Patents

Literature

1447 results about "Ball grid array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

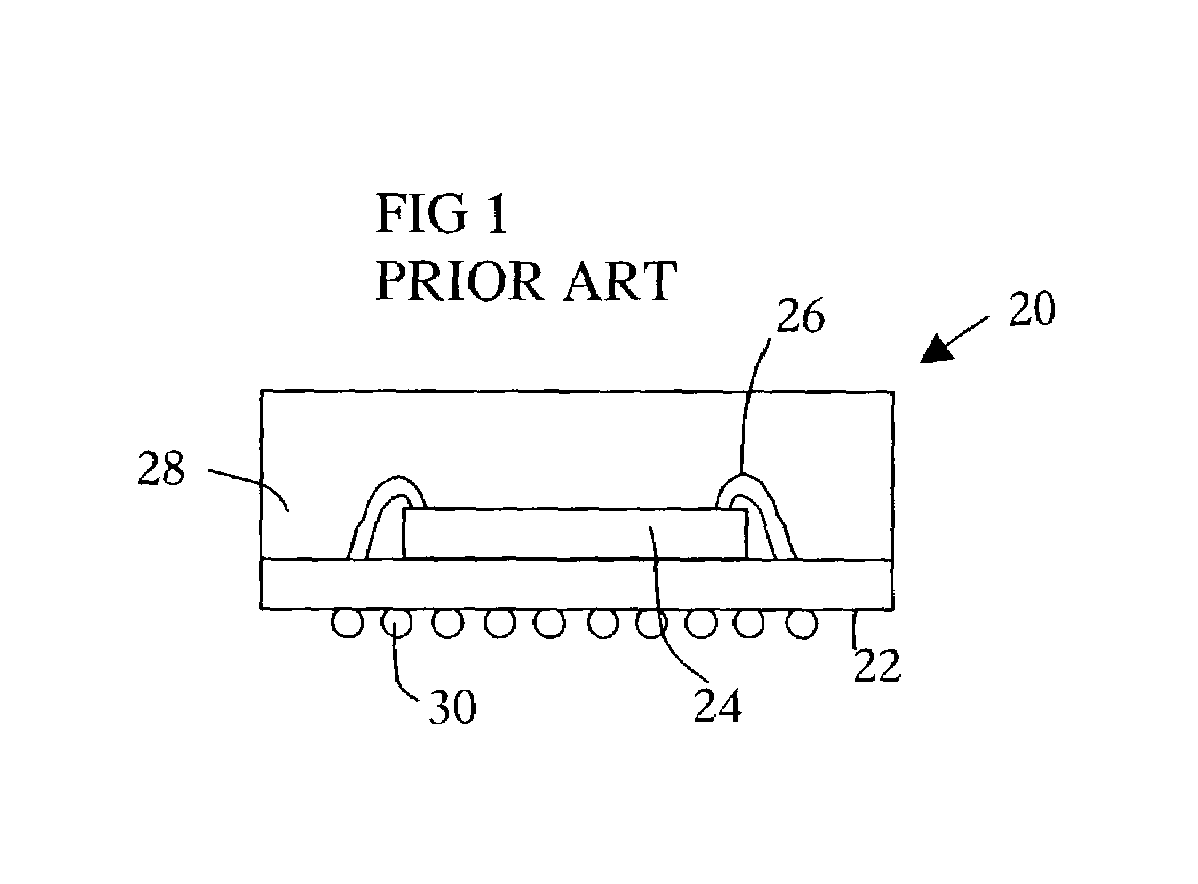

A ball grid array (BGA) is a type of surface-mount packaging (a chip carrier) used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors. A BGA can provide more interconnection pins than can be put on a dual in-line or flat package. The whole bottom surface of the device can be used, instead of just the perimeter. The traces connecting the package's leads to the wires or balls which connect the die to package are also on average shorter than with a perimeter-only type, leading to better performance at high speeds.

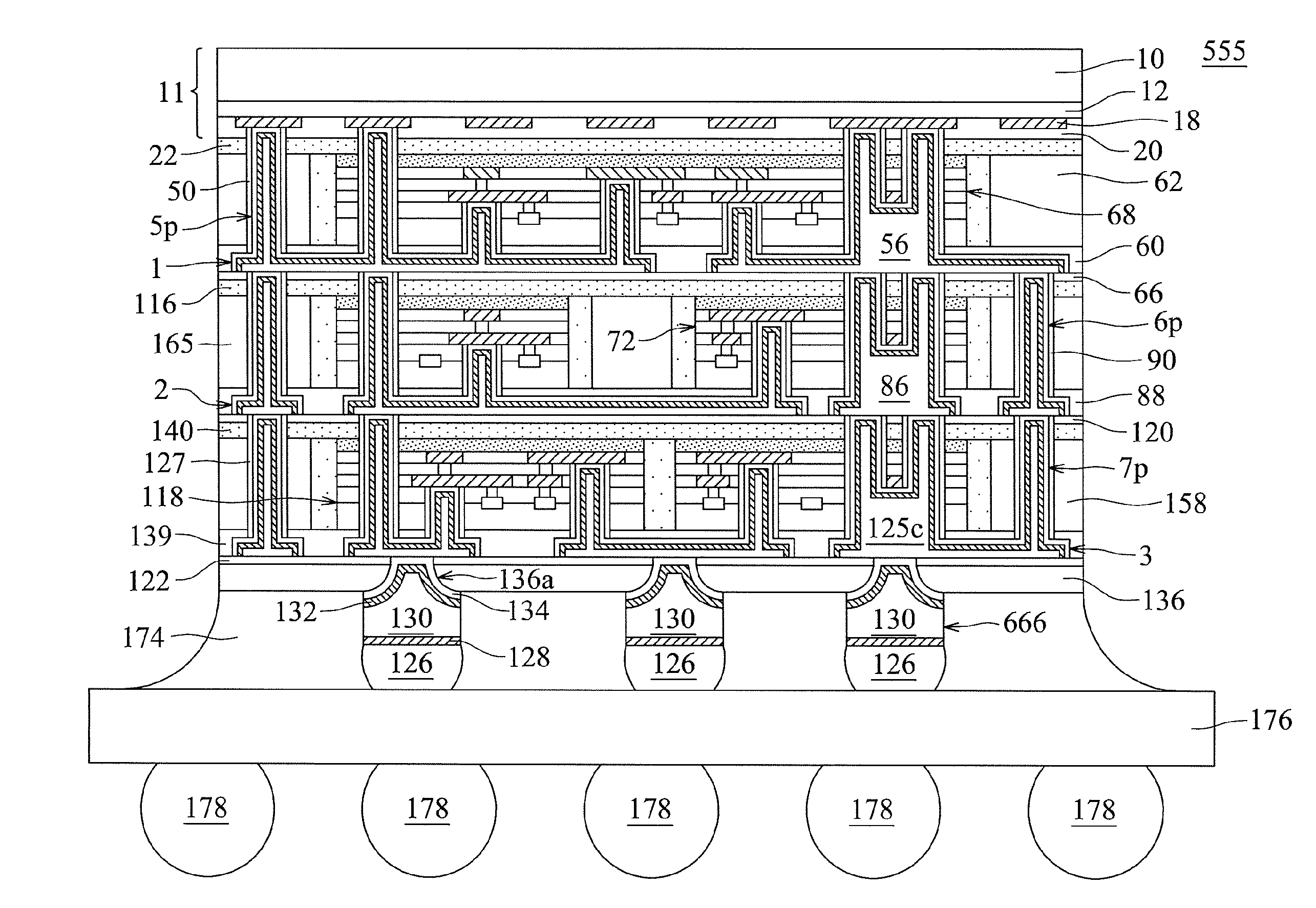

System-in packages

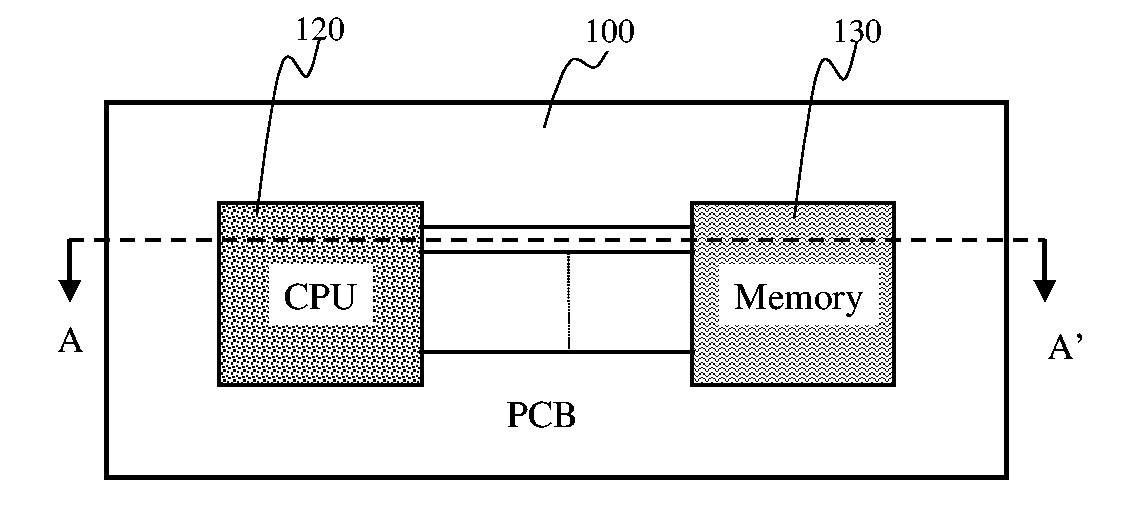

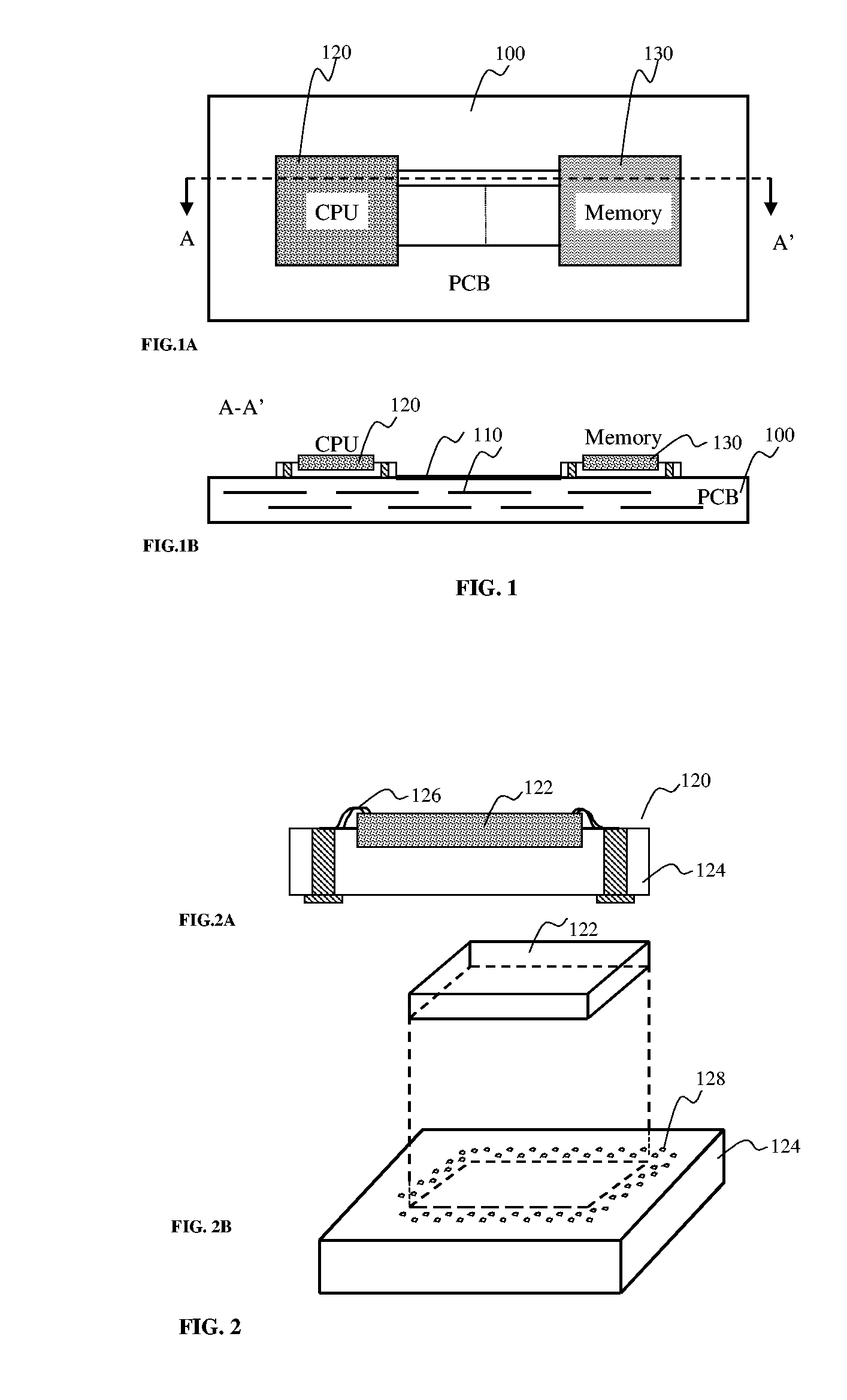

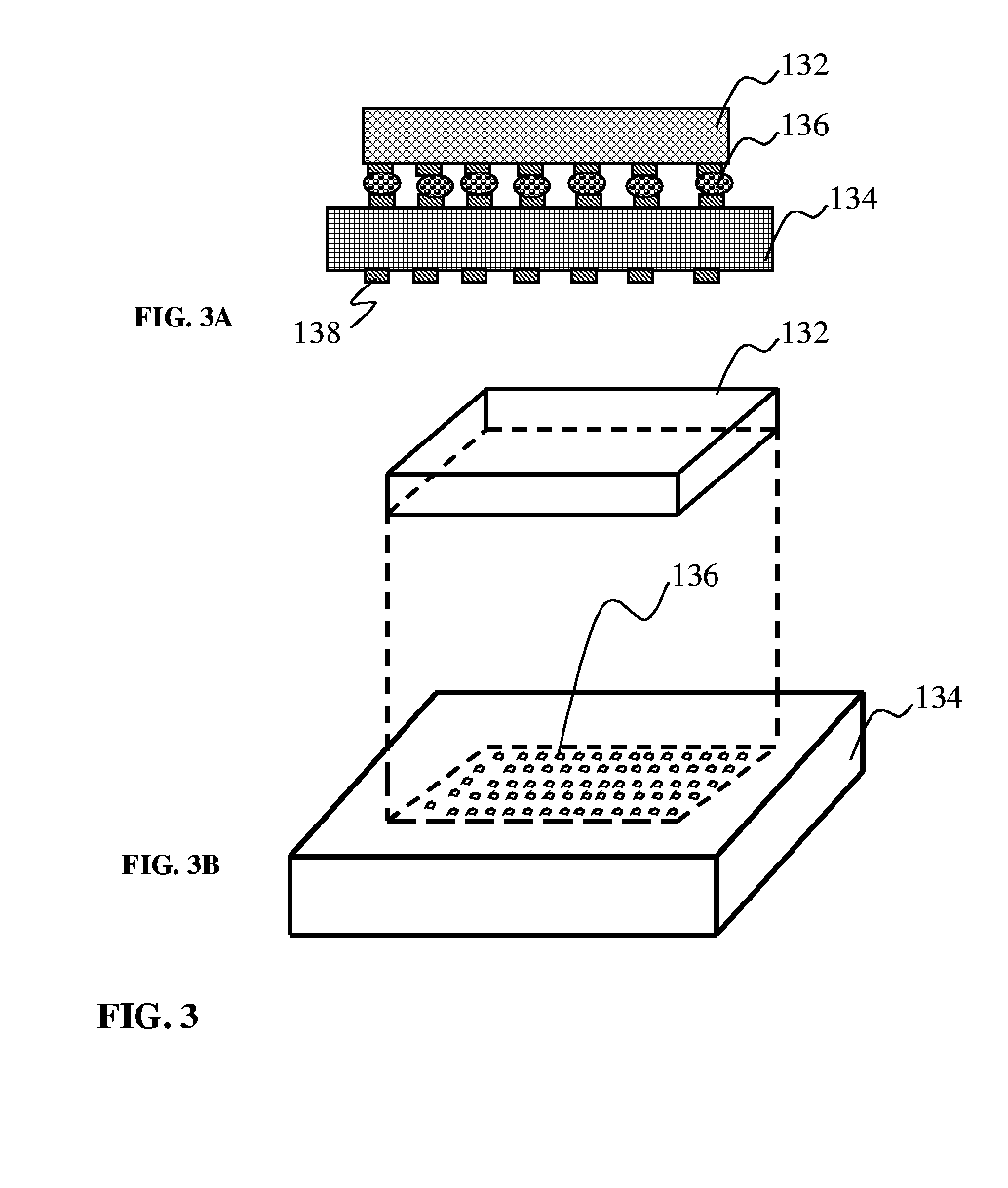

ActiveUS20110026232A1Improve uniformitySemiconductor/solid-state device detailsCircuit arrangements on support structuresMetal interconnectSystem in package

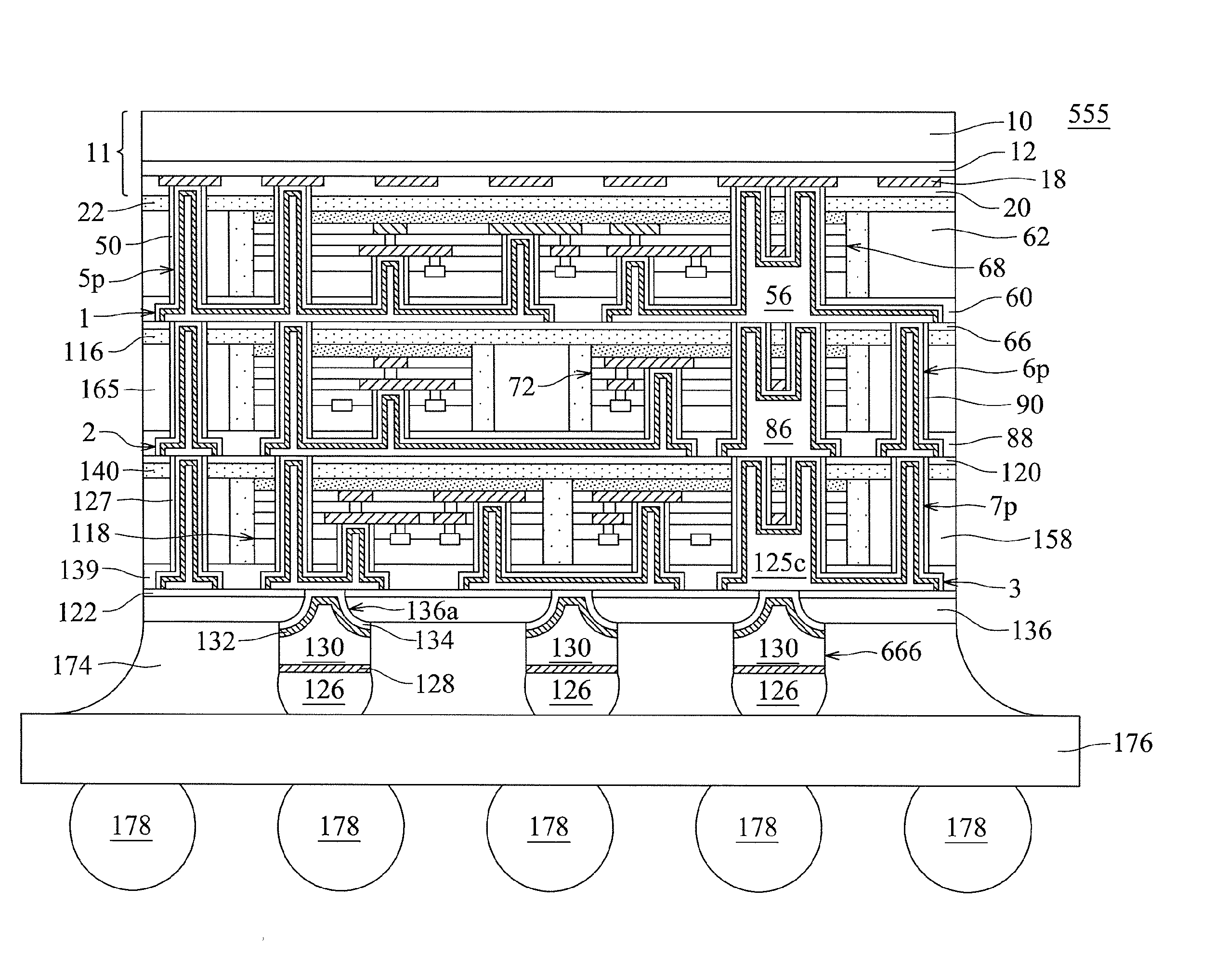

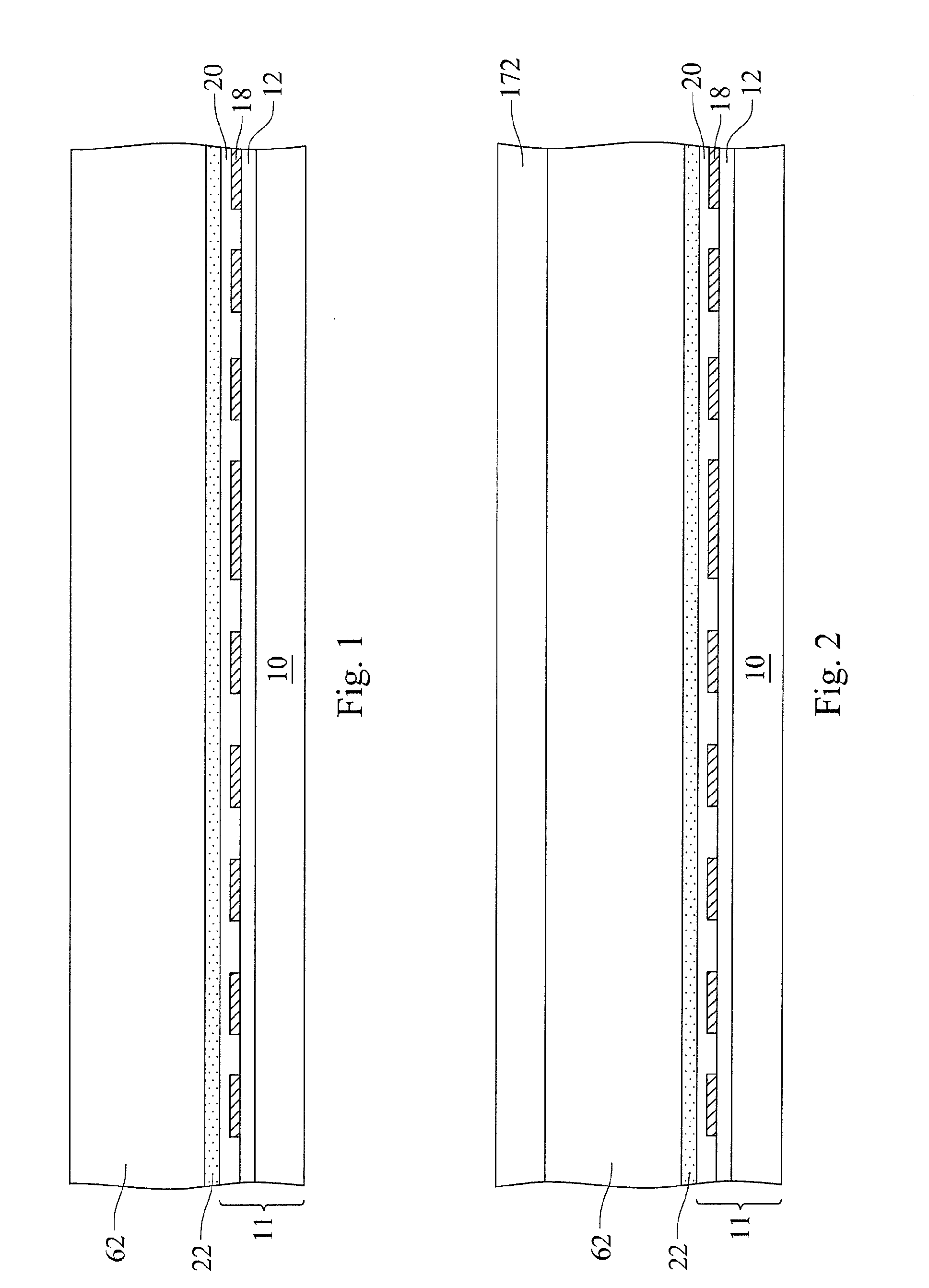

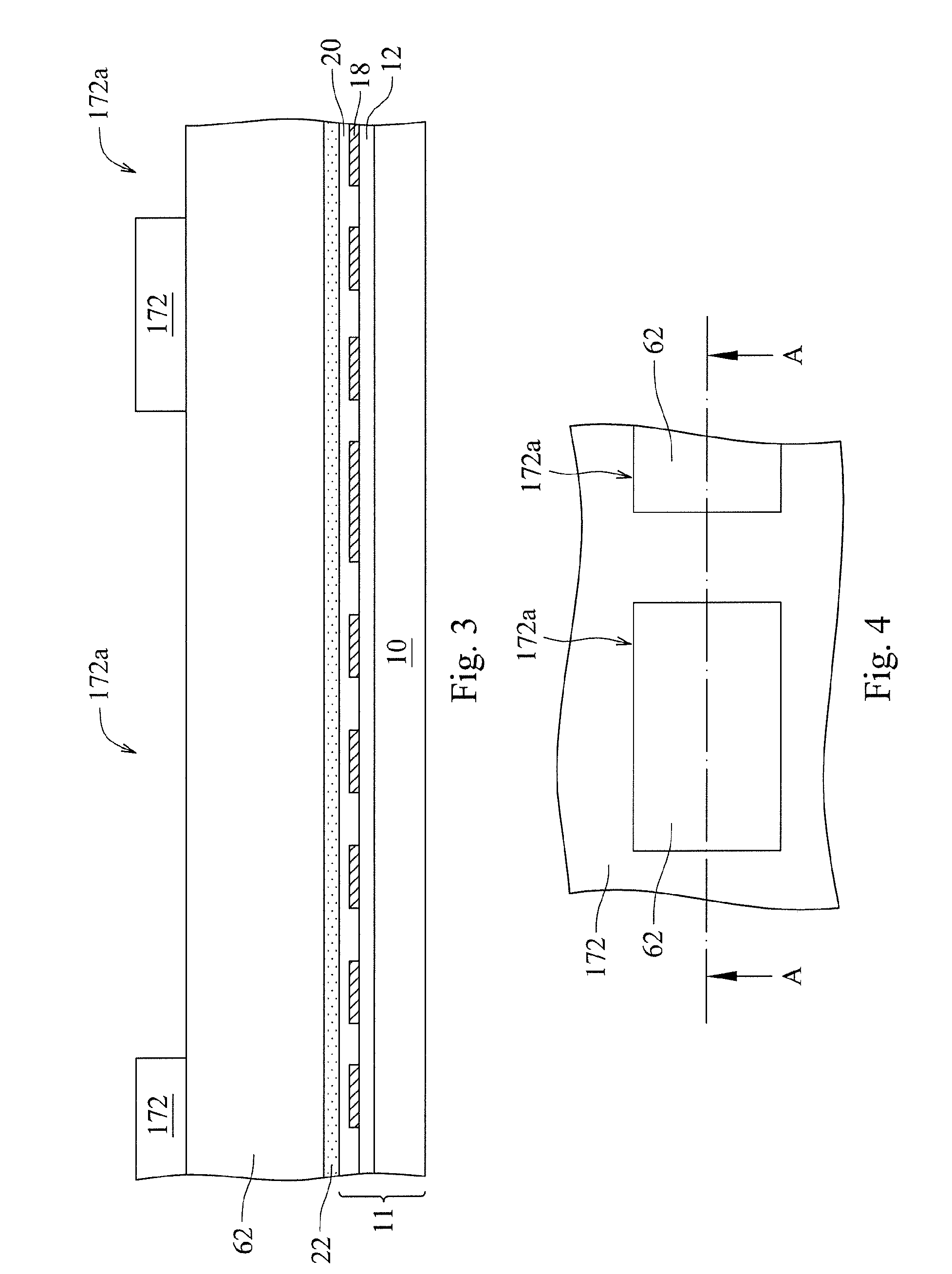

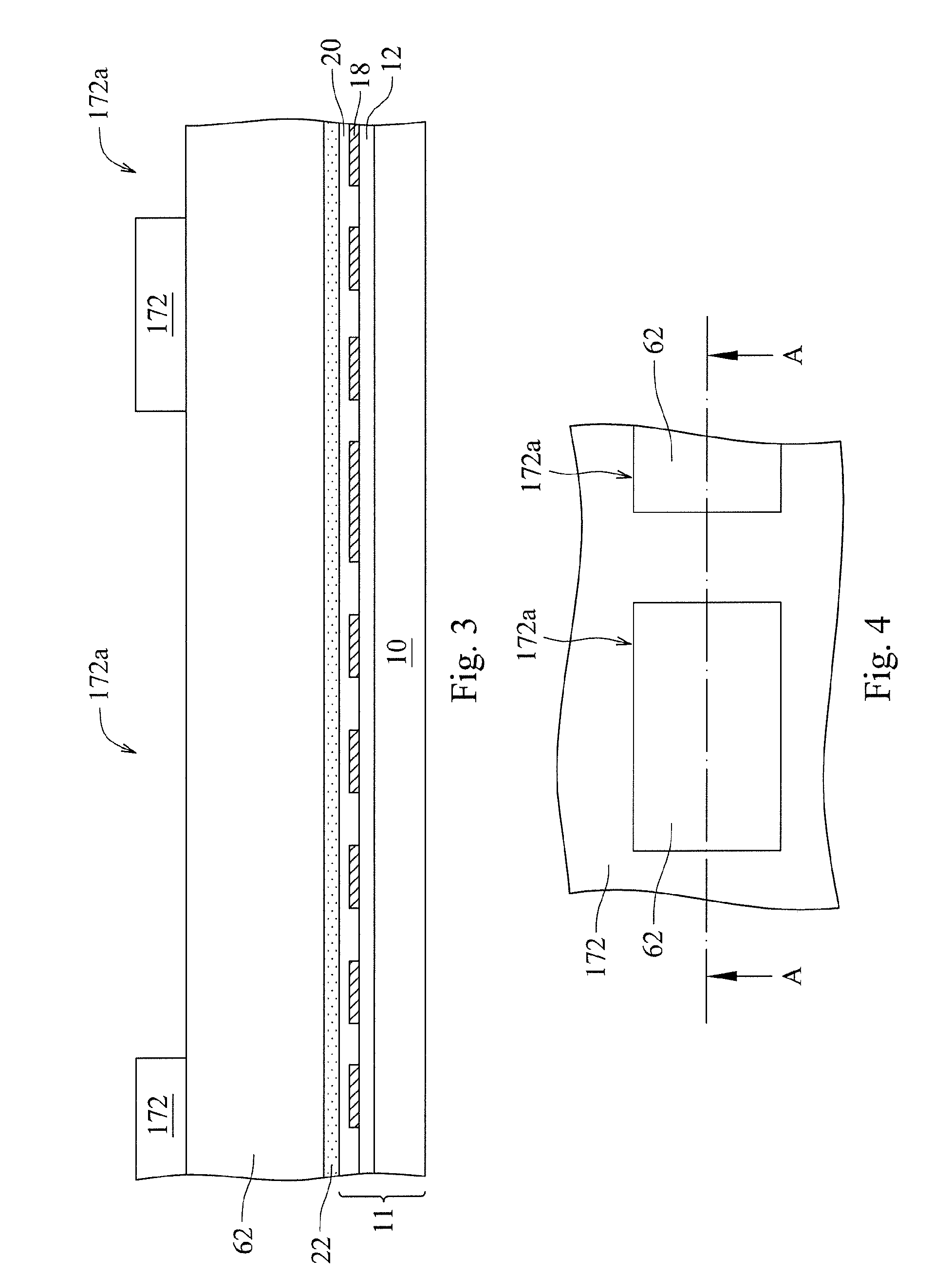

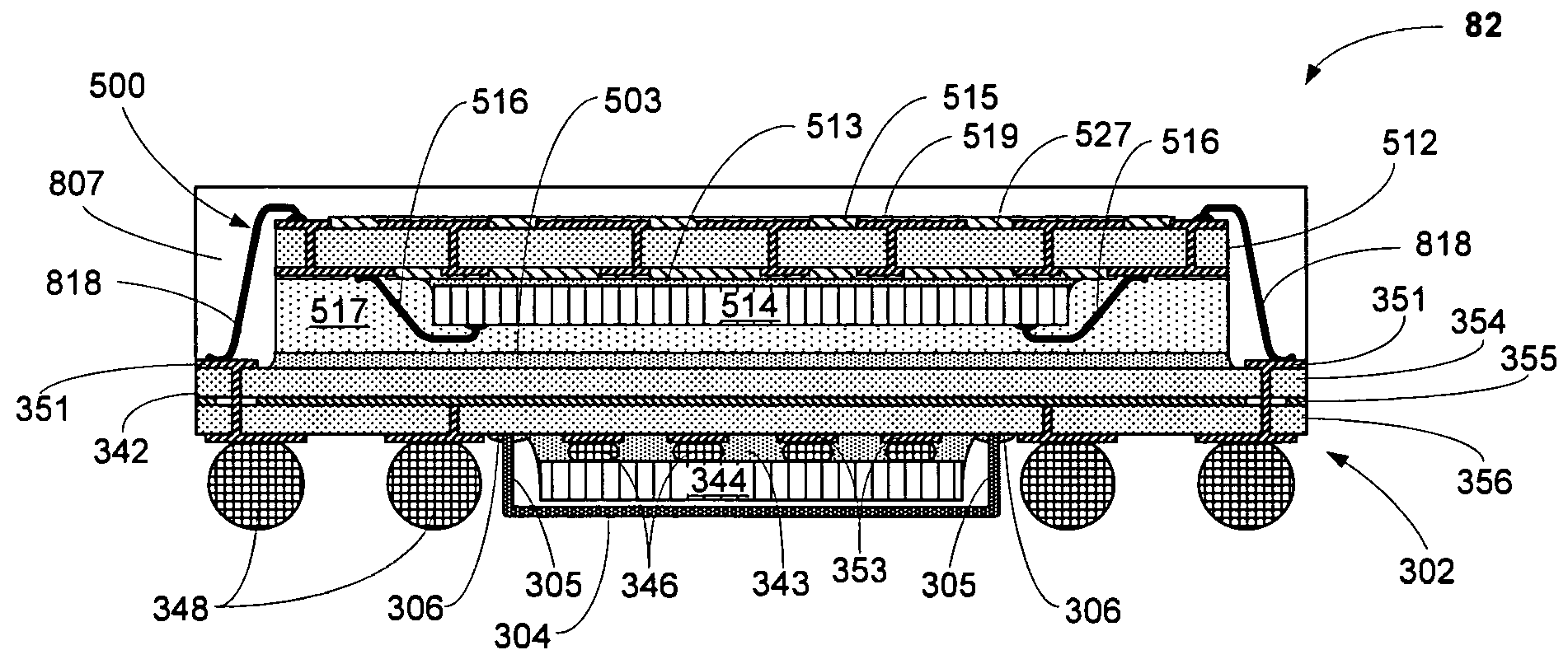

System-in packages, or multichip modules, are described which can include multi-layer chips and multi-layer dummy substrates over a carrier, multiple through vias blindly or completely through the multi-layer chips and completely through the multi-layer dummy substrates, multiple metal plugs in the through vias, and multiple metal interconnects, connected to the metal plugs, between the multi-layer chips. The multi-layer chips can be connected to each other or to an external circuit or structure, such as mother board, ball grid array (BGA) substrate, printed circuit board, metal substrate, glass substrate, or ceramic substrate, through the metal plugs and the metal interconnects.

Owner:QUALCOMM INC

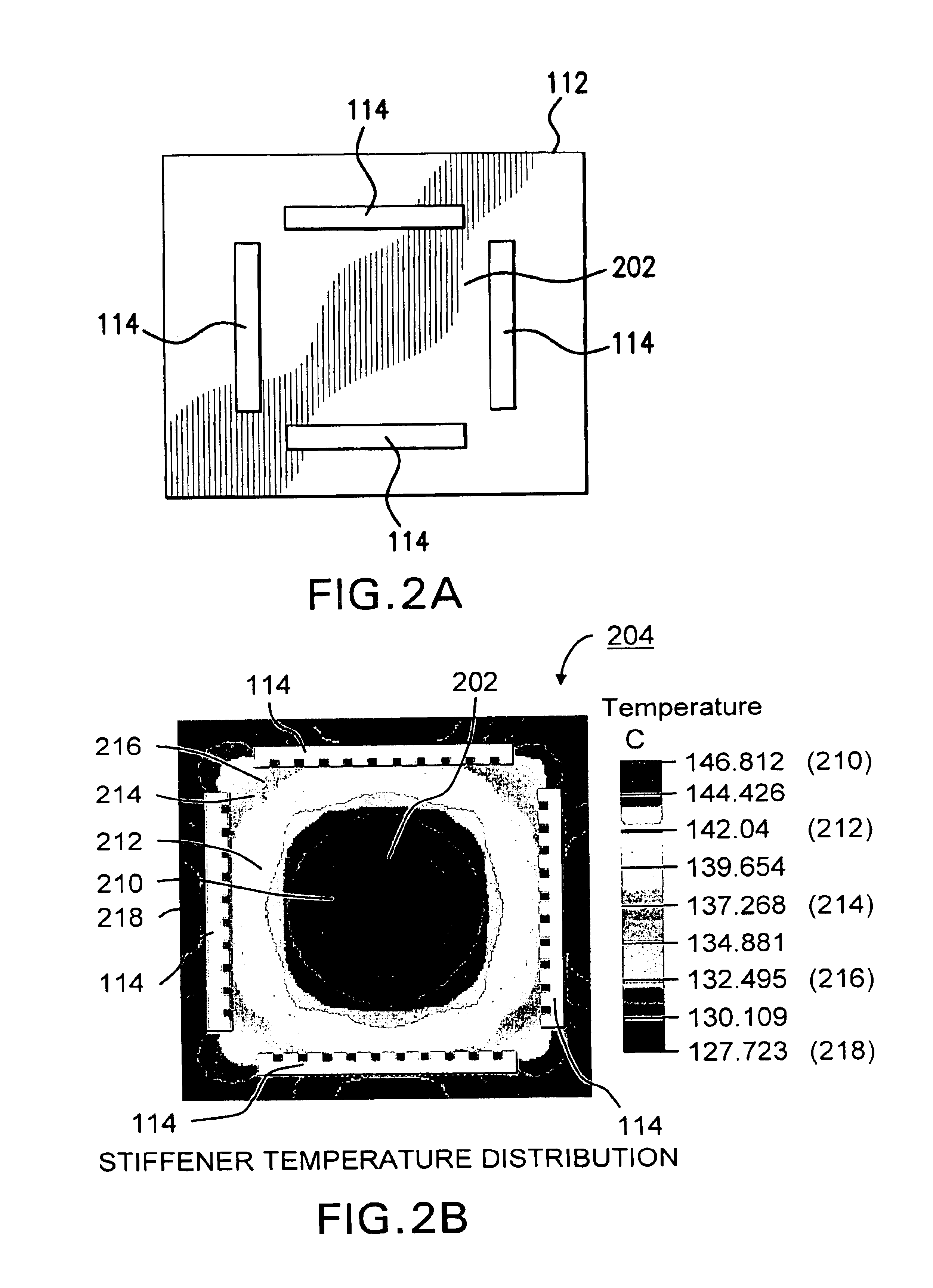

Stackable ceramic FBGA for high thermal applications

InactiveUS6297548B1Increase speedEasy to operateSemiconductor/solid-state device detailsSolid-state devicesDevice materialBall grid array

An apparatus package for high temperature thermal applications for ball grid array semiconductor devices and a method of packaging ball grid array semiconductor devices.

Owner:MICRON TECH INC

System-in packages

ActiveUS8503186B2Improve uniformityCircuit arrangements on support structuresSemiconductor/solid-state device detailsMetal interconnectSystem in package

Owner:QUALCOMM INC

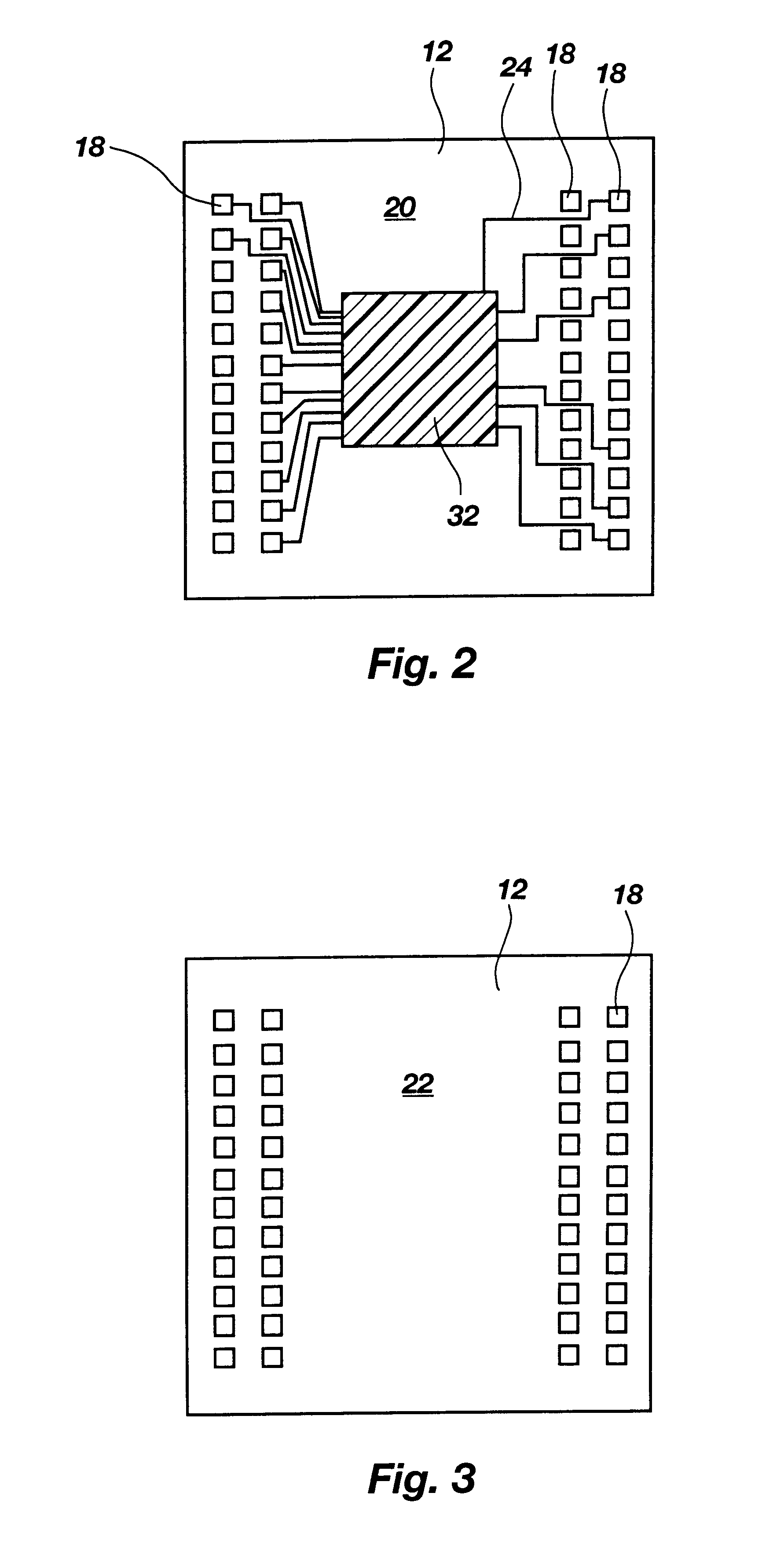

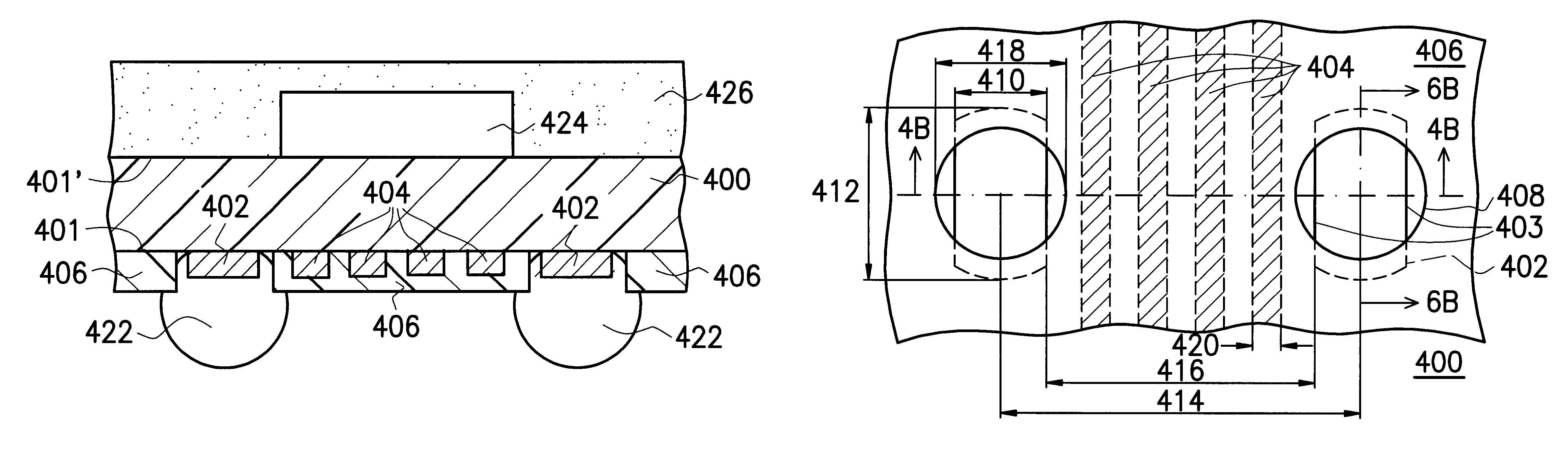

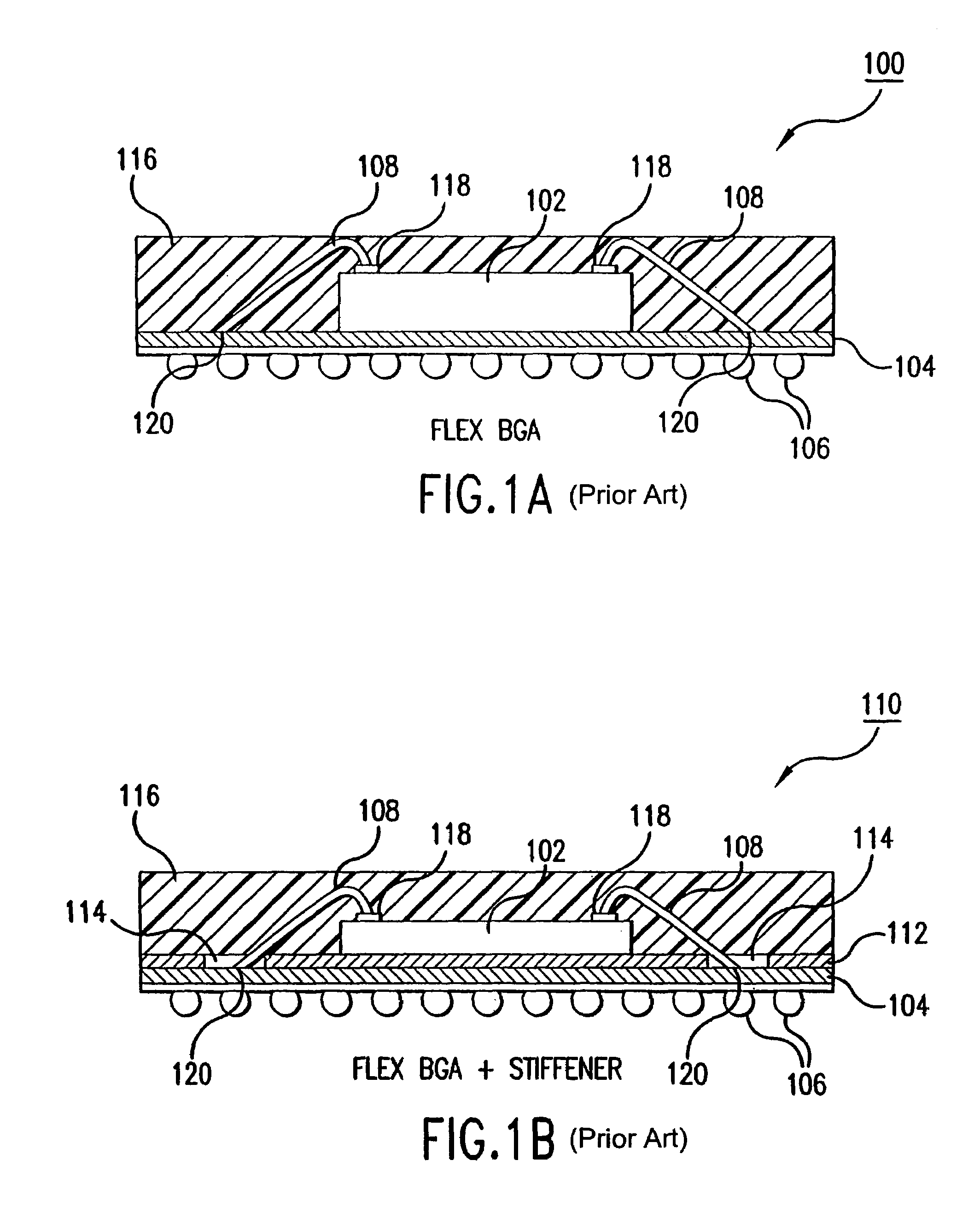

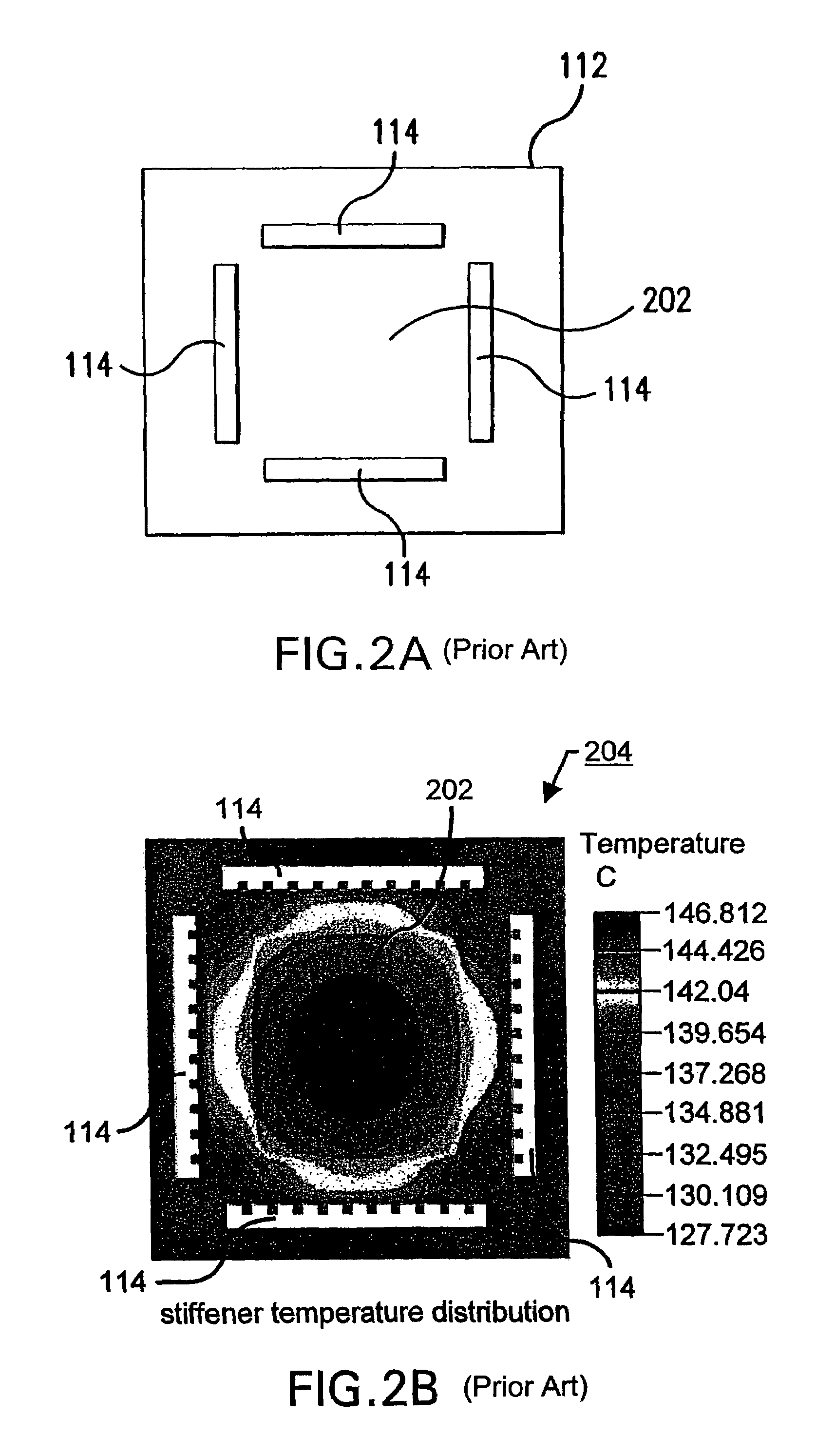

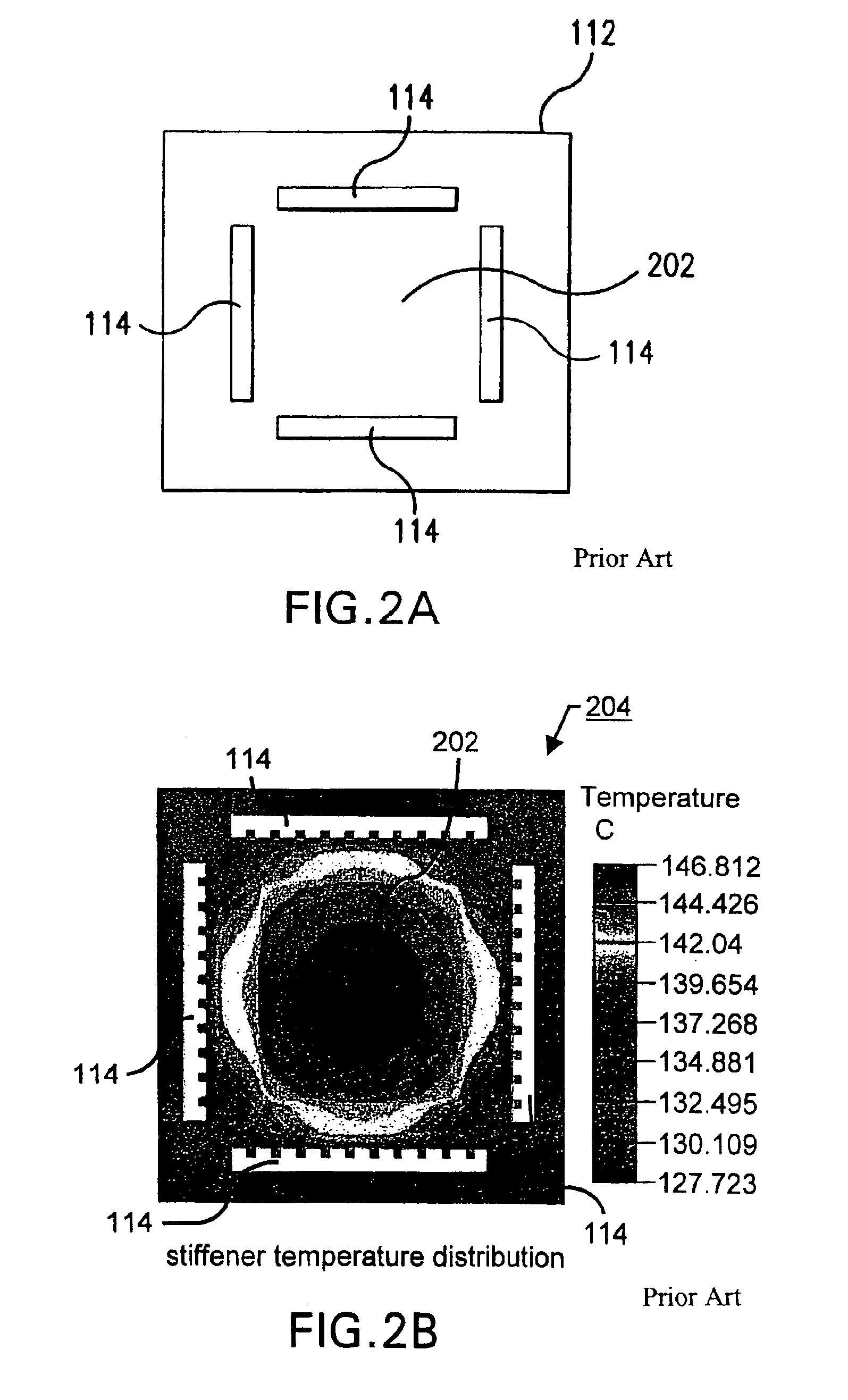

Ball grid array package with patterned stiffener layer

InactiveUS6906414B2Semiconductor/solid-state device detailsSolid-state devicesContact padEngineering

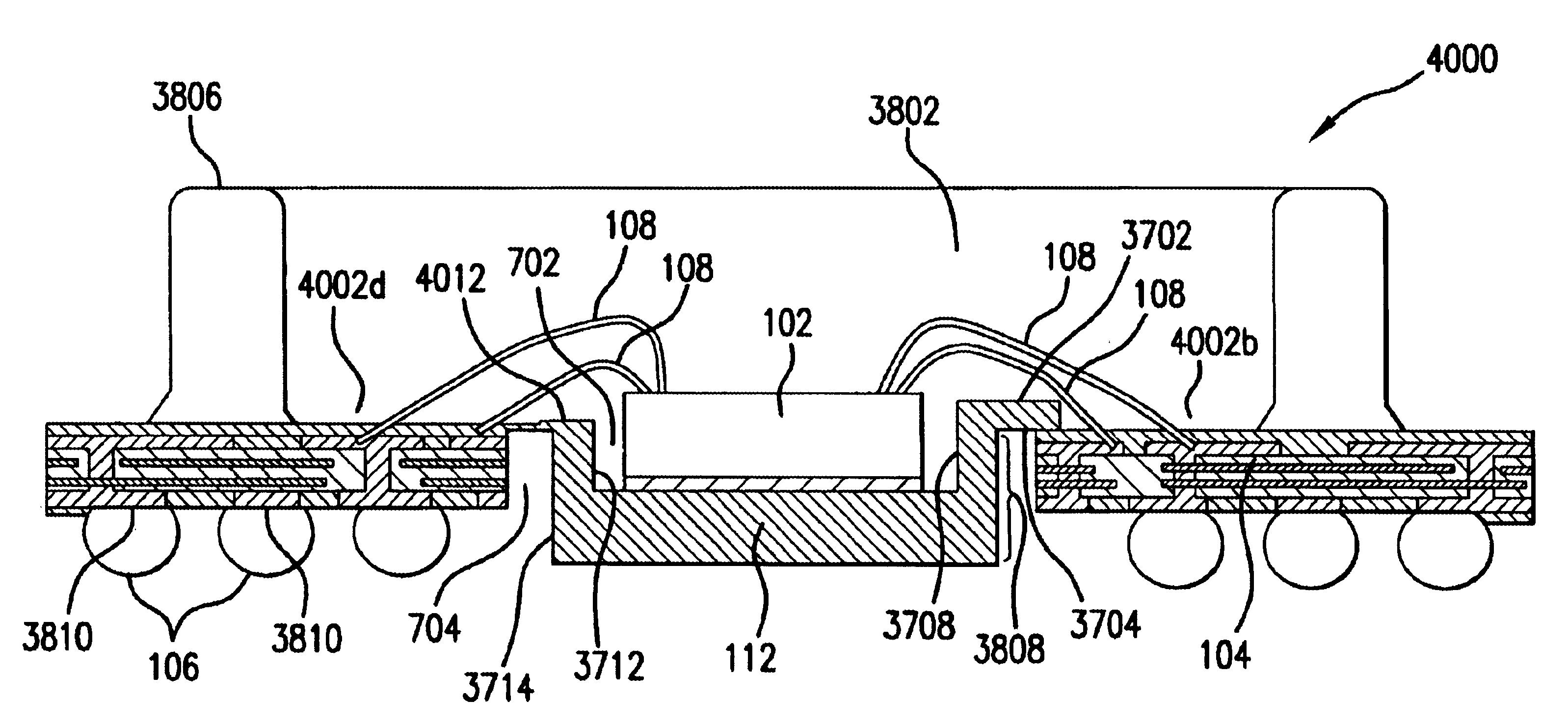

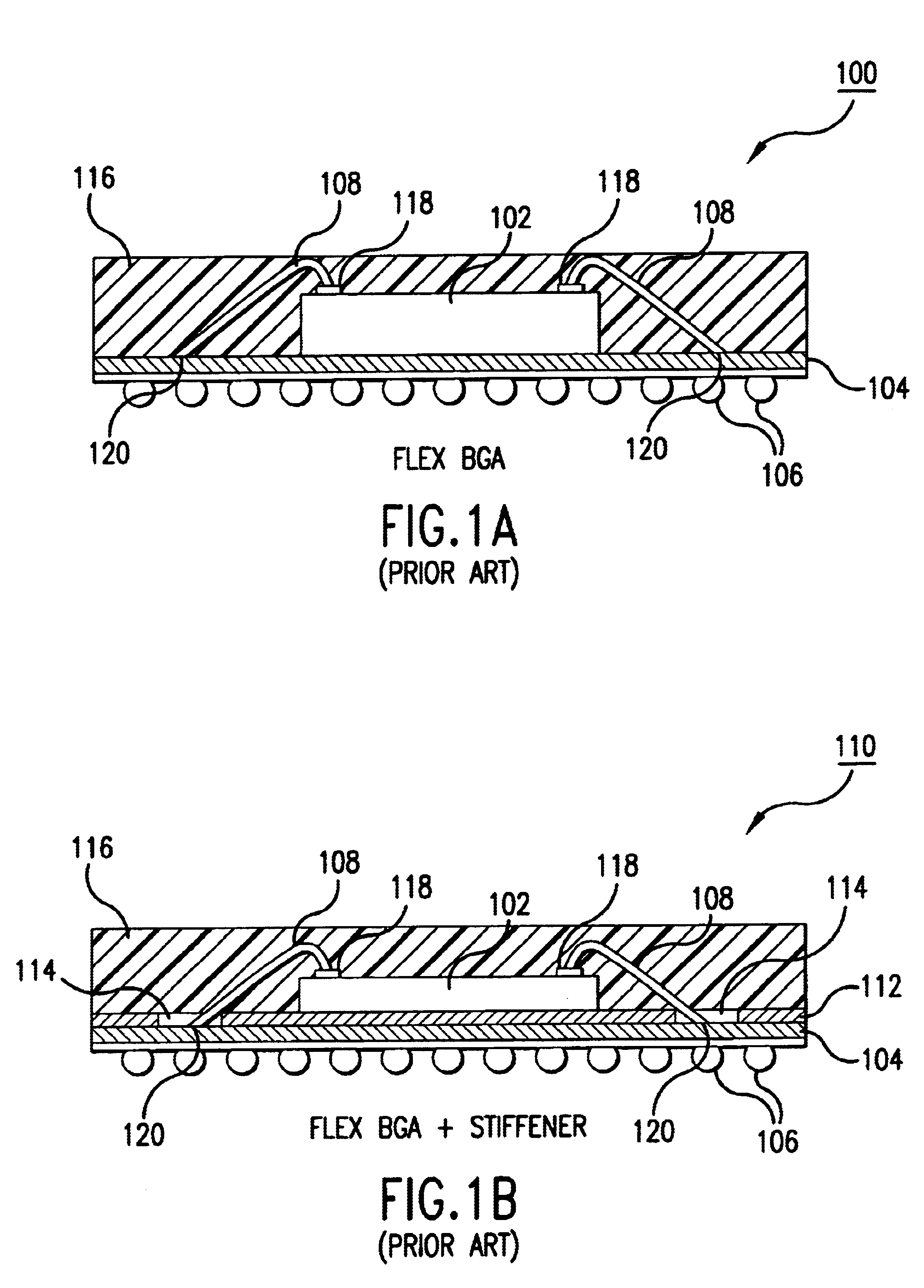

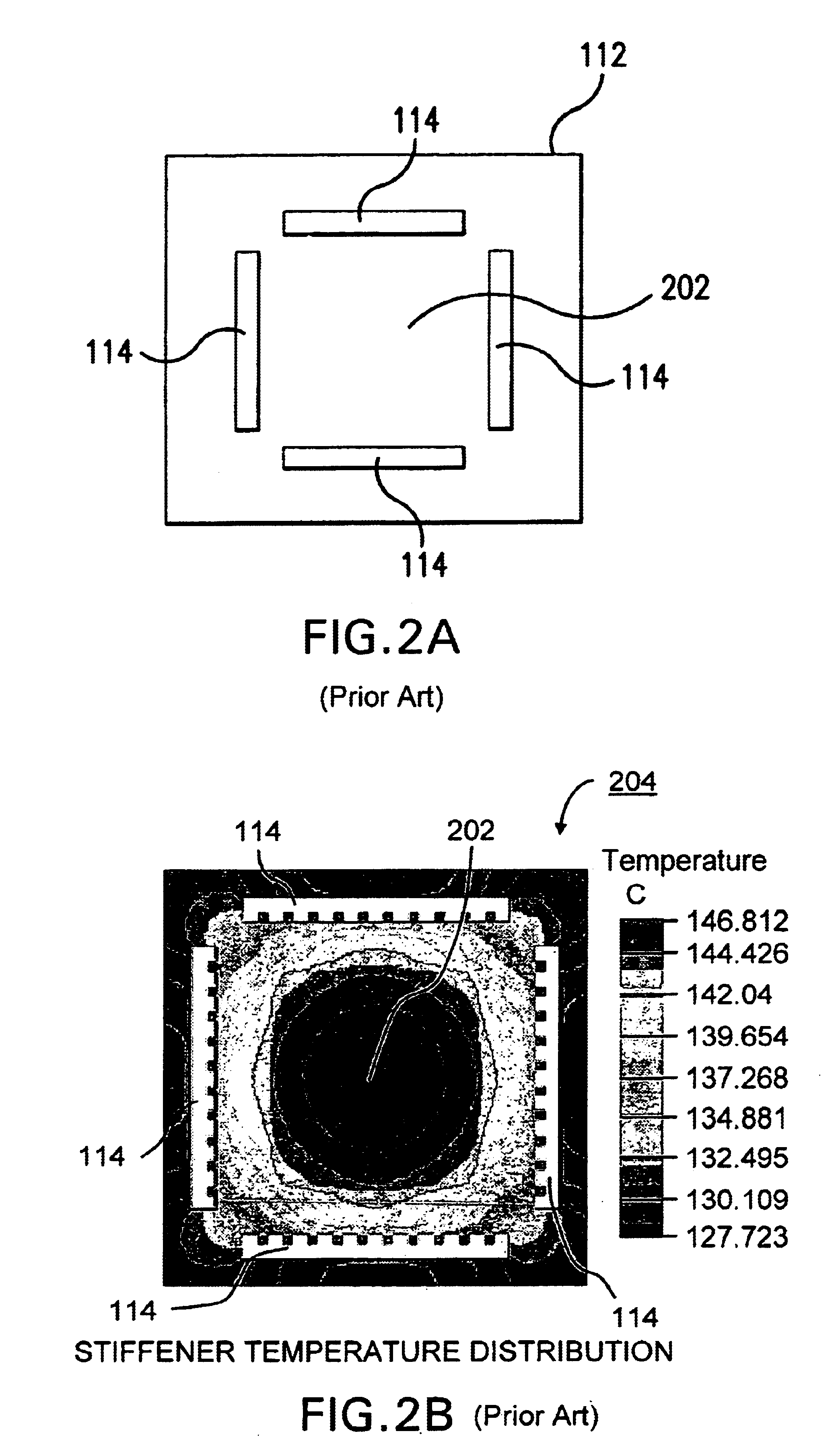

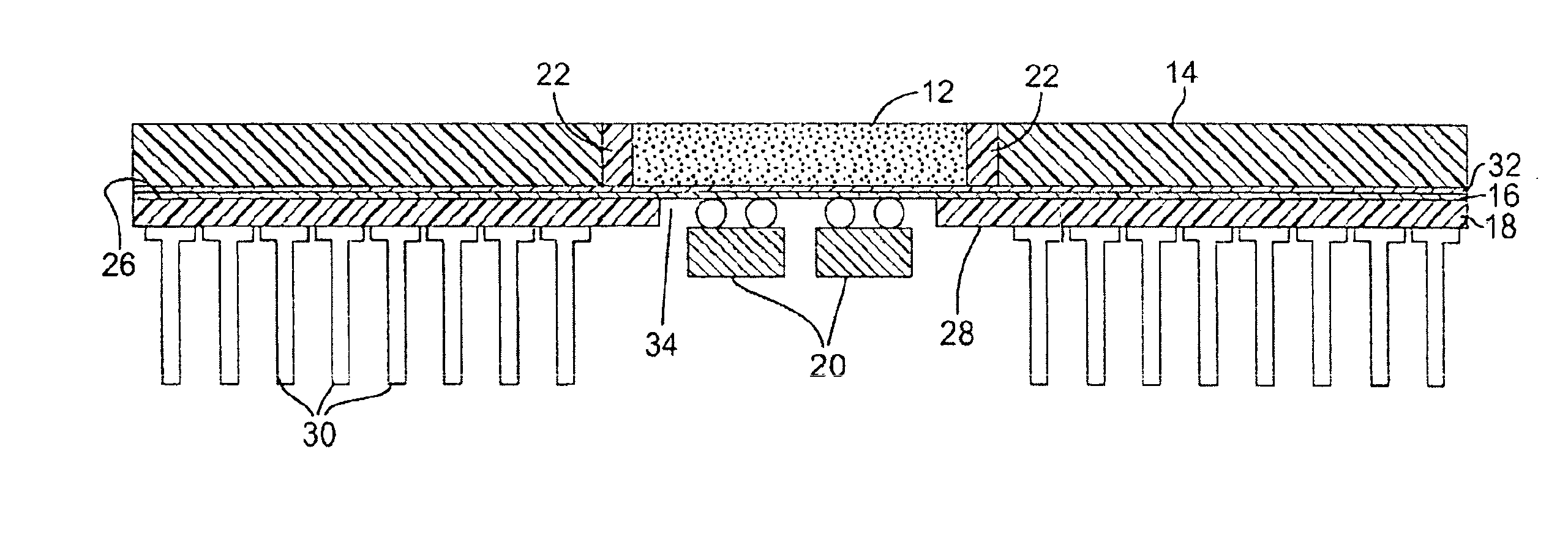

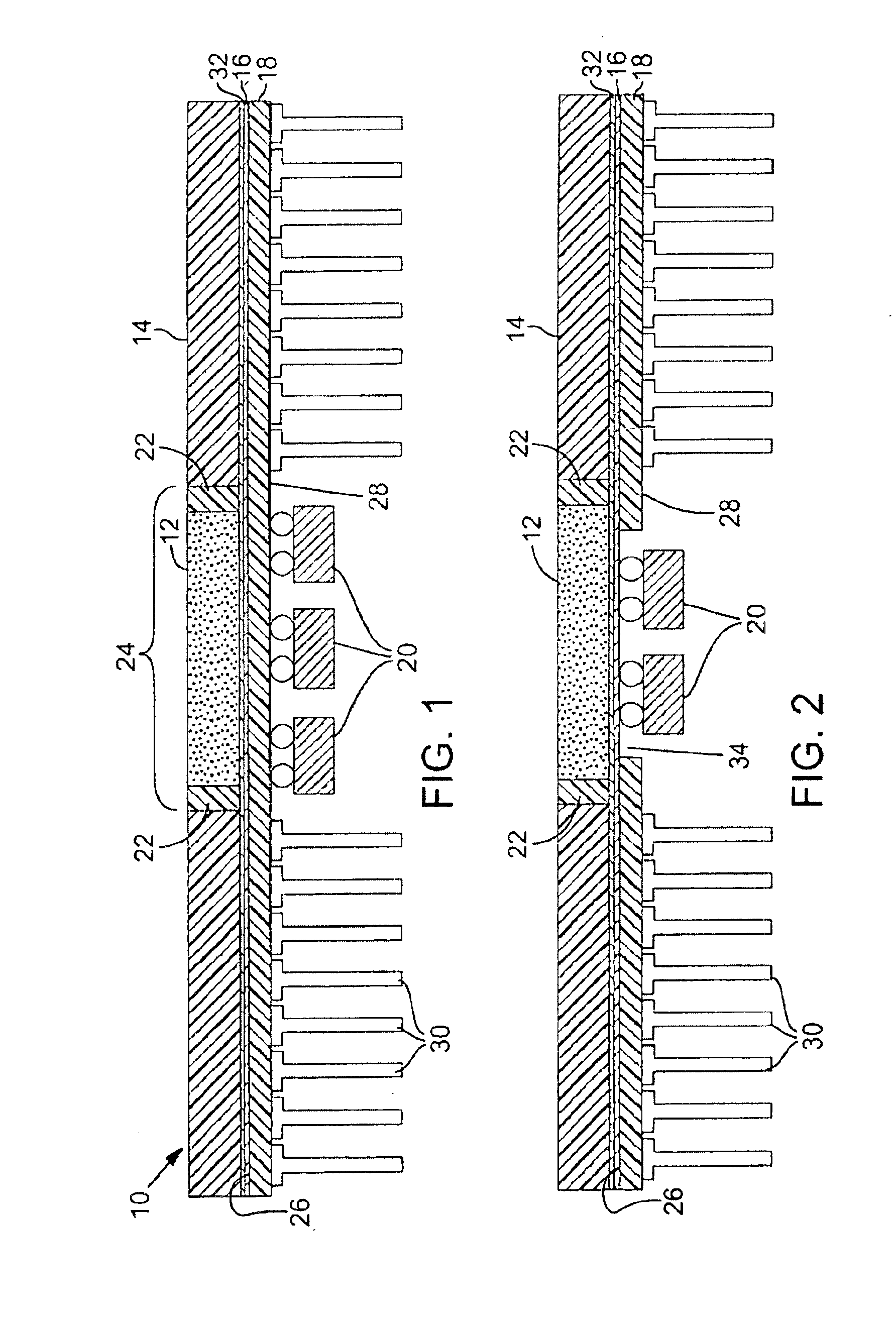

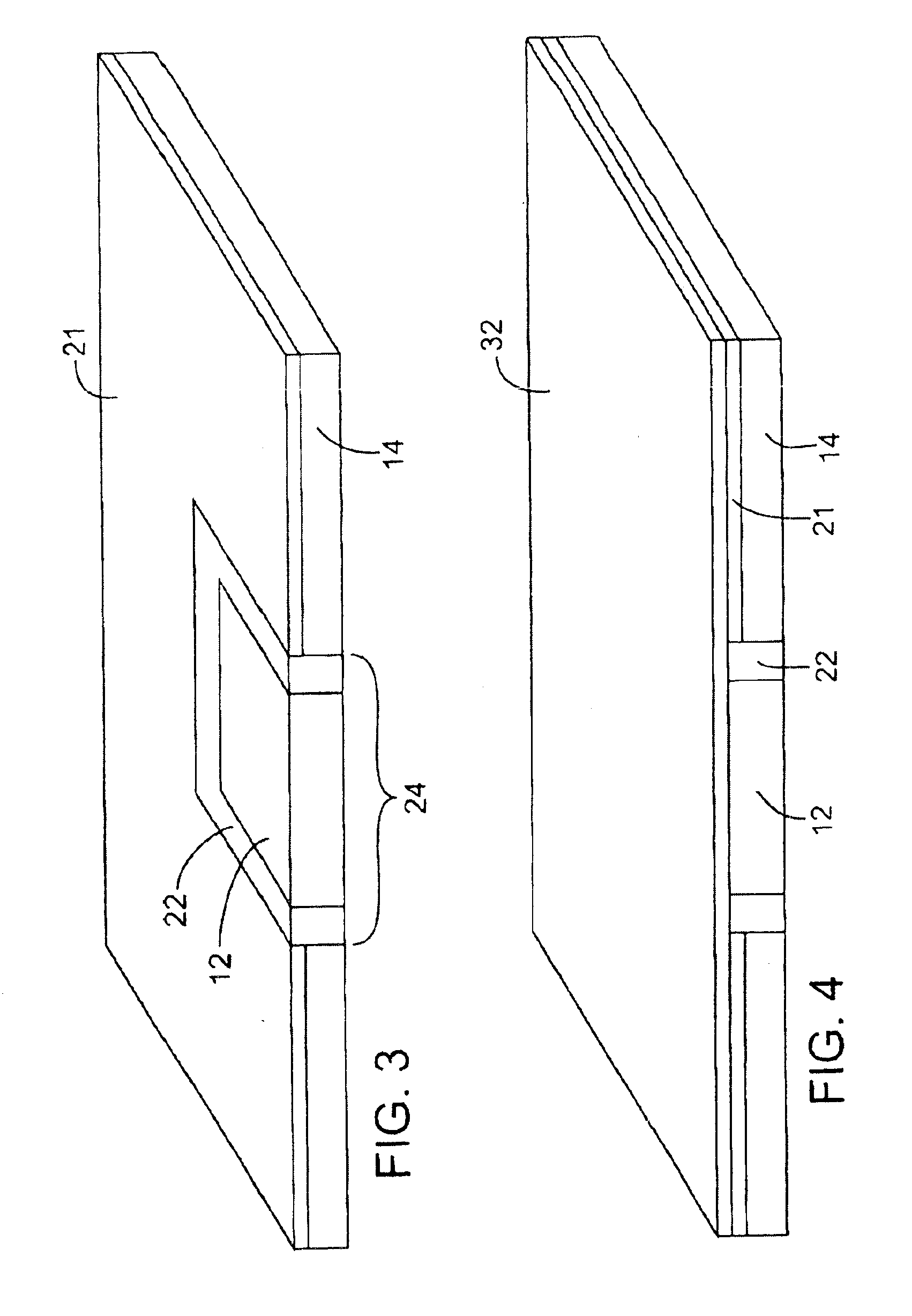

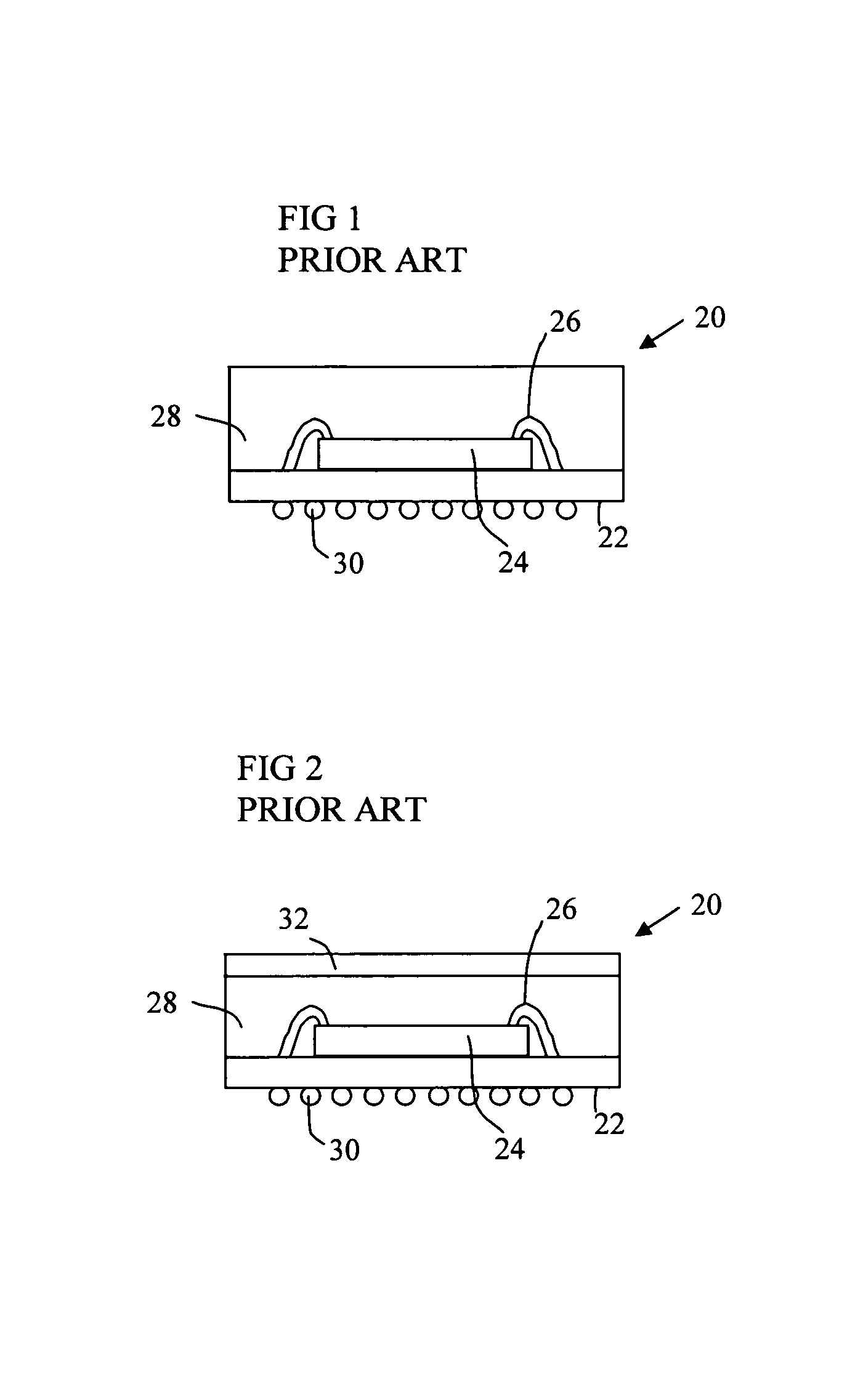

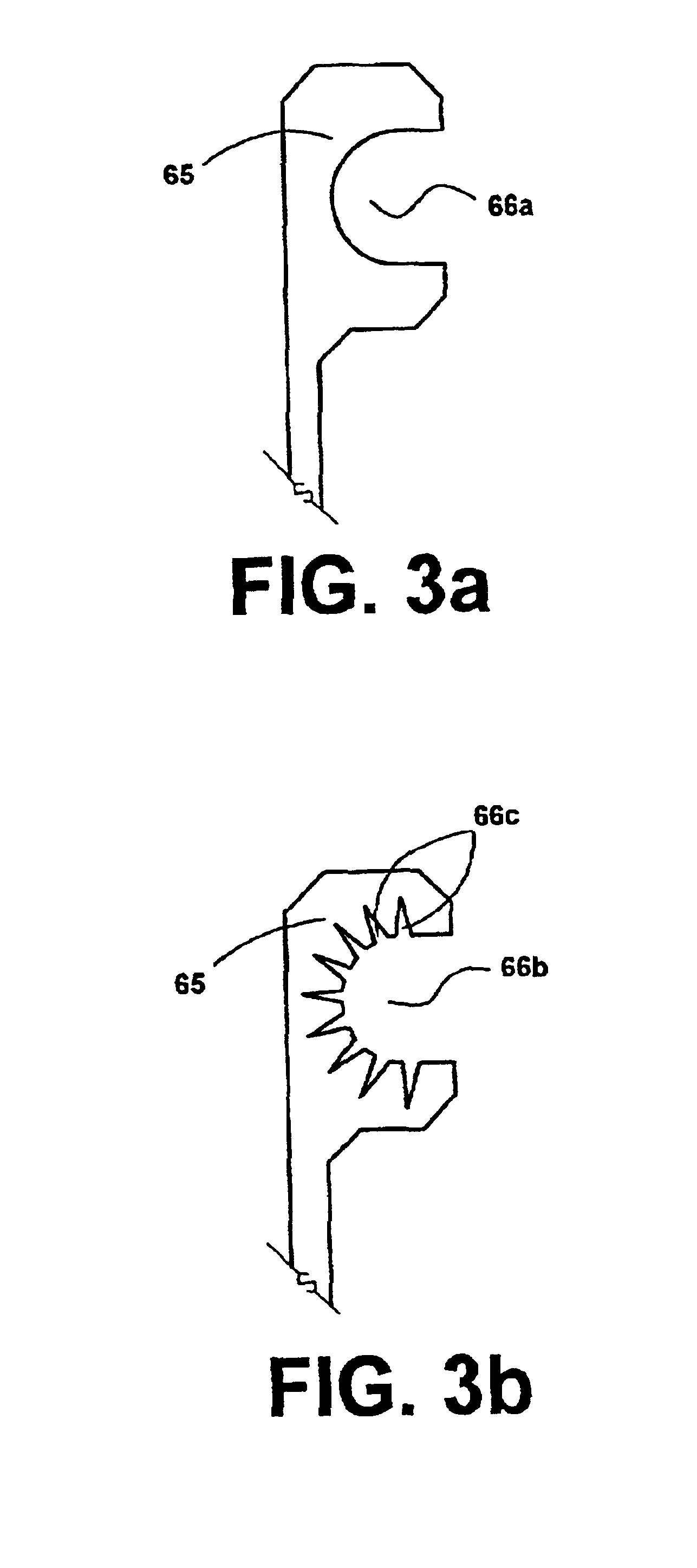

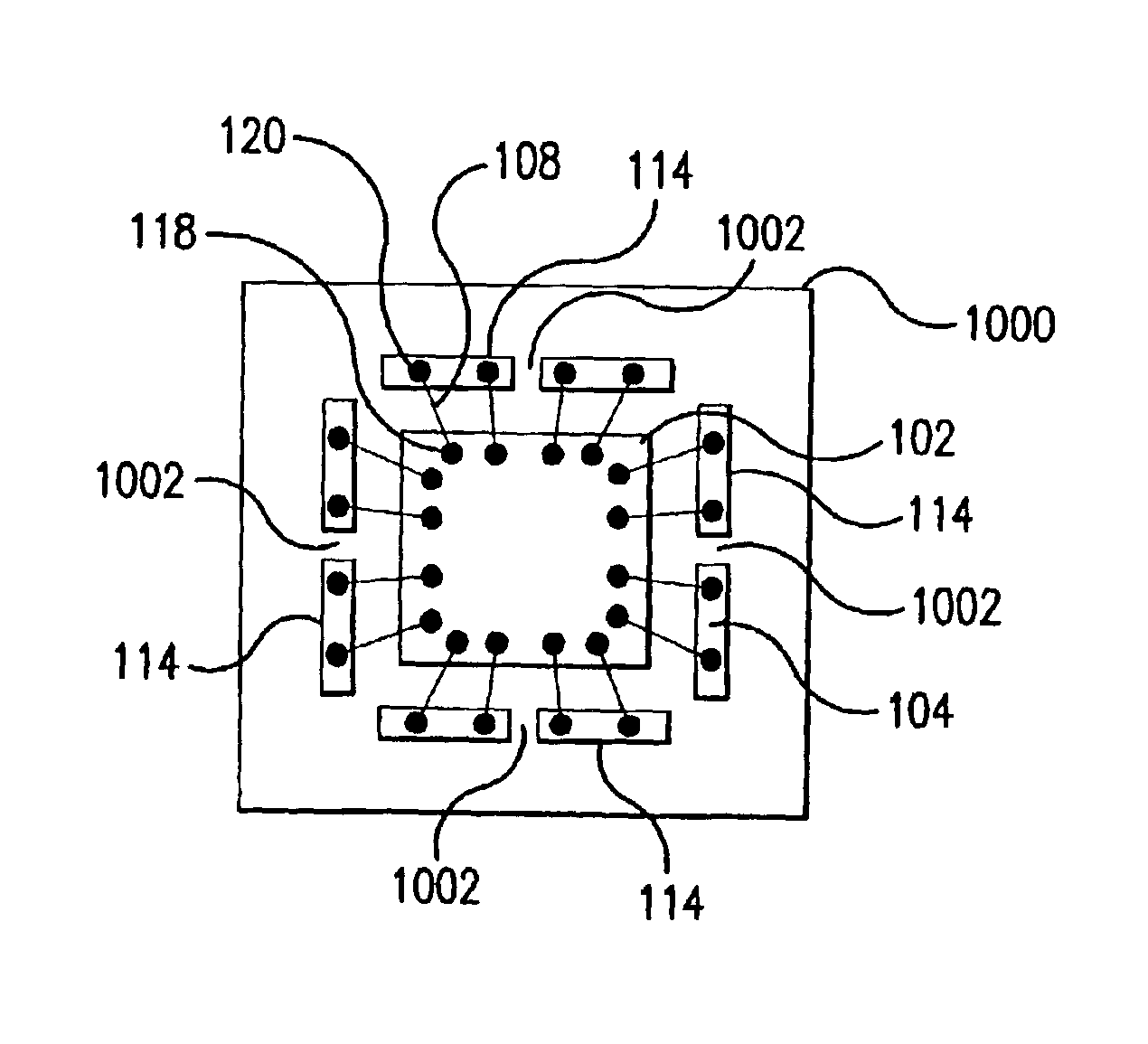

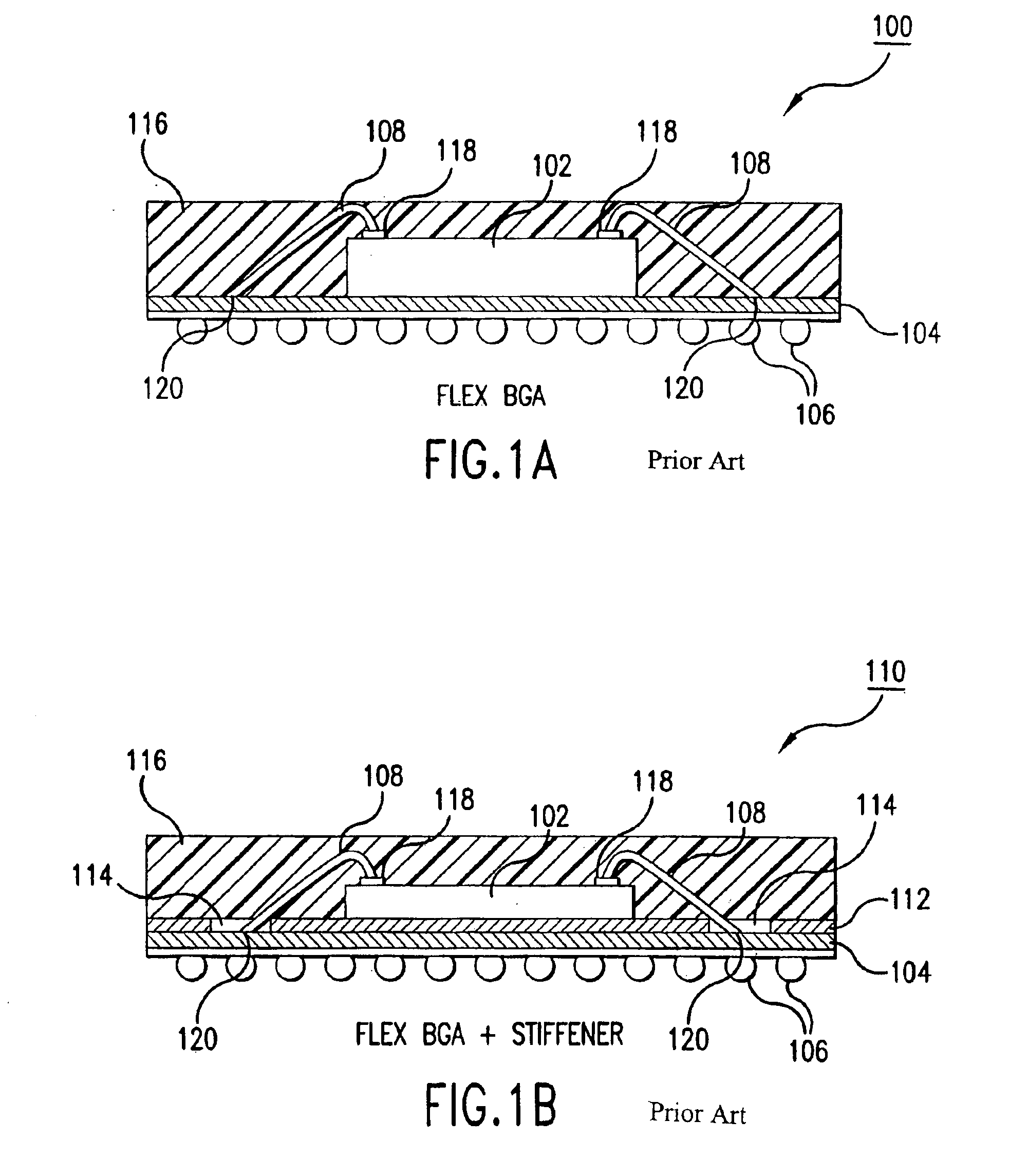

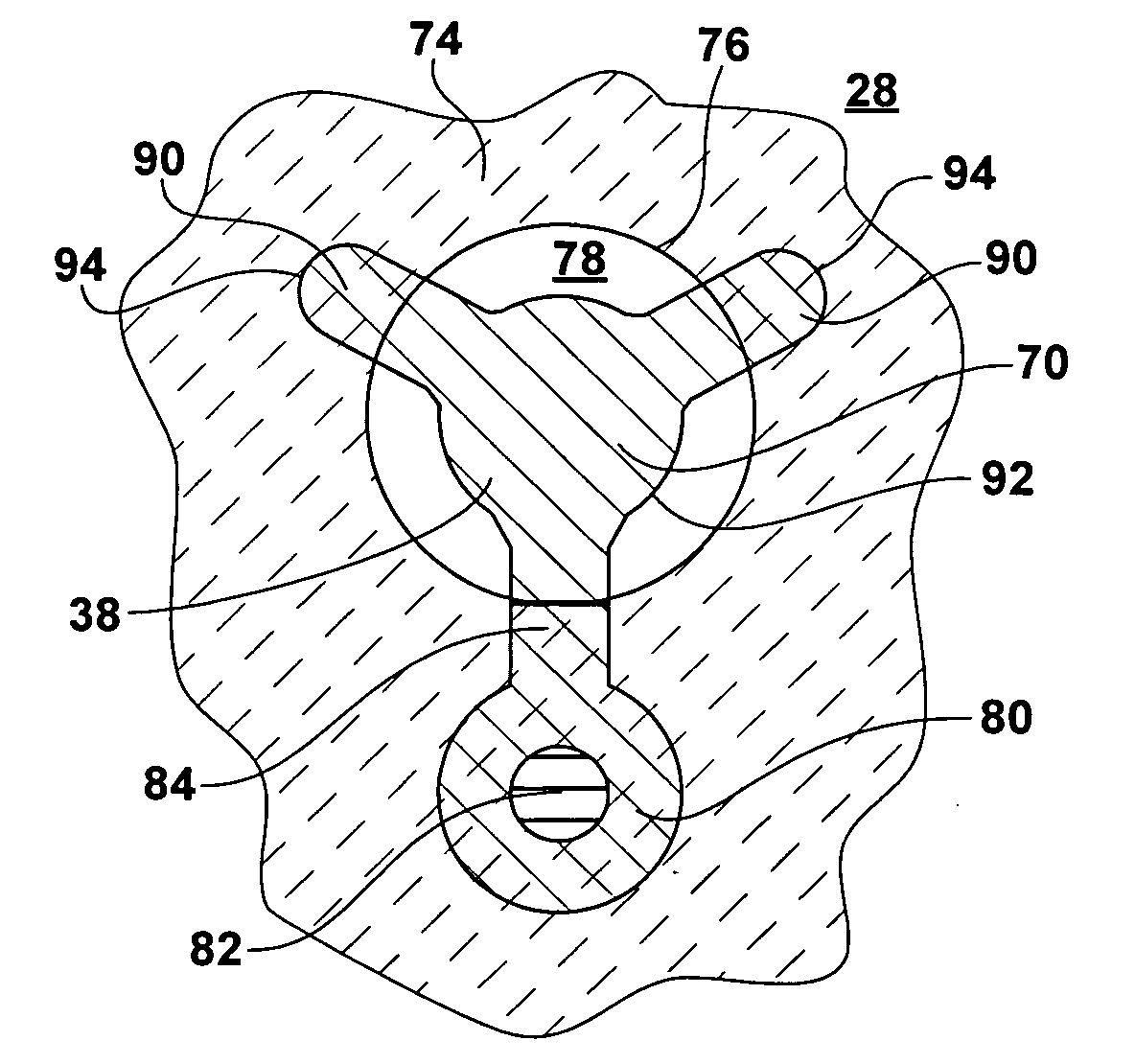

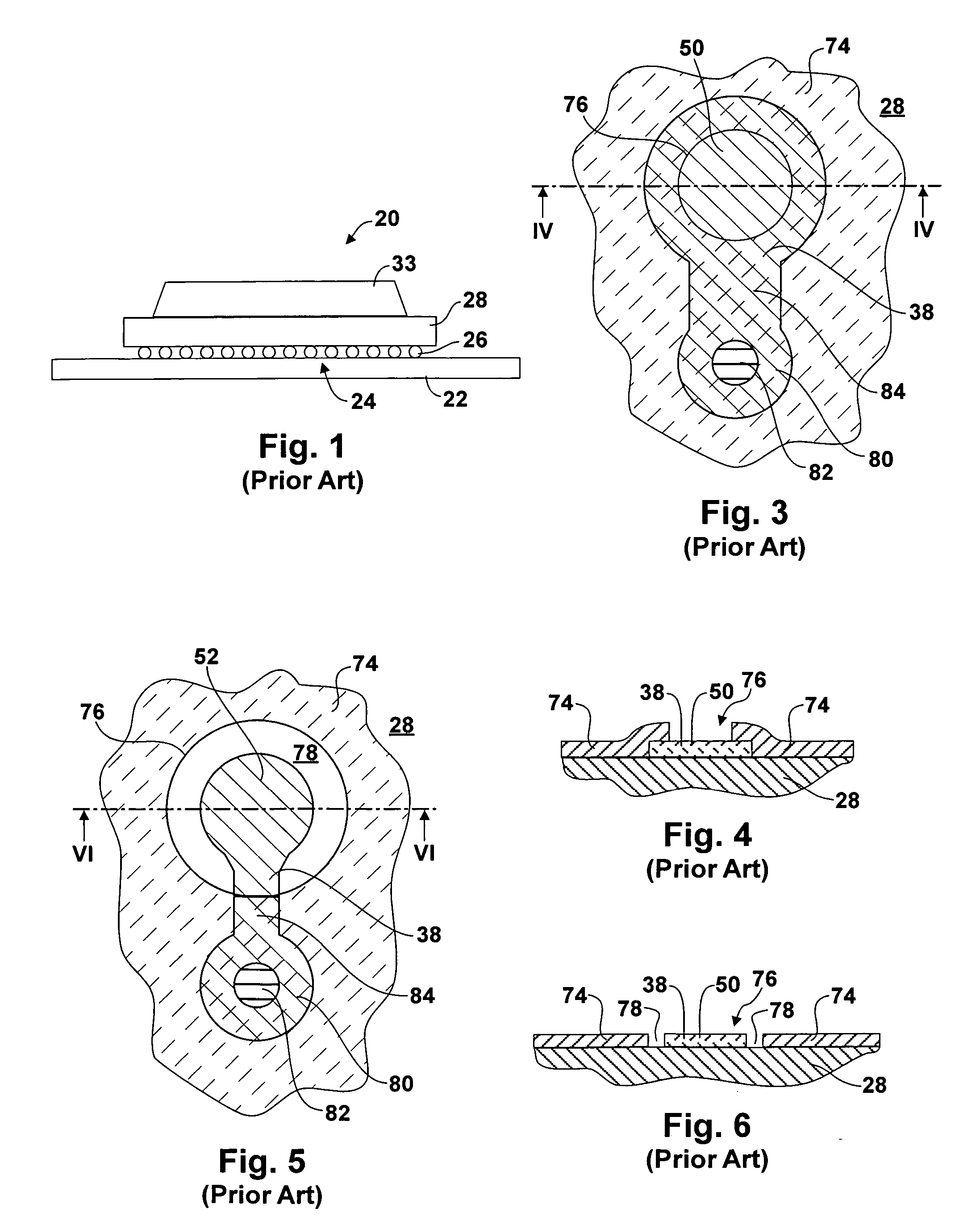

Electrically, mechanically, and thermally enhanced ball grid array (BGA) packages are described. An IC die is mounted in a centrally located cavity of a substantially planar first surface of a stiffener. The first surface of a substrate is attached to a substantially planar second surface of the stiffener. The second surface of the stiffener is opposed to the first surface of the stiffener. A centrally located protruding portion on the second surface of the stiffener is opposed to the centrally located cavity. The protruding portion extends through an opening in the substrate. A wire bond is coupled from a bond pad of the IC die to a contact pad on the first surface of the substrate through a through-pattern in the stiffener. The through-pattern in the stiffener is one of an opening through the stiffener, a recessed portion in an edge of the stiffener, a notch in an edge of the recessed portion, and a notch in an edge of the opening.

Owner:AVAGO TECH INT SALES PTE LTD

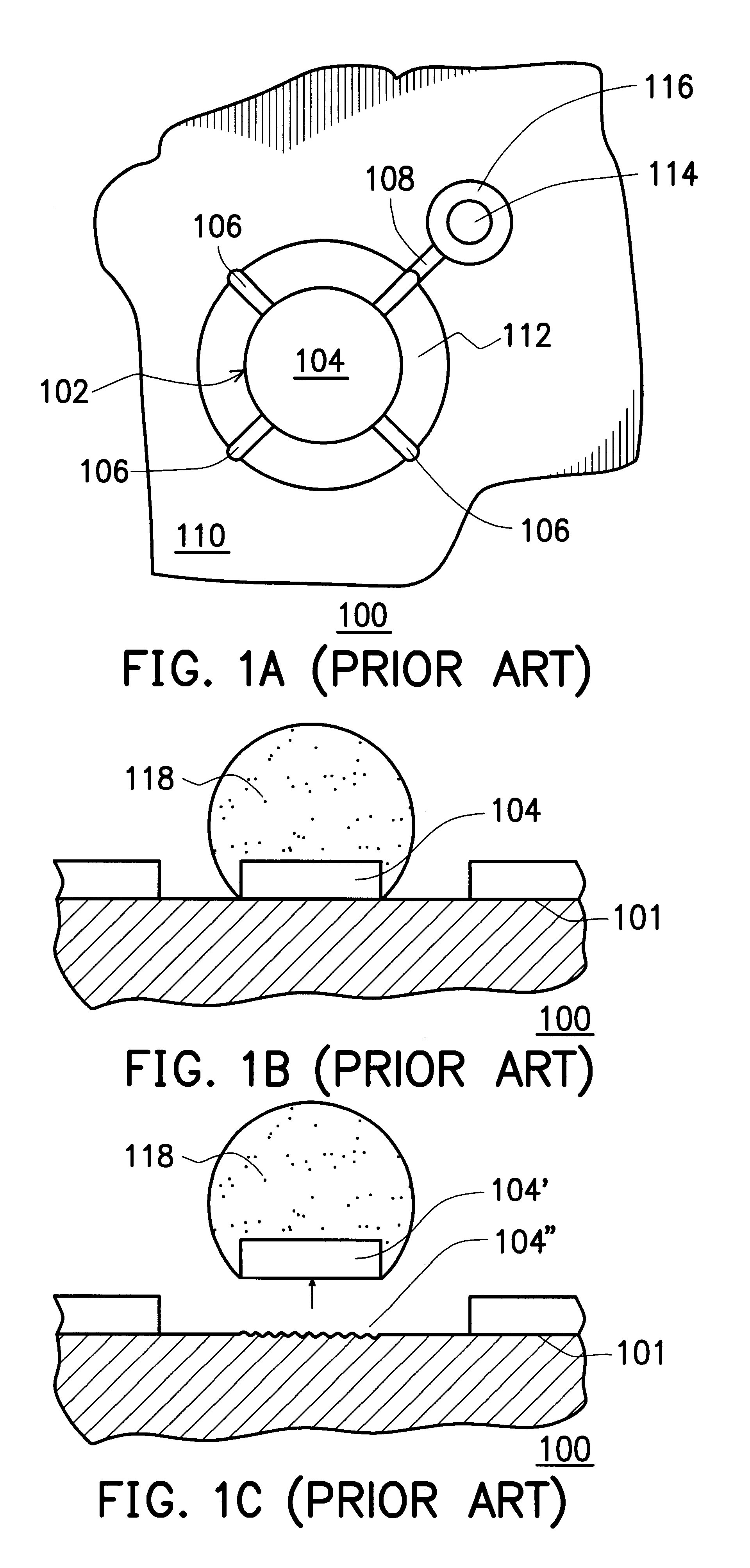

Backside contact for touchchip

InactiveUS6326689B1Semiconductor/solid-state device detailsSolid-state devicesContact formationContact pad

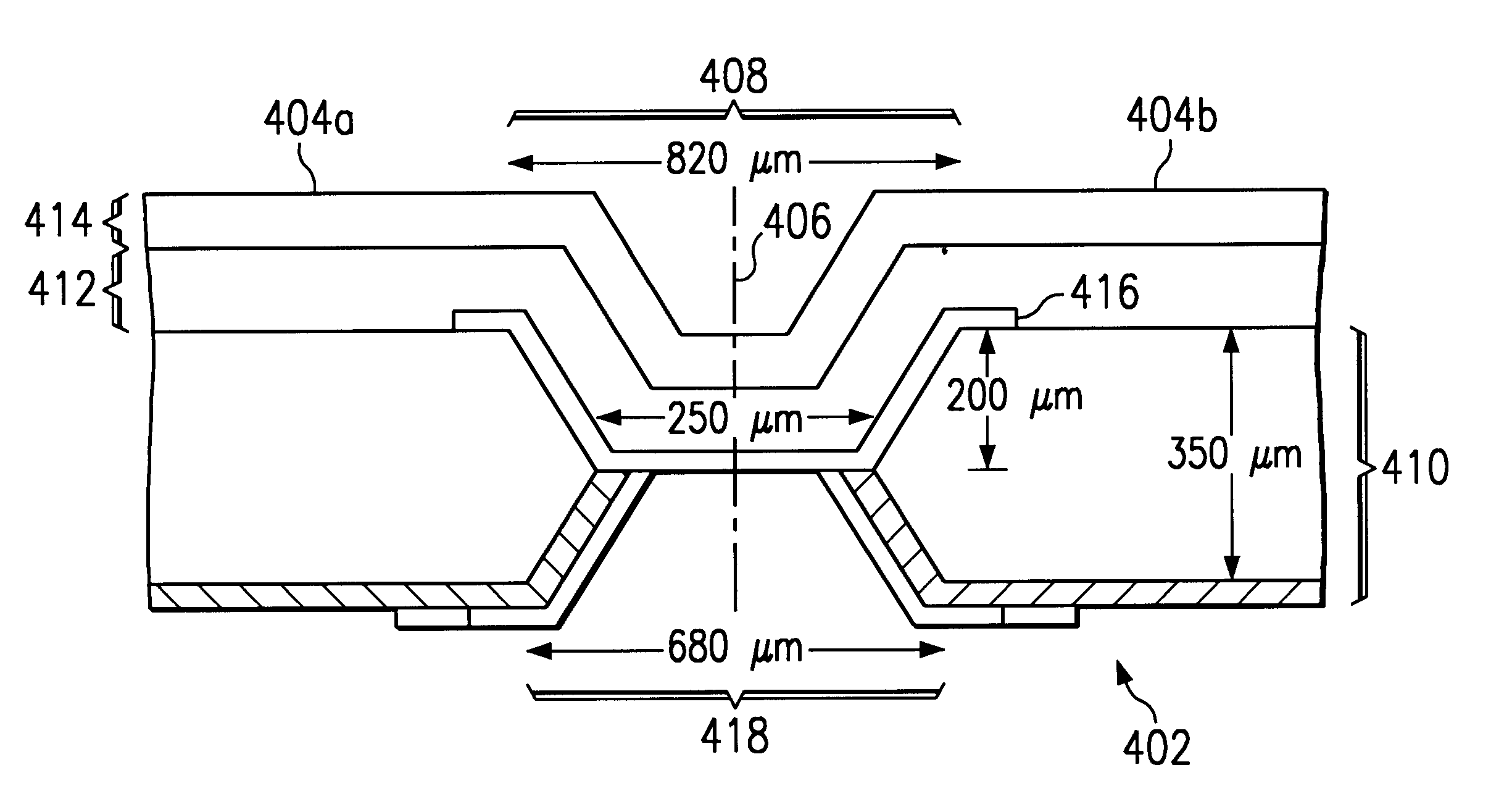

A contact is formed within an active region of a substrate at the edge of a die, preferably within the first metallization level in the active region of the substrate. An opening having sloped sidewalls is then etched into the back side of the substrate, exposing a portion of the active region contact. An interconnect is formed on the opening sidewall to connect the active region contact with a die contact pad on the backside surface of the substrate. The active region contact preferably spans a boundary between two die, with the opening preferably etched across the boundary to permit inter-connects on opposing sidewalls of the opening to each contact the active region contact within different die, connecting the active region contact to die contact pads on different dice. The dice are then separated along the boundary, through the active region contact which becomes two separate active region contacts. By forming a shared contact opening spanning two dice, the backside contact is formed around the die edge and the backside surface area necessary for the contact opening is minimized. The backside contact allows direct placement of the integrated circuit die on contacts within the packaging, such as a ball grid array, eliminating the need for wire bonds. The need for a pad etch through passivation material overlying active devices on the front side of the die is also eliminated, and no mask levels are added for the devices formed on the front side.

Owner:STMICROELECTRONICS SRL

System and method of plating ball grid array and isolation features for electronic components

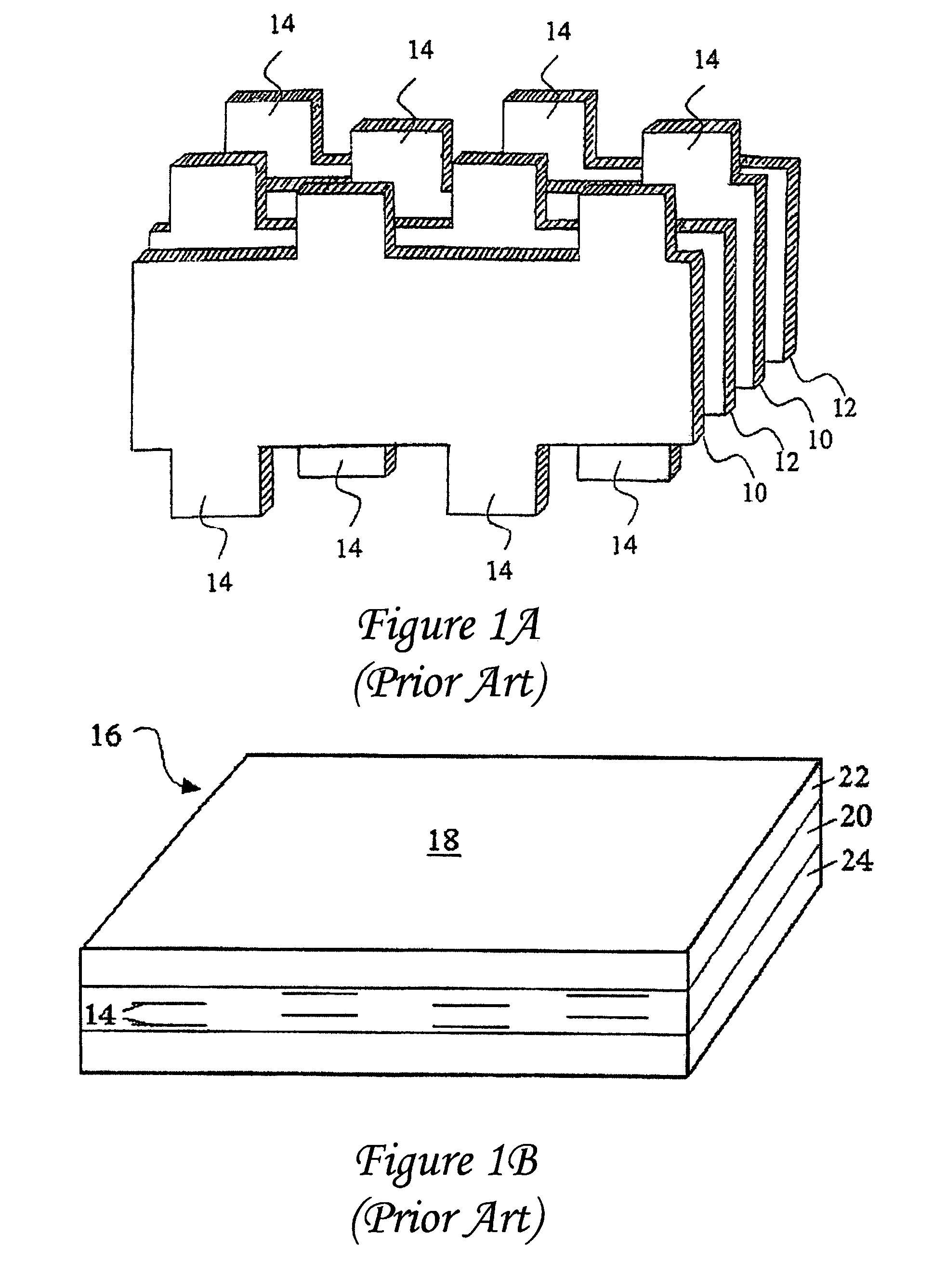

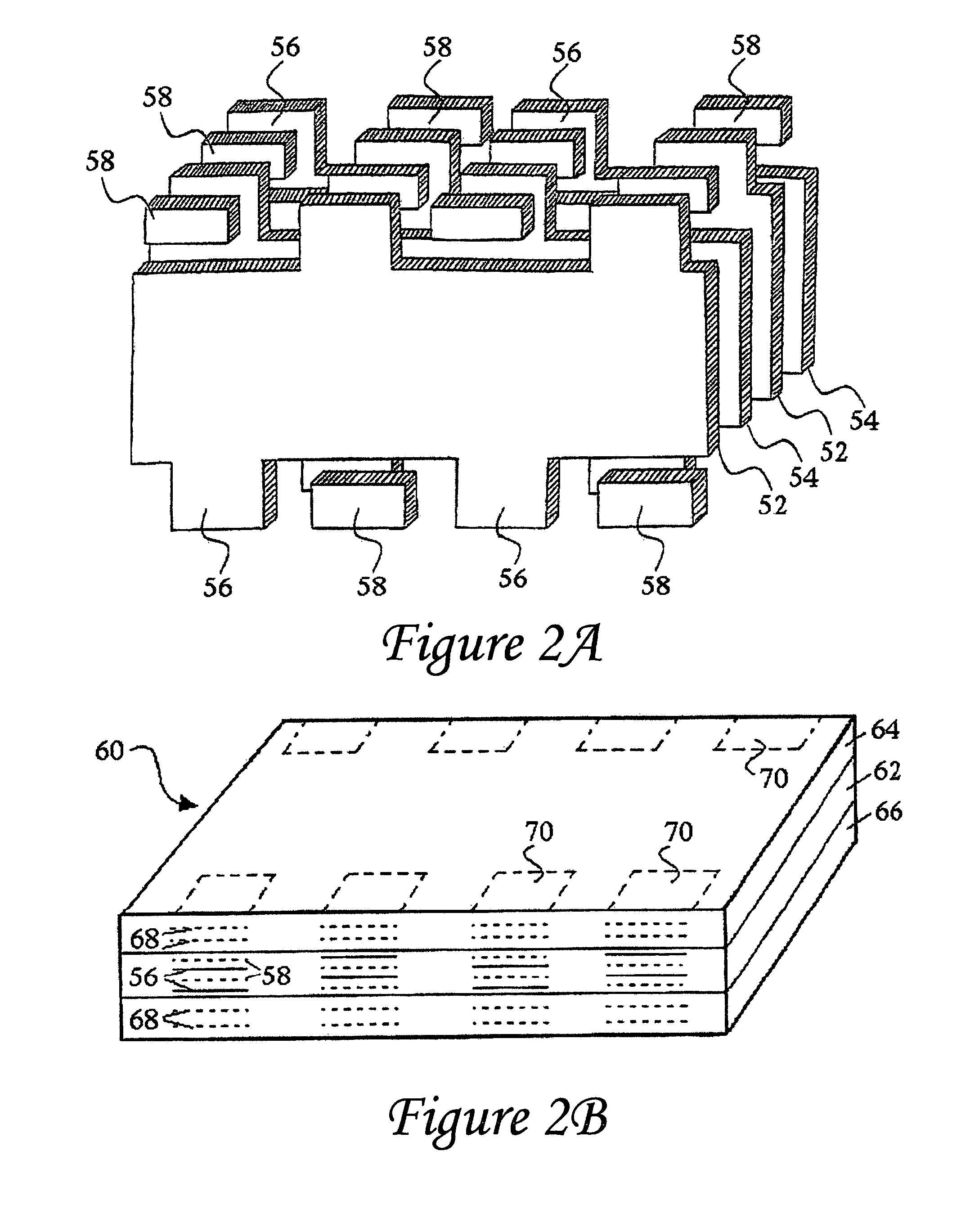

InactiveUS7463474B2Improved termination featureEliminate or greatly simplify thick-film stripesFixed capacitor dielectricStacked capacitorsEngineeringElectronic component

Owner:KYOCERA AVX COMPONENTS CORP

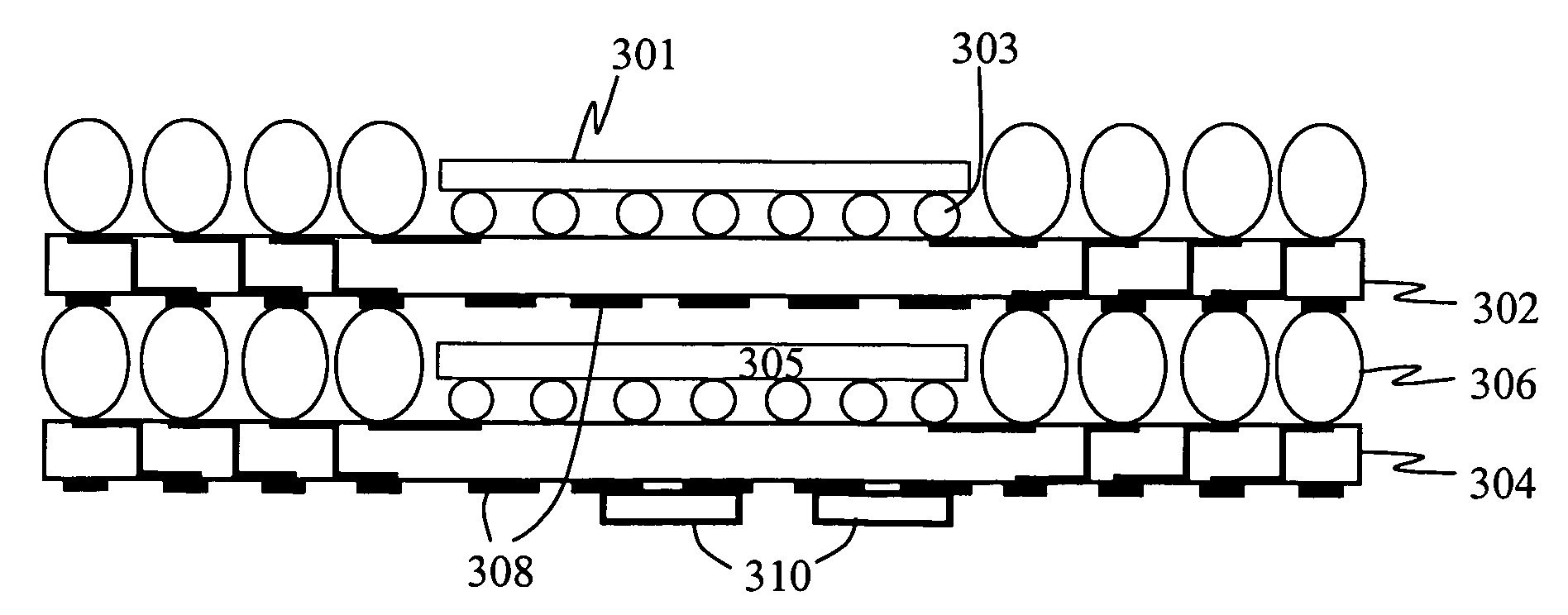

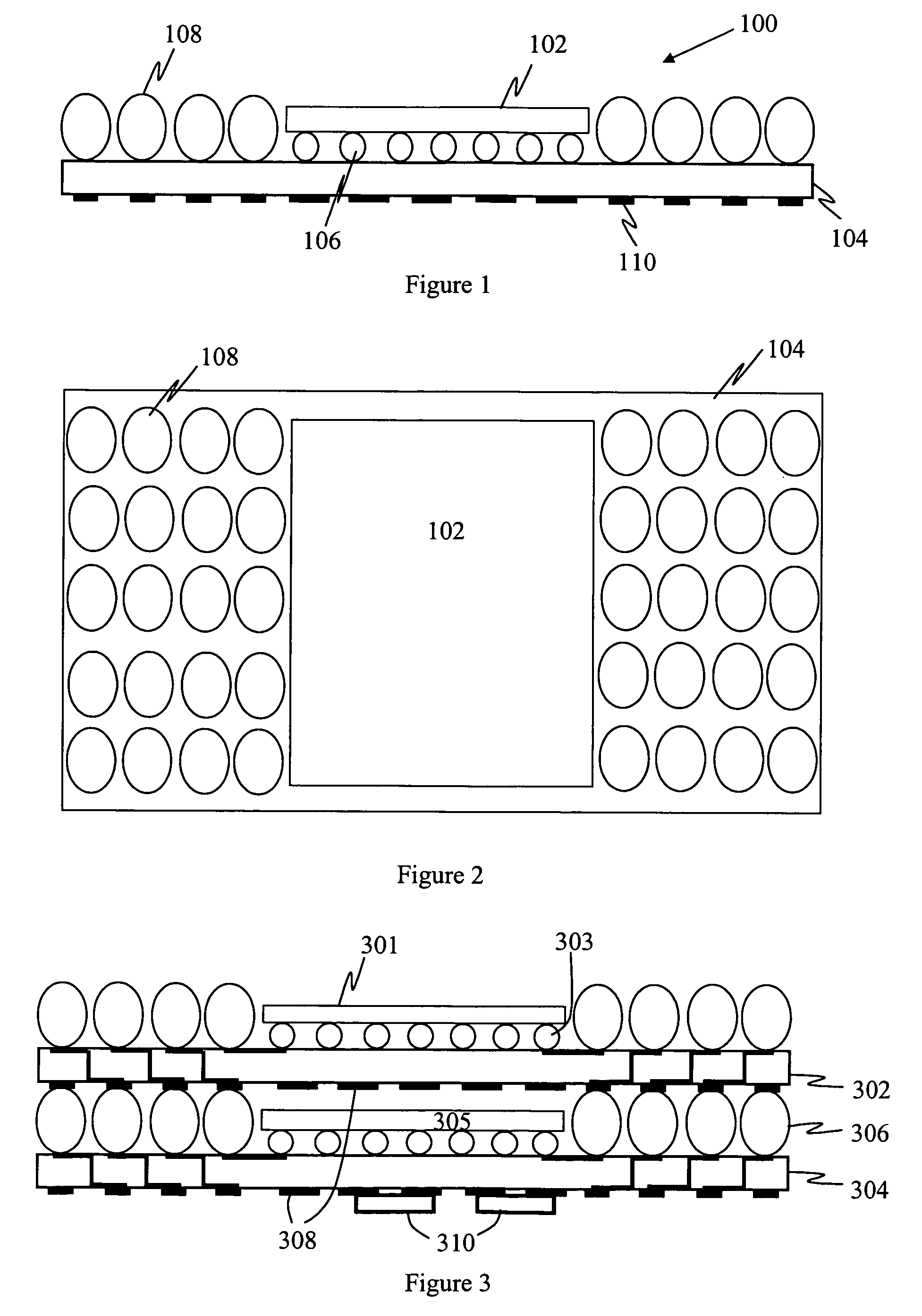

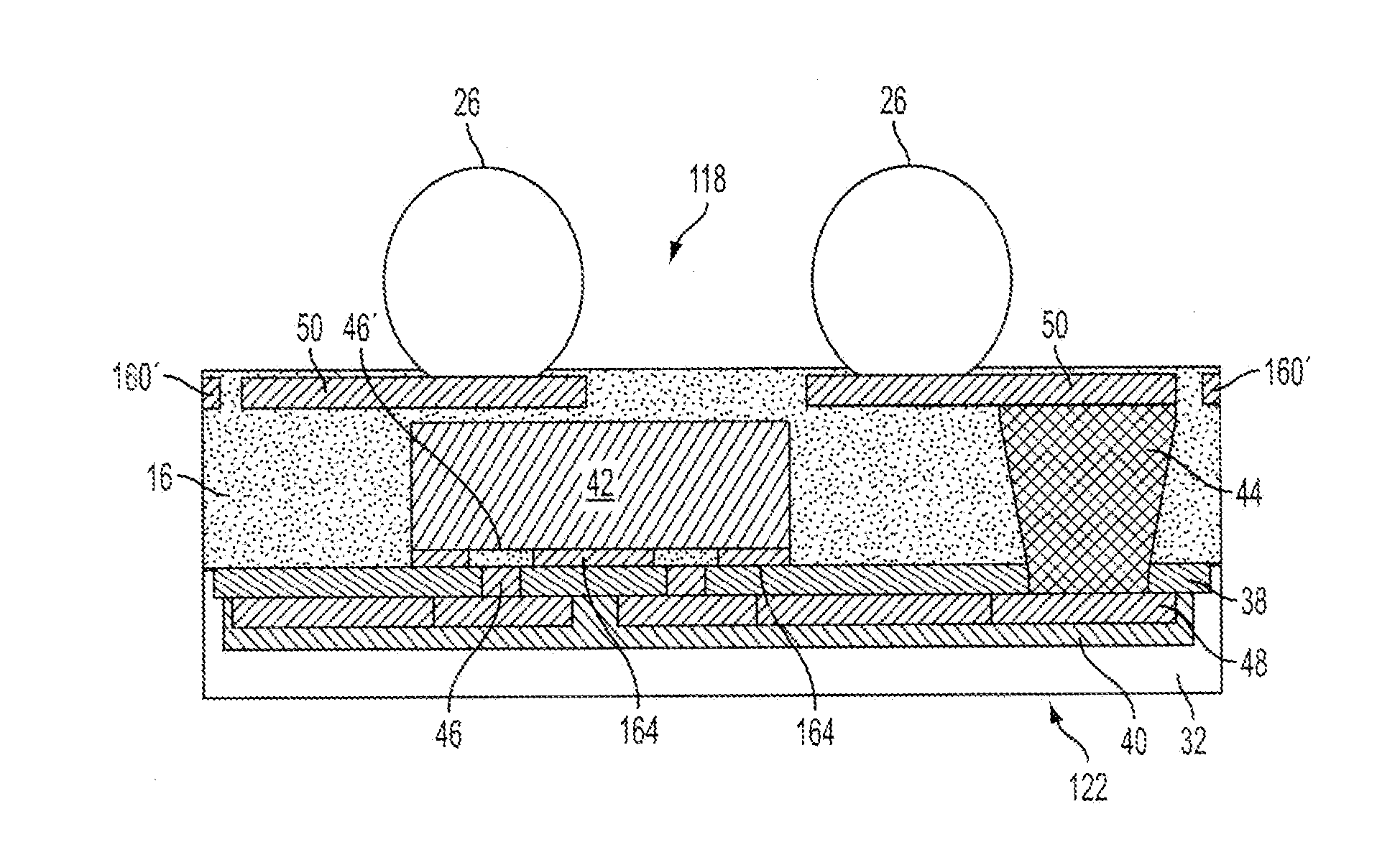

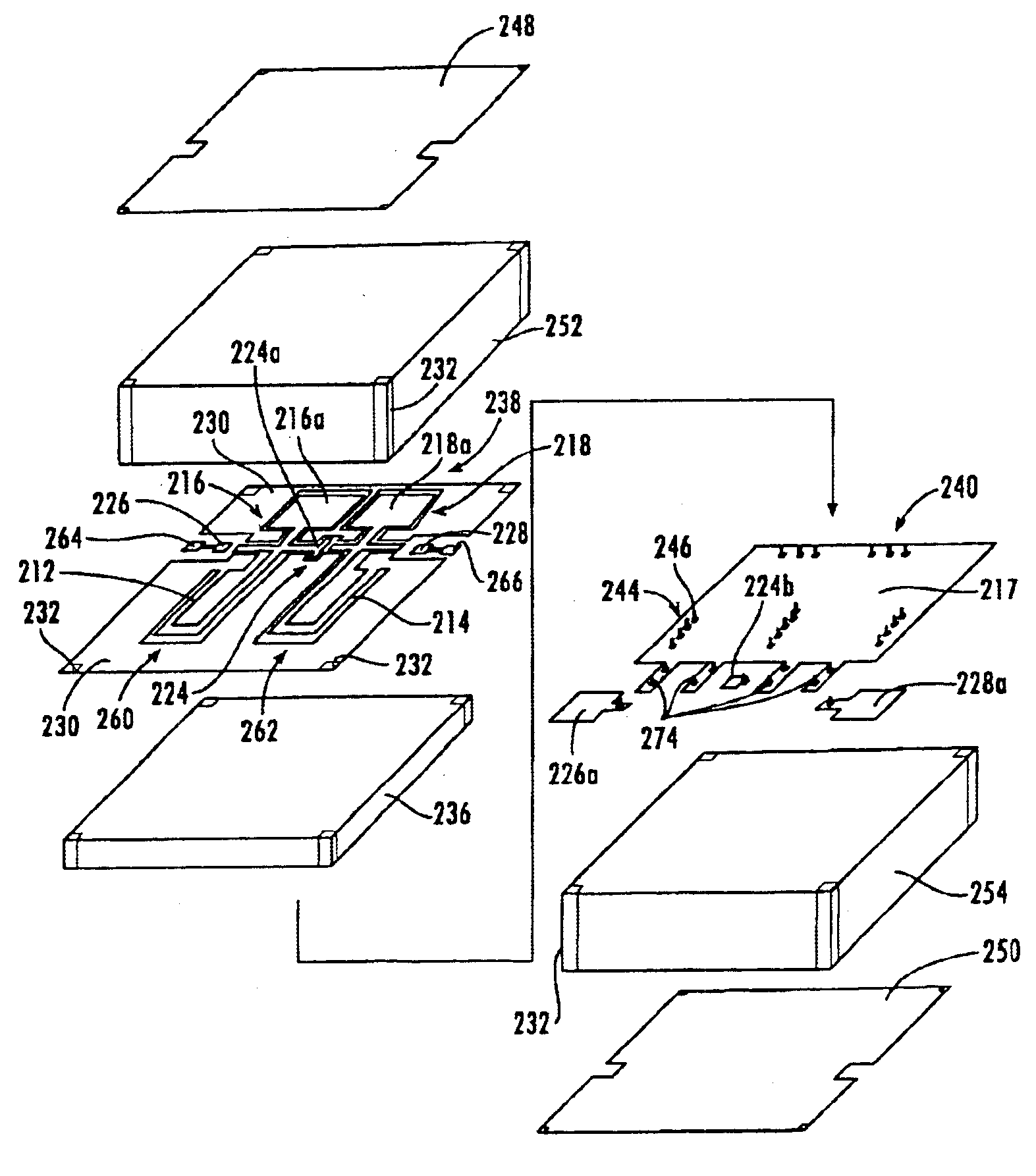

Ball grid array package with multiple interposers

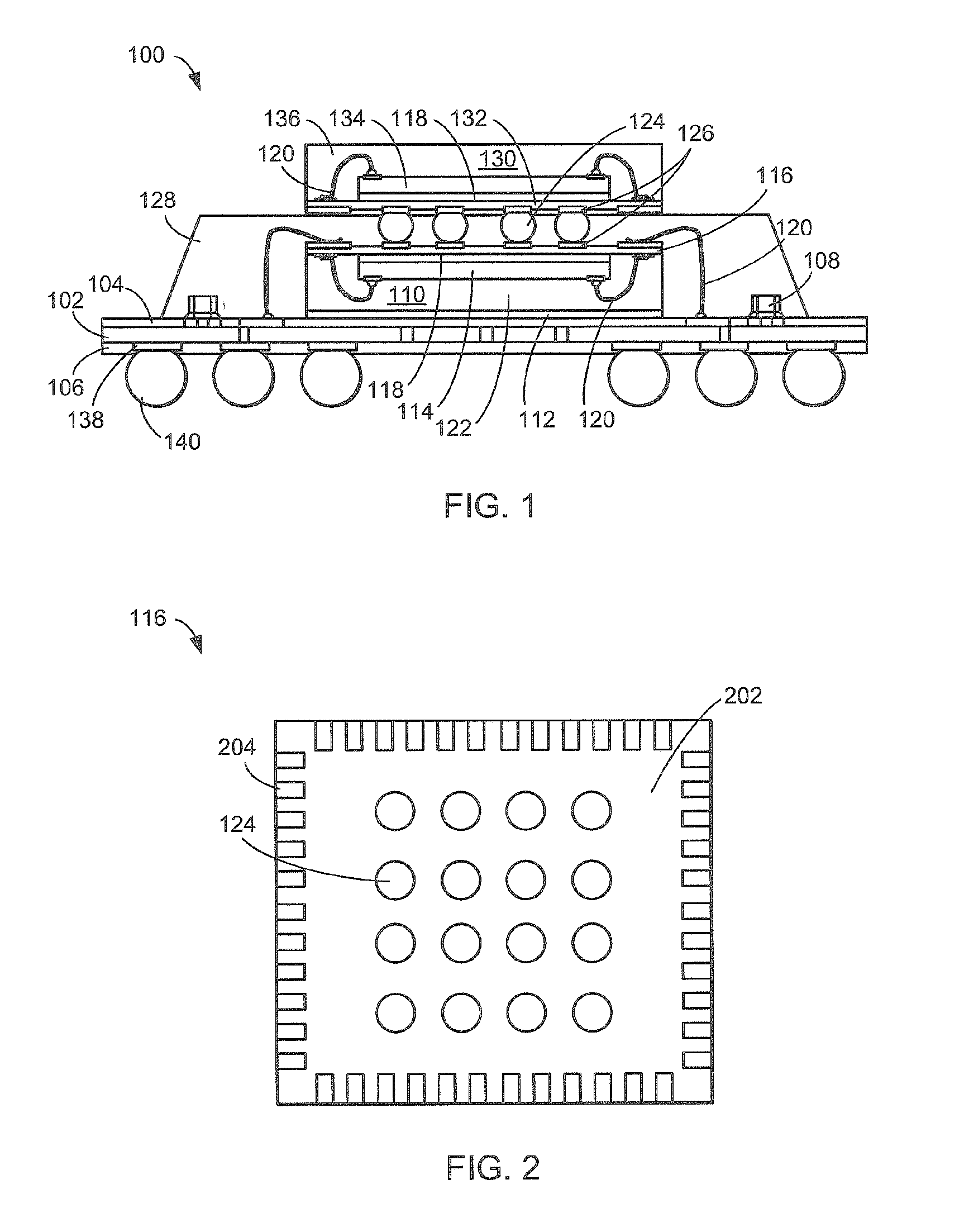

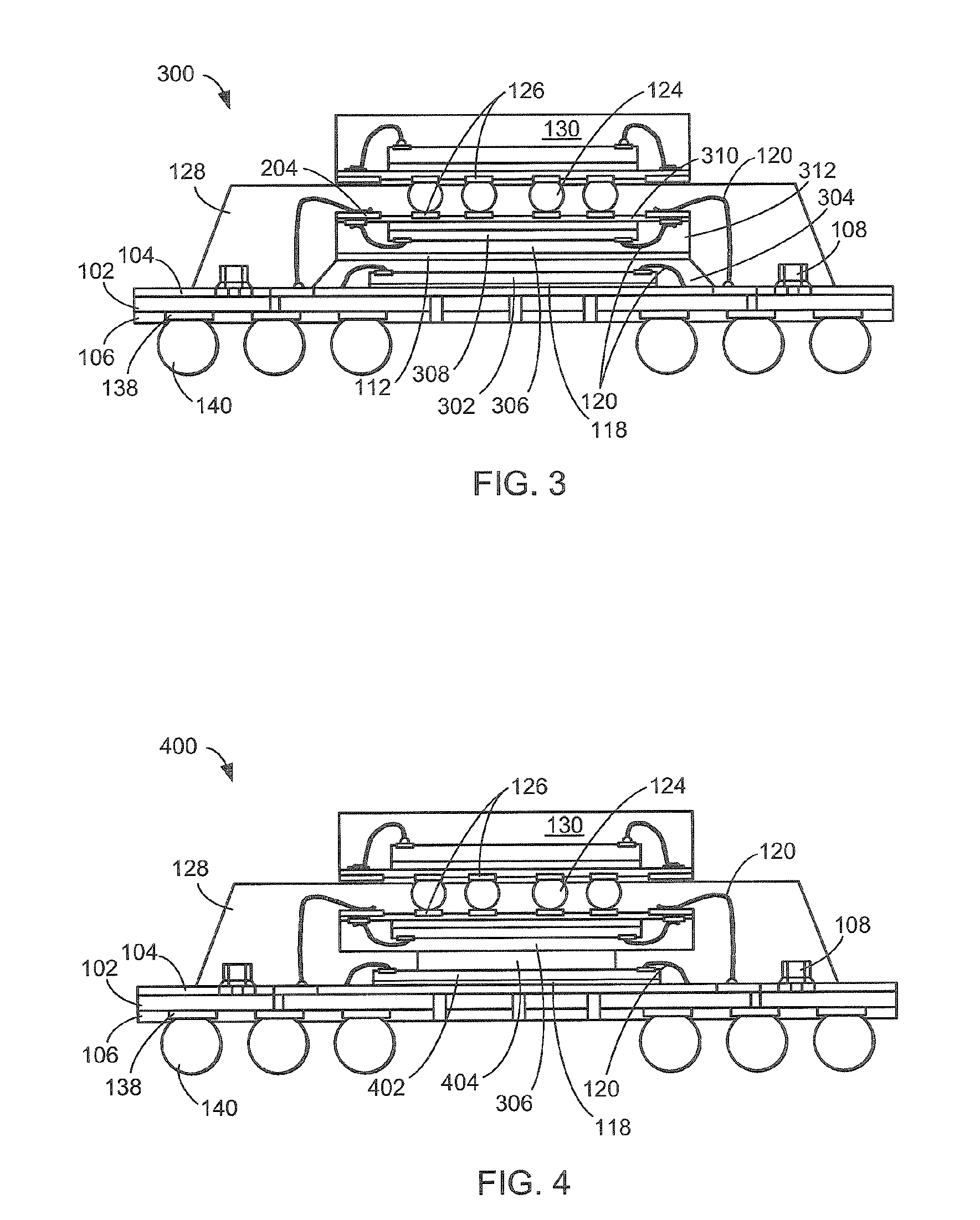

InactiveUS6861750B2Increase stiffness/rigidityImprove heat transfer performanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContact padPlanar substrate

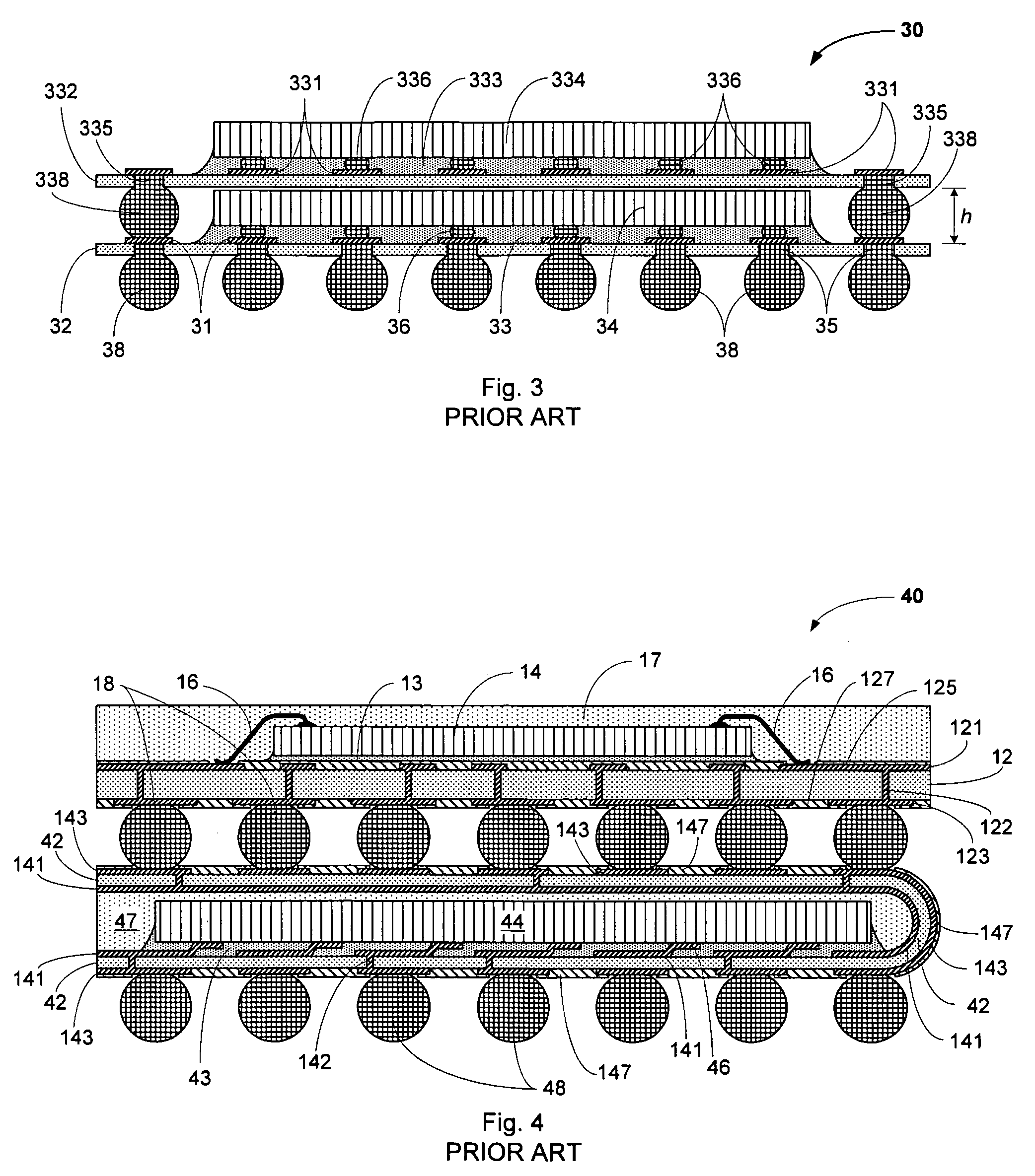

Electrically, thermally and mechanically enhanced ball grid array (BGA) packages are described. An IC die is mounted to a first surface of a first stiffener. A peripheral edge portion of a second surface of the first stiffener is attached to a first surface of a second stiffener to cover an opening through the second stiffener that is open at the first surface and a second surface of the second stiffener. The second surface of the second stiffener is attached to a first surface of a substantially planar substrate that has a plurality of contact pads on the first surface of the substrate. The plurality of contact pads are electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

Ball grid array package

InactiveUS6396707B1Printed circuit assemblingSemiconductor/solid-state device detailsSolder maskSolder ball

A ball grid array package comprises a substrate having a first surface and a second surface, a chip, an insulating material, and a solder ball. The surface of the substrate comprises ball pads, conducting traces, and solder masks wherein the conducting traces are disposed in between the adjacent ball pads, and are covered by the solder mask, in addition, a portion of each of the ball pads is also covered by the solder mask. The solder mask includes an opening positioned in the area corresponding to the ball pads wherein the opening exposes a portion of the surface the ball pad and a portion of the side wall of the ball pad. The chip is disposed on the second surface of the substrate, and is sealed and encapsulated by the insulated material. The solder balls are disposed on the first surface of the substrate, and are positioned at the openings of the ball pads. Additionally, the solder balls are electrically connected to a portion of the surface of the ball pads and a portion of the side wall of the ball pads disposed at the ball pad openings.

Owner:SILICONWARE PRECISION IND CO LTD

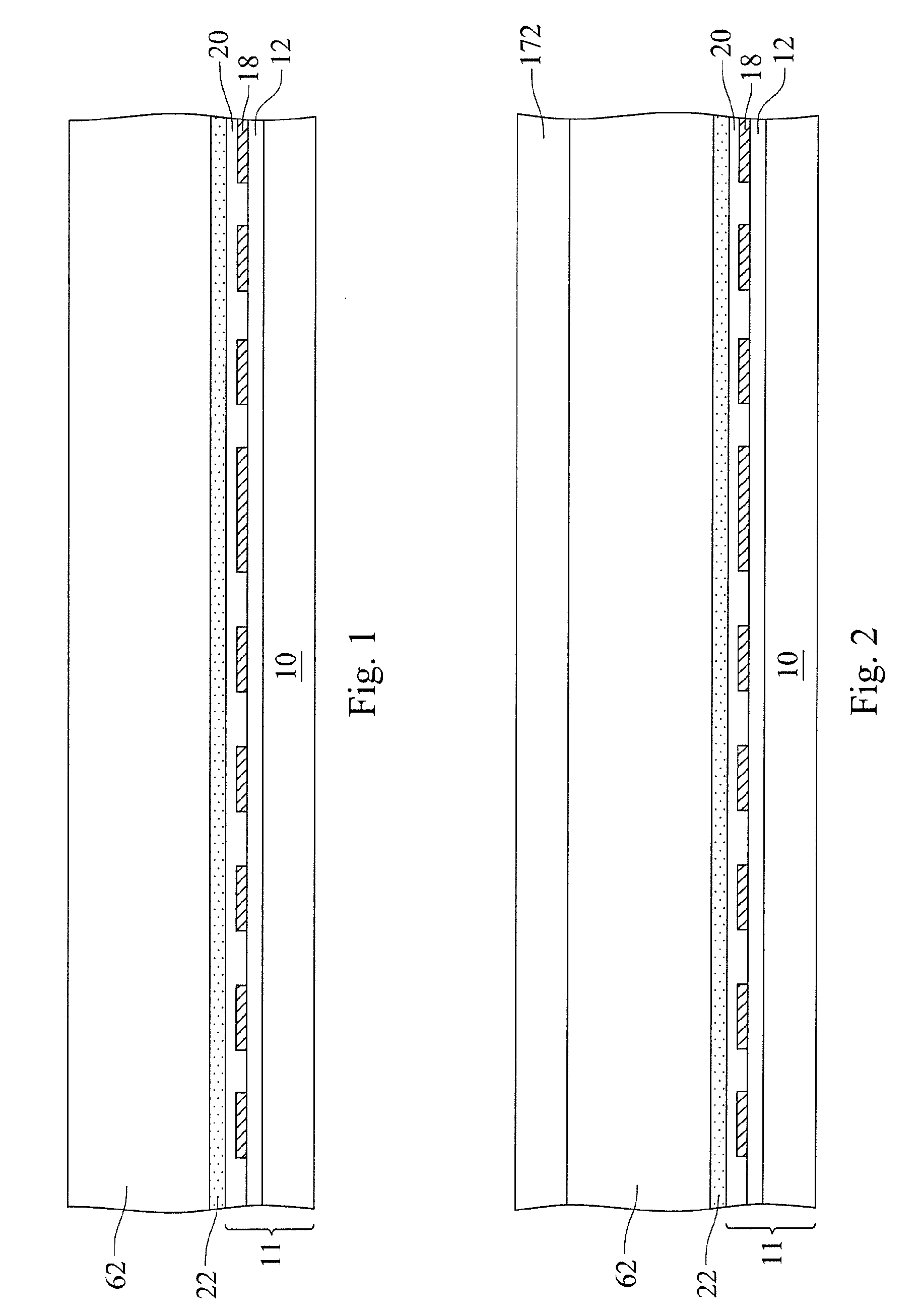

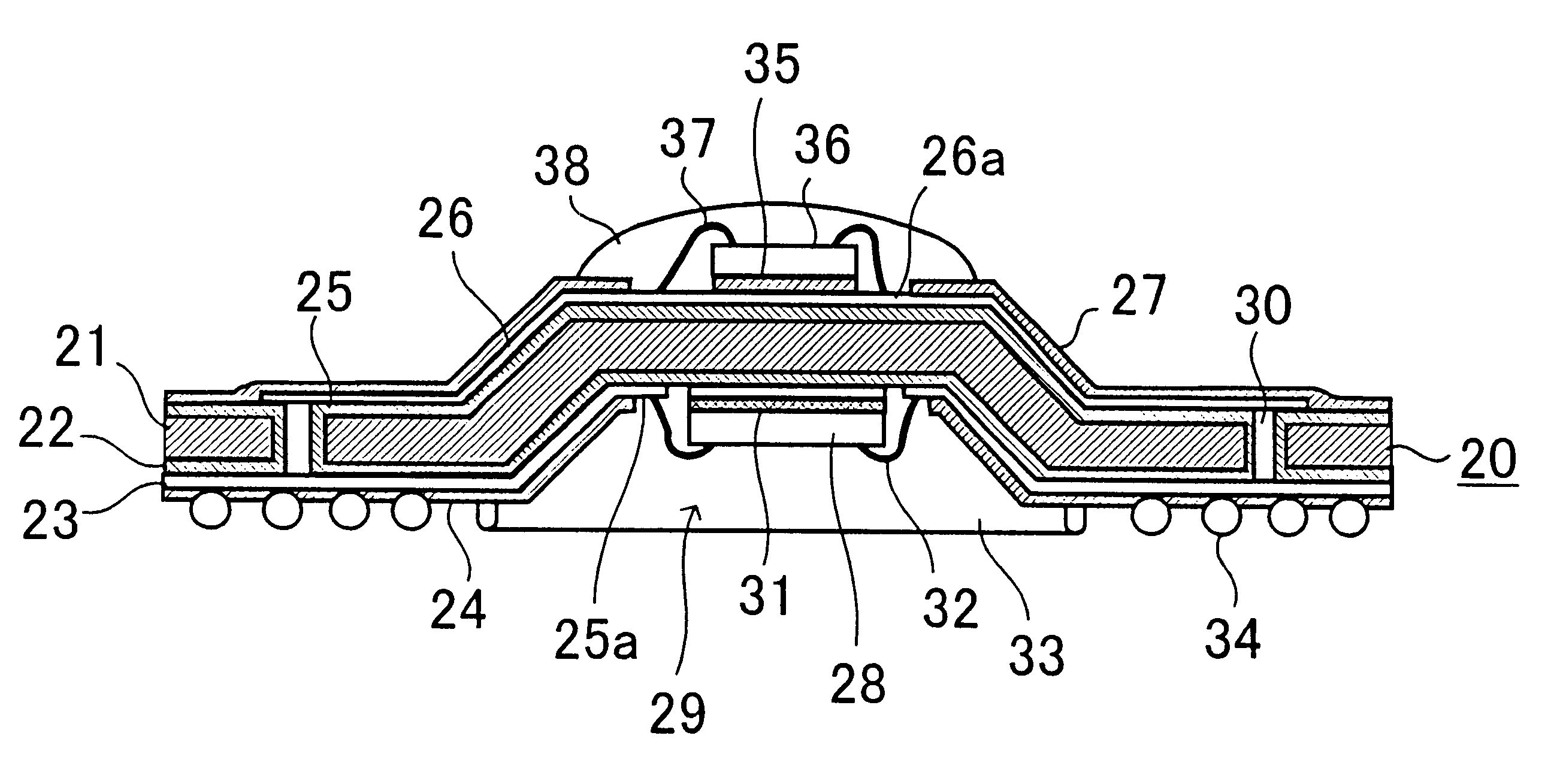

Stackable optoelectronics chip-to-chip interconnects and method of manufacturing

ActiveUS20050224946A1Minimize skewEasily stackable/mountableCircuit optical detailsSemiconductor/solid-state device detailsElectrical conductorEngineering

An optoelectronics chip-to-chip interconnects system is provided, including packaged chips to be connected on printed-circuit-board (PCB), multiple-packaged chip, optical-electrical(O-E) conversion means, waveguide-board, and PCB. Single to multiple chips interconnects can be possible using this technique. The packaged-chip includes semiconductor-die and its package based on the ball-grid array or chip-scale-package. The O-E board includes the optoelectronics components and multiple electrical contacts. The waveguide board includes electrical conductors transferring signal from O-E board to PCB and the flex optical waveguide easily stackable onto the PCB, to guide optical signal from one chip-to-other chip. The chip-to-chip interconnects system is pin-free and compatible with the PCB. The main advantages are that standard packaged-chip and conventional PCB technology can be used for low speed electrical signal connection. Also, the part of the heat from the packaged chip can be transmitted to PCB through conductors, so that complex cooling system can be avoided.

Owner:BANPIL PHOTONICS

High performance, low cost microelectronic circuit package with interposer

InactiveUS6888240B2Semiconductor/solid-state device detailsSolid-state devicesPin grid arrayInterposer

A low cost technique for packaging microelectronic circuit chips fixes a die within an opening in a package core. At least one metallic build up layer is then formed on the die / core assembly and a grid array interposer unit is laminated to the build up layer. The grid array interposer unit can then be mounted within an external circuit using any of a plurality of mounting technologies (e.g., ball grid array (BGA), land grid array (LGA), pin grid array (PGA), surface mount technology (SMT), and / or others). In one embodiment, a single build up layer is formed on the die / core assembly before lamination of the interposer.

Owner:INTEL CORP

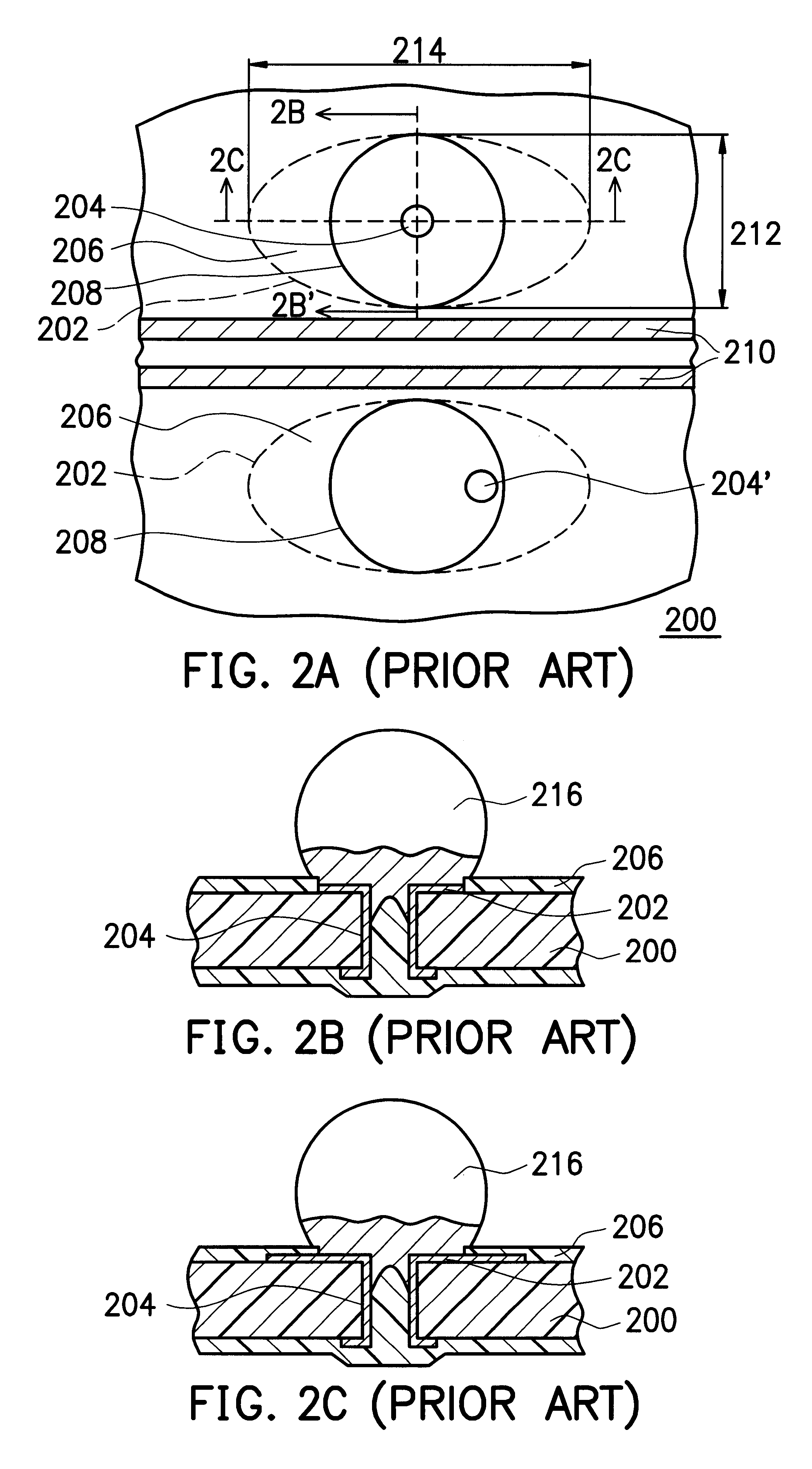

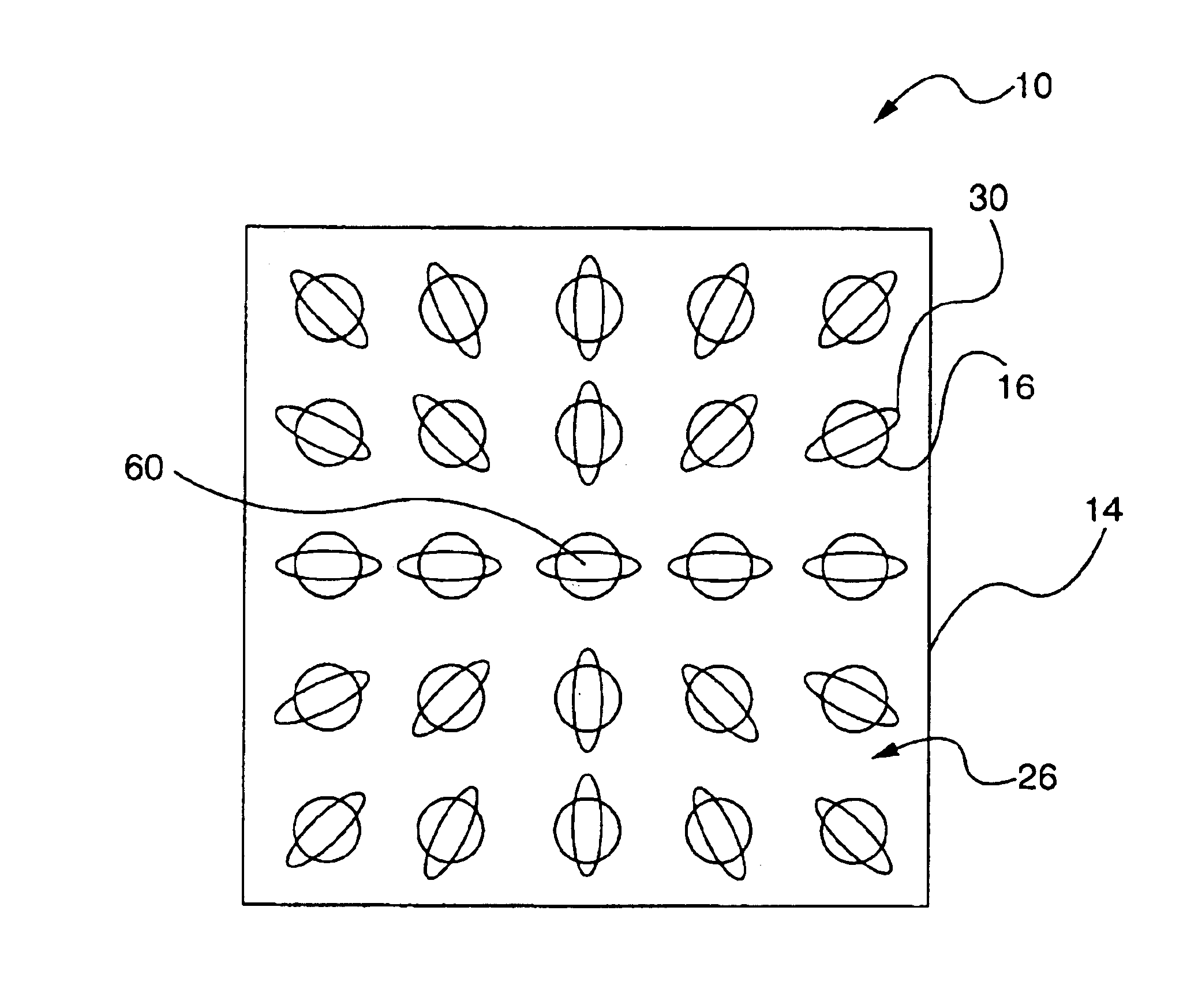

Partially captured oriented interconnections for BGA packages and a method of forming the interconnections

InactiveUS6913948B2Improve fatigue lifeEnhanced pad adhesionPrinted circuit assemblingSemiconductor/solid-state device detailsIncreased fatigueEngineering

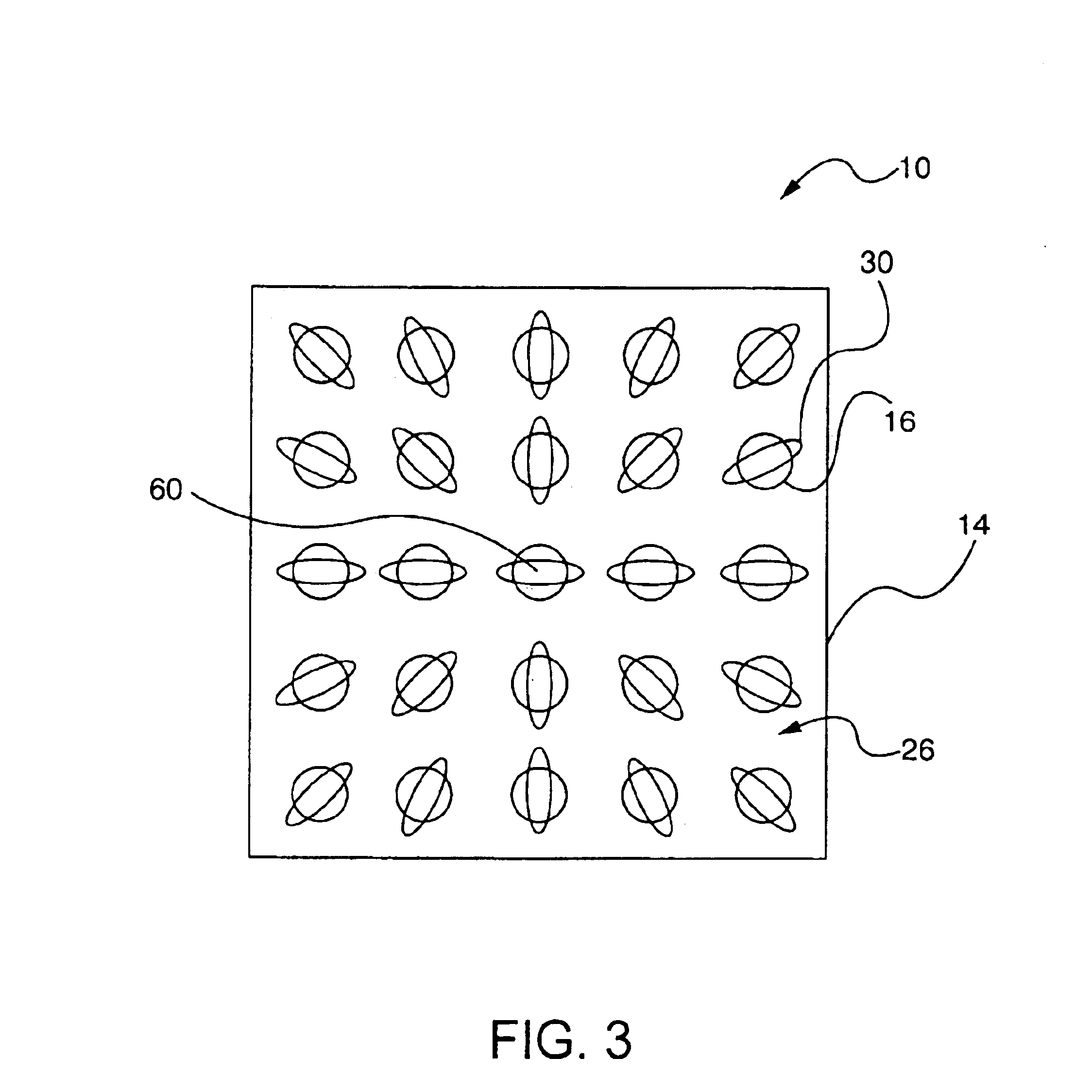

A Ball Grid Array package having an increased fatigue life and improved conductive pad adhesion strength, as well as providing sufficient wiring space within the package, is disclosed. In particular, solder joints having a combination of mask-defined and pad-defined solder joint profiles are formed using a mask having non-circular elongated openings. The non-circular elongated openings of the mask have a major axis and a minor axis, such that the dimension of the openings along the major axis is greater than the diameter of the conductive pads, and the dimension of the openings along the minor axis is less than the diameter of the conductive pads. In addition, the major axis of the openings within the mask are selectively oriented in the direction of highest stress for each solder joint within the package, while providing ample wiring space therein.

Owner:IBM CORP

Ball grid array package and process for manufacturing same

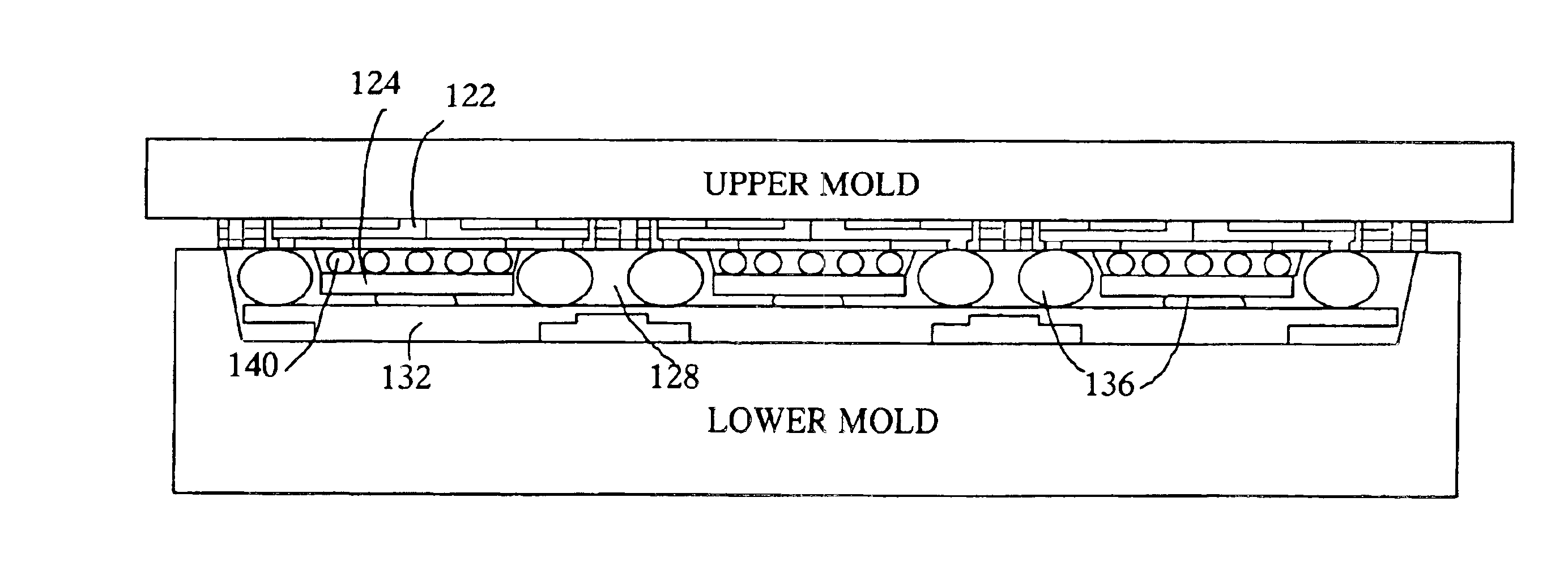

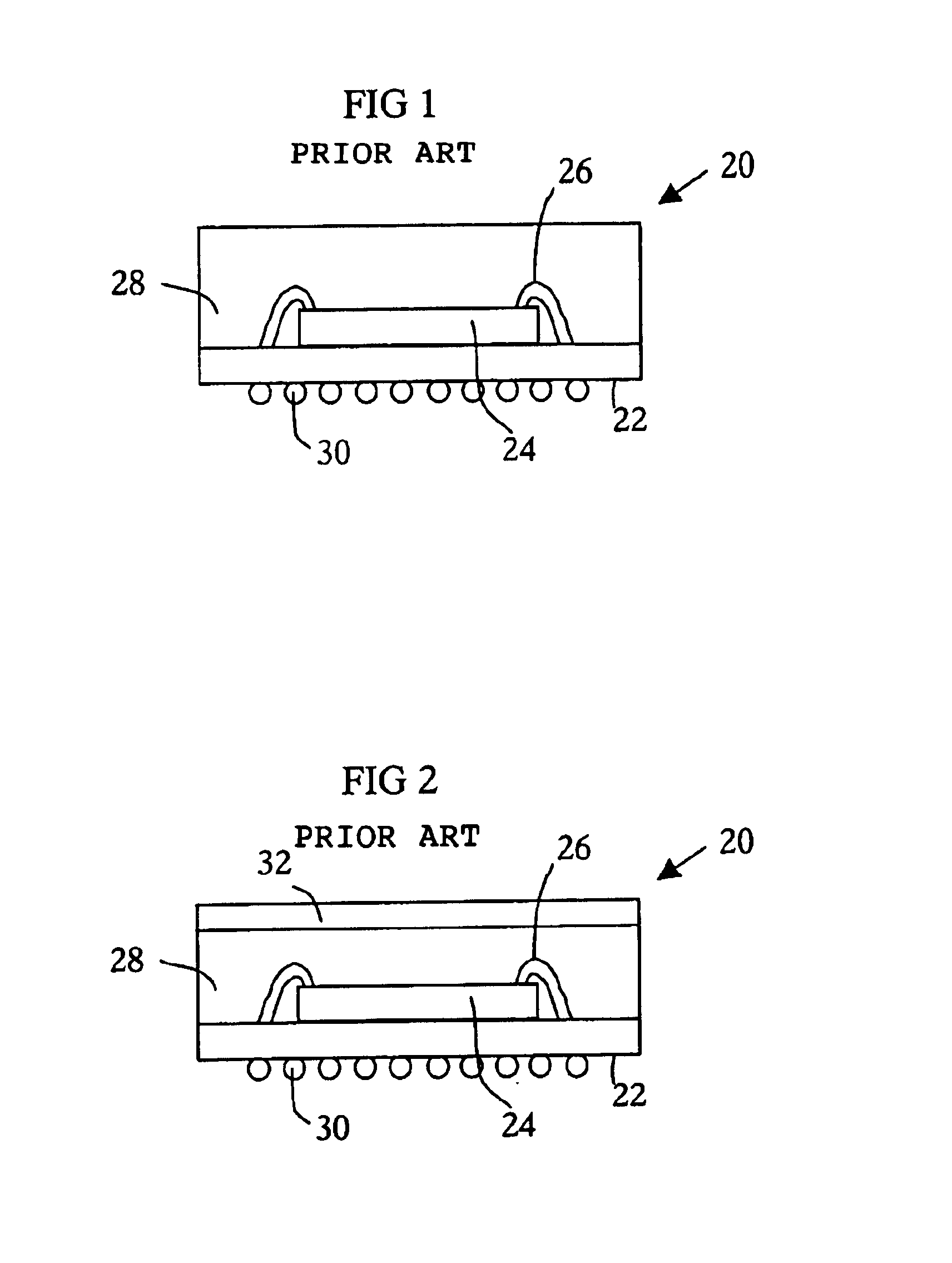

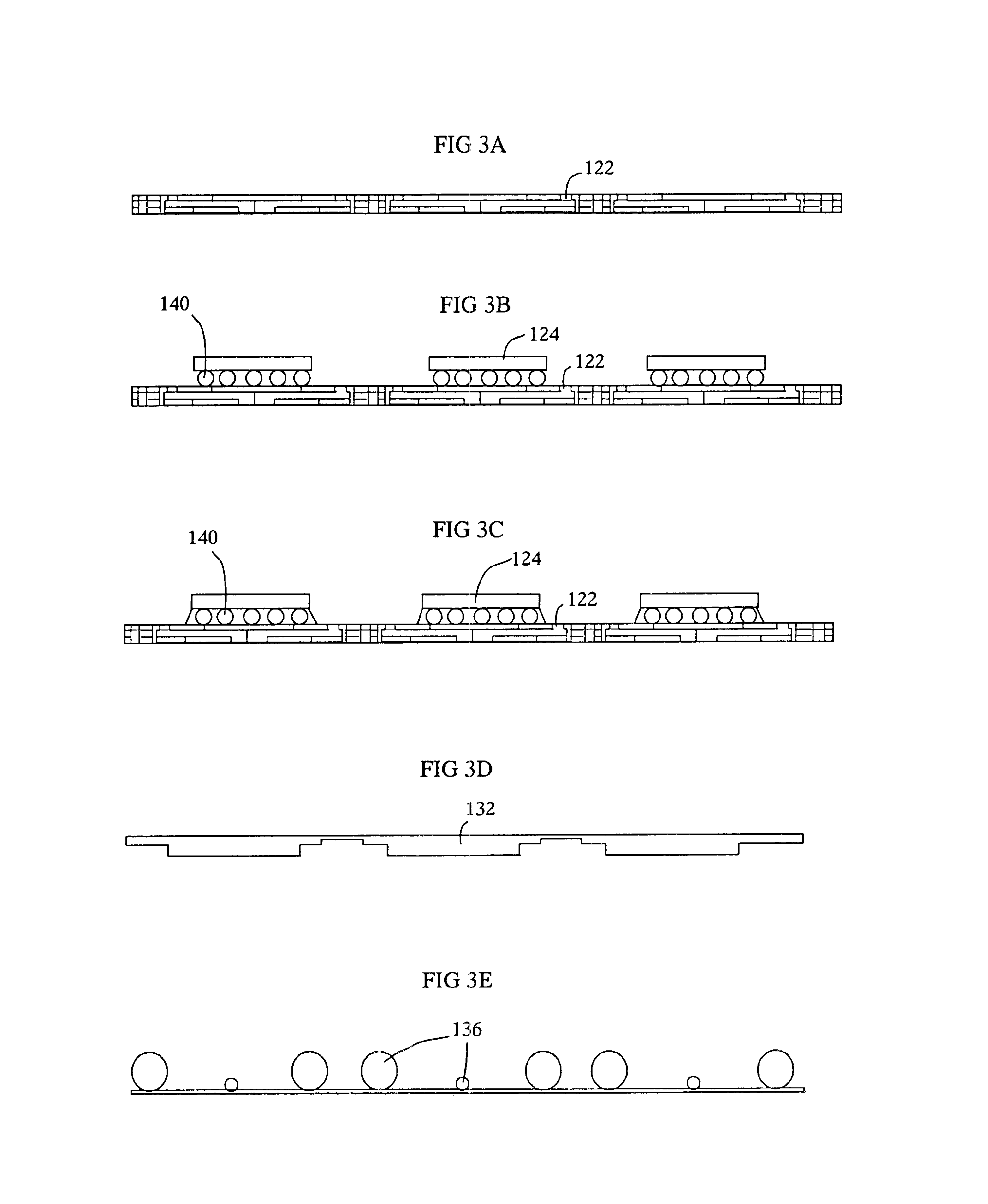

InactiveUS6987032B1Inhibiting mold flashReducing mold flashSemiconductor/solid-state device detailsSolid-state devicesBall grid arraySemiconductor

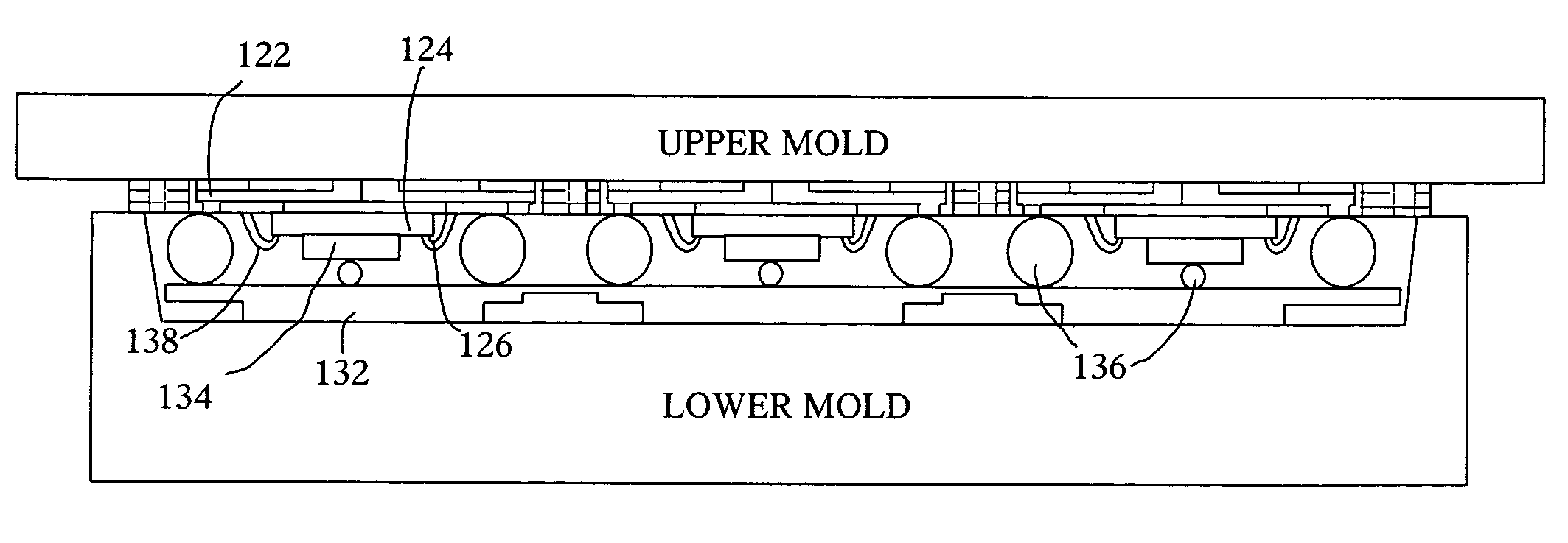

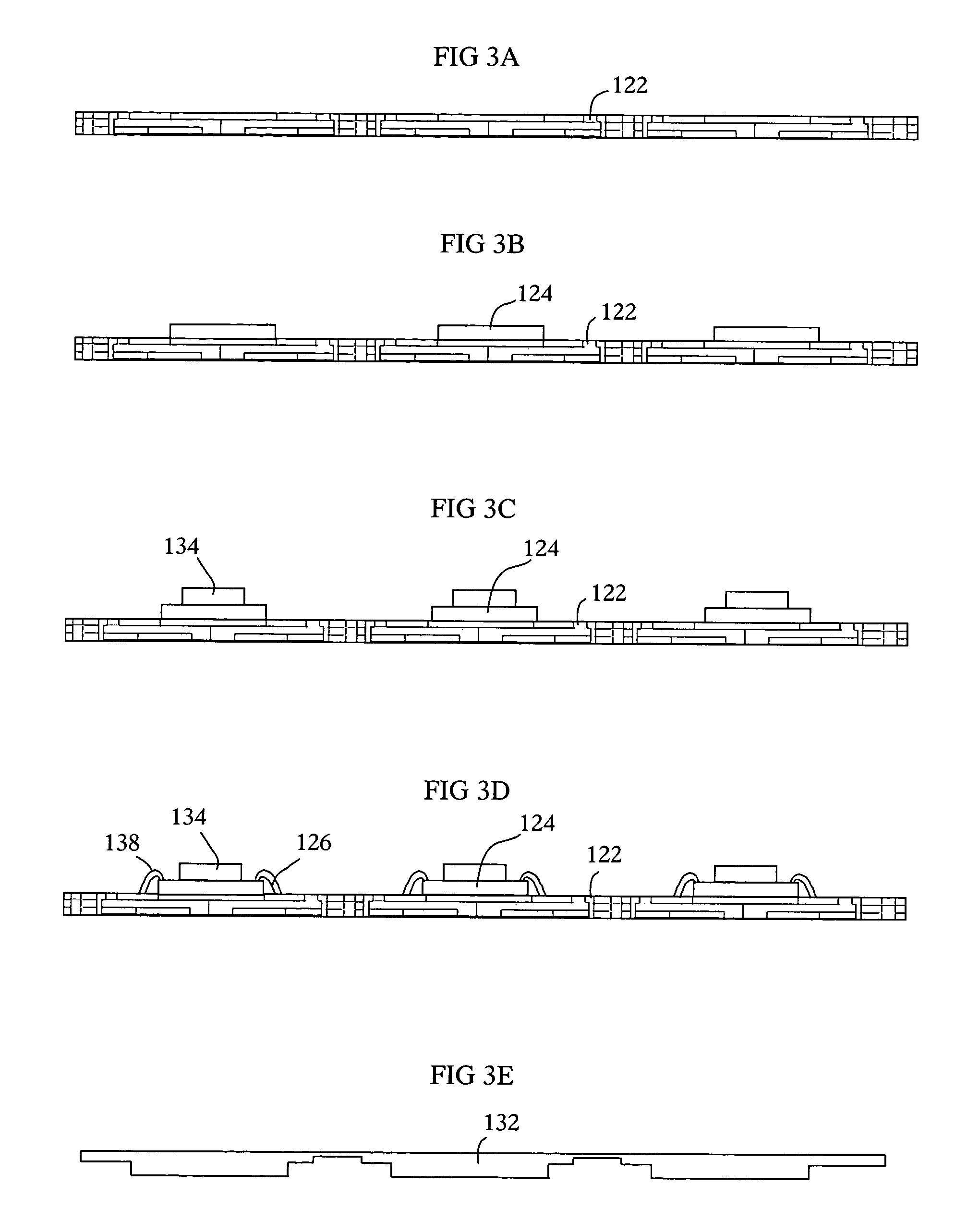

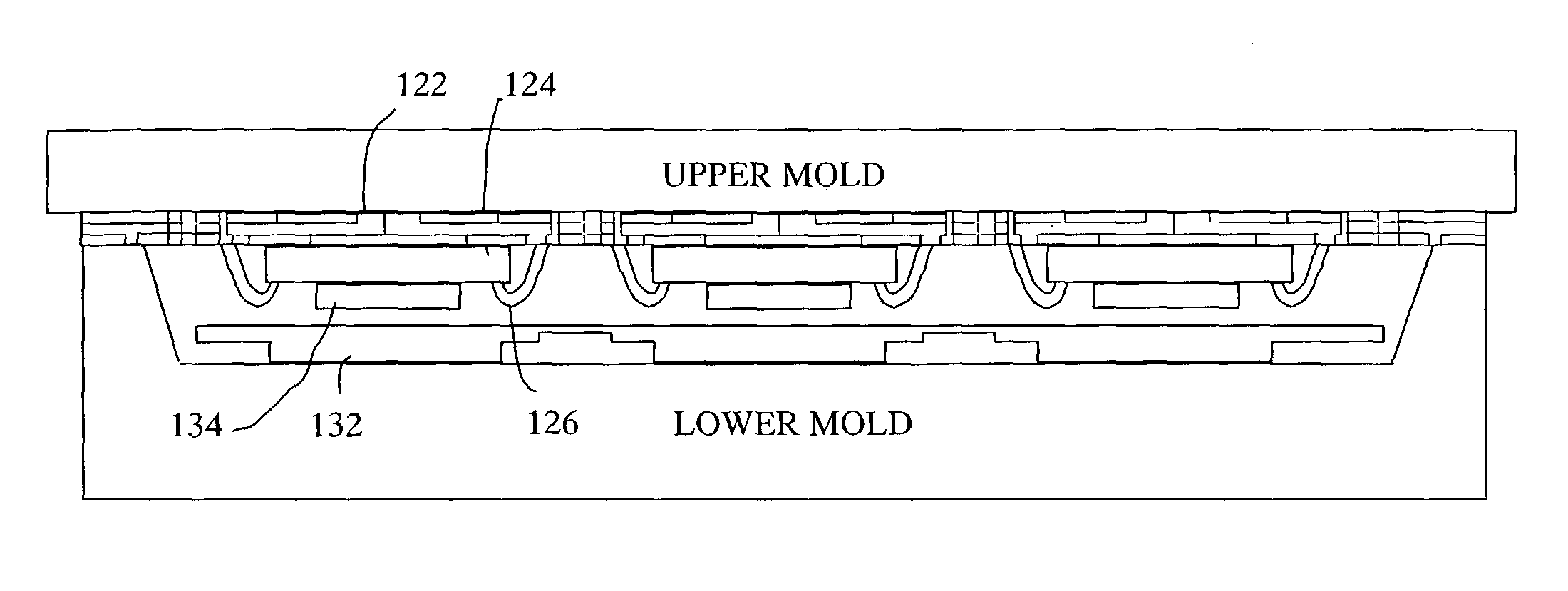

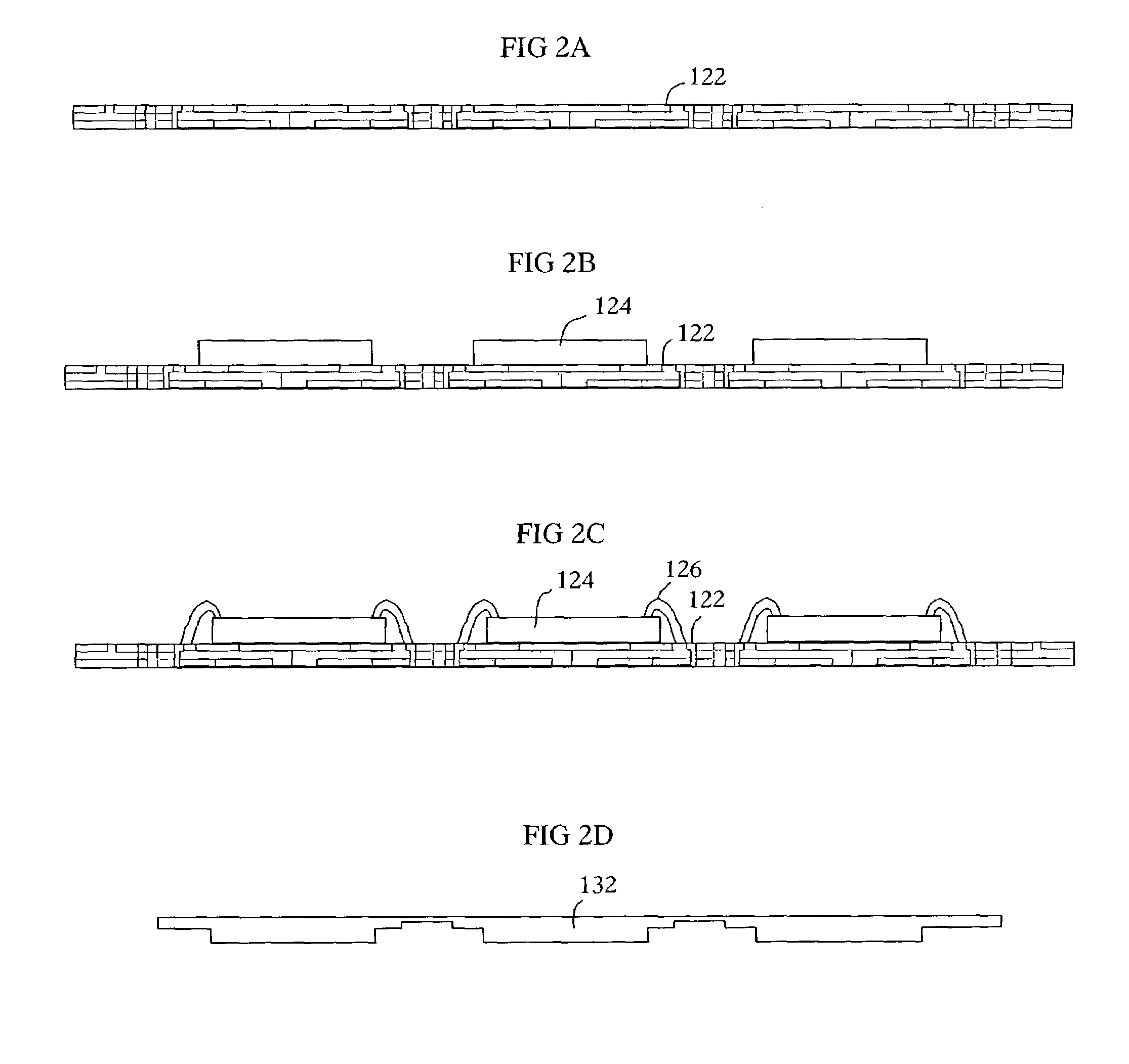

A ball grid array package is manufactured by mounting a semiconductor die to a first surface of a substrate and mounting a die adapter to the semiconductor die. The semiconductor die is wire bonded to ones of conductive traces of the substrate. A collapsible spacer is mounted to the substrate and the substrate is releasably clamped to an upper side of a mold cavity. A heat spreader and at least one collapsible spacer are placed in the mold cavity such that the collapsible spacer is disposed between the heat spreader and the substrate. A molding compound is molded in the mold, thereby molding the semiconductor die, the substrate, the wire bonds, the die adapter, the at least one collapsible spacer and the heat spreader into the molding compound to provide a molded package. A ball grid array is formed on a second surface of the substrate, bumps of the ball grid array being electrically connected to the conductive traces and the integrated circuit package is singulated.

Owner:UTAC HEADQUARTERS PTE LTD

Ball grid array package and process for manufacturing same

InactiveUS6933176B1Inhibiting mold flashReducing mold flashSemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyBall grid array

A ball grid array integrated circuit package is manufactured by mounting a semiconductor die, to a surface of a substrate such that bumps on the semiconductor die are electrically connected to conductive traces of the substrate. At least one collapsible spacer is mounted to at least one of a heat spreader, the semiconductor die and the substrate. The heat spreader is fixed to the at least one of the first surface of the substrate and the semiconductor die such that he at least one collapsible spacer is disposed therebetween. A ball grid array is formed on a second surface of the substrate, bumps of the ball grid array being electrically connected to the conductive traces and the integrated circuit package is singulated.

Owner:UTAC HEADQUARTERS PTE LTD

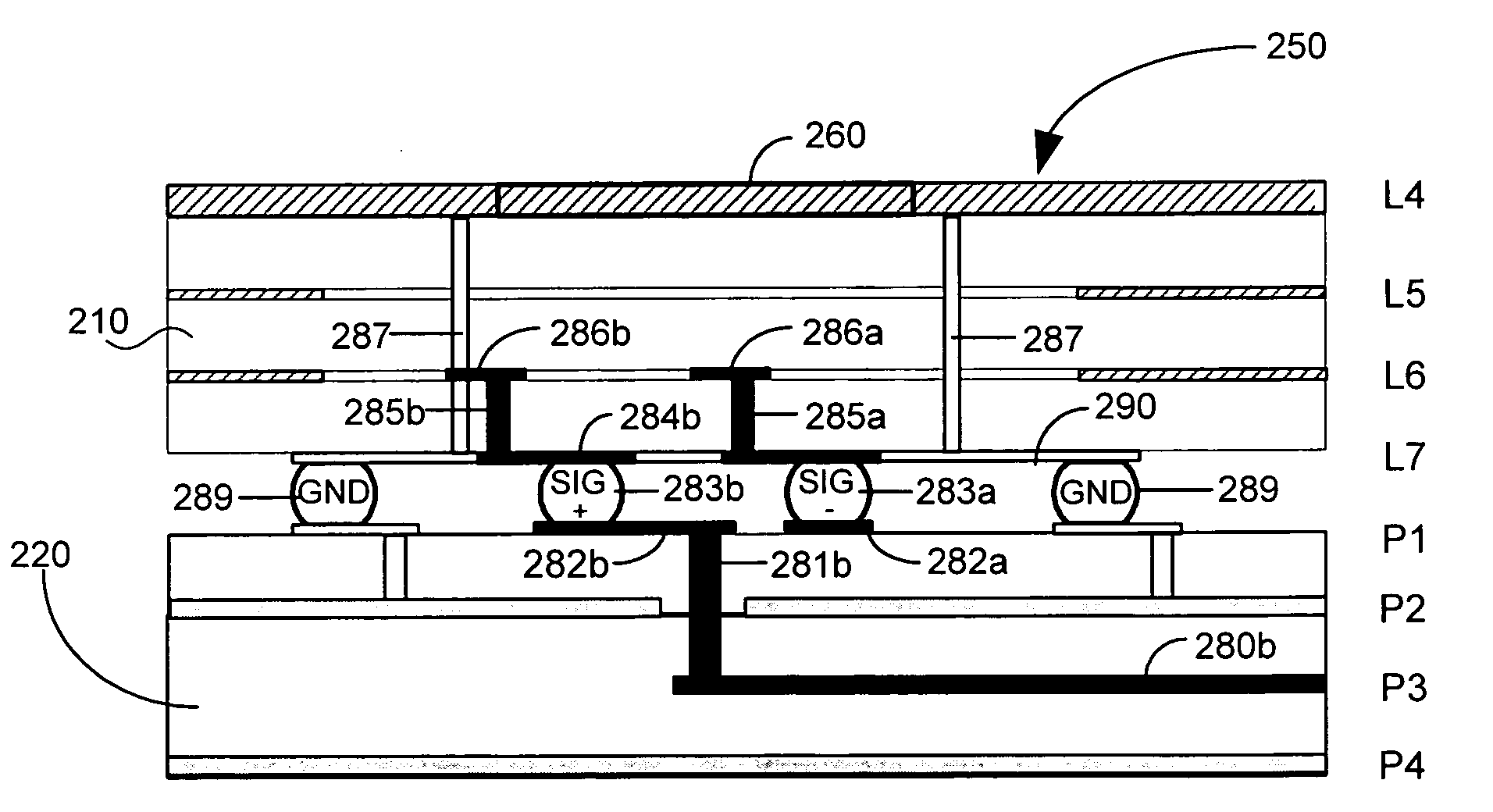

Ball grid array package-to-board interconnect co-design apparatus

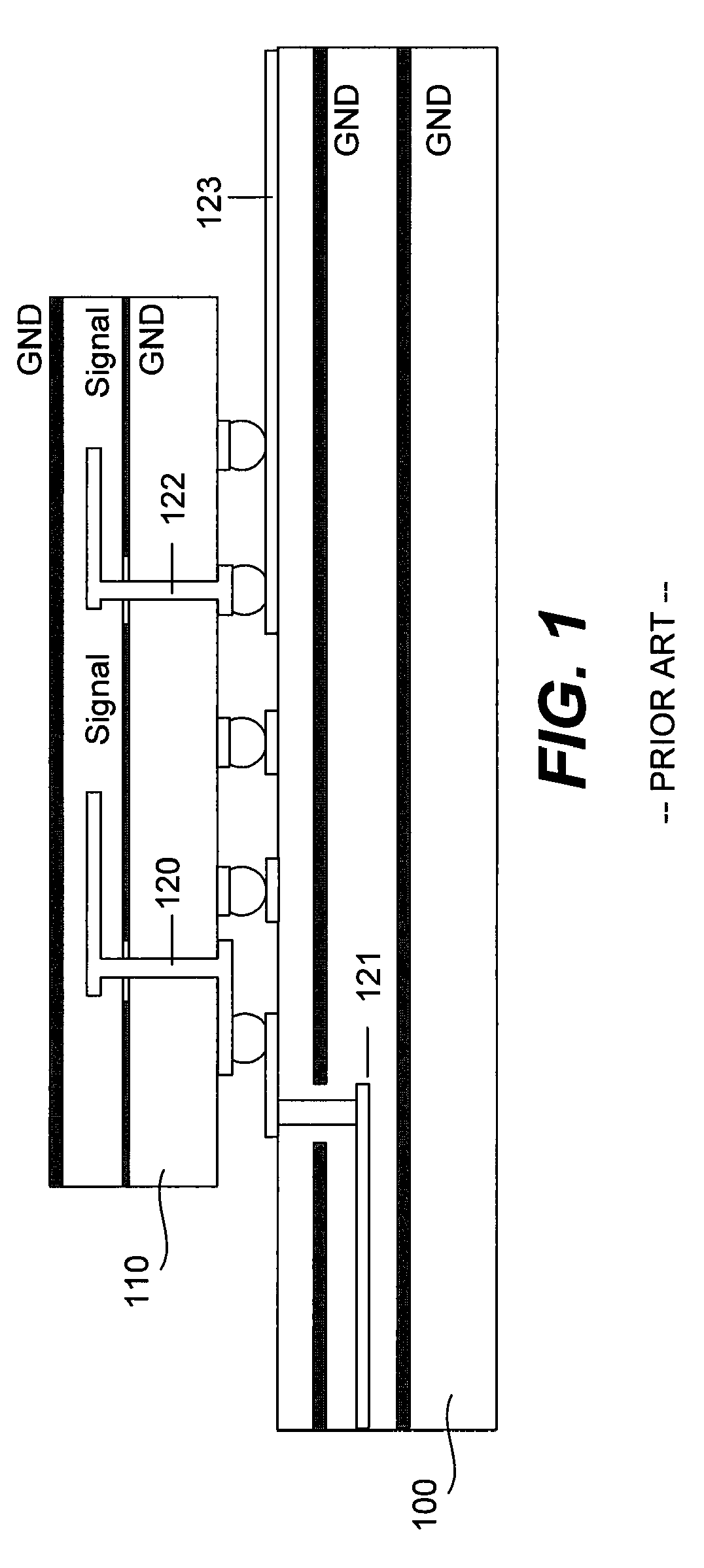

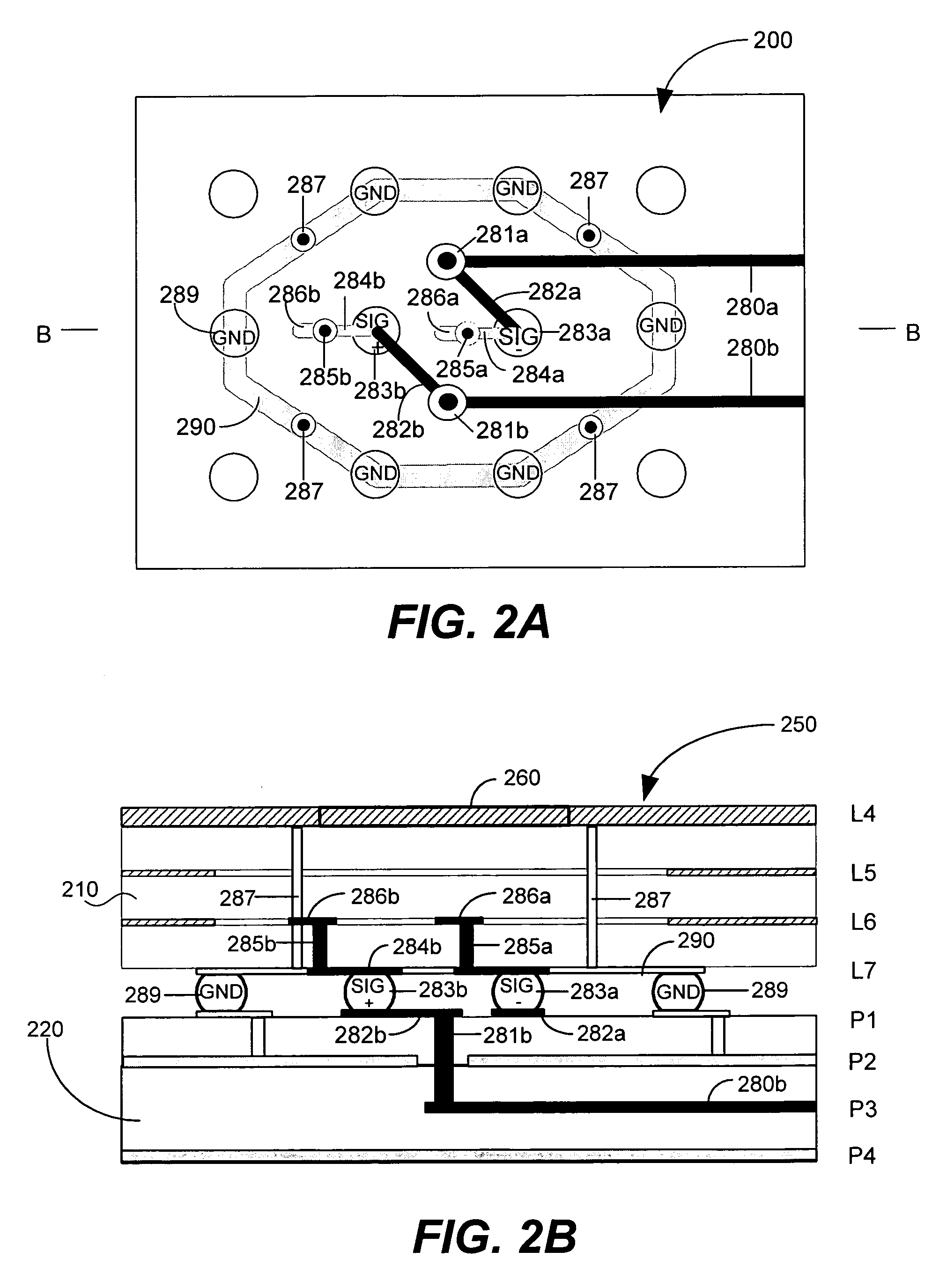

InactiveUS7405477B1Signal transmission is convenientAvoid reflectionsSemiconductor/solid-state device detailsPrinted circuit aspectsCopper interconnectData stream

A package-board co-design methodology preserves the signal integrity of high-speed signals passing from semiconductor packages to application PCBs. An optimal architecture of interconnects between package and PCB enhances the signal propagation, minimizes parasitic levels, and decreases electromagnetic interference from adjacent high frequency signals. The invention results in devices with superior signal quality and EMI shielding properties with enhanced capability for carrying data stream at multiple-gigabit per second bit-rates.

Owner:TAHOE RES LTD

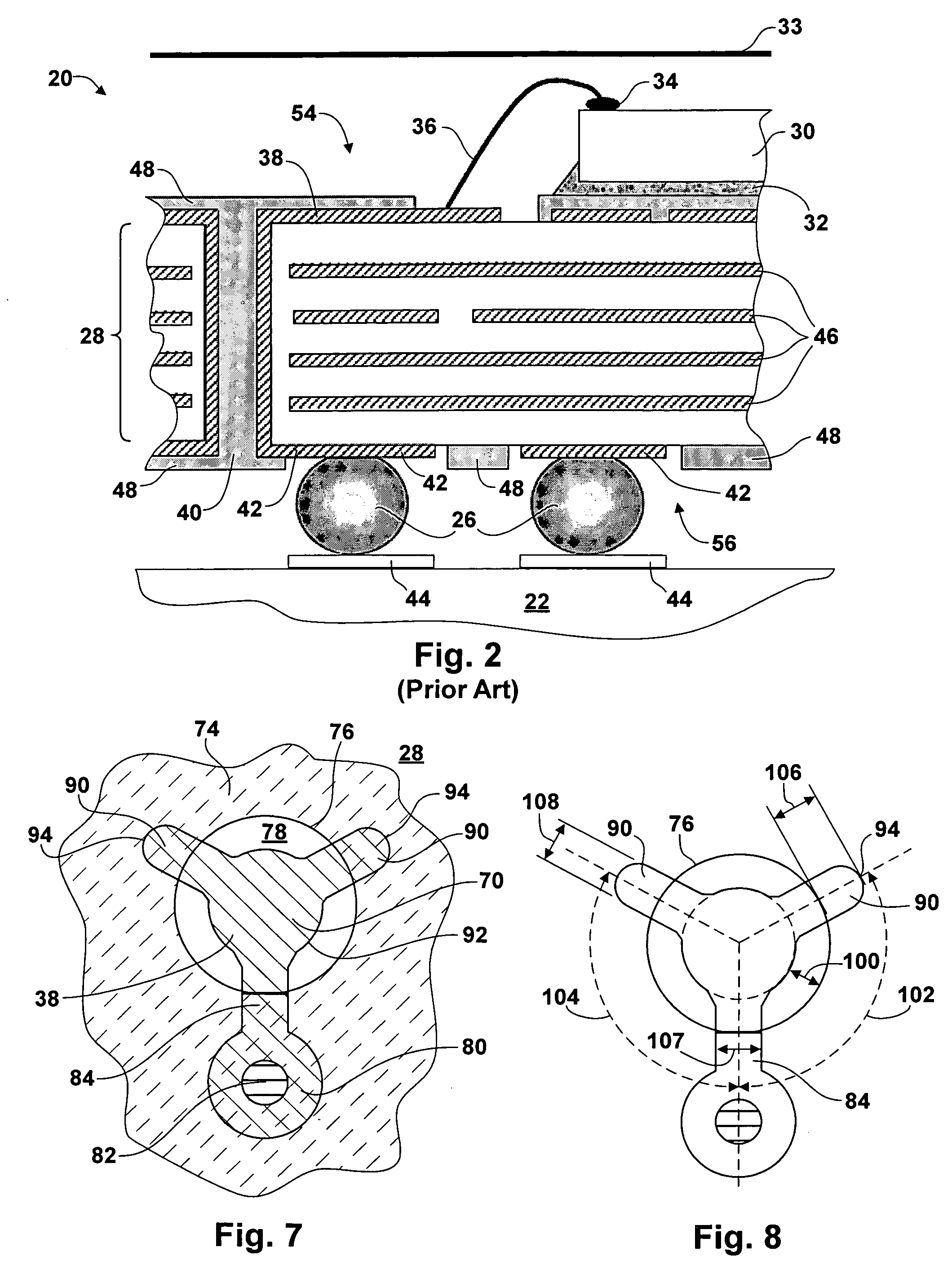

Embedded heat spreader ball grid array

InactiveUS7126218B1Reduce thermal resistanceSacrificing thermal performanceSemiconductor/solid-state device detailsSolid-state devicesInterconnectionBall grid array

A heat slug or spreader is attached directly to a surface of the die in a ball grid array (BGA) package. The heat spreader roughly conforms to the topological profile of the die, underlying substrate, and electrical interconnections between the die and the substrate, such as bond wires. The outer portion of the heat spreader substantially cover the outer portion of the substrate, or alternatively, cover only those portions extending in laterally from the sides of the chip and not the corners. An encapsulant completely covers the heat spreader and die.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

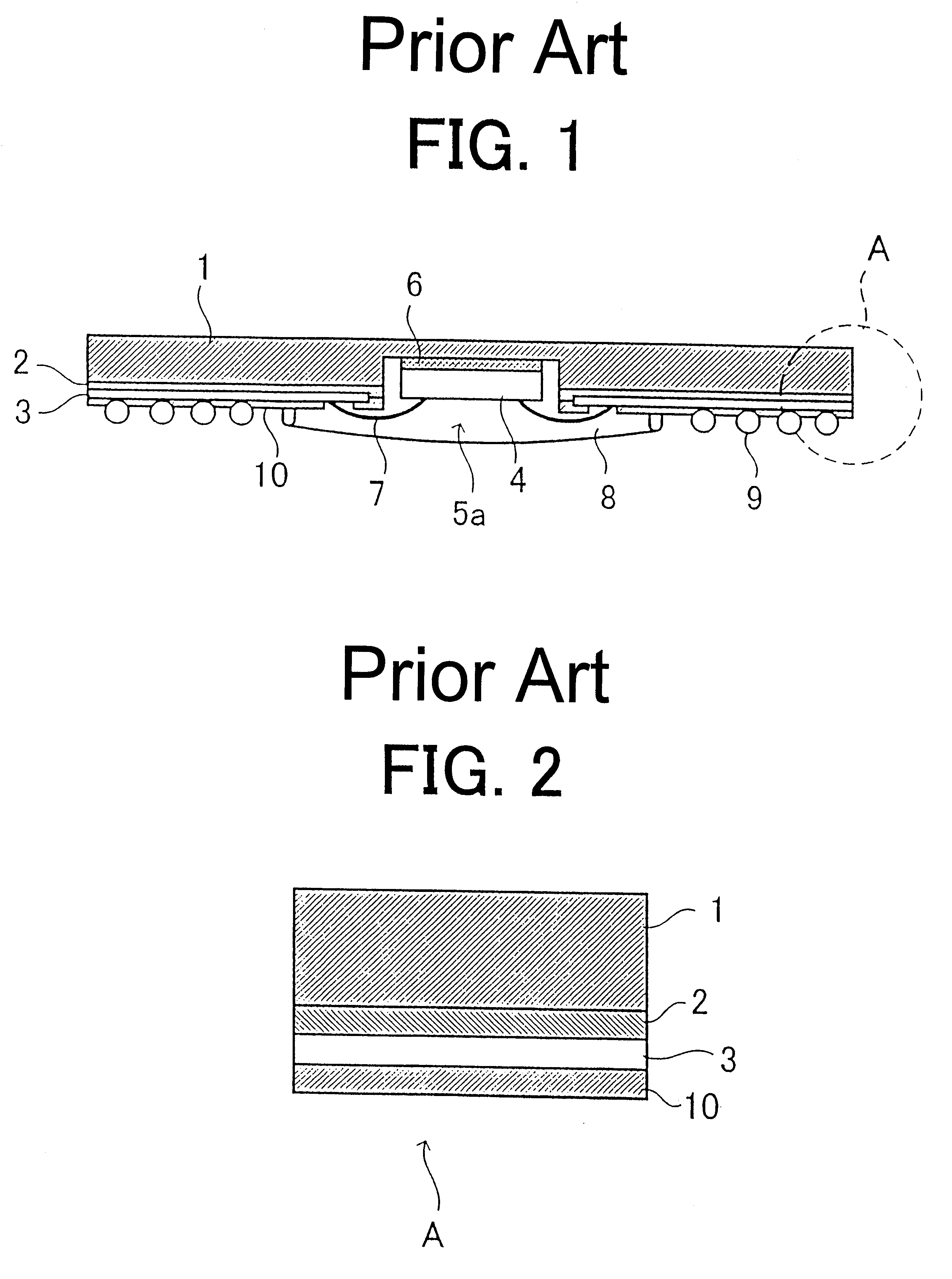

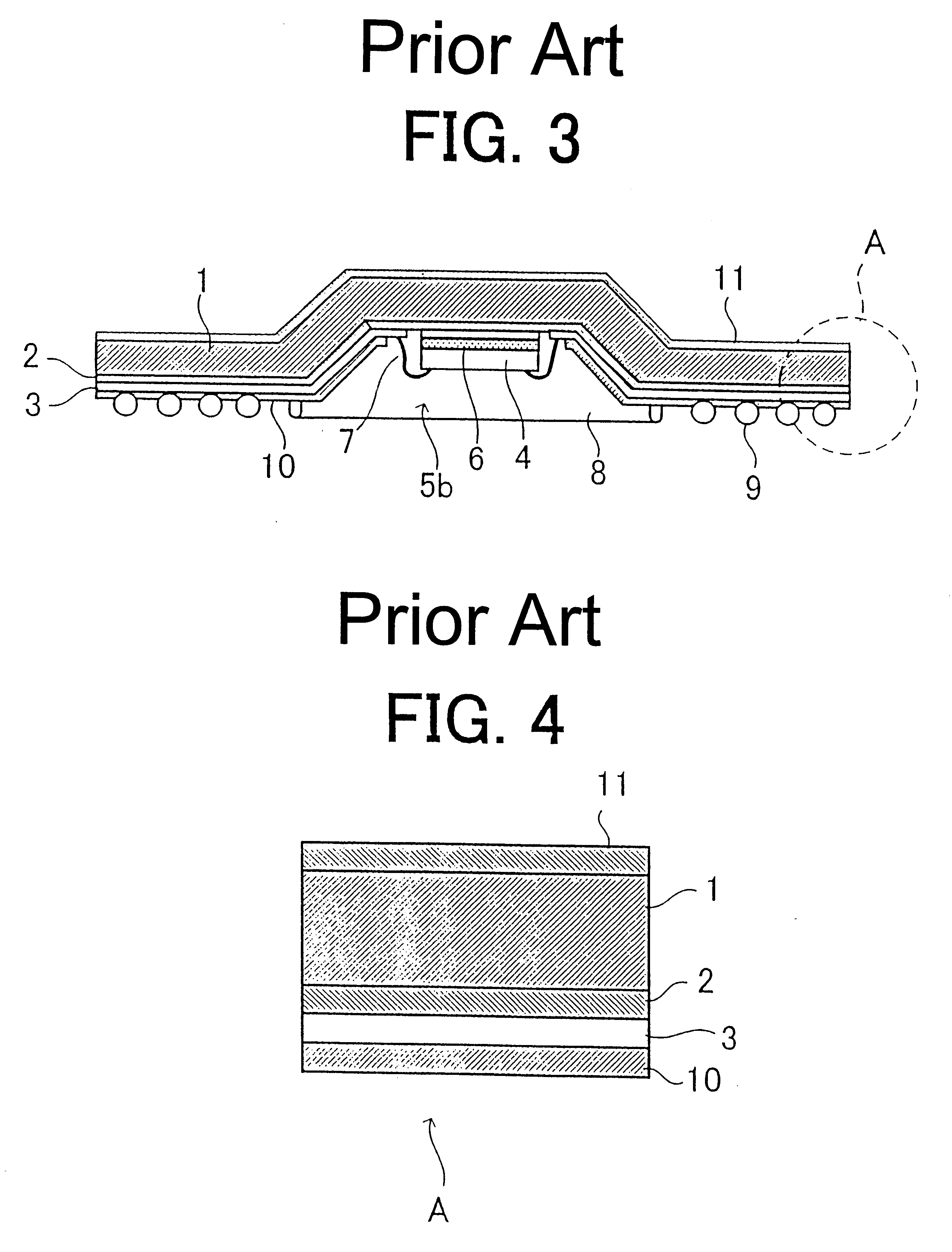

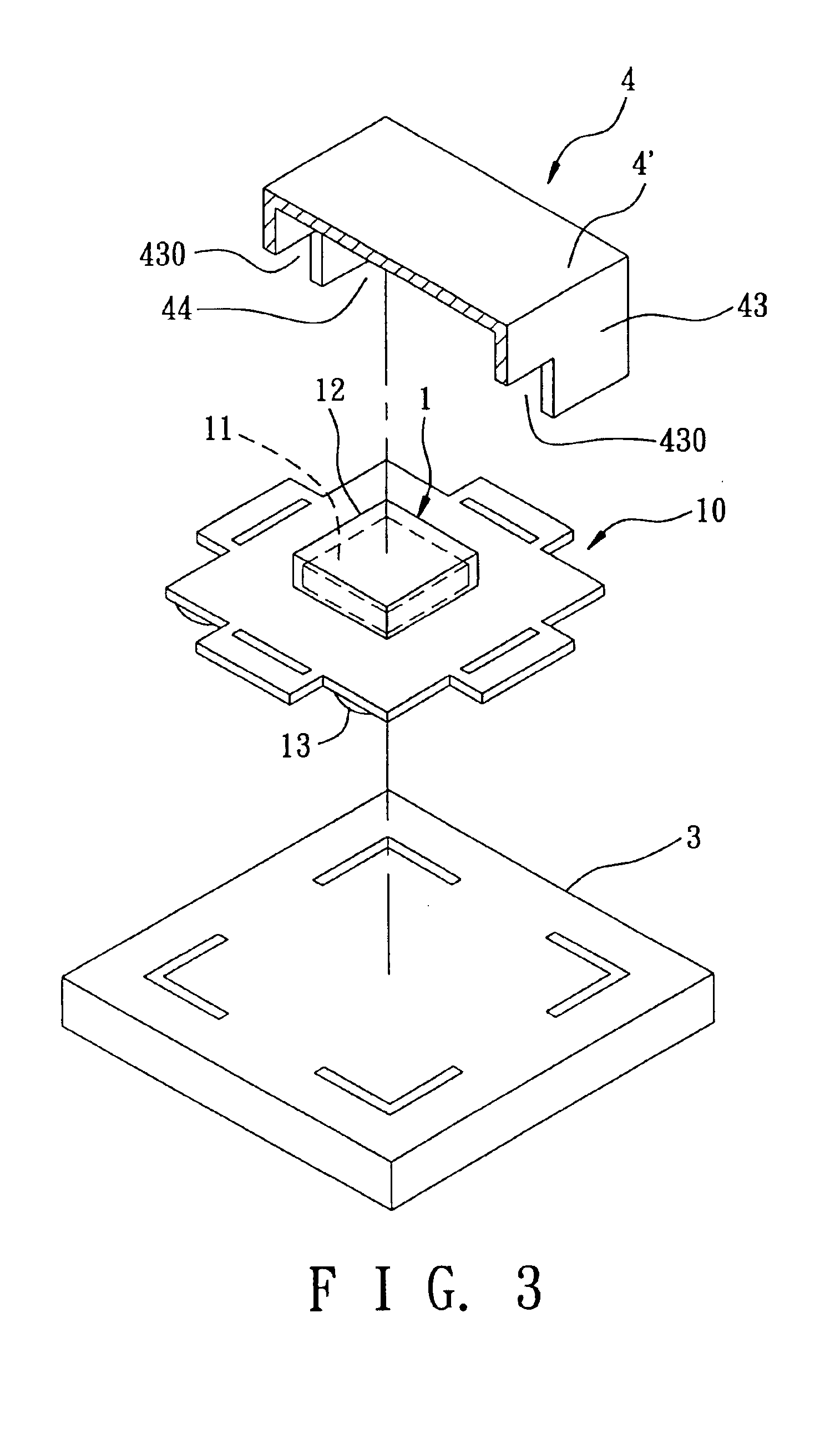

Non-solder mask defined (NSMD) type wiring substrate for ball grid array (BGA) package and method for manufacturing such a wiring substrate

ActiveUS7098407B2Reduce crackingReduce stress concentrationPrinted circuit assemblingSemiconductor/solid-state device detailsStress concentrationSolder mask

In one embodiment, a pad is formed on a substrate surface. The pad is connected with a connecting pattern. A first mask is formed on the substrate. The first mask has a first opening exposing at least a portion of the pad and a portion of the connecting pattern. A second mask is formed on the first mask. The second mask has a second opening exposing at least a portion of the pad and a portion of the connecting pattern. A boundary surface or sidewall of the first opening is not coplanar with a boundary surface or sidewall of the second opening. Therefore, stresses may be prevented from concentrating on the boundary surface of the first opening, thereby allowing dispersion of the stresses and restraining pattern cracks.

Owner:SAMSUNG ELECTRONICS CO LTD

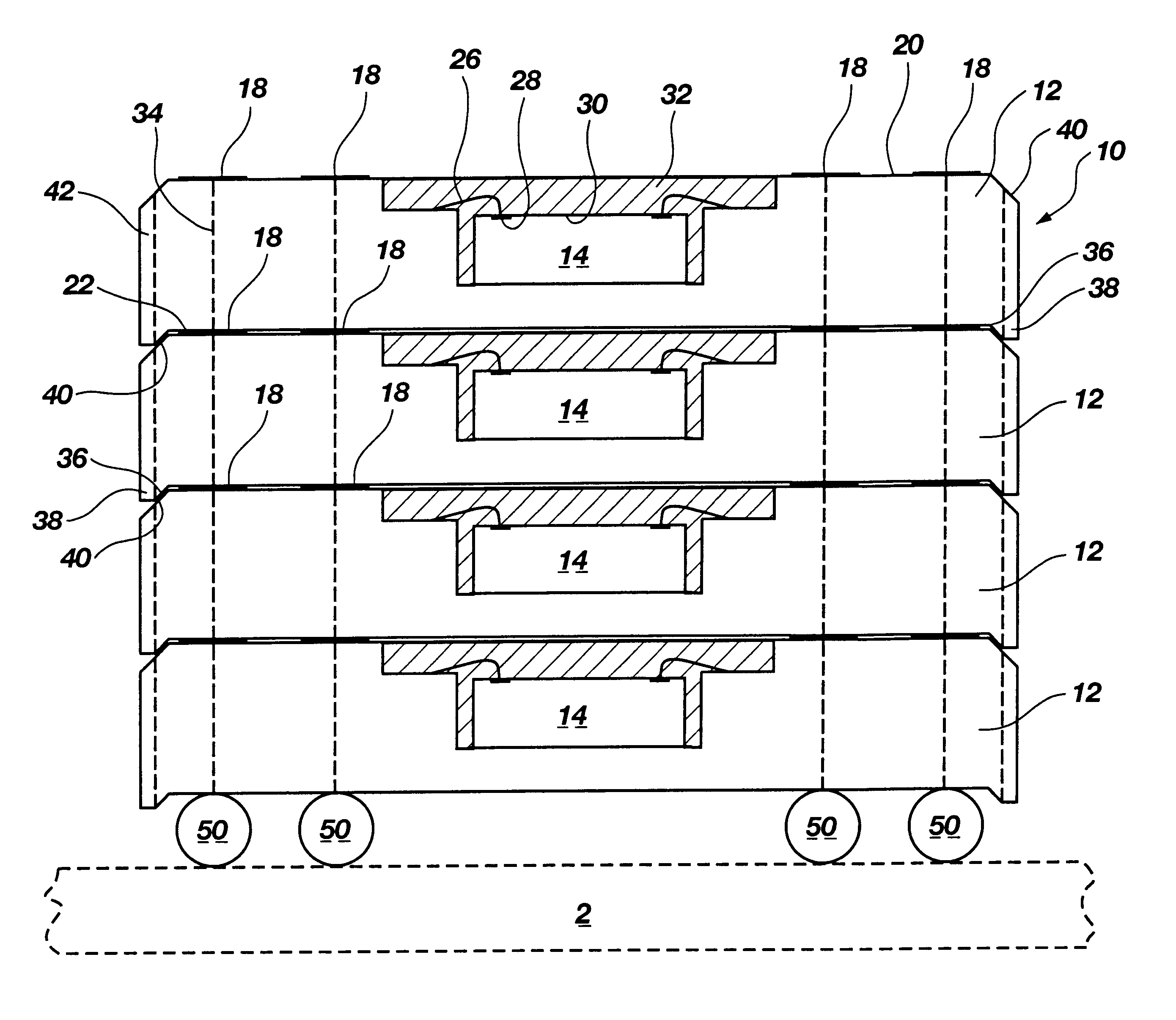

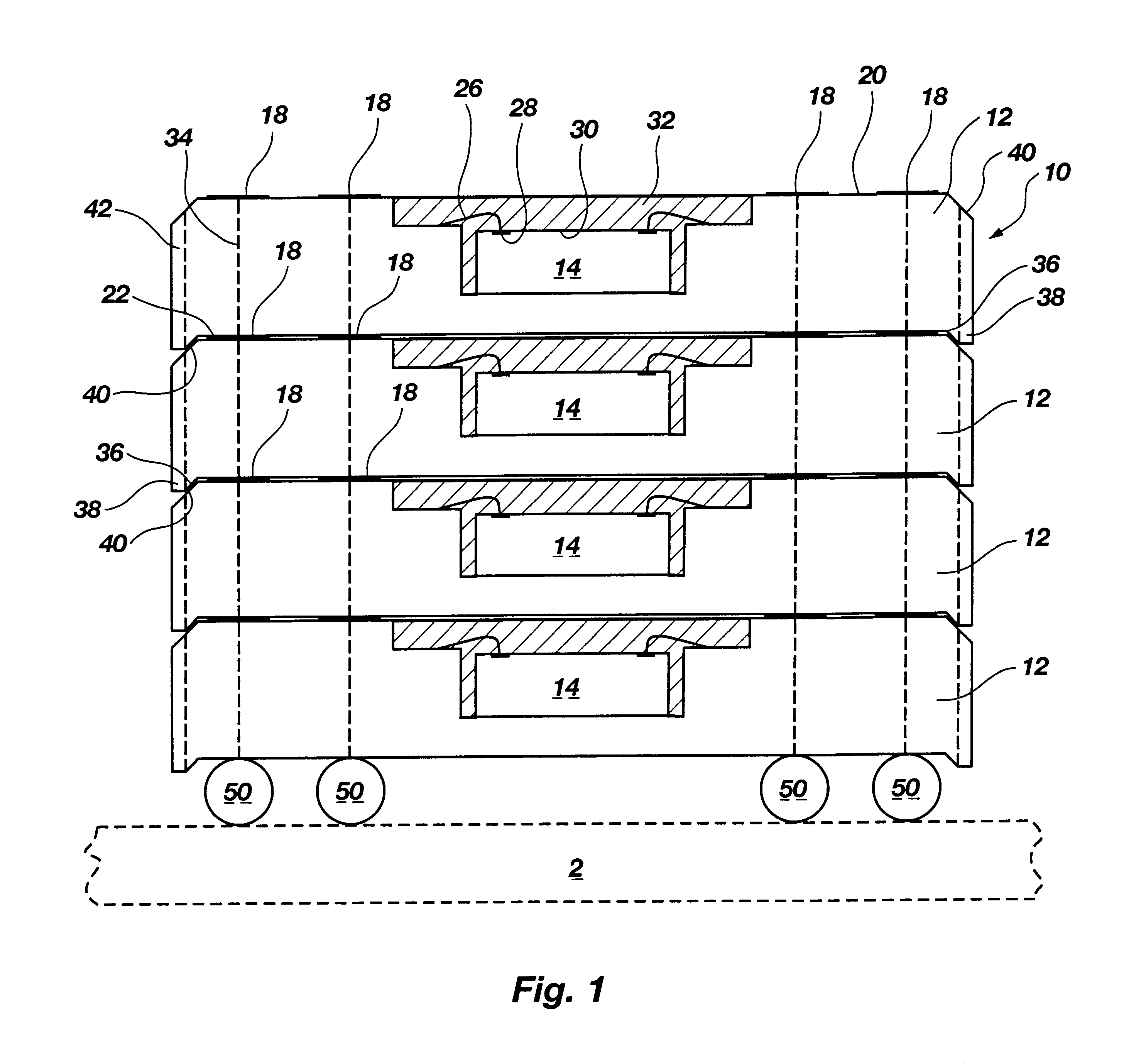

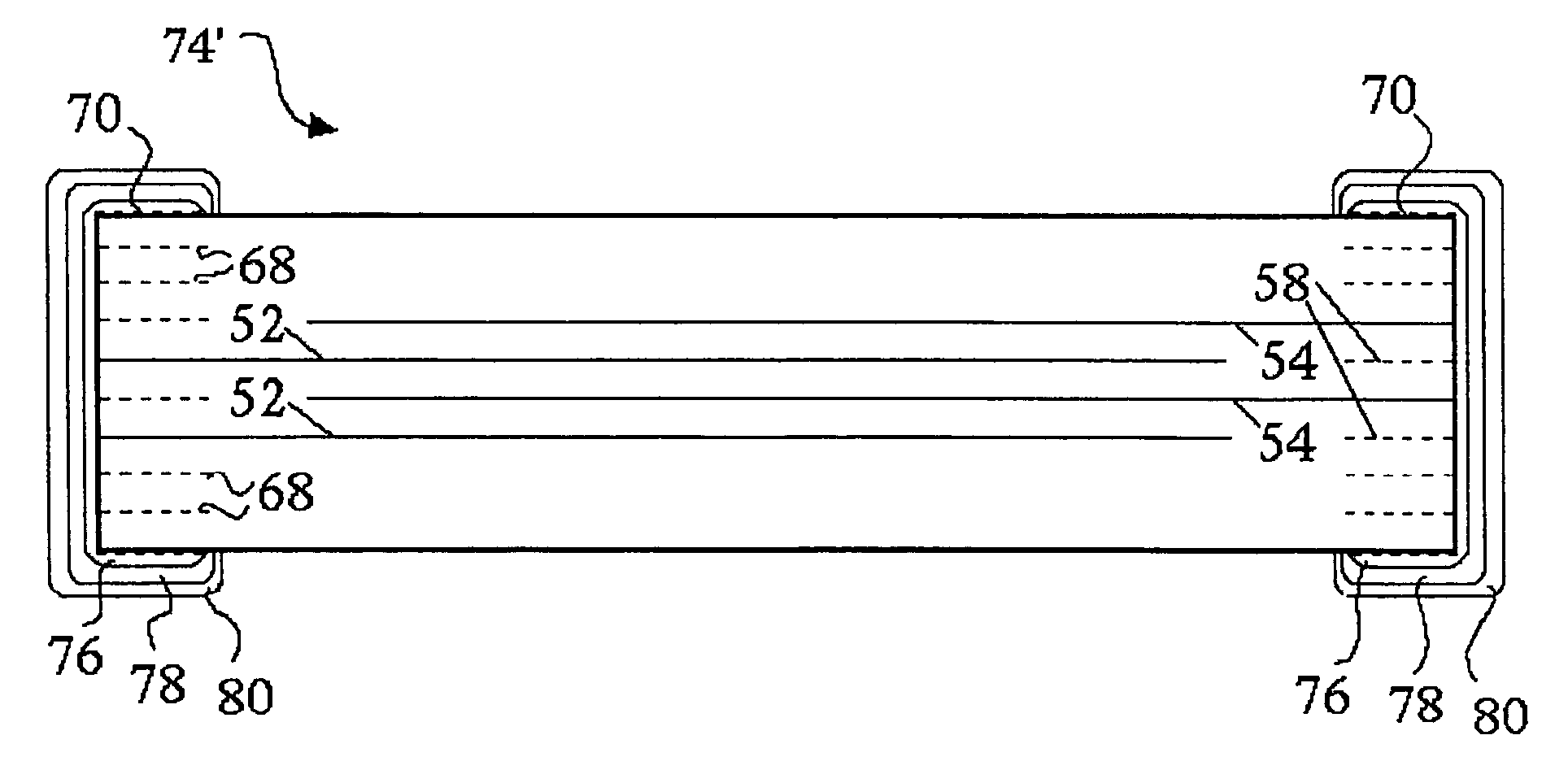

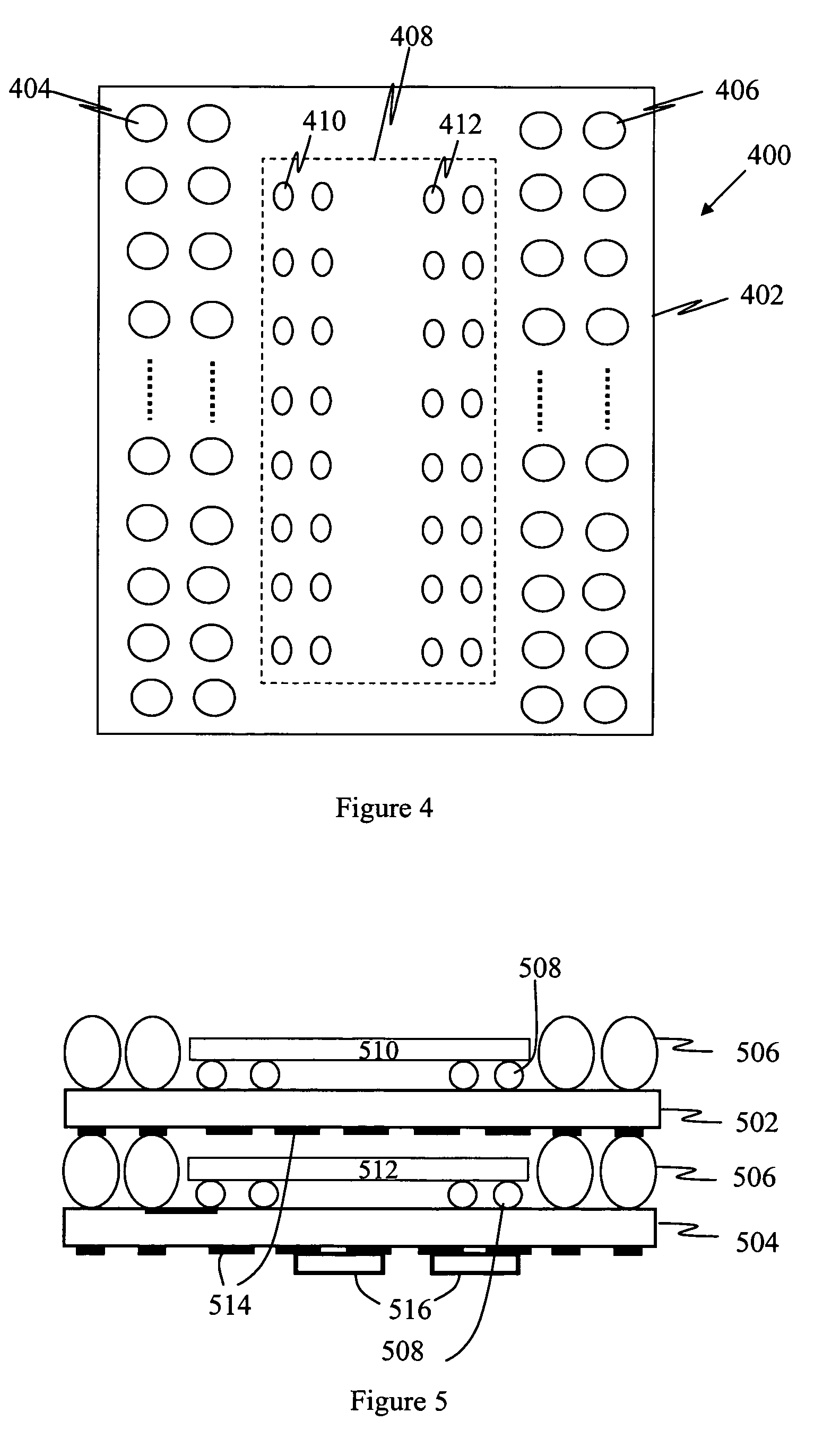

Stackable electronic assembly

InactiveUS7180165B2Reduce crackingImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesCombined useEngineering

On implementation of the invention provides a stackable chip-scale package for improving memory density that may be mounted within a limited area or module. A novel staggered routing scheme enables the use of the same trace routing at every level of the stacked architecture for efficiently accessing individual memory devices in a chip-scale package stack. The use of a ball grid array chip-scale package architecture in combination with thermally compatible materials decreases the risk of thermal cracking while improving heat dissipation. Moreover, this architecture permits mounting support components, such as capacitors and resistors, on the chip-scale package.

Owner:SANMINA-SCI CORPORATION

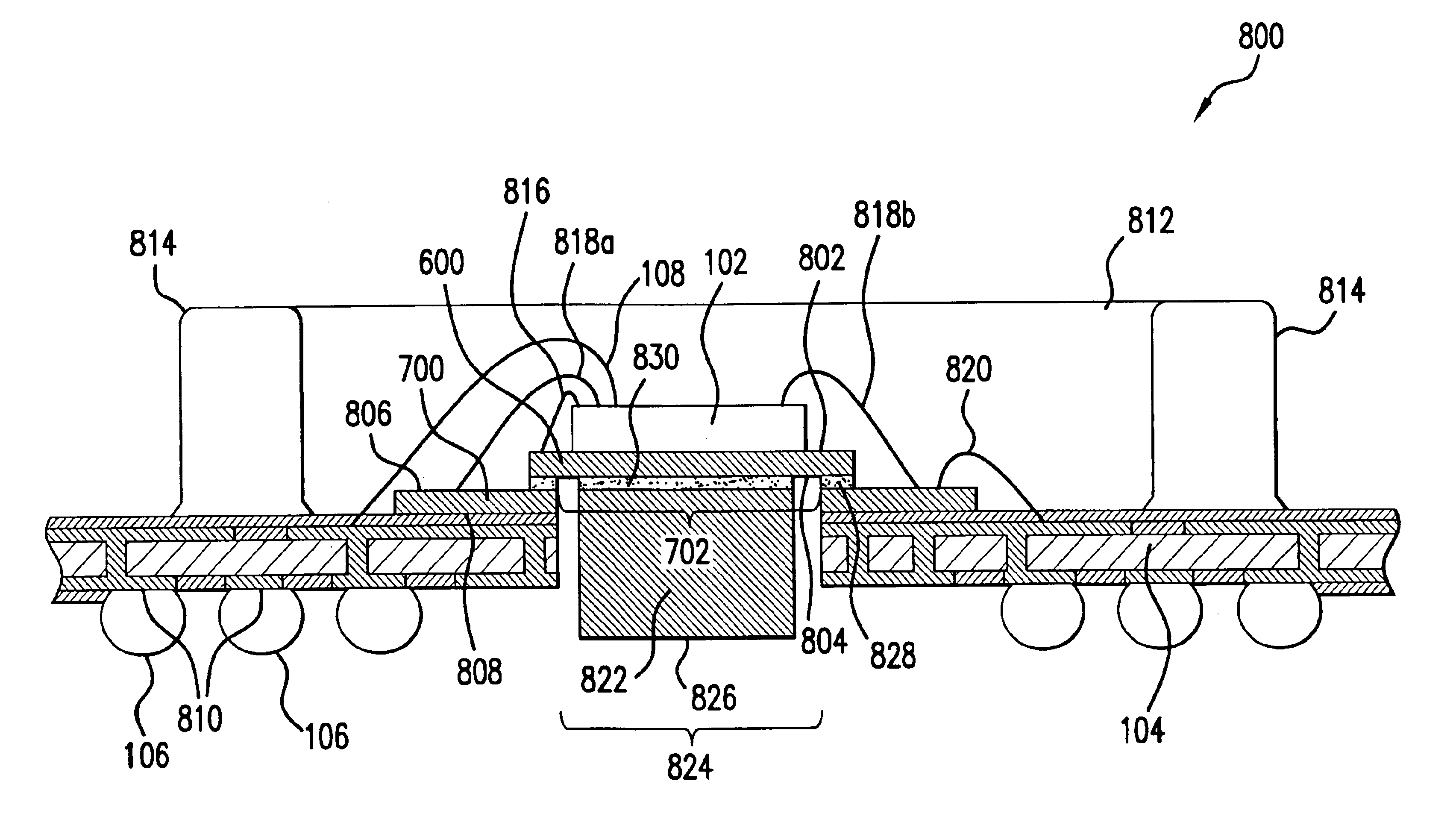

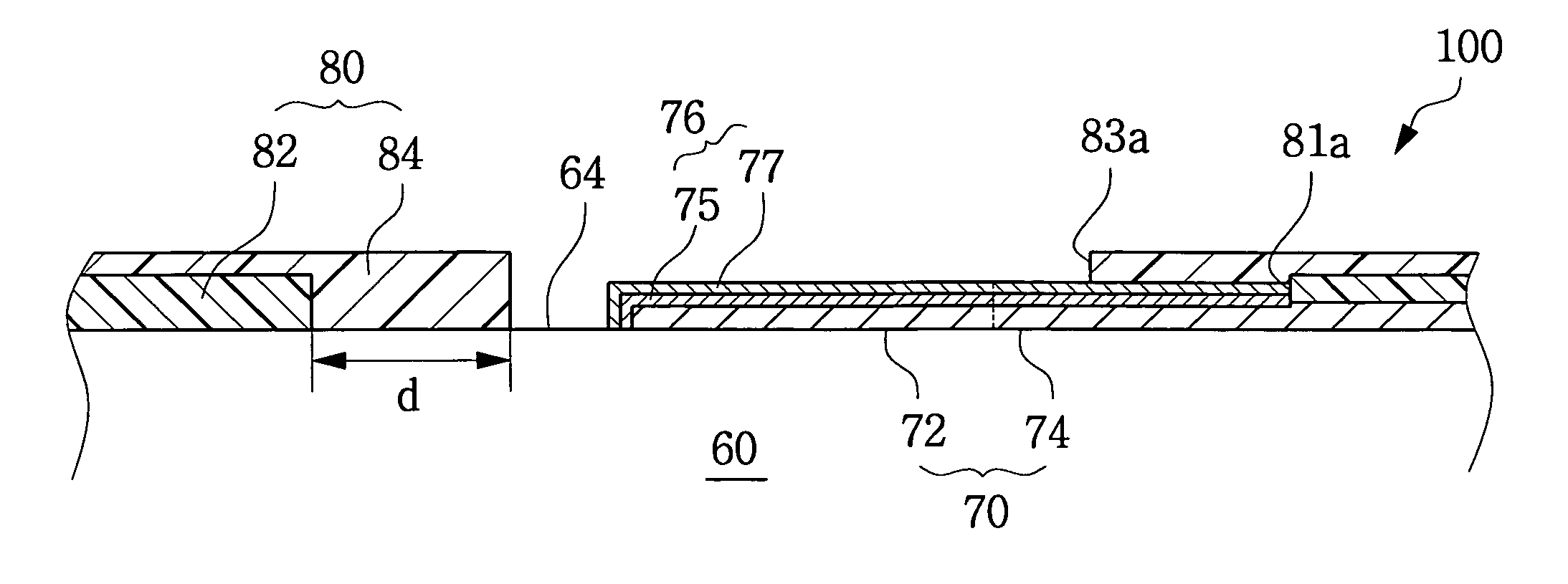

Ball grid array package enhanced with a thermal and electrical connector

InactiveUS7161239B2Improve electricityImprove thermal characteristicsSemiconductor/solid-state device detailsSolid-state devicesElectrical connectorBall grid array

Electrically, mechanically, and thermally enhanced ball grid array (BGA) packages are described. A substrate has a surface, wherein the surface has an opening therein. A stiffener has a surface coupled to the surface of the substrate. An area of the surface of the stiffener can be greater than, equal to, or less than an area of the surface of the substrate. A thermal connector is coupled to the surface of the stiffener through the opening. A surface of the thermal connector is capable of attachment to a printed circuit board (PCB) when the BGA package is mounted to the PCB. The thermal connector can have a height such that the thermal connector extends into a cavity formed in a surface of the PCB when the BGA package is mounted to the PCB. Alternatively, the stiffener and thermal connector may be combined into a single piece stiffener, wherein the stiffener has a protruding portion. The protruding portion extends through the opening when the stiffener is coupled to the substrate, and is capable of attachment to the PCB.

Owner:AVAGO TECH INT SALES PTE LTD

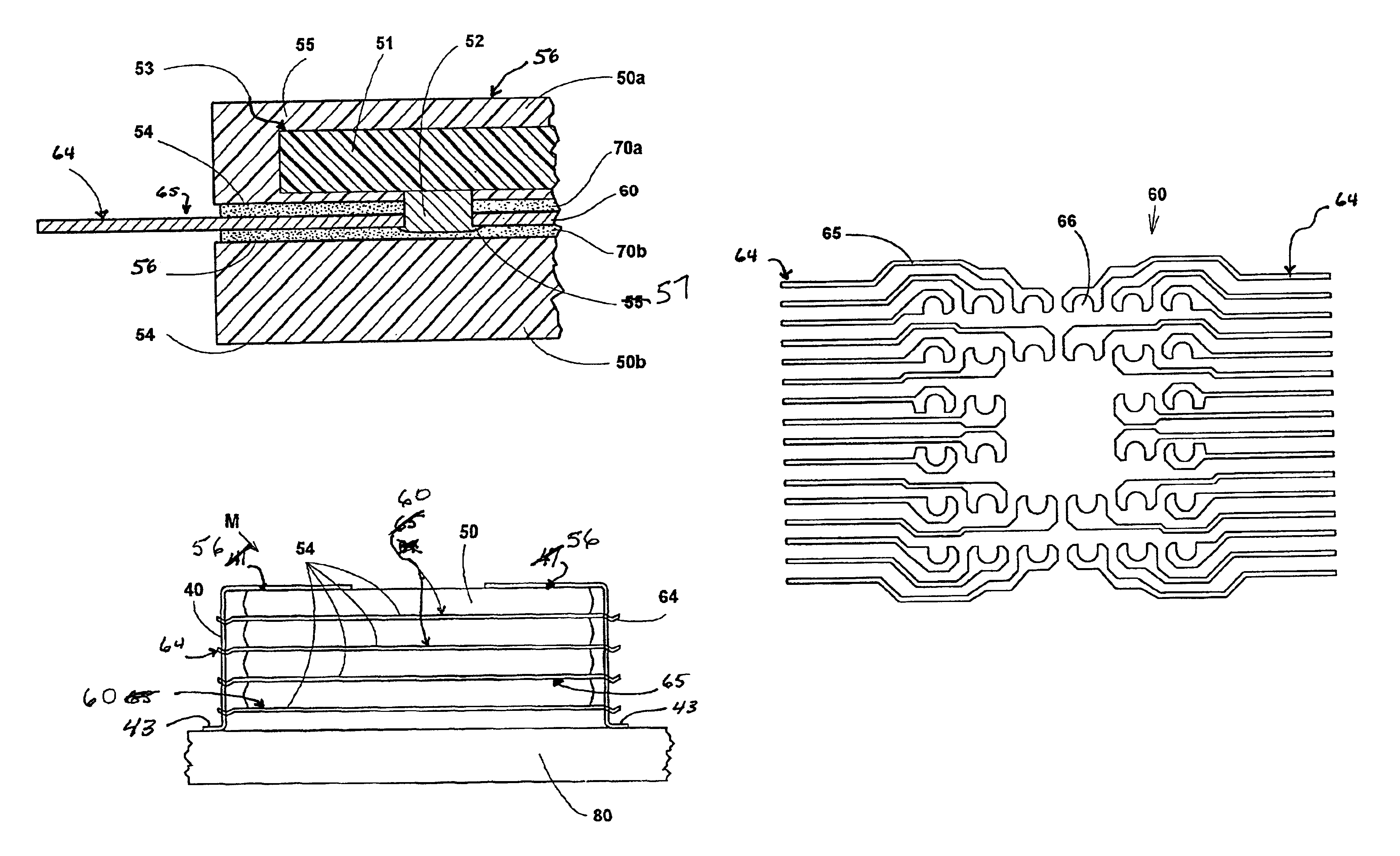

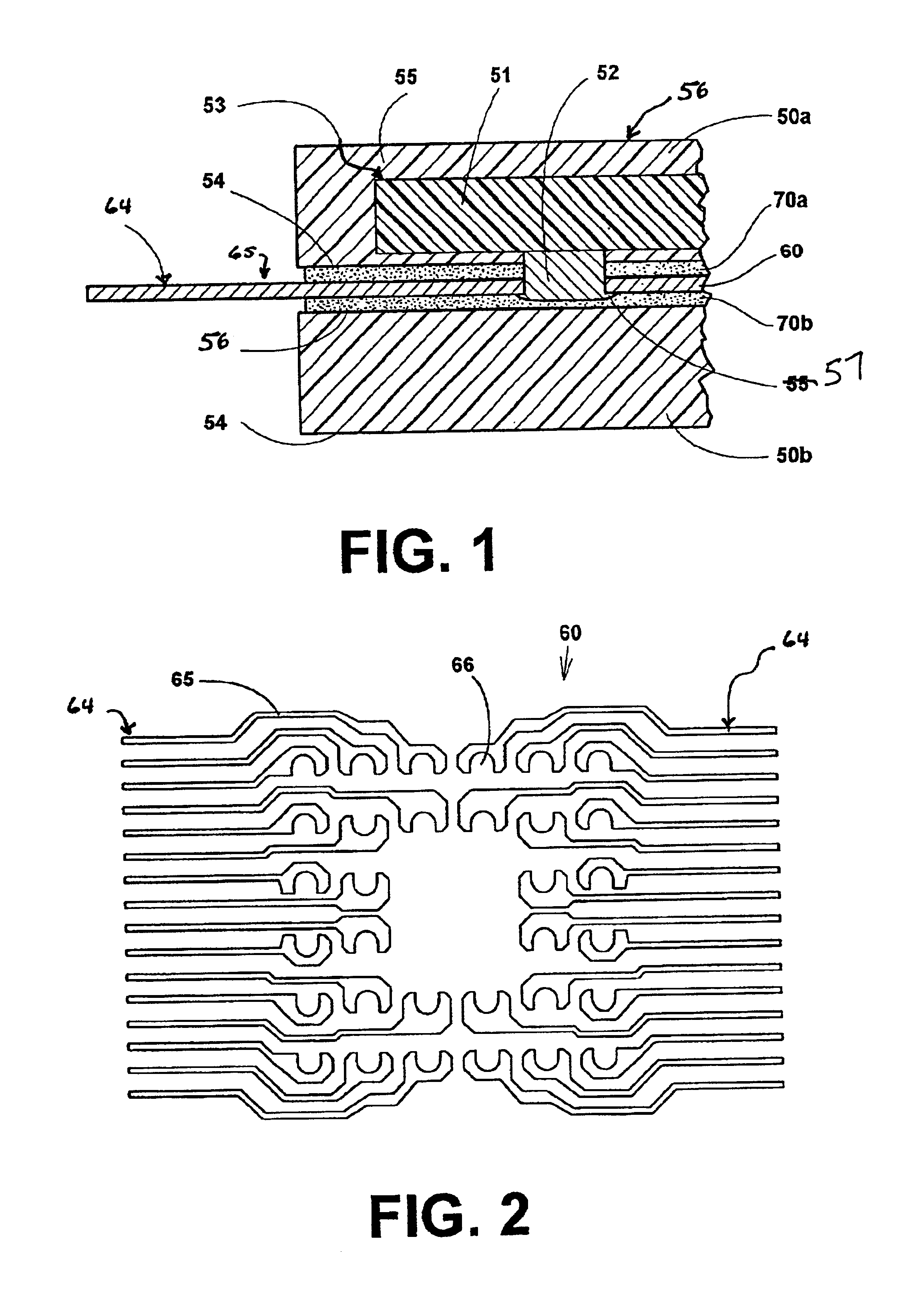

High density integrated circuit module

InactiveUS6919626B2Improve cooling effectImprove space efficiencyPrinted circuit assemblingLine/current collector detailsAdhesiveFlexible circuits

The present invention provides a method and apparatus for fabricating densely stacked ball-grid-array packages into a three-dimensional multi-package array. Integrated circuit packages are stacked on one another to form a module. Lead carriers provide an external point of electrical connection to buried package leads. Lead carriers are formed with apertures that partially surround each lead and electrically and thermally couple conductive elements or traces in the lead carrier to each package lead. Optionally thin layers of thermally conductive adhesive located between the lead carrier and adjacent packages facilitates the transfer of heat between packages and to the lead carrier. Lead carriers may be formed of custom flexible circuits having multiple layers of conductive material separated by a substrate to provide accurate impedance control and providing high density signal trace routing and ball-grid array connection to a printed wiring board.

Owner:OVID DATA CO

Process for manufacturing ball grid array package

InactiveUS6979594B1Reducing mold flashSemiconductor/solid-state device detailsSolid-state devicesSolder ballEngineering

A ball grid array package is manufactured by mounting a semiconductor die to a first surface of a substrate array. Wires are bonded between the semiconductor die and ones of conductive traces of the substrate array. The heat spreader is disposed in a mold and the substrate array is releasably clamped to a top die of the mold. The semiconductor die, the substrate array, the wire bonds and the heat spreader are molded into a molding material to provide a molded package. Next, the molded package is removed from the mold and a plurality of solder balls are added in the form of a ball grid array on a second surface of the substrate array such that bumps of the ball grid array are electrically connected to the conductive traces. The integrated circuit package is then singulated from a remainder of the substrate array.

Owner:UTAC HEADQUARTERS PTE LTD

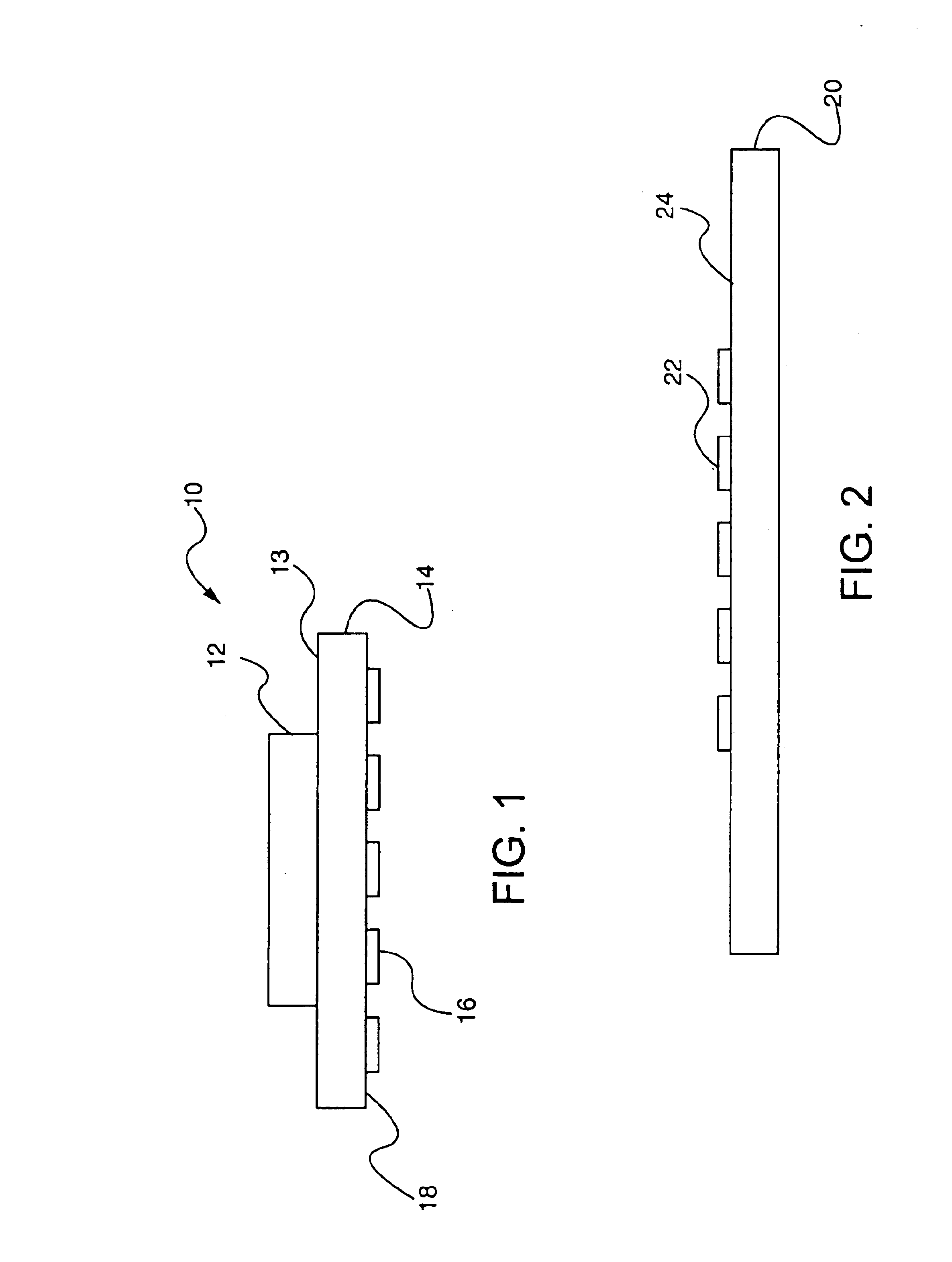

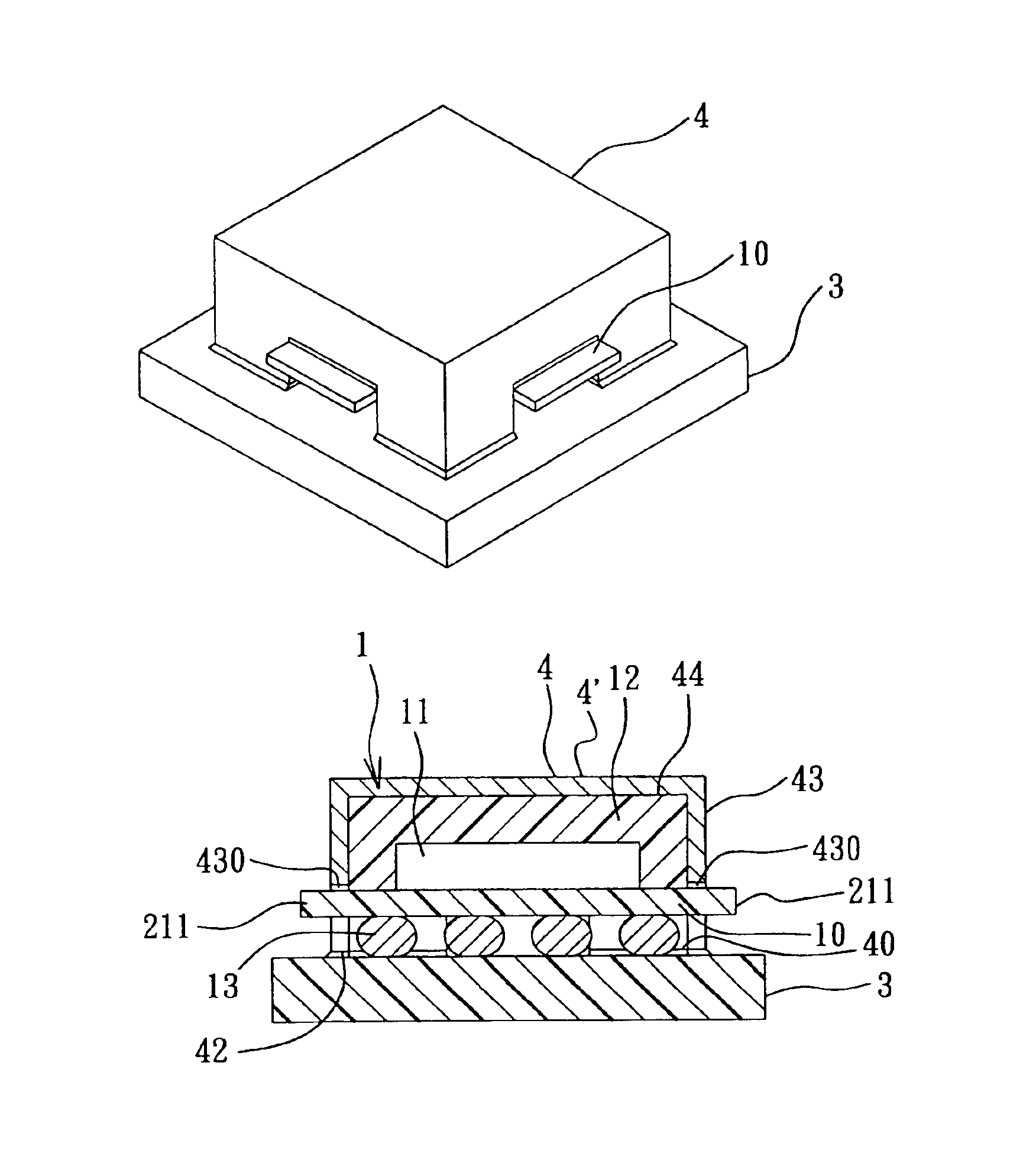

BGA package and method for fabricating the same

InactiveUS6472732B1Small sizeEasy to integrateSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A ball grid array (BGA) package includes a substrate (20) having first and second surfaces. and through holes (30) passing through it. The package further includes a first semiconductor chip (28) which is mounted on the first surface of the substrate (20); a second semiconductor chip (36) which is mounted on the second surface of the substrate (20); and solder balls (34) which are provided on the first surface of the substrate (20) and are electrically connected to the first semiconductor chip (28). The second semiconductor chip (36) is electrically connected via the through holes (30) to the solder balls (34).

Owner:LAPIS SEMICON CO LTD

3-d package stacking system

ActiveUS20070187826A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringBall grid array

The present invention provides a system for 3D package stacking system, comprising providing a substrate, attaching a ball grid array package, in an inverted position, to the substrate, forming a lower package, the lower package having the ball grid array package and the substrate encapsulated by a molding compound and attaching a second integrated circuit package over the lower package.

Owner:STATS CHIPPAC LTD

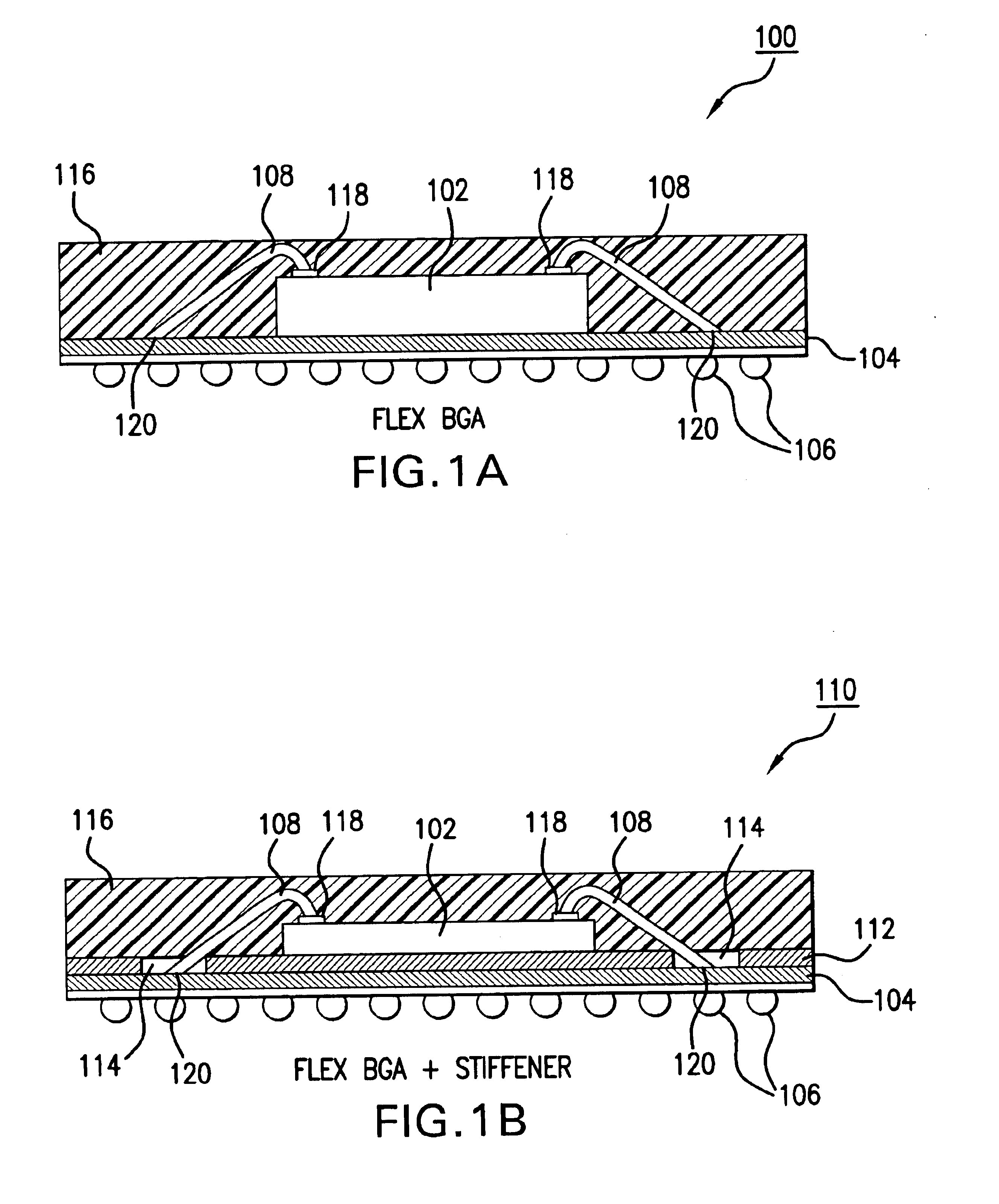

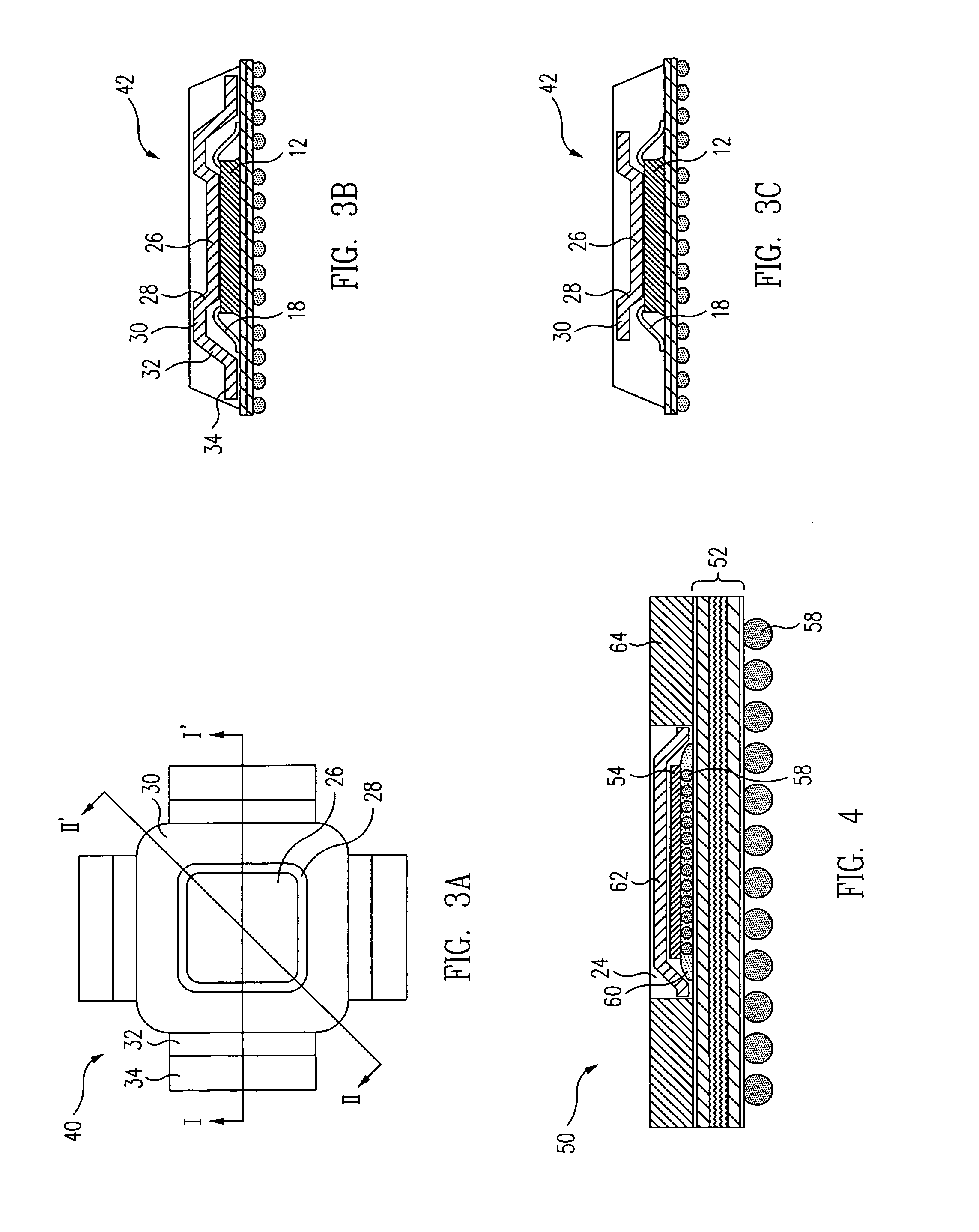

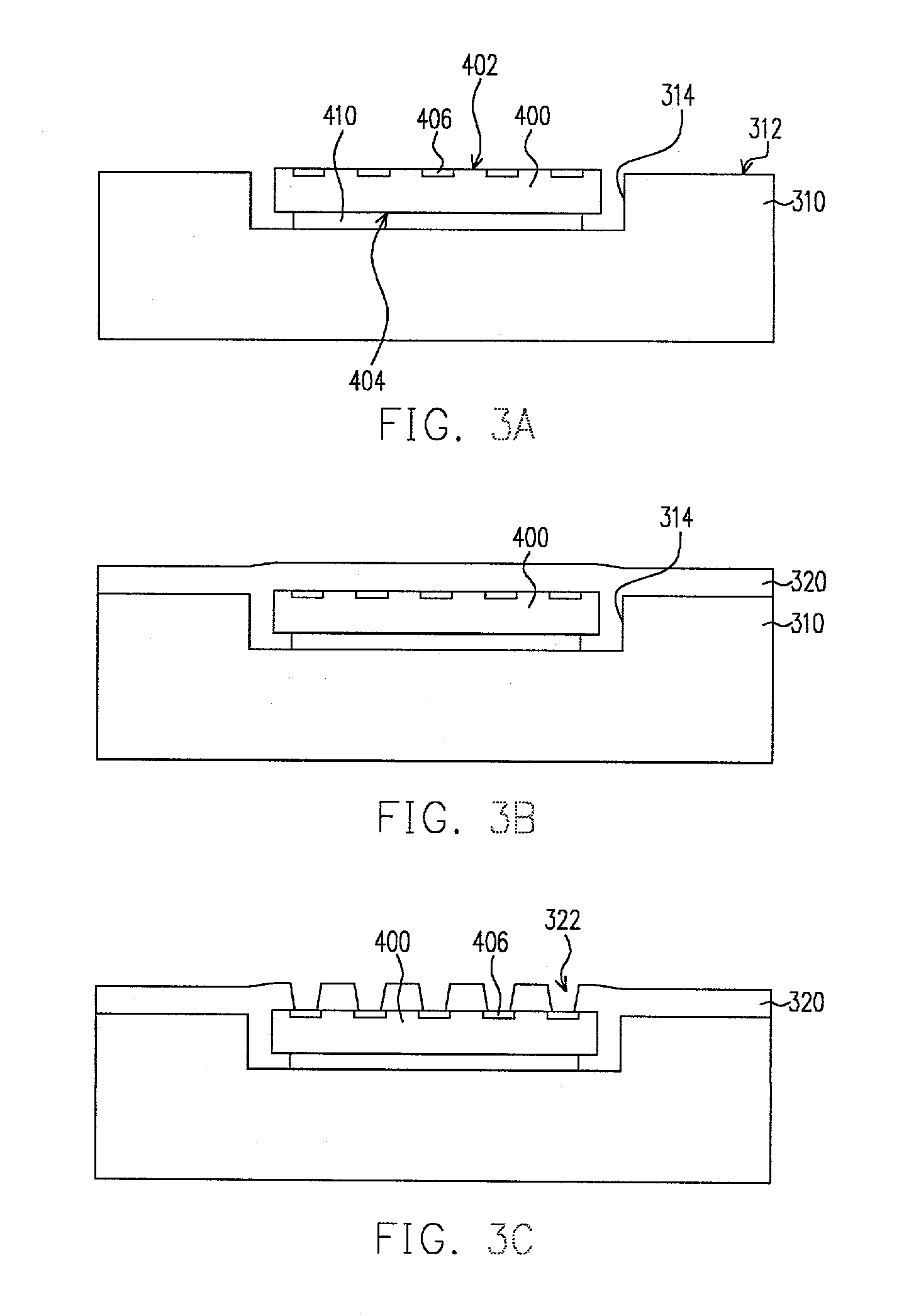

Die-up ball grid array package with patterned stiffener opening

InactiveUS6989593B2Semiconductor/solid-state device detailsSolid-state devicesSolder ballWindow opening

An electrically and thermally enhanced die-up tape substrate ball grid array (BGA) package and die-up plastic substrate BGA package are described. A substrate that has a first surface and a second surface is provided. The stiffener has a first surface and a second surface. The second stiffener surface is attached to the first substrate surface. An IC die has a first surface and a second surface. The first IC die surface is mounted to the first stiffener surface. A plurality of solder balls is attached to the second substrate surface. In one aspect, a heat spreader is mounted to the second IC die surface. In another aspect, the stiffener is coupled to ground to act as a ground plane. In another aspect, the substrate has a window opening that exposes a portion of the second stiffener surface. The exposed portion of the second stiffener surface is configured to be coupled to a printed circuit board (PCB). In another aspect, a metal ring is attached to the first stiffener surface. In another aspect, wire bond openings in the stiffener are bridged by one or more studs.

Owner:AVAGO TECH INT SALES PTE LTD

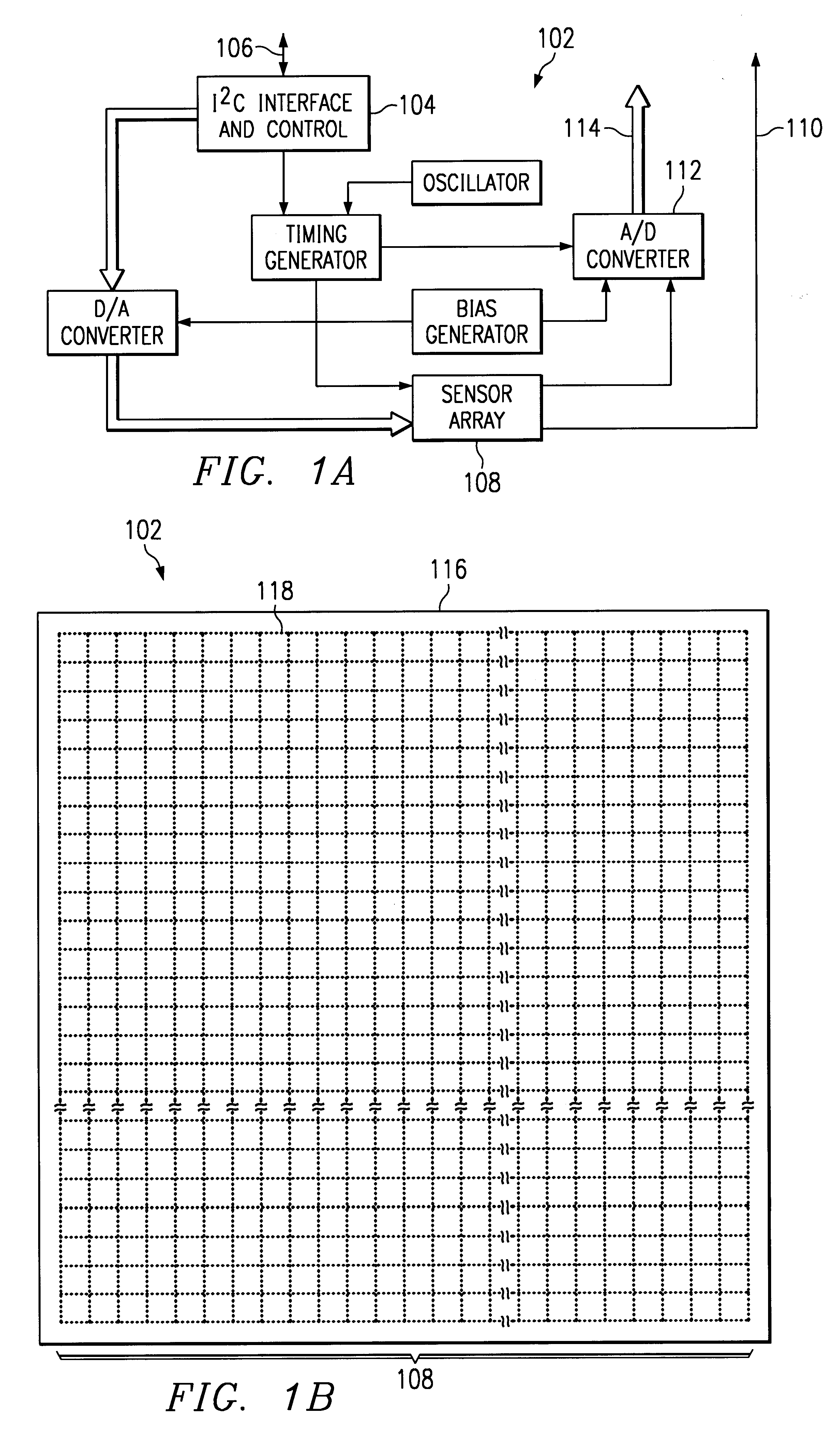

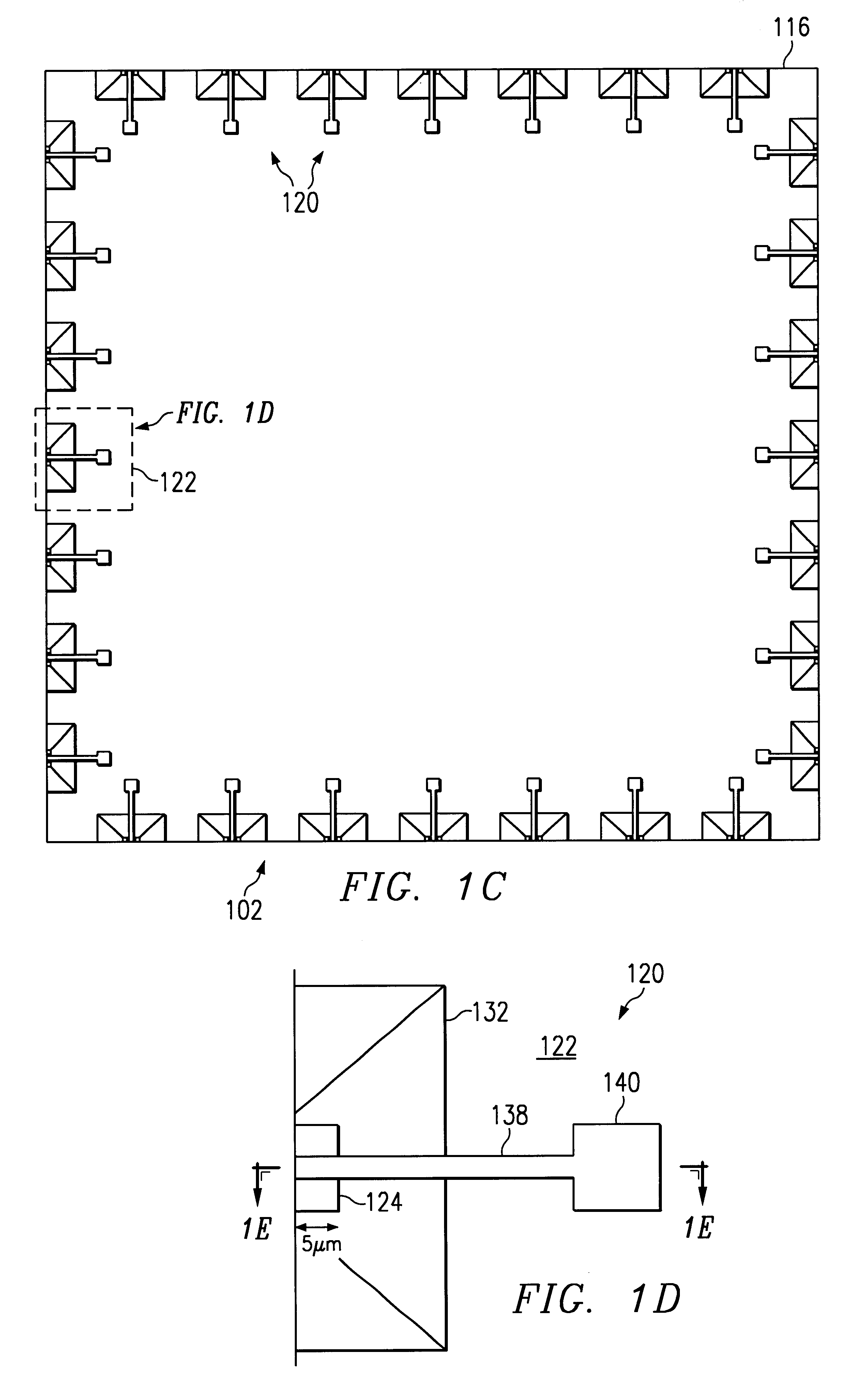

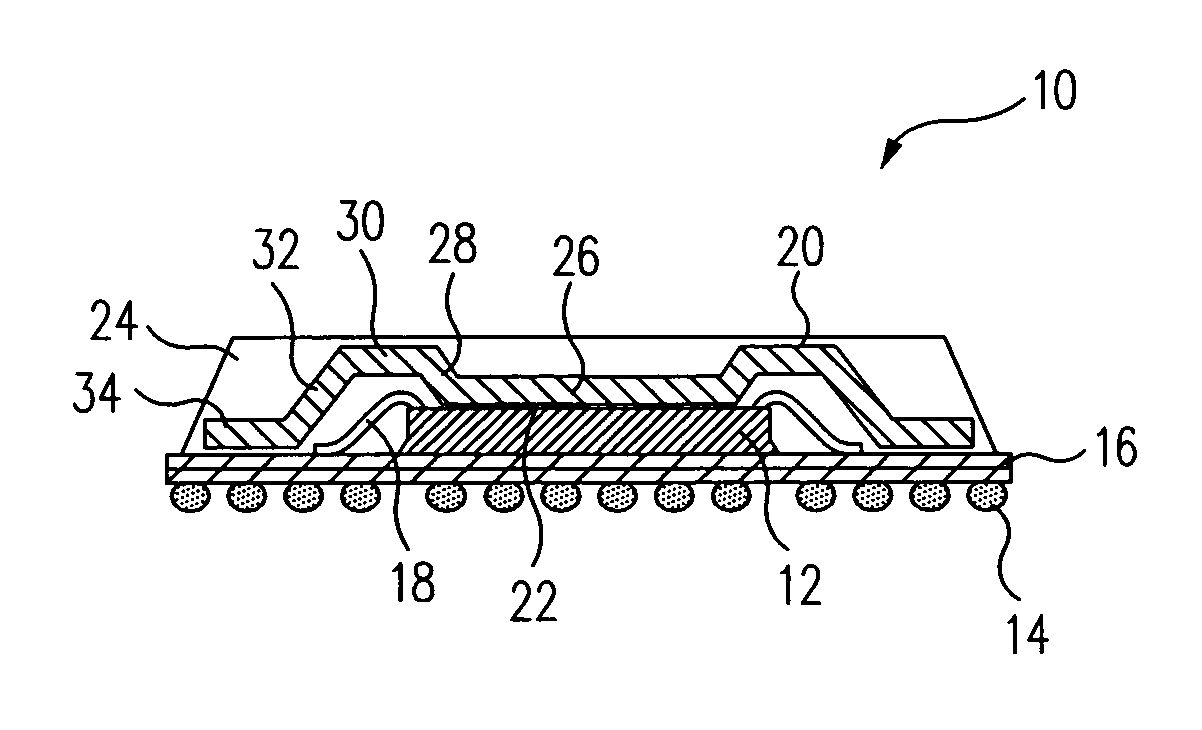

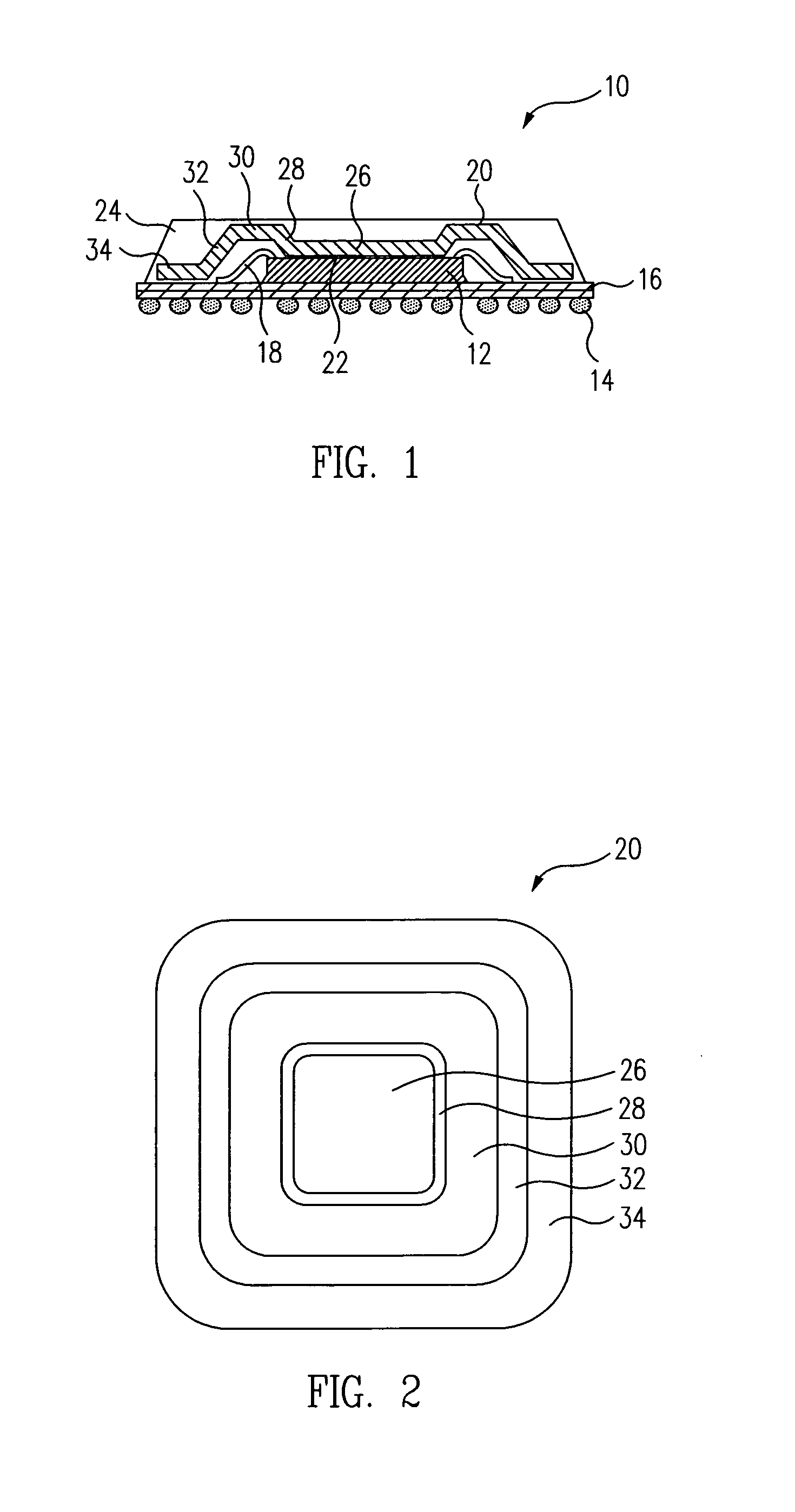

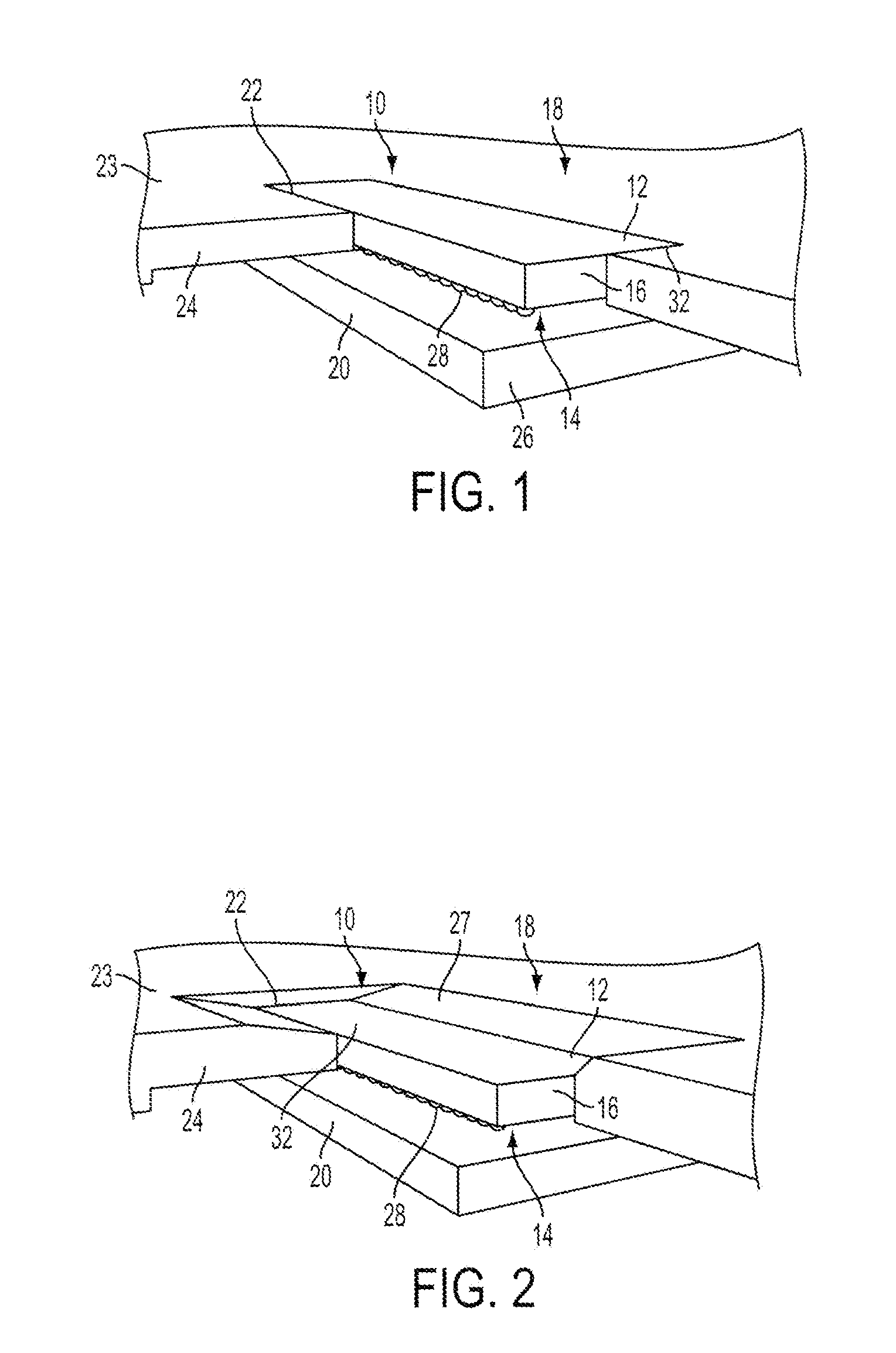

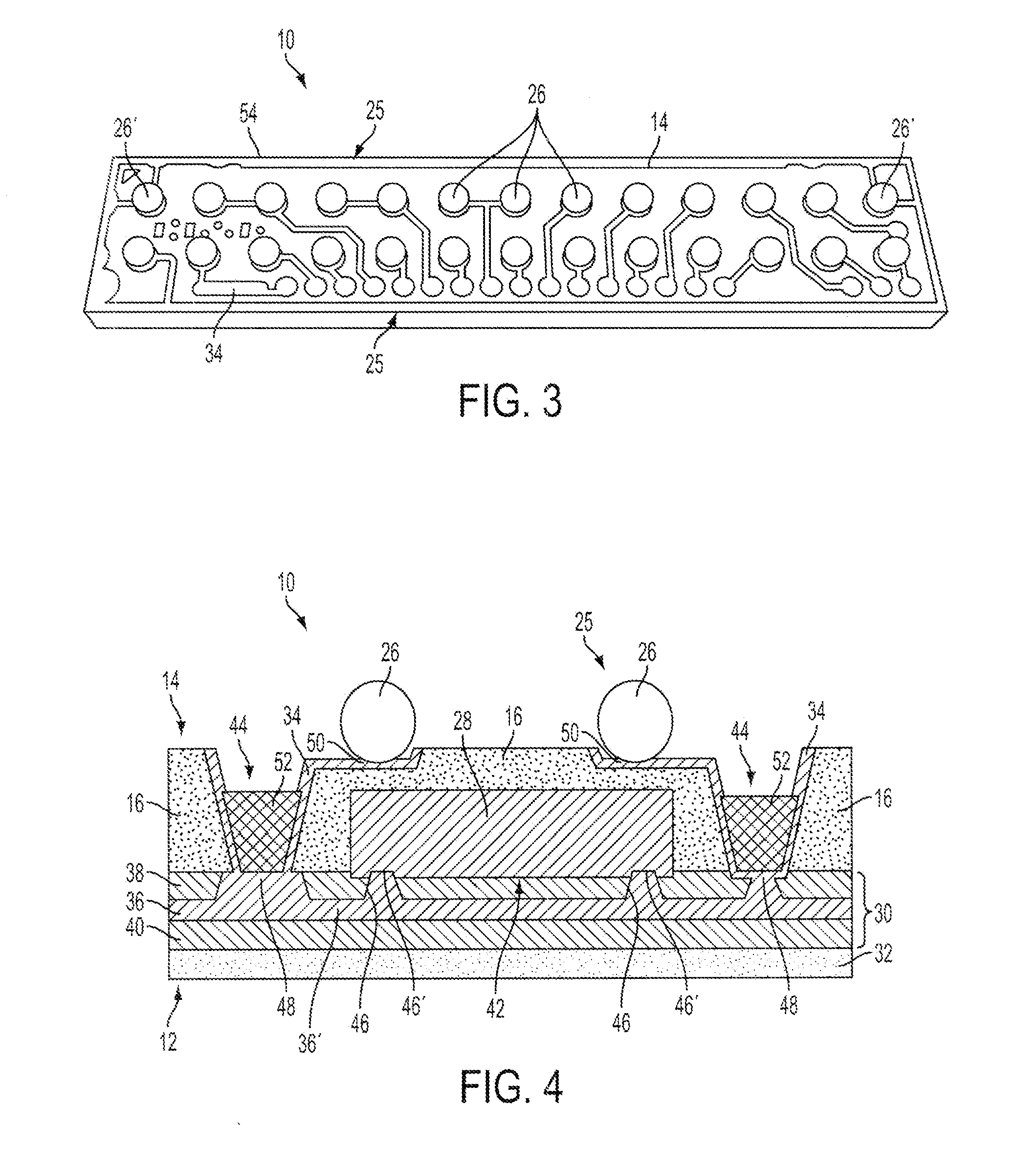

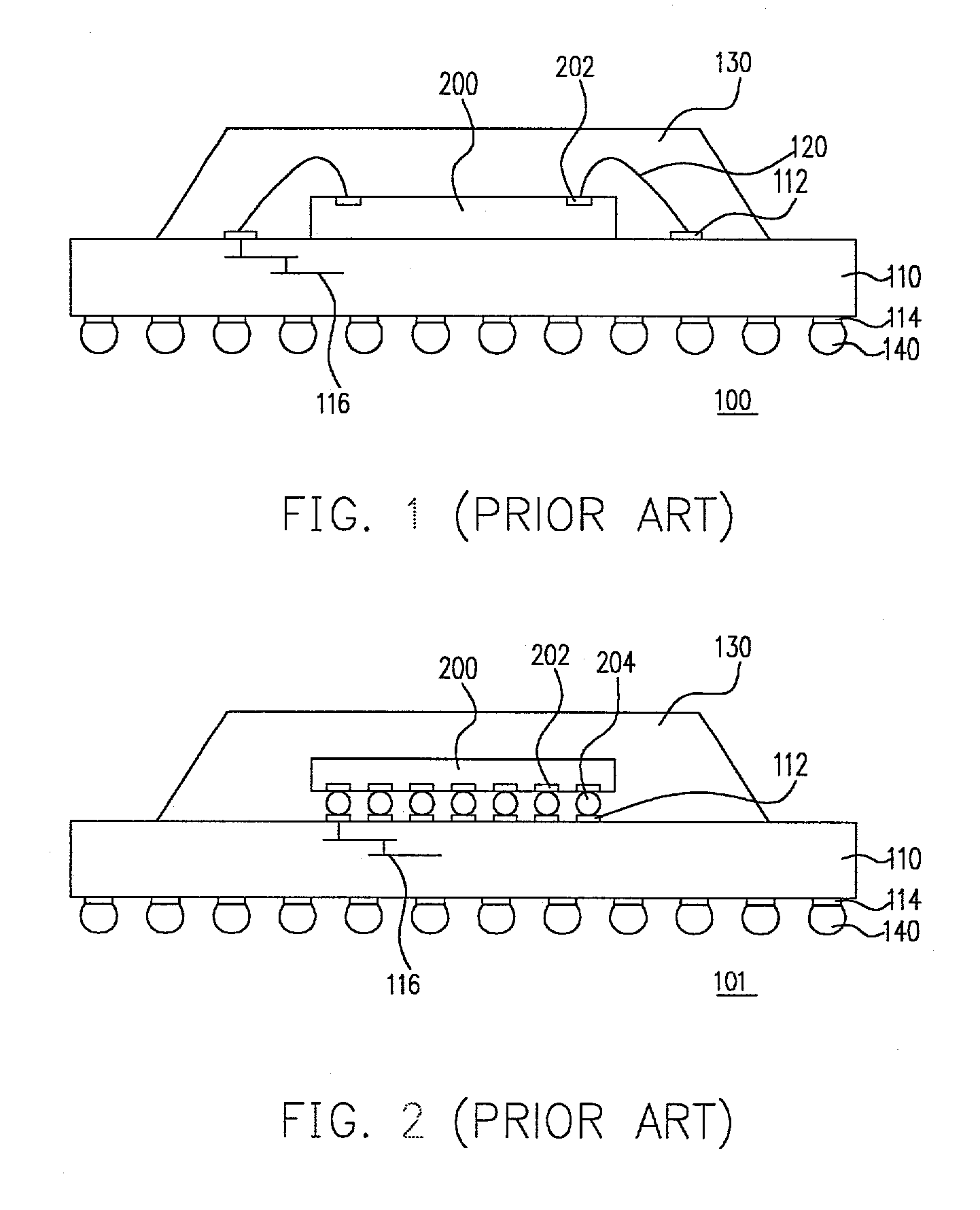

Packaging for fingerprint sensors and methods of manufacture

ActiveUS20120256280A1Semiconductor/solid-state device detailsSolid-state devicesElectricityRedistribution layer

A fingerprint sensor package, including a sensing side for sensing fingerprint information and a separate connection side for electrically connecting the fingerprint sensor package to a host device, is disclosed. The fingerprint sensor package can also include a sensor integrated circuit facing the sensing side and substantially surrounded by a fill material. The fill material includes vias at peripheral locations around the sensor integrated circuit. The fingerprint sensor package can further include a redistribution layer on the sensing side which redistributes connections of the sensor integrated circuit to the vias. The connections can further be directed through the vias to a ball grid array on the connection side. Some aspects also include electrostatic discharge traces positioned at least partially around a perimeter of the connection side. Methods of manufacturing arc also disclosed.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

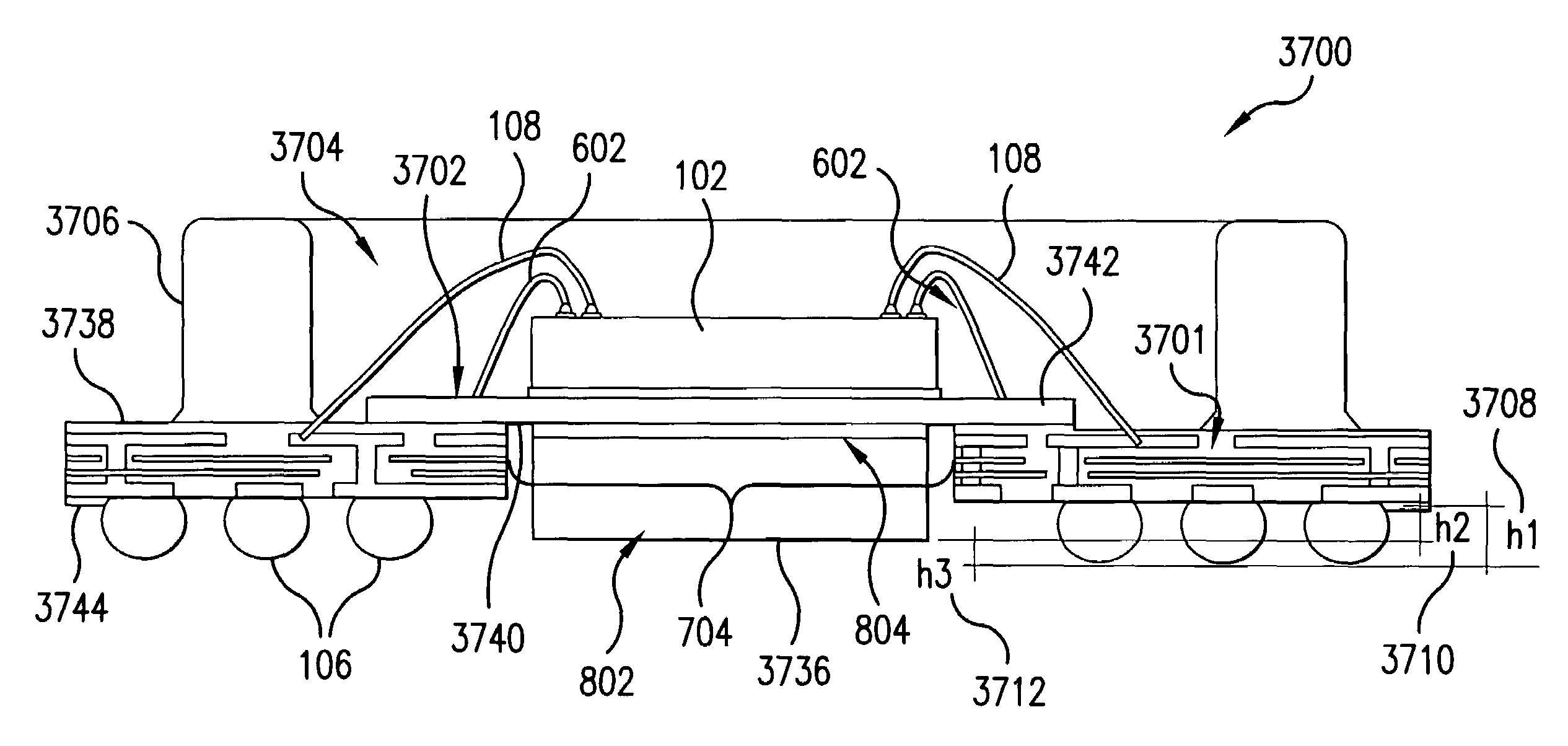

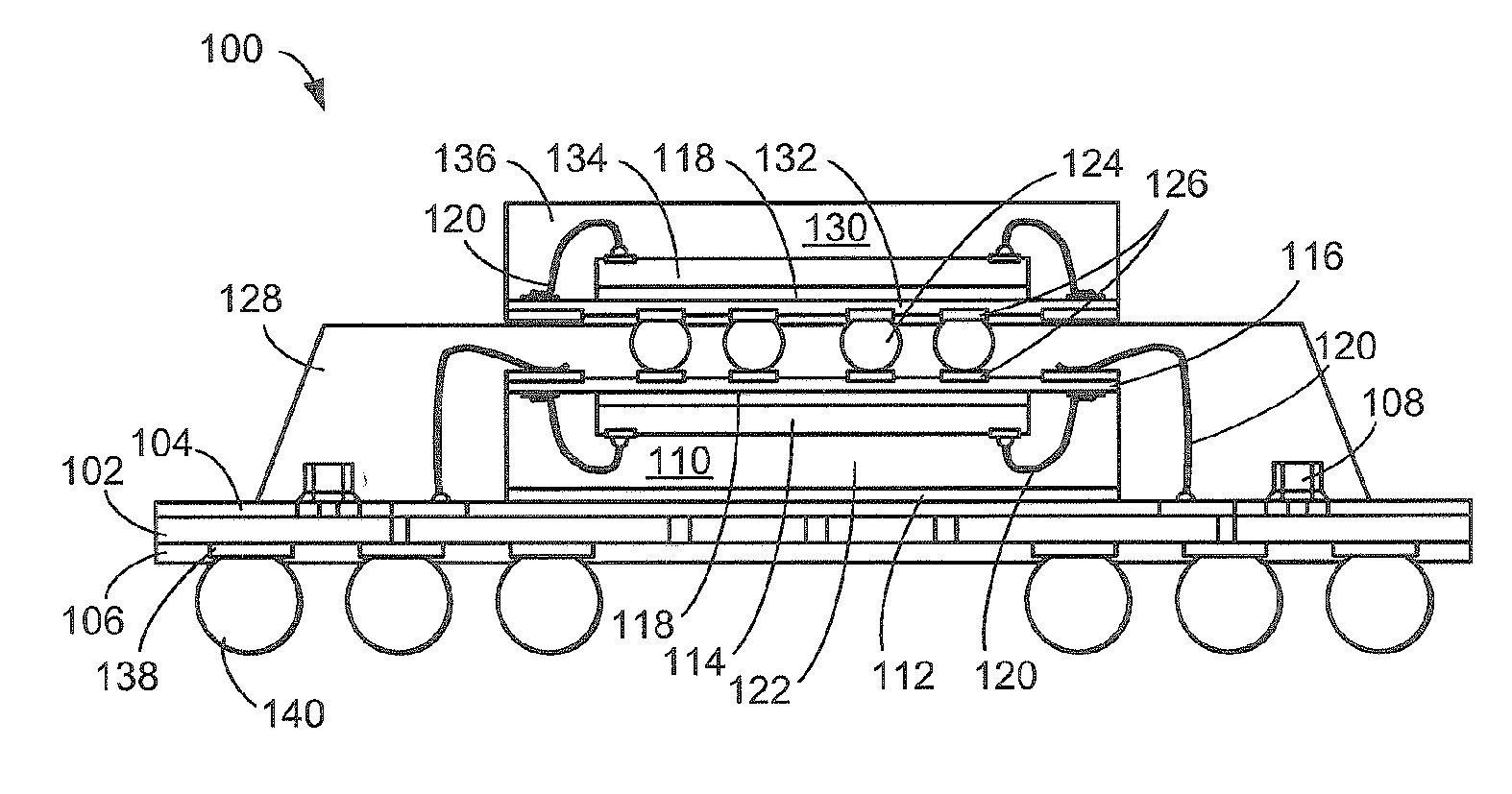

Semiconductor multi-package module having inverted second package stacked over die-up flip-chip ball grid array (BGA) package

ActiveUS7101731B2Low production costOverall design flexibilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor multi-package module has stacked lower and upper packages, each of which includes a die attached to a substrate, in which the second package is inverted, and in which the first and second substrates are interconnected by wire bonding, and in which the first package includes a flip-chip ball grid array package having a flip-chip in a die-down configuration. Also, a method for making a semiconductor multi-package module, by providing a lower molded package including a lower substrate and a flip-chip in a die-down configuration, affixing an upper molded package including an upper substrate in inverted orientation onto the upper surface of the lower package, and forming z-interconnects between the upper and lower substrates.

Owner:STATS CHIPPAC LTD

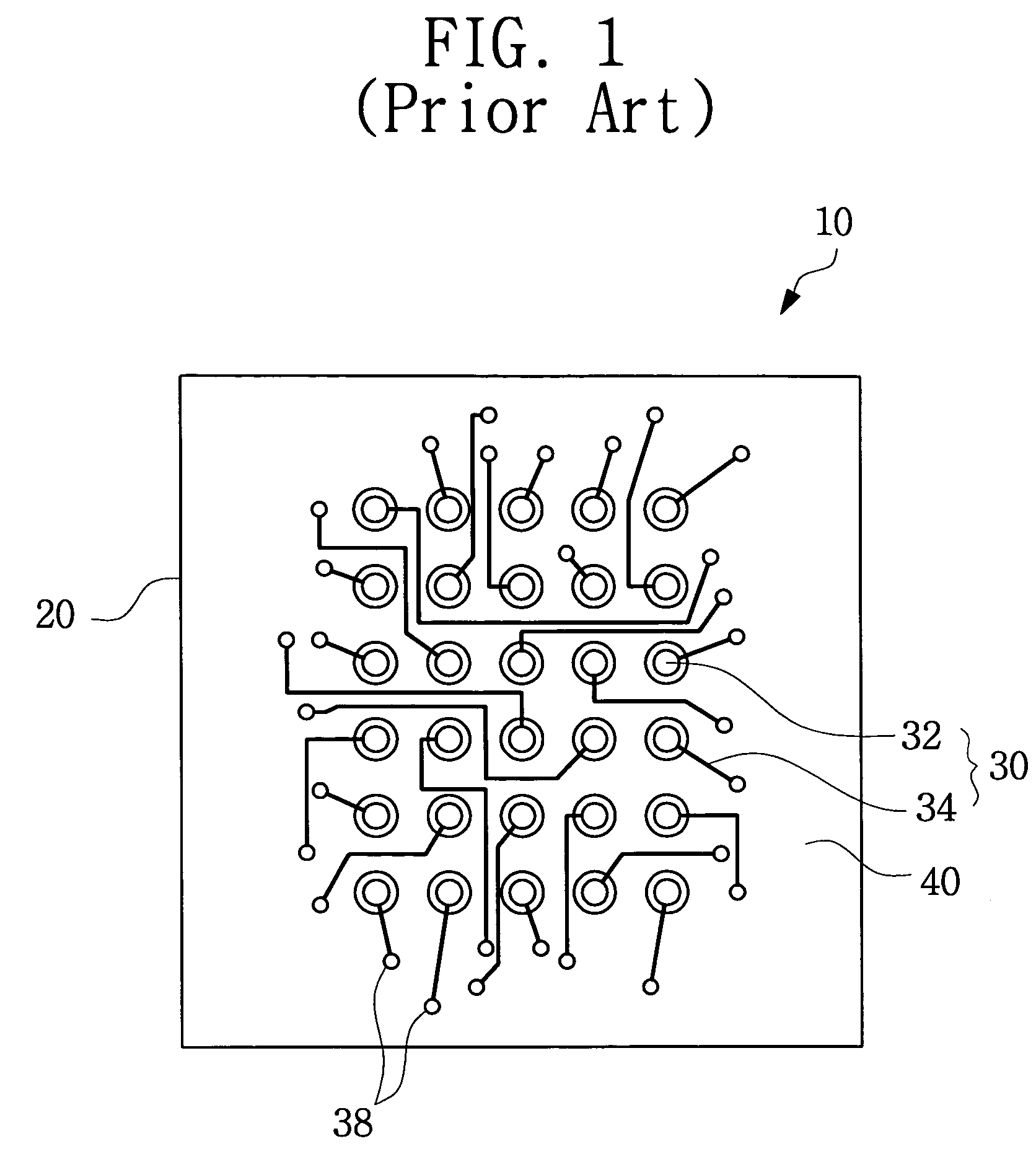

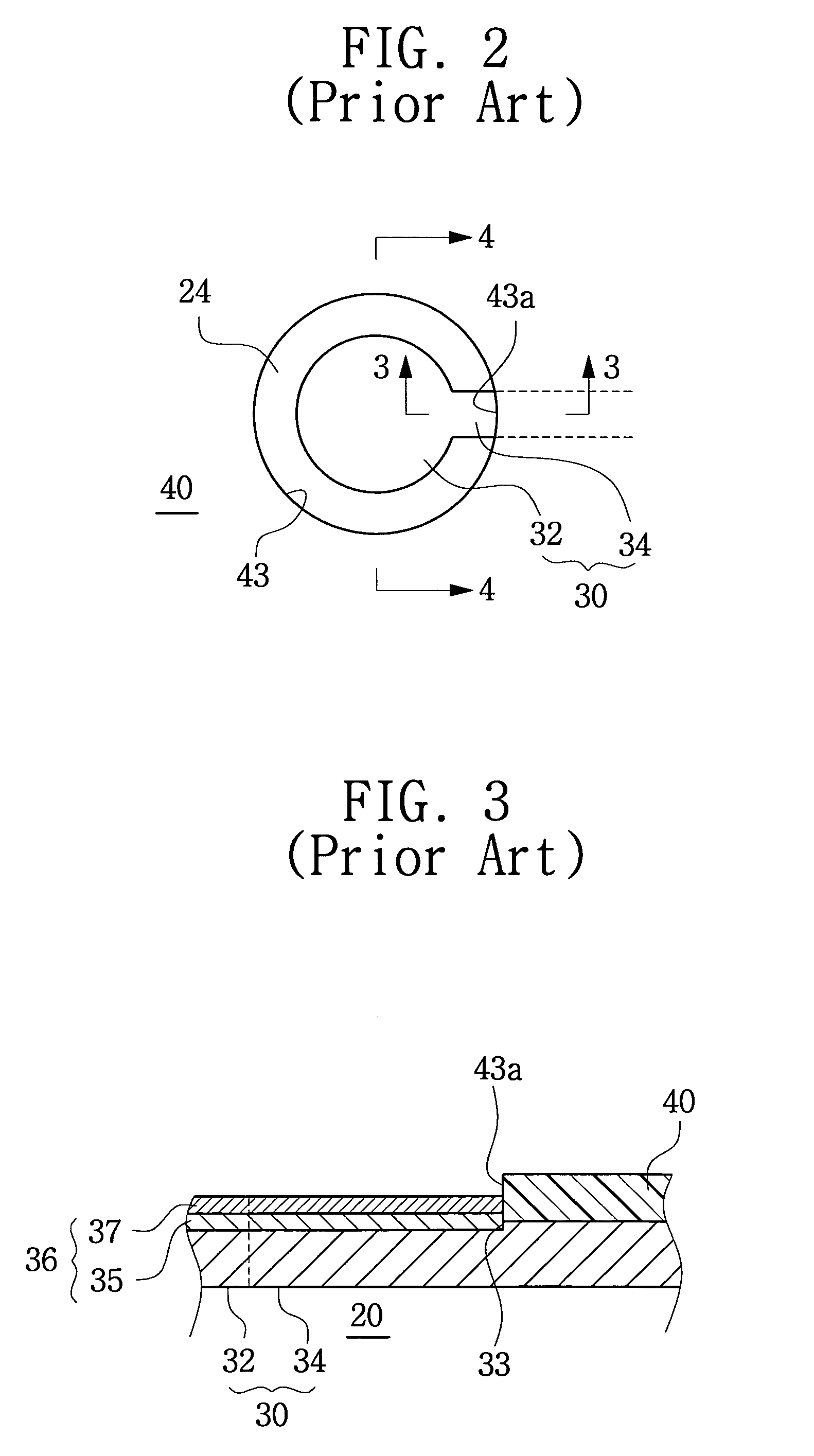

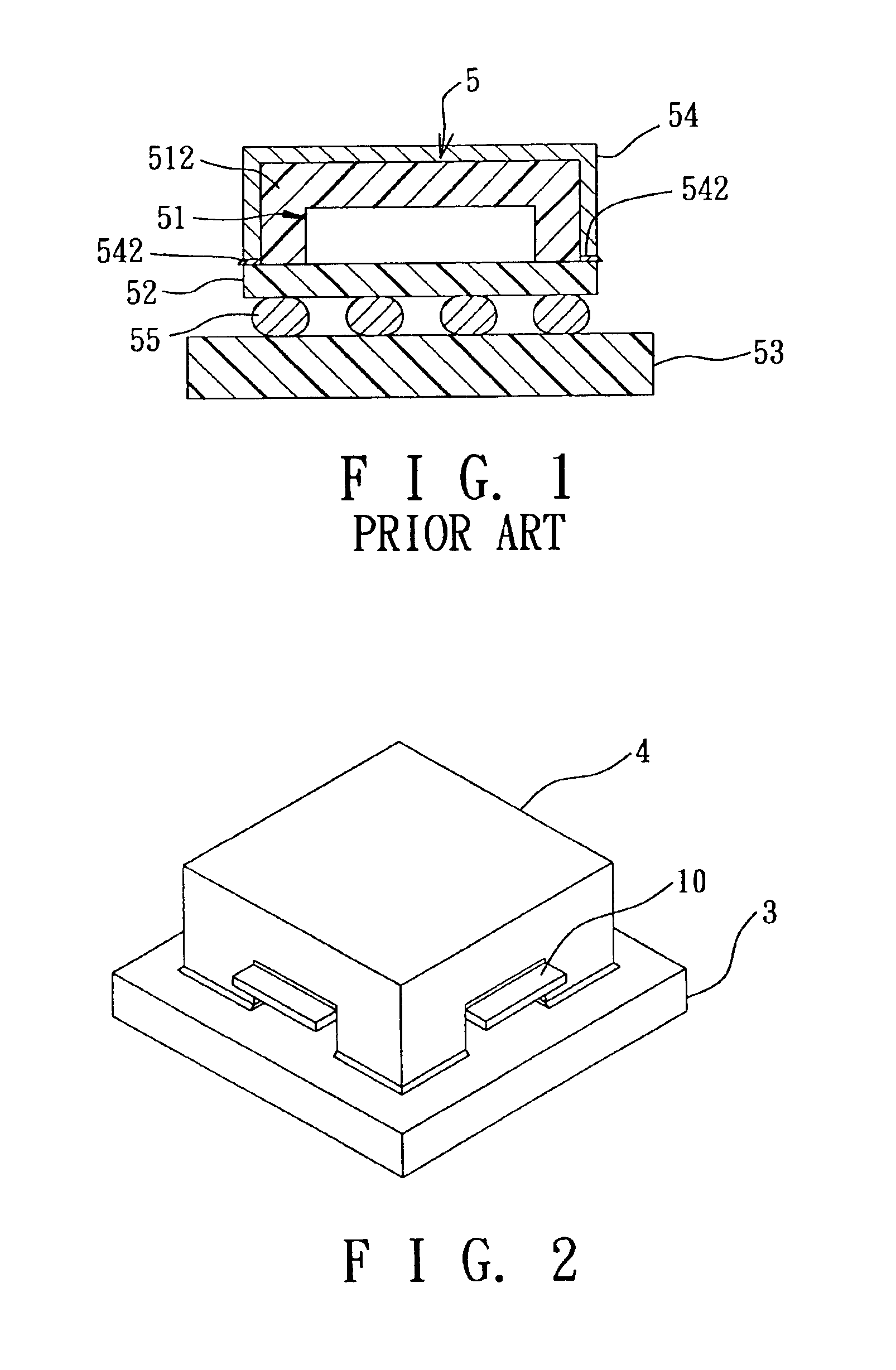

Anchored non-solder mask defined ball pad

InactiveUS20060131758A1Semiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorSolder mask

A ball grid pad for connecting a ball grid array package to a printed circuit board includes a circular pad area adhered on a ball grid connection surface. A solder mask on the ball grid connection surface has an opening surrounding and spaced apart from the circular pad area. The ball pad includes an anchor trace on the ball grid connection surface wherein the ball pad conductor material extends radially from the edge of the circular pad area to a terminating point beyond the opening of the solder mask so that a portion of the anchor trace is covered by the solder mask. The ball grid connection surface may be an integrated circuit package substrate or a printed circuit board surface.

Owner:STMICROELECTRONICS SRL

Ball grid array package with an electromagnetic shield connected directly to a printed circuit board

InactiveUS6947295B2Printed circuit assemblingMagnetic/electric field screeningEngineeringElectromagnetic shielding

A ball grid array package includes a chip having a substrate with a bottom surface, a plurality of solder bumps projecting outwardly from the bottom surface of the substrate, and an electromagnetic shield including a housing that defines an inner space which receives the chip and the solder bumps therein, and a bottom opening for access into the inner space. The solder bumps project outwardly of the inner space through the bottom opening in the housing.

Owner:BENQ CORP

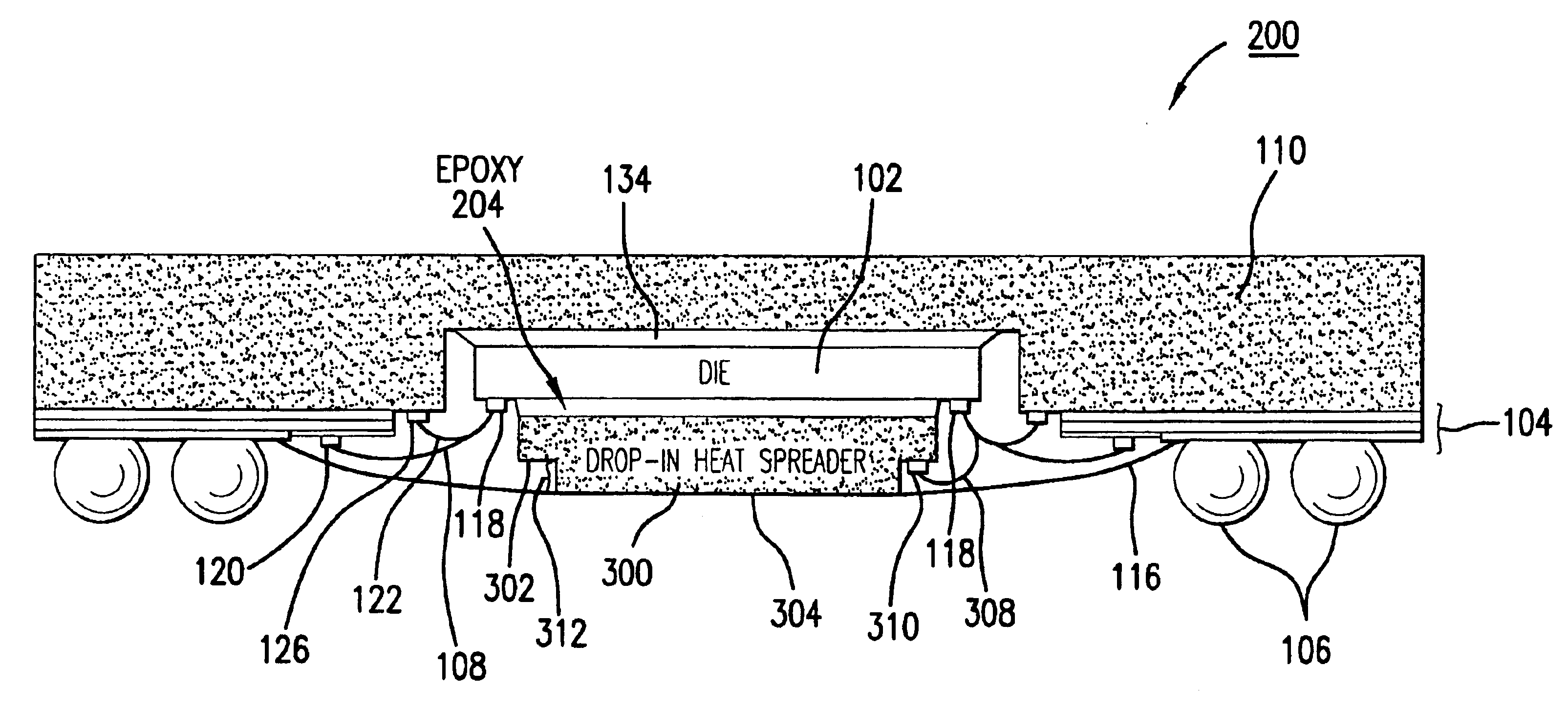

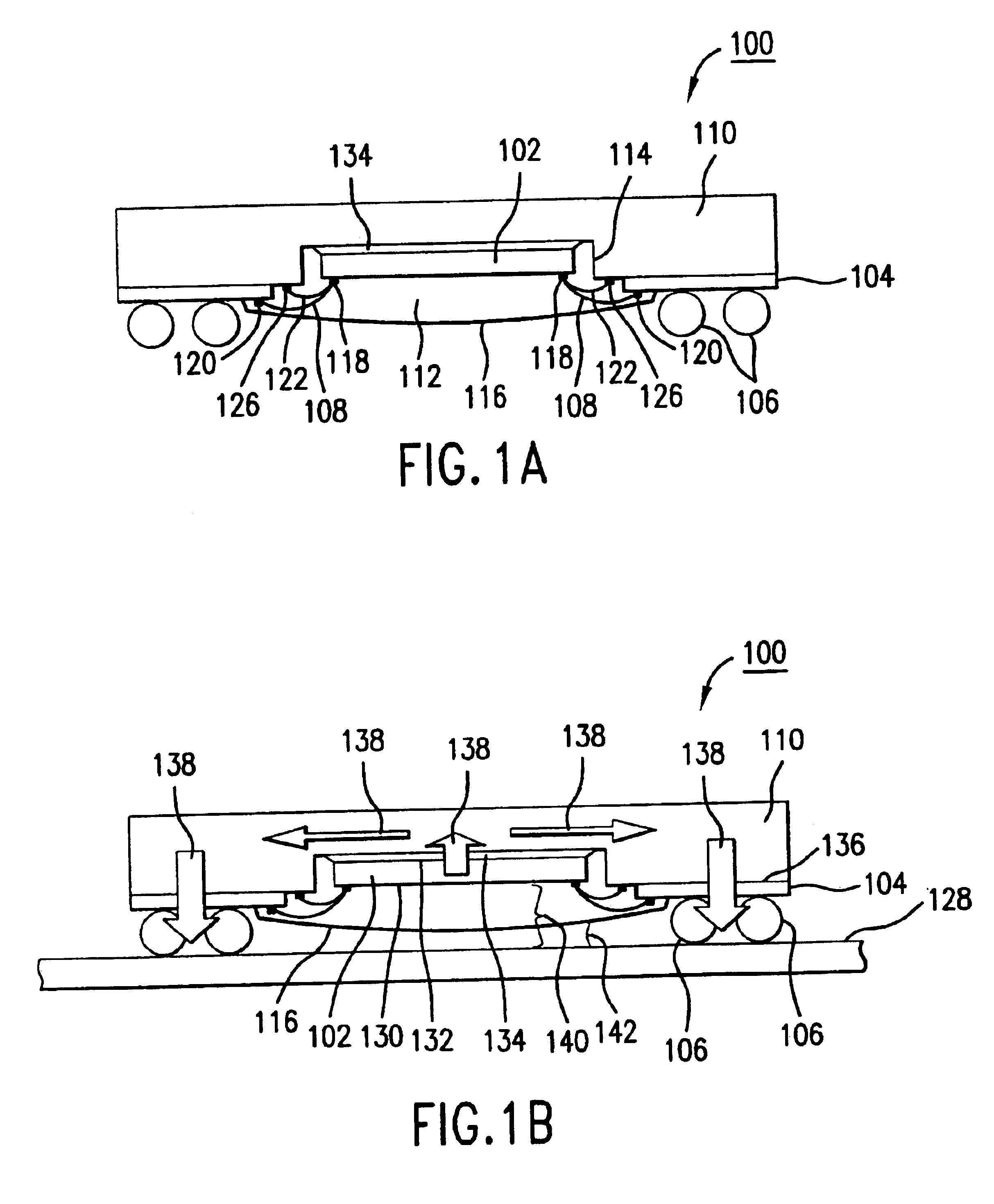

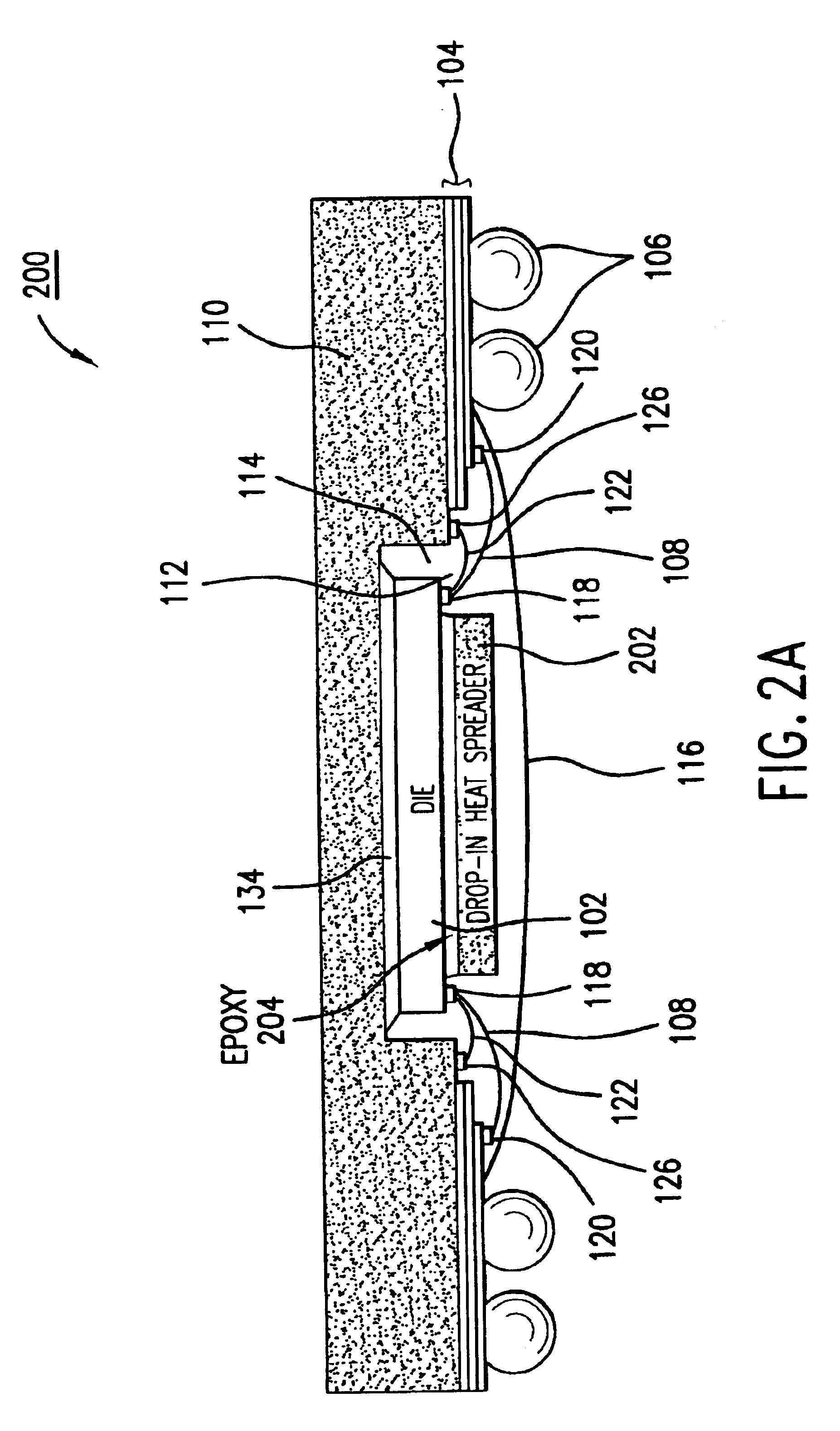

Die-down ball grid array package with die-attached heat spreader and method for making the same

InactiveUS6853070B2Semiconductor/solid-state device detailsSolid-state devicesSurface mountingEngineering

An apparatus, system, and method for assembling a ball grid array (BGA) package is described. A stiffener / heat spreader is provided. A substrate has a first surface and a second surface. The substrate has a central window-shaped aperture that extends through the substrate from the first substrate surface to the second substrate surface. The first substrate surface is attached to a surface of the stiffener / heat spreader. A portion of the stiffener / heat spreader is accessible through the central window-shaped aperture. An IC die has a first surface and a second surface. The first IC die surface is mounted to the accessible portion of the stiffener / heat spreader. A drop-in heat spreader has a surface that is mounted to the second IC die surface.

Owner:AVAGO TECH INT SALES PTE LTD

Integrated passive devices fabricated utilizing multi-layer, organic laminates

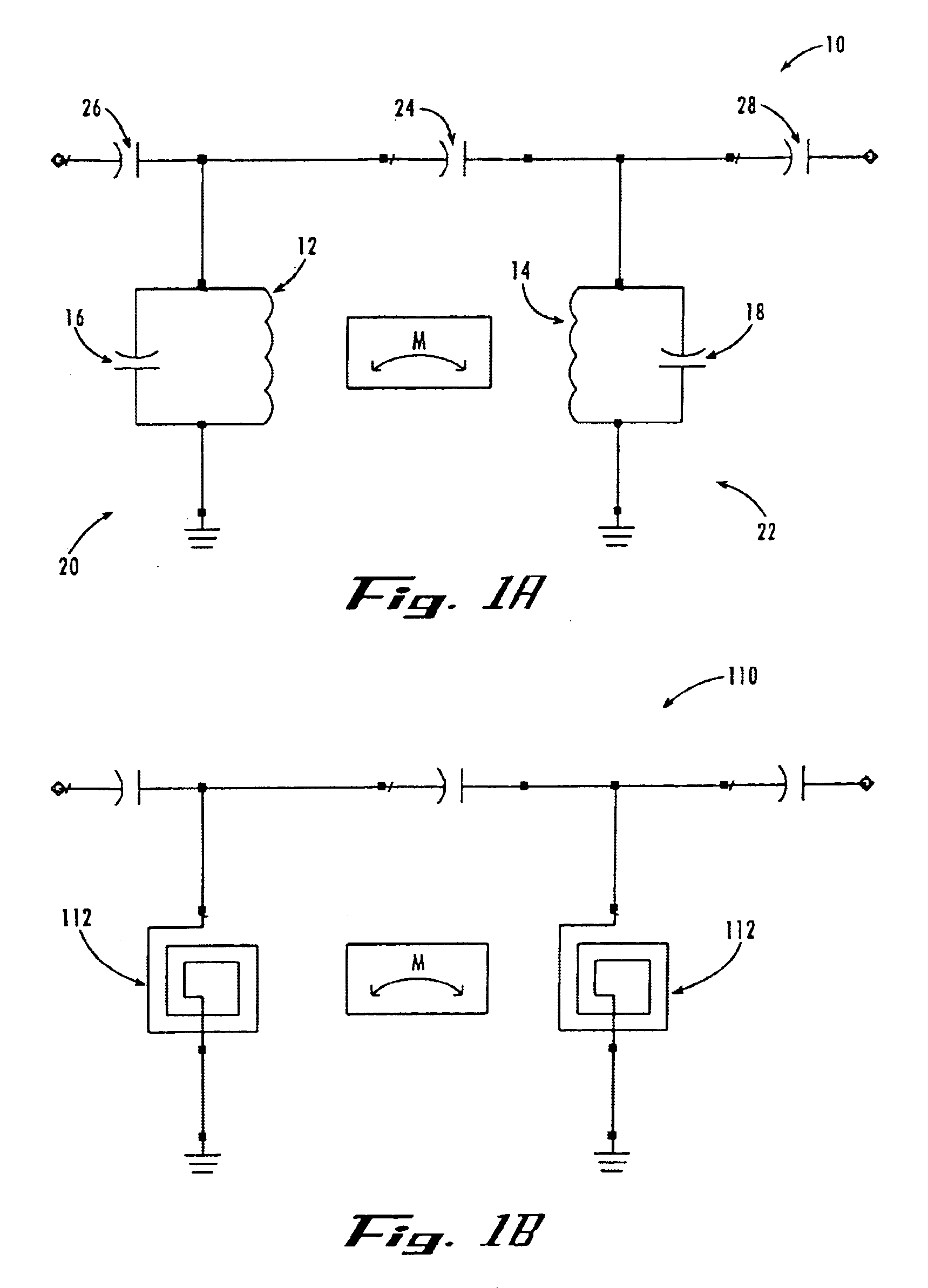

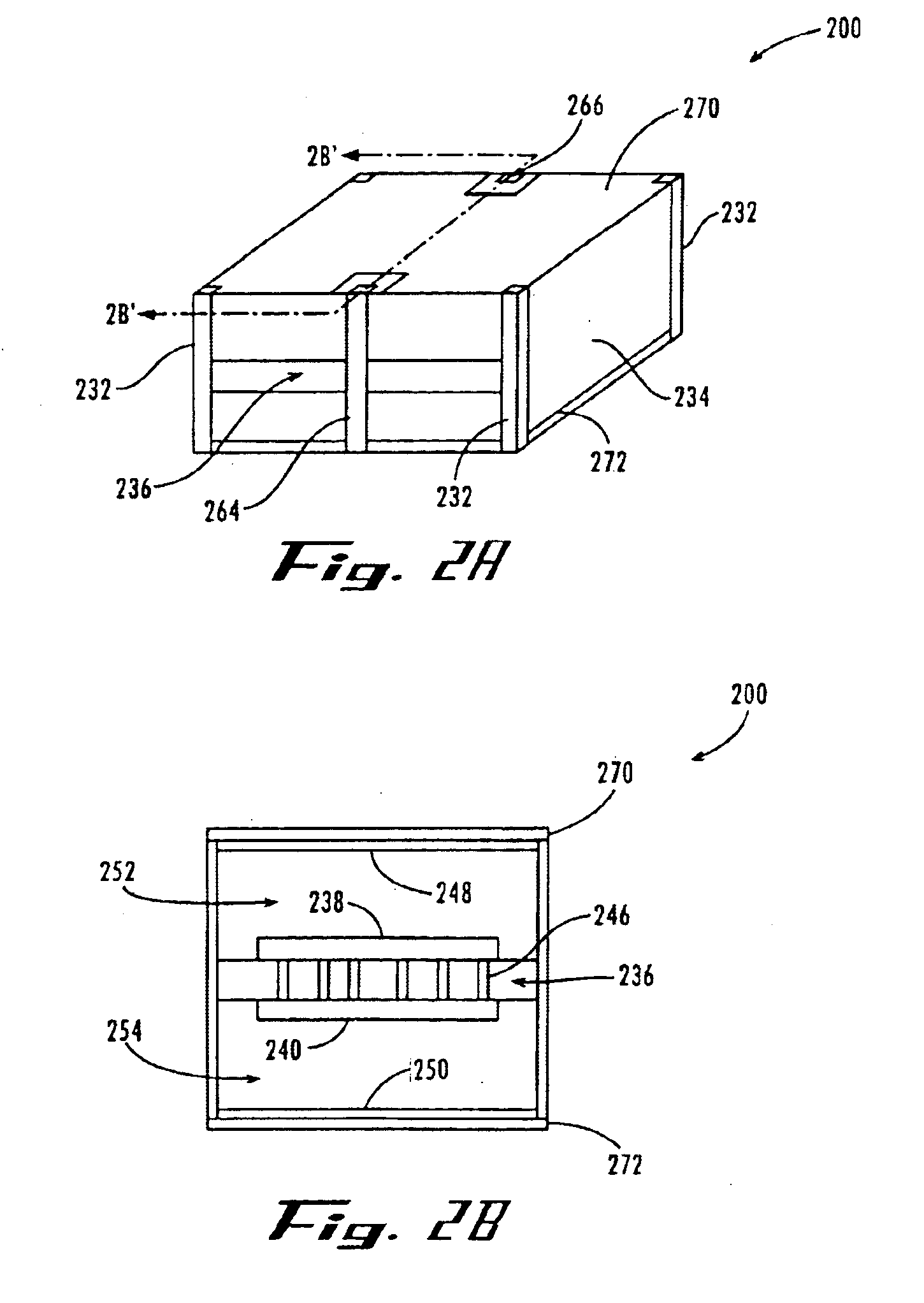

InactiveUS6900708B2Easy to integrateLow costMultiple-port networksSolid-state devicesSurface mountingBall grid array

The present invention includes an organic device that can be integrated in a multilayer board made of organic material. The passive devices can be integrally fabricated on a circuit board in either surface mount device (SMD) or ball grid array (BGA) form. Alternatively, the passive device can be constructed in a stand alone SMD or BGA / chip scale package (CSP) form to make it mountable on a multilayer board, ceramic carrier or silicon platform in the form of an integrated passive device. The passive device includes side shielding on two sides in the SMD form and four sides in the BGA / CSP form. The side shielding can be external or in-built.

Owner:GEORGIA TECH RES CORP

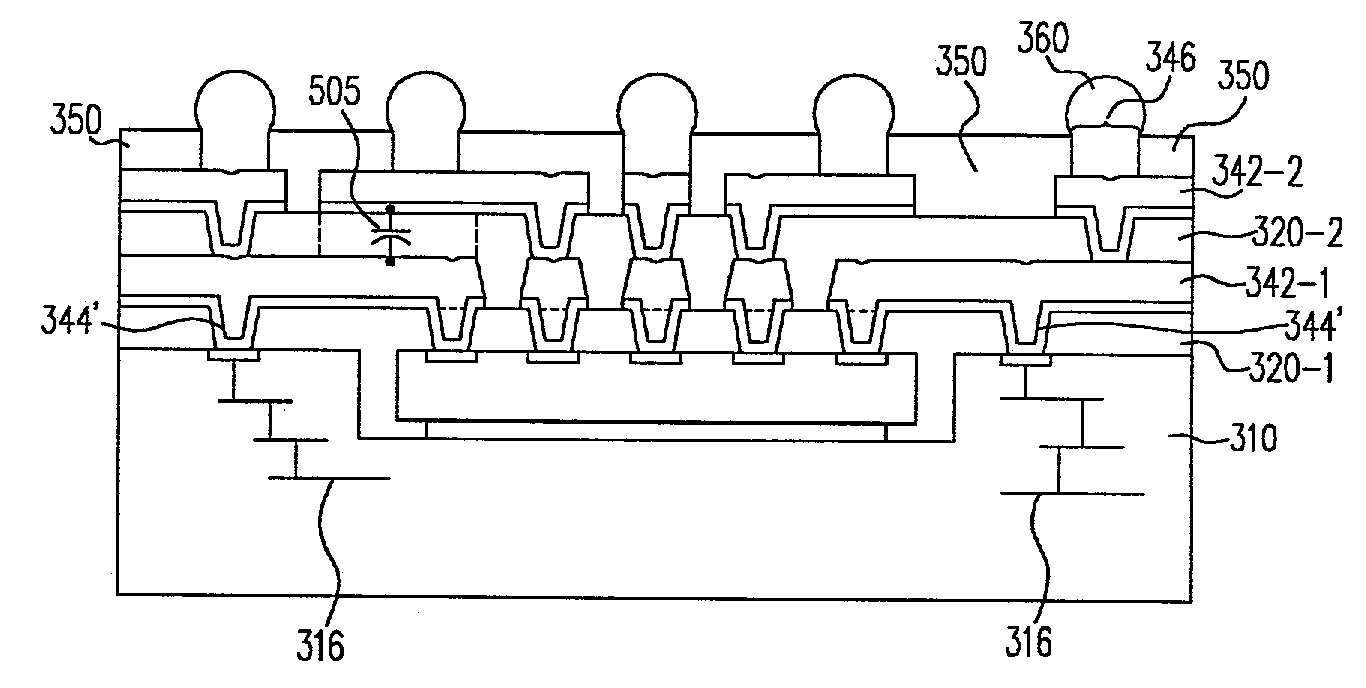

Integrated circuit package and method of manufacture

InactiveUS7087991B2Eliminates connective requirementImprove cooling effectPrinted circuit assemblingSemiconductor/solid-state device detailsInsulation layerSolder ball

An integrated circuit package and a method of manufacturing the package. A silicon chip is attached to the surface of a substrate or attached to the bottom surface of a cavity in the substrate so that the active surface of the chip is exposed. One or more build-up circuit structures are formed over the substrate. Each build-up circuit structure has at least one insulation layer, at least one patterned circuit layer and a plurality of via openings with conductive material therein so that bonding pads on the active surface of the chip connect electrically with the patterned circuit layer through the vias. To form a ball grid array package, solder balls may also be attached to the solder ball pads on the patterned circuit layer so that the bonding pads on the chip are electrically connected to an external circuit through the build-up circuit structure and the solder balls.

Owner:VIA TECH INC