Patents

Literature

86 results about "Pin grid array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

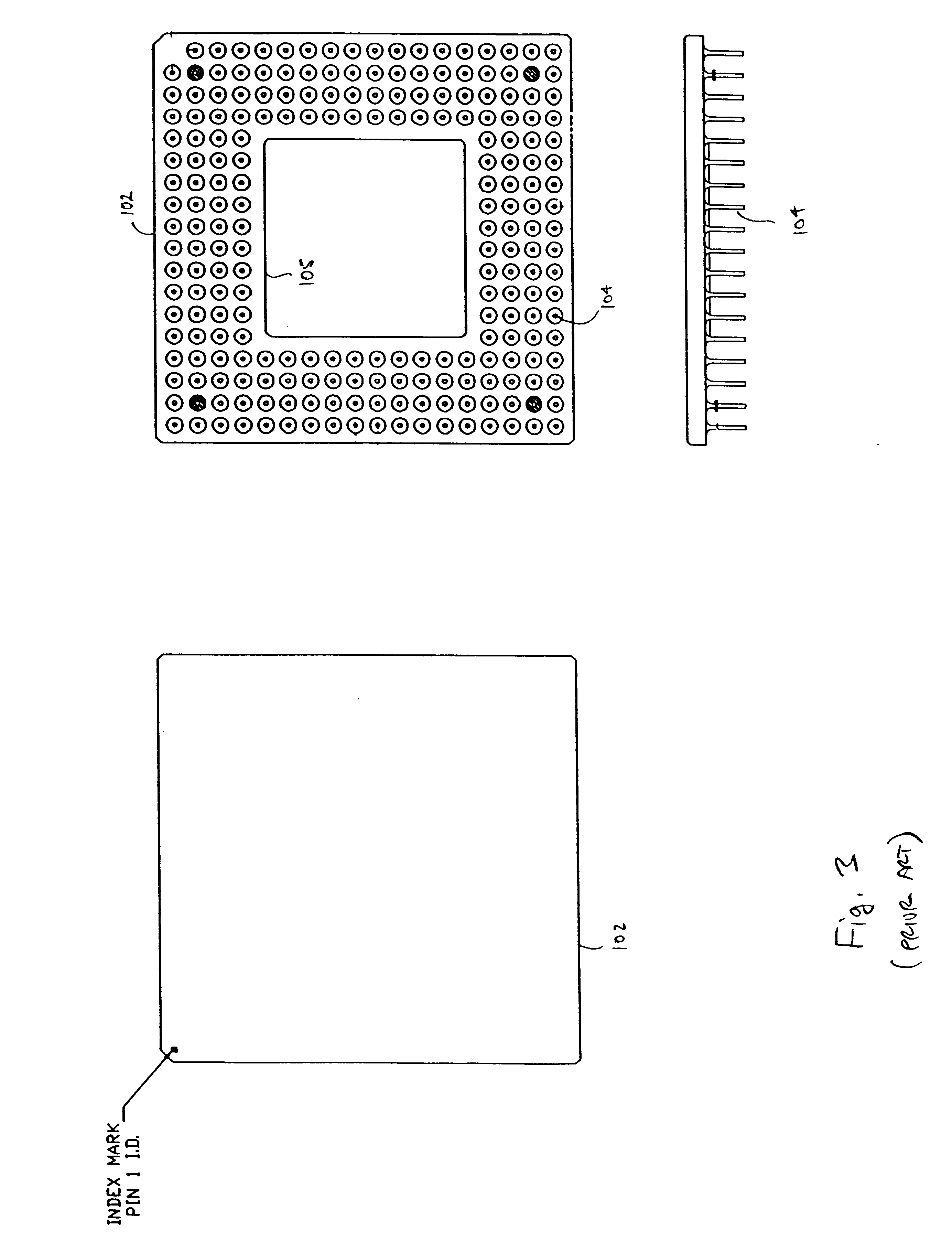

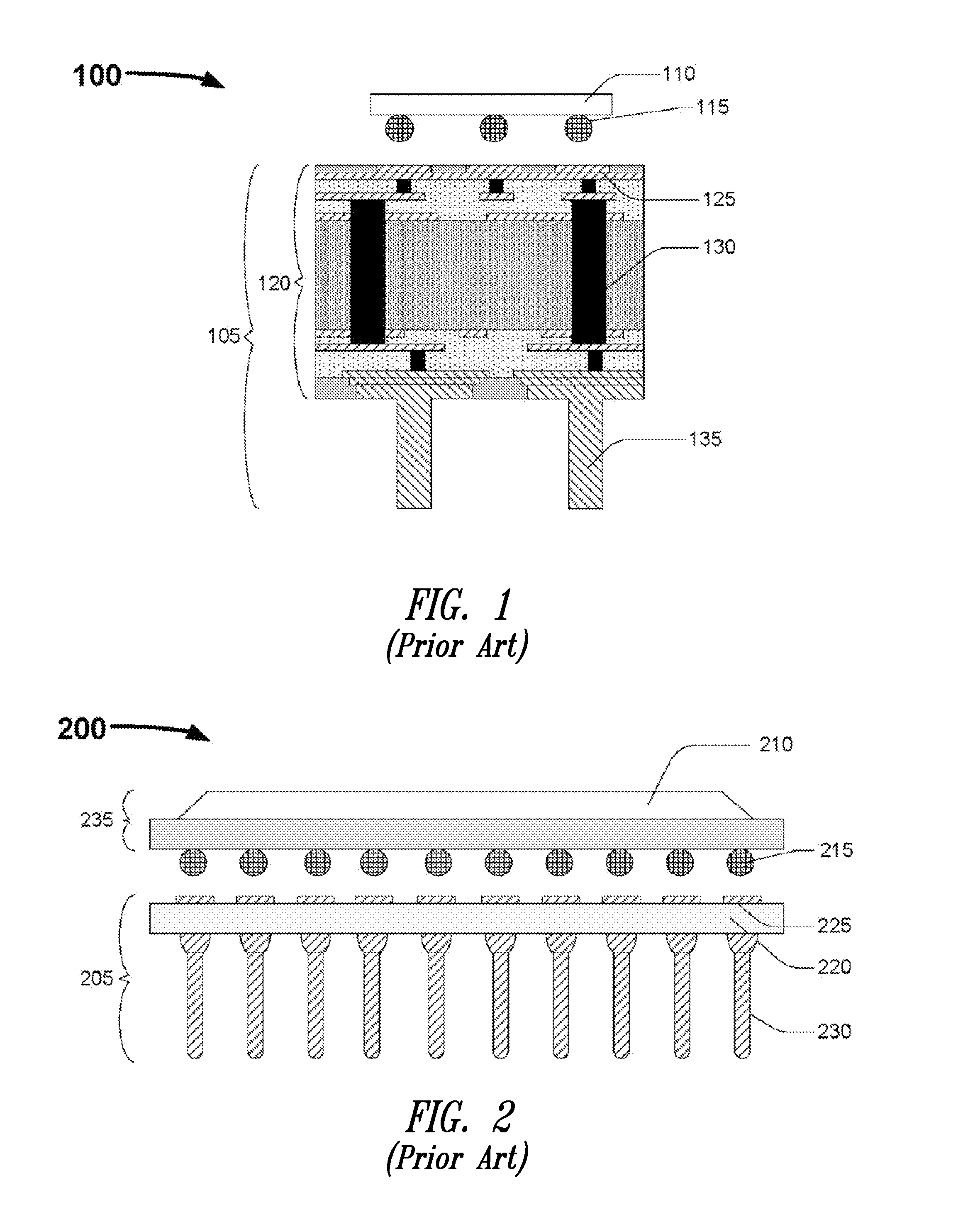

A pin grid array (PGA) is a type of integrated circuit packaging. In a PGA, the package is square or rectangular, and the pins are arranged in a regular array on the underside of the package. The pins are commonly spaced 2.54 mm (0.1") apart, and may or may not cover the entire underside of the package.

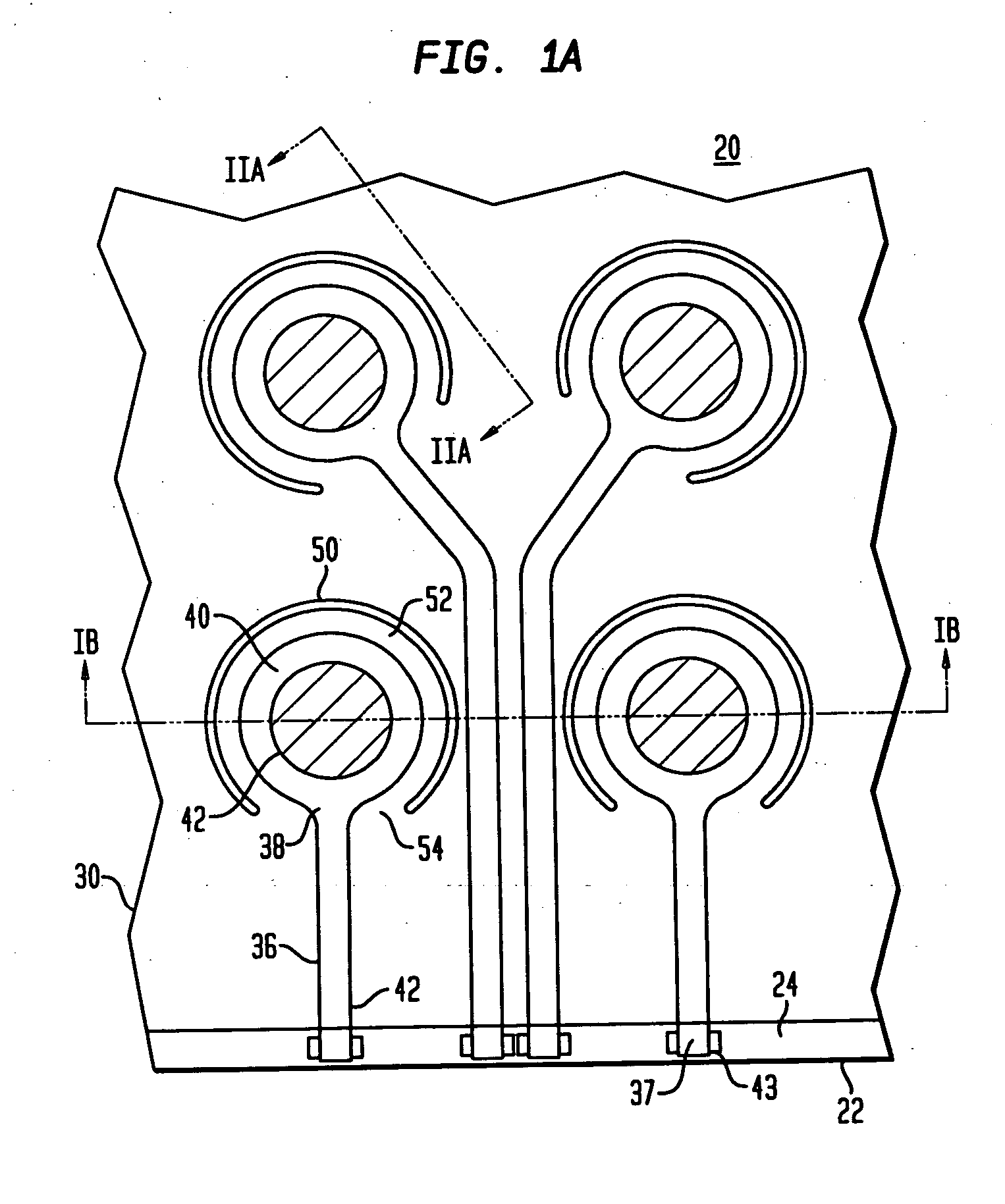

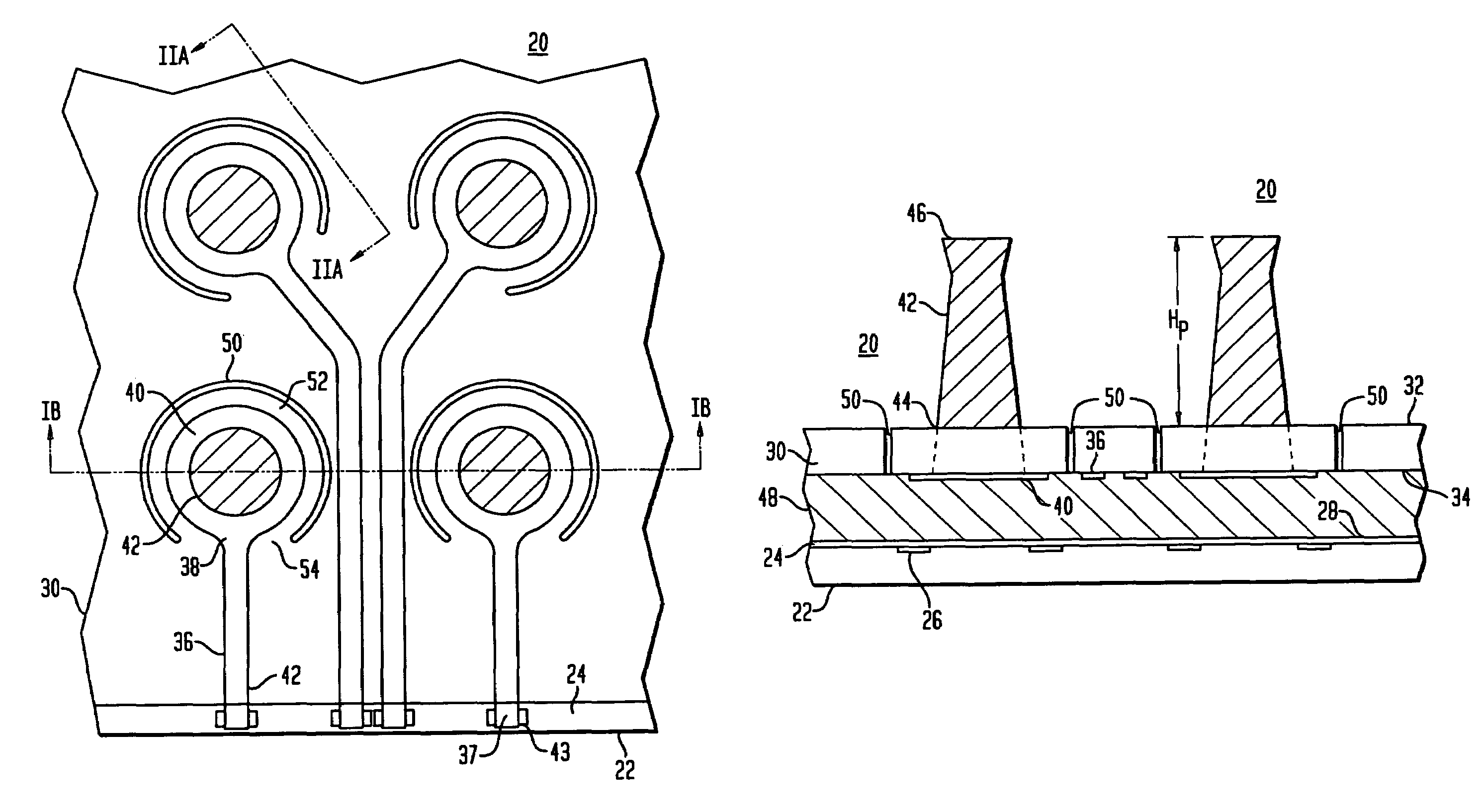

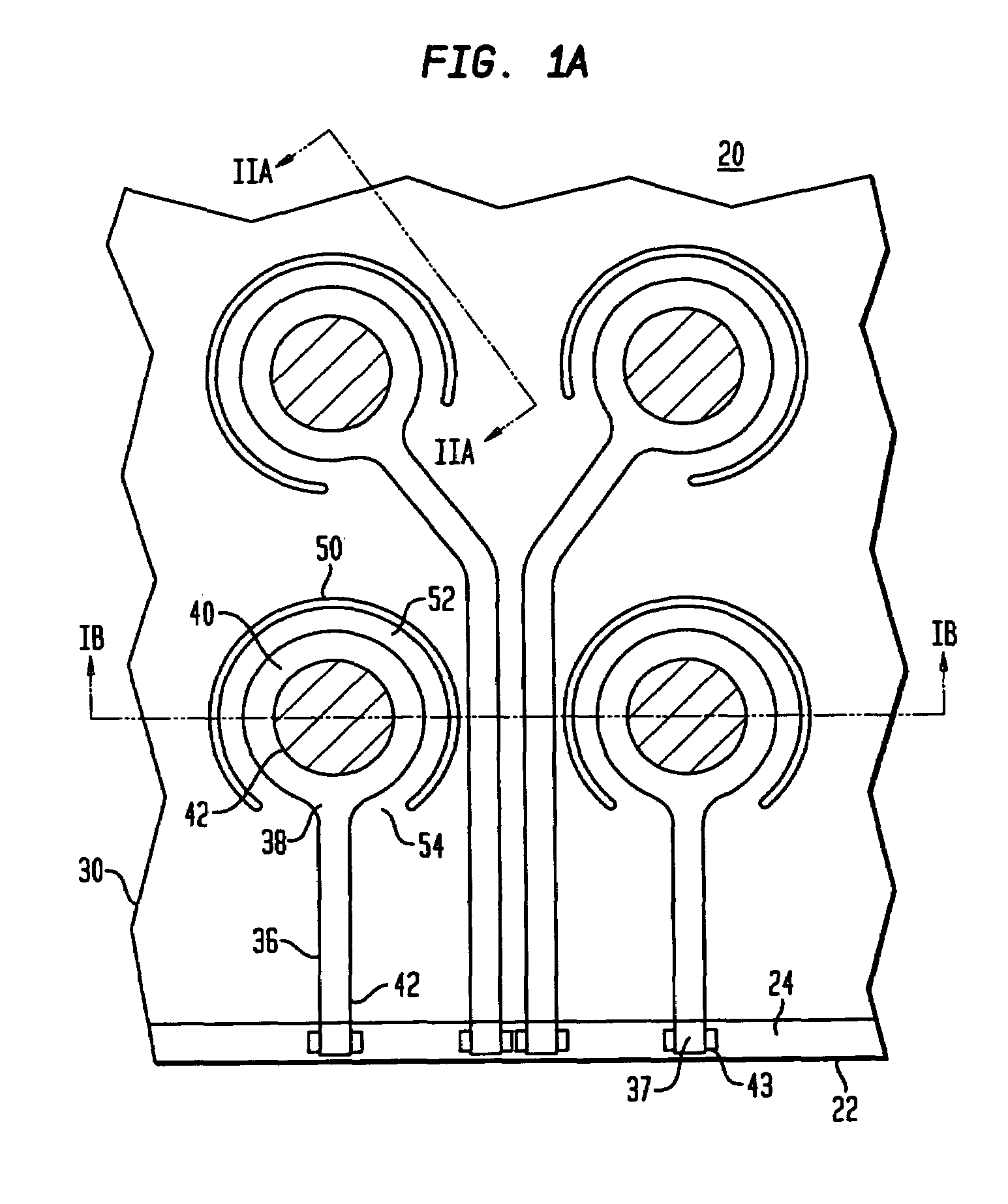

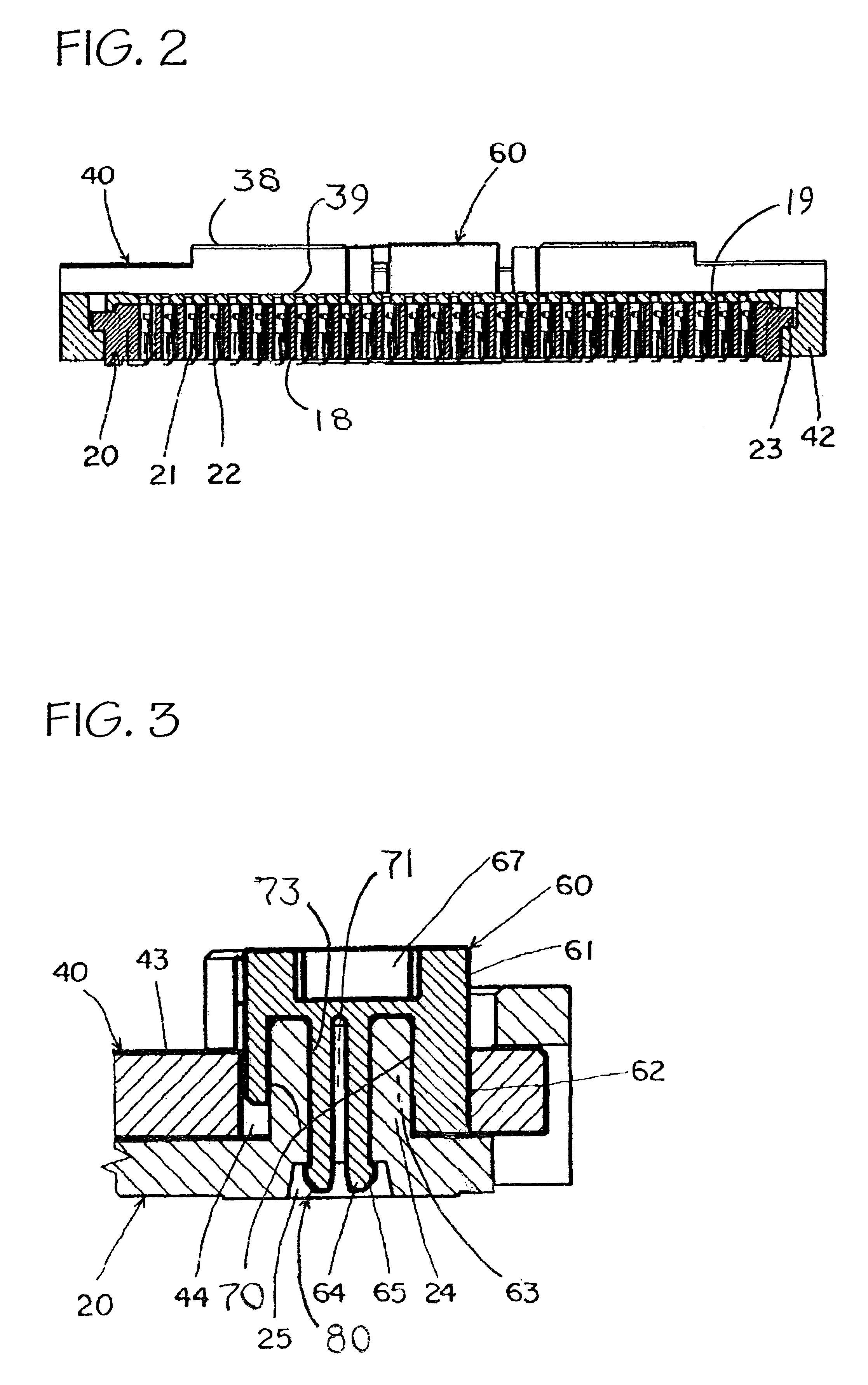

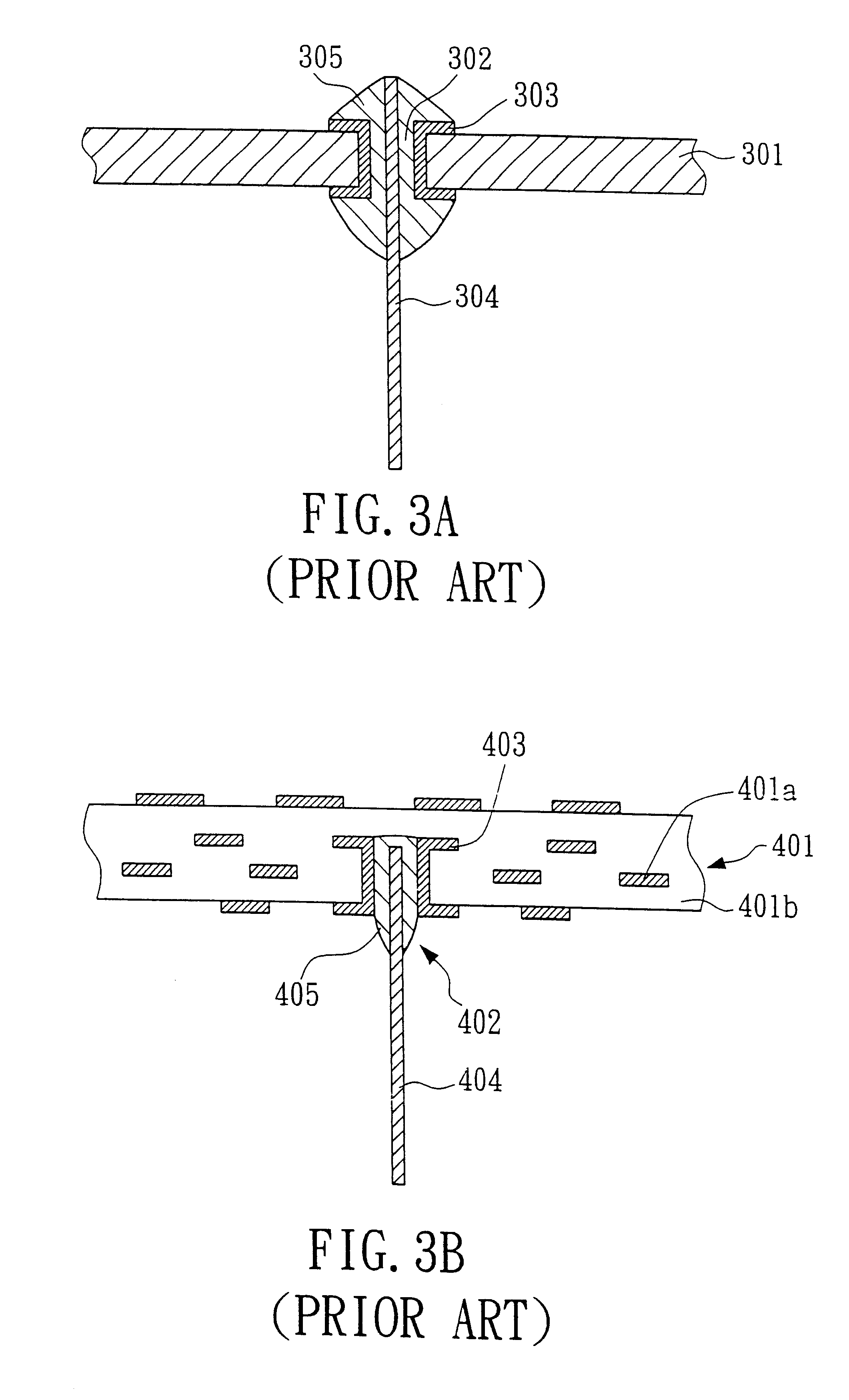

Micro pin grid array with wiping action

ActiveUS20050181655A1Promote formationIncrease in sizeEngagement/disengagement of coupling partsSemiconductor/solid-state device detailsContact padPin grid array

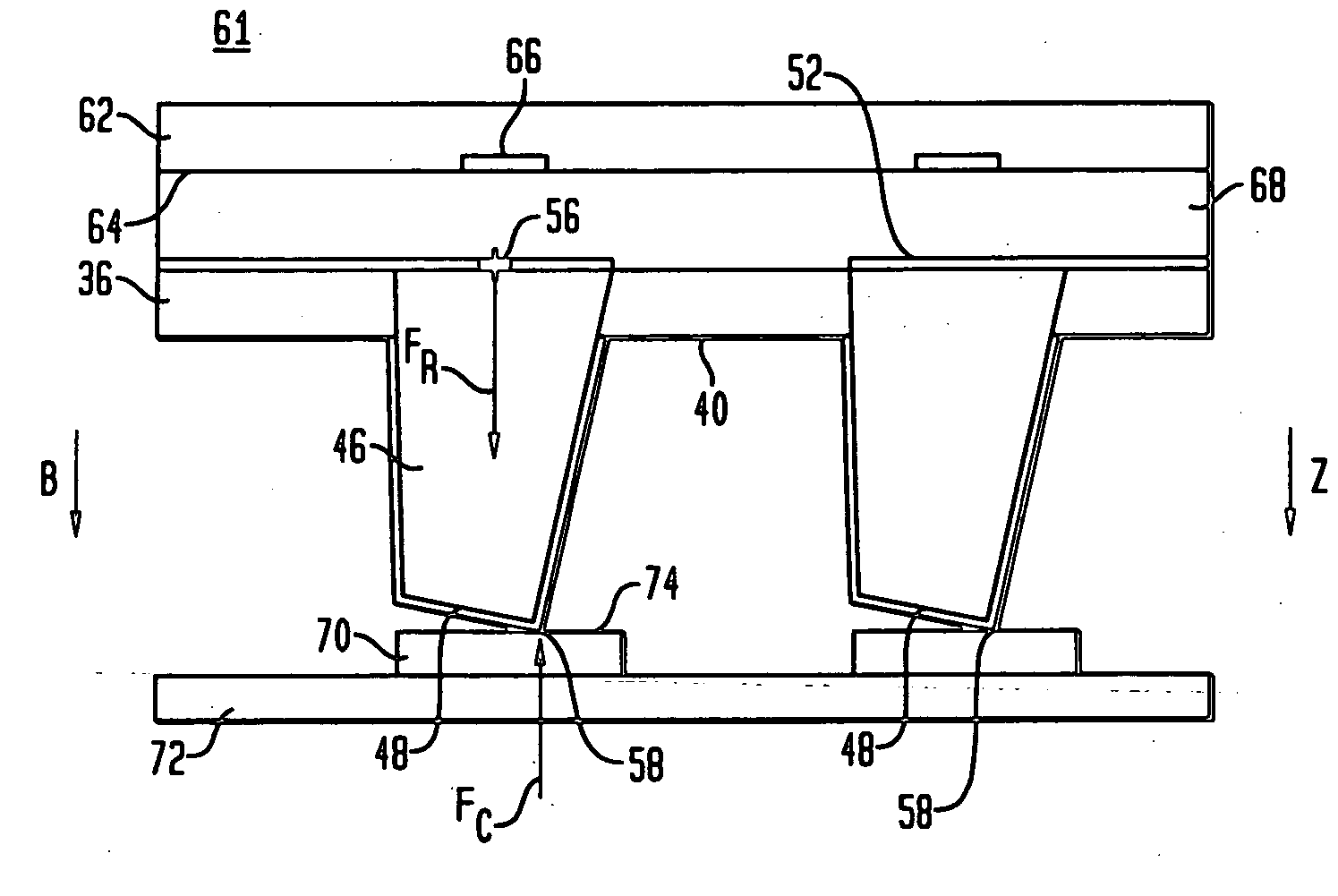

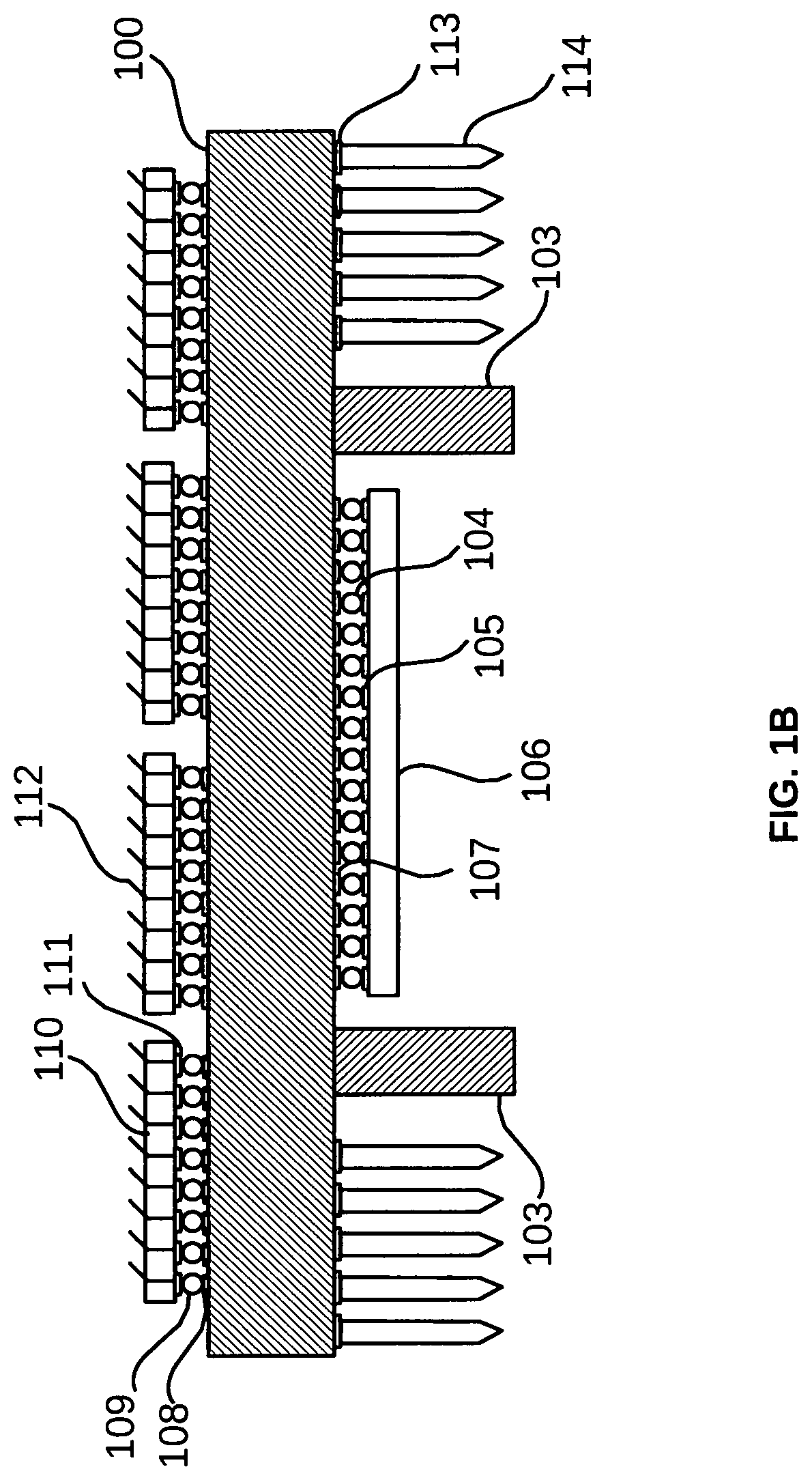

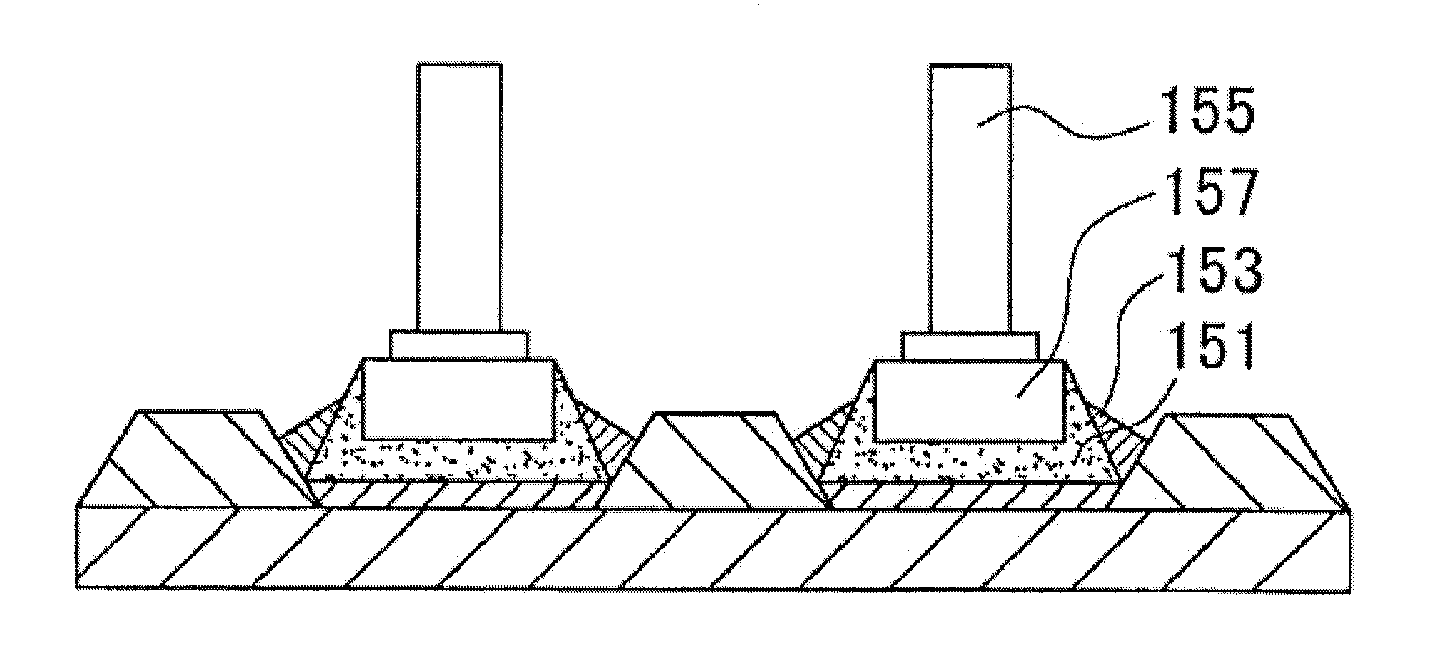

A microelectronic package includes a mounting structure, a microelectronic element associated with the mounting structure, and a plurality of conductive posts physically connected to the mounting structure and electrically connected to the microelectronic element. The conductive posts project from the mounting structure in an upward direction, at least one of the conductive posts being an offset post. Each offset post has a base connected to the mounting structure, the base of each offset post defining a centroid. Each offset post also defines an upper extremity having a centroid, the centroid of the upper extremity being offset from the centroid of the base in a horizontal offset direction transverse to the upward direction. The mounting structure is adapted to permit tilting of each offset post about a horizontal axis so that the upper extremities may wipe across a contact pad of an opposing circuit board.

Owner:TESSERA INC

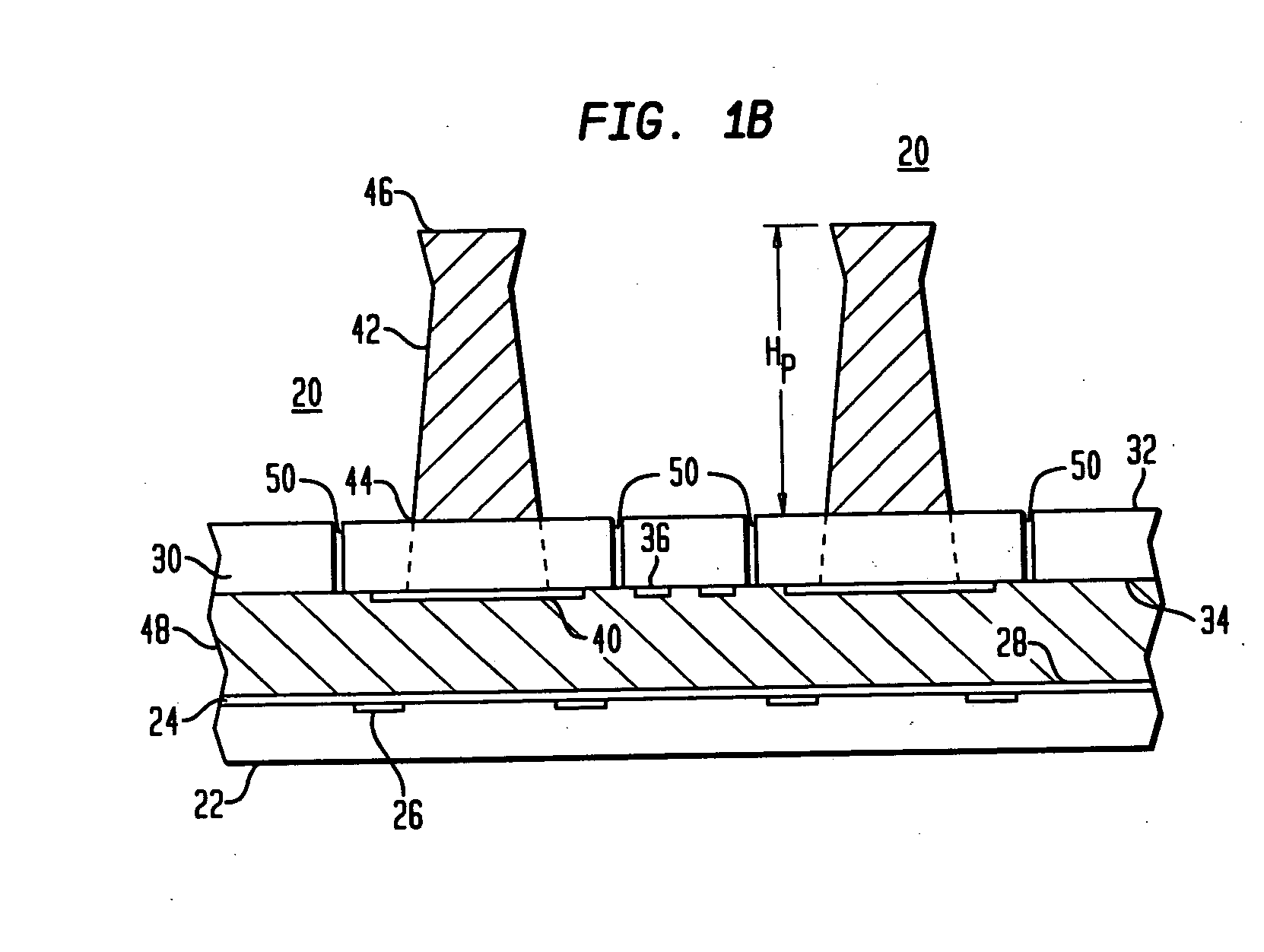

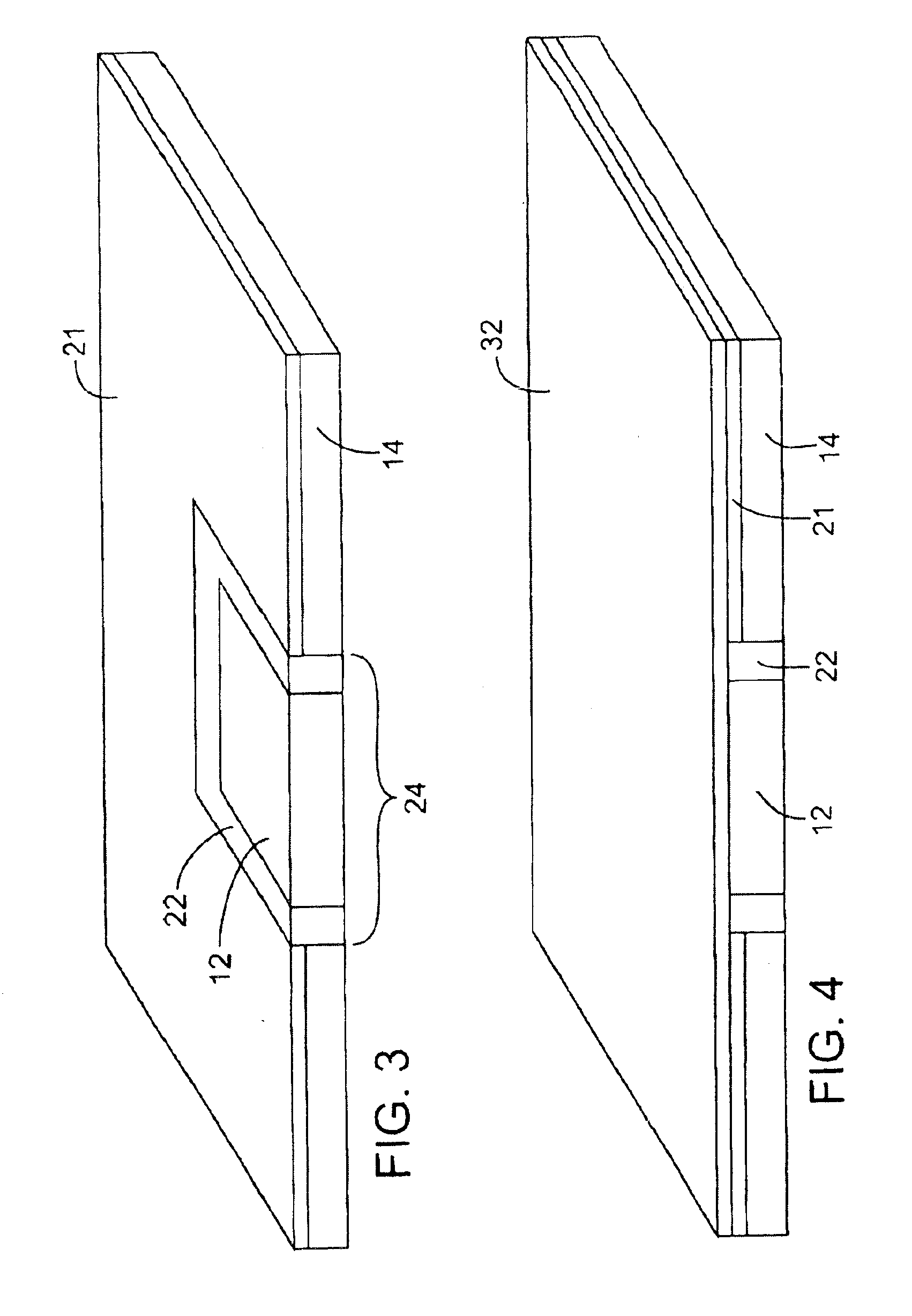

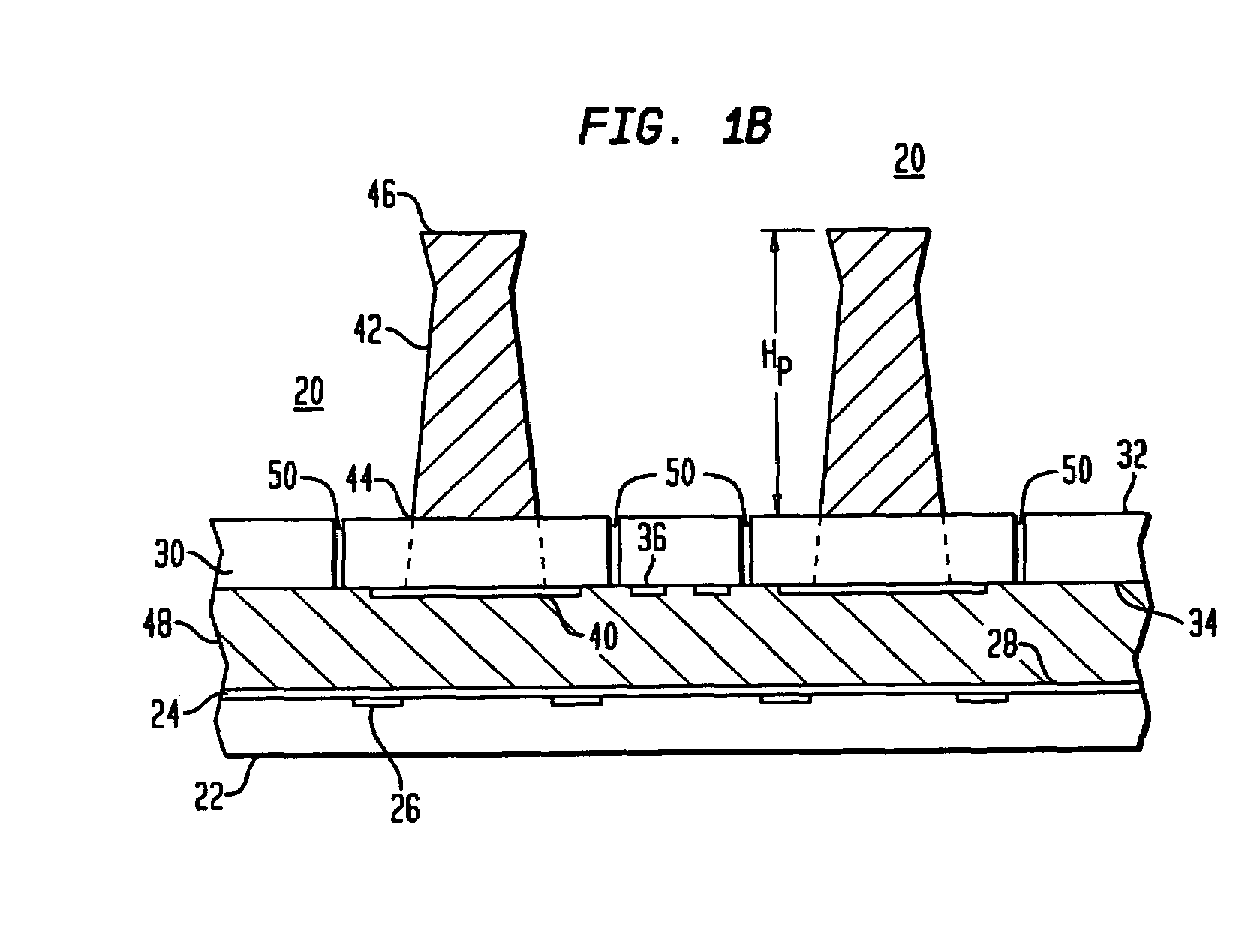

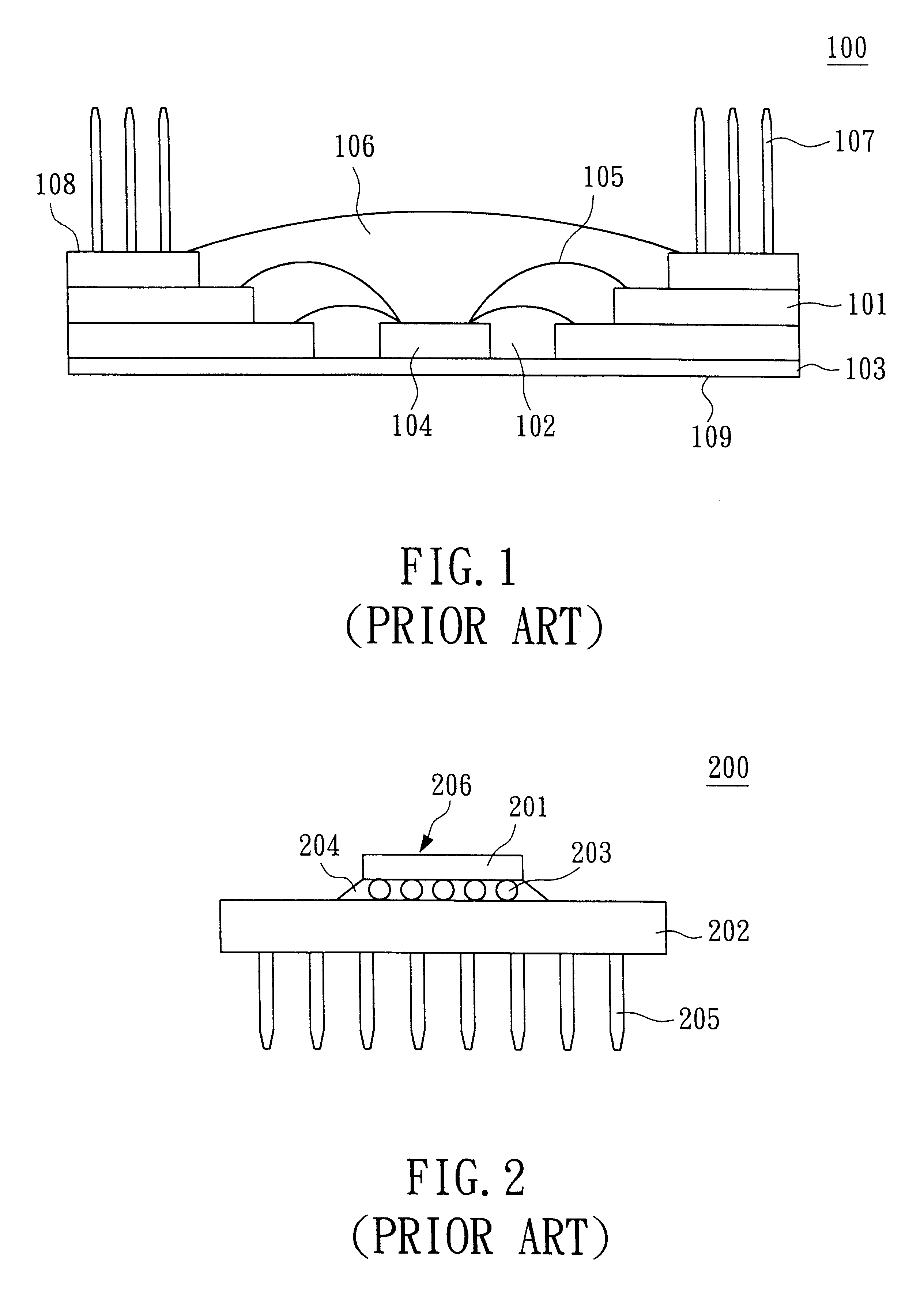

Micro pin grid array with pin motion isolation

InactiveUS20050173805A1Promote sportsFacilitates flexing of the substratePrinted circuit assemblingSemiconductor/solid-state device detailsPin grid arrayPartial alignment

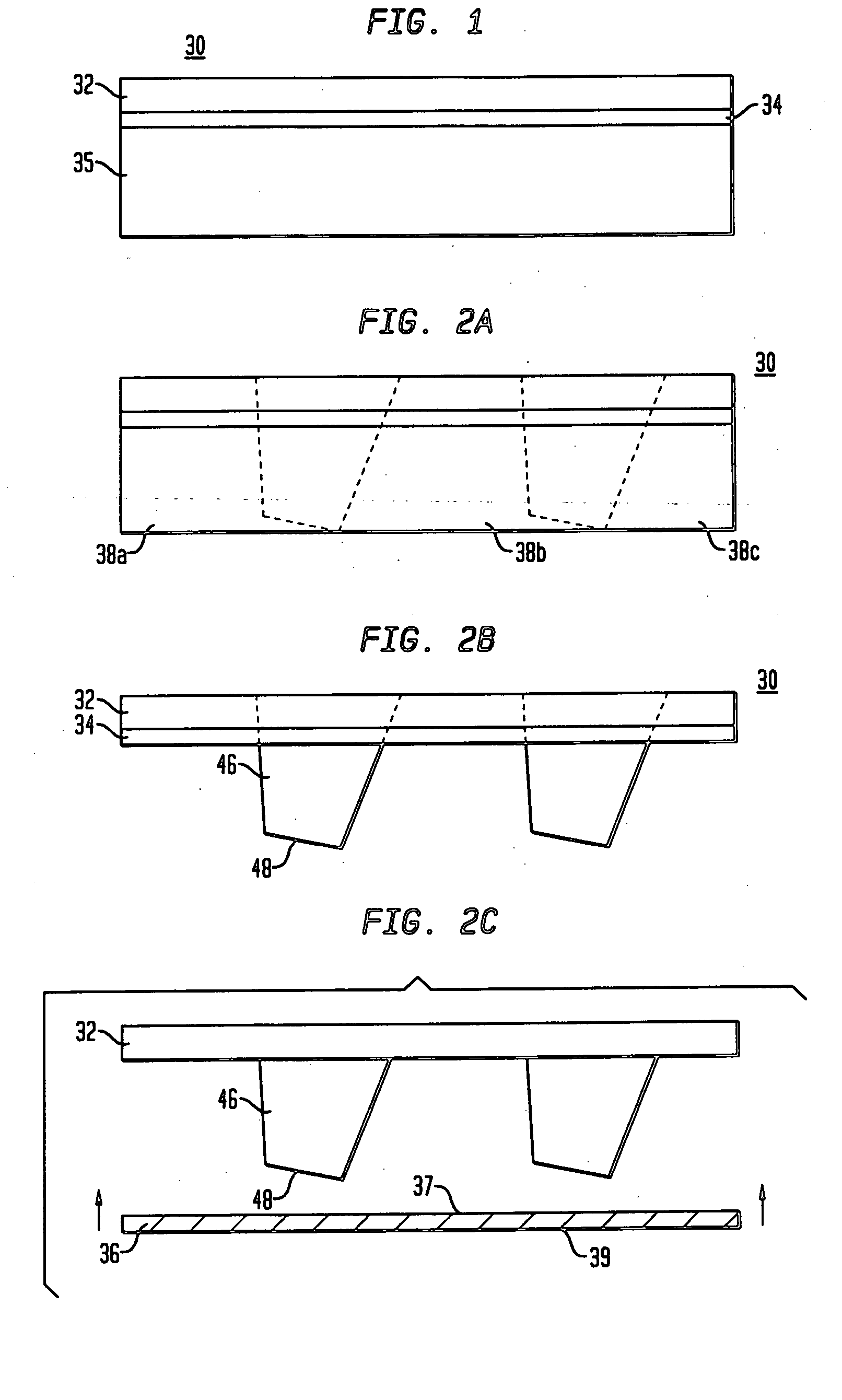

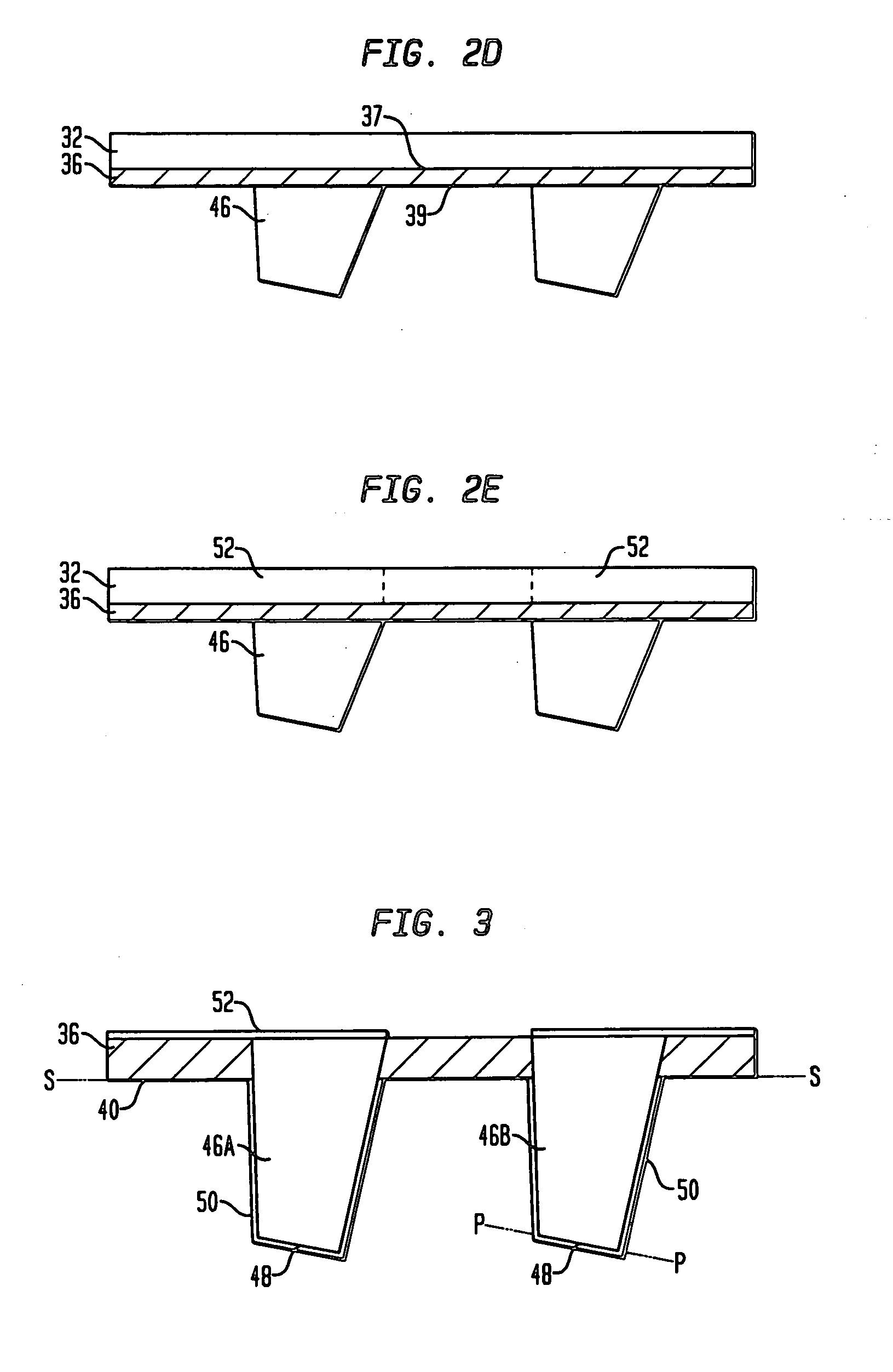

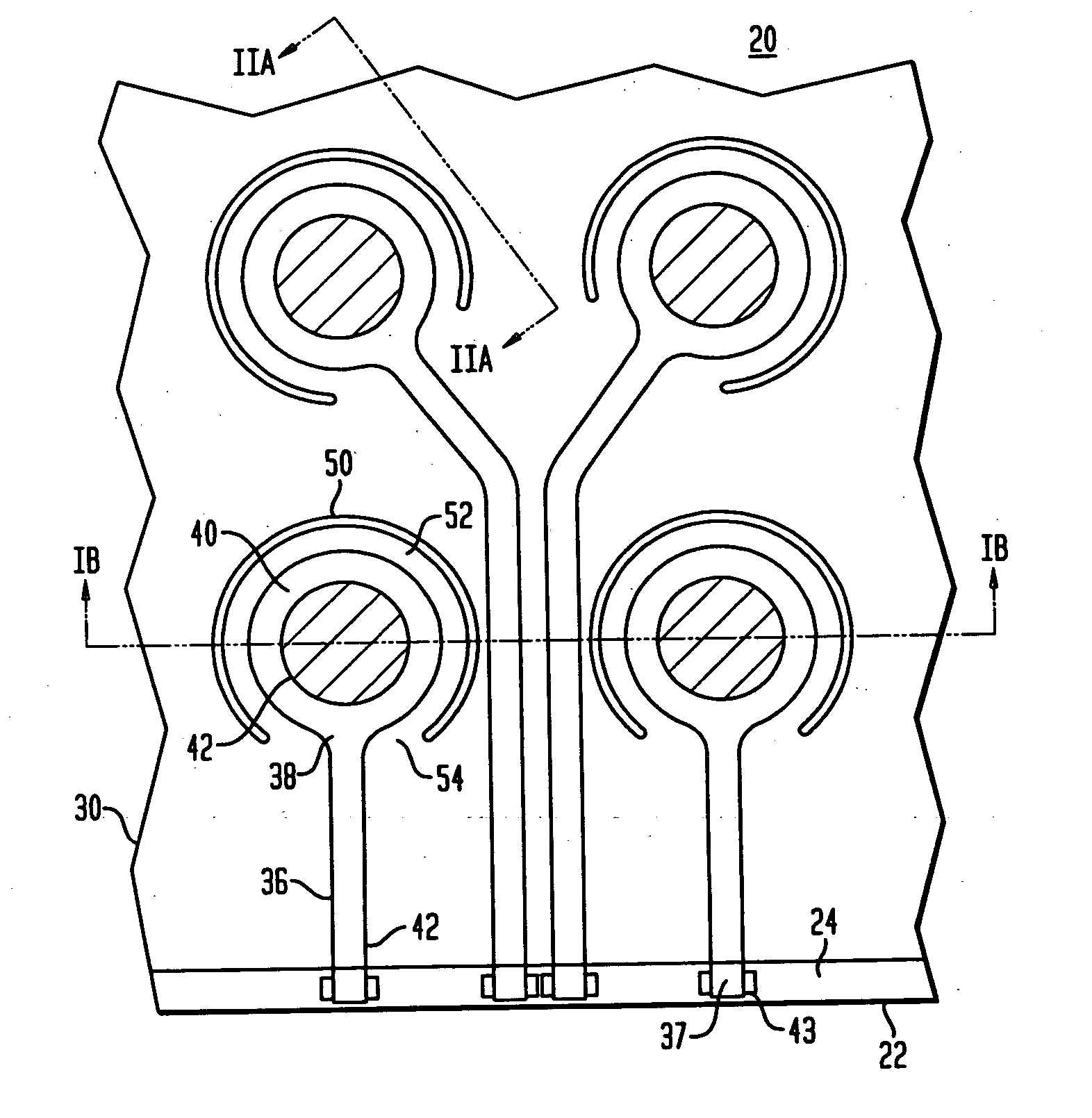

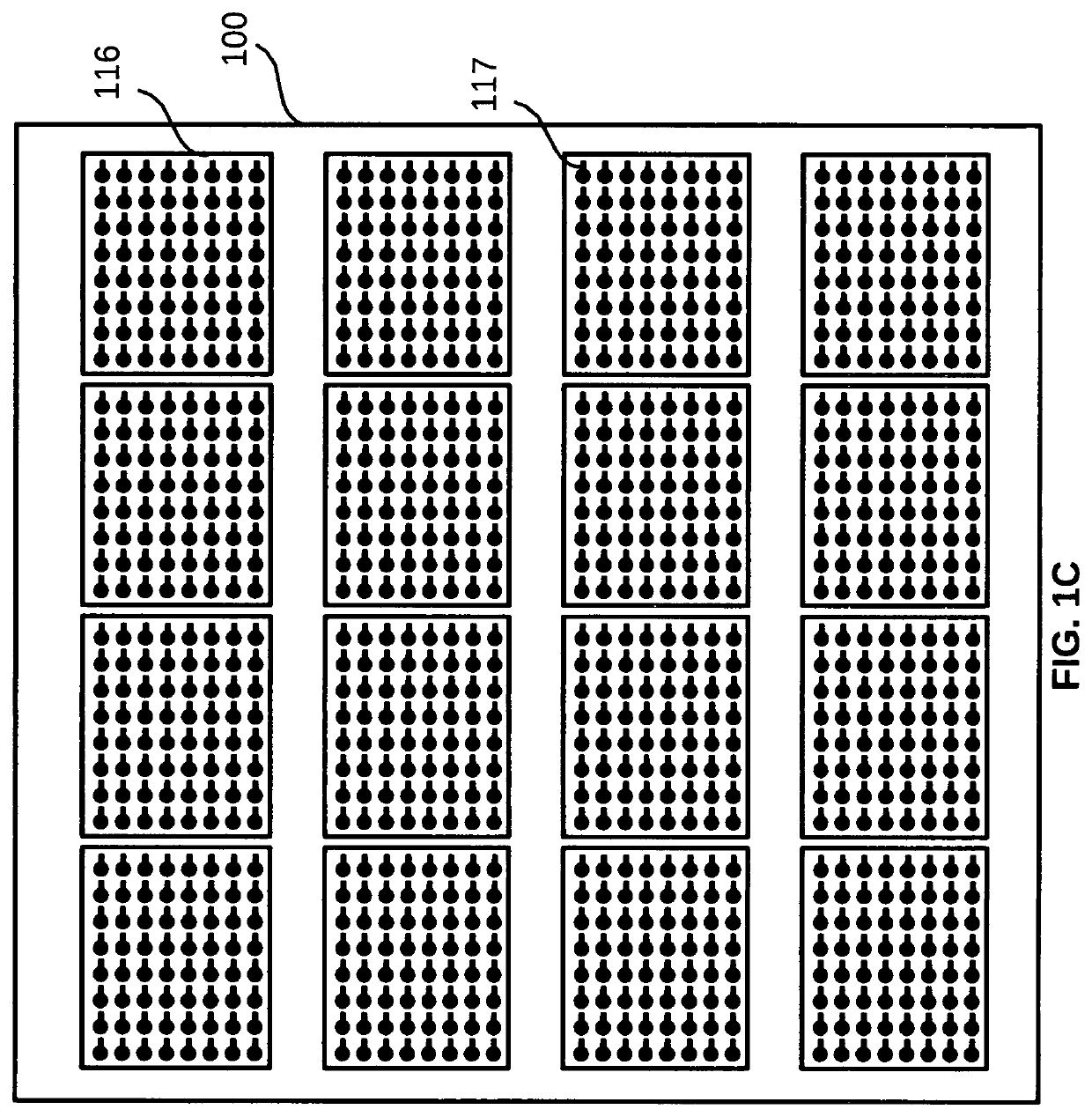

A microelectronic package includes a microelectronic element having faces and contacts, a flexible substrate overlying and spaced from a first face of the microelectronic element, and a plurality of conductive terminals exposed at a surface of the flexible substrate. The conductive terminals are electrically interconnected with the microelectronic element and the flexible substrate includes a gap extending at least partially around at least one of the conductive terminals. In certain embodiments, the package includes a support layer, such as a compliant layer, disposed between the first face of the microelectronic element and the flexible substrate. In other embodiments, the support layer includes at least one opening that is at least partially aligned with one of the conductive terminals.

Owner:TESSERA INC

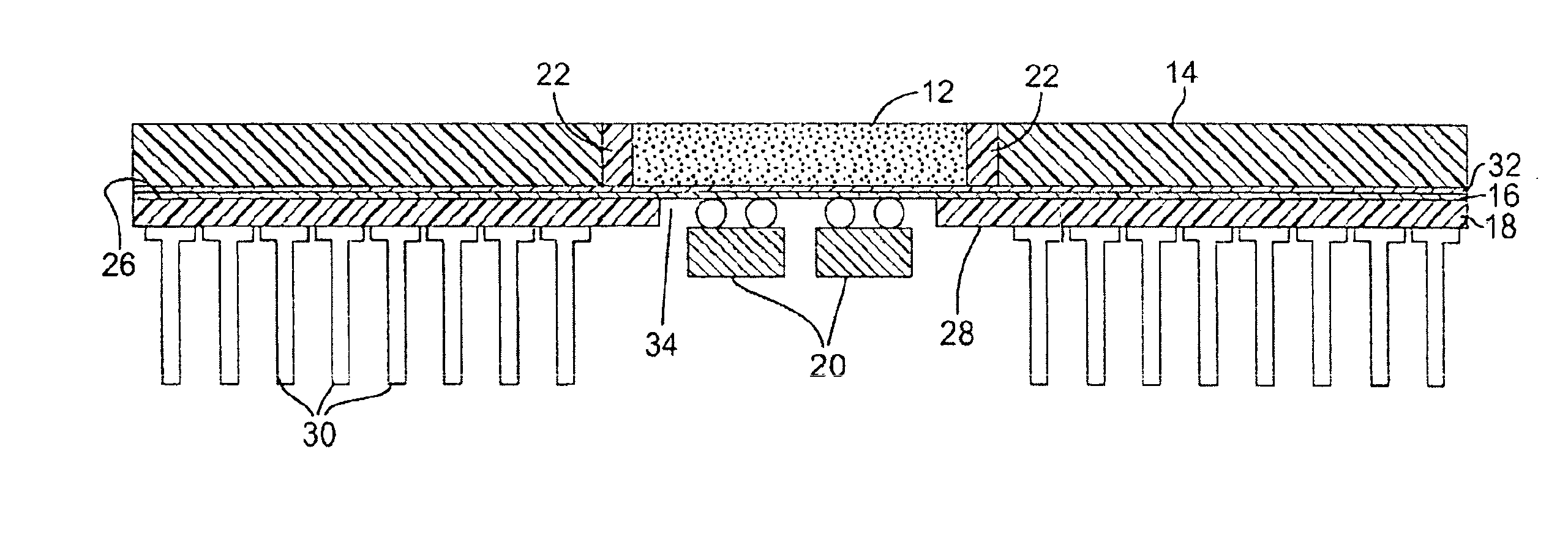

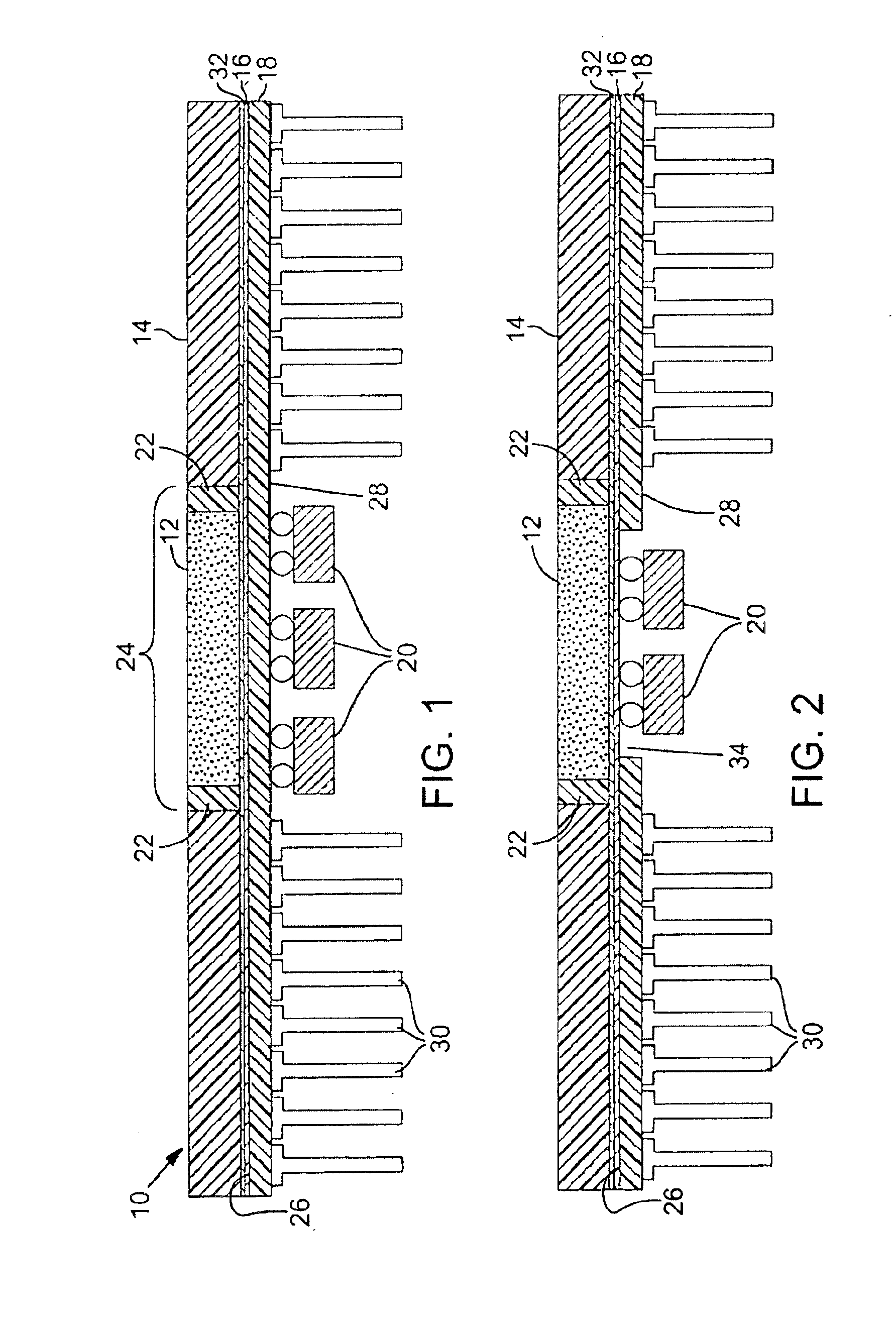

High performance, low cost microelectronic circuit package with interposer

InactiveUS6888240B2Semiconductor/solid-state device detailsSolid-state devicesPin grid arrayInterposer

A low cost technique for packaging microelectronic circuit chips fixes a die within an opening in a package core. At least one metallic build up layer is then formed on the die / core assembly and a grid array interposer unit is laminated to the build up layer. The grid array interposer unit can then be mounted within an external circuit using any of a plurality of mounting technologies (e.g., ball grid array (BGA), land grid array (LGA), pin grid array (PGA), surface mount technology (SMT), and / or others). In one embodiment, a single build up layer is formed on the die / core assembly before lamination of the interposer.

Owner:INTEL CORP

Micro pin grid array with pin motion isolation

InactiveUS7709968B2Facilitates flexing of the substratePromote sportsPrinted circuit assemblingSemiconductor/solid-state device detailsPin grid arrayEngineering

A microelectronic package includes a microelectronic element having faces and contacts, a flexible substrate overlying and spaced from a first face of the microelectronic element, and a plurality of conductive terminals exposed at a surface of the flexible substrate. The conductive terminals are electrically interconnected with the microelectronic element and the flexible substrate includes a gap extending at least partially around at least one of the conductive terminals. In certain embodiments, the package includes a support layer, such as a compliant layer, disposed between the first face of the microelectronic element and the flexible substrate. In other embodiments, the support layer includes at least one opening that is at least partially aligned with one of the conductive terminals.

Owner:TESSERA INC

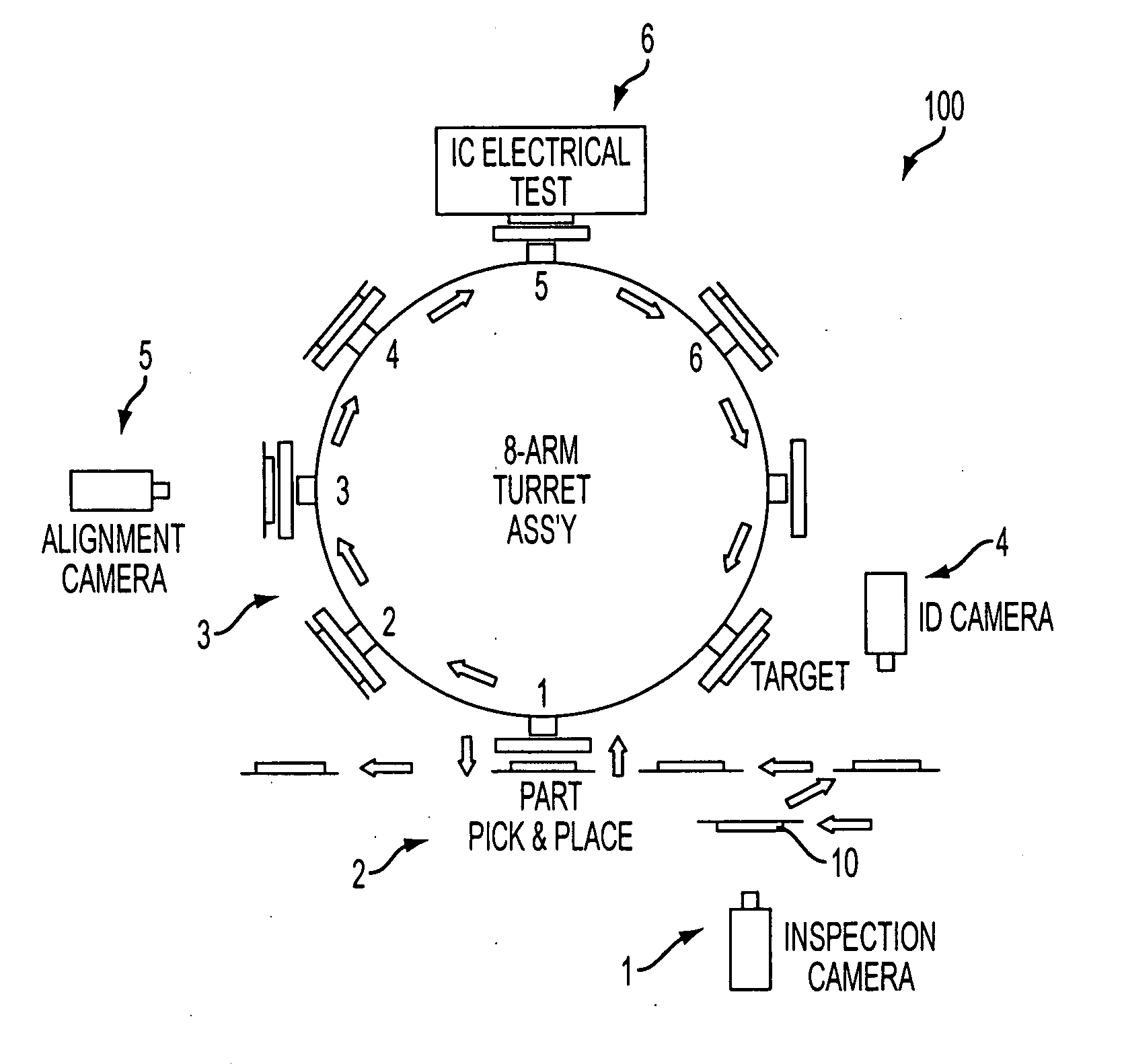

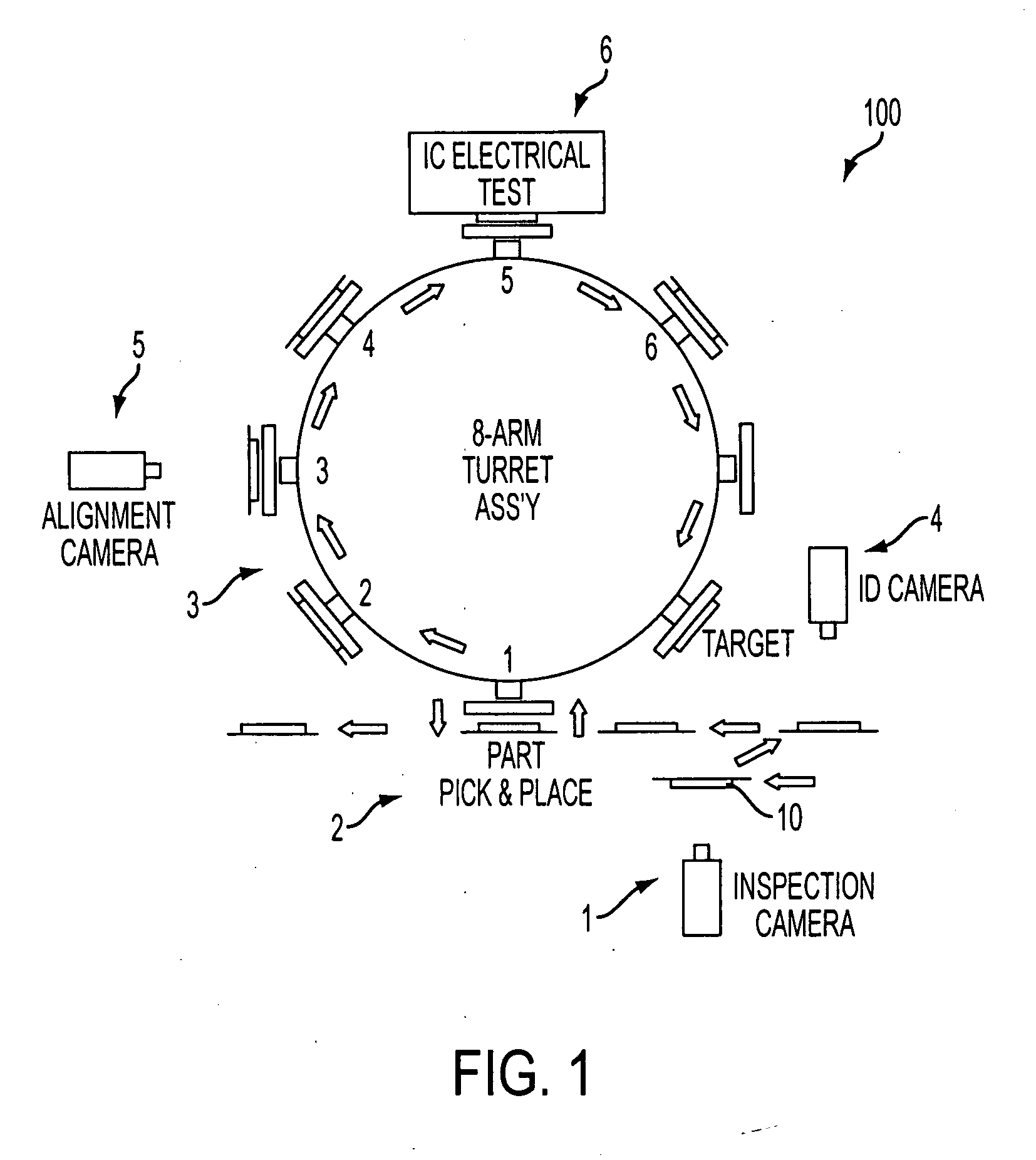

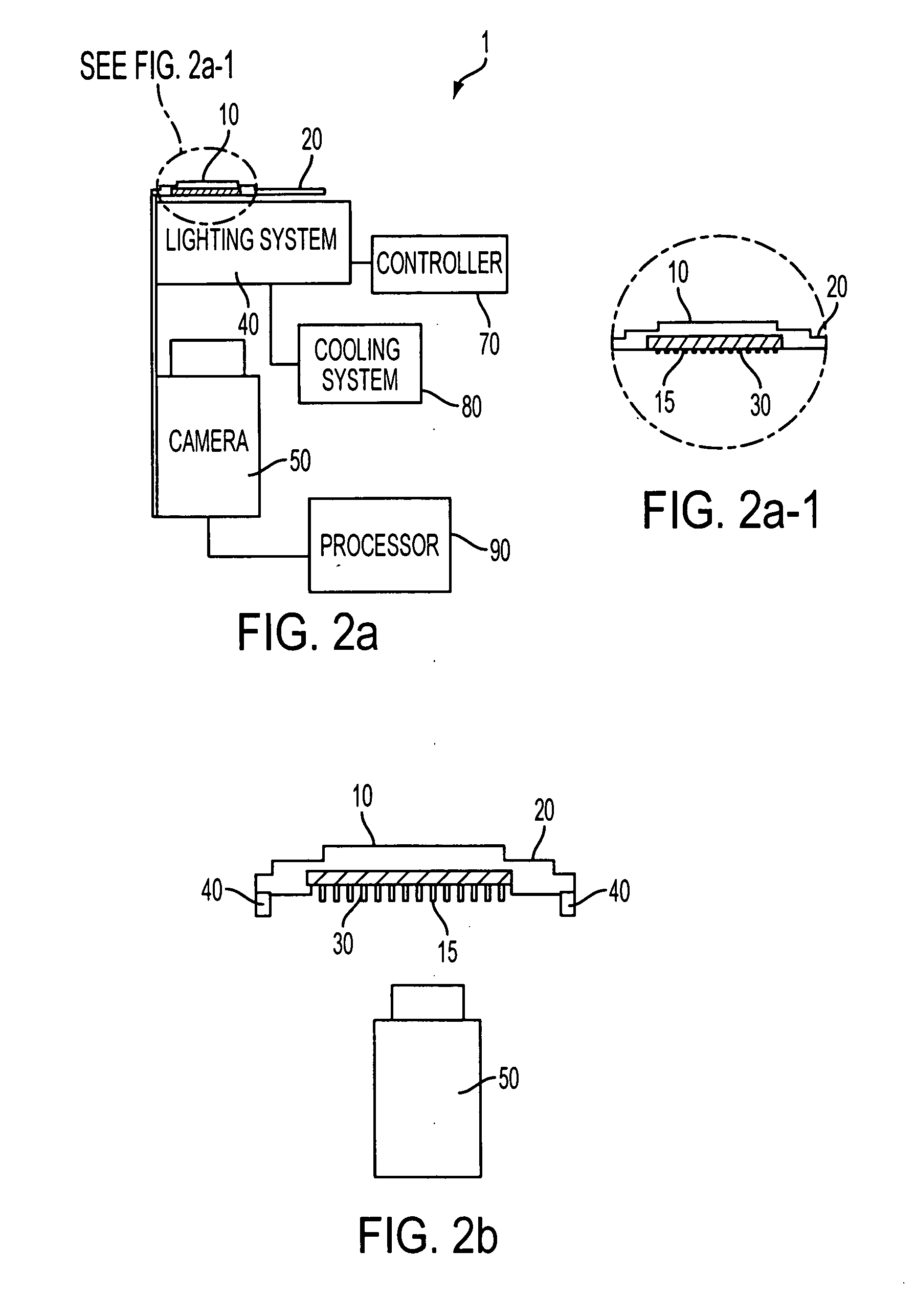

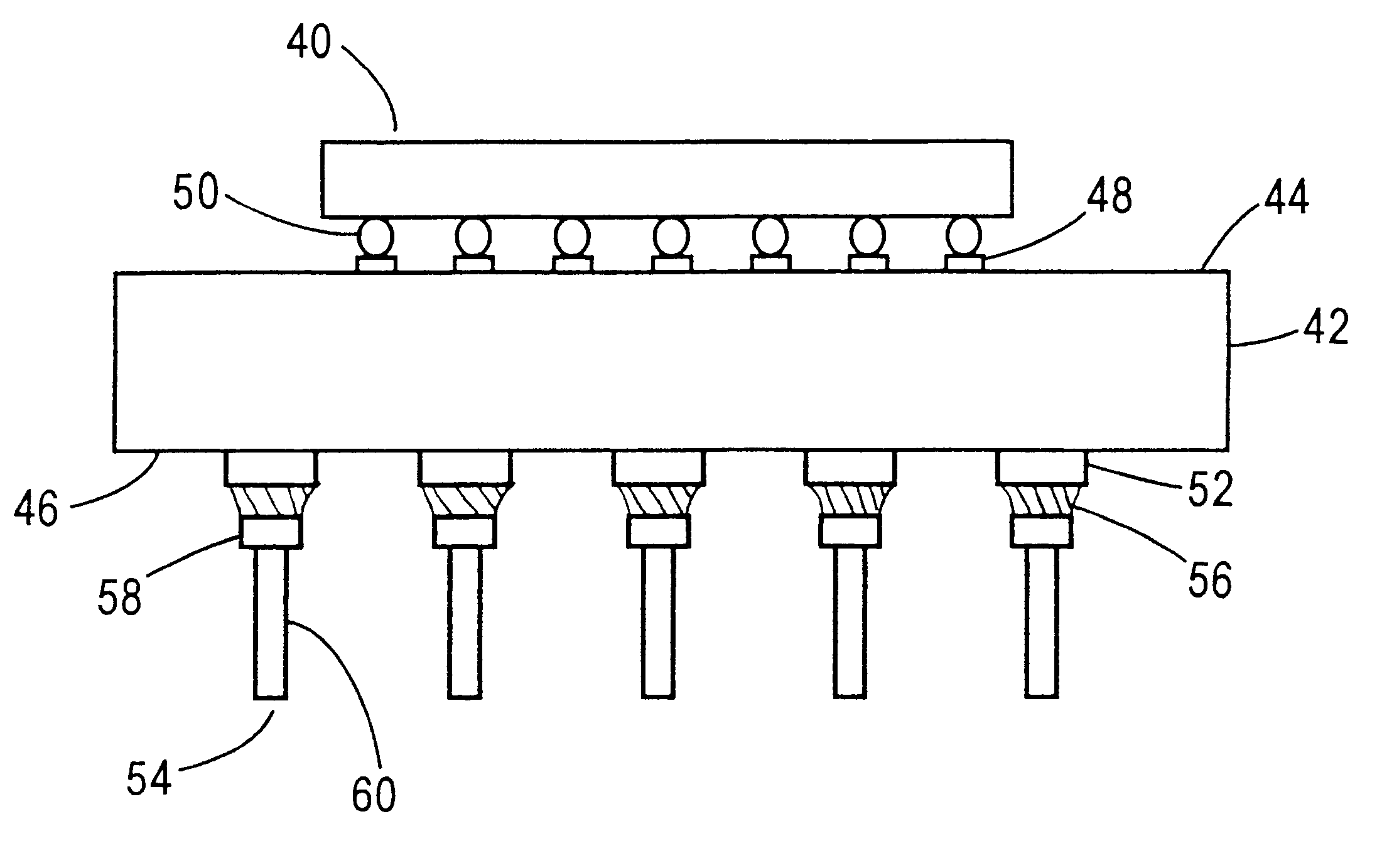

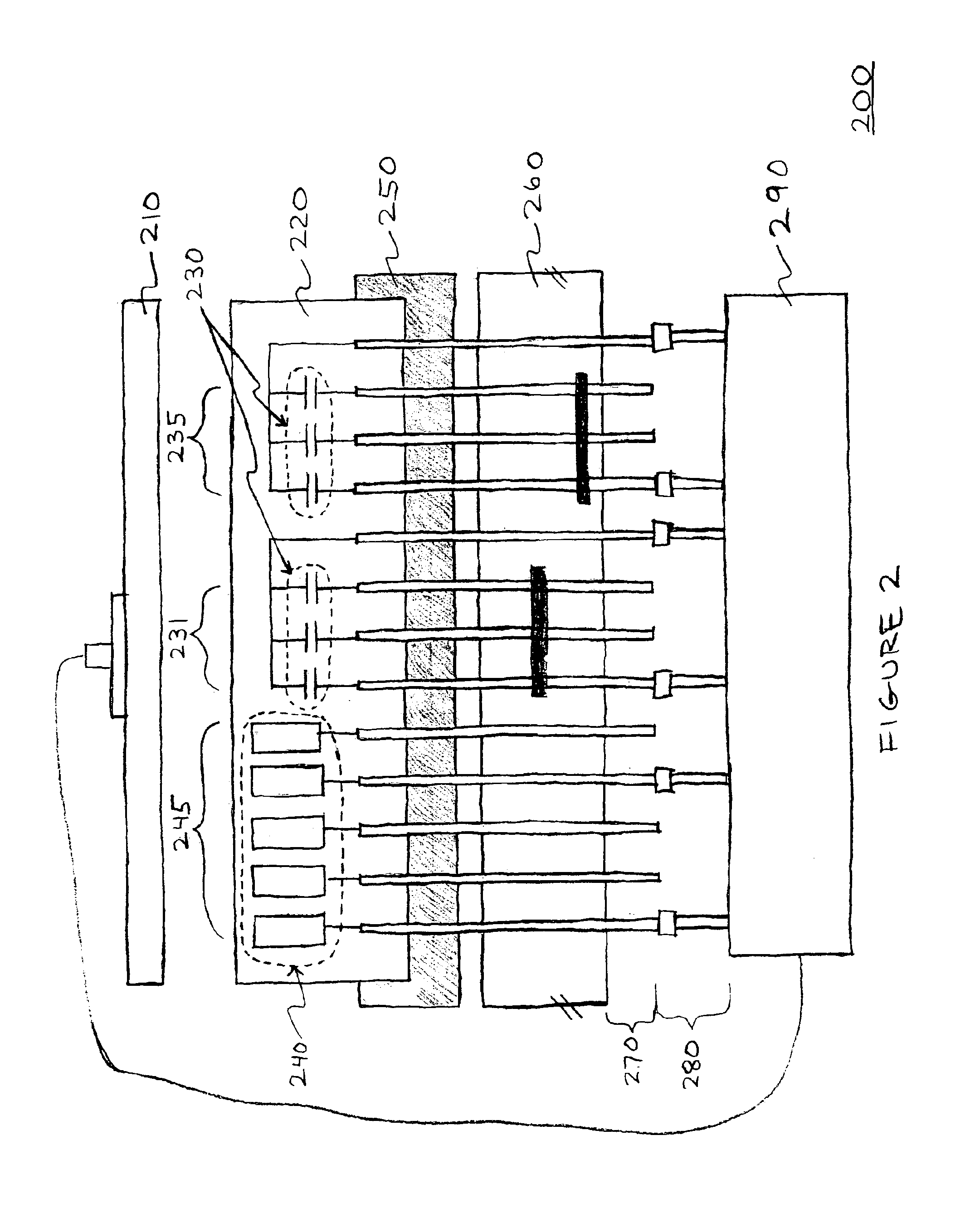

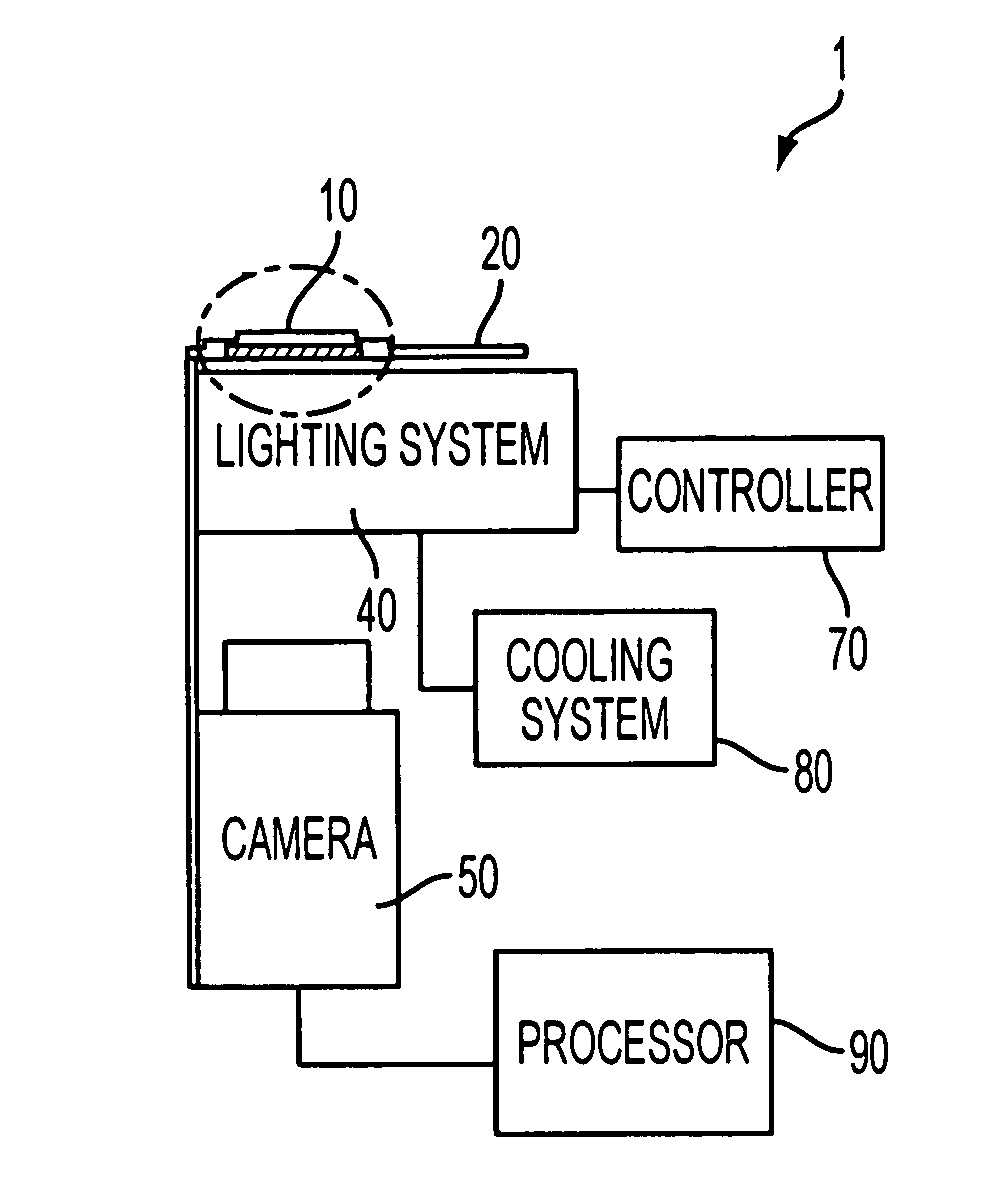

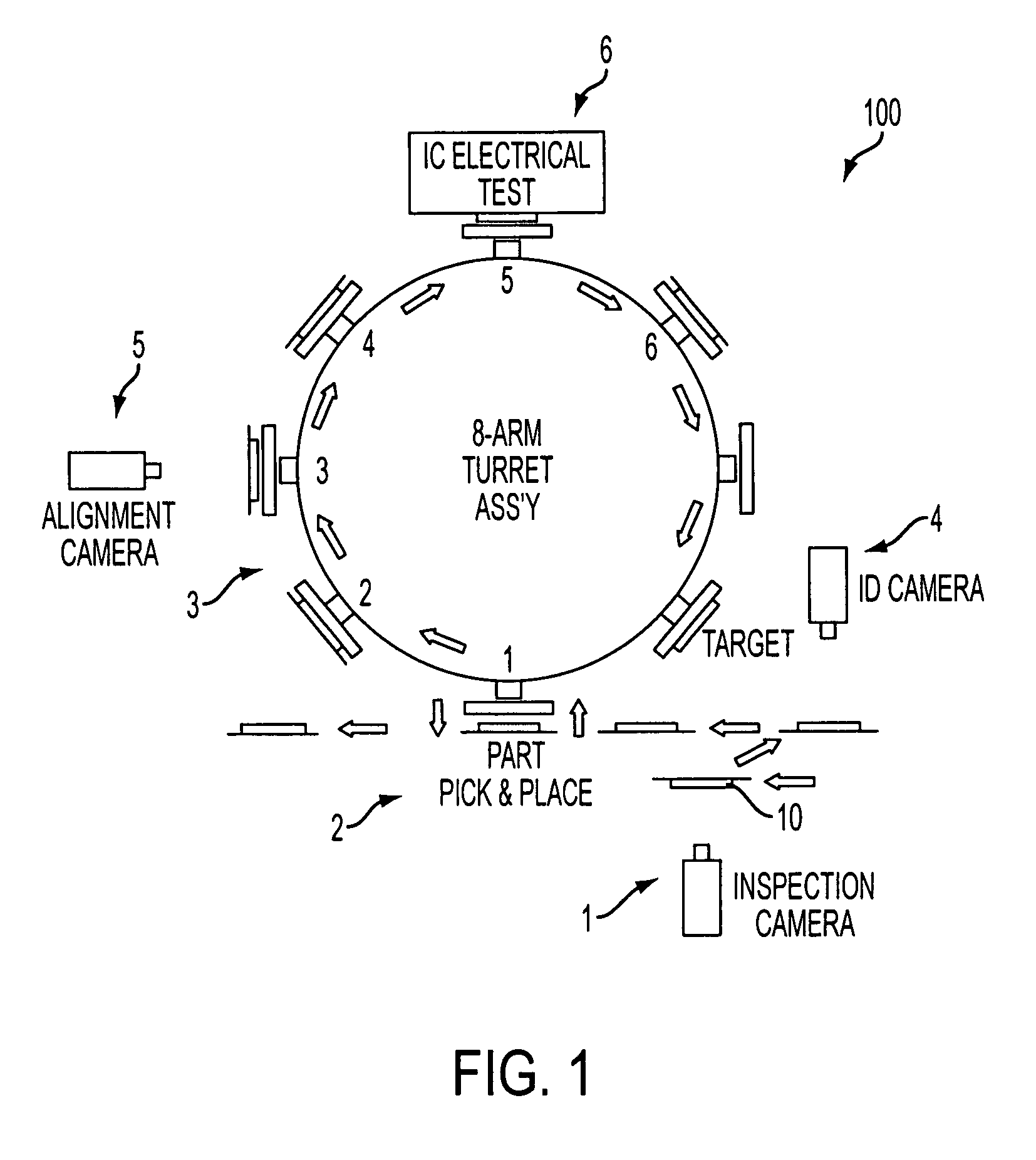

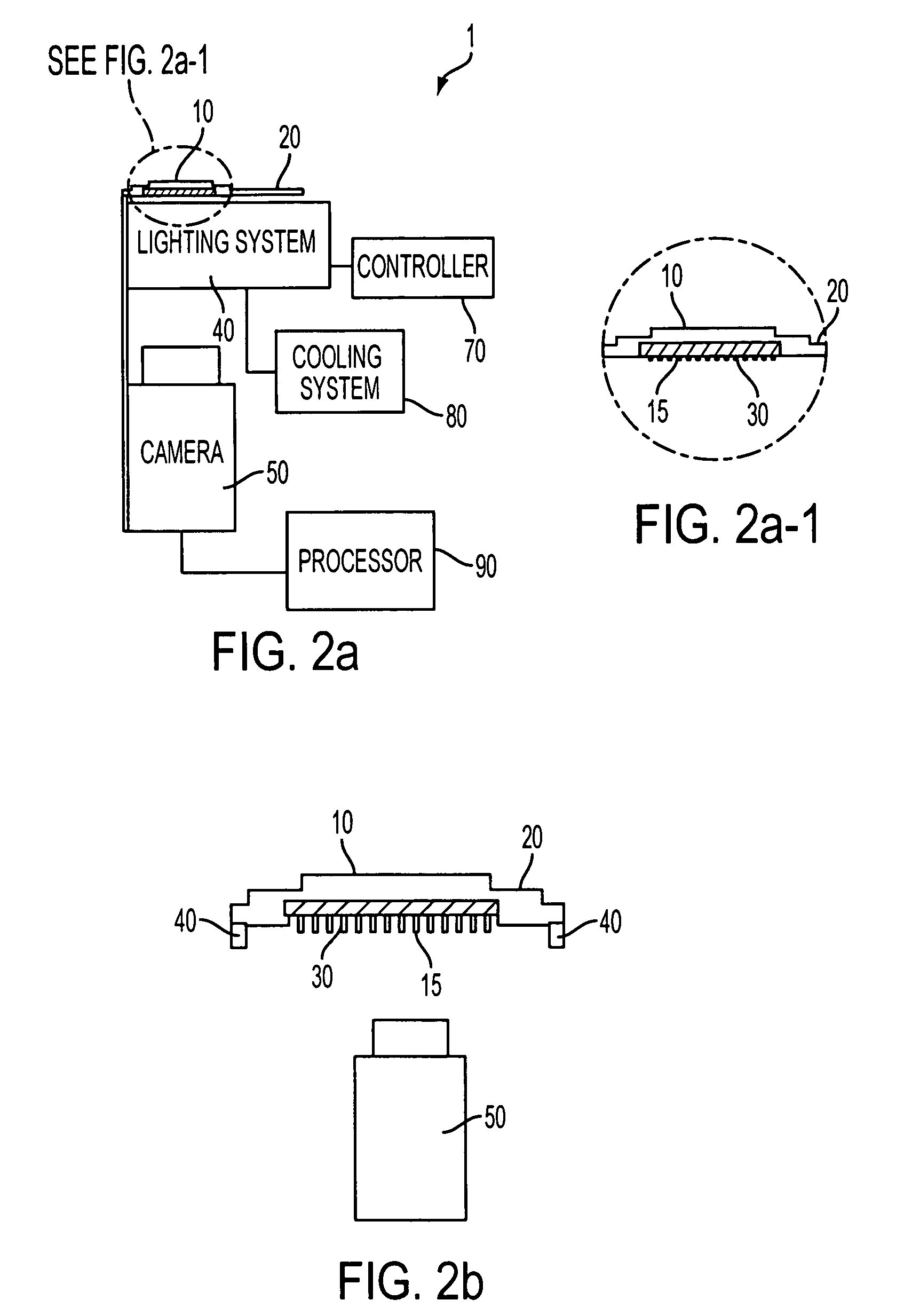

Camera based pin grid array (PGA) inspection system with pin base mask and low angle lighting

InactiveUS20070080703A1Detection of defectElectric connection testingMaterial analysis by optical meansPin grid arrayEffect light

An inspection system, for inspecting pin grid arrays on integrated circuit devices includes a pin base mask configured to receive a device having a pin grid array. A dark-field, low-angle lighting system emits light onto the pin grid array. The pin base mask and low-angle lighting system provide for a clear and definitive image of the pin grid array. A camera captures the image of the pin grid array. A processor, coupled to the camera, analyzes the images captured by the camera. Based on the captured image, the processor determines whether any pins on the pin grid array are bent or missing, or whether there are extra pins present.

Owner:DELTA DESIGN

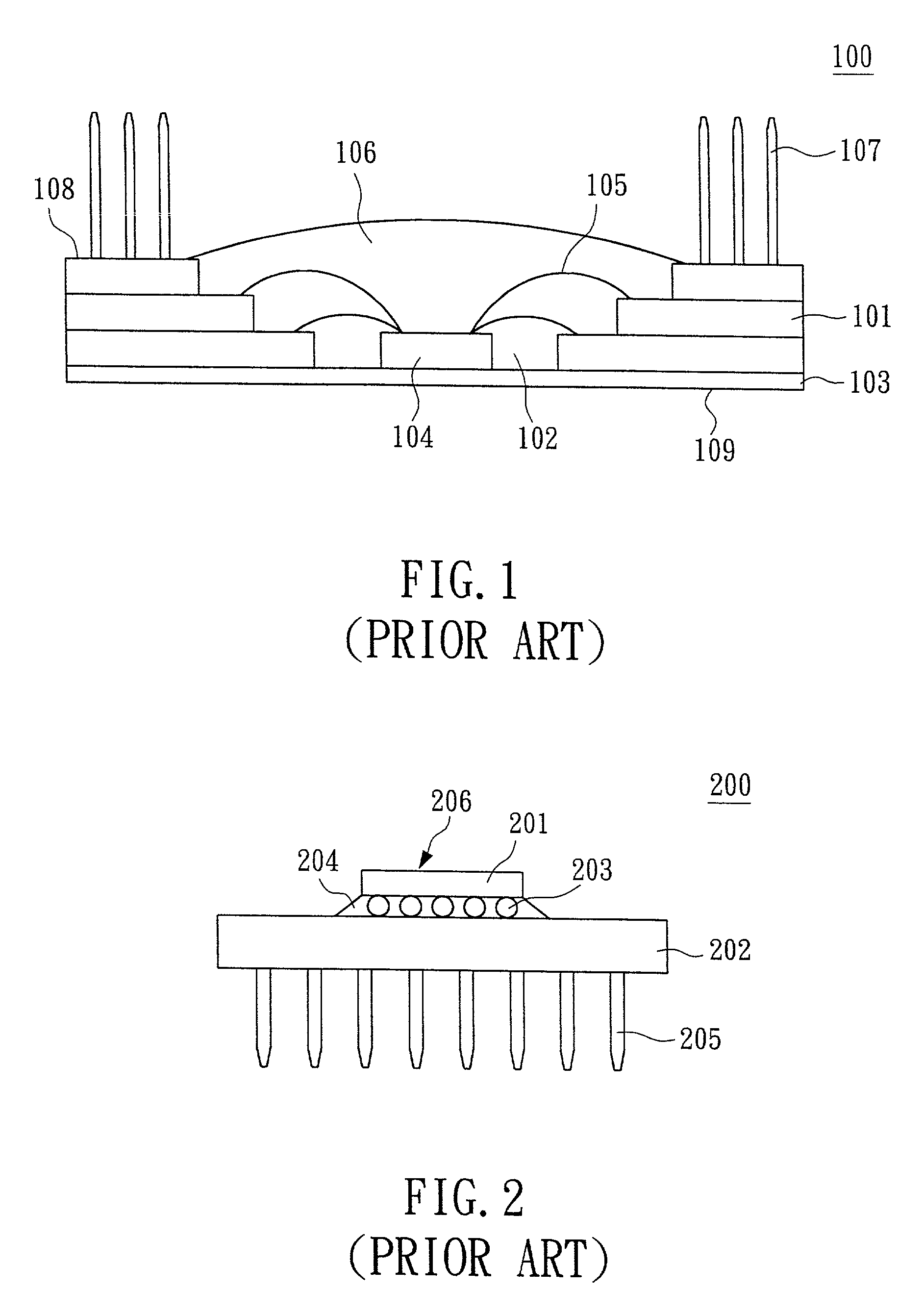

Organic pin grid array flip chip carrier package

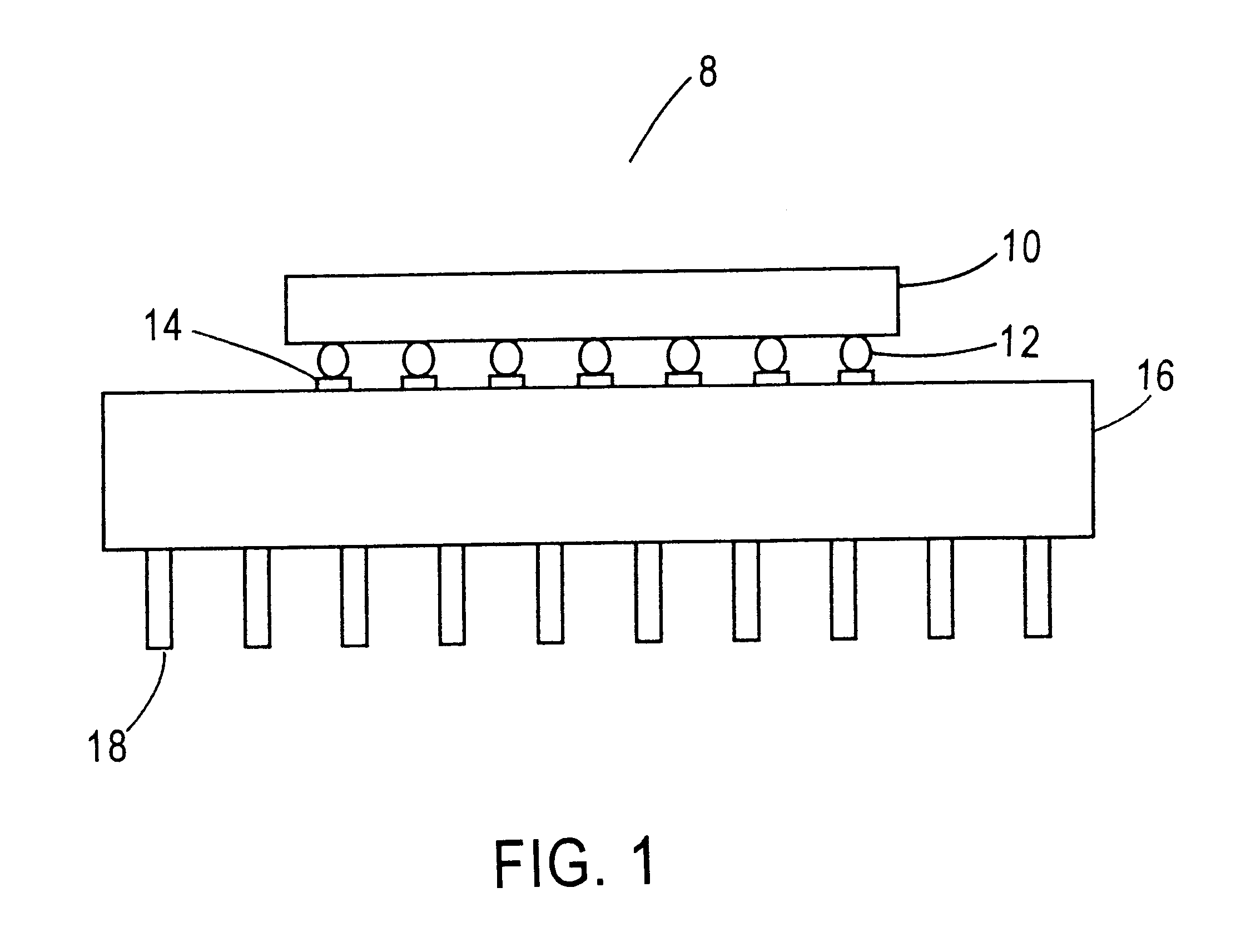

InactiveUS6229207B1Printed circuit assemblingSemiconductor/solid-state device detailsDevice materialPin grid array

An organic carrier member for mounting a semiconductor device is provided that has a plurality of pin leads joined to conductive pads on the carrier member by a solder fillet having a reflow temperature higher than the temperature necessary to attach the semiconductor device. Embodiments include a bismaleimide-triazine epoxy laminate carrier member having an array of pins joined to the carrier member by a solder fillet having a reflow temperature of no greater than 275° C.

Owner:ADVANCED MICRO DEVICES INC

Socket connection test modules and methods of using the same

InactiveUS6956387B2Resistance/reactance/impedenceElectronic circuit testingCapacitancePin grid array

Test modules, systems, and methods employing capacitors for the testing of the solder joint connections between a printed circuit board (PCB) and a socket of a device are presented in embodiments of the current invention. A test module having capacitors in parallel, and in particular embedded capacitors, can be used to test tied traces and their solder joint connections by measuring the total capacitance of the capacitors. Embodiments of the current invention present no-power tests that can be used with a variety of testing platforms and test fixtures, such as in-circuit testing (ICT) and manufacturing defect analysis (MDA.) Additionally, the test module can be used with a variety of sockets, such as a ball grid array, a pinned grid array, and a land grid array.

Owner:INTEL CORP

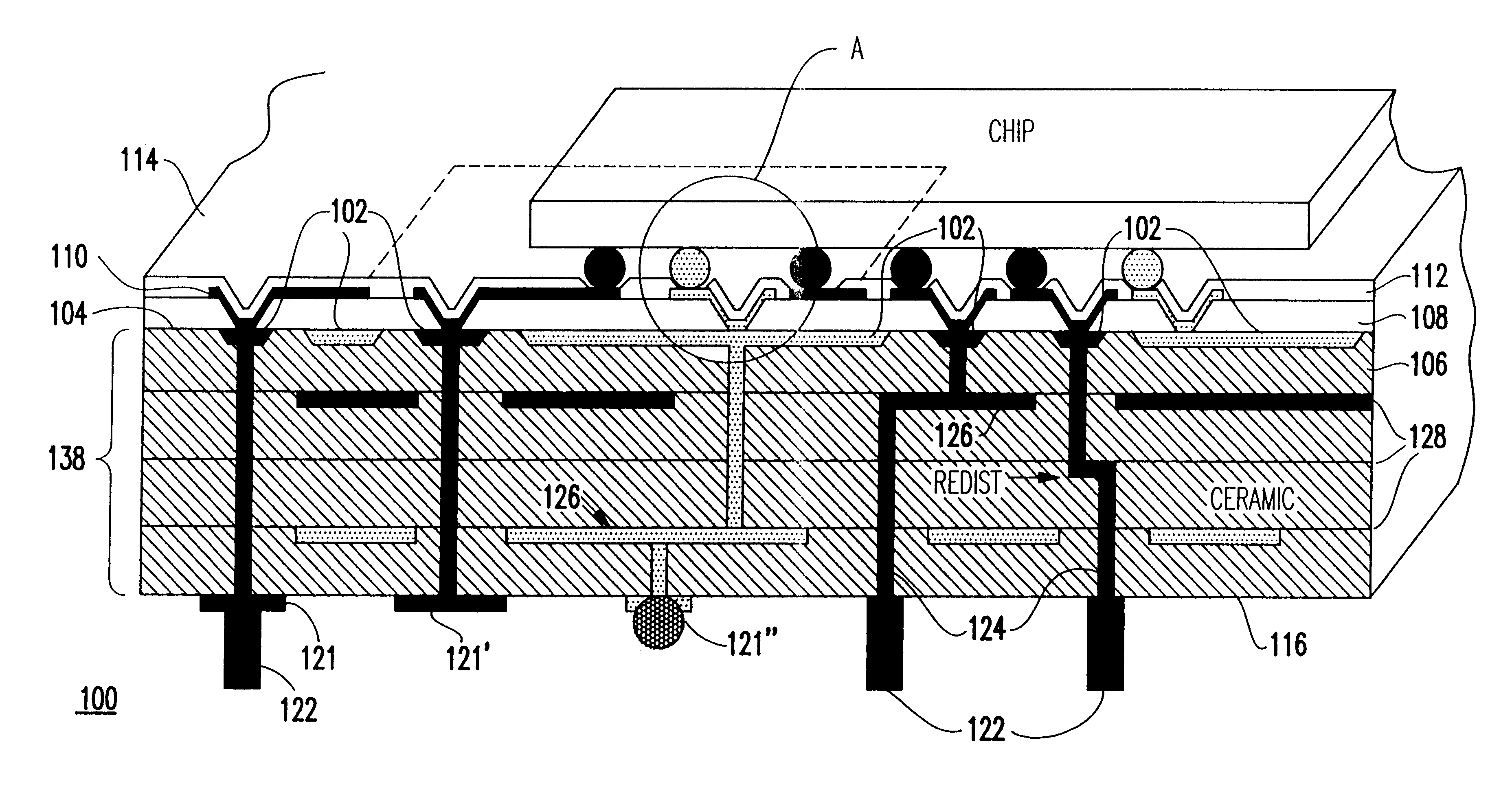

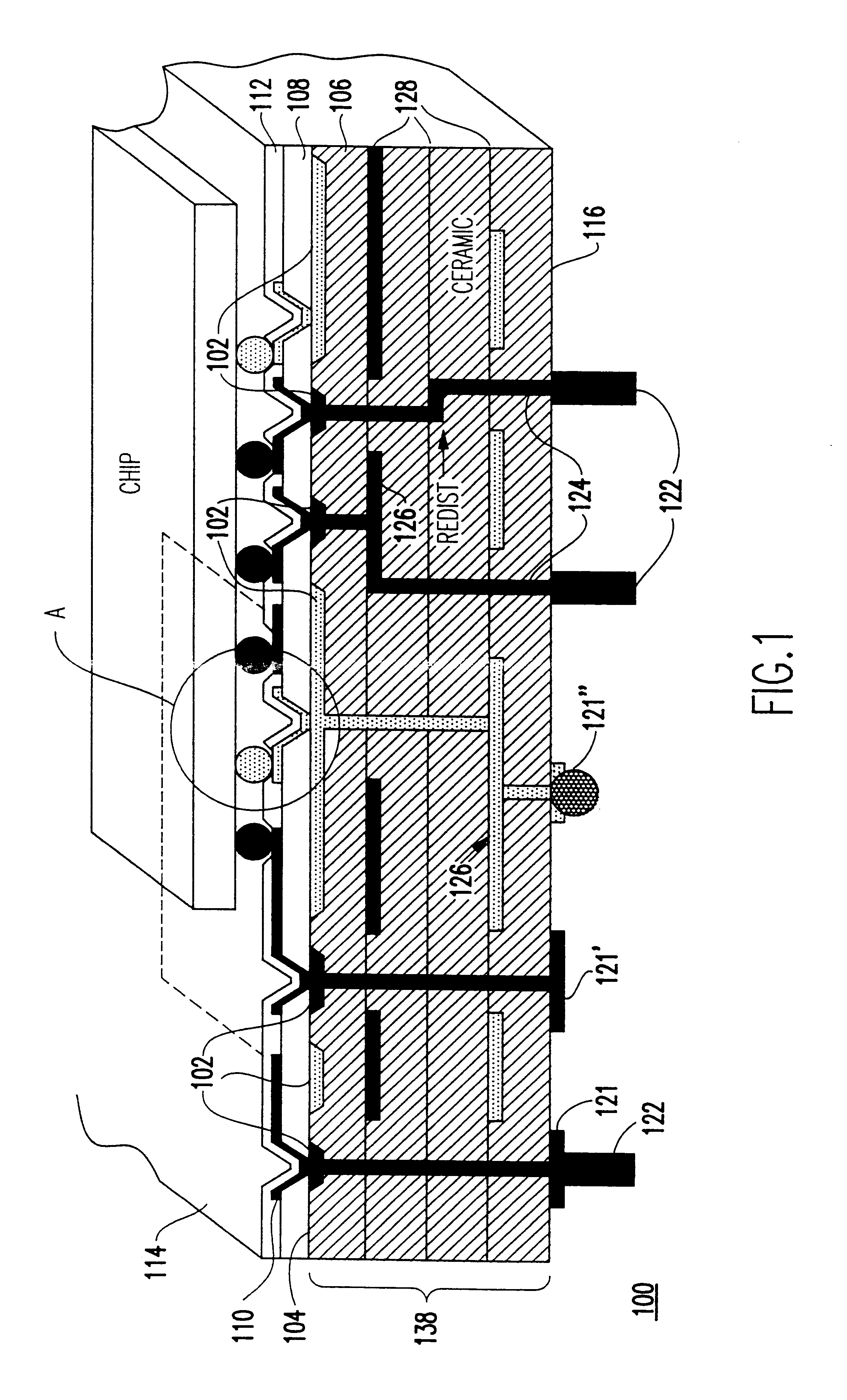

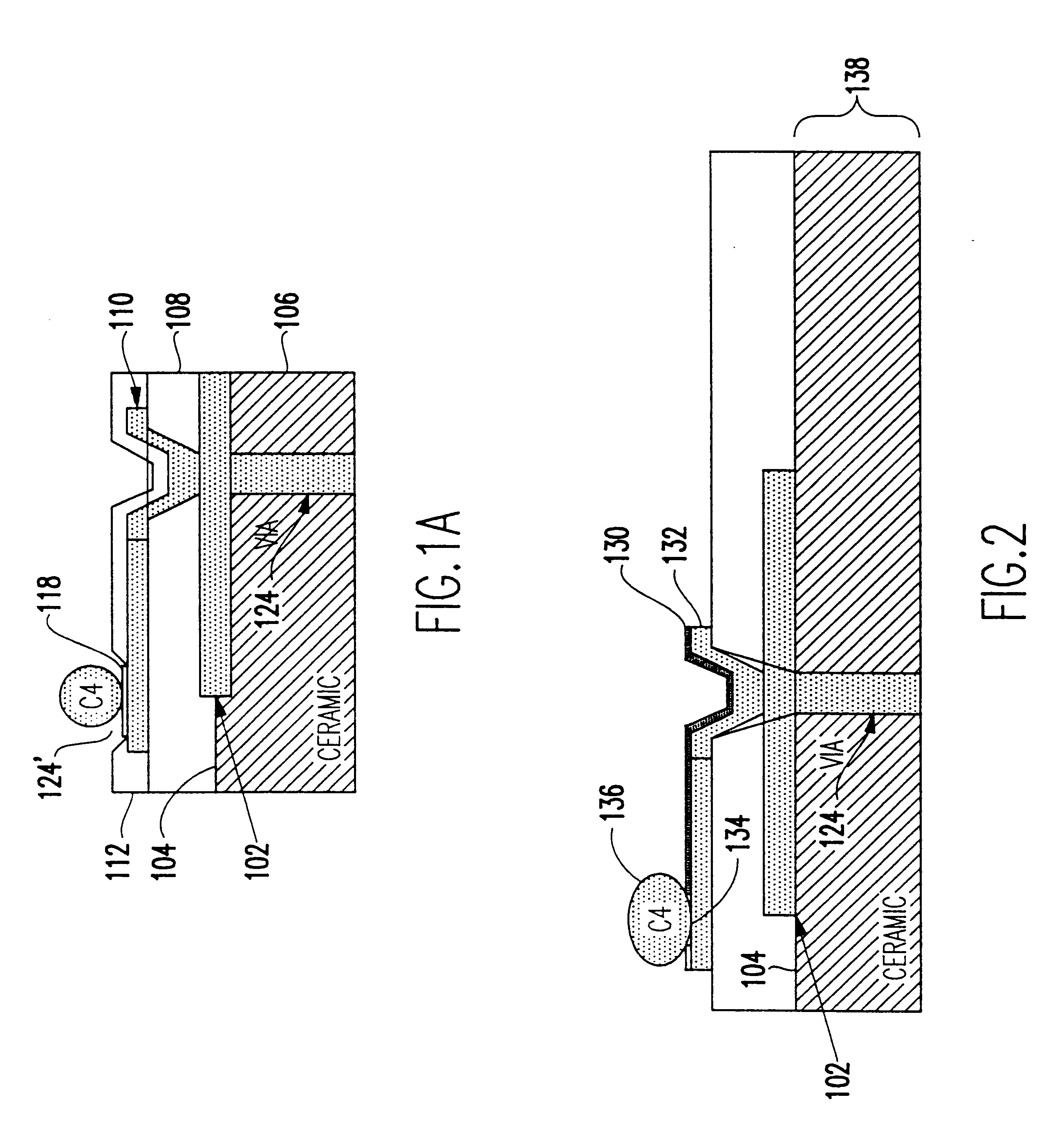

Direct deposit thin film single/multi chip module

InactiveUS6261467B1Semiconductor/solid-state device detailsSolid-state devicesGas phaseThick film technology

A high performance TF-ceramic module for mounting integrated circuit chips thereto and a method of fabricating the module at reduced cost. The substrate includes thin film (TF) layers formed directly on a layered ceramic base. A first thick film wiring layer is formed on or embedded in a top surface of the thick film layered ceramic base using thick film techniques. A first dielectric layer of a polyimide or other organic material, or an insulating material different than the ceramic material is formed on top of the first wiring layer. The dielectric layer may be spun on or sprayed on and baked; vapor deposited; laminated to the ceramic base; or an inorganic layer may be deposited using plasma enhanced chemical vapor deposition (PECVD). Vias are formed through the first dielectric layer. A second wiring layer is formed on the first dielectric layer. A second dielectric layer is formed on the second wiring layer. At least one mounting location suitable for mounting an electronic component is formed on the second dielectric layer. The substrate may be attached a printed circuit board by direct attachment, pin grid array (PGA), land grid array (LGA), ball grid array (BGA), column grid array (CGA) and miniBGA on the bottom layer of the ceramic base.

Owner:INT BUSINESS MASCH CORP

Socket connection test modules and methods of using the same

InactiveUS20050035754A1Resistance/reactance/impedenceElectronic circuit testingCapacitancePin grid array

Test modules, systems, and methods employing capacitors for the testing of the solder joint connections between a printed circuit board (PCB) and a socket of a device are presented in embodiments of the current invention. A test module having capacitors in parallel, and in particular embedded capacitors, can be used to test tied traces and their solder joint connections by measuring the total capacitance of the capacitors. Embodiments of the current invention present no-power tests that can be used with a variety of testing platforms and test fixtures, such as in-circuit testing (ICT) and manufacturing defect analysis (MDA.) Additionally, the test module can be used with a variety of sockets, such as a ball grid array, a pinned grid array, and a land grid array.

Owner:INTEL CORP

Multistage connector for carriers with combined pin-array and pad-array

InactiveUS6106316APromote repairEngagement/disengagement of coupling partsCoupling contact membersPin grid arrayIntegrated circuit

A socket for connecting to an integrated circuit module containing pin grid array contacts and land grid array contacts thereon. The socket has a first portion containing openings therein for the pin grid array contacts and a second portion for contacting the land grid array contacts. The first portion of the socket is disposed around the second portion of the socket, and the second portion is movable with respect to the first portion. The second portion is located in a position wherein the pin grid array contacts on the integrated circuit module are received in the openings in the first portion before the land grid array contacts on the integrated circuit module contact the second portion, the second portion being biased toward the integrated circuit module by a spring. The socket further includes movable connectors in the openings in the first portion of the socket for releasably securing the pin grid array contacts, such that the pin grid array and land grid array contacts on the integrated circuit module are simultaneously in contact with the respective portions of the socket. The connectors comprise leaf connectors movable in a direction lateral to the pin grid array contacts to open while receiving the pin grid array contacts and close to secure the pin grid array contacts in the openings. Inflatable bladders are employed to simultaneously move the leaf connectors between the open and closed positions.

Owner:IBM CORP

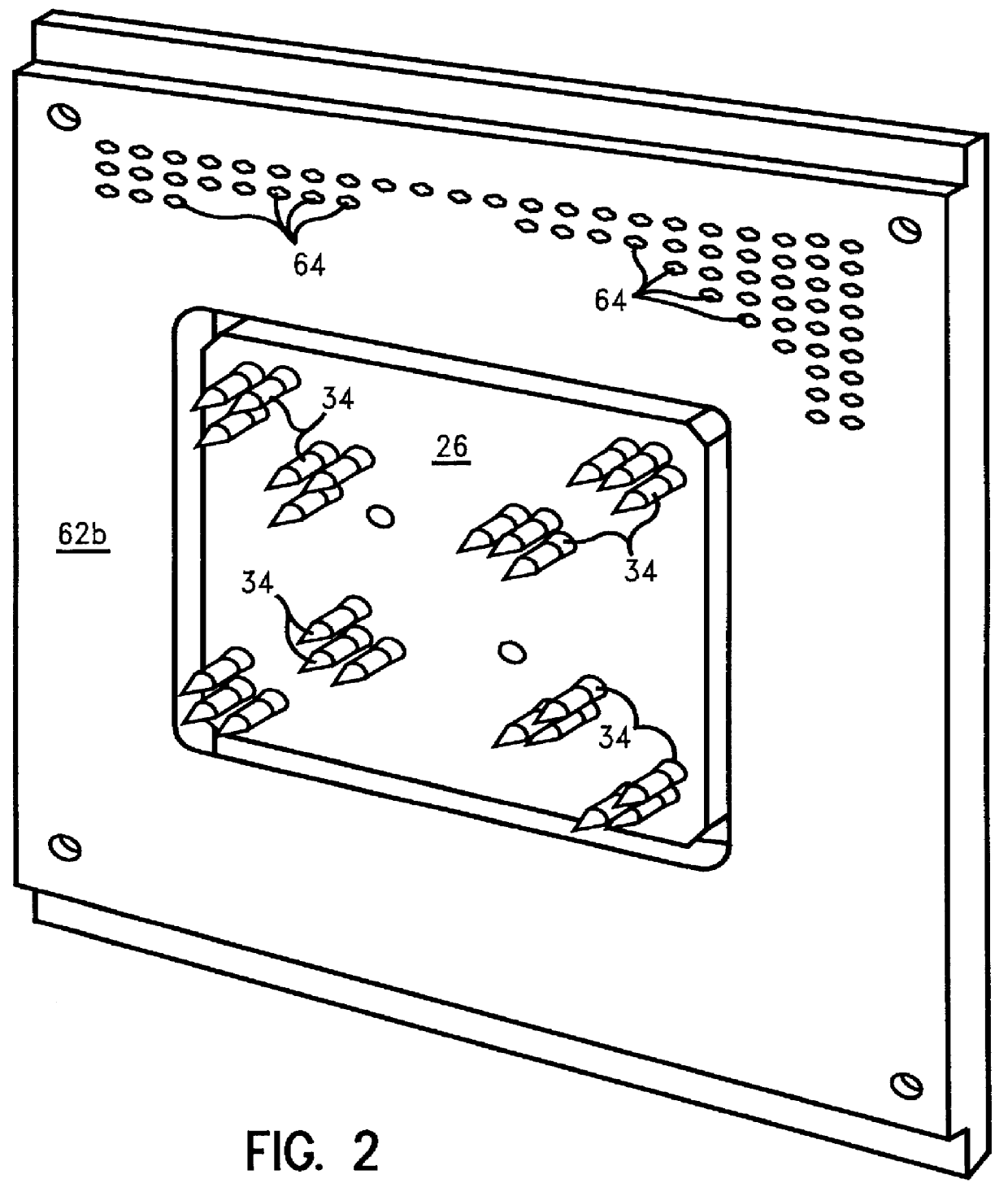

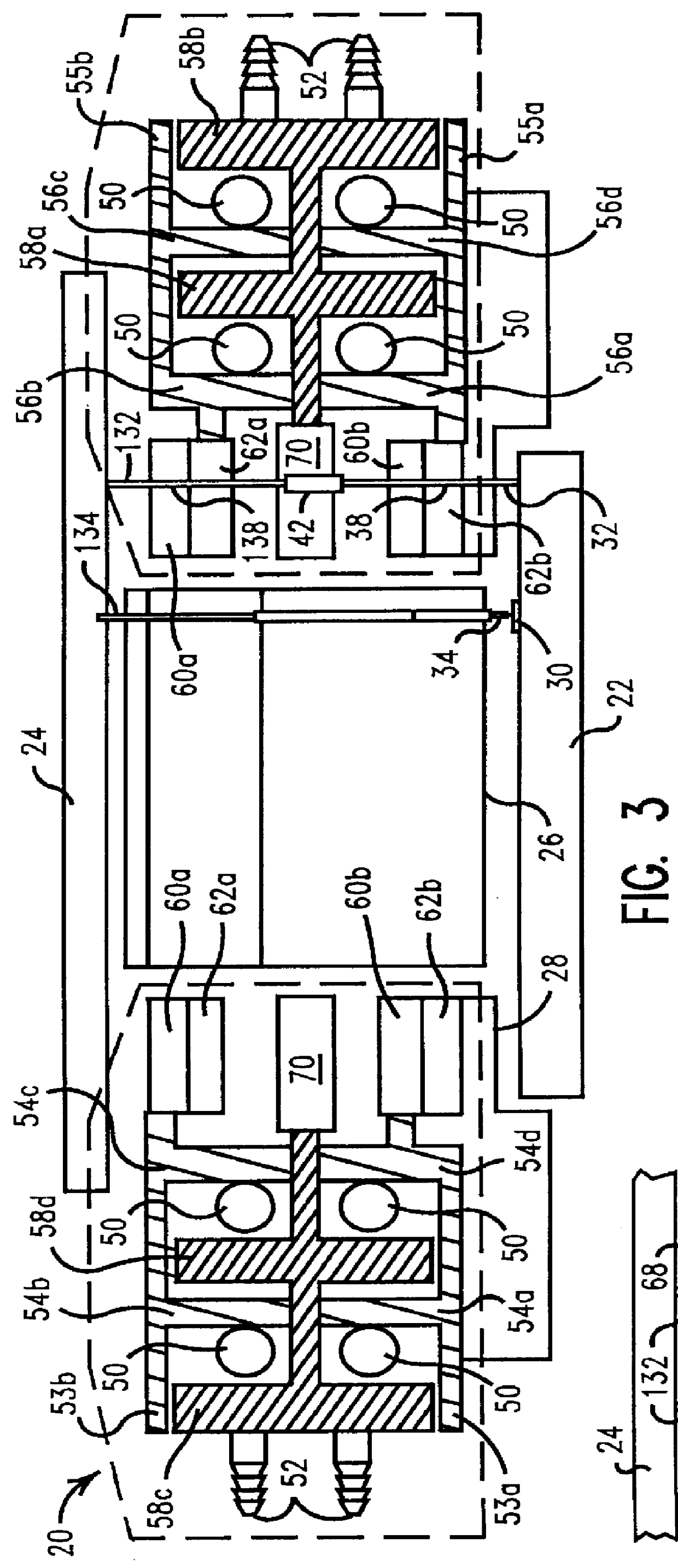

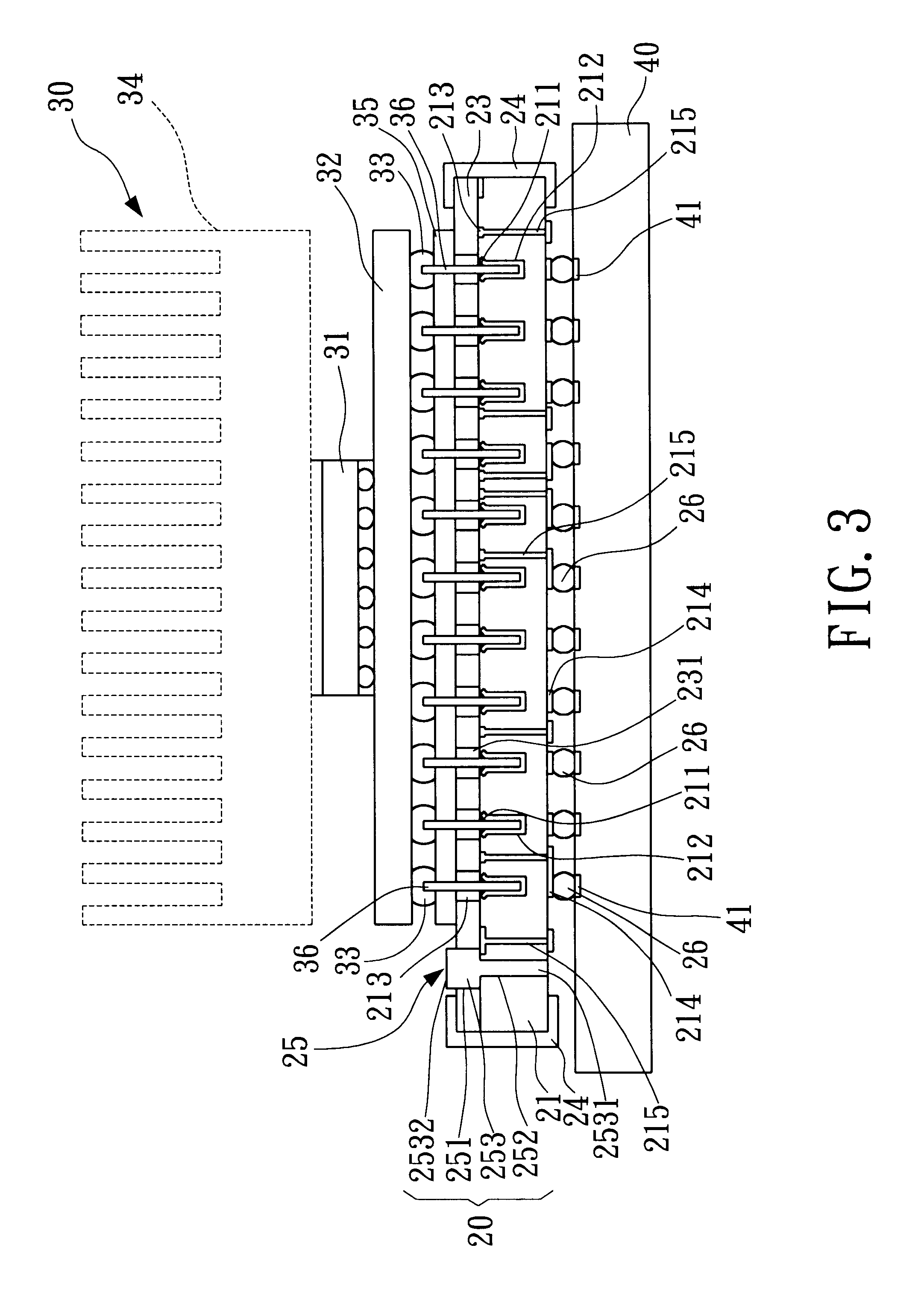

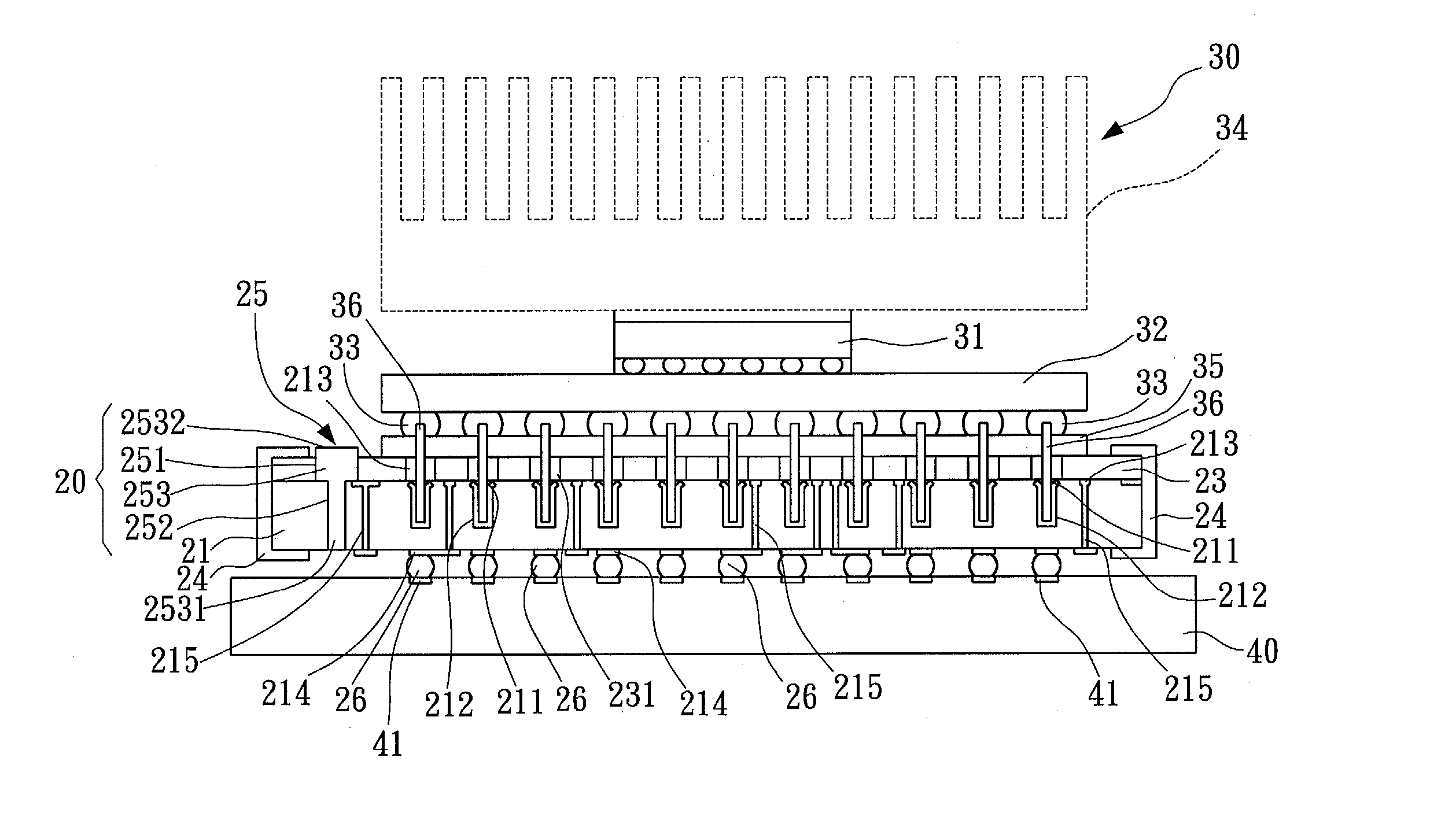

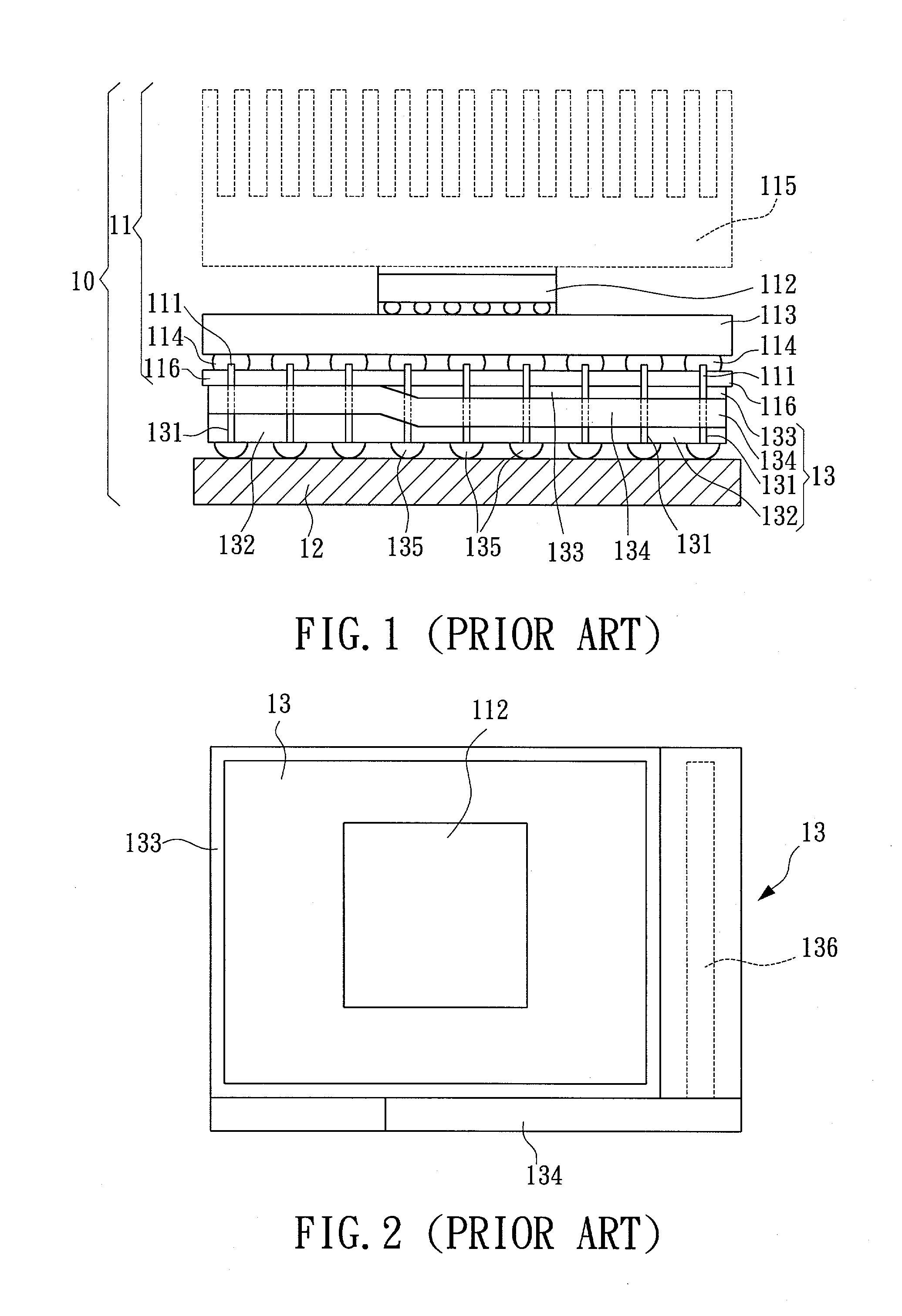

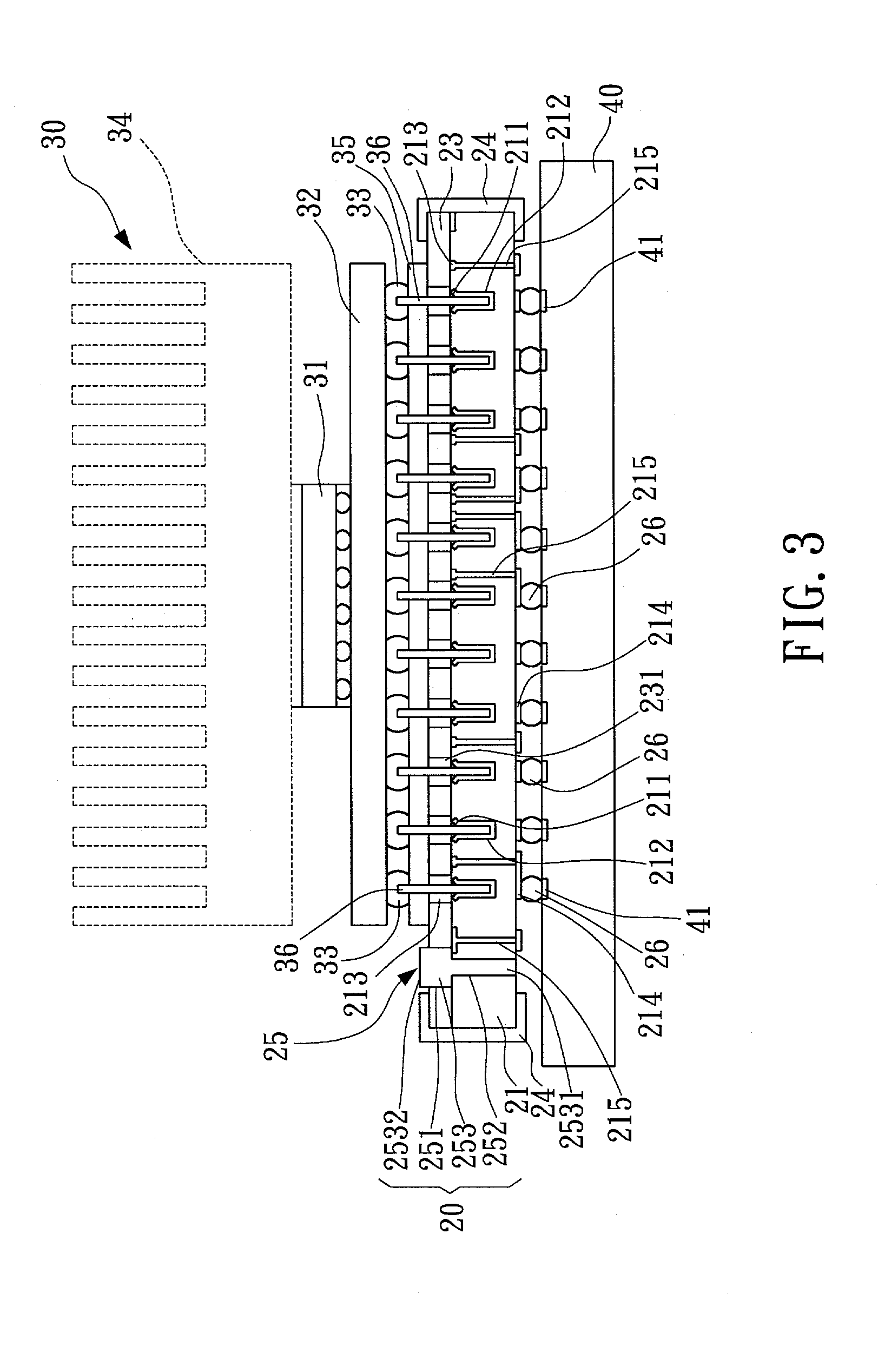

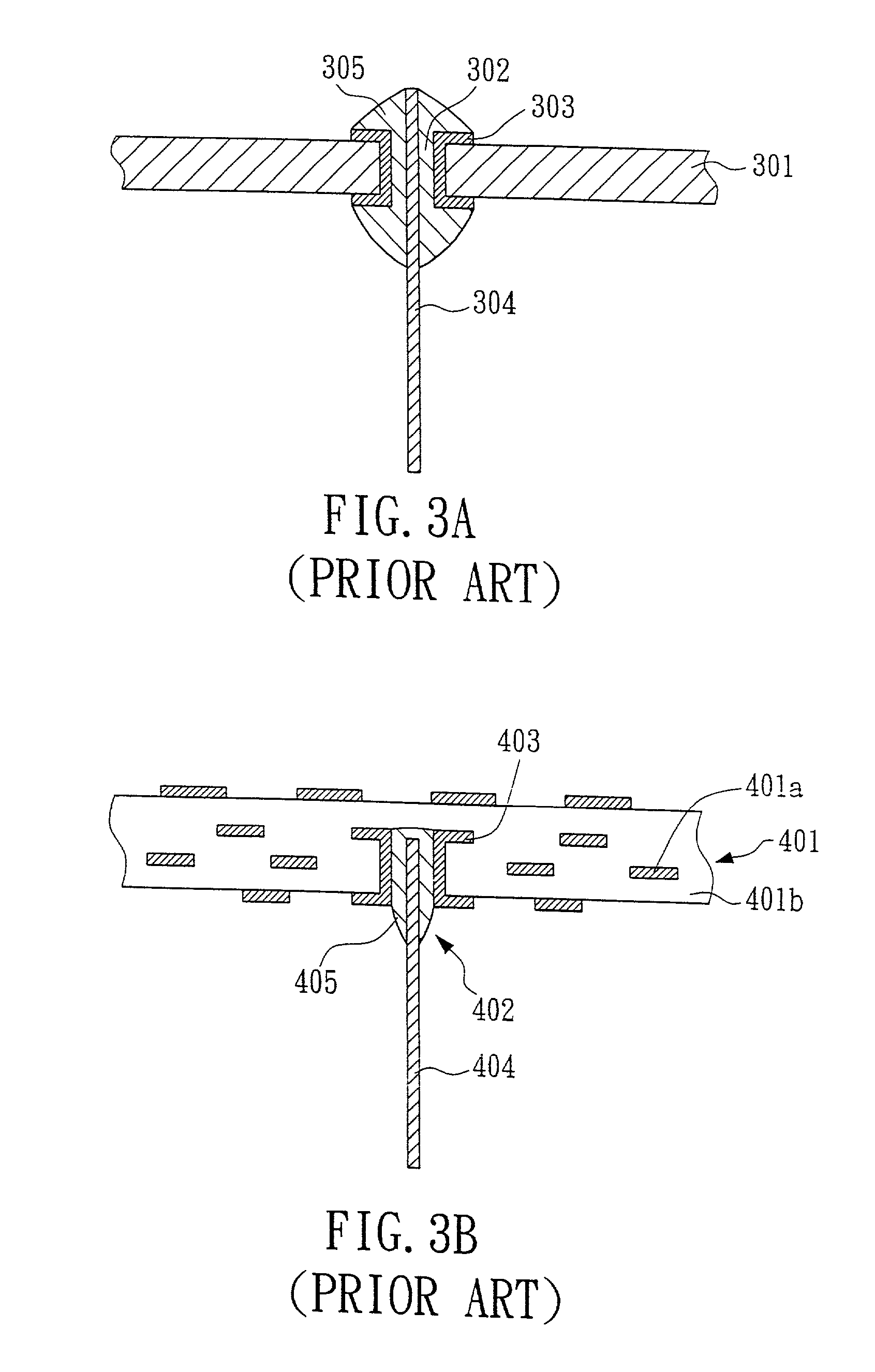

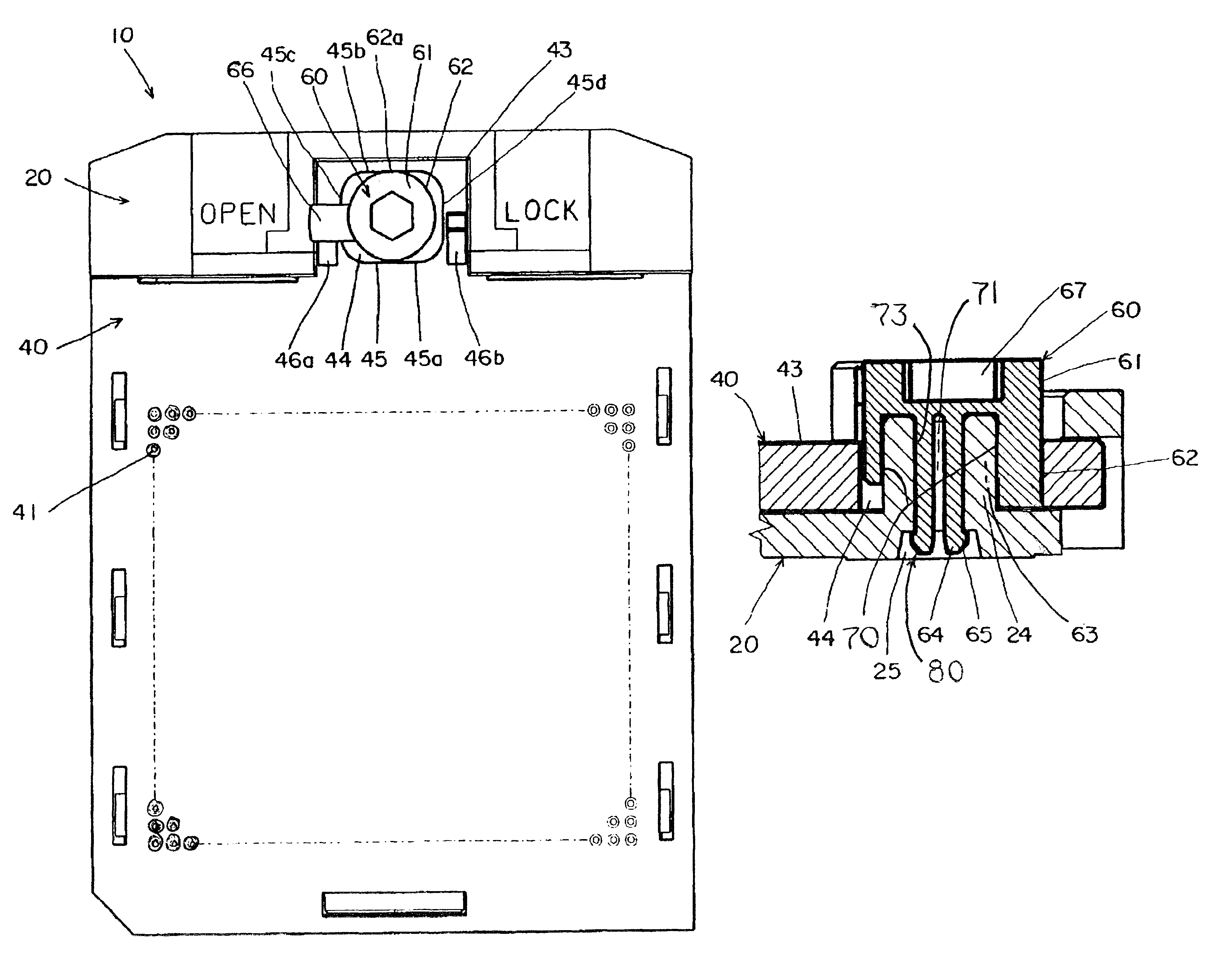

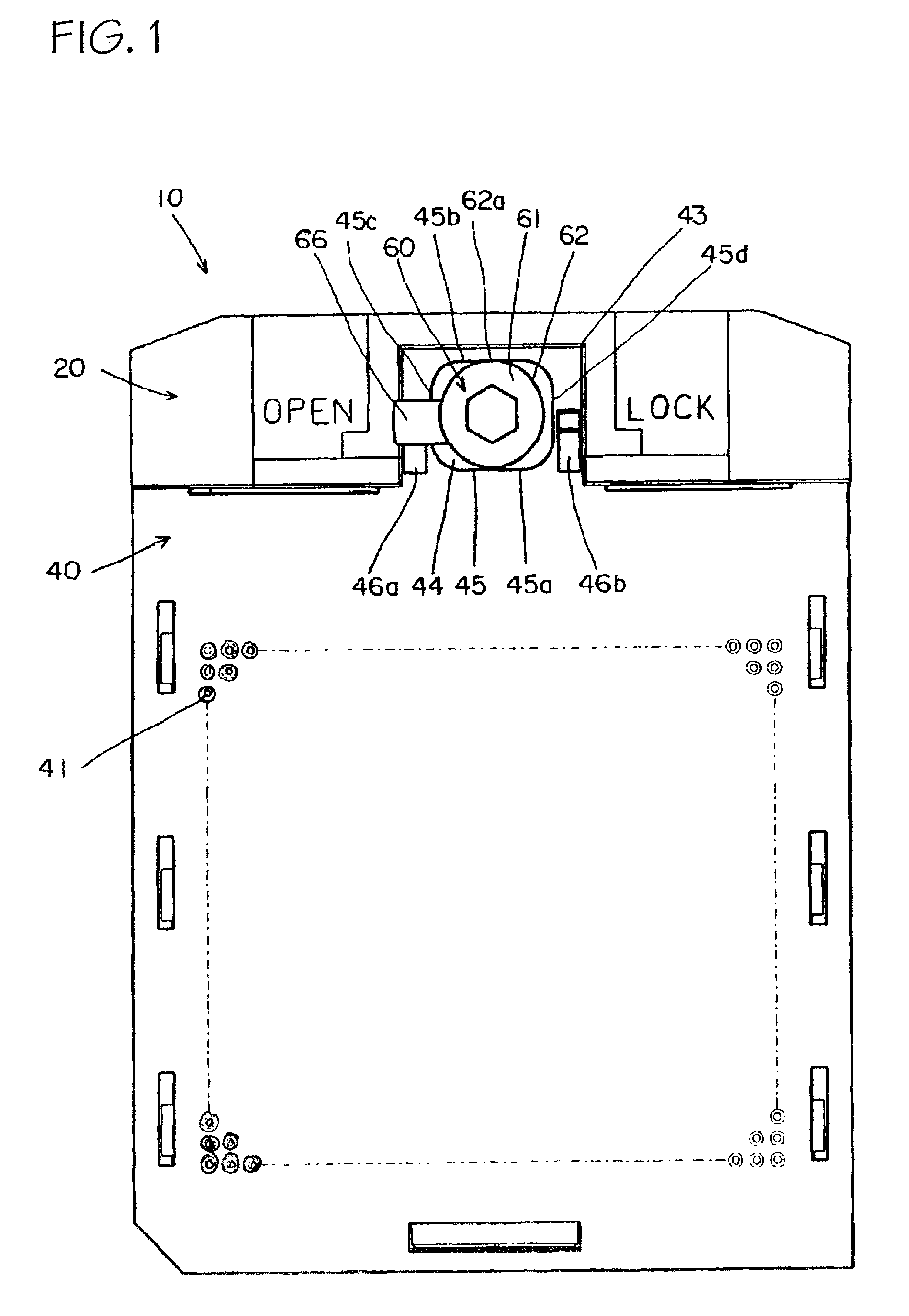

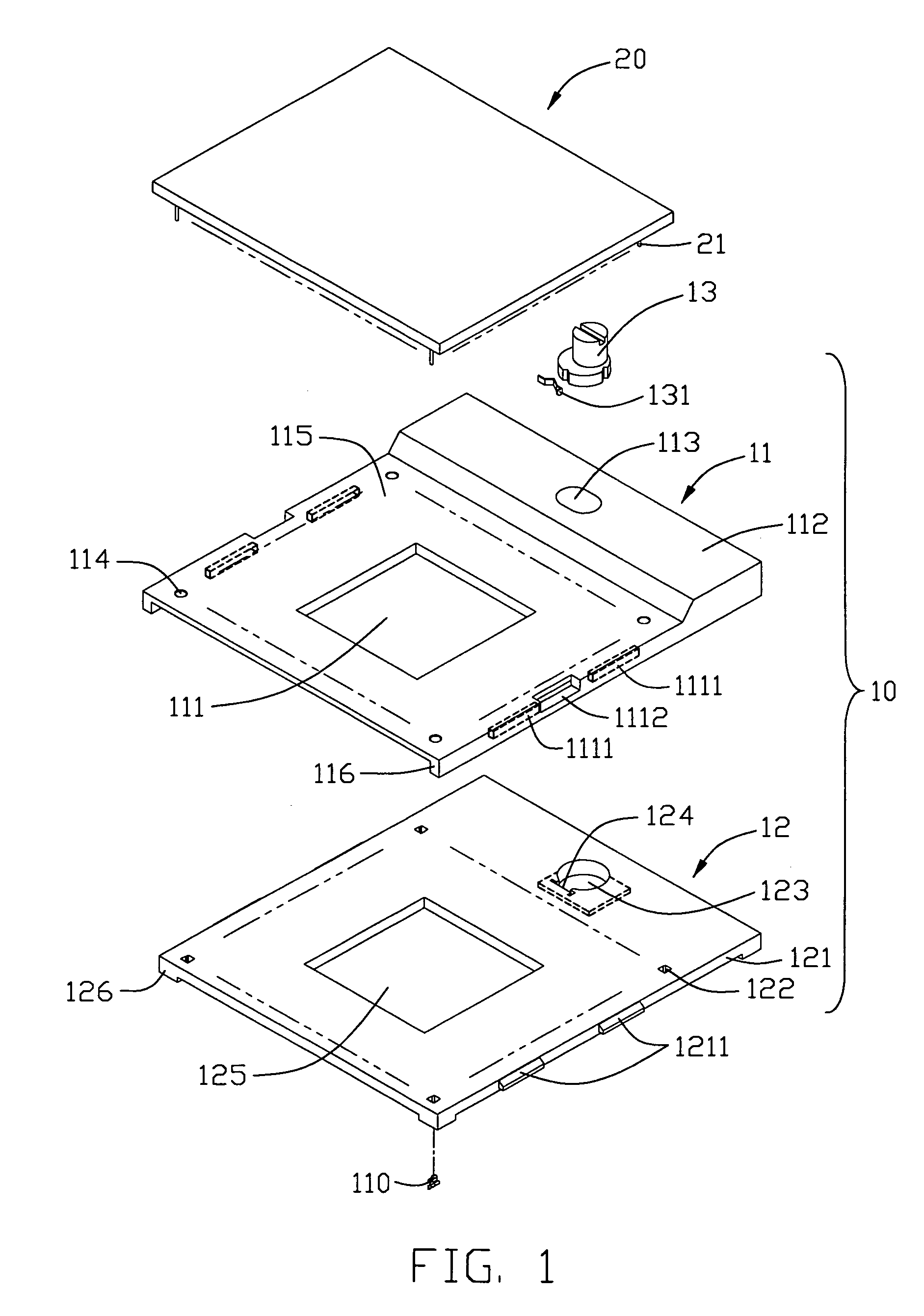

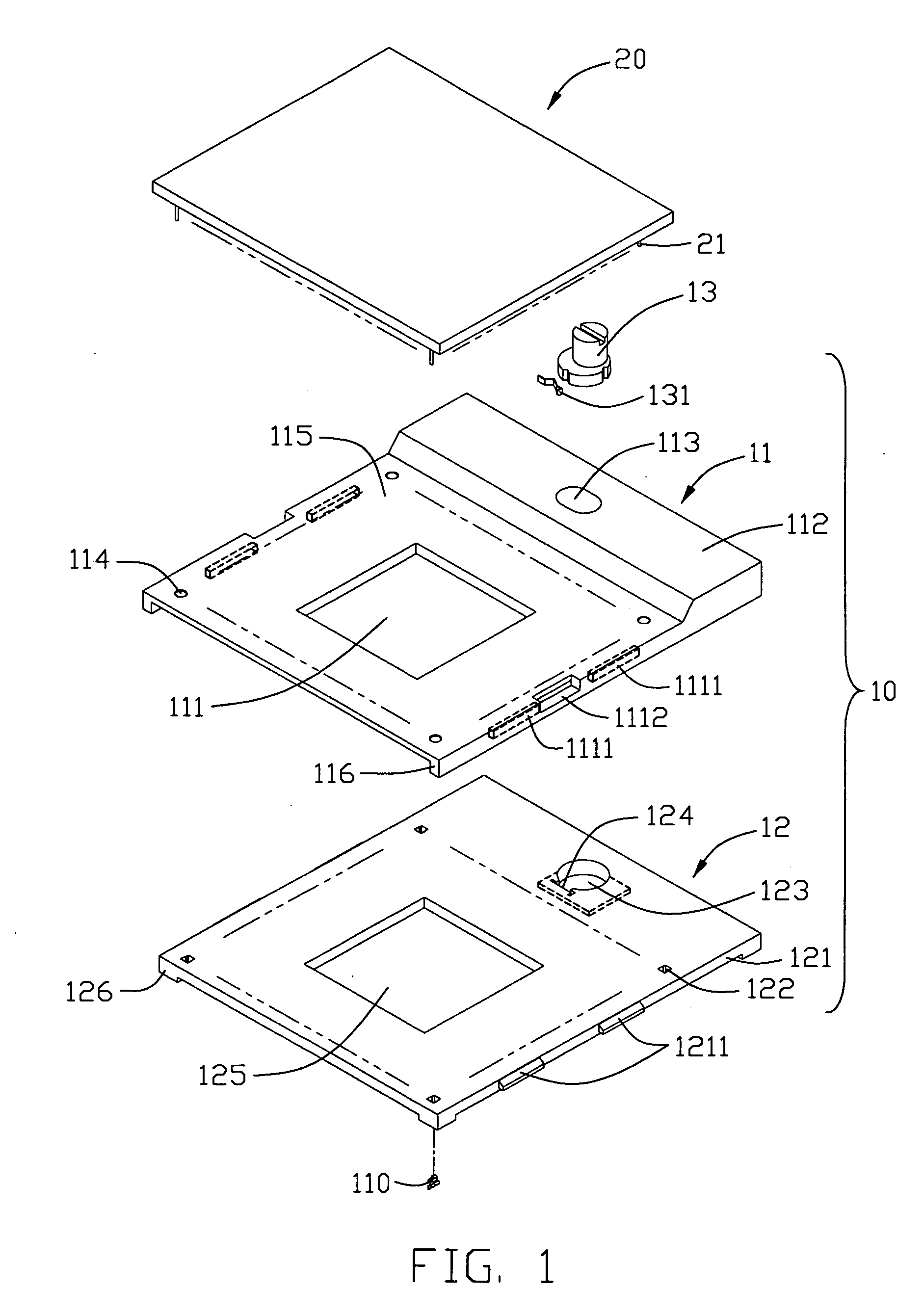

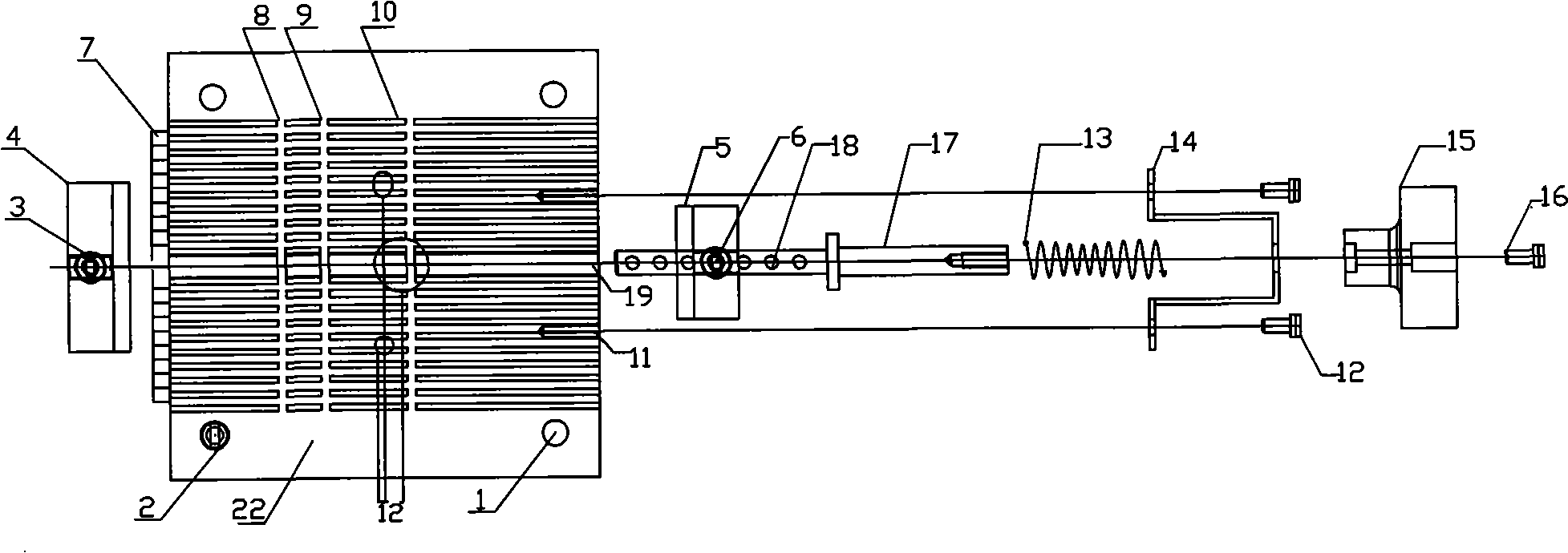

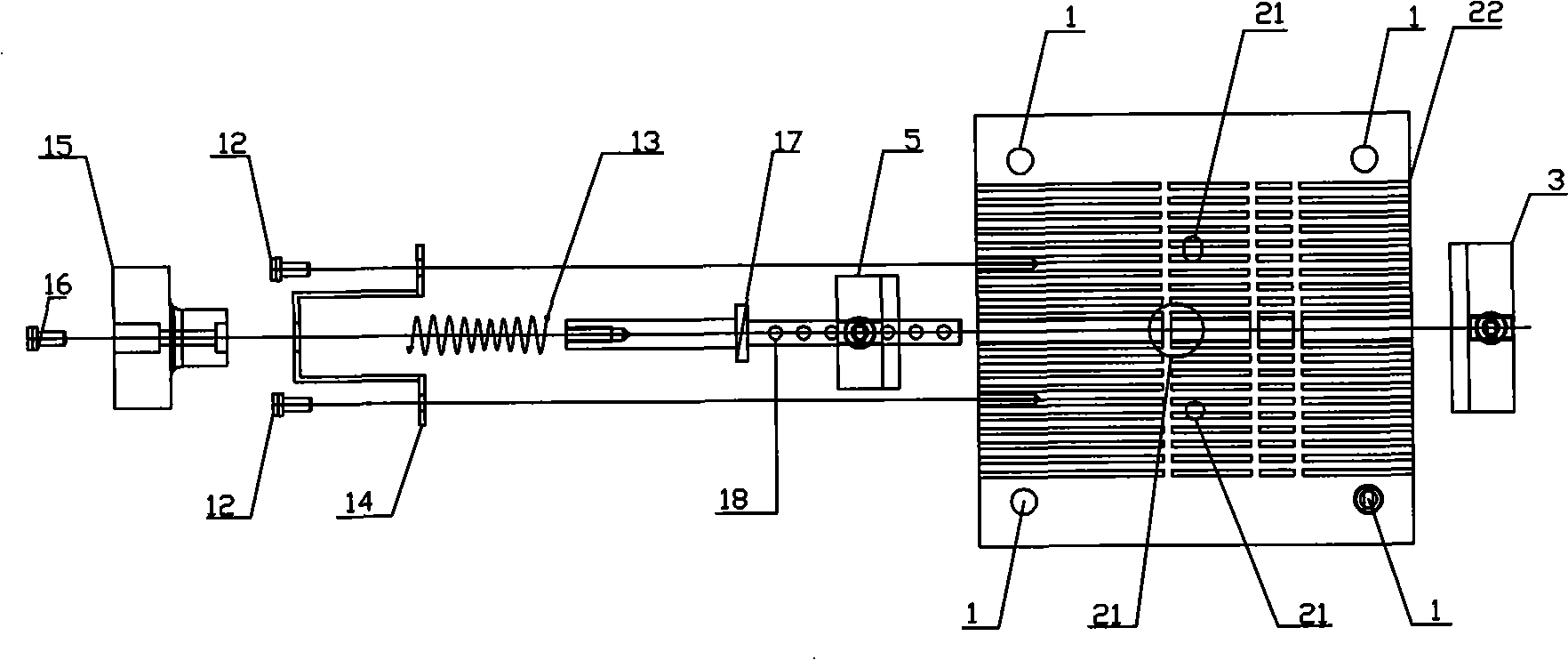

Pin grid array integrated circuit connecting device

InactiveUS6699046B2Engagement/disengagement of coupling partsPrinted circuit assemblingPin grid arrayEngineering

A pin grid array integrated circuit connecting device which including a substrate, a sliding slice, a guiding frame and a driving apparatus. Said substrate further includes multiple holes to hold pins of a integrated circuit package, multiple conductive positioning components in the holes to hold said pins and connect said pins electrically, circuit device with proper circuit layout and multiple electrical connecting spots on the bottom of said substrate which connecting said multiple conductive positioning components thru said circuit device. The extra electronic components placed on said substrate will provide the additional function. Said sliding slice is placed on the top of said substrate and can be moved relatively. Multiple holes are placed on said sliding slice and positioned correspondingly to the holes on said substrate. Said guiding frame is placed on at least the two opposite sides of said substrate which guide said sliding move linearly along the extension of said guiding frame. Said driving apparatus is connecting to said sliding slice and, by rotating horizontally, drive said sliding slice to move in a proper manner linearly.

Owner:VIA TECH INC

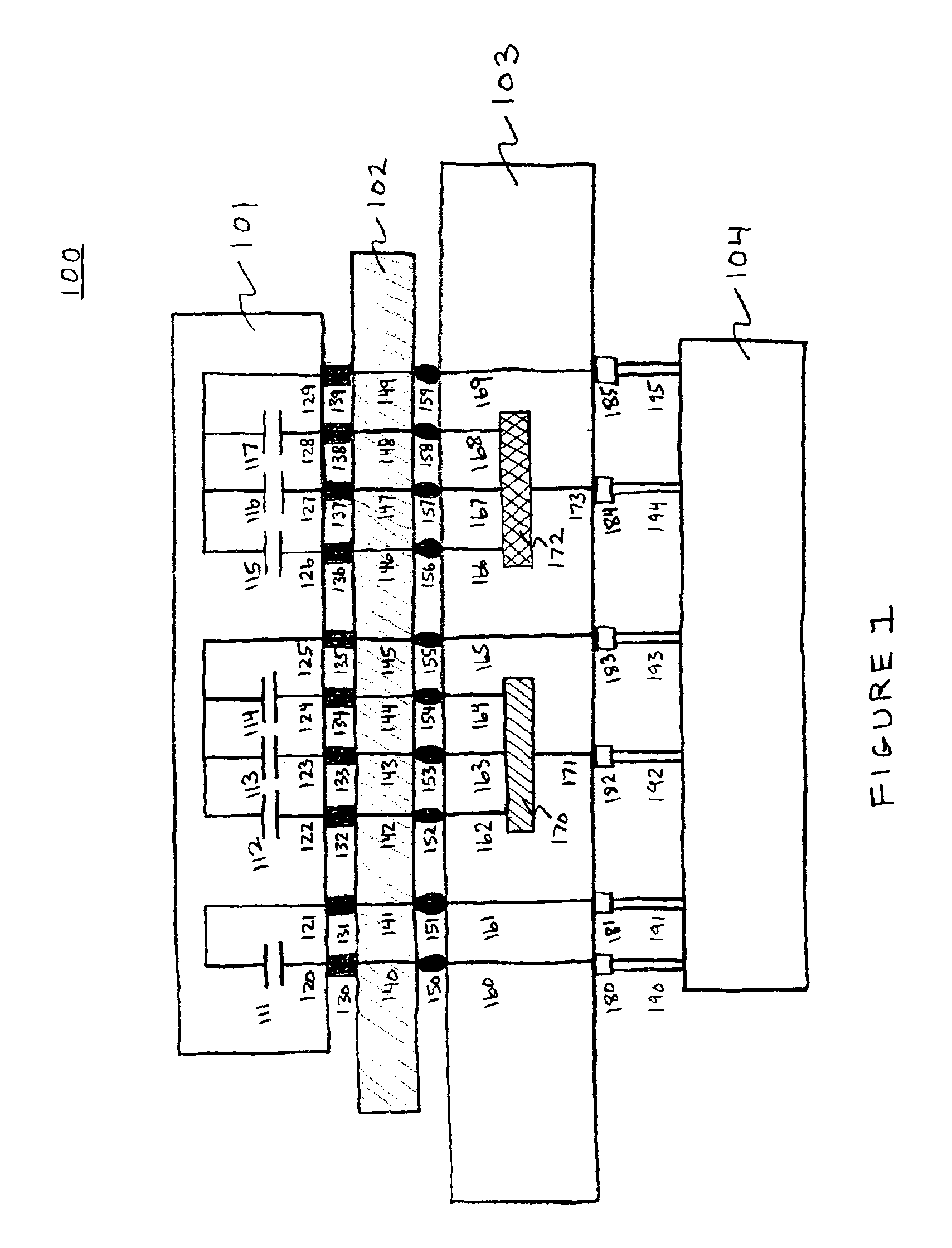

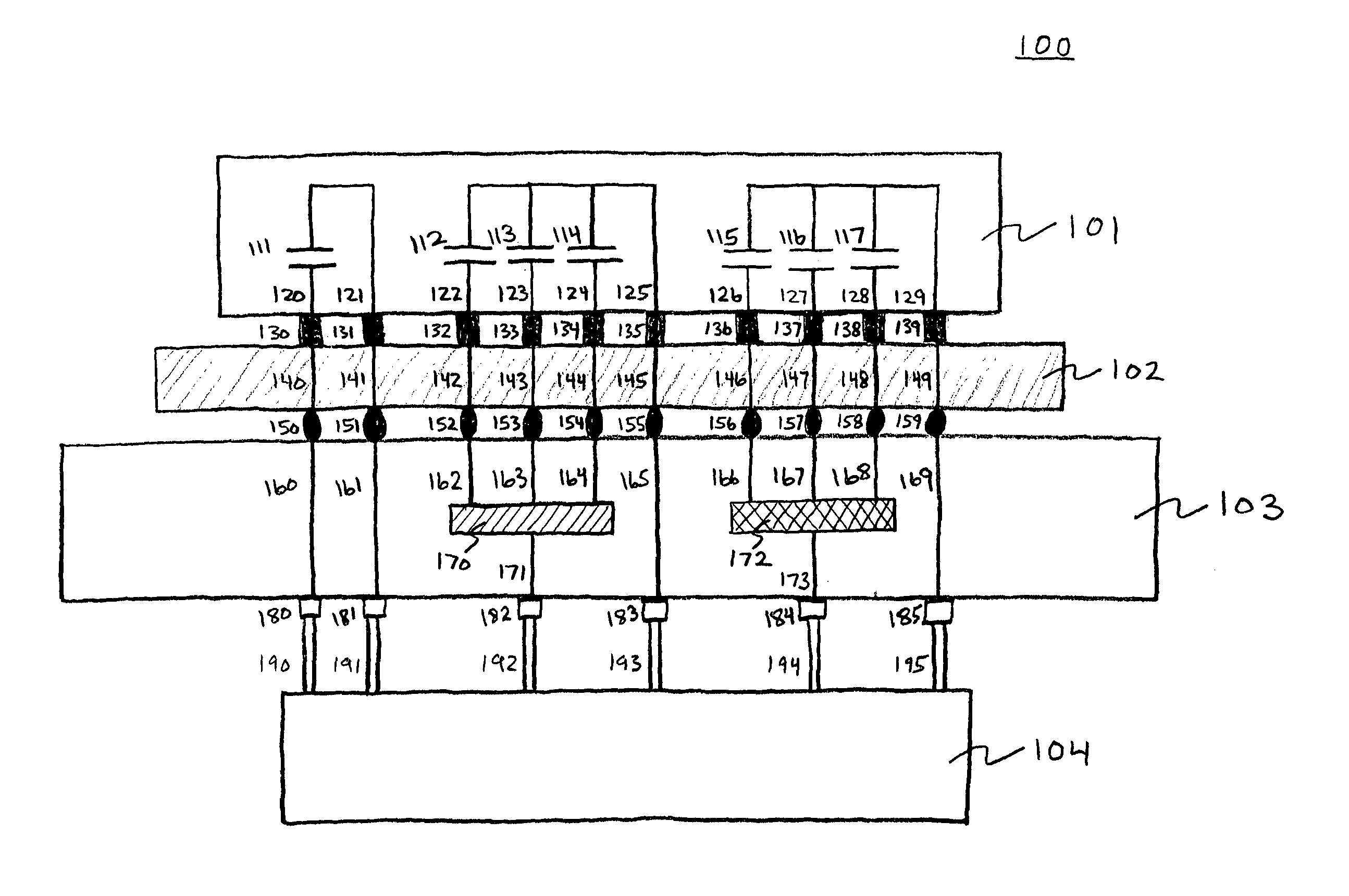

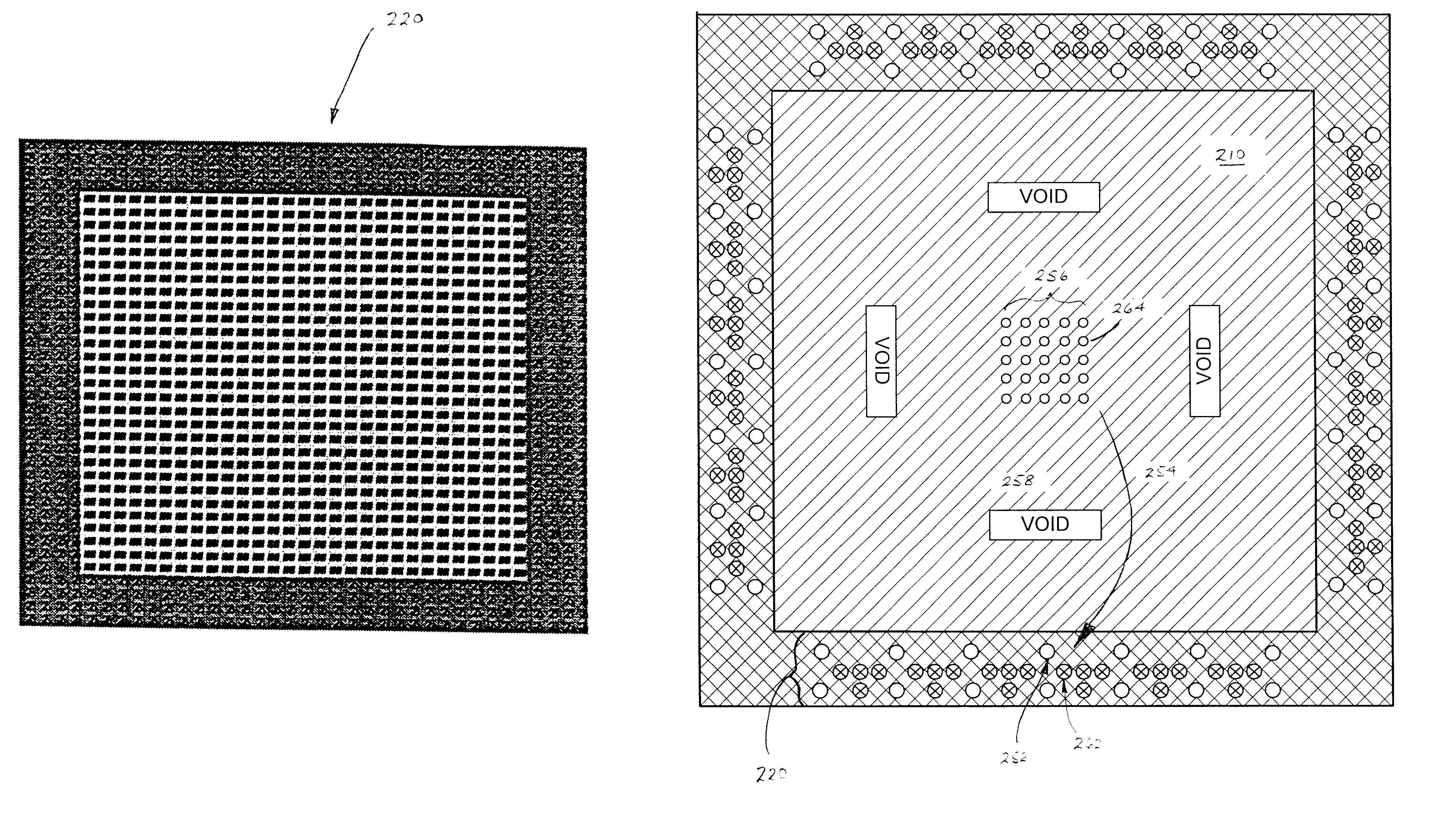

Integrated circuit carrier arrangement for reducing non-uniformity in current flow through power pins

InactiveUS6496383B1Semiconductor/solid-state device detailsMaterial analysis using microwave meansContact padEngineering

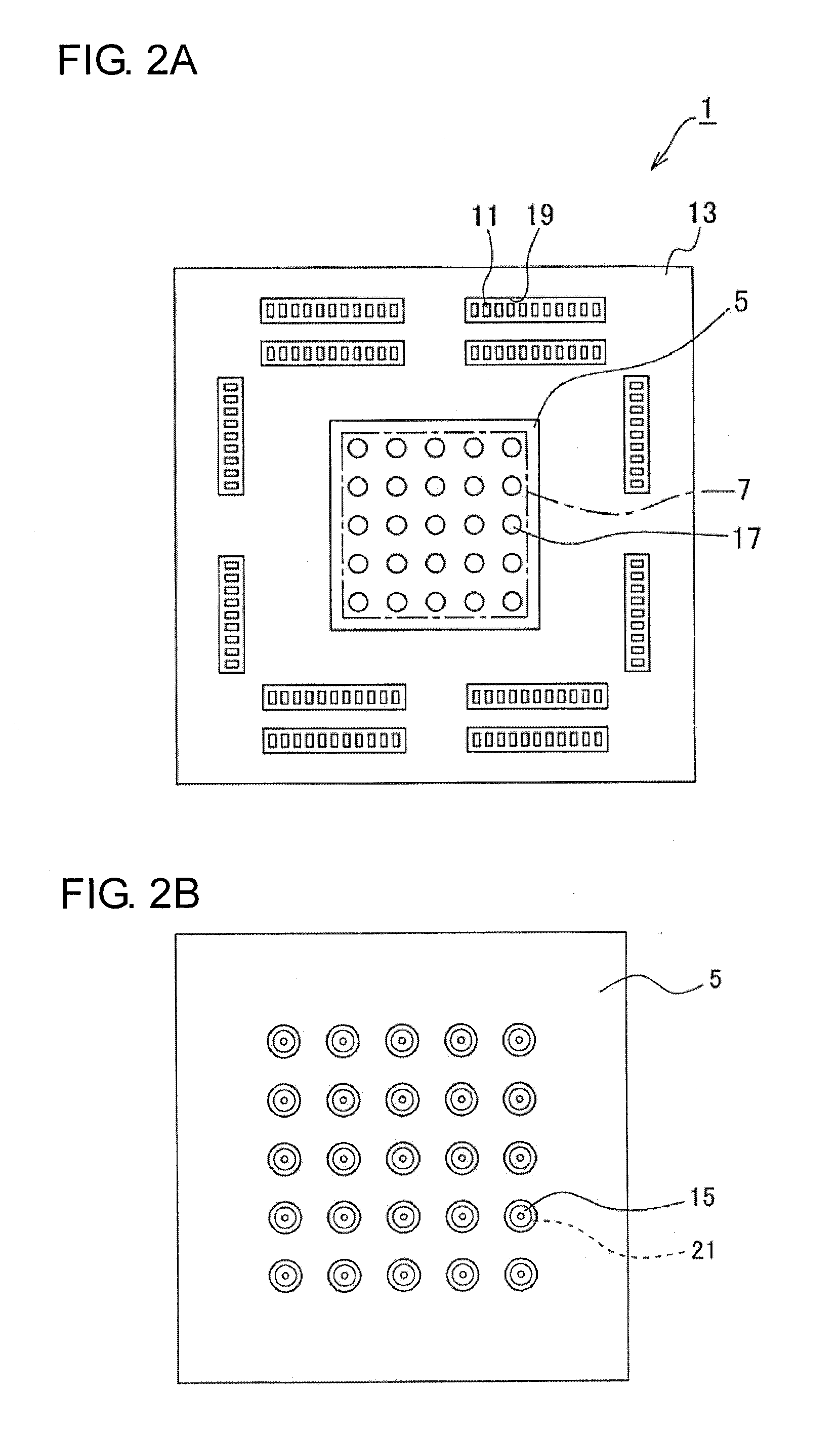

In an integrated circuit carrier having a large number of power pins allocated to an internal power plane, the current flowing through the power pins may divide very unevenly, and result in current flow through some of the power pins which exceeds the maximum specification for either the package pin or for the socket into which the package may be inserted. In such a package, the magnitude of the current flowing through the highest current power pin may be reduced by configuring the resistance of the power plane(s) and vias to provide approximately the same total resistance to every power pin location. Slots may be cut in a package power plane to alter the current path and raise the impedance of the conduction path between some of the package power pins and the internal contact pads otherwise having the lowest impedance. If the package, such as a pin-grid-array package, includes more than one row of pins along an edge of the package, the internal package vias may be arranged to provide an impedance from die footprint to the outer row of pins which is not substantially higher than that of the inner row of pins. In this fashion the aggregate current carrying capacity of the carrier may be increased by reducing the difference in current flow between power pins having the highest current flow and power pins having the lowest current flow. The current flow through all the power pins may then be operated nearer to the design maximum of the particular connector used, or the design maximum of the carrier itself.

Owner:GLOBALFOUNDRIES INC

Pin grid array integrated circuit connecting device

InactiveUS20030096514A1Engagement/disengagement of coupling partsPrinted circuit assemblingPin grid arrayEngineering

A pin grid array integrated circuit connecting device which comprises a substrate, a sliding slice, a guiding frame and a driving apparatus. Said substrate further comprises multiple holes to hold pins of a integrated circuit package, multiple conductive positioning components in the holes to hold said pins and connect said pins electrically, circuit device with proper circuit layout and multiple electrical connecting spots on the bottom of said substrate which connecting said multiple conductive positioning components thru said circuit device. The extra electronic components placed on said substrate will provide the additional function. Said sliding slice is placed on the top of said substrate and can be moved relatively. Multiple holes are placed on said sliding slice and positioned correspondingly to the holes on said substrate. Said guiding frame is placed on at least the two opposite sides of said substrate which guide said sliding move linearly along the extension of said guiding frame. Said driving apparatus is connecting to said sliding slice and, by rotating horizontally, drive said sliding slice to move in a proper manner linearly.

Owner:VIA TECH INC

Socket connection test modules and methods of using the same

InactiveUS20060006894A1Electronic circuit testingElectrical measurement instrument detailsCapacitancePin grid array

Test modules, systems, and methods employing capacitors for the testing of the solder joint connections between a printed circuit board (PCB) and a socket of a device are presented in embodiments of the current invention. A test module having capacitors in parallel, and in particular embedded capacitors, can be used to test tied traces and their solder joint connections by measuring the total capacitance of the capacitors. Embodiments of the current invention present no-power tests that can be used with a variety of testing platforms and test fixtures, such as in-circuit testing (ICT) and manufacturing defect analysis (MDA.) Additionally, the test module can be used with a variety of sockets, such as a ball grid array, a pinned grid array, and a land grid array.

Owner:INTEL CORP

Ball grid array to pin grid array conversion

ActiveUS20130127041A1Semiconductor/solid-state device detailsSoldering apparatusContact padPin grid array

Ball grid array to pin grid array conversion methods are provided. An example method can include coupling a plurality of solder balls to a respective plurality of pin grid array contact pads. Each of the plurality of solder balls is encapsulated in a fixed material. A portion of the plurality of solder balls and a portion of the fixed material is removed to provide a plurality of exposed solder balls. The exposed solder balls are softened and each of a plurality of pin members is inserted in a softened, exposed, solder ball. The plurality of pin members forms a pin grid array package.

Owner:STMICROELECTRONICS SRL

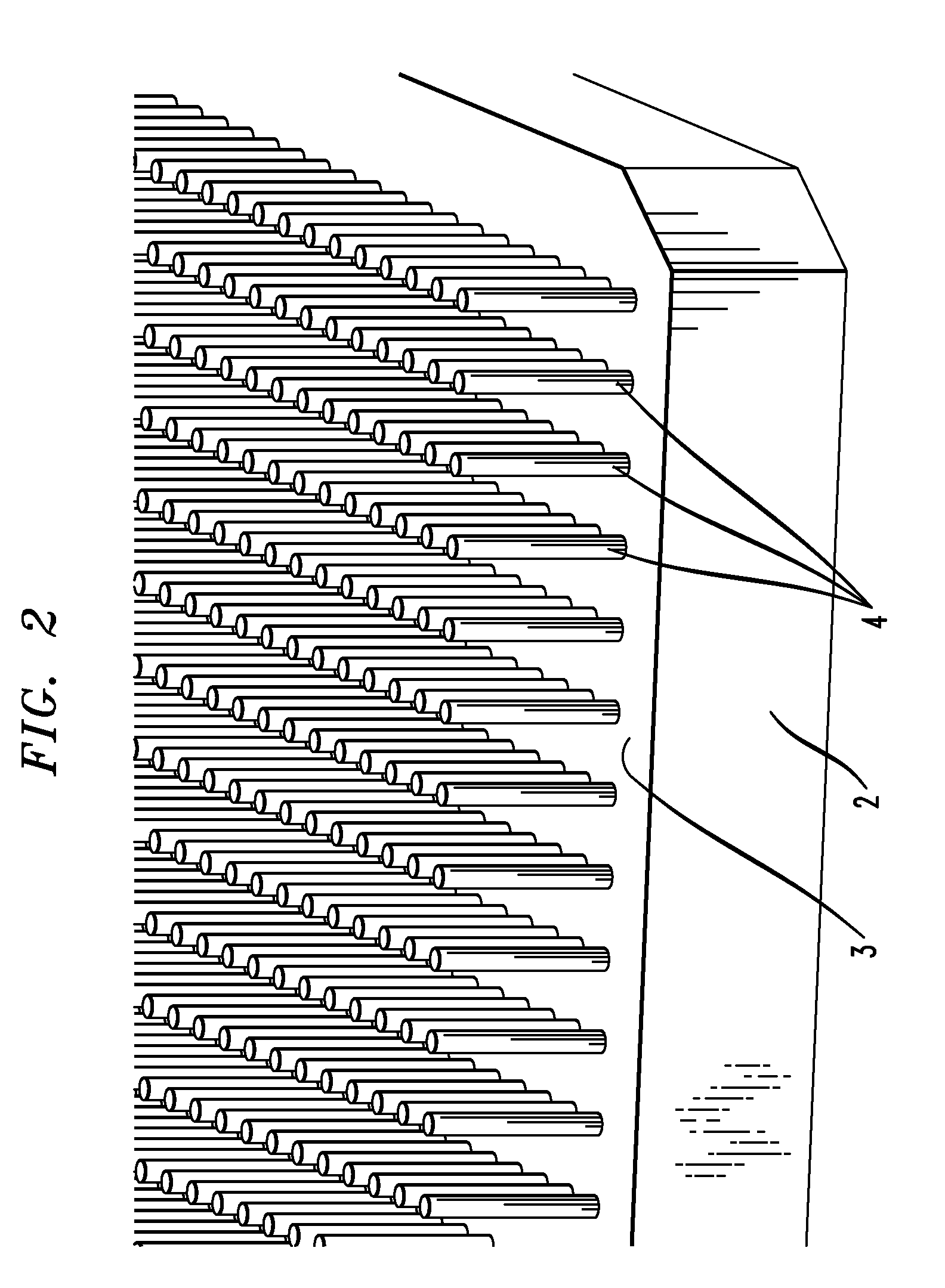

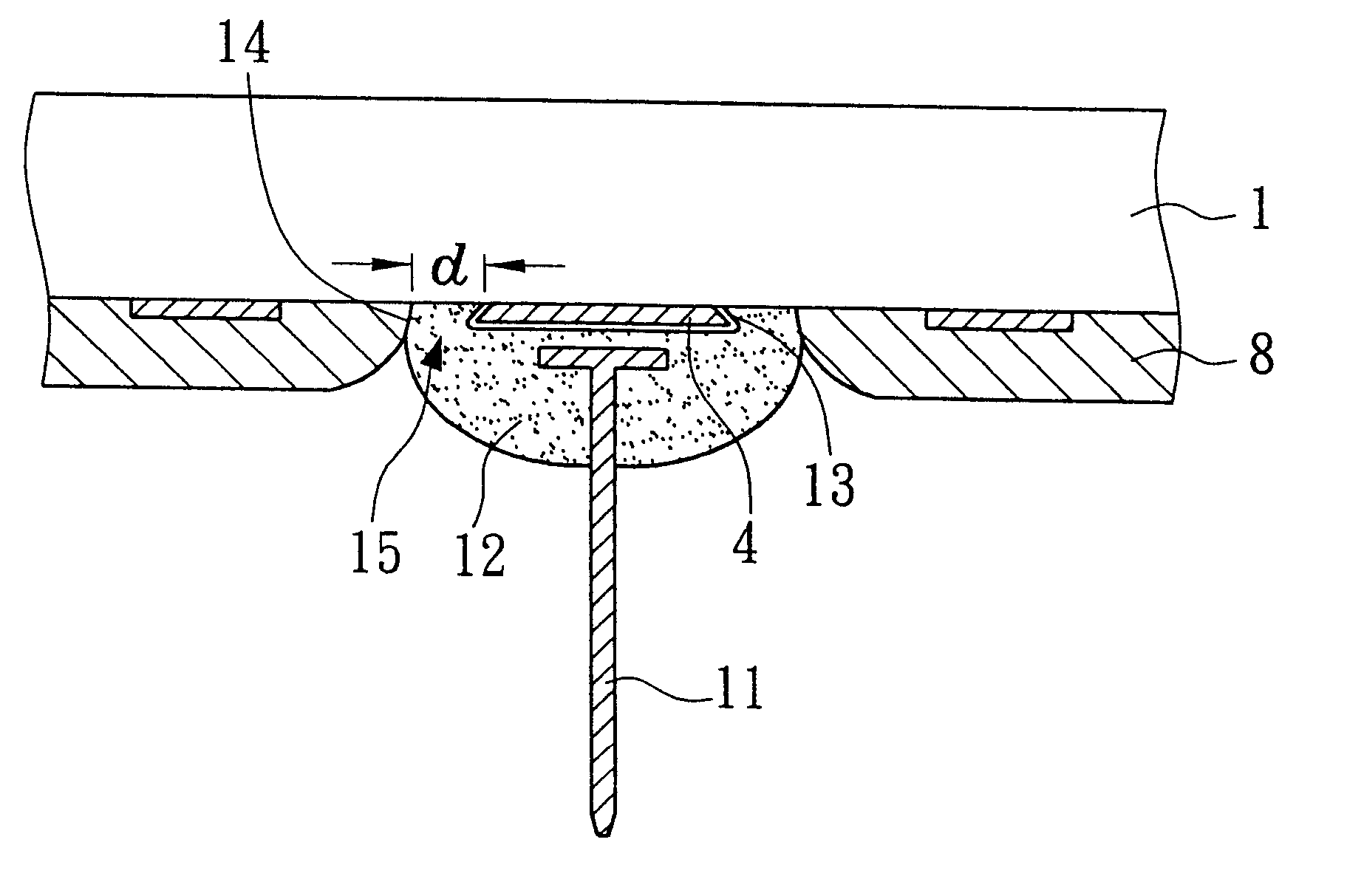

Pin attachment by a surface mounting method for fabricating organic pin grid array packages

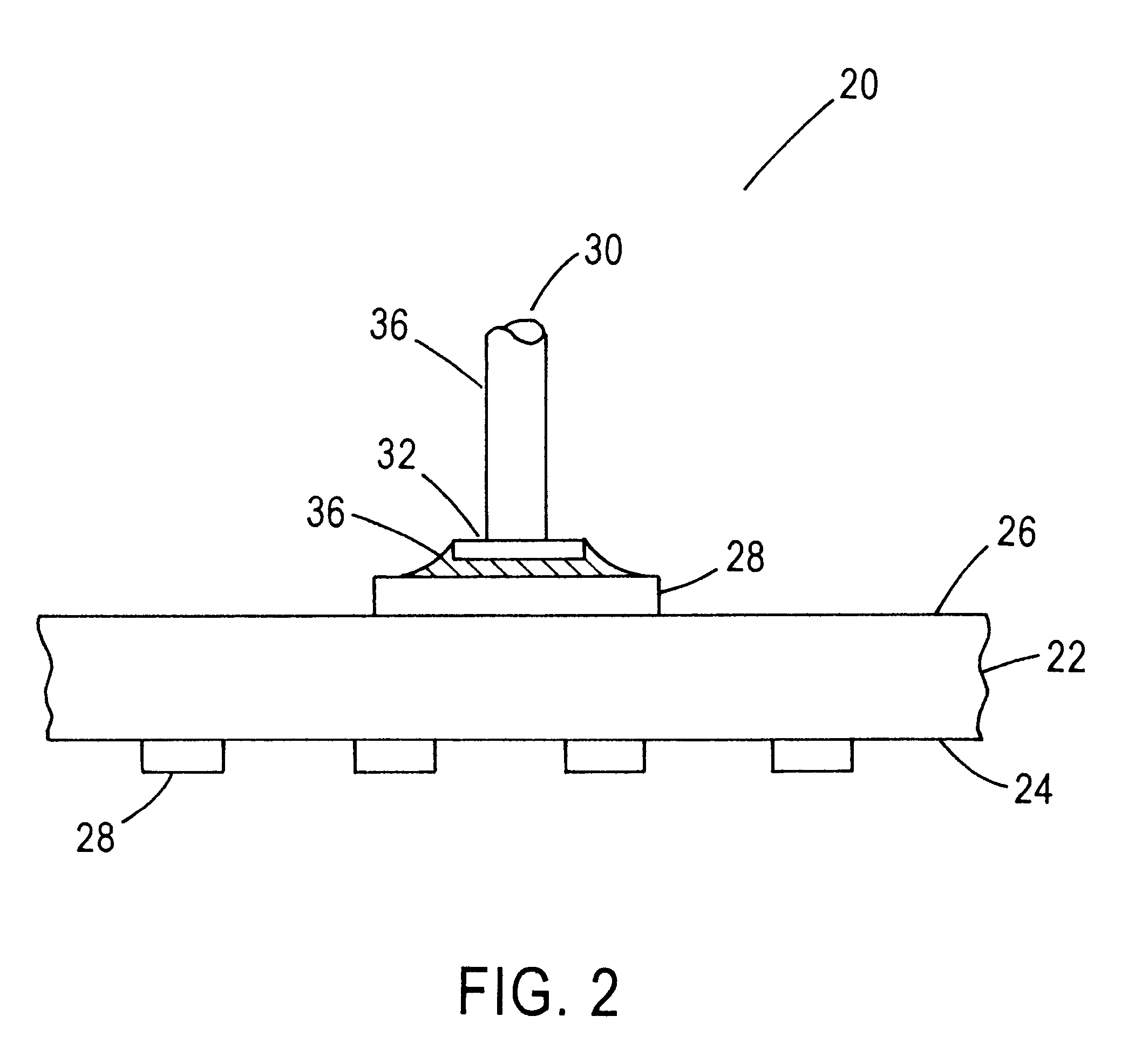

InactiveUS20020179692A1High strengthImprove reliabilityPrinted circuit assemblingFinal product manufactureSolder maskContact pad

A pin attachment method for mounting the pins on a wiring substrate for fabricating a pin grid array package is disclosed. There is provided an organic wiring board including a surface bearing electrical circuitry which includes at least one contact pad for receiving a pin. A solder mask layer which is placed on the board surface and patterned to expose the pad. The solder mask layer which does not cover any portion of the pad and forms a well by the perimeter of the solder mask layer around the pad. Subsequently, a pin and a solder material which are placed over said pad in the well. The pin which is soldered to the pad by a temperature sufficient to melt the solder material.

Owner:PHOENIX PRECISION TECH CORP

Camera based pin grid array (PGA) inspection system with pin base mask and low angle lighting

InactiveUS7755376B2Electric connection testingMaterial analysis by optical meansPin grid arrayEffect light

An inspection system, for inspecting pin grid arrays on integrated circuit devices includes a pin base mask configured to receive a device having a pin grid array. A dark-field, low-angle lighting system emits light onto the pin grid array. The pin base mask and low-angle lighting system provide for a clear and definitive image of the pin grid array. A camera captures the image of the pin grid array. A processor, coupled to the camera, analyzes the images captured by the camera. Based on the captured image, the processor determines whether any pins on the pin grid array are bent or missing, or whether there are extra pins present.

Owner:DELTA DESIGN

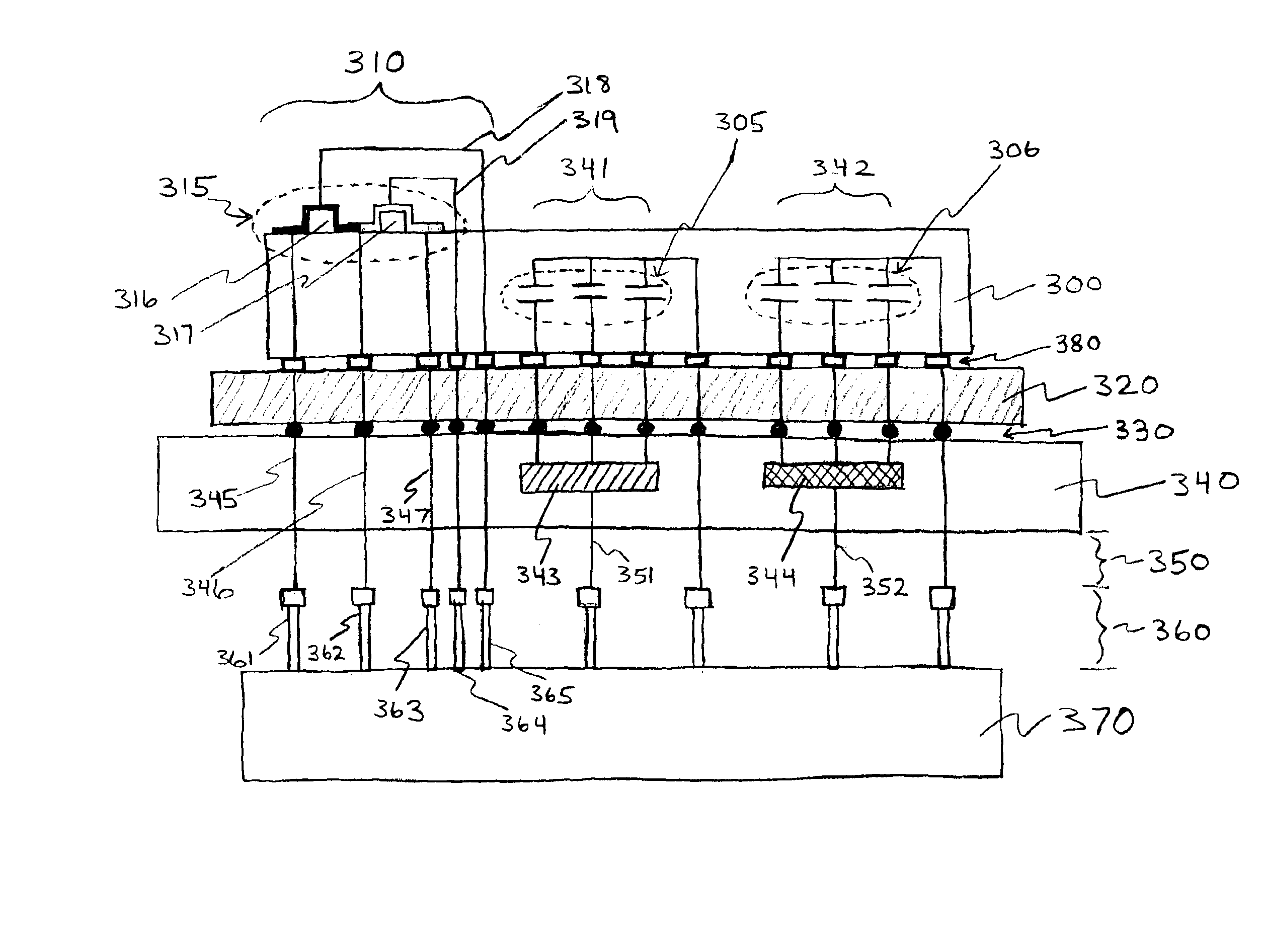

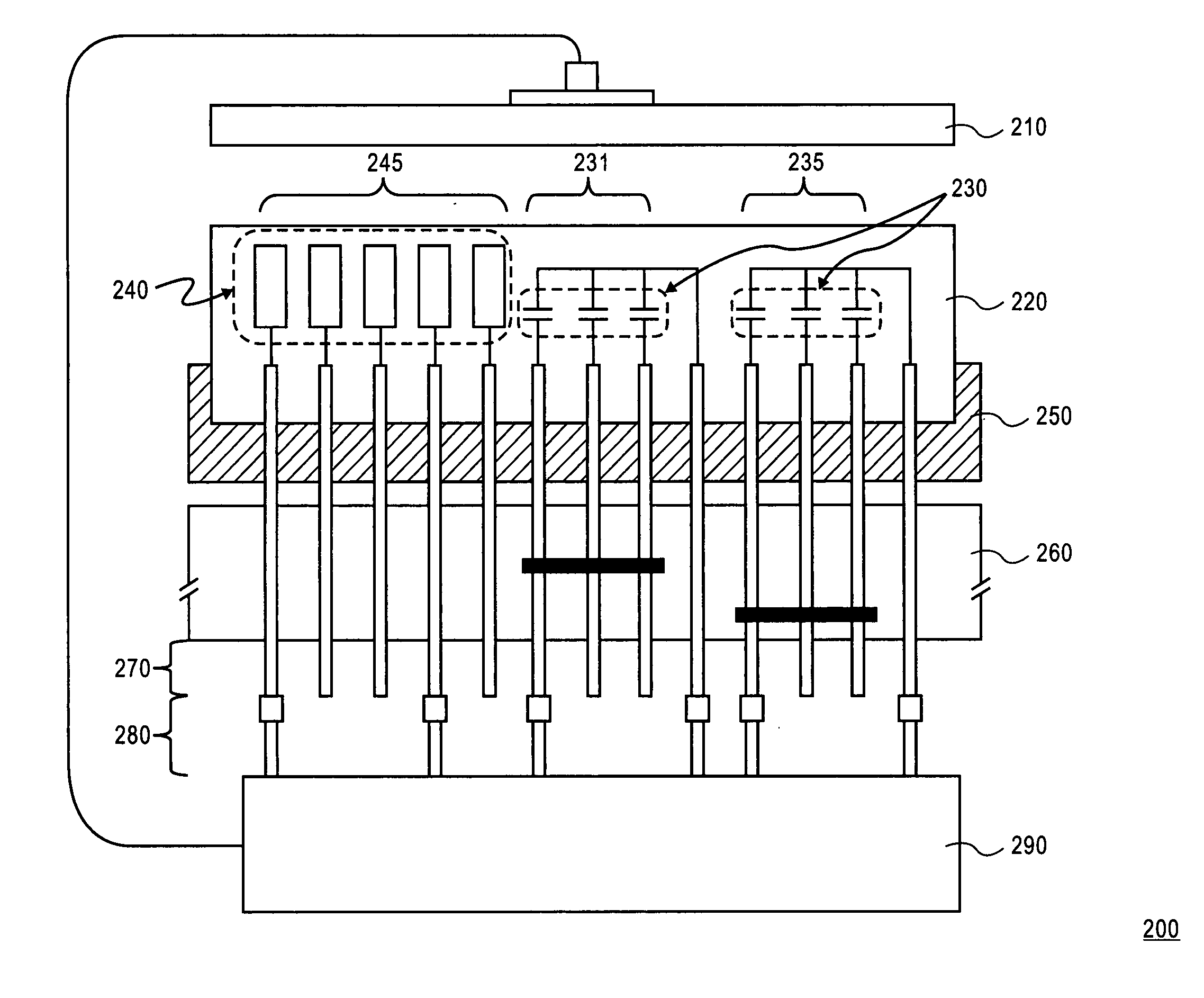

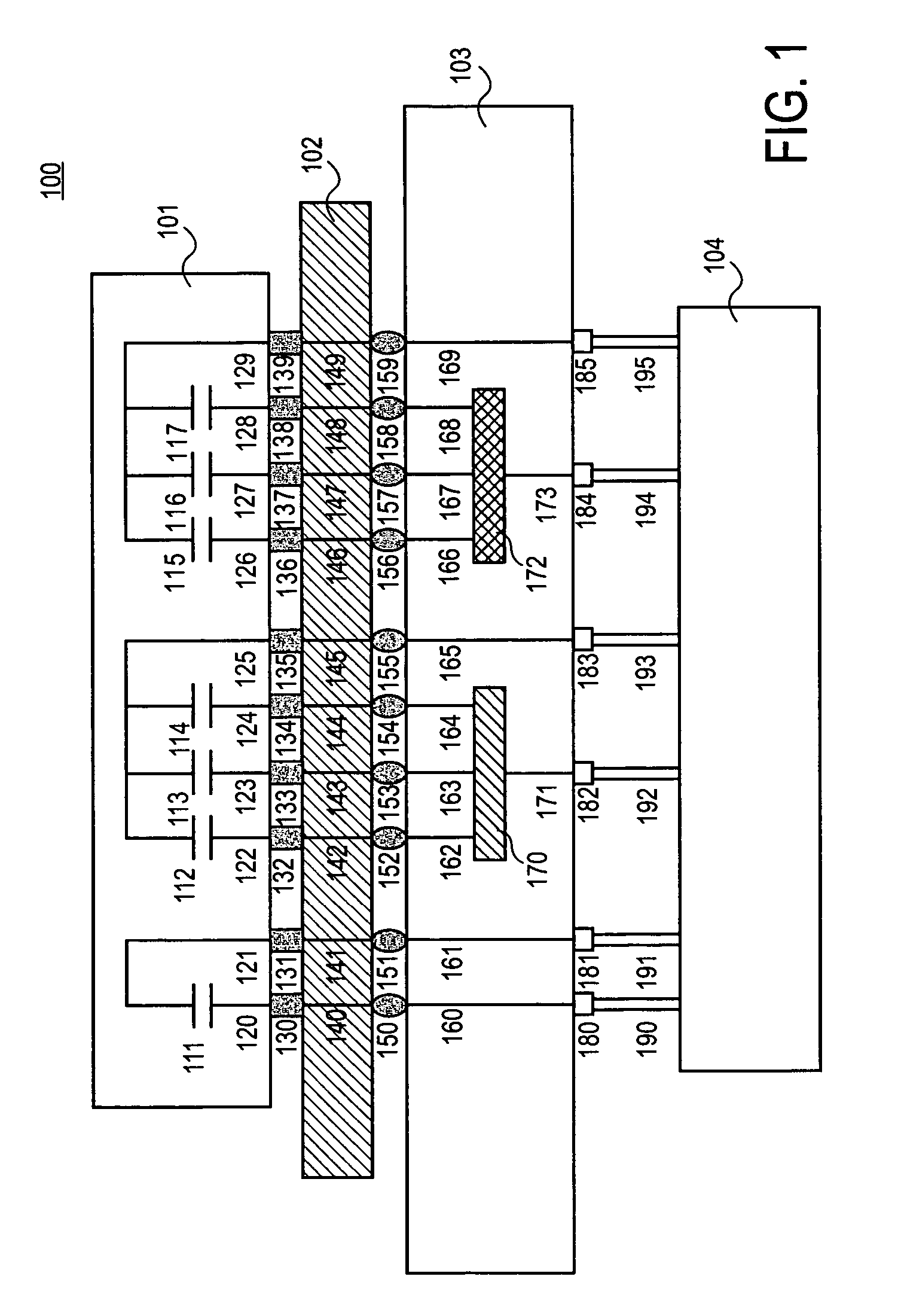

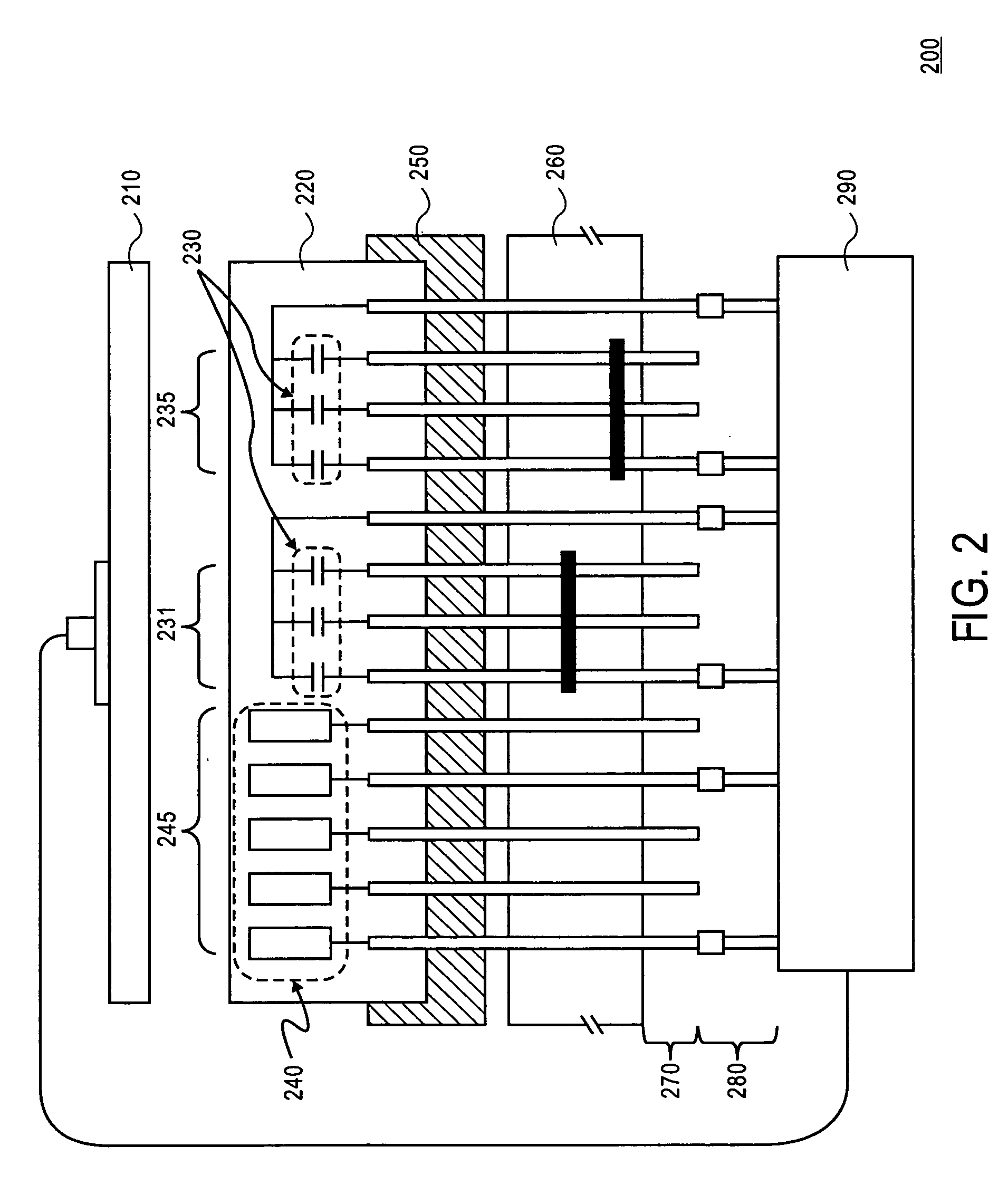

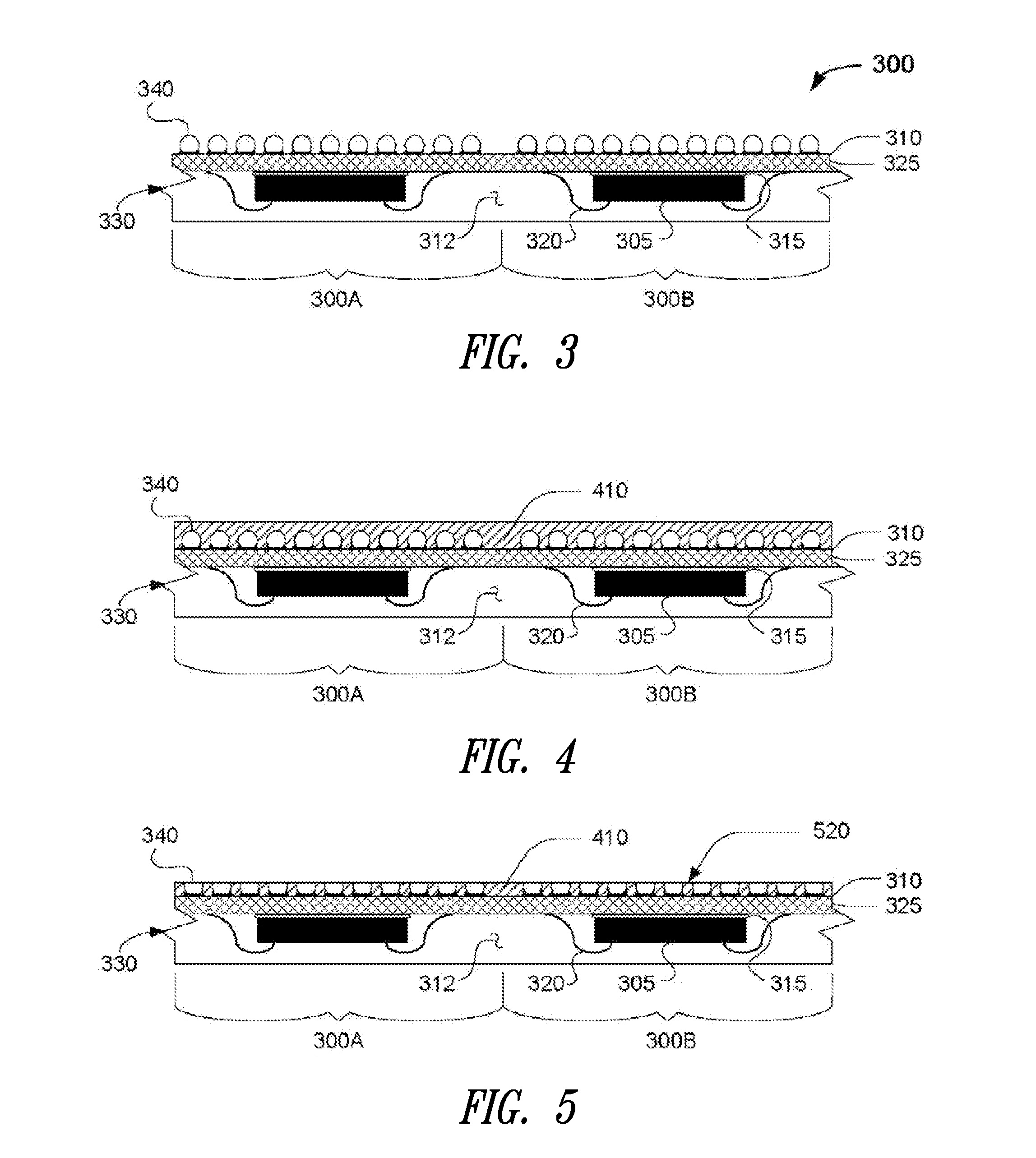

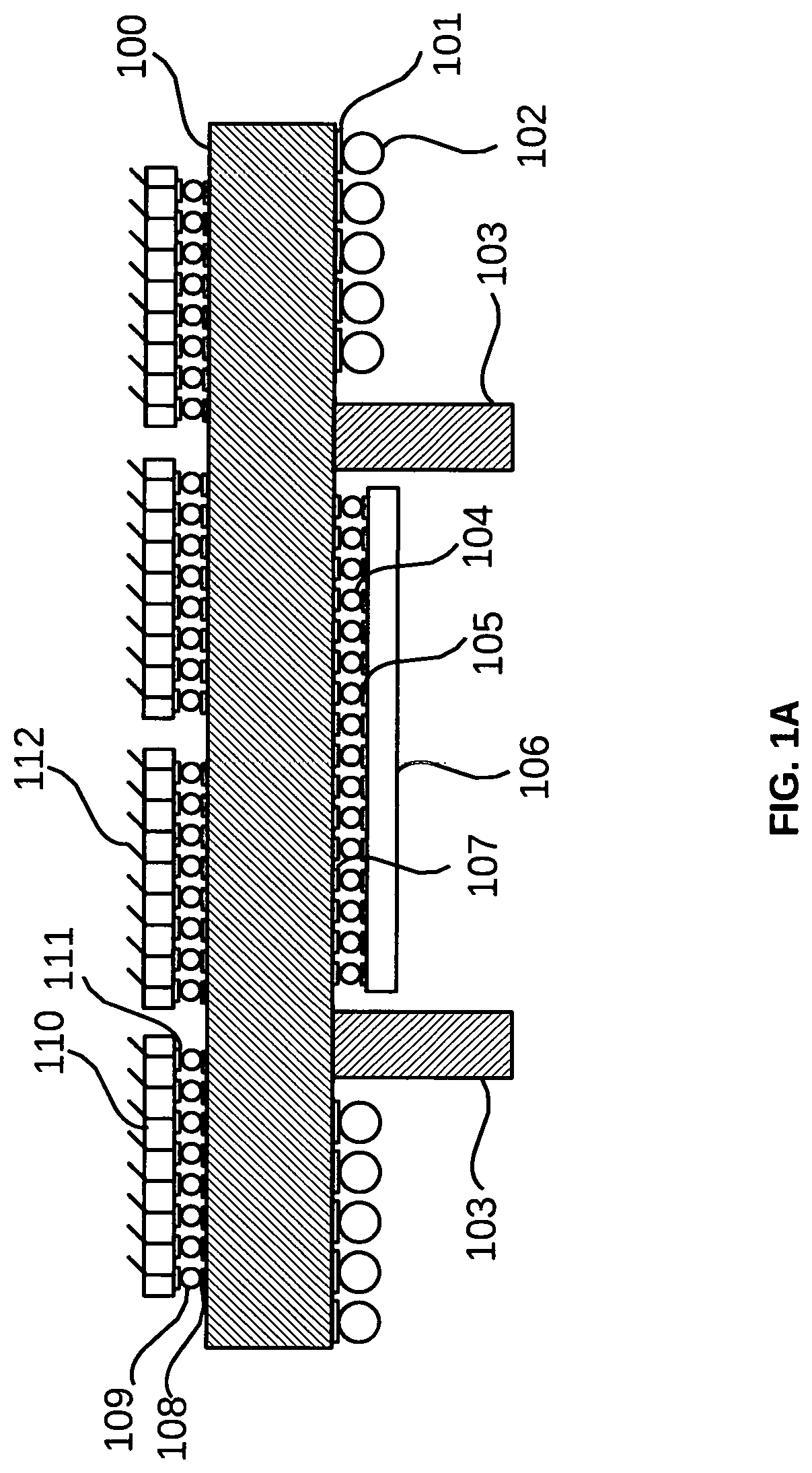

Method and system for co-packaging photonics integrated circuit with an application specific integrated circuit

ActiveUS10866376B1Semiconductor/solid-state device detailsSolid-state devicesThermal isolationEngineering

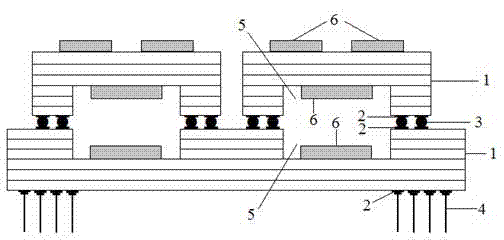

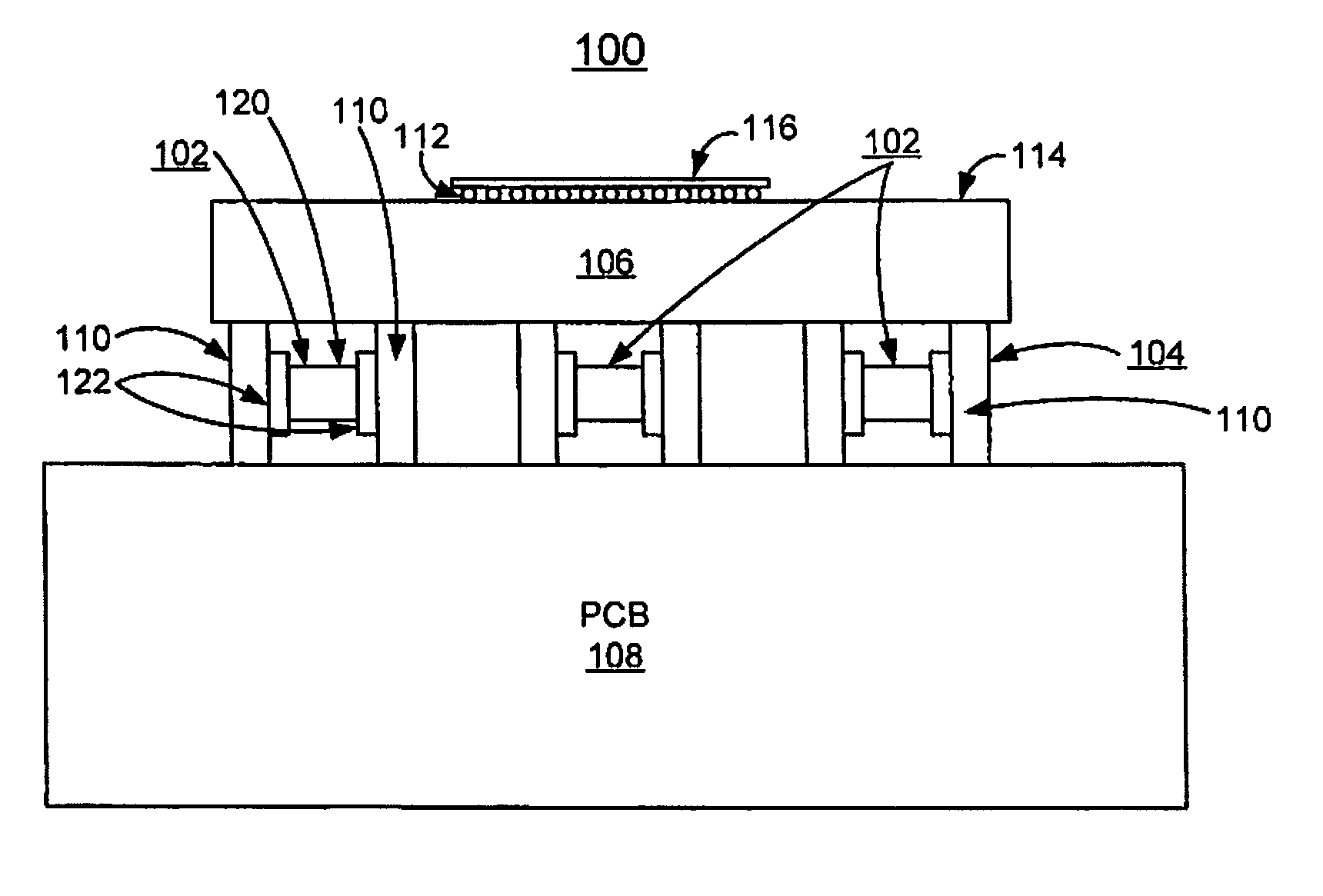

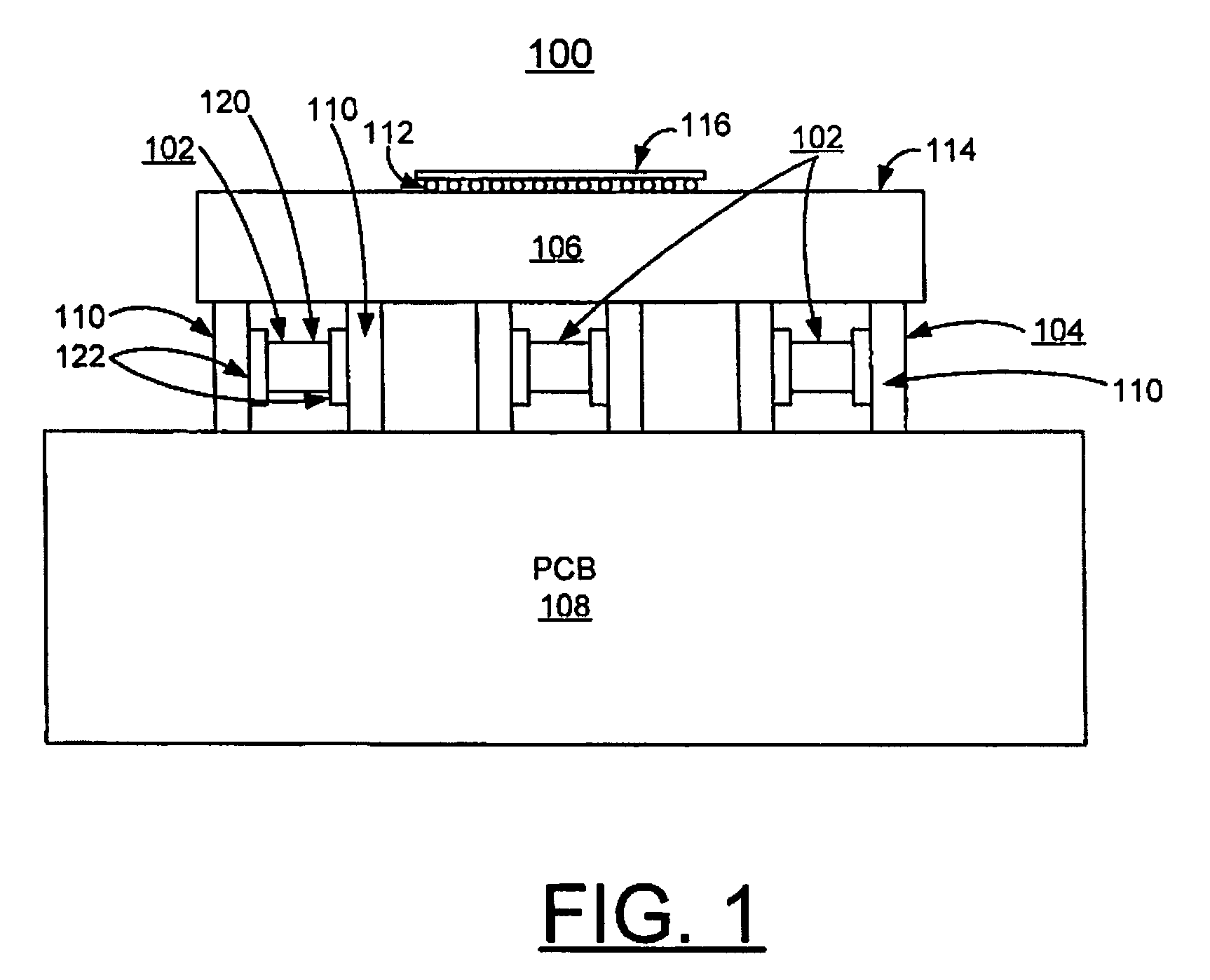

A method and system of co-packaging optoelectronics components or photonic integrated circuit (PIC) with application specific integrated circuits (ASICs) are disclosed and may include package substrate, several electronics die, passive components, socket assembly, and heat sinks. The said method converts ASIC high speed signals to optical signals by eliminating intermediary electrical interface between the ASIC and conventional optical modules. The method described provides many advantages of pluggable optical modules such as configurability, serviceability, and thermal isolation from the ASIC heat, while eliminating bandwidth bottlenecks as result of the ASIC package, host or linecard printed circuit board (PCB) traces, and the optical module connector. The high-power consumption ASIC is mounted below the package substrate, but sensitive optoelectronics and PIC components are mounted on top of the package substrate assembly for thermal isolation and serviceability. The package assembly ball grid array (BGA) or pin grid array (PGA) contacts are on the same side of the package substrate surface as ASIC die. The co-packaged package assembly is attached to the host or linecard PCB having a cutout for ASIC with the heatsink mounted from the bottom onto the ASIC die.

Owner:GHIASI ALI

PGA/BGA (Pin Grid Array/Ball Grid Array) three-dimensional structure for assembling components and production method thereof

ActiveCN103489847AImprove protectionImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPin grid arrayBall grid array

The invention discloses a PGA / BGA (Pin Grid Array / Ball Grid Array) three-dimensional structure for assembling components. The PGA / BGA three-dimensional structure comprises a T / R module with a leading-out end which is in a BGA structure and a subsystem plate with a leading-out end which is in a PGA structure, wherein the T / R module comprises a T / R module base plate and a component connected to the T / R module base plate; the subsystem plate comprises a subsystem base plate and a component connected to the subsystem base plate; each of the T / R module base plate and the subsystem base plate is further provided with a cavity for mounting the component; the T / R module base plate and the subsystem base plate are LTCC (Low Temperature Co-Fired Ceramic) base plates. The PGA / BGA three-dimensional structure adopts the cavities and a BGA leading-out structure so as to realize the three-layered stereoscopic assembling of the components, reduce the assembling area, improve the assembling density and lighten the system weight. The cavity structures can protect the components well and the length of a lead wire is further optimized; the reliability of the T / R module is improved; the subsystem plate can be used for a plane mother plate and can also be used for assembling a curved-surface mother plate.

Owner:NO 43 INST OF CHINA ELECTRONICS TECH GRP CETC

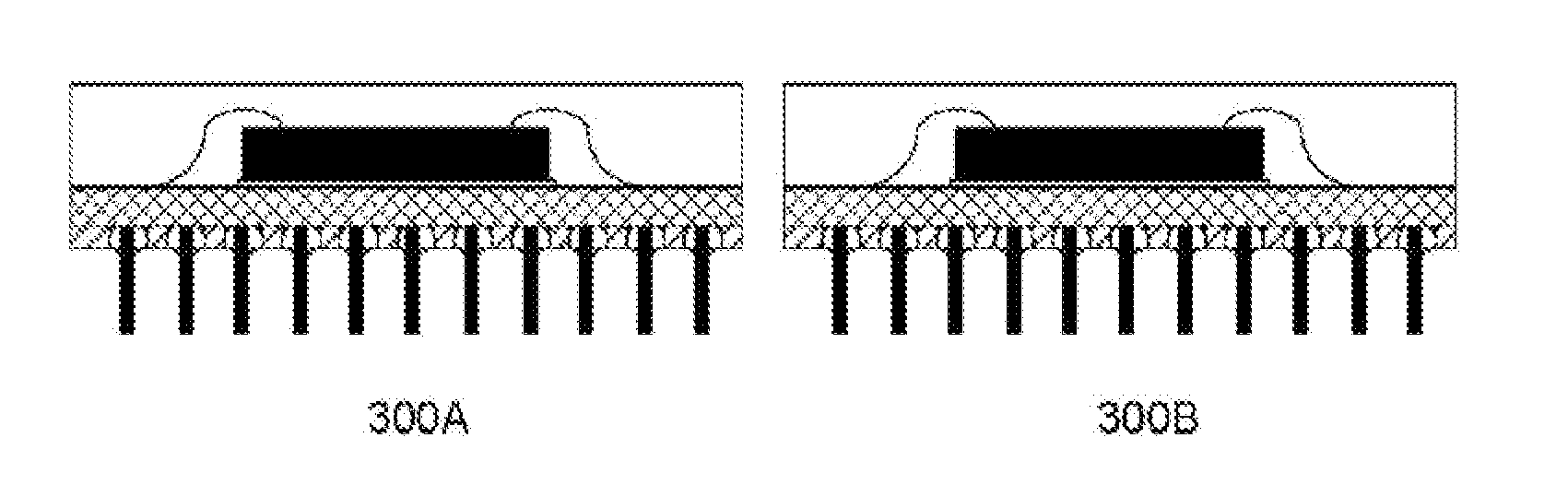

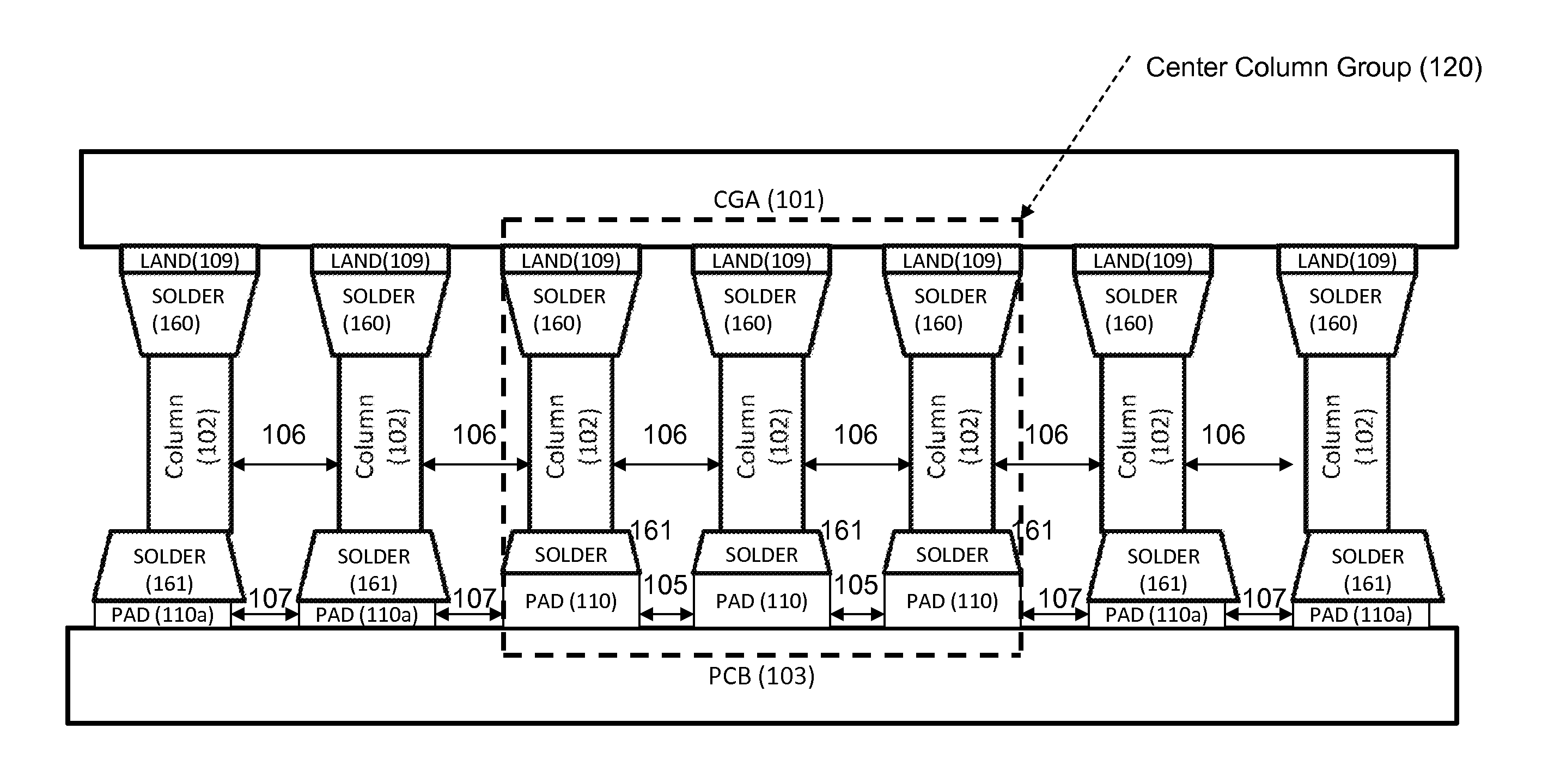

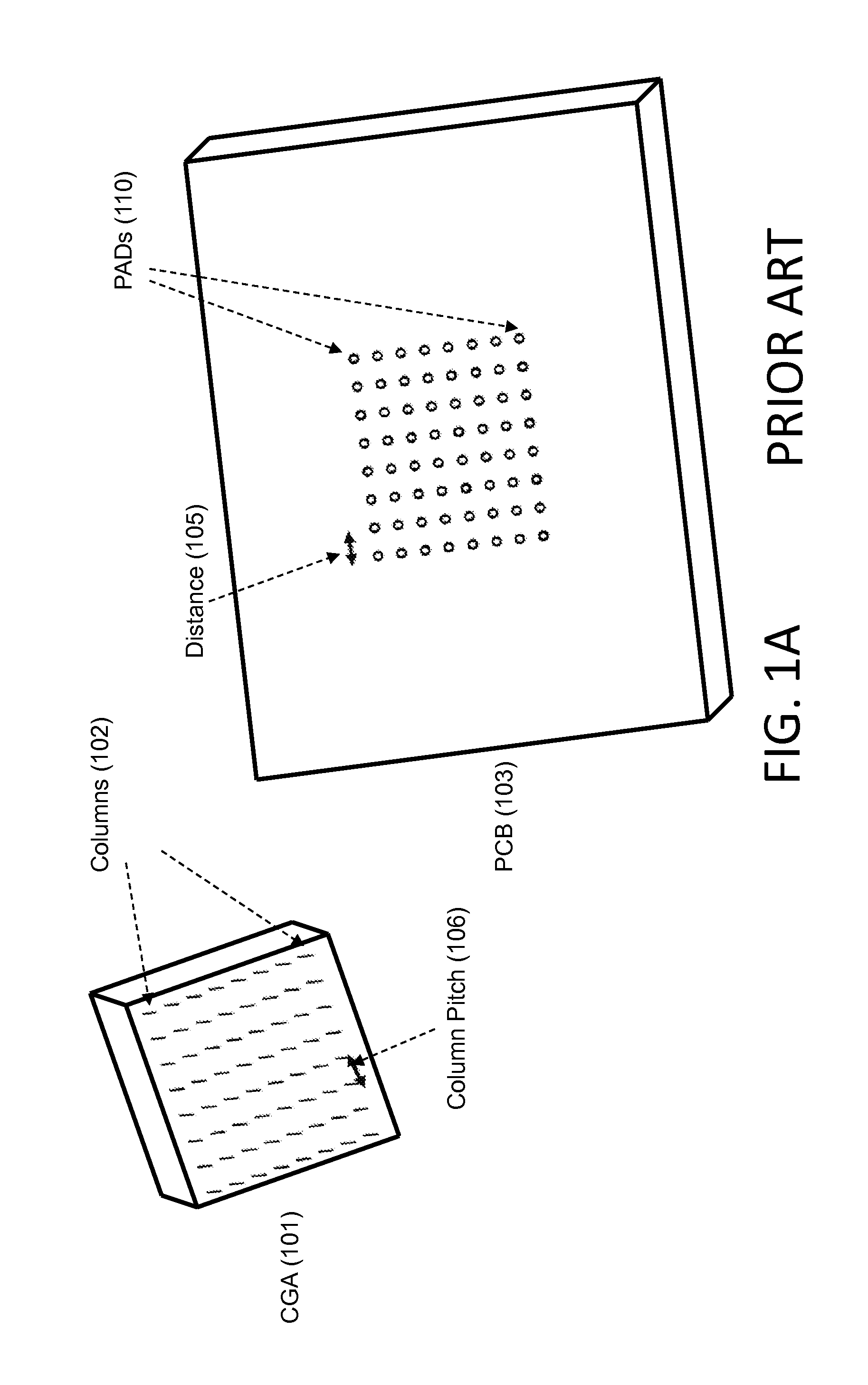

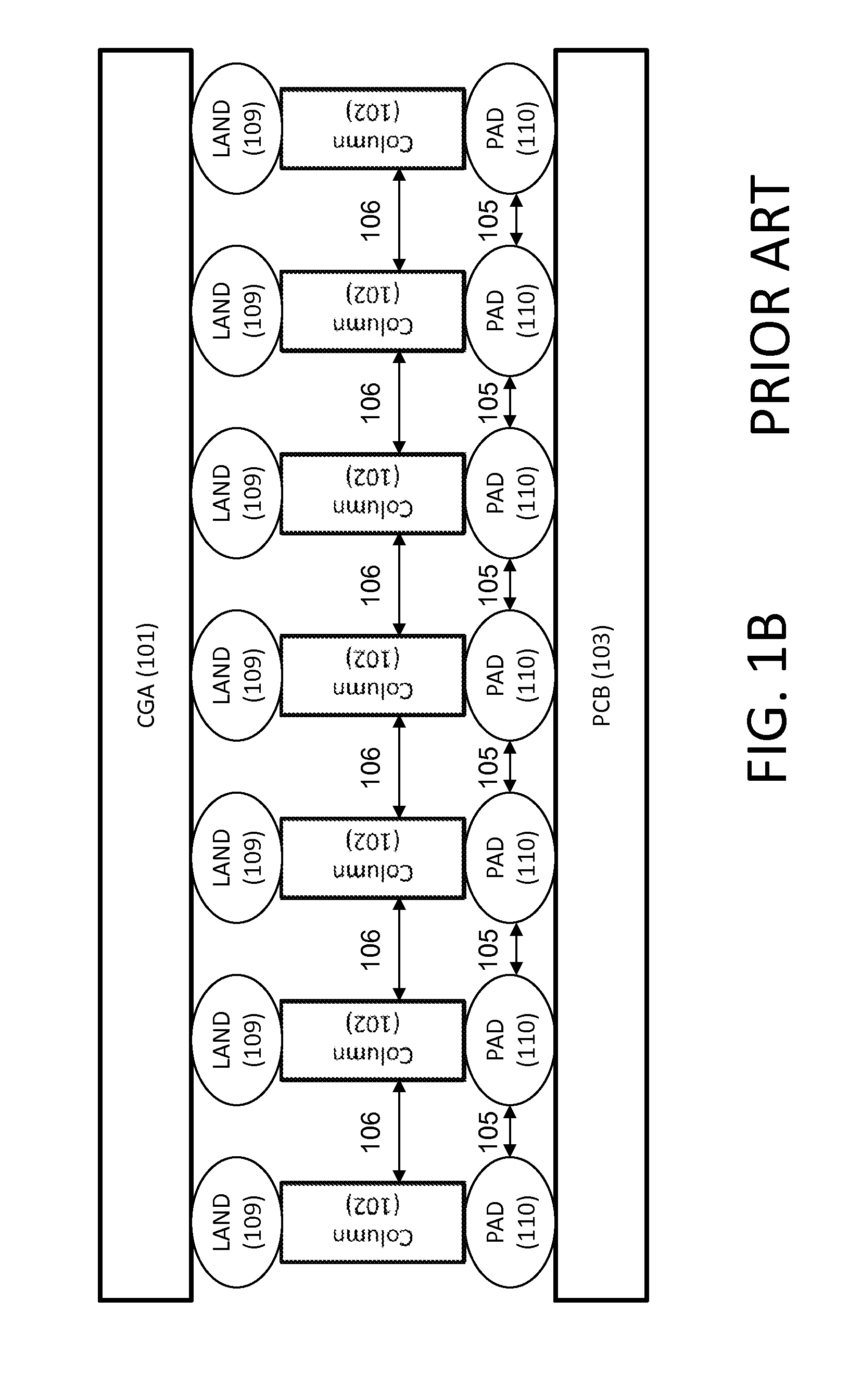

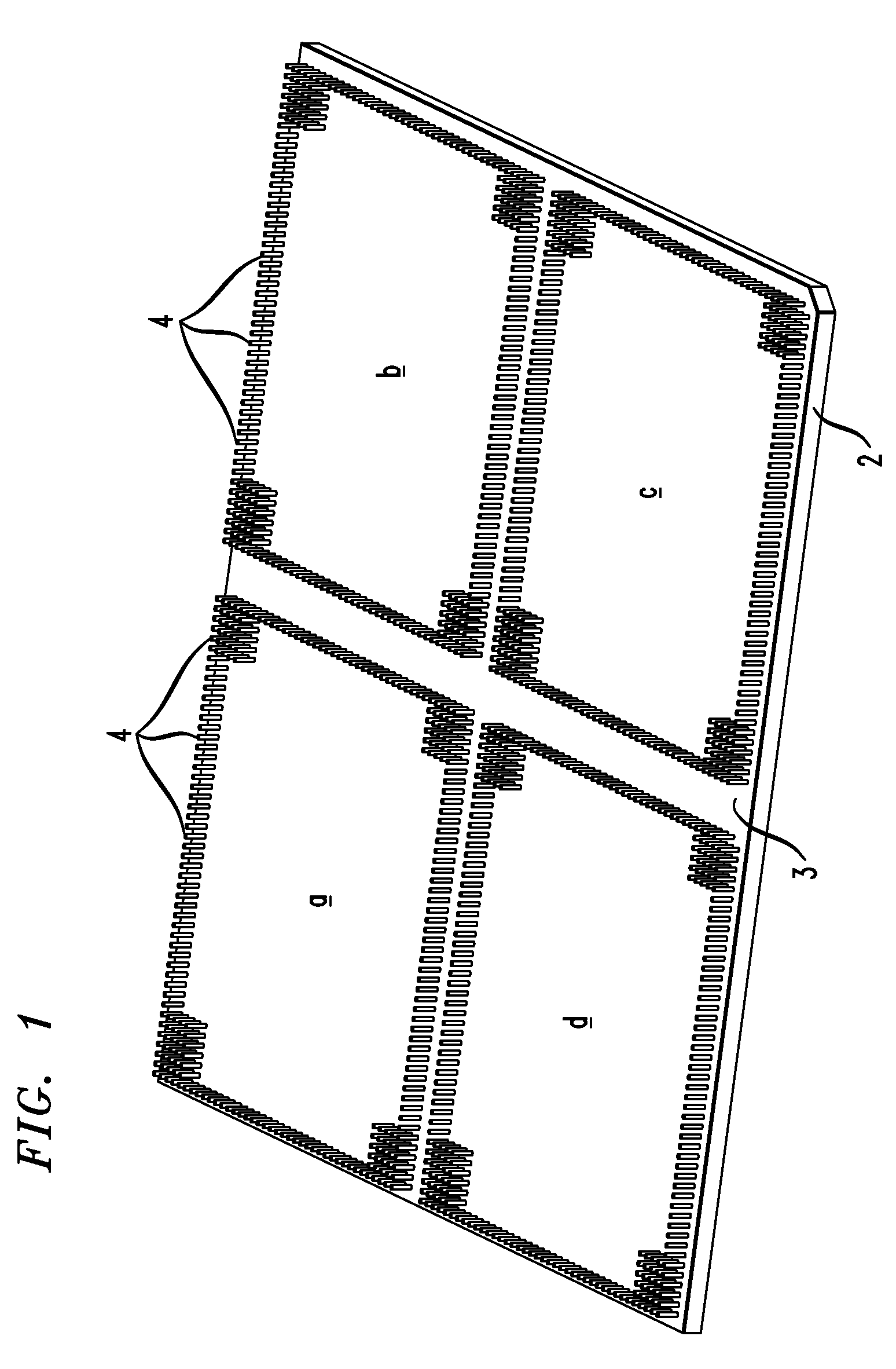

Grid Arrays with Enhanced Fatigue Life

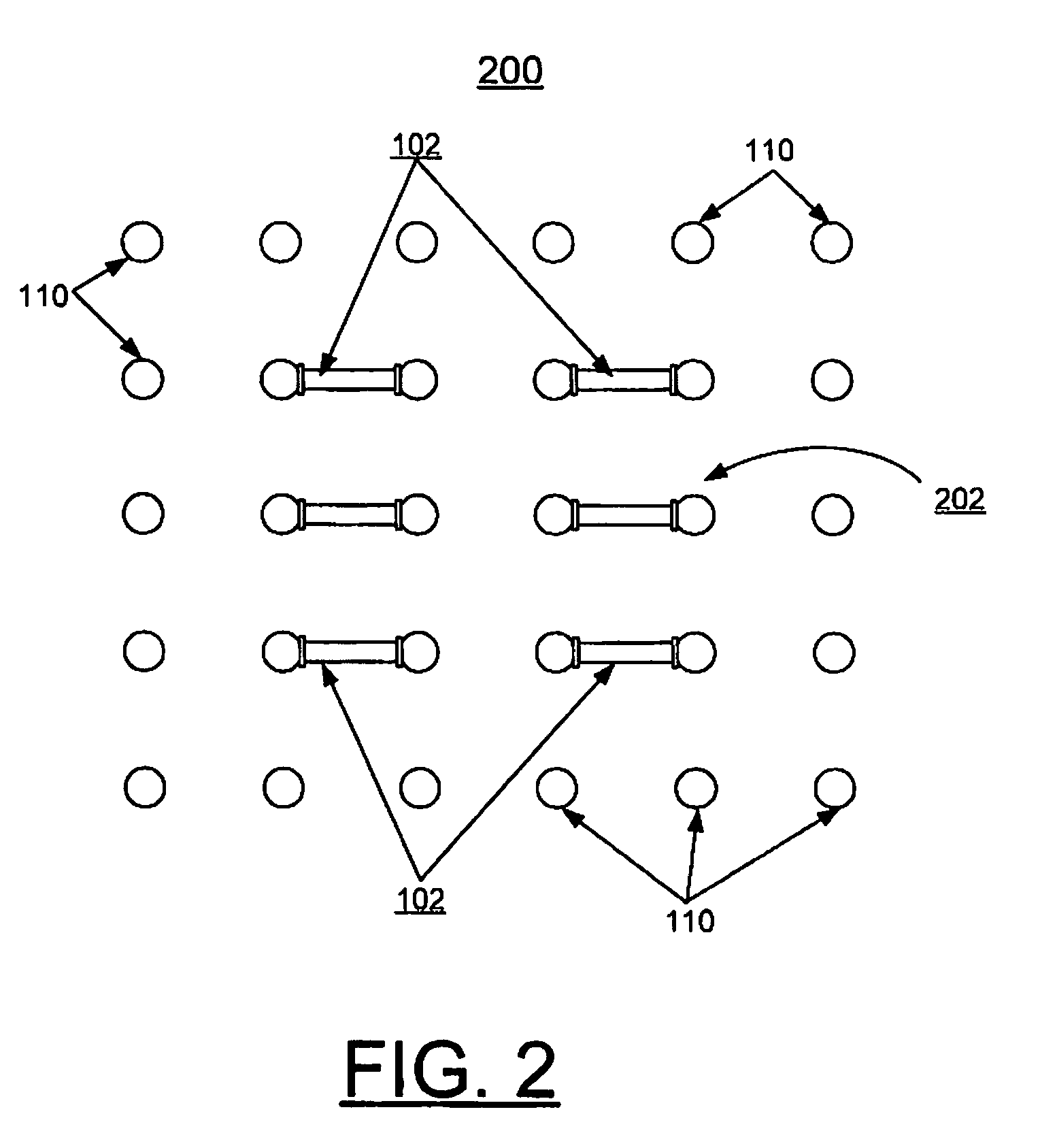

ActiveUS20130313007A1Improve reliabilityImprove fatigue lifePrinted circuit assemblingFinal product manufactureShear stressPin grid array

Reliability is improved for the mechanical electrical connection formed between a grid array device, such as a pin grid array device (PGA) or a column grid array device (CGA), and a substrate such as a printed circuit board (PCB). Between adjacent PCB pads, a spacing pattern increases toward the periphery of the CGA, creating a misalignment between pads and columns. As part of the assembly method, columns align with the pads, resulting in column tilt that increases from the center to the periphery of the CGA. An advantage of this tilt is that it reduces the amount of contractions and expansions of columns during thermal cycling, thereby increasing the projected life of CGA. Another advantage of the method is that it reduces shear stress, further increasing the projected life of the CGA.

Owner:MASSACHUSETTS INST OF TECH

Cam retaining means for ZIF electrical connector

InactiveUS6457986B2Electric discharge tubesSemiconductor/solid-state device detailsPin grid arrayEngineering

A electrical connector for a pin grid array package includes a base housing for mounting a plurality of terminals in grid array fashion, and a slide plate formed with through holes in grid array fashion corresponding to each of the terminals and overlaid on the upper side of the base housing. The slide plate slides between a position in which a pin of the pin grid array package is held adjacent to one of the terminals position and a position in which the pin is engaged with the terminal. A cam member is inserted through a cam opening formed in the slide plate and rotatably supported on the base housing so that a cam surface and an opening edge are mutually opposed. Engaging means rotatably secure the cam member in proper axial position with respect to the base housing. A flat surface formed on the cam surface abuts a straight edge formed on the cam opening when the slide plate is in the position in which the pin is engaged with the terminals.

Owner:MOLEX INC

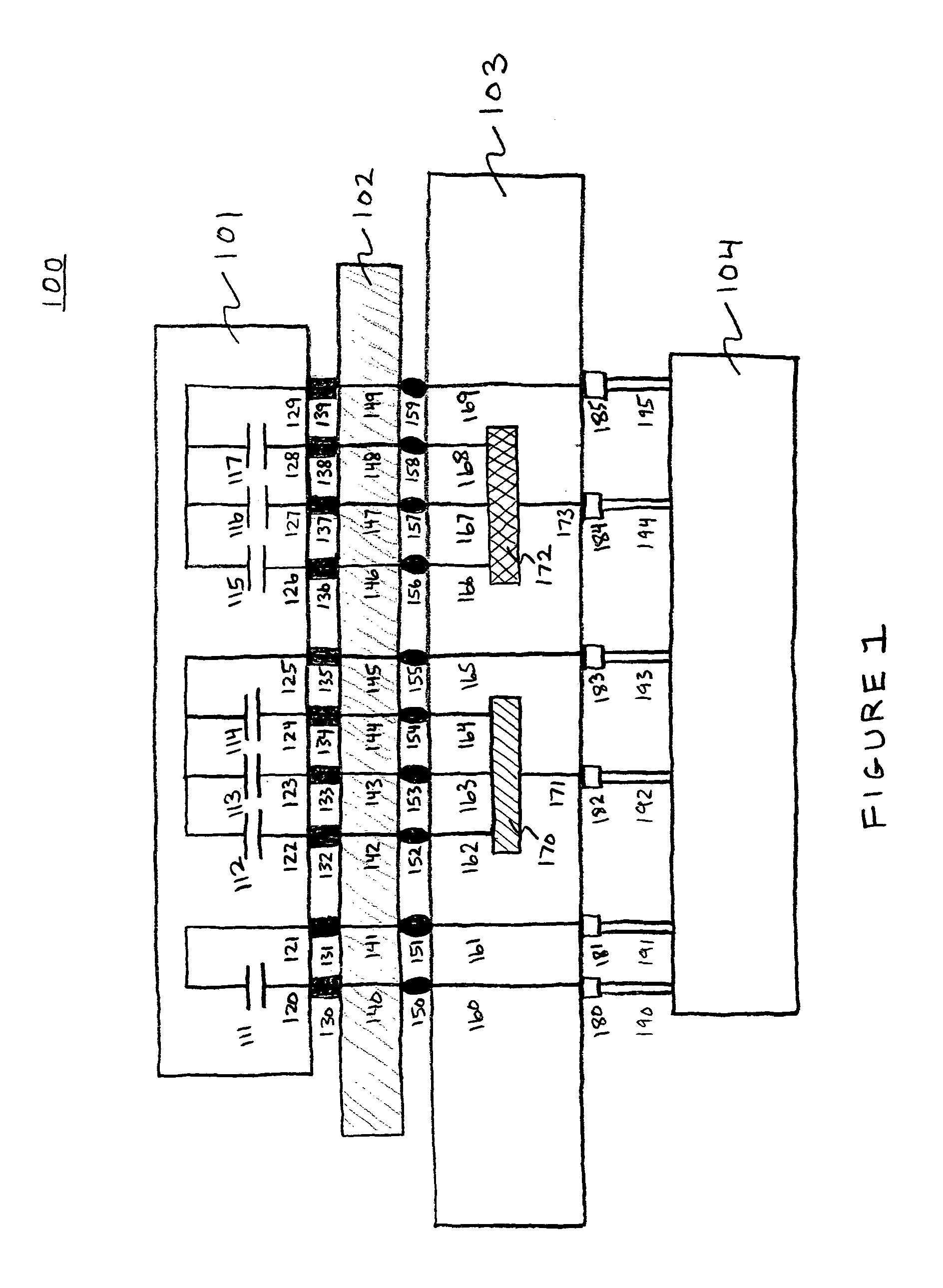

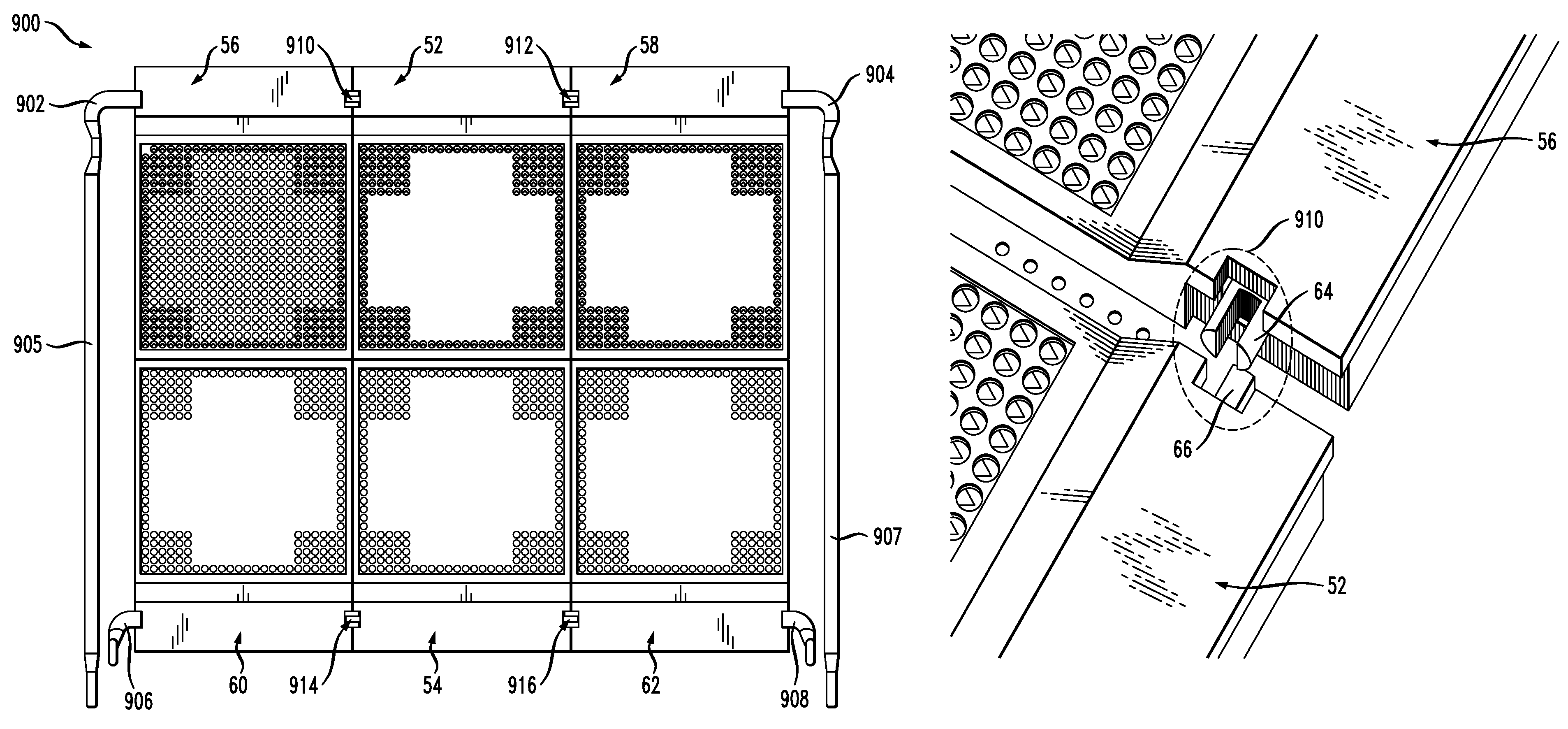

Pin grid array zero insertion force connectors configurable for supporting large pin counts

InactiveUS7322844B1Large I/O pin countFine pitchCoupling device detailsElectrical apparatus contructional detailsPin grid arrayEngineering

Owner:GLOBALFOUNDRIES INC

Pin attachment by a surface mounting method for fabricating organic pin grid array packages

InactiveUS6543676B2Improved strength and reliabilityPrinted circuit assemblingFinal product manufactureSolder maskContact pad

A pin attachment method for mounting the pins on a wiring substrate for fabricating a pin grid array package is disclosed. There is provided an organic wiring board including a surface bearing electrical circuitry which includes at least one contact pad for receiving a pin. A solder mask layer which is placed on the board surface and patterned to expose the pad. The solder mask layer which does not cover any portion of the pad and forms a well by the perimeter of the solder mask layer around the pad. Subsequently, a pin and a solder material which are placed over said pad in the well. The pin which is soldered to the pad by a temperature sufficient to melt the solder material.

Owner:PHOENIX PRECISION TECH CORP

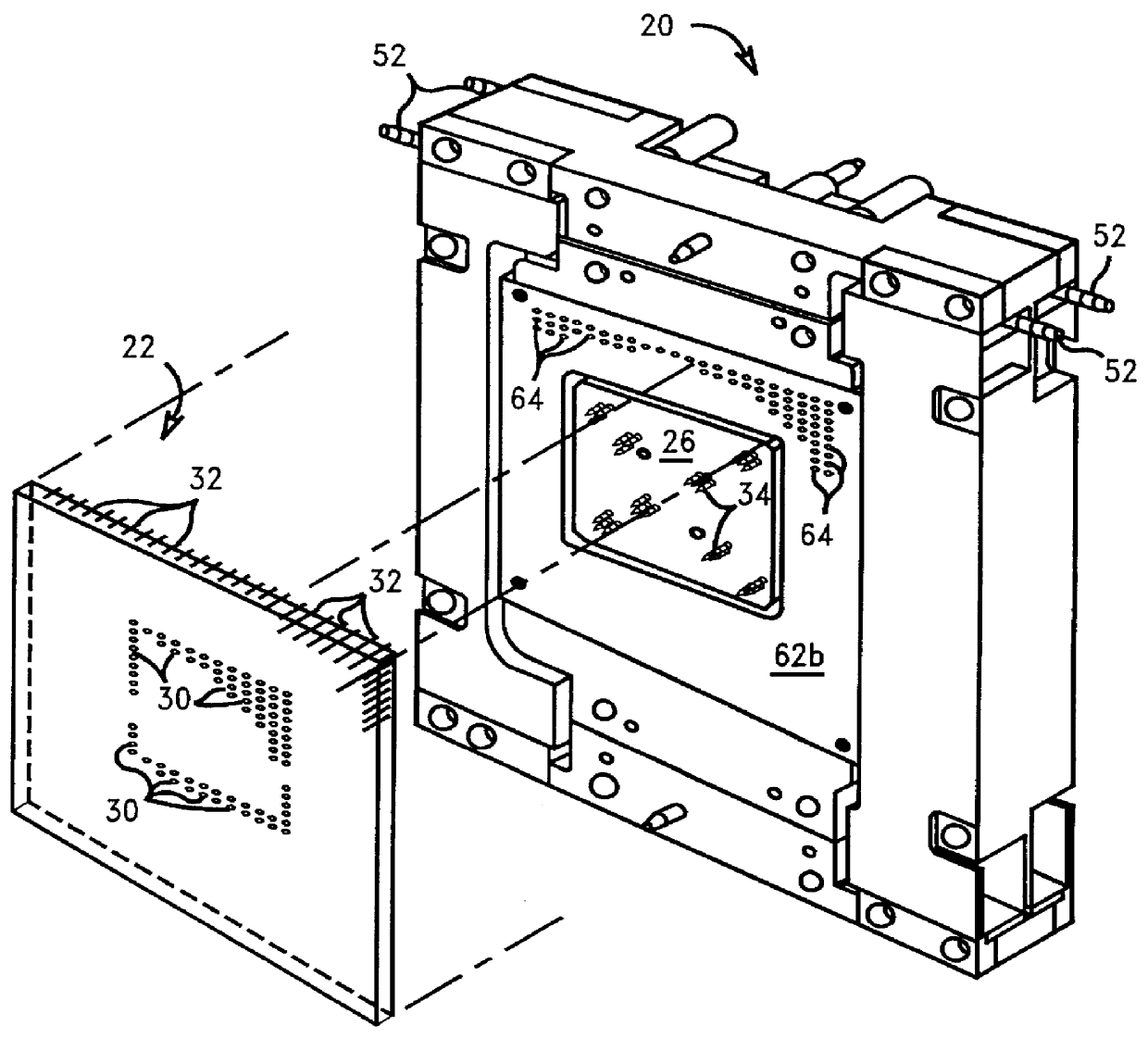

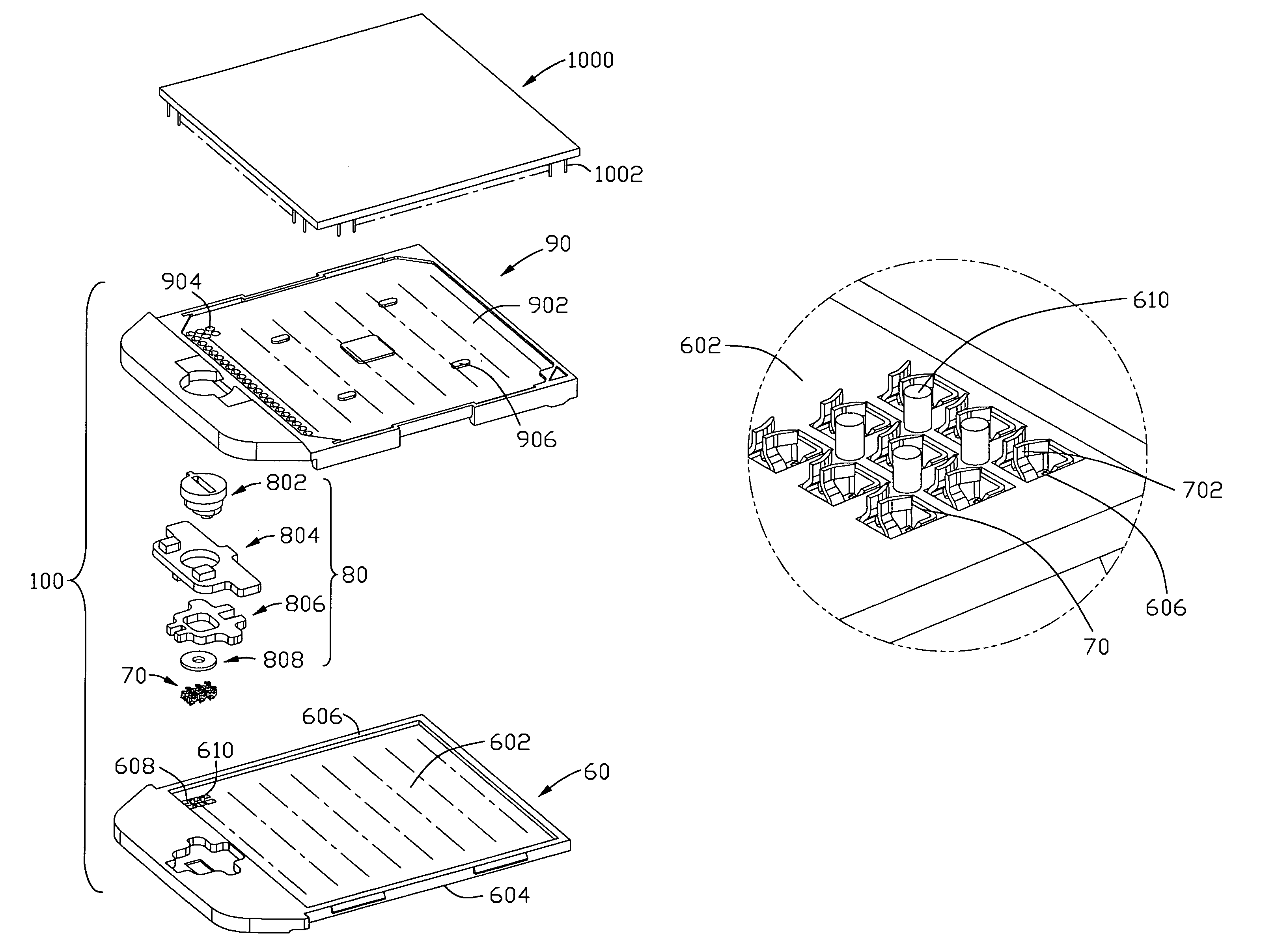

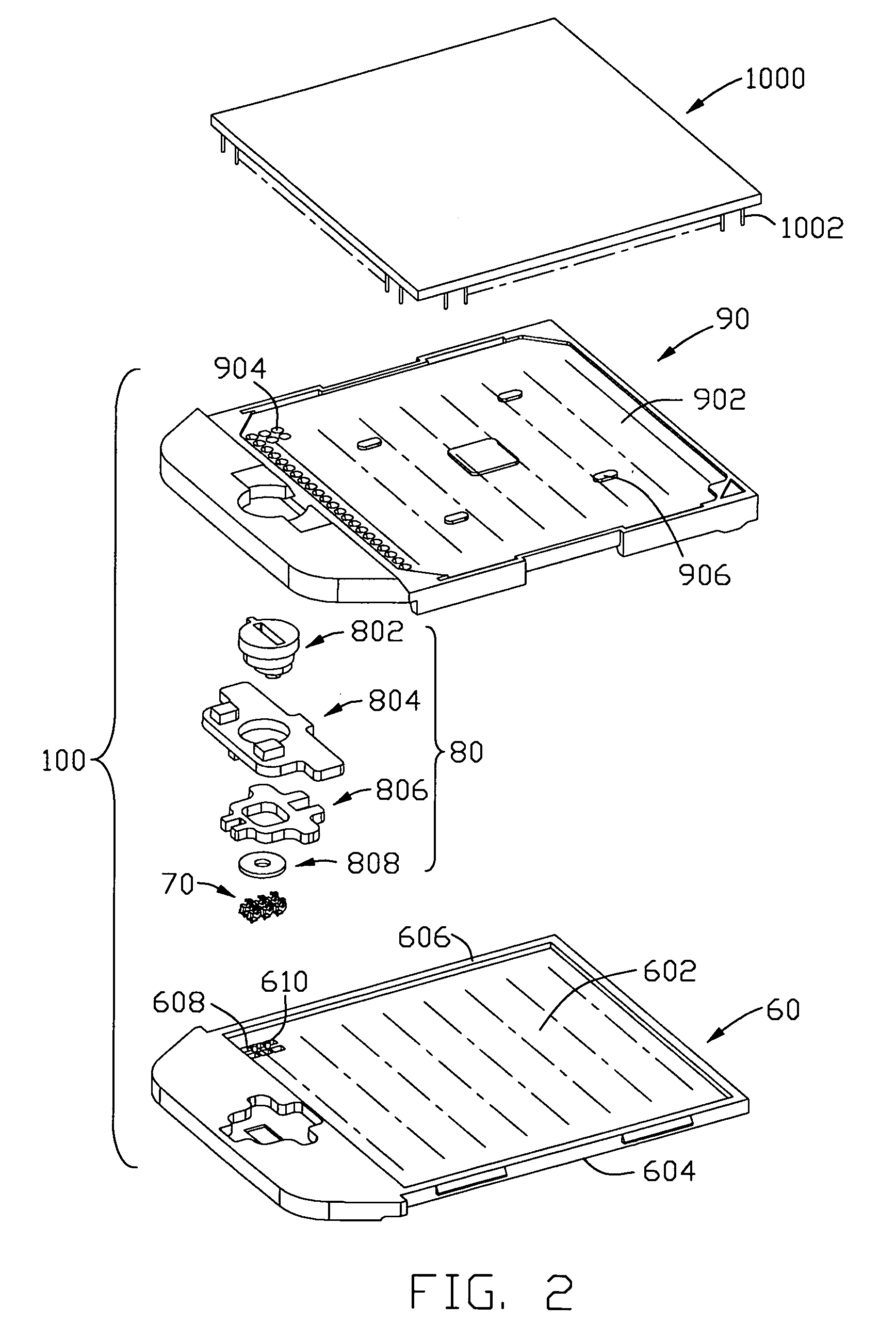

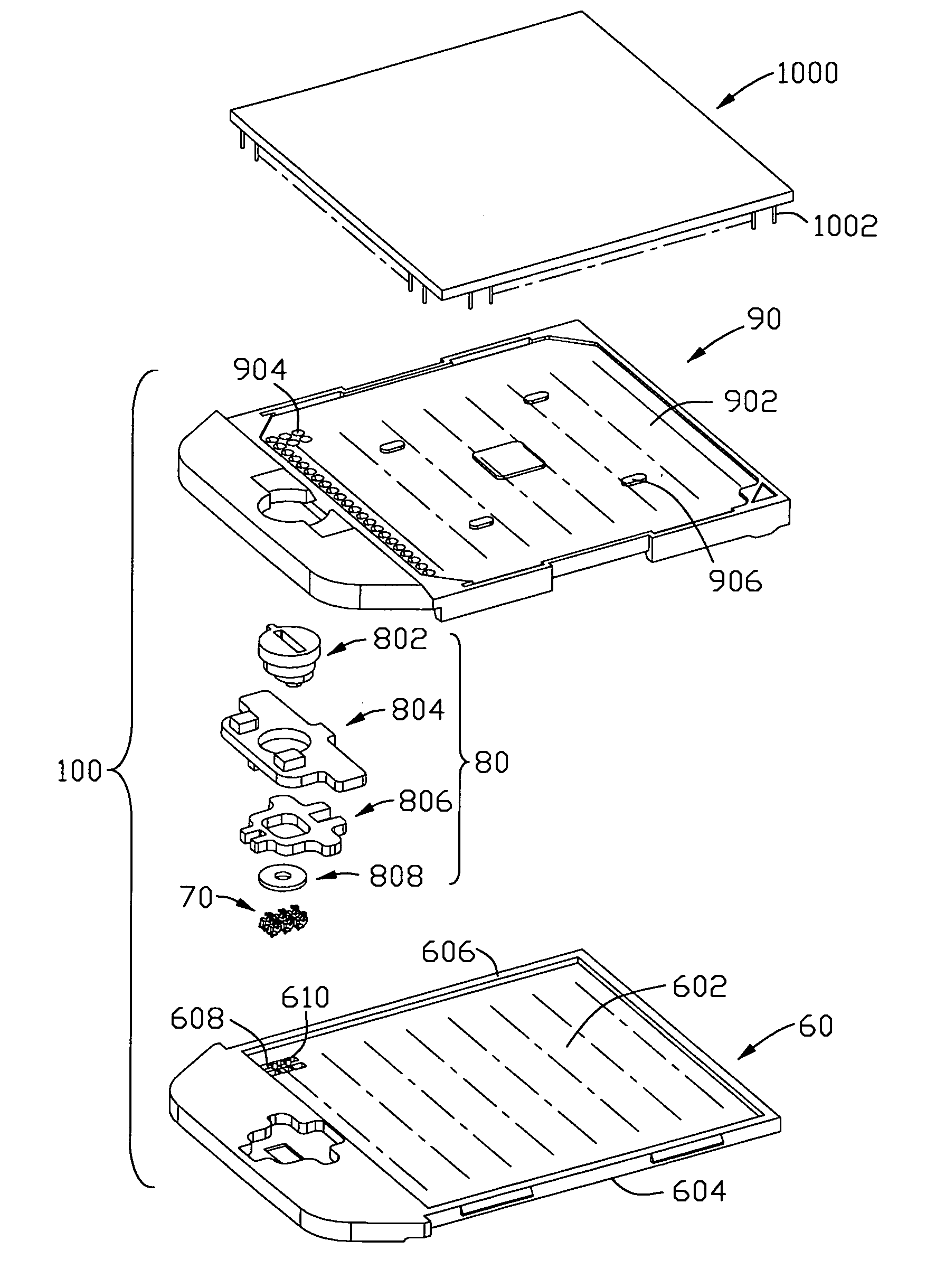

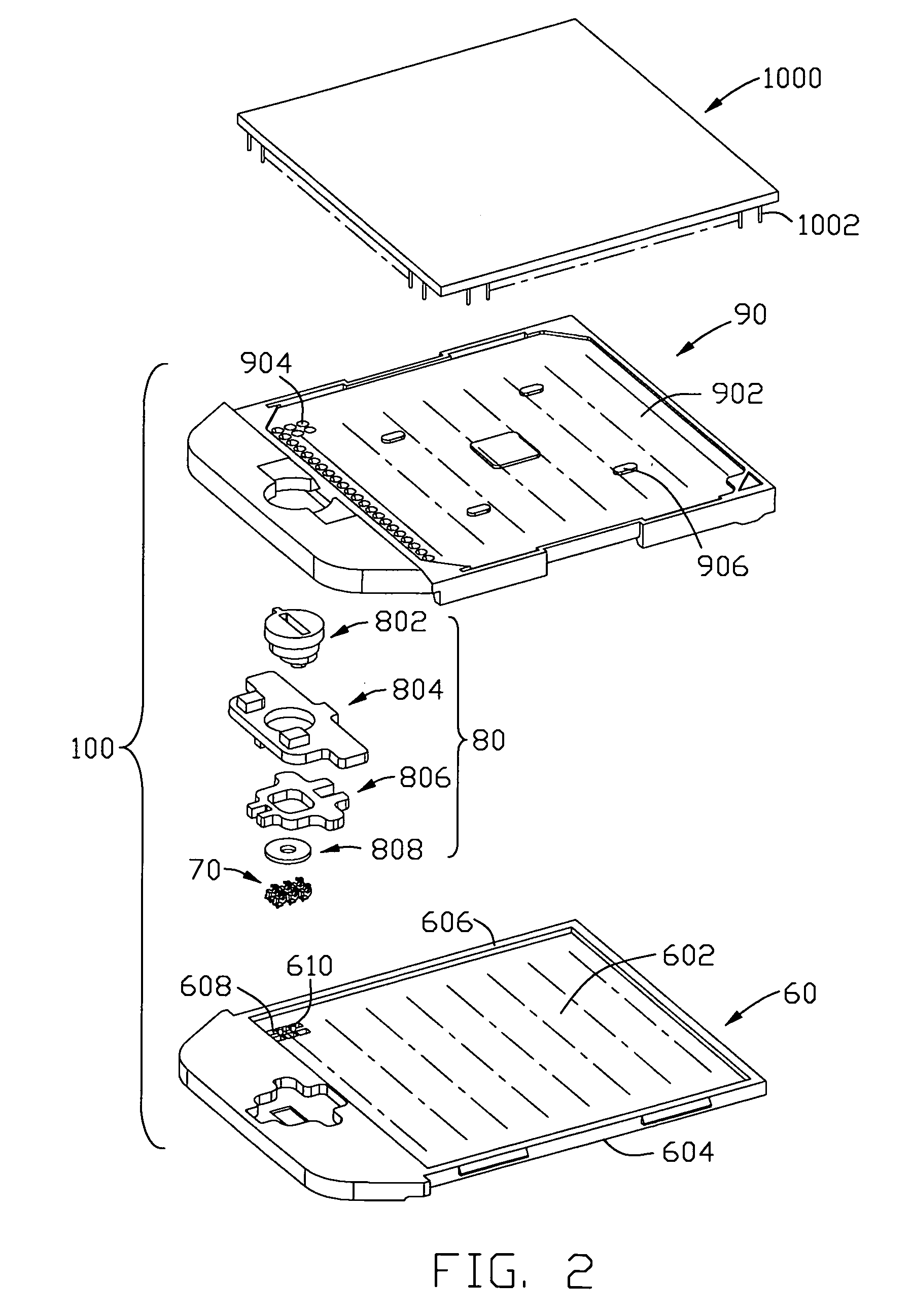

Pin grid array socket having a base with interior standoffs and hightening peripheral walls

InactiveUS7651358B2Avoid deformationLine/current collector detailsCoupling device detailsPin grid arrayMechanical engineering

A socket connector is provided for securely mounting an electronic device (1000) on a printed circuit board, said socket connector comprises an insulatve base (60) and heightened perimeter walls (606) upward extending therefrom to define an inner cavity. The top surface (602) of the inner cavity comprises a plural of passageways (608) in which a plural of contacts (70) hold. Furthermore, there are a plural of standoffs (610) between the adjacent passageways (608) co-worked with the heightened perimeter walls (606) for effectively preventing a cover (90) from deformation.

Owner:HON HAI PRECISION IND CO LTD

Pin grid array socket having a base with interior standoffs and hightening peripheral walls

InactiveUS20080311777A1Avoid deformationCoupling device detailsPrinted circuit manufacturePin grid arrayEngineering

A socket connector is provided for securely mounting an electronic device (1000) on a printed circuit board, said socket connector comprises an insulatve base (60) and heightened perimeter walls (606) upward extending therefrom to define an inner cavity. The top surface (602) of the inner cavity comprises a plural of passageways (608) in which a plural of contacts (70) hold. Furthermore, there are a plural of standoffs (610) between the adjacent passageways (608) co-worked with the heightened perimeter walls (606) for effectively preventing a cover (90) from deformation.

Owner:HON HAI PRECISION IND CO LTD

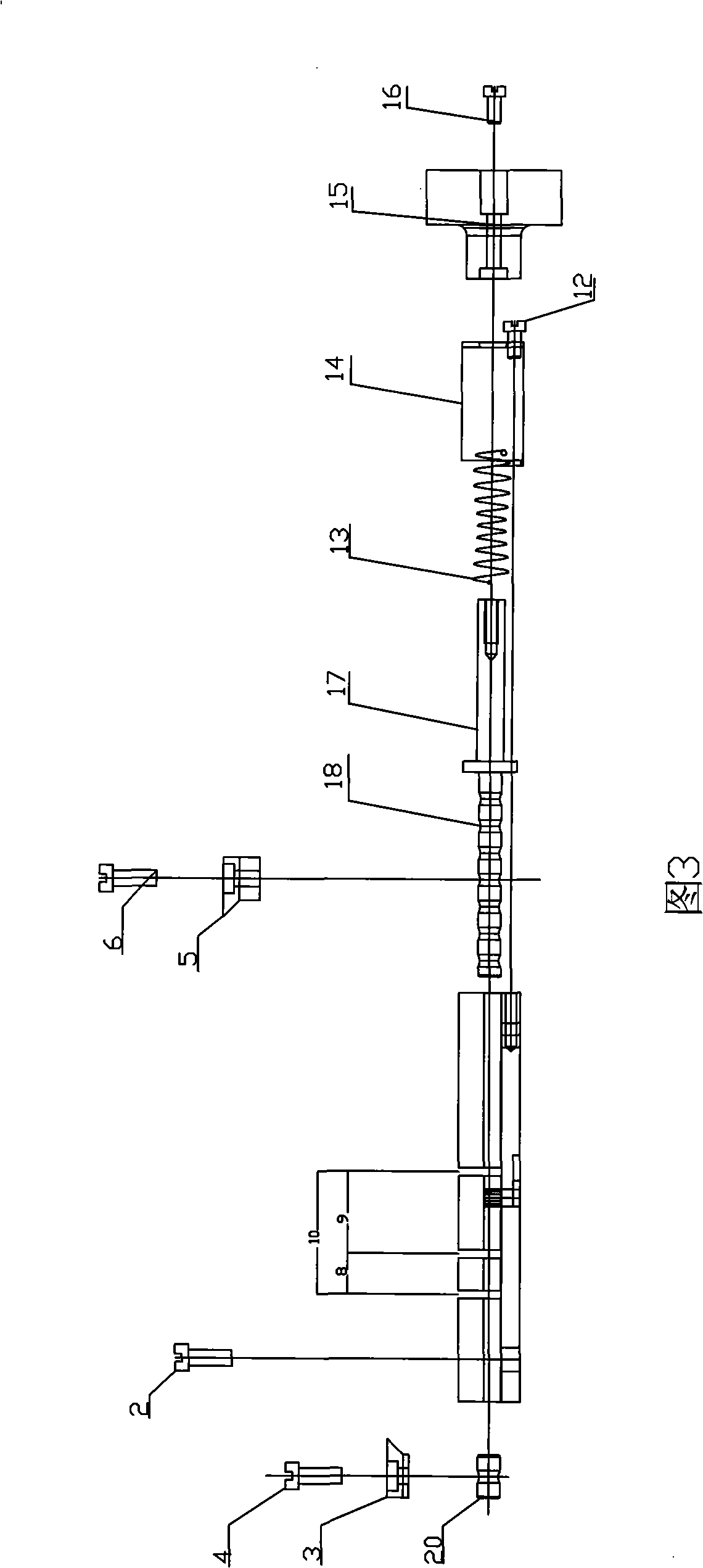

Multipurpose clamper for bonding machine worktable

ActiveCN101303999ANo damageNo deformationSemiconductor/solid-state device manufacturingPin grid arrayEngineering

The invention relates to a multipurpose fixture for a bonder worktable, which is characterized in that a fixture body is provided with a chute, in which a slide bar is inserted; a hold-down spring is sheathed into the slide bar, and a hold-down spring stopper is sheathed into the slide bar; a hold-down spring handle is sheathed into the slide bar and is tightened. According to different types and spans of components, the fixture body is provided with different first fixing grooves, second fixing grooves, third fixing grooves and fourth fixing grooves. The fixture body is provided with an adjustable locating block and a location distance regulation orifice. The fixture body is equipped with a first upper hypotenuse clamping squash and a second upper hypotenuse clamping squash. The multipurpose fixture can fix various ceramic dual-in-line package components, various leadless components and various pin grid array components with different spans; the fixture can meet the clamping and fixing requirements in packaging and bonding without component damage or lead deformation in clamping and fixing.

Owner:WUXI ZHONGWEI GAOKE ELECTRONICS +1

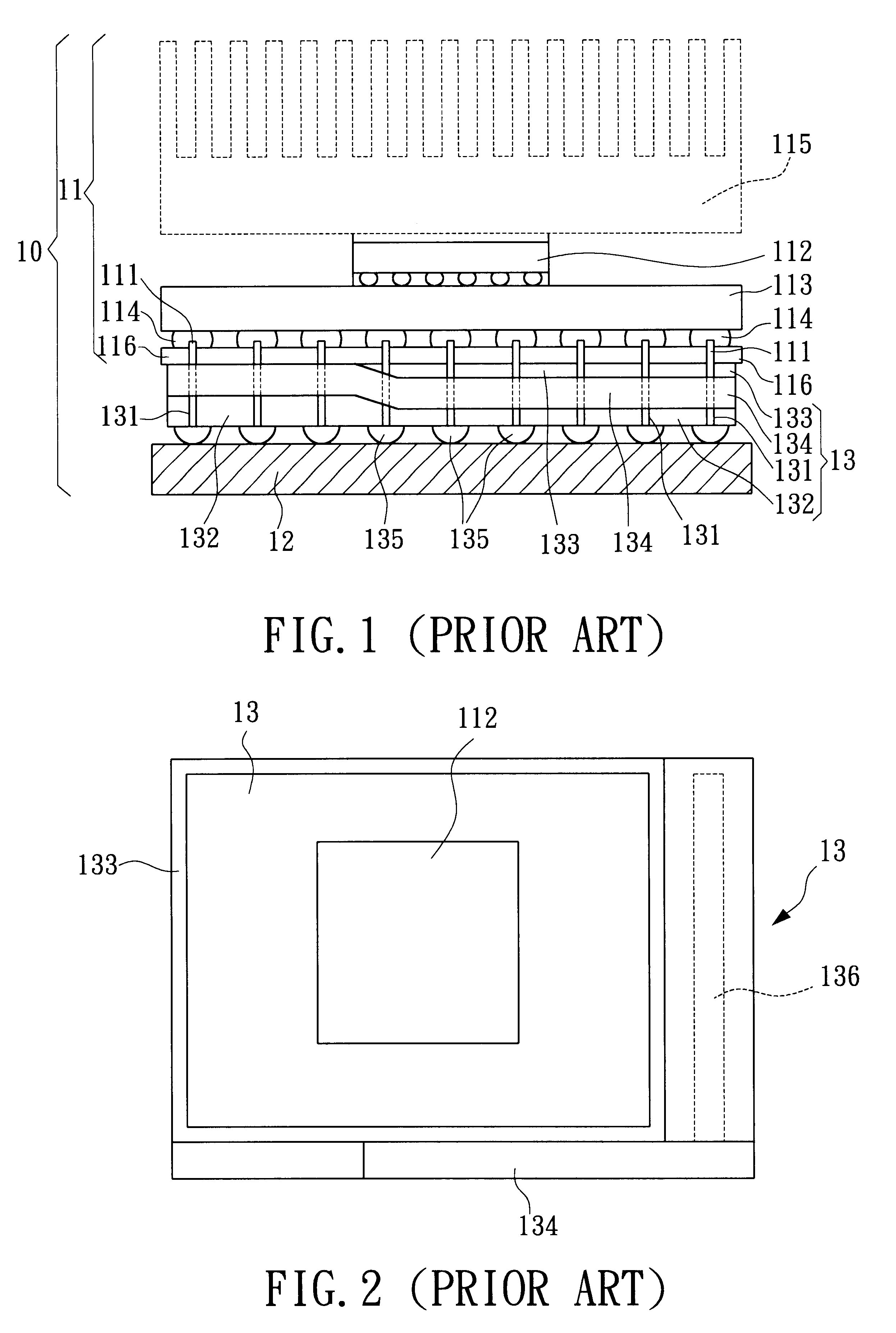

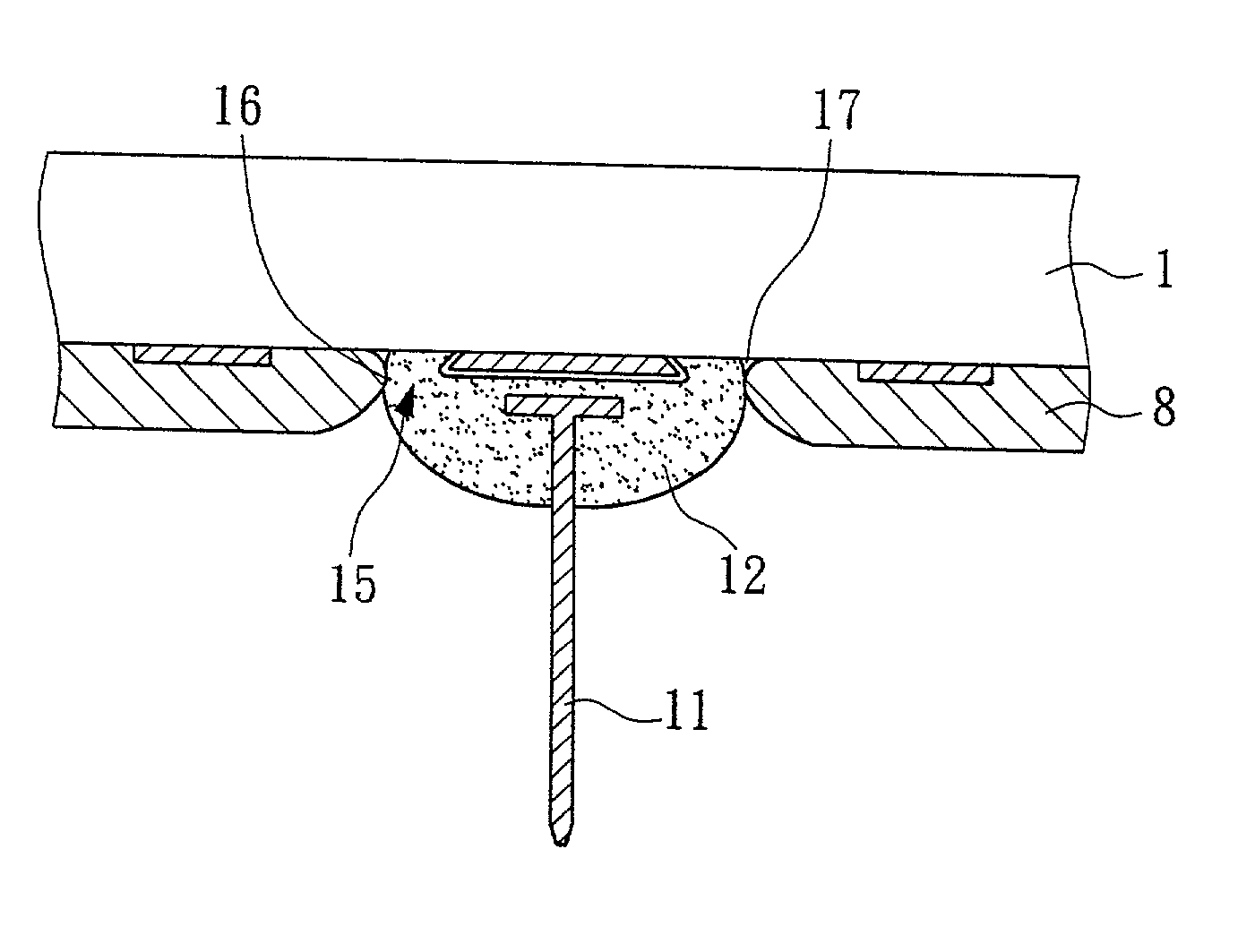

Wiring board and method for manufacturing the same

InactiveUS20120186864A1Simple manufacturing processEasy to controlPrinted circuit detailsSemiconductor/solid-state device detailsSurface layerPin grid array

A wiring board and a method for manufacturing the wiring board reinforced by means of a resin is provided. Embodiments of the wiring board allow for reliable attachment of a connection member, like a socket, to a terminal member. For example, a base of terminal pins is put on pin grid array (PGA) terminal pads, and a bonding material paste including solder and an electric insulation material made of a resin is placed on each of the PGA terminal pads. The bonding material paste is then heated to fuse the solder and soften the electric insulation material. Subsequently, the bonding material paste is cooled to solidify the solder and bond each of the bases to a corresponding PGA terminal pad and form an electric insulation surface layer on an exposed surface of each of solder junctions to which the respective bases are bonded.

Owner:NGK SPARK PLUG CO LTD

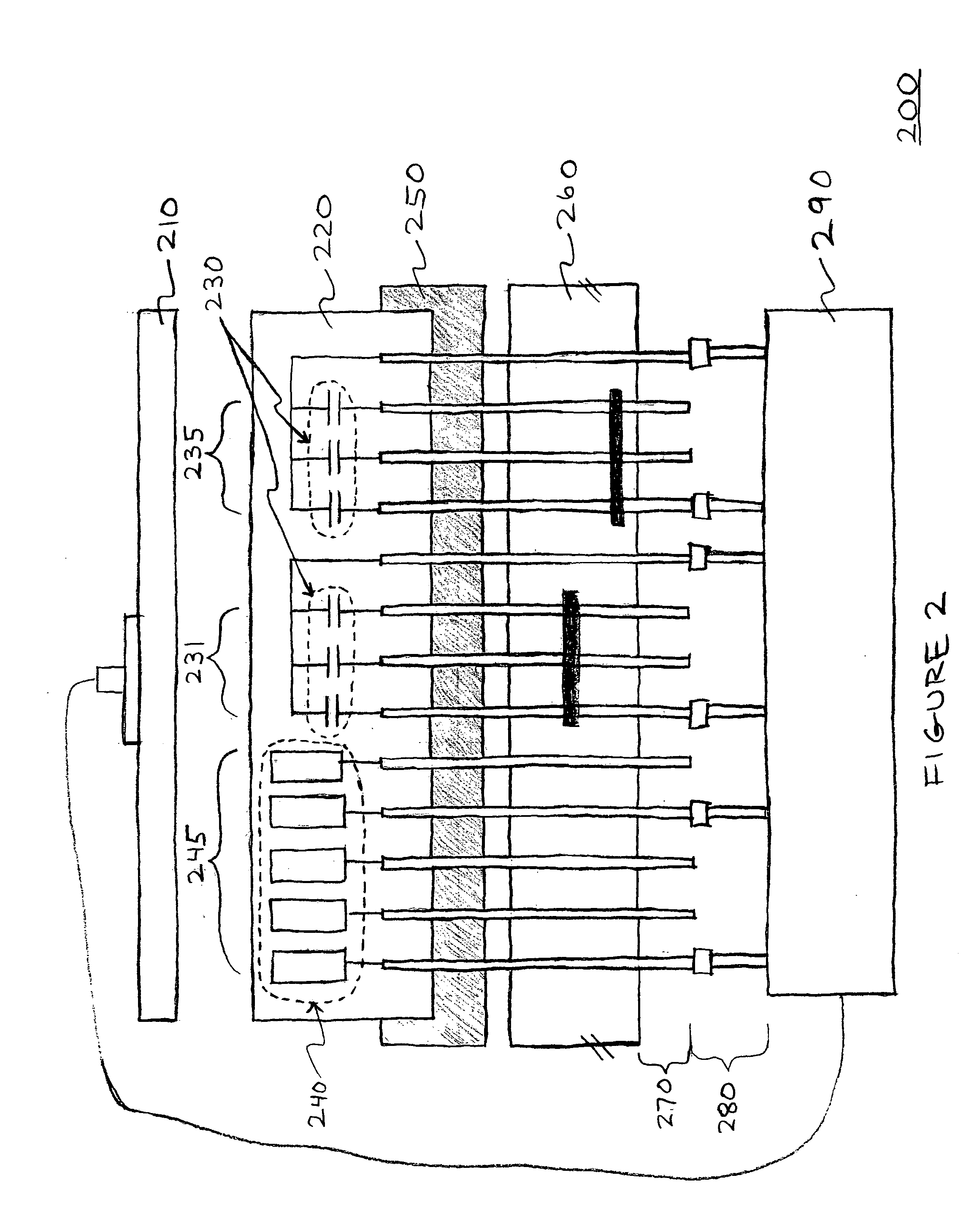

Method for implementing component placement suspended within grid array packages for enhanced electrical performance

InactiveUS7553696B2Improve electrical performanceLine/current collector detailsHydroxy compound active ingredientsPin grid arrayEngineering

A method and structure are provided for implementing component placement suspended within electrical pin grid array packages for enhanced electrical performance. A solder column grid array is coupled between a printed circuit board and a first level package. A component is connected between a predefined pair of adjacent columns in the solder column grid array suspended between the printed circuit board and the first level package.

Owner:IBM CORP

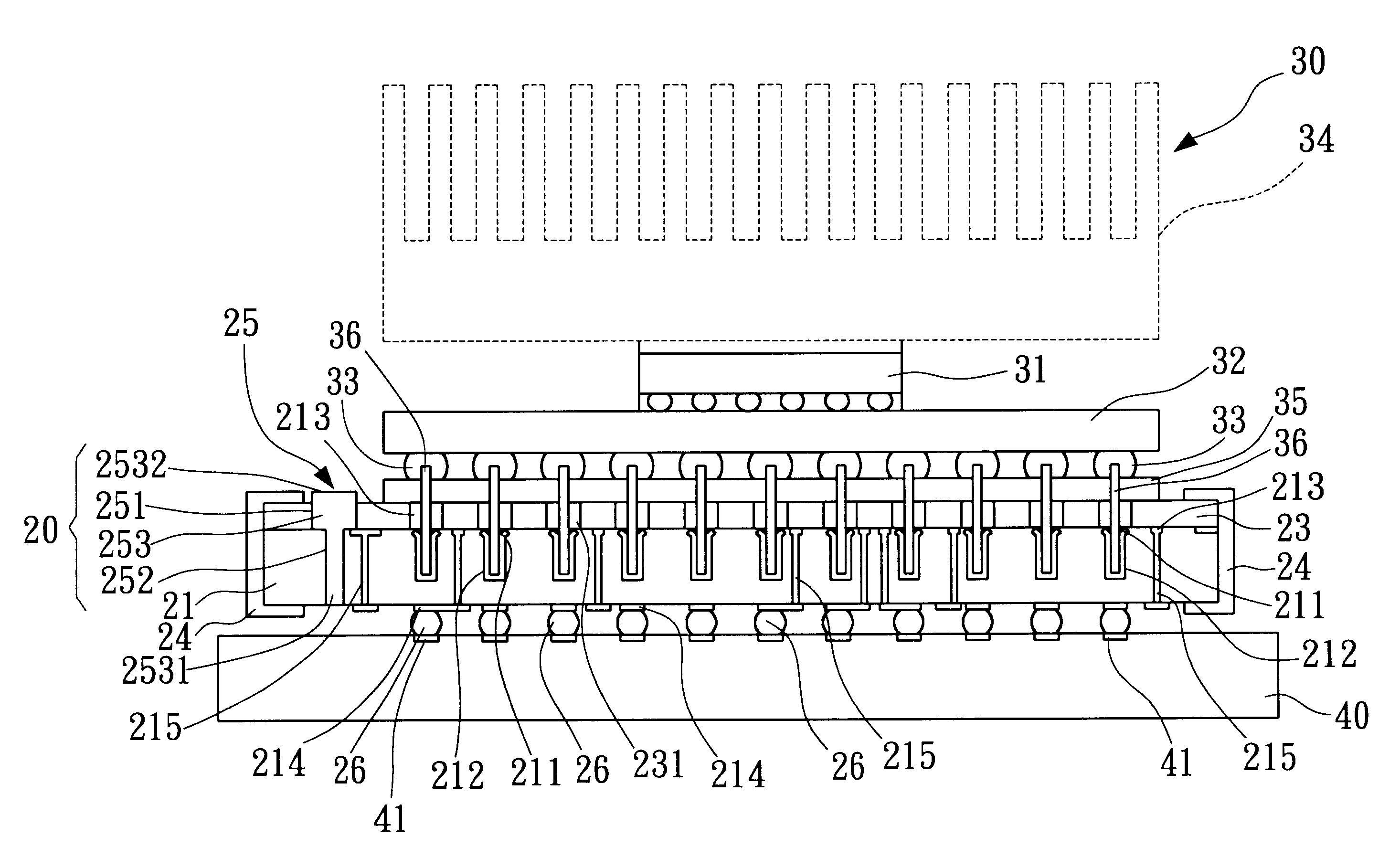

Circuit carrier and fabrication method thereof

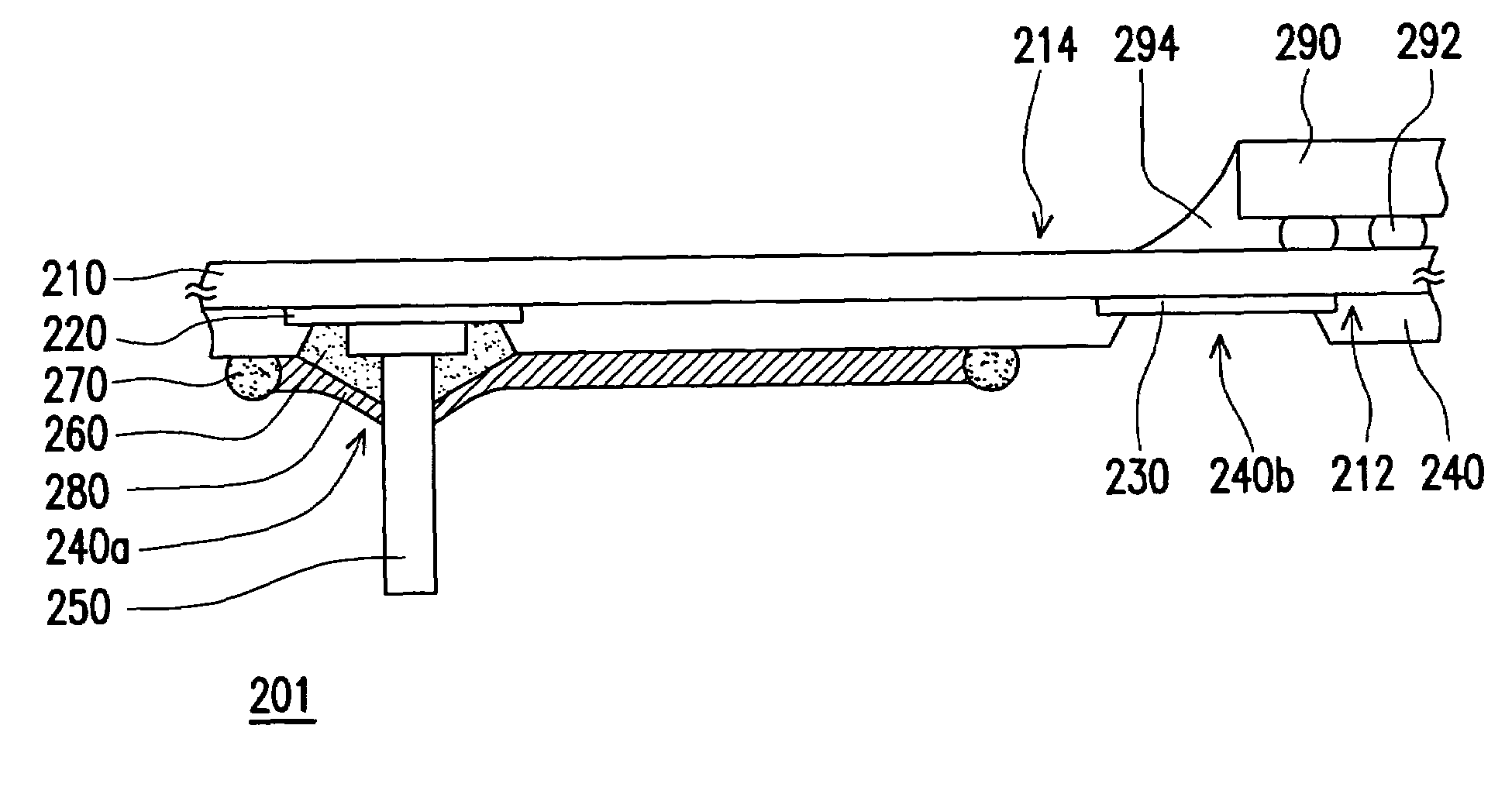

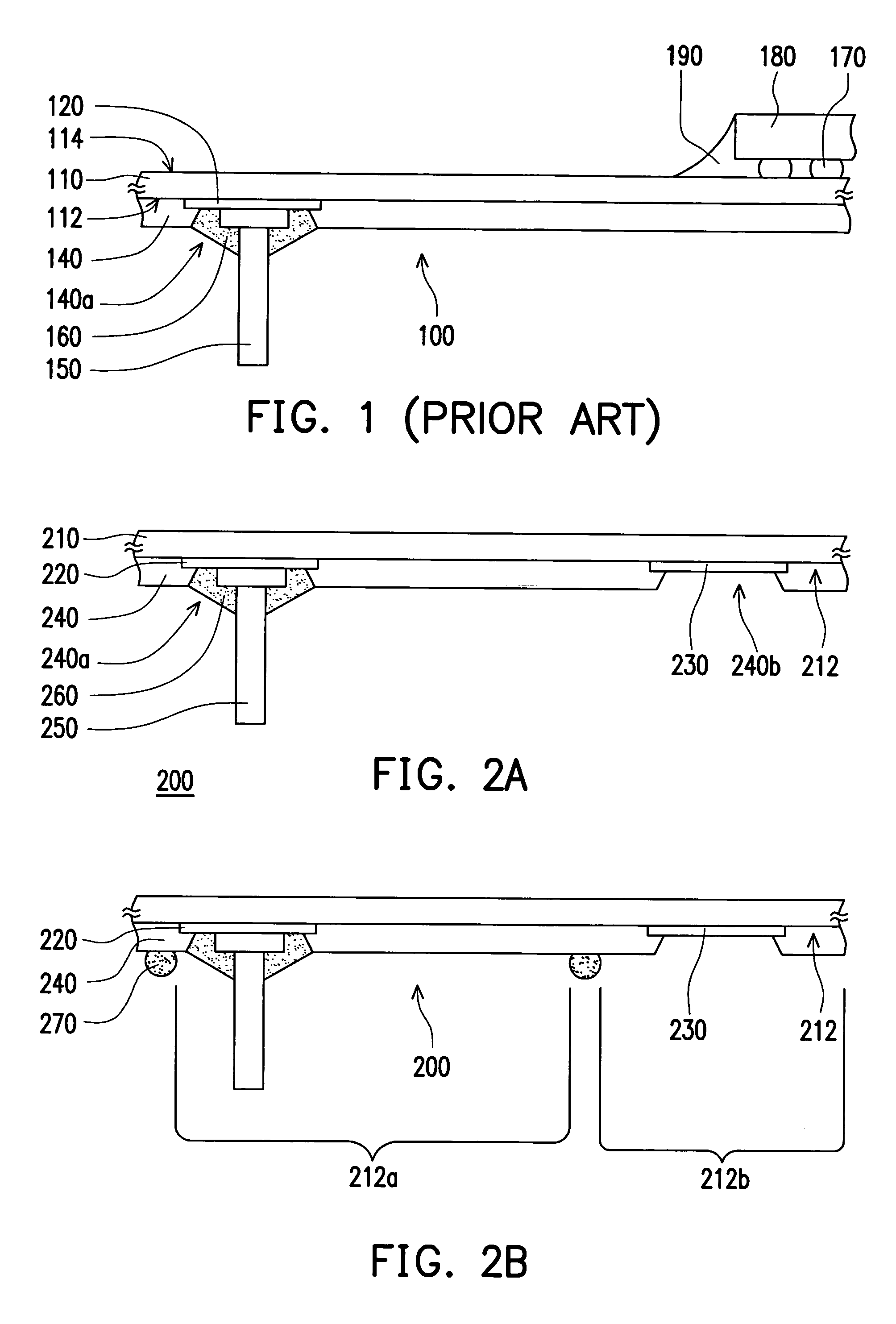

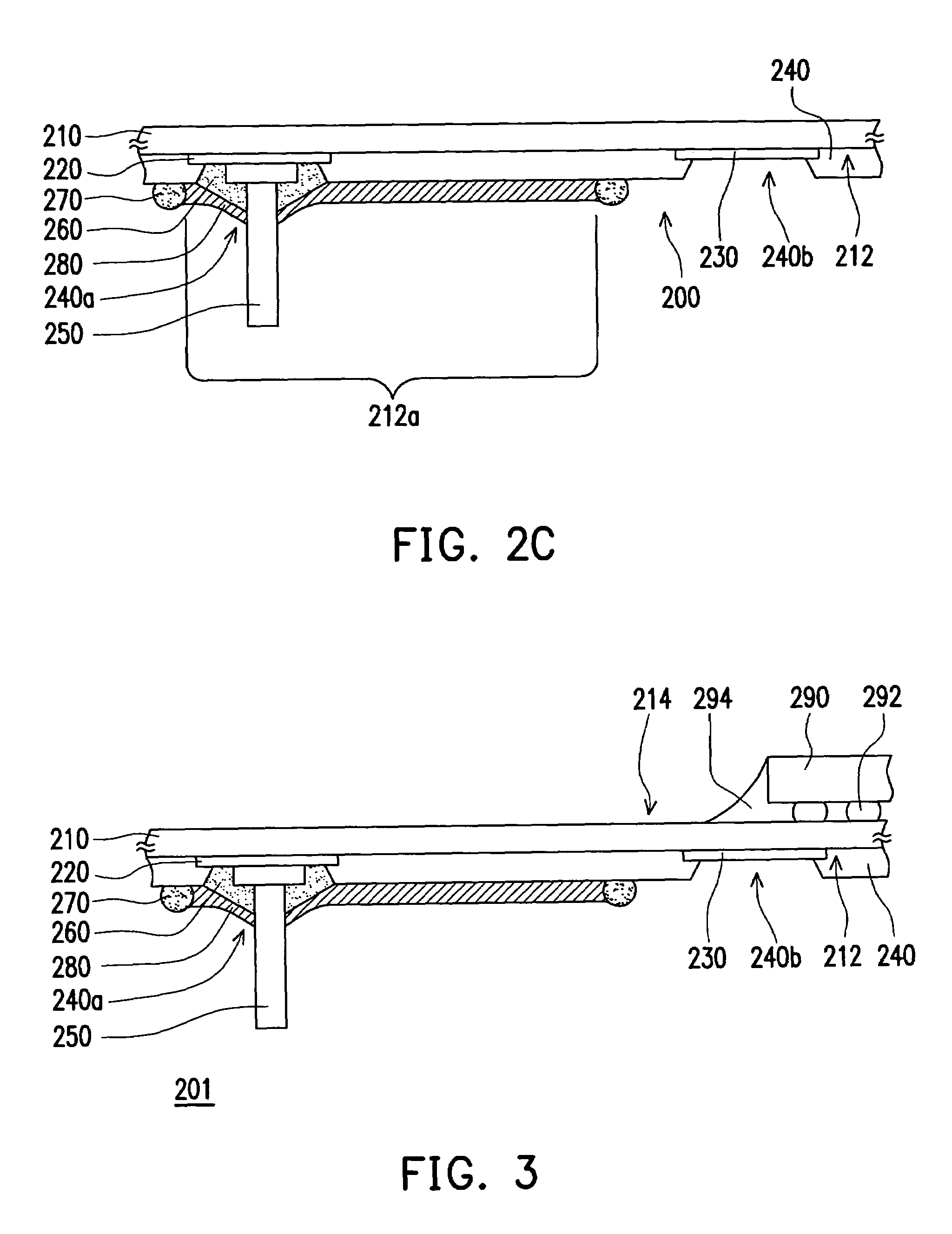

ActiveUS7102230B2Improve manufacturing yieldIncrease productionPrinted circuit assemblingFinal product manufactureSolder maskPin grid array

A circuit carrier adapted for a pin grid array (PGA) package is disclosed. The circuit carrier comprises a substrate, at least one pin pad, at least one solder mask layer, at least one solder layer, at least one pin and a fixing layer. The pin pad is disposed over the surface of the substrate. The solder mask layer is disposed over the surface of the substrate, and exposing at least a portion of the pin pad. The solder layer is disposed over the pin pad. One end of the pin connects to the pin pad through the solder layer. The fixing layer is disposed over the solder mask layer, and covering the solder layer and a portion of a side surface of the pin. When the solder layer melts due to a high process temperature, the fixing layer helps to fix the pin to the pin pad.

Owner:VIA TECH INC

Gender identification method based on face shape and generalized self-organizing mapping

InactiveCN102682294AHigh precisionThe adverse effects of reducing the recognition accuracyCharacter and pattern recognition3D modelling3d shapesInternational standard

The invention discloses a gender identification method based on a face shape and generalized self-organizing mapping. The method comprises the following steps of firstly establishing a face three-dimensional (3D) shaped recovery model by pin grid array (PGA) technology based on an international standard MAXPLANCK3D face database; secondly, studying the 3D face library by growing self-organizing map (G-SOM), obtaining the distribution rules of 3D characteristics of face gender; at the identification stage, recovering a 3D shape information of a 2D face image on a 3D shape recovering model by firstly using a PGASFS technology, and then inputting the 3D shape information obtained by recovering to the G-SOM, and performing gender identification by using a Soft-KNN algorithm. The method provided by the invention has the advantages that the adverse effect to identification precision caused by changes of face gesture, expression and illumination conditions is reduced; secondly, the mode intrinsic topology can be kept better by the use of G-SOM; and thirdly, the links between the local structure and overall structure of the face is utilized by the gender identification method, thus, the recognition rate is improved.

Owner:CHANGSHU RES INSTITUE OF NANJING UNIV OF SCI & TECH +1