Patents

Literature

1996 results about "Electronic packaging" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electronic packaging is the design and production of enclosures for electronic devices ranging from individual semiconductor devices up to complete systems such as a mainframe computer. Packaging of an electronic system must consider protection from mechanical damage, cooling, radio frequency noise emission and electrostatic discharge. Product safety standards may dictate particular features of a consumer product, for example, external case temperature or grounding of exposed metal parts. Prototypes and industrial equipment made in small quantities may use standardized commercially available enclosures such as card cages or prefabricated boxes. Mass-market consumer devices may have highly specialized packaging to increase consumer appeal. Electronic packaging is a major discipline within the field of mechanical engineering.

Precision spray processes for direct write electronic components

InactiveUS6251488B1Keep for a long timeIncrease probabilityMolten spray coatingVacuum evaporation coatingElectrical resistance and conductanceElectronic component

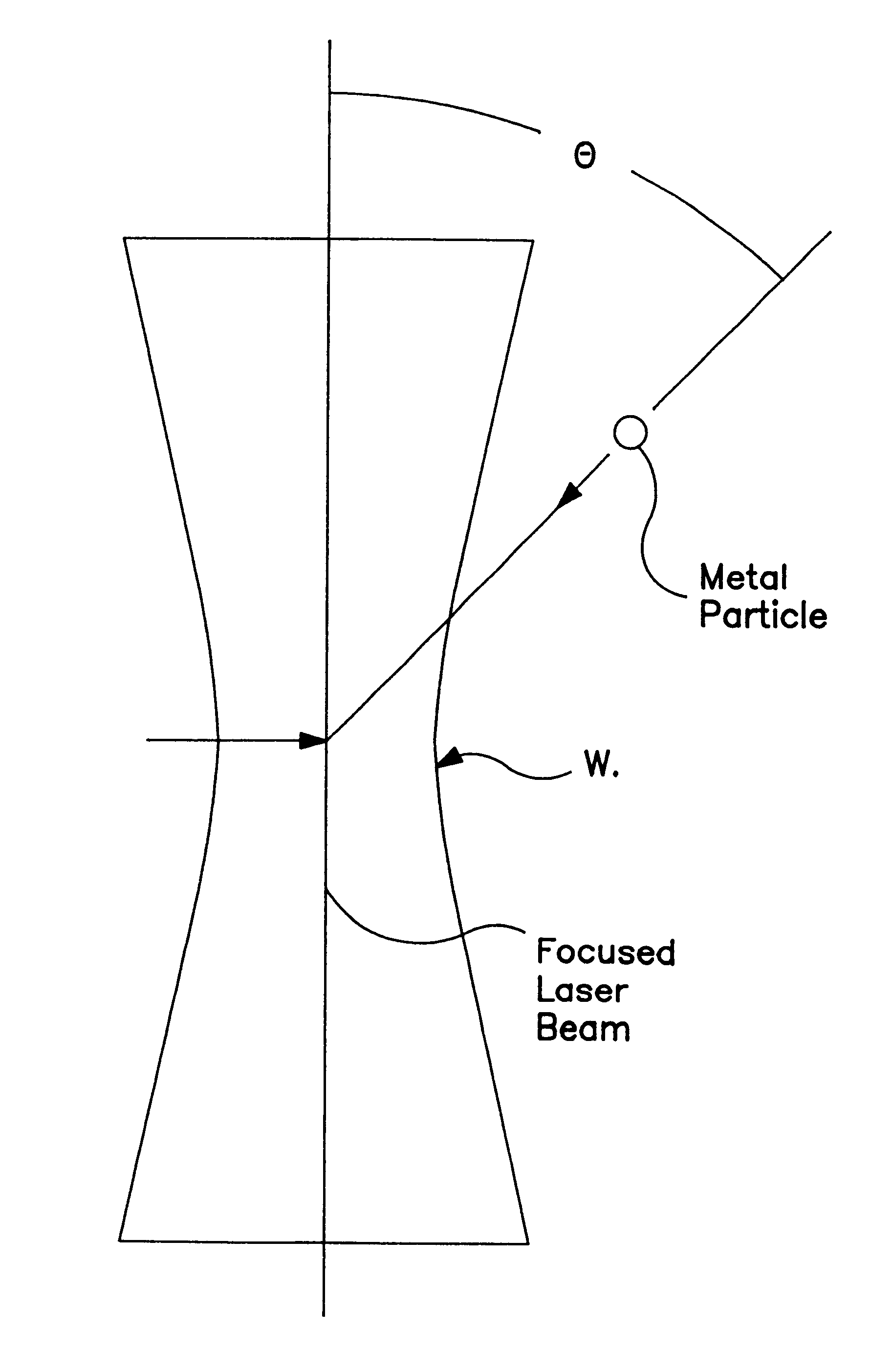

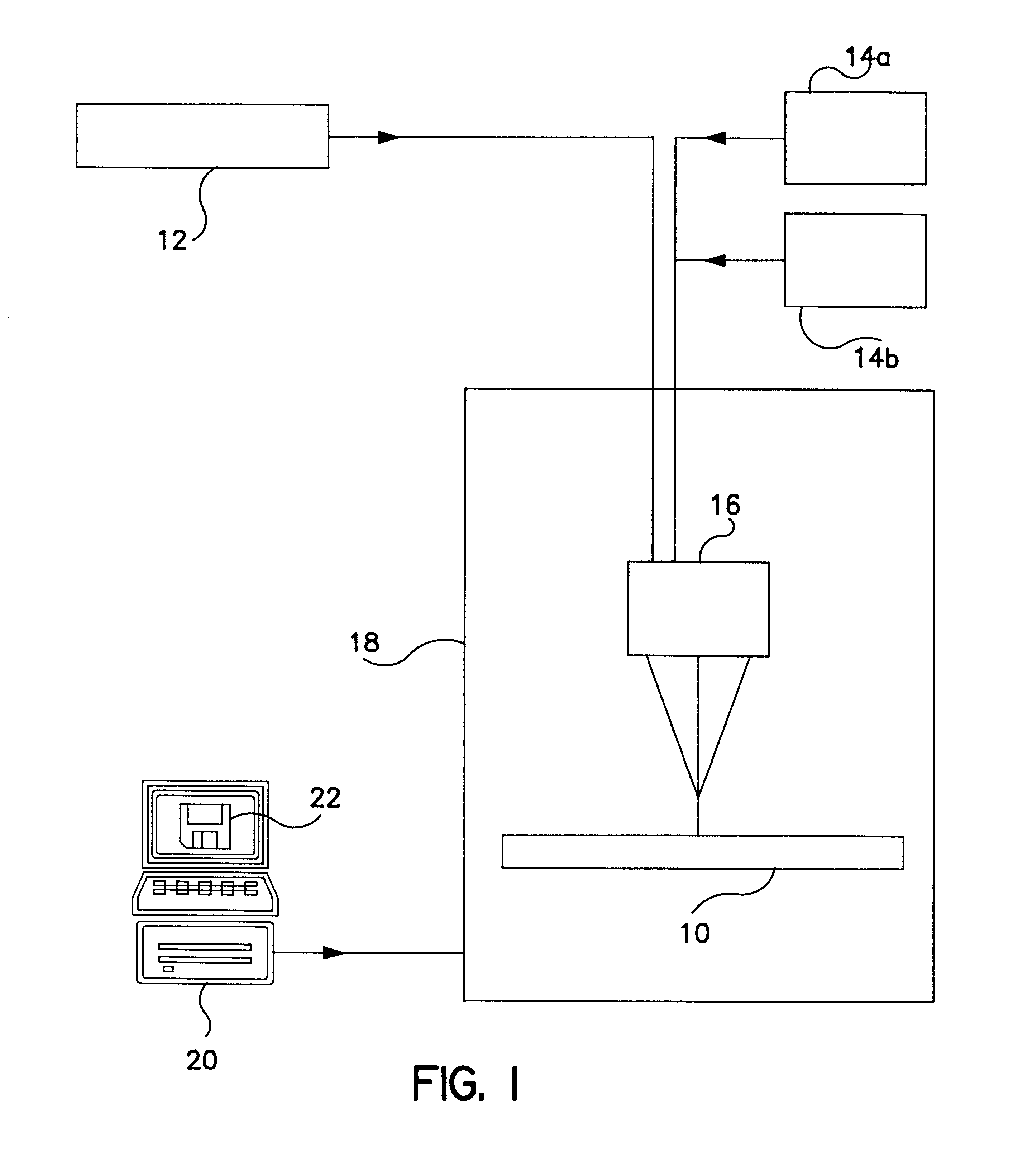

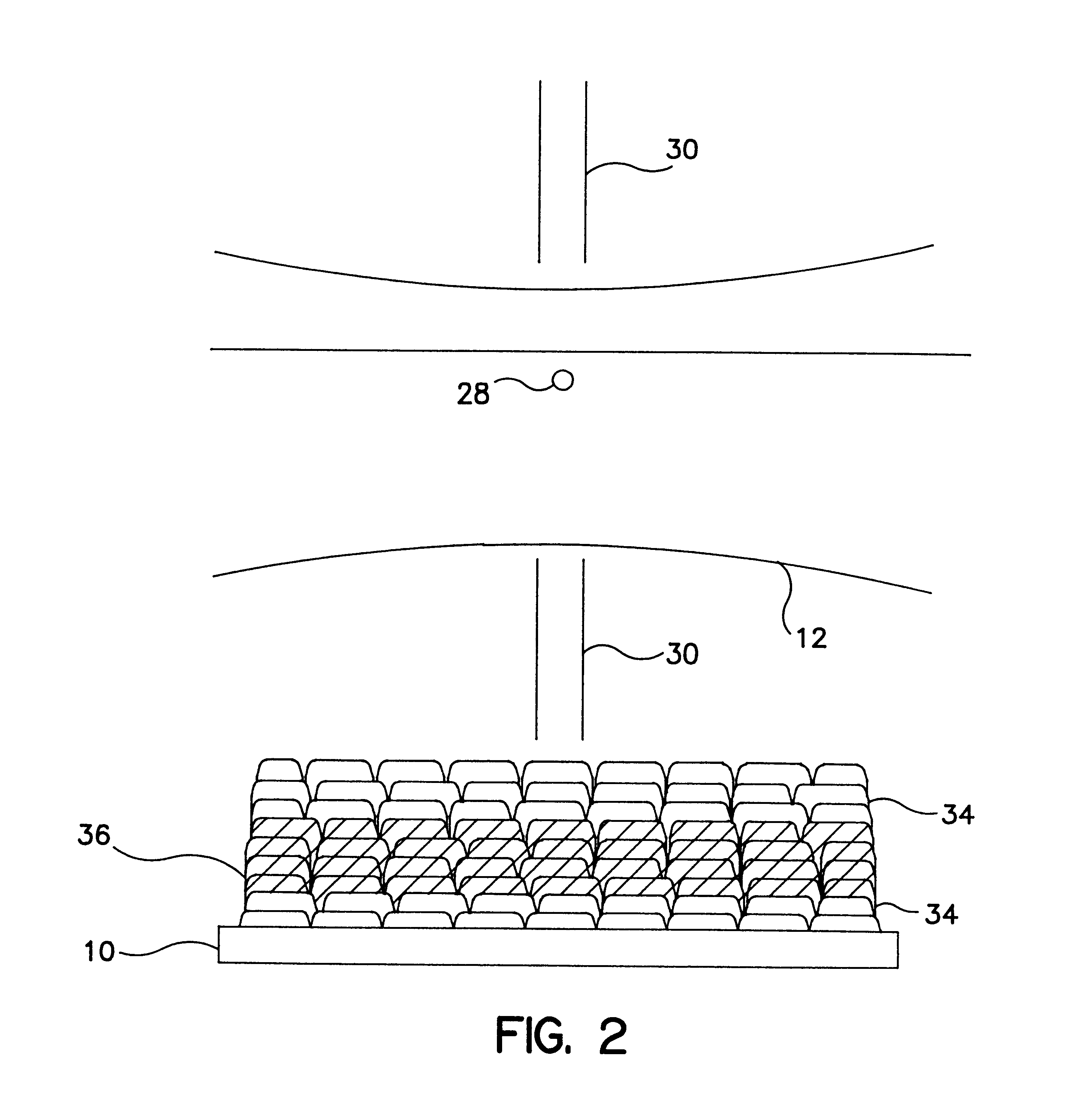

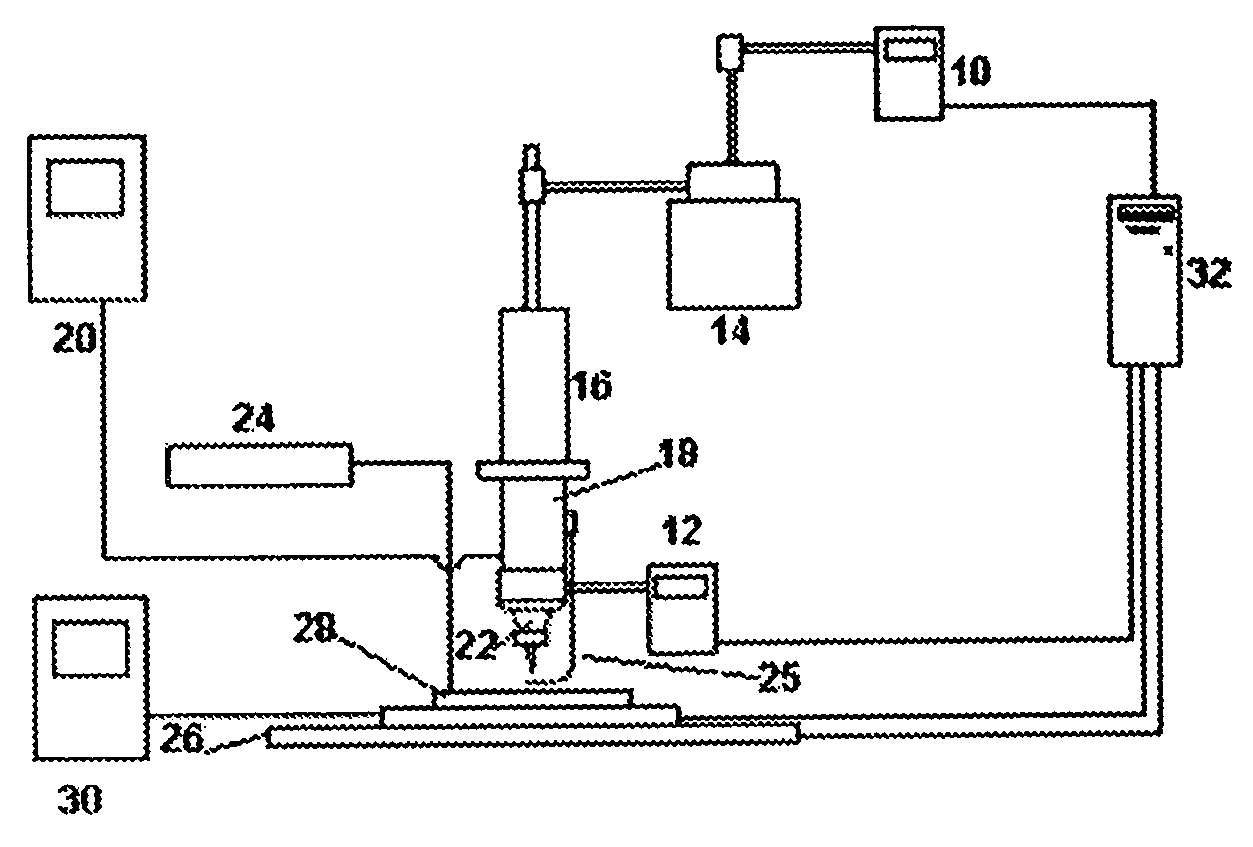

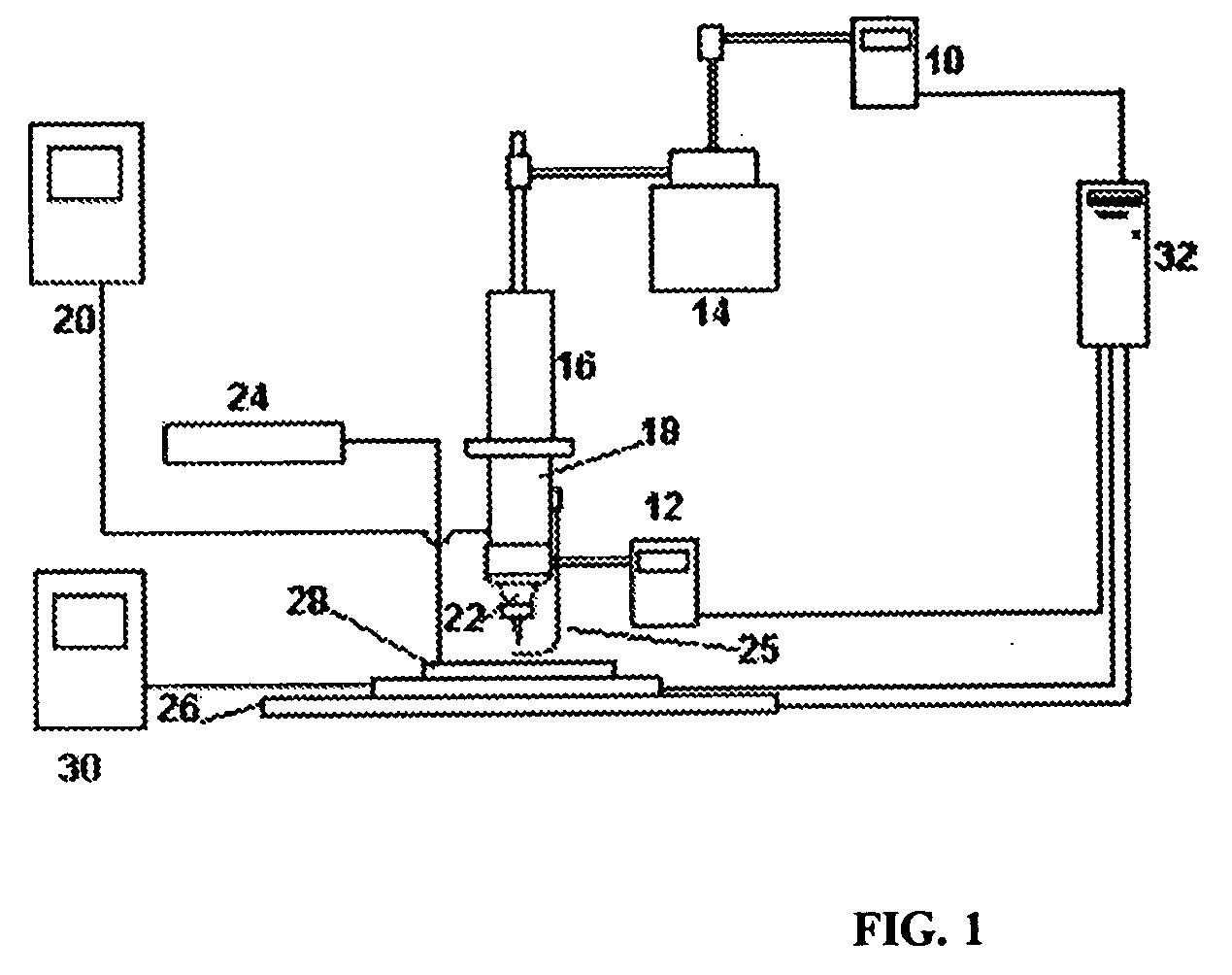

This invention combines the precision spray process with in-flight laser treatment in order to produce direct write electronic components. In addition to these components, the process can lay down lines of conductive, inductive, and resistive materials. This development has the potential to change the approach to electronics packaging. This process is revolutionary in that components can be directly produced on small structures, thus removing the need for printed circuit boards.

Owner:OPTOMEC DESIGN CO

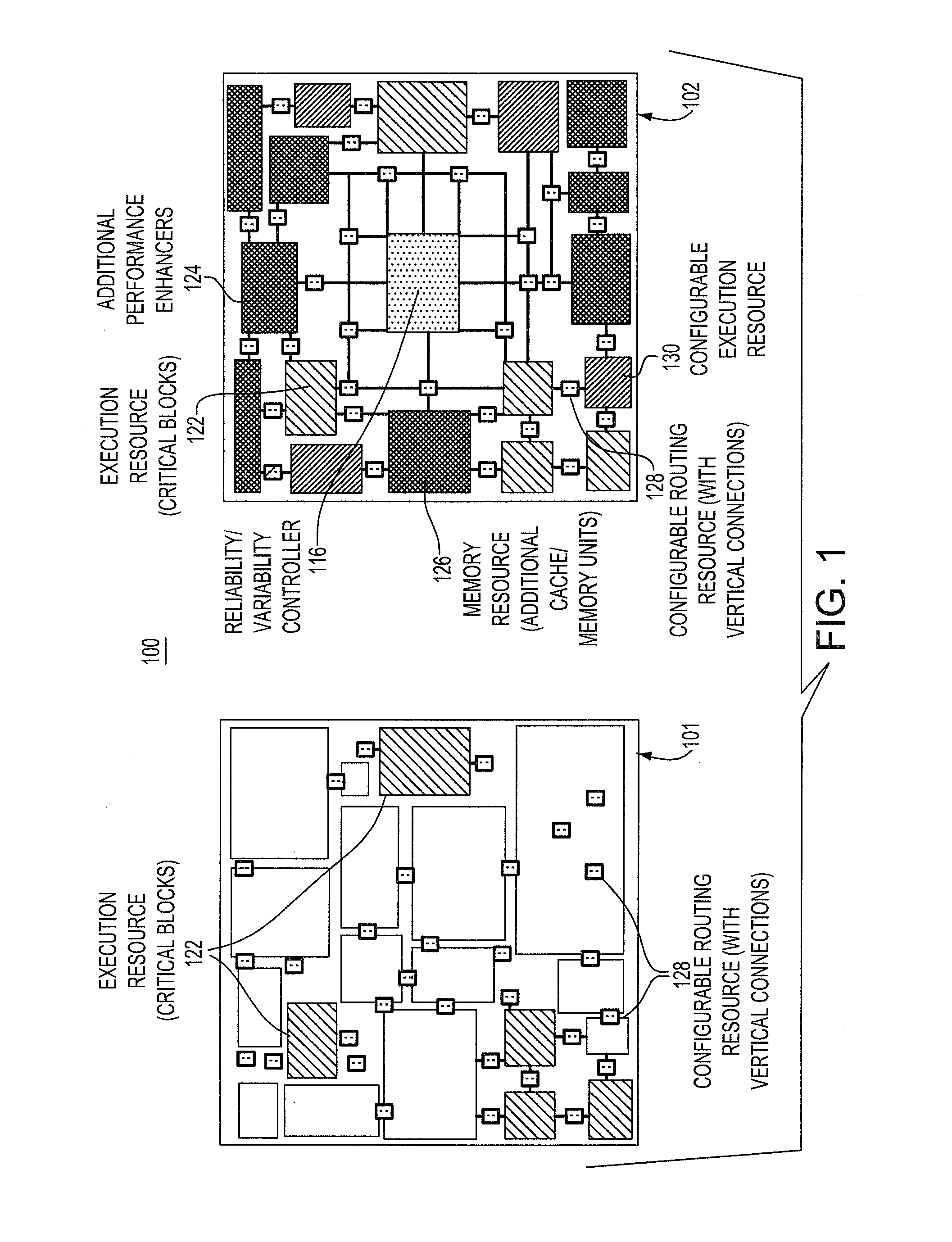

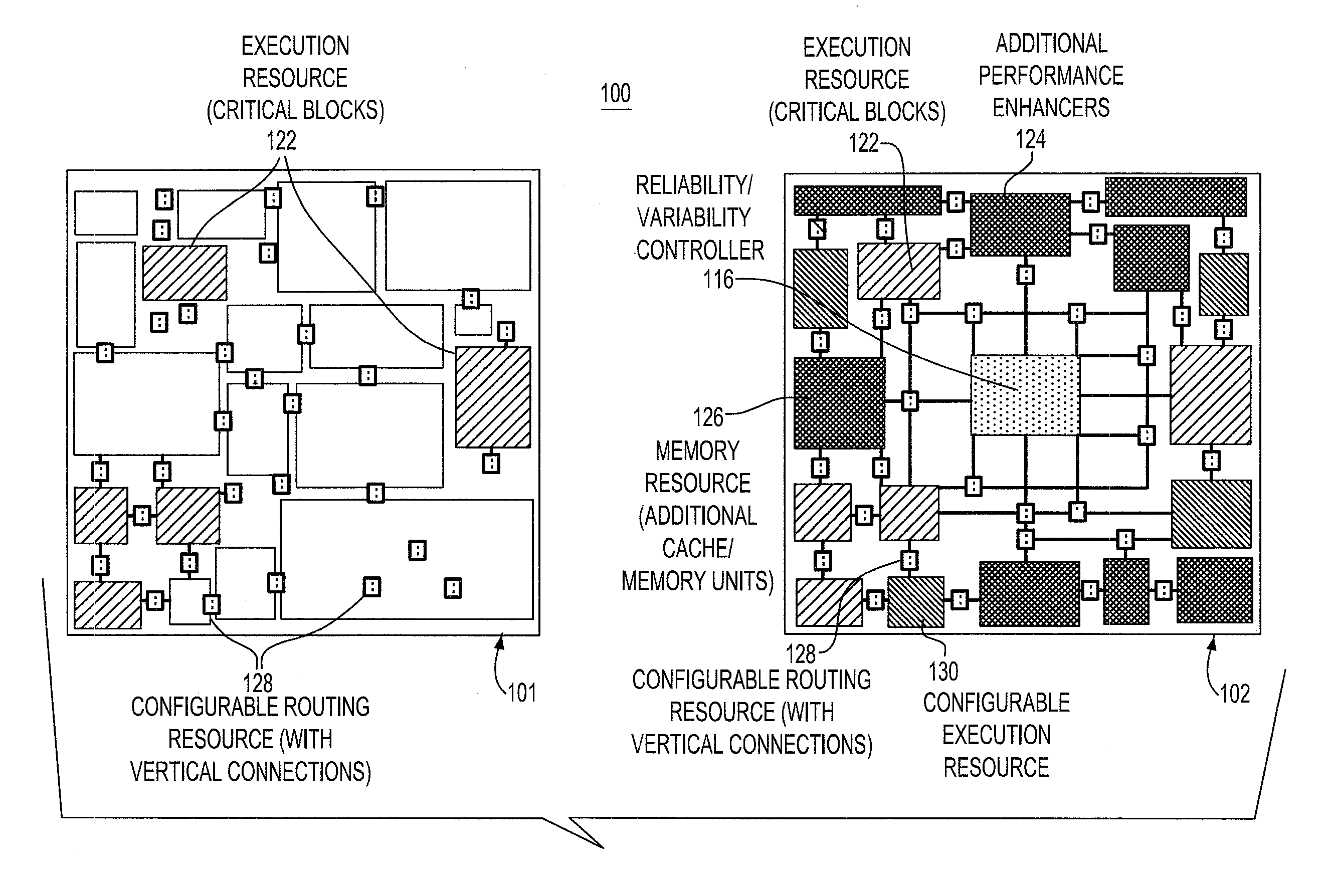

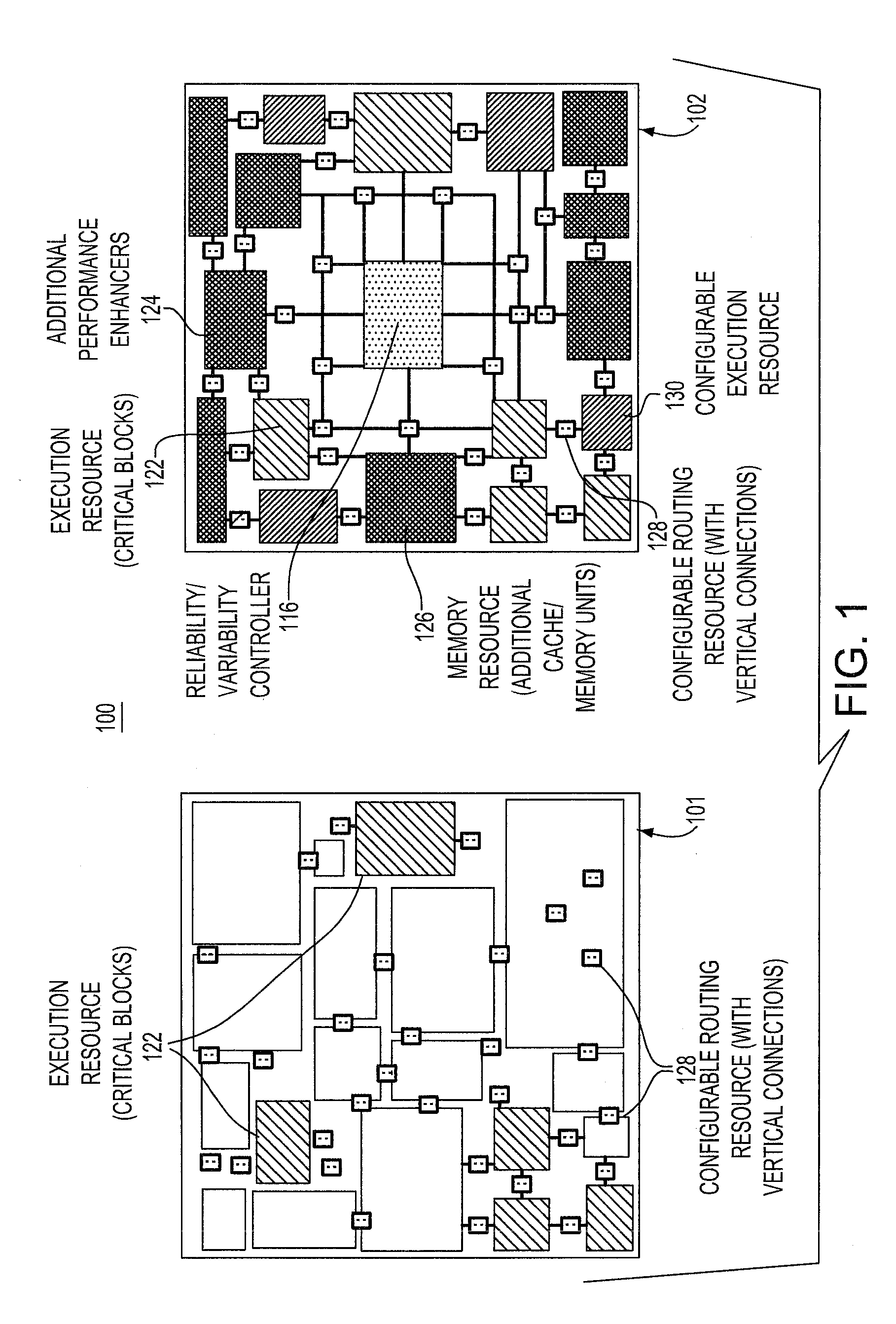

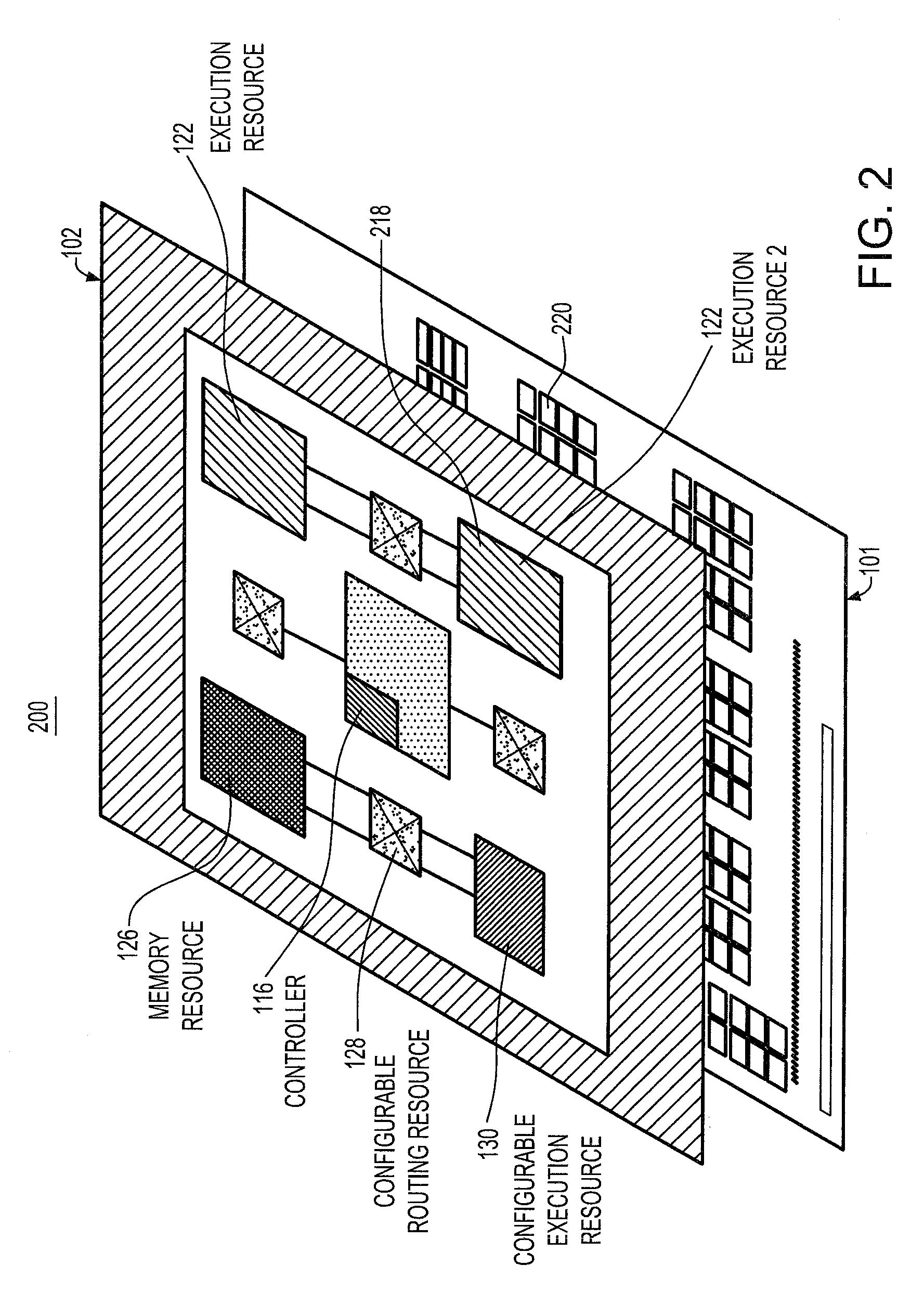

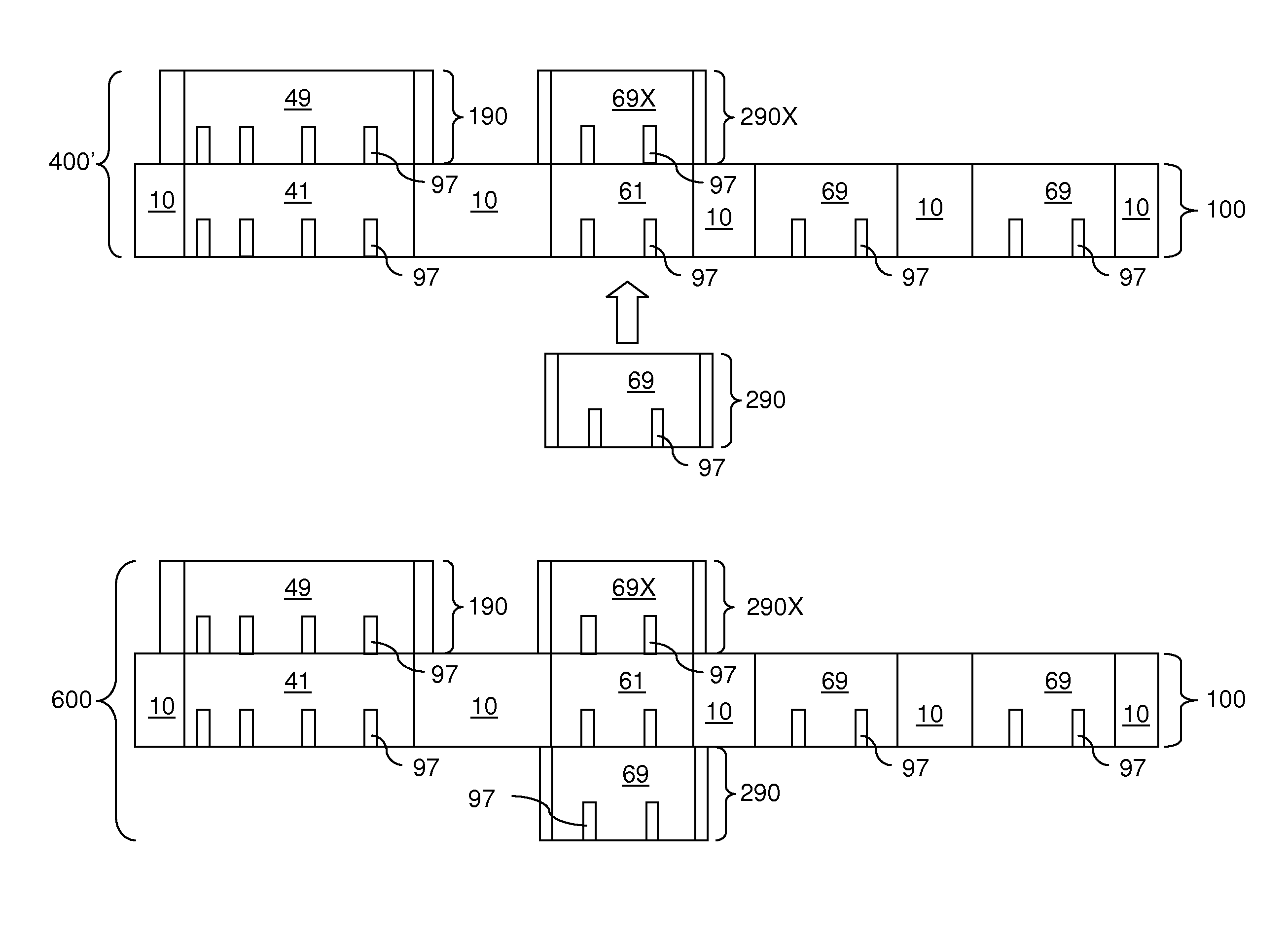

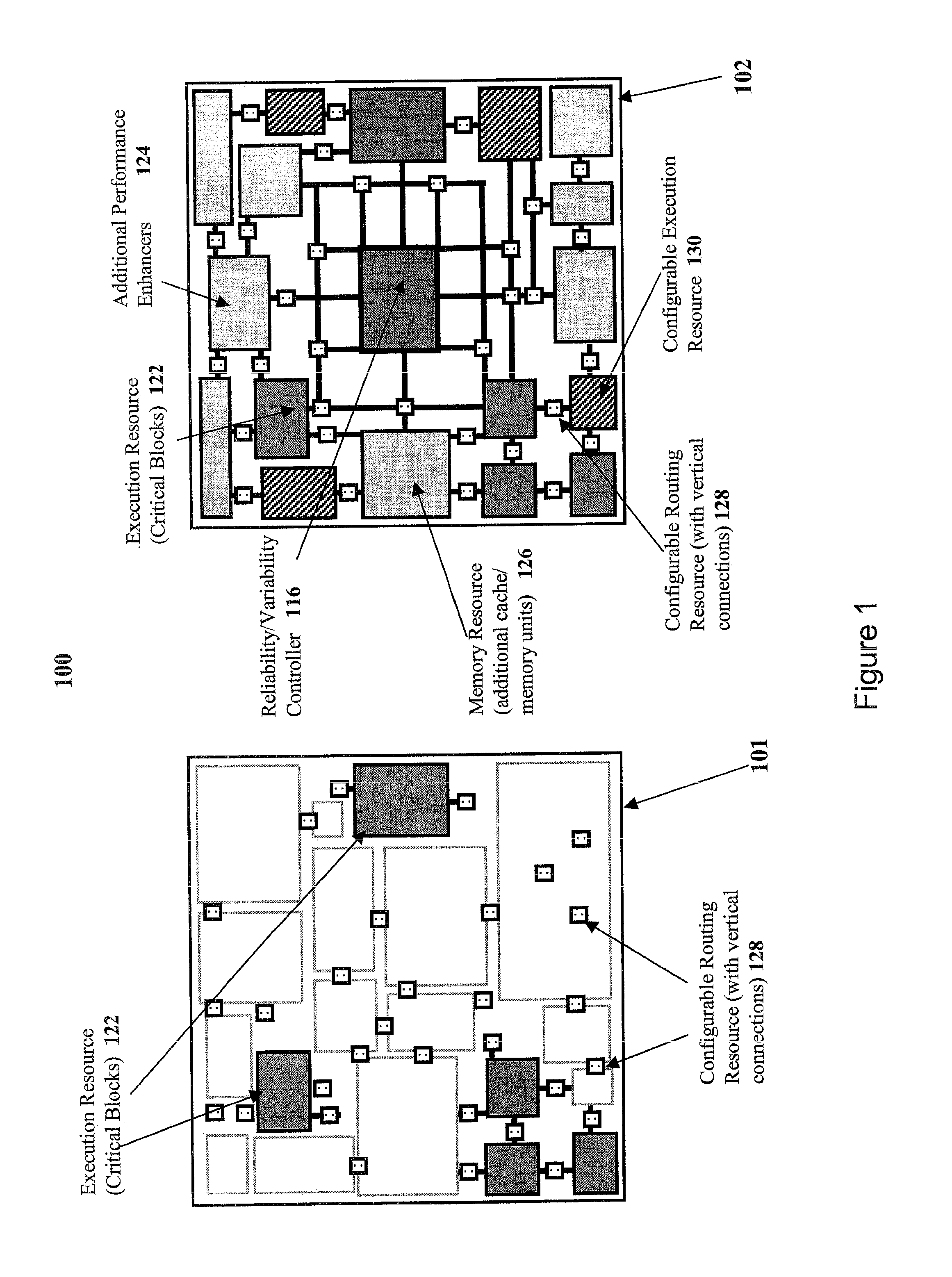

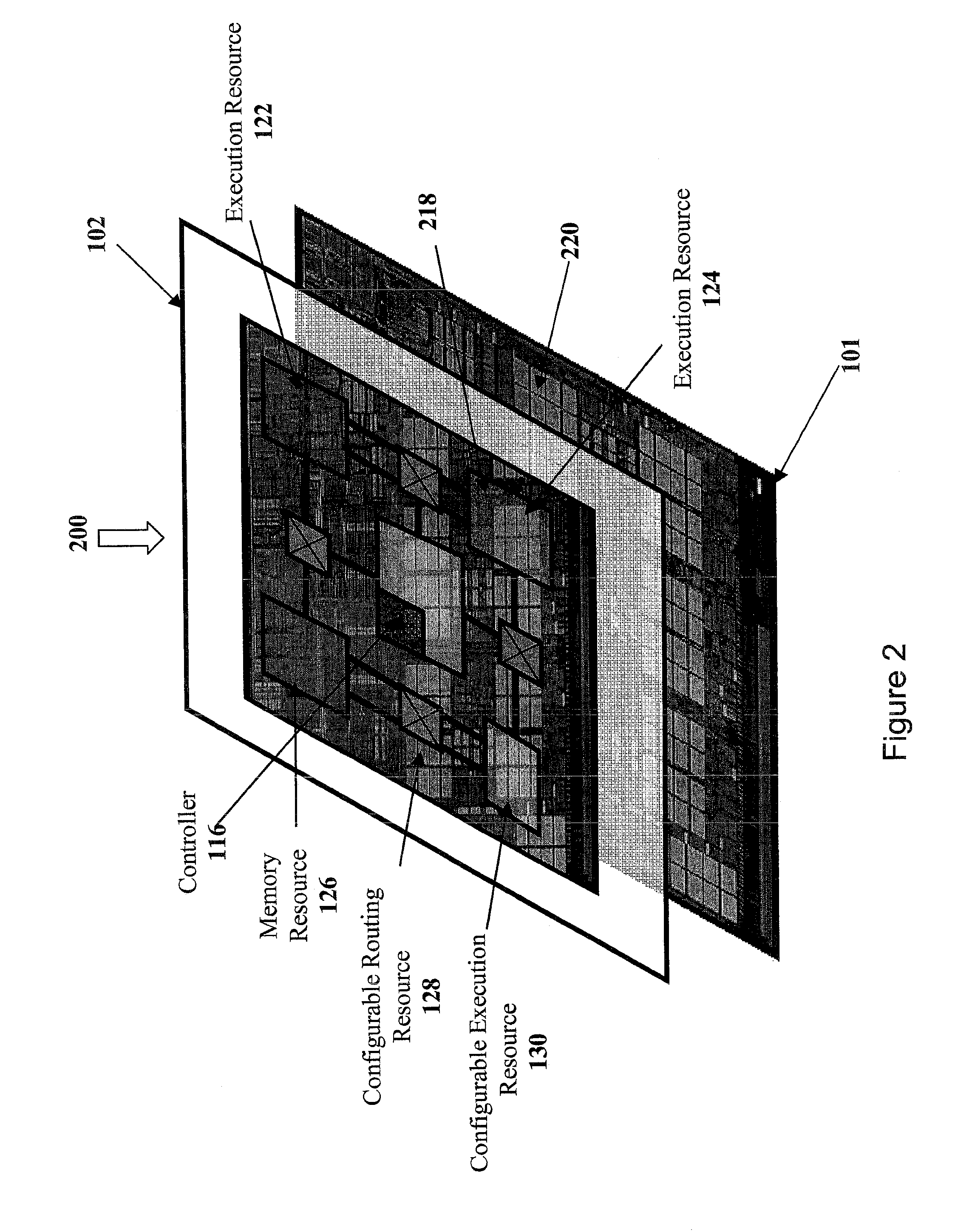

Method and on-chip control apparatus for enhancing process reliability and process variability through 3D integration

InactiveUS20090144678A1Alleviate lifetime reliabilityAlleviate process variability issueError detection/correctionSoftware simulation/interpretation/emulationSemiconductor chipEngineering

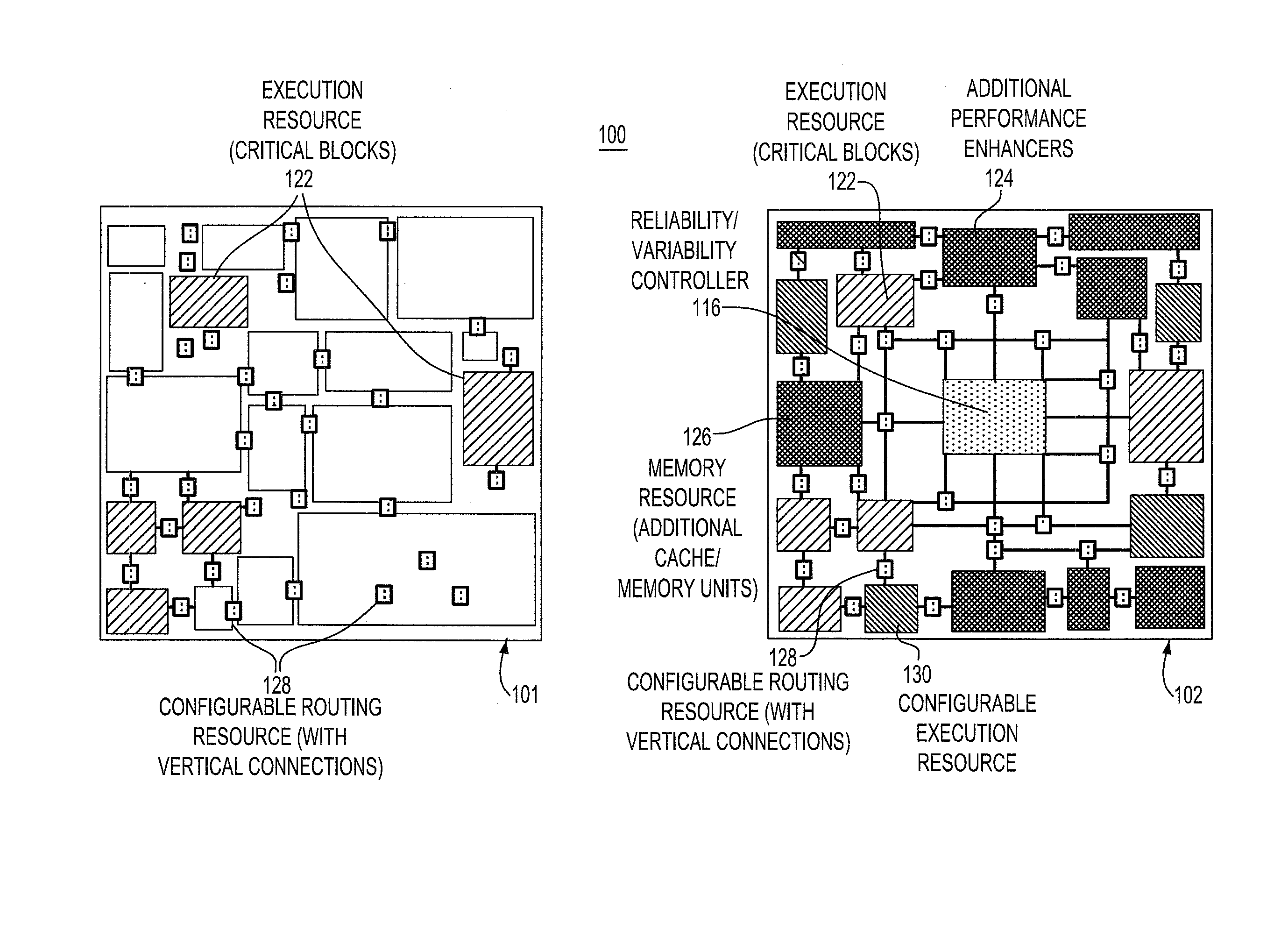

A method and on-chip controller for enhancing semiconductor chip process variability and lifetime reliability through a three-dimensional (3D) integration applied to electronic packaging. Also provided is an on-chip reliability / variability controller arrangement for implementing the inventive method.

Owner:GLOBALFOUNDRIES INC

Nanocoated primary particles and method for their manufacture

InactiveUS6913827B2Granule coatingSemiconductor/solid-state device detailsConformal coatingElectronic packaging

Particles have an ultrathin, conformal coating are made using atomic layer deposition methods. The base particles include ceramic and metallic materials. The coatings can also be ceramic or metal materials that can be deposited in a binary reaction sequence. The coated particles are useful as fillers for electronic packaging applications, for making ceramic or cermet parts, as supported catalysts, as well as other applications.

Owner:UNIV OF COLORADO THE REGENTS OF

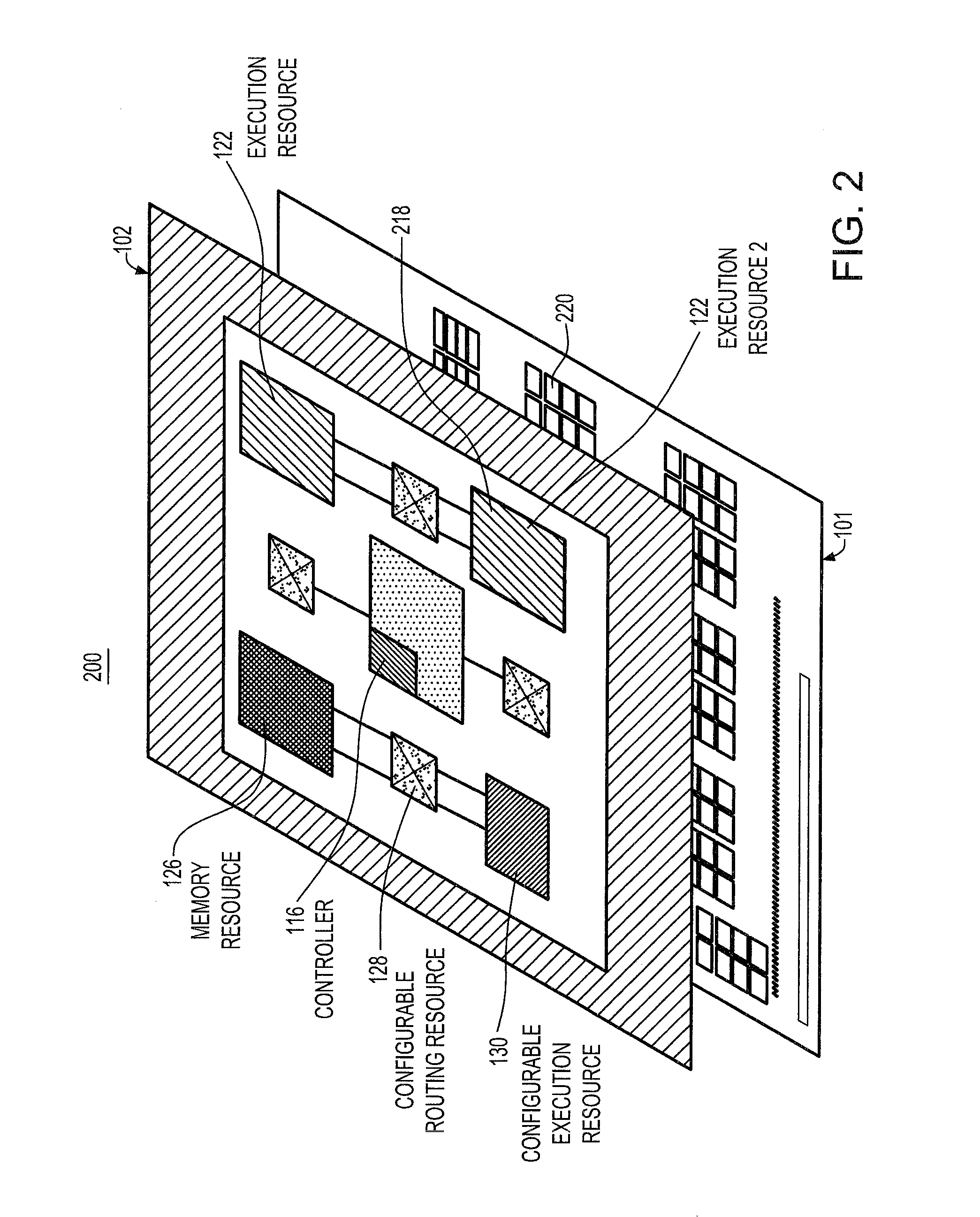

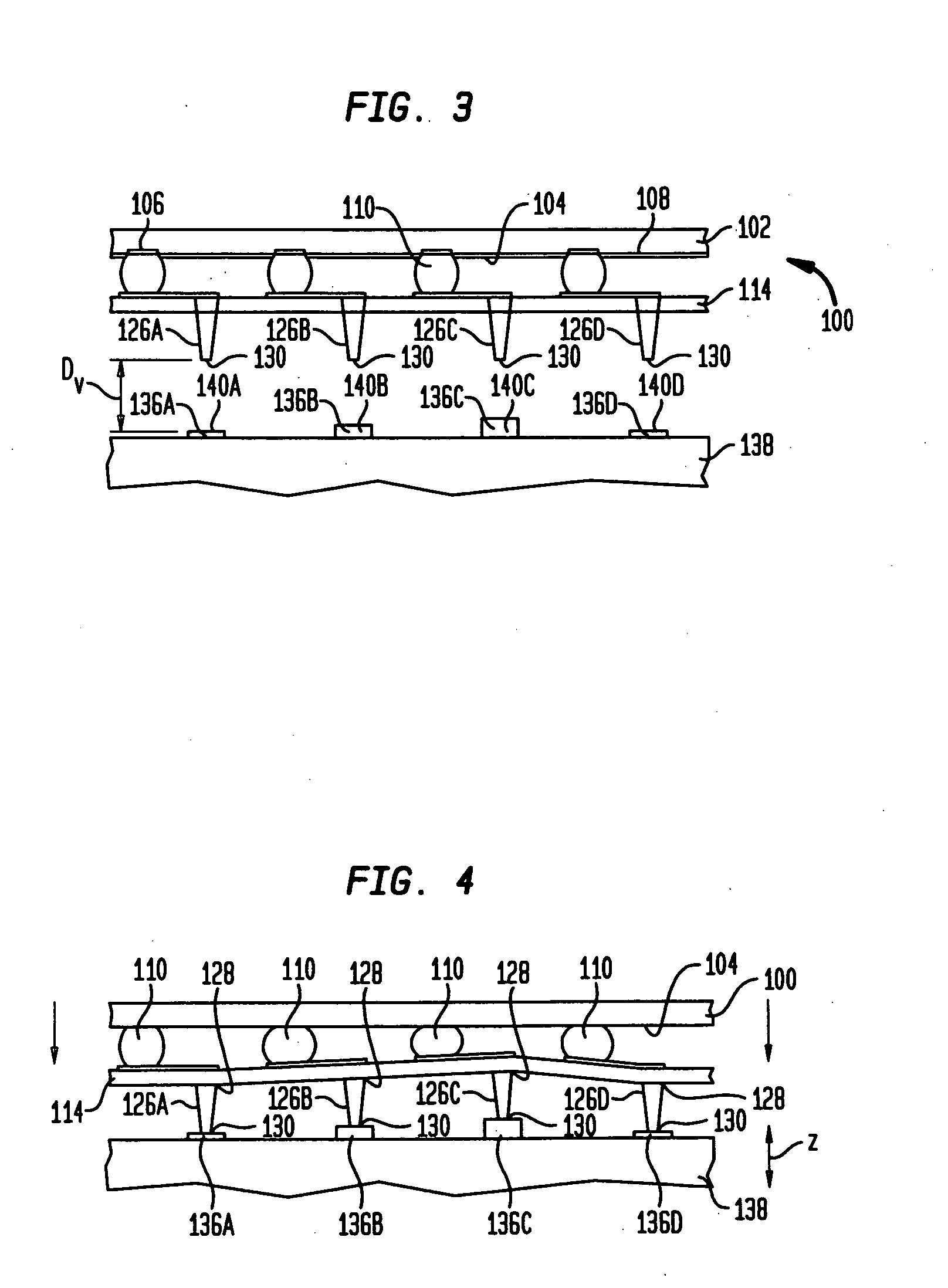

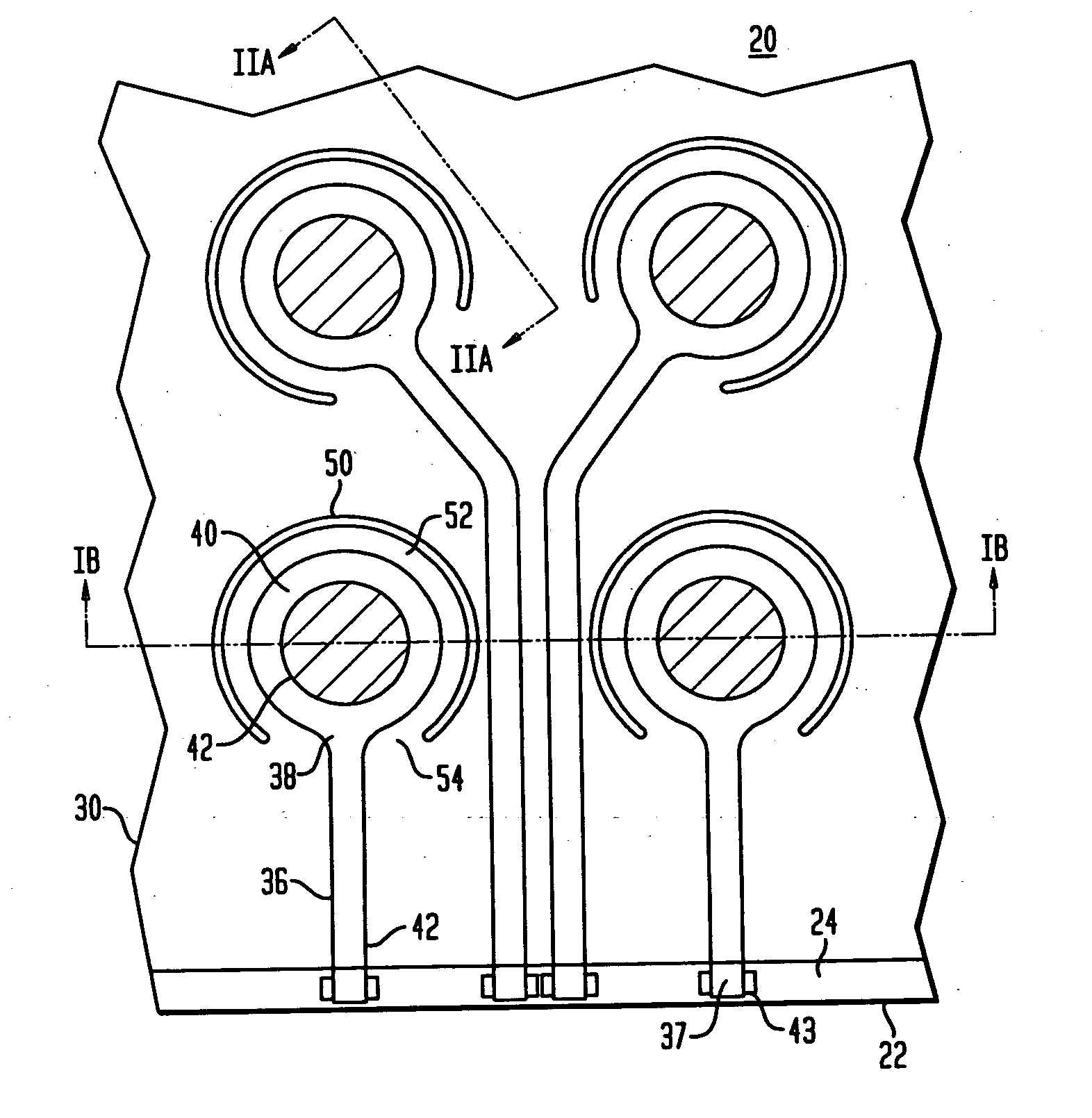

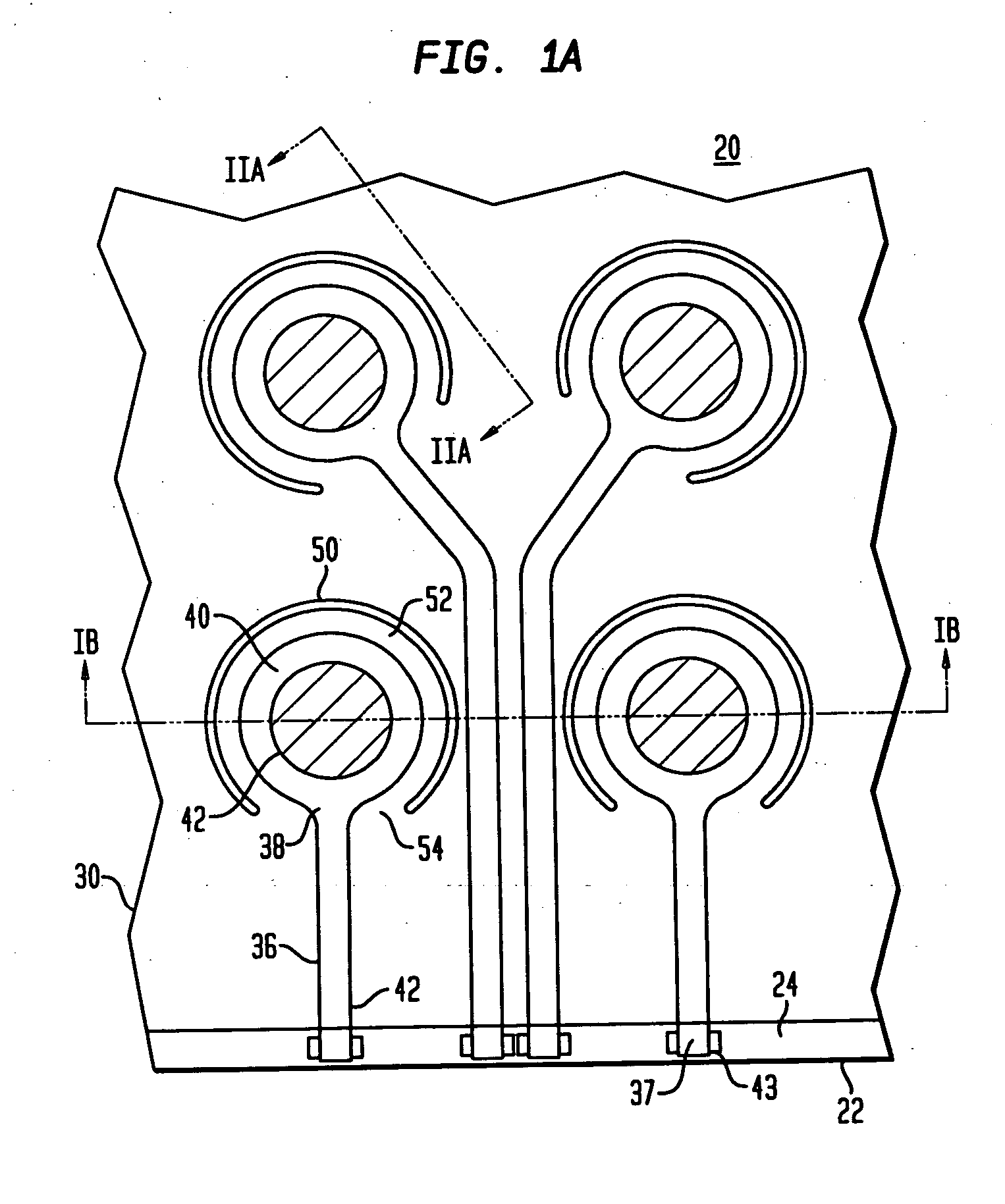

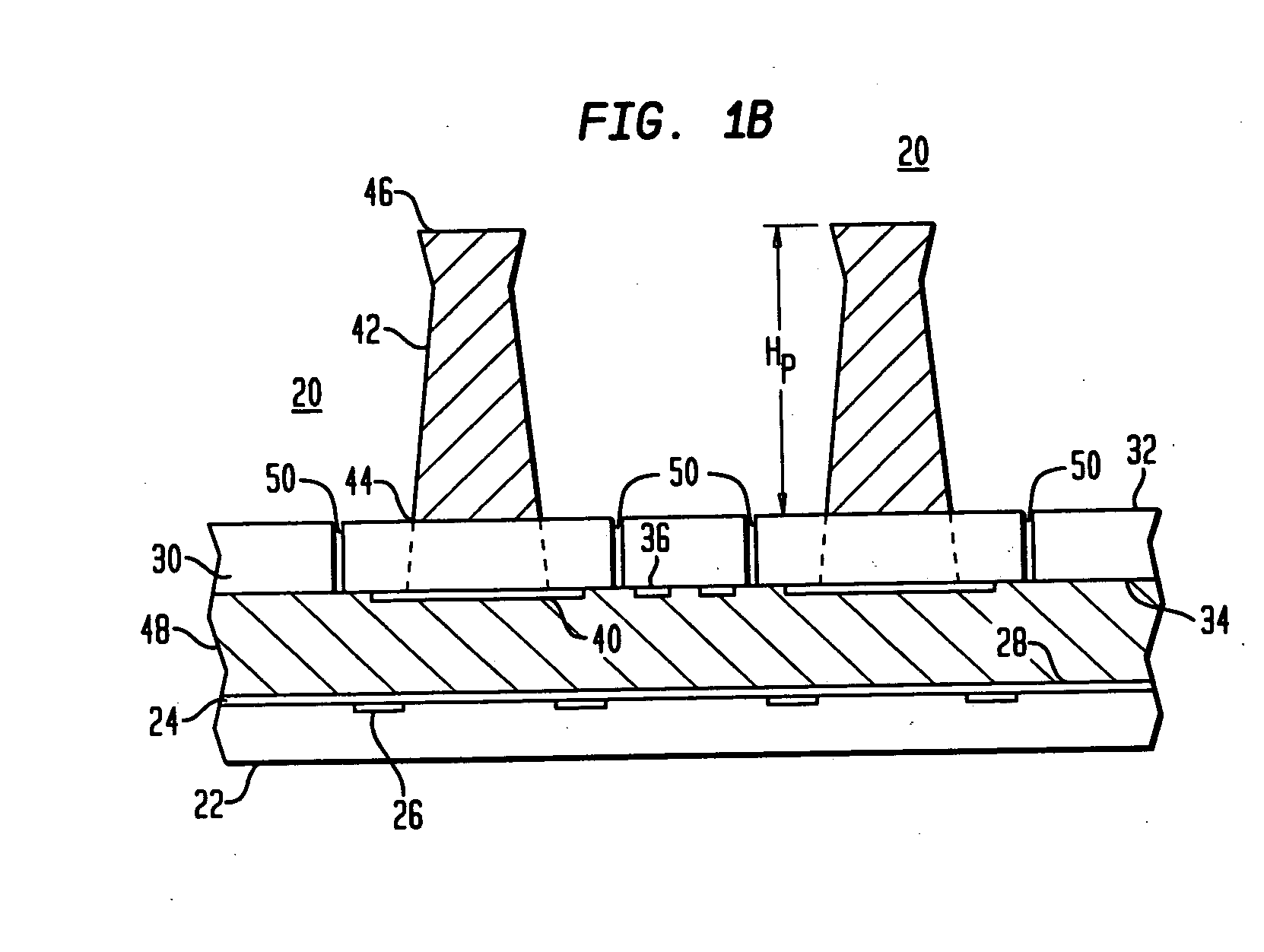

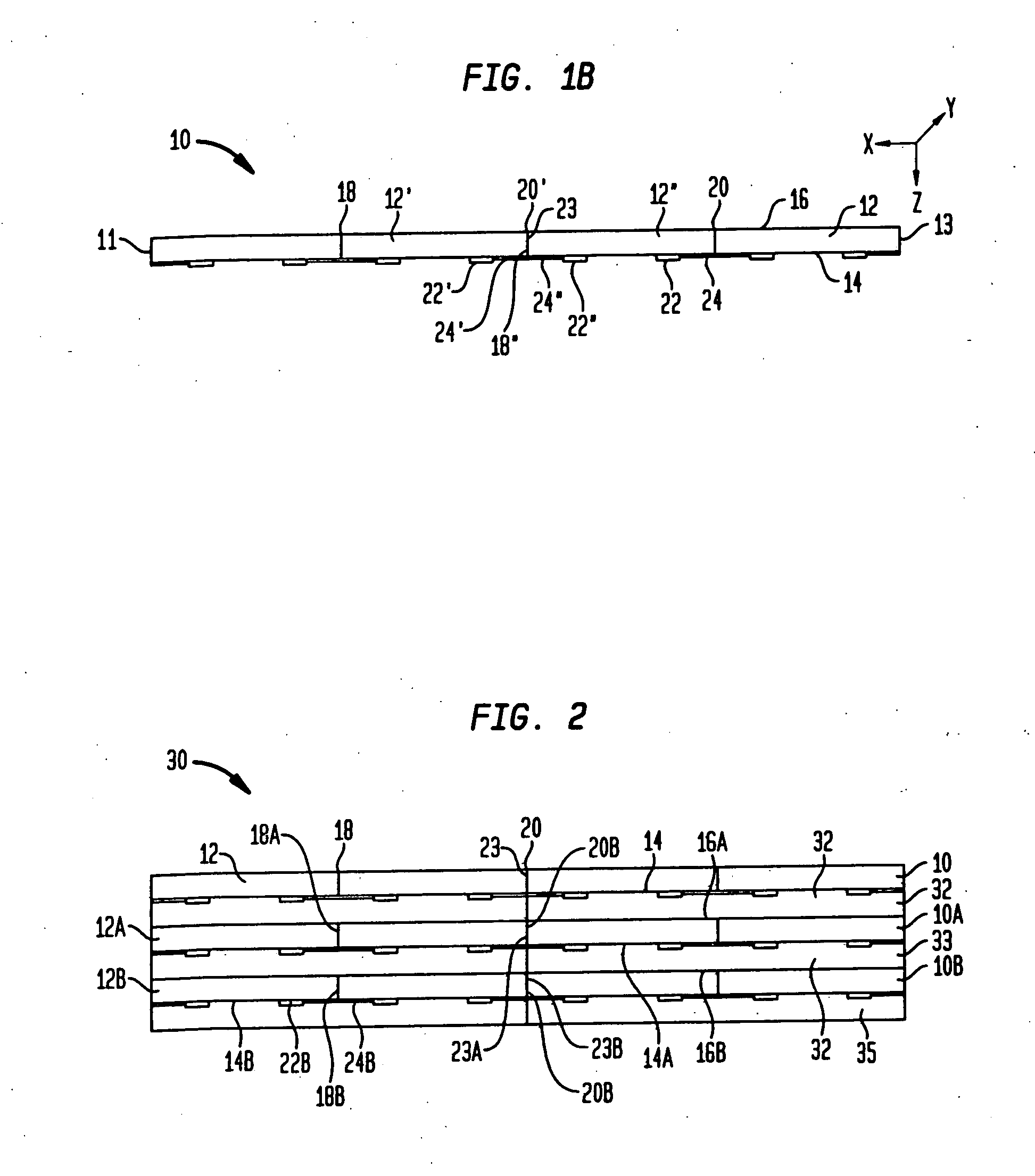

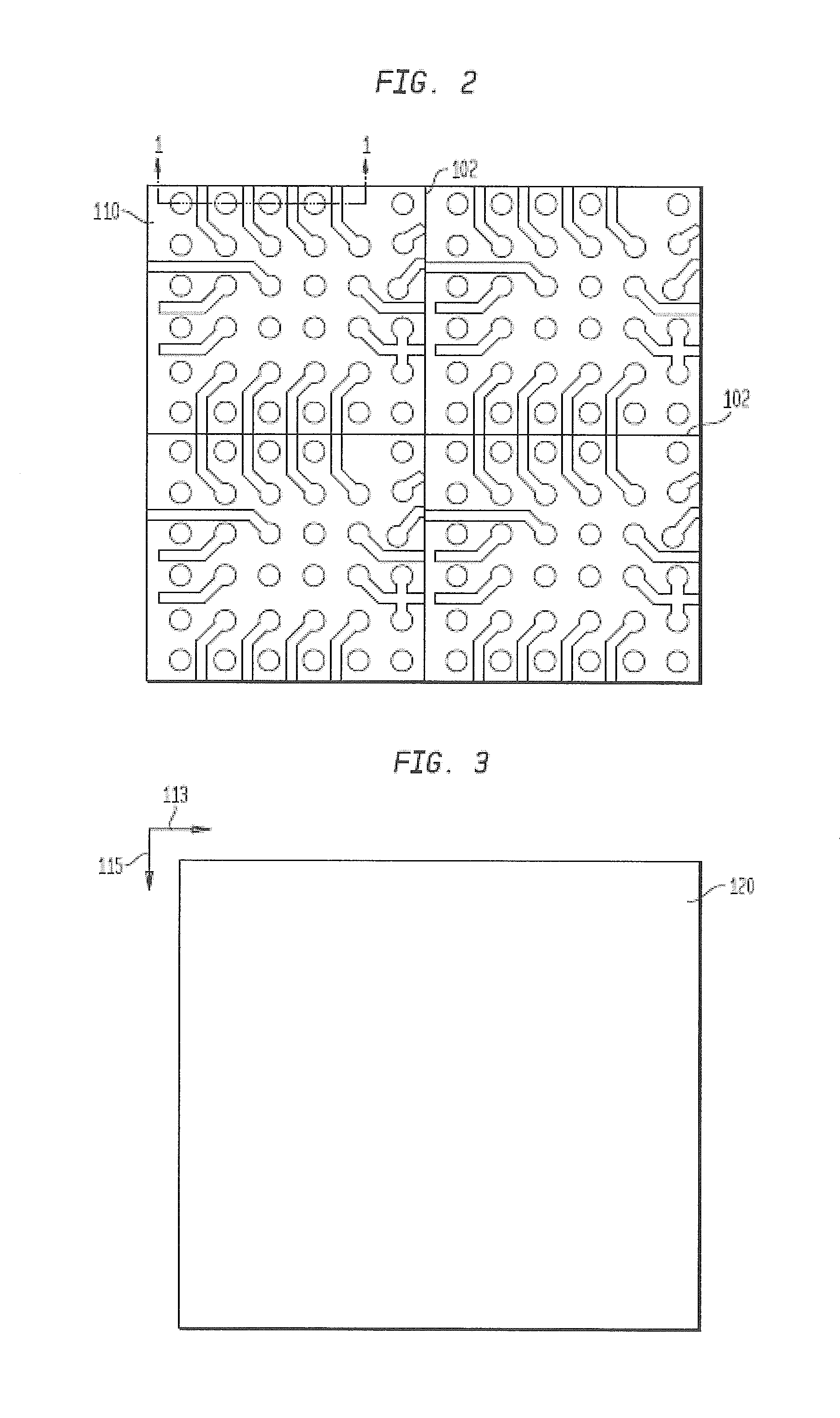

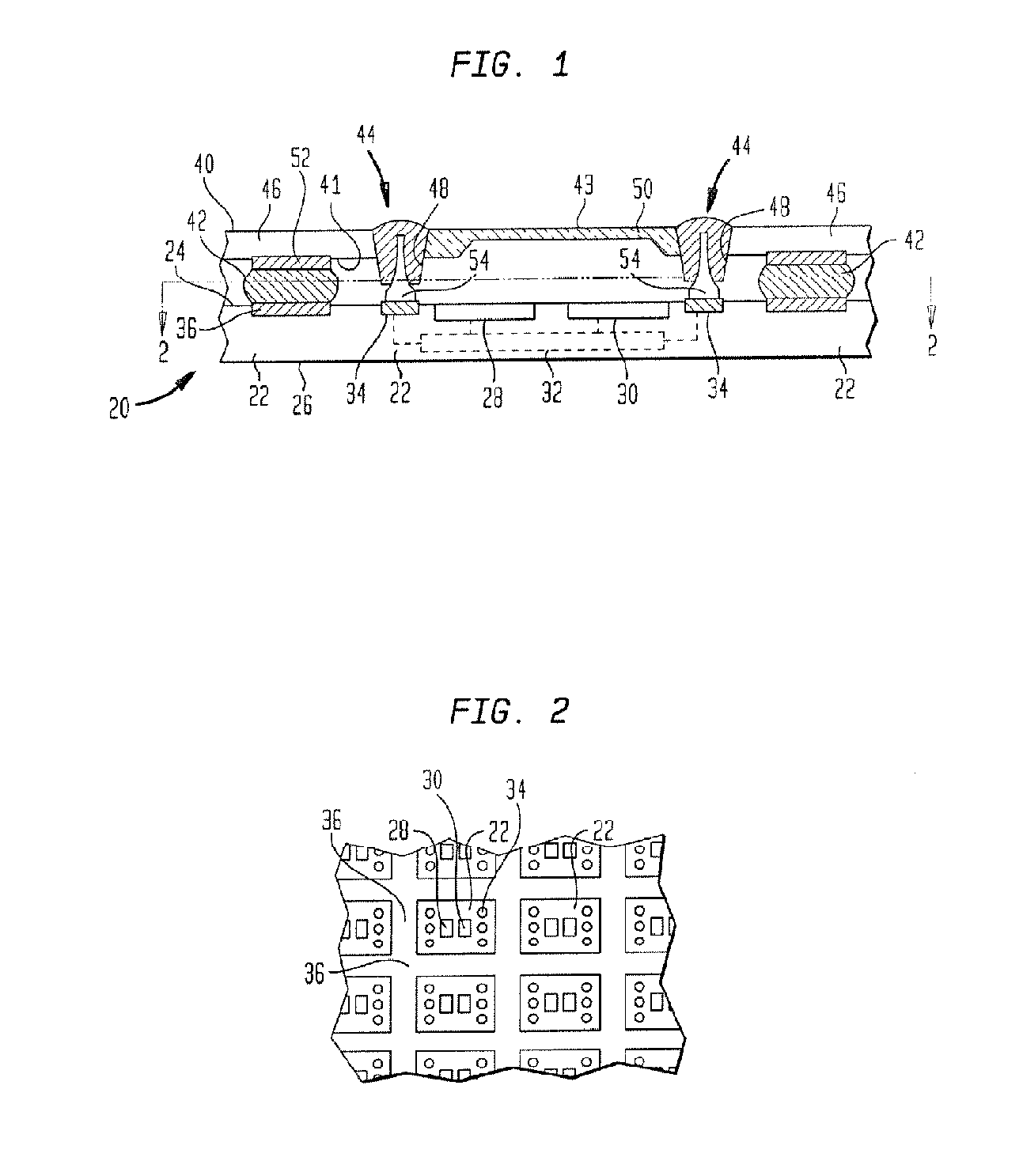

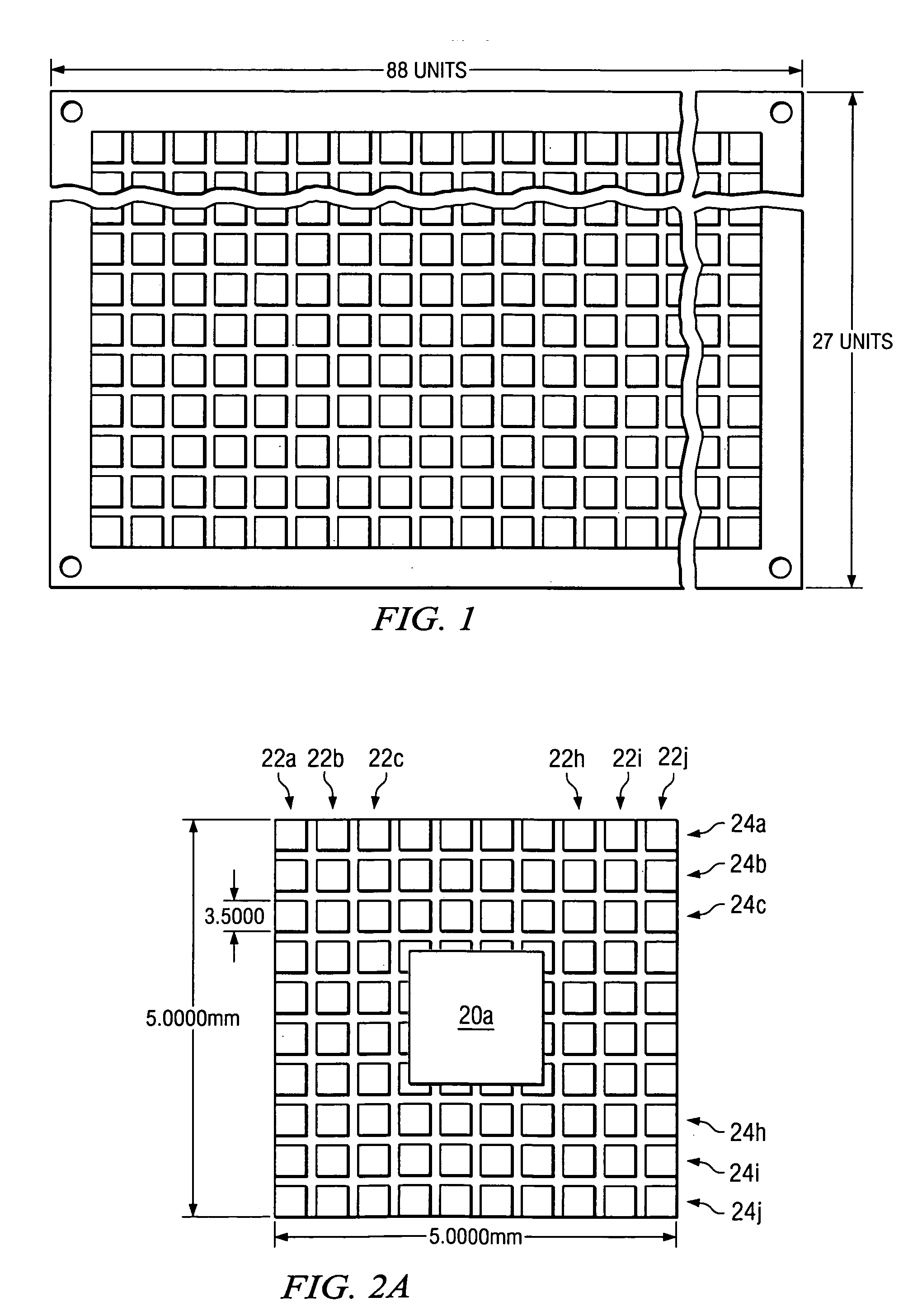

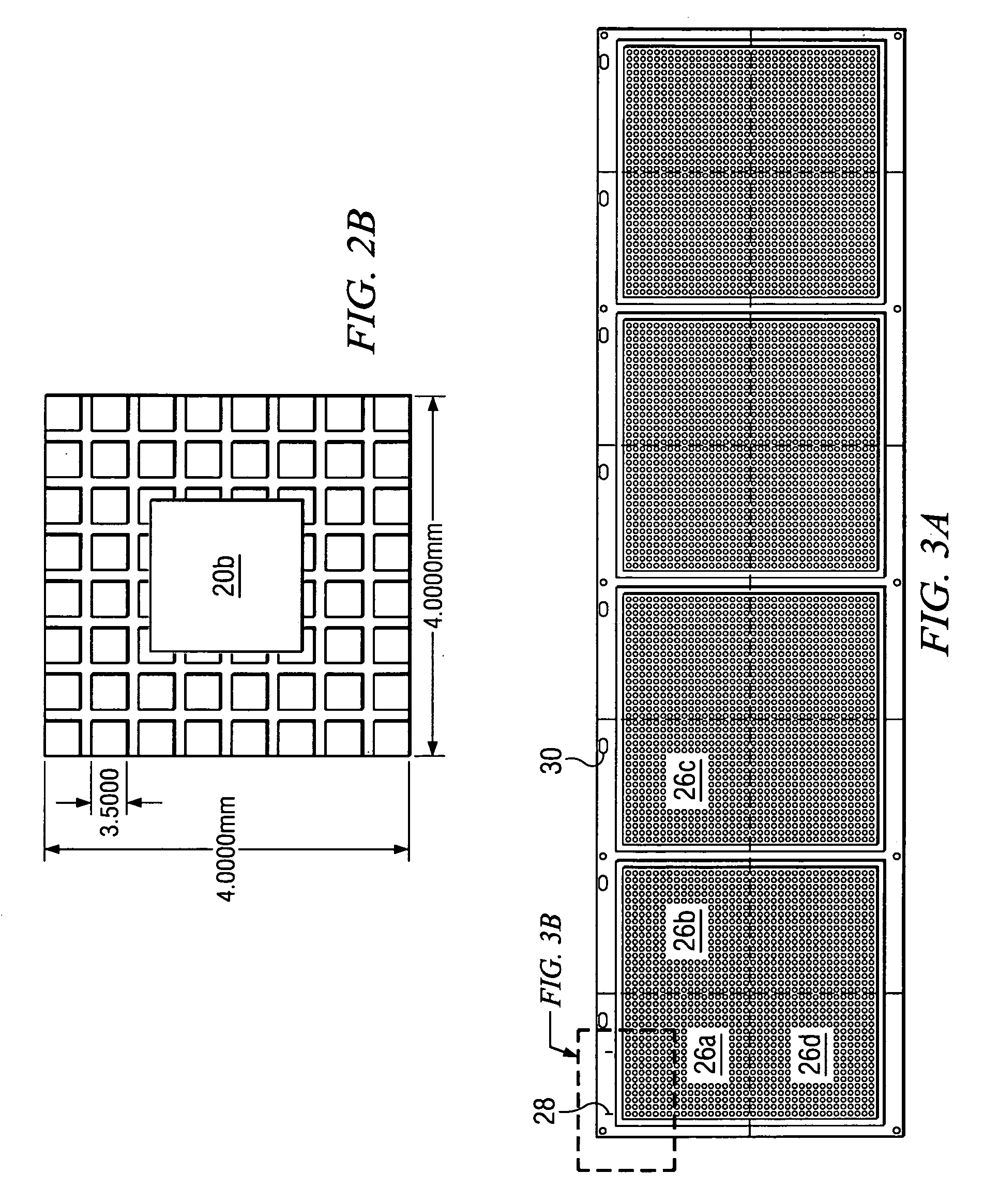

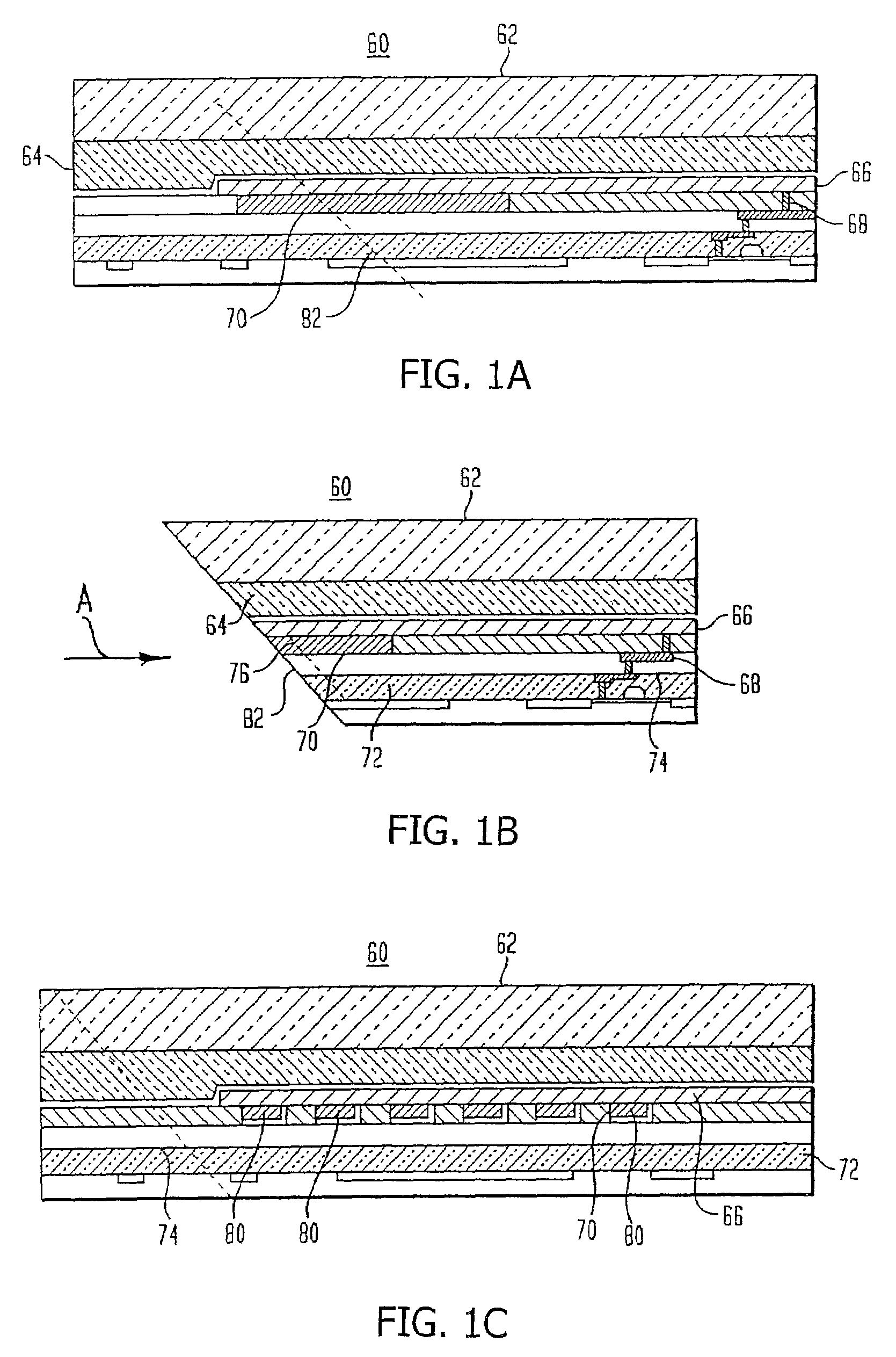

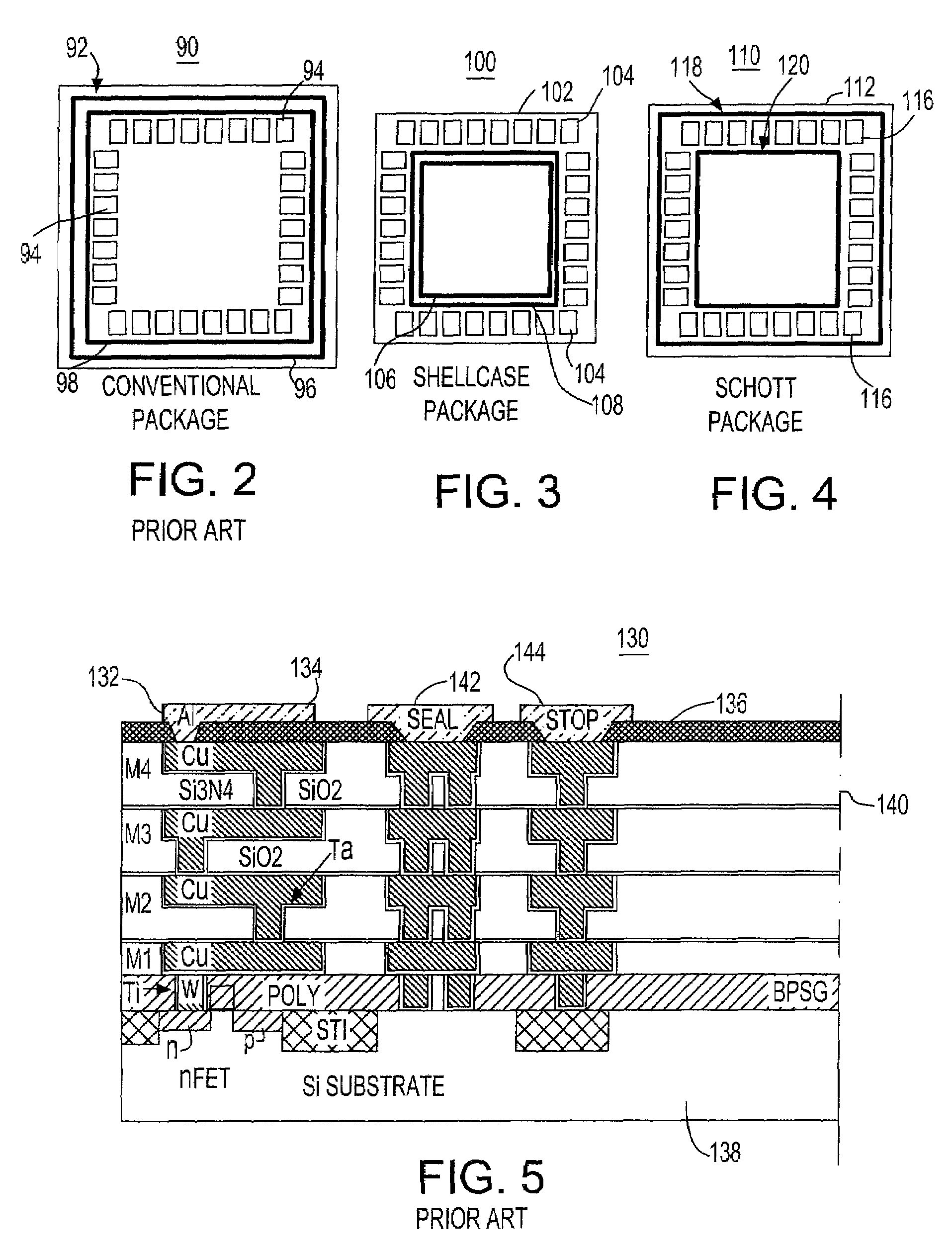

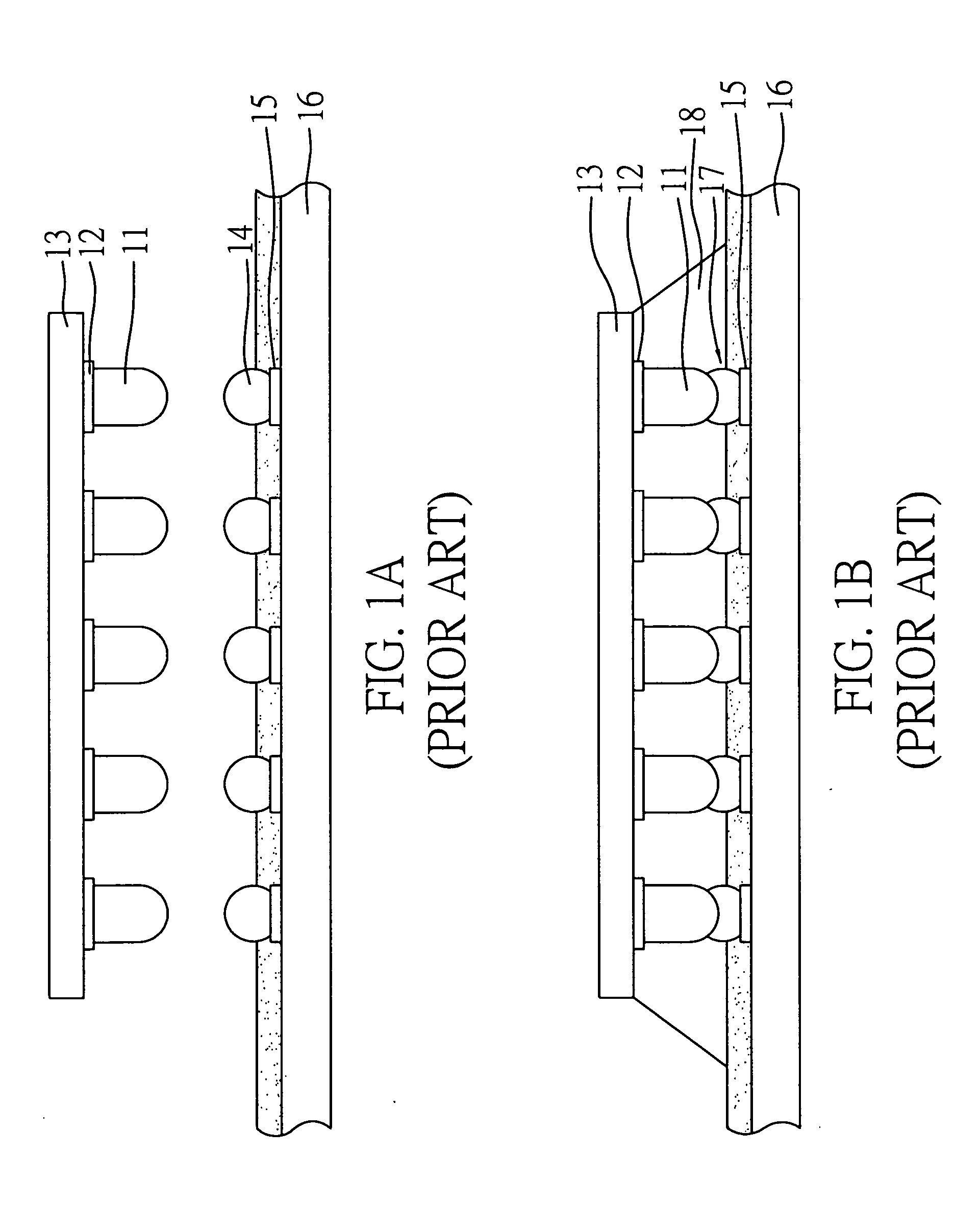

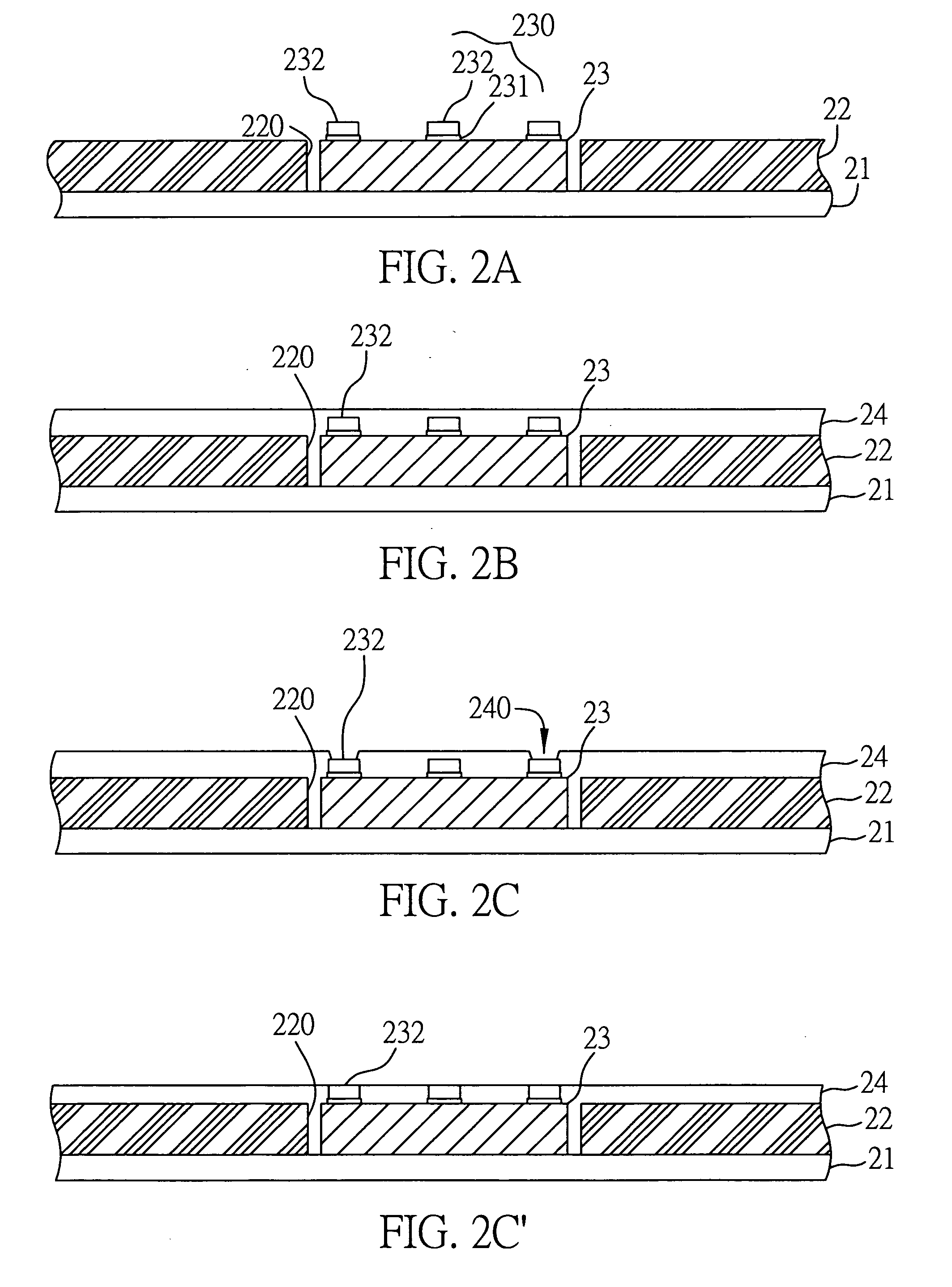

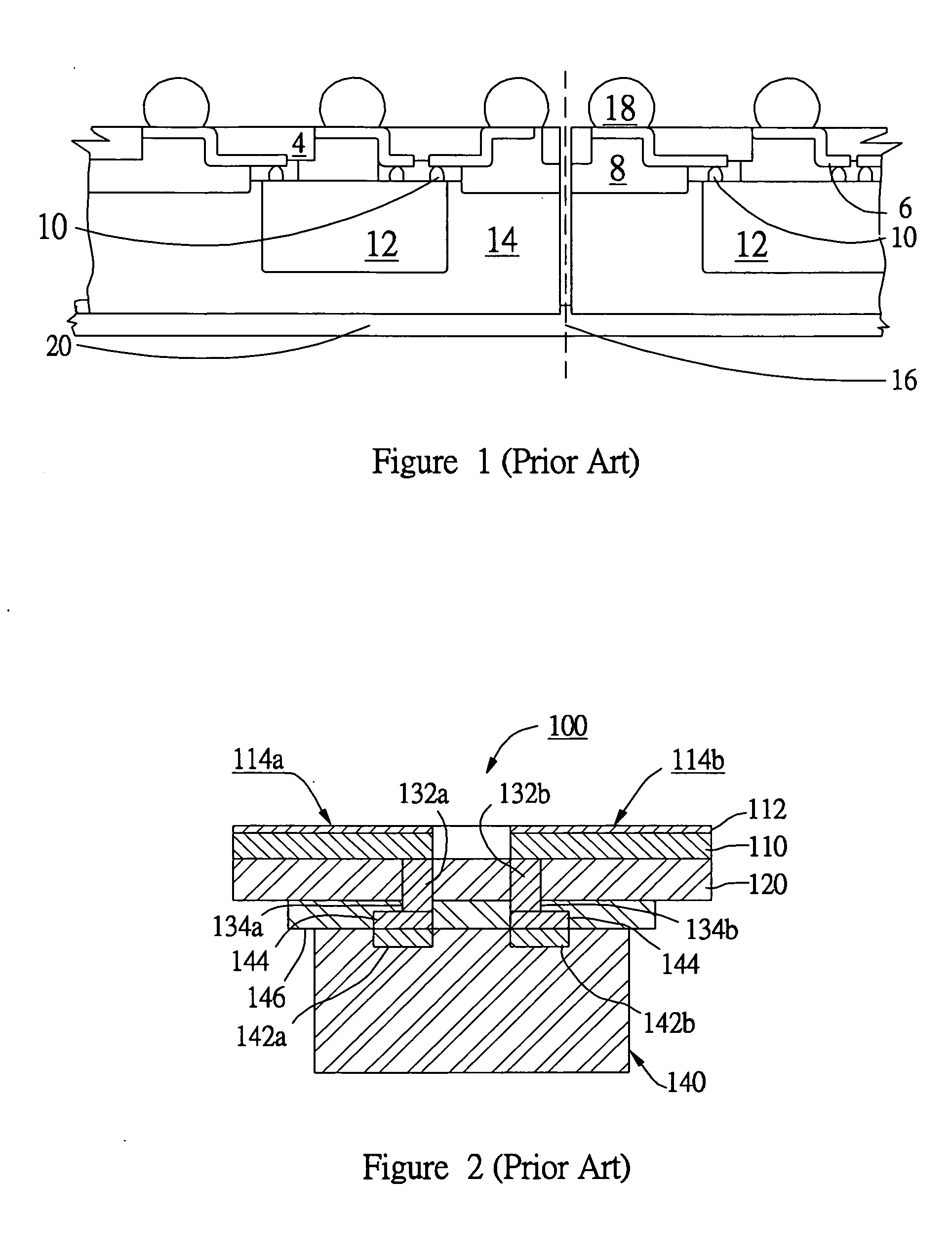

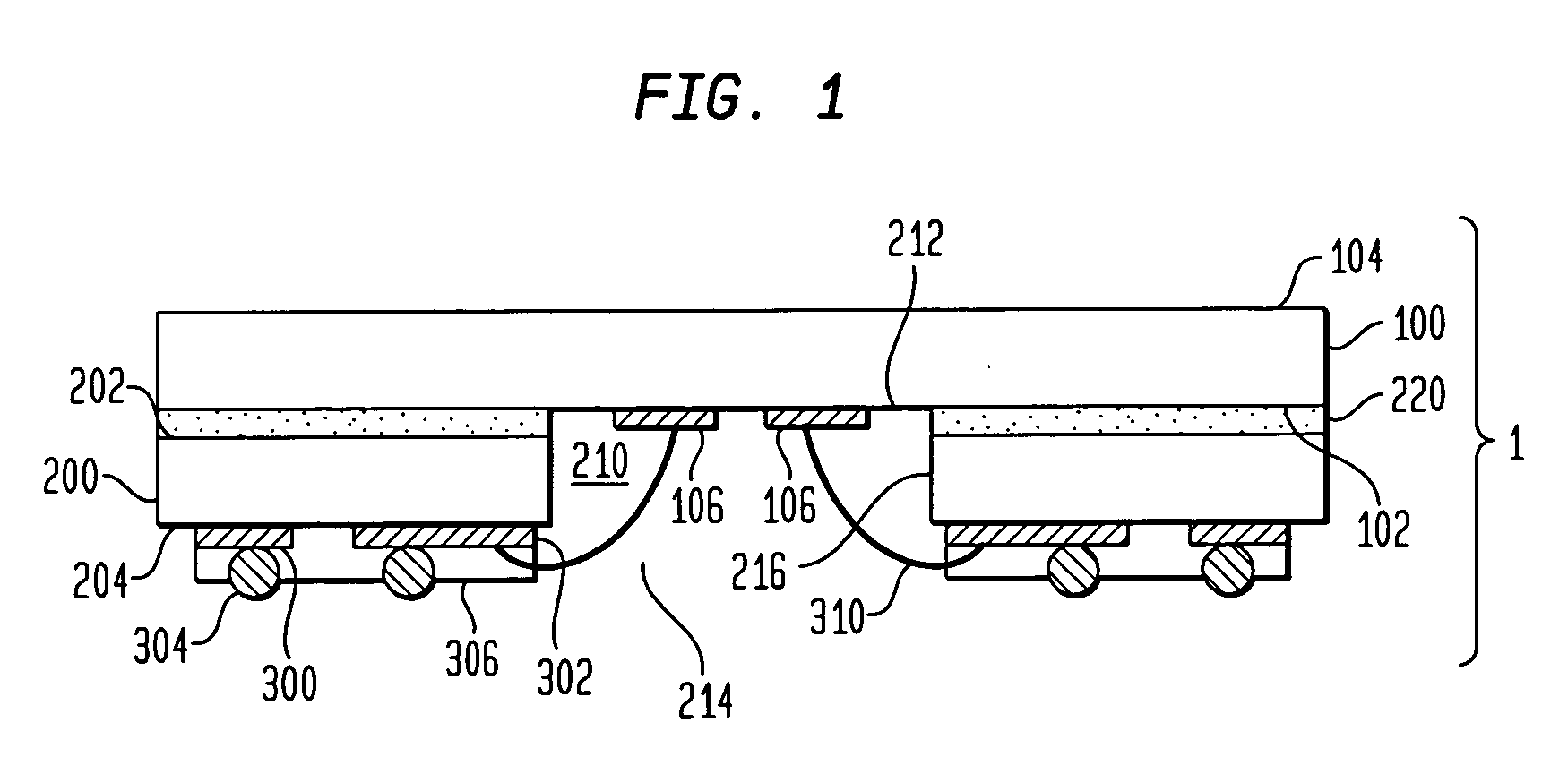

Microelectronic packages and methods therefor

ActiveUS20070148822A1Easy to testAvoid the needSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A method of making a microelectronic assembly includes providing a microelectronic package having a substrate, a microelectronic element overlying the substrate and at least two conductive elements projecting from a surface of the substrate, the at least two conductive elements having surfaces remote from the surface of the substrate. The method includes compressing the at least two conductive elements so that the remote surfaces thereof lie in a common plane, and after the compressing step, providing an encapsulant material around the at least two conductive elements for supporting the microelectronic package and so that the remote surfaces of the at least two conductive elements remain accessible at an exterior surface of the encapsulant material.

Owner:TESSERA INC

Method and arrangement for enhancing process variability and lifetime reliability through 3D integration

InactiveUS20090144669A1Improve lifetime reliabilityEnhancing process variabilitySolid-state devicesWork holdersSemiconductor chipDependability

A method of enhancing semiconductor chip process variability and lifetime reliability through a three-dimensional (3D) integration applied to electronic packaging. Also provided is an arrangement for implementing the inventive method.

Owner:IBM CORP

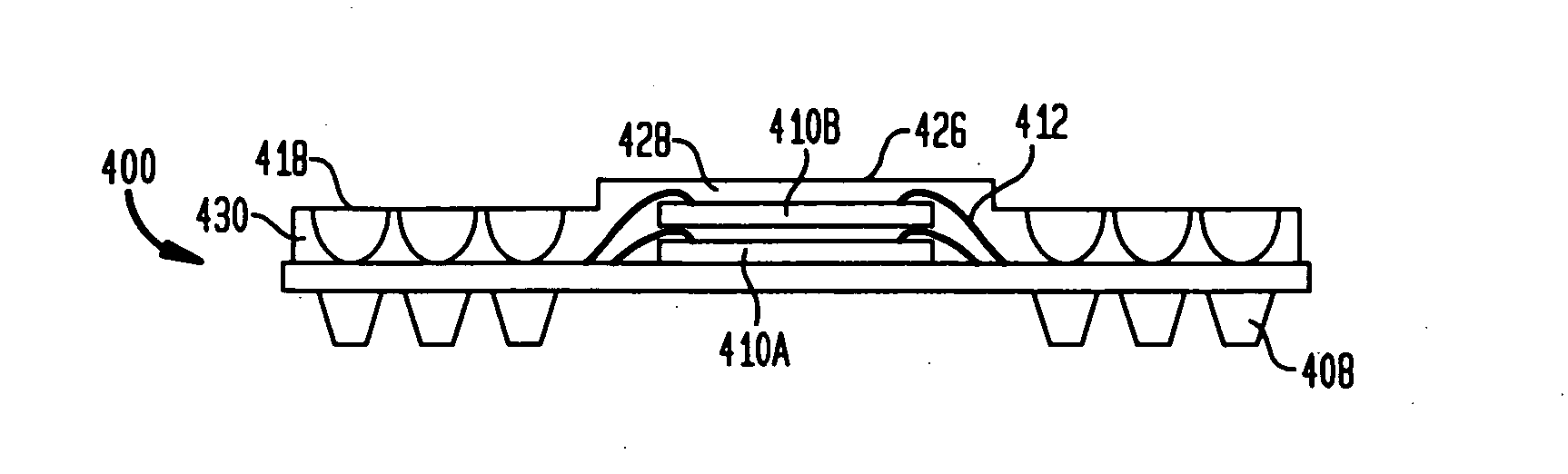

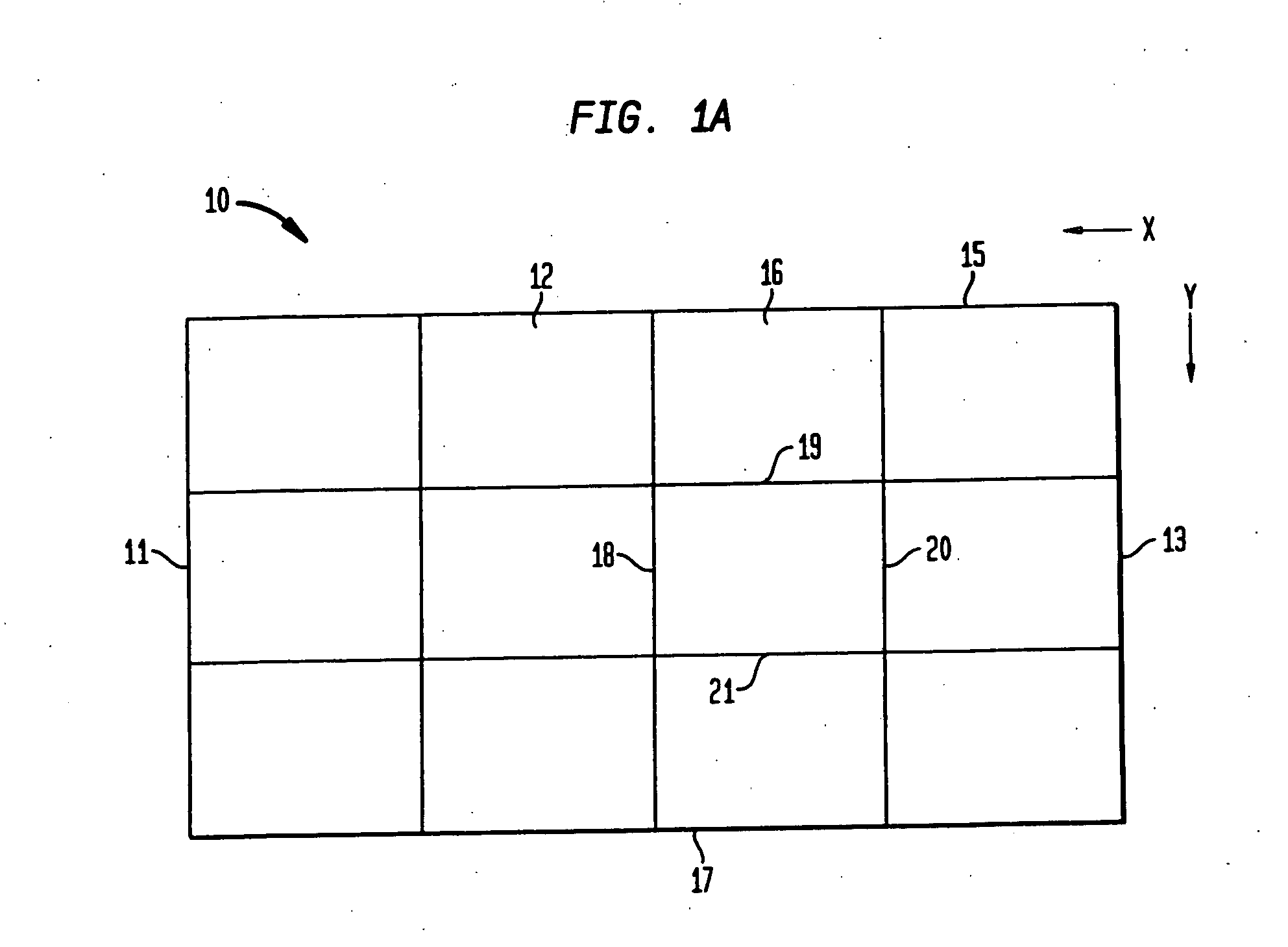

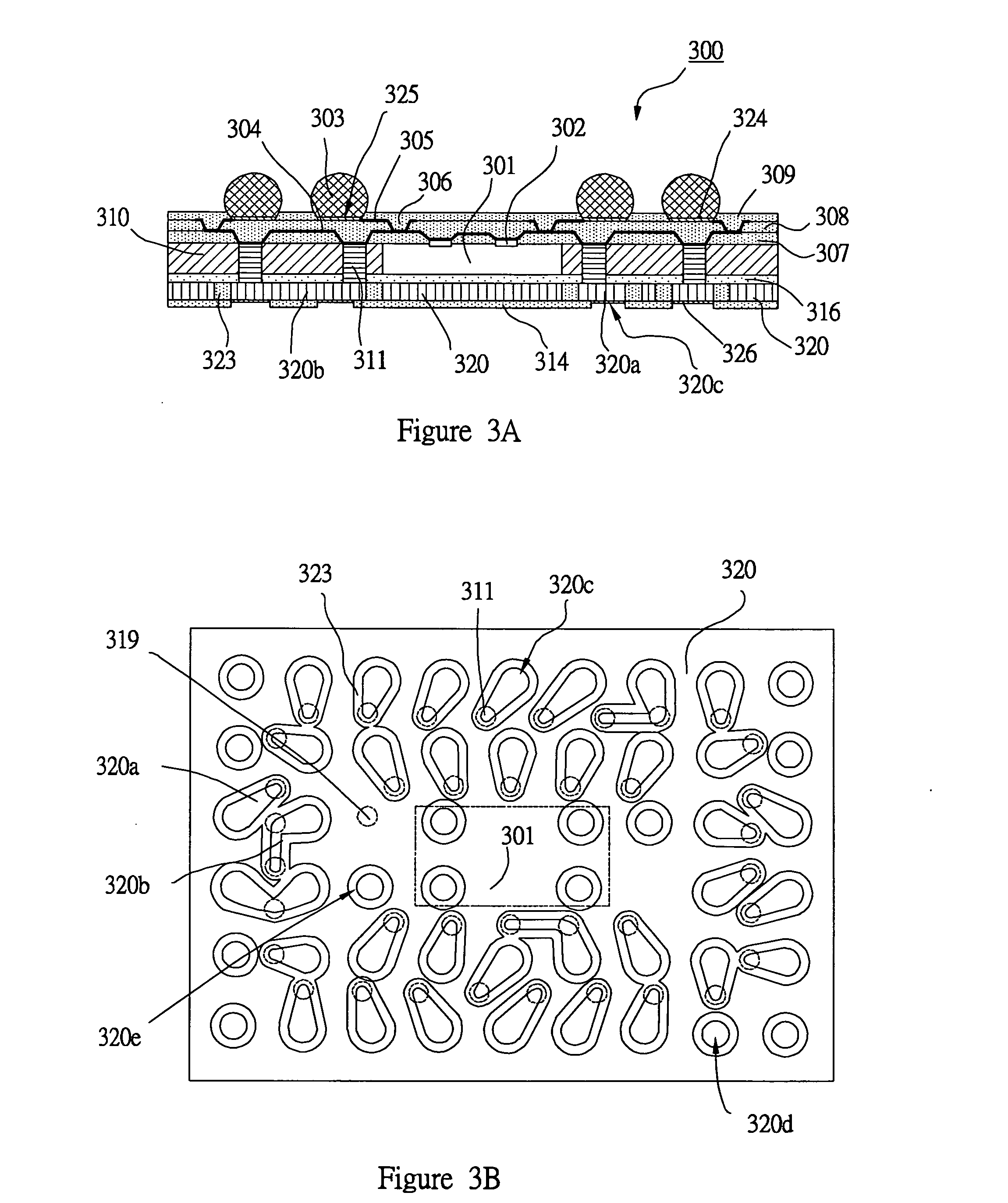

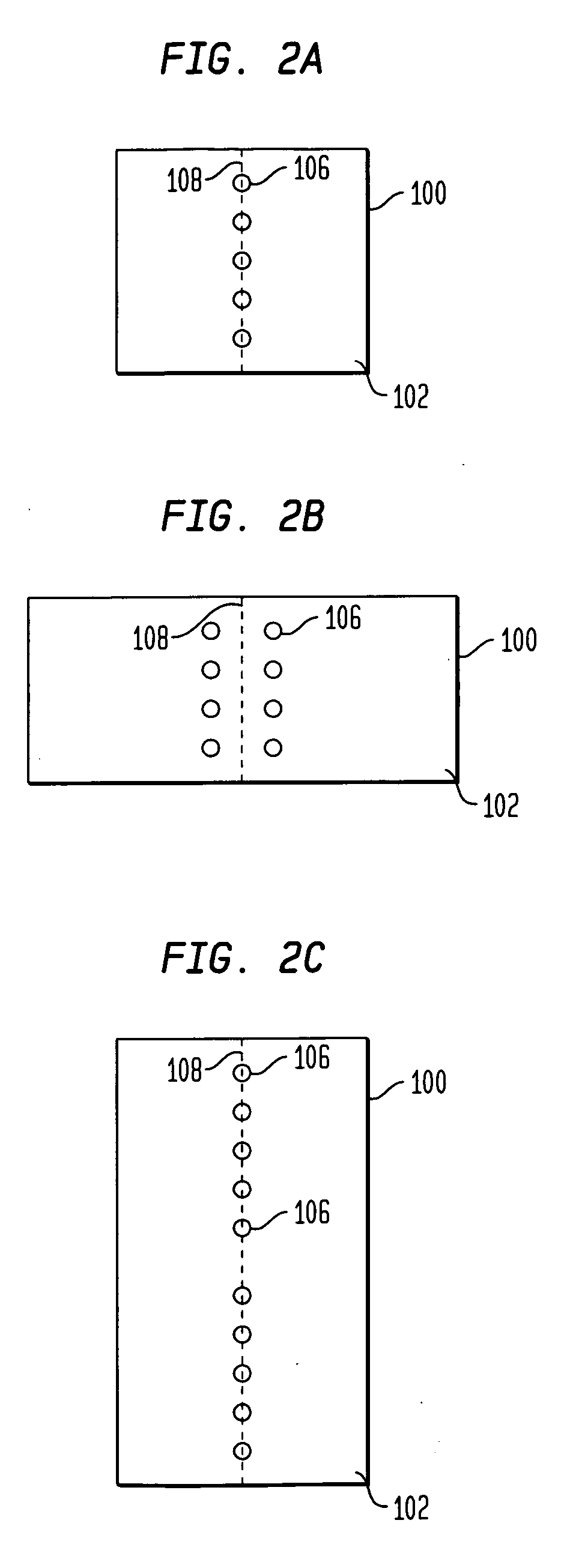

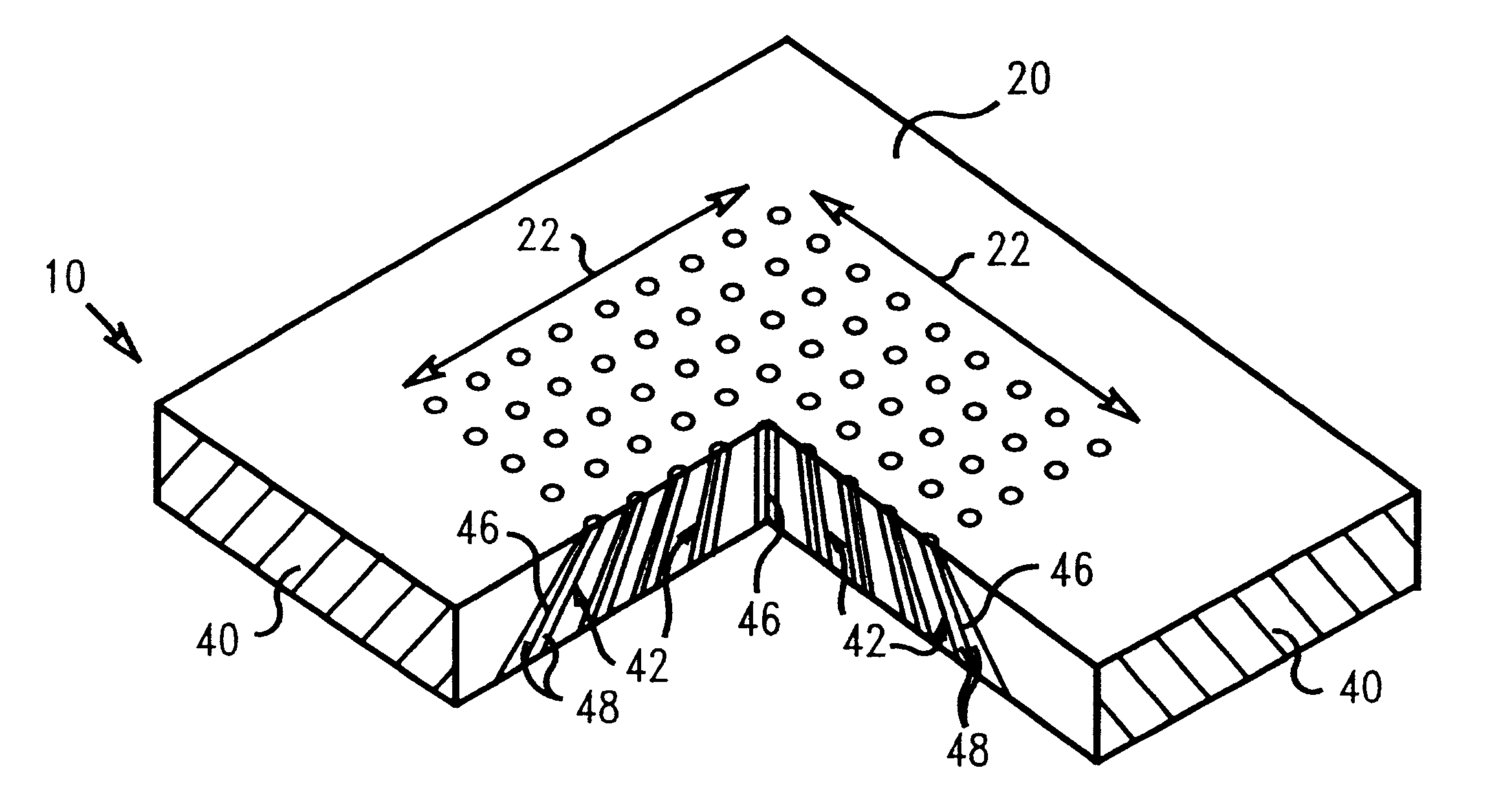

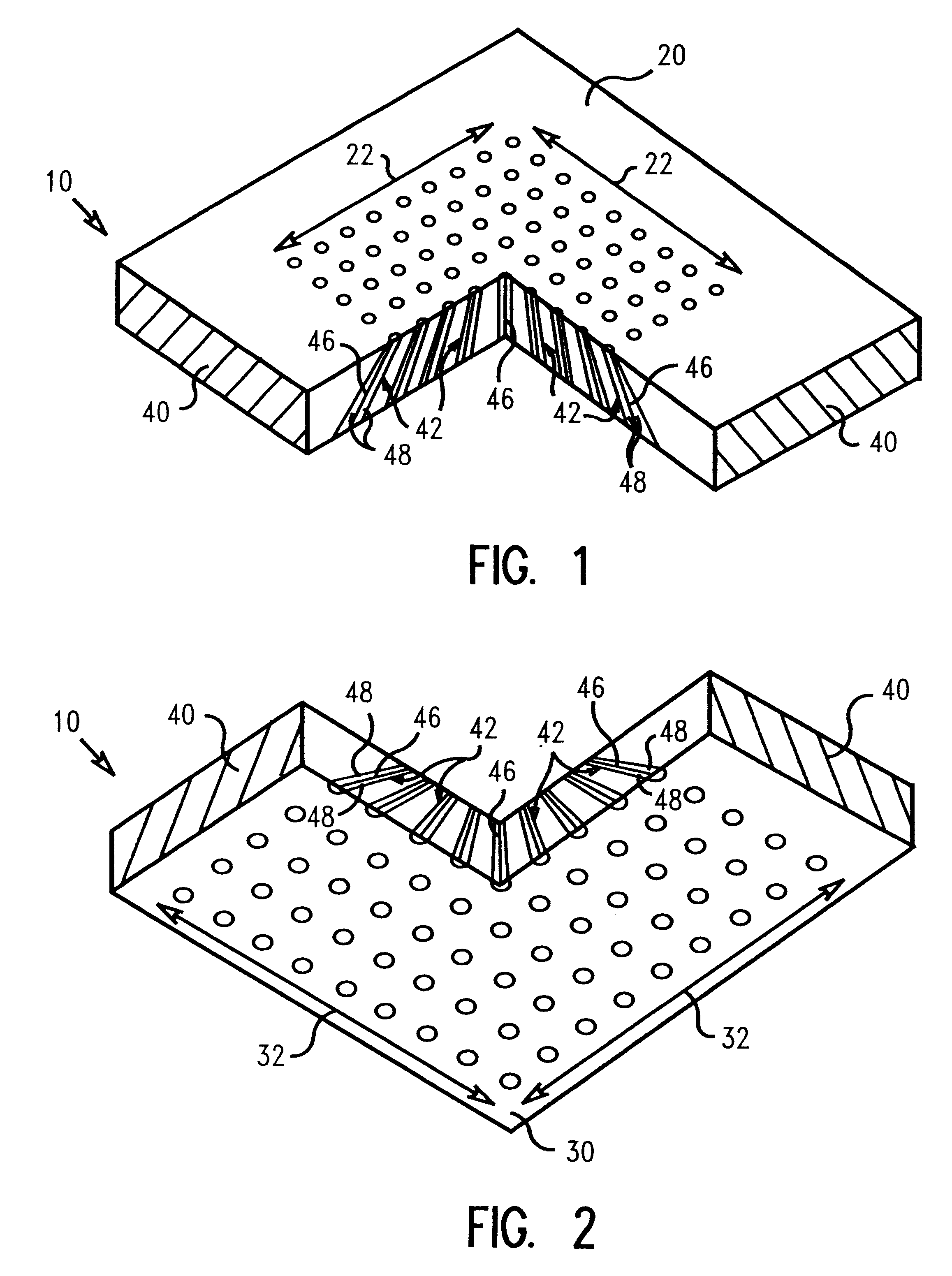

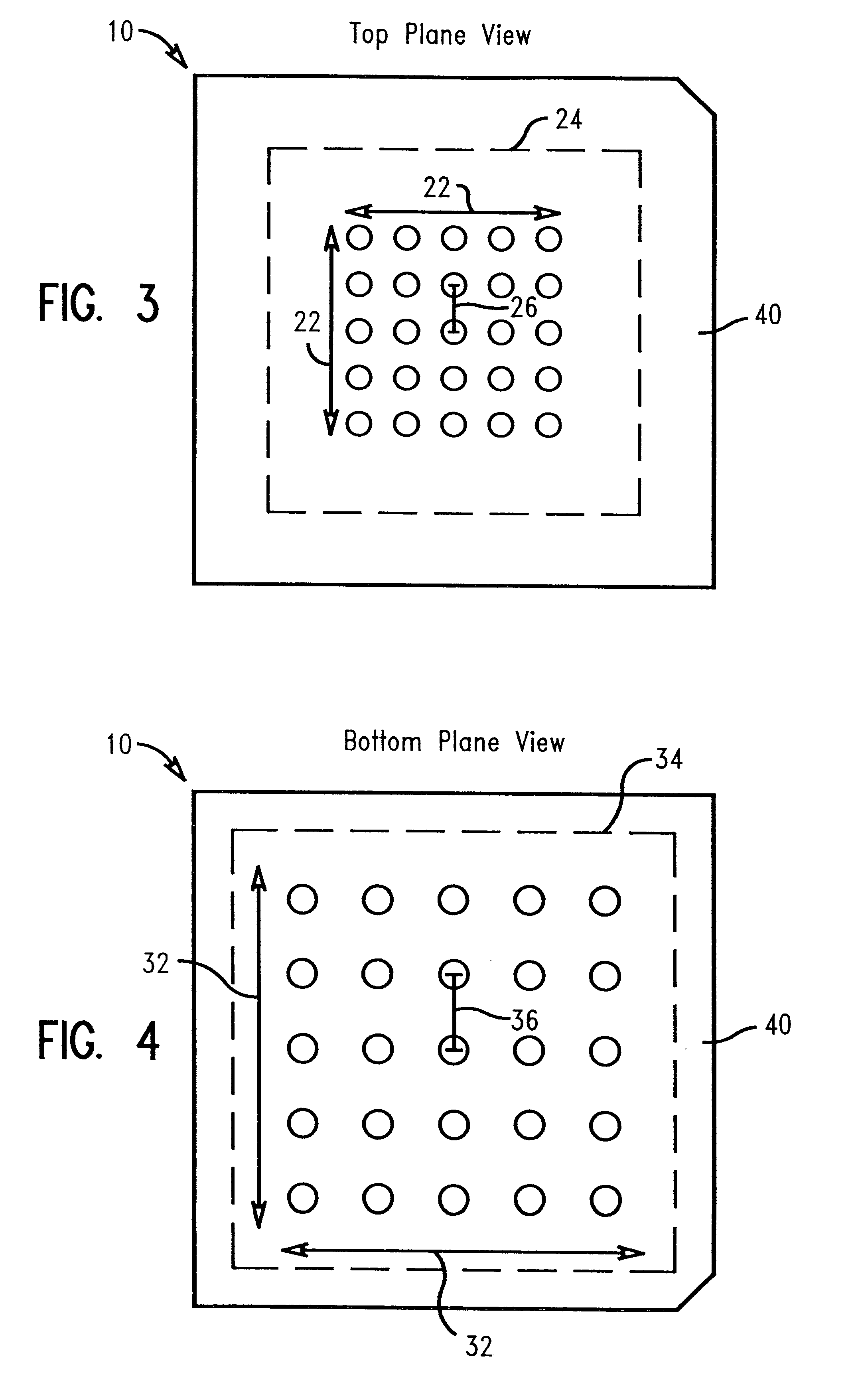

Micro pin grid array with pin motion isolation

InactiveUS20050173805A1Promote sportsFacilitates flexing of the substratePrinted circuit assemblingSemiconductor/solid-state device detailsPin grid arrayPartial alignment

A microelectronic package includes a microelectronic element having faces and contacts, a flexible substrate overlying and spaced from a first face of the microelectronic element, and a plurality of conductive terminals exposed at a surface of the flexible substrate. The conductive terminals are electrically interconnected with the microelectronic element and the flexible substrate includes a gap extending at least partially around at least one of the conductive terminals. In certain embodiments, the package includes a support layer, such as a compliant layer, disposed between the first face of the microelectronic element and the flexible substrate. In other embodiments, the support layer includes at least one opening that is at least partially aligned with one of the conductive terminals.

Owner:TESSERA INC

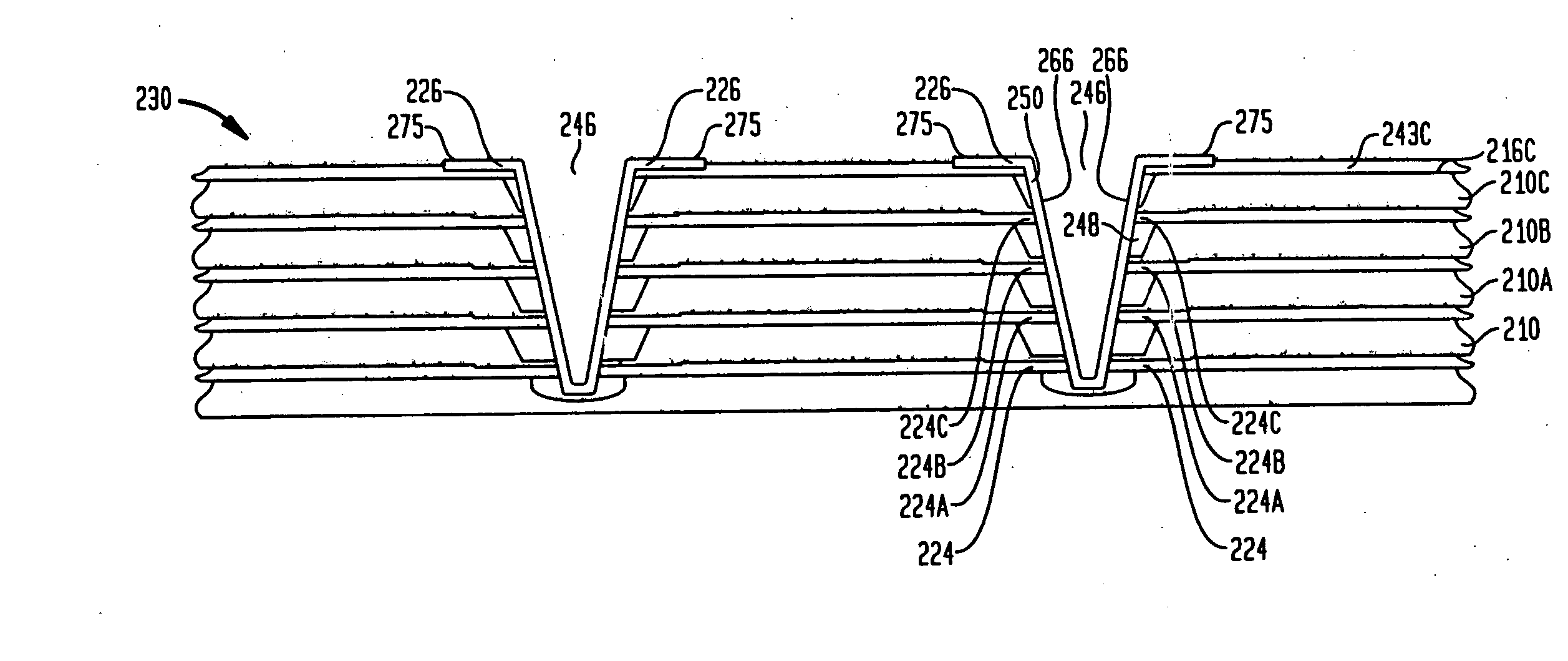

Edge connect wafer level stacking

ActiveUS20080083976A1Low costSmall sizeSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A method of making a stacked microelectronic package by forming a microelectronic assembly by stacking a first subassembly including a plurality of microelectronic elements onto a second subassembly including a plurality of microelectronic elements, at least some of the plurality of microelectronic elements of said first subassembly and said second subassembly having traces that extend to respective edges of the microelectronic elements, then forming notches in the microelectronic assembly so as to expose the traces of at least some of the plurality of microelectronic elements, then forming leads at the side walls of the notches, the leads being in electrical communication with at least some of the traces and dicing the assembly into packages. Additional embodiments include methods for creating stacked packages using substrates and having additional traces that extend to both the top and bottom of the package.

Owner:TESSERA INC

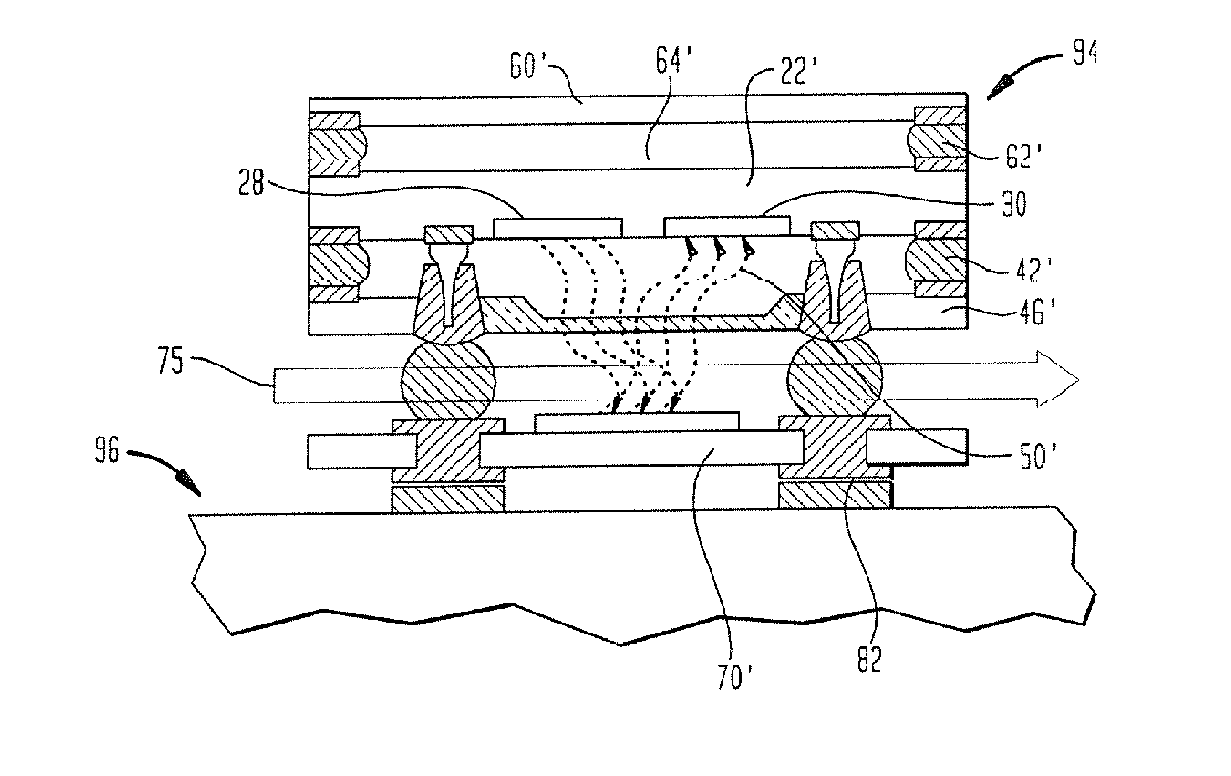

Microelectronic packages with nanoparticle joining

A method of making an assembly includes the steps of applying metallic nanoparticles to exposed surfaces of conductive elements of either of or both of a first component and a second component, juxtaposing the conductive elements of the first component with the conductive elements of the second component with the metallic nanoparticles disposed therebetween, and elevating a temperature at least at interfaces of the juxtaposed conductive elements to a joining temperature at which the metallic nanoparticles cause metallurgical joints to form between the juxtaposed conductive elements. The conductive elements of either of or both of the first component and the second component can include substantially rigid posts having top surfaces projecting a height above the surface of the respective component and edge surfaces extending at substantial angles away from the top surfaces thereof.

Owner:TESSERA INC

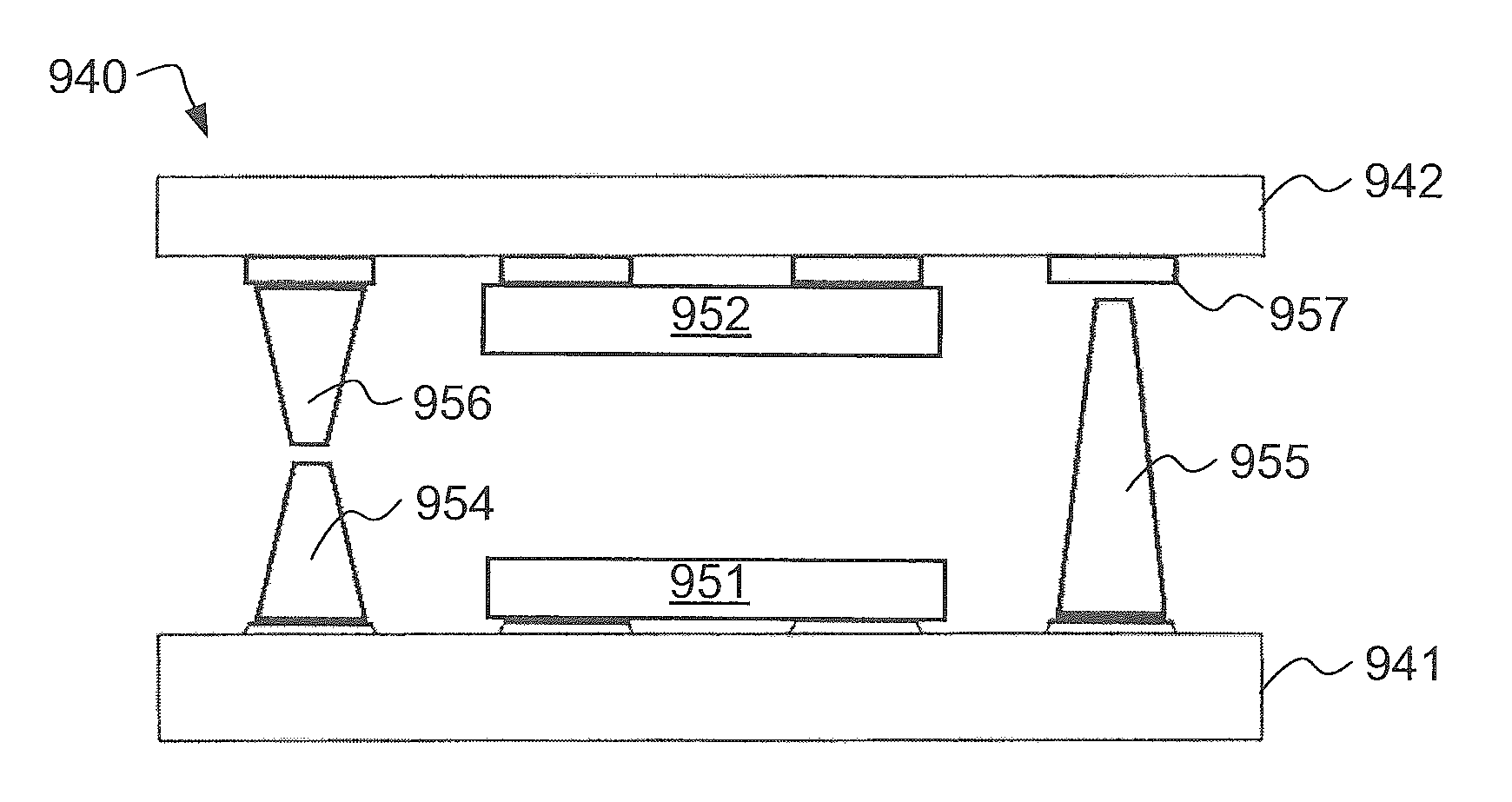

Semiconductor chip repair by stacking of a base semiconductor chip and a repair semiconductor chip

InactiveUS8679861B2Improve performanceSimple processSemiconductor/solid-state device testing/measurementSolid-state devicesSemiconductor chipElectronic packaging

In one aspect, a method of enhancing semiconductor chip process variability and lifetime reliability through a three-dimensional (3D) integration applied to electronic packaging is disclosed. Also provided is an arrangement for implementing the inventive method. In another aspect, a method and on-chip controller are disclosed for enhancing semiconductor chip process variability and lifetime reliability through a three-dimensional (3D) integration applied to electronic packaging. Also provided is an on-chip reliability / variability controller arrangement for implementing the inventive method. In yet another aspect, base semiconductor chips, each comprising a plurality of chiplets, are manufactured and tested. For a base semiconductor chip having at least one non-functional chiplet, at least one repair semiconductor chiplet chiplet is vertically stacked. A functional multi-chip assembly is formed, which provides the same functionality as a base semiconductor chip in which all chiplets are functional.

Owner:GLOBALFOUNDRIES INC

Apparatus, methods and precision spray processes for direct write and maskless mesoscale material deposition

InactiveUS20040197493A1Reduce package sizeElectric discharge heatingVacuum evaporation coatingOptoelectronicsBiological materials

Apparatuses and processes for maskless deposition of electronic and biological materials. The process is capable of direct deposition of features with linewidths varying from the micron range up to a fraction of a millimeter, and may be used to deposit features on substrates with damage thresholds near 100° C. Deposition and subsequent processing may be carried out under ambient conditions, eliminating the need for a vacuum atmosphere. The process may also be performed in an inert gas environment. Deposition of and subsequent laser post processing produces linewidths as low as 1 micron, with sub-micron edge definition. The apparatus nozzle has a large working distance-the orifice to substrate distance may be several millimeters-and direct write onto non-planar surfaces is possible. This invention is also of combinations of precision spray processes with in-flight laser treatment in order to produce direct write electronic components, and additionally lines of conductive, inductive, and resistive materials. This development has the potential to change the approach to electronics packaging in that components can be directly produced on small structures, thus removing the need for printed circuit boards.

Owner:OPTOMEC DESIGN CO

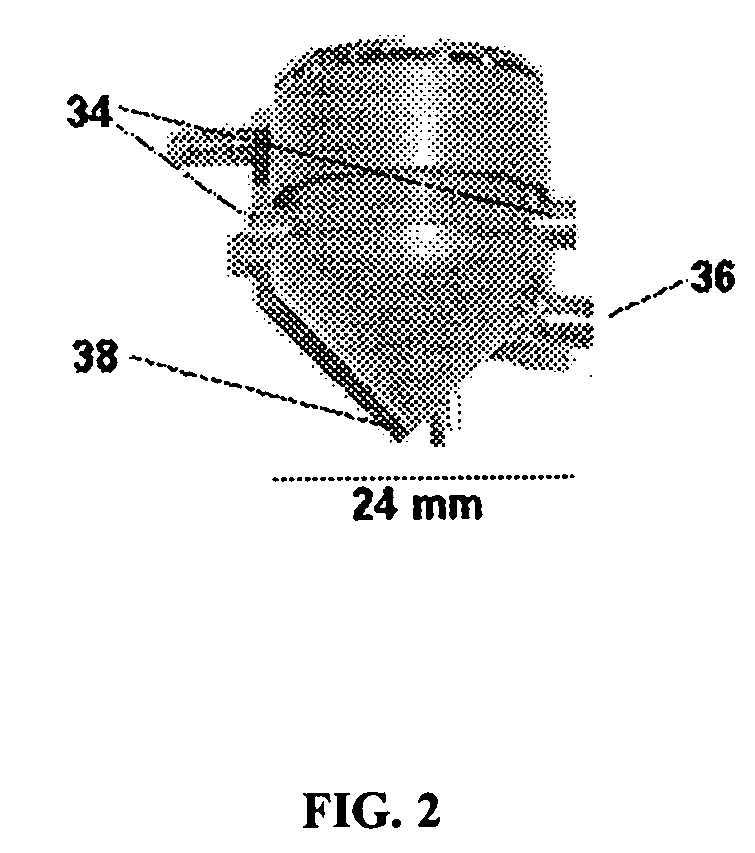

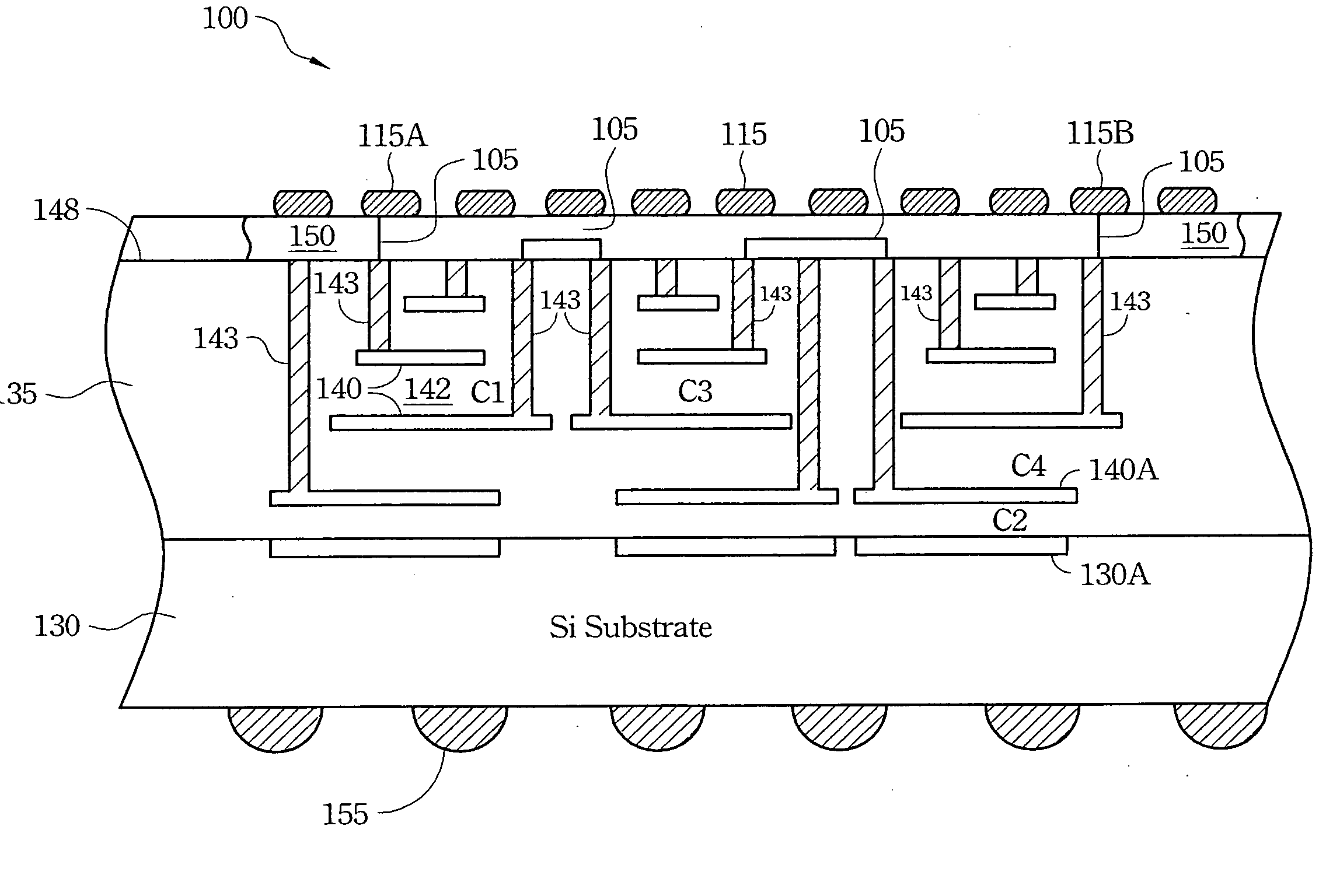

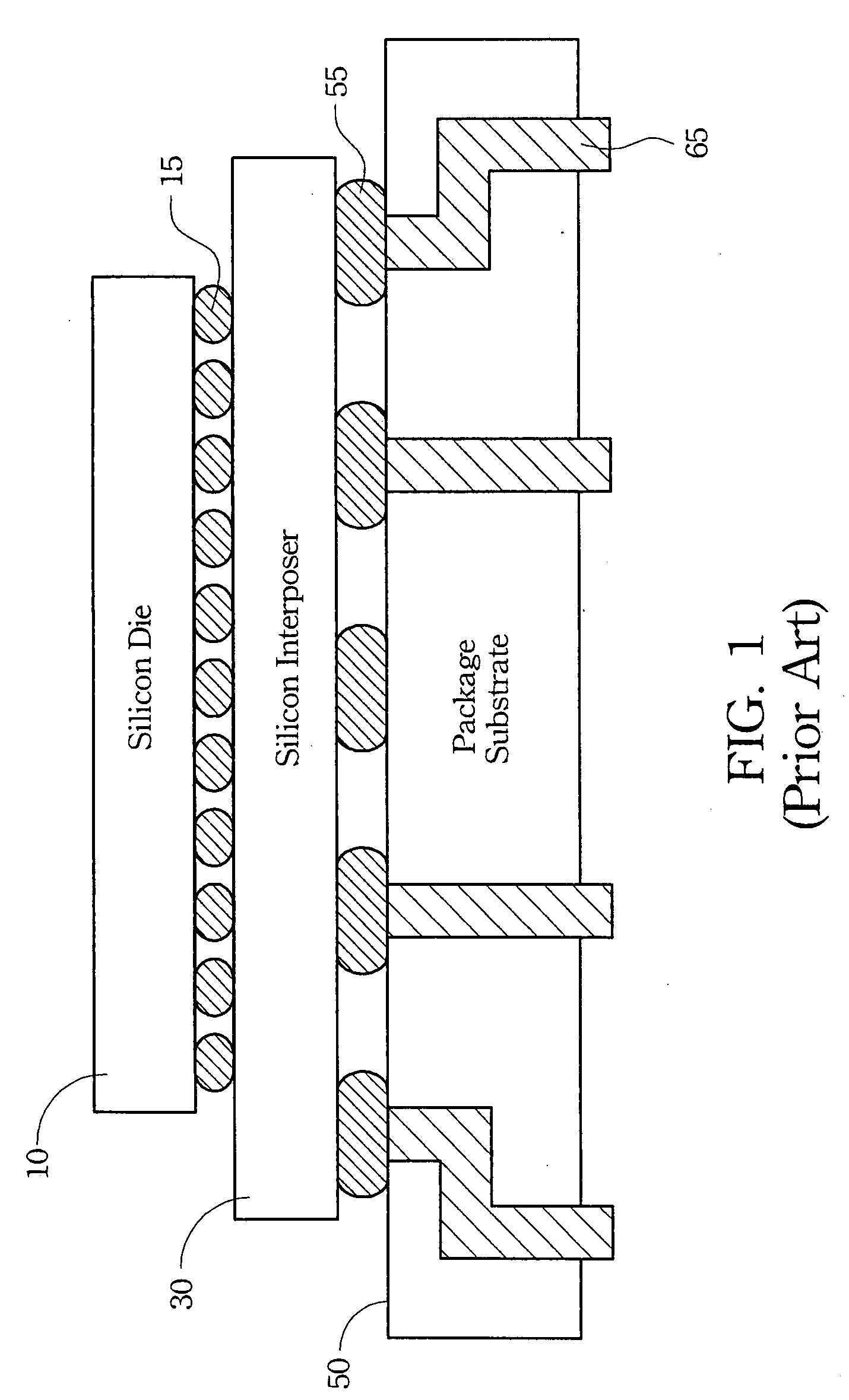

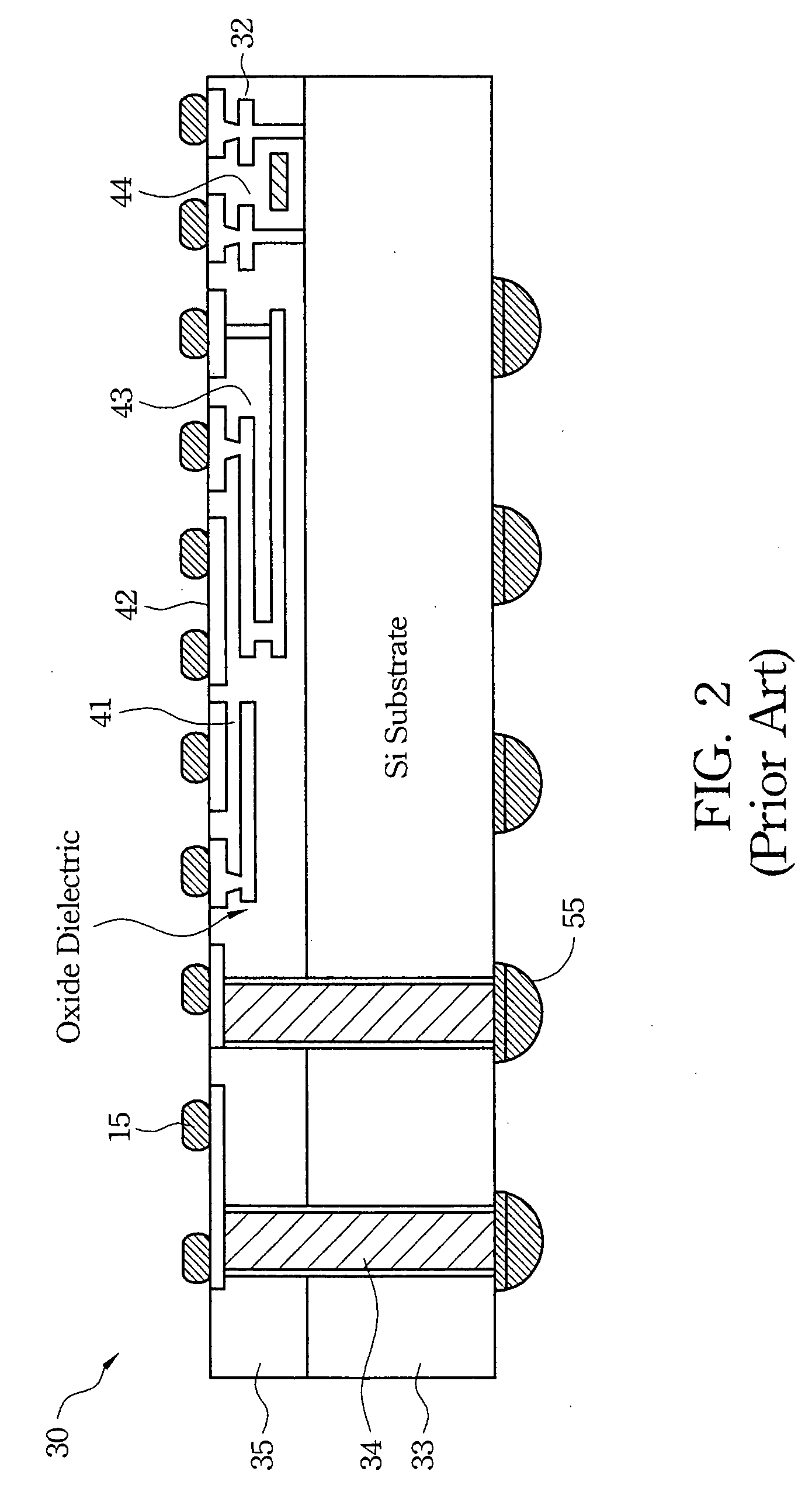

Programmable semiconductor interposer for electronic package and method of forming

ActiveUS20080296697A1Low costShorten the timeSemiconductor/solid-state device detailsSolid-state devicesContact padInterposer

Various structures of a programmable semiconductor interposer for electronic packaging are described. An array of semiconductor devices having various values is formed in said interposer. A user can program said interposer and form a “virtual” device having a desired value by selectively connecting various one of the array of devices to contact pads formed on the surface of said interposer. An inventive electronic package structure includes a standard interposer having an array of unconnected devices of various values and a device selection unit, which selectively connects various one of the array of devices in said standard interposer to an integrated circuit die encapsulated in said electronic package. Methods of forming said programmable semiconductor interposer and said electronic package are also illustrated.

Owner:TAIWAN SEMICON MFG CO LTD

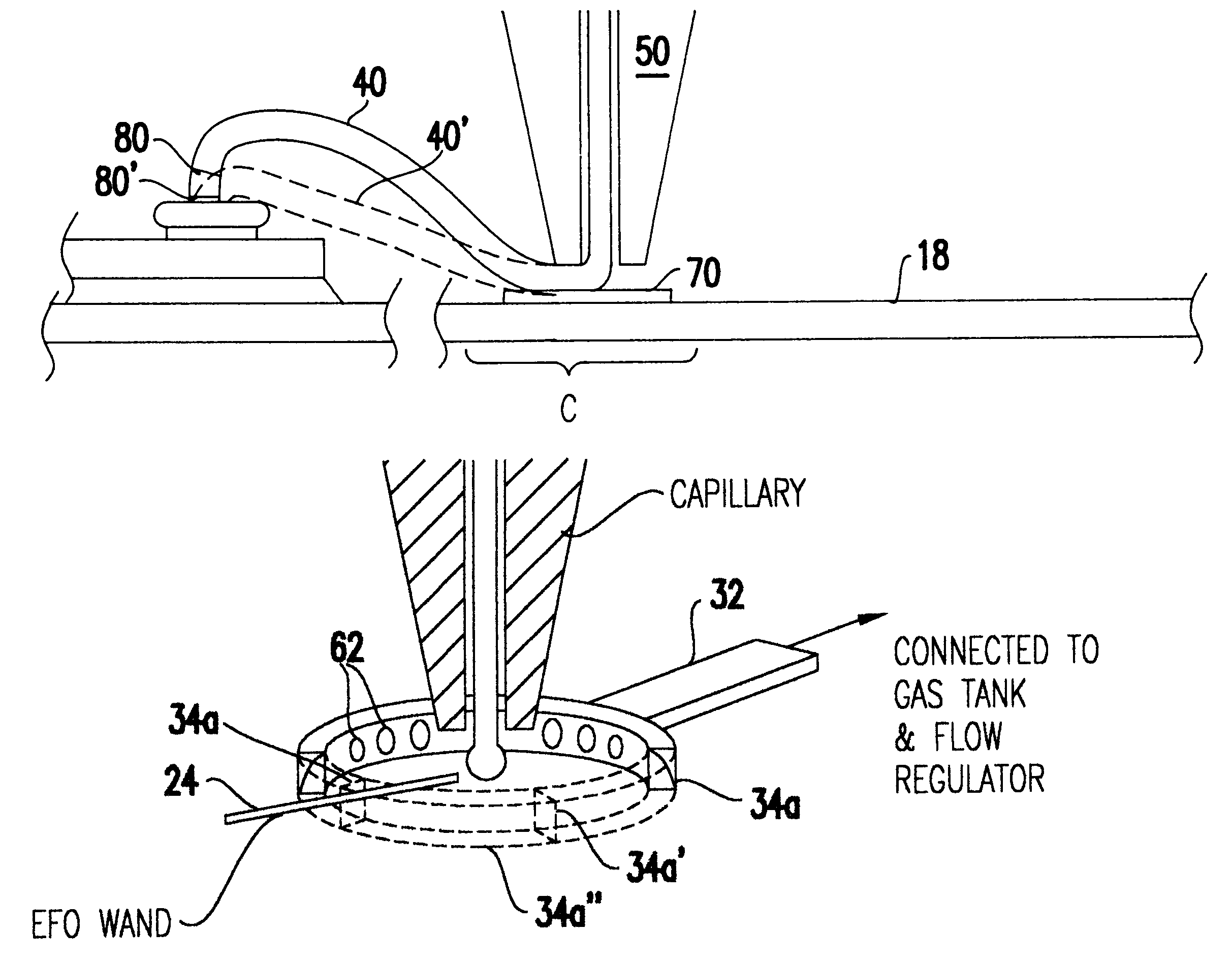

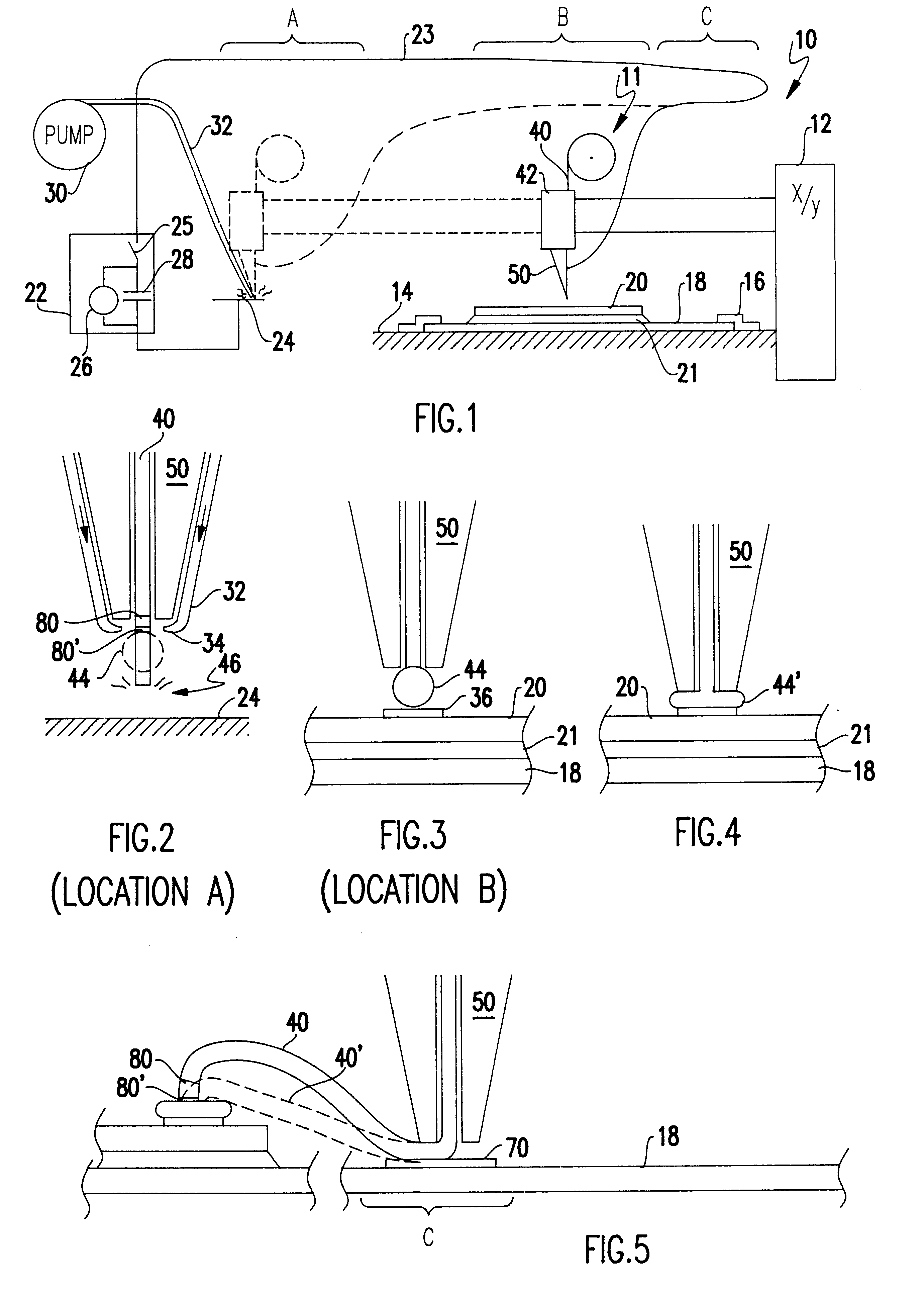

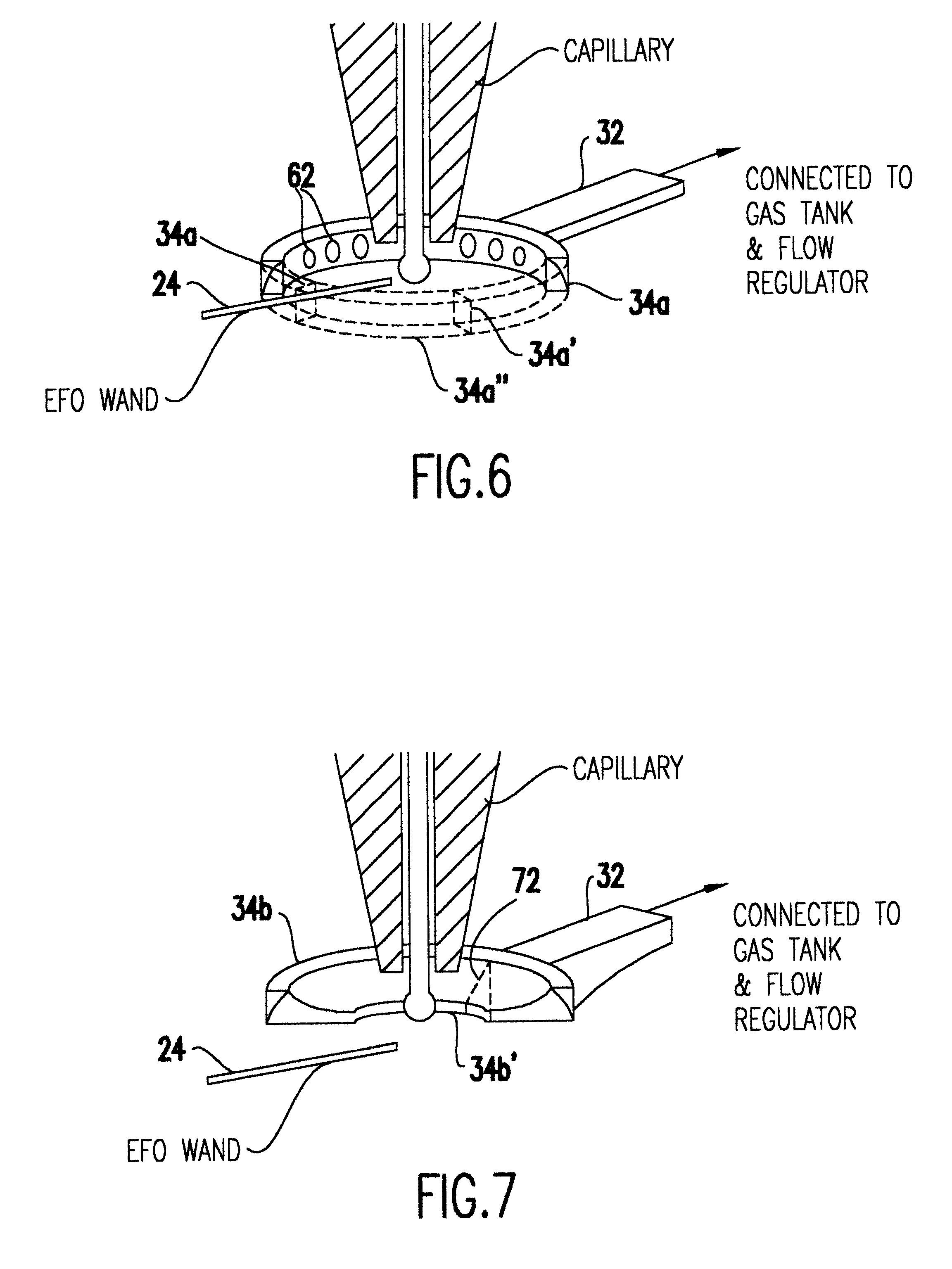

Control of size and heat affected zone for fine pitch wire bonding

InactiveUS6180891B1Electrically conductive connectionsSemiconductor/solid-state device detailsHeat-affected zoneLead bonding

The amount of melting of the bonding wire is closely regulated, and reduction of size and improvement of uniformity of the free air ball is obtained for ball bonding at pitches of less than ninety mils even when bonding wire of reduced diameter is employed. Quenching of the bonding wire adjacent to the free air ball also limits the temperature rise in the bonding wire and the extent of a heat affected zone having less tensile strength and stiffness to less than one micron and with reduced grain enlargement. The present invention provides such a bond for electronic packaging of increased reliability, potential functionality, increased manufacturing yield and reduced process complexity.

Owner:IBM CORP

Heat spreader

InactiveUS20100149756A1Wave amplification devicesSemiconductor/solid-state device detailsEngineeringElectronic packaging

The present invention relates to a package comprising a plate formed from a diamond-composite material and a frame and its use as a lid or cavity lid in electronic packaging applications.

Owner:ROWCLIFFE DAVID +1

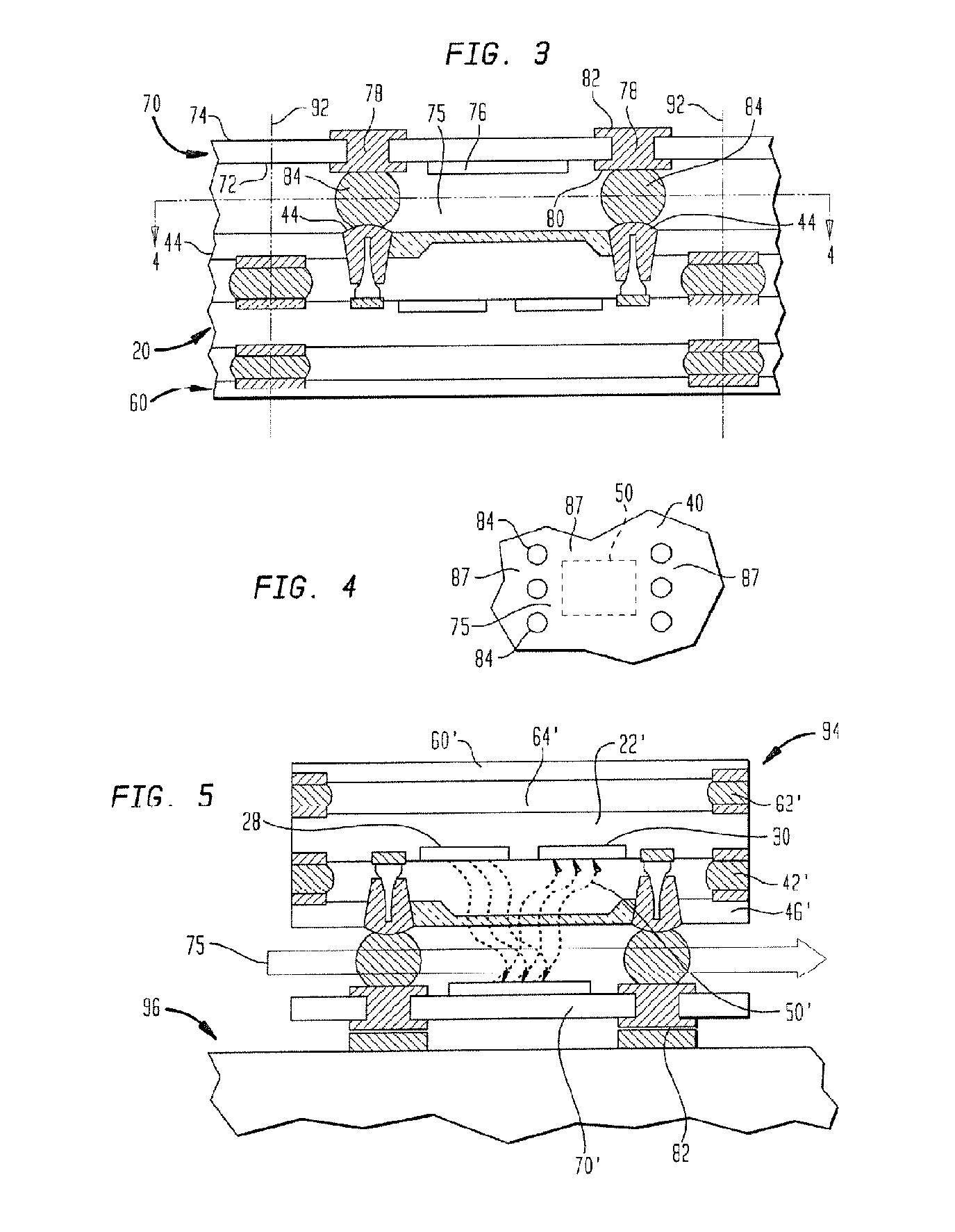

Wafer level microelectronic packaging with double isolation

InactiveUS20060081983A1Improved thermal isolationSemiconductor/solid-state device detailsSolid-state devicesThermal isolationAnalyte

A microelectronic package may include front and rear covers overlying the front and rear surfaces of a microelectronic element such as an infrared sensor and spaces between the microelectronic element and the covers to provide thermal isolation. A sensing unit including a microelectronic package may include a reflector spaced from the front cover to provide an analyte space, and the microelectronic element may include an emitter and a detector so that radiation directed from the emitter will be reflected by the sensor to the detector, and such radiation will be affected by the properties of the analyte in the analyte space. Such a unit provides a compact, economical chemical sensor. Other packages include elements such as valves for passing fluids into and out of the spaces within the package itself.

Owner:TESSERA INC

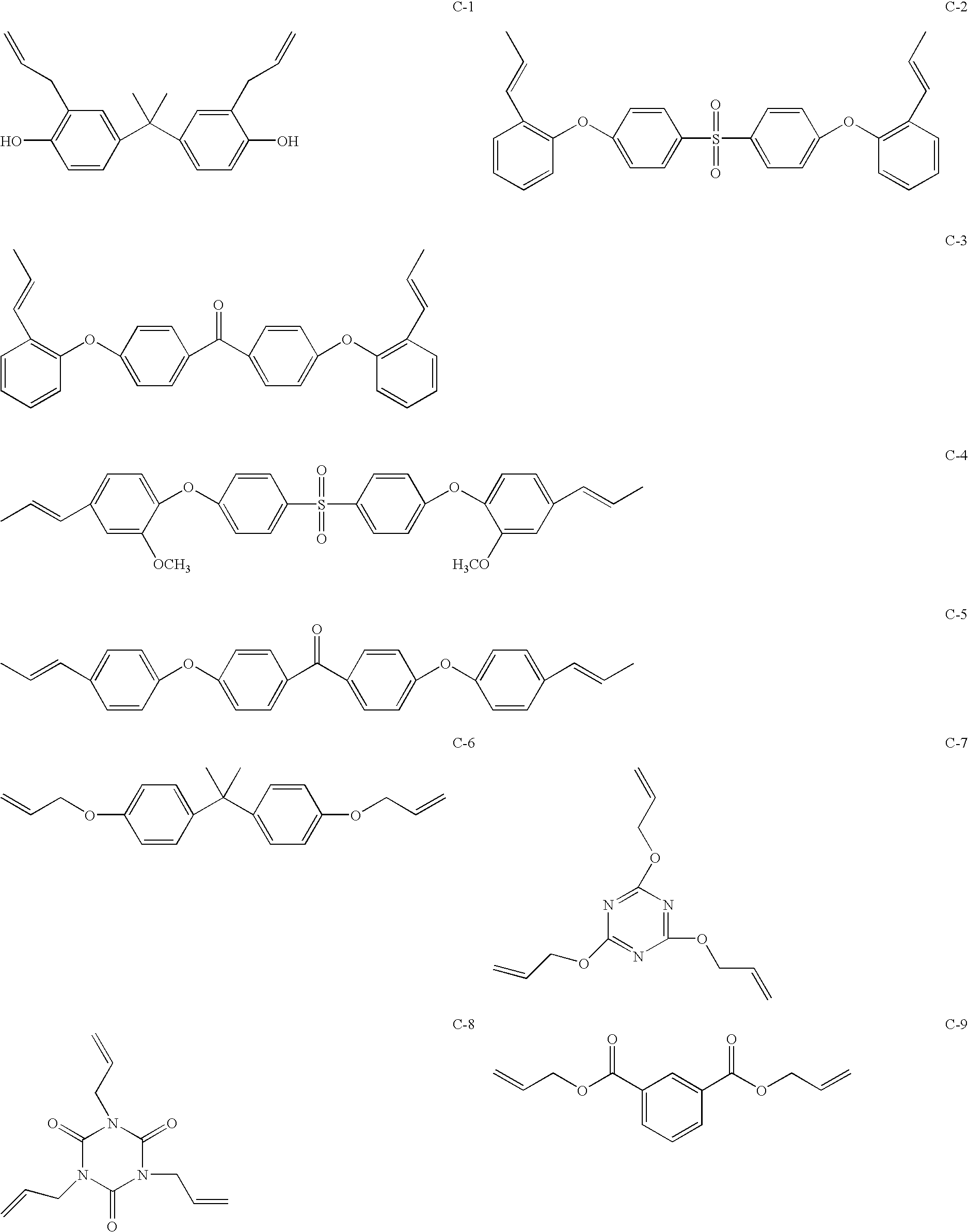

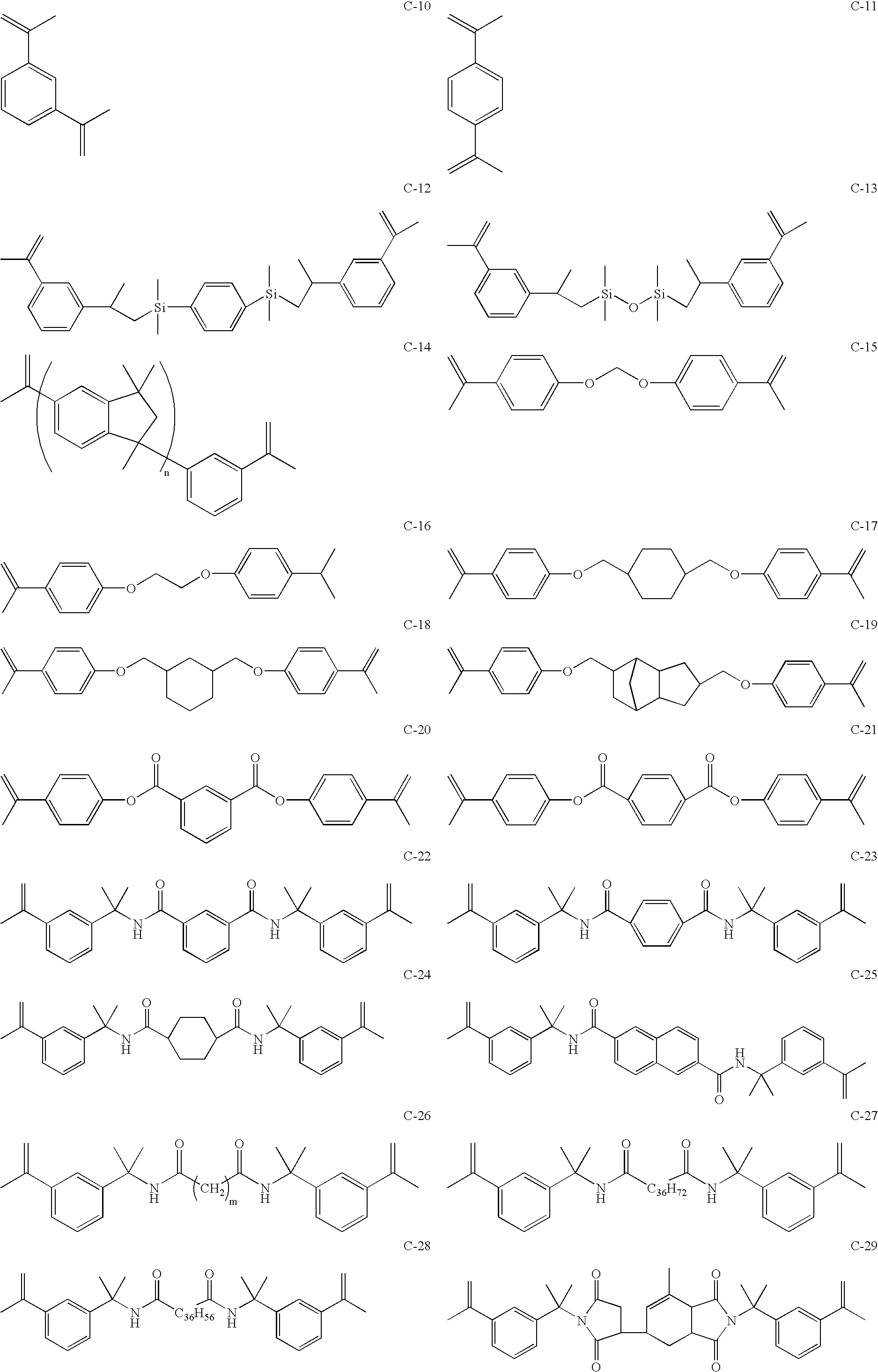

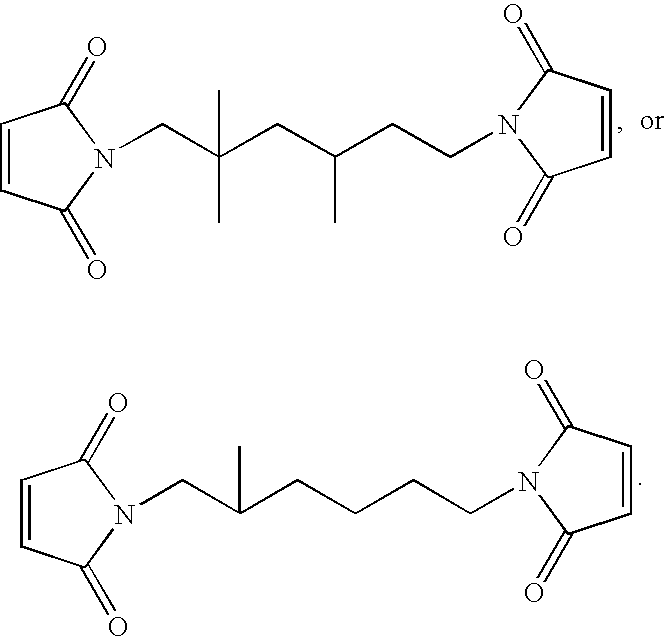

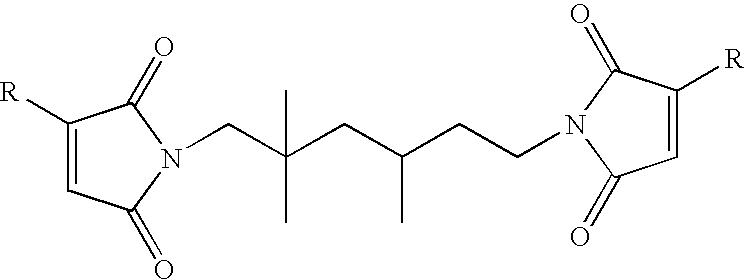

Maleimide compositions and methods for use thereof

ActiveUS20080075965A1Efficient curingIncrease application of useMixing methodsConductive materialElectronic packagingMaleimide

The invention is based on the discovery that compositions containing certain maleimide compounds and aromatic diene compounds are useful as thermosetting resins for the electronic packaging industry. The invention compositions described herein can be cured in a variety of ways, with or without a catalyst. In some embodiments, the well-known “ene” reaction can be used to cure the compositions described herein, and therefore no catalyst is required.

Owner:DESIGNER MOLECULES

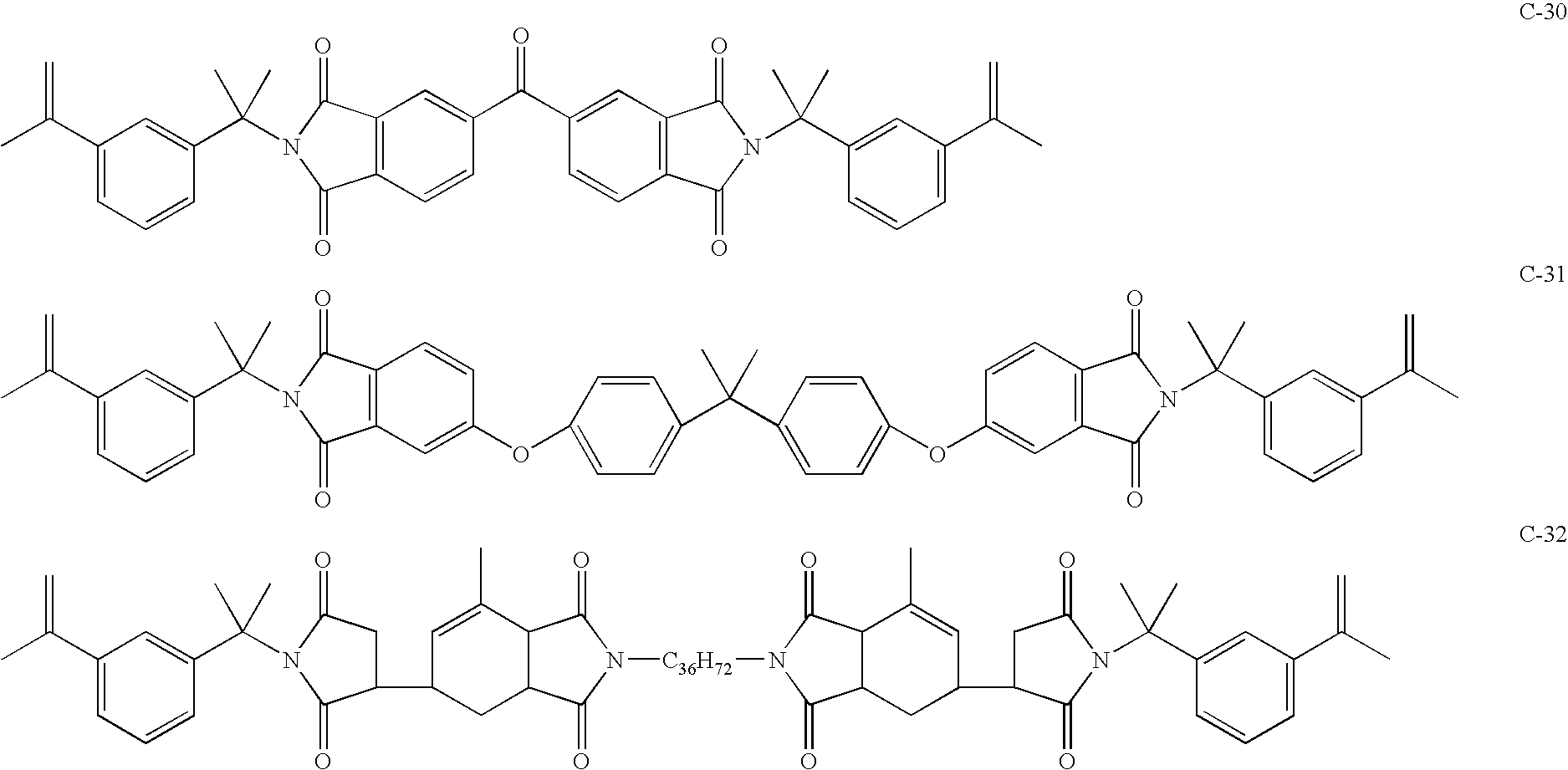

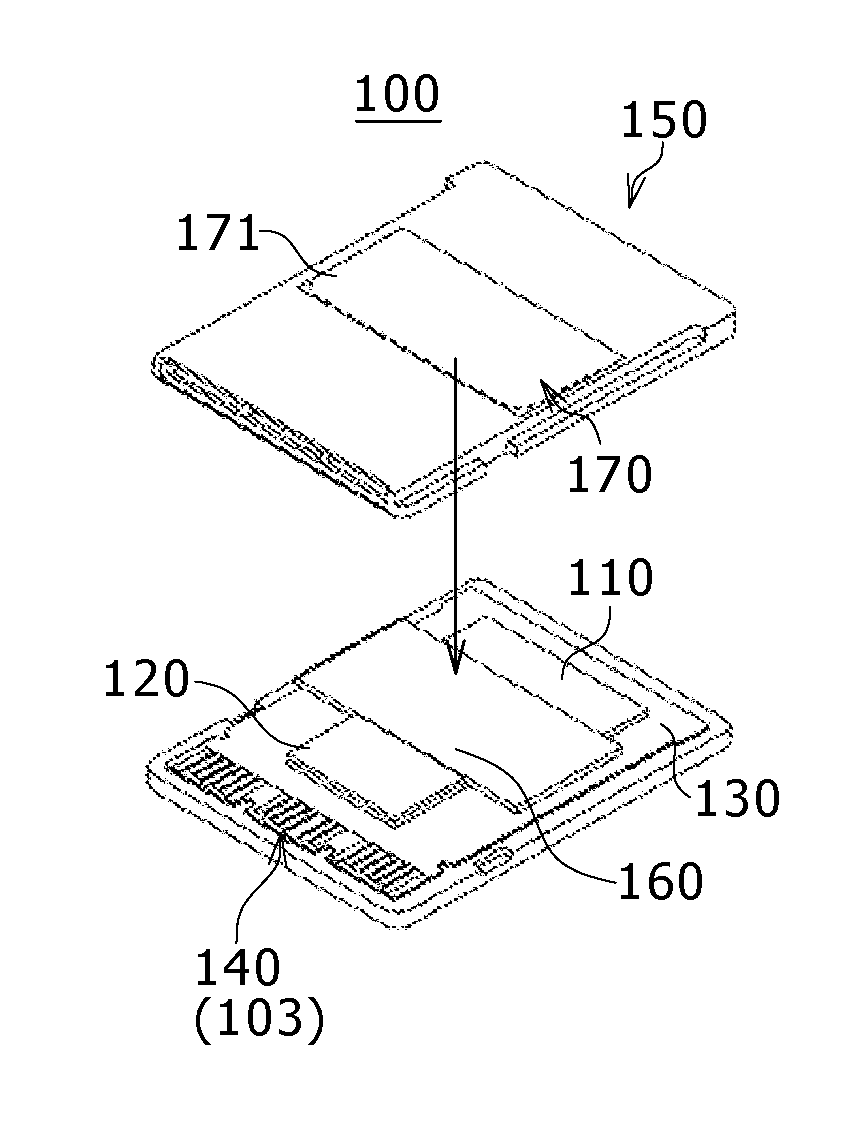

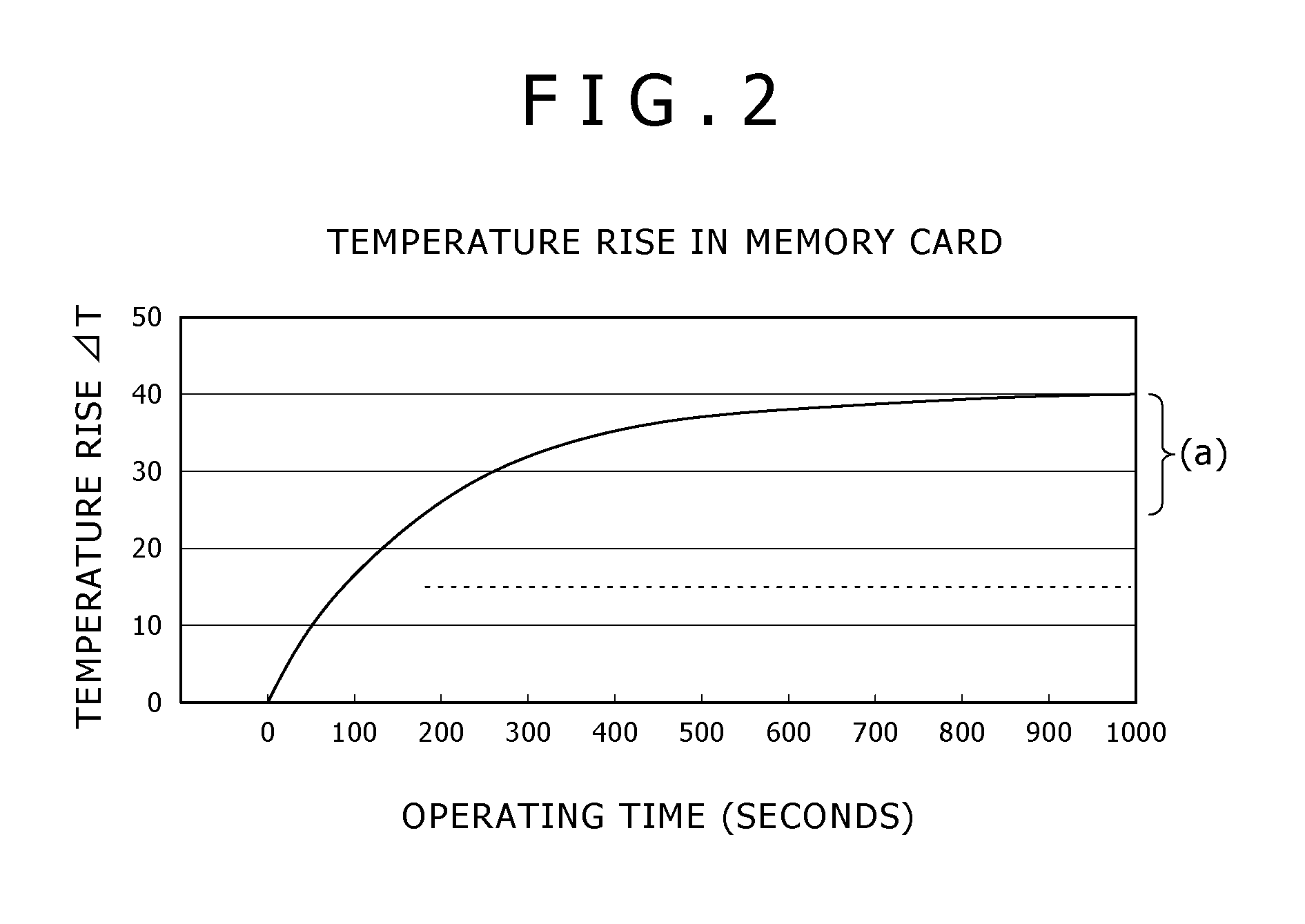

Card-type peripheral apparatus

InactiveUS20110103027A1Increased power consumptionImprove data transfer rateDigital data processing detailsSemiconductor/solid-state device detailsConductive materialsEngineering

Disclosed herein is a card-type peripheral apparatus including: a case body configured to accommodate an electronic package including a circuit board between a first surface and a second surface that are opposite to each other; a first electronic package including a memory mounted on the circuit board; a second electronic package including an electronic part for controlling the memory mounted on the circuit board; a first thermal conductive material arranged inside the case body, the first thermal conductive material in contact with a surface of at least one of the first electronic package and the second electronic package; and a second thermal conductive material formed with the first surface and the second surface of the case body, wherein the first thermal conductive material and the second thermal conductive material are in contact with each other inside the case body.

Owner:SONY CORP

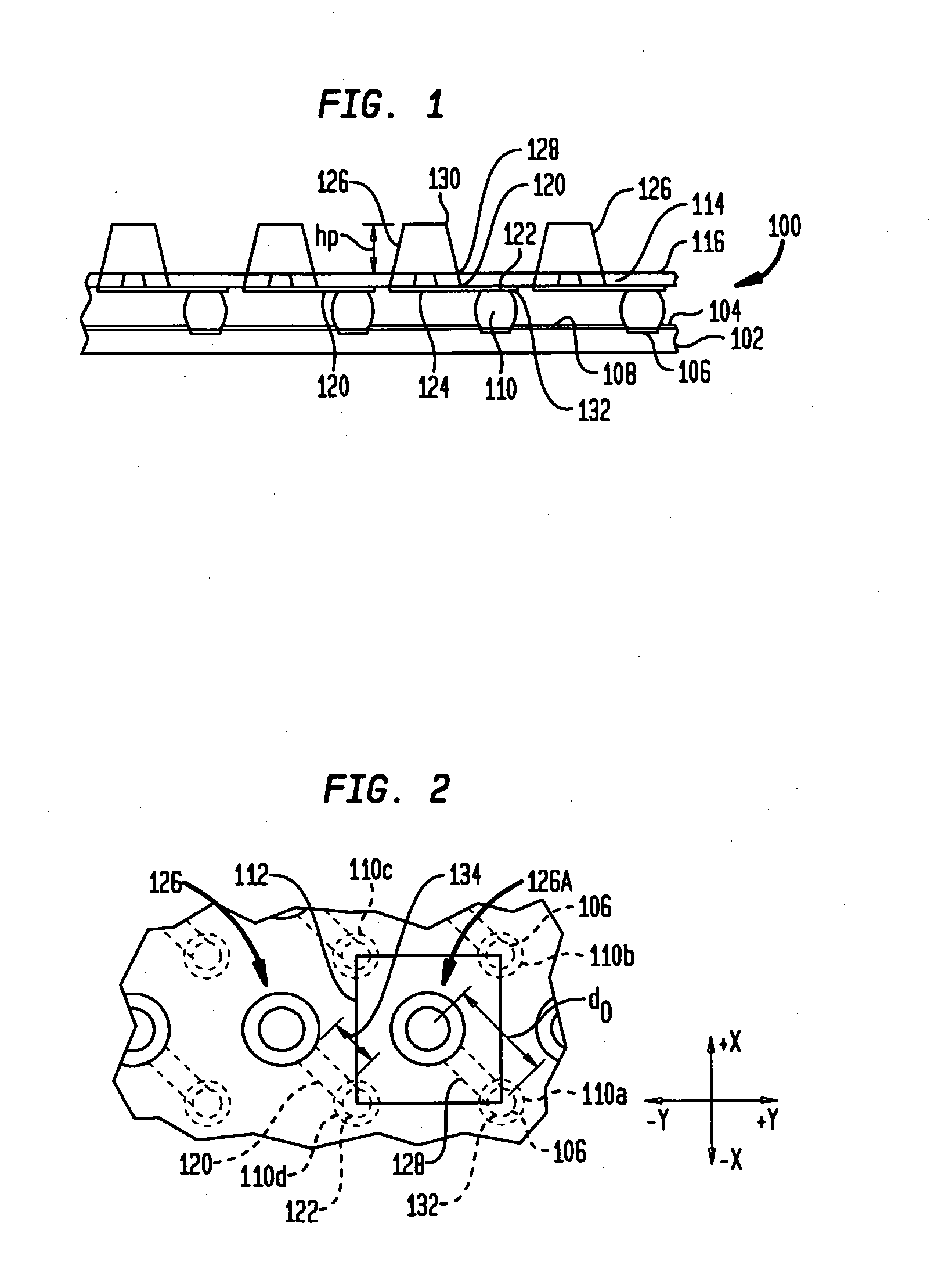

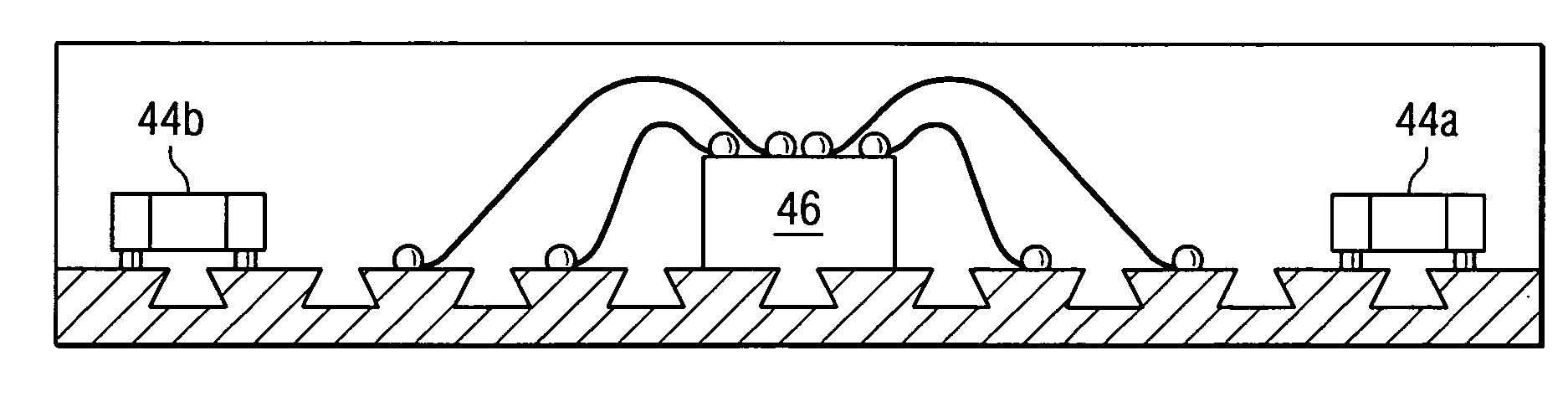

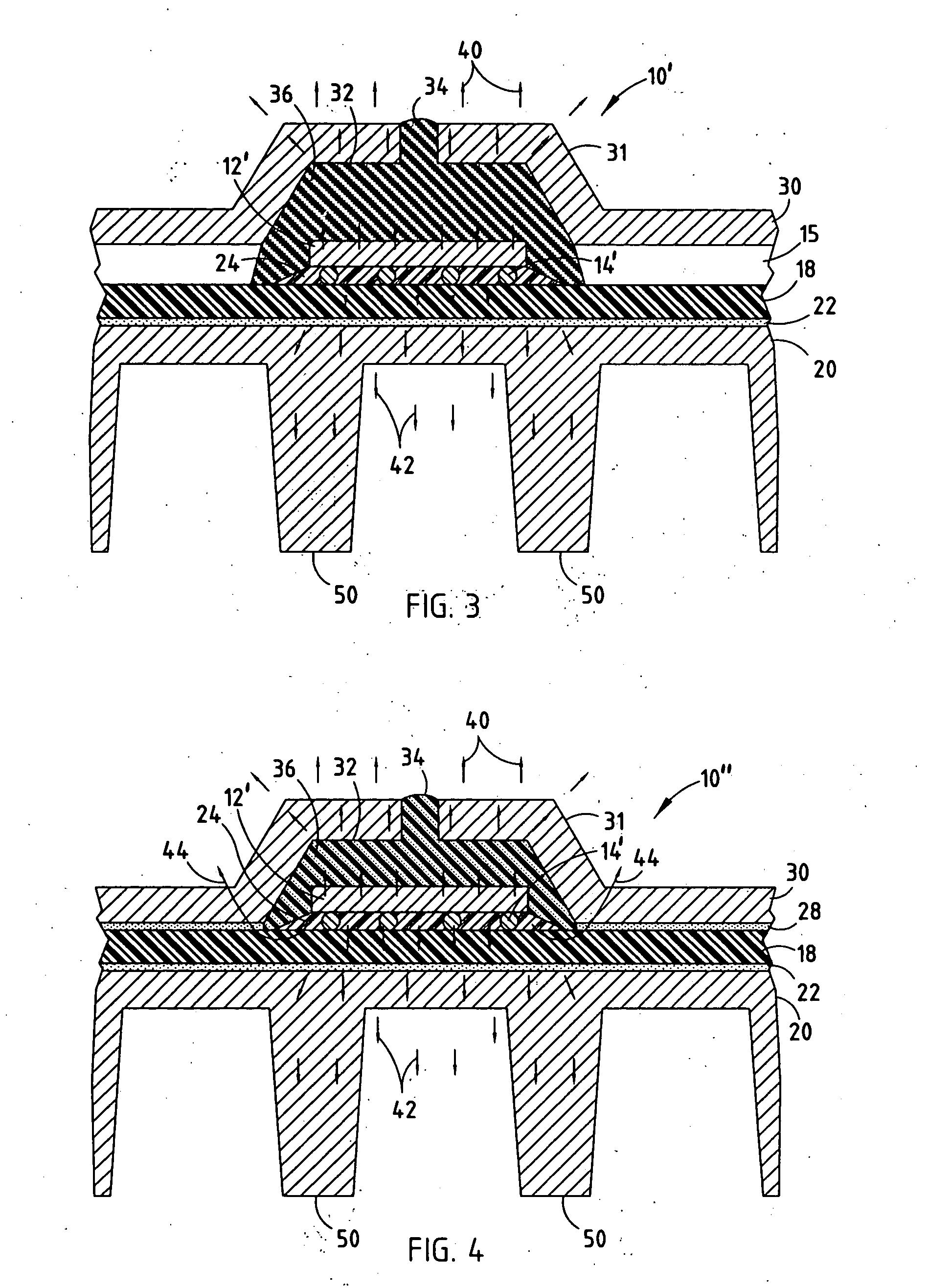

Method and apparatus for packaging an electronic chip

InactiveUS20060170081A1Accurate locationRemove heatSemiconductor/solid-state device detailsSolid-state devicesLead bondingLead frame

An electronic packaging combines features of a MAP (molded array package) and a lead frame package. The package includes an electrically conductive substrate somewhat like a lead frame package but defines a grid of conductive pads rather than a multiplicity of leads as is common with a lead frame package. An electronic chip is attached to the top surface of the lead frame, and the output terminals of the electronic chip are individually electrically connected to selected connecting pads of the lead frame grid array. Both flip chips and wire bond chips may be connected to the grid array. The channels defining the grid of connecting pads extend part way through the conductive substrate and increase in width from the top surface of the lead frame to the bottom of the channel such that the molding compound is locked in place when it cures and hardens. The grid pads are then singulated by sawing or etching channels from the bottom surface of the lead frame substrate that correspond to the channels defining the connecting pads on the top surface.

Owner:TEXAS INSTR INC

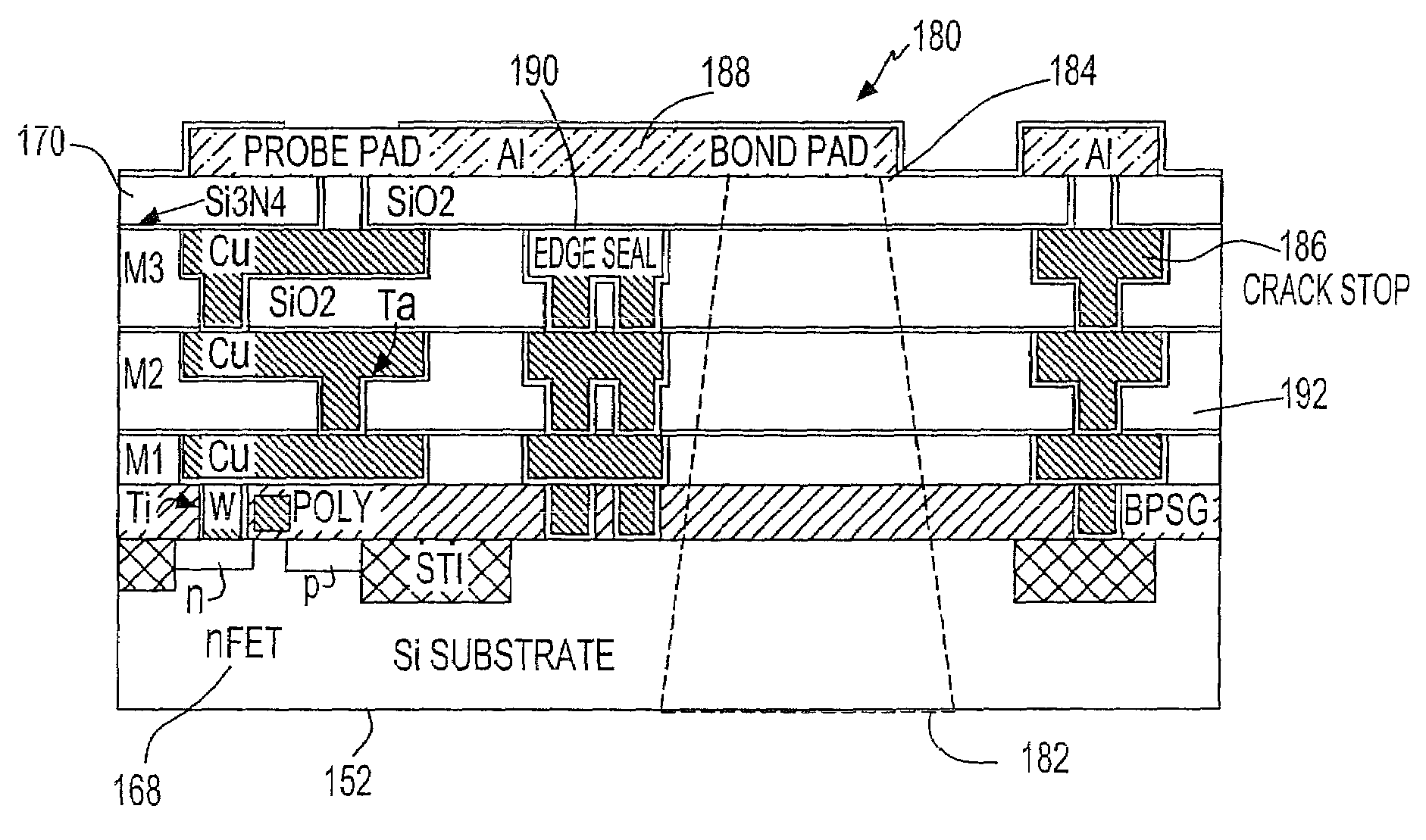

Bond pad for wafer and package for CMOS imager

An electronic packaging having at least one bond pad positioned on a chip for effectuating through-wafer connections to an integrated circuit. The electronic package is equipped with an edge seal between the bond pad region and an active circuit region, and includes a crack stop, which is adapted to protect the arrangement from the entry of deleterious moisture and combination into the active regions of the chip containing the bond pads.

Owner:SMARTSENS TECH CAYMAN CO LTD

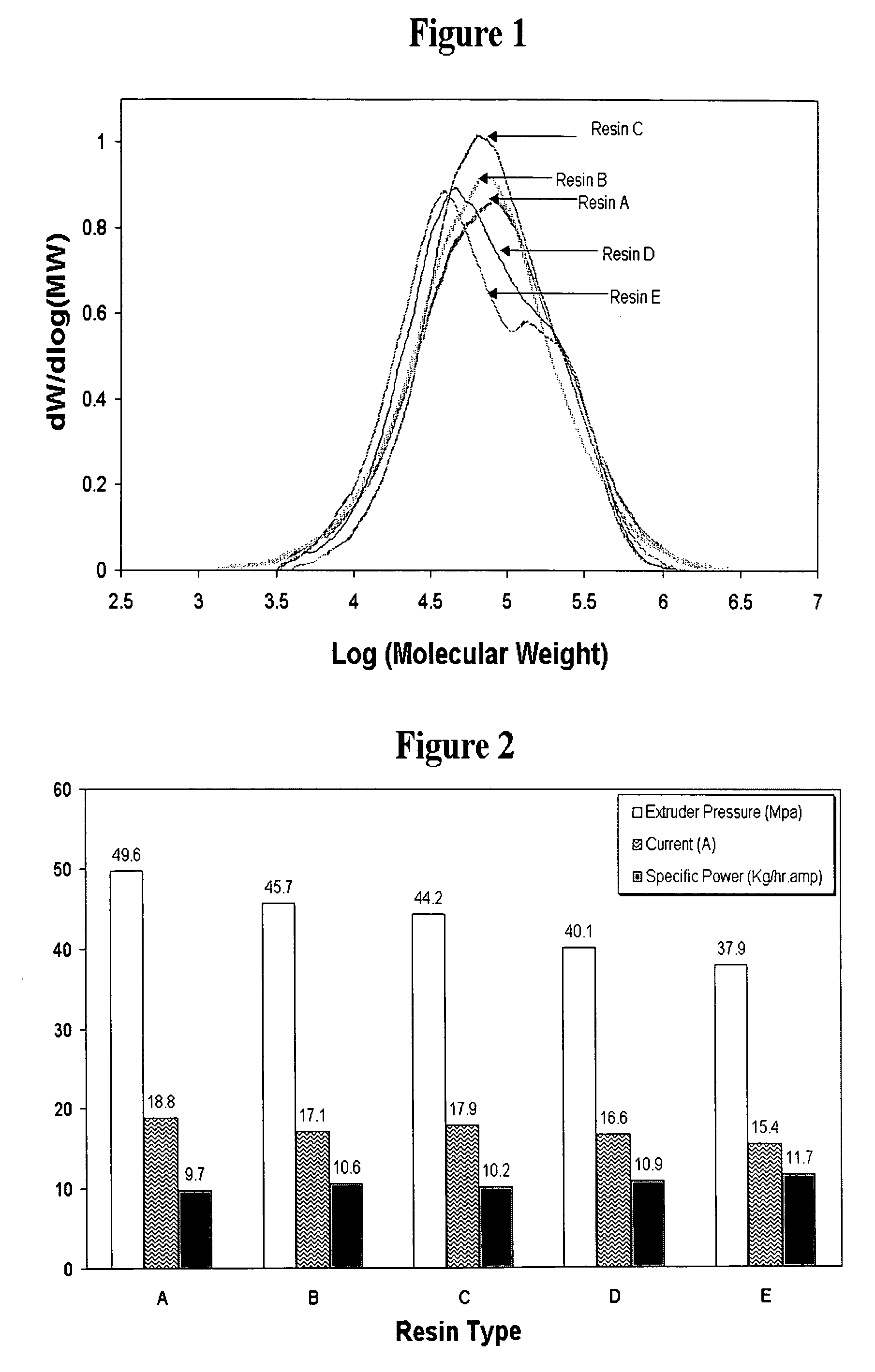

Dual reactor polyethylene resins for electronic packaging-films, tapes, bags and pouches

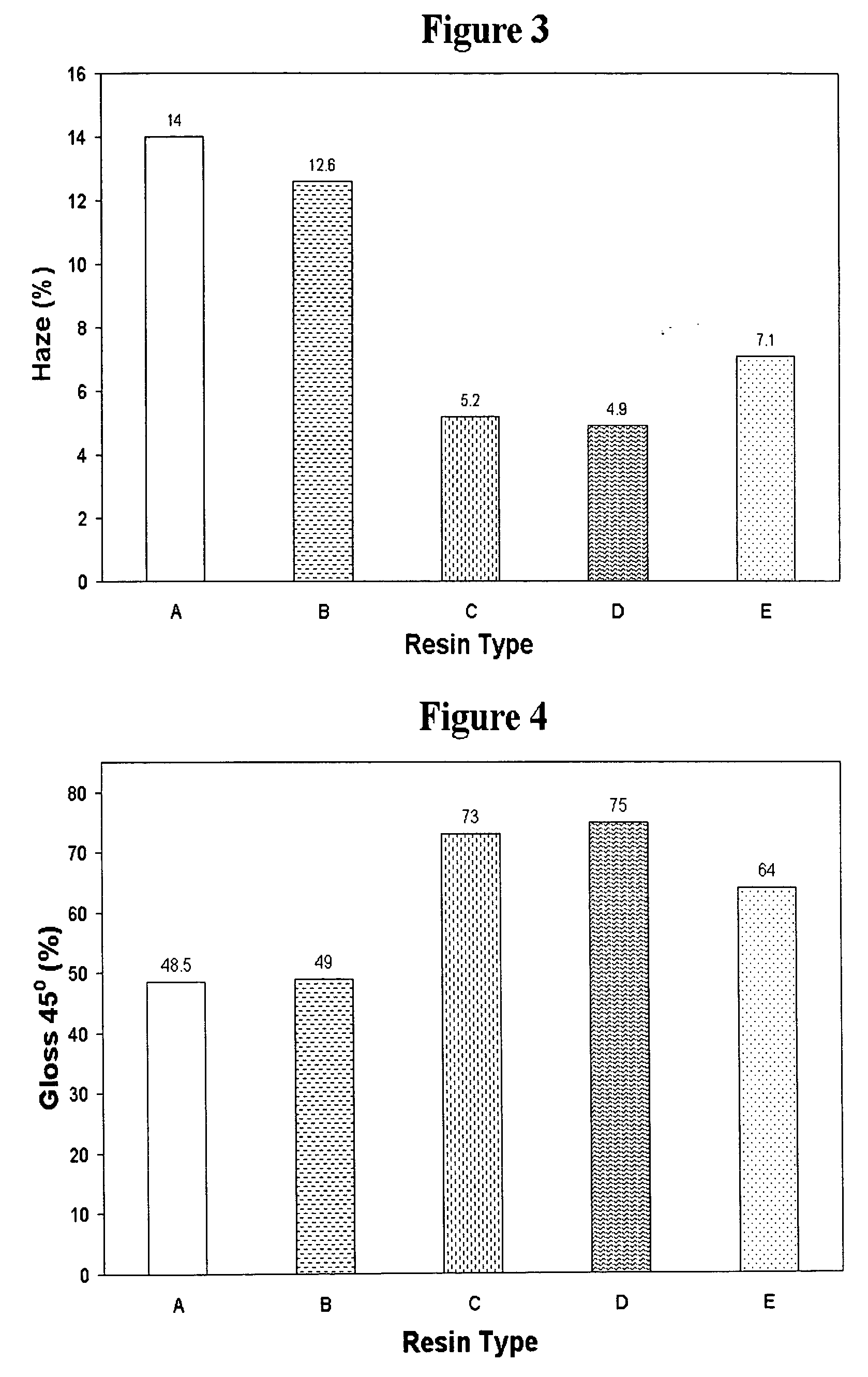

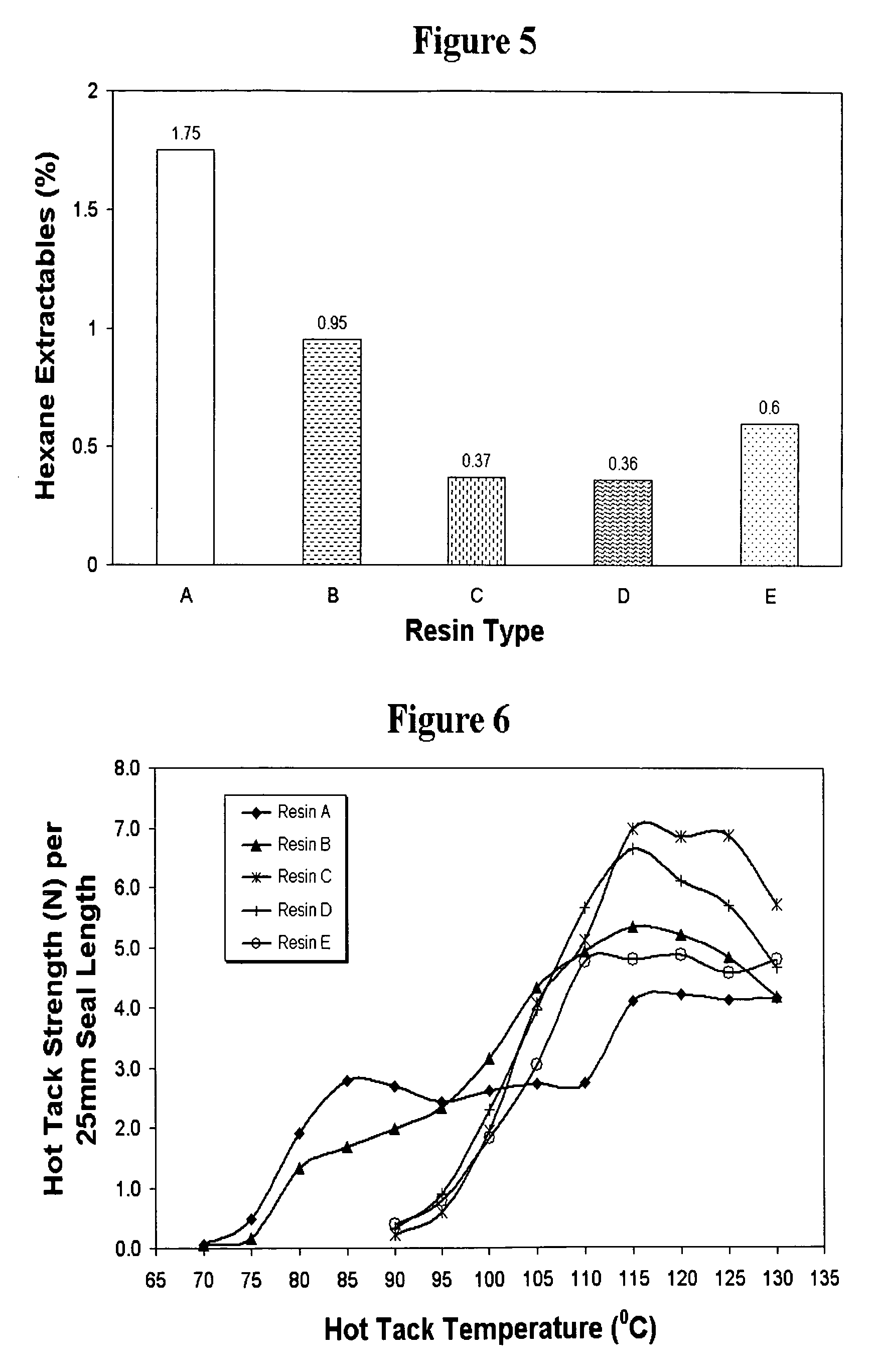

InactiveUS20060247373A1Good optical performanceHeat sealabilityLinear low-density polyethylenePolymer science

Owner:NOVA CHEM (INT) SA

Coated particles and sunscreen and cosmetic products containing same

InactiveUS20070280895A1Increasing bed volumeEqually distributedCosmetic preparationsToilet preparationsMetallic materialsConformal coating

Particles have an ultrathin, conformal coating are made using atomic layer deposition methods. The base particles include ceramic and metallic materials. The coatings can also be ceramic or metal materials that can be deposited in a binary reaction sequence. The coated particles are useful as fillers for electronic packaging applications, for making ceramic or cermet parts, as supported catalysts, as well as other applications.

Owner:WEIMER ALAN W +1

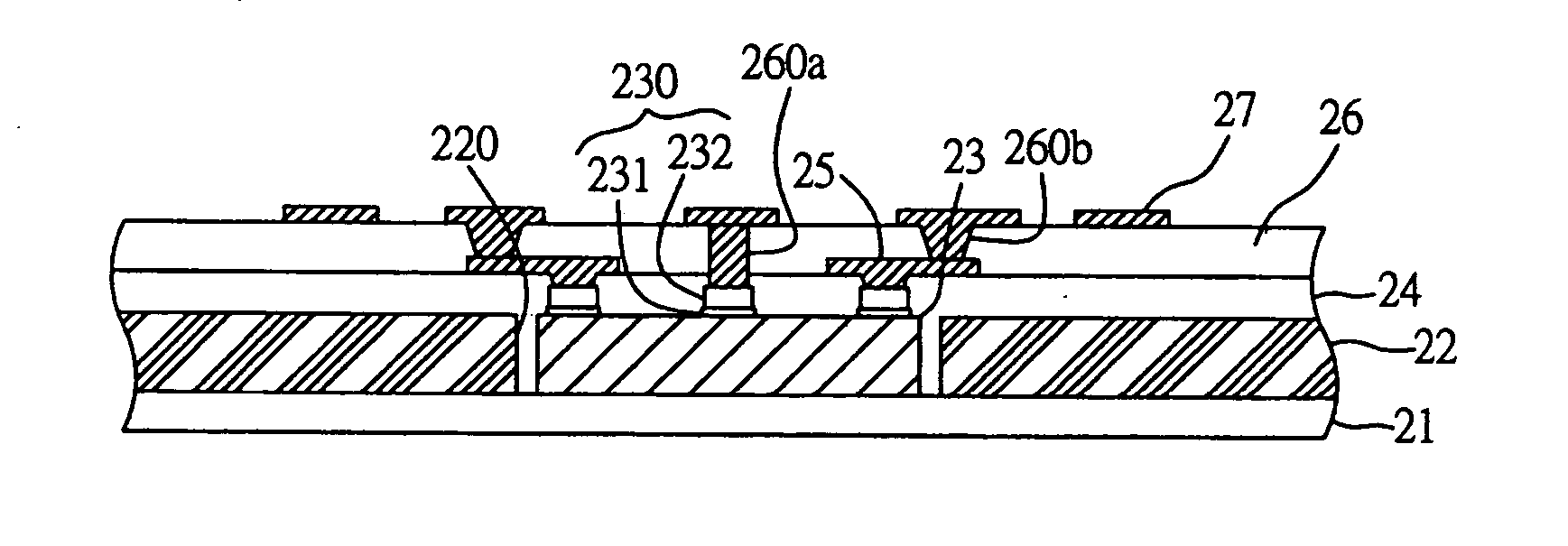

Micro-electronic package structure and method for fabricating the same

InactiveUS20060043549A1Simplify the manufacturing processImprove responseSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionSemiconductor chip

A micro-electronic package structure and a method for fabricating the same are proposed. A carrier is prepared and provided with a cavity for receiving at least one semiconductor chip having a plurality of electrical connection contacts. A dielectric layer is formed on the carrier, with the electrical connection contacts being exposed from the dielectric layer. A first circuit layer is formed on the dielectric layer and electrically connected to a portion of the electrical connection contacts of the chip. Another dielectric layer is formed on the first circuit layer and said dielectric layer, and a second circuit layer is formed on this dielectric layer and electrically connected to the rest of the electrical connection contacts of the chip and the first circuit layer by conductive vias, such that the chip is integrated into the carrier.

Owner:PHOENIX PRECISION TECH CORP

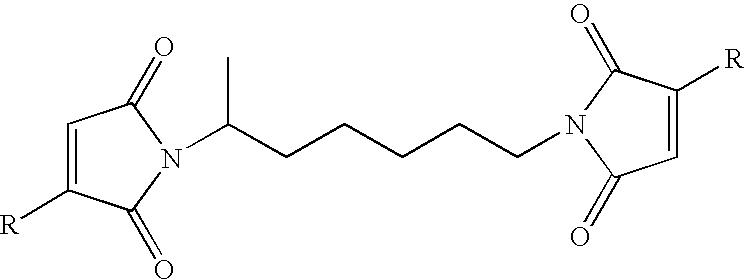

Low temperature curing acrylate and maleimide based formulations and methods for use thereof

ActiveUS20100063184A1Non-fibrous pulp additionFilm/foil adhesivesLow temperature curingElectronic packaging

The present invention is based on the discovery that certain electron poor olefins combined with nucleophiles and a base catalyst are useful as adhesive compositions for the electronic packaging industry. In particular, the adhesive formulations set forth herein are useful as low temperature curing formulations with high adhesion to a variety of substrates. Invention formulations typically cure at about 80° C. and have a potlife of about 24 hours. The formulations cure by the well-known Michael addition reaction.

Owner:DESIGNER MOLECULES

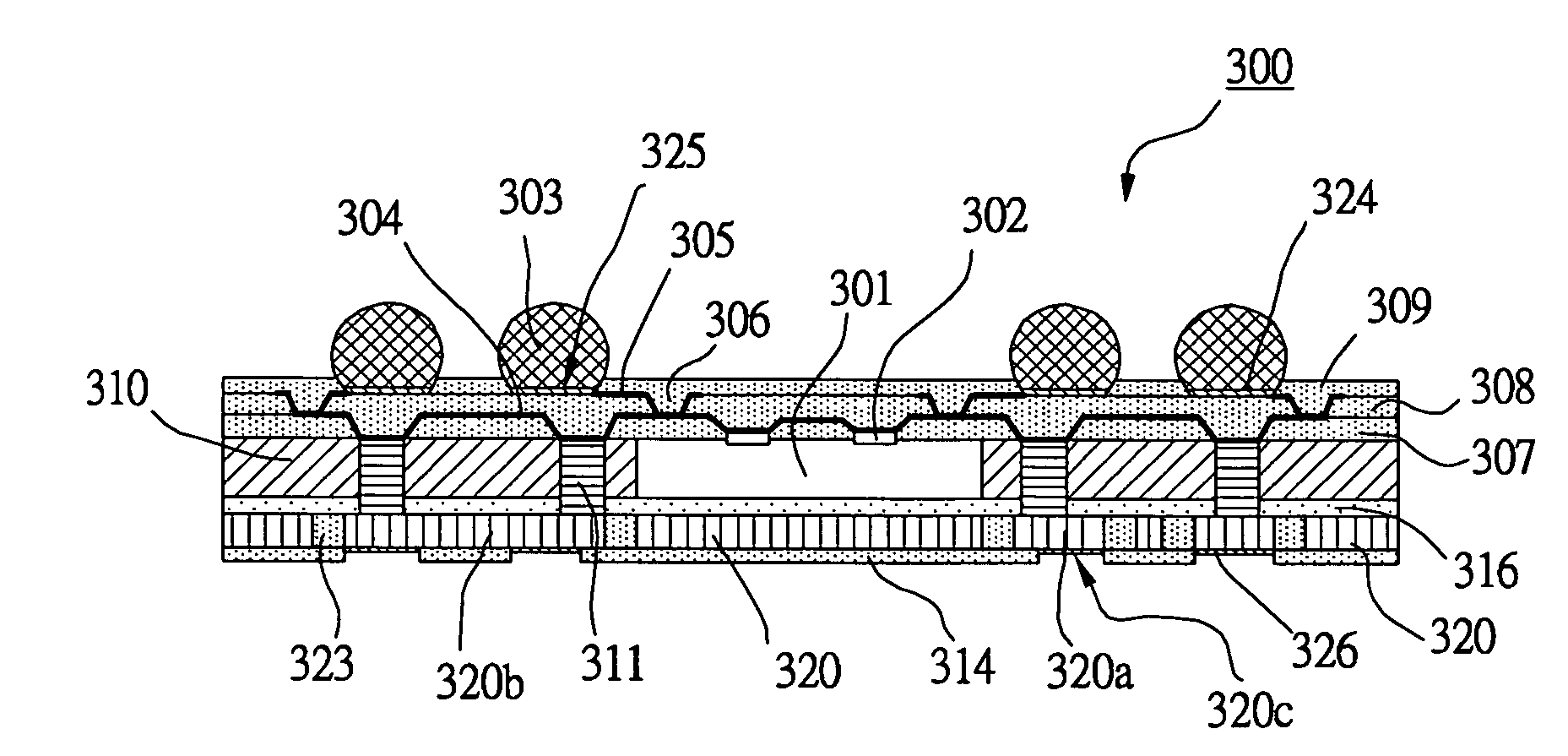

3D electronic packaging structure having a conductive support substrate

ActiveUS20070296065A1Shorten the signal transmission pathShorten the timeSemiconductor/solid-state device detailsSolid-state devicesElectronic componentElectronic packaging

The present invention provides a 3D electronic packaging unit having a conductive supporting substrate that can achieve multi-chip stacking through the signal contacts on the both sides of the unit. The packaging unit can be batched manufactured on wafers or substrates, and thus reduce the manufacturing cost of each individual packaging unit; moreover, the conductive supporting substrate can be utilized to provide signal transmission of the electronic elements, and the supporting substrate can be used as a ground terminal for the carried electronic elements to enhance electric performance of the electronic elements. The supporting substrate is also a good thermal conductor that can release effectively heat energy generated by the electronic elements and accumulated inside the package to the outside of the package along the substrate to enhance reliability of the packaging structure.

Owner:ADVANCED CHIP ENG TECH

Microelectronic packages using a ceramic substrate having a window and a conductive surface region

InactiveUS20060138626A1Semiconductor/solid-state device detailsSolid-state devicesElectronic packagingSubstrate surface

A microelectronic package includes a microelectronic device, a unitary ceramic substrate, and a plurality of terminals. The microelectronic device has a front surface and a plurality of electrical contacts thereon. The substrate has first and second opposing surfaces. A window extends from a first opening on the first surface along a side wall to a second opening on the second surface. A conductive region may be provided on the side wall and / or the second substrate surface. The substrate is located between the device and the terminals such that the first surface of the substrate faces the front surface of the device and the first opening is aligned with at least one contact on the front device surface. Also provided are methods for producing microelectronic packages and wafer-scale assemblies.

Owner:TESSERA INC

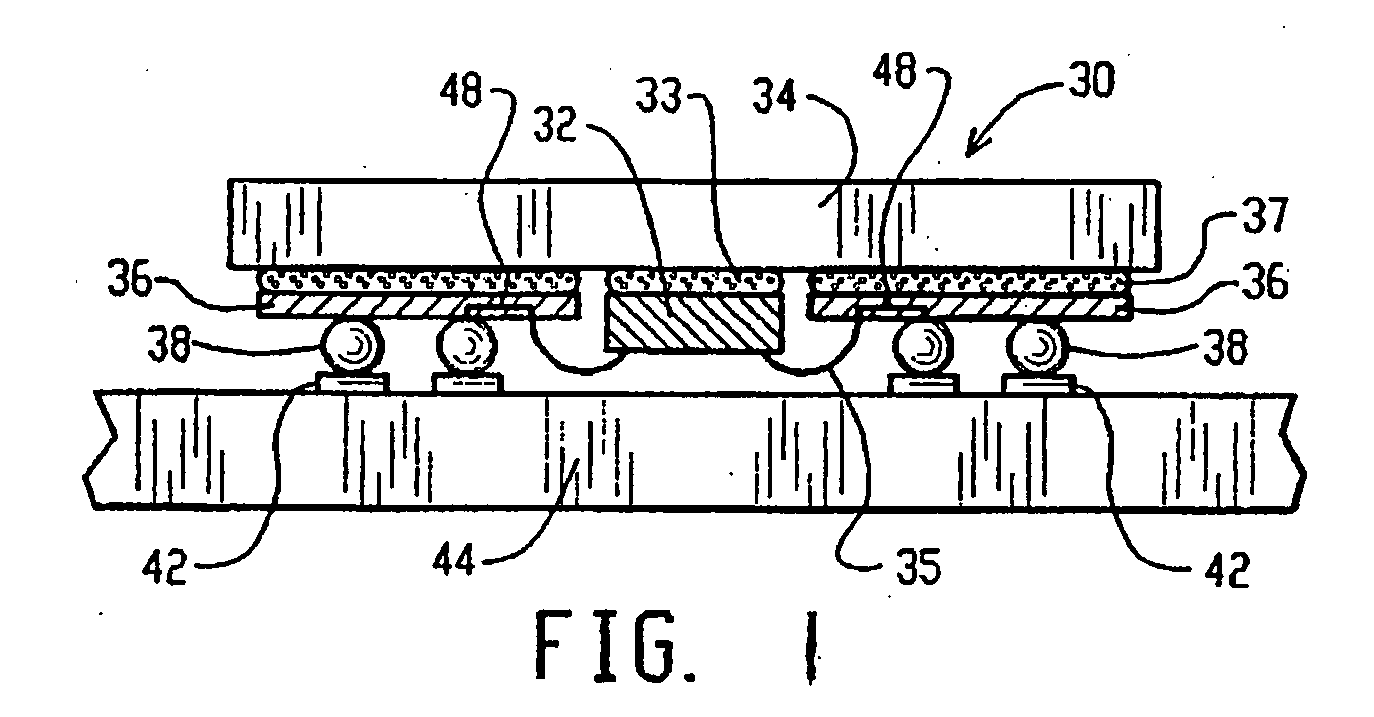

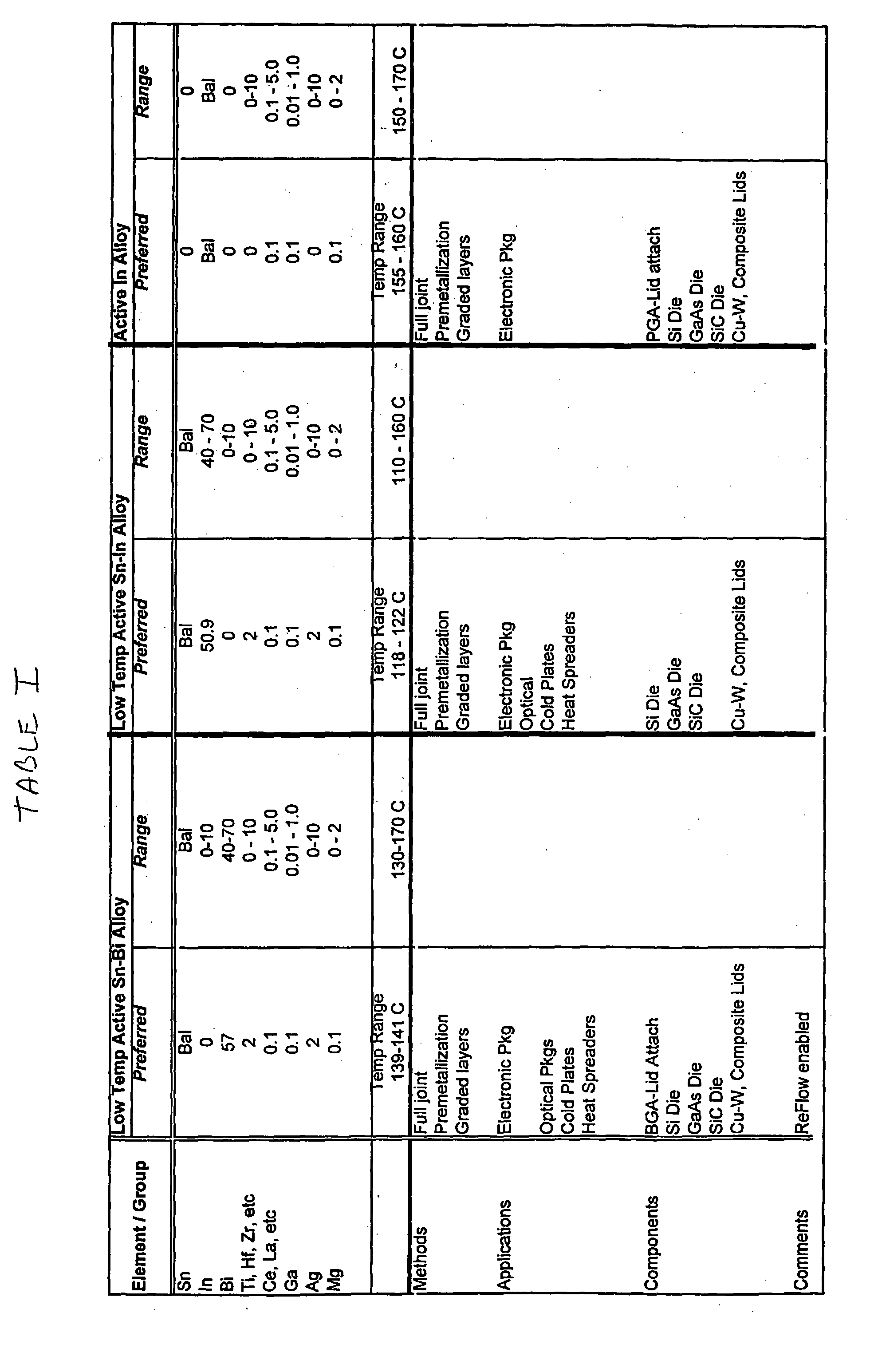

Electronic Package Formed Using Low-Temperature Active Solder Including Indium, Bismuth, and/or Cadmium

InactiveUS20070228109A1Increase concentrationHigh-strength, high-thermal conductivity jointsCooking-vessel materialsExhaust apparatusIndiumNiobium

An active solder alloy, an electronic device package including the active solder alloy bonding an electronic device to a substrate, and a method of forming high-strength joints by soldering using the solder alloy. The alloy contains up to about 10% by weight of an element or a mixture of elements selected from the group consisting of titanium, zirconium, hafnium, vanadium, niobium, or tantalum; between about 0.1 and 5% by weight of an element or a mixture of elements selected from the group of the lanthanides (rare earths); between about 0.01 and 1% by weight of gallium up to about 10% by weight of silver; up to about 2% by weight of magnesium; and a remainder consisting of tin, bismuth, indium, cadmium, or a mixture of two or more of these elements. The alloy enables low-temperature (less than about 180° C.) soldering within relatively narrow melting ranges (less than about 10° C.).

Owner:S BOND TECH

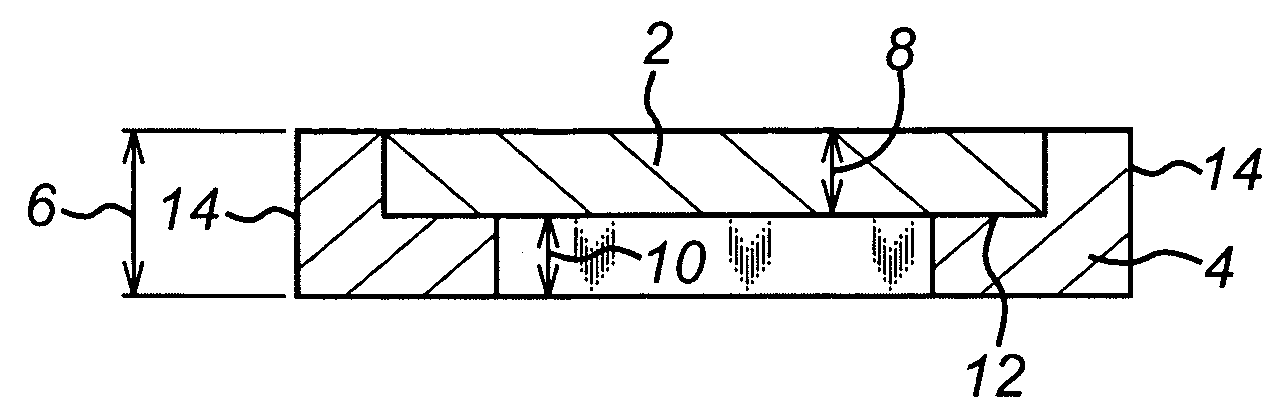

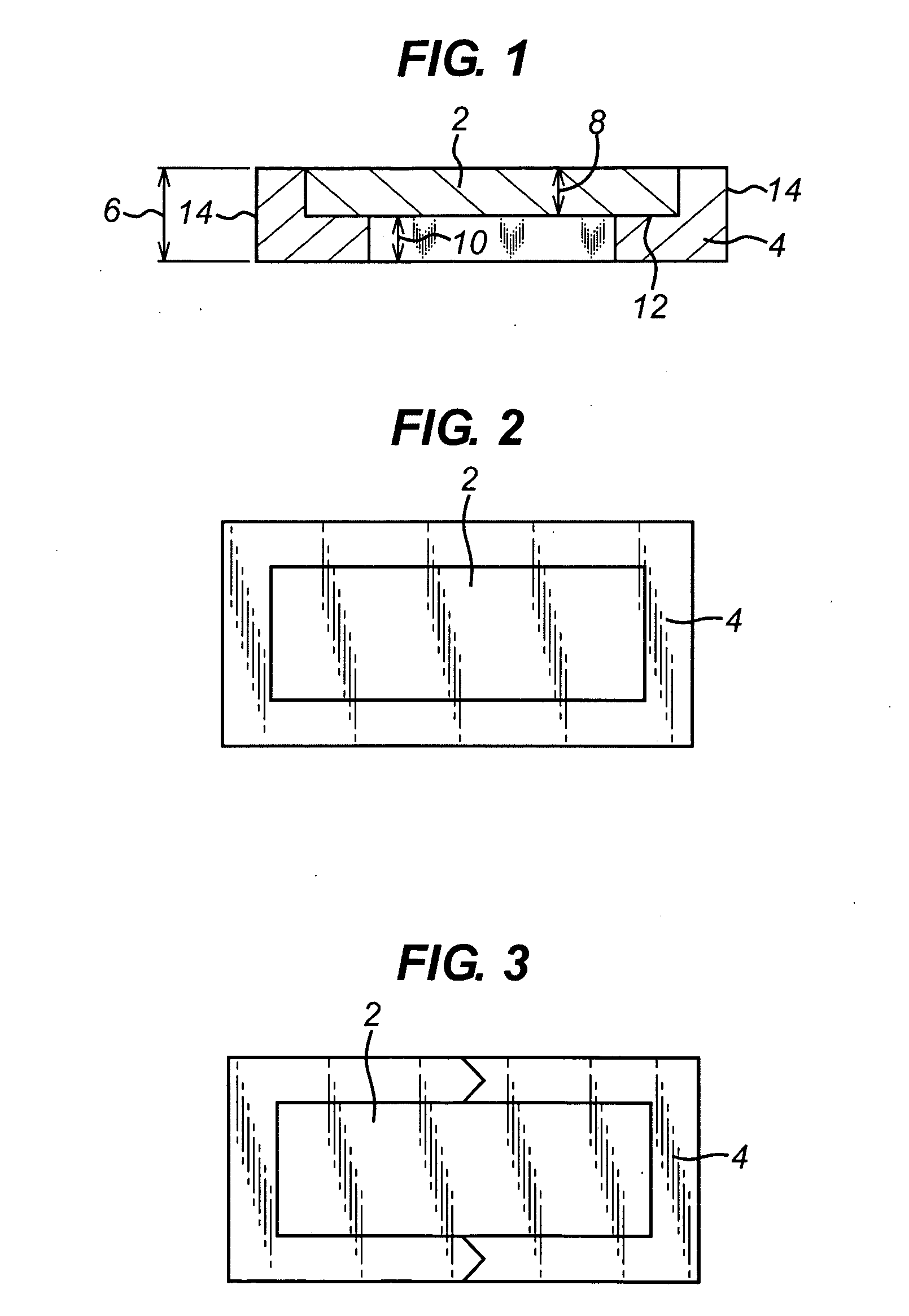

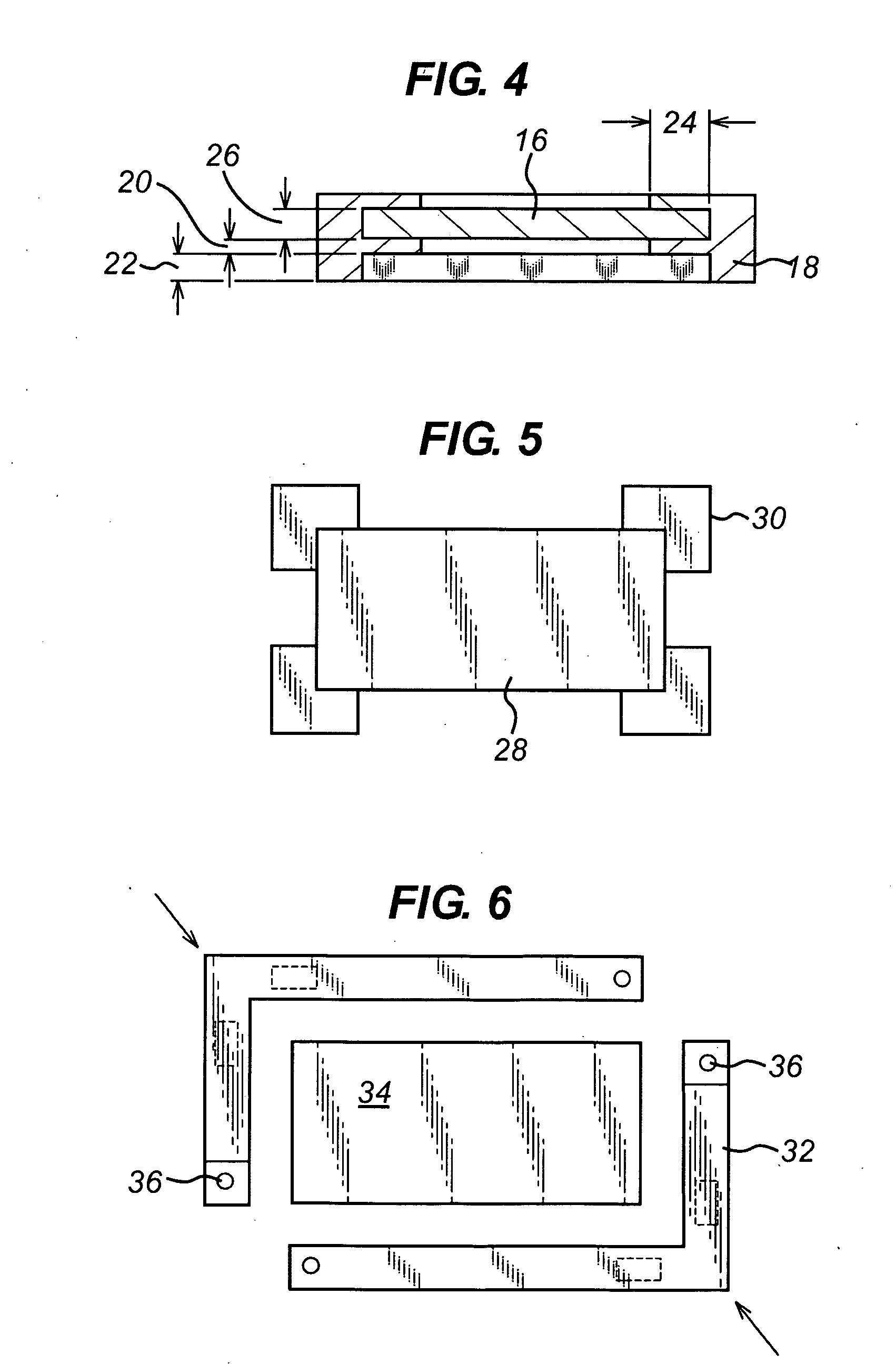

Spatial transformation interposer for electronic packaging

InactiveUS6332782B1Firmly connectedSmall sizePrinted circuit assemblingSemiconductor/solid-state device detailsInterposerInterconnection

An interconnect substrate structure for electrical interconnection between two electronic modules having differing conductive array parameters. The interconnect structure comprises an interposer having a top surface and a bottom surface; a first set of conductive arrays having a first conductive array parameter on the top surface, and a second set of conductive arrays having a second conductive array parameter on the bottom surface, the second conductive array and the first conductive array having differing parameters. A plurality of conductors traverses a thickness of the interposer, with the conductors comprising a conductive material optionally coated with a dielectric material, the conductors having a first end at the first conductive arrays and a second end at the second conductive arrays, whereby the conductors connecting the first and second conductive arrays therein are adapted to spatially transform the differing parameters to provide an electrical interconnection. A conductive matrix surrounds the conductors. The first set of conductive arrays comprise the same conductive array parameters as a first electronic module and the second set of conductive arrays comprise the same conductive array parameters as a second electronic module.

Owner:IBM CORP

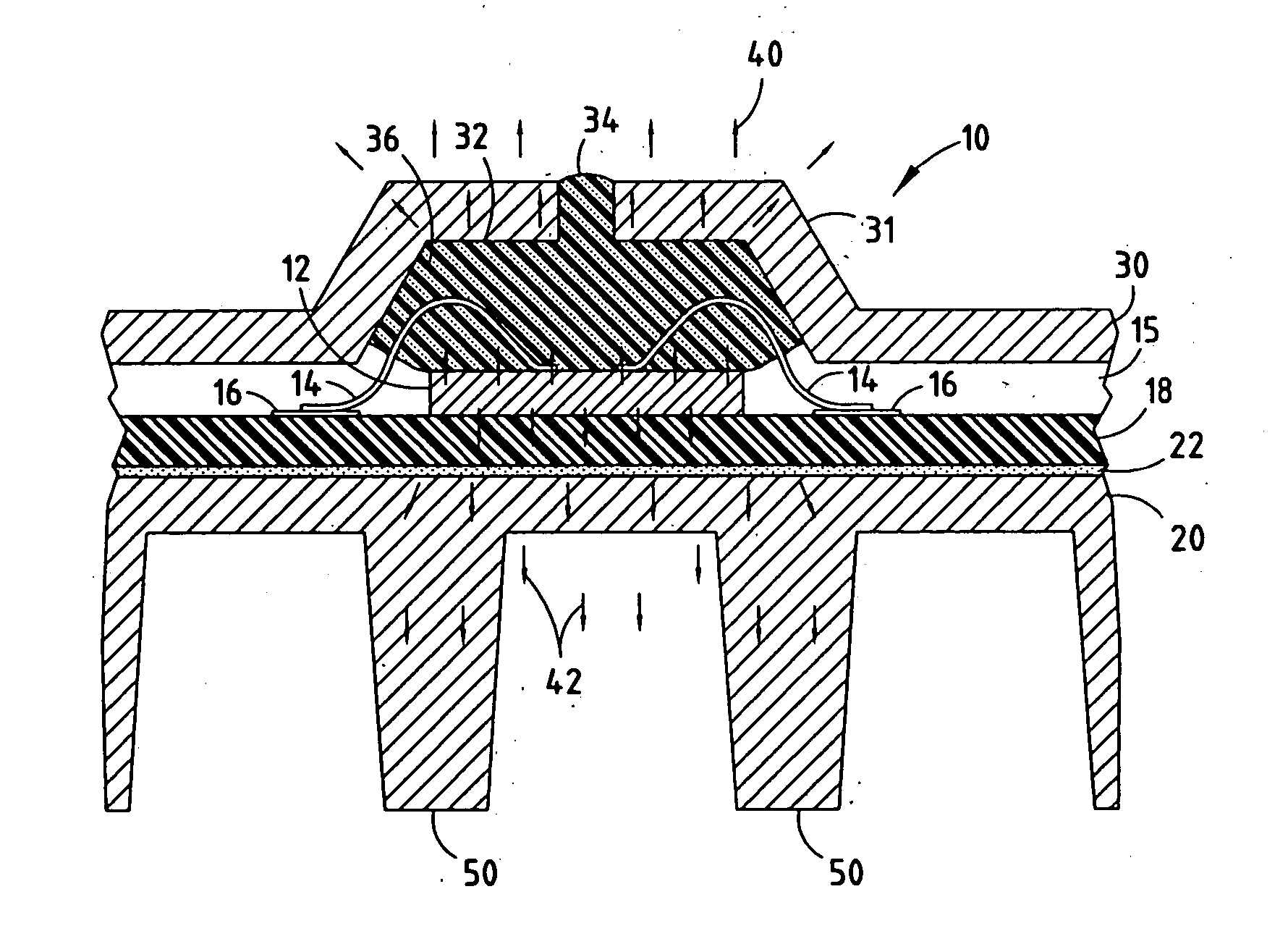

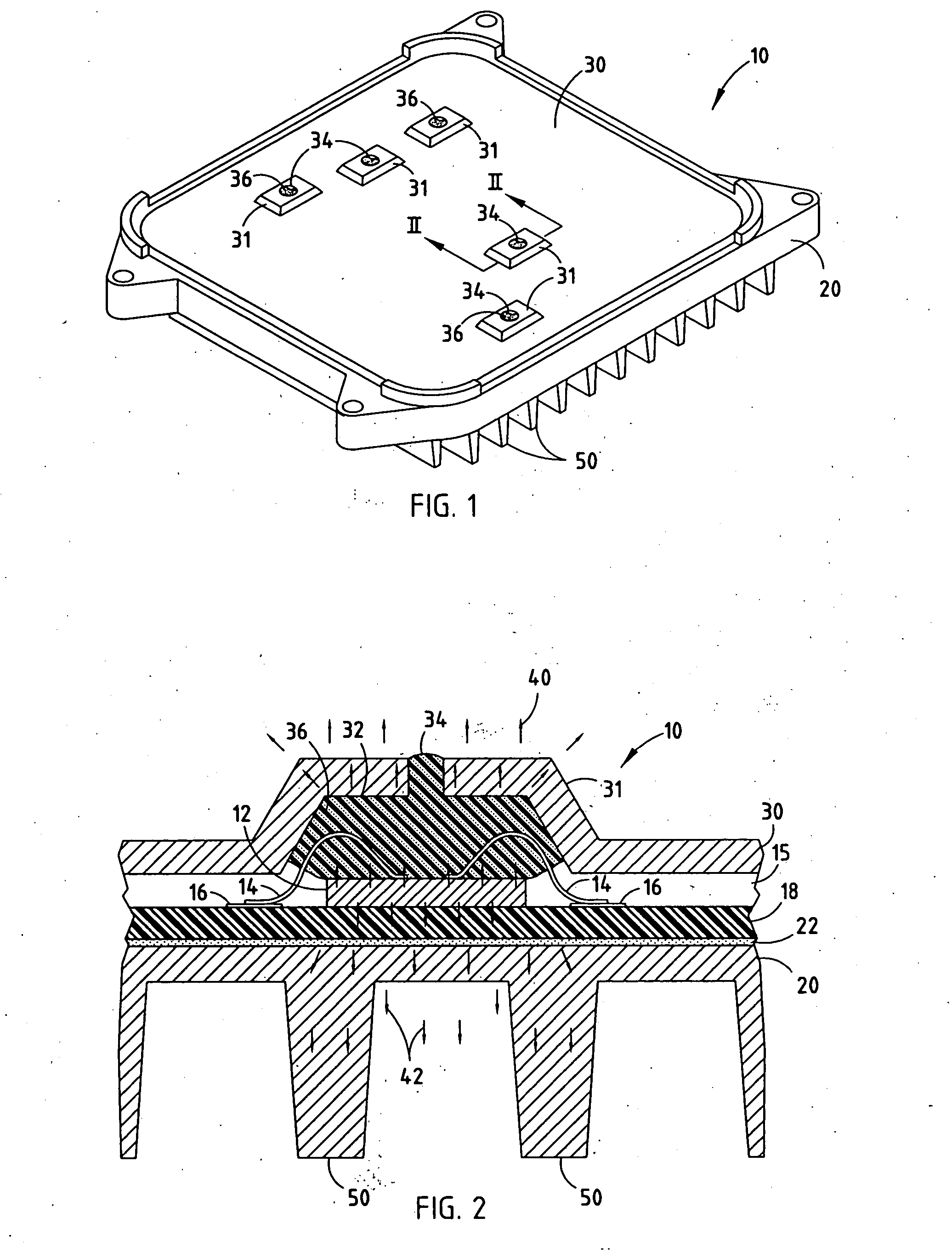

Semiconductor device heat sink package and method

InactiveUS20050077614A1Improve cooling effectSemiconductor/solid-state device detailsSolid-state devicesDevice materialElectronic packaging

An electronic package having enhanced heat dissipation is provided exhibiting dual conductive heat paths in opposing directions. The package includes a substrate and a semiconductor device mounted to the substrate. The semiconductor device has electrical circuitry a first surface, and a second surface oppositely disposed from the first surface. A thermally conductive heat sink is assembled over the semiconductor device such that a cavity is formed between the semiconductor device and the heat sink. A thermally conductive and electrically insulative material is disposed in the cavity between the semiconductor device and the heat sink.

Owner:DELPHI TECH INC

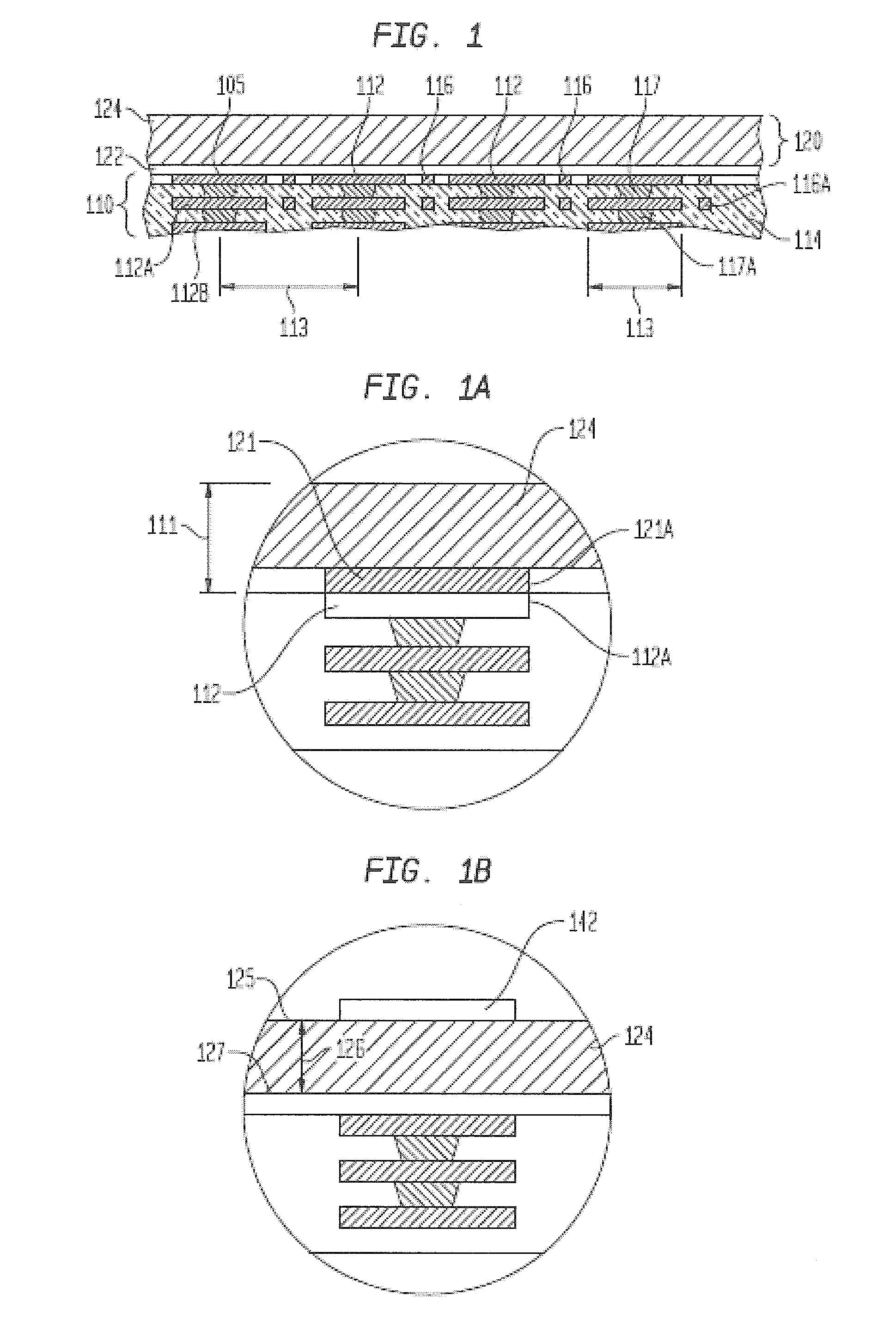

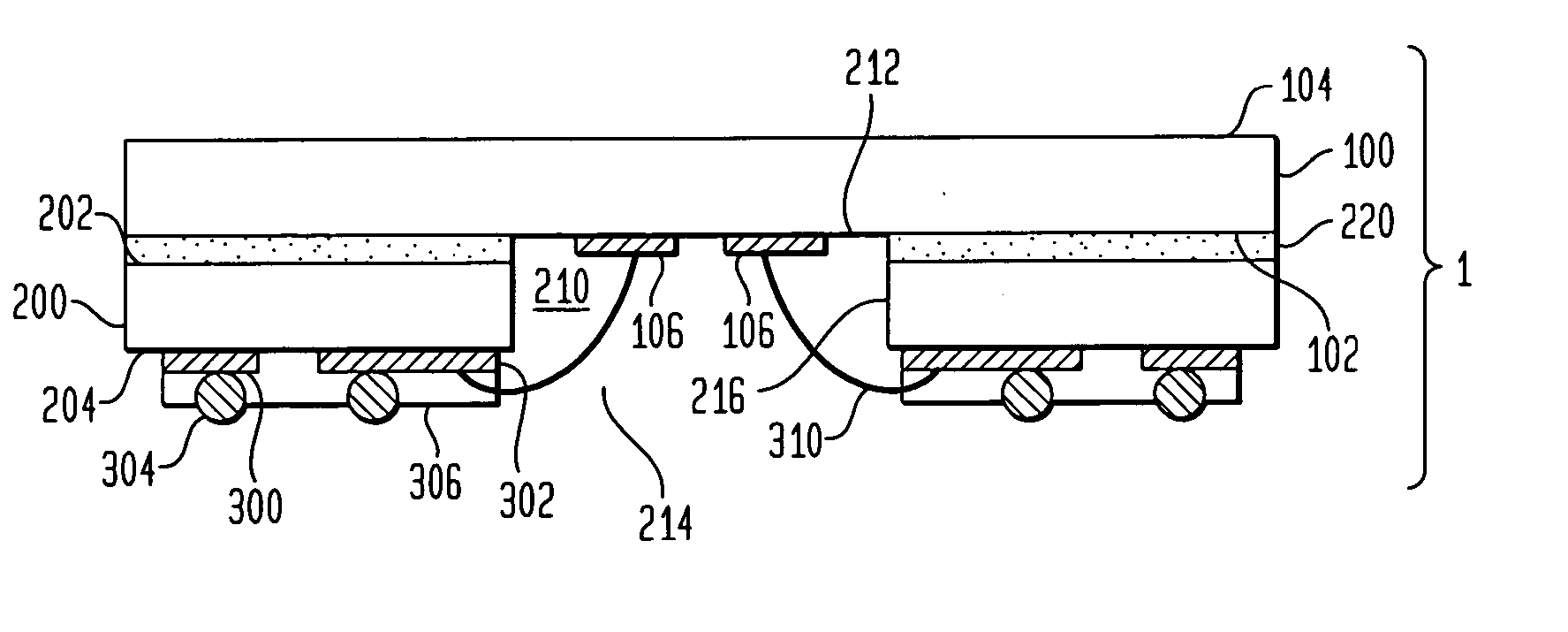

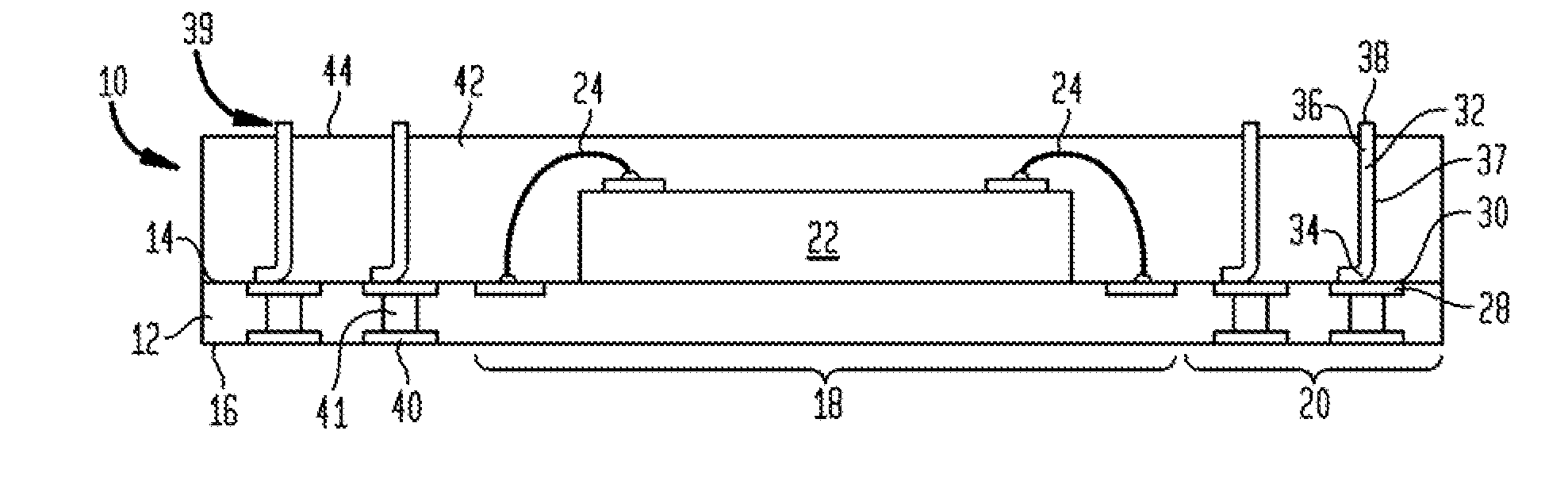

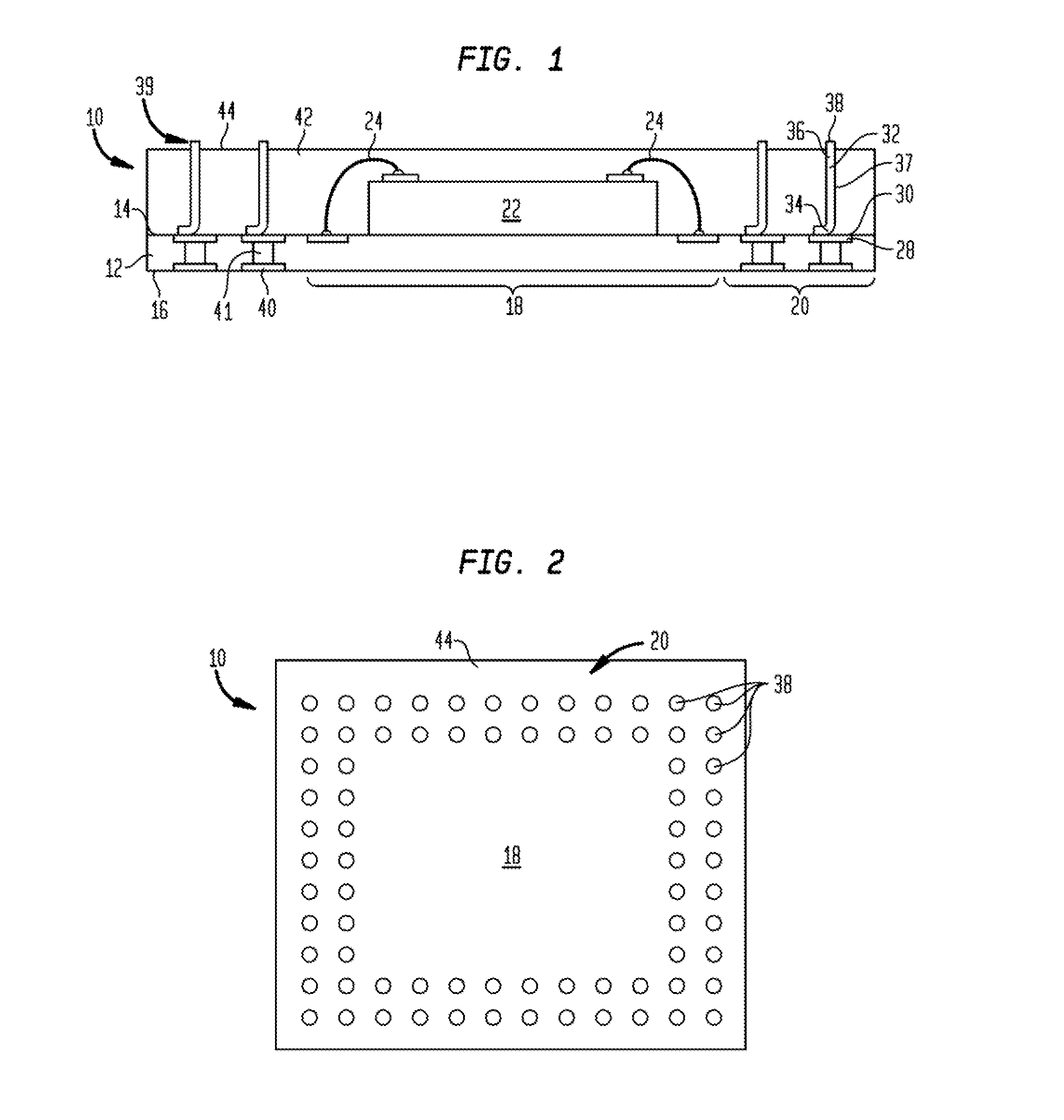

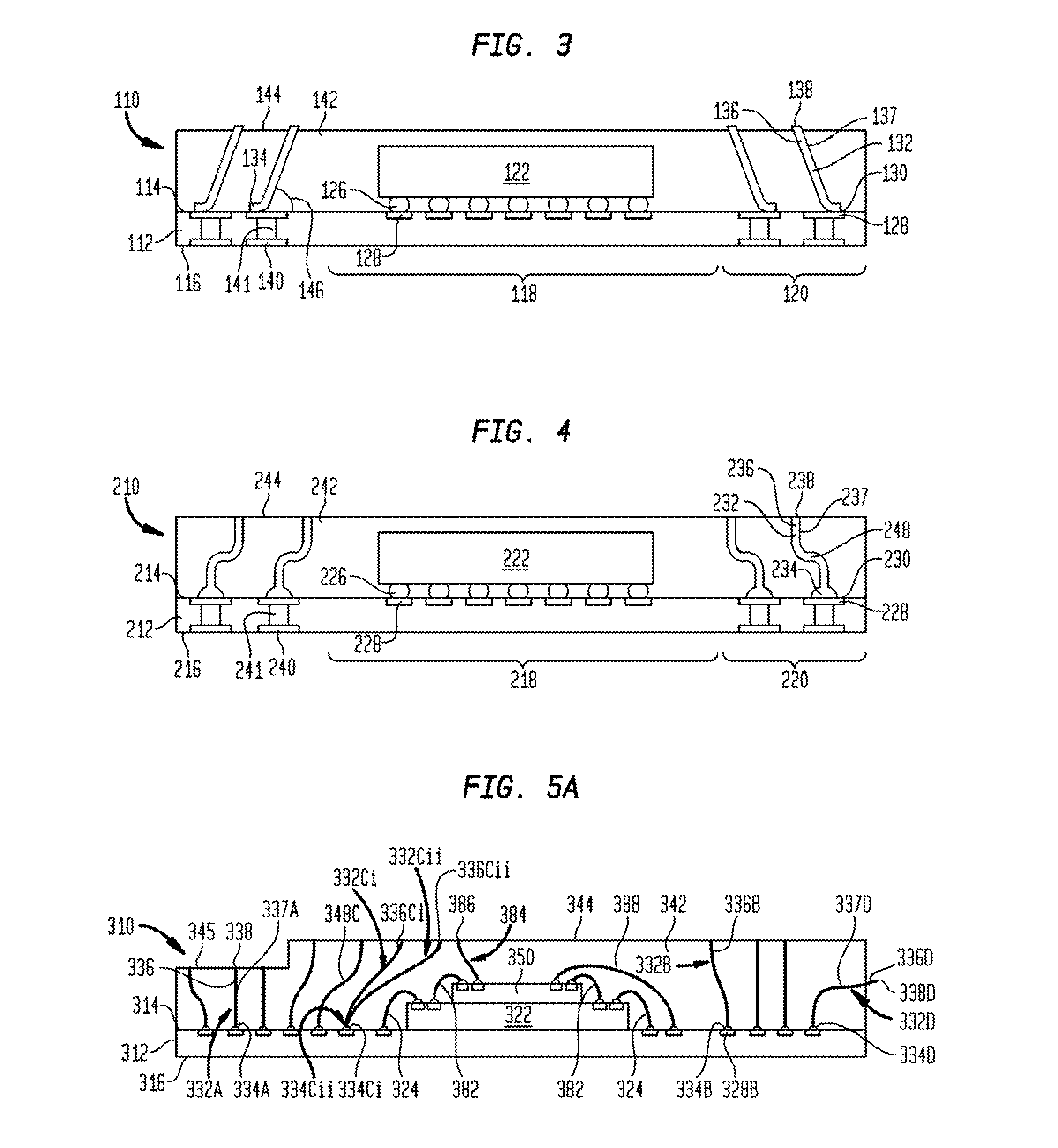

Package-on-package assembly with wire bond vias

ActiveUS20130095610A1Semiconductor/solid-state device detailsPrinted circuit aspectsEdge surfaceLead bonding

A microelectronic package can include wire bonds having bases bonded to respective ones of conductive elements exposed at a surface of a substrate. The wire bonds may have exterior edge surfaces disposed at an angle between 25° and 92° relative to the bases, and ends remote, e.g., opposite, from the bases, and remote from the ends which are connected to the bases. A dielectric encapsulation layer extends from the substrate and covers portions of the wire bonds such that covered portions of the wire bonds are separated from one another by the encapsulation layer, wherein unencapsulated portions of the wire bonds are defined by portions of the wire bonds that are uncovered by the encapsulation layer, the unencapsulated portions including the ends of the wire bonds.

Owner:INVENSAS LLC

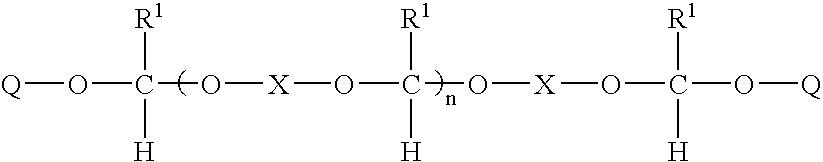

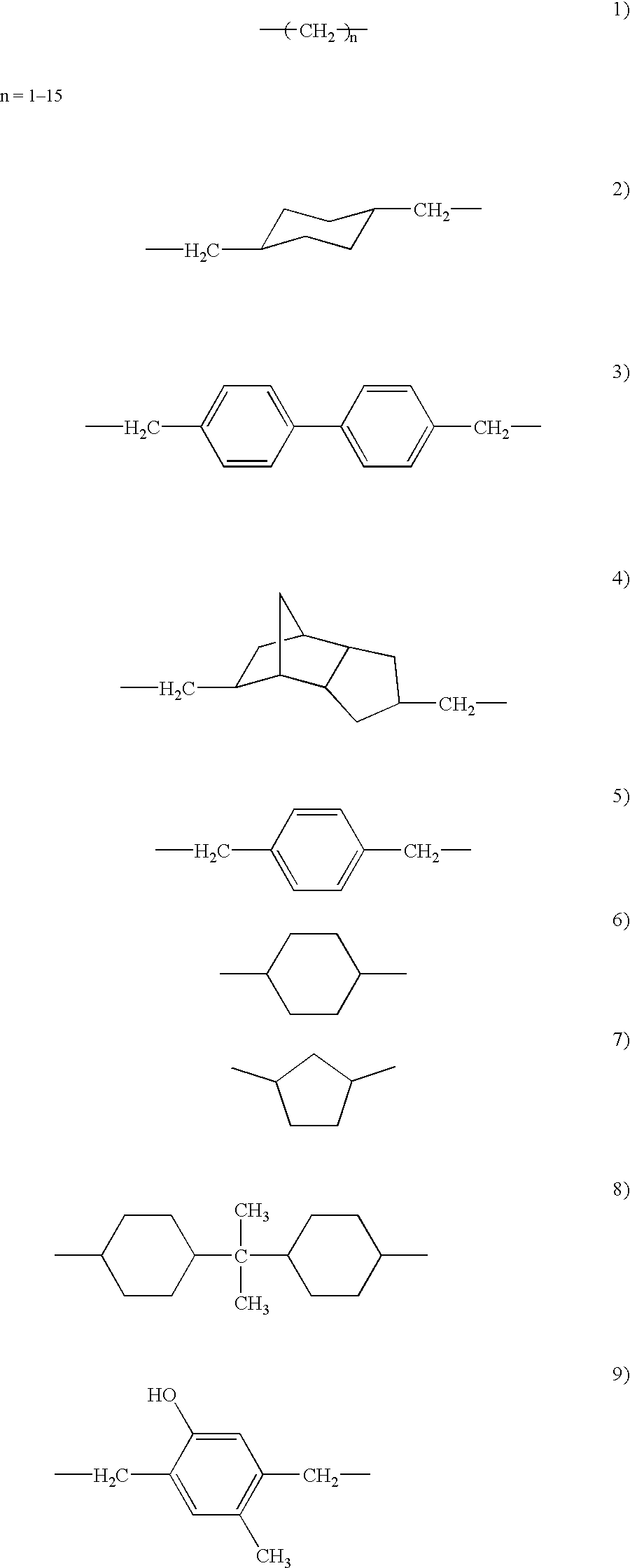

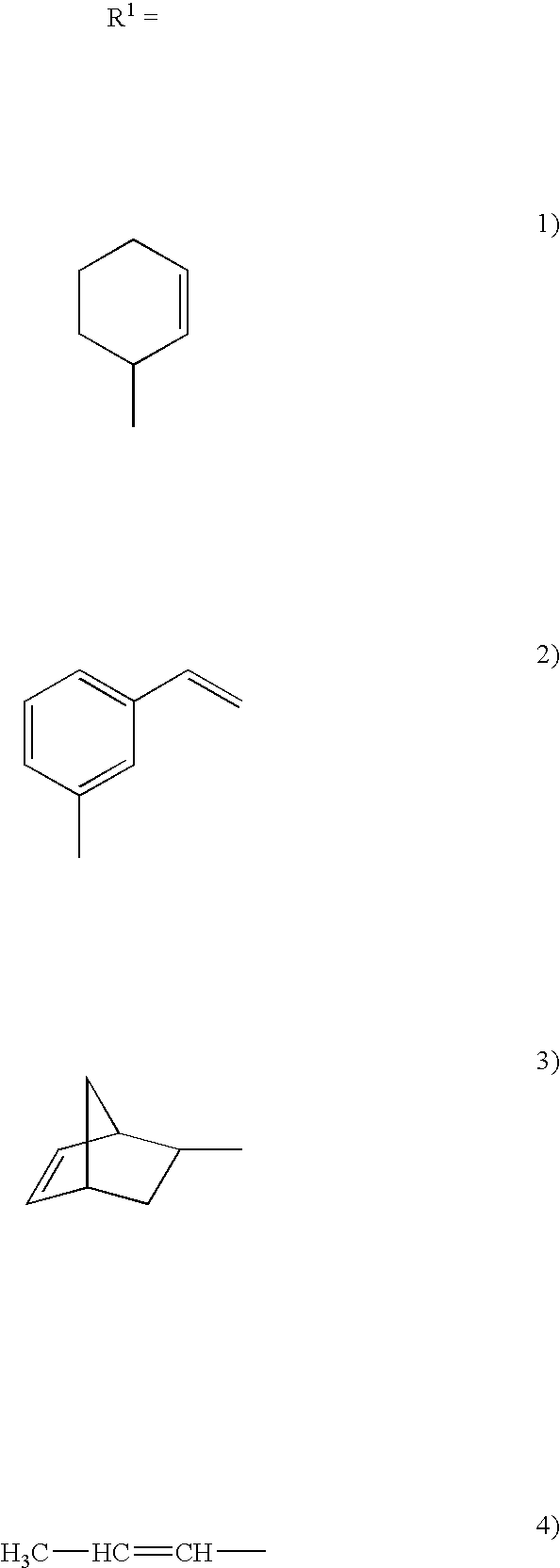

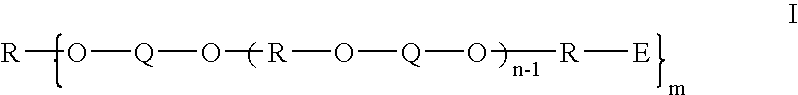

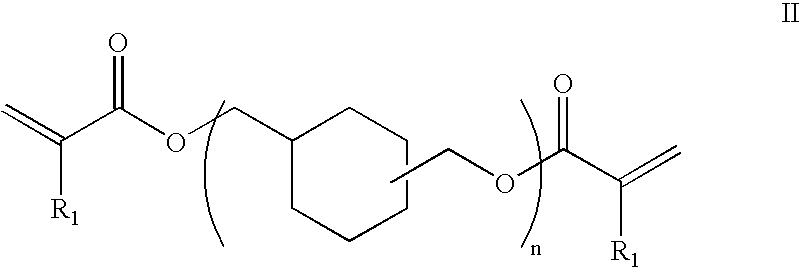

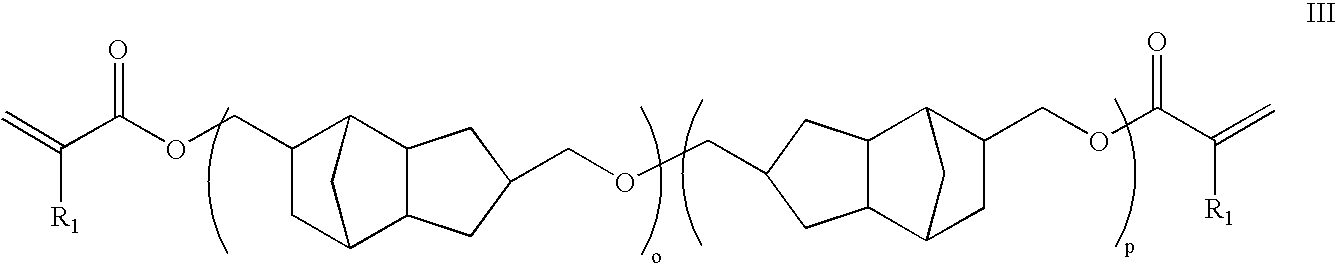

Thermosetting polyether oligomers, compostions and methods for use thereof

InactiveUS20090061244A1Low viscosityImprove conductivityOrganic chemistryOrganic compound preparationOligomerAdhesive

The invention is based on the discovery that certain polyether oligomers bearing curable moieties are useful as adhesives for the microelectonic packaging industry. Specifically, certain thermoset adhesive compositions containing polyether oligomers of the invention have good adhesion with lower viscosity, lower resistivity, higher conductivity and higher thixotropy when compared to acrylate- and maleimide-based thermoset adhesives.

Owner:DESIGNER MOLECULES