Patents

Literature

62results about How to "Shorten the signal transmission path" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

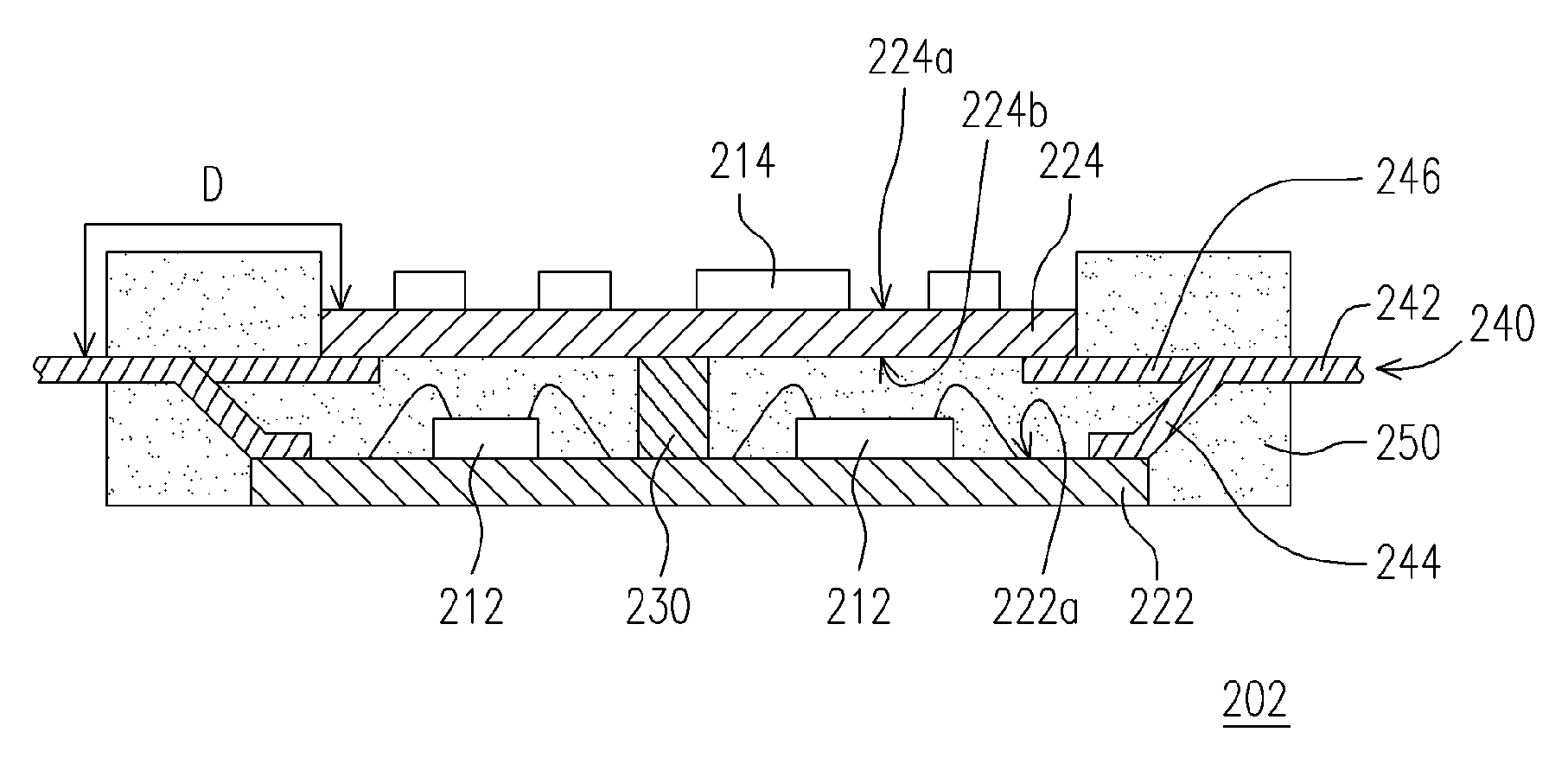

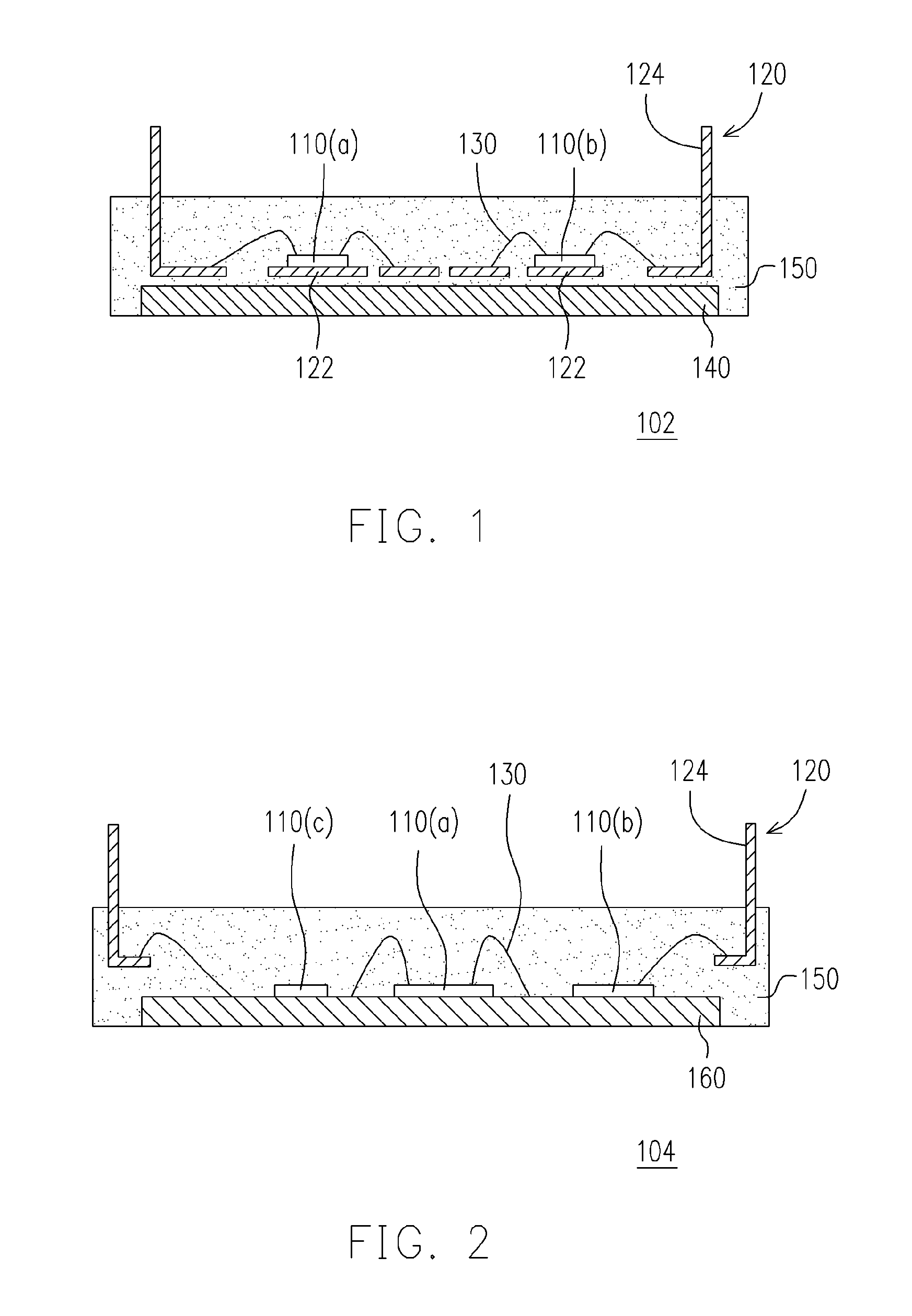

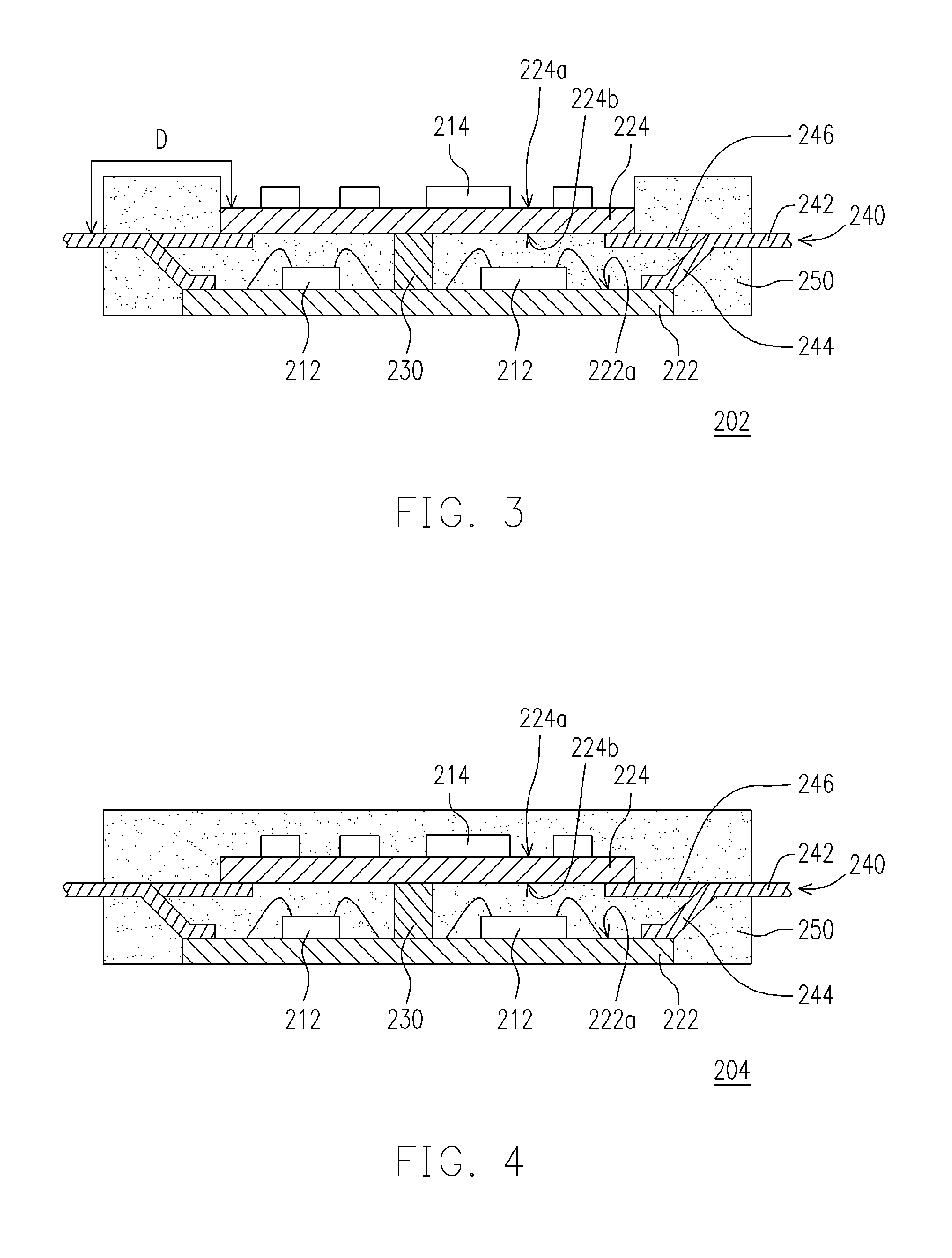

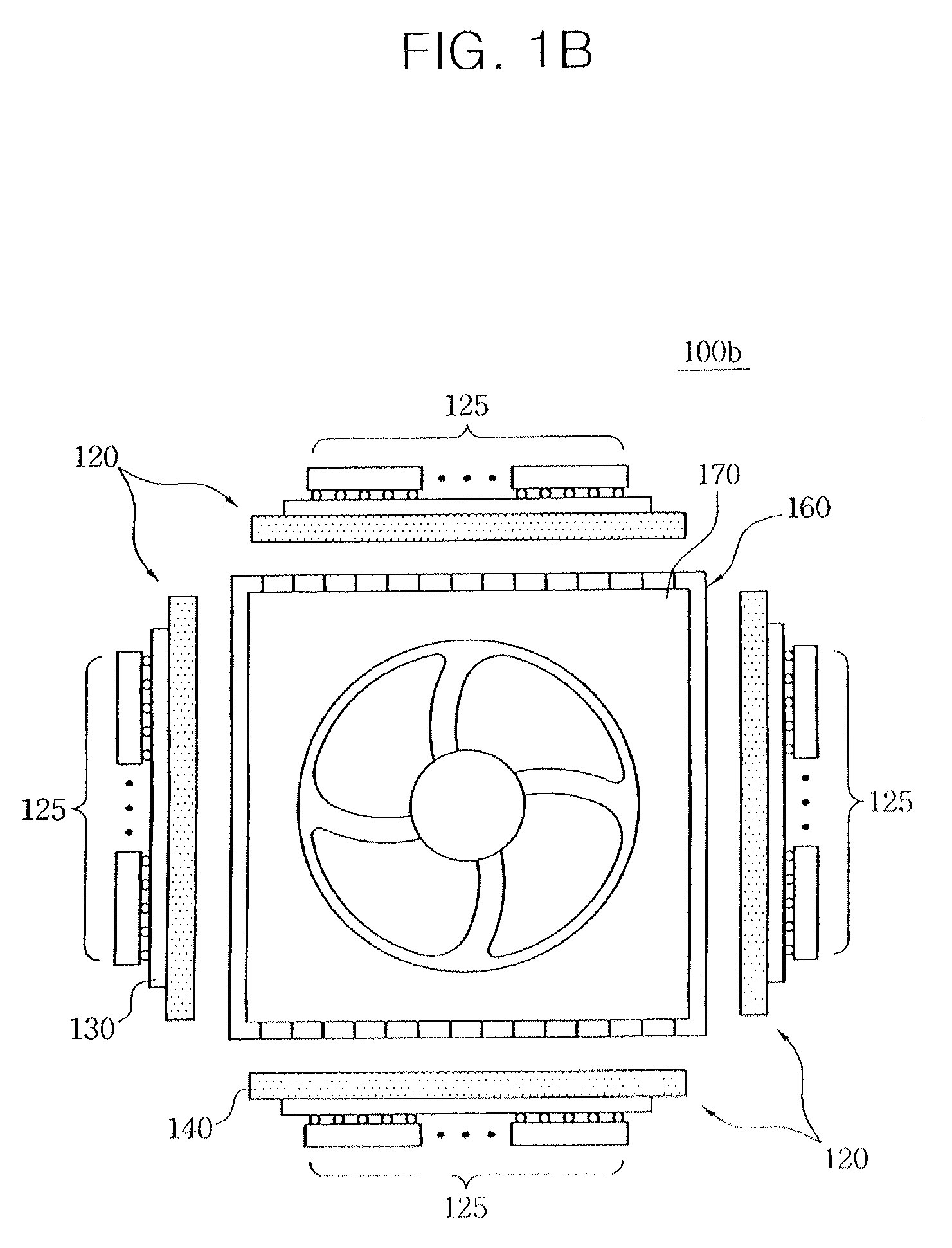

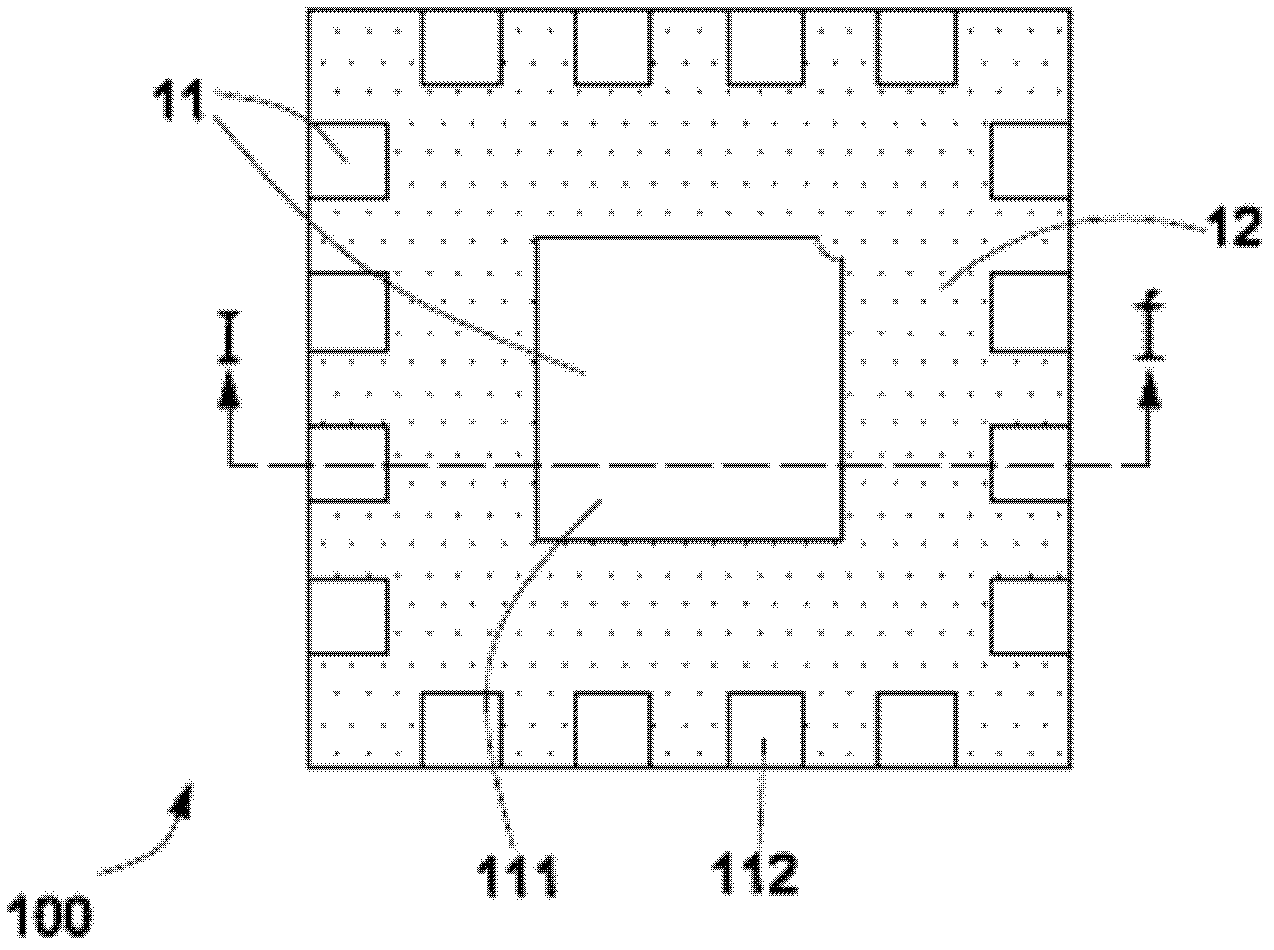

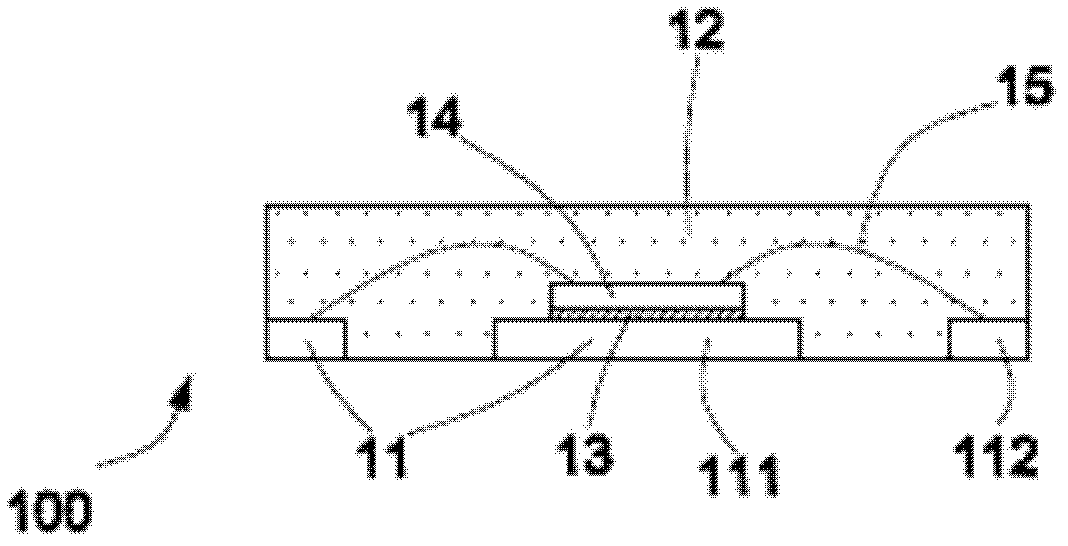

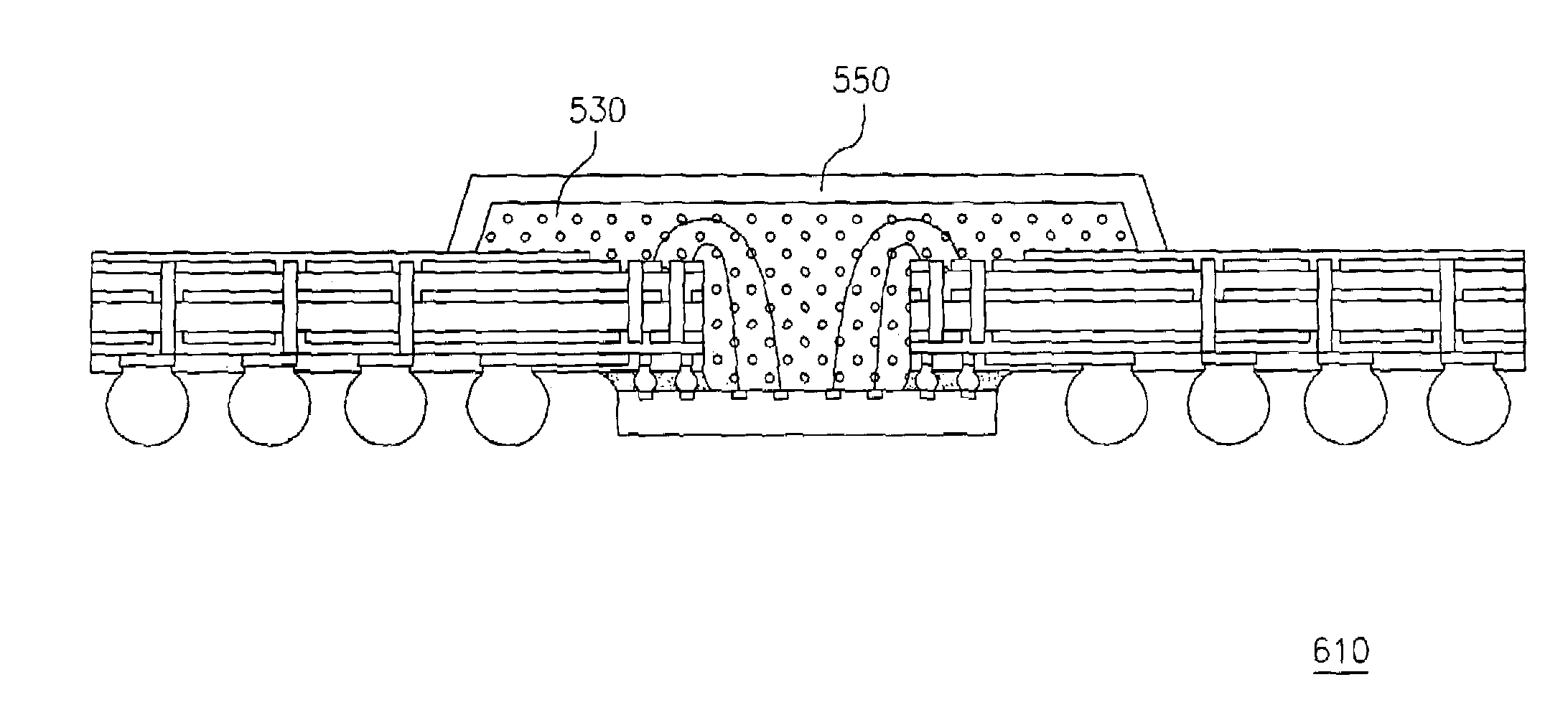

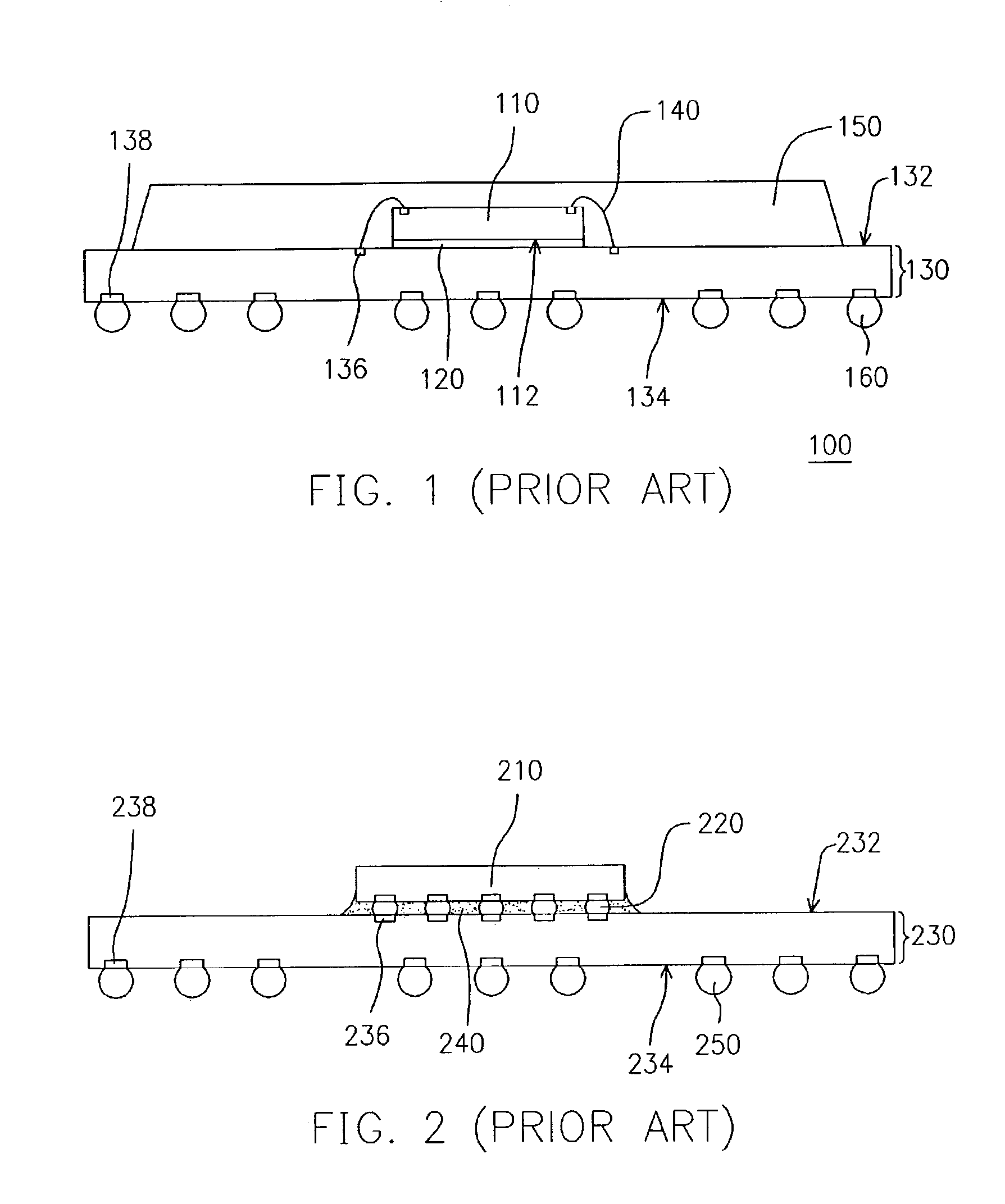

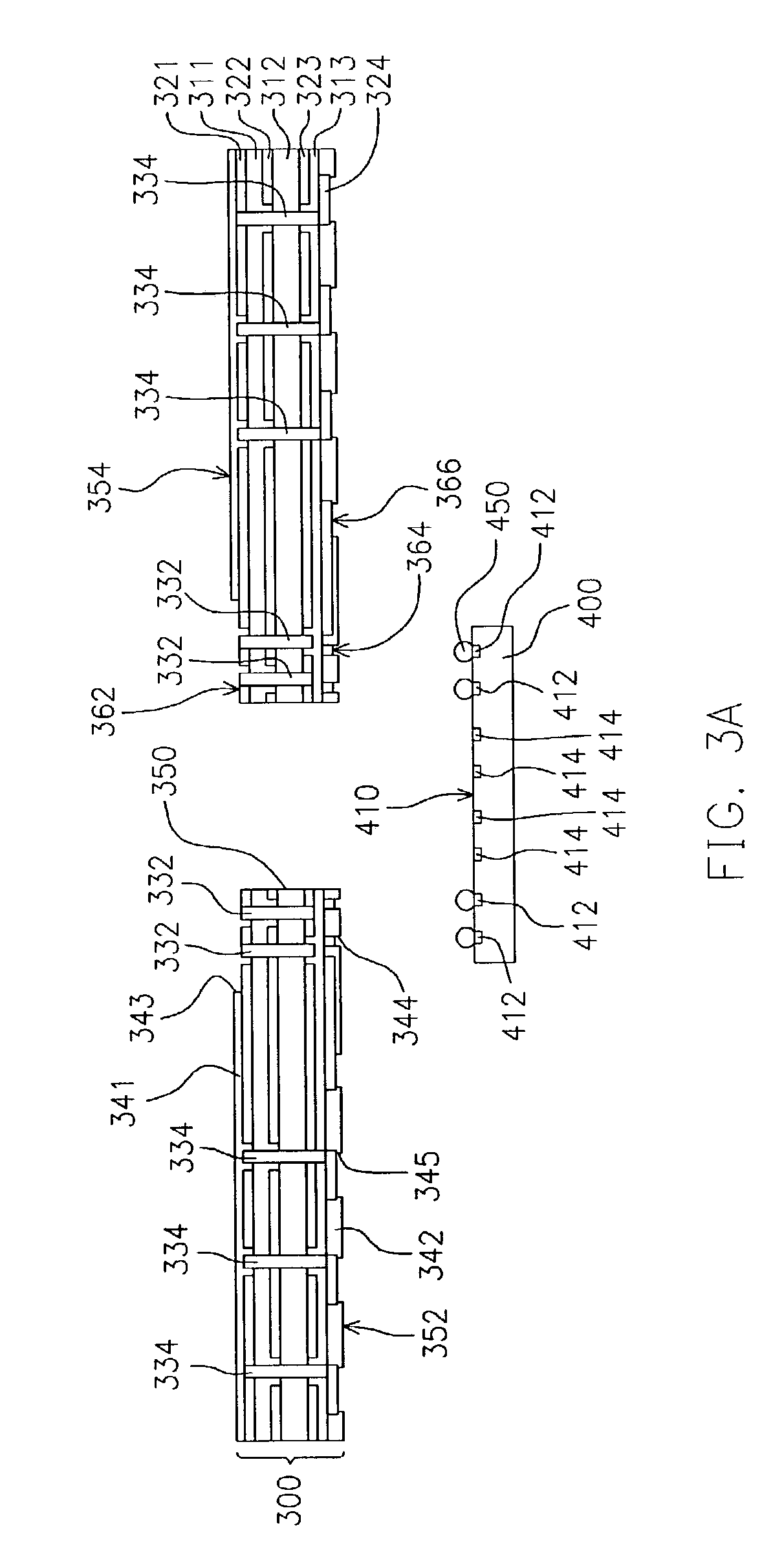

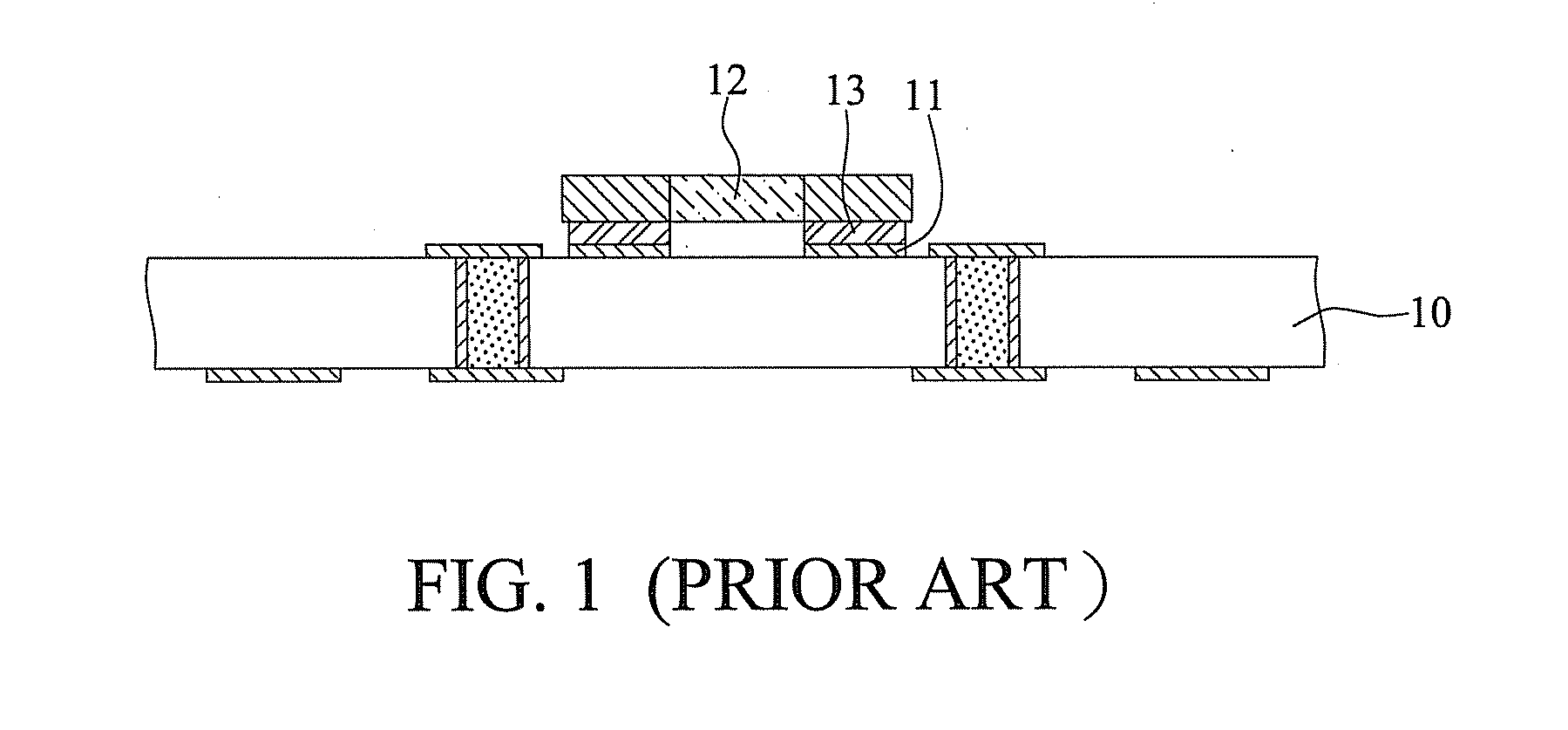

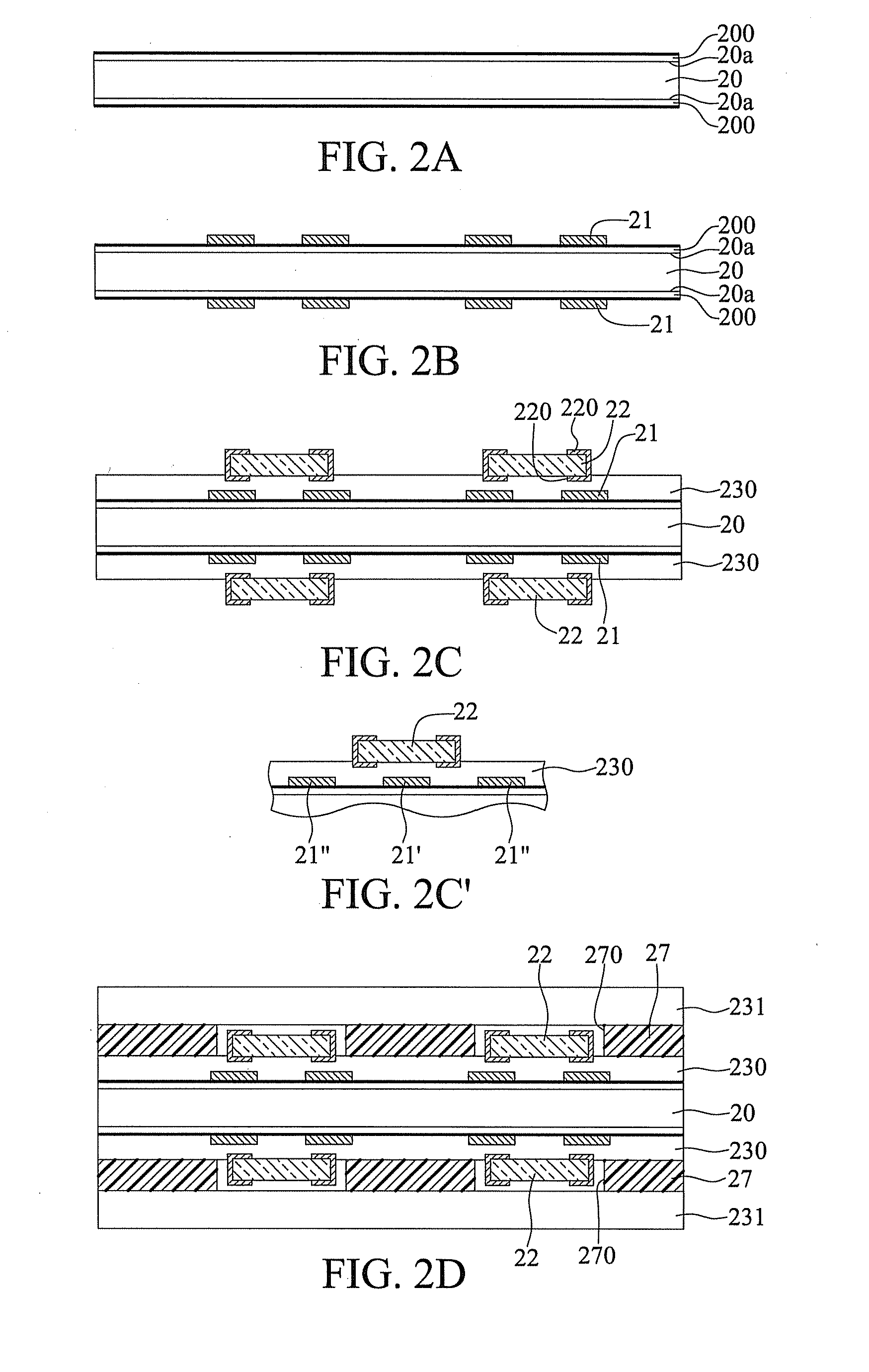

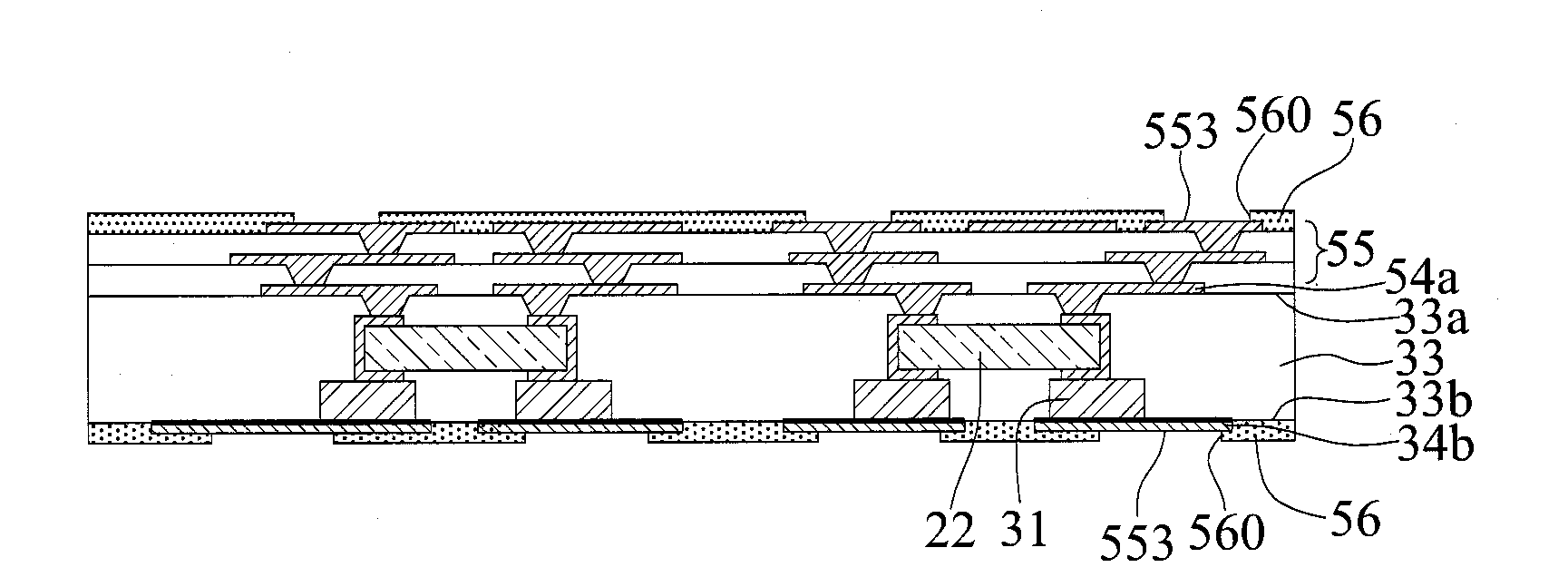

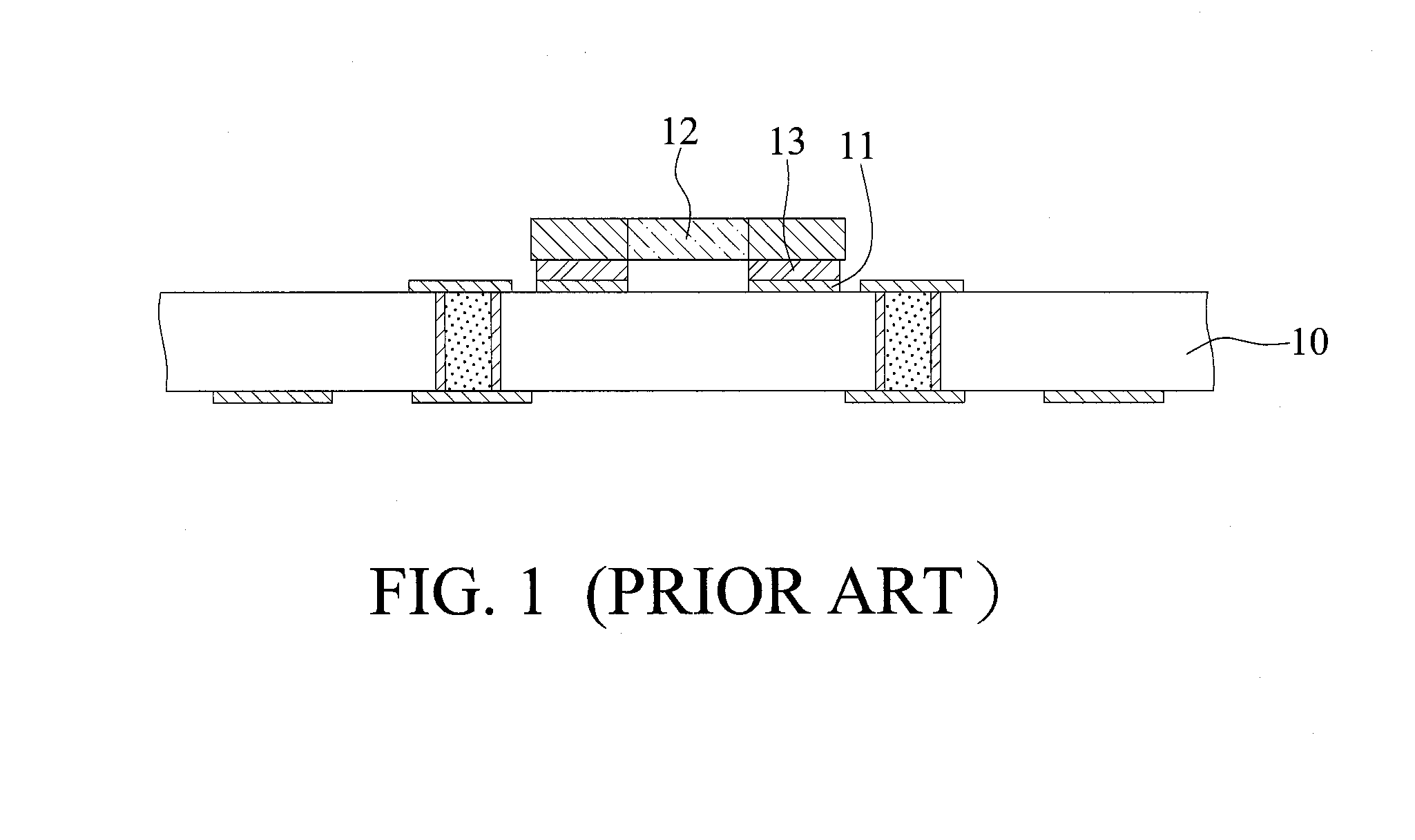

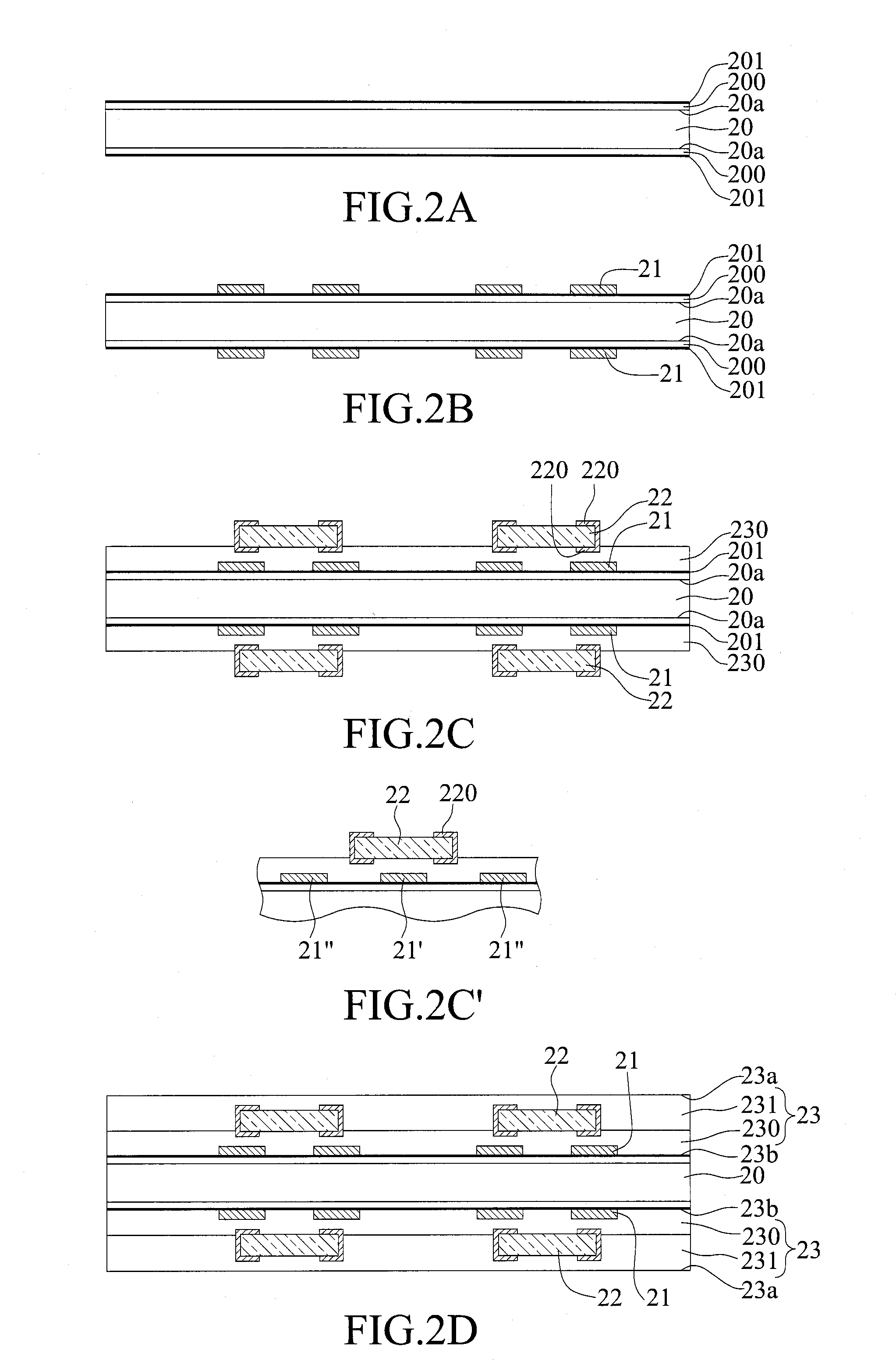

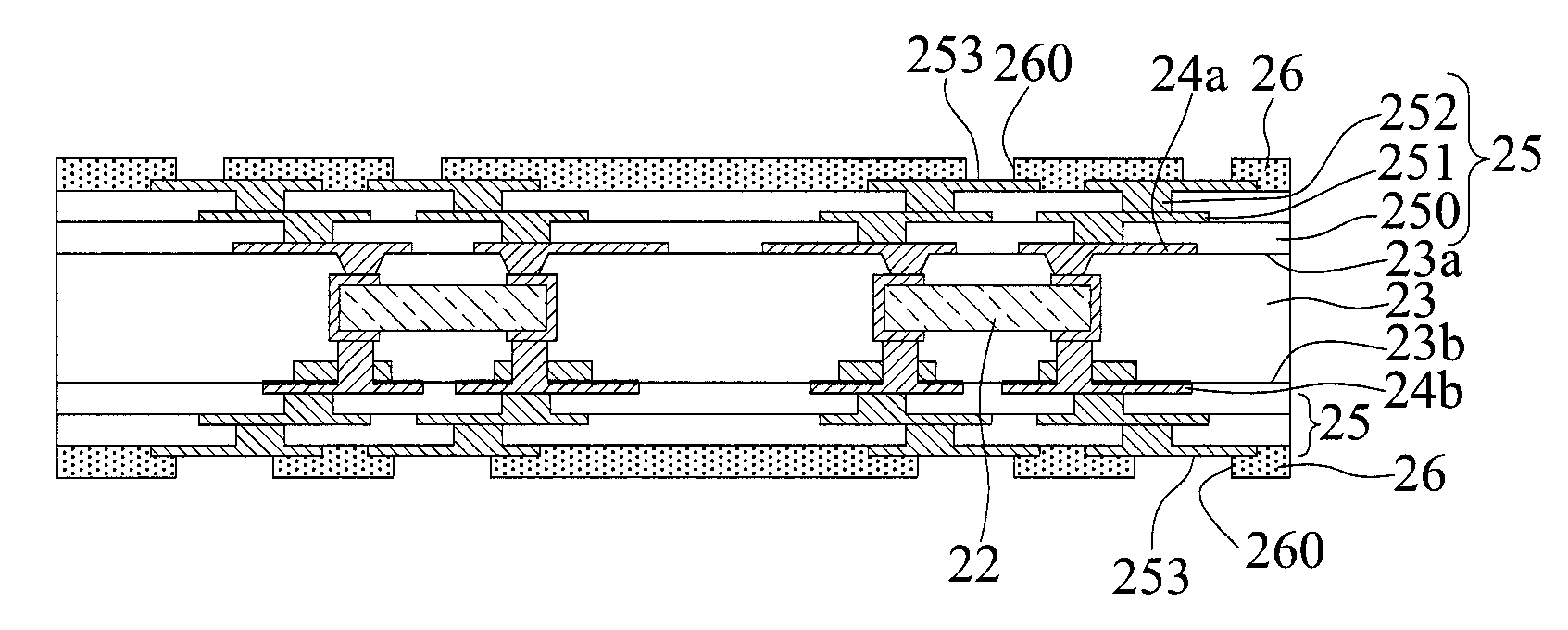

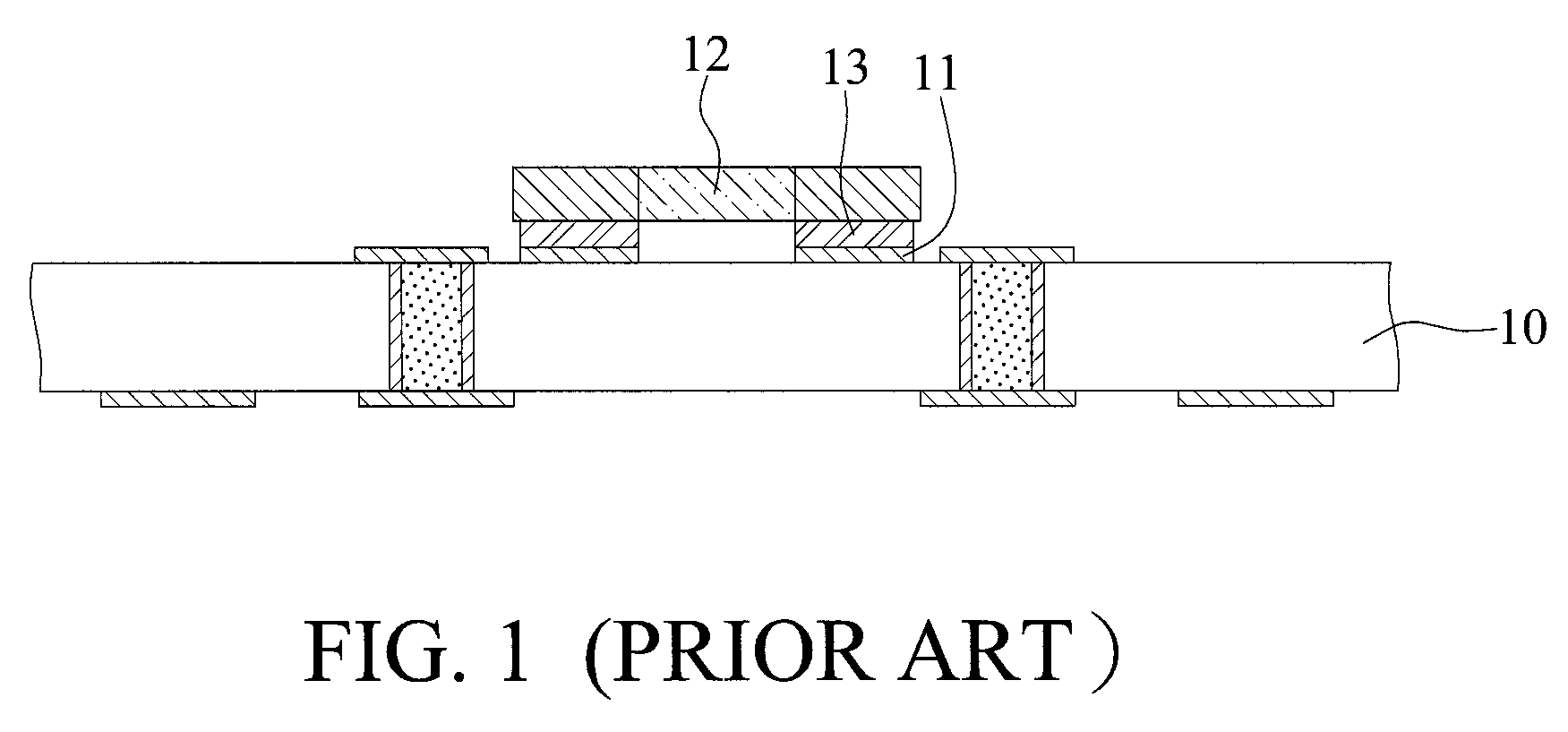

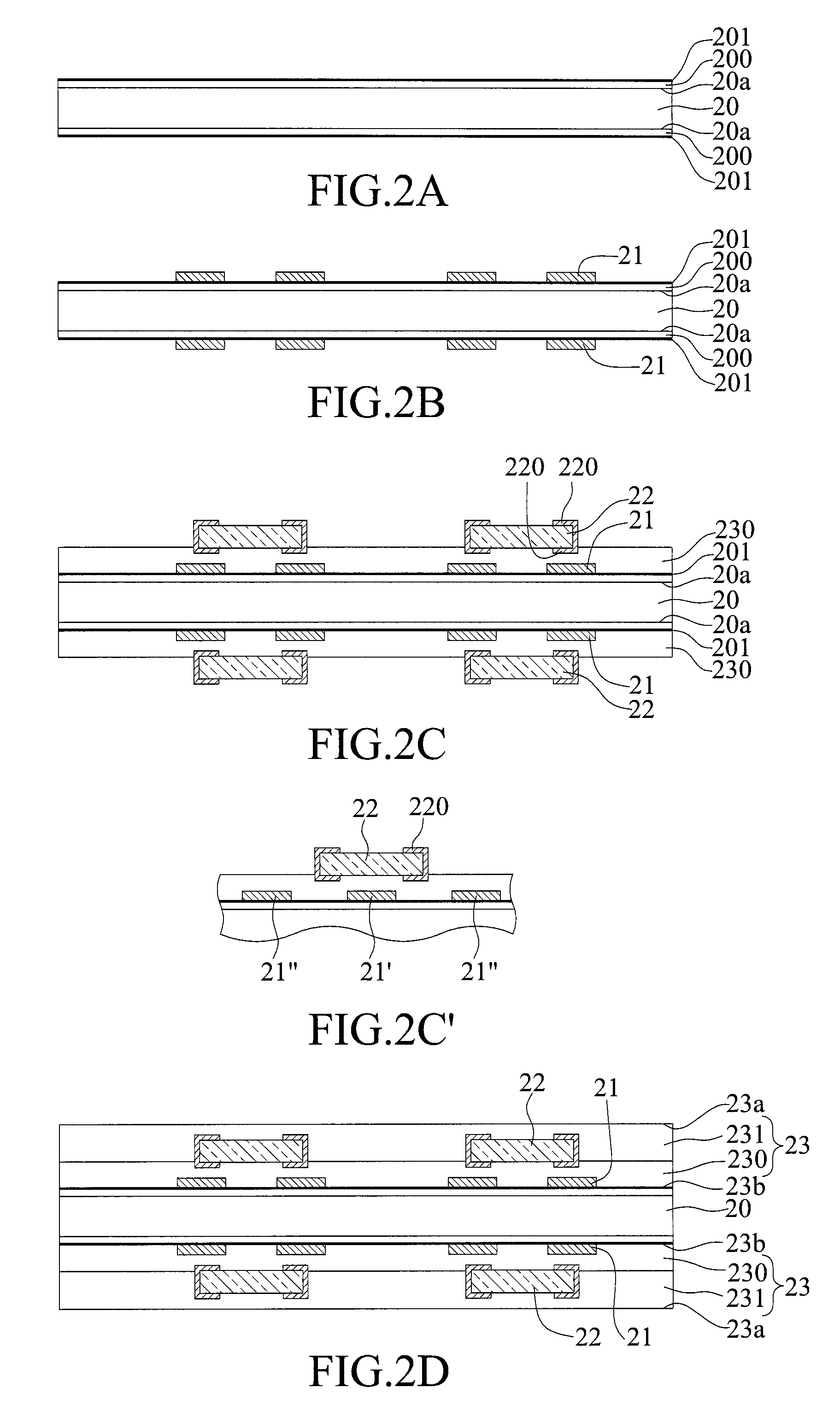

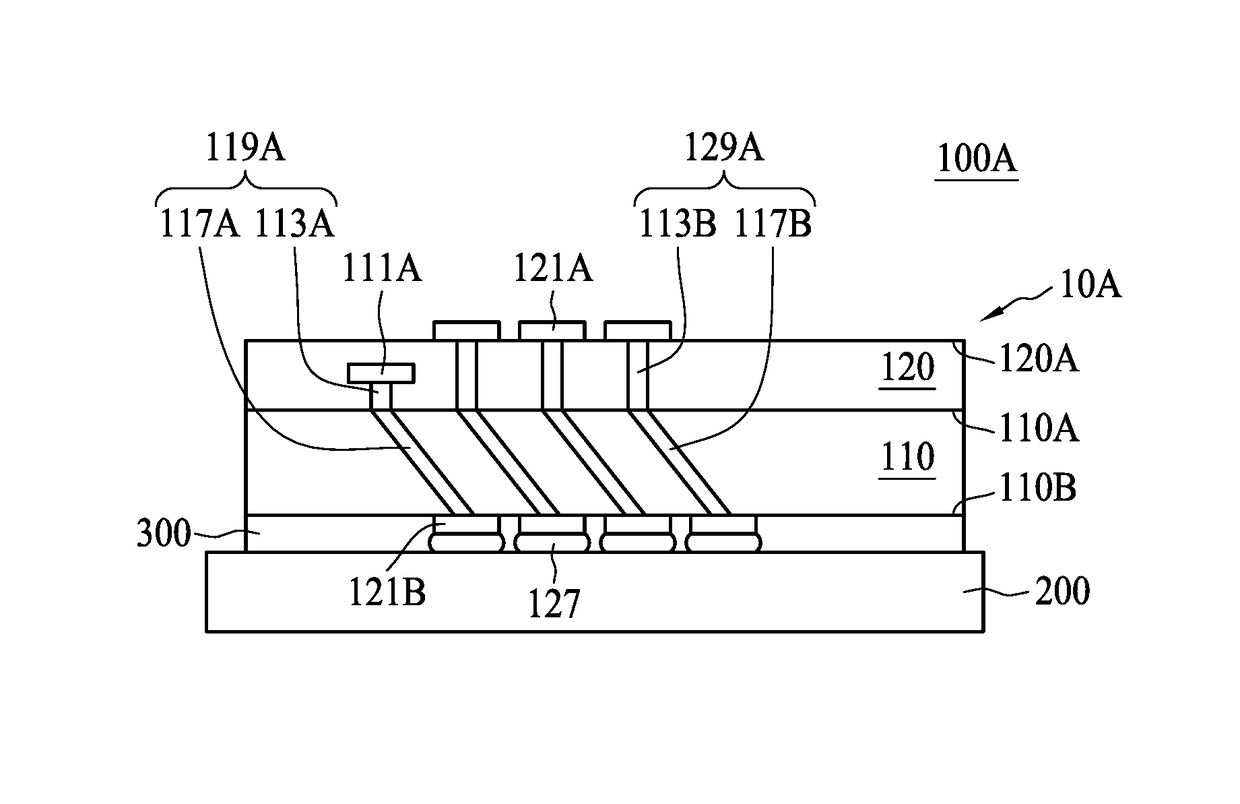

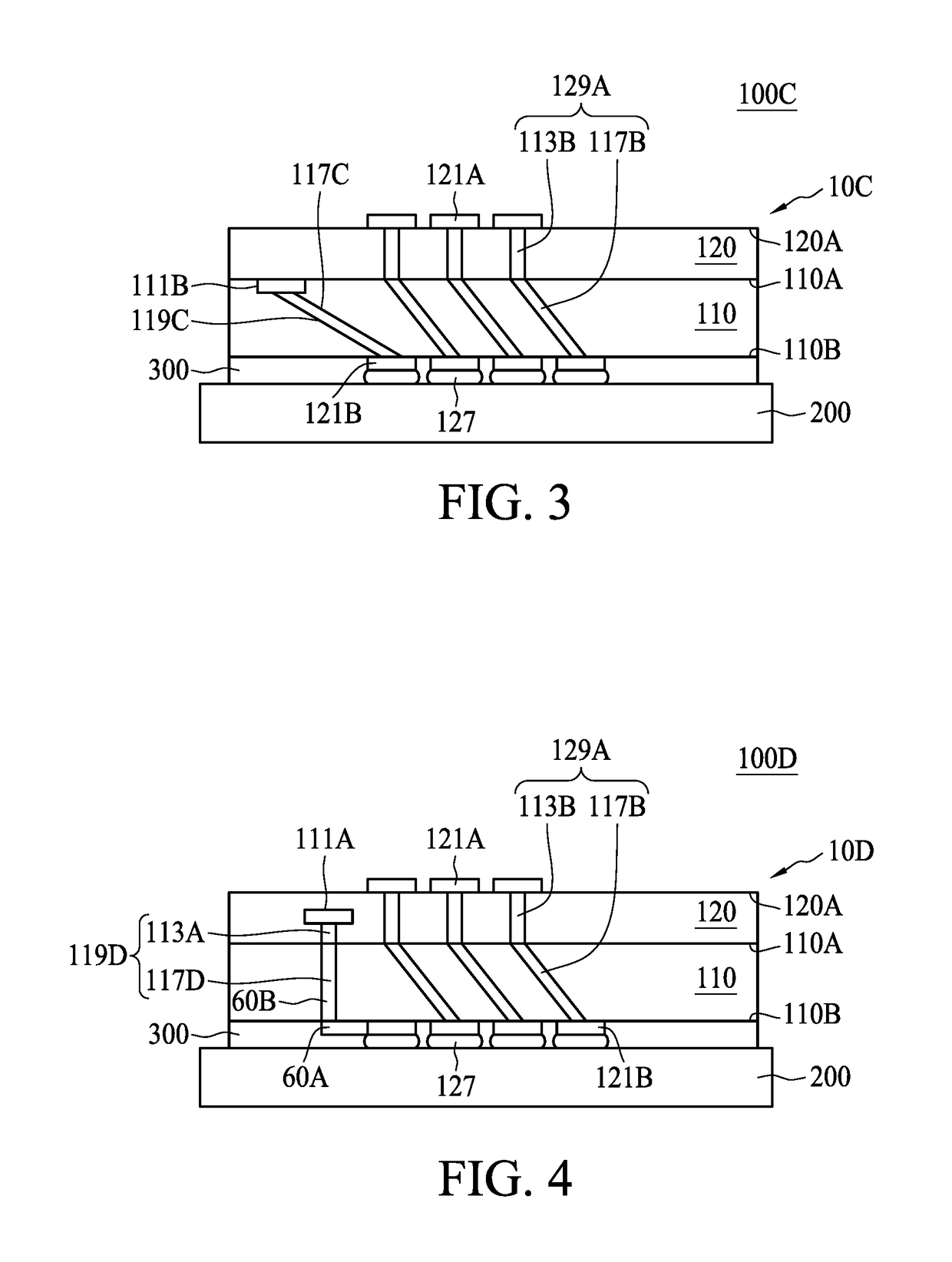

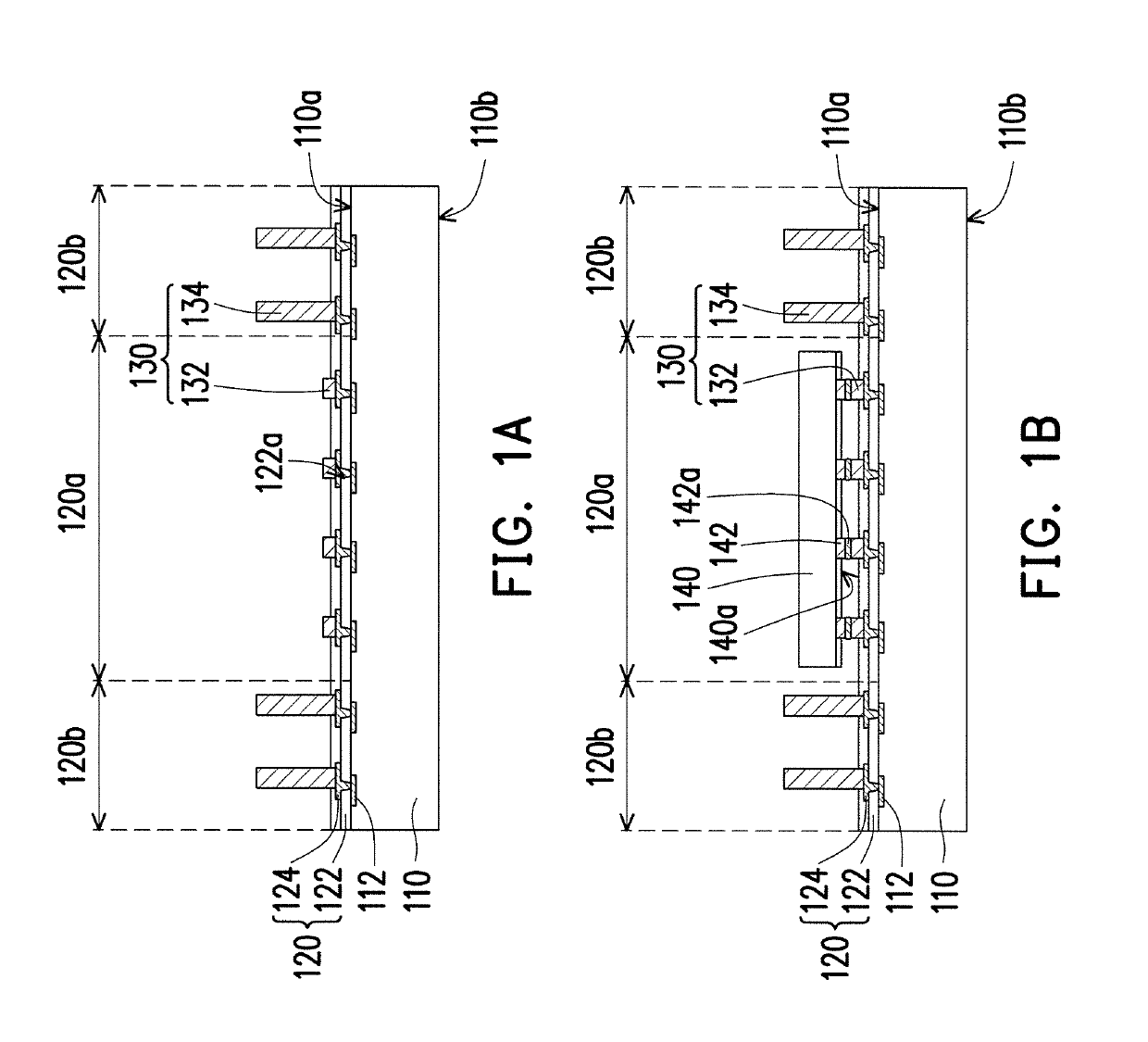

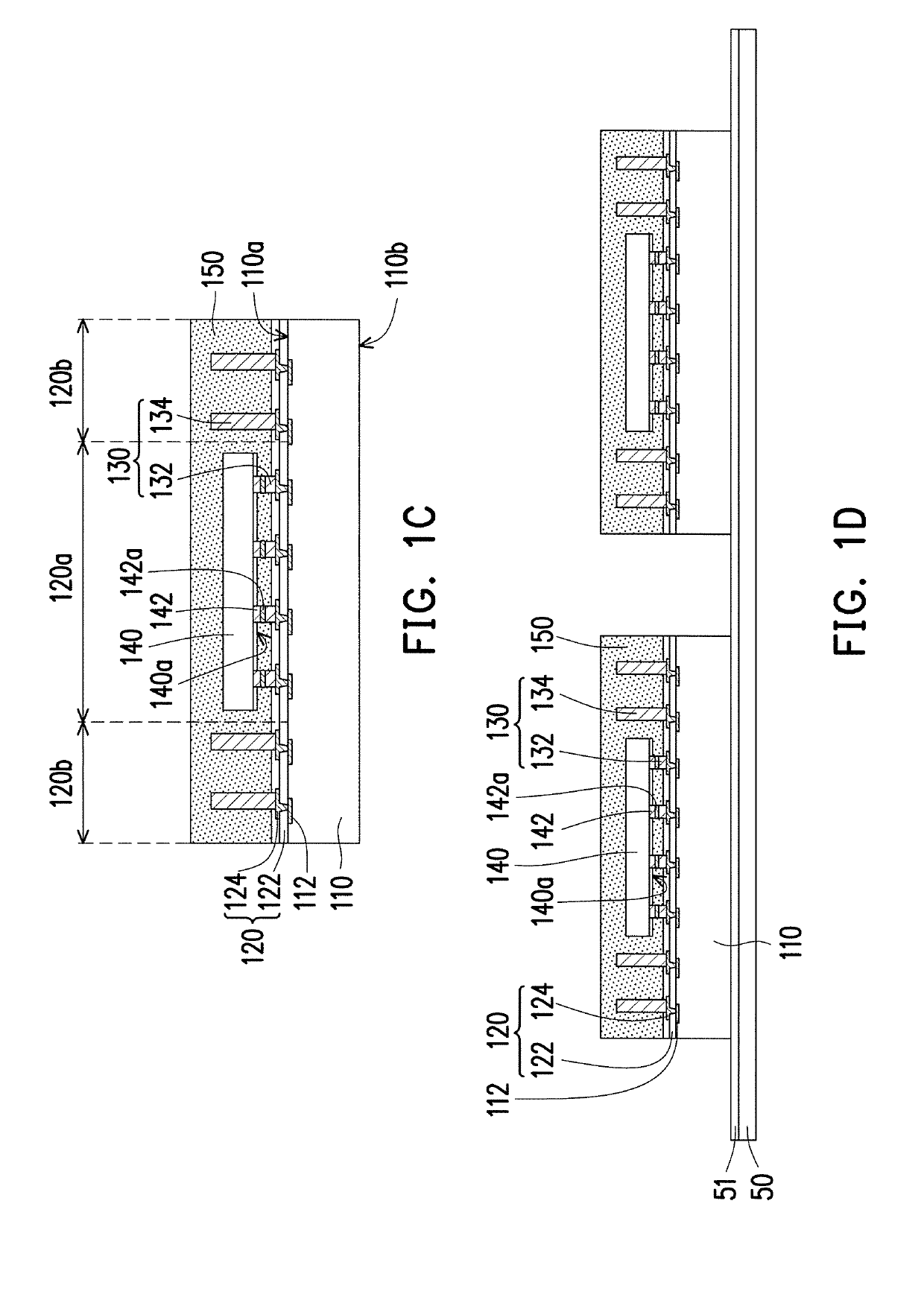

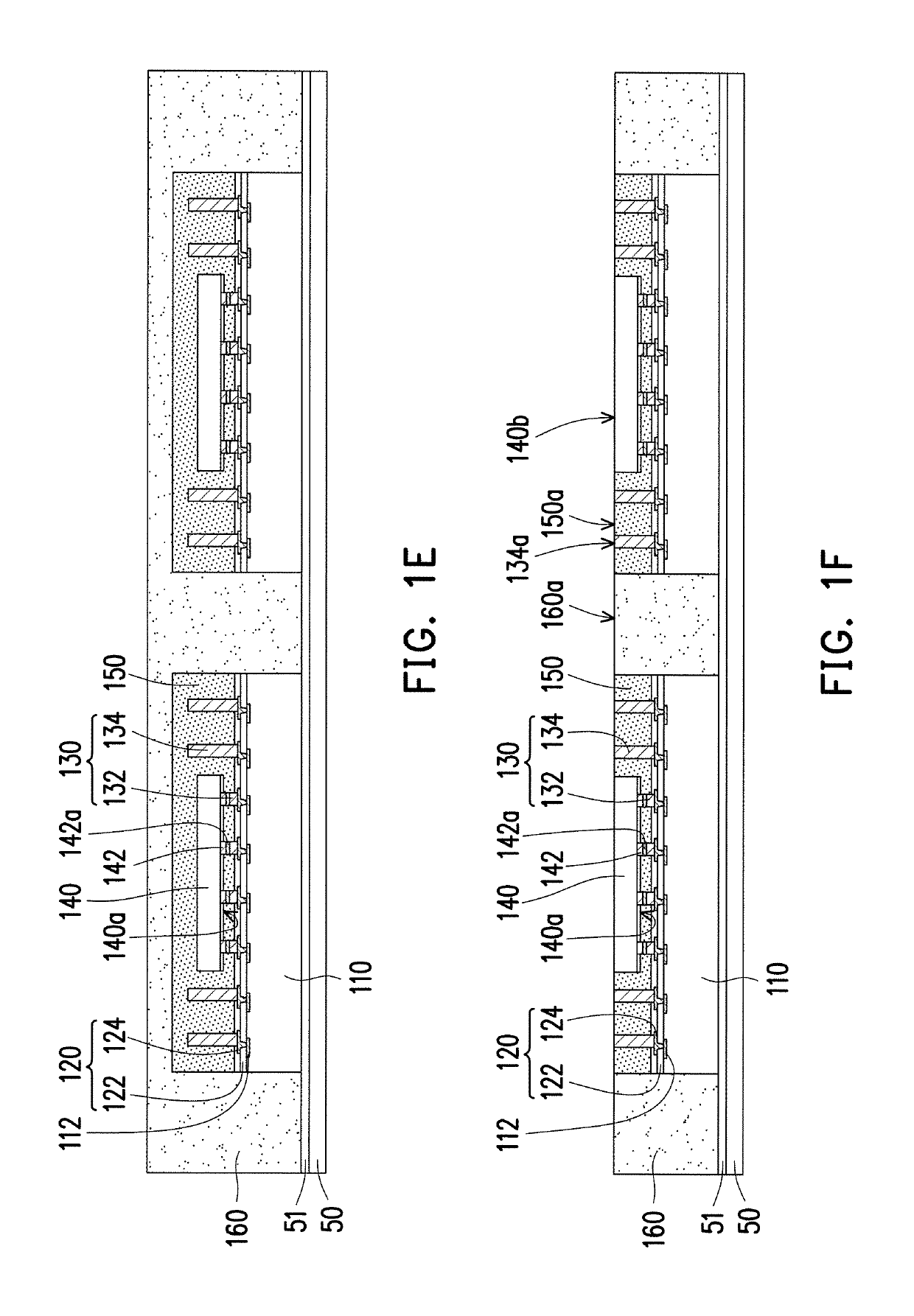

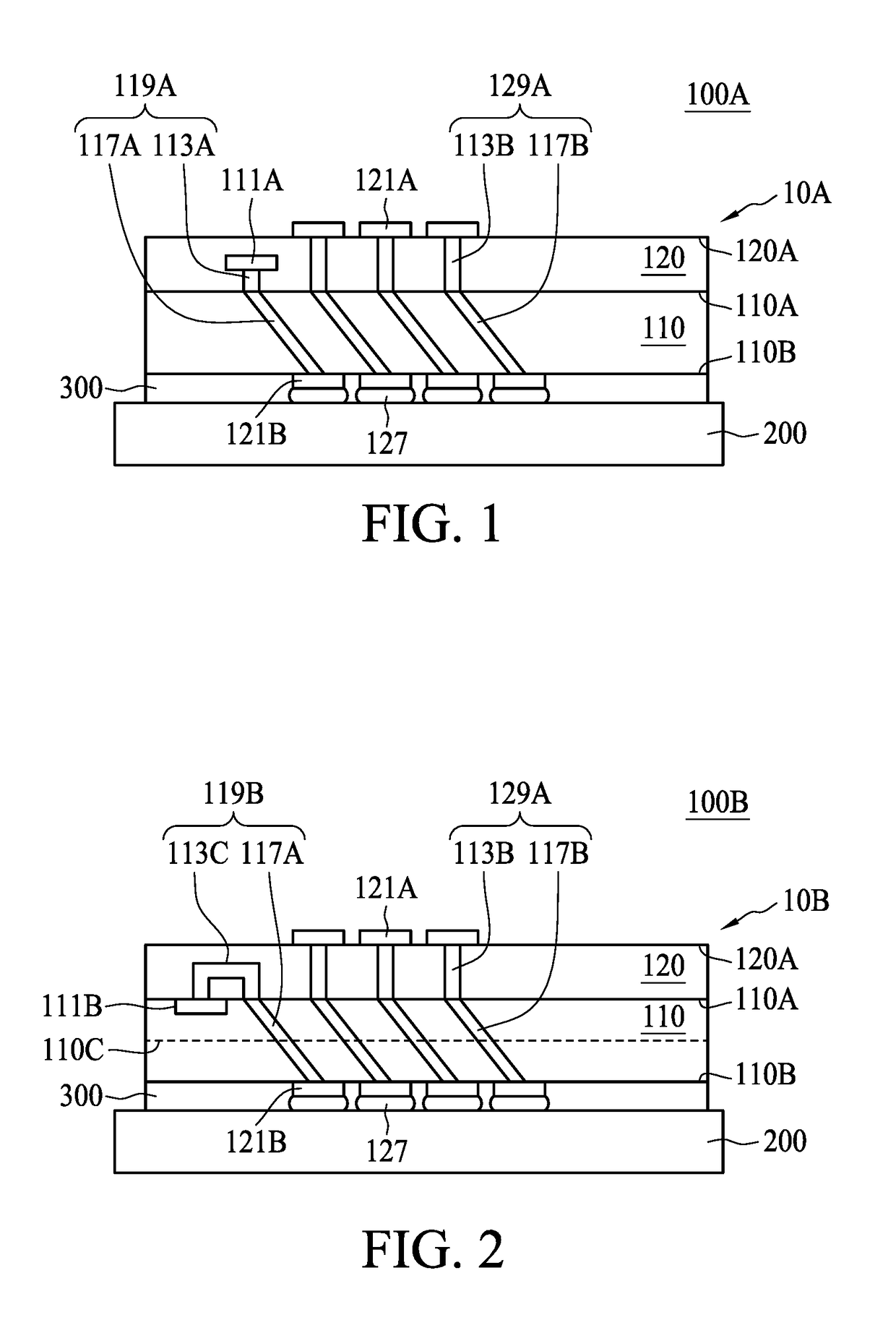

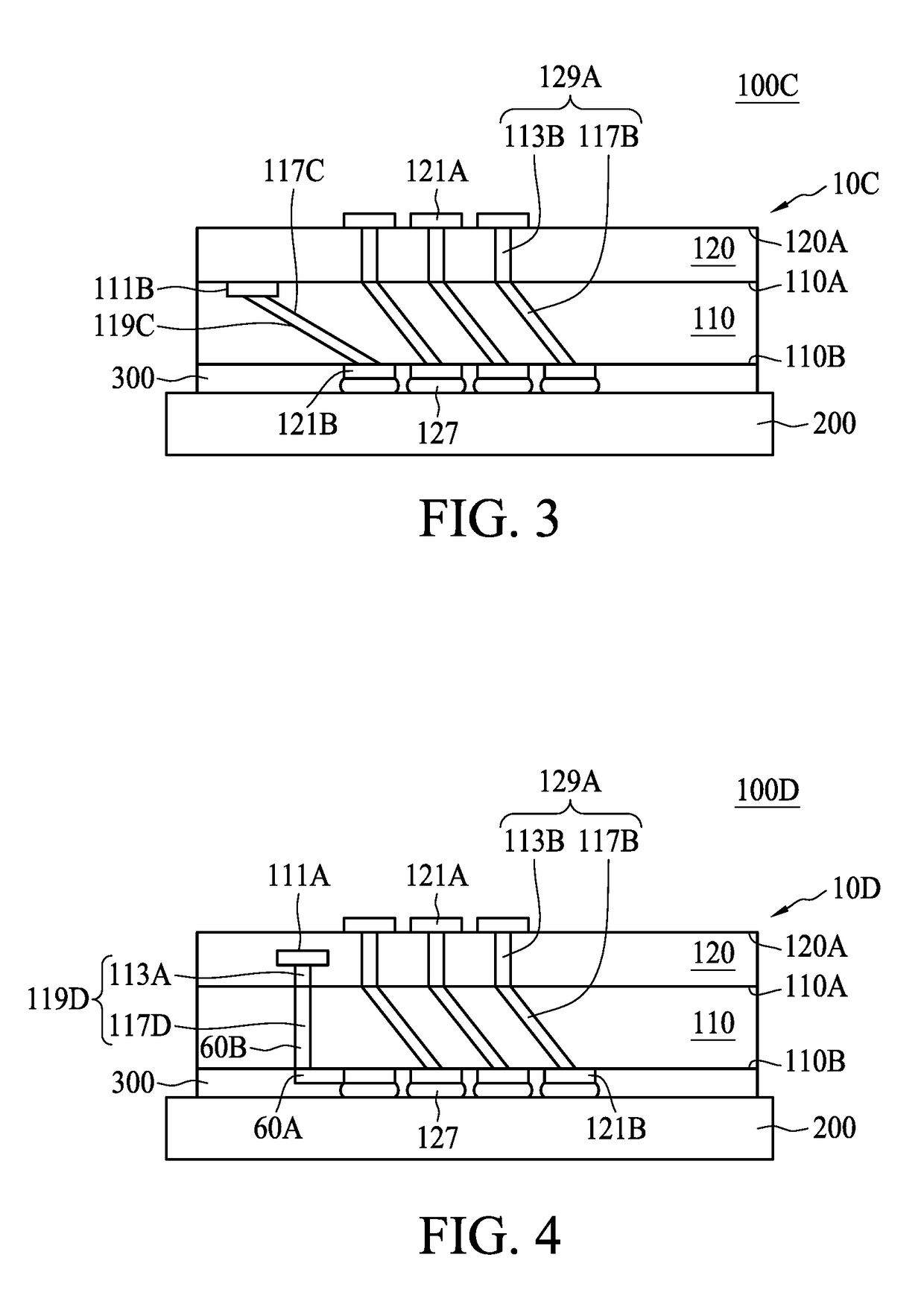

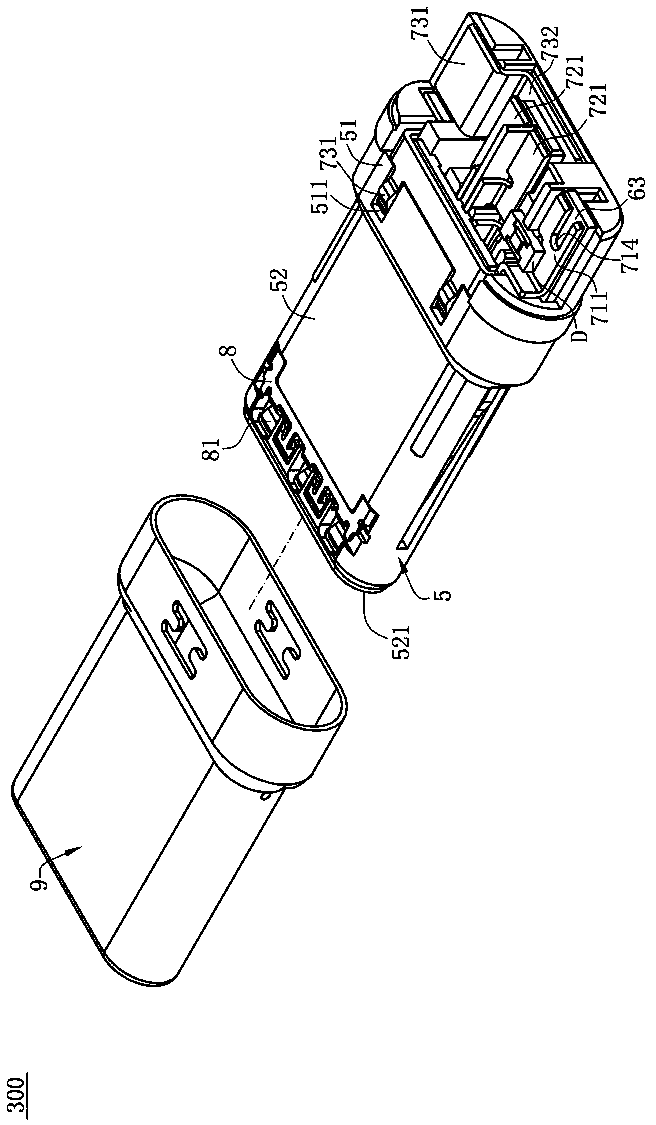

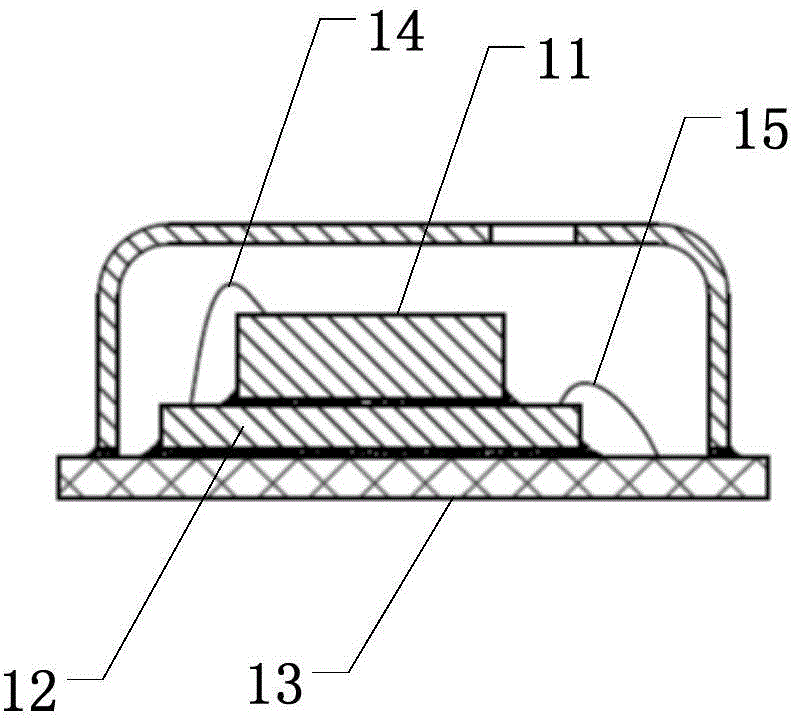

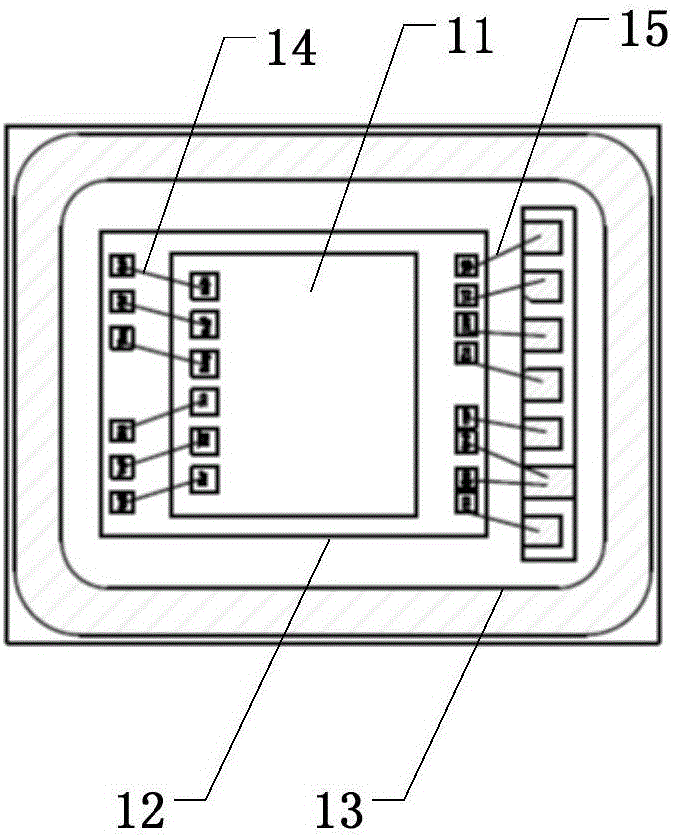

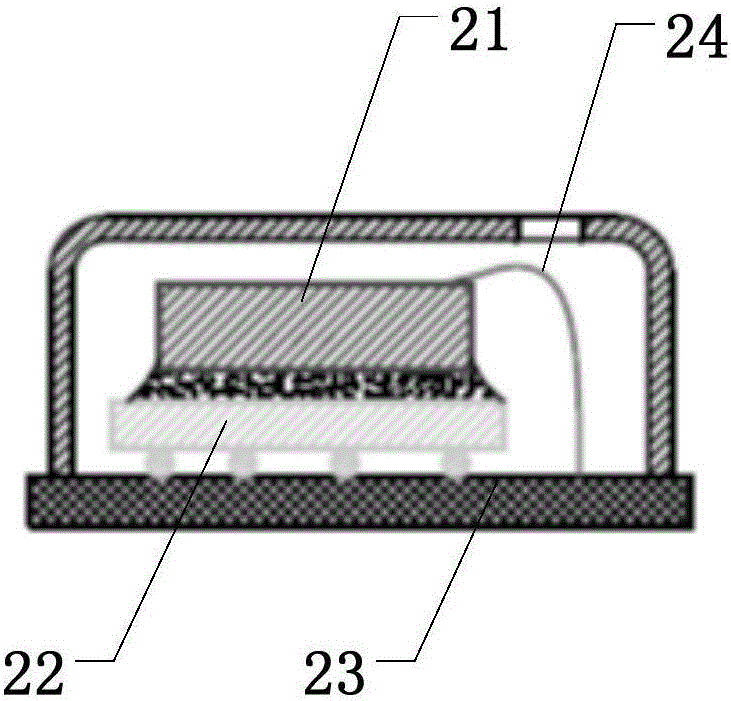

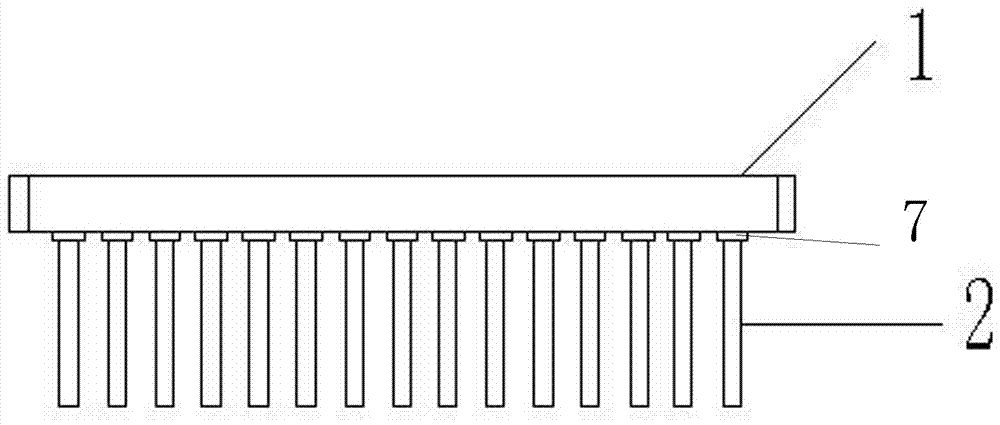

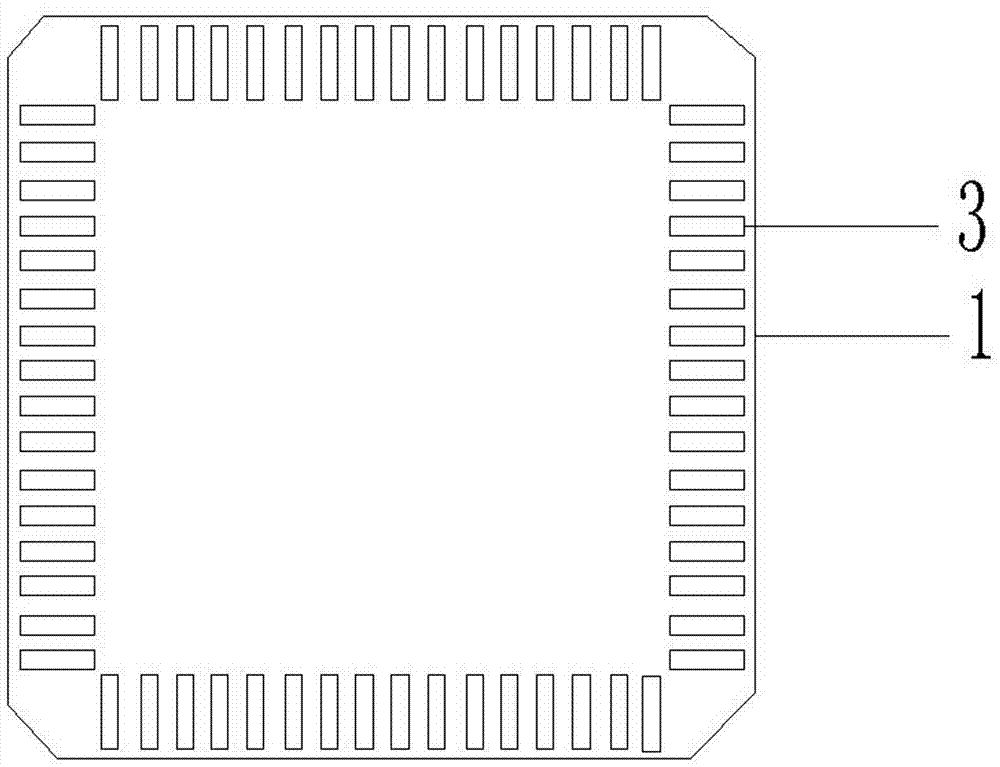

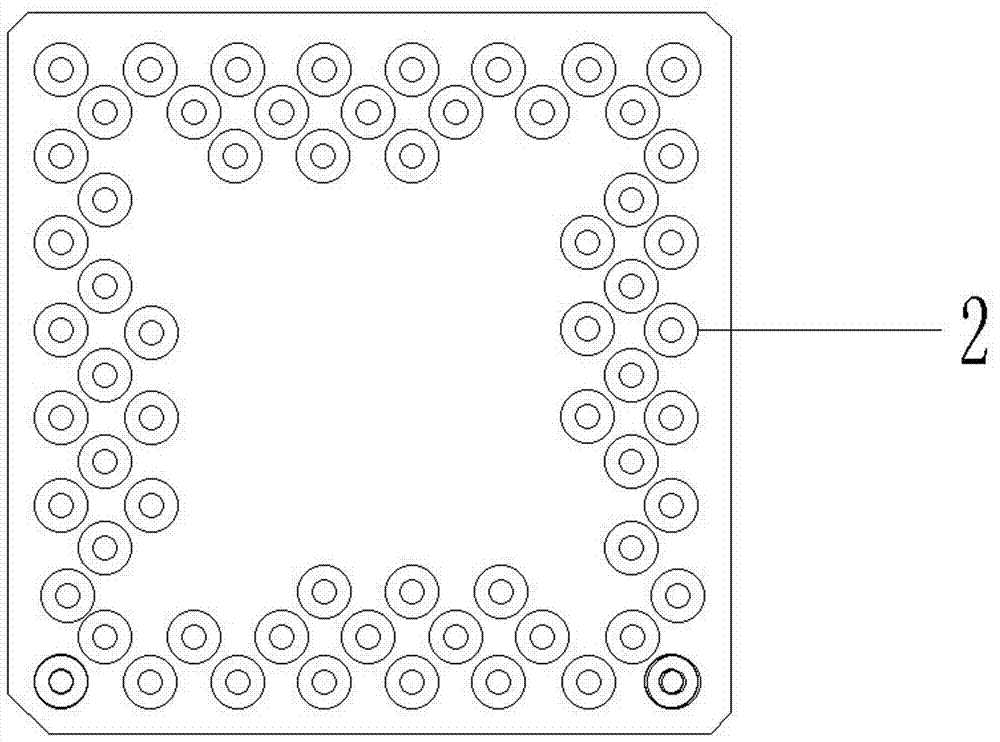

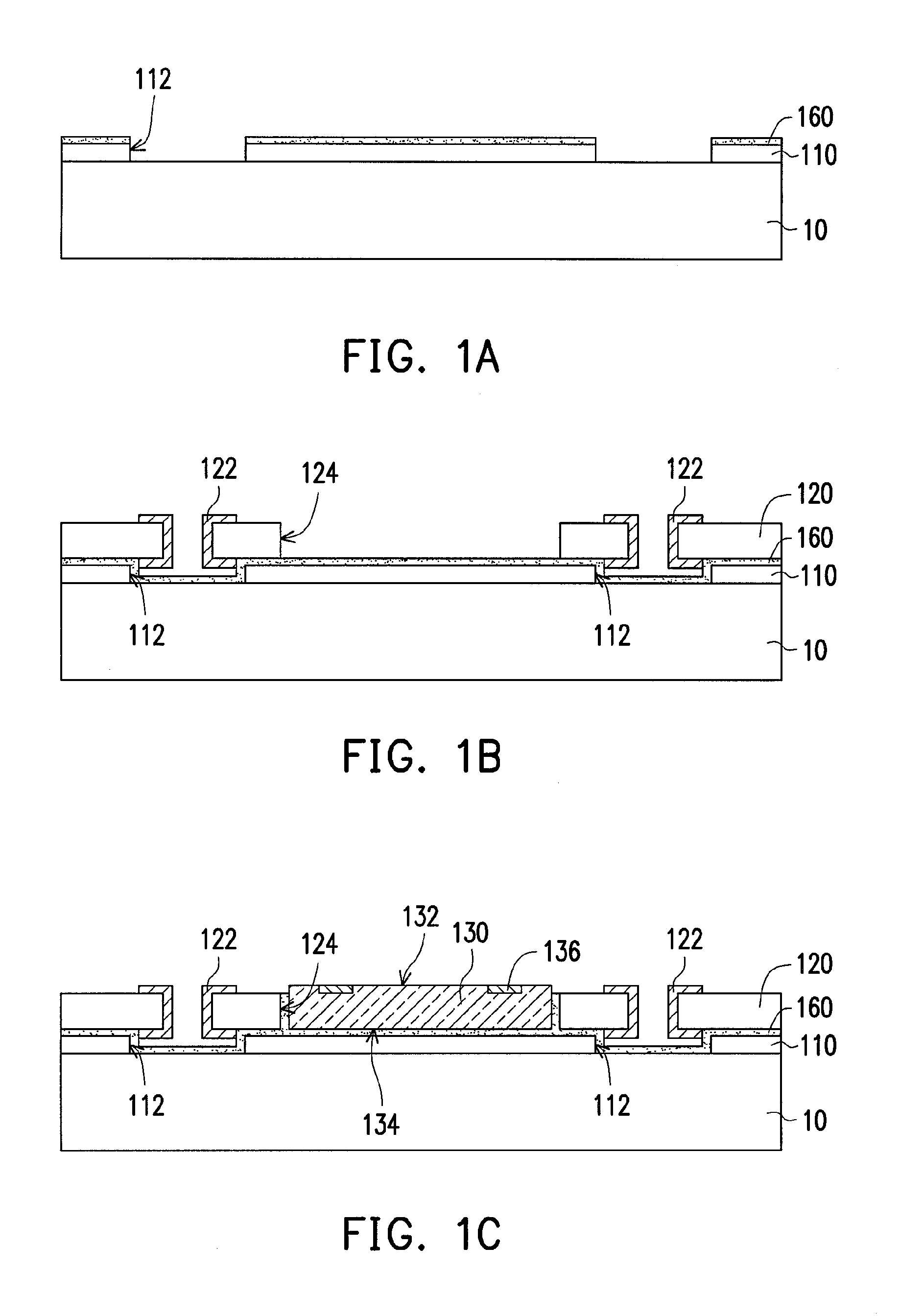

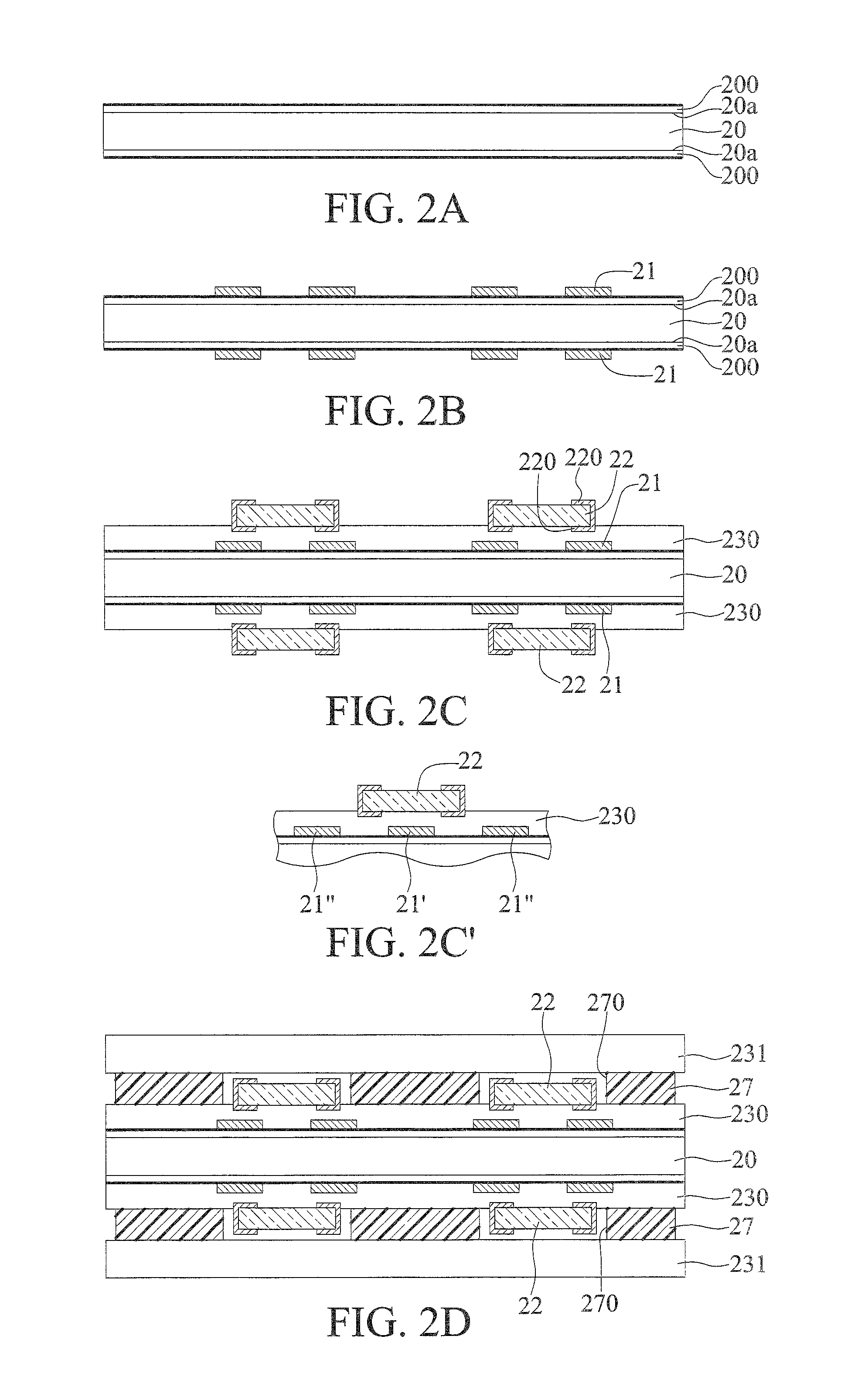

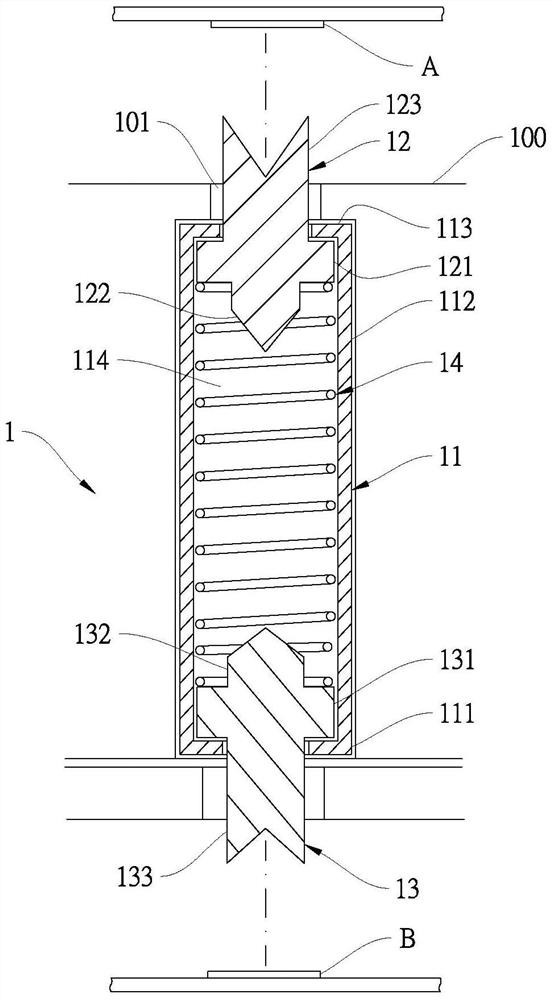

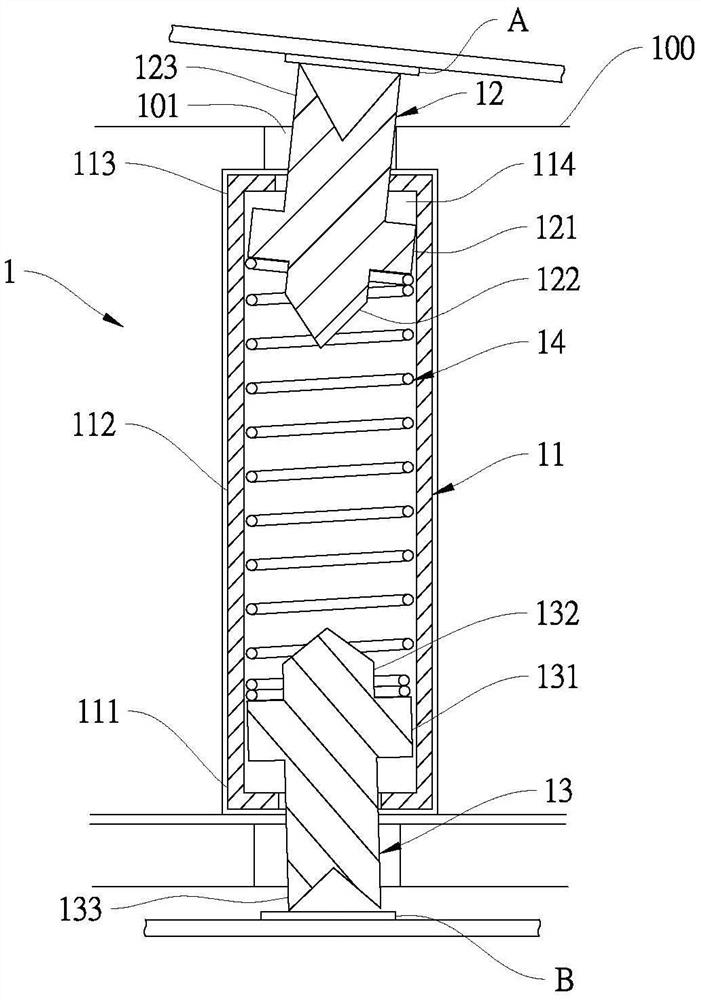

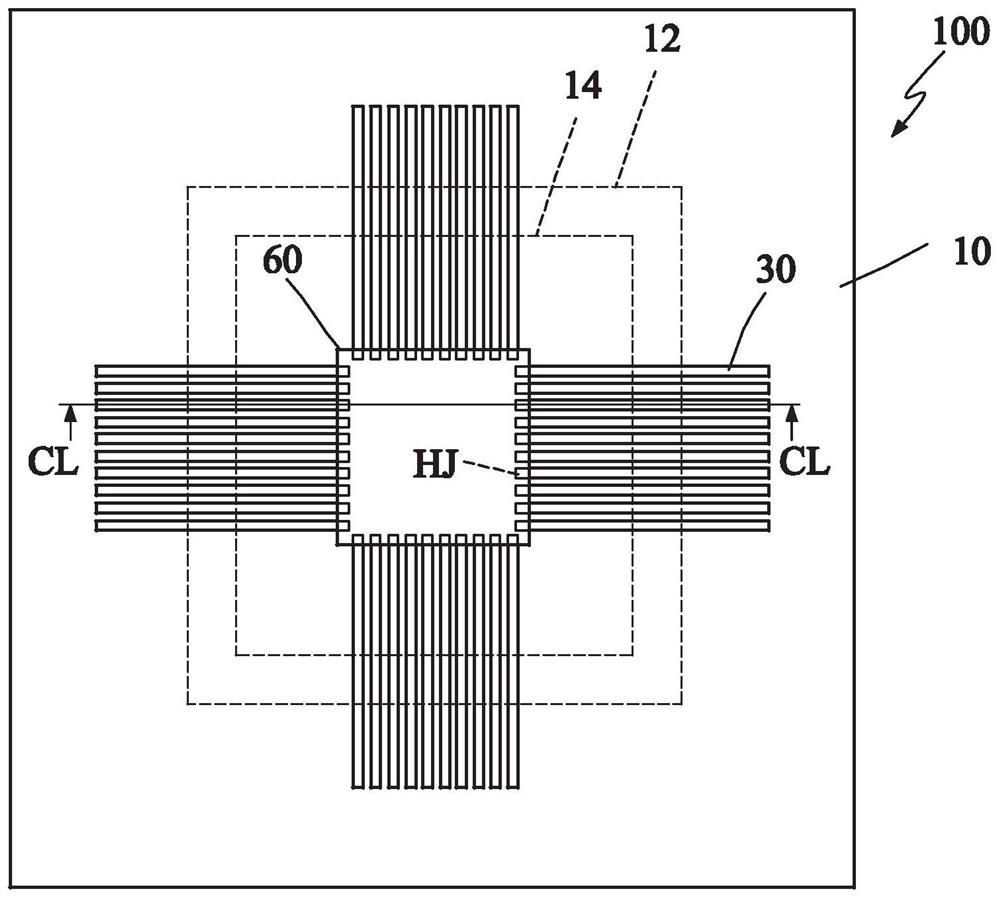

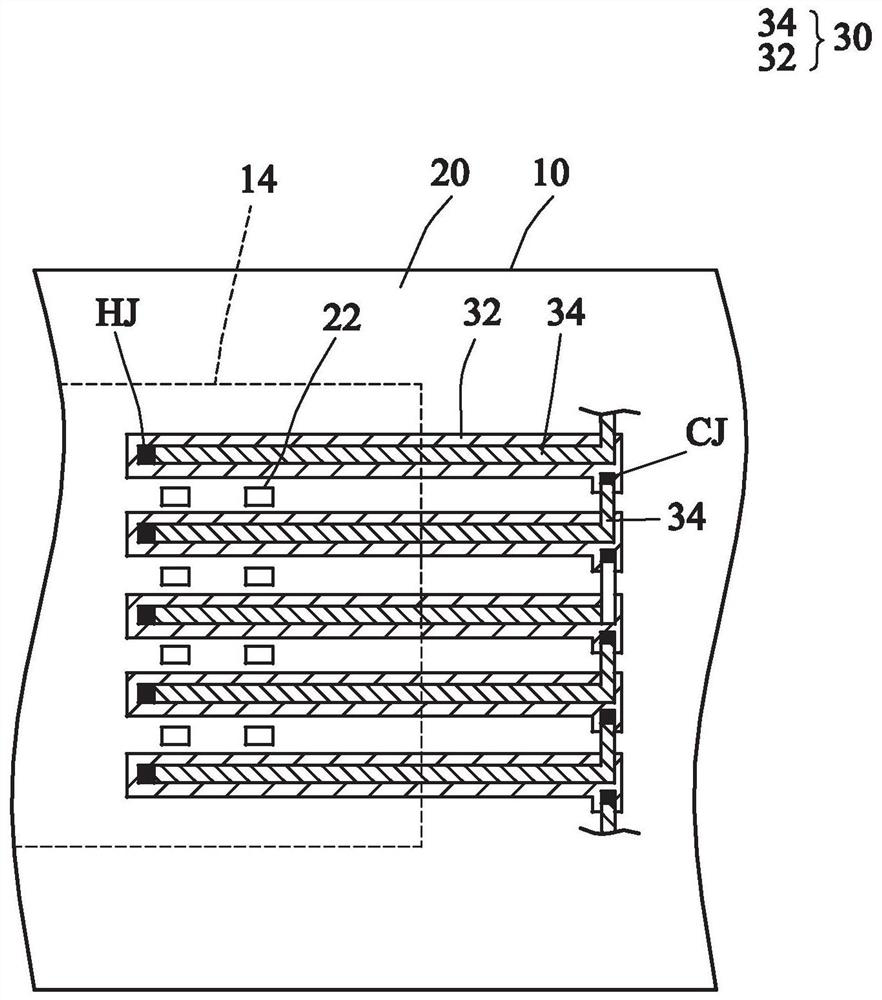

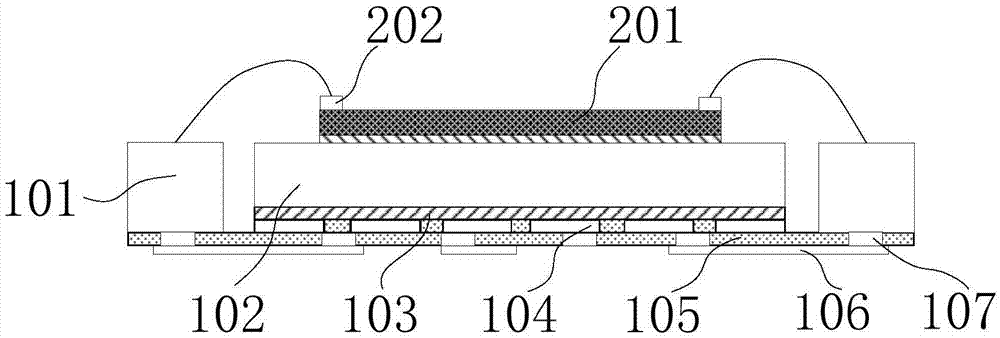

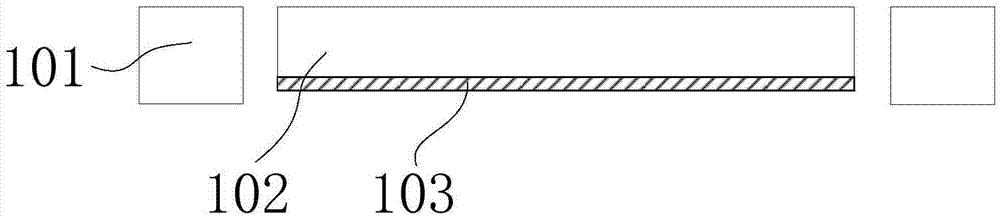

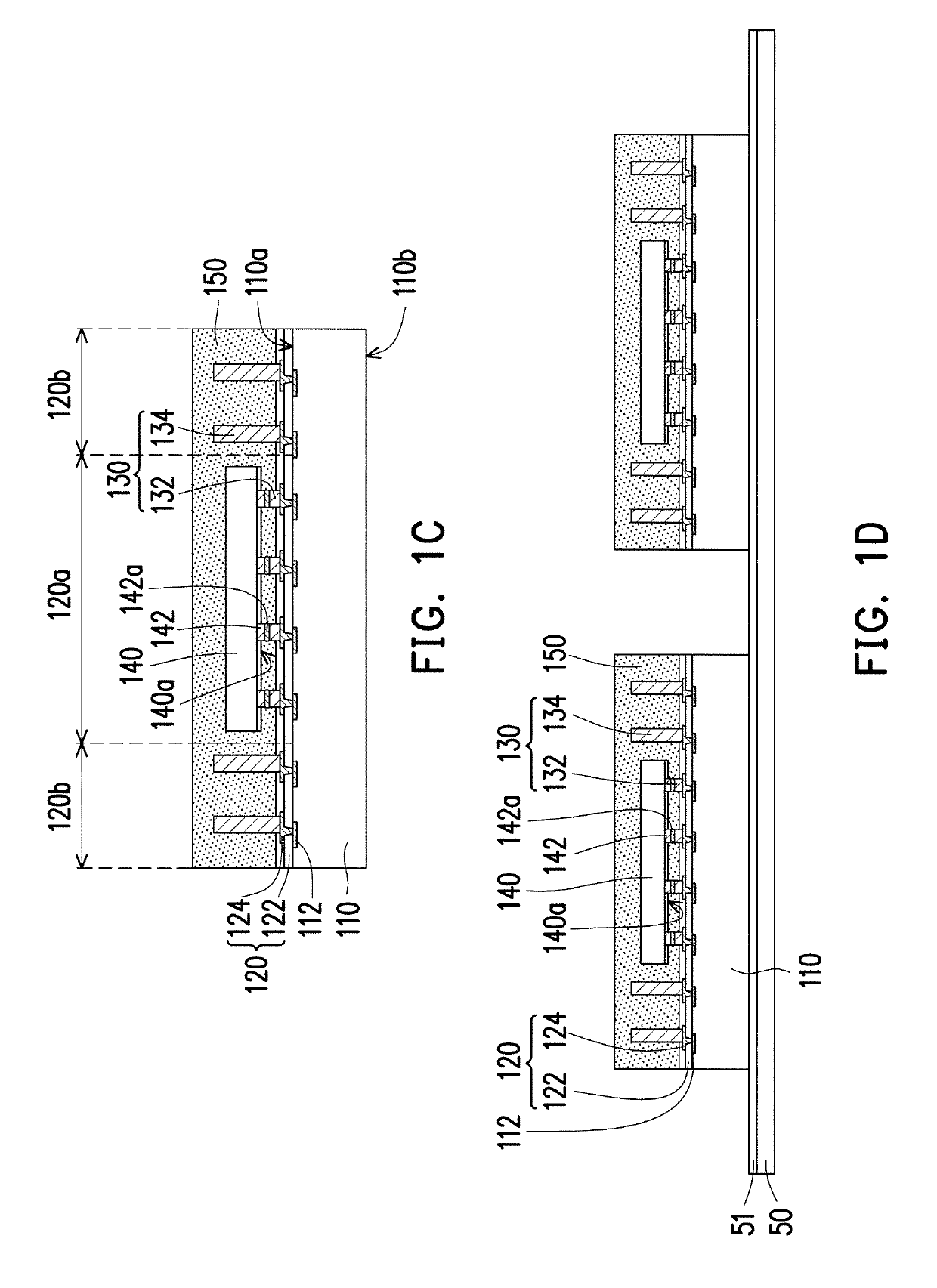

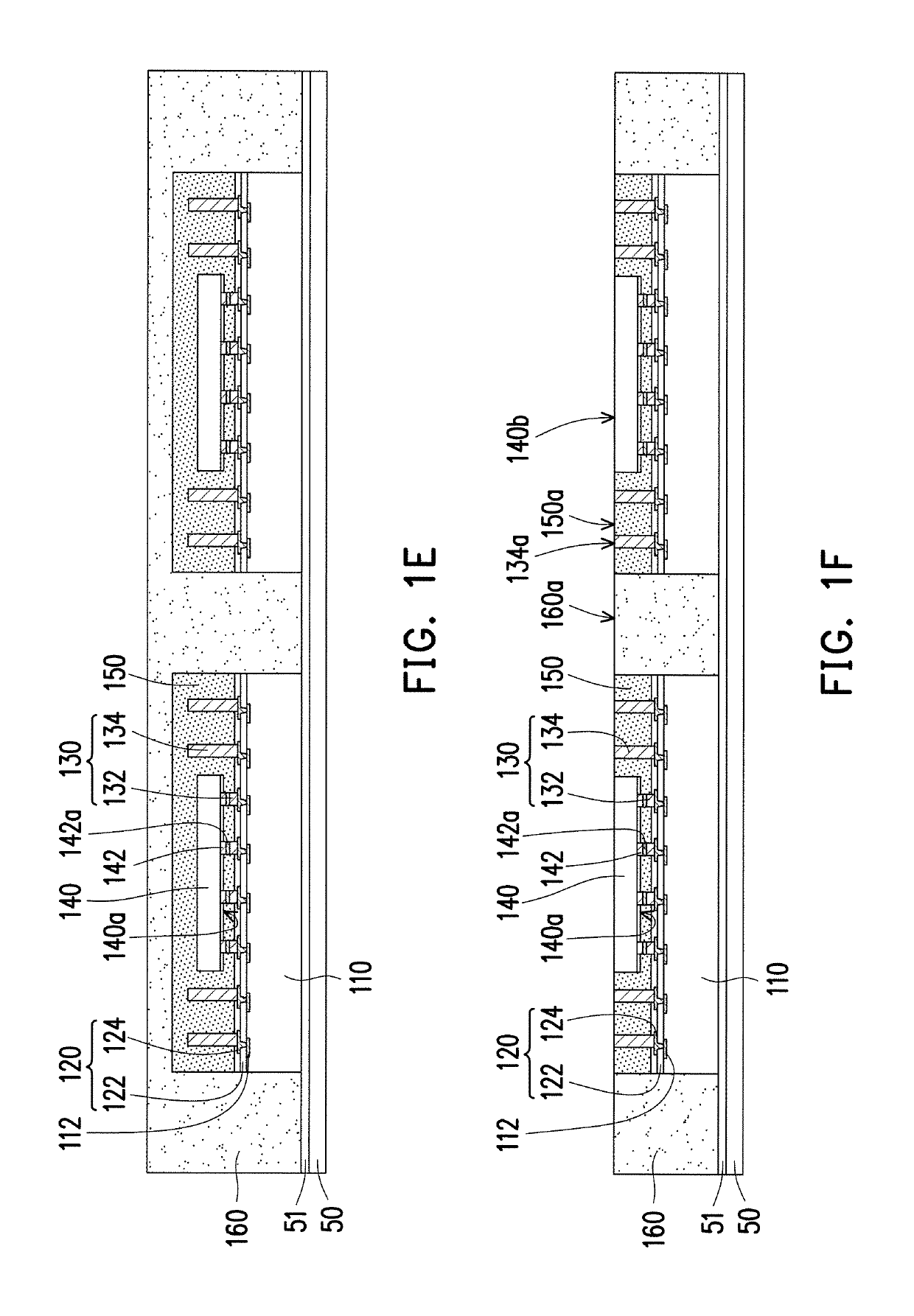

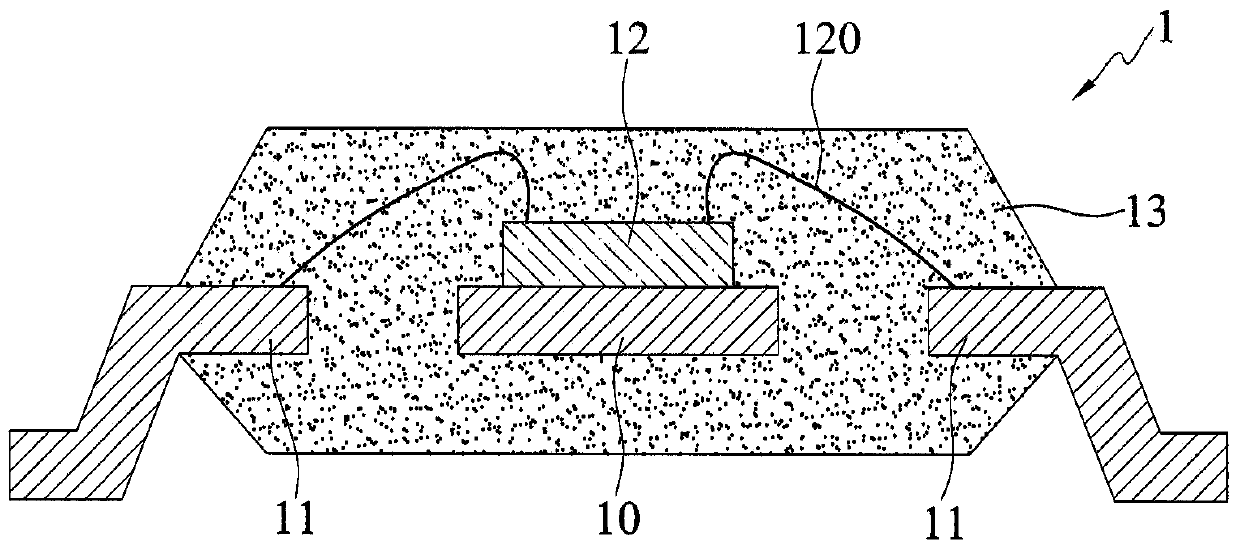

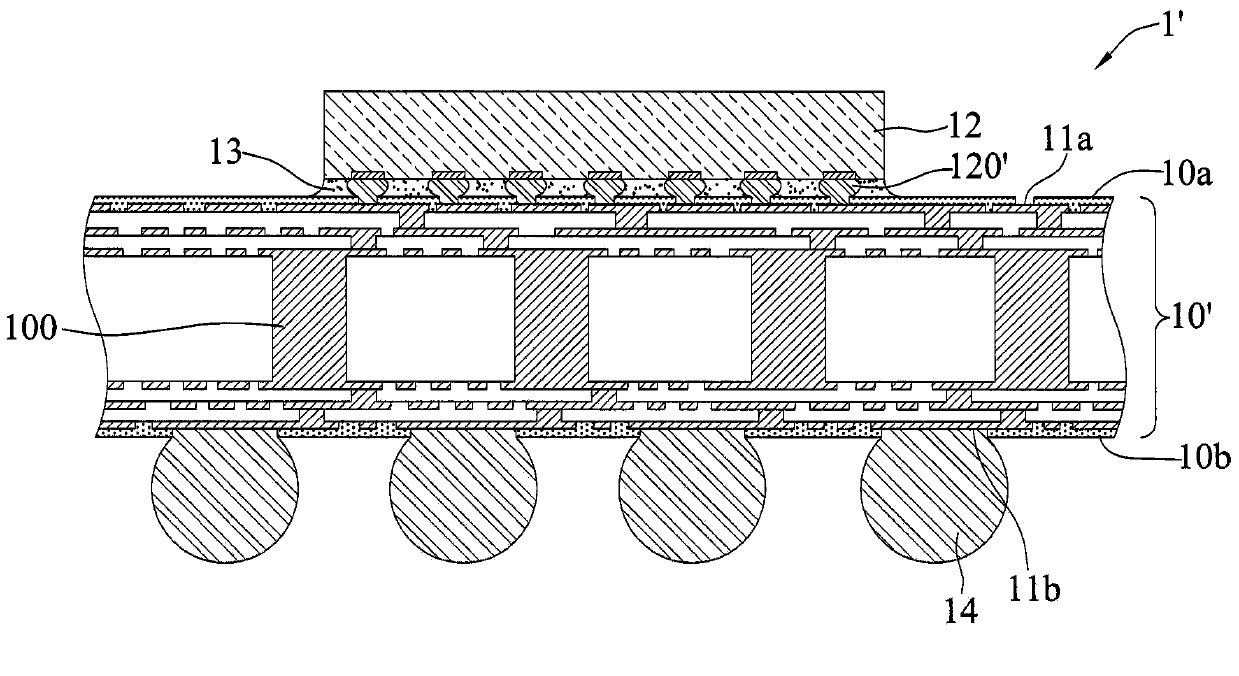

[package with stacked substrates]

InactiveUS20050205970A1High mechanical strengthImprove electrical performancePrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringLead frame

A package having a plurality of stacked substrates is provided. The package has at least two substrates. One substrate is stacked over the other to construct a three-dimensional circuit structure. Elements are disposed on the respective substrates. At least a conductive column is disposed between the two substrates. A lead-frame is connected to the substrates or the elements. The lead-frame also has a plurality of leads. The two neighboring substrates are electrically connected through the conductive column so that the average signal transmission length is shortened and the signal transmission quality is improved. Furthermore, the conductive column increases the mechanical strength of the package and reduces the degree of warping in the package so that a longer life span can be expected.

Owner:CYNTEC

Package with stacked substrates

InactiveUS6972479B2High mechanical strengthImprove electrical performancePrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringLead frame

A package having a plurality of stacked substrates is provided. The package has at least two substrates. One substrate is stacked over the other to construct a three-dimensional circuit structure. Elements are disposed on the respective substrates. At least a conductive column is disposed between the two substrates. A lead-frame is connected to the substrates or the elements. The lead-frame also has a plurality of leads. The two neighboring substrates are electrically connected through the conductive column so that the average signal transmission length is shortened and the signal transmission quality is improved. Furthermore, the conductive column increases the mechanical strength of the package and reduces the degree of warping in the package so that a longer life span can be expected.

Owner:CYNTEC

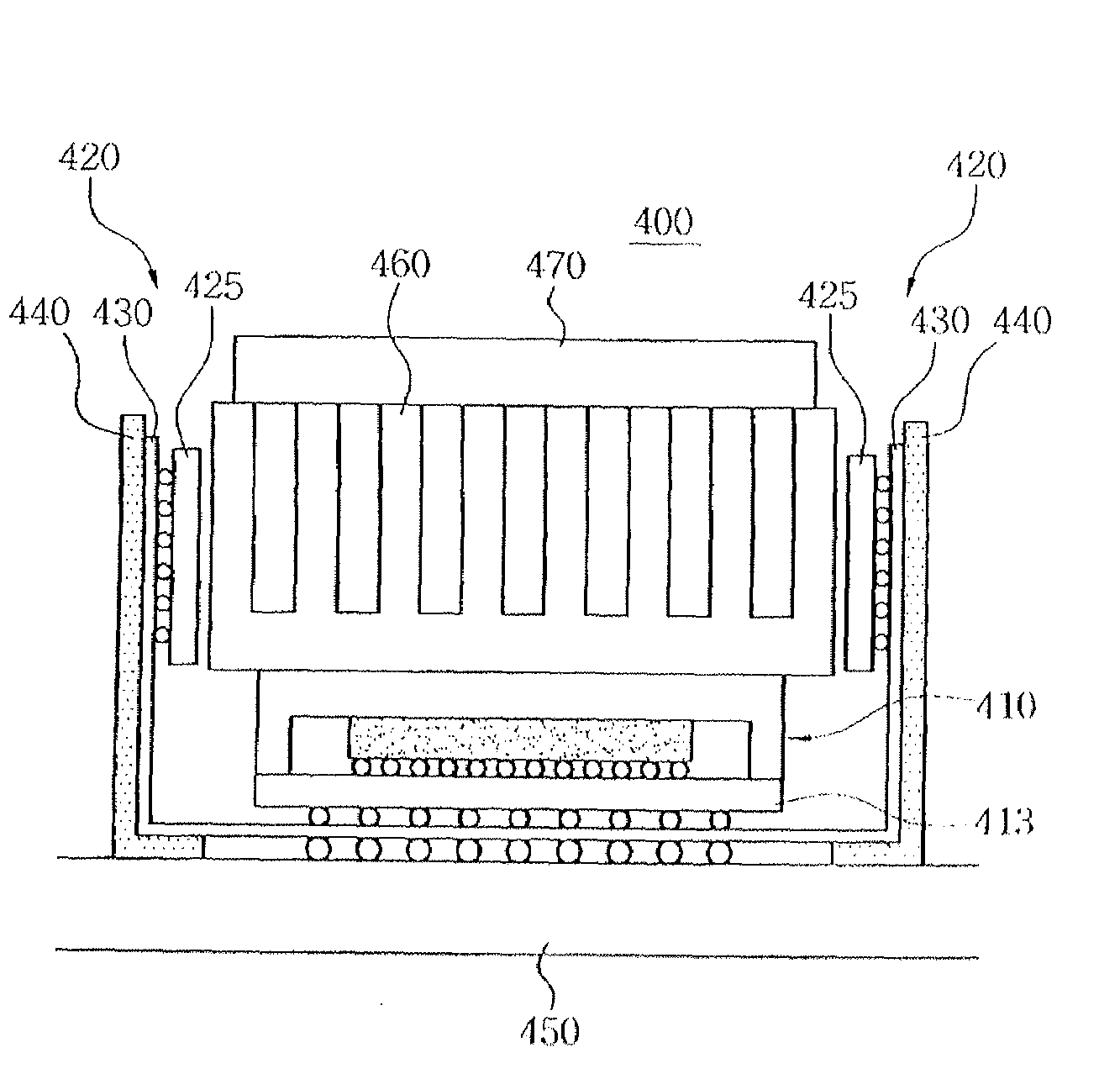

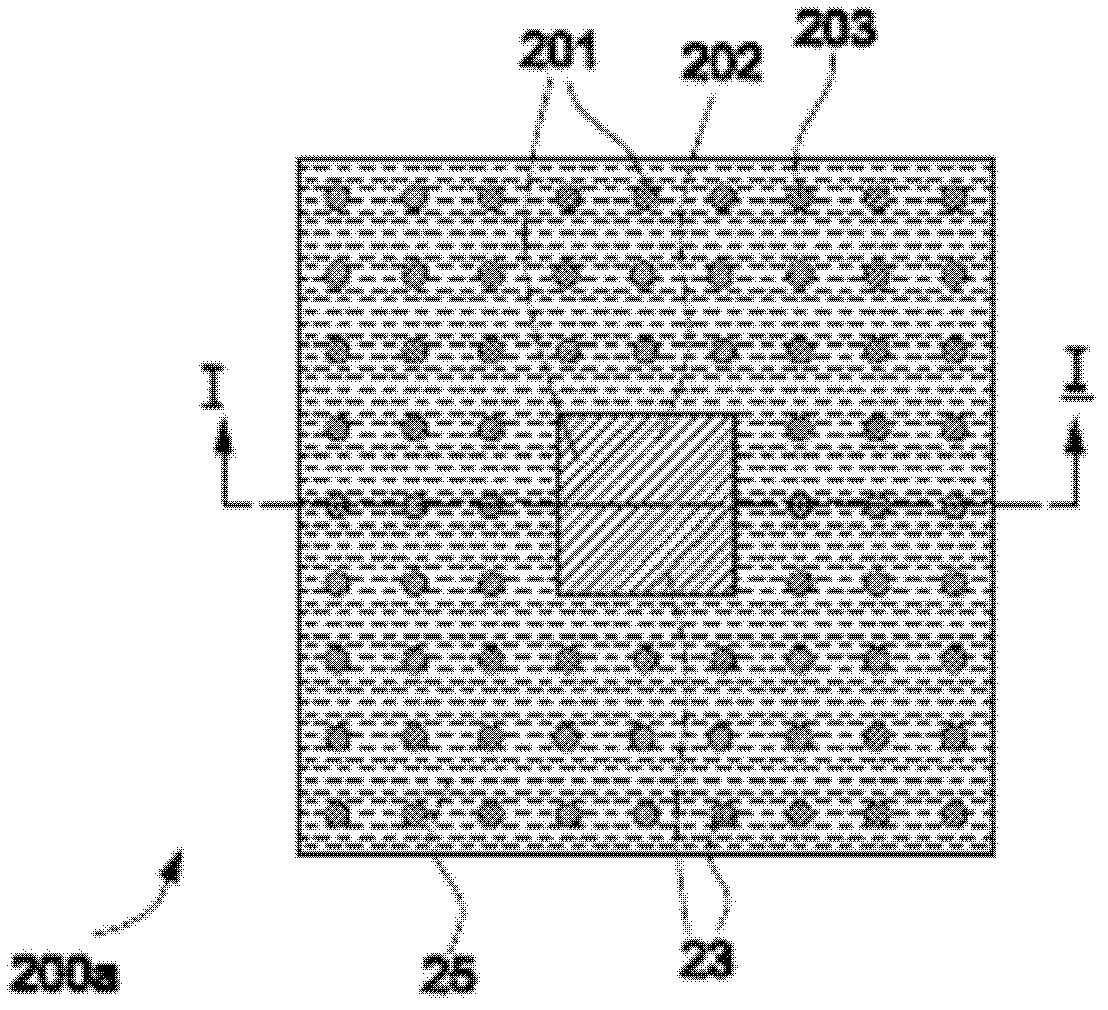

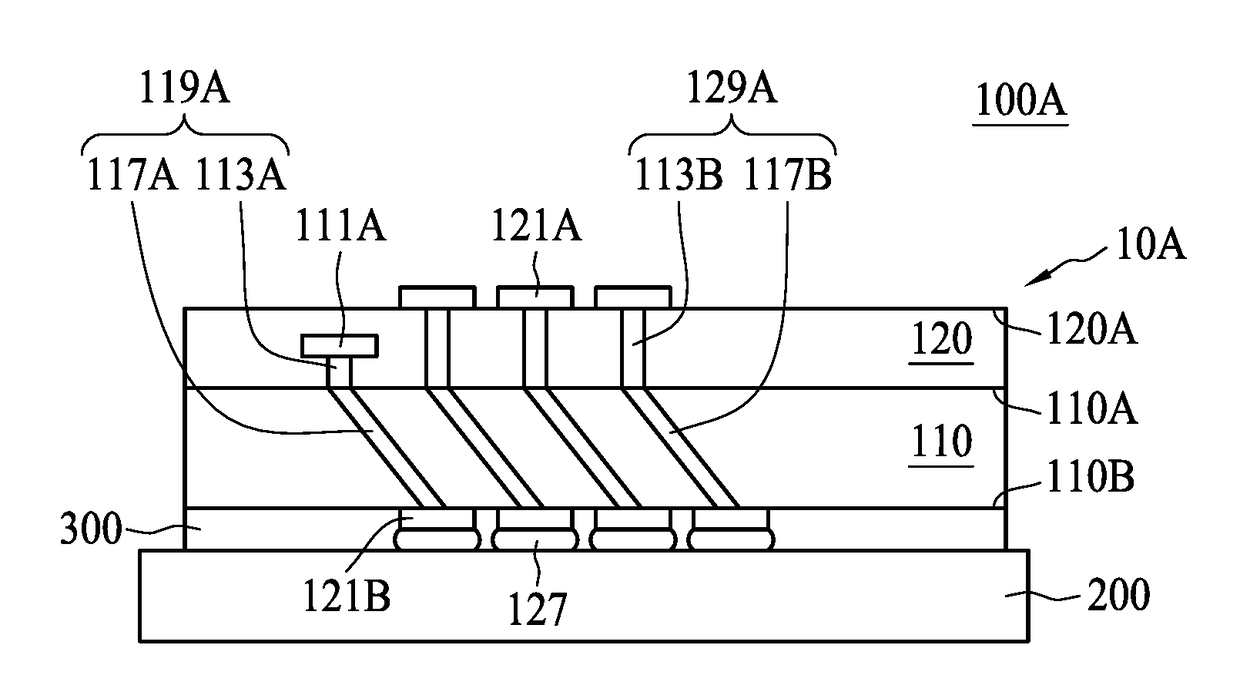

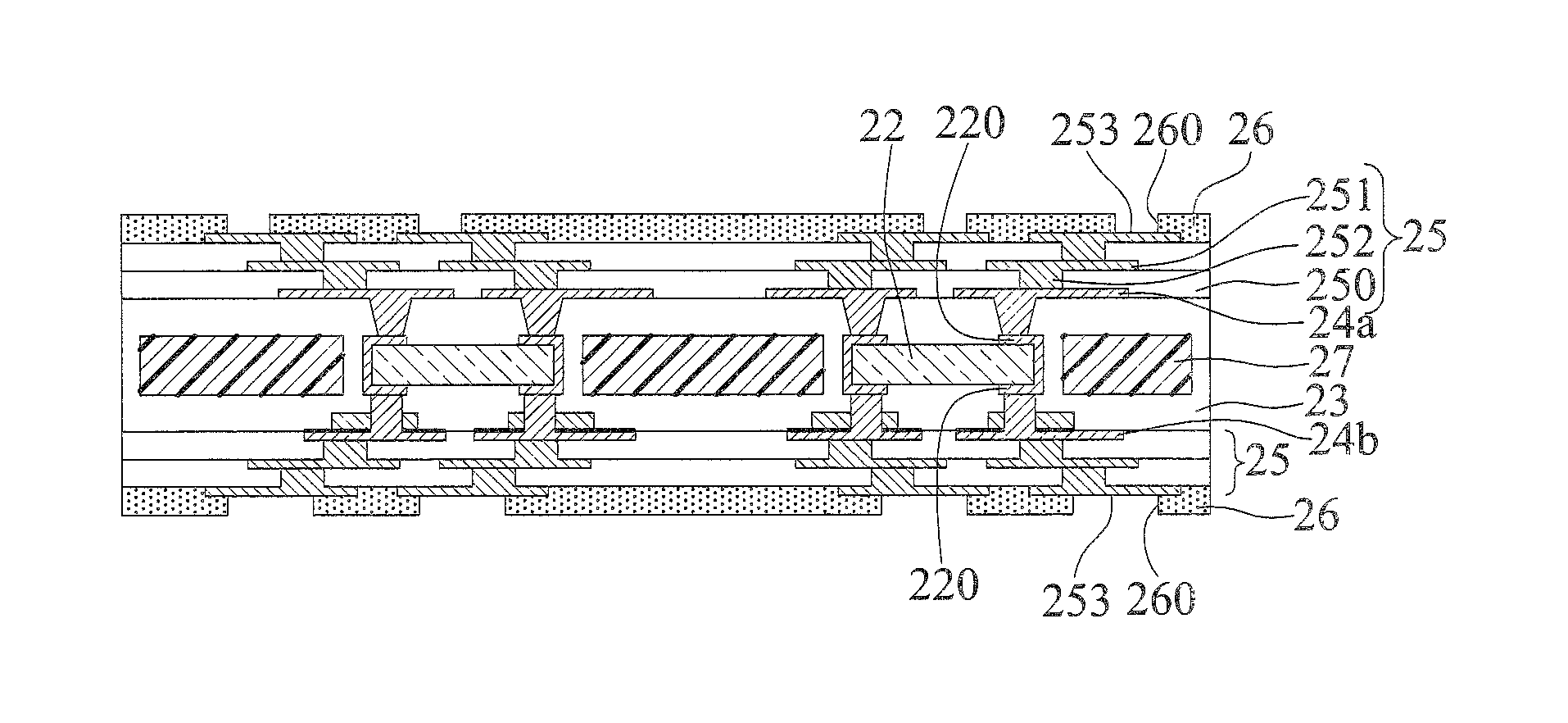

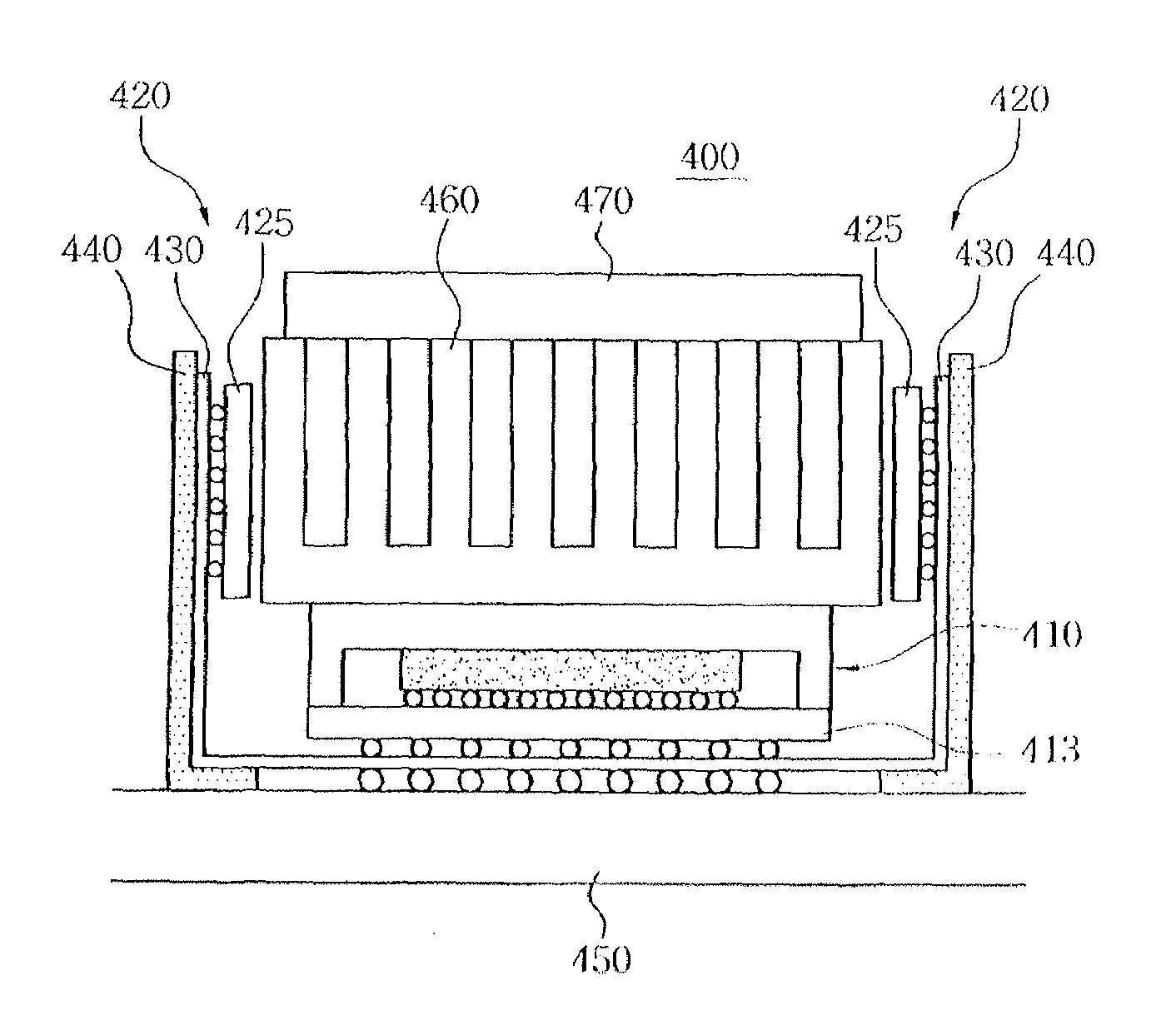

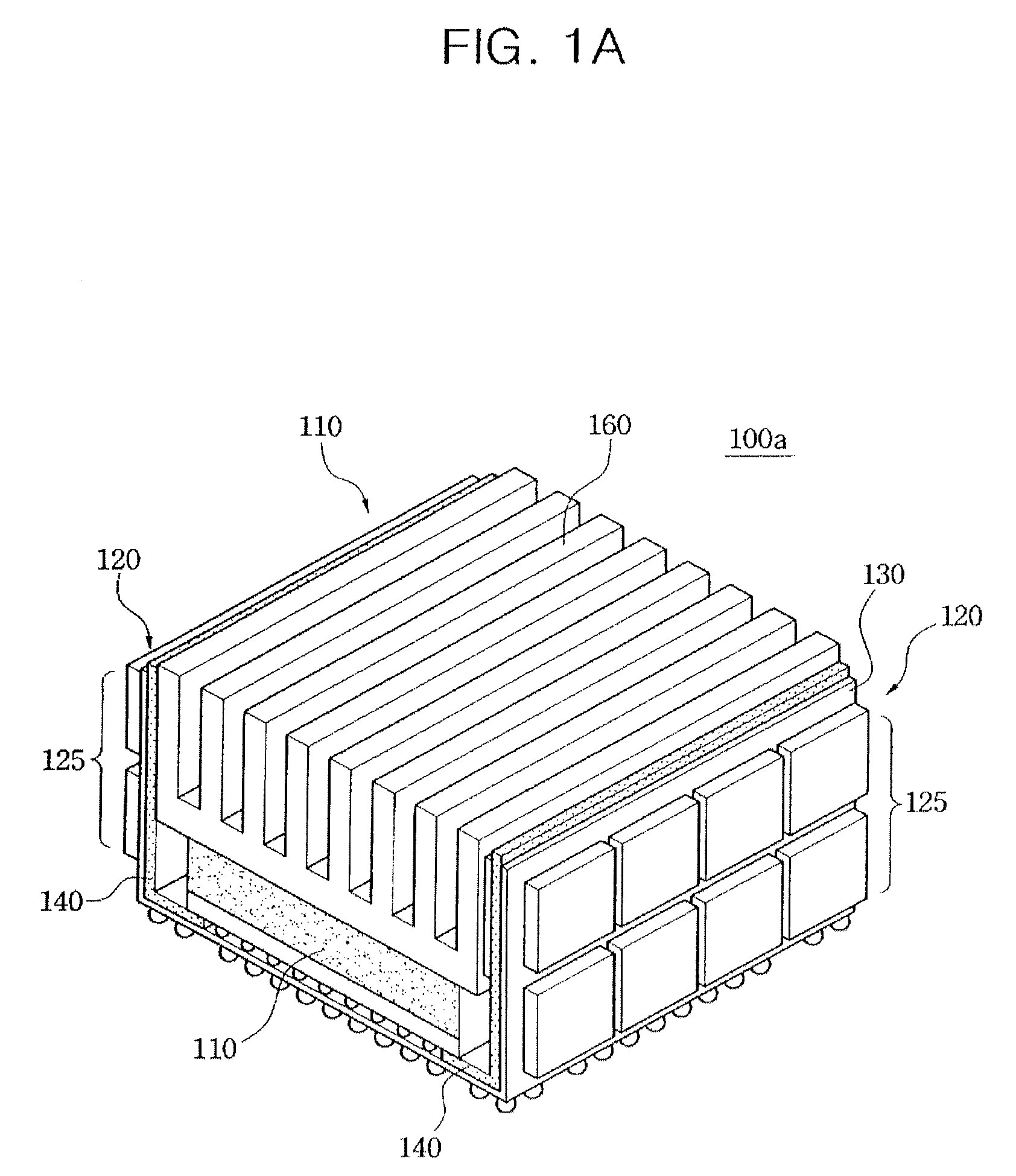

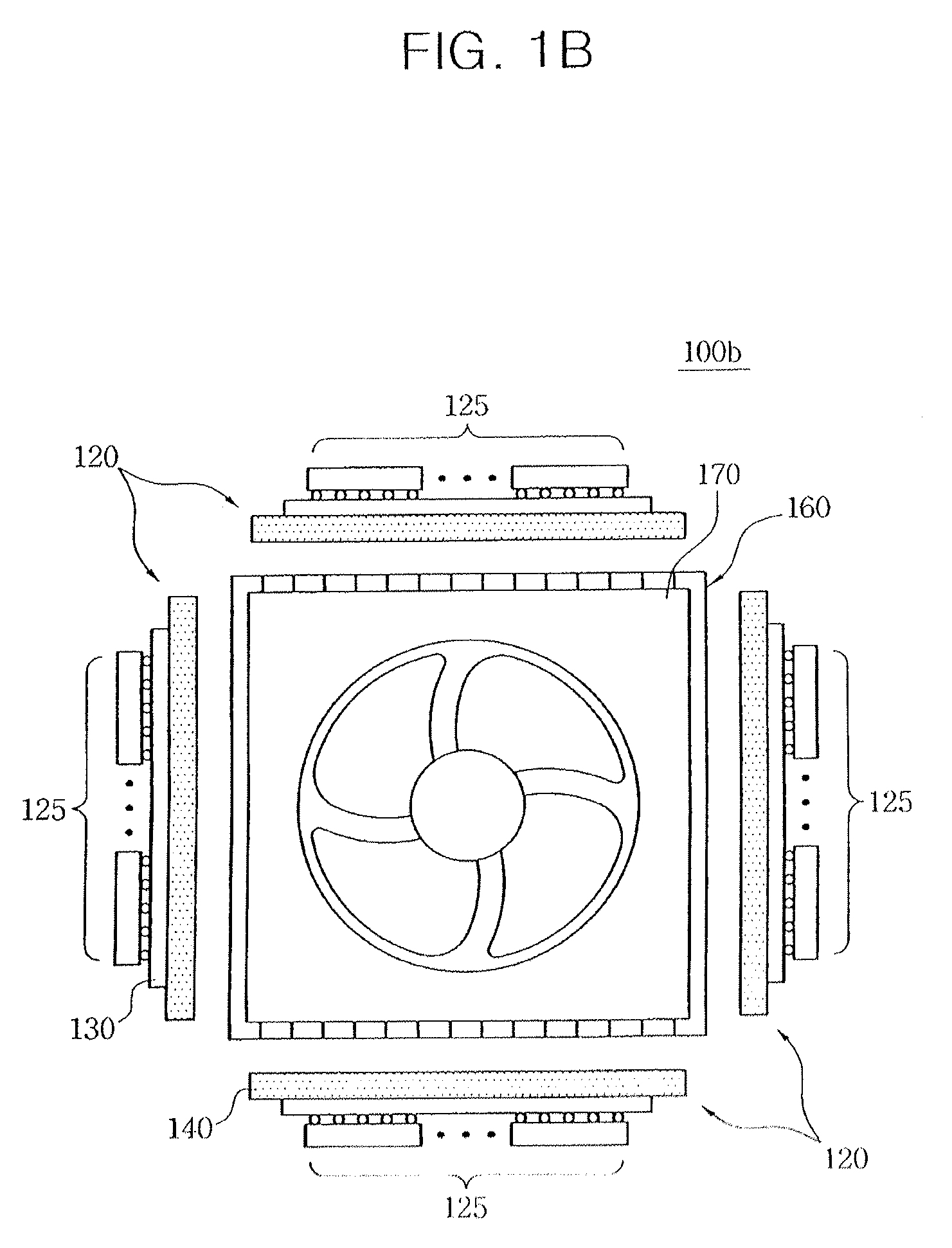

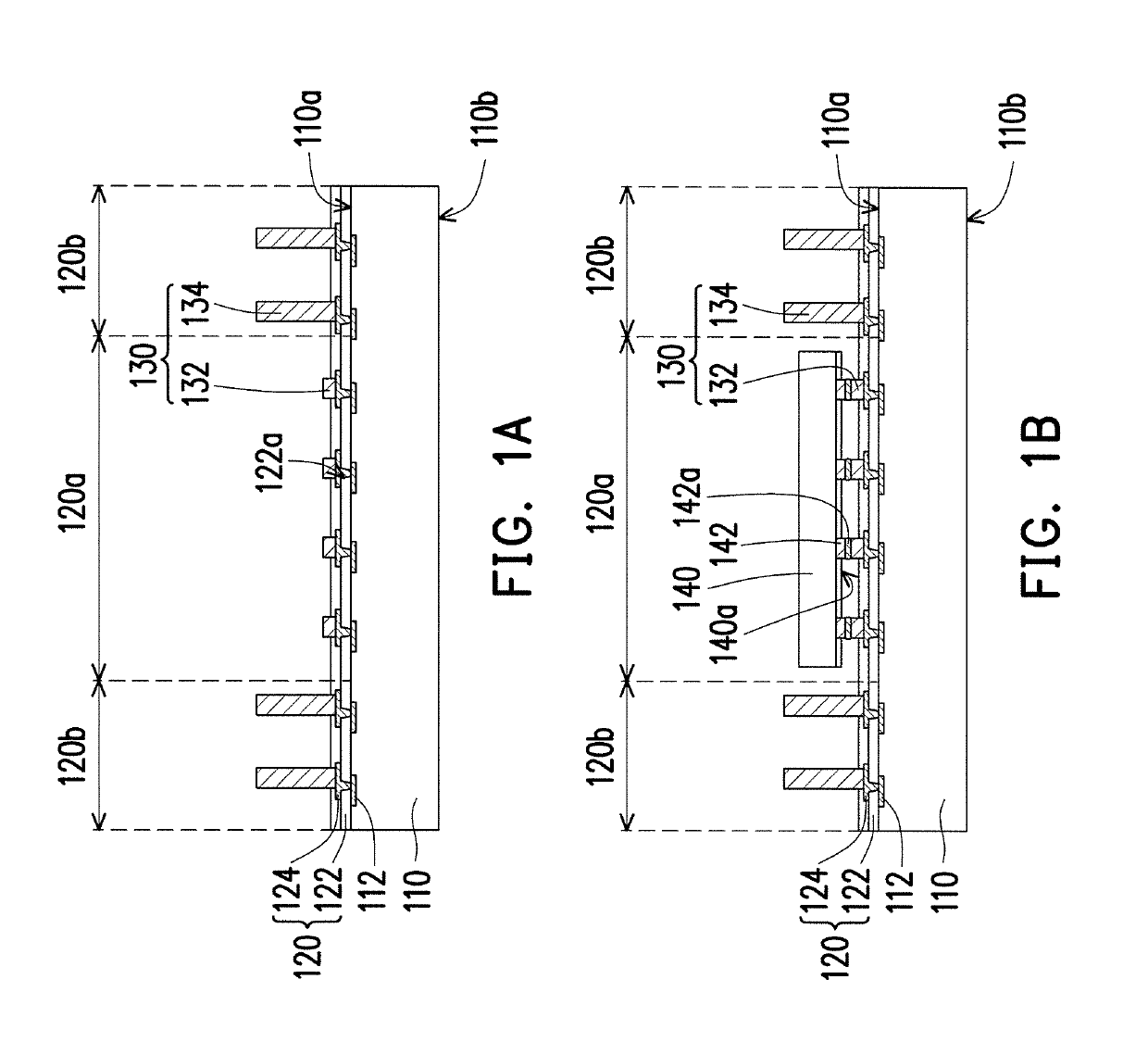

Semiconductor module and an electronic system including the same

ActiveUS20100059880A1Shorten the signal transmission pathImprove cooling efficiencySubstation/switching arrangement detailsSemiconductor/solid-state device detailsElectronic systemsDevice form

A three-dimensional semiconductor module and an electronic system including the same are provided. The semiconductor module includes a module substrate, a logic device formed on a part of the module substrate, and a plurality of memory devices formed on another part of the module substrate, wherein the plurality of memory devices are disposed perpendicular to the logic device, and the module substrate on which the plurality of memory devices are formed is supported by a supporter. The electronic system includes the semiconductor module.

Owner:SAMSUNG ELECTRONICS CO LTD

Package and manufacture method for thermal enhanced quad flat no-lead flip chip

InactiveCN102543907AImprove thermal conductivityImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesFilling materialsHeat conducting

The invention discloses a packaging and manufacturing method for a thermal enhanced quad flat no-lead flip chip. A thermal enhanced quad flat no-lead flip chip package piece structure comprises a lead framework, a first metal material layer, a second metal material layer, IC chips with convex points, an insulating filler material, a sticking material, radiating fins, heat conducting spacers and a plastic package material, wherein the lead framework comprises a chip carrier and a plurality of pins arranged in multiple circles around the chip carrier; the first metal material layer and the second metal material layer are respectively configured on the upper surface and the lower surface of the lead framework; the IC chips with the convex points are invertedly welded and configured at the position of the first metal material on the upper surface of the lead framework; the insulating filler material is configured below the stepped structure of the lead framework; the heat conducting spacers are configured between the IC chips and the chip carrier through the sticking material; and the radiating fins are configured on the edgeless surfaces of the IC chips through the sticking material and wrapped by the plastic package material to form a package piece. The QFN (Quad Flat No-lead) package piece structure provided by the invention has the advantages of high reliability, low cost and high I / O (Input / Output) density.

Owner:BEIJING UNIV OF TECH

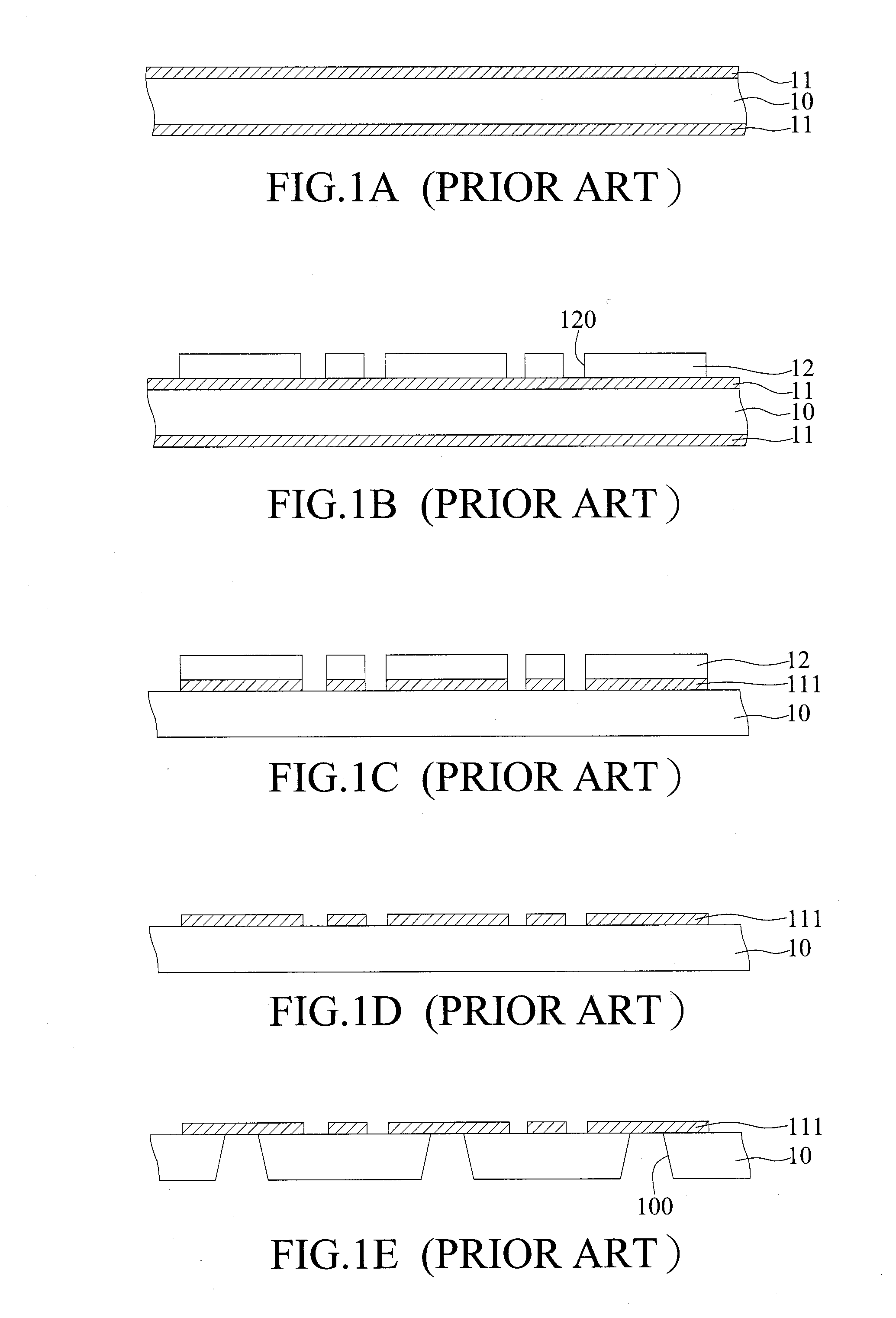

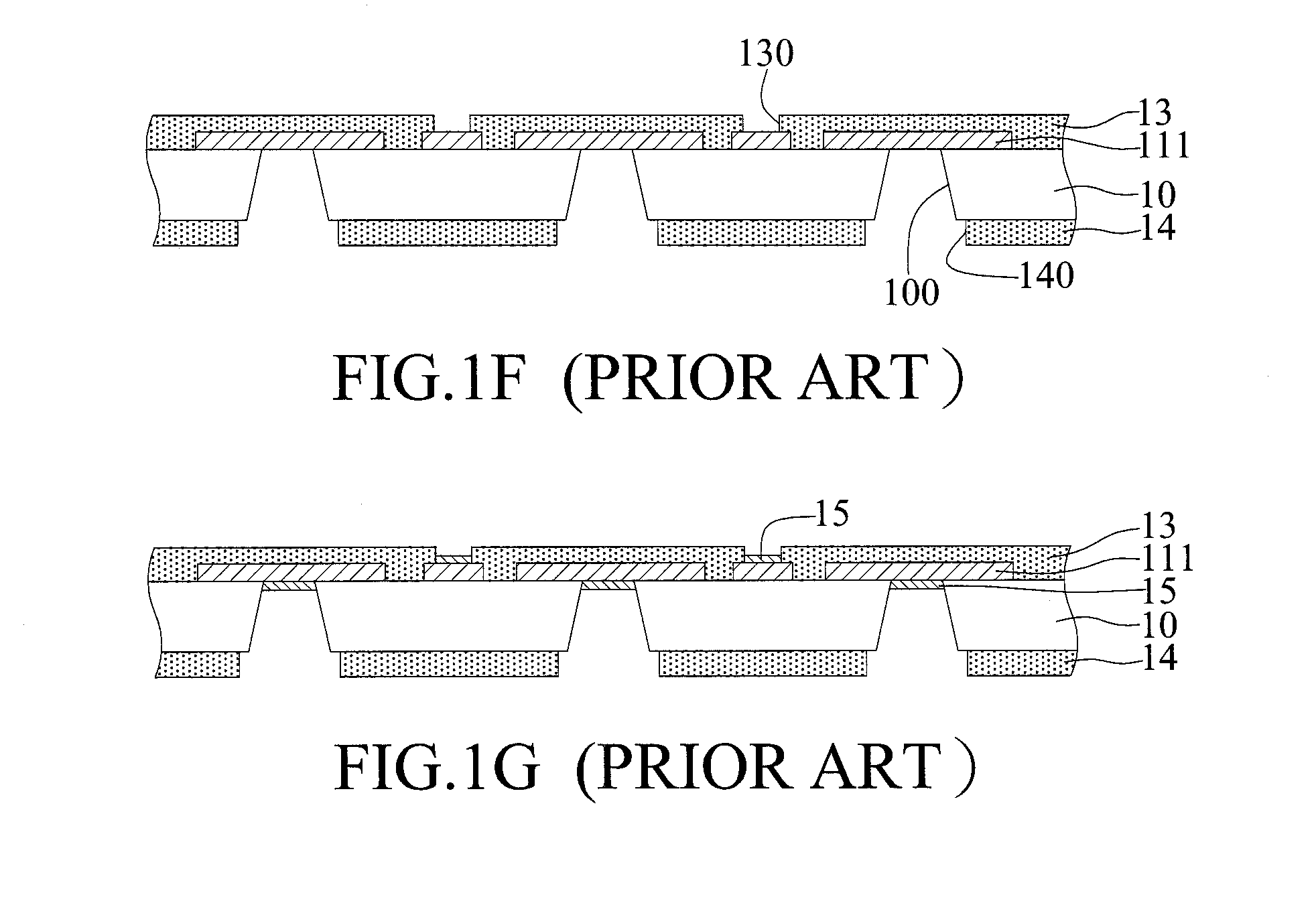

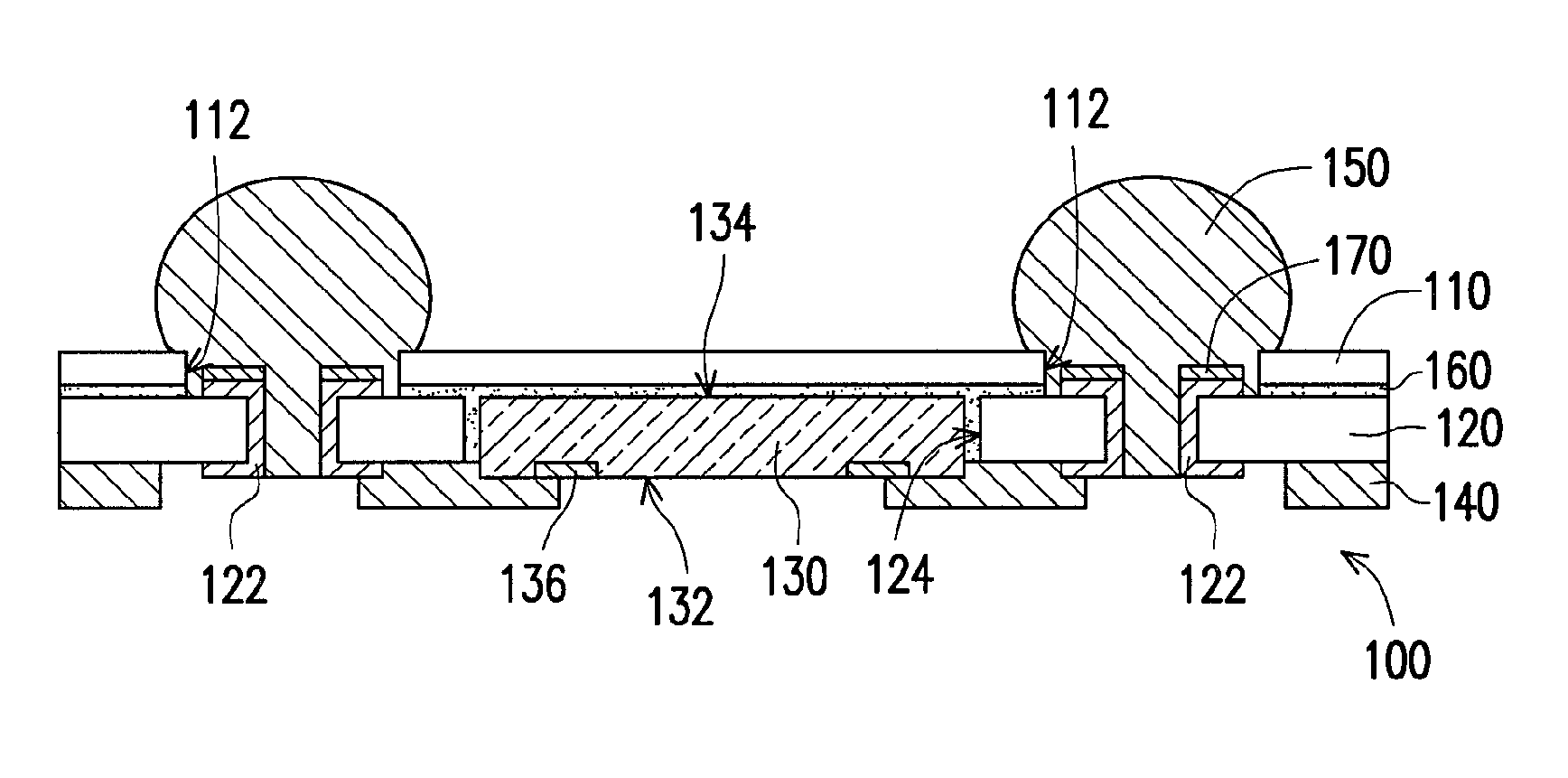

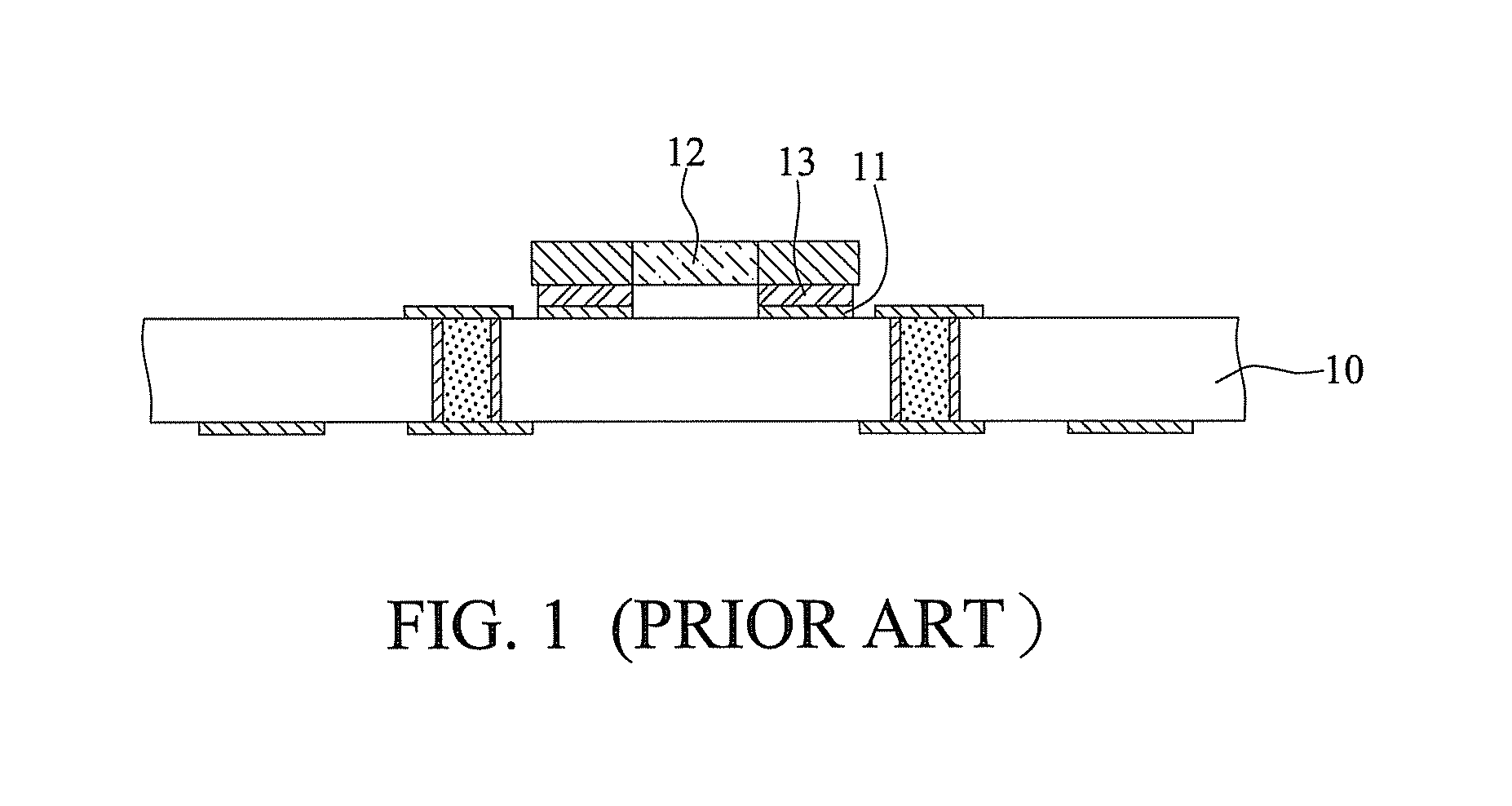

Chip package and process for forming the same

ActiveUS7078794B2Improve chip performanceLow production costSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A chip package structure comprising a substrate, a chip, a plurality of bumps, a plurality of conductive wires and an insulating material is provided. The substrate has a first surface and a corresponding second surface. The substrate has a slot that penetrates the substrate. The chip is attached to the first surface of the substrate in a position that covers the slot. The conductive wires pass through the slot such that one end of each conductive wire is attached to a contact point on the chip while the other end of the conductive wire is attached to a contact point on the second surface of the substrate. The insulating material fills the space between the chip and the substrate and the slot so that the conductive wires and the bumps are enclosed.

Owner:VIA TECH INC

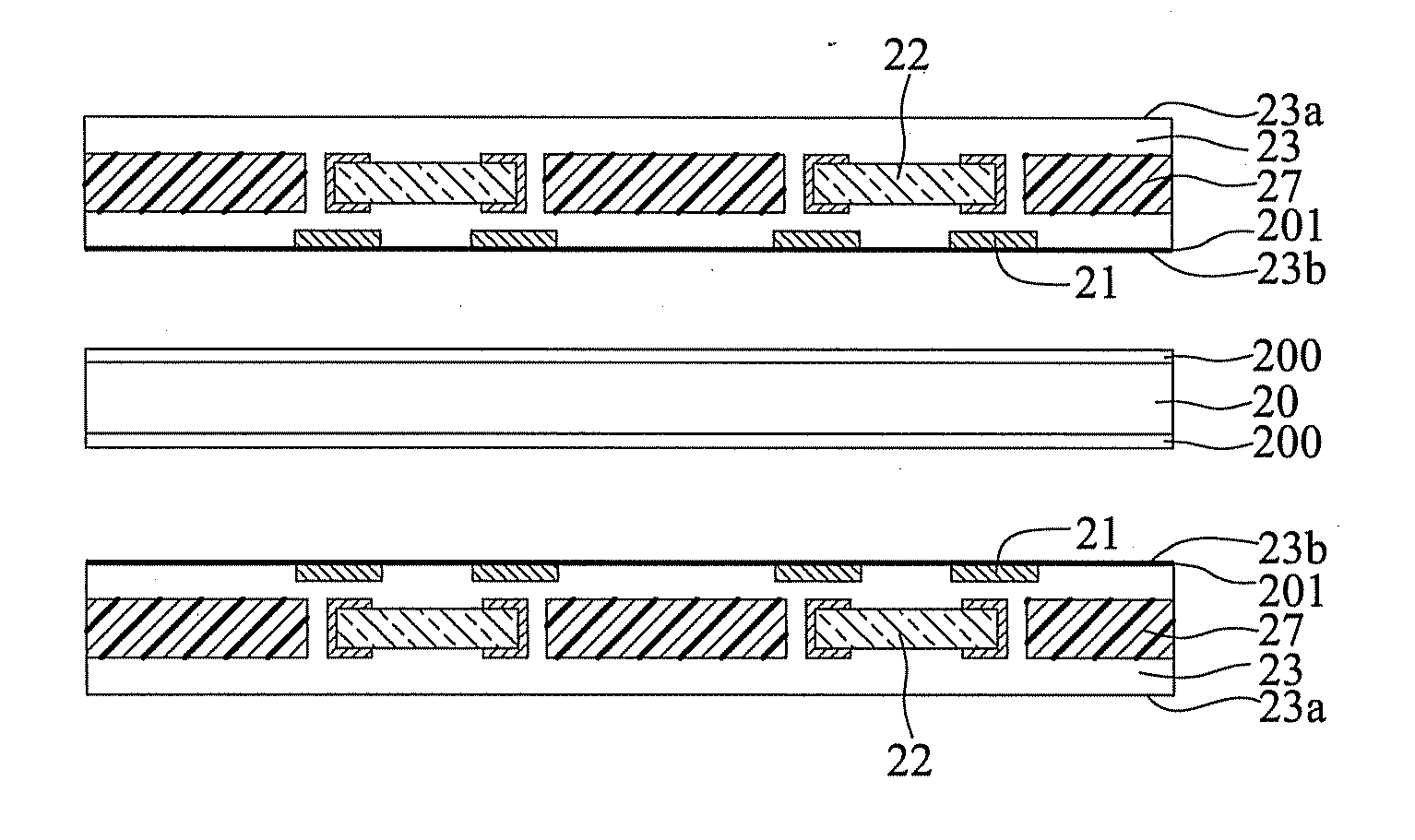

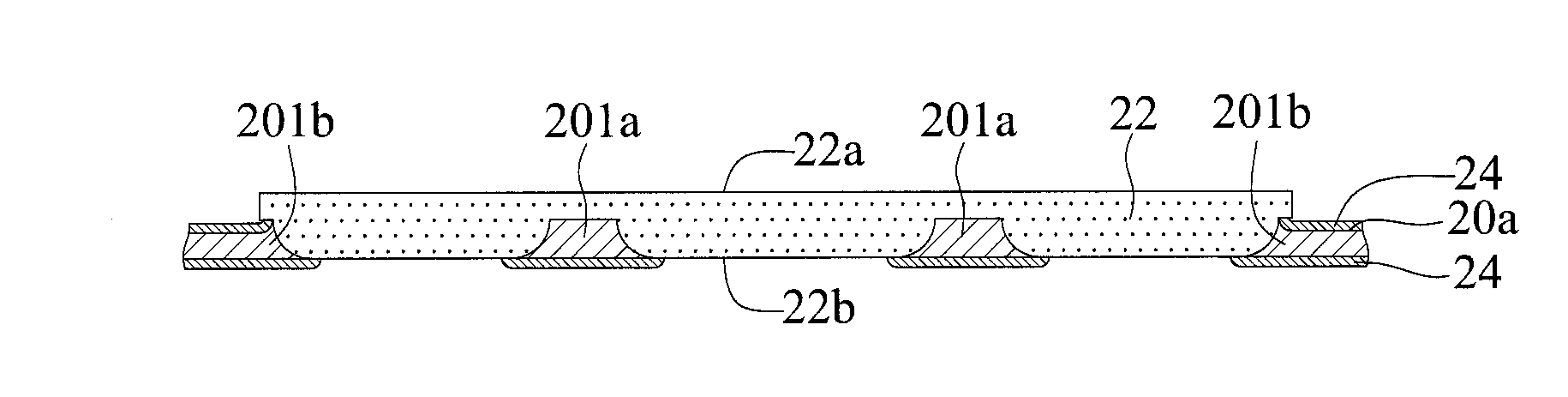

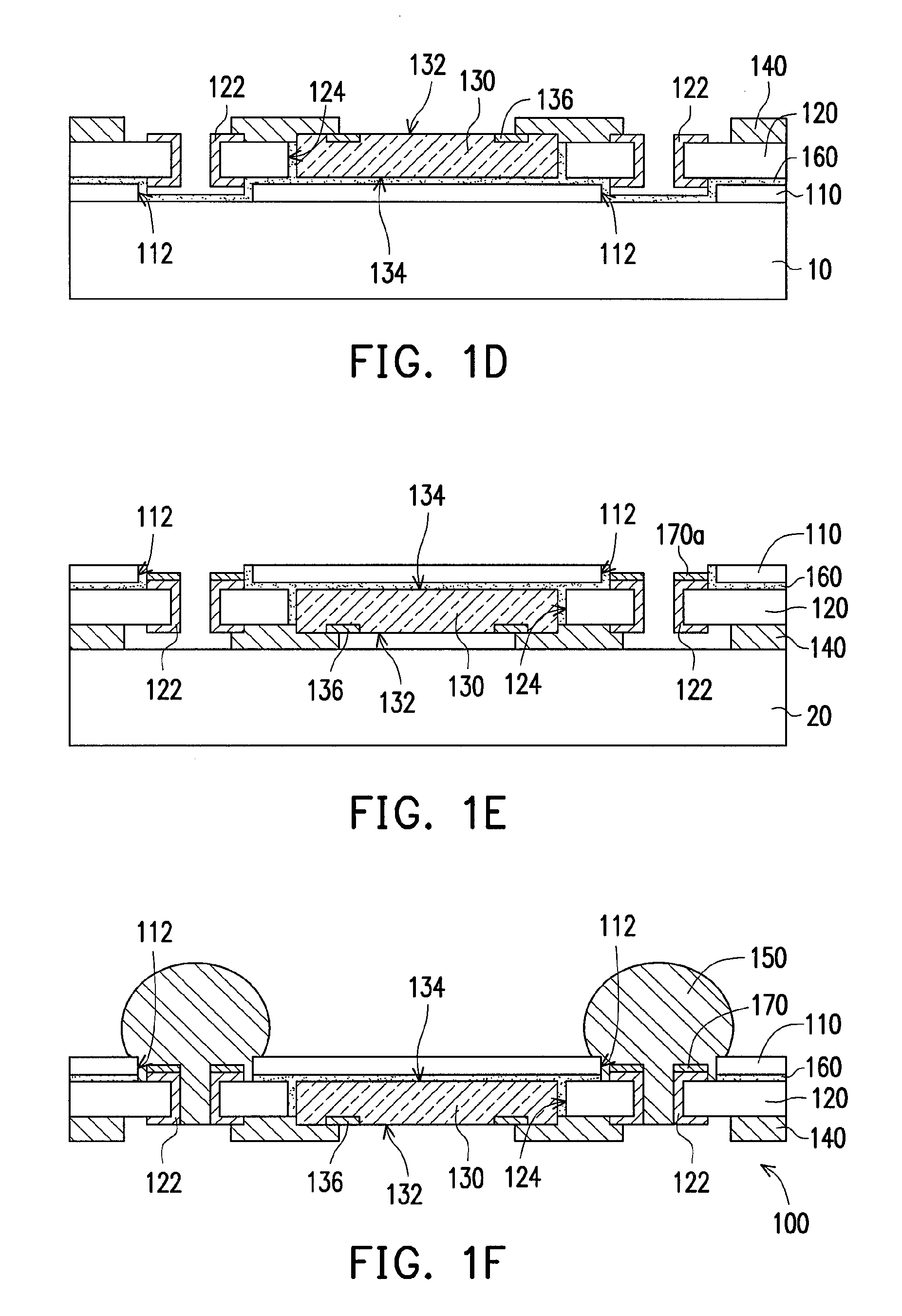

Packaging substrate having embedded passive component and fabrication method thereof

ActiveUS20120037411A1Reduce the overall heightShorten the signal transmission pathPrinted circuit assemblingPrinted electric component incorporationEngineeringDielectric layer

A packaging substrate includes: a core board with at least a cavity; a dielectric layer unit having upper and lower surfaces and encapsulating the core board and filling the cavity; a plurality of positioning pads embedded in the lower surface of the dielectric layer unit; at least a passive component having upper and lower surfaces with electrode pads disposed thereon and embedded in the dielectric layer unit so as to be received in the cavity of the core board at a position corresponding to the positioning pads; first and second wiring layers disposed on the upper and lower surfaces of the dielectric layer unit and electrically connected to the electrode pads of the upper and lower surfaces of the passive component through conductive vias, respectively. By embedding the passive component in the core board and the dielectric layer unit, the invention effectively reduces the height of the overall structure.

Owner:UNIMICRON TECH CORP

Packaging substrate having a passive element embedded therein and method of fabricating the same

ActiveUS20120037404A1Reduce the height of the structureShorten the signal transmission pathSemiconductor/solid-state device detailsSolid-state devicesDielectric layerElectrical and Electronics engineering

A packaging substrate includes: a dielectric layer unit having top and bottom surfaces; a positioning pad embedded in the bottom surface of the dielectric layer unit; at least a passive element having a plurality of electrode pads disposed on upper and lower surfaces thereof, the passive element being embedded in the dielectric layer unit and corresponding to the positioning pad; a first circuit layer disposed on the top surface of the dielectric layer unit, the first circuit layer having first conductive vias electrically connected to the electrode pads disposed on the upper surface of the passive element; and a second circuit layer disposed on the bottom surface of the dielectric layer unit, the second circuit layer having second conductive vias electrically connected to the electrode pads disposed on the lower surface of the passive element. Through the embedding of the passive element, the overall structure may have a reduced height.

Owner:UNIMICRON TECH CORP

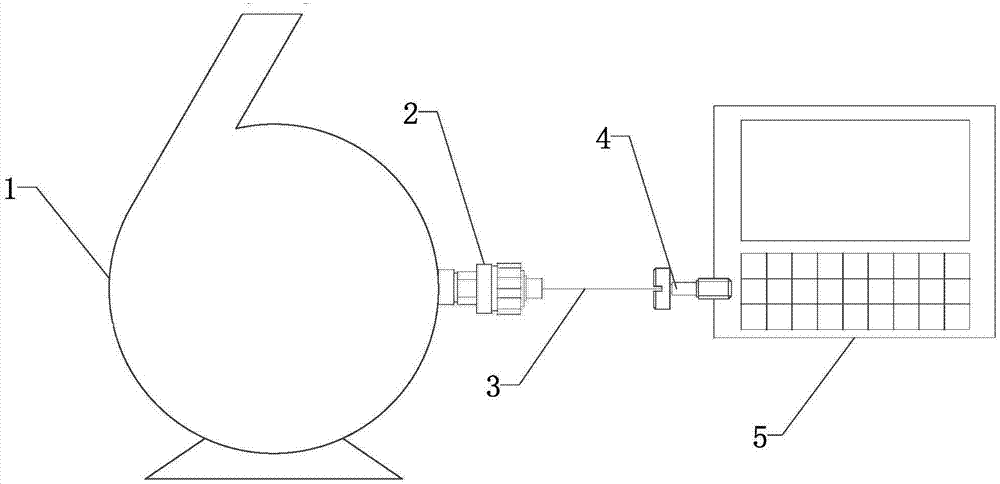

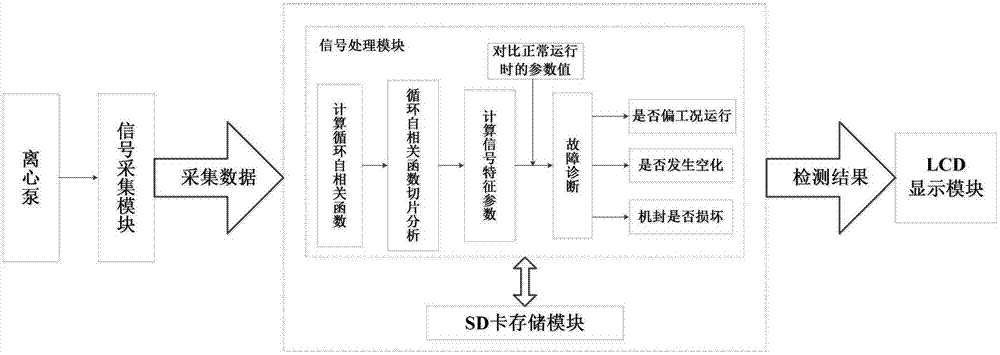

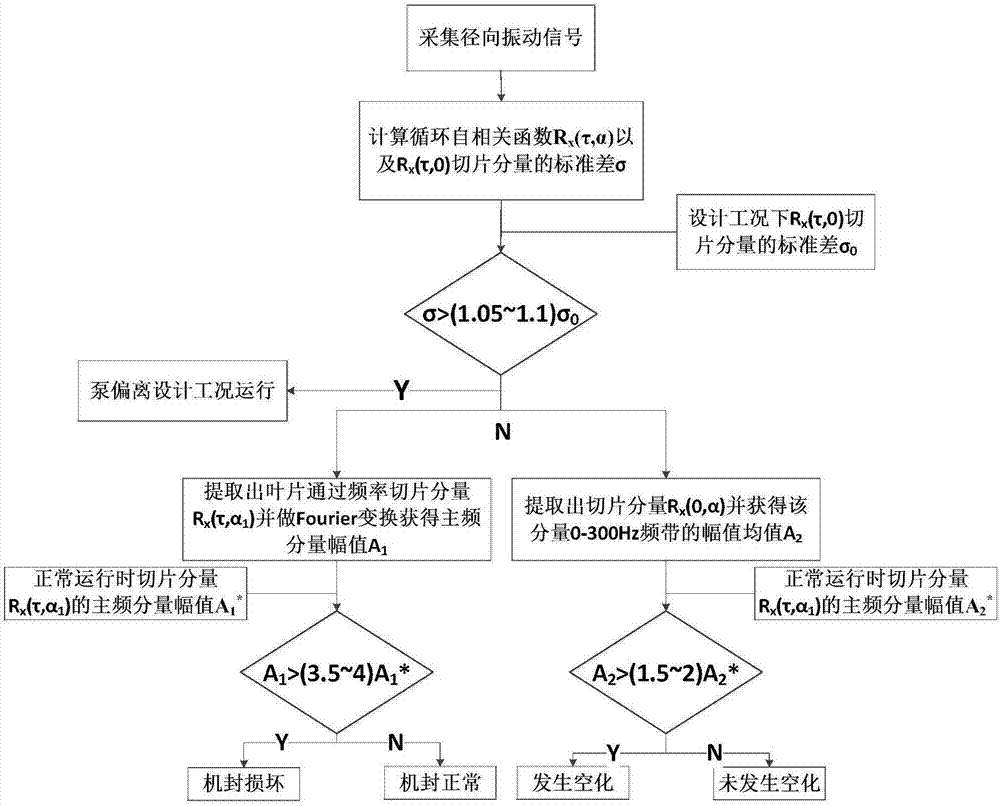

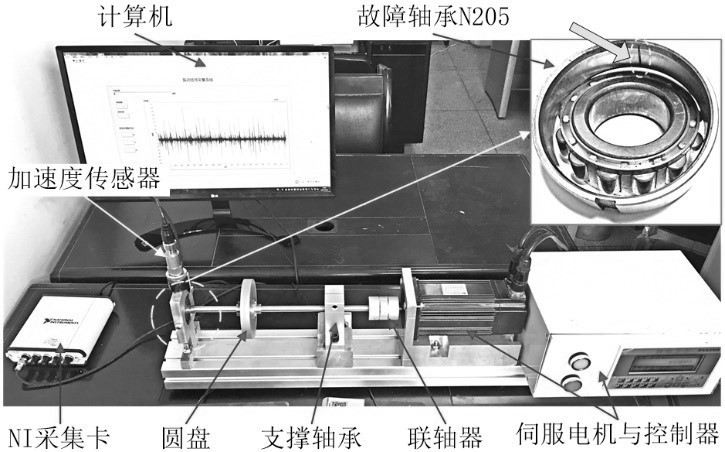

Online fault diagnosis method and system for centrifugal pump

InactiveCN107461342AImprove reliabilityProvide timely operation status monitoring resultsPump controlNon-positive displacement fluid enginesAnti jammingCavitation

The invention discloses an online fault diagnosis method and system for a centrifugal pump. According to the method, a vibration sensor is utilized for measuring a radial vibration signal in the operating process of a pump; the radial vibration signal is transmitted to a signal processing module; analysis treatment is conducted based on the cyclostationary theory so that a cyclic autocorrelation function can be obtained and subjected to slice analysis; feature parameters for distinguishing whether the pump breaks down or not and recognizing the breakdown type after it is determined that the pump breaks down are obtained; and a relevant breakdown diagnosis result is obtained by performing comparison and analysis on the feature parameters and corresponding parameters generated when the pump runs normally under the design working condition. According to the online fault diagnosis method and system for the centrifugal pump, diagnosis on mechanical seal damage and cavitation failures can be achieved by measuring the radial vibration signal of the pump, the running feature information of the pump can be reflected in the vibration signal in real time, the information integration degree is high, the number of signal transfer paths is small, the anti-jamming capability is high, and measurement reliability is high; and by analyzing stable components in the cyclic autocorrelation function of the signal, the situation that running is unstable due to the bias condition and consequently signal analysis is disturbed can be avoided, and specific reasons which cause unstable flowing of the centrifugal pump are identified.

Owner:JIANGSU UNIV

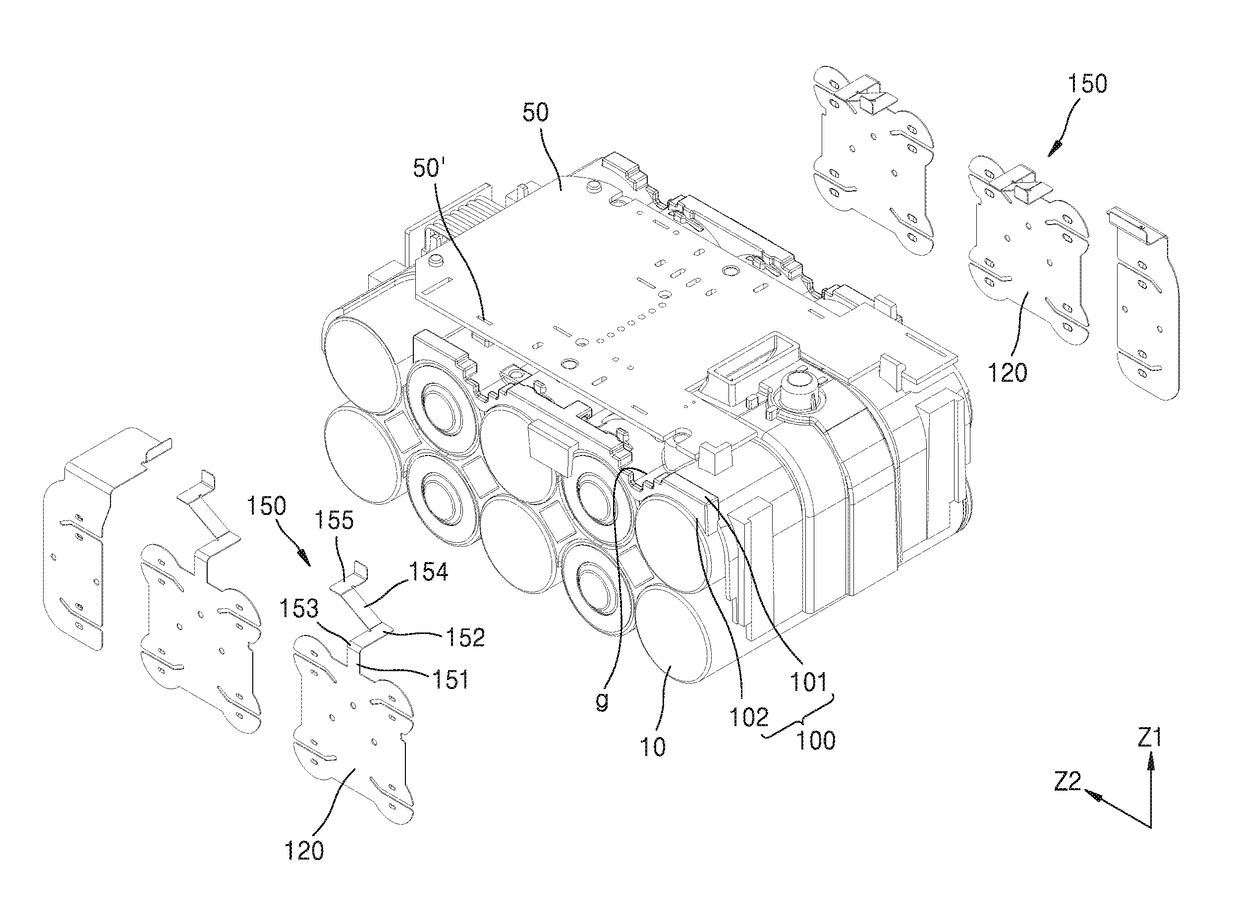

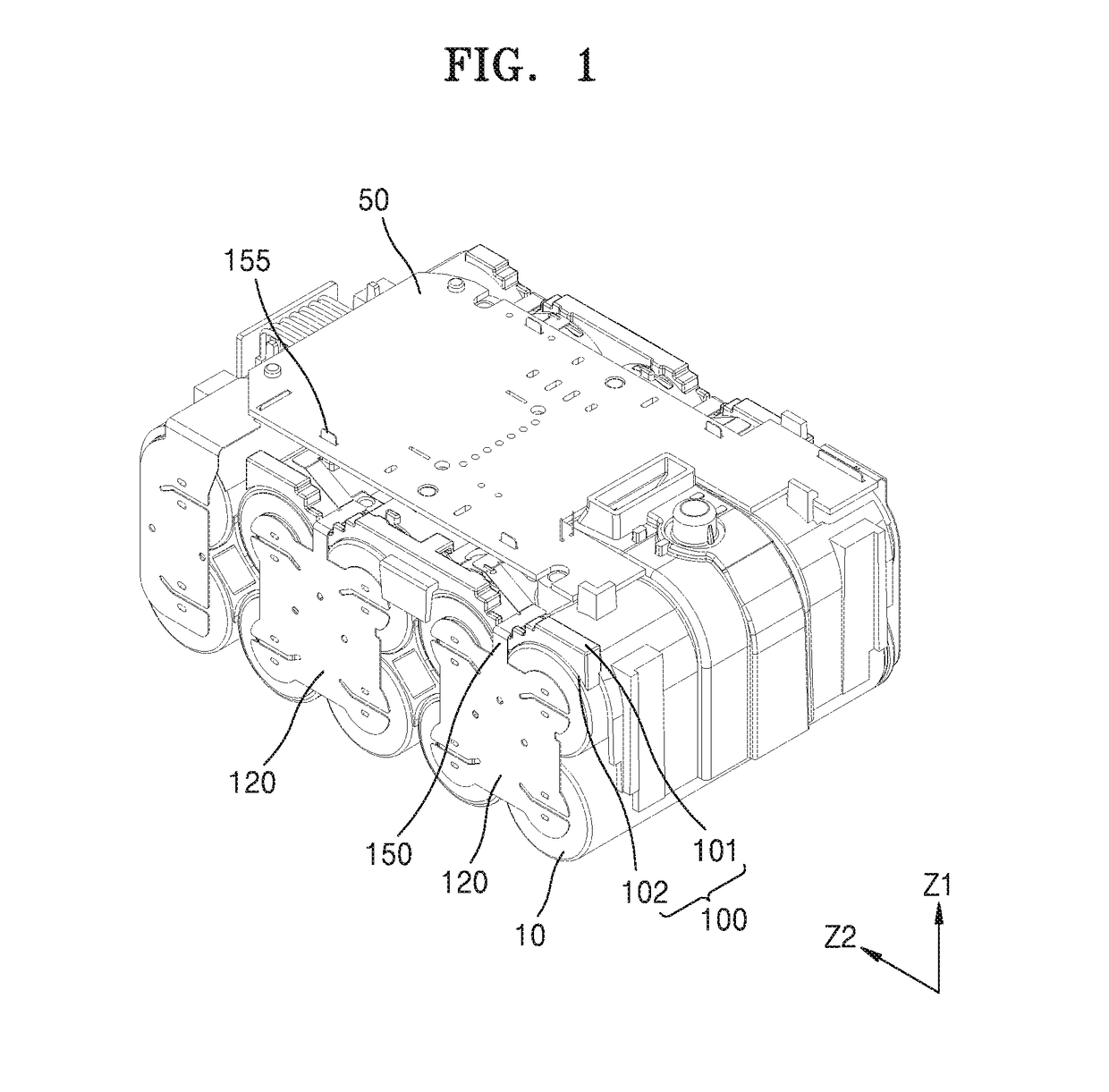

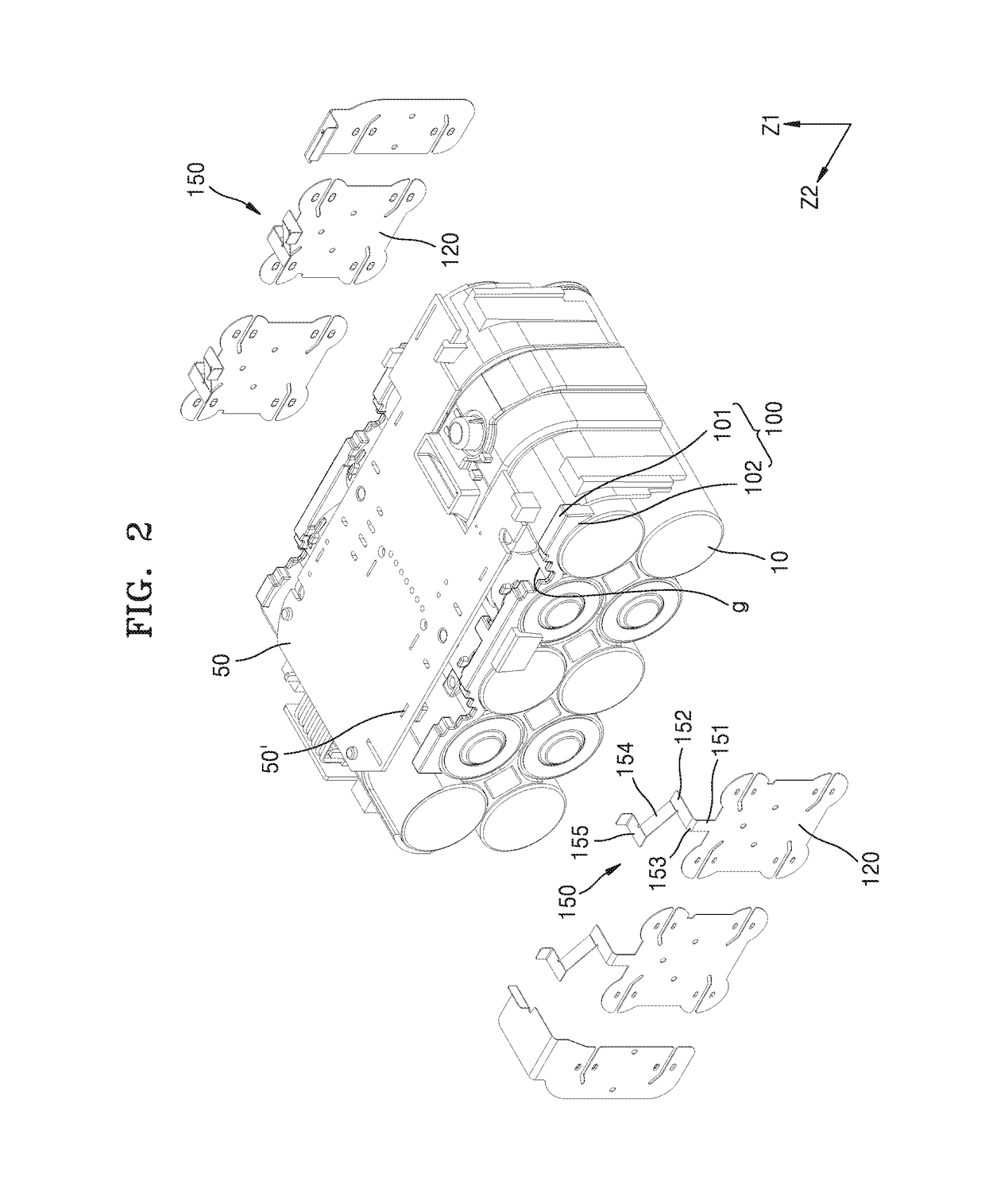

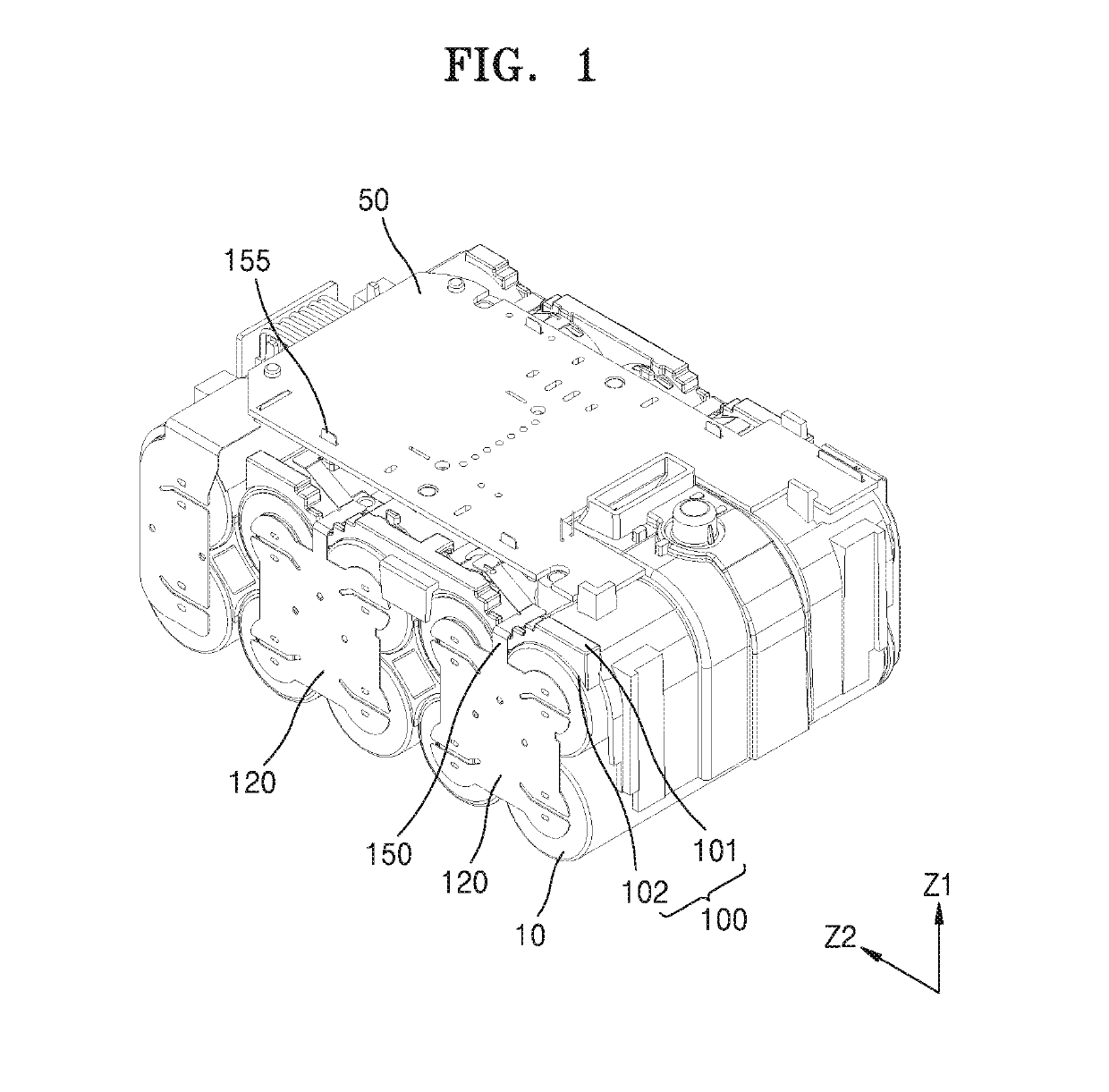

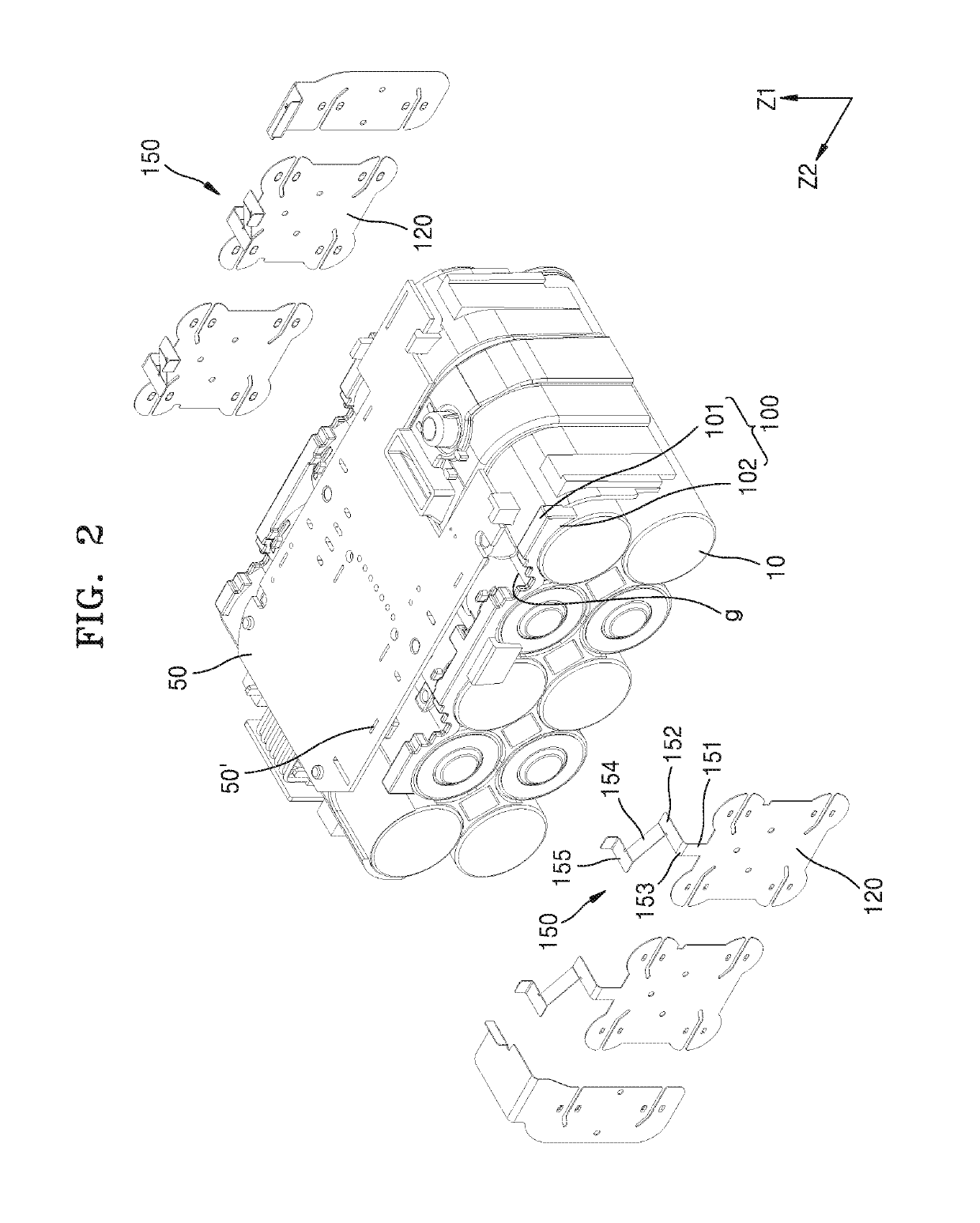

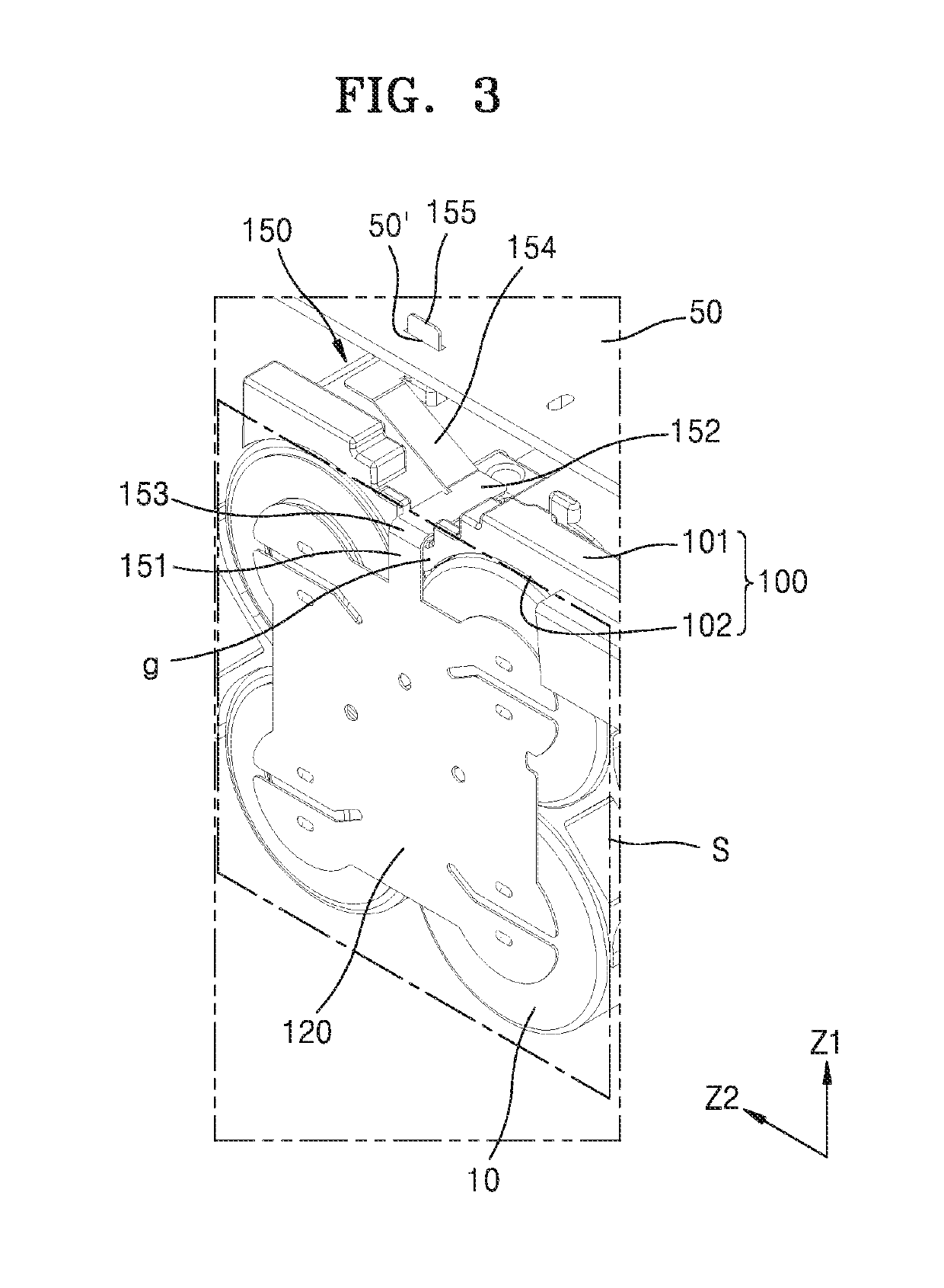

Battery pack

ActiveUS20170264107A1Reduce connection tabShorten the signal transmission pathFinal product manufactureCylindrical casing cells/batteryElectrical batteryCharge and discharge

A battery pack includes at least two battery cells; a circuit board to control charging and discharging operations of the battery cells; and a connection tab electrically connected to the battery cells, extending towards the circuit board, and including a bent portion proximal to the battery cells and located within a battery area defined by the battery cells. A battery pack suitable for a compact type device is provided and a low-resistive design may be applied to the battery pack.

Owner:SAMSUNG SDI CO LTD

Packaging substrate having a passive element embedded therein and method of fabricating the same

ActiveUS8829356B2Shorten the signal transmission pathReduce the height of the structureFinal product manufactureElectric spark ignitersDielectric layerElectrical and Electronics engineering

Owner:UNIMICRON TECH CORP

Chip package having tilted through silicon via

ActiveUS9831155B2Shorten the signal transmission pathSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

A chip package includes at least one integrated circuit die. The integrated circuit die includes a substrate portion having an internal plane between a front side and a back side, an electrical interconnect portion on the front side, a plurality of first connection terminals on an upper surface of the electrical interconnect portion, a plurality of second connection terminals on the back side of the substrate portion, a plurality of connection wirings electrically connecting the first connection terminals and the second connection terminals, a chip selection terminal between the internal plane of the substrate portion and the upper surface of the electrical interconnect portion, and a chip selection wiring connected to the chip selection terminal and one of the second connection terminals and the first connection terminals. At least one of the chip selection wiring and the plurality of connection wirings includes a tilted portion with respect to the back side of the substrate portion.

Owner:NAN YA TECH

Semiconductor package and manufacturing method thereof

ActiveUS20190214347A1Reduce fabrication costReduced packaging volumeSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package including a stacked-die structure, a second encapsulant laterally encapsulating the stacked-die structure and a redistribution layer disposed on the second encapsulant and the staked-die structure is provided. The stacked-die structure includes a first semiconductor die including a first active surface, a circuit layer disposed on the first active surface, a second semiconductor die including a second active surface facing towards the first active surface, a plurality of conductive features distributed at the circuit layer and electrically connected to the first and second semiconductor die and a first encapsulant encapsulating the second semiconductor die and the conductive features. A portion of the conductive features surrounds the second semiconductor die. The redistribution layer is electrically connected to the staked-die structure. A manufacturing method of a semiconductor package is also provided.

Owner:POWERTECH TECHNOLOGY

Chip package having tilted through silicon via

ActiveUS20170263536A1Shorten signal transmission pathShorten the signal transmission pathSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitThrough-silicon via

A chip package includes at least one integrated circuit die. The integrated circuit die includes a substrate portion having an internal plane between a front side and a back side, an electrical interconnect portion on the front side, a plurality of first connection terminals on an upper surface of the electrical interconnect portion, a plurality of second connection terminals on the back side of the substrate portion, a plurality of connection wirings electrically connecting the first connection terminals and the second connection terminals, a chip selection terminal between the internal plane of the substrate portion and the upper surface of the electrical interconnect portion, and a chip selection wiring connected to the chip selection terminal and one of the second connection terminals and the first connection terminals. At least one of the chip selection wiring and the plurality of connection wirings includes a tilted portion with respect to the back side of the substrate portion.

Owner:NAN YA TECH

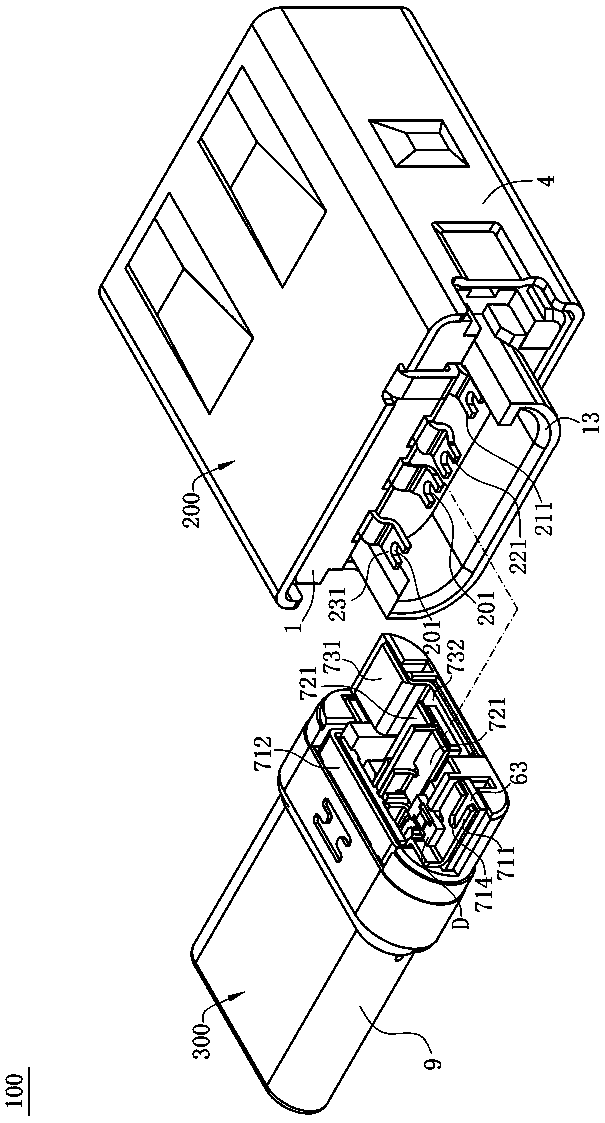

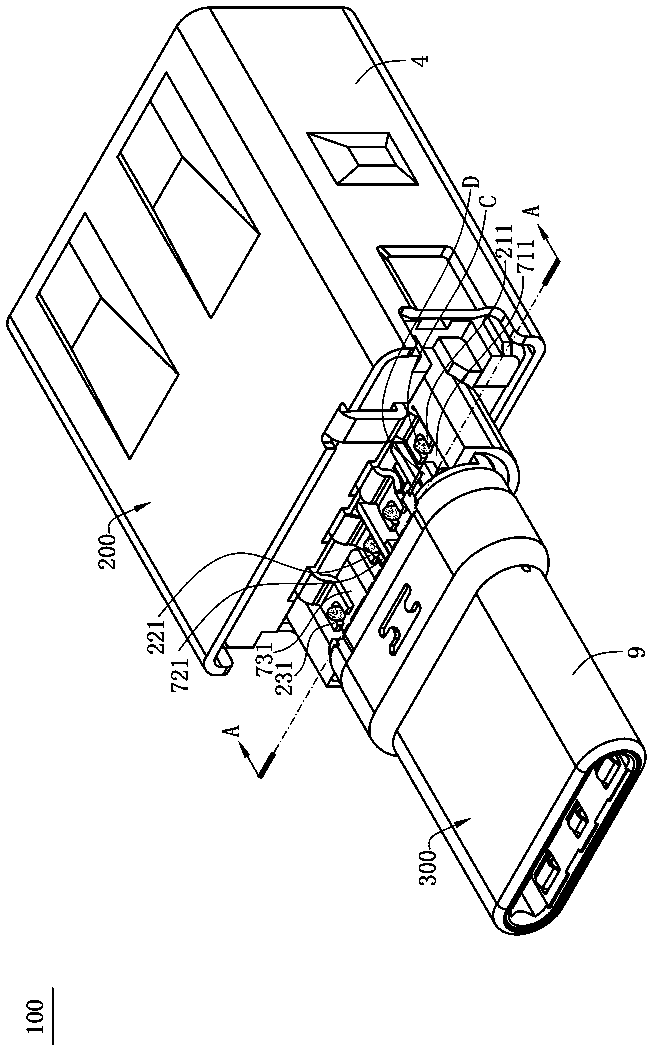

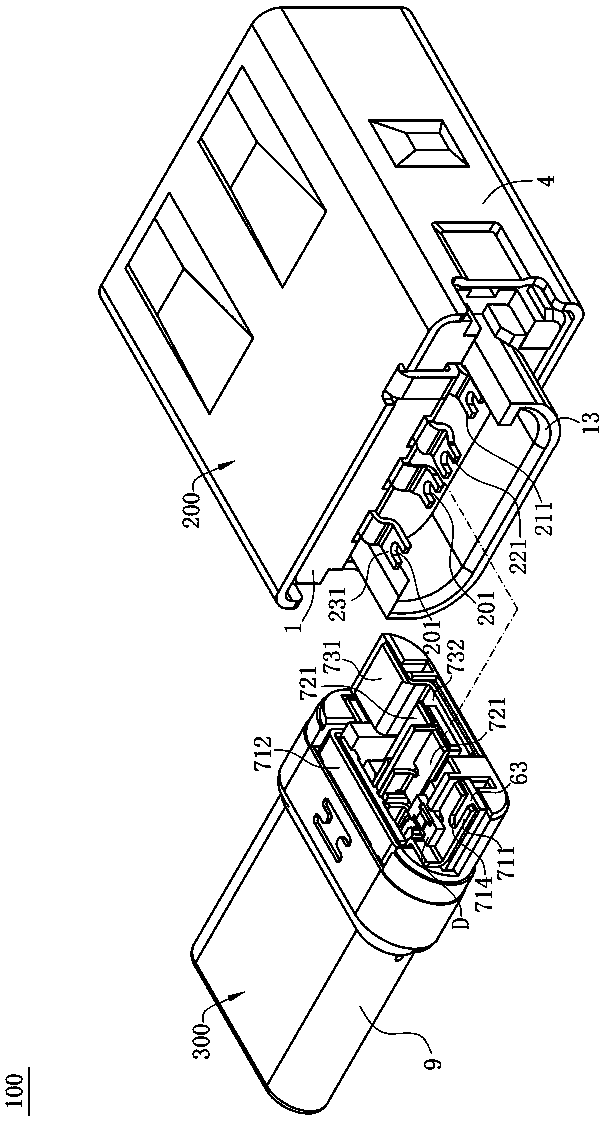

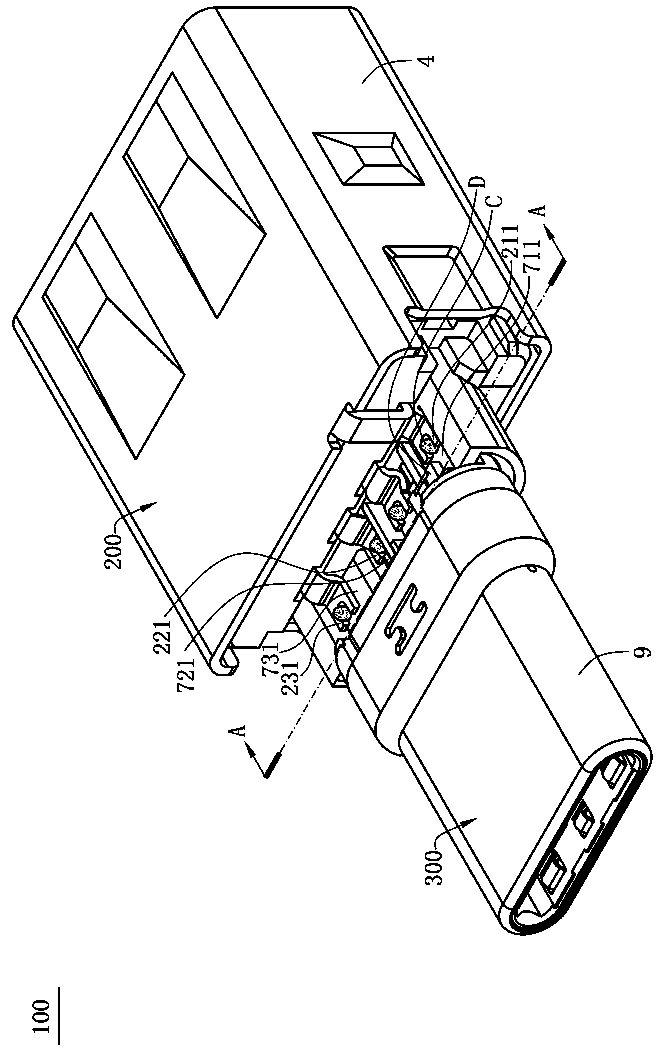

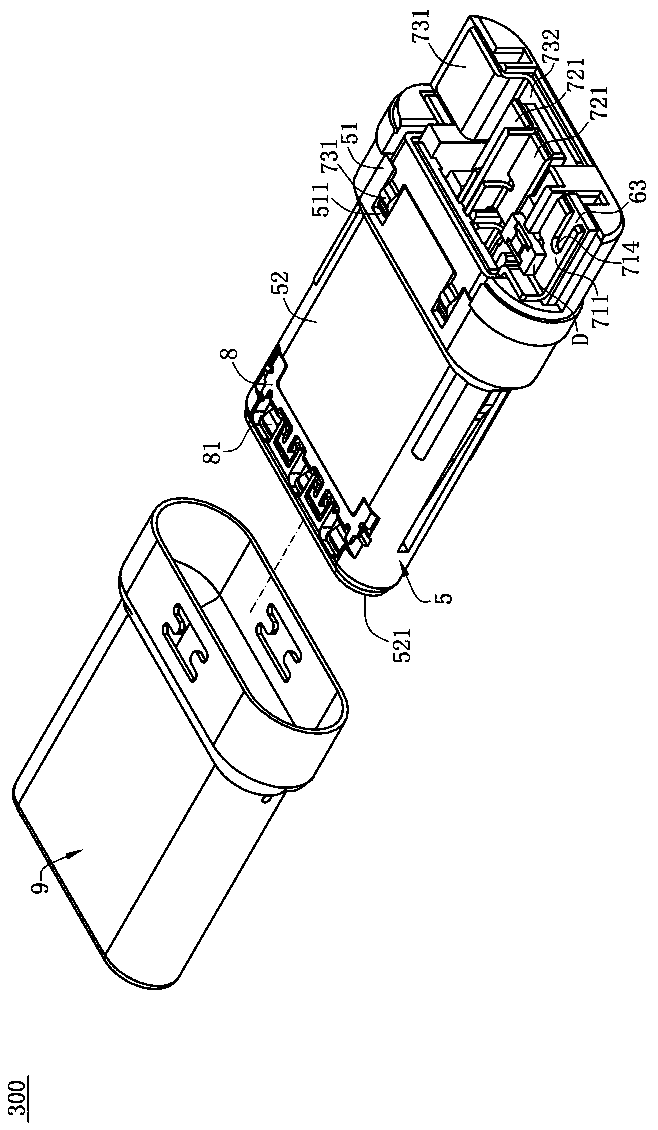

Adapter

ActiveCN108321573AReduce the number of partsMiniaturizationSoldered/welded conductive connectionsCoupling contact membersMiniaturizationEngineering

The present invention discloses an adapter. The adapter includes a first connector and a second connector which is located behind the first connector and is electrically connected with the first connector; the first connector comprises a first body; a first grounding terminal is fixed to the first body; the second connector comprises a second body; a second grounding terminal and a shielding terminal are fixed to the second body; and the first grounding terminal, the second grounding terminal, and the shielding terminal all directly contact with one another. According to the adapter, a PCBA isnot required to be adopted to connect the terminal of the first connector and the terminals of the second connector, and therefore, the number of the parts of the adapter is decreased, the miniaturization of the adapter can be facilitated, and the production cost of the adapter can be decreased.

Owner:DEYI PRECISION ELECTRONIC IND CO LTD PANYU

Packaging substrate and method of fabricating the same

InactiveUS20120097430A1Shortening electrical signal transmission pathShort production processSemiconductor/solid-state device detailsSolid-state devicesEngineeringWire bonding

A packaging substrate and a method of fabricating the packaging substrate. The packaging substrate includes: a dielectric layer that has an external contact surface and an opposing chip mounting surface; a circuit layer that is embedded in the dielectric layer and exposed from the external contact surface and the chip mounting surface, the circuit layer having wire-bonding pads, conductive pads, and a circuit that electrically connects the wire-bonding pads and the conductive pads, wherein the widths of the wire-bonding pads, conductive pads, and the circuit narrow gradually from chip mounting surface to the external contact surface; and a first insulating protective layer disposed on the external contact surface of the dielectric layer and covering the dielectric layer and the circuit layer, a plurality of conductive pad openings being formed in the first insulating protective layer for exposing the conductive pads. The dielectric layer is used directly as a foundation of the packaging substrate, thereby providing advantage in miniaturization, simpler fabrication procedure, and thus low cost production.

Owner:UNIMICRON TECH CORP

Packaging structure of MEMS (Micro Electro Mechanical Systems) chip integration

InactiveCN106335868AAvoid oversized requirementsSmall sizeSolid-state devicesFluid speed measurementLead bondingParasitic capacitance

The invention discloses a packaging structure of MEMS (Micro Electro Mechanical Systems) chip integration. On an ASIC (Application Specific Integrated Circuit) chip, a silicon through hole is manufactured to lead signal output on the front side of the ASIC chip to the back surface of the ASIC chip, and the electrical interconnection of the ASIC chip and a base plate is realized through a metal re-wiring layer and solder bumps on the back surface. According to the way, a signal transmission path is reduced, meanwhile, a phenomenon that a lead bonding connection way requires an overlarge base plate area is avoided, and the size of the packaging structure is reduced. The front side of the MEMS chip and the front side of the ASIC chip are electrically connected directly through a metal lead to guarantee the minimum path of signal transmission and avoid introducing stray capacitance. Or a silicon through hole technology is used for leading the signal output on the front side of the MEMS chip to the back surface of the MEMS chip, then the electric interconnection of the MEMS chip and the ASIC chip is realized through the metal re-wiring layer and the solder bumps, furthermore, the signal transmission path is reduced, and the connection way of lead bonding is completely avoided so as to further reduce the size of the packaging structure of the chip.

Owner:GOERTEK INC

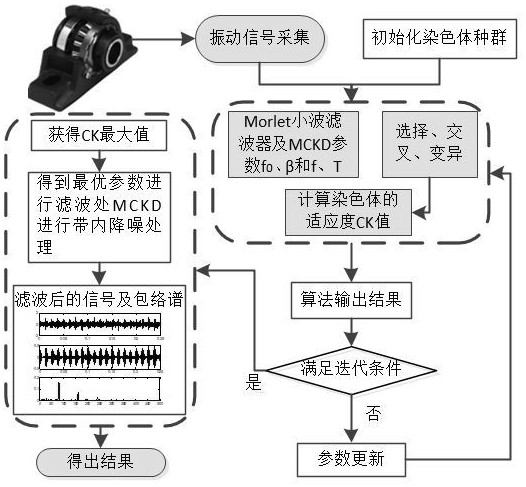

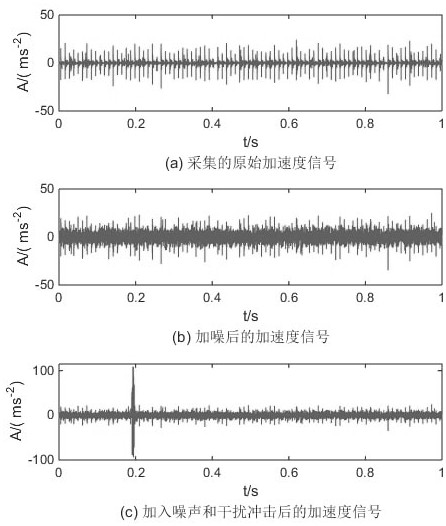

Bearing fault diagnosis method based on synchronous optimization of wavelet filter and MCKD by using NGAs

ActiveCN111896260AGuaranteed validityElimination of high-amplitude occasional shocksMachine part testingGenetic algorithmsGenetics algorithmsWavelet filter

The invention discloses a bearing fault diagnosis method based on synchronous optimization of wavelet filter and MCKD by using NGAs. The method comprises the steps: firstly, collecting an original vibration signal with a sensor and inputting the original vibration signal; setting an initial condition of an ecological niche genetic algorithm (NGAs); synchronously and jointly optimizing the centralfrequency and bandwidth of a Morlet wavelet filter and the length and period of a maximum correlation kurtosis deconvolution (MCKD) filter by using NGAs; taking correlation kurtosis (CK) of bearing fault impact period generation characteristics as an optimization index, and realizing parameter adaptive synchronization optimization of the front and back two processing steps; conducting in-band noise reduction processing on filtering signals by adopting Morlet band-pass filtering preprocessing and MCKD; and finally, judging whether faults exist or not and fault types through an envelope spectrumof the signals obtained after MCKD in-band noise reduction. Analysis of simulation signals, laboratory signals and experimental data shows that the method provided by the invention can effectively eliminate external accidental interference impact influences and reduce signal transmission paths and noise influences, and the effectiveness of bearing fault diagnosis is ensured.

Owner:EAST CHINA JIAOTONG UNIVERSITY

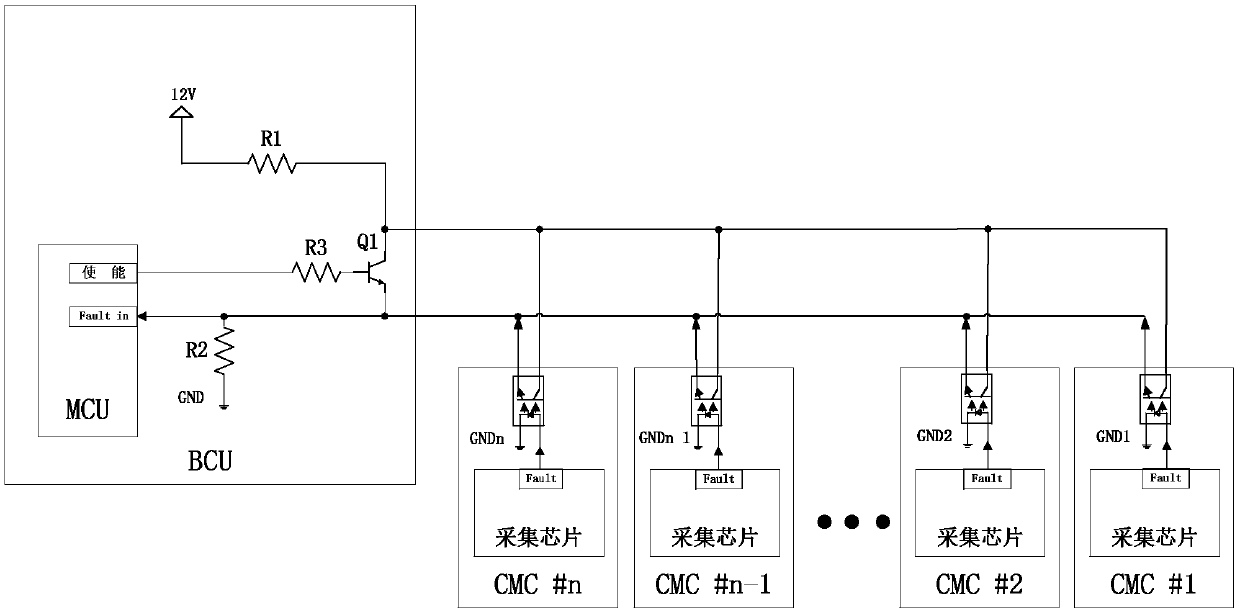

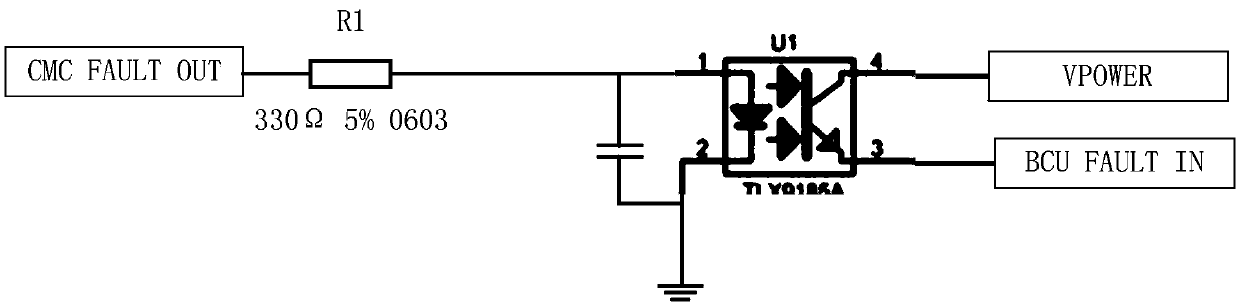

Battery cell fault detection circuit and detection method

InactiveCN109633469AShorten the signal transmission pathReduce failure rateElectrical testingSecondary cells testingFailure rateBattery cell

The invention provides a battery cell fault detection circuit and a detection method. The battery cell fault detection circuit is added to a battery pack formed by a plurality of cells which are connected to each other. The circuit comprises a controller, acquisition chips and processing and sending units, wherein the acquisition chips correspond to each cell, detect the fault of each cell and output a fault signal when the cell has a fault; the processing and sending units correspond to the plurality of the acquisition chips; and each processing and sending unit is used to receive the fault signal sent by the corresponding acquisition chip and process the signal, and then send the signal to the controller. In the technical scheme, when any cell has the fault, a Fault signal is generated by the acquisition chip corresponding to the cell which has the fault and is directly sent to the controller after being processed so that a signal transmission path is effectively shortened and a failure rate is reduced.

Owner:SVOLT ENERGY TECHNOLOGY CO LTD

Ceramic adapter plate used for mounting large-size ceramic tube shell

PendingCN106952889AReduce installation usageReduce reliability risksSemiconductor/solid-state device detailsSolid-state devicesThermal expansionLarge size

The invention discloses a ceramic adapter plate used for mounting a large-size ceramic tube shell, and relates to the ceramic packaging technology field. The ceramic adapter plate comprises a ceramic substrate. The front side of the ceramic substrate is provided with a metal conduction layer, and the back side of the ceramic substrate is provided with metal pin leads. The metal pin leads are communicated with the metal conduction layer. Reliability hidden troubles caused by a situation that the thermal expansion coefficient of a large-size ceramic tube shell and the thermal expansion coefficient of a PCB are mismatched can be effectively reduced, a signal transmission path can be shortened while the contour size of a large-size ceramic lead-free carrier is guaranteed, the loss is reduced, and the usage reliability is improved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Semiconductor package structure and manufacturing method thereof

ActiveUS20130049197A1Improve reliabilitySmall package thicknessSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor package

A manufacturing method of semiconductor package structure includes: providing a first dielectric layer having multiple through holes; providing a second dielectric layer having multiple conductive vias and a chip-containing opening; laminating the second dielectric layer onto the first dielectric layer; disposing a chip in the chip-containing opening and adhering a rear surface of the chip onto the first dielectric layer exposed by the chip-containing opening; forming a redistribution circuit layer on the second dielectric layer wherein a part of the redistribution circuit layer extends from the second dielectric layer onto an active surface of the chip and the conductive vias so that the chip electrically connects the conductive vias through the partial redistribution circuit layer; forming multiple solder balls on the first dielectric layer wherein the solder balls are in the through holes and electrically connect the chip through the conductive vias and the redistribution circuit layer.

Owner:CHIPMOS TECH INC

Packaging substrate having embedded passive component and fabrication method thereof

ActiveUS9179549B2Reduce the overall heightShorten the signal transmission pathPrinted circuit assemblingFinal product manufactureEngineeringDielectric layer

A packaging substrate includes: a core board with at least a cavity; a dielectric layer unit having upper and lower surfaces and encapsulating the core board and filling the cavity; a plurality of positioning pads embedded in the lower surface of the dielectric layer unit; at least a passive component having upper and lower surfaces with electrode pads disposed thereon and embedded in the dielectric layer unit so as to be received in the cavity of the core board at a position corresponding to the positioning pads; first and second wiring layers disposed on the upper and lower surfaces of the dielectric layer unit and electrically connected to the electrode pads of the upper and lower surfaces of the passive component through conductive vias, respectively. By embedding the passive component in the core board and the dielectric layer unit, the invention effectively reduces the height of the overall structure.

Owner:UNIMICRON TECH CORP

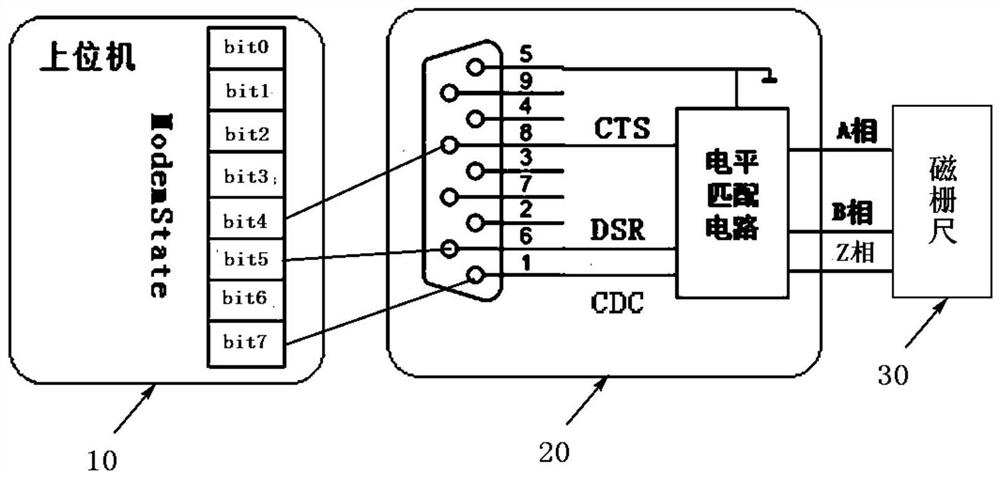

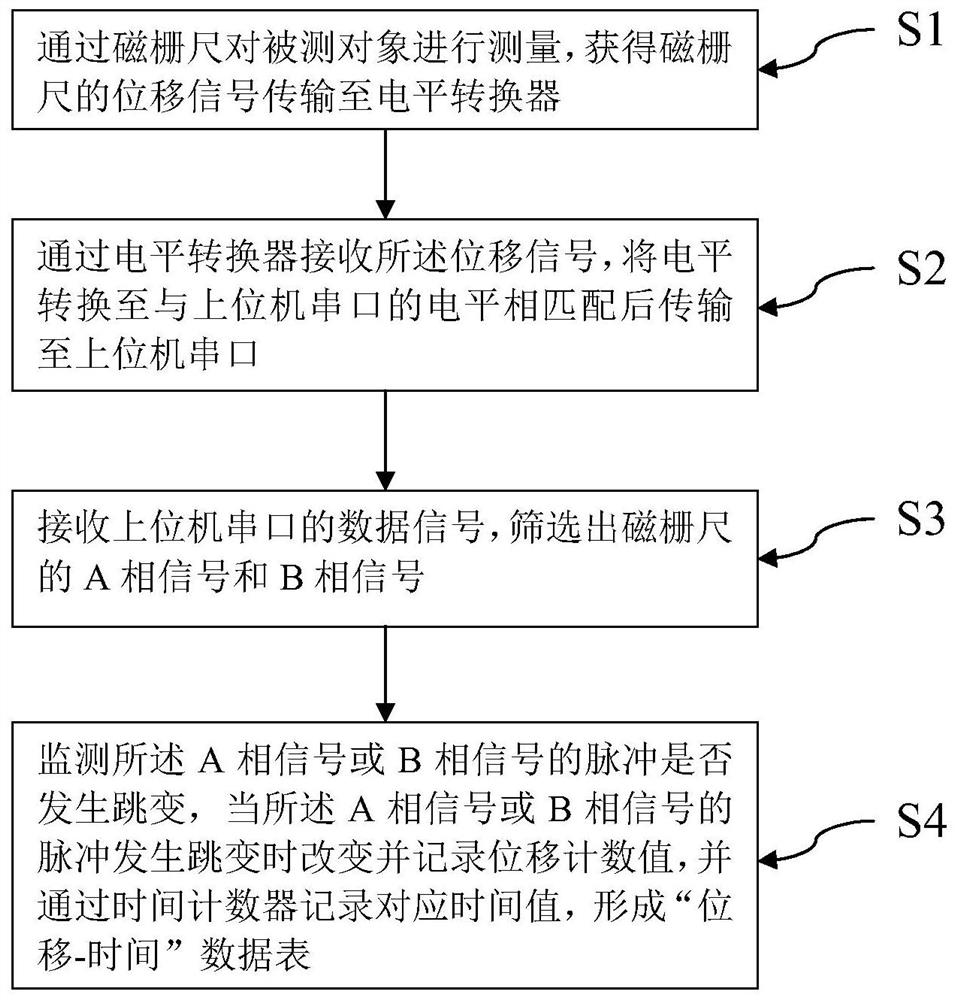

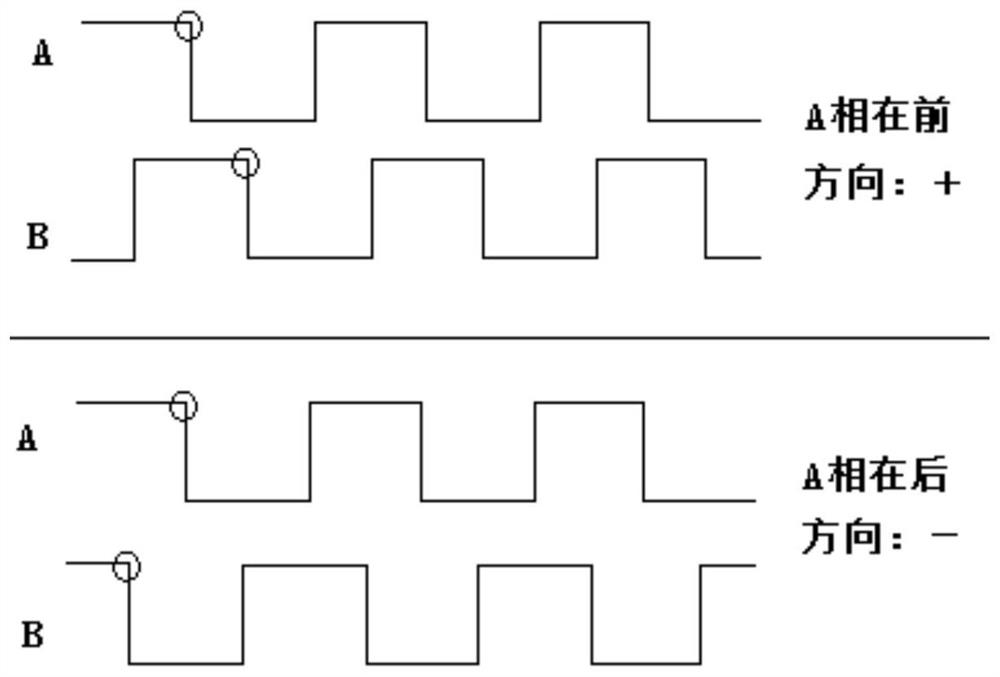

Magnetic grating ruler reading receiving method and device and electronic equipment

PendingCN111814650AShorten the signal transmission pathHigh speedWelding/cutting auxillary devicesCharacter and pattern recognitionConvertersLevel shifting

The invention provides a magnetic grating ruler reading receiving method and device, and the magnetic grating ruler reading receiving method comprises the following steps: carrying out the measurementof a measured object through a magnetic grating ruler, obtaining a displacement signal of the magnetic grating ruler, and transmitting the displacement signal to a level converter; receiving the displacement signal through a level converter, carrying out level conversion, and then transmitting the displacement signal to an upper computer serial port; receiving a data signal of an upper computer serial port, and screening out an A-phase signal and a B-phase signal of the magnetic railing ruler; and monitoring whether the pulse of the A-phase signal or the B-phase signal jumps or not, changingand recording a displacement count value when the pulse of the A-phase signal or the B-phase signal jumps, and recording a corresponding time value through a time counter. The magnetic grating ruler reading receiving method has the advantages of short signal transmission path, high signal transmission speed and high reliability.

Owner:珠海市迈卡威超声波技术有限公司

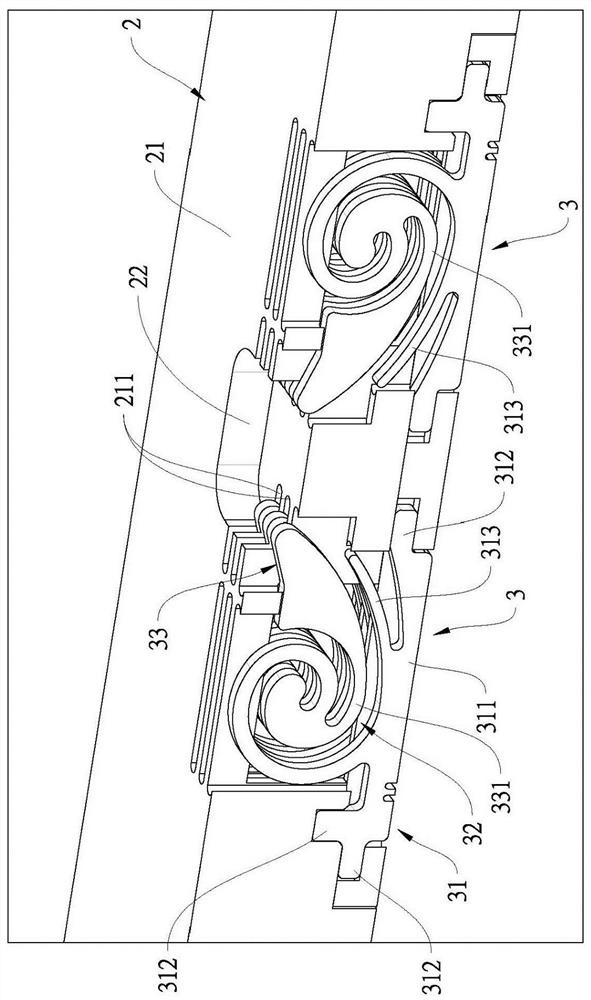

Probe and test device

PendingCN112526178AAchieving test efficacyTest fitElectrical measurement instrument detailsElectrical testingEngineeringMechanical engineering

The invention discloses a probe and a test device, which are used for testing a chip, the probe is arranged in a mounting hole of a test seat, the probe is in a sheet shape and is made of a conductivematerial, and the probe comprises a base part, a buffer part and a contact part, wherein the base part is located in the mounting hole and clamped on the test seat, the buffer part is located in themounting hole and integrally and spirally extends outwards from the base part, and the contact part is located in the mounting hole and integrally extends from the buffer part to be separated from thebase part; a tail end of the contact part protrudes out of the mounting hole and extends into the test space. The probe is integrally formed, so impedance and noise can be reduced, manufacturing costof the testing device comprising the probe is reduced, and assembling convenience is improved.

Owner:吴俊杰

Heterogeneously integrated thermal infrared sensing element and thermal infrared sensor

InactiveCN112393806AWon't breakConditions that will not damage the circuitPyrometry using electric radation detectorsInfraredElectrical conductor

A heterogeneously integrated thermal infrared sensing element includes: a substrate; the sensing circuit that is positioned in or on the substrate; the cavity that is located in or on the substrate, and the sensing circuit is located below the cavity; the thermocouple that is made of a material which is manufactured on the second substrate and transferred above the cavity in a bonding mode, the thermocouple comprises a first conductor and a second conductor, the first ends of the first conductor and the second conductor of the thermocouple are connected to a hot end located above the cavity, and the second end of the first conductor and the second conductor of the thermocouple are connected to a hot end located above the cavity; the second ends of the first conductor and the second conductor of the thermocouple are cold ends arranged at the edge of the cavity and are electrically connected to the sensing circuit.

Owner:李美燕

Semiconductor module and an electronic system including the same

ActiveUS8456000B2Shorten the signal transmission pathImprove cooling efficiencySubstation/switching arrangement detailsSemiconductor/solid-state device detailsElectronic systemsDevice form

A three-dimensional semiconductor module and an electronic system including the same are provided. The semiconductor module includes a module substrate, a logic device formed on a part of the module substrate, and a plurality of memory devices formed on another part of the module substrate, wherein the plurality of memory devices are disposed perpendicular to the logic device, and the module substrate on which the plurality of memory devices are formed is supported by a supporter. The electronic system includes the semiconductor module.

Owner:SAMSUNG ELECTRONICS CO LTD

Battery pack

ActiveUS10454282B2Shorten the signal transmission pathImprove support strengthFinal product manufactureCylindrical casing cells/batteryEngineeringBattery cell

A battery pack includes at least two battery cells; a circuit board to control charging and discharging operations of the battery cells; and a connection tab electrically connected to the battery cells, extending towards the circuit board, and including a bent portion proximal to the battery cells and located within a battery area defined by the battery cells. A battery pack suitable for a compact type device is provided and a low-resistive design may be applied to the battery pack.

Owner:SAMSUNG SDI CO LTD

Frame packaging structure integrating passive device and manufacturing method thereof

ActiveCN106935517AShorten the signal transmission pathImprove integration densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

The invention discloses a frame packaging structure integrating a passive device and a manufacturing method thereof. The frame packaging structure integrating the passive device comprises a bare chip pad, a first insulation dielectric layer, a metal structure layer, a second insulation dielectric layer and at least one conductive pad, wherein the first insulation dielectric layer is arranged below the bare chip pad; the metal structure layer is arranged below the first insulation dielectric layer; the second insulation dielectric layer is arranged below the metal structure layer; and the at least one conductive pad is arranged at a periphery of the bare chip pad. The at least one conductive pad is connected to the second insulation dielectric layer. At least one active chip is arranged on the bare chip pad. The at least one active chip is electrically connected to the conductive pad.

Owner:SANECHIPS TECH CO LTD

Semiconductor package and manufacturing method thereof

ActiveUS10431549B2Provide rigidityAvoid damageSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package including a stacked-die structure, a second encapsulant laterally encapsulating the stacked-die structure and a redistribution layer disposed on the second encapsulant and the staked-die structure is provided. The stacked-die structure includes a first semiconductor die including a first active surface, a circuit layer disposed on the first active surface, a second semiconductor die including a second active surface facing towards the first active surface, a plurality of conductive features distributed at the circuit layer and electrically connected to the first and second semiconductor die and a first encapsulant encapsulating the second semiconductor die and the conductive features. A portion of the conductive features surrounds the second semiconductor die. The redistribution layer is electrically connected to the staked-die structure. A manufacturing method of a semiconductor package is also provided.

Owner:POWERTECH TECHNOLOGY

Package structure and method of fabricating the same

InactiveCN105514081AShorten the signal transmission pathReduce signal lossSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A package structure and a method for fabricating a package structure are provided. The method includes the steps of forming a wiring layer on a carrier by electroplating; disposing at least one electronic component on the wiring layer; forming on the carrier an insulating layer that encapsulates the wiring layer and the electronic component; and removing the carrier. With the single wiring layer having one surface electrically connected the at least one electronic component and the other surface electrically connected to a plurality of conductive elements, the package structure has a signal transmission path that is shortened.

Owner:PHOENIX & CORP

Adapter

ActiveCN108321573BReduce the number of partsMiniaturizationSoldered/welded conductive connectionsCoupling contact membersMiniaturizationMechanical engineering

The present invention discloses an adapter. The adapter includes a first connector and a second connector which is located behind the first connector and is electrically connected with the first connector; the first connector comprises a first body; a first grounding terminal is fixed to the first body; the second connector comprises a second body; a second grounding terminal and a shielding terminal are fixed to the second body; and the first grounding terminal, the second grounding terminal, and the shielding terminal all directly contact with one another. According to the adapter, a PCBA isnot required to be adopted to connect the terminal of the first connector and the terminals of the second connector, and therefore, the number of the parts of the adapter is decreased, the miniaturization of the adapter can be facilitated, and the production cost of the adapter can be decreased.

Owner:DEYI PRECISION ELECTRONIC IND CO LTD PANYU

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com

![[package with stacked substrates] [package with stacked substrates]](https://images-eureka.patsnap.com/patent_img/033ecdfa-f56f-4924-ae63-d5295ab45a5a/US20050205970A1-20050922-D00000.png)

![[package with stacked substrates] [package with stacked substrates]](https://images-eureka.patsnap.com/patent_img/033ecdfa-f56f-4924-ae63-d5295ab45a5a/US20050205970A1-20050922-D00001.png)

![[package with stacked substrates] [package with stacked substrates]](https://images-eureka.patsnap.com/patent_img/033ecdfa-f56f-4924-ae63-d5295ab45a5a/US20050205970A1-20050922-D00002.png)