Patents

Literature

39922results about "Pump control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

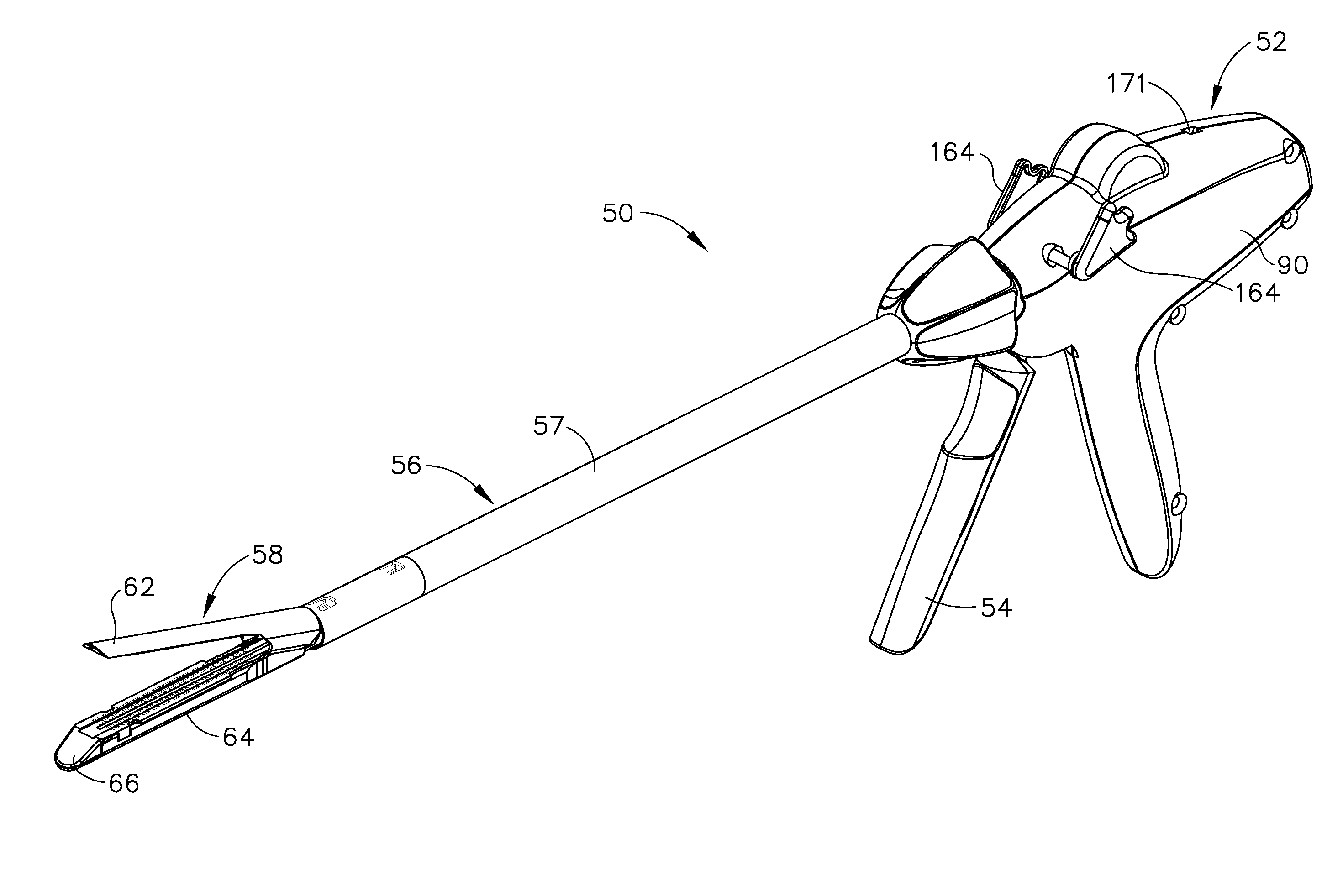

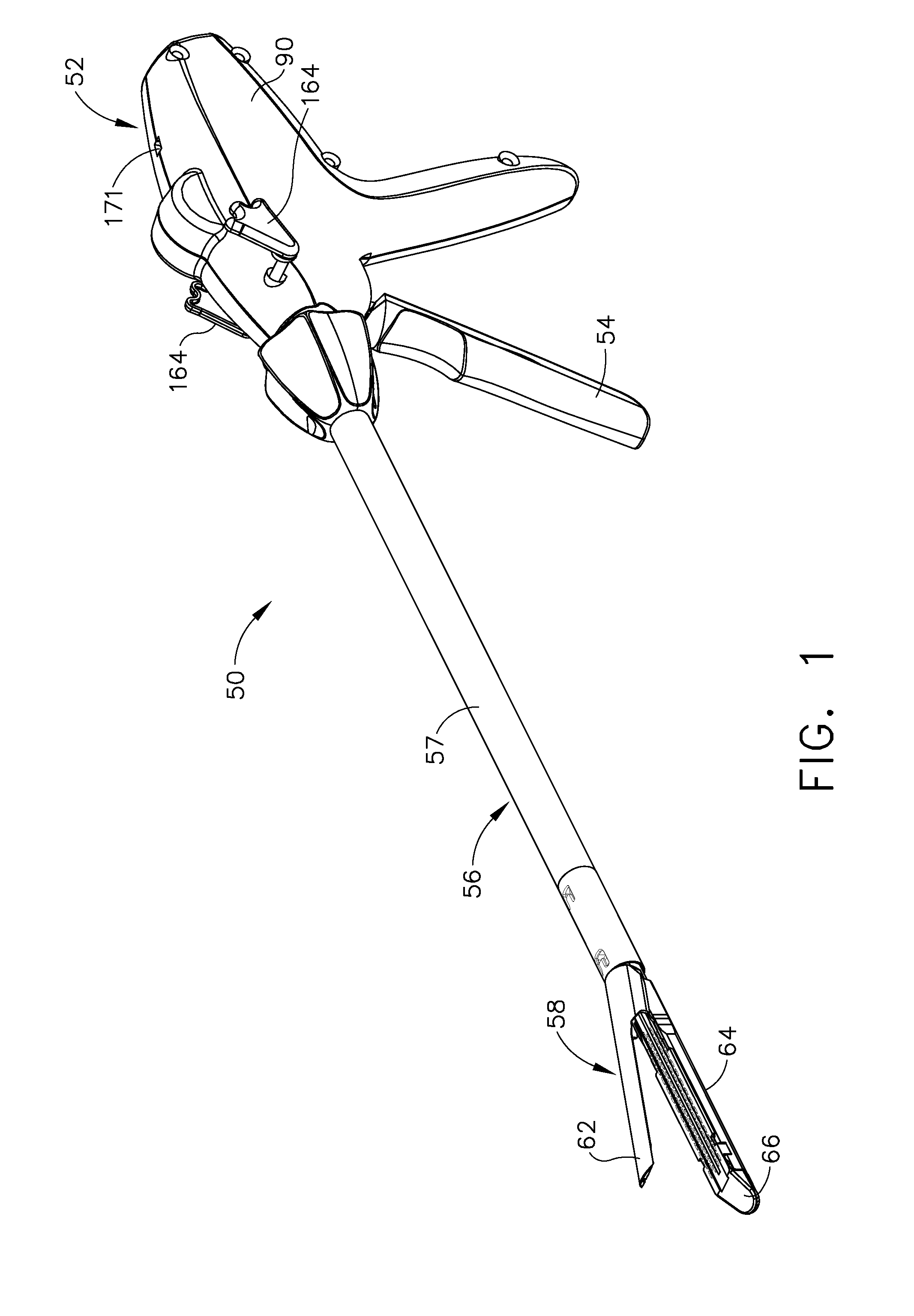

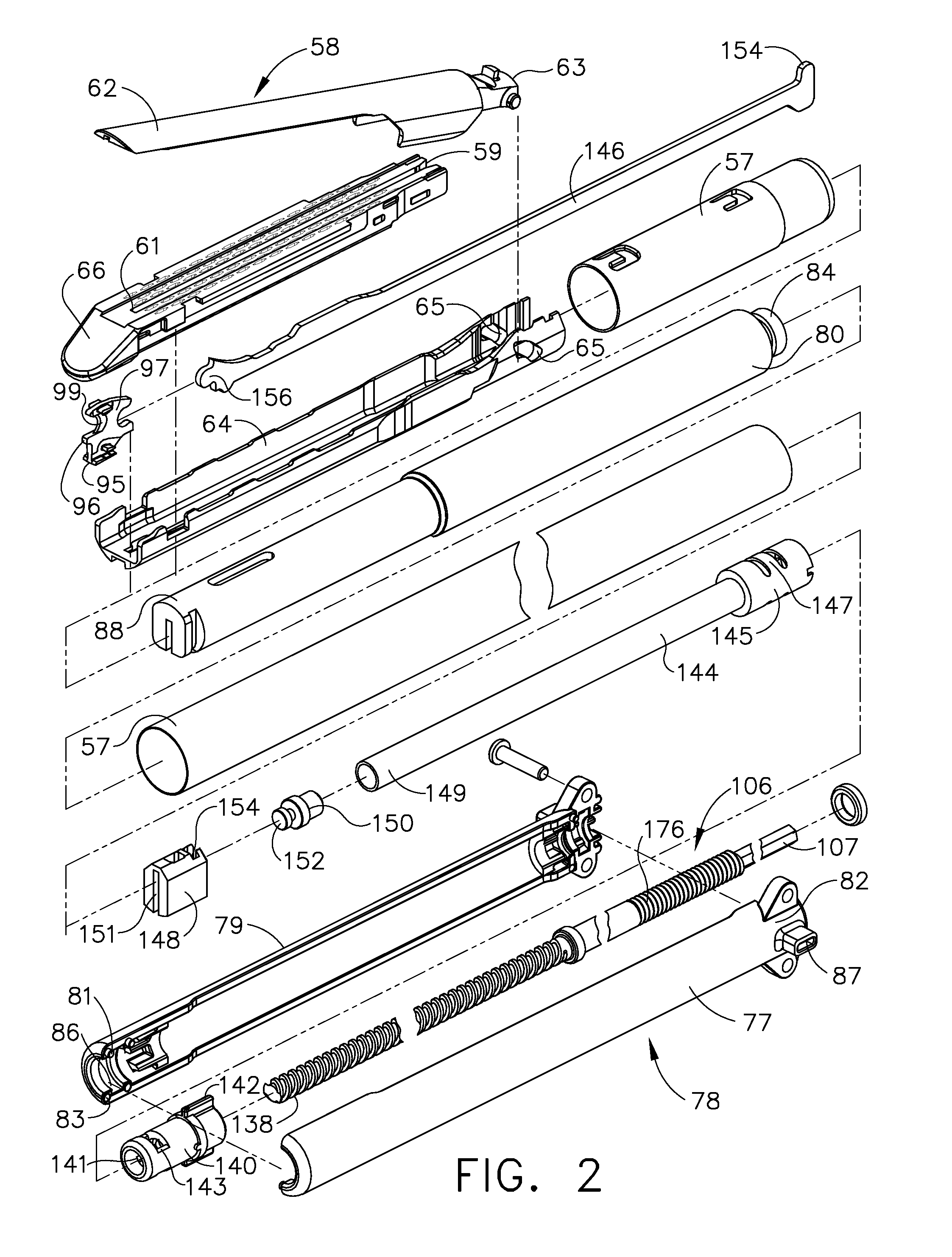

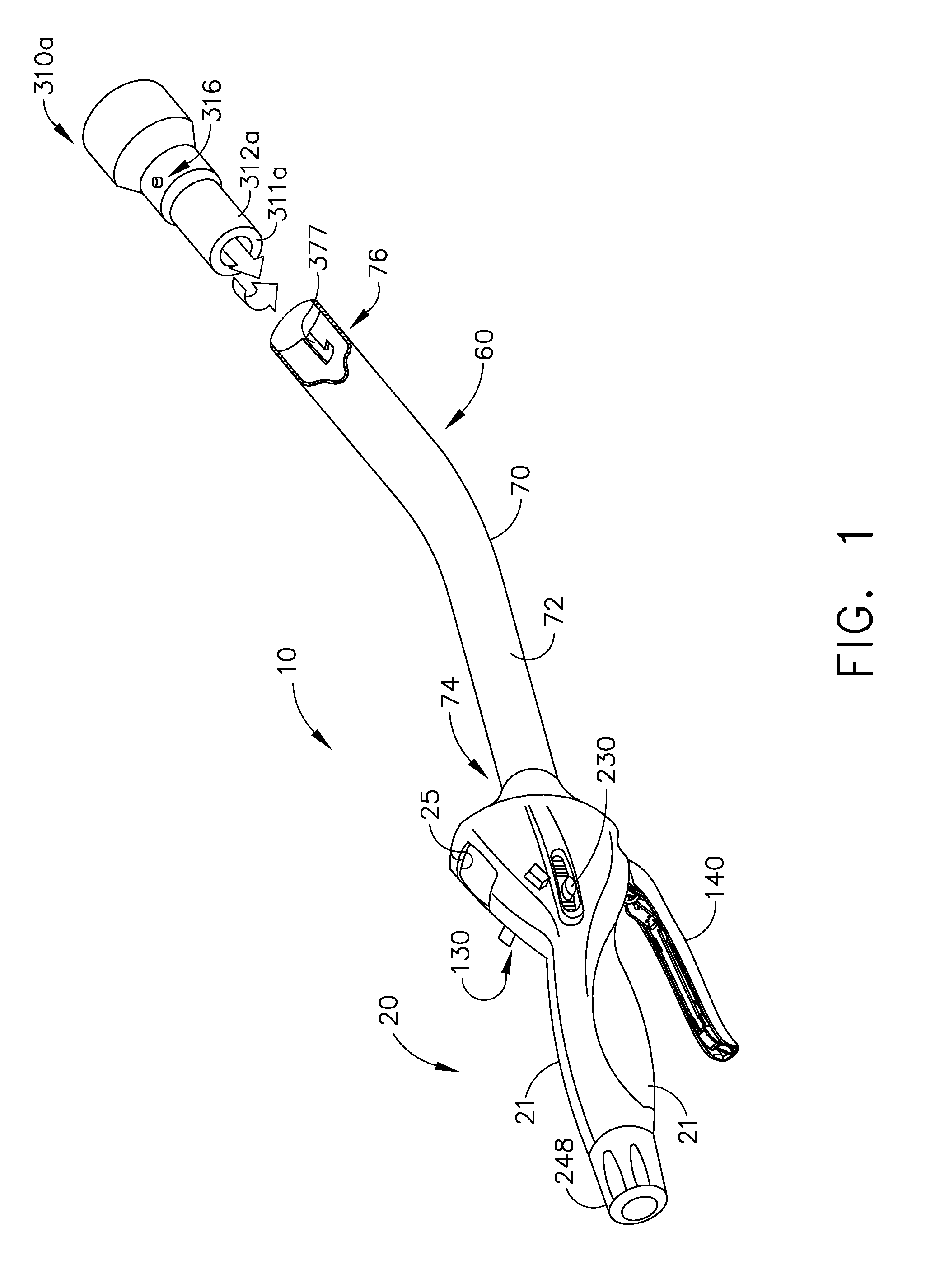

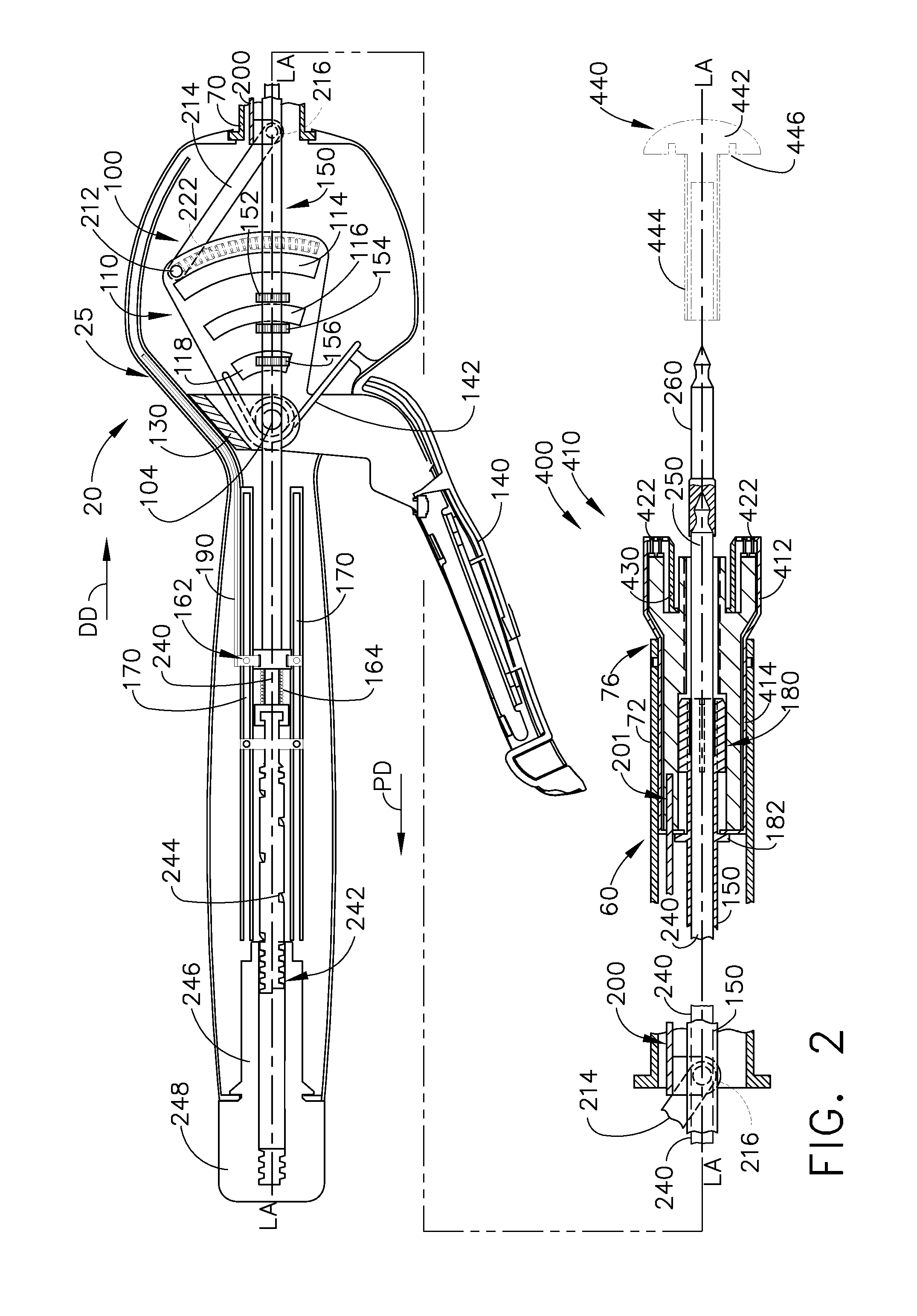

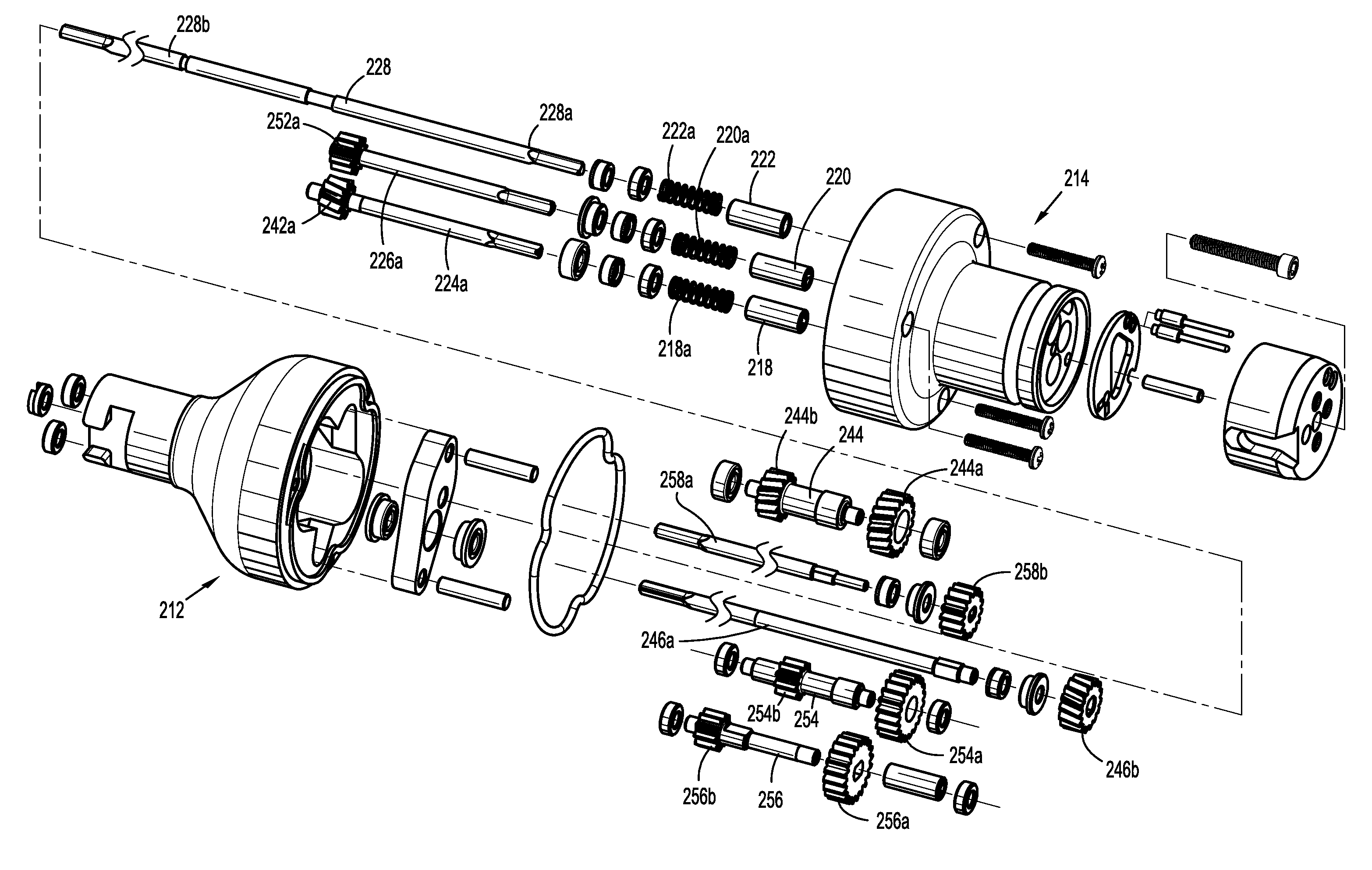

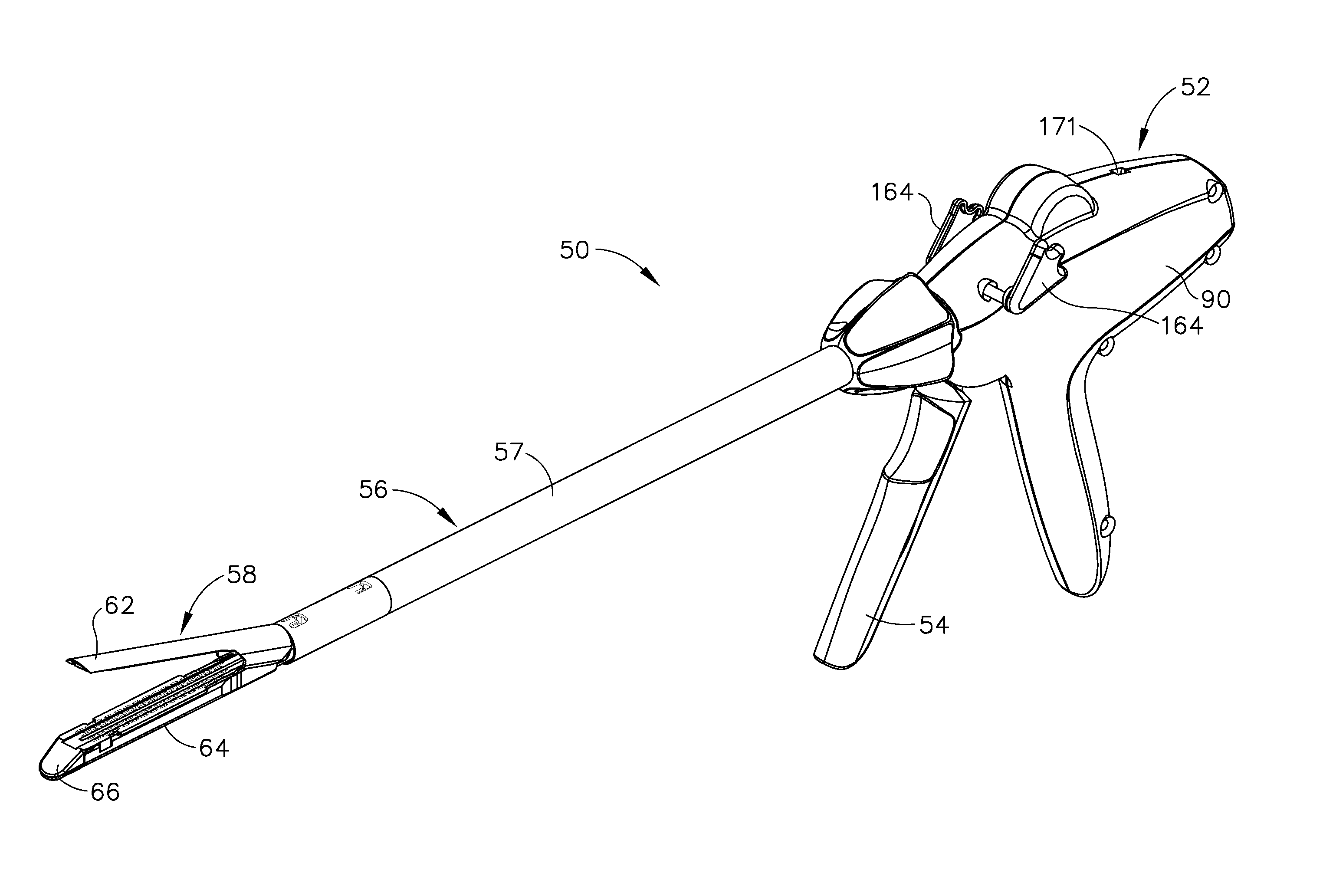

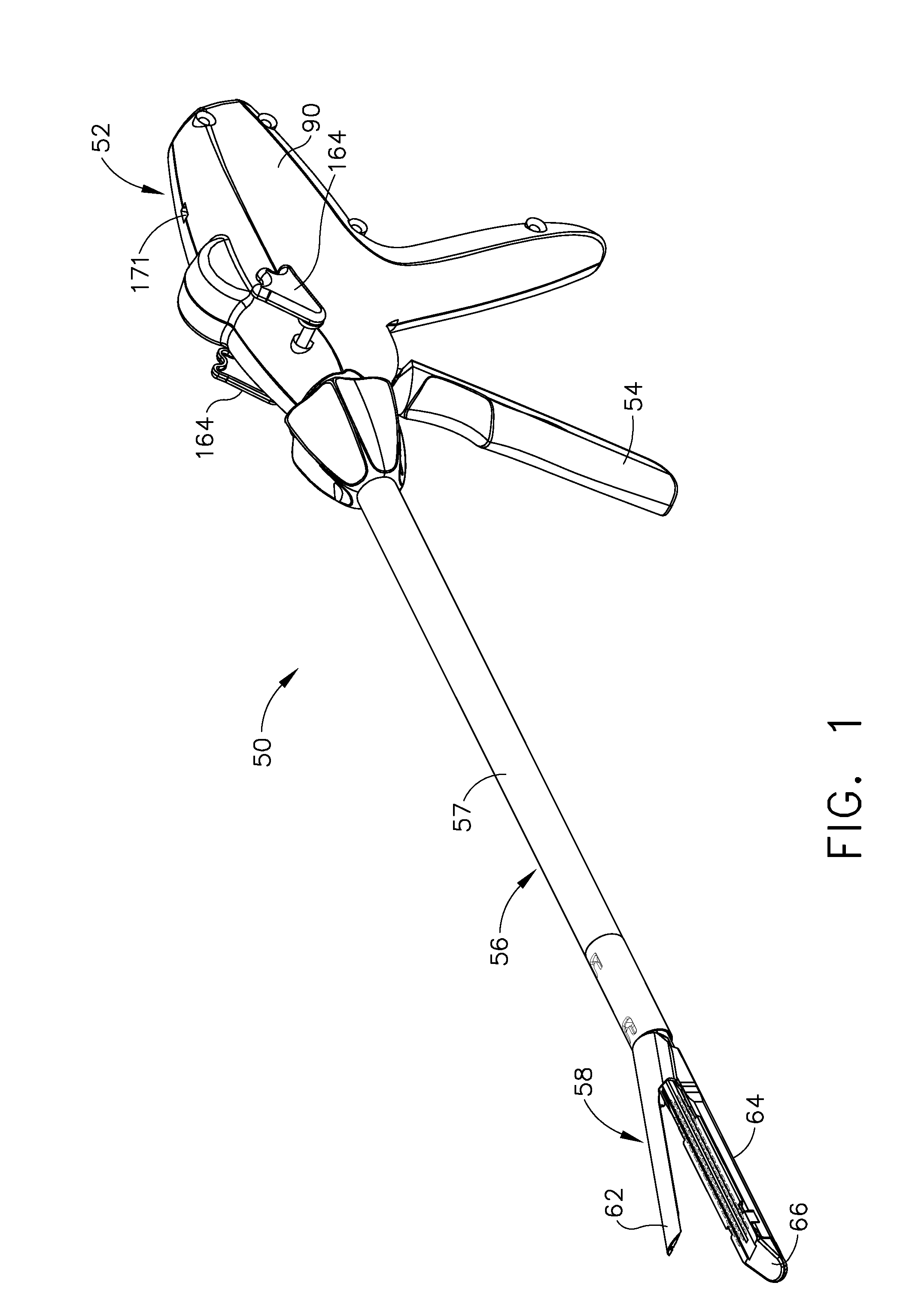

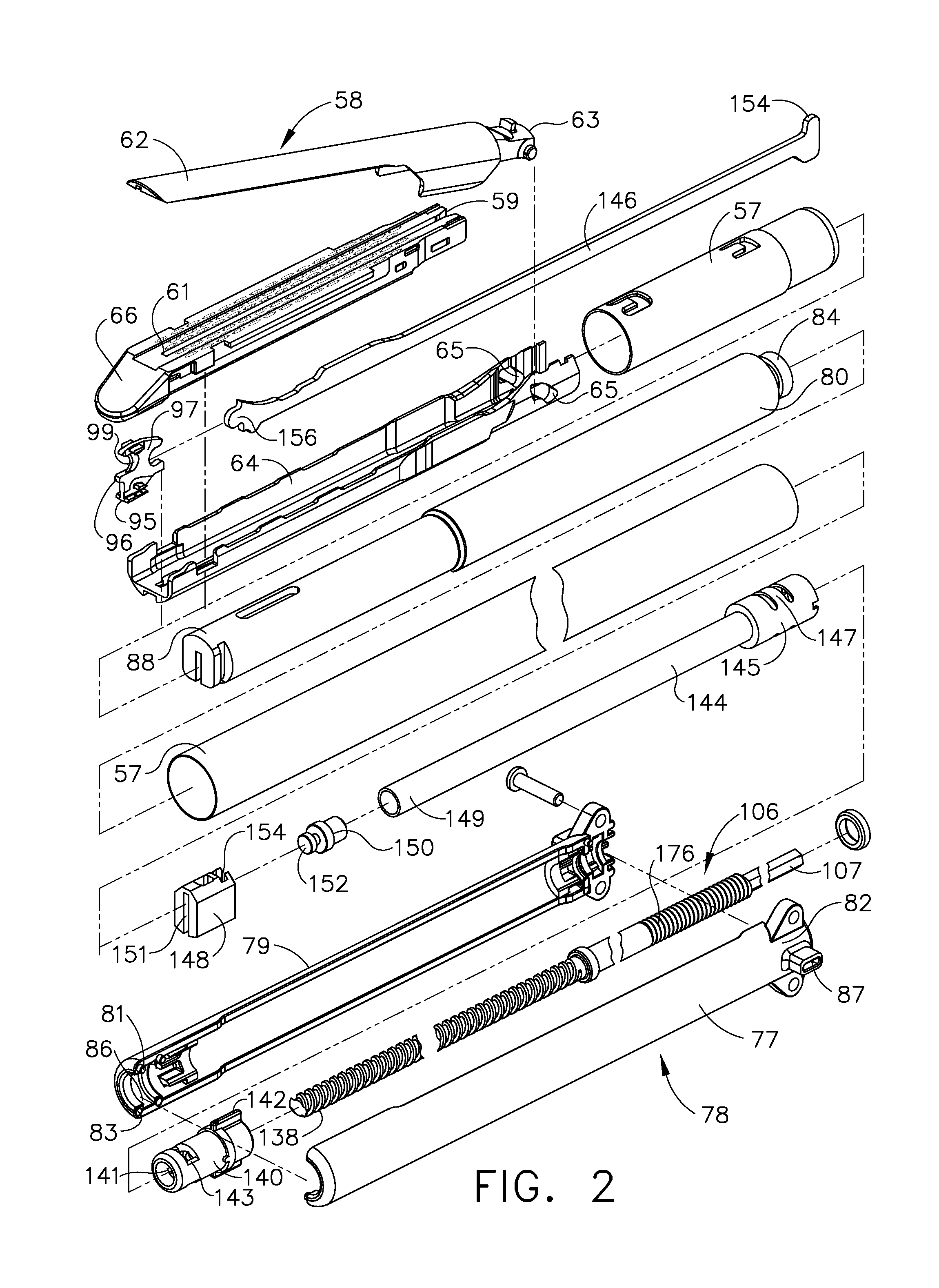

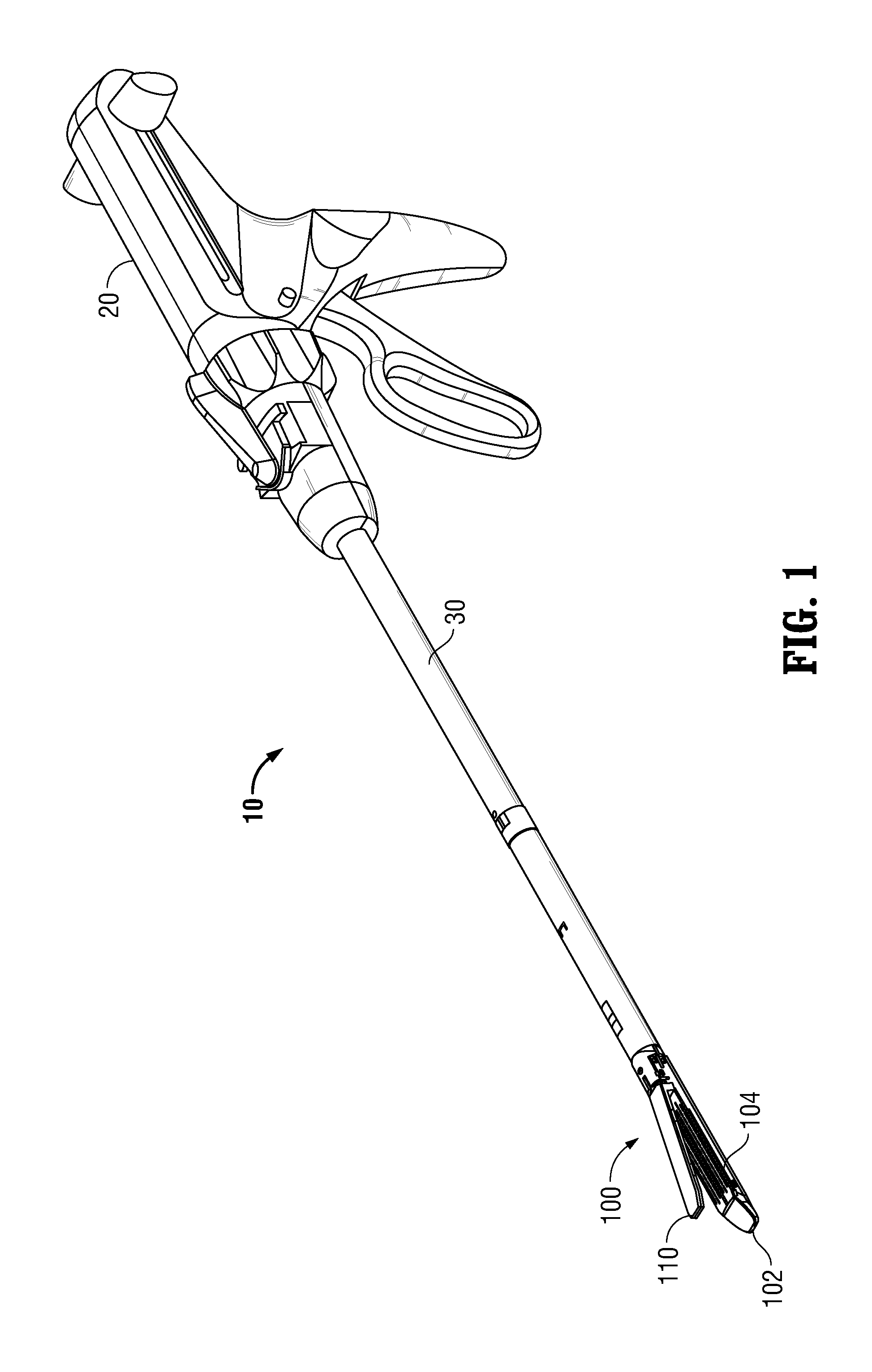

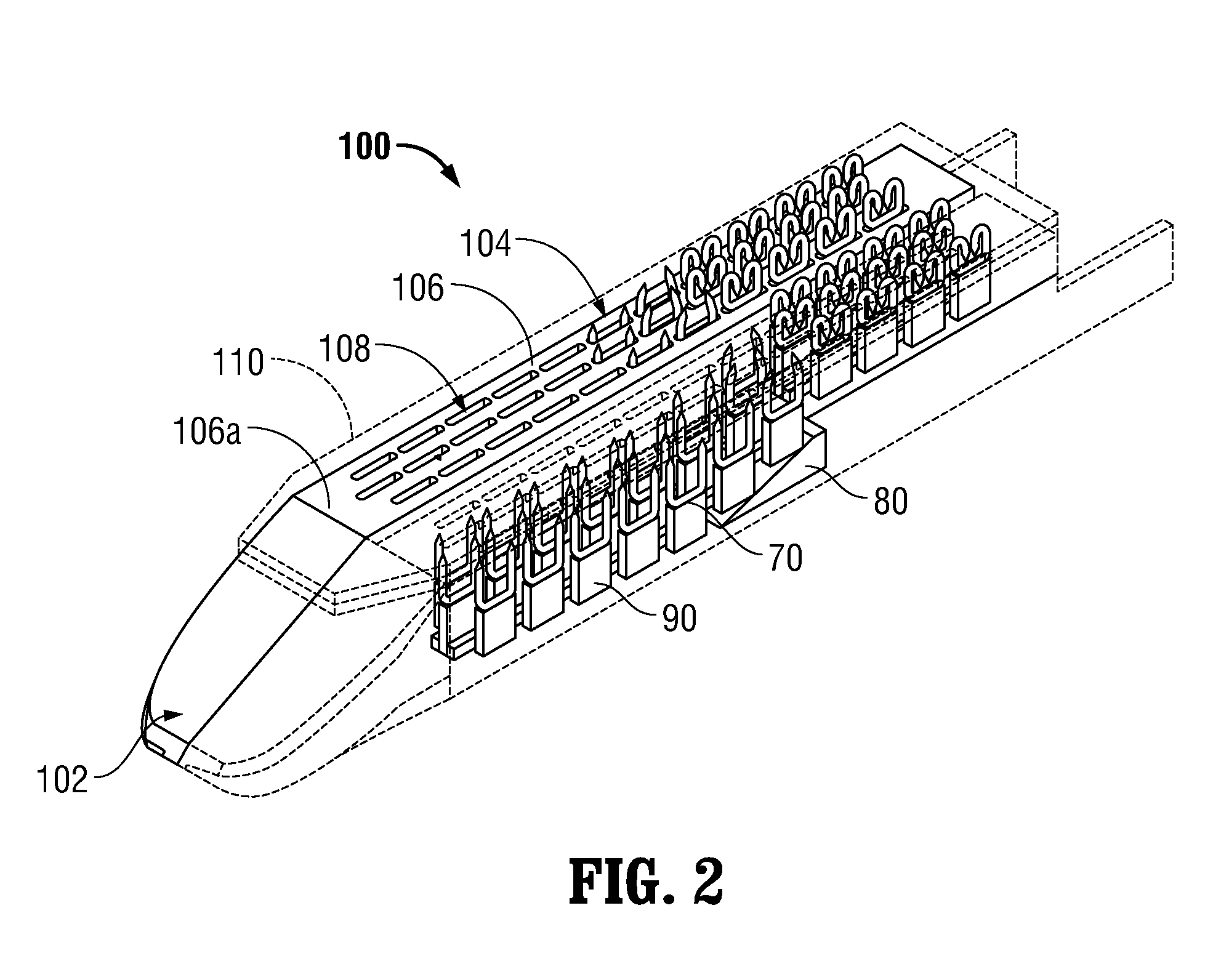

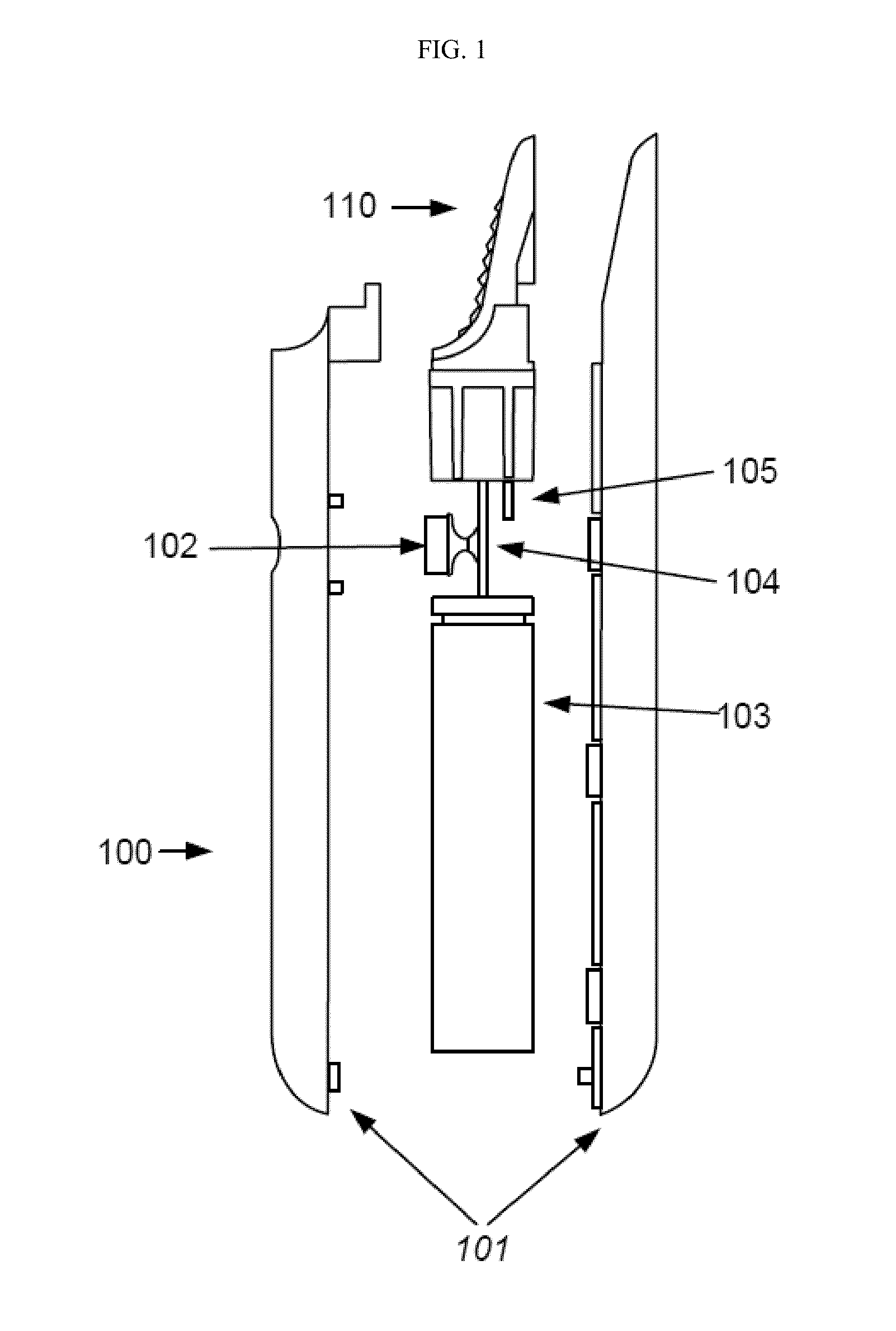

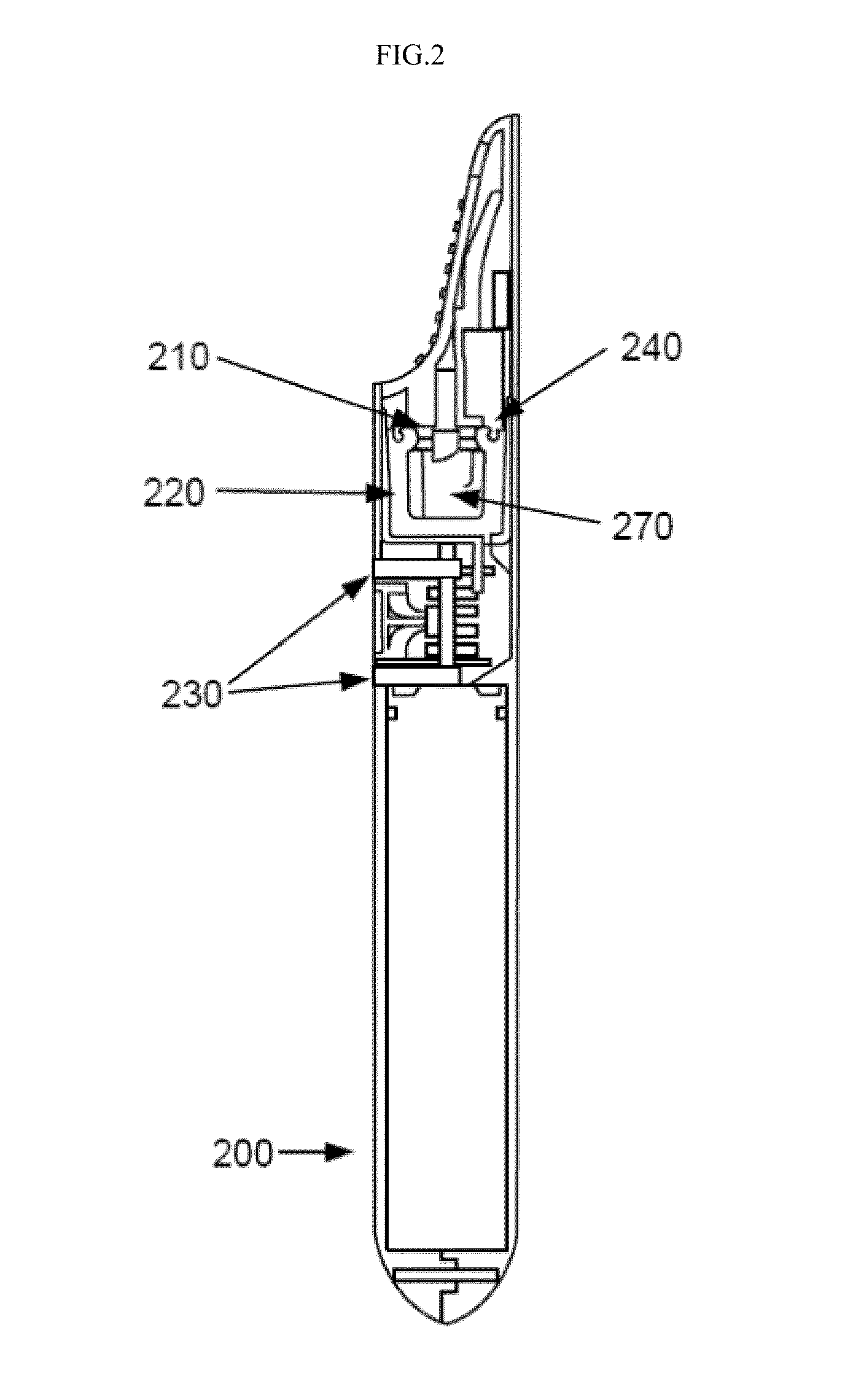

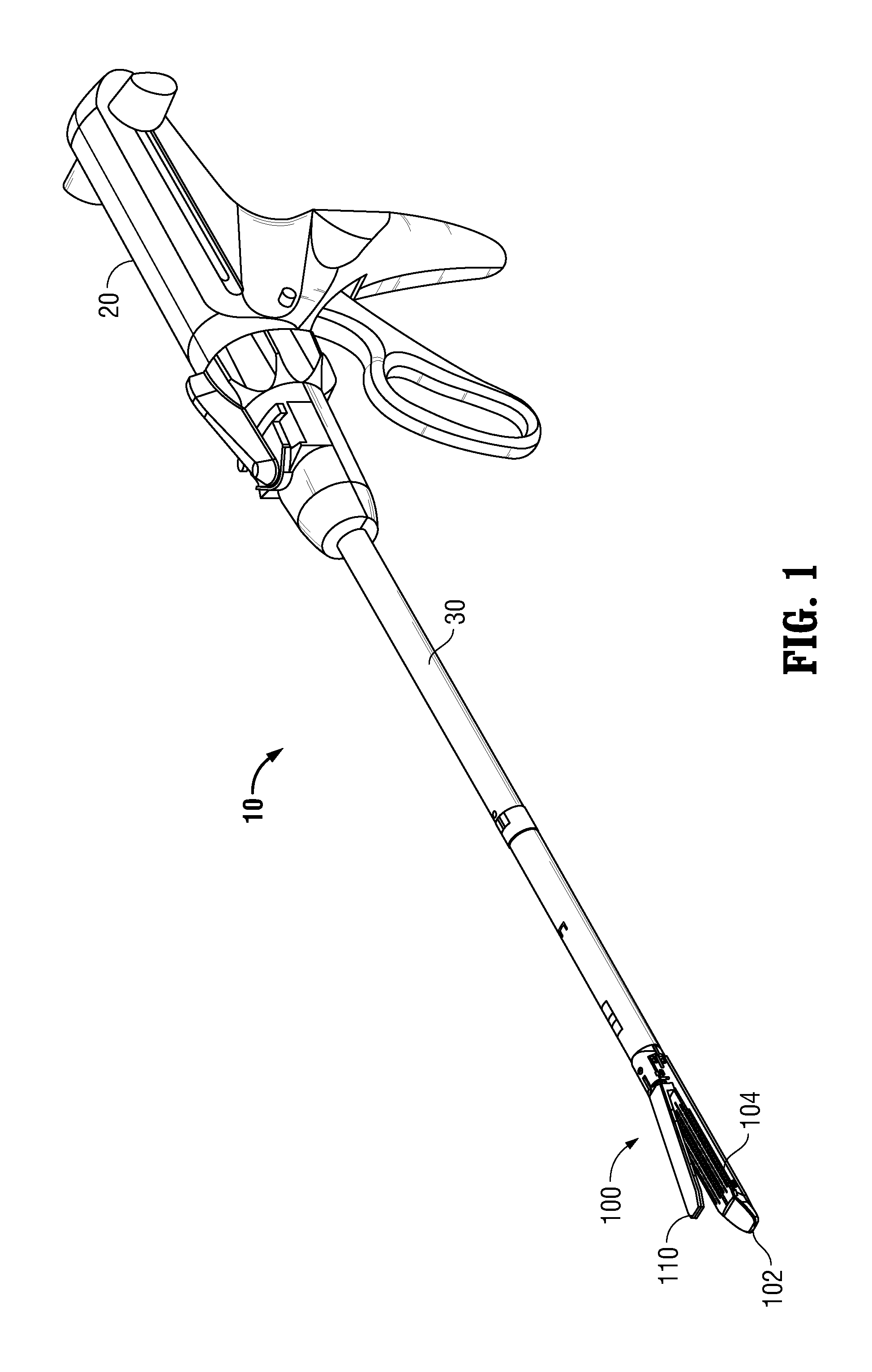

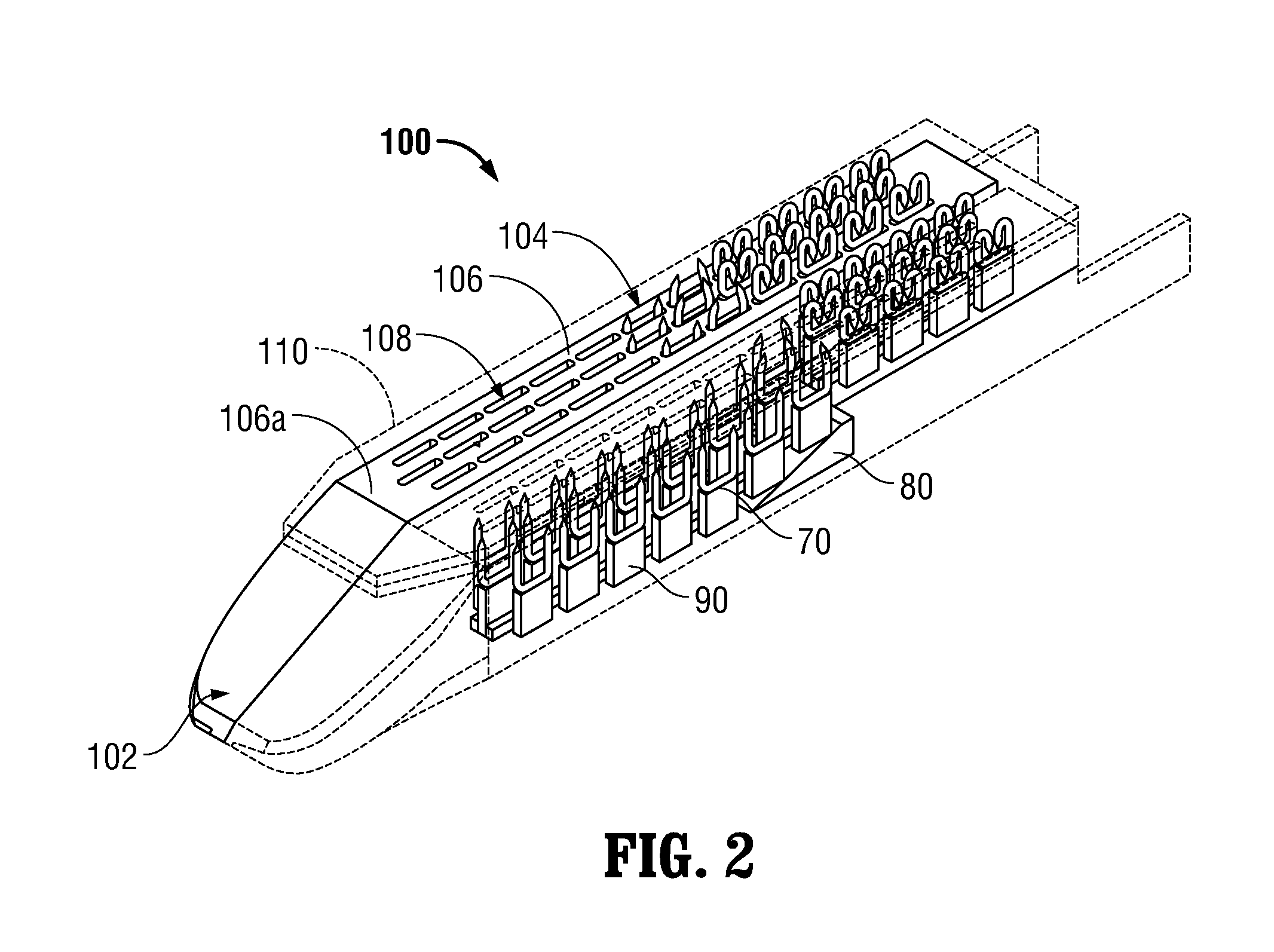

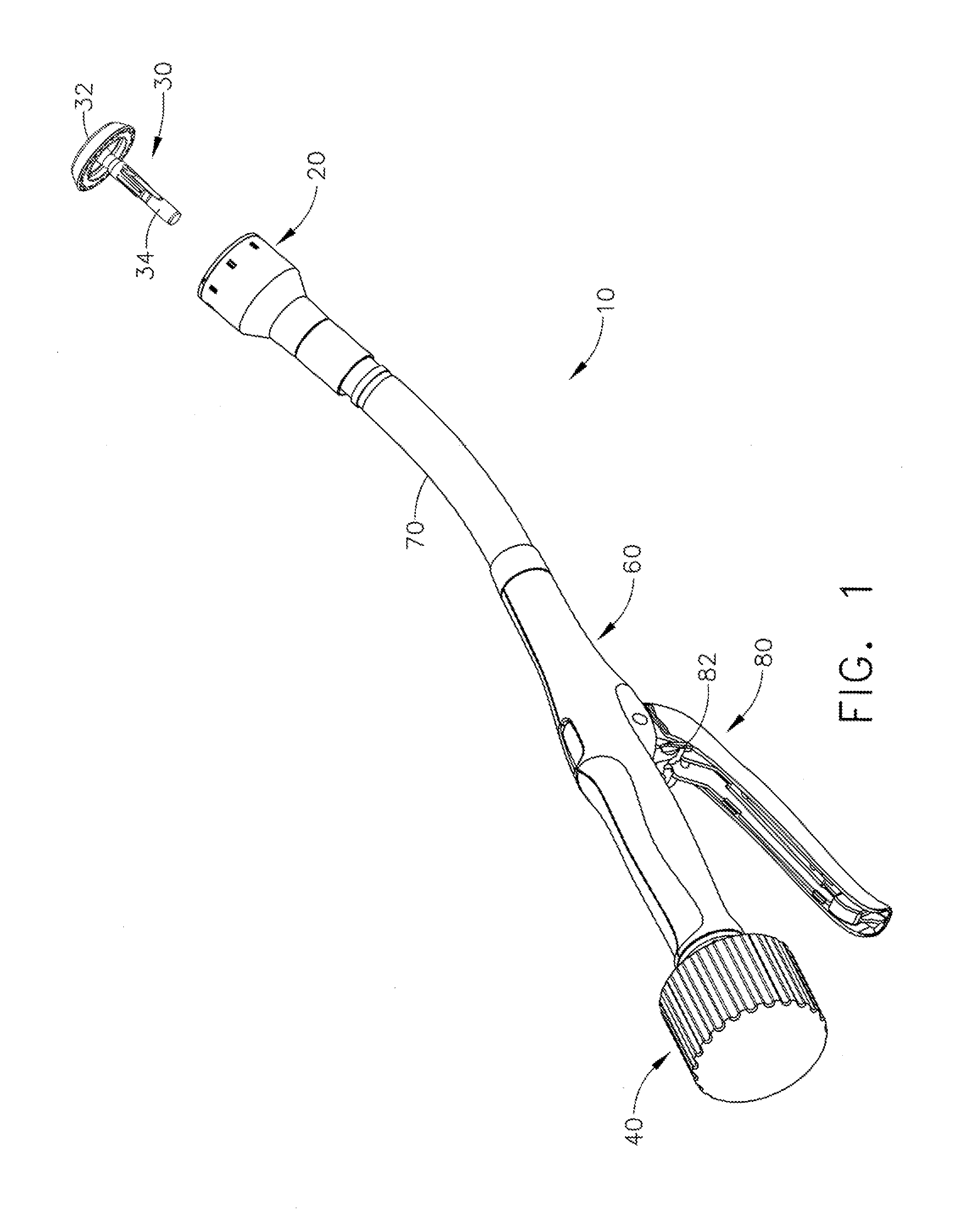

Surgical instrument having a multiple rate directional switching mechanism

A surgical instrument having a remotely controllable user interface, and a firing drive configured to generate a rotary firing motion upon a first actuation of the remotely controllable user interface and a rotary refraction motion upon an other actuation of remotely controllable user interface. The instrument is such that when the remotely controllable user interface operates a first drive member, the first actuation advances a cutting member a first distance, wherein, when the remotely controllable user interface operates a second drive member, the other actuation retracts the cutting member a second distance, and wherein the second distance is greater than the first distance.

Owner:CILAG GMBH INT

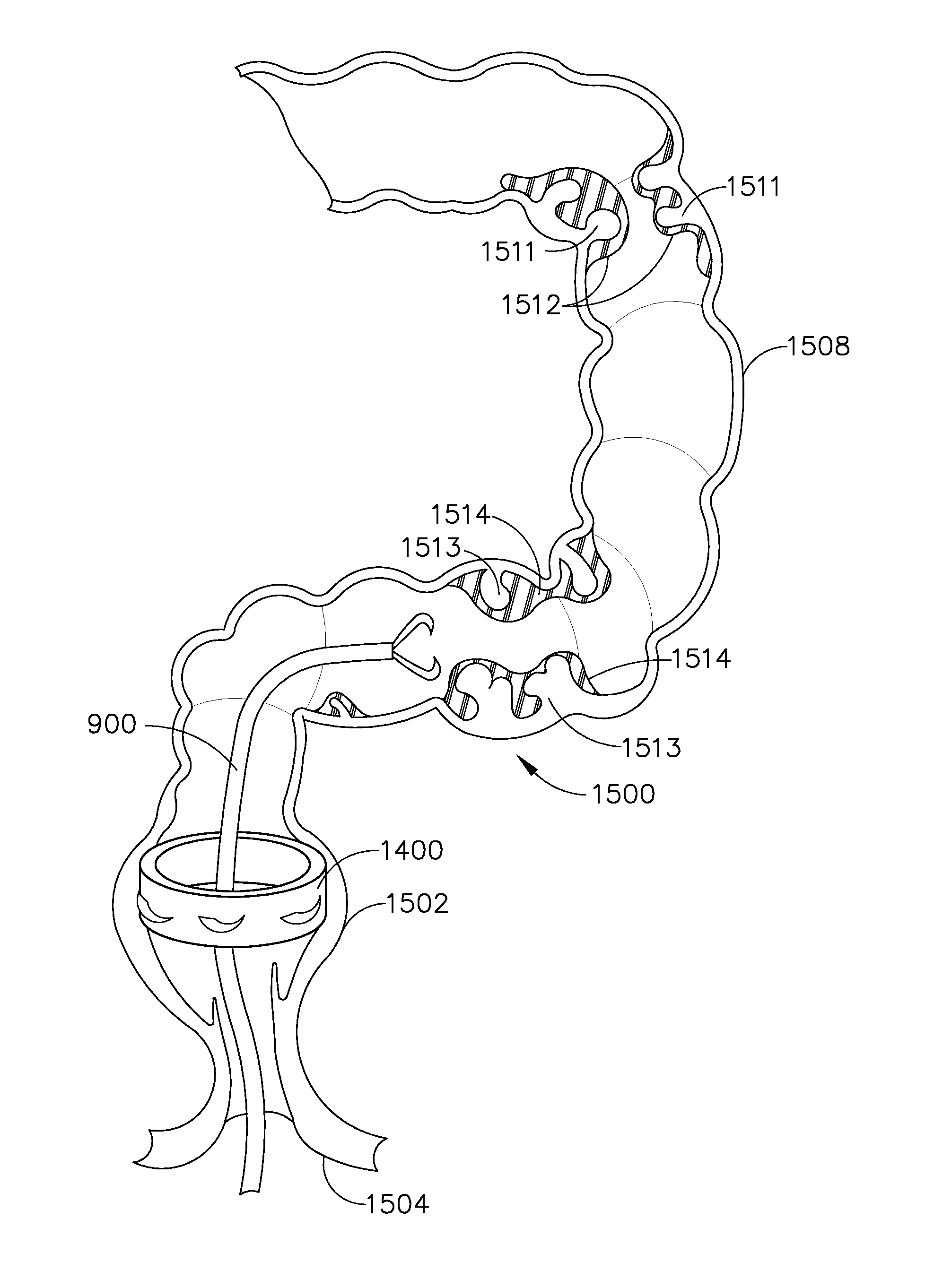

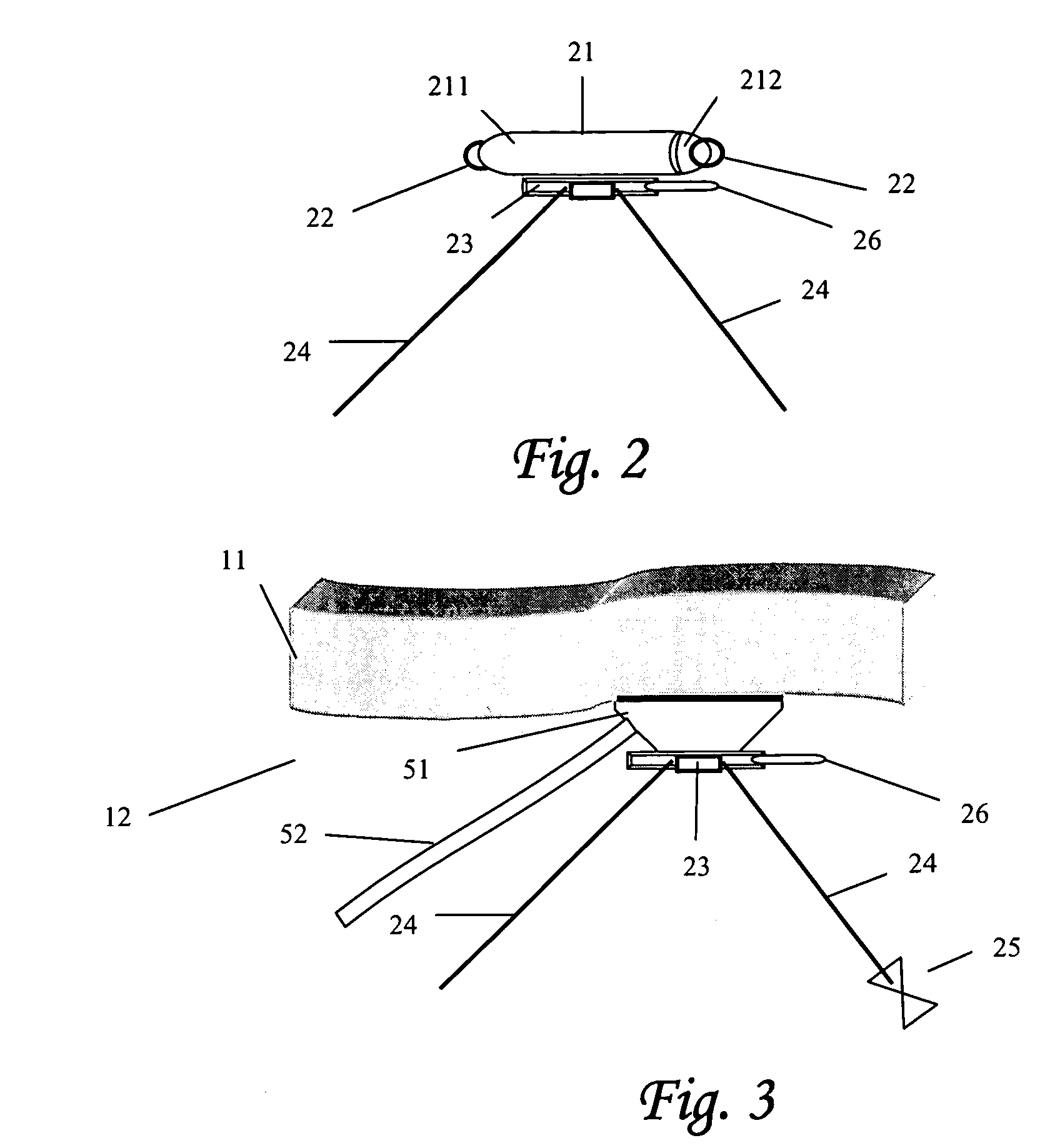

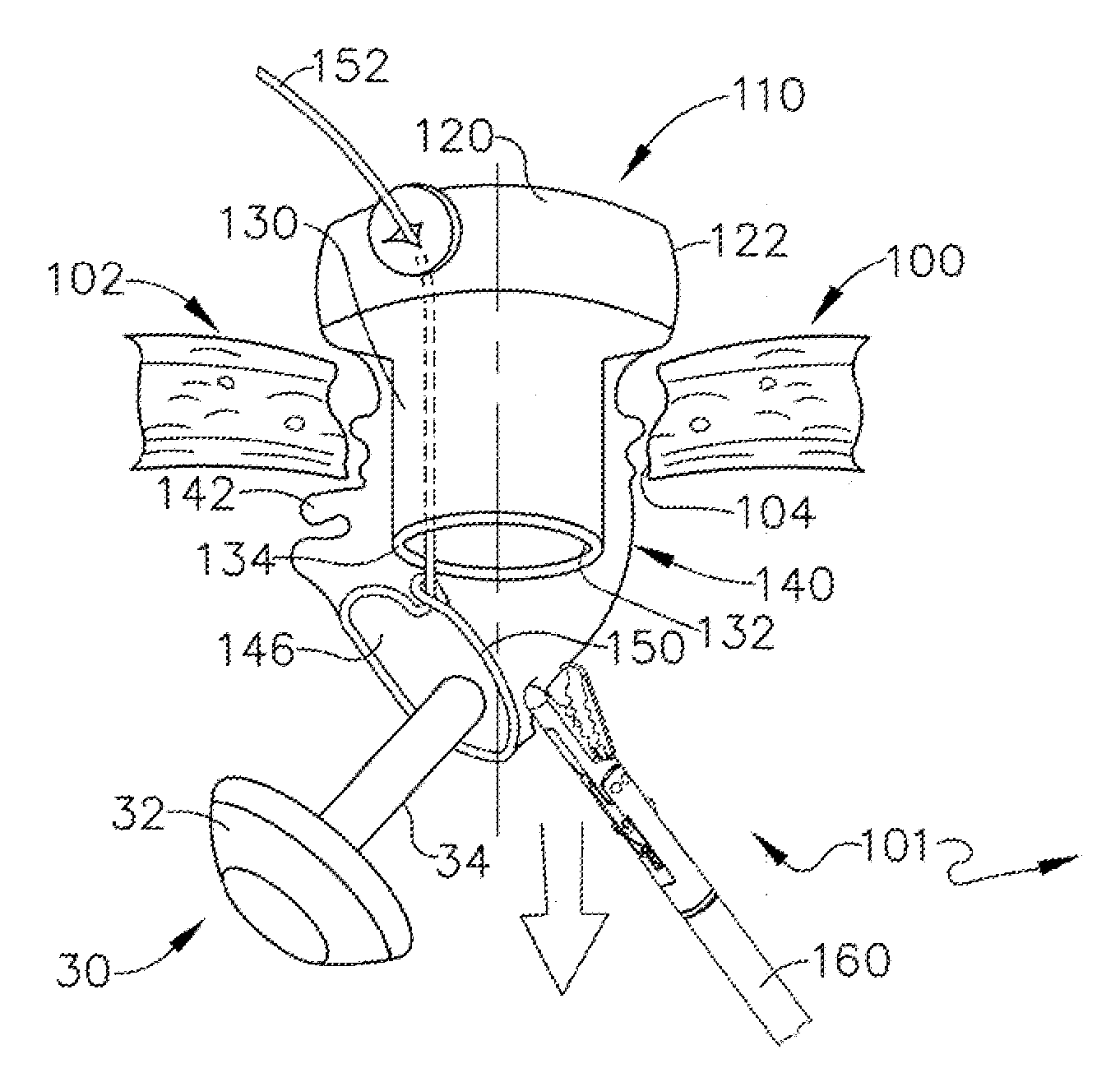

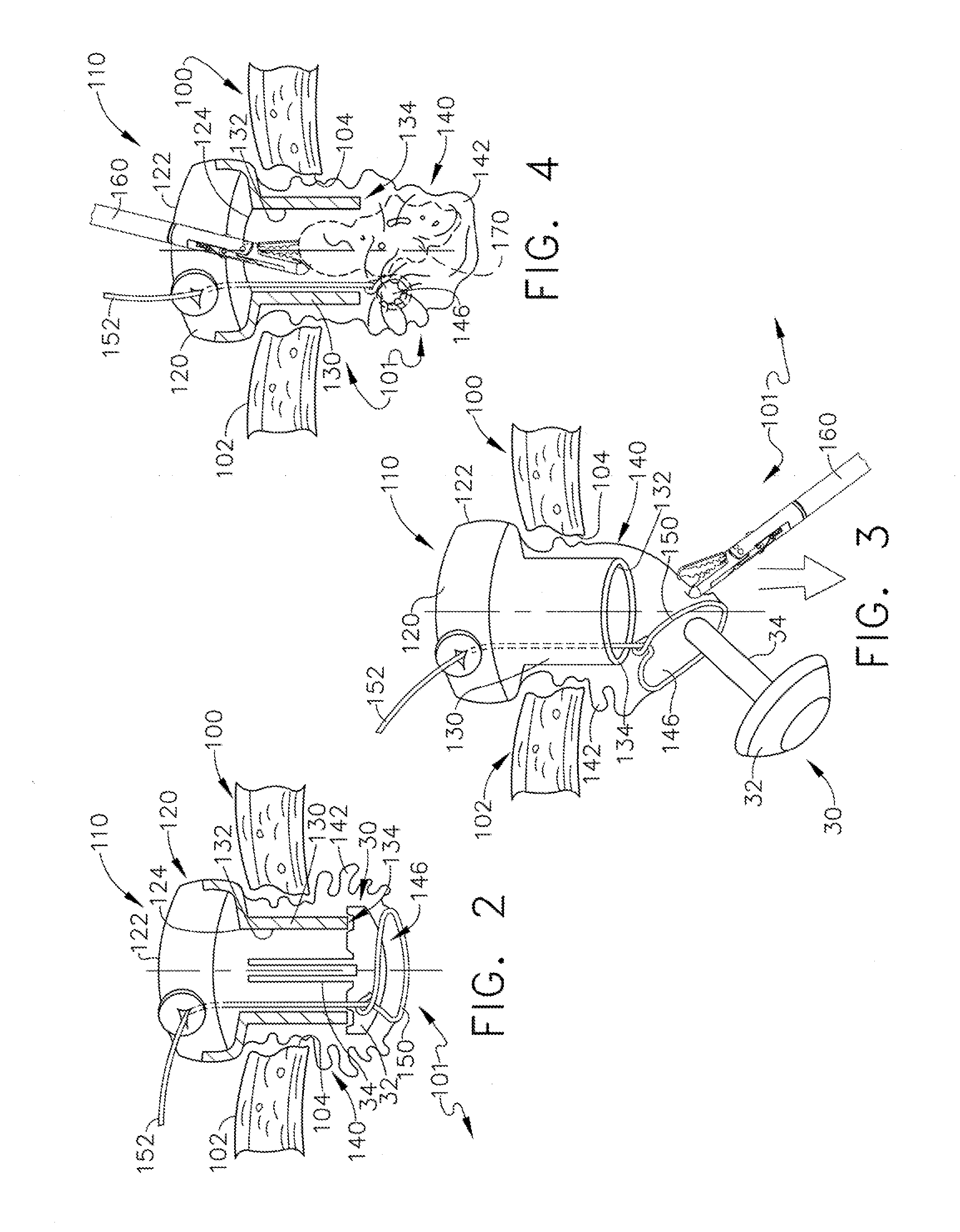

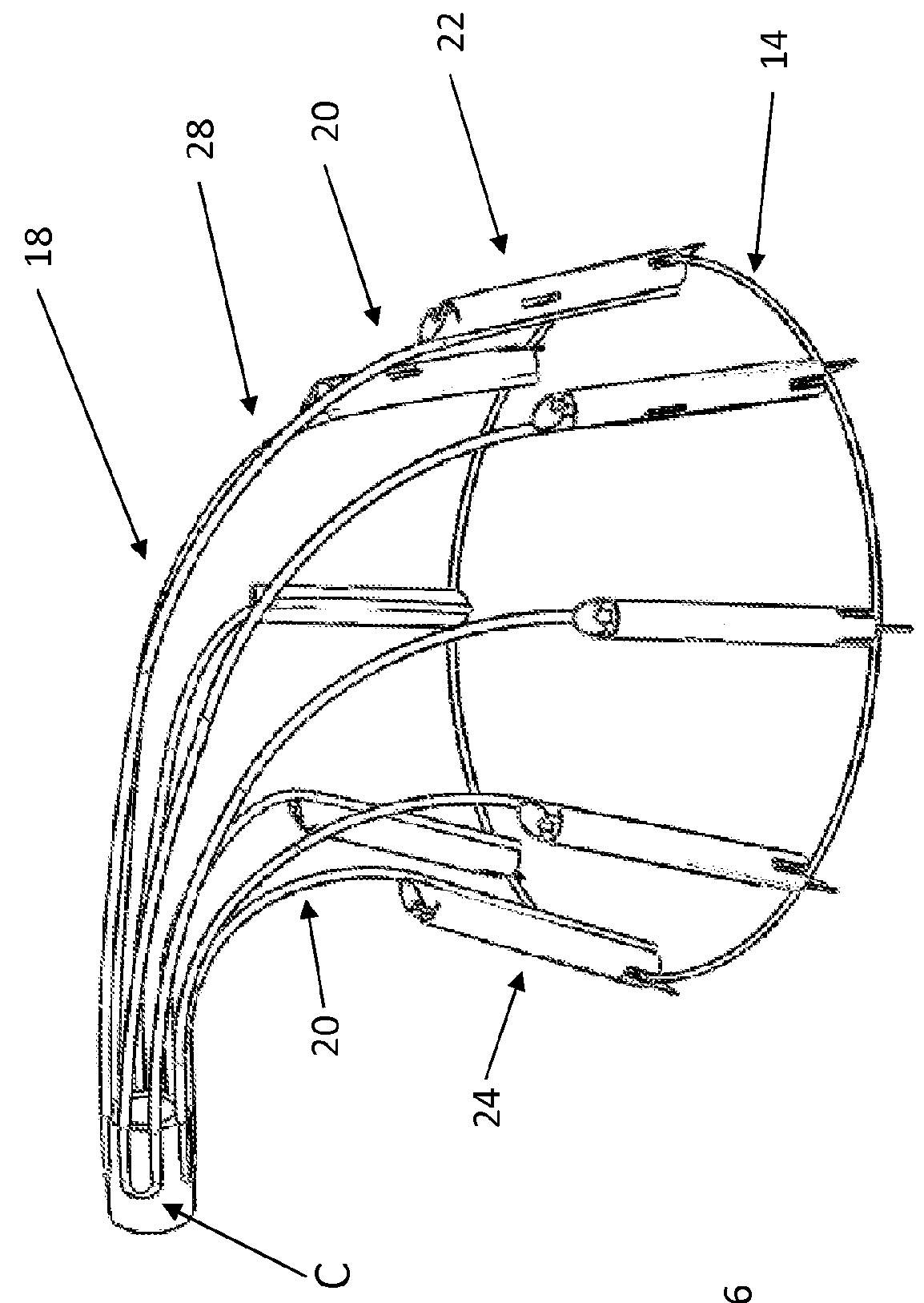

Trans-rectum universal ports

Various universal ports for installation into a colon are disclosed. Various embodiments include expandable port bodies that may employ selectively deployable tissue-engaging barbs for securing the port in position within the colon. Some embodiments also employ tissue cutting members that may be deployed to sever the colon. Some embodiments also employ a flexible sleeve that may extend from the port out through the anus to provide a passageway for passing surgical instruments and into and out of the rectum and also for removing severed specimens therefrom.

Owner:CILAG GMBH INT

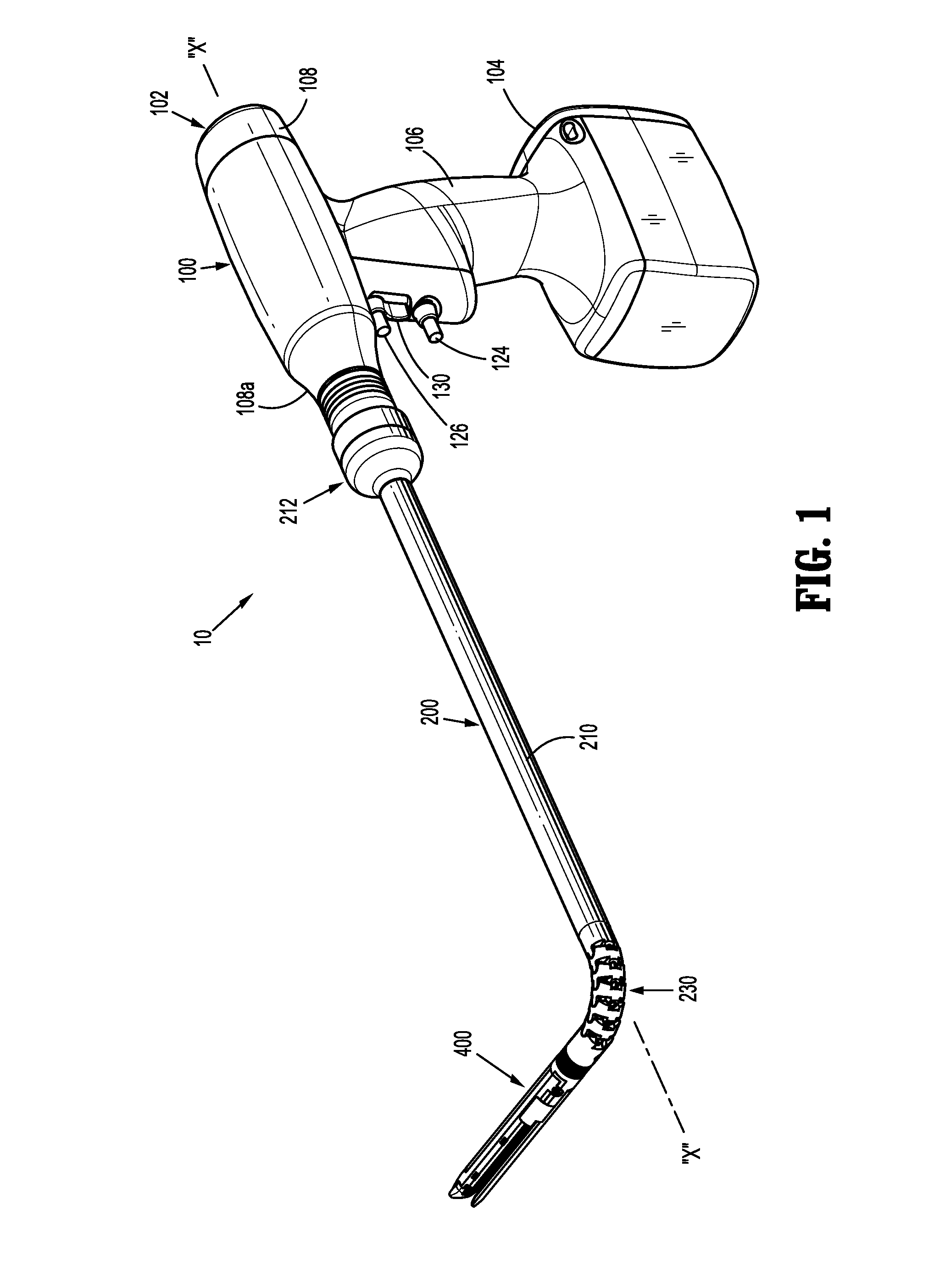

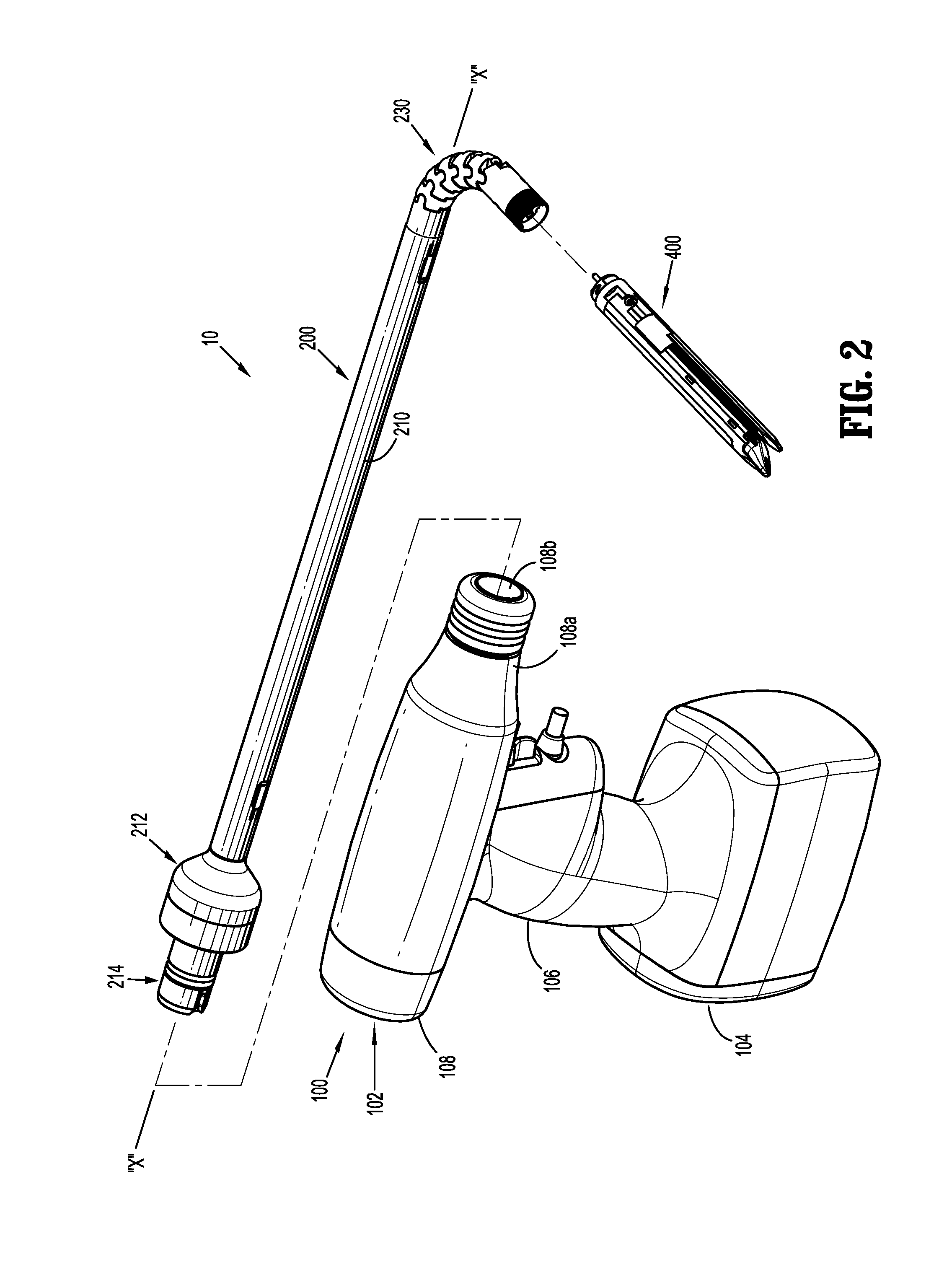

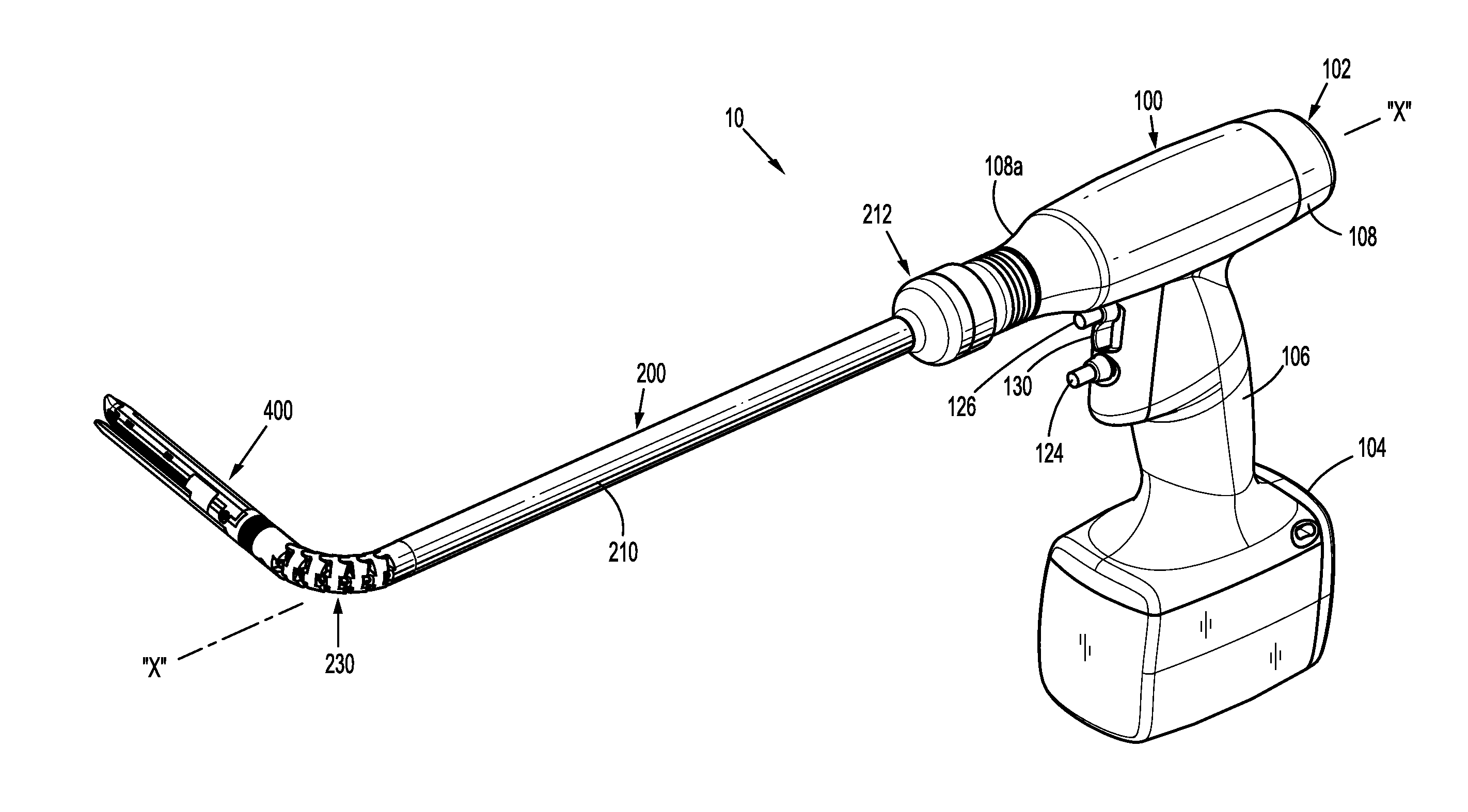

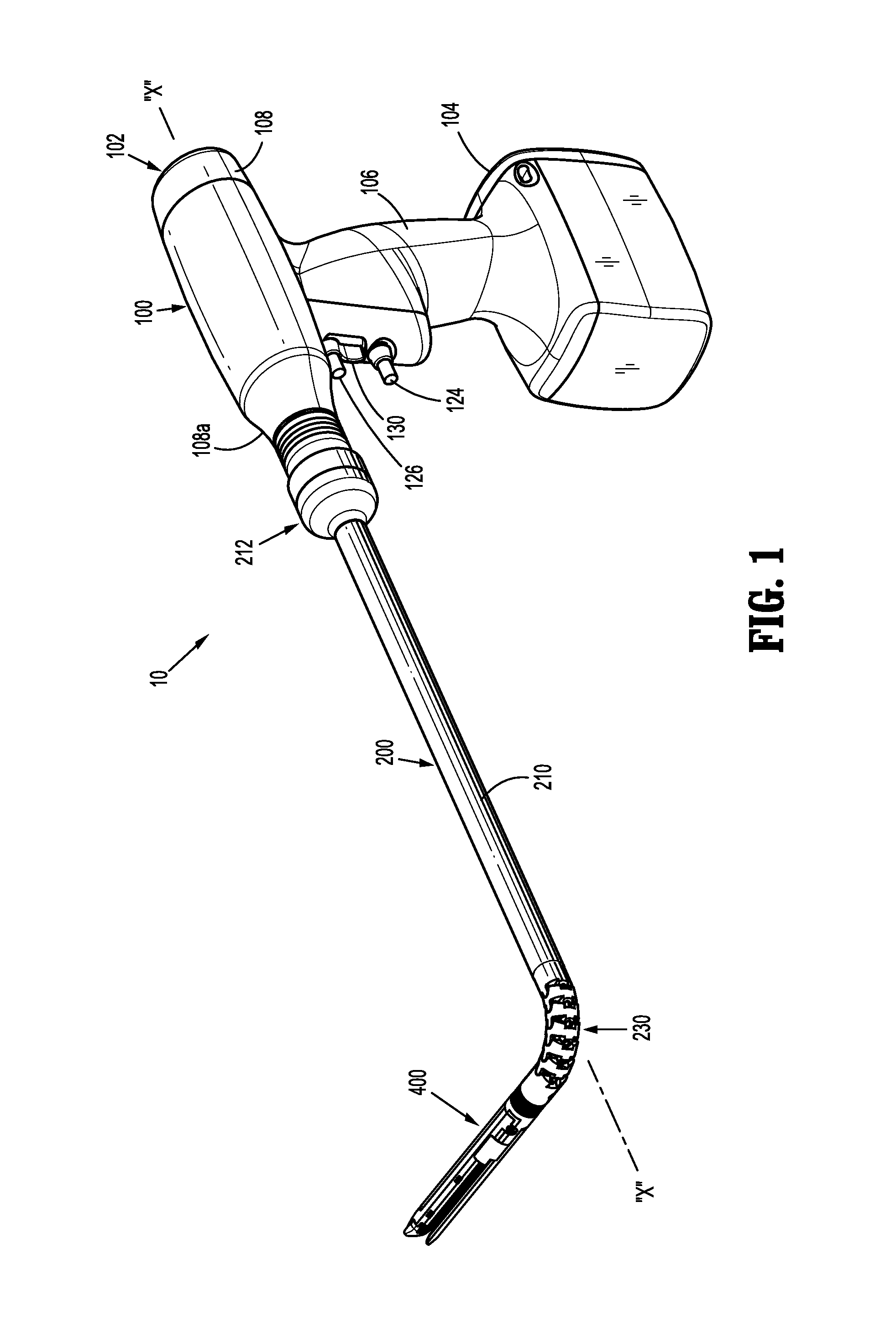

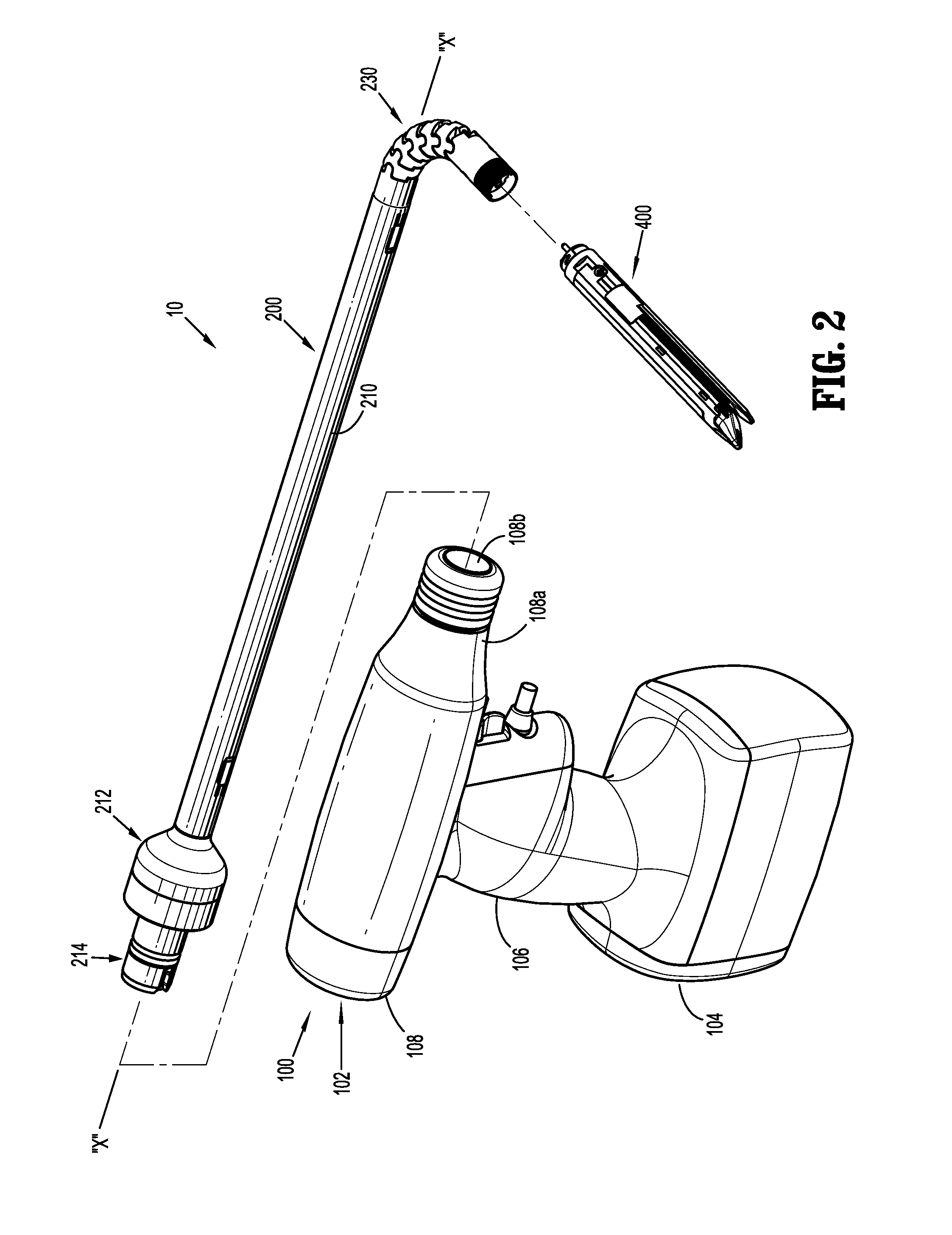

Apparatus for endoscopic procedures

An electromechanical surgical system is provided including a hand-held surgical instrument; an end effector; and a shaft assembly for selectively interconnecting the end effector and the surgical device. The shaft assembly includes a transmission housing; an outer tubular body; a distal neck housing for interconnecting a rotatable drive member of the surgical instrument and a rotation receiving member supported in the end effector, wherein the distal neck housing includes at least one gear system configured to convert a rotational input of the rotatable drive member into at least two output forces to the end effector; and an articulating neck assembly interconnecting the tubular body and the distal neck housing. The articulating neck assembly enables off-axis articulation of the distal neck assembly, and wherein the rotatable drive member extends through the articulating neck assembly.

Owner:TYCO HEALTHCARE GRP LP

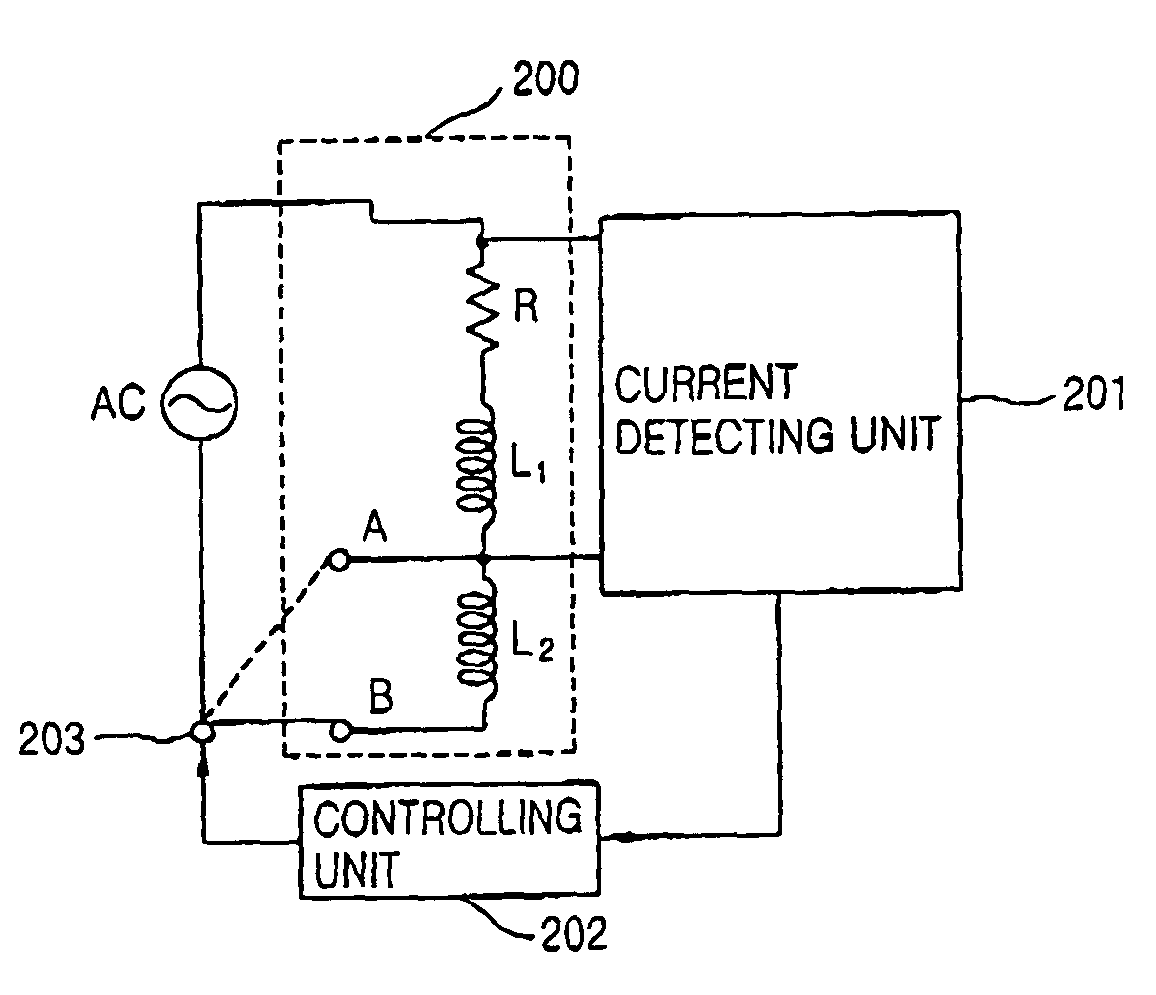

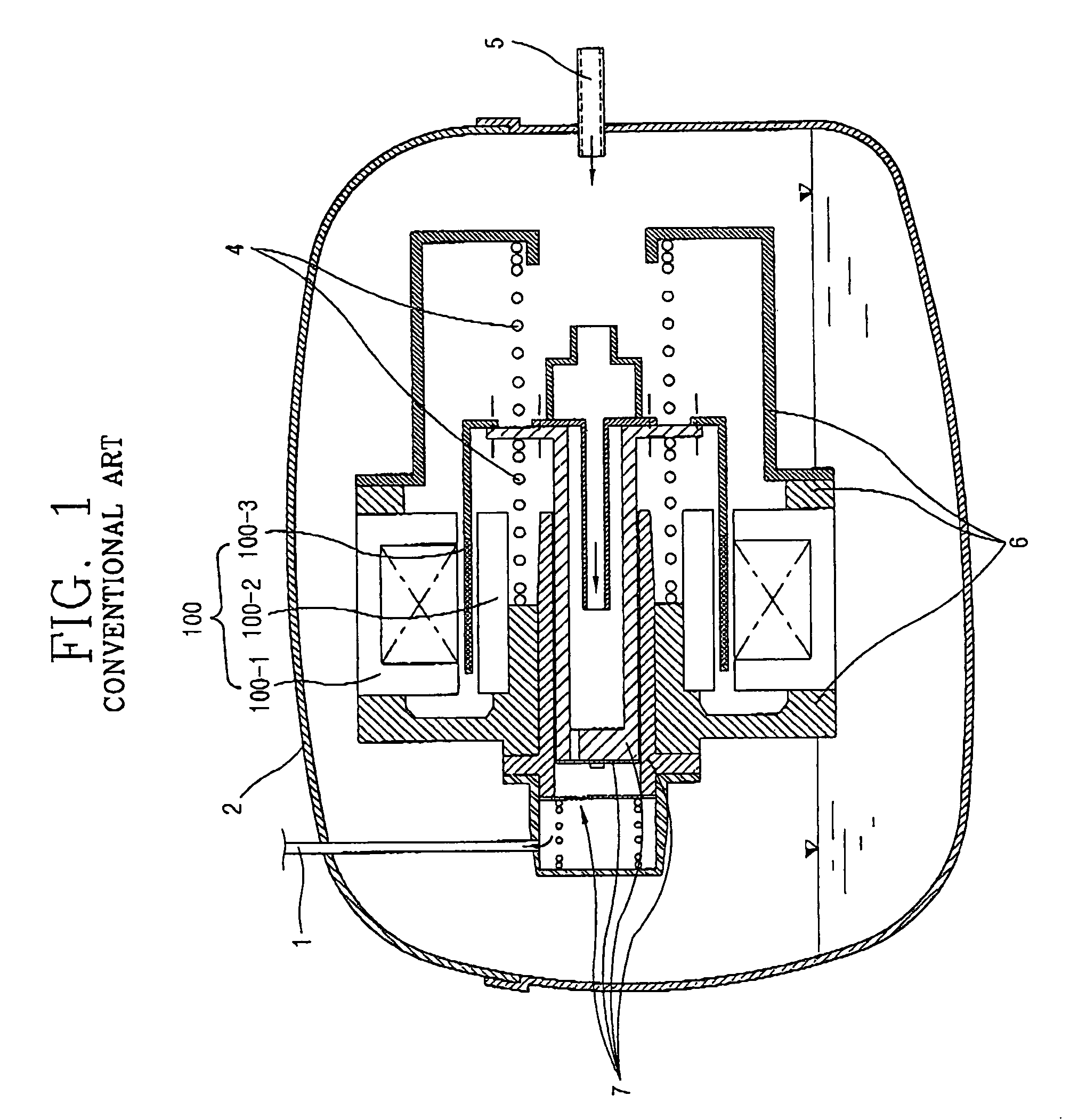

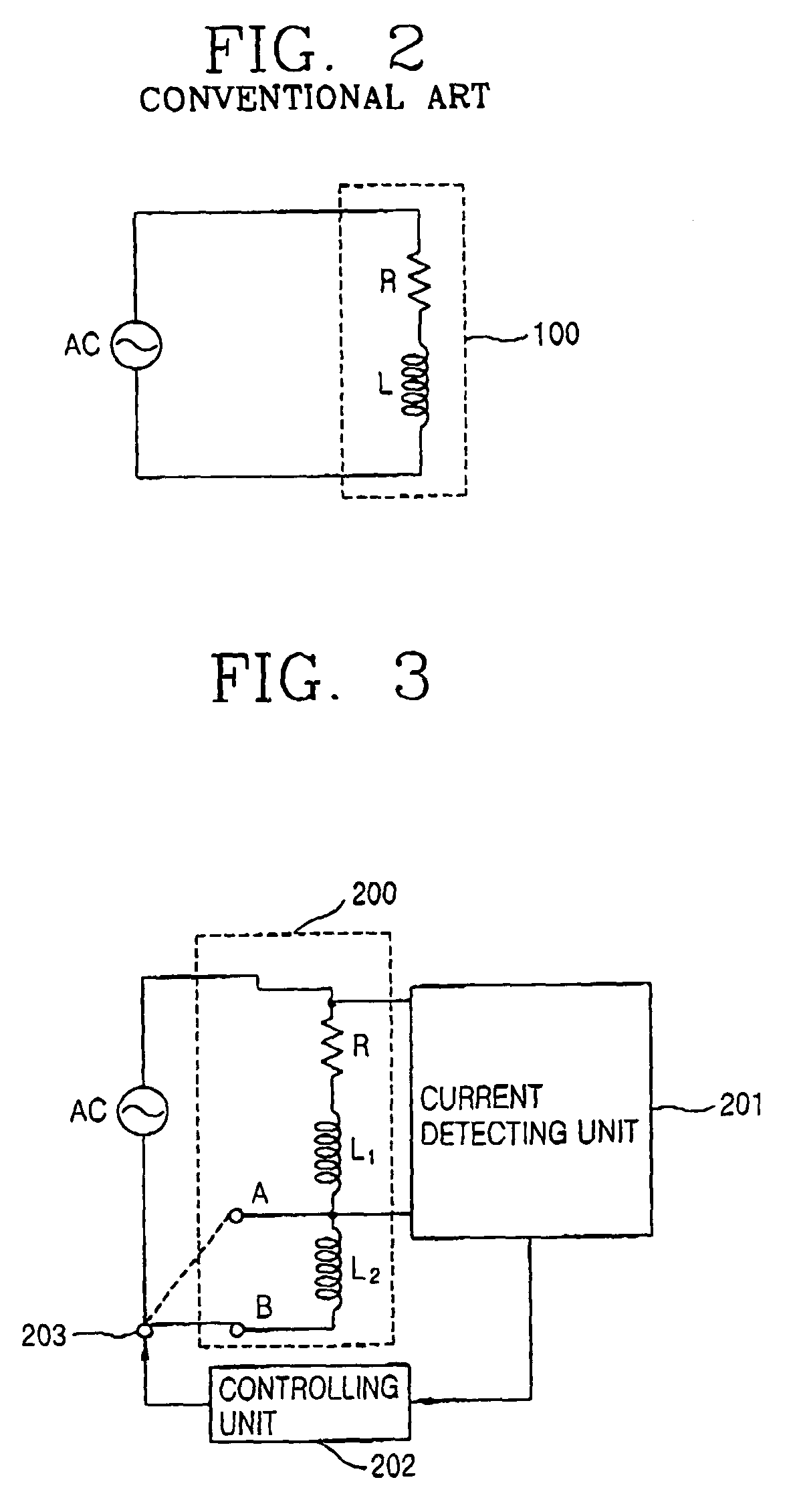

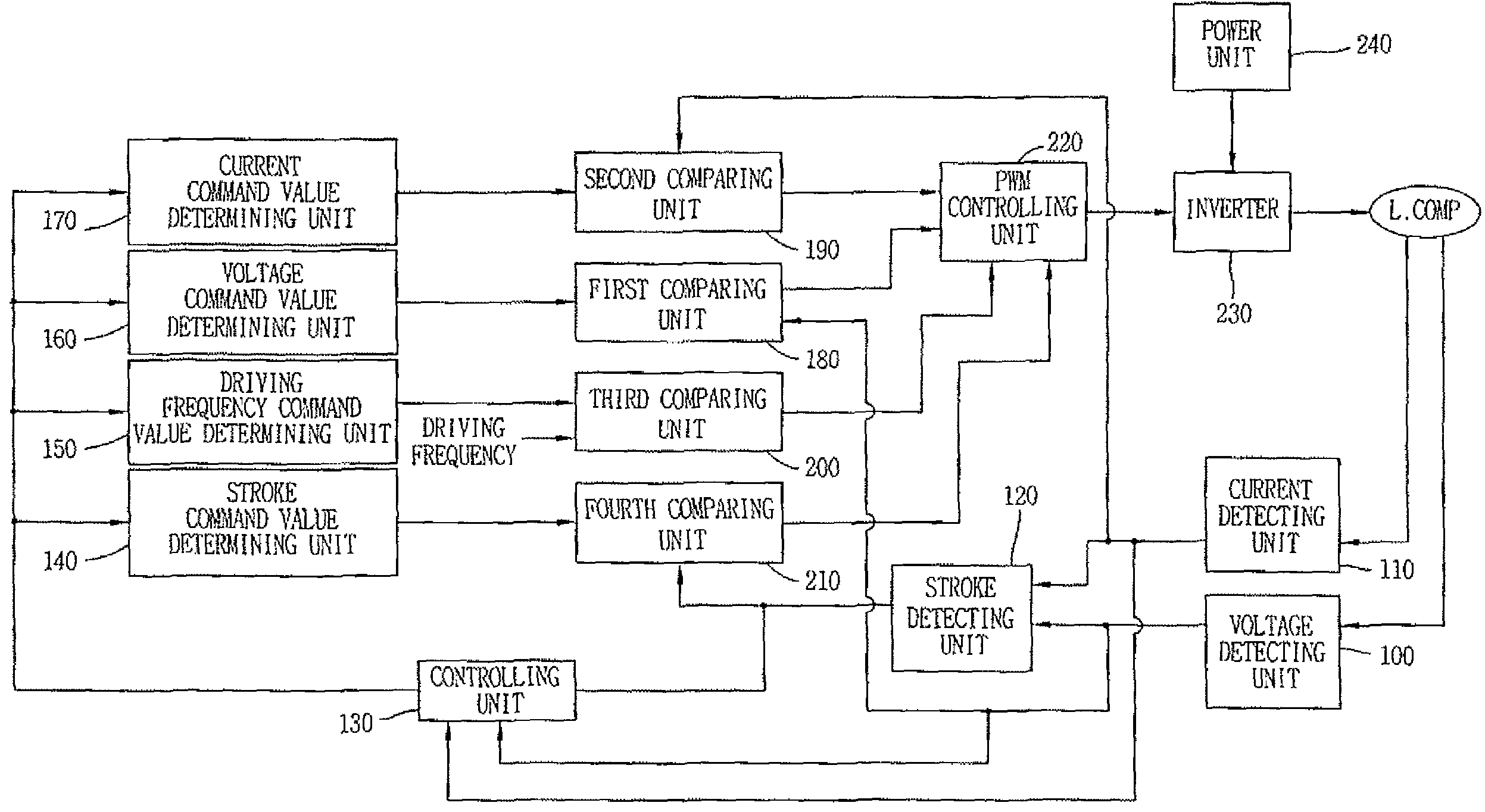

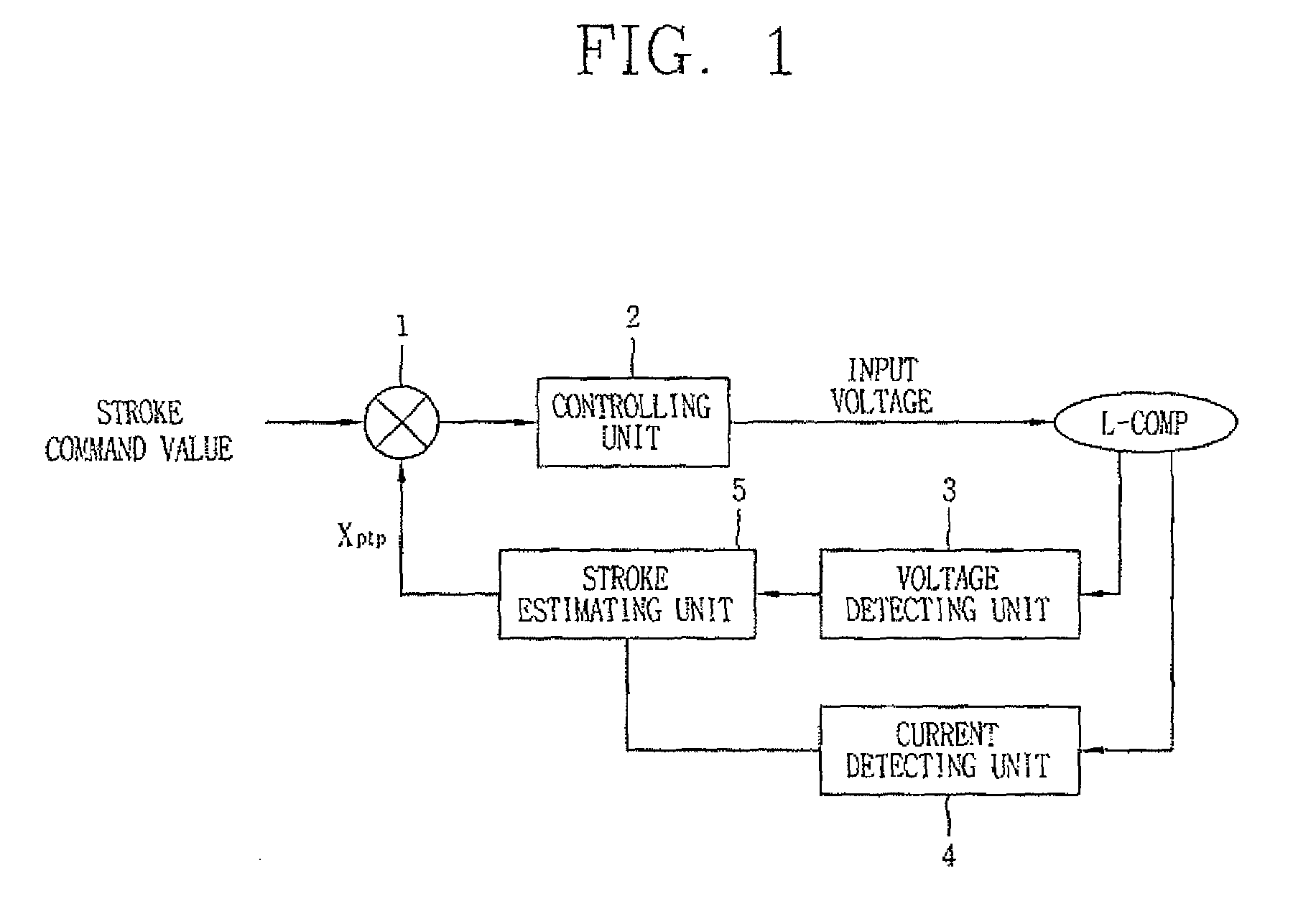

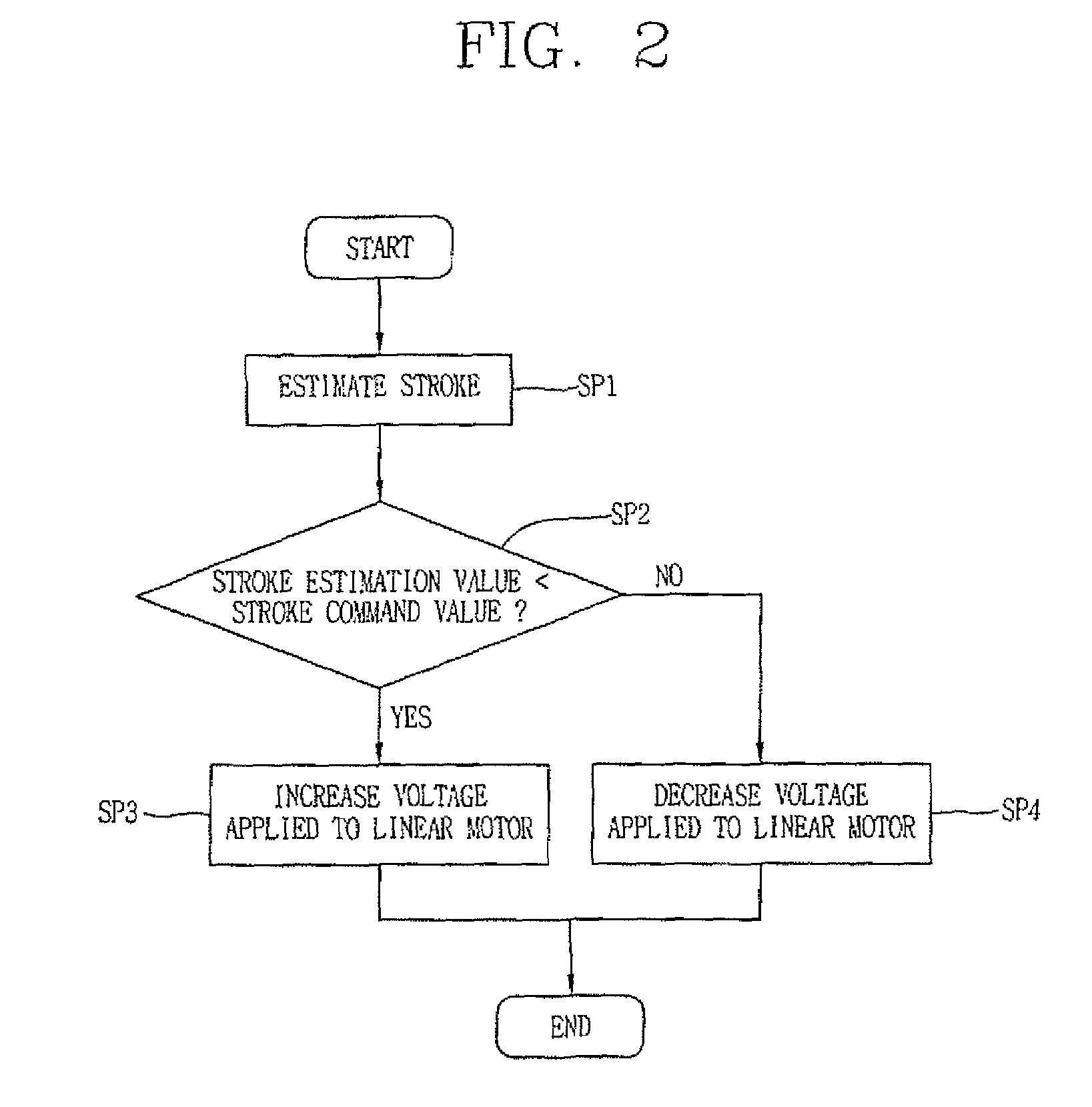

Apparatus and method for controlling driving of linear motor

InactiveUS6998736B2Increase efficiency of linearMotor/generator/converter stoppersDC motor speed/torque controlControl signalLinear compressor

Owner:LG ELECTRONICS INC

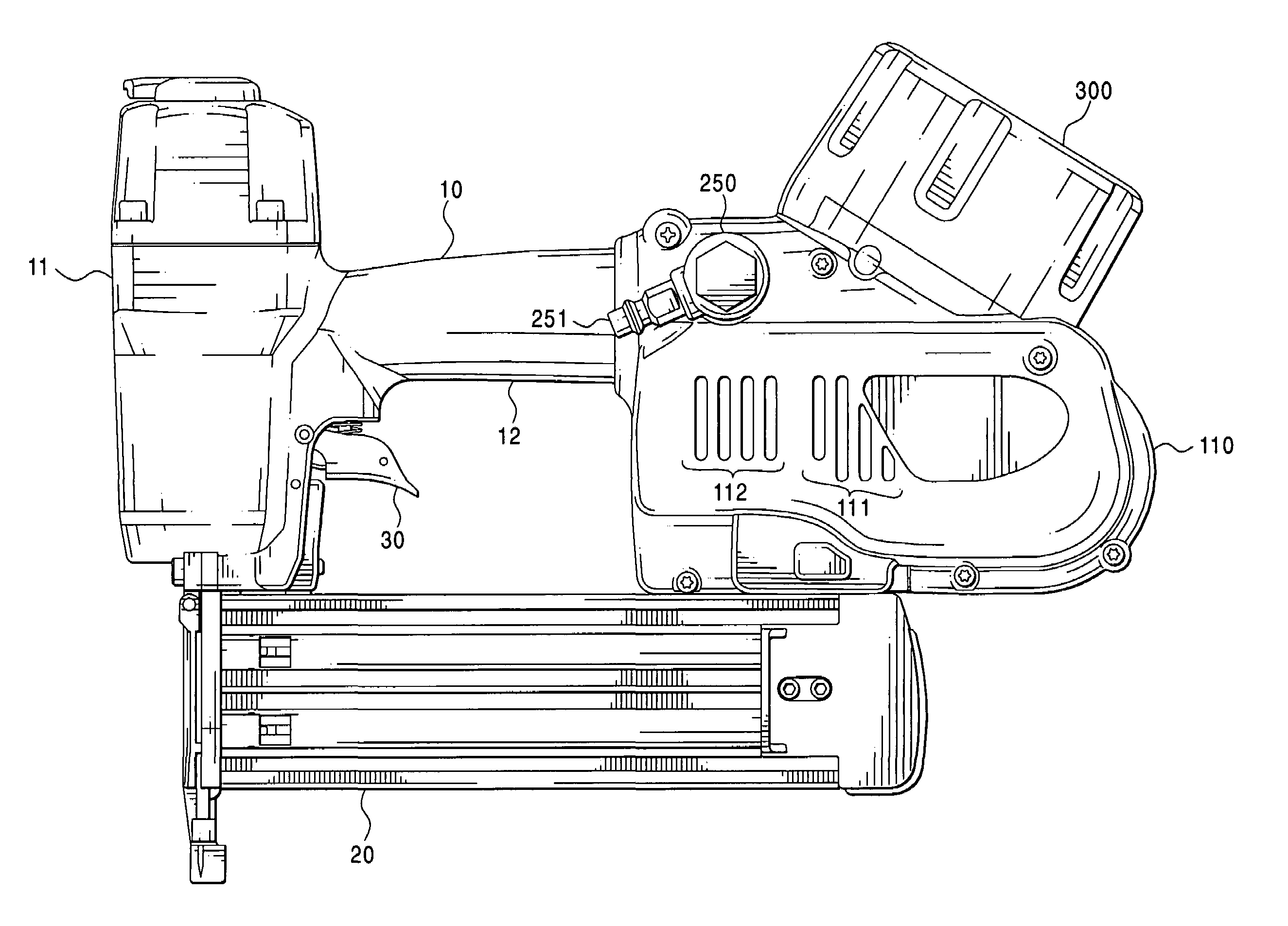

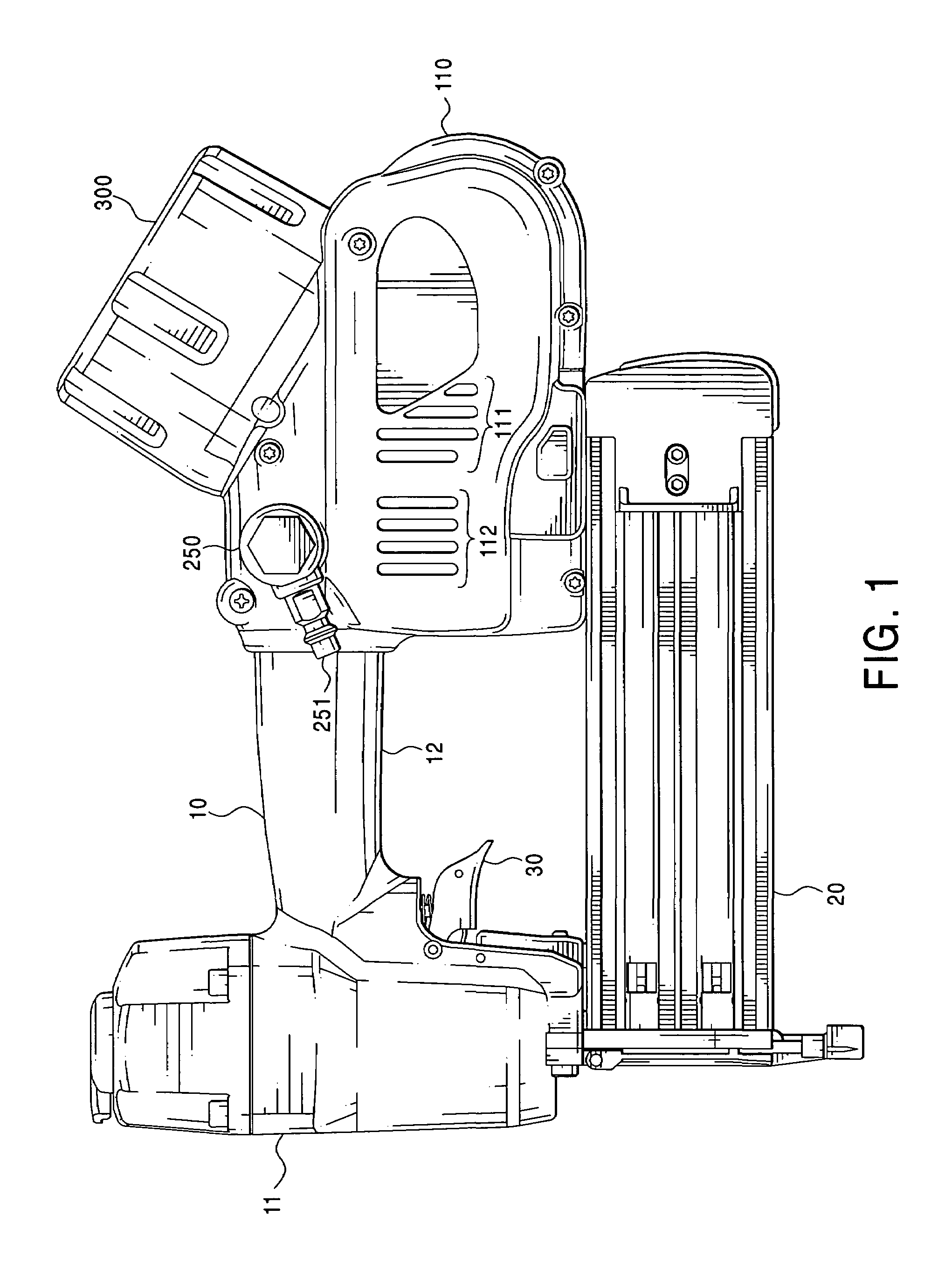

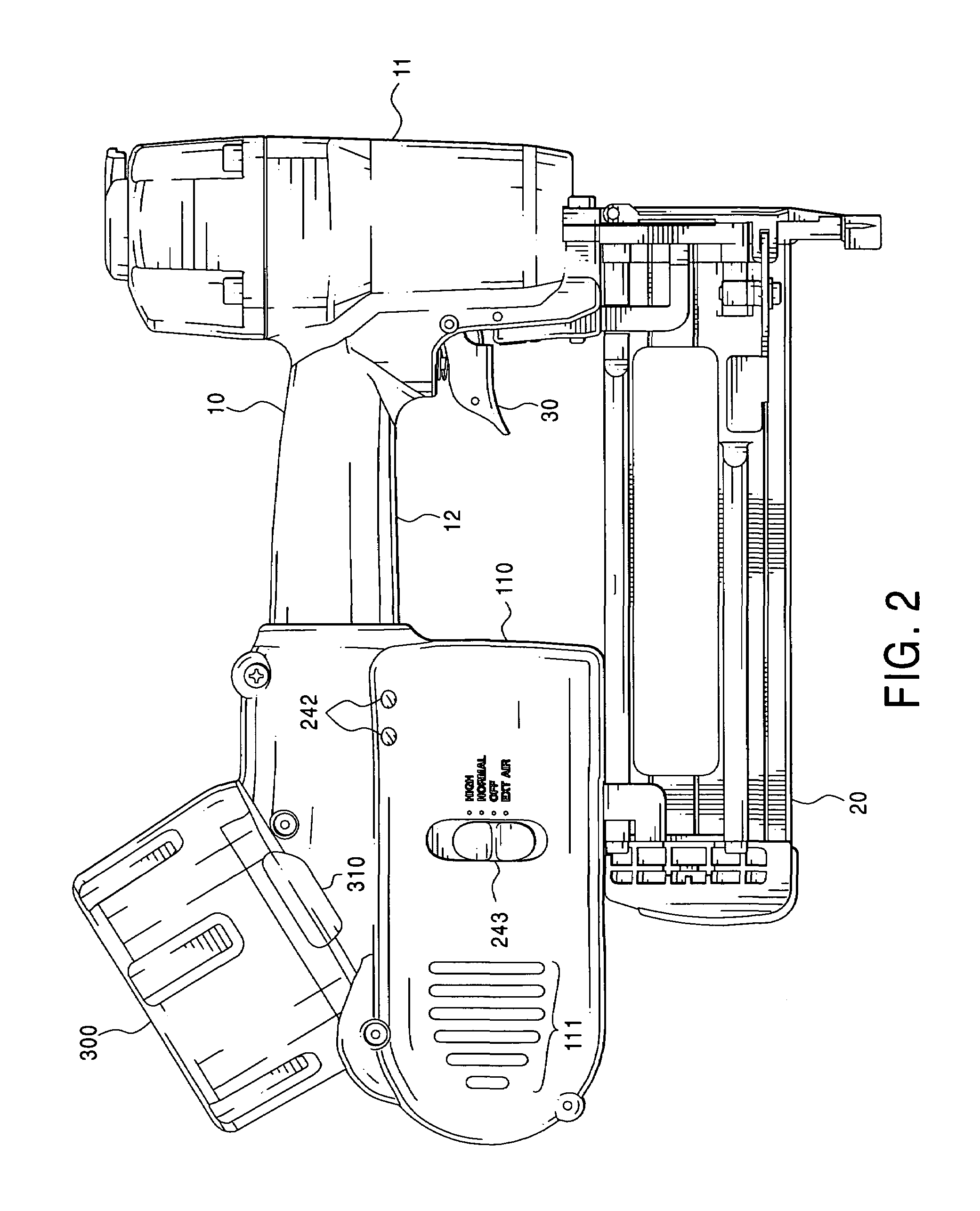

Portable, battery-powered air compressor for a pneumatic tool system

Owner:BLACK & DECKER INC +1

Surgical Instrument Having A Multiple Rate Directional Switching Mechanism

A surgical instrument having a remotely controllable user interface, and a firing drive configured to generate a rotary firing motion upon a first actuation of the remotely controllable user interface and a rotary refraction motion upon an other actuation of remotely controllable user interface. The instrument includes a first drive member, wherein remotely controllable user interface is selectively engageable with the first drive member, and a second drive member, wherein the remotely controllable user interface is selectively engageable with the second drive member. The instrument also includes an elongate shaft assembly operably engaged with the first drive member and the second drive member. The instrument further includes an end effector coupled to the elongate shaft assembly. The end effector includes an elongate channel configured to operably support a staple cartridge therein, and an anvil movably coupled to the elongate channel. The end effector also includes a cutting member operably supported within the elongate channel, wherein the cutting member is operably engaged with the elongate shaft assembly. The instrument is such that when the remotely controllable user interface operates the first drive member, the first actuation advances the cutting member a first distance, wherein, when the remotely controllable user interface operates the second drive member, the other actuation retracts the cutting member a second distance, and wherein the second distance is greater than the first distance.

Owner:CILAG GMBH INT

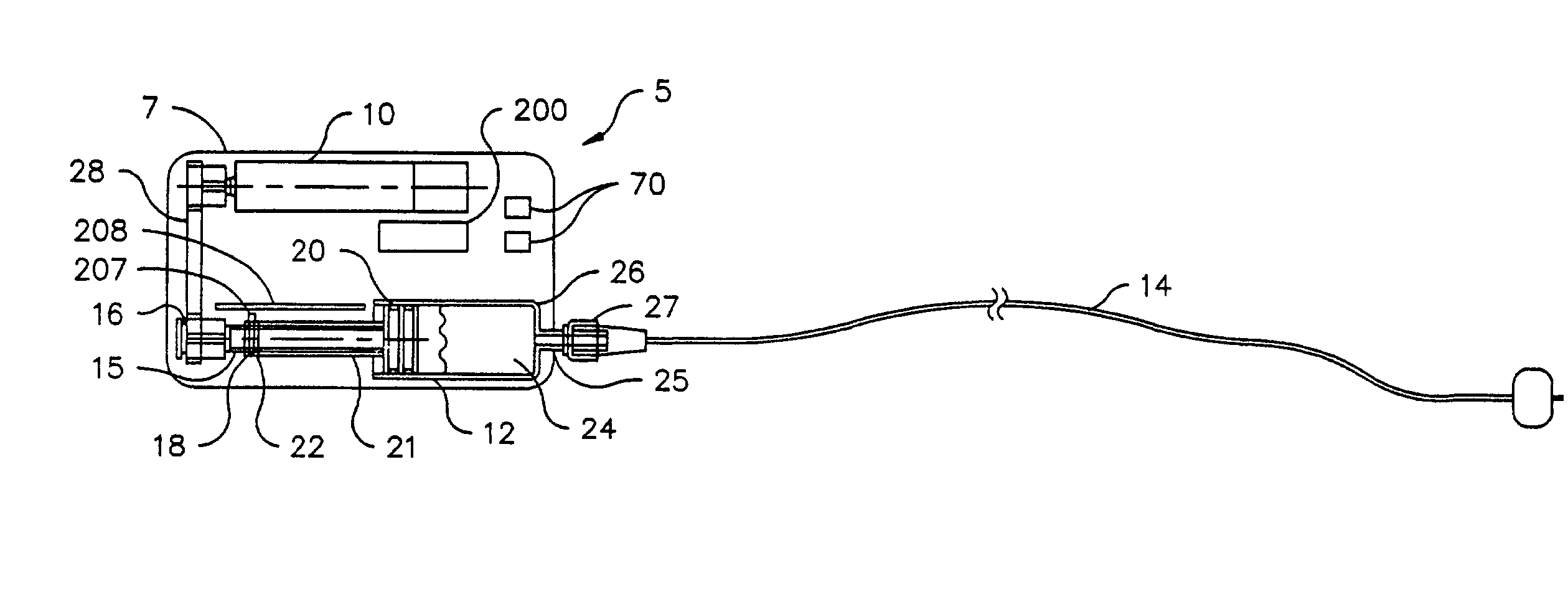

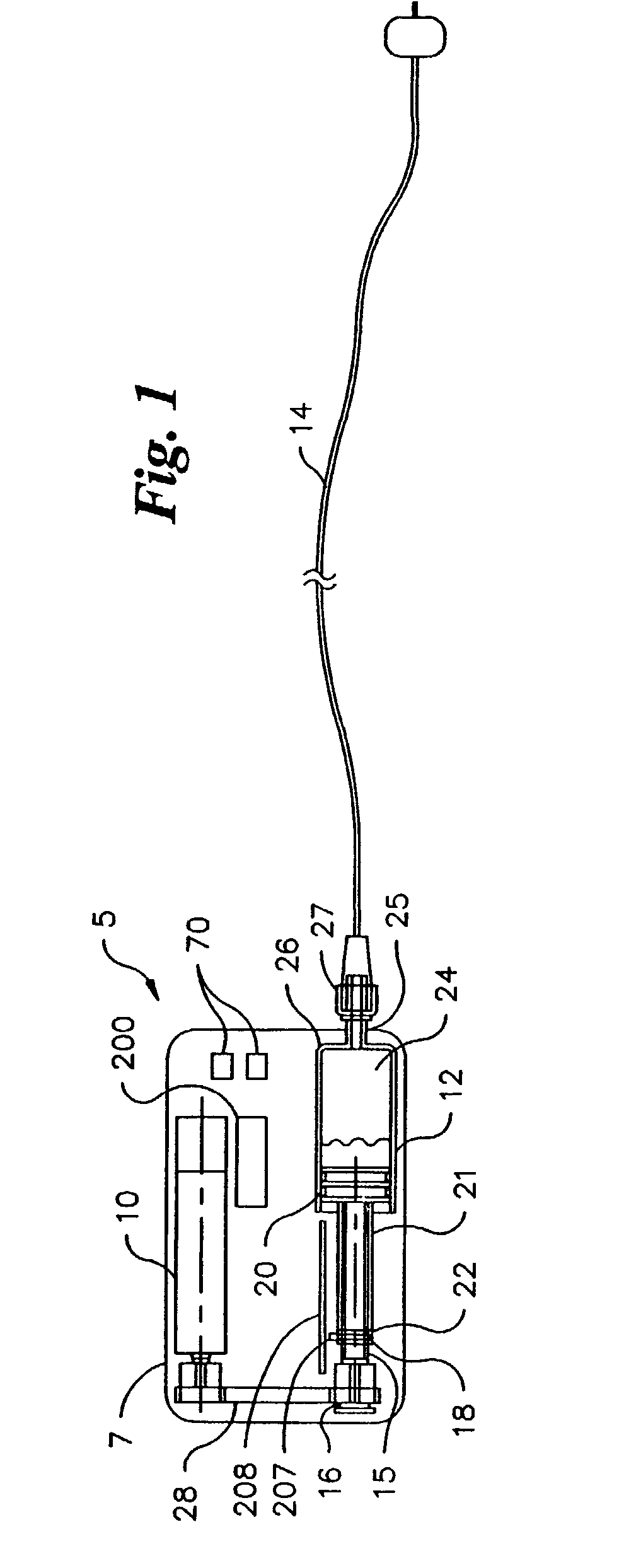

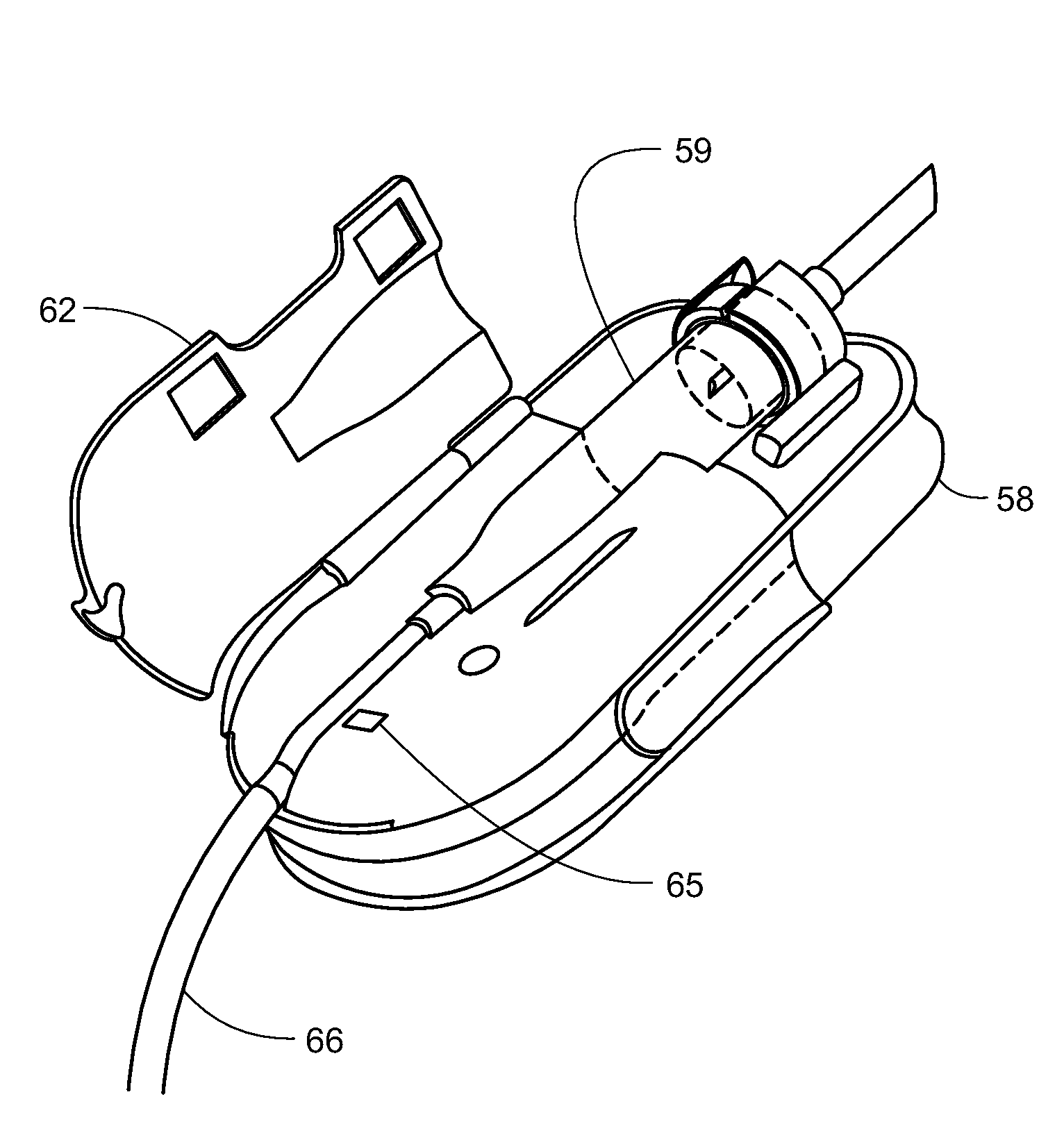

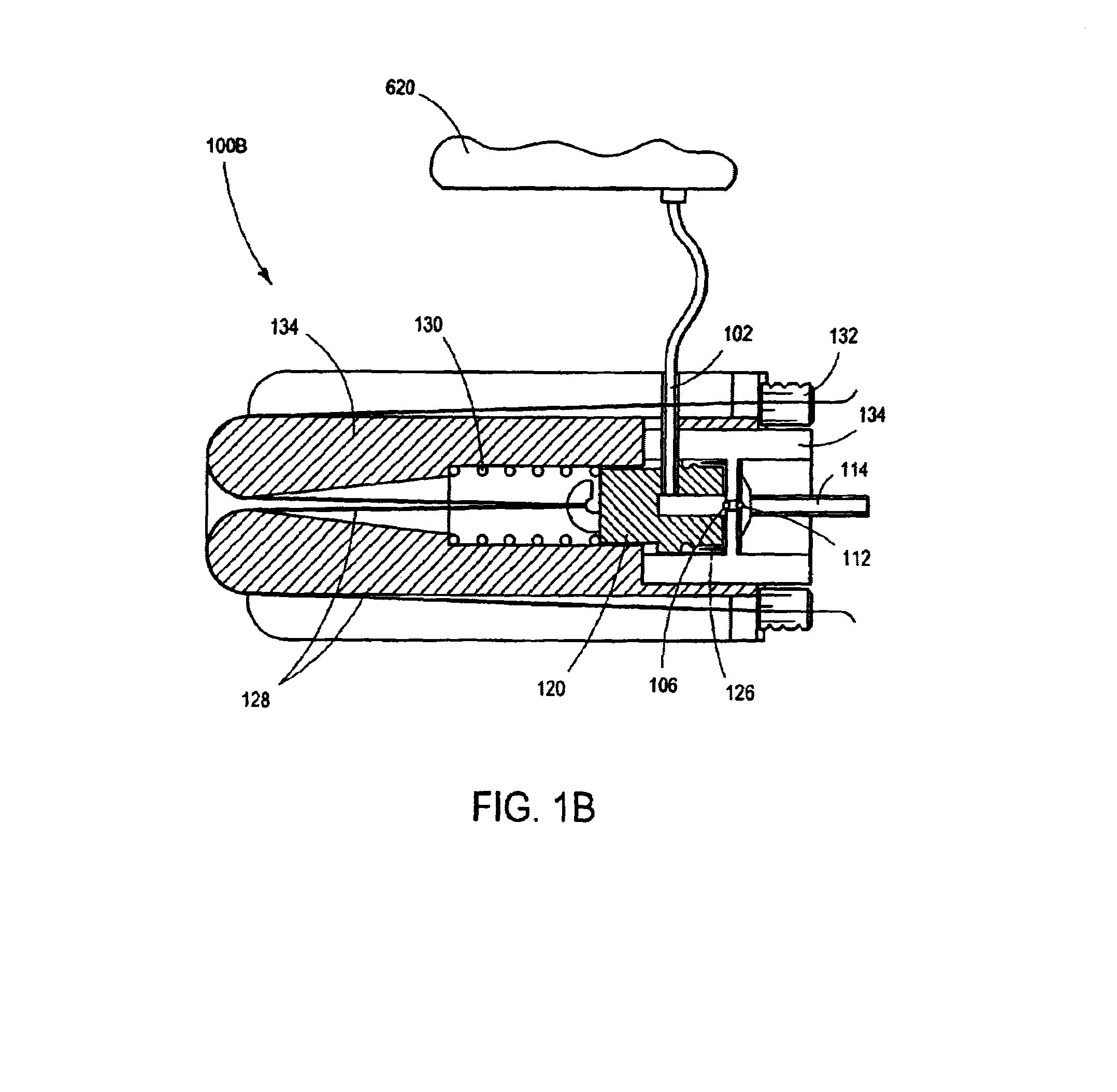

Infusion pump with a sealed drive mechanism and improved method of occlusion detection

InactiveUS20020128594A1Error minimizationImprove accuracyFlexible member pumpsSurgeryOcclusion detectionImproved method

A piston-type infusion pump is provided having an improved method of occlusion detection. The infusion pump includes processing circuitry for controlling the drive mechanism to infuse medication to a patient, including a sensor to track the position of the syringe plunger, thereby metering the amount of medication dispensed to the patient. The processing circuitry also includes a force sensor for providing signals indicative of the presence of occlusions along the infusion path. The operation of the drive mechanism causes delivery of medication to the patient. The infusion pump is constructed to be watertight.

Owner:LIFESCAN IP HLDG LLC

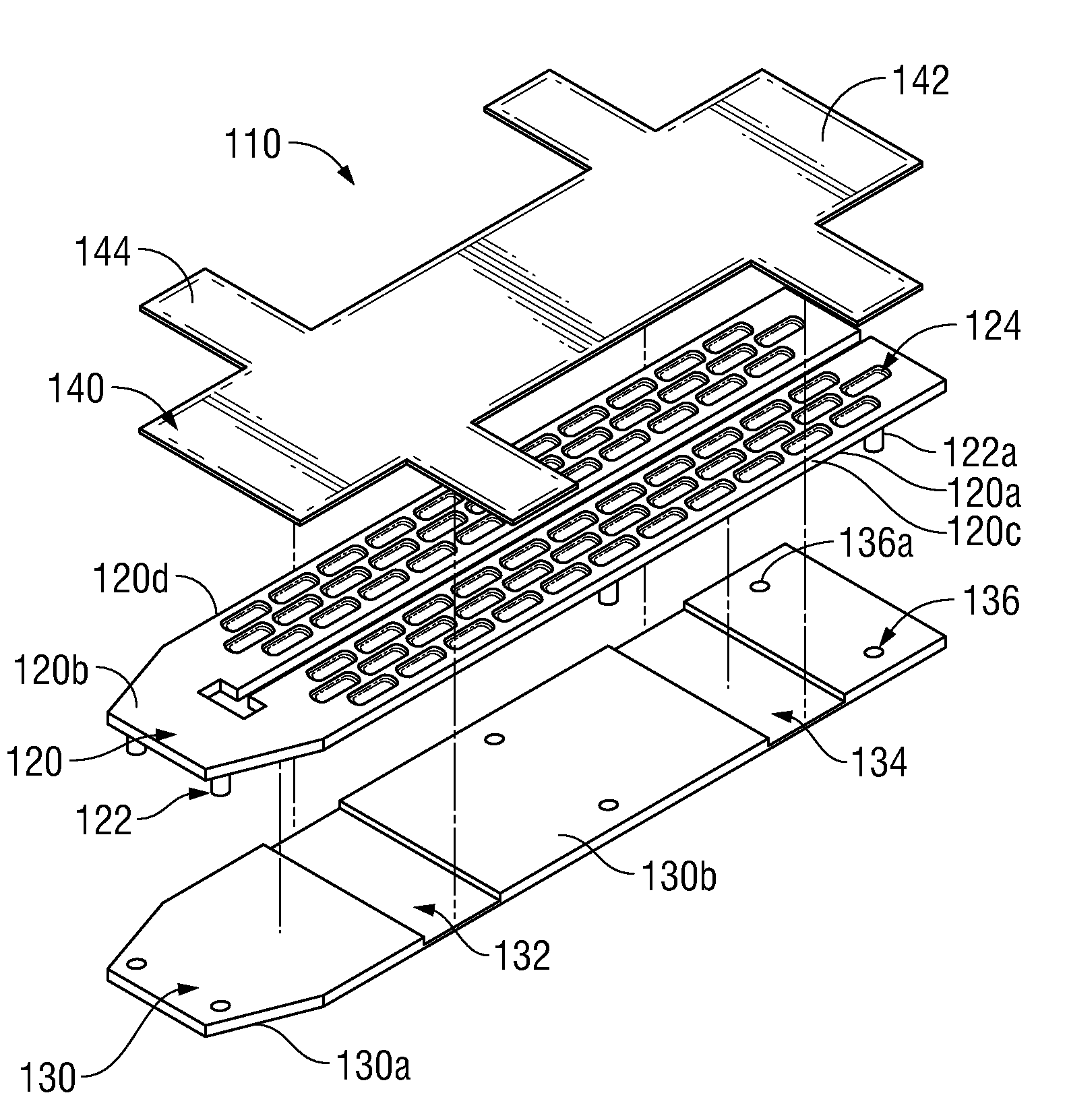

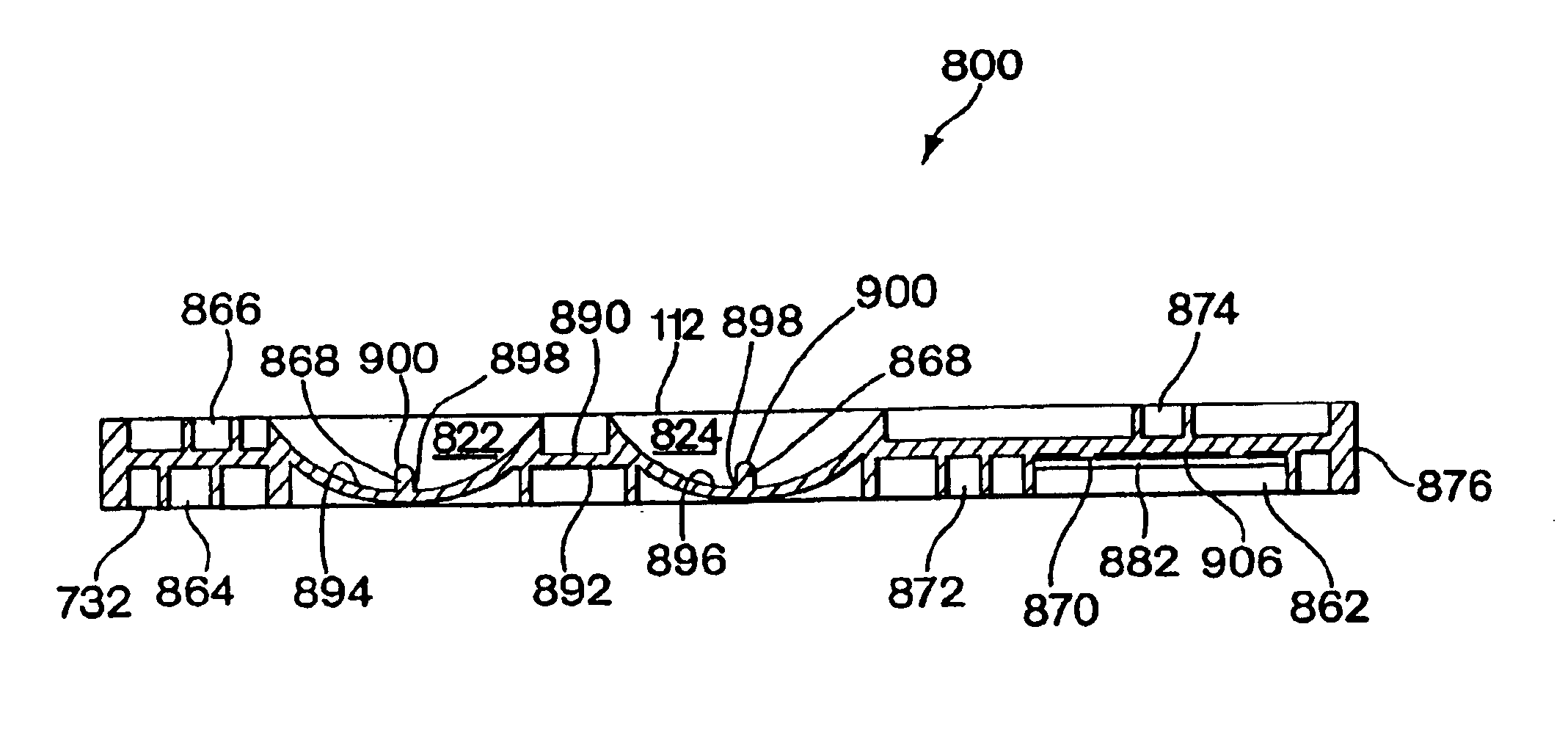

Surgical apparatus including surgical buttress

An end effector for a surgical stapling apparatus is provided which includes an anvil assembly and a surgical buttress. The anvil assembly includes an anvil body and an anvil plate. The anvil plate includes a bottom surface that defines a plurality of staple forming pockets. The anvil body and the anvil plate are selectively connectable. The surgical buttress includes a buttress body and a plurality of arms extending from the body. The arms are disposable between a top surface of the anvil plate and a bottom surface of the anvil body to support the buttress body against the bottom surface of the anvil plate when the anvil plate and the anvil body are connected to one another.

Owner:TYCO HEALTHCARE GRP LP

Device and method employing shape memory alloy

InactiveUS6916159B2Low costSmall size and weightTesting/calibration apparatusVolume/mass flow measurementShape-memory alloyEngineering

Owner:THERASENSE

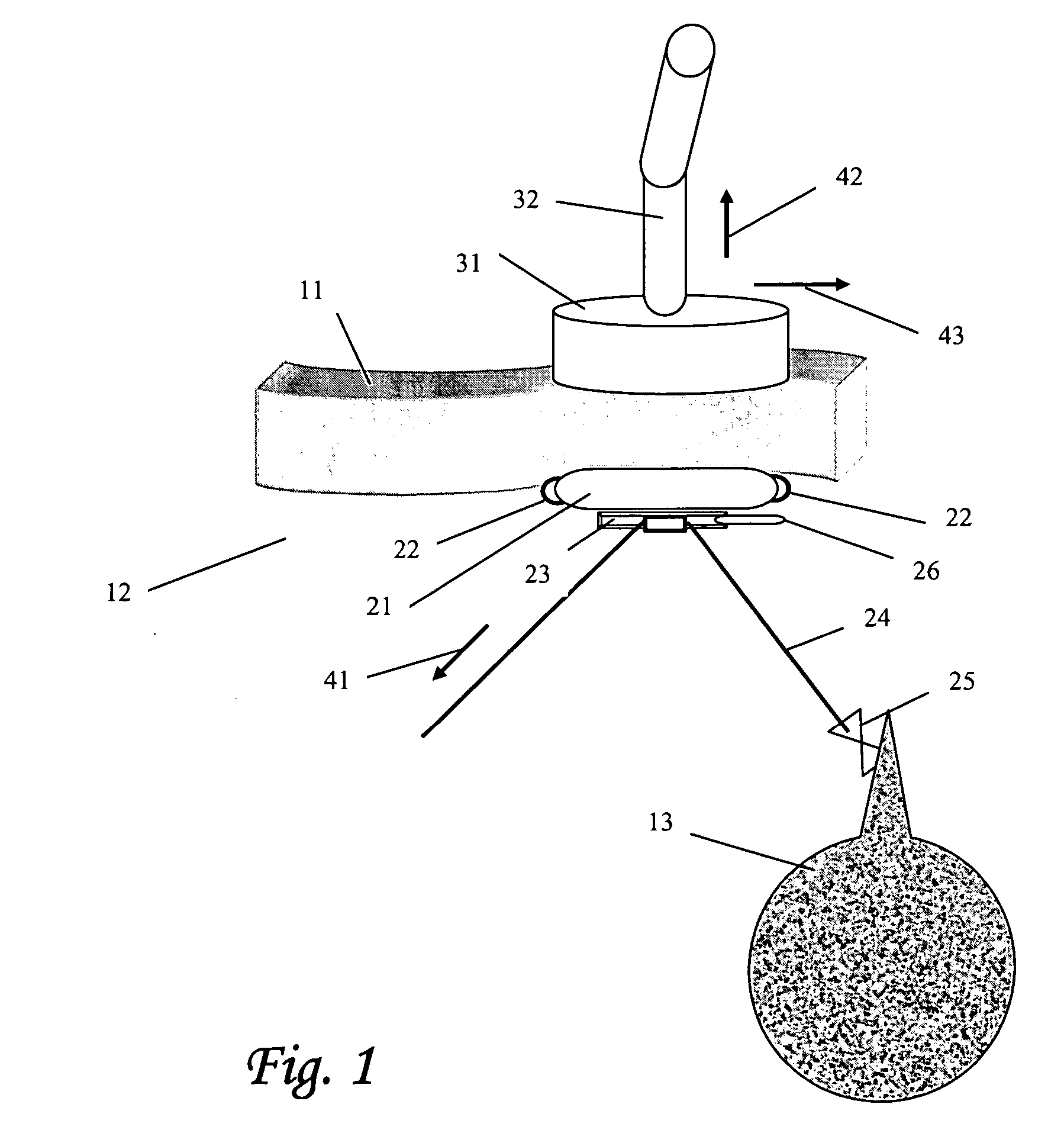

Low temperature electronic vaporization device and methods

ActiveUS20130042865A1Maintain efficiencyReduce the temperatureInput/output for user-computer interactionTobacco treatmentInhalationEnvironmental health

Low temperature electronic vaporization devices and method are described herein for emulating smoking wherein the devices generate an aerosol for inhalation by a subject by heating a viscous material that can have a tactile response in the mouth or respiratory tract.

Owner:JLI NAT SETTLEMENT TRUST

Apparatus for endoscopic procedures

An electromechanical surgical system is provided including a hand-held surgical instrument; an end effector; and a shaft assembly for selectively interconnecting the end effector and the surgical device. The shaft assembly includes a transmission housing; an outer tubular body; a distal neck housing for interconnecting a rotatable drive member of the surgical instrument and a rotation receiving member supported in the end effector, wherein the distal neck housing includes at least one gear system configured to convert a rotational input of the rotatable drive member into at least two output forces to the end effector; and an articulating neck assembly interconnecting the tubular body and the distal neck housing. The articulating neck assembly enables off-axis articulation of the distal neck assembly, and wherein the rotatable drive member extends through the articulating neck assembly.

Owner:TYCO HEALTHCARE GRP LP

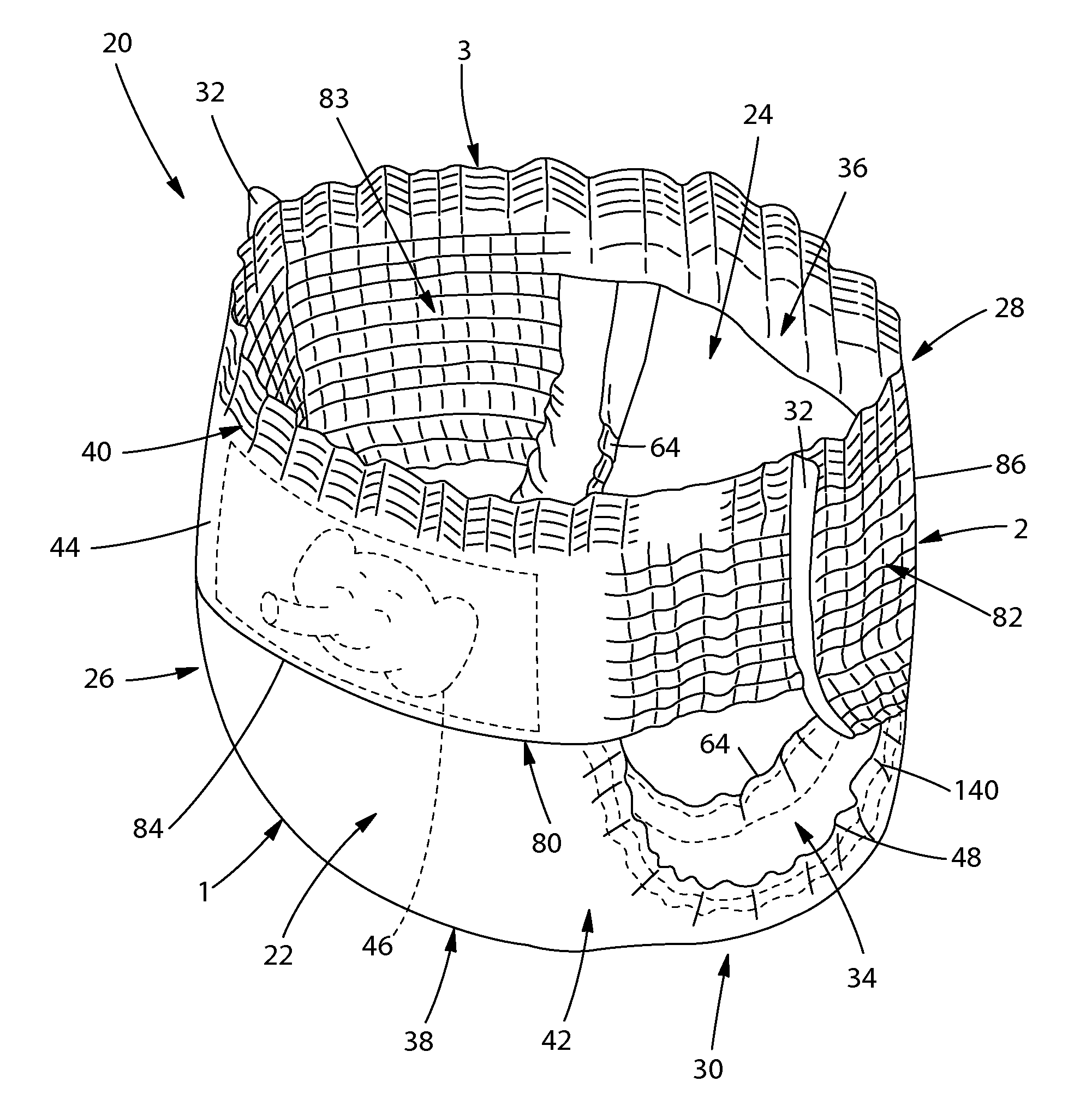

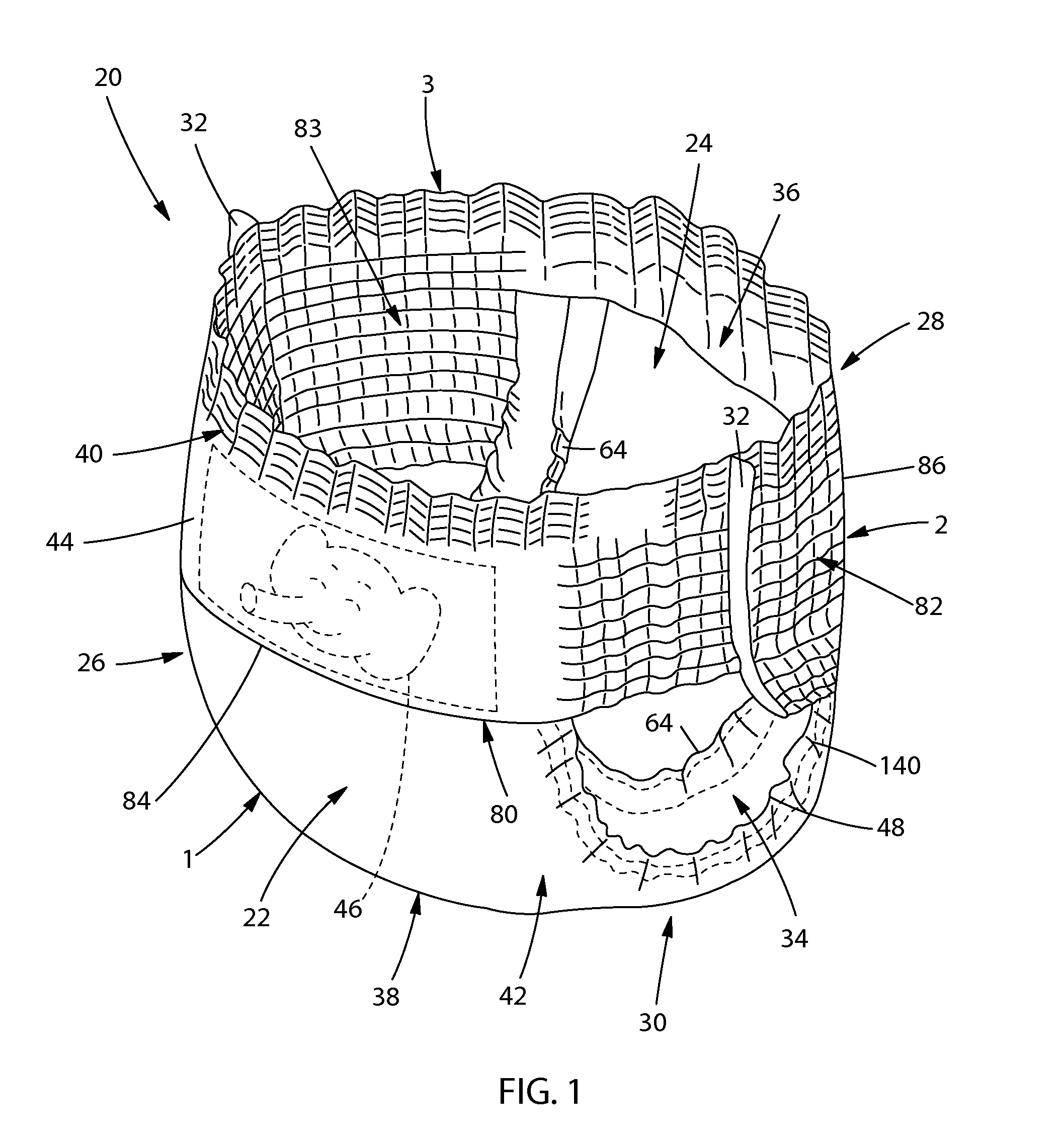

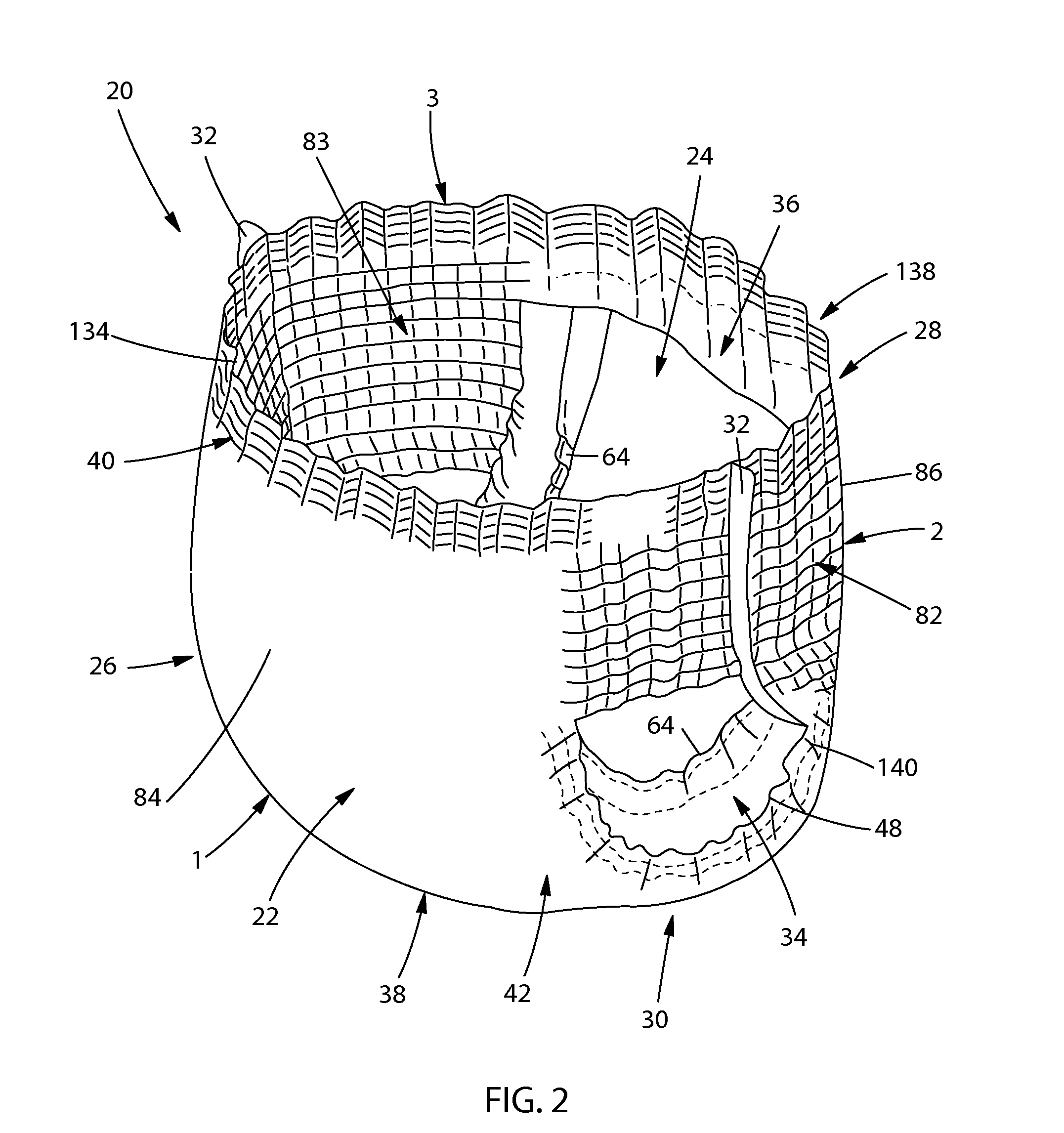

Disposable pull-on garment

An absorbent article having a longitudinal centerline, a front region, a crotch region, and a back region. The absorbent article has a main portion, a side portion, and a waist portion. The waist portion has a belt portion that has a front belt portion having elastomeric material and a back belt portion having elastomeric material. The front belt portion has a first elastic section and a second elastic section, each section having force zones. The back belt portion has a third elastic section and a fourth elastic section, each section having force zones. The force zones in the portions alternate between a high force zone and a low force zone in at least one belt portion.

Owner:THE PROCTER & GAMBLE COMPANY

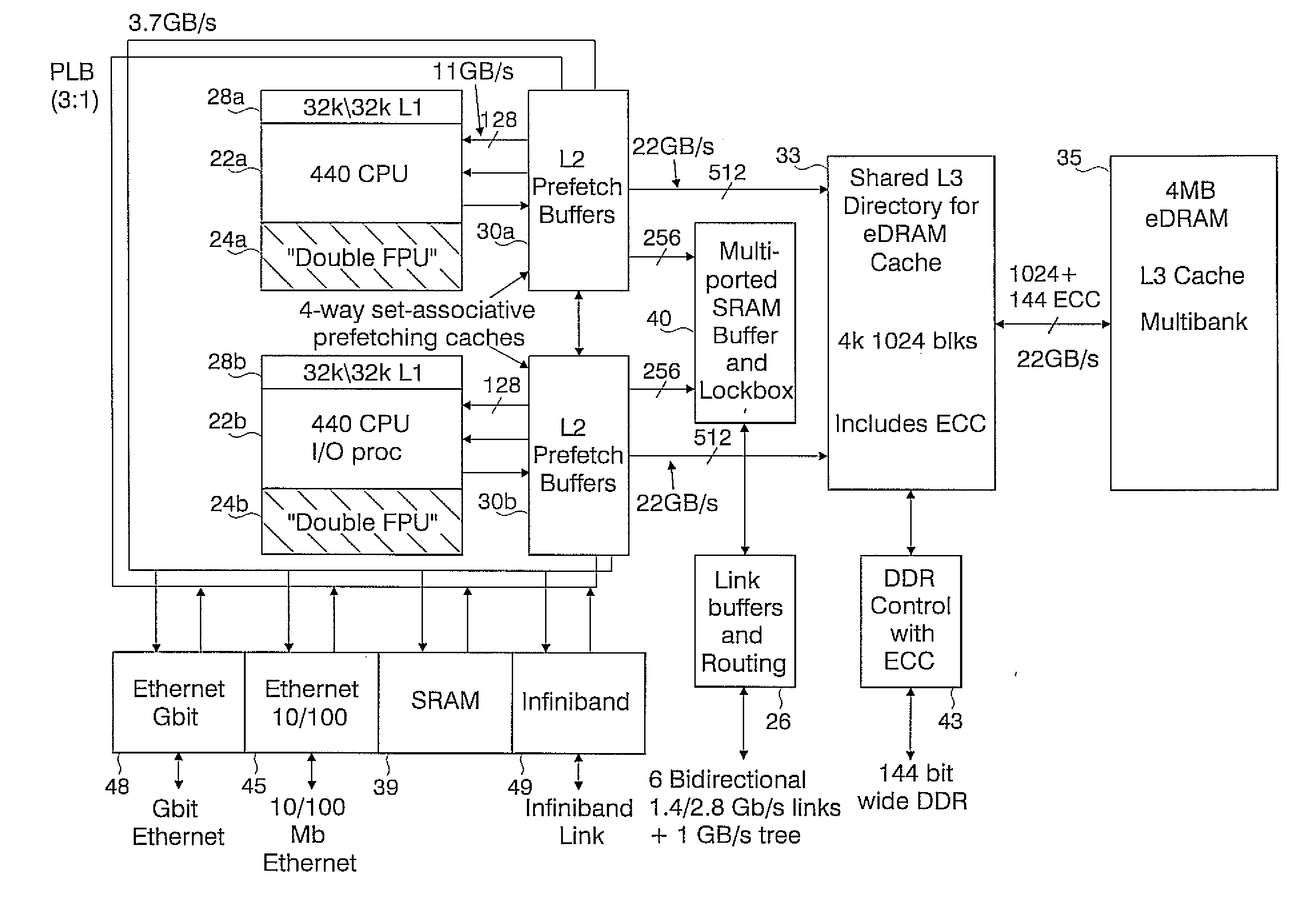

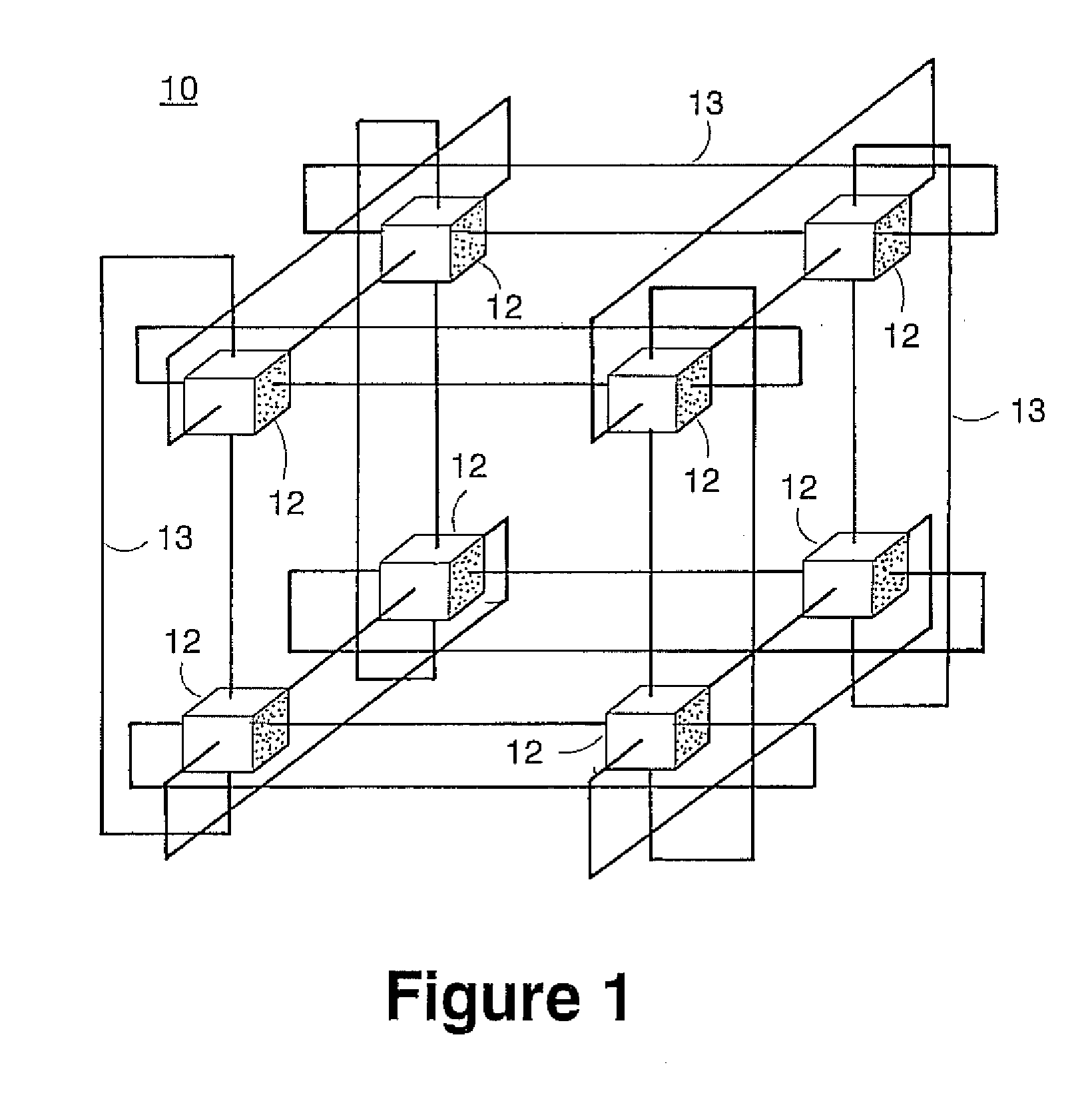

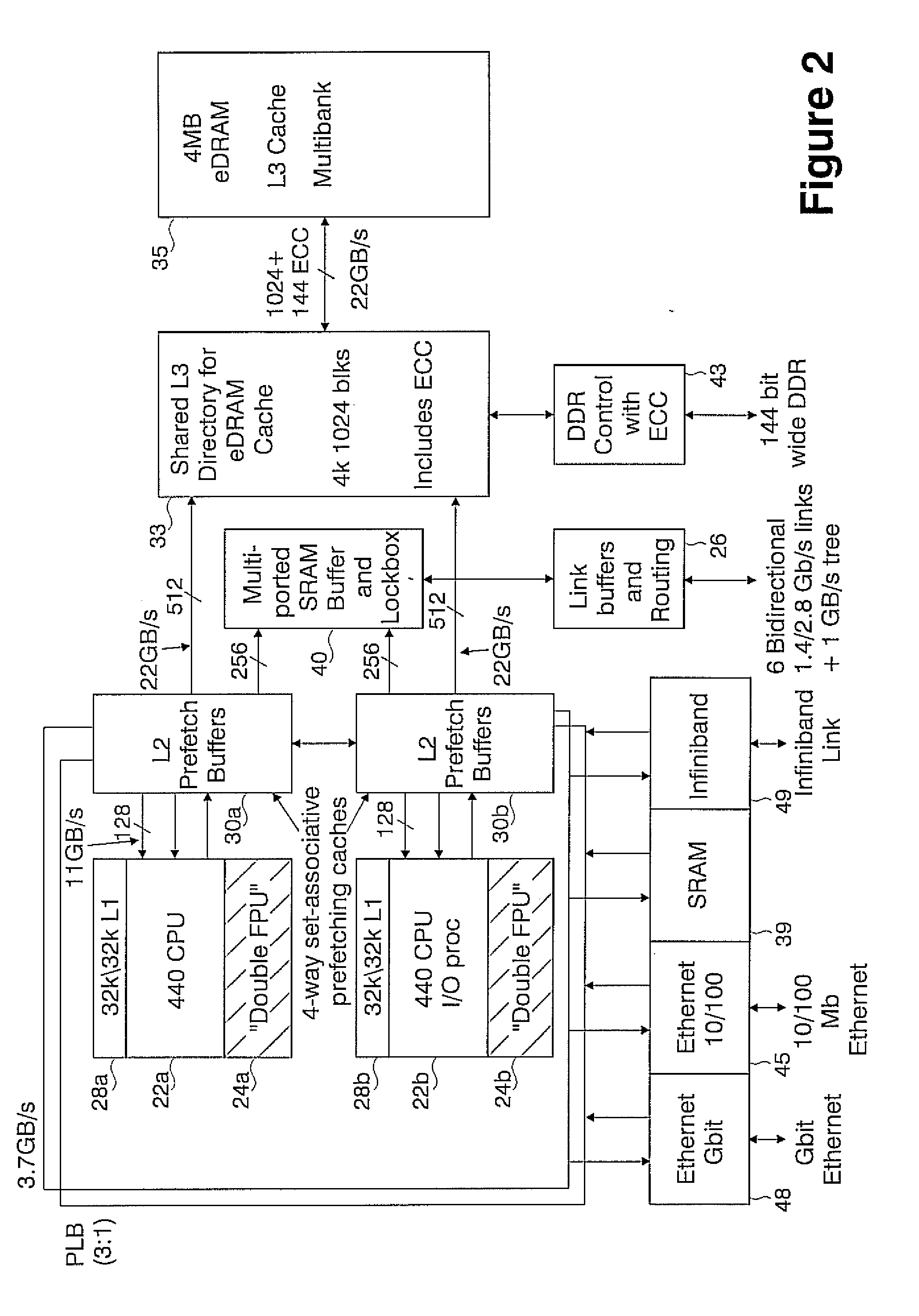

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

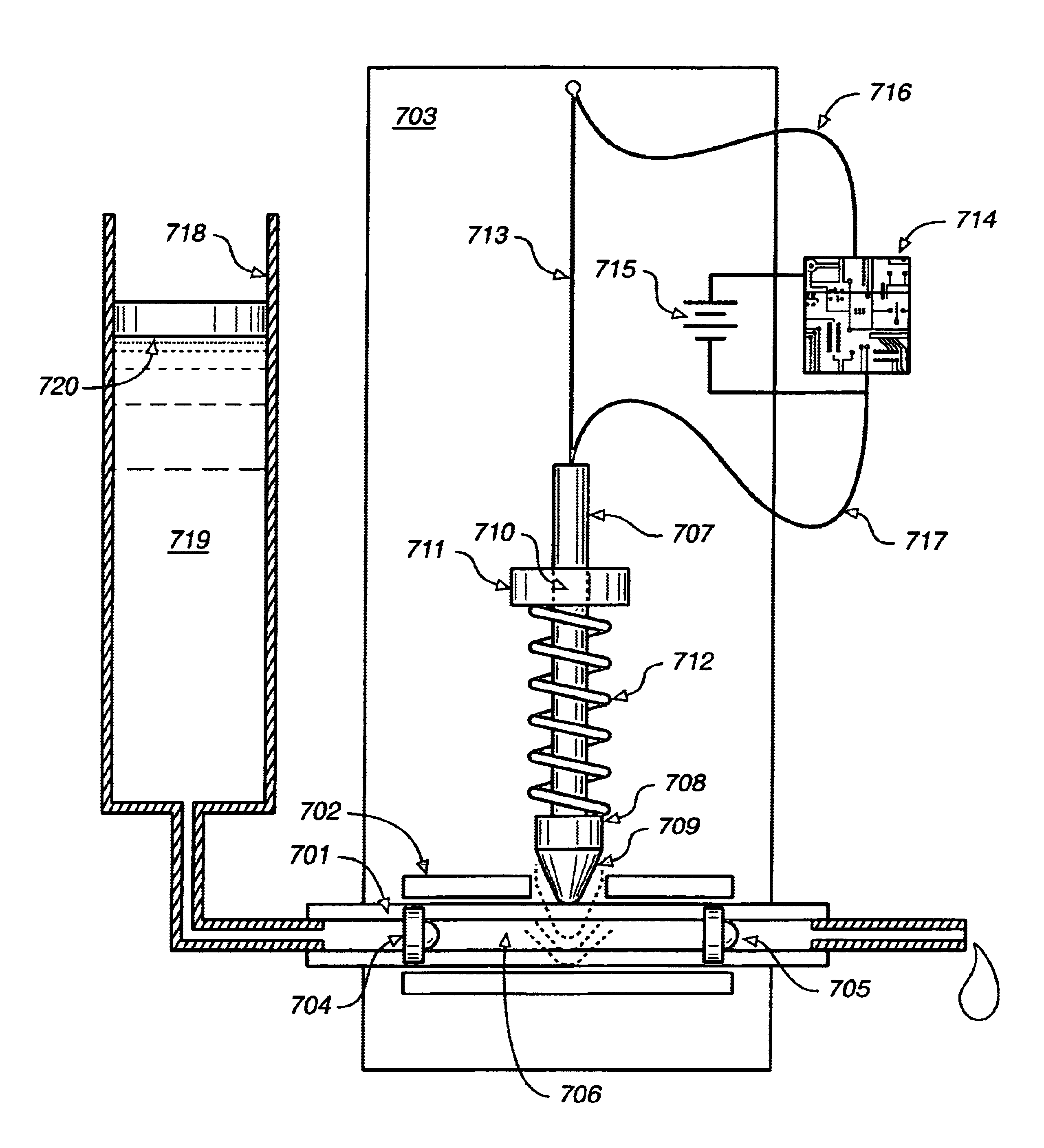

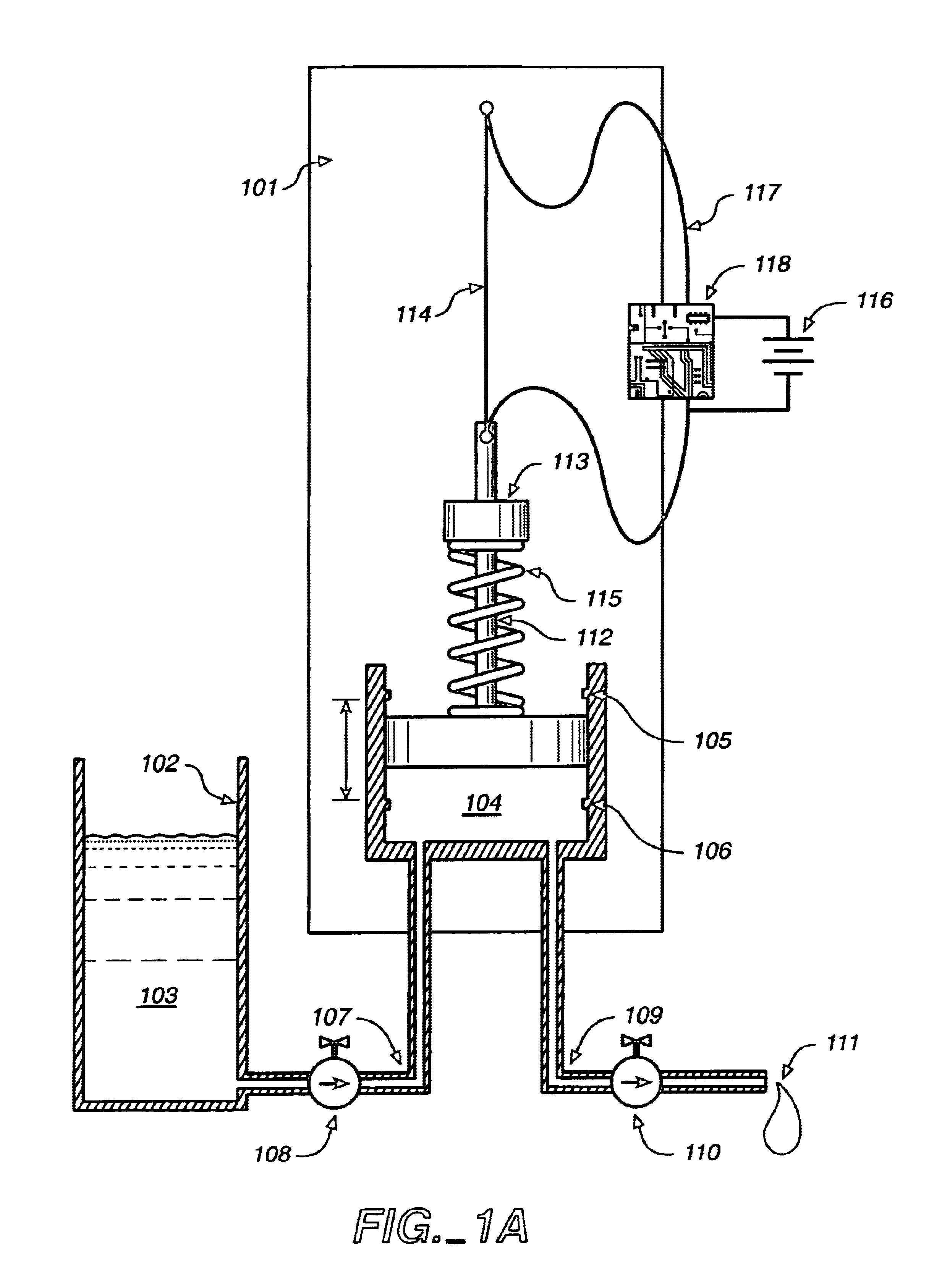

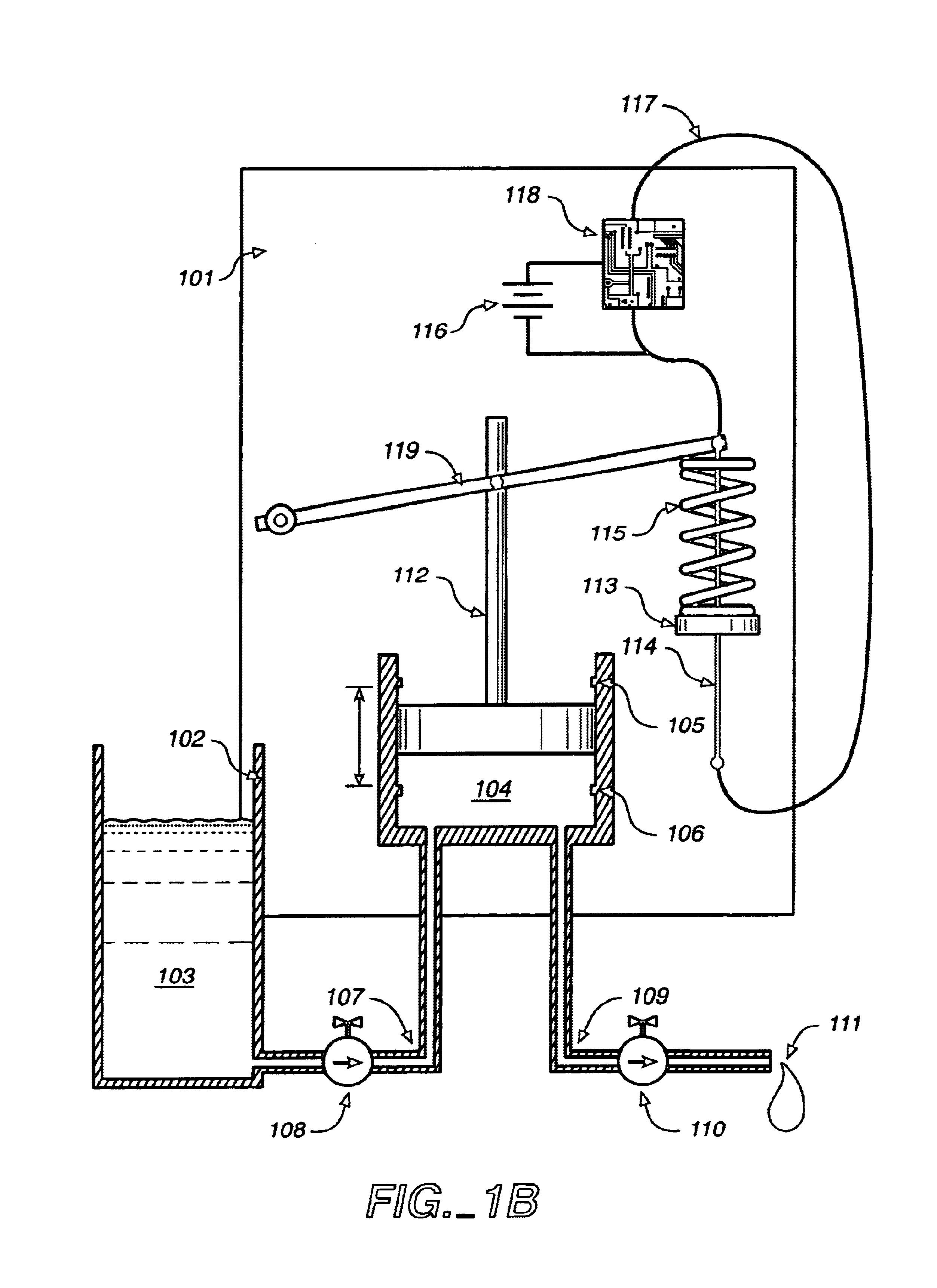

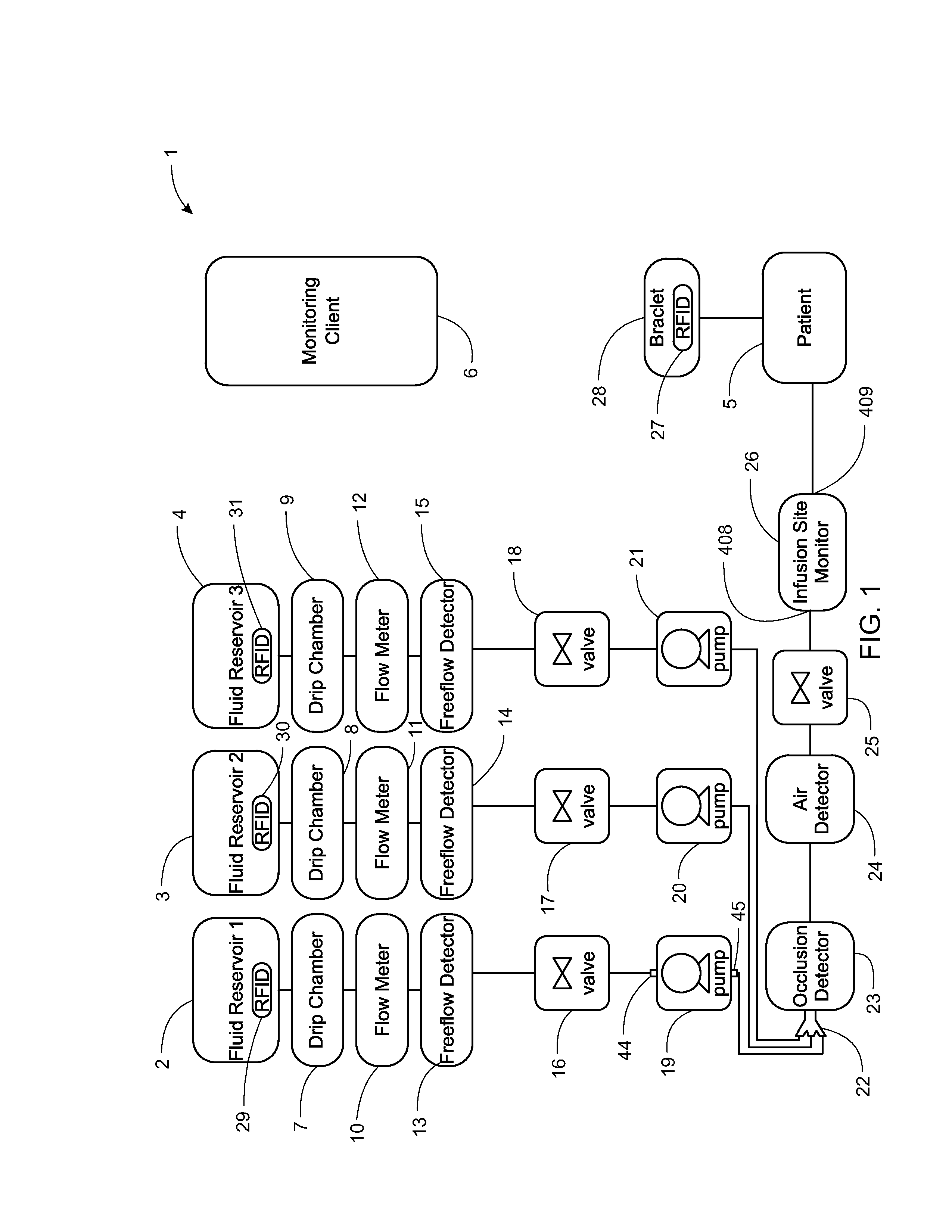

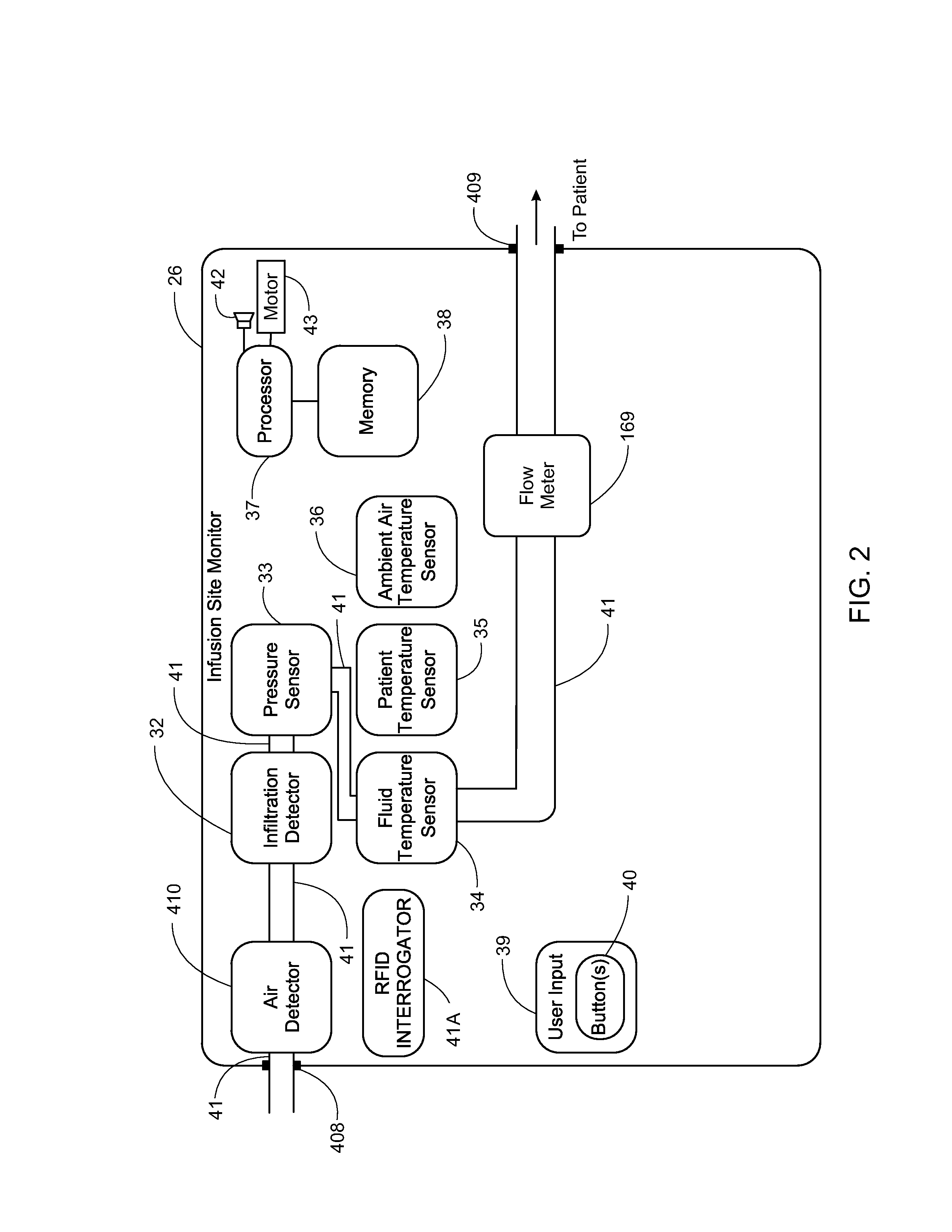

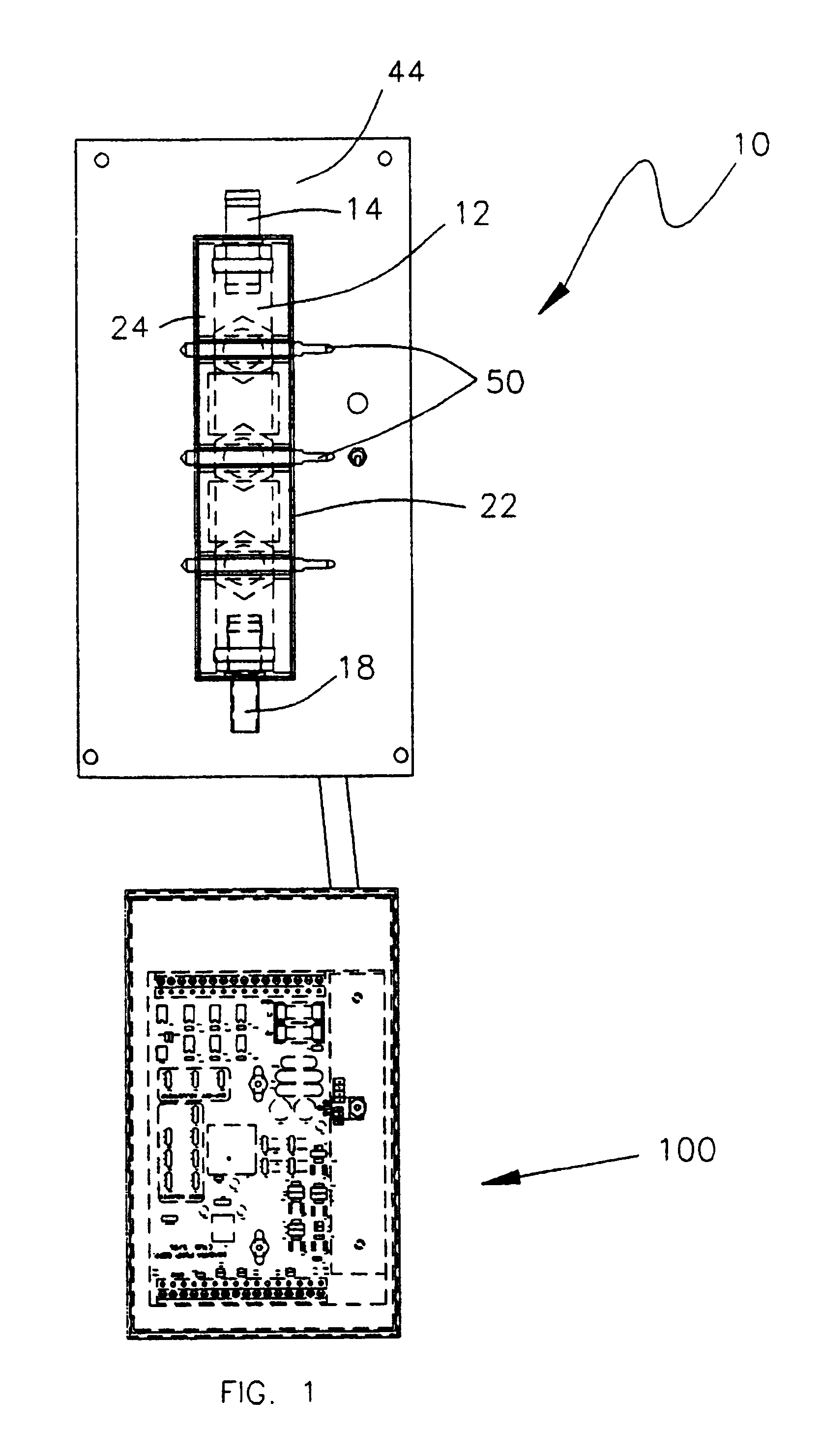

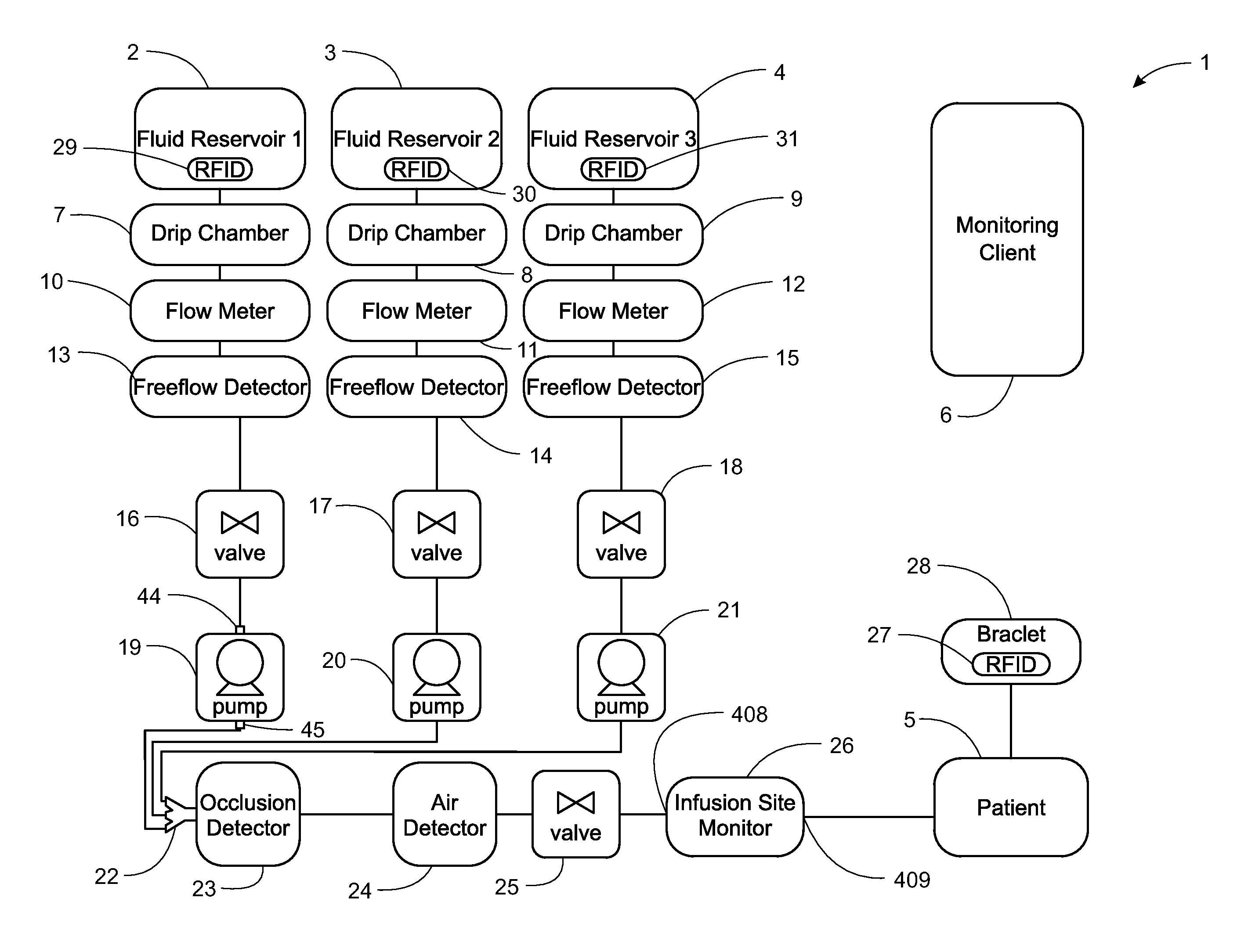

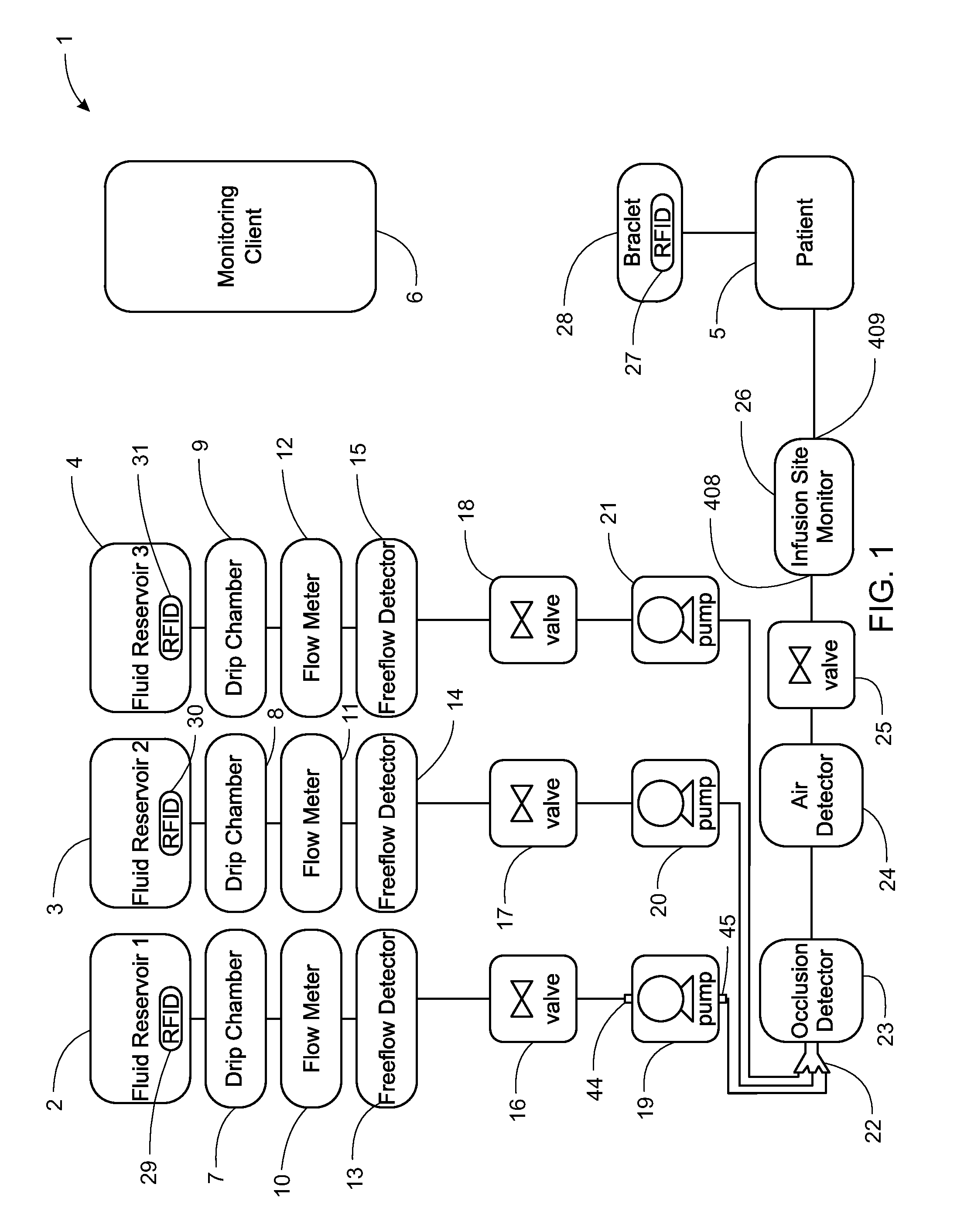

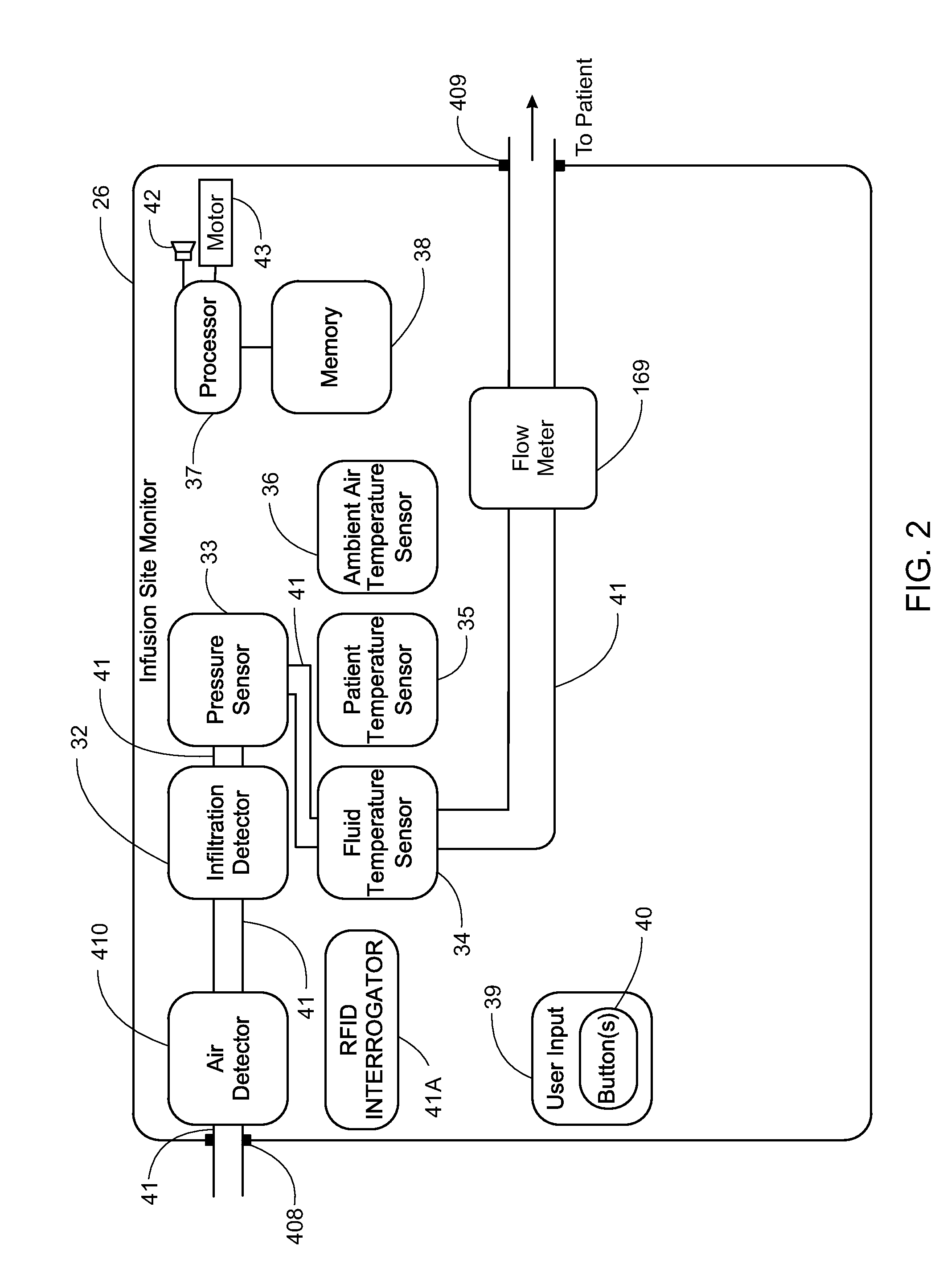

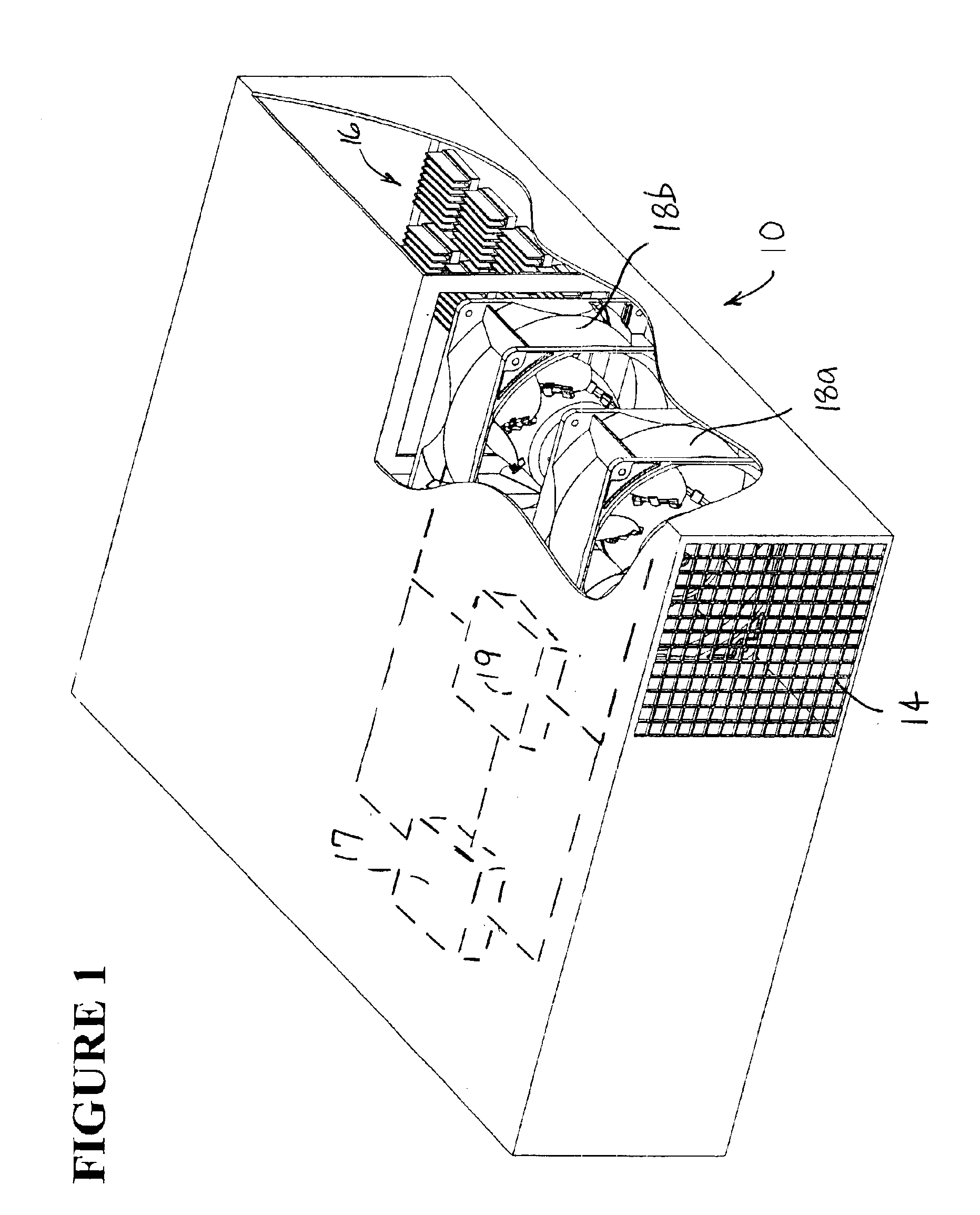

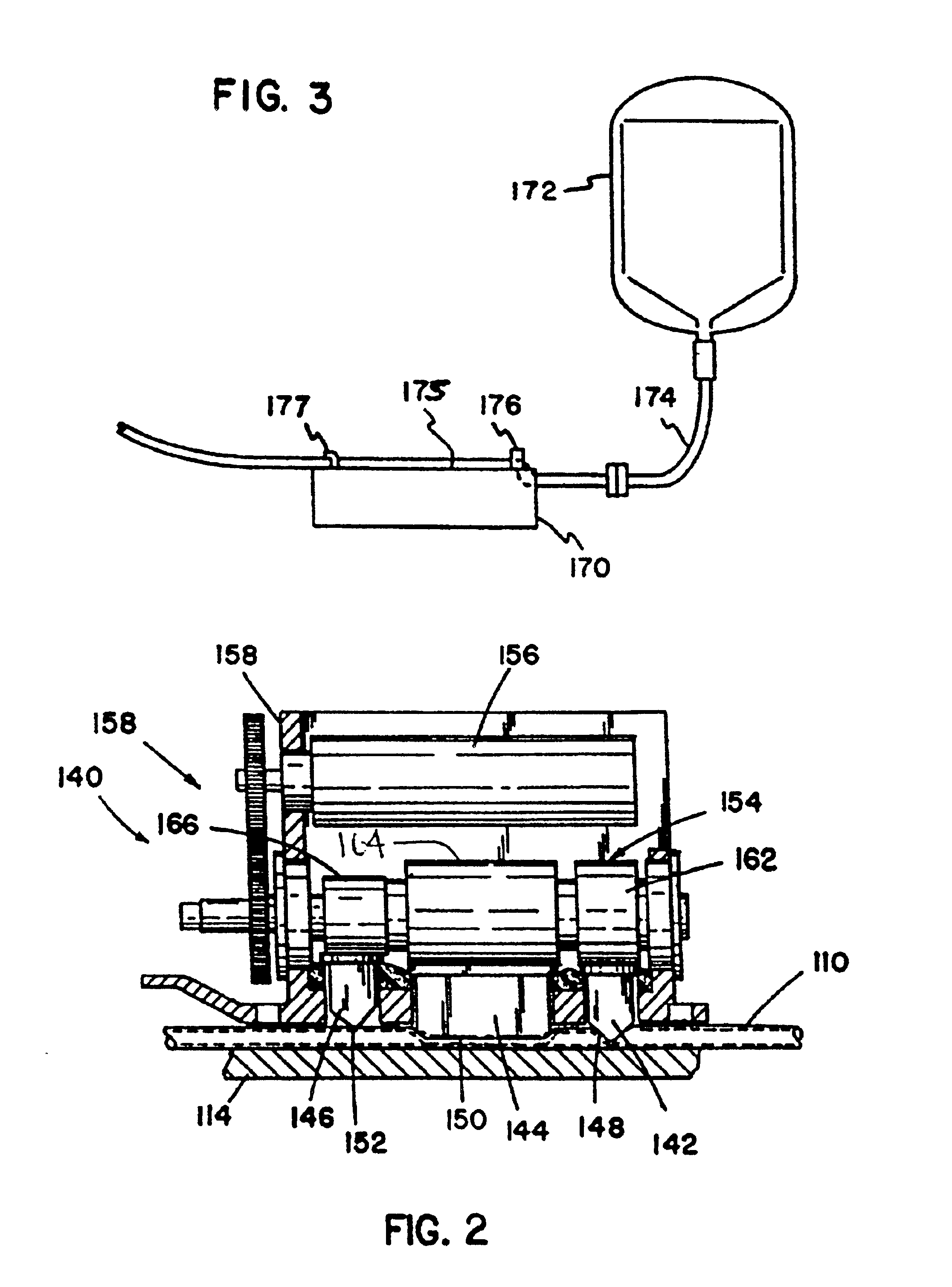

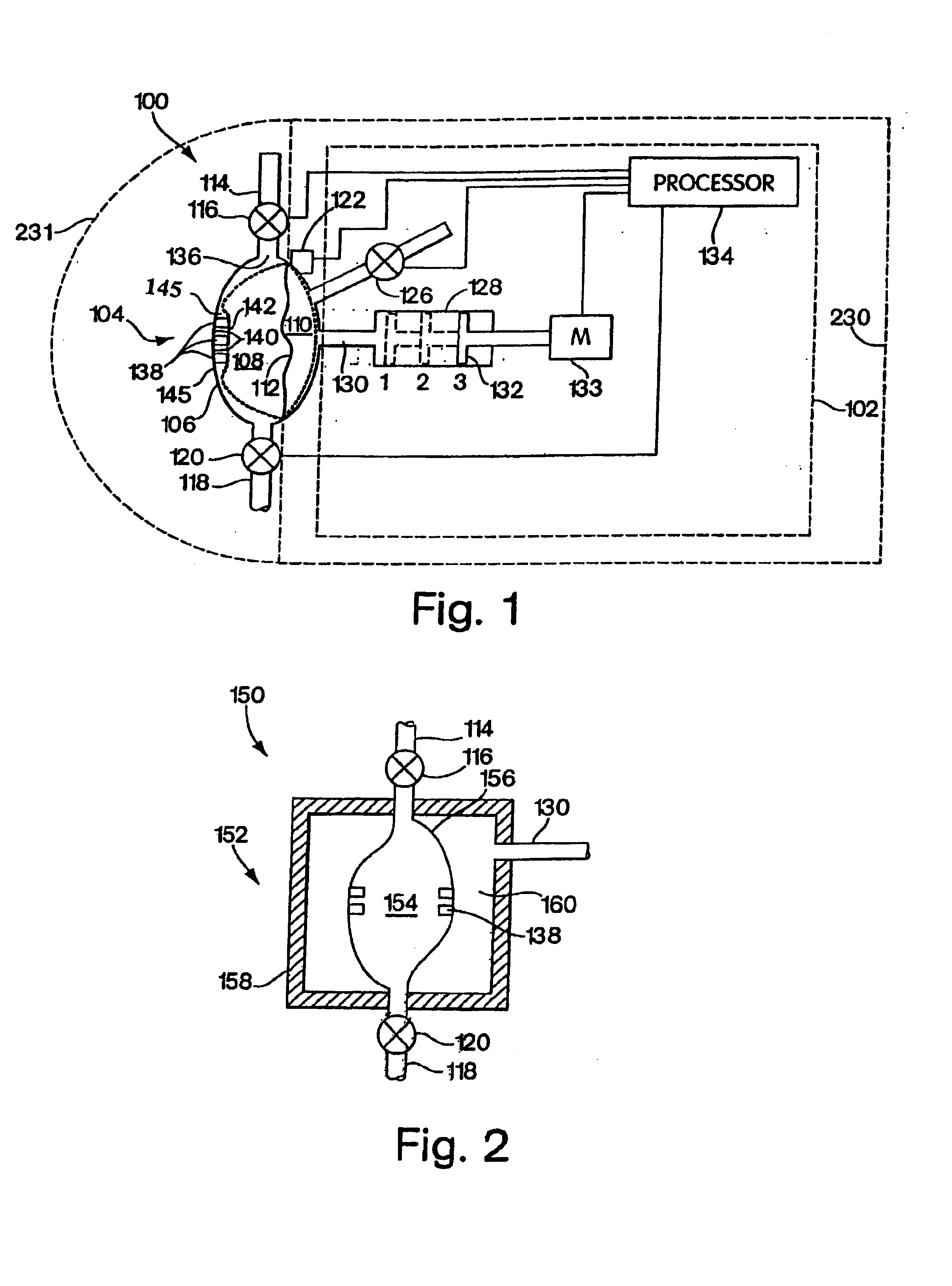

System, Method, and Apparatus for Infusing Fluid

ActiveUS20130177455A1Reduce peak torqueDrug and medicationsFlexible member pumpsPeristaltic pumpPinch valve

A peristaltic pump, and related system method are provided. The peristaltic pump includes a cam shaft, first and second pinch-valve cams, first and second pinch-valve cam followers, a plunger cam, a plunger-cam follower, a tube receiver, and a spring-biased plunger. The first and second pinch-valve cams are coupled to the cam shaft. The first and second pinch-valve cam followers each engage the first and second pinch-valve cams, respectively. The plunger cam is coupled to the cam shaft. The plunger-cam follower engages the plunger cam. The tube receiver is configured to receive a tube. The spring-biased plunger is coupled to the plunger-cam follower such that the expansion of the plunger cam along a radial angle intersecting the plunger-cam follower as the cam shaft rotates pushes the plunger cam follower towards the plunger and thereby disengages the spring-biased plunger from the tube. A spring coupled to the spring-biased plunger biases the spring-biased plunger to apply the crushing force to the tube.

Owner:DEKA PROD LLP

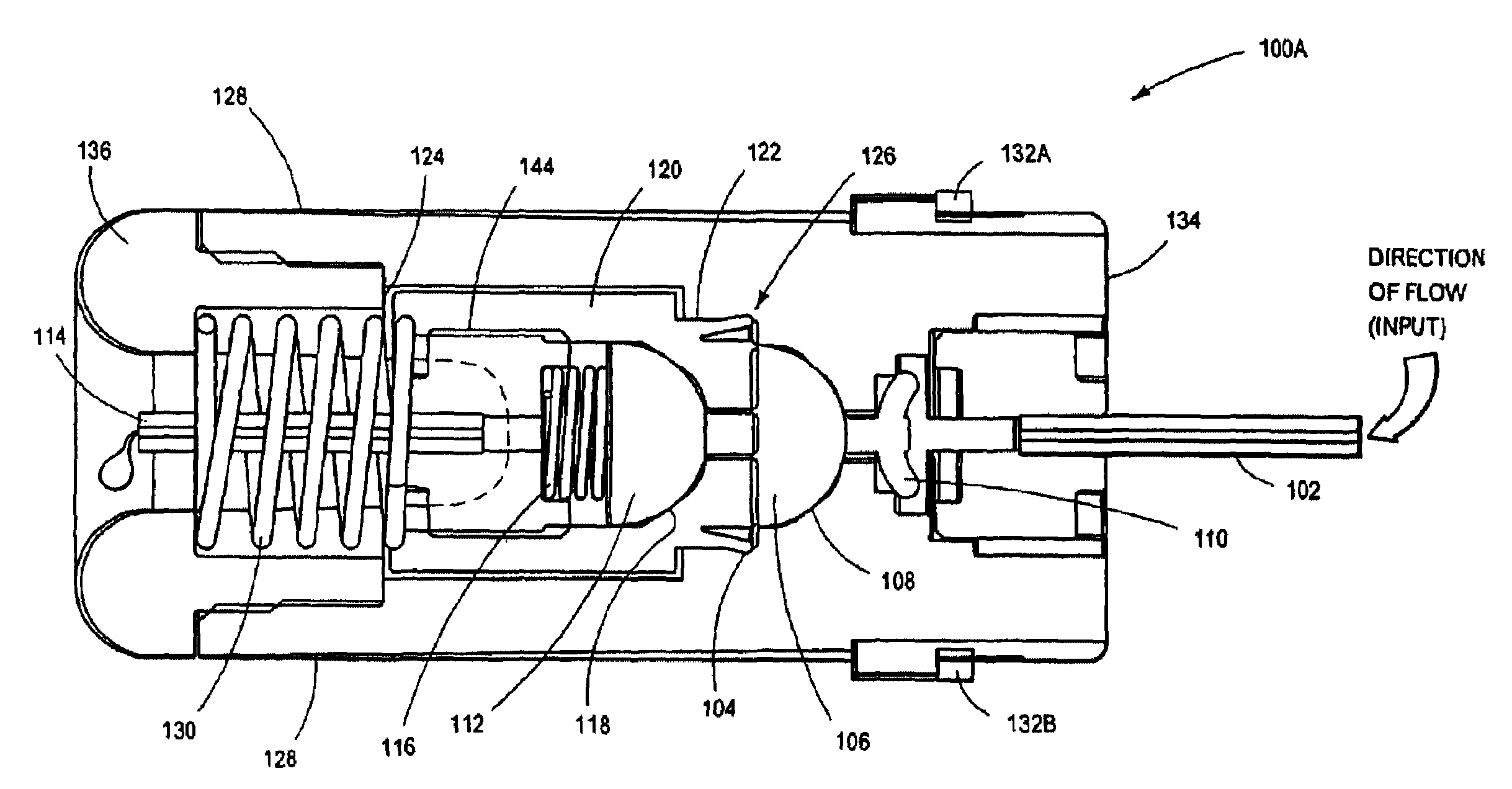

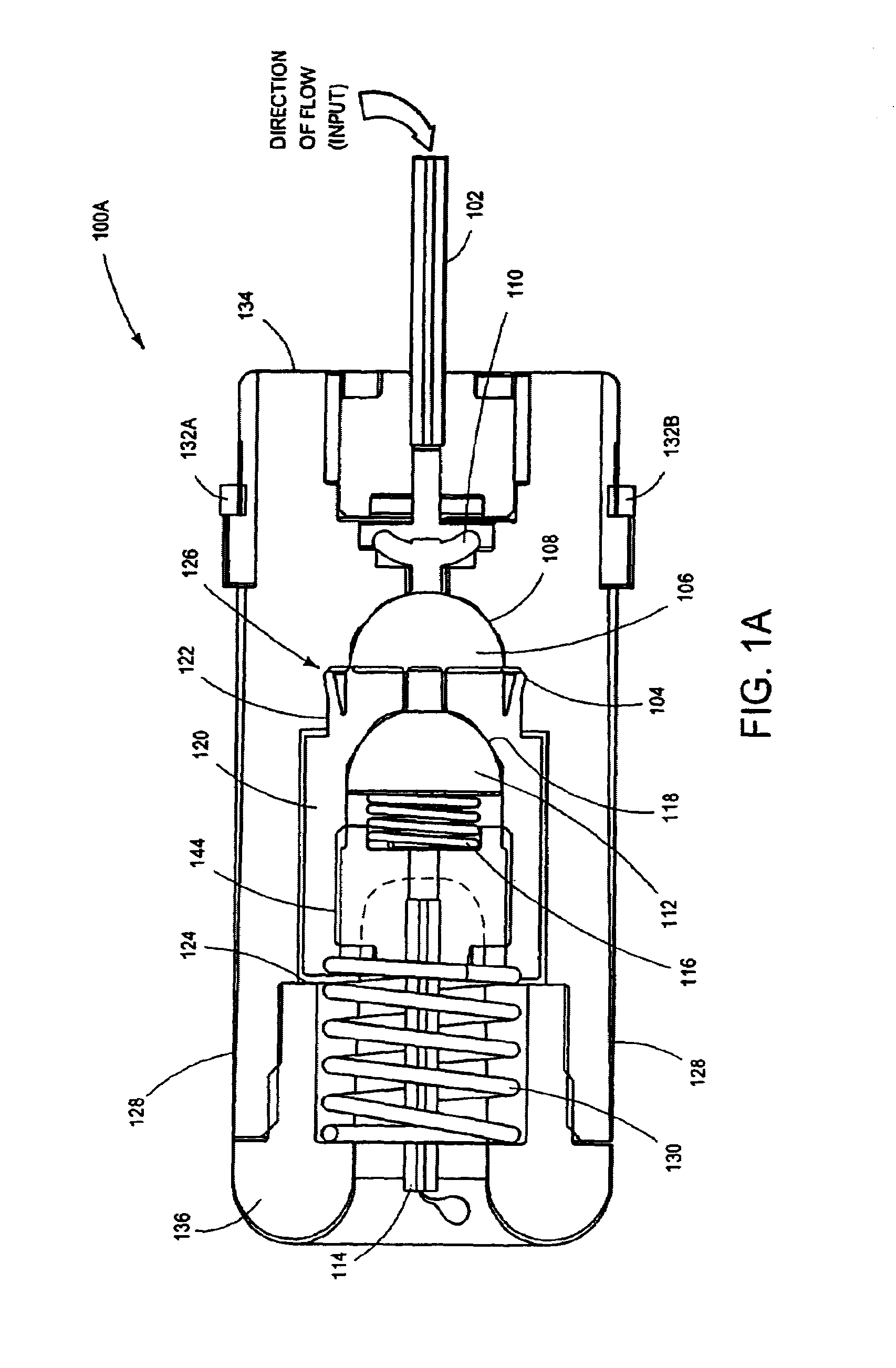

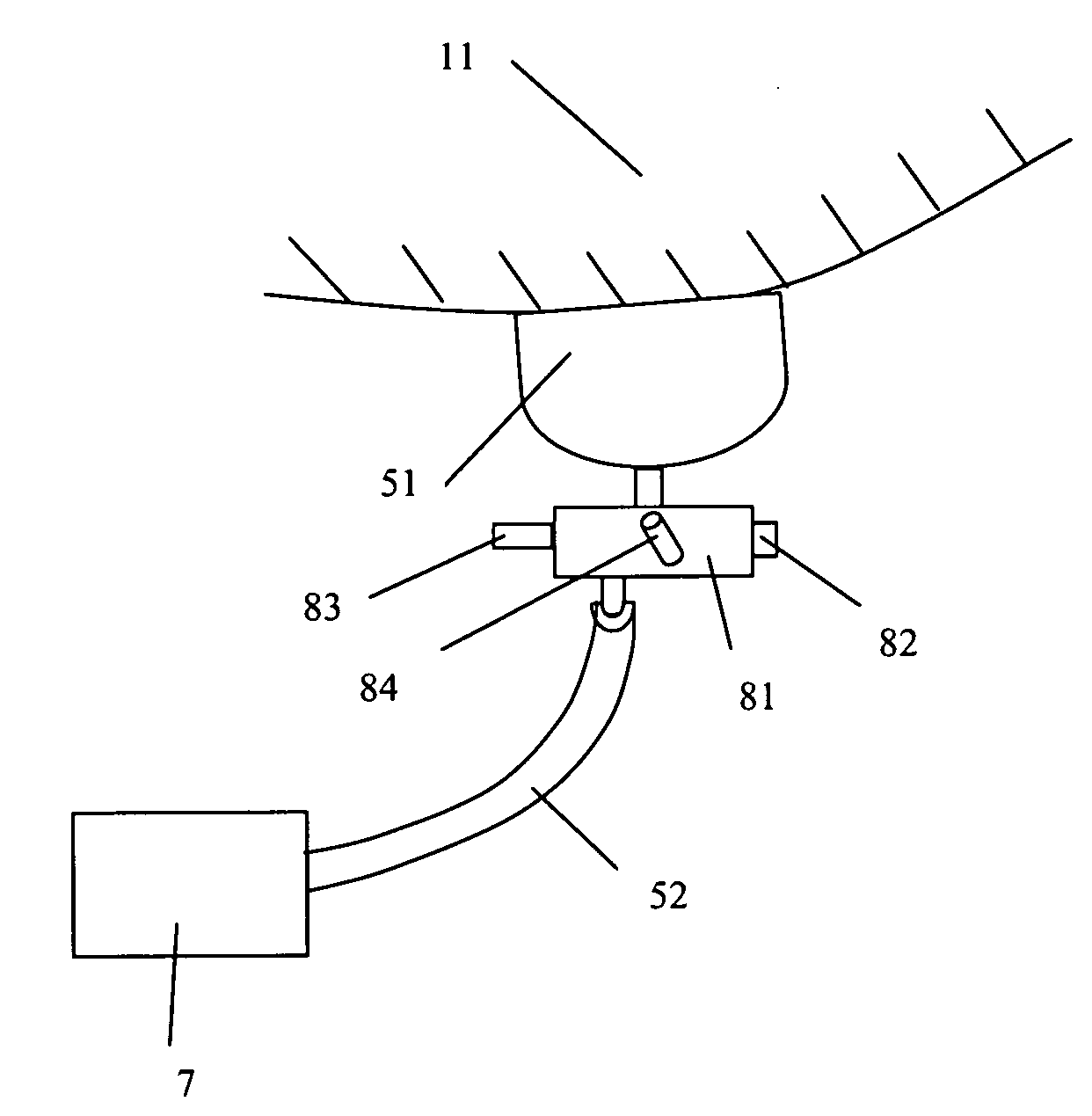

Shape memory alloy wire driven positive displacement micropump with pulsatile output

InactiveUS7052251B2Reliable outputLow costFlexible member pumpsMedical devicesControl electronicsShape-memory alloy

Apparatuses and methods for pumping fluid are disclosed. An exemplary apparatus is a miniature pump that includes a shape memory wire that obtains a plastic condition below a transformation temperature and has a memorized shape such that the shape memory wire produces a work stroke by returning to the memorize shape at least at the transformation temperature. A spring biased against the shape memory wire is deflected by the work stroke to deform the shape memory wire from the memorized shape below the transformation temperature. A fluid pump is coupled to the shape memory wire and driven by the biased spring and shape memory wire to produce a fluid flow. The miniature pump can be incorporated into a self-contained infusion device in the form of a compact self-adhesive patch including a fluid reservoir, control electronics and power supply that is place directly at the infusion site of a user.

Owner:MEDTRONIC MIMIMED INC

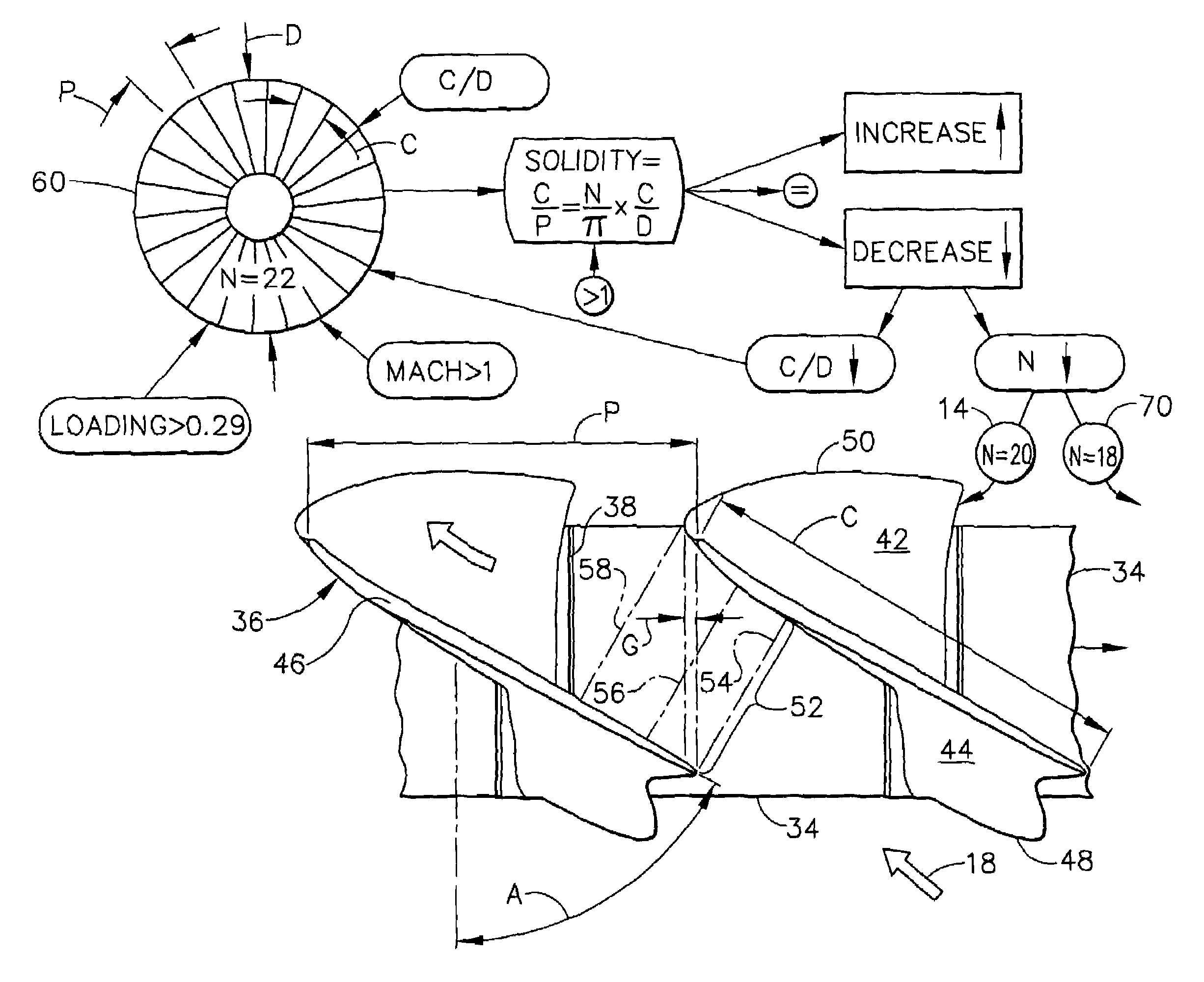

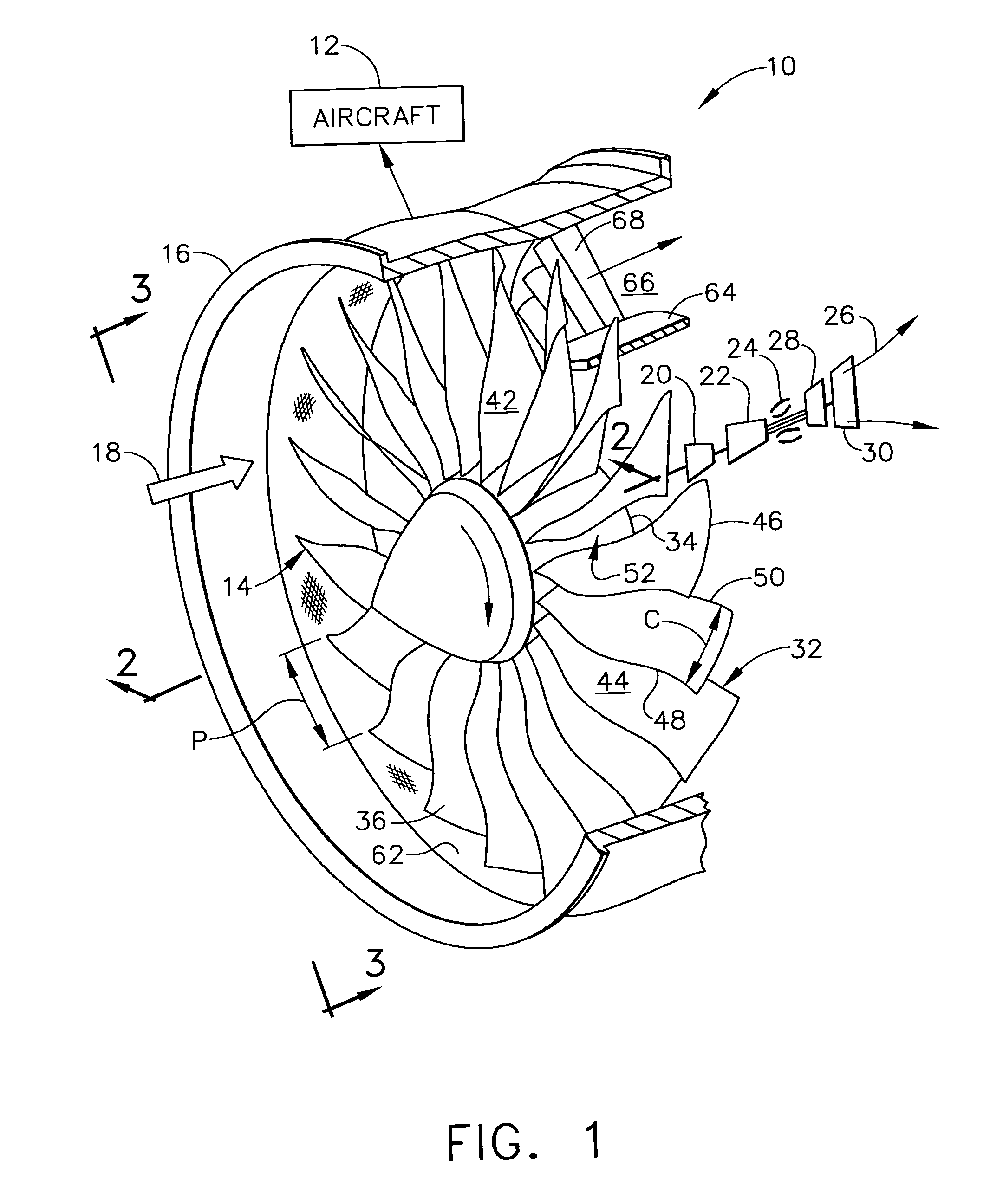

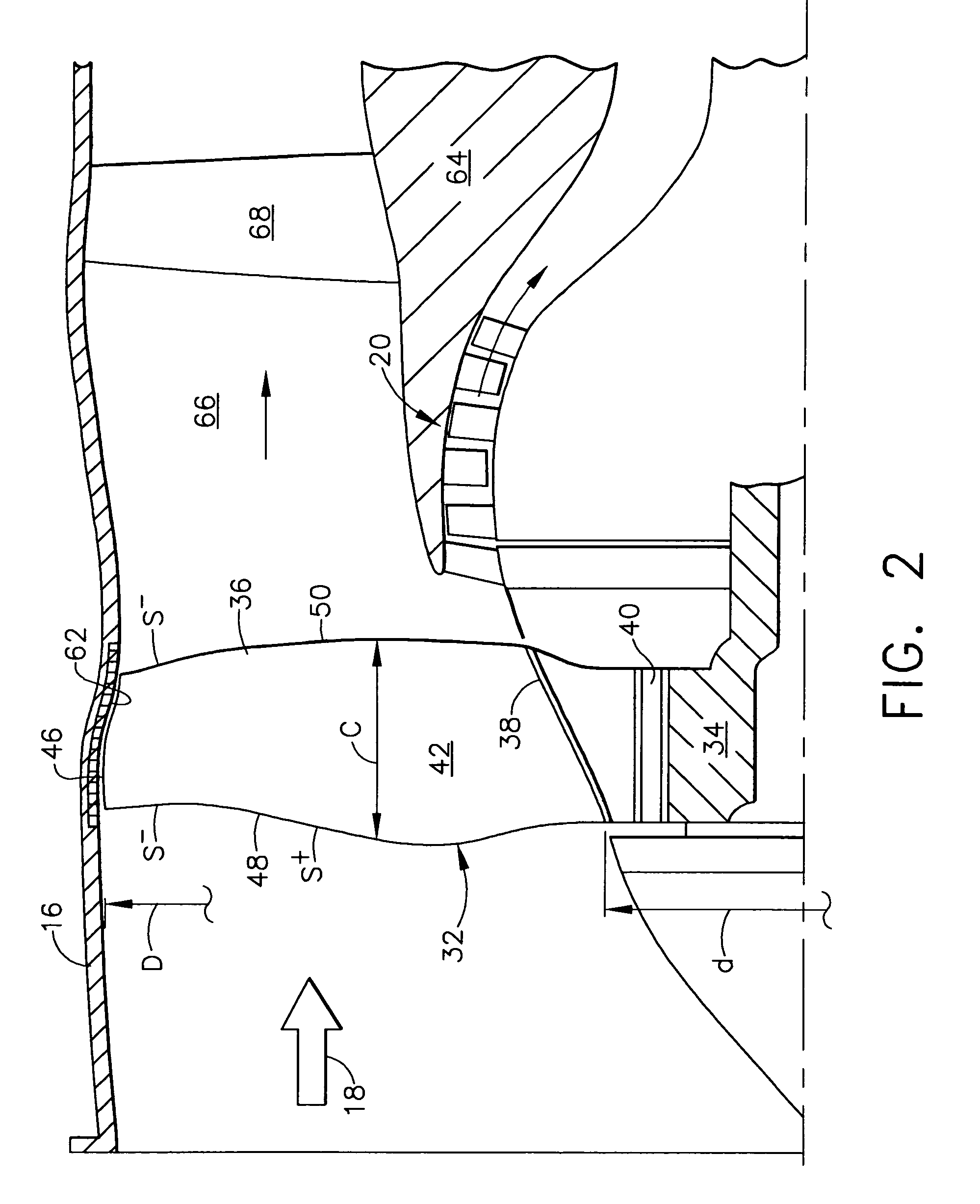

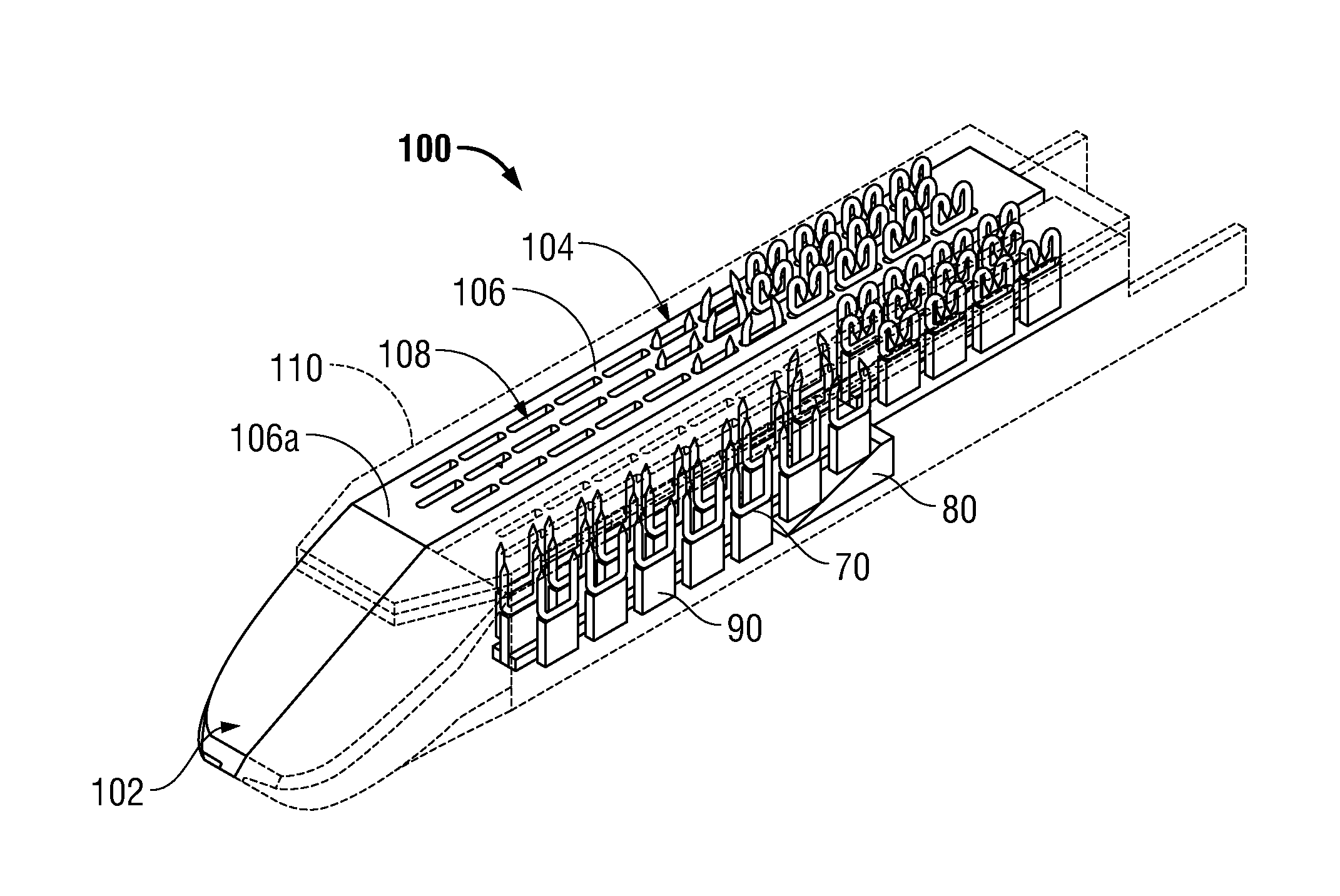

Low solidity turbofan

A turbofan includes a row of fan blades extending from a supporting disk inside an annular casing. Each blade includes an airfoil having opposite pressure and suction sides extending radially in span between a root and tip and axially in chord between leading and trailing edges. Adjacent airfoils define corresponding flow passages therebetween for pressurizing air. Each airfoil includes stagger increasing between the root and tip, and the flow passage has a mouth between the airfoil leading edge and the suction side of an adjacent airfoil and converges to a throat aft from the mouth. The row includes no more than twenty fan blades having low tip solidity for increasing the width of the passage throat.

Owner:GENERAL ELECTRIC CO

Driving controlling apparatus for linear compressor and method thereof

Owner:LG ELECTRONICS INC

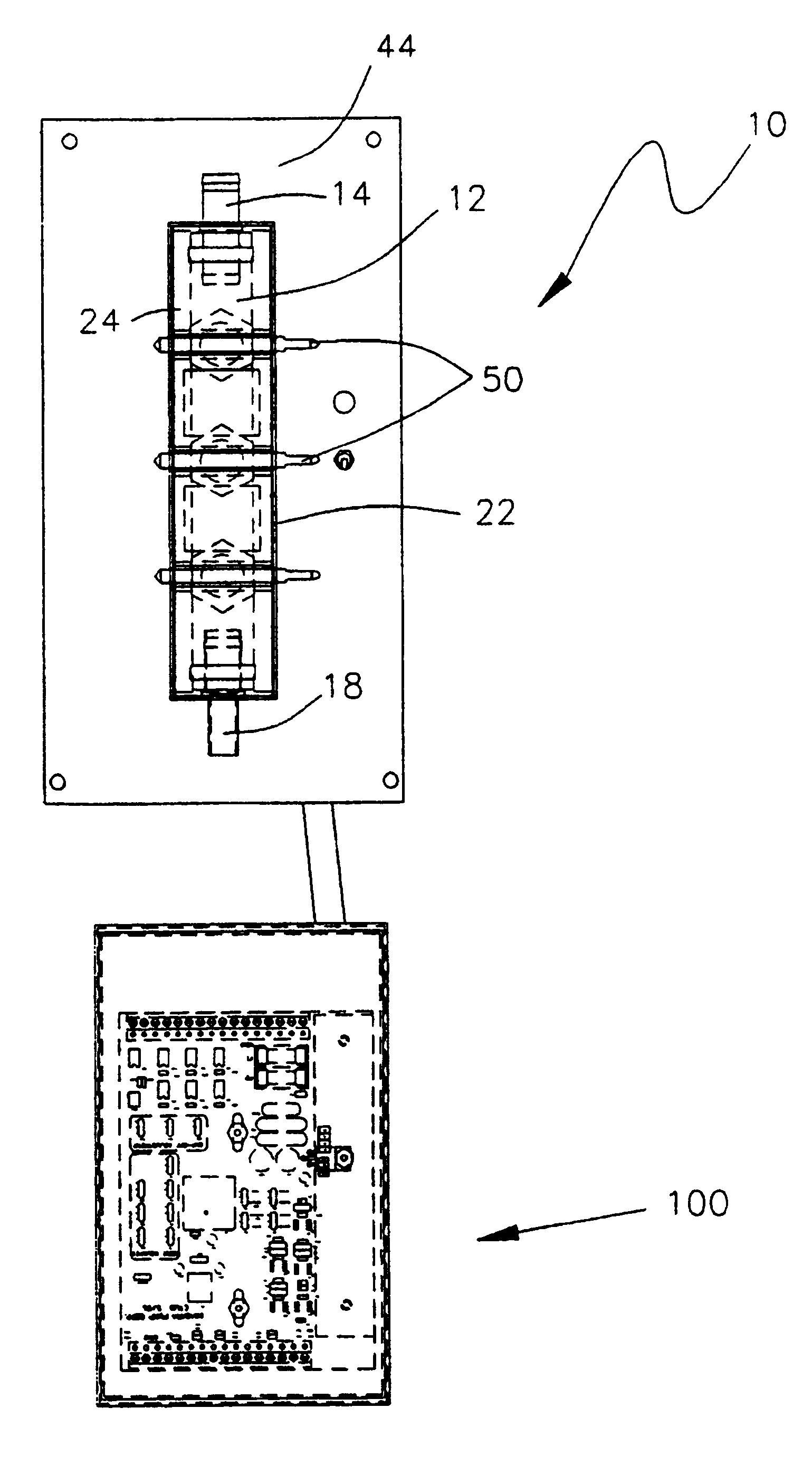

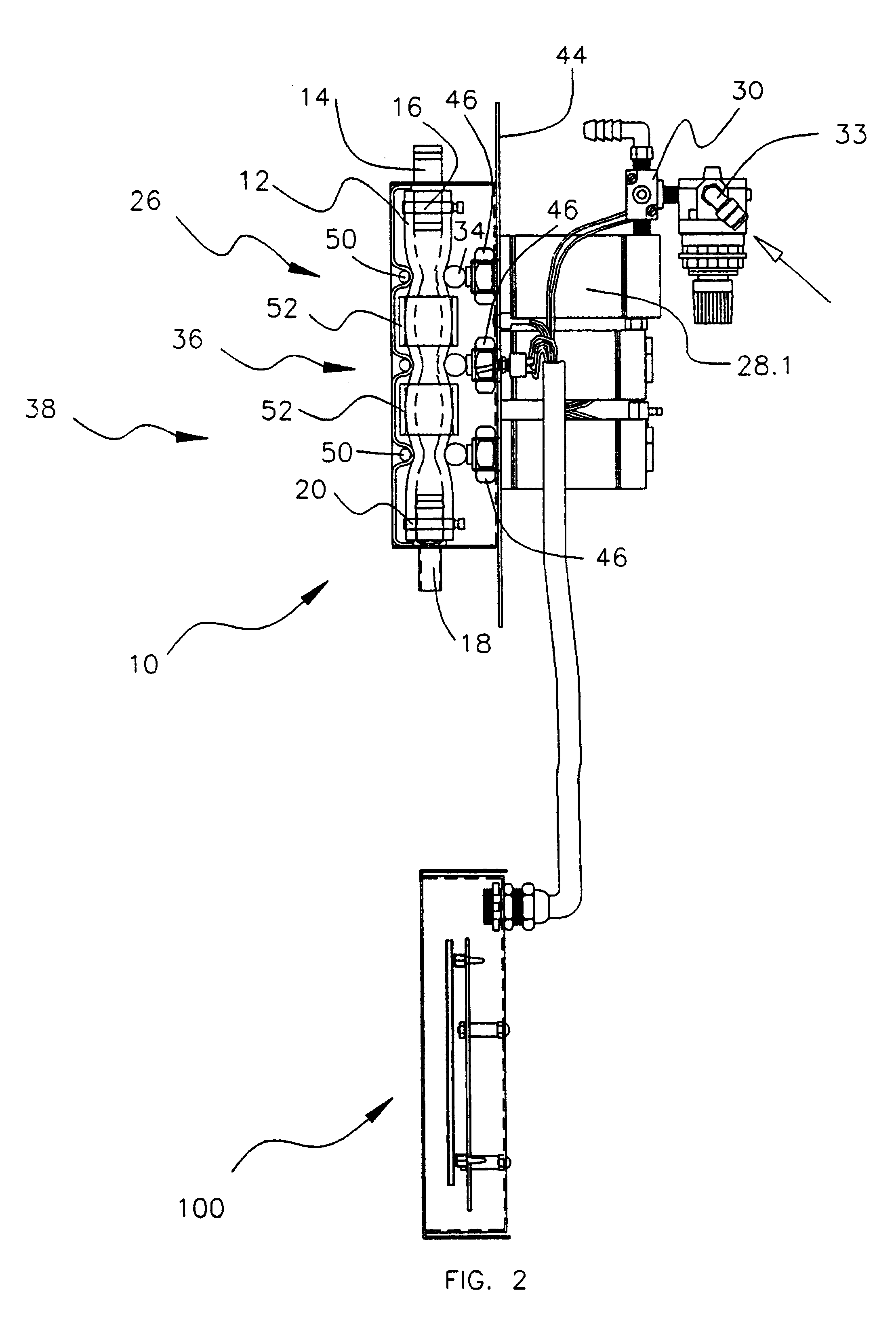

Linear peristaltic pump

InactiveUS6213739B1High liquid pumping pressureExtends useful pump tube lifeFluid parameterFlexible member pumpsPeristaltic pumpActuator

A liquid pumping apparatus for pumping liquids, more specifically a linear peristaltic pump apparatus. The apparatus consists of a high durometer compressible elastomeric liquid flow tube (12), an infeed valve assembly (26), an outfeed valve assembly (38), an extensible and retractable actuator anvil (34) having a round surface which engages the flow tube (12) at all times, an opposed anvil (24.1) having a round surface in engagement with the flow tube at all times, the flow tube being held between the anvils (34, 24.1) in a slightly compressed state when the anvil (34) is retracted, and a control assembly (100) for causing the movable anvil to be sequentially extended and retracted to cause flow within the flow tube (12) from the infeed valve assembly (26) to the outfeed valve assembly (38). With this apparatus the lumen of the flow tube (12) to the sides of the anvils is not completely reduced to zero volume during displacement compression whereby gas embolisms do not erupt or explode when discharged. Two principal embodiments are disclosed, one having infeed and outfeed check valves which oclude the flow tube, and the other having check valves.

Owner:NIAGARA PUMP CORP

Virtual ports devices and method

A device auxiliary to surgery, for anchoring and lifting cavity walls or internal organs of a patient. The device provides a virtual port, that is an instrument that can he non-invasively, or minimally invasively and removably attached to the undersurface of a patient's cavity, or to various tissues within a cavity, and to which various retracting means are attached. The device includes means allowing it to be moved from one position to another and reattached to the undersurface of the abdominal wall, or to various tissues within a cavity, without creating any additional openings in the cavity wall. The device includes means for attaching various retractors.

Owner:VIRTUAL PORTS

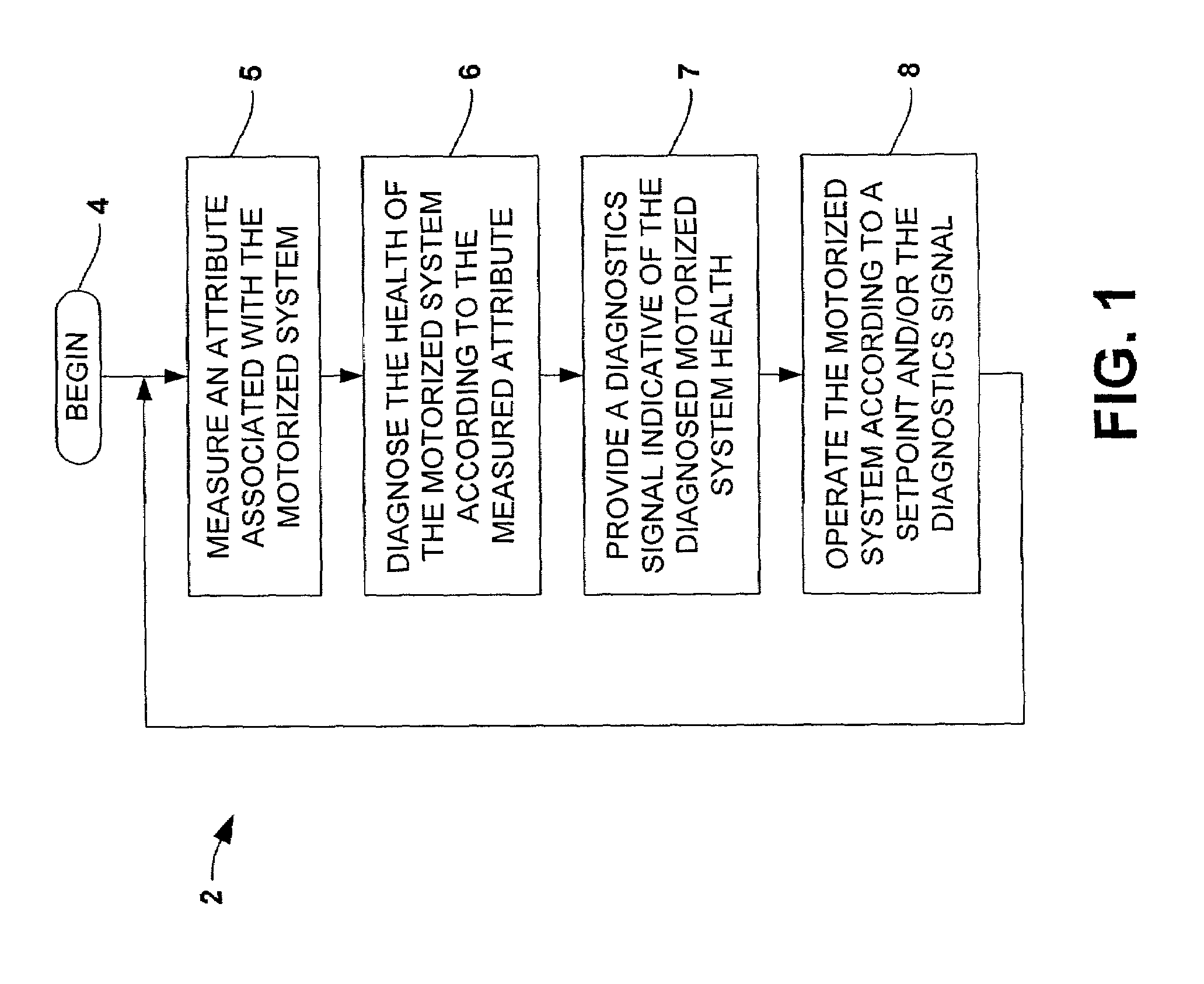

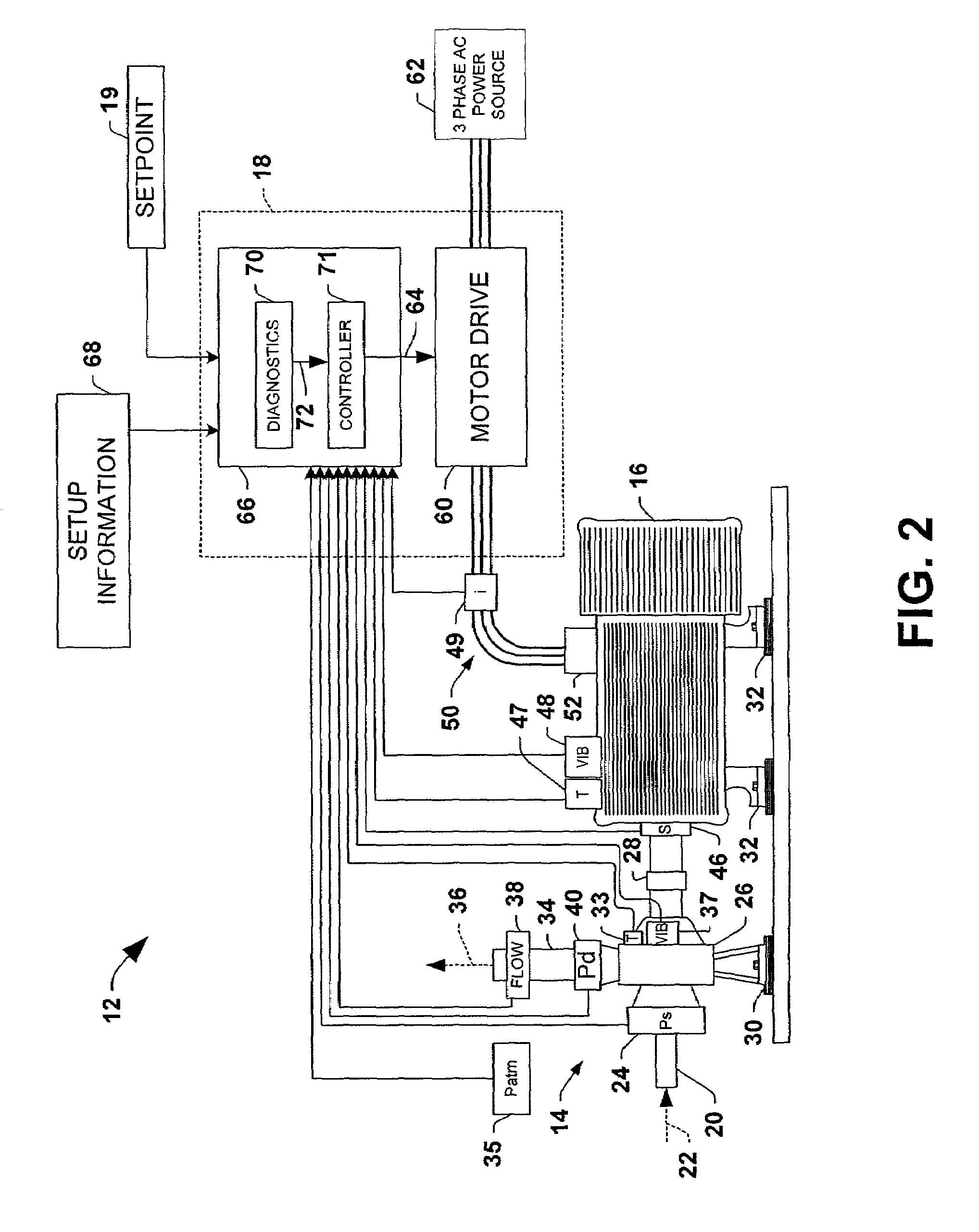

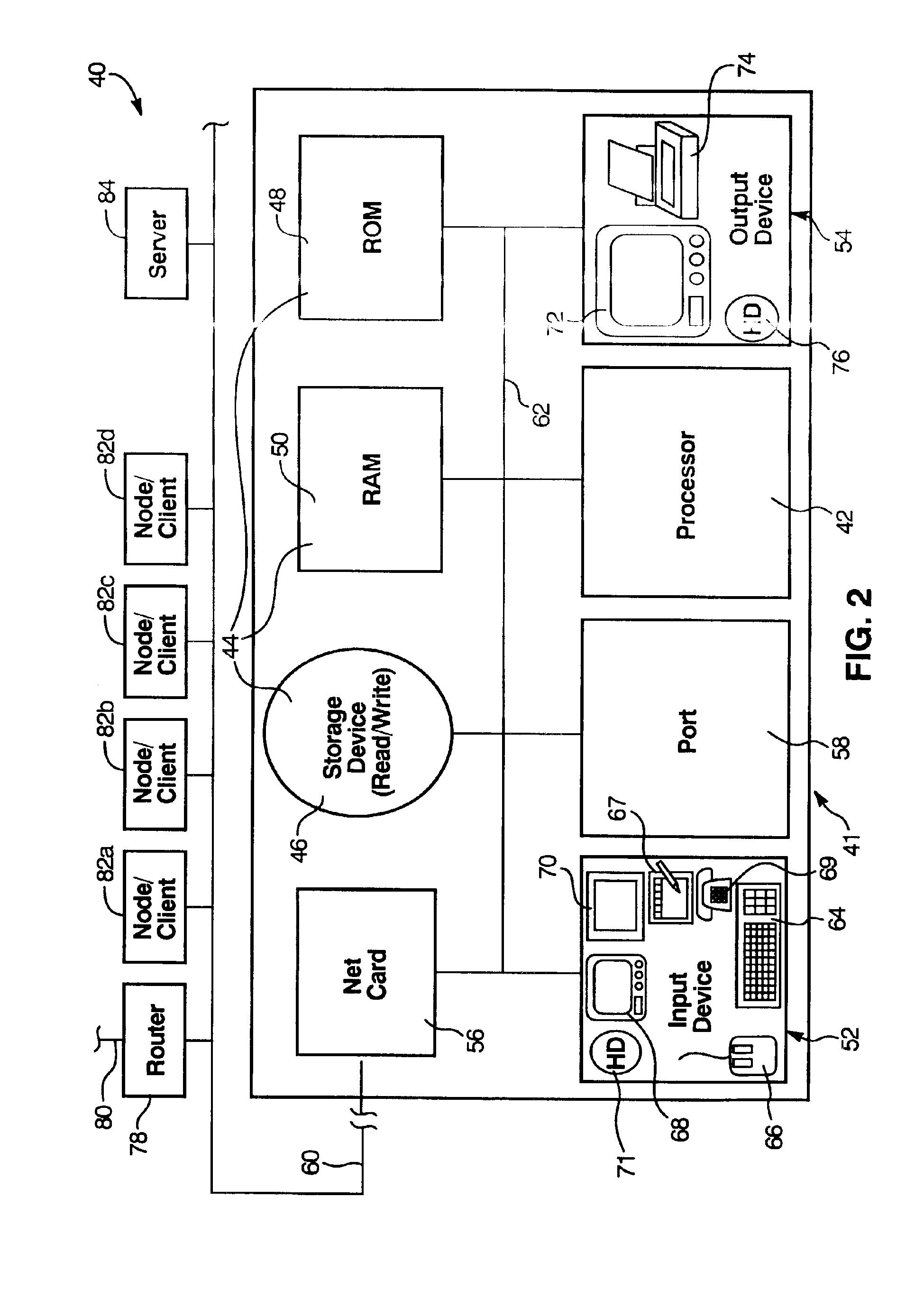

Motorized system integrated control and diagnostics using vibration, pressure, temperature, speed, and/or current analysis

InactiveUS7539549B1Condition be reduced and eliminatedAdvantageously employedPump componentsTesting/monitoring control systemsCurrent analysisDiagnostic system

Systems and methods are disclosed for controlling and diagnosing the health of a motorized system. The systems may comprise a diagnostics system and a controller, wherein the diagnostics system employs a neural network, an expert system, and / or a data fusion component in order to assess the health of the motorized system according to one or more attributes associated therewith. The controller may operate the motorized system in accordance with a setpoint and / or a diagnostics signal from the diagnostics system. Also disclosed are methodologies for controlling and diagnosing the health of a motorized system, comprising operating a motor in the motorized system in a controlled fashion, and diagnosing the health of the motorized system according to a measured attribute associated with the motorized system, wherein the motor may be operated according to a setpoint and / or the diagnostics signal.

Owner:ROCKWELL AUTOMATION TECH

Surgical apparatus including surgical buttress

An end effector for a surgical stapling apparatus is provided which includes an anvil assembly and a surgical buttress. The anvil assembly includes an anvil body and an anvil plate. The anvil plate includes a bottom surface that defines a plurality of staple forming pockets. The anvil body and the anvil plate are selectively connectable. The surgical buttress includes a buttress body and a plurality of arms extending from the body. The arms are disposable between a top surface of the anvil plate and a bottom surface of the anvil body to support the buttress body against the bottom surface of the anvil plate when the anvil plate and the anvil body are connected to one another.

Owner:TYCO HEALTHCARE GRP LP

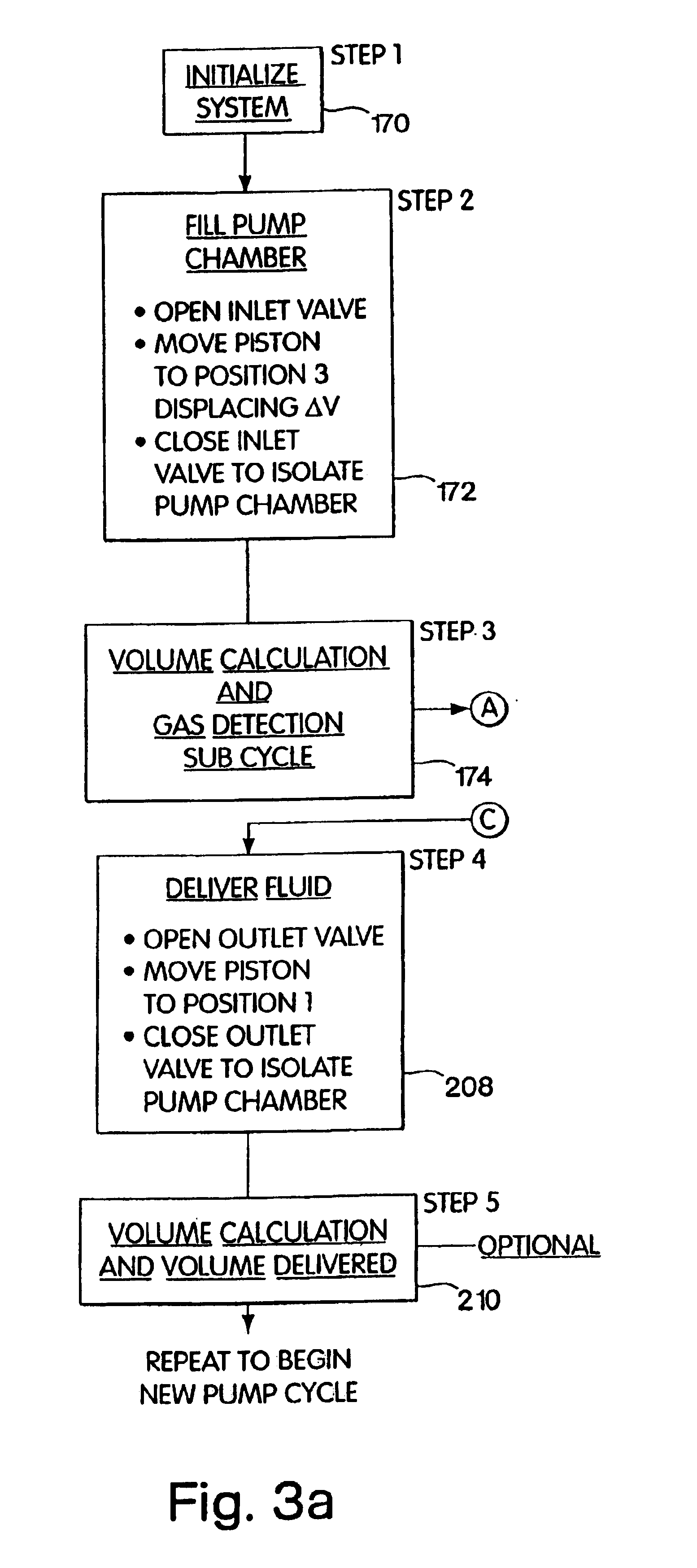

Apparatus for Infusing Fluid

A pump for pumping fluid includes a tube platen, a plunger, a bias member, inlet and outlet valves, an actuator mechanism, a position sensor, and a processor. The plunger is configured for actuation toward and away from the infusion-tube when the tube platen is disposed opposite to the plunger. The tube platen can hold an intravenous infusion tube. The bias member is configured to urge the plunger toward the tube platen.

Owner:DEKA PROD LLP

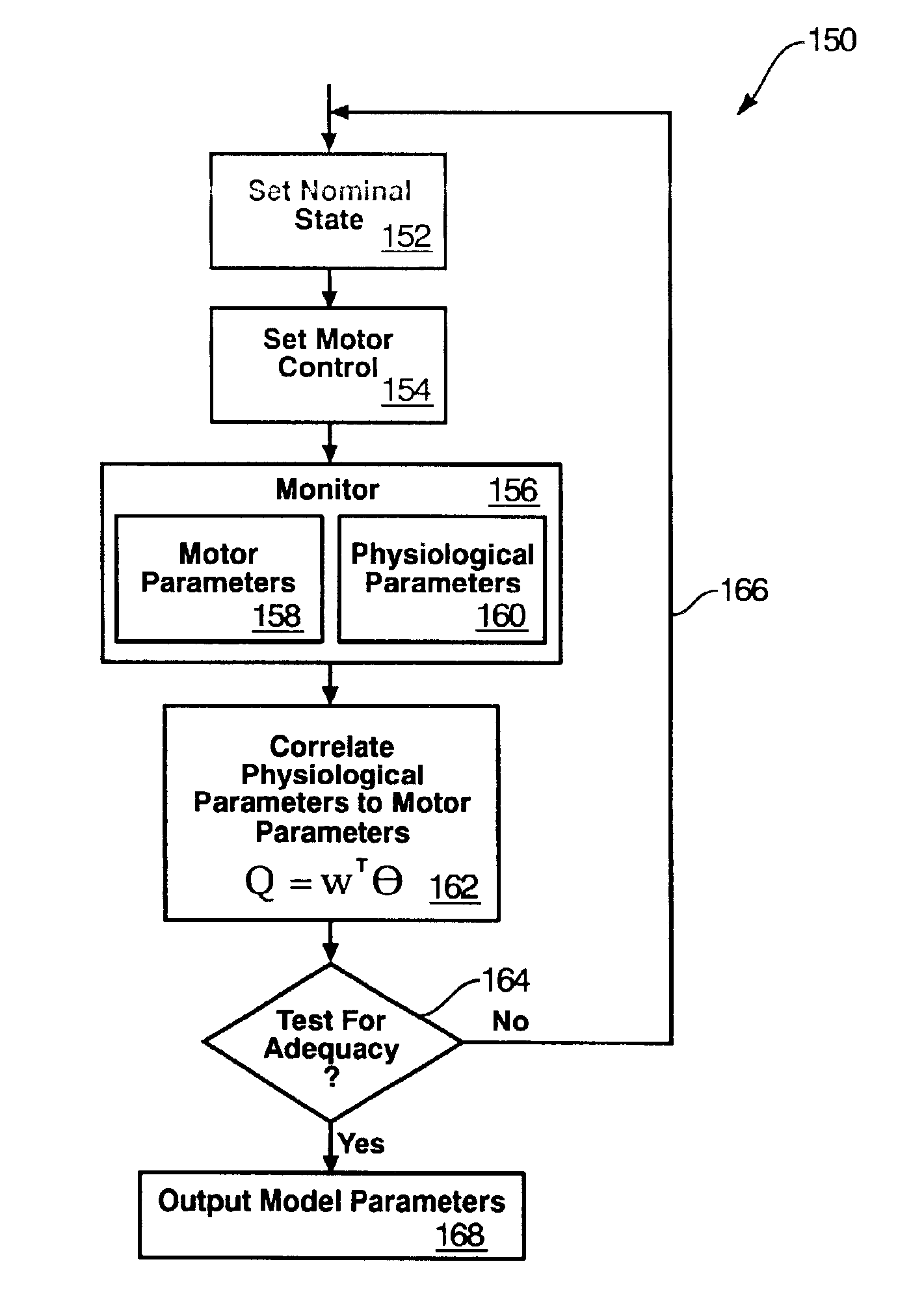

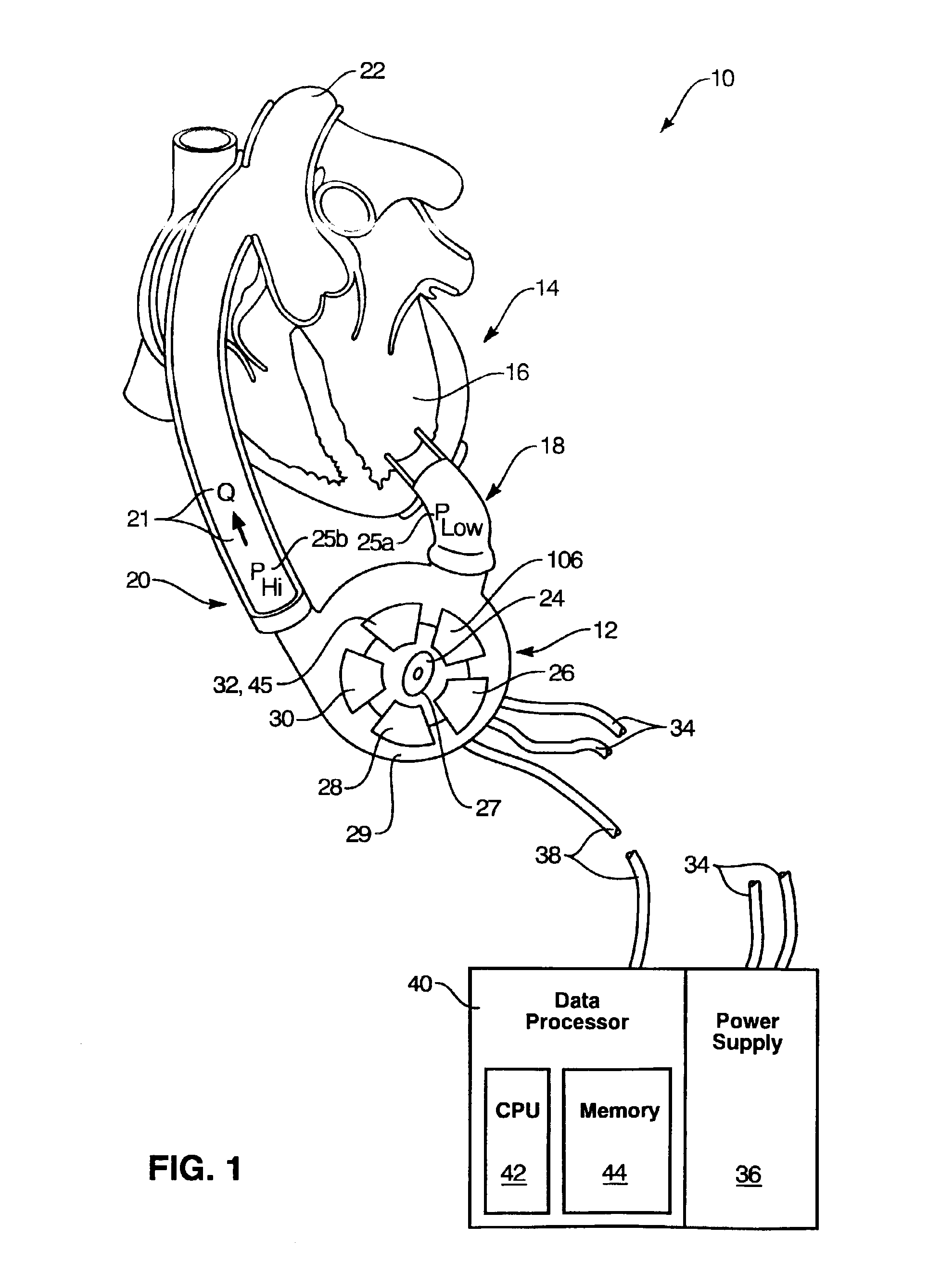

Rotary blood pump diagnostics and cardiac output controller

A method and apparatus for controlling a ventricular assist device are disclosed. The method includes the step of providing a ventricular assist device which can be defined in terms of operational parameters such as pump speed or current. Measuring at least one physiological parameter reflecting a physiological state corresponding to a patient. Correlating at least one physiological parameter measured from the patient to at least one operational parameter using an estimation method. Selecting a physiological state definable by desired values of the physiological parameters. Monitoring at least one operational parameter. Controlling input values of the operational parameter based on output from the monitoring step. The apparatus includes a pump driven by a motive drive and having an impeller. A sensor detects the value of an operational parameter of the pump. A processor provides a statistical correlation between patients physiological parameter and the operational parameter of the pump and adjusts the operational parameter to affect a predetermined optimal physiological state.

Owner:WORLD HEART

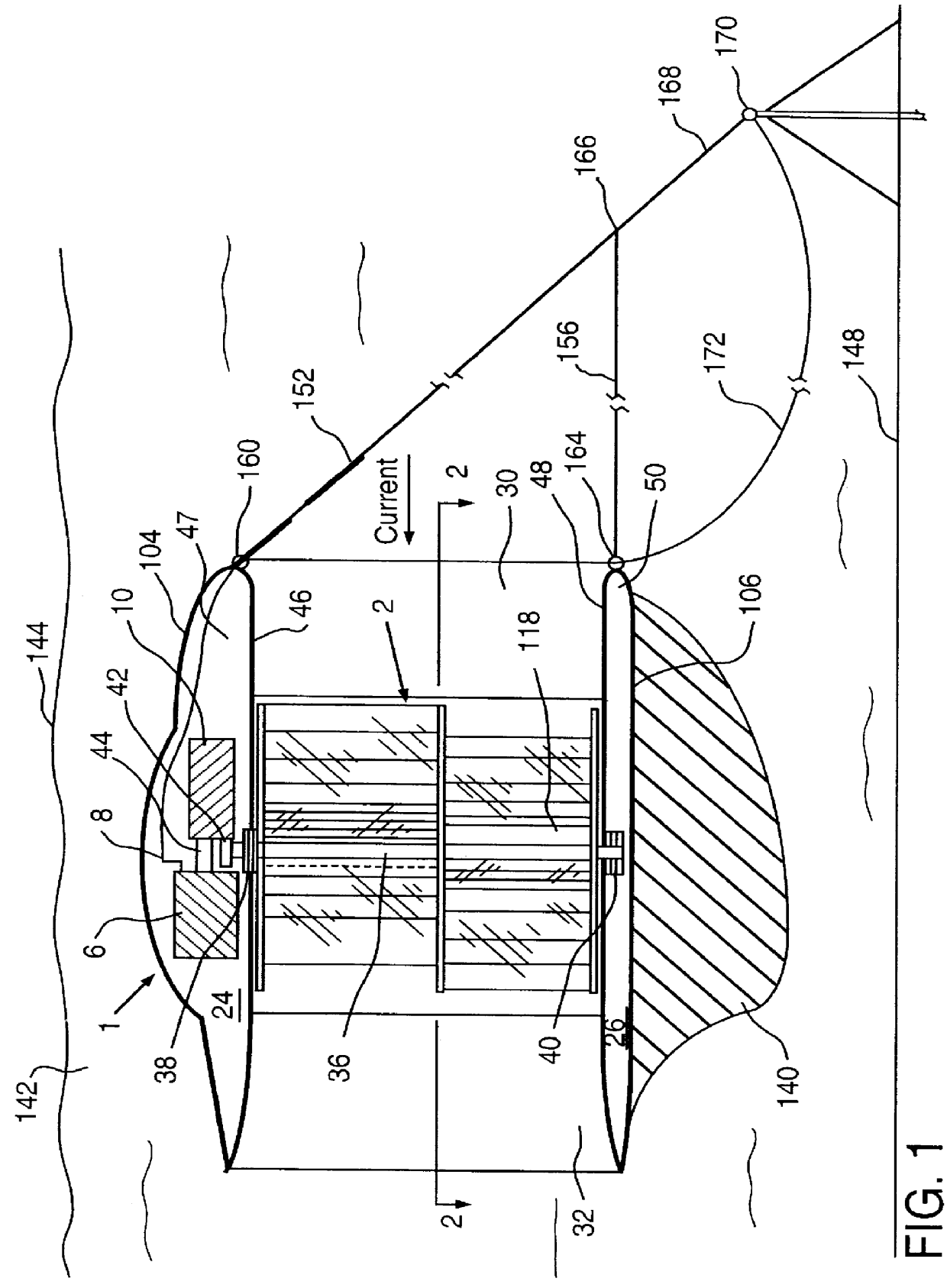

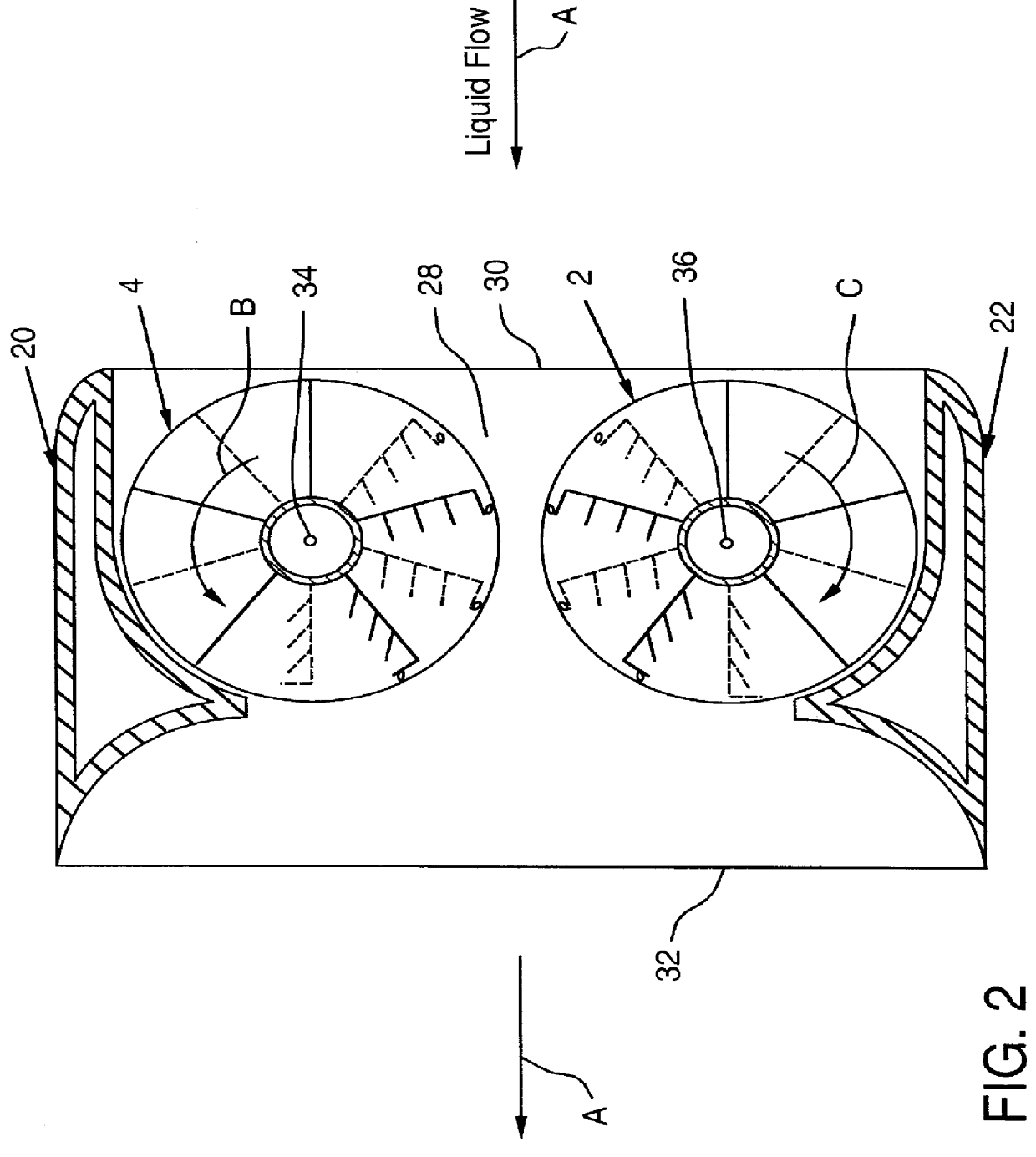

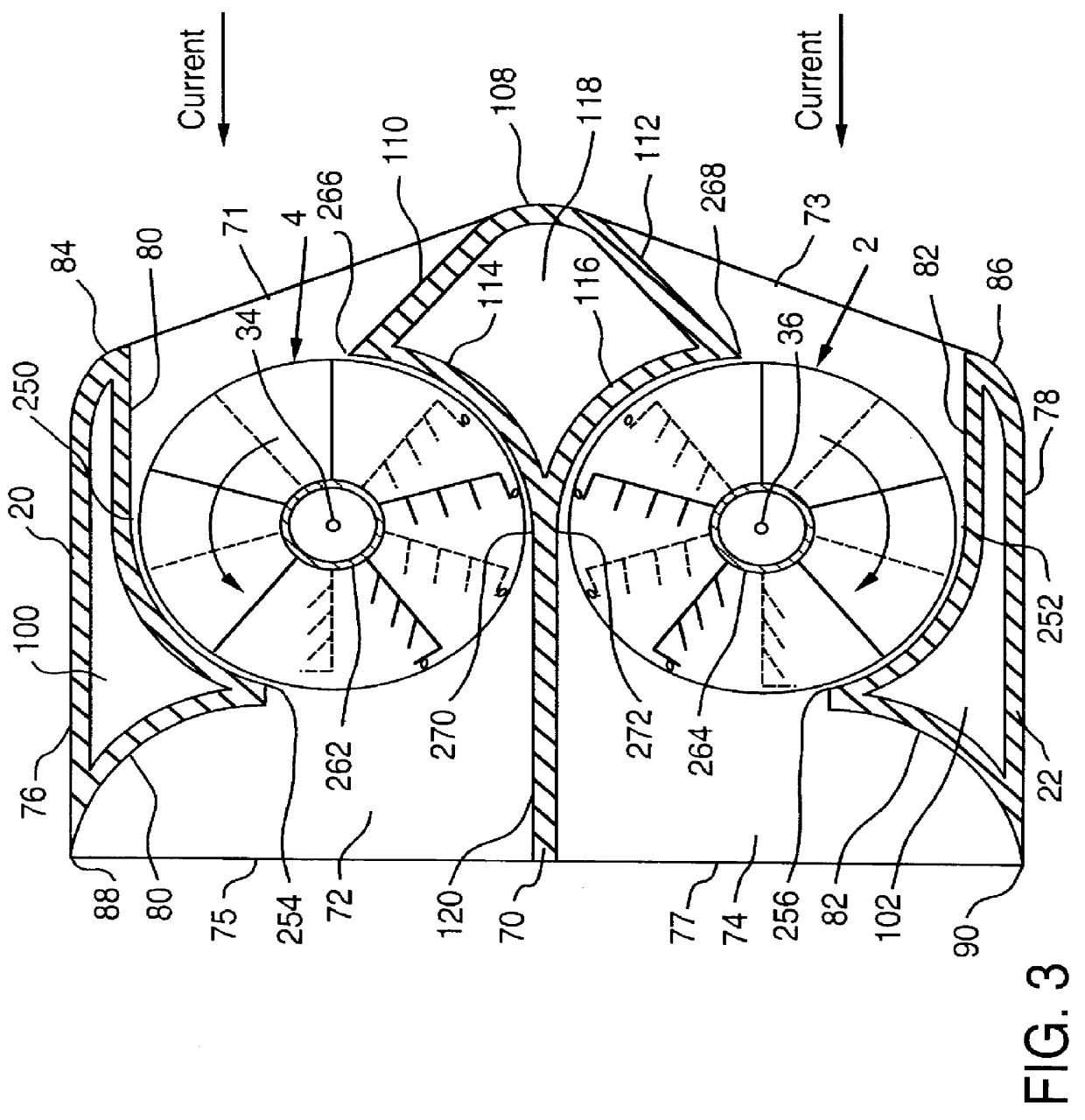

Submersible appartus for generating electricity and associated method

InactiveUS6109863AReduce the impactReduce impactCircumferential flow pumpsWind motor controlElectricityMarine engineering

A fully submersible apparatus for generating electricity from liquid flow as in an ocean or river current. A buoyant structure is fully submersible and has at least one pair of counter-rotating side-by-side motors with a plurality of angularly spaced radial vanes each having a plurality of rotatable subvanes such that current impinging upon the motor will impinge on a closed or solid vane to effect rotation of the motor and its shaft during a first phase of the rotational cycle and will impinge on open vanes for free passage therethrough on the return or second phase of rotation of the motor. Motors may also be provided with vanes in overlying and underlying relationship. An associated method is provided.

Owner:MILLIKEN LARRY D

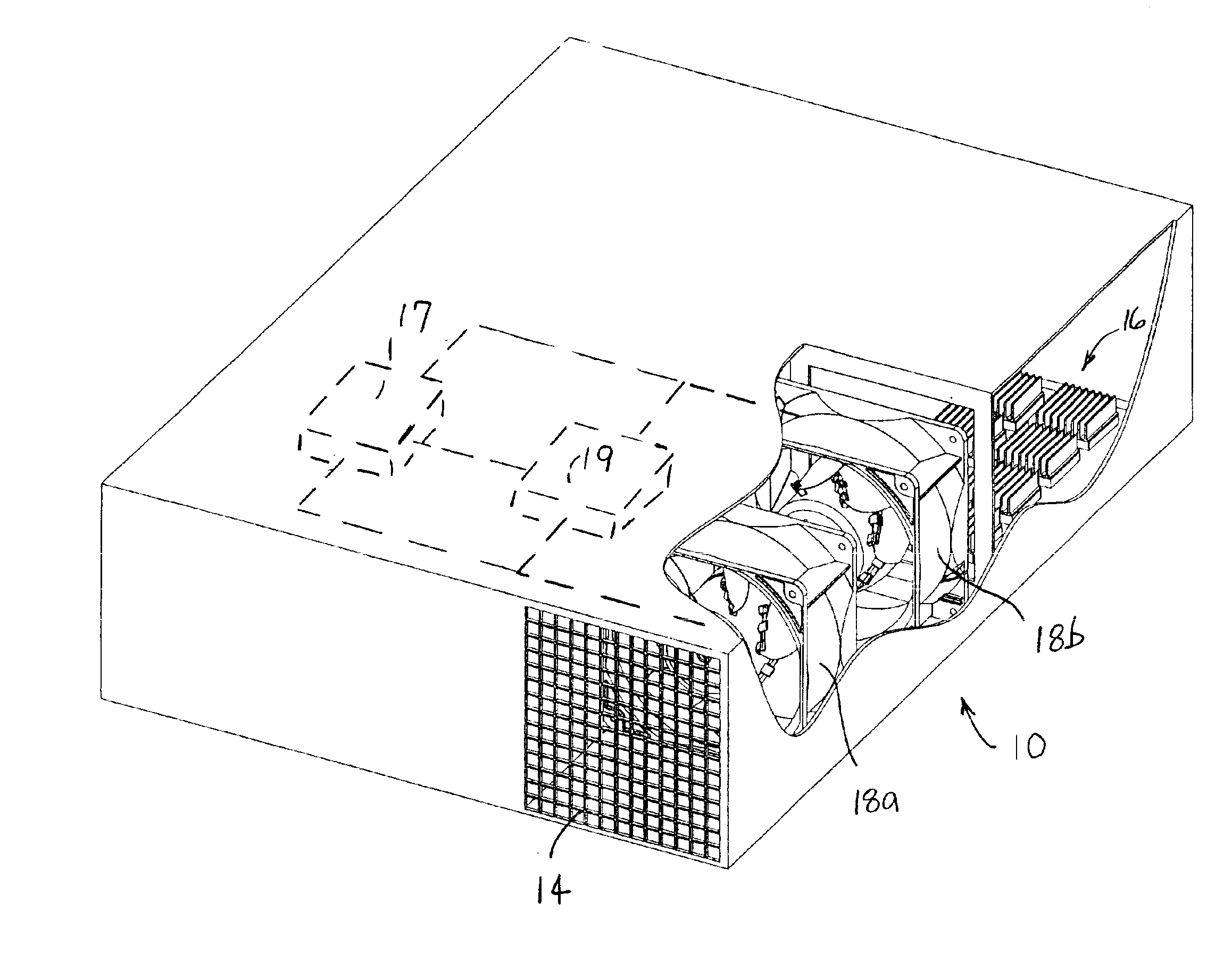

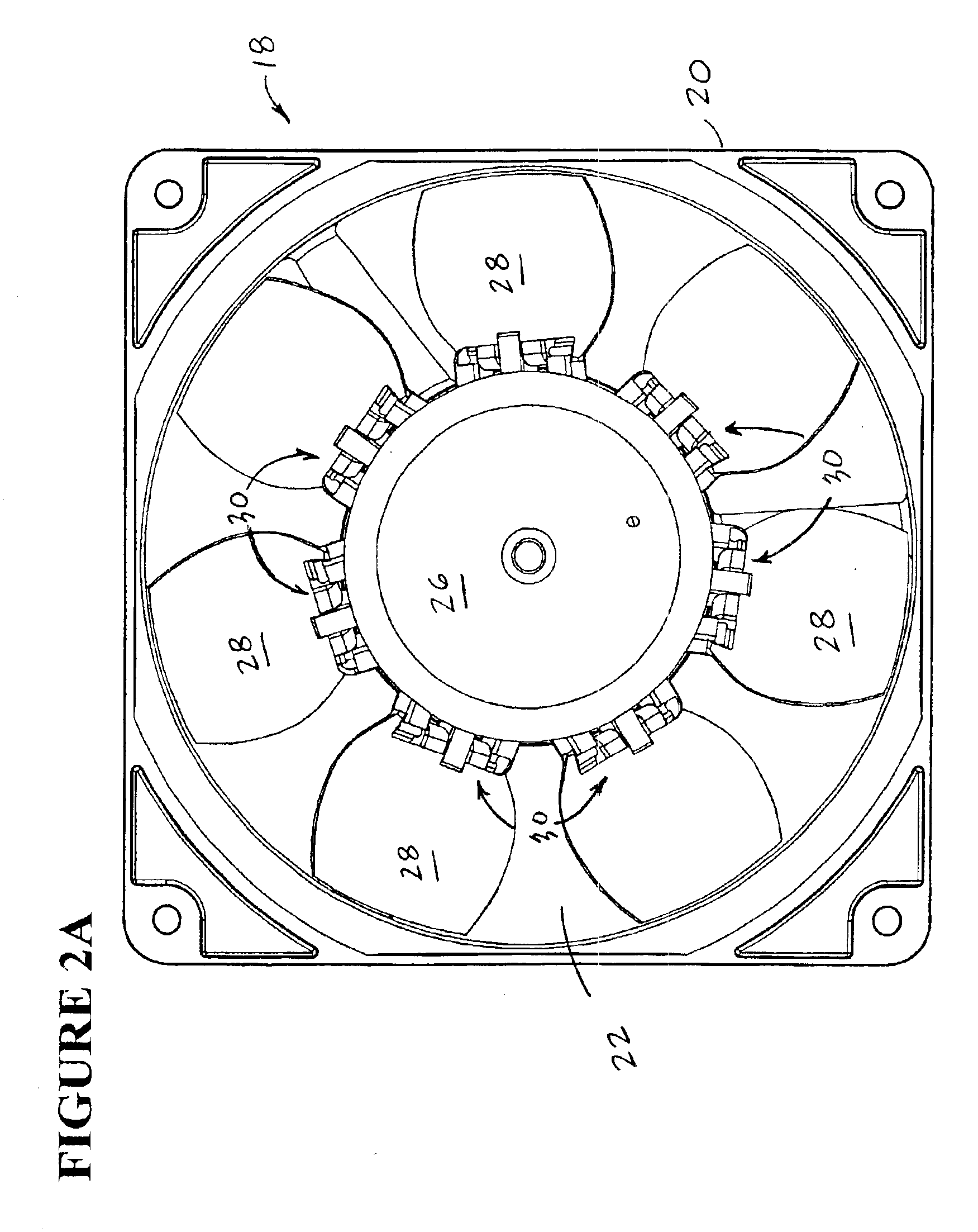

Fan with collapsible blades, redundant fan system, and related method

InactiveUS6860713B2Reduces fan inefficiencyPrevent undesirable blockagePropellersPump componentsFan bladeAirflow

A redundant fan system for a computer includes two fans installed in series with at least one of the fans having collapsible blades. A fan system of this type reduces the fan inefficiency caused when one fan in a series mounted pair is not operating, either because it is free-wheeling or in a locked rotor condition. When non-operational, the fan blades of the collapsible fan fold inward due to airflow generated by the operational fan over the collapsible blades. The ability of the blades to fold reduces the inefficiency of the operational fan, having less of an effect on fan life. Also, because the flow of air is less restricted, proper airflow can be maintained, thus preventing overheating of the computer.

Owner:NIDEC AMERICA CORP

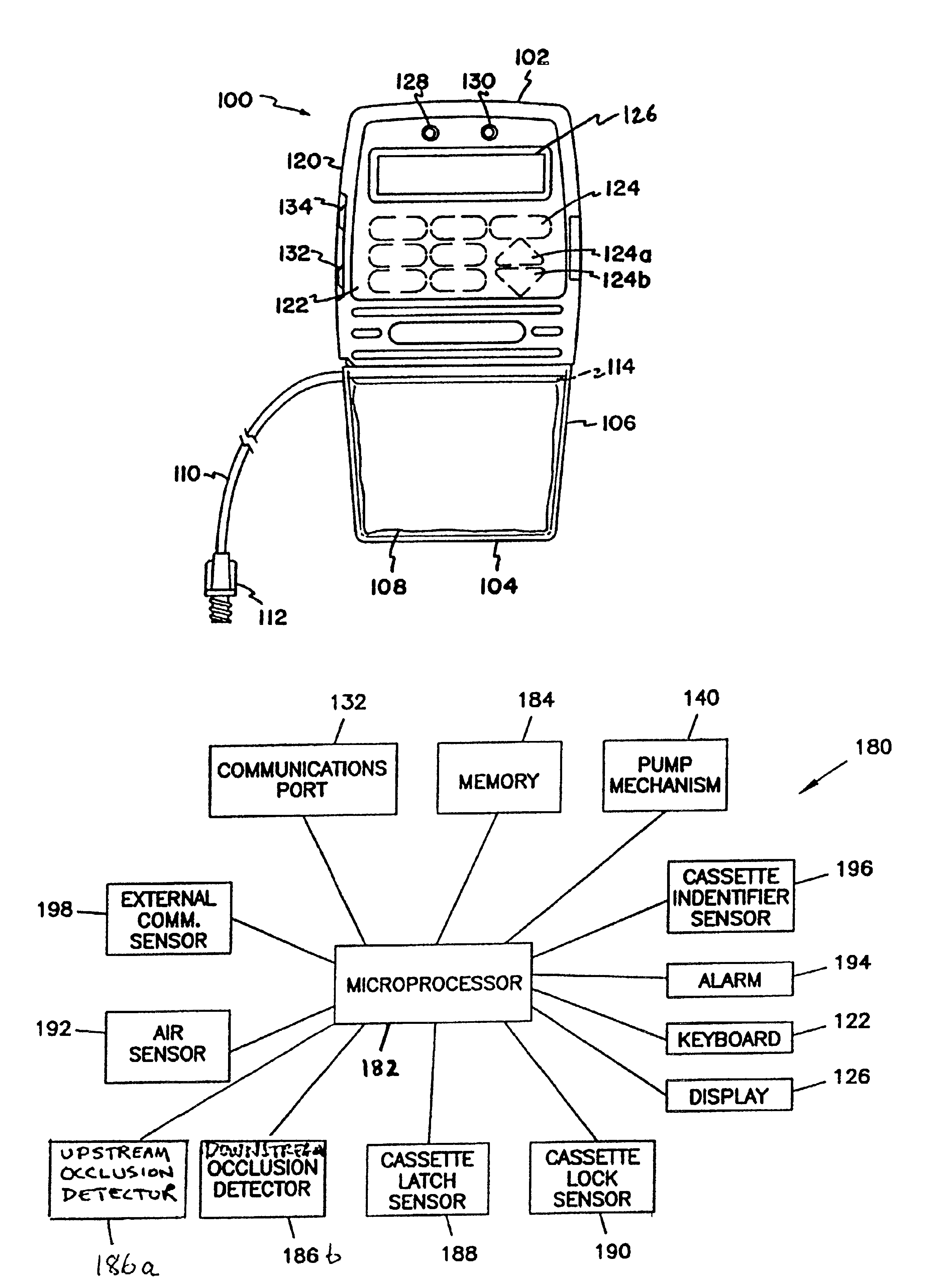

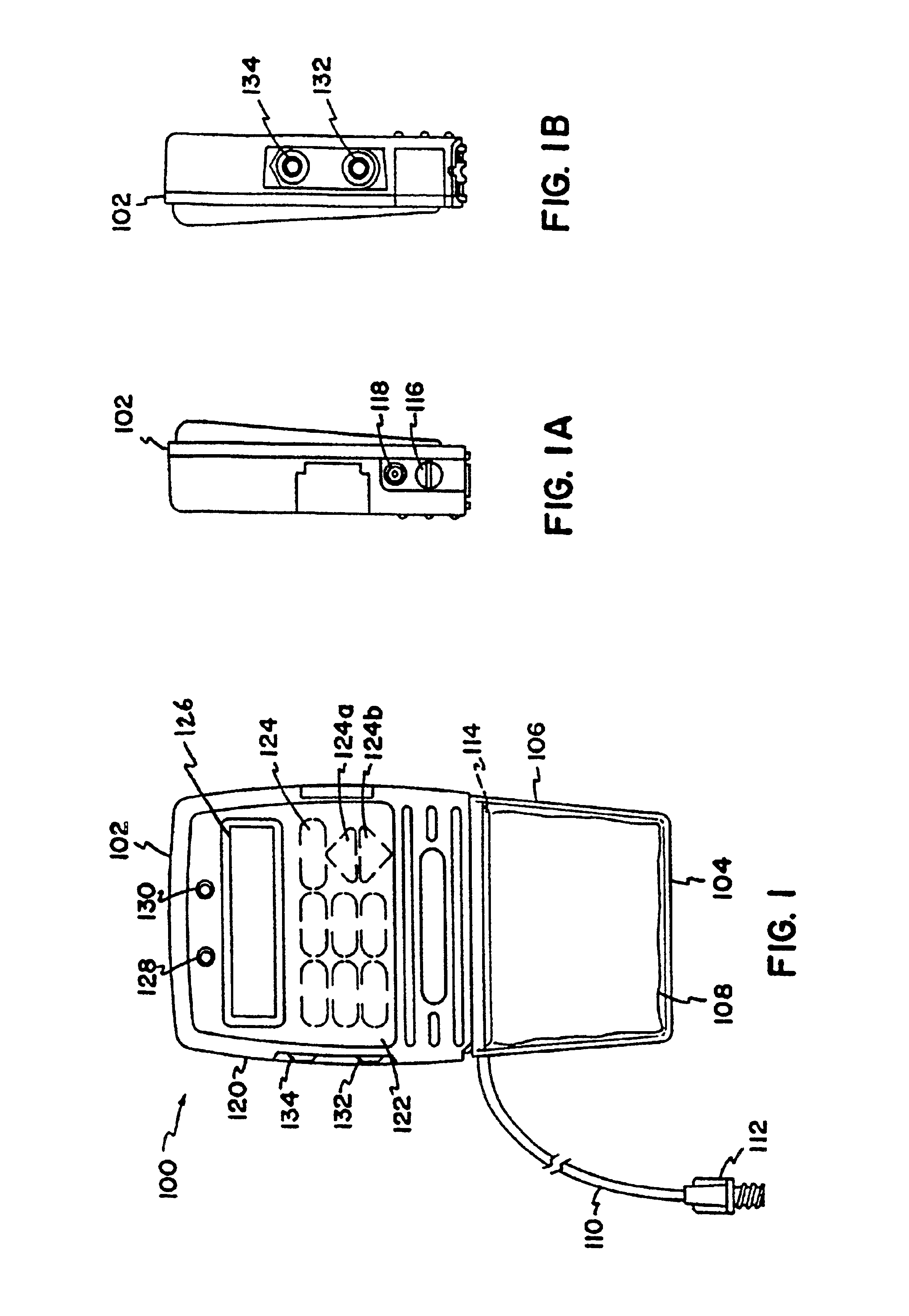

Drug pump systems and methods

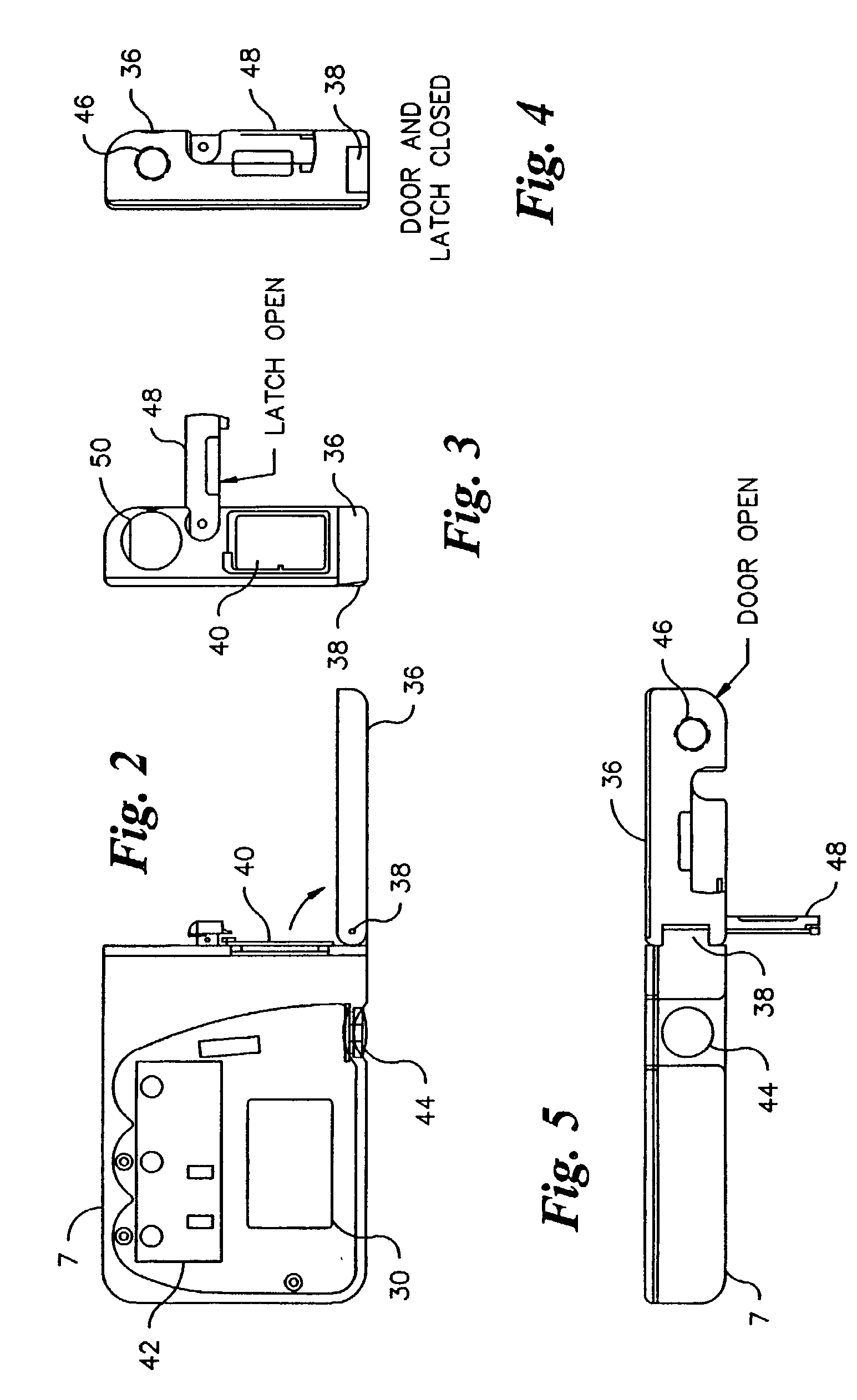

A menu driven reprogrammable drug pump is provided with a memory, such as flash memory, a display, a keyboard, and a communications port to allow a generic pump to be programmed with a desired pump application (therapy) program and patient specific settings. Programming and data transfer with another pump or a computer to and from the patient pump is by the communications port that allows local and / or remote communications with the pump. Flash memory stores the pump application program during use. Patient safety is provided by a cassette identification system, an occlusion detection system, and a latch / lock detection system. Automated testing of the pump is by a closed loop testing system.

Owner:SMITHS MEDICAL ASD INC

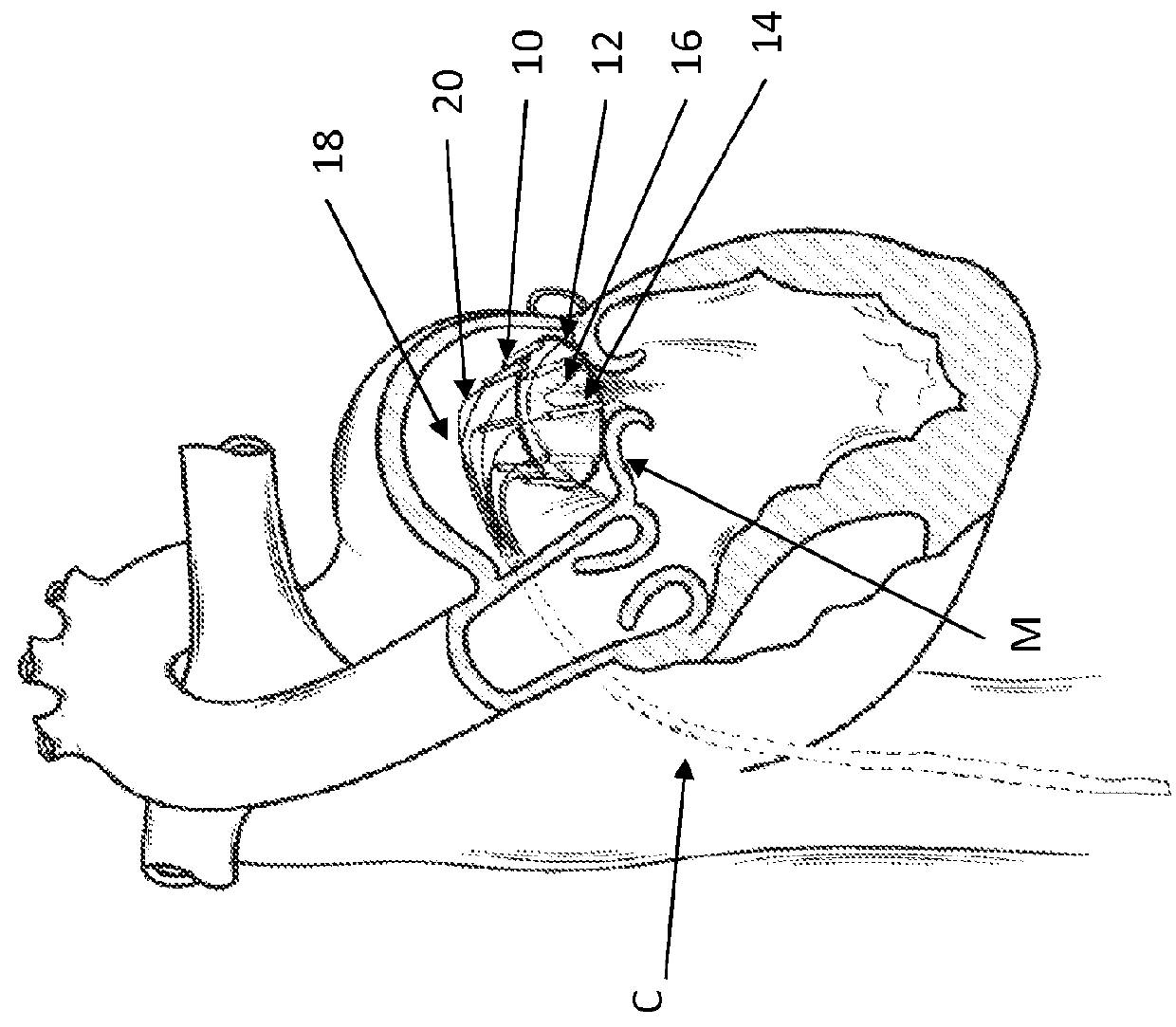

Surgical access devices with anvil introduction and specimen retrieval structures

Surgical access devices are disclosed. In various forms, the access devices form at least one passageway through which various surgical instruments and tools may be admitted into the body cavity. Various embodiments may be configured to support an anvil for a circular stapling device therein. Various forms employ a flexible bag for retrieval of specimen from the body cavity.

Owner:CILAG GMBH INT

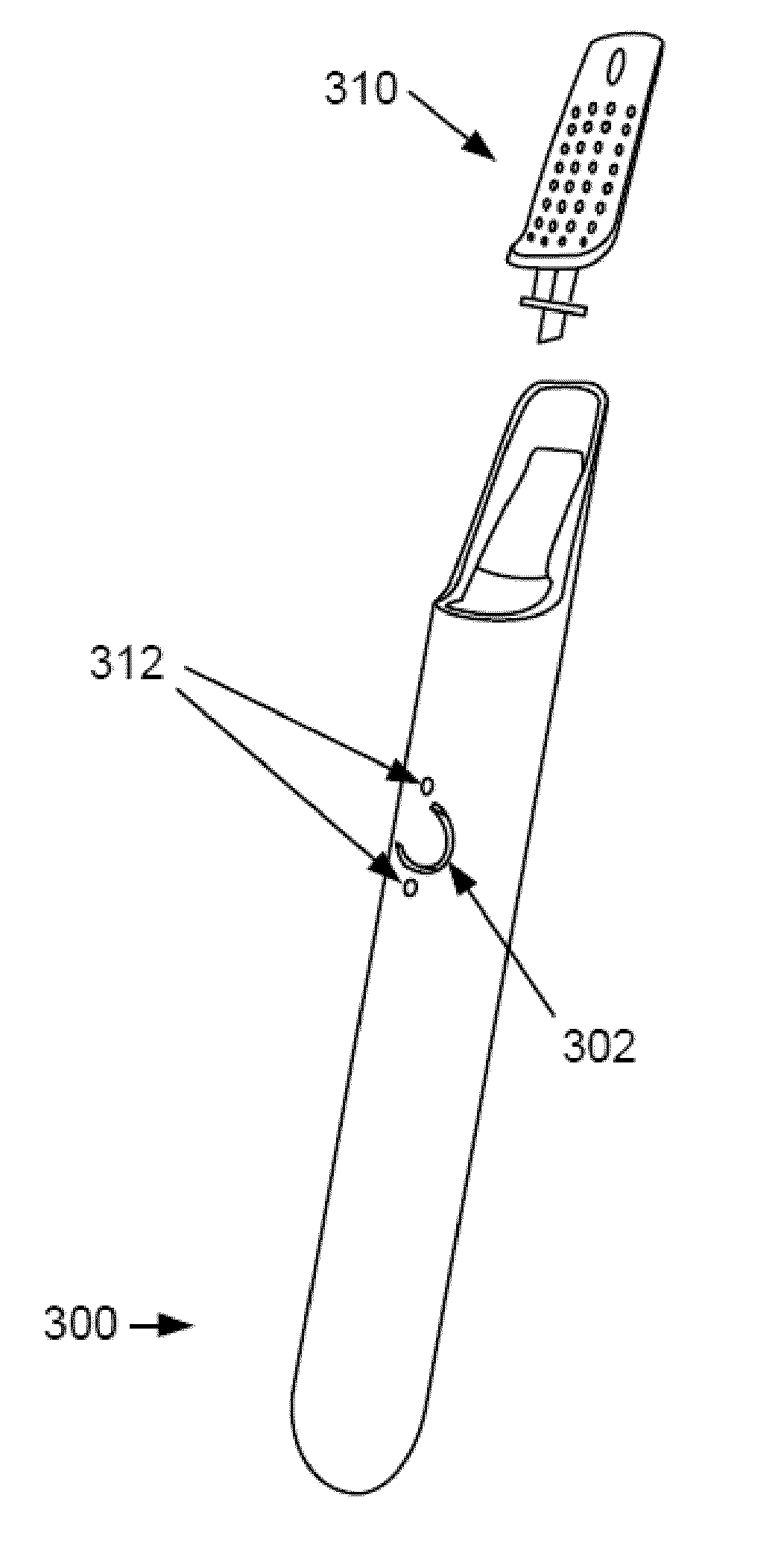

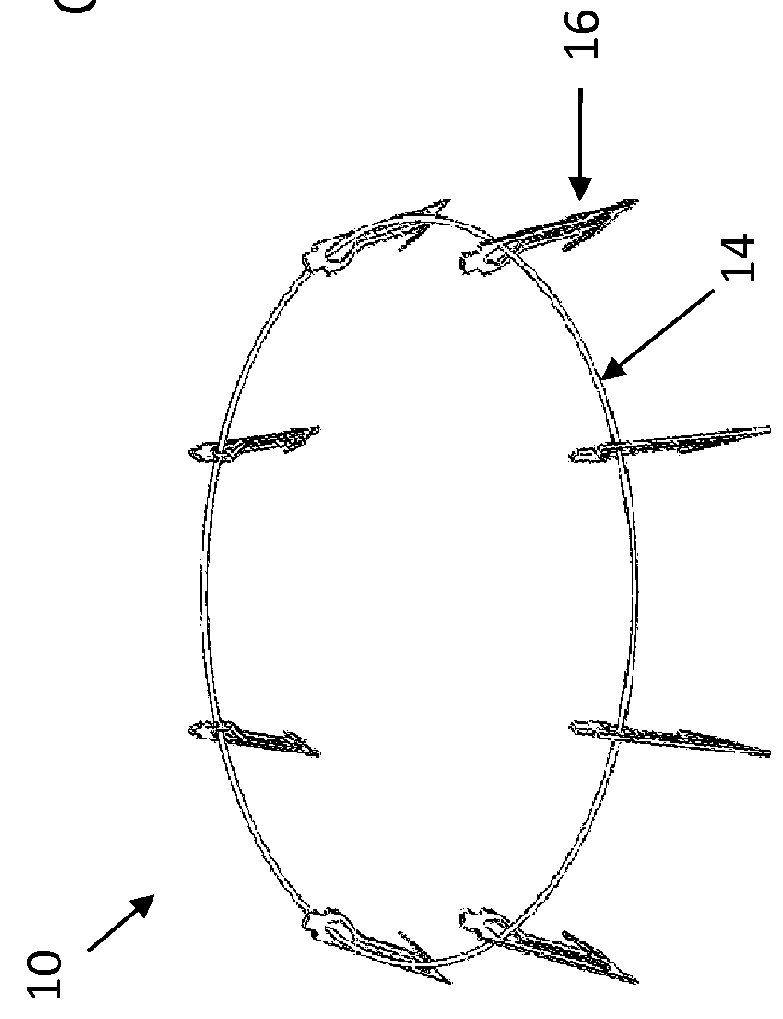

Heart Valve Repair Device

ActiveUS20140309730A1Suture equipmentsAnnuloplasty ringsFront and back endsHeart Valve Annulus Repair

A heart valve annulus repair device having a tissue engaging member and a plurality of anchors. The tissue engaging member includes a loop of wire. Each of the anchors has a pointy front end and a back end and a slot that runs in a front-to-back direction. The anchors are distributed about the loop of wire with the front ends of the plurality of anchors facing the heart valve annulus and with the loop of wire passing through the slots. The device further includes means for implanting the anchors into the heart valve annulus tissue so that the tissue engaging member becomes affixed to the heart valve annulus.

Owner:CARDIAC IMPLANTS

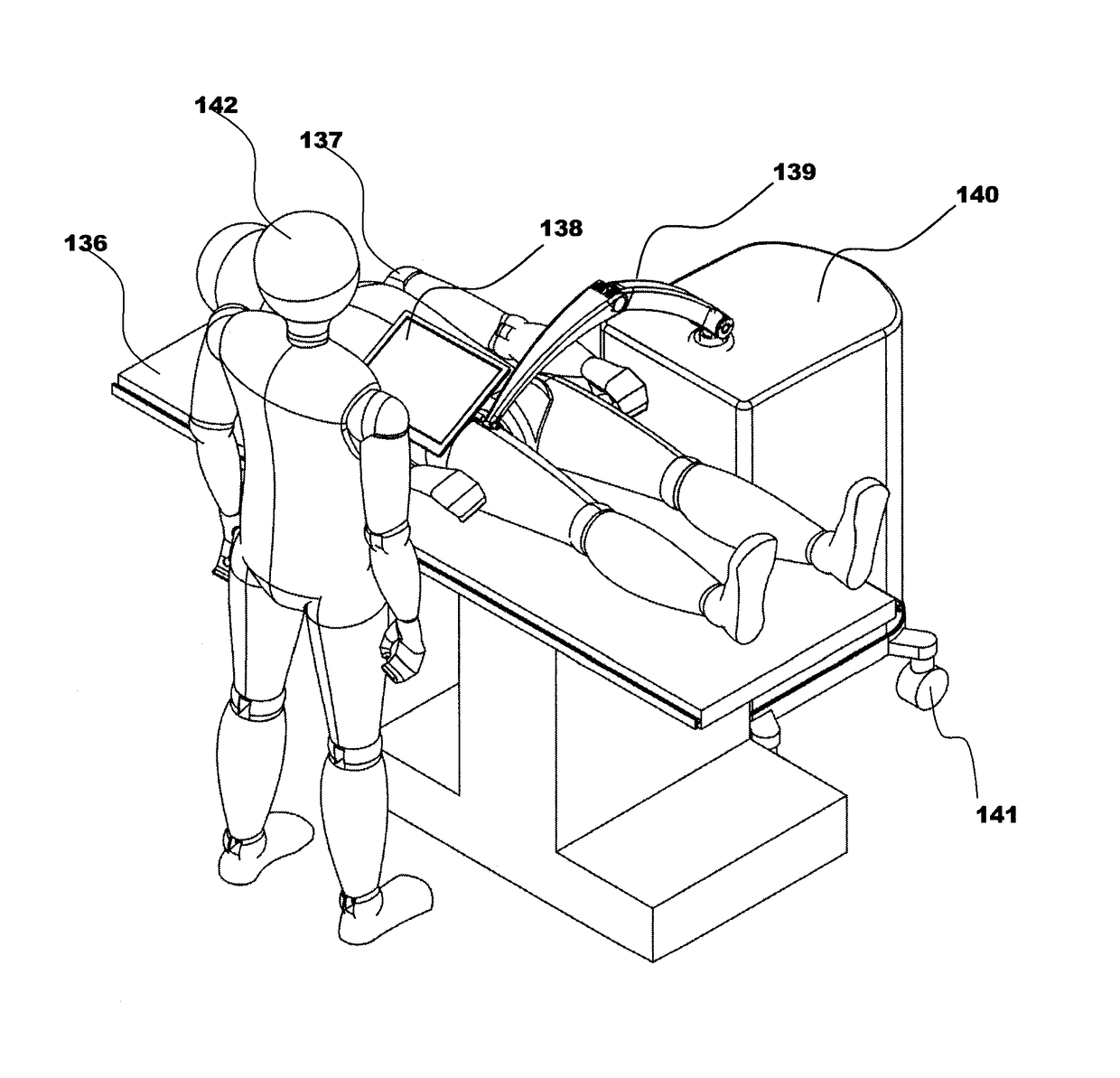

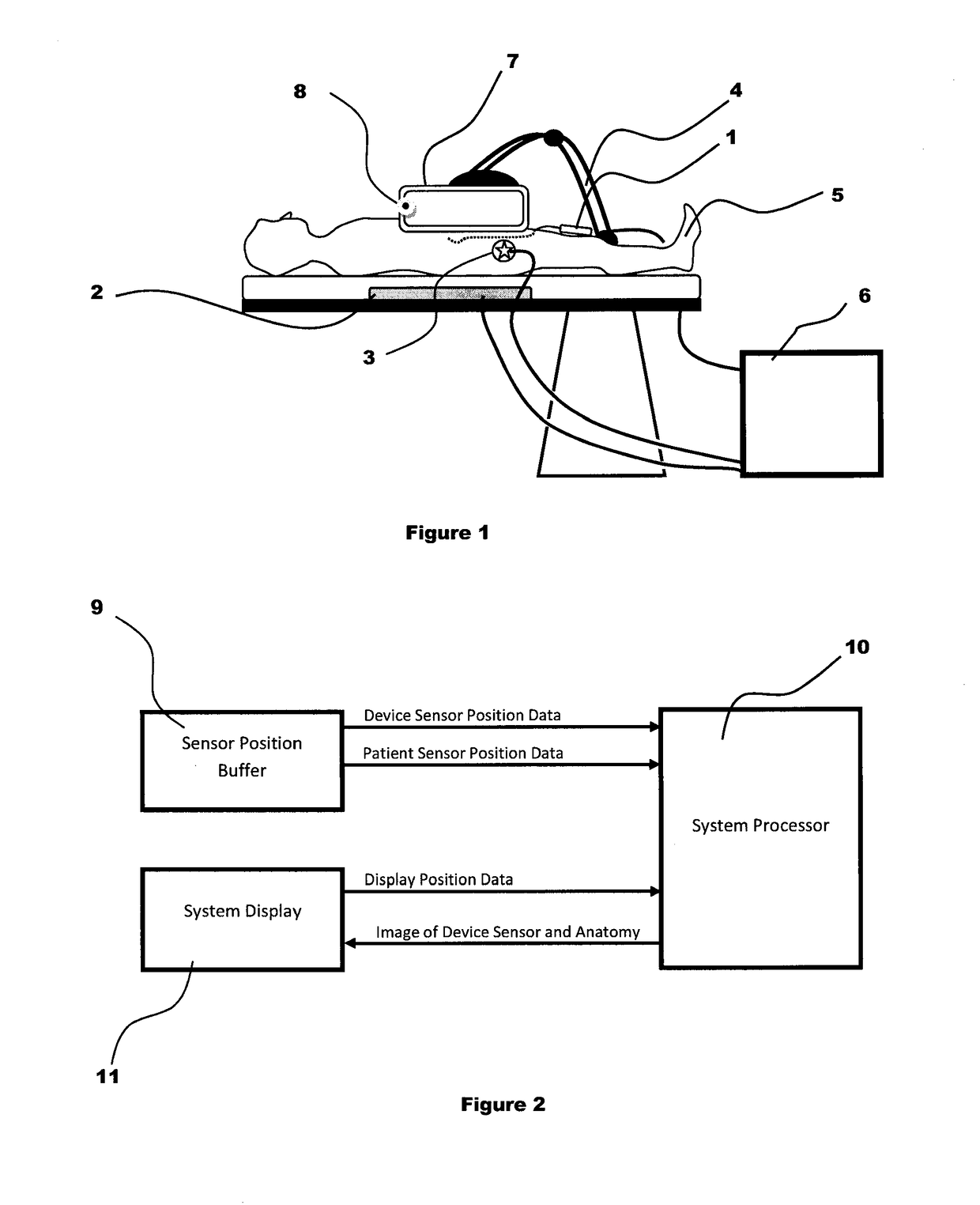

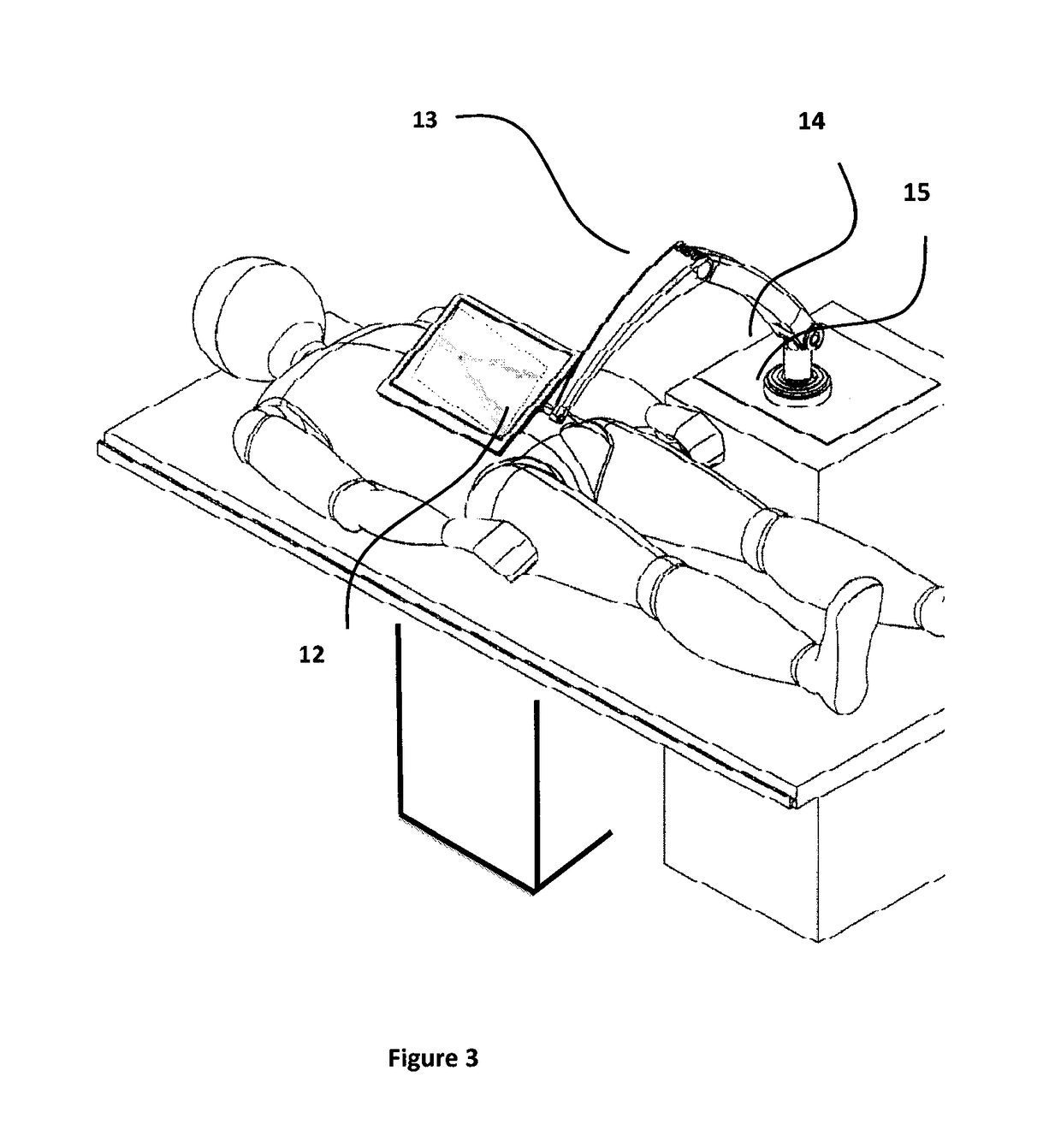

System and method for virtually tracking a surgical tool on a movable display

ActiveUS9918681B2Increase workspaceImprove ergonomicsUltrasonic/sonic/infrasonic diagnosticsSurgical navigation systemsDisplay deviceVisual perception

The invention comprises a virtual window system that creates a visual coherency between the image of the patient and his or her anatomy and the patient by aligning the image of the patient anatomy on the display to the patient and presenting the image to the user that feels as if the user is looking directly into the patient through the display. The invention is designed to also display medical devices, such as a minimally invasive tool. The system substantially unifies the coordinate systems of the patient, the medical device, the display, and the physician's hands. The invention creates a visual coherency between the motion of the medical device in the image and the motion of the physician's hands manipulating the device. This invention also creates a visual coherency between the motion of the image in the display and of that display.

Owner:AURIS HEALTH INC

Pumping cartridge having an integrated filter and method for filtering a fluid with the cartridge

InactiveUS6905479B1Positive displacement pump componentsOther blood circulation devicesParticulatesEngineering

The present invention involves, in some embodiments, reusable pump drive systems, which are coupled to removable, and preferably disposable, pumping cartridges. The invention provides, in some embodiments, novel pumping cartridges for use in pumping systems. One such cartridge includes an integrated filter element therein for filtering fluids, for example fluids pumped to the body of a patient in a medical procedure. In some embodiments, the integrated filter is utilized as a blood clot removal filter and in other embodiments is used to remove particulates liquids infused to a patient. The filter element includes a filter with pores therein that are preferably sized to permit essentially unrestricted flow of individual human blood cells therethrough and to block or collect blood clots, cell clumps, particulates etc. with sizes substantially larger than the average size of a human blood cell.

Owner:DEKA PROD LLP