Patents

Literature

64results about How to "Reduce fabrication cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Steel sheet with high mechanical strength, ductility and formability properties, production method and use of such sheets

ActiveUS20140170439A1Reduce fabrication costSimplifies fabricationFurnace typesThin material handlingDuctilityMicrometer

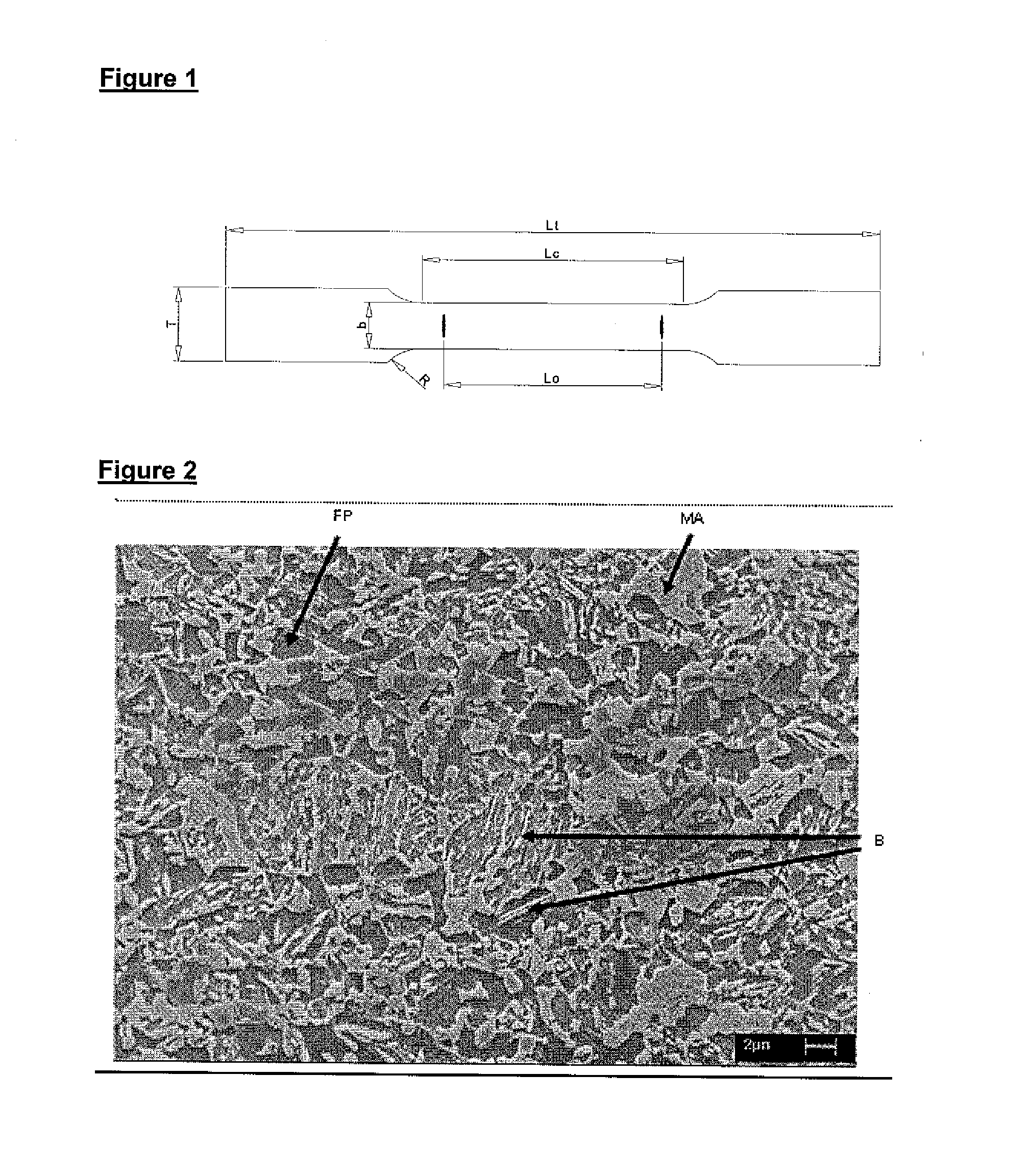

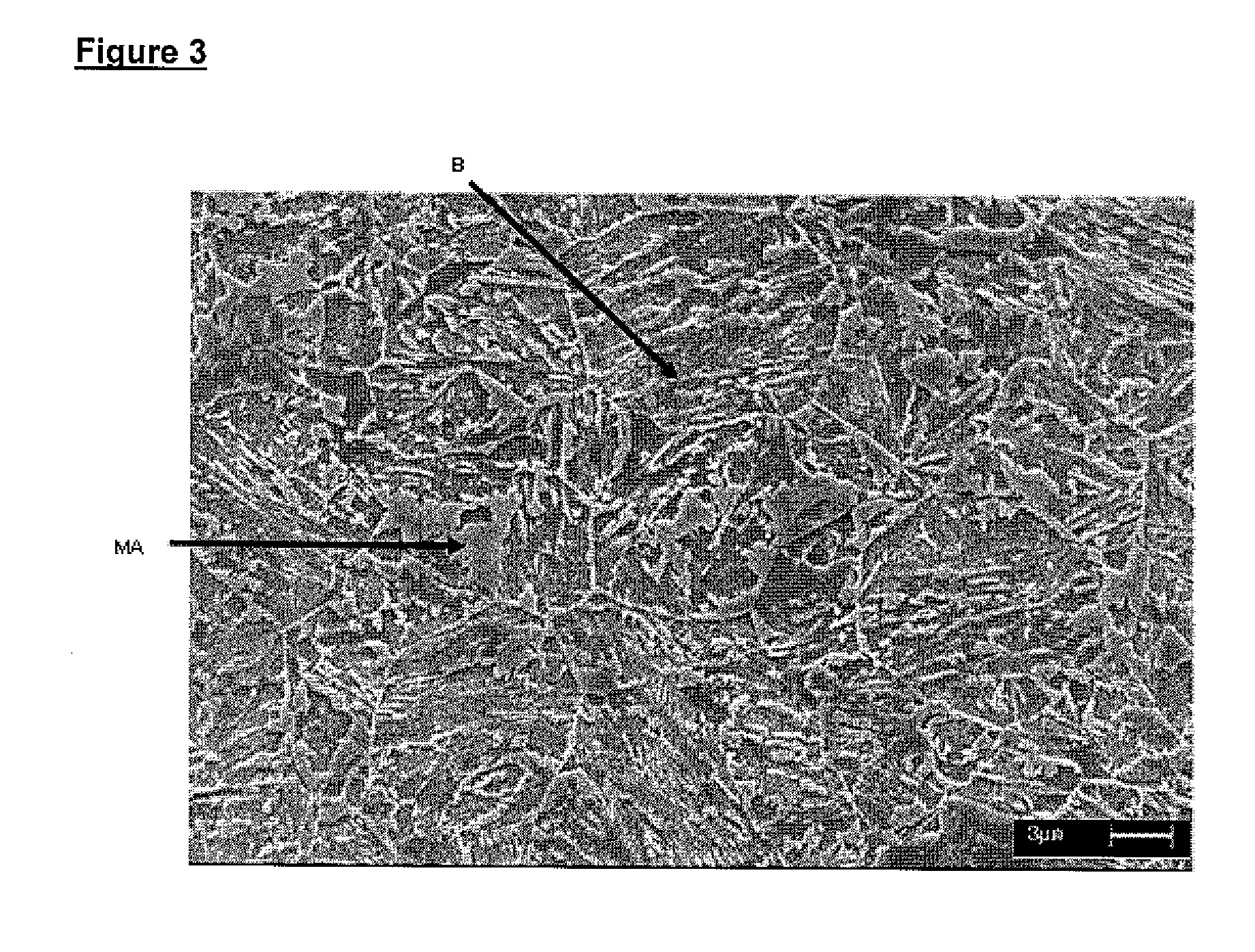

The present invention provides a cold rolled steel sheet. The steel sheet has a strength greater than 1000 MPa, a uniform elongation greater than 12% and a V-bendability greater than 90°. The composition of the steel sheet includes, expressed in per cent by weight, 0.15%≦C≦0.25%, 1.8%≦Mn≦3.0%, 1.2%≦Si≦2%, 0%≦Al≦0.10%, 0%≦Cr≦0.50%, 0%≦Cu≦1%, 0%≦Ni≦1%, 0%≦S≦0.005%, 0%≦P≦0.020%, Nb≦0.015%, Ti≦0.020%, V≦0.015%, Co≦1%, N≦0.008%, B≦0.001% whereby Mn+Ni+Cu≦3%. The remainder of the composition consists of iron and inevitable impurities resulting from processing. The microstructure includes, in area percentage, 5 to 20% polygonal ferrite, 10 to 15% residual austenite, 5 to 15% martensite and a balance of bainite. The bainite is in the form of laths and includes carbides between the laths. A number N of inter-lath carbides larger than 0.1 micrometers per unit of surface area is less than or equal to 50000 / mm2. A fabrication method and a motor vehicle are also provided.

Owner:ARCELORMITTAL INVESTIGACION Y DESARROLLO SL

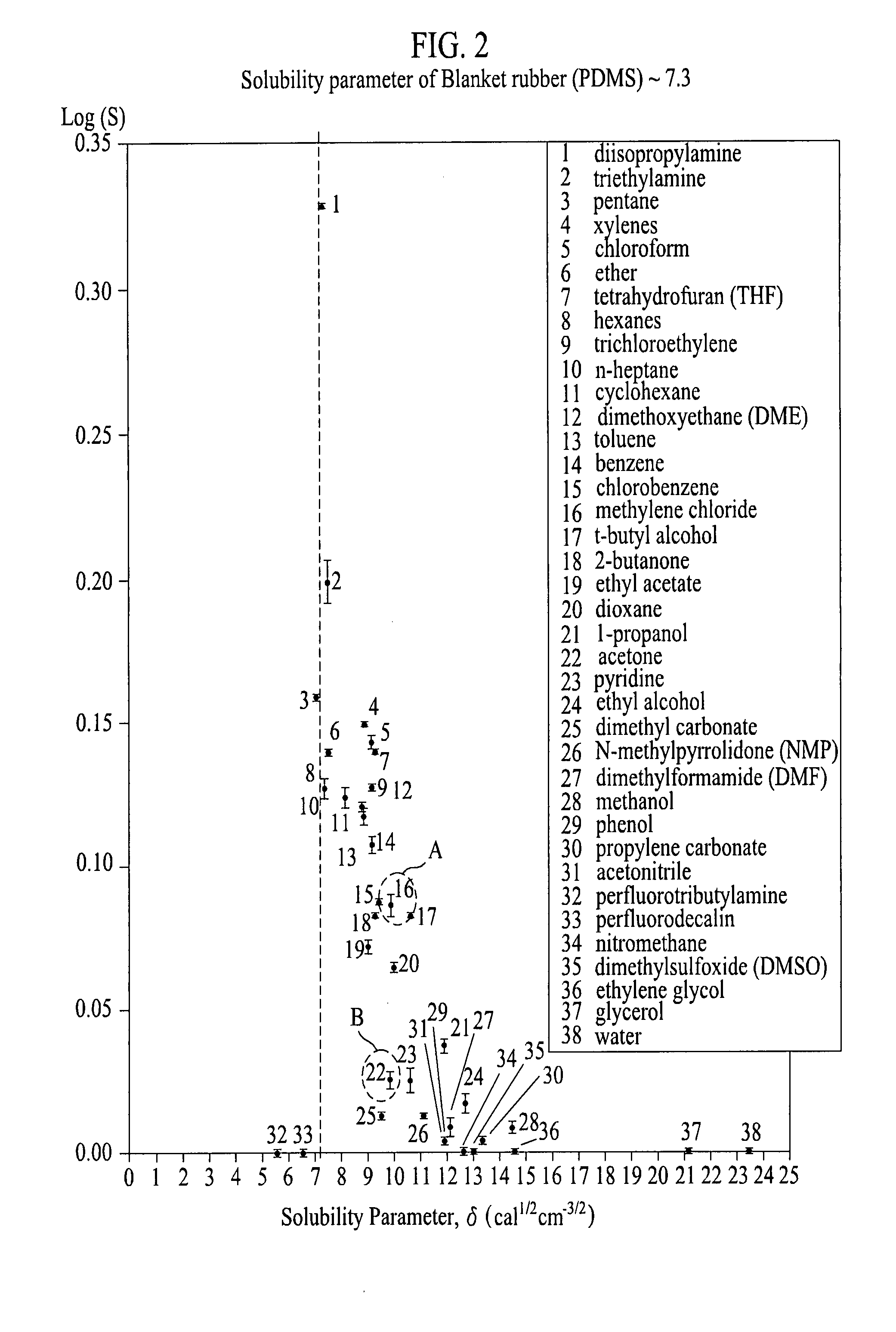

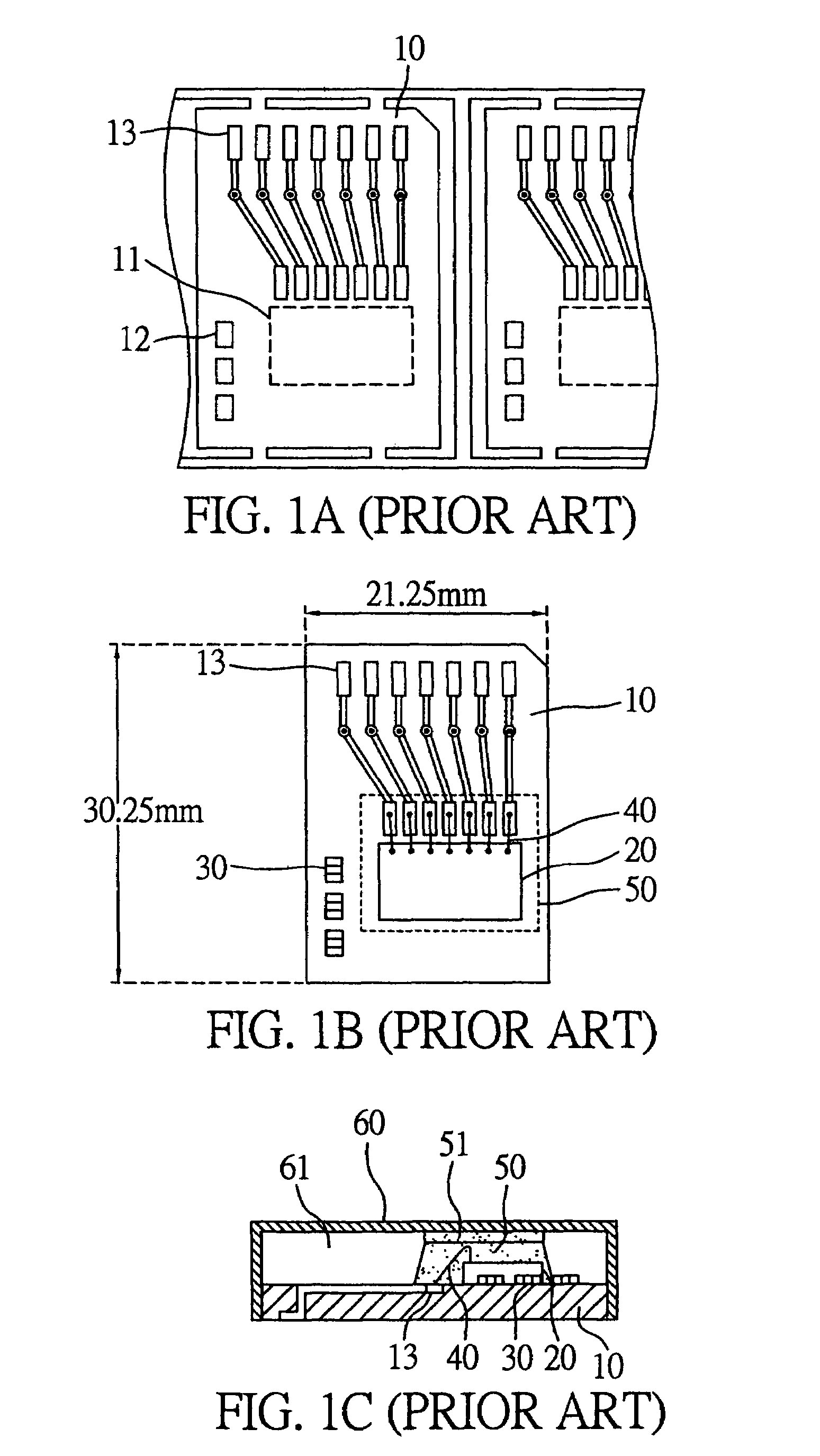

Etch resist solution, method of fabricating thin film pattern using the same and method of fabricating an LCD device using the same

ActiveUS20080173615A1Reduce fabrication costFabrication reliability be improveAfter-treatment detailsDecorative surface effectsSolventResist

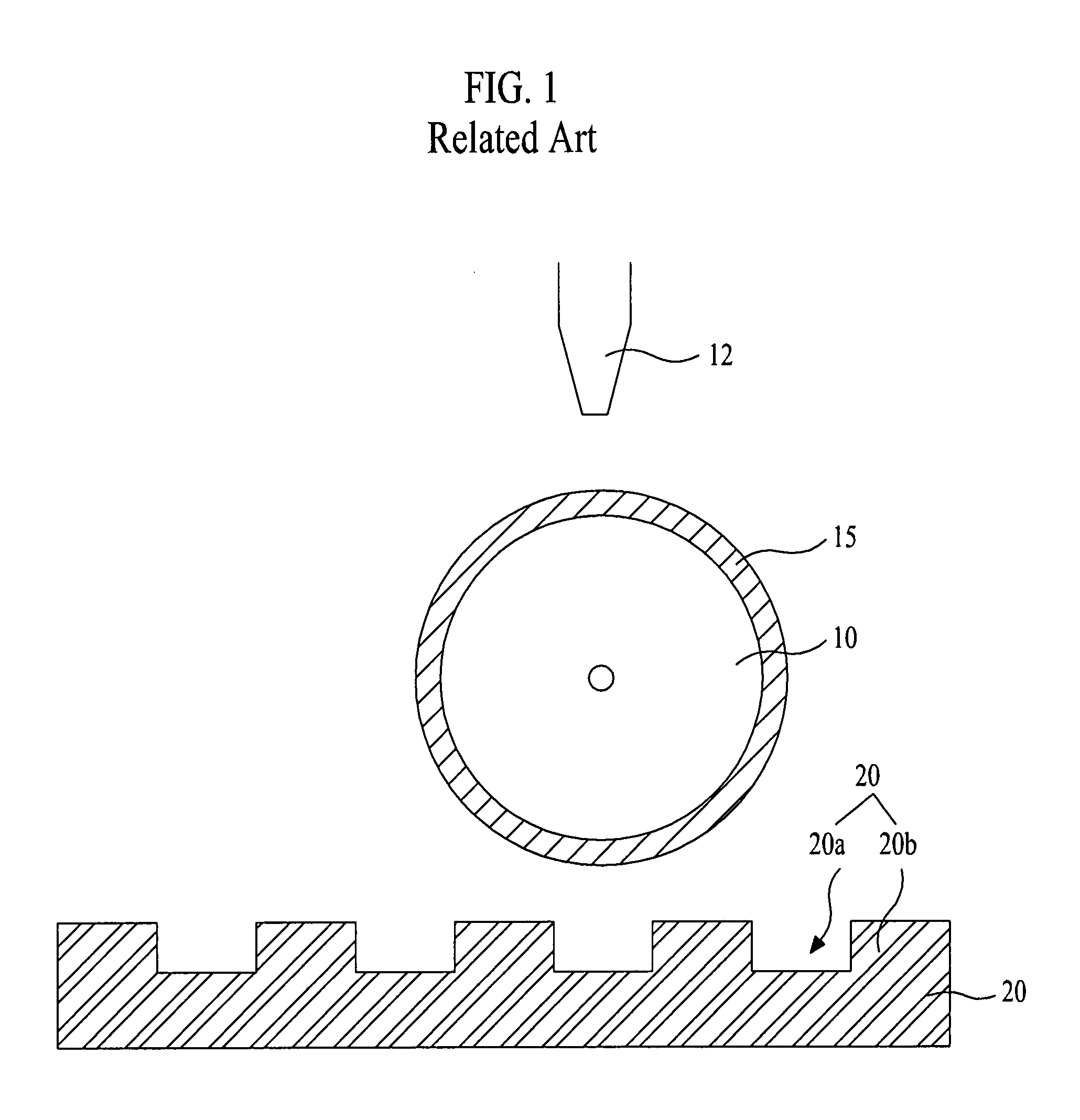

A method of fabricating a thin film pattern improve the life of a blanket and reduce the cost and improve reliability in forming the thin film pattern. The method includes injecting an etch resist solution into a blanket on a printing roller, wherein the etch resist solution includes a printing solvent that satisfies the condition 6>δsolvent or δsolvent>11, where δsolvent is the solubility parameter of the solvent, or satisfies the condition 6<δsolvent<11 and μ<2(D), where μ is the dipole moment of the solvent; rotating the printing roller to uniformly coat the etch resist solution on the blanket; rolling the printing roller coated with the etch resist solution onto a printing plate to pattern the etch resist solution to thereby form an etch resist pattern; transferring the etch resist pattern from the printing roller to a substrate; hardening the etch resist pattern; and forming a desired thin film pattern on the substrate using the etch resist pattern.

Owner:LG DISPLAY CO LTD

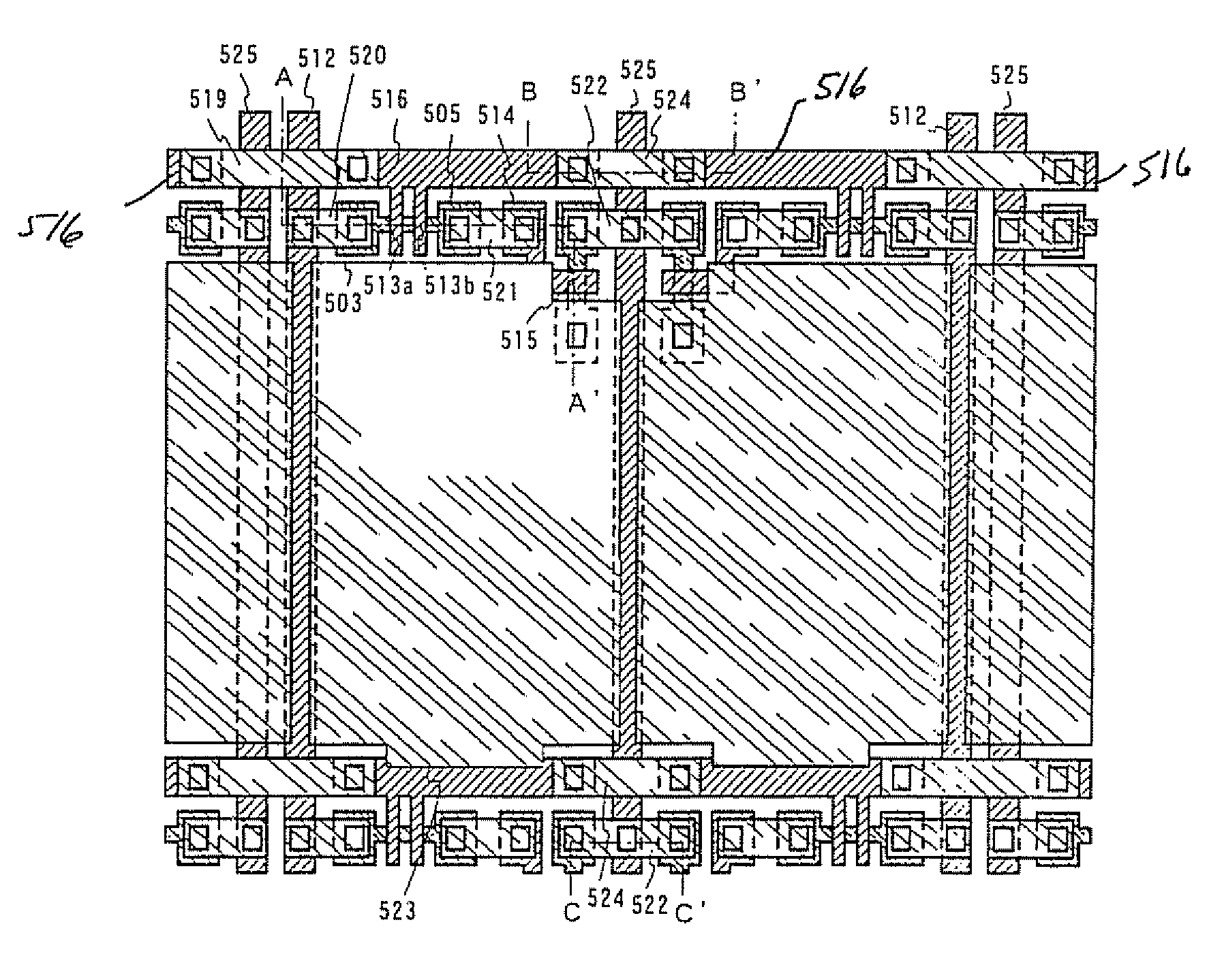

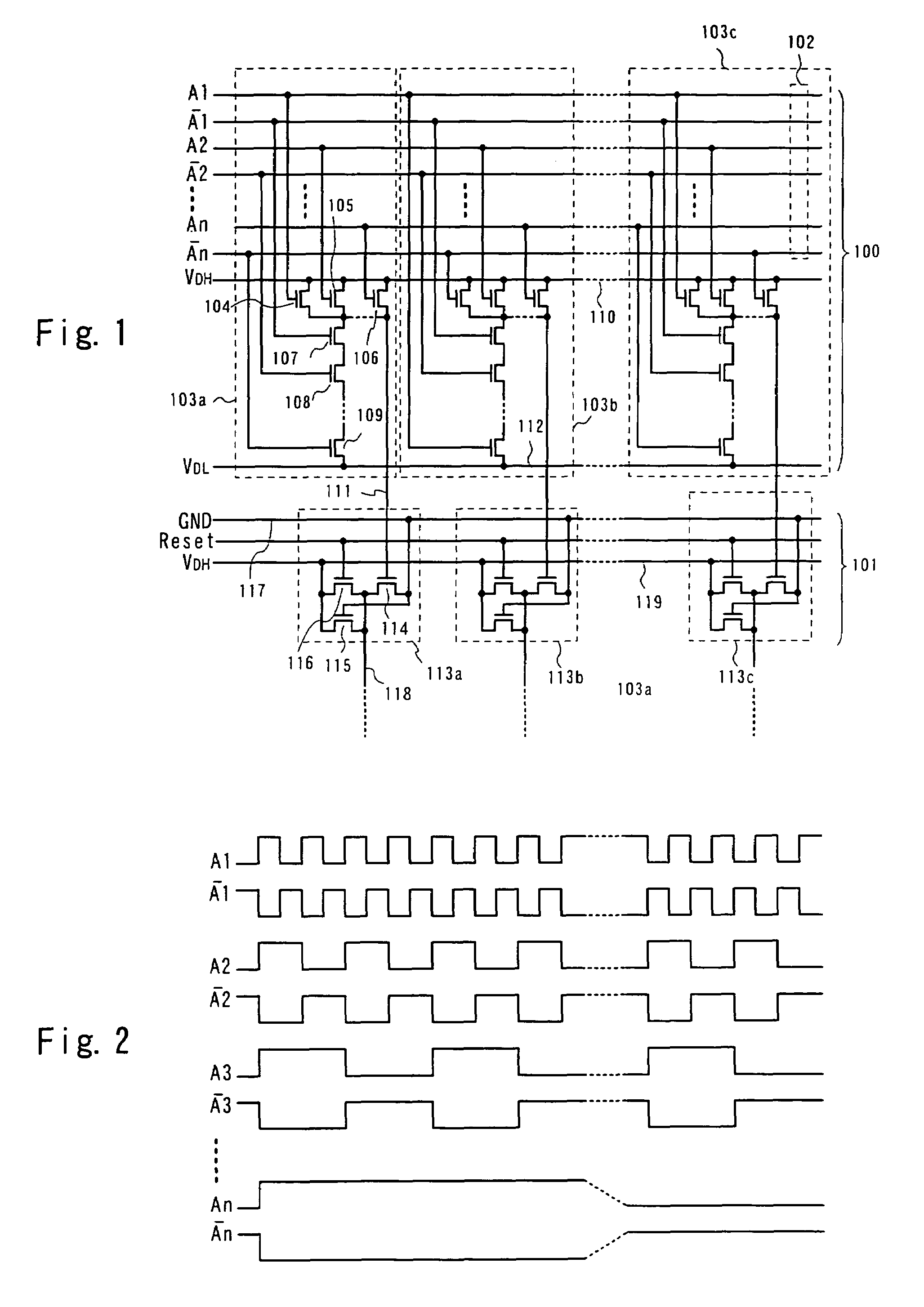

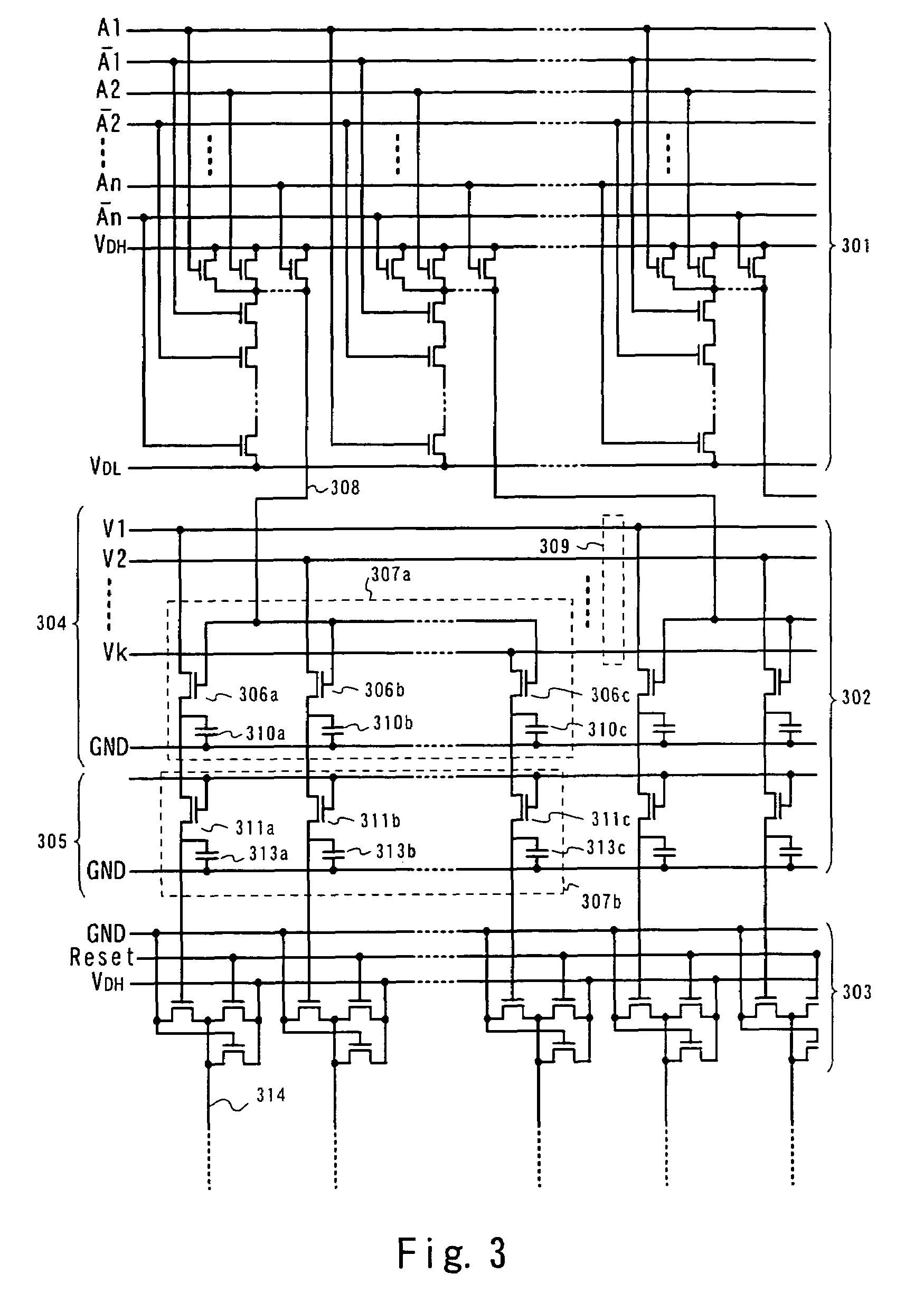

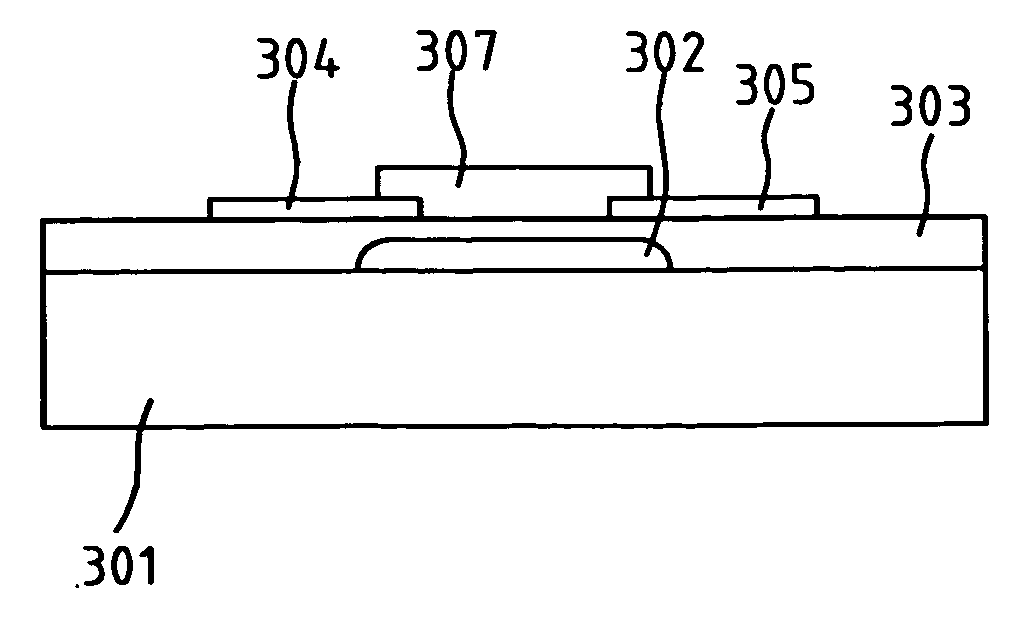

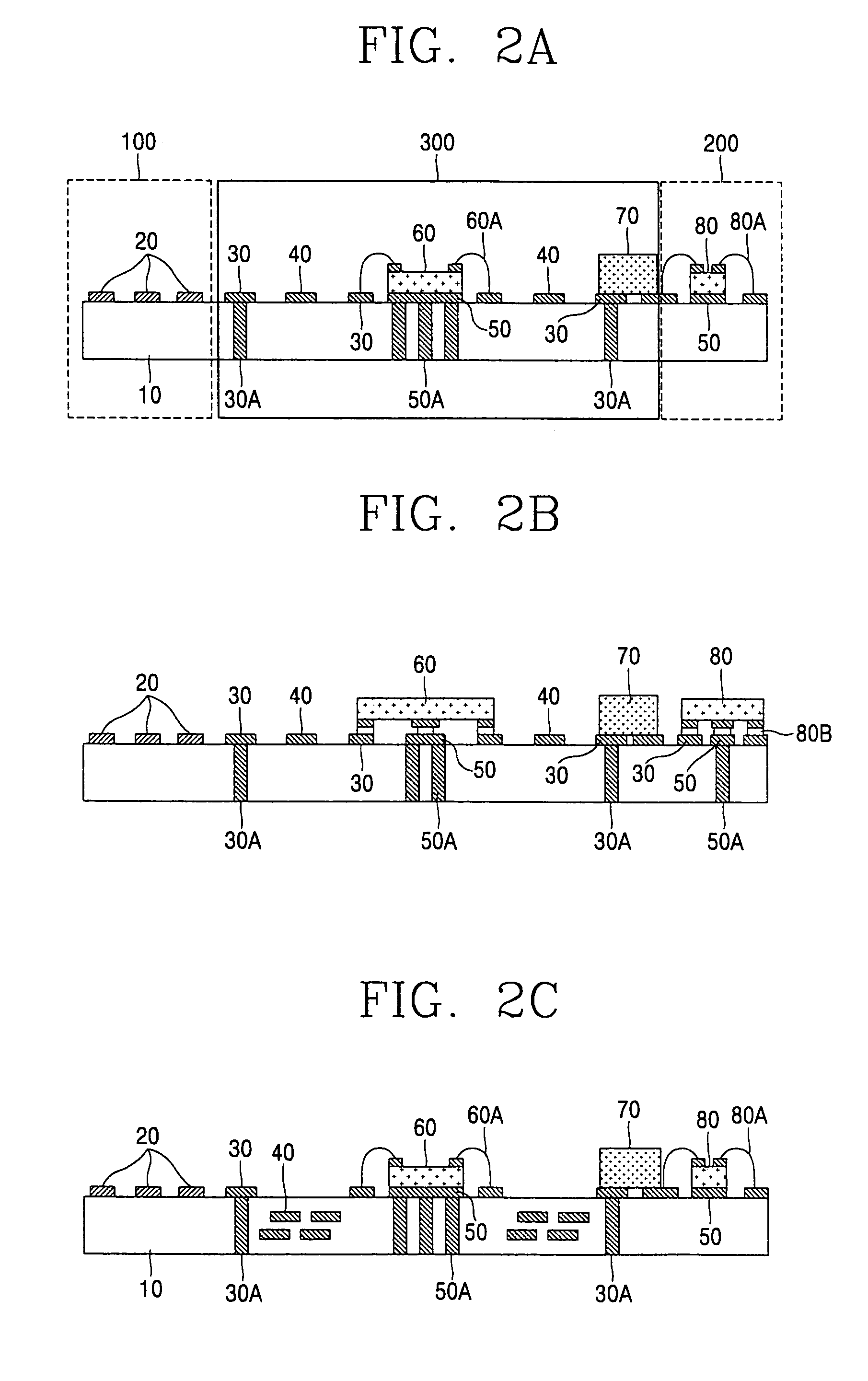

Display device and method for fabricating the same

InactiveUS7612753B2Reduce fabrication costFabrication process can be shortenedStatic indicating devicesFinal product manufactureP channelDisplay device

An inexpensive display device, as well as an electrical apparatus employing the same, can be provided. In the display device in which a pixel section and a driver circuit are included on one and the same insulating surface, the driver circuit includes a decoder 100 and a buffer section 101. The decoder 100 includes a plurality of NAND circuits each including p-channel TFTs 104 to 106 connected to each other in parallel and other p-channel TFTs 107 to 109 connected to each other in series. The buffer section 101 includes a plurality of buffers each including three p-channel TFTs 114 to 116.

Owner:SEMICON ENERGY LAB CO LTD

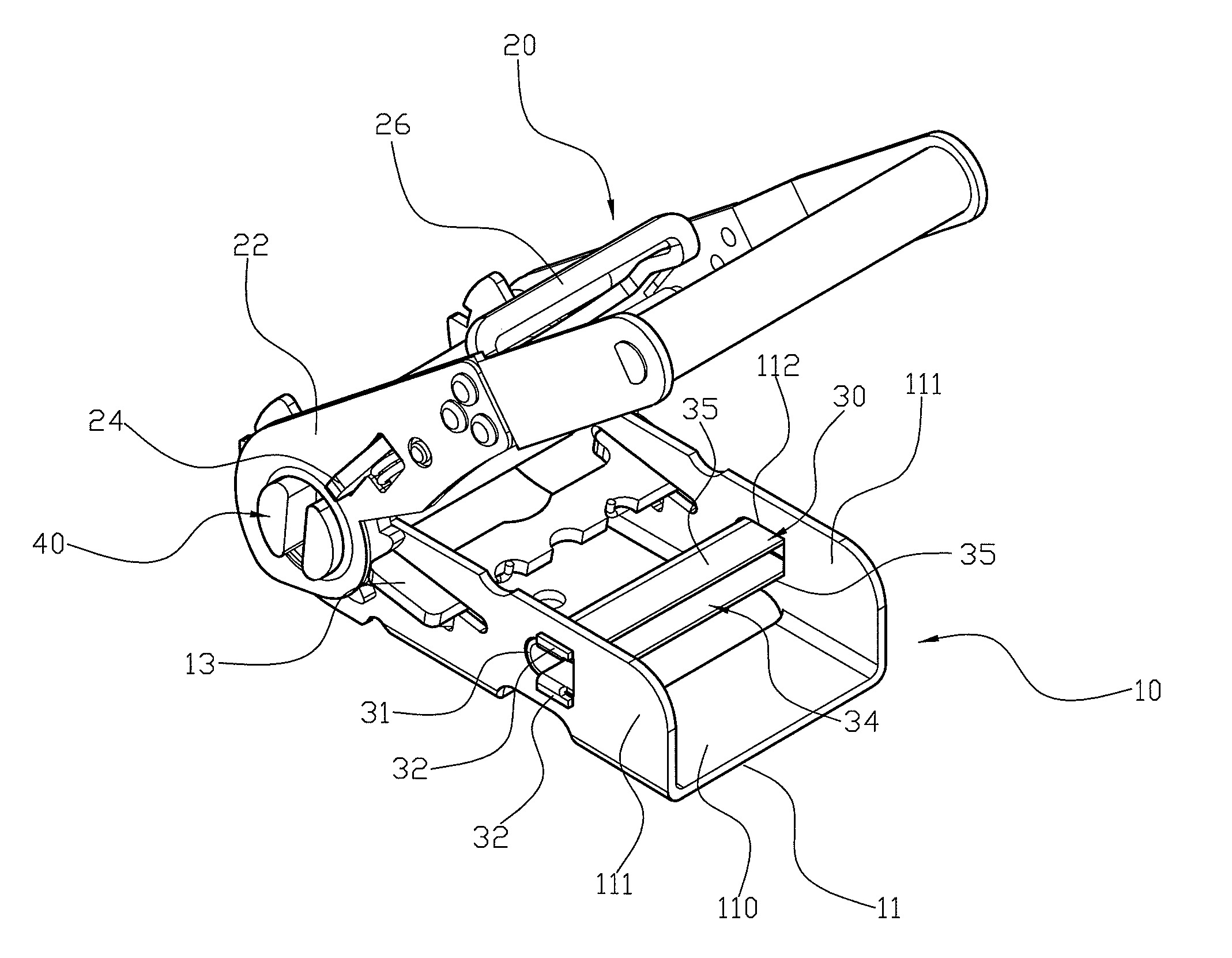

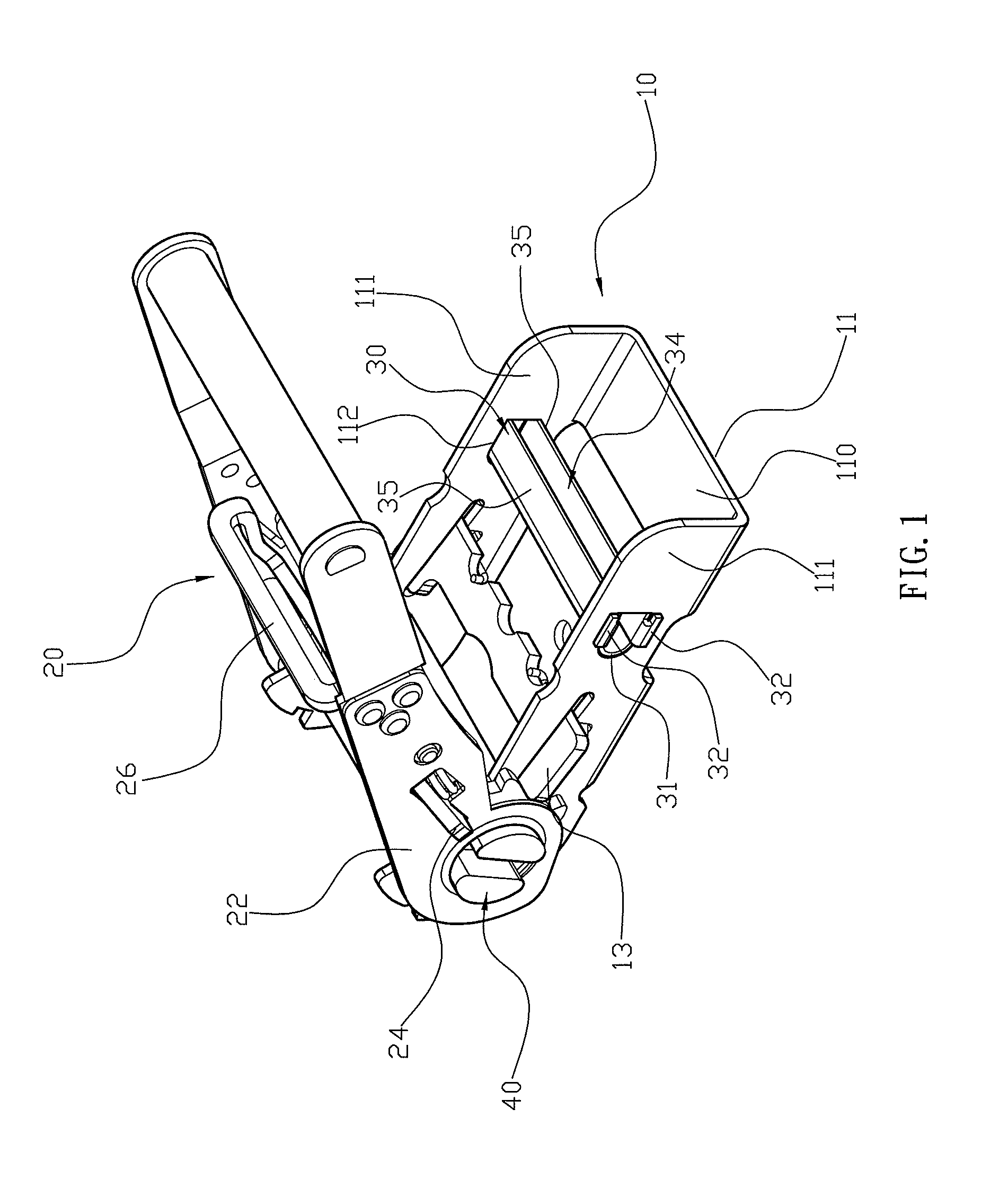

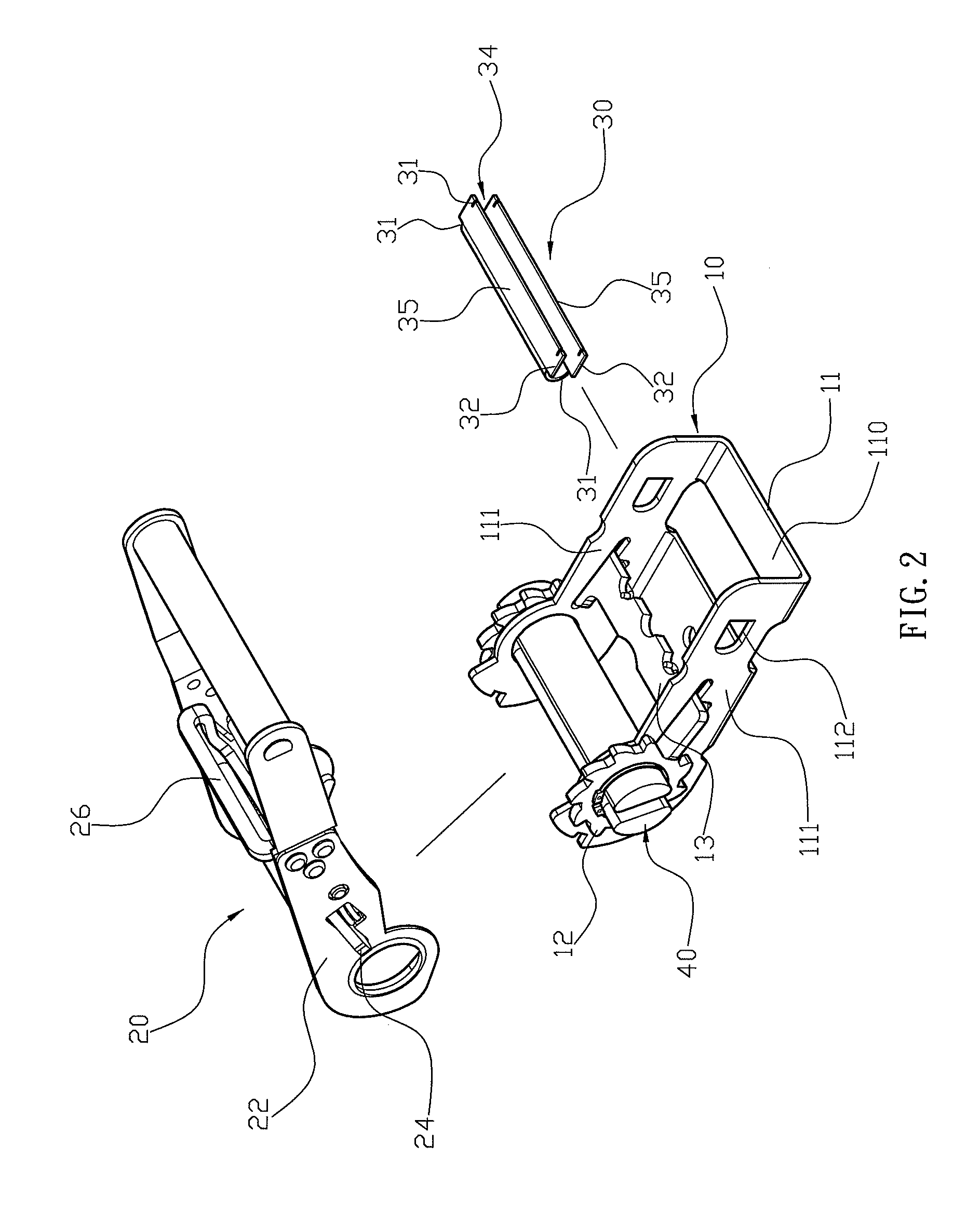

Cable tightening device with a base having a lower cost of fabrication

InactiveUS7651072B1Reduce fabrication costSaving price of materialSnap fastenersLifting devicesEngineeringElectric cables

A cable tightening device includes a fixed unit including a base, a rotation member rotatably mounted on a first end of the base, a movable unit including a movable member rotatably mounted on the rotation member and movable relative to the base, and a holding member secured on a second end of the base. Thus, the base of the fixed unit is integrally combined with the holding member without having to provide a bolt and a nut, thereby decreasing the costs of fabrication. In addition, the holding member is integrally combined with the base of the fixed unit by punching so that the holding member will not detach from the base of the fixed unit, thereby facilitating operation of the cable tightening device.

Owner:CHANG WEN CHENG

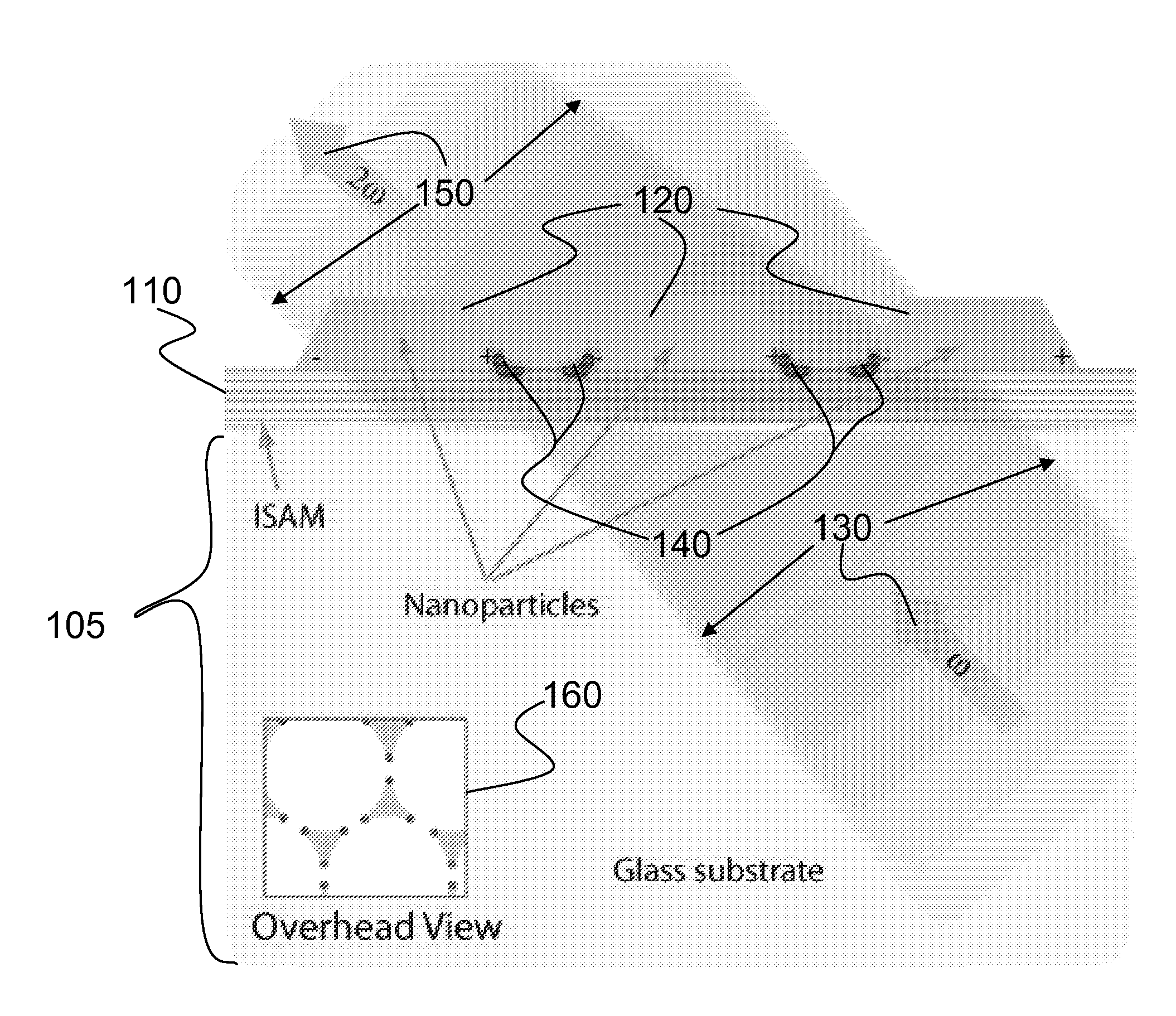

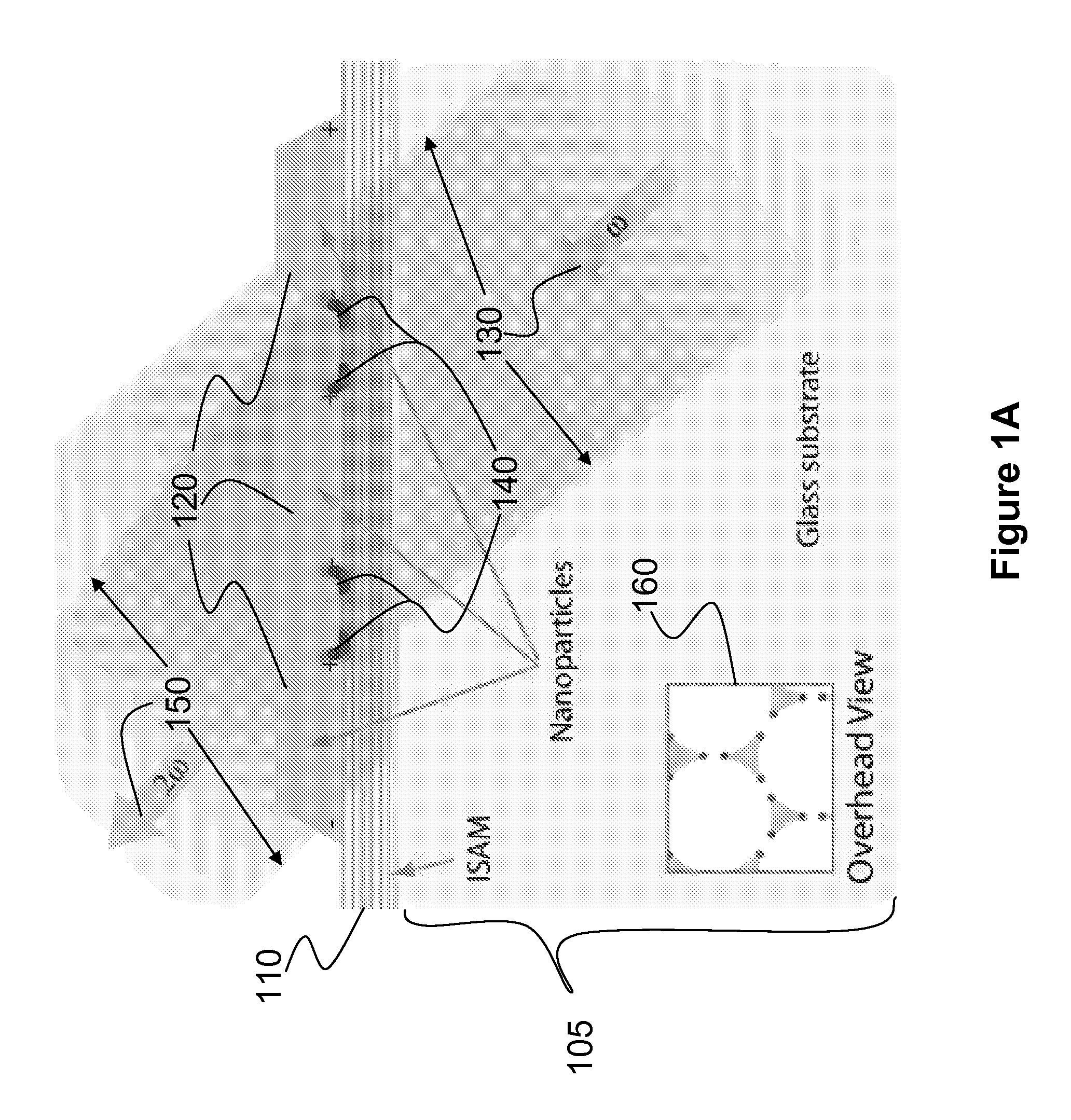

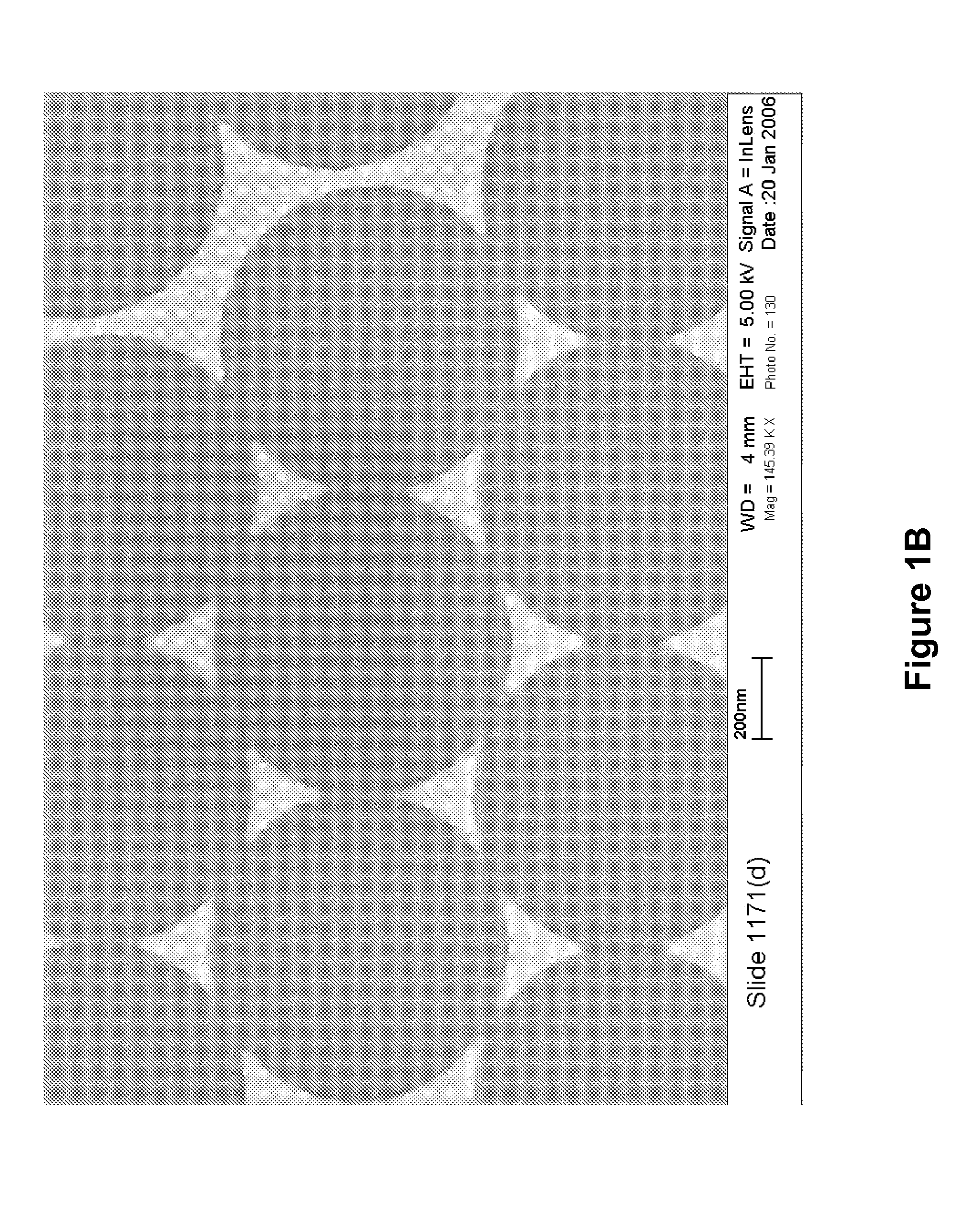

Enhancement of second-order non-linear optical susceptibilities in organic film materials using non-centrosymmetric nanoparticles

ActiveUS20080044148A1Enhance emissionReduce fabrication costNanoopticsOptical light guidesNanometreCu nanoparticles

A non-linear optical material comprising a plurality of non-centrosymmetric nanoparticles juxtaposed to non-linear optical (NLO) film at a localized surface Plasmon resonance (LSPR) of the nanoparticles. The LSPR is resonant at a wavelength of an incident light source, wherein a second-order non-linear susceptibility (χ(2)) of the NLO film with respect to the incident light is enhanced by the juxtaposition to the LSPR of the nanoparticles. The non-linear optical material lacks global inversion symmetry.

Owner:VIRGINIA TECH INTPROP INC

Method for manufacturing thin film transistors

InactiveUS20060286725A1Low fabrication costReduce fabrication costLight-sensitive devicesSemiconductor/solid-state device manufacturingCompound (substance)Oxide

A method for manufacturing TFTs is provided. It can be applied to both inverted staggered and co-planar TFT structures. The manufacturing method for the staggered TFT includes the formation of a gate electrode, a gate insulator, an active channel layer, a drain electrode, and a source electrode on a substrate. It emphasizes the use of metal oxides or II-VI compounds semiconductors and low-temperature CBD process to form the active channel layer. In a CBD process, the active channel layers are selectively deposited on the substrates immersed in the solution through controlling solution temperature and PH value. The invention offers the advantages of low deposition temperature, selective deposition, no practical limit of panel size, and low fabrication cost. Its low deposition temperature allows the use of flexible substrates, such as plastic substrates.

Owner:IND TECH RES INST

Steel sheet having very high mechanical properties of strength and ductility, manufacturing method and use of such sheets

ActiveUS20160160309A1Reduce fabrication costLess scatterHot-dipping/immersion processesFurnace typesDuctilityBainite

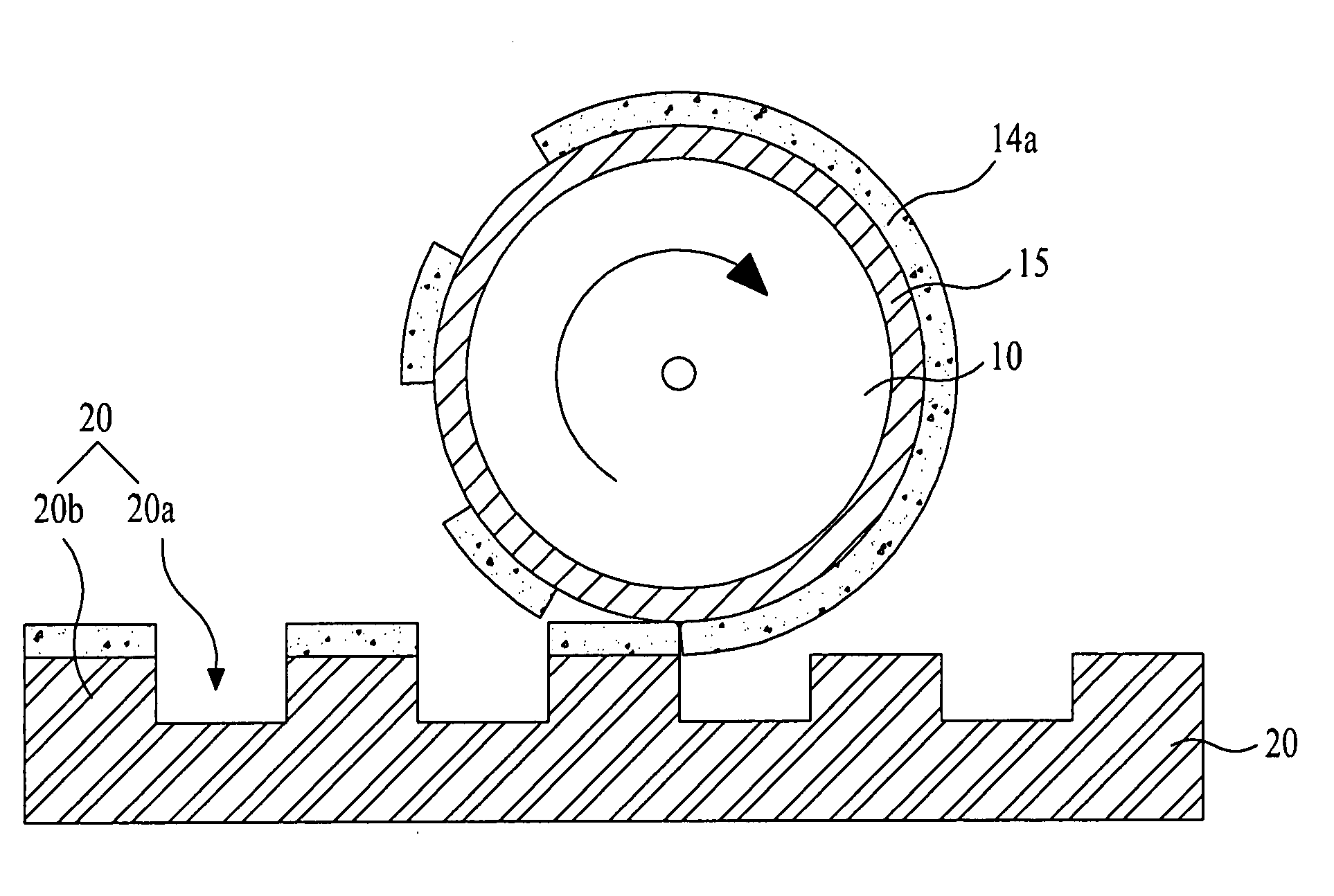

The invention relates to the manufacture of a cold-rolled steel sheet having a strength of more than 900 MPa, an elastic limit of more than 700 MPa and distributed elongation of more than 12%, the composition of which includes, the contents being expressed as weight percentages: 0.26%≦C≦0.45%, 1.0%≦Mn≦3.0%, 1.0%≦Si≦3.0%, Al≦0.10%, 0%≦Cr≦1.5% %, S≦0.005%, P≦0.020%, Nb≦0.1%, Ti≦0.020%, V≦0.015%, N≦0.01%, the remainder of the composition being iron and inevitable impurities resulting from the production process. The microstructure, given in surface proportions, comprises 13% to 25% residual austenite and 13% to 30% MA islands, the remainder consisting of bainite and possibly ferrite.

Owner:ARCELOR FRANCE SA

Communication apparatus, electronic apparatus, imaging apparatus

InactiveUS20060173986A1Reduce fabrication costMaintain performanceDigital computer detailsOther printing apparatusData bufferAddress mapping

A communication apparatus is disclosed that includes a transmission circuit configured to transmit transmission data to a communication counterpart; a reception circuit configured to receive reception data from the communication counterpart; a storage device configured as at least two buffers including a transmission buffer that stores the transmission data and a reception buffer that stores the reception data; and an address mapping unit configured to perform address mapping of the buffers including the transmission buffer and the reception buffer on the storage device, and adjust the storage capacity of the transmission buffer and the storage capacity of the reception buffer.

Owner:RICOH KK

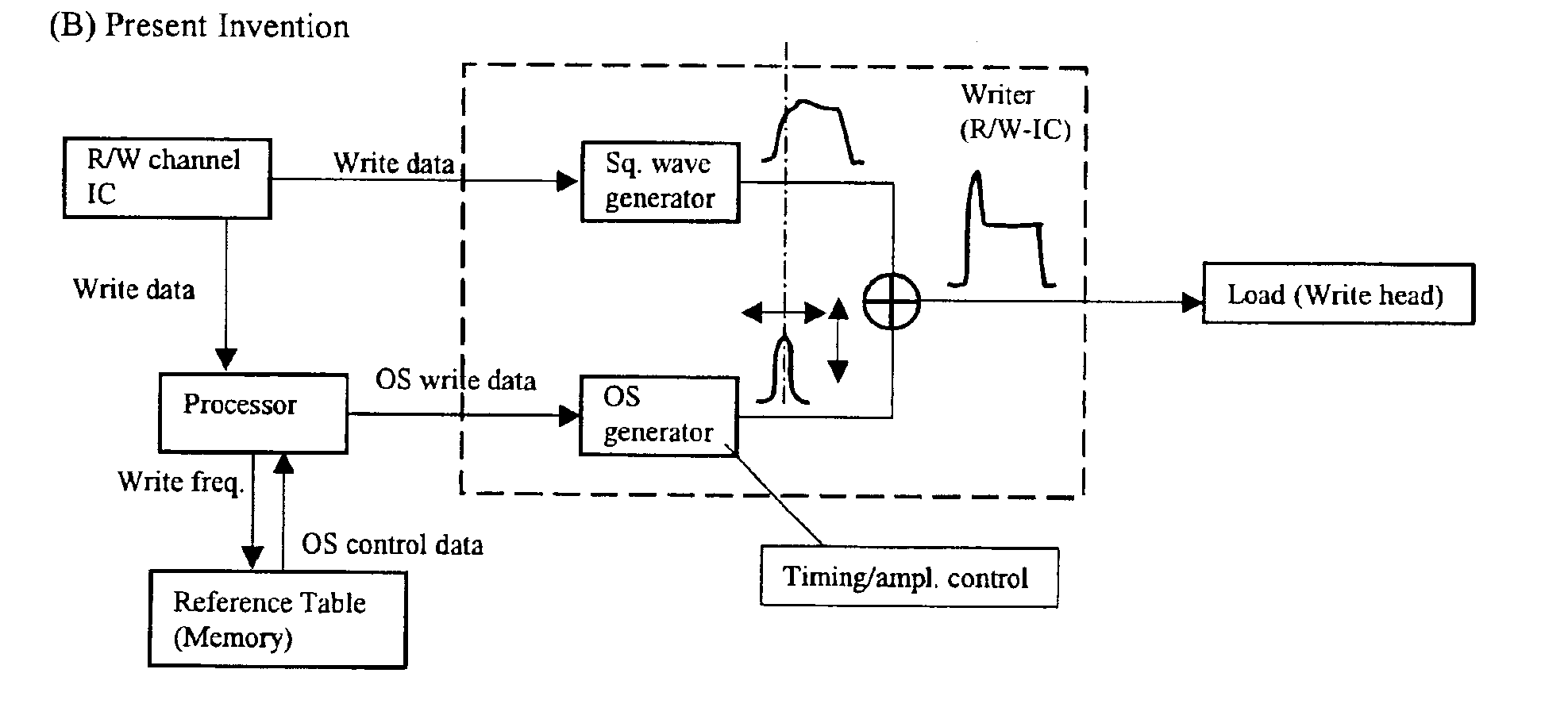

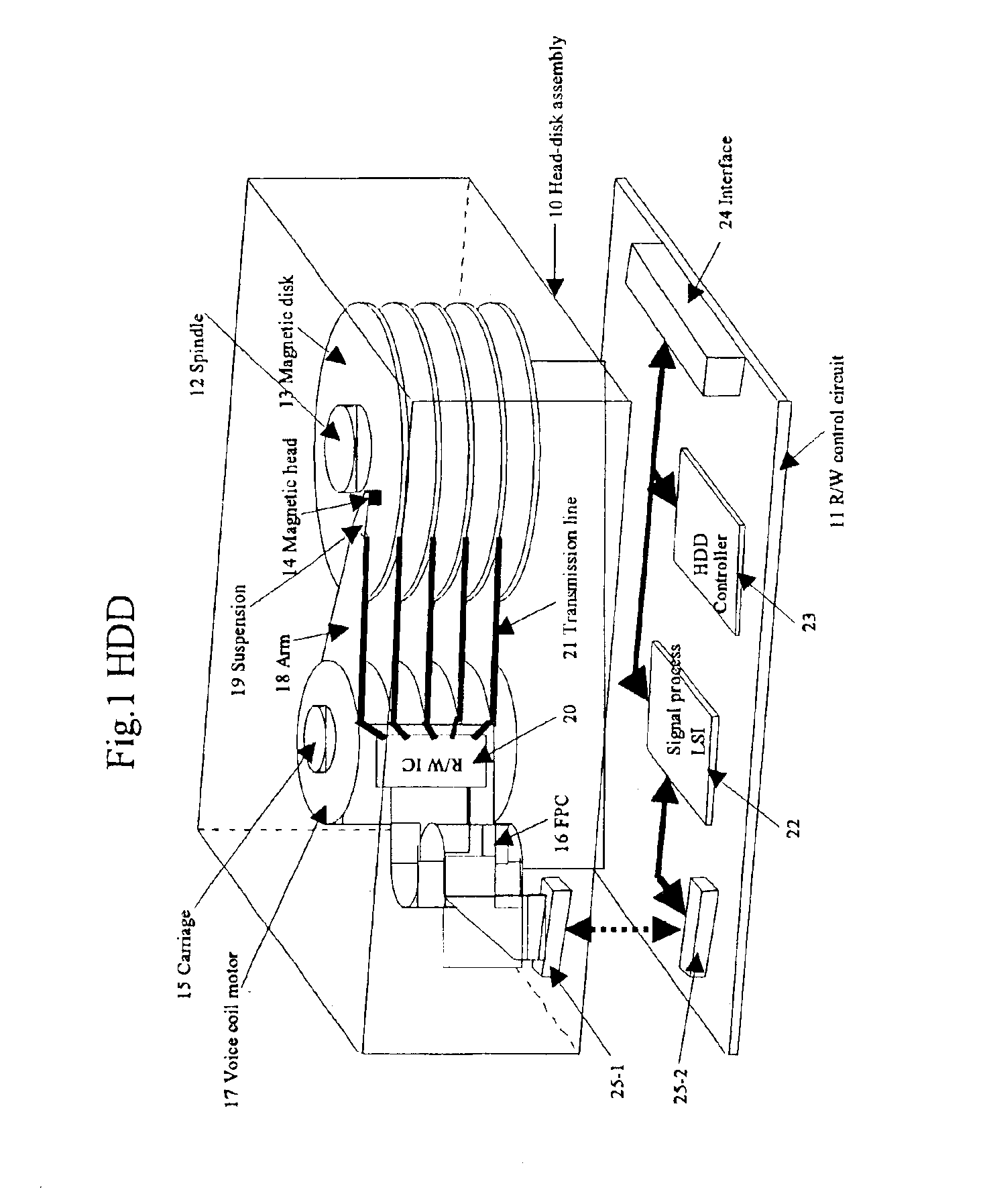

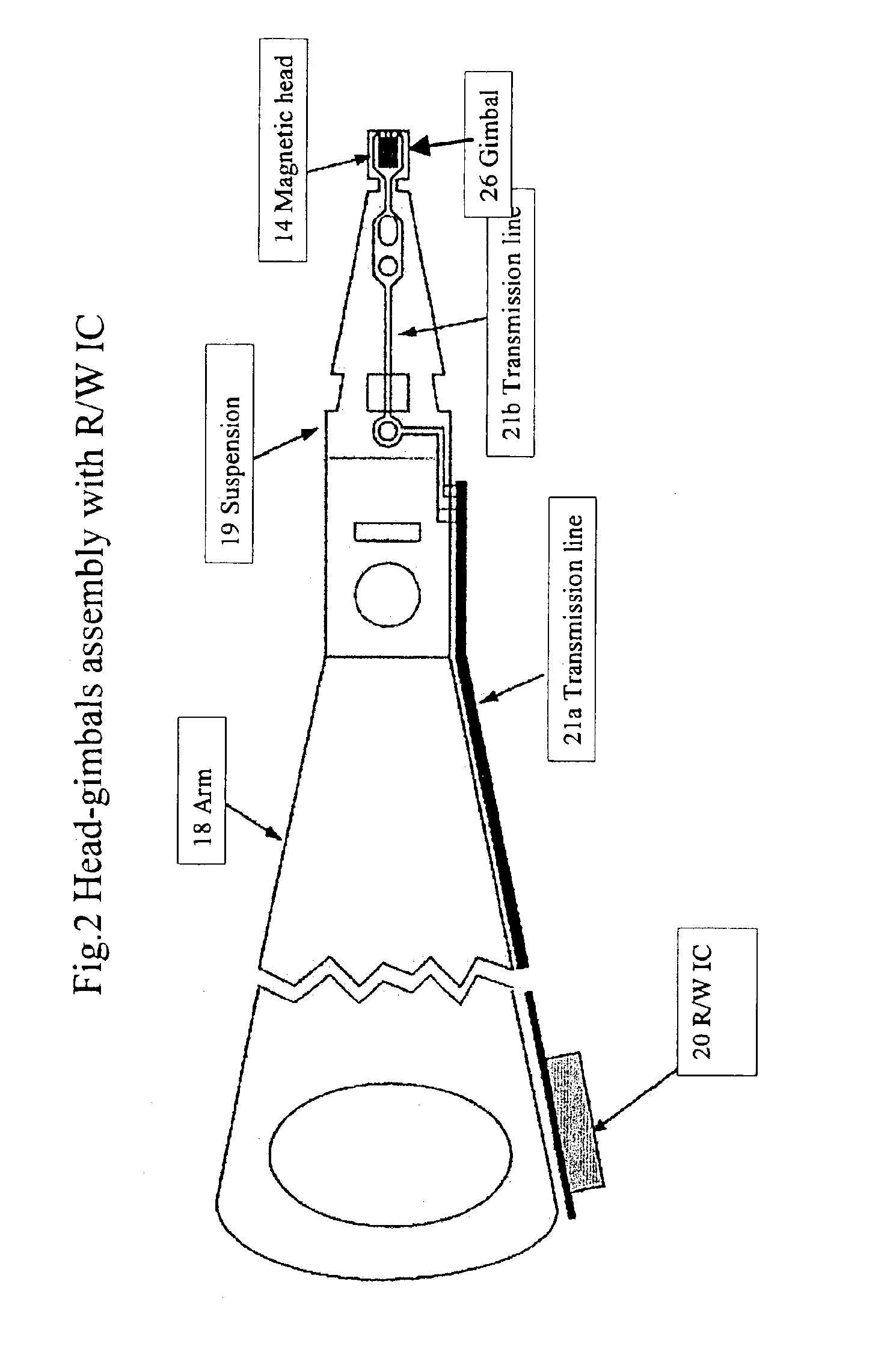

Overshoot current phase/amplitude control for hard disk drive write current

InactiveUS6870697B2Reduce fabrication costReduce manufacturing costModification of read/write signalsRecord information storageHard disc driveWrite current

Devices and methods for generating a magnetic head-specific overshoot current which is combined with an alternating current waveform into a write current used by the magnetic head to store information on a magnetic medium. A processor analyzes the frequency of incoming write data and retrieves from a data table of an overshoot current amplitude and an overshoot current phase. This amplitude and phase information is sent to an overshoot current generator to generate an overshoot current that is responsive to the dynamic impedance properties of a magnetic write head during operation. The data table may have information related to one or many write heads, and the data table may be further subdivided based on additional dynamic characteristics of a write head that may affect the impedance thereof.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD

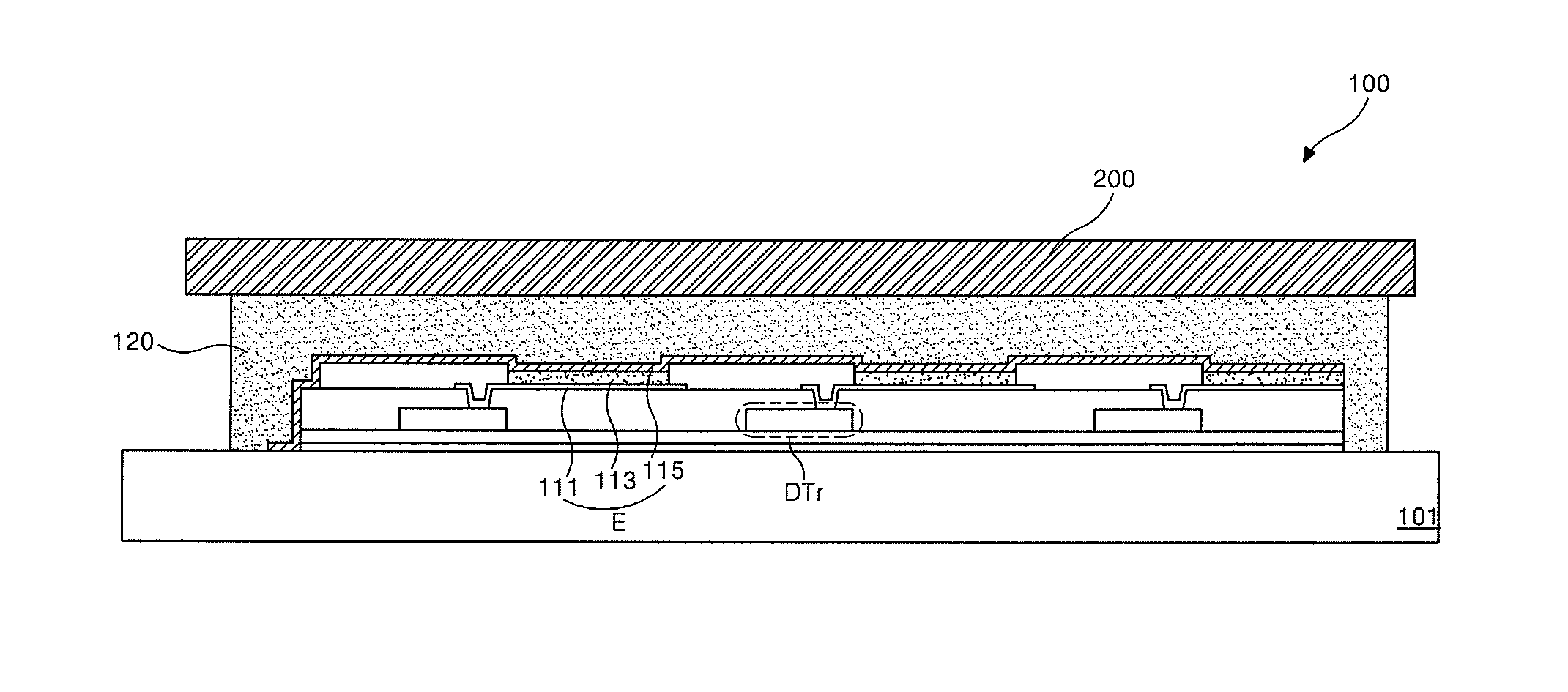

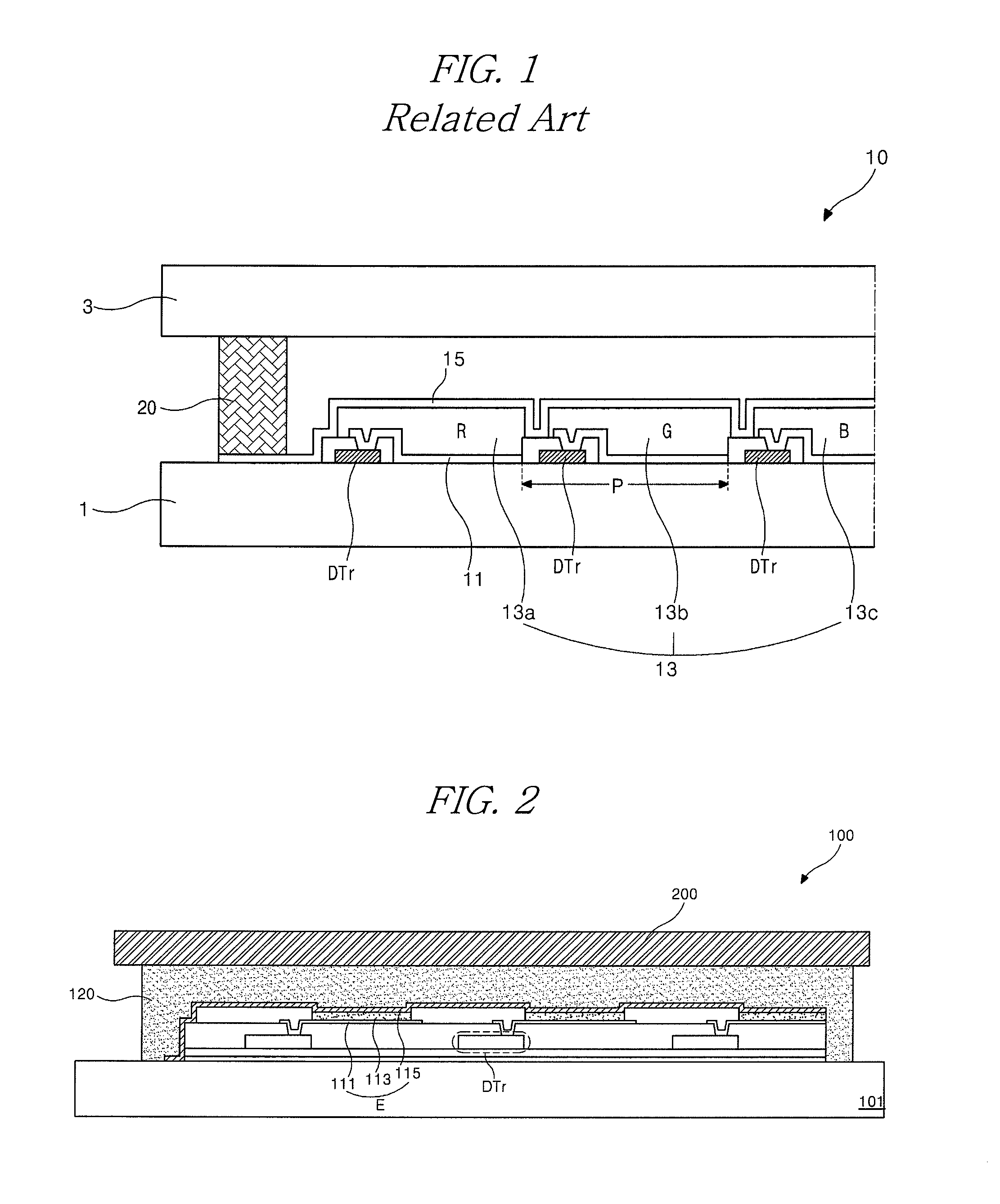

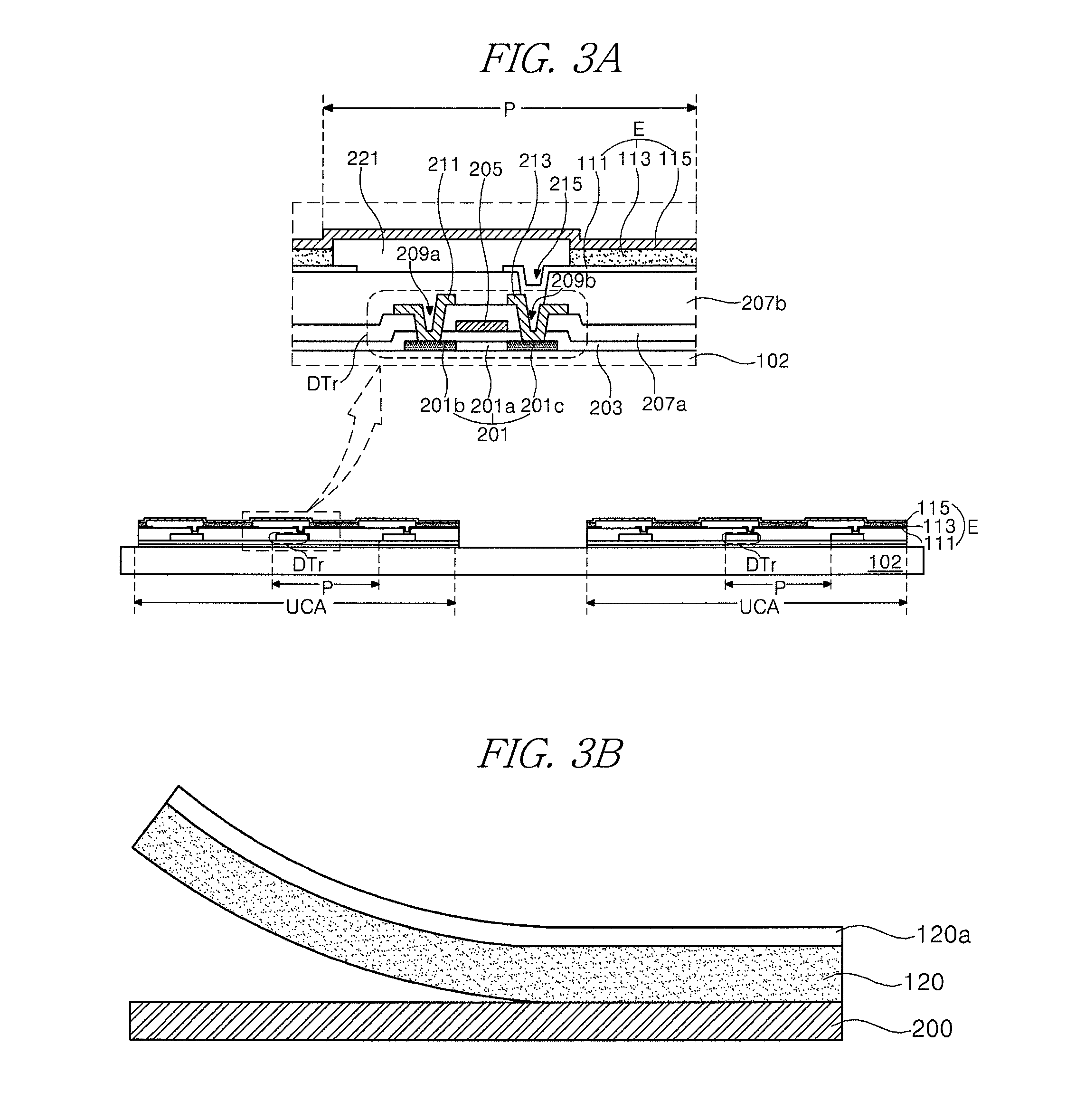

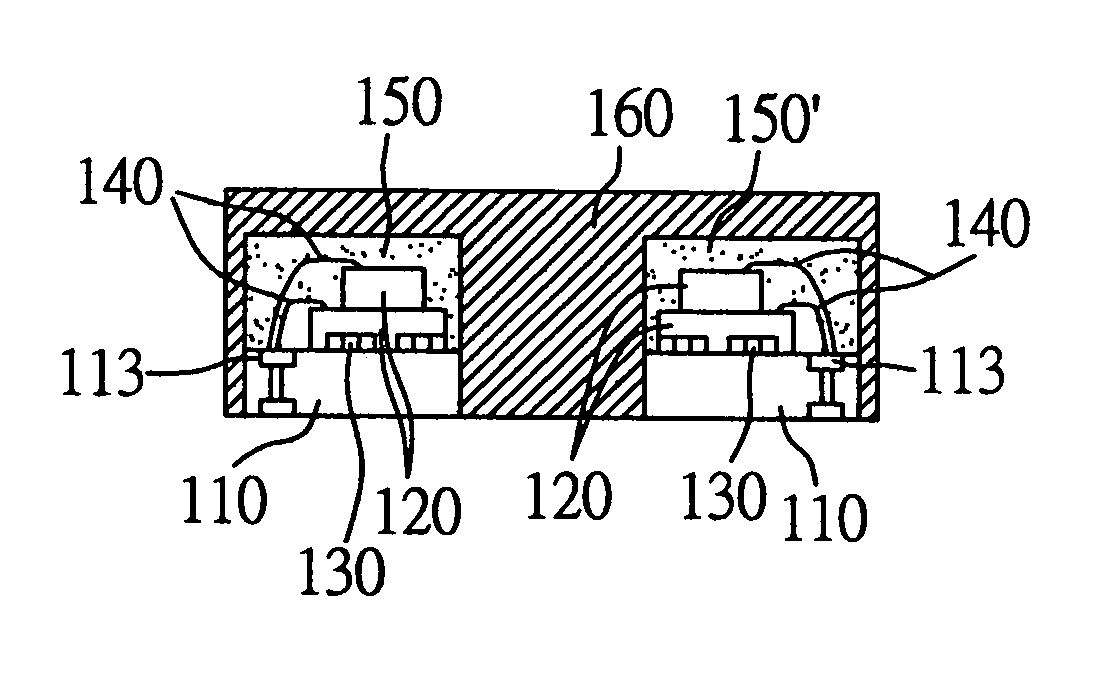

Organic electroluminescent display device and method of fabricating the same

ActiveUS20110101853A1Reduce fabrication costEfficiently radiatedDischarge tube luminescnet screensElectroluminescent light sourcesOrganic electroluminescenceMetal foil

A method for fabricating an organic electroluminescent display device includes: forming a switching thin film transistor, a driving thin film transistor and an organic electroluminescent diode on a mother substrate having a plurality of unit cell areas; forming a cutting portion in a metal foil having a plurality of unit metal foil areas, the metal foil having a size corresponding to the mother substrate; forming an adhesive layer on the metal foil; attaching the mother substrate and the metal foil such that the adhesive layer contacts the mother substrate; and cutting the mother substrate and the metal foil along the cutting portion.

Owner:LG DISPLAY CO LTD

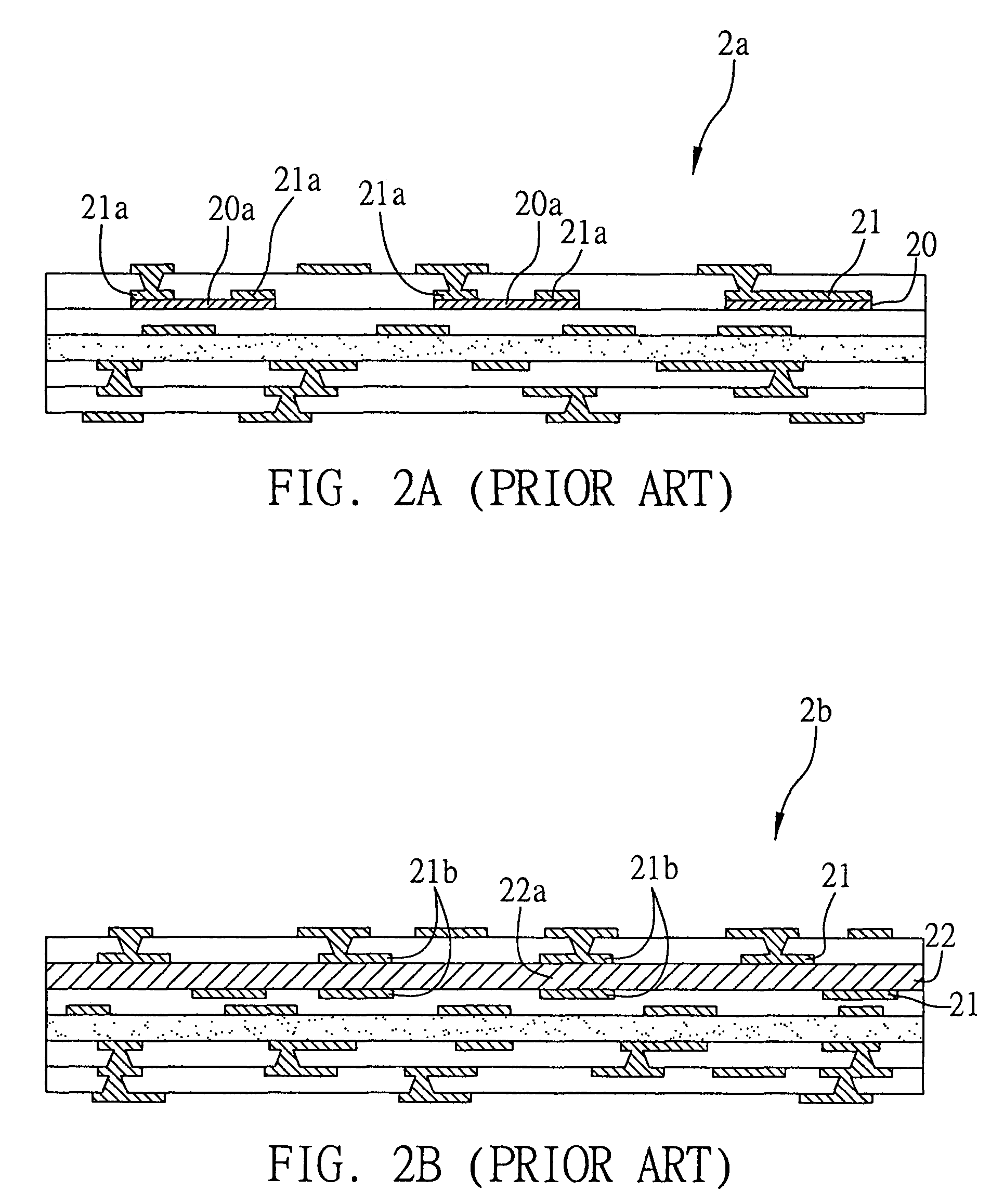

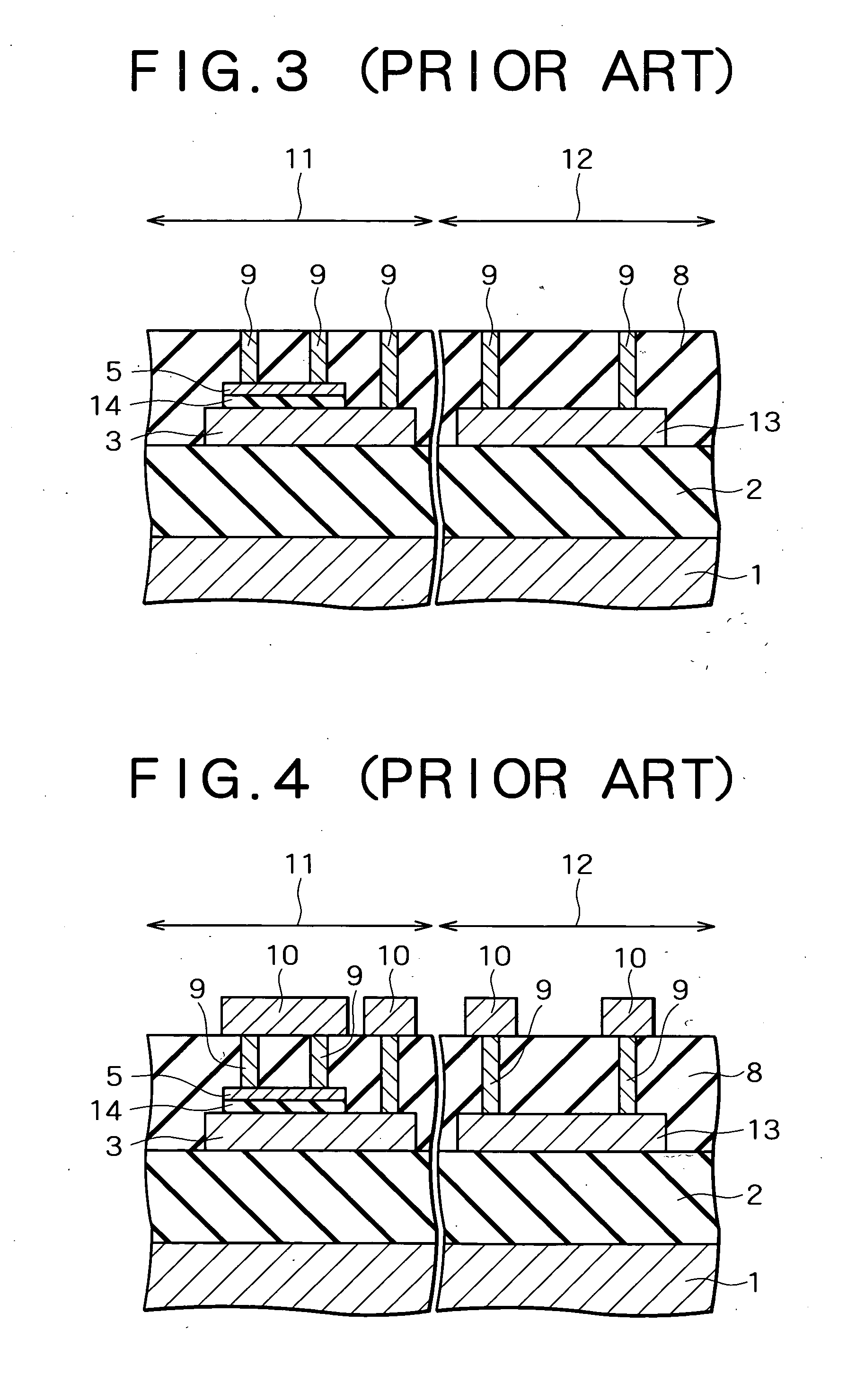

Integrated library core for embedded passive components and method for forming electronic device thereon

InactiveUS7190592B2Reduce fabrication costIncrease numberSemiconductor/solid-state device detailsSolid-state devicesElectrically conductivePrinted circuit board

An integrated library core for embedded passive components and a method for forming an electronic device on the library core are provided. An insulating core layer is formed with a plurality of openings penetrating therethrough and with electrically conductive layers on upper and lower surfaces thereof. The openings of the core layer are filled with materials for forming passive components such as resistors and capacitors. This thereby provides an integrated library core on which the electrically conductive layers of the core layer can be desirably patterned to electrically interconnect the passive components, and this library core can be electrically connected to an electronic device such as substrate or printed circuit board to enhance performances of electrical characteristics for the electronic device.

Owner:PHOENIX PRECISION TECH CORP

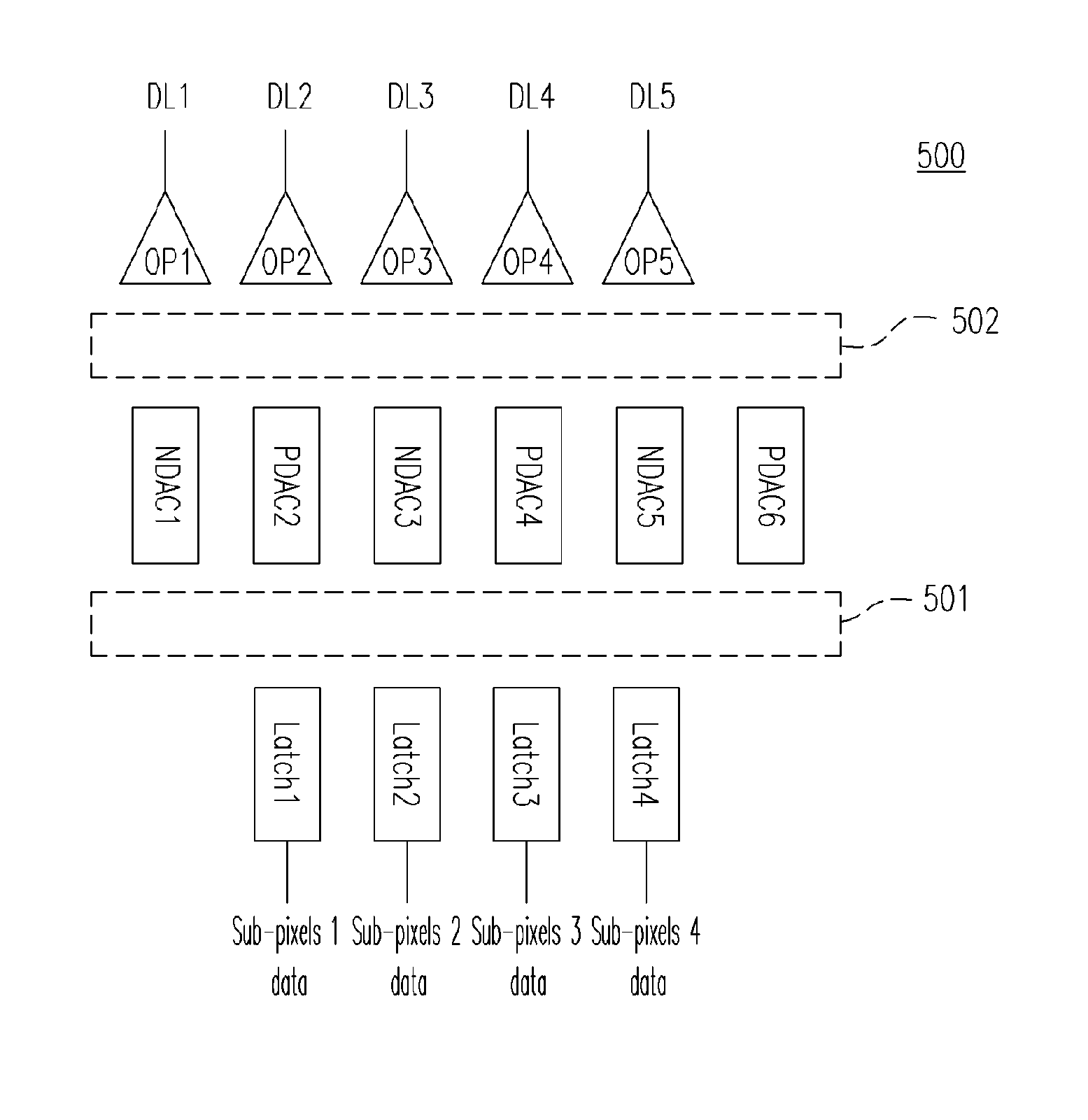

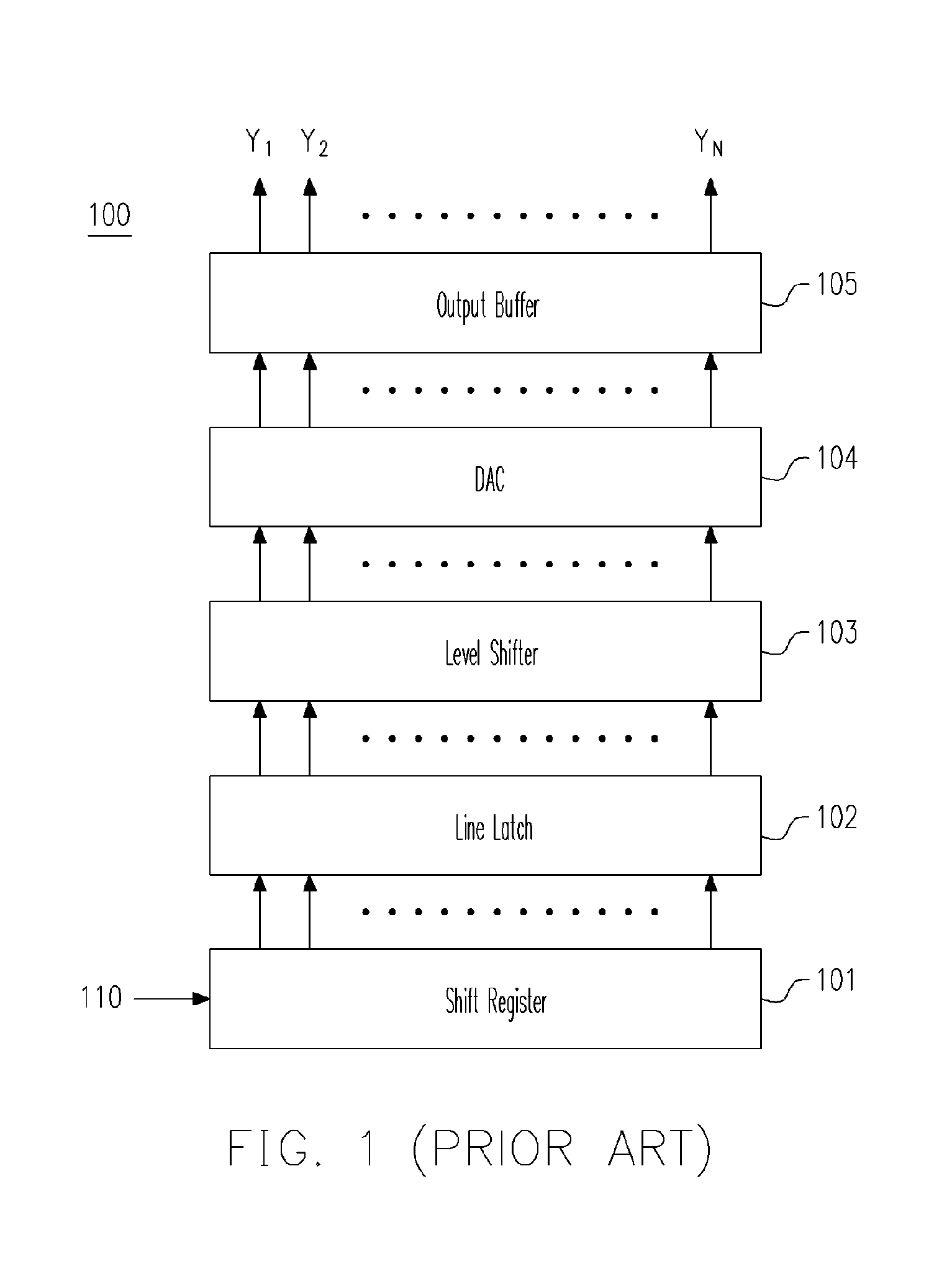

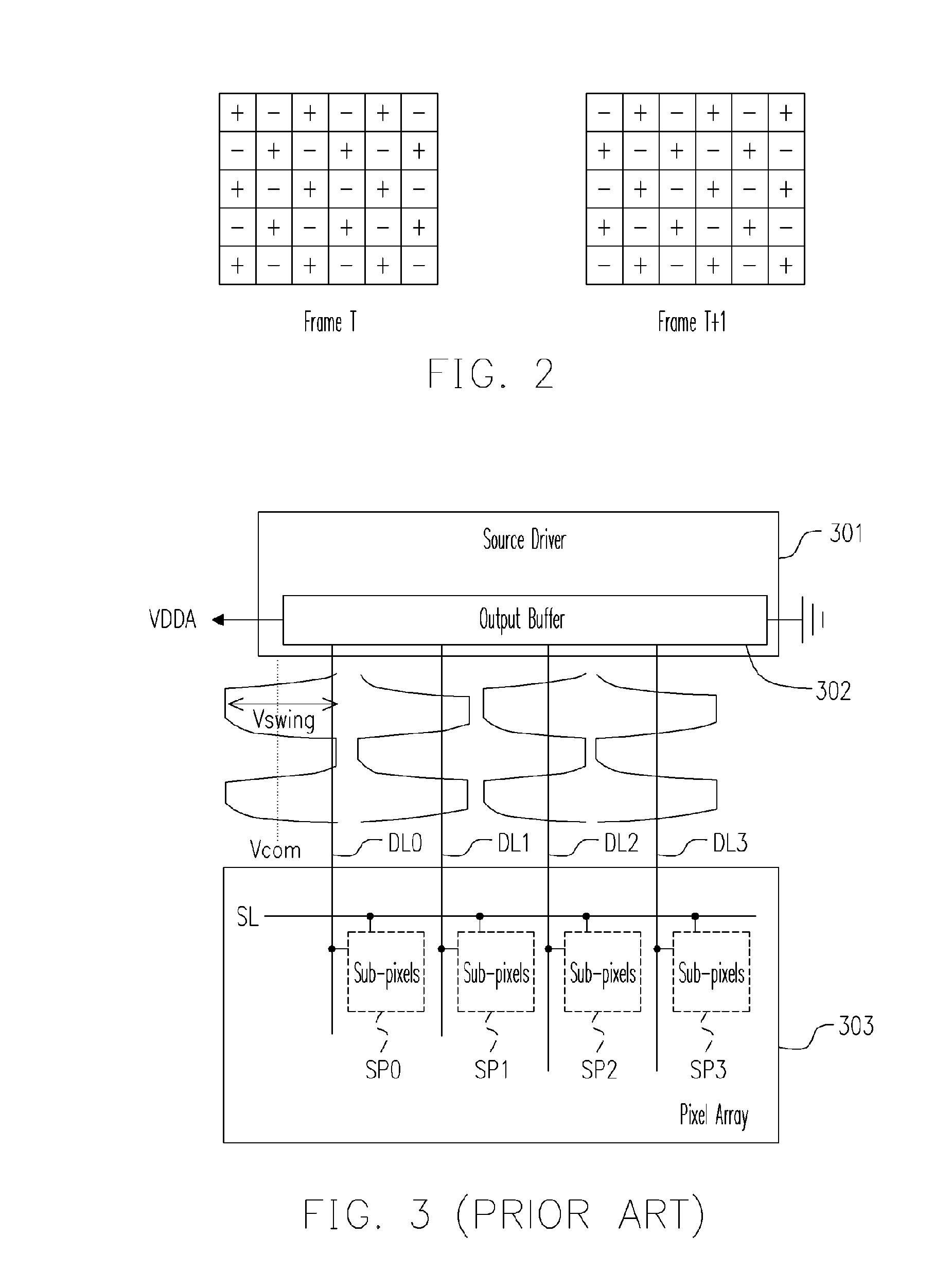

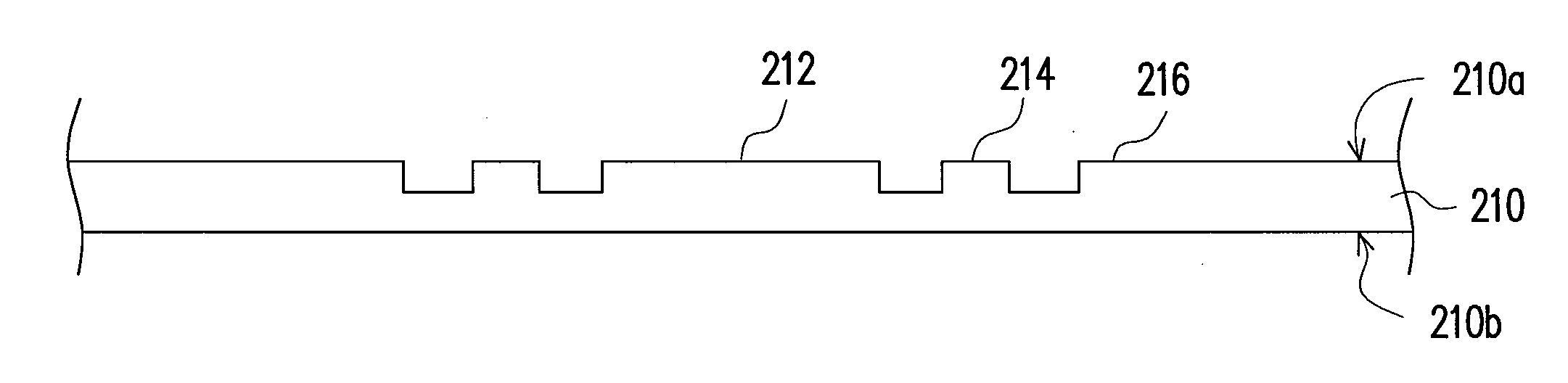

Source driver and internal data transmission method thereof

ActiveUS20070013639A1Reduce power consumptionReduce fabrication costCathode-ray tube indicatorsInput/output processes for data processingData transmissionDigital-to-analog converter

A source driver and an internal data transmission method are provided. The present invention employs specially designed switch units and creates specially designed data paths in a source driver, which matches with the driving method for dot invesion and the specially designed pixel array. When the dot inversion driving method is used on a pixel array of a specific design, each output buffer and digital-to-analog converter inside the source driver continuously output voltages of positive polarity and voltages of negative polarity, instead of switching between positive and negative polarities. Consequently, the swing voltages that the source driver outputs can be lowered, the power consumption can also be reduced accordingly, a smaller area is occupied, and the costs are reduced.

Owner:NOVATEK MICROELECTRONICS CORP

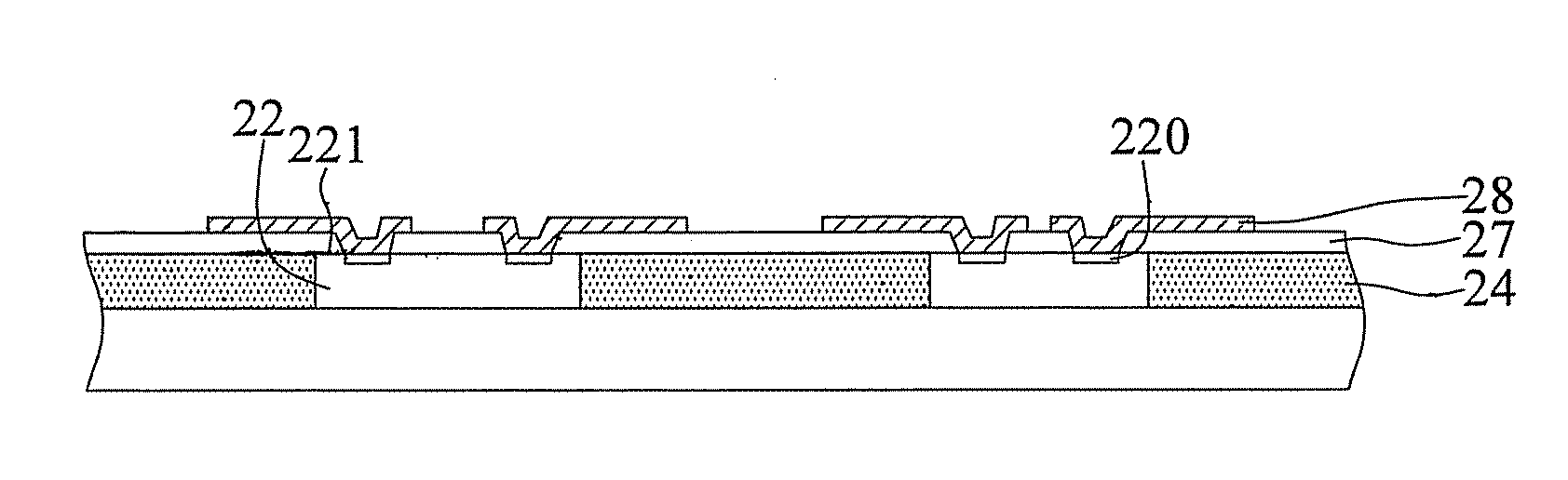

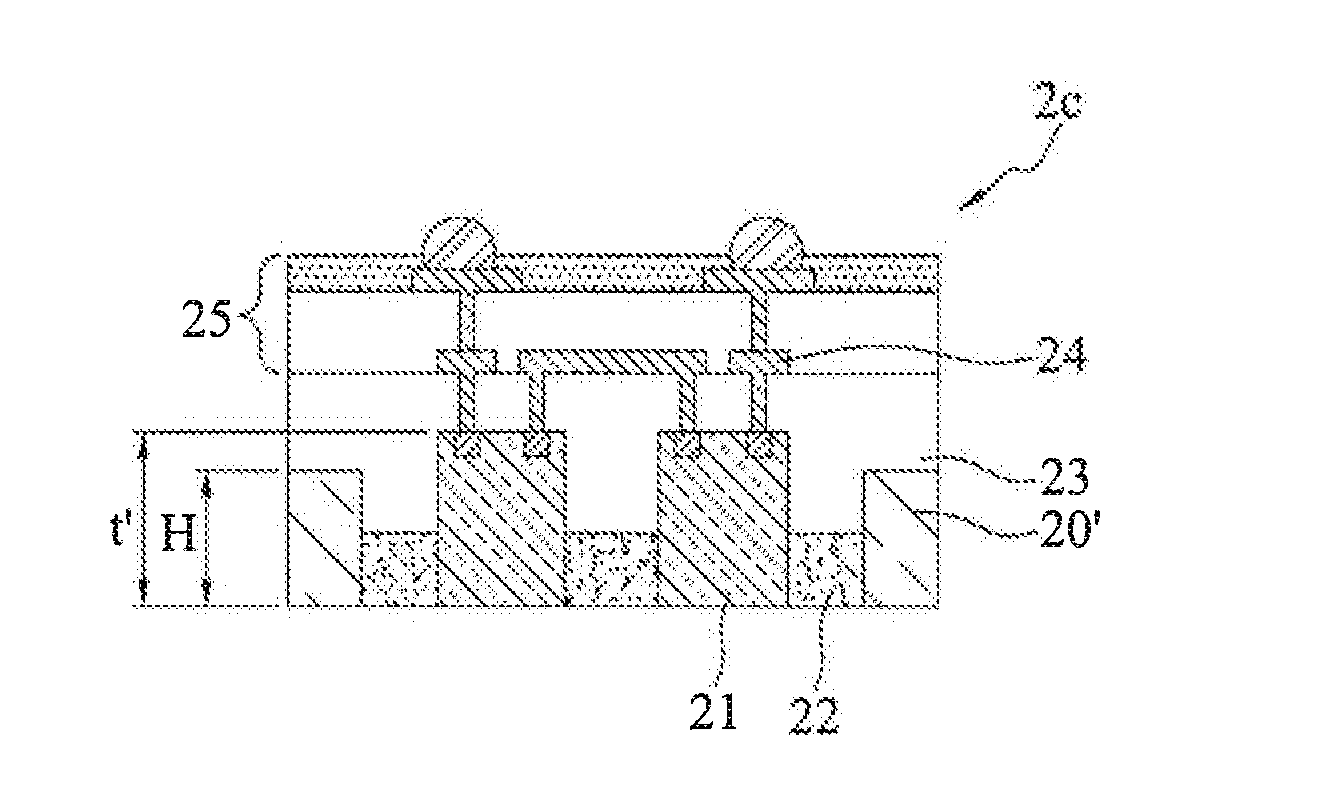

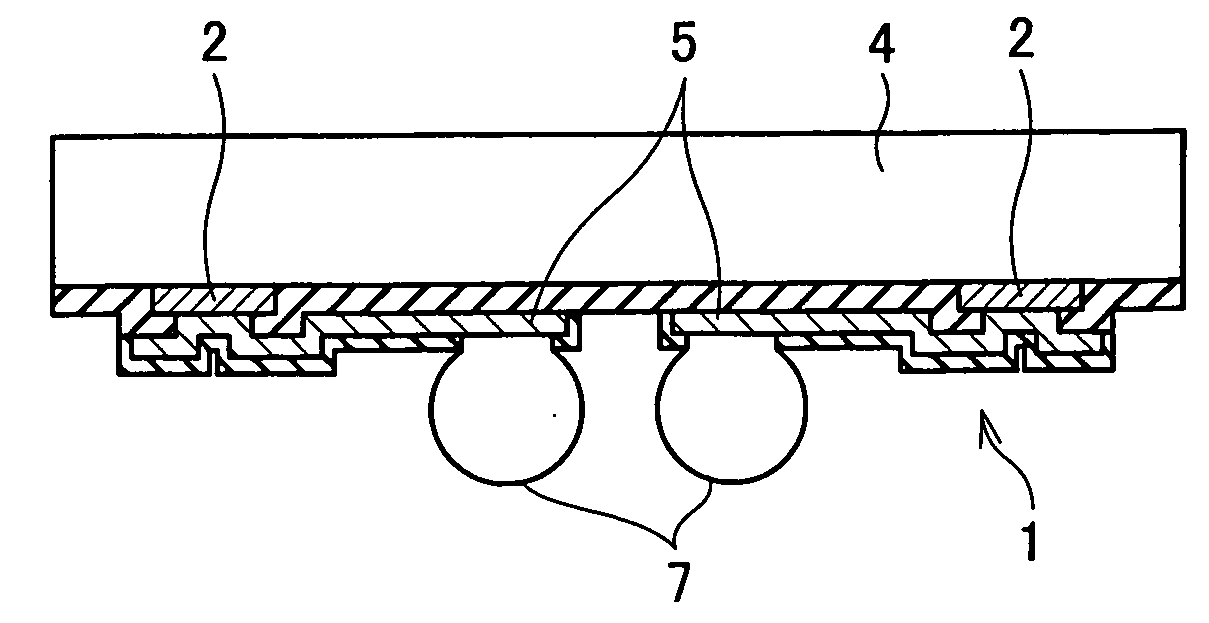

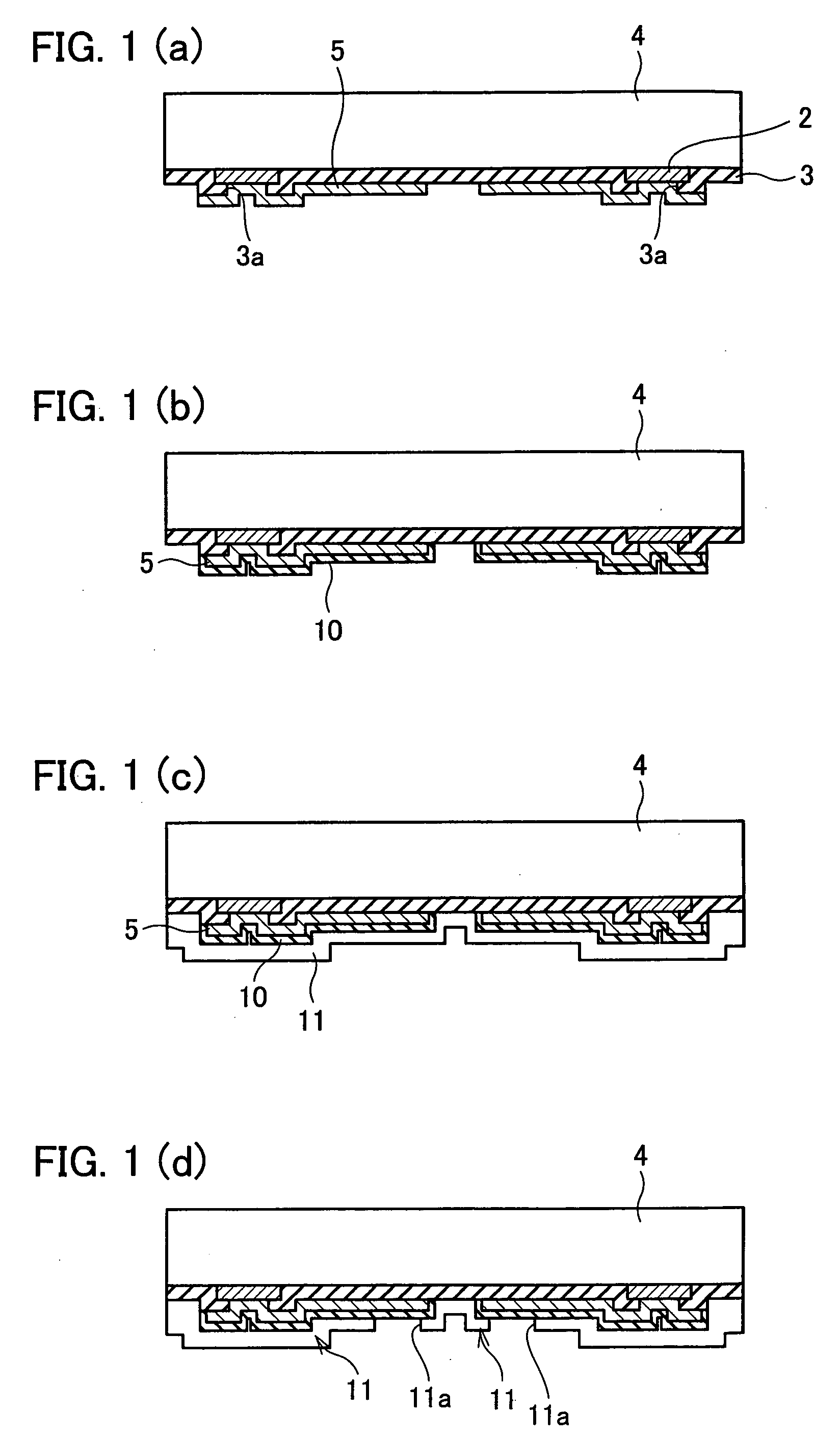

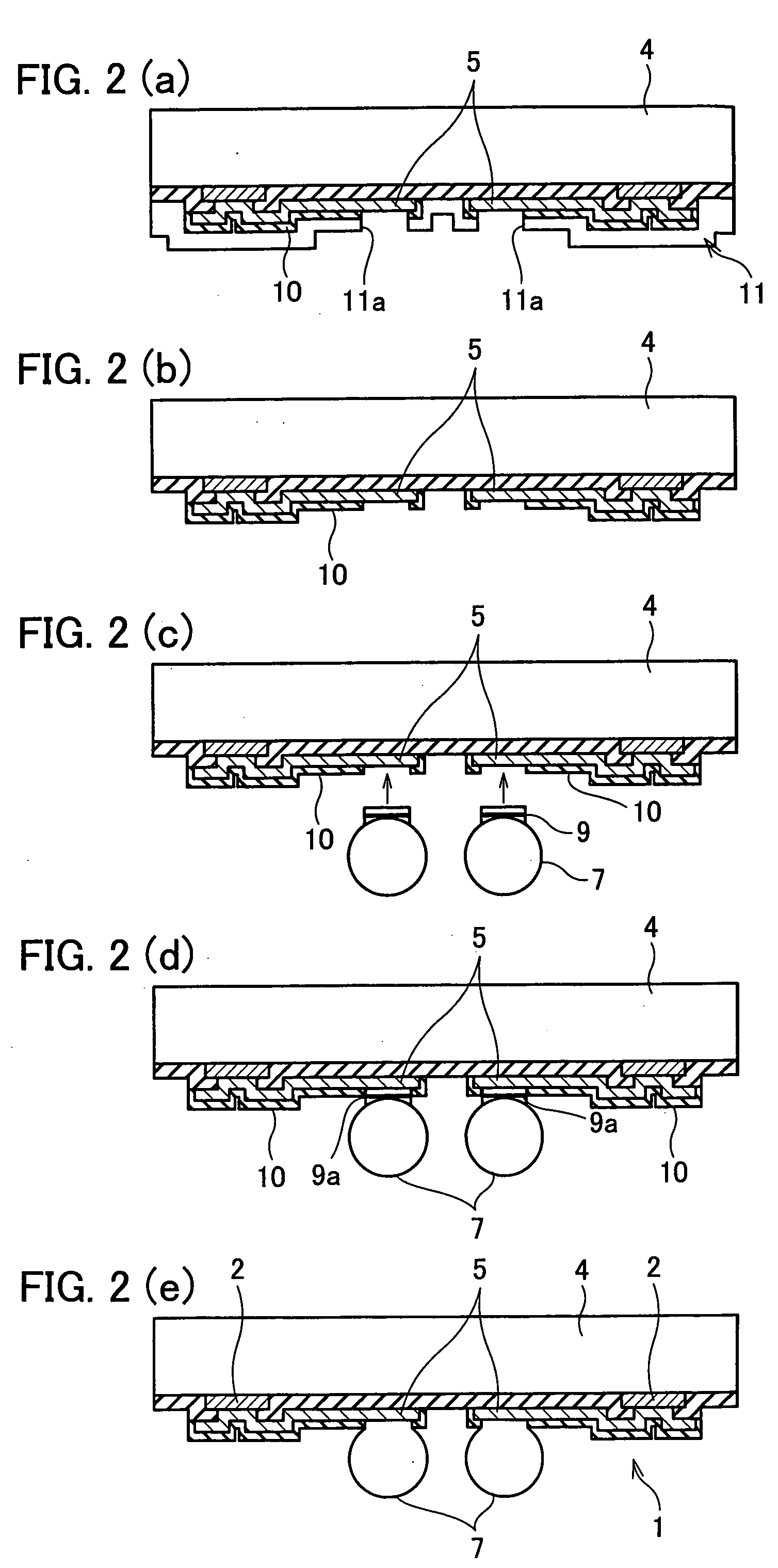

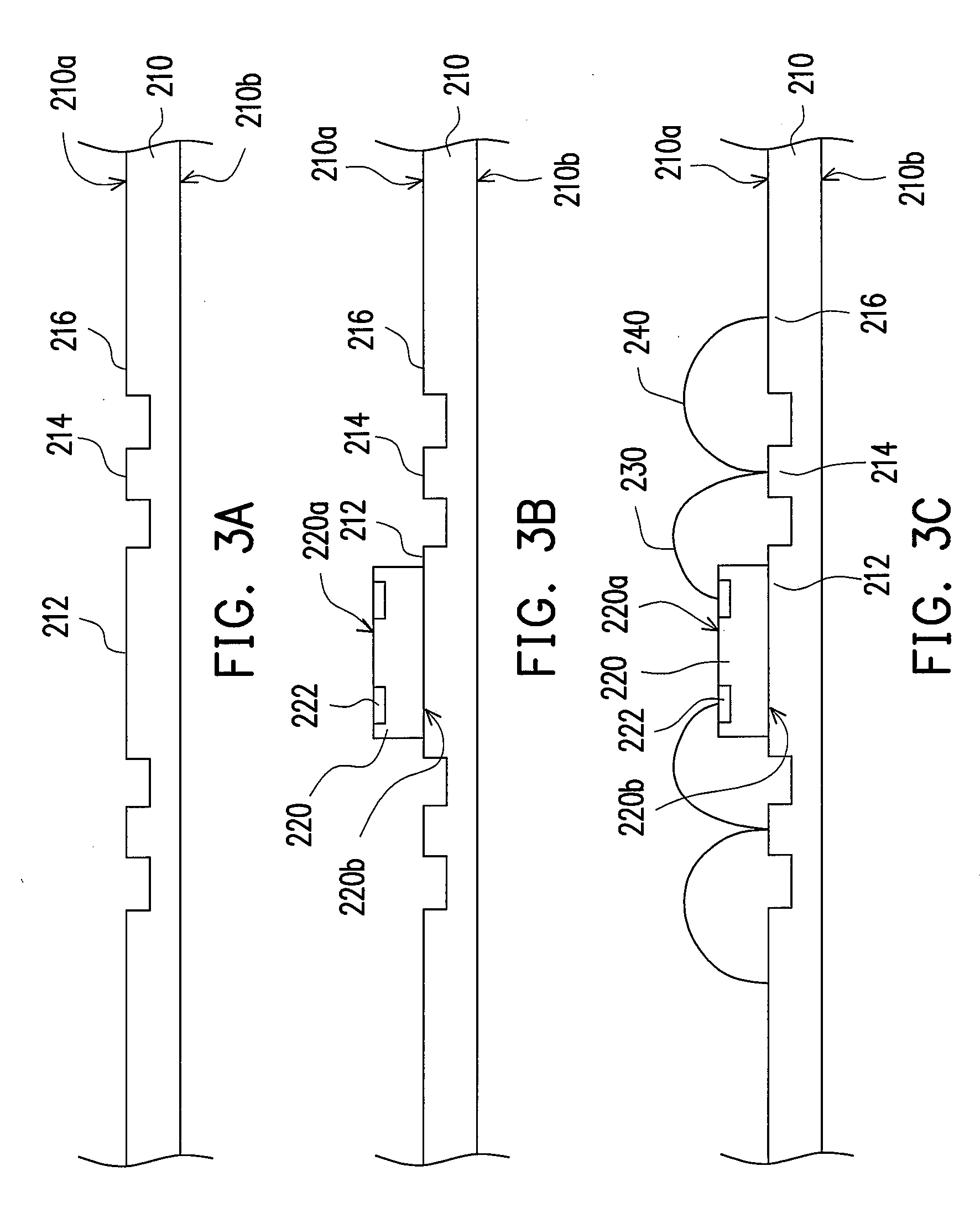

Chip scale package and fabrication method thereof

ActiveUS20120032347A1Avoid warpageReduce fabrication costSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionWaste product

A fabrication method of a chip scale package includes providing electronic components, each having an active surface with electrode pads and an opposite inactive surface, and a hard board with a soft layer disposed thereon; adhering the electronic components to the soft layer via the inactive surfaces thereof; pressing the electronic components such that the soft layer encapsulates the electronic components while exposing the active surfaces thereof; forming a dielectric layer on the active surfaces of the electronic components and the soft layer; and forming a first wiring layer on the dielectric layer and electrically connected to the electrode pads, thereby solving the conventional problems caused by directly attaching a chip on an adhesive film, such as film-softening, encapsulant overflow, warpage, chip deviation and contamination that lead to poor electrical connection between the electrode pads and the wiring layer formed in a subsequent RDL process and even waste product.

Owner:SILICONWARE PRECISION IND CO LTD

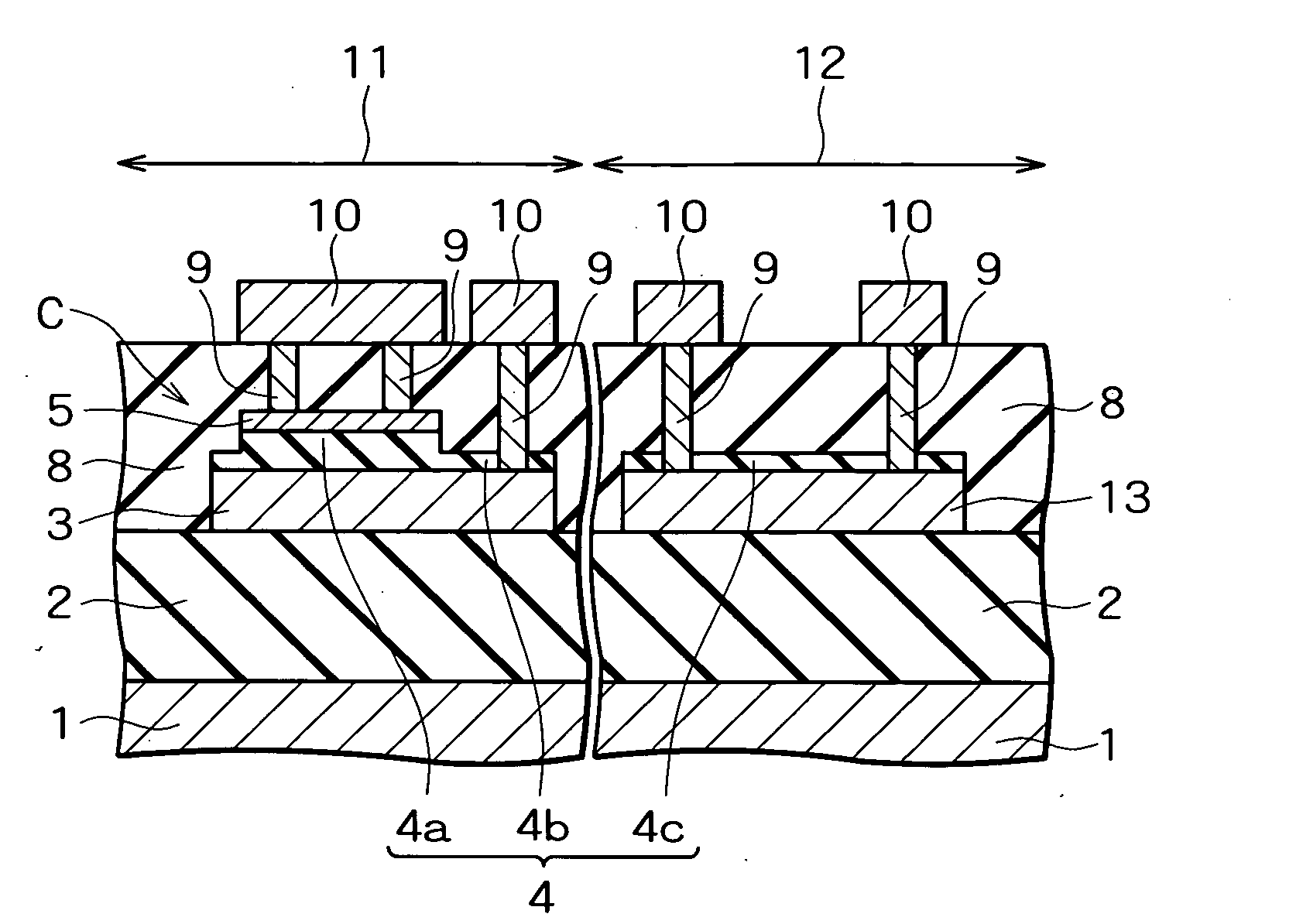

Semiconductor device and fabrication method thereof

ActiveUS20050139956A1Reduce fabrication costPrevent conductionSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor

On a silicon substrate, a first insulation layer, a lower conductive layer, a capacitor-insulator layer, and an upper conductive layer are formed in that order. Then, a first resist pattern is formed, the upper conductive layer is etched to form an upper electrode, and the capacitor-insulator layer is successively etched partway under the same etching condition as that of the upper conductive layer. Next, second resist pattern is formed, the remaining part of the capacitor-insulator layer is etched to form a second insulation layer, and the lower conductive layer is successively etched under the same etching condition as that of the capacitor-insulator layer so as to form a lower electrode and a lower wiring. In this manner, an MiM capacitor element constituted by the upper electrode, a part of the second insulation layer, and the lower electrode can be fabricated.

Owner:RENESAS ELECTRONICS CORP

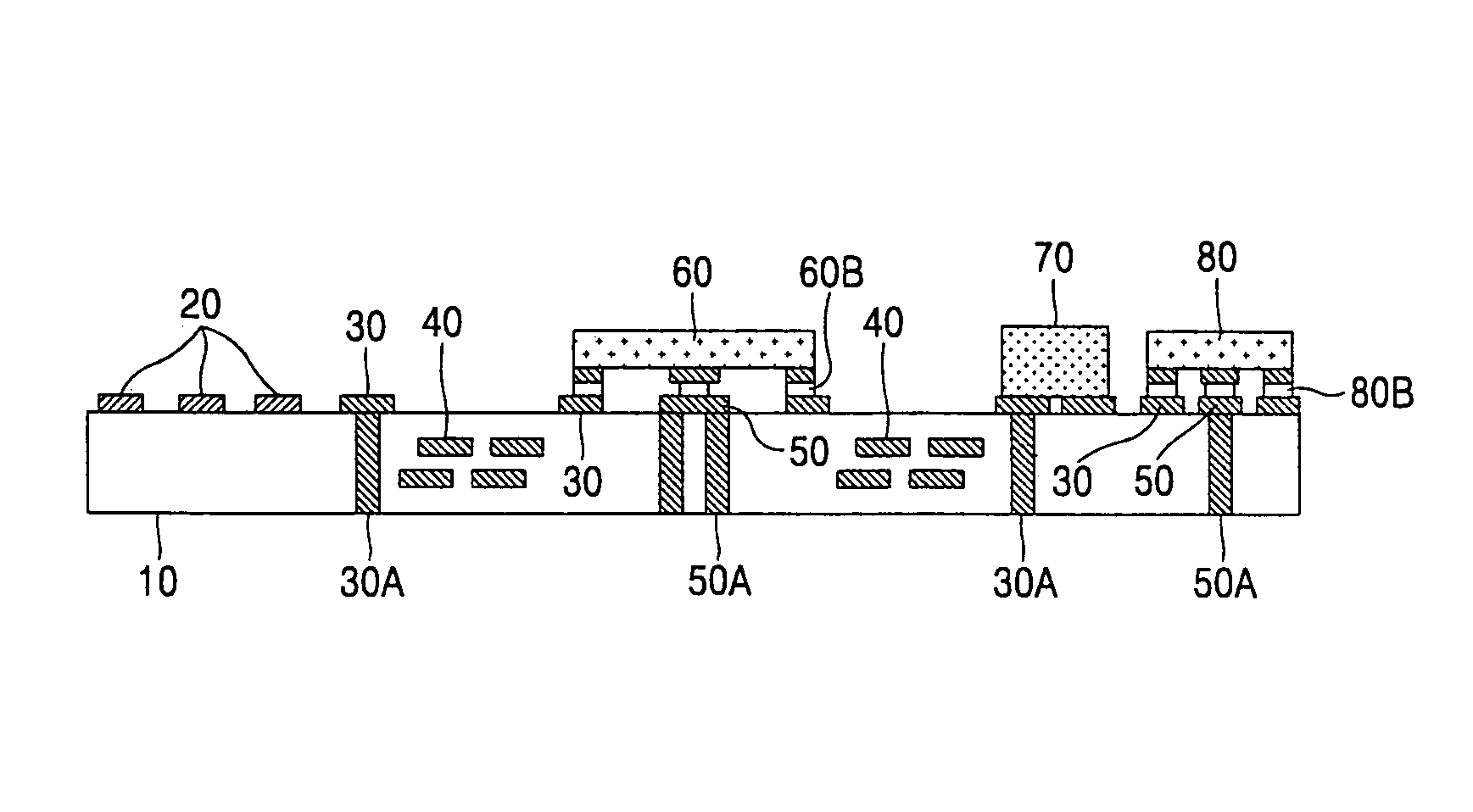

Active smart antenna system and fabrication method thereof

InactiveUS7365683B2Reduce fabrication costHigh resistanceAntenna arraysSimultaneous aerial operationsSmart antennaEngineering

Disclosed are an active smart antenna system and a method thereof. The system comprises: an antenna for receiving a signal; a low noise amplifier for amplifying a signal received through the antenna so as to minimize a noise generation; and a phase shifter for controlling a phase of the amplified signal. The antenna, the low noise amplifier, and the phase shifter are formed on one high resistance substrate.

Owner:LG ELECTRONICS INC

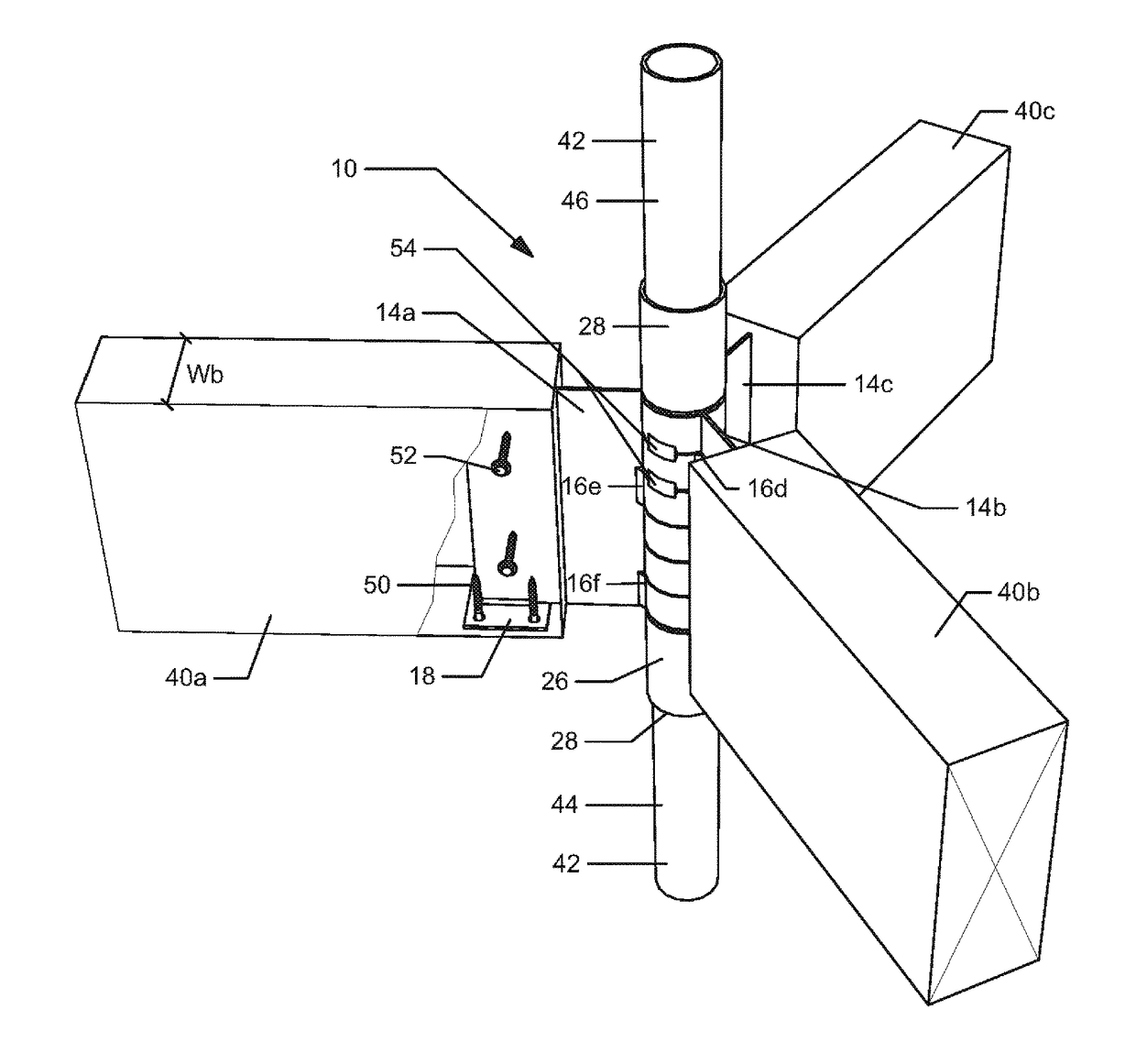

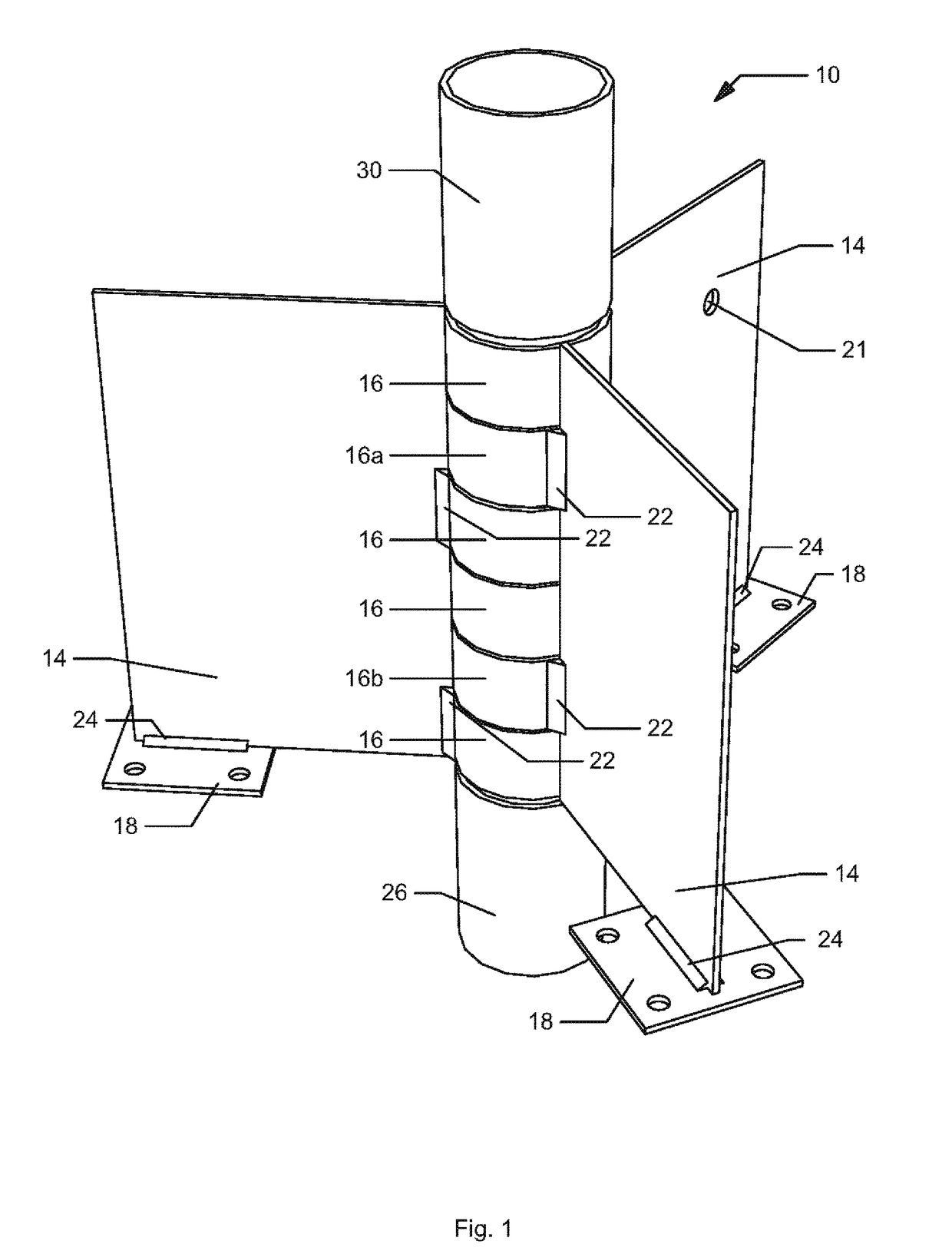

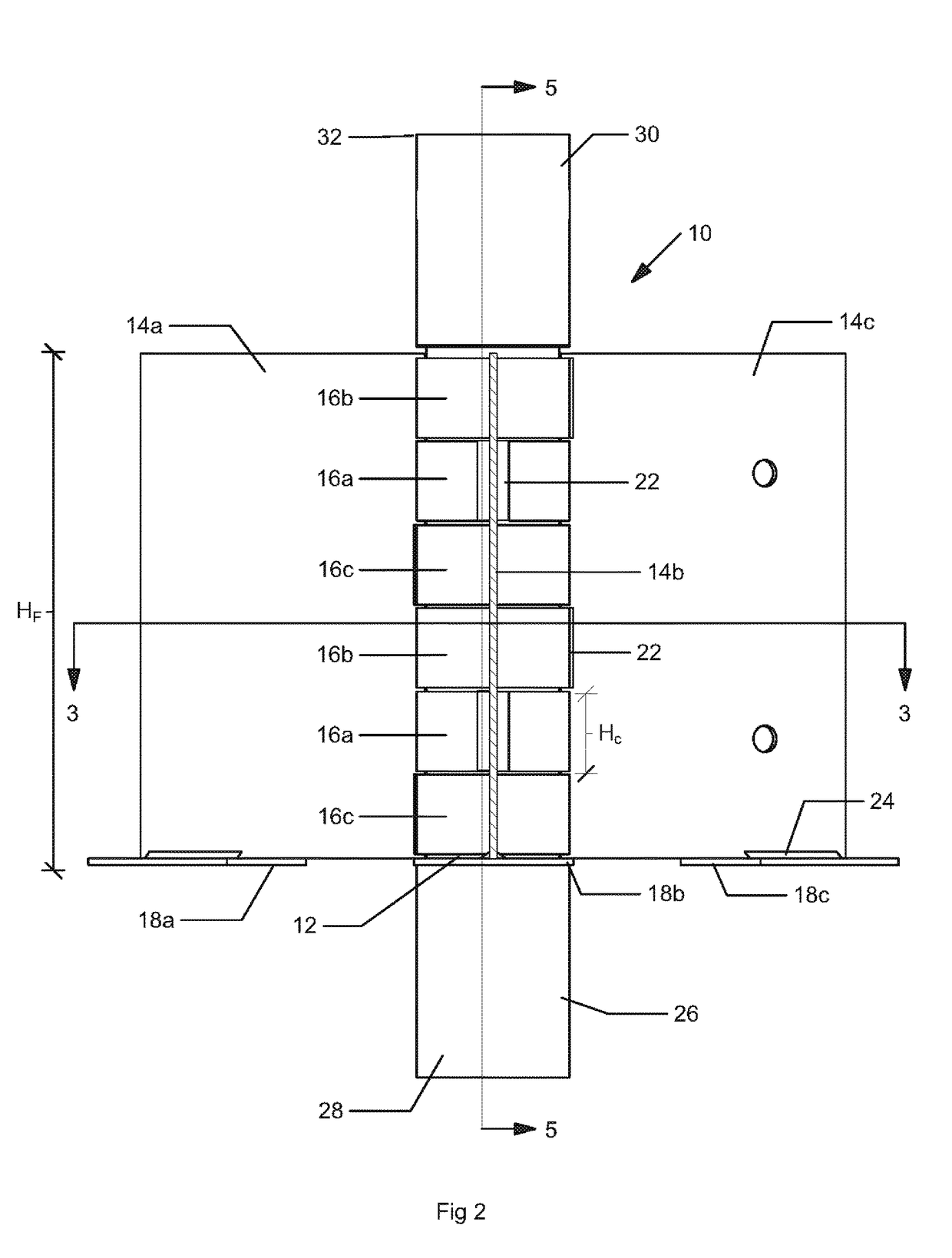

Building frame connector and method of use

InactiveUS20170130444A1Reduce errorReduce fabrication costBuilding constructionsEngineeringMechanical engineering

A building frame connector for connecting beams to columns to create a building frame. The building frame connector includes a pin member and plurality of fins mounted on said pin member for rotation relative to said pin. The pin may be in alignment with the column, and the fins allow connection of the beams to the columns The fins may be disposed to rotate relative to said pin member about a longitudinal axis of the pin. In one embodiment the pin member may have an outer diameter and the fins have a collar with an inner diameter is greater than said outer diameter of said pin allowing for the collars to rotate about the pin member. The present building frame connector may also include at least one coupling member coupled to the pin member, wherein the coupling member facilitates the connection of the building frame connector to a building column.

Owner:CARBON DEV SERVICES LLC

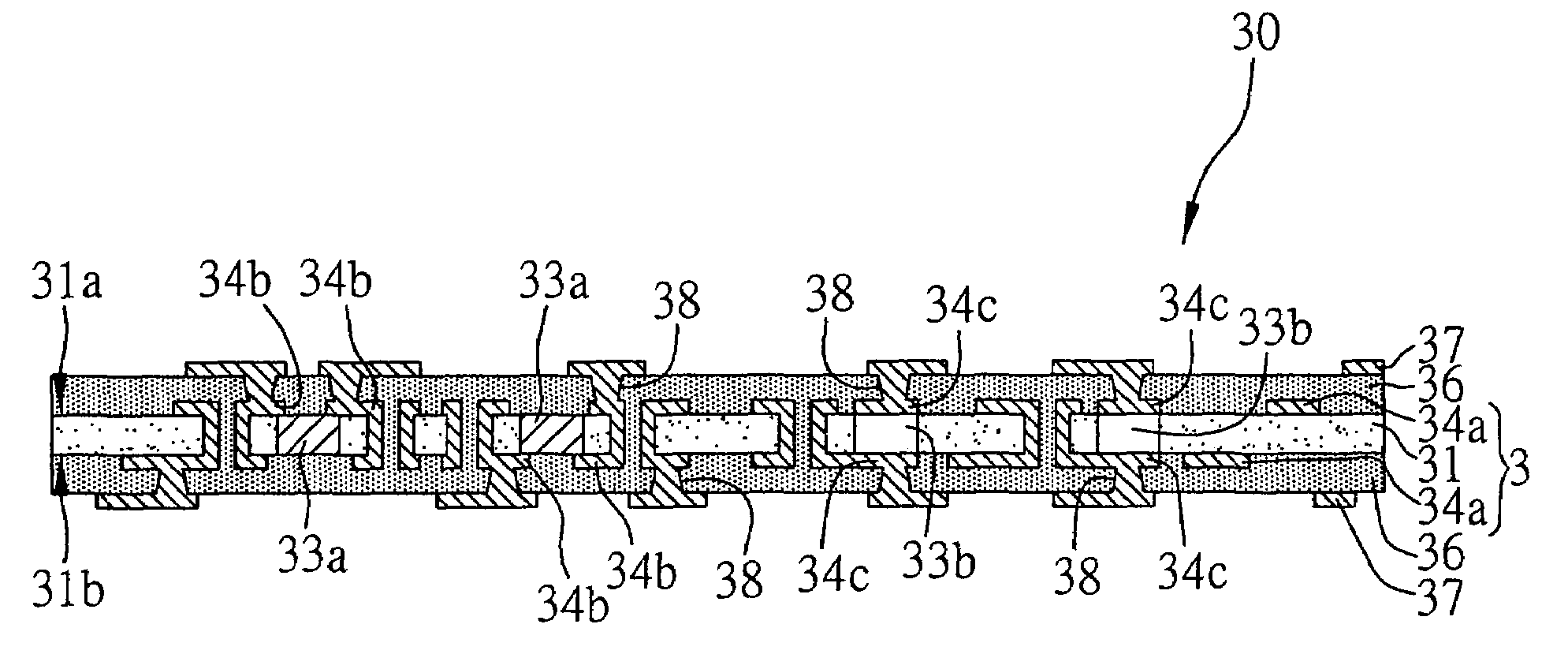

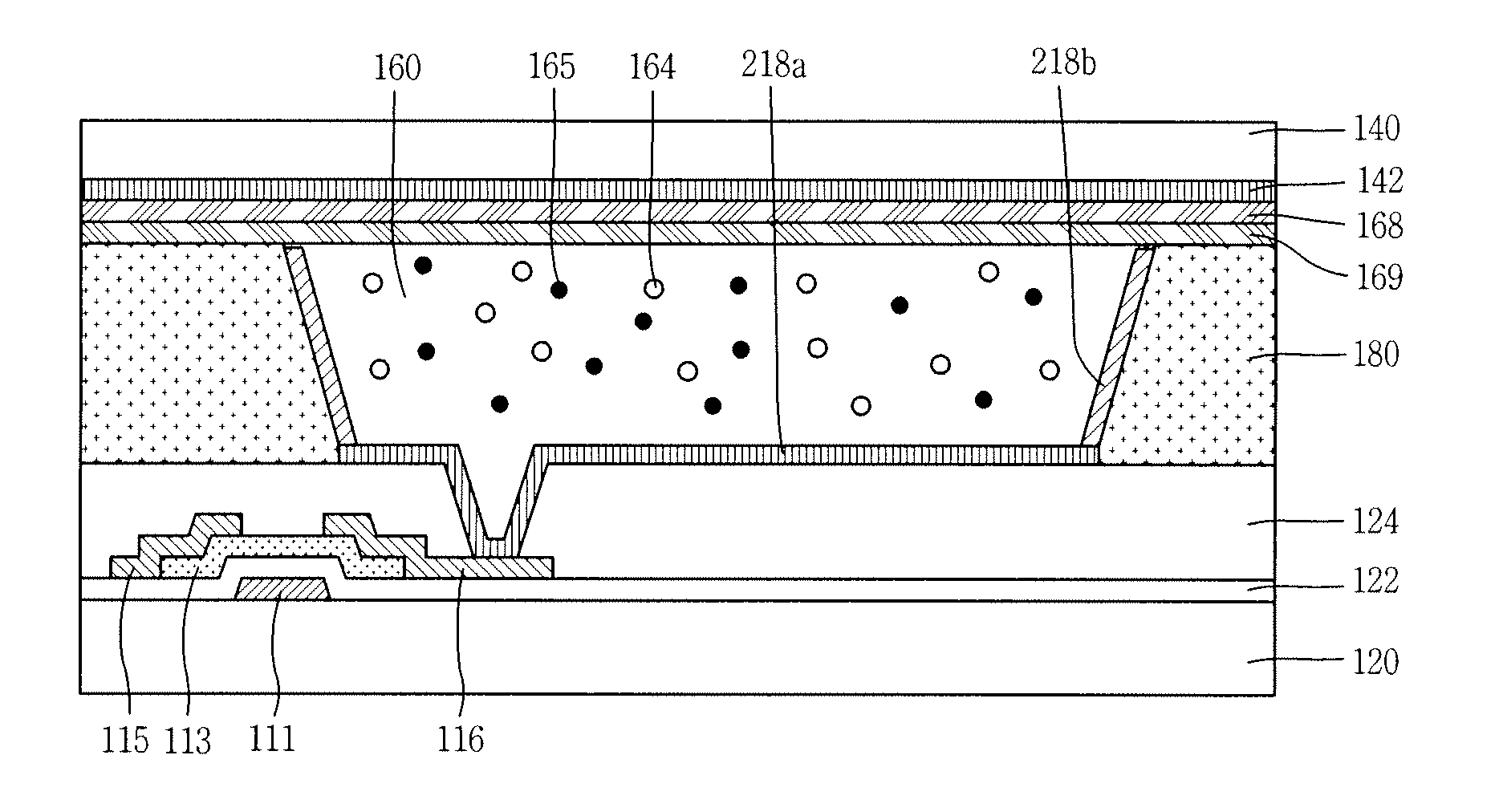

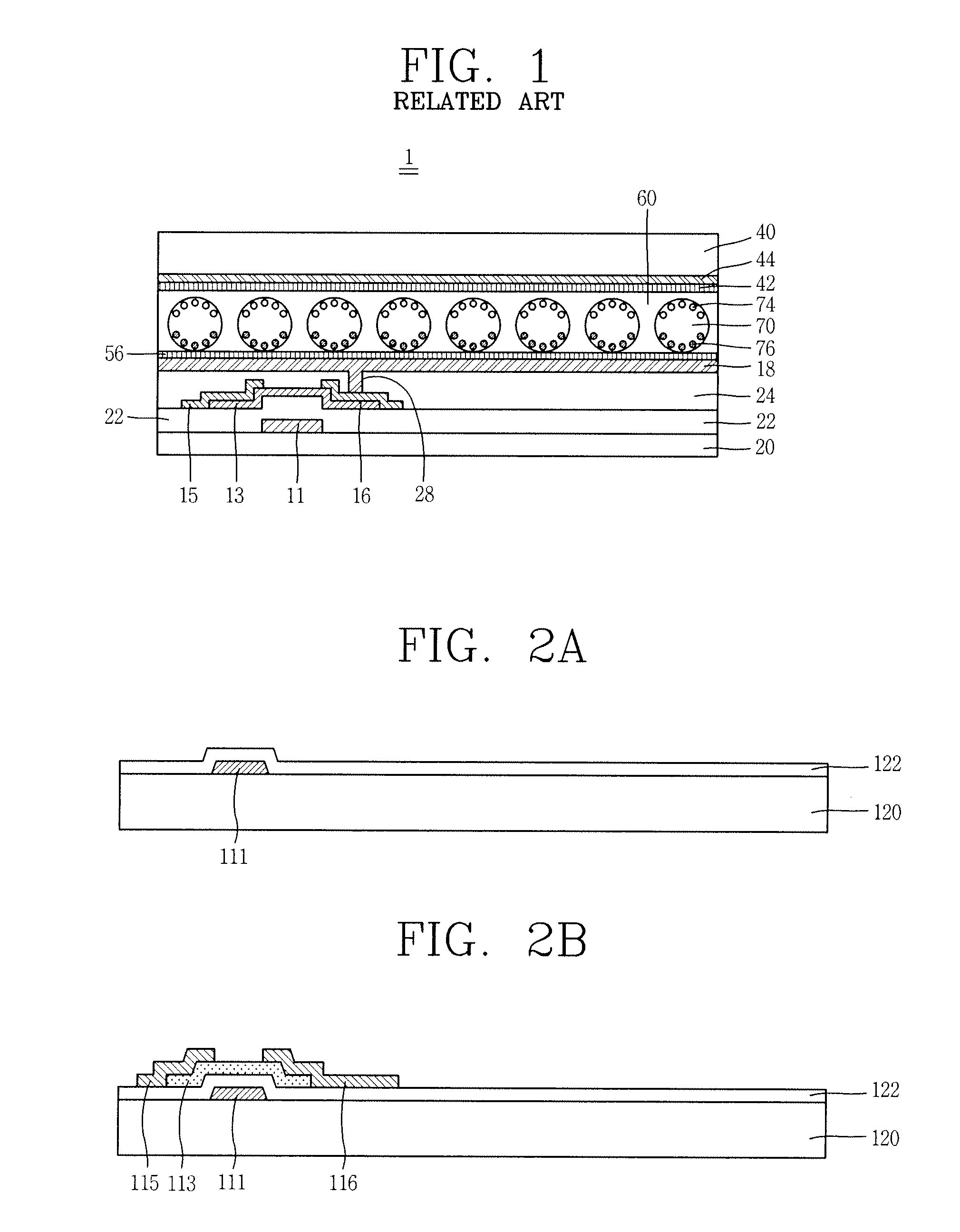

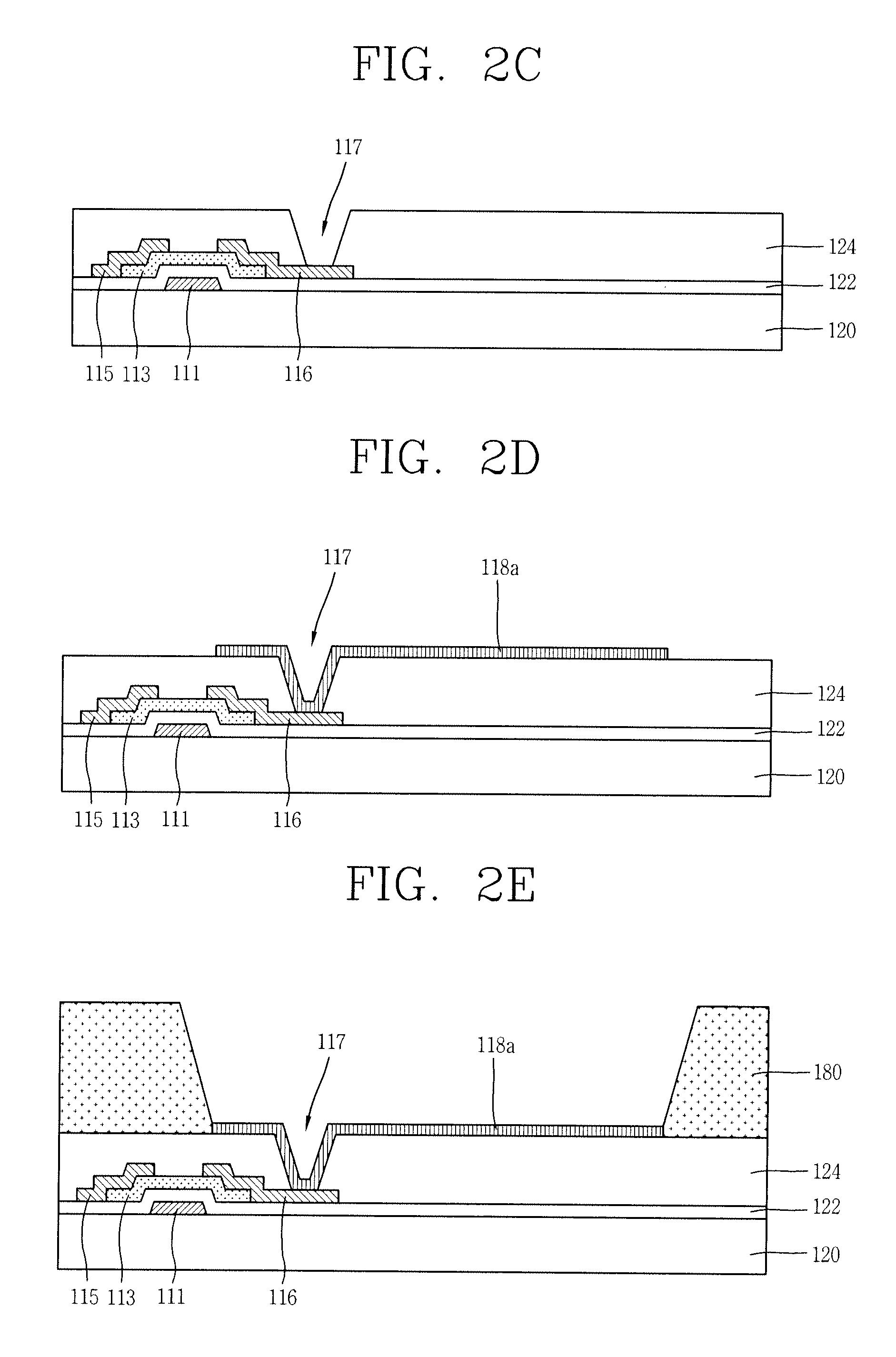

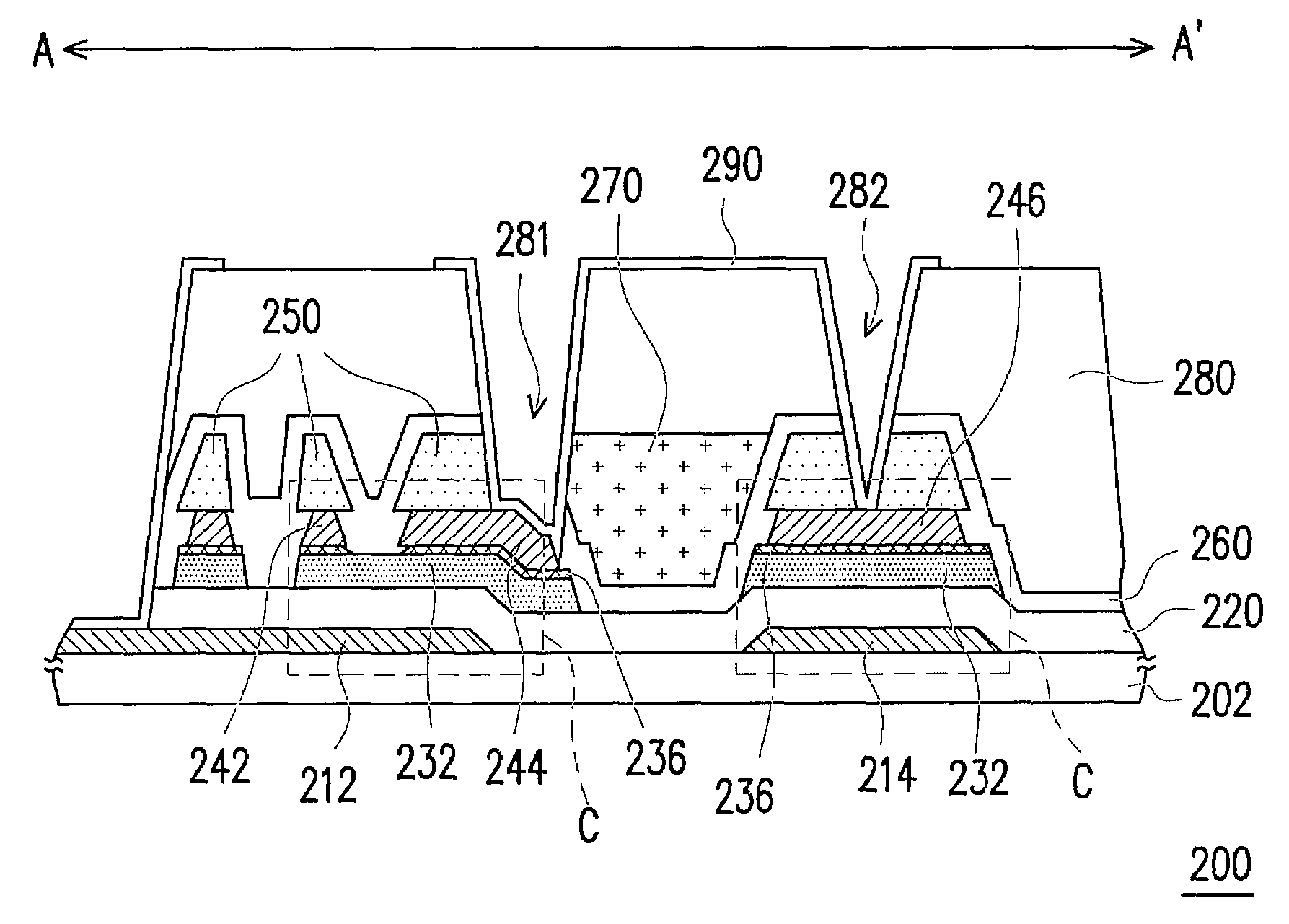

Electrophoretic display device and method of fabrication thereof

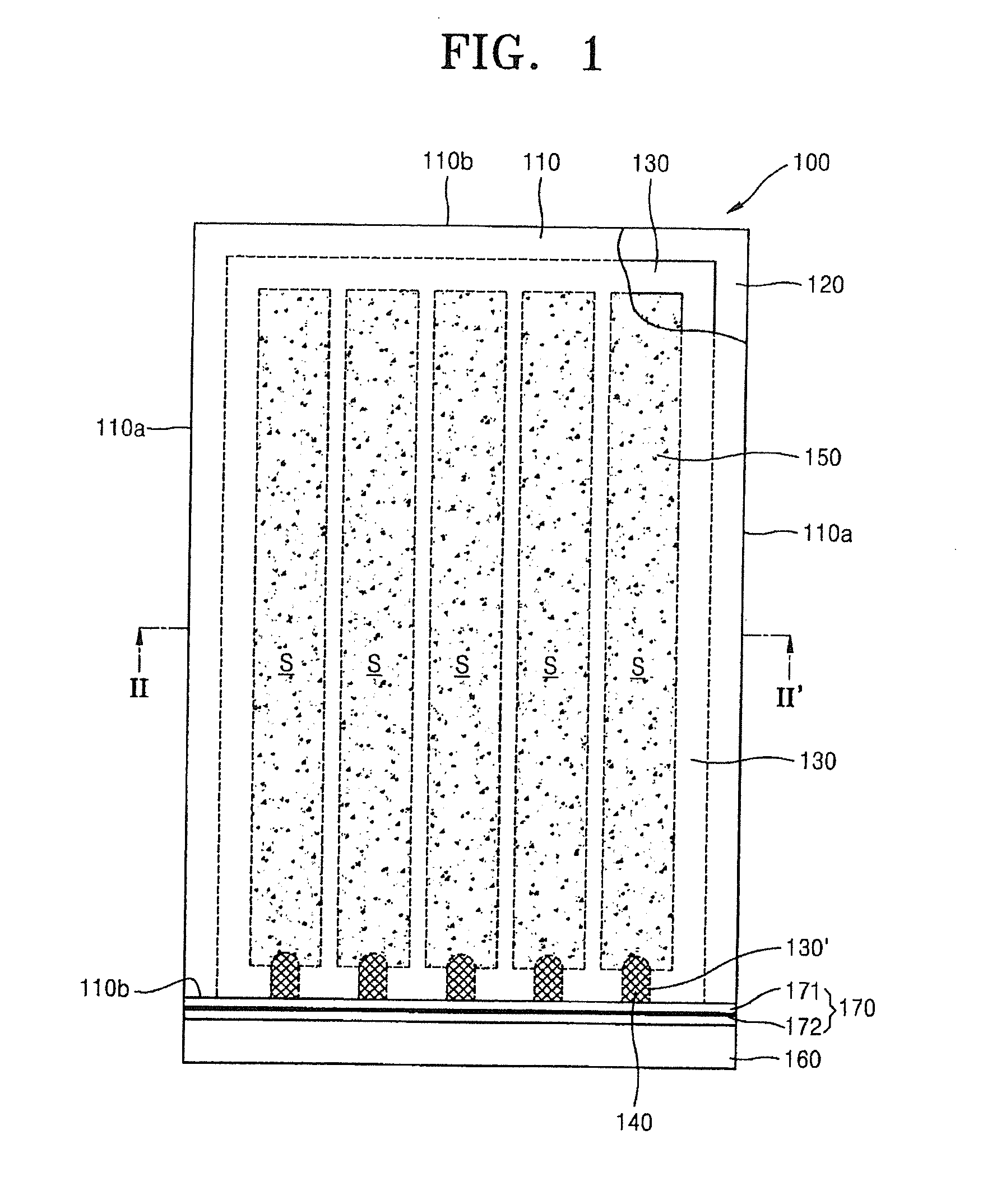

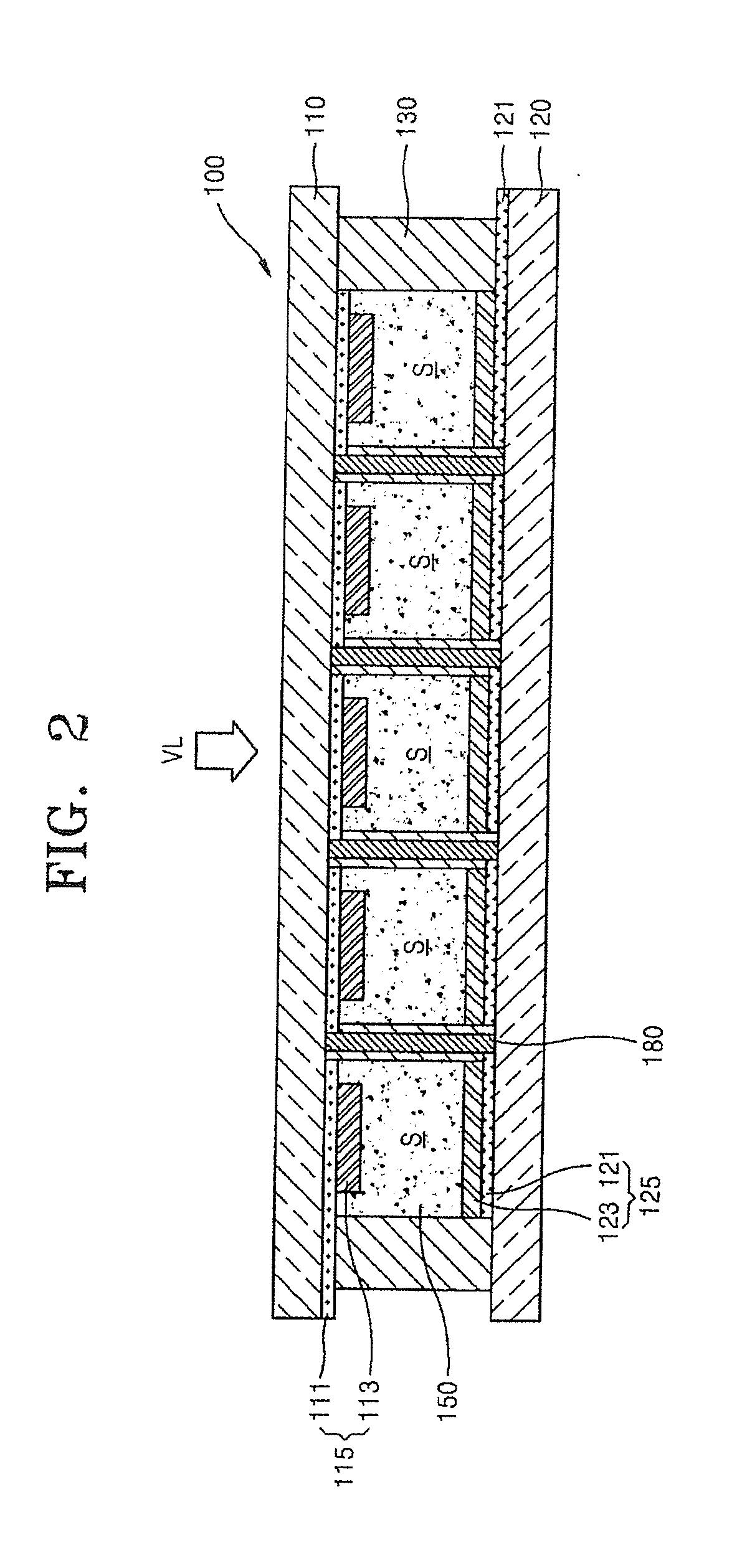

ActiveUS20120008191A1Reduce fabrication costSimplify fabrication processSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringImaging quality

Disclosed is an electrophoretic display (EPD) device and fabrication method thereof that has a simplified fabrication process and reduced fabrication costs. In the EPD device, a partition wall is formed directly on a first substrate having a pixel electrode and extended up a lateral surface of the partition wall to prevent dead areas in the pixel region, provide increased aperture ratio, and enhanced image quality.

Owner:LG DISPLAY CO LTD

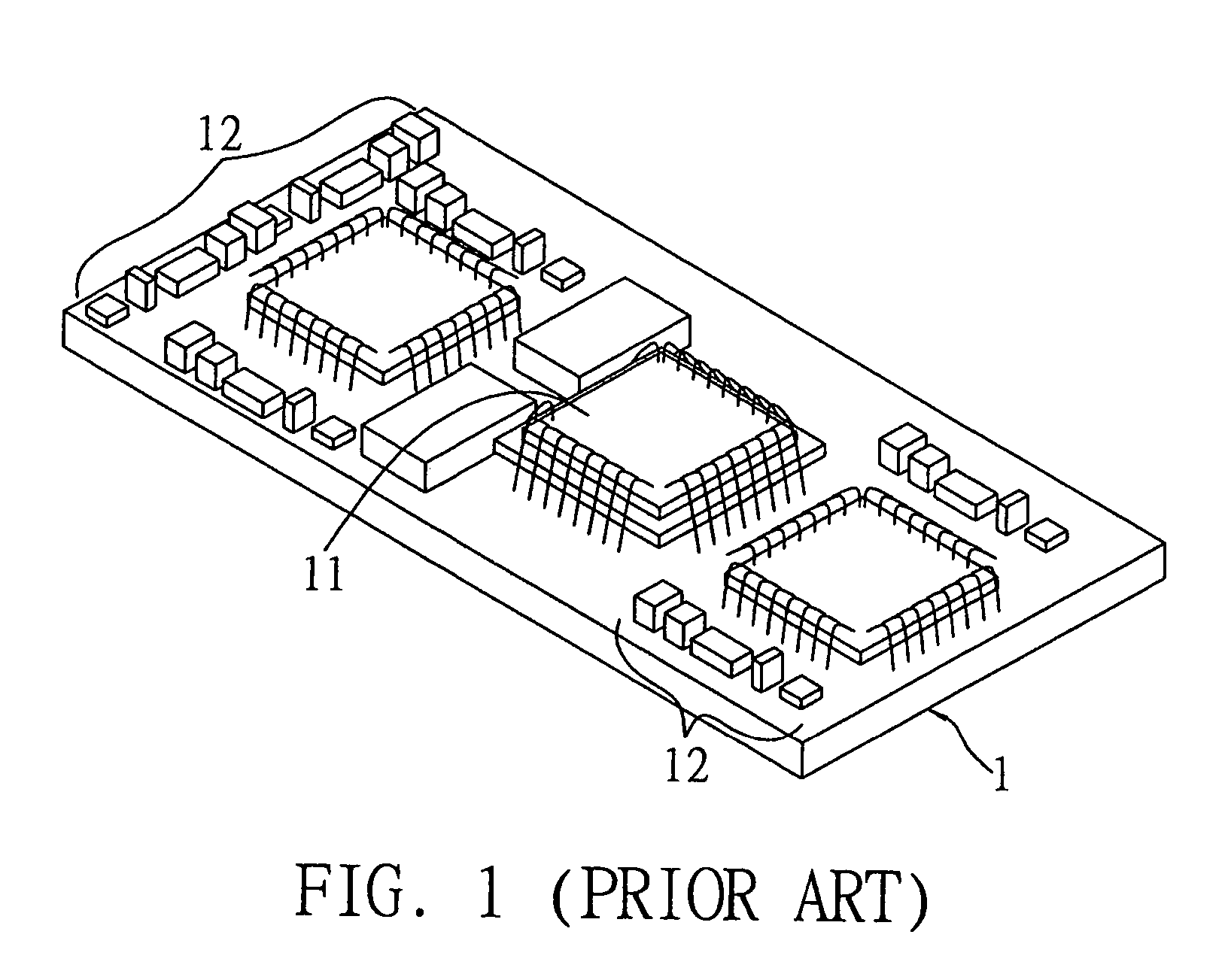

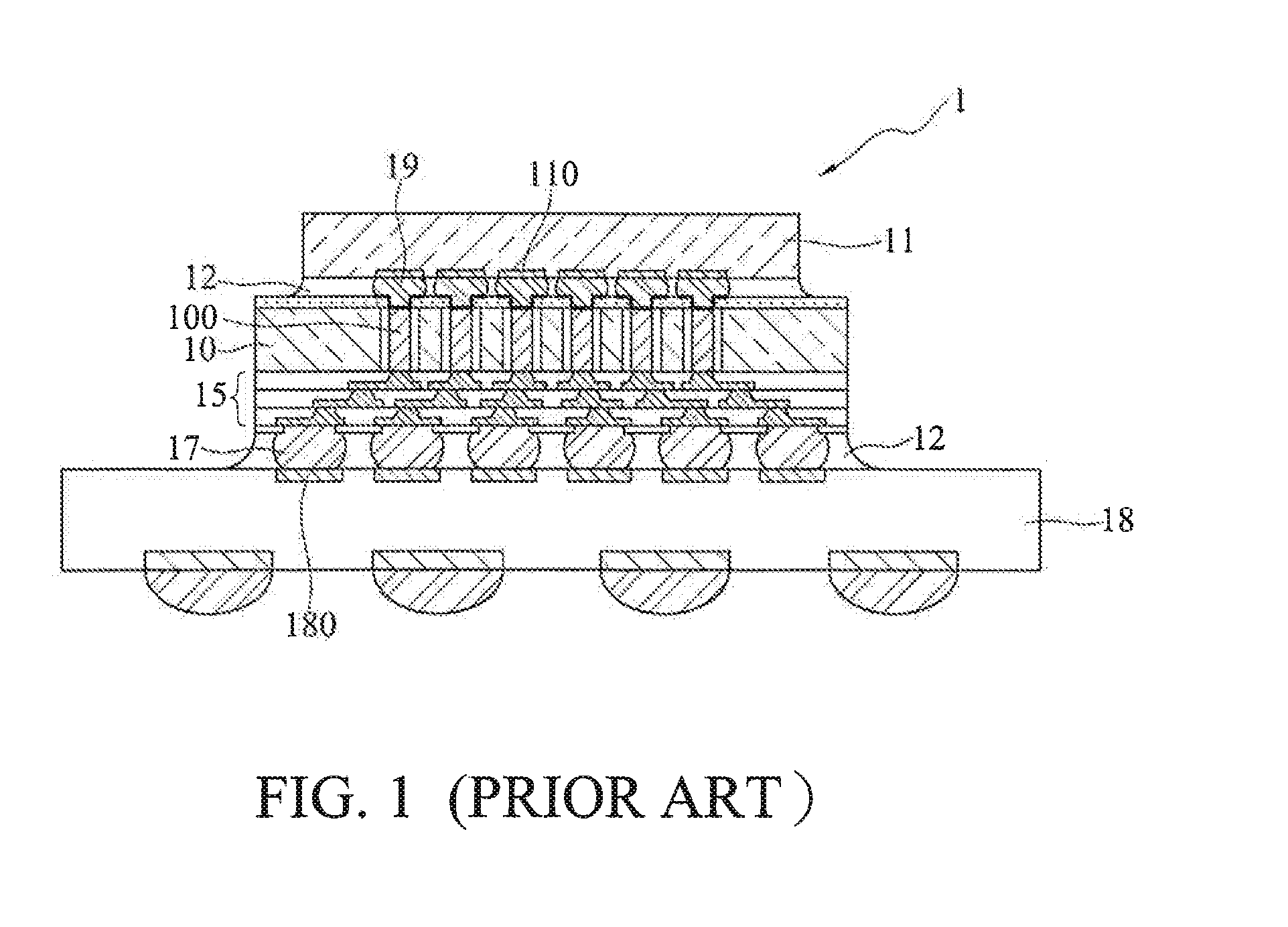

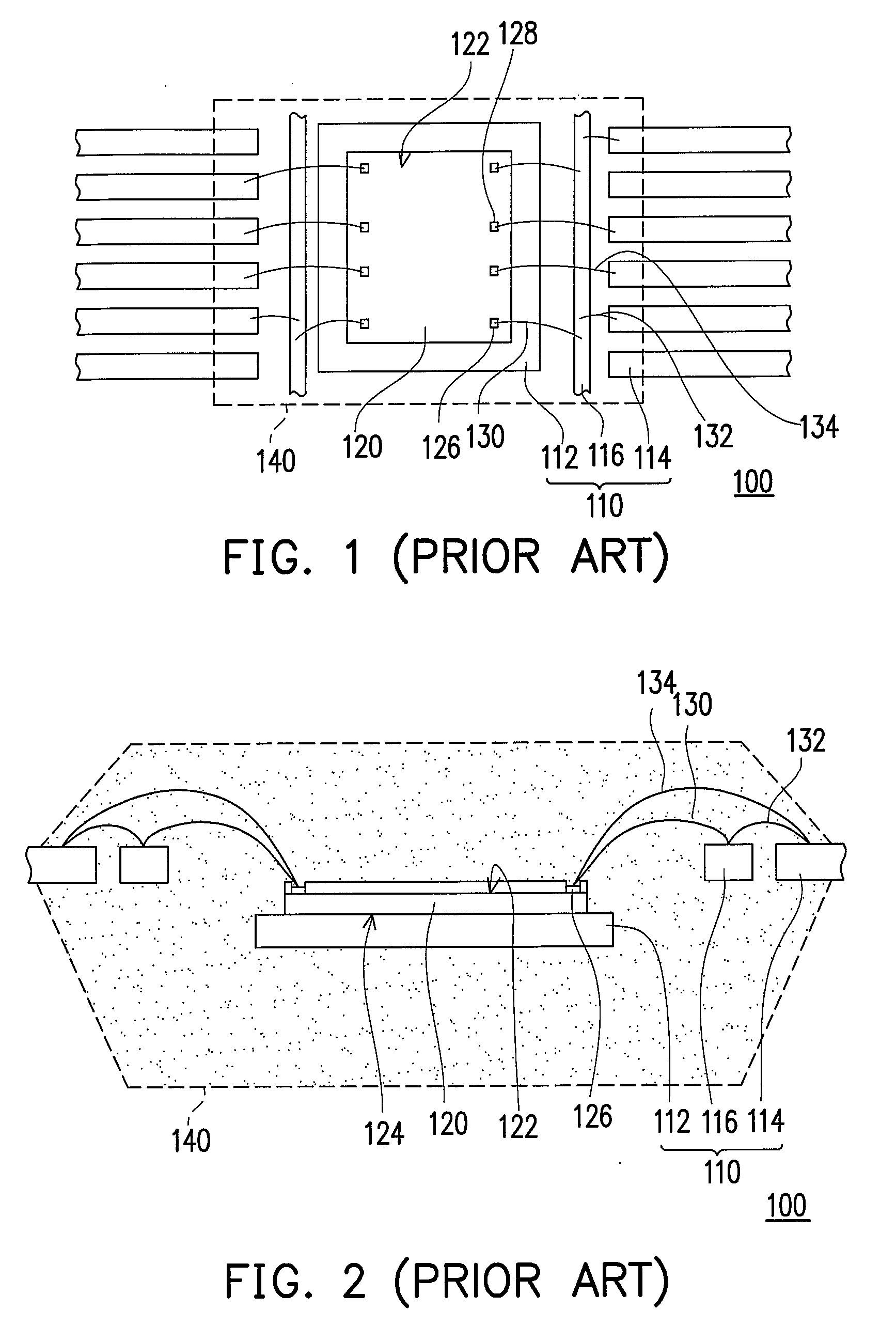

Semiconductor package and method of fabricating the same

InactiveUS20150035164A1Reduce fabrication costSimplify fabrication processSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor components

The present invention provides a semiconductor package and a method of fabricating the same, including: placing in a groove of a carrier a semiconductor element having opposing active and non-active surfaces, and side surfaces abutting the active surface and the non-active surface; applying an adhesive material in the groove and around a periphery of the side surfaces of the semiconductor element; forming a dielectric layer on the adhesive material and the active surface of the semiconductor element; forming on the dielectric layer a circuit layer electrically connected to the semiconductor element; and removing a first portion of the carrier below the groove to keep a second portion of the carrier on a side wall of the groove intact for the second portion to function as a supporting member. The present invention does not require formation of a silicon interposer, and therefore the overall cost of a final product is much reduced.

Owner:SILICONWARE PRECISION IND CO LTD

Semiconductor package for memory chips

InactiveUS6963135B2Enhance performance and memory capacityReduce fabrication costSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

A semiconductor package includes two substrates each having a plurality of electrical connection pads, at least one chip mounted on each of the substrates, an encapsulation body formed on each of the substrates for encapsulating the chip, and an cover for receiving the substrates and the chips therein. The chip is electrically connected to the electrical connection pads. The electrical connection pads are exposed from the cover and located on the same surface or oppositely arranged. The substrates and the cover each substantially has a rectangular shape, with a longer side of each of the substrates being vertical to a longer side of the cover. The semiconductor package is incorporated with multiple chips to enhance the performance and memory capacity thereof, and the substrates are smaller than those in the prior art and thus are more cost-effective to fabricate.

Owner:SILICONWARE PRECISION IND CO LTD

Display panel

ActiveUS20130044046A1Reduce fabrication costImprove reliabilityStatic indicating devicesSolid-state devicesPhysicsComposite material

A display panel includes a substrate, a TFT device, a patterned dielectric layer, a patterned metal layer and a bridge line. The TFT device is disposed in a display region. The patterned dielectric layer includes an ILD layer disposed over the TFT device, and a sealant stage disposed in a peripheral region. The patterned metal layer includes a signal line disposed on the ILD layer, and a first connecting line and a second connecting line. The first connecting line is disposed in an inner side of the sealant stage facing the display region, and the first connecting line is electrically connected to the signal line. The second connecting line is disposed in an outer side of the sealant stage opposite to the display region. The bridge line is disposed under the sealant stage, and the first connecting line and the second connecting line are electrically connected through the bridge line.

Owner:AU OPTRONICS CORP

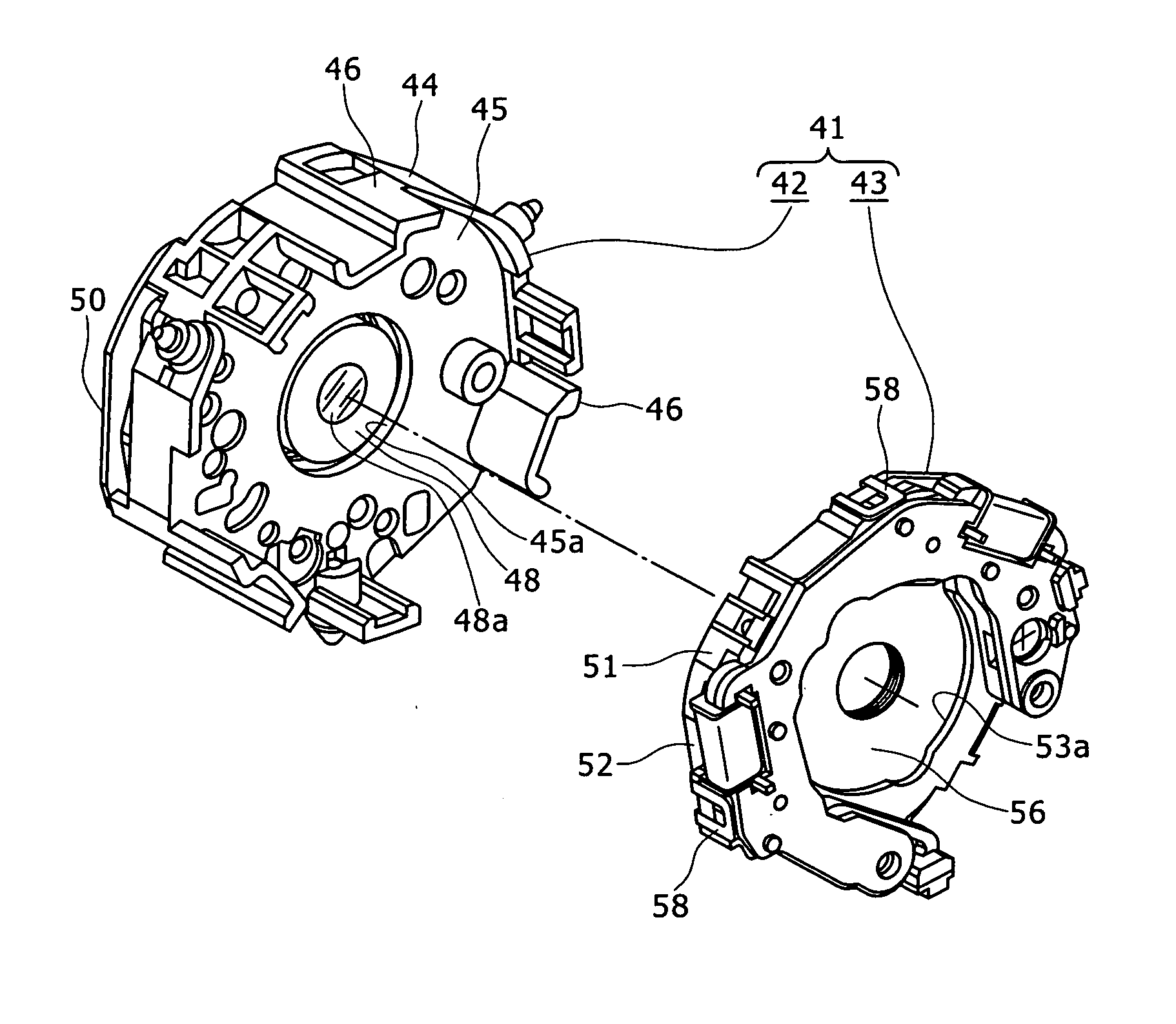

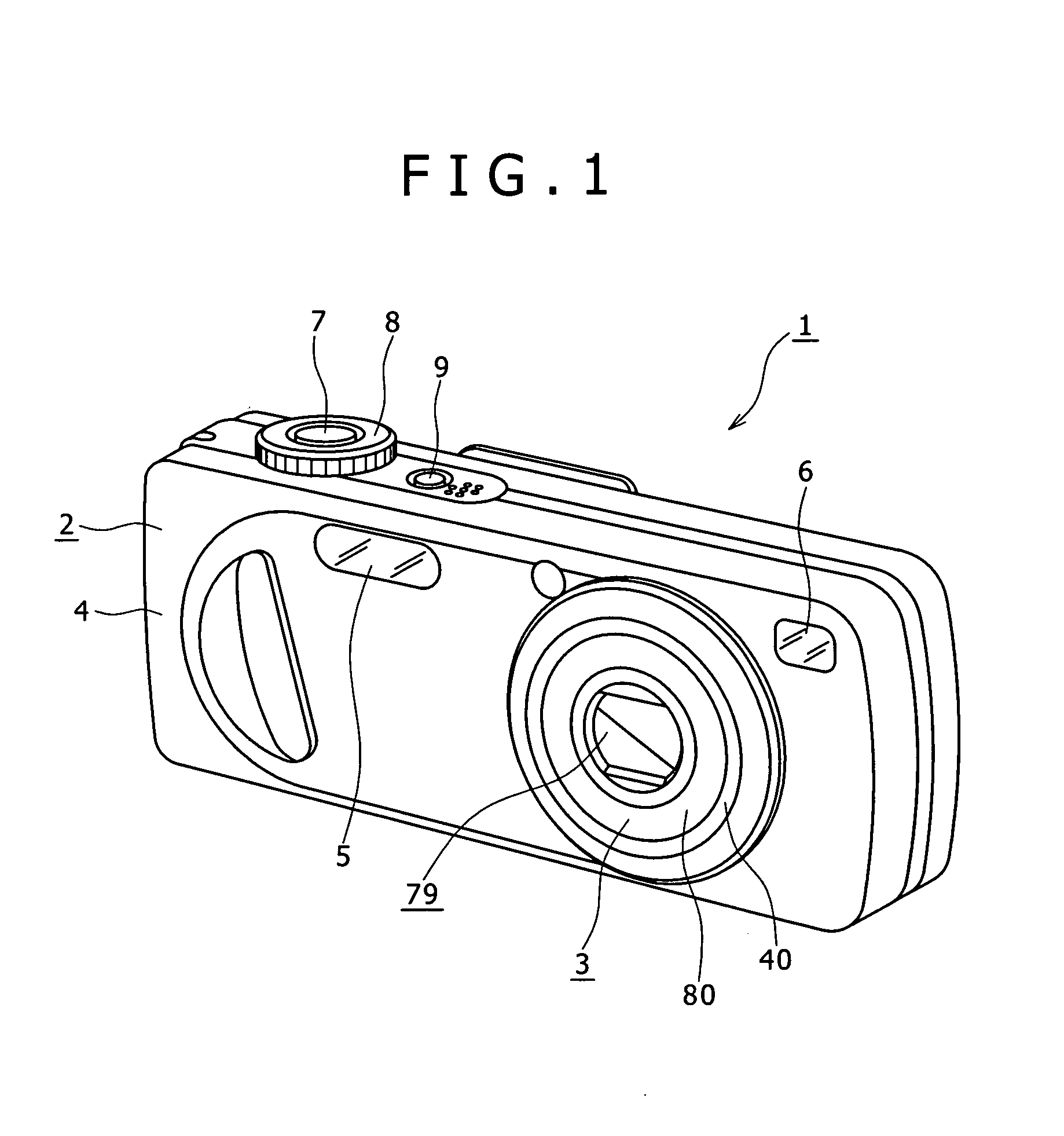

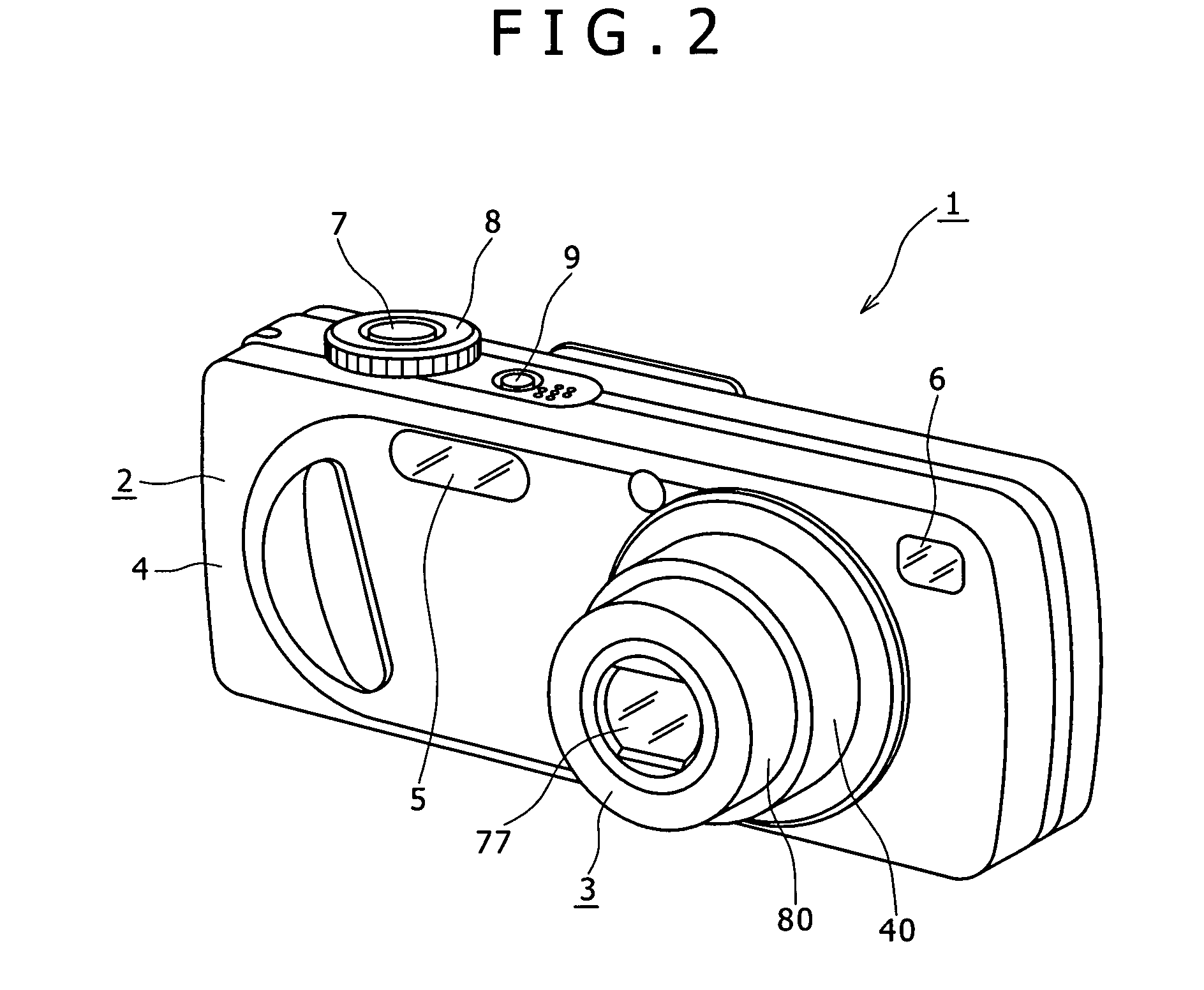

Light amount adjustment apparatus and image pickup apparatus

InactiveUS20080175584A1Improve assemblabilityReduce fabrication costShuttersMechanical energy handlingEmbedded systemMagnet

Disclosed herein is a light amount adjustment apparatus, including: a shutter blade and a filter blade each configured to operate in a predetermined direction to adjust the amount of light transmitted through a lens group; a first magnet configured to drive the shutter blade; a first core and a first coil; a second magnet configured to drive the filter blade; and a second core and a second coil. The filter blade has a control portion for controlling and adjusts the amount of light transmitted through the lens group. The filter blade has at least one hole or one cutaway portion formed at a portion of the filter blade other than the control portion.

Owner:SONY CORP

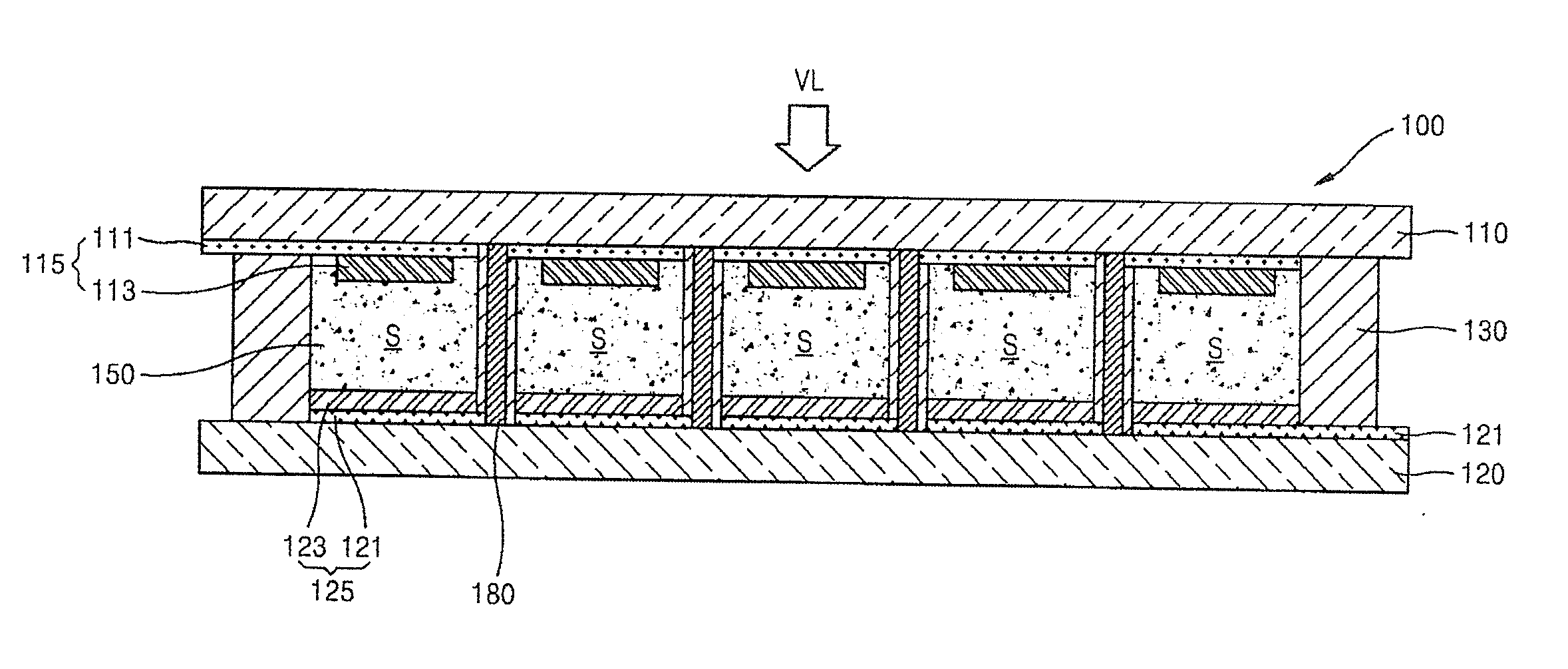

Photoelectric conversion module

InactiveUS20110174352A1Reduce fabrication costSimplifying fabrication processElectrolytic capacitorsPV power plantsElectrolyteMechanical engineering

A photoelectric conversion module including a first substrate; a second substrate spaced apart from the first substrate in a first direction; a plurality of photoelectric cells between the first and second substrates, each including an electrolyte; and a sealing member between the first and second substrates, the sealing member surrounding the plurality of photoelectric cells and extending between adjacent photoelectric cells of the plurality of photoelectric cells, wherein the sealing member has at least one electrolyte injecting portion for receiving the electrolyte into the photoelectric cells.

Owner:SAMSUNG SDI CO LTD

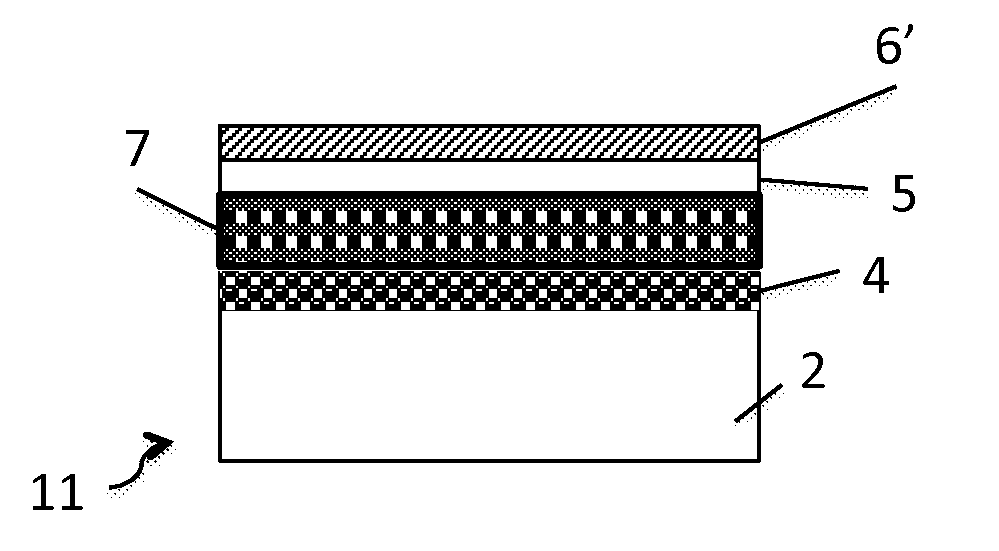

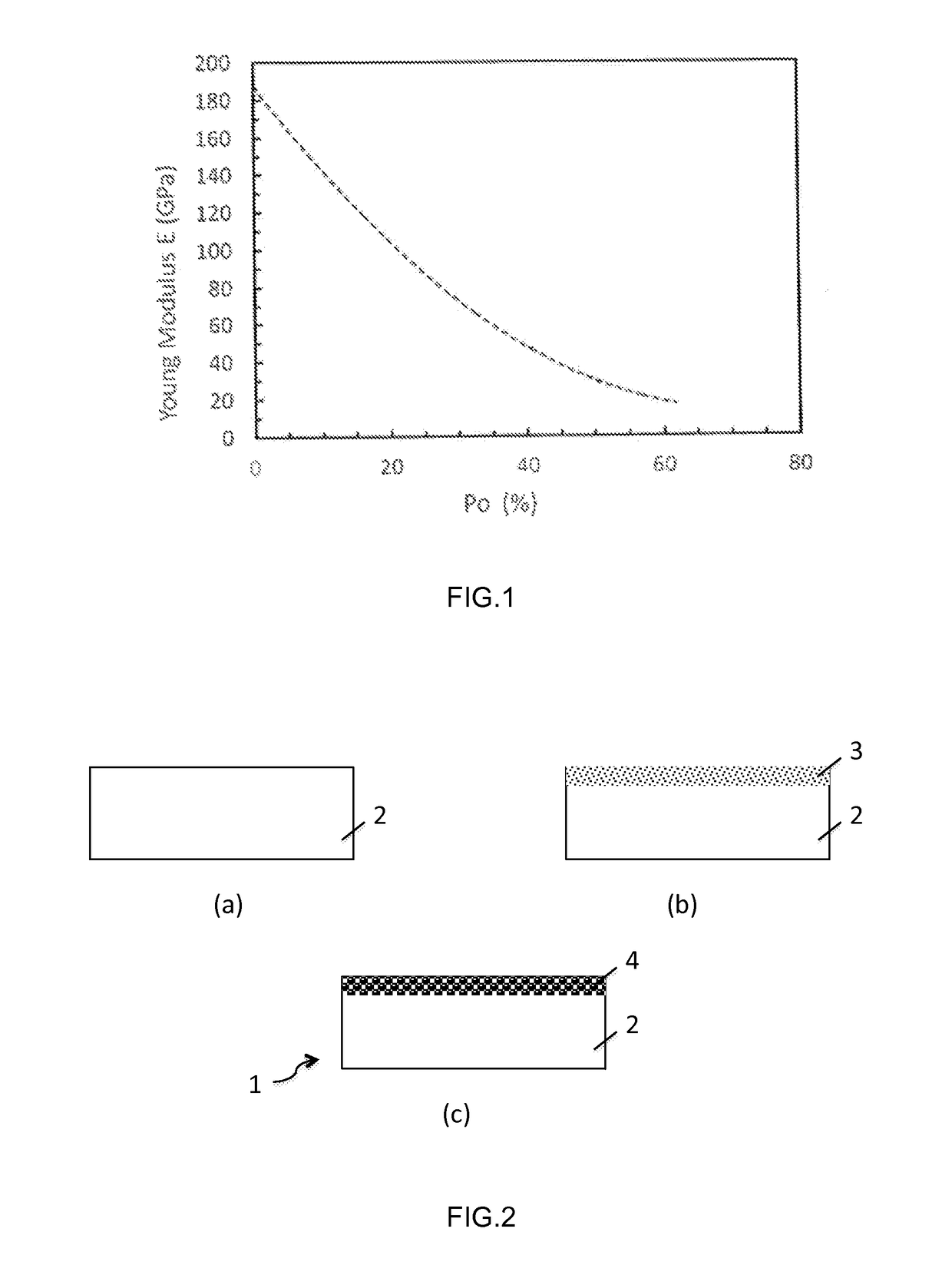

Structure for radio-frequency applications

ActiveUS20170221839A1Reduce fabrication costReduce manufacturing costImpedence networksSemiconductor/solid-state device detailsRadio frequencyP type doping

A structure for radiofrequency applications includes: a support substrate of high-resistivity silicon comprising a lower part and an upper part having undergone a p-type doping to a depth D; mesoporous trapping layer of silicon formed in the doped upper part of the support substrate. The depth D is less than 1 micron and the trapping layer has a porosity rate of between 20% and 60%.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

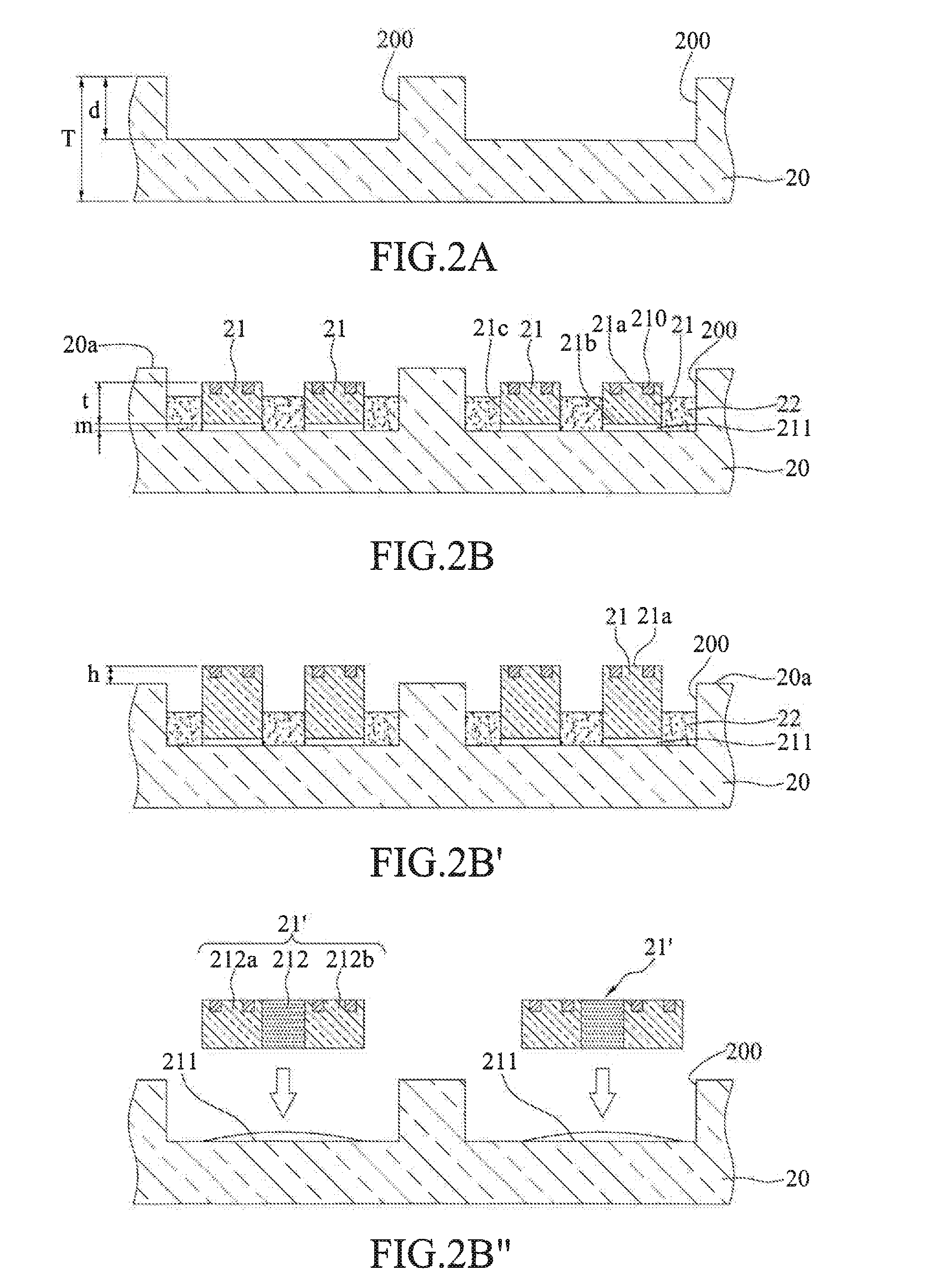

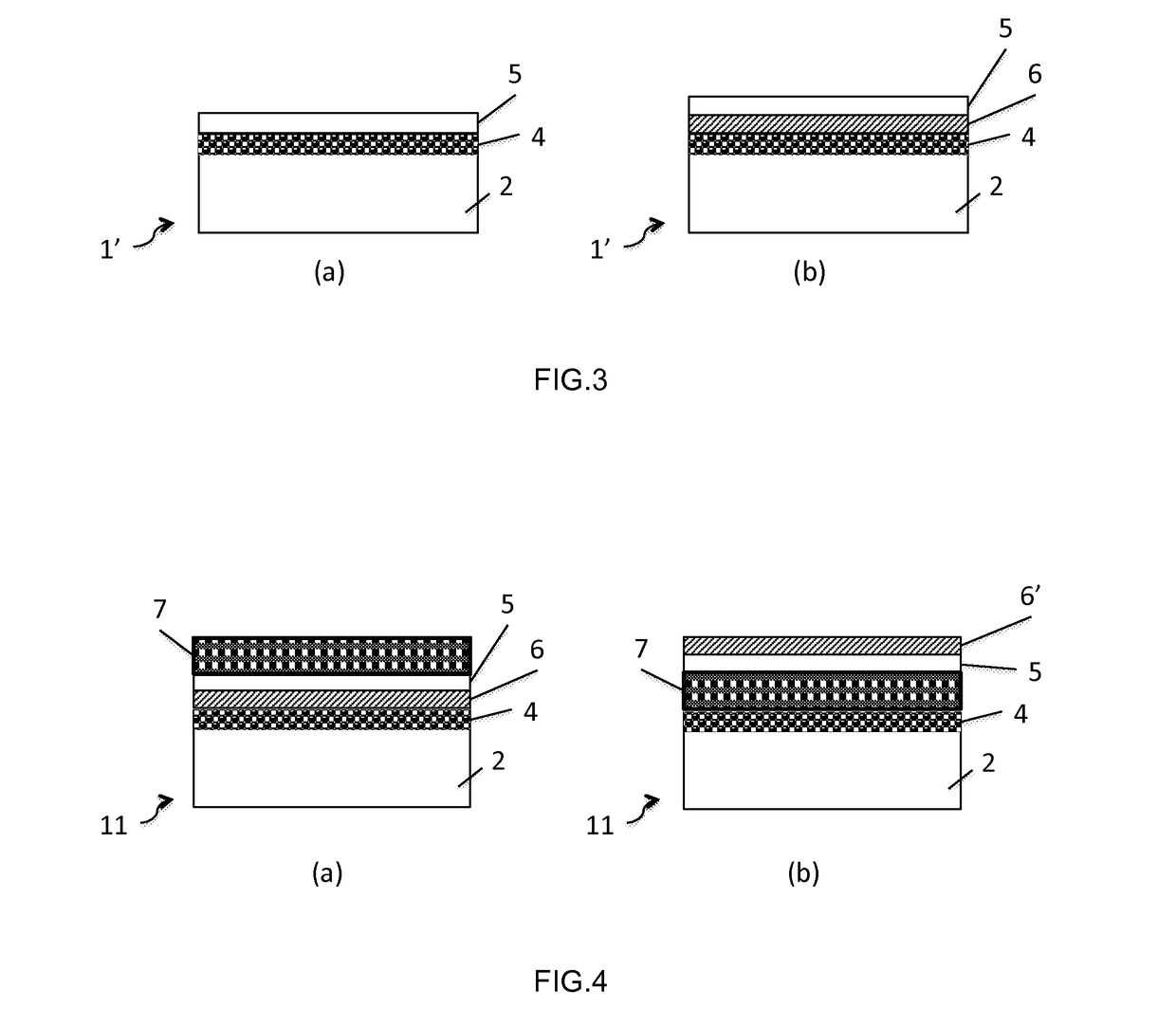

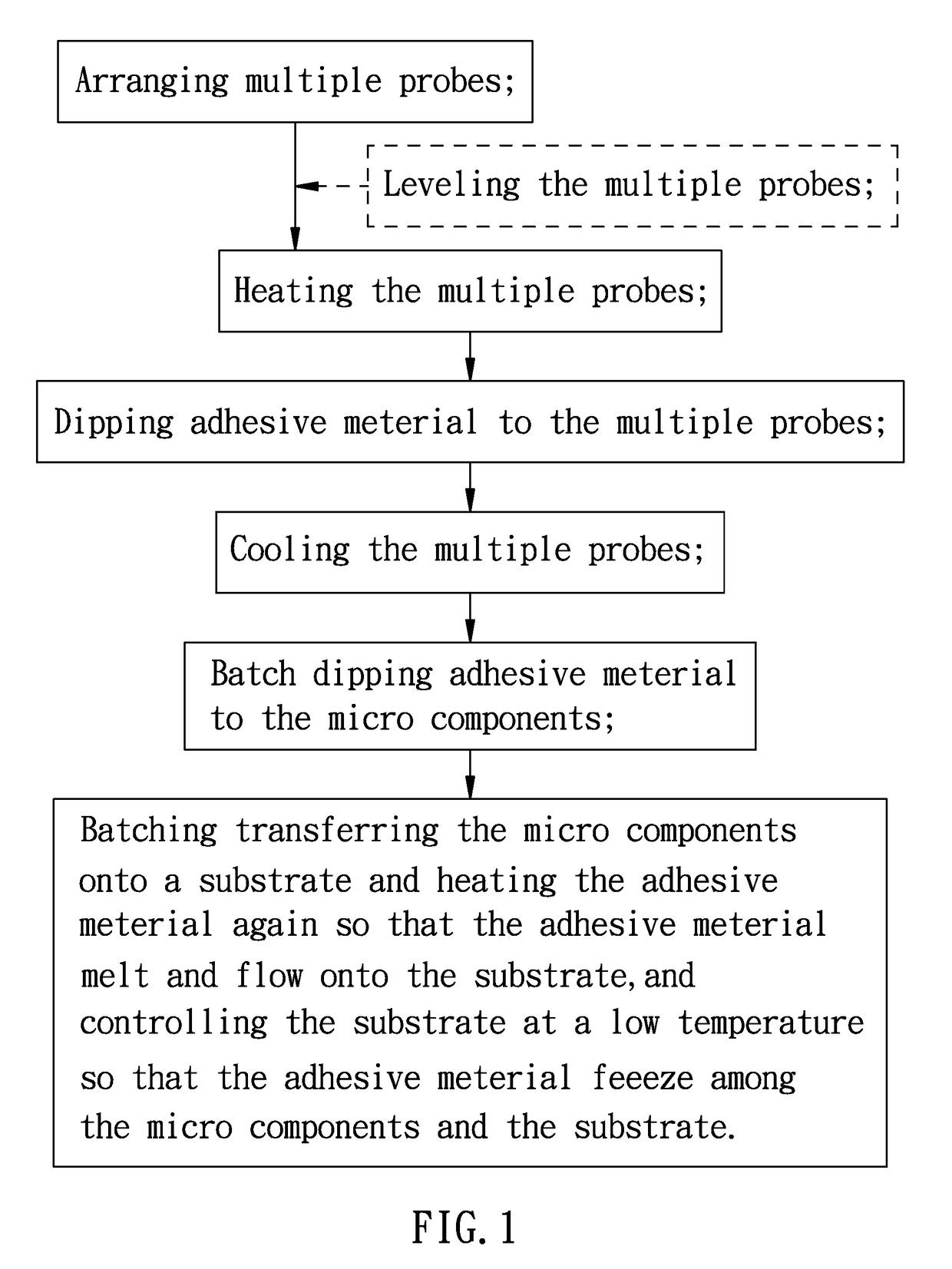

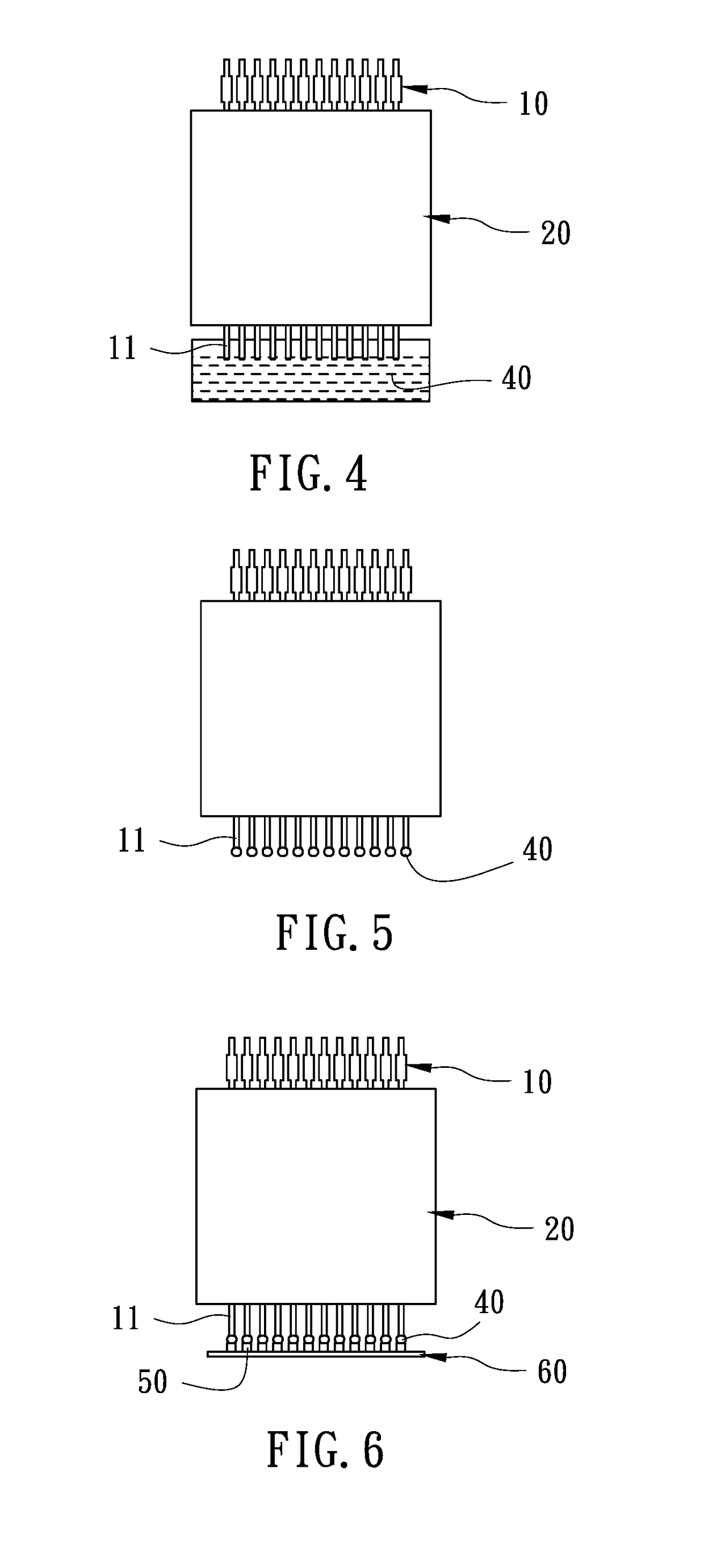

Method and device of batch transferring micro components

ActiveUS20190035662A1Accelerate speedReduce fabrication costSolid-state devicesSemiconductor/solid-state device manufacturingMicro componentsEngineering

A method of batch transferring micro components comprising steps of: A. arranging multiple probes in array on a carrying unit and extending multiple columns of the multiple probes out of a bottom of the carrying unit; B. providing a temperature control conduit in the carrying unit into which hot water is fed; C. driving the carrying unit so that the multiple columns of the multiple probes dip an adhesive material; D. feeding cold water into the temperature control conduit; E. moving the carrying unit on micro components and pressing the multiple probes of the carrying unit downward; F. moving the carrying unit onto a substrate and pressing the micro components to desired positions respectively; and G. heating adhesive material again as pressing the micro components and controlling the substrate at a low temperature so that the adhesive material freezes among the micro components and the substrate.

Owner:INNOSERV

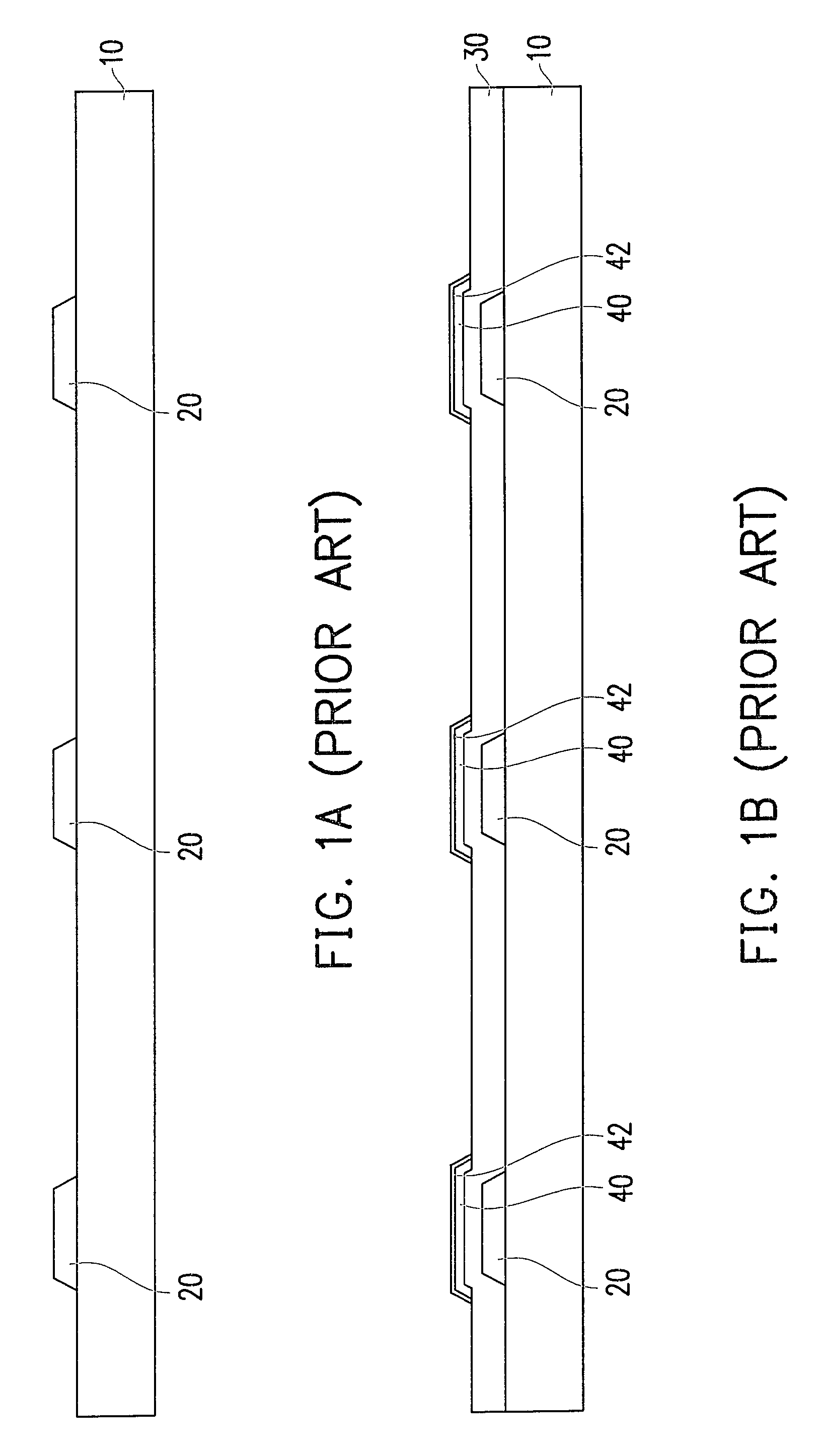

Method for fabricating pixel structure

ActiveUS7598102B1Reduce fabrication costReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingInkjet printingSemiconductor

A fabricating method for a pixel structure including following procedures is provided. First, a gate and a gate insulator layer are formed sequentially on a substrate. Next, a semiconductor layer, a conductive layer and a photosensitive black matrix having a color filter containing opening are sequentially formed on the gate insulator layer. The photosensitive black matrix includes a first portion and a second portion. A thickness of the first portion is smaller than that of the second portion. A channel, a source and a drain are formed simultaneously using the photosensitive black matrix as a mask. A passivation is formed on the substrate, and a color filer layer is formed within the color filter containing opening via an inkjet printing process and a dielectric layer is formed thereon. Next, a patterning process is applied to expose the drain. Ultimately, a pixel electrode connected to the drain is formed.

Owner:AU OPTRONICS CORP

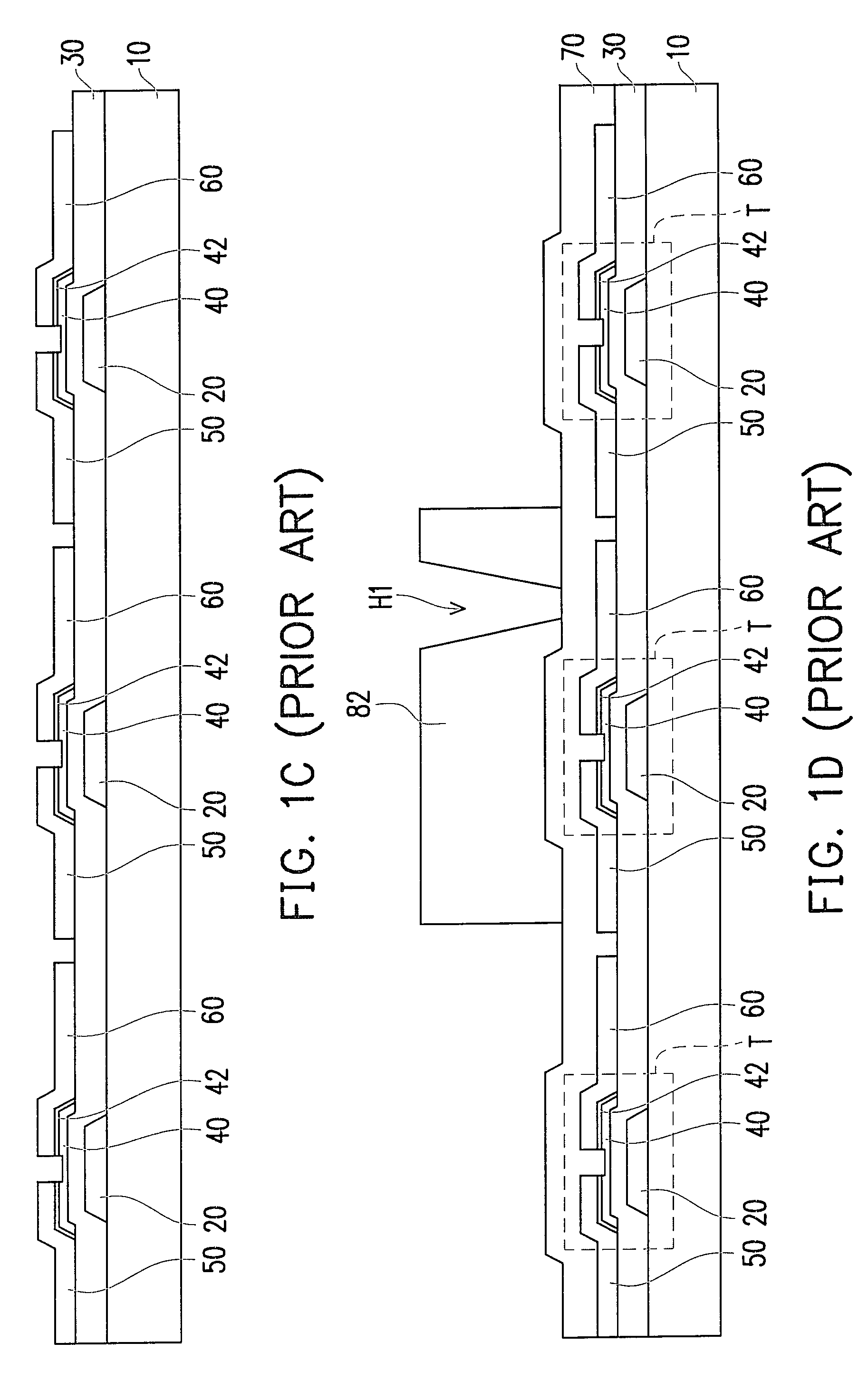

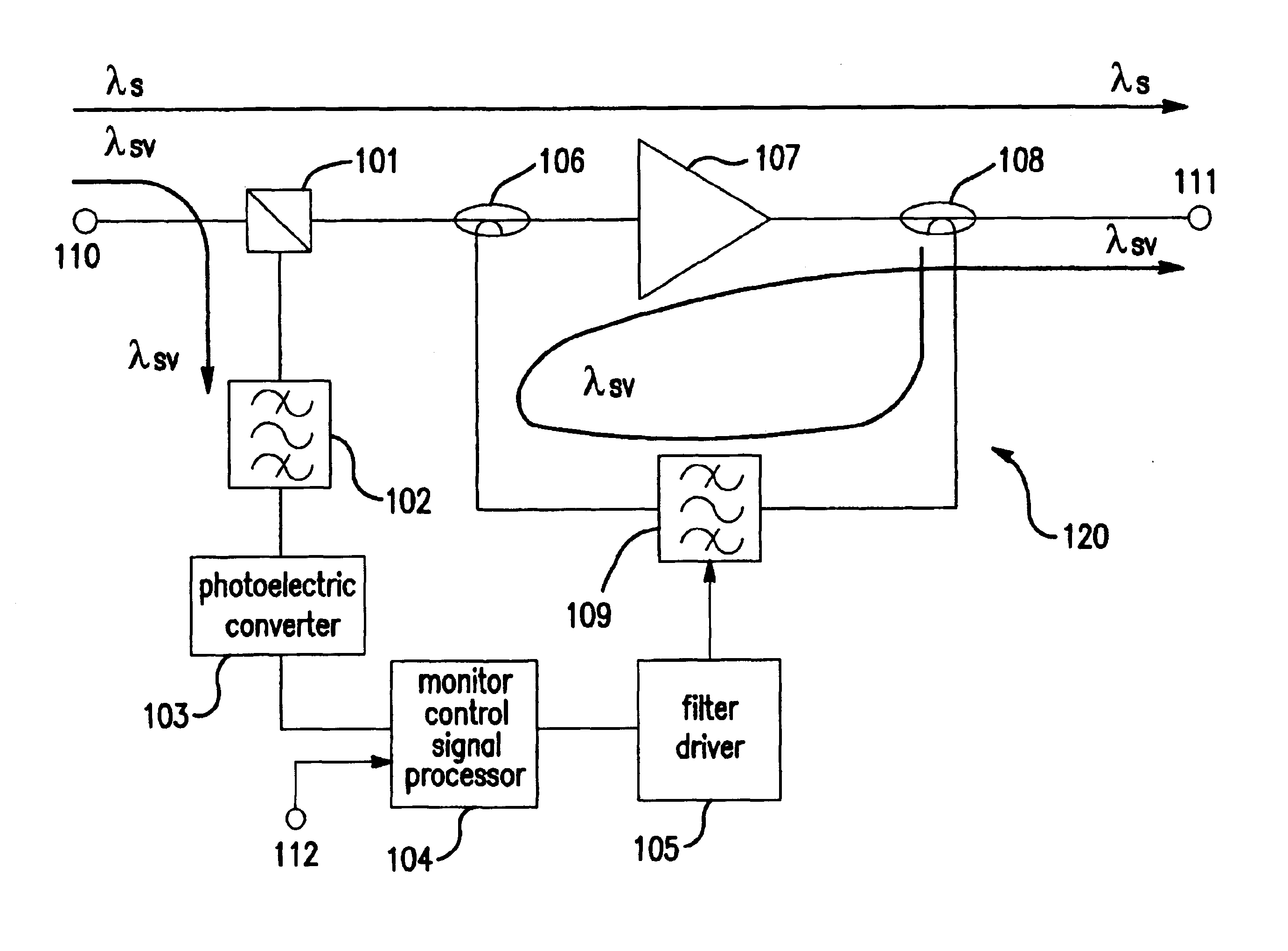

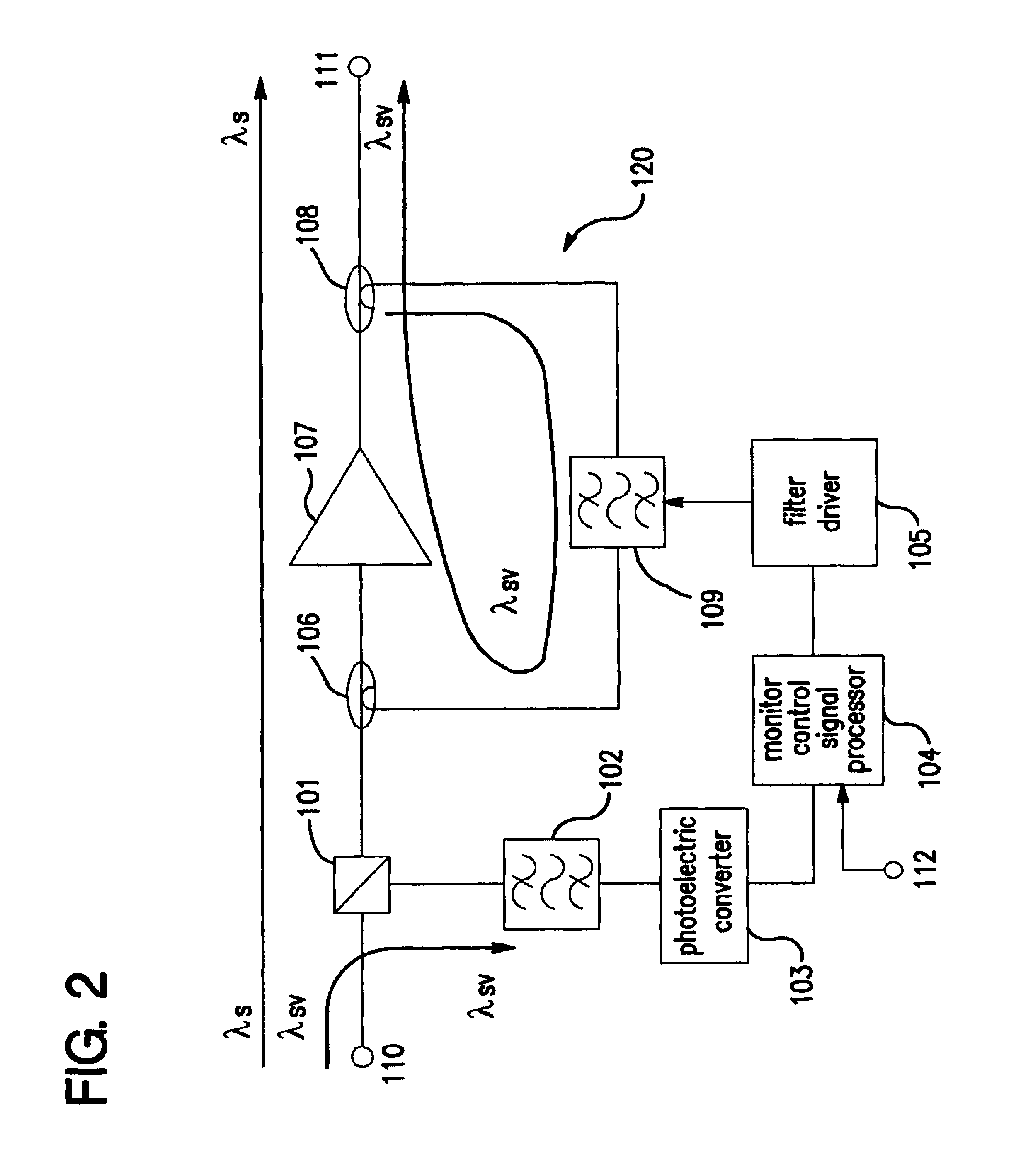

Apparatus for transferring monitor signals in photo-transfer system

InactiveUS6909853B1Reduce fabrication costSimplify structure of apparatusBaseband system detailsTransmission monitoringOptical couplerTransfer system

An apparatus for transferring monitor signals, which apparatus receives a primary signal, and a secondary signal for monitoring a wavelength, and outputs the primary signal and the modulated secondary signal. The apparatus includes an optical coupler to which the primary signal is input, a first optical branching filter optically connected to a signal output terminal, a first optical amplifier optically connected in series between the optical coupler and the first optical branching filter, and a first optical band-pass filter optically connected in series between the optical coupler and the first optical branching filter, but optically connected in parallel with the first optical amplifier. The primary signal is input into the optical coupler and output from the signal output terminal through the first optical amplifier and the first optical branching filter. The primary signal is divided into two parts by the first optical branching filter, and one of the two parts is input again into the first optical amplifier through the first optical band-pass filter and the optical coupler. The apparatus makes it possible to generate a monitor signal without employing a laser module.

Owner:NEC CORP

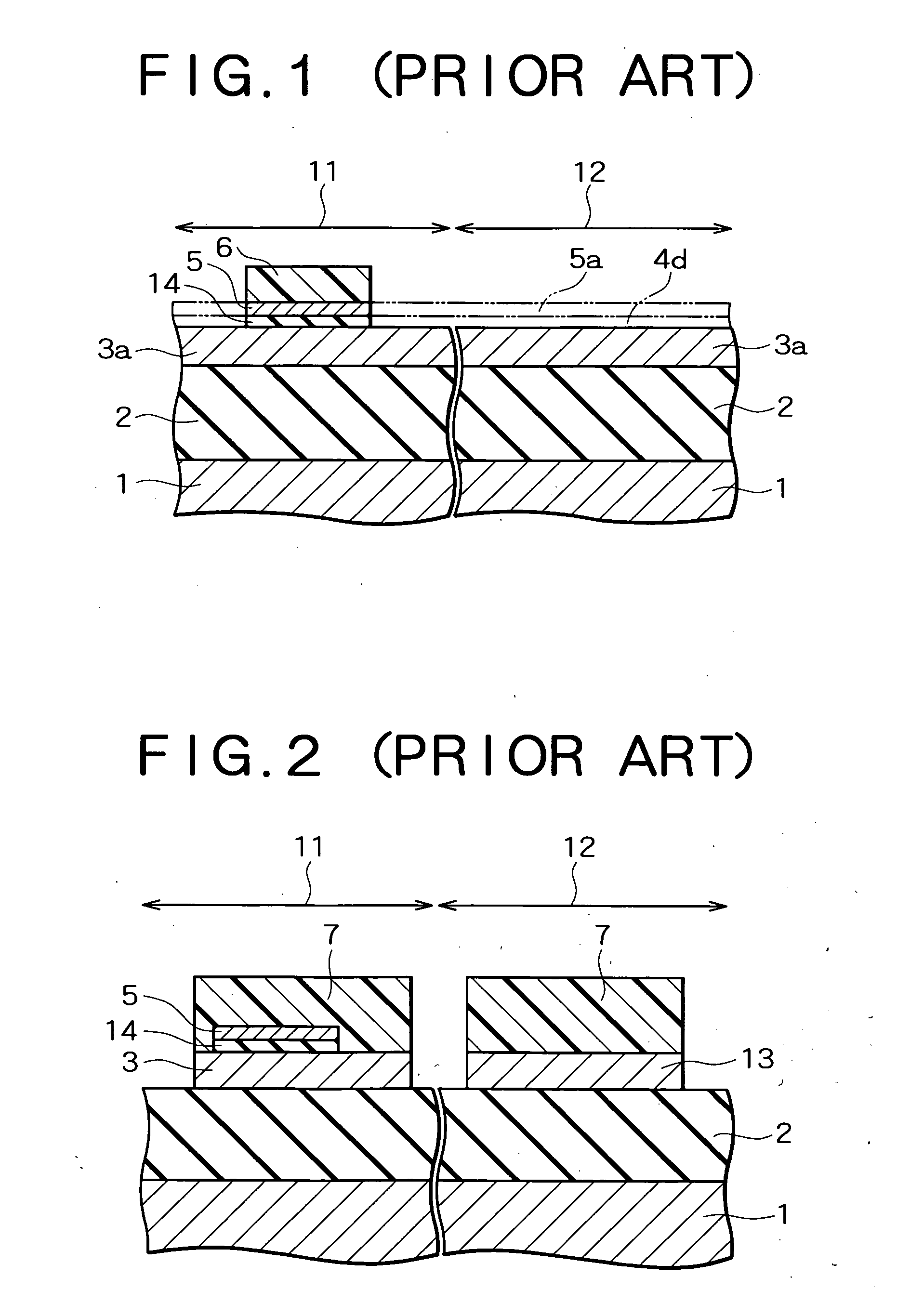

Semiconductor device and manufacturing method for the same

InactiveUS20050194686A1Decrease reliabilityReduce fabrication costPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringOxide

A semiconductor device according to the present invention comprises an electrode pad electrically conducted to an electric circuit formed on an element-formed surface of a silicon wafer; a wiring pattern re-wired by being electrically conducted to the electrode pad; and an oxide film formed on a surface of the wiring pattern, the oxide film being formed by subjecting the wiring pattern to oxidization. With the provision of oxide film, the semiconductor device prevents a decrease in reliability in terms of electric characteristic or the like, and also achieves reduction in fabrication cost compared to a conventional semiconductor device.

Owner:SHARP KK

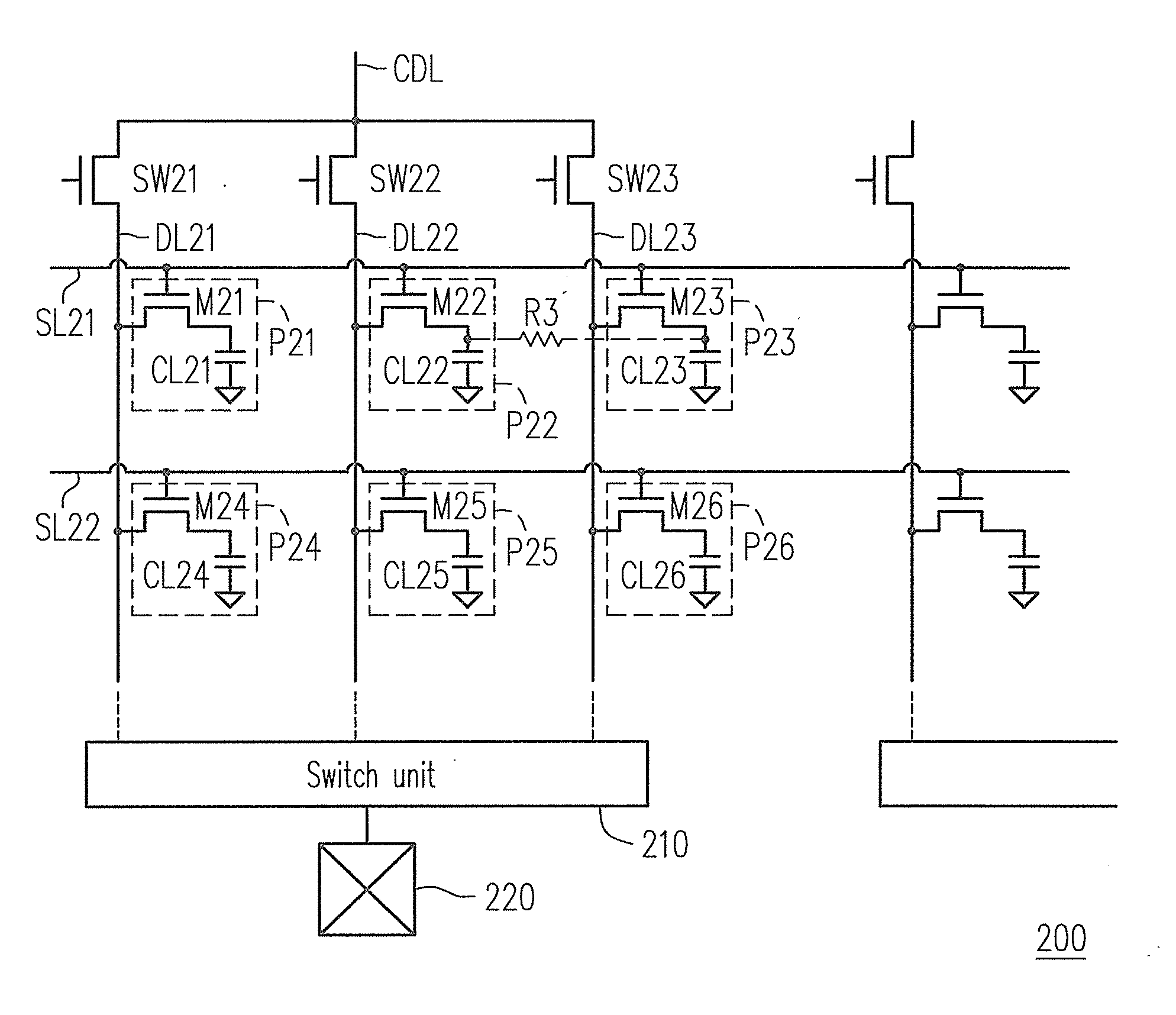

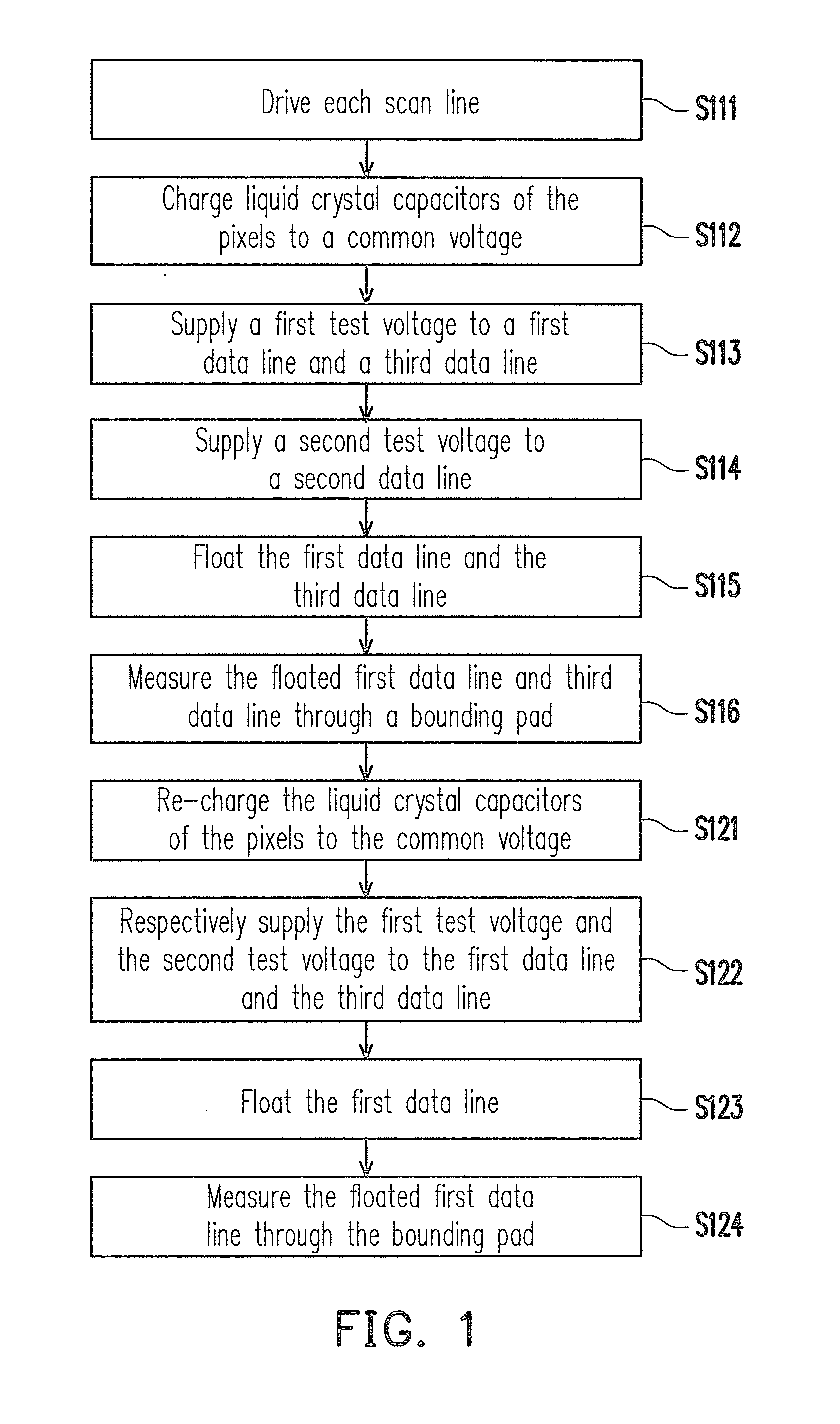

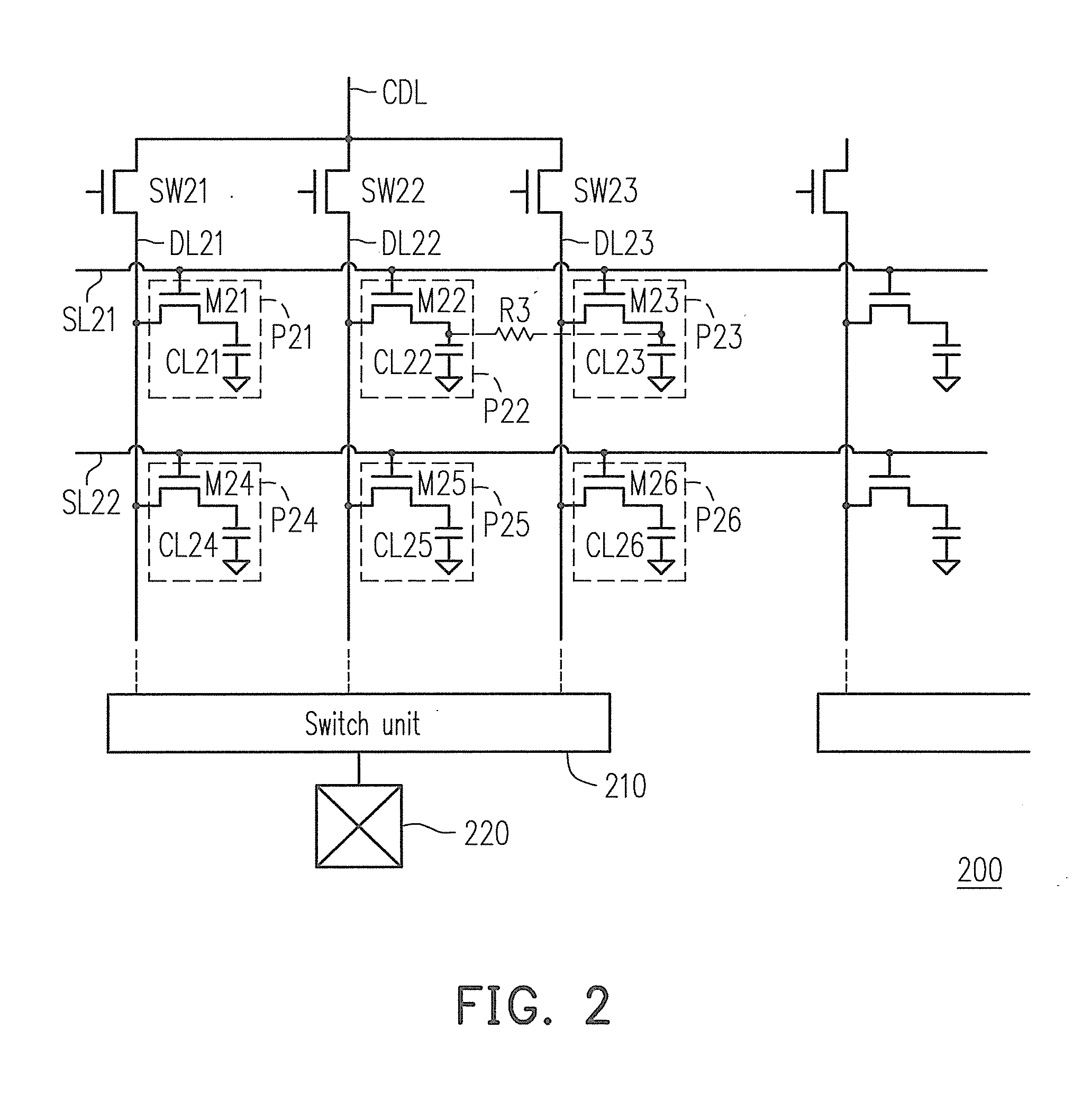

Test method of liquid crystal display panel

ActiveUS20120062263A1Fabrication timeReduce fabrication costStatic indicating devicesIndividual semiconductor device testingLiquid-crystal displayElectricity

A test method of a liquid crystal display panel is provided. The liquid crystal display panel includes a plurality of pixels and a testing pad. The pixels are disposed at intersections between a first, a second, and a third data lines and a plurality of scan lines. In the test method, each of the scan lines is driven to connect liquid crystal capacitors of the pixels to the first, the second, and the third data lines. A first and a second test voltages are respectively supplied to the first and the second data lines, wherein the first test voltage is not equal to the second test voltage. The first data line is floated. The floated first data line is measured through the testing pad to determine whether the liquid crystal capacitors of the pixels electrically connected to the first and the second data lines are electrically connected with each other.

Owner:HIMAX DISPLAY INC

Chip package and method of fabricating the same

InactiveUS20080224277A1High costReduce fabrication costSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A method of fabricating a chip package is provided. A thin metal plate having a first protrusion part, a second protrusion part and a plurality of third protrusion parts are provided. A chip is disposed on the thin metal plate, and a plurality of bonding wires for electrically connecting the chip to the second protrusion part and the second protrusion part to the third protrusion parts is formed. An upper encapsulant and a lower encapsulant are formed on the upper surface and the lower surface of the thin metal plate respectively. The lower encapsulant has a plurality of recesses for exposing a portion of the thin metal plate at locations where the first protrusion part, the second protrusion part and the third protrusion parts are connected to one another. Finally, the thin metal plate is etched by using the lower encapsulant as an etching mask.

Owner:CHIPMOS TECH INC

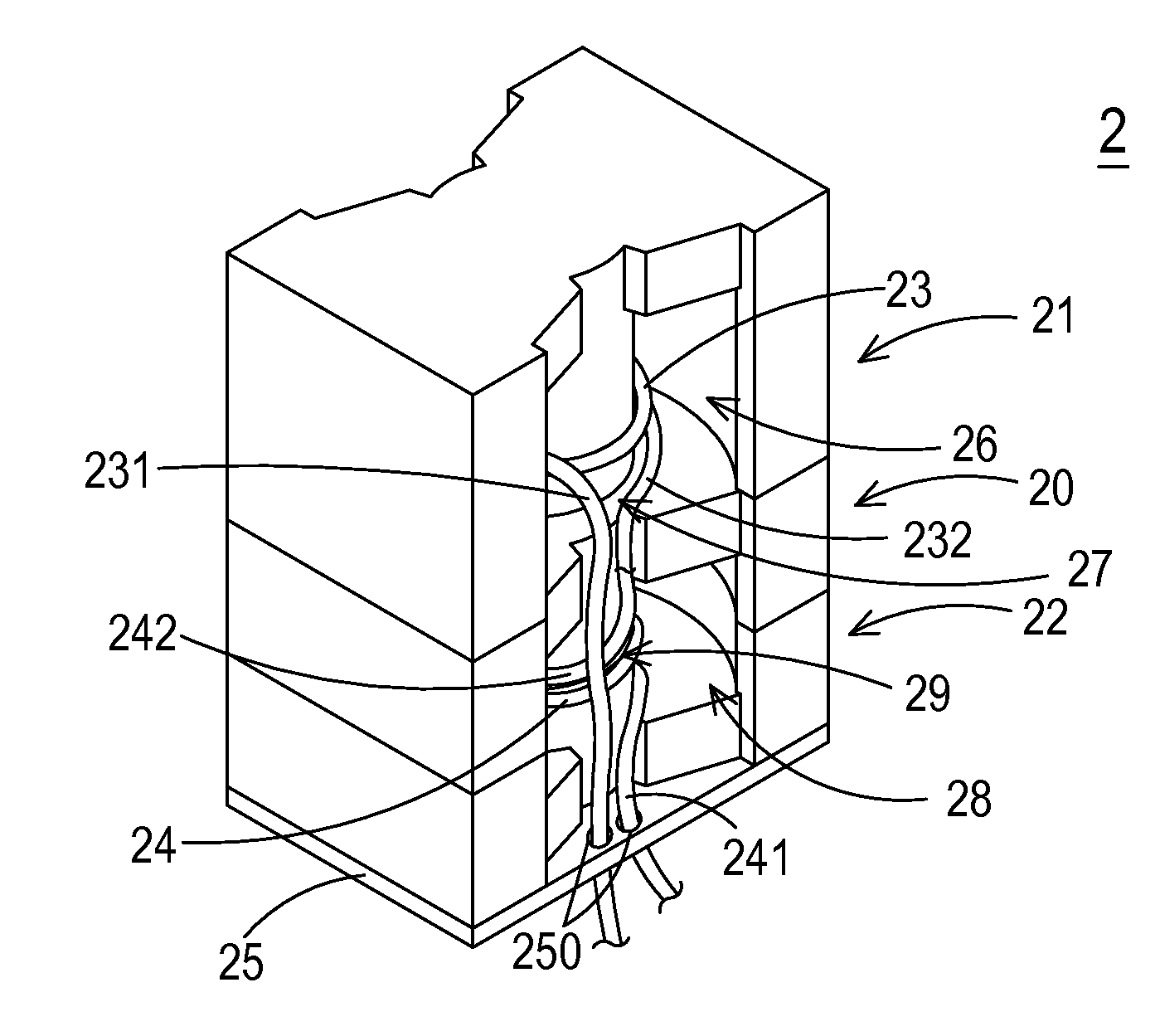

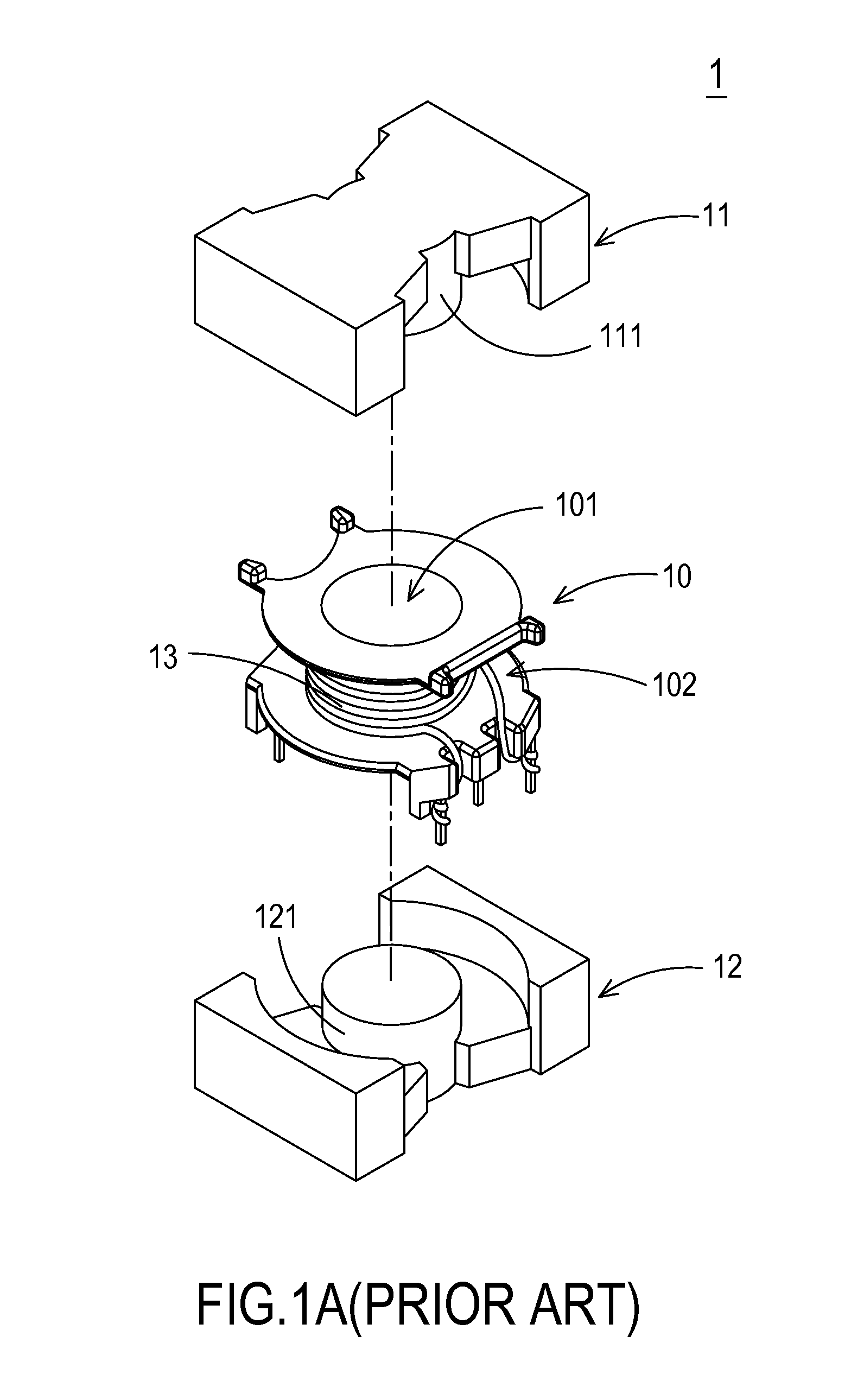

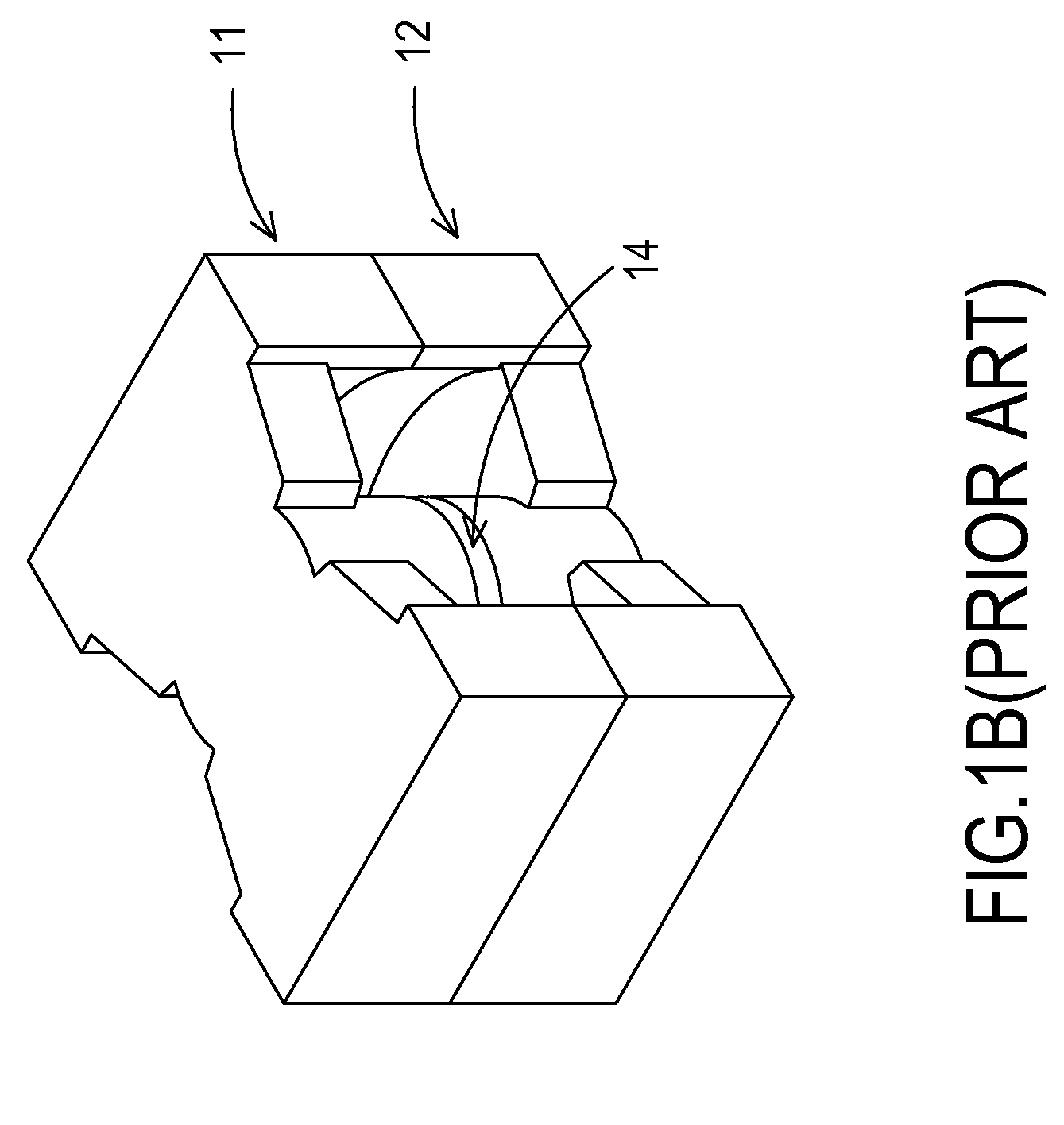

Magnetic element with multiple air gaps

ActiveUS20150302968A1Reduce fabrication costEnhance utilityTransformers/inductances casingsTransformers/inductances coils/windings/connectionsPhysicsMagnetic core

A magnetic element includes a first magnetic core, a second magnetic core, an intermediate magnetic core, a first winding coil, and a second winding coil. The intermediate magnetic core is arranged between the first magnetic core and the second magnetic core. After the first magnetic core and the intermediate magnetic core are coupled with each other, a first winding space and a first air gap are defined. After the second magnetic core and the intermediate magnetic core are coupled with each other, a second winding space and a second air gap are defined. The first winding coil is disposed within the first winding space and arranged around the first air gap. The second winding coil is disposed within the second winding space and arranged around the second air gap. The first winding coil and the second winding coil are connected with each other in series.

Owner:DELTA ELECTRONICS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com