Patents

Literature

52results about How to "Reliably fabricated" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

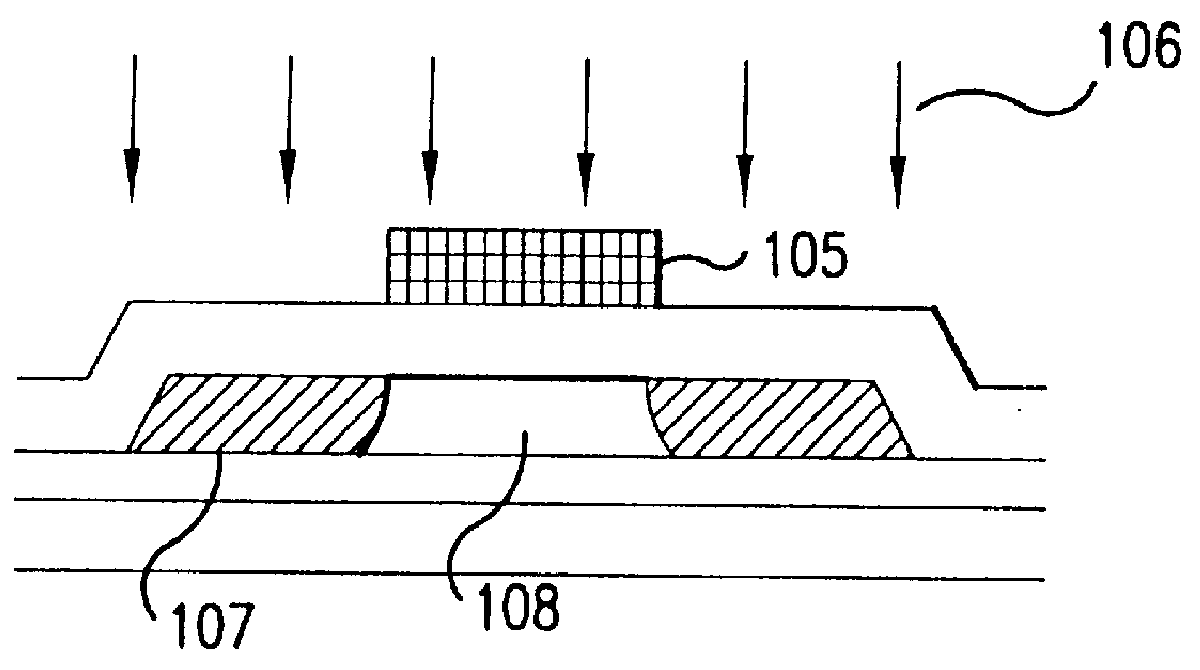

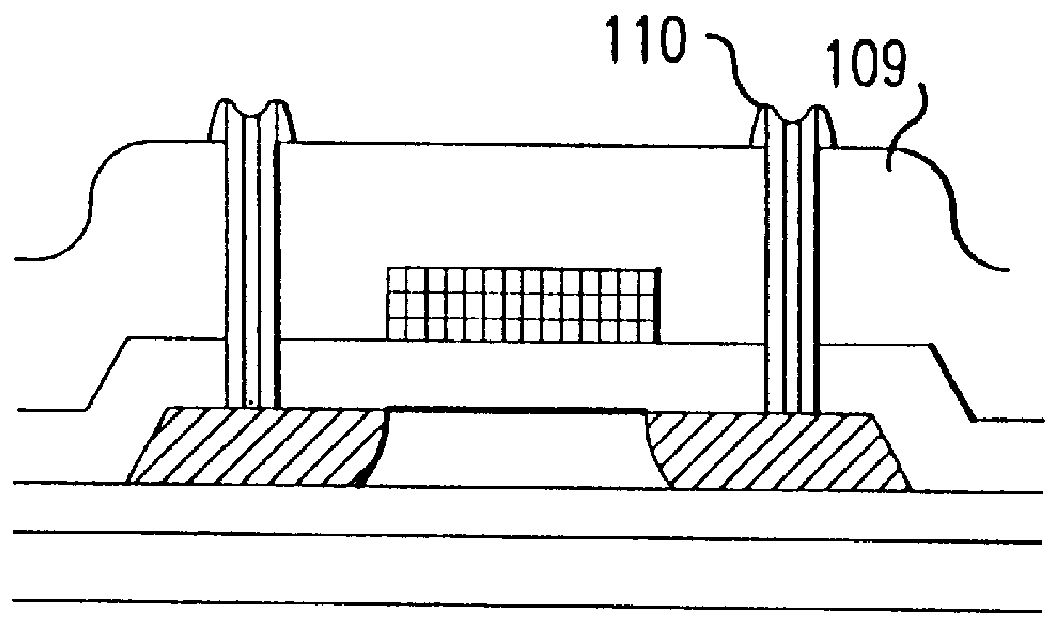

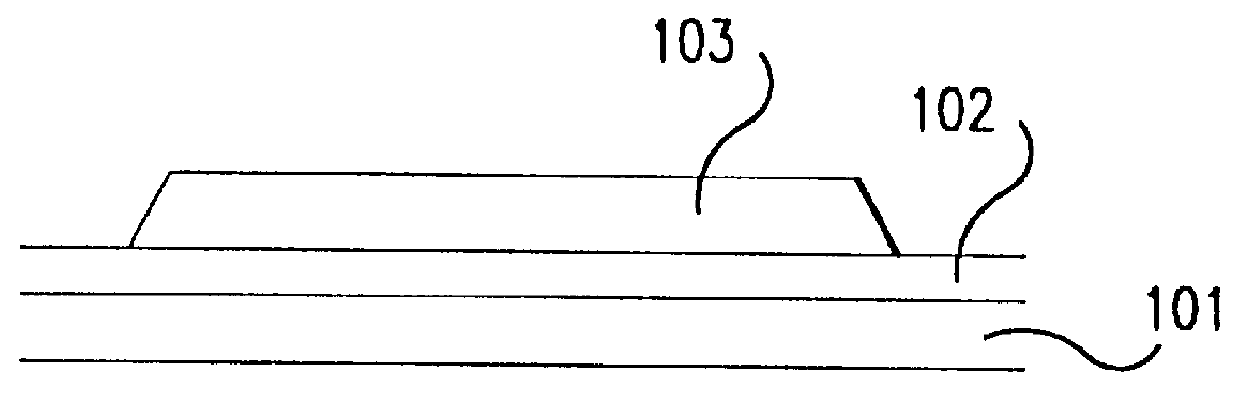

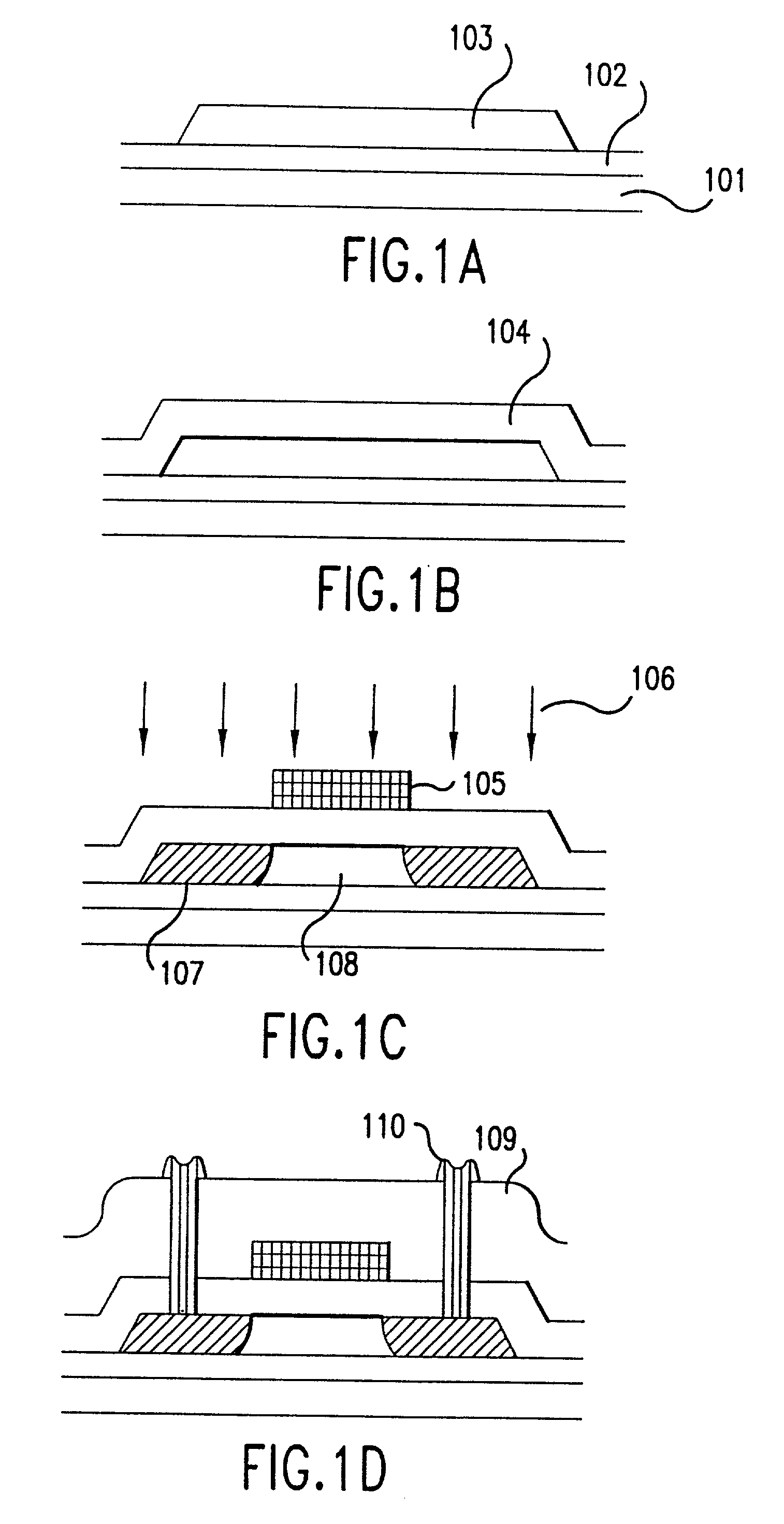

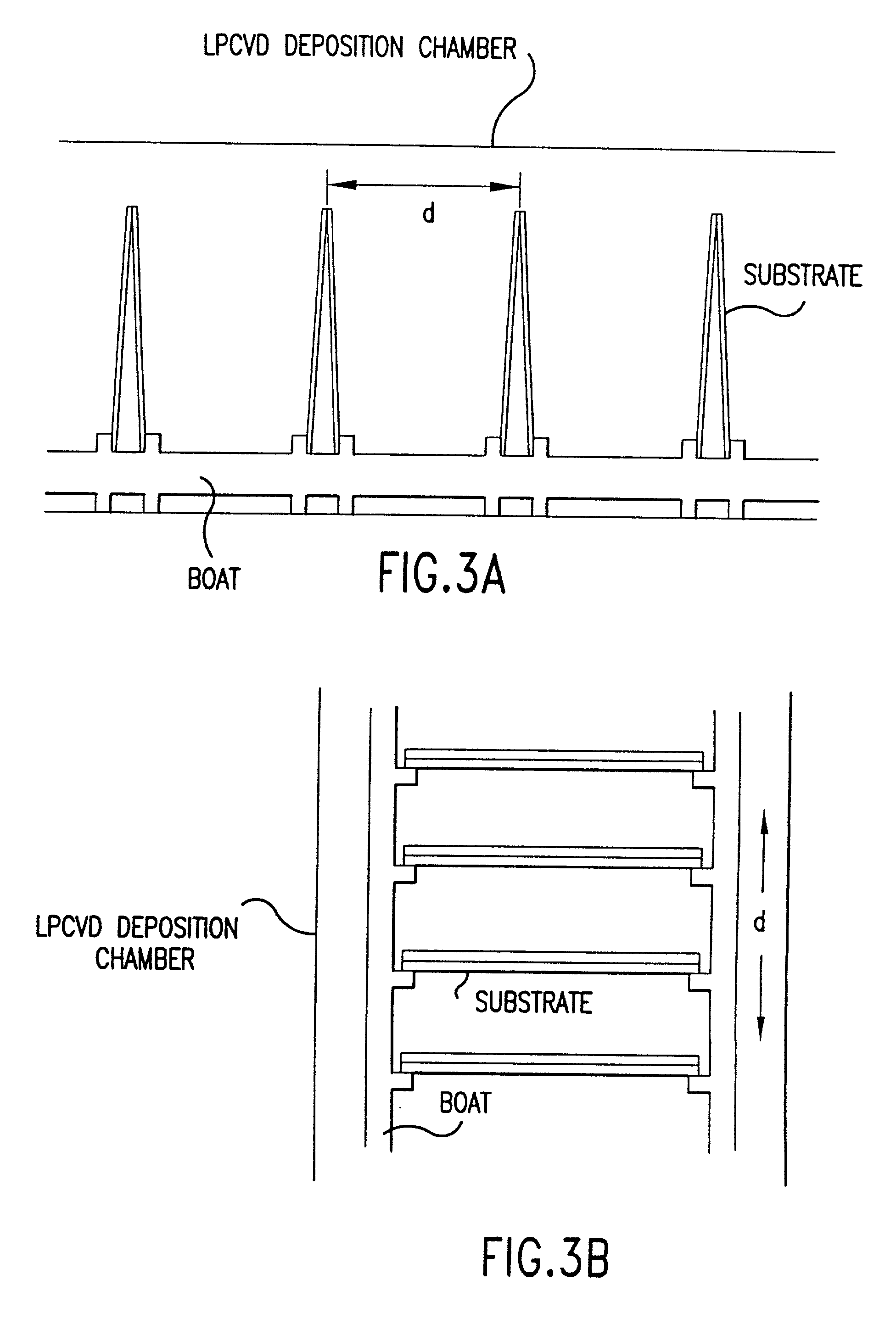

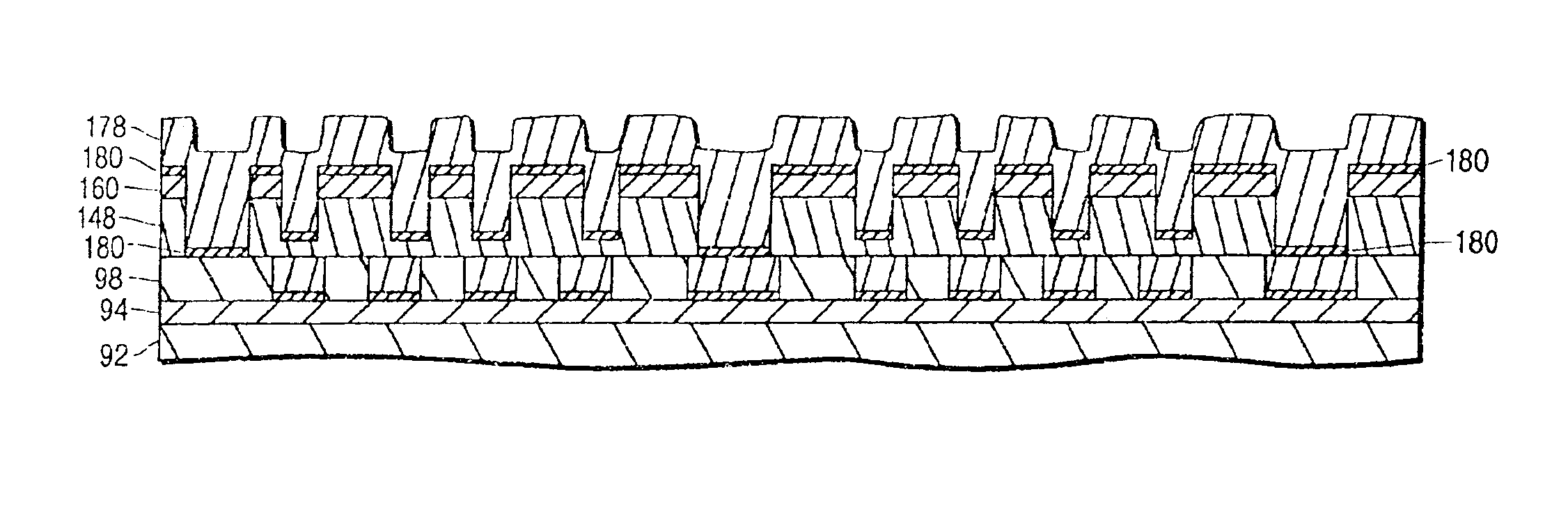

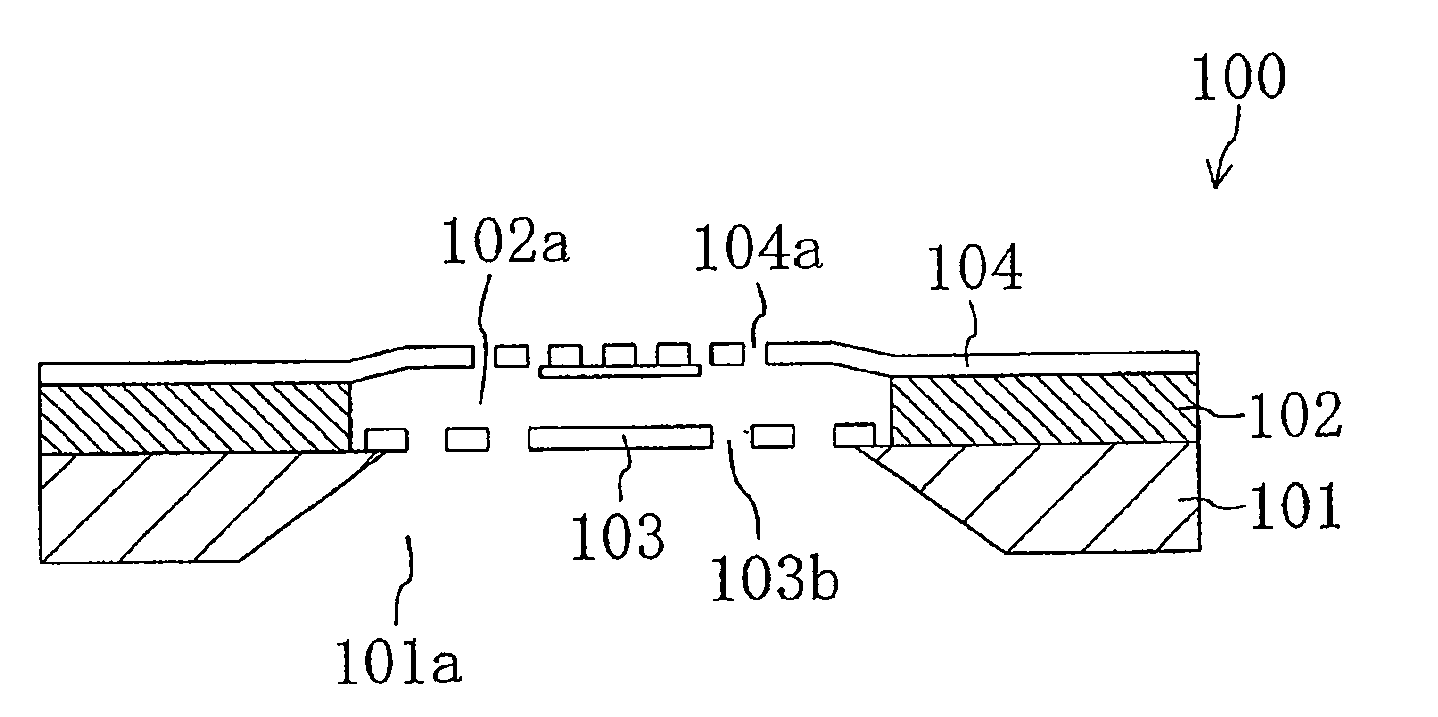

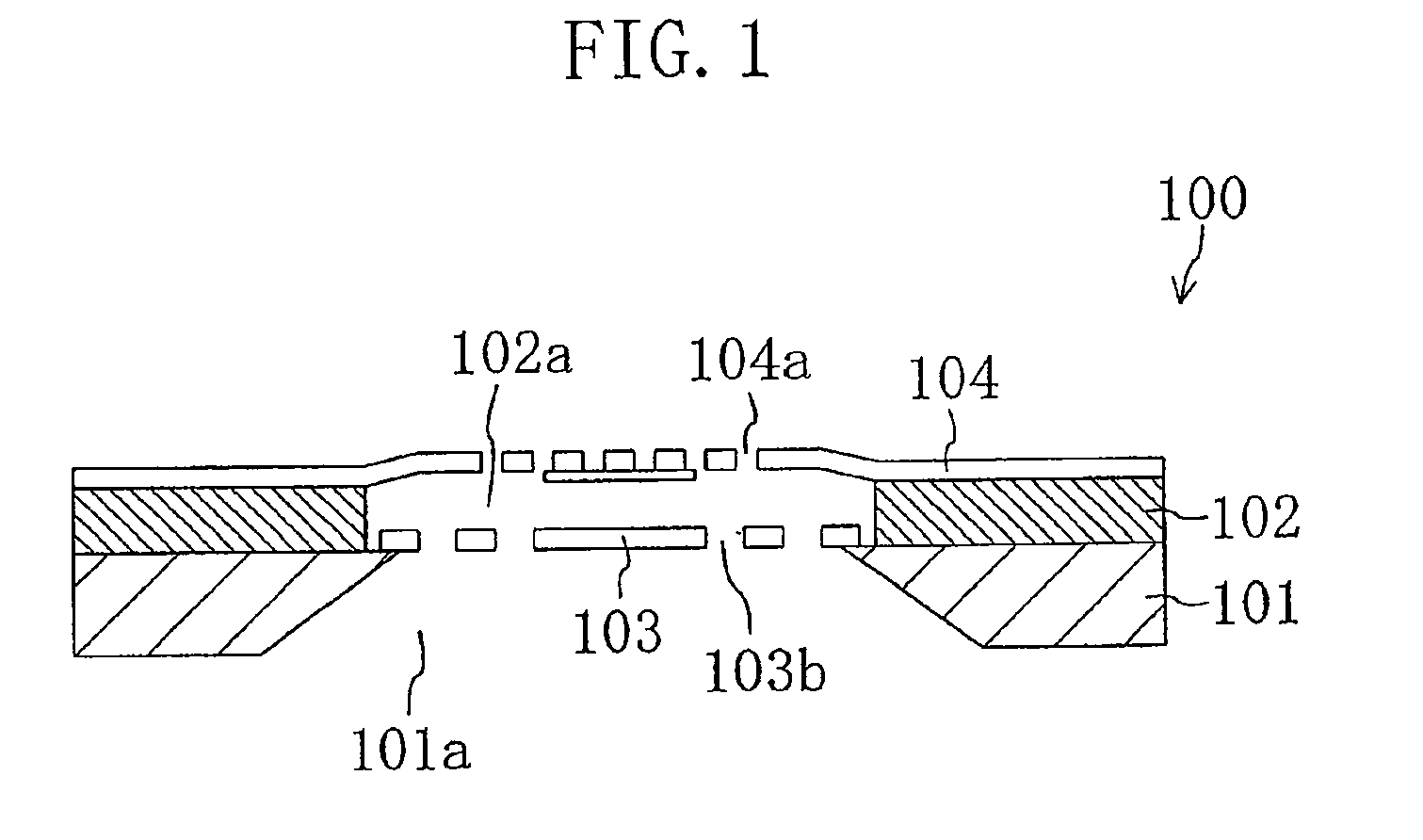

Fabrication method for a thin film semiconductor device, the thin film semiconductor device itself, liquid crystal display, and electronic device

InactiveUS6017779AImprove propertiesWell formedTransistorLinear bearingsElectronic circuitLiquid-crystal display

In order to fabricate a high performance thin film semiconductor device using a low temperature process in which it is possible to use low price glass substrates, a thin film semiconductor device has been fabricated by forming a silicon film at less than 450 DEG C., and, after crystallization, keeping the maximum processing temperature at or below 350 DEG C. In applying the present invention to the fabrication of an active matrix liquid crystal display, it is possible to both easily and reliably fabricate a large, high-quality liquid crystal display. Additionally, in applying the present invention to the fabrication of other electronic circuits as well, it is possible to both easily and reliably fabricate high-quality electronic circuits.

Owner:INTELLECTUAL KEYSTONE TECH

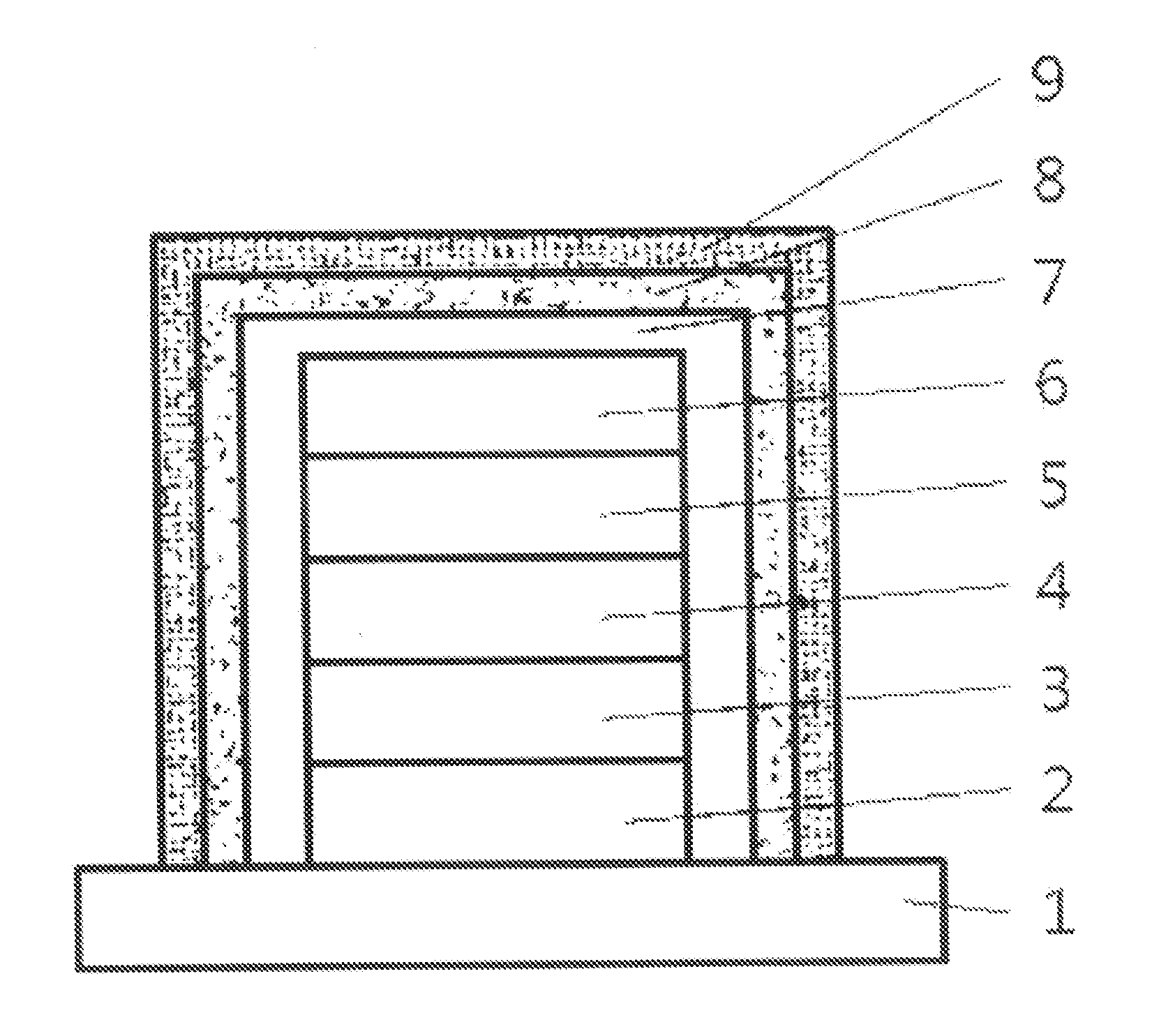

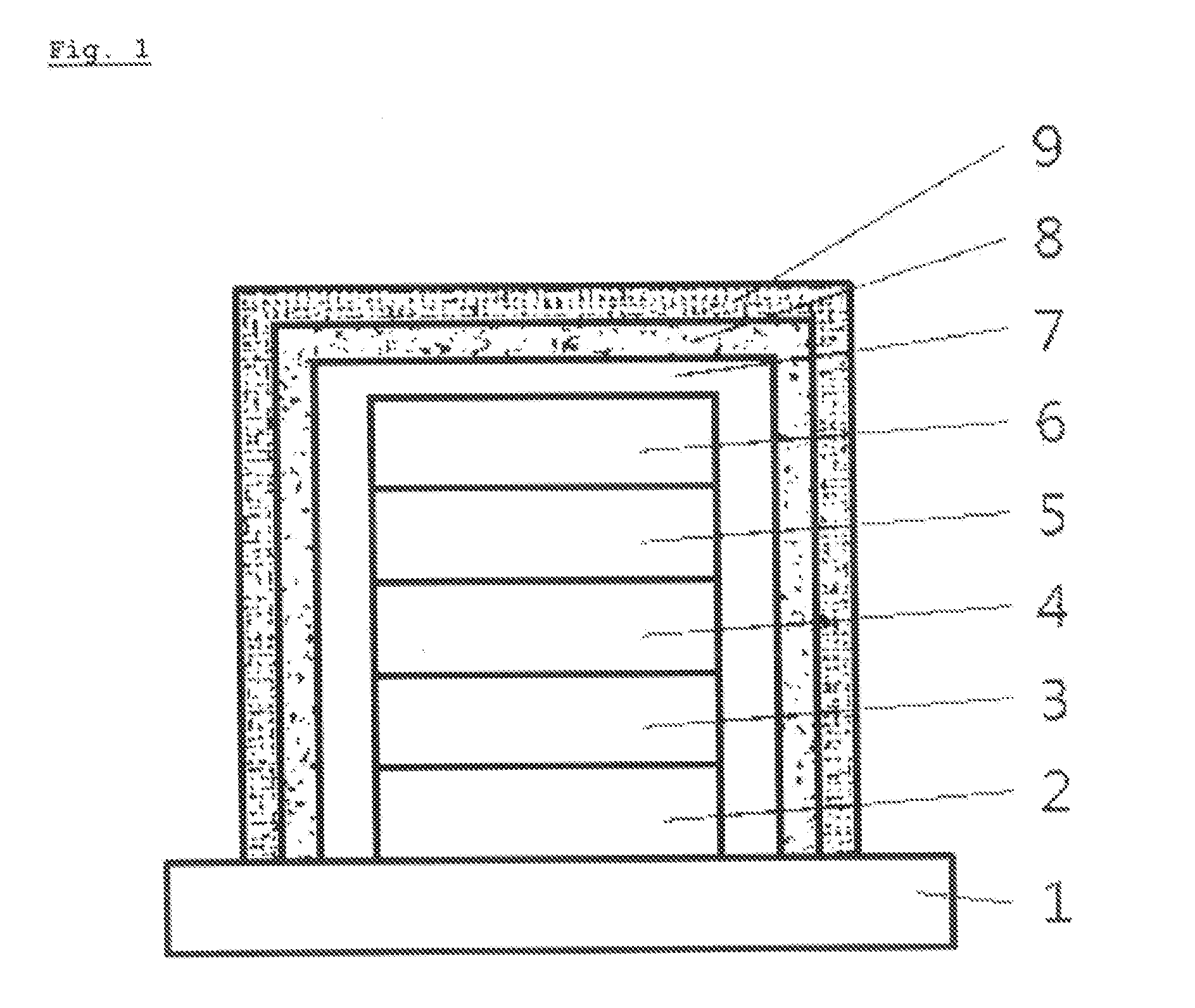

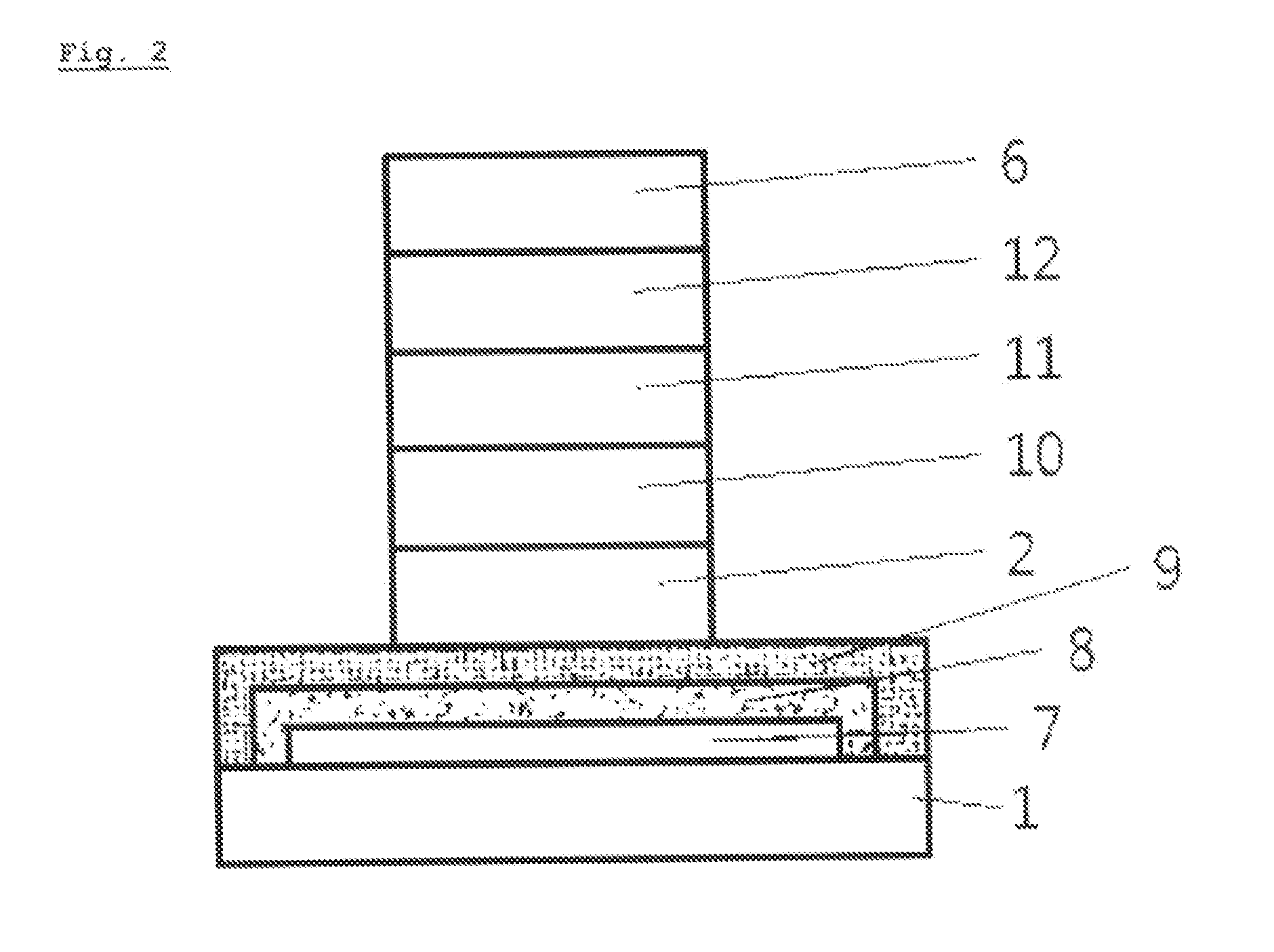

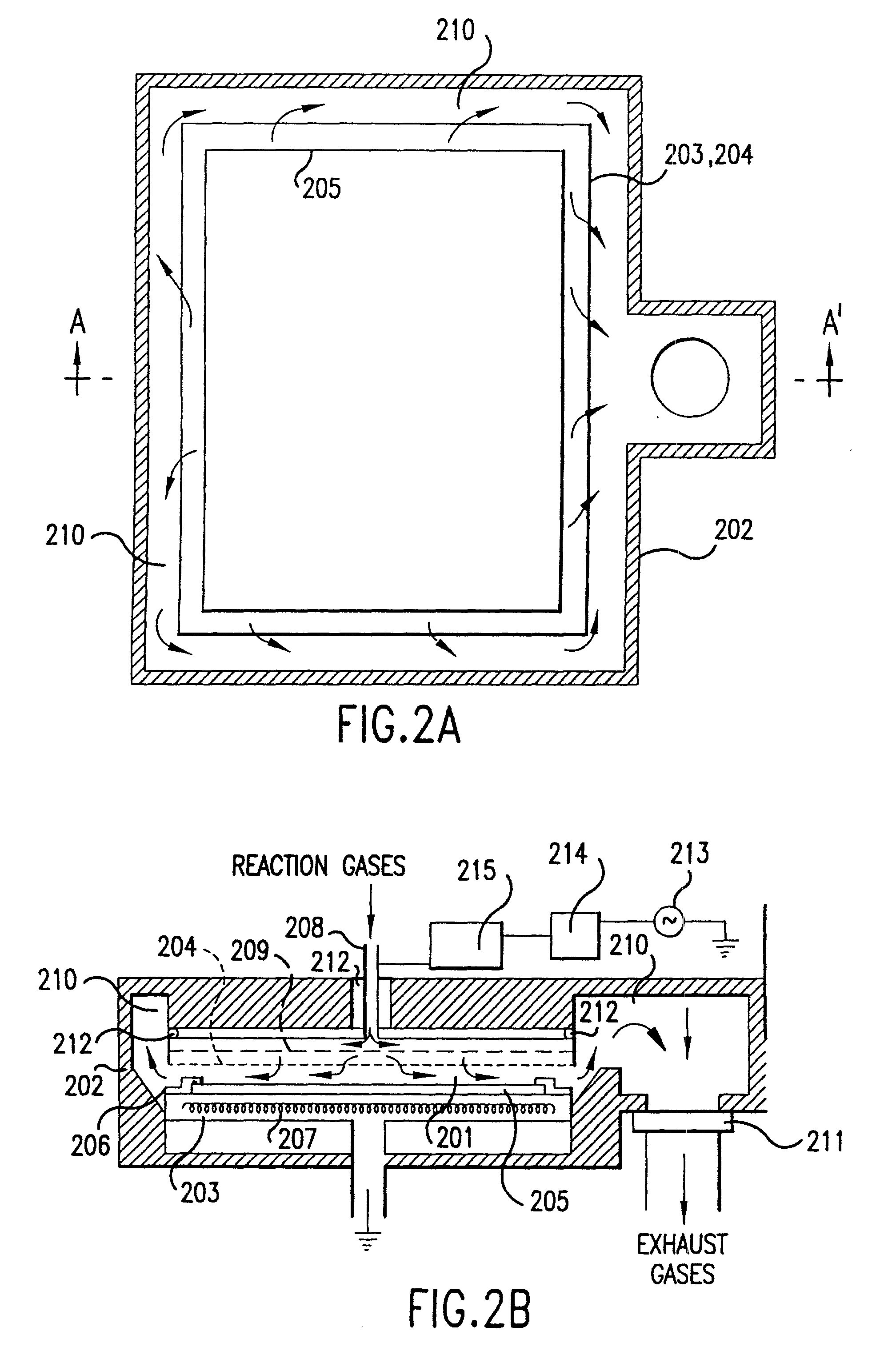

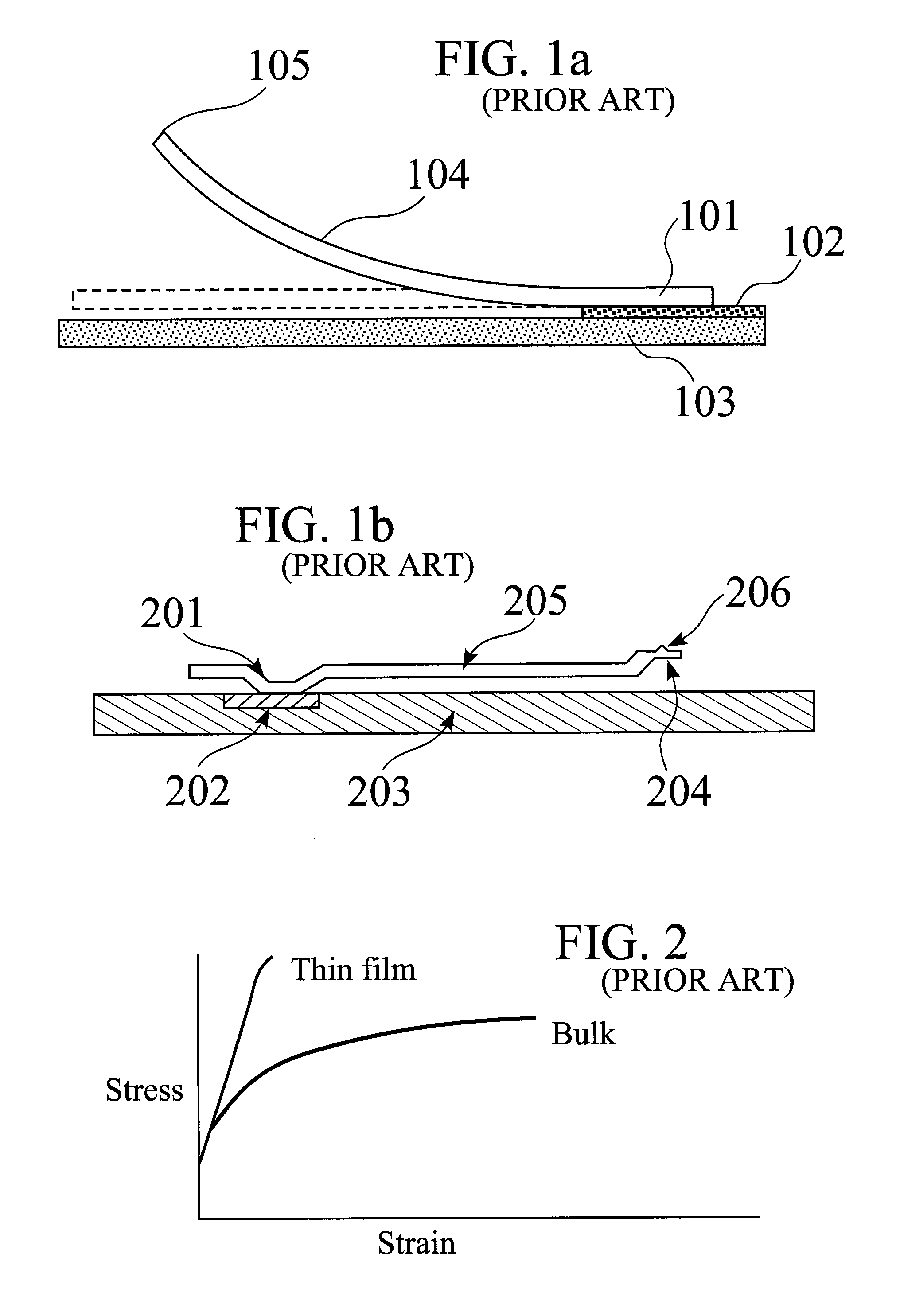

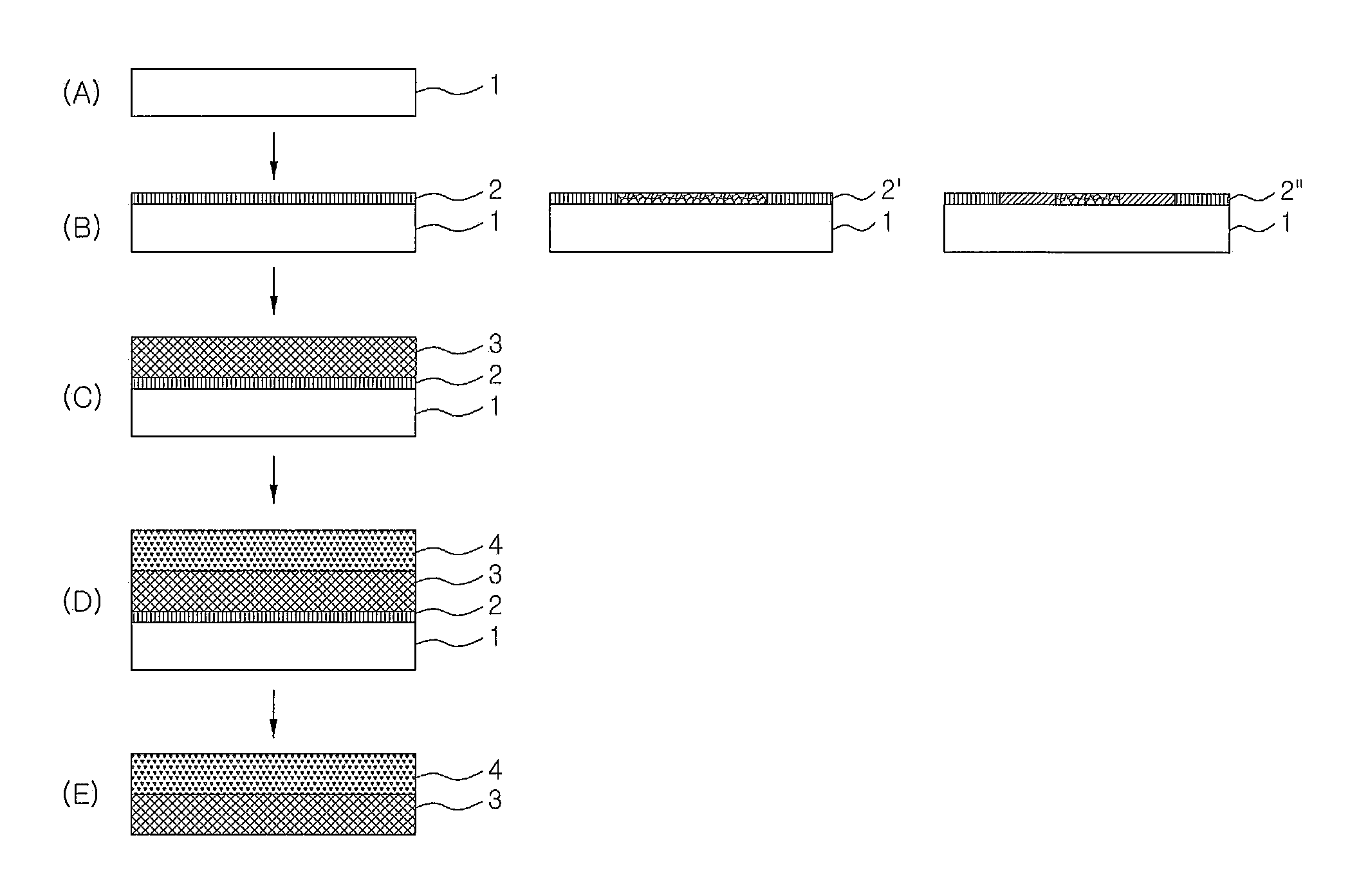

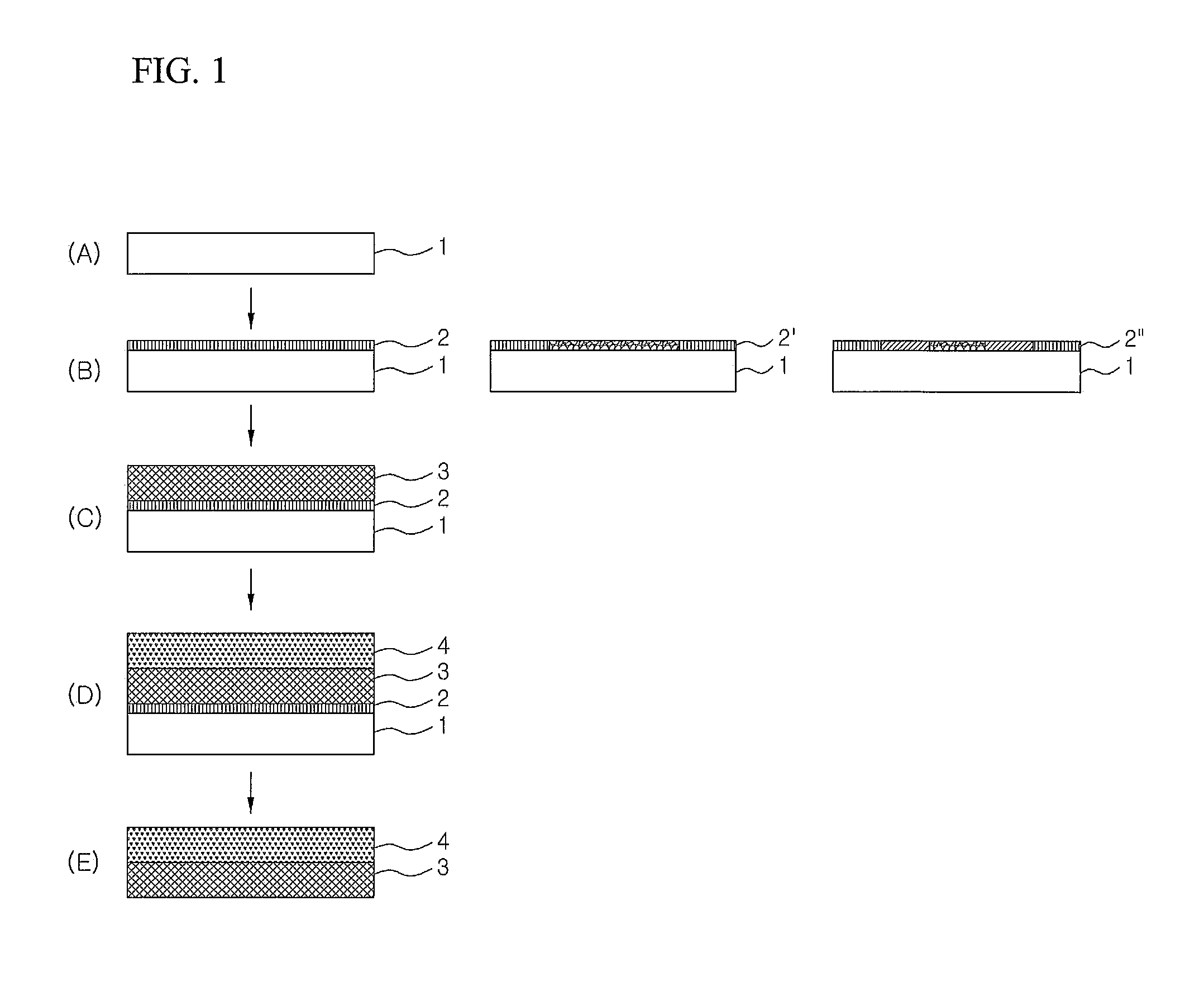

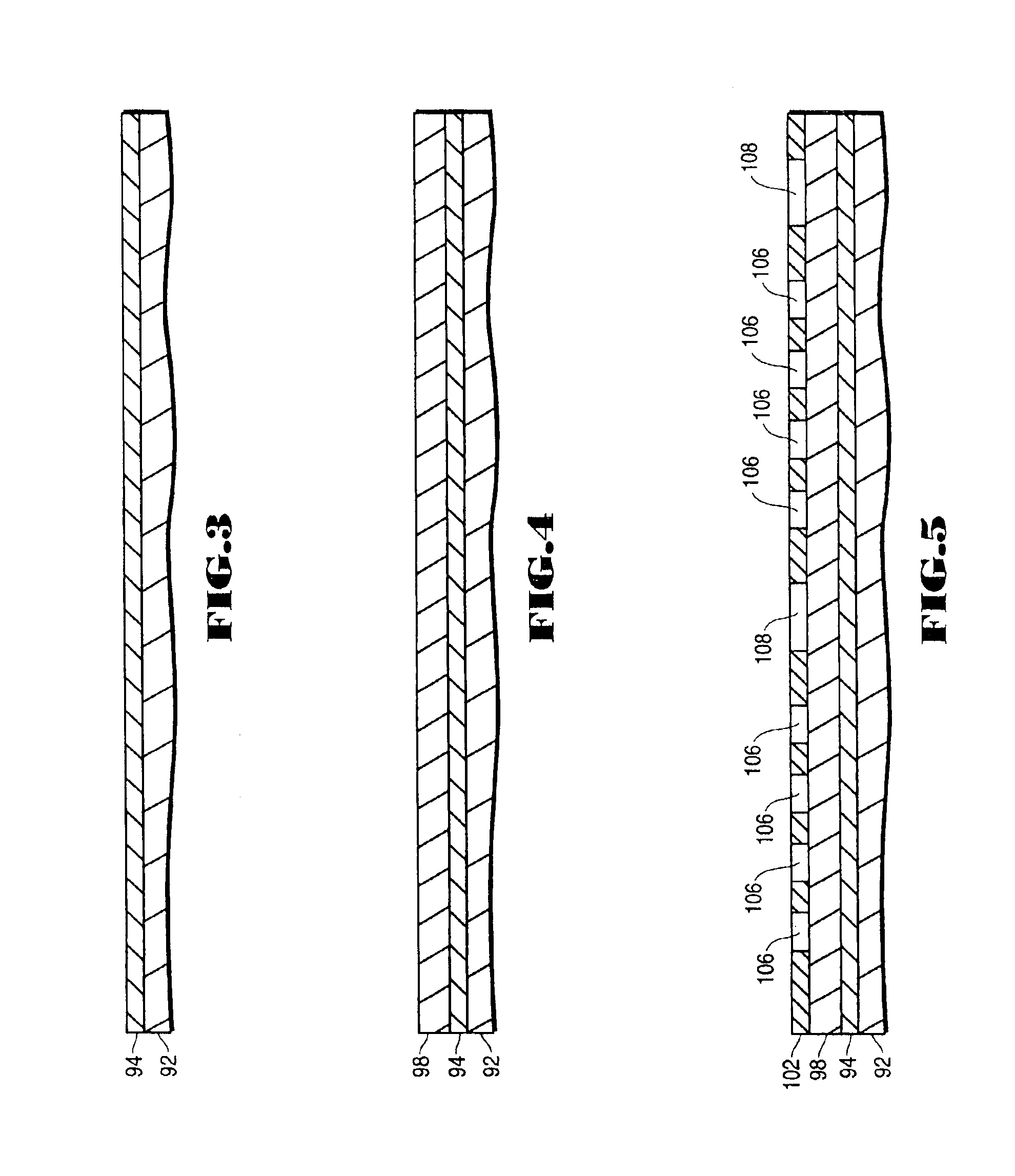

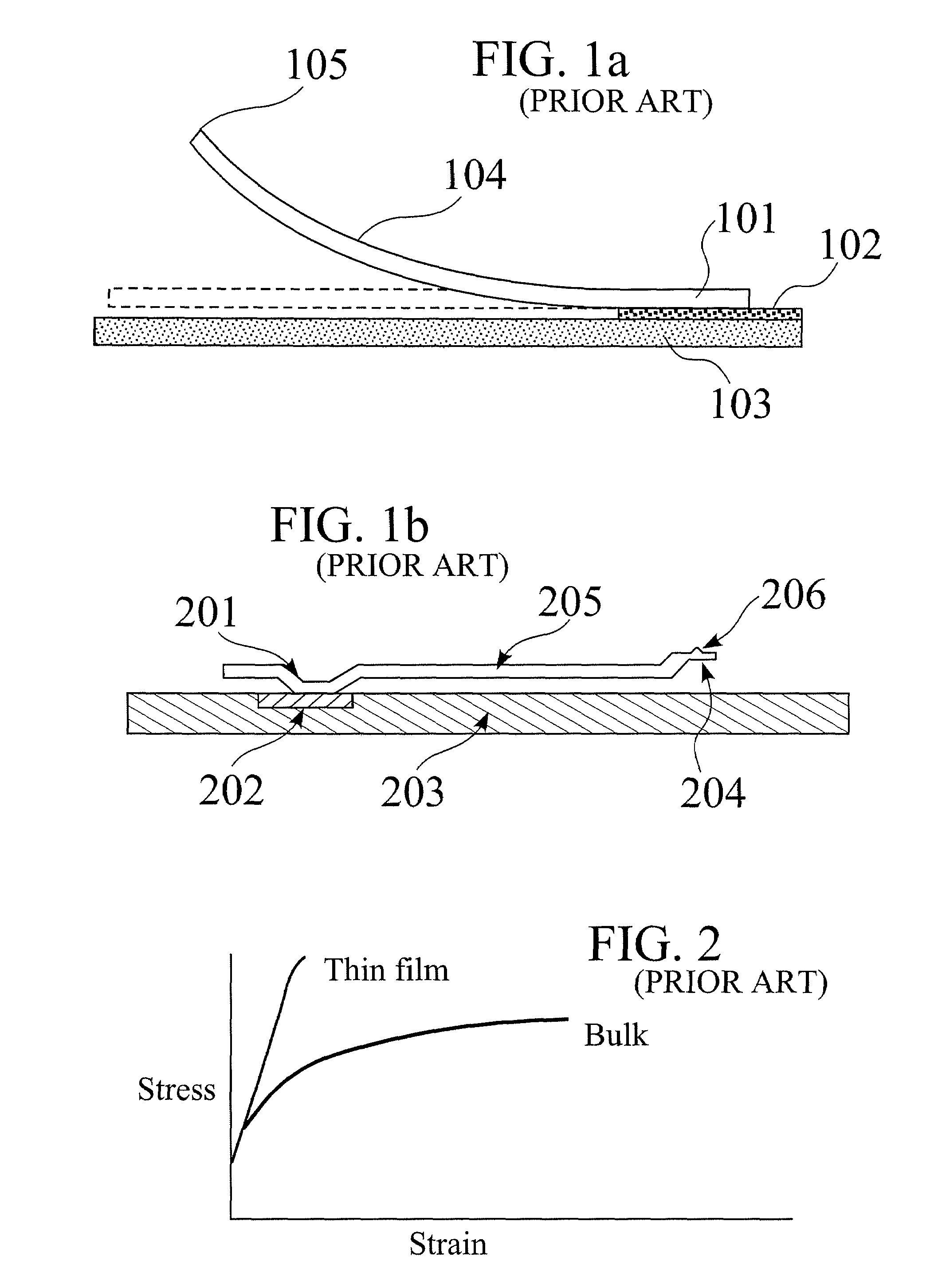

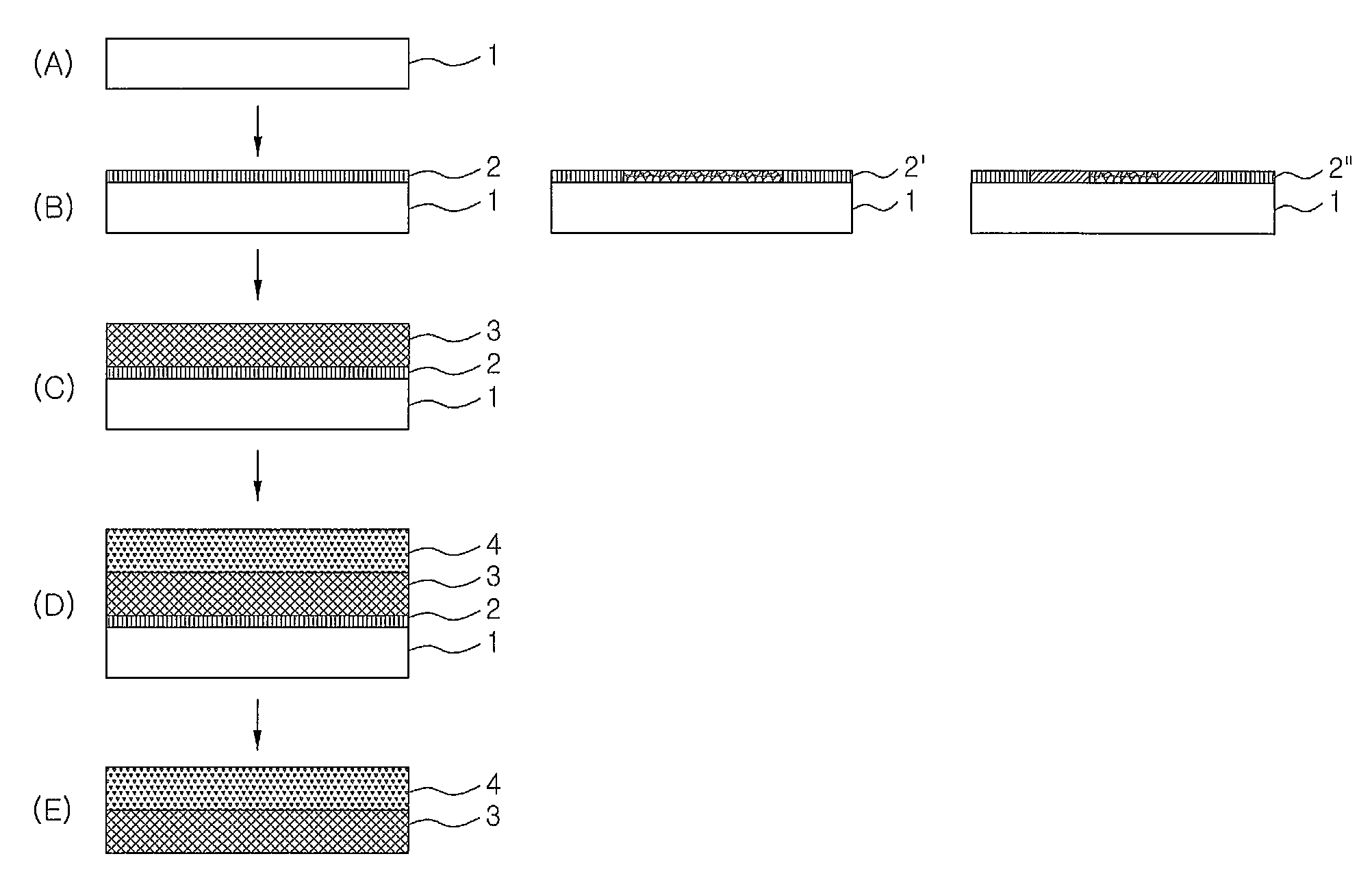

Multi-layer thin film for encapsulation and method thereof

InactiveUS20110100458A1Increase brightnessLow level of moistureLiquid surface applicatorsFinal product manufactureHigh resistanceMoisture penetration

A multi-layer thin film for encapsulation and the method thereof are provided. The multi-layer thin film for encapsulation includes a protective layer composed of aluminum oxide, a single or double barrier layer composed of silicon nitride (SiNx), and a mechanical protective layer composed of silicon dioxide (SiO2). The multi-layer thin film can be economically fabricated by using the existing equipment, and has a high level of light transmission over 85% while showing a low level of oxygen and moisture penetration. Additionally, due to superior adhesive strength between the thin films, and high resistance against impacts by heat or ion during a fabricating process, reliability of fabrication is enhanced, and it can thus efficiently used in encapsulating an organic light-emitting device (OLED), a flexible organic light emitting device (FOLED) in a display field, and the cells such as a thin film battery and a solar cell.

Owner:KOREA INST OF MASCH & MATERIALS

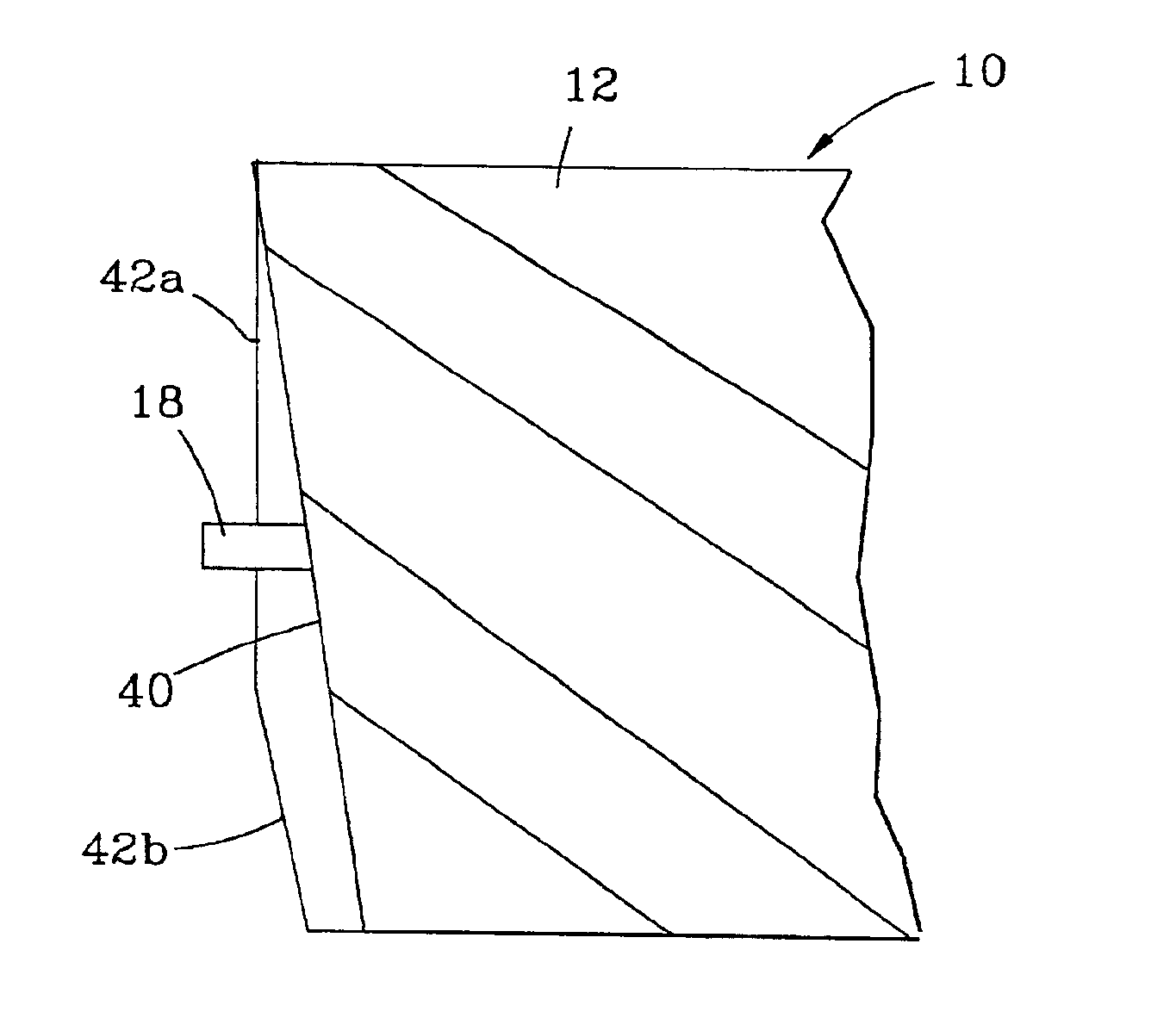

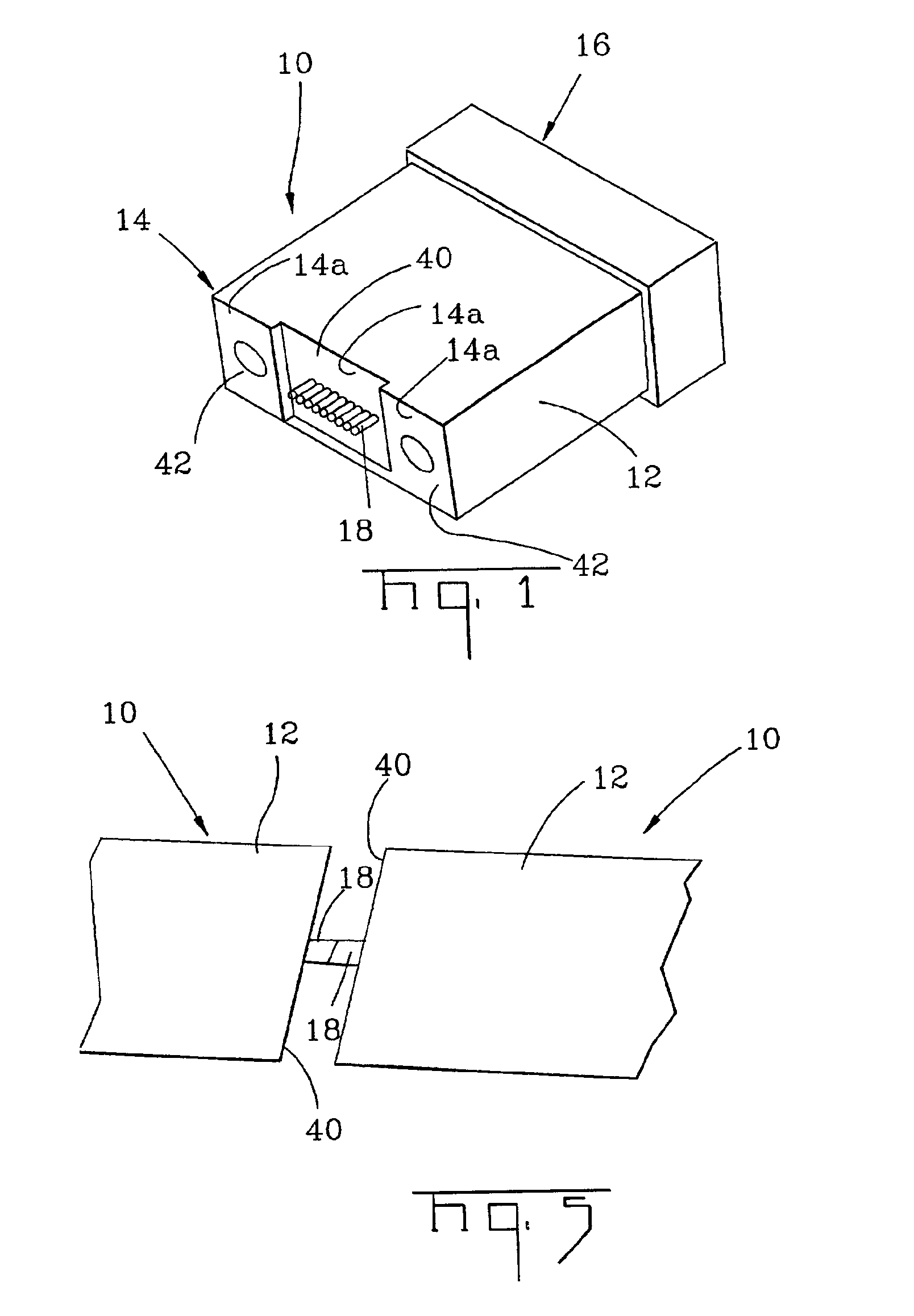

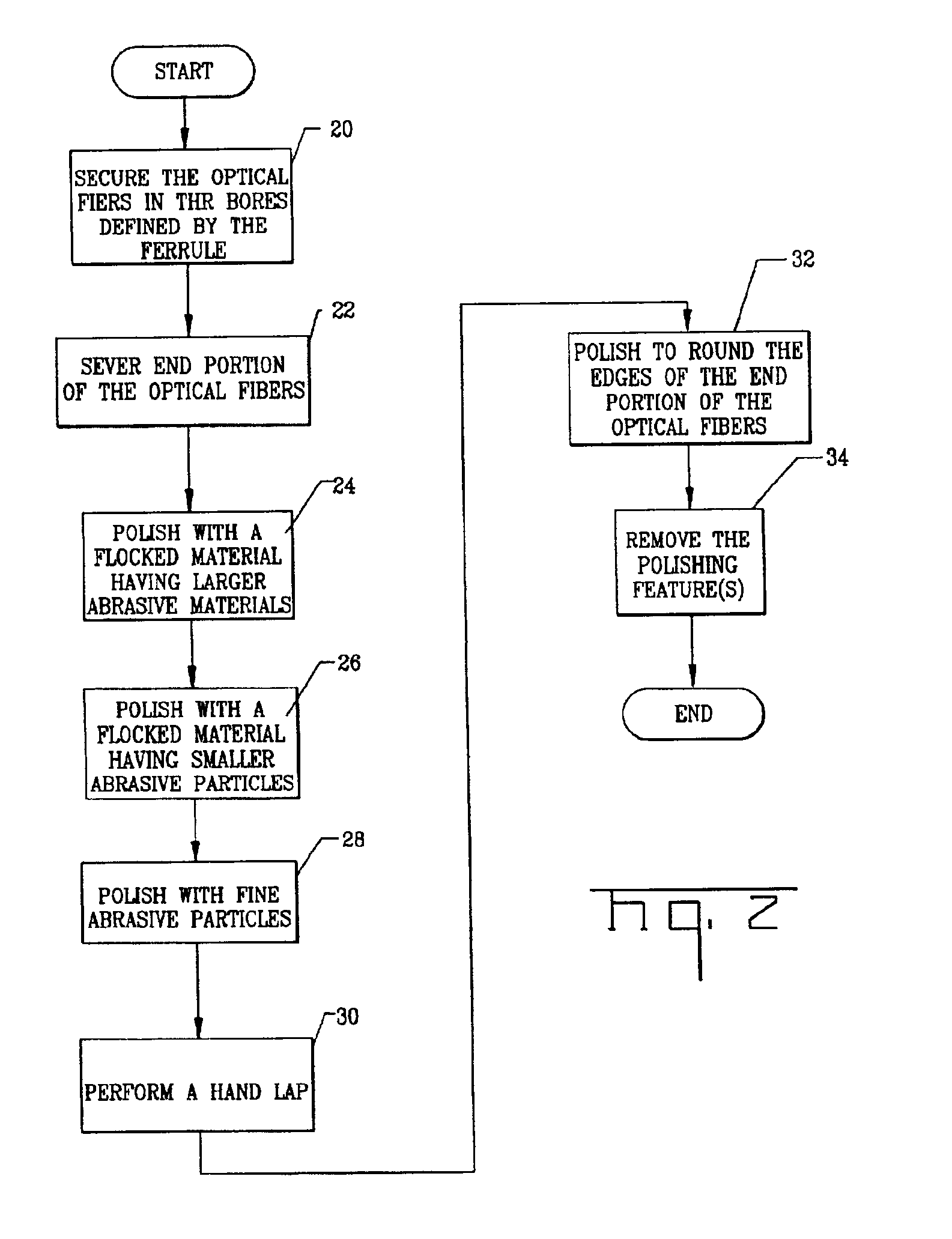

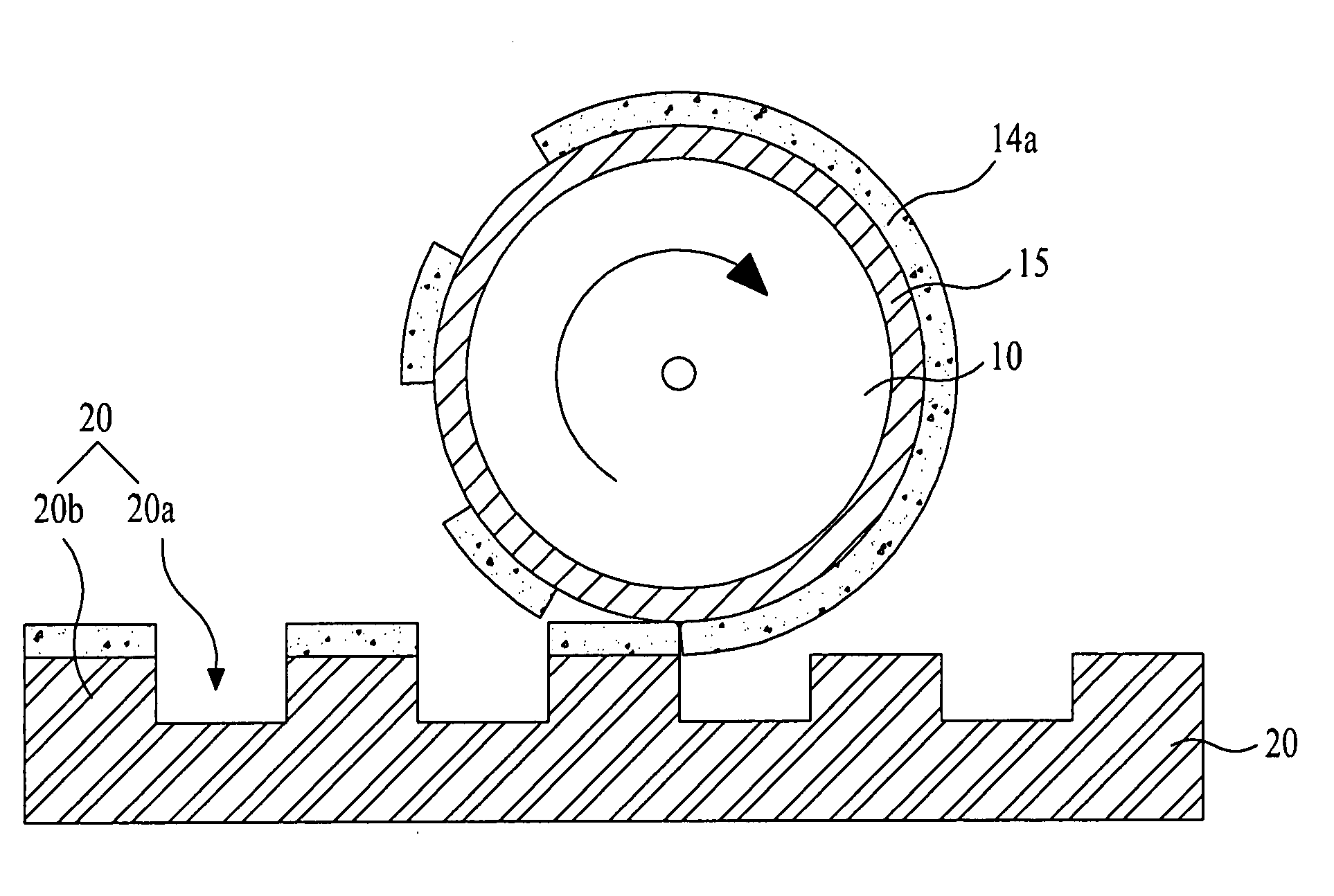

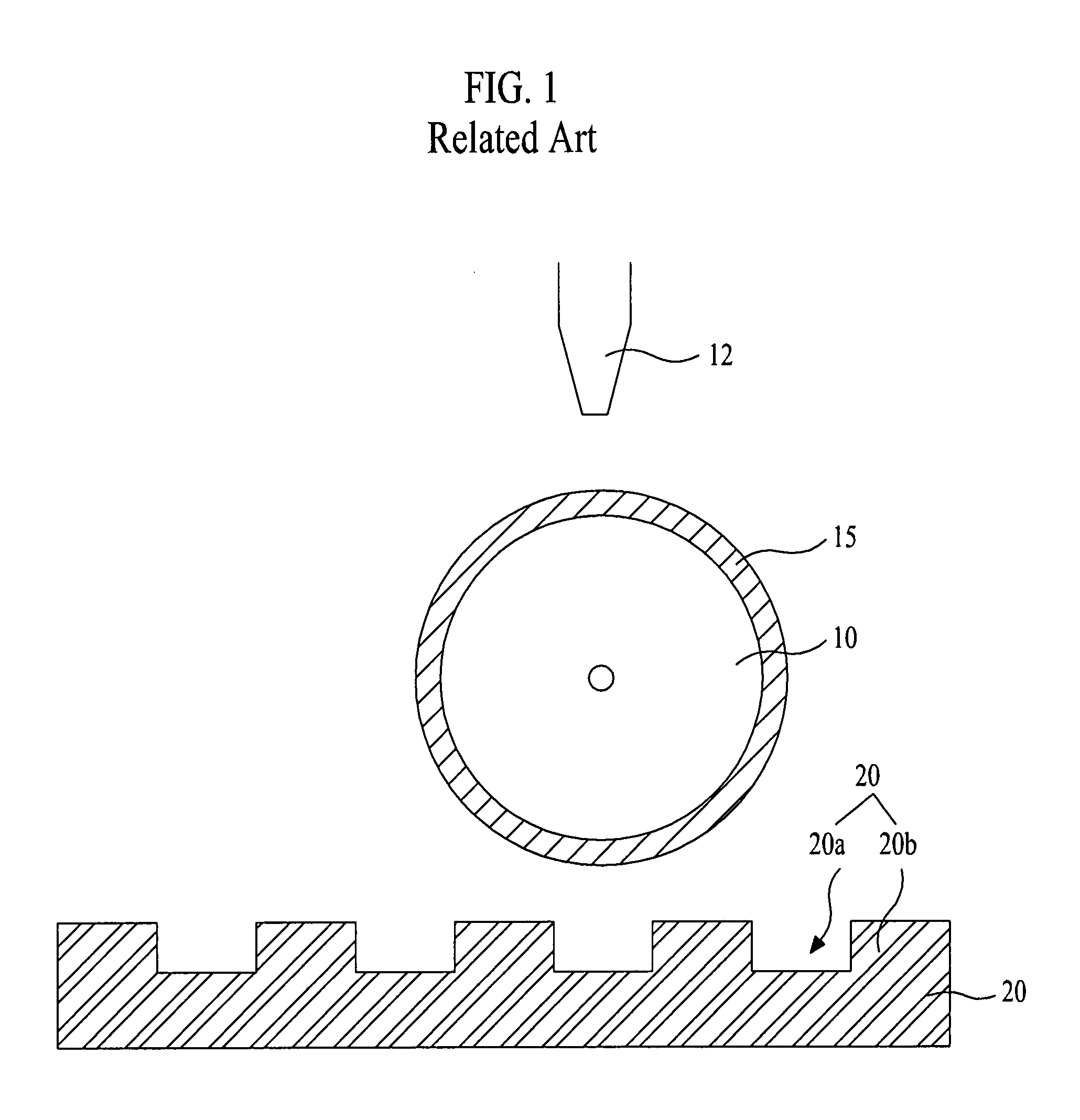

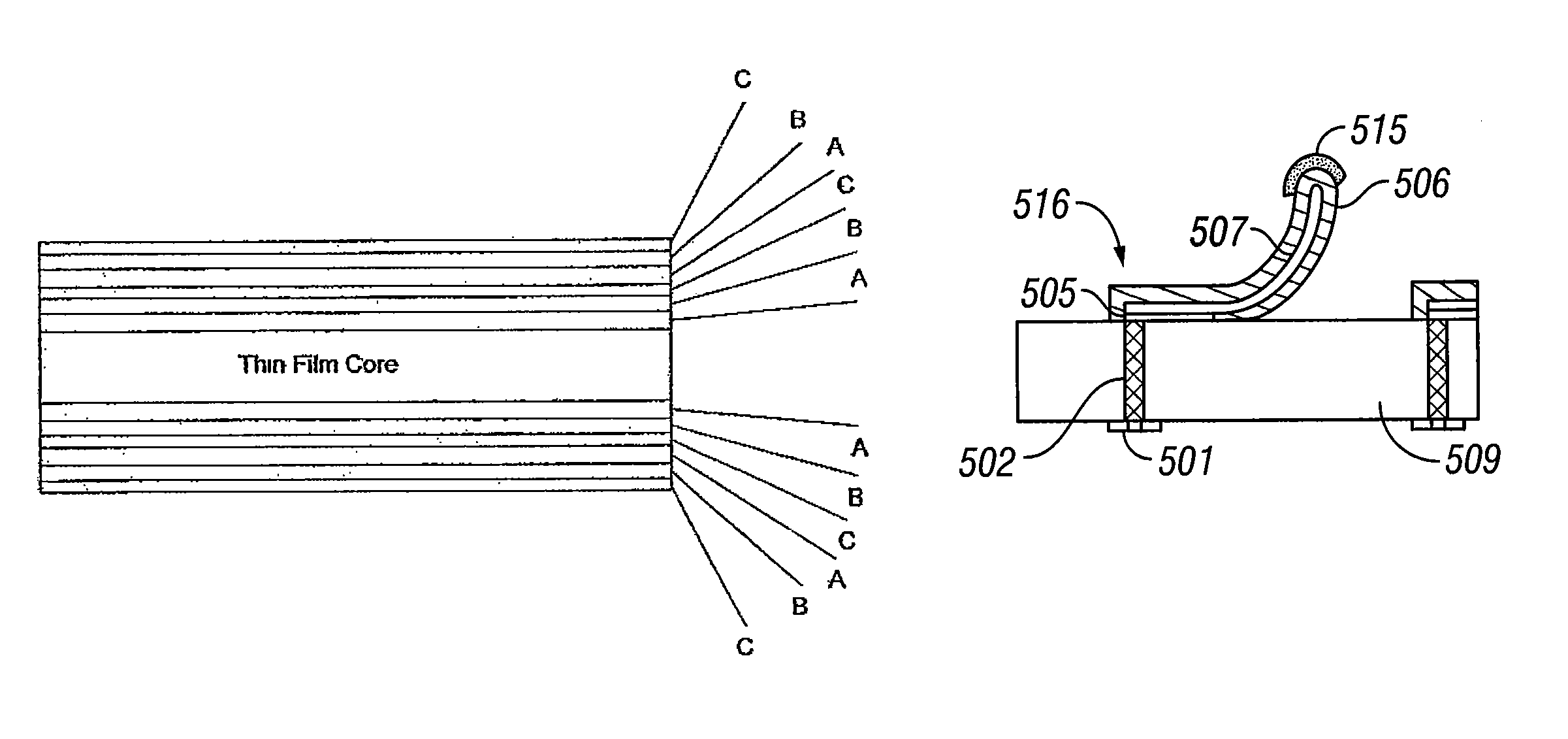

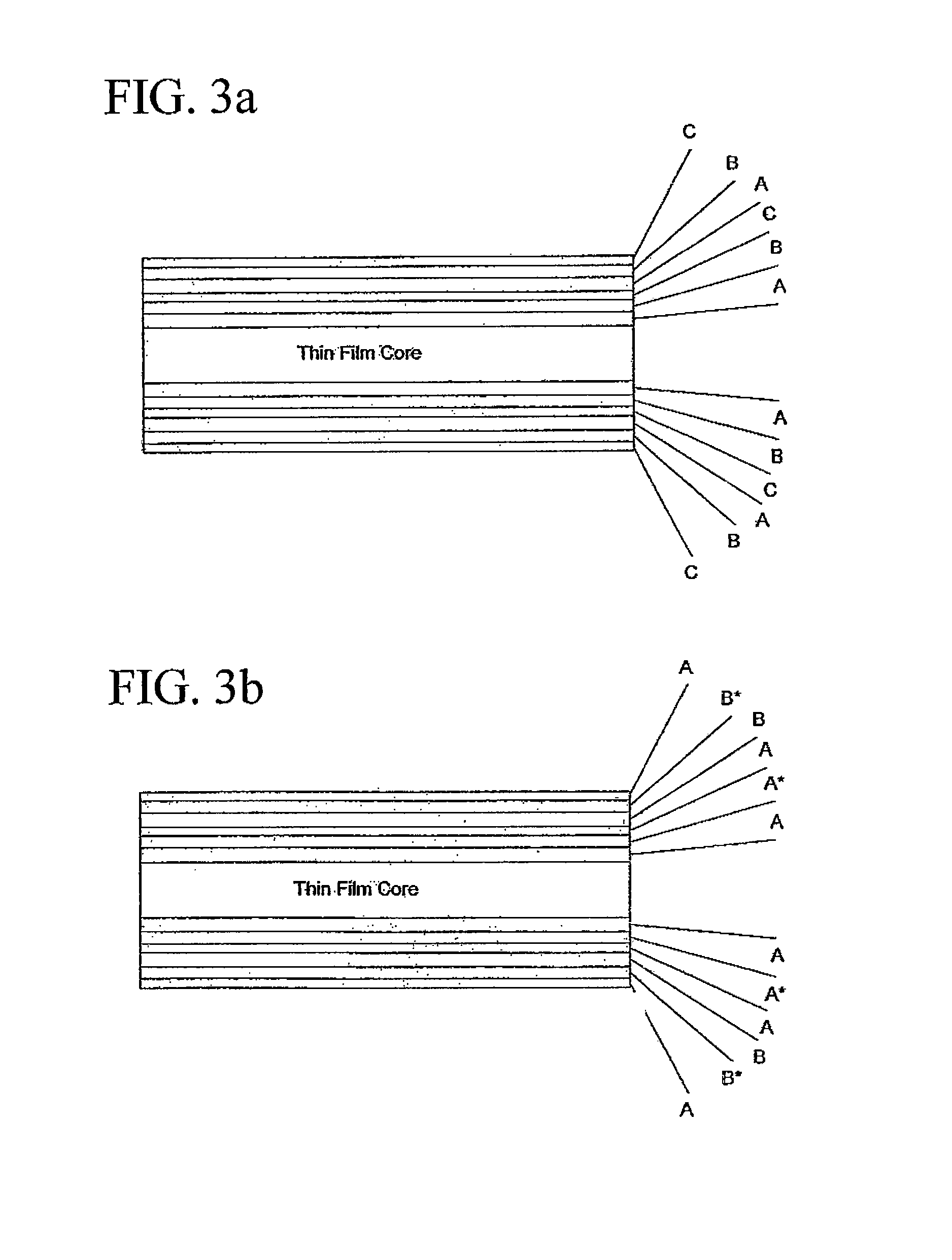

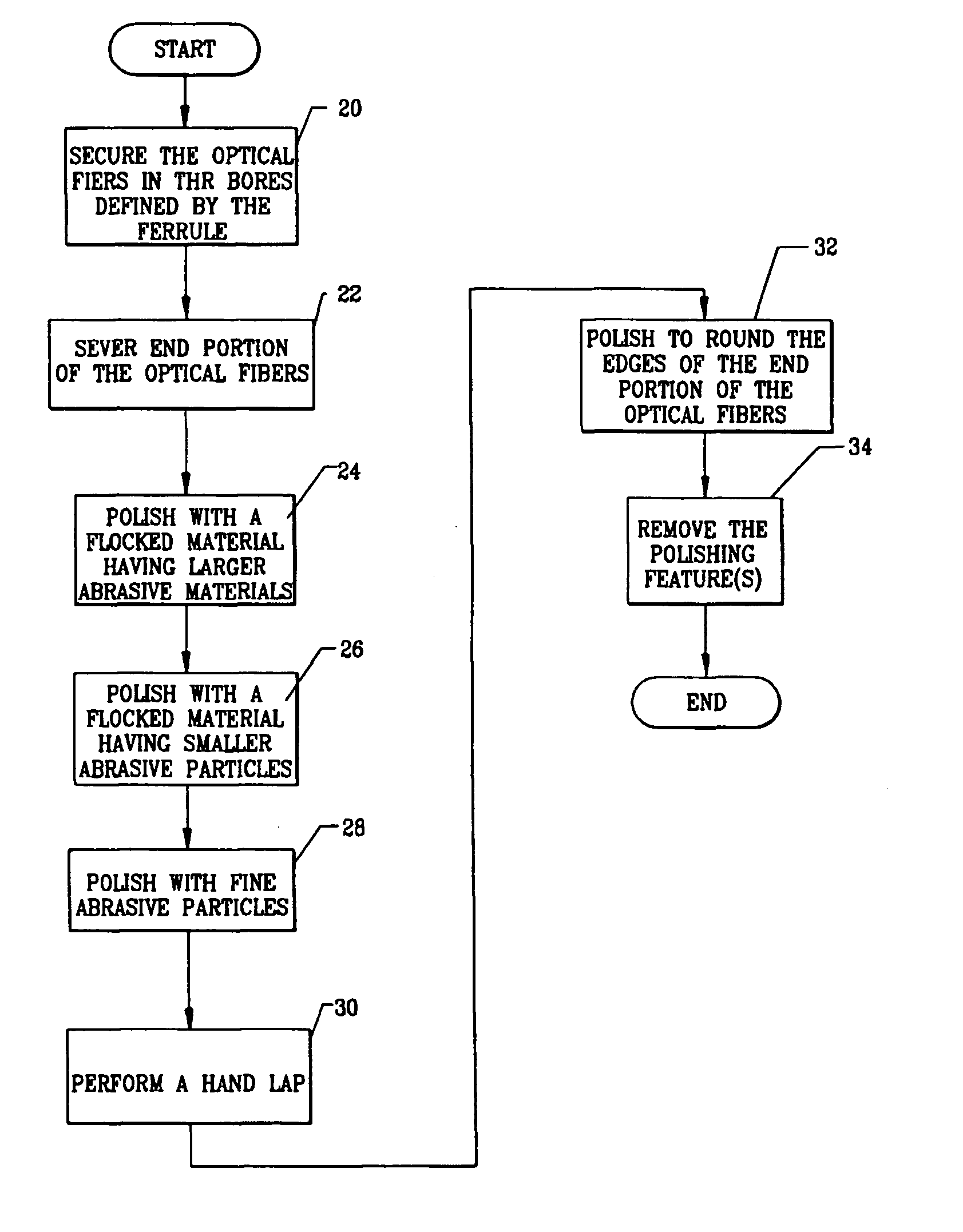

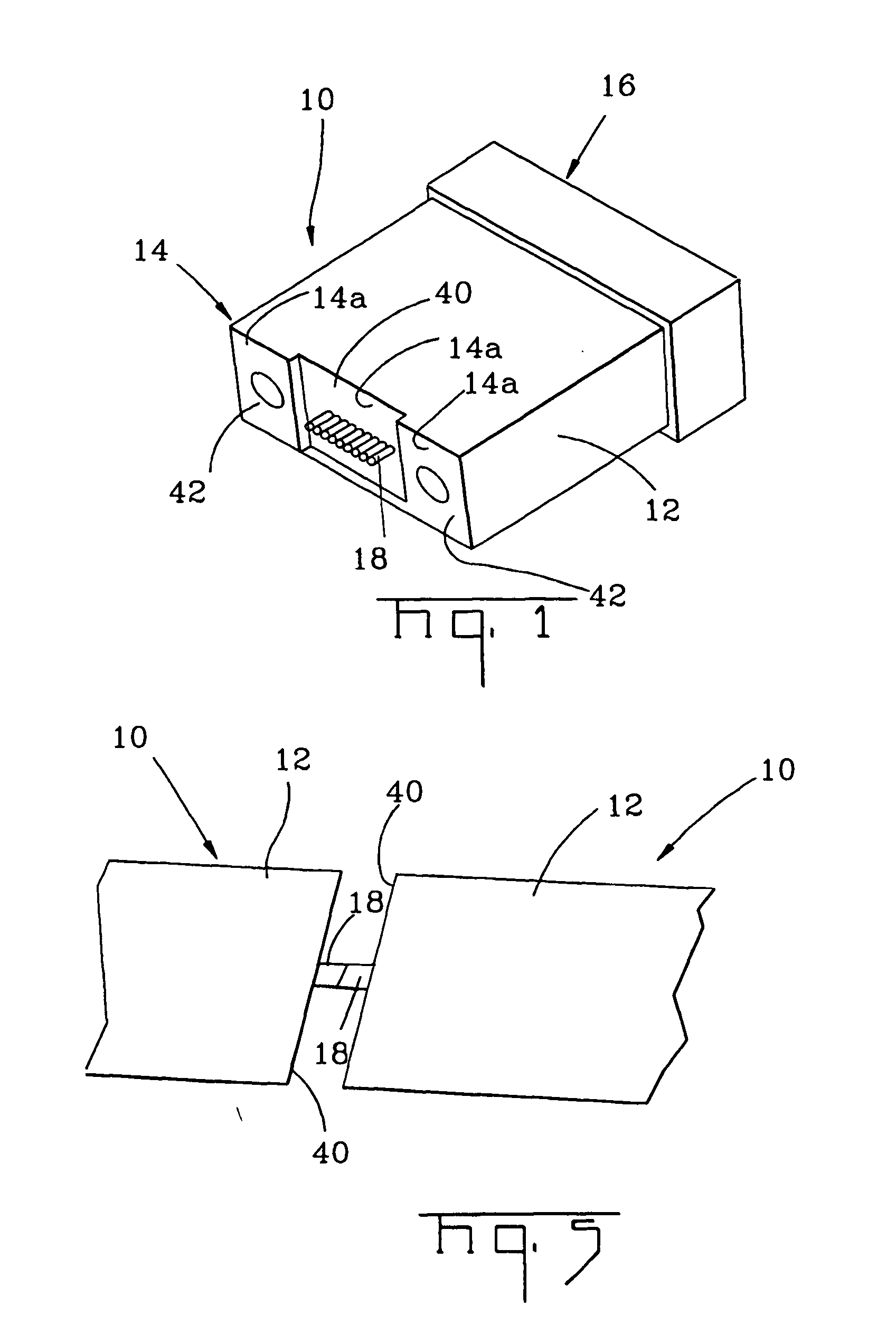

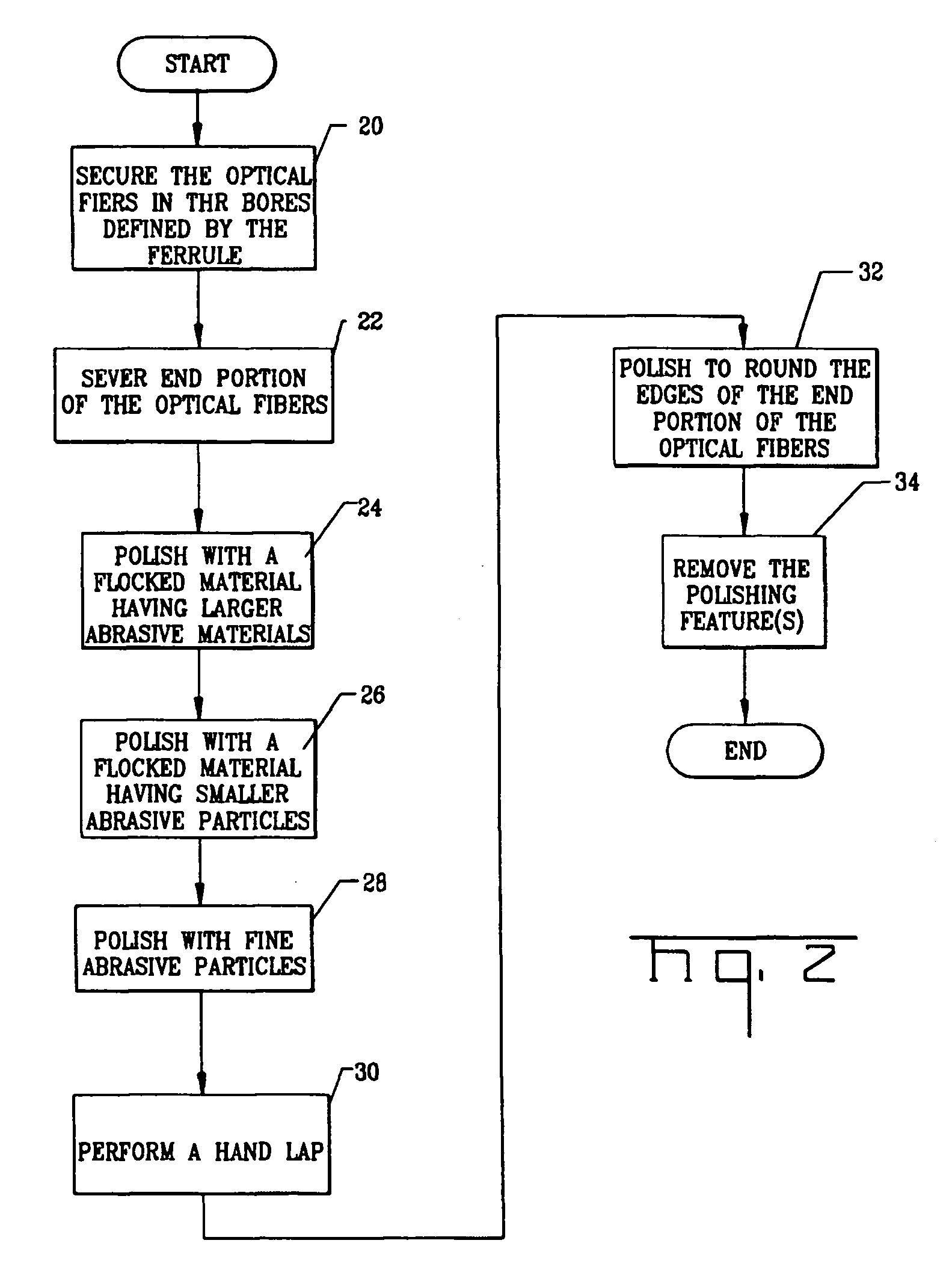

Ferrule assembly having highly protruding optical fibers and an associated fabrication method

InactiveUS6957920B2Reduce protrusionEffectively fabricatesCoupling light guidesBiomedical engineeringOptical fiber cable

A ferrule assembly having highly protruding optical fibers and a corresponding method of efficiently, precisely and repeatedly fabricating the ferrule assemblies are provided. In this regard, a ferrule assembly is provided that includes a plurality of optical fibers extending at least about 3.5 μm beyond the front face. The end portions of the optical fibers of the ferrule assembly may also be substantially coplanar with the end portions of the optical fibers differing in position from one another by no more than 100 nm. The ferrule assembly may be efficiently fabricated by polishing the optical fibers to a desired protrusion without first grinding or polishing the optical fibers to be flush with the front face of the ferrule. The ferrule assembly may be even more efficiently fabricated in instances in which the ferrule includes at least one polishing feature, such as an outwardly extending pedestal or a recessed portion.

Owner:CORNING OPTICAL COMM LLC

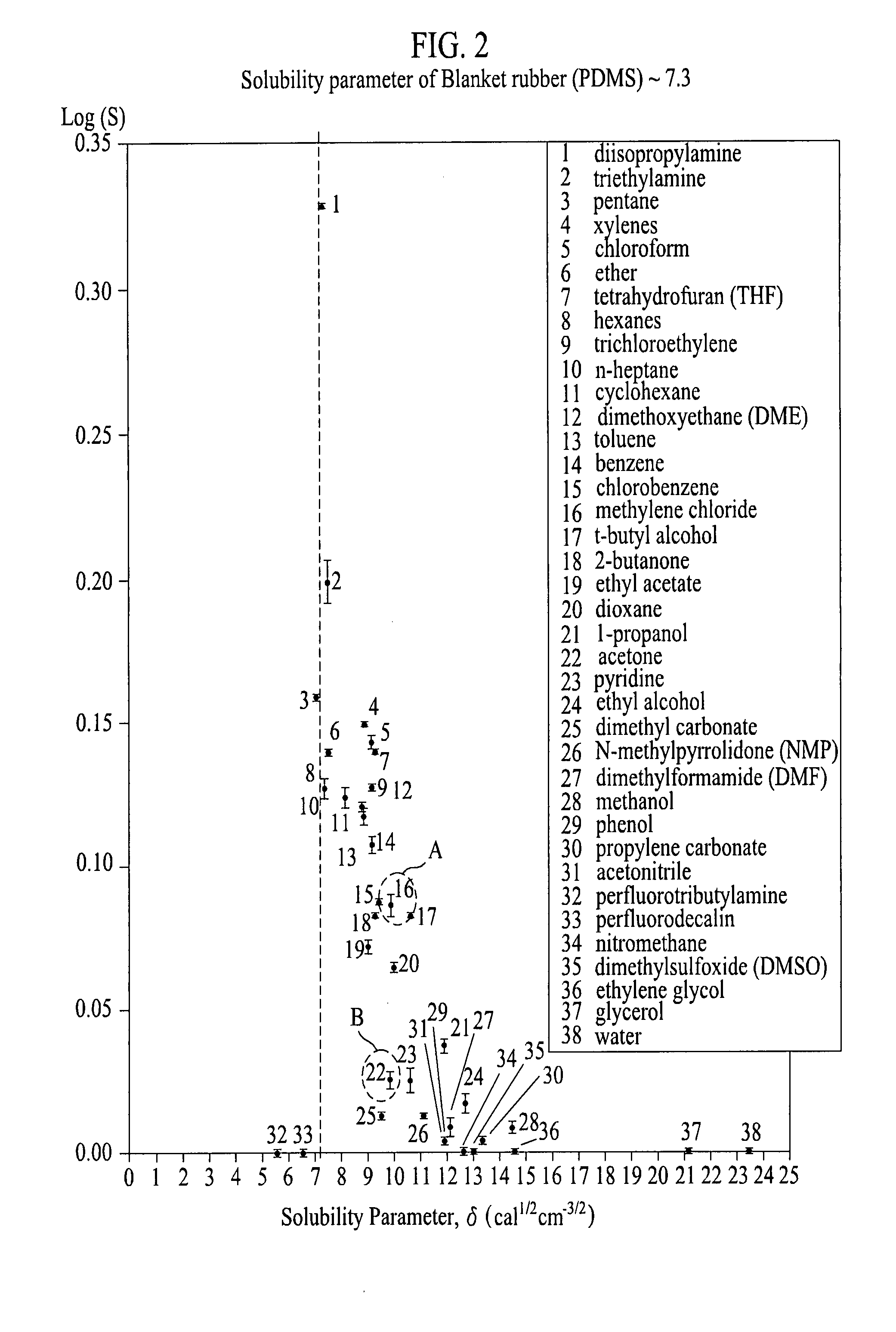

Etch resist solution, method of fabricating thin film pattern using the same and method of fabricating an LCD device using the same

ActiveUS20080173615A1Reduce fabrication costFabrication reliability be improveAfter-treatment detailsDecorative surface effectsSolventResist

A method of fabricating a thin film pattern improve the life of a blanket and reduce the cost and improve reliability in forming the thin film pattern. The method includes injecting an etch resist solution into a blanket on a printing roller, wherein the etch resist solution includes a printing solvent that satisfies the condition 6>δsolvent or δsolvent>11, where δsolvent is the solubility parameter of the solvent, or satisfies the condition 6<δsolvent<11 and μ<2(D), where μ is the dipole moment of the solvent; rotating the printing roller to uniformly coat the etch resist solution on the blanket; rolling the printing roller coated with the etch resist solution onto a printing plate to pattern the etch resist solution to thereby form an etch resist pattern; transferring the etch resist pattern from the printing roller to a substrate; hardening the etch resist pattern; and forming a desired thin film pattern on the substrate using the etch resist pattern.

Owner:LG DISPLAY CO LTD

Fabrication method for a thin film semiconductor device, the thin film semiconductor device itself, liquid crystal display, and electronic device

InactiveUS20010013607A1Improve propertiesWell formedTransistorLinear bearingsActive-matrix liquid-crystal displayLiquid-crystal display

In order to fabricate a high performance thin film semiconductor device using a low temperature process in which it is possible to use low price glass substrates, a thin film semiconductor device has been fabricated by forming a silicon film at less than 450° C., and, after crystallization, keeping the maximum processing temperature at or below 350° C. In applying the present invention to the fabrication of an active matrix liquid crystal display, it is possible to both easily and reliably fabricate a large, high-quality liquid crystal display. Additionally, in applying the present invention to the fabrication of other electronic circuits as well, it is possible to both easily and reliably fabricate high-quality electronic circuits.

Owner:INTELLECTUAL KEYSTONE TECH LLC

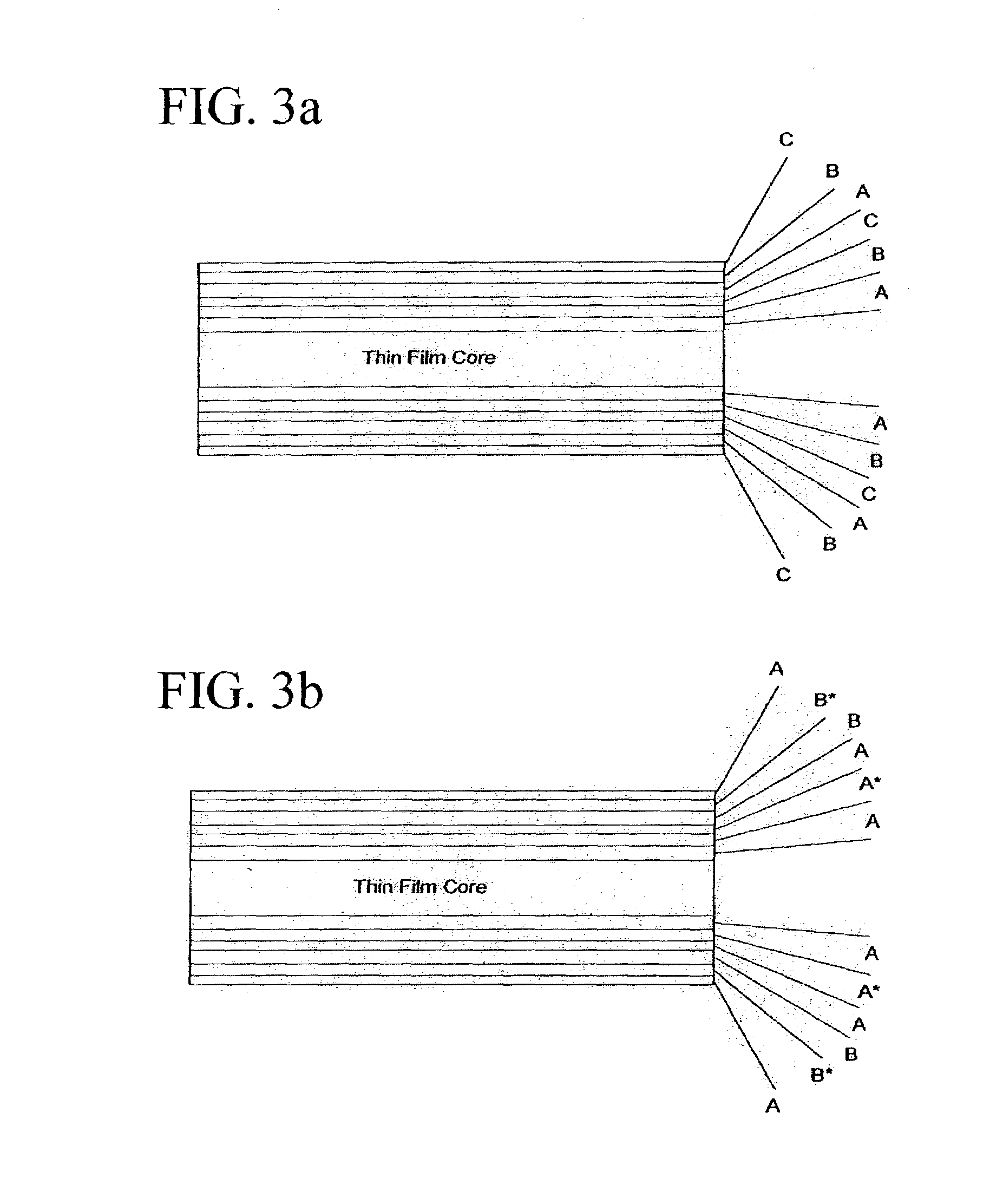

Miniaturized contact spring

InactiveUS7126220B2Increase yield strength and fatigue strengthReliably fabricateSemiconductor/solid-state device detailsSolid-state devicesContact padLife time

This invention provides a solution to increase the yield strength and fatigue strength of miniaturized springs, which can be fabricated in arrays with ultra-small pitches. It also discloses a solution to minimize adhesion of the contact pad materials to the spring tips upon repeated contacts without affecting the reliability of the miniaturized springs. In addition, the invention also presents a method to fabricate the springs that allow passage of relatively higher current without significantly degrading their lifetime.

Owner:ADVANTEST SINGAPORE PTE LTD

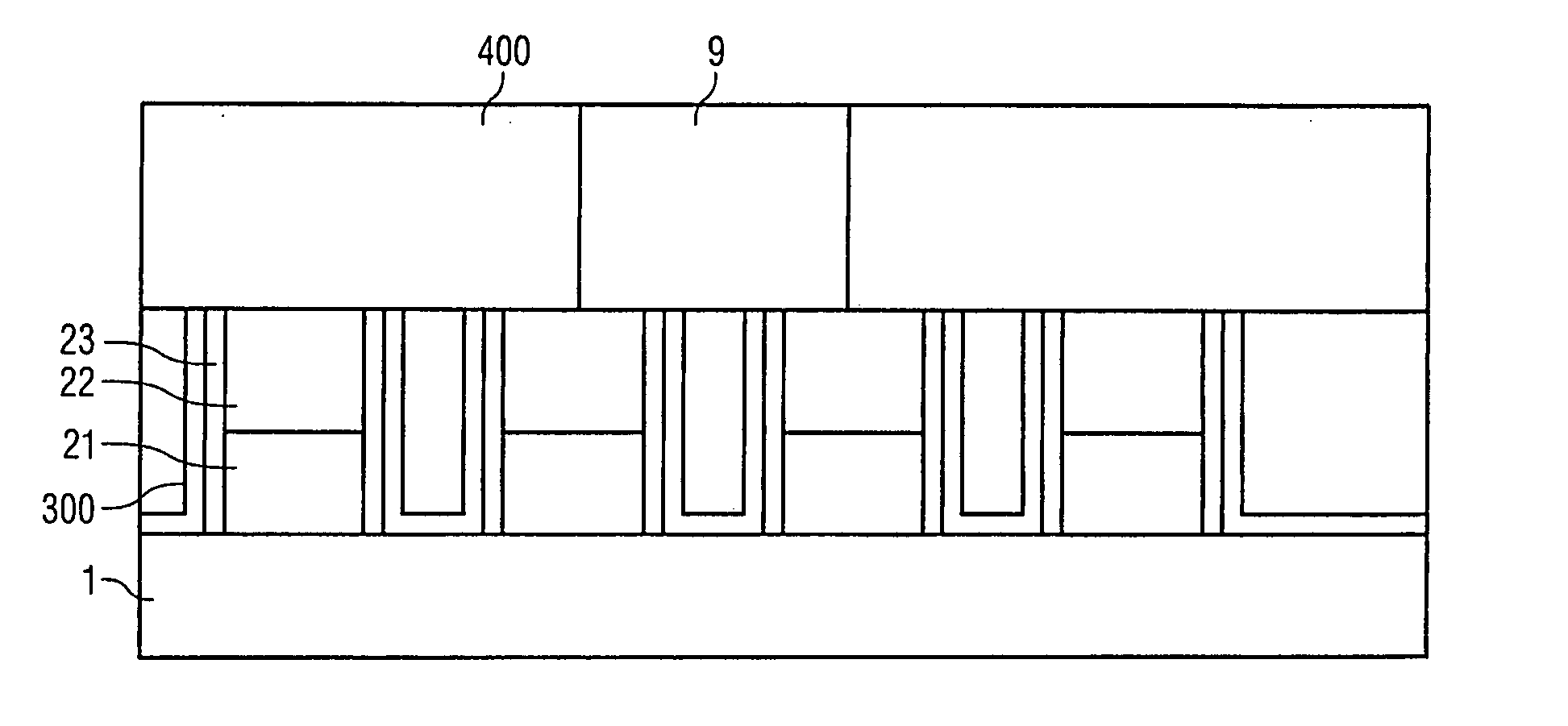

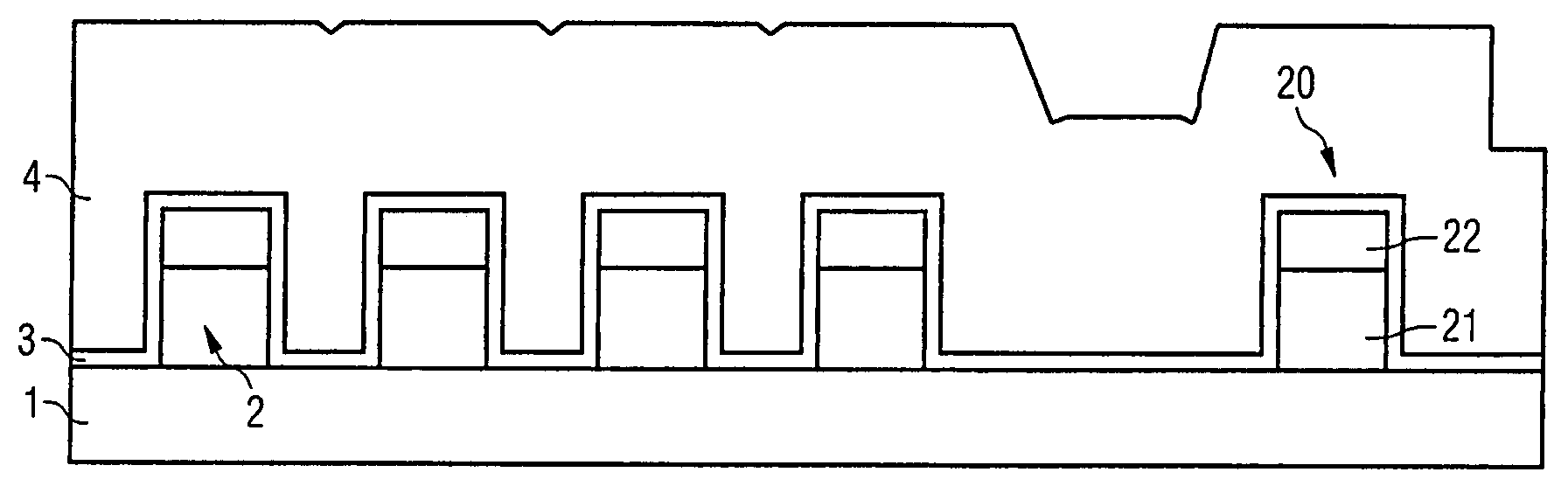

Method for fabricating a contact hole plane in a memory module

InactiveUS20050003308A1Reduce coupling capacitanceReliably fabricatedSolid-state devicesPhotomechanical apparatusConductive materialsSemiconductor

In order to fabricate a contact hole plane in a memory module with an arrangement of memory cells each having a selection transistor, on a semiconductor substrate with an arrangement of mutually adjacent gate electrode tracks on the semiconductor surface, an insulator layer is formed on the semiconductor surface and a sacrificial layer is subsequently formed on the insulator layer, then material plugs are produced on the sacrificial layer for the purpose of defining contact openings between the mutually adjacent gate electrode tracks, the sacrificial layer is etched to form material plugs with the underlying sacrificial layer blocks, after the production of the vitreous layer with uncovering of the sacrificial layer blocks above the contact openings between the mutually adjacent gate electrode tracks, an essentially planar surface being formed, then the sacrificial layer material is etched out from the vitreous layer and the uncovered insulator material is removed above the contact openings on the semiconductor surface and, finally, the contact opening regions are filled with a conductive material.

Owner:POLARIS INNOVATIONS LTD

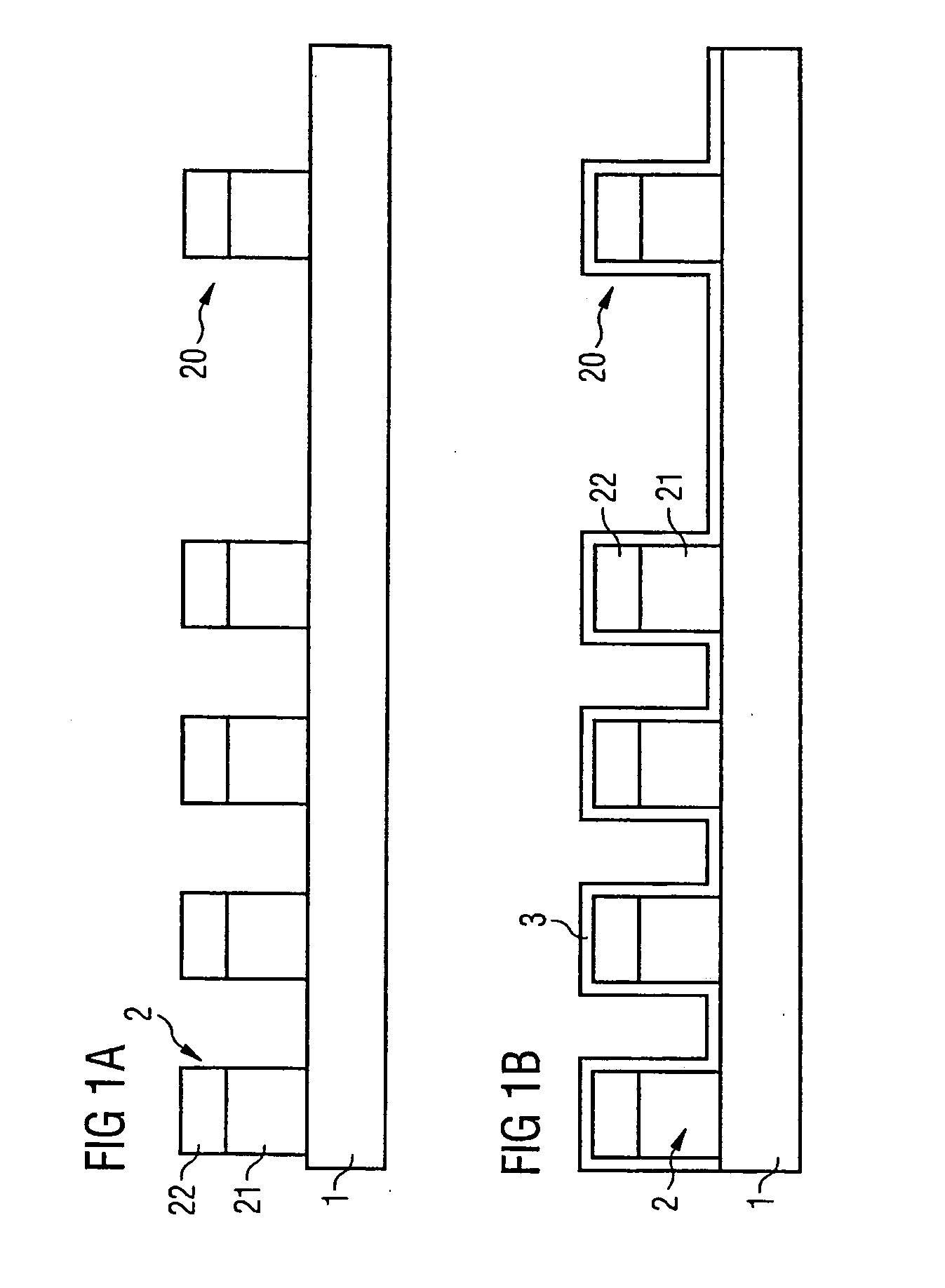

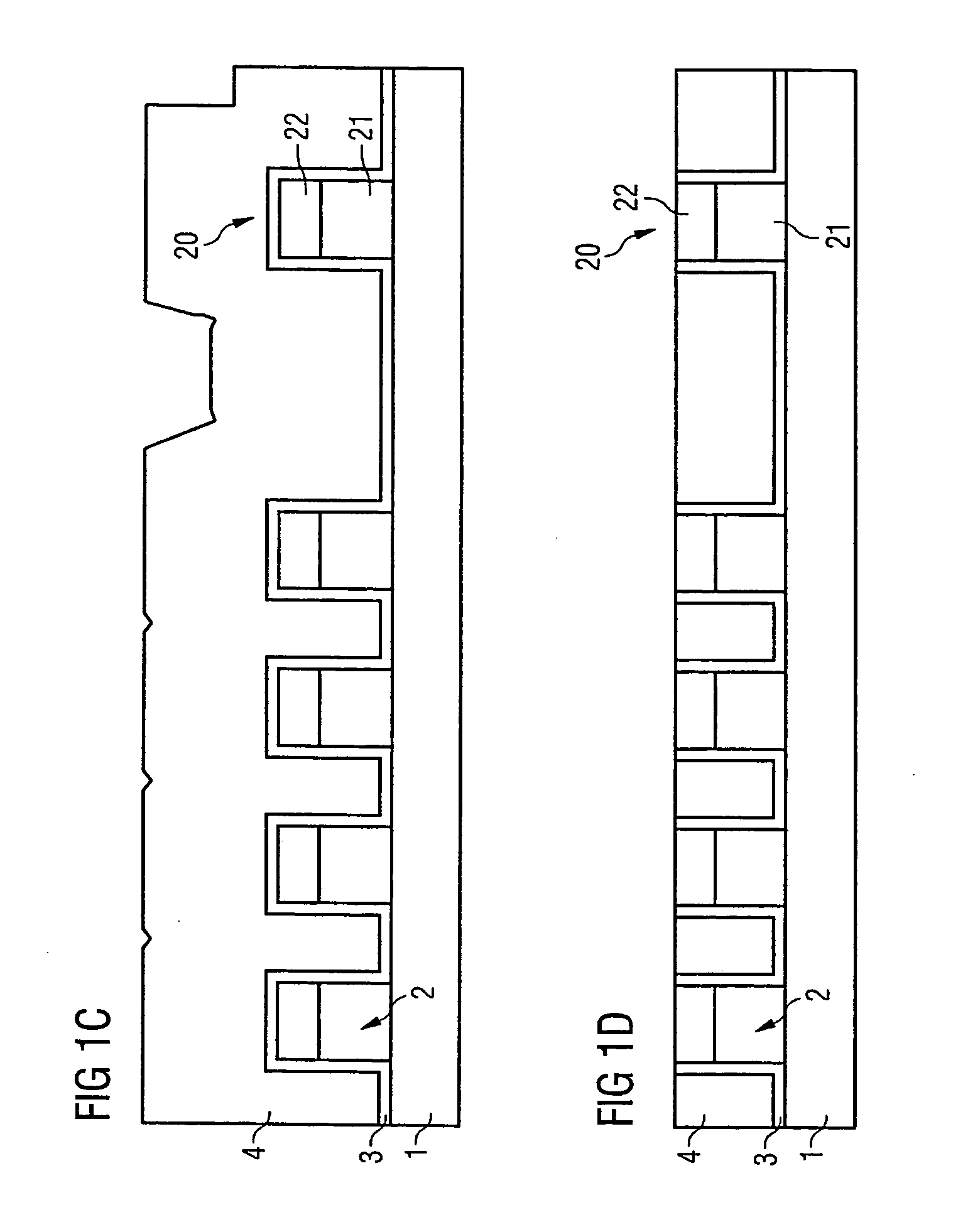

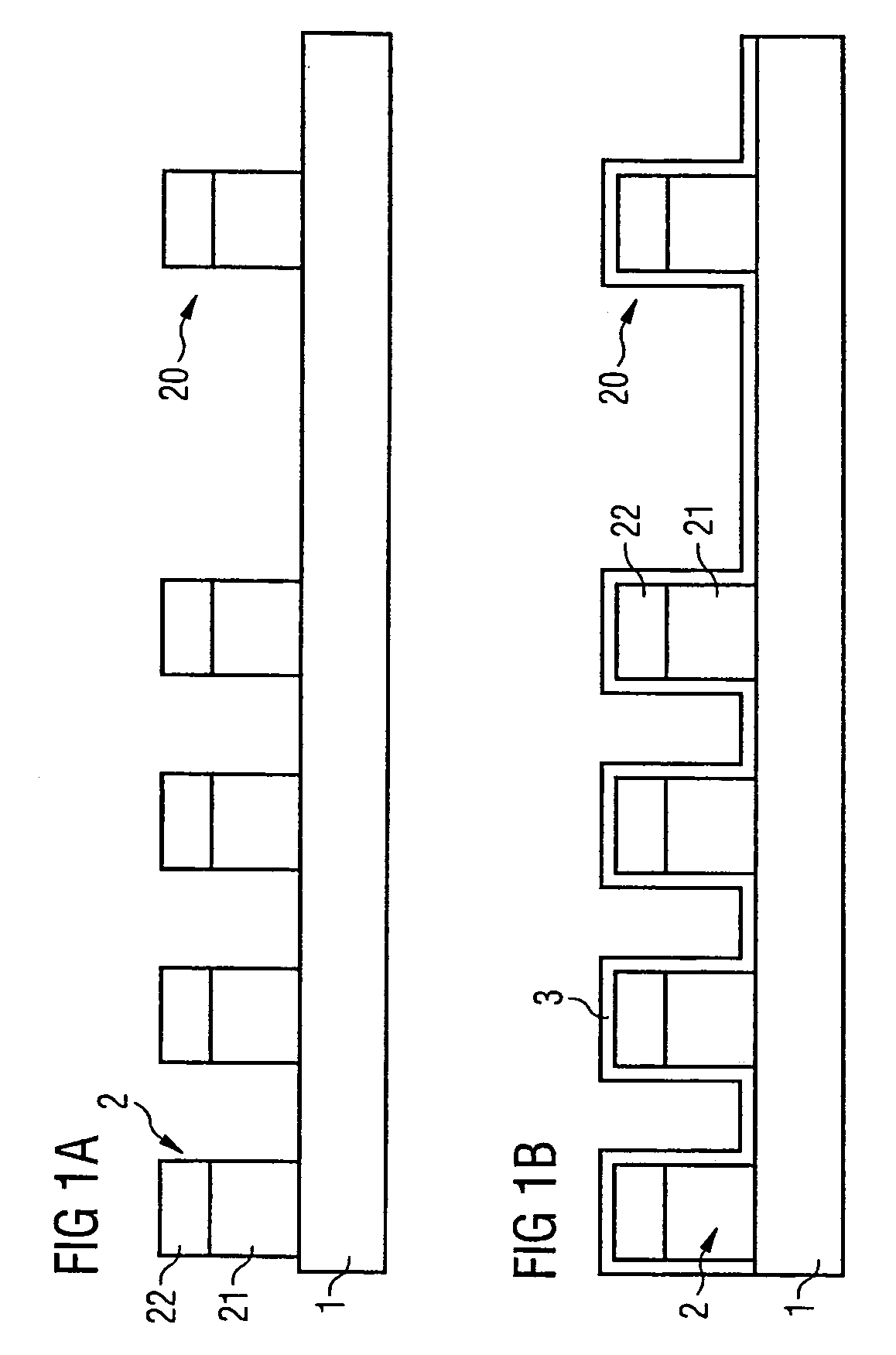

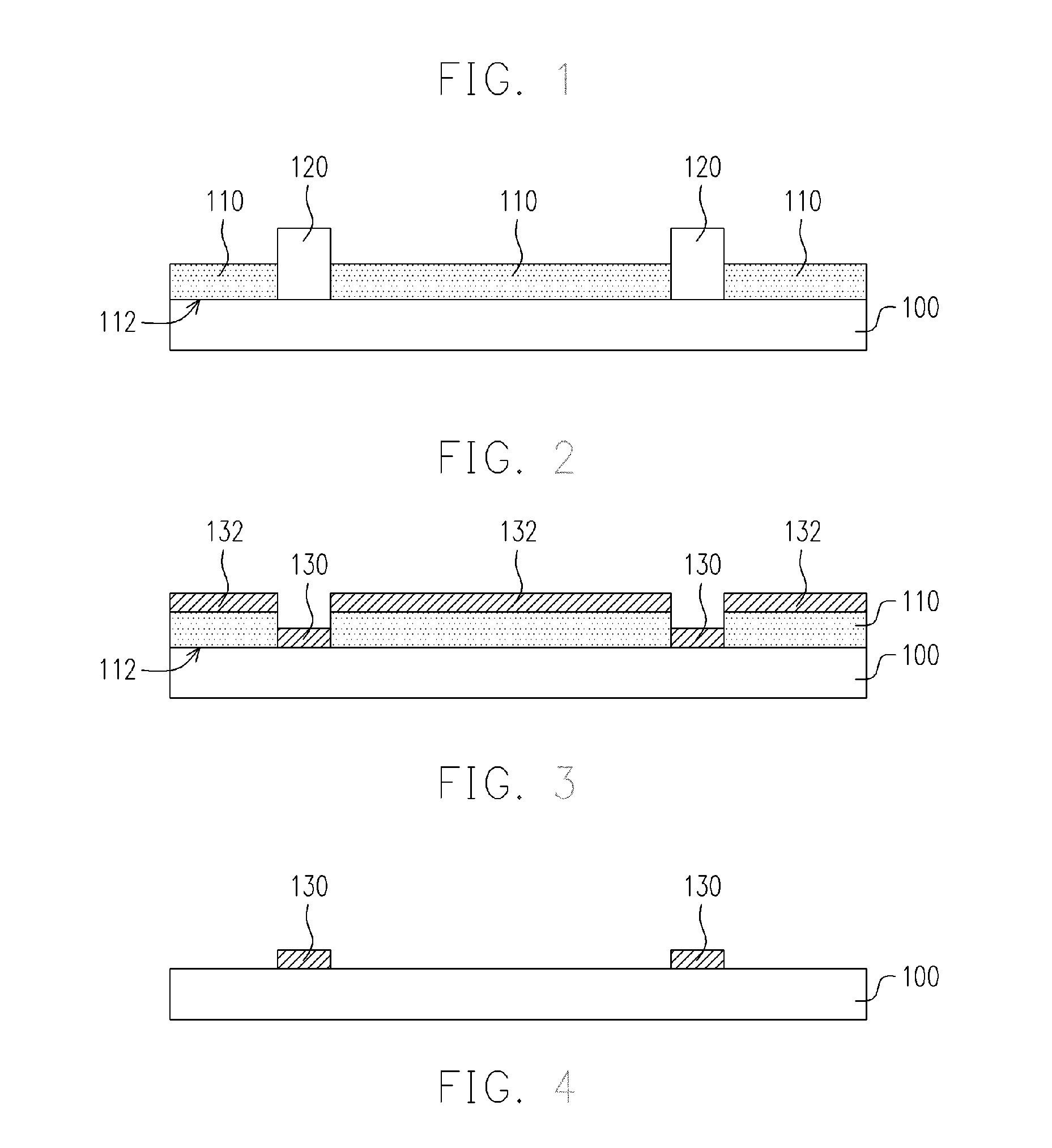

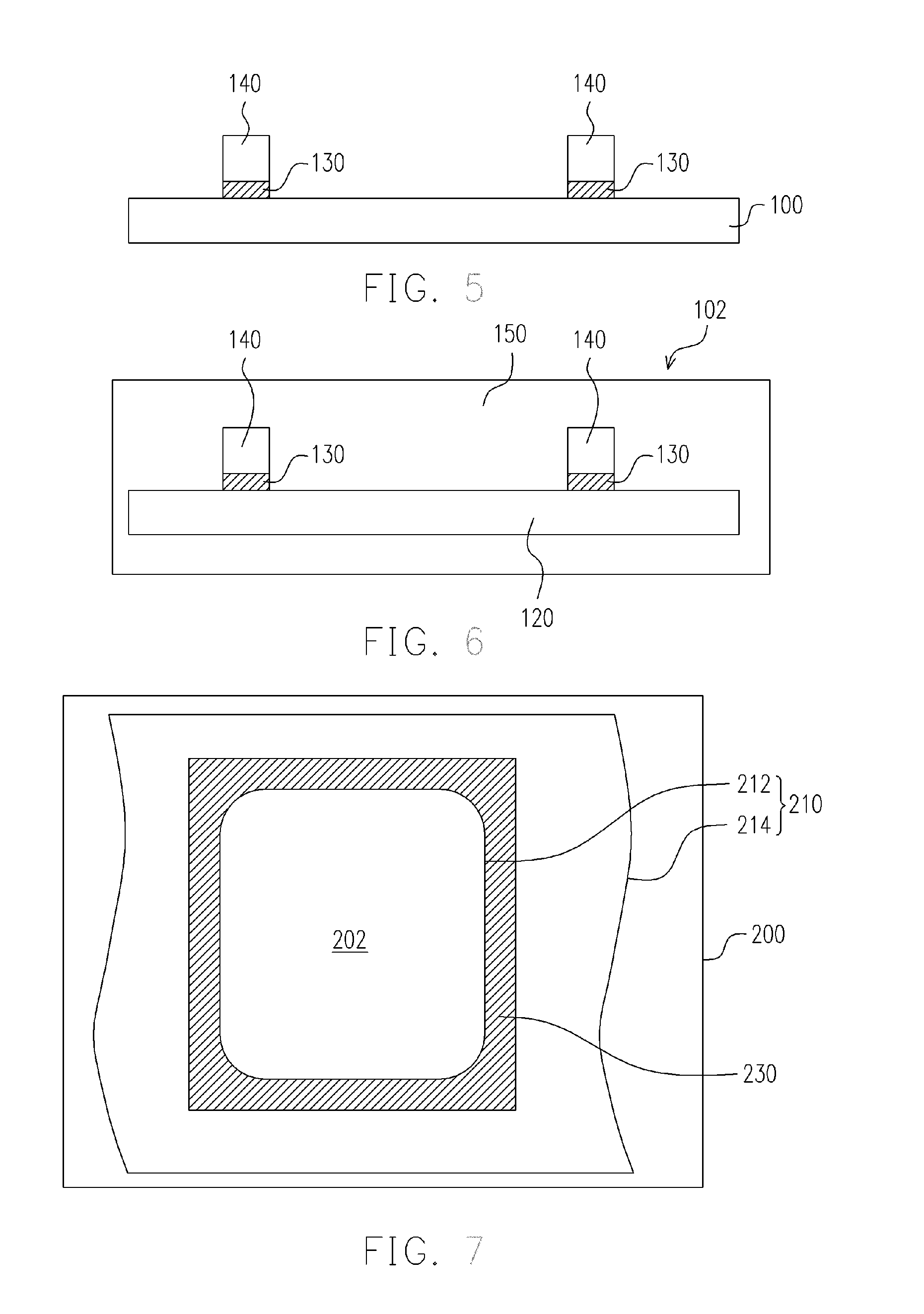

Fabrication Method of Flexible Devices

ActiveUS20120061881A1Easy to separateReliably fabricatedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSolvent

Disclosed is a method of fabricating a flexible device, which includes surface-treating one or both sides of a carrier plate so that regions with different surface-treatments are formed on the same side of the carrier plate, forming a glass-filler reinforced plastic substrate film on the surface-treated carrier plate, forming thin film patterns on the glass-filler reinforced plastic substrate film, and separating the glass-filler reinforced plastic substrate film having the thin film patterns formed thereon from the carrier plate, and in which the surface-treating of the carrier plate enables the glass-filler reinforced plastic substrate film to be easily separated from the carrier plate without an additional process such as using a solvent or a laser release technique.

Owner:KOREA ADVANCED INST OF SCI & TECH

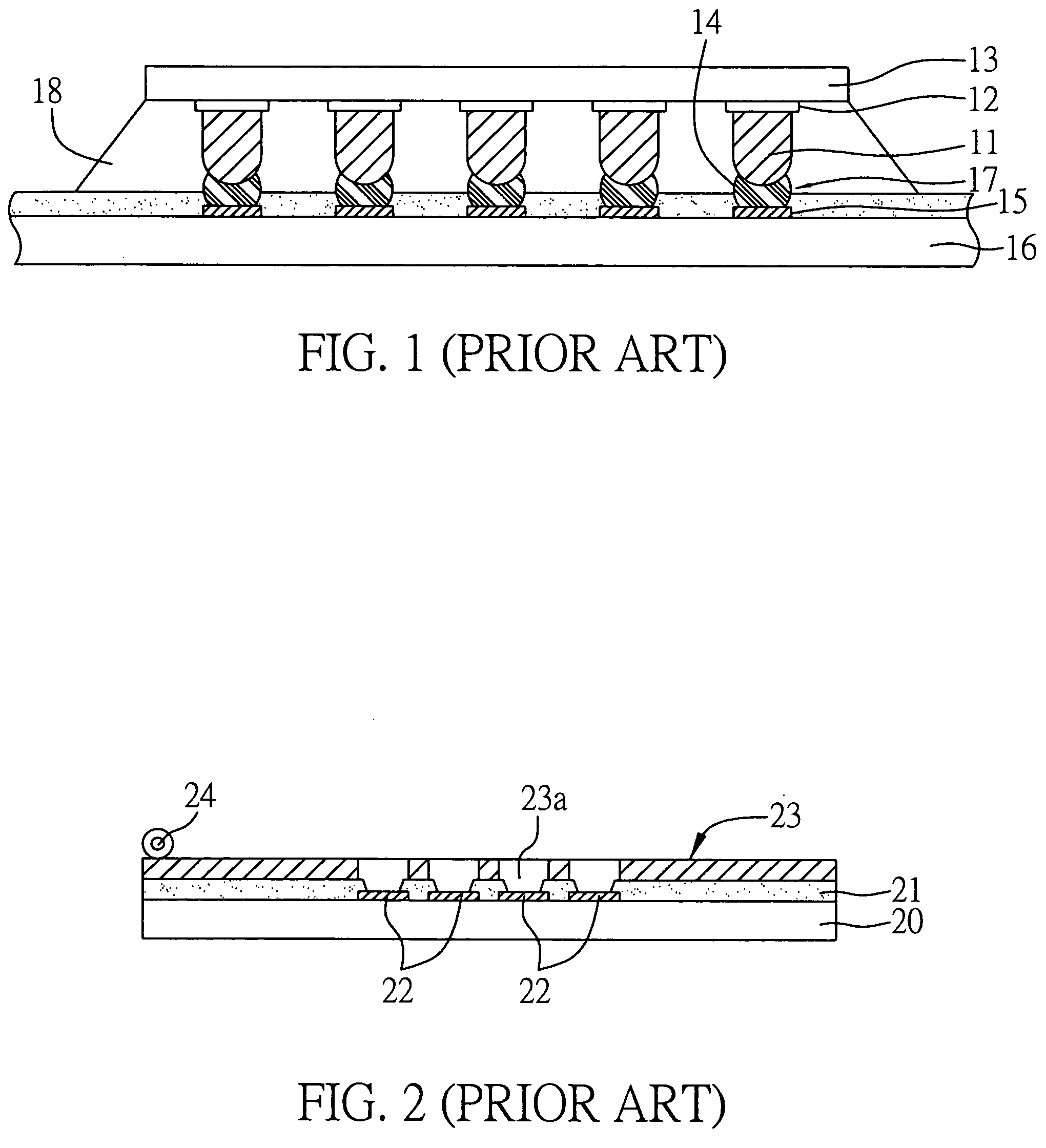

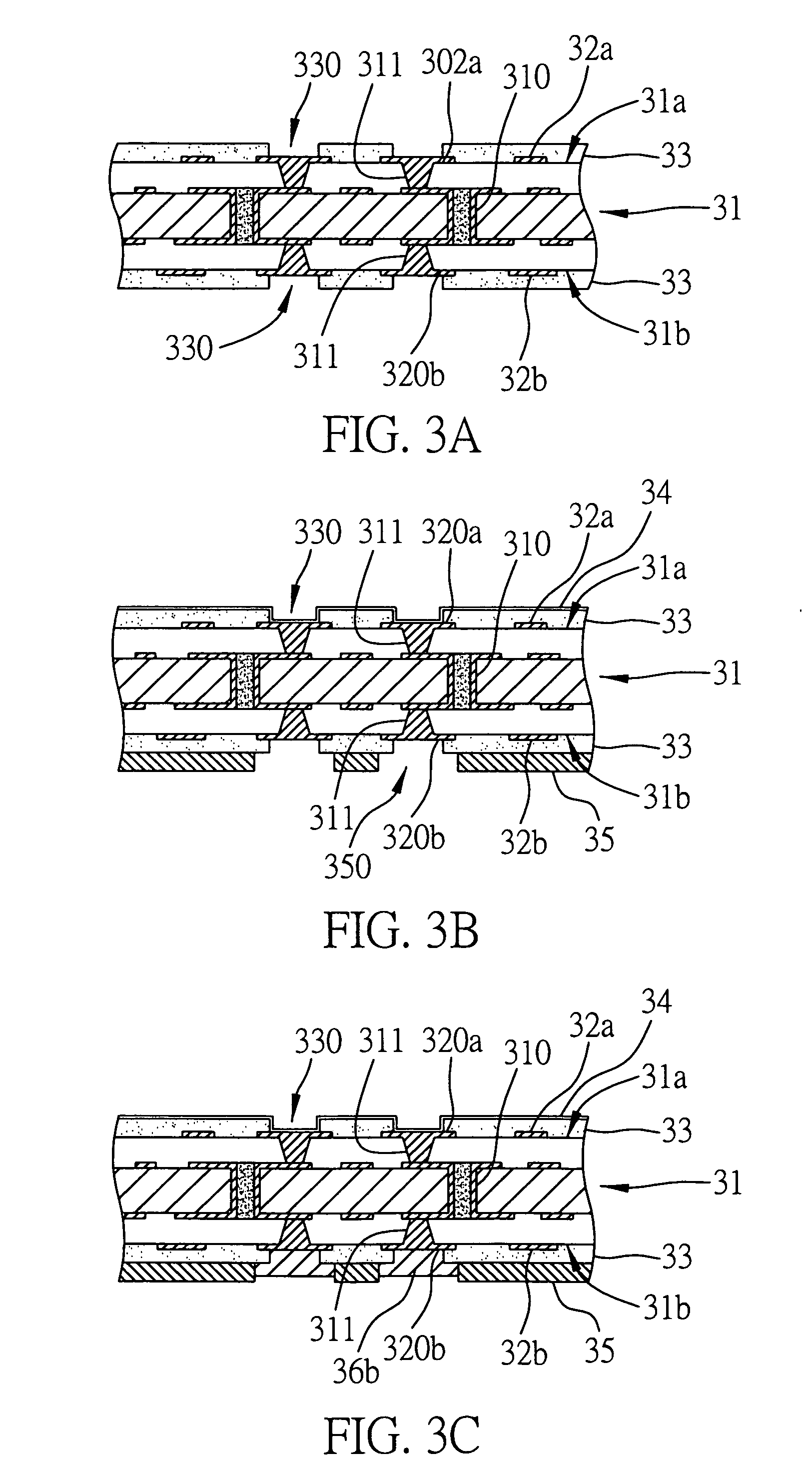

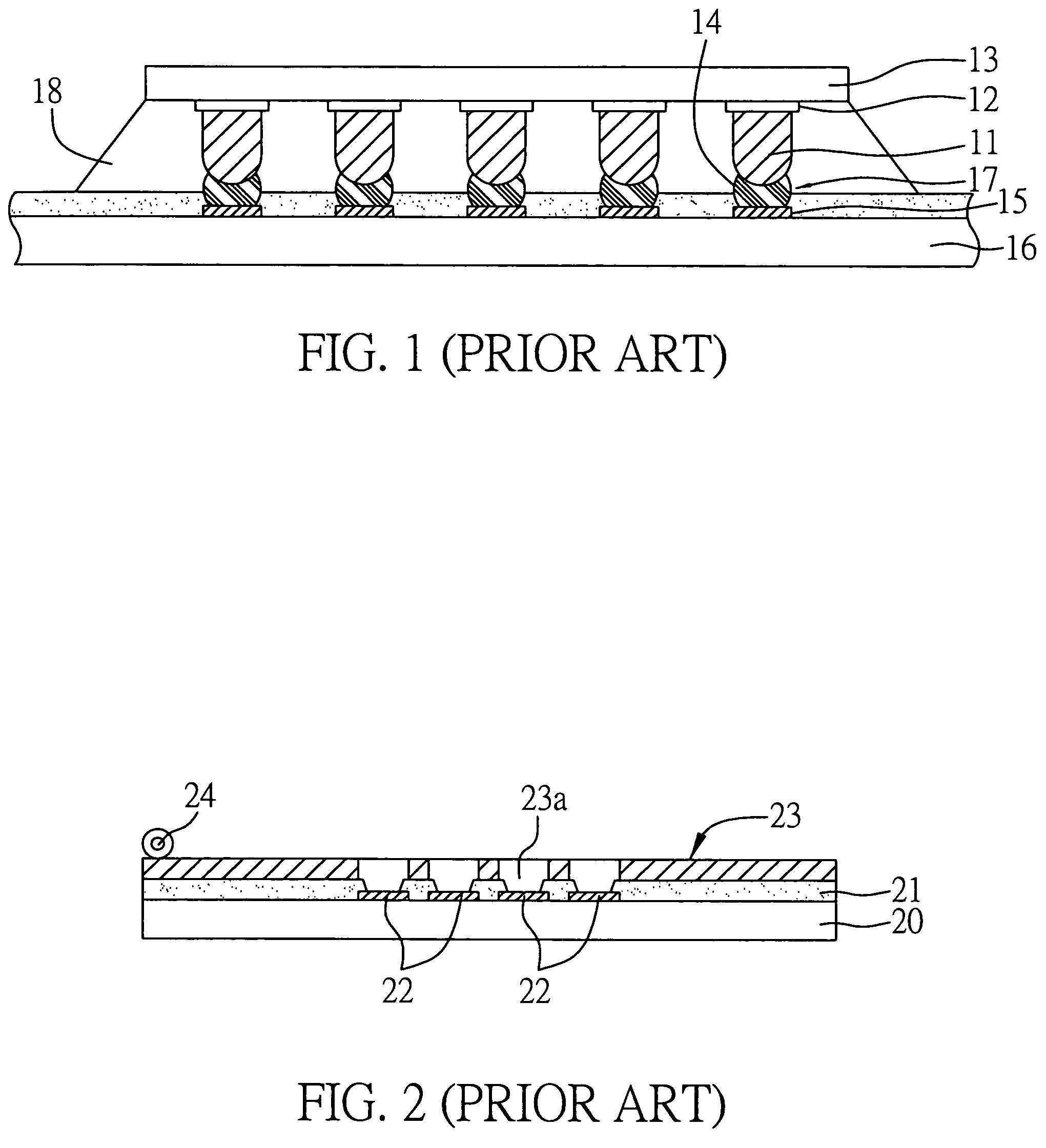

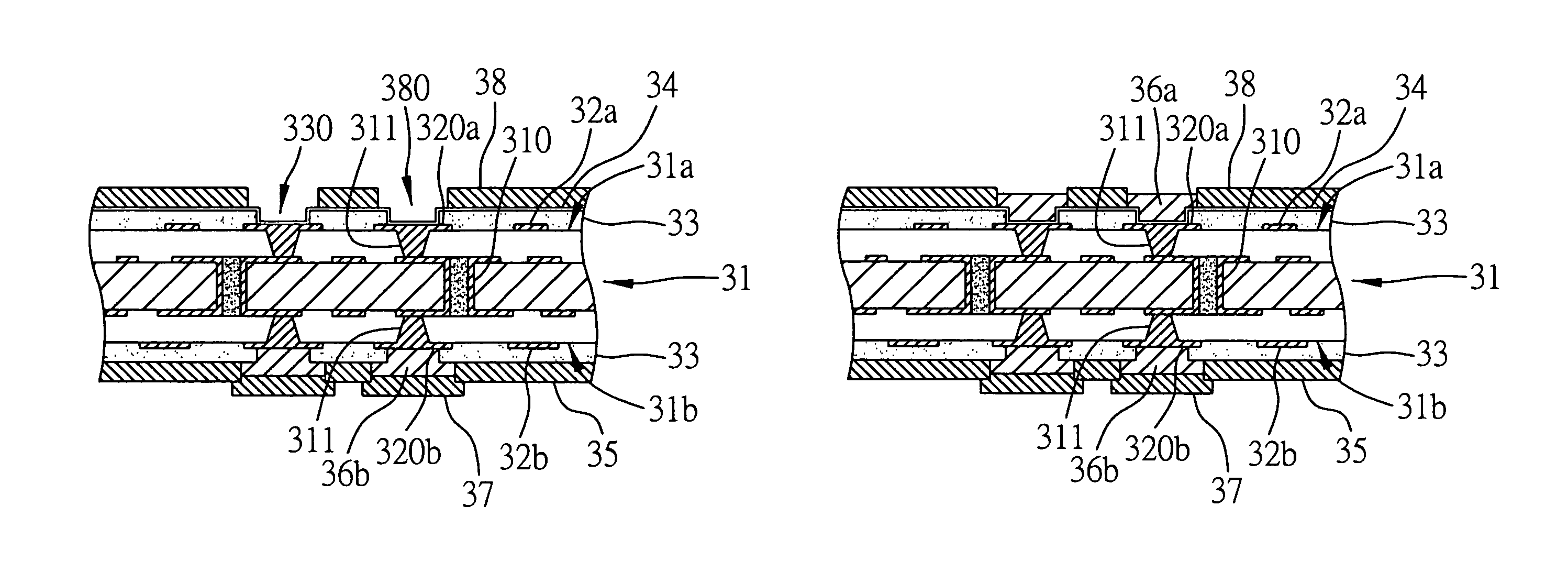

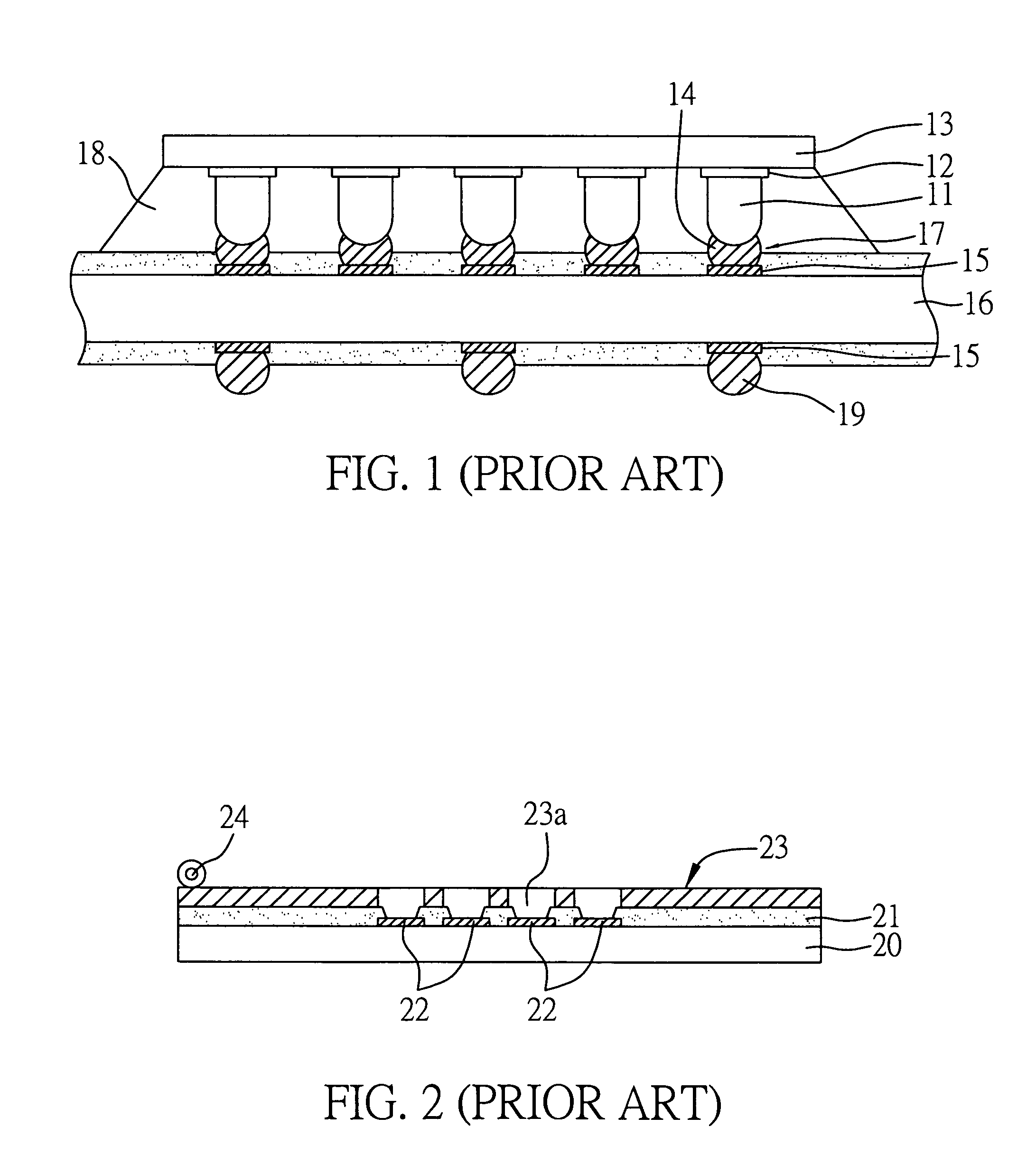

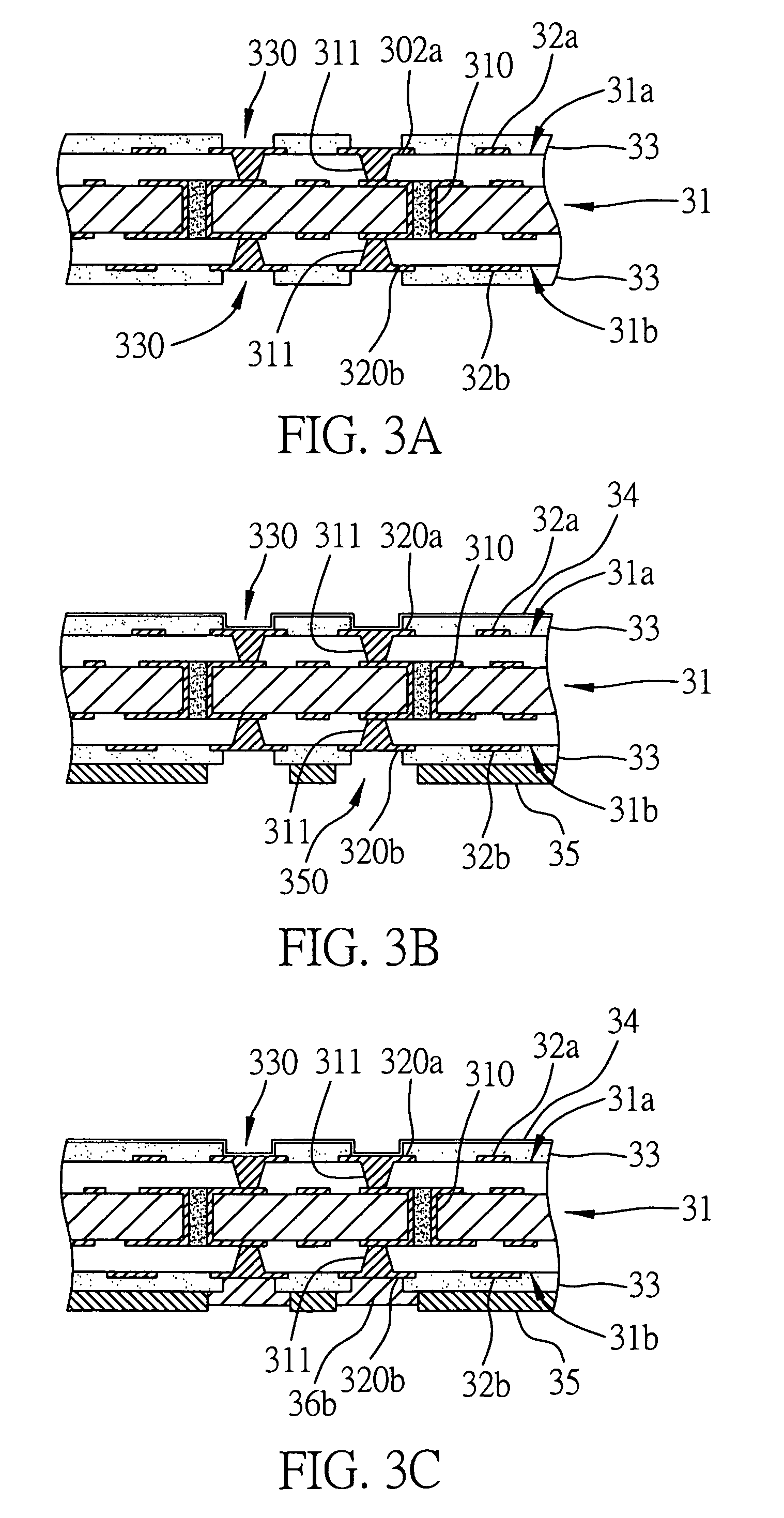

Method for fabricating electrical connection structure of circuit board

ActiveUS20060000877A1Pitches canSmallness of the opening of the stencil can be eliminatedDecorative surface effectsMultilayer circuit manufactureElectricityElectrical connection

A method for fabricating an electrical connection structure of a circuit board is proposed. The circuit board is provided with a plurality of pads on a surface thereof and with a plurality of conductive structures therein for electrically connecting the pad. A plurality of openings is formed penetrating through an insulating layer provided on the circuit board to expose the pad. Subsequently, a conductive base is attached to one surface of the circuit board for electrically connecting the pad. By such arrangement, a conductive material can be formed on the pad located on the other surface of the circuit board by an electroplating process via the conductive base, the pad on the surface, and the conductive structure within the circuit board.

Owner:PHOENIX PRECISION TECH CORP

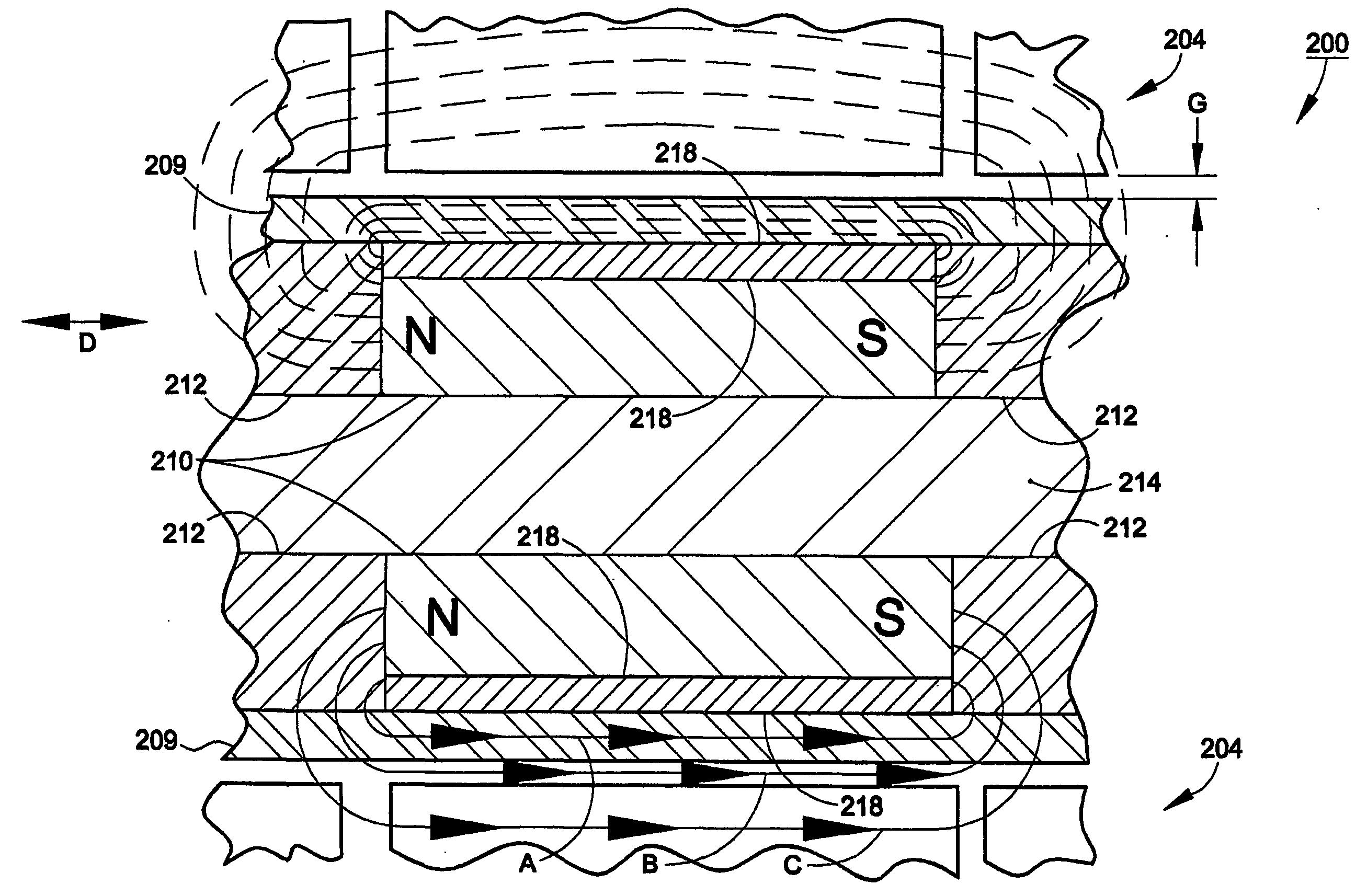

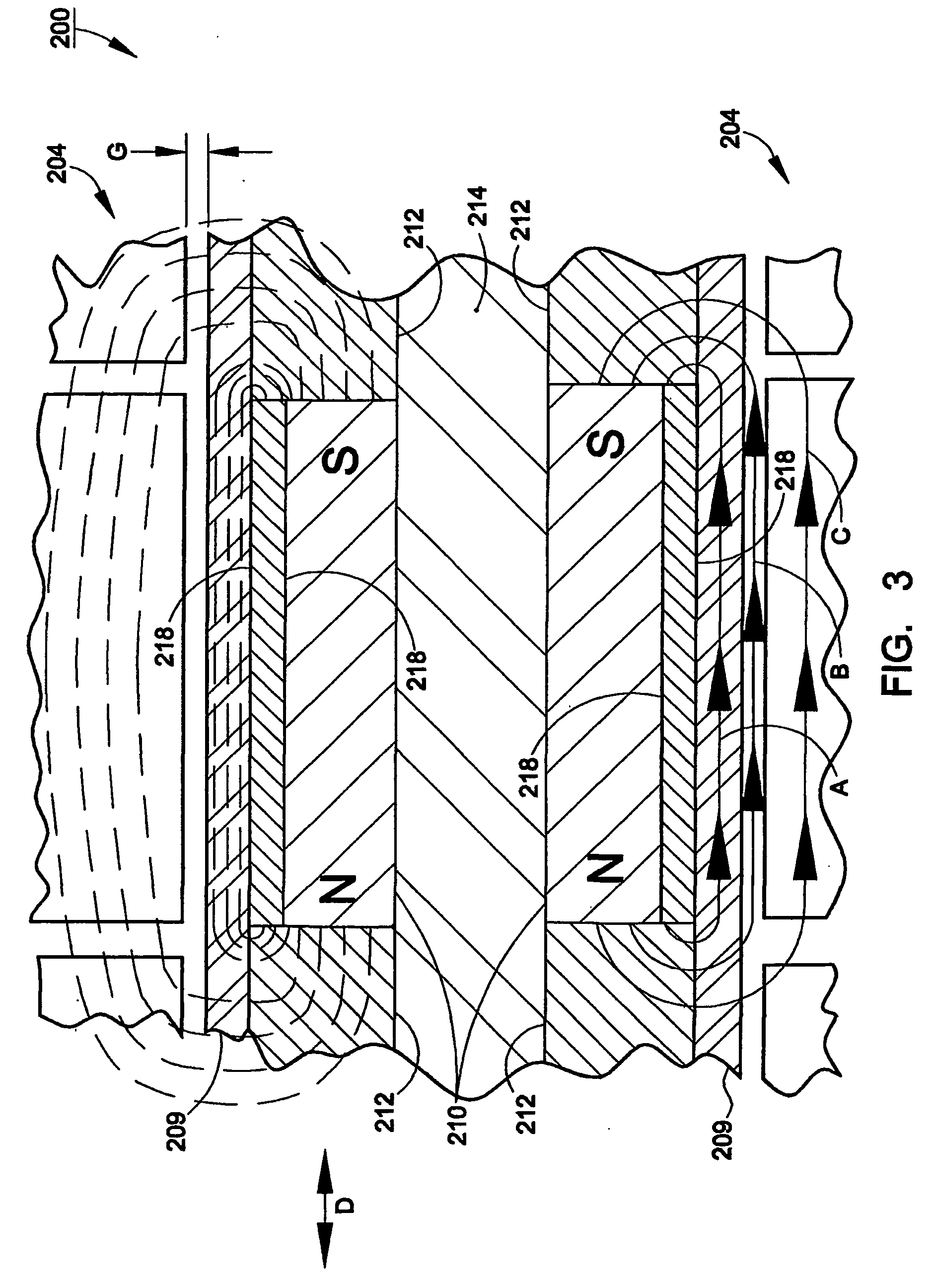

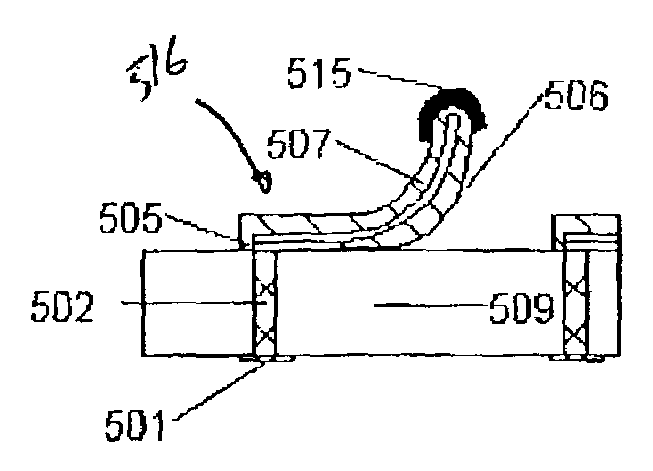

Bearing surface layer for magnetic motor

InactiveUS20050006971A1Conducive to maintenanceGood wearDynamo-electric brakes/clutchesMagnetic circuit rotating partsBearing surfaceThermal treatment

Magnetic motor component sleeves (209) for motor components with the sleeves (209) having various helpful magnetic characteristics, such as high magnetic permeability; magnetic saturation; residual (or remanent) magnetization; anisotropic magnetic properties. Method for making a magnetic linear motor shaft (202), including thermal treatment to temporarily change the dimensions of various shaft components to allow tight assembly.

Owner:MOOG INC

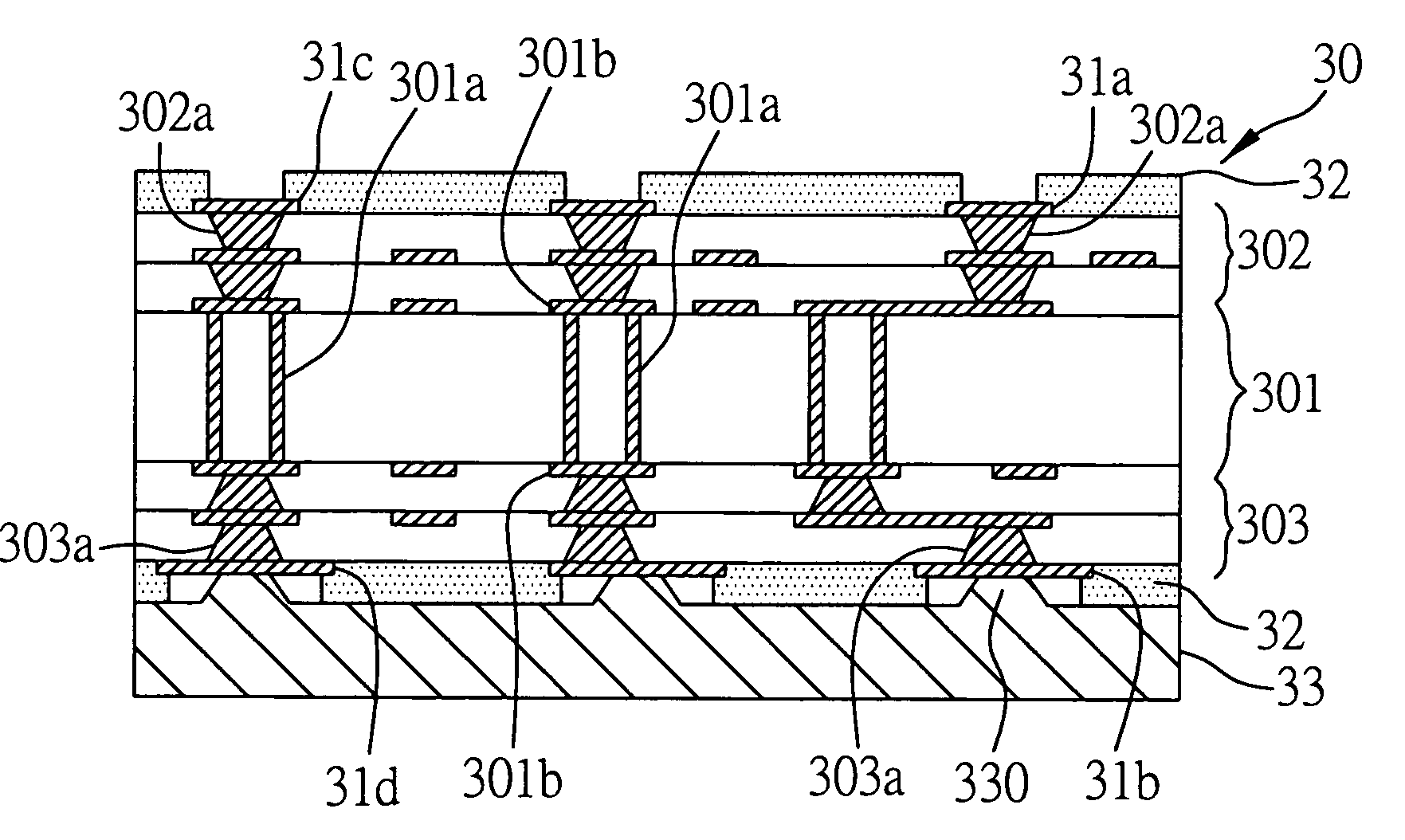

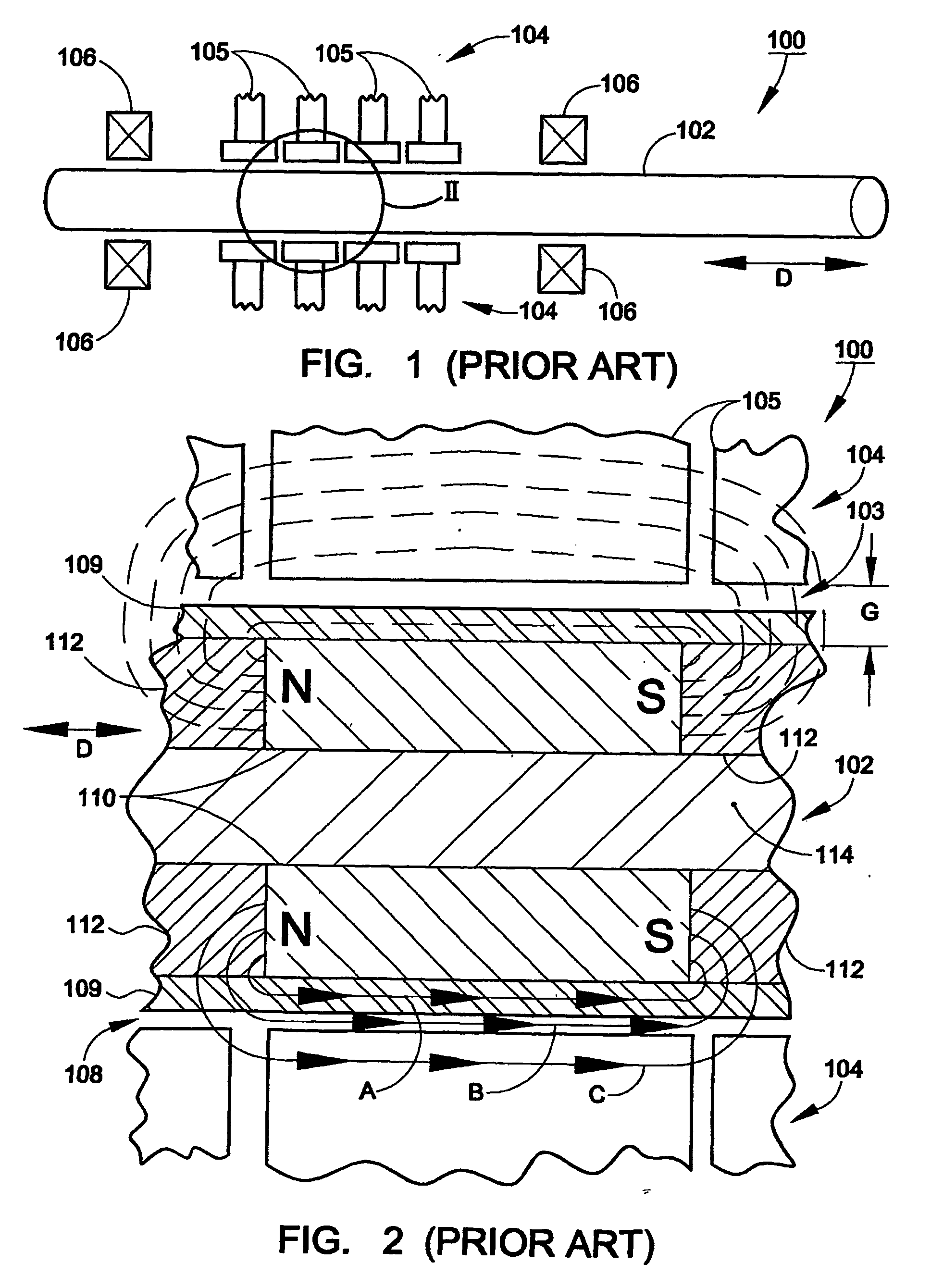

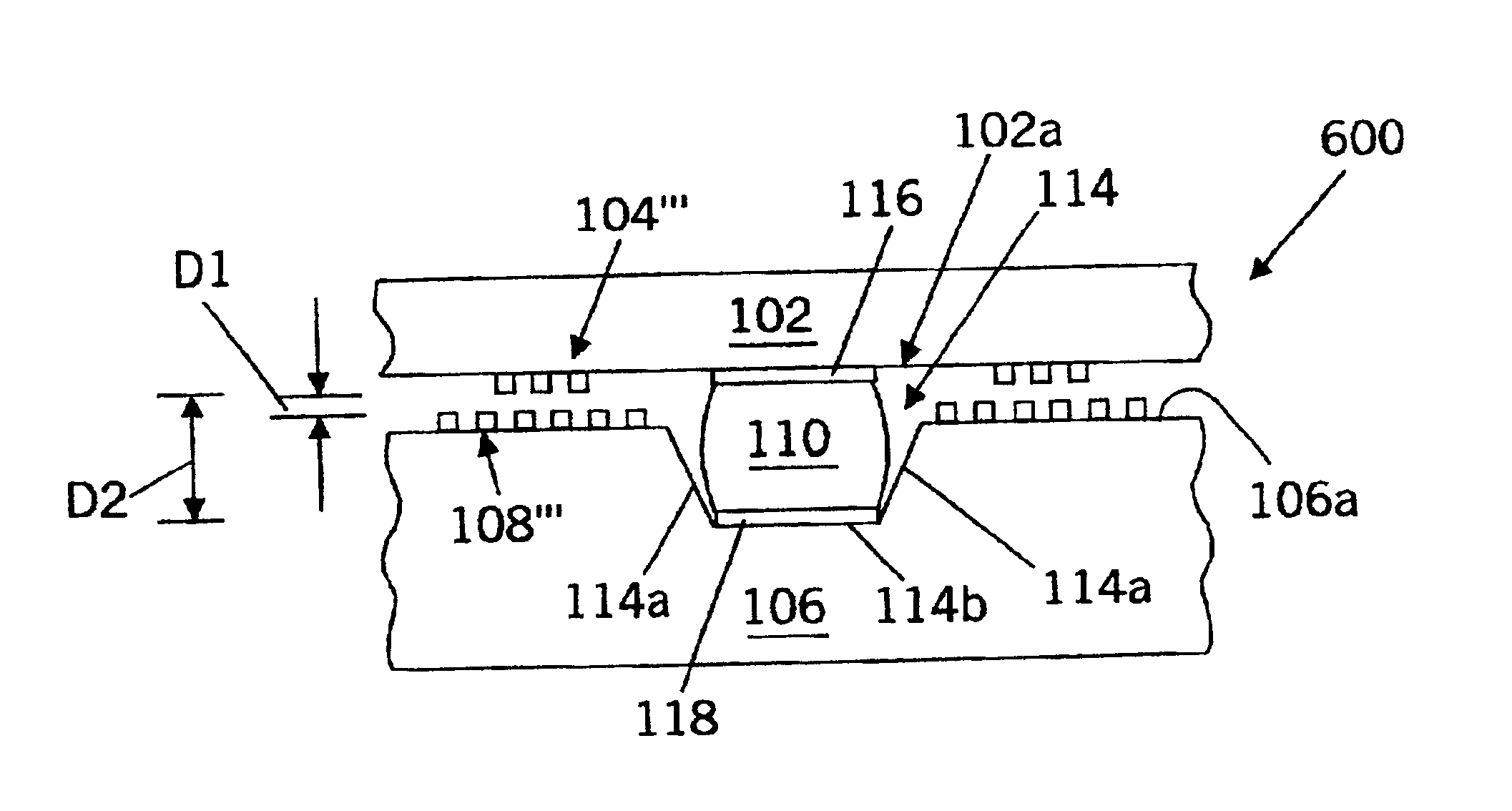

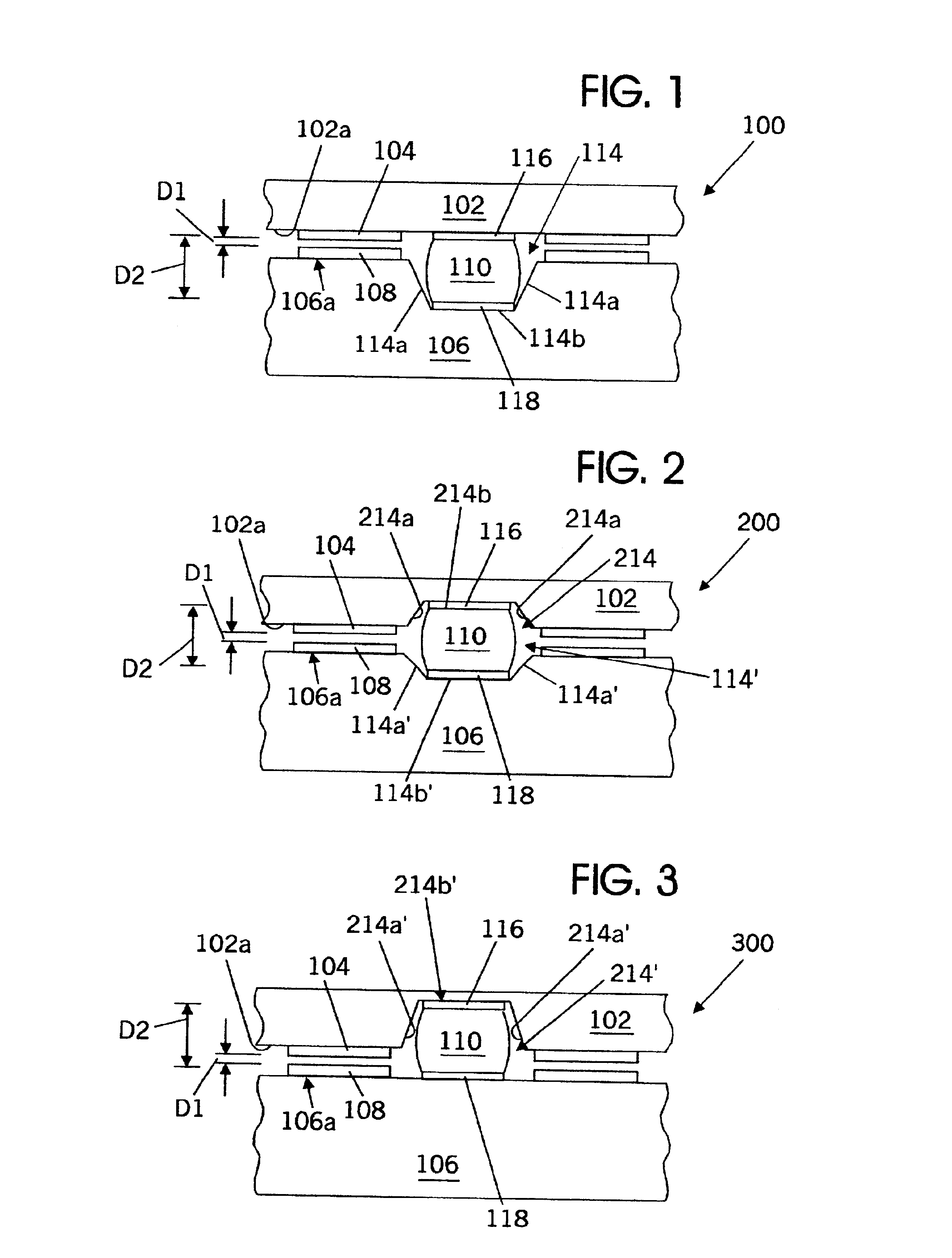

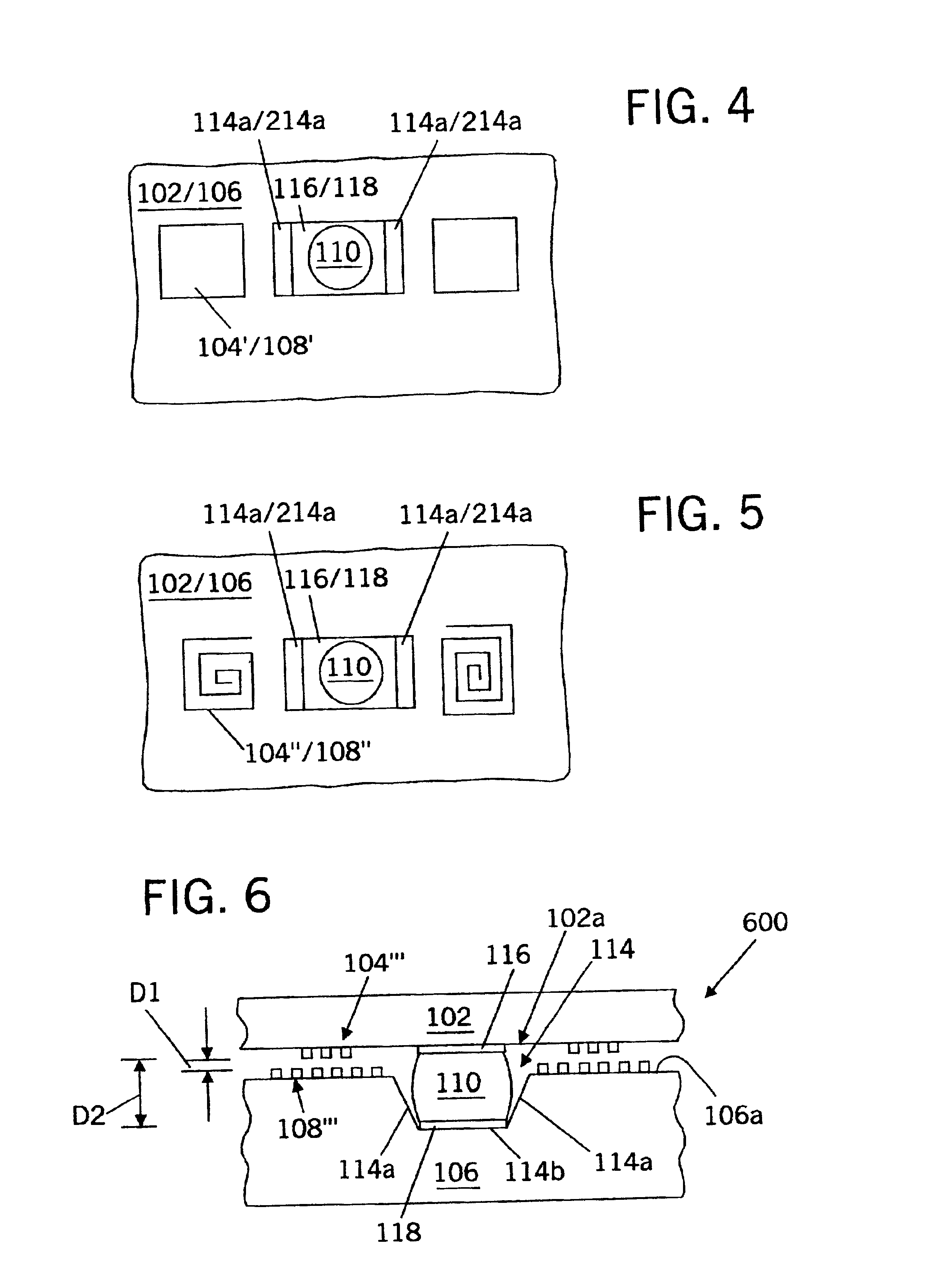

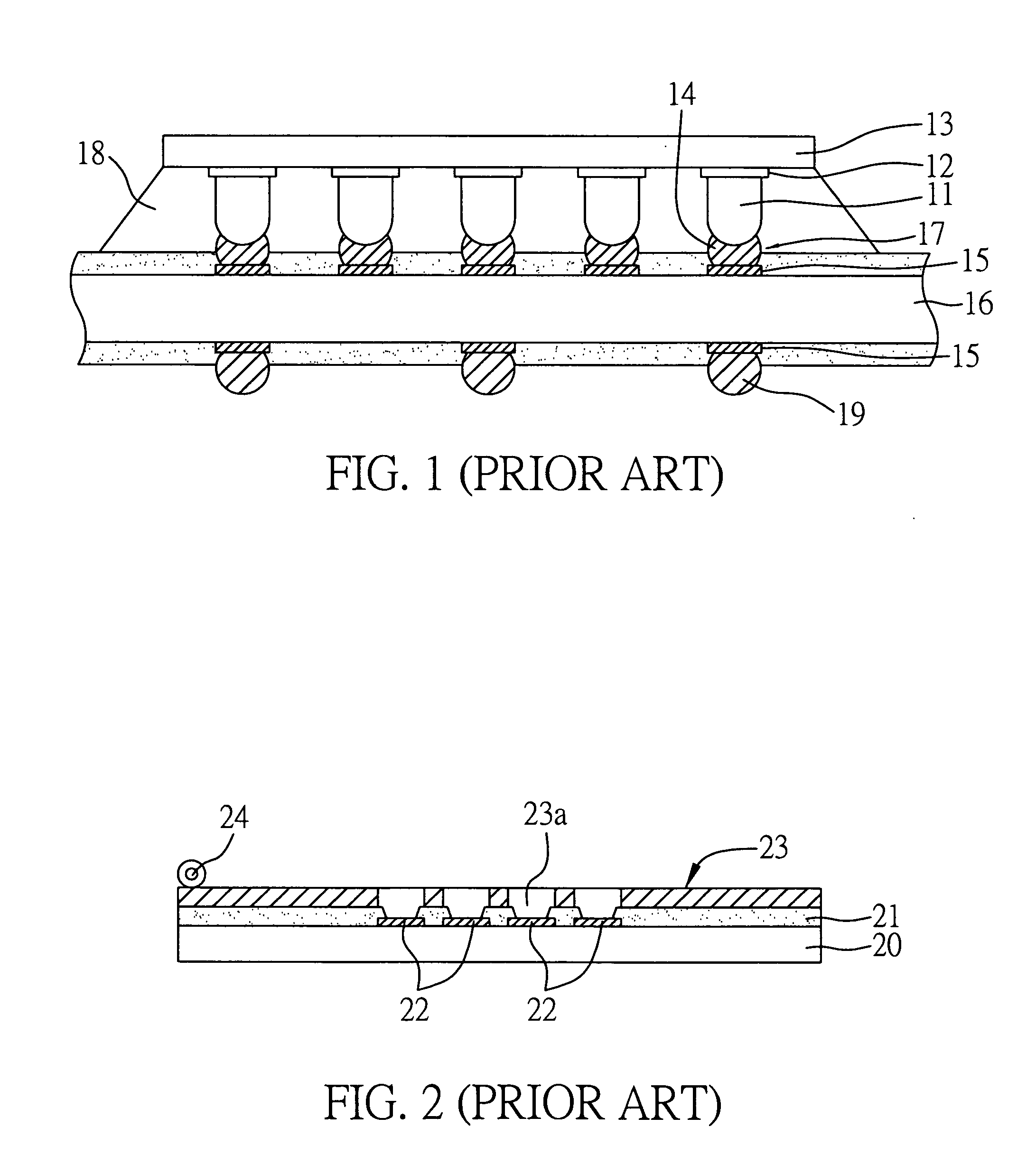

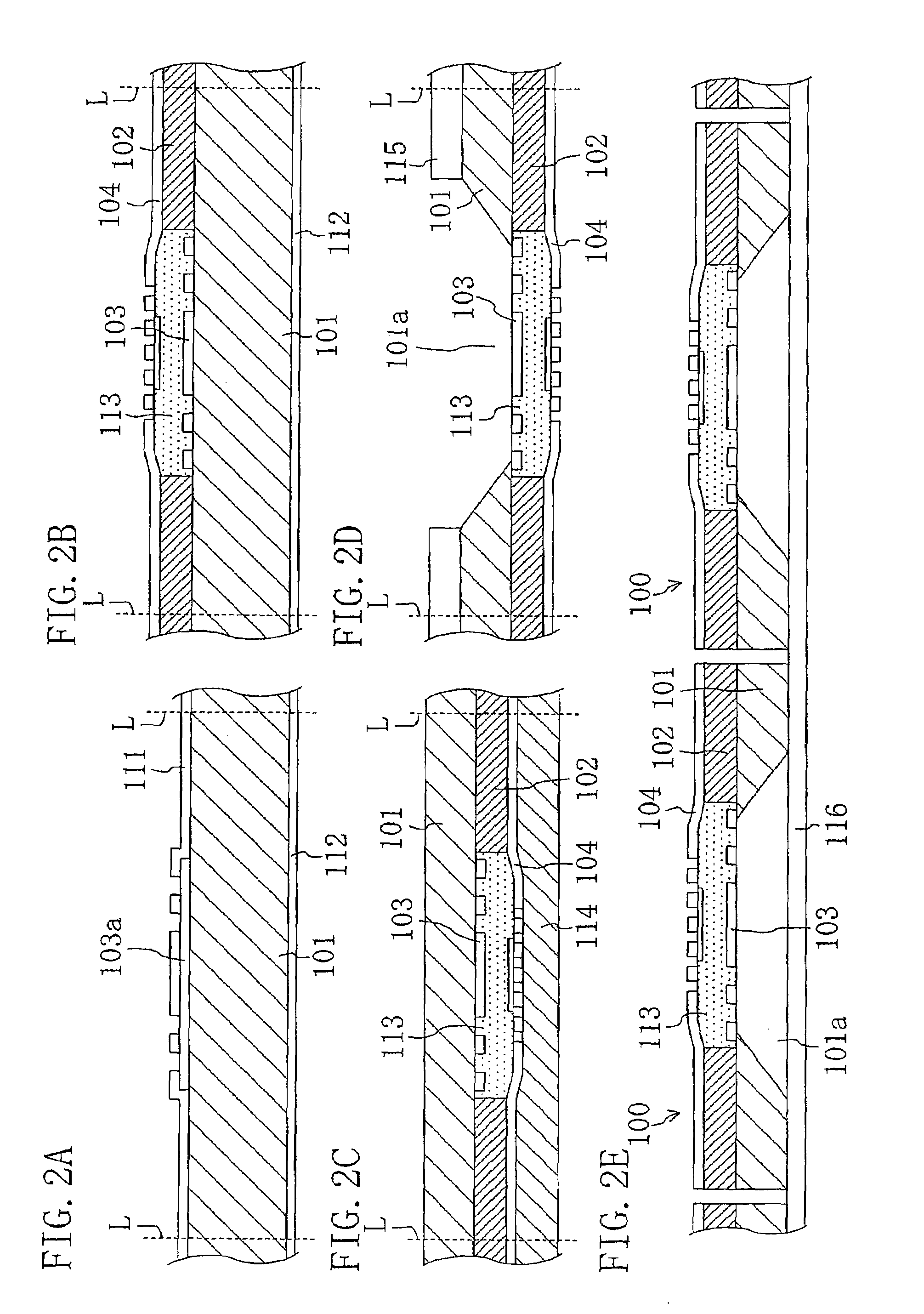

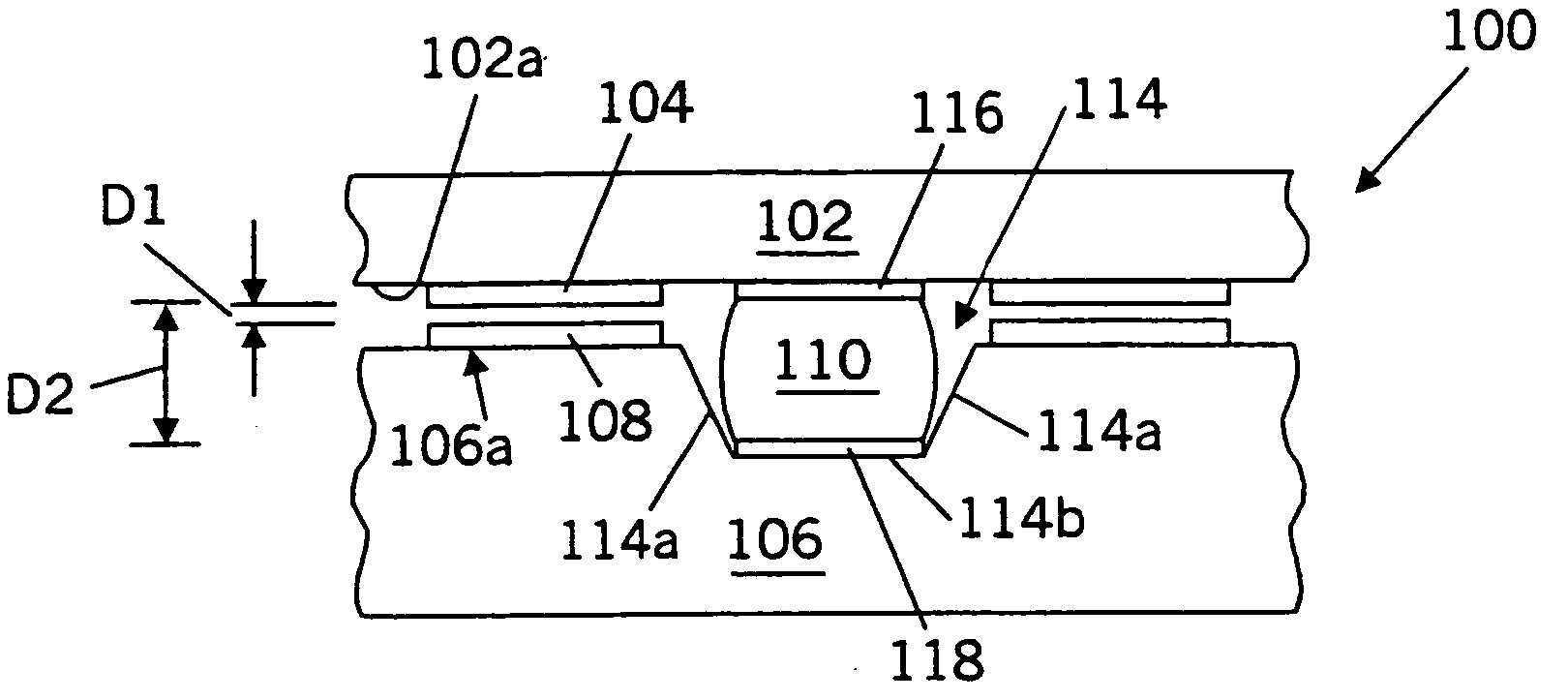

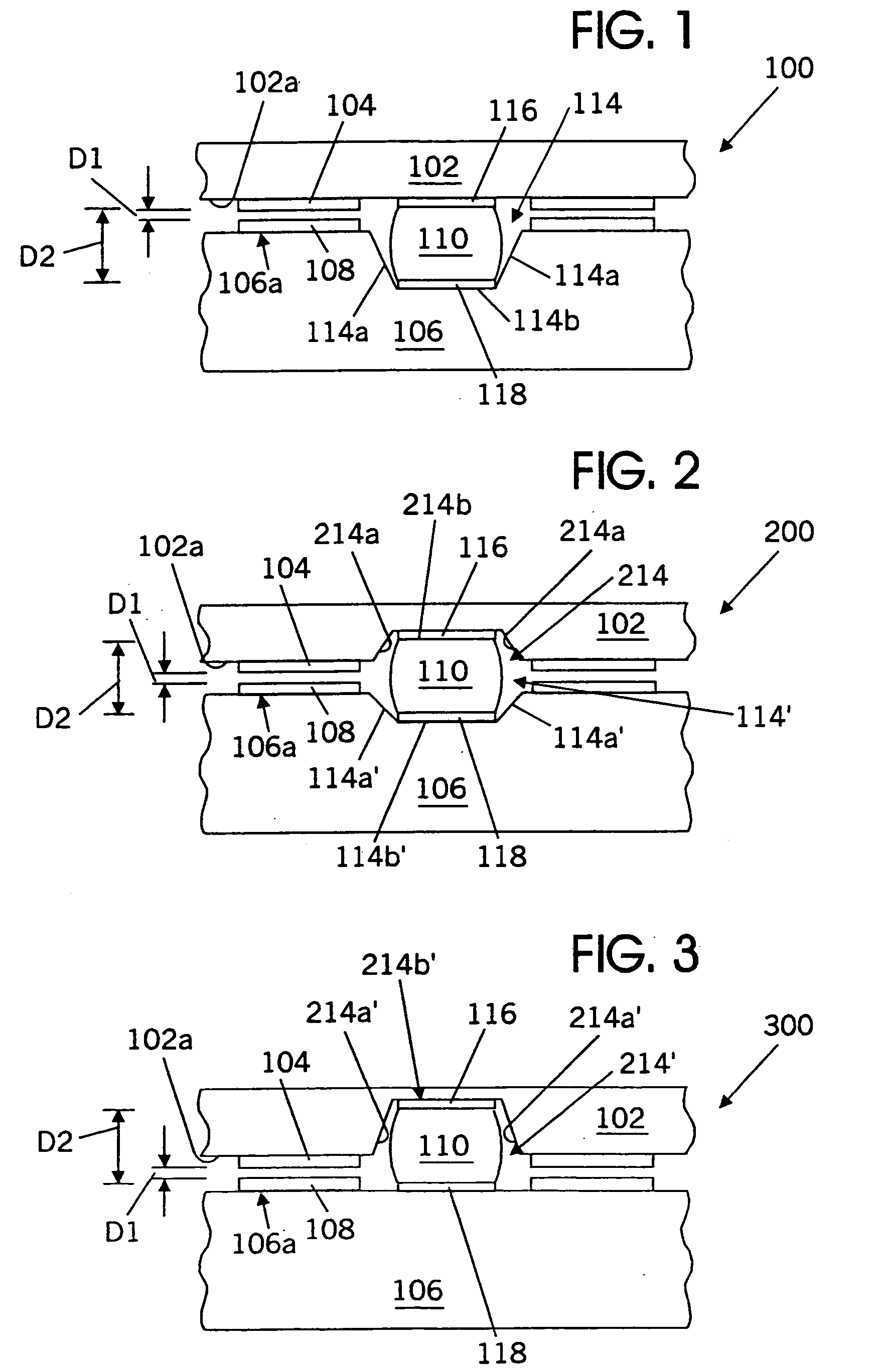

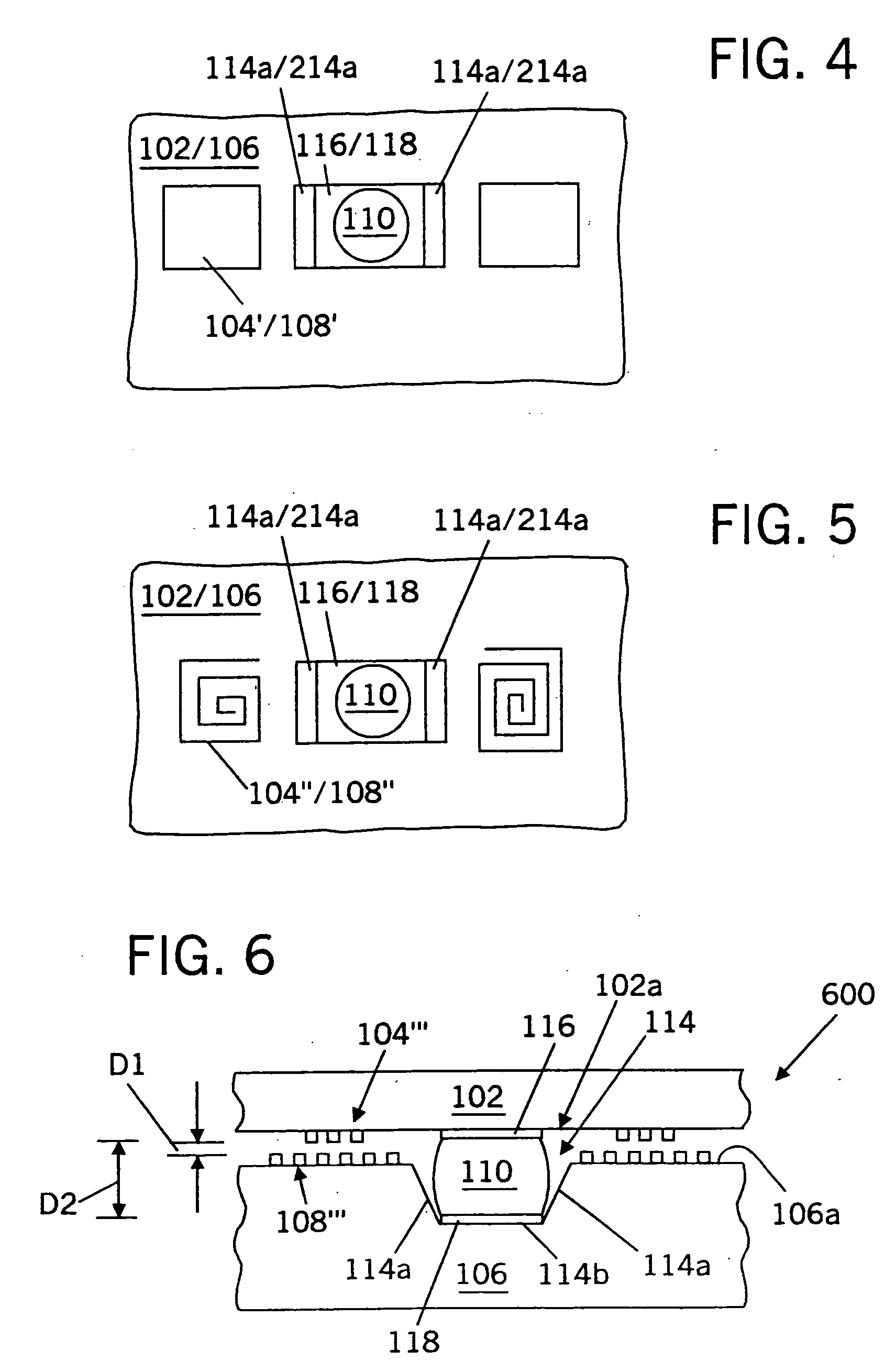

Inductively coupled electrical connectors

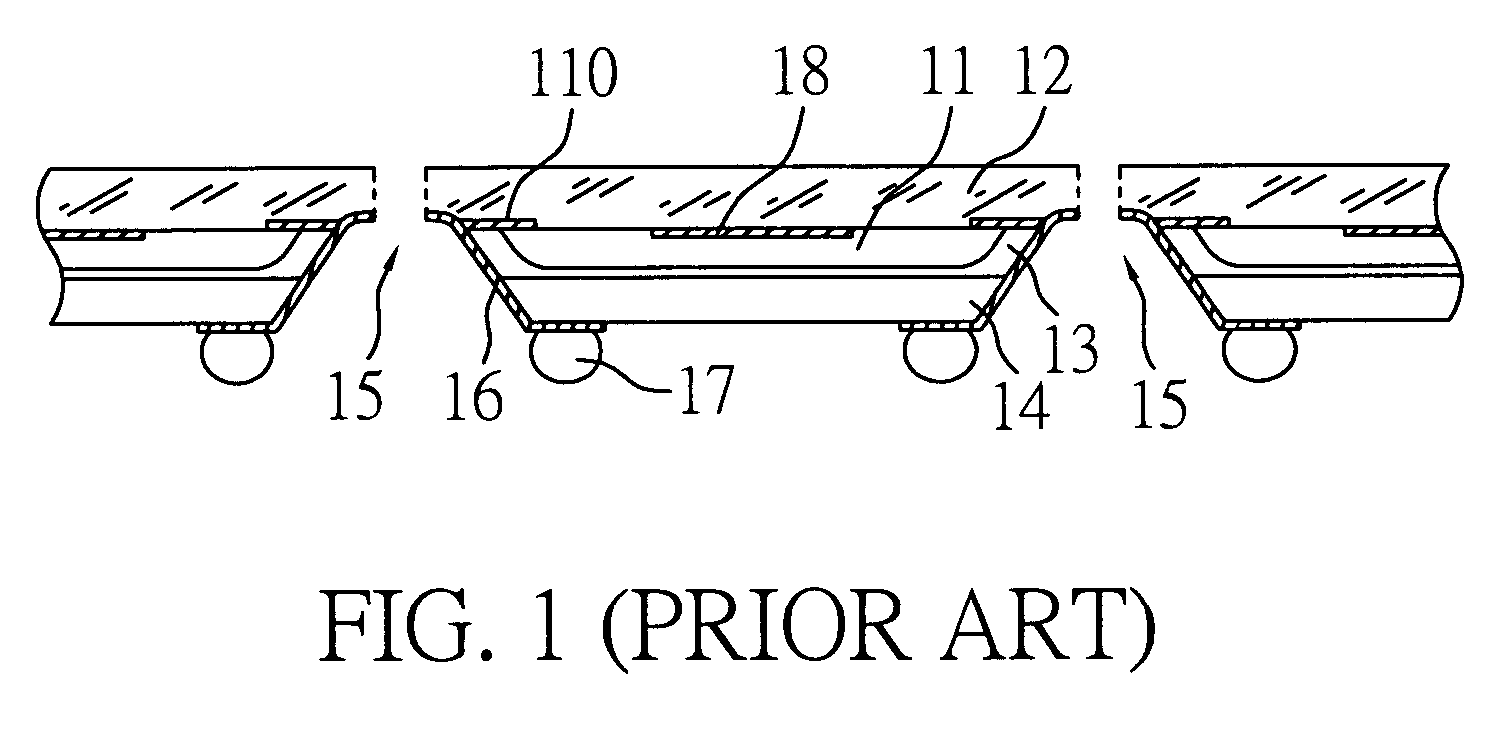

InactiveUS6885090B2Sufficient complianceAvoid excessive distancePrinted circuit assemblingSemiconductor/solid-state device detailsElectricityInductor

Microelectronic packages include a first microelectronic substrate having a first face and a first AC-coupled interconnect element on the first face. A second microelectronic substrate includes a second face and a second AC-coupled interconnect element on the second face. A buried solder bump extends between the first and second faces, and is at least partially buried beneath the first and / or second faces, to maintain the first and second AC-coupled interconnect elements in closely spaced apart relation. The buried solder bump also may couple DC power between the first and second substrates. Other technologies also may be used to maintain the AC-coupled interconnect elements in closely spaced apart relation and to couple DC power between the substrates. The first and second AC-coupled interconnect elements may be first and second capacitor plates, first and second inductors and / or first and second combined inductive and capacitive elements.

Owner:NORTH CAROLINA STATE UNIV

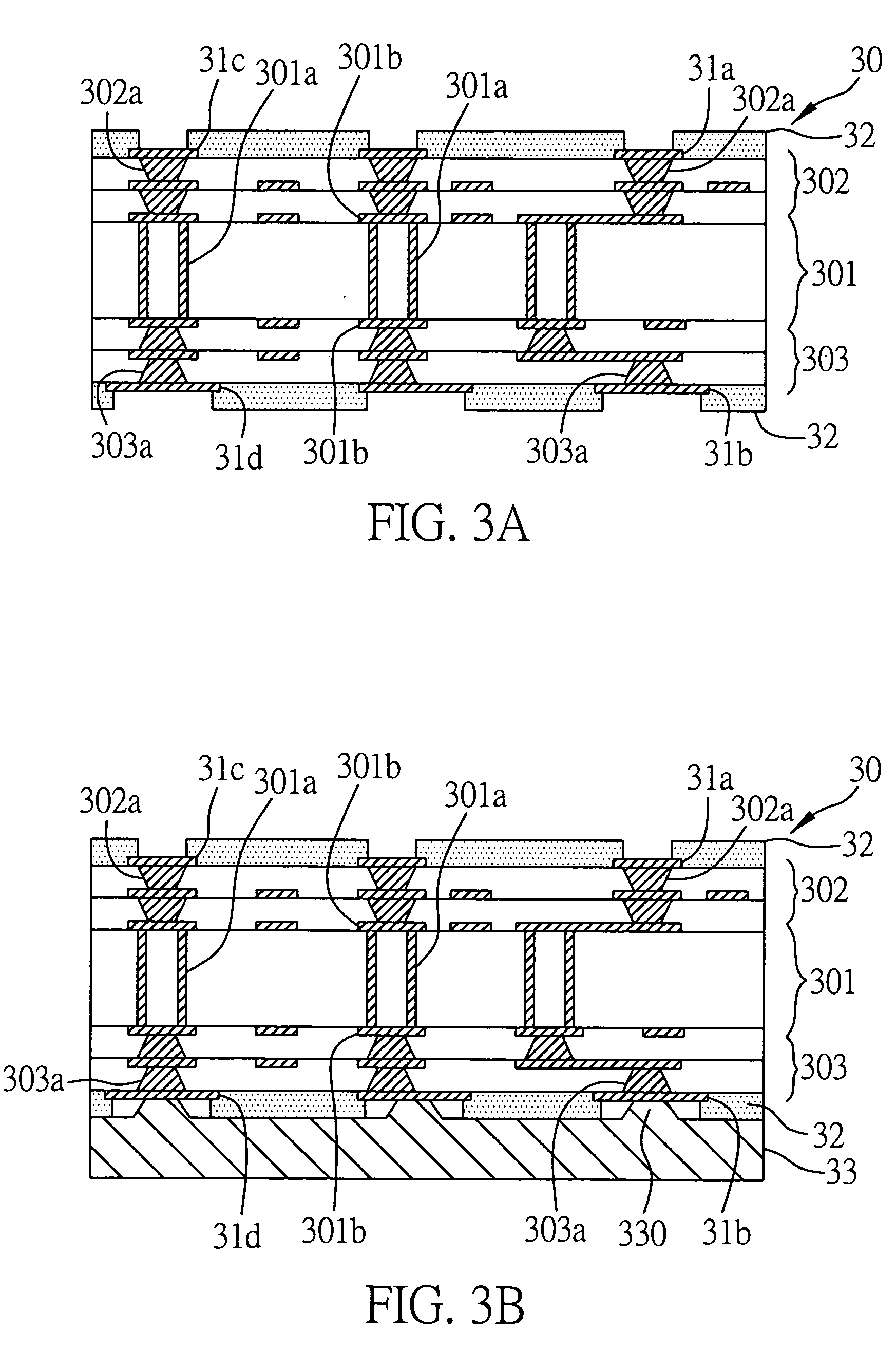

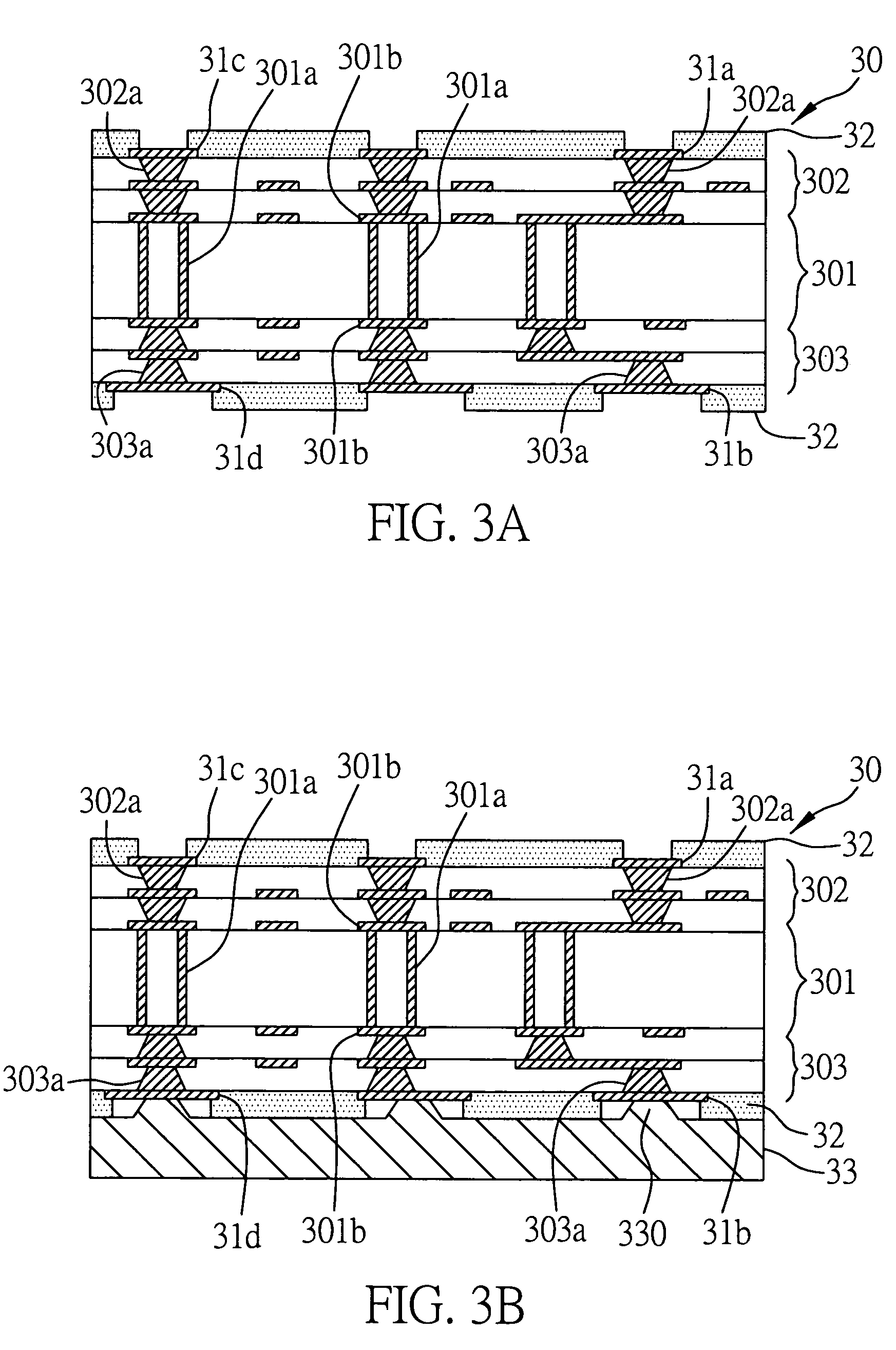

Method for fabricating conductive bump of circuit board

ActiveUS20060051952A1High manufacturing reliabilityReduce spacingSemiconductor/solid-state device detailsPrinted circuit aspectsResistEngineering

A method for fabricating conductive bumps of a circuit board is proposed. First of all, a circuit board having a first surface and a corresponding second surface is provided. A circuit structure having a plurality of conductive pads is formed on each of the first surface and the second surface, and conductive structures are formed in the circuit board for electrically connecting the circuit structures. Also, an insulating layer having a plurality of openings penetrating therethrough is formed on the circuit board for exposing the conductive pad. Then, a conductive layer is formed on a surface of the insulating layer having the opening formed on the first surface of the circuit board. An electroplating process is performed via the conductive layer and the conductive structure, such that a conductive bump is formed on the conductive pad located on the second surface of the circuit board. Subsequently, a resist layer is formed on the second surface of the circuit board to cover the conductive bump, and another resist layer having openings penetrating therethrough is formed on the first surface of the circuit board to expose the conductive pad. Finally, a conductive bump is formed on the conductive pad located on the first surface of the circuit board by an electroplating process. By such arrangement, the conductive bumps are successively formed on the first surface and the second surface of the circuit board.

Owner:PHOENIX PRECISION TECH CORP

Magnetic head induction coil fabrication method utilizing aspect ratio dependent etching

InactiveUS6913704B2Reliably fabricatedReduce spacingConstruction of head windingsDecorative surface effectsEtchingInsulation layer

A magnetic head including a dual layer induction coil. Following the deposition of a first magnetic pole (P1) a first induction coil is fabricated. Following a chemical mechanical polishing (CMP) step a layer of etchable insulation material is deposited followed by the fabrication of a second induction coil etching mask. A reactive ion etch process is then conducted to etch the second induction coil trenches into the second etchable insulation material layer. The etching depth is controlled by the width of the trenches in an aspect ratio dependent etching process step. The second induction coil is next fabricated into the second induction coil trenches, preferably utilizing electrodeposition techniques. Thereafter, an insulation layer is deposited upon the second induction coil, followed by the fabrication of a second magnetic pole (P2) upon the insulation layer.

Owner:WESTERN DIGITAL TECH INC

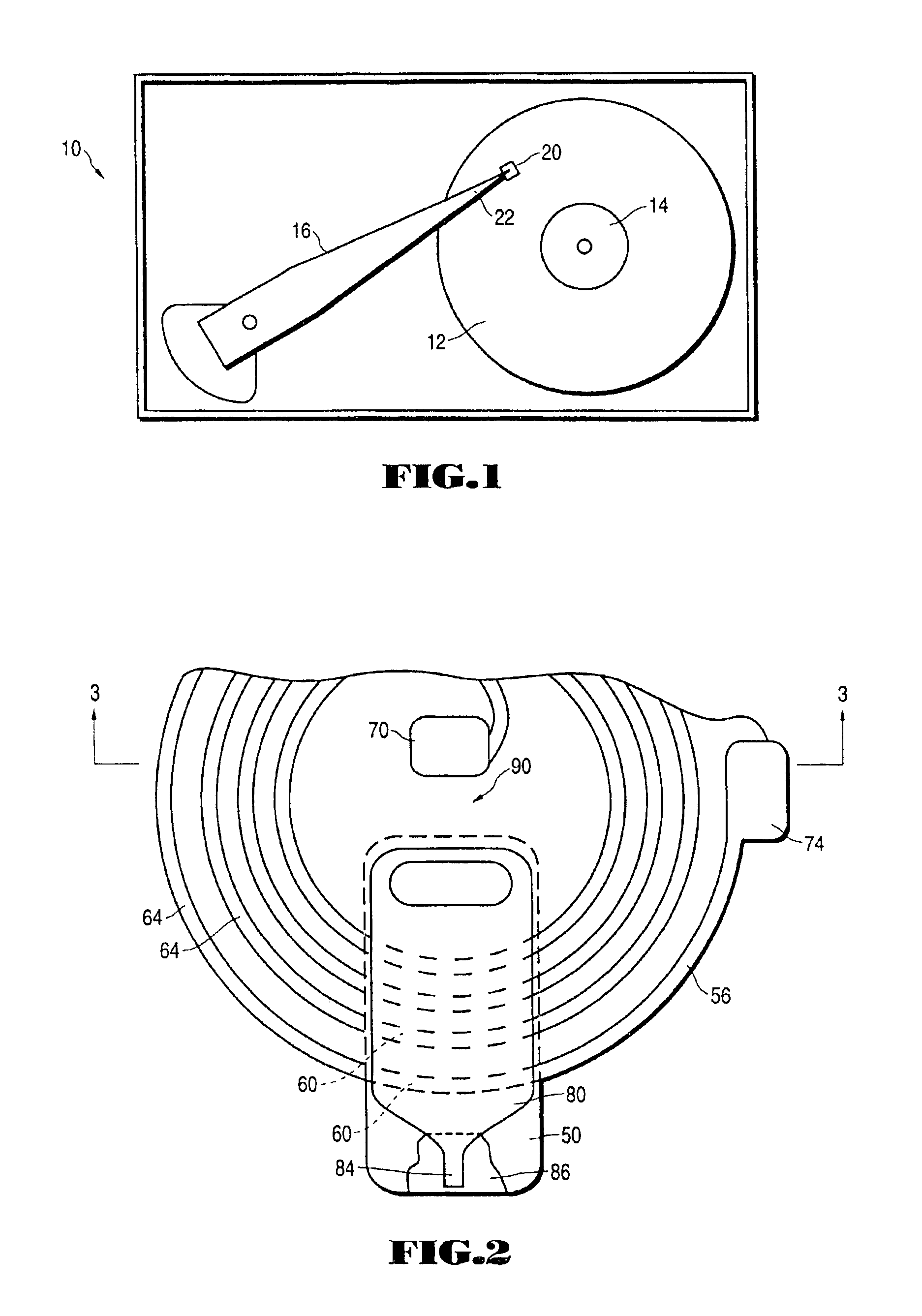

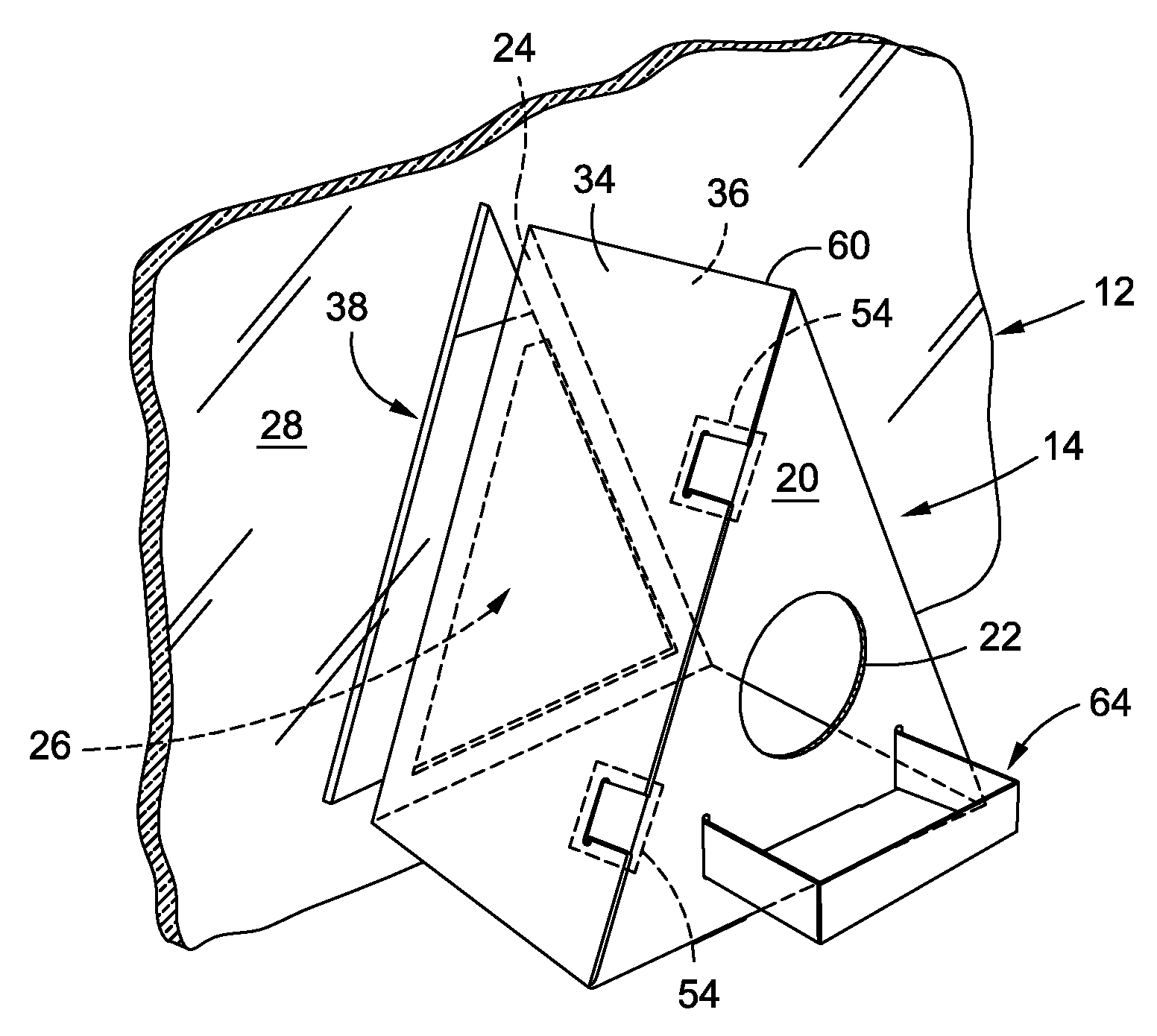

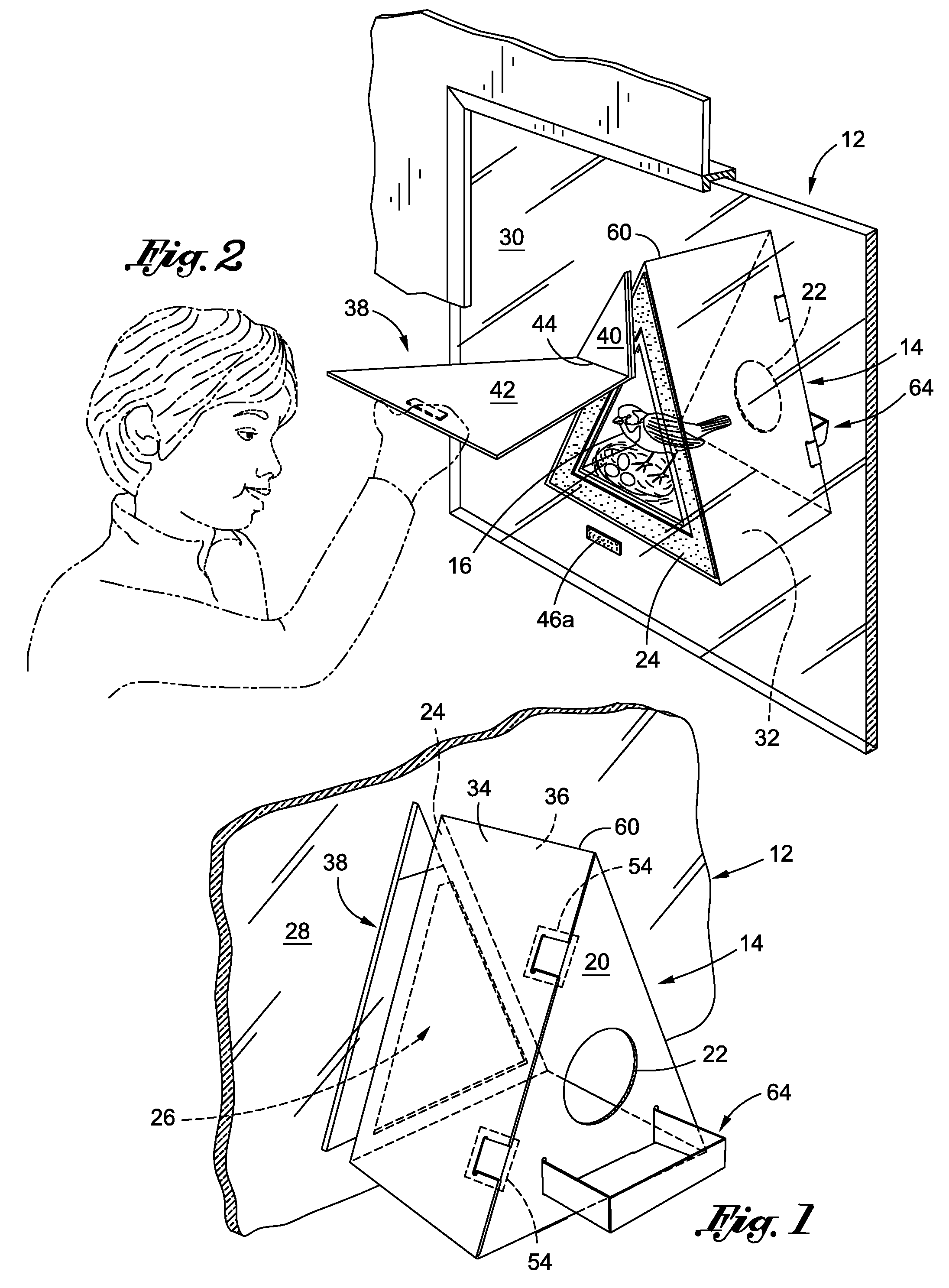

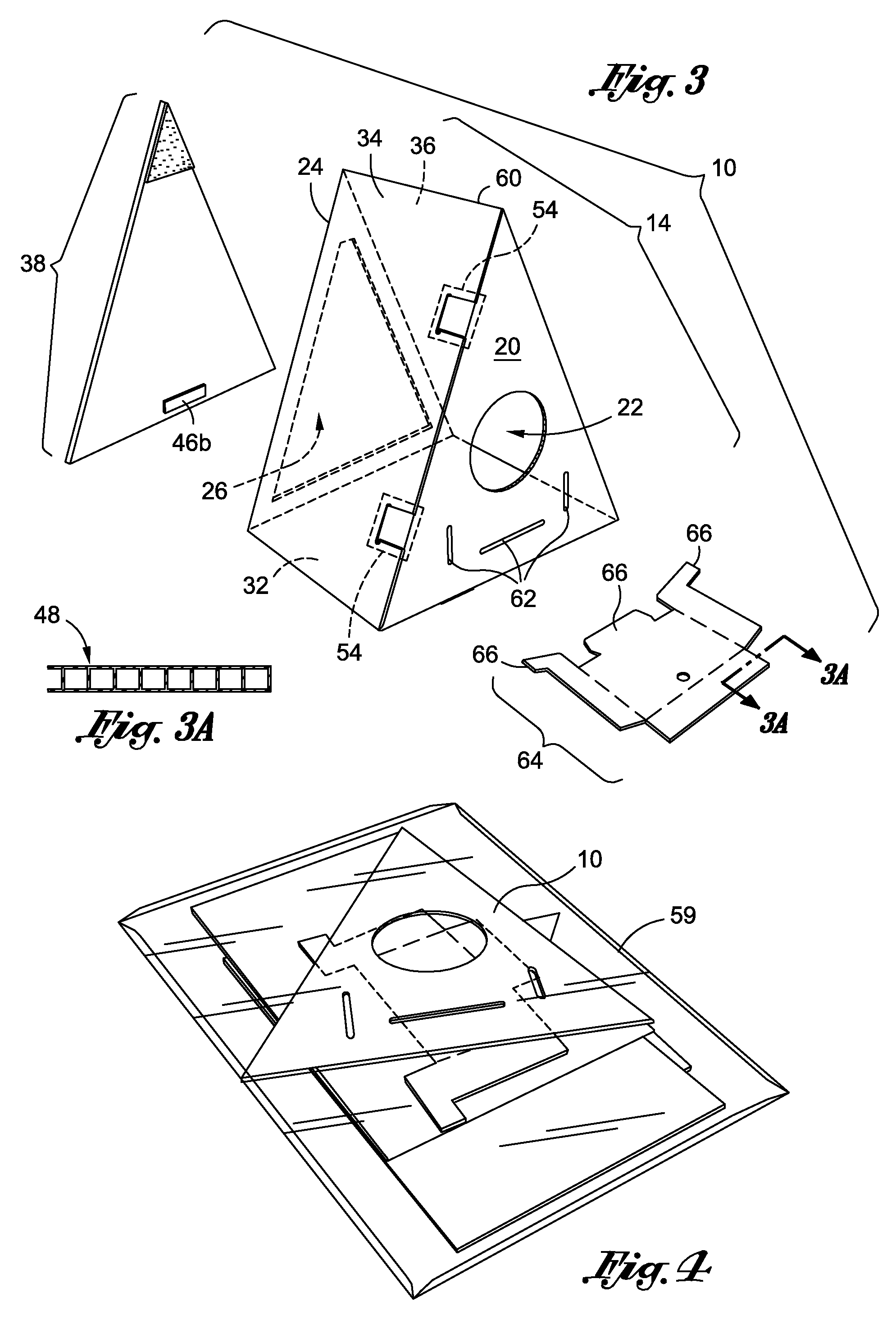

Window Bird House

InactiveUS20100175630A1Conveniently attach to windowEasy to assembleBird housingsEngineeringPlastic film

A window bird house is advantageously configured for easy transport and storage, and is a low cost alternative to prior art bird houses. The window bird house includes a housing having a plurality of walls and a floor which are collapsible upon each other for compact transport and storage. One of the walls includes a viewing opening for observing birds in the housing. Additionally, the rear wall may be removably secured to a first side of a window so that inside of the housing is visible from a second side of the window. Also, one of the walls includes an opening for ingress and egress of birds. A cover may be attached to the second side of the window for selecting covering the viewing opening thereby mitigating disruptions to the birds. The window bird house may be fabricated from die cut corrugated plastic sheet.

Owner:STETABON MICHAEL A

Miniaturized contact spring

InactiveUS7137830B2High strengthMinimize adhesionSemiconductor/solid-state device detailsSolid-state devicesContact padMiniaturization

Owner:ADVANTEST SINGAPORE PTE LTD

Method for fabricating semiconductor device

ActiveUS20100022046A1Reliably fabricatedPoor-strength structureSemiconductor/solid-state device manufacturingWelding/soldering/cutting articlesEngineeringSemiconductor

Owner:TDK CORPARATION

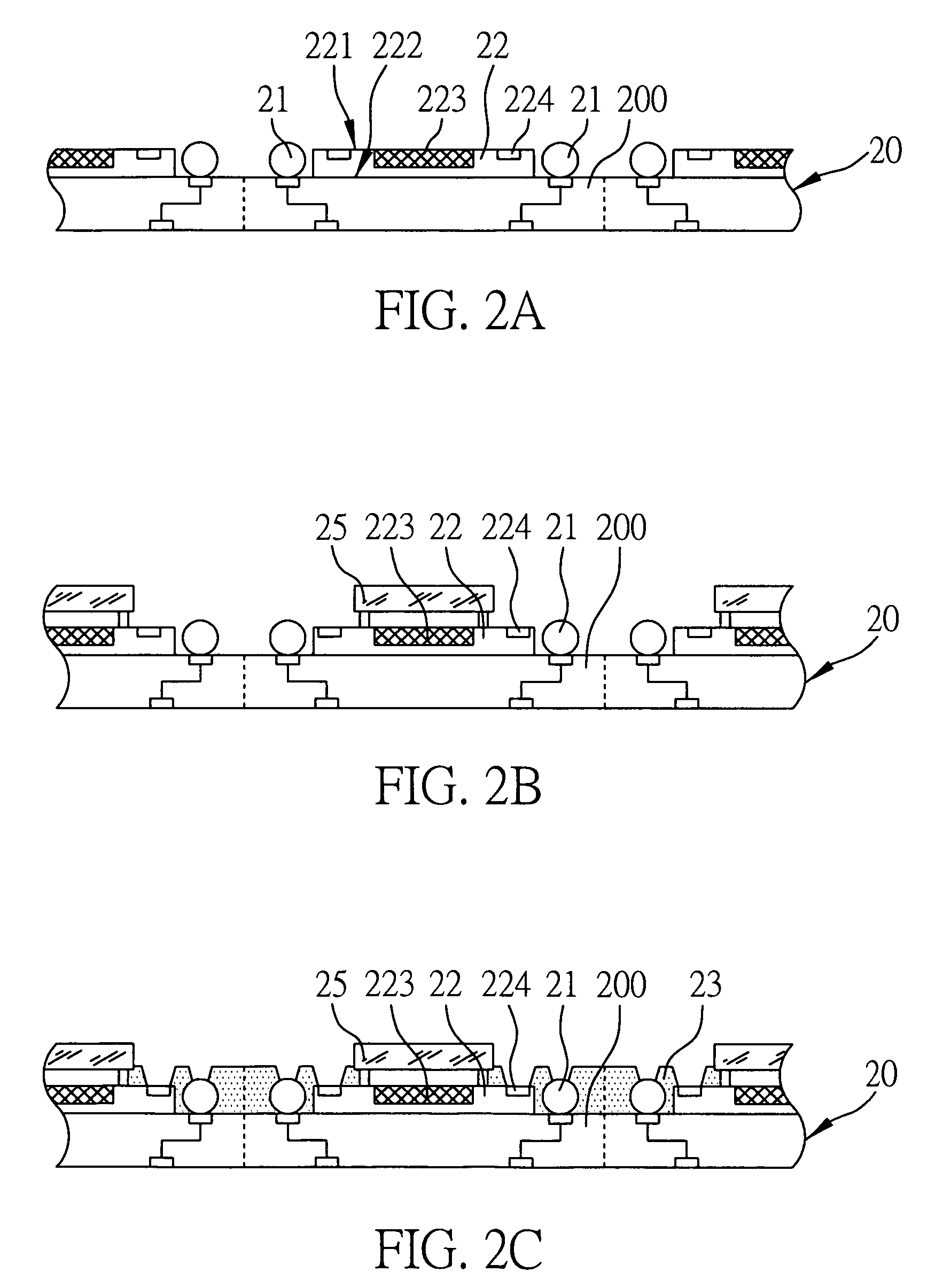

Sensor semiconductor device and fabrication method of the sensor semiconductor device

ActiveUS7446307B2Avoid crackingReliably fabricatedSemiconductor/solid-state device detailsSolid-state devicesState of artSolder ball

A sensor semiconductor device and a fabrication method thereof are provided. The fabrication method includes mounting a sensor chip on a surface of a substrate; forming a transparent cover on the sensor chip; forming a dielectric layer and a circuit layer on the substrate, wherein the sensor chip is electrically connected to the substrate through the circuit layer and the transparent cover is exposed from the dielectric layer such that light can pass through the transparent cover to reach a sensor region of the sensor chip and allow the sensor chip to operate; and implanting a plurality of solder balls on another surface of the substrate to electrically connect the sensor chip to an external device. The sensor semiconductor device can be cost-effectively fabricated, and the circuit cracking and known good die (KGD) problems of the prior art can be avoided.

Owner:SILICONWARE PRECISION IND CO LTD

Method for fabricating a contact hole plane in a memory module

InactiveUS7018781B2Reduce coupling capacitanceReliably fabricatedSolid-state devicesPhotomechanical apparatusComputer moduleMemory module

Owner:POLARIS INNOVATIONS LTD

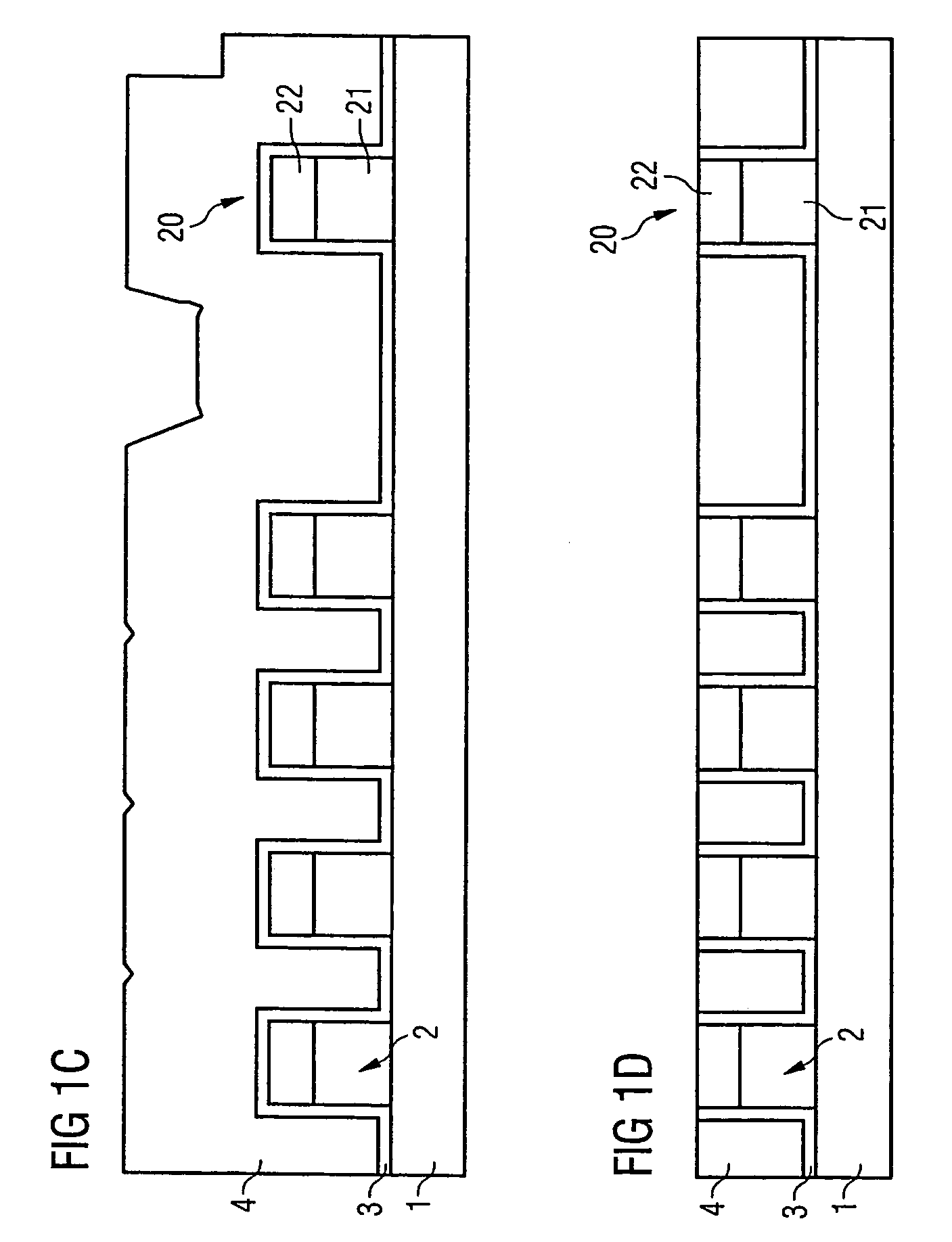

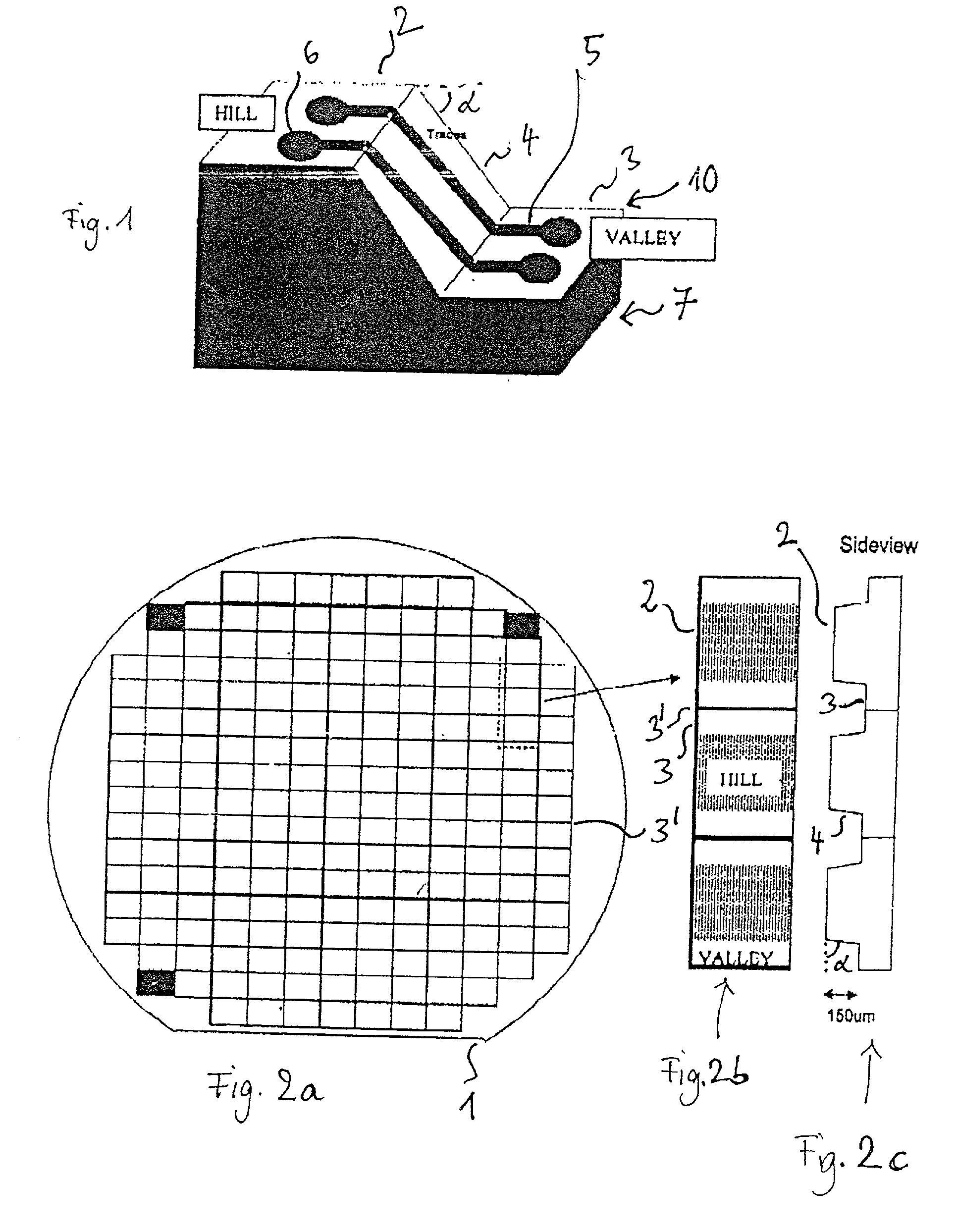

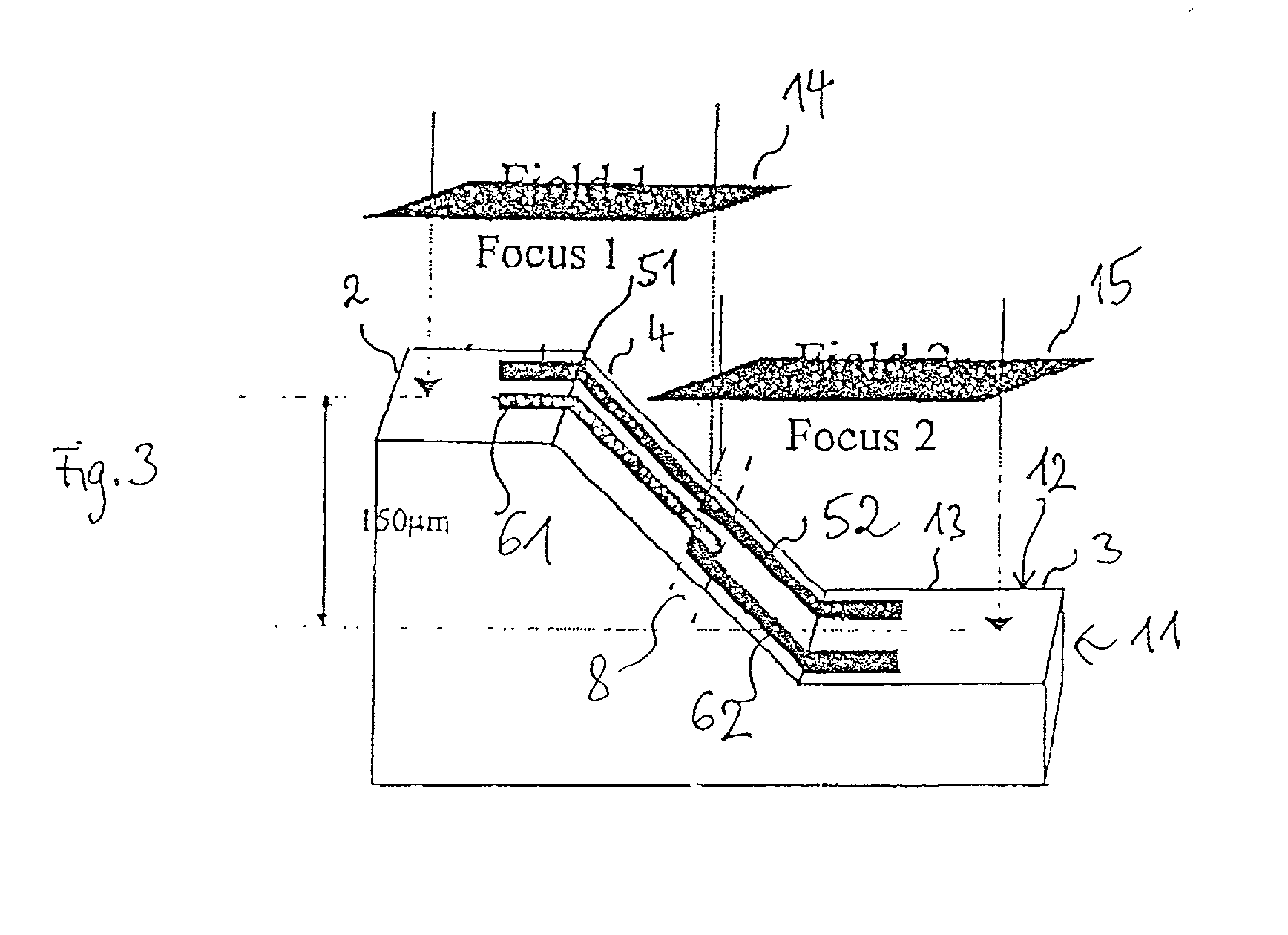

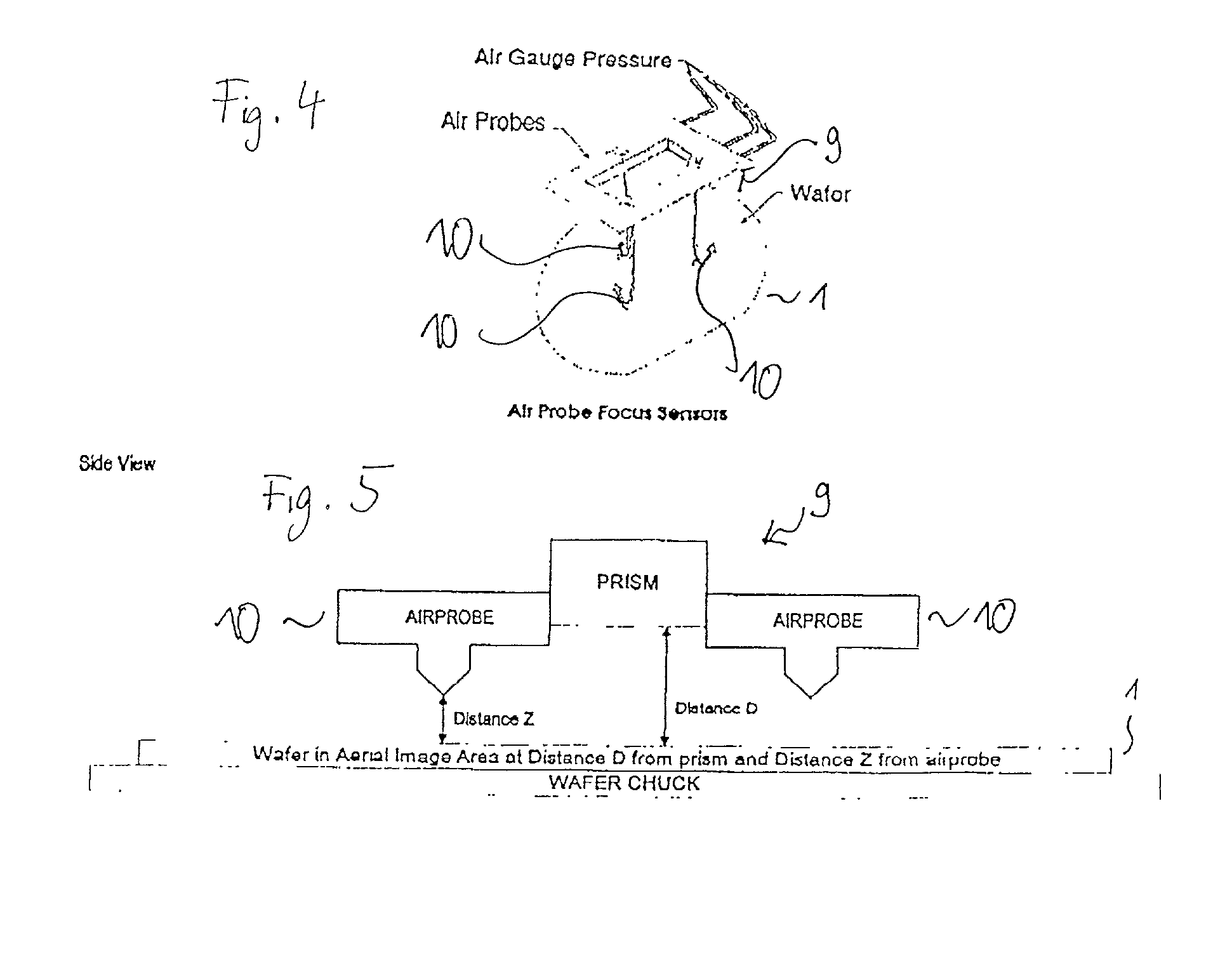

Structuring method

InactiveUS20030022112A1Reliability exposureReliably fabricatedSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusStructured methodologyOptics

The invention provides a structuring method, in particular for stepped wafer or die surfaces. The method includes photolithographically exposing a pattern comprising at least a first pattern portion and a second pattern portion onto a surface, said surface comprising at least a first surface portion at which a tangential plane to the surface extends in a first plane and a second surface portion at which a tangential plane to the surface extends in a second plane not coinciding with the first plane. The method comprises a first exposure step, in which the first pattern portion is exposed. Therein, the first pattern portion is focused into a first focal plane. The method further comprises a second exposure step, in which the second pattern portion is exposed. Therein, the second pattern portion is focused into a second focal plane which is different from the first focal plane.

Owner:HEWLETT PACKARD DEV CO LP

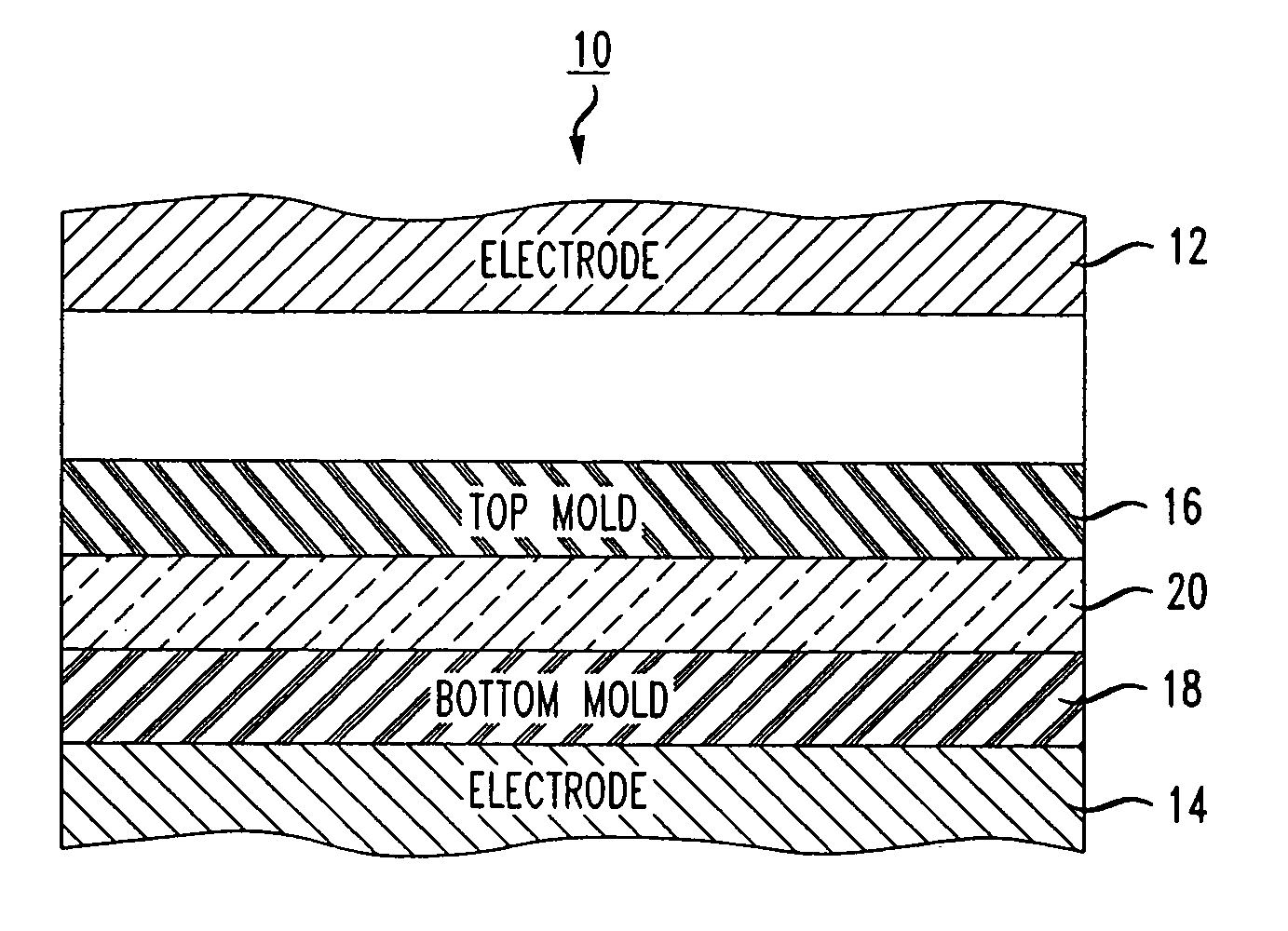

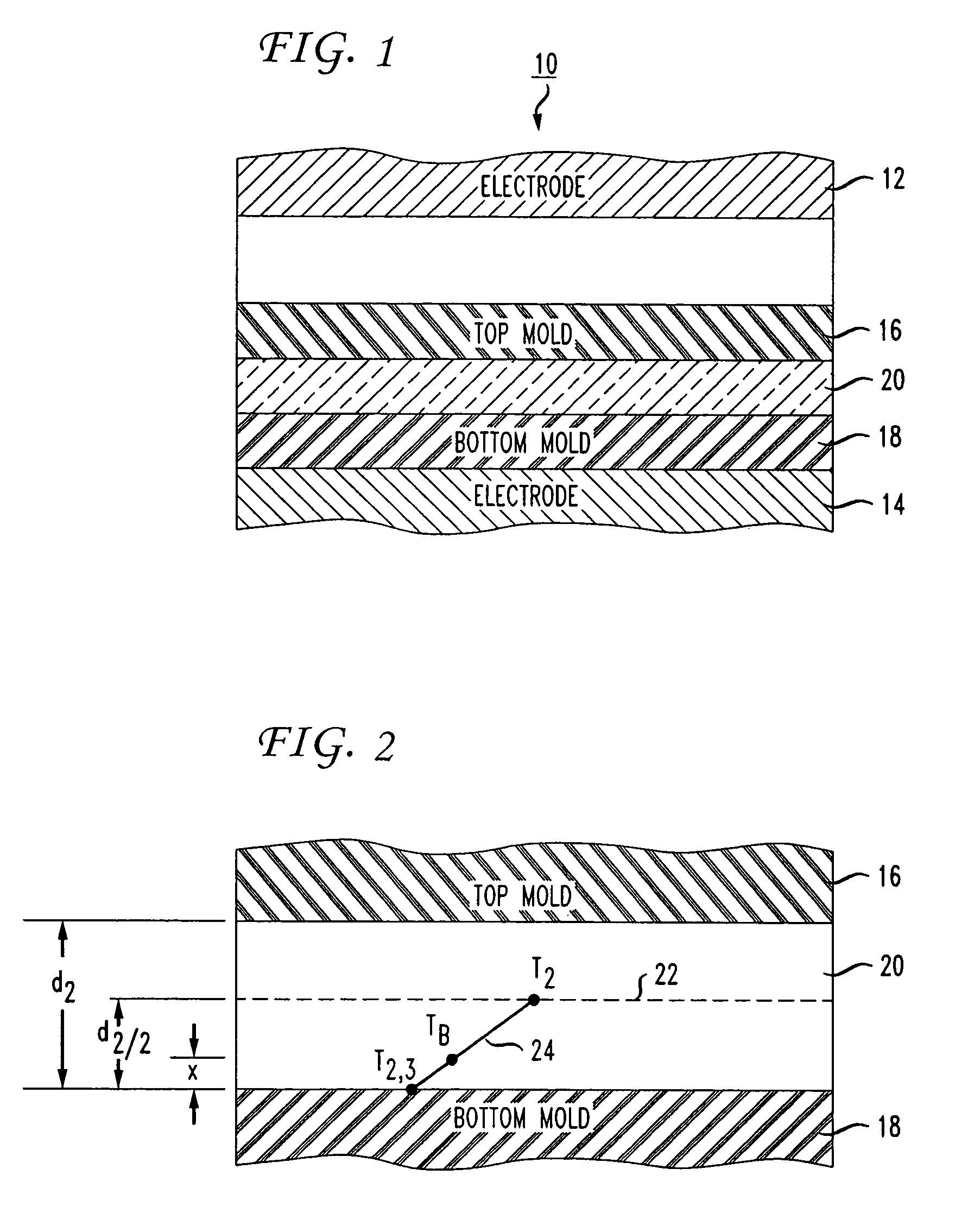

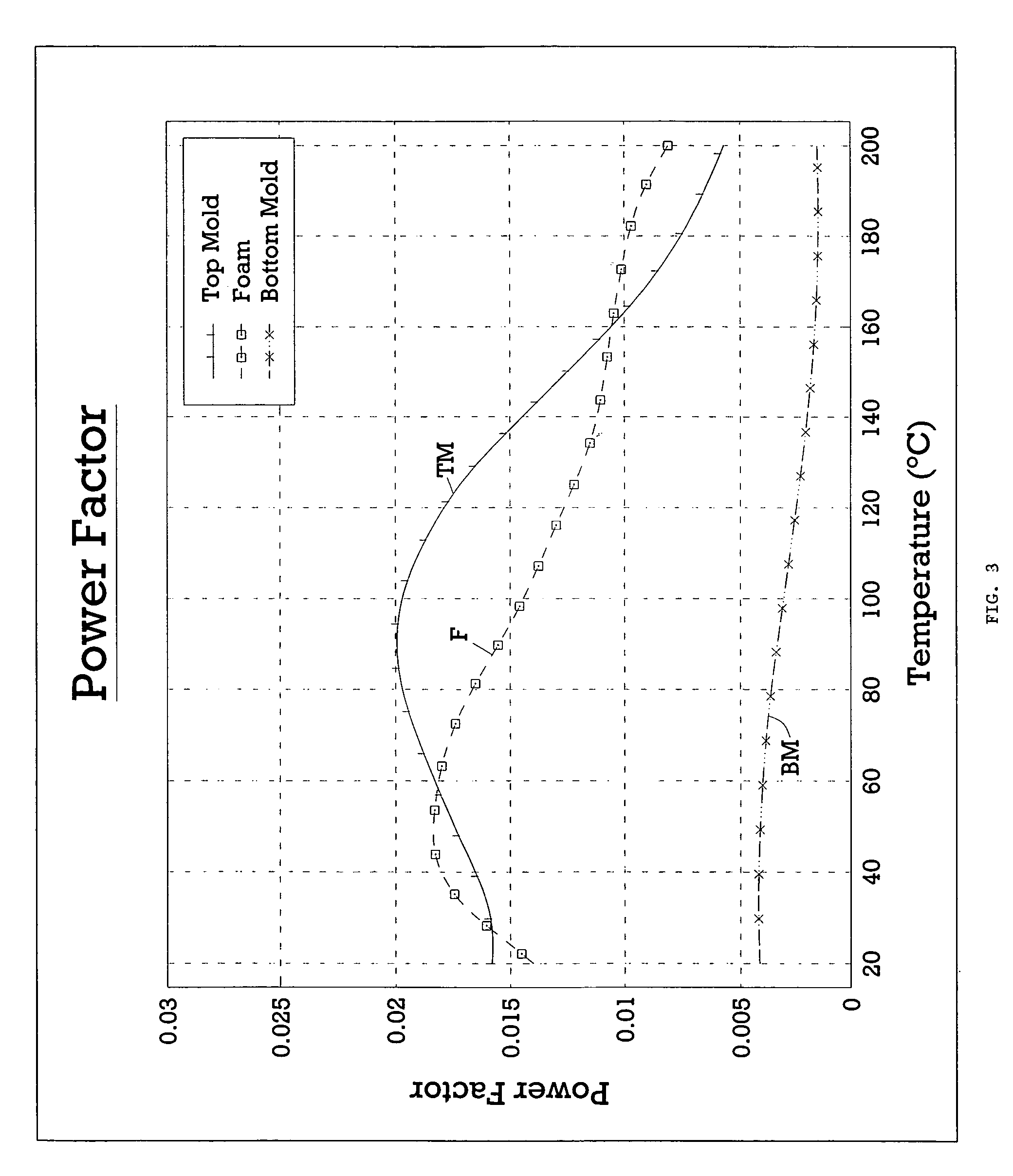

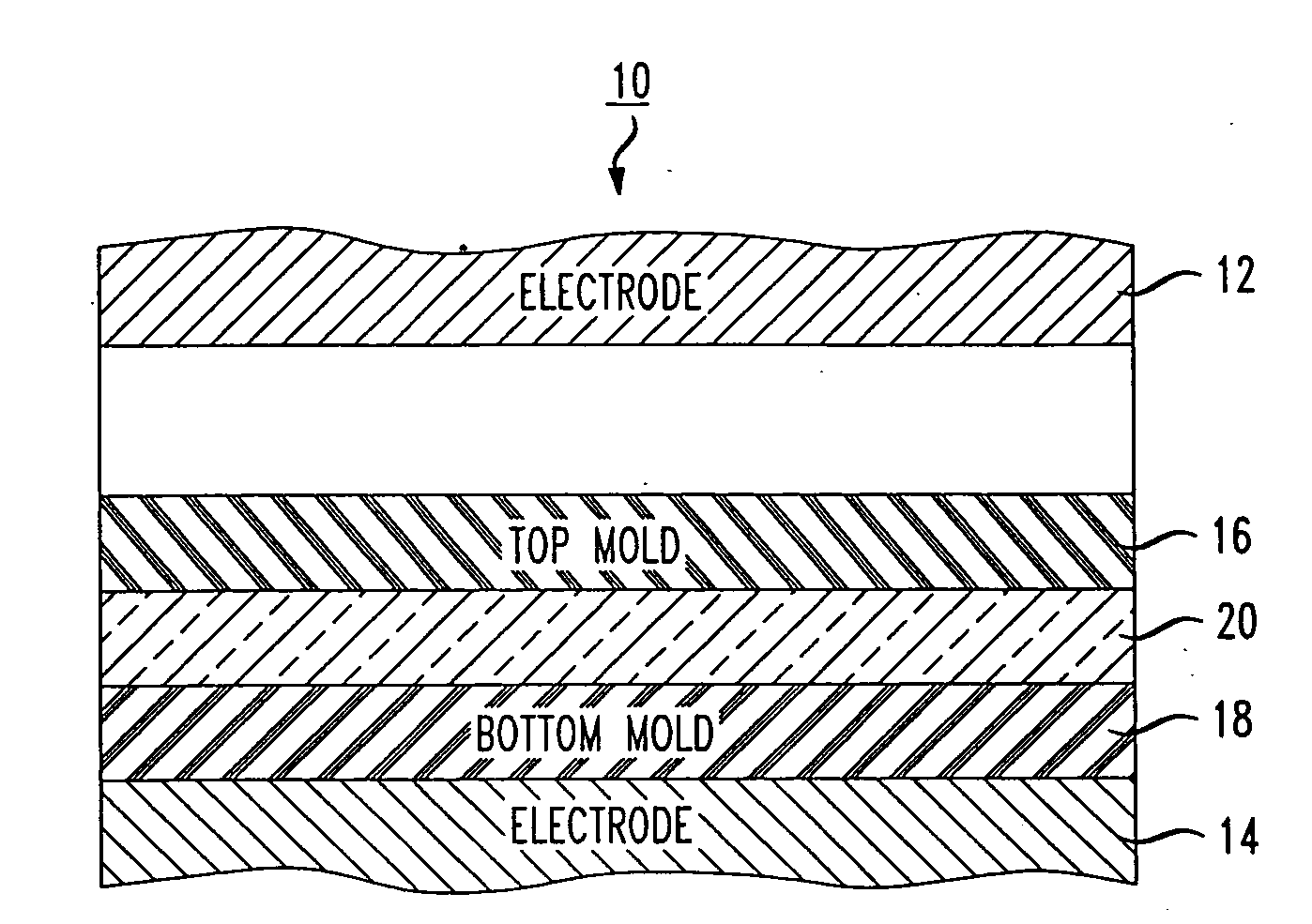

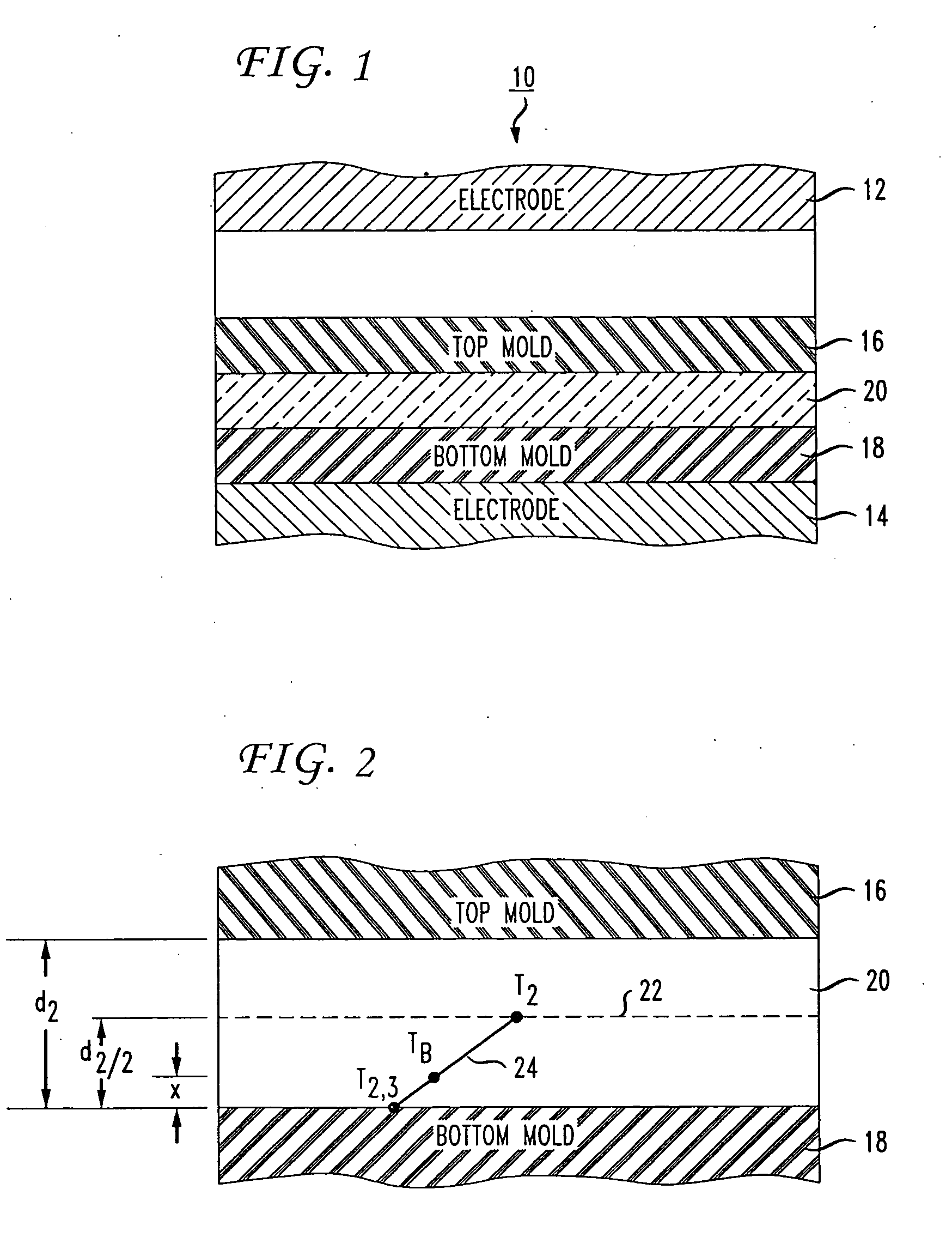

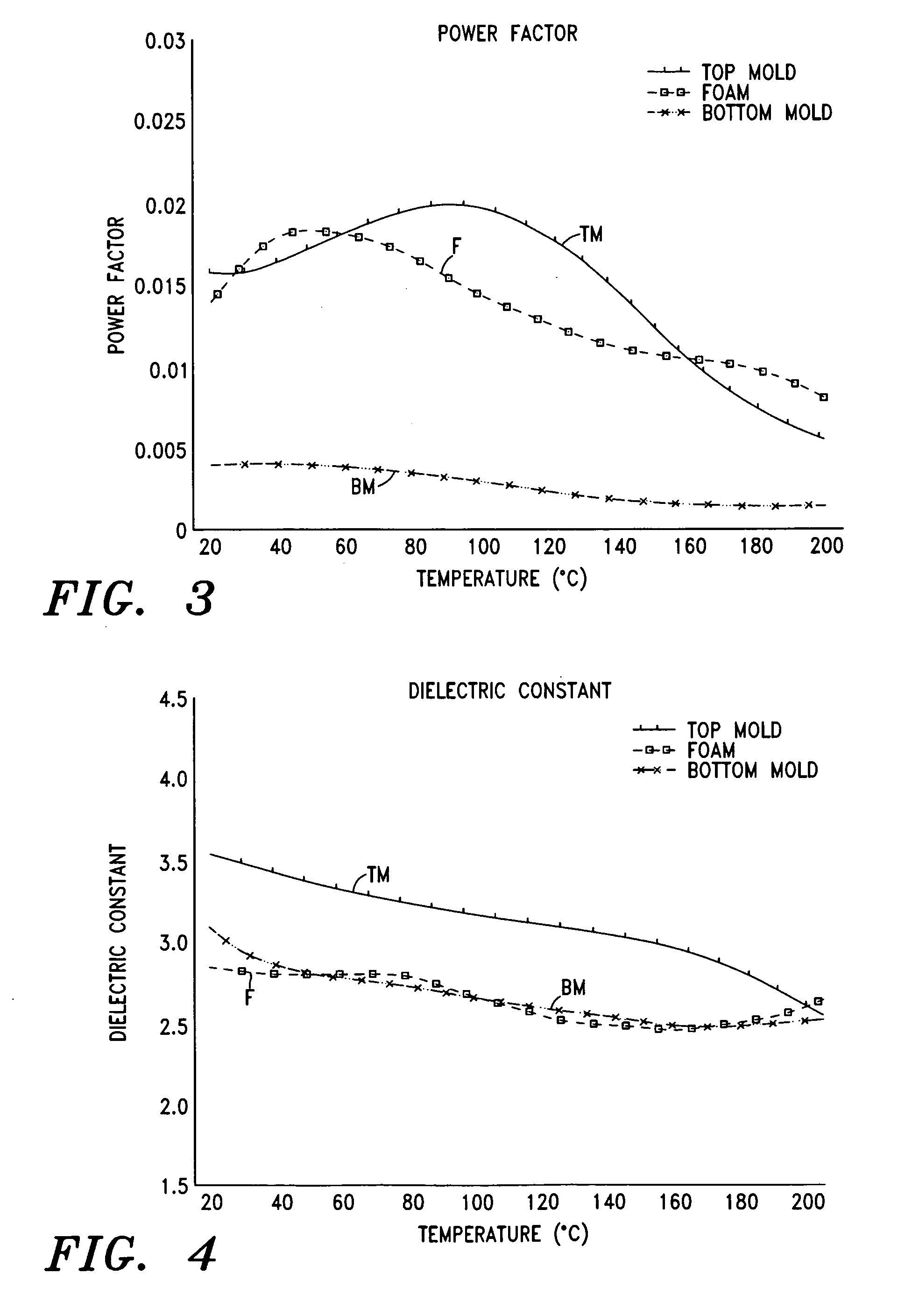

Method of forming a hardened skin on a surface of a molded article

ActiveUS7837910B2Easy to cleanReliably fabricatedElectric discharge heatingLaminationFoaming agentShell molding

A method of forming a hardened skin on a surface of a molded article. In an exemplary method, a formable material is mixed with a blowing agent to form a foam material. The foam material is placed in a flow molding apparatus such that the top surface of the foam material is in contact with the top mold of the apparatus and the bottom surface of the foam material is in contact with the bottom mold of the apparatus. In operation, an alternating dielectric field is applied across the foam material to form the molded article. At the end of the molding cycle, the bottom surface of the foam material remains under the decomposition temperature of the blowing agent so as to form a hardened skin on the molded article.

Owner:NOVATION IQ LLC

Method for fabricating electrical connection structure of circuit board

ActiveUS7340829B2Pitches canSmallness of the opening of the stencil can be eliminatedDecorative surface effectsMultilayer circuit manufactureElectrical connectionConductive materials

A method for fabricating an electrical connection structure of a circuit board is proposed. The circuit board is provided with a plurality of pads on a surface thereof and with a plurality of conductive structures therein for electrically connecting the pad. A plurality of openings is formed penetrating through an insulating layer provided on the circuit board to expose the pad. Subsequently, a conductive base is attached to one surface of the circuit board for electrically connecting the pad. By such arrangement, a conductive material can be formed on the pad located on the other surface of the circuit board by an electroplating process via the conductive base, the pad on the surface, and the conductive structure within the circuit board.

Owner:PHOENIX PRECISION TECH CORP

Method of Forming a Hardened Skin on a Surface of a Molded Article

ActiveUS20100096780A1Easy to cleanReliably fabricatedDielectric heatingLaminationPolymer scienceBlowing agent

A method of forming a hardened skin on one or more surfaces of a molded article. In an exemplary method, a formable material is mixed with a blowing agent to form a foam material. The foam material is placed in a flow molding apparatus such that a first surface of the foam material is in contact with a first mold section and a second surface of the foam material is in contact with a second mold section. In operation, an alternating dielectric field is applied across the foam material to form the molded article. At the end of the molding cycle, the first and / or second surfaces of the foam material remain under the decomposition temperature of the blowing agent and are not blown so as to form one or more thicknesses of hardened skin on the molded article.

Owner:NOVATION IQ LLC

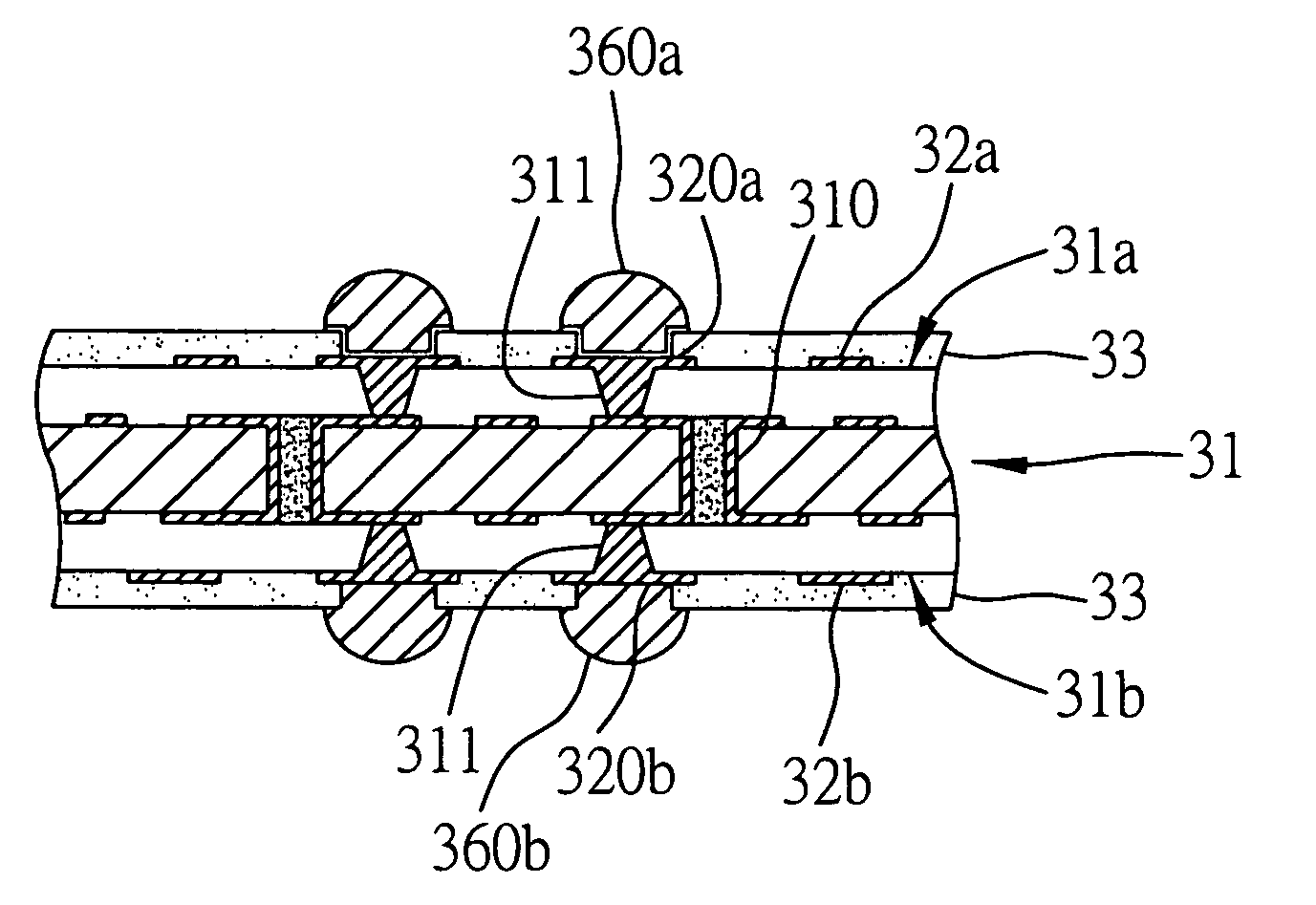

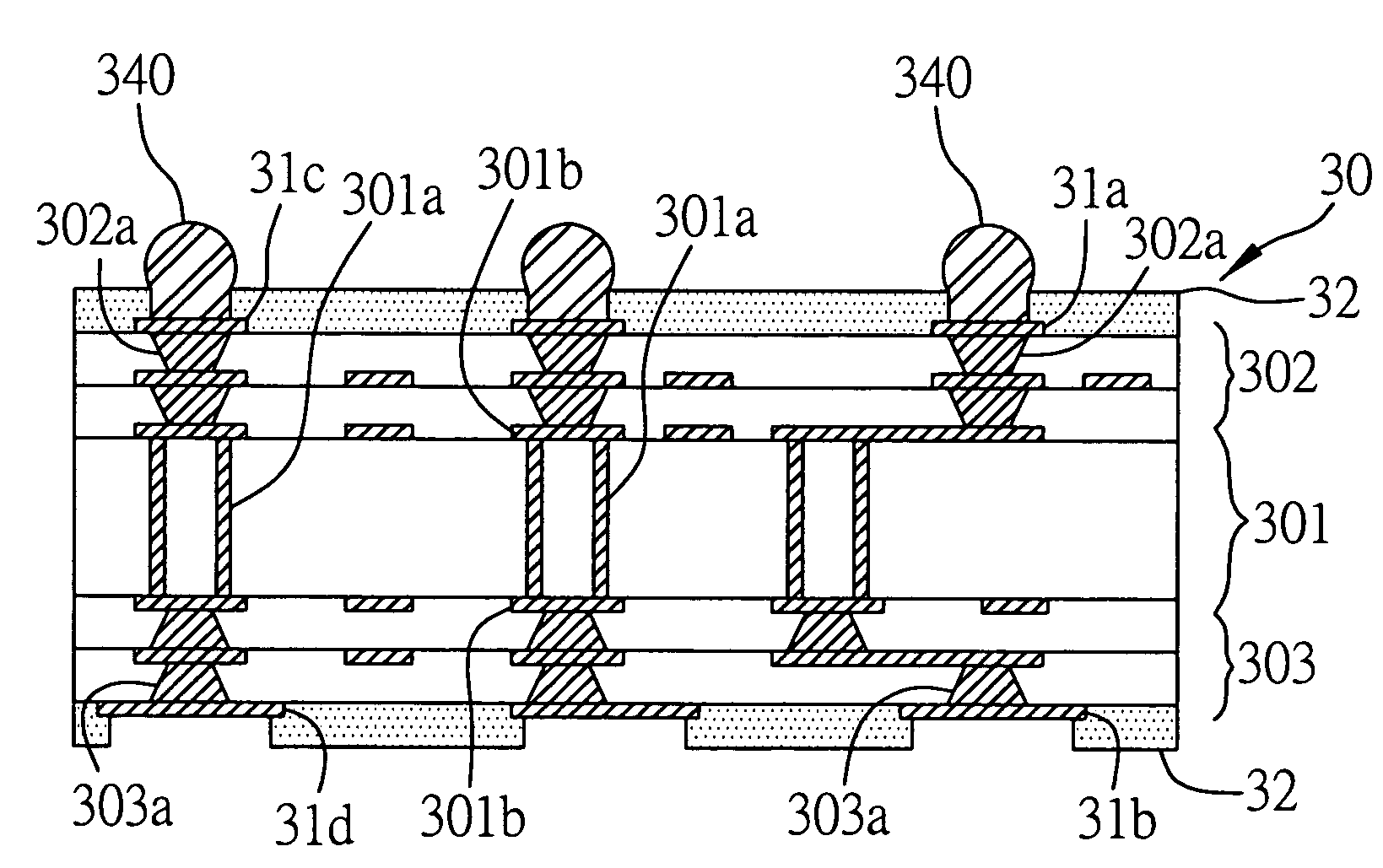

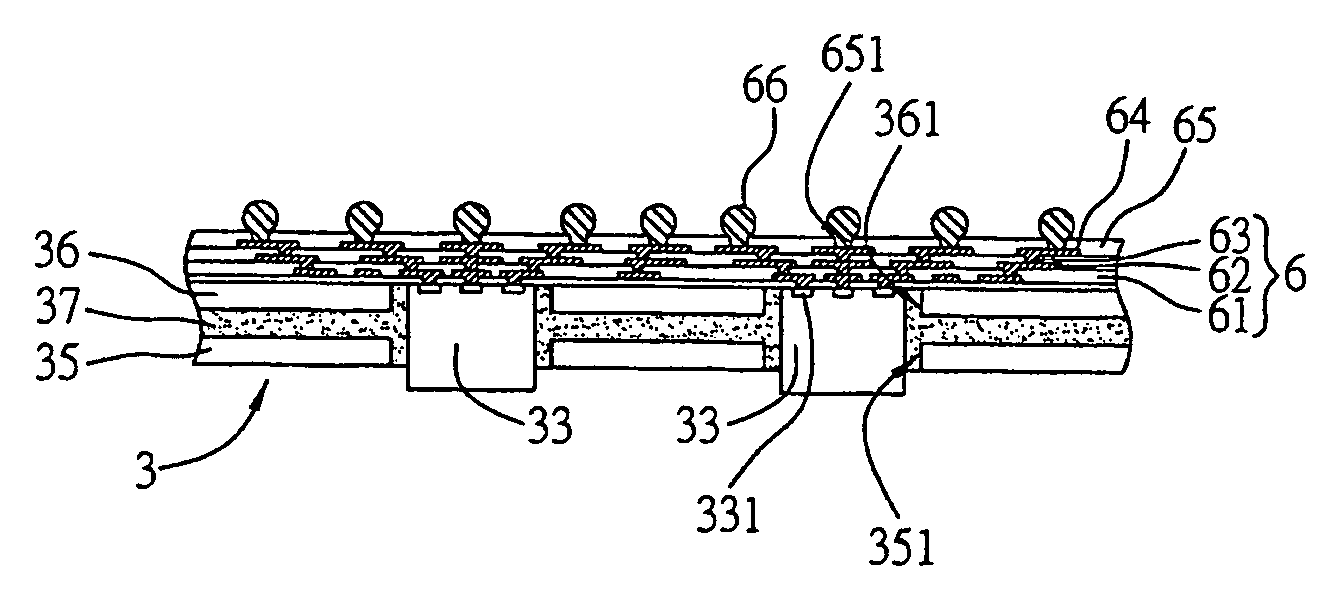

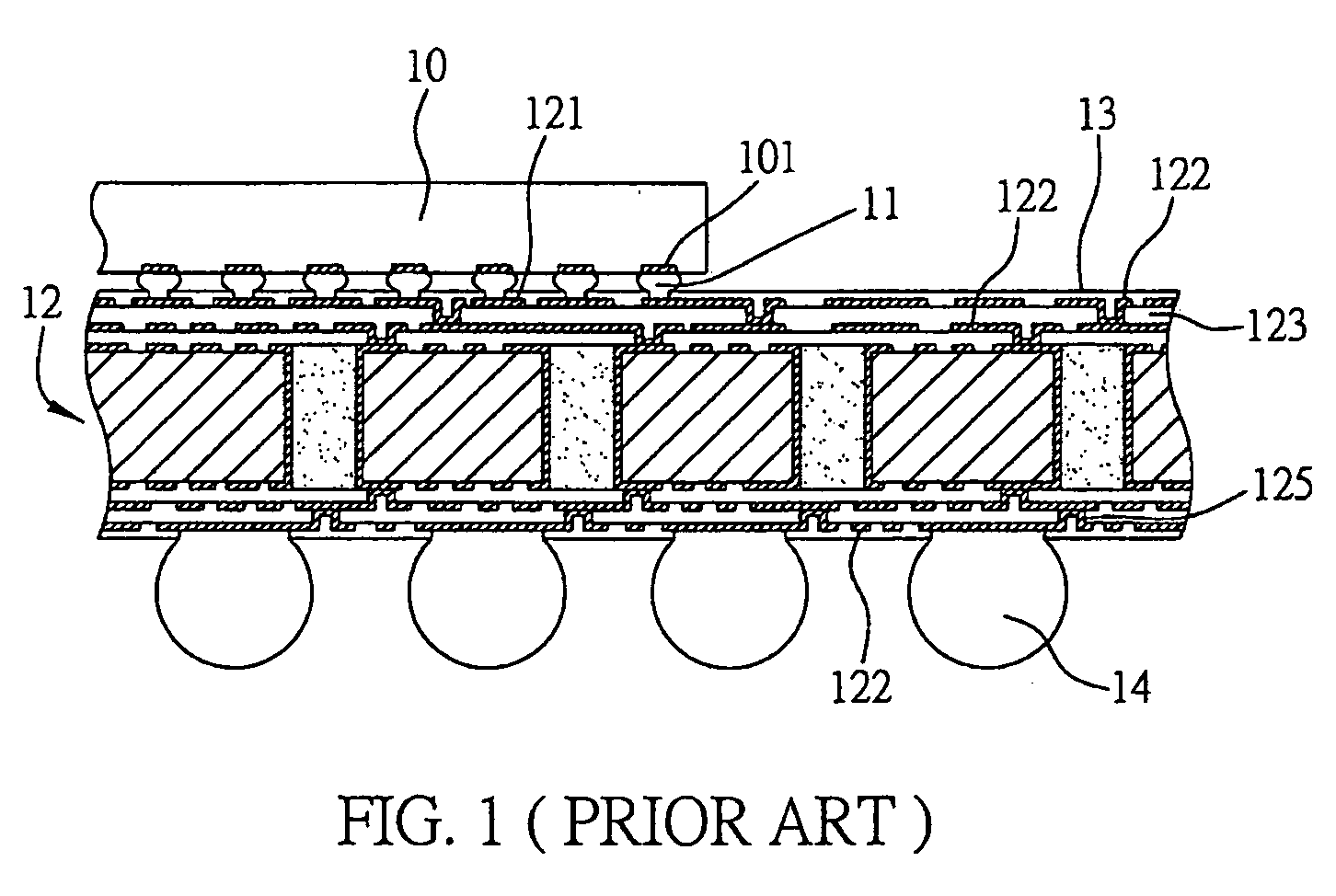

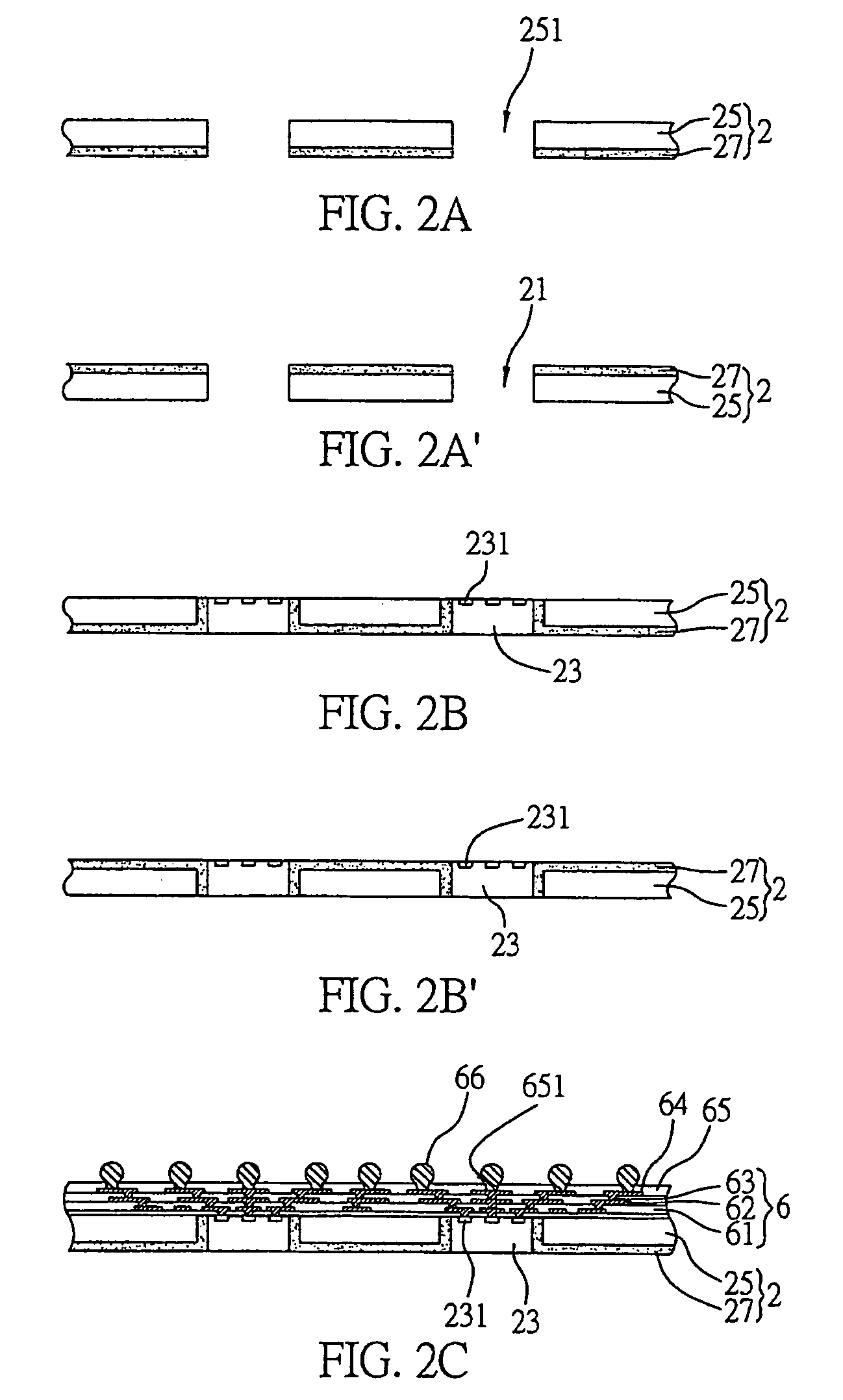

Carrying structure of electronic components

ActiveUS20060237854A1Manufacturing process is complexLow costSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A carrying structure of electronic components is proposed. The carrying structure includes at least one supporting board with at least one cavity disposed thereon, at least one adhesive layer formed on the supporting board, and at least one electronic component having an active face and a non-active face located in the cavity. The gap between the cavity and the electronic component is filled with a portion of the adhesive layer, and thus the electronic component is fixed in the cavity of the supporting board.

Owner:PHOENIX PRECISION TECH CORP

Fabrication method of flexible devices

ActiveUS8801997B2Easy to separateReliably fabricatedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSolvent

Disclosed is a method of fabricating a flexible device, which includes surface-treating one or both sides of a carrier plate so that regions with different surface-treatments are formed on the same side of the carrier plate, forming a glass-filler reinforced plastic substrate film on the surface-treated carrier plate, forming thin film patterns on the glass-filler reinforced plastic substrate film, and separating the glass-filler reinforced plastic substrate film having the thin film patterns formed thereon from the carrier plate, and in which the surface-treating of the carrier plate enables the glass-filler reinforced plastic substrate film to be easily separated from the carrier plate without an additional process such as using a solvent or a laser release technique.

Owner:KOREA ADVANCED INST OF SCI & TECH

Ferrule assembly having highly protruding optical fibers and an associated fabrication method

InactiveUS20060018605A1Reduce protrusionEffectively fabricatesCoupling light guidesBiomedical engineeringFerrule

A ferrule assembly having highly protruding optical fibers and a corresponding method of efficiently, precisely and repeatedly fabricating the ferrule assemblies are provided. In this regard, a ferrule assembly is provided that includes a plurality of optical fibers extending at least about 3.5 μm beyond the front face. The end portions of the optical fibers of the ferrule assembly may also be substantially coplanar with the end portions of the optical fibers differing in position from one another by no more than 100 nm. The ferrule assembly may be efficiently fabricated by polishing the optical fibers to a desired protrusion without first grinding or polishing the optical fibers to be flush with the front face of the ferrule. The ferrule assembly may be even more efficiently fabricated in instances in which the ferrule includes at least one polishing feature, such as an outwardly extending pedestal or a recessed portion.

Owner:CORNING OPTICAL COMM LLC

In-mold decoration fabrication of injection molding

InactiveUS20060214322A1Improve reliabilityAvoid layeringCoatingsInjection mouldingElectrical and Electronics engineering

An in-mold decoration fabrication of injection molding is provided as follows. First, a plastic substrate is provided and a mask is disposed on the plastic substrate. A patterned metal film is formed on a surface of the plastic substrate without covering the mask. After the mask is removed, an ink pattern is formed selectively on the patterned metal film. Then, a plurality of forming units on the plastic substrate are preformed and separated to each other by trimming the plastic substrate. Finally, a step of resin injection is provided to cover the patterned metal film, ink pattern of each of the forming units and the exposed surface thereof.

Owner:SPEED TECH

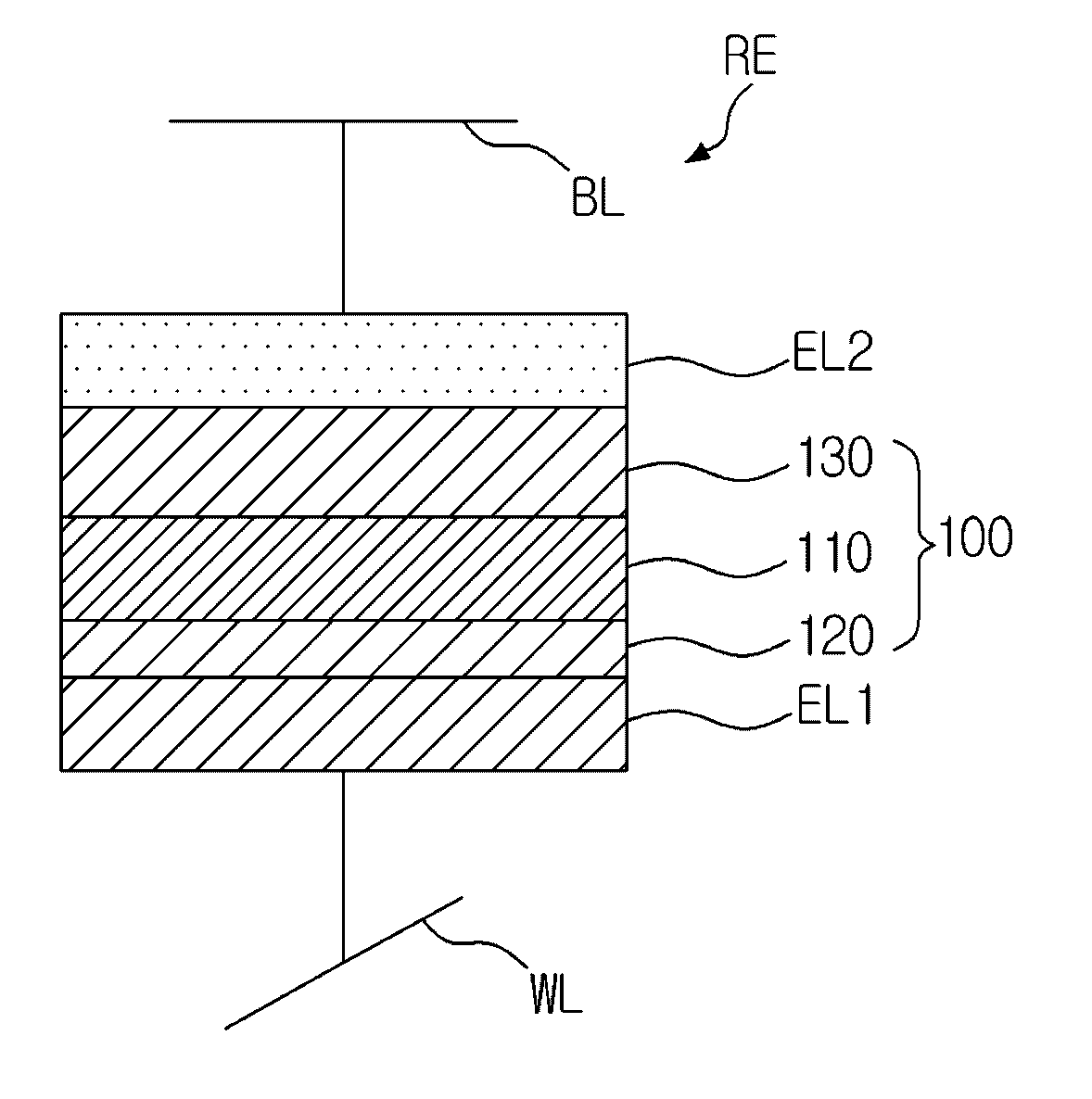

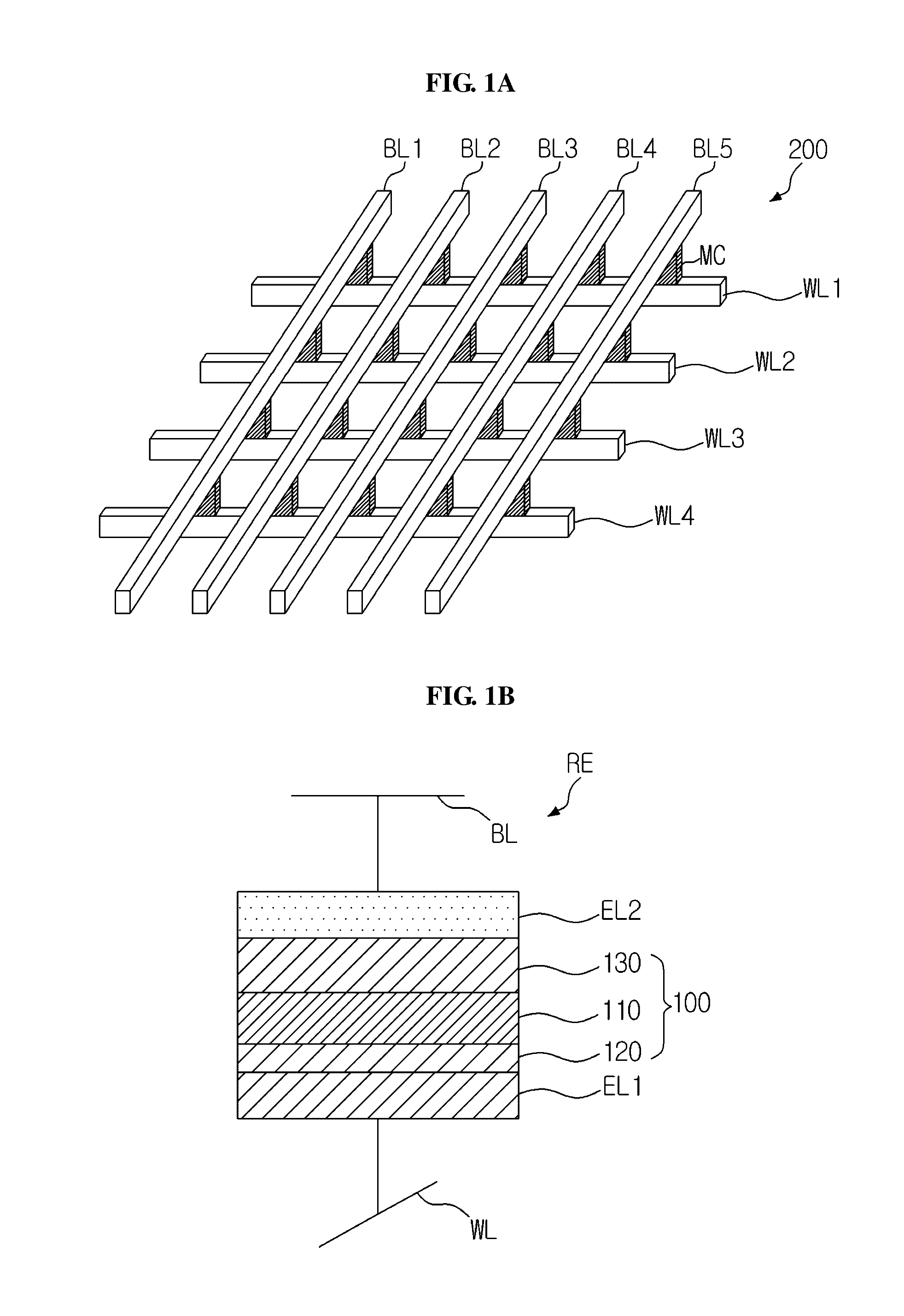

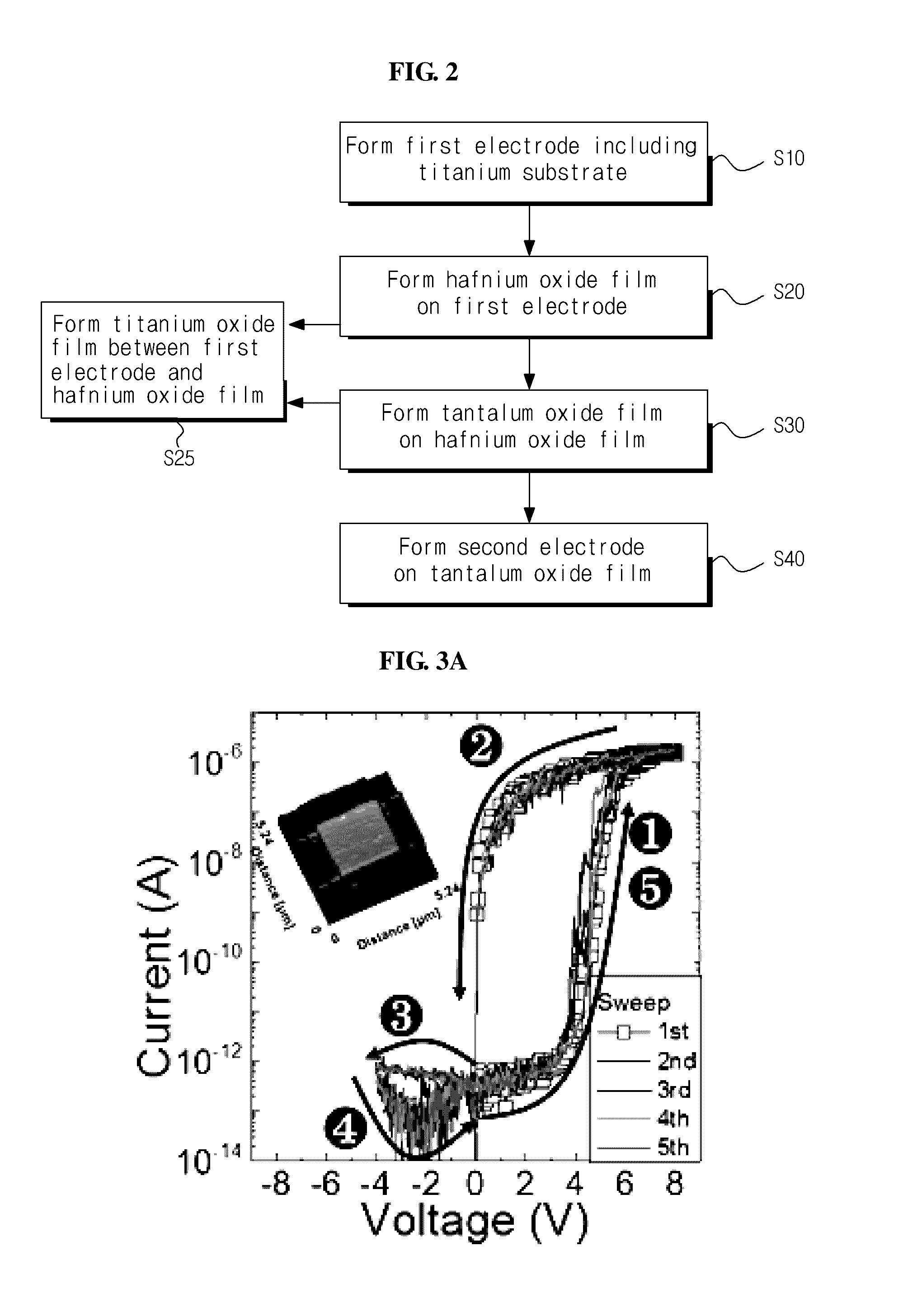

Variable resistor, non-volatile memory device using the same, and method of fabricating thereof

ActiveUS20170005262A1Reduce power consumptionSimple structureSolid-state devicesSemiconductor devicesSchottky barrierEngineering

Provided are a semiconductor technique, and more particularly, to a variable resistor, a non-volatile memory device using the same, and a method of fabricating the same. The variable resistor may include a first electrode including titanium (Ti); a second electrode for forming a Schottky barrier; and a stacked structure including an oxygen-deficient hafnium oxide film (HfO2-x, 0<x<2) between the first electrode and the second electrode, an oxygen-deficient titanium oxide (TiOx) film between the oxygen-deficient hafnium oxide film and the first electrode, and a stoichiometric tantalum oxide (Ta2O5) film between the oxygen-deficient hafnium oxide film and the second electrode.

Owner:SEOUL NAT UNIV R&DB FOUND

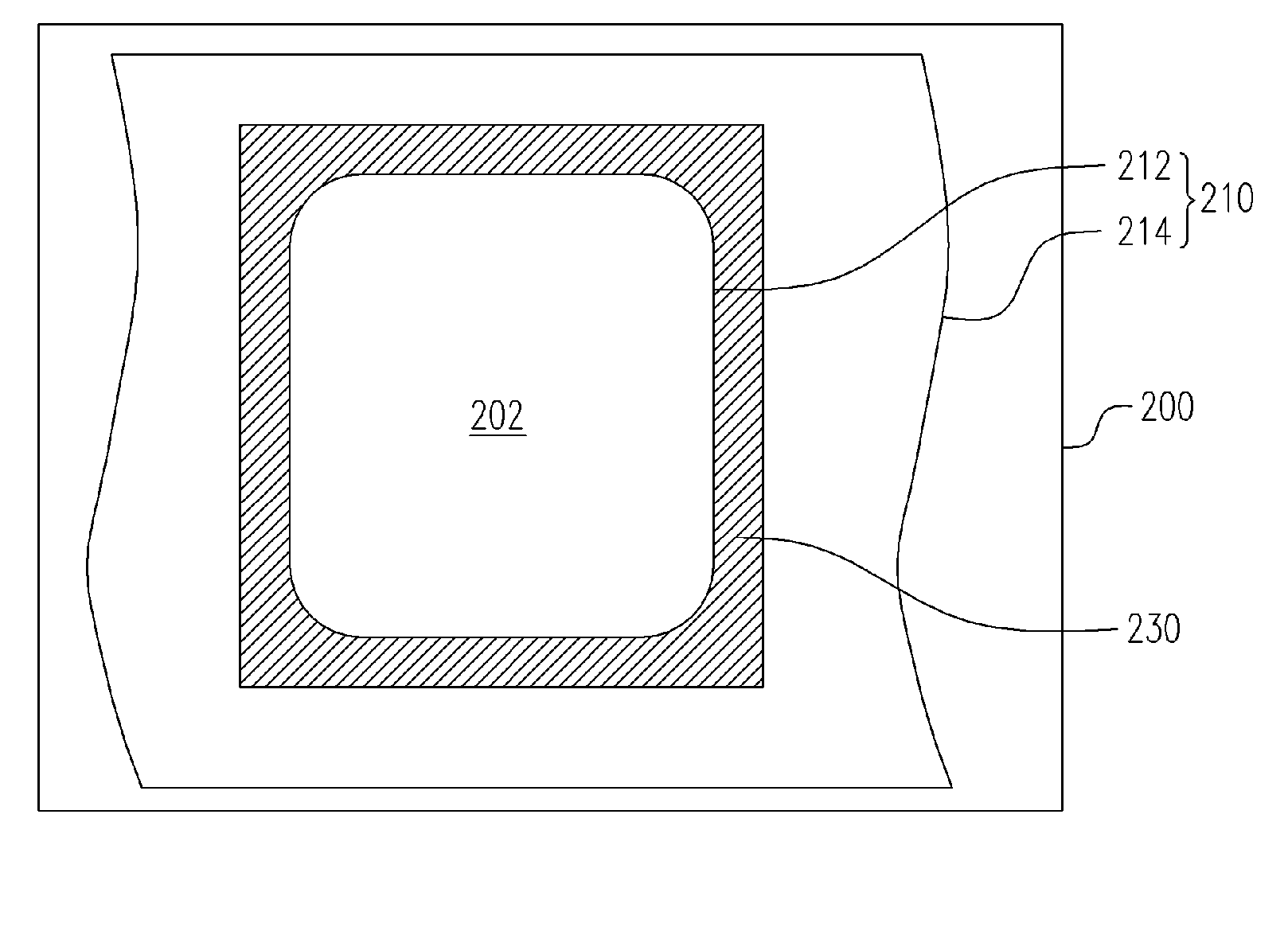

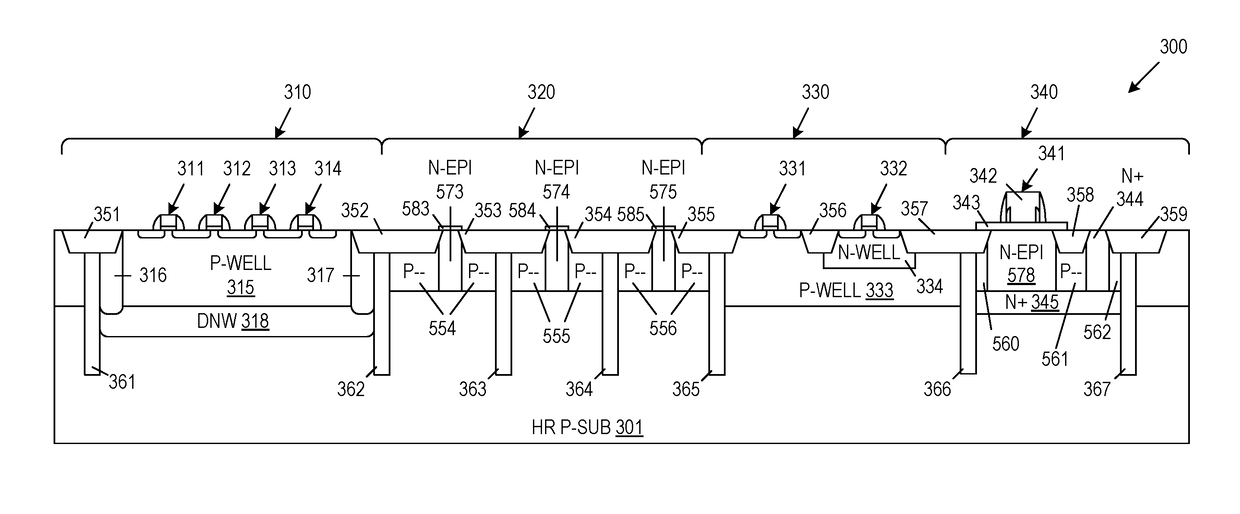

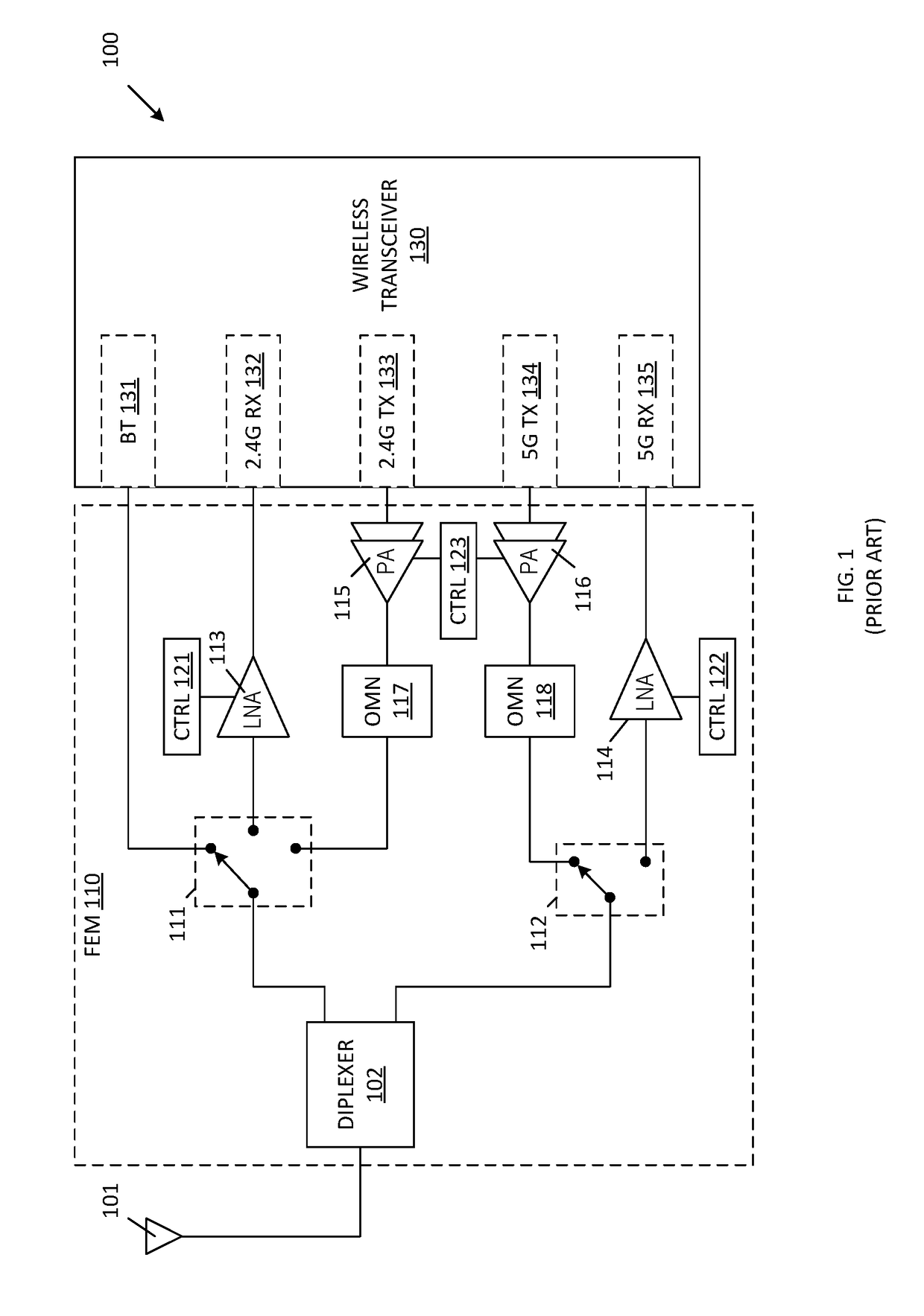

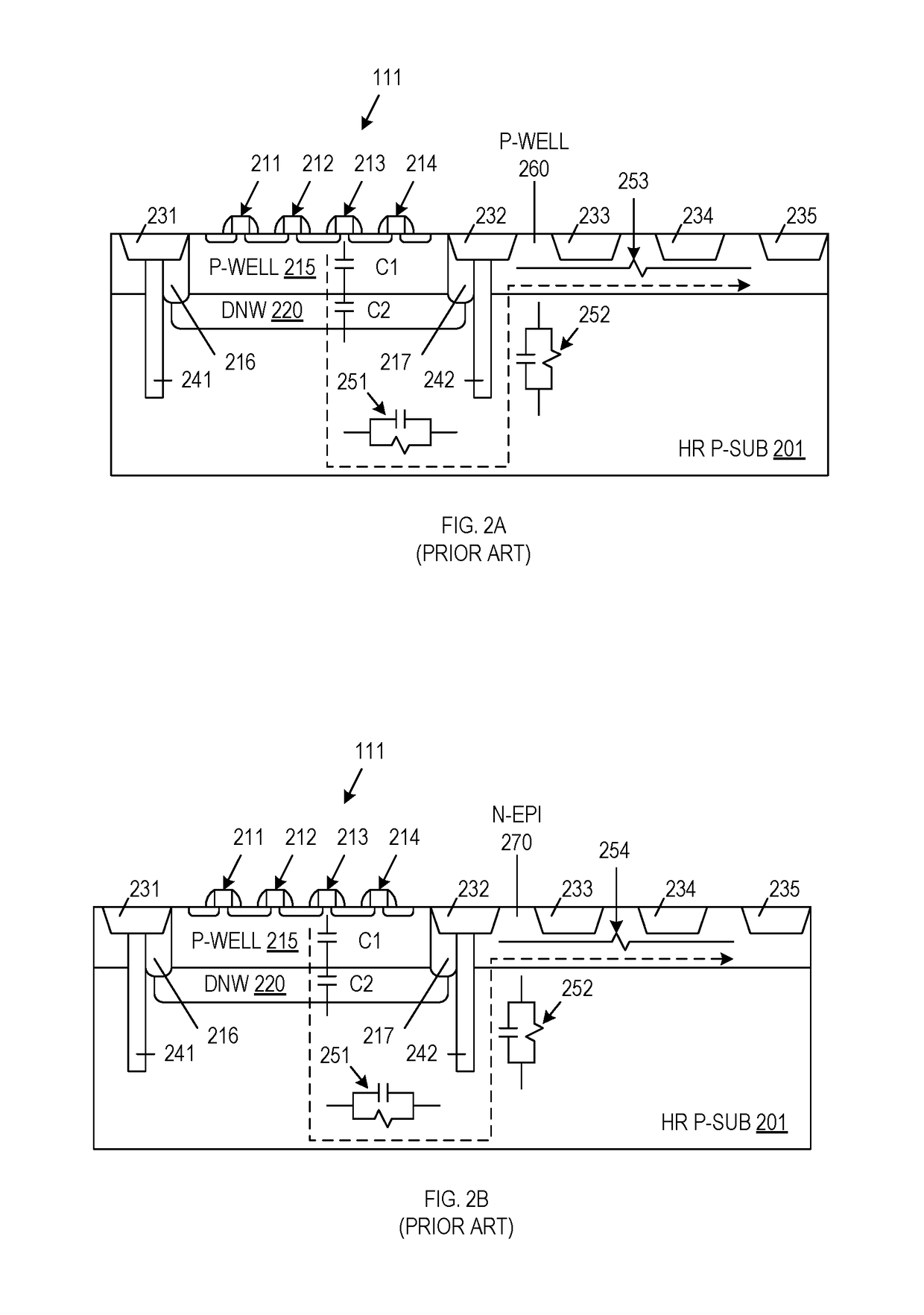

Substrate Isolation For Low-Loss Radio Frequency (RF) Circuits

ActiveUS20180323187A1Reliably fabricatedEasy to useTransistorSemiconductor/solid-state device detailsEngineeringRadio frequency

Methods and structures for improved isolation in a SiGe BiCMOS process or a CMOS process are provided. In one method, shallow trench isolation (STI) regions are formed in a first semiconductor region located over a semiconductor substrate. Dummy active regions of the first semiconductor region extend through the STI regions to an upper surface of the first semiconductor region. A grid of deep trench isolation (DTI) regions is also formed in the first semiconductor region, wherein the DTI regions extend entirely through the first semiconductor region. The grid of DTI regions includes a pattern that exhibits only T-shaped or Y-shaped intersections. The pattern defines a plurality of openings, wherein a dummy active region is located within each of the openings.

Owner:NEWPORT FAB

Method for fabricating conductive bump of circuit board

ActiveUS7341934B2Reduce spacingSmallness of the opening can be eliminatedSemiconductor/solid-state device detailsStacked resist layersResistEngineering

A method for fabricating conductive bumps of a circuit board is proposed. First of all, a circuit board having a first surface and a corresponding second surface is provided. A circuit structure having a plurality of conductive pads is formed on each of the first surface and the second surface, and conductive structures are formed in the circuit board for electrically connecting the circuit structures. Also, an insulating layer having a plurality of openings penetrating therethrough is formed on the circuit board for exposing the conductive pad. Then, a conductive layer is formed on a surface of the insulating layer having the opening formed on the first surface of the circuit board. An electroplating process is performed via the conductive layer and the conductive structure, such that a conductive bump is formed on the conductive pad located on the second surface of the circuit board. Subsequently, a resist layer is formed on the second surface of the circuit board to cover the conductive bump, and another resist layer having openings penetrating therethrough is formed on the first surface of the circuit board to expose the conductive pad. Finally, a conductive bump is formed on the conductive pad located on the first surface of the circuit board by an electroplating process. By such arrangement, the conductive bumps are successively formed on the first surface and the second surface of the circuit board.

Owner:PHOENIX PRECISION TECH CORP

Buried solder bumps for AC-coupled microelectronic interconnects

InactiveUS20050046037A1Sufficient complianceAvoid excessive distancePrinted circuit assemblingSemiconductor/solid-state device testing/measurementCapacitanceEngineering

Microelectronic packages include a first microelectronic substrate having a first face and a first AC-coupled interconnect element on the first face. A second microelectronic substrate includes a second face and a second AC-coupled interconnect element on the second face. A buried solder bump extends between the first and second faces, and is at least partially buried beneath the first and / or second faces, to maintain the first and second AC-coupled interconnect elements in closely spaced apart relation. The buried solder bump also may couple DC power between the first and second substrates. Other technologies also may be used to maintain the AC-coupled interconnect elements in closely spaced apart relation and to couple DC power between the substrates. The first and second AC-coupled interconnect elements may be first and second capacitor plates, first and second inductors and / or first and second combined inductive and capacitive elements.

Owner:NORTH CAROLINA STATE UNIV