Patents

Literature

109results about "Stacked resist layers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

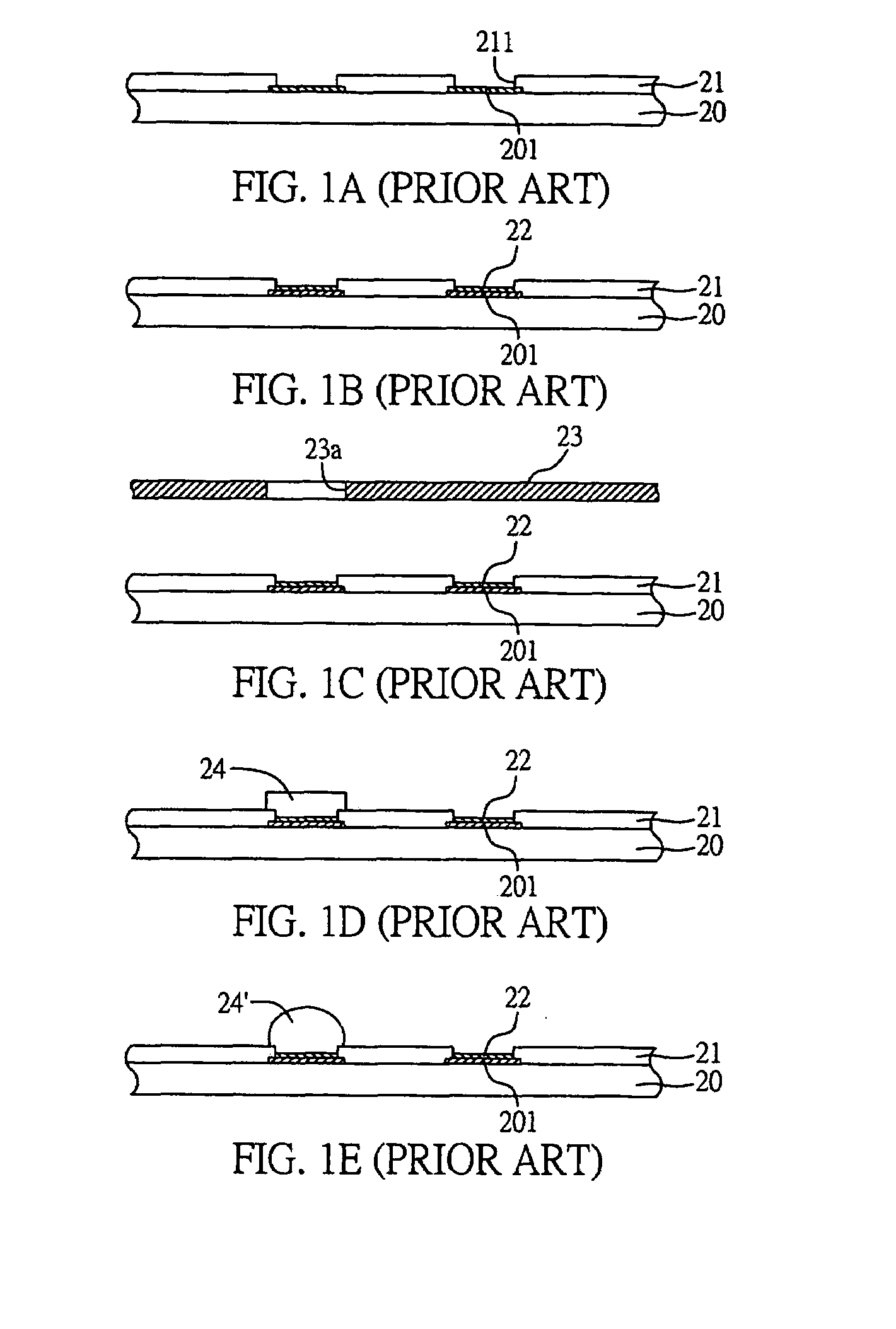

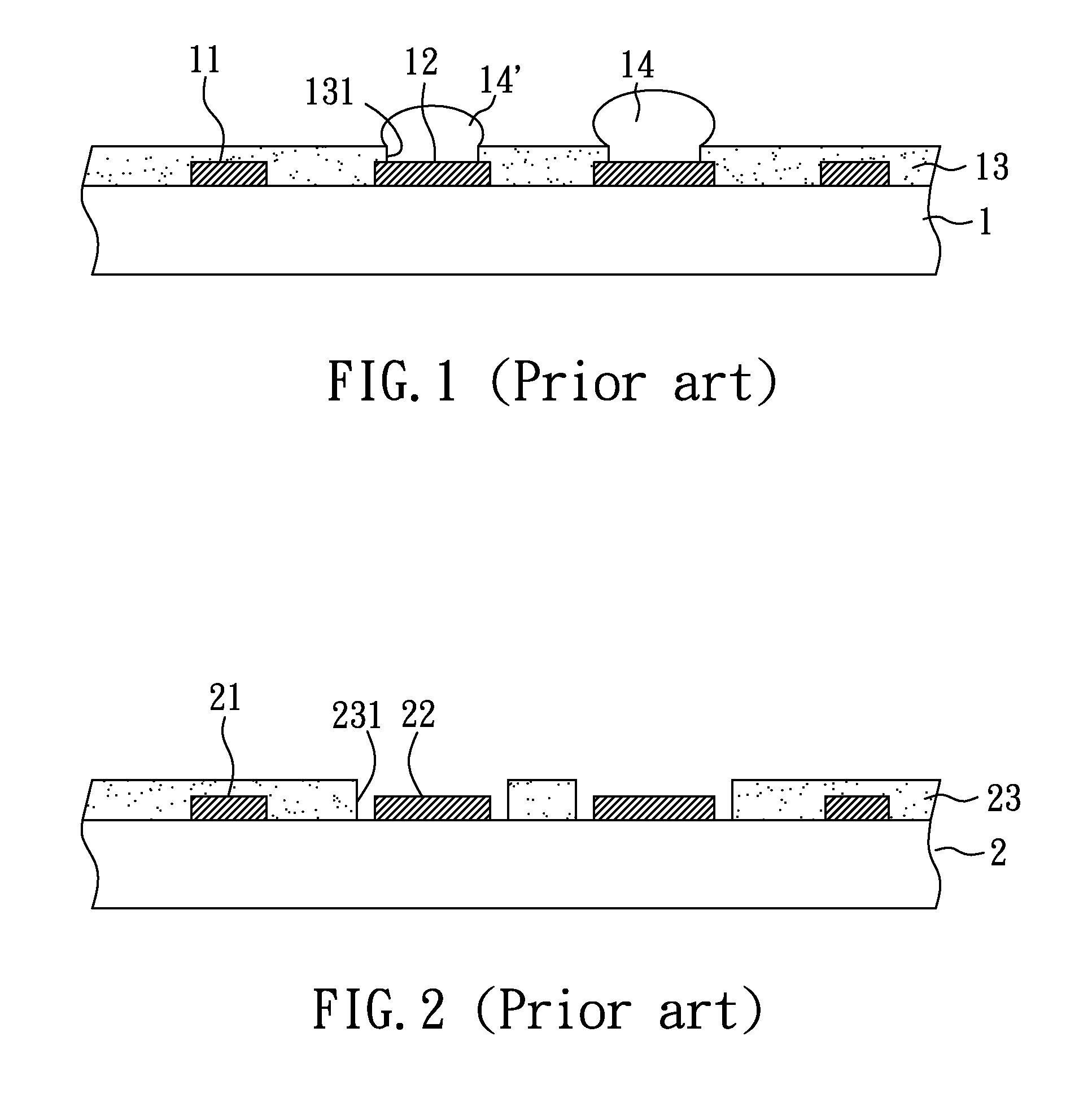

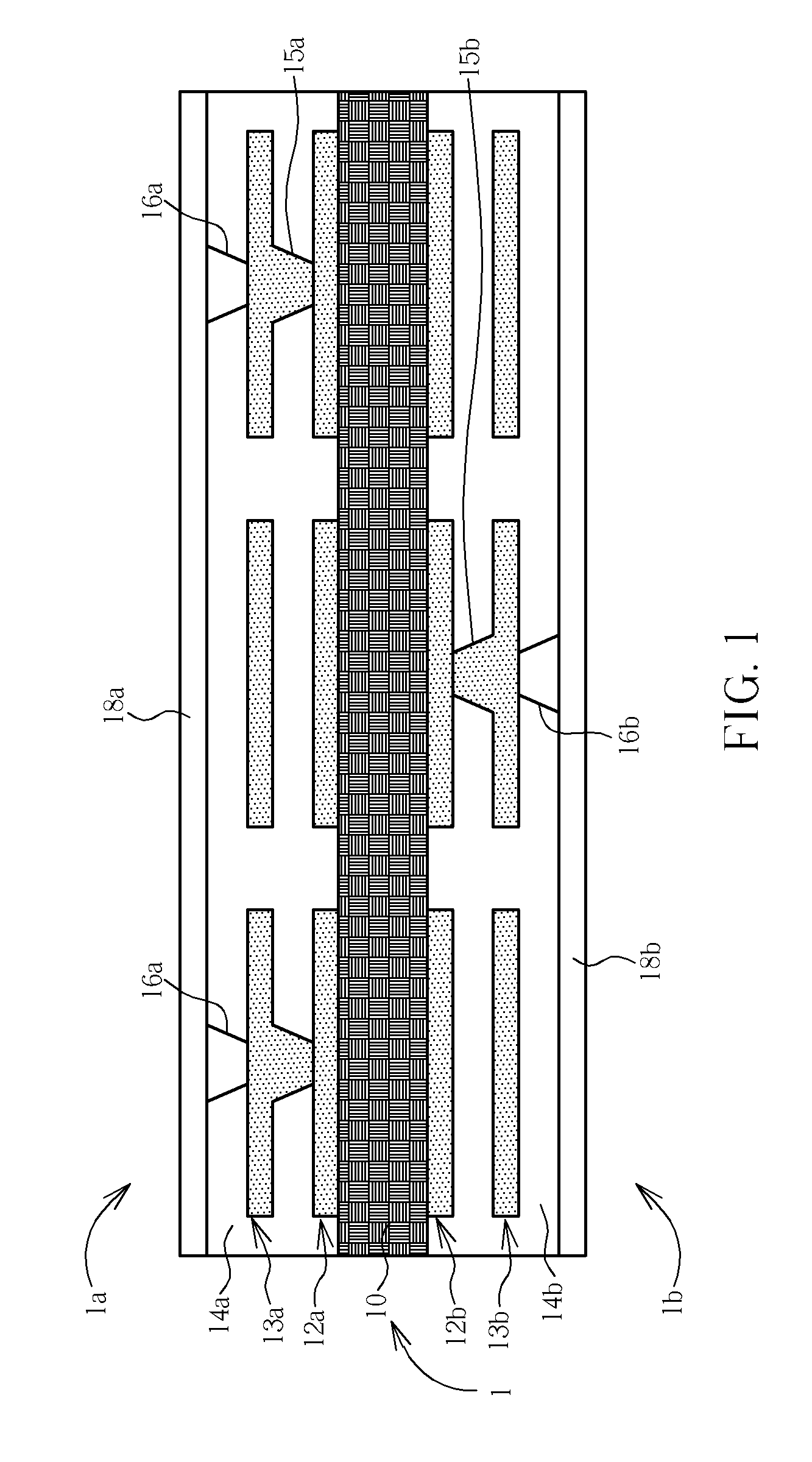

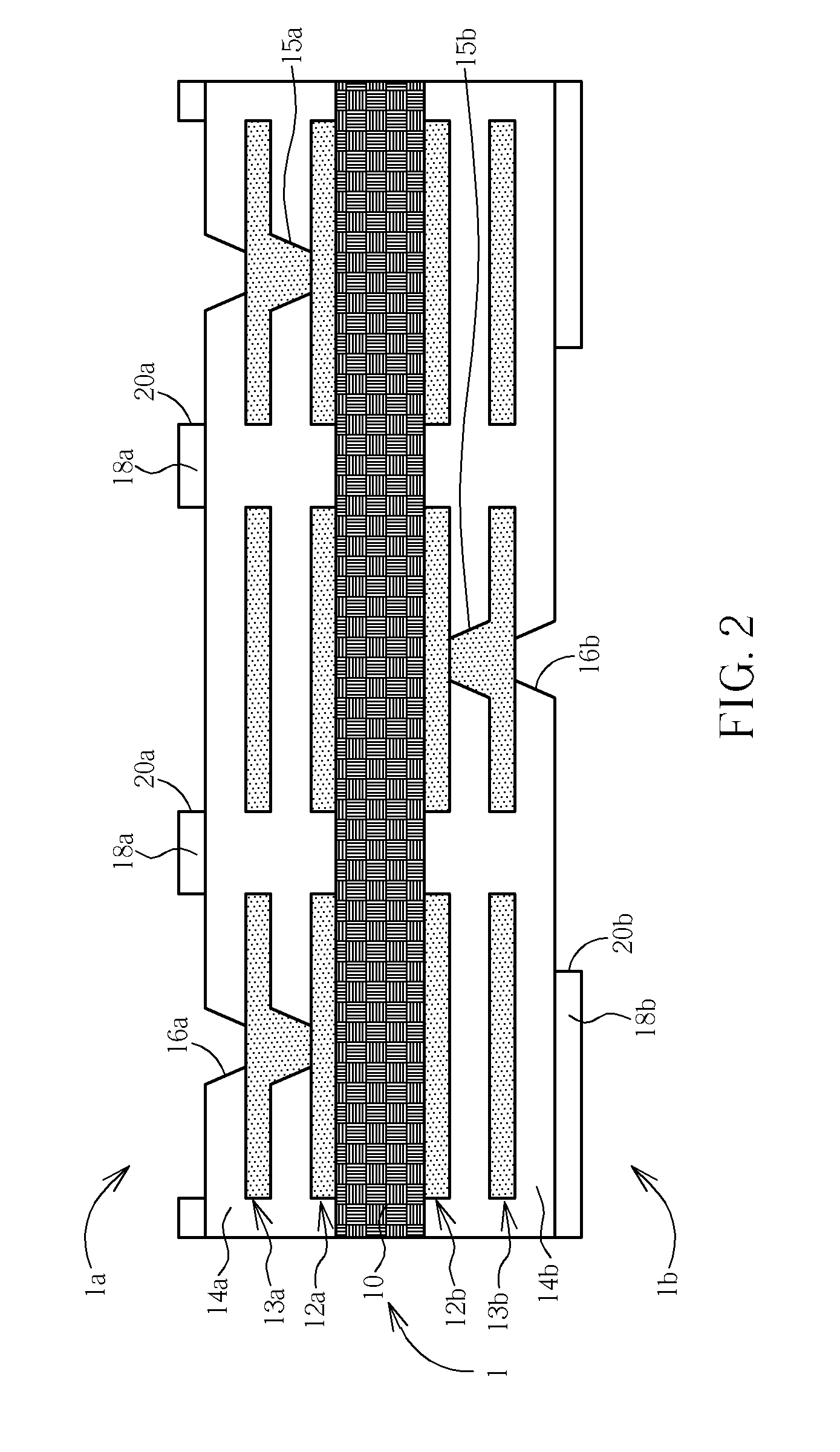

Package substrate, method of fabricating the same and chip package

InactiveUS20080179740A1Improve chip reliabilityIncrease distribution densitySemiconductor/solid-state device detailsStacked resist layersSolder maskEngineering

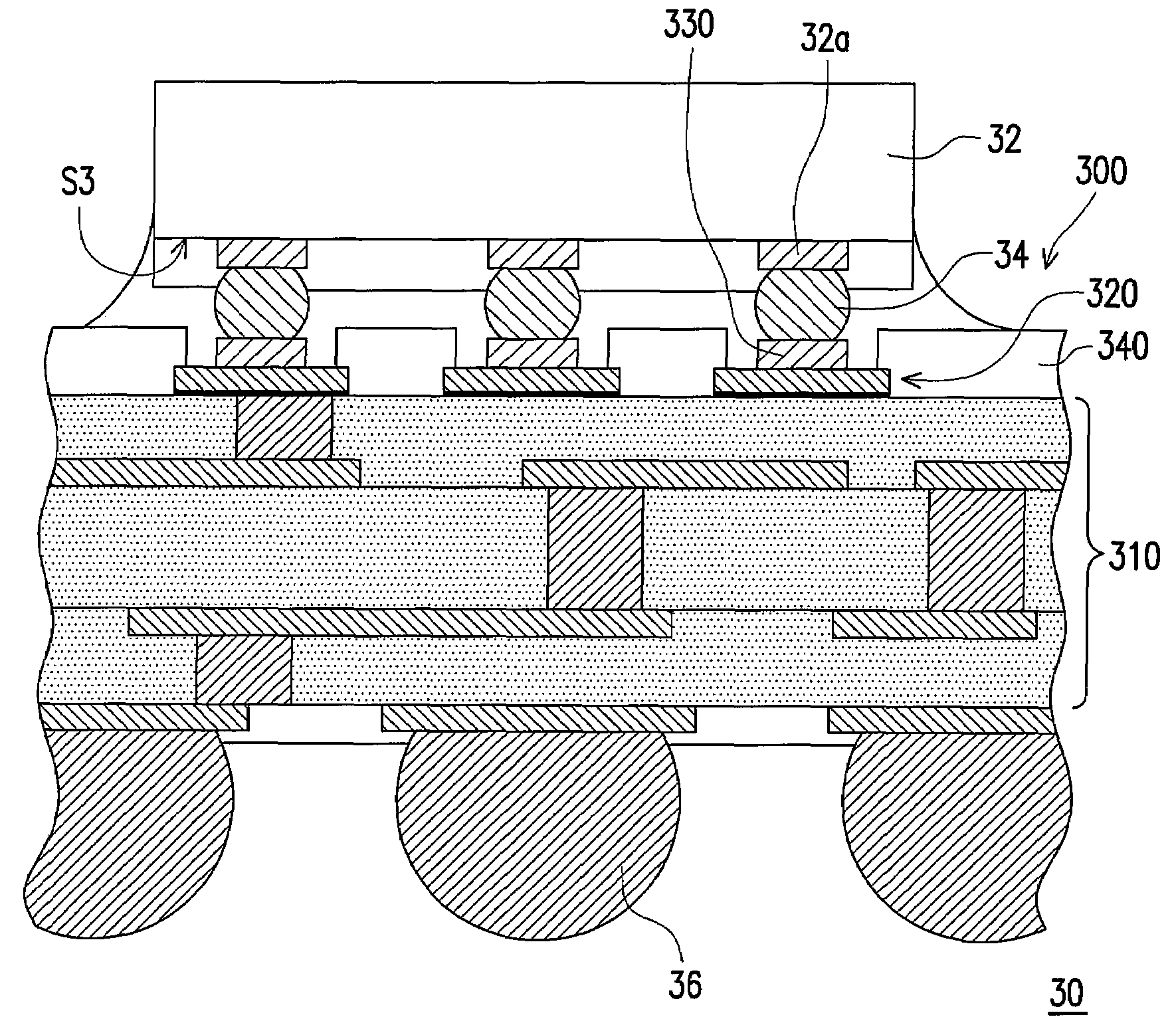

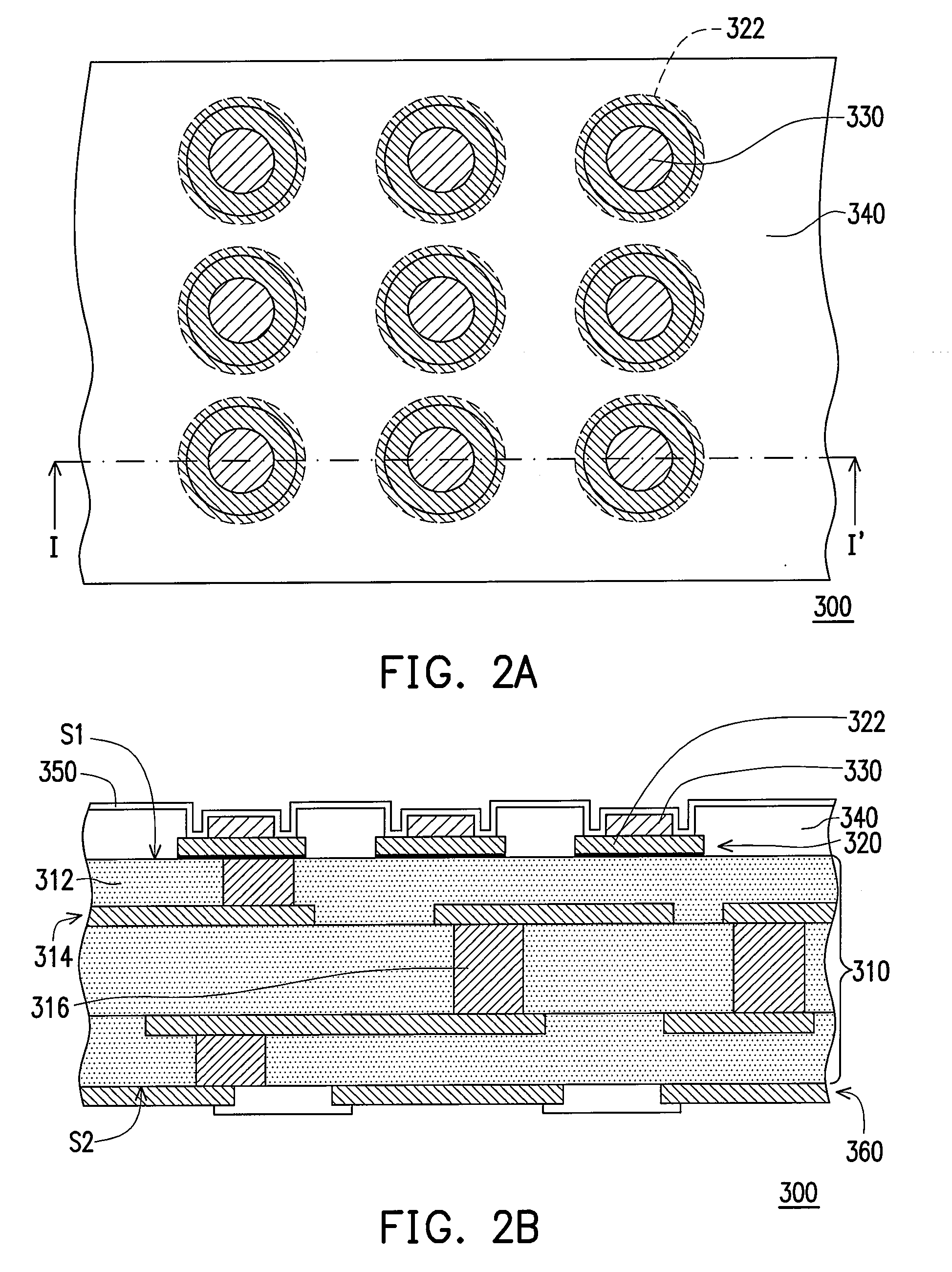

A package substrate, including a base layer, a surface circuit layer, a plurality of conductive bumps, and a patterned solder mask layer, is provided. The surface circuit layer having a plurality of bonding pads is disposed on a surface of the base layer. The conductive bumps are disposed on the bonding pads individually. The patterned solder mask layer is disposed on the surface of the base layer and outside a corresponding region occupied by the conductive bumps, so as to expose the conductive bumps. In addition, a method of fabricating the package substrate and a chip package structure employing the package substrate are also provided.

Owner:ADVANCED SEMICON ENG INC

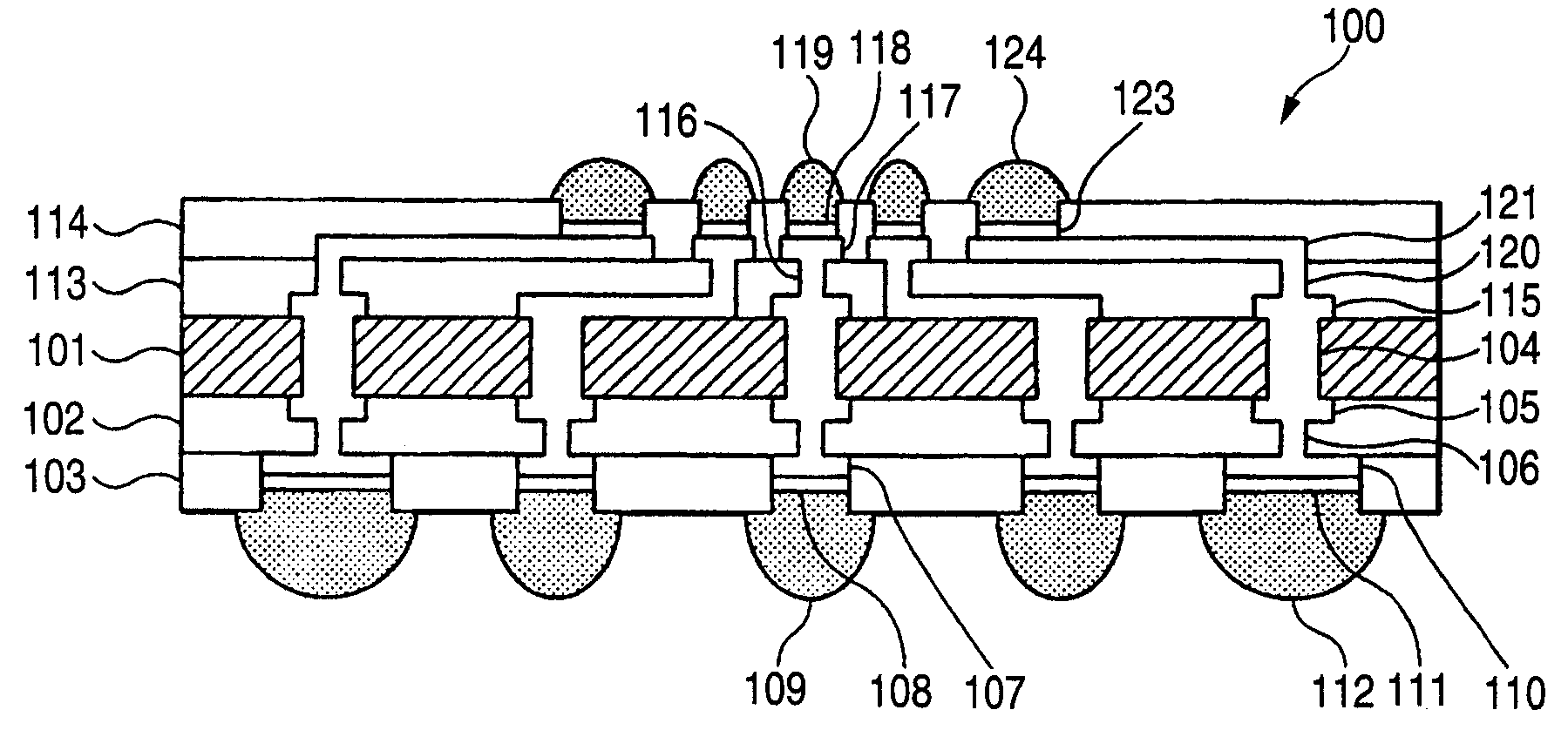

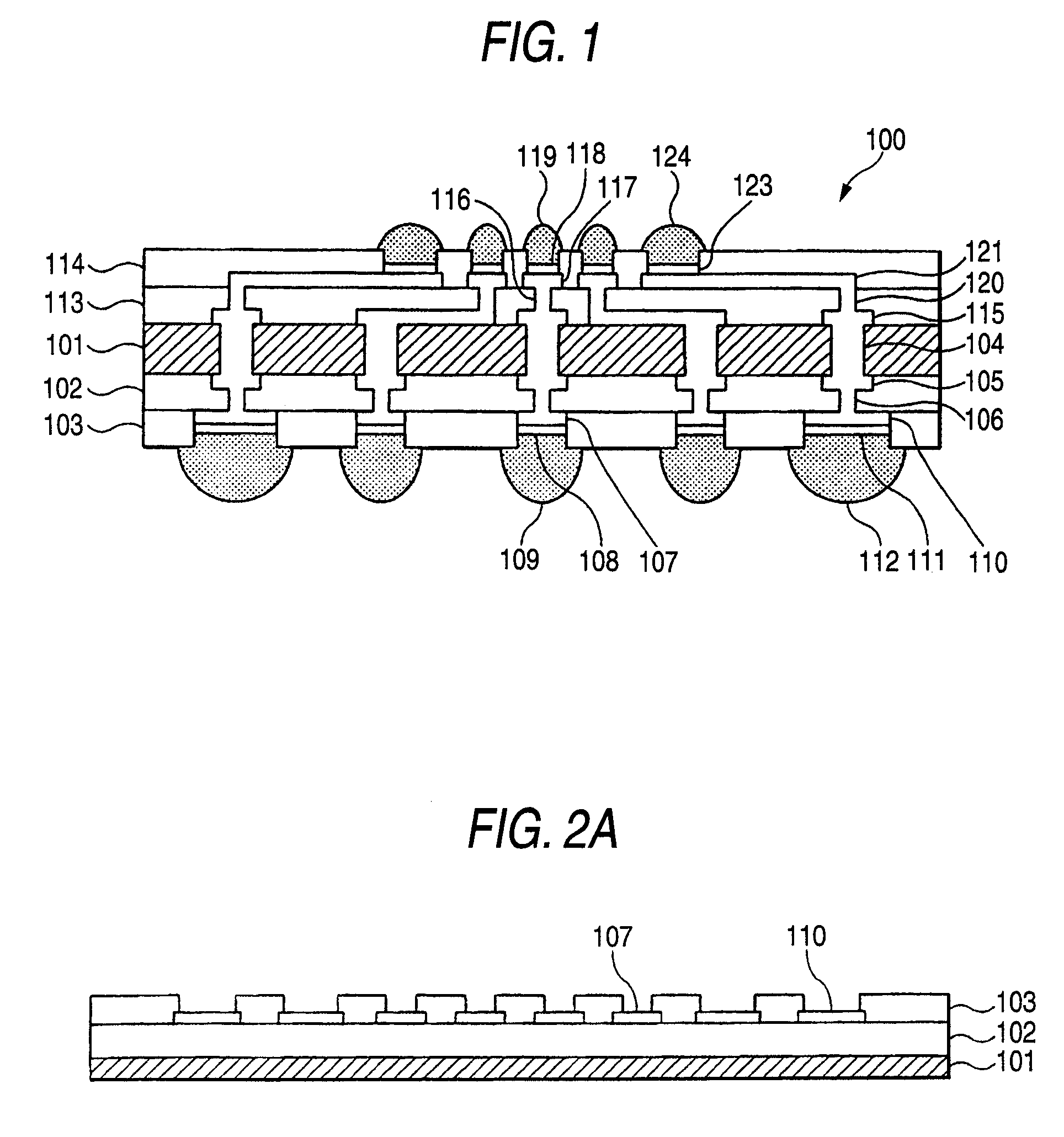

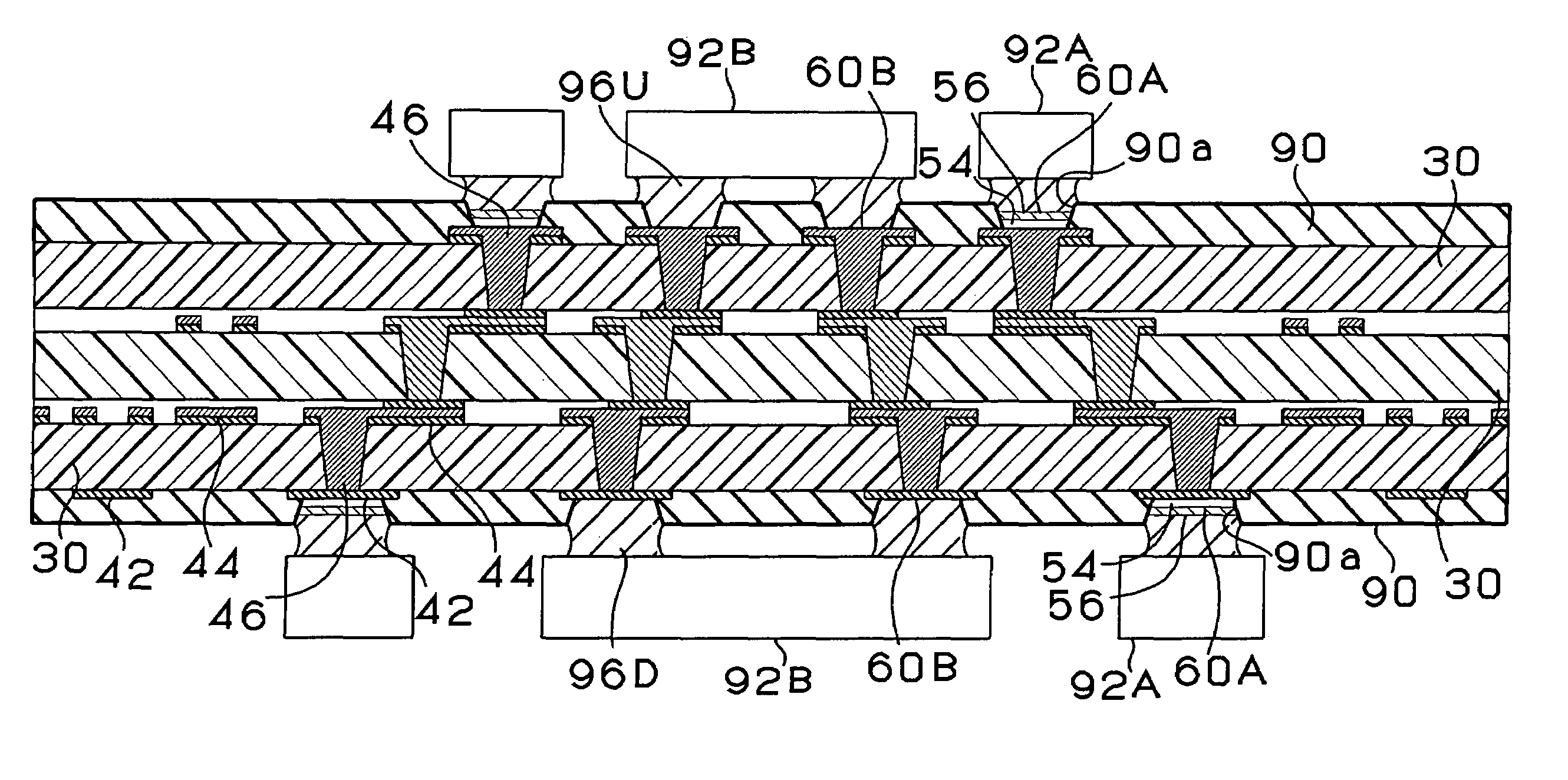

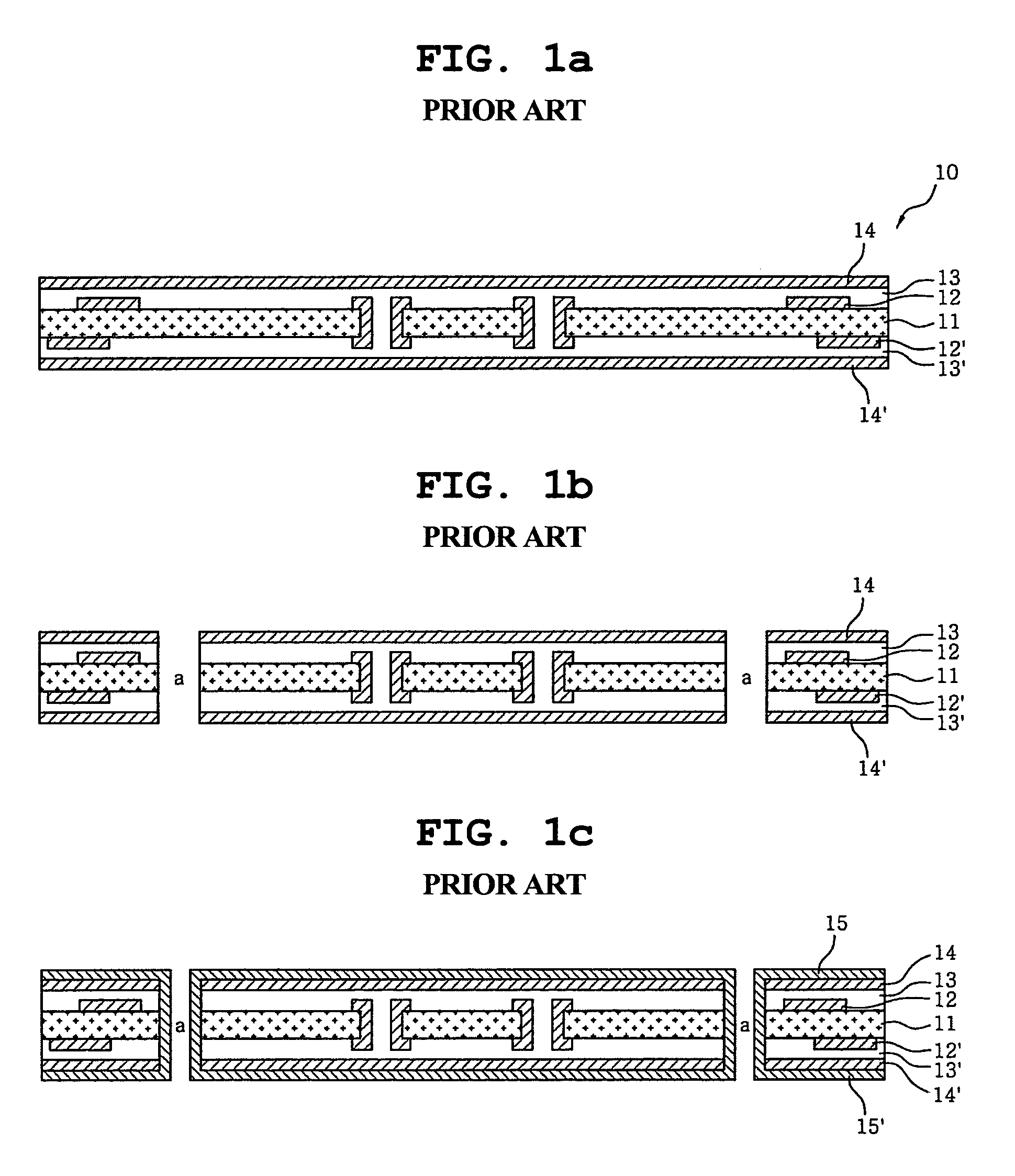

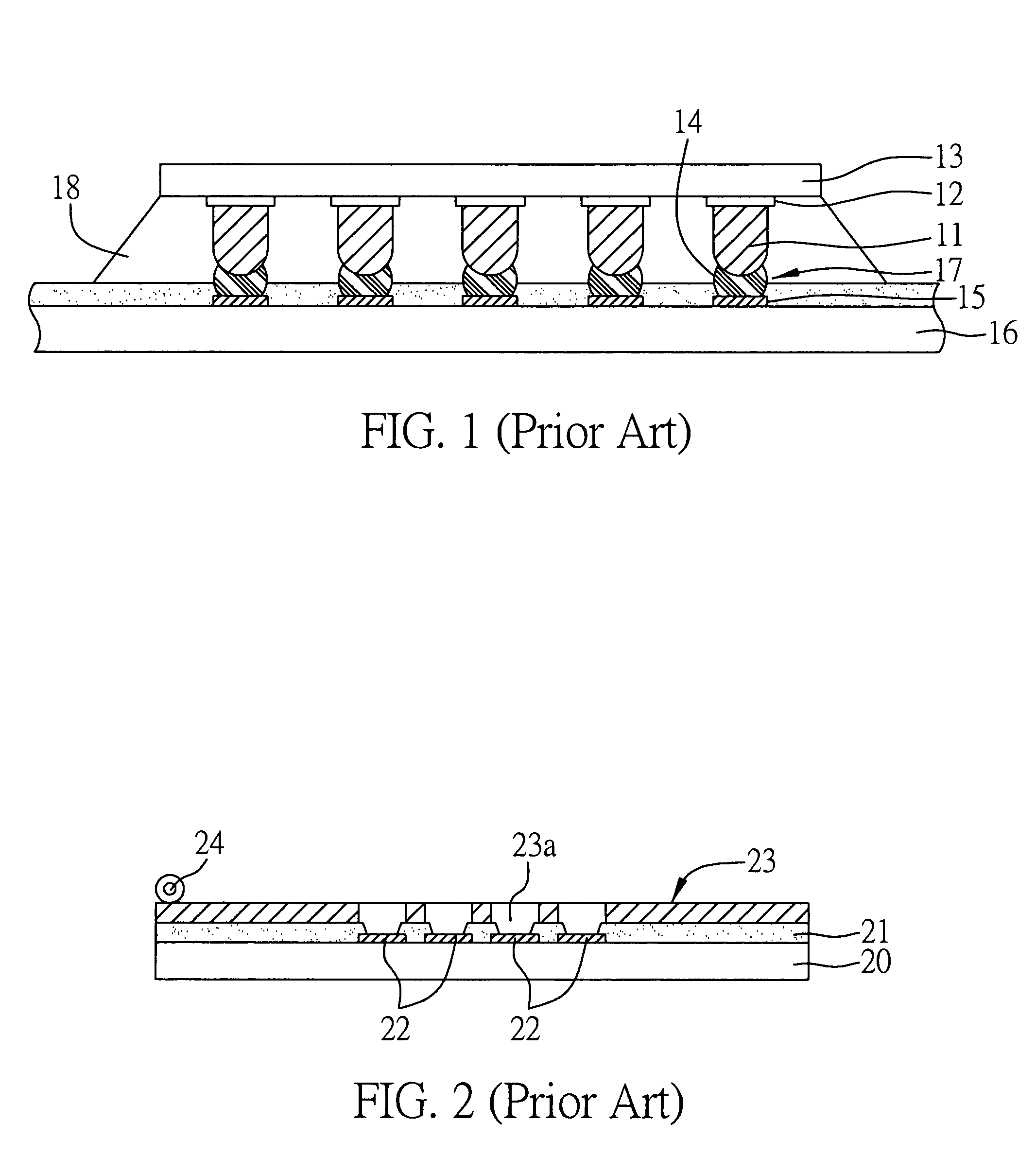

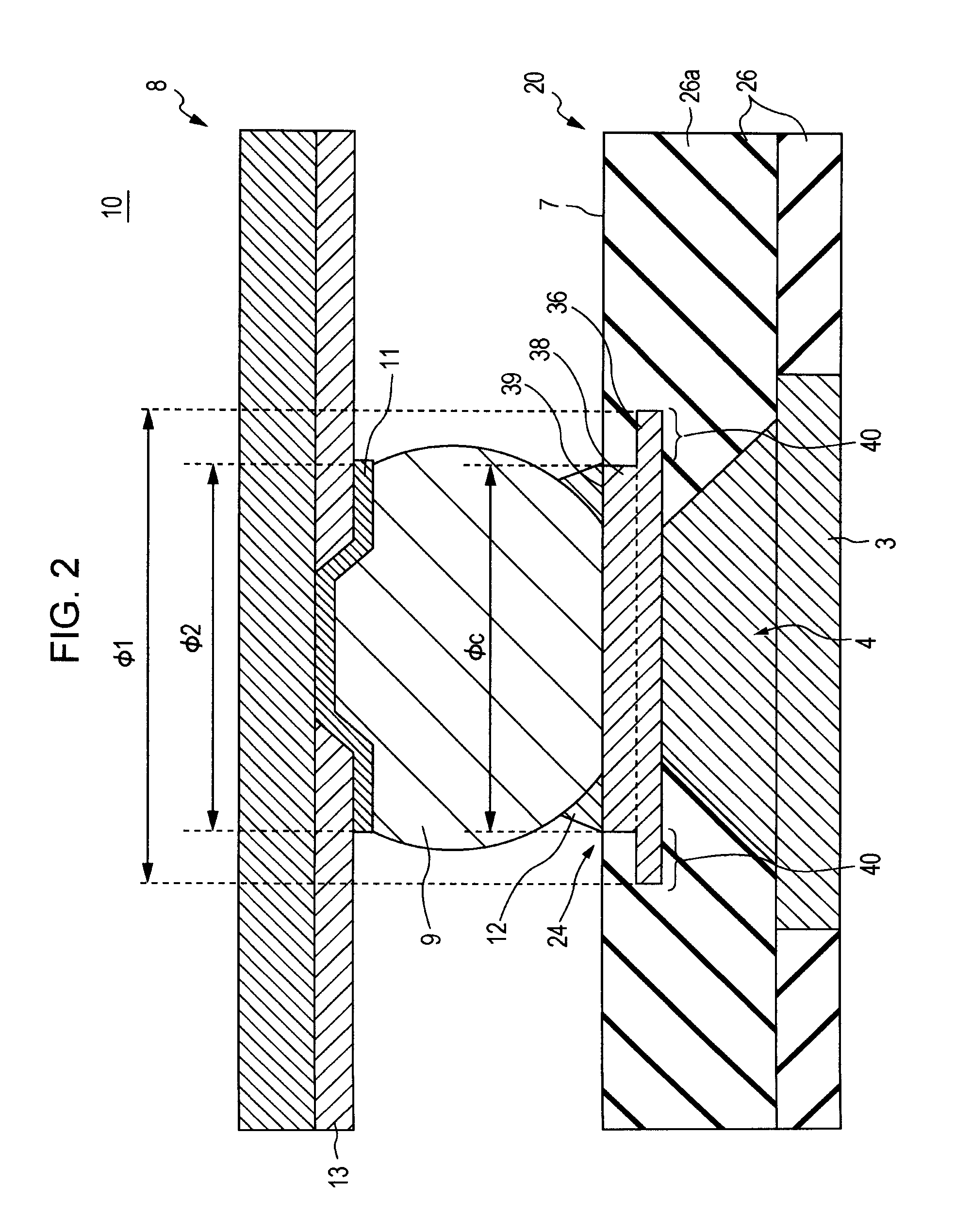

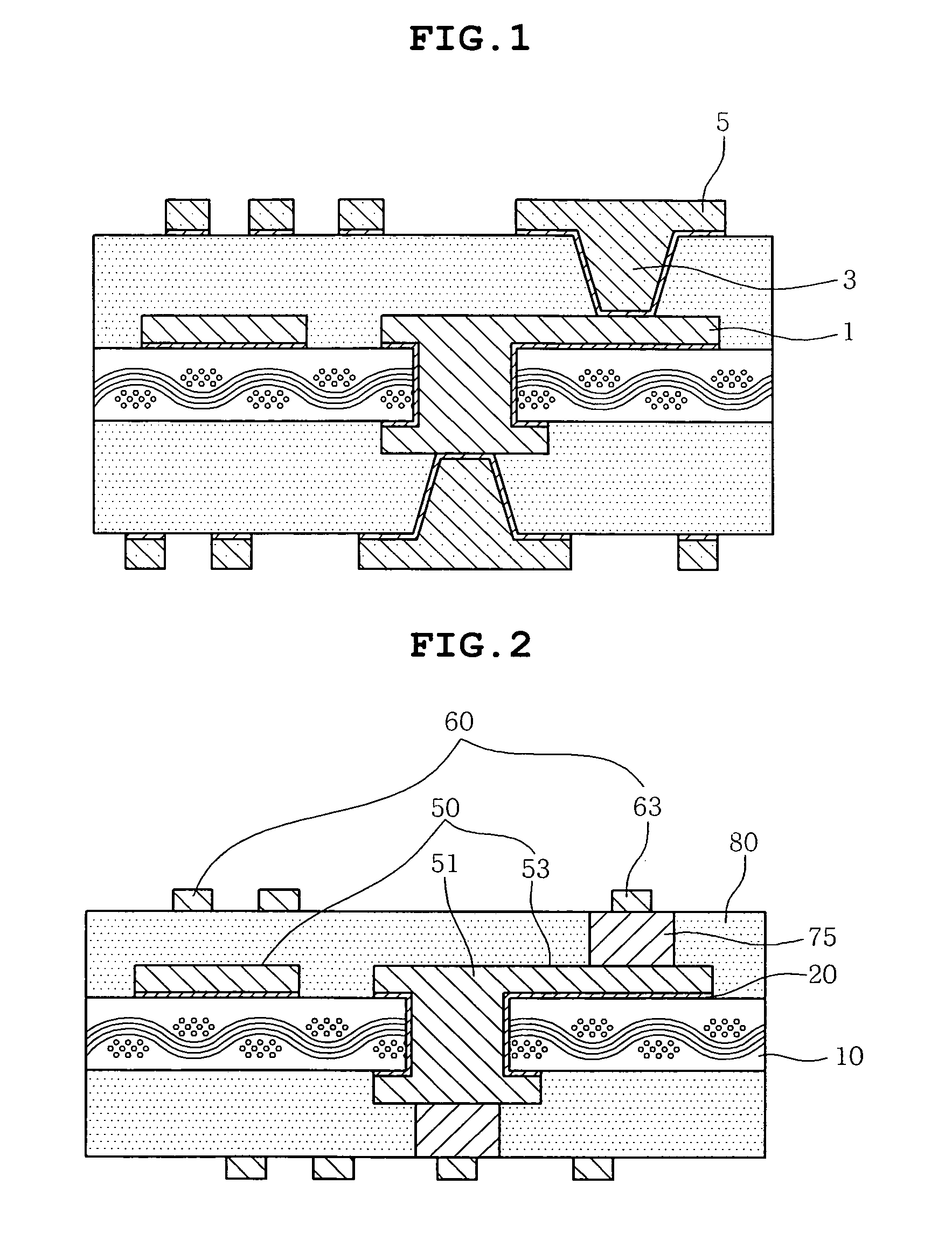

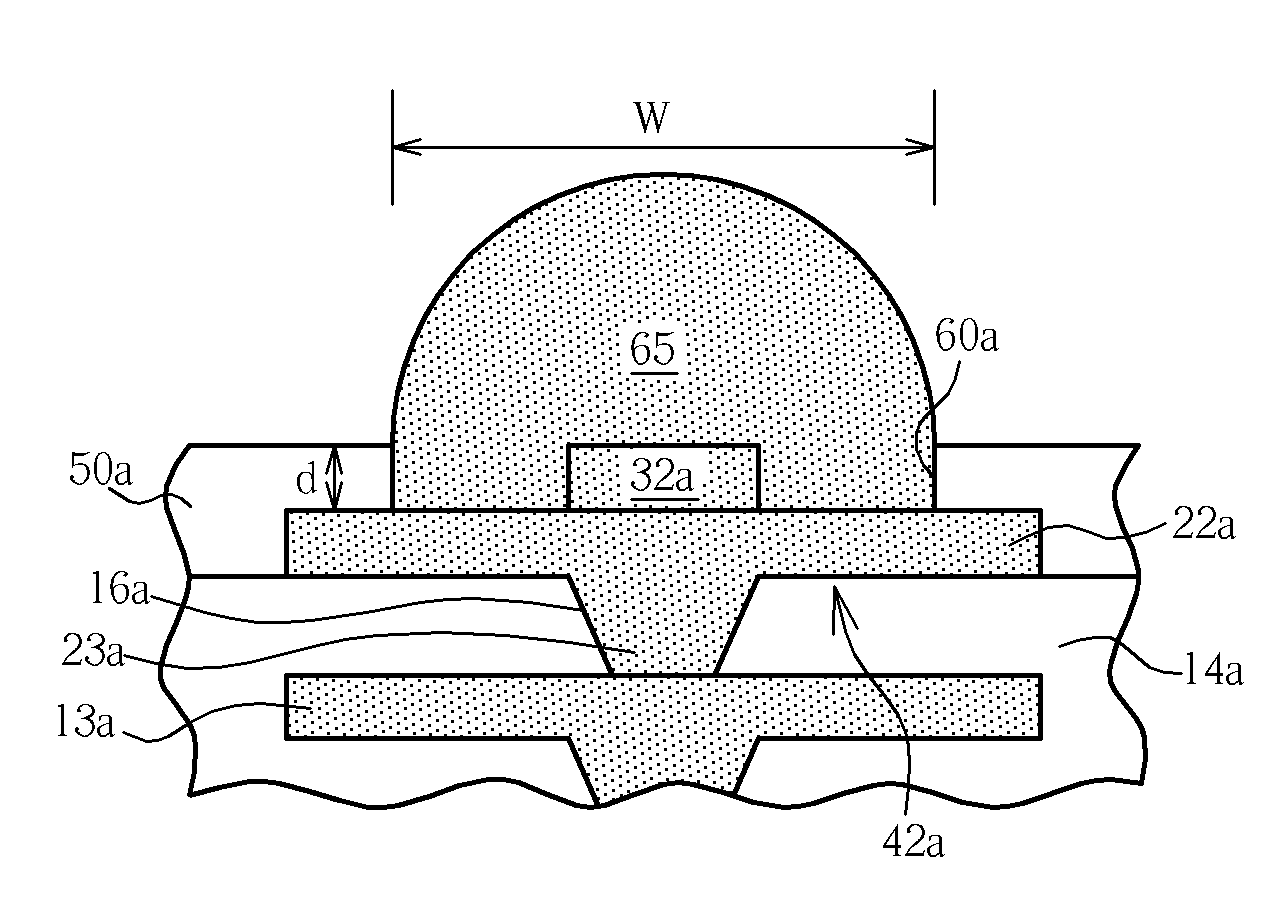

Multilayer printed wiring board and manufacturing method of the multilayer printed wiring board

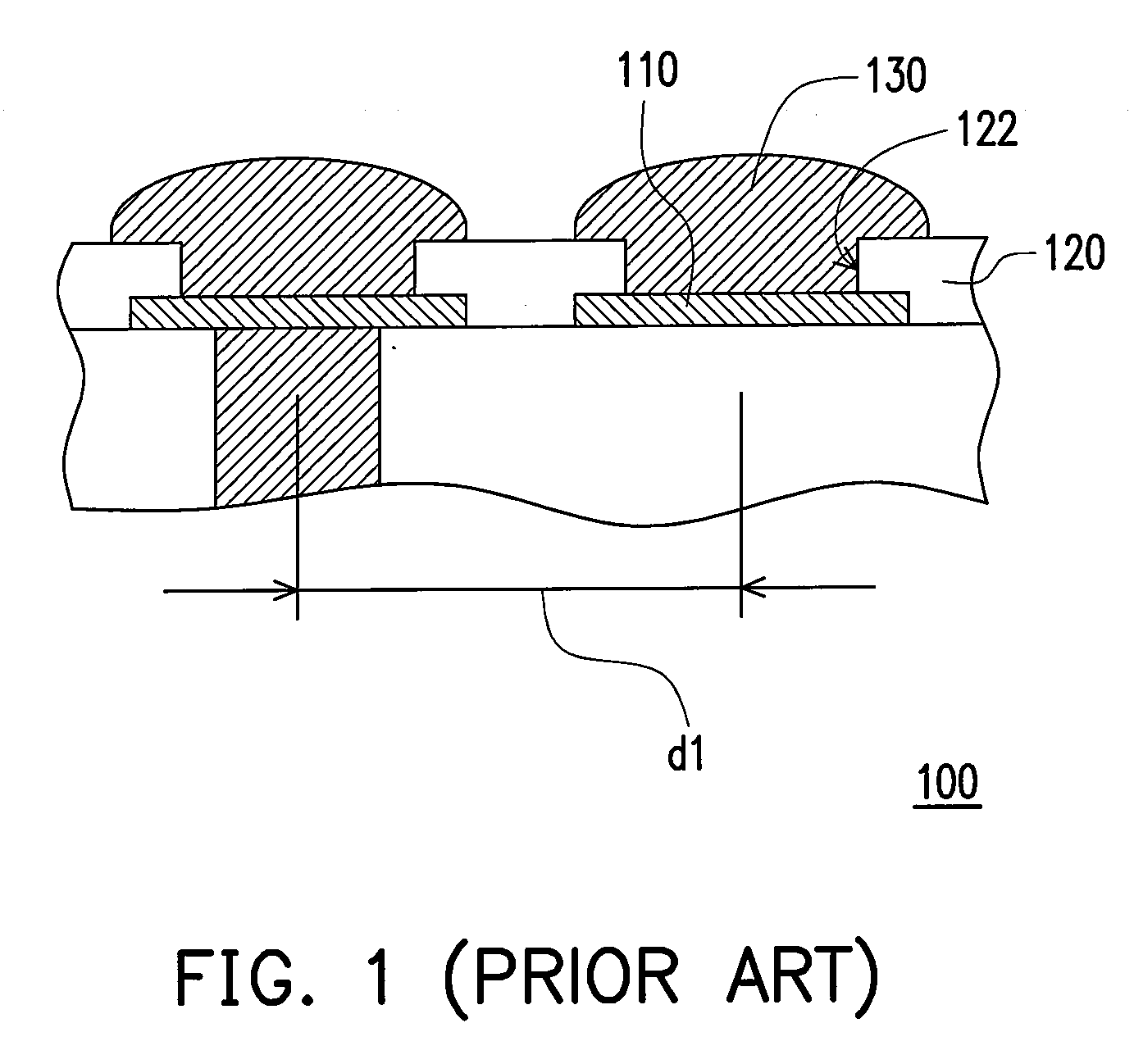

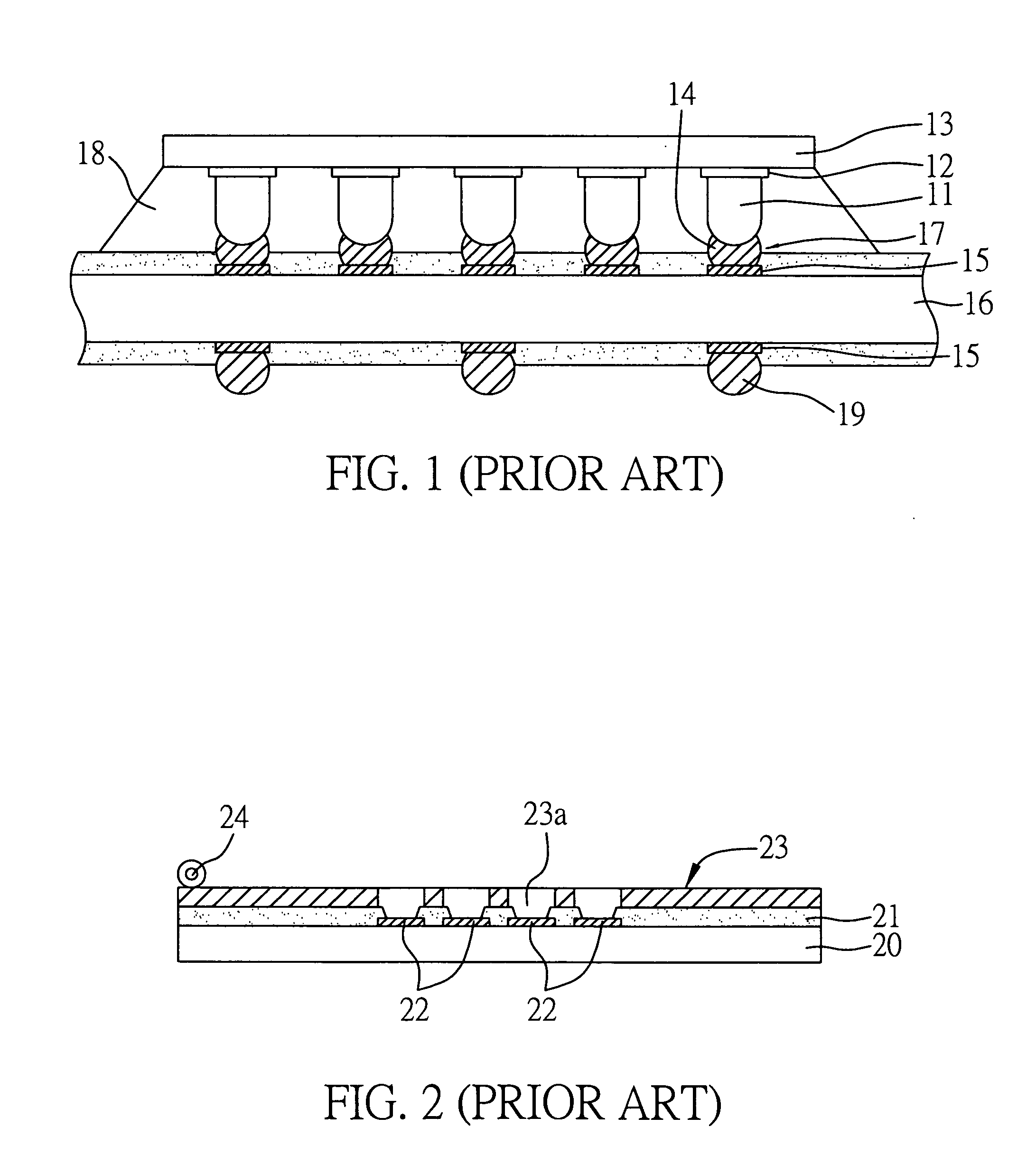

ActiveUS20060102384A1Improve buffering effectMore reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectricityDrop tests

This invention provides a multilayer printed wiring board in which electric connectivity and functionality are obtained by improving reliability and particularly, reliability to the drop test can be improved. No corrosion resistant layer is formed on a solder pad 60B on which a component is to be mounted so as to obtain flexibility. Thus, if an impact is received from outside when a related product is dropped, the impact can be buffered so as to protect any mounted component from being removed. On the other hand, land 60A in which the corrosion resistant layer is formed is unlikely to occur contact failure even if a carbon pillar constituting an operation key makes repeated contacts.

Owner:IBIDEN CO LTD

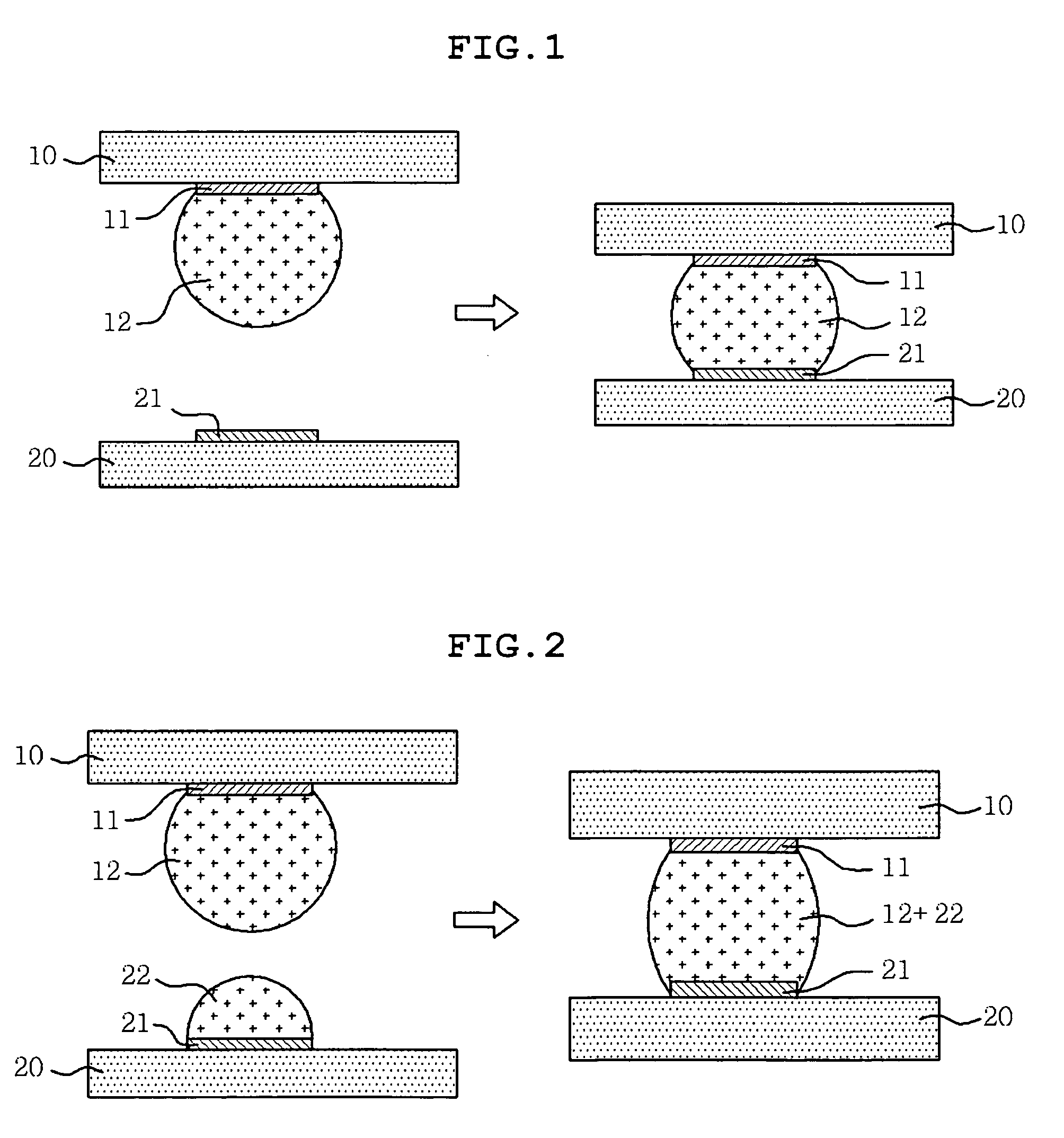

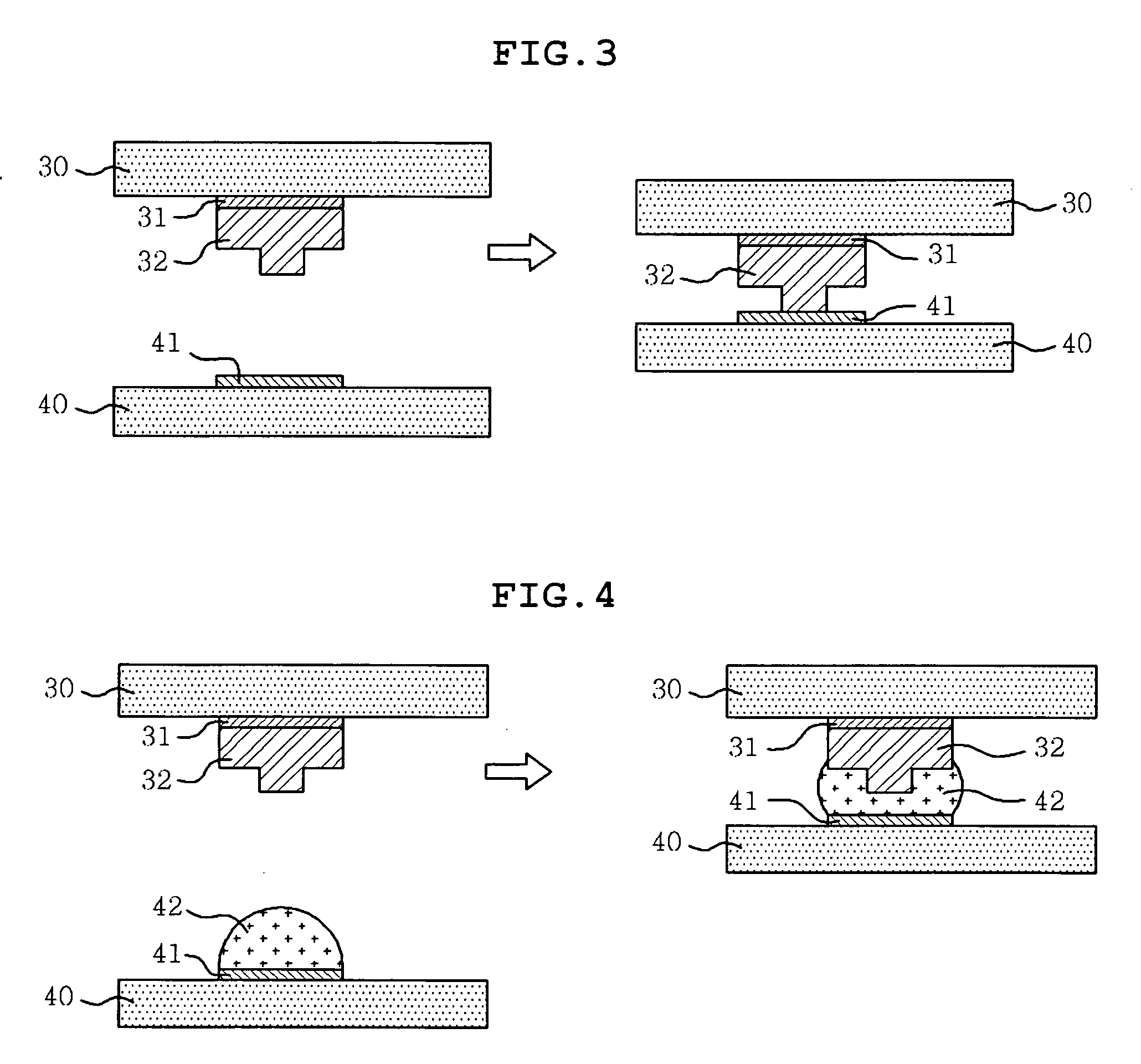

Method of forming solder connection portions, method of forming wiring substrate and method of producing semiconductor device

ActiveUS20070234563A1Improve reliabilitySemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor

A method of forming solder connection portions on first electrode pads and on second electrode pads, comprises a first step of arranging solder balls on the first electrode pads by arranging a first mask on a base mask; a second step of arranging solder balls on the second electrode pads by arranging a second mask on the base mask; and a third step of melting the solder balls. The base mask has first opening portions corresponding to the first electrode pads and second opening portions corresponding to the second electrode pads and having a size different from that of the first opening portions. The first mask has opening portions corresponding to the first opening portions and covering the second opening portions. The second mask has opening portions corresponding to the second opening portions and covers the first opening portions.

Owner:SHINKO ELECTRIC IND CO LTD

Multilayer printed wiring board and manufacturing method of the multilayer printed wiring board

ActiveUS7626829B2Improve buffering effectMore reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectricityDrop tests

This invention provides a multilayer printed wiring board in which electric connectivity and functionality are obtained by improving reliability and particularly, reliability to the drop test can be improved. No corrosion resistant layer is formed on a solder pad 60B on which a component is to be mounted so as to obtain flexibility. Thus, if an impact is received from outside when a related product is dropped, the impact can be buffered so as to protect any mounted component from being removed. On the other hand, land 60A in which the corrosion resistant layer is formed is unlikely to occur contact failure even if a carbon pillar constituting an operation key makes repeated contacts.

Owner:IBIDEN CO LTD

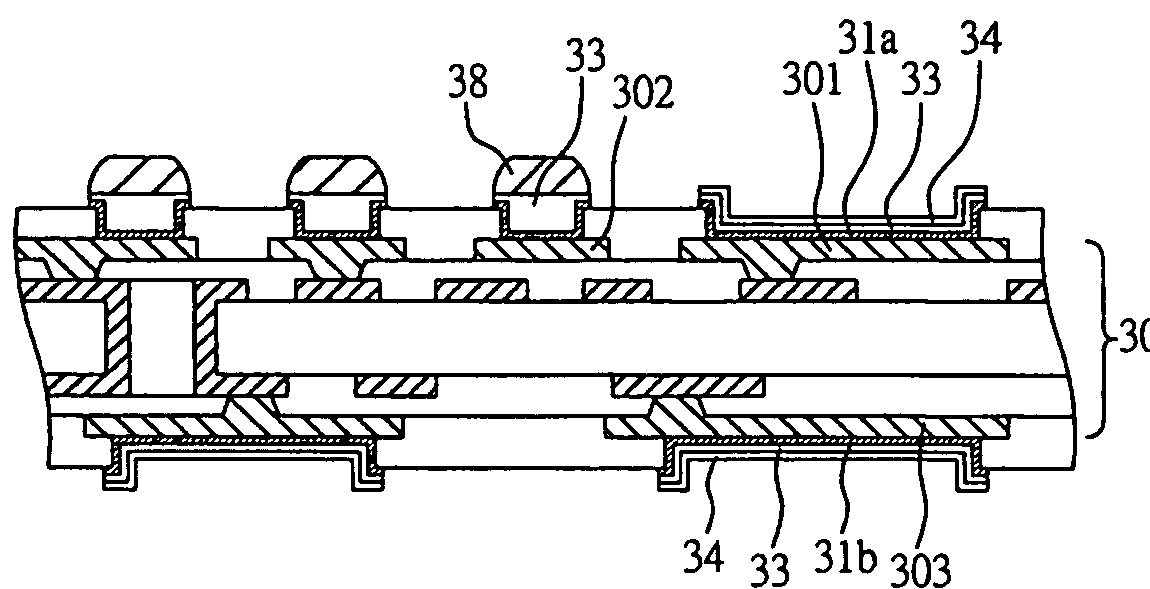

BGA package board and method for manufacturing the same

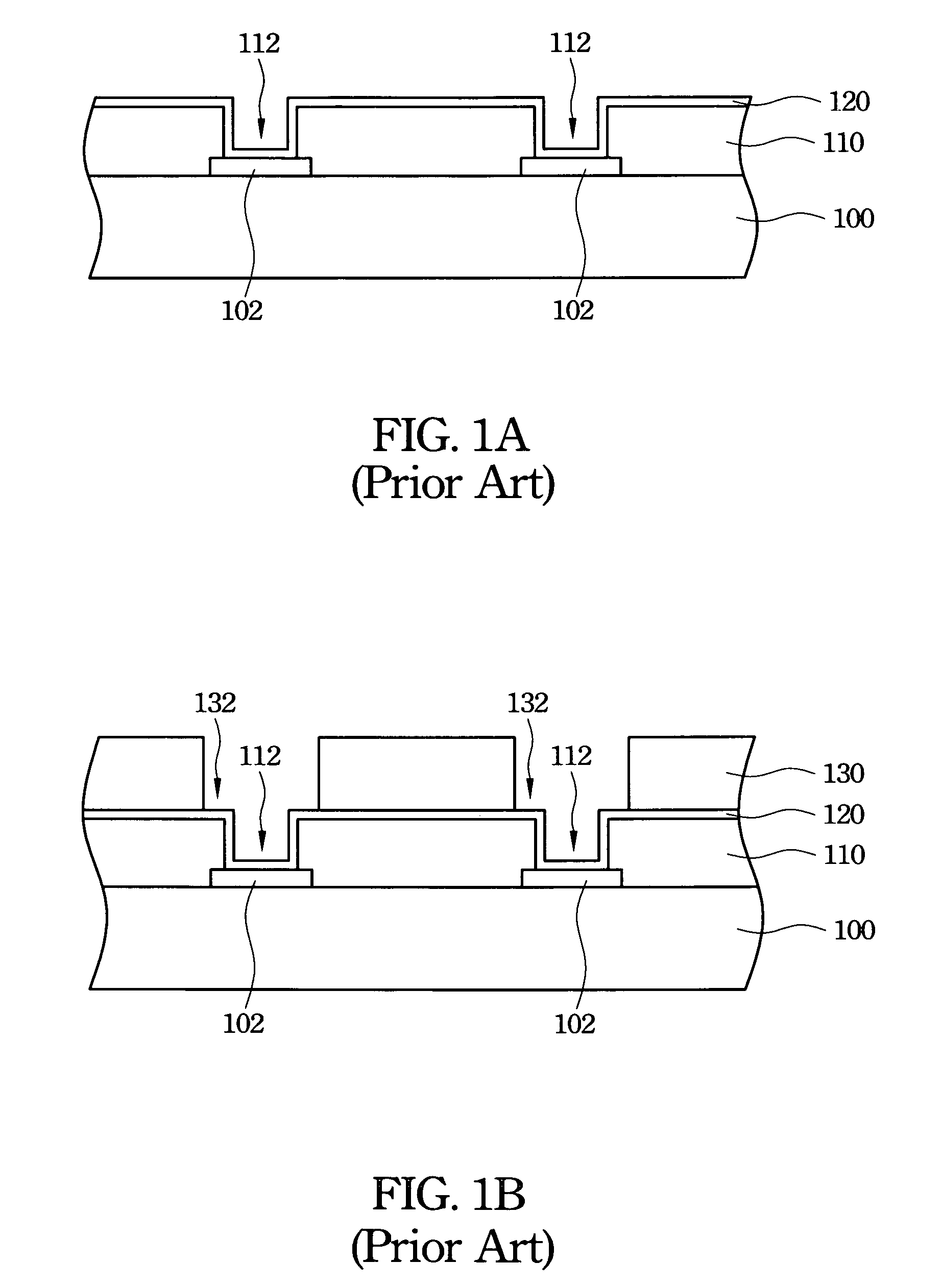

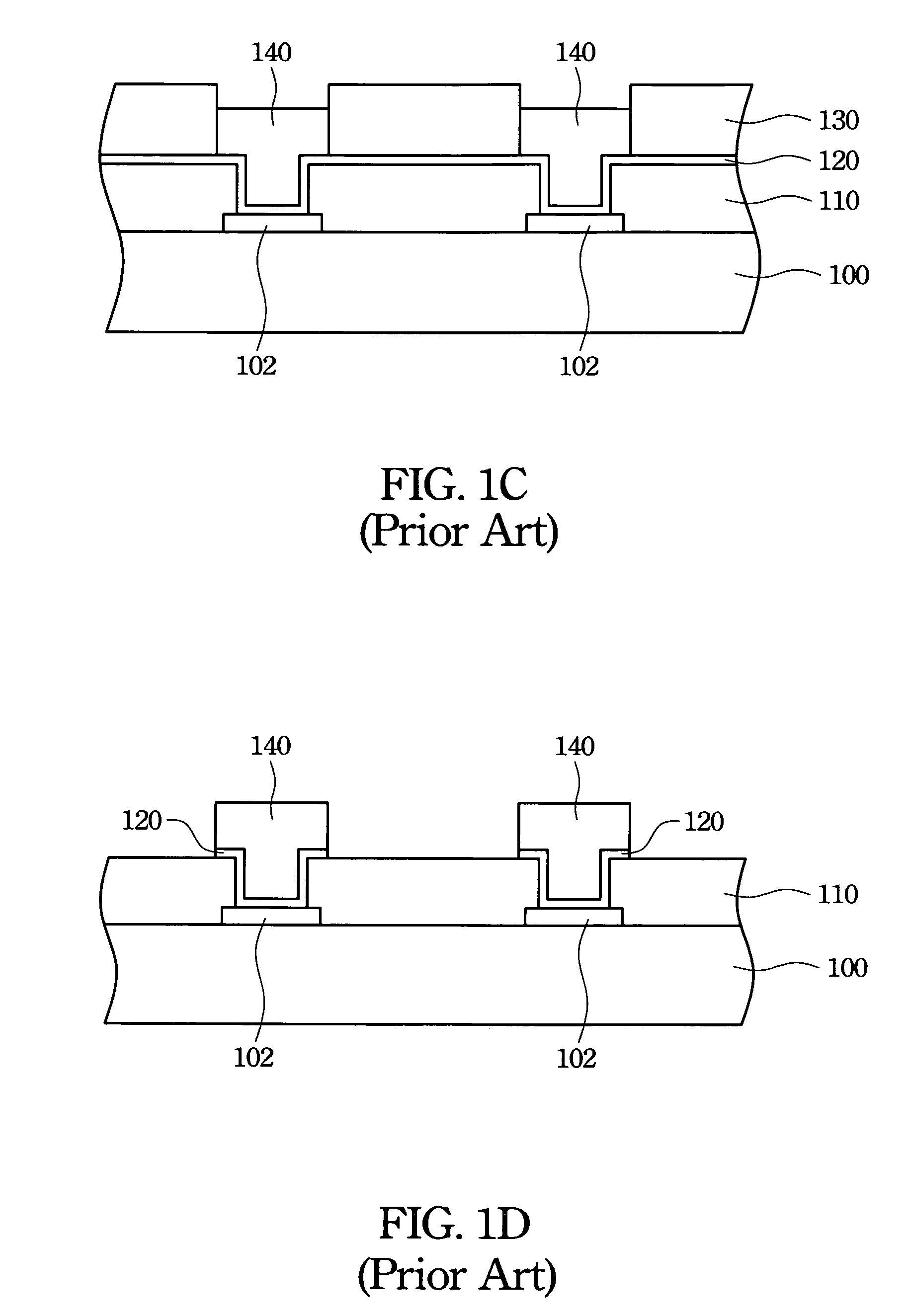

ActiveUS7408261B2Avoid stickingAdapt effectivelySemiconductor/solid-state device detailsStacked resist layersResistLead bonding

Disclosed herein is a Ball Grid Array (BGA) package board. The BGA package board includes a first external layer on which a pattern comprising a circuit pattern and a wire bonding pad pattern is formed, a second external layer on which a pattern comprising a circuit pattern and a solder ball pad pattern is formed, an insulating layer formed between the first and second external layers, a first outer via hole to electrically connect the first and second external layers to each other, and a solder resist layer formed on each of the first and second external layers, with portions of the solder resist layer corresponding to the wire bonding pad pattern and the solder ball pad pattern being opened. The solder ball pad pattern is thinner than the circuit pattern of the second external layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

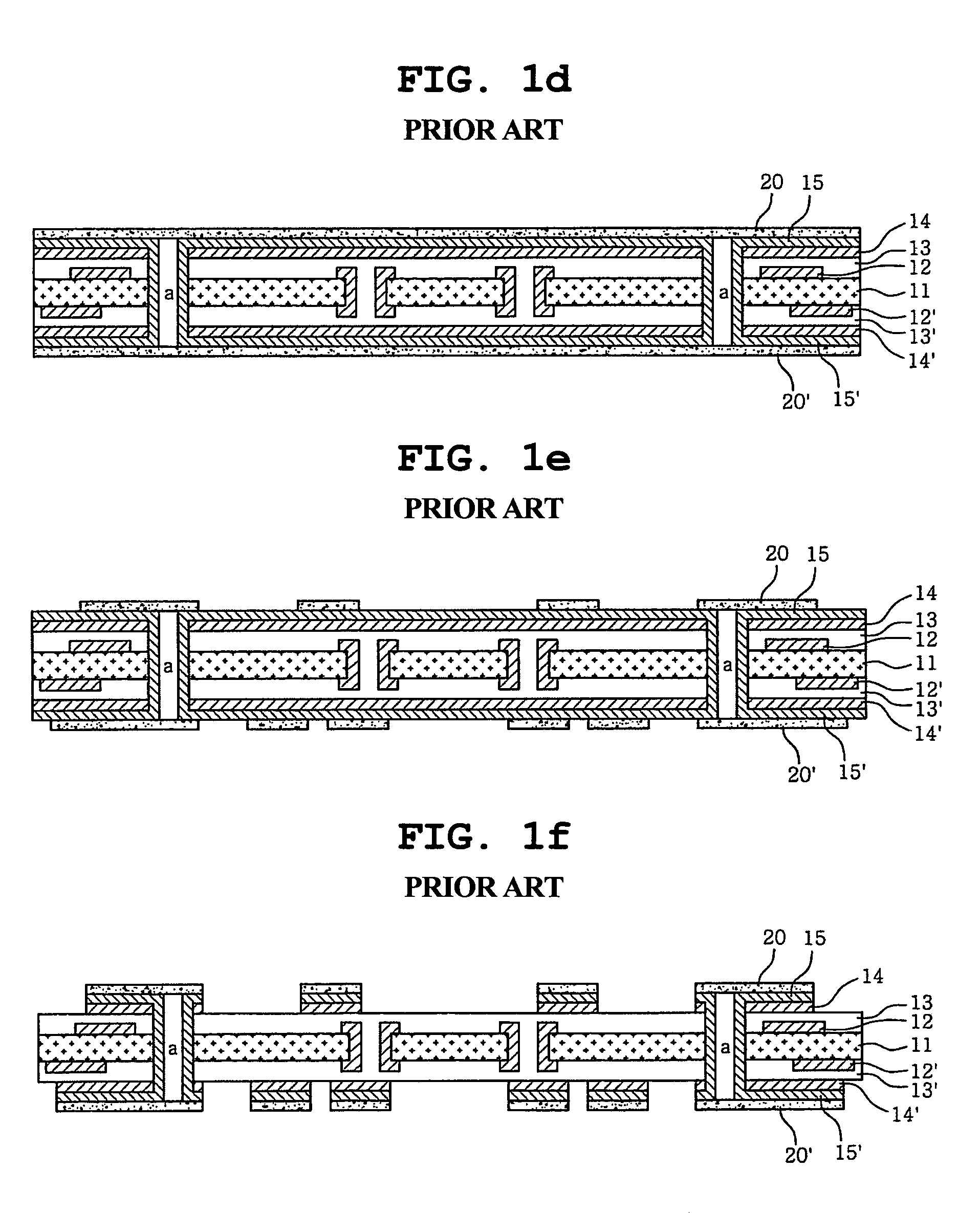

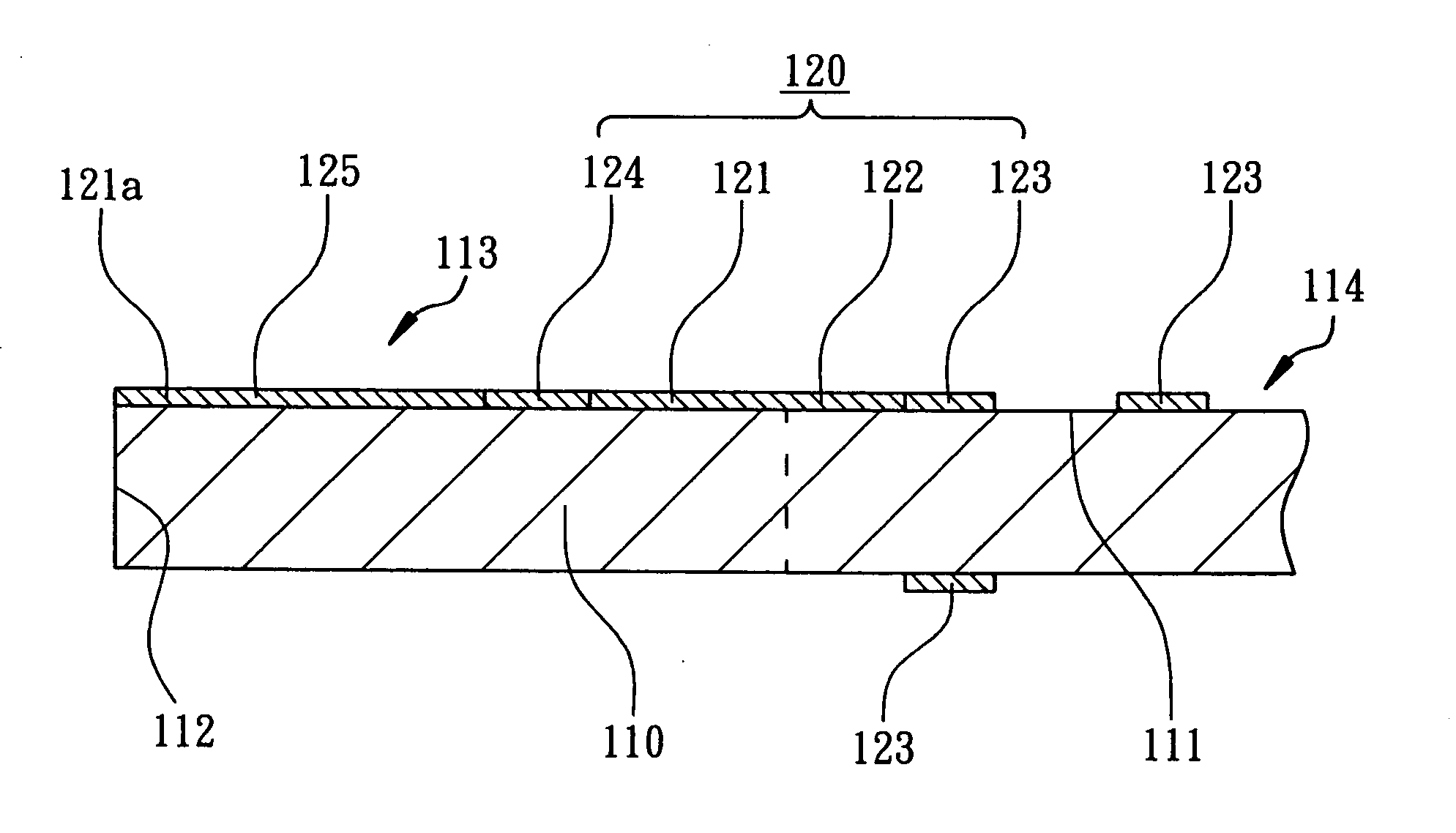

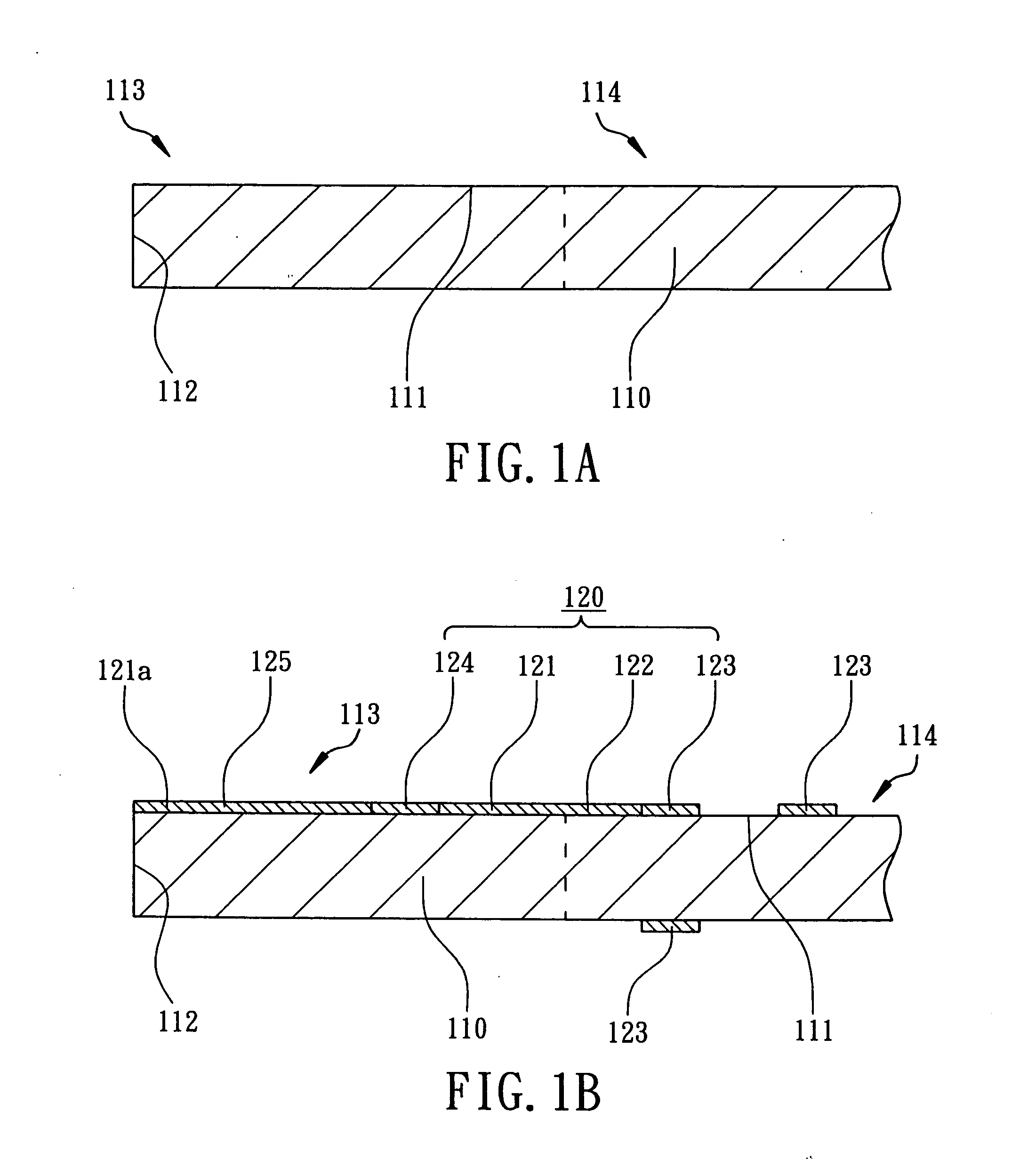

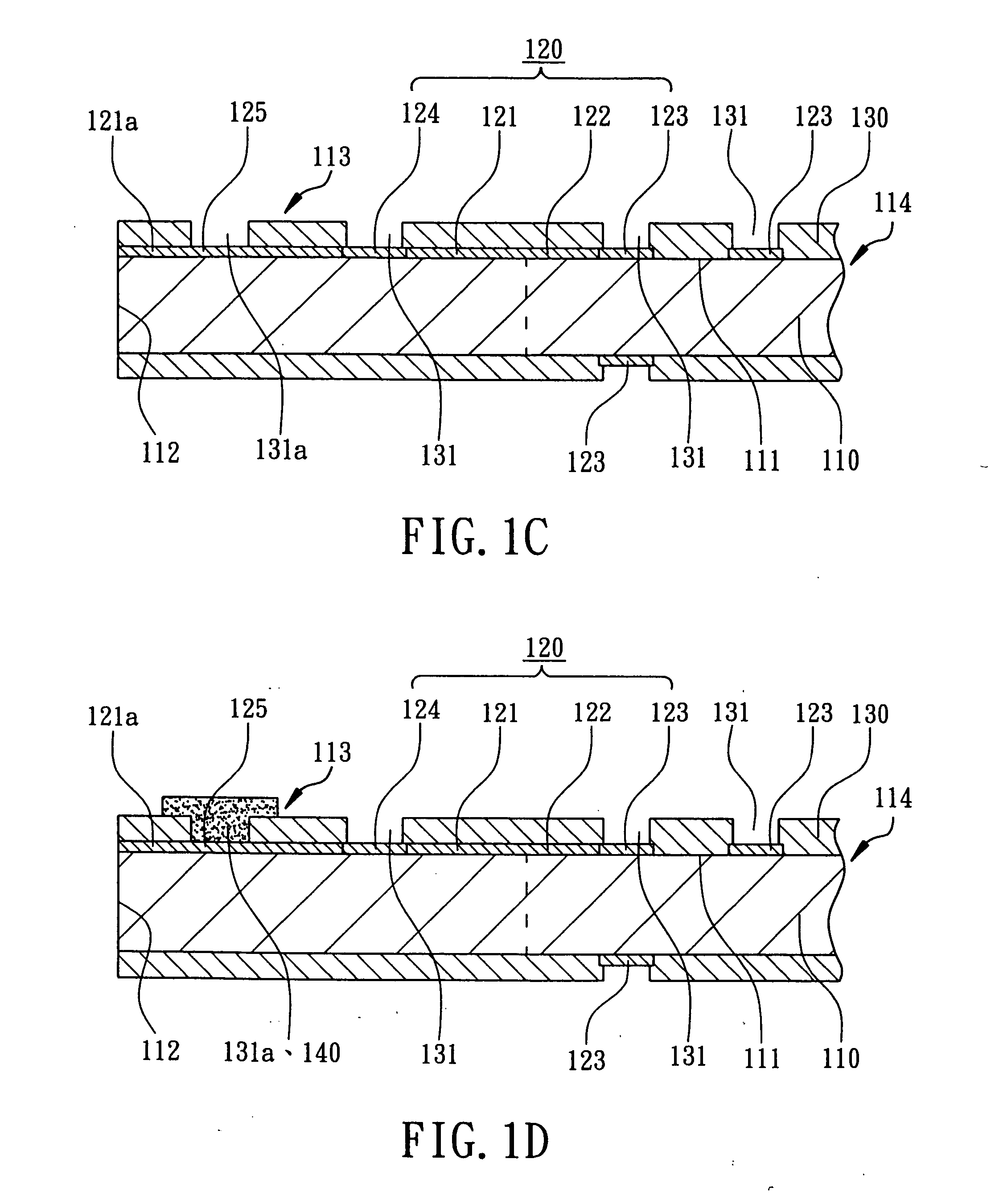

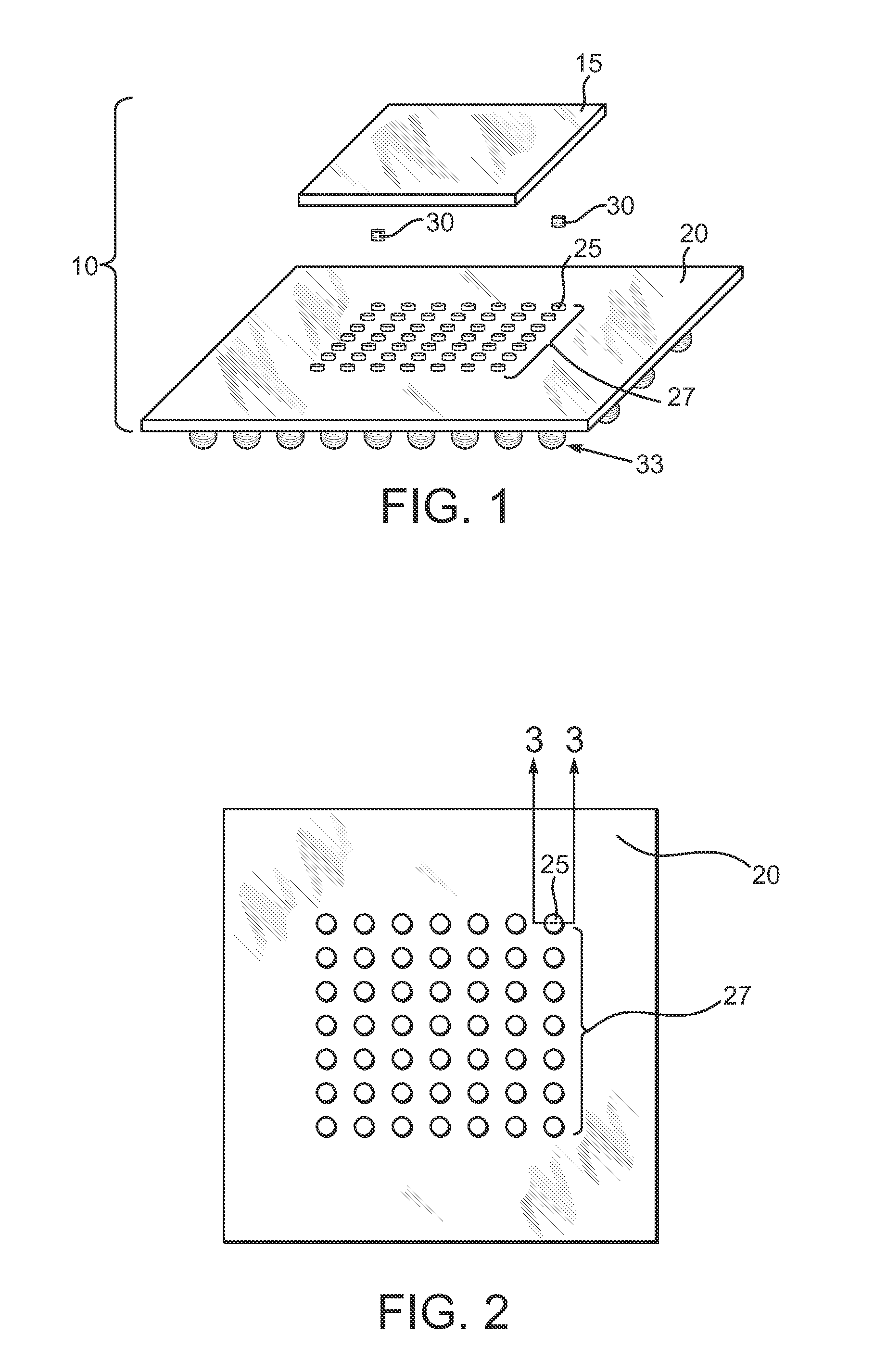

Semiconductor Package Having Buss-Less Substrate

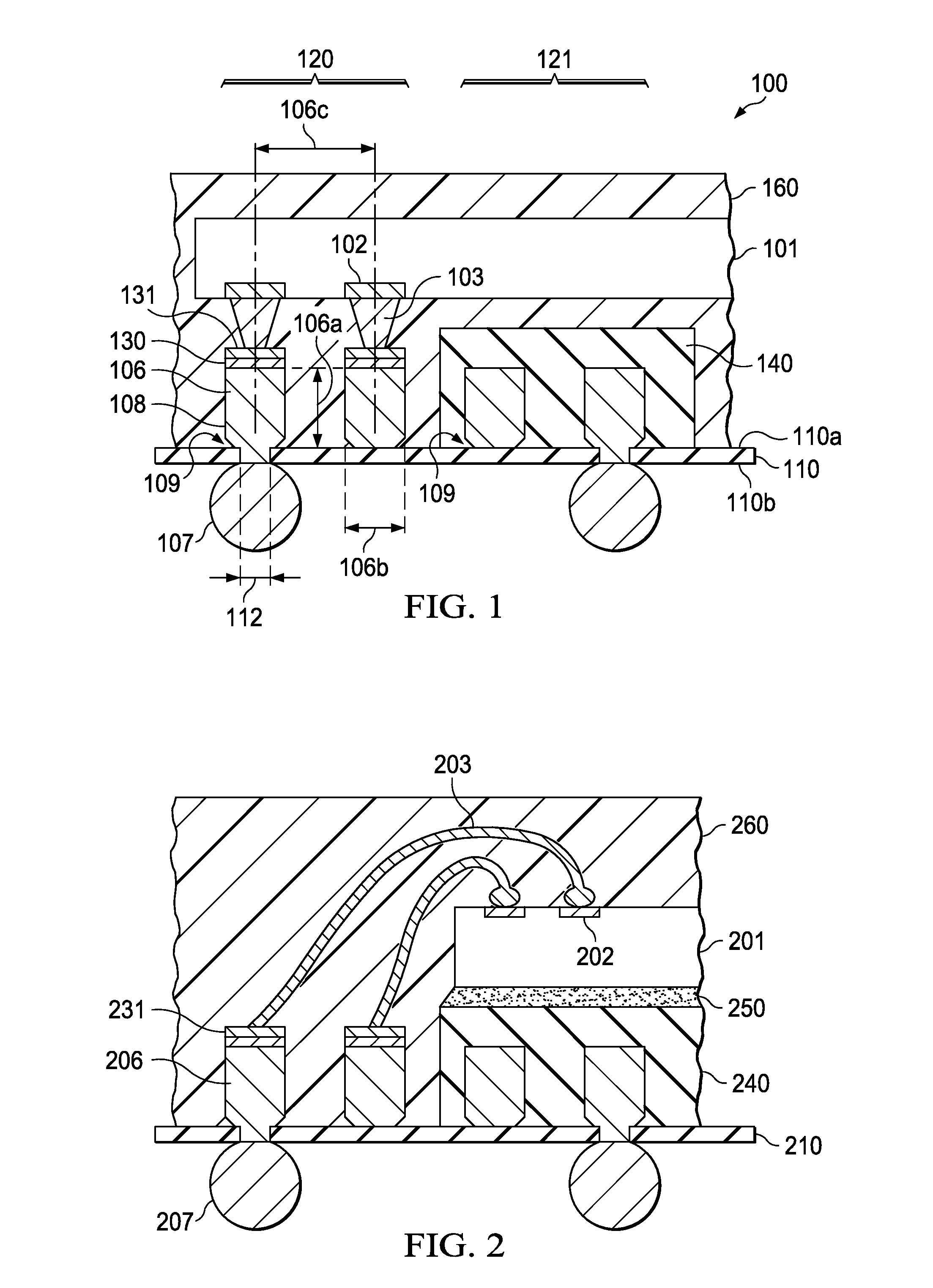

ActiveUS20090051036A1Improve adhesionAvoid elevationSemiconductor/solid-state device detailsStacked resist layersSemiconductor chipSemiconductor package

A ball grid array device with an insulating substrate (110) having metal traces (106, for example copper, about 18 μm thick) with sidewalls (108) at right angles to the trace top. The traces are grouped in a first (120) and a second set (121). The first set traces have the top surface covered by a thin noble metal (for example a nickel layer (130) about 0.1 μm thick and an outermost gold layer (131) about 0.5 μm thick), while the sidewalls are un-covered by the noble metal. About 1.5 μm are thus gained for the trace spacing; oxidation of the trace sidewalls is enabled. The second set traces have the top surface un-covered by the noble metal; the traces are covered by an insulating soldermask. A semiconductor chip (101) with terminals (102) is attached to the substrate with the terminals connected to the noble metal of the first set traces, either by bonding wires (for example gold) or by metal studs (for example gold). The assembled chip and the first set traces are encapsulated in a polymerized compound (160), which adheres to the oxidized trace sidewalls and locks into the trace undercuts at the substrate interface.

Owner:TEXAS INSTR INC

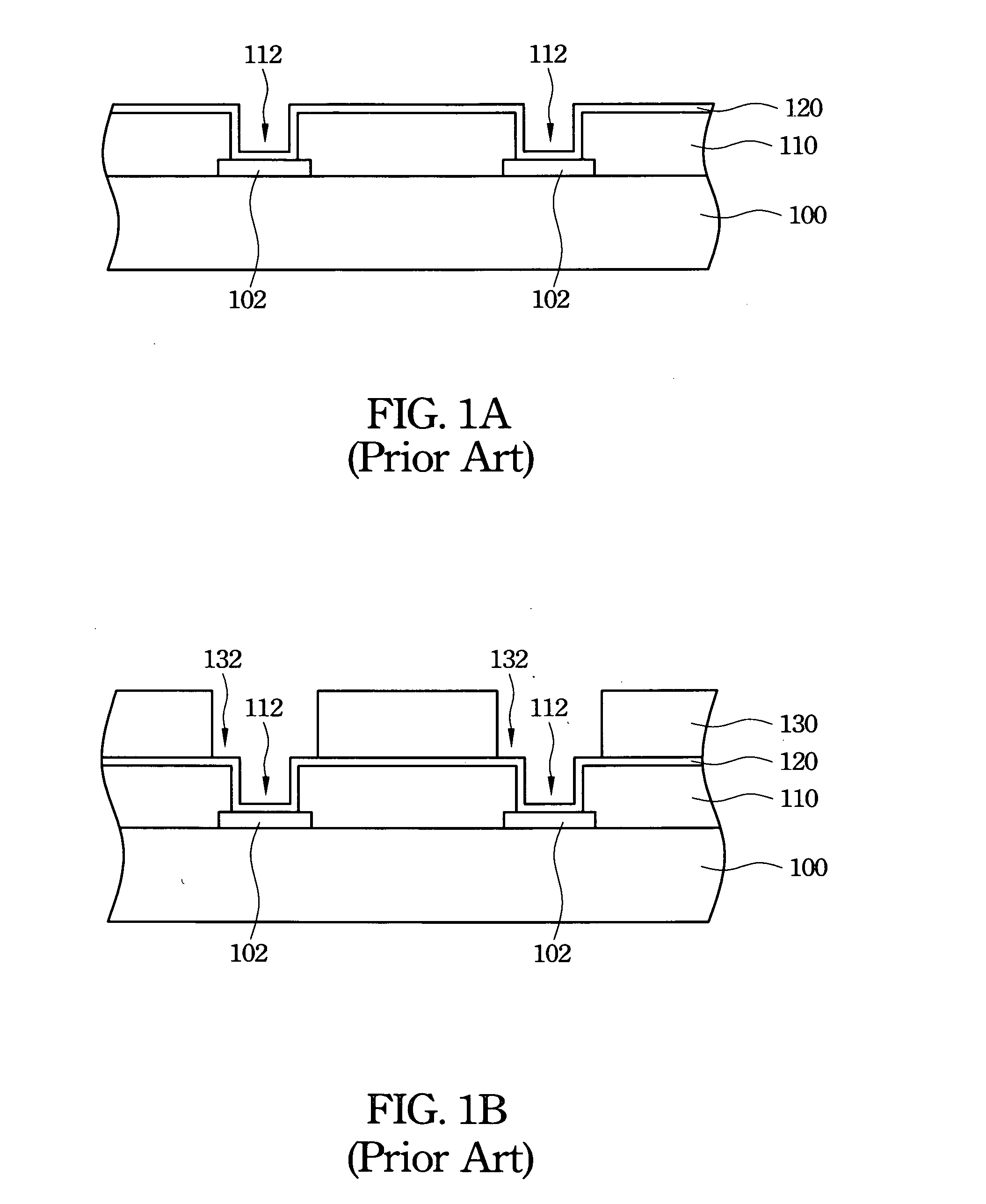

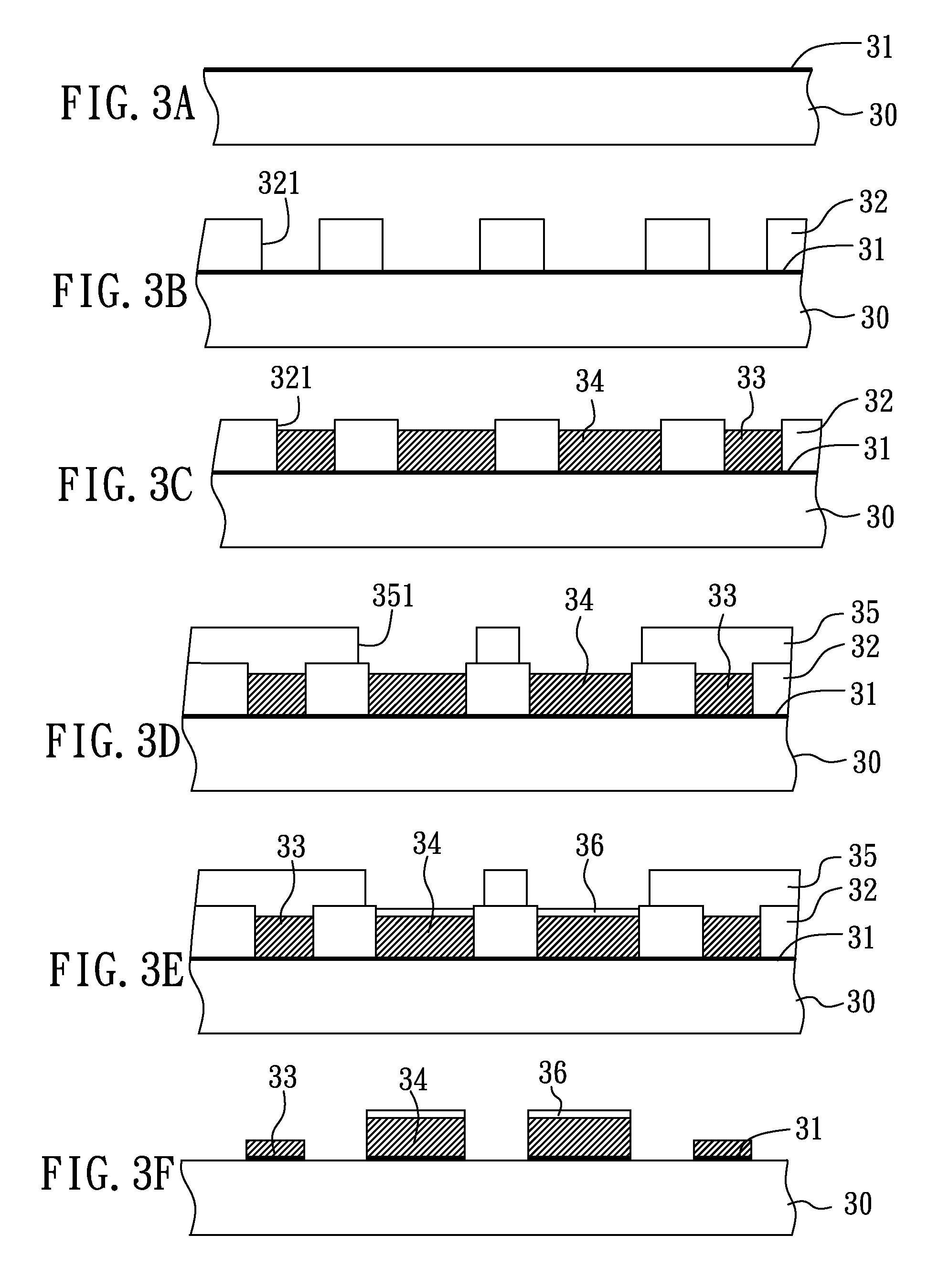

Conductive structures for electrically conductive pads of circuit board and fabrication method thereof

ActiveUS20070161223A1Preventing metal interface problemImprove conductivityPrinted circuit aspectsStacked resist layersResistMetal

Conductive structures for electrically conductive pads of a circuit board and fabrication method thereof are proposed. The fabrication method includes: providing a circuit board with a plurality of first, second and third electrically conductive pads; forming first and second conductive layers on the circuit board; forming first and second resist layers respectively on the first and second conductive layers, the resist layers having a plurality of openings for exposing the conductive layers on the pads; forming a metal layer in the openings of the first and second resist layers; and forming a first connecting layer on the metal layer; forming third and fourth resist layers on the first and second resist layers respectively, the third resist layer having a plurality of openings for exposing the first connecting layer on the metal layer on the second electrically

Owner:PHOENIX PRECISION TECH CORP

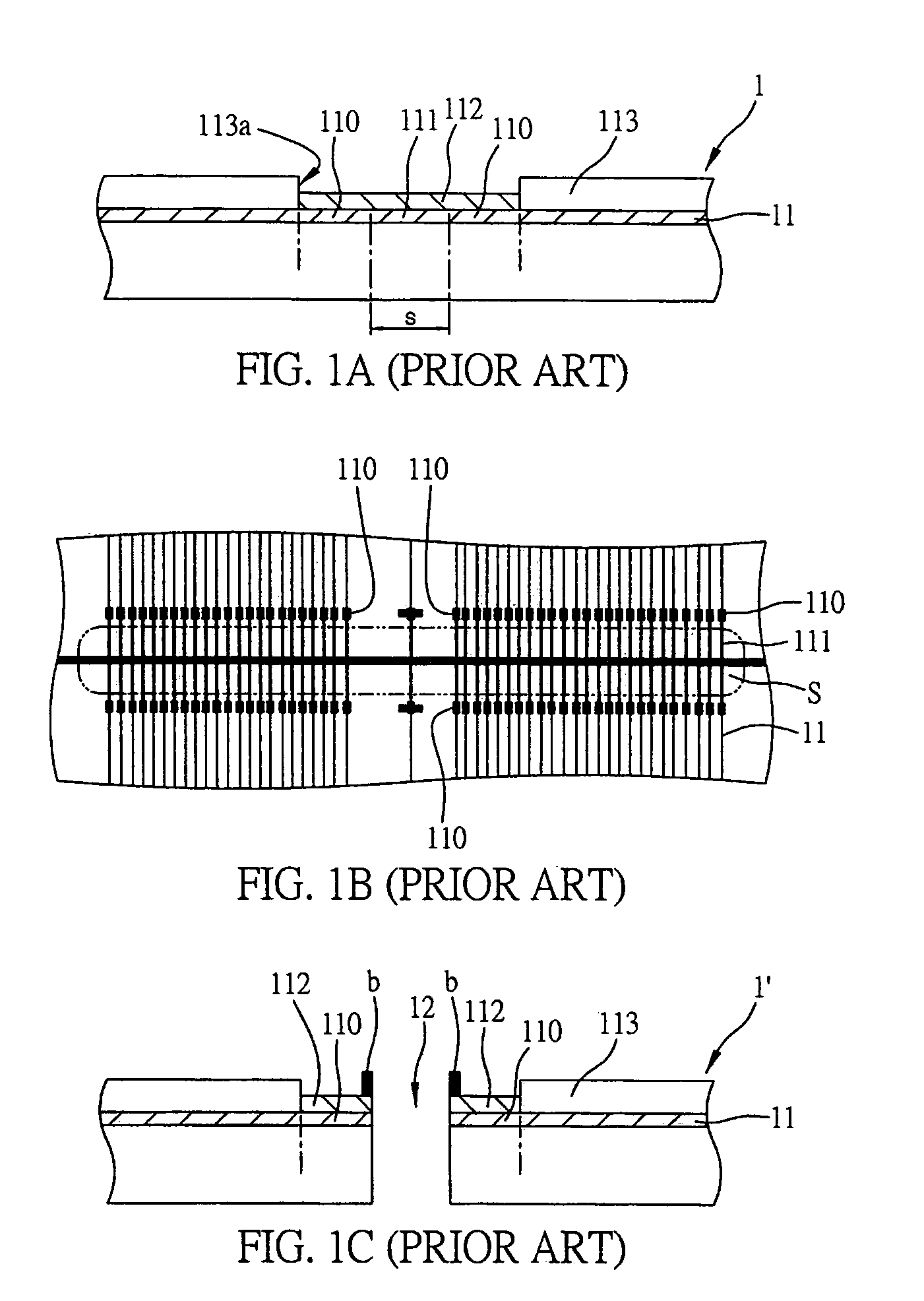

Method and structure for prevention leakage of substrate strip

InactiveUS20050051881A1Large caliberImprove package yieldSemiconductor/solid-state device detailsStacked resist layersSolder maskContact pad

The present invention provides a structure and a method for prevention leakage of a substrate strip. The substrate strip includes an edge portion and a plurality of units. A patterned metal layer on a surface of the substrate strip includes at least one plating bus extended to the edge portion, a plurality of plating lines at the units, a plurality of contact pads at the units and a plurality of fiducial marks at the edge portion. The plating bus has an extended trail having one end exposed out of the sidewall of the substrate strip. The fiducial marks and the contact pads are exposed out of a plurality of first openings of a solder mask. The solder mask also has a second opening at the edge portion exposing a portion of the plating bus to define a breaking hole. After forming a surface layer on the fiducial marks and the contact pads, the exposed portion of the plating bus is void of the surface layer. By removing the exposed portion of the plating bus, the breaking hole is formed to electrically isolate the extended trail from the contact pads in order to prevent a chip on the substrate strip from being damaged by ESD (Electrostatic Discharge) during packaging processes.

Owner:ADVANCED SEMICON ENG INC

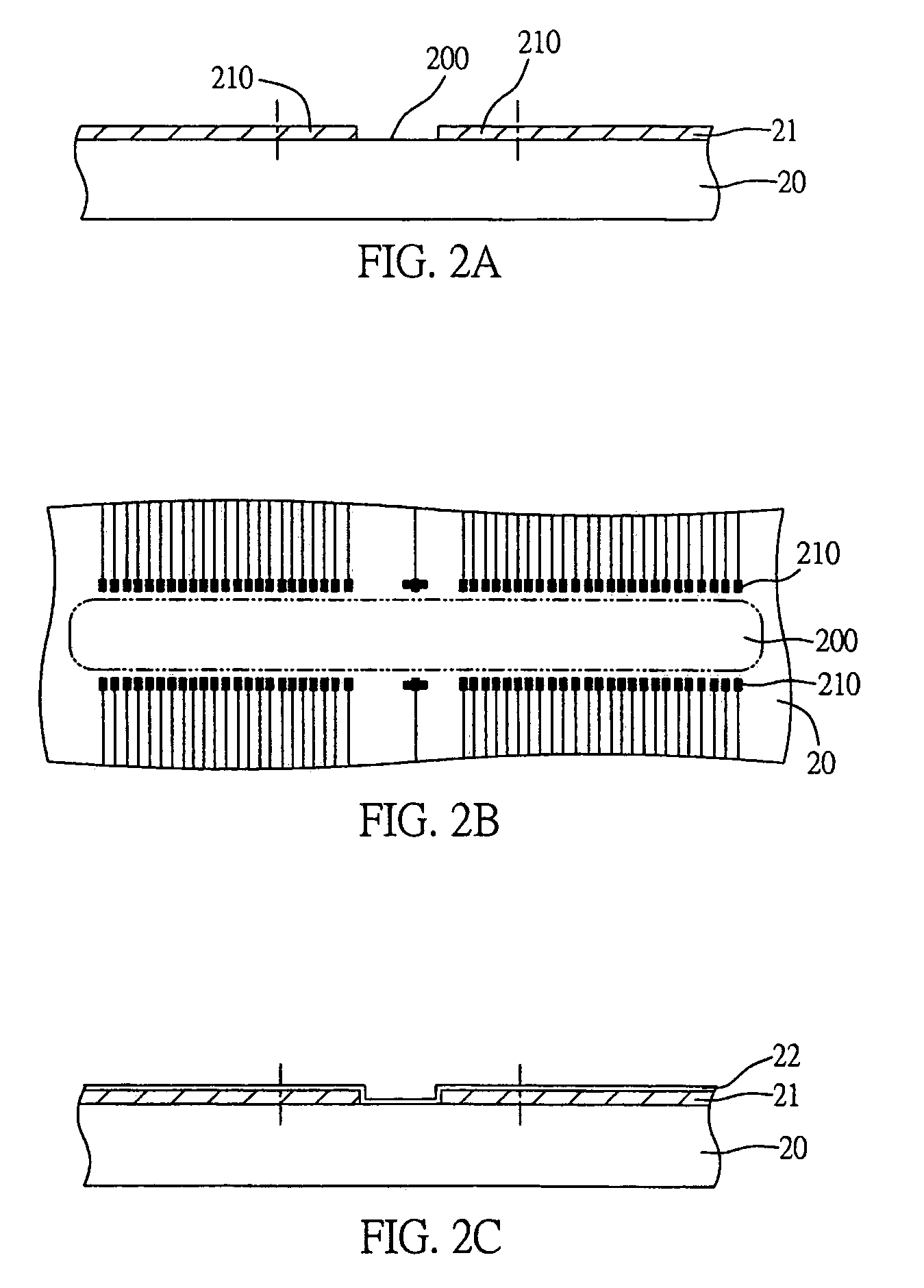

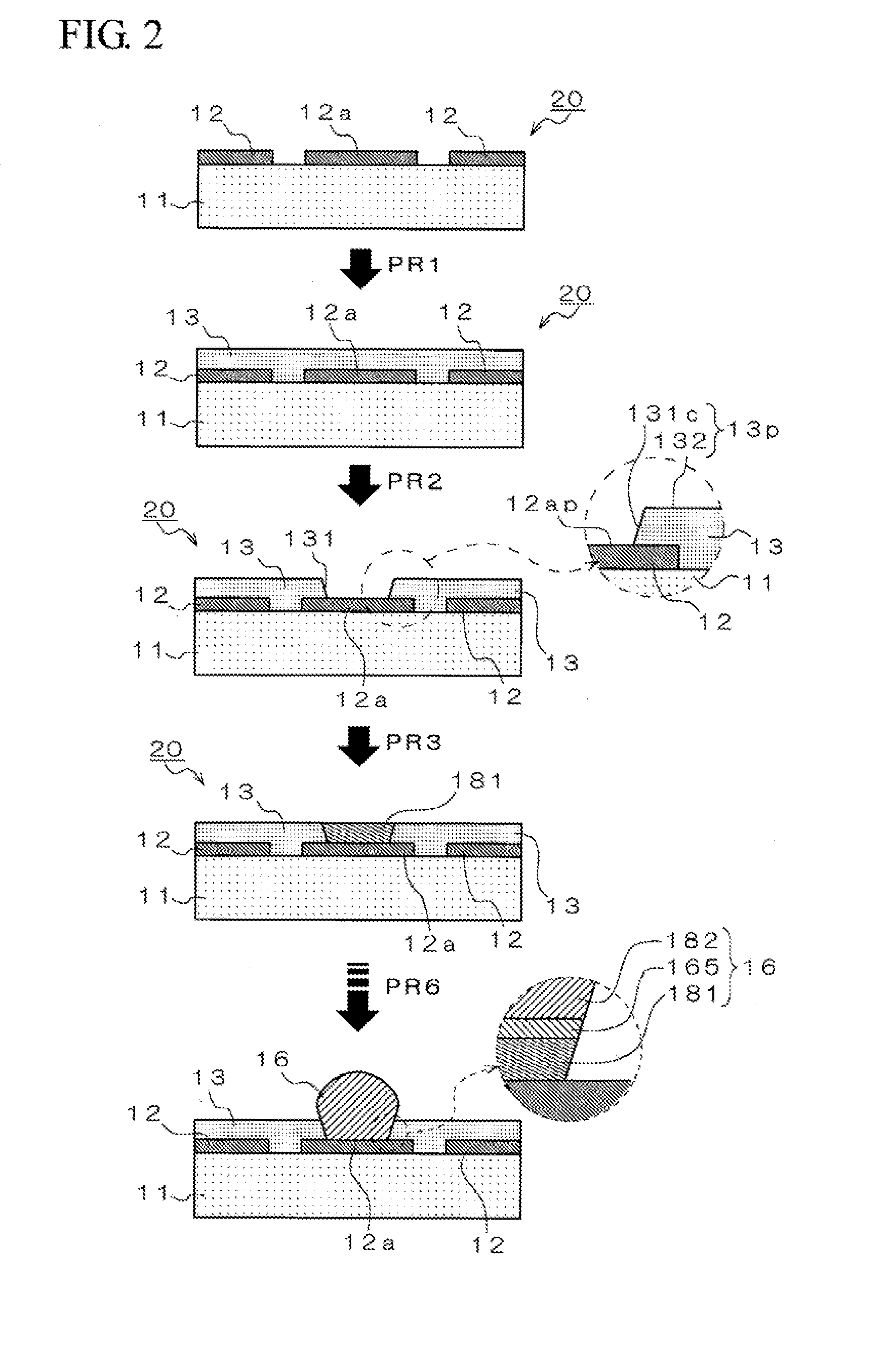

Method for forming metal bumps

InactiveUS20070218676A1Quality improvementLow costStacked resist layersPrinted circuit aspectsSolder maskOptoelectronics

A method for forming metal bumps is disclosed. Steps of the method include supplying a substrate containing a plurality of pads; forming a first photoresist layer on the substrate, herein the first photoresist layer covers the pads; performing a planarization step to remove a portion of the first photoresist layer so as to expose the pads; forming a conductive layer on the first photoresist layer and the pads; electroplating a metal layer on the conductive layer; forming a patterned second photoresist layer on the metal layer; a portion of the metal layer and the conductive layer which are not covered by the patterned second photoresist layer is removed by using the patterned second photoresist layer as a mask; removing the patterned second photoresist layer; and forming a solder mask on the substrate, wherein the solder mask has a plurality of openings to expose the metal layer located on the pads.

Owner:ADVANCED SEMICON ENG INC

Substrate with surface finished structure and method for making the same

InactiveUS20080093109A1Prevent oxidationPrinted circuit aspectsStacked resist layersSurface finishSolder mask

A substrate with surface finished structure and a method for manufacturing the same are disclosed. The method comprises: forming a circuit layer and a solder mask on the surface of the substrate in sequence, wherein a plurality of openings are formed in the solder mask to expose the portion of the circuit layer to be electrical contact pads which having at least a wire bonding pad and a plurality of solder pads; and forming a Ni / Au layer on the surface of the wire bonding pad and a chemical gold layer on the surface of the solder pads. Therefore, the disclosed structure can prevent the electrical contact pads from oxidation for a long time.

Owner:PHOENIX PRECISION TECH CORP

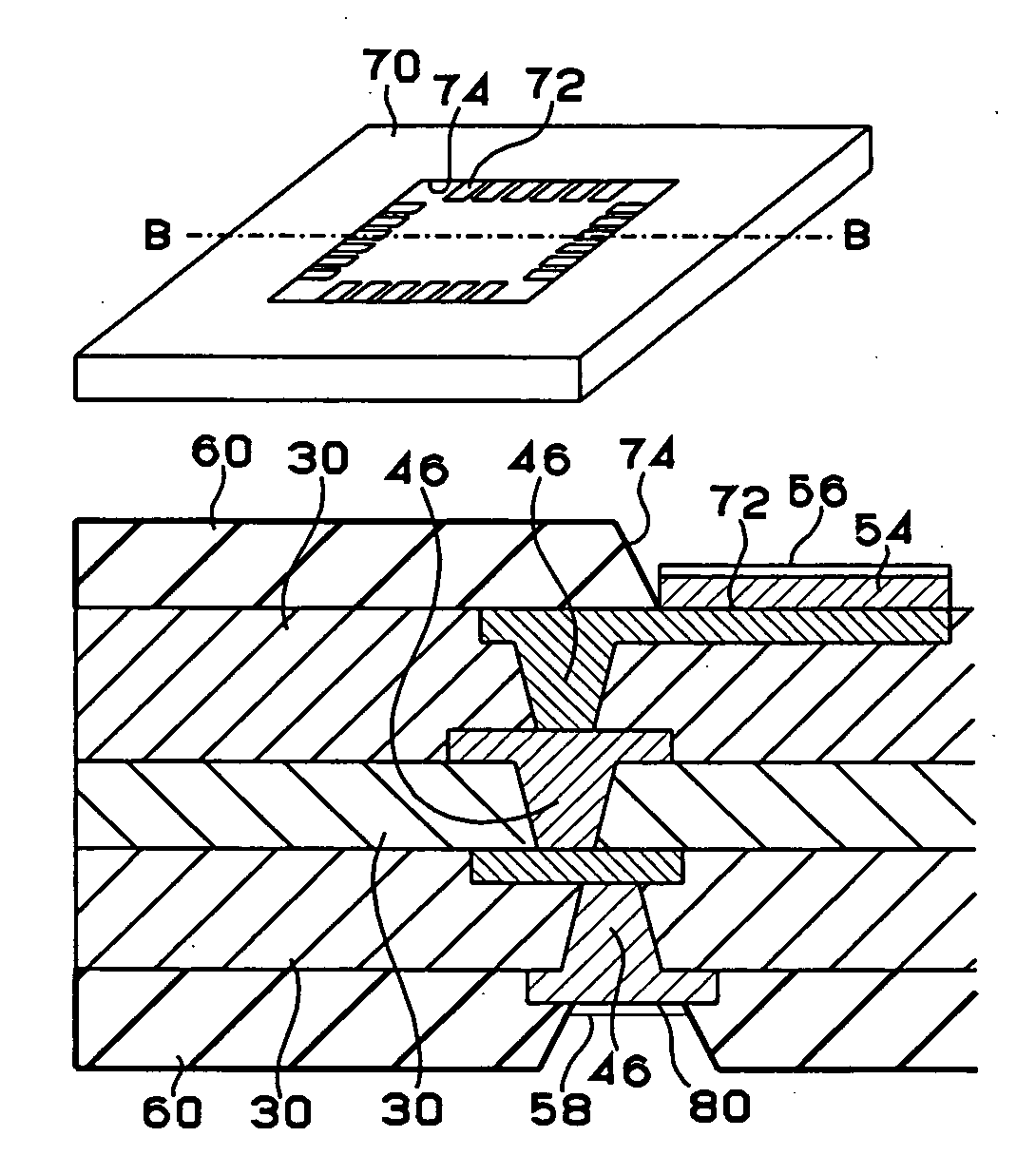

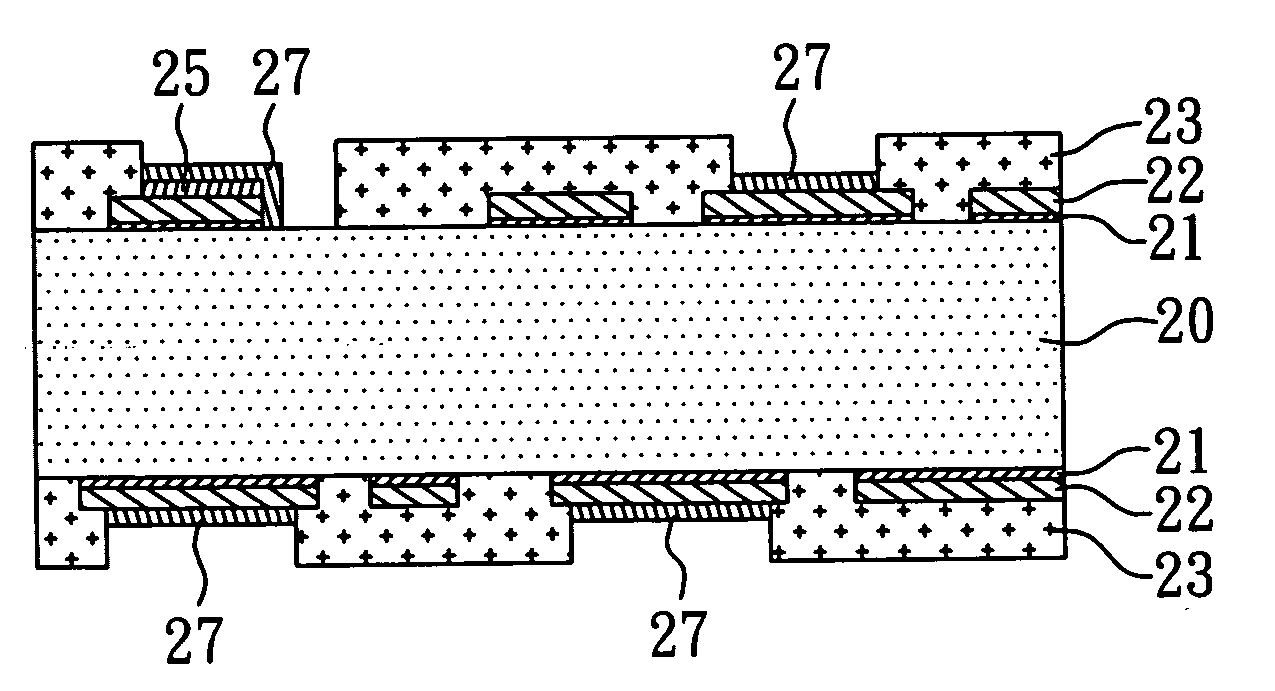

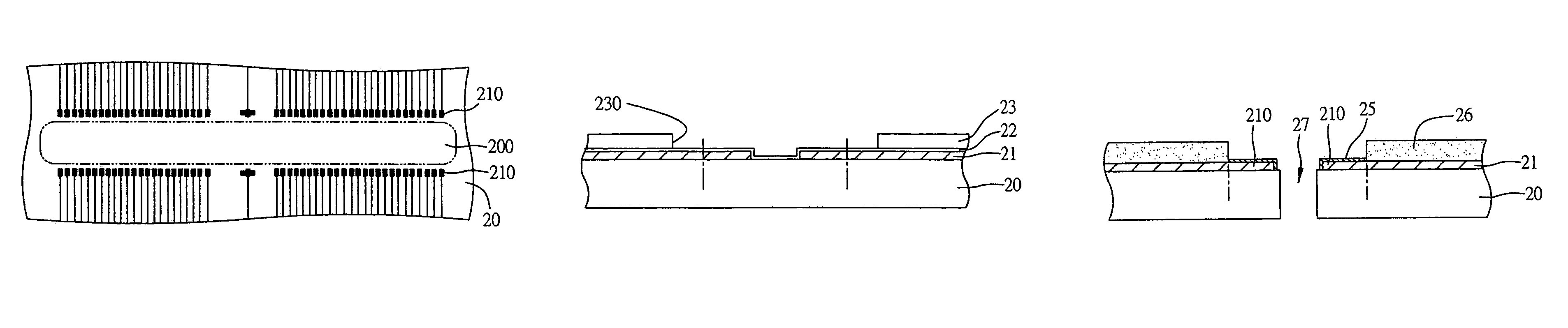

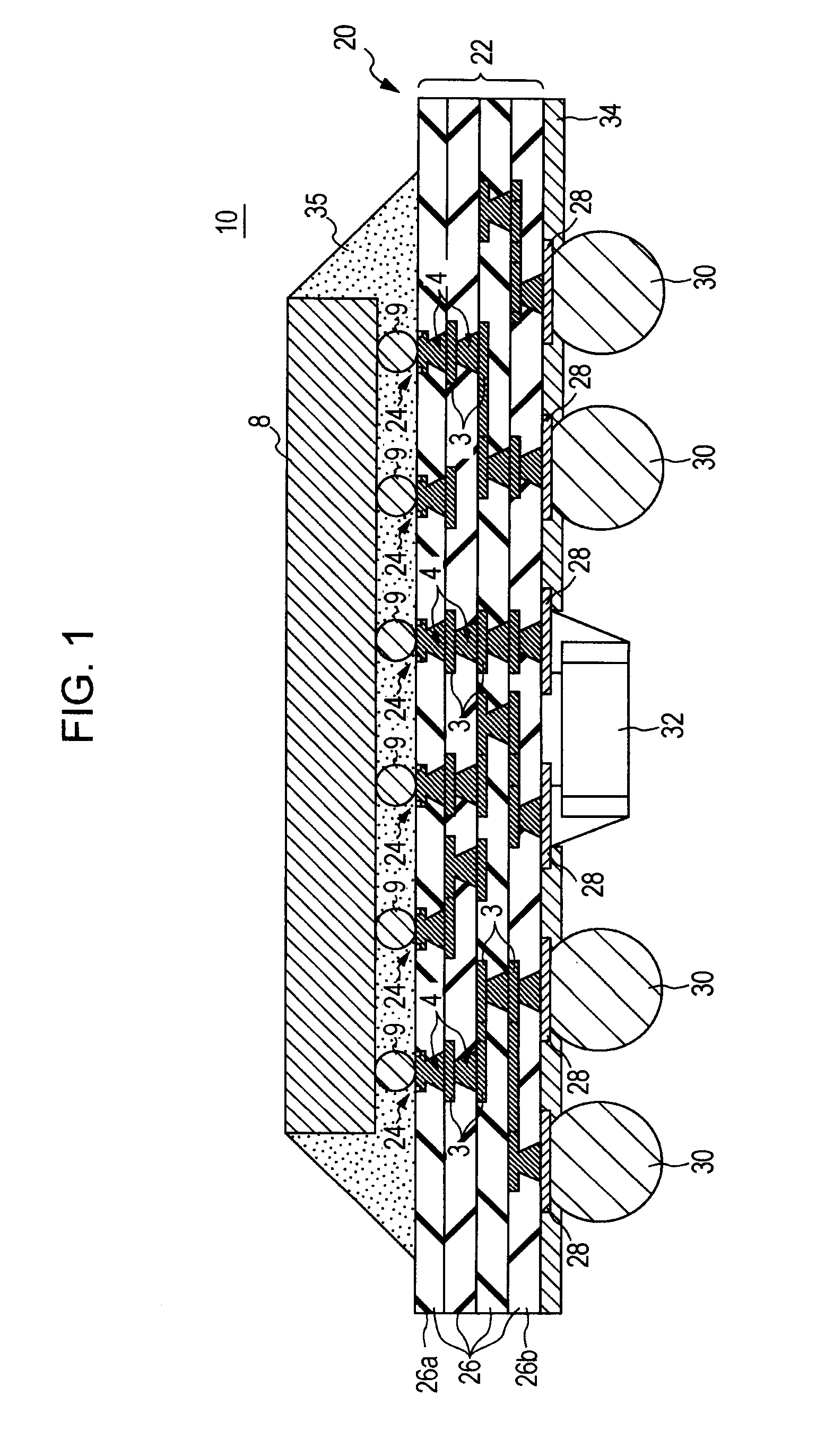

Electronic part module and method of making the same

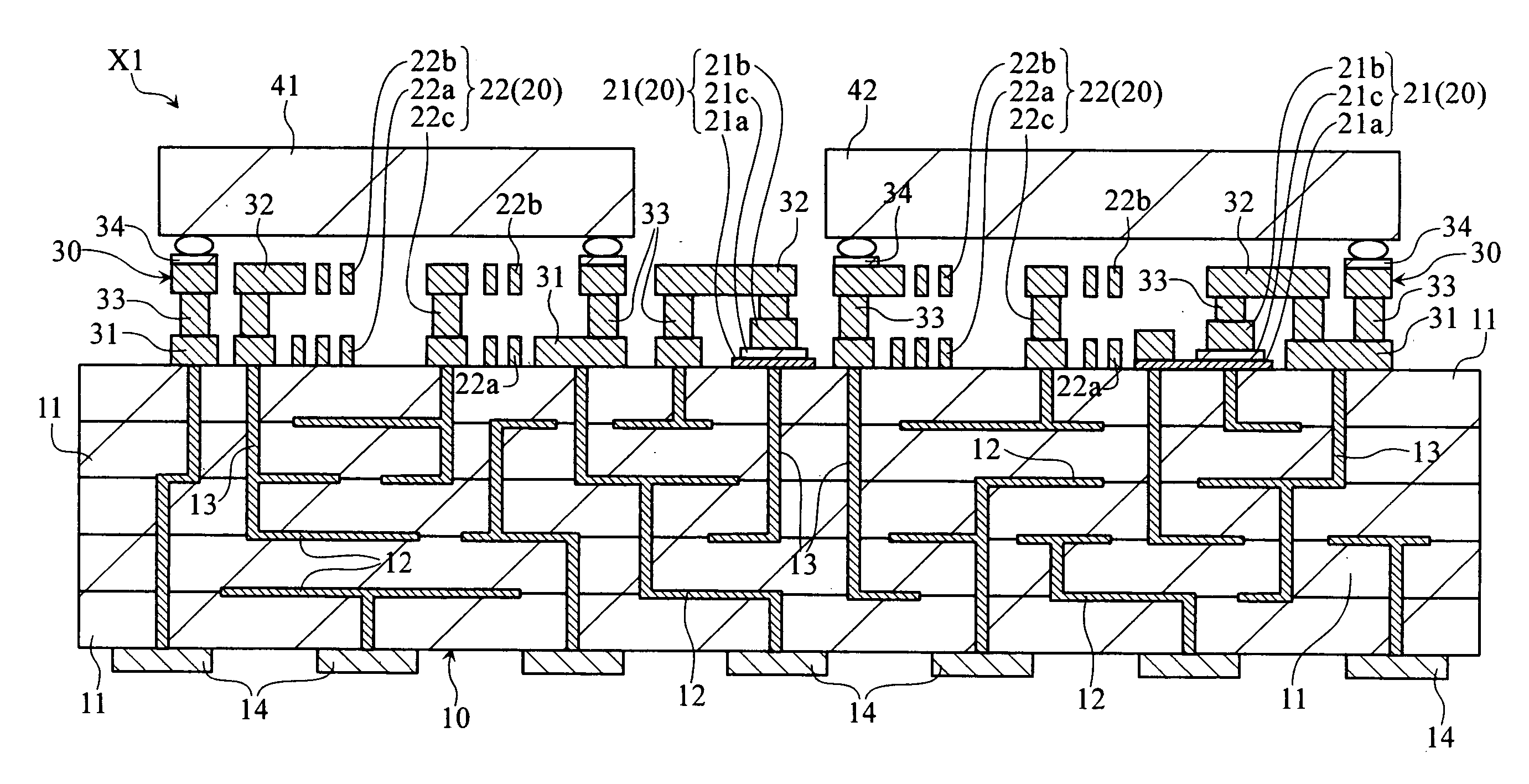

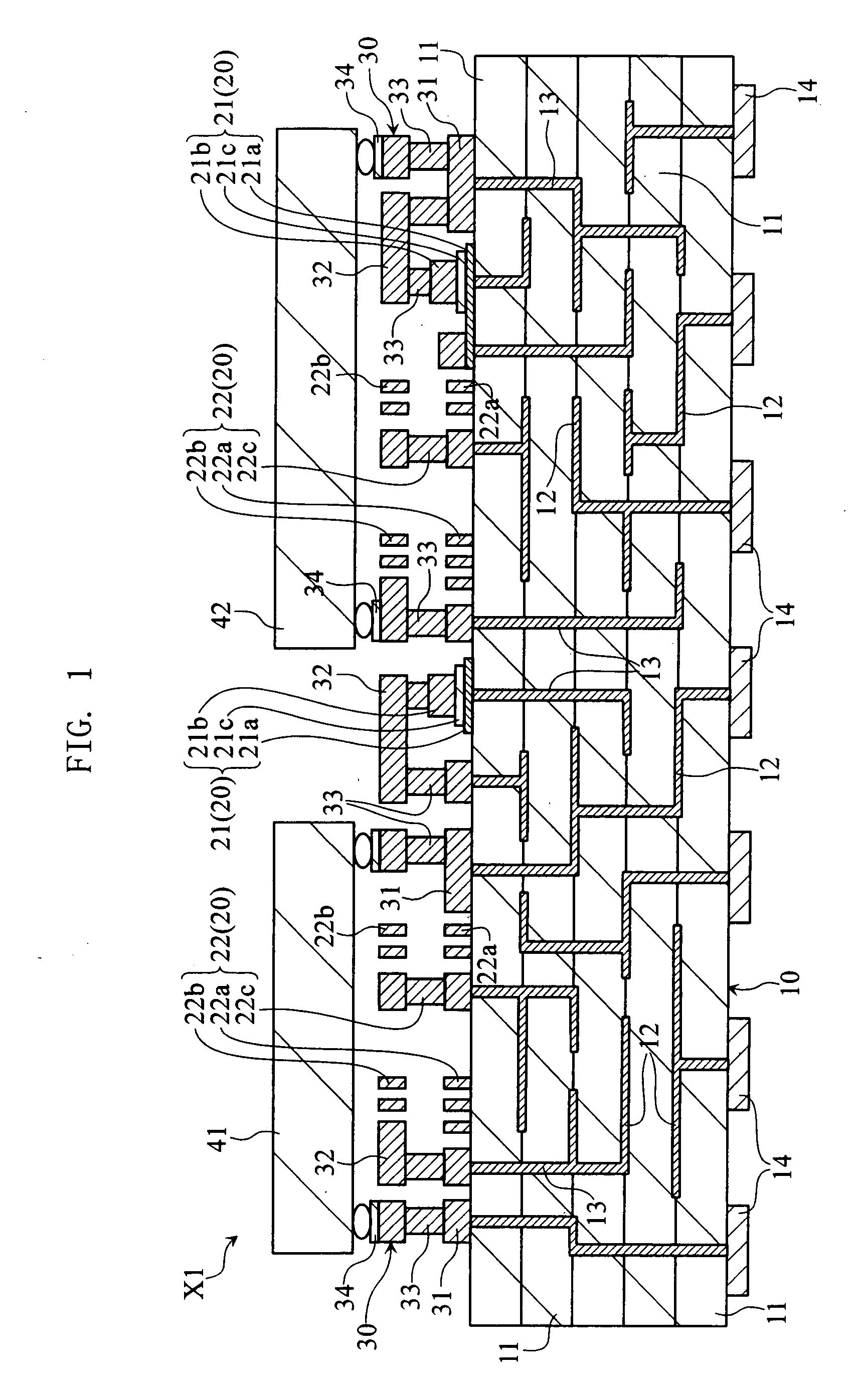

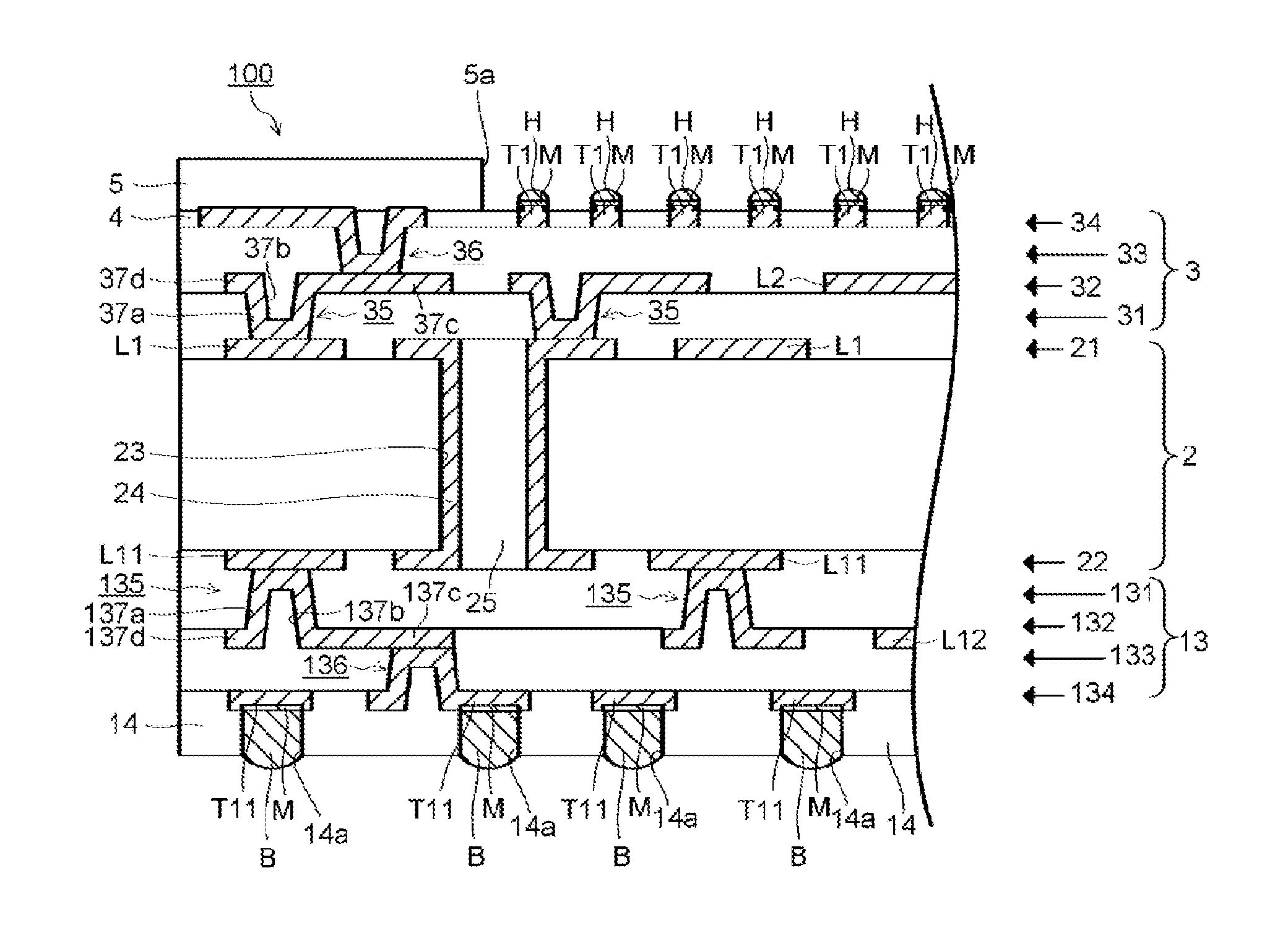

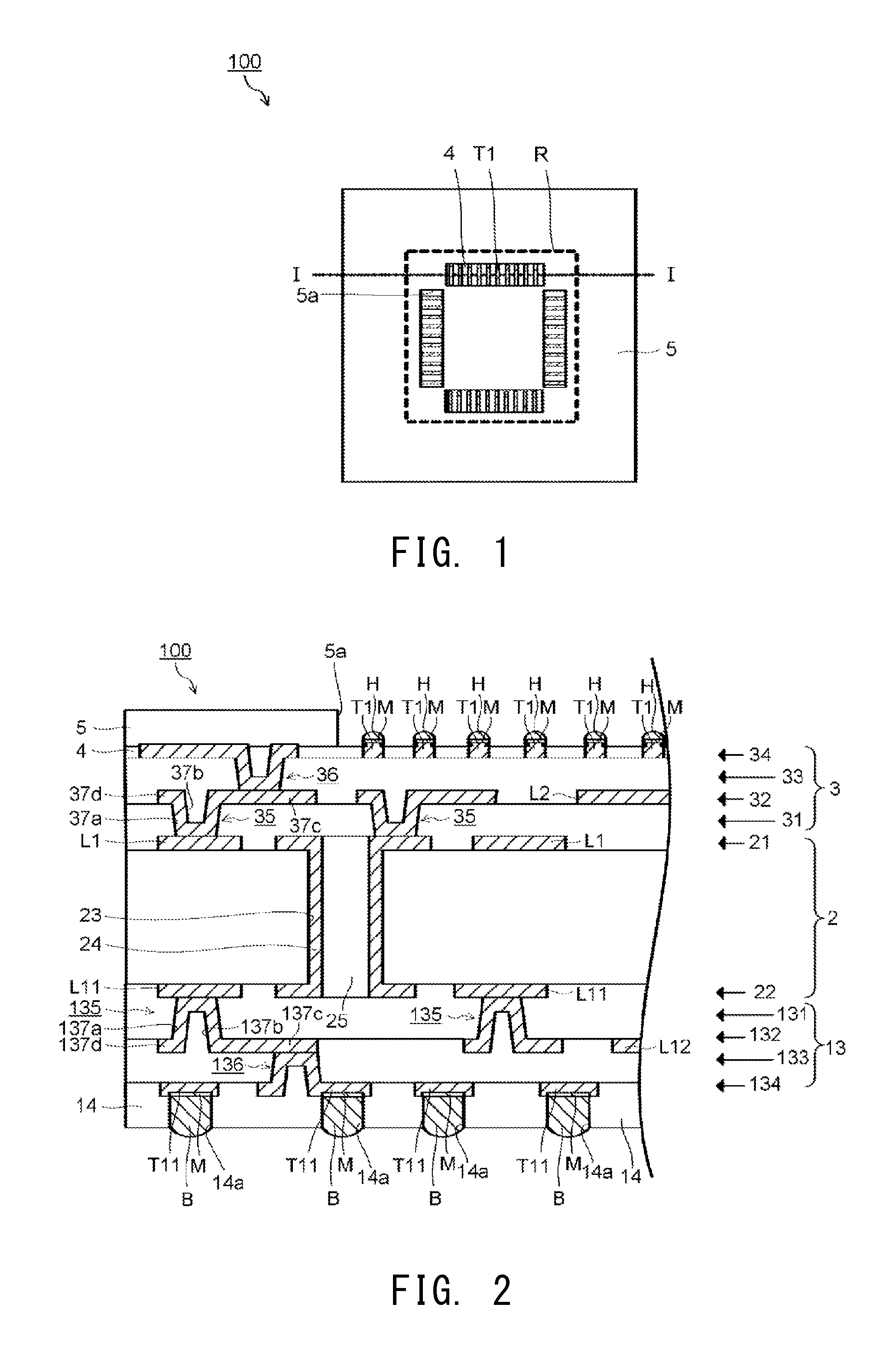

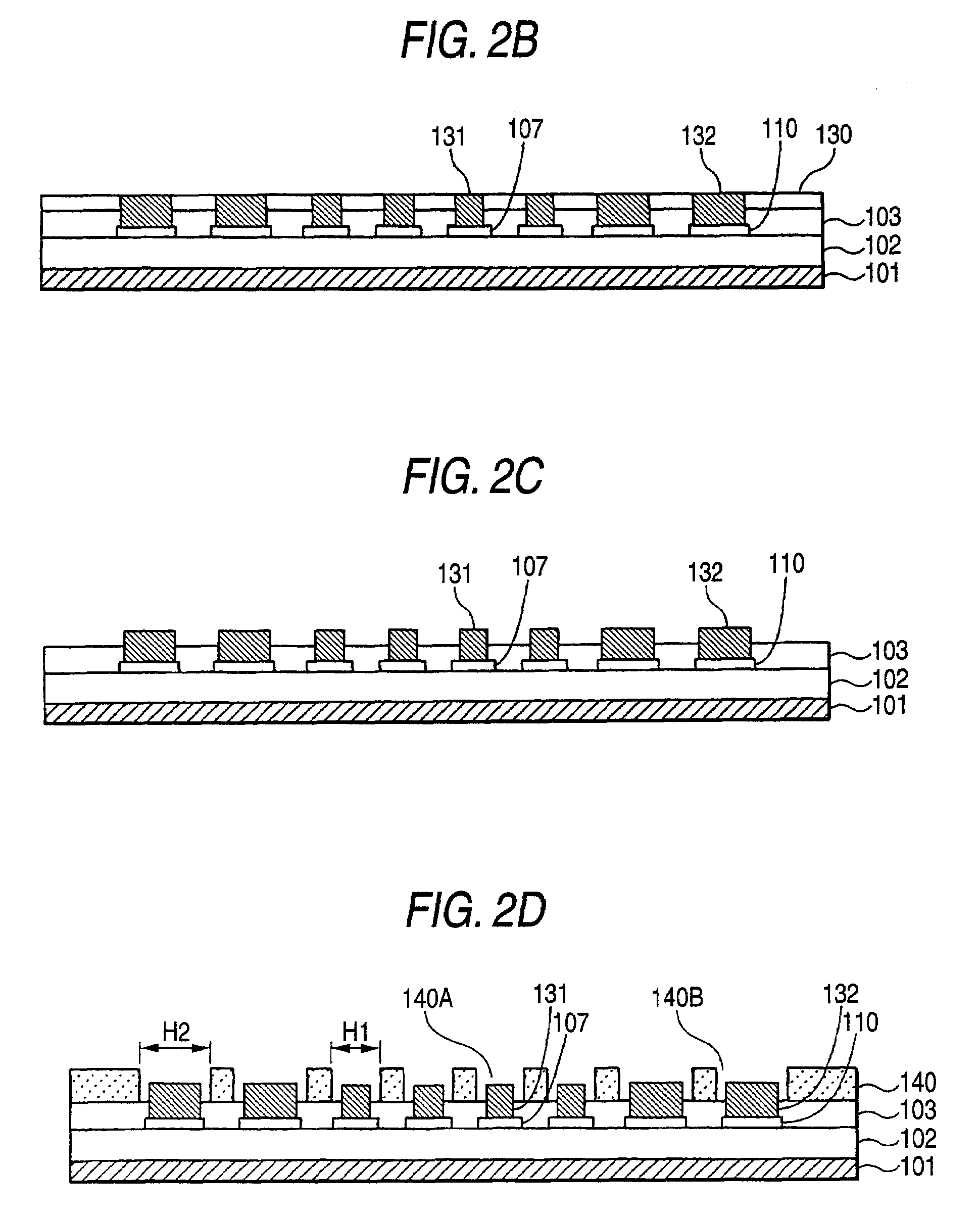

ActiveUS20080055873A1Appropriately manufacturedImprove production efficiencyPrinted circuit assemblingSemiconductor/solid-state device detailsDevice formEngineering

An electronic part module includes a wiring substrate, a passive device group of passive devices formed on the wiring substrate, and device chips mounted on the wiring substrate. Such an electronic part module is made in the following manner. First, a wiring substrate wafer is made, to include a plurality of electronic part module formation areas. Then, a plurality of passive devices are formed in each of the electronic part module formation areas on the wiring substrate wafer. Then, the device chips are formed on each of the electronic part module formation areas on the wiring substrate wafer. Finally, the wiring substrate wafer is divided.

Owner:TAIYO YUDEN KK

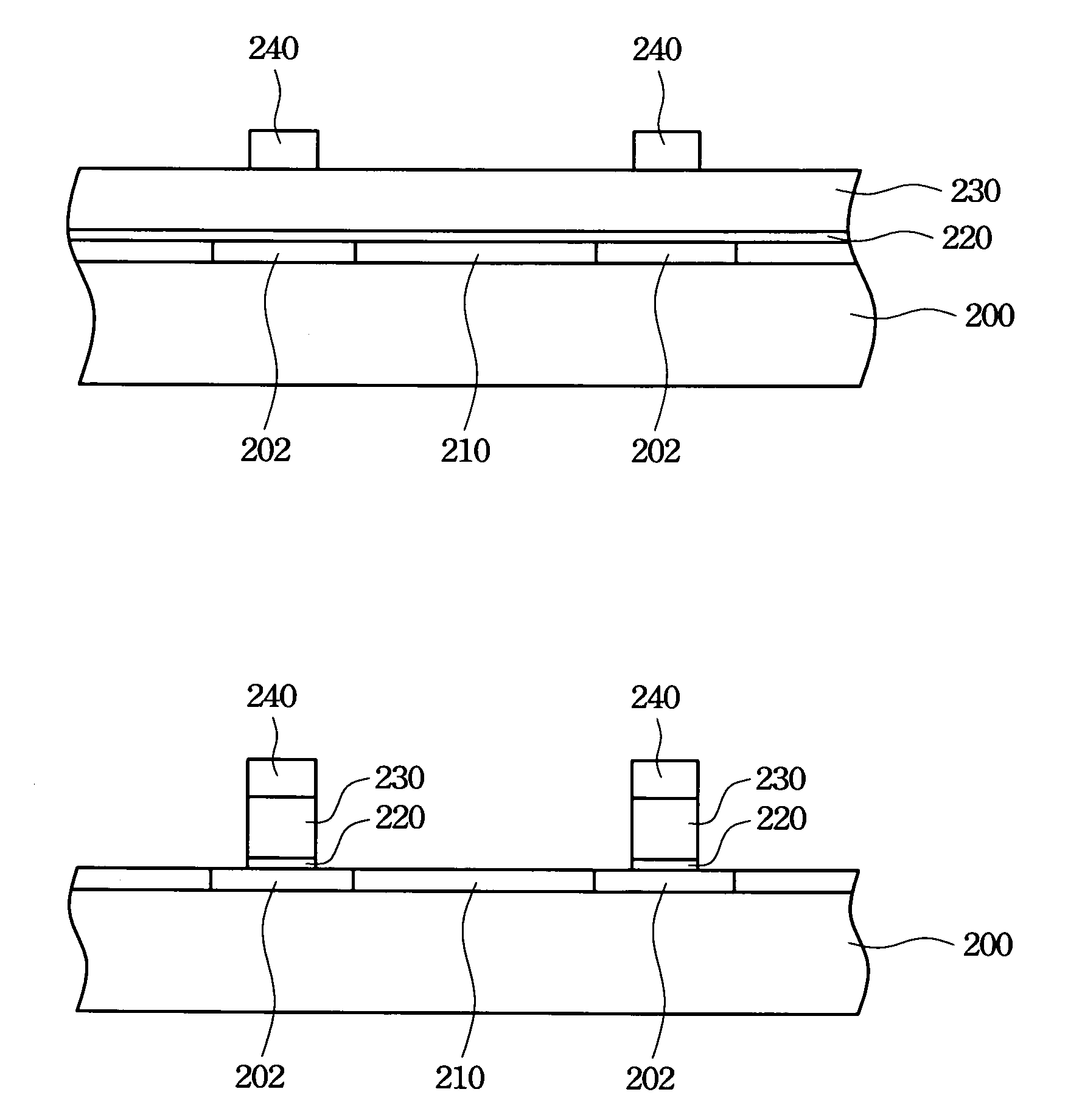

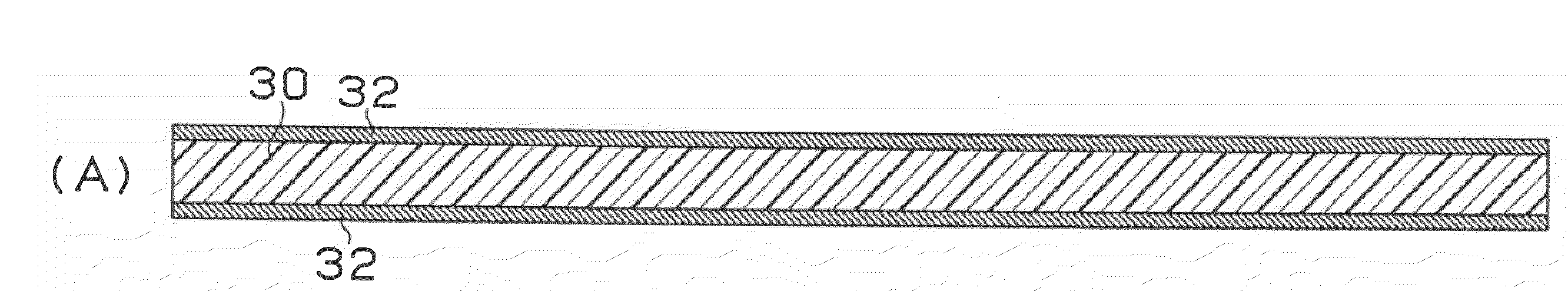

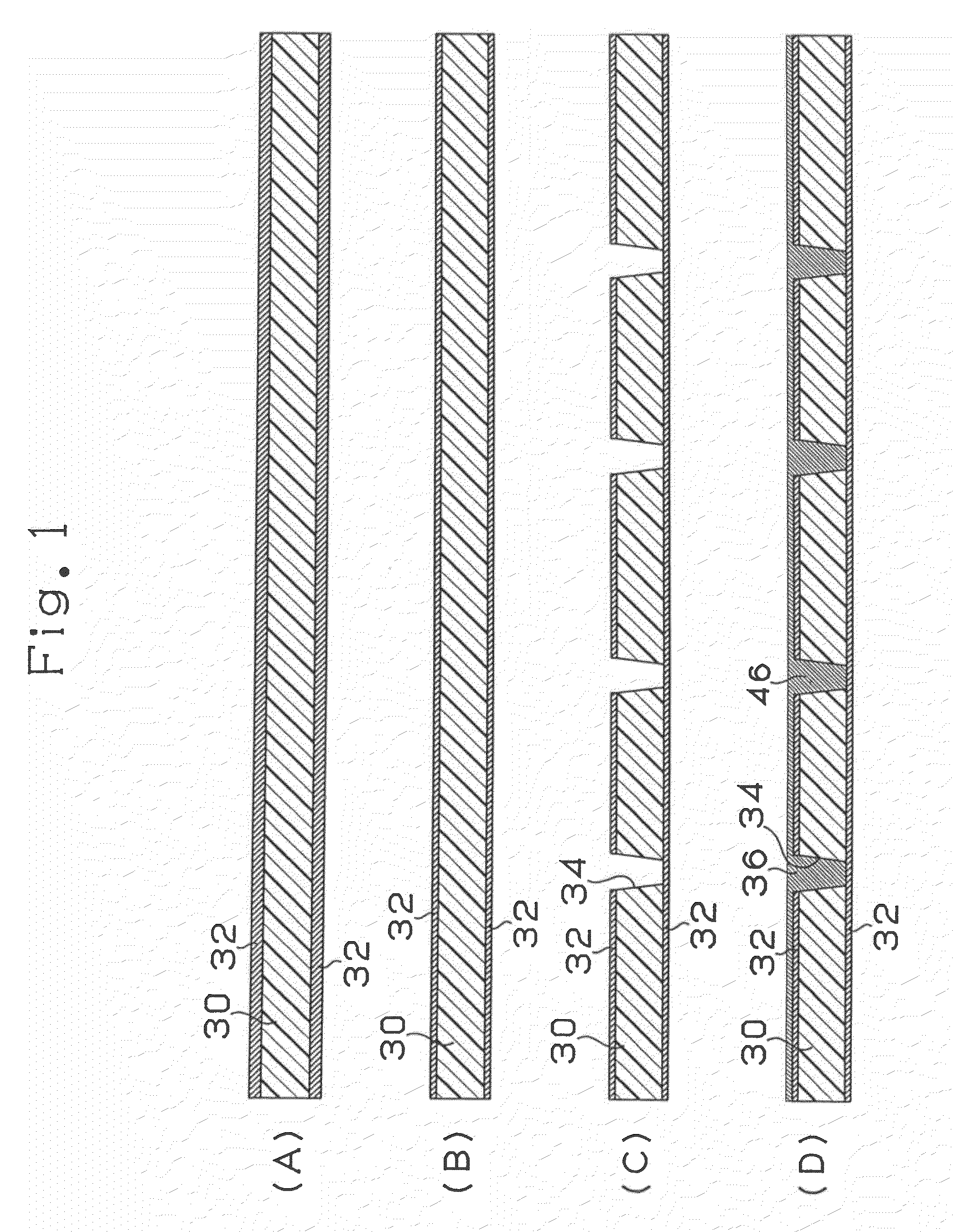

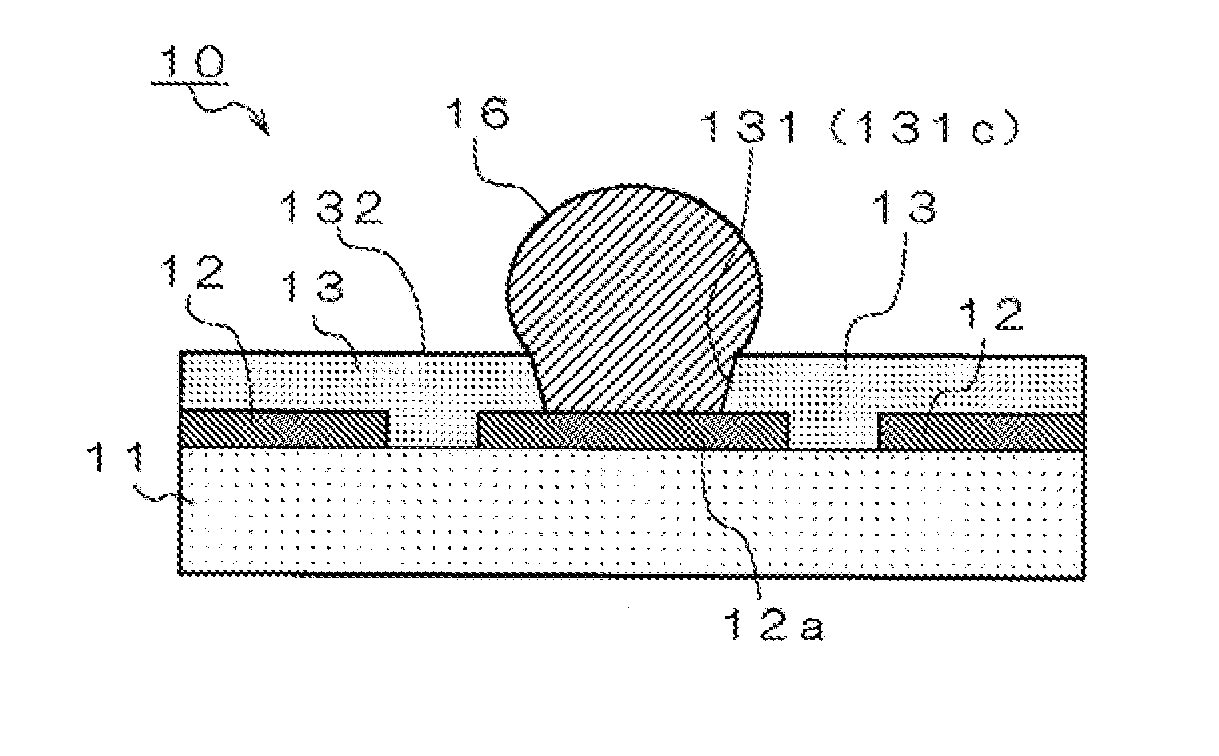

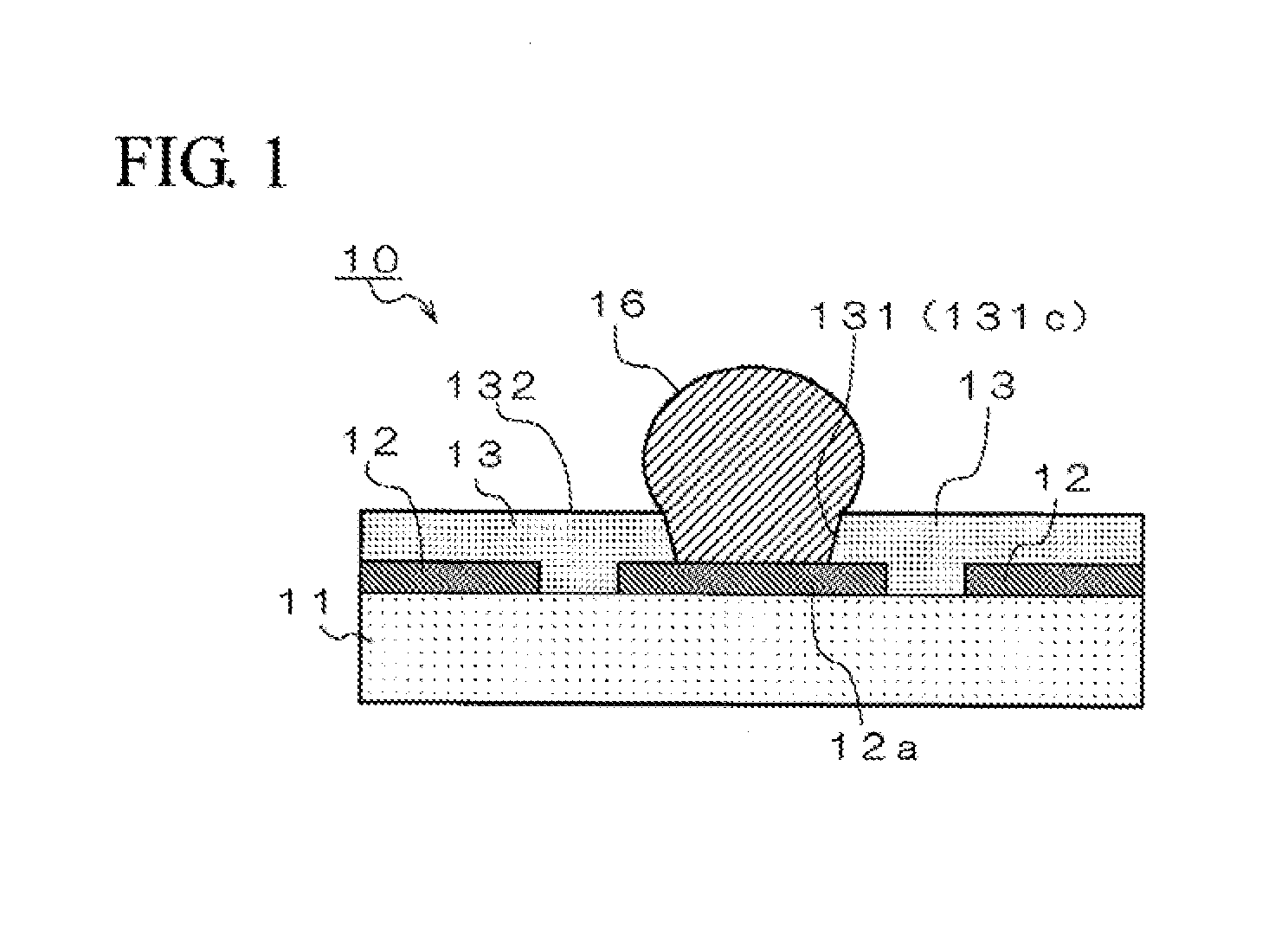

Wiring substrate and method for producing the same

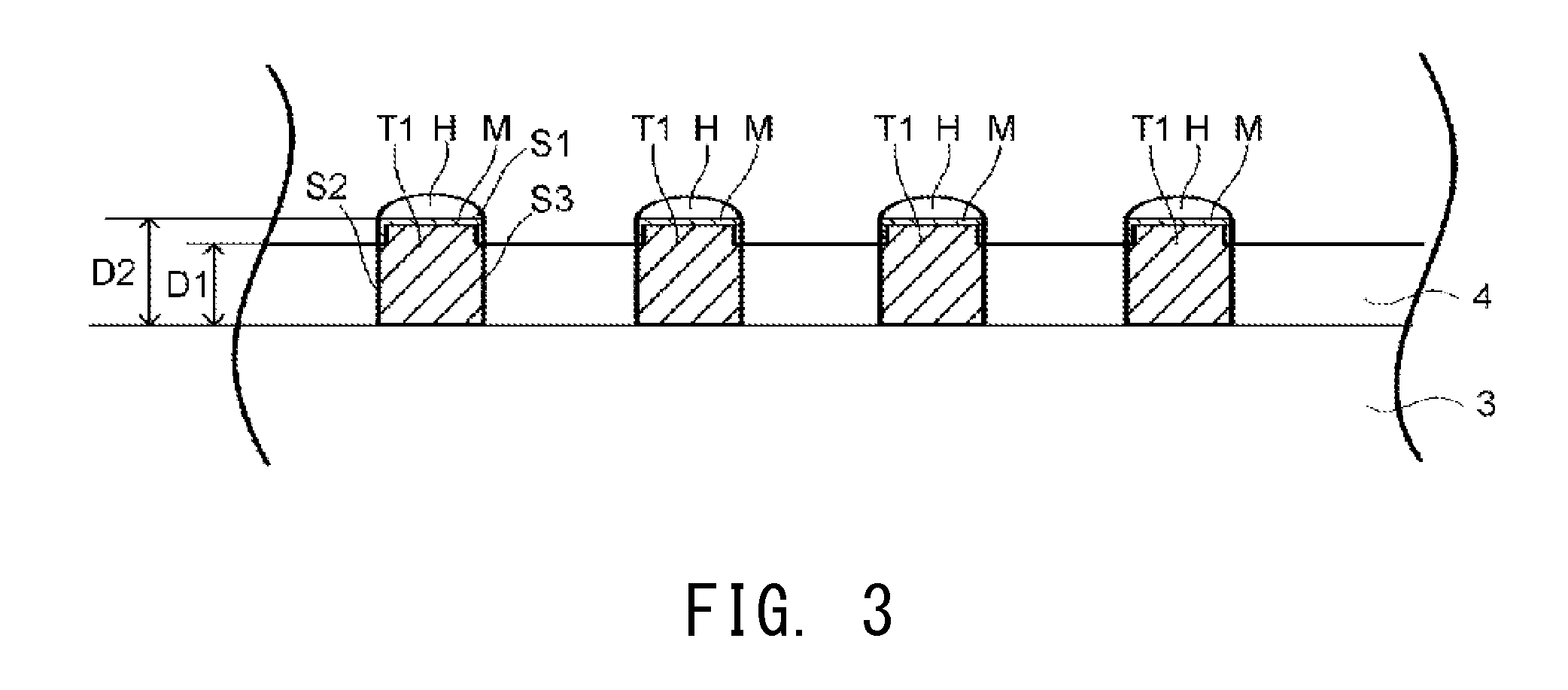

InactiveUS20140097007A1Avoid it happening againIncrease the areaExhaust apparatusStacked resist layersInsulation layerEngineering

Embodiments of the present wiring substrate include a stacked body including one or more insulation layers and one or more conductive layers, wherein the wiring substrate has a plurality of connection terminals formed on the stacked body, each connection terminal has a top surface whose area is smaller than that of each of opposite side surfaces thereof, and a filling member provided in a filling manner between the connection terminals. The top surface of each connection terminal has an area larger than that of a portion of each side surfaces portion exposed from the filling member, and a bonding layer containing a solder is formed on the top surface.

Owner:NGK SPARK PLUG CO LTD

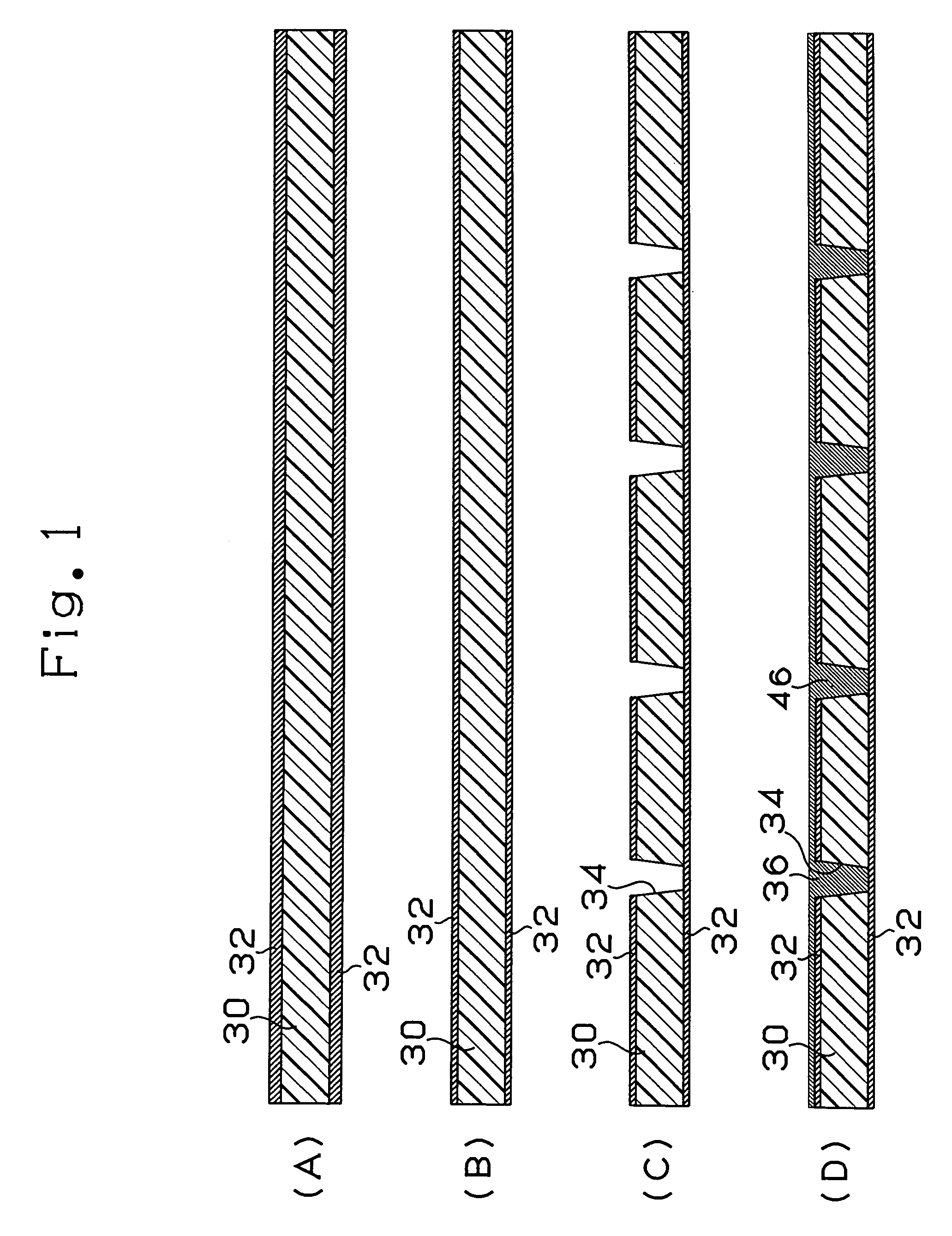

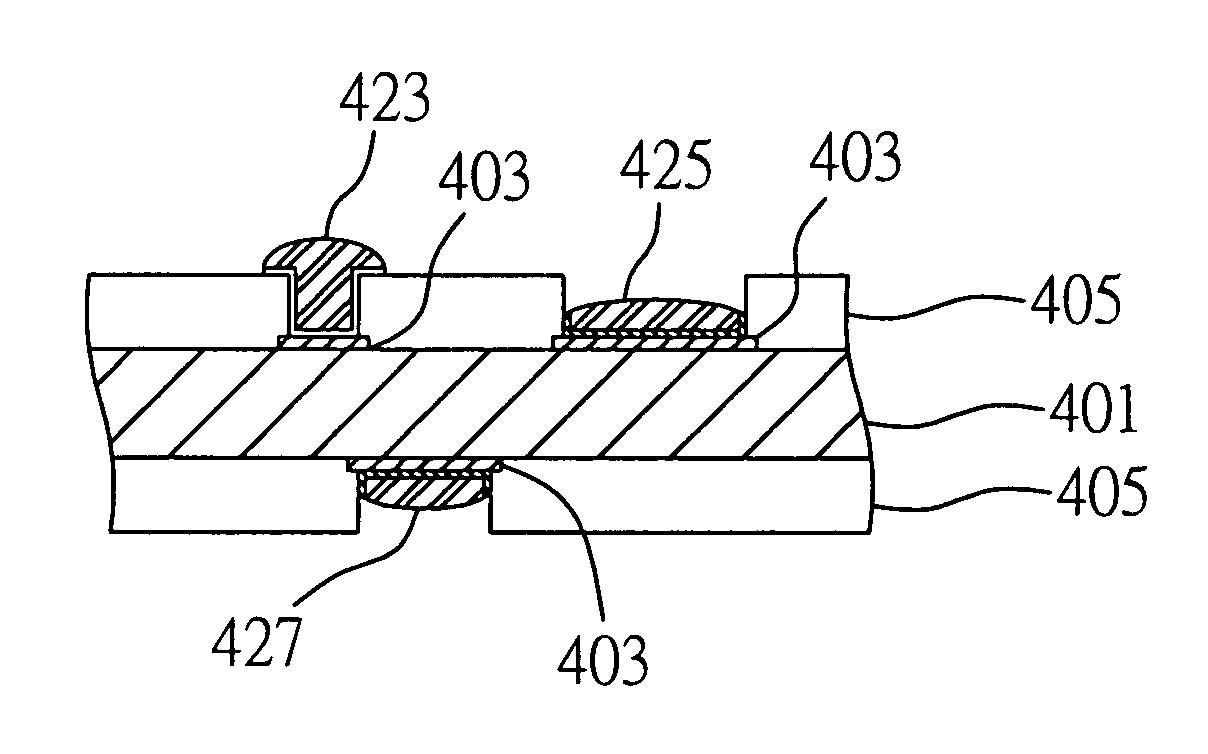

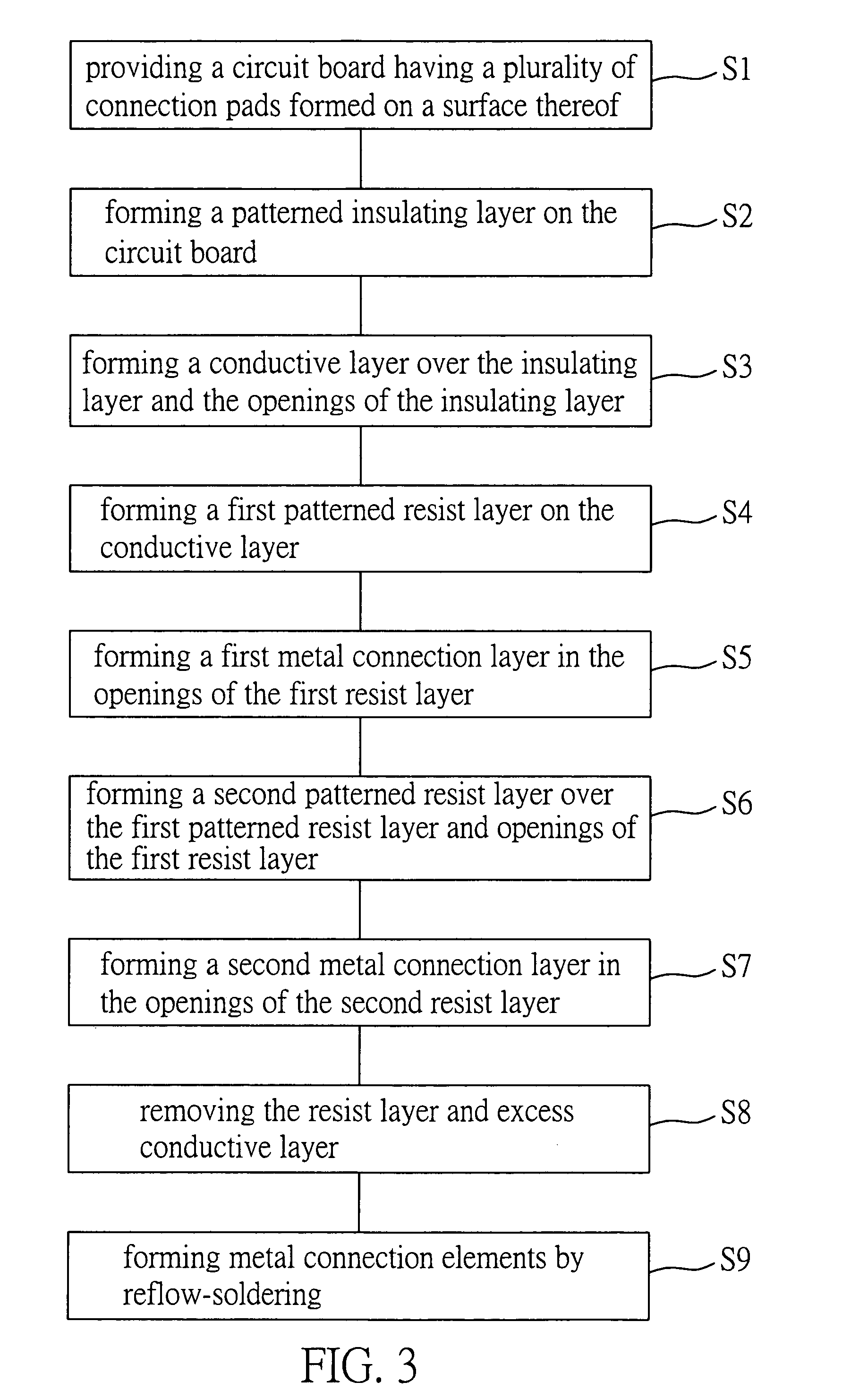

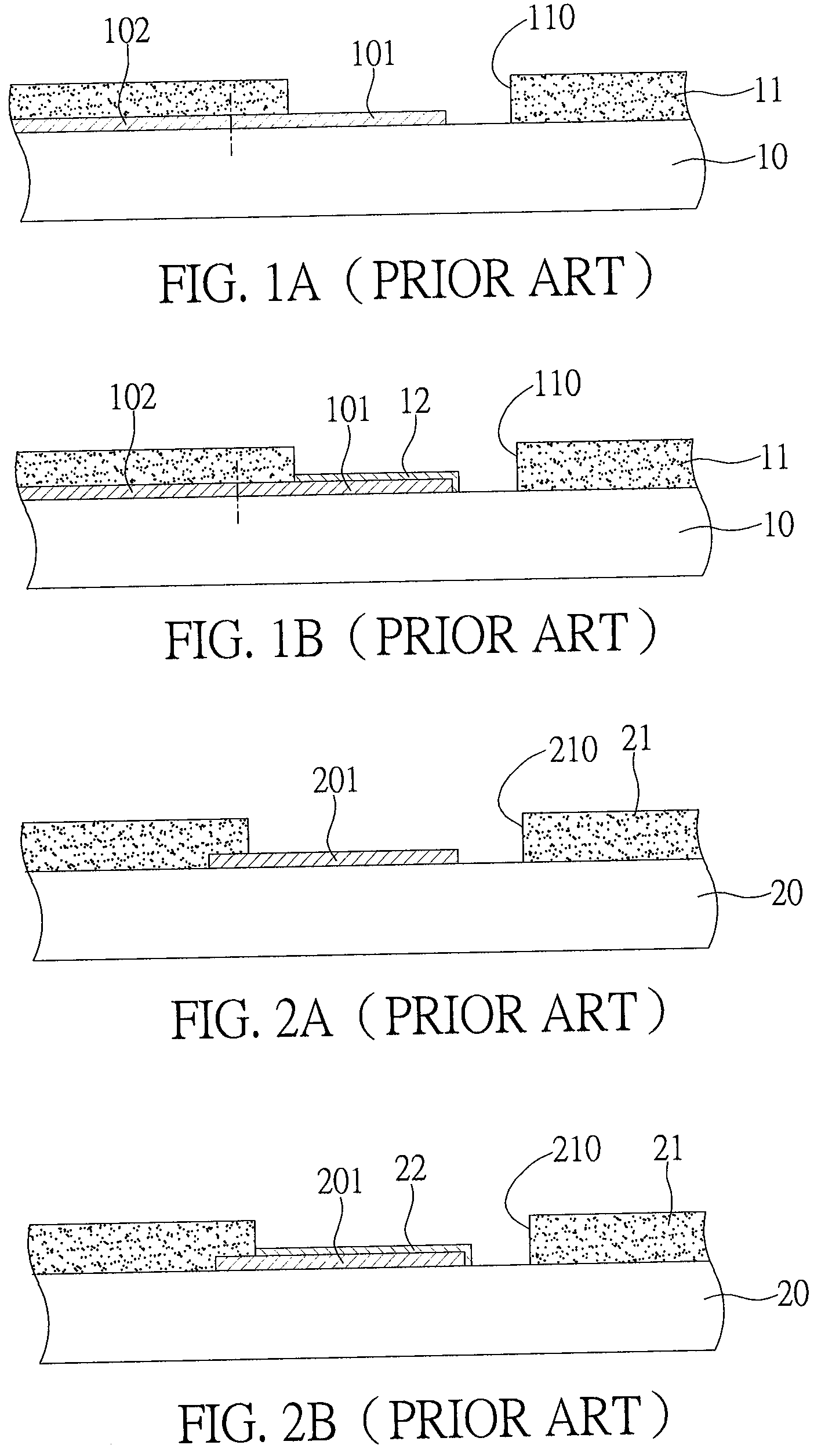

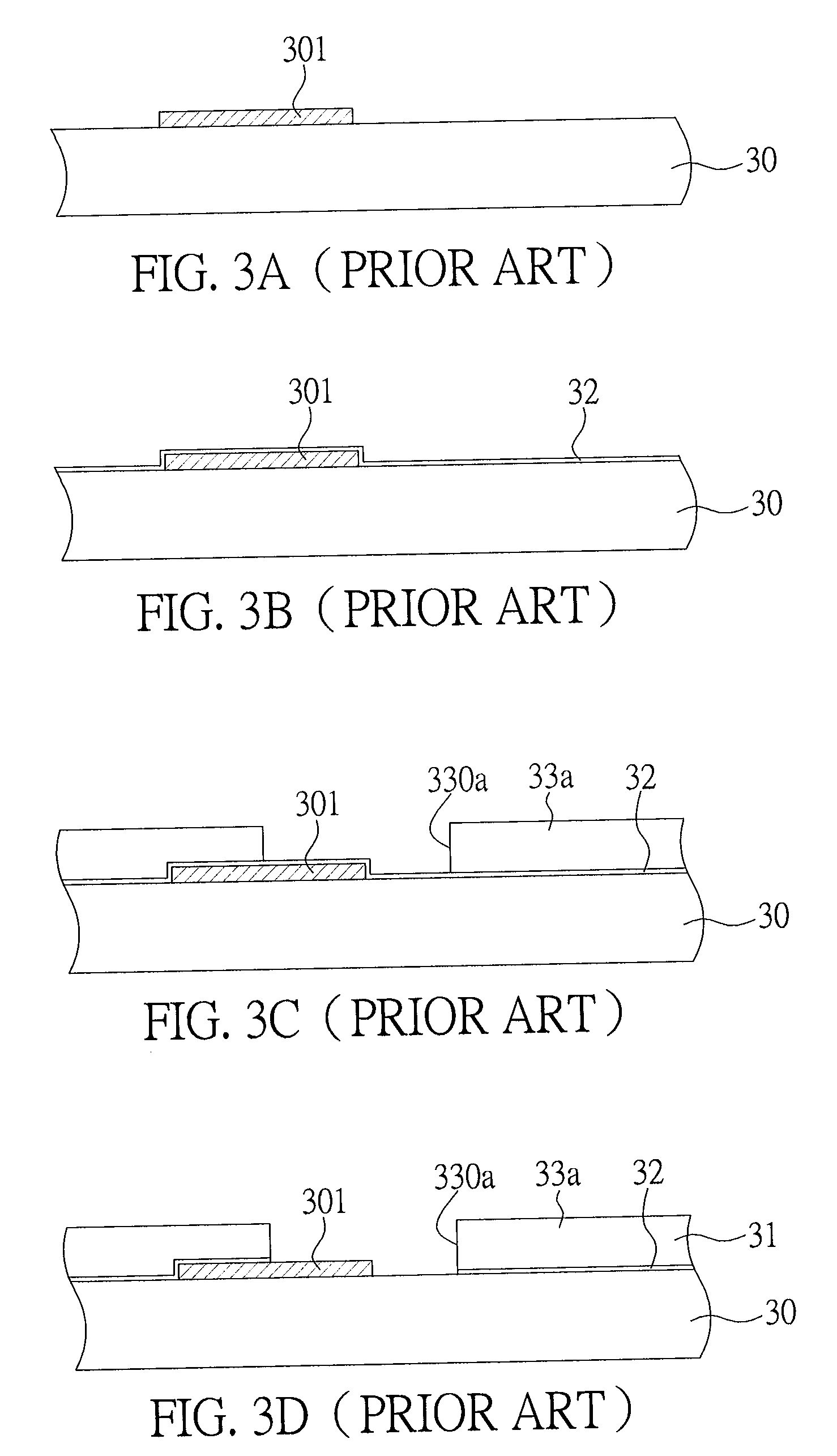

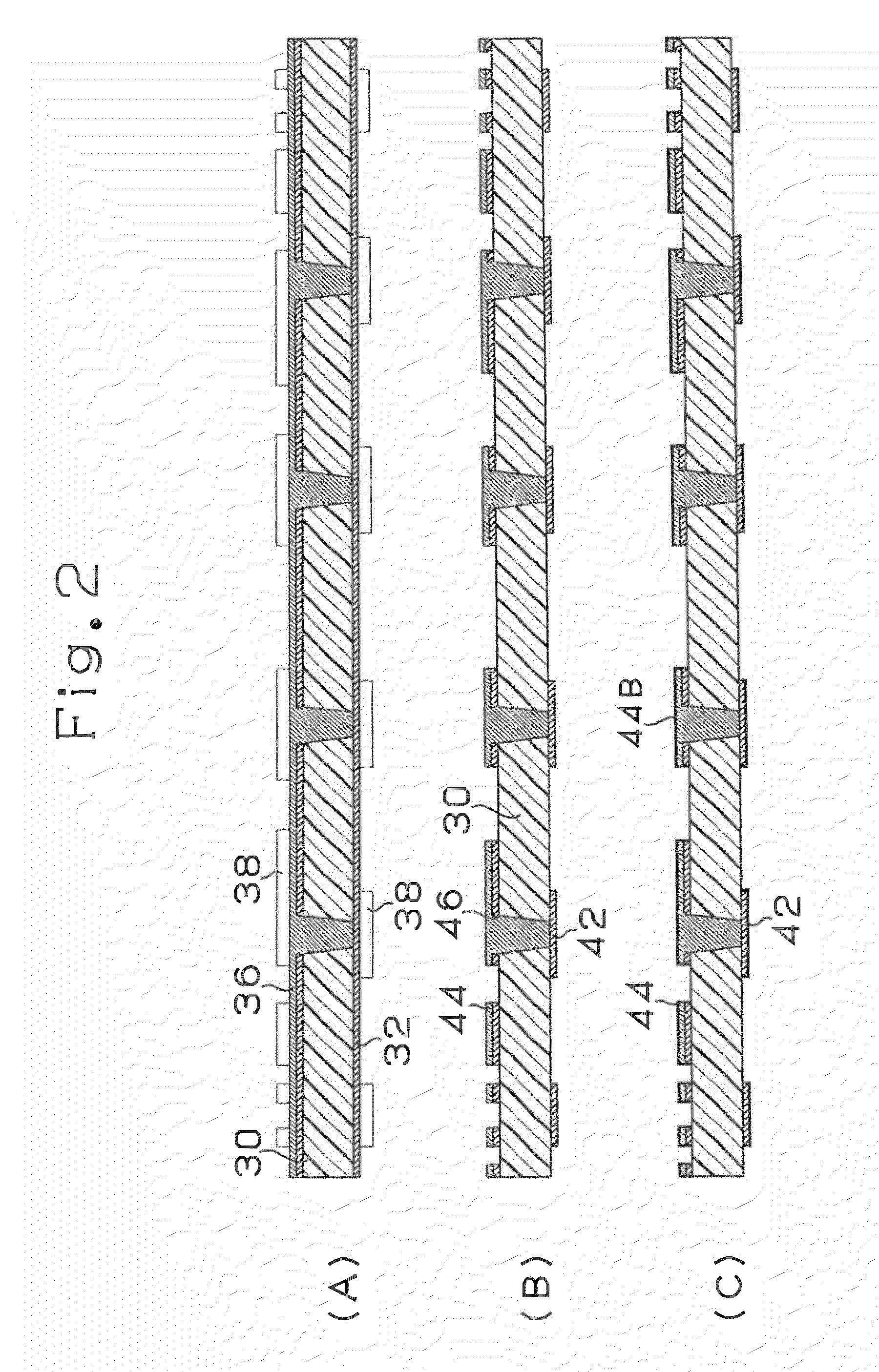

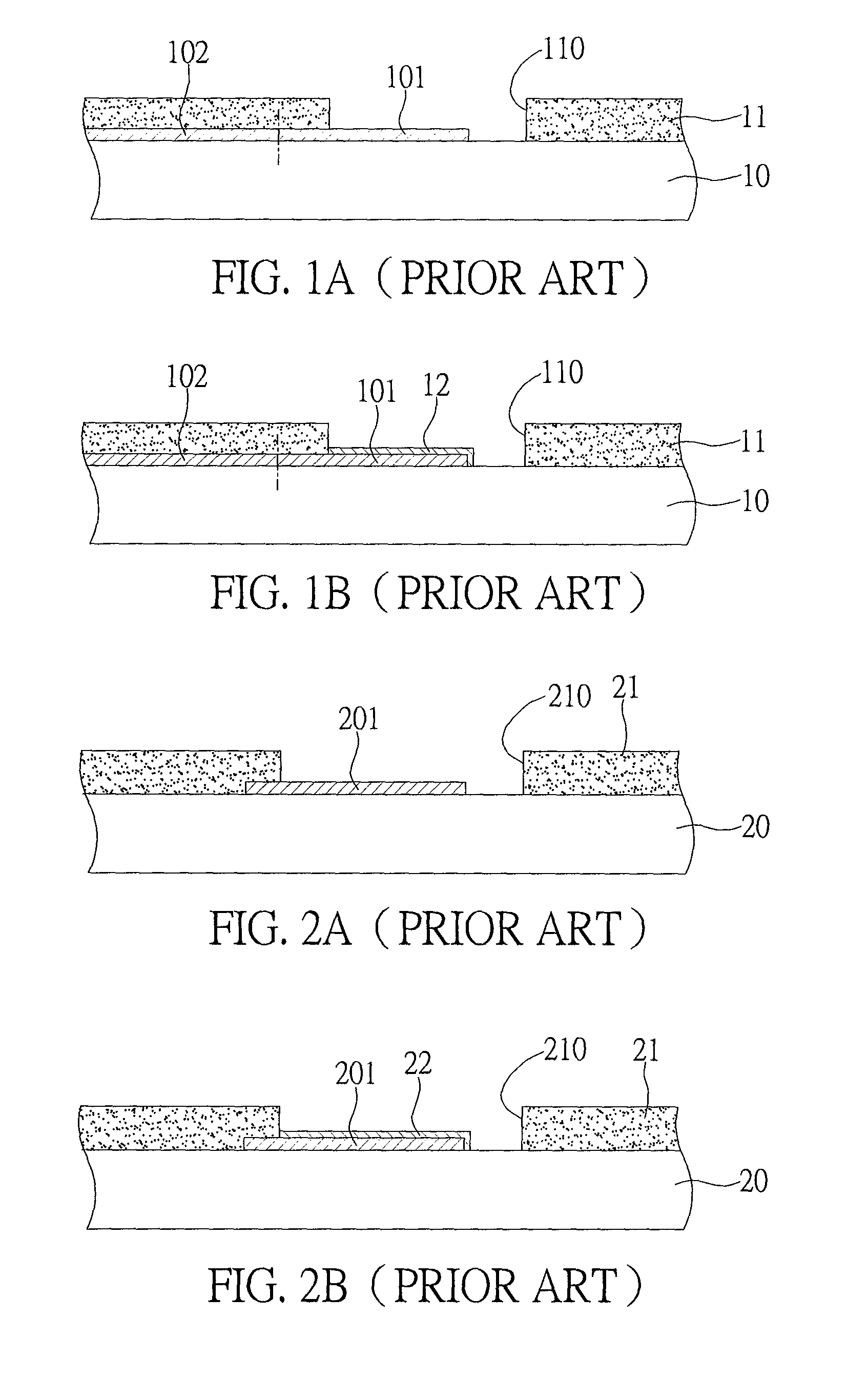

Method for fabricating connection terminal of circuit board

ActiveUS7174630B2Reduced yieldIncreased complexityContact member manufacturingElectrically conductive connectionsResistElectroplating

A method for fabricating connection terminals of a circuit board is proposed. The method involves providing a circuit board with connection pads thereon, forming an insulating layer with first openings over the circuit board to expose the connection pads, forming a conductive layer over the insulating layer, forming a first resist layer with second openings over the conductive layer to partially expose the conductive layer, electroplating a first metal connection layer on the exposed conductive layer, followed by forming a second resist layer with third openings over the first conductive layer to partially expose the first metal connection layer, and electroplating a second metal connection layer on the exposed first connection layer, and removing portions of the first and second resist layers and conductive layer covered by the first and second resist layers to form metal connection material of different heights and sizes on the connection pads.

Owner:PHOENIX PRECISION TECH CORP

Method for manufacturing semiconductor package substrate

ActiveUS7399399B2Eliminate burrsIncrease productionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectroplating

A method for manufacturing a semiconductor package is proposed. A circuit board with a circuit layer on at least one surface thereof is provided. The circuit board has at least one free area, and the circuit layer has a plurality of electrically connecting pads distributed on the periphery of the free area. A metal protecting layer is plated on the electrically connecting pads by non-plating line. The free area is removed, to form a cavity penetrating the circuit board. The present invention prevents burrs which may otherwise form on the periphery of a cavity, to increase the yield and throughput.

Owner:PHONEIX PRECISION TECH

Method of forming solder connection portions, method of forming wiring substrate and method of producing semiconductor device

ActiveUS7507655B2Improve reliabilitySemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor

A method of forming solder connection portions on first electrode pads and on second electrode pads, comprises a first step of arranging solder balls on the first electrode pads by arranging a first mask on a base mask; a second step of arranging solder balls on the second electrode pads by arranging a second mask on the base mask; and a third step of melting the solder balls. The base mask has first opening portions corresponding to the first electrode pads and second opening portions corresponding to the second electrode pads and having a size different from that of the first opening portions. The first mask has opening portions corresponding to the first opening portions and covering the second opening portions. The second mask has opening portions corresponding to the second opening portions and covers the first opening portions.

Owner:SHINKO ELECTRIC IND CO LTD

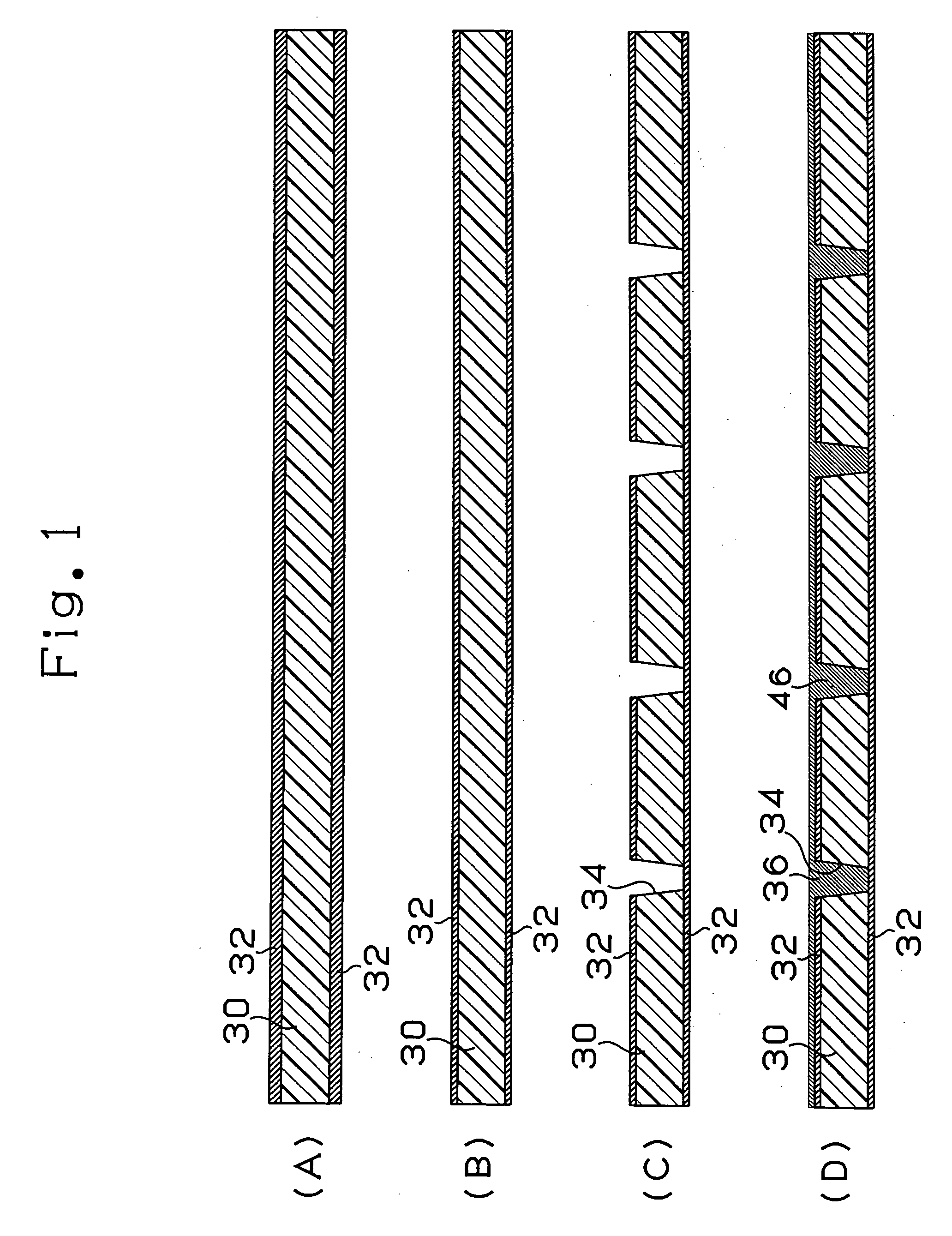

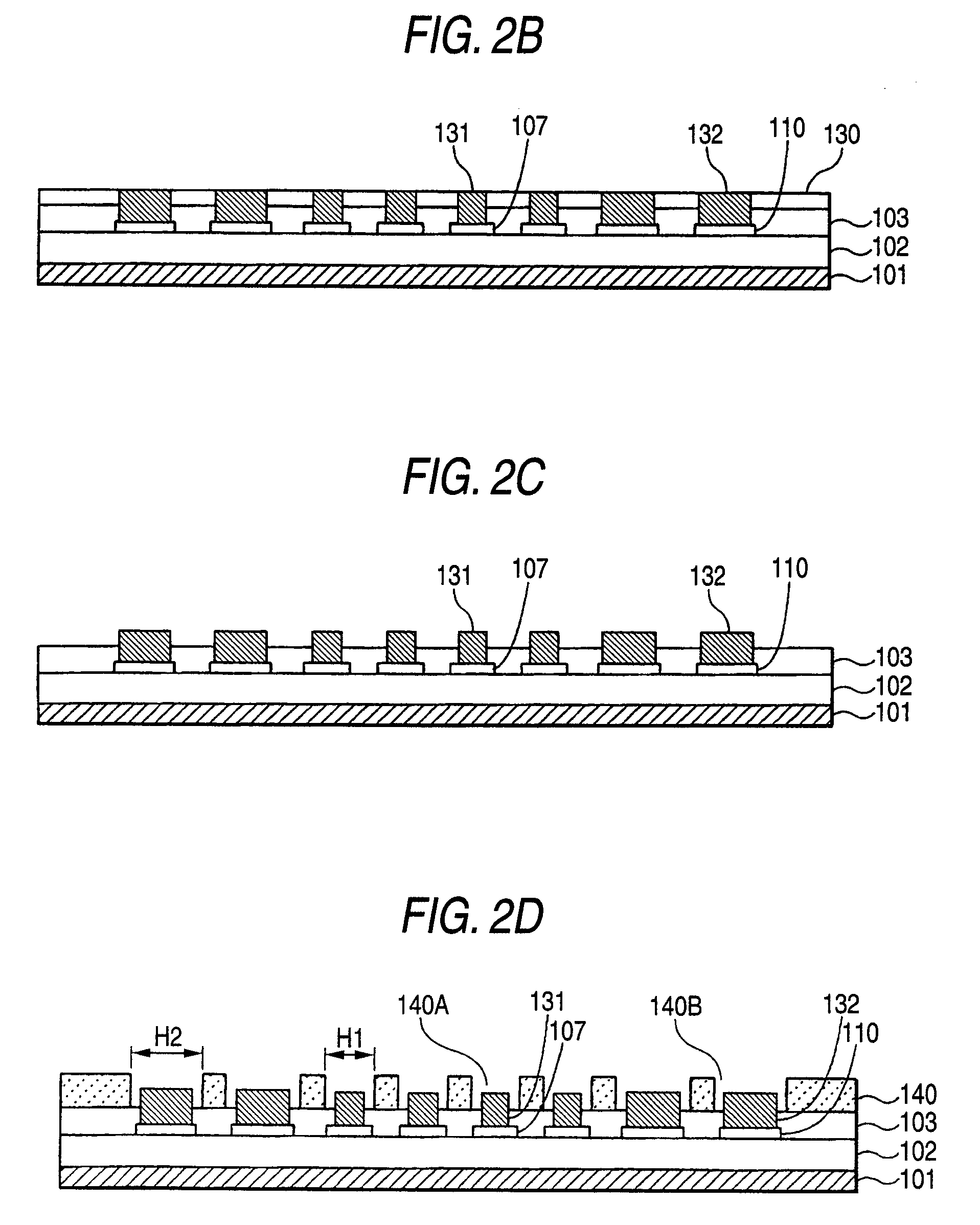

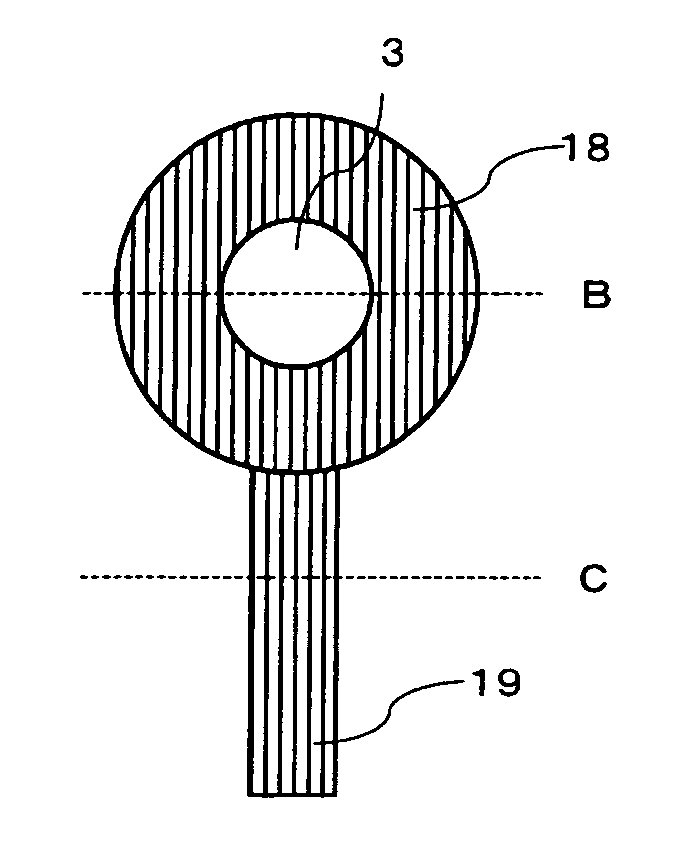

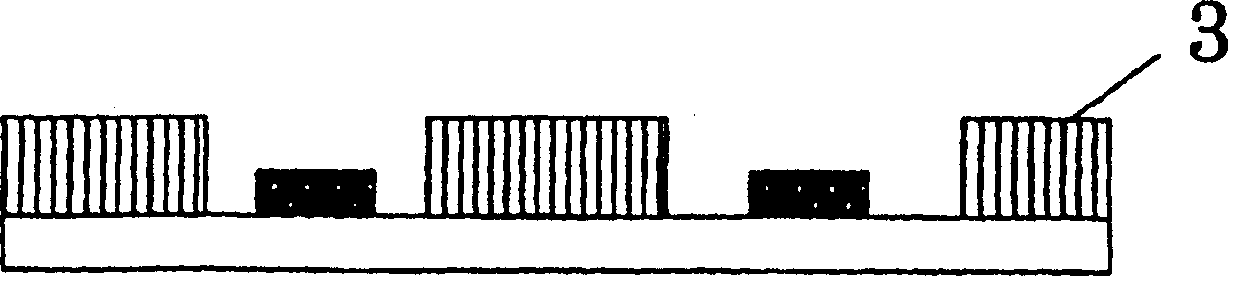

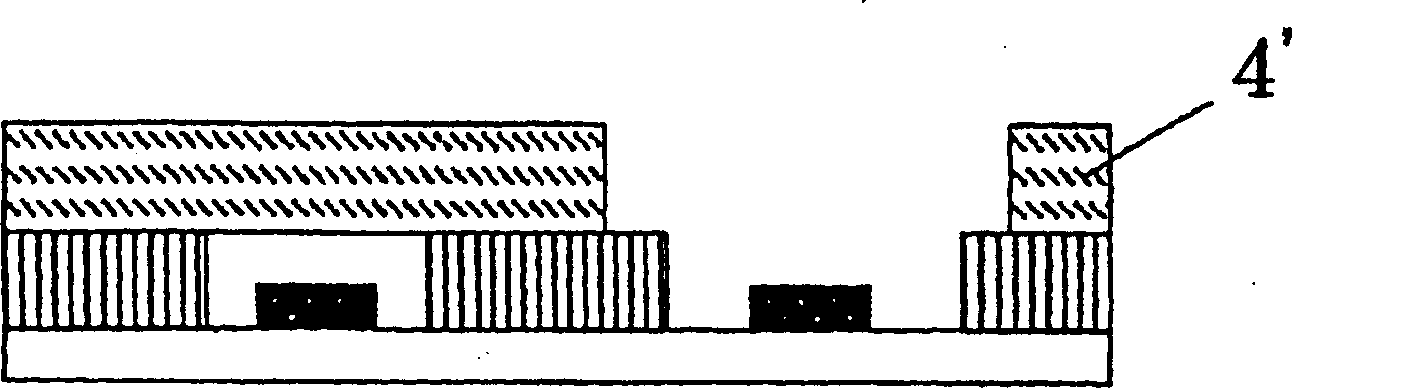

Method for Forming Resist Pattern, Method for Producing Circuit Board, and Circuit Board

InactiveUS20090236137A1Forming accuratelyAccurate removalPrinted circuit aspectsStacked resist layersResistHigh density

There are provided a method for forming a resist pattern for preparing a circuit board having a landless or small-land-width through-hole(s) to realize a high-density circuit board, a method for producing a circuit board, and a circuit board. A method for forming a resist pattern, comprising the steps of forming a resin layer and a mask layer on a first surface of a substrate having a through-hole(s), and removing the resin layer on the through-hole(s) and on a periphery of the through-hole(s) on the first surface by supplying a resin layer removing solution from a second surface opposite to the first surface of the substrate, and a method for producing a circuit board using the method for forming a resist pattern, and a circuit board.

Owner:MITSUBISHI PAPER MILLS LTD +1

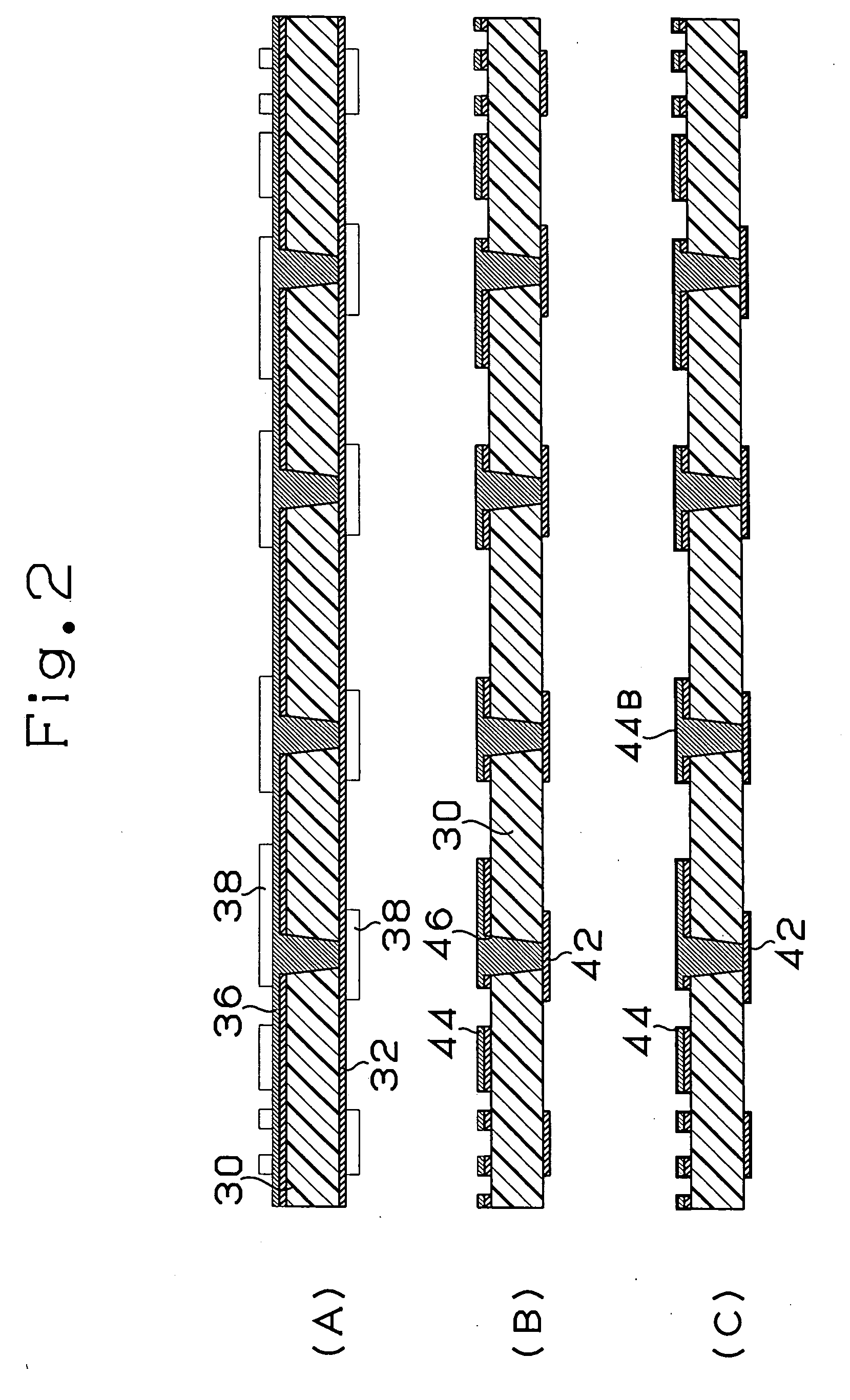

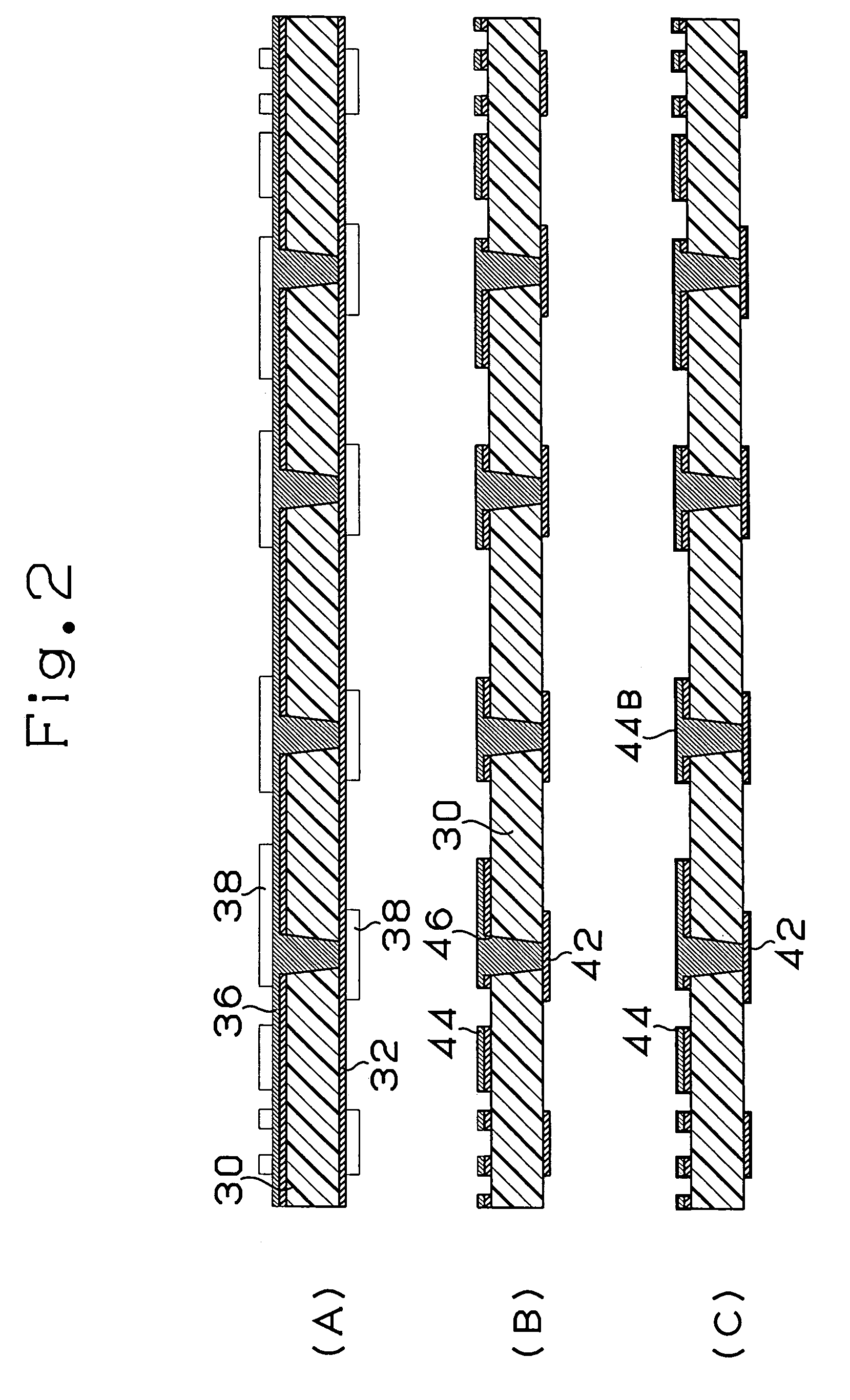

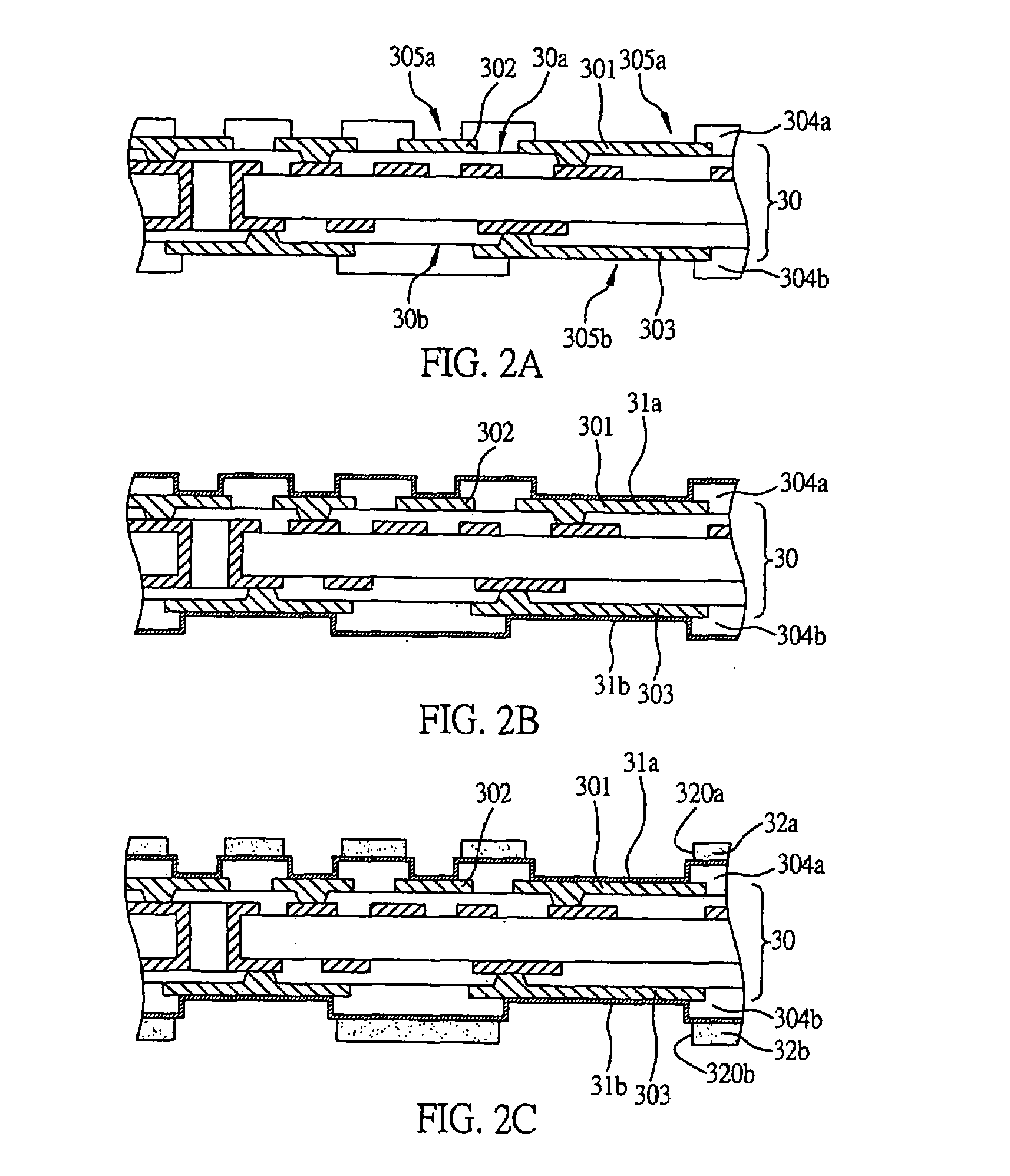

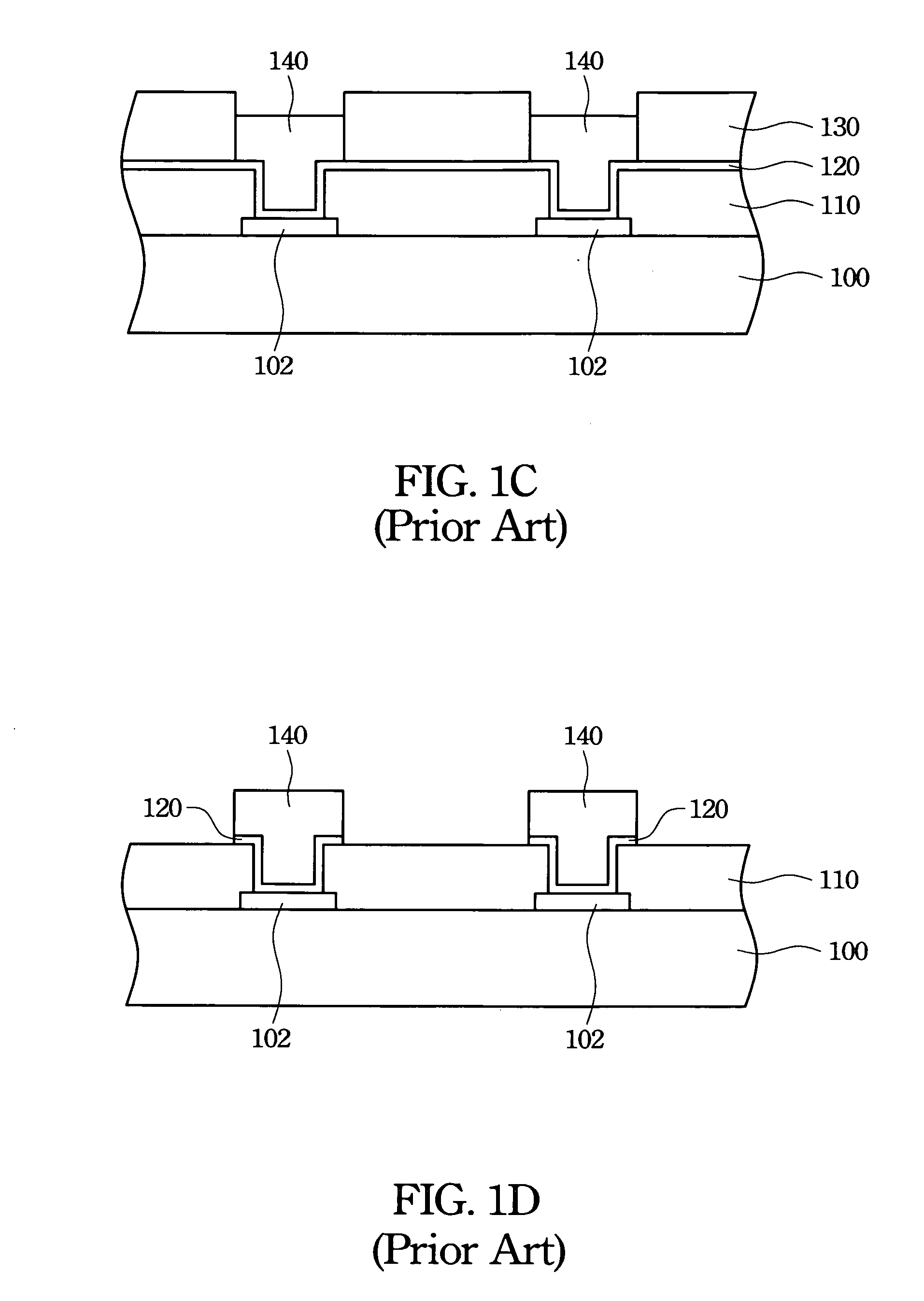

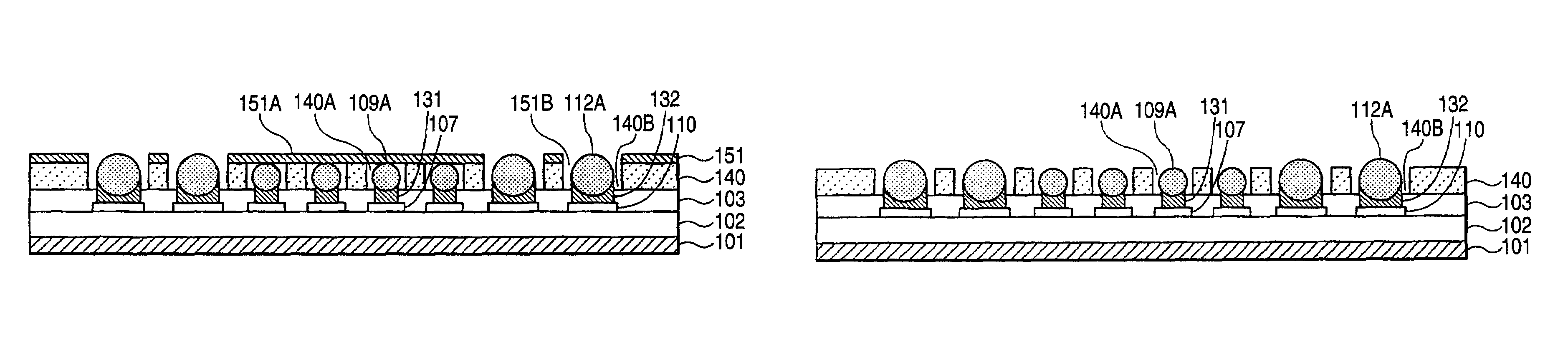

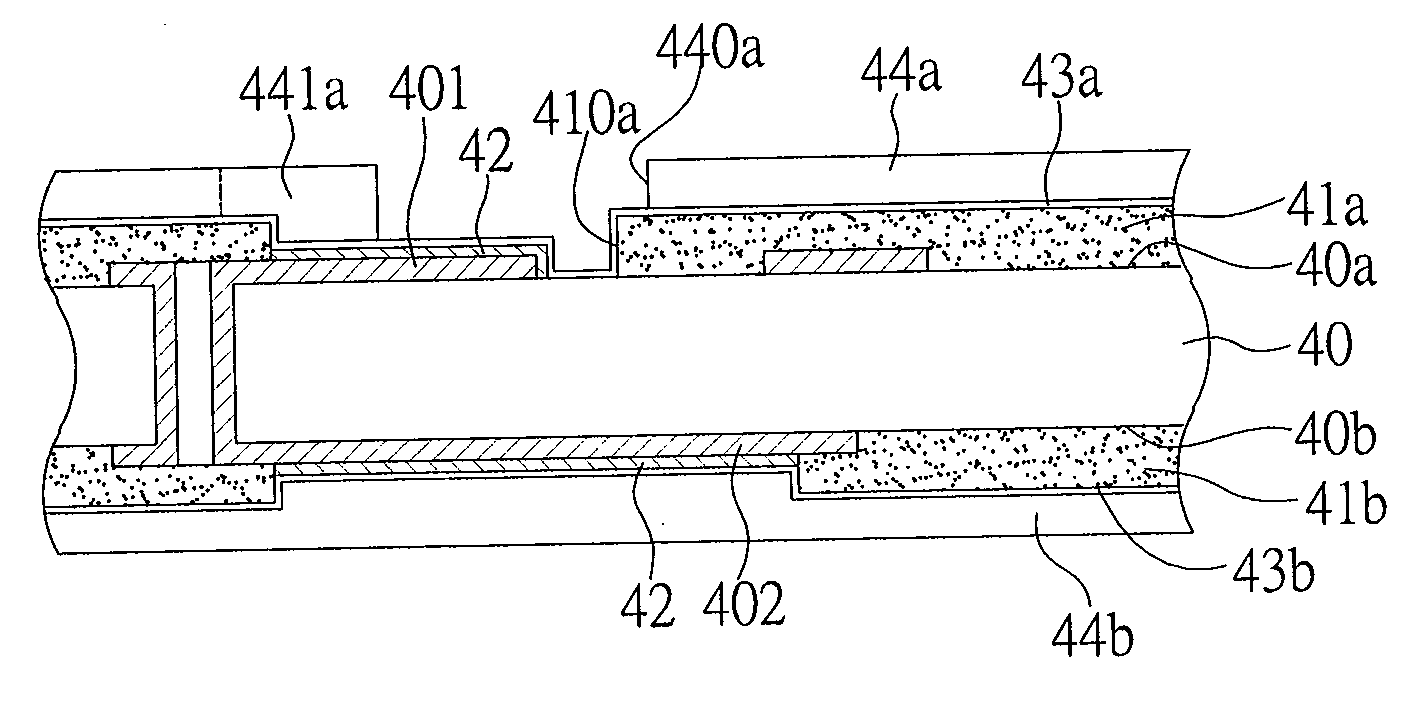

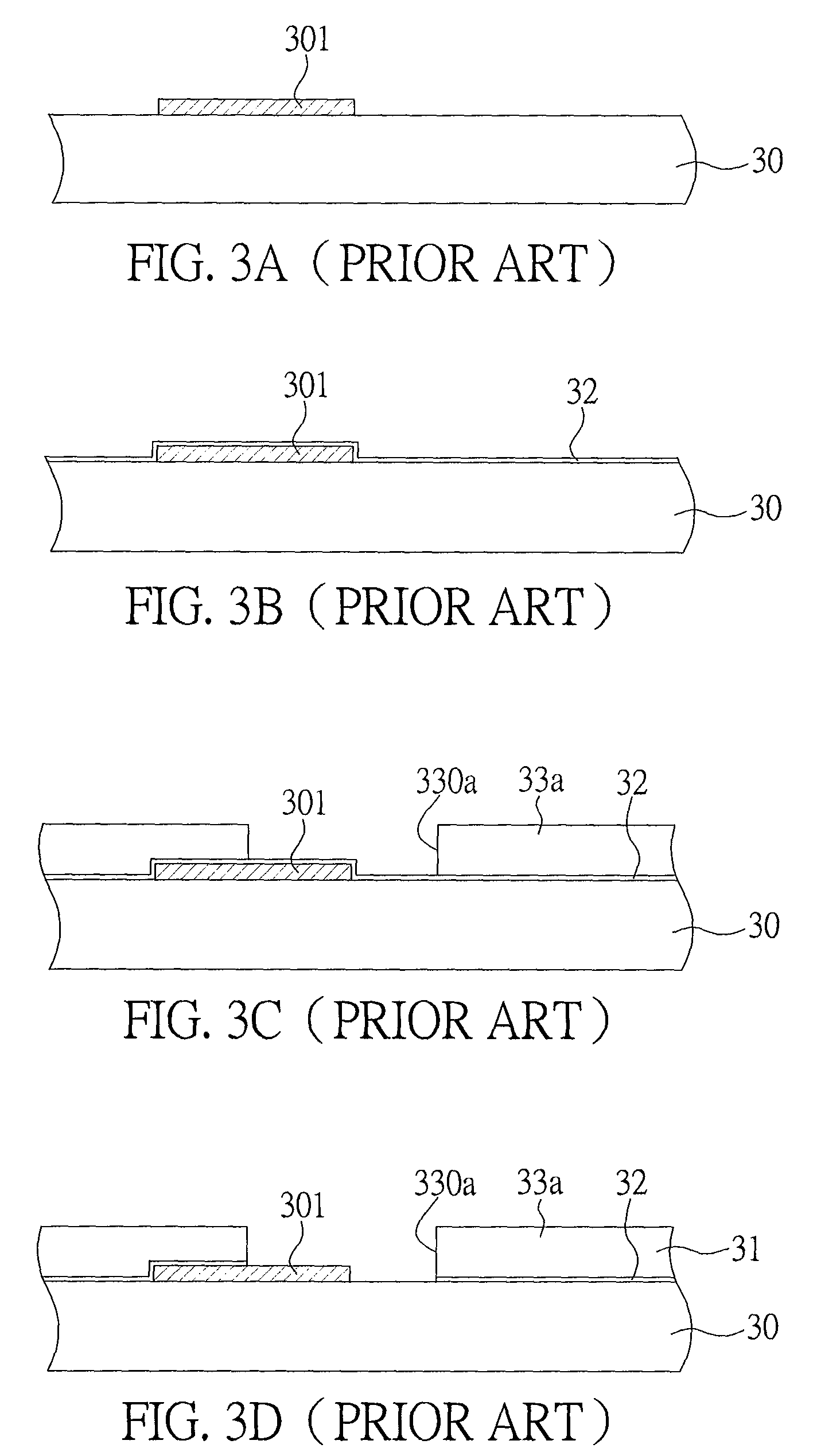

Method for fabricating conductive bump of circuit board

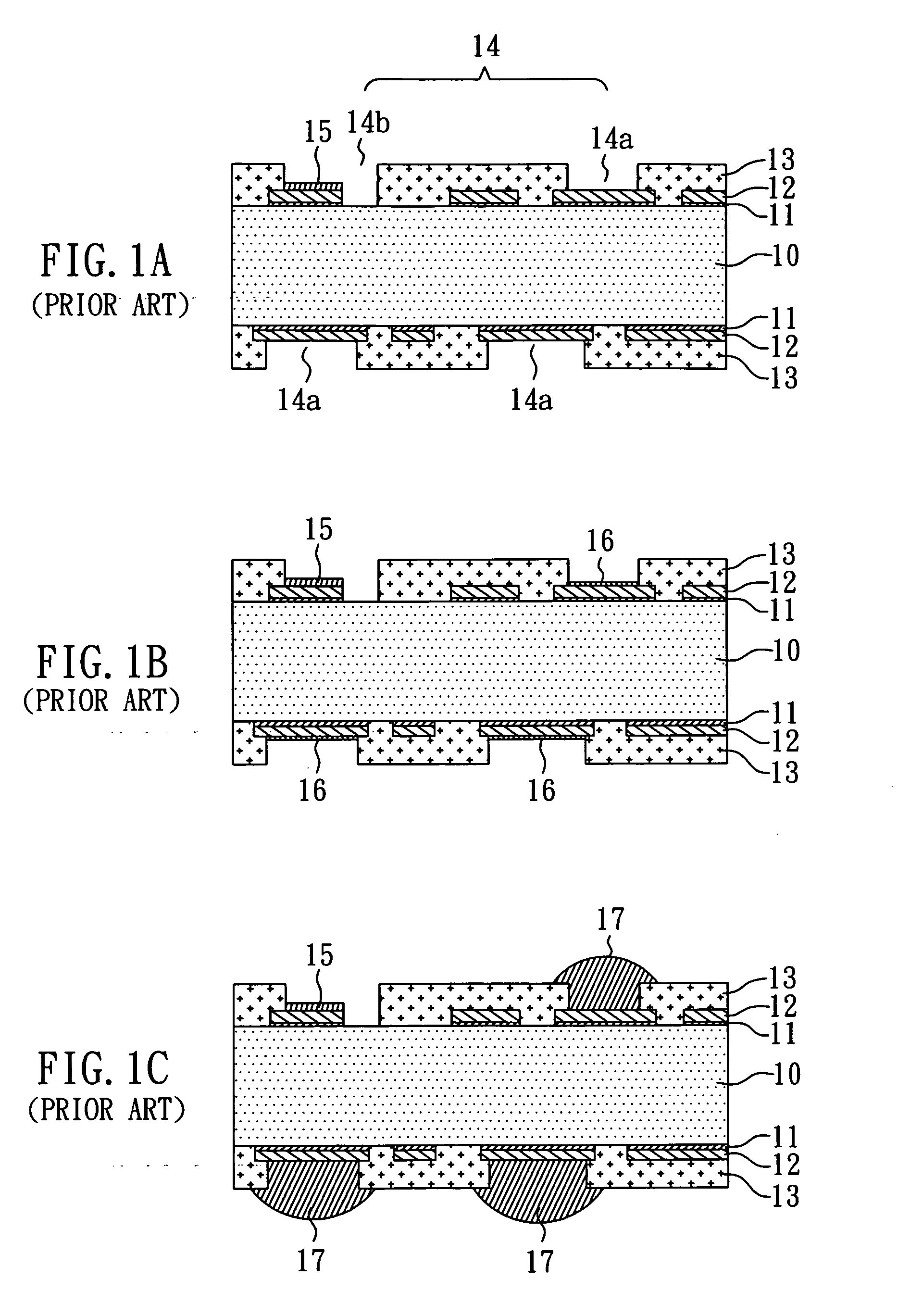

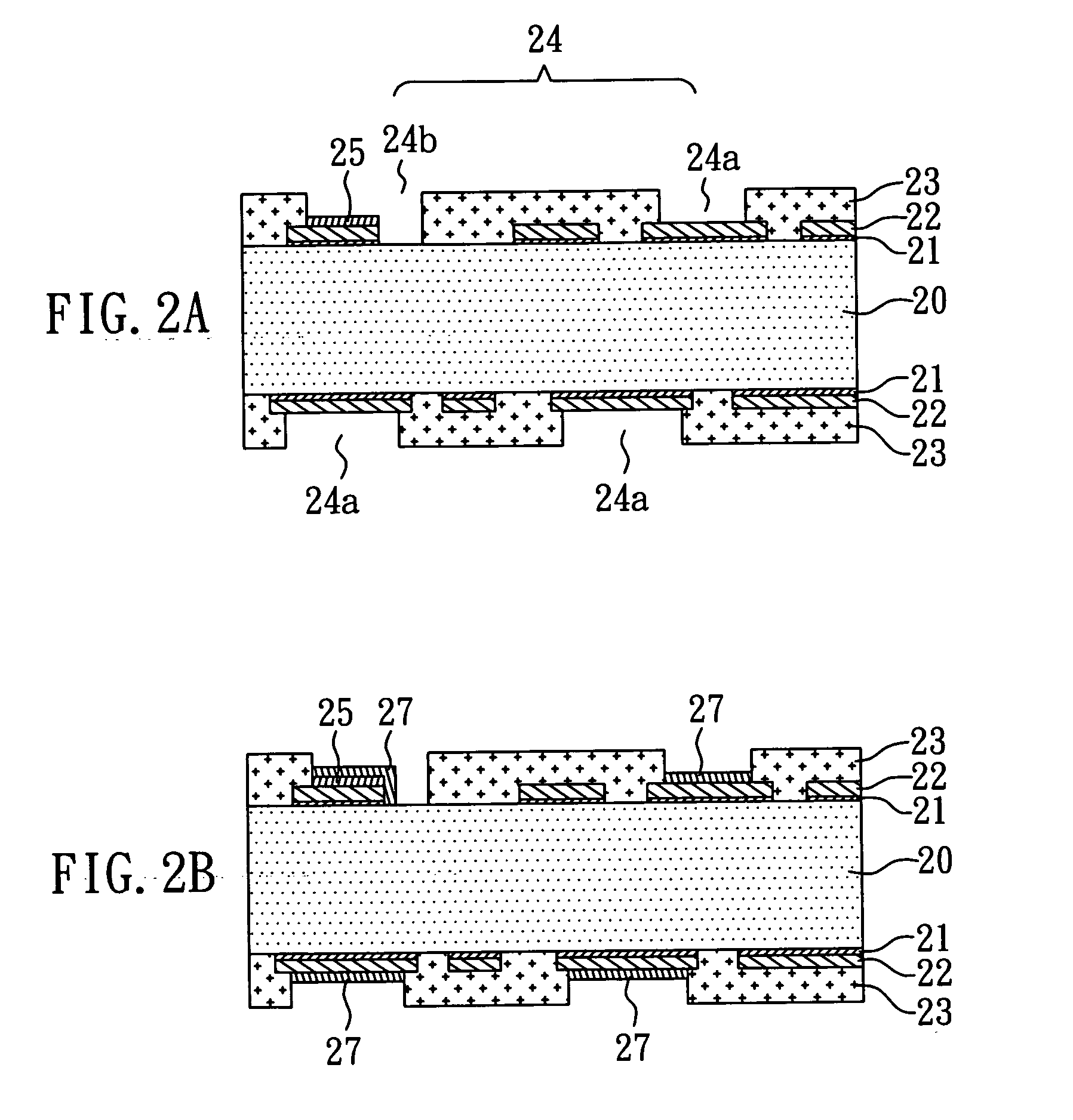

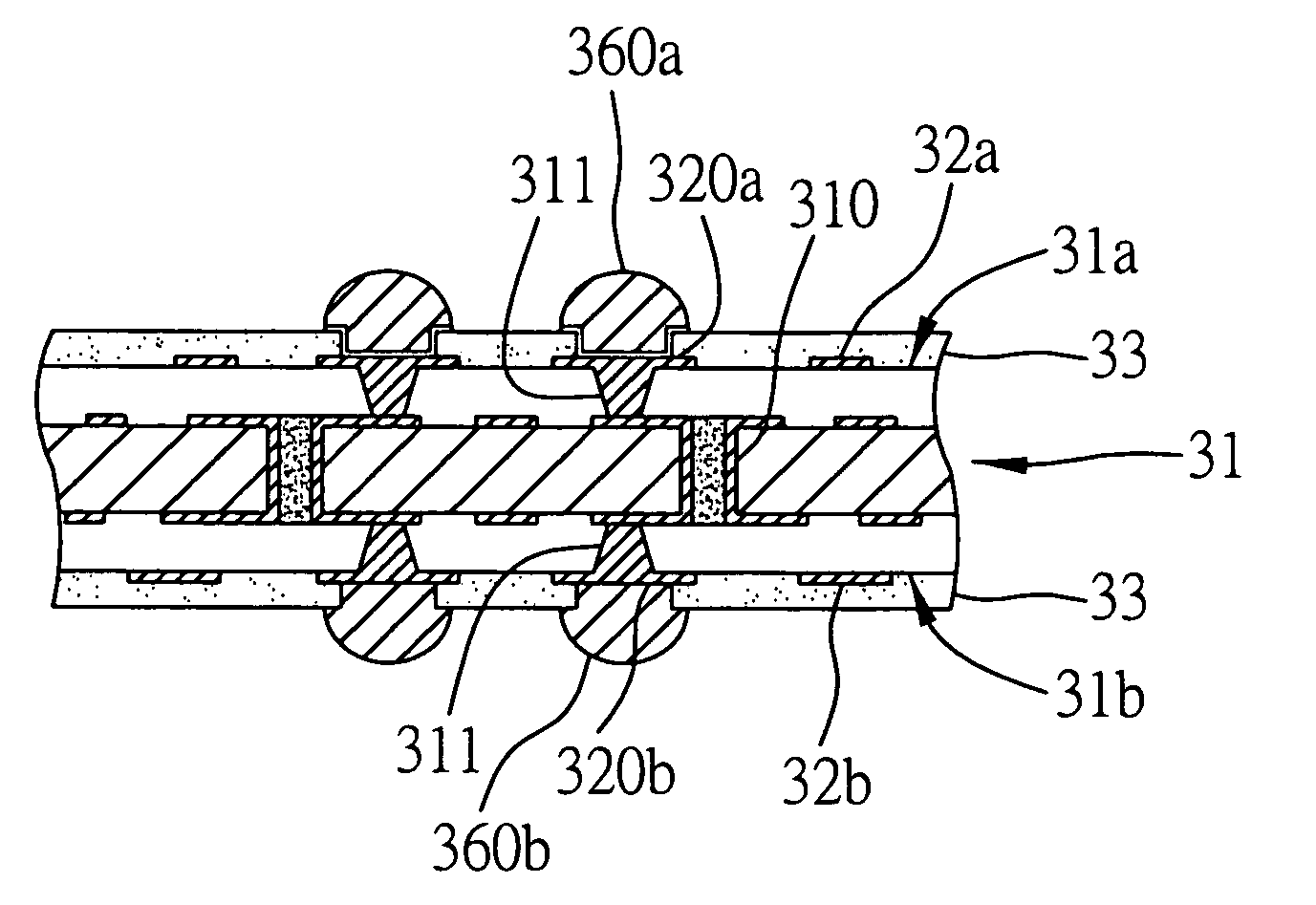

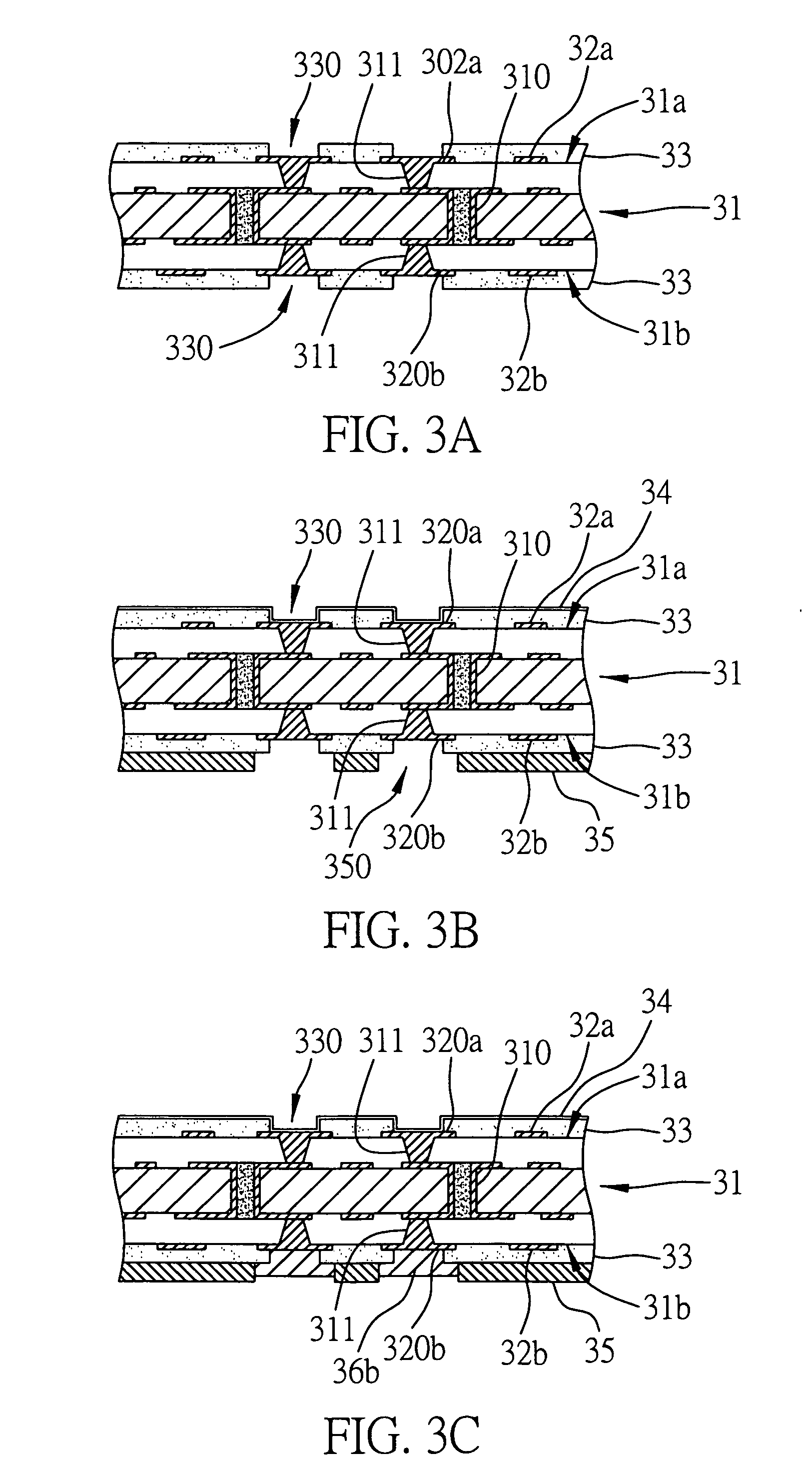

ActiveUS20060051952A1High manufacturing reliabilityReduce spacingSemiconductor/solid-state device detailsPrinted circuit aspectsResistEngineering

A method for fabricating conductive bumps of a circuit board is proposed. First of all, a circuit board having a first surface and a corresponding second surface is provided. A circuit structure having a plurality of conductive pads is formed on each of the first surface and the second surface, and conductive structures are formed in the circuit board for electrically connecting the circuit structures. Also, an insulating layer having a plurality of openings penetrating therethrough is formed on the circuit board for exposing the conductive pad. Then, a conductive layer is formed on a surface of the insulating layer having the opening formed on the first surface of the circuit board. An electroplating process is performed via the conductive layer and the conductive structure, such that a conductive bump is formed on the conductive pad located on the second surface of the circuit board. Subsequently, a resist layer is formed on the second surface of the circuit board to cover the conductive bump, and another resist layer having openings penetrating therethrough is formed on the first surface of the circuit board to expose the conductive pad. Finally, a conductive bump is formed on the conductive pad located on the first surface of the circuit board by an electroplating process. By such arrangement, the conductive bumps are successively formed on the first surface and the second surface of the circuit board.

Owner:PHOENIX PRECISION TECH CORP

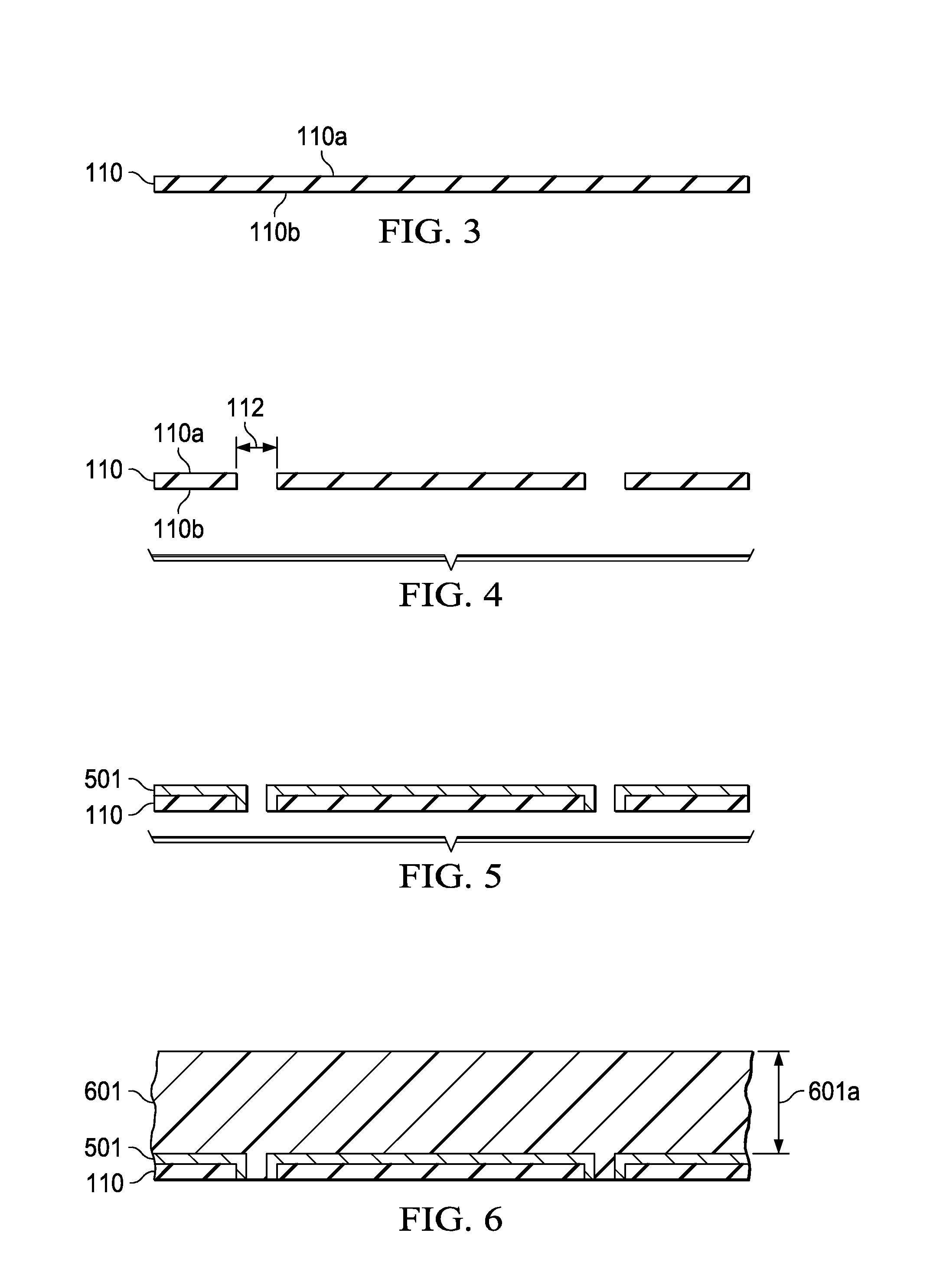

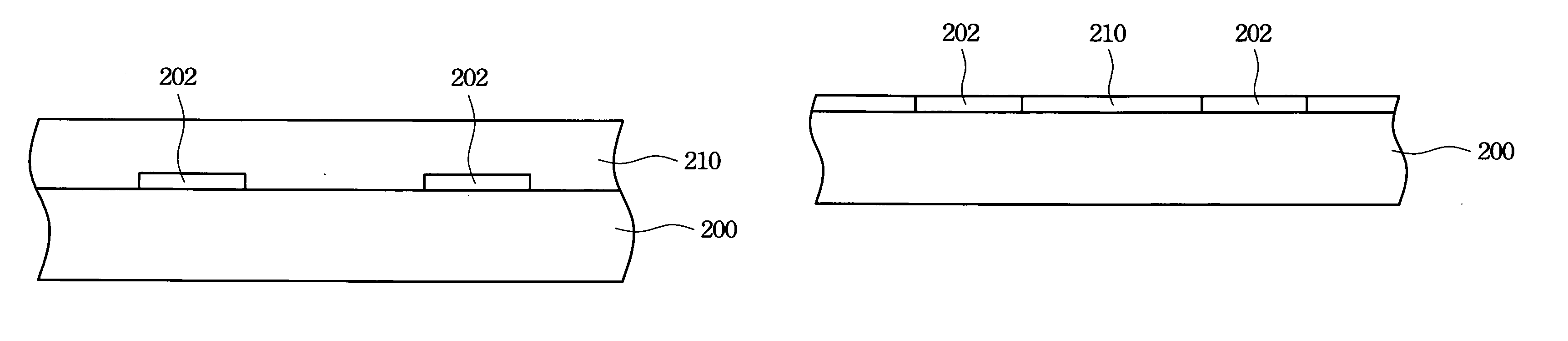

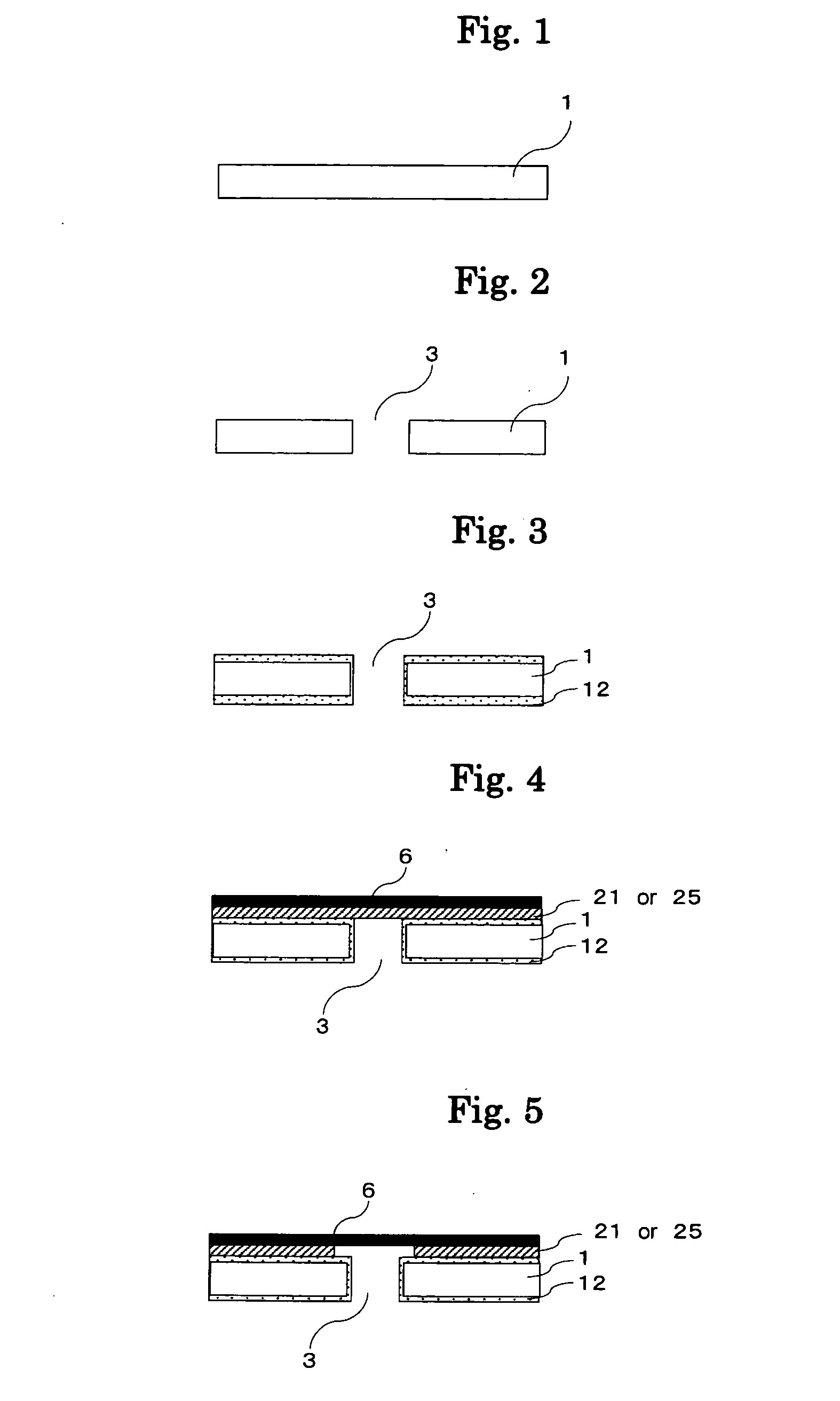

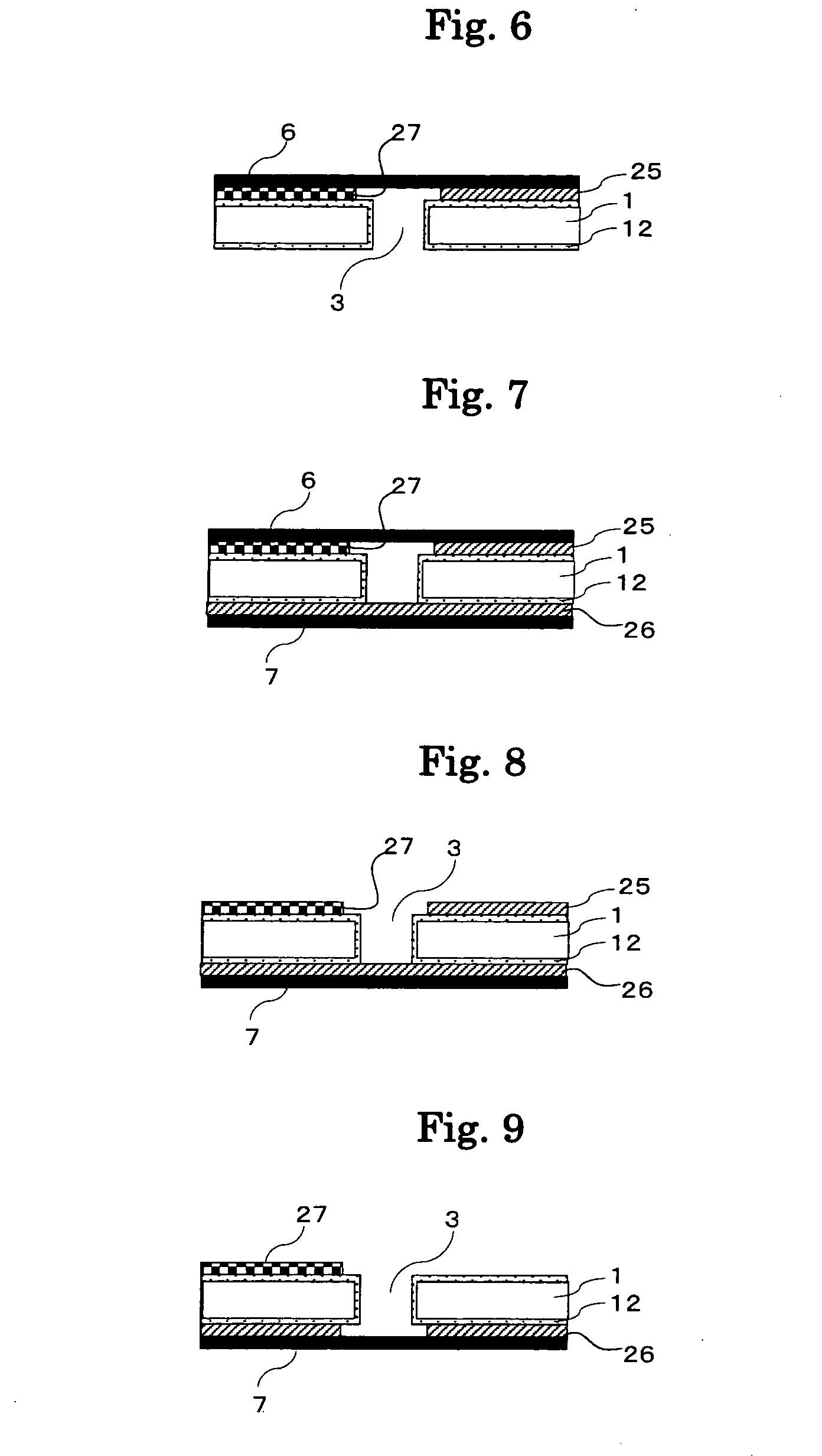

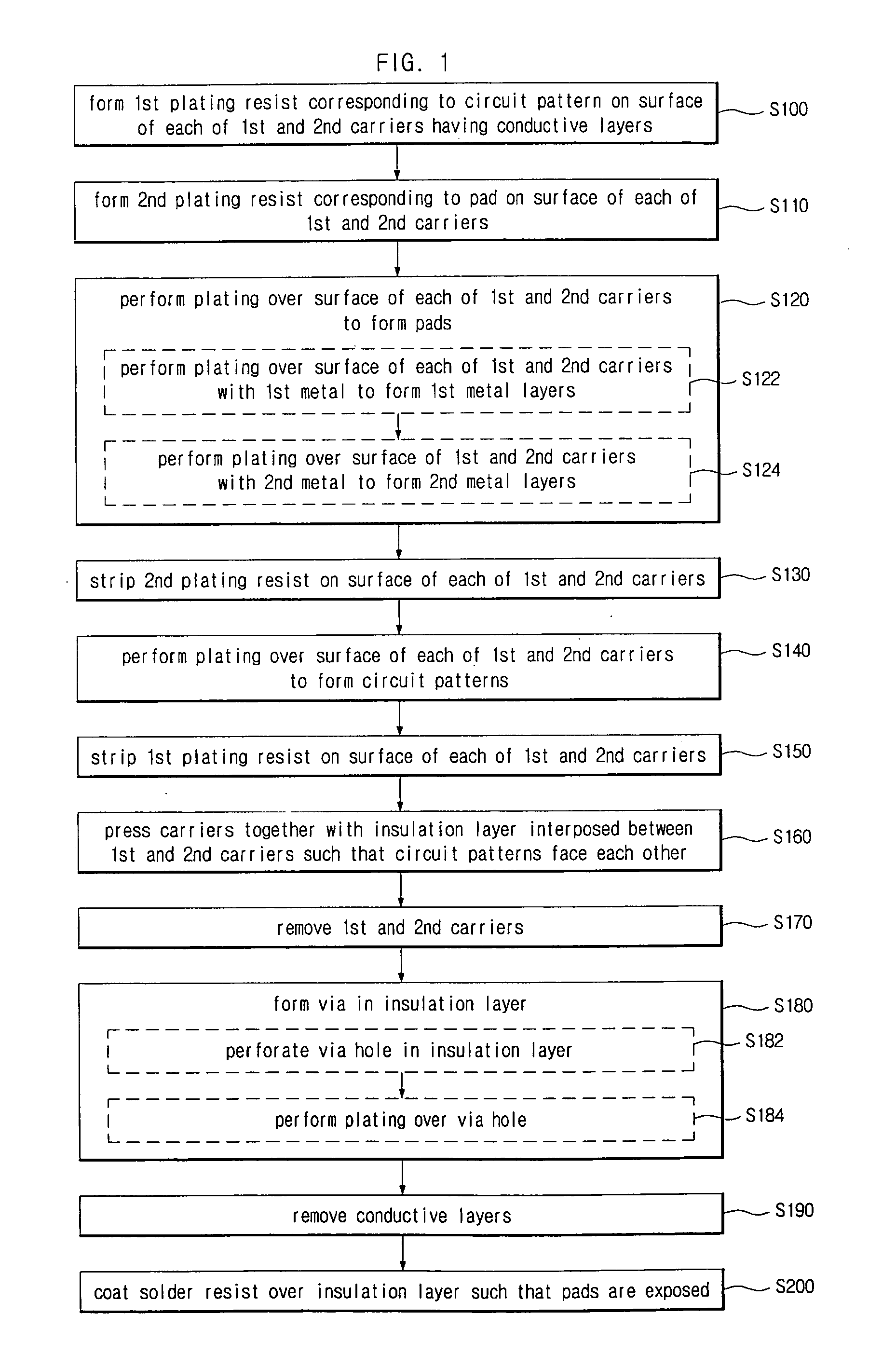

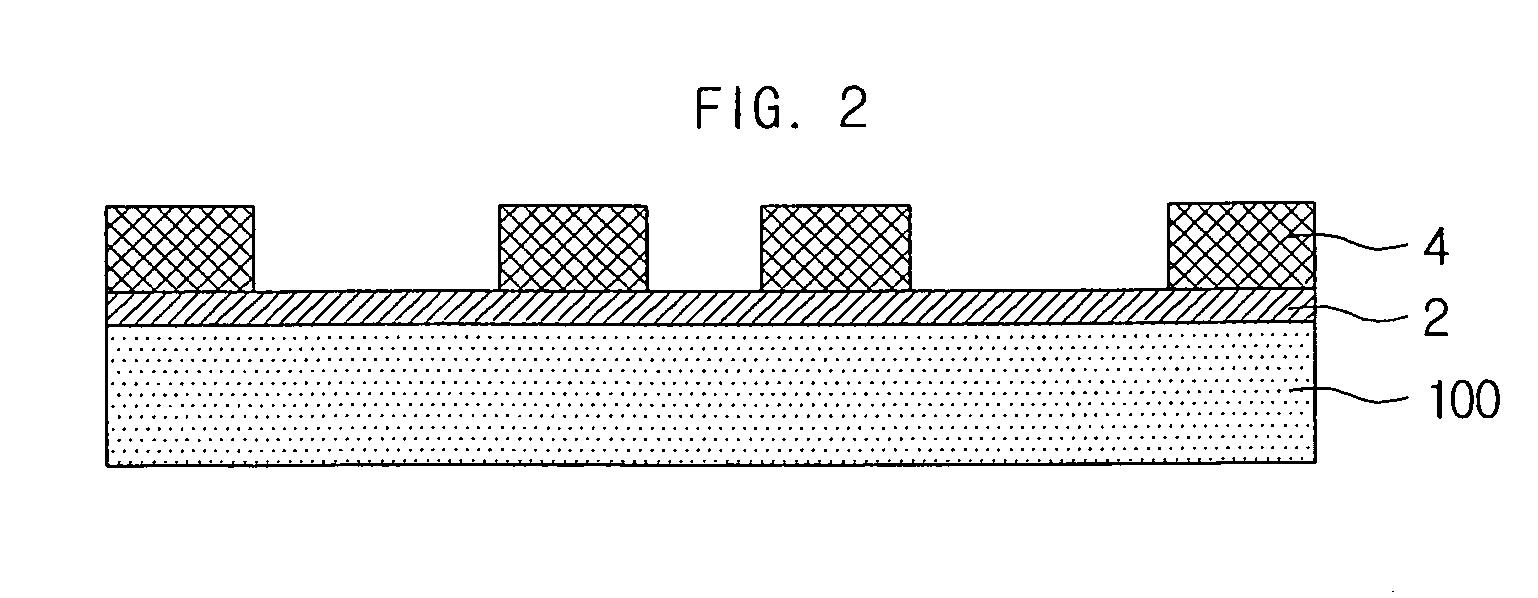

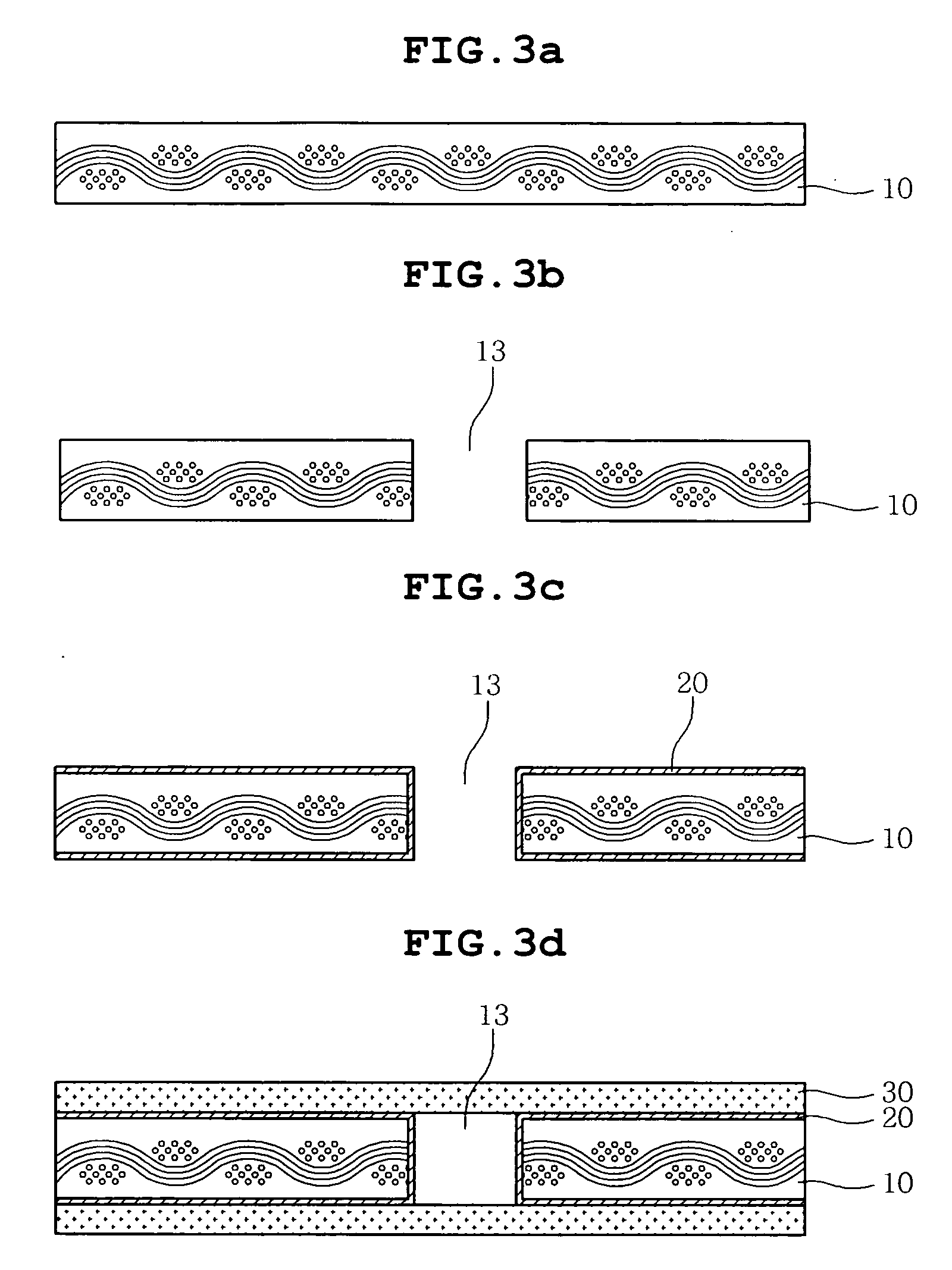

Printed circuit board and method for manufacturing the same

A printed circuit board and a method for manufacturing the same are disclosed. The manufacturing method includes: forming a first plating resist corresponding to the circuit pattern on a surface of each of a first carrier and a second carrier; forming a second plating resist corresponding to the pad on each of the surfaces; forming the pad by performing plating over each of the surfaces; stripping the second plating resists; forming the circuit pattern by performing plating over each of the surfaces; pressing the first carrier and the second carrier with an insulation layer interposed between the first carrier and the second carrier such that the circuit patterns face each other; and removing the first carrier and the second carrier. Since plating bars need not be used, the degree of freedom in designing circuits can be increased, and circuits of higher densities can be designed.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

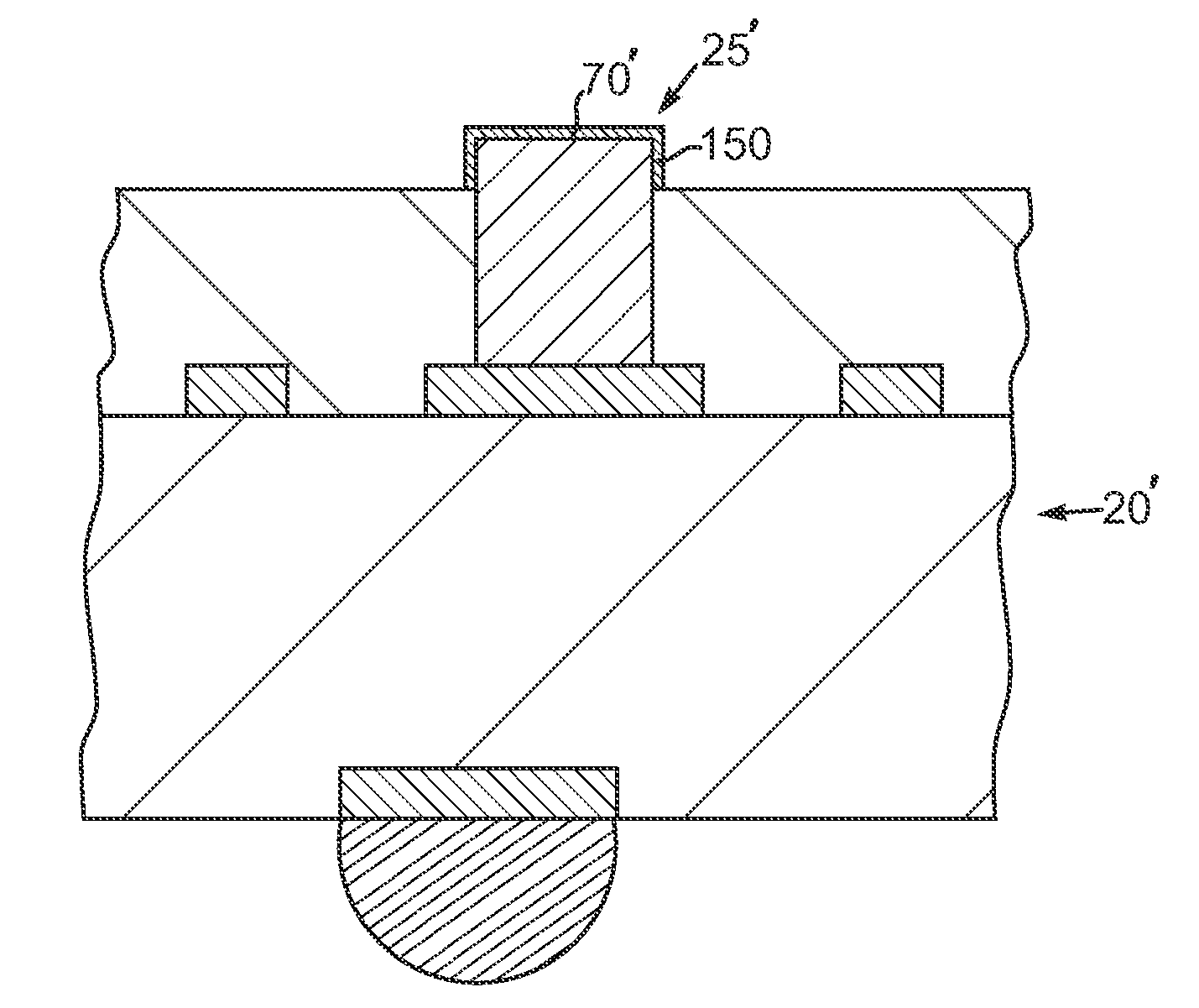

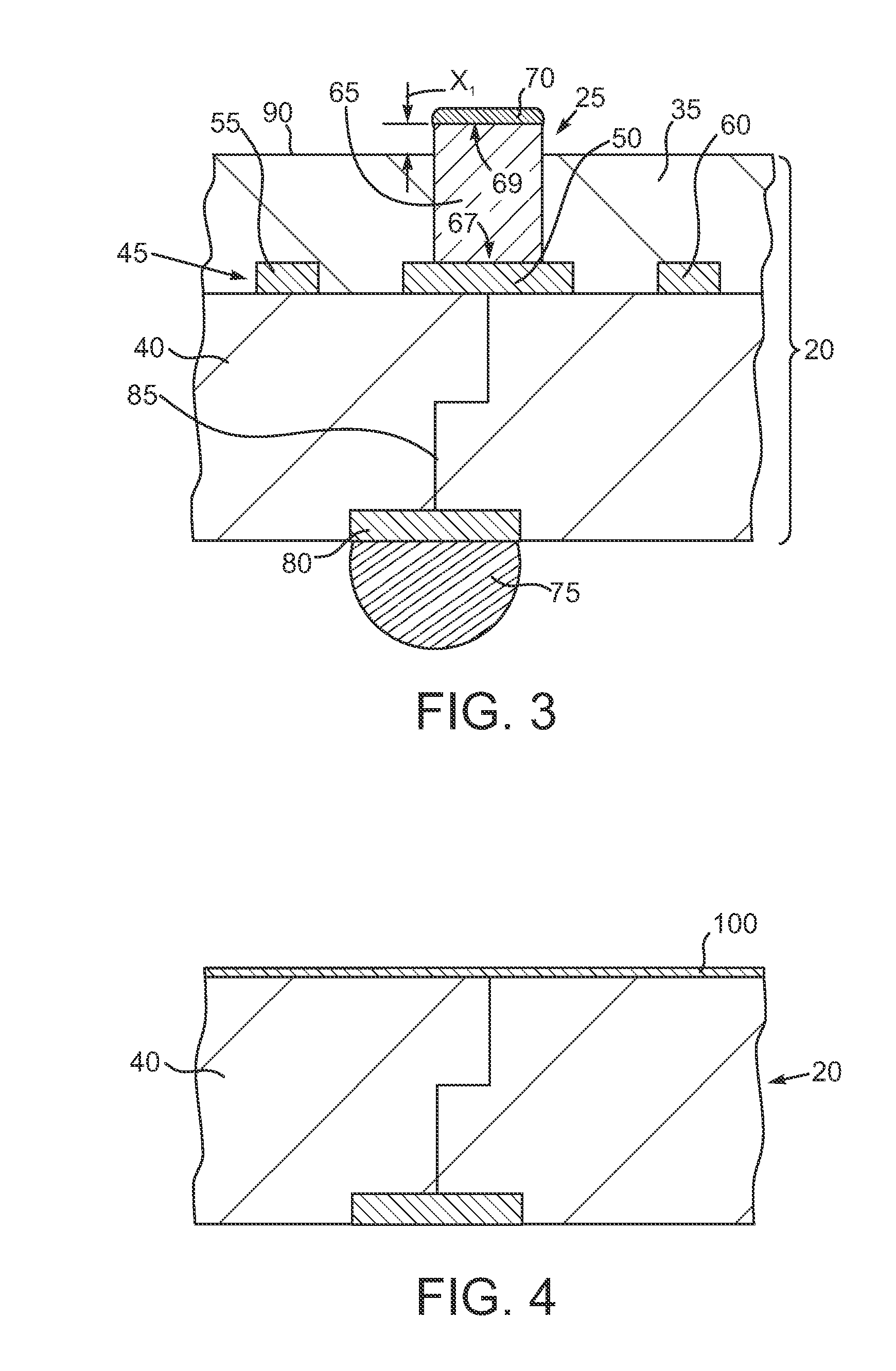

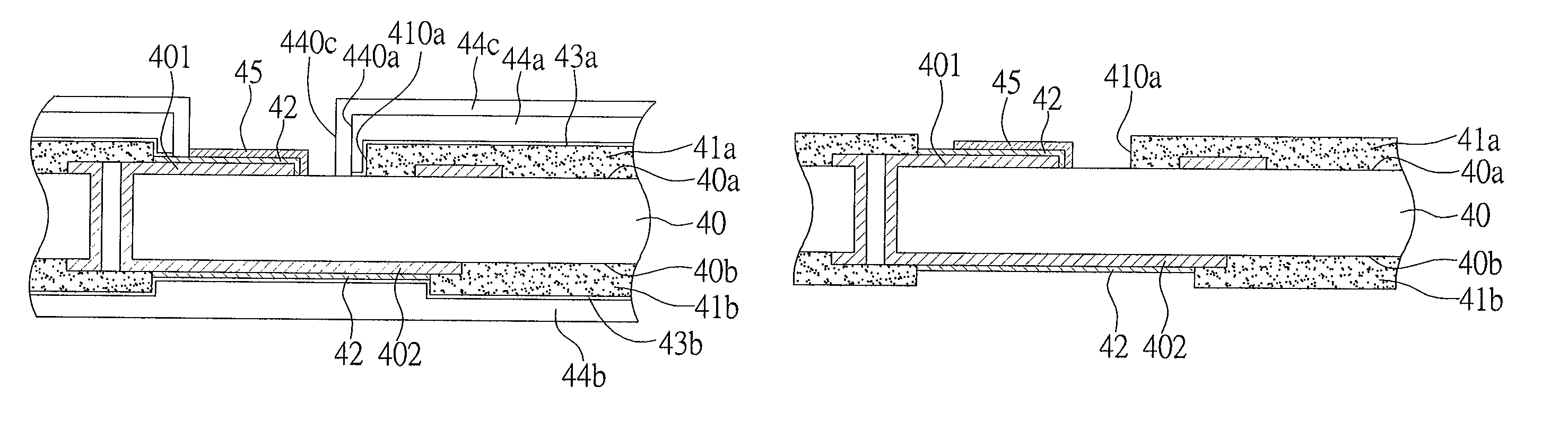

Circuit board with conductor post structure

InactiveUS20110299259A1Reduce thicknessElectrically conductive connectionsSemiconductor/solid-state device detailsSolder maskElectrical conductor

Owner:ADVANCED MICRO DEVICES INC

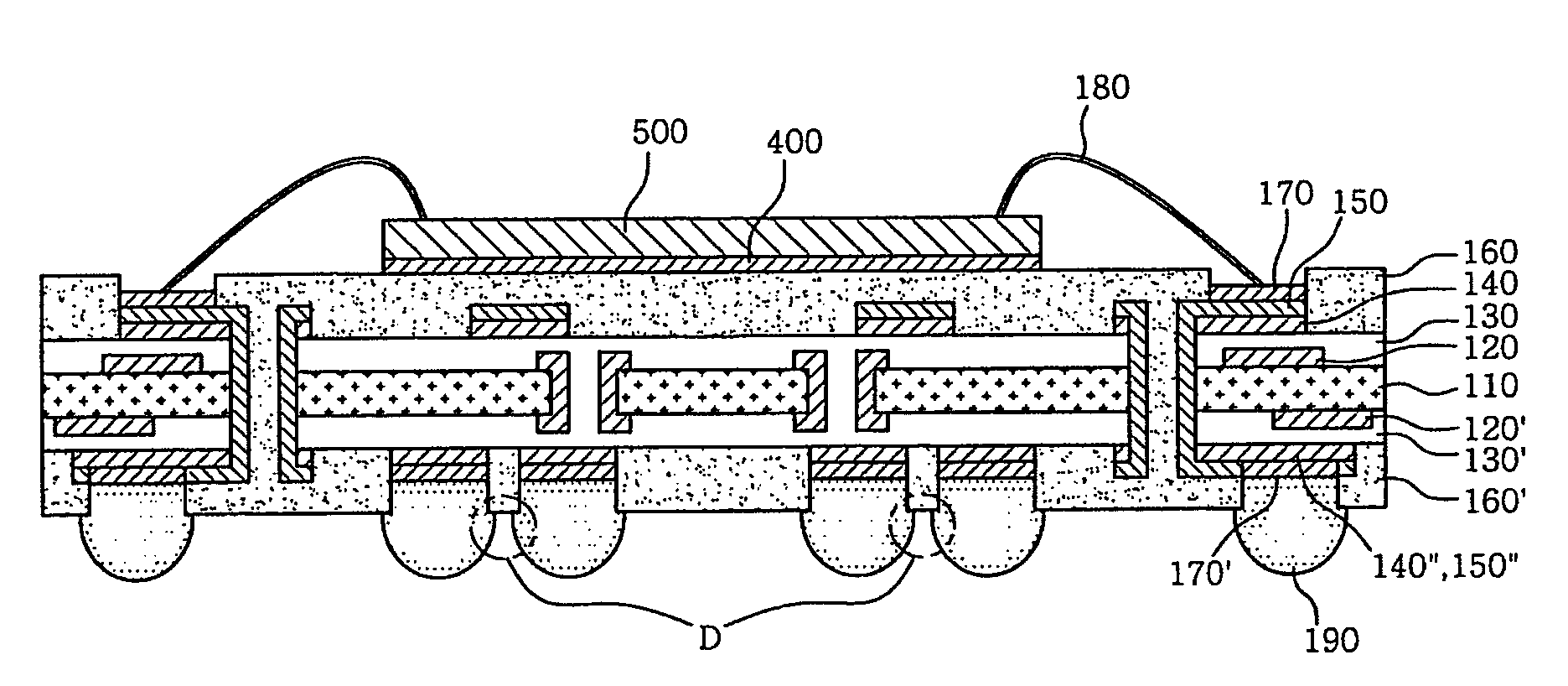

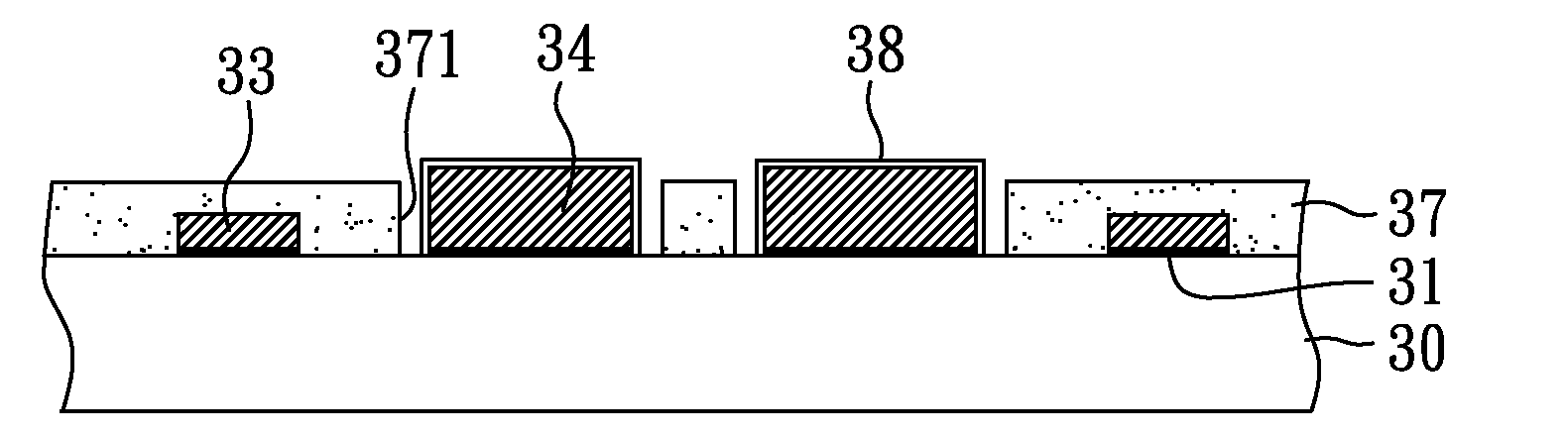

Package substrate and method for fabricating the same

ActiveUS20090096099A1Hard textureImprove bindingSemiconductor/solid-state device detailsStacked resist layersChemical platingLead bonding

A package substrate and a method for fabricating the same are provided according to the present invention. The package substrate includes: a substrate body with a die attaching side and a ball implanting side lying opposite each other, having a plurality of wire bonding pads and a plurality of solder ball pads respectively, and having a first insulating passivation layer and a second insulating passivation layer respectively, wherein a plurality of first apertures and a plurality of second apertures are formed in the first insulating passivation layer and the second insulation passivation layer respectively to corresponding expose the wire bonding pads and the solder ball pads; a chemical plating metal layer formed on the wire bonding pads and solder ball pads respectively; and a wire bonding metal layer formed on a surface of the chemical plating metal layer of the wire bonding metal layer.

Owner:PHOENIX PRECISION TECH CORP

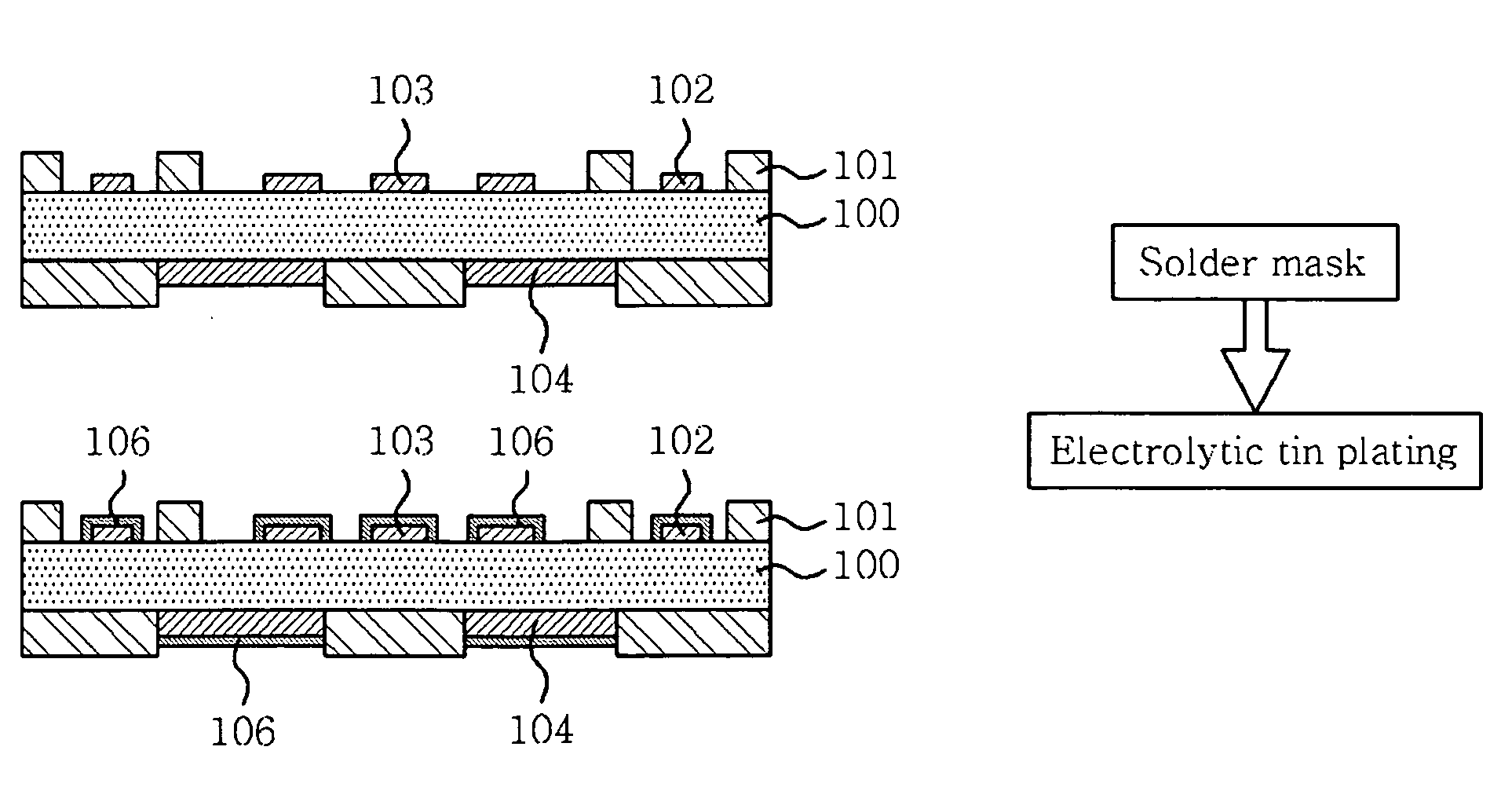

Printed circuit board for semiconductor package and method of manufacturing the same

InactiveUS20070170586A1Reduce manufacturing costFine pitchSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageAlloy

Disclosed are a printed circuit board for a semiconductor package and a method of manufacturing the same. Specifically, a printed circuit board for a semiconductor package includes predetermined circuit patterns, having a wire bonding portion and a bump portion for mounting a semiconductor and a soldering portion for connection to external parts, in which the bump portion has a pre-solder formed using a tin or tin alloy electroplating process. According to this invention, the pre-solder, which is formed by reflow using an electroplating process, permits easy increase of the height thereof to thus enhance bondability and underfilling capability, may be formed to a desired thickness by controlling a plating thickness, and furthermore, may be applied to a fine pitch through a masking process.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Method for forming metal bumps

InactiveUS7550375B2Improve processing yieldReduce manufacturing costStacked resist layersPrinted circuit aspectsSolder maskOptoelectronics

A method for forming metal bumps is disclosed. Steps of the method include supplying a substrate containing a plurality of pads; forming a first photoresist layer on the substrate, herein the first photoresist layer covers the pads; performing a planarization step to remove a portion of the first photoresist layer so as to expose the pads; forming a conductive layer on the first photoresist layer and the pads; electroplating a metal layer on the conductive layer; forming a patterned second photoresist layer on the metal layer; a portion of the metal layer and the conductive layer which are not covered by the patterned second photoresist layer is removed by using the patterned second photoresist layer as a mask; removing the patterned second photoresist layer; and forming a solder mask on the substrate, wherein the solder mask has a plurality of openings to expose the metal layer located on the pads.

Owner:ADVANCED SEMICON ENG INC

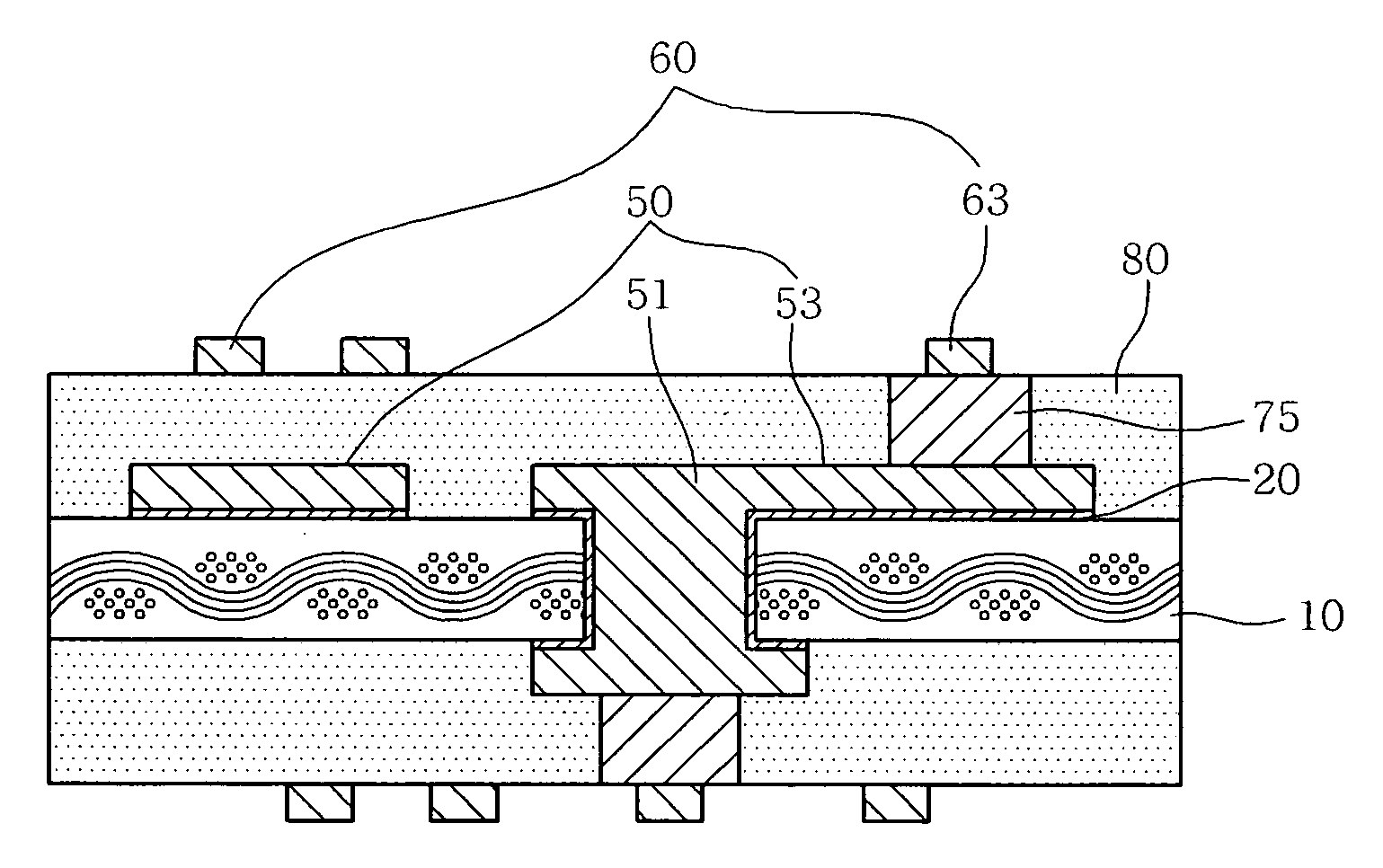

Multilayer printed wiring board and manufacturing method of the multilayer printed wiring board

ActiveUS20100000087A1Improve buffering effectMore reliabilityPrinted circuit assemblingContact member manufacturingDrop testsContact failure

This invention provides a multilayer printed wiring board in which electric connectivity and functionality are obtained by improving reliability and particularly, reliability to the drop test can be improved. No corrosion resistant layer is formed on a solder pad 60B on which a component is to be mounted so as to obtain flexibility. Thus, if an impact is received from outside when a related product is dropped, the impact can be buffered so as to protect any mounted component from being removed. On the other hand, land 60A in which the corrosion resistant layer is formed is unlikely to occur contact failure even if a carbon pillar constituting an operation key makes repeated contacts.

Owner:IBIDEN CO LTD

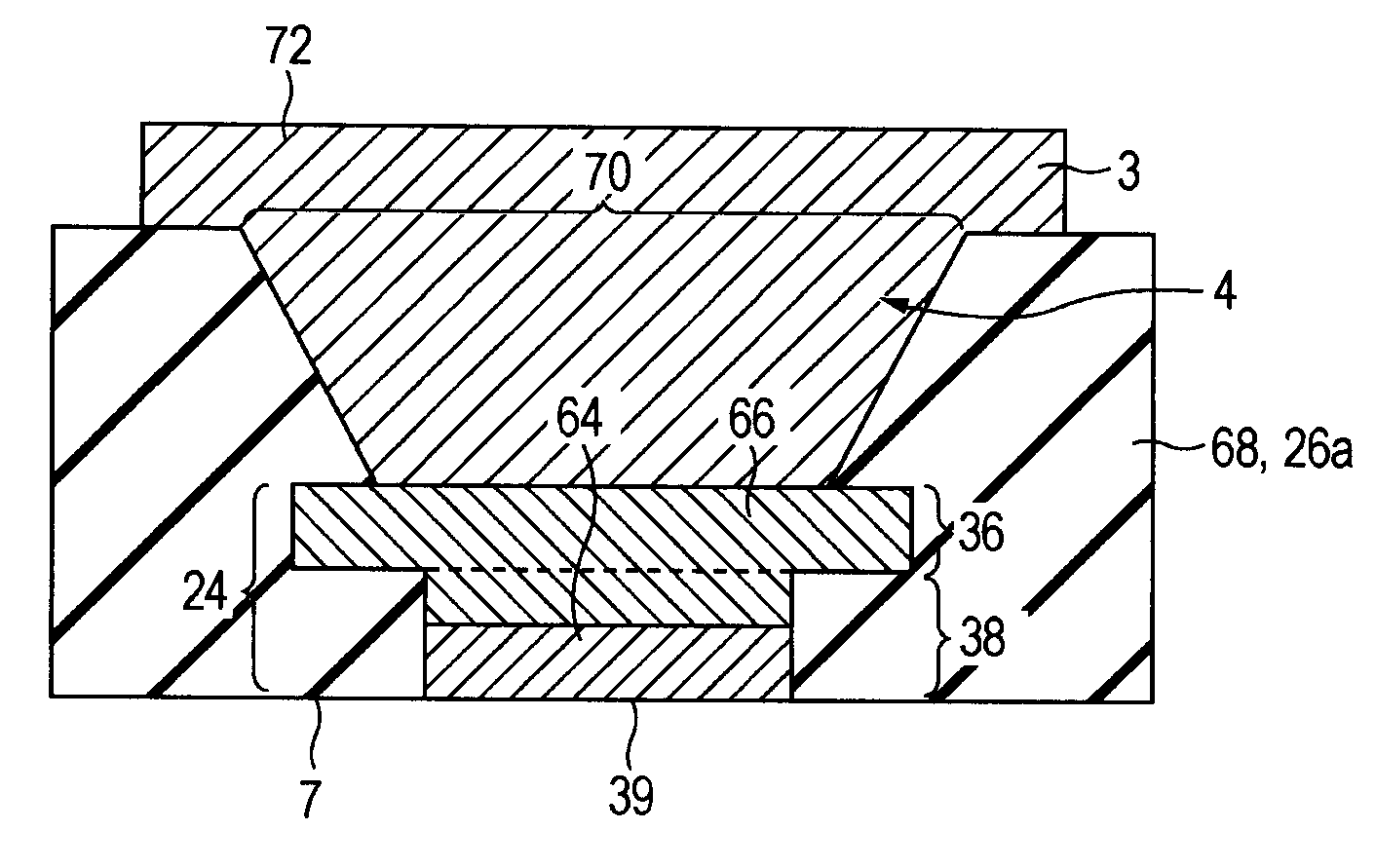

Printed wiring board and method for manufacturing the same

InactiveUS20100096744A1Easy to manufactureAvoid breakingSemiconductor/solid-state device detailsStacked resist layersSemiconductor chipEngineering

Embodiments of the present invention provide a printed wiring board in which solder bumps of a mounted semiconductor chip are less prone to be ruptured. The printed wiring board includes a coreless substrate which includes: a dielectric layer having a main surface and a connecting pad embedded in the dielectric layer. The connecting pad is shaped like a brimmed hat. That is, the connecting pad includes a plate portion whose diameter φ1 is about 95 μm and a contact portion whose diameter φc is about 75 μm. The main surface of the contact portion is exposed at the main surface of the dielectric layer. Since diameter φc of the contact portion is substantially the same as diameter φ2 of an under bump metal at the semiconductor chip side, even if mechanical stress is applied in a direction in which the semiconductor chip is peeled off from the coreless substrate, the stress disperses evenly to both of the connecting pad and the under bump metal, and thus rupture is less prone to occur.

Owner:IBM CORP

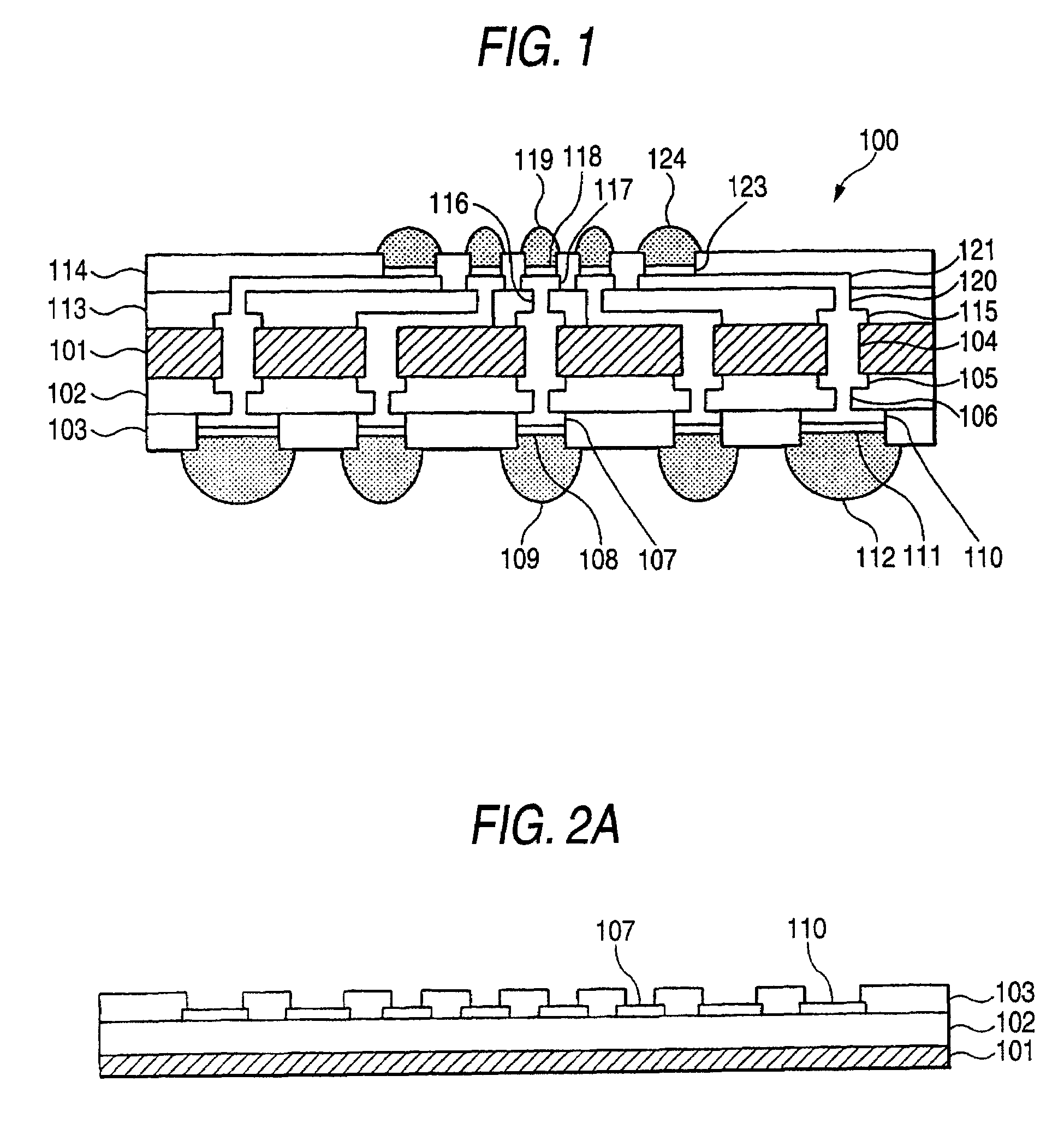

Wiring board and method of manufacturing the same

InactiveUS20120152598A1Efficiently obtainedImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesResistElectrical conductor

Disclosed is a method for manufacturing a wiring board including a conductor layer, a solder resist layer laminated on the conductor layer, and a conductor post to be electrically connected to a conductor layer which is disposed in a lower portion of a through-hole provided in the solder resist layer, the method including a through-hole boring process of boring the through-hole in the solder resist layer containing a thermosetting resin to expose the conductor layer within the through-hole; a first conductor part forming process of forming a first conductor part composed mainly of copper within the through-hole; and a second conductor part forming process of forming a second conductor part composed mainly of tin, copper, or a solder on the first conductor part, in this order.

Owner:NGK SPARK PLUG CO LTD

Method for mfg. printed wiring board and photosenstive resin compsn. to be used for it

InactiveCN1500232AExcellent plating resistanceExcellent peelabilitySecond resist patternStacked resist layersResistSolder mask

An object of the present invention is to provide a process for producing a printed wiring board, which is advantageous not only in that the reduction in size and increase in density of the wiring board are achieved and further the steps are simplified, but also in that the connection reliability of mount parts and the yield are improved, and a photosensitive resin composition used in the process. The present invention is directed to a process for producing a printed wiring board, comprising the steps of: (i) forming a solder resist on a wiring board having a circuit; (ii) laminating a preliminarily molded layer of a photosensitive resin composition on the solder resist; (iii) subjecting the layer of the photosensitive resin composition to exposure and development to form a resist pattern of the photosensitive resin composition; (iv) subjecting the entire surface of the resultant board to electroless plating, and (v) stripping the layer of the photosensitive resin composition, wherein the steps are conducted in this order, as well as a photosensitive resin composition and the layer thereof used in the process.

Owner:RESONAC CORPORATION

Printed circuit board and method of manufacturing the same

InactiveUS20090260868A1High-density circuit patternSmall line widthStacked resist layersPrinted circuit aspectsElectrical connectionEngineering

The printed circuit board includes the via formed with the electroplating layer unlike a conventional via formed with an electroless plating layer and an electroplating layer and having a cylindrical shape, and thus exhibits good interlayer electrical connection and high reliability of physical contact upon thermal stress caused by the variance in physical properties of material depending on changes in temperature. The via has no upper land, and thus a fine circuit pattern of the circuit layer can be formed on the via.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Package substrate and method for fabricating the same

ActiveUS7718470B2High densityLarge spacingSemiconductor/solid-state device detailsStacked resist layersChemical platingLead bonding

A package substrate and a method for fabricating the same are provided according to the present invention. The package substrate includes: a substrate body with a die attaching side and a ball implanting side lying opposite each other, having a plurality of wire bonding pads and a plurality of solder ball pads respectively, and having a first insulating passivation layer and a second insulating passivation layer respectively, wherein a plurality of first apertures and a plurality of second apertures are formed in the first insulating passivation layer and the second insulation passivation layer respectively to corresponding expose the wire bonding pads and the solder ball pads; a chemical plating metal layer formed on the wire bonding pads and solder ball pads respectively; and a wire bonding metal layer formed on a surface of the chemical plating metal layer of the wire bonding metal layer.

Owner:PHOENIX PRECISION TECH CORP

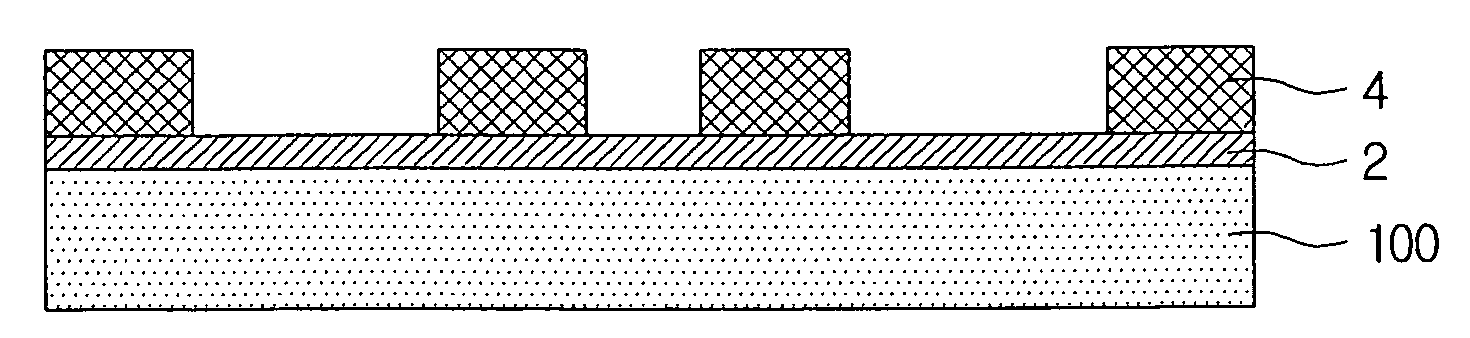

Packaging substrate structure and method for manufacturing the same

InactiveUS20090071699A1Improve product reliabilityCost is economizedSemiconductor/solid-state device detailsStacked resist layersEngineeringProtection layer

The present invention relates to a packaging substrate and a method for manufacturing the same. The packaging substrate comprises: a substrate body, wherein a surface thereof has a circuit layer comprising a plurality of circuits and a plurality of conductive pads, and the conductive pads are higher than the circuits; and an insulating protection layer disposed on the surface of the substrate body, wherein the insulating protection layer has a plurality of openings exposing the conductive pads, and the size of the openings is larger than or equal to that of the conductive pads. Accordingly, the packaging substrate structure of the present invention can be employed in a flip-chip packaging structure of fine-pitch.

Owner:PHOENIX PRECISION TECH CORP

Solder pad and method of making the same

ActiveUS20080251917A1Easy to optimizeSemiconductor/solid-state device detailsStacked resist layersResistInsulation layer

A solder pad structure includes a first metal layer disposed on an insulation layer, wherein the first metal layer is electrically connected with an underlying interconnection circuit layer through a conductive through hole disposed in the insulation layer. A solder resist layer having an opening exposing a central portion of the first metal layer is disposed on the insulating layer. A pillar-shaped second metal layer is disposed within the opening directly on the first metal layer. A solder ball filled into the opening is in contact with the pillar-shaped second metal layer.

Owner:NAN YA PRINTED CIRCUIT BOARD CORPORATION

Popular searches

Conductive pattern formation Electrical connection printed elements Semiconductor devices Circuit susbtrate materials Multilayer circuit manufacture Metallic pattern materials Component plug-in assemblages Resilient/clamping means Non-metallic protective coating application Semiconductor/solid-state device manufacturing