Patents

Literature

2784results about "Resilient/clamping means" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

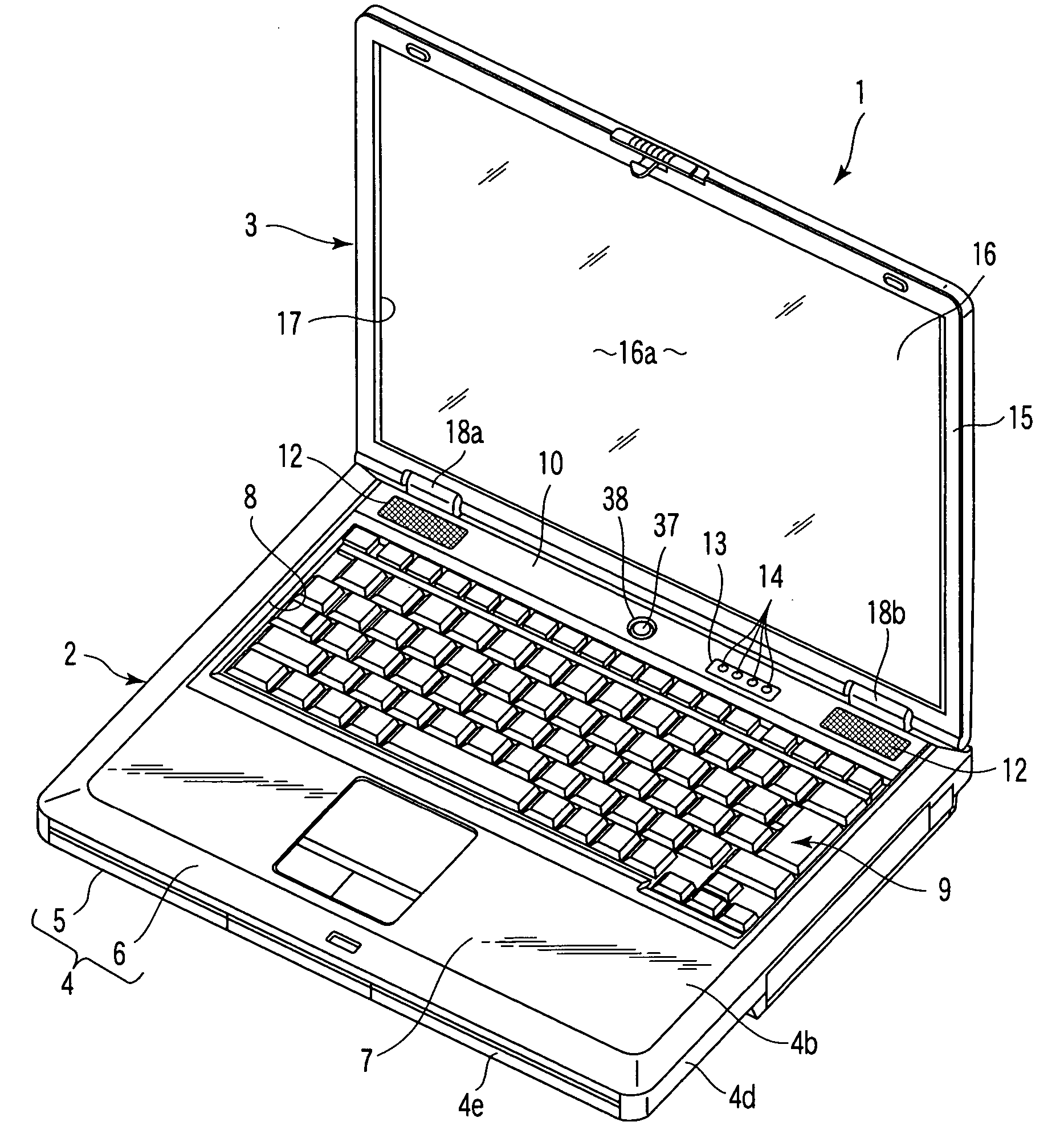

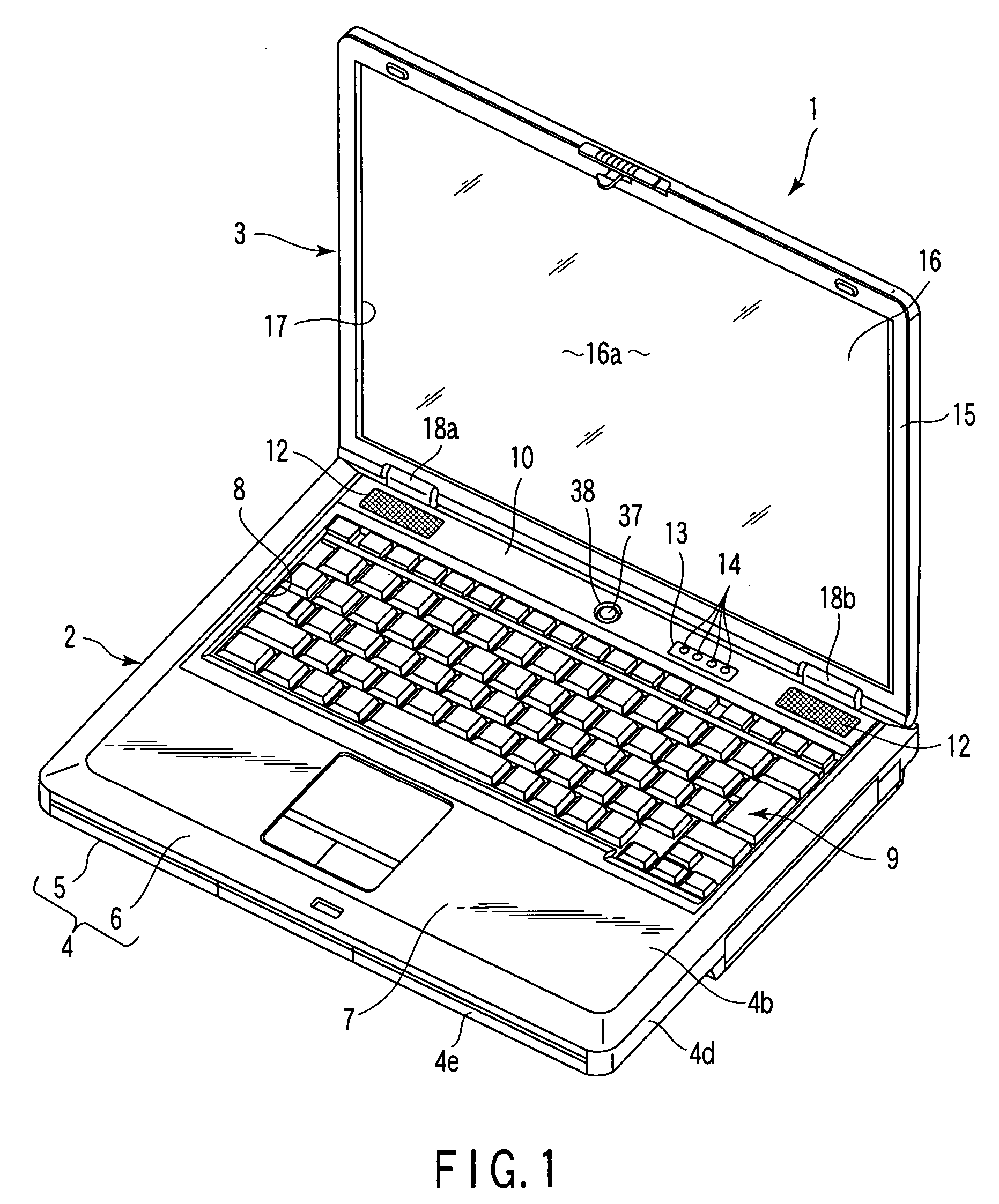

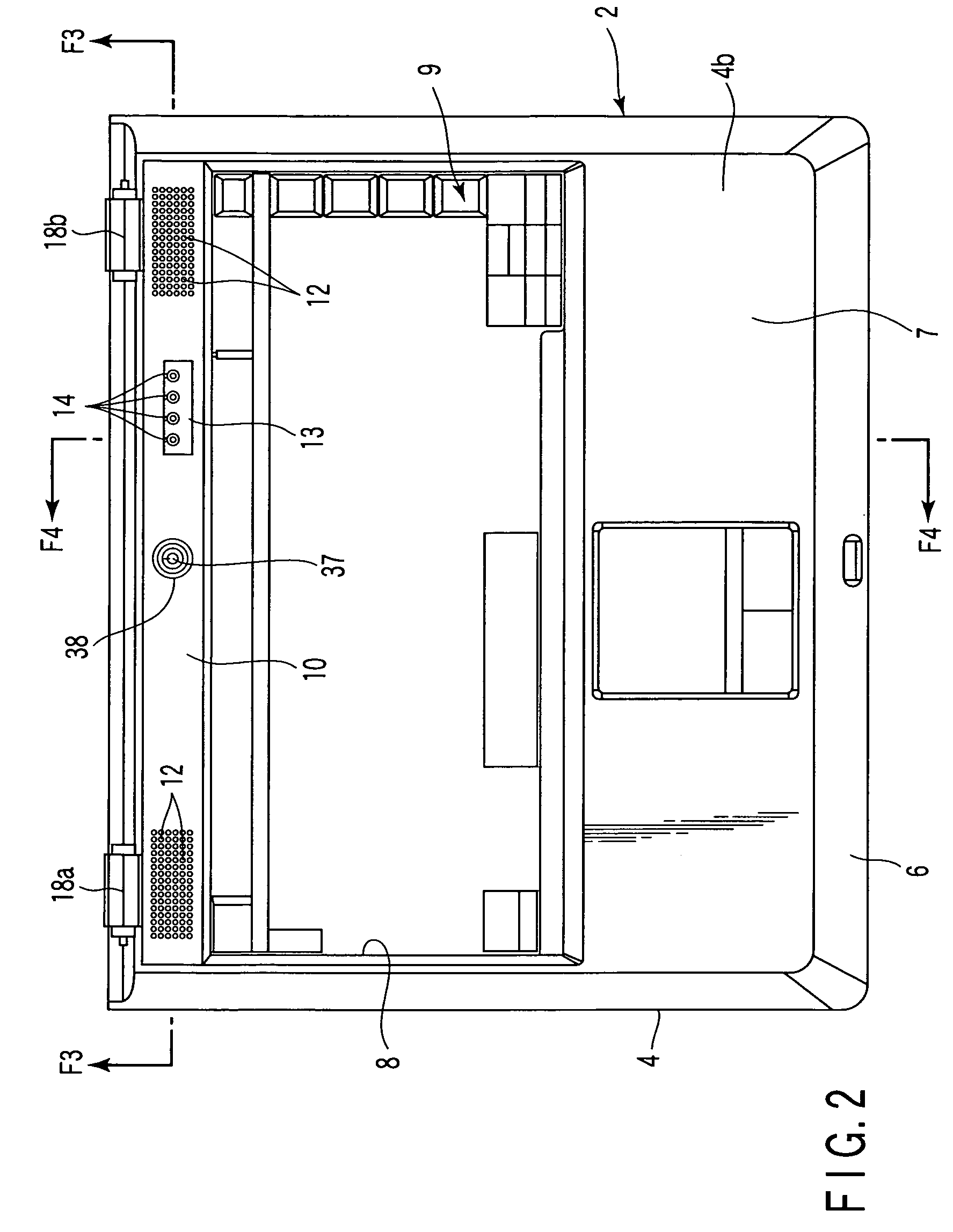

Electronic apparatus including optical guide that guides light from light-emitting diode to outside of housing

Owner:KK TOSHIBA

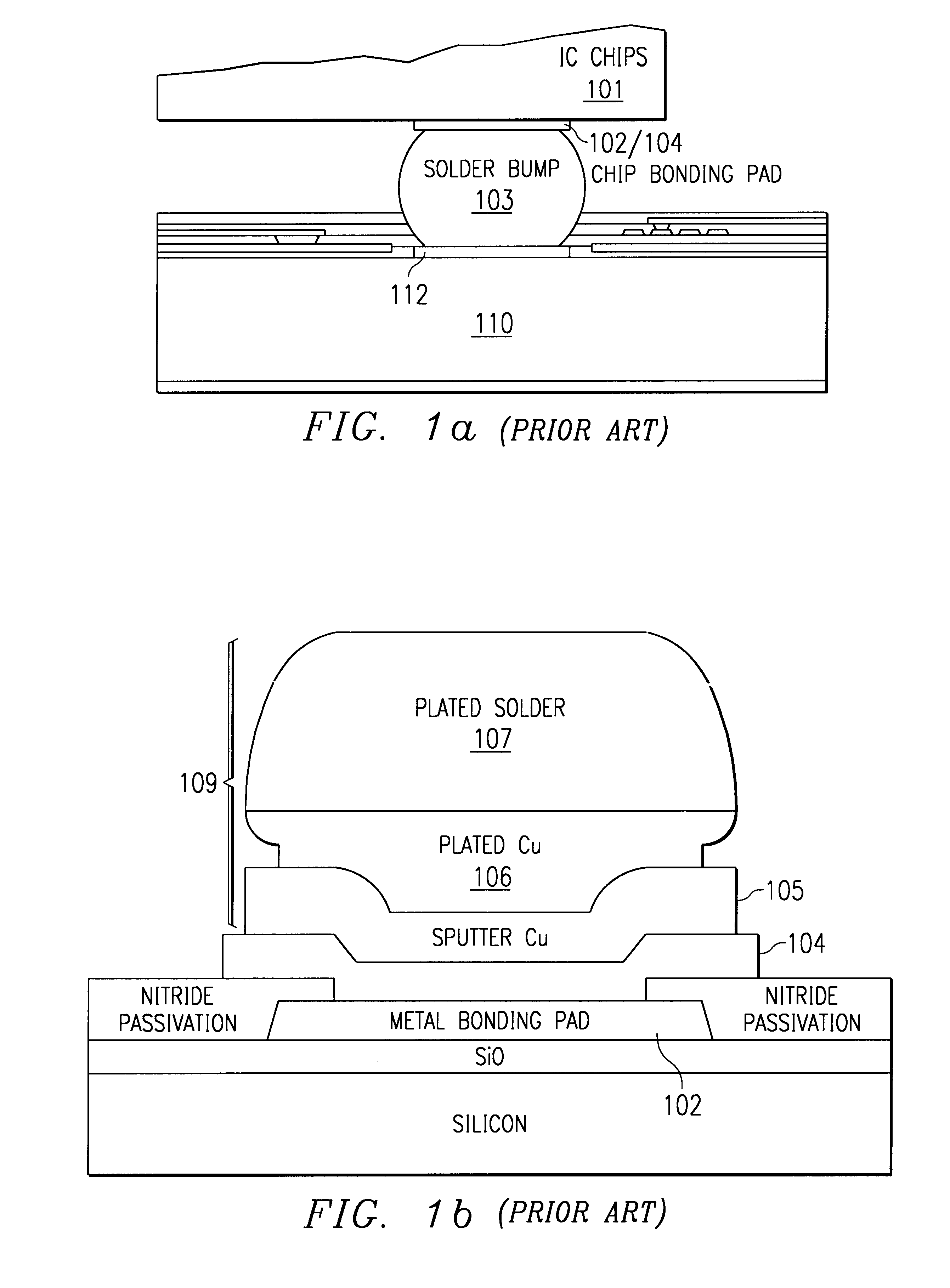

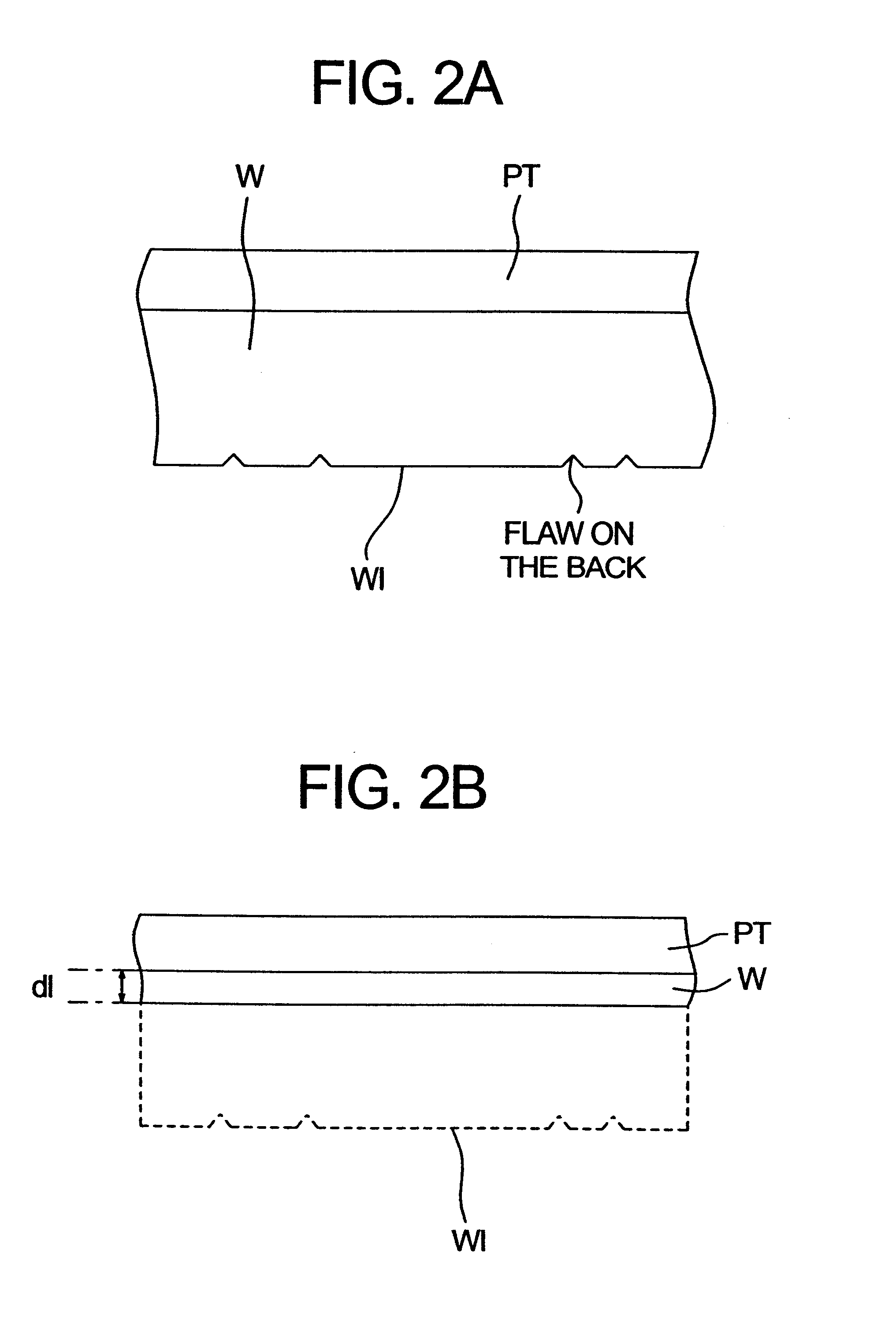

Method and apparatus for a semiconductor package for vertical surface mounting

InactiveUS6291894B1Electrically conductive connectionsDigital data processing detailsDevice materialSurface mounting

A method for packaging a semiconductor device includes connecting a plurality of wire leads to a corresponding plurality of electrical connection pads on the semiconductor device, covering at least a portion of the semiconductor device and at least a portion of each of the wire leads with an encapsulating material, and removing a portion of the encapsulating material and a portion of each of the wire leads to form a packaged semiconductor device wherein each of the wire leads has an exposed portion only at an end. The invention also includes a packaged semiconductor device having an integrated circuit device with a plurality of electrical connection pads, a plurality of wire leads coupled to the plurality of electrical connection pads, and a covering of encapsulating material covering at least a portion of the integrated circuit device and covering each of the wire leads, wherein each of the wire leads has an exposed end. The present invention contemplates wire bonding and encapsulation of individual die as well as multiple die on a single wafer.

Owner:MICRON TECH INC

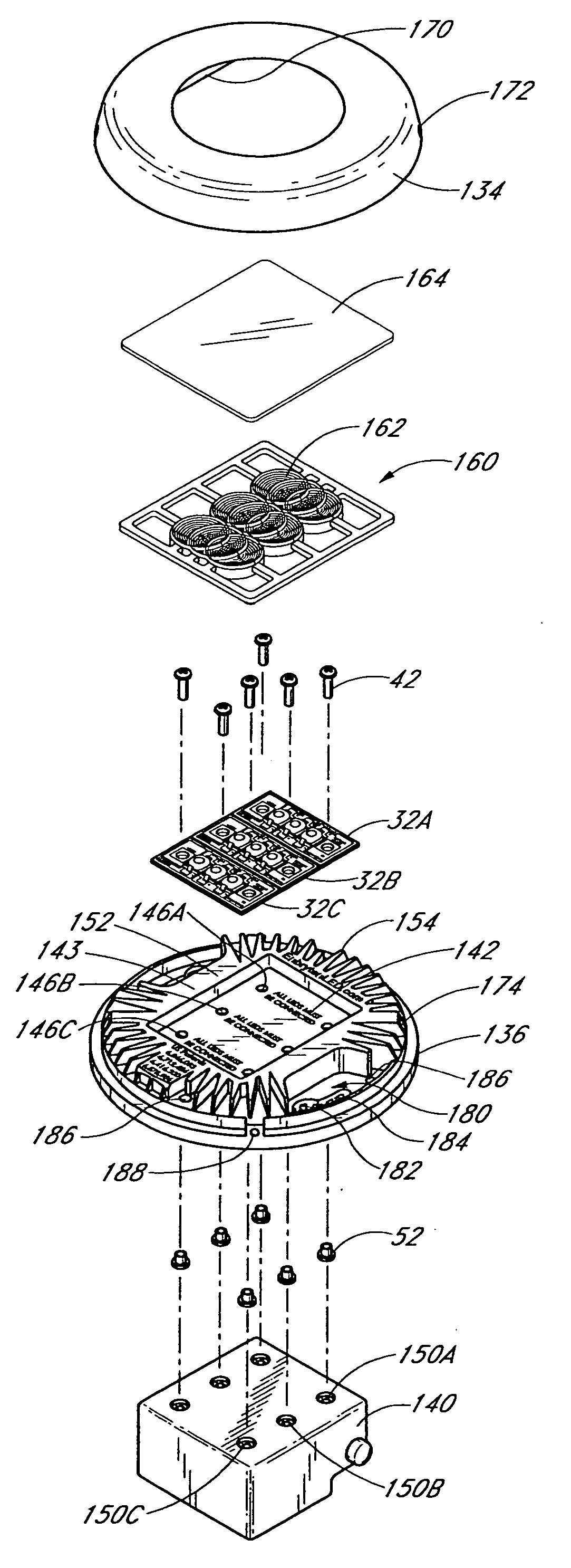

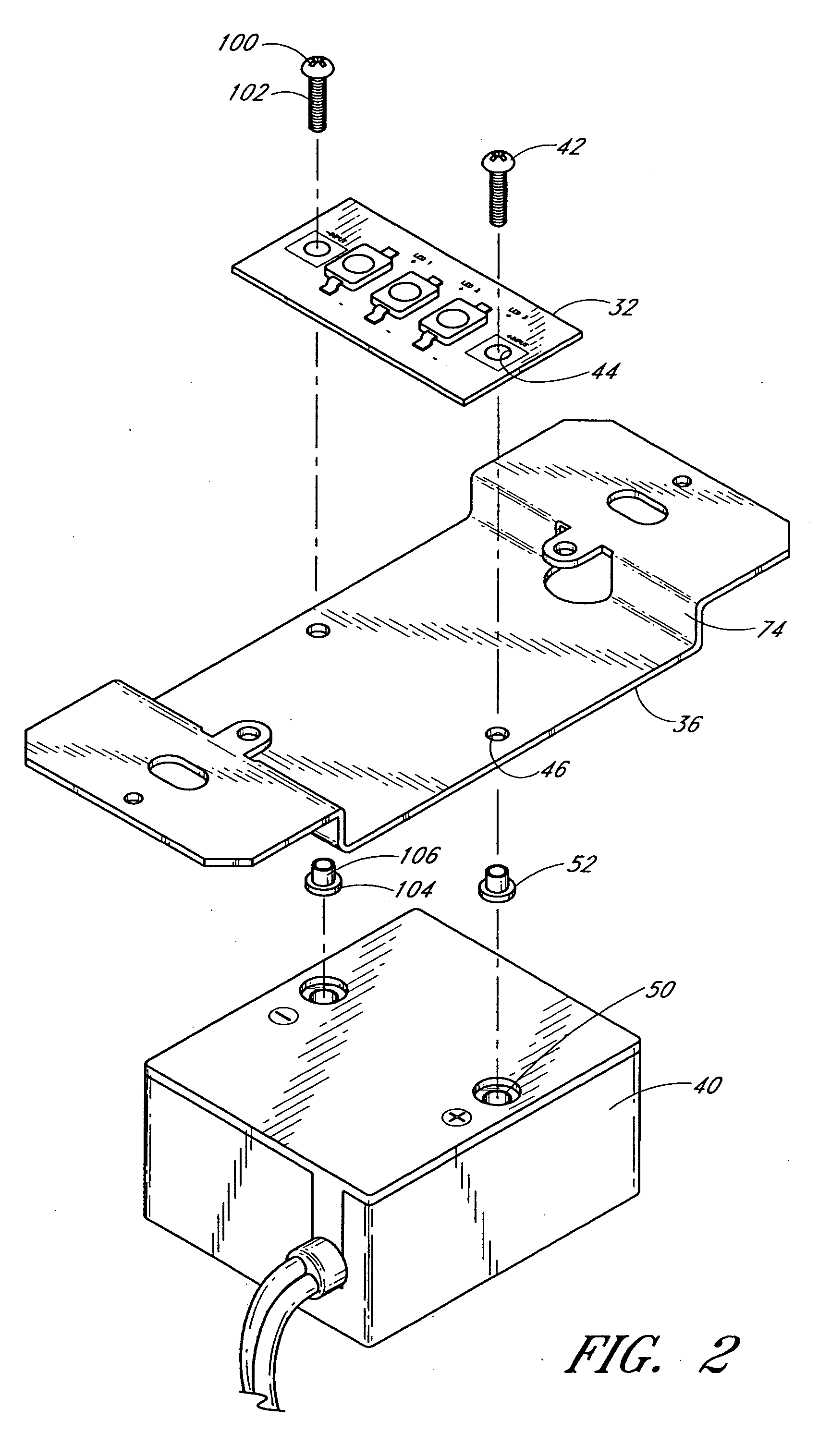

LED-based luminaire

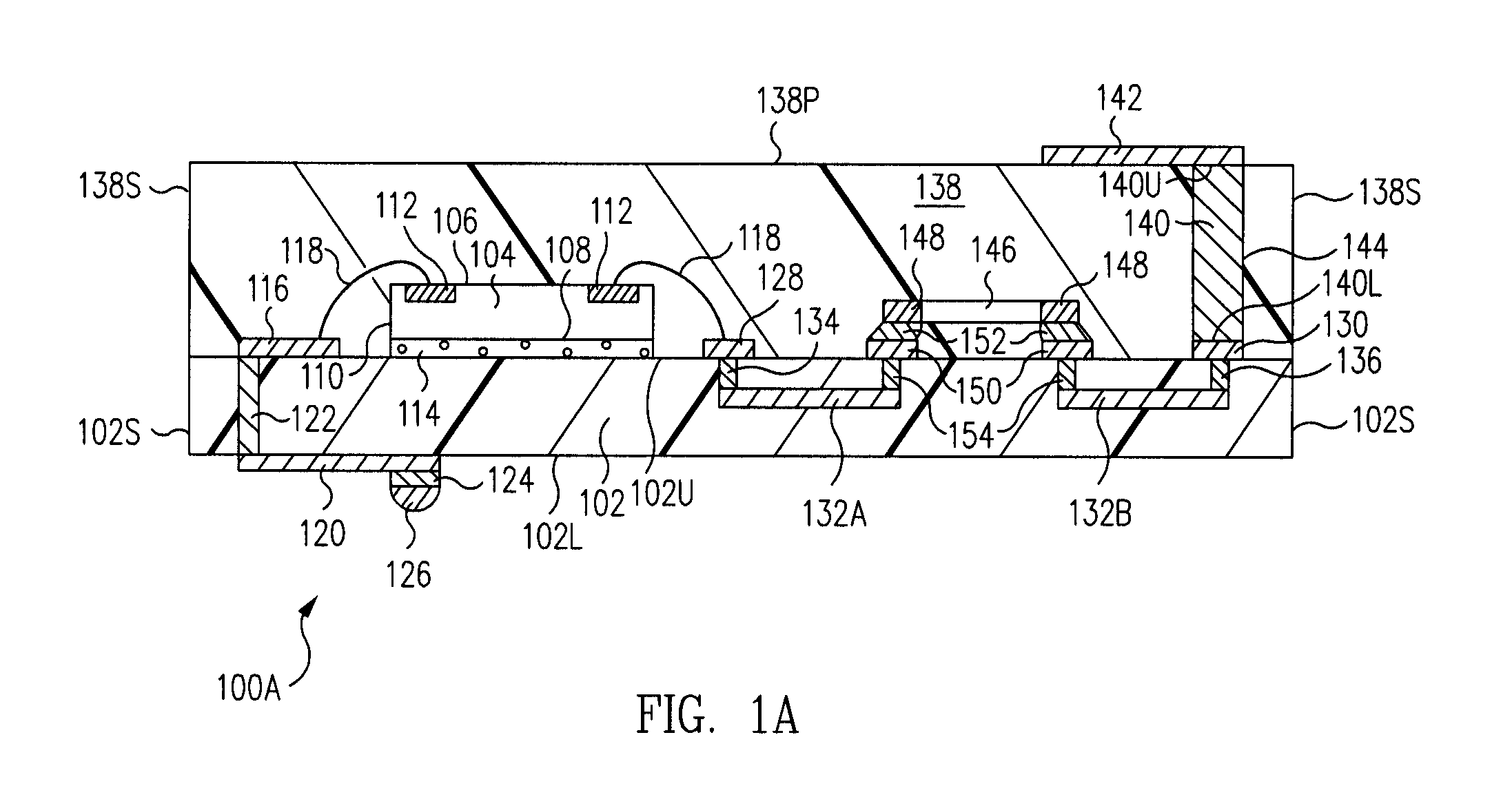

InactiveUS20070041220A1Maximize lighting effectivenessLow costCoupling device connectionsPlanar light sourcesEffect lightEngineering

An LED-based luminaire includes a driver configured to convert line voltage into a desired power configuration. Elongate fasteners attach one or more LED-based lighting modules to a mount member and also to energized poles of the power driver. The fasteners communicate electrical energy from the power driver to the lighting module. In one embodiment, the mount member functions as a heat sink, and it includes a bumpy surface coating having a texture with sufficient feature heights to enhance heat transfer between the heat sink and the surrounding environment.

Owner:DIAMOND CREEK CAPITAL LLC

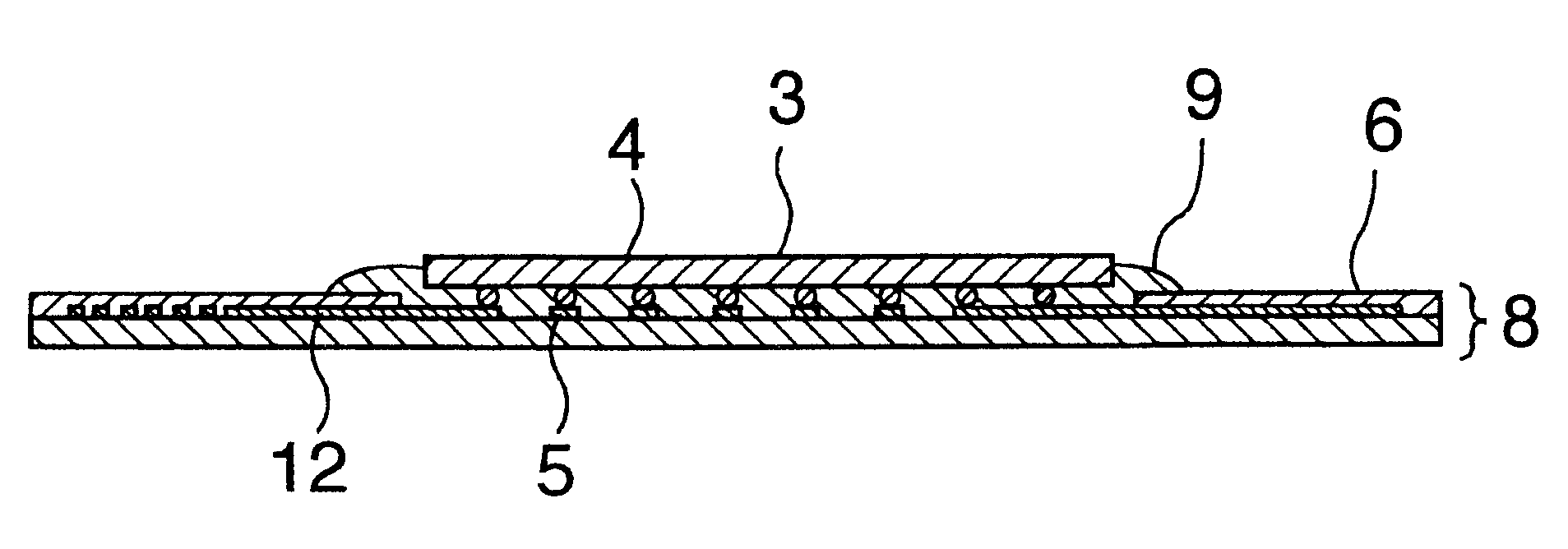

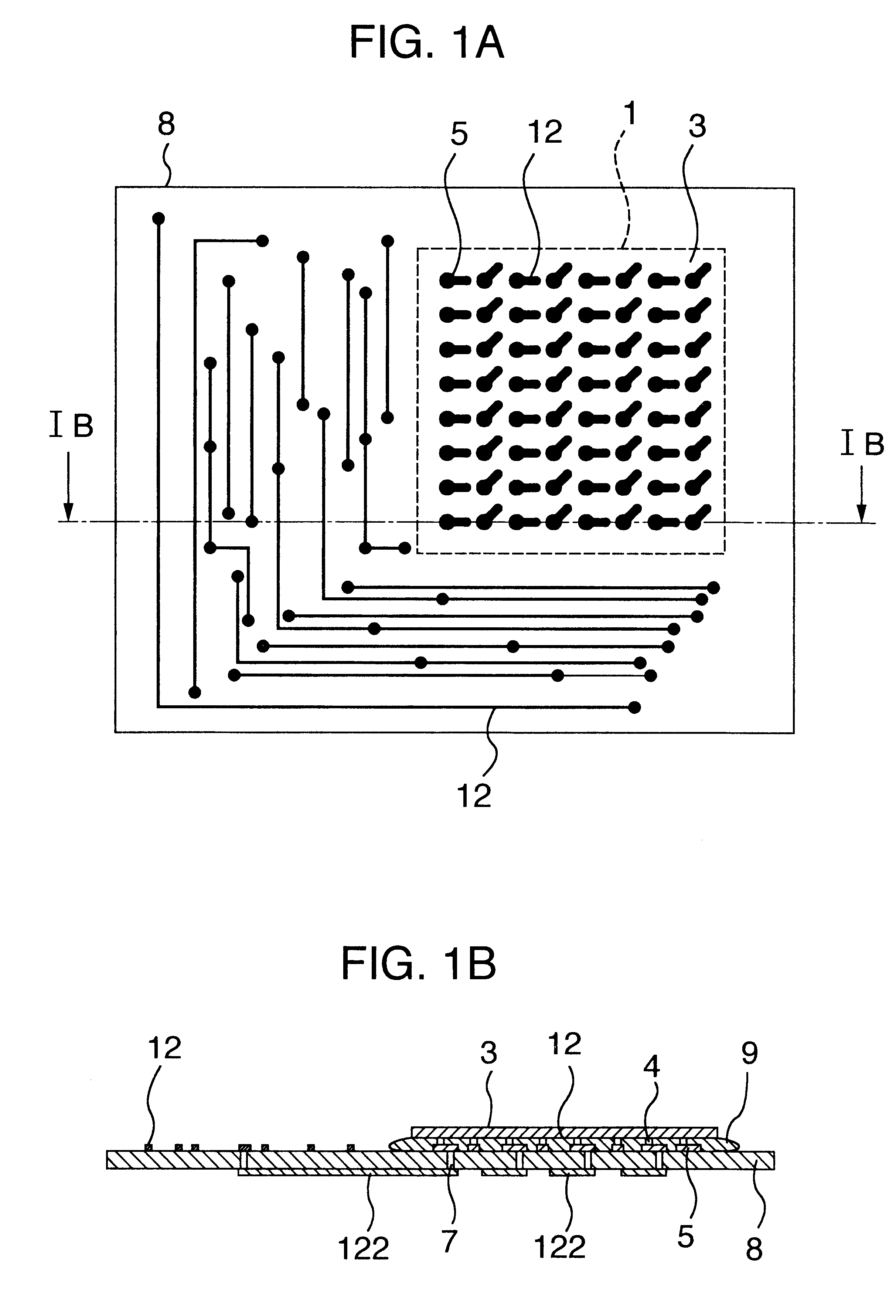

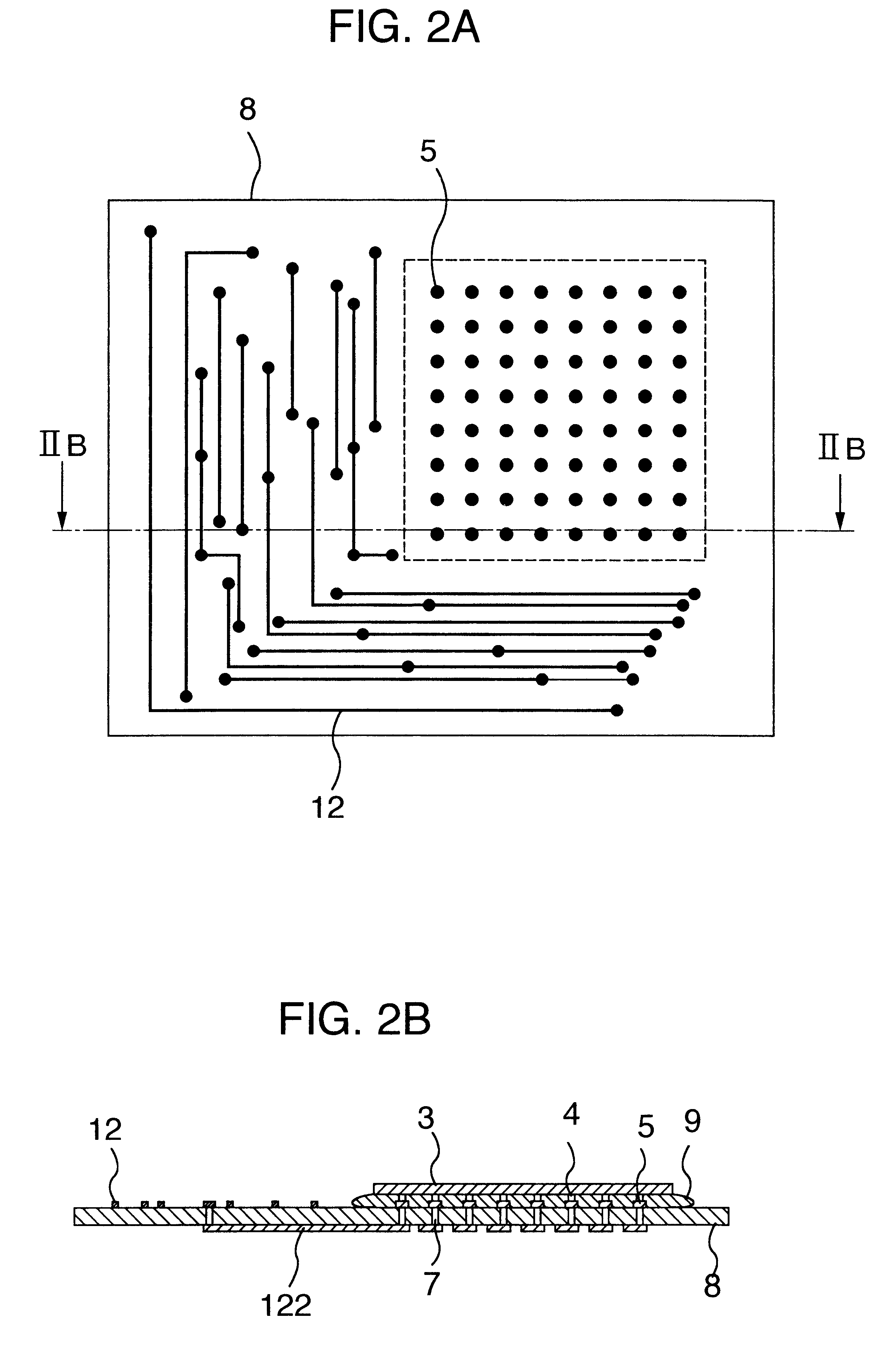

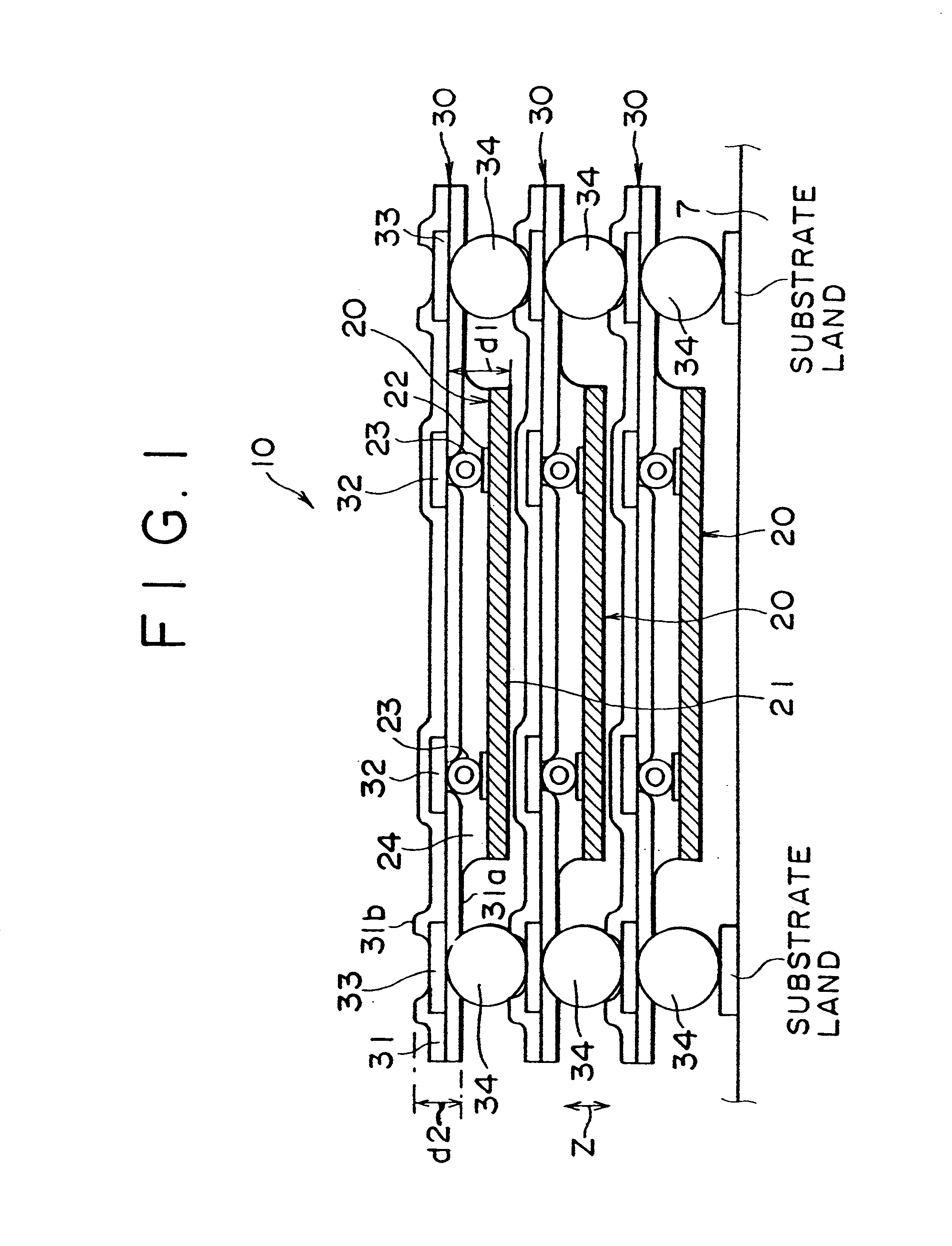

Substrate for mounting semiconductor chips

InactiveUS6281450B1Improve connection reliabilityImprove batch productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical conductor

A substrate for mounting a semiconductor chip having bumps using an adhesive thereon, said substrate being, for instance, provided with an insulating coating having an opening in the semiconductor chip mounting area so that the wiring conductors will not be exposed to the substrate surface near the boundary of the semiconductor chip mounting area, is improved in connection reliability and has high mass productivity.

Owner:HITACHI CHEM CO LTD

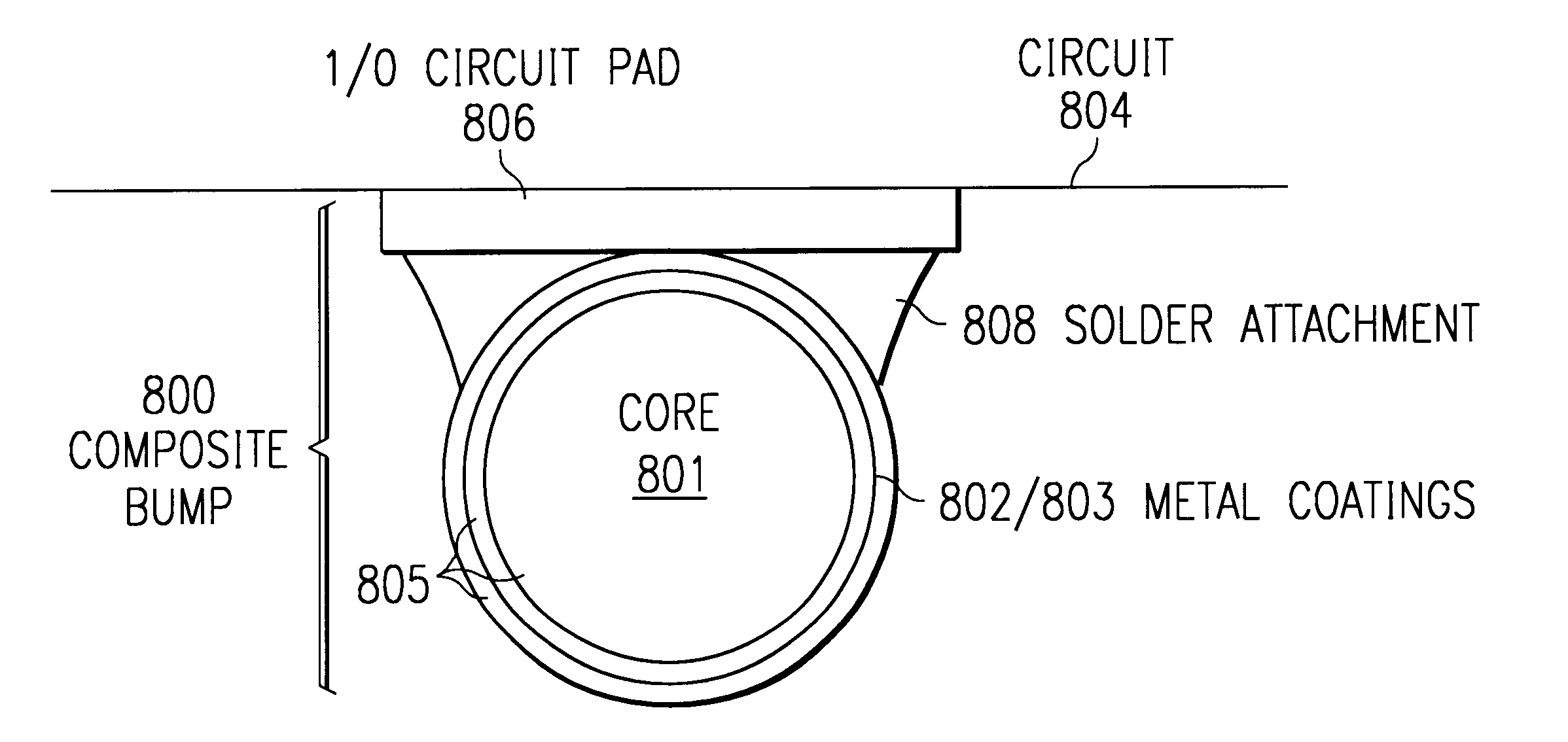

Composite connection structure and method of manufacturing

InactiveUS6337445B1Improve reliability and performanceImprove thermal conductivityPrinted circuit assemblingFinal product manufactureContact padSolder paste

A bump connection structure and a method of attachment to integrated circuits or packages is provided which comprises a prefabricated core structure coated with solderable metal layers to form a composite bump. Said composite bump is aligned to contact pads of the chip or package which have been coated with solder paste, and the assembly heated to form a metallurgical bond. The prefabricated core structures are comprised of metal, plastic or ceramic of the size and dictated by package standards. The connection structure is preferably lead free.

Owner:TEXAS INSTR INC

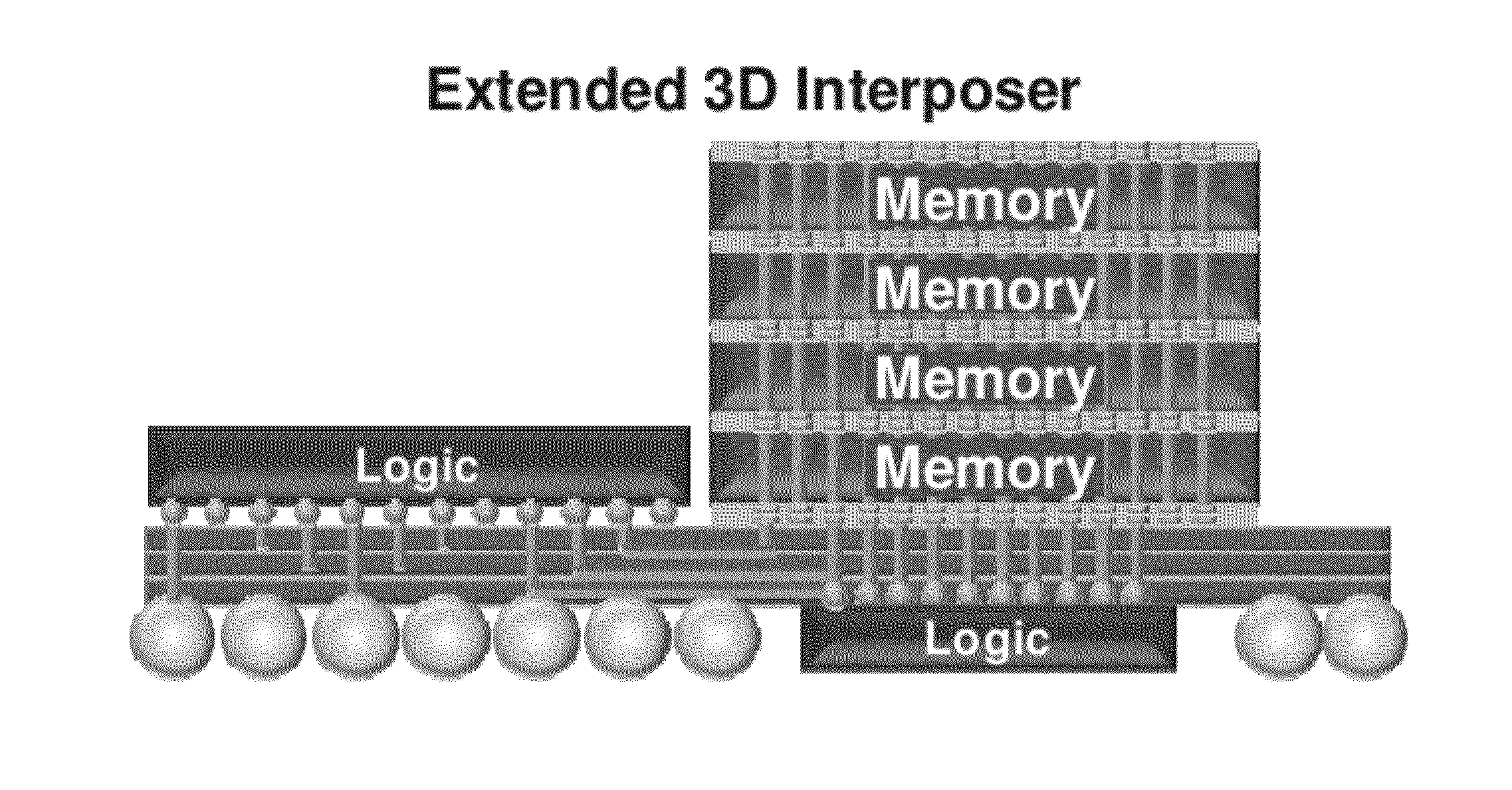

Ultra-thin interposer assemblies with through vias

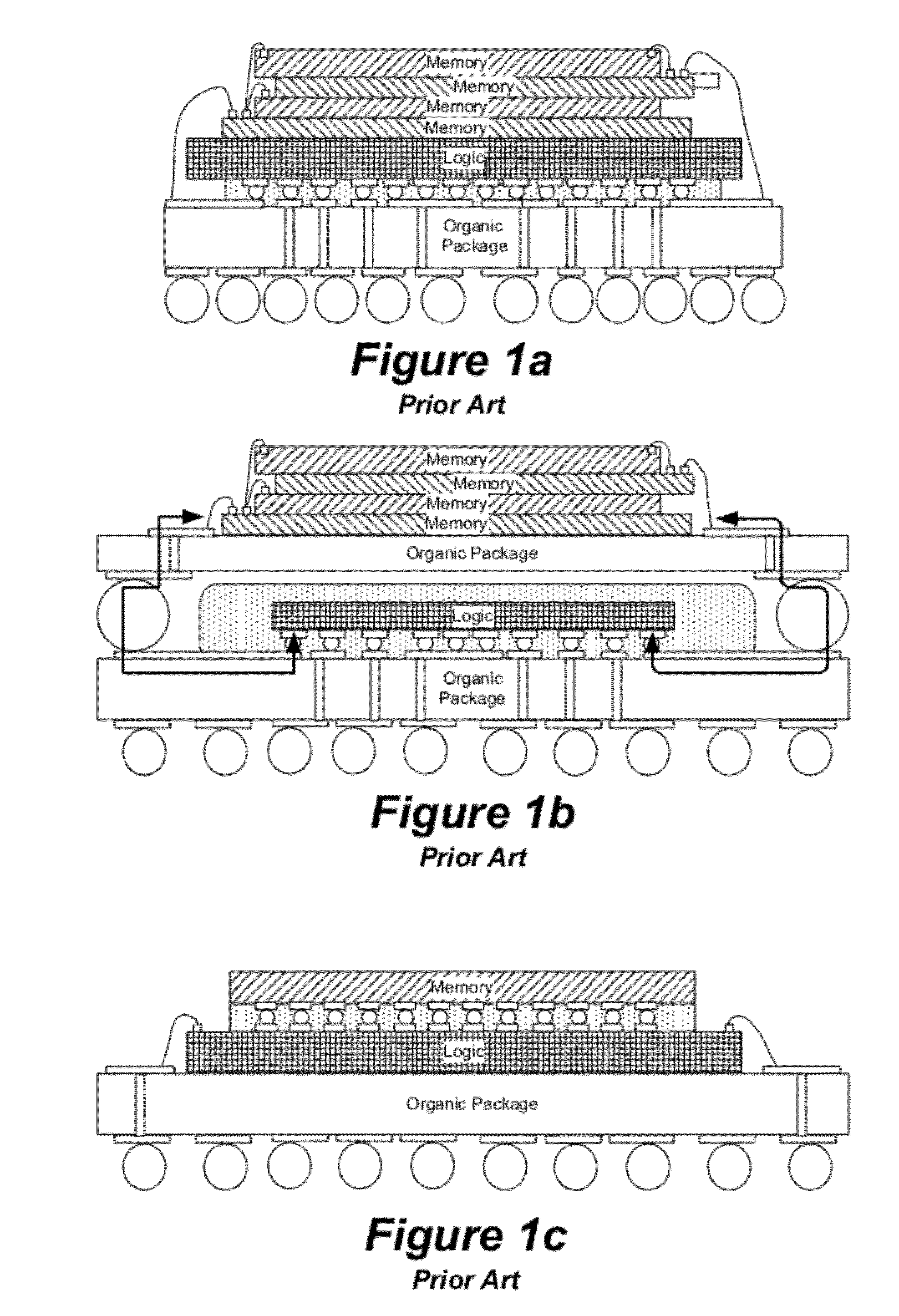

ActiveUS20120106117A1Semiconductor/solid-state device detailsPrinted circuit aspectsGraphicsElectricity

A 3D interconnect structure comprising an ultra-thin interposer having a plurality of ultra-high density of through-via interconnections defined therein. The 3D interposer electrically connects first and second electronic devices in vertical dimension and has the same or similar through-via density as the first or second electronic devices it connects. The various embodiments of the interconnect structure allows 3D ICs to be stacked with or without TSVs and increases bandwidth between the two electronic devices as compared to other interconnect structures of the prior art. Further, the interconnect structure of the present invention is scalable, testable, thermal manageable, and can be manufactured at relatively low costs. Such a 3D structure can be used for a wide variety of applications that require a variety of heterogeneous ICs, such as logic, memory, graphics, power, wireless and sensors that cannot be integrated into single ICs.

Owner:GEORGIA TECH RES CORP

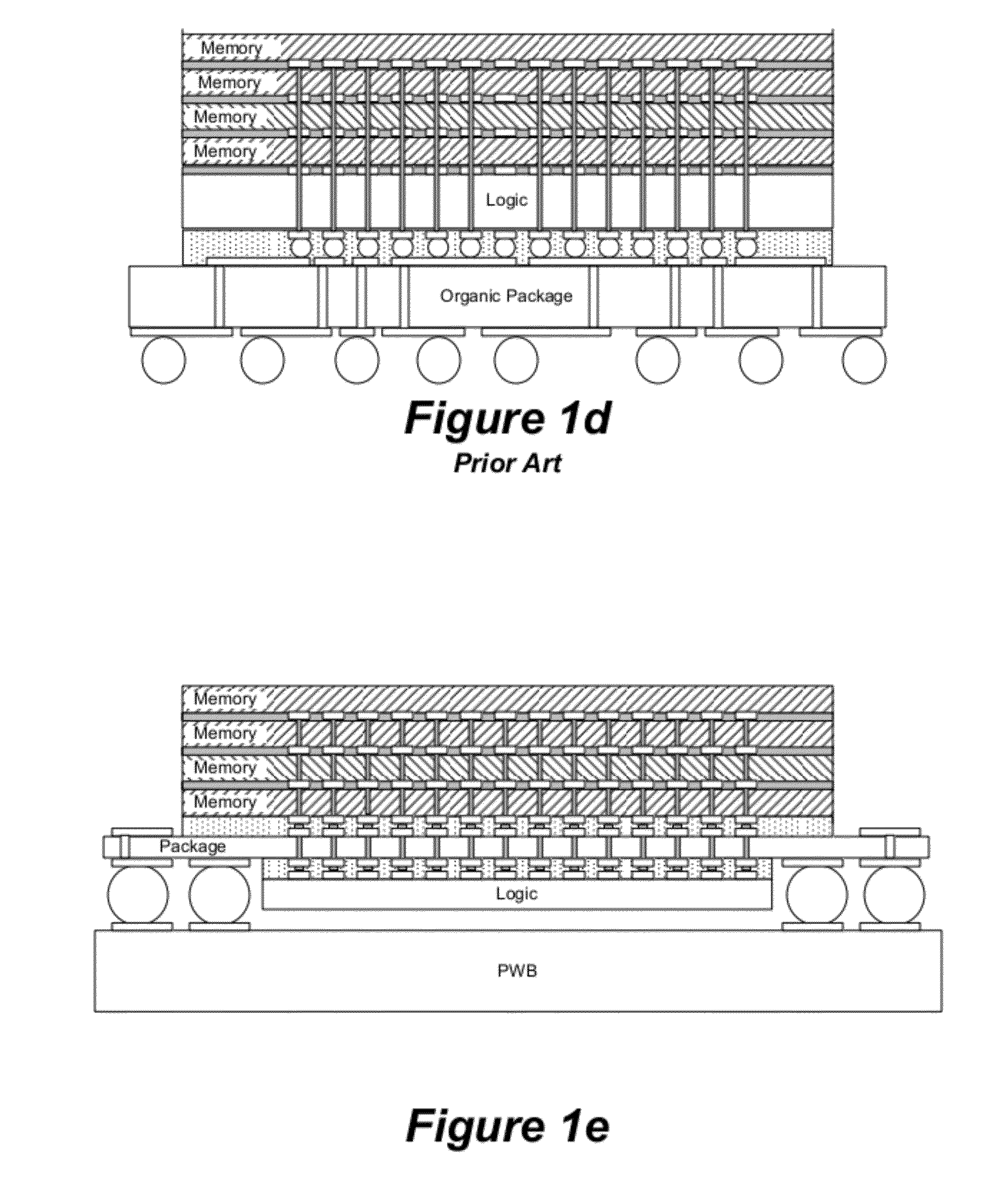

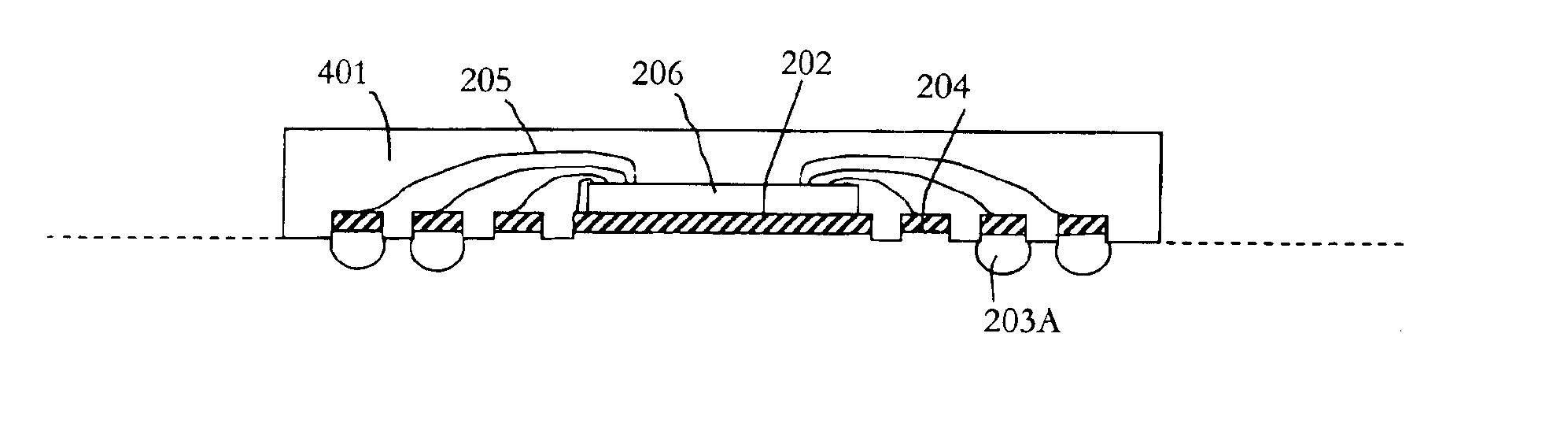

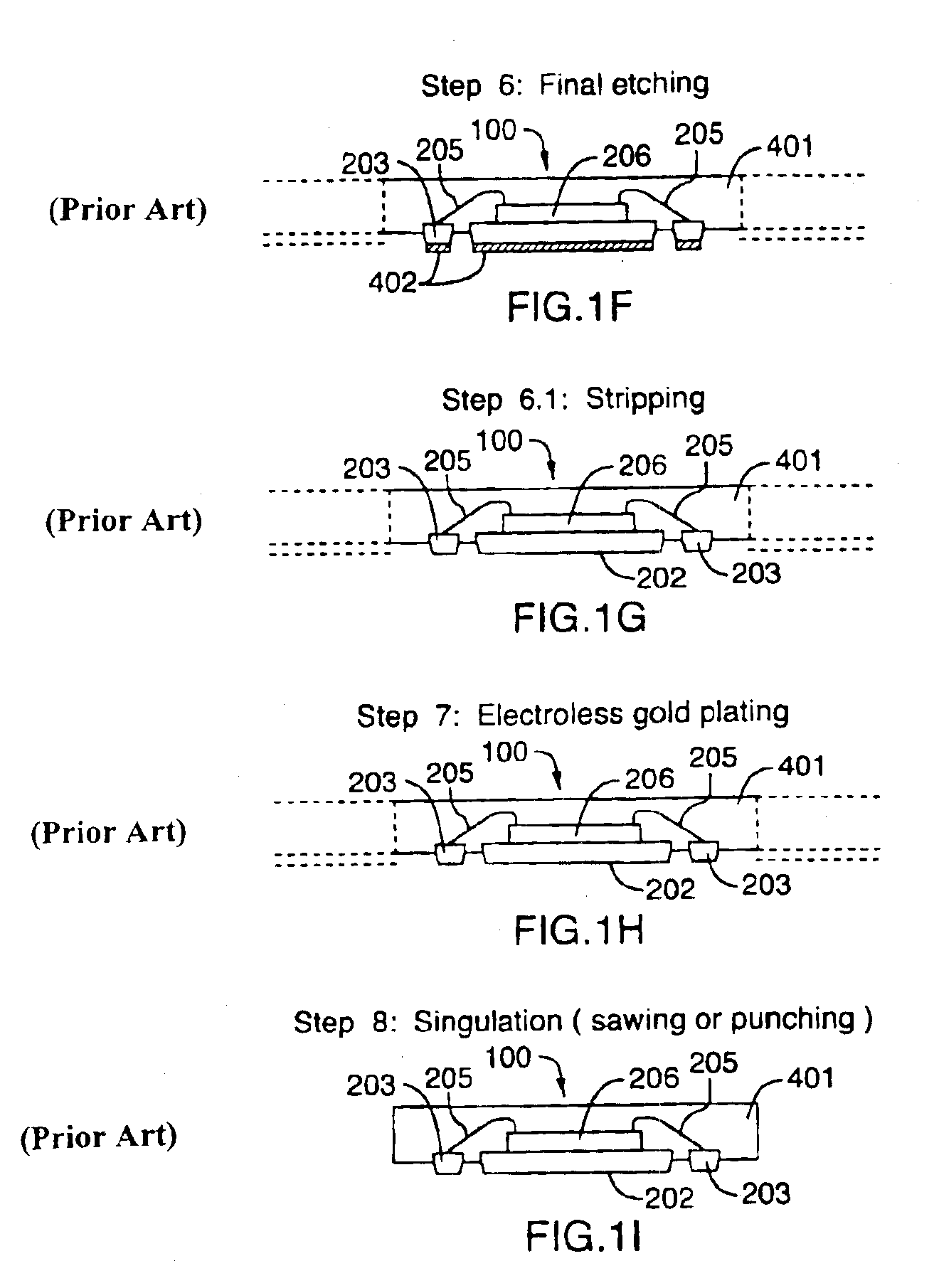

Leadless plastic chip carrier with etch back pad singulation

InactiveUS6933594B2Improve interlockEasy alignmentSemiconductor/solid-state device detailsSolid-state devicesEtchingPunching

A leadless plastic chip carrier is constructed by half etching one or both sides of the package design onto a leadframe strip so as to create unique design features such as power and / or ground ring surrounding the die attach pad, interlocking rivet head construction for the contact pads, and an interlocking pattern for the die attach pad. After wire bonding and molding, a further etching is performed to isolate and expose contact pads. Singulation of individual chip packages from the leadframe strip is then performed by saw singulation or die punching.

Owner:UTAC HEADQUARTERS PTE LTD

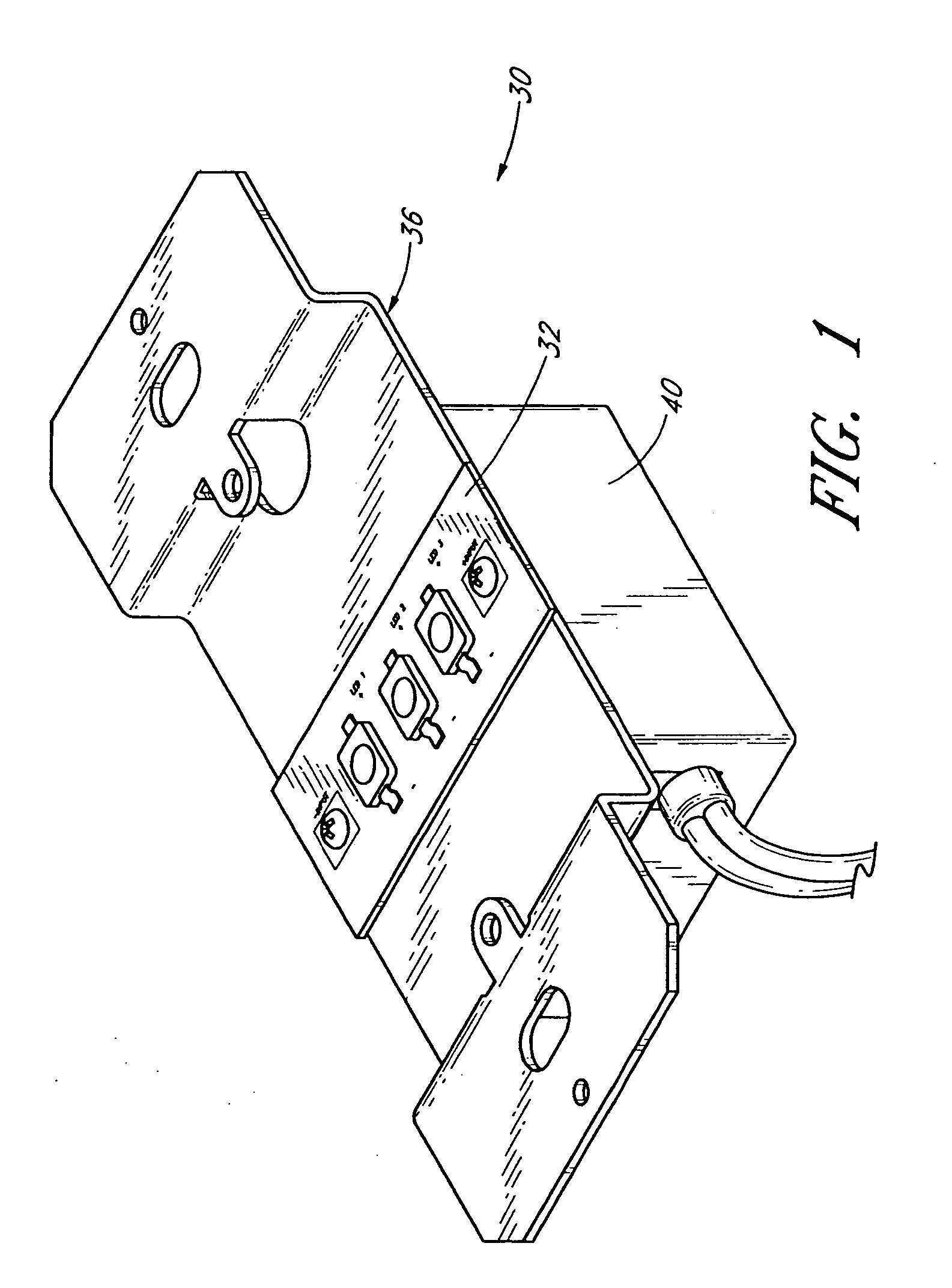

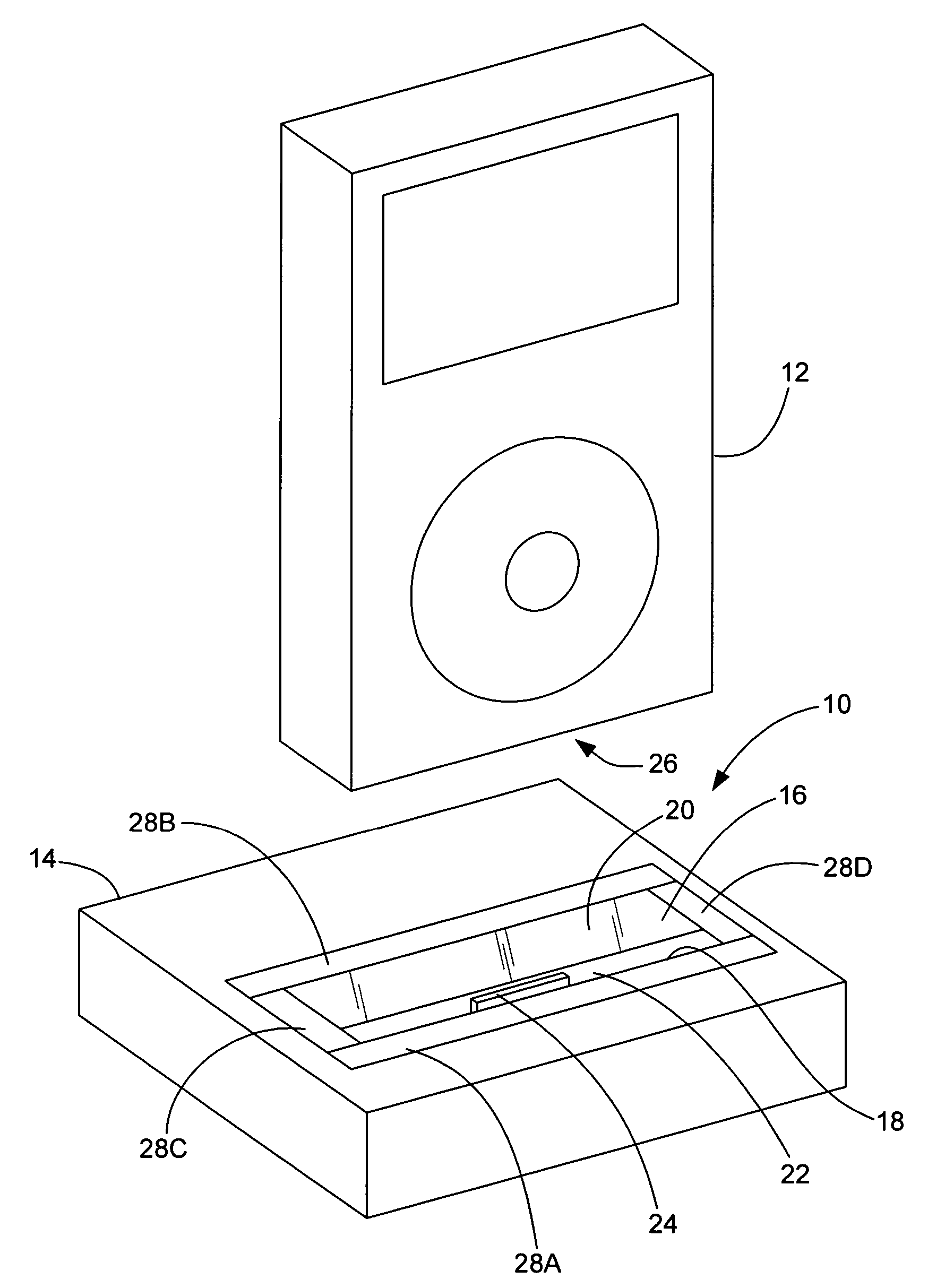

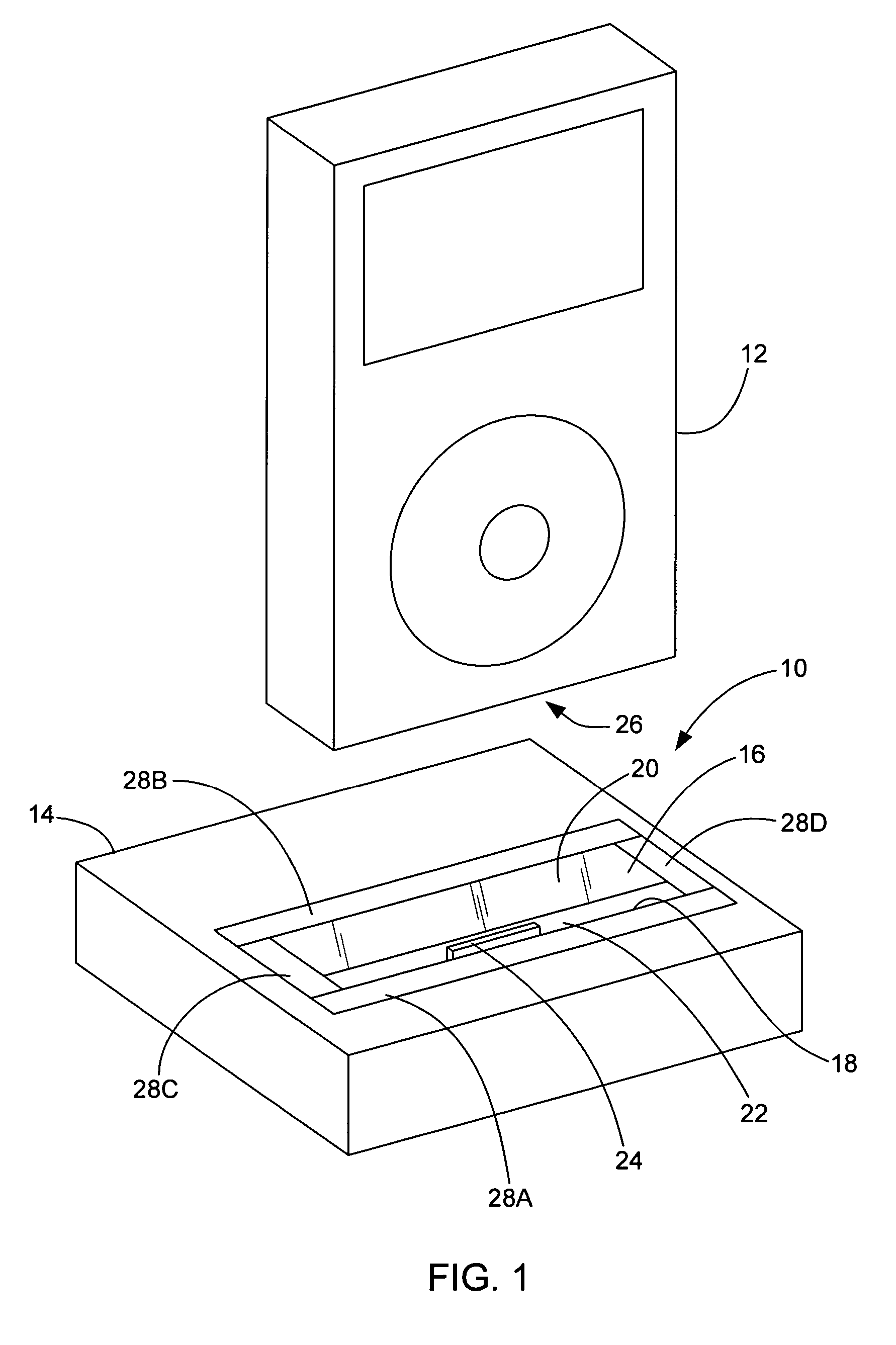

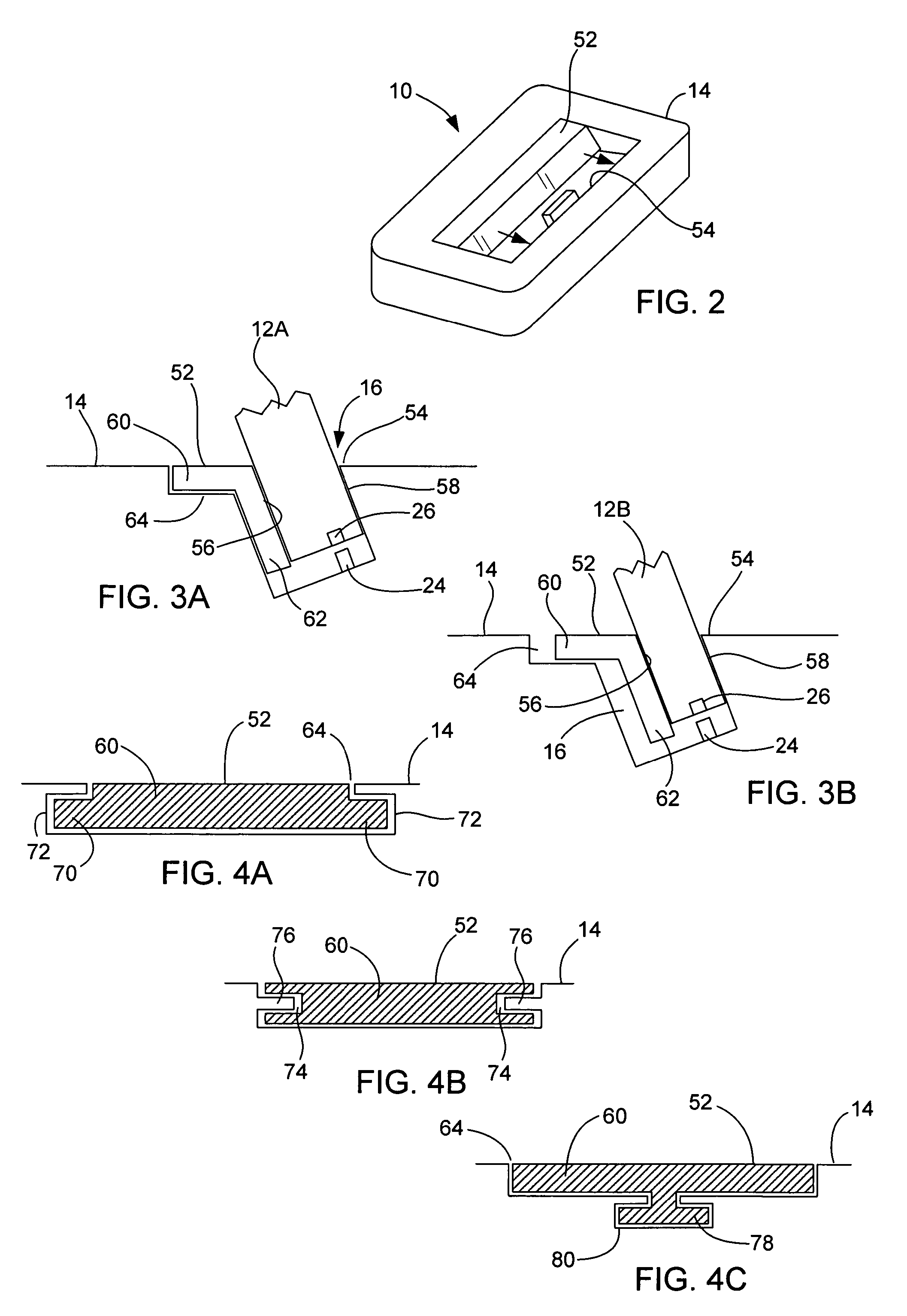

Universal docking station for hand held electronic devices

A docking station is disclosed. The docking station has an adjustable opening that accommodates portable electronic devices with differing sizes and shapes. The opening is capable of expanding to accommodate larger devices and retracting to accommodate smaller devices while still supporting the portable electronic device in its proper position within the docking station.

Owner:APPLE INC

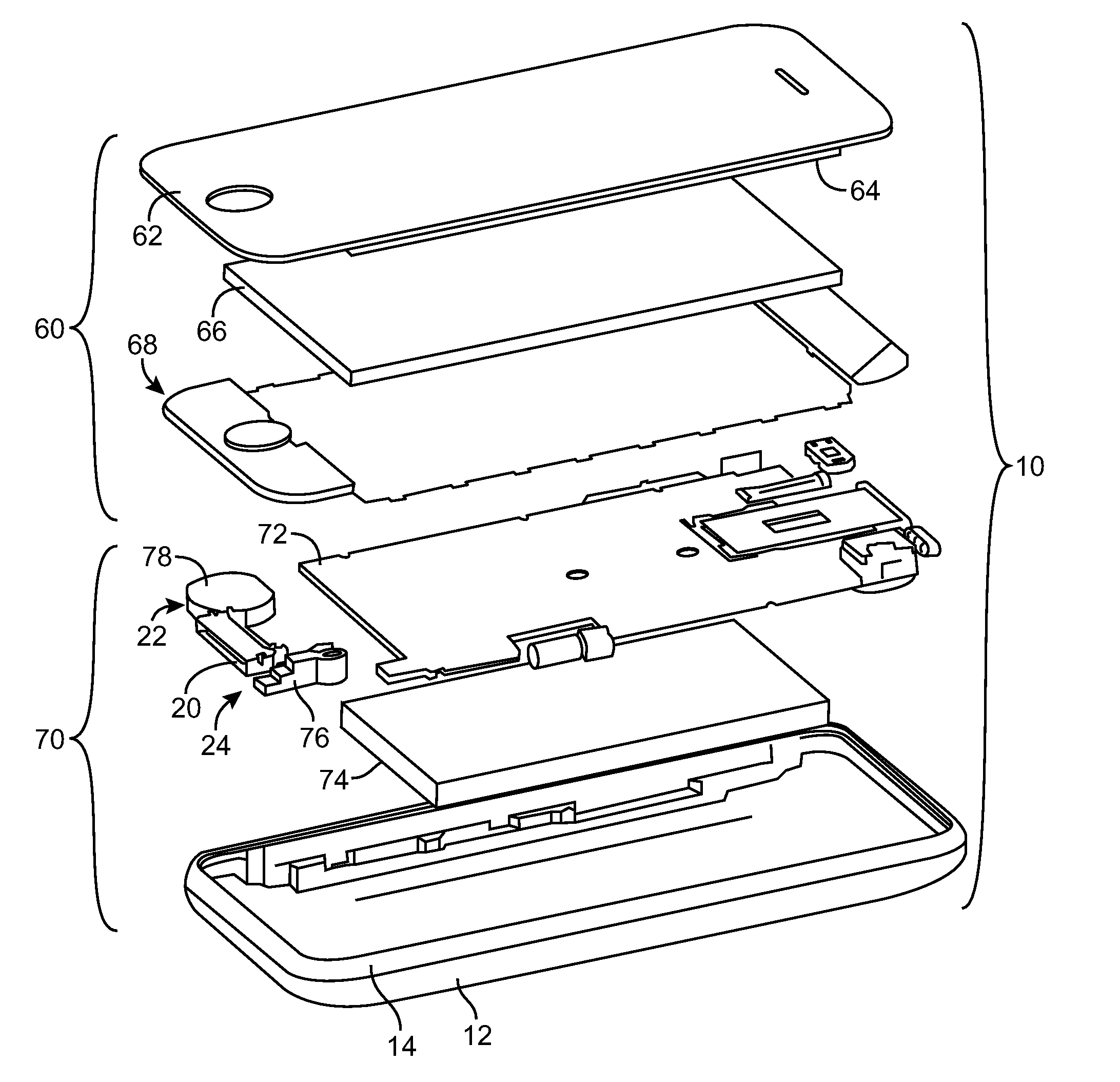

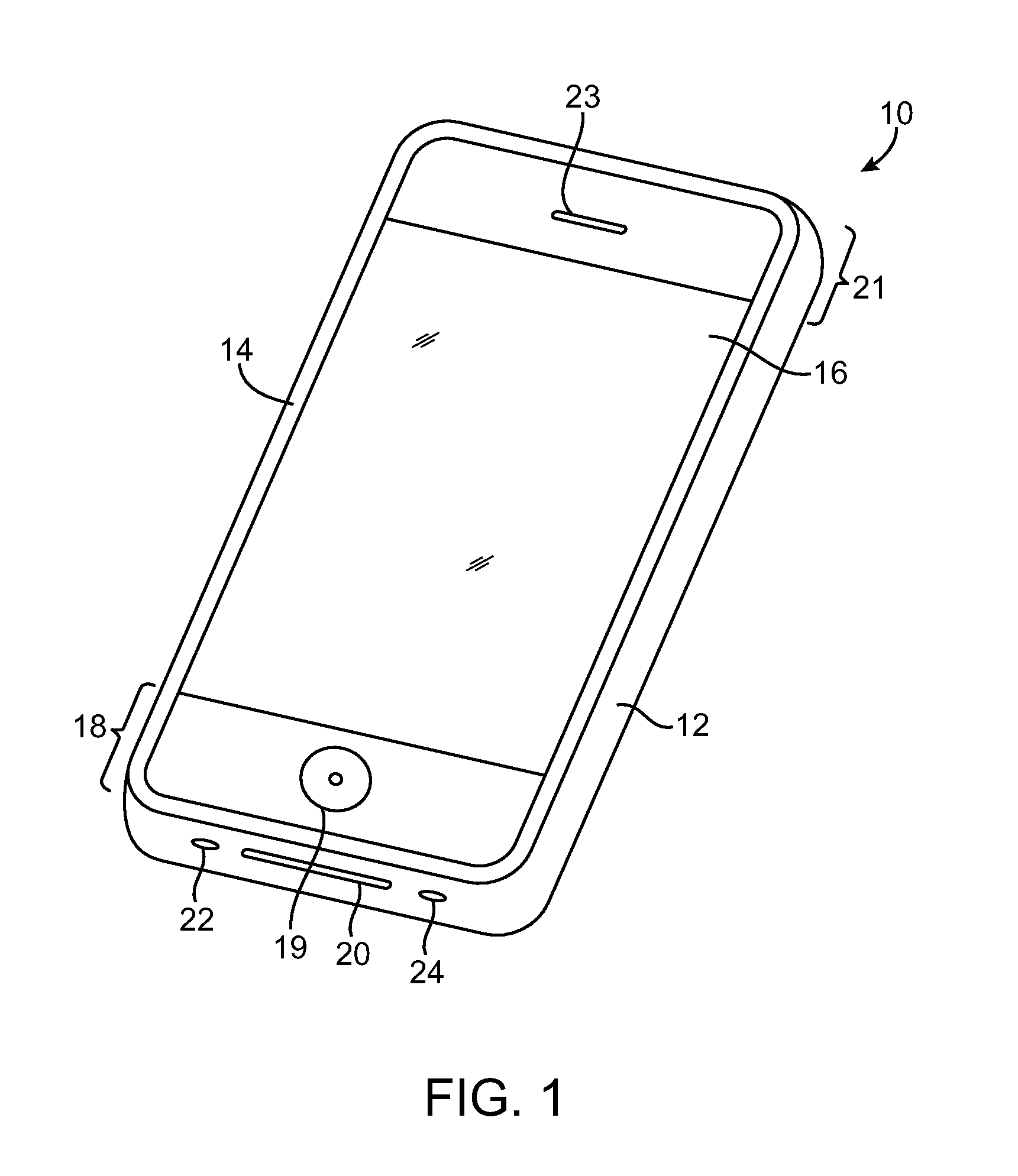

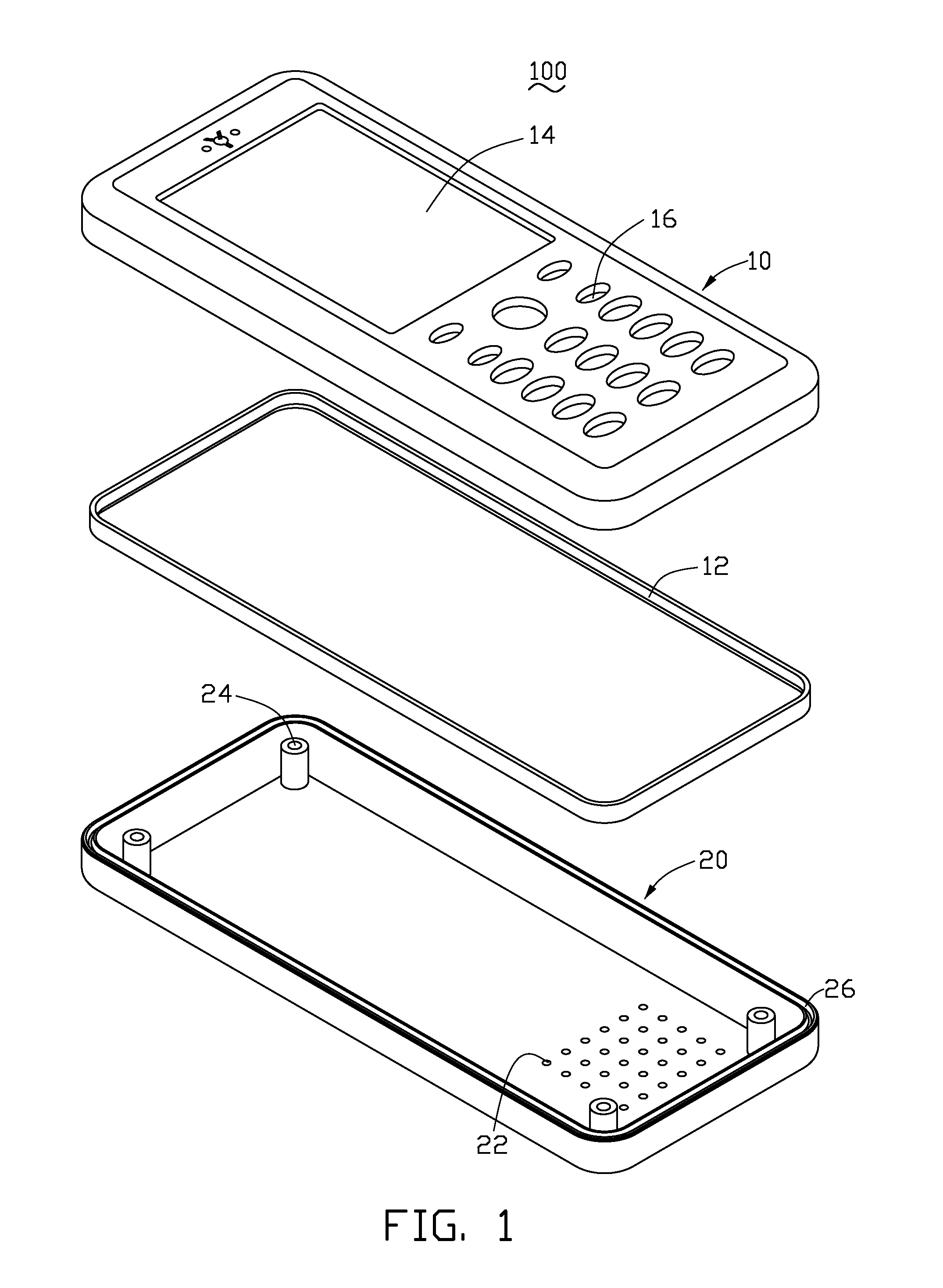

Portable electronic device with two-piece housing

ActiveUS7933123B2Avoid scratchesDisassembled for rework or repair operationsDigital data processing detailsSubstation equipmentEngineeringCover glass

Owner:APPLE INC

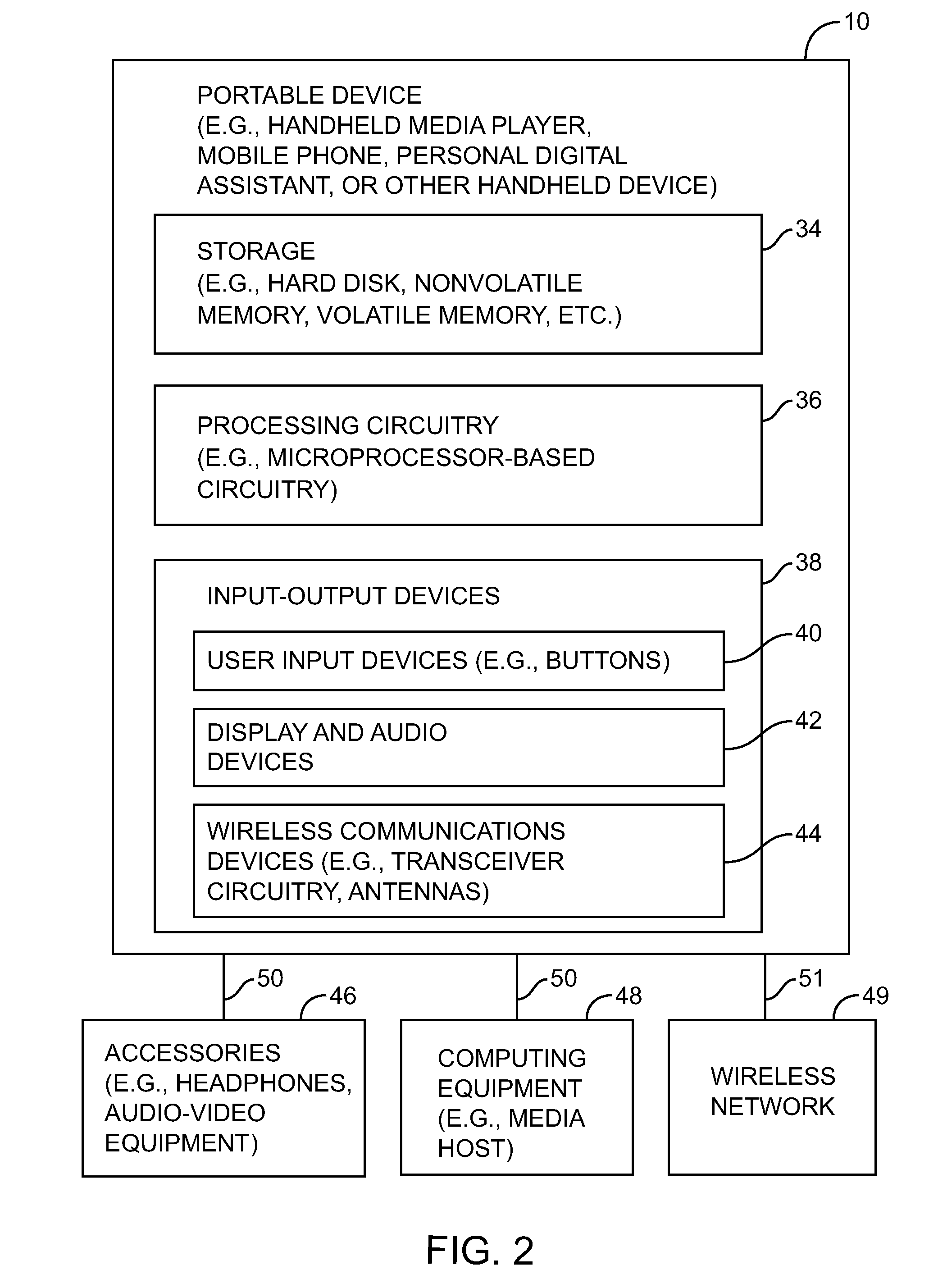

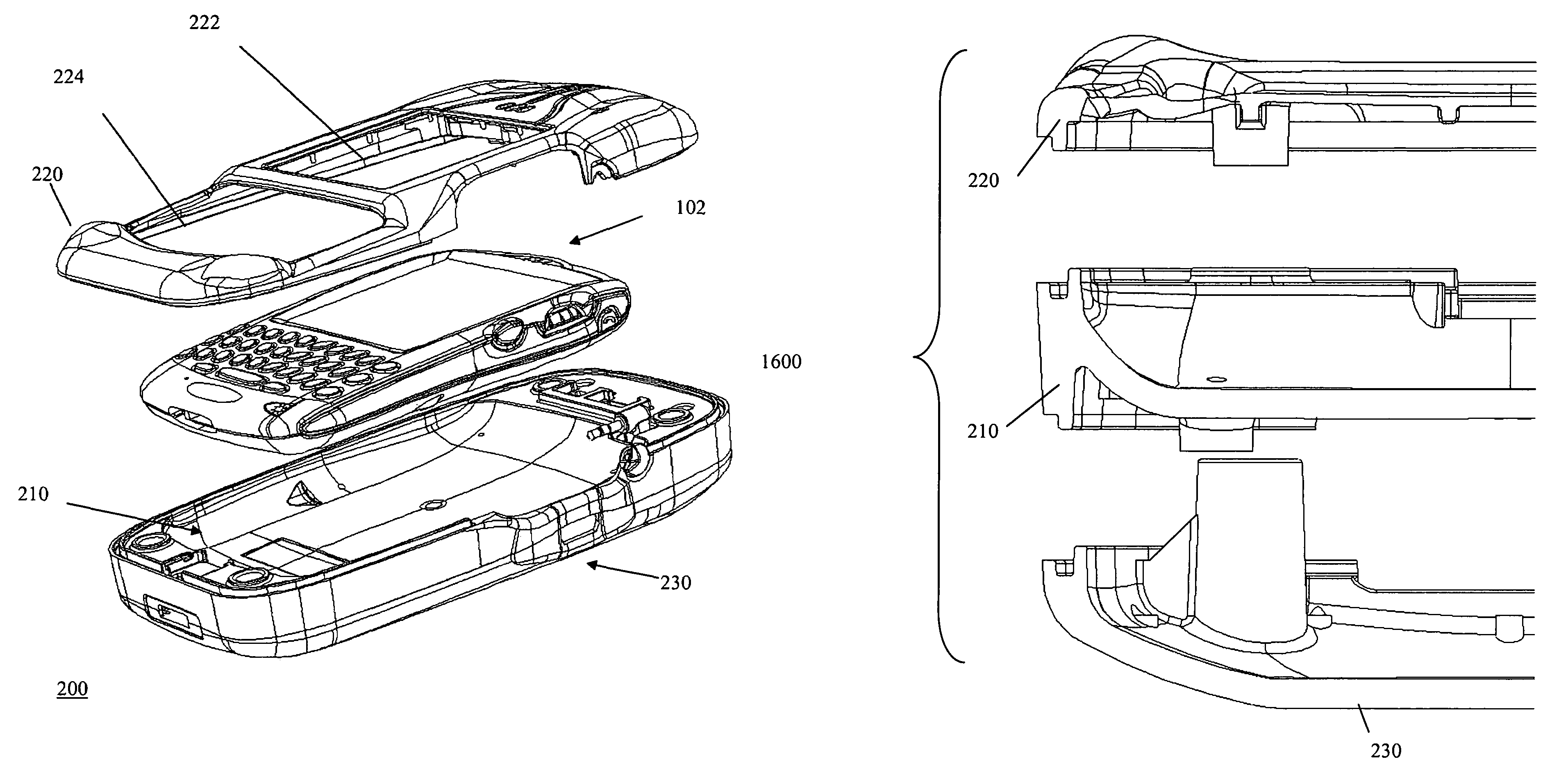

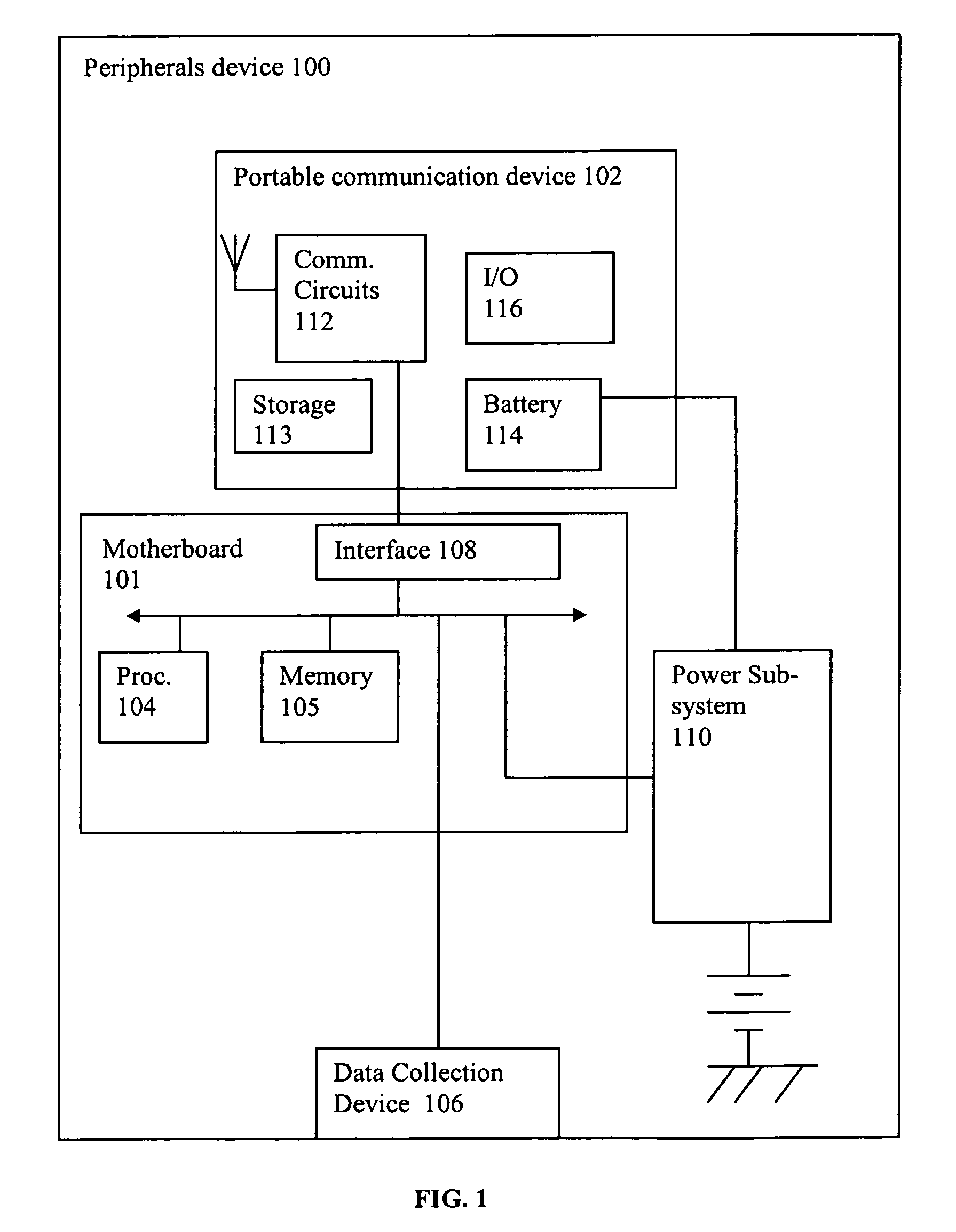

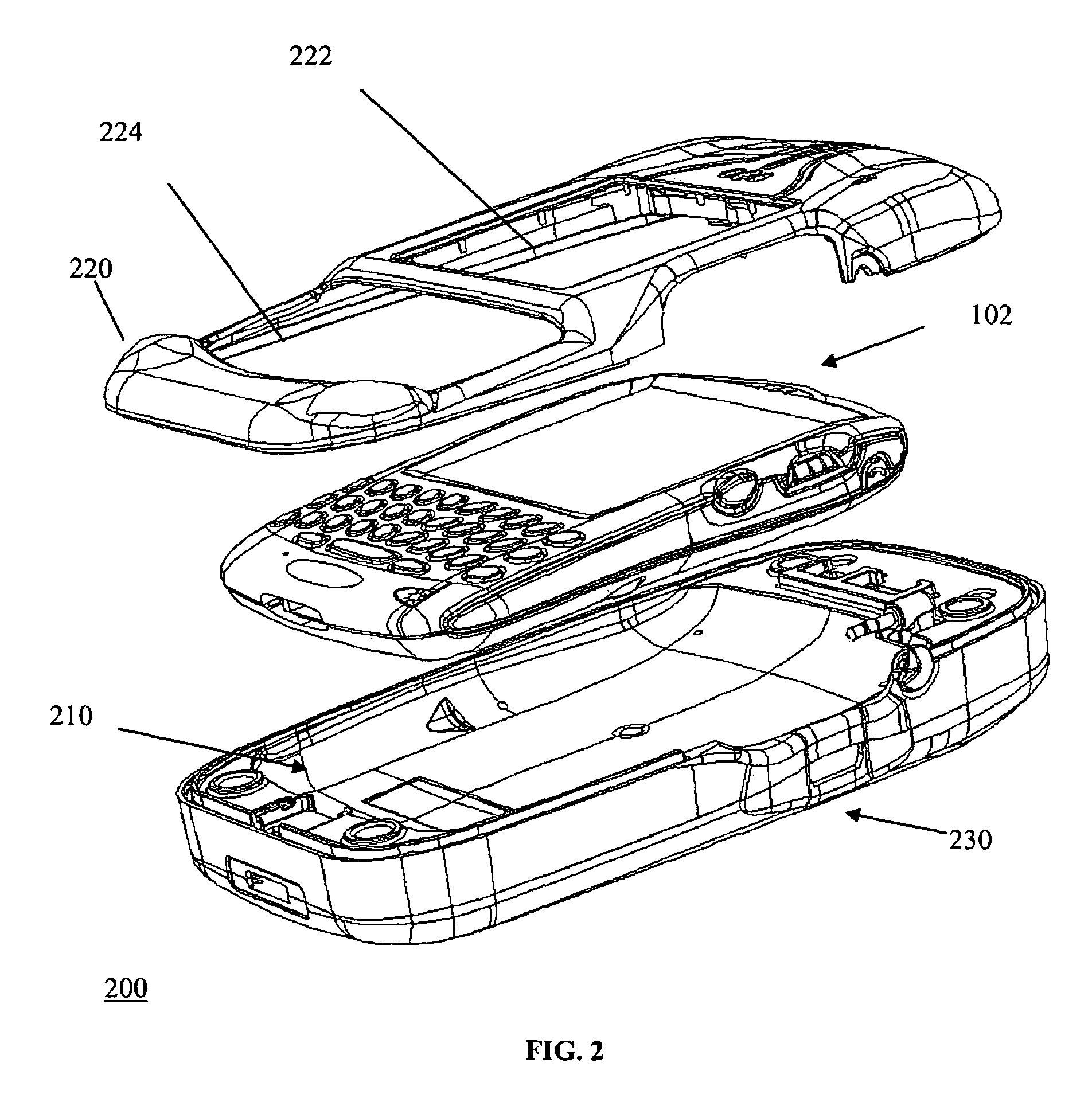

Modular protective housing with peripherals for a handheld communications device

InactiveUS7663878B2Digital data processing detailsSubstation equipmentComputer hardwareElectric power system

A peripherals device for coupling with a handheld communication device includes an interface to the handheld communication device and a processor for performing functions complementary to the communications device. According to another embodiment, the peripherals device includes a conformal cavity for receiving a handheld communications device in a secure fashion. According to yet another embodiment, the peripherals device includes a data collection device for collecting data and using the interface for sending the collected data to a remote processor for further processing. The data collection device can include an image reader, a barcode reader, a signature capture device, an optical character recognition. In yet another embodiment, there is a power subsystem that powers the peripherals device and the handheld communications device. The power system has a low power state to conserve energy. In another embodiment, the peripherals device comprises a plurality of processors that automatically reconfigure themselves to work with the communication device to which the peripherals device is connected.

Owner:SD X INTERACTIVE

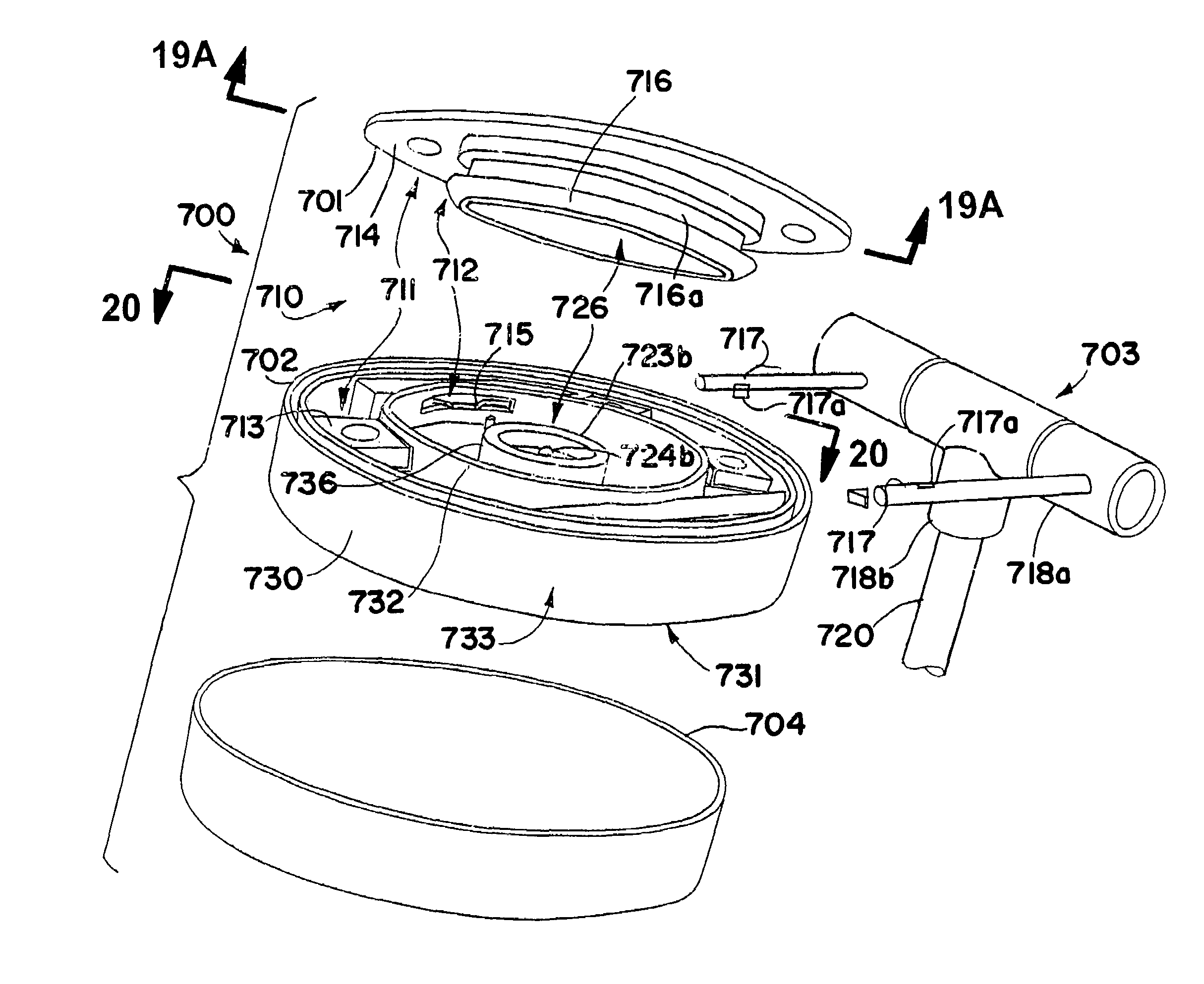

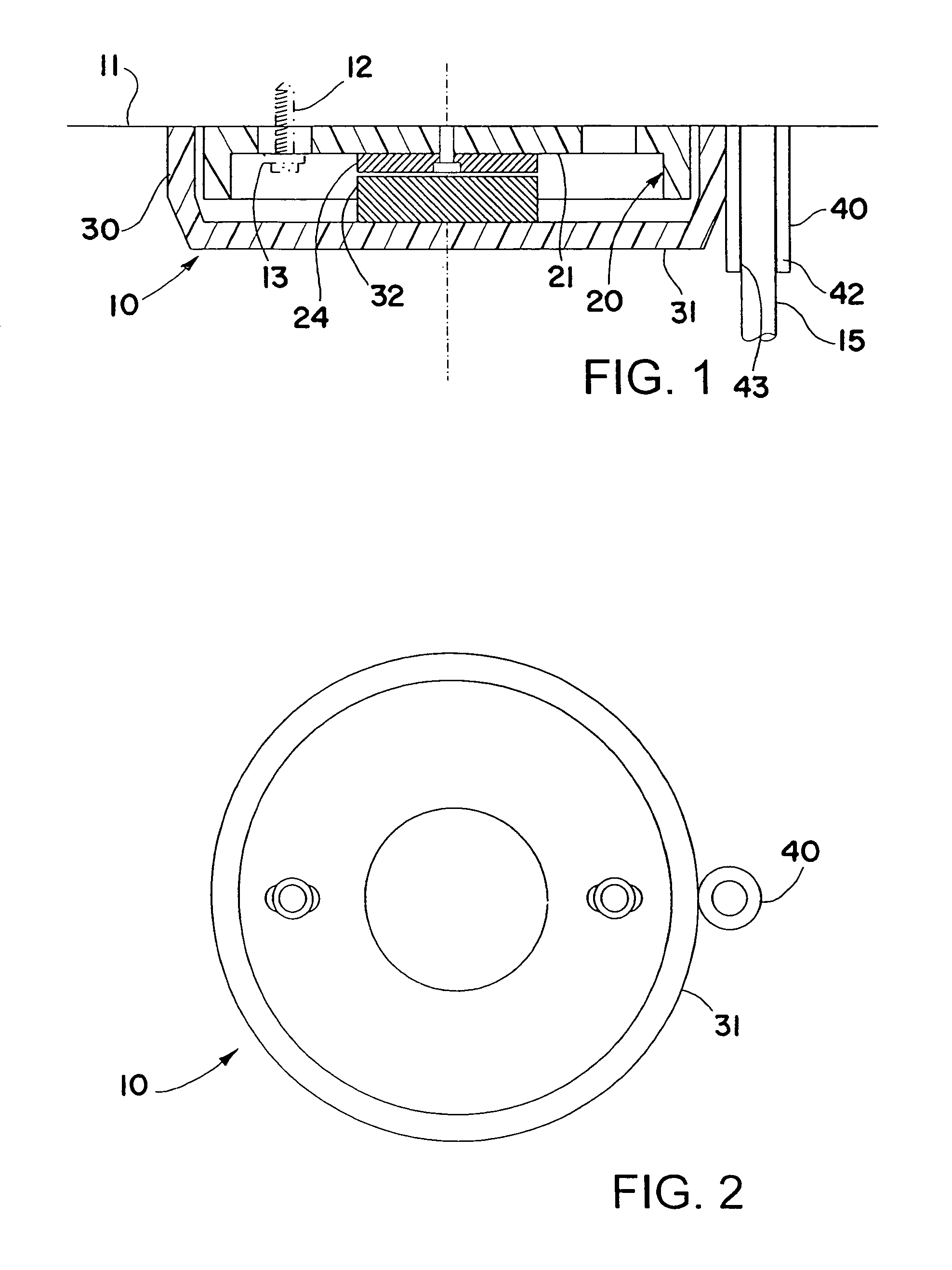

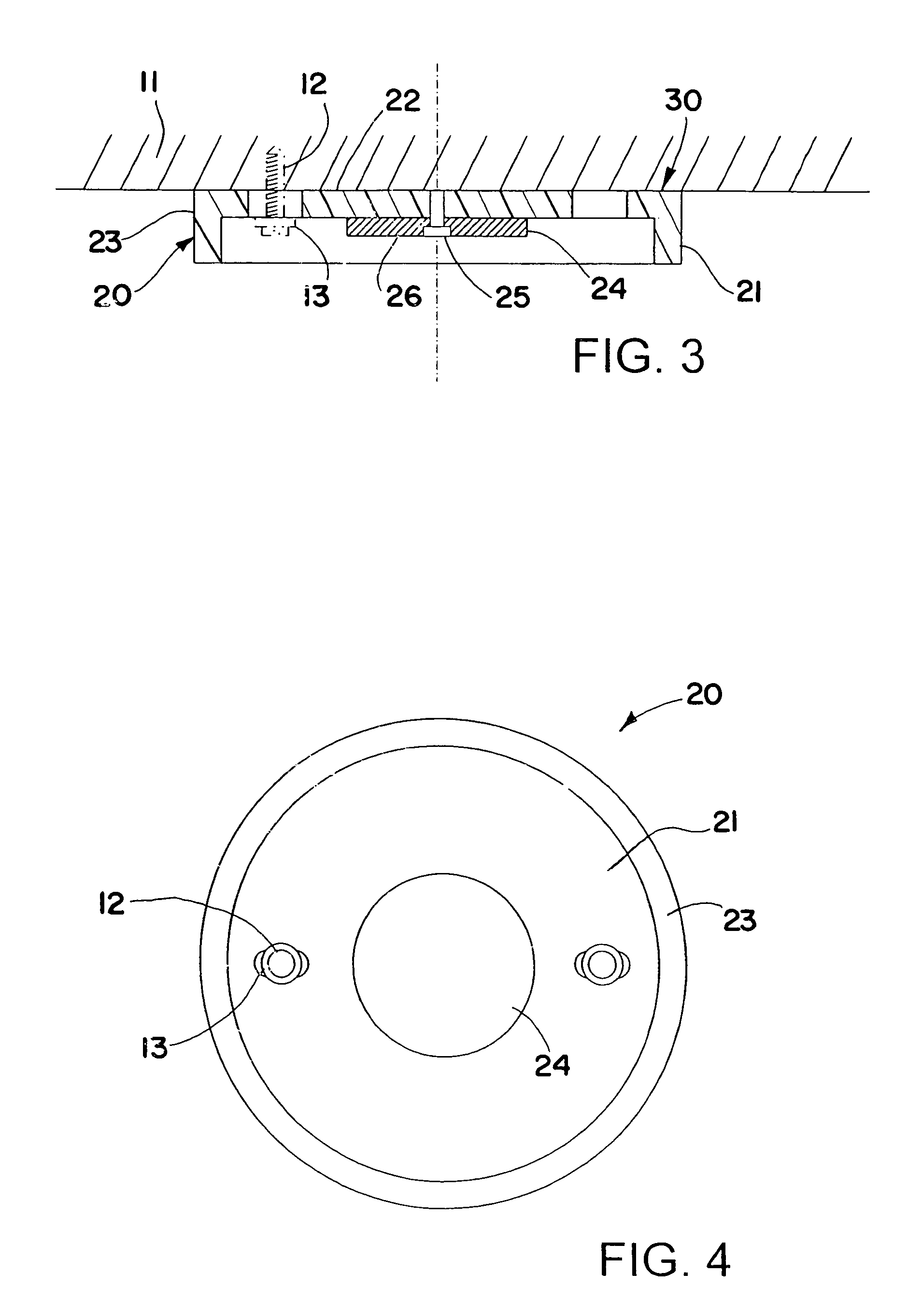

Remotely attachable and separable coupling

InactiveUS7287738B2Easy to disengageSecure supportSubstation/switching arrangement detailsPicture framesSmoke detectorsCoupling

An article for mounting from or against the ceiling is removably coupled to a base fixedly secured to the ceiling, by a person standing on the floor, supporting the article on an elongated rod, and thrusting the article against the base to couple the article and the secured base. The article is removed by inserting the rod into the article, exerting a force on the rod to uncouple the article from the base, and supporting the article on the rod as the article is lowered. The article is thus positioned on or hung from the ceiling, without being manually contacted by the person. The article may be used to mount other devices, such as a sign, smoke detector, etc. or may include such device as a part of the mount.

Owner:ACCESSMOUNT LLC

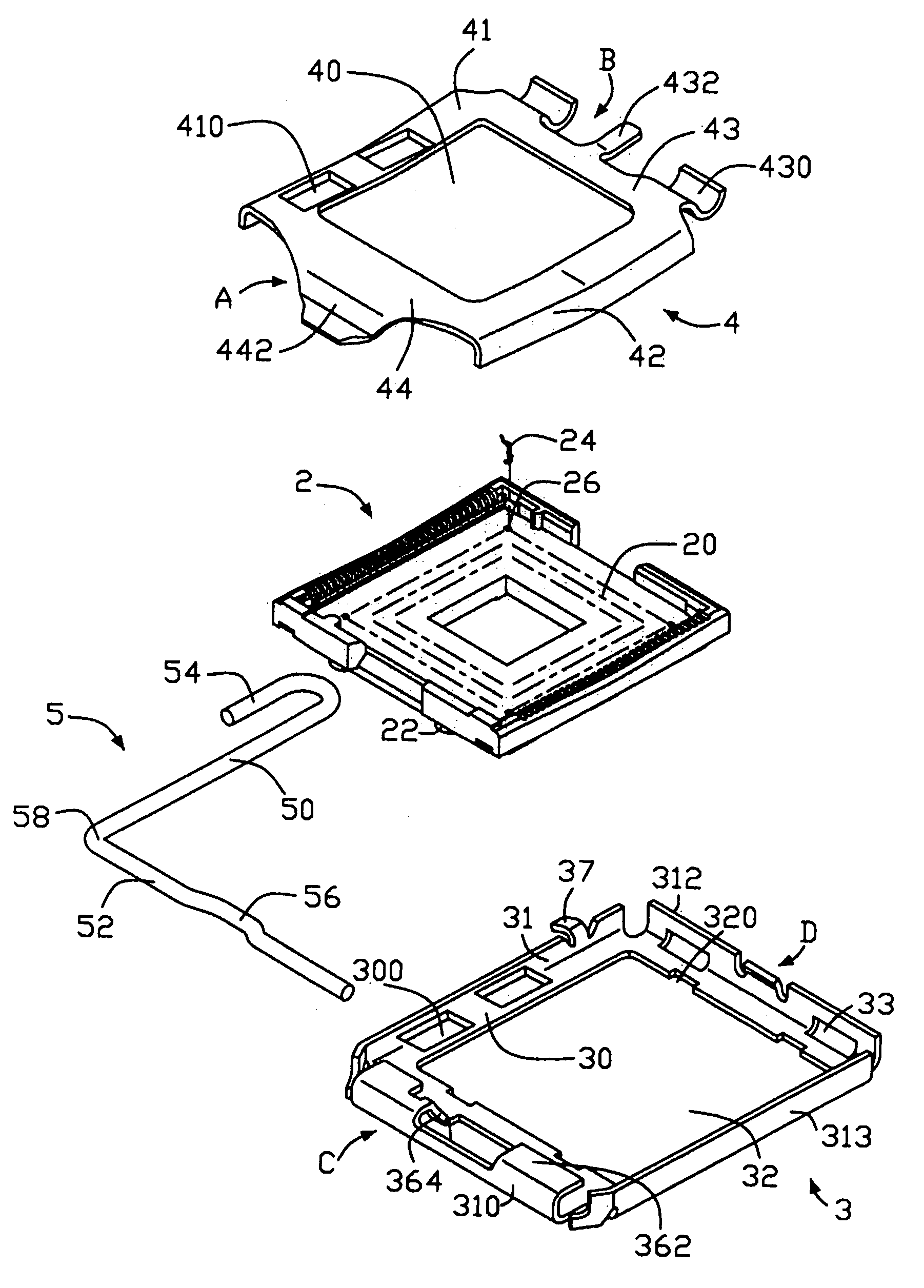

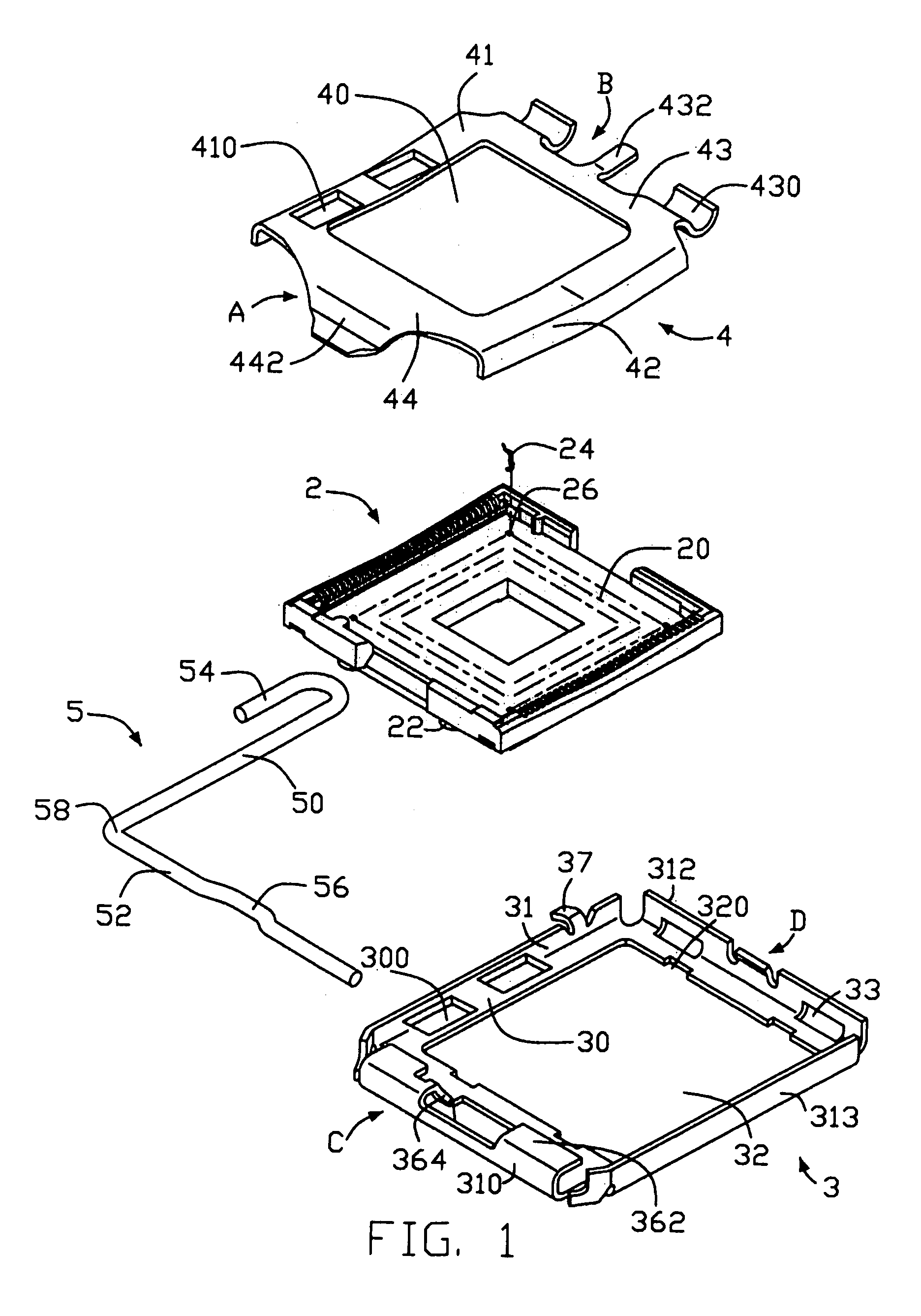

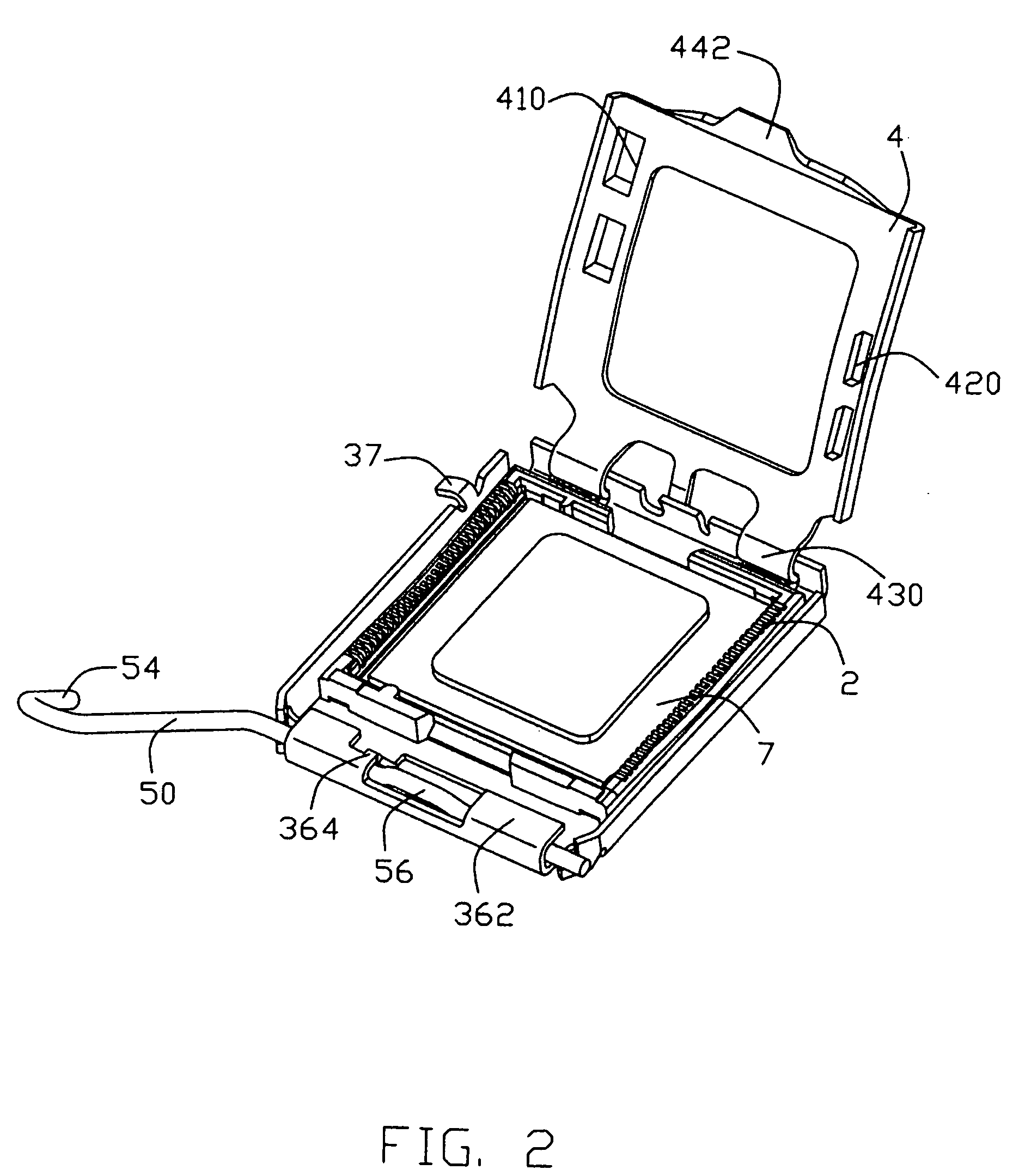

LGA socket

InactiveUS7101210B2Possibility to failAvoid possibilityEngagement/disengagement of coupling partsElectric discharge tubesEngineeringPrinted circuit board

Owner:HON HAI PRECISION IND CO LTD

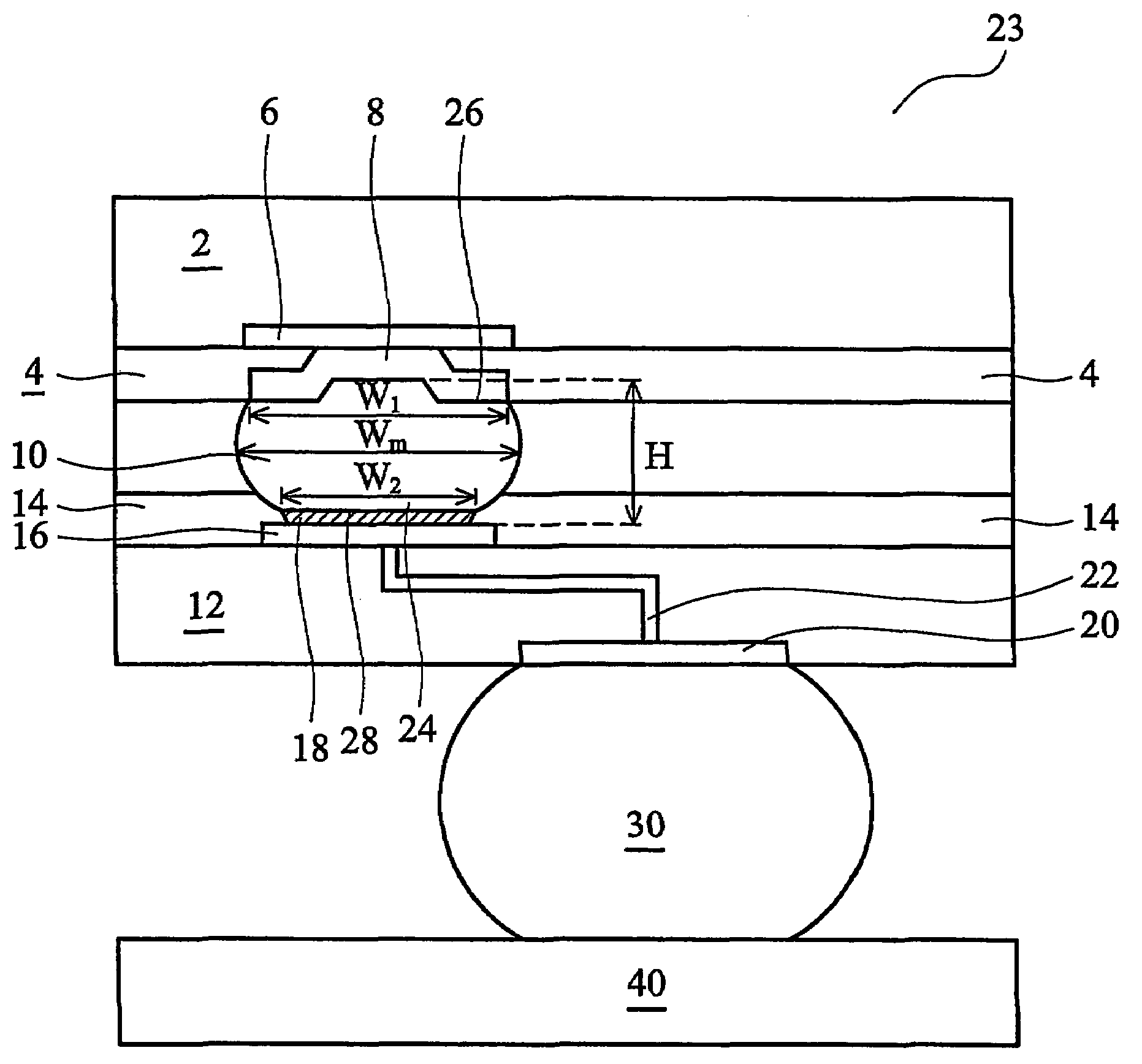

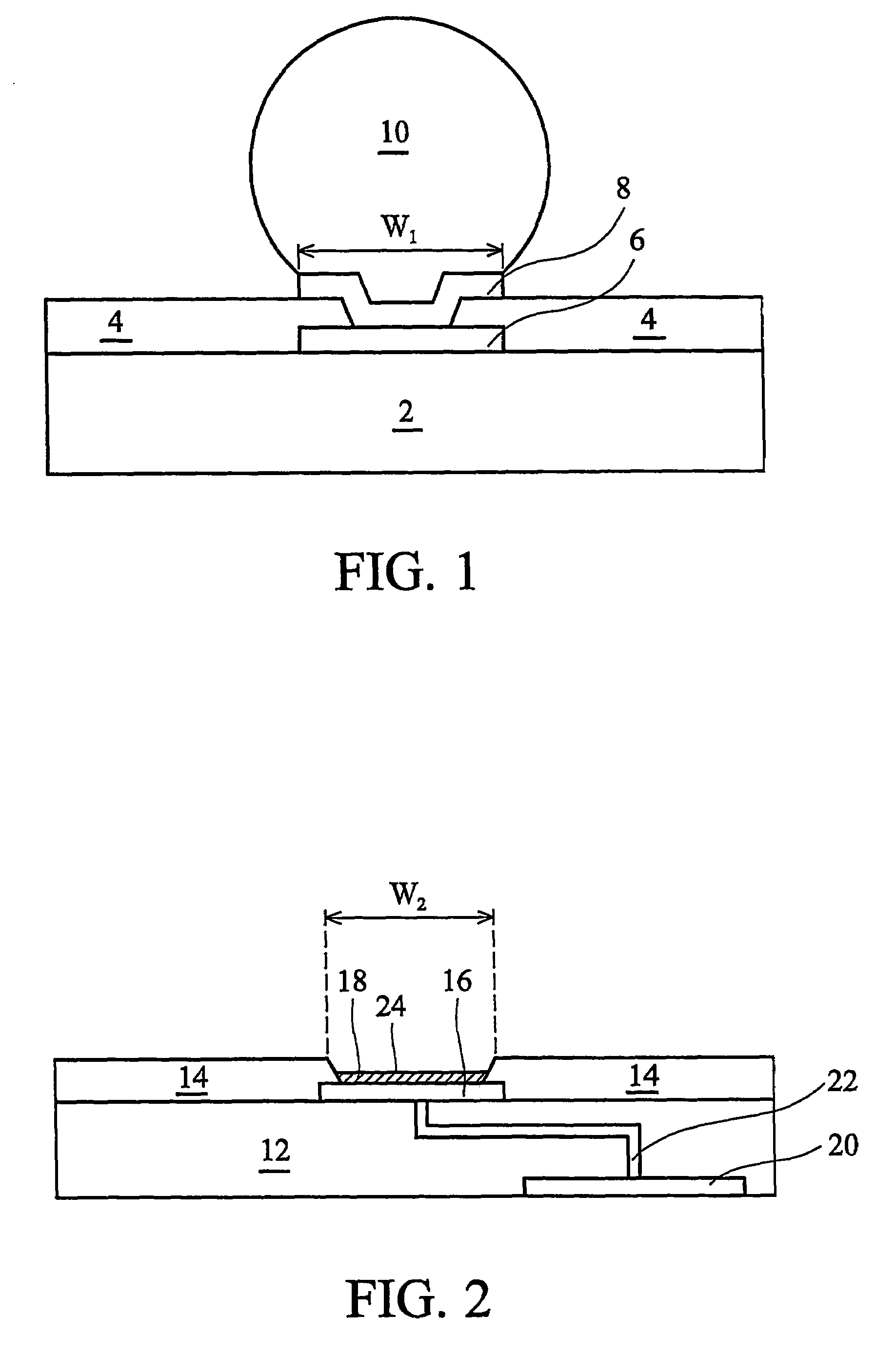

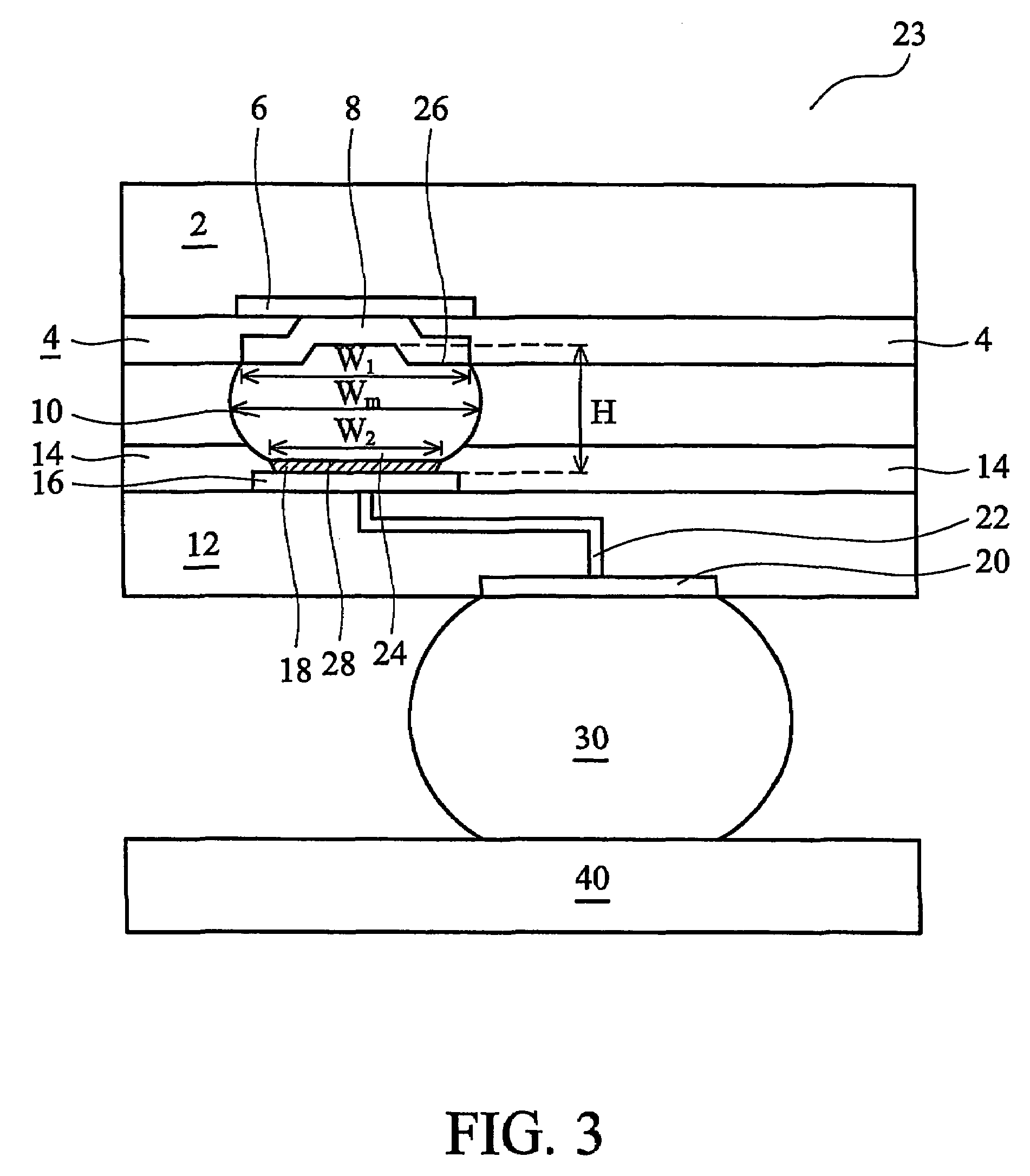

Reducing cracking of high-lead or lead-free bumps by matching sizes of contact pads and bump pads

ActiveUS7361990B2Relieve pressureReliable resultsSemiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor package

A semiconductor package assembly comprises a first conductive pad on a semiconductor substrate; a second conductive pad on a package substrate; a bump physically coupled between the first conductive pad and the second conductive pad, wherein the bump is substantially lead-free or high-lead-containing; the bump has a first interface with the first conductive pad, the first interface having a first linear dimension; the bump has a second interface with the second conductive pad, the second interface having a second linear dimension; and wherein the ratio of the first linear dimension and the second linear dimension is between about 0.7 and about 1.7.

Owner:MICROSOFT TECH LICENSING LLC

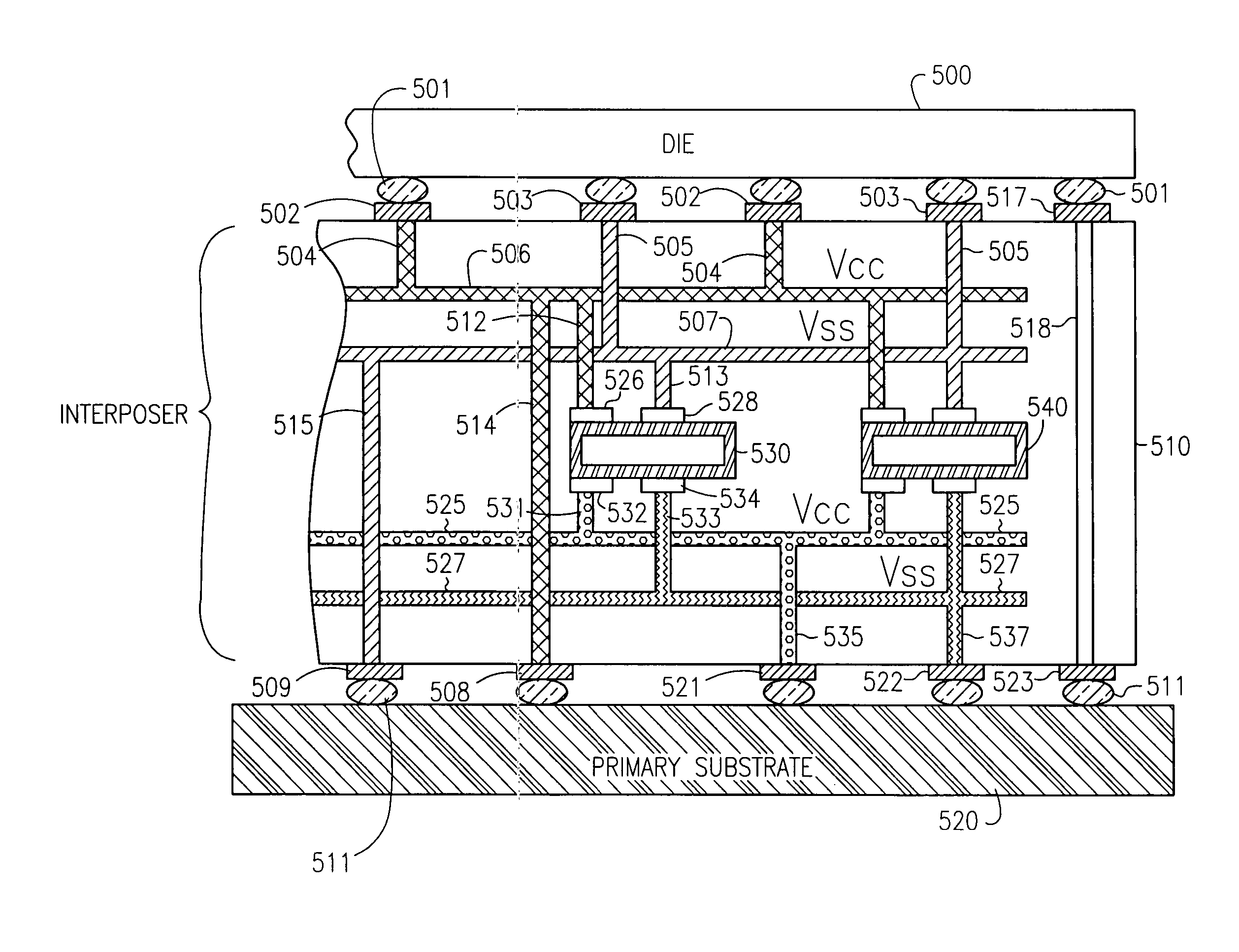

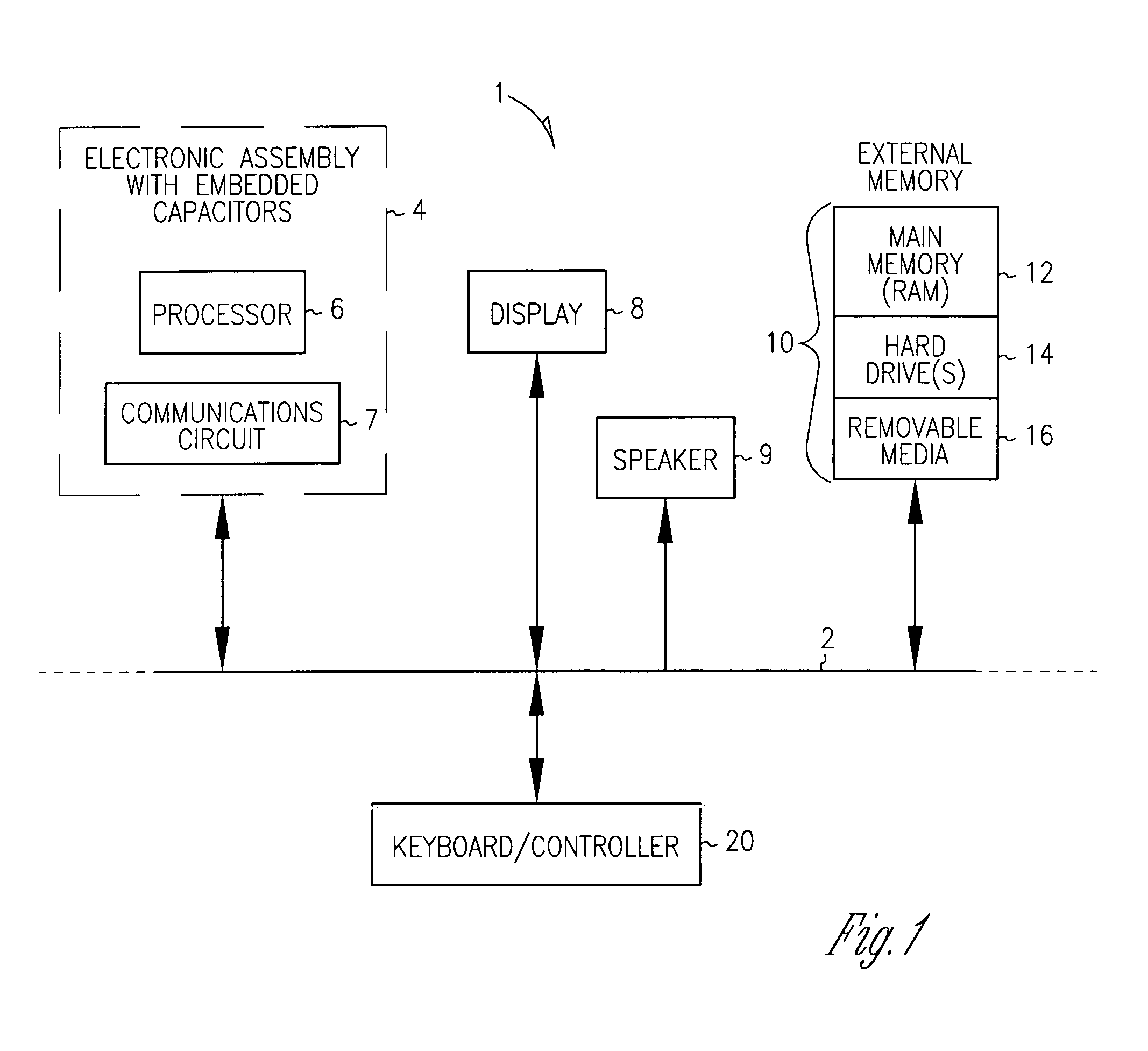

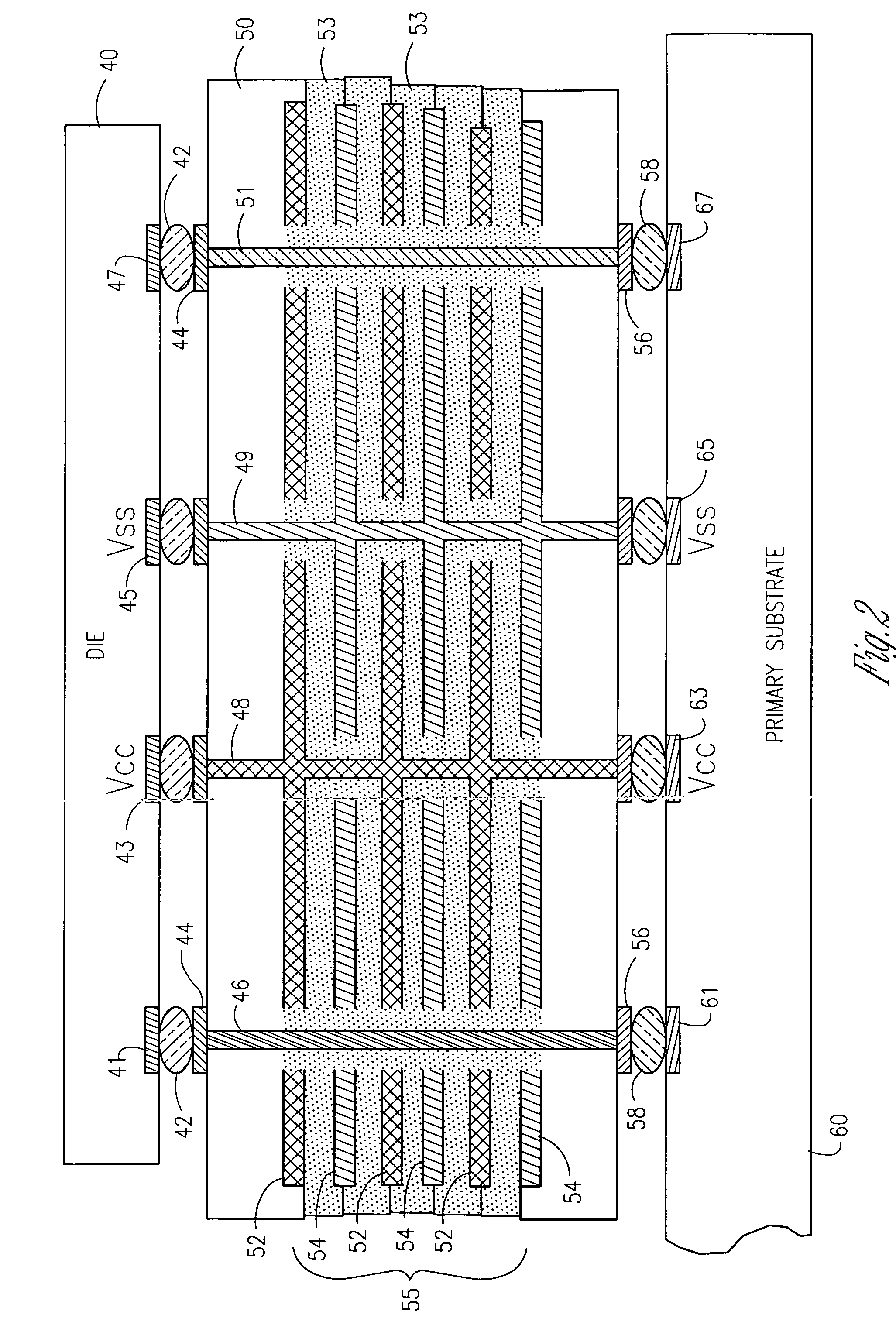

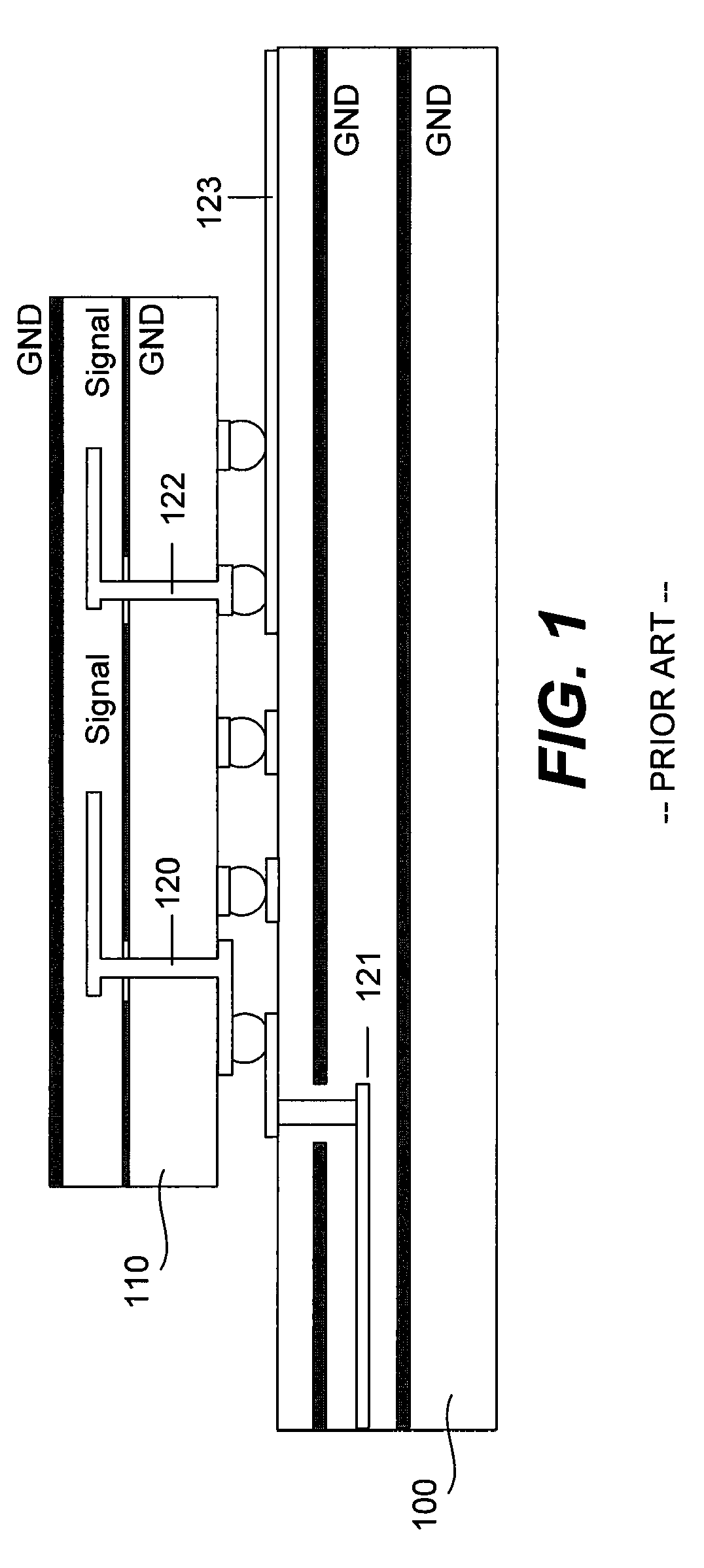

Electronic assemblies and systems comprising interposer with embedded capacitors

InactiveUS20060012966A1Semiconductor/solid-state device detailsSolid-state devicesData processing systemElectrical conductor

To reduce switching noise, the power supply terminals of an integrated circuit die are coupled to the respective terminals of at least one capacitor embedded in an interposer that lies between the die and a substrate. In an embodiment, the interposer is a multilayer ceramic structure that couples power and signal conductors on the die to corresponding conductors on the substrate. The capacitor is formed of at least one high permittivity layer and in an embodiment comprises several high permittivity layers interleaved with conductive layers. Alternatively, the capacitor can comprise at least one embedded discrete capacitor. Also described are an electronic system, a data processing system, and various methods of manufacture.

Owner:INTEL CORP

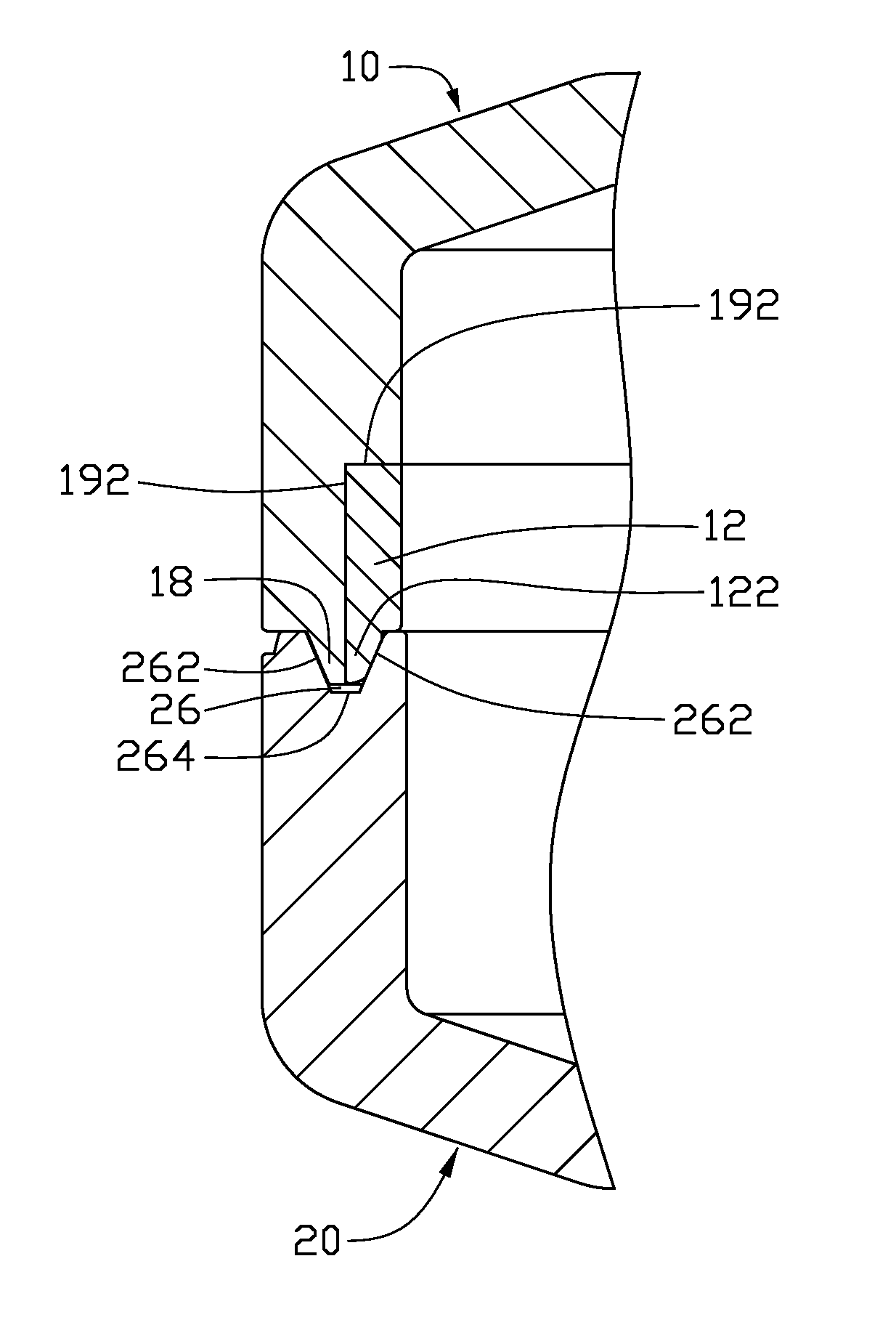

Housing mechanism for electronic device and method for making the same

InactiveUS7436653B2Digital data processing detailsResilient/clamping meansEngineeringElectronic equipment

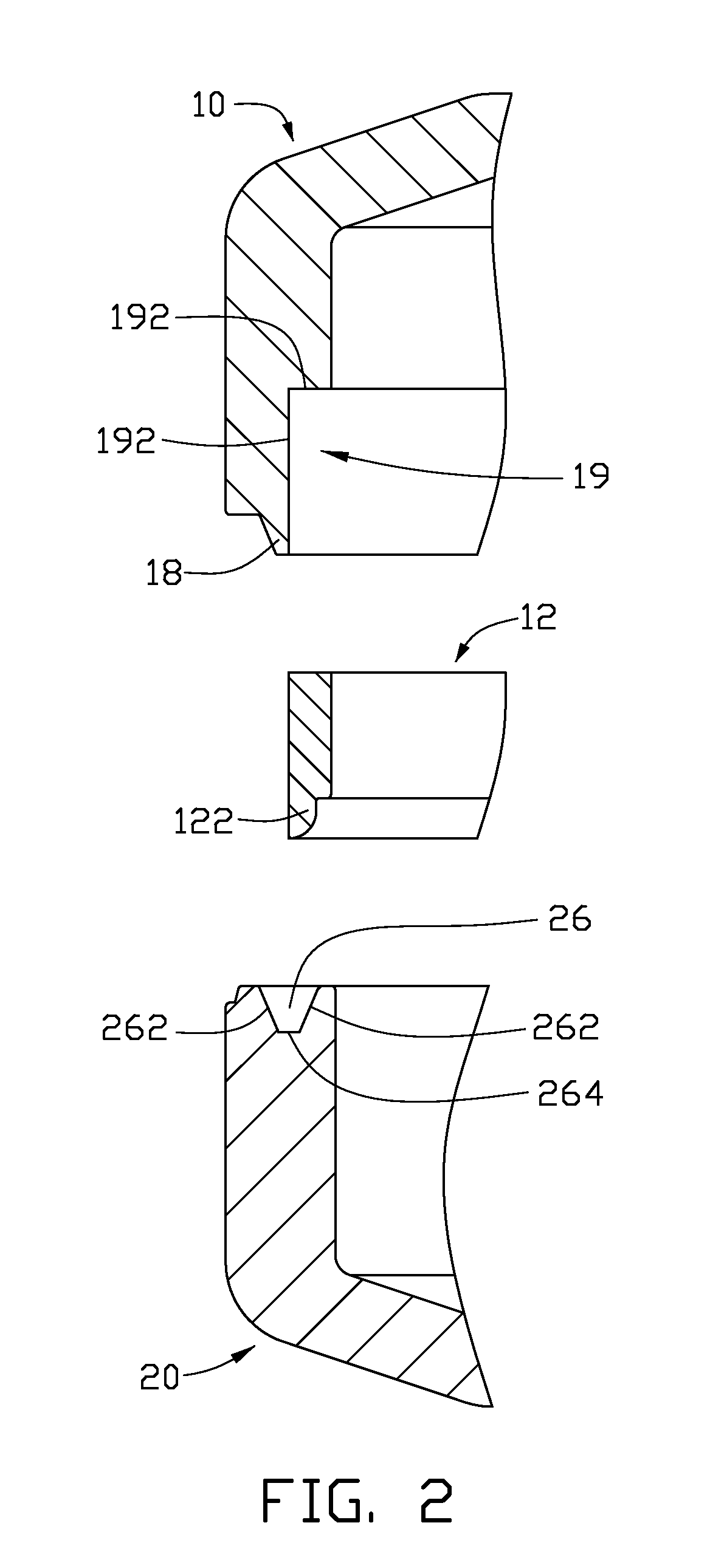

An exemplary housing mechanism (100) for an electronic device includes a front cover (10), a back cover (20), and an elastic sealing element (12). The front cover has a projecting edge (18) defined thereon. The back cover has a recessed edge (26) defined therein. The elastic sealing element has a tip portion (122) and is formed or sealed together with the front cover. The projecting edge of the front cover and the tip portion of the elastic sealing element are configured to be press fit into the recessed edge of the back cover.

Owner:GOLD CHARM LTD

Heat sink formed with conformal shield

ActiveUS20090000114A1Printed circuit assemblingWave amplification devicesEngineeringElectromagnetic shielding

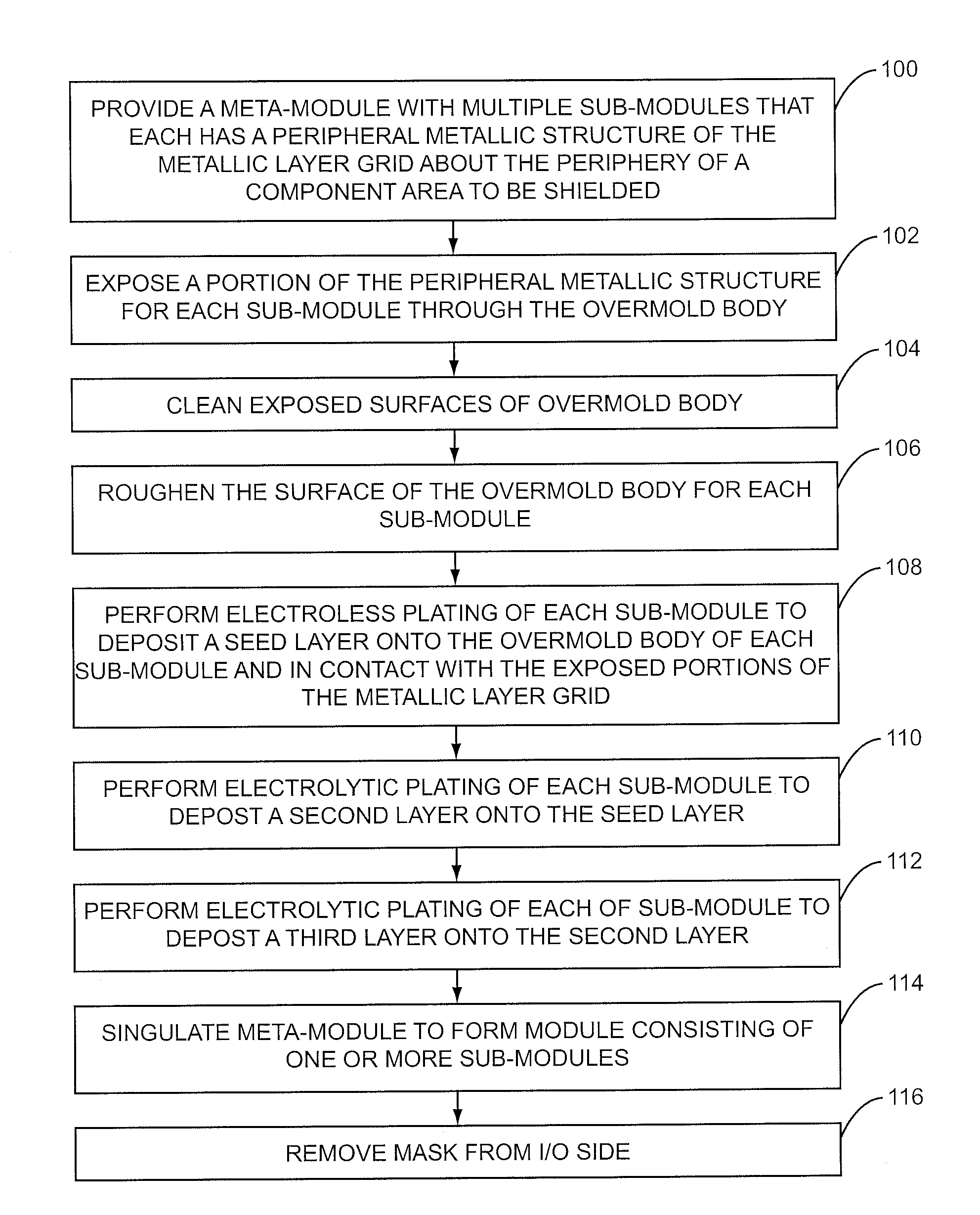

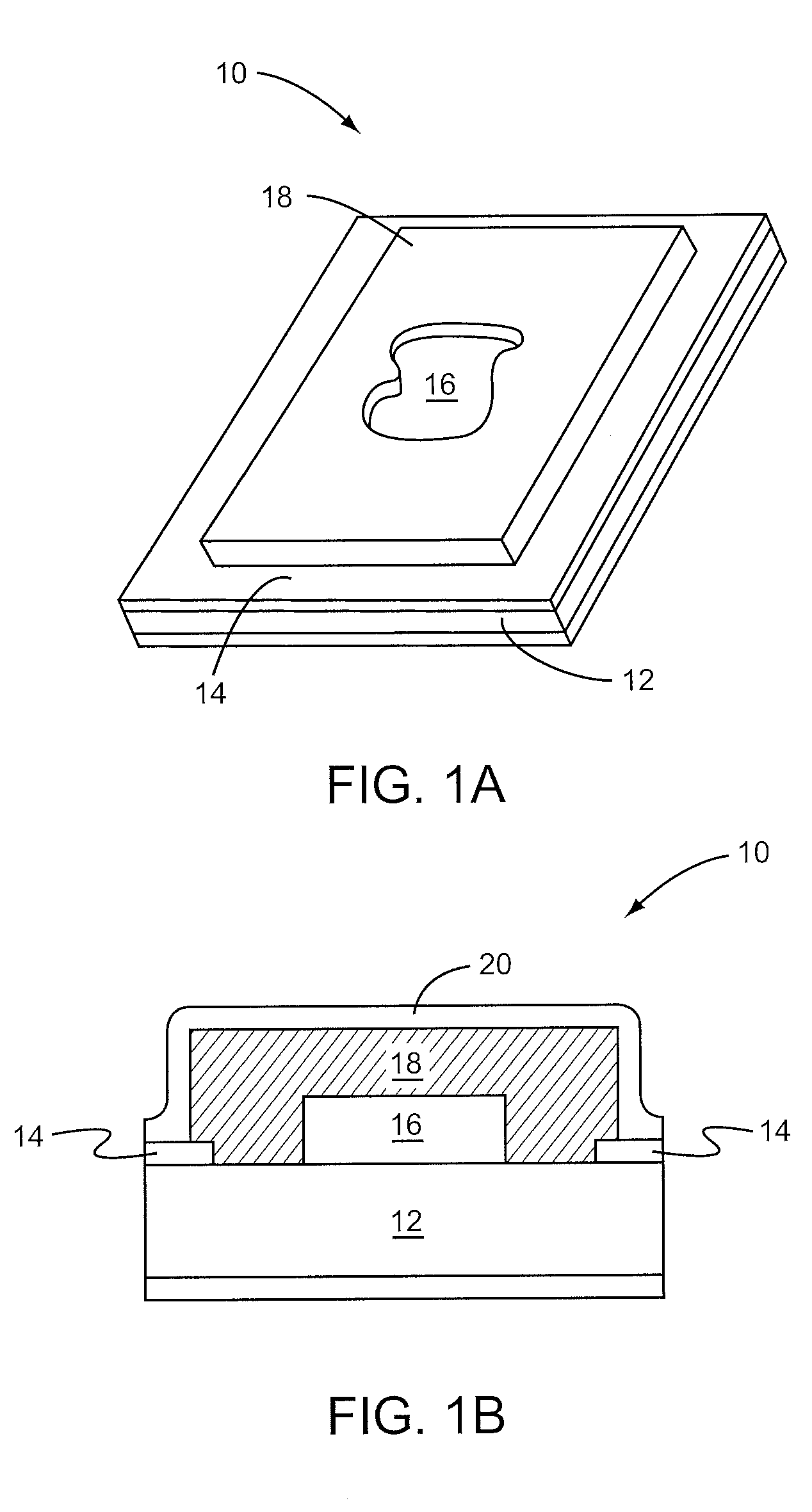

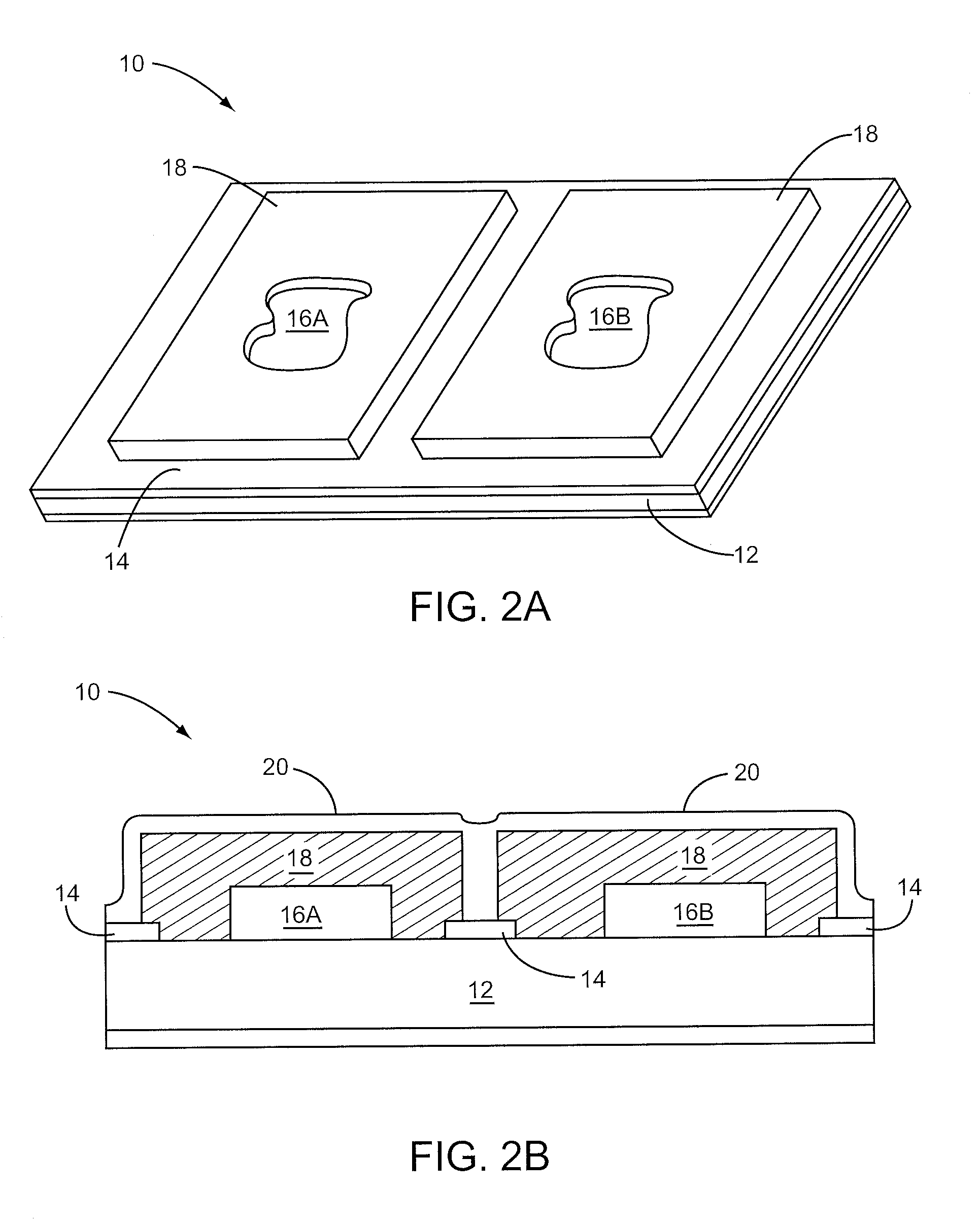

In one embodiment, a meta-module having circuitry for two or more modules is formed on a substrate, which is preferably a laminated substrate. The circuitry for the different modules is initially formed on the single meta-module. Each module will have one or more component areas in which the circuitry is formed. A metallic structure is formed on or in the substrate for each component area to be shielded. A single body, such as an overmold body, is then formed over all of the modules on the meta-module. At least a portion of the metallic structure for each component area to be shielded is then exposed through the body by a cutting, drilling, or like operation. Next, an electromagnetic shield material is applied to the exterior surface of the body of each of the component areas to be shielded and in contact with the exposed portion of the metallic structures.

Owner:QORVO US INC

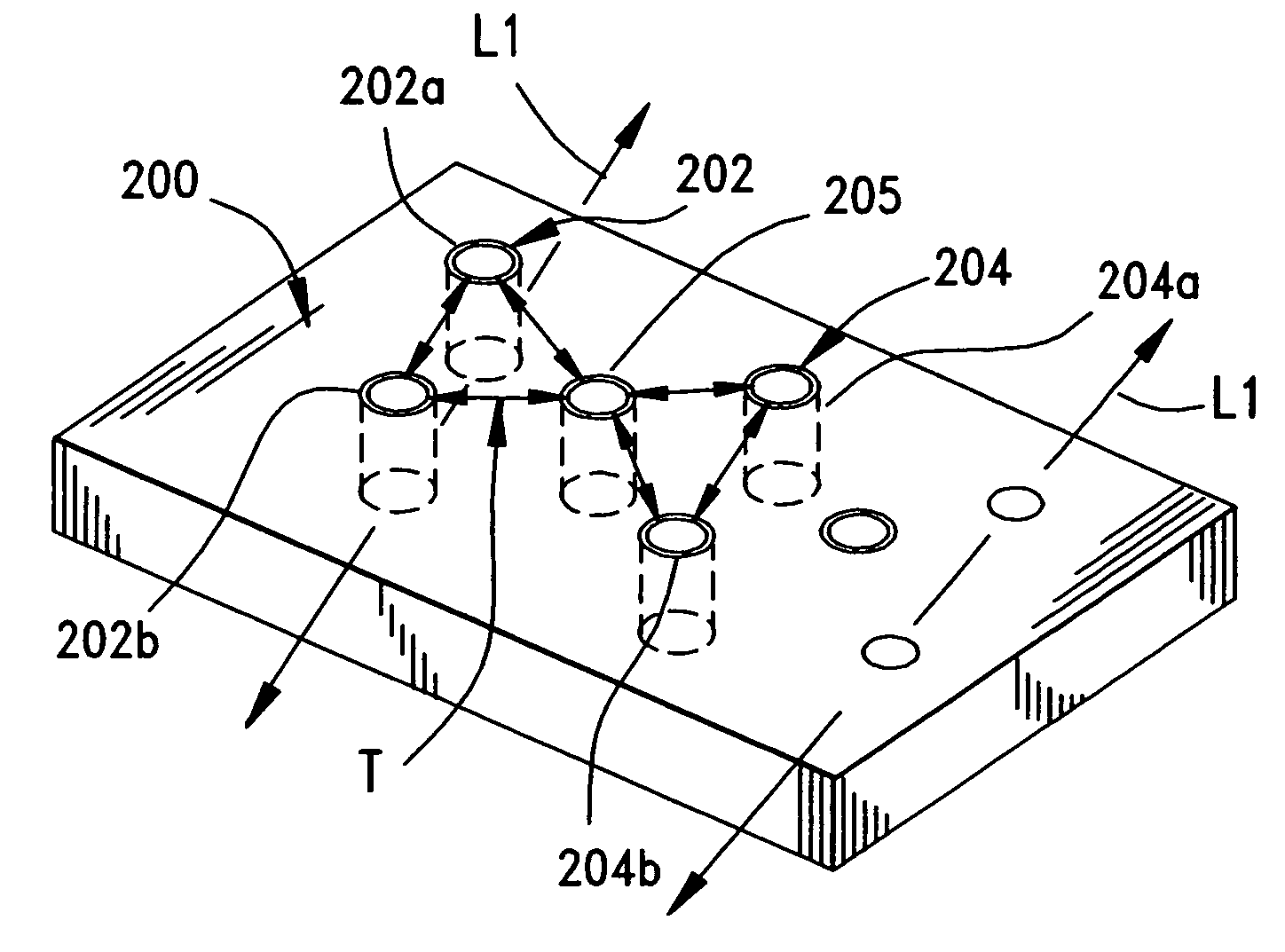

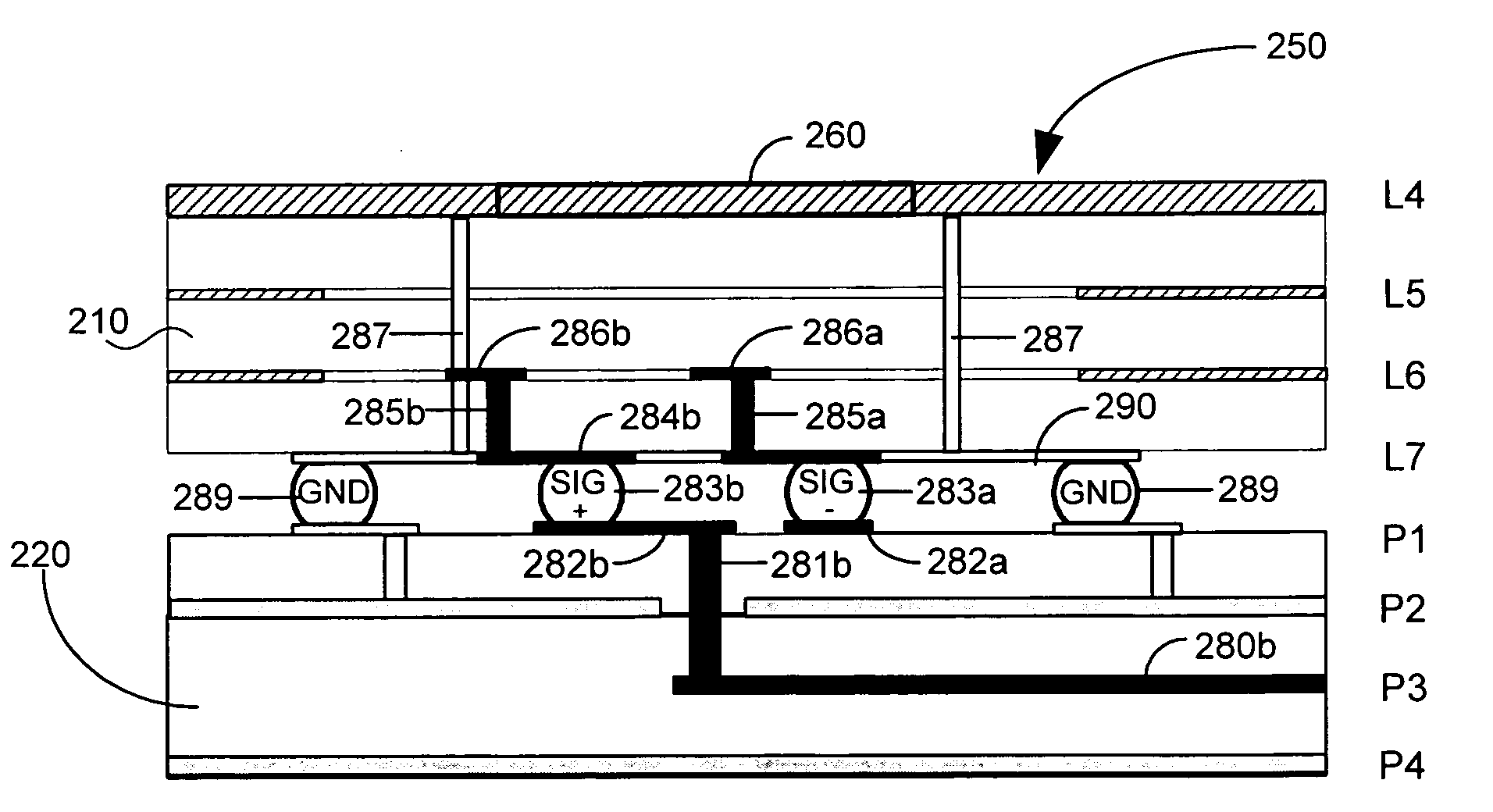

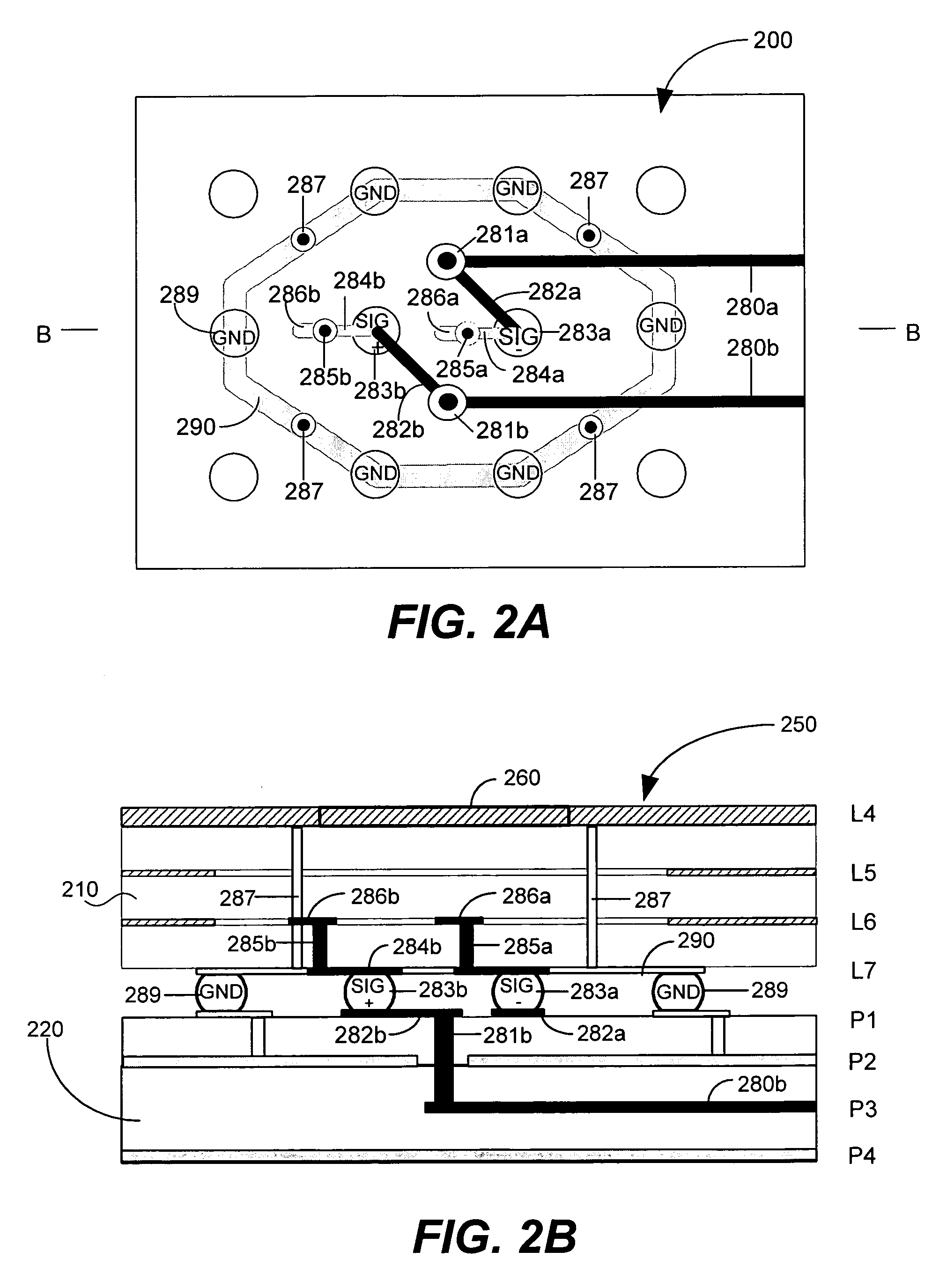

Preferential via exit structures with triad configuration for printed circuit boards

ActiveUS20050202722A1Promotes capacitive couplingSimple structureElectrically conductive connectionsPrinted circuit aspectsEngineeringGround plane

A circuit board design is disclosed that is useful in high-speed differential signal applications uses either a via arrangement or a circuit trace exit structure. A pair of differential signal vias in a circuit board are surrounded by an opening that is formed within a ground plane disposed on another layer of the circuit board. The vias are connected to traces on the circuit board by way of an exit structure that includes two flag portions and associated angled portions that connect the flag portions to circuit board traces. In an alternate embodiment, the circuit board traces that leave the differential signal vias are disposed in one layer of the circuit board above a wide ground strip disposed on another layer of the circuit board.

Owner:MOLEX INC

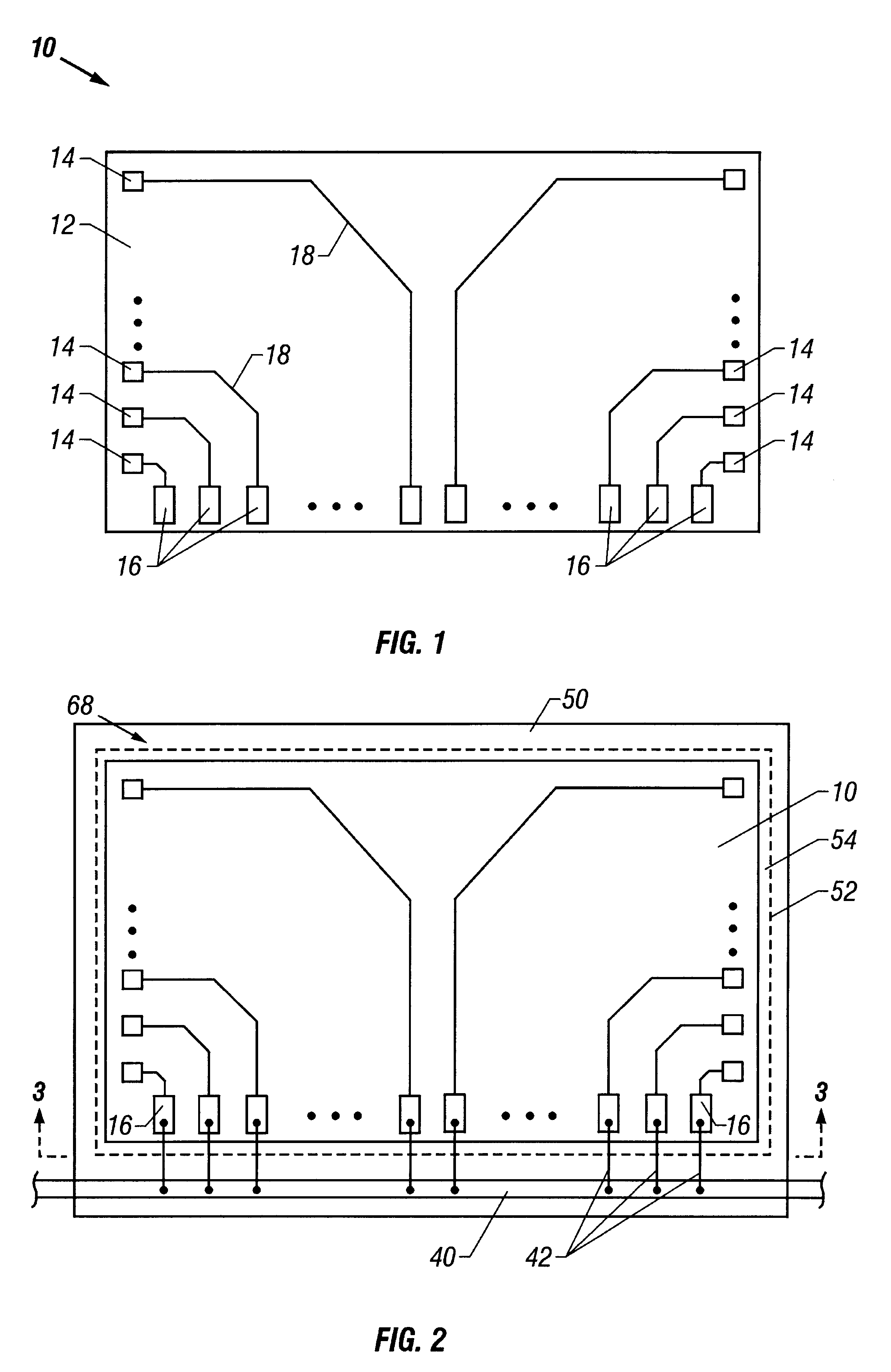

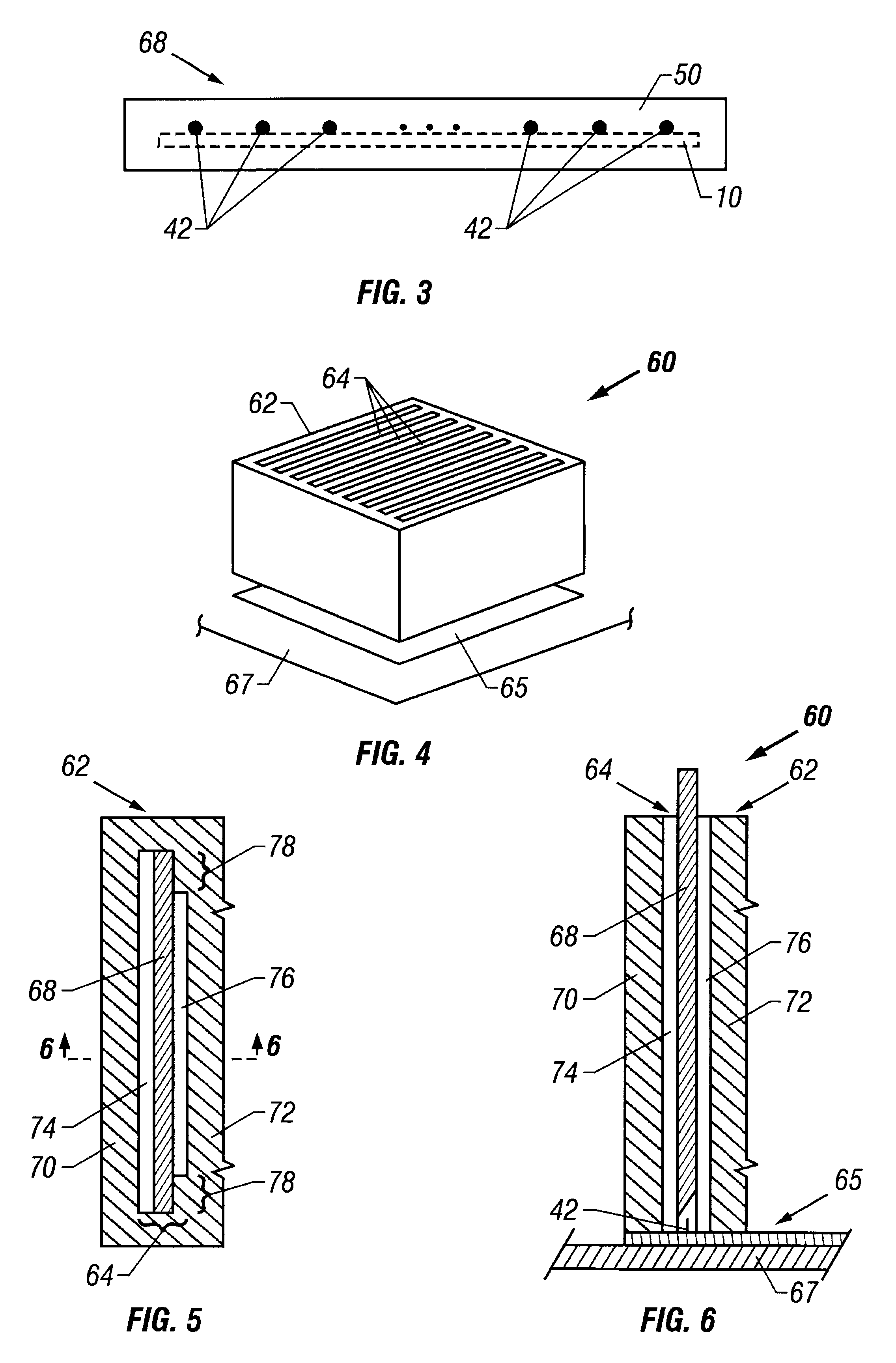

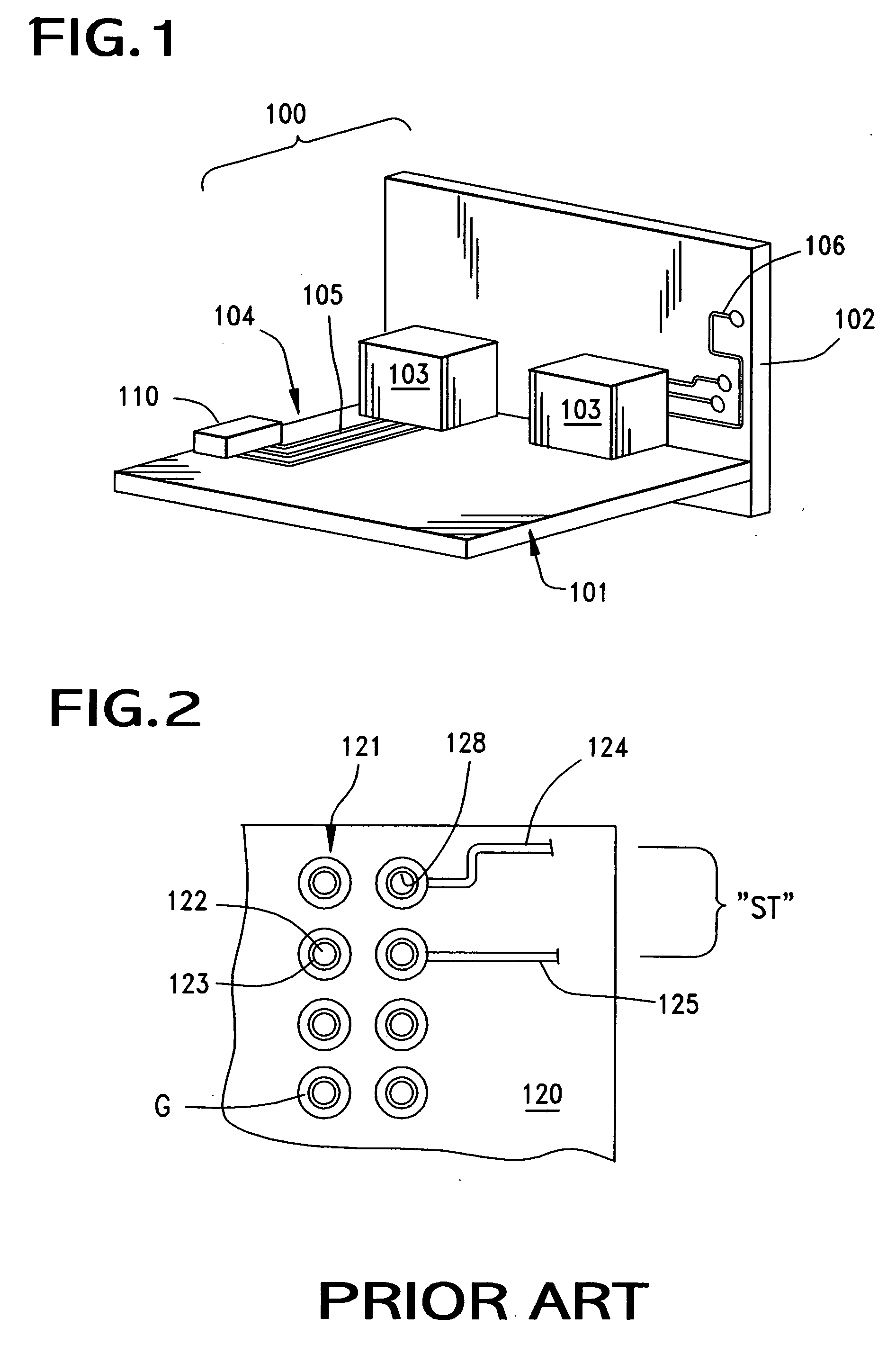

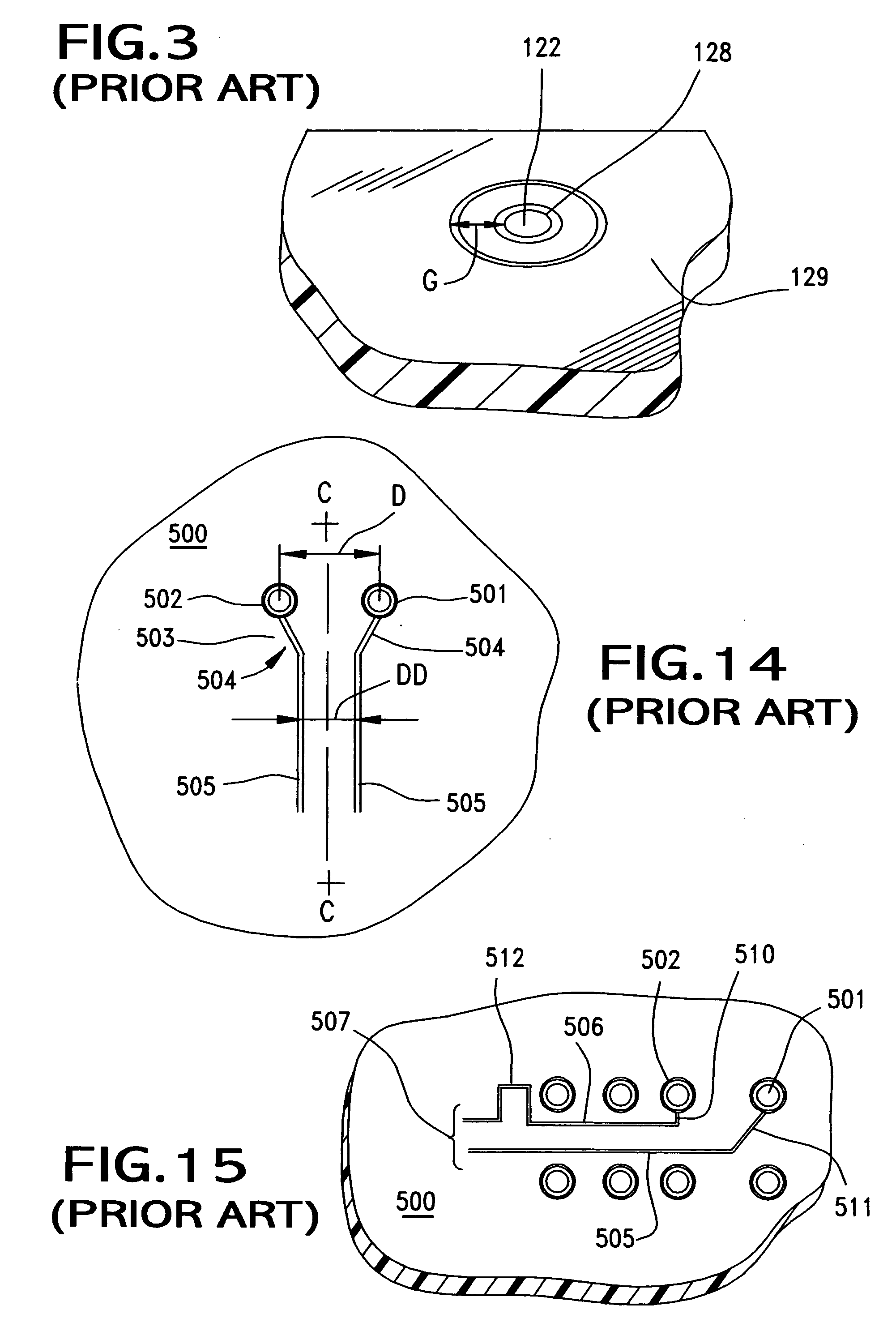

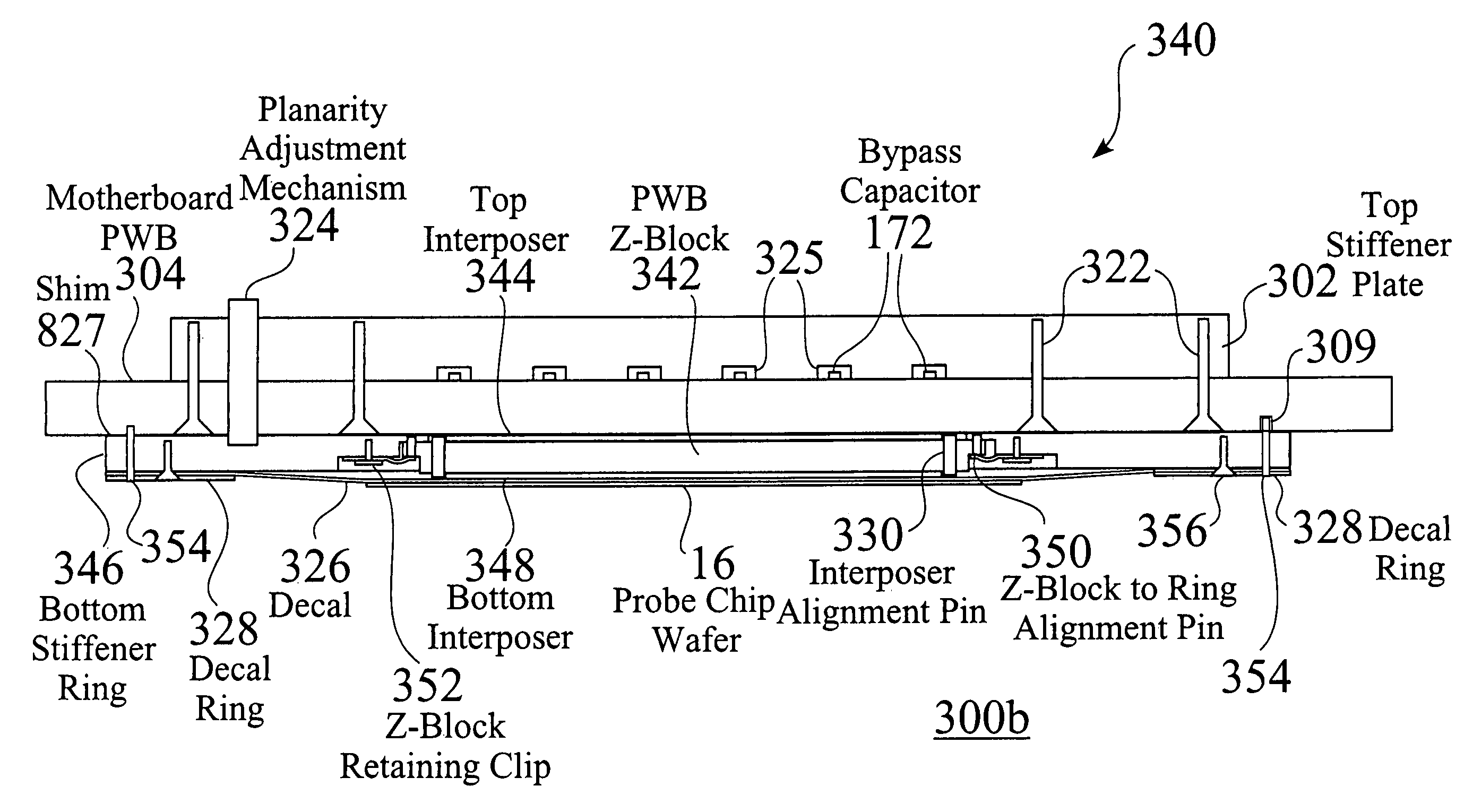

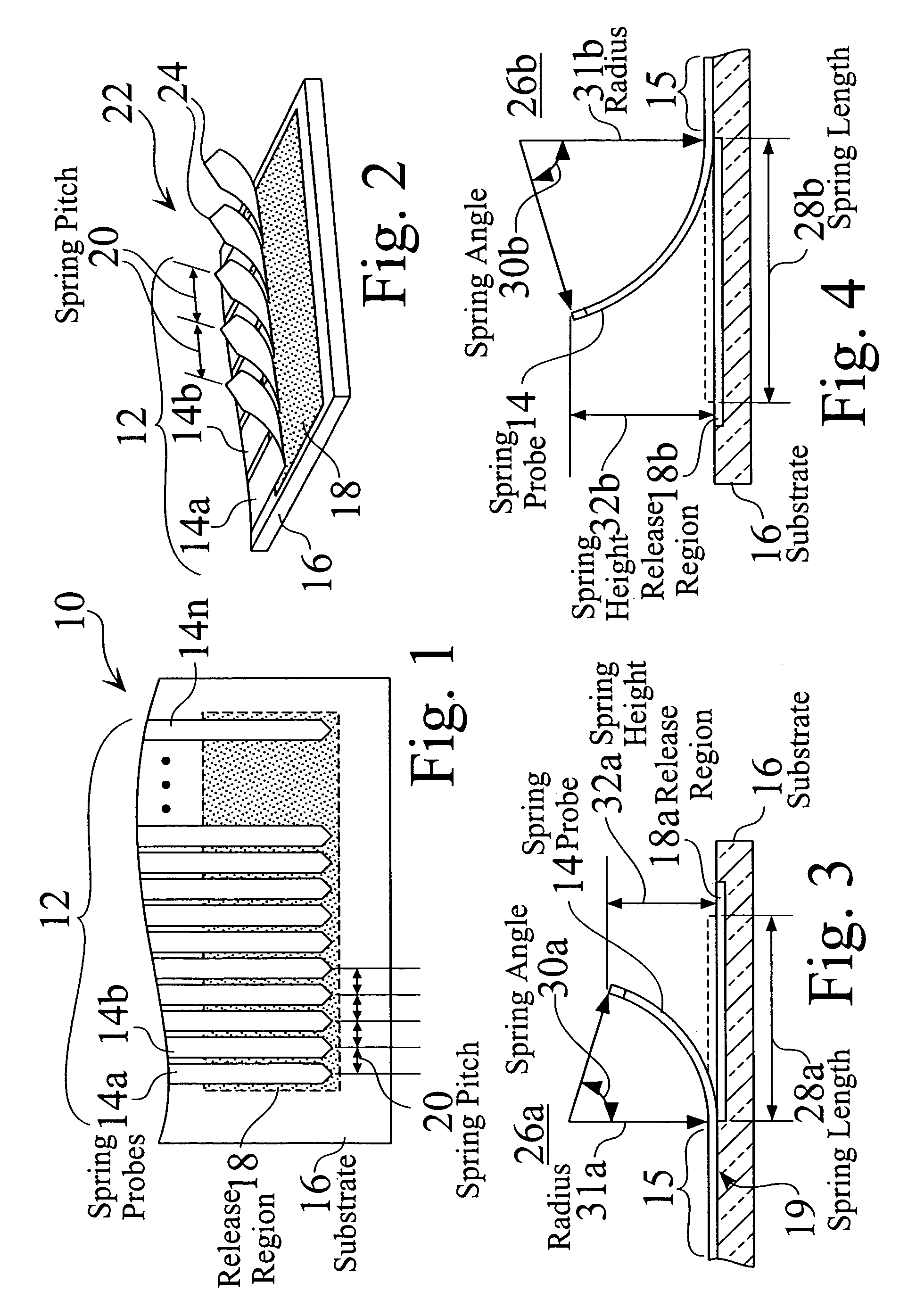

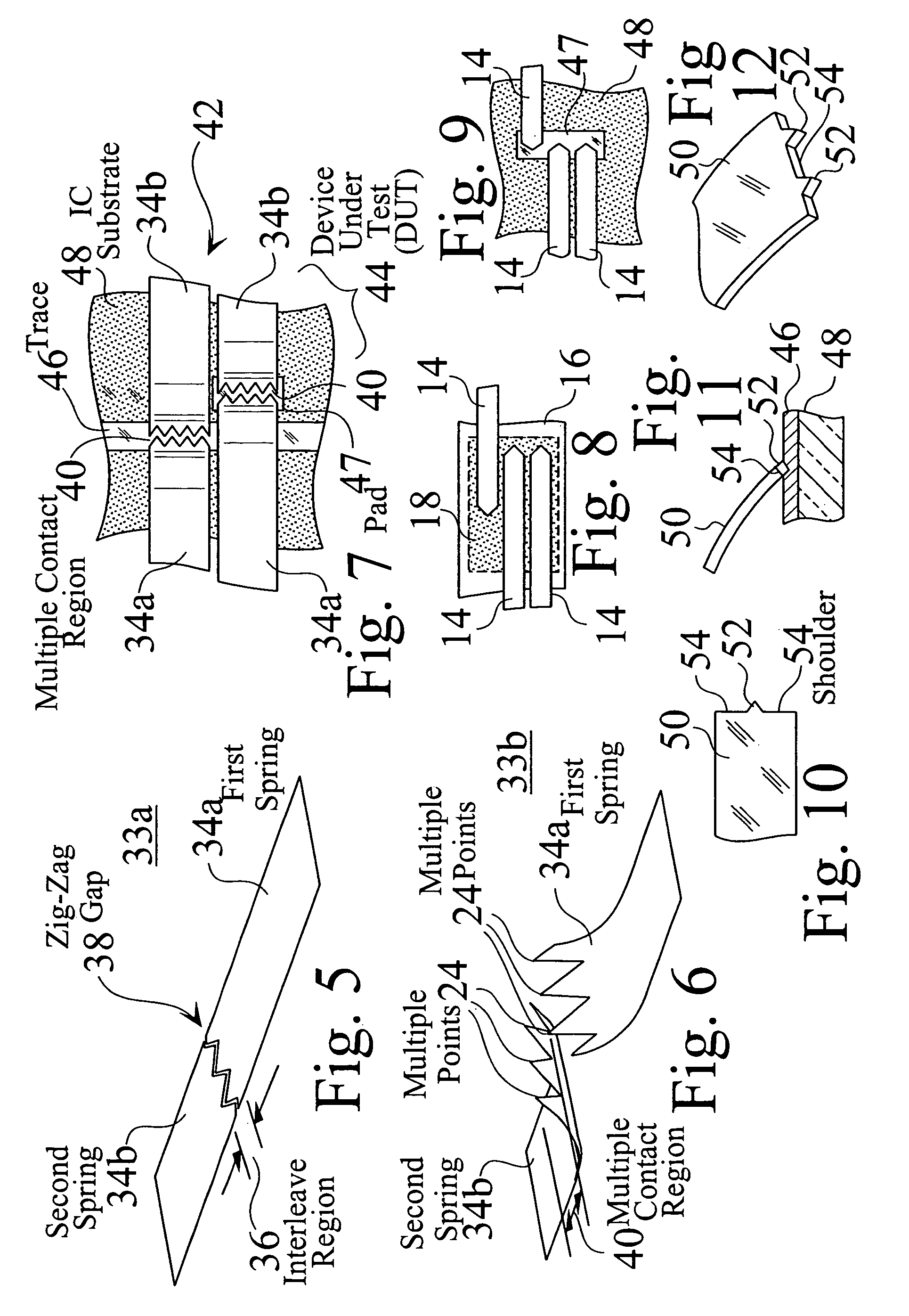

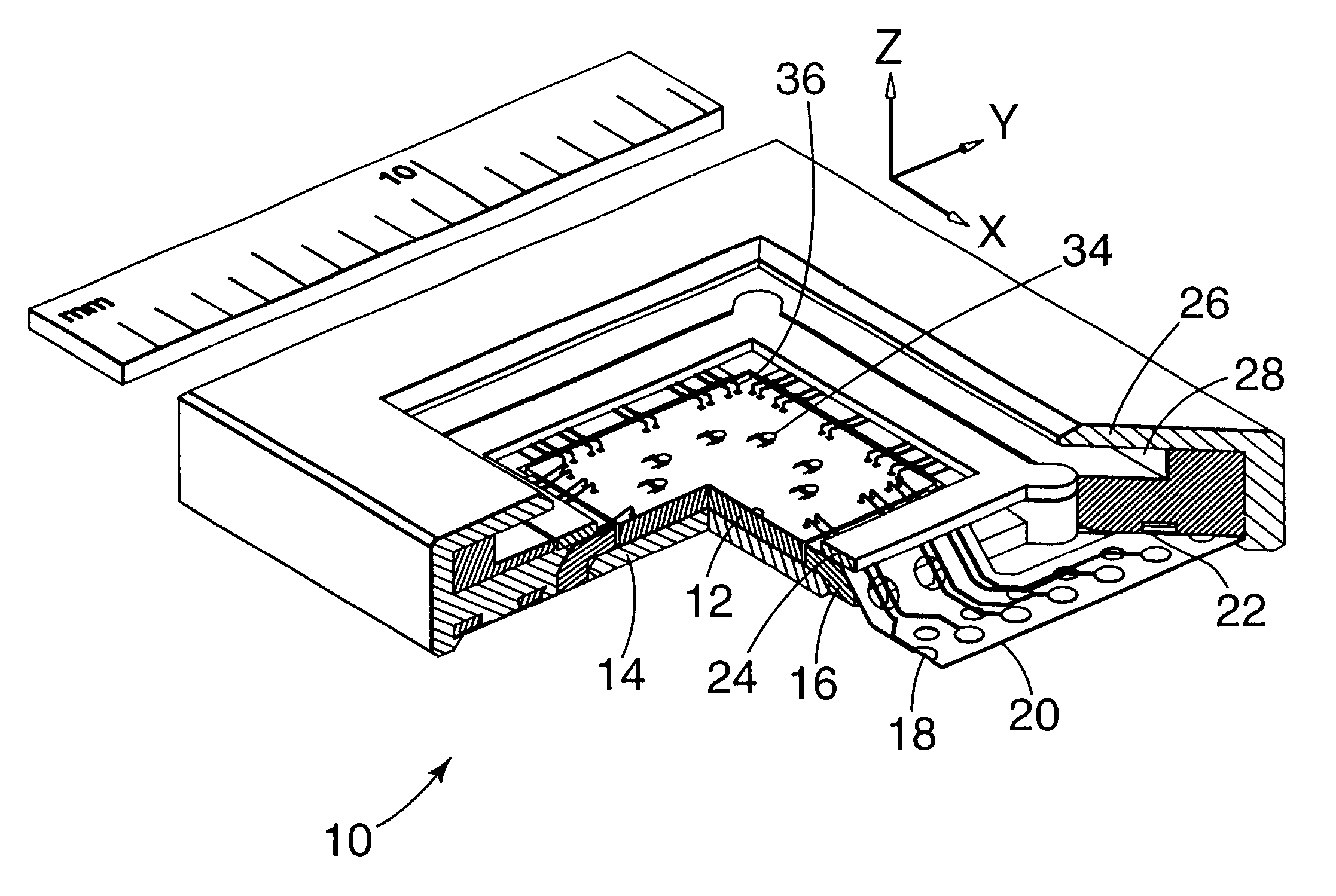

Enhanced compliant probe card systems having improved planarity

InactiveUS7349223B2Improve complianceImprove the level ofCoupling device connectionsSubstation/switching arrangement detailsProbe cardAssembly structure

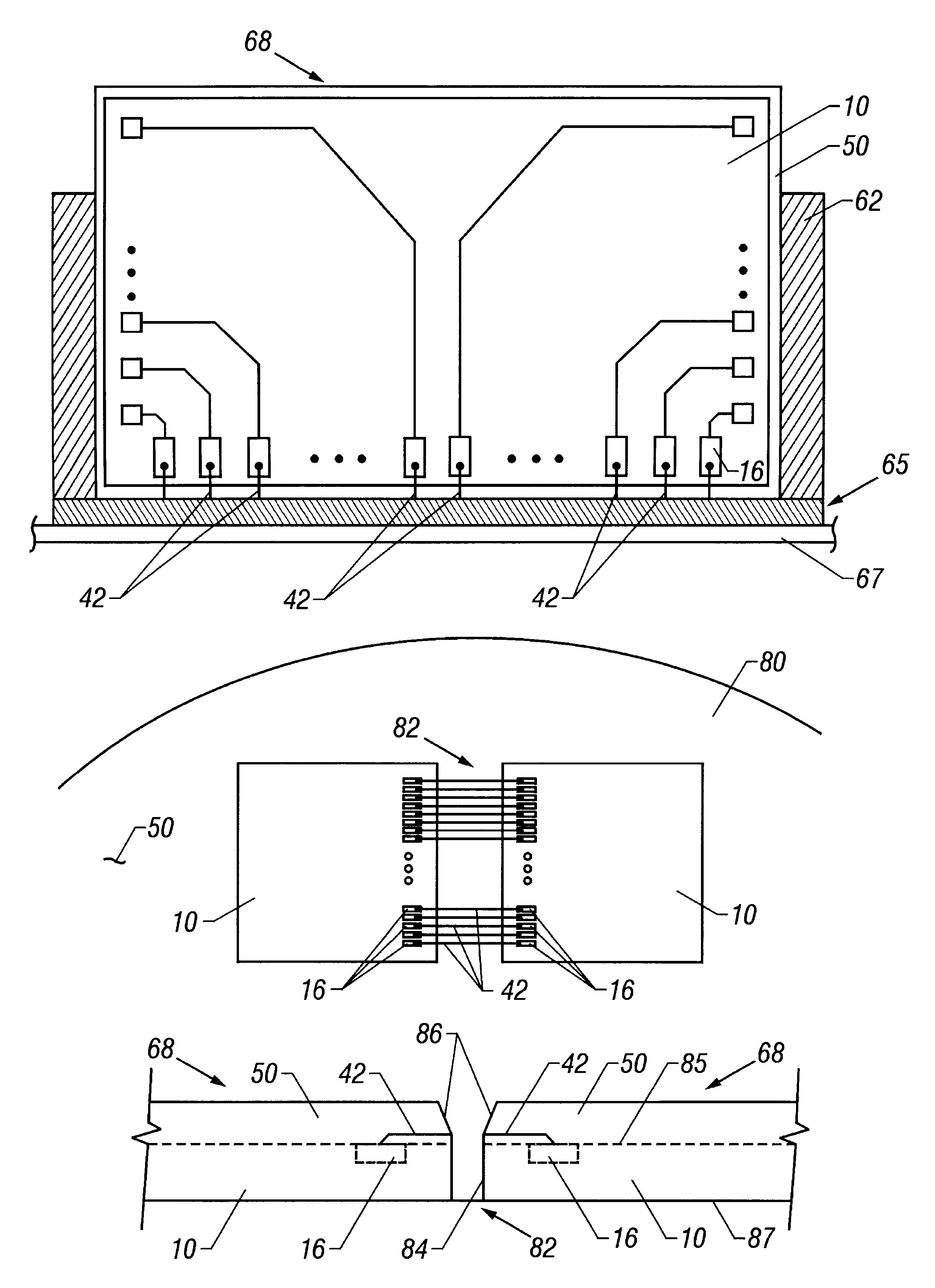

Several embodiments of enhanced integrated circuit probe card and package assemblies are disclosed, which extend the mechanical compliance of both MEMS and thin-film fabricated probes, such that these types of spring probe structures can be used to test one or more integrated circuits on a semiconductor wafer. Several embodiments of probe card assemblies, which provide tight signal pad pitch compliance and / or enable high levels of parallel testing in commercial wafer probing equipment, are disclosed. In some preferred embodiments, the probe card assembly structures include separable standard components, which reduce assembly manufacturing cost and manufacturing time. These structures and assemblies enable high speed testing in wafer form. The probes also have built in mechanical protection for both the integrated circuits and the MEMS or thin film fabricated spring tips and probe layout structures on substrates. Alternate card assembly structures comprise a stiffening structure and a compliant carrier structure, such as a decal or screen, which is fixedly attached to the probe chip substrate.

Owner:ADVANTEST SINGAPORE PTE LTD

Ball grid array package-to-board interconnect co-design apparatus

InactiveUS7405477B1Signal transmission is convenientAvoid reflectionsSemiconductor/solid-state device detailsPrinted circuit aspectsCopper interconnectData stream

A package-board co-design methodology preserves the signal integrity of high-speed signals passing from semiconductor packages to application PCBs. An optimal architecture of interconnects between package and PCB enhances the signal propagation, minimizes parasitic levels, and decreases electromagnetic interference from adjacent high frequency signals. The invention results in devices with superior signal quality and EMI shielding properties with enhanced capability for carrying data stream at multiple-gigabit per second bit-rates.

Owner:TAHOE RES LTD

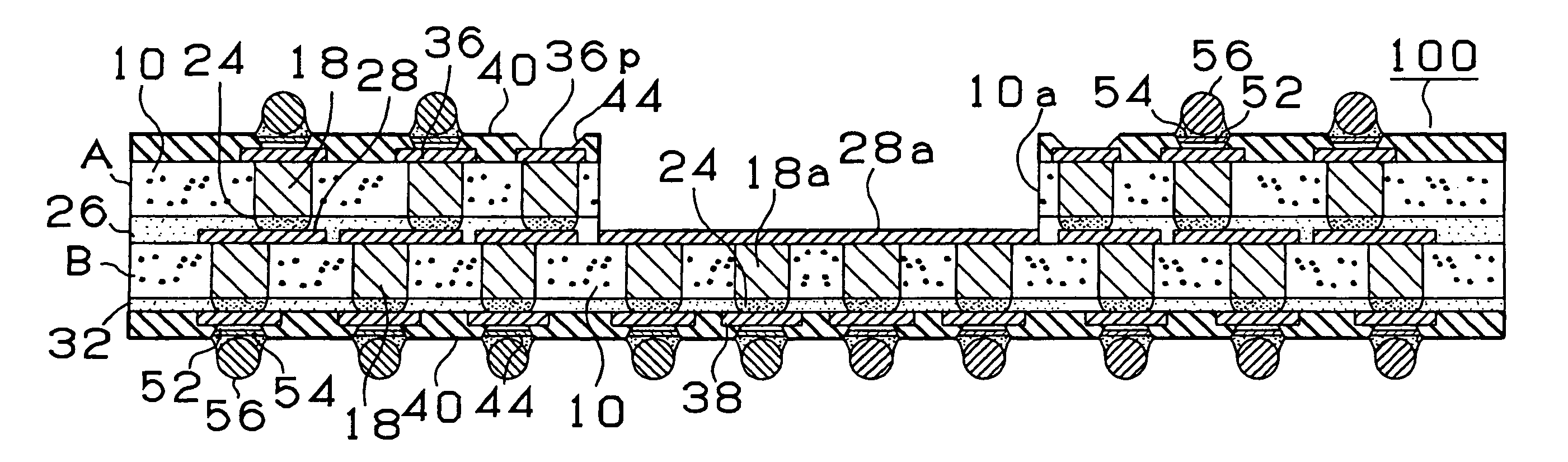

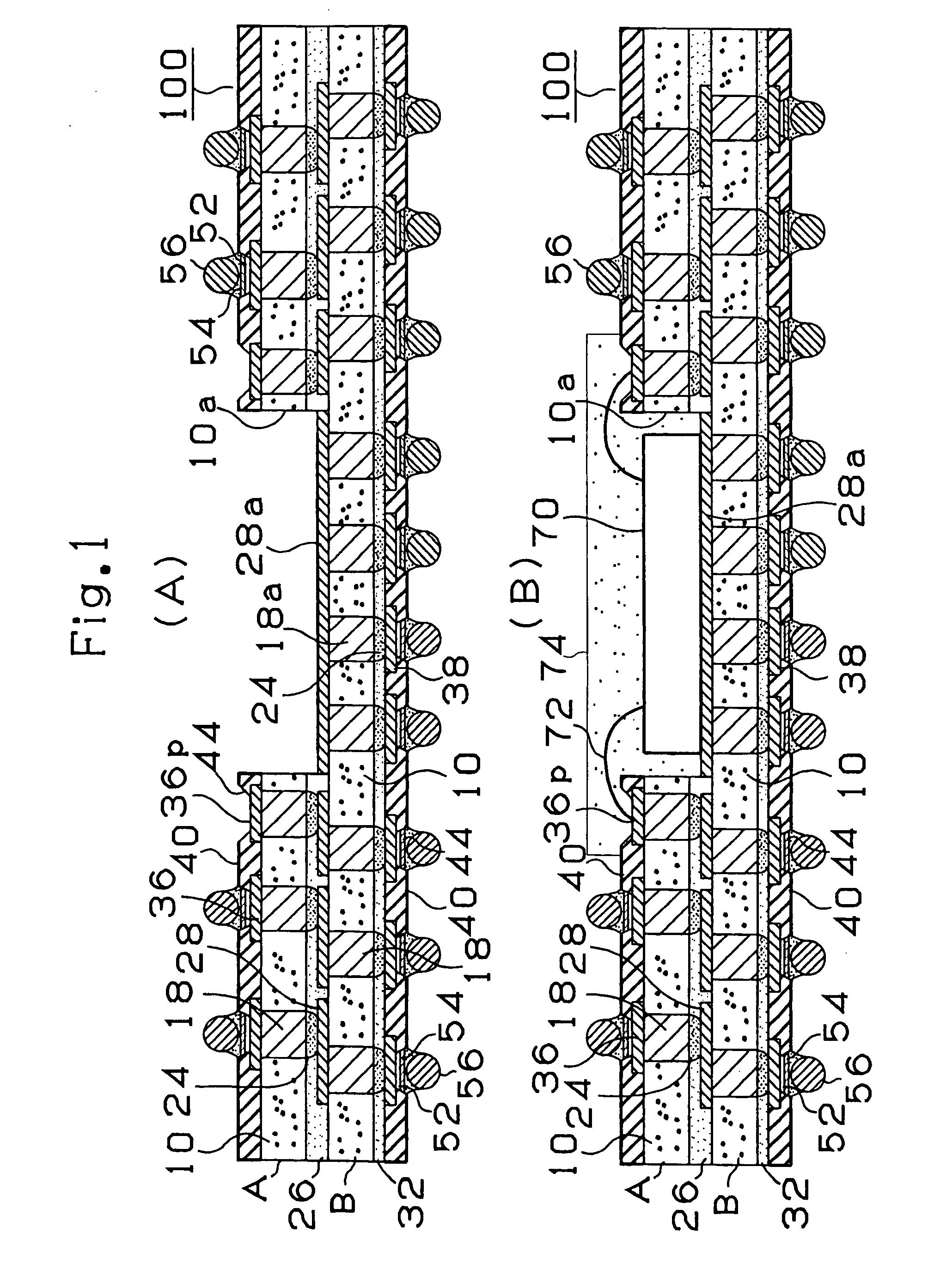

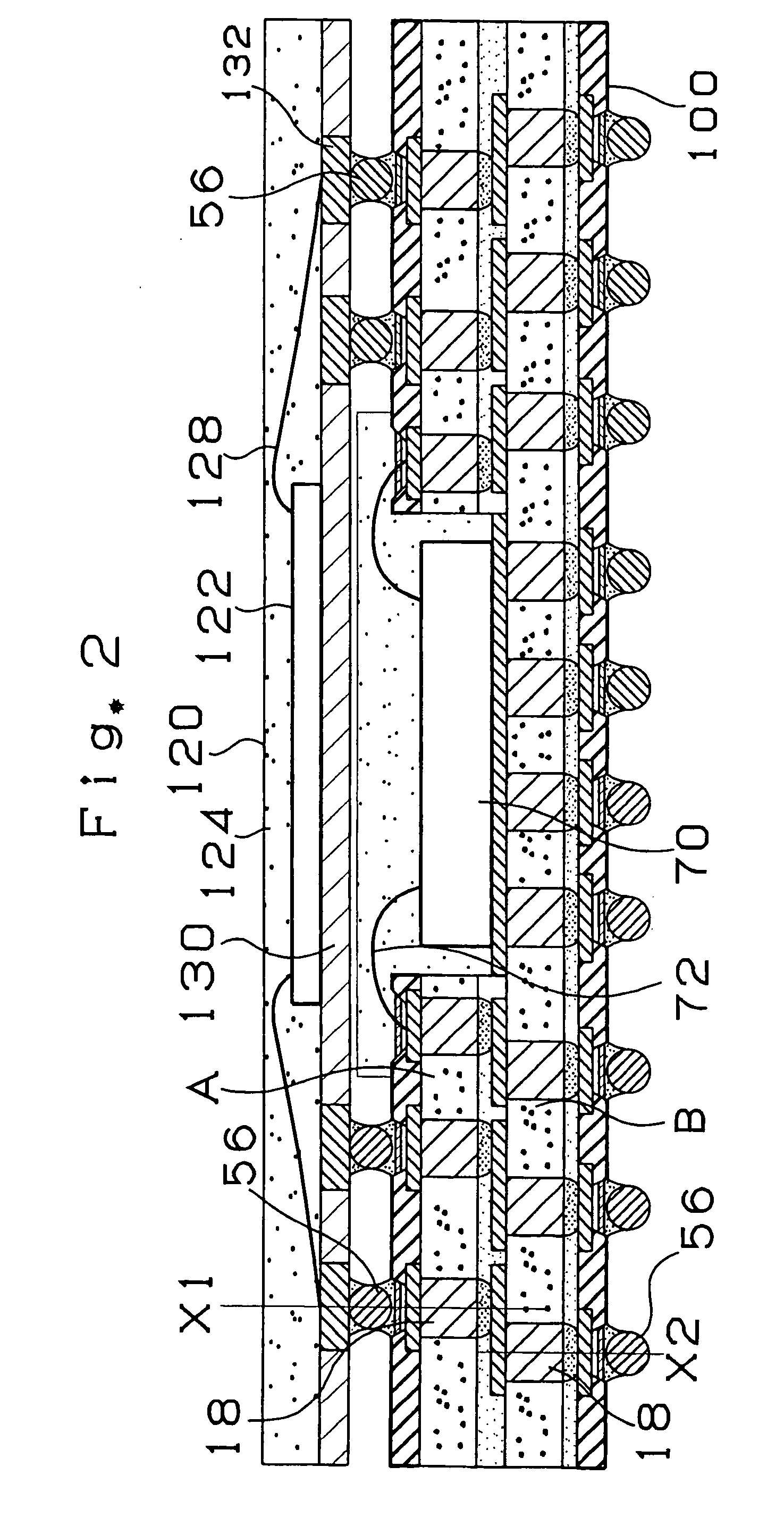

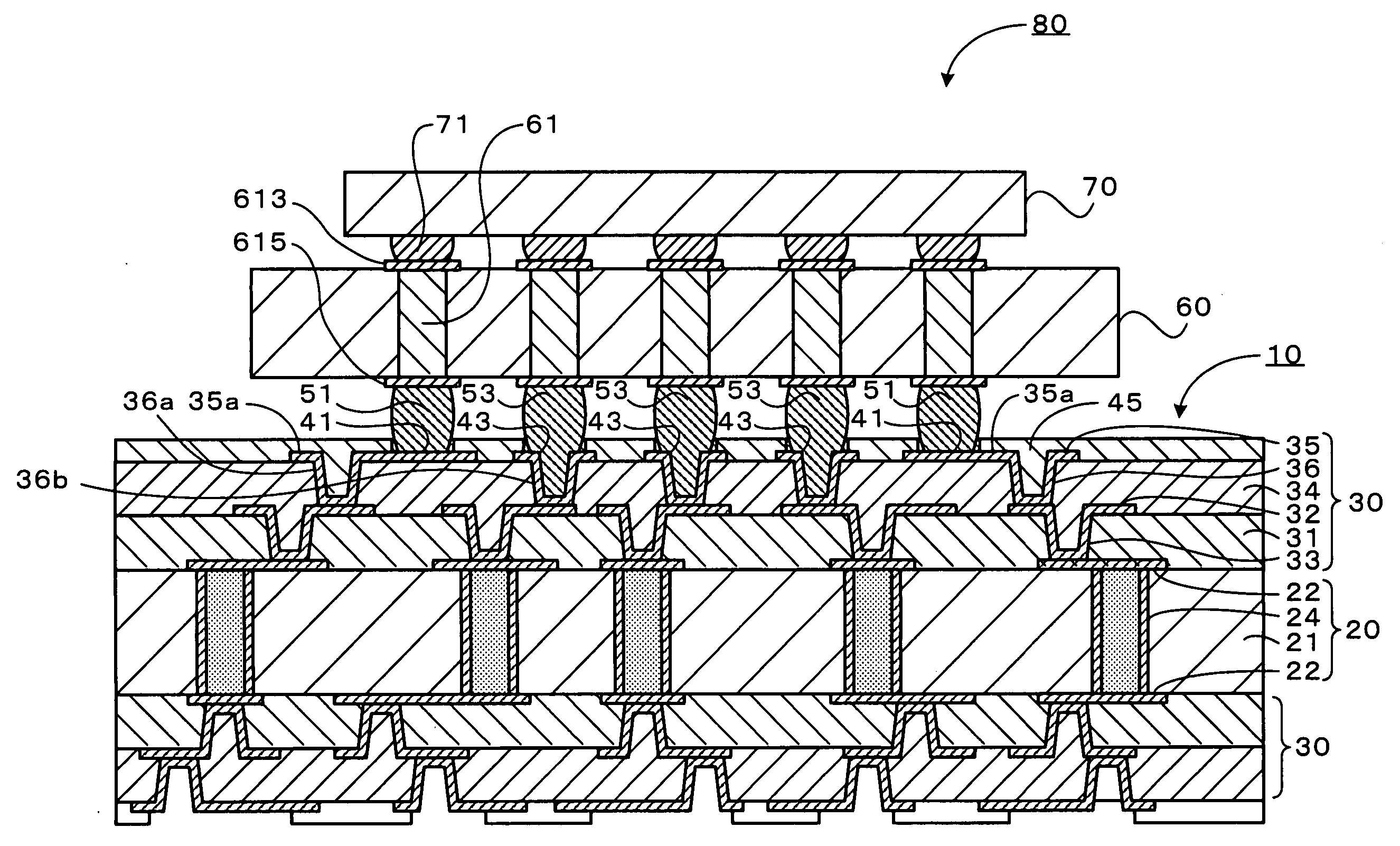

Multilayer printed wiring board

ActiveUS20060237225A1Improve adhesionEffective applicationSemiconductor/solid-state device detailsPrinted electric component incorporationEngineeringElectrical and Electronics engineering

In a multi-layer printed wiring board 100 comprising single side circuit boards A, B and for accommodating an IC chip 70, BGAs 56 are disposed on its front and rear faces, so that with an IC module 120 mounted through the BGA 56 on the front face, this board can be connected to a printed wiring board through the BGA 56 on the rear face. Thus, freedom in the configuration of the IC module mounted increases so that various kinds of the IC modules can be loaded.

Owner:IBIDEN CO LTD

Thin multi-chip flex module

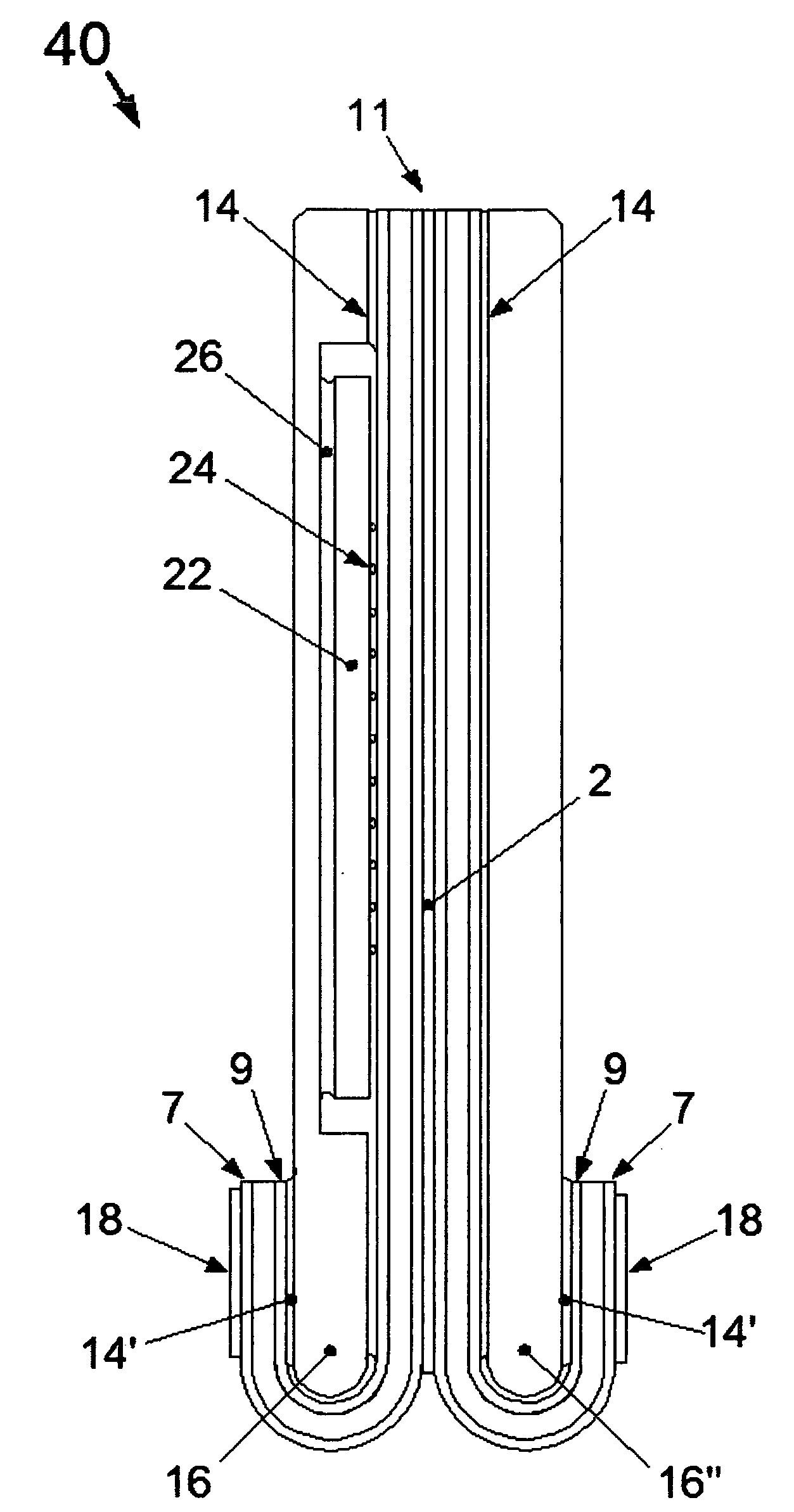

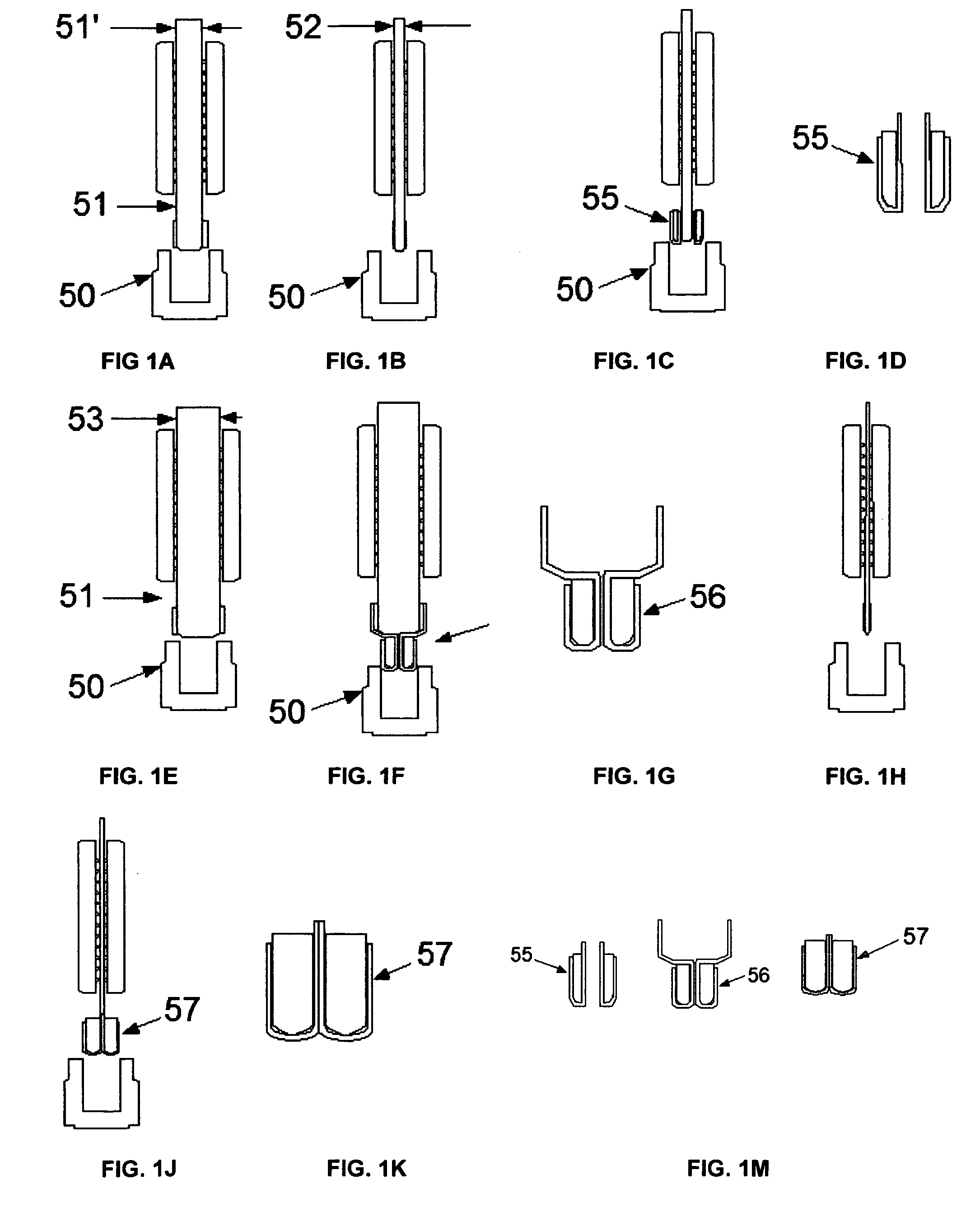

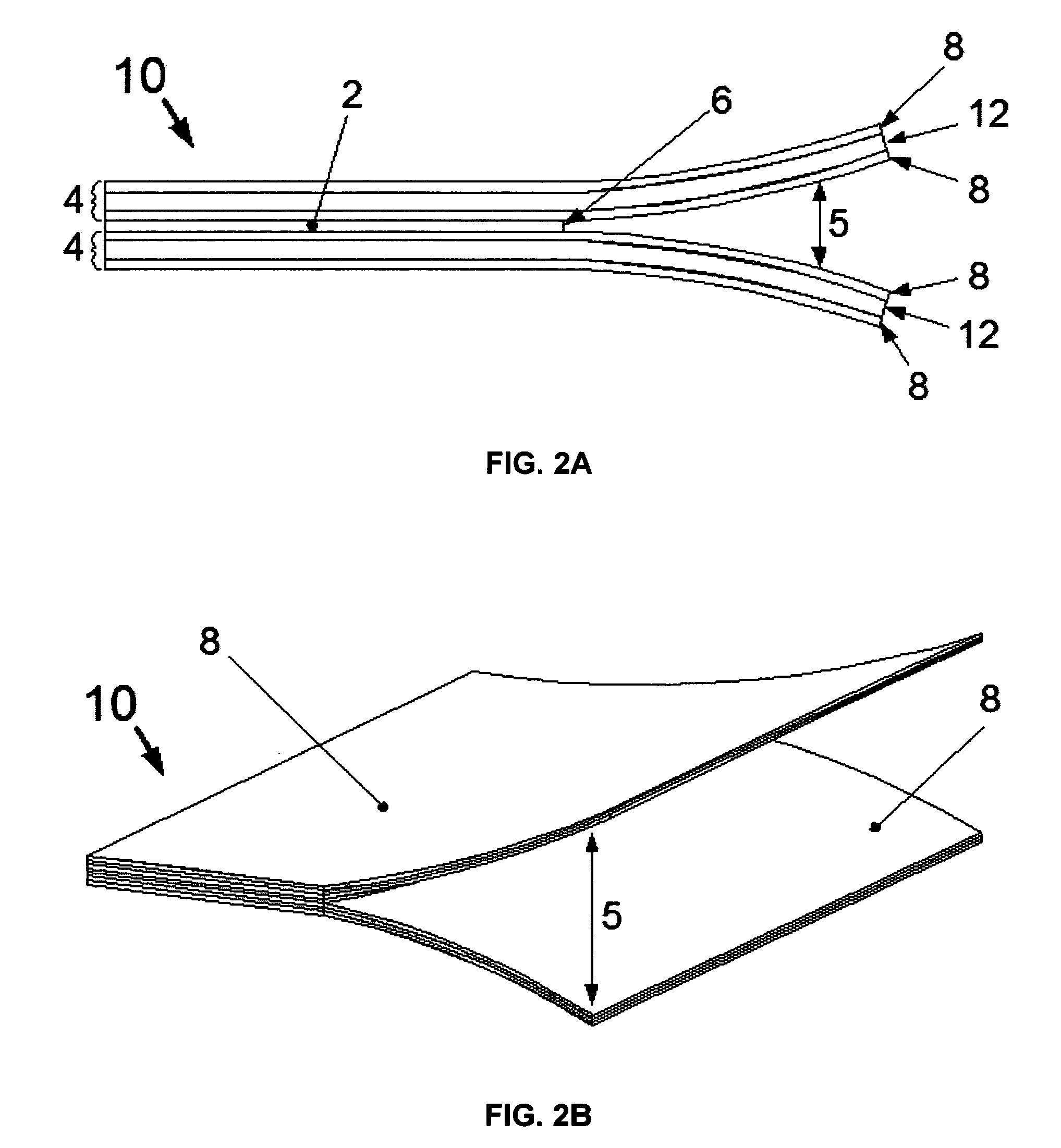

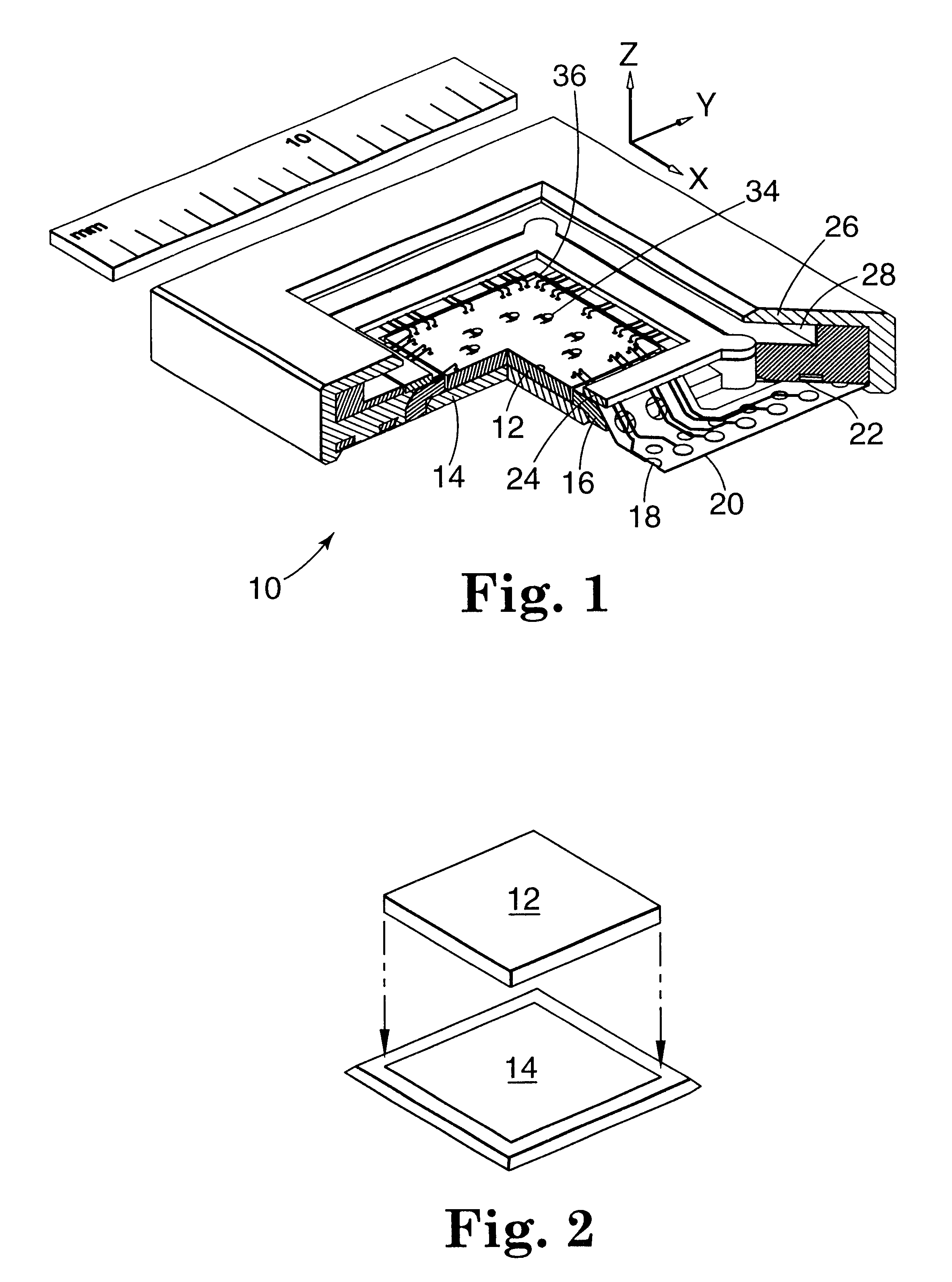

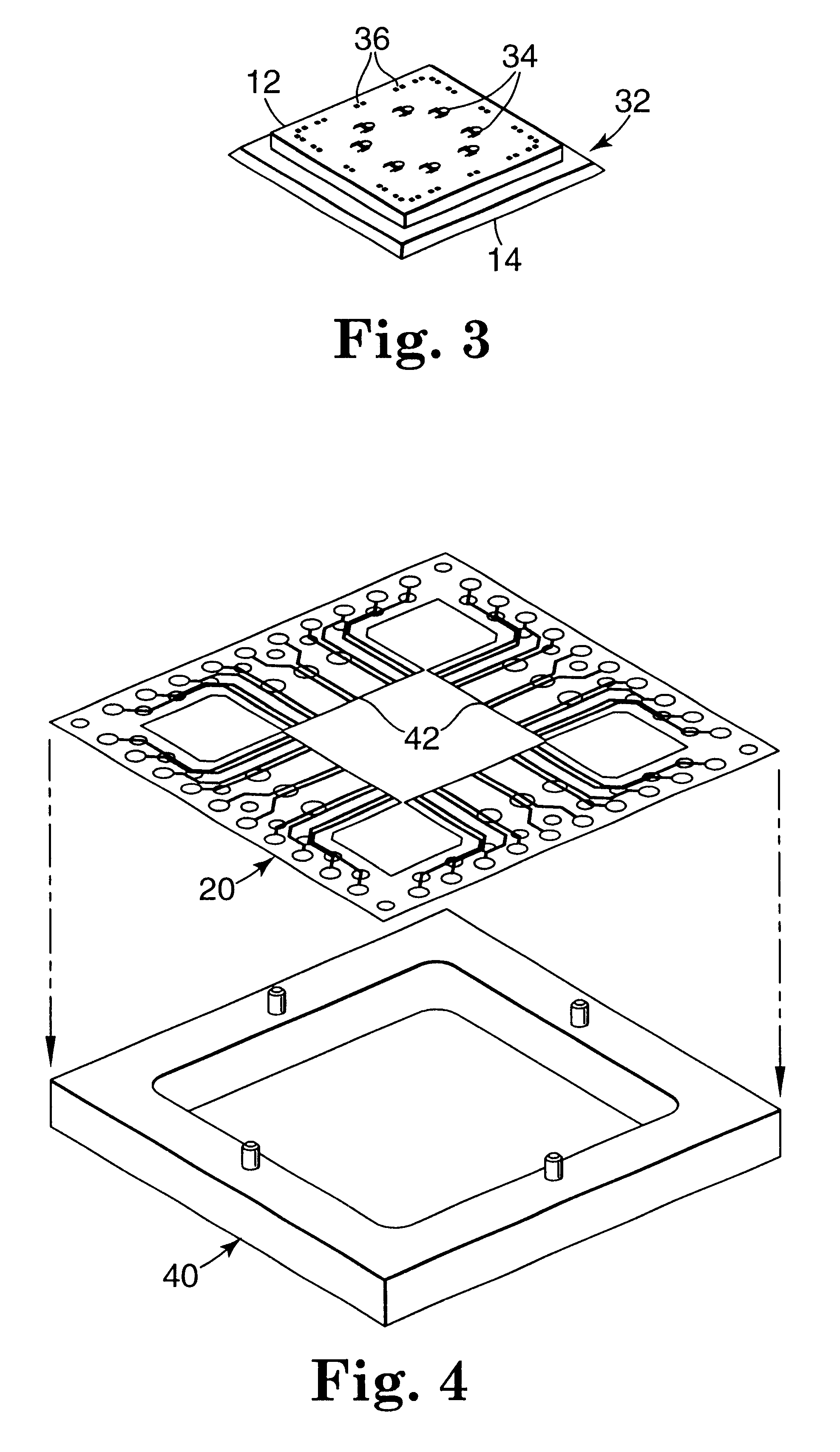

InactiveUS7796399B2Engagement/disengagement of coupling partsSemiconductor/solid-state device detailsPin arrayRigid frame

A multichip module comprises a multilayer substrate circuit having conductive patterns on its surface(s) to which microelectronic device(s) are attached. The conductive patterns include a series of electrical contacts adjacent to one edge of the substrate. The substrate is bonded to two rigid frames, one on each opposite surface. Each substrate has a series of castellations on one edge that are aligned and electrically connected to the respective contacts on the substrate, preferably by soldering. The castellations can serve as a self-aligning mechanism when the module is brought into contact with a low-profile pin array, and the module may be held in place on a motherboard by guide rails in a socket that engages the edges perpendicular to the castellated edge of the module. The module may further be provided with protective heat spreading covers.

Owner:MICROELECTRONICS ASSEMBLY TECH

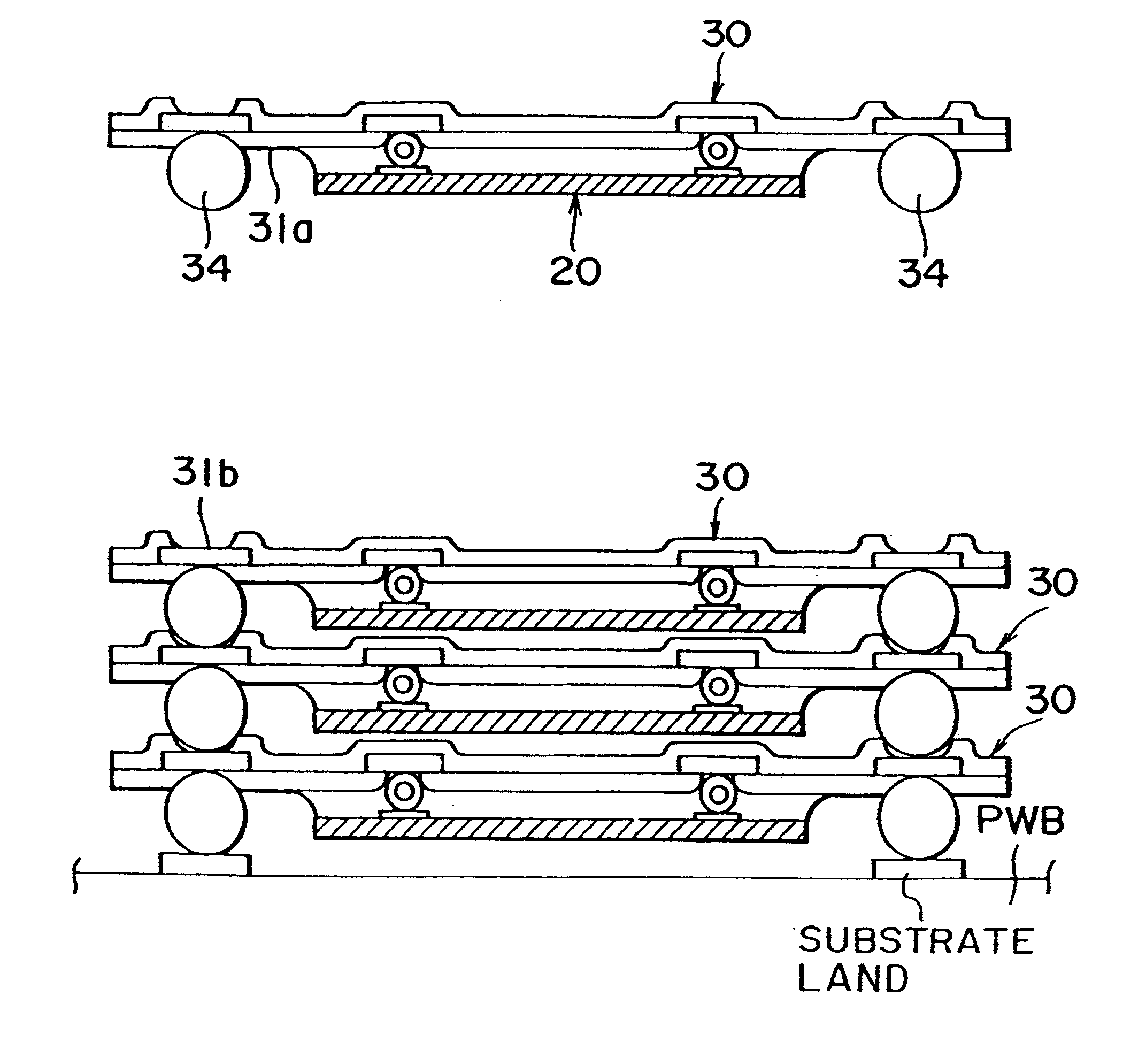

Stackable semiconductor device and method for manufacturing the same

InactiveUS6504241B1Semiconductor/solid-state device detailsSolid-state devicesMiniaturizationSemiconductor chip

There is provided a semiconductor device having a semiconductor chip in which a first protrusion electrode is formed on the semiconductor substrate; and an intermediate substrate which comprises a base substrate, a first external terminal provided in said base substrate, which is joined to said first protrusion electrode, a second external terminal provided in said base substrate, an electrode section being exposed on both surfaces of said base substrate, and a second protrusion electrode formed at one end face of said second external terminal, a plurality of said intermediate substrates being stacked in layers by joining said second protrusion electrode to the other end face of said second external terminal, thus enabling miniaturizing and lightening electronic equipment and realizing high reliability and high performance.

Owner:SONY CORP

Top feature package and method

ActiveUS8199518B1Minimizing overall package manufacturing costMinimizing overall package sizePrinted circuit groundingCross-talk/noise/interference reductionElectricityEngineering

An electronic component package includes a substrate and an electronic component mounted to the substrate, the electronic component including a bond pad. A first antenna terminal is electrically connected to the bond pad, the first antenna terminal being electrically connected to a second antenna terminal of the substrate. A package body encloses the electronic component, the package body having a principal surface. An antenna is formed on the principal surface by applying an electrically conductive coating. An embedded interconnect extends through the package body between the substrate and the principal surface and electrically connects the second antenna terminal to the antenna. Applying an electrically conductive coating to form the antenna is relatively simple thus minimizing the overall package manufacturing cost. Further, the antenna is relatively thin thus minimizing the overall package size.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

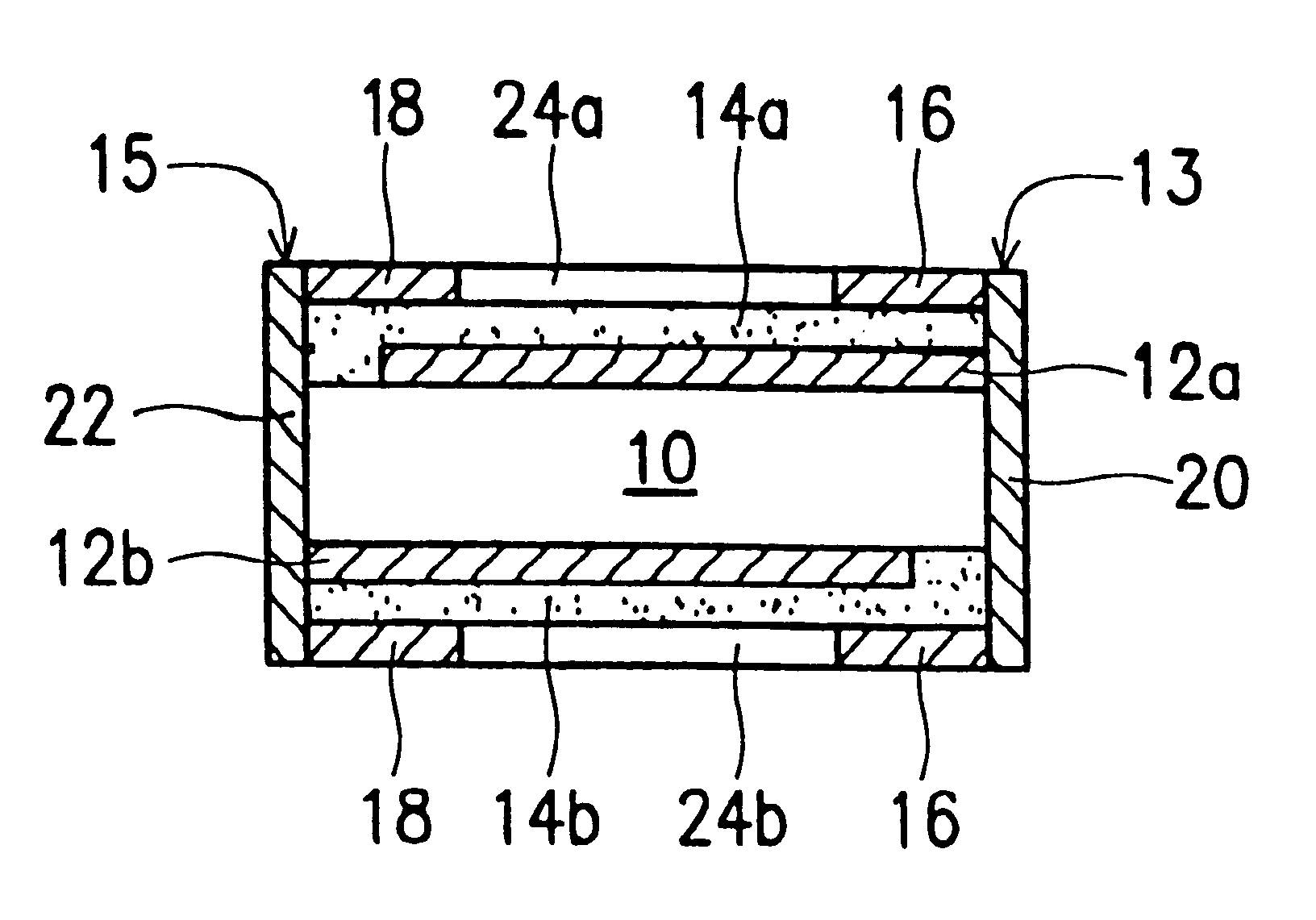

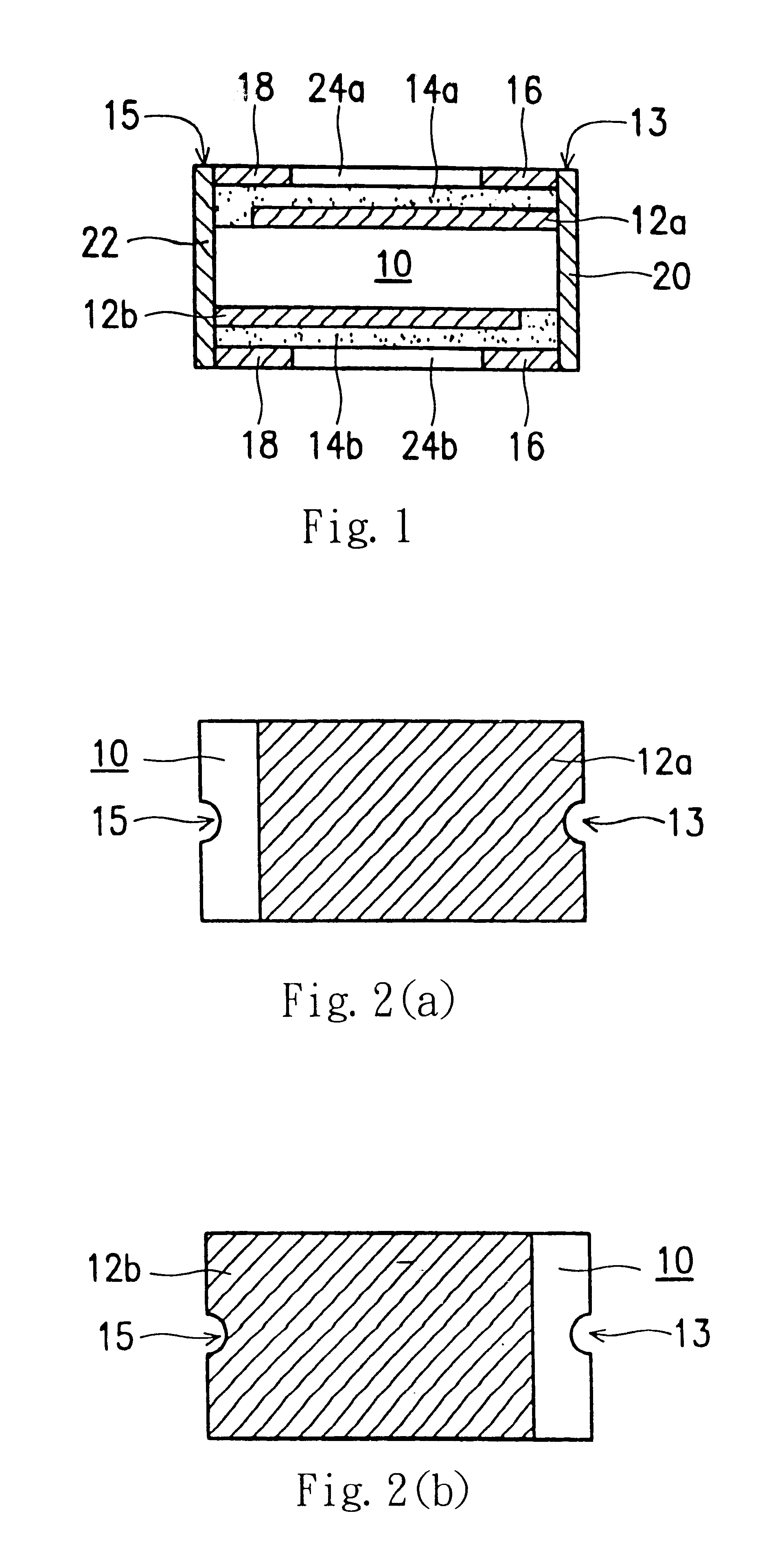

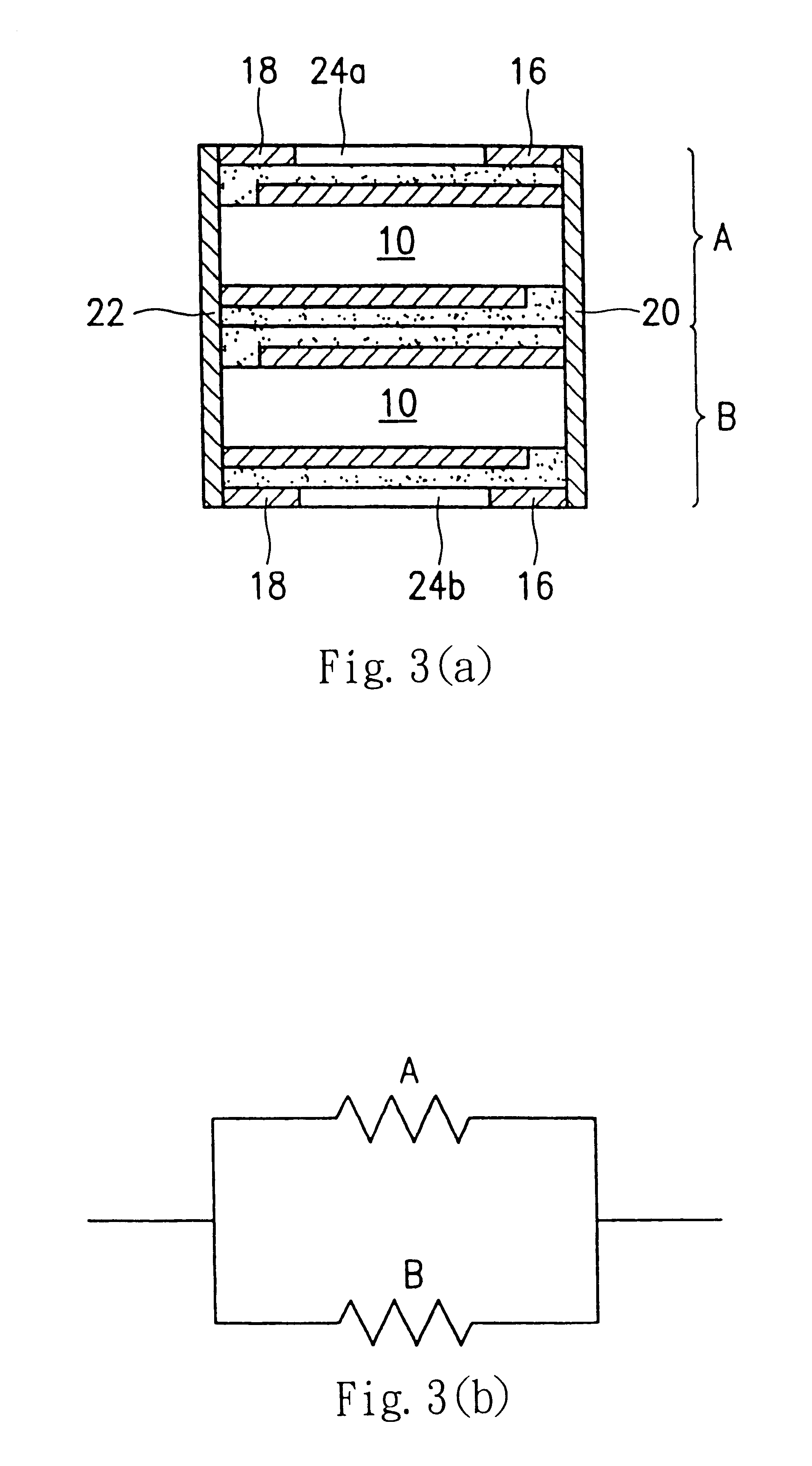

Surface mountable over-current protecting device

InactiveUS6377467B1Easy to installGood dimensional stabilityResistor terminals/electrodesNegative temperature coefficient thermistorsElectrical resistance and conductancePlanar electrode

The present invention relates to a novel thermal-sensitive resistive apparatus, such as PTC and NTC, which allocates planar electrode films on the top and bottom surfaces of a prior art thermal-sensitive resistive apparatus, such as a PTC apparatus, to laminate with an outer electrode layer. A plurality of interconnection vias are electroplated with conductive material to connect to any plane. It is convenient to surface mount the apparatus of the present invention on a printed circuit board. The present invention can largely increase the dimensional stability of components and overcome the disadvantage that thermal diffusion of the prior are surface mounted resistive apparatus is affected easily by line width and environments.

Owner:POLYTRONICS TECH

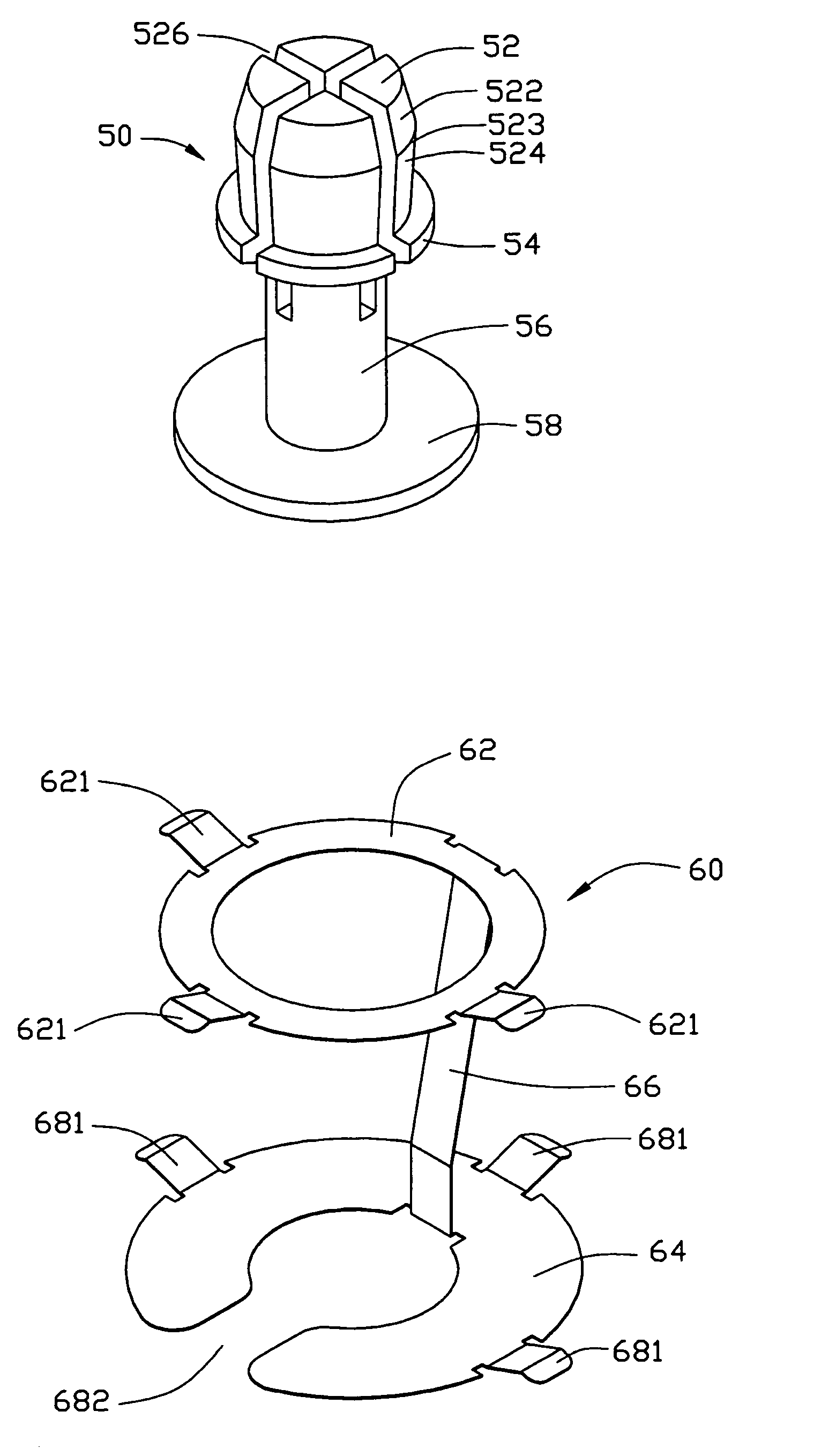

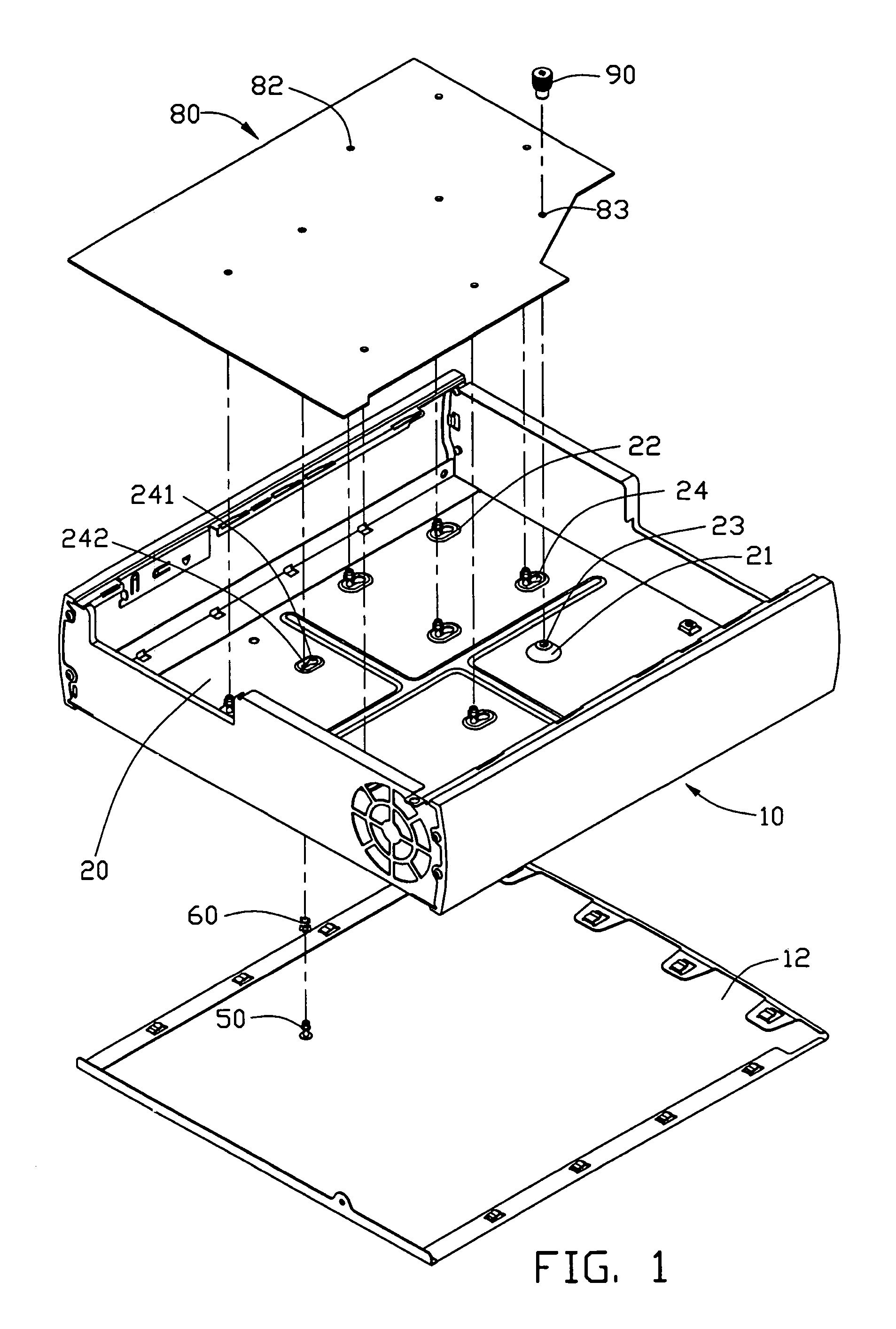

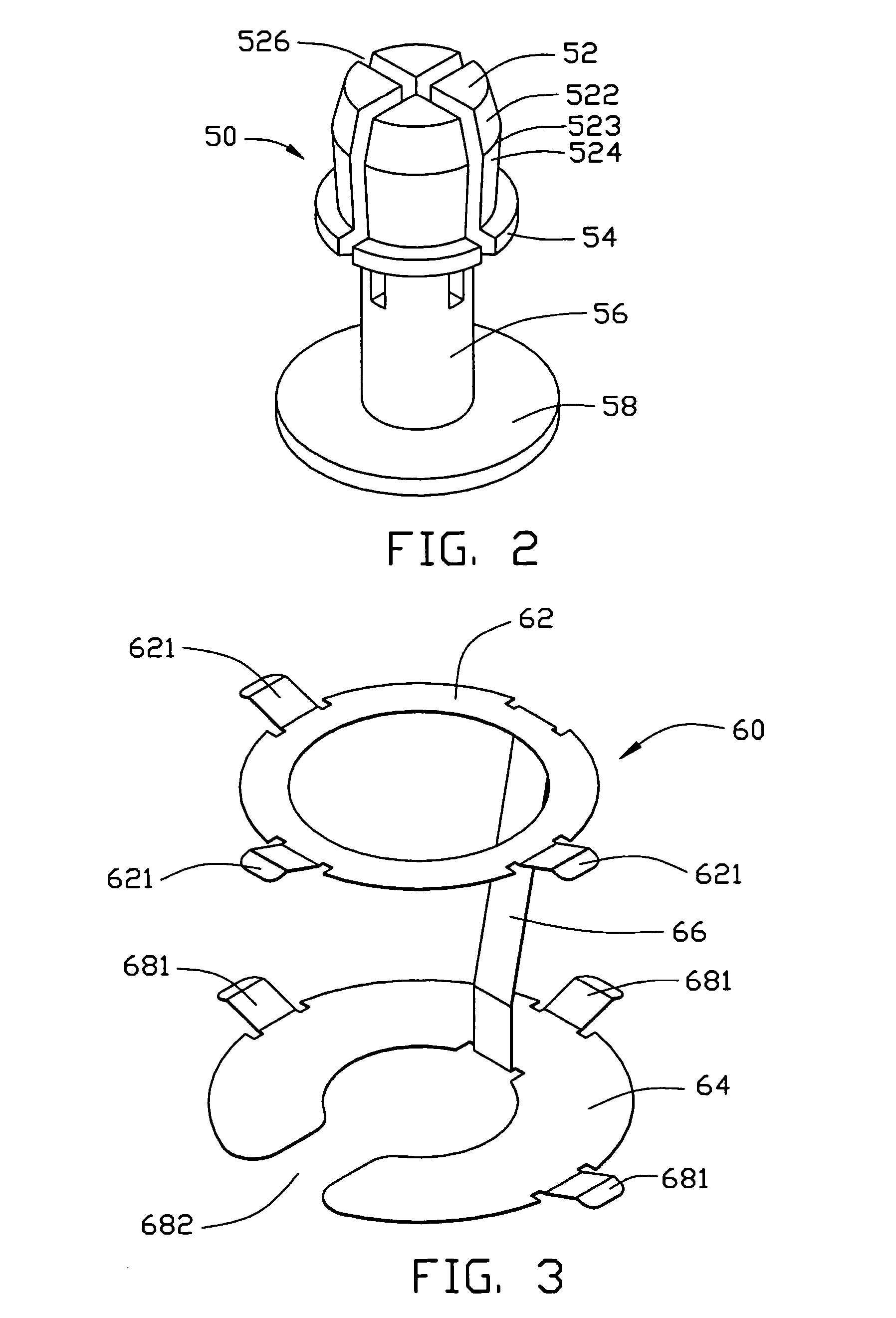

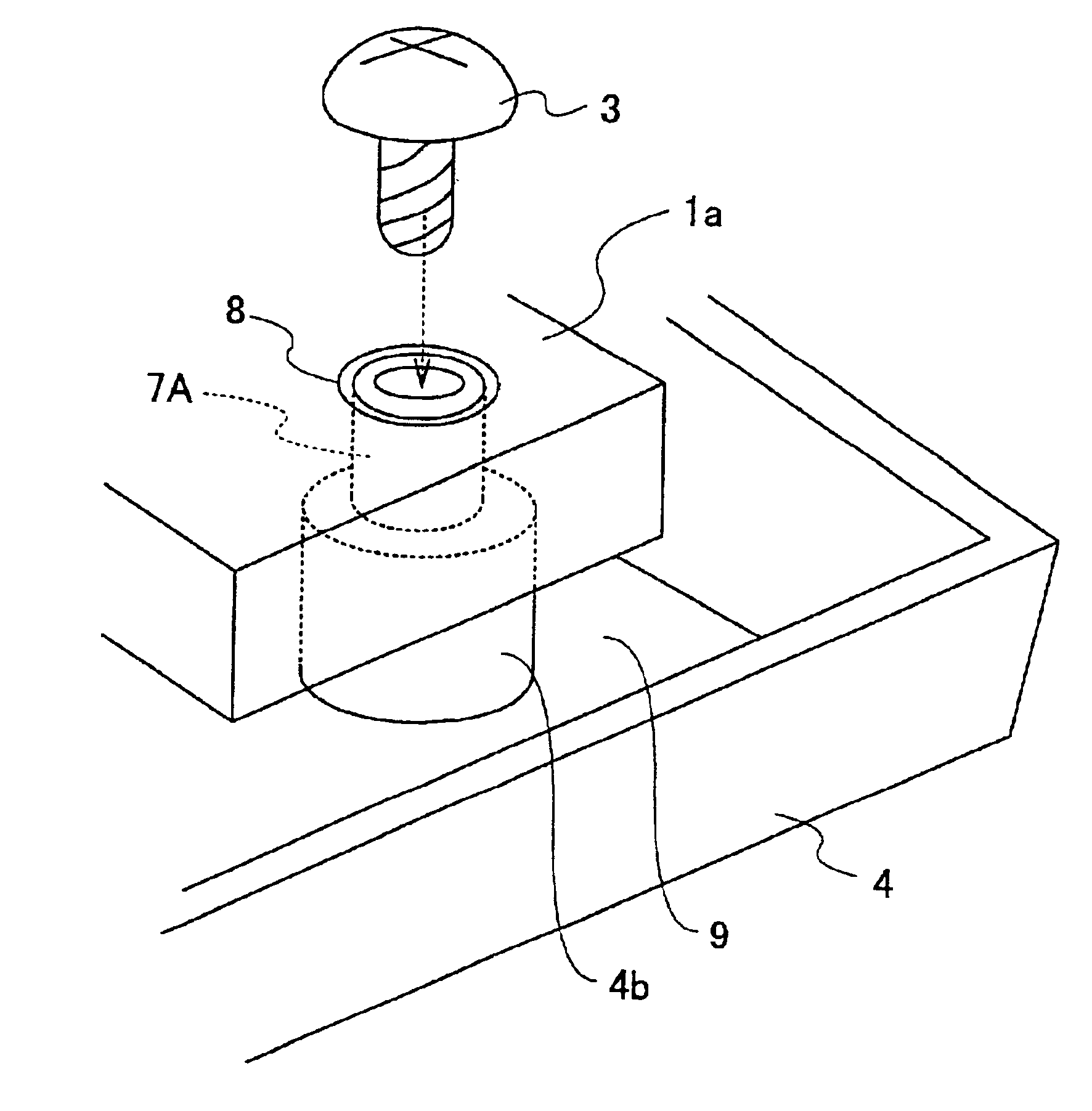

Mounting apparatus for PCB

InactiveUS7034223B2Quickly and readily attachmentQuickly and readily and removalPrinted circuit assemblingCasings/cabinets/drawers detailsEngineeringConductive materials

A PCB mounting apparatus includes a supporting plate (20) defining a number of through holes, a number of standoffs (50) engaging in the through holes, and a number of grounding members (60) attached to the standoffs. The standoff each includes a head (52) having a holding portion, a flange (54), a post (56), and a base (58). The grounding member each includes a first ring (62) supported on the flange, a second ring (68) supported on the base, and a band (66) connecting therebetween. The PCB (80) defines a number of fixing apertures (82). The combined standoff and grounding member is disposed in the through hole. The PCB is placed upon the supporting plate with the fixing apertures engaging the holding portions of the standoffs and contacts the first rings of the grounding members. The standoffs and the grounding members are made of conductive materials.

Owner:HON HAI PRECISION IND CO LTD

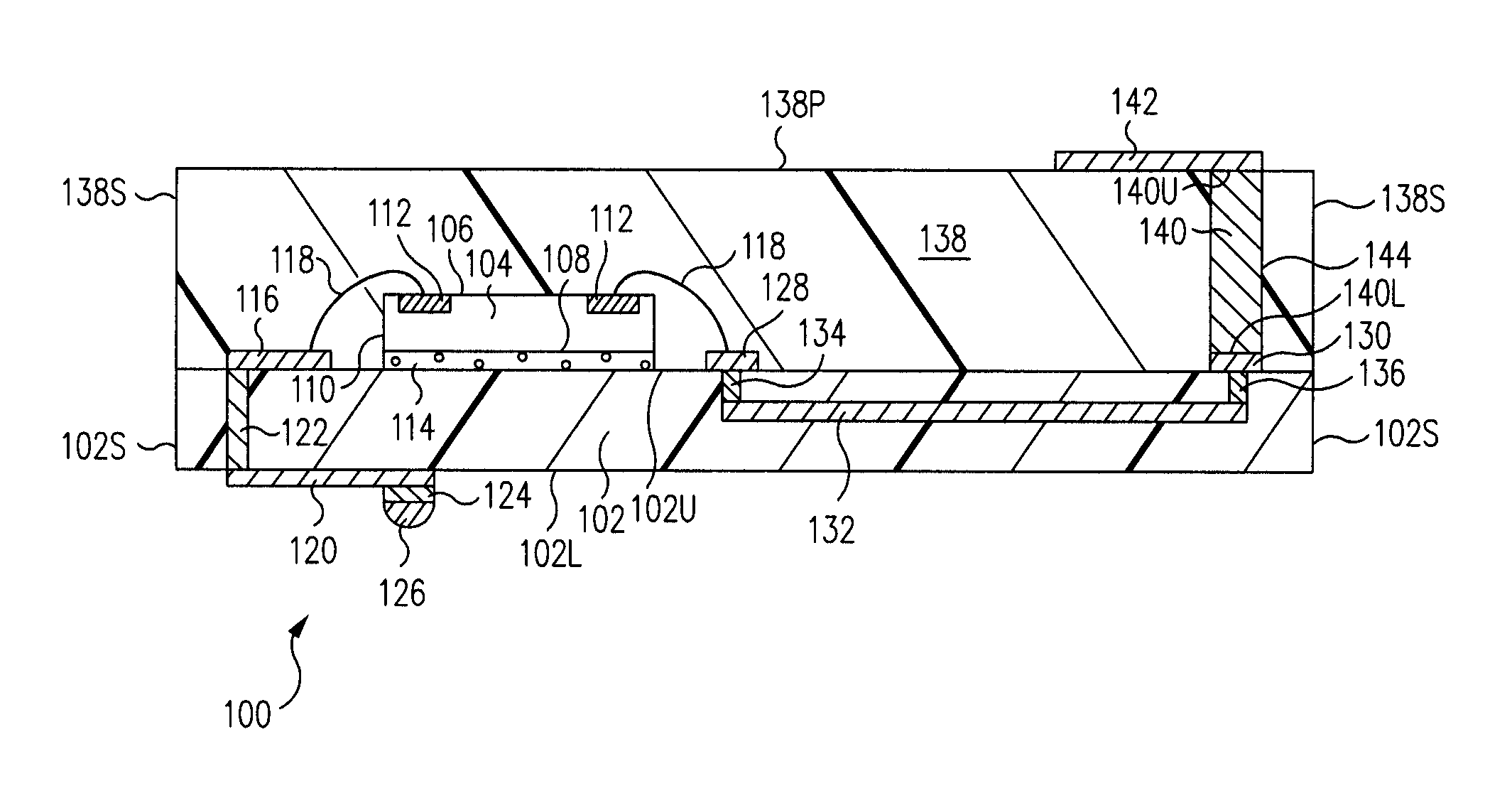

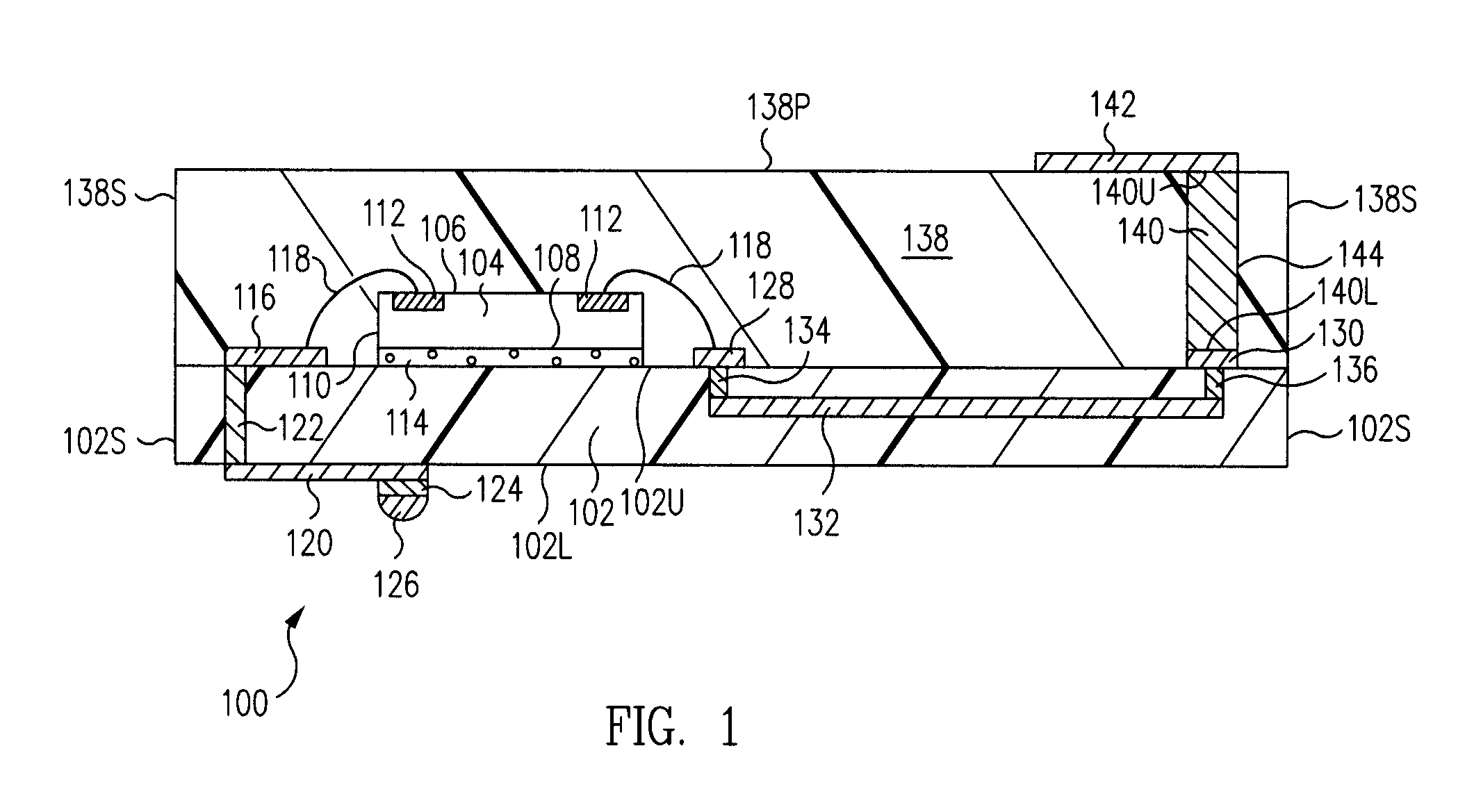

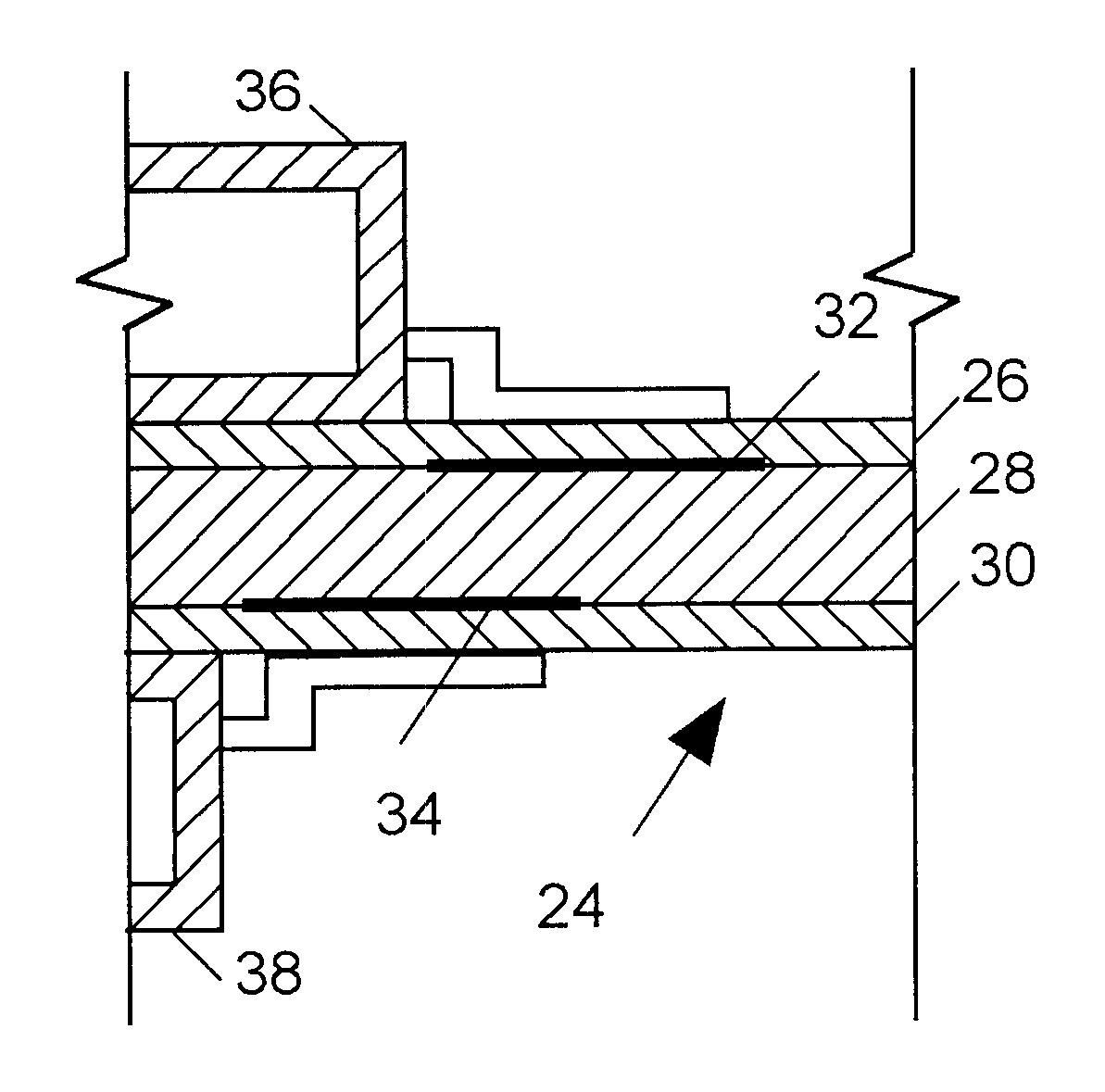

MEMS package with flexible circuit interconnect

InactiveUS6469909B2Facilitates back-end release processSemiconductor/solid-state device detailsSolid-state devicesFlexible circuitsEngineering

A method of fabricating a package for a micro-electromechanical systems (MEMS) device. A flex circuit interconnect subassembly for the package is made by placing a flex circuit on a pad insert, attaching a carrier insert to the pad insert to deflect the lead portions of the flex circuit, and applying a cover insert to the pad insert, after the attachment of the carrier insert, to re-deflect the lead portions of the flex circuit toward the device bond sites. The flex circuit interconnect subassembly may be combined with an electronic device die / carrier subassembly to form a completed electronic device package. The flex circuit interconnect subassembly and the die / carrier subassembly are joined using mechanical interlocking layers. The invention is particularly suited for making such an electronic device die / carrier subassembly which has a MEMS die permanently affixed to a carrier. The carrier is advantageously utilized during the process of releasing a protective coating from the surface of the MEMS die which support the various MEMS components. The MEMS components on the MEMS die are hermetically sealed, such as by bonding a cover to the upper package body or the lower package body. The cover may have features such as ports which allow the MEMS components to interact with the external environment.

Owner:3M INNOVATIVE PROPERTIES CO

Self-heating circuit board

InactiveUS6396706B1Inexpensive and convenientSemiconductor/solid-state device detailsSolid-state devicesVoltage pulseAdhesive

Separate heating elements are embedded in a printed circuit board near integrated circuit (IC) packages or other parts mounted on the circuit board. Each heating element supplies heat to the part residing near it in response to an input voltage pulse. The heating elements are used to selectively melt solder or adhesives attaching the parts to the circuit board so that they can be easily removed or to temporarily melt solder or cure adhesive when the parts are mounted on the circuit board. The heating elements are also used to supply heat to IC packages for regulating their operating temperatures.

Owner:MA ZHONGXIN +1

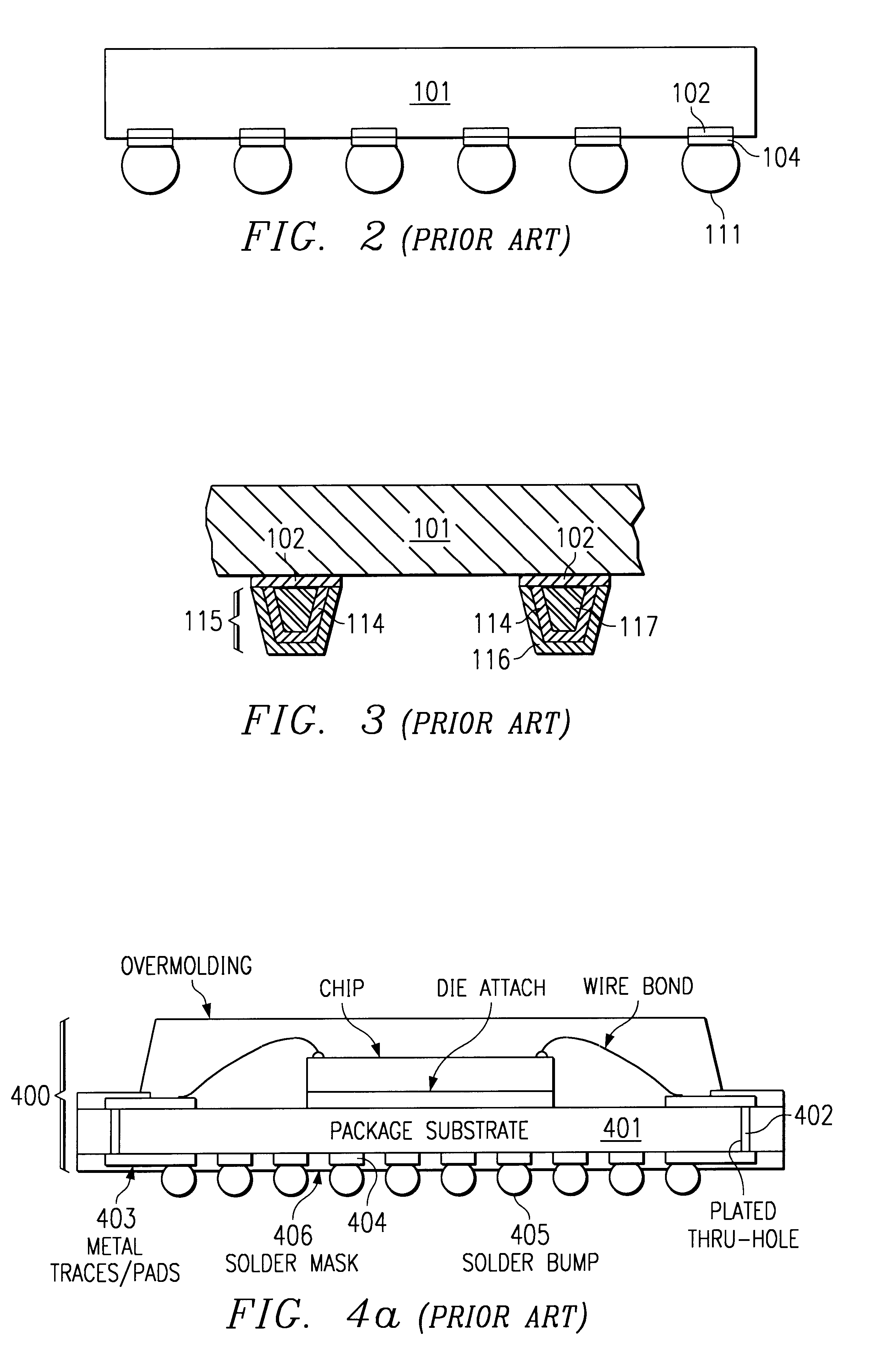

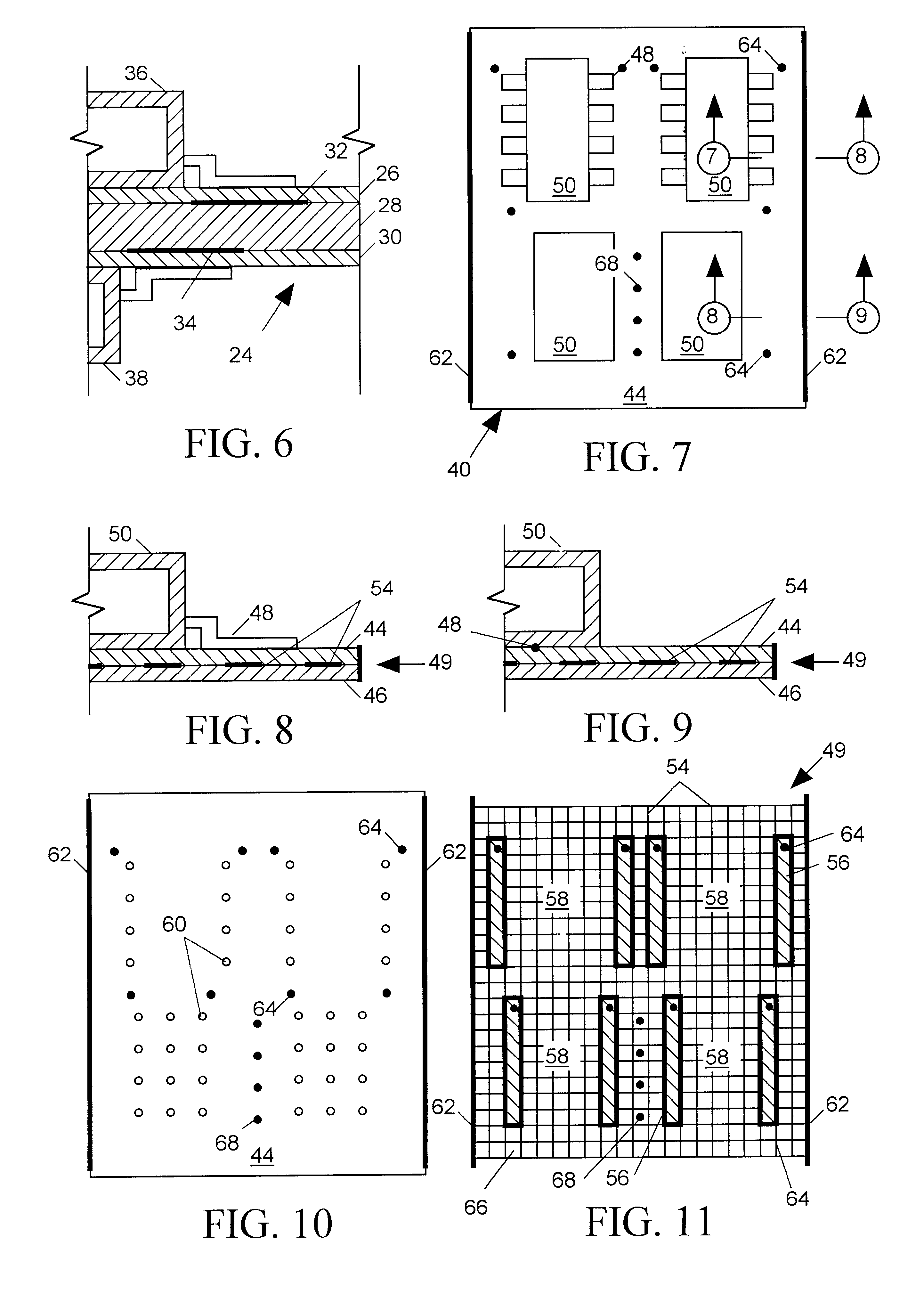

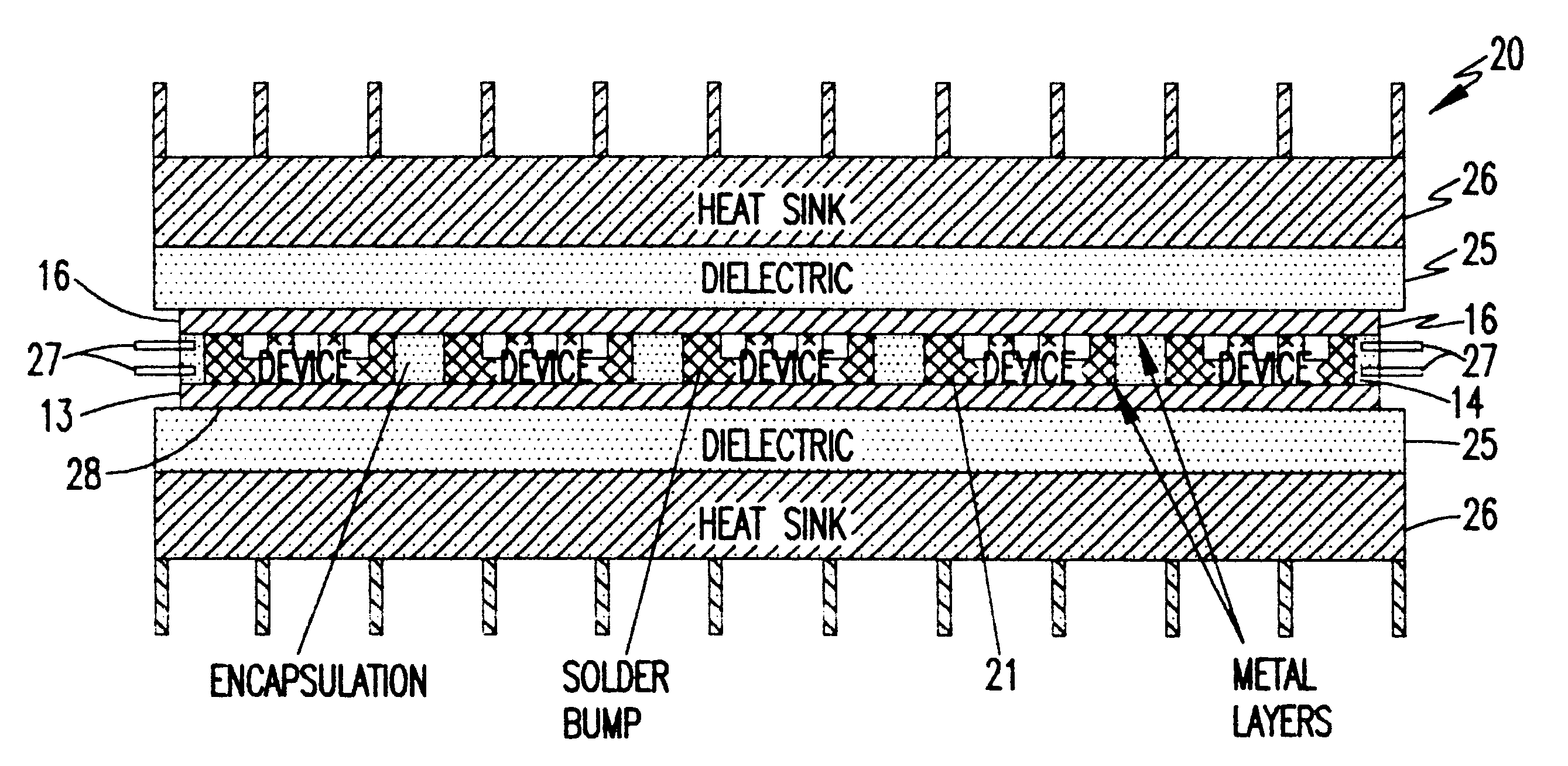

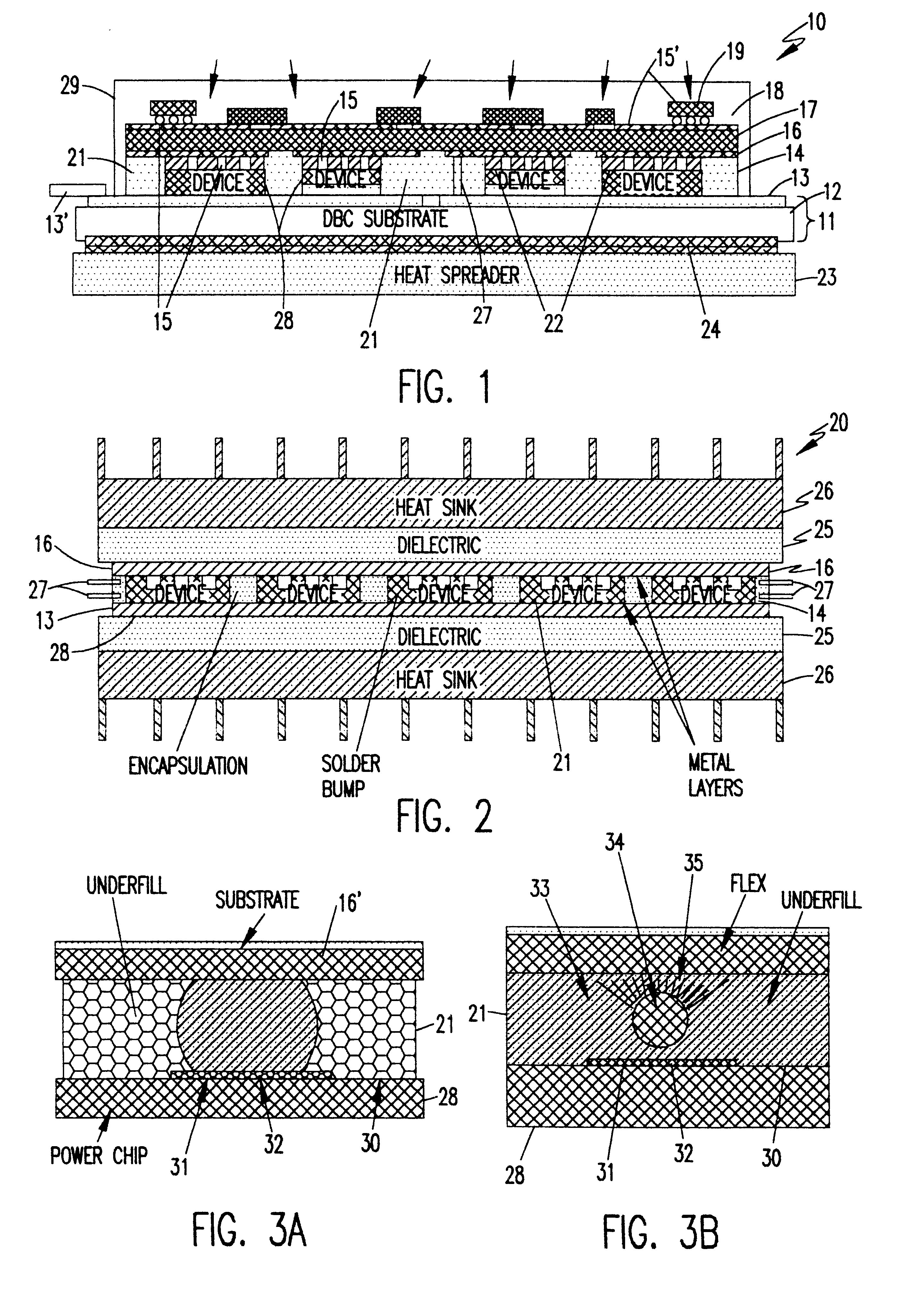

Low-cost 3D flip-chip packaging technology for integrated power electronics modules

InactiveUS6442033B1Improve performanceLow costSemiconductor/solid-state device detailsSolid-state devicesVoltage overshootLead bonding

Resistance and parasitic inductance resulting from interconnection of semiconductor chips in power modules are reduced to negligible levels by a robust structure which completely avoids use of wire bonds through use of ball bonding and flip-chip manufacturing processes, possibly in combination with chip scale packaging and hourglass shaped stacked solder bumps of increased compliance and controlled height / shape. Turn-off voltage overshoot is reduced to about one-half or less than a comparable wire bond packaged power module. Hourglass shaped solder bumps provide increased compliance and reliability over much increased numbers of thermal cycles over wide temperature excursions.

Owner:VIRGINIA TECH INTPROP INC

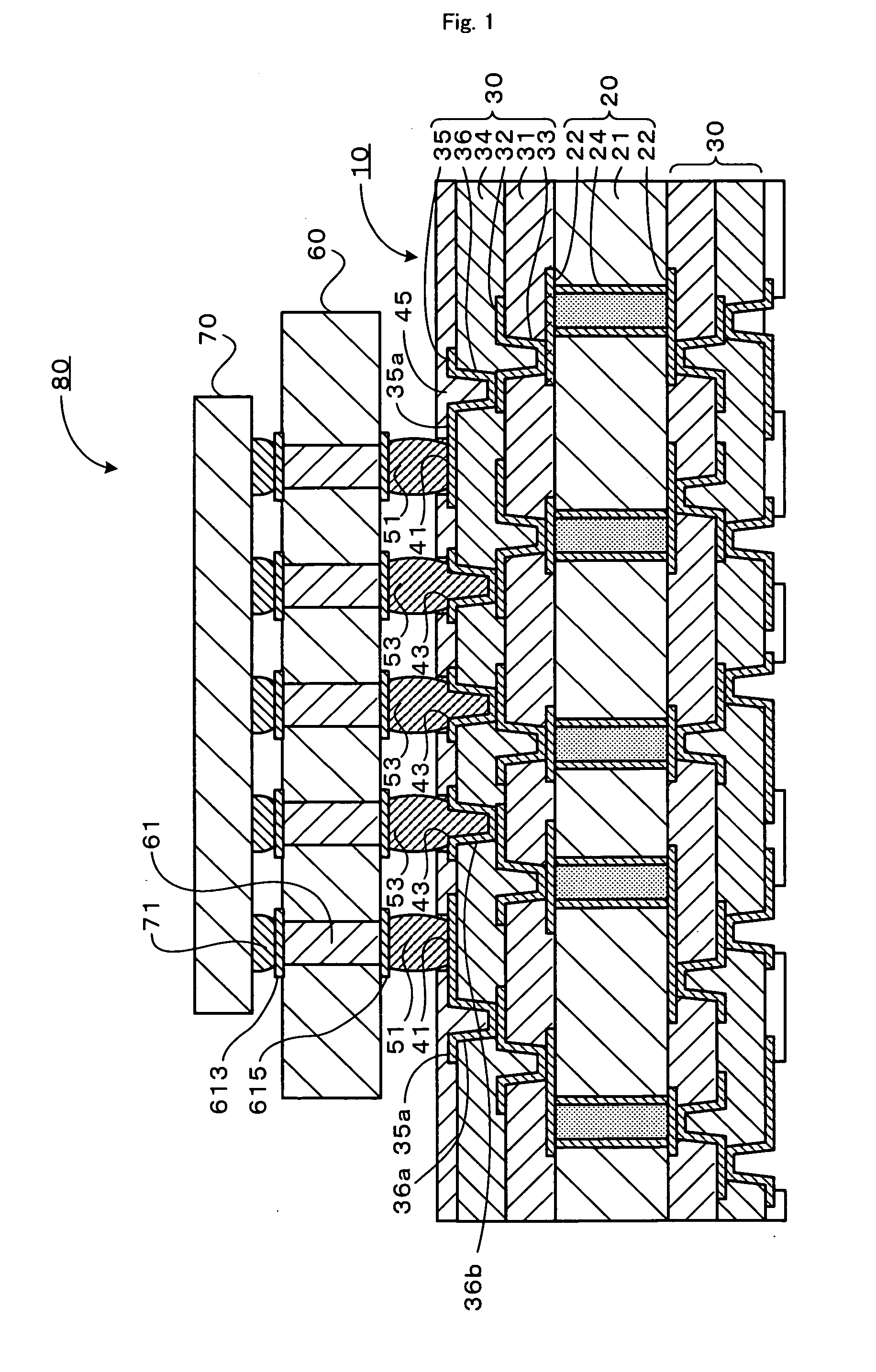

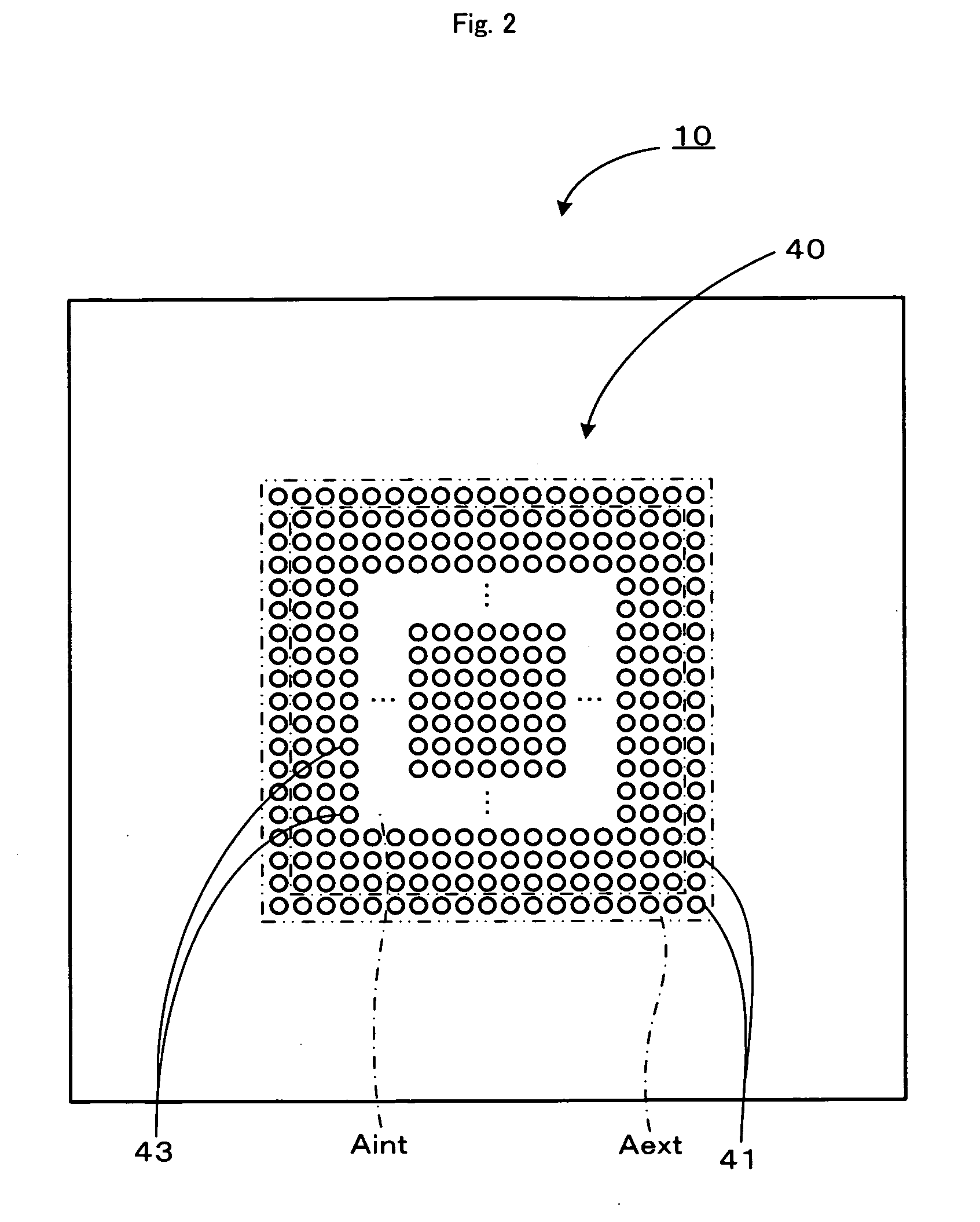

Semiconductor mounting board

ActiveUS20060163740A1Increased durabilityGreat shearing stressSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor

A semiconductor mounting board 80 is prepared by electrically joining an IC chip 70 via an interposer 60 of high rigidity to external pads 41 and internal pads 43, which are formed on the uppermost surface of a build-up layer 30. When the IC chip 70 generates heat, since pads 41 are positioned away from the center, a large shearing stress is applied to the portions at which pads 41 are joined to the interposer 60 in comparison to the portions at which pads 43 are joined to the interposer 60. Here, pads 41 are formed at substantially flat wiring portions and thus when joined to the interposer 60 by means of solder bumps 51, voids and angled portions, at which stress tends to concentrate, are not formed in the interiors of solder bumps 51. The joining reliability is thus high.

Owner:IBIDEN CO LTD

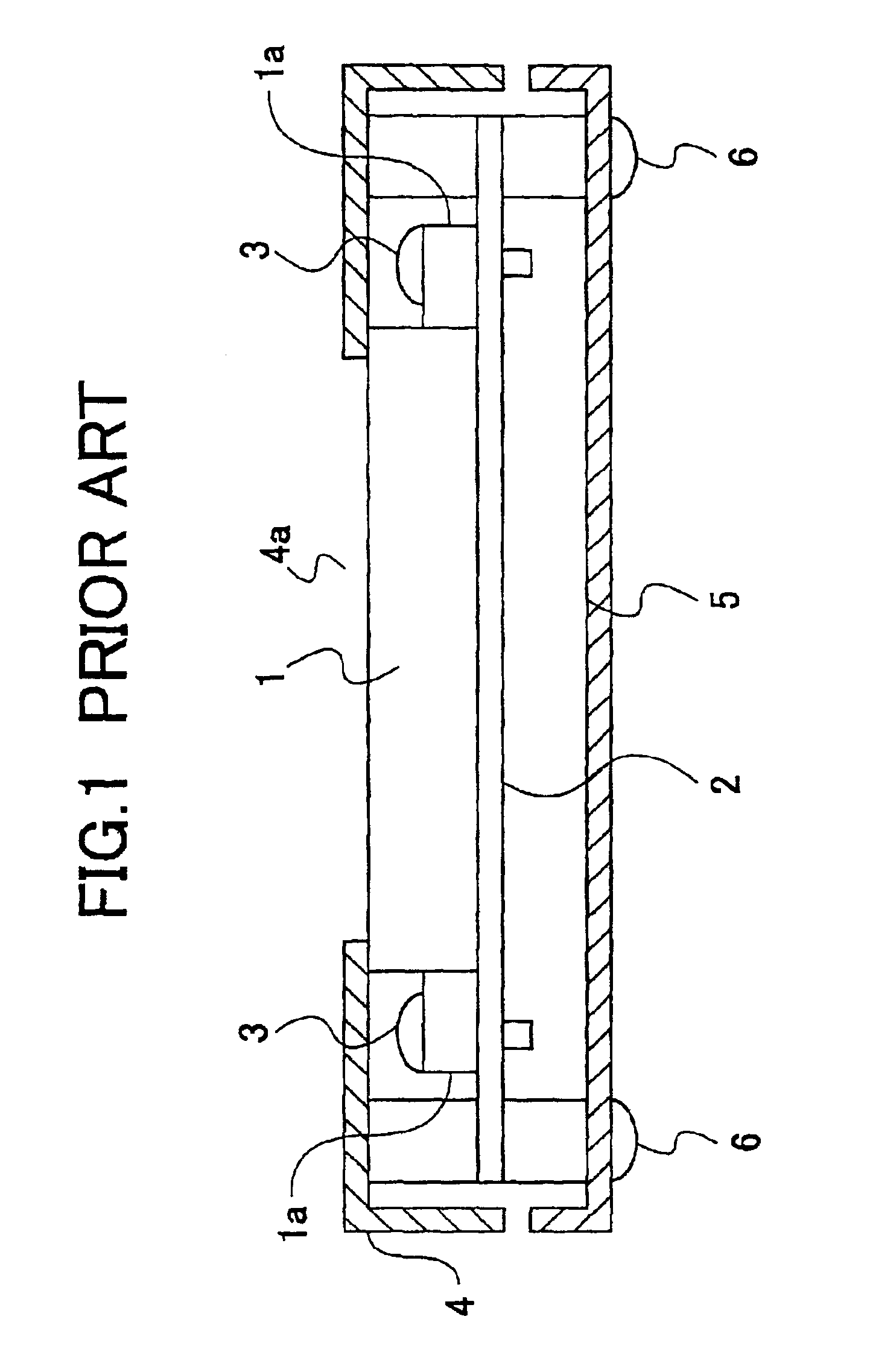

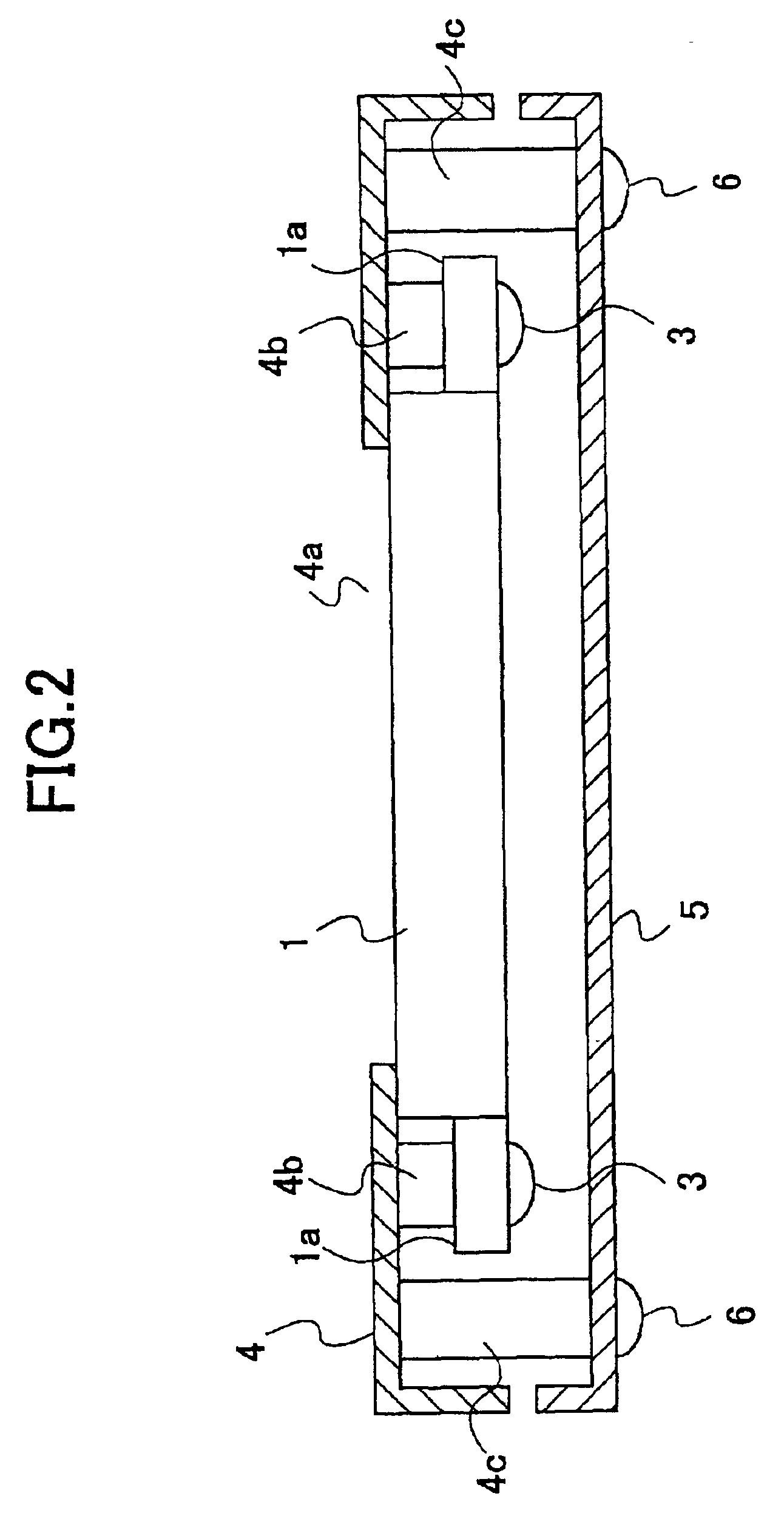

Display device

InactiveUS6867824B2Precise positioningReduce manufacturing costCasings/cabinets/drawers detailsResilient/clamping meansLiquid-crystal displayDisplay device

A liquid crystal display unit having a liquid crystal display element is accommodated in a housing having an opening for exposing the display portion of the display element to the exterior. The housing comprises a display face cover and a rear cover and the liquid crystal display unit is mounted directly relative to the display face cover. A positioning pin is provided so as to extend out from the display face cover in order to position the liquid crystal display unit relative to the display face cover, and a positioning hole, which engages the positioning pin, is provided on the liquid crystal unit.

Owner:SHARP KK

Popular searches

Details for portable computers Electrical apparatus casings/cabinets/drawers Component plug-in assemblages Printed circuits structural associations Printed circuit non-printed electric components association Semiconductor devices Support structures on hinges/pivots Elongate light sources Semiconductor devices for light sources Non-electric lighting