Patents

Literature

228 results about "Pin array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

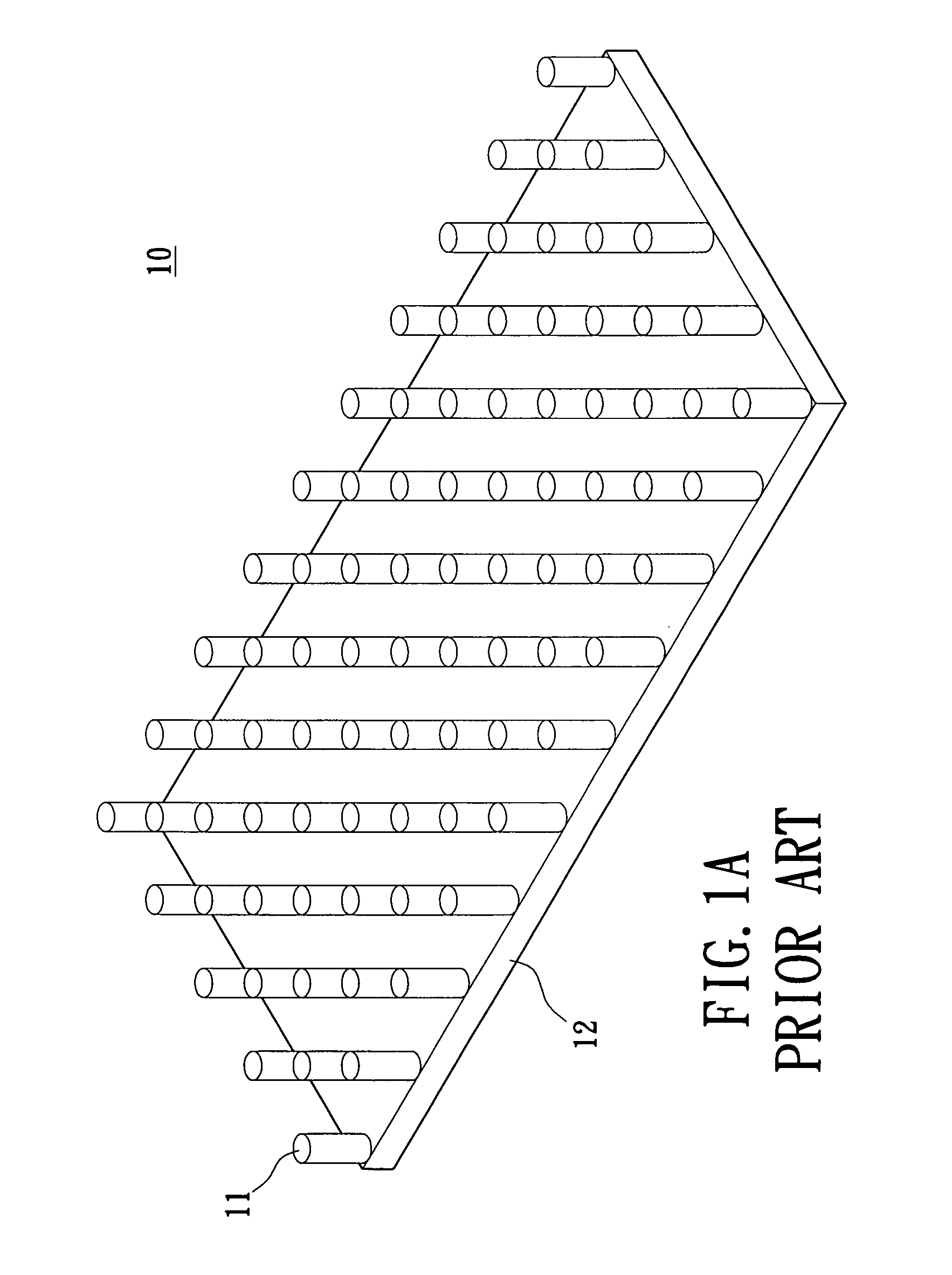

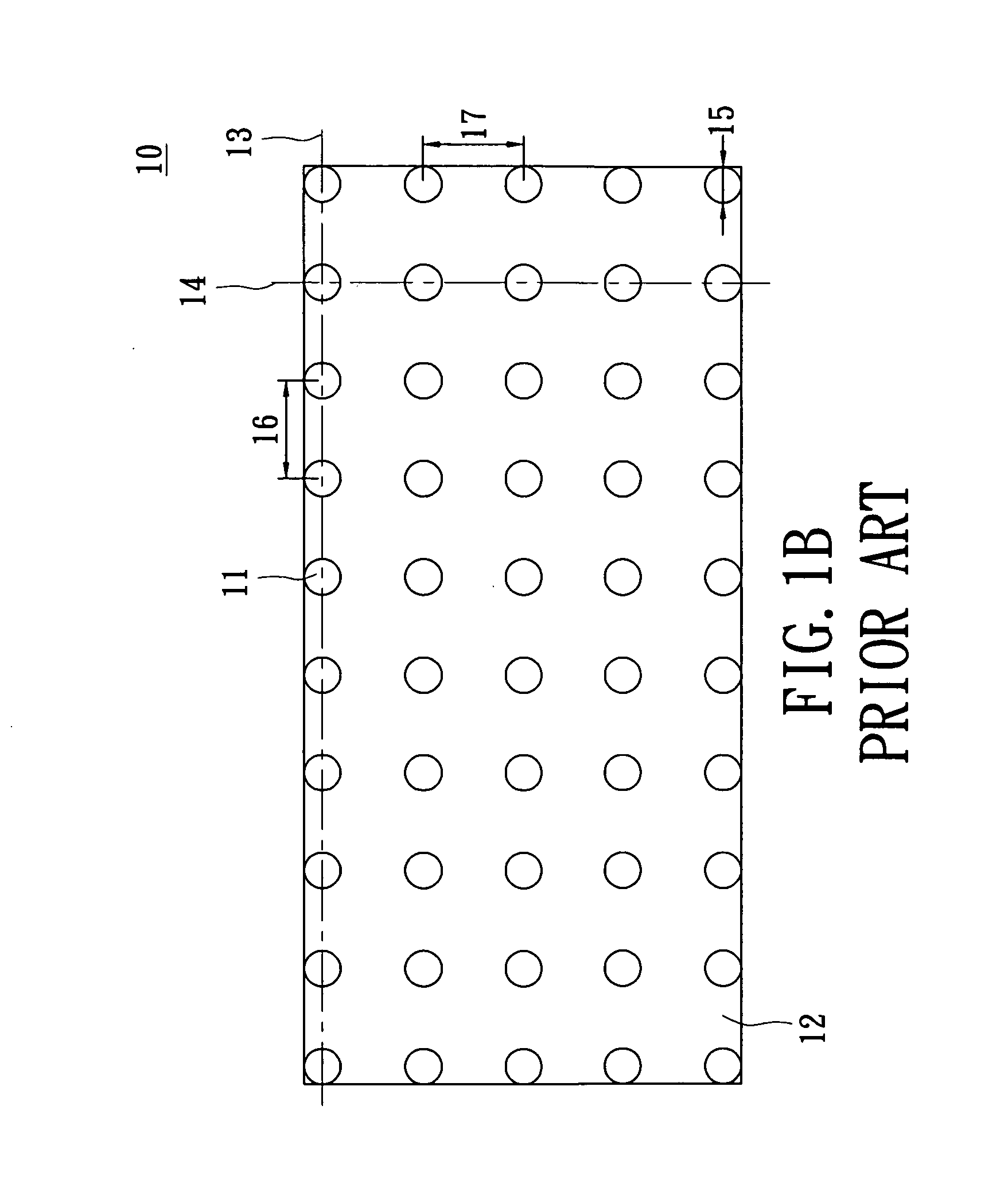

A pin grid array (PGA) is the integrated circuit packaging standard used in most second- through fifth-generation processors. Pin grid array packages were either rectangular or square in shape, with pins arranged in a regular array.

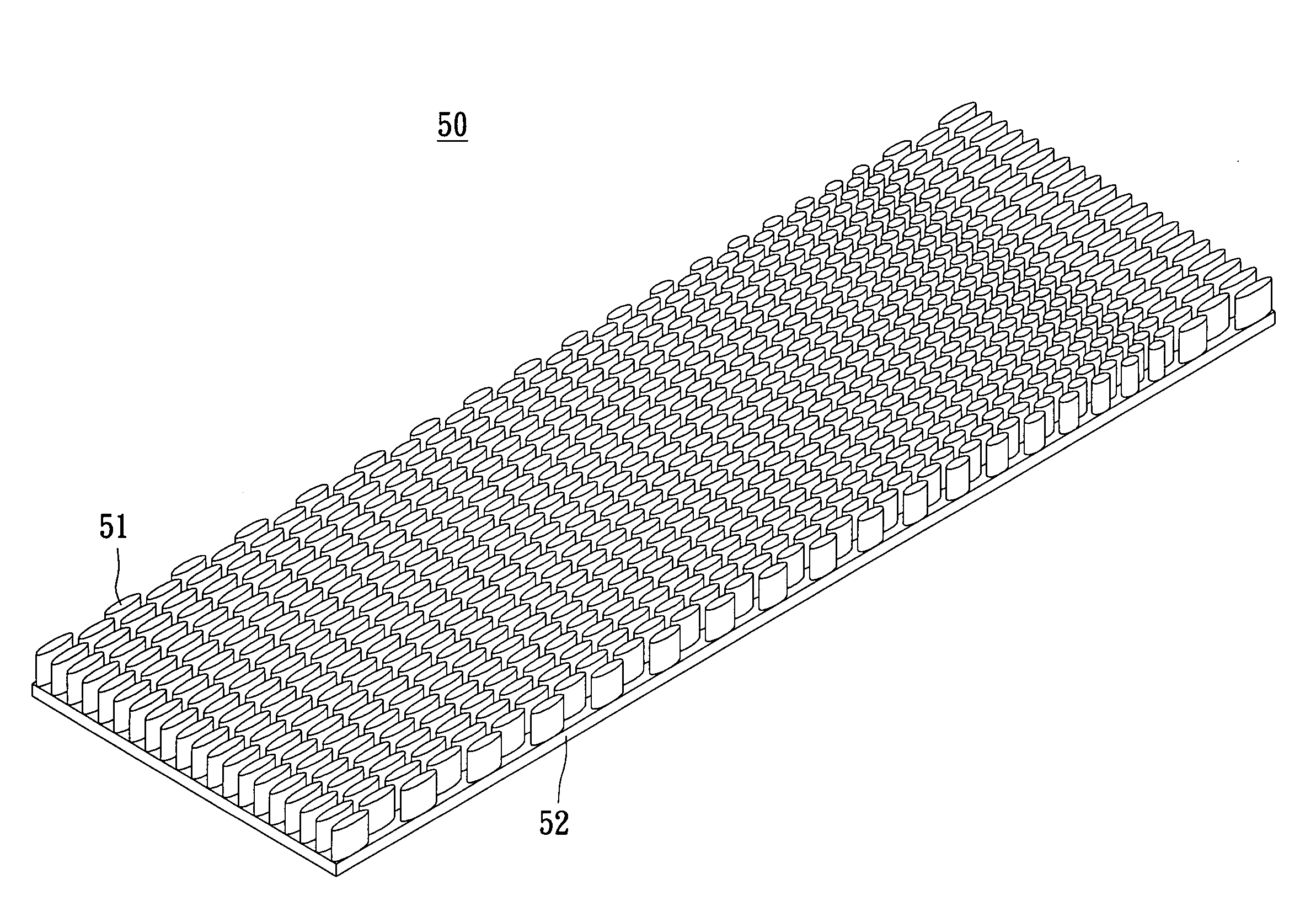

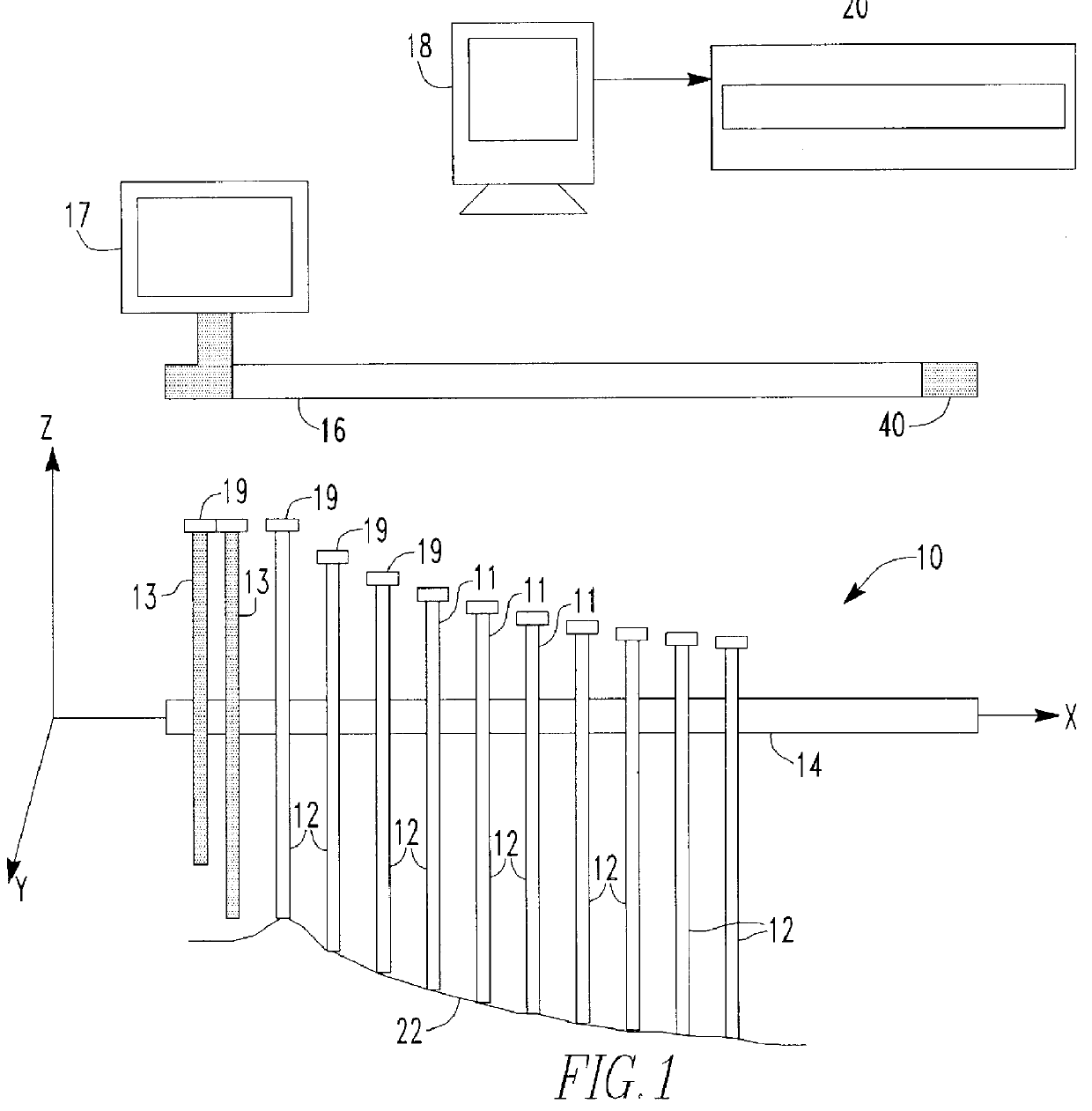

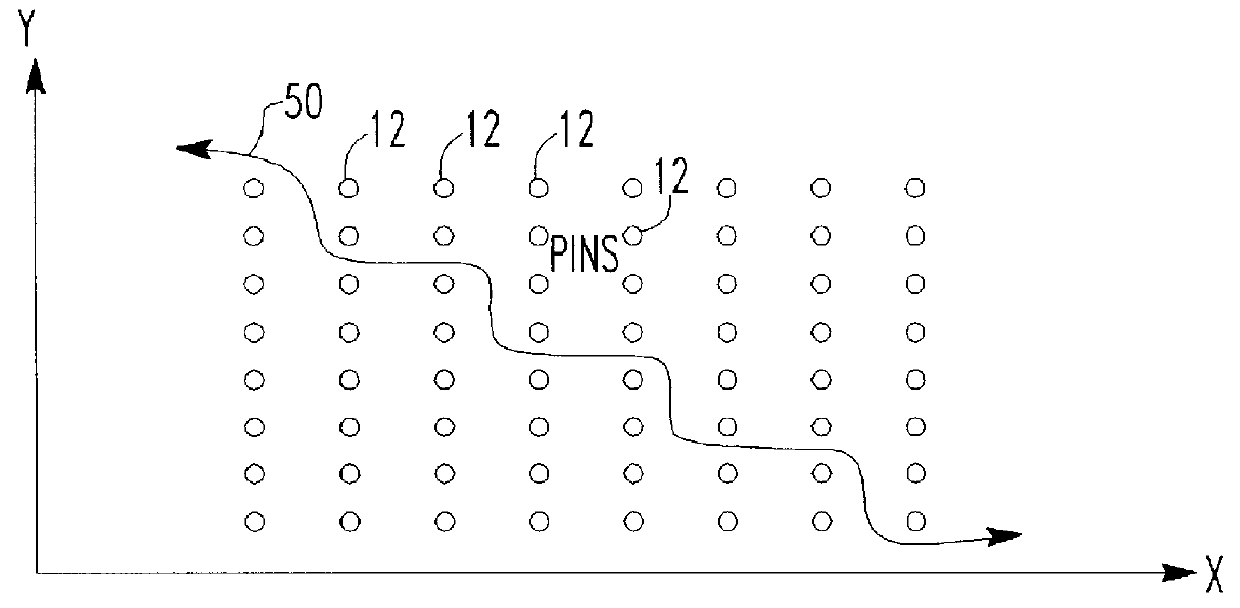

Non-linear fin heat sink

InactiveUS20090145581A1Improve power densityDissipating/removing heatSemiconductor/solid-state device detailsSolid-state devicesCoolant flowEngineering

A non-linear fin heat sink is provided for dissipating / removing heat uniformly from a device, where the heat generation is non-uniform over that device, while also providing a small and relatively lightweight heat sink. The heat sink has extended surface protrusions that are optimally shaped in recognition of convective heat transfer, conductive heat transfer, and flow resistance allowing the heat sink to offset the temperature rise of a coolant media and provide enhanced cooling for the coolant temperature, deliver optimized cooling efficiency per the local physical properties of the coolant media, be used with a fluid for effectuating heat transfer; either liquid coolant, gas coolant or a combination thereof. Furthermore the heat sink features turbulence enhancement of the coolant stream by a pin array through which coolant stream passes, such fin array featuring a non-linear shape, spacing, and height pattern to provide optimal cooling while simultaneously reducing volume and flow resistance.

Owner:THERMAL TECH

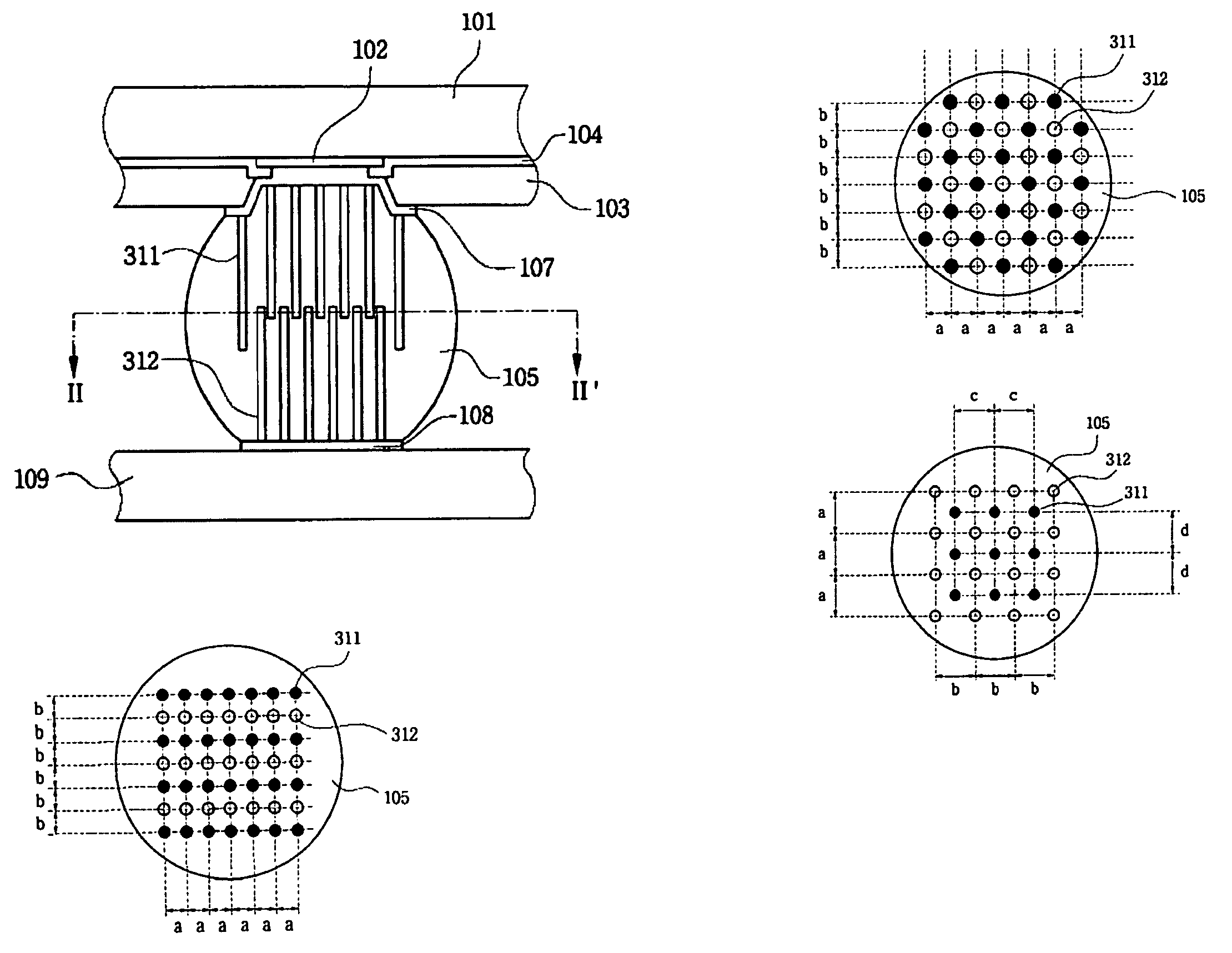

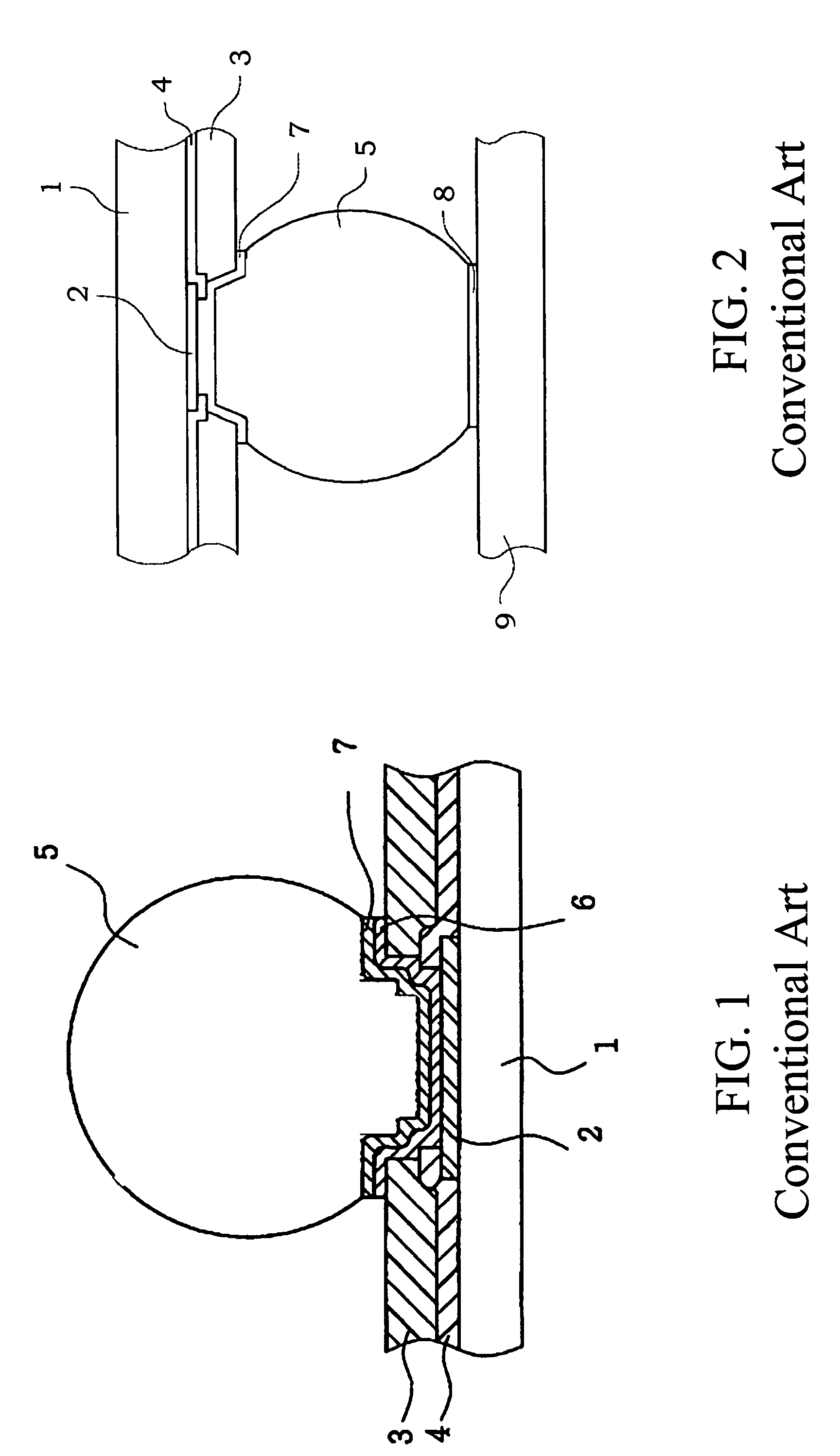

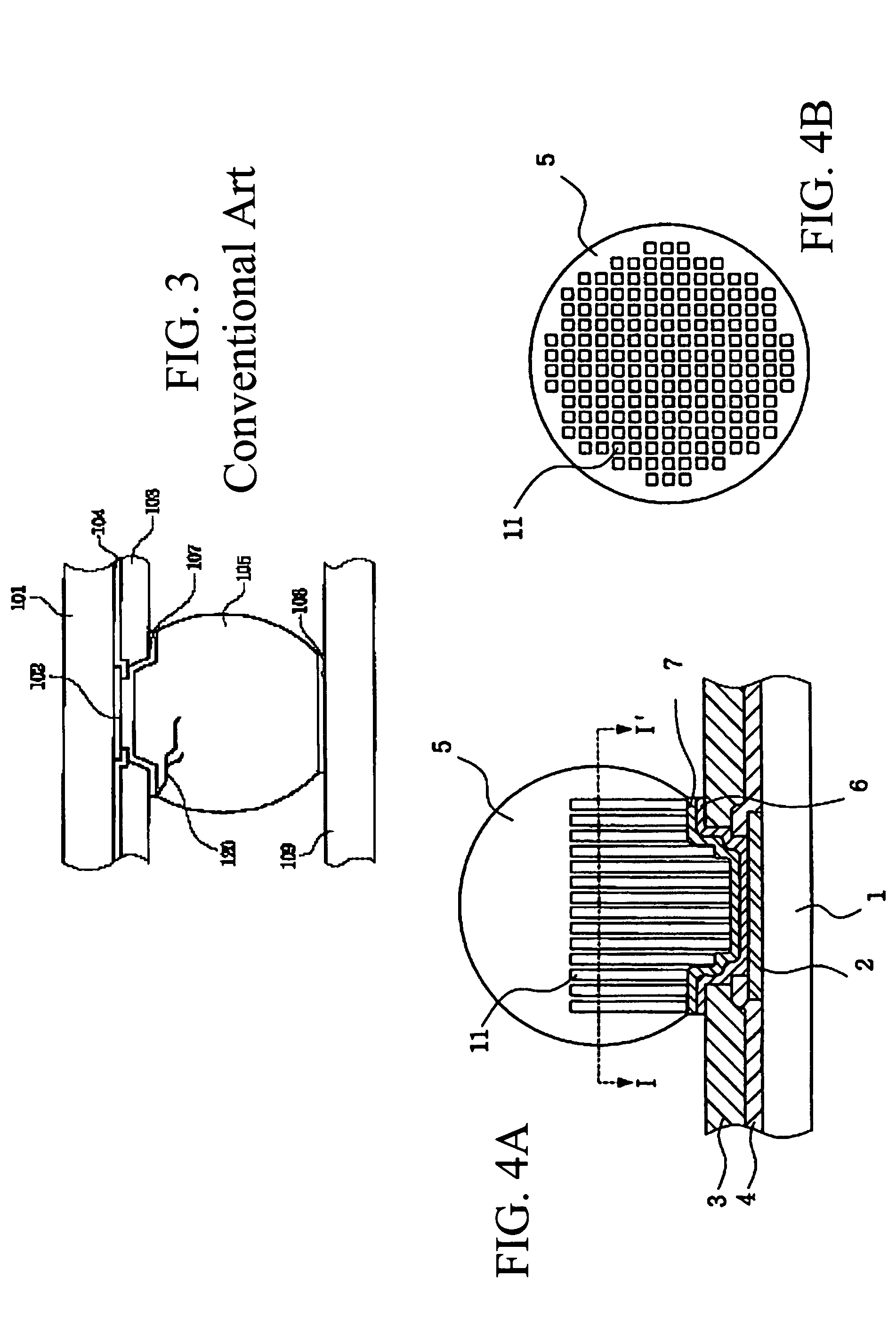

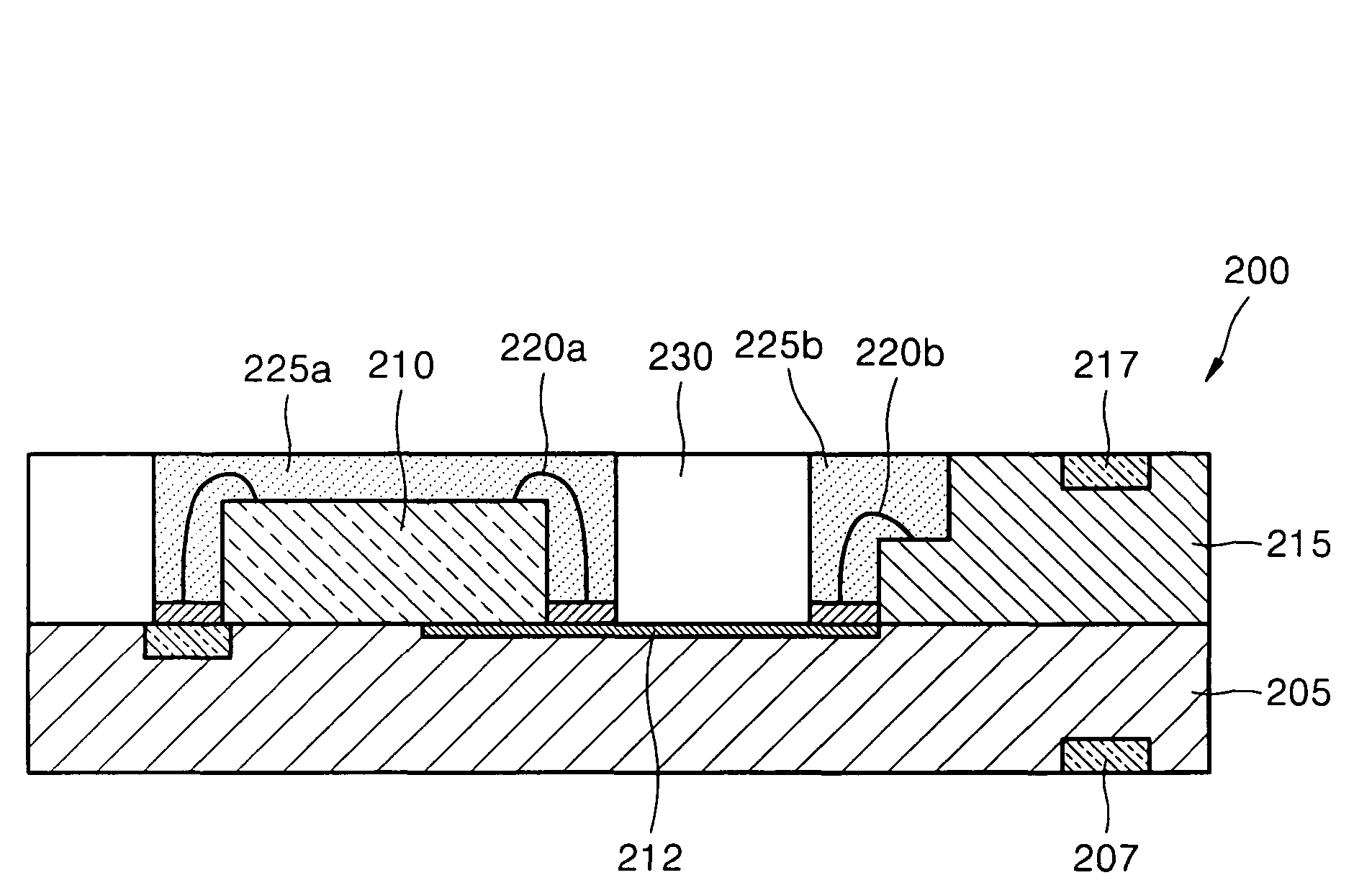

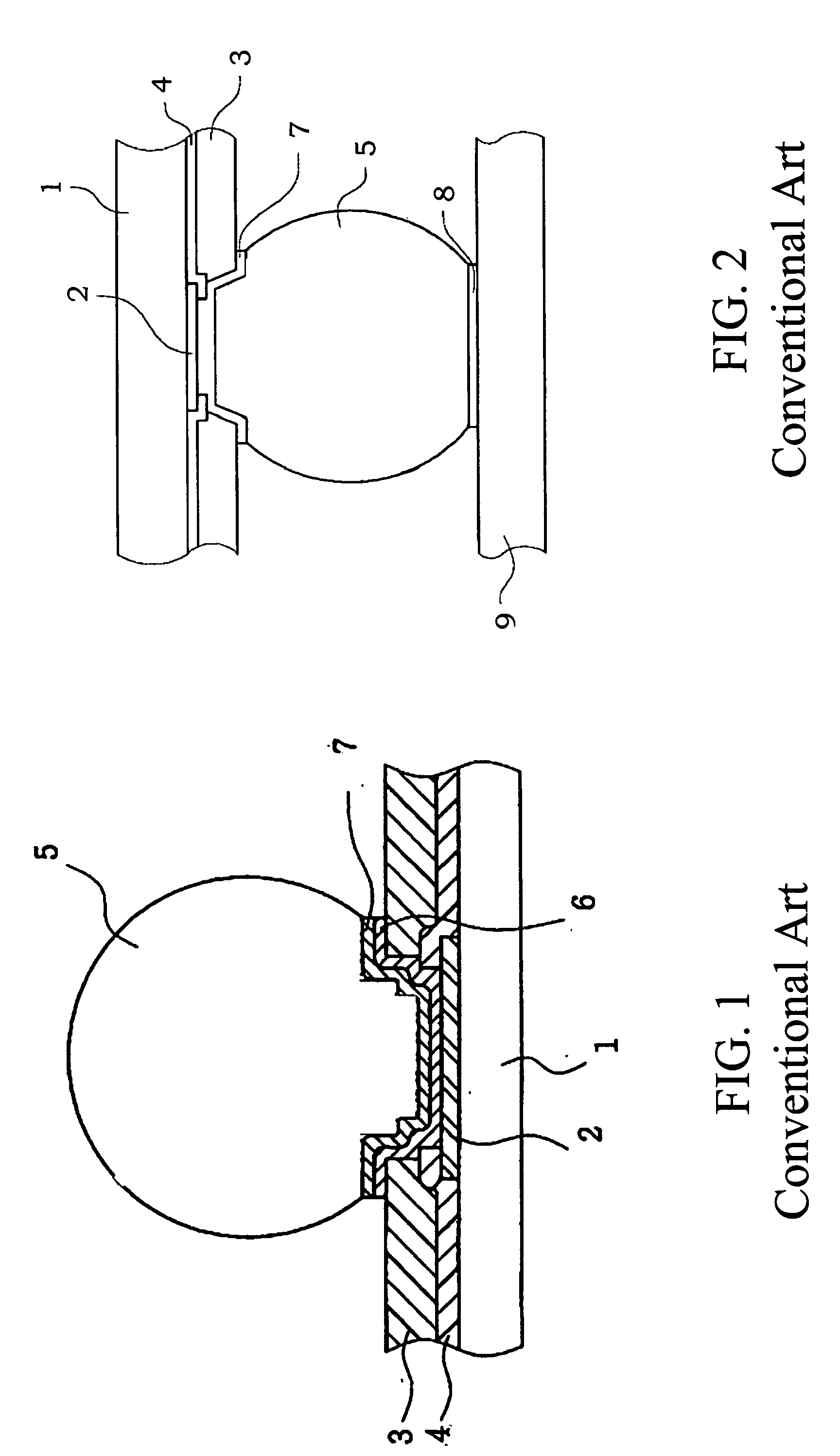

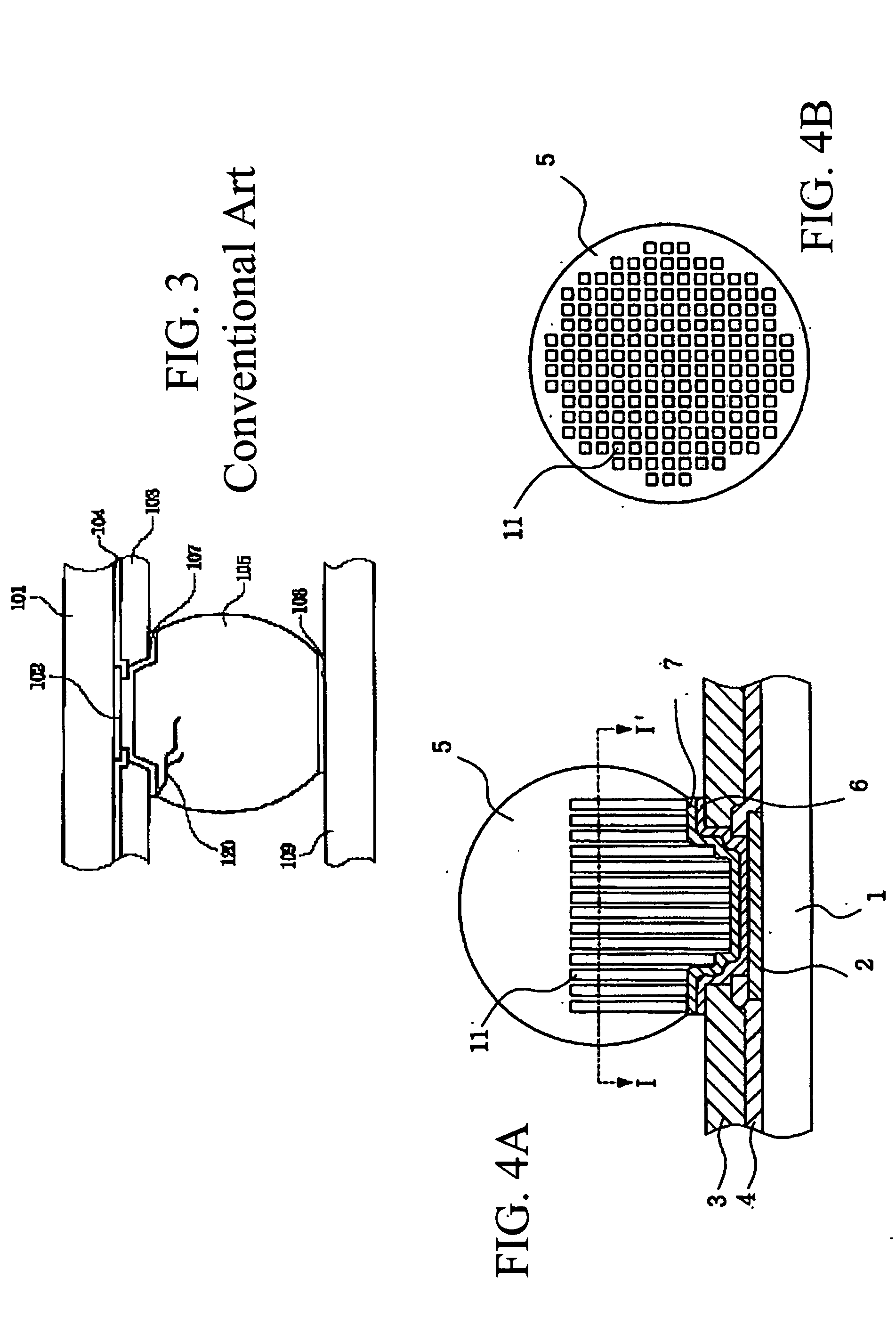

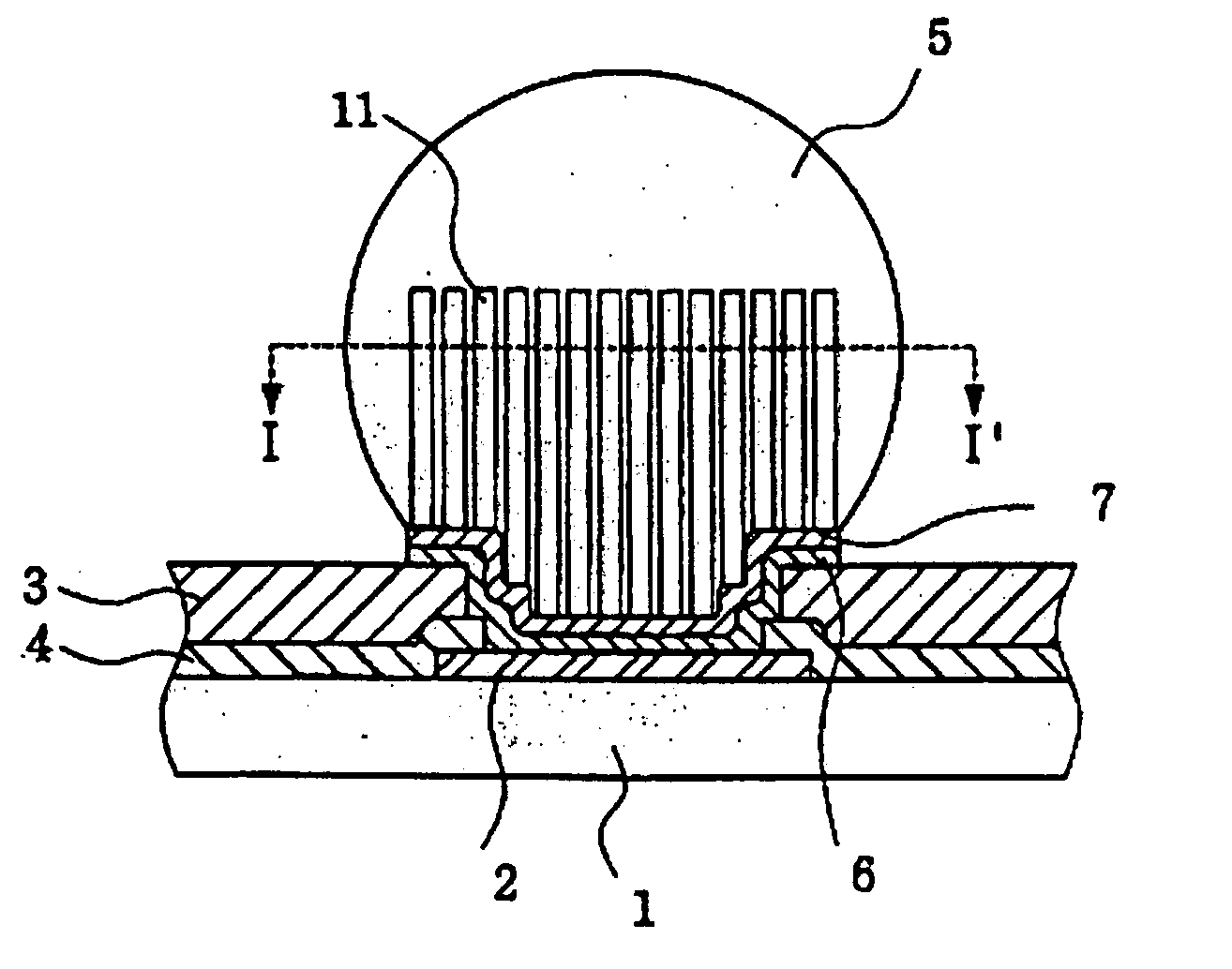

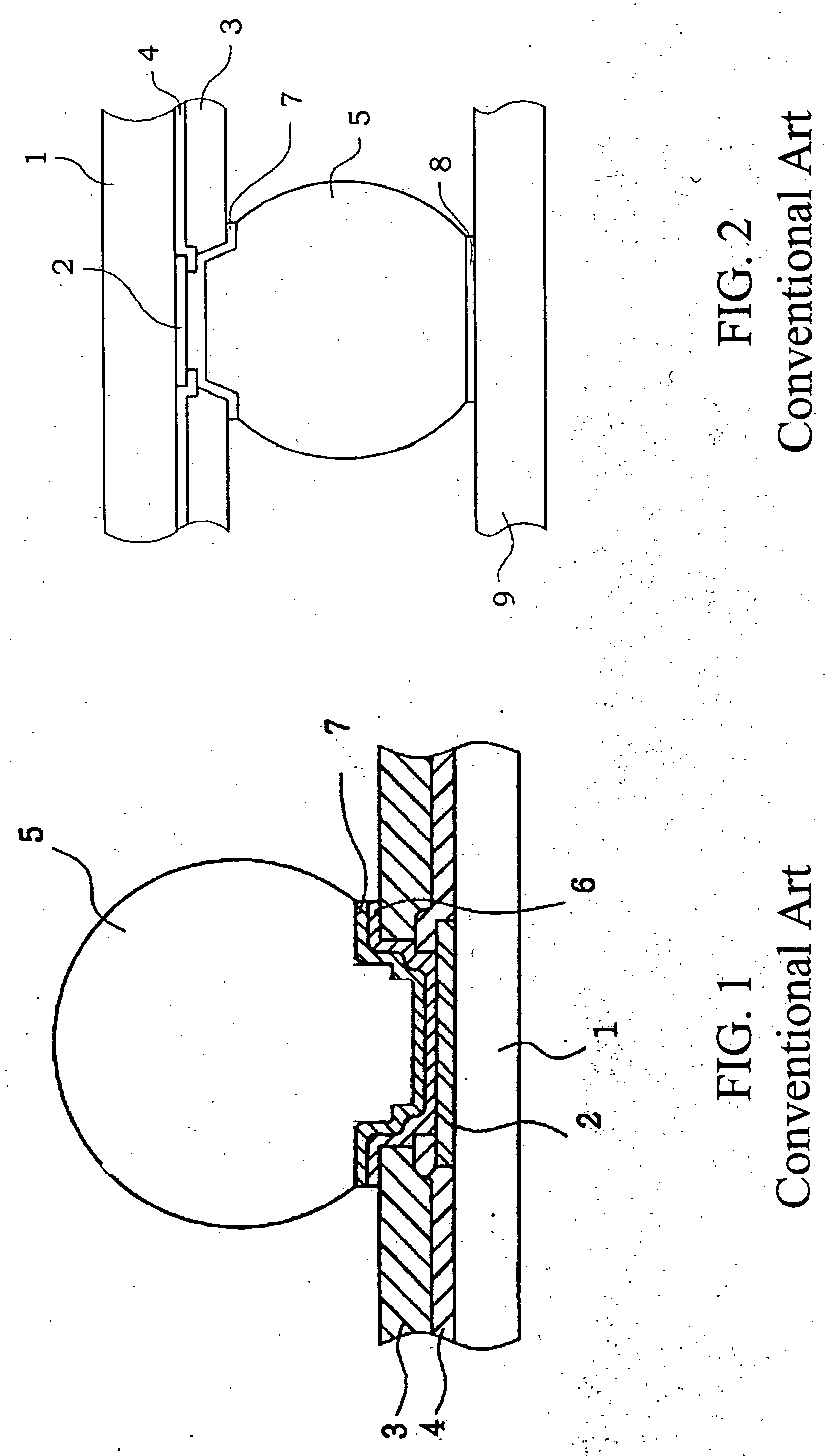

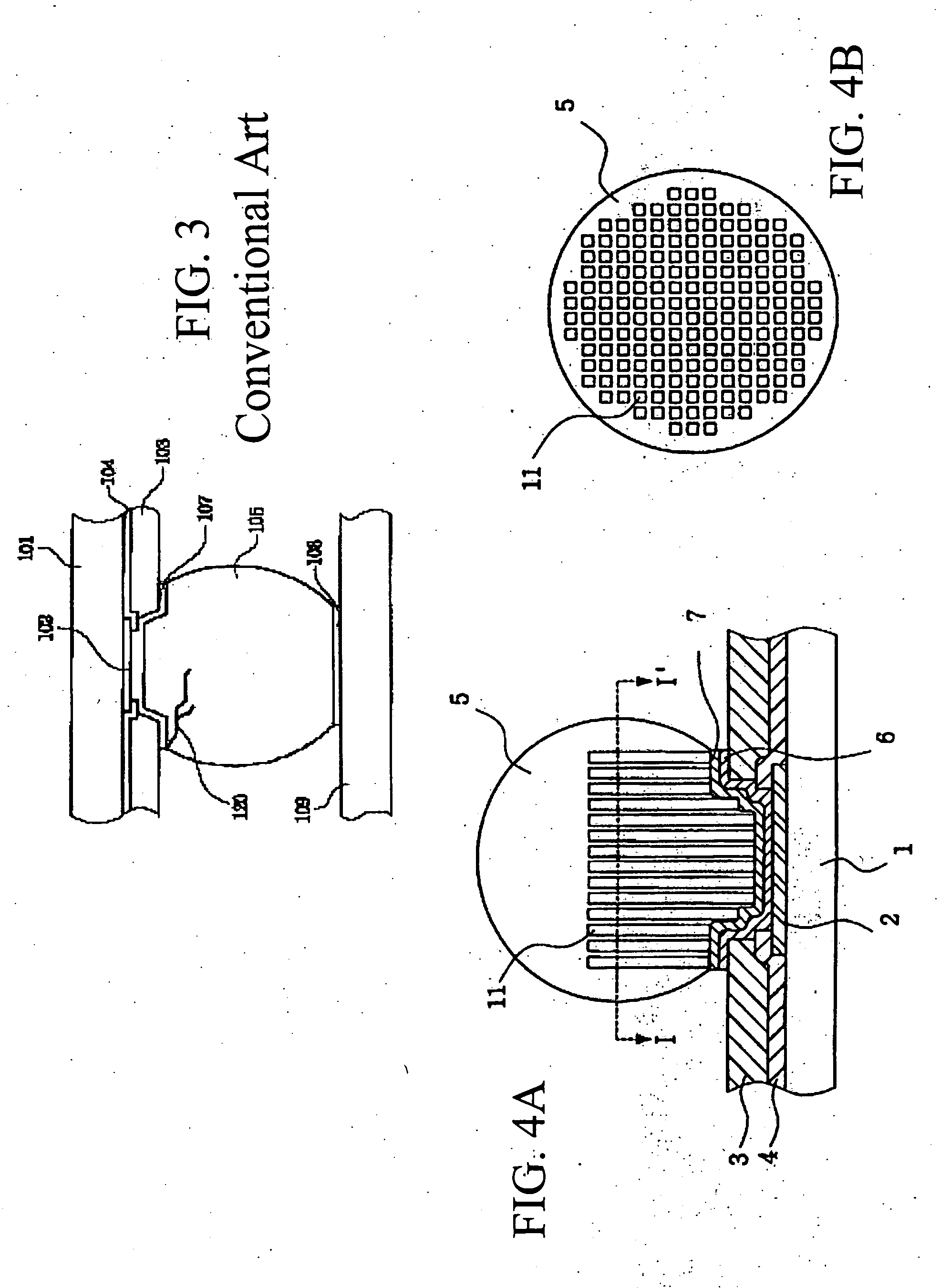

Reinforced solder bump structure and method for forming a reinforced solder bump

A reinforced solder bump connector structure is formed between a contact pad arranged on a semiconductor chip and a ball pad arranged on a mounting substrate. The semiconductor chip includes at least one reinforcing protrusion extending upwardly from a surface of an intermediate layer. The mounting substrate includes at least one reinforcing protrusion extending upwardly from a ball pad, the protrusions from both the chip and the substrate being embedded within the solder bump connector. In some configurations, the reinforcing protrusion from the contact pad and the ball pad are sized and arranged to have overlapping under portions. These overlapping portions may assume a wide variety of configurations that allow the protrusions to overlap without contacting each other including pin arrays and combinations of surrounding and surrounded elements. In each configuration, the reinforcing protrusions will tend to suppress crack formation and / or crack propagation thereby improving reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

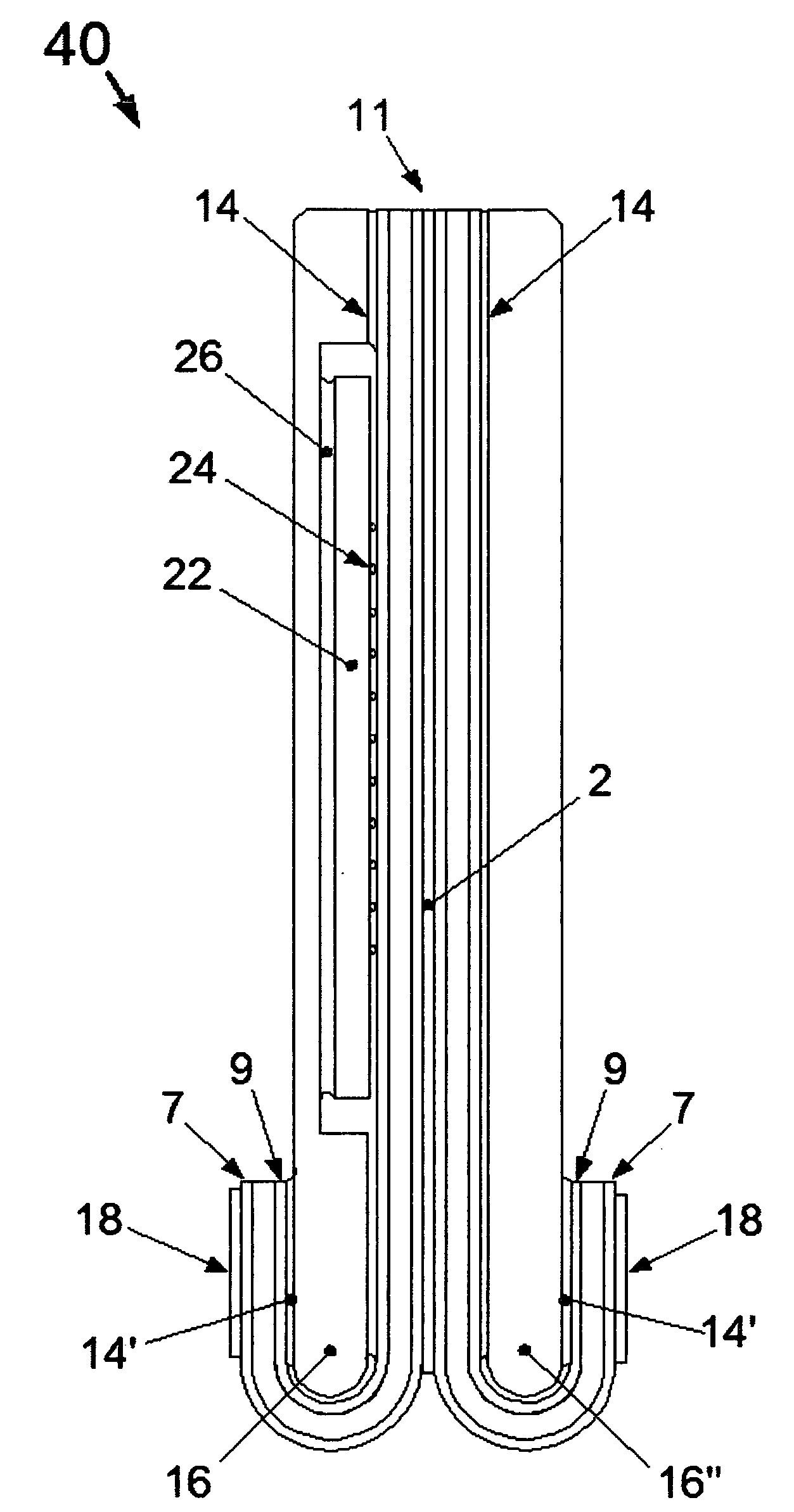

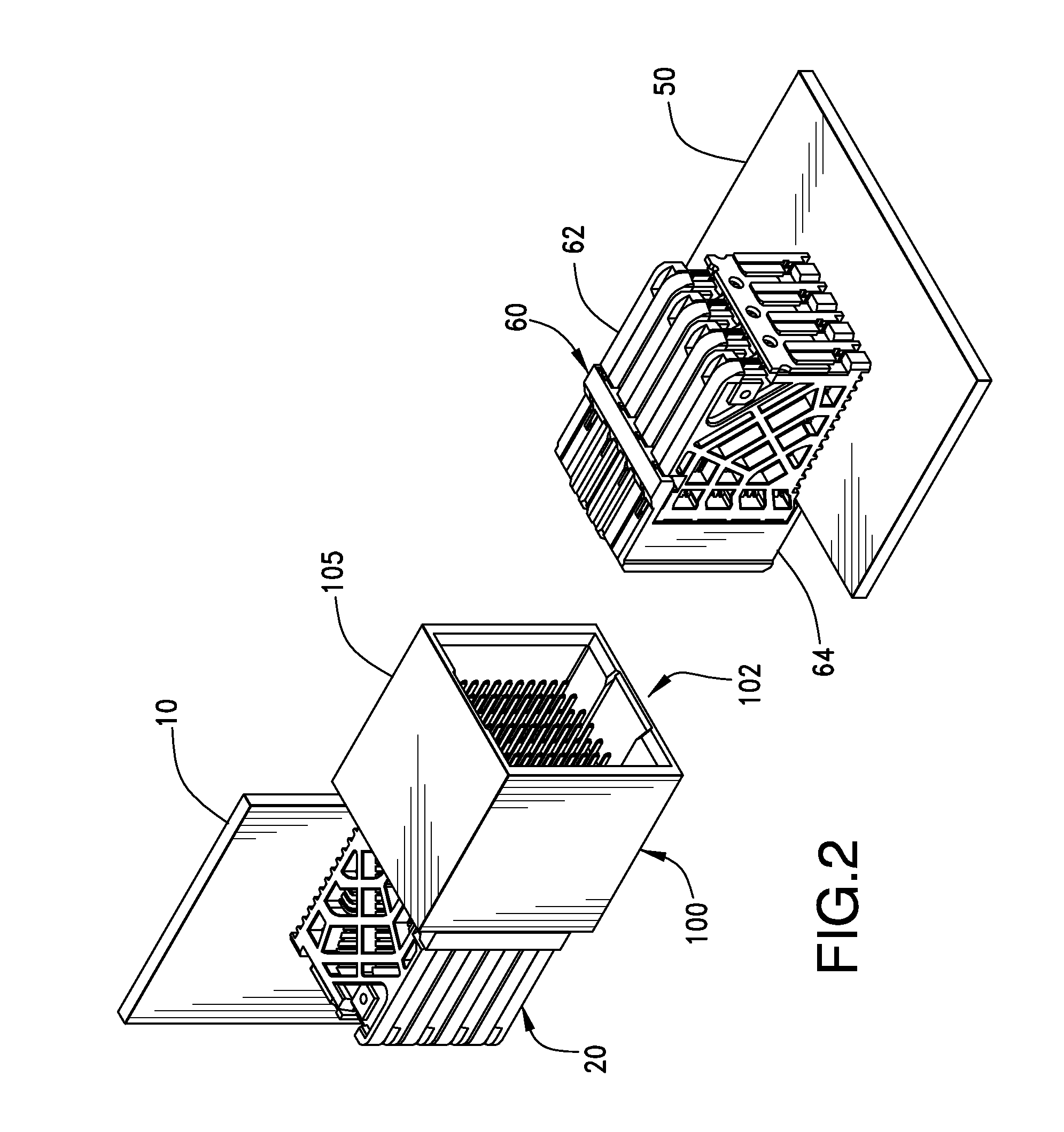

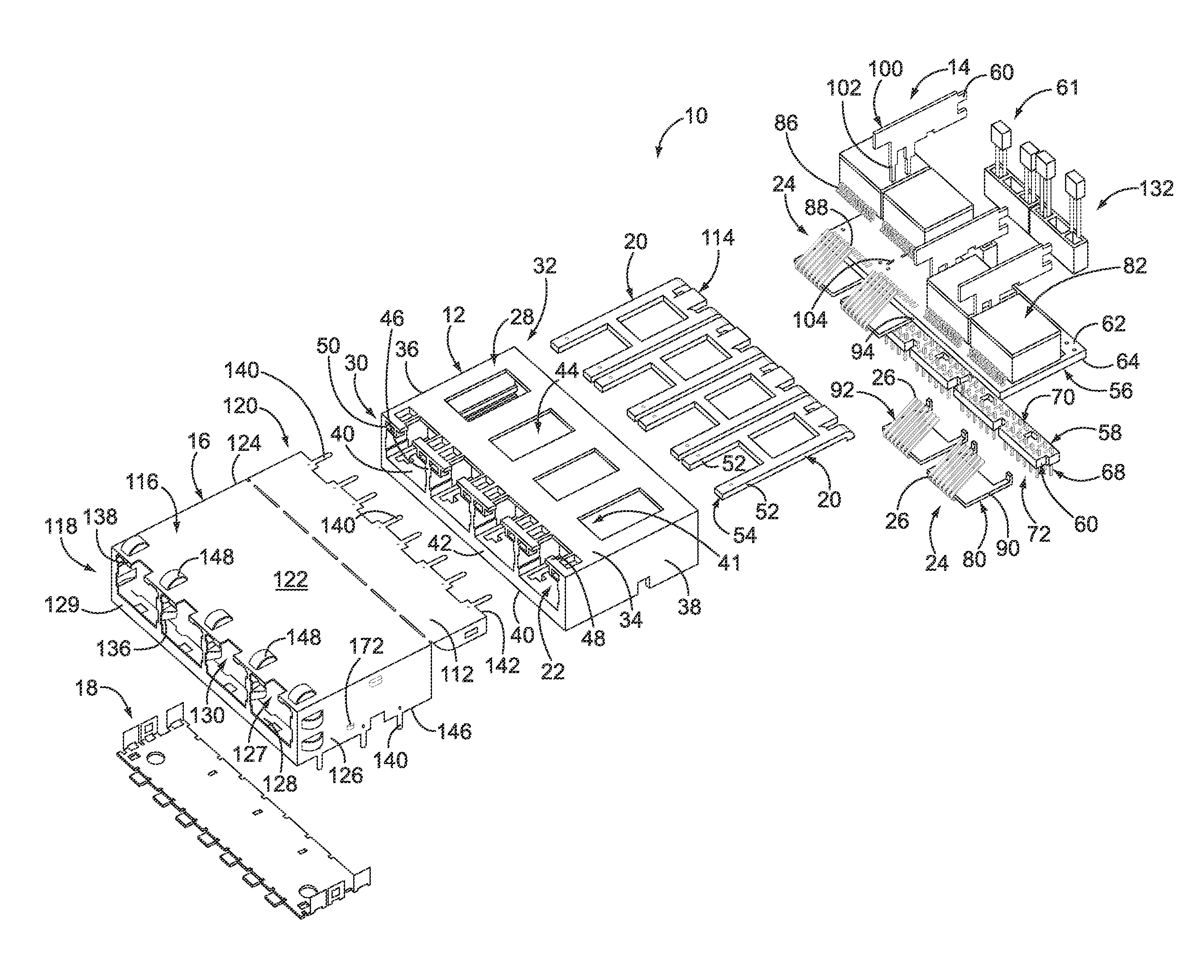

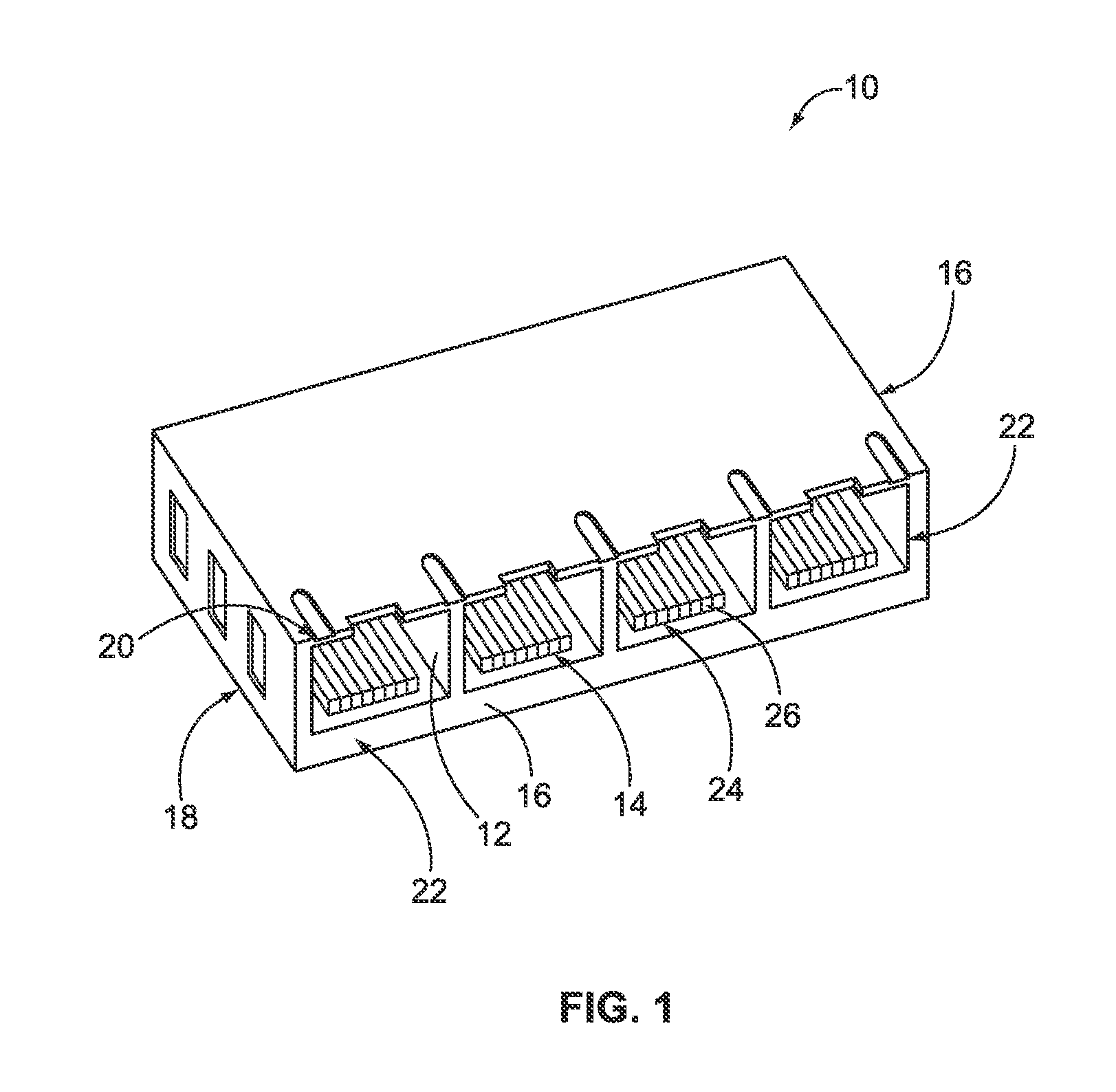

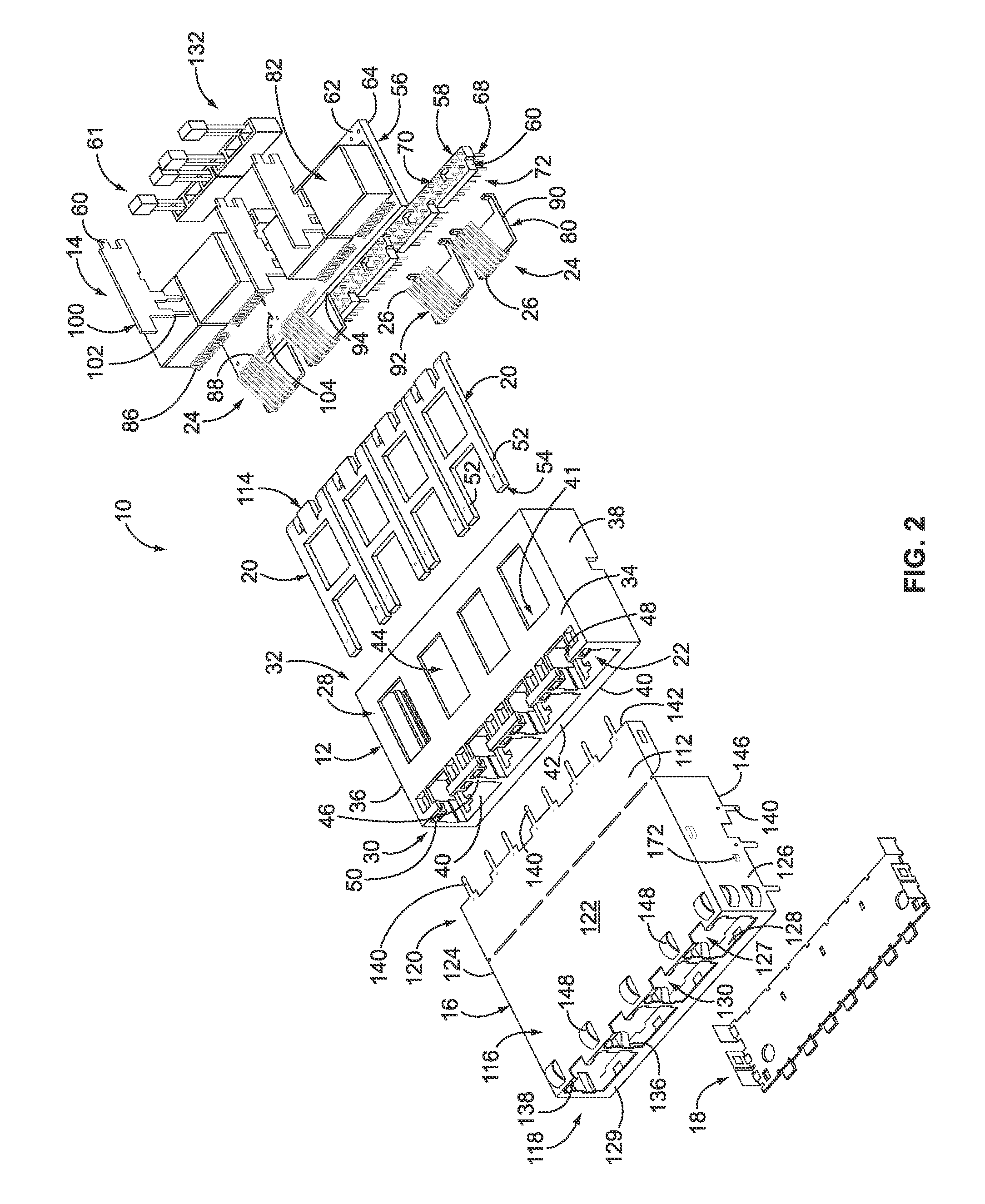

Thin multi-chip flex module

InactiveUS7796399B2Engagement/disengagement of coupling partsSemiconductor/solid-state device detailsPin arrayRigid frame

A multichip module comprises a multilayer substrate circuit having conductive patterns on its surface(s) to which microelectronic device(s) are attached. The conductive patterns include a series of electrical contacts adjacent to one edge of the substrate. The substrate is bonded to two rigid frames, one on each opposite surface. Each substrate has a series of castellations on one edge that are aligned and electrically connected to the respective contacts on the substrate, preferably by soldering. The castellations can serve as a self-aligning mechanism when the module is brought into contact with a low-profile pin array, and the module may be held in place on a motherboard by guide rails in a socket that engages the edges perpendicular to the castellated edge of the module. The module may further be provided with protective heat spreading covers.

Owner:MICROELECTRONICS ASSEMBLY TECH

Semiconductor device and method of manufacturing the same

InactiveUS7850087B2Coupling device connectionsSemiconductor/solid-state device detailsPin arraySemiconductor

Owner:SAMSUNG ELECTRONICS CO LTD

Reinforced solder bump structure and method for forming a reinforced solder bump

A reinforced solder bump connector structure is formed between a contact pad arranged on a semiconductor chip and a ball pad arranged on a mounting substrate. The semiconductor chip includes at least one reinforcing protrusion extending upwardly from a surface of an intermediate layer. The mounting substrate includes at least one reinforcing protrusion extending upwardly from a ball pad, the protrusions from both the chip and the substrate being embedded within the solder bump connector. In some configurations, the reinforcing protrusion from the contact pad and the ball pad are sized and arranged to have overlapping under portions. These overlapping portions may assume a wide variety of configurations that allow the protrusions to overlap without contacting each other including pin arrays and combinations of surrounding and surrounded elements. In each configuration, the reinforcing protrusions will tend to suppress crack formation and / or crack propagation thereby improving reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

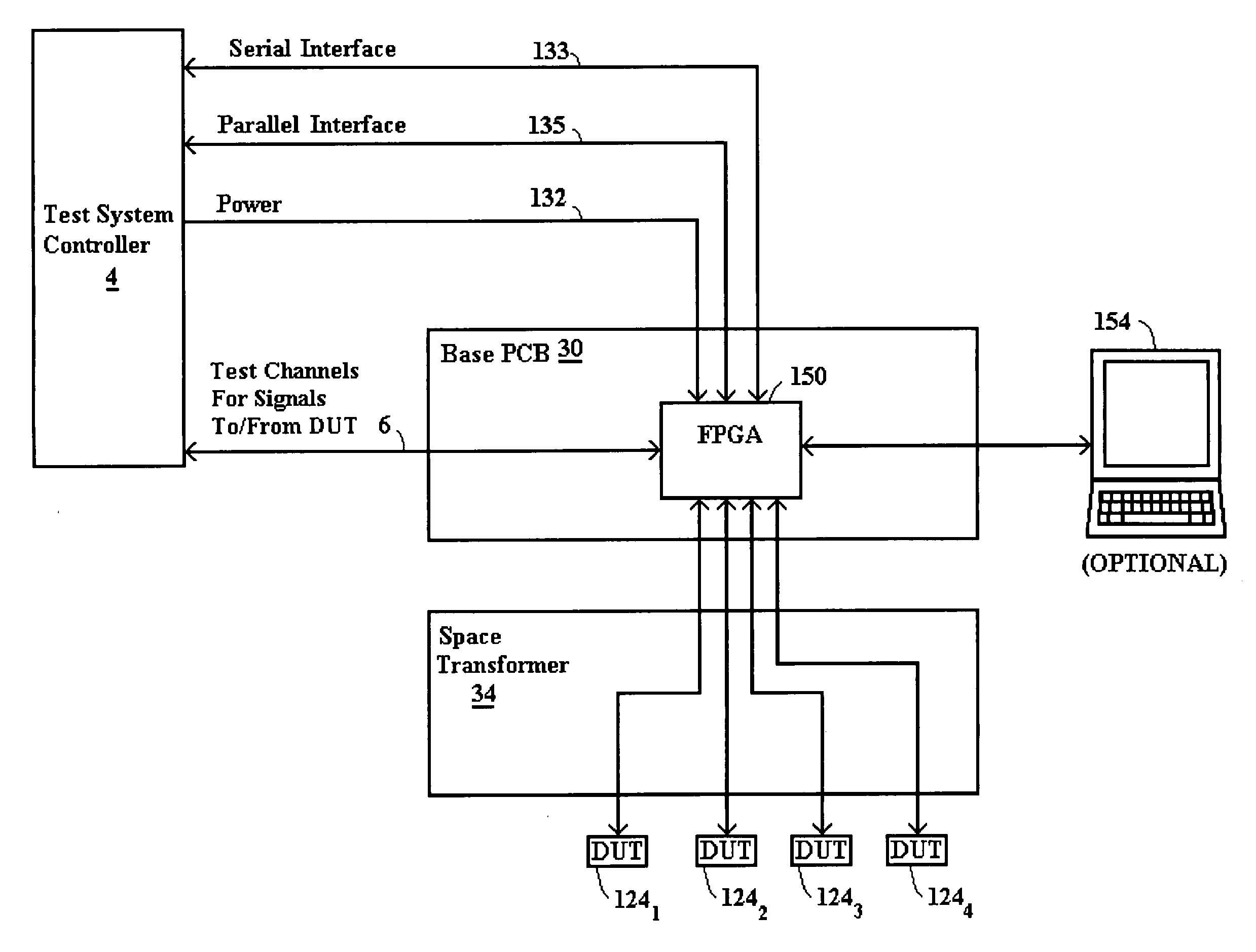

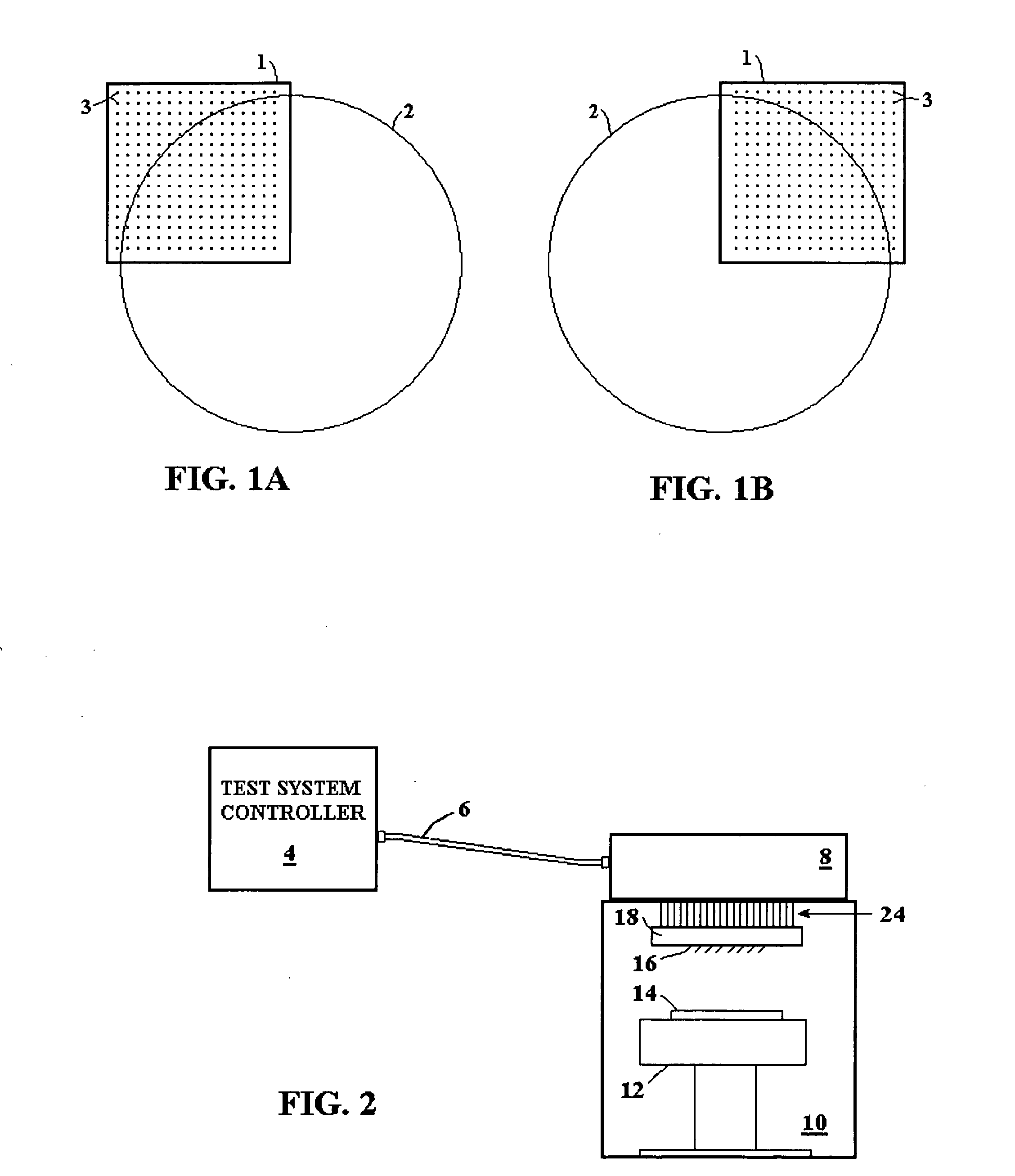

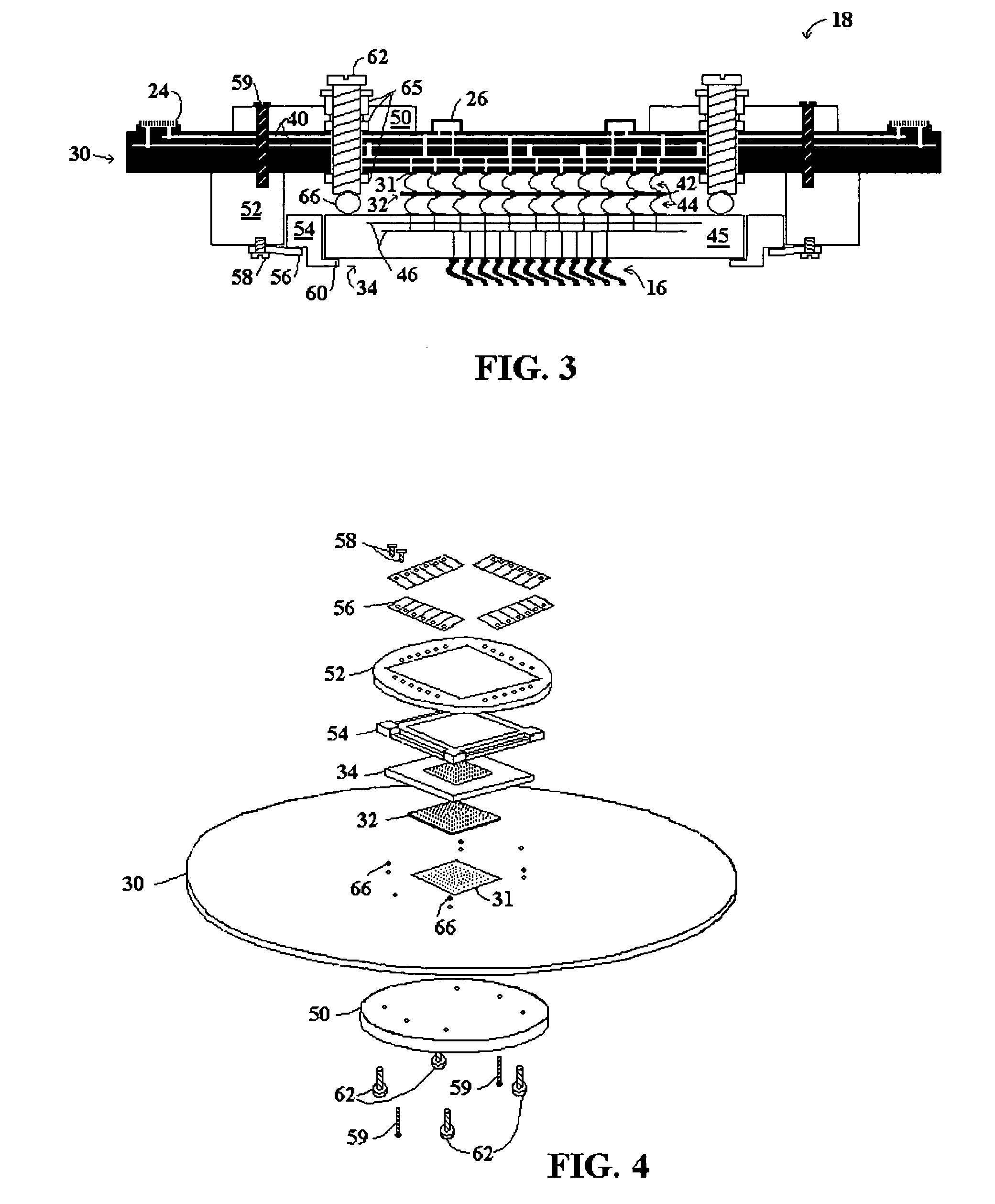

Programmable devices to route signals on probe cards

InactiveUS20060170435A1Great switching densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

A probe card of a wafer test system includes one or more programmable ICs, such as FPGAs, to provide routing from individual test signal channels to one of multiple probes. The programmable ICs can be placed on a base PCB of the probe card, or on a daughtercard attached to the probe card. With programmability, the PCB can be used to switch limited test system channels away from unused probes. Programmability further enables a single probe card to more effectively test devices having the same pad array, but having different pin-outs for different device options. Reprogrammability also allows test engineers to re-program as they are debugging a test program. Because the programmable IC typically includes buffers that introduce an unknown delay, in one embodiment measurement of the delay is accomplished by first programming the programmable IC to provide a loop back path to the test system so that buffer delay can be measured, and then reprogramming the programmable IC now with a known delay to connect to a device being tested.

Owner:FORMFACTOR INC

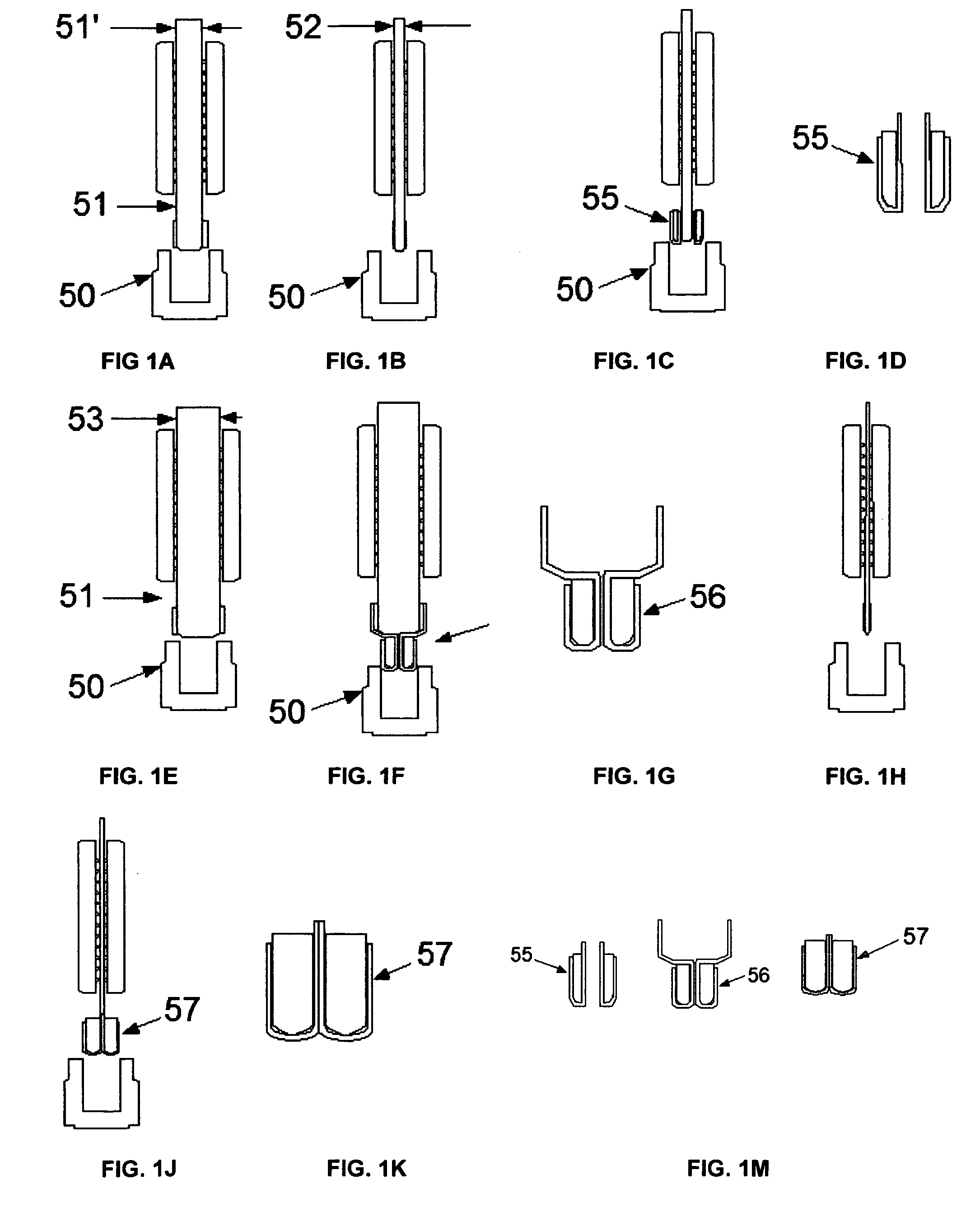

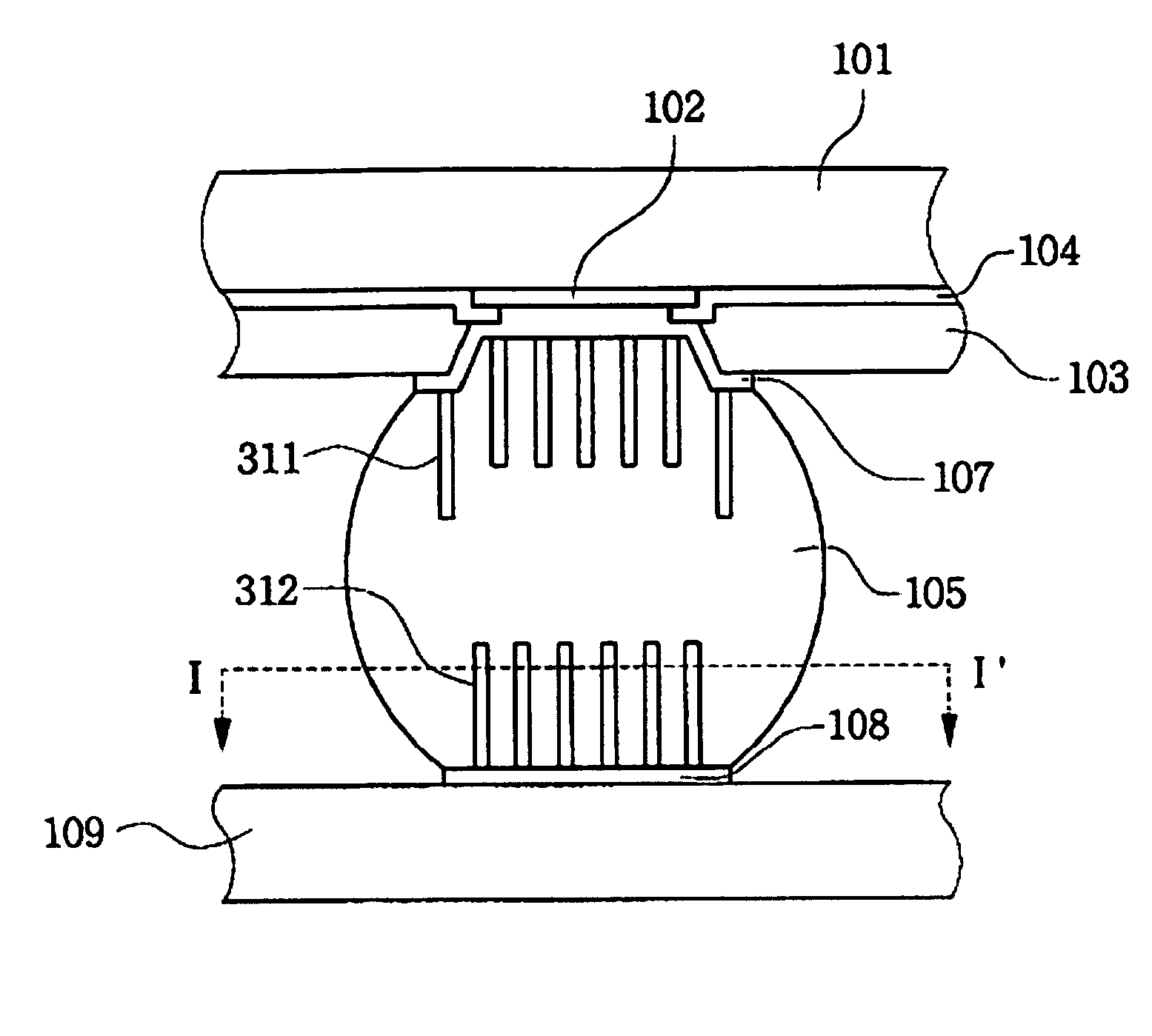

Semiconductor device and method of manufacturing the same

InactiveUS20060118641A1Coupling device connectionsSemiconductor/solid-state device detailsDevice materialPin array

A semiconductor device and method of fabricating the same. The semiconductor device includes at least one first contact pin on a first substrate and at least one second contact pin on a second substrate. The at least one first and second contact pins may be included in first and second contact pin arrays. The first and second contact pins of the first and second contact pin arrays may be aligned.

Owner:SAMSUNG ELECTRONICS CO LTD

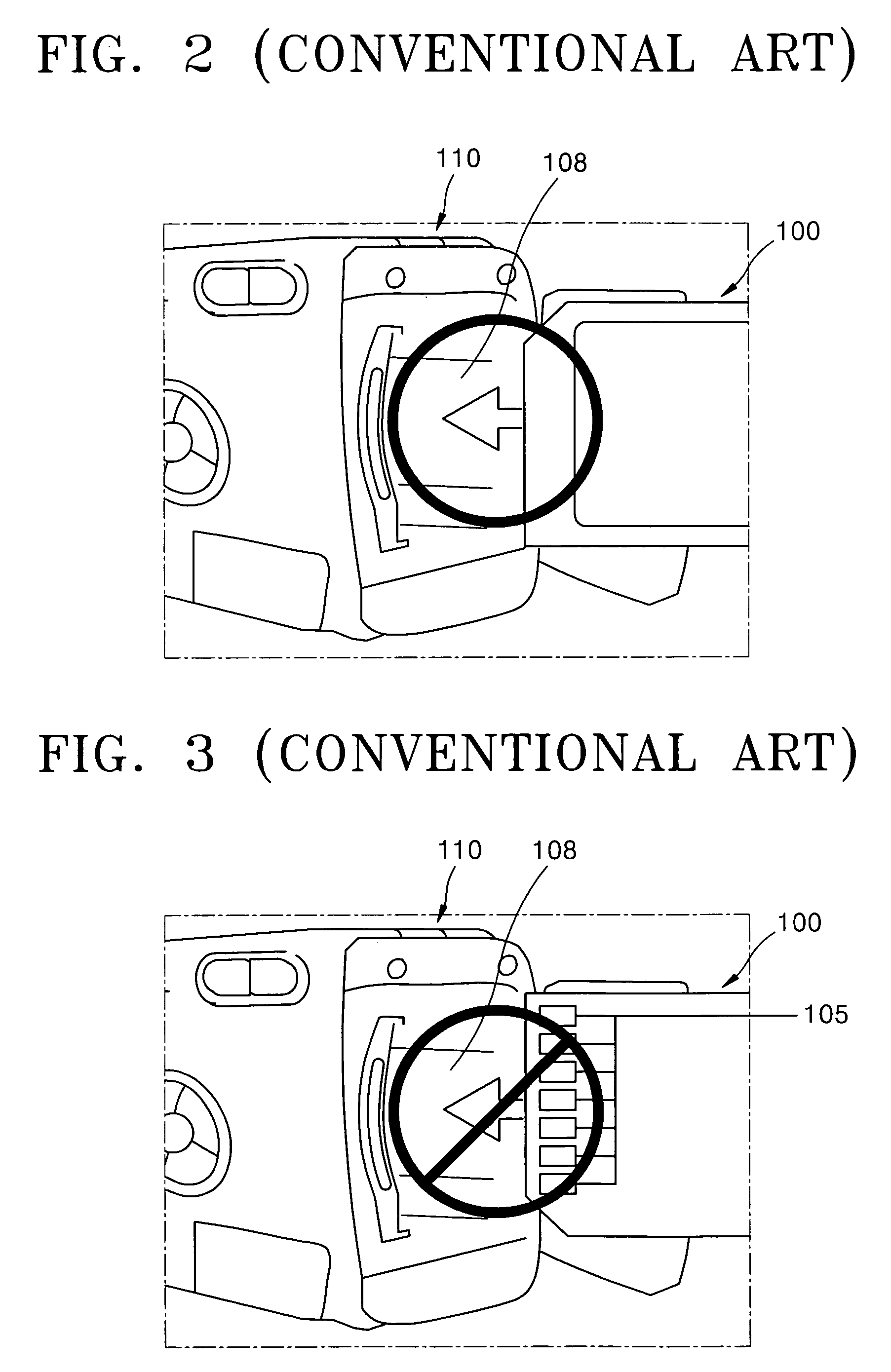

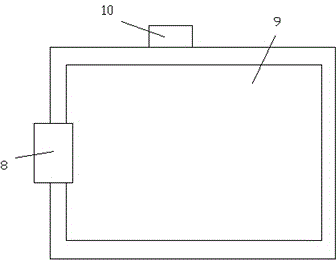

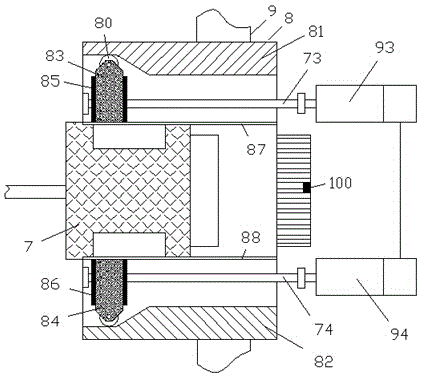

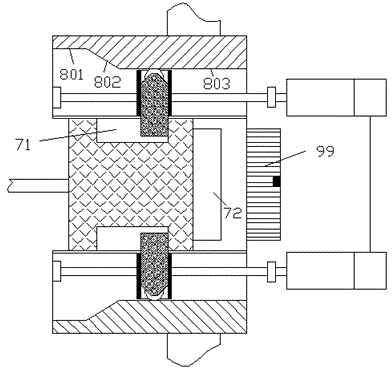

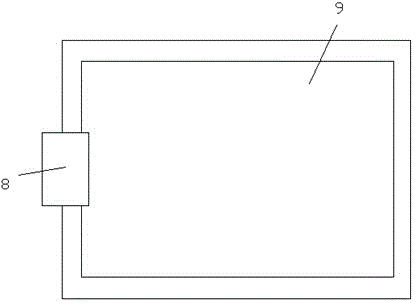

Circuit board plug-in subassembly with LED indicator light

InactiveCN104836087ASmooth side to side movementAchieve lockingCoupling device detailsIdler-wheelPin array

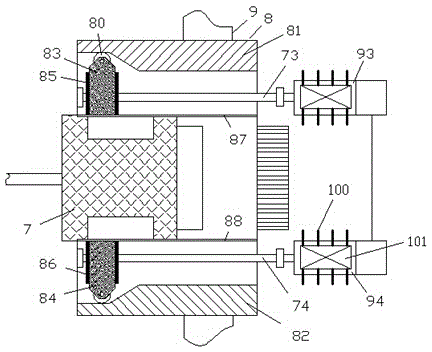

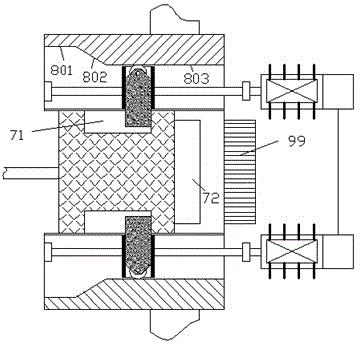

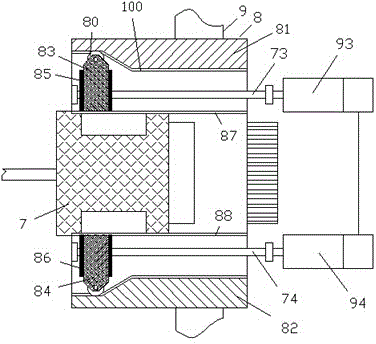

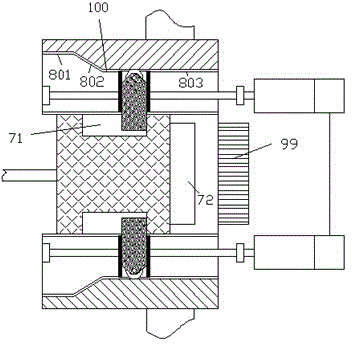

A circuit board plug-in subassembly with an LED indicator light of the invention comprises circuit board equipment (9) and an interface device (8) which is arranged at the left side of the circuit board equipment (9). The LED indicator light (10) is arranged at the top of the circuit board equipment (9), and the interface device (8) comprises a shell which is composed of an upper outline part (81) and a lower outline part (82). A contact pin array (99) is arranged at the part of the plate of the circuit board equipment (9) adjacent to the inner side of the shell and is used for engaging with a jack array (72) which is inserted into a plug (7) between the upper outline part (81) and the lower outline part (82) of the interface device (8), and the upper outline part (81) and the lower outline part (82) are respectively engaged with idler wheels (80), which are arranged on an upper sliding block subassembly (83) and a lower sliding block subassembly (84).

Owner:汪贤女

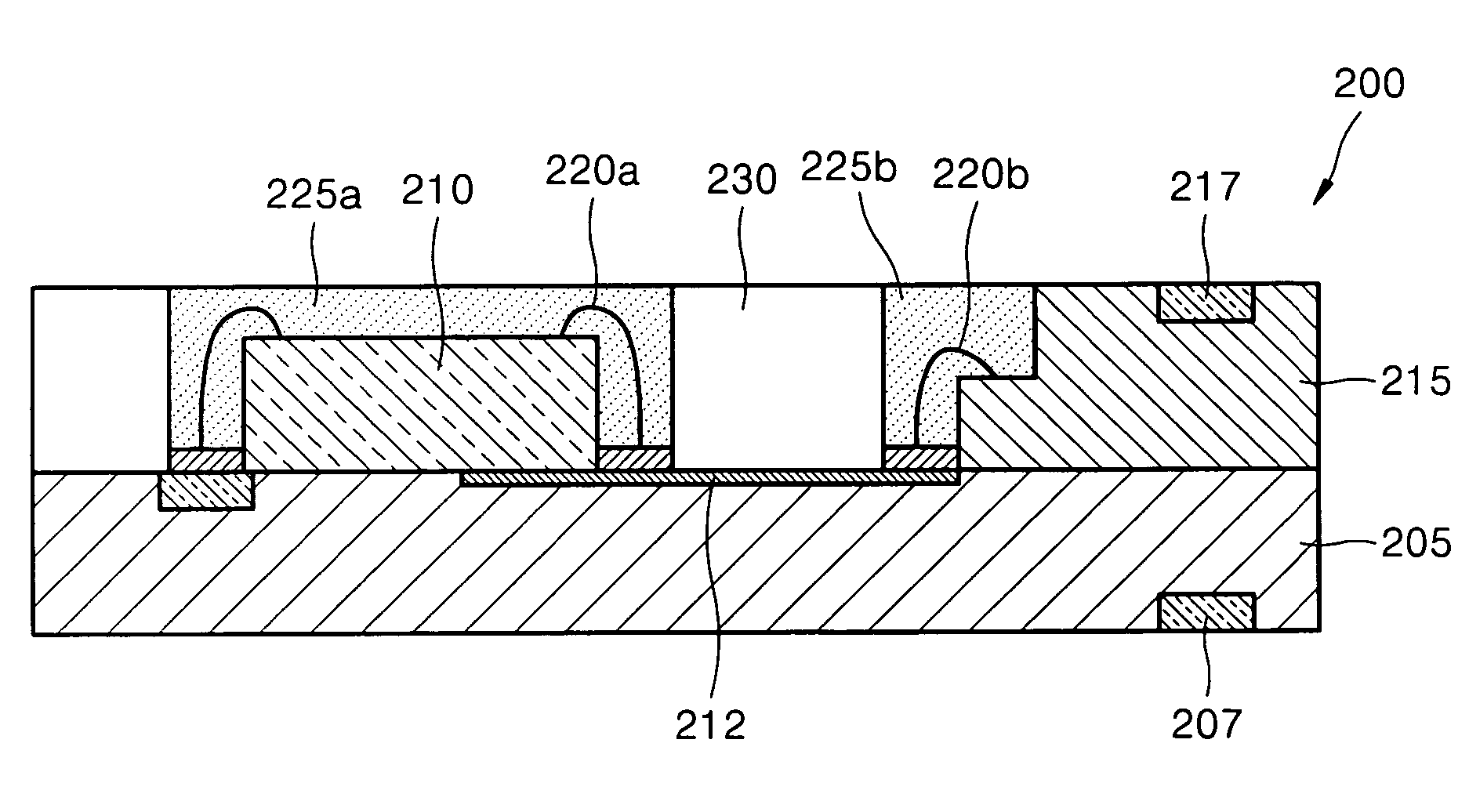

Reinforced solder bump structure and method for forming a reinforced solder bump

InactiveUS20060113681A1Printed circuit assemblingFinal product manufactureContact padSemiconductor chip

A reinforced solder bump connector structure is formed between a contact pad arranged on a semiconductor chip and a ball pad arranged on a mounting substrate. The semiconductor chip includes at least one reinforcing protrusion extending upwardly from a surface of an intermediate layer. The mounting substrate includes at least one reinforcing protrusion extending upwardly from a ball pad, the protrusions from both the chip and the substrate being embedded within the solder bump connector. In some configurations, the reinforcing protrusions from the contact pad and the ball pad are sized and arranged to have overlapping upper portions. These overlapping portions may assume a wide variety of configurations that allow the protrusions to overlap without contacting each other including pin arrays and combinations of surrounding and surrounded elements. In each configuration, the reinforcing protrusions will tend to suppress crack formation and / or crack propagation thereby improving reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

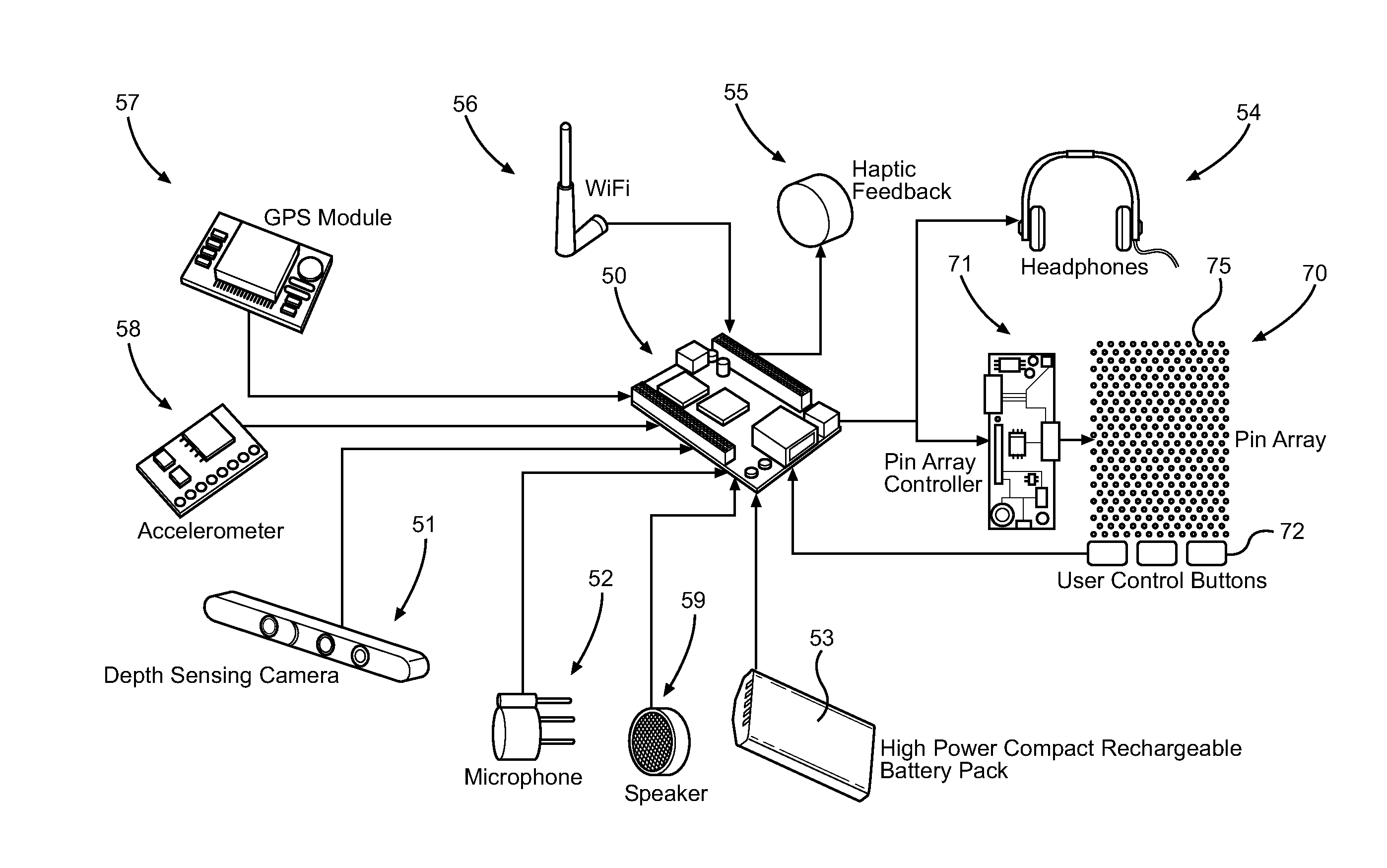

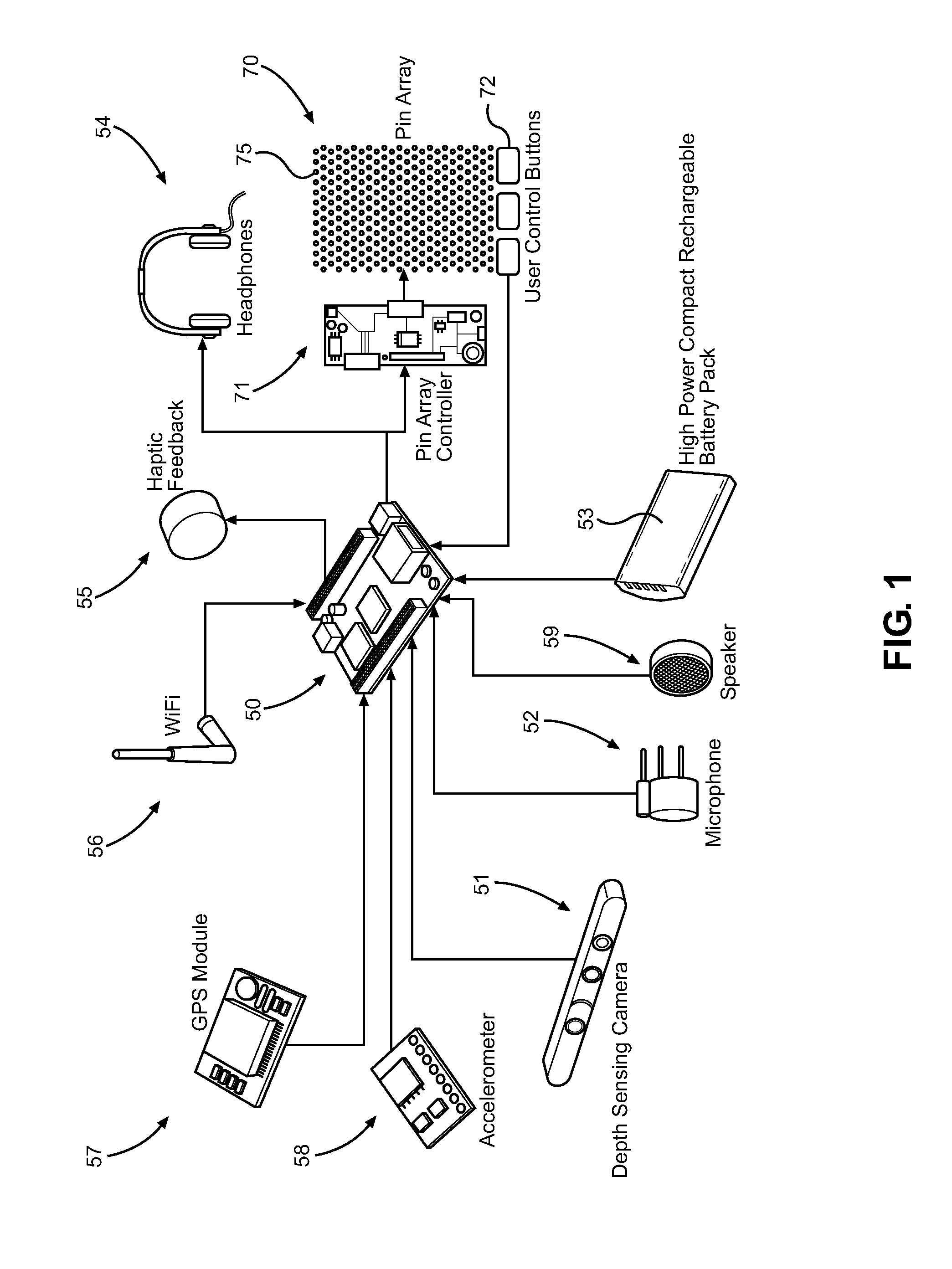

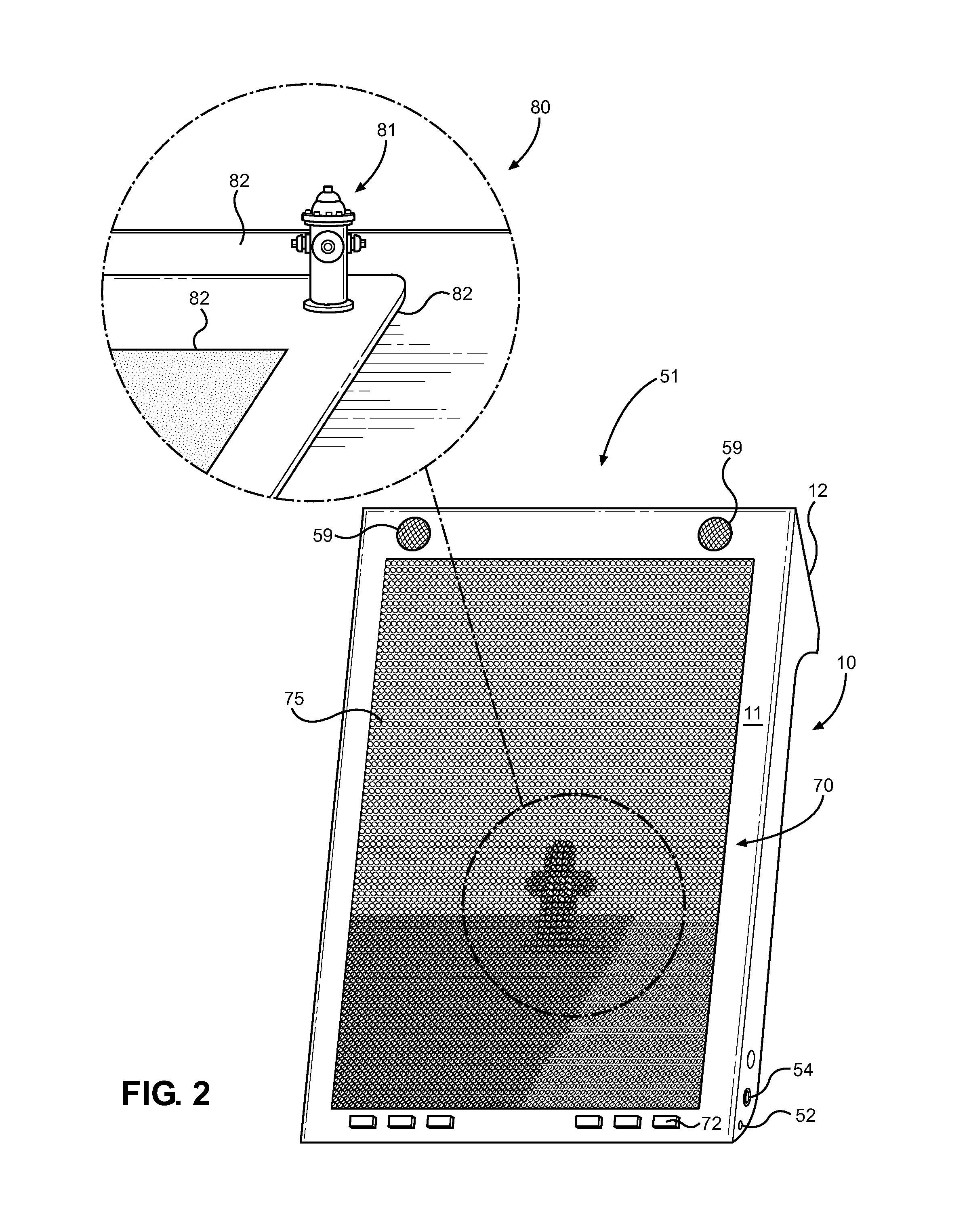

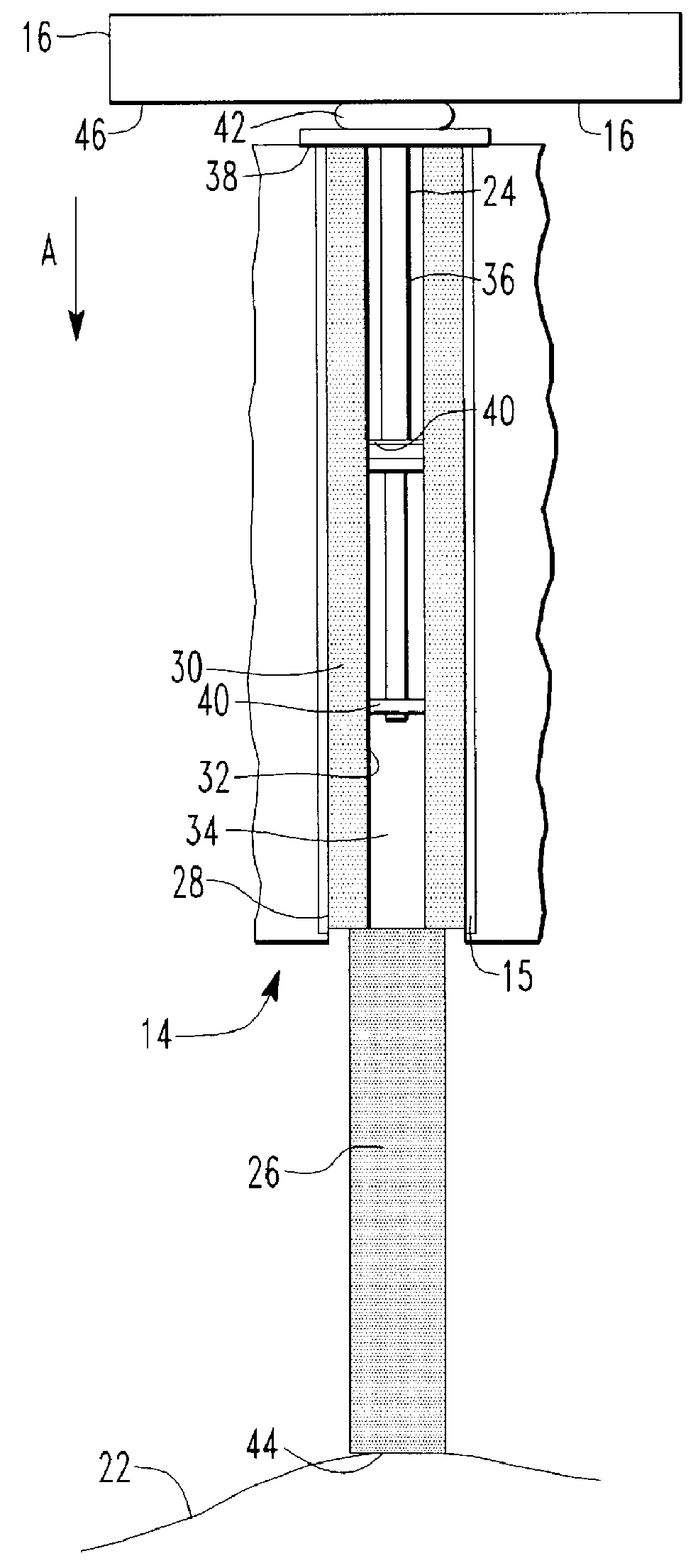

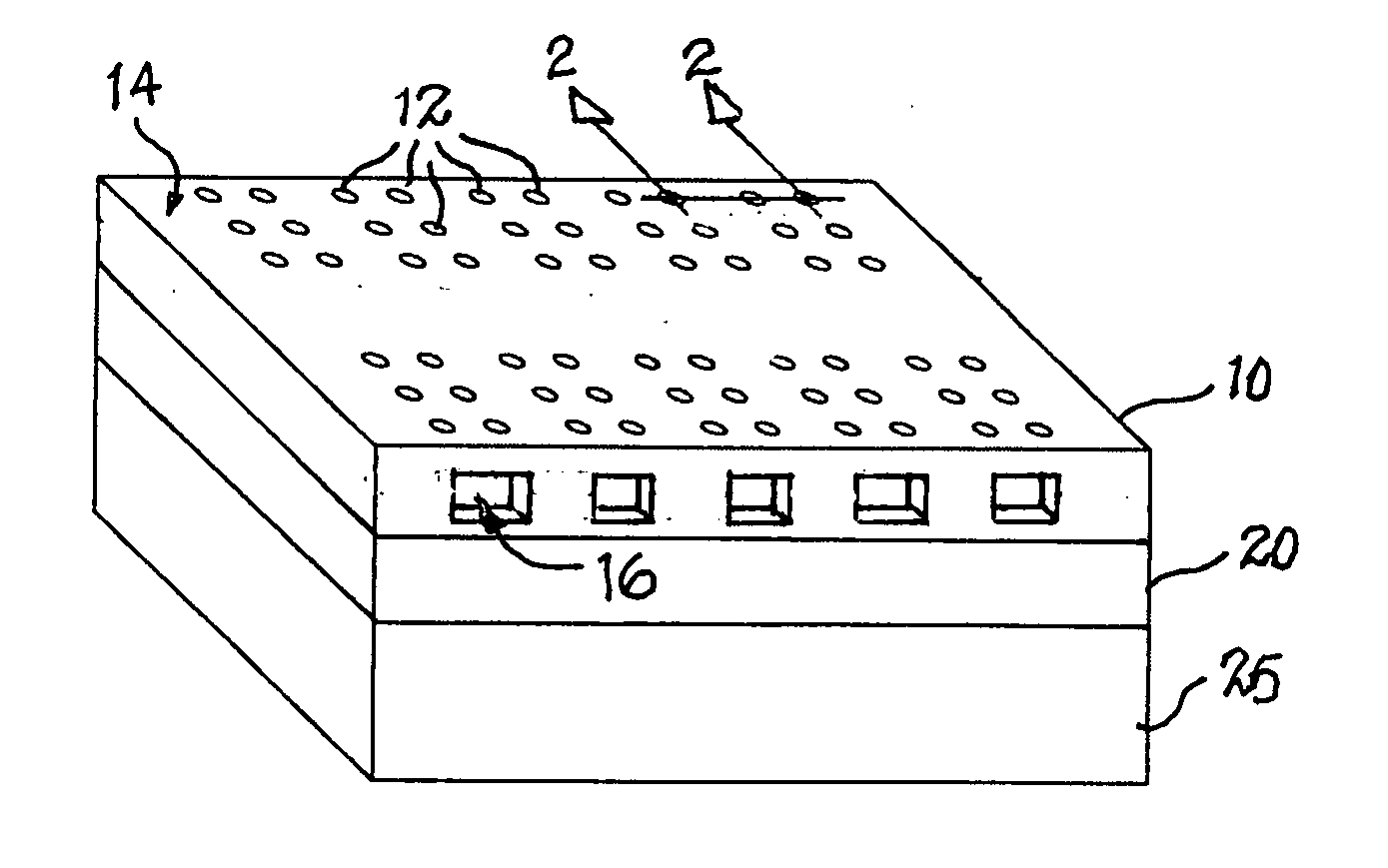

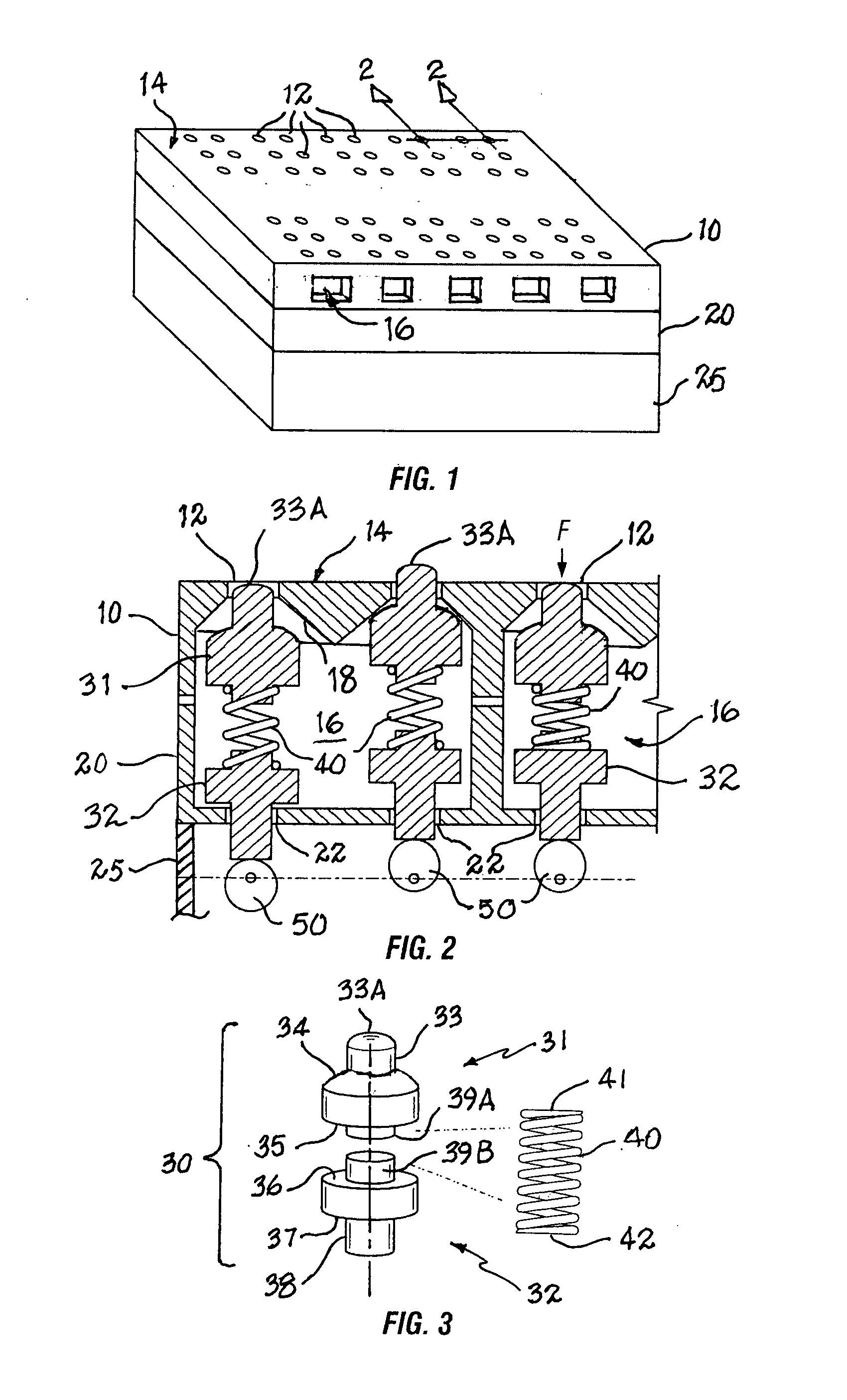

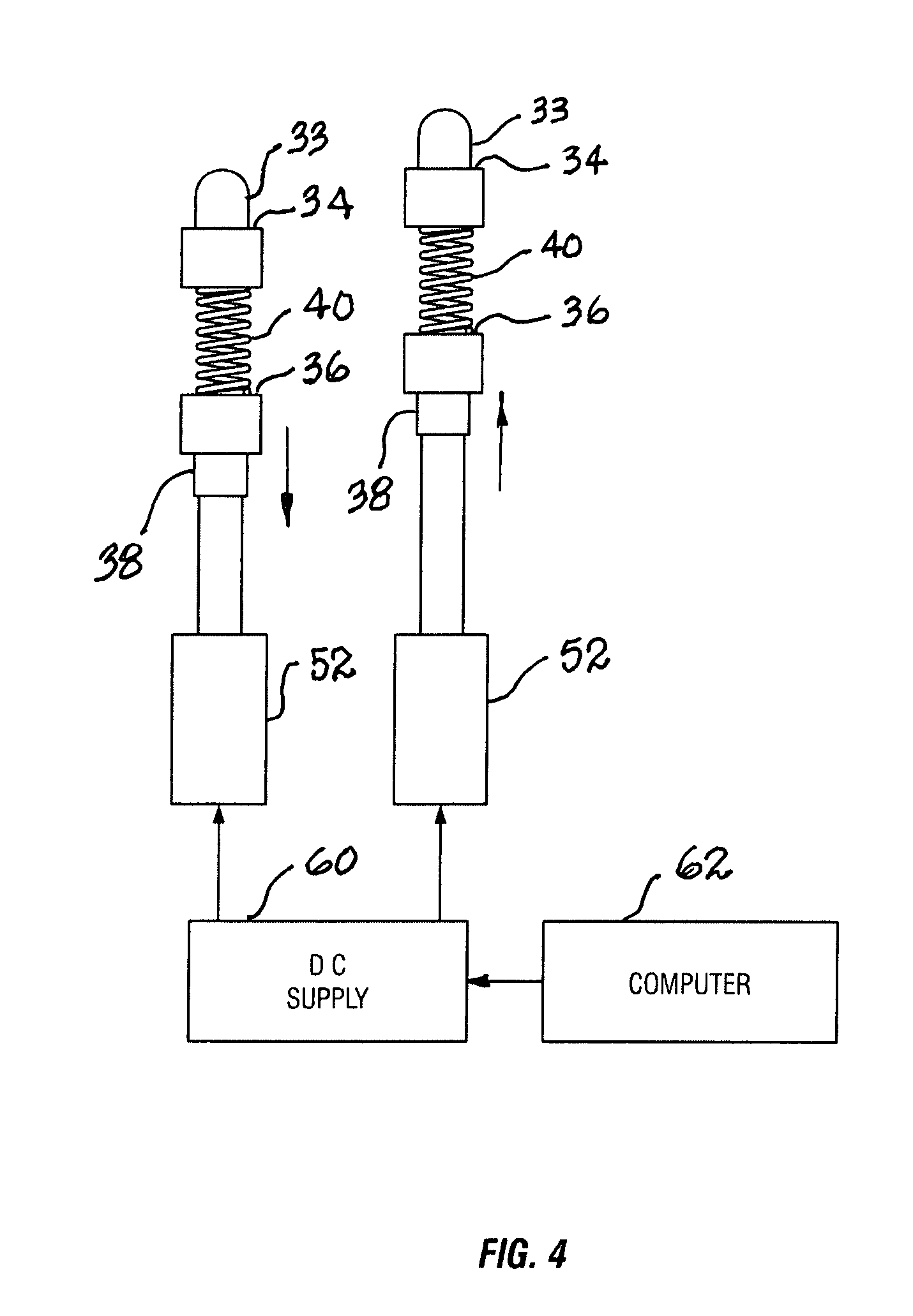

Tactile Pin Array Device

A handheld electronic device having a tactile pin array thereon is provided for assisting those with vision impairments. The device comprises a set of cameras that can capture a forward image, whereby the image is processed and used to output a three dimensional representation of the image on the tactile pin array. This allows one to recognize objects and obstacles in the area in front of the device, while the pin array may also be deployed as an adaptive braille reader. A specific pin assembly is contemplated using a micro stepper motor, while the overall system provides several functions for visually impaired users, including navigation capabilities, facial recognition, connection to wireless networks, and various input / output means.

Owner:CHANDRASHEKHAR NAIR SRIJIT +1

Contour replicating and measuring device

InactiveUS6125338AAccurately and inexpensively and quickly measureSimple designFeeler-pin gaugesMechanical counters/curvatures measurementsPin arrayComputer science

Owner:PITTSBURGH UNIV OF

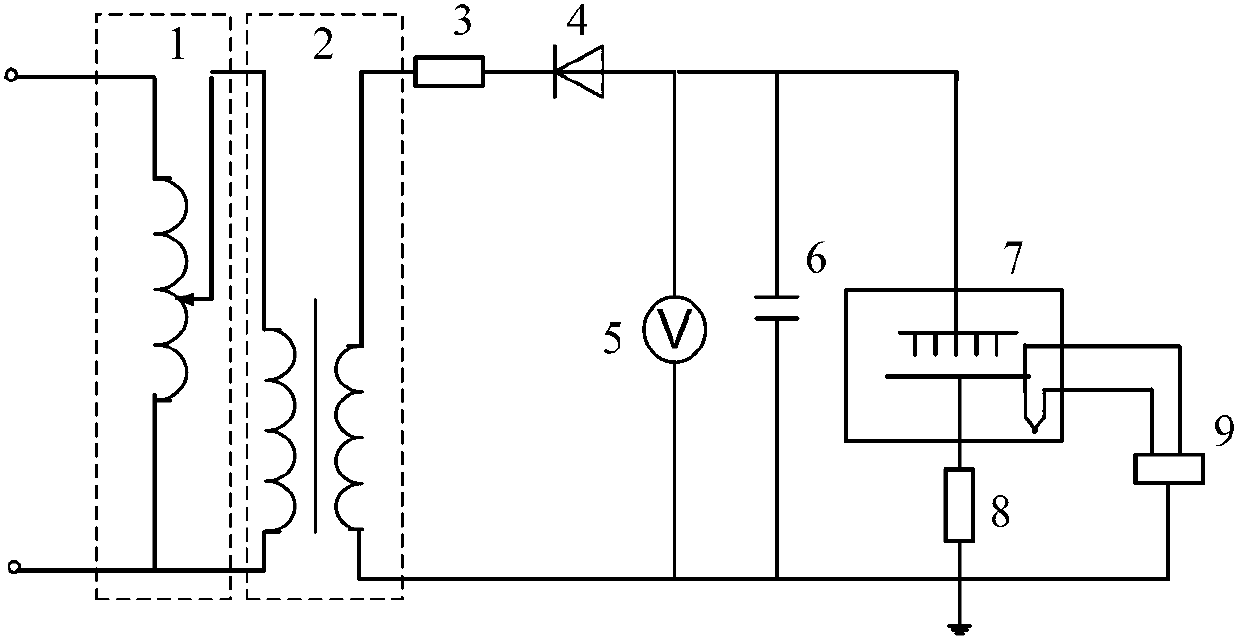

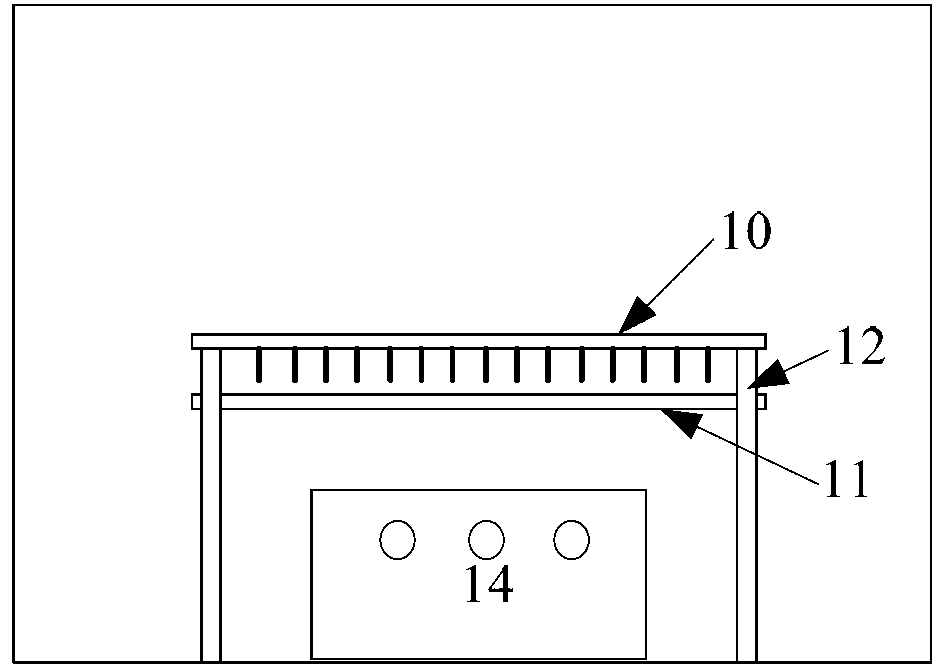

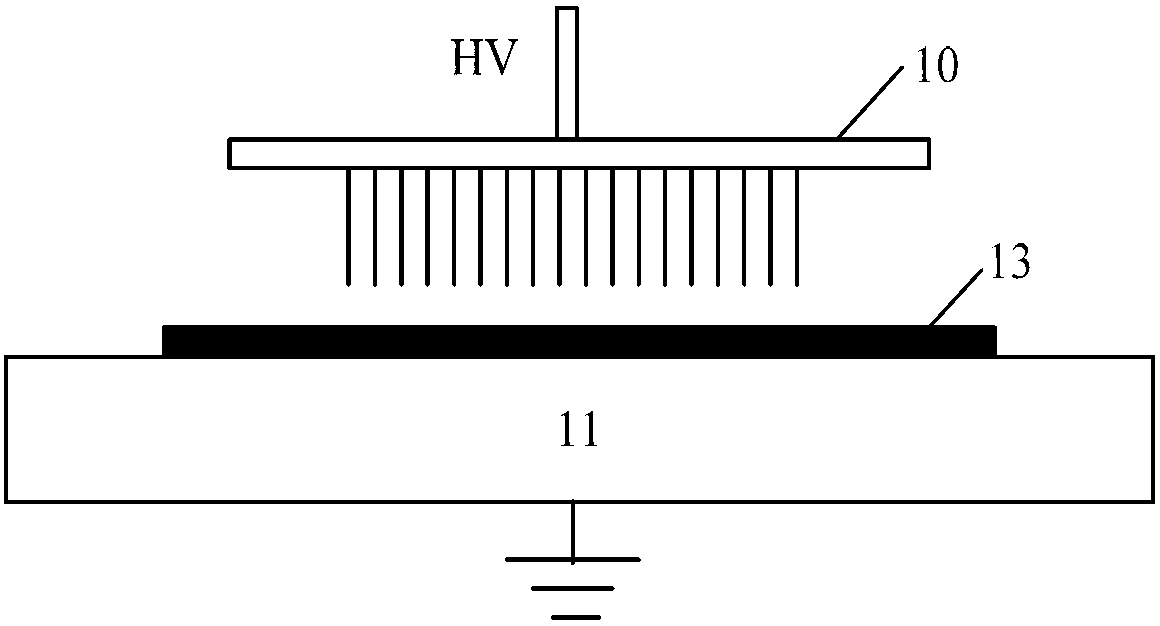

Corona aging acceleration device and method for polymer insulating material

InactiveCN103278752ALow requirements for experimental conditionsEasy to operateTesting dielectric strengthPolymer insulationCorona discharge

The invention discloses a corona aging acceleration device and a corona aging acceleration method for a polymer insulating material. The device comprises a sealed corona aging experimental case in which a pin array electrode and a metal plate electrode are arranged, wherein the pin array electrode is connected with a high voltage generation device; the metal plate electrode is grounded; a pinpoint array is arranged on the pin array electrode; a test sample is arranged on the metal plate electrode, and is opposite to the pinpoint array; and after voltage is applied, uniform corona discharge is generated between the pin array electrode and the metal plate electrode to perform corona aging on the test sample. The device and the method have the advantages of low requirements on experimental conditions, convenience for operation and quantitative control over aging factors in an experiment, and short experimental period, and are applied to researches on the corona aging resistance of insulating materials in a laboratory.

Owner:XI AN JIAOTONG UNIV +1

Braille module with compressible pin arrays

A refreshable tactile reader apparatus for Braille text and graphics, utilizing a plurality of compressible tactile pins that can absorb strong downward forces. Such strong forces transmitted through tactile pins can damage pin actuation mechanisms. The physical enclosure of the reader provides open channels that allow the apparatus to be more easily cleaned than prior art enablements.

Owner:TACTICLE DISPLAY

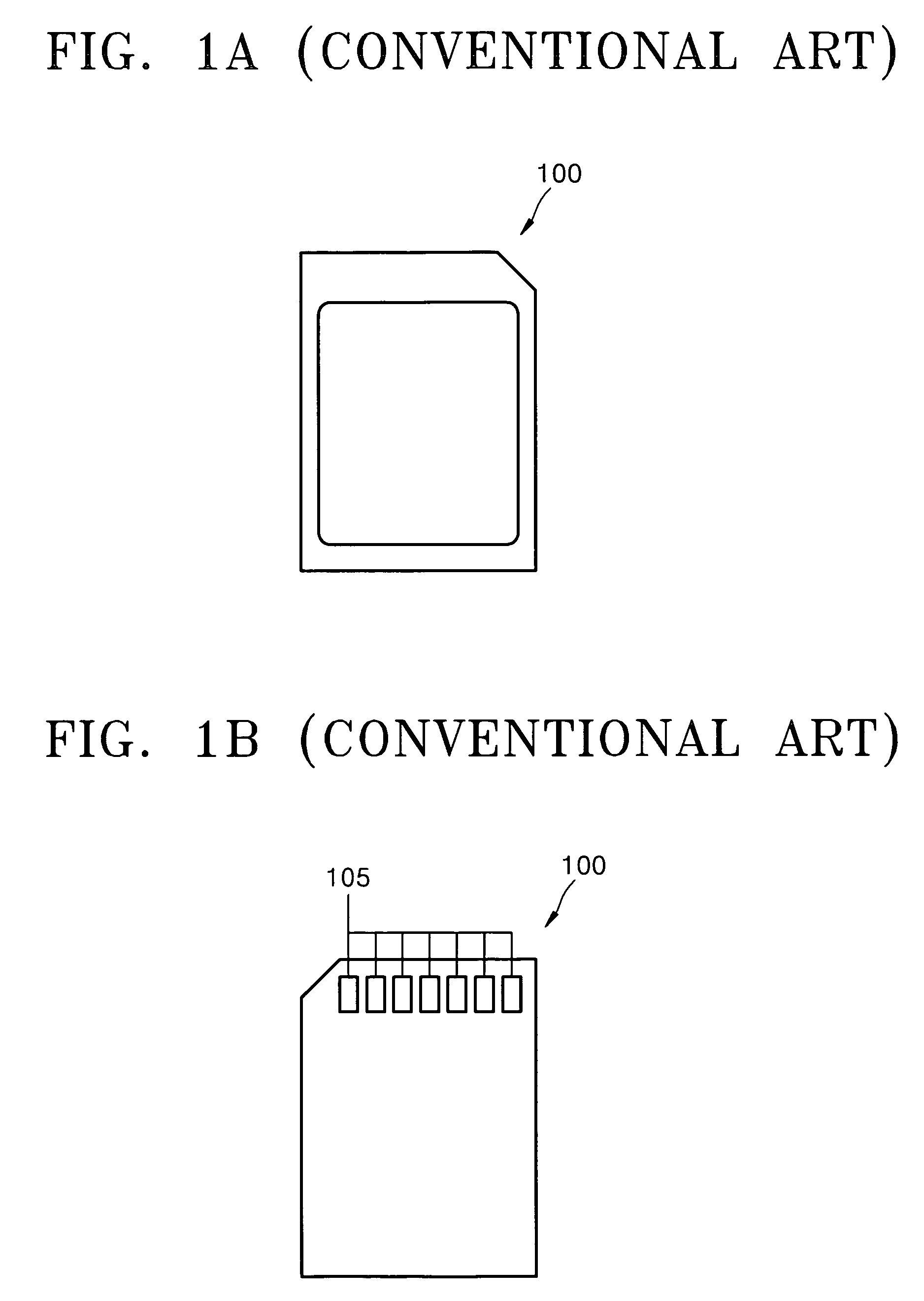

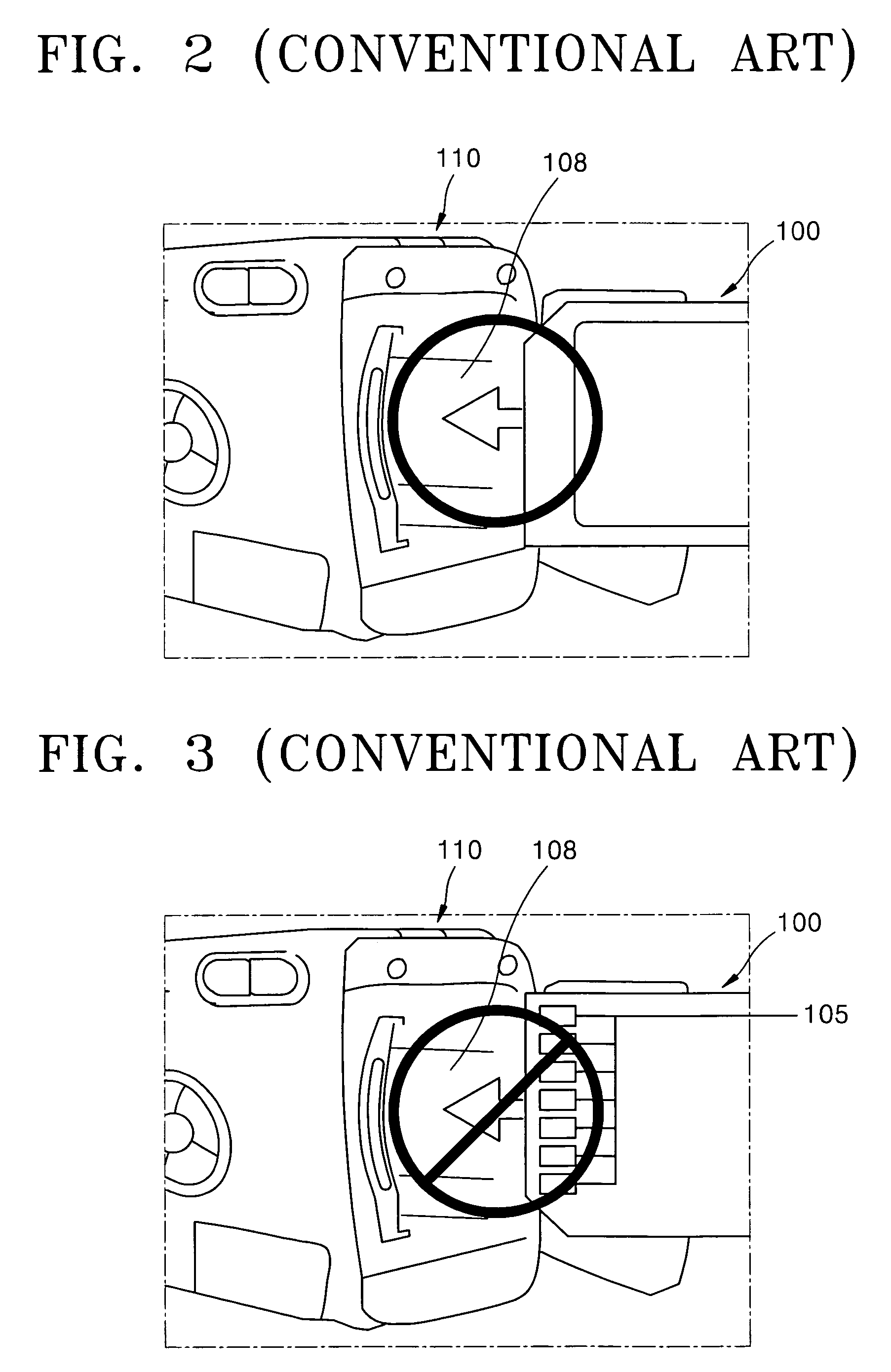

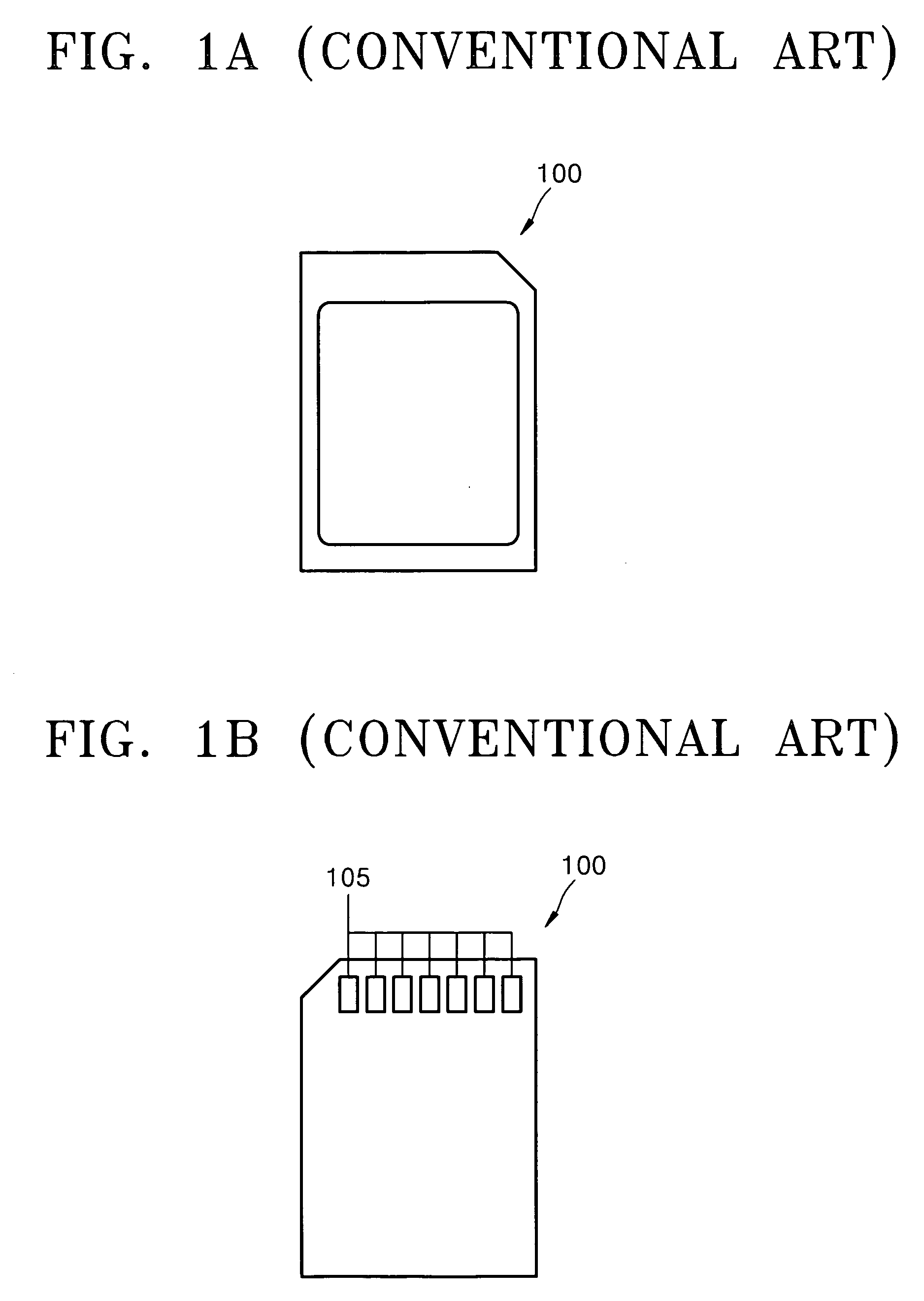

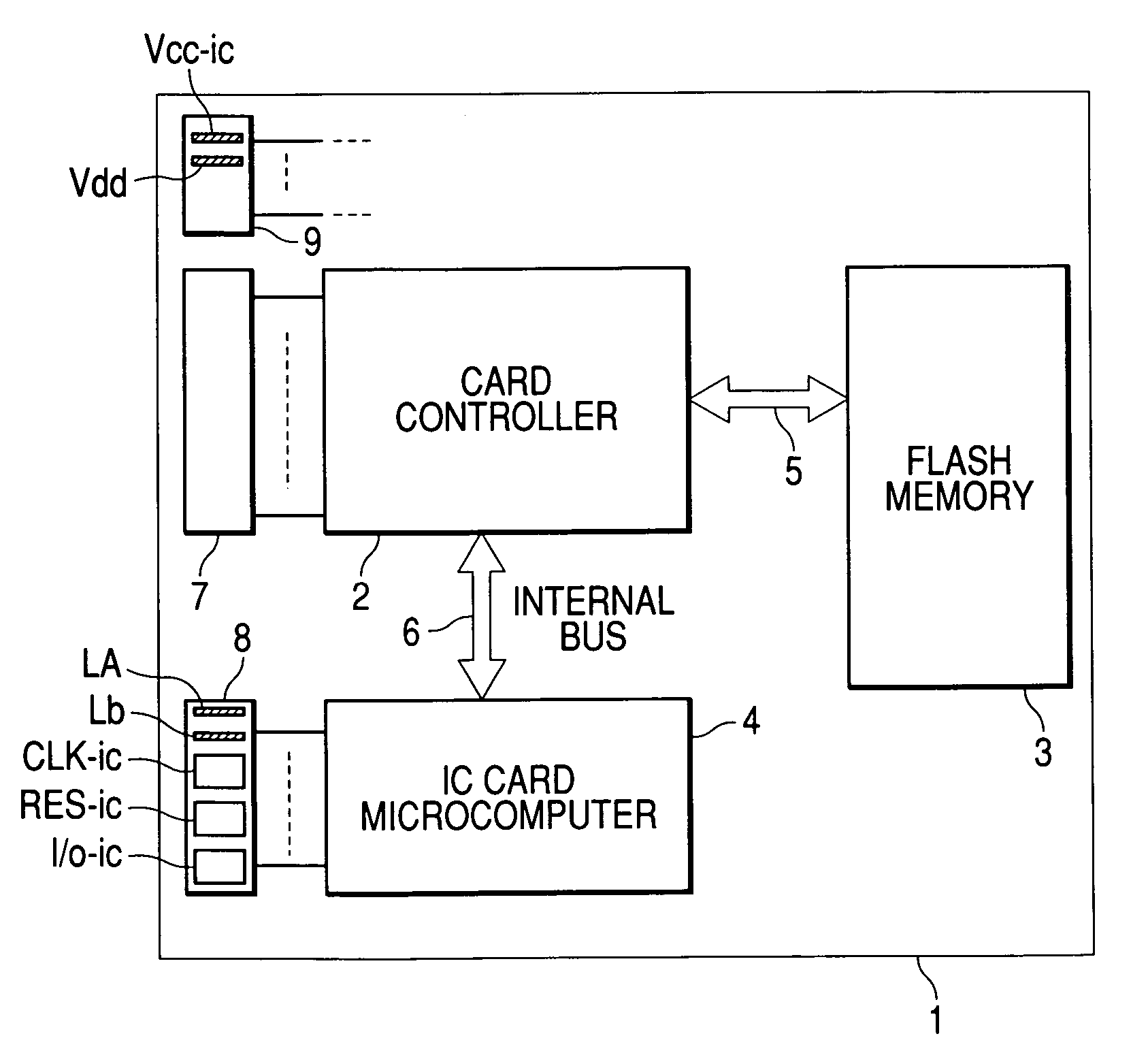

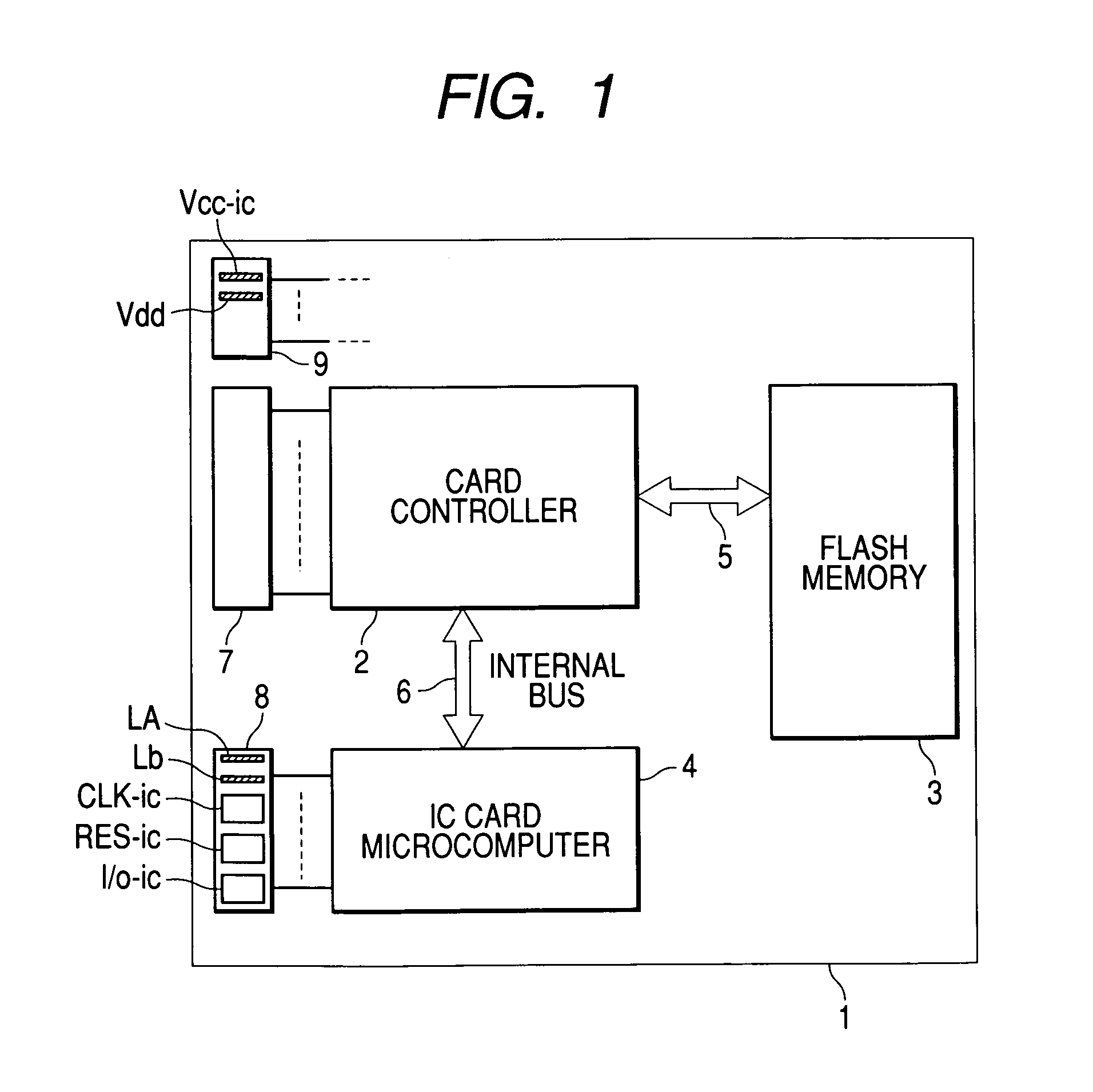

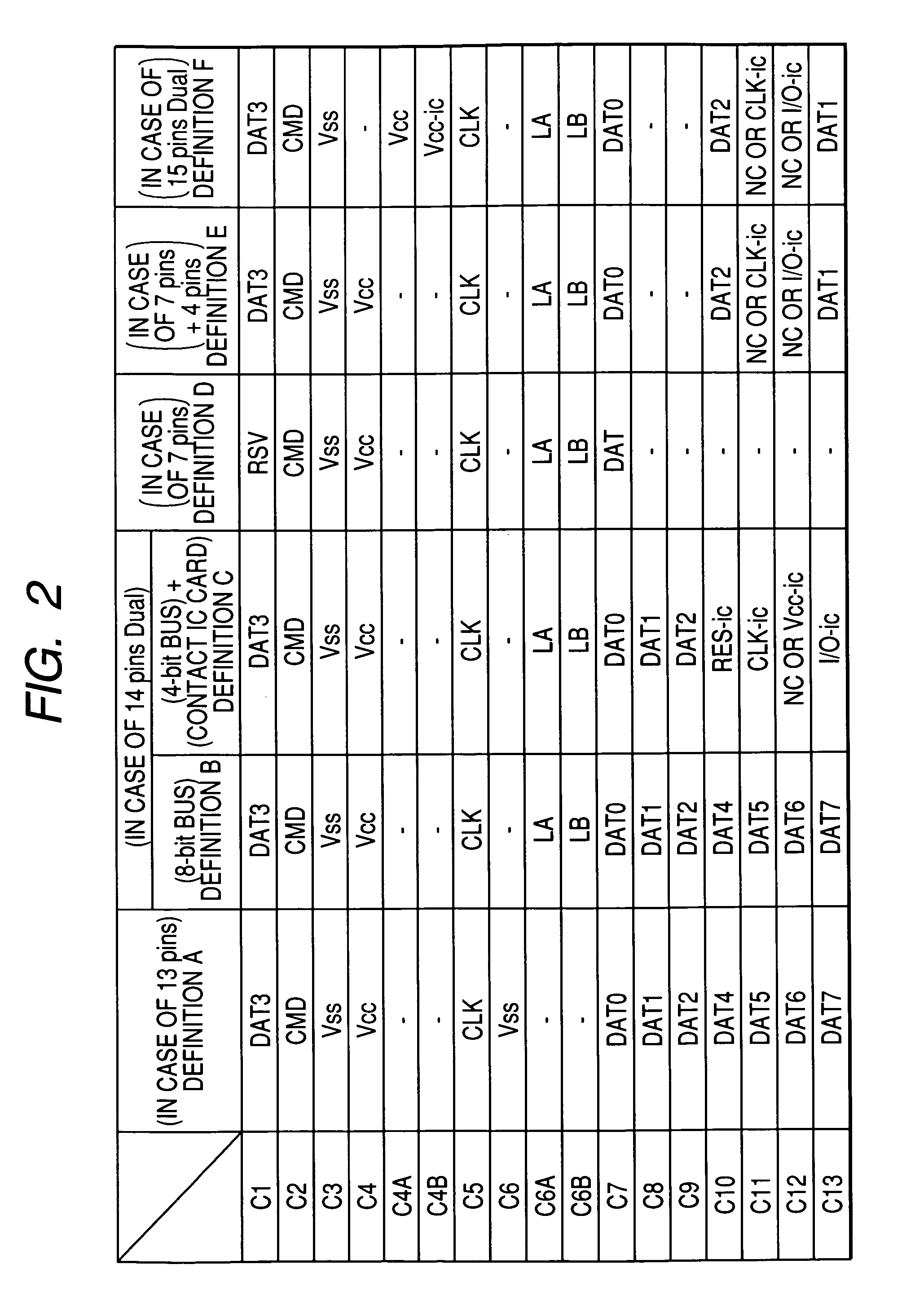

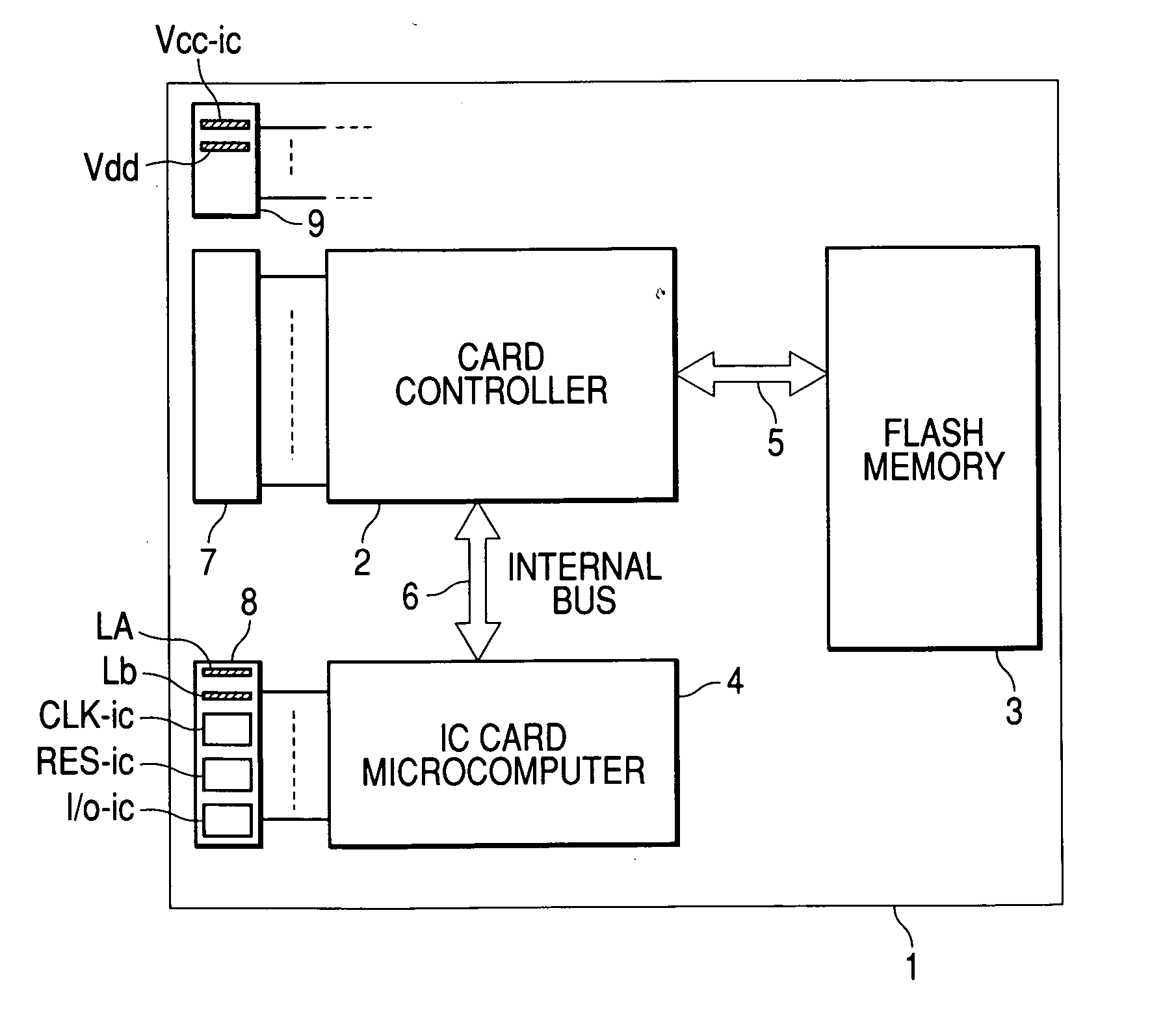

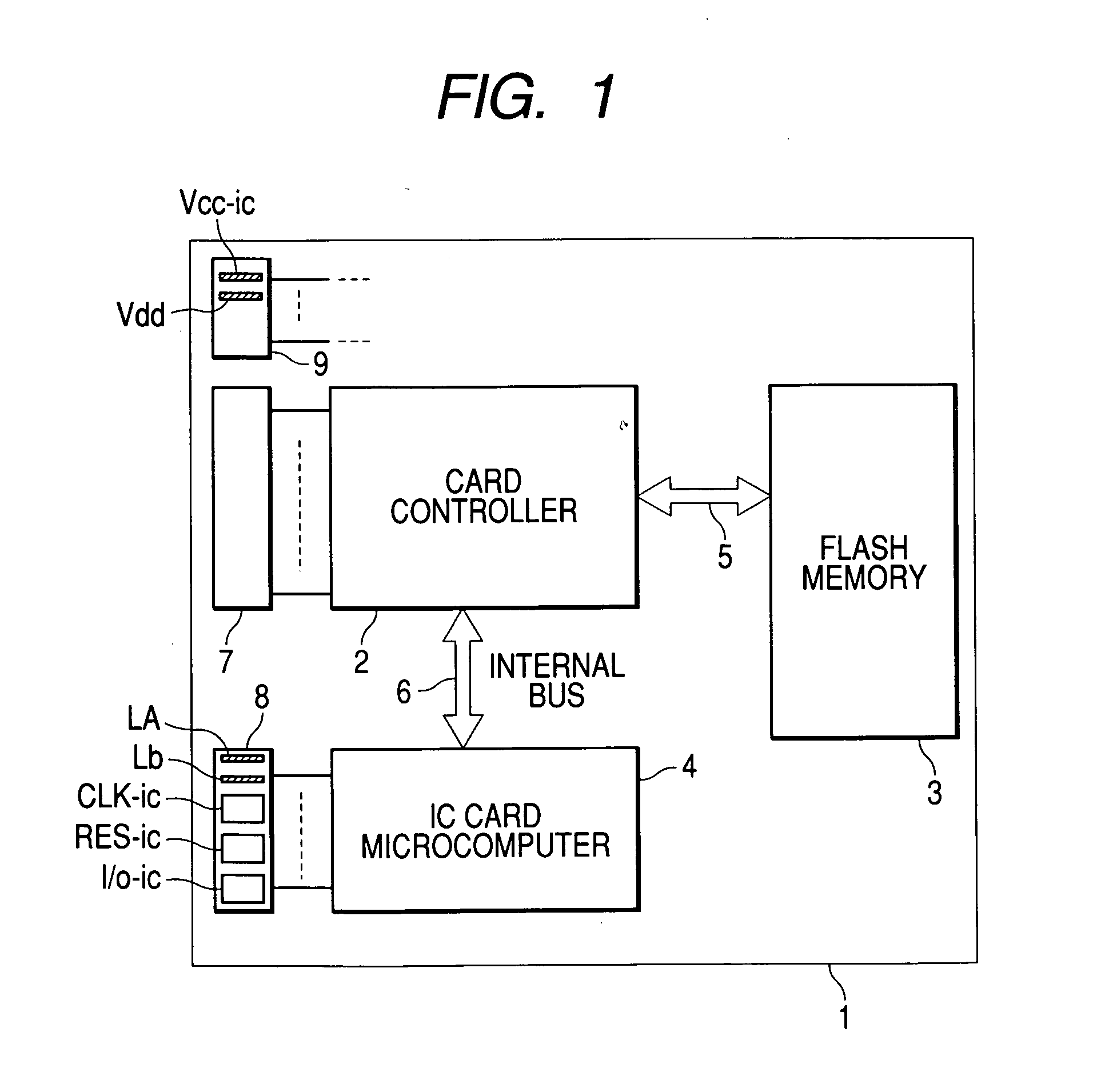

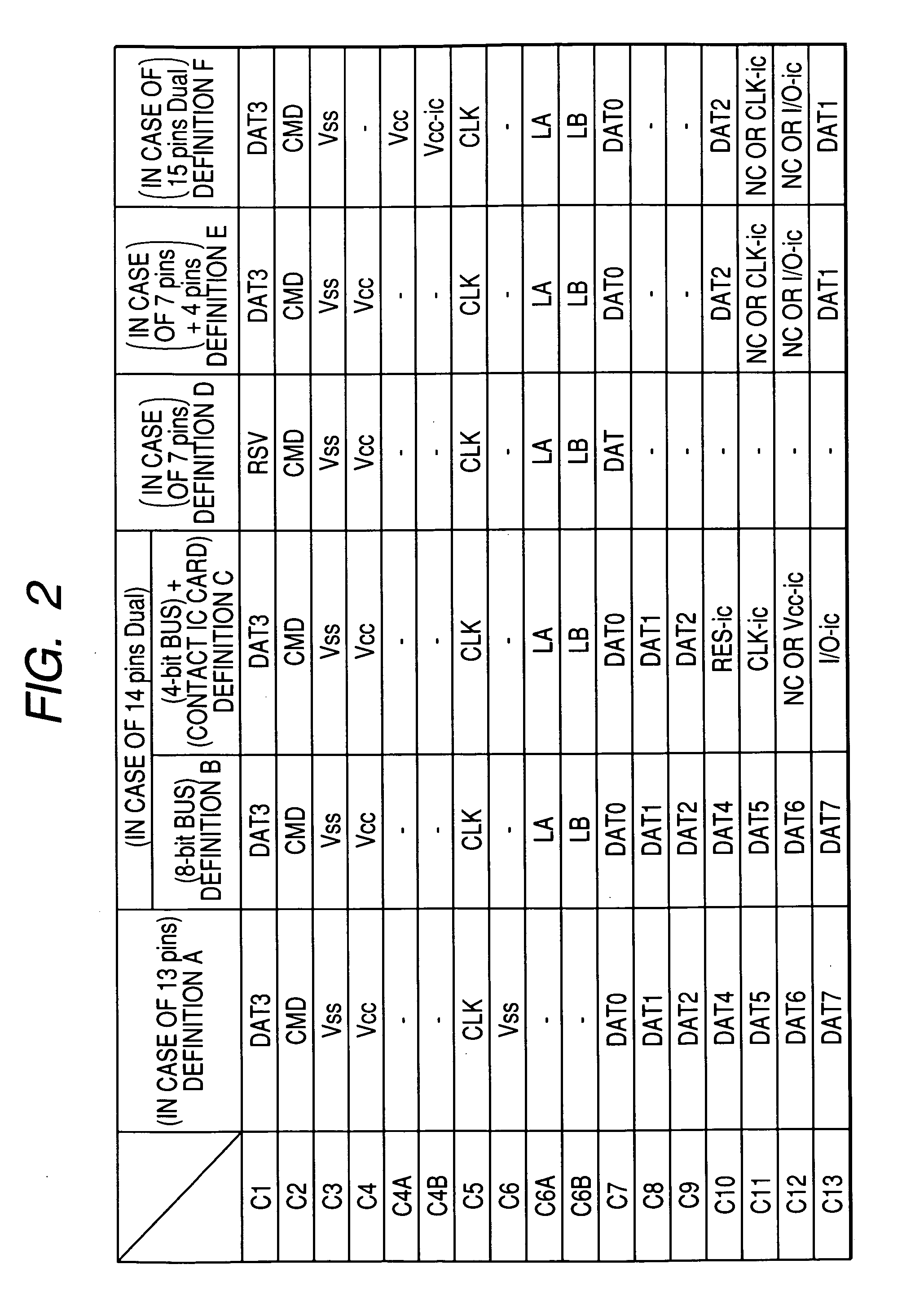

Memory card and semiconductor device

An antenna connection function for a noncontact interface is provided by suppressing a modification in a pin arrangement and a pin shape of a memory card that does not correspond to the noncontact interface. Two antenna connecting pins having the memory card are divided into two areas in which a size of one potential supply pin is the largest and used as a split pin arranged at intervals. Because a size of the two antenna connecting pins is at maximum as large as the size of the potential supply pin, the two antenna connecting pins are provided and the memory card that corresponds to the noncontact interface is obtained by devoting a pin area having the size of the one potential supply pin to the memory card that does not correspond to the noncontact interface.

Owner:RENESAS ELECTRONICS CORP

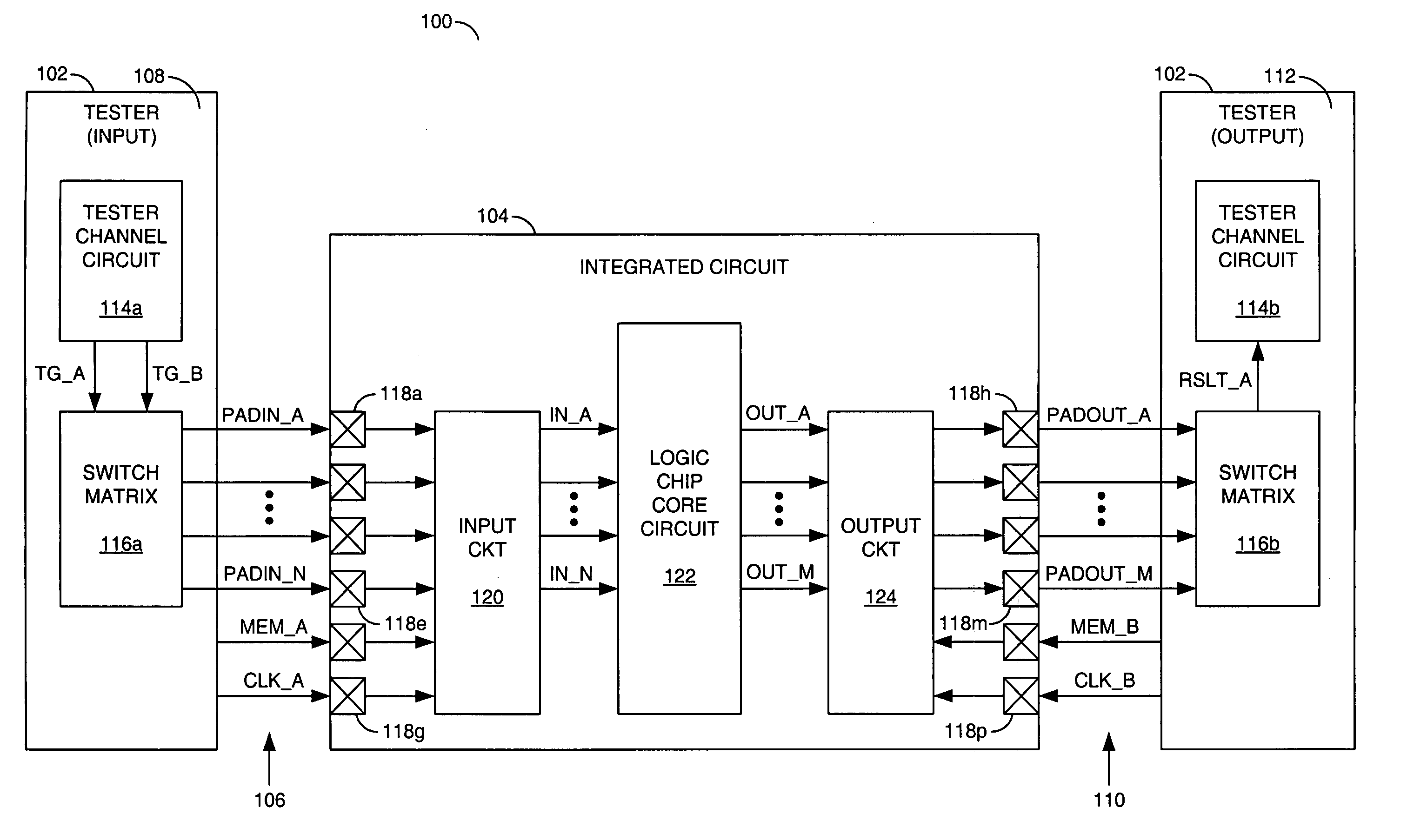

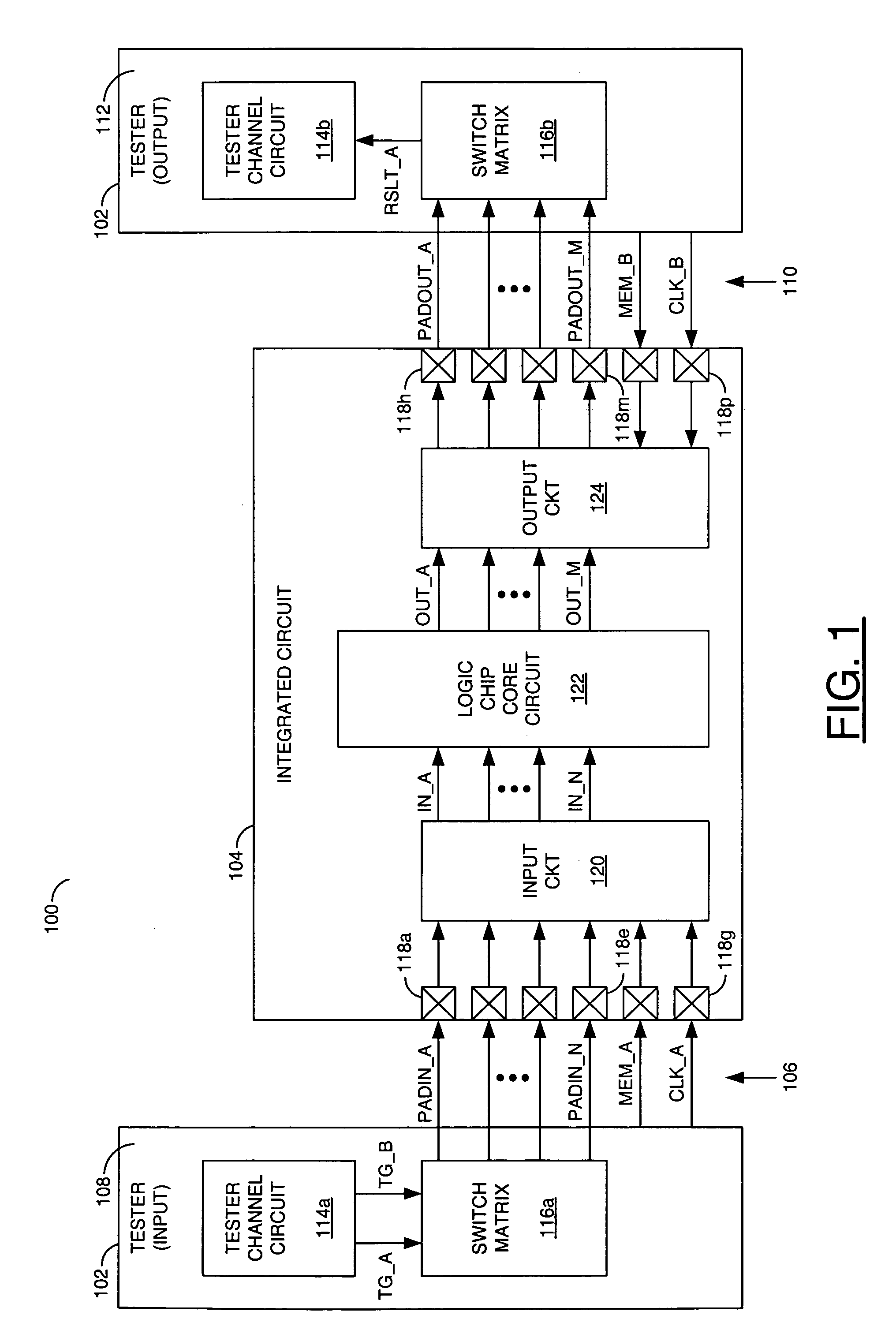

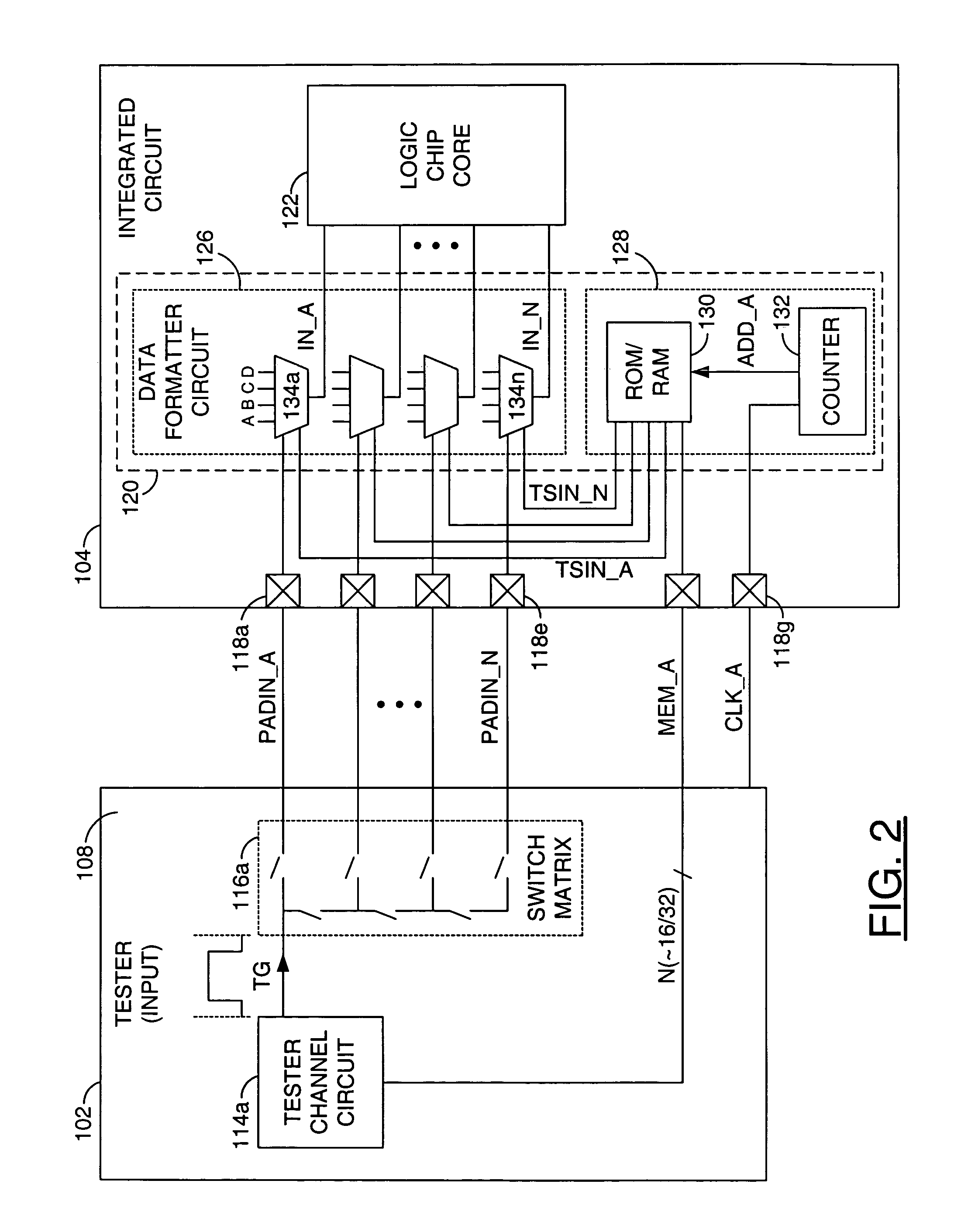

Reducing tester channels for high pinout integrated circuits

InactiveUS6971045B1Short test timeReduce testing costsDigital circuit testingError detection/correctionEngineeringOperation mode

An integrated circuit generally comprising a plurality of input pads, an input circuit, and a core circuit. The input pads may be configured to receive a plurality of first input signals. The input circuit may be configured to generate a plurality of second input signals (i) equal to the first input signals while in an operational mode and (ii) responsive to a plurality of test vectors with timing generation determined by the first signals while in a test mode. The core circuit may be responsive to the second input signals.

Owner:MONTEREY RES LLC

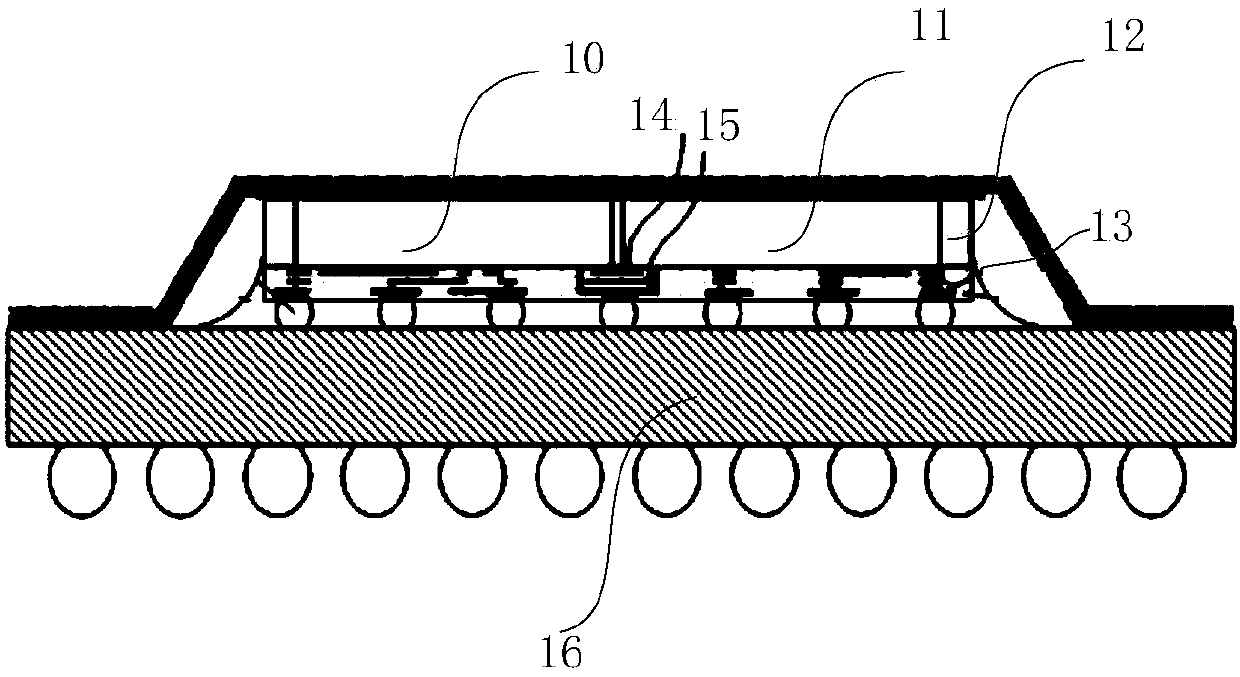

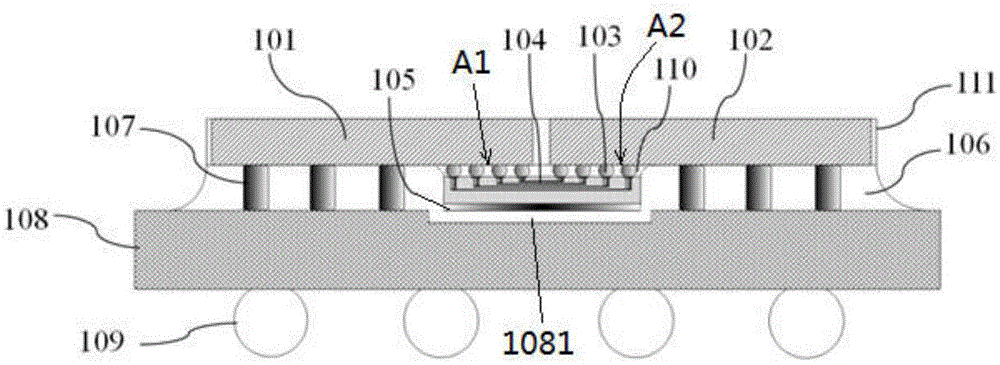

Chip and packaging method thereof

InactiveCN110197793ALow costSmall sizeSemiconductor/solid-state device detailsSolid-state devicesHigh densityShortest distance

The embodiment of the application discloses a chip and a packaging method thereof. In the chip, the respective first bonding pads on a first bonding pad array on a first substrate are attached to respective corresponding second pins in second pin arrays on different bare chips, thereby achieving short-distance high-density interconnection between bare chips. A plastic package body is used for wrapping first pins, the second pins, the first bonding pads and the first substrate, so that a fan-out unit and the first substrate are plastically packaged into a unitary structure. In the unitary structure, the bottoms of the respective first pins of the first pin array on the bare chips to be electrically connected to the peripheries of the chips are not wrapped in the plastic package body, such that the respective first pins can be directly electrically connected to the peripheries of the chips. The overall size of the chip provided by the embodiment of the application is mainly determined bythe size of the plurality of integrated bare chips. Compared with the prior art, the chip provided by the embodiment of the application is small in overall size, and can meet a chip miniaturization requirement.

Owner:HUAWEI TECH CO LTD

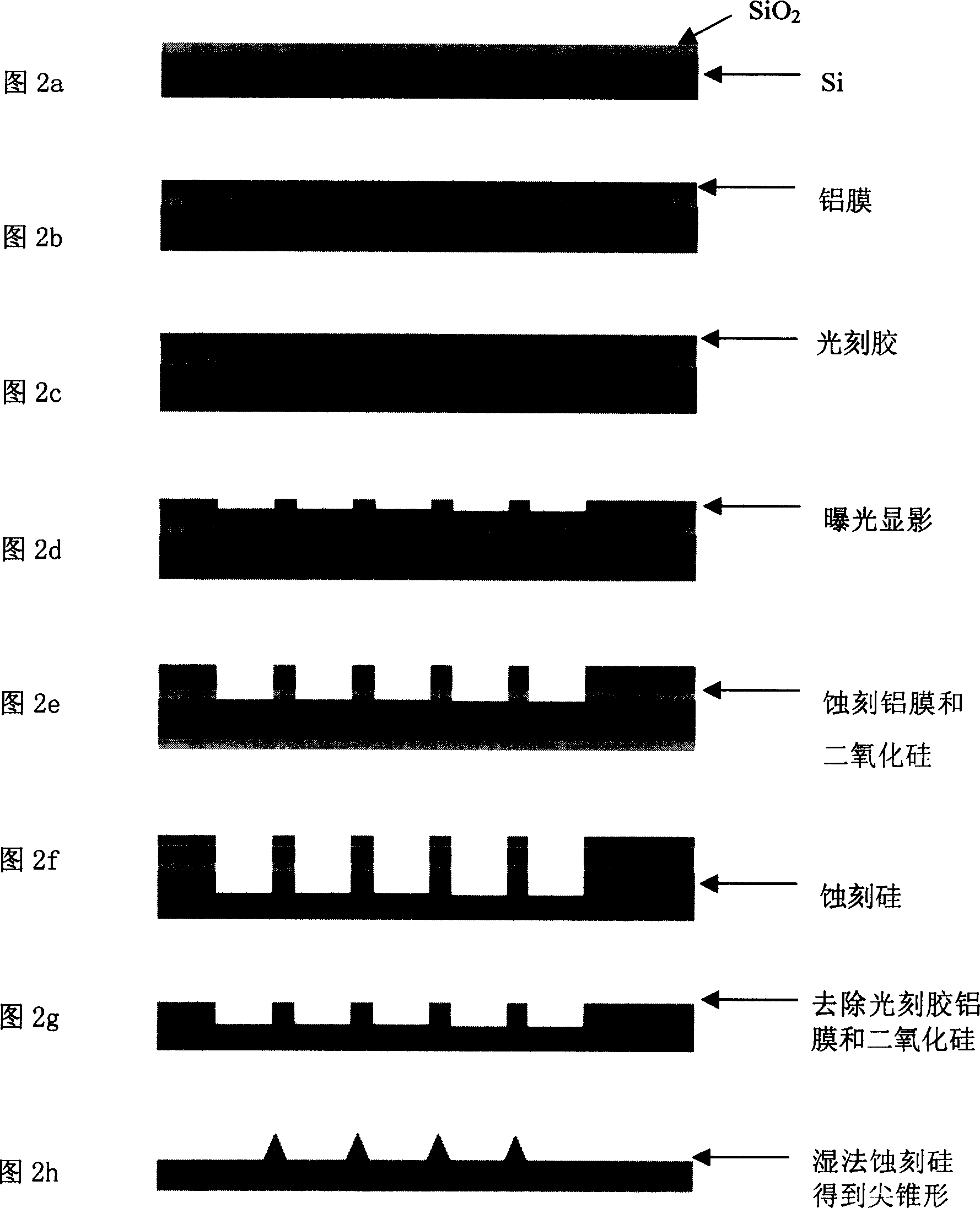

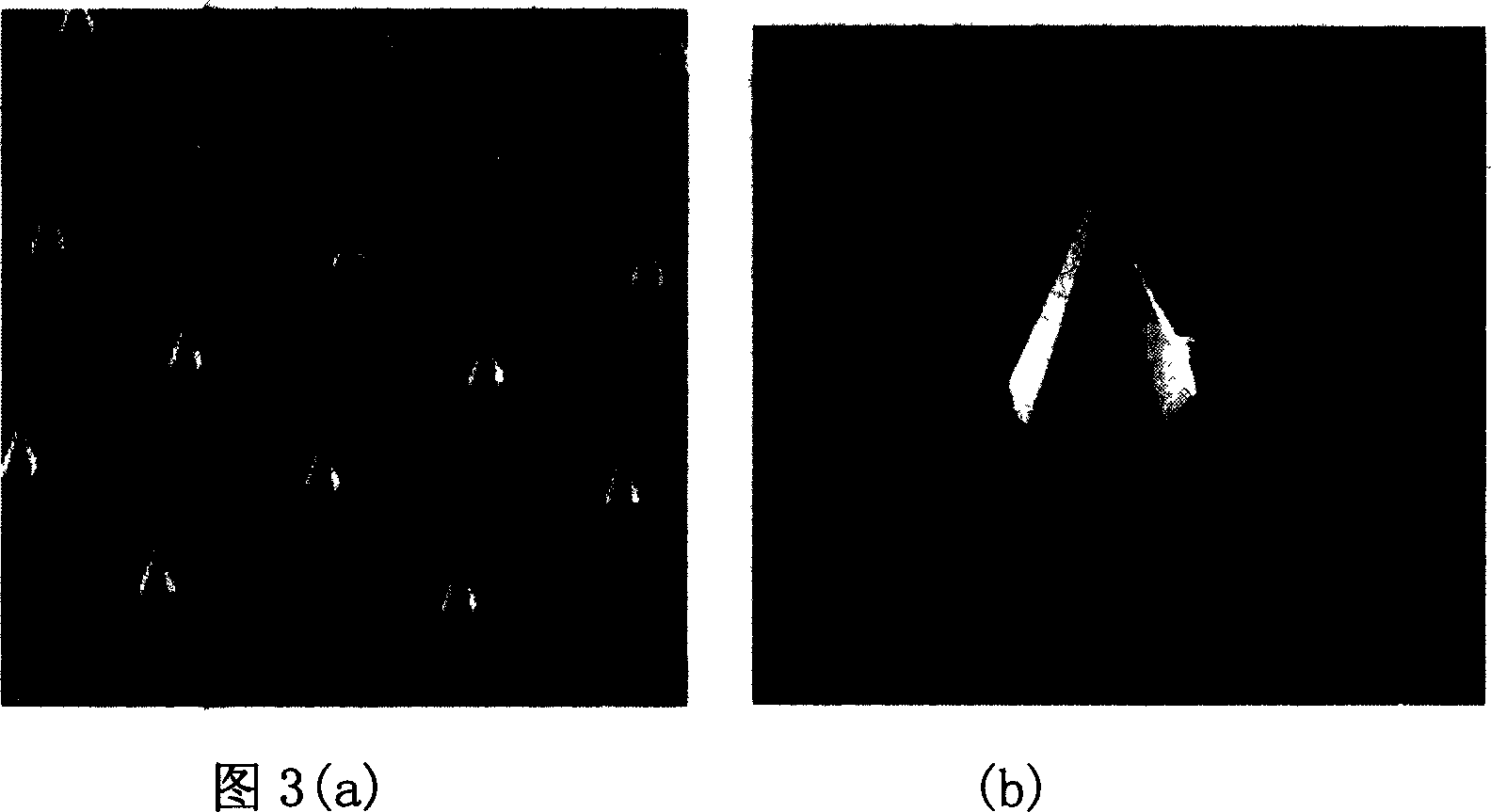

Minisize solid silicon needle array chip and its preparation method and use

ActiveCN1569271AIncrease absorption rateHigh mechanical strengthMicroneedlesMedical devicesMicroelectromechanical systemsDrug release

The invention belongs to a transdermal drug releasing device field. It relates in particular to a preparing method and usage of the minitype solid silicon pin array chip by monocrystalline silicon and Microelectromechanical systems(MEMS) technology. The minitype solid silicon pin array chip is processed by the adoption of photoengraving, wet etching, plasma dry etching, filming and other MEMS technologies. A side groove opens on the side of the mini pins, one or a plurality of drug storage pool being manufactured on the back of the solid mini pins by the combined utilization of double face alignment light photo technology, the drug dosage can be increased by the connection of the drug storage pool and the solid mini pin surface. The present invention has simple process and durable solid mini pins, being suitable for transdermal drug release of bio drug with macromolecules in particular.

Owner:SUZHOU NANOMED BIOMED CO LTD

A circuit board plug assembly dissipating heat by utilizing heat-dissipation fans

InactiveCN104822248ASmooth side to side movementAchieve lockingCoupling device detailsCooling/ventilation/heating modificationsPin arrayElectrical and Electronics engineering

The invention provides a circuit board plug assembly dissipating heat by utilizing heat-dissipation fans. The circuit board plug assembly comprises a circuit board device (9) and an interface device (8) arranged at the left side of the circuit board device (9). The interface device (8) comprises a housing formed by an upper contour portion (81) and a lower contour portion (82); the place, adjacent to the inner side of the housing, of a board body of the circuit board device (9) is provided with an insertion pin array (99) for connecting with insertion hole array (72) in a plug (7) plugged between the upper contour portion (81) and the lower contour portion (82) of the interface device (8); and the upper contour portion (81) and the lower contour portion (82) are connected with roller wheels (80) of an upper slide block assembly (83) and a lower slide block assembly (84) respectively.

Owner:叶吉利

Right angle adaptor

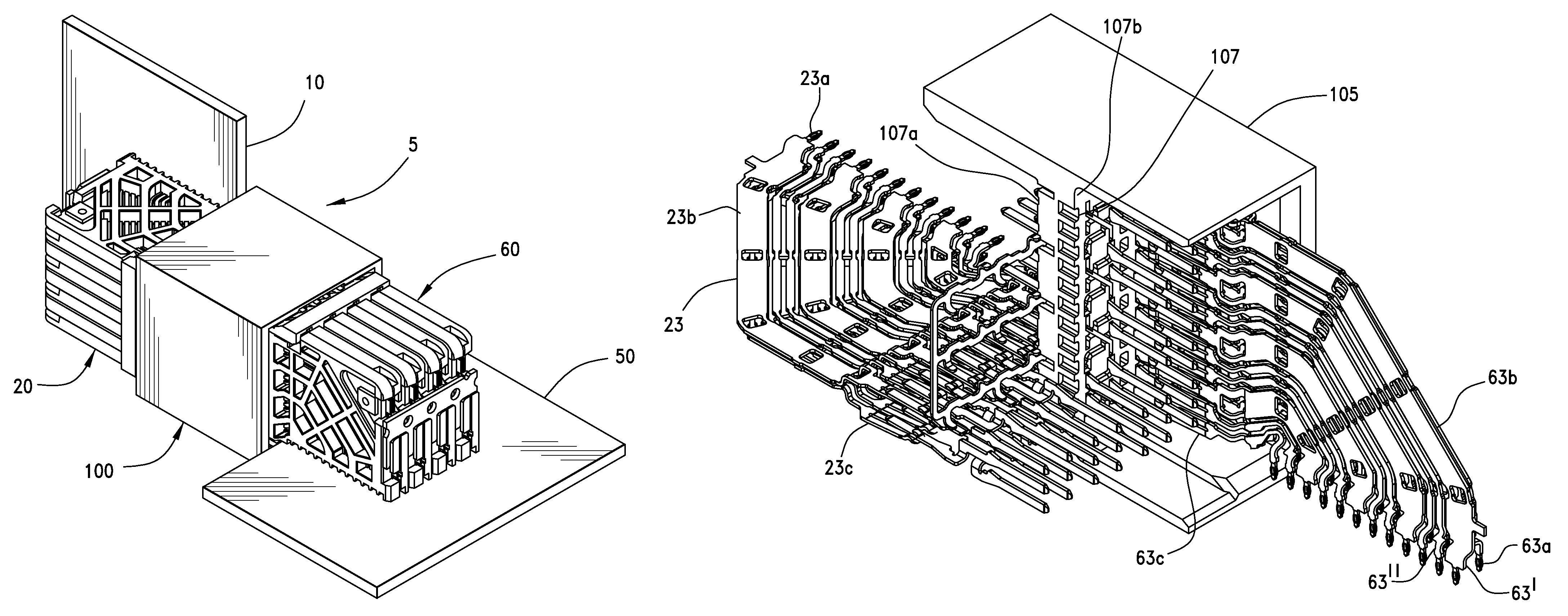

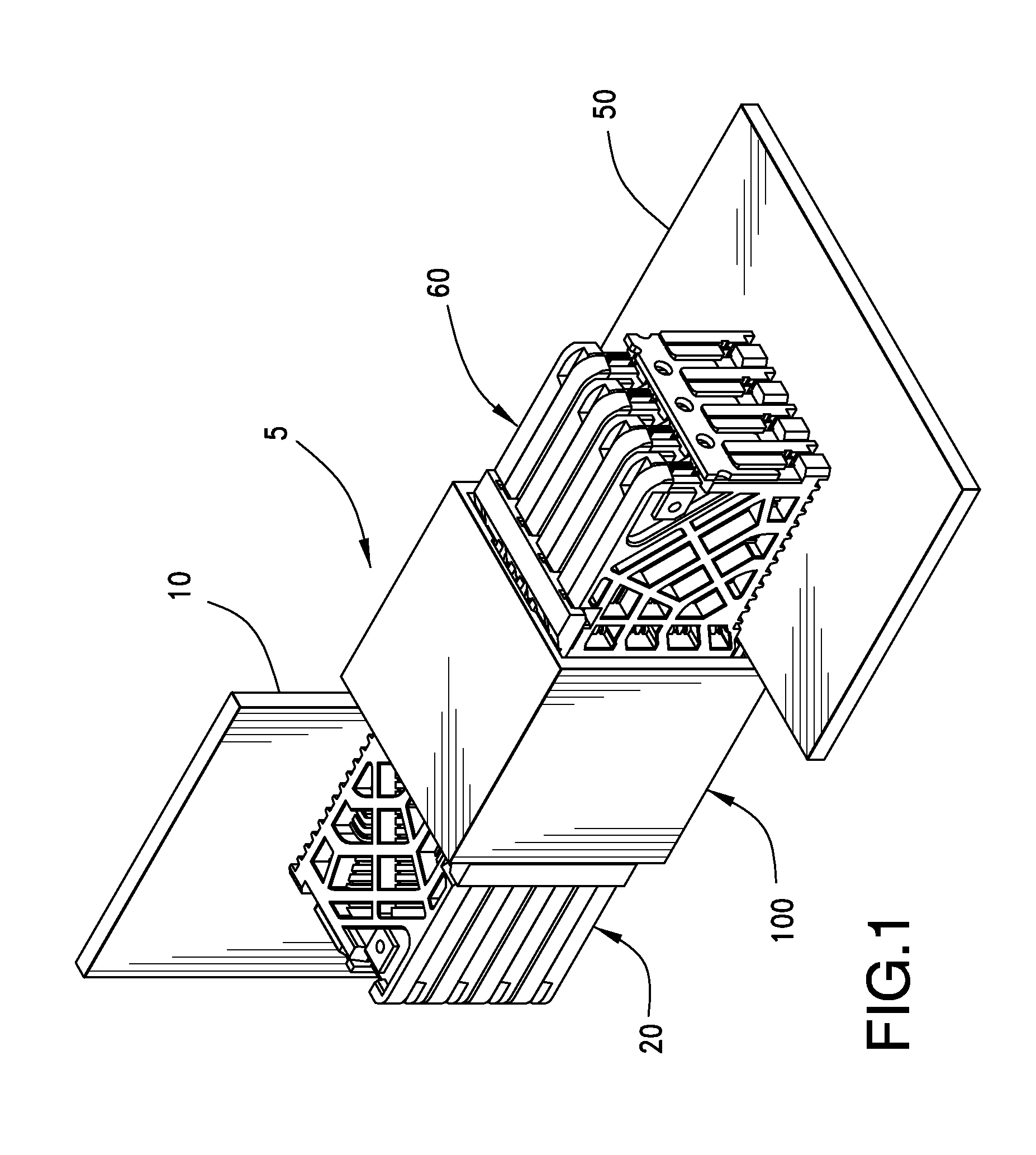

ActiveUS8628356B2Improve electrical performanceCoupling device detailsFour or more pole connectionsPin arrayElectrical and Electronics engineering

An adaptor includes a first and second recess that face in opposing directions and that are configured to receive a first and second connector. A floor in the adaptor can separate the first recess from the second recess. A pin array can be positioned in the floor and the pin array can extend in two directions from the floor so as to extend into the first and second recess. The pin array can include terminals that are configured with first and second contact ends that are respectively positioned in the first and second recess. The first and second contact ends can be respectively configured with a first and second orientation that are at a right angle with respect to each other.

Owner:MOLEX INC

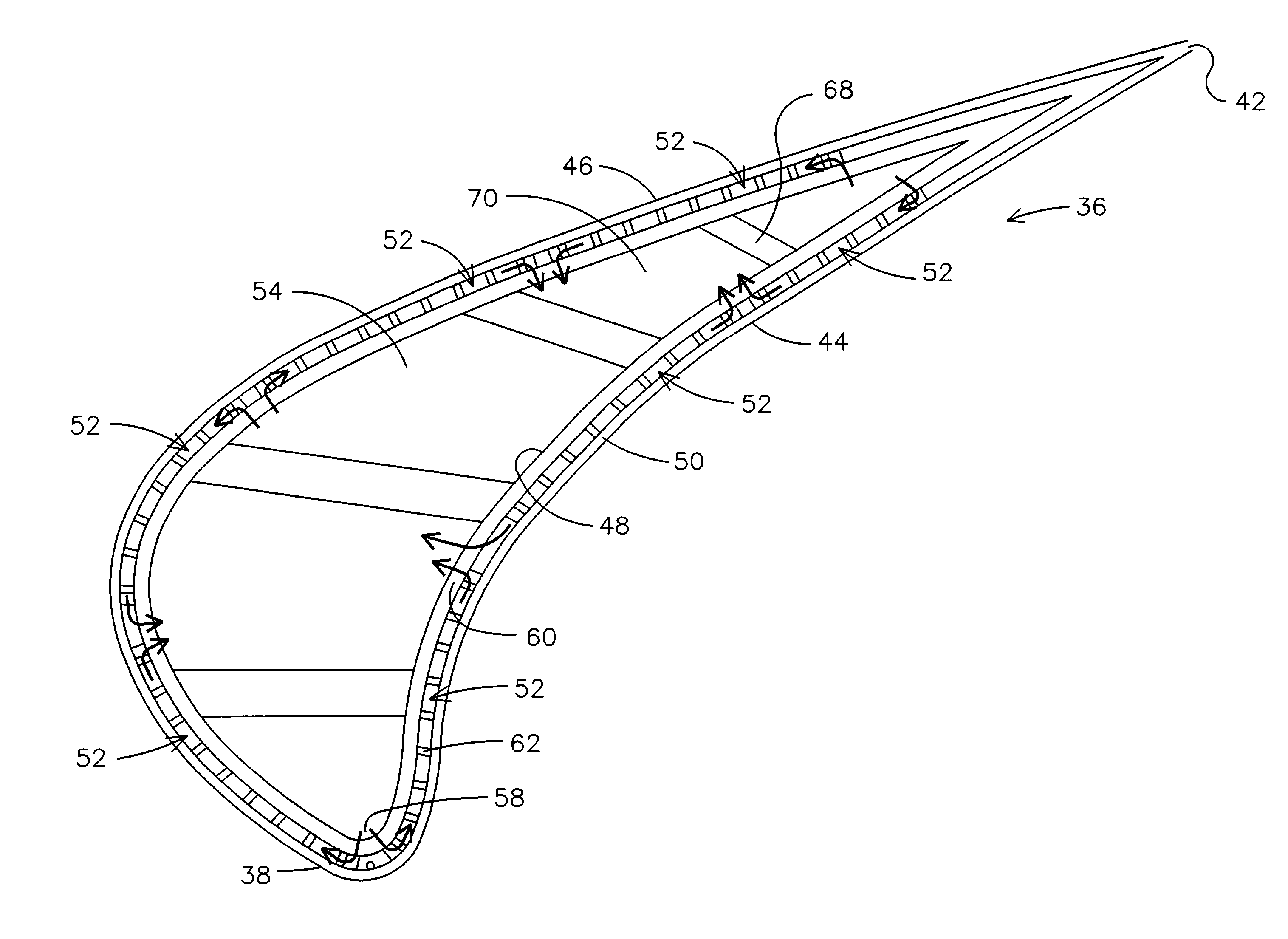

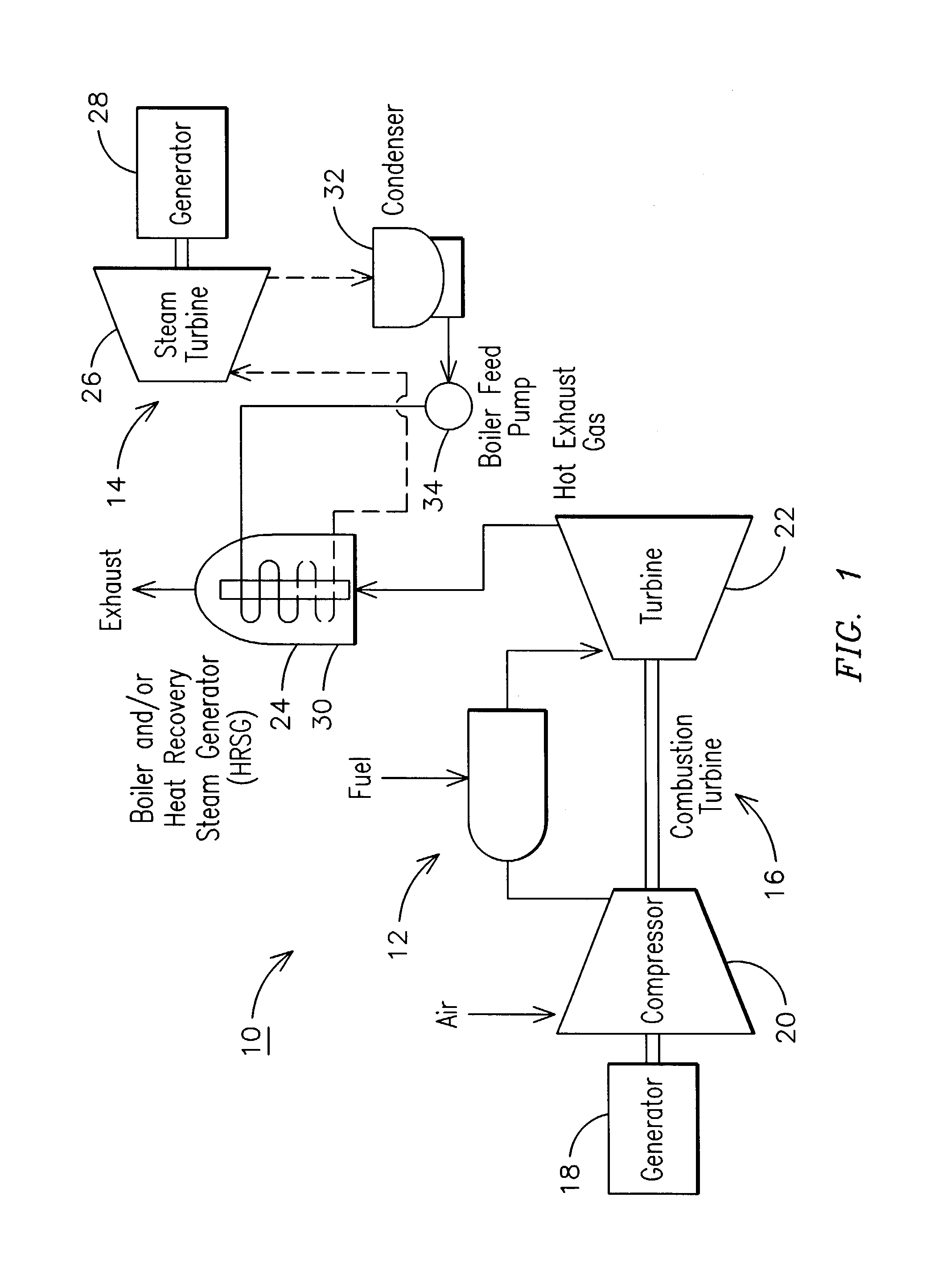

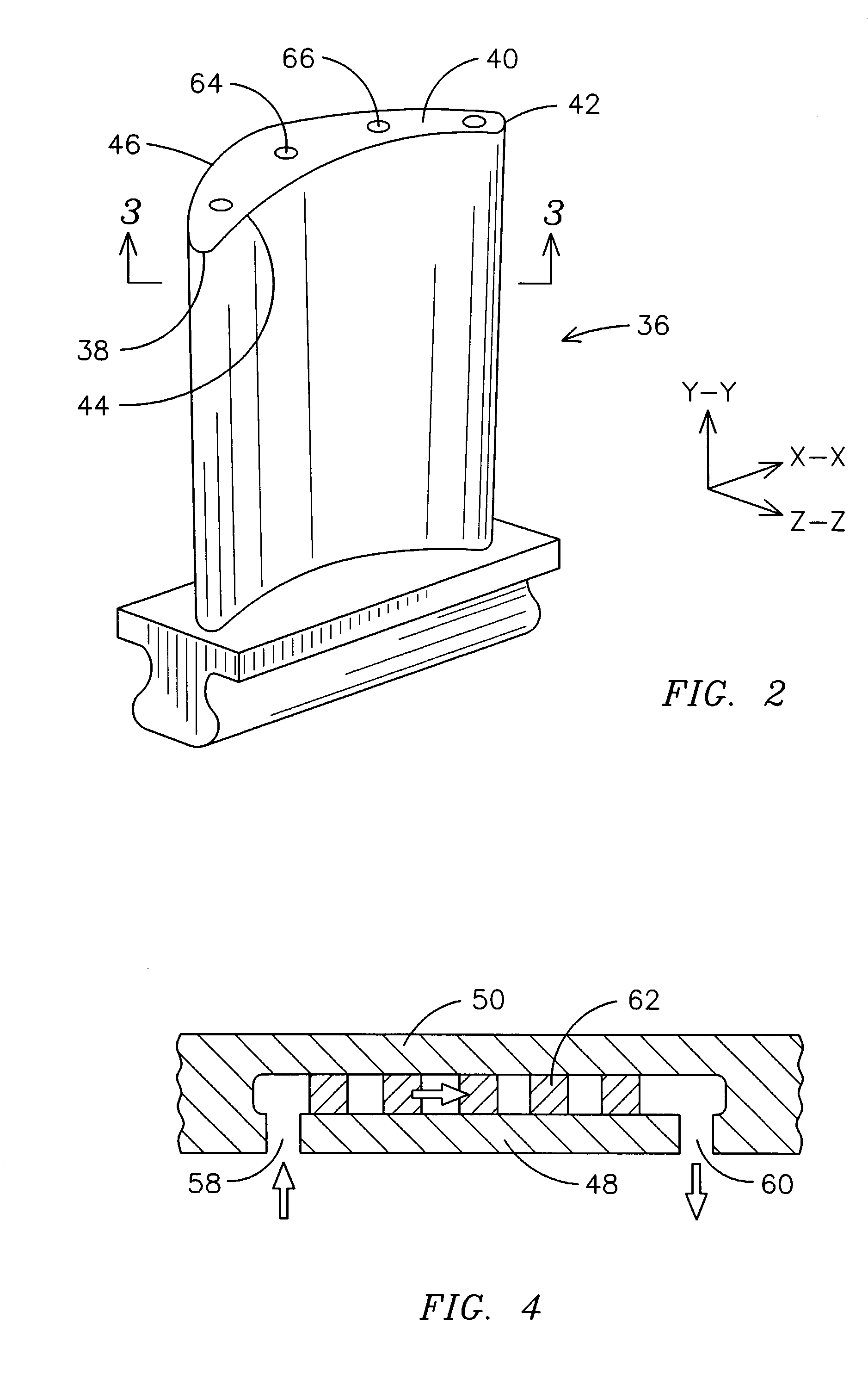

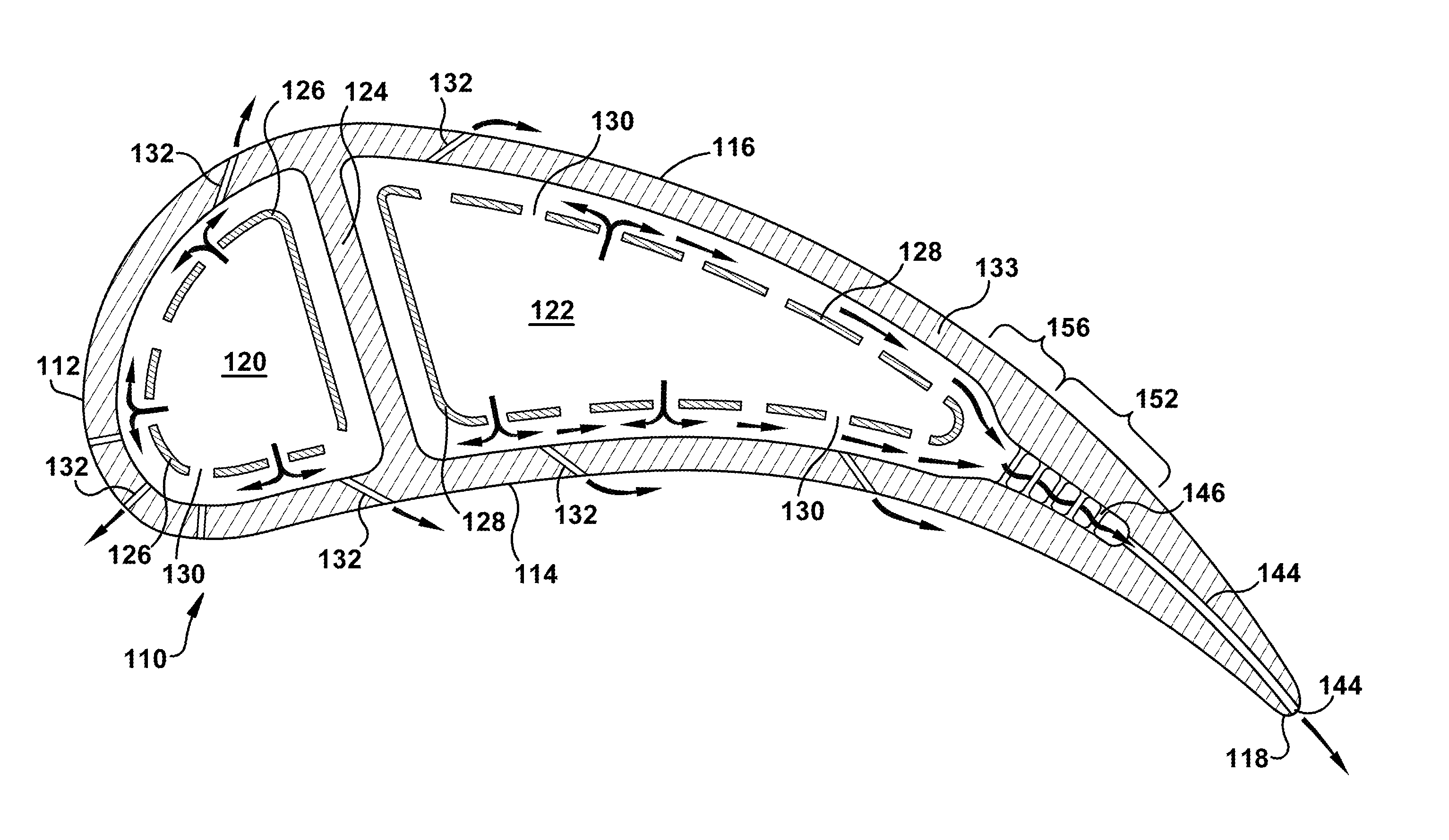

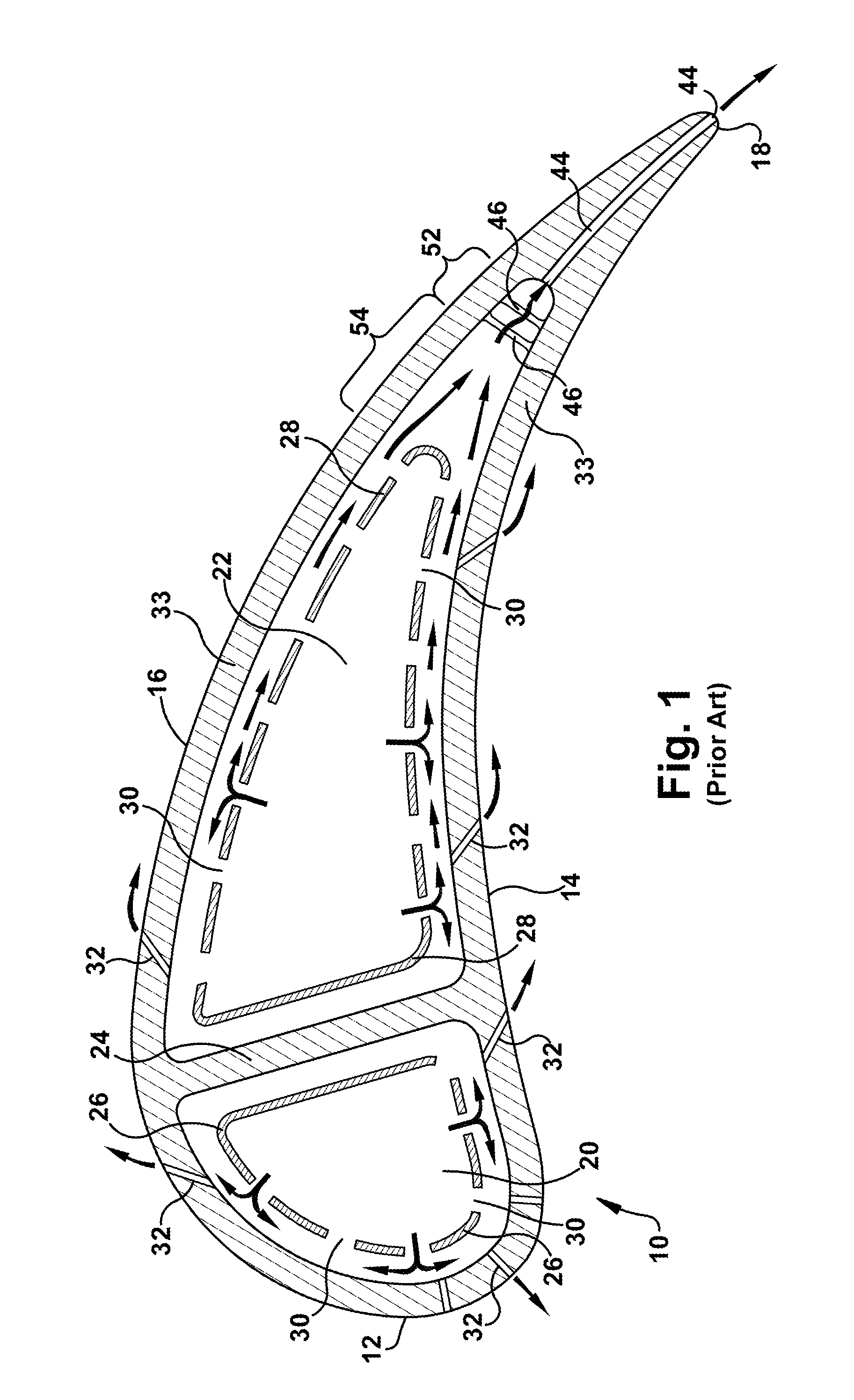

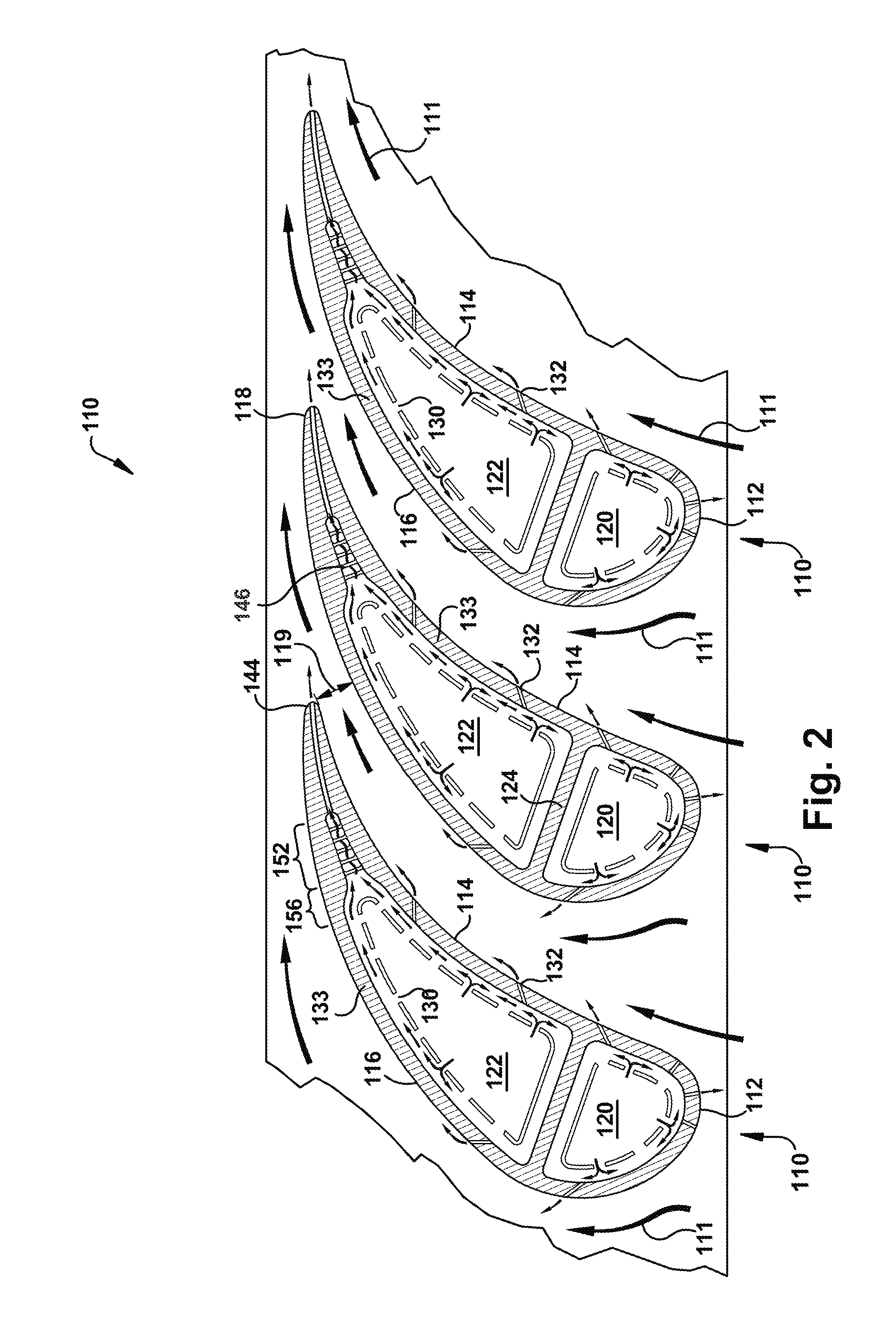

Closed loop steam cooled airfoil

An airfoil, a method of manufacturing an airfoil, and a system for cooling an airfoil is provided. The cooling system can be used with an airfoil located in the first stages of a combustion turbine within a combined cycle power generation plant and involves flowing closed loop steam through a pin array set within an airfoil. The airfoil can comprise a cavity having a cooling chamber bounded by an interior wall and an exterior wall so that steam can enter the cavity, pass through the pin array, and then return to the cavity to thereby cool the airfoil. The method of manufacturing an airfoil can include a type of lost wax investment casting process in which a pin array is cast into an airfoil to form a cooling chamber.

Owner:SIEMENS ENERGY INC

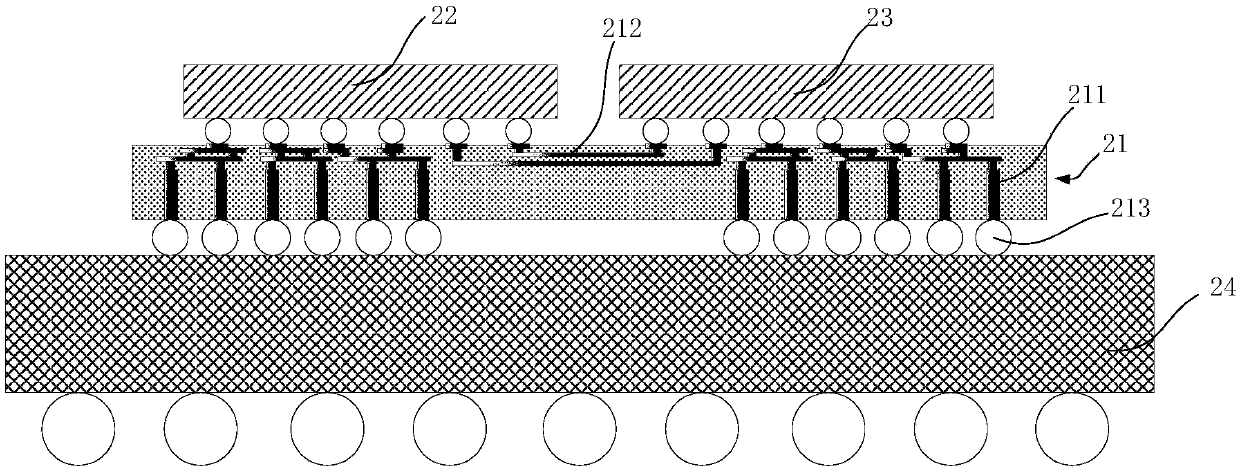

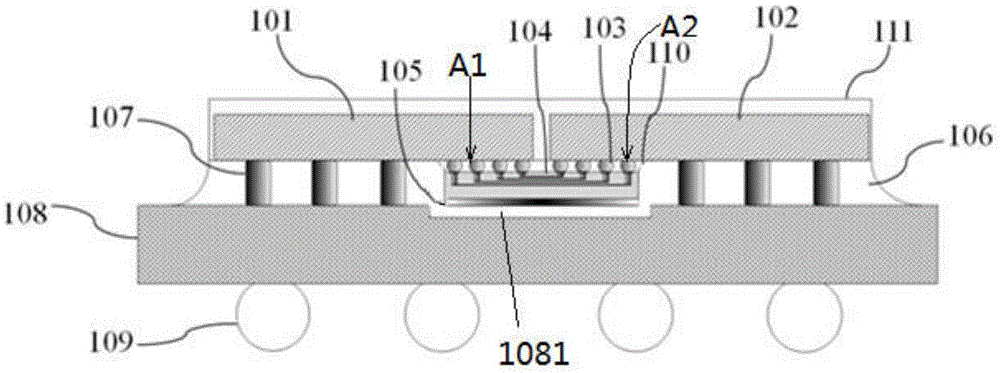

Encapsulation structure, electronic equipment and encapsulation method

ActiveCN105655310ASimple preparation processLow costSemiconductor/solid-state device detailsSolid-state devicesMiniaturizationElectrical connection

The invention discloses an encapsulation structure which comprises a substrate, a fan-out unit and a wiring layer, wherein the fan-out unit comprises a first chip and a second chip; the first chip comprises a first pin array; the second chip comprises a second pin array; the fan-out unit also comprises a third pin array; the first pin array, the second pin array and the third pin array are opposite to the substrate; the wiring layer is bridged between the first pin array and the second pin array and used for connecting the first pins in the first pin array to corresponding second pin in the second pin array; the substrate is provided with a welding pad electrically connected with the wiring layer in the substrate; the third pin array is connected with the welding pad. The invention also discloses electronic equipment and an encapsulation method. The encapsulation structure disclosed by the invention has the advantages of low difficulty in production, low cost and miniaturization.

Owner:HUAWEI TECH CO LTD

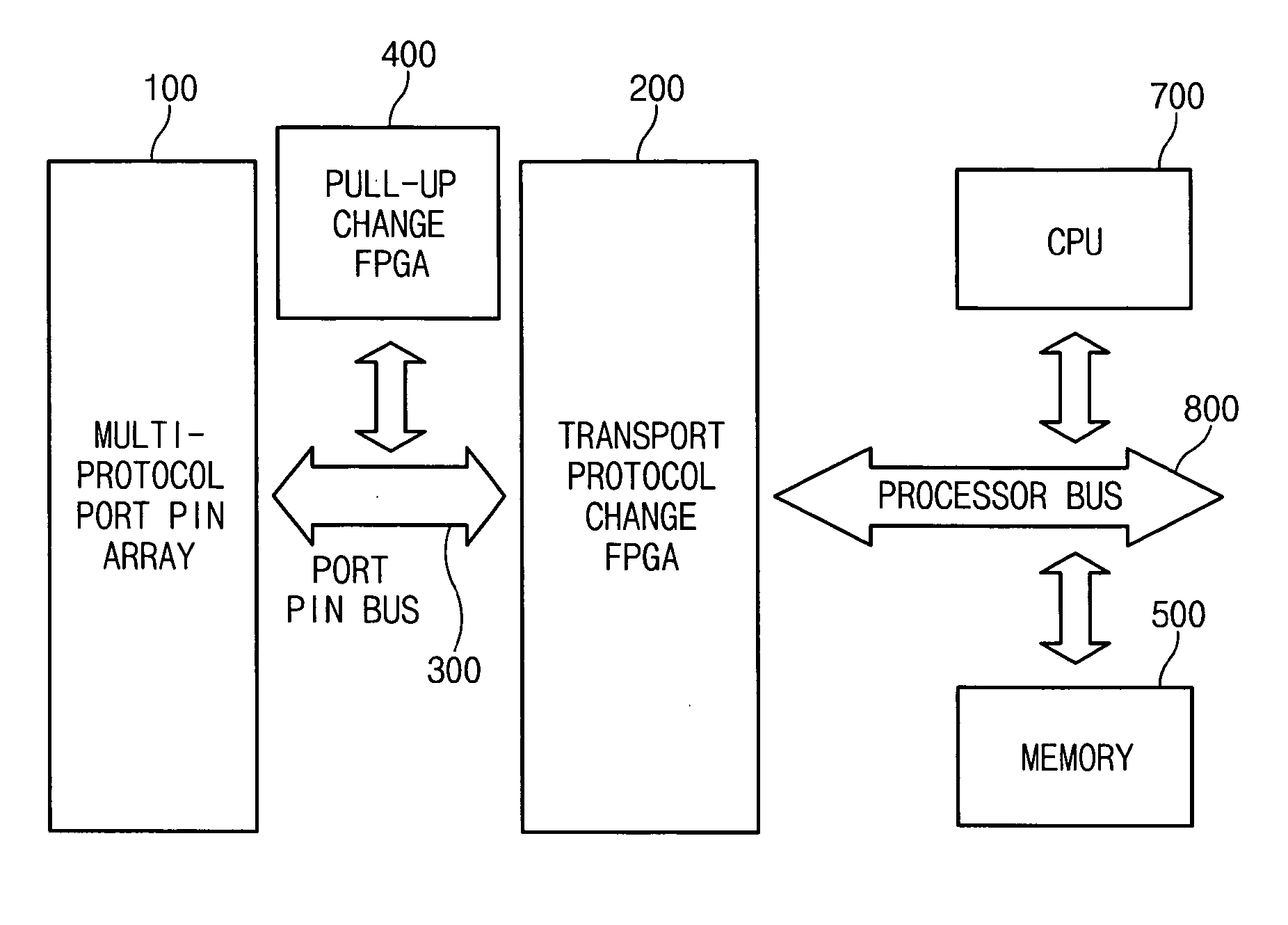

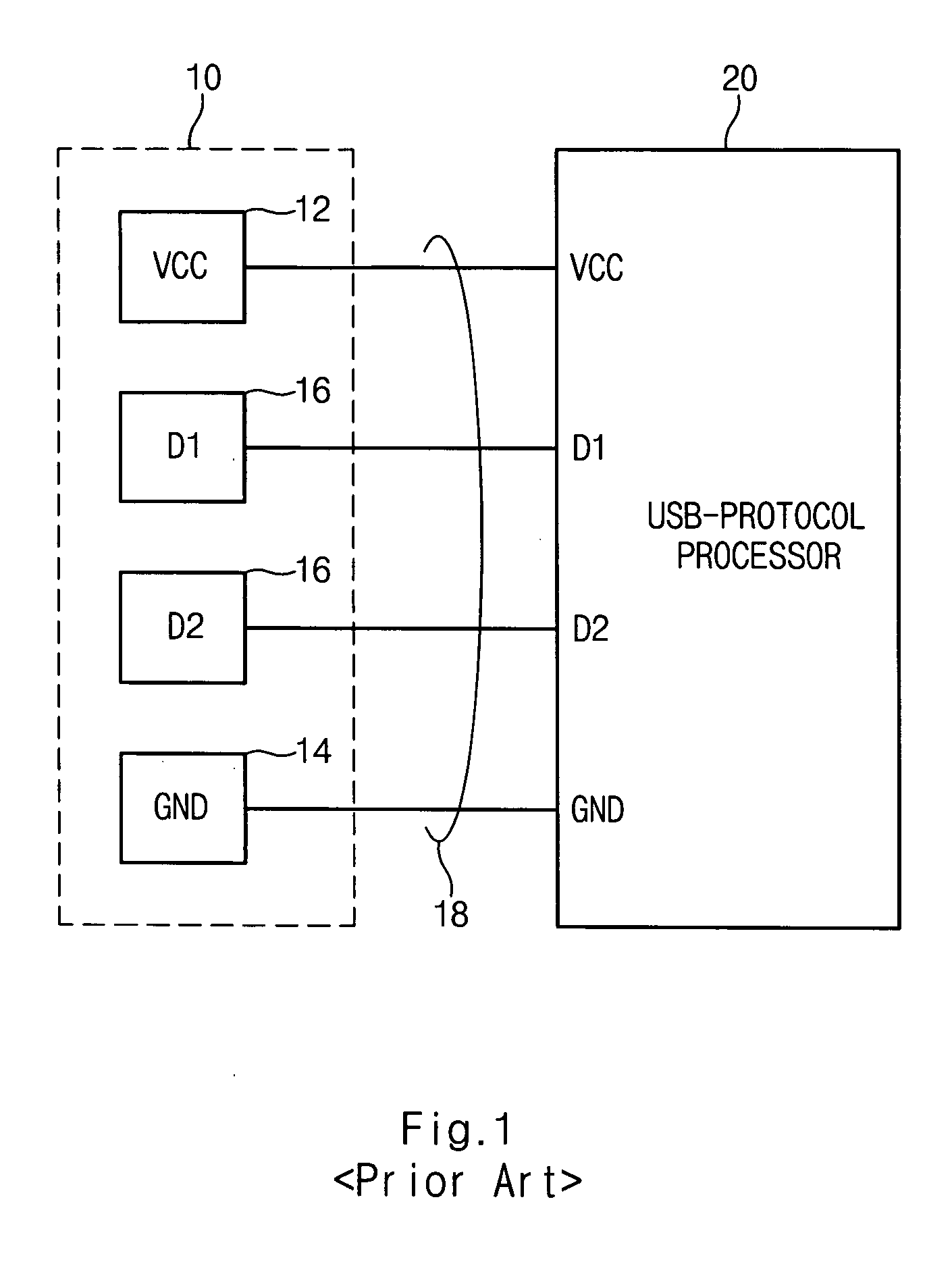

Multi-protocol serial interface system

ActiveUS20050235088A1Energy efficient ICTDigital computer detailsTransmission protocolMulti protocol

A multi-protocol serial interface system comprises a multi-protocol port pin array, a transport protocol change FPGA, a pull-up change FPGA and a memory. The multi-protocol port pin array comprises a plurality of port pins which interface with an external system for exchanging data with the external system. The transport protocol change FPGA determines roles of port pins of the multi-protocol port pin array depending on a variably changed protocol by selecting one of the plurality of programmed transport protocol circuits in response to code data. The pull-up change FPGA regulates pull-up load of the port pins corresponding to the roles of the port pins determined in the transport protocol change FPGA. The memory stores data processed in the transport protocol change FPGA unit and exchanged with the external system.

Owner:SK HYNIX INC

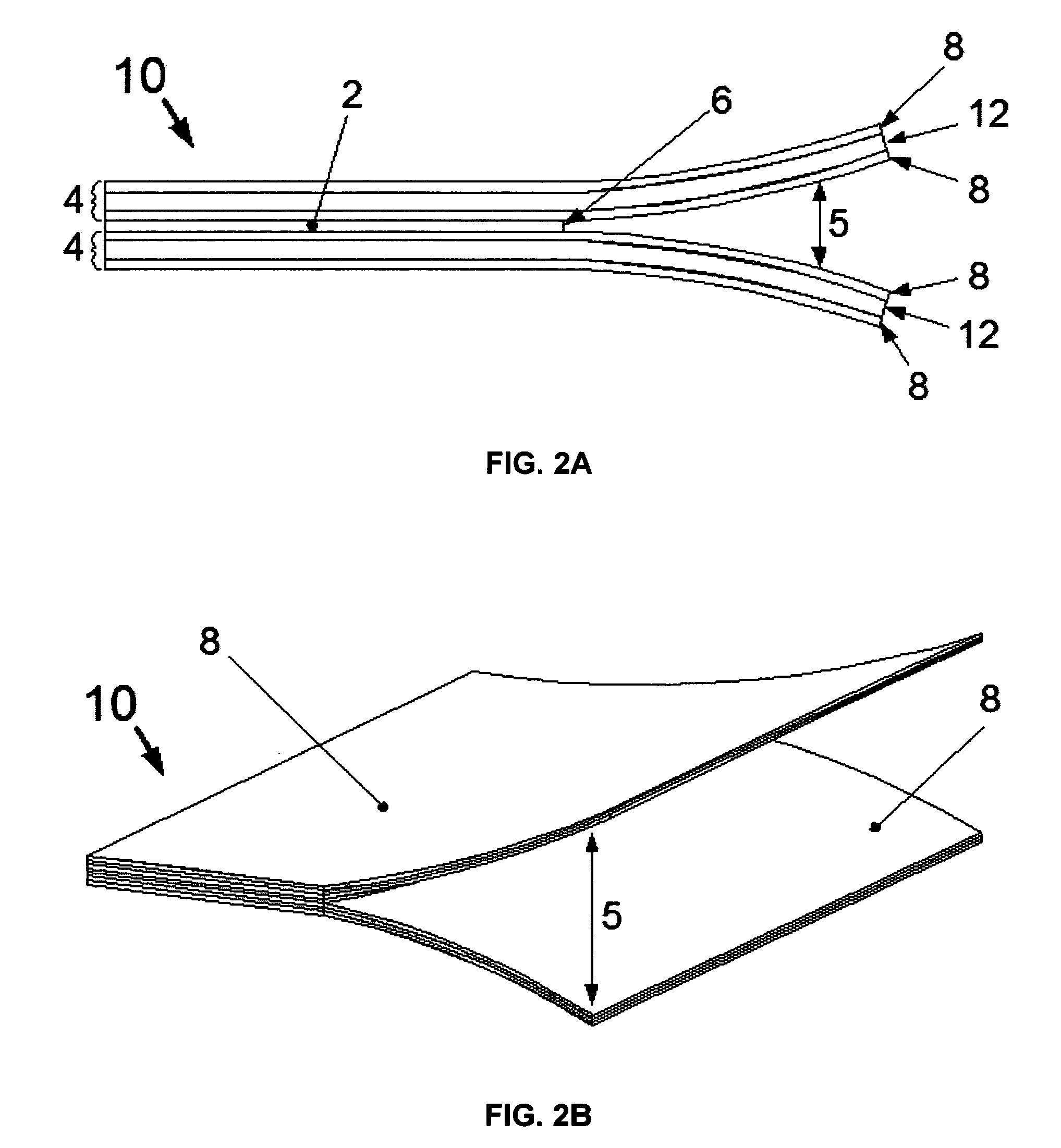

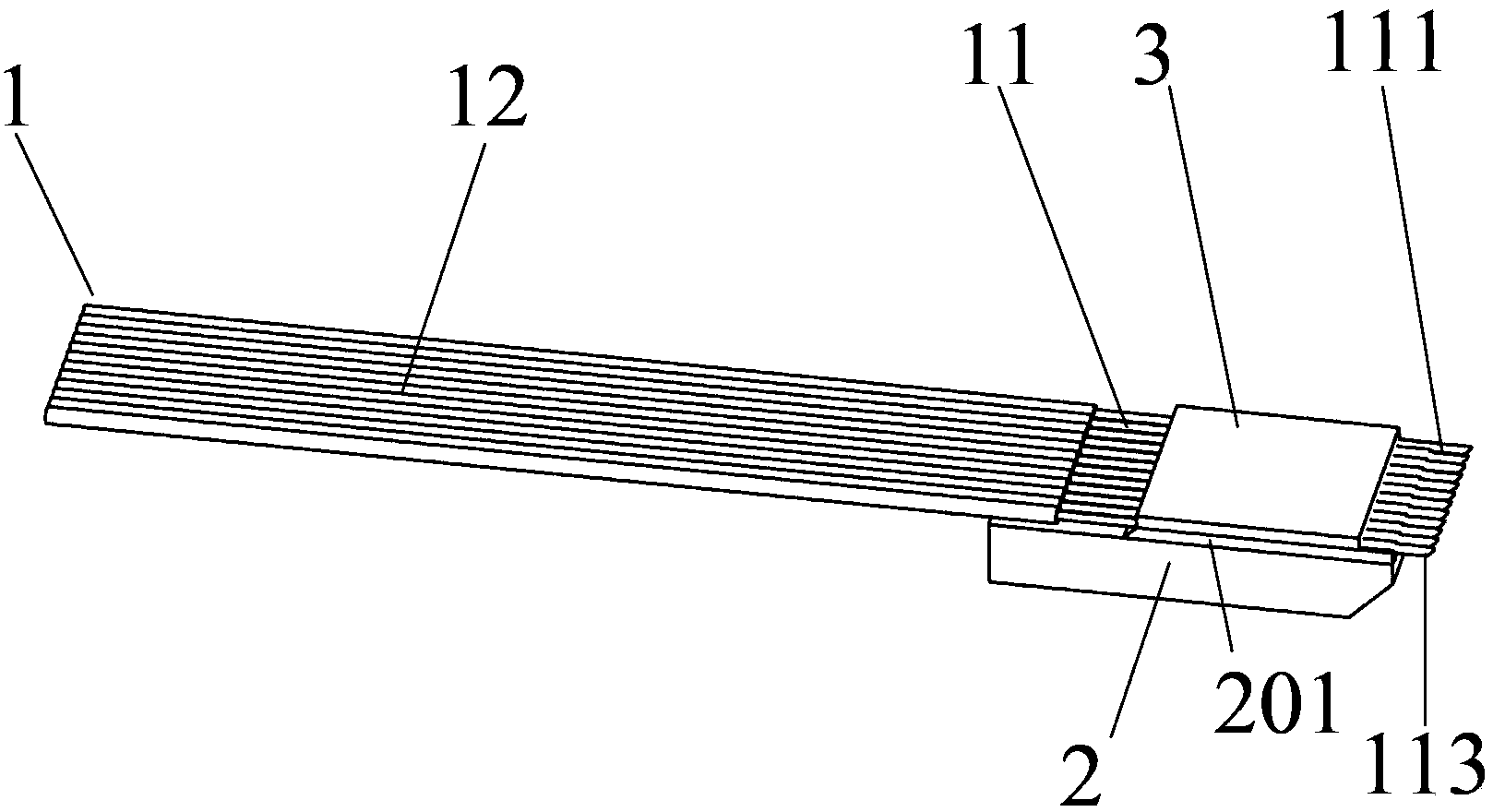

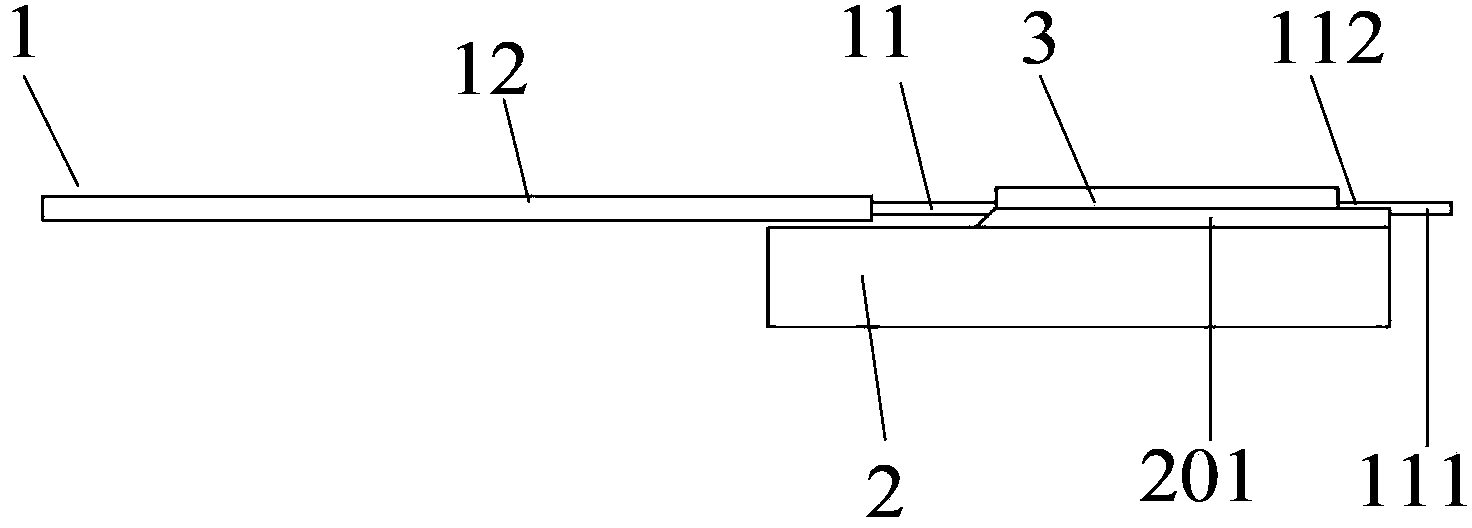

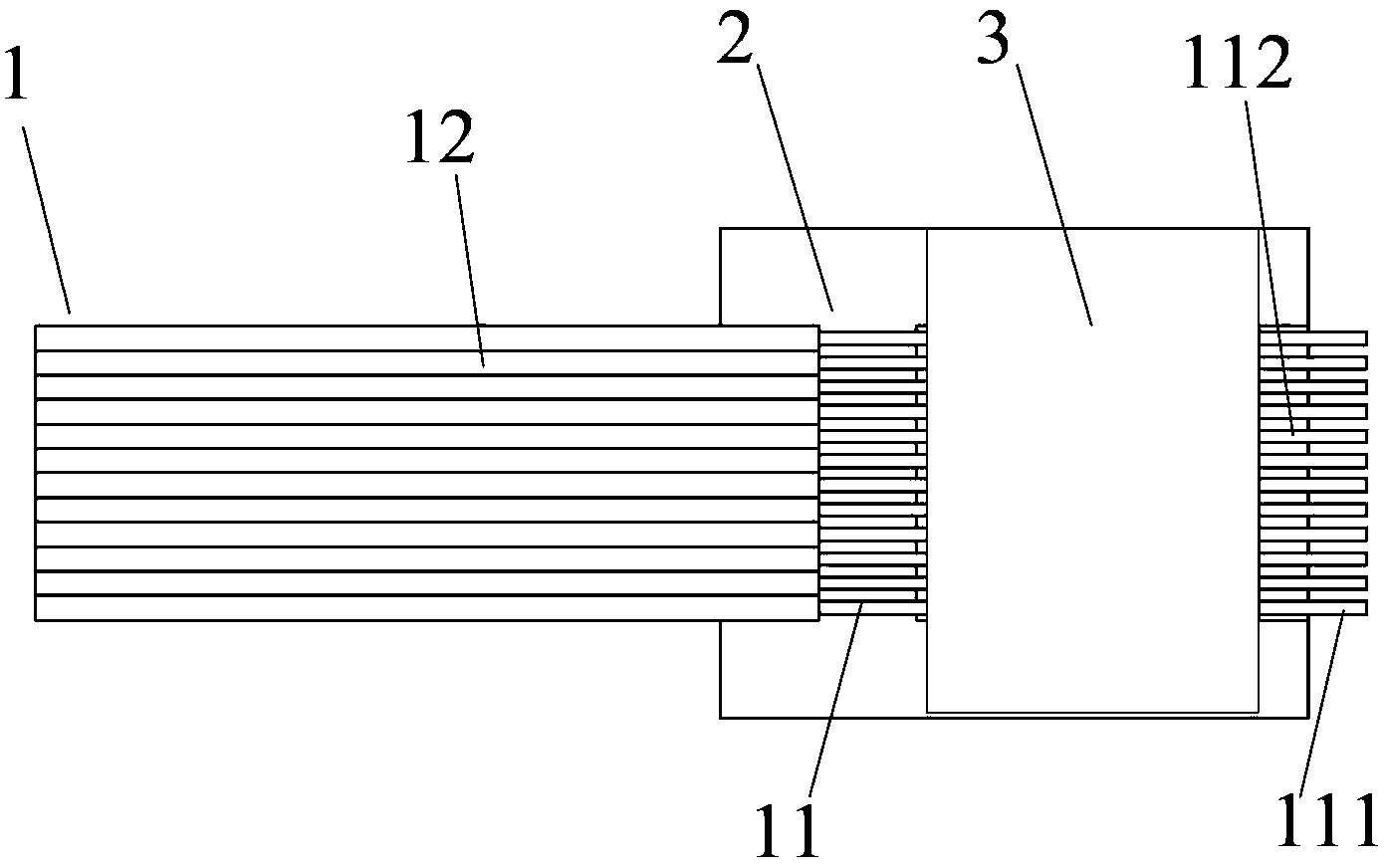

Fiber array coupled with VSCEL or PIN array and manufacturing method of fiber array

ActiveCN103383482AEfficient couplingAvoiding Adjustment Coupling Distance IssuesCoupling light guidesFiberCoupling

The invention relates to a fiber array coupled with a VSCEL or PIN array and a manufacturing method of the fiber array. The fiber array comprises a cover slip, a carving groove substrate and a fiber micro-strip, the fiber micro-strip comprises an exposed fiber micro-strip portion without a fiber coating, a V-shaped carving groove for holding the exposed fiber micro-strip portion is formed in the carving groove substrate, the cover slip presses the groove of the exposed fiber micro-strip portion, the carving groove substrate, the cover slip and the exposed fiber micro-strip portion are fixedly connected through binding agents, the cover slip is shorter than the V-shaped carving groove, the end face of the exposed fiber micro-strip portion is an optical plane with a 45-degree oblique angle, and the optical plane faces the carving groove substrate. The coupling distance between the 45-degree optical plane of the exposed fiber micro-strip portion and the VSCEL or PIN array is controlled by the aid of the cover slip of the fiber array, the thickness of the cover slip can be customized, and high-efficiency coupling is realized. The method for manufacturing the fiber array is simple, easy to implement and low in cost.

Owner:WUHAN POWERISE OPTOELECTRONICSAL TECH

Shielded integrated connector module

ActiveUS8007318B1Electrically conductive connectionsCoupling device detailsEngineeringElectrical connector

An electrical connector assembly is provided for mating with electrical plugs. The electrical connector assembly includes a housing having a top wall and a bottom wall that is opposite the top wall. The housing includes a mating face having ports that are configured to receive the electrical plugs therein. A jack sub-assembly is held by the housing. The jack sub-assembly includes jacks having electrical contacts held within the ports for engagement with the electrical plugs. The jack sub-assembly includes a signal pin array having signal pins for connection to a host circuit board. The signal pin array includes a front side extending along the bottom wall of the housing. An electrically conductive outer shield covers the top wall of the housing. The outer shield includes a bottom flap covering an end of the bottom wall of the housing. An electrically conductive bottom shield covers the bottom wall of the housing between the bottom flap of the outer shield and the front side of the signal pin array.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

Turbine blade cooling with a hollow airfoil configured to minimize a distance between a pin array section and the trailing edge of the air foil

ActiveUS8231329B2Improve viewing effectIncrease the areaPropellersRotary propellersLeading edgeTurbine blade

Owner:GENERAL ELECTRIC CO

Memory card and semiconductor device

An antenna connection function for a noncontact interface is provided by suppressing a modification in a pin arrangement and a pin shape of a memory card that does not correspond to the noncontact interface. Two antenna connecting pins having the memory card are divided into two areas in which a size of one potential supply pin is the largest and used as a split pin arranged at intervals. Because a size of the two antenna connecting pins is at maximum as large as the size of the potential supply pin, the two antenna connecting pins are provided and the memory card that corresponds to the noncontact interface is obtained by devoting a pin area having the size of the one potential supply pin to the memory card that does not correspond to the noncontact interface. Accordingly, the pin area of the memory card that corresponds to the noncontact interface can be formed without departing from the pin area of the memory card that does not correspond to the noncontact interface.

Owner:RENESAS ELECTRONICS CORP

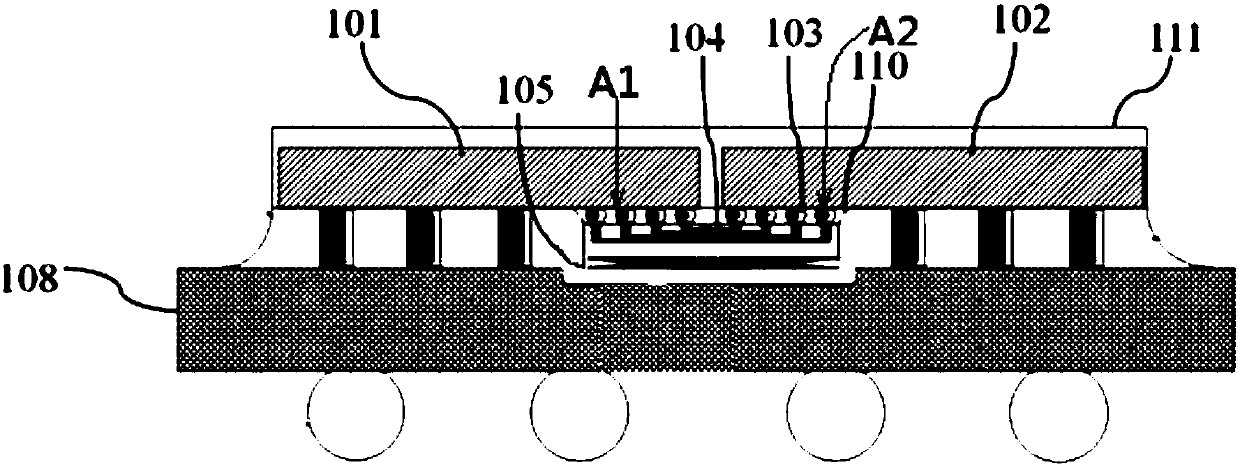

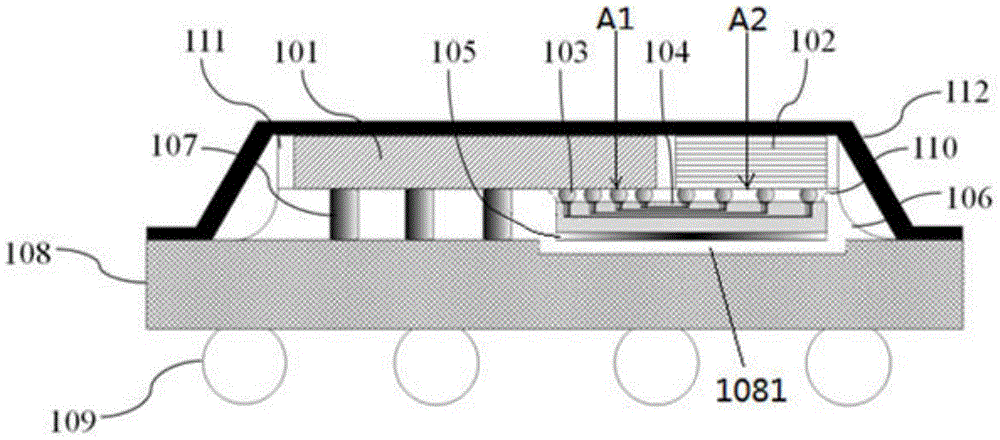

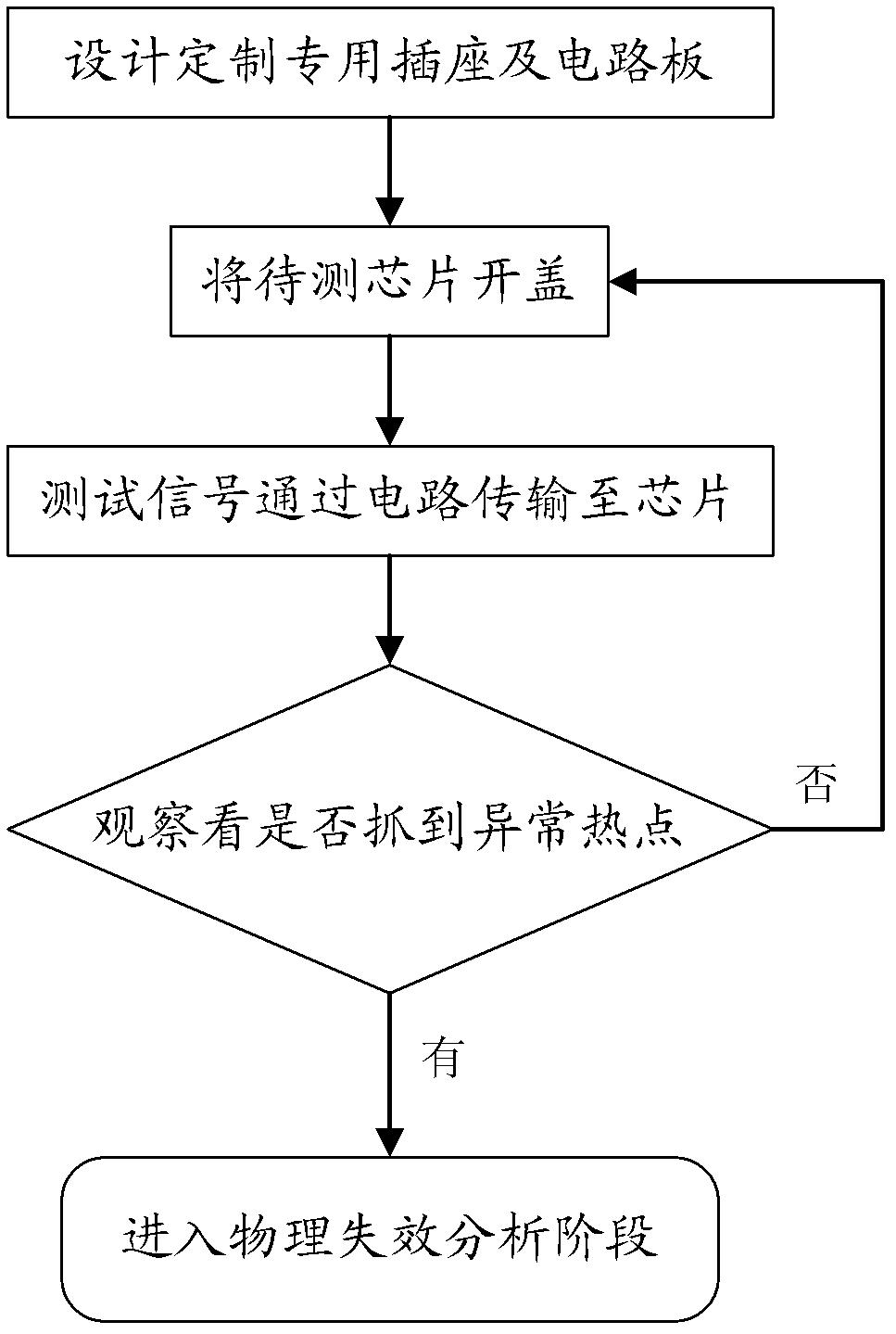

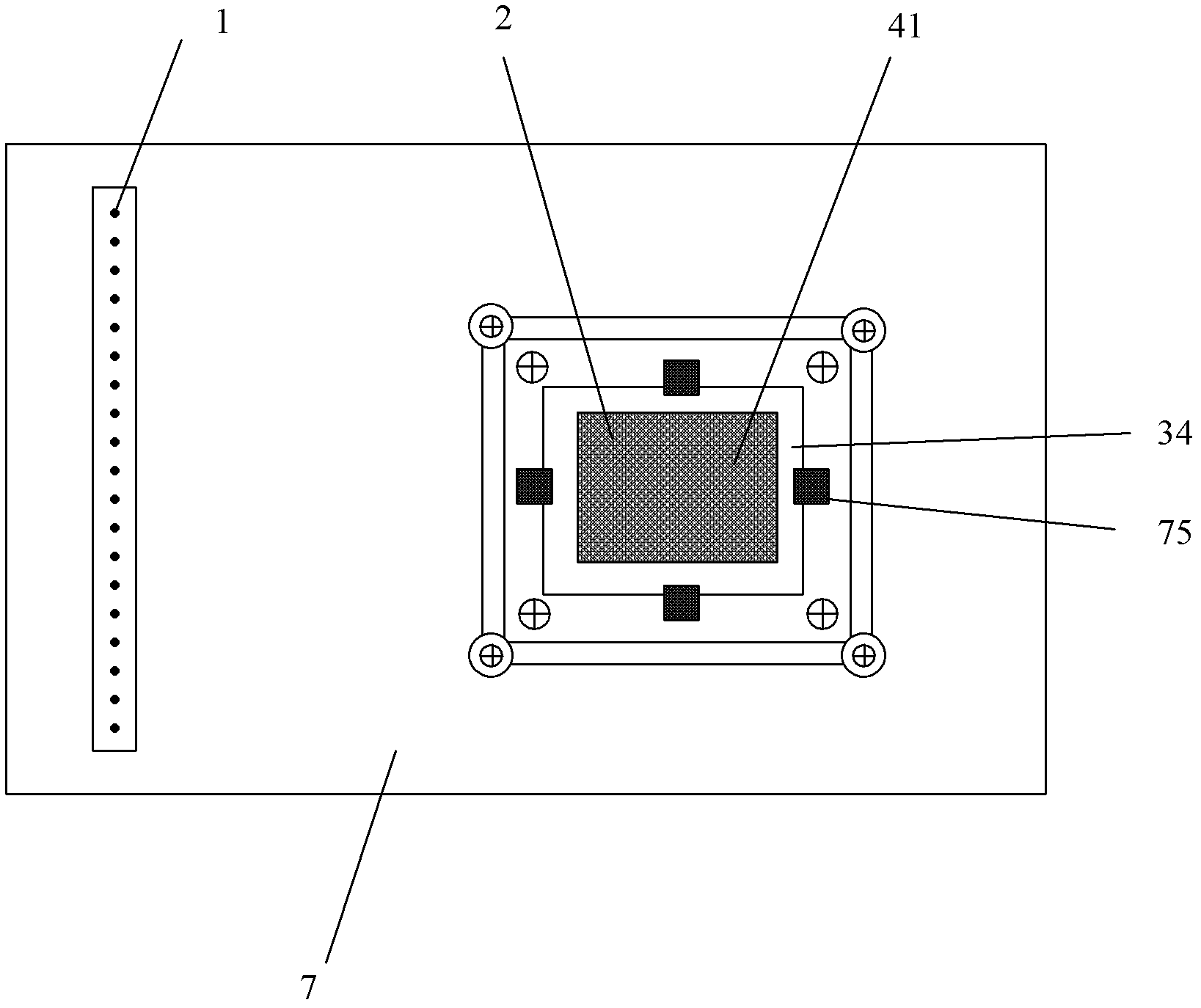

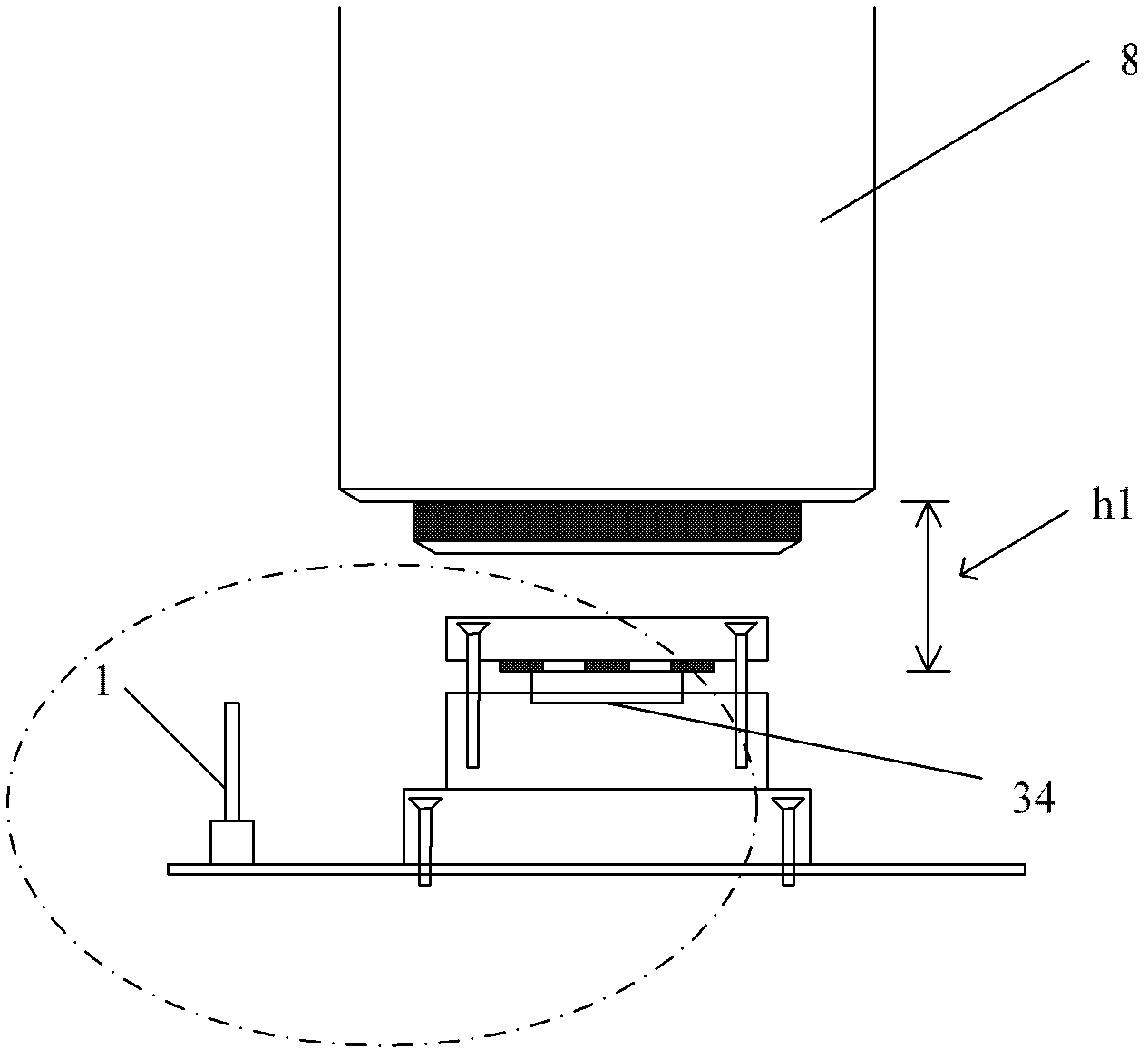

Support plate for failure analysis, test equipment, and method for chip electrical failure analysis

ActiveCN103185856AEasy to completeMethods for Implementing Failure AnalysisElectronic circuit testingOptically investigating flaws/contaminationElectrical FailureFailure analysis

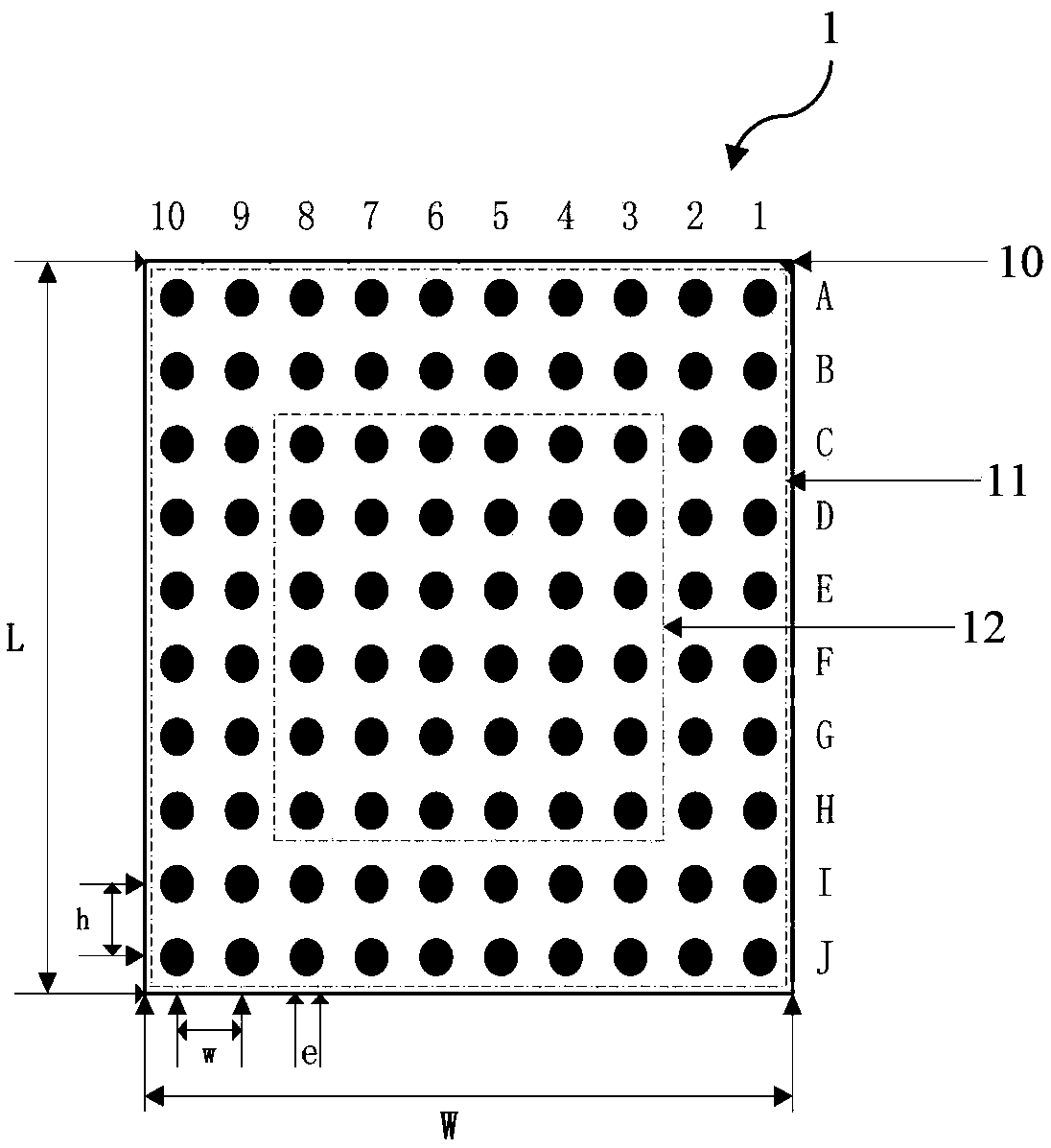

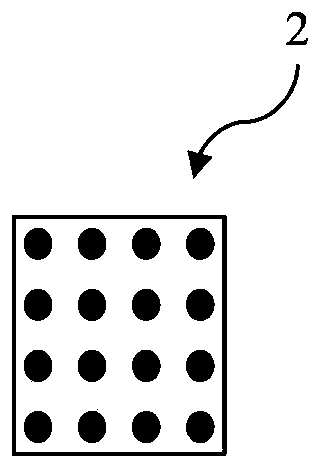

The invention provides a support plate specially designed for a chip to be tested, test equipment, and a method for chip electrical failure analysis. According to the method, the support plate is specially designed for the chip to be tested, wherein the support plate comprises a pad array located in a containing area of the chip to be tested, a pin array used for realizing signal transmission with a test machine, and metal cables used for connecting the pin array and the pad array, and the chip to be tested is stuck to the support plate with the surface mounted technology (SMT). According to the method for the chip electrical failure analysis, the support plate used for the chip electrical failure analysis and the test equipment, hardware preparation can be achieved conveniently and fast, and the chip electrical failure analysis of tests of chips with a large amount of pins can be achieved easily.

Owner:SEMICON MFG INT (SHANGHAI) CORP

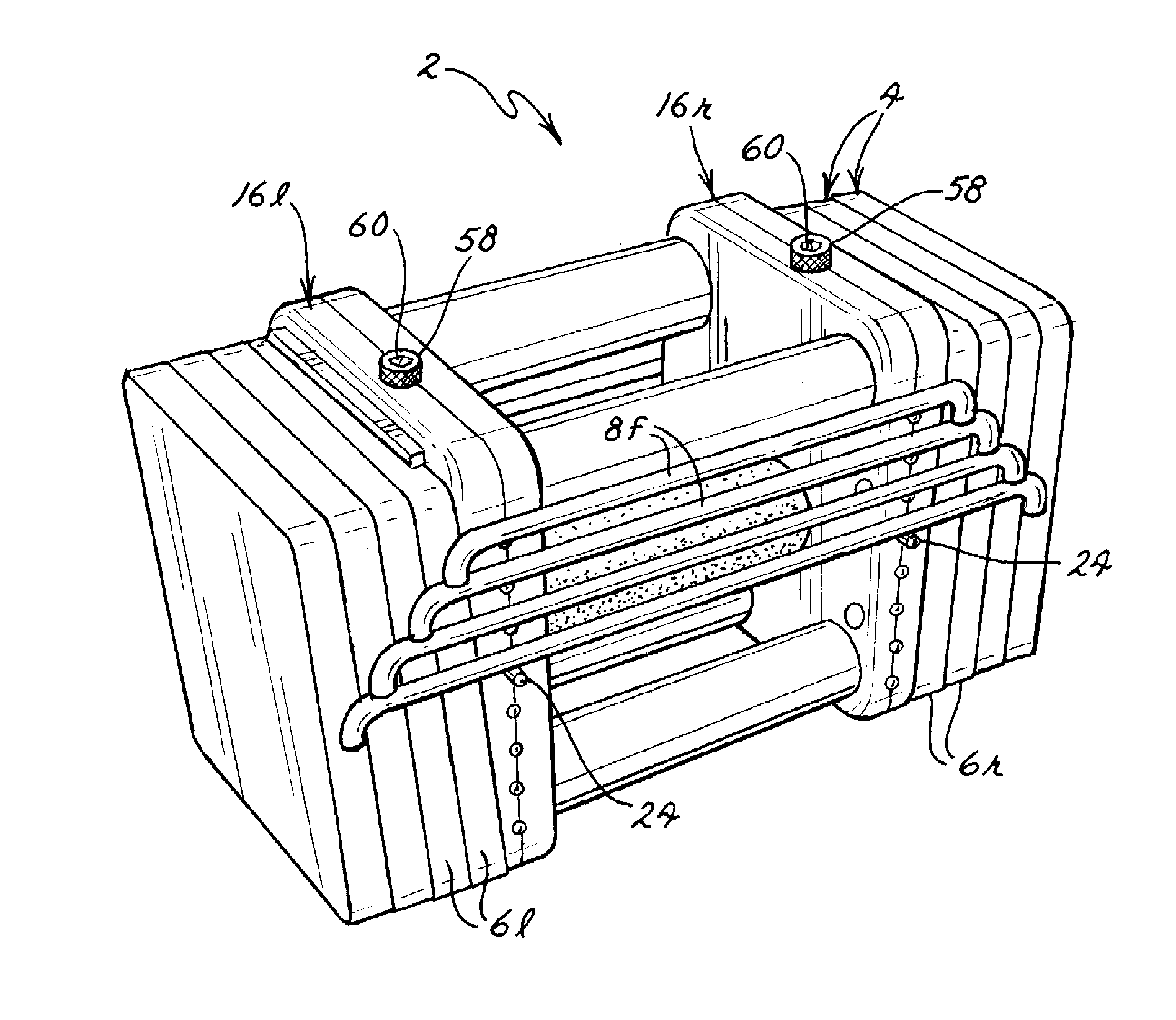

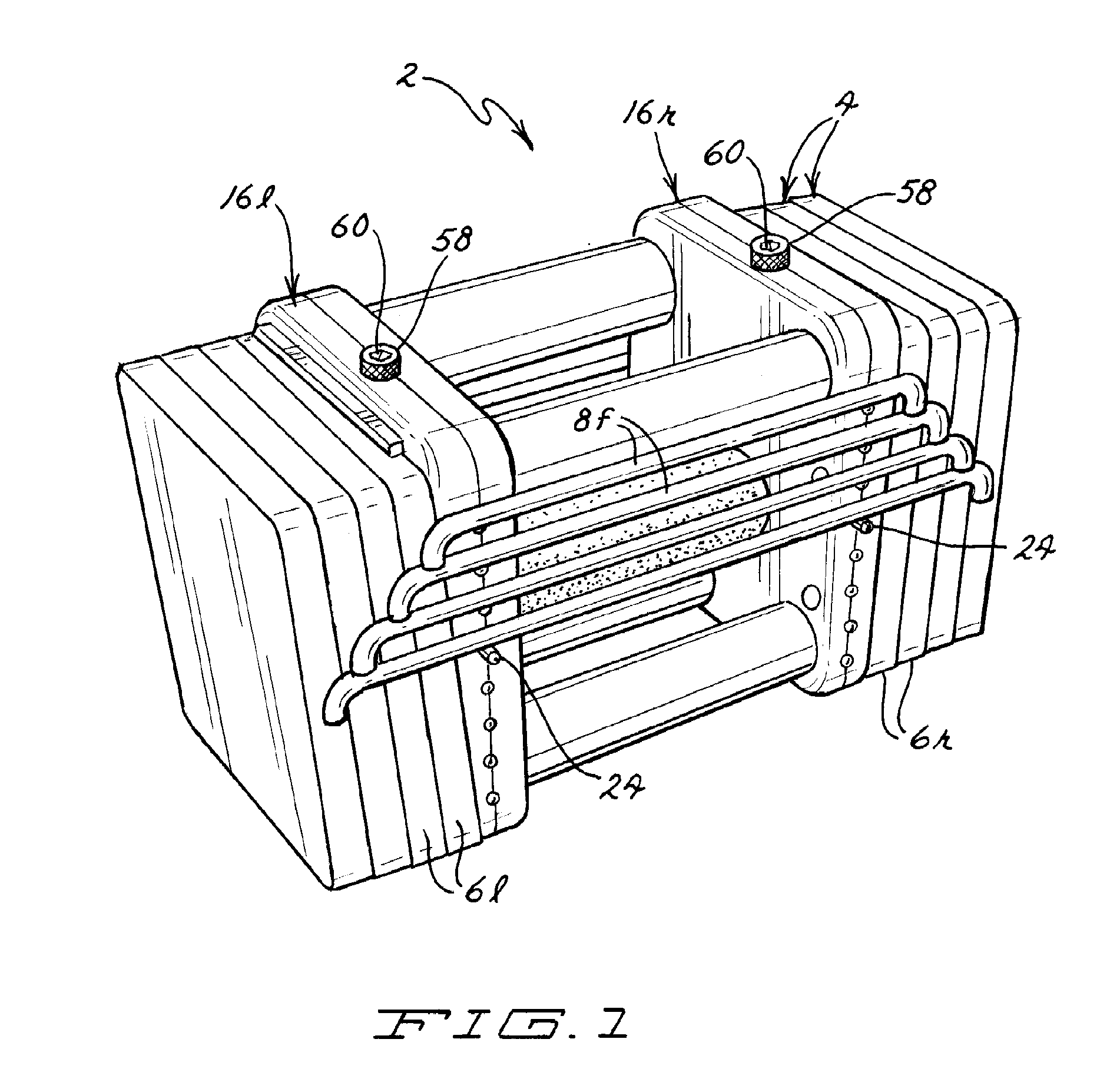

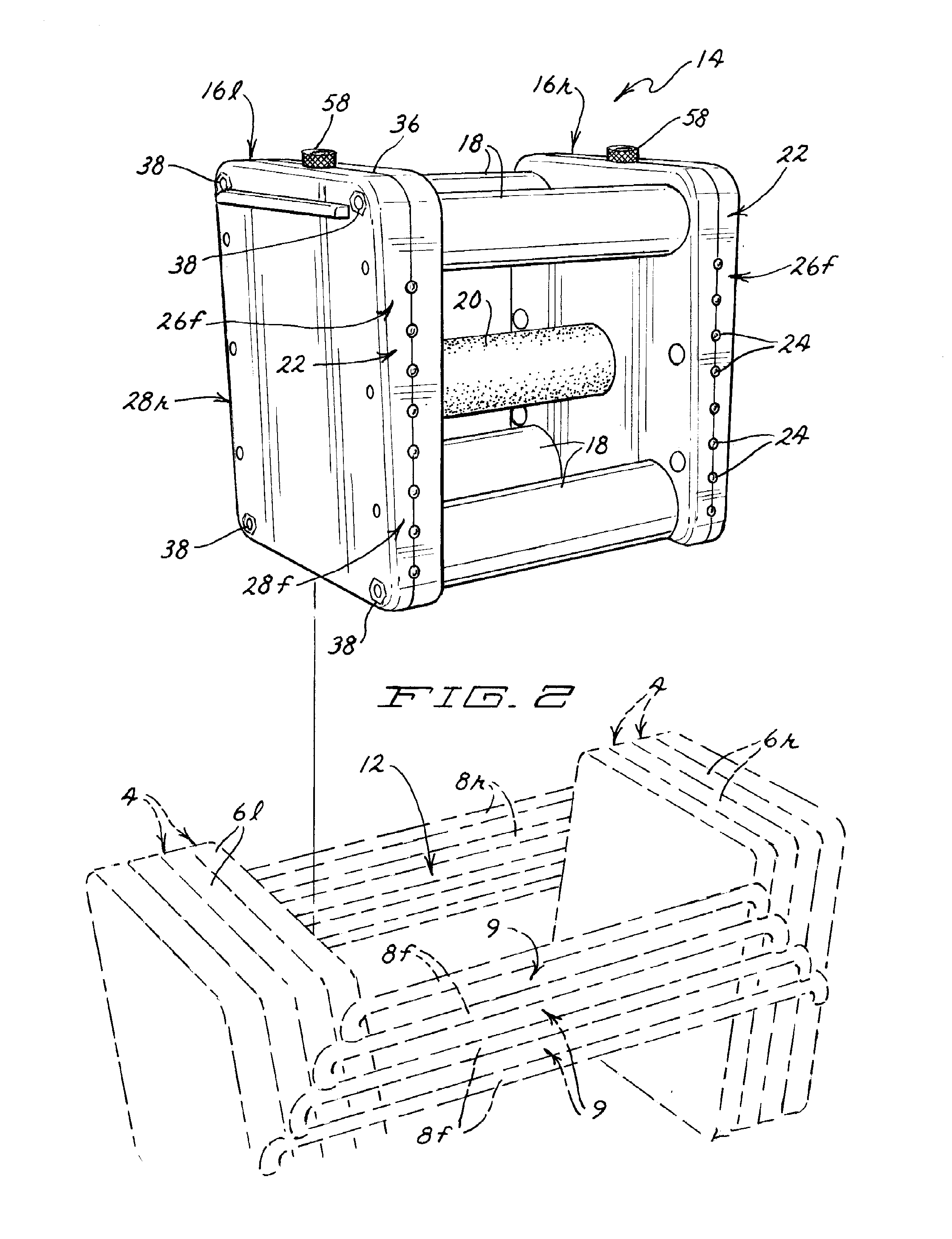

Selectorized dumbbell with selector comprising weight connecting pins carried in each end of handle

A selectorized dumbbell comprises a plurality of nested weights which have front and rear arrays of rails with the rails being vertically spaced from one another with a space beneath each rail. A handle is insertable into a gap between stacks of nested left and right weight plates. A selector comprises front and rear pin arrays in each end of the handle with the pins in these arrays being selectively movable in a horizontal direction into extended positions located in the spaces beneath the rails for coupling different weights to the handle. The pins in the arrays are movable into their extended positions by a single vertically movable member carried on a vertically rotatable shaft in the handle end or by a plurality of independently movable members in the handle end that are moved by a plurality of keys carried on a top side of the handle end.

Owner:POWERBLOCK HLDG

Circuit board plug-in component with roller groove

InactiveCN104953366ASmooth side to side movementAchieve lockingCoupling device detailsEngineeringPin array

The invention relates to a circuit board plug-in component with a roller groove. The circuit board plug-in component comprises circuit board equipment (9) and an interface device (8) disposed on the left side of the circuit board equipment (9). The interface device (8) comprises a shell formed by an upper contour part (81) and a lower contour part (82). A part, adjacent to the inner side of the shell, of the board of the circuit board equipment (9) is provided with a contact pin array (99) used for being connected with the jack array (72) of a plug (7) inserted between the upper contour part (81) and the lower contour part (82) of the interface device (8). The upper contour part (81) and a lower contour part (82) are respectively connected with rollers (80) on an upper slider component (83) and a lower slider component (84).

Owner:汪贤女

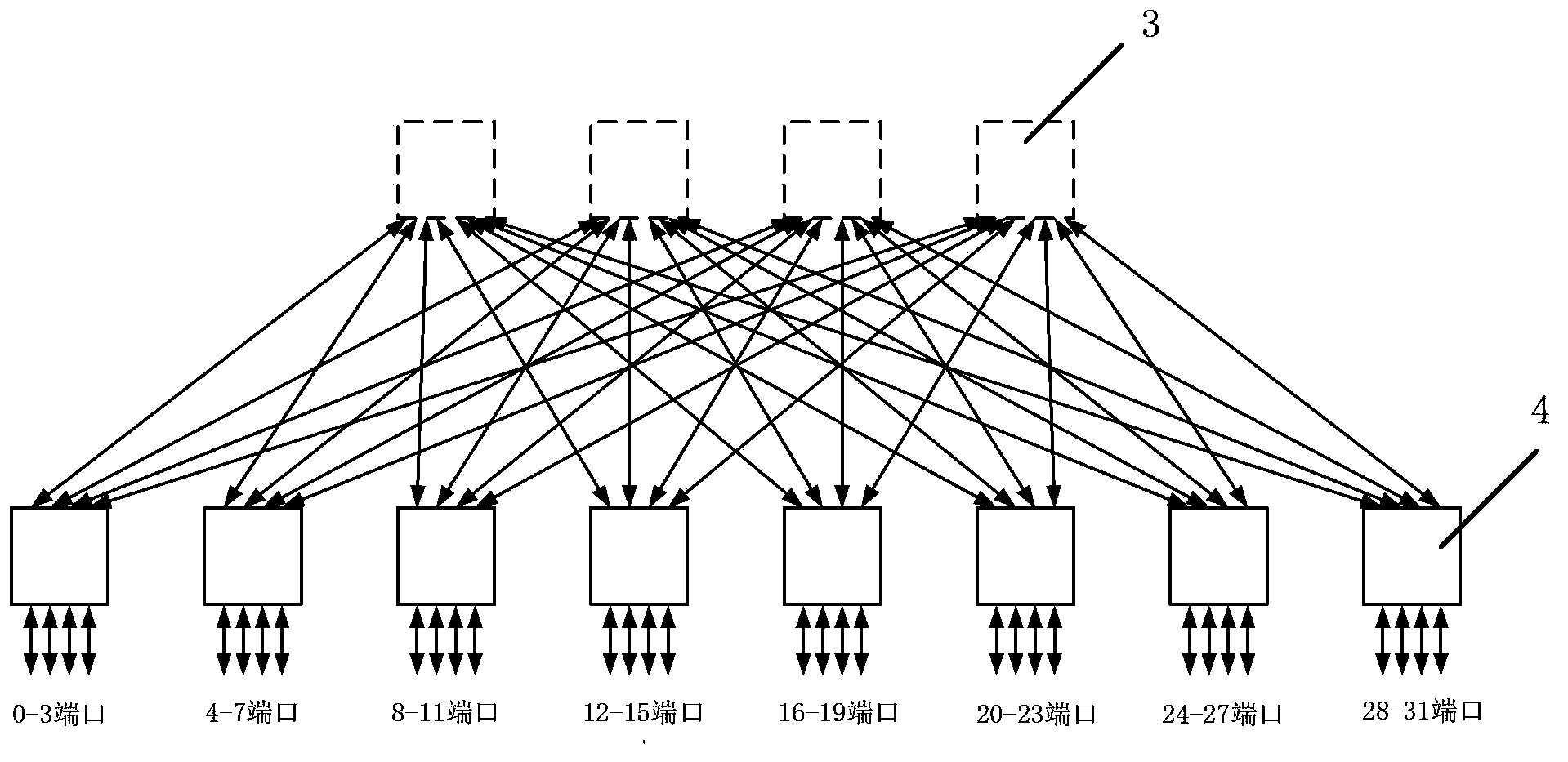

Substrate/multi-chip-integrated large port interconnection chip and realization method thereof

ActiveCN103413796AManufacturing technology requirements are lowIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyEngineering

The invention provides a multilayer wiring substrate / multi-chip integration-based large port interconnection chip interconnection construction and physical realization method and relates to a multi-chip interconnection structure, a multi-chip interconnection structure construction method, multi-chip layout, substrate pin array partitioning and distribution, distribution of high-speed differential signal pin pairs, effective partition of substrate wiring and a partition method of the substrate wiring as well as a corresponding multi-chip interconnection chip device which are applicable to substrate integration. According to the invention, large-port interconnection chips can be effectively and equivalently realized based on substrate encapsulation size. Compared with a corresponding single-chip integration implementation method, the method of the invention can support multiple kinds of interconnection structures, and is compatible with interconnection sub-chips be of a variety of micro-system structures, can effectively utilize the characteristics of different functional interconnection sub-chips, and has better performance in implementation cost of the chips, scalability, flexibility, compatibility and the like; and at the same time, the method of the invention has lower requirements for manufacturing technology for realizing a required integrated circuit and can provide interconnection chips having different specifications and different number of ports, and can more flexibly adapt to market demands.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI