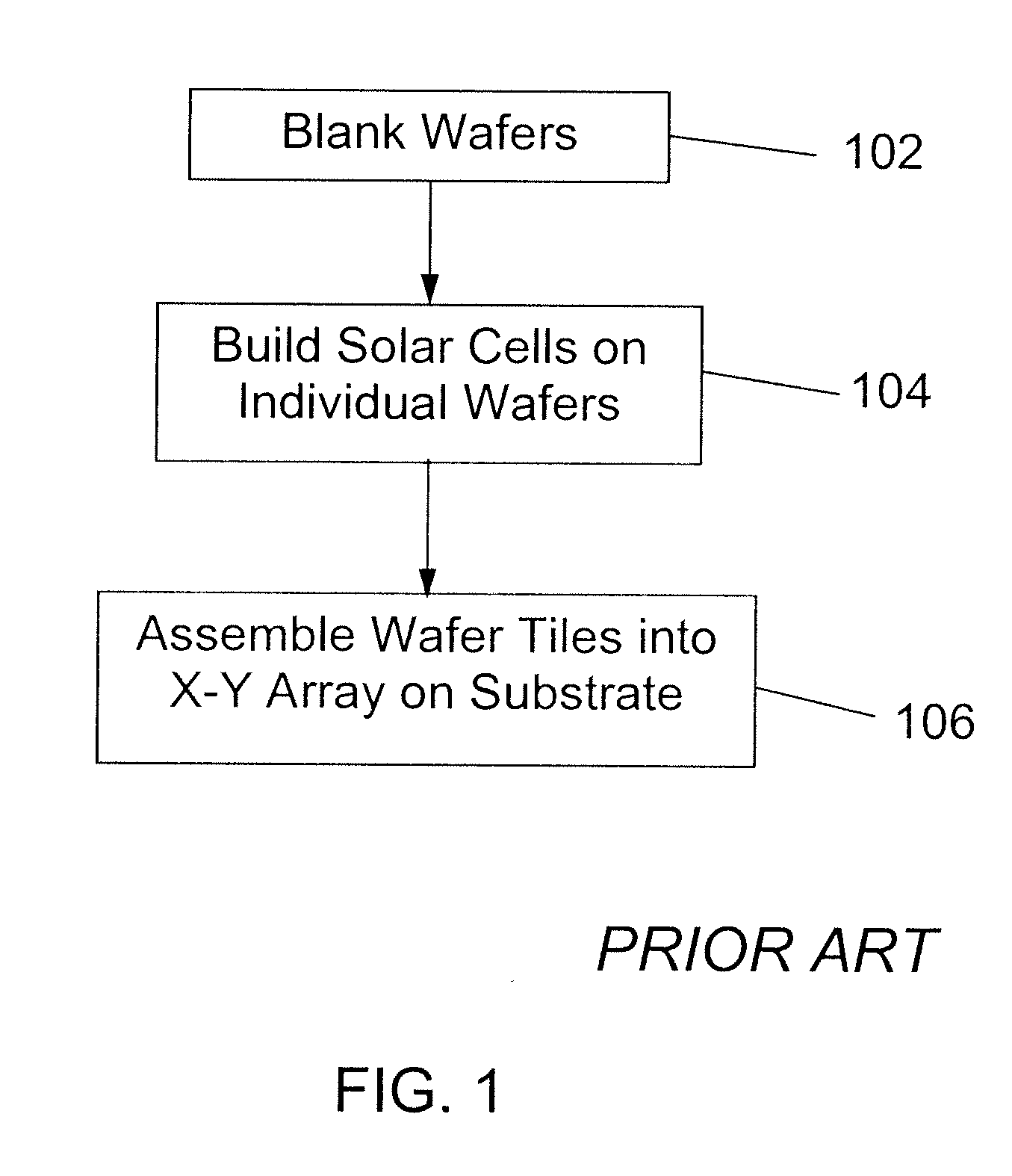

Patents

Literature

823 results about "Monocrystalline silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Monocrystalline silicon (also called single-crystal silicon (or Si), mono c-Si or simply mono-Si) is the base material for silicon-based discrete components and integrated circuits used in virtually all modern electronic equipment. Mono-Si also serves as a photovoltaic, light-absorbing material in the manufacture of solar cells.

Integrated circuit memory with single crystal silicon on silicide driver and manufacturing method

ActiveUS20100171086A1Excellent ElectricalExcellent structural characteristicSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitMonocrystalline silicon

A memory device includes a diode driver and a data storage element, such as an element comprising phase change memory material, and in which the diode driver comprises a silicide element on a silicon substrate with a single crystal silicon node on the silicide element. The silicide element separates the single crystal silicon node from the underlying silicon substrate, preventing the flow of carriers from the single crystal silicon node into the substrate, and is capable of acting as a conductive element for interconnecting devices on the device. The single crystal silicon node acts as one terminal of a diode, and a second semiconductor node is formed on top of it, acting as the other terminal of the diode.

Owner:MACRONIX INT CO LTD

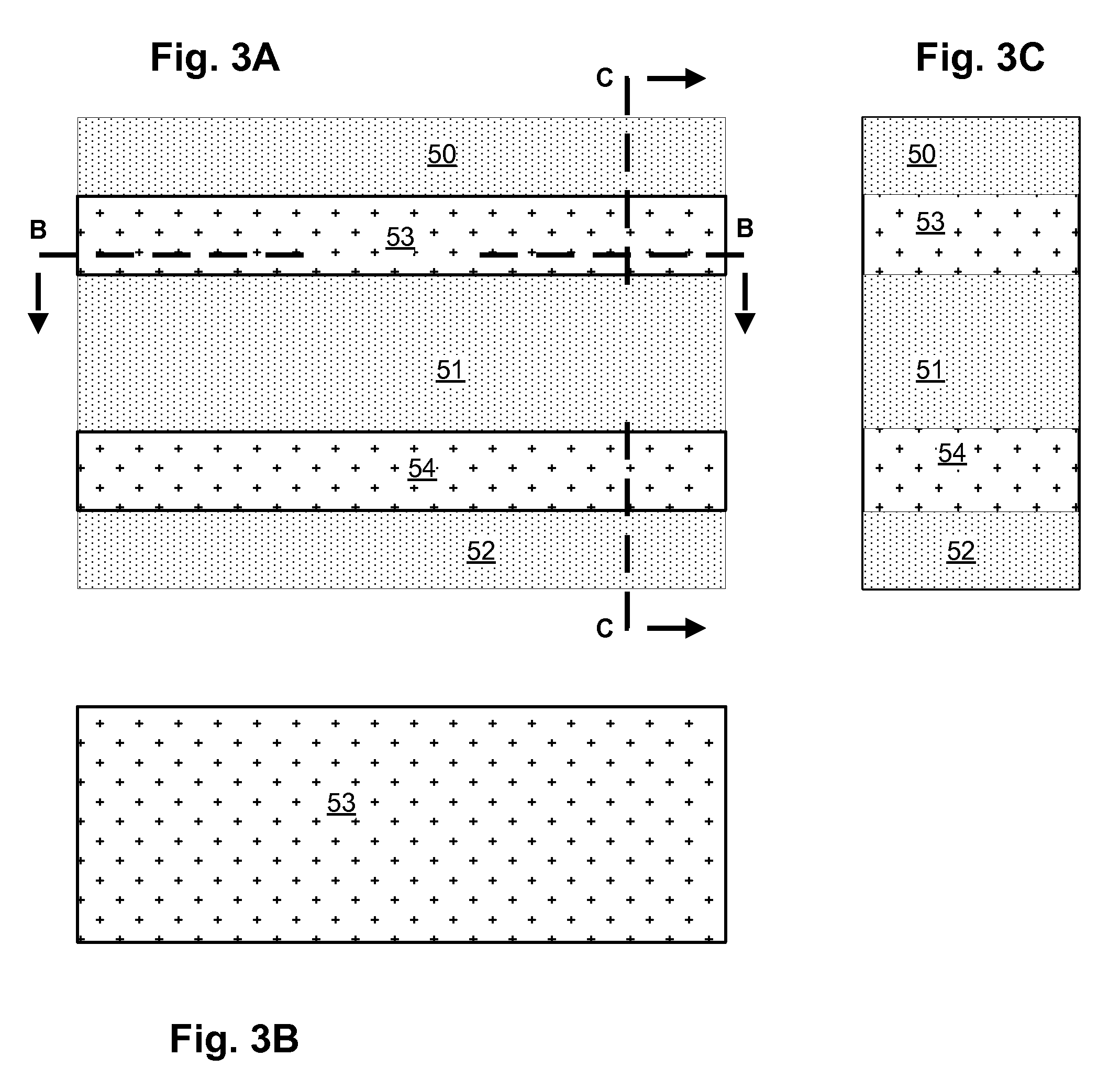

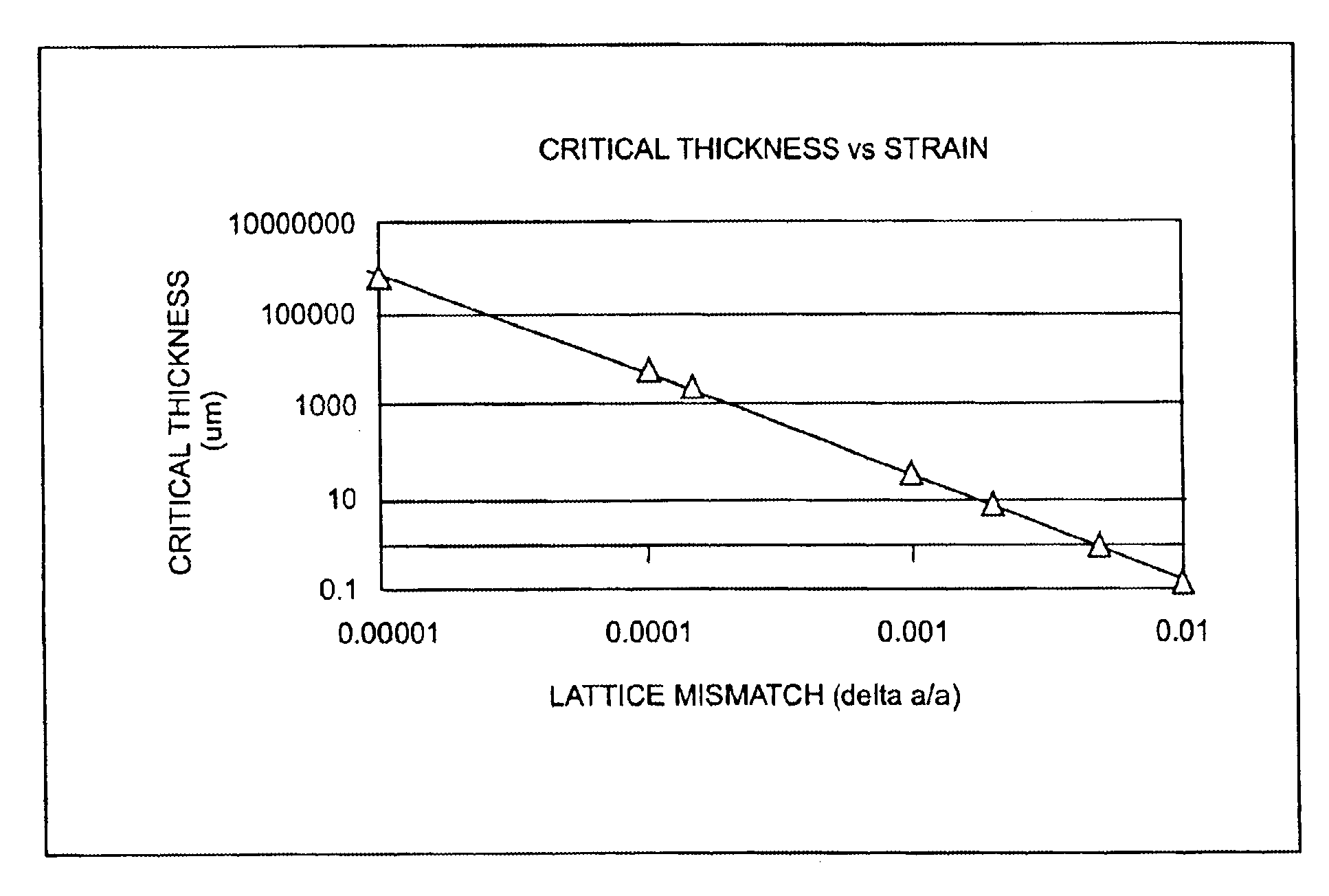

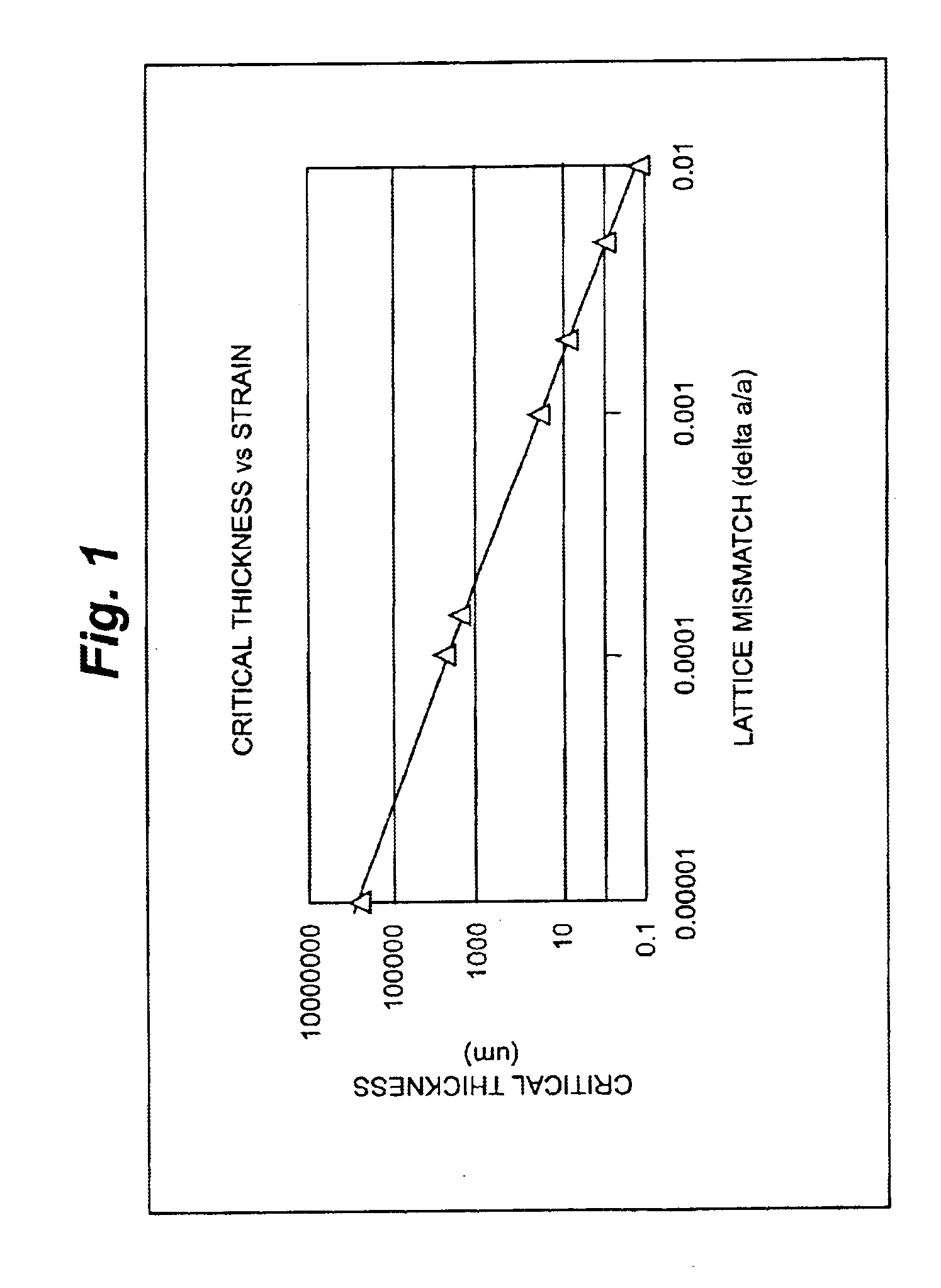

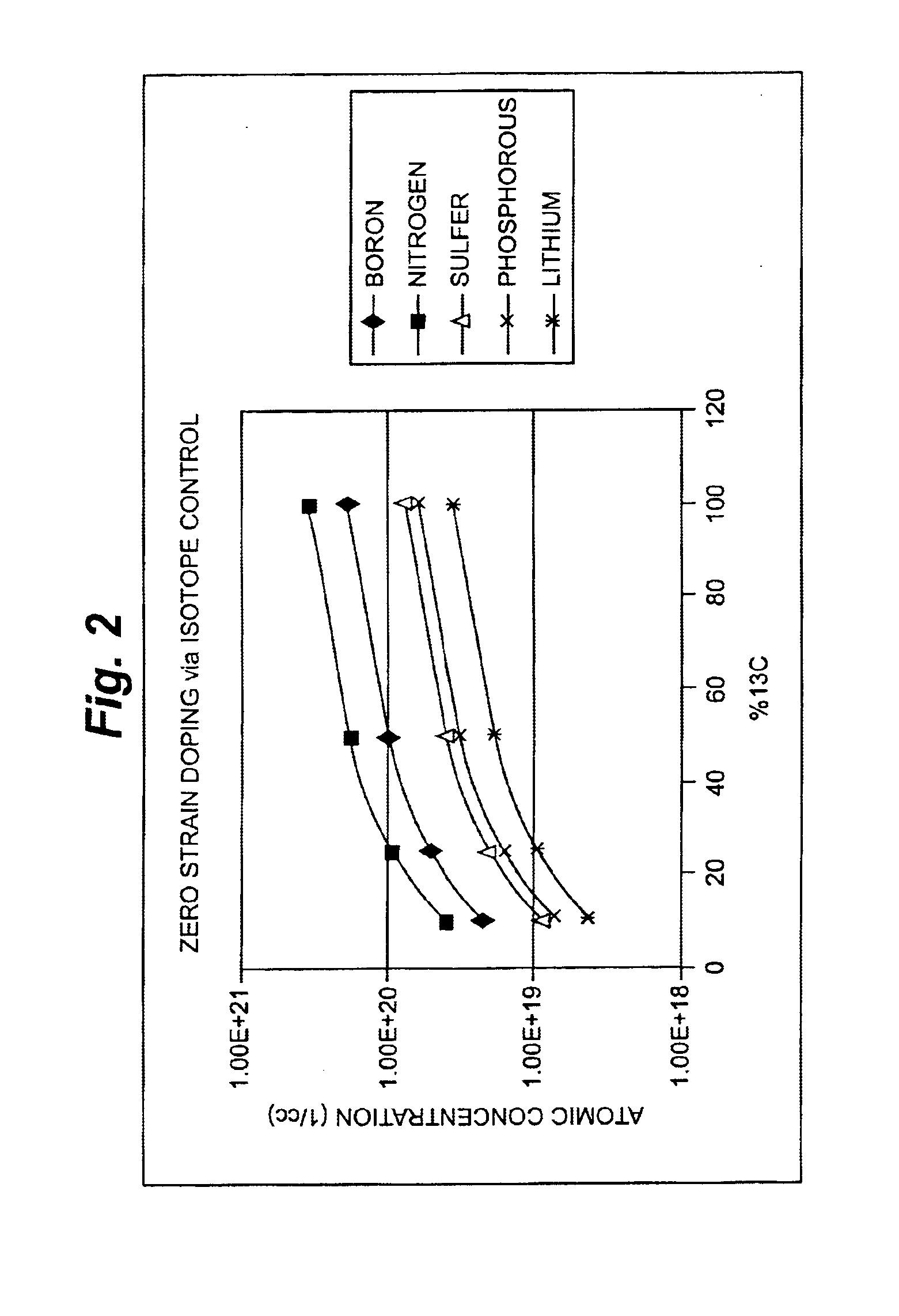

Tunable CVD diamond structures

InactiveUS6858080B2Improve propertiesPolycrystalline material growthUltra-high pressure processesLattice mismatchMonocrystalline silicon

Monocrystalline diamond, adapted for use as in applications such as semiconductor devices, optical waveguides, and industrial applications, in the form of a single crystalline diamond structure having one or more diamond layers, at least one of which is formed by a CVD process. The diamond layers are “lattice-matched” or “lattice-mismatched” to each other to provide a desired level of strain.

Owner:SCIO DIAMOND TECHNOLOGY CORPORATION

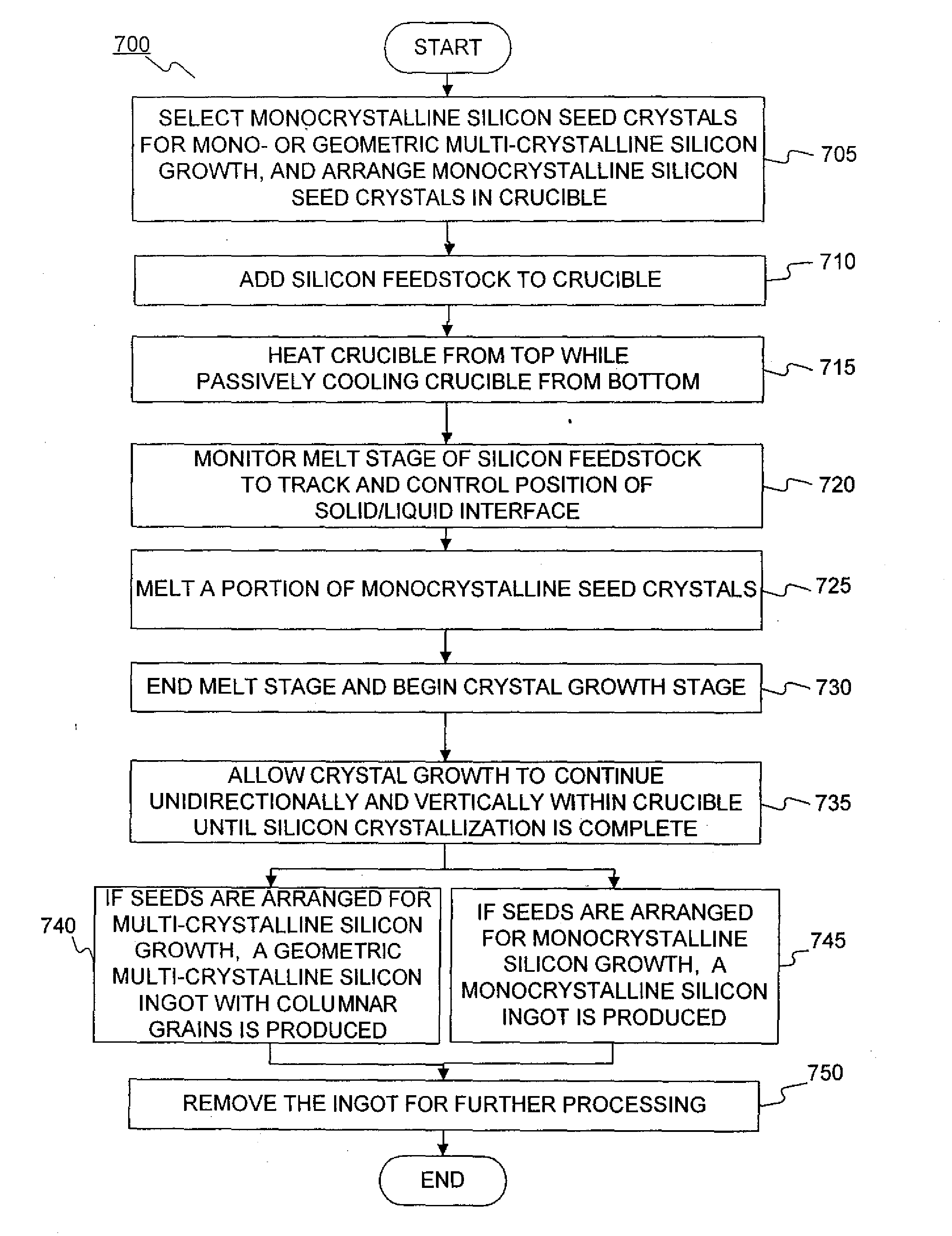

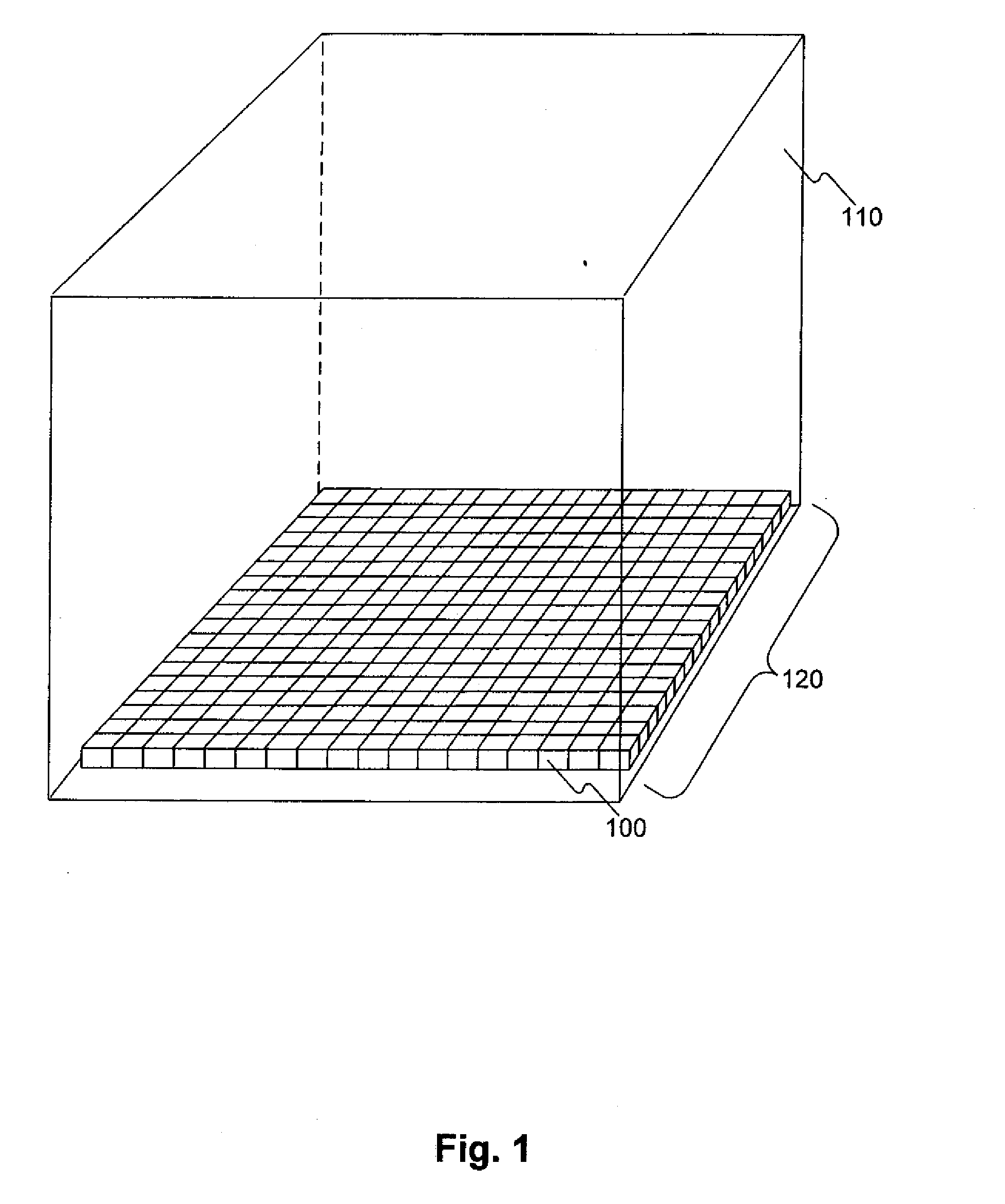

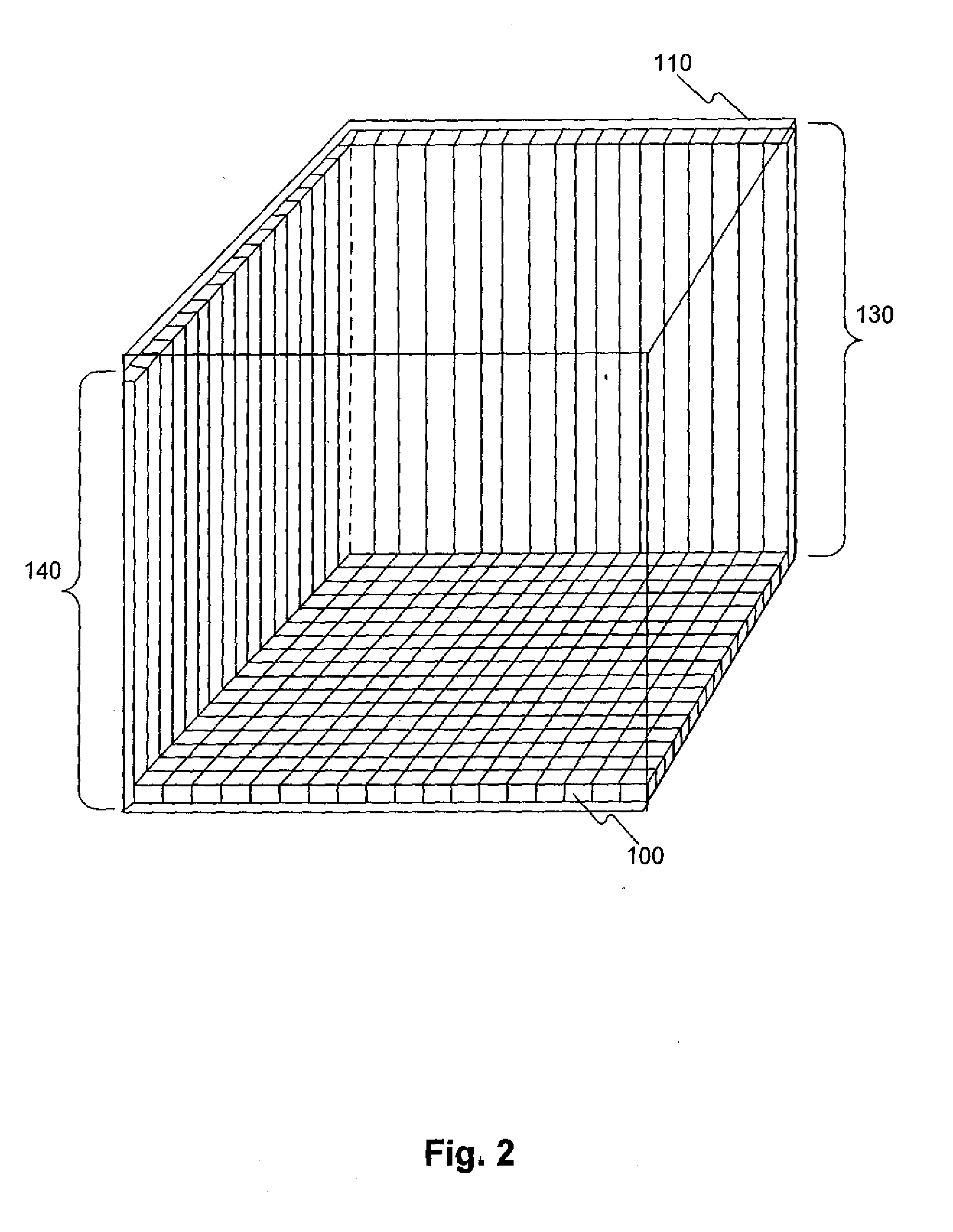

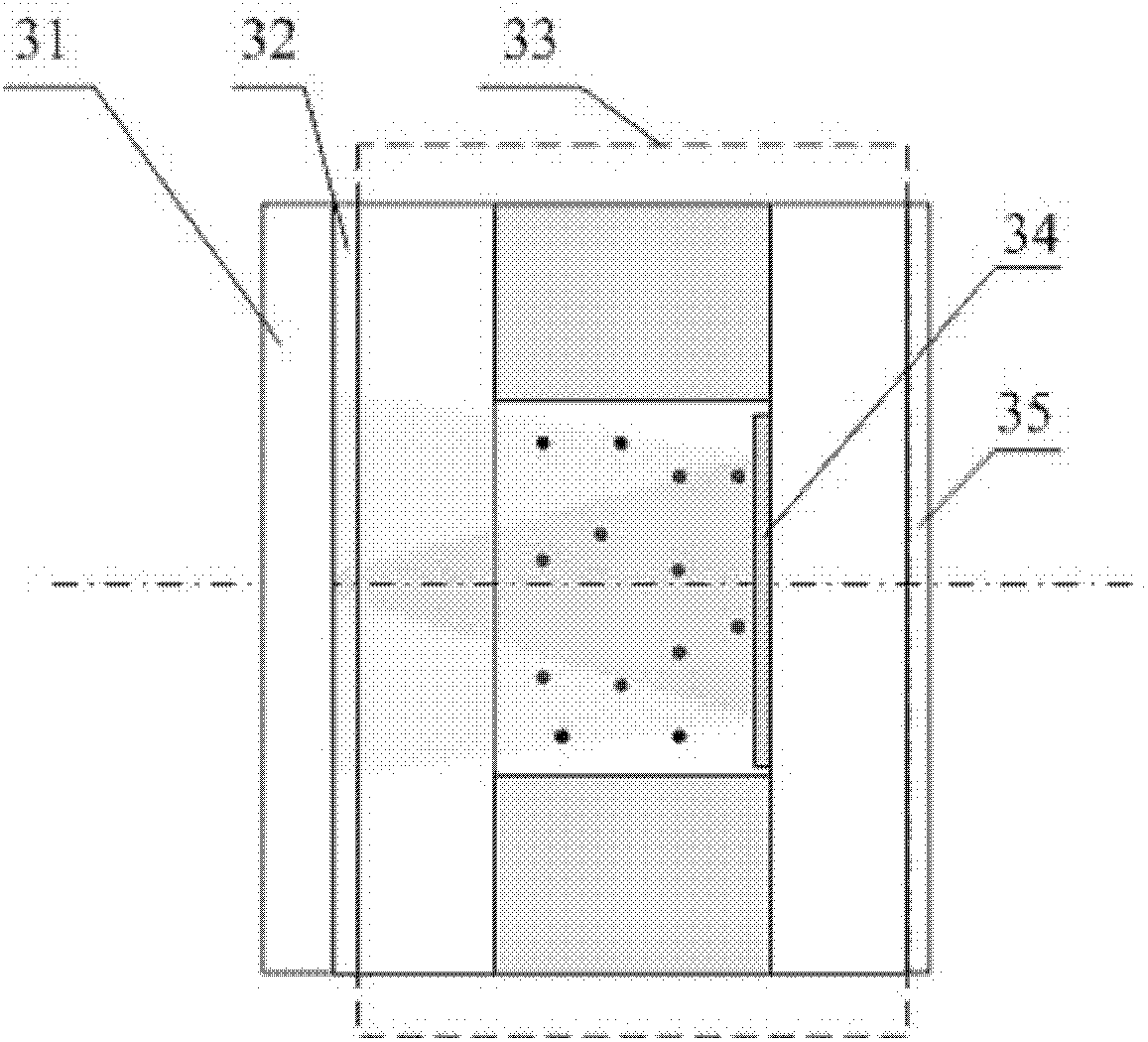

Methods and Apparatuses for Manufacturing Monocrystalline Cast Silicon and Monocrystalline Cast Silicon Bodies for Photovoltaics

InactiveUS20070169684A1Polycrystalline material growthFinal product manufactureMonocrystalline siliconSingle crystal

Methods and apparatuses are provided for casting silicon for photovoltaic cells and other applications. With such methods and apparatuses, a cast body of monocrystalline silicon may be formed that is free of, or substantially free of, radially-distributed impurities and defects and having at least two dimensions that are each at least about 35 cm is provided.

Owner:THE UNITED STATES AS REPRESENTED BY THE DEPARTMENT OF ENERGY +1

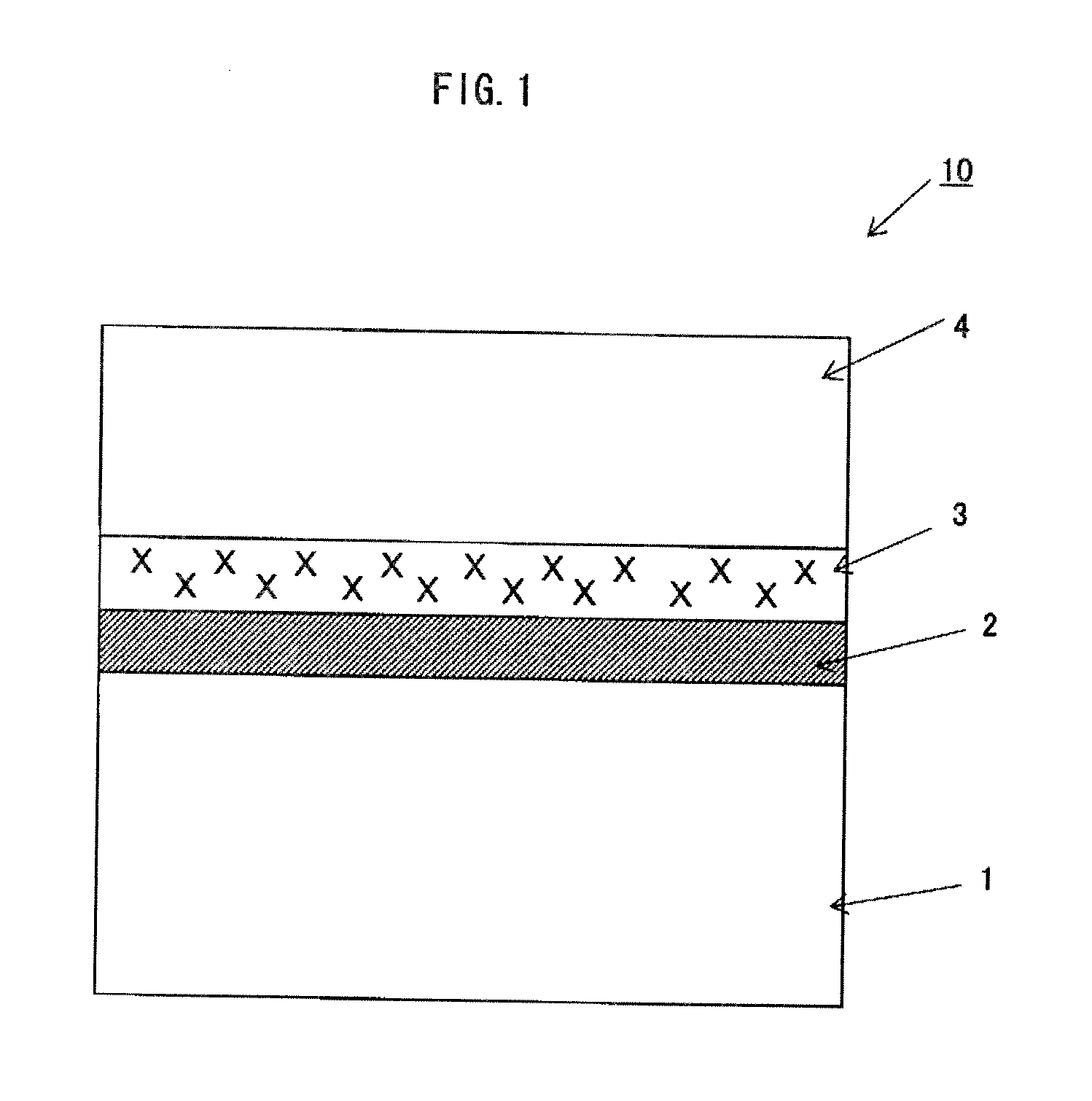

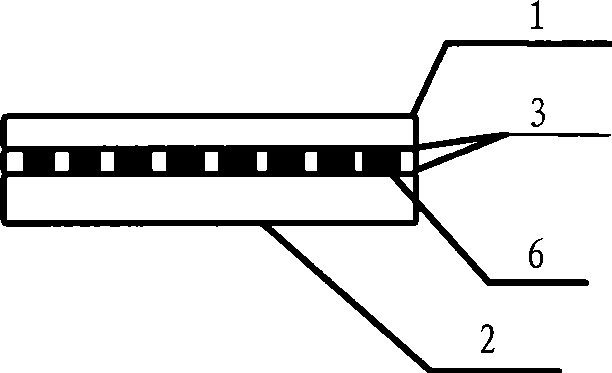

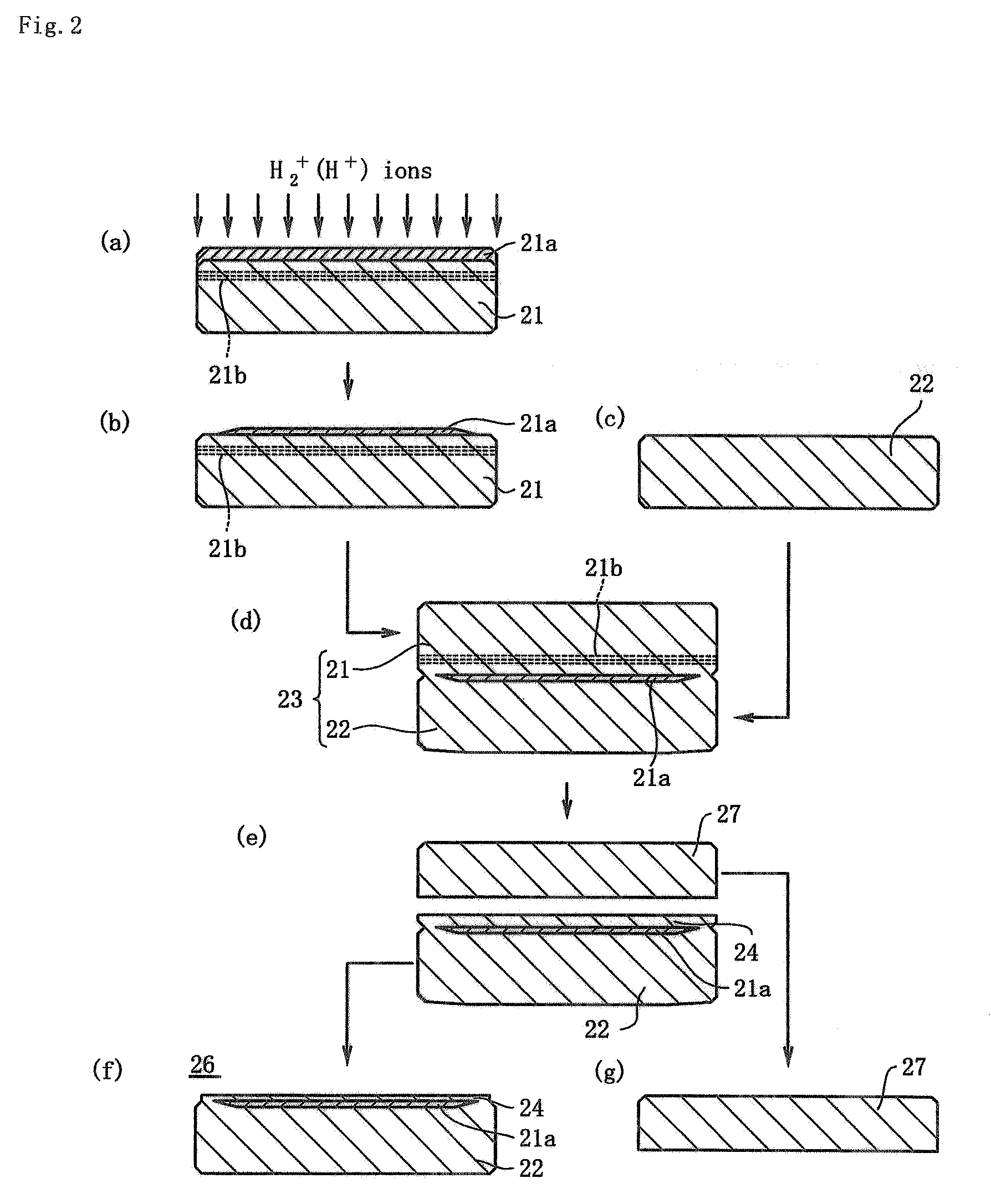

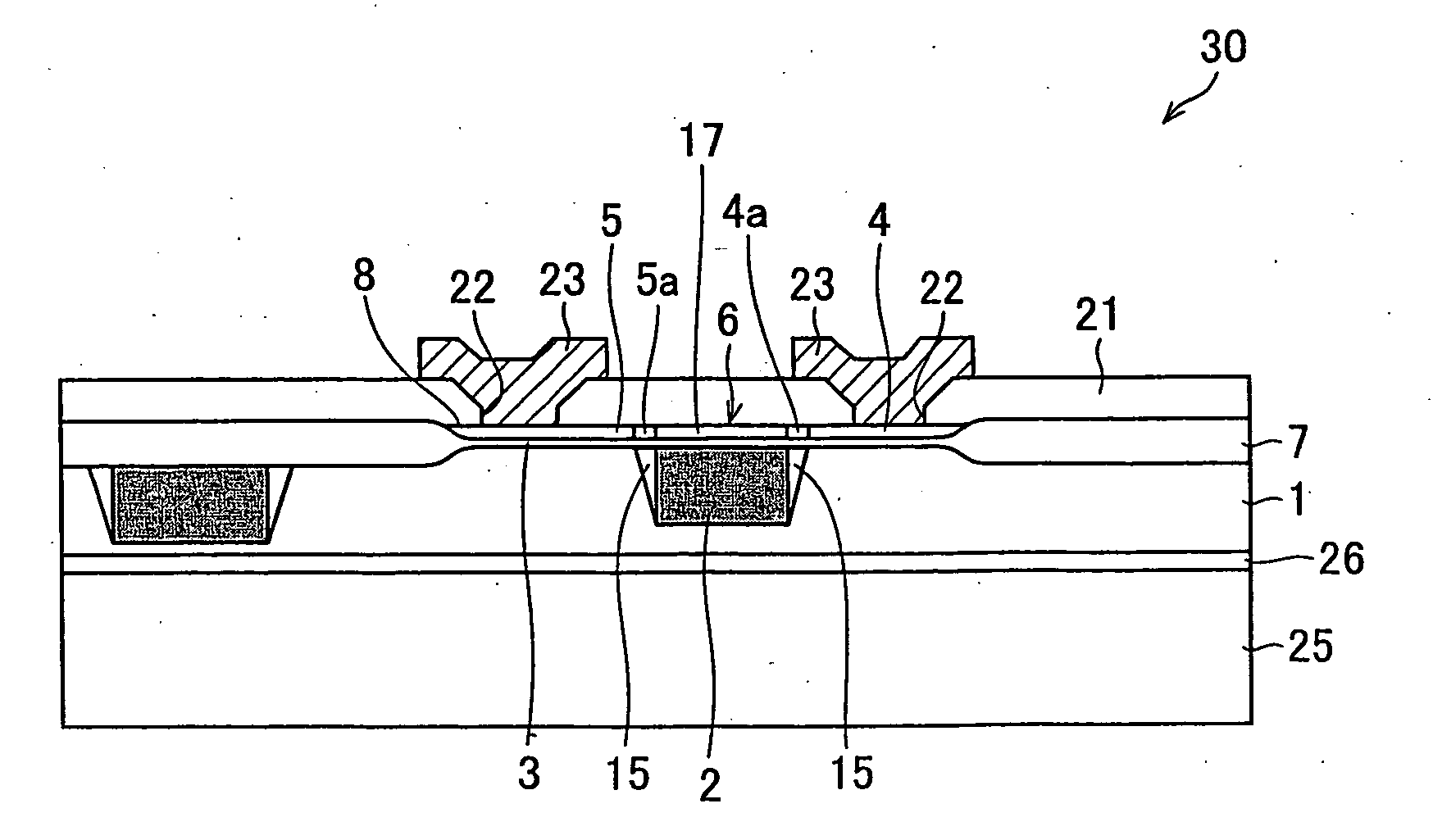

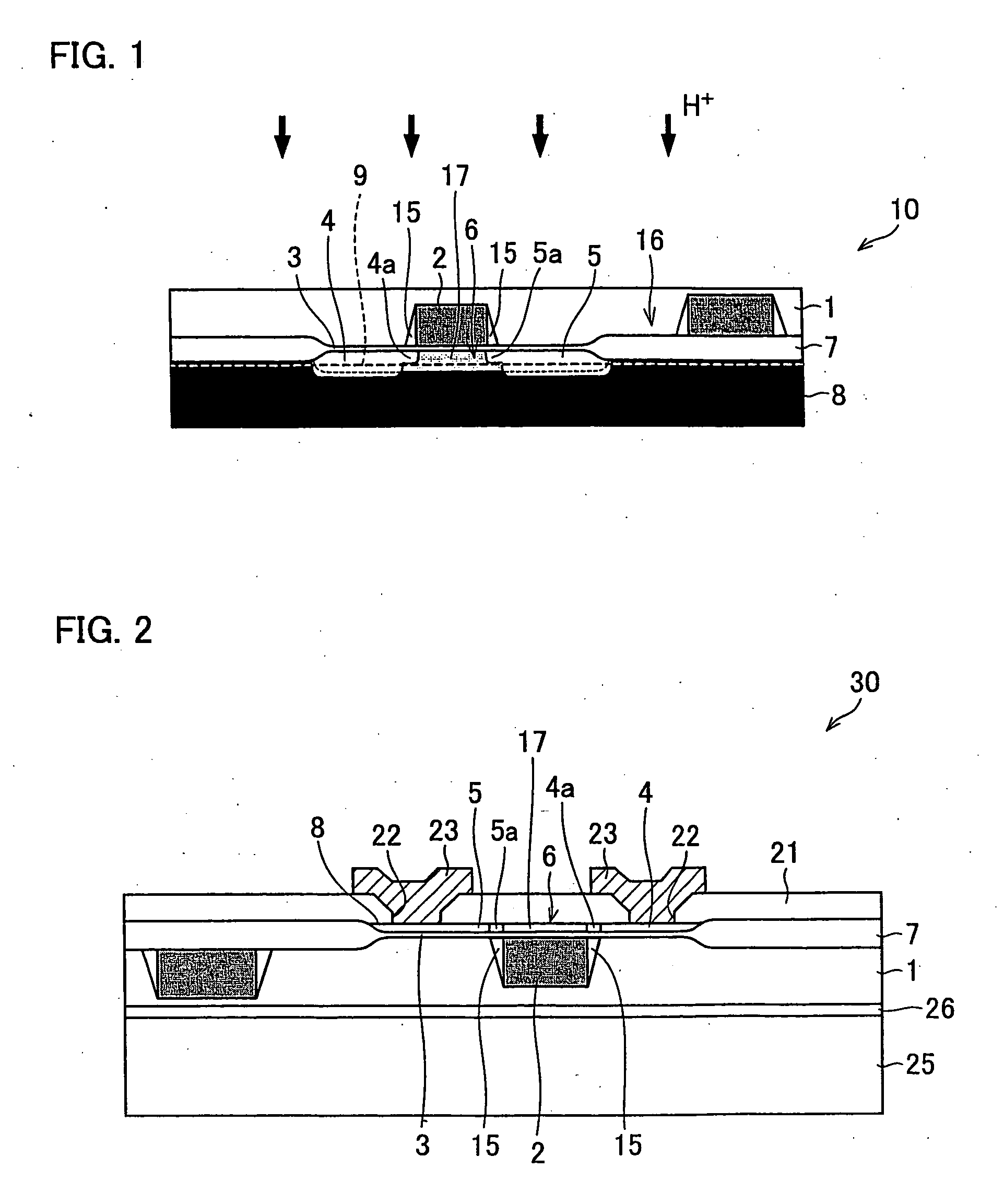

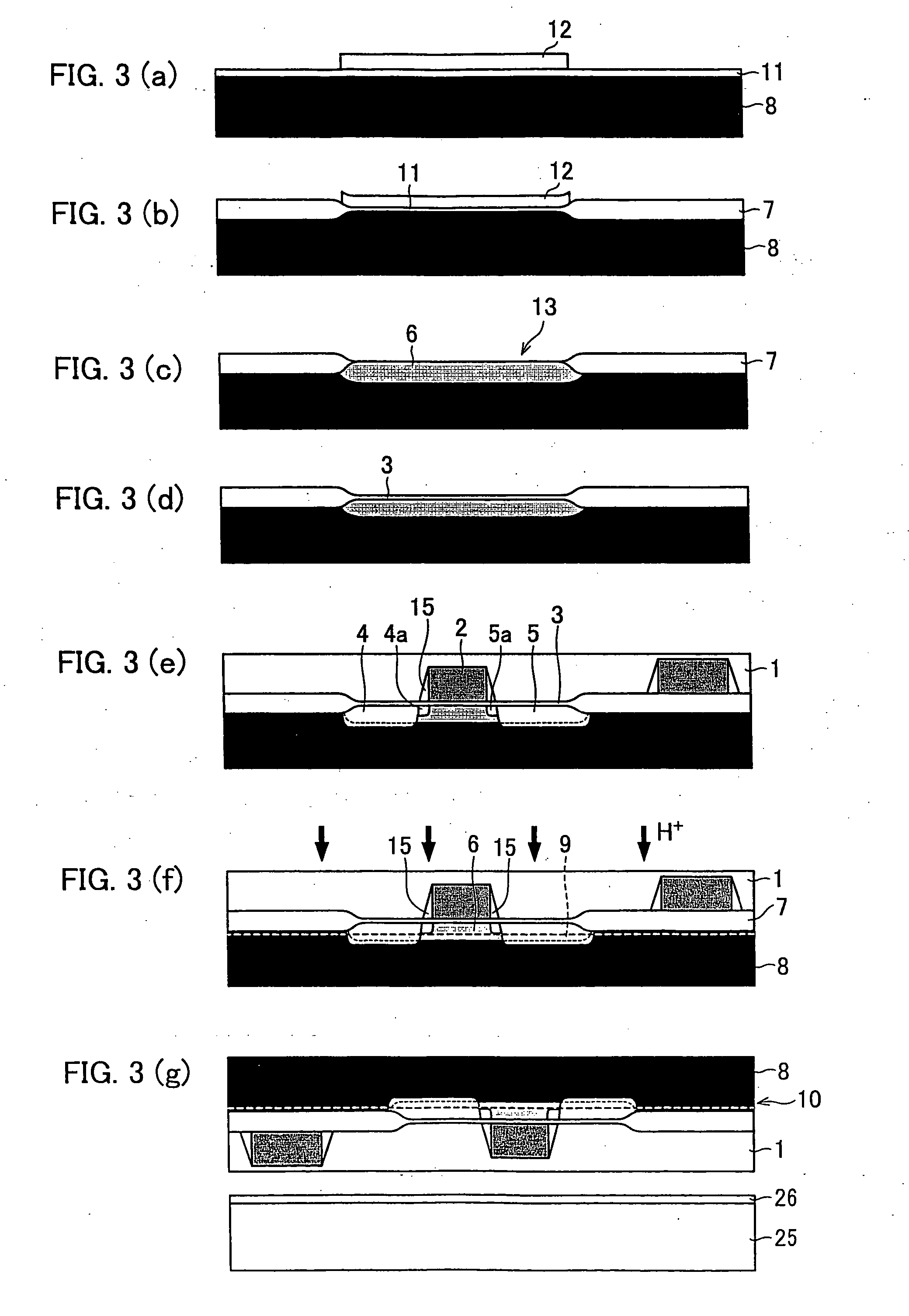

Soi wafer, method for producing same, and method for manufacturing semiconductor device

ActiveUS20110298083A1Promote precipitationImprove inhalation capacitySolid-state devicesSemiconductor/solid-state device manufacturingNitrogenOxygen

An SOI wafer including: a supporting substrate 1; a BOX layer 2 provided above the supporting substrate 1, the BOX layer 2 being formed by a thermal oxidization; a gettering layer 3 provided immediately on the BOX layer 2 and mainly composed of a silicon which contains one or more of oxygen, carbon and nitrogen and contains at least oxygen; and an S layer 4 in which semiconductor devices are to be formed, the S layer 4 being mainly composed of a monocrystalline silicon.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

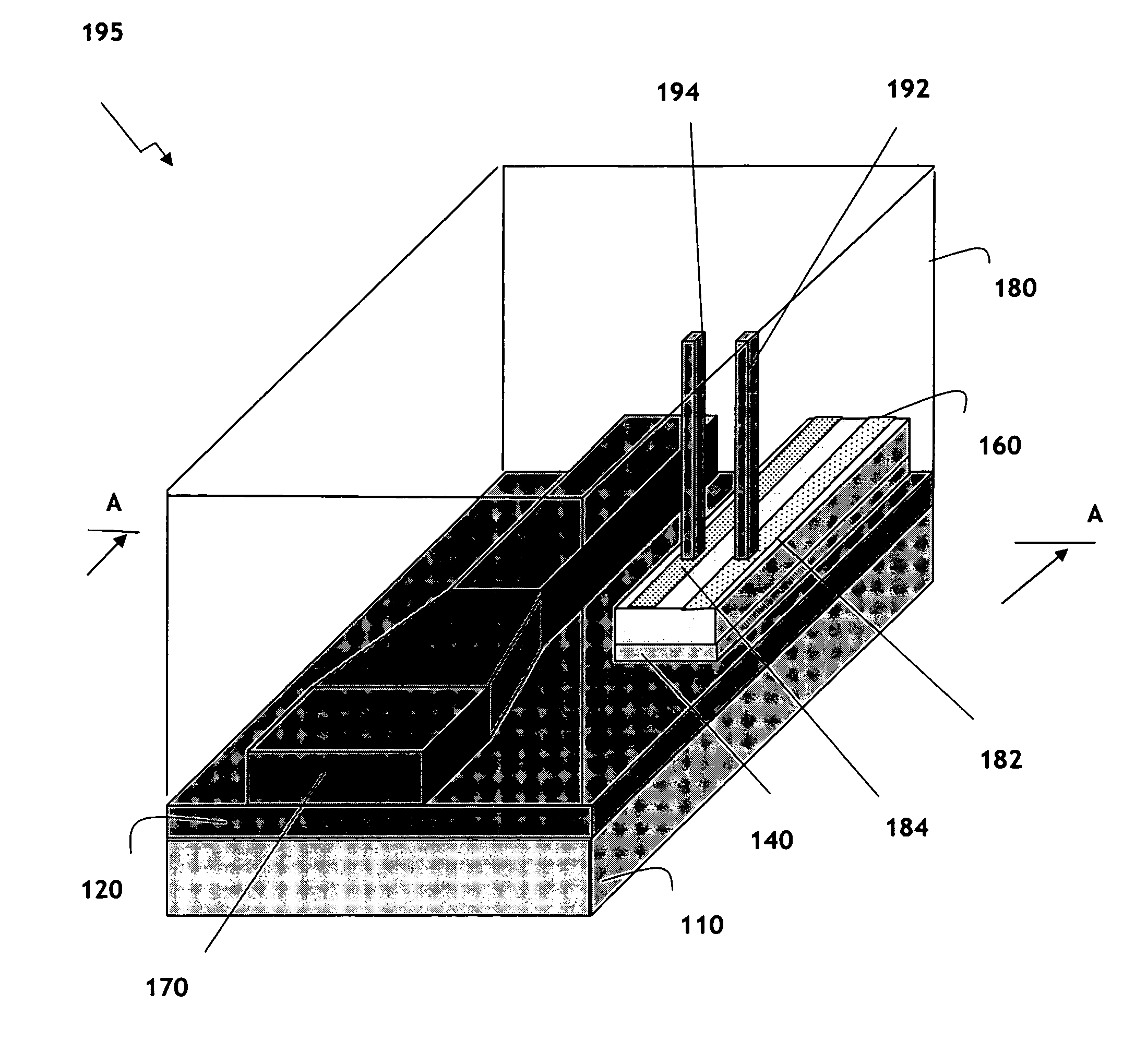

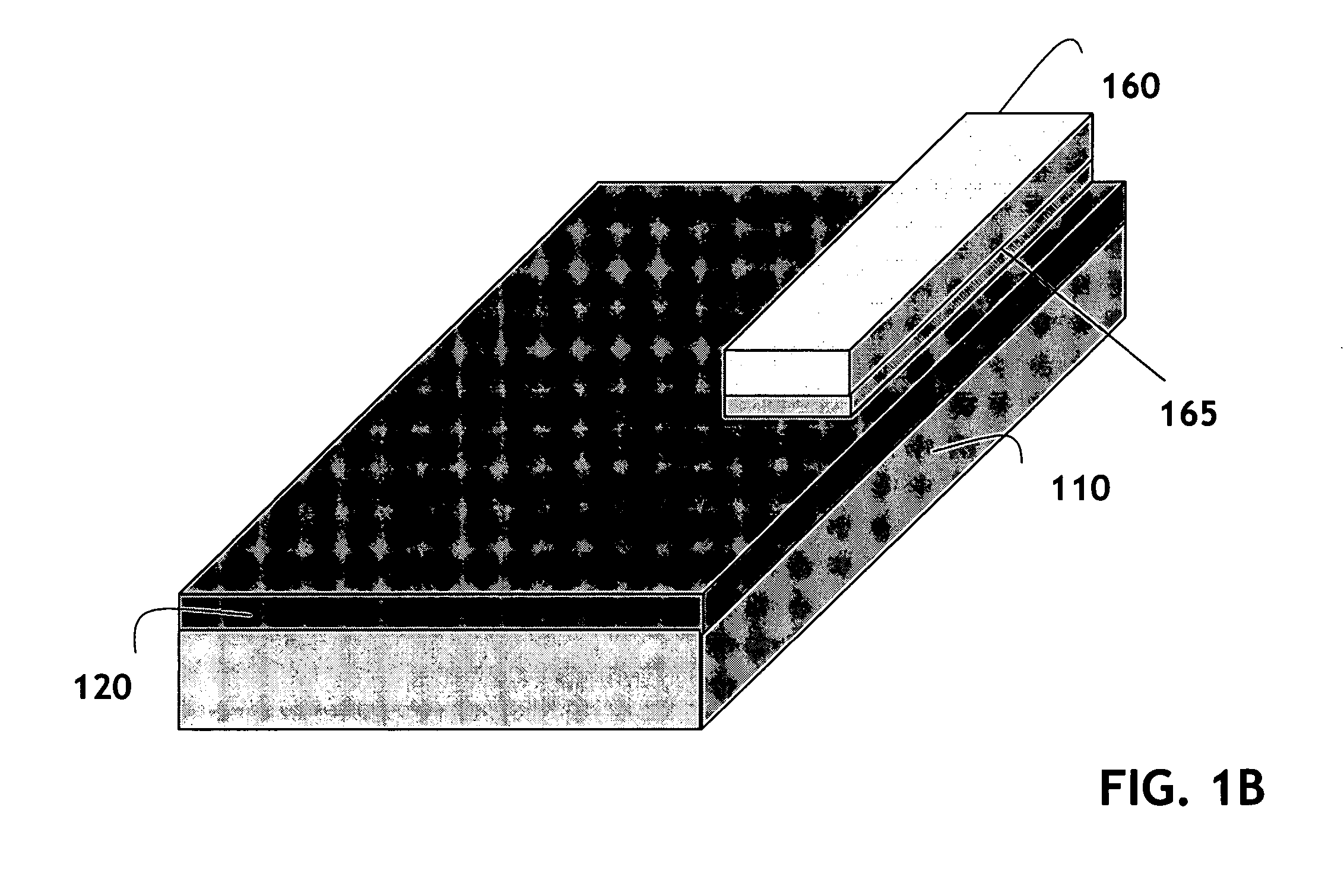

Integrated waveguide photodetector apparatus with matching propagation constants and related coupling methods

ActiveUS20070104410A1Increase data rateCoupling light guidesOptical waveguide light guideCMOSPhotovoltaic detectors

High-speed optoetectronic devices having a waveguide densely integrated with and efficiently coupled to a photodetector are fabricated utilizing methods generally compatible with CMOS processing techniques. In various implementations, the waveguide consists essentially of single-crystal silicon and the photodetector contains, or consists essentially of, epitaxially grown germanium or a silicon-germanium alloy having a germanium concentration exceeding about 90%.

Owner:MASSACHUSETTS INST OF TECH

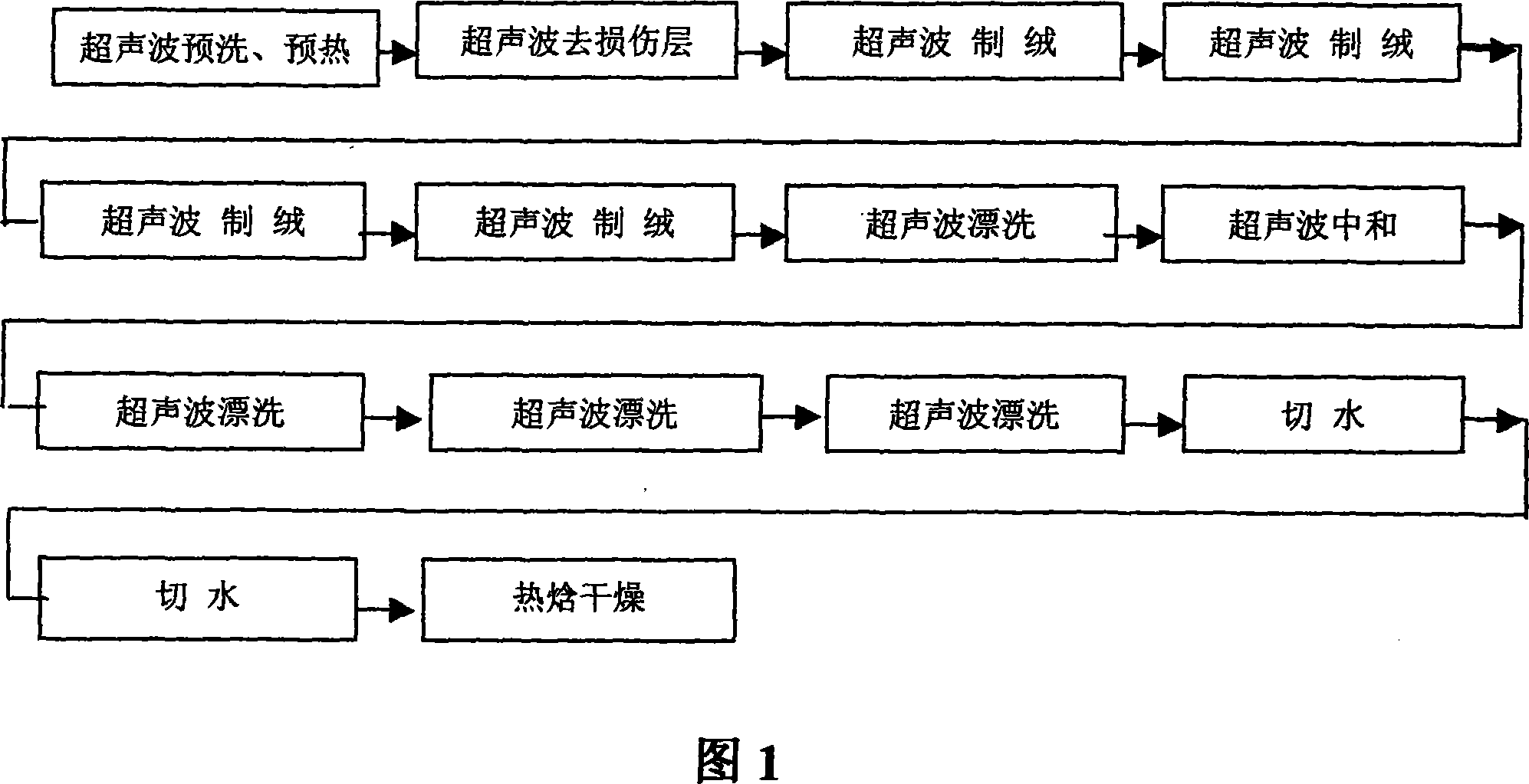

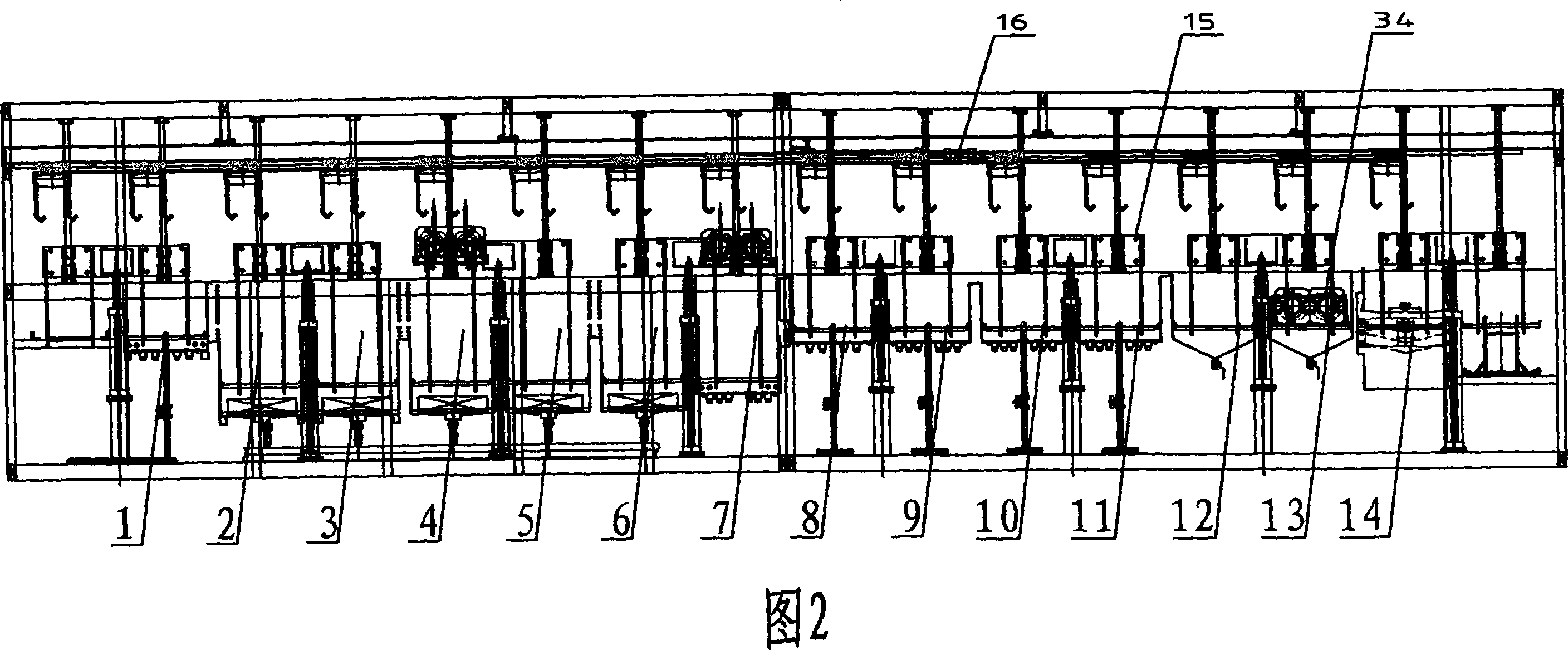

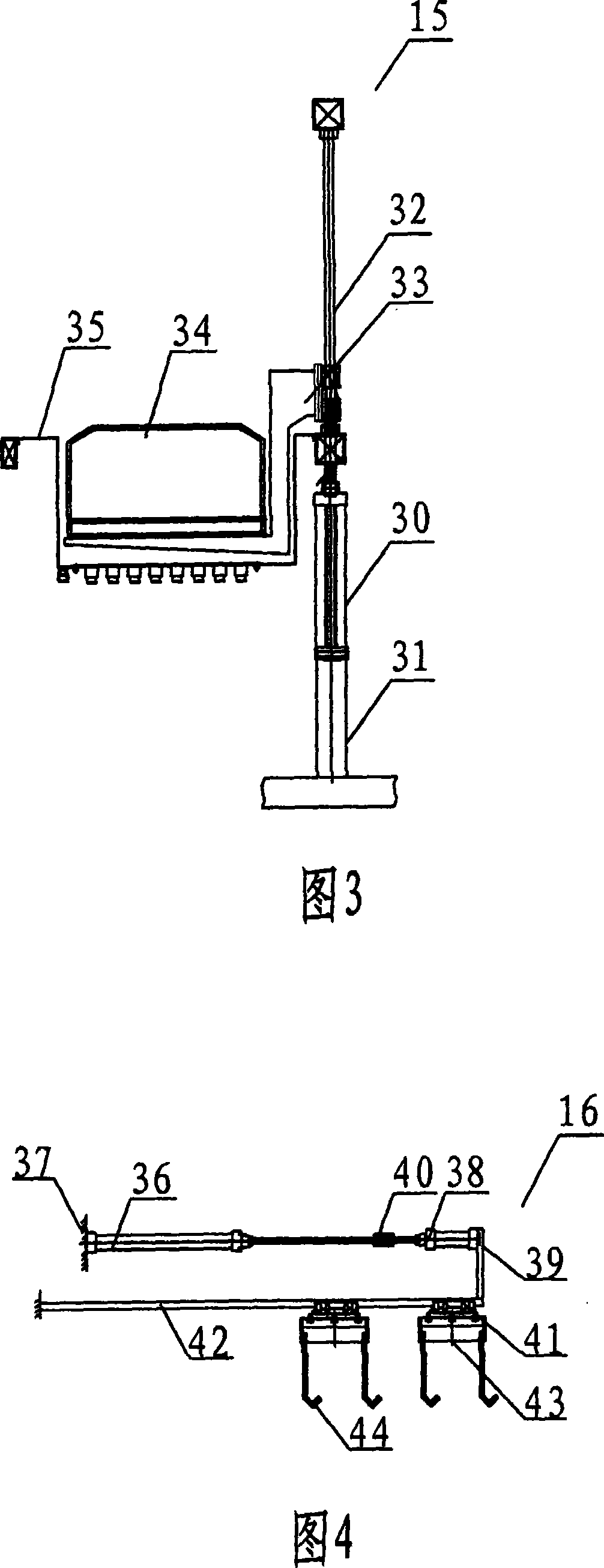

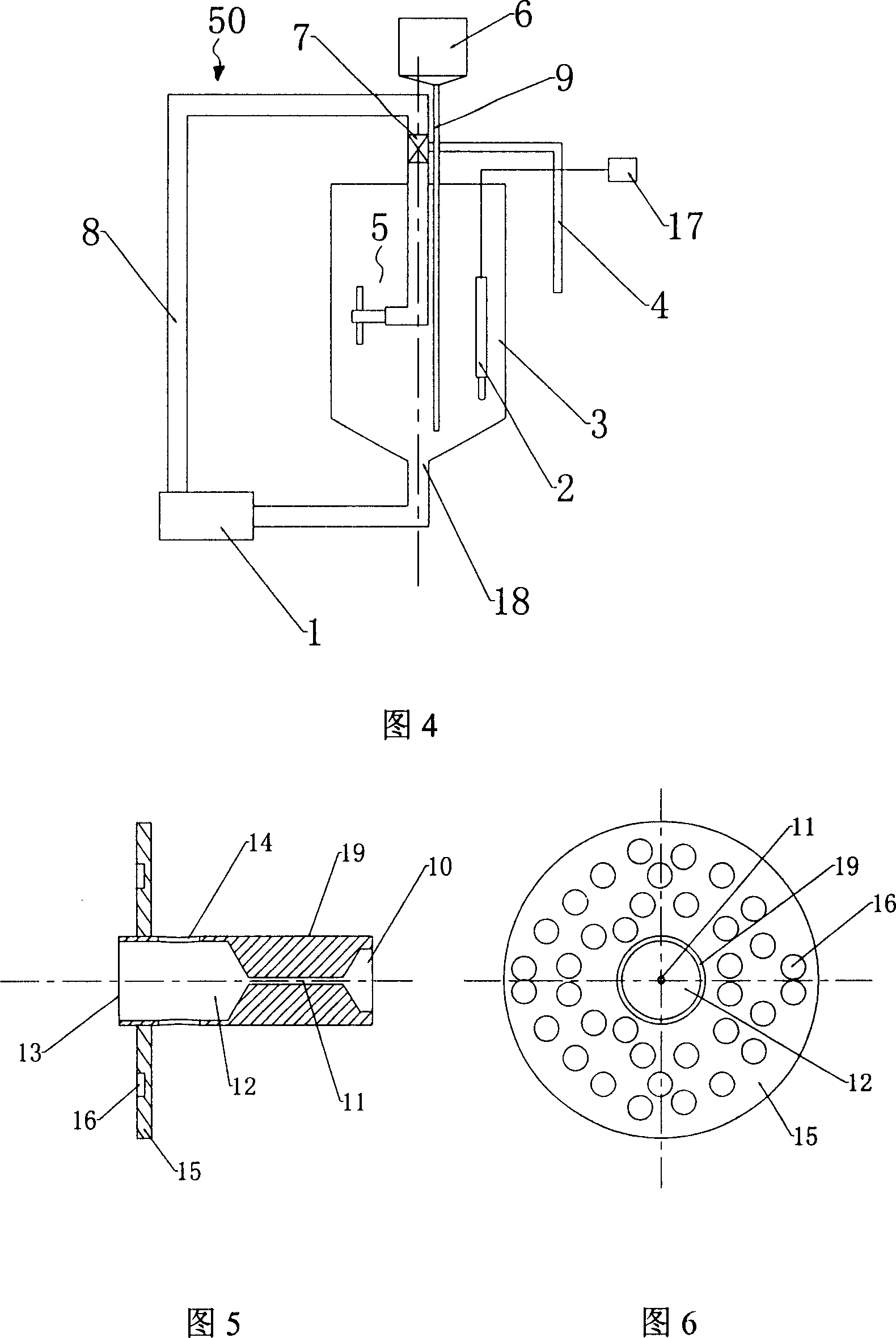

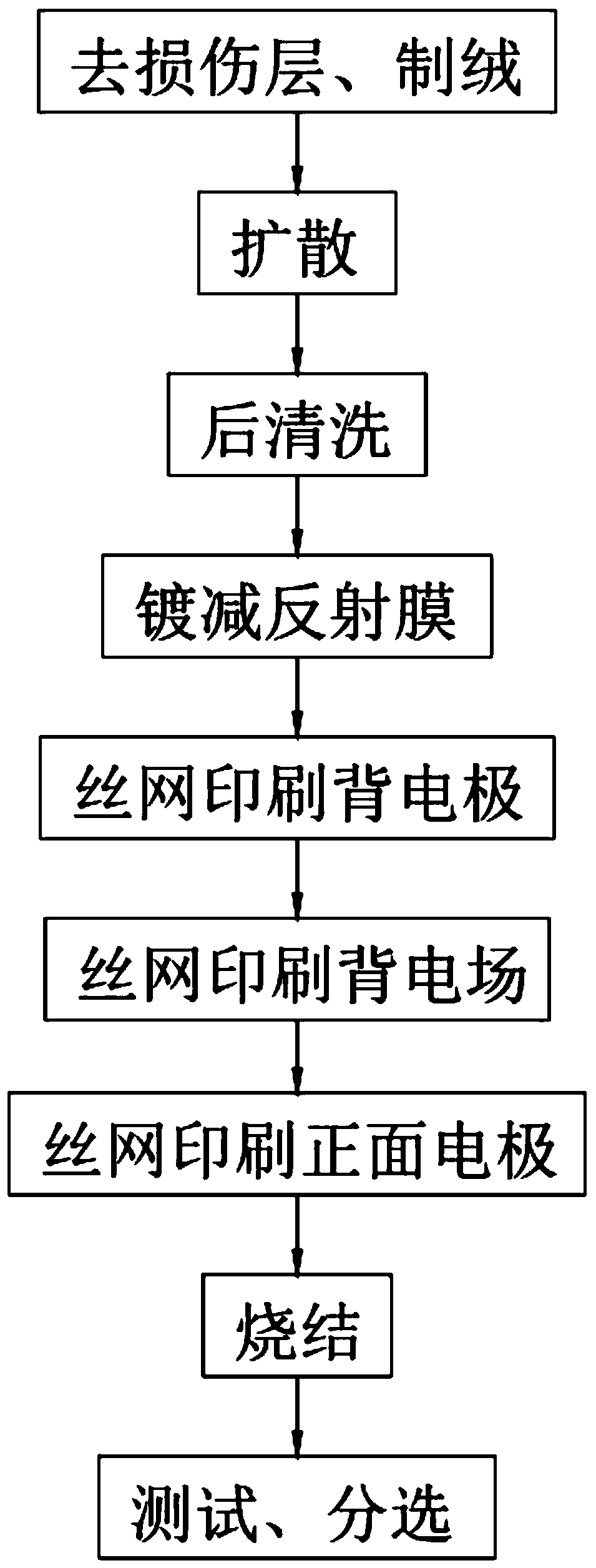

Chemical etching, cleaning and drying method of single-crystal silicon solar battery and integrated processing machine

InactiveCN101087007AImprove reflective effectAvoid secondary pollutionFinal product manufactureSemiconductor devicesEtchingWater source

Monocrystalline silicon solaode chemical etching, washing, drying method and integral processor belong to technique field of chemical etching technique and washing. It characterized in that it not only includes water, acid, alkali, but also ultrasonic participates in etching and washing course: it includes following steps: (1) ultrasonic washes and heats in advance, (2) ultrasonic removes damnification layer, (3) ultrasonic makes herbs into wool, (4) ultrasonic rinses, (5) washing with acid to counteract, (6) ultrasonic rinses, (7) cutting water, (8) hot enthalpy to dry. Positive effects of the invention are: adopting ultrasonic to etch and wash, liquid of making wool can be acted with silicon piece, similar coarseness degree can be generated on surface, perfect pyramid pattern can be obtained; it also eliminates kalium, natrium ion from alkalescent solution, and extends service life of silicon piece; pollution can be decreased, energy consumption and water source can be saved greatly, it is a practical invention.

Owner:SHANGHAI MINGXING KAICHENG ULTRASONIC TECH +2

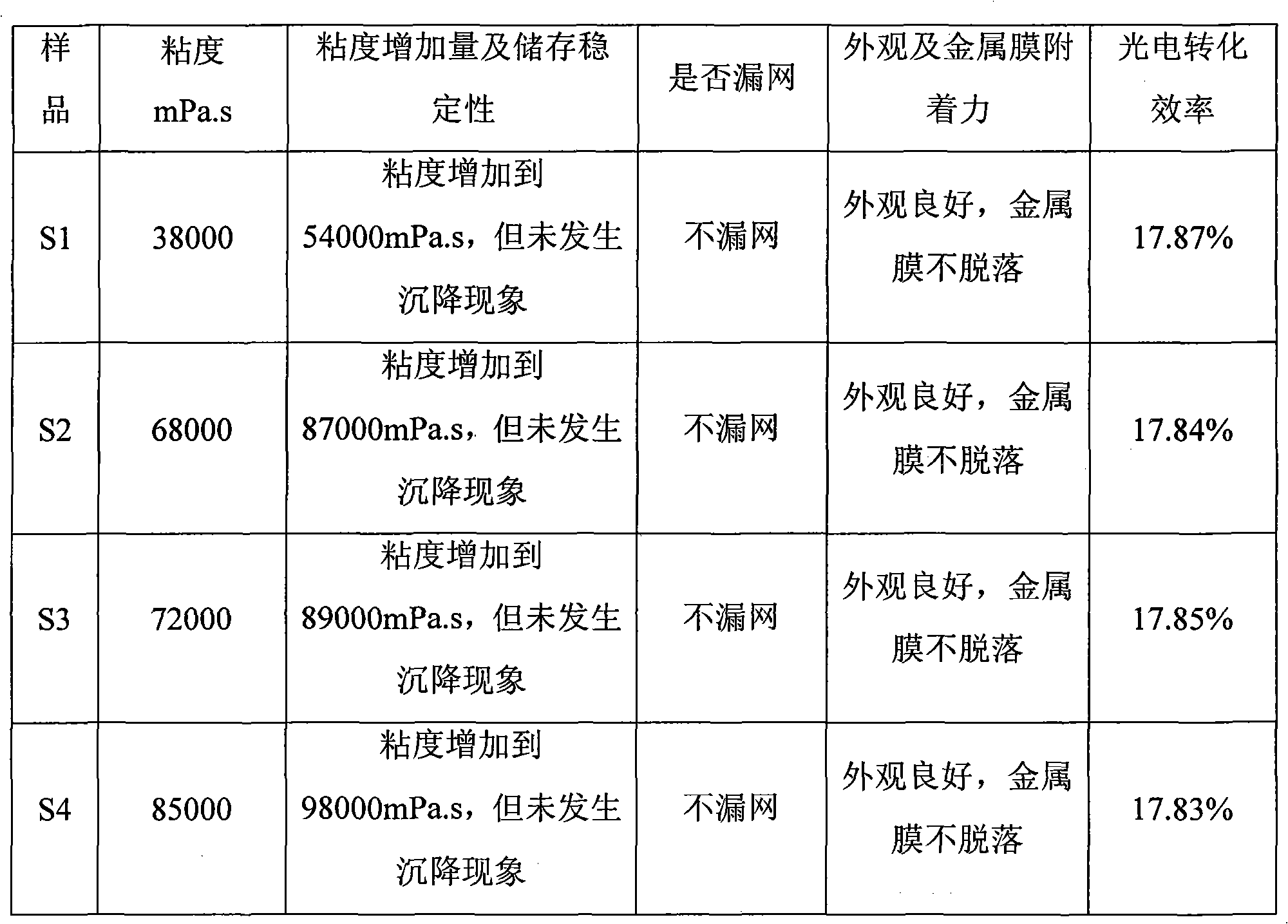

Conductive paste for solar cell and preparation method thereof

InactiveCN102034877AImprove performanceNo sedimentation and caking phenomenonConductive materialInksSilicon matrixSilicon solar cell

The invention provides a conductive paste for a solar cell, comprising the following components based on the total weight: 60-85 percent by weight of conductive metal powder, 0.5-10.0 percent by weight of inorganic binder, 10.0-30.0 percent by weight of water-borne binder and 0.05-5.0 percent by weight of additive, wherein the water-borne binder is a solution formed by dissolving a water-borne polymer into the water. The conductive paste for the solar cell, provided by the invention, has no organic solvent and pollution, is environment-friendly and has low cost of materials; the mesh leakage can be avoided when the conductive paste is stood in a screen mesh; the phenomena of settling and aggregation can be avoided after the conductive paste is stored for a long time; after being subjected to the silk-screen sintering, the conductive paste has firm adhesive force to a silicon matrix and excellent electrical performance; and the average photoelectric conversion efficiency of the produced monocrystal silicon solar cell is more than 17.80 percent.

Owner:BYD CO LTD

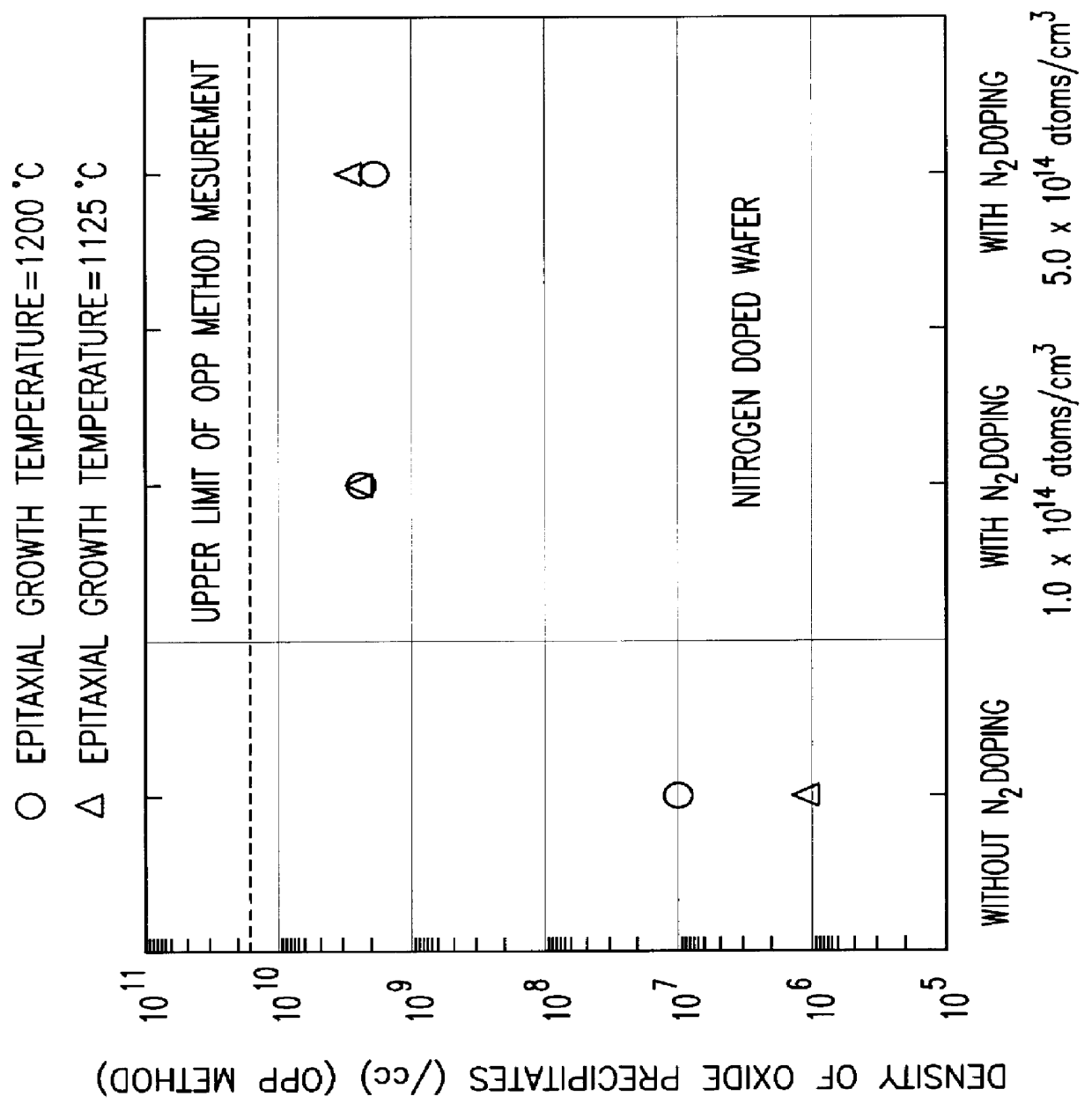

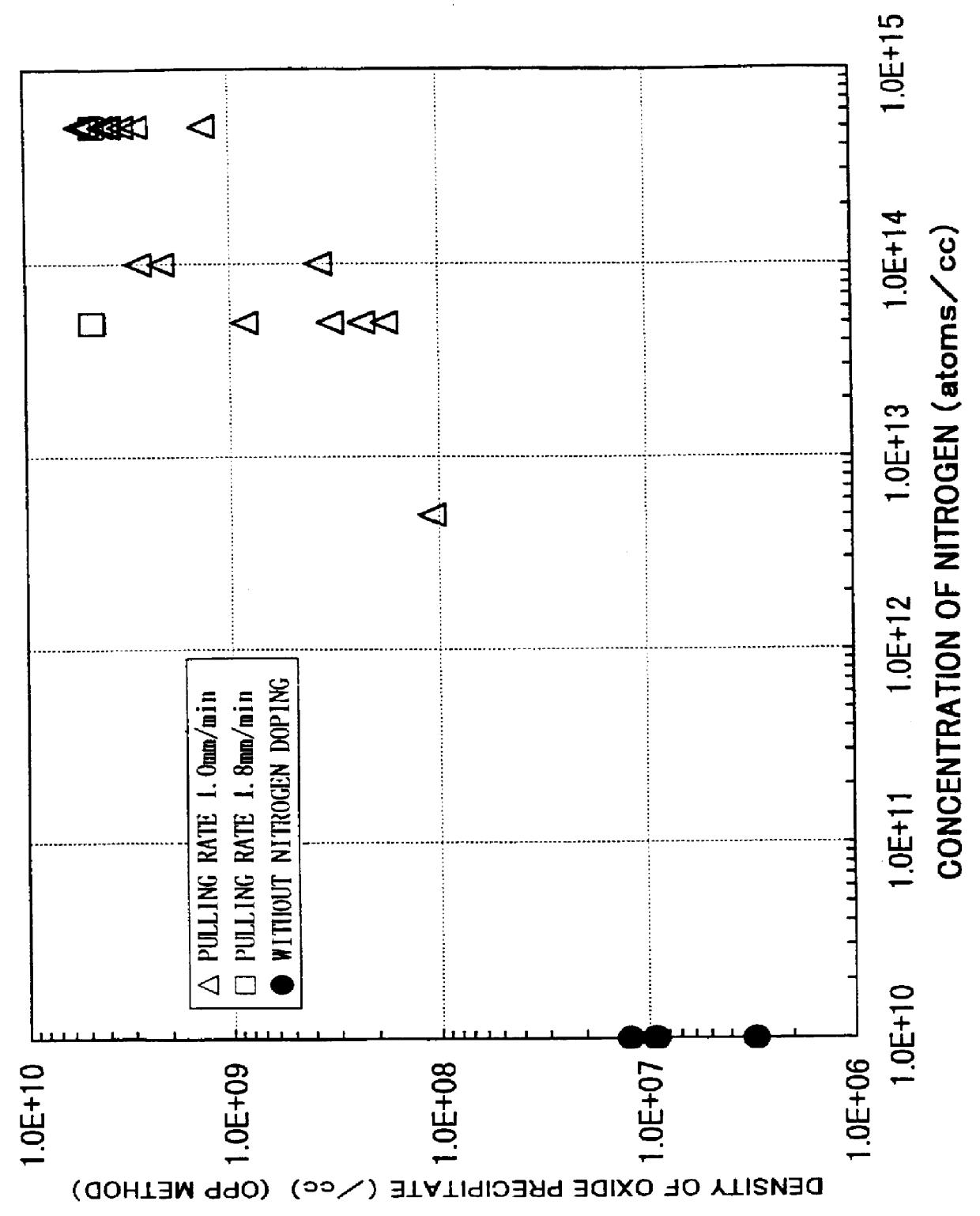

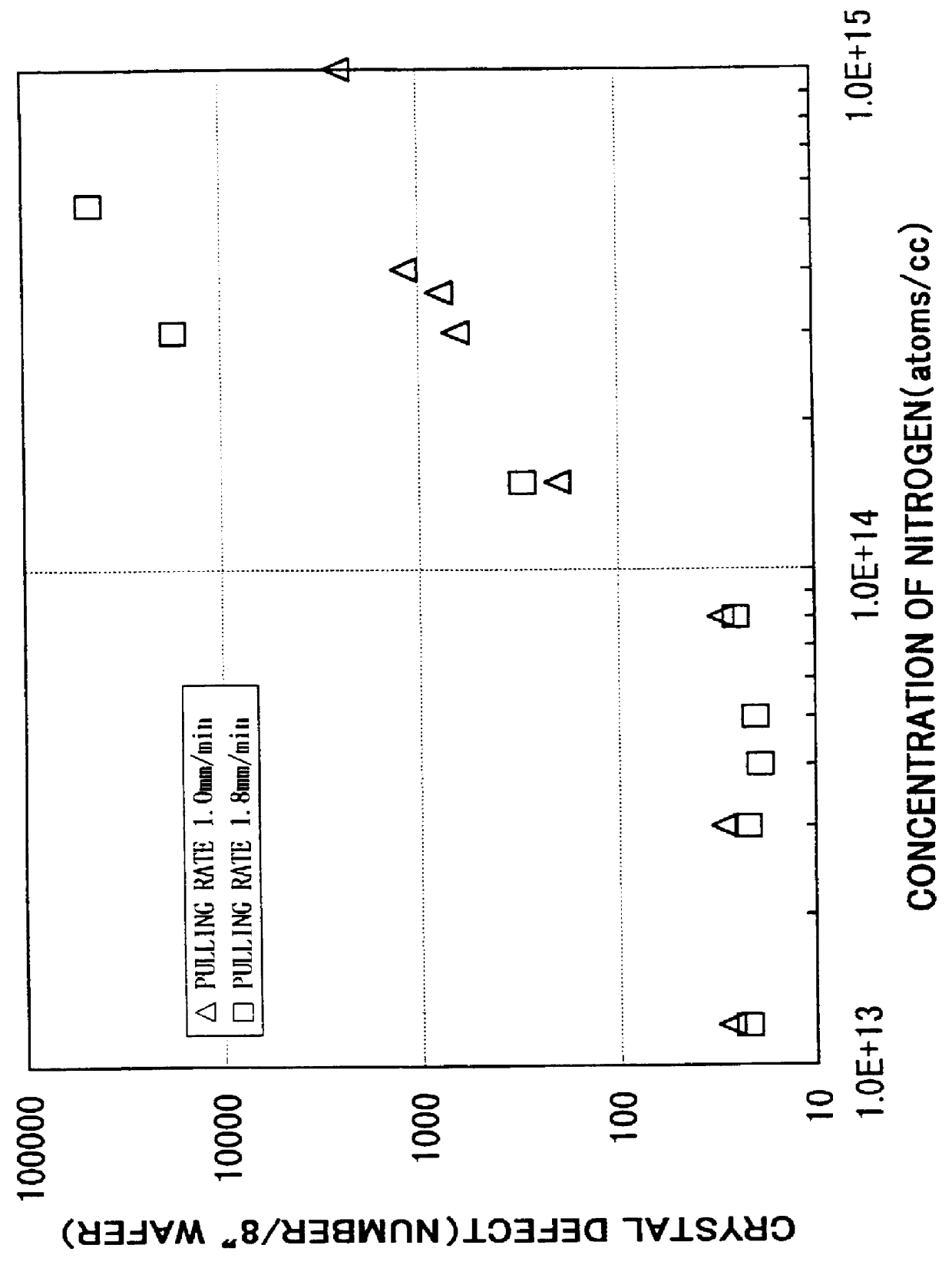

Method for producing an epitaxial silicon single crystal wafer and the epitaxial silicon single crystal wafer

InactiveUS6162708AReduce concentrationEasy to producePolycrystalline material growthSemiconductor/solid-state device manufacturingSingle crystalCrystallinity

There is disclosed a method for producing an epitaxial silicon single crystal wafer comprising the steps of growing a silicon single crystal ingot wherein nitrogen is doped by Czochralski method, slicing the silicon single crystal ingot to provide a silicon single crystal wafer, and forming an epitaxial layer in the surface layer portion of the silicon single crystal wafer. There can be manufactured easily and in high productivity an epitaxial silicon monocrystal wafer which has high gettering capability when a substrate having a low boron concentration is used, a low concentration of heavy metal impurity, and an excellent crystallinity.

Owner:SHIN-ETSU HANDOTAI CO LTD

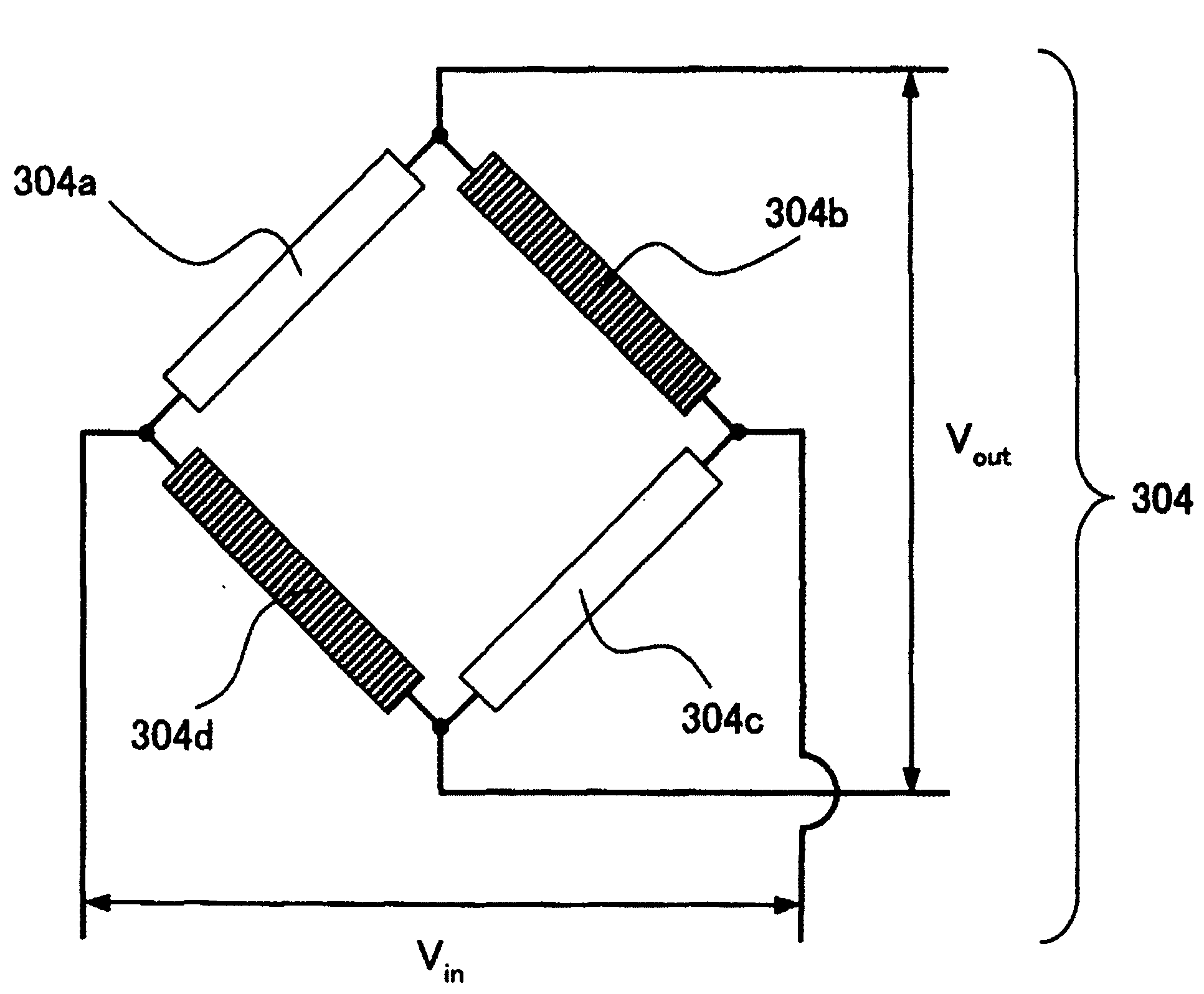

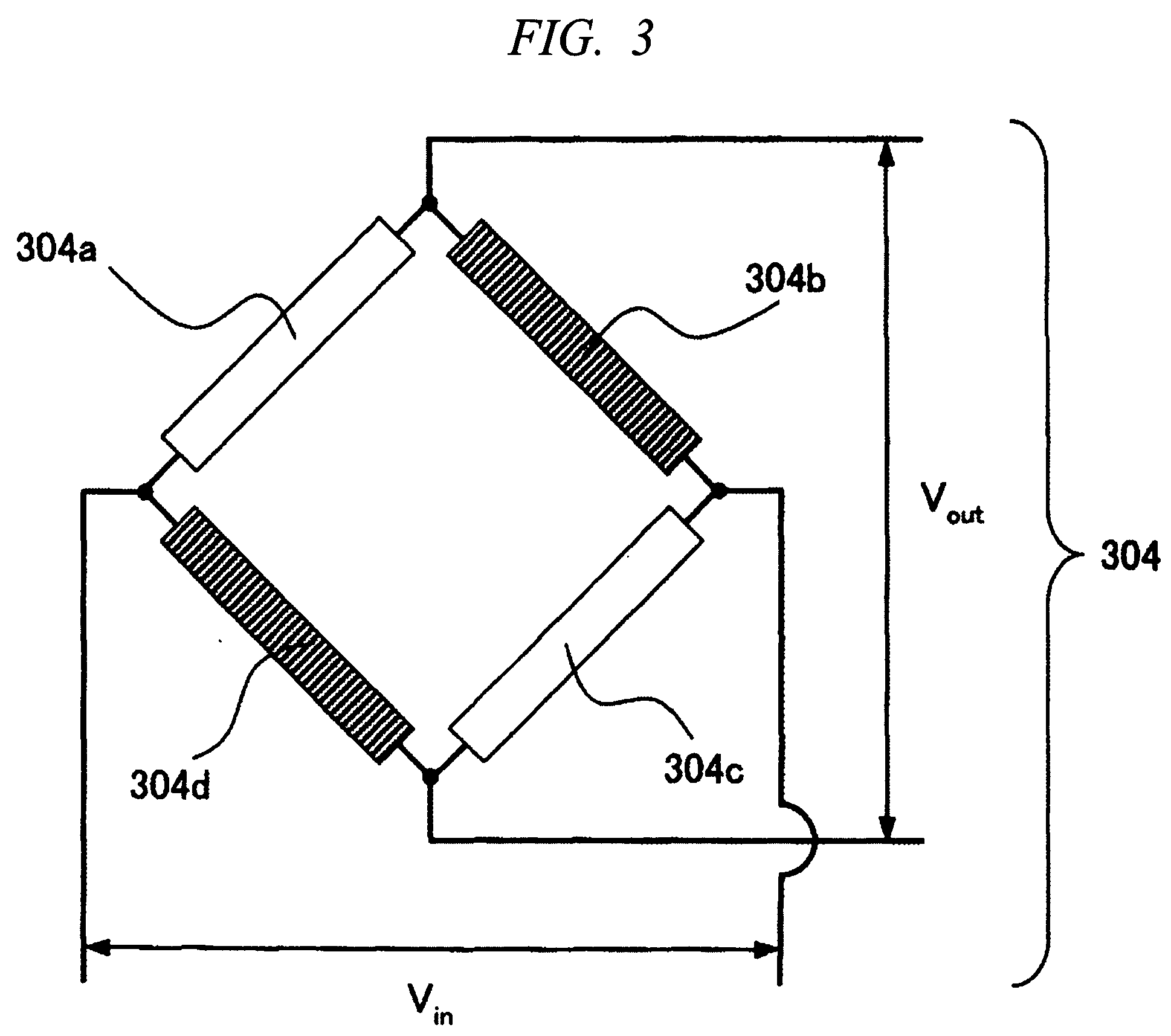

Mechanical-Quality measuring device

ActiveUS20070228500A1Improve accuracyHigh sensitivityAcceleration measurement using interia forcesSolid-state devicesElectrical resistance and conductanceMeasurement device

A mechanical-quantity measuring device capable of measuring a strain component in a specific direction with high precision is provided.At least two or more pairs of bridge circuits are formed inside a semiconductor monocrystal substrate and a semiconductor chip, and one of these bridge circuits forms a n-type diffusion resistor in which a direction of a current flow and measuring variation of a resistor value are in parallel with a <100> direction of the semiconductor monocrystal silicon substrate, and an another bridge circuit is composed of combination of p-type diffusion resistors in parallel with a <110> direction.

Owner:HITACHI LTD

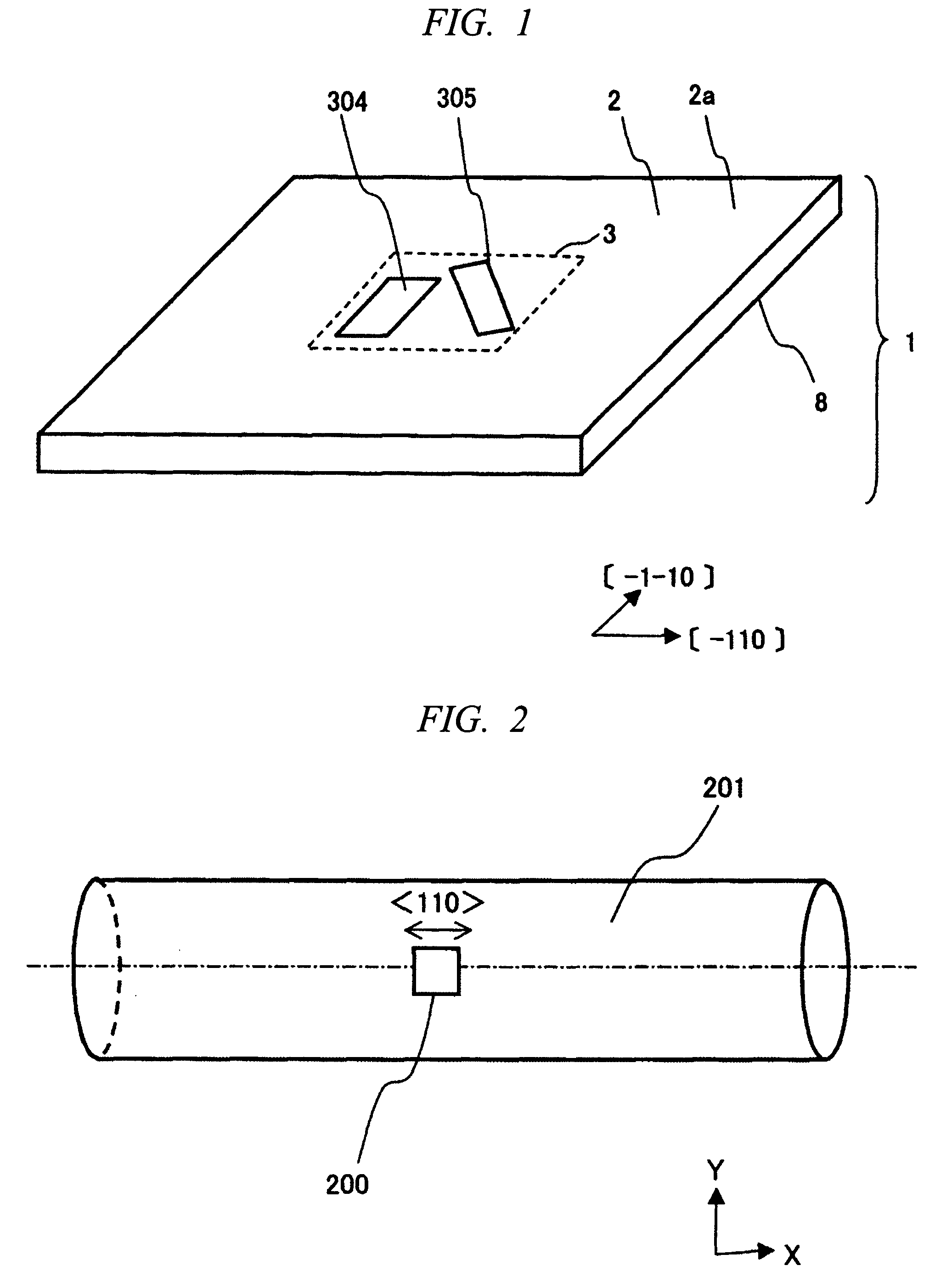

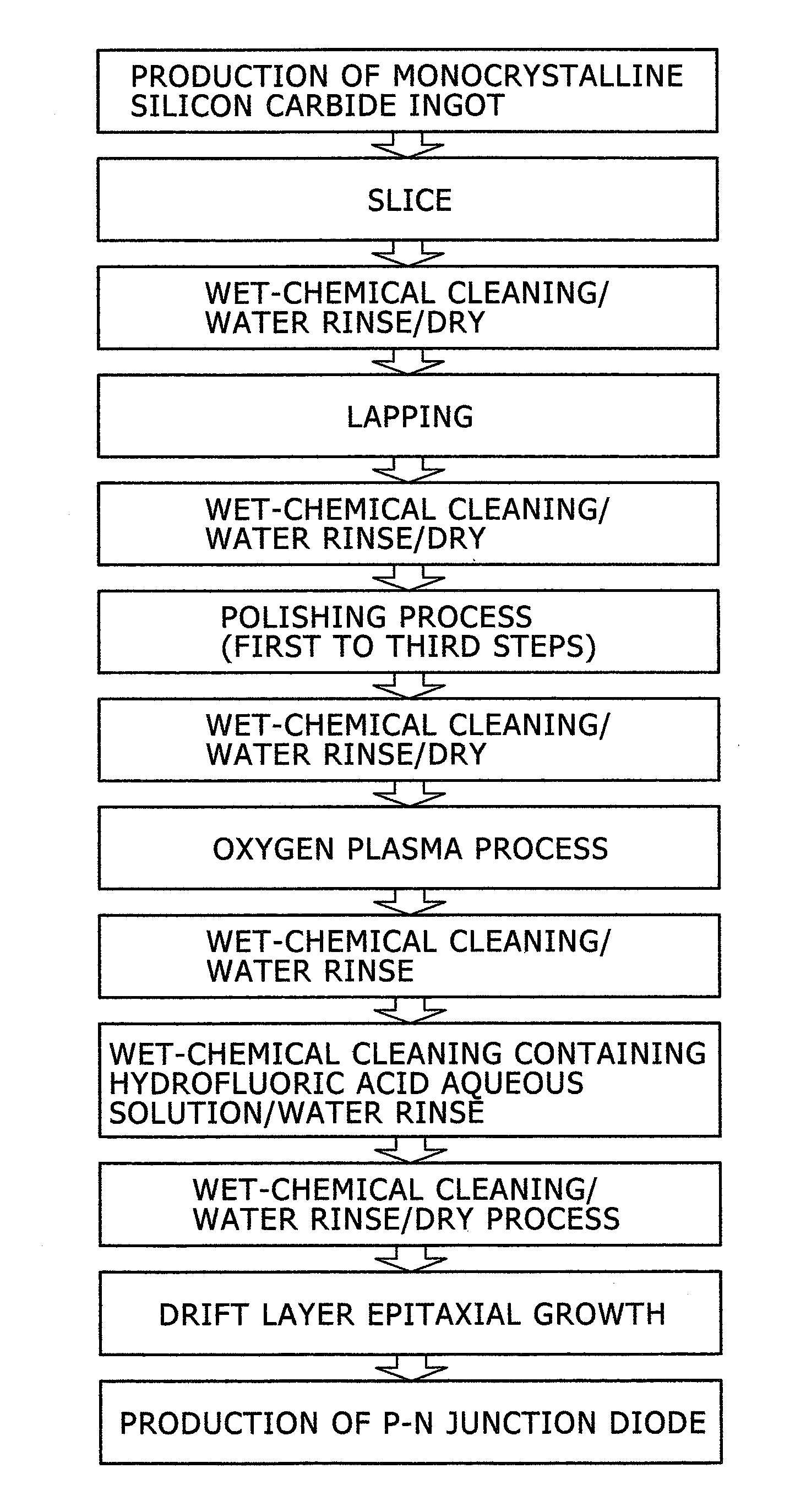

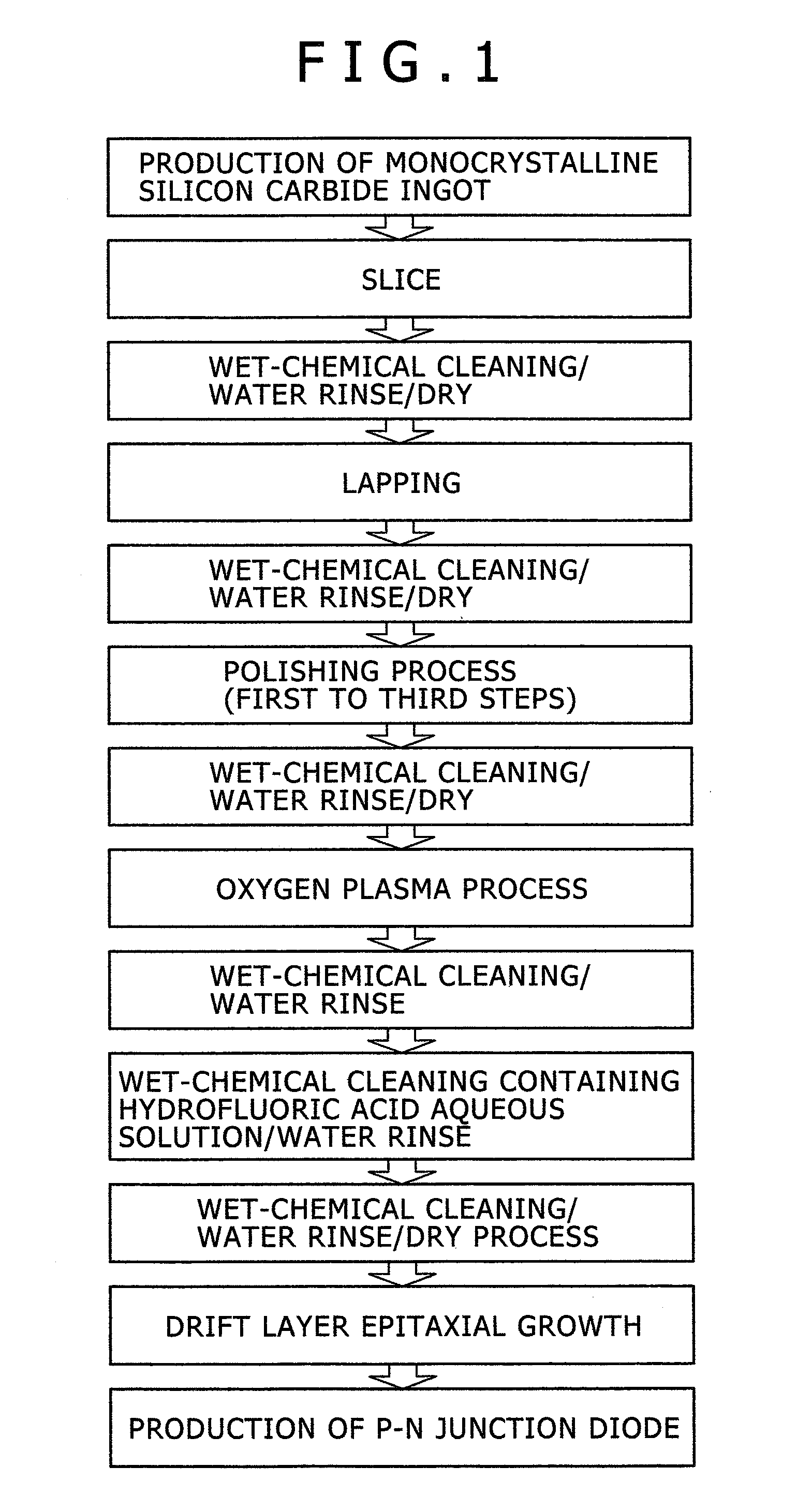

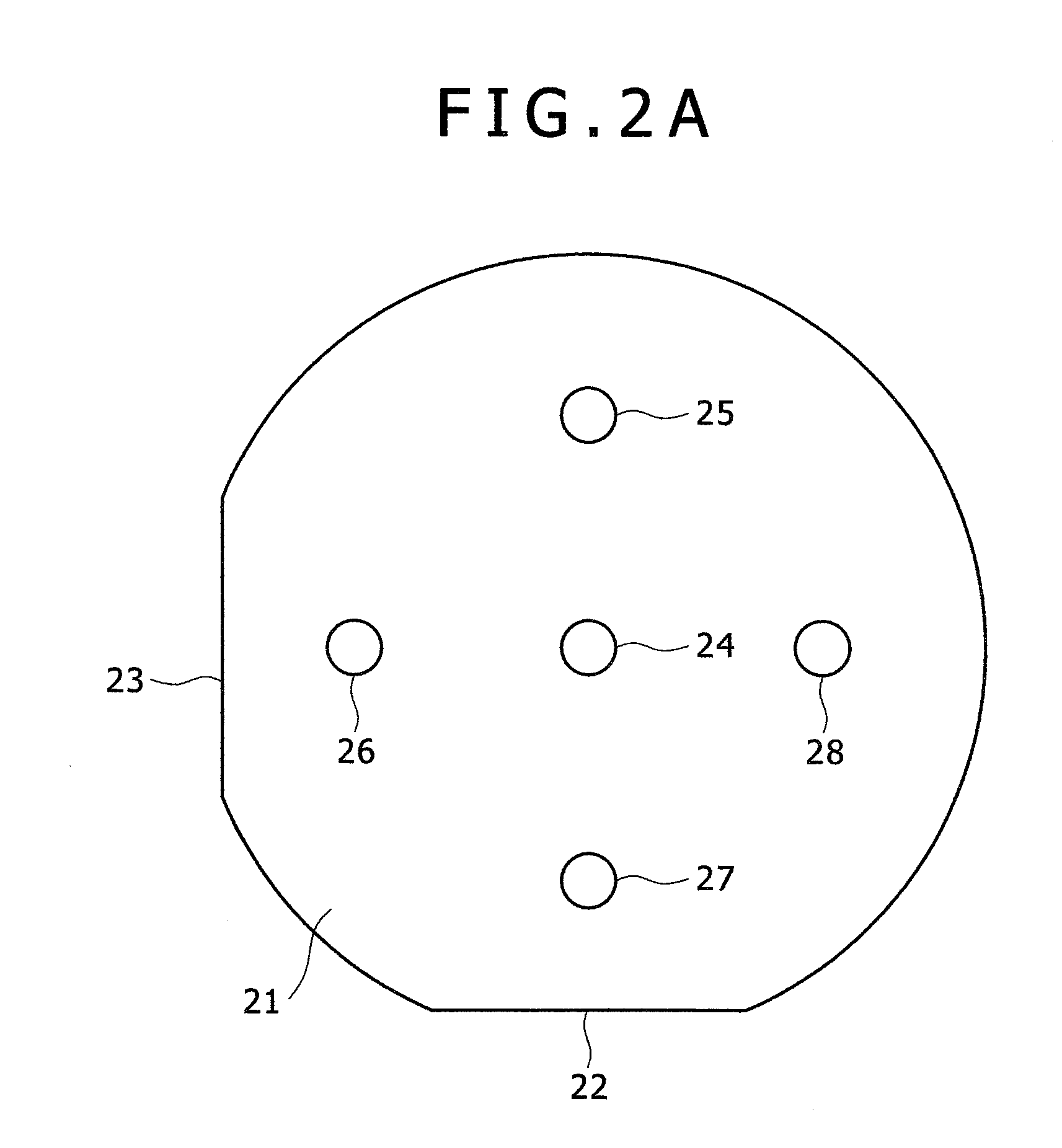

Manufacturing method of semiconductor device

ActiveUS20090209090A1Surface cleaningEasy to spreadSemiconductor/solid-state device manufacturingSemiconductor devicesMetal contaminationMonocrystalline silicon

A problem in the conventional technique is that metal contamination on a silicon carbide surface is not sufficiently removed in a manufacturing method of a semiconductor device using a monocrystalline silicon carbide substrate. Accordingly, there is a high possibility that the initial characteristics of a manufactured silicon carbide semiconductor device are deteriorated and the yield rate is decreased. Further, it is conceivable that the metal contamination has an adverse affect even on the long-term reliability of a semiconductor device. In a manufacturing method of a semiconductor device using a monocrystalline silicon carbide substrate, there is applied a metal contamination removal process, on a silicon carbide surface, including a step of oxidizing the silicon carbide surface and a step of removing a film primarily including silicon dioxide formed on the silicon carbide surface by the step.

Owner:HITACHI POWER SEMICON DEVICE

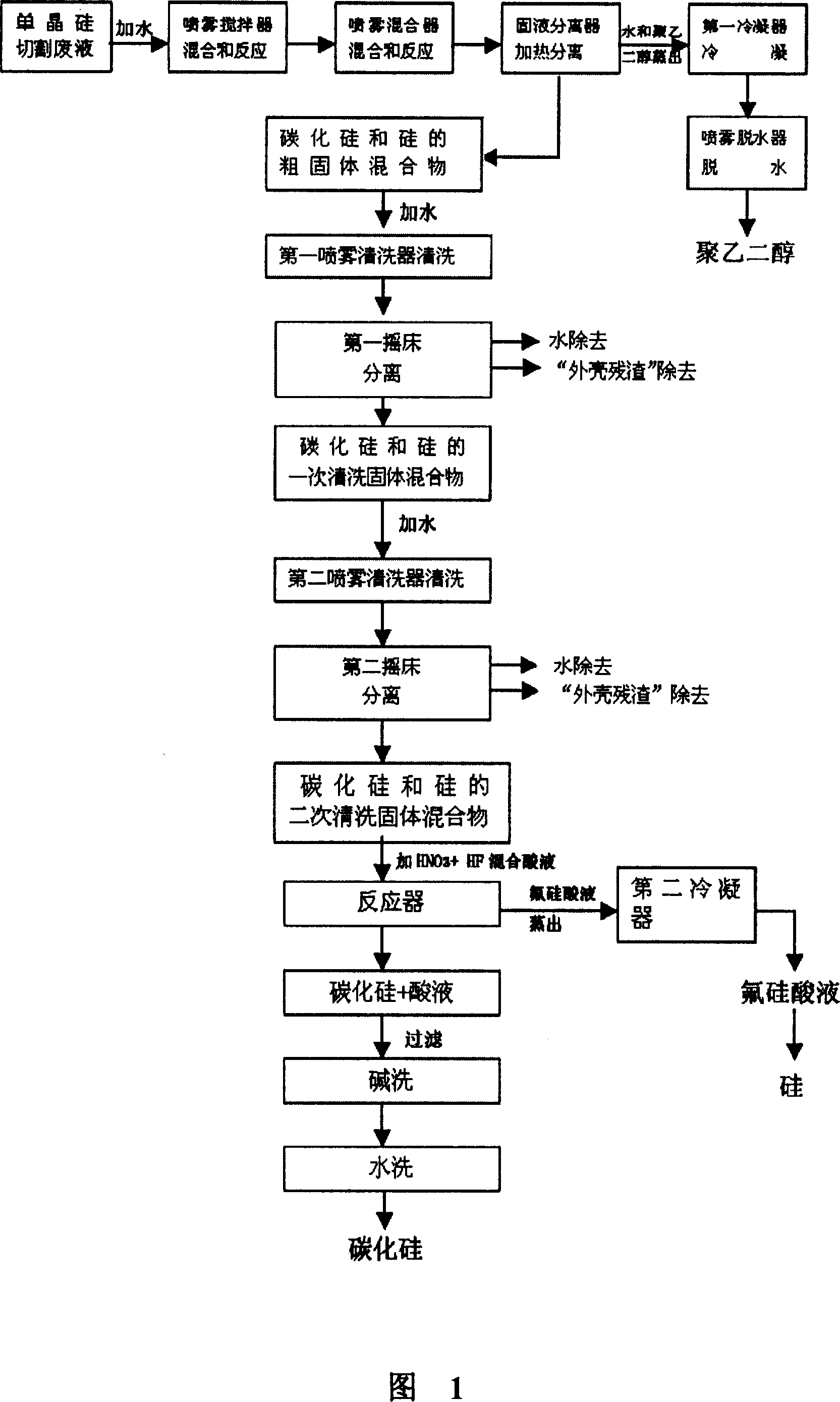

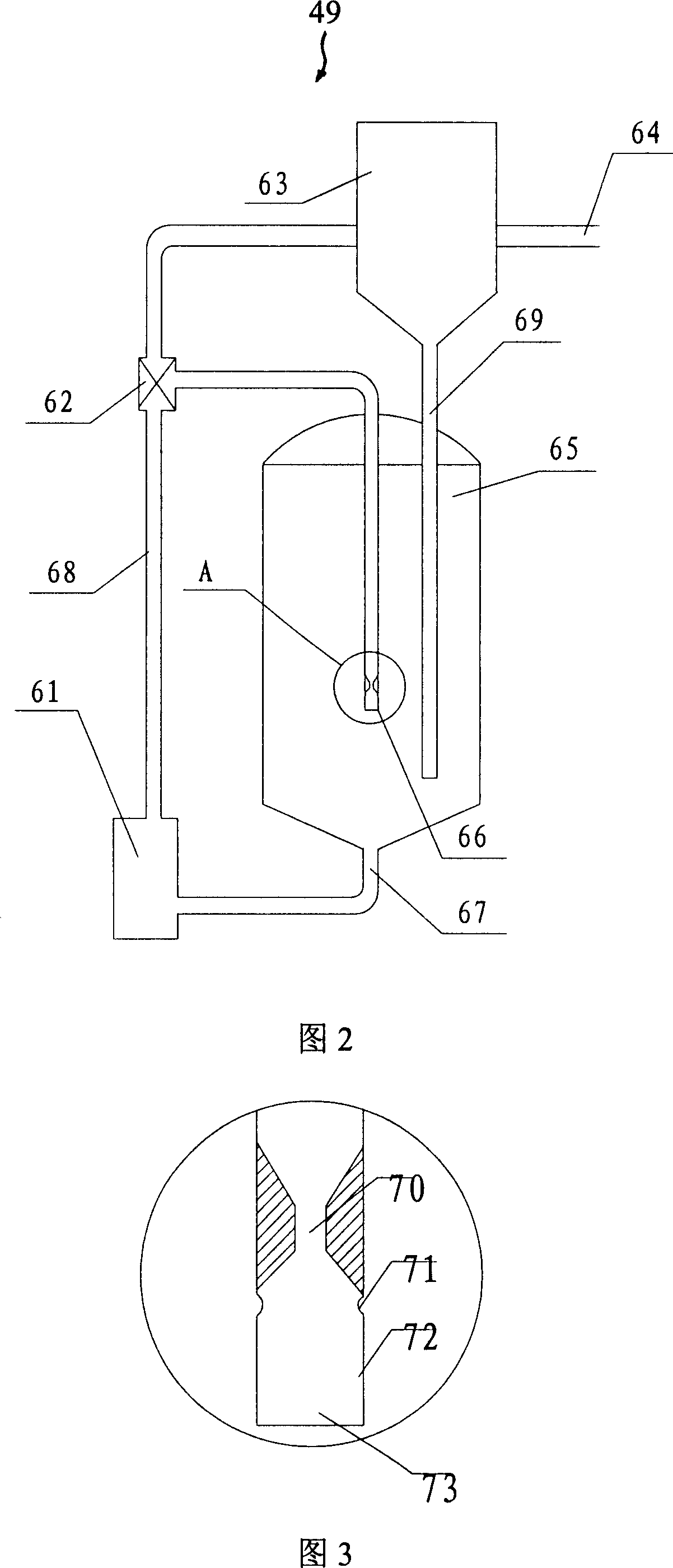

Treatment recovery method for monocrystalline silicon cutting waste liquor

InactiveCN101113029AParticle refinementWell mixedSiliconEnergy based wastewater treatmentRecovery methodLiquid waste

A treatment and reclaim method of single crystal silicon cutting waste liquid comprises the steps: (1). the waste liquid is treated with diluted hydrochloric acid then is stirred and mixed to enable the liquid to become a flowable mixture; (2). the mixed material is heated to separate solid and liquid, by which water and polyethylene glycol are extracted. The polyethylene glycol is obtained by the process of condensation, dehydration and recovery. The solid after being separated is a crude solid mixture of silicon carbide and silicon; (3). the quadratic-cleaning solid mixture of silicon diluted and silicon is obtained after quadratic cleaning to the crude solid mixture obtained in step 2; (4). the mixture is treated by mixed acid liquid comprising HNO3+HF to recover and get silicon diluted and silicon. The method has easy operation, simple equipment, low cost, high efficiency in treatment and recovery. The allover recovery rate calculated based on the weight of waste liquid can reach 26-46 percent and the recovering material can reach or close to the standard index, and can be directly used in solar energy battery production, so the invented method has good economic benefit and also can greatly contribute to environment protective, thereby having large exploration prospect.

Owner:金柏林

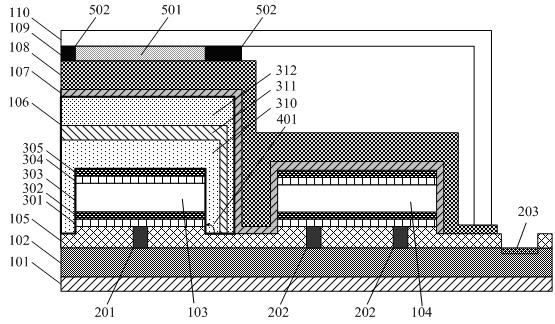

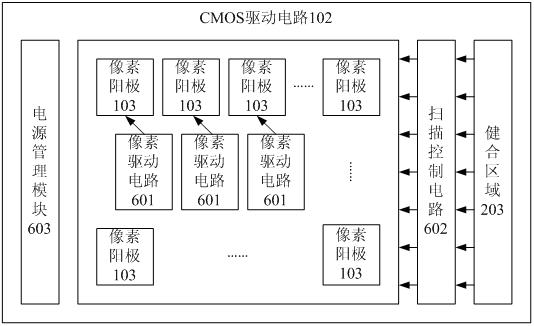

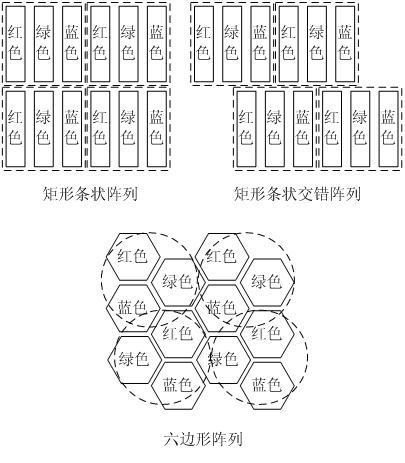

Silicon substrate top emission organic light emitting microdisplay and method for producing same

ActiveCN102629667AAvoid secondary processingSimple processStatic indicating devicesSolid-state devicesTitanium nitrideDisplay device

The invention relates to a silicon substrate top emission organic light emitting microdisplay and method for producing the same. An organic light emitting device is arranged on the surface of a silicon-based chip, and a driving circuit and a controlling circuit of the organic light emitting device are integrated in the silicon-based chip. The structure (from bottom to top) of the microdisplay is a monocrystalline silicon substrate, the driving circuit, a top through-hole layer and a top through-hole, a pixel anode and a common-cathode, an organic layer, a transparent cathode layer, a multi-layer film packaging layer, a color filtering layer and a glass sealing cap, wherein the pixel anode adopts a vertical five-layer structure and the five layers are titanium, titanium nitride, aluminum, titanium and titanium nitride; the organic layer comprises at least a hole transporting layer, a multi-layer organic light emitting layer and an electron transporting layer. The organic light emitting pixel unit area of the microdisplay is less than 100 square microns and the pixel resolution is more than 640*480. Besides, a processing procedure of chip cutting is performed before production of the organic light emitting layer and the film packaging layer, and various masks are used for producing organic displaying devices, so that laser etchers with high cost cannot be introduced.

Owner:LUMICORE MICROELECTRONICS SHANGHAI CO LTD

Soi device and method for its fabrication

A silicon on insulator (SOI) device and methods for fabricating such a device are provided. The device includes an MOS capacitor coupled between voltage busses and formed in a monocrystalline semiconductor layer overlying an insulator layer and a semiconductor substrate. The device includes at least one electrical discharge path for discharging potentially harmful charge build up on the MOS capacitor. The MOS capacitor has a conductive electrode material forming a first plate of the MOS capacitor and an impurity doped region in the monocrystalline silicon layer beneath the conductive electrode material forming a second plate. A first voltage bus is coupled to the first plate of the capacitor and to an electrical discharge path through a diode formed in the semiconductor substrate and a second voltage bus is coupled to the second plate of the capacitor.

Owner:GLOBALFOUNDRIES US INC

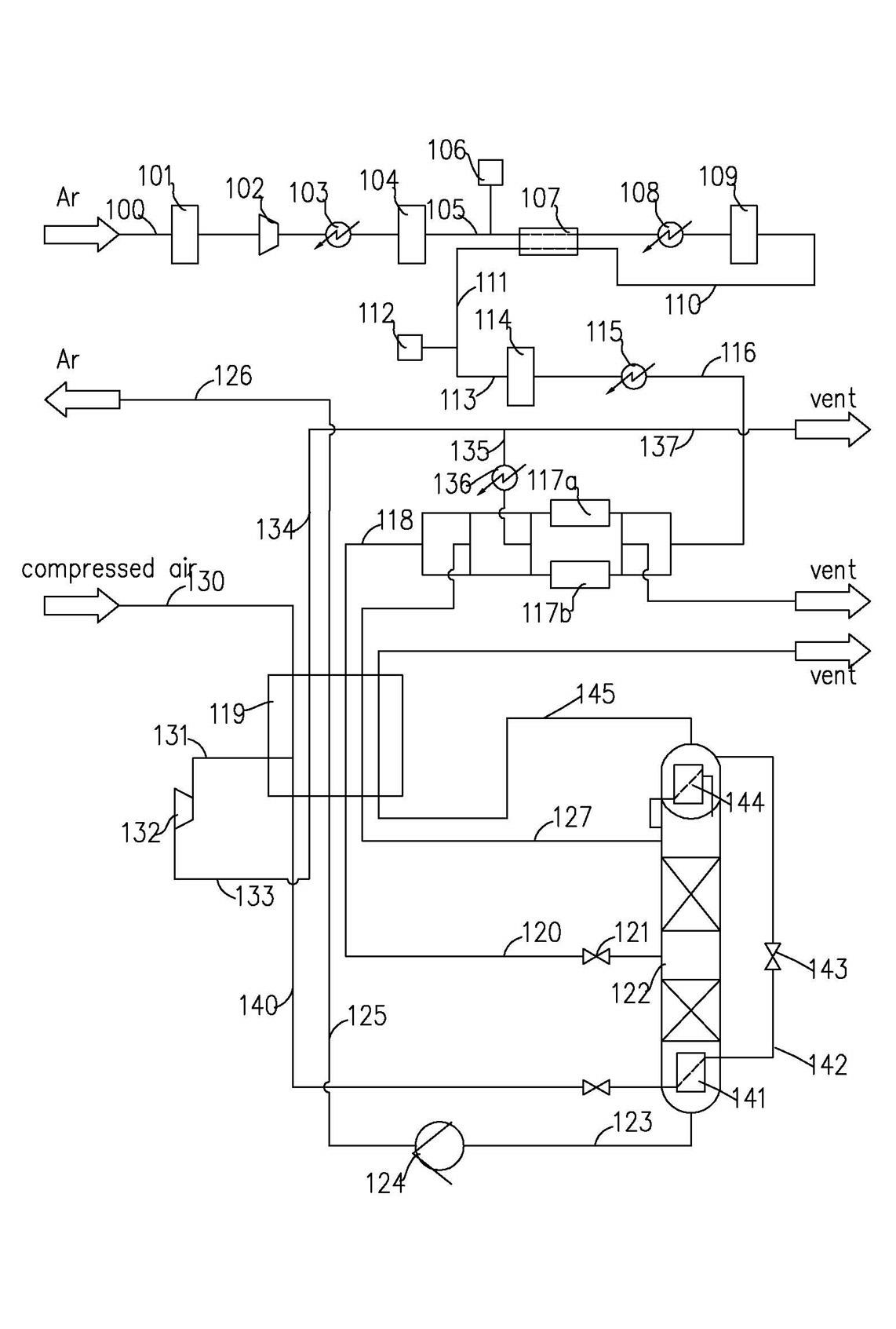

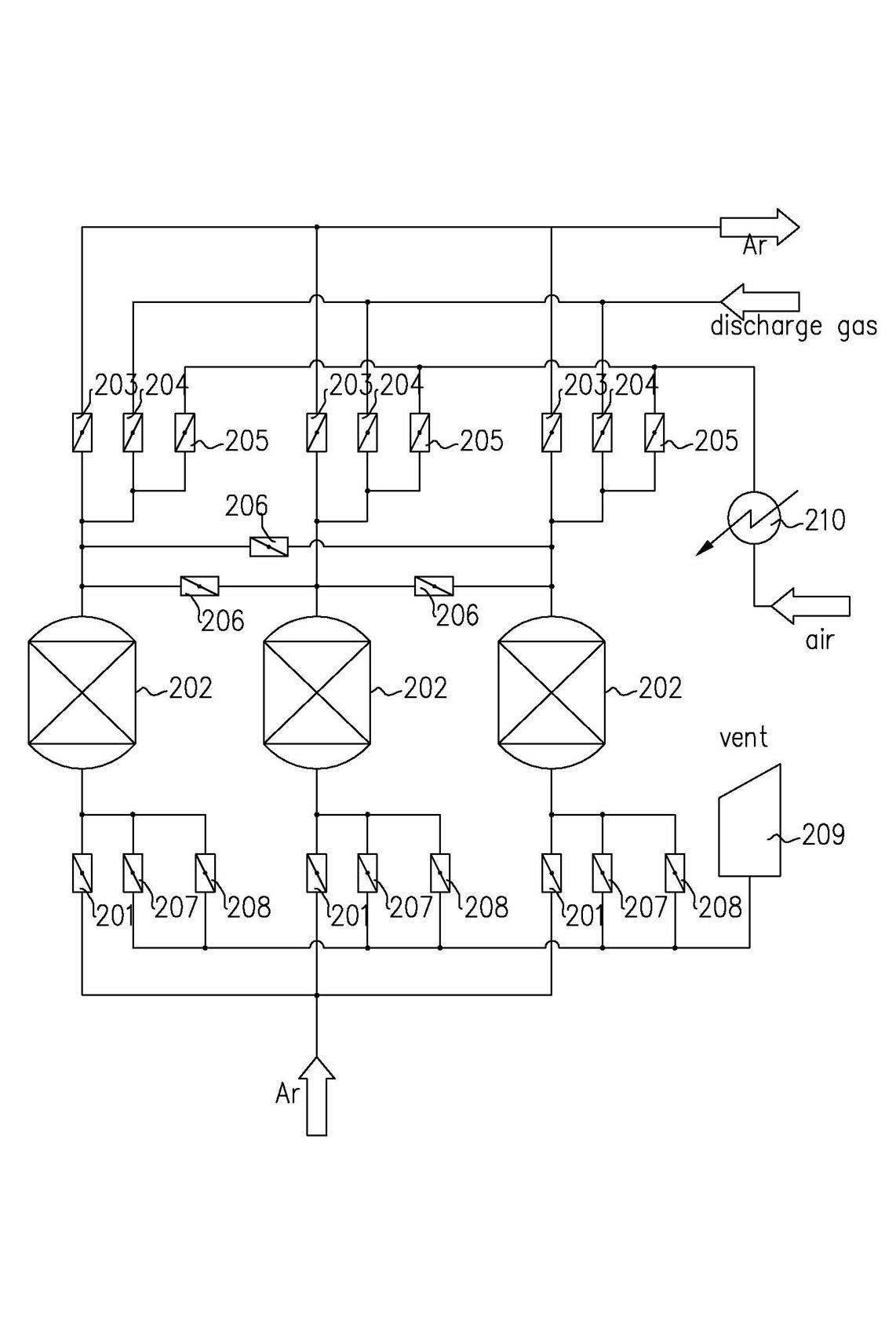

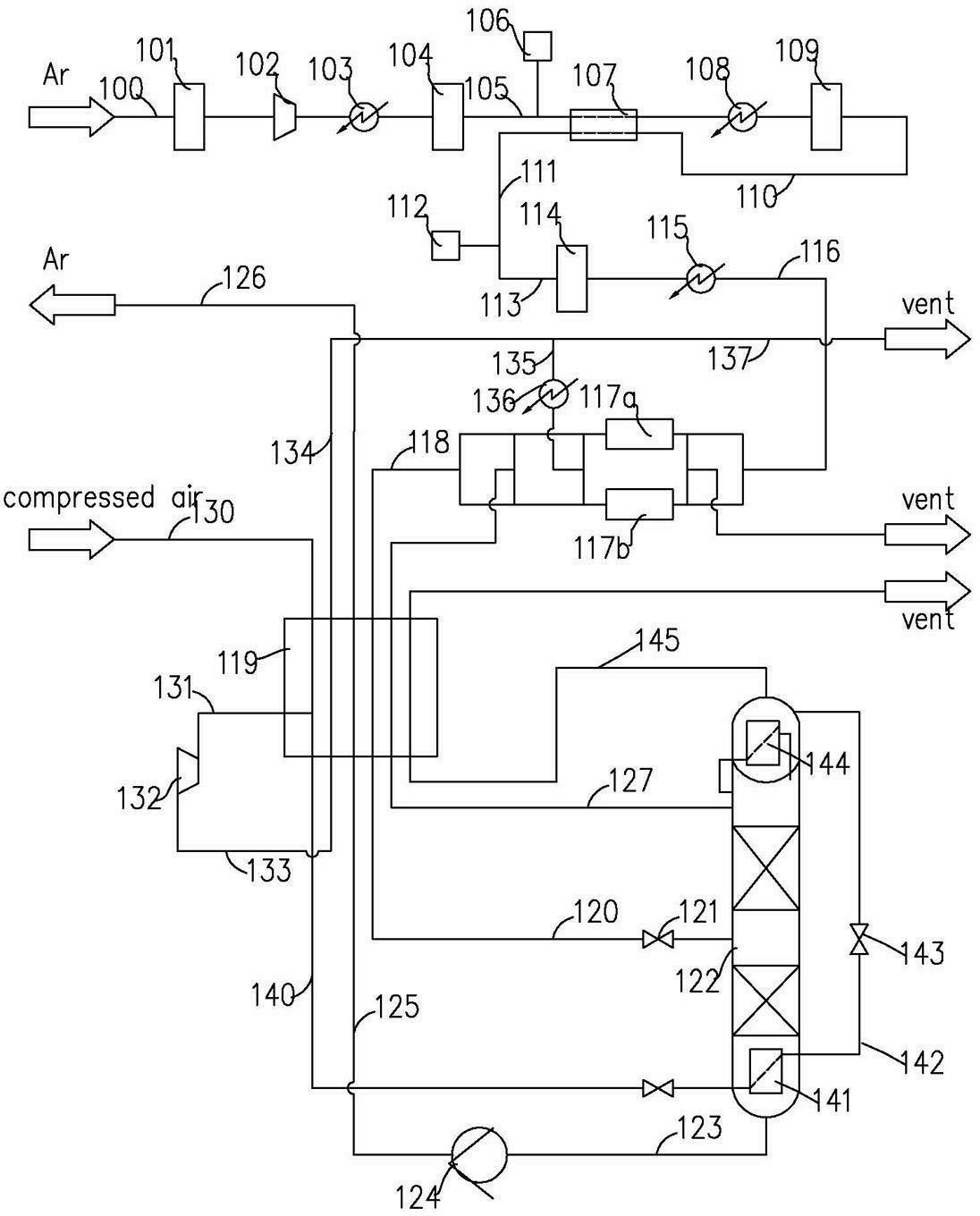

Method and device for recovering and purifying argon in monocrystalline silicon production

ActiveCN102583281AThorough responseHigh recovery rateNoble gas compoundsPtru catalystCatalytic oxidation

Provided is a method and a device for recovering and purifying argon in monocrystalline silicon production. The method comprises firstly conducting coarse oil removal on argon recovered from a single crystal furnace, compressing, cooling and conducting high-precision oil removal and dedusting; secondly enabling hydrocarbon such as methane and carbon monoxide to be reacted with oxygen to generate water and carbon dioxide through a high temperature catalytic reaction and guaranteeing the oxygen to be excessive in the catalytic reaction; thirdly enabling excessive oxygen to be reacted with added hydrogen to generate the water under effects of a catalytic agent after cooling and enabling argon after two catalytic reactions to penetrate through a normal temperature adsorption unit to absorb the water and the carbon dioxide; cooling the argon, sending a low temperature rectifying tower, enabling the argon, the nitrogen and the hydrogen to produce rectification separation, obtaining pure liquid argon, and conducting repeated heating to obtain pure argon products. The device mainly comprises an oil filter, a catalytic reactor of the hydrocarbon of high temperature catalytic oxidation carbon monoxide and methane and the like, a normal temperature hydrogenation deoxygenization catalytic reactor, a normal temperature adsorption unit for absorbing the carbon dioxide and the water at the normal temperature and the low temperature rectifying tower for rectifying and separating the hydrogen and the nitrogen at the low temperature. The device has the advantages of being high in argon recovery rate, high in purity of recovered argon, low in oxygen content, low in energy consumption for recovery and purification and the like.

Owner:HANGZHOU HANGYANG

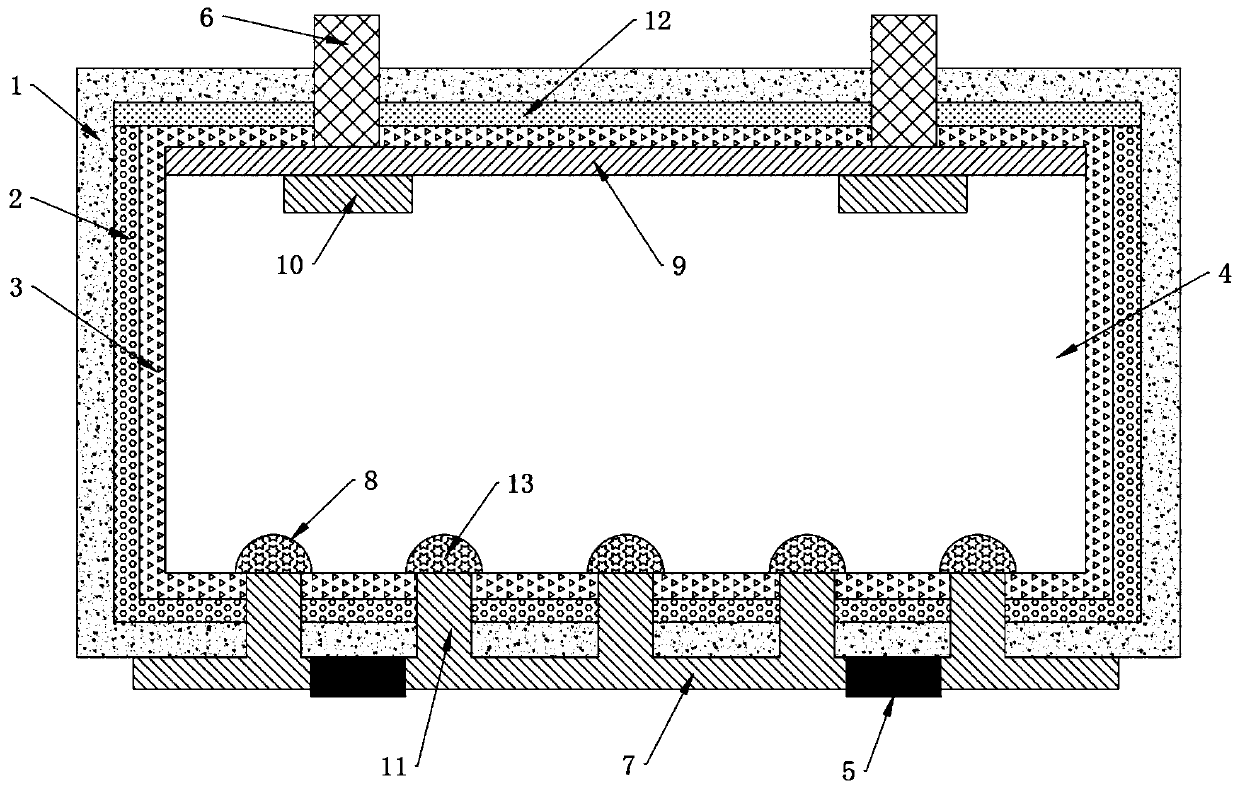

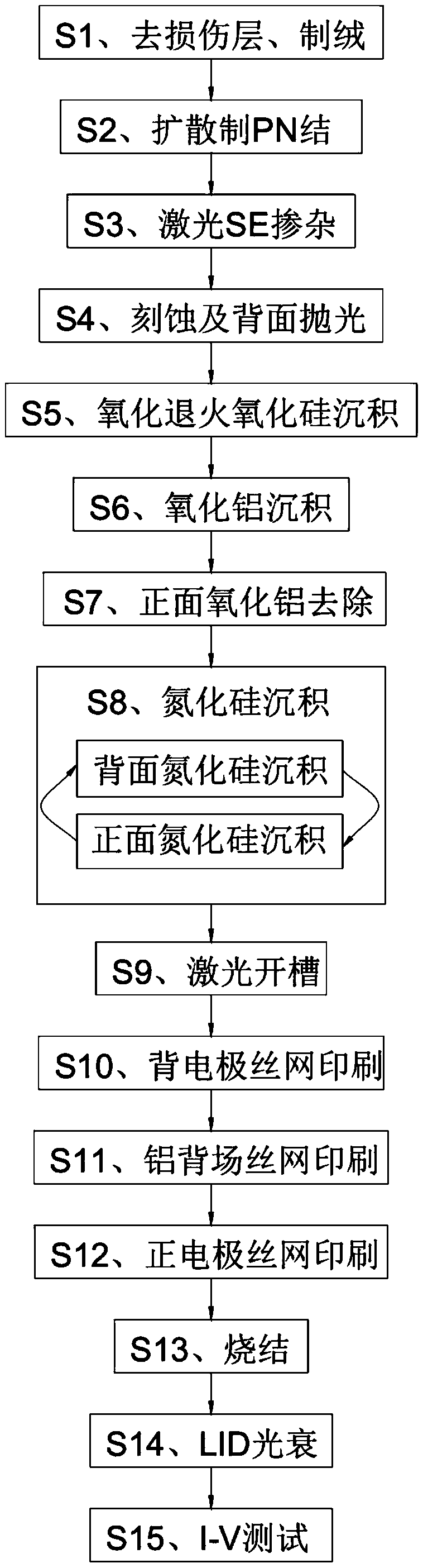

Solar cell with composite dielectric passivation layer structure and preparation process thereof

PendingCN110459615AIncrease short circuit currentIncrease the open circuit voltageFinal product manufacturePhotovoltaic energy generationDielectricRefractive index

The invention discloses a solar cell with a composite dielectric passivation layer structure and a preparation process thereof. A silicon oxide film, an alumina film and a silicon nitride or silicon oxynitride film are deposited in turn on the front, back and sides of a p-type silicon substrate to form a composite dielectric film on the whole surface, and windows are opened locally to lead electrodes out. Through aluminum oxide, silicon dioxide, silicon oxynitride, silicon nitride with different refractive indexes and a back surface passivation layer with a laminated structure of the materials, the back surface recombination rate is greatly reduced, the back reflectivity is improved, the CTM of a module is reduced, and the light attenuation and heat-assisted light attenuation and the anti-PID performance of the cell are improved. The structure can be made on a boron / gallium-doped p-type monocrystalline silicon, p-type polycrystalline silicon or p-type monocrystalline-silicon-like substrate, and a passivation method based on the composite dielectric film passivation structure can be used to manufacture PERC cells, double-sided PERC+ cells and imbricate PERC cells. Based on the preparation process steps and sequence, the corresponding preparation mode and the process parameter range of the laminated structure, the making of the cell can be well completed.

Owner:TONGWEI SOLAR ENERGY CHENGDU CO LID +2

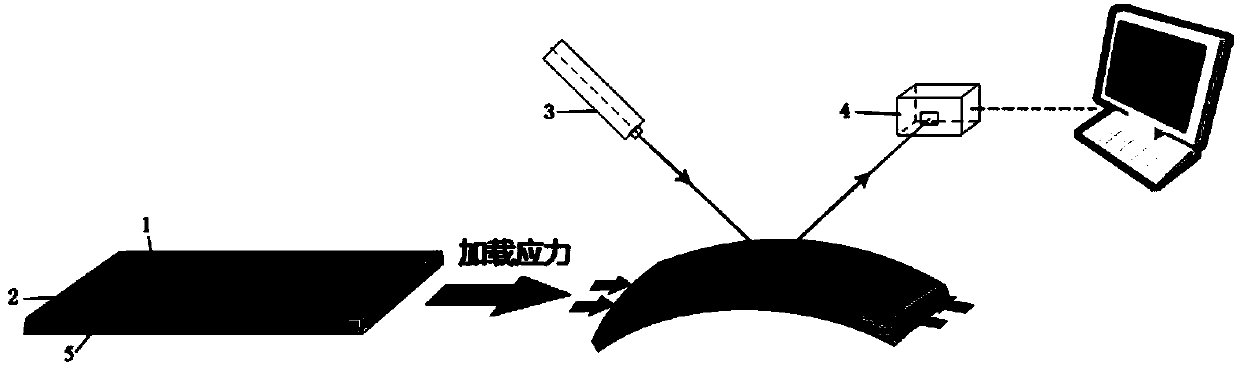

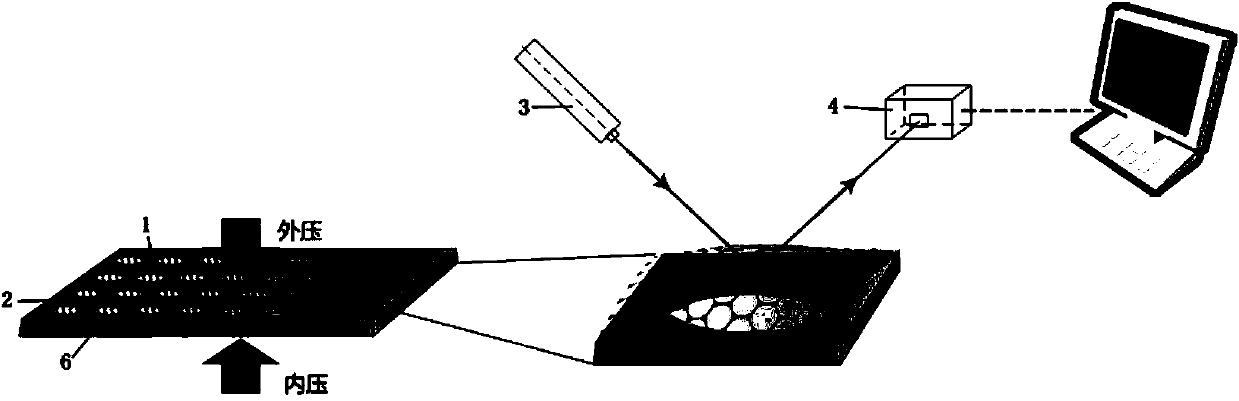

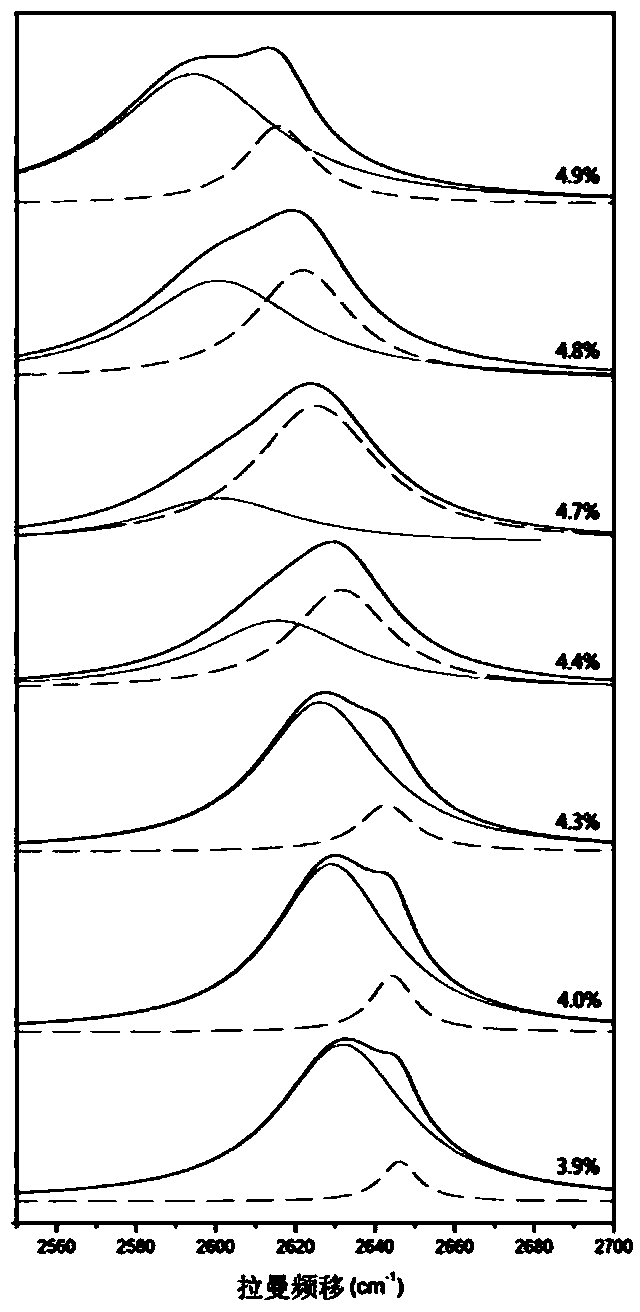

Device for measuring object stress by utilizing graphene membrane, and preparation method and testing method of device

ActiveCN103630272ASimple structureEasy to operateUsing optical meansChemical vapor deposition coatingStress measurementTechnical design

The invention discloses a device for measuring object stress by utilizing a graphene membrane, and a preparation method and a testing method of the device. The testing method is characterized in that graphene is arranged on a flexible stretchable substrate by utilizing a growth and transfer technology of the graphene and is tightly adhered to the surface of a to-be-measured object or a single crystal silicon substrate which is provided with a through hole, a characteristic peak of a Raman spectrum of the graphene can be subjected to shifting and splitting when the to-be-measured object is subjected to deformation or gas pressure difference exists between the internal part and the external part of the through hole, and sensing on strain or gas pressure can be realized basing on shifting and splitting amount of the characteristic peak. According to the device, the preparation method and the testing method, disclosed by the invention, the technical design is simple, the performance is stable, non-contact with the to-be-measured object is realized, and the complexity of an electrical measurement method which is in need of arranging leading wires can be avoided; the strain loading range is large, and the stress measurement accuracy degree is high.

Owner:西安超宇微晶新材料技术有限公司

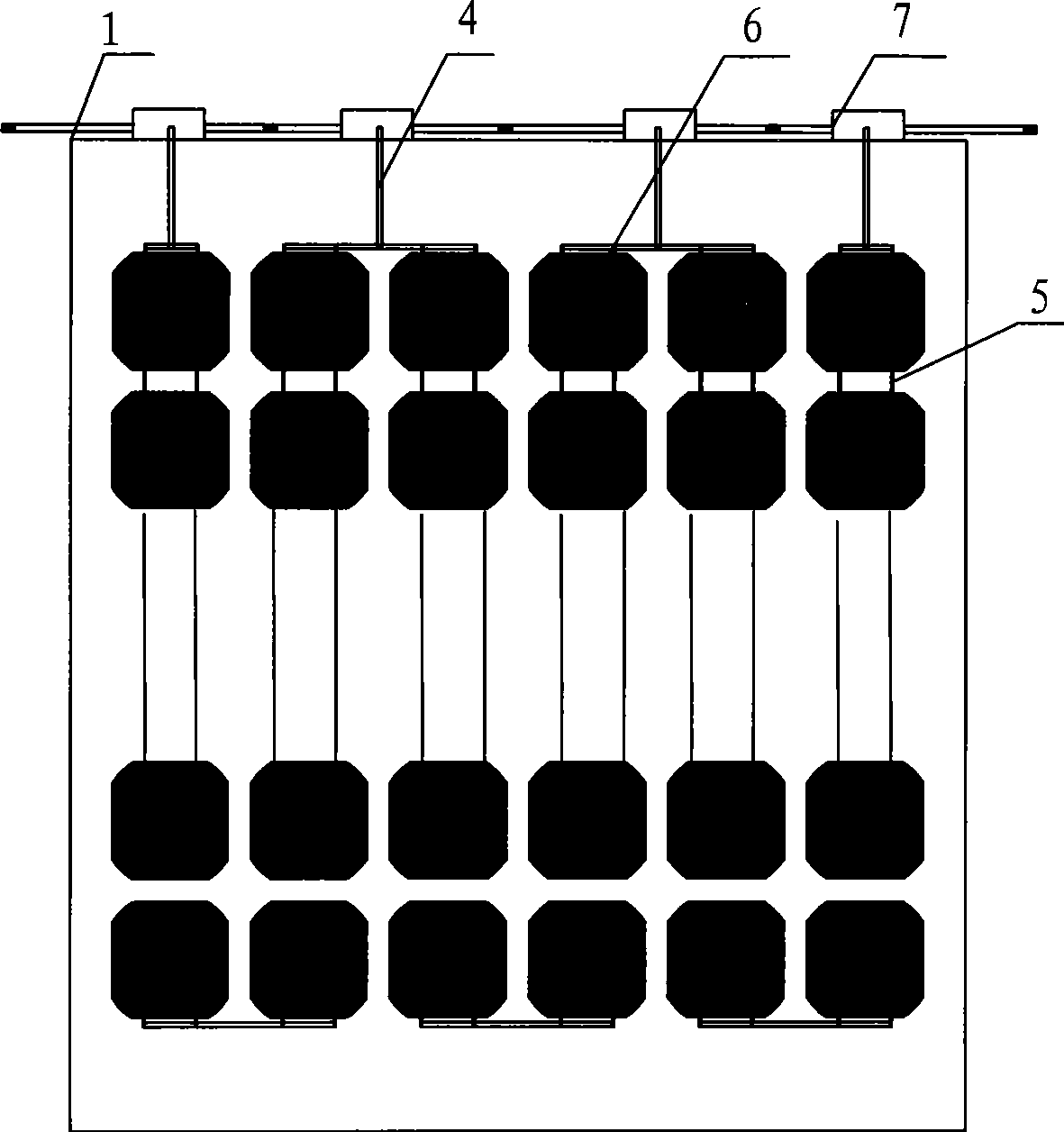

Double side photovoltaic battery wall component and manufacturing process thereof

InactiveCN101478010ASolve the use problemWith heat insulationWallsPhotovoltaic energy generationSolar lightElectrical battery

The invention belongs to the field of photoelectricity and building materials and particularly relates to a double-side photovoltaic battery curtain wall assembly and the fabrication method thereof. The double-side photovoltaic battery curtain wall assembly comprises an upper glass layer, a bottom glass layer, and solar battery slices, wherein the upper glass layer, the bottom glass layer and the solar battery slices are hermetically bonded with each other through EVA; the solar battery slice is a double-side monocrystalline silicon solar battery slice; double-side monocrystalline silicon solar battery slices are connected with each other through interconnection strips; and each solar battery slice groups is connected with a terminal box through a bus bar. The fabrication method of the double-side photovoltaic battery curtain wall assembly is also provided. The invention can solve the purpose problem of double-side battery, so that the double-side batteries can be used in the photoelectrical field more generally. The double-side solar battery, i.e. the positive and the negative side of the battery slice, can generate corresponding power under the irradiation of solar light, so that the power of the photovoltaic assembly is increased indirectly, the conversion efficiency of the single battery slice is improved.

Owner:山东科明太阳能光伏有限公司

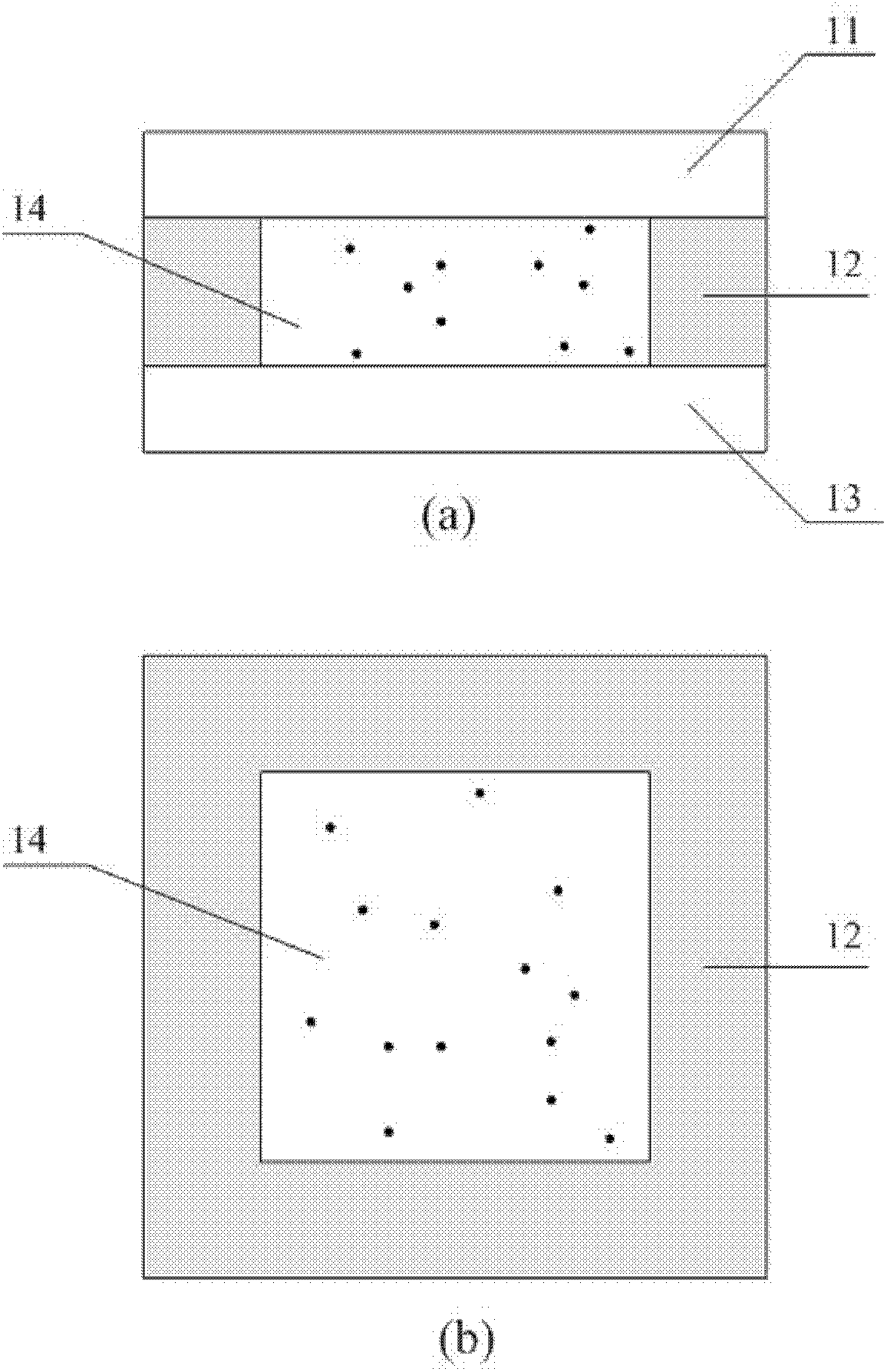

Groove type atomic gas cavity and atomic clock physical system formed by same

ActiveCN102323738ALower working temperatureUnlimited thicknessApparatus using atomic clocksCrystal planeParticle physics

The invention relates to a groove type atomic gas cavity produced by applying MEMS technology and an atomic clock physical system formed by the same. The cavity is characterized in that the cavity is formed in such a manner that a silicon wafer with a groove and Pyrex glass sheets define a cavity structure through bonding; the cavity structure is used for alkali metal atom vapor and buffer gases to fill in; the cross section of the groove is in a shape of inverted trapezoid; and the groove comprises a bottom surface and side walls forming included angles with the bottom surface. The cavity is manufactured based on MEMS (micro-electro-mechanical system) technology. The silicon groove is formed through anisotropic etching of the (100) monocrystalline wafer. The groove type cavity is manufactured through silicon-glass anode bonding. The side walls of the cavity are {111} crystal planes of the silicon wafer. The cavity and the system have the following beneficial effects: by utilizing the cavity, the distance between two reflectors in the cavity is easy to enlarge through atomic cavity dimension design, thus increasing the length of the interaction space between laser and atomic gas, enhancing the signal to noise ratio of the CPT (coherent population trapping) signal and being beneficial to improvement of the frequency stability of the micro CPT atomic clock.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Corrosive liquid for preparing monocrystal silicon textured surface and method thereof

InactiveCN101634026AHigh thermodynamic stabilityGood chemical stabilityAfter-treatment detailsSemiconductor devicesPotassium hydroxidePerfluorooctanoic acid

The invention relates to a corrosive liquid for preparing monocrystal silicon textured surfaces and a method thereof. The corrosive liquid comprises an alkali solution, sodium silicate and isopropanol, and is characterized by also comprising a perfluoro octoate aqueous solution, wherein the perfluoro octoate aqueous solution has the volume percent of 0.2-1 percent and the concentration within a range of 5*10<-5>-5*10<-3>mol / L; the alkali solution has the mass percent of 1-2.5 percent, the sodium silicate has the mass percent of 0.1-2 percent, and the isopropanol has the volume percent of 0.3-2 percent; and the alkali solution is sodium hydroxide or potassium hydroxide or sodium carbonate. The corrosive liquid has low cost, pyramids formed on the prepared monocrystal silicon textured surfaces have small and uniform sizes, and the corrosive liquid is favorable for solar energy absorption and can be widely applied to the field of solar batteries.

Owner:BEIJING SOLAR ENERGY INST +1

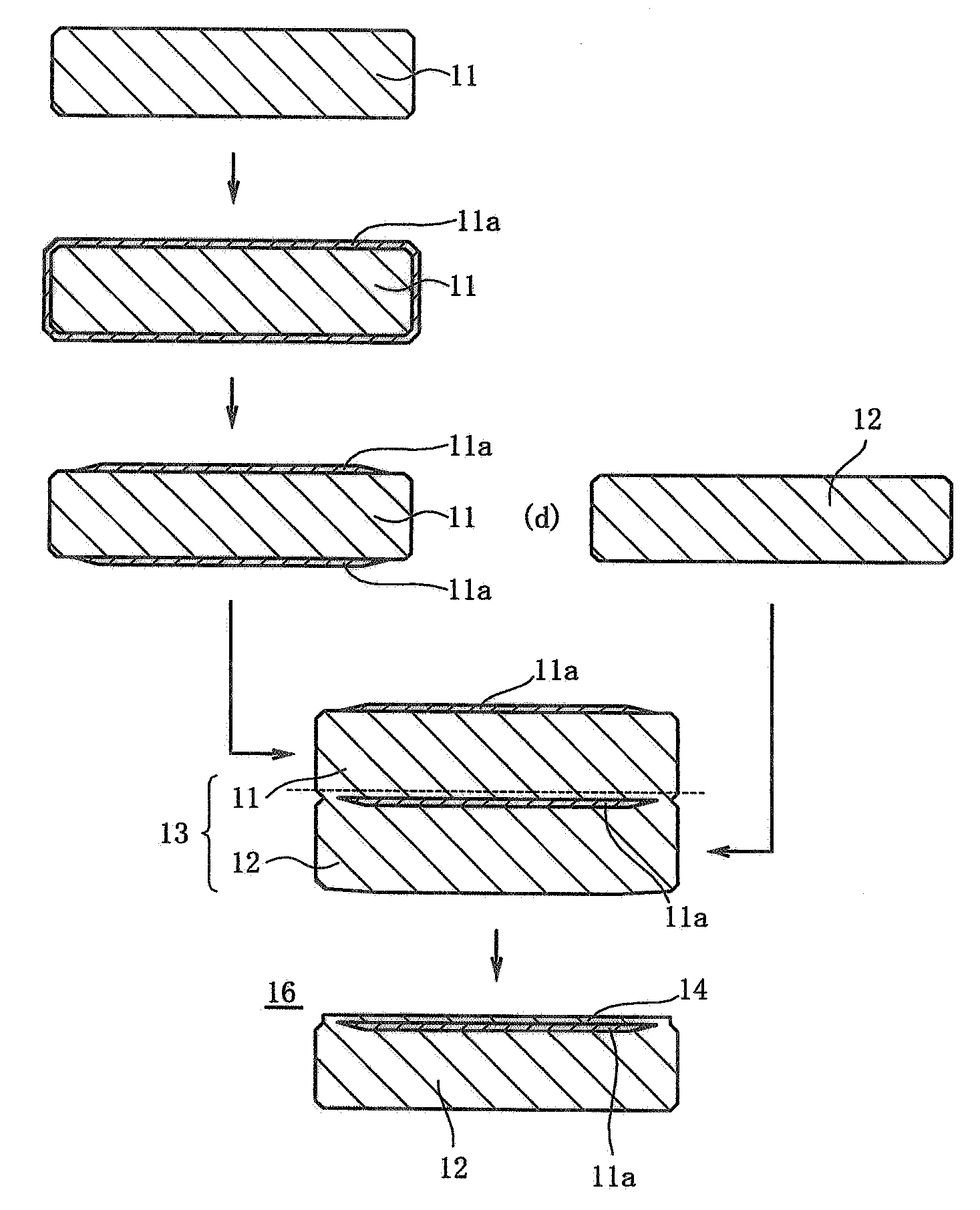

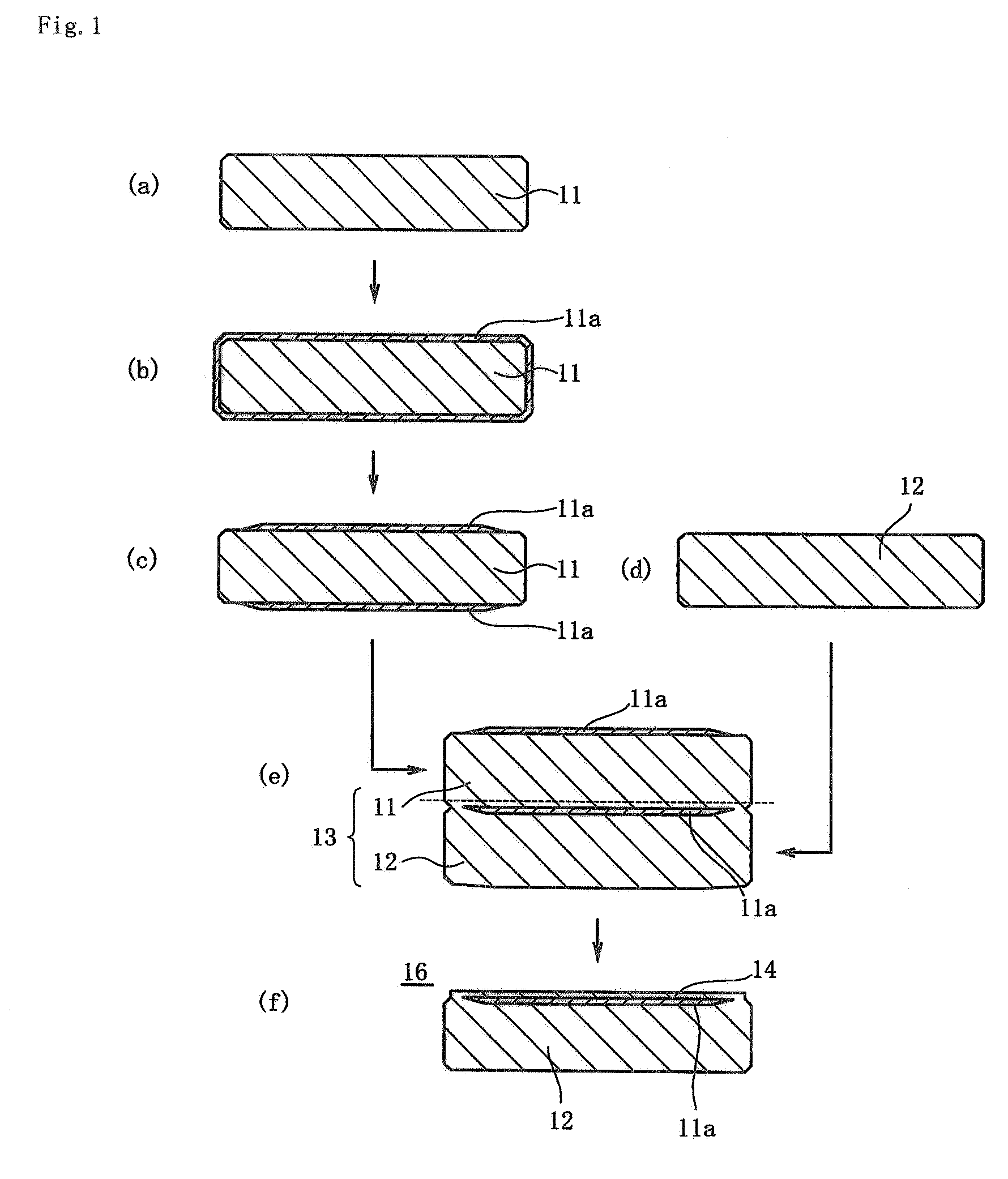

Method for Manufacturing Direct Bonded SOI Wafer and Direct Bonded SOI Wafer Manufactured by the Method

ActiveUS20070148912A1Reduce manufacturing costReduce yieldSemiconductor/solid-state device manufacturingWaferingThin membrane

There are provided a method for manufacturing a direct bonded SOI wafer in which the entire buried oxide film layer is covered and not exposed and a direct bonded SOI wafer. This is the improvement of a method for manufacturing a direct bonded SOI wafer comprising the process of (A) forming a laminated body by laminating a semiconductor wafer and a support wafer via an oxide film; and (B) forming a thin-film single crystal silicon layer on the support wafer using a buried oxide film layer by film-thinning the semiconductor wafer to a predetermined thickness, wherein in a process (C) the entire buried oxide film layer is covered by a main surface on the laminating side of the support wafer and the single crystal silicon layer. The covering of the entire buried oxide film layer is carried out by, between process (A) and (B), removing the oxide film formed on the circumferential end edge of the main surface on the laminating side and the chamfered portion to leave the oxide film only on the laminated surface except the circumferential end edge.

Owner:SUMCO CORP

Preparation and purification process for arenaceous quartz and quartz powder, and products produced thereby

InactiveCN101367609AGood effectAvoid pollutionSilicaGlass shaping apparatusWet grindingMonocrystalline silicon

The invention discloses a preparation and purification process of quartz sand and quartz powder and products thereof. The preparation and purification process of quartz sand comprises raw quartz ore, rough separation, fragmentation, water separation, roasting, water fragmentation, soaking in oxalic acid or citric acid, dry grinding or wet grinding, high-gradient magnetic separation, classification, combined process washing, floatation, deionized water washing, special drying. The preparation and purification process of quartz powder comprises quartz sand flotation, ultra fine grinding (dry grinding or wet grinding ), combined process washing, high-gradient magnetic separation, electrostatic separation, deionized water washing, classification, special drying, and vacuum packing. The quartz sand and quartz powder produced with the process of the invention can not foam in the production of glass and chips, an optical fibre and an optical cable can not be broken, the glass does not have water streaks, and the application area is widened. The quartz sand and the quartz powder is suitable for being applied in the fields of monocrystal line silicon, chips, optical fibre and optical cables, war industry, fine chemistry industry and micro-electronics.

Owner:刘少云

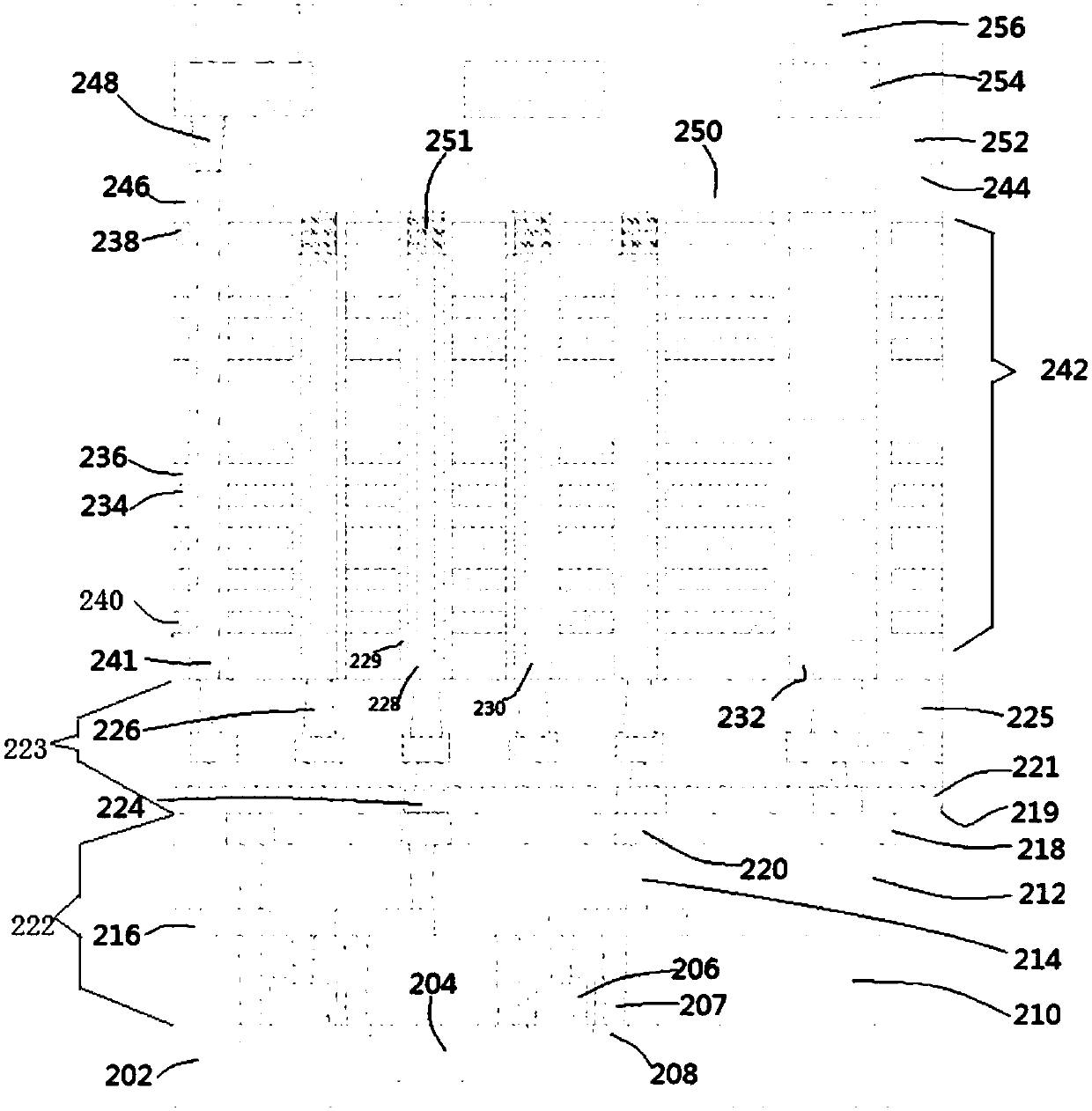

Semiconductor substrate, semiconductor device, and manufacturing methods for them

InactiveUS20050245046A1Improve performanceLess varied in characteristicTransistorStatic indicating devicesLOCOSEngineering

The present invention provides a semiconductor substrate, which comprises a singlecrystalline Si substrate which includes an active layer having a channel region, a source region, and a drain region, the singlecrystalline Si substrate including at least a part of a device structure not containing a well-structure or a channel stop region; a gate insulating film formed on the singlecrystalline Si substrate; a gate electrode formed on the gate insulating film; a LOCOS oxide film whose thickness is more than a thickness of the gate insulating film, the LOCOS oxide film being formed on the singlecrystalline Si substrate by surrounding the active layer; and an insulating film formed over the gate electrode and the LOCOS oxide film. On this account, on fabricating the semiconductor device having a high-performance integration system by forming the non-singlecrystalline Si semiconductor element and the singlecrystalline Si semiconductor element on the large insulating substrate, the process for making the singlecrystalline Si is simplified. Further, the foregoing arrangement provides a semiconductor substrate and a fabrication method thereof, which ensures device isolation of the minute singlecrystalline Si semiconductor element without highly-accurate photolithography, when the singlecrystalline Si semiconductor element is transferred onto the large insulating substrate.

Owner:SHARP KK

Method for manufacturing photoelectric conversion device

InactiveUS20100047952A1High Photoelectric Conversion EfficiencyReduce consumptionFinal product manufactureSemiconductor/solid-state device manufacturingMonocrystalline siliconSilanes

Owner:SEMICON ENERGY LAB CO LTD

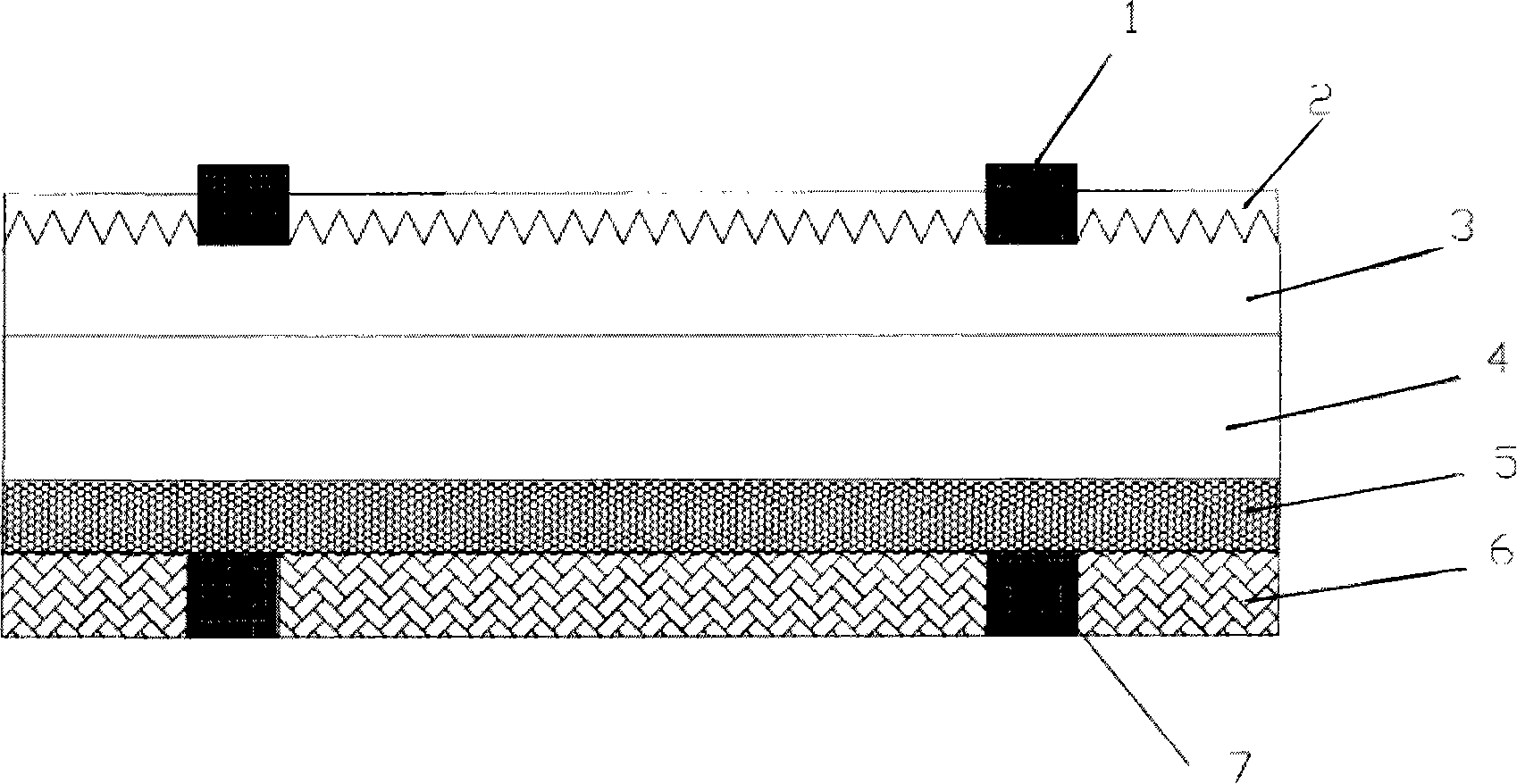

Novel aluminum emitter junction N type single crystal silicon solar battery

ActiveCN101150148ASolderabilitySolve problems that cannot be solved by firmness problemsFinal product manufacturePhotovoltaic energy generationScreen printingGrating

This invention provides a new type of type-N monocrystal silicon solar cells of Al back emission junction including: 1, Ag grating positive electrode, 2, SiNx reduction reflection layer of 80nm thick, 3, a positive N+phosphor diffusion layer of 0.3-0.5um thick, 4, type-N monocrystal silicon chip with the resistivity of 0.2-15ohmcm, 5, a P+ Al-Si alloy layer, 6,a back Al electrode, 7, a back AgAl master grating elctrode, in which, sintering of AlSi alloy and that of the back electrode are separated by two times of silk screen printing Al slurry and two times of sintering.

Owner:NINGBO ULICA SOLAR SCIENCE & TECHNOLOGY CO LTD

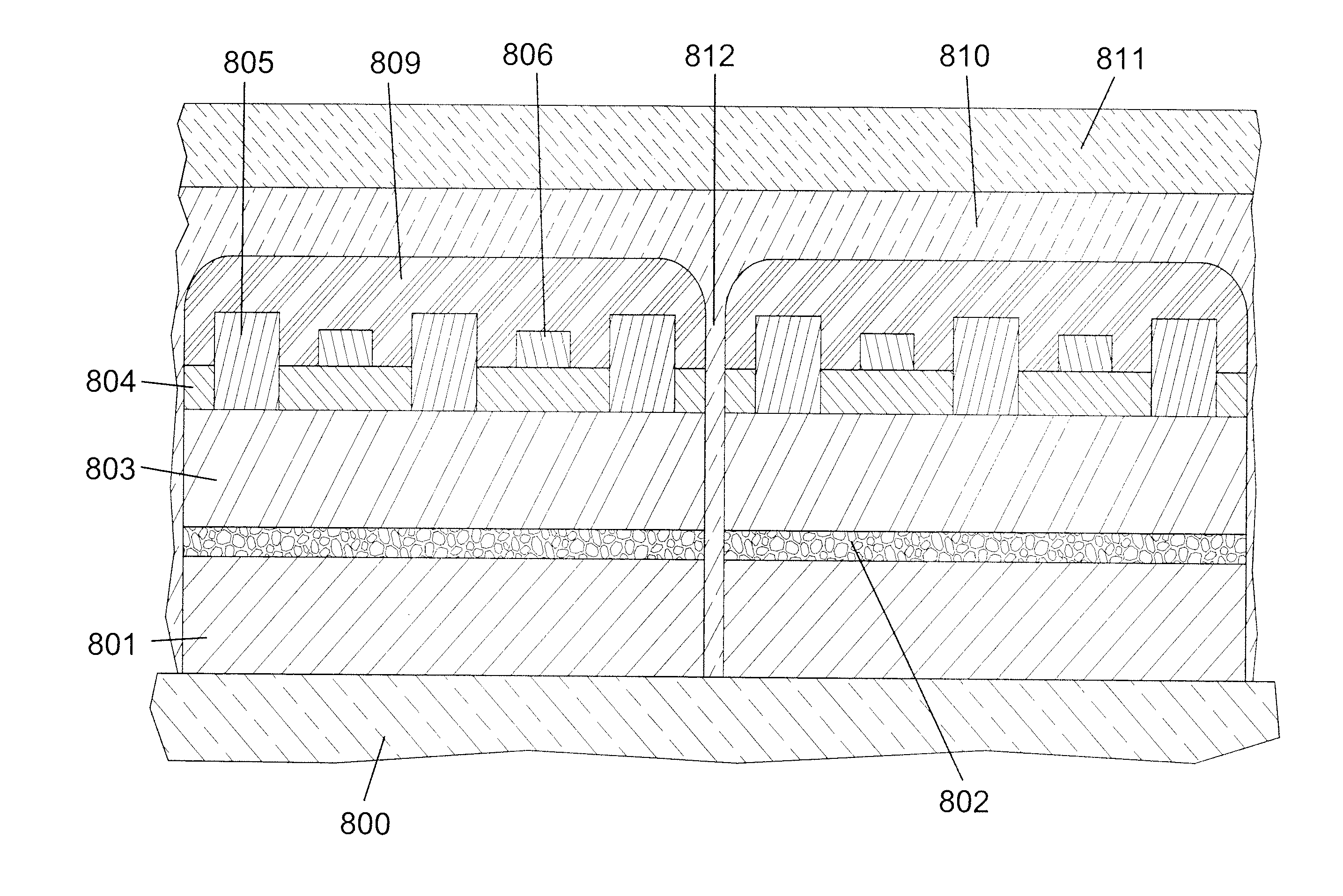

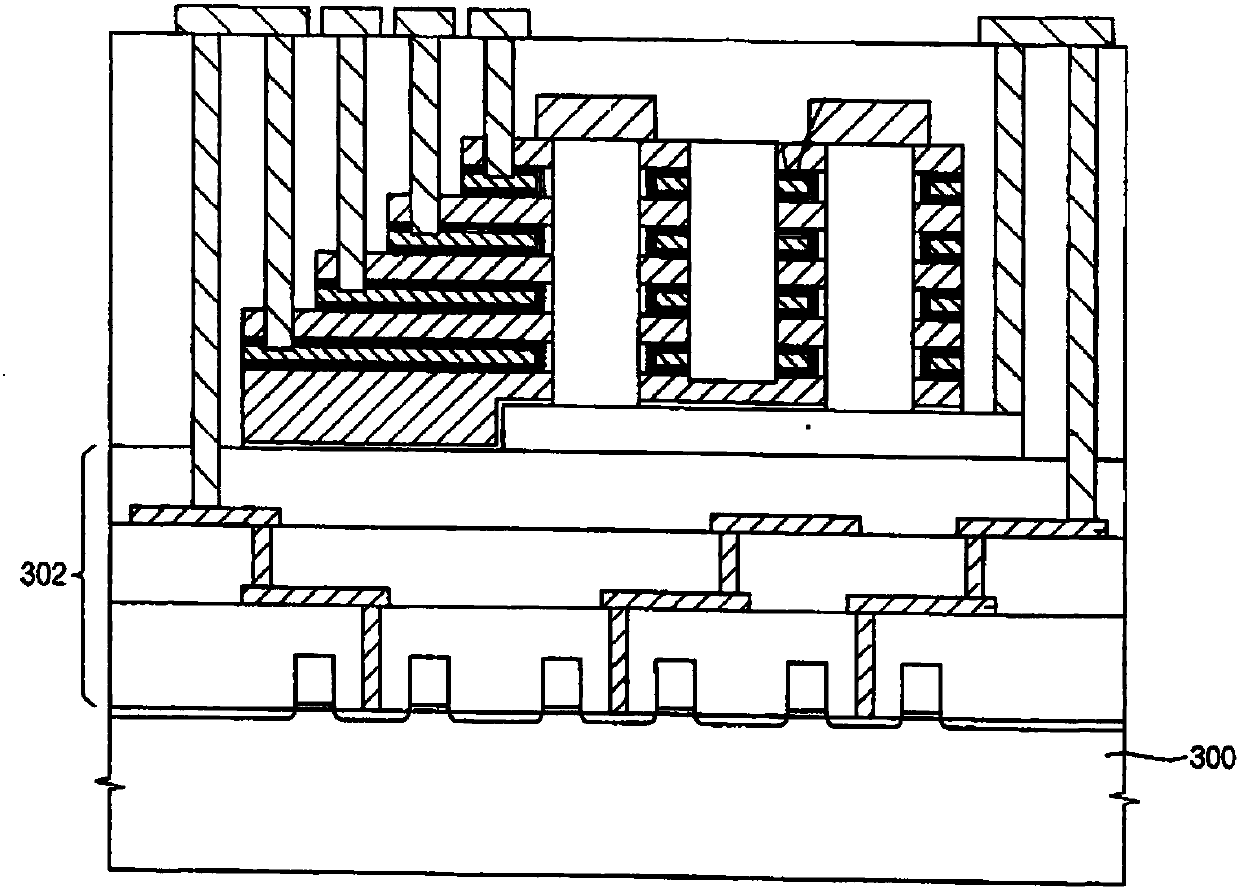

NAND memory and preparing method thereof

ActiveCN107731828ASolve the problem of temperature limitAvoid mutual influenceSolid-state devicesSemiconductor devicesElectrical conductorComputer science

The invention relates to a NAND memory and a preparing method thereof. The NAND memory comprises a plurality of NAND strings and a monocrystalline silicon layer formed on the plurality of NAND strings. The monocrystalline silicon layer is in contact connection with the NAND strings. Each of the said NAND strings comprises a plurality of conductors / insulator lamination layers, a semi-conductor channel which extends at the vertical direction and traverses through the plurality of conductors / insulator lamination layers; a tunnel layer formed between the plurality of conductors / insulator lamination layers and the semi-conductor channel; and a memory cell layer formed between the tunnel layer and the plurality of conductors / insulator lamination layers. The invention is advantageous in that through separating the preparation of array devices and peripheral devices, it can be prevented that the producing of one device will affect that of the other device; the problem of the prior art that thetemperature is limited due to the fact that the producing of the latter layer is affected by the producing of the former layer can be resolved; good peripheral device performance can be obtained; asthe array device is superposed on the peripheral device, high device density can be realized.

Owner:YANGTZE MEMORY TECH CO LTD

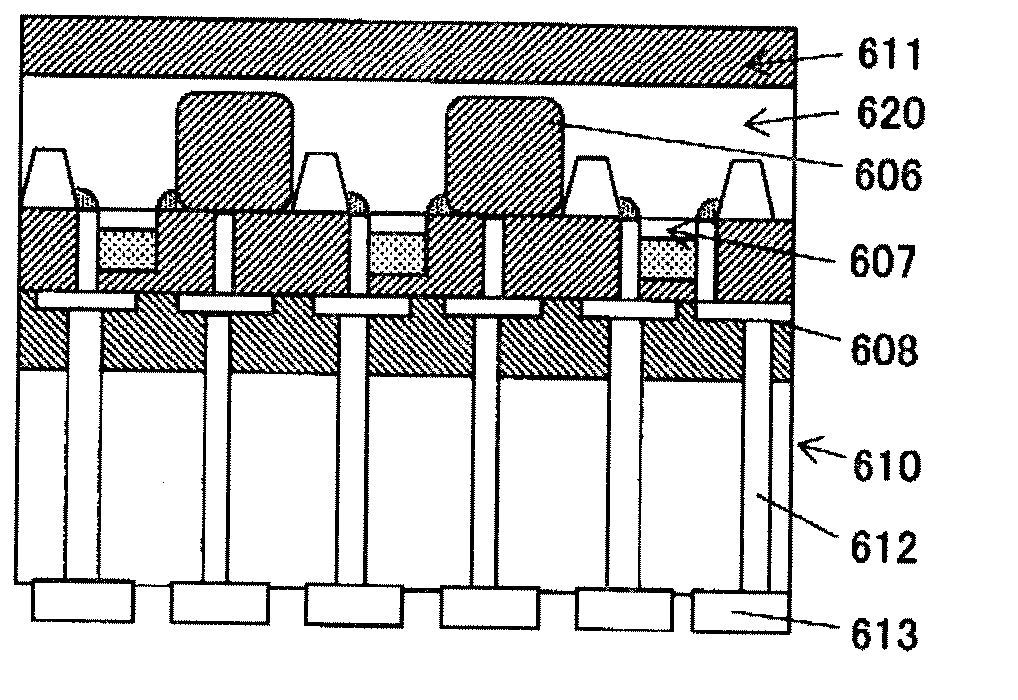

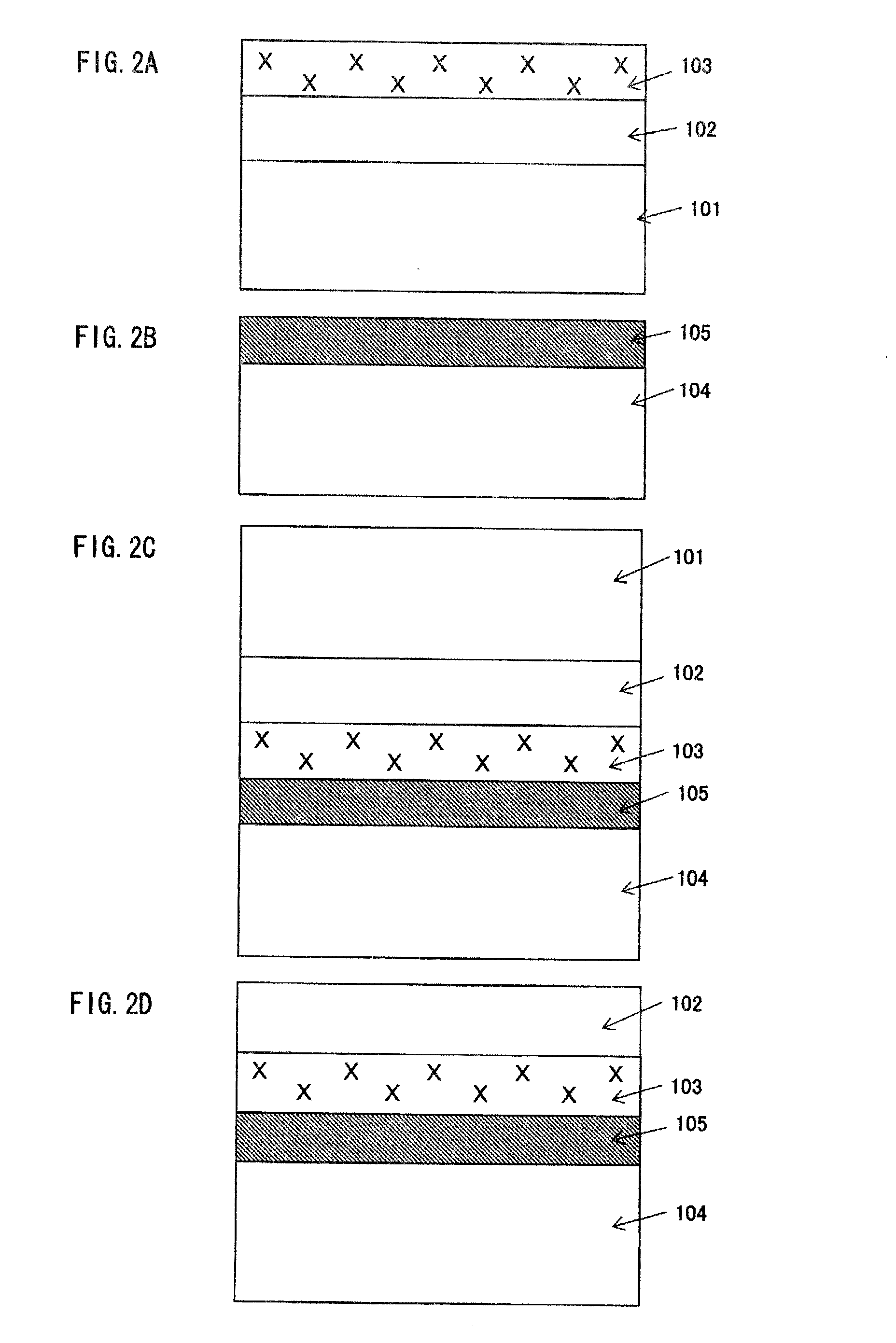

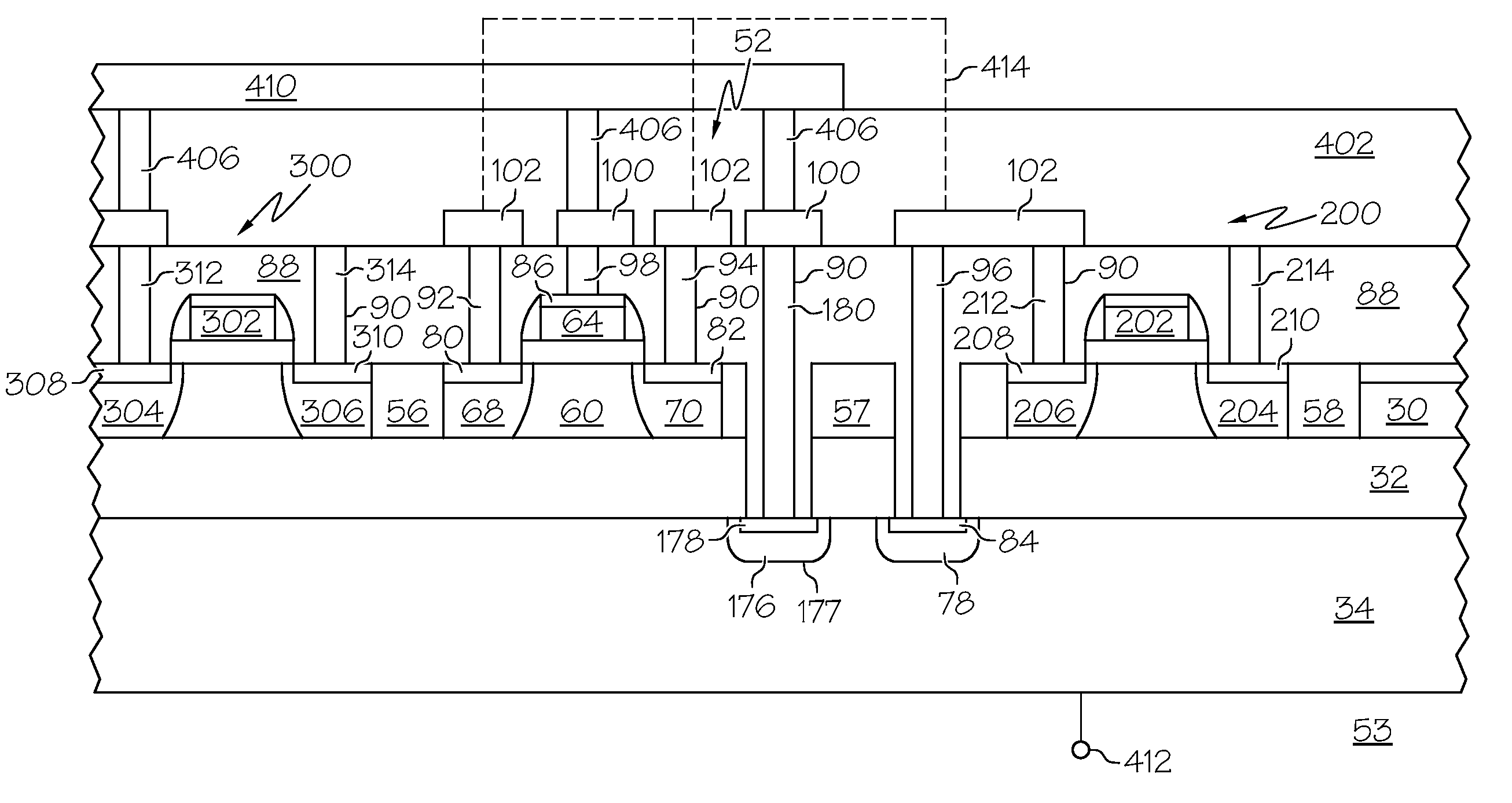

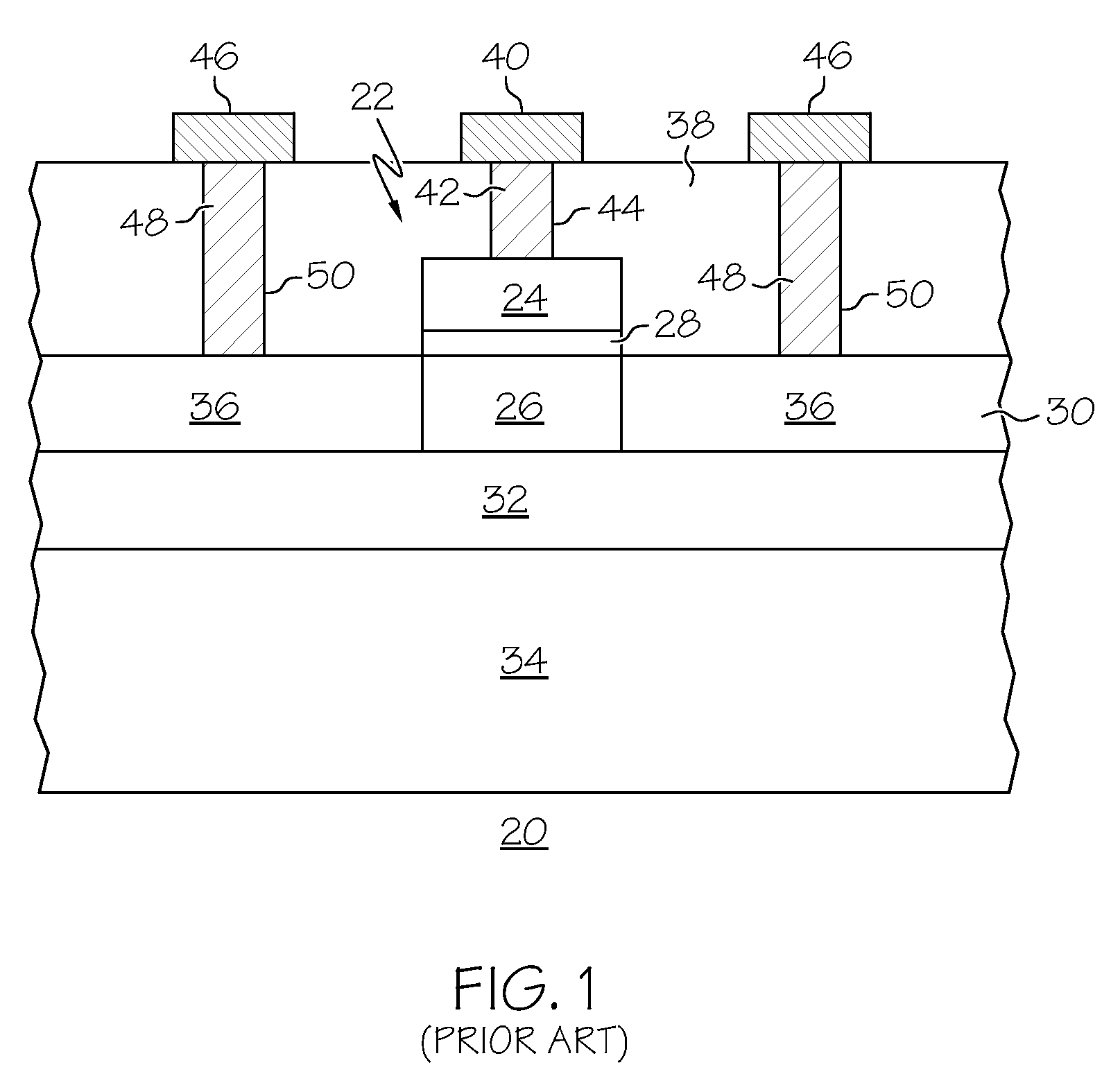

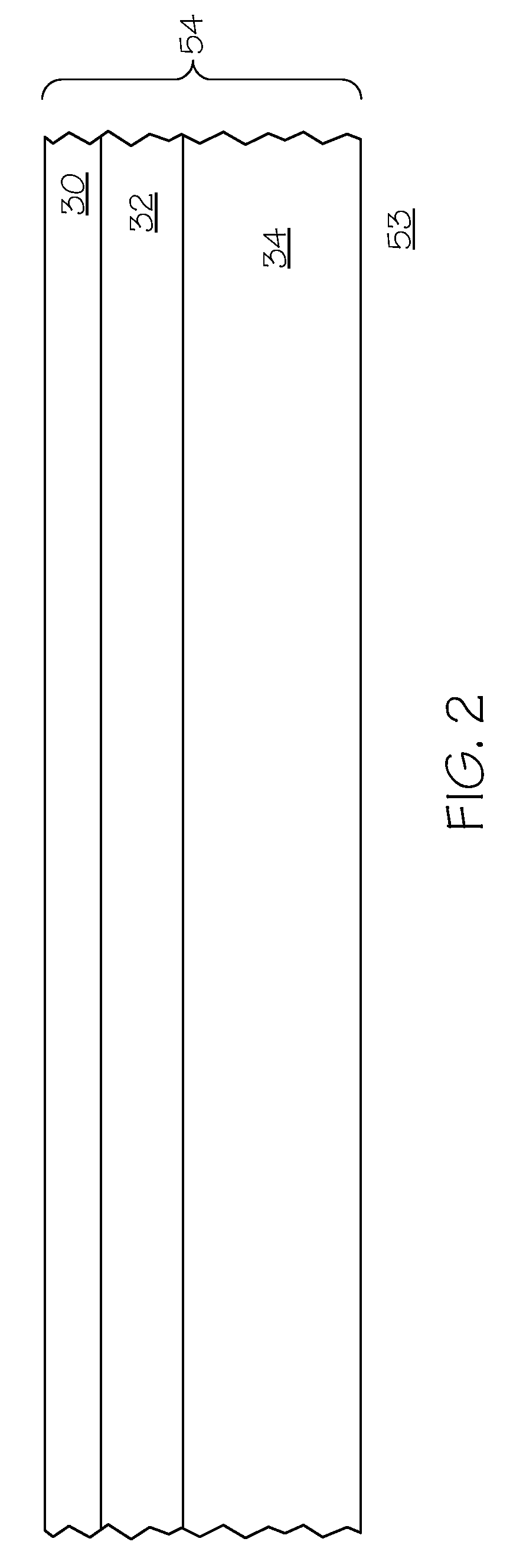

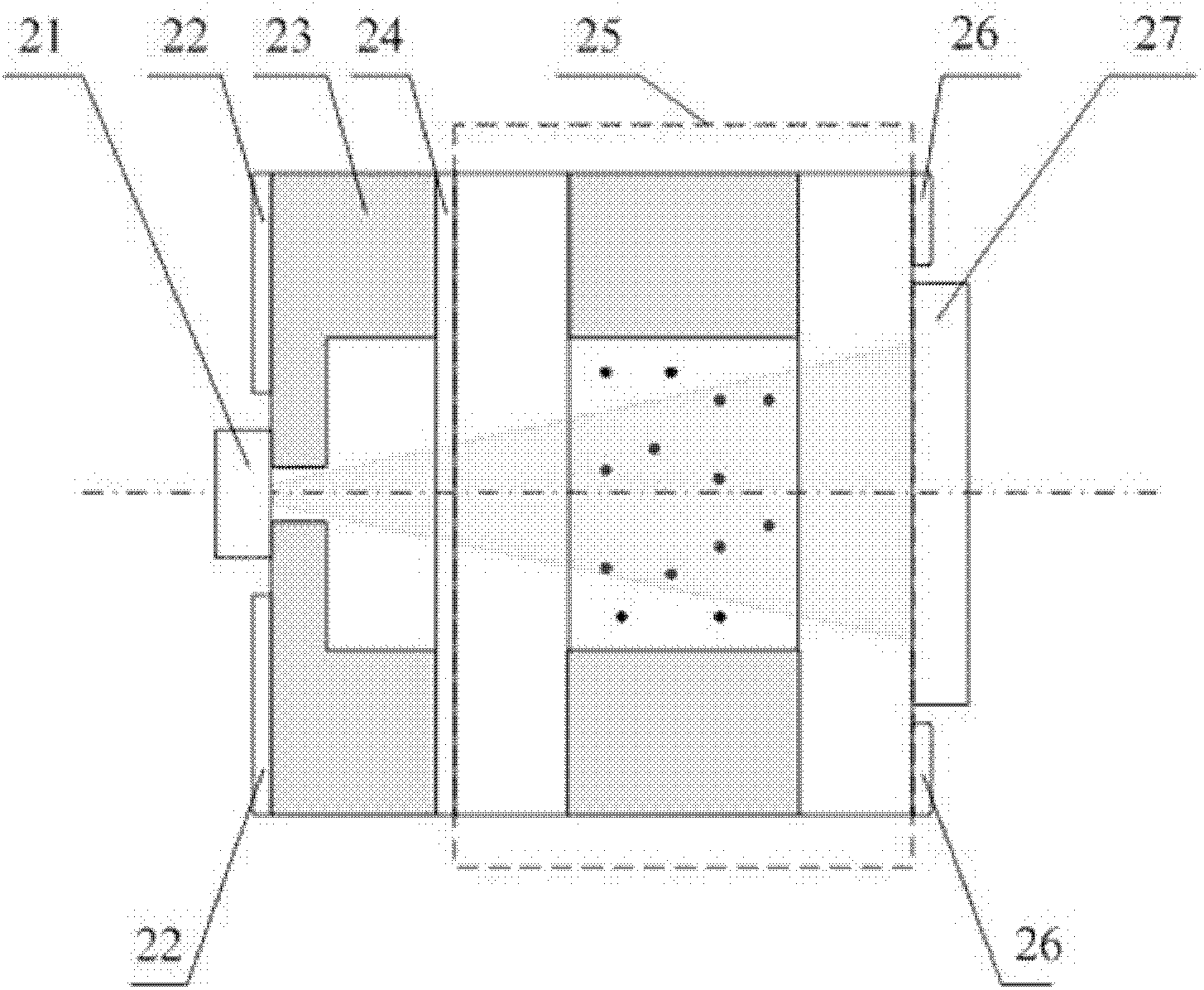

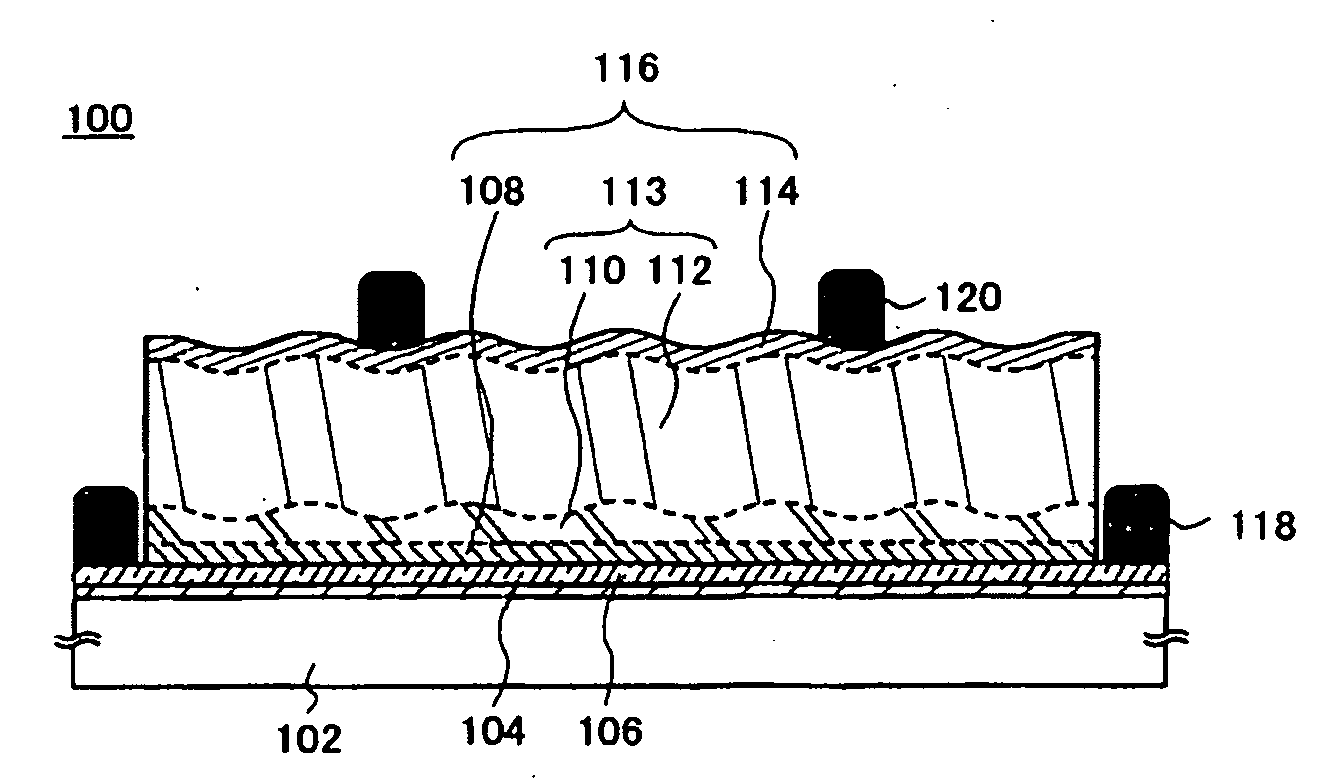

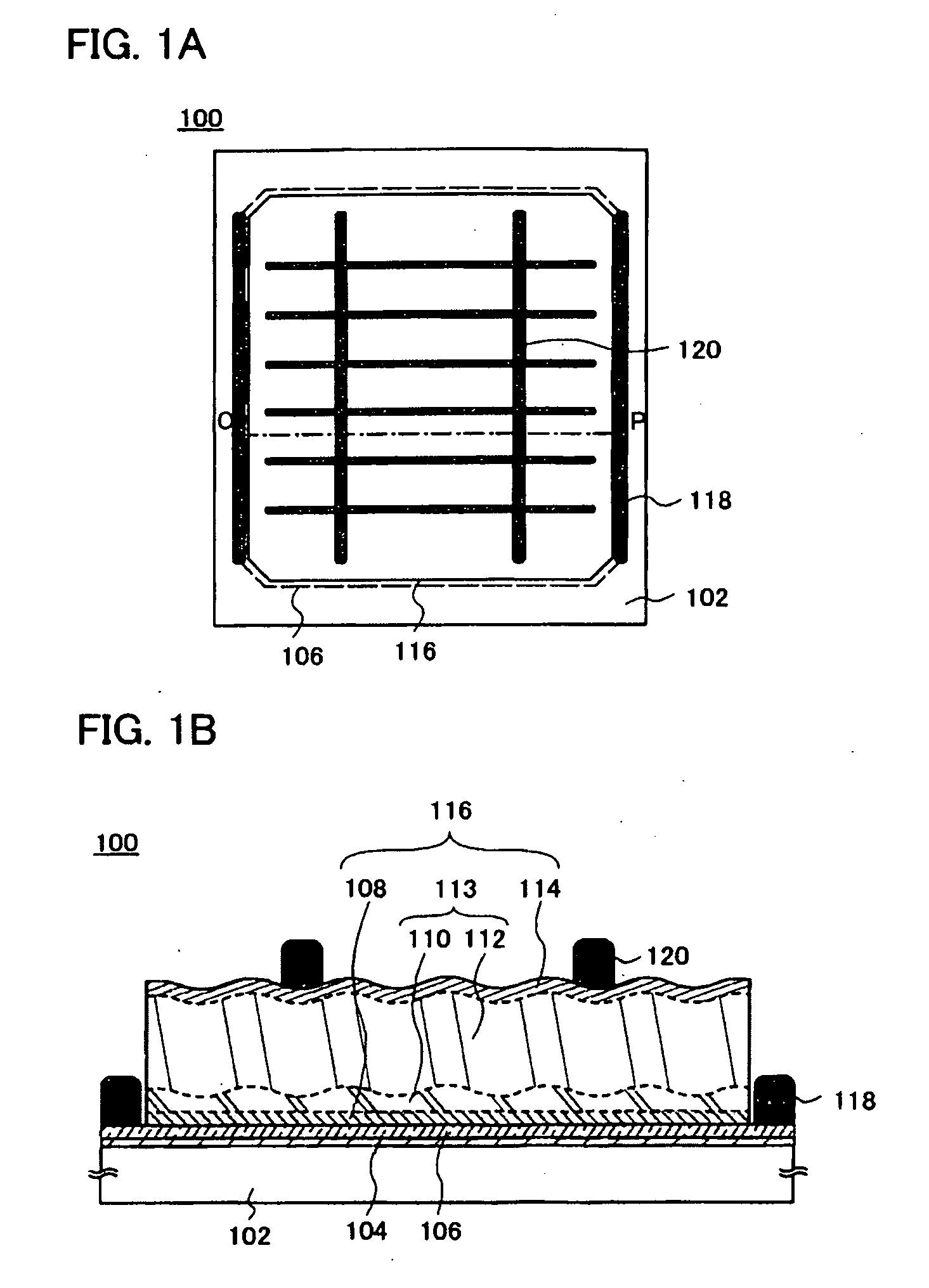

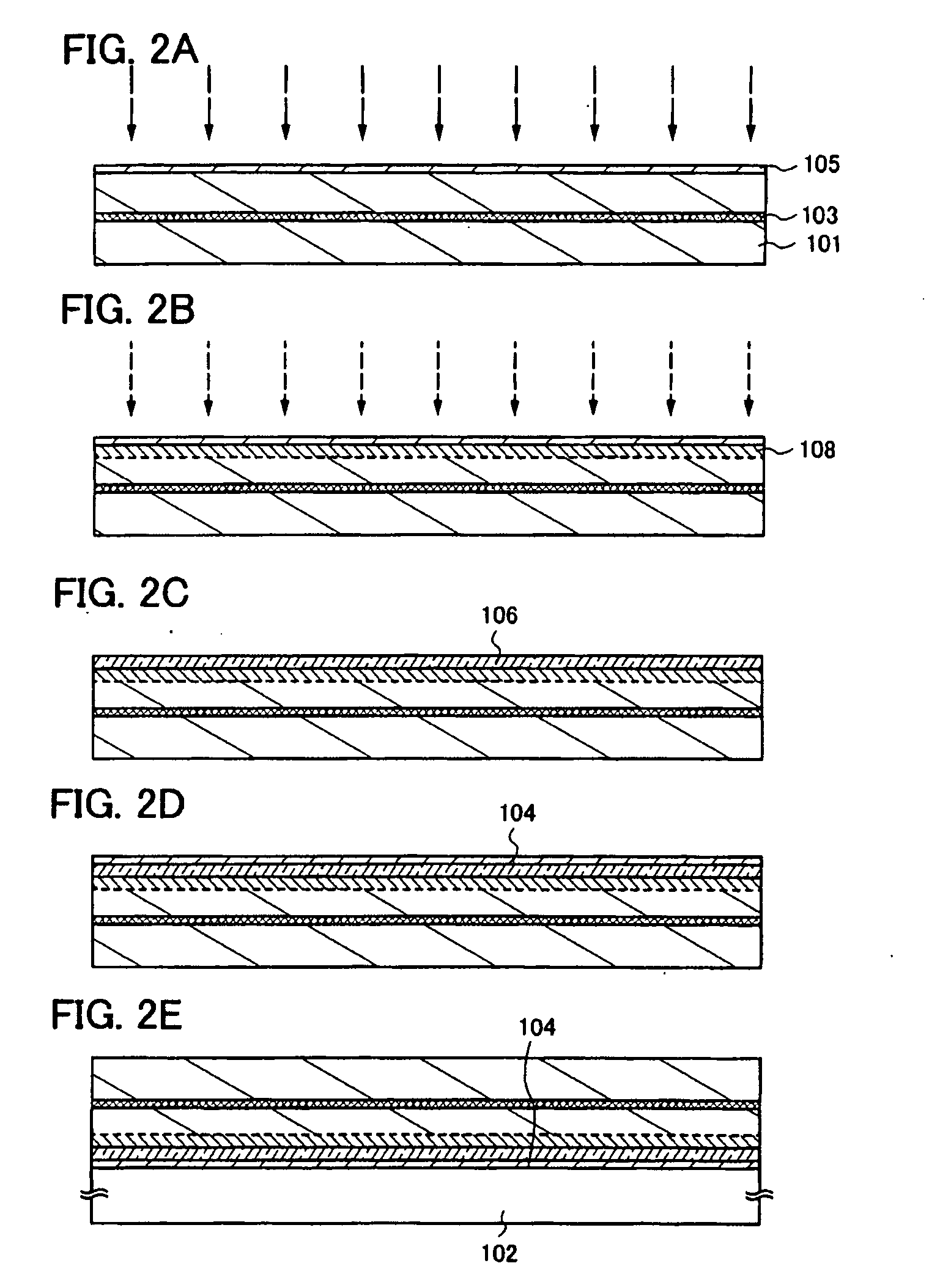

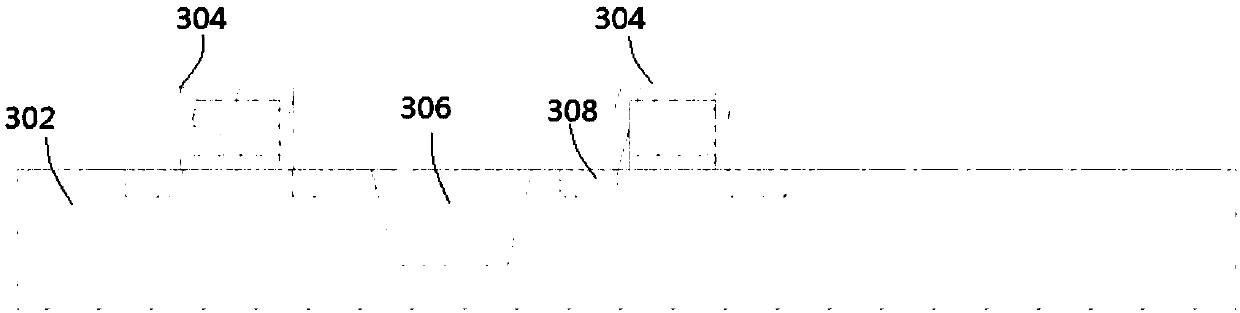

[methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof]

ActiveUS20050062079A1Total current dropUniform characteristicsTransistorSolid-state devicesProgrammable read-only memoryAmorphous silicon

A method for forming a PN junction is described. A stacked structure consisting of an N-doped (or P-doped) layer, a dielectric layer and a nucleation layer is formed, and then an insulating layer is formed having an opening therein. A P-doped (or N-doped) polysilicon or amorphous silicon layer is filled into the opening, and then annealed to convert into a single-crystal silicon layer. Then, the dielectric layer is broken down to form a PN junction.

Owner:MACRONIX INT CO LTD

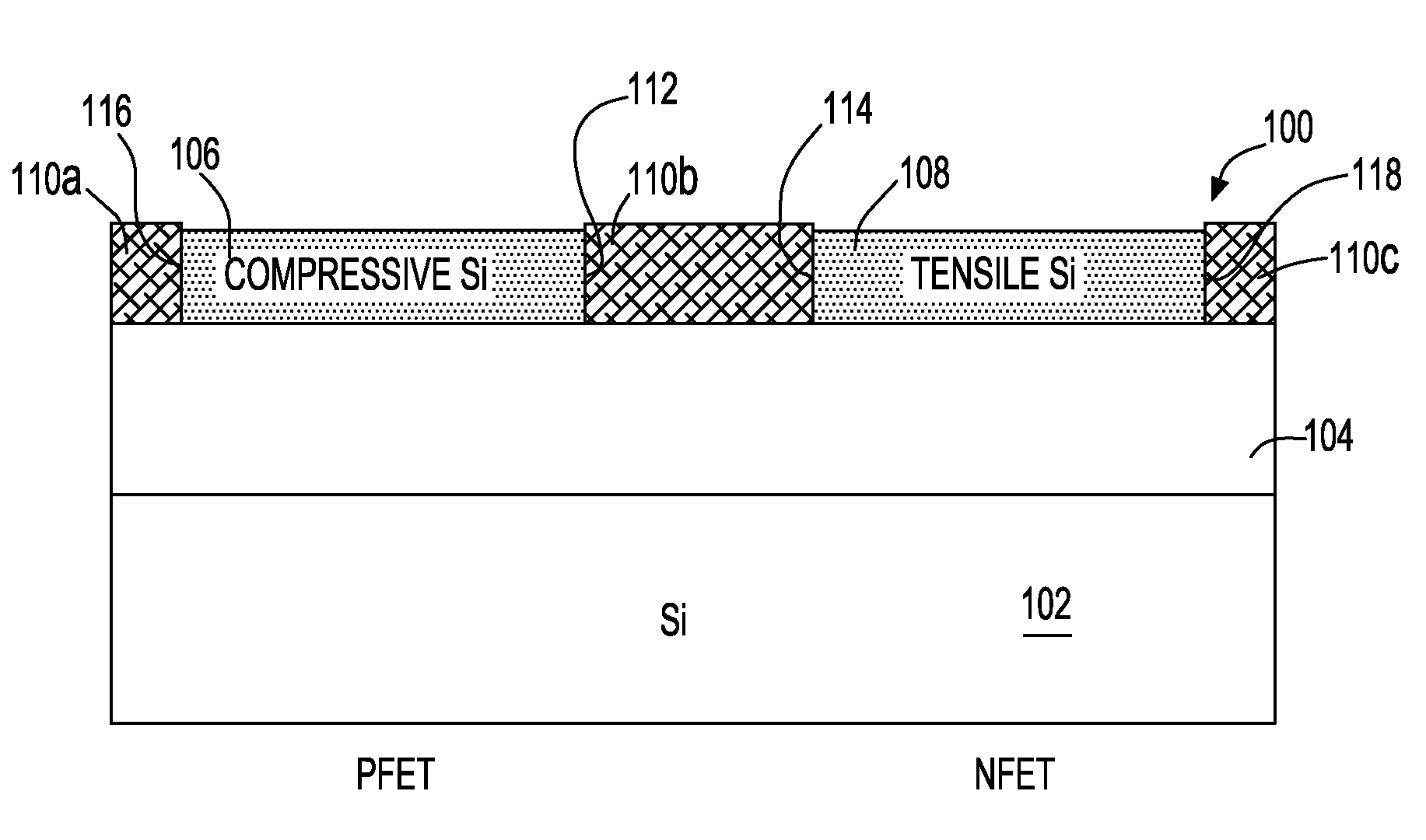

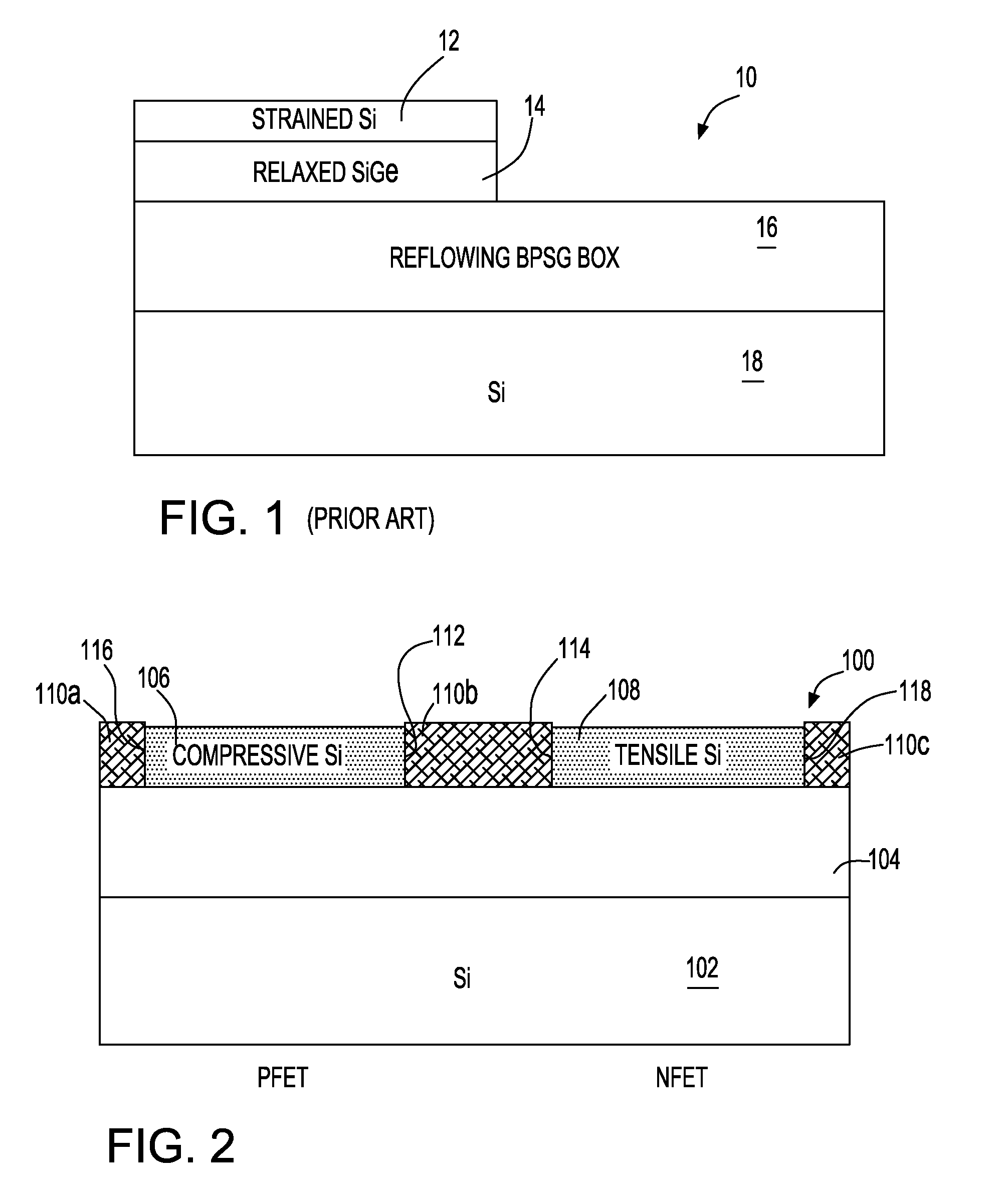

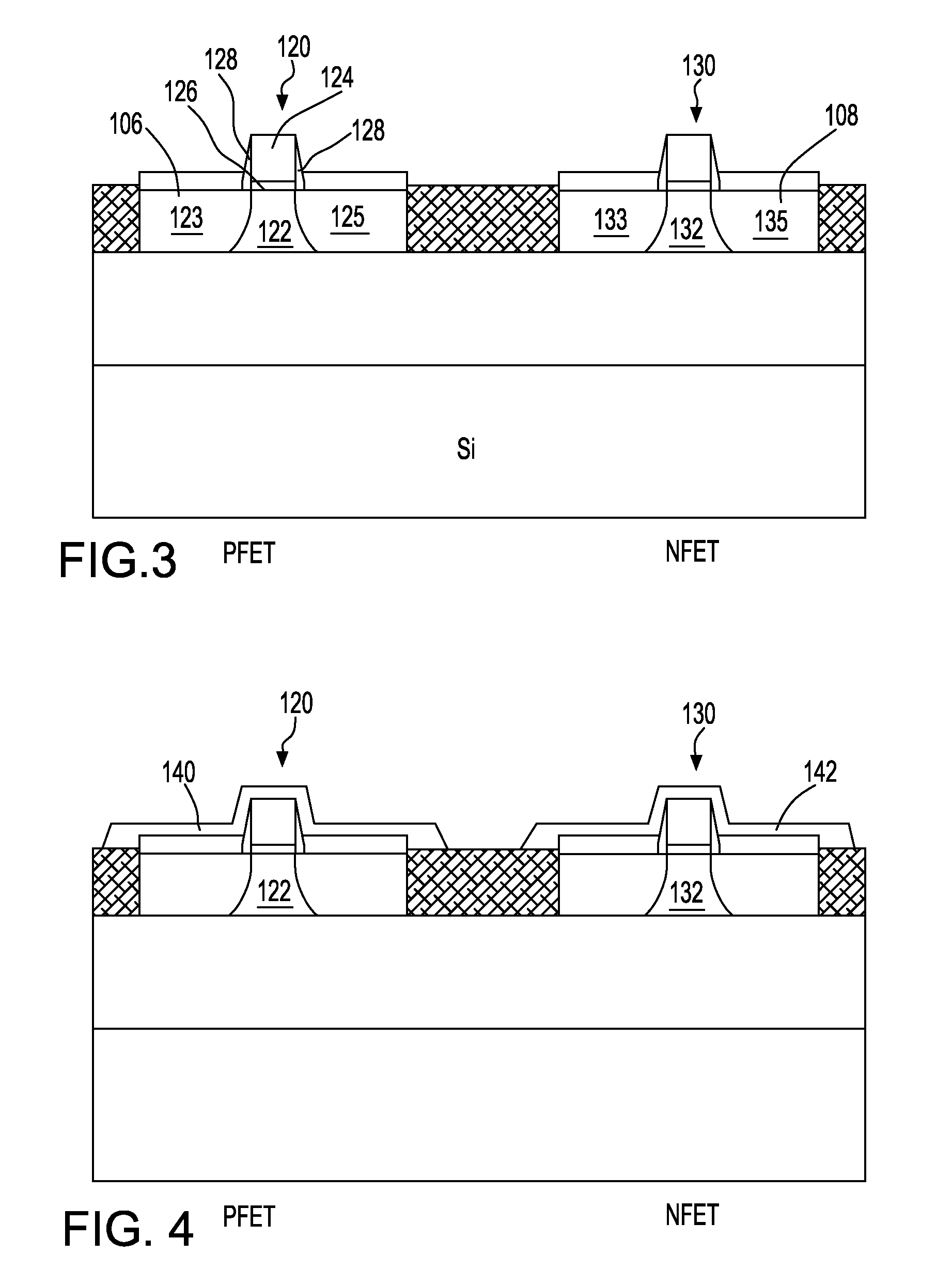

Method of forming stressed SOI FET having doped glass box layer using sacrificial stressed layer

InactiveUS7888197B2Solid-state devicesSemiconductor/solid-state device manufacturingSilicate glassField effect

A method is provided for fabricating a semiconductor-on-insulator (“SOI”) substrate. In such method an SOI substrate is formed to include (i) an SOI layer of monocrystalline silicon separated from (ii) a bulk semiconductor layer by (iii) a buried oxide (“BOX”) layer including a layer of doped silicate glass. A sacrificial stressed layer is deposited onto the SOI substrate to overlie the SOI layer. Trenches are then etched through the sacrificial stressed layer and into the SOI layer. The SOI substrate is heated with the sacrificial stressed layer sufficiently to cause the glass layer to soften and the sacrificial stressed layer to relax, to thereby apply a stress to the SOI layer to form a stressed SOI layer. The trenches in the stressed SOI layer are then filled with a dielectric material to form trench isolation regions contacting peripheral edges of the stressed SOI layer, the trench isolation regions extending downwardly from a major surface of the stressed SOI layer towards the BOX layer. The sacrificial stressed layer is then removed to expose the stressed SOI layer. Field effect transistors can then be formed in the stressed SOI layer.

Owner:ELPIS TECH INC

Crucible coating layer for polycrystal silicon or single crystal silicon and preparation method thereof

The invention relates to a crucible coating layer and a preparation method thereof, in particular to a crucible coating layer for polycrystal silicon or single crystal silicon and a preparation method thereof, which are especially applicable to preparation of special-shaped and small-sized crucible coating layers for polycrystal silicon or single crystal silicon. The invention aims at providing the crucible coating layer for polycrystal silicon or single crystal silicon and the preparation method thereof, wherein the density range of the coating layer is 0.75-1.8g / cm<3>; the preparation method comprises the following operation steps that: silicon nitride powdery particles is adopted to be mixed with a solvent to obtain silicon nitride suspending liquid which is used as raw material for preparing the coating layer, wherein the silicon nitride suspending liquid is injected into a crucible; the silicon nitride suspending liquid is absorbed on the inner wall of the crucible; and the residual silicon nitride suspending liquid in the crucible is discharged. The coating layer provided by the invention has high strength, good density, and short needed time for preparation time, can utilize the silicon nitride powdery particles for preparing the coating layer completely and also improves the working environment for preparing the coating layer greatly and simultaneously.

Owner:JIANGXI SAI WEI LDK SOLAR HI TECH CO LTD

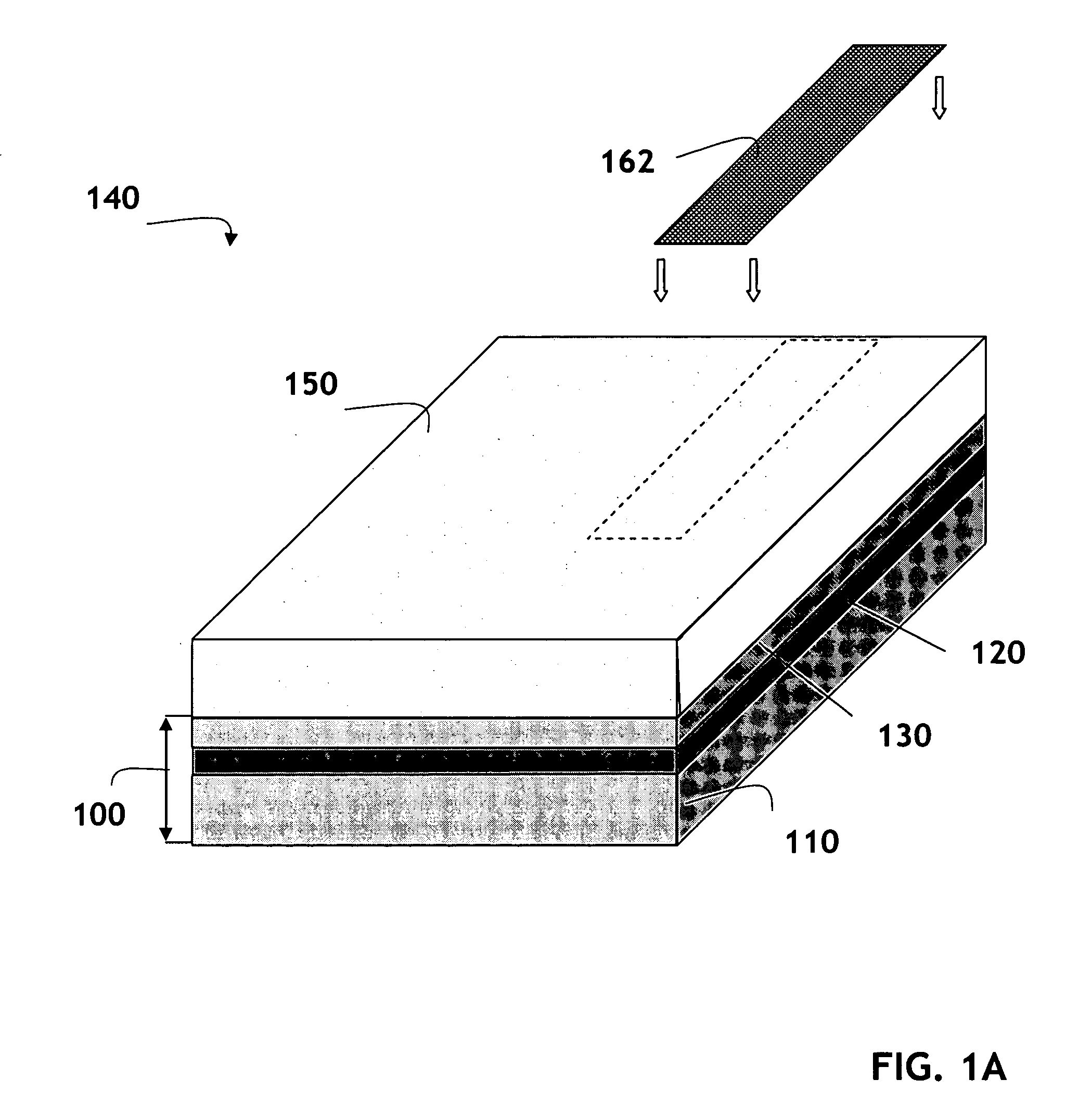

Thin film solar cell with ceramic handling layer

ActiveUS20110186117A1Low costEliminate needPV power plantsFinal product manufactureSusceptorMaterials science

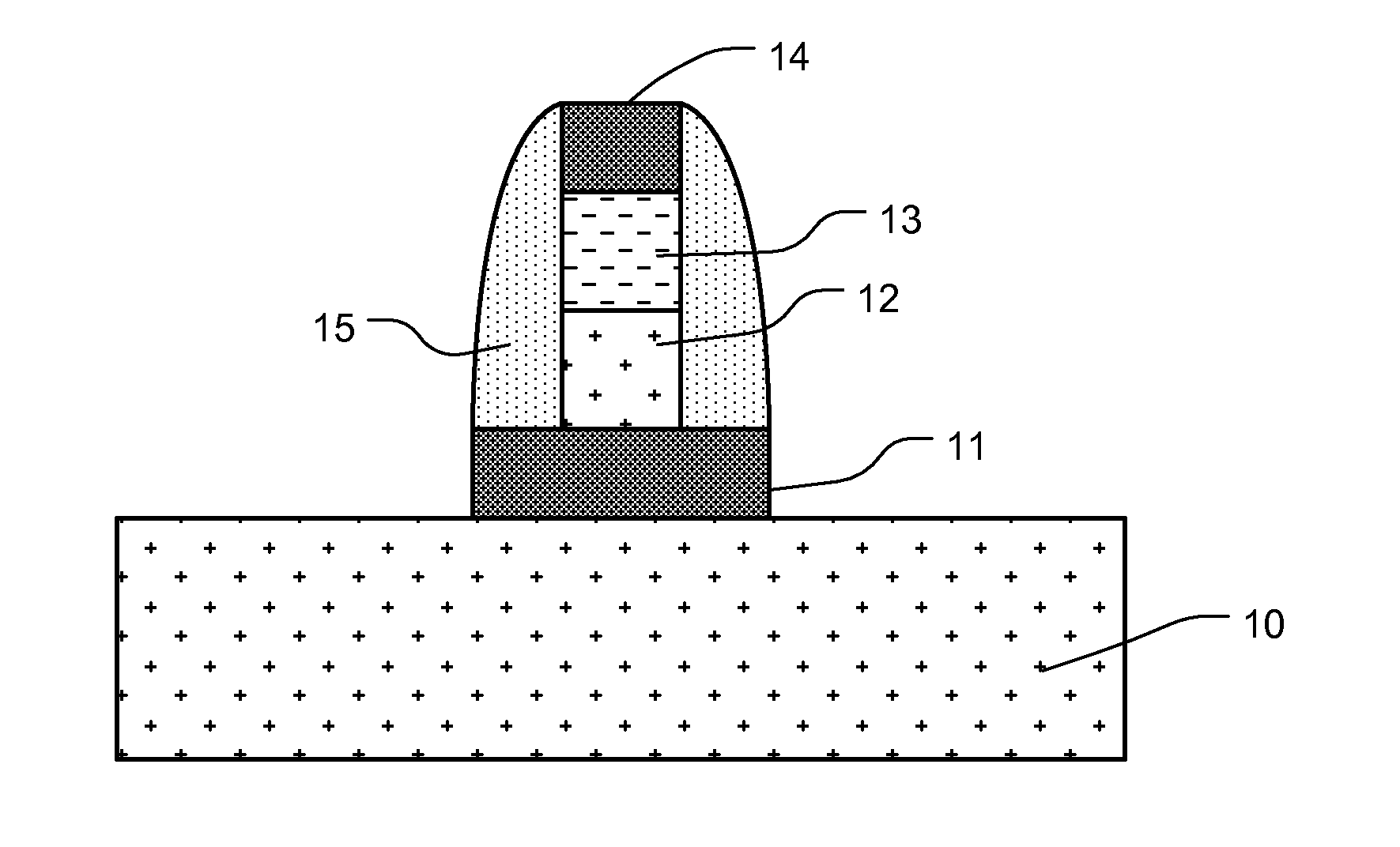

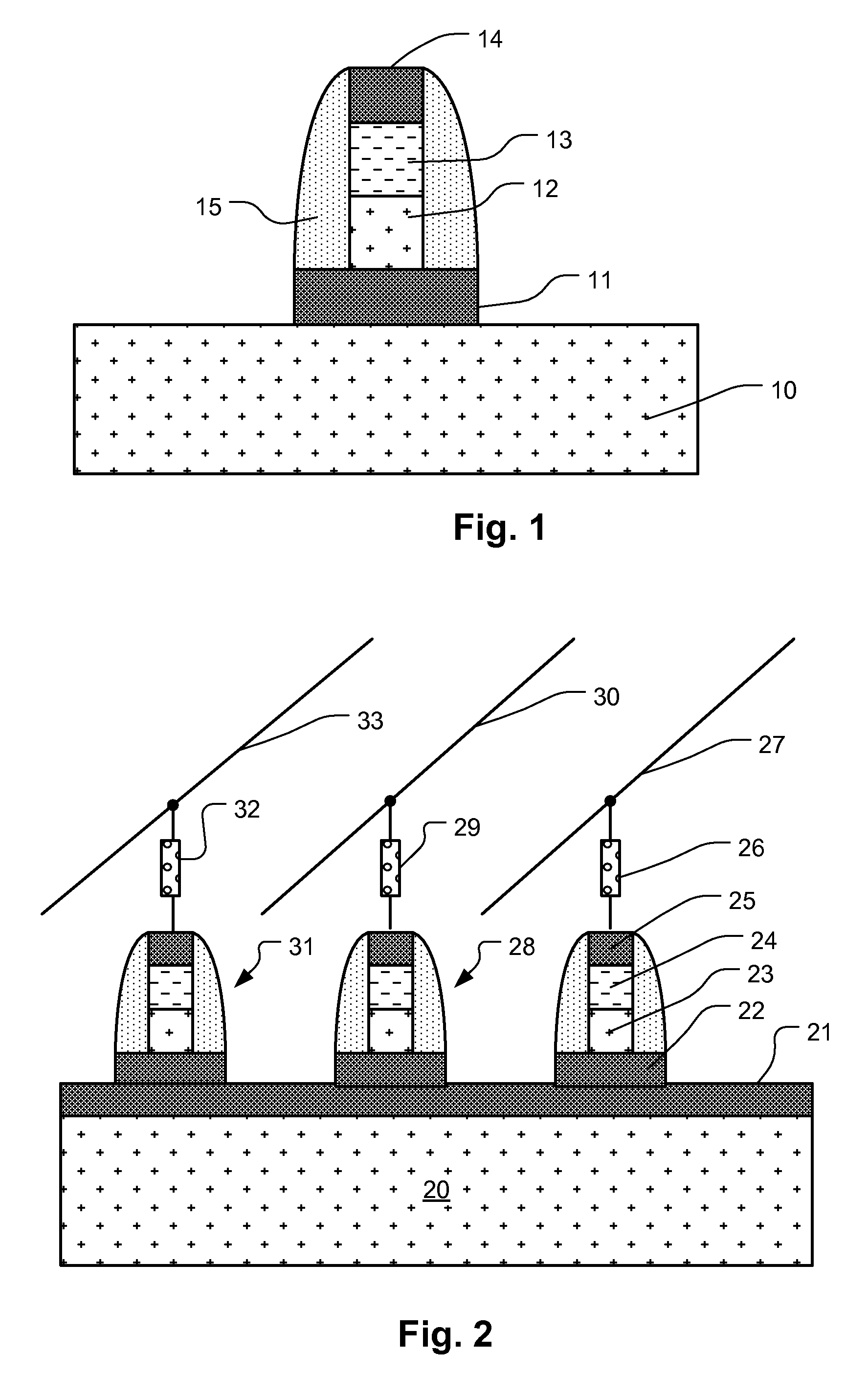

A method for fabricating a photovoltaic (PV) cell panel wherein all PV cells are formed simultaneously on a two-dimensional array of monocrystalline silicon mother wafers affixed to a susceptor is disclosed. Porous silicon separation layers are anodized in the surfaces of the mother wafers. The porous film is then smoothed to form a suitable surface for epitaxial film growth. An epitaxial reactor is used to grow n- and p-type films forming the PV cell structures. A glass / ceramic handling layer is then formed on the PV cell structures. The PV cell structures with handling layers are then exfoliated from the mother wafer. The array of mother wafers may be reused multiple times, thereby reducing materials costs for the completed solar panels. The glass / ceramic handling layers provide structural integrity to the thin epitaxial solar cells during the separation process and subsequent handling.

Owner:SVAGOS TECHNICK INC

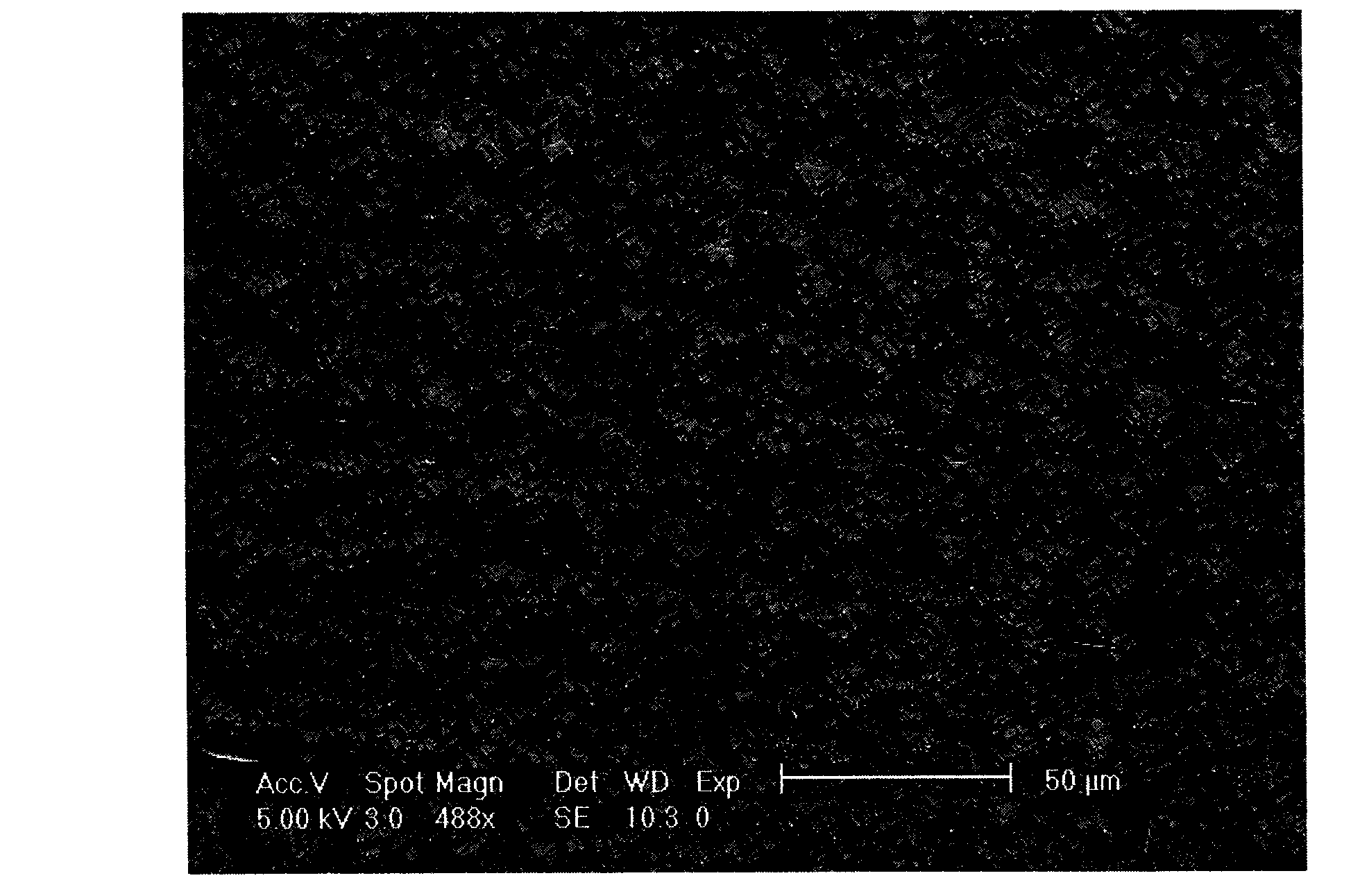

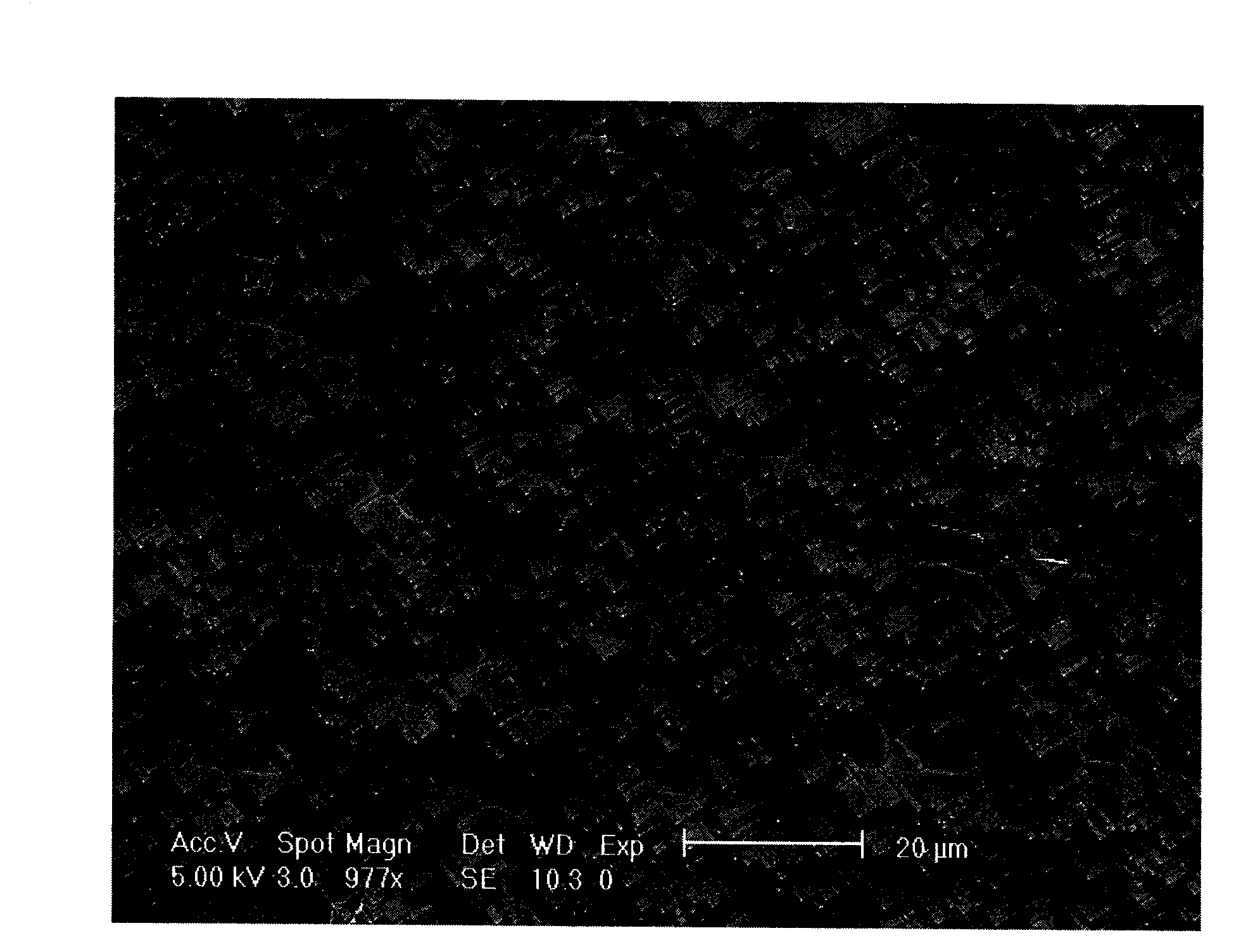

Monocrystalline silicon wafer alcohol-free texturing process and texturing additive

ActiveCN104576831AReduce CODReduce the cost of cashmereAfter-treatment detailsFinal product manufactureAlcohol freePotassium hydroxide

The invention relates to a monocrystalline silicon wafer alcohol-free texturing process and a texturing additive. Firstly, a silicon wafer is placed in preprocessing liquid so as to be preprocessed for 60 s to 300 s, and the silicon wafer is then placed in texturing liquid for texturing. The monocrystalline silicon texturing process includes the steps that deionized water is heated to 70 DEG C to 90 DEG C, sodium hydroxide or potassium hydroxide is added, and monocrystalline silicon texturing corrosive liquid is acquired. When the texturing additive is adopted for texturing, isopropanol or ethyl alcohol is not needed, tiny, even and dense pyramid texturing faces can be acquired, texturing cost is reduced, and environmental pollution is avoided. The preprocessing process is added before the texturing step, the silicon wafer acquired after texturing can be cleaner, rework caused by white spot fingerprints and the like can be reduced, and certain practical value is achieved.

Owner:JIANGSU SHUNFENG PHOTOVOLTAIC TECH CO LTD

![[methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof] [methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof]](https://images-eureka.patsnap.com/patent_img/511fe210-dbeb-4c72-b386-616e96a7a6c3/US20050062079A1-20050324-D00000.png)

![[methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof] [methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof]](https://images-eureka.patsnap.com/patent_img/511fe210-dbeb-4c72-b386-616e96a7a6c3/US20050062079A1-20050324-D00001.png)

![[methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof] [methods for forming pn junction, one-time programmable read-only memory and fabricating processes thereof]](https://images-eureka.patsnap.com/patent_img/511fe210-dbeb-4c72-b386-616e96a7a6c3/US20050062079A1-20050324-D00002.png)