Soi device and method for its fabrication

a technology of semiconductor devices and dielectric materials, applied in semiconductor devices, diodes, electrical apparatus, etc., can solve problems such as destructive discharge through capacitor dielectric materials, significant voltage spikes on bus, and affecting the yield and reliability of integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011]The following detailed description is merely exemplary in nature and is not intended to limit the invention or the application and uses of the invention. Furthermore, there is no intention to be bound by any expressed or implied theory presented in the preceding technical field, background, brief summary or the following detailed description.

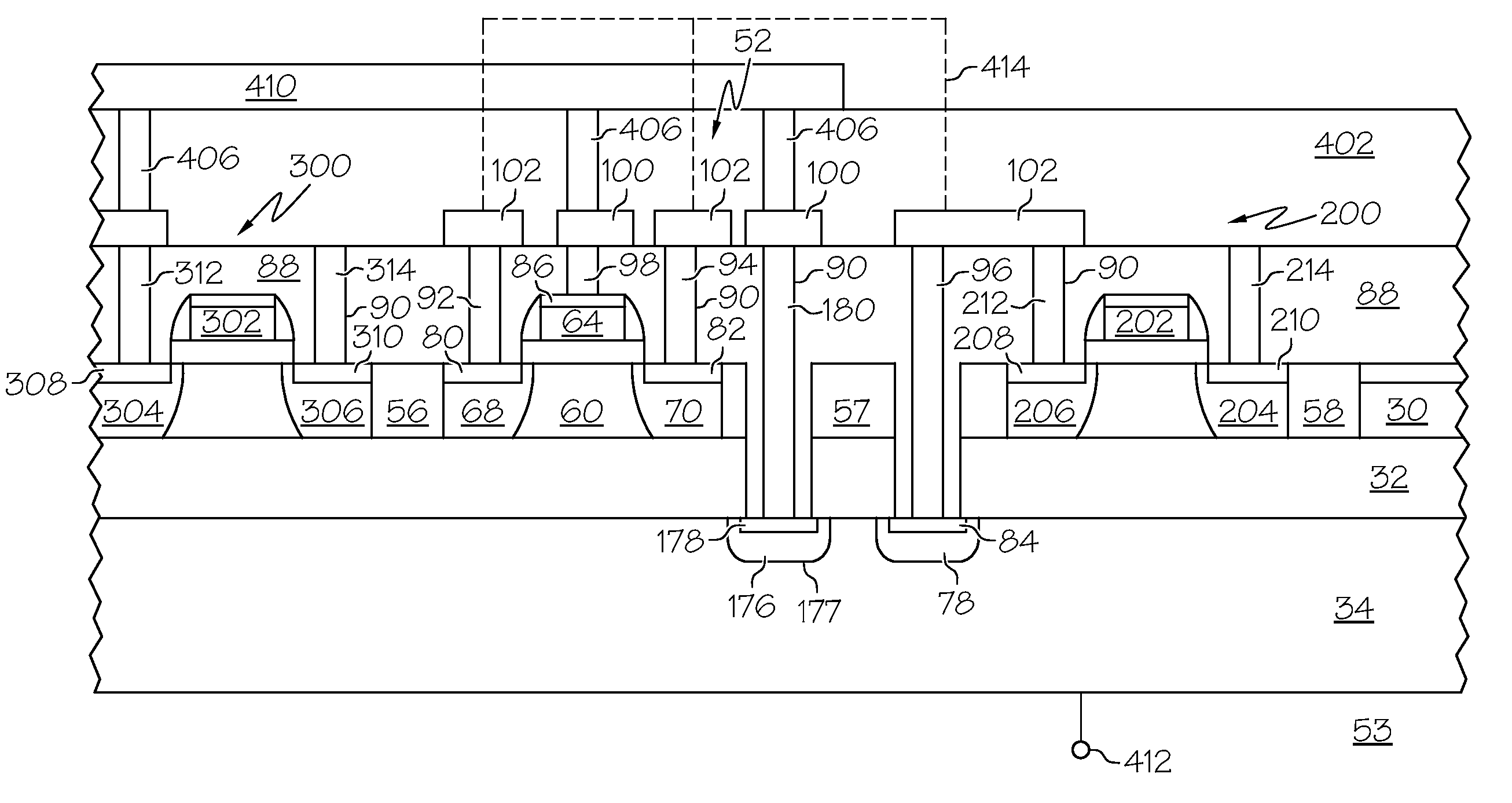

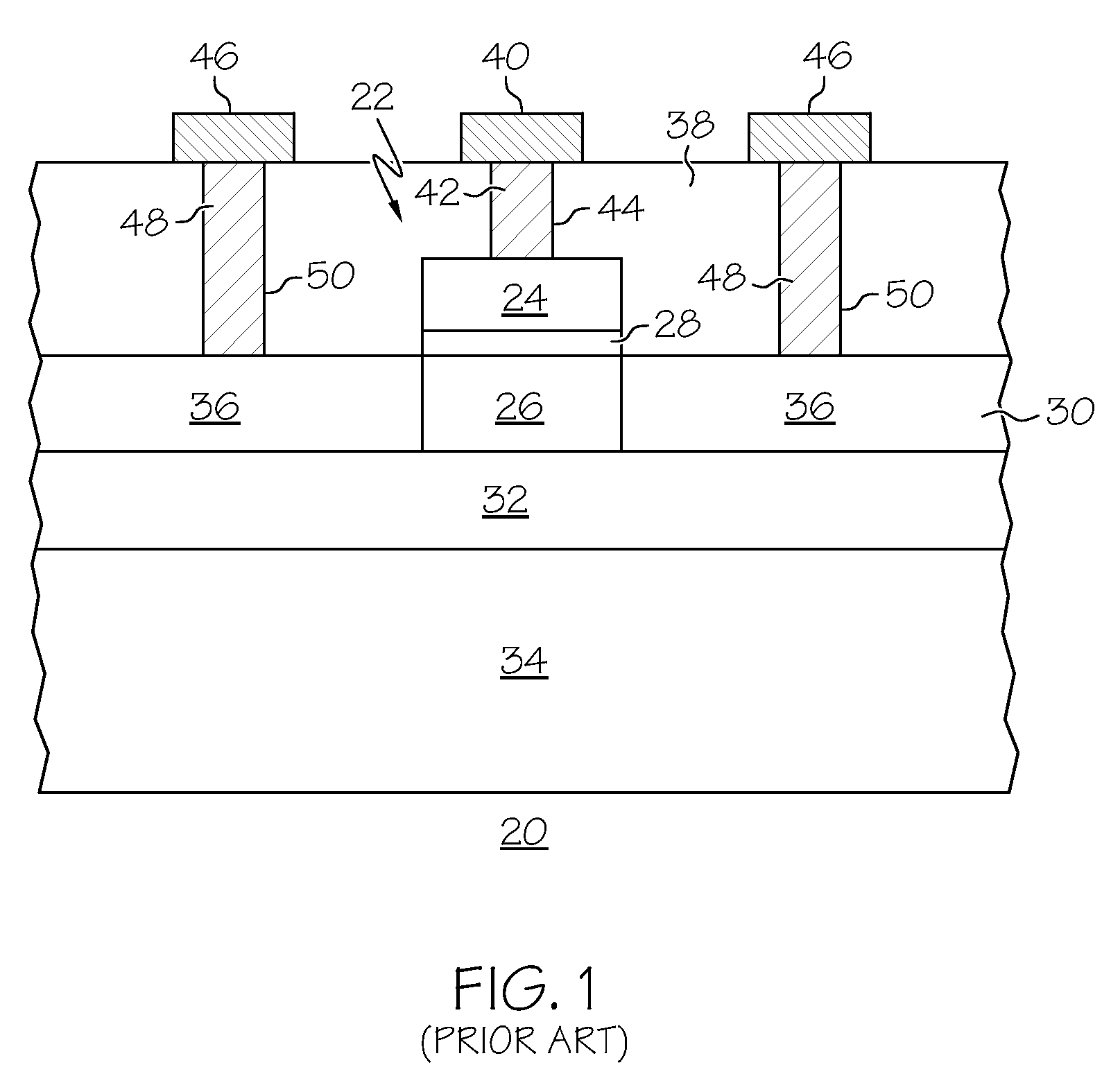

[0012]FIG. 1 illustrates, in partial cross section, elements of a conventional decoupling capacitor structure 20 implemented in a portion of a silicon on insulator (SOI) integrated circuit (IC) device structure. Such an IC structure might include a plurality of distributed MOS capacitors 22 (only one of which is illustrated), each of which includes a top plate 24, a bottom plate 26 and a capacitor dielectric 28. Top plate 24 generally is formed from the same material as are the gate electrodes of the MOS transistor that make up the remainder of the IC. Capacitor dielectric 28 generally is formed of the same material used for the gate diele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More