Patents

Literature

1042 results about "Decoupling capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

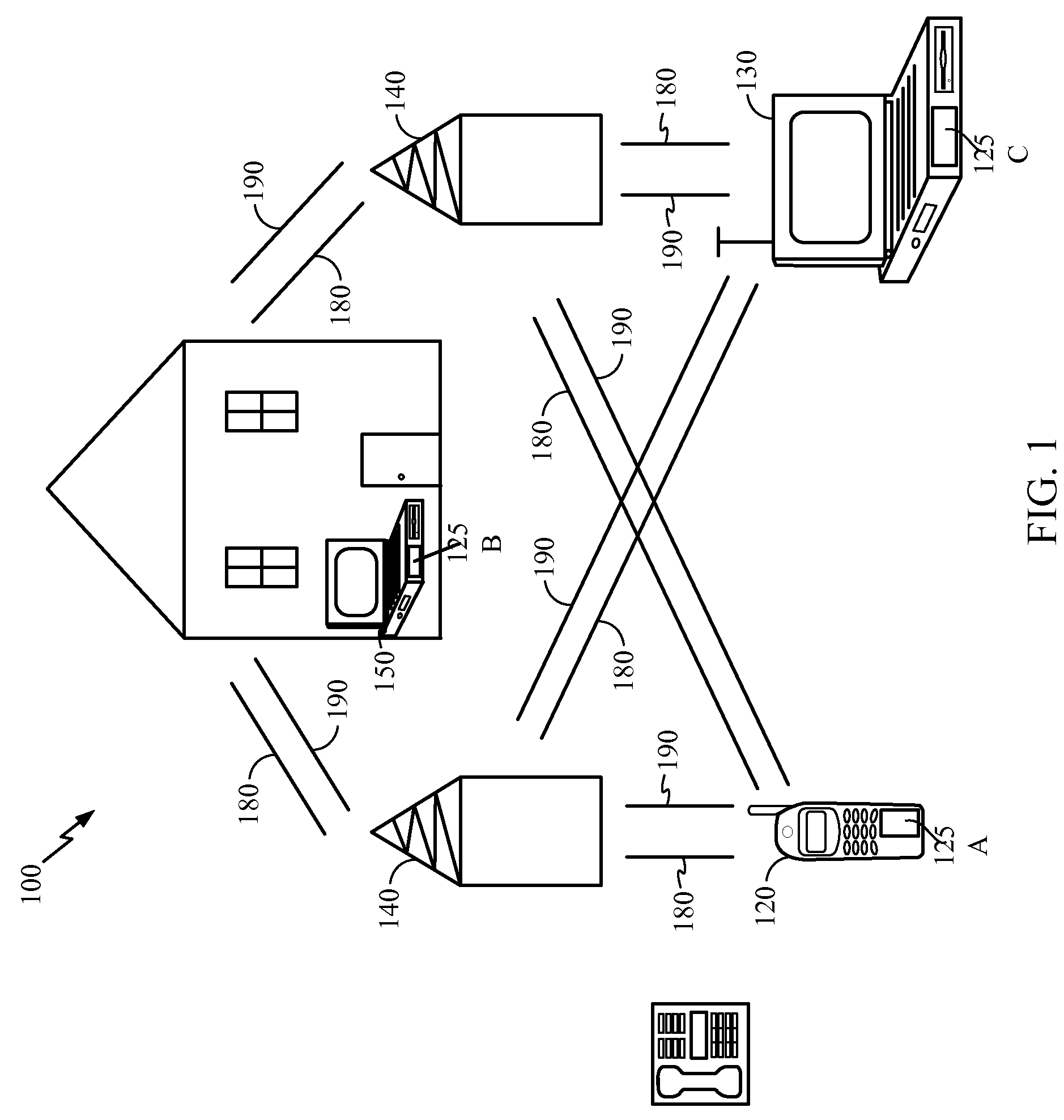

A decoupling capacitor is a capacitor used to decouple one part of an electrical network (circuit) from another. Noise caused by other circuit elements is shunted through the capacitor, reducing the effect it has on the rest of the circuit. An alternative name is bypass capacitor as it is used to bypass the power supply or other high impedance component of a circuit.

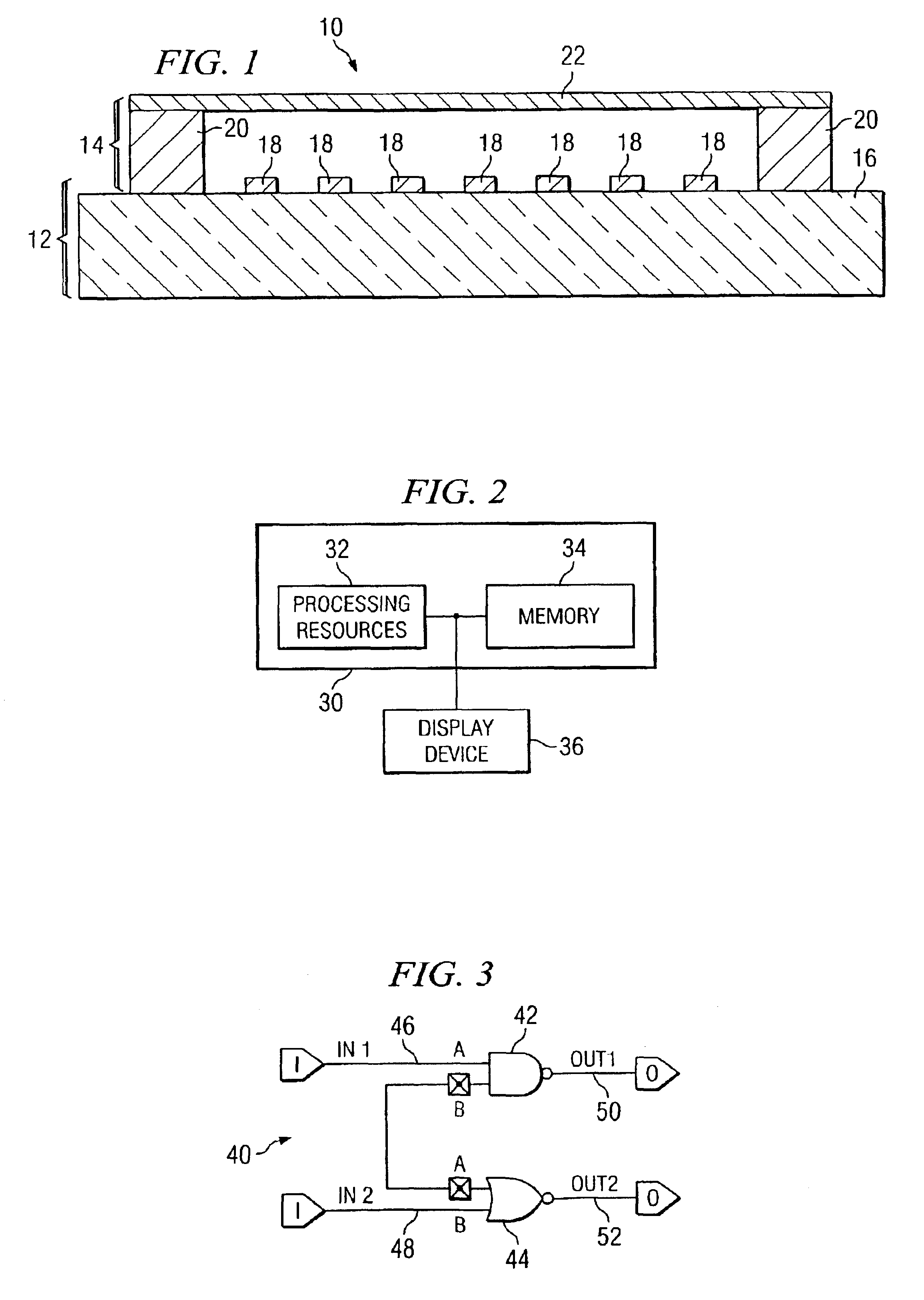

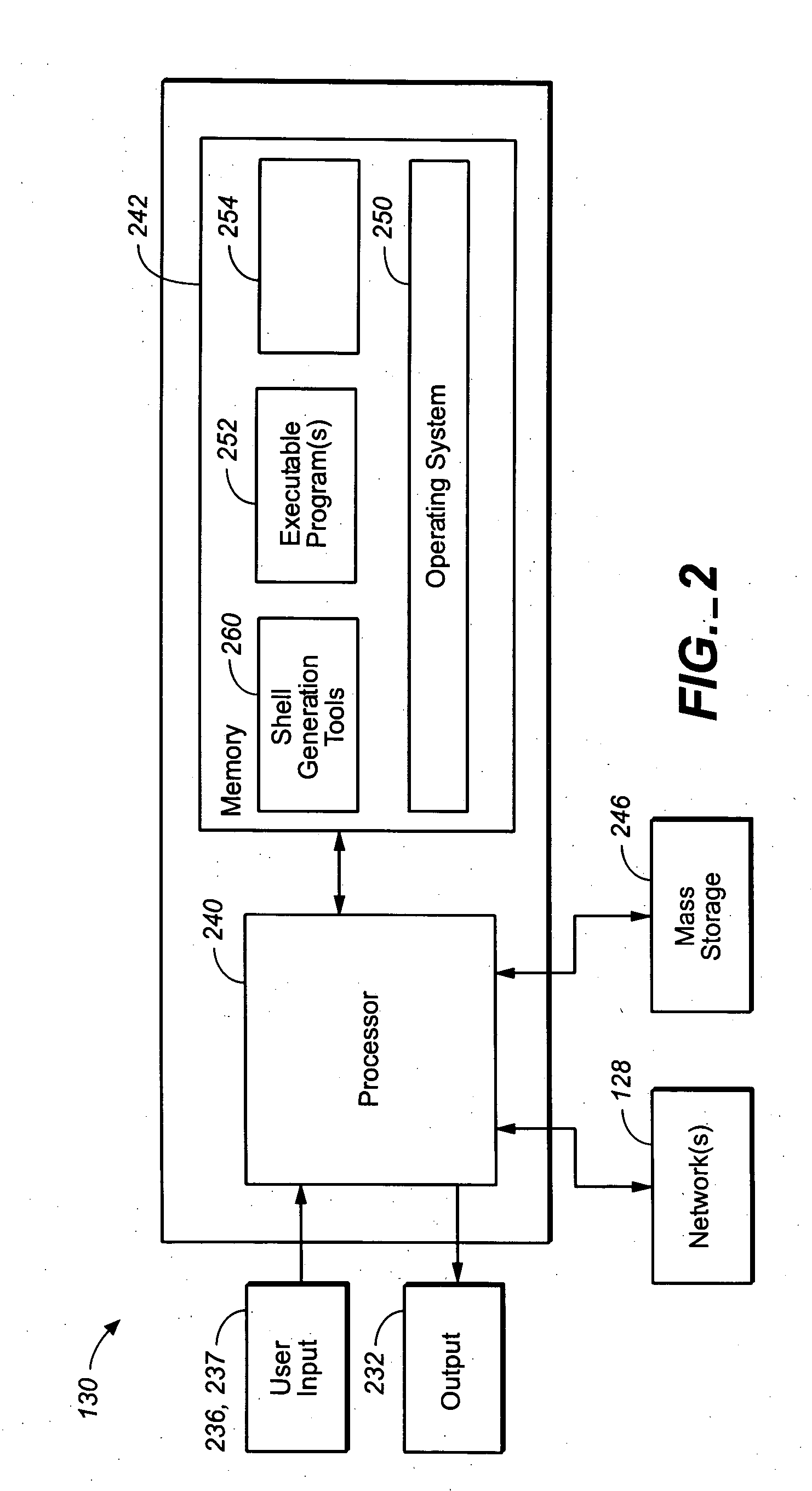

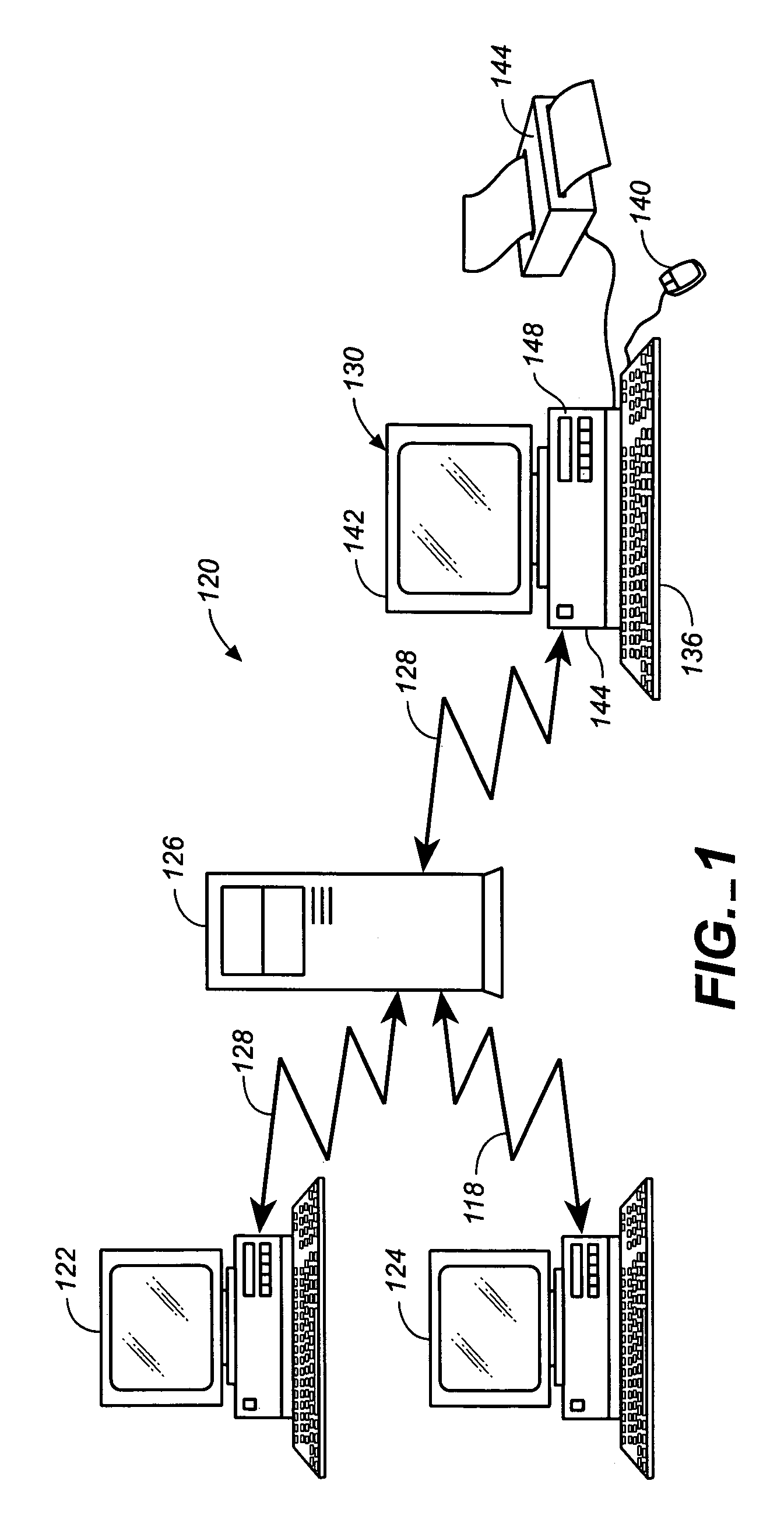

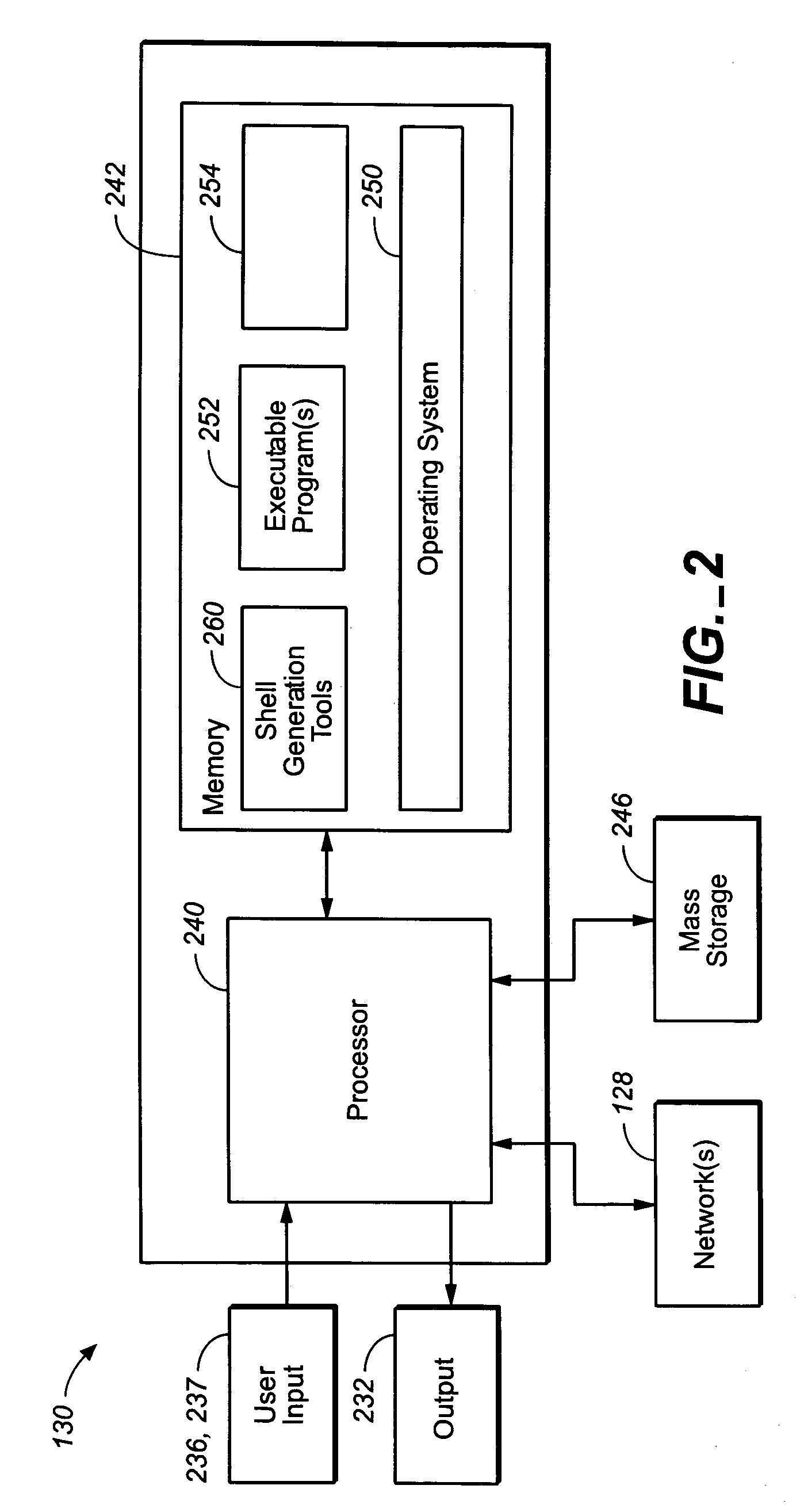

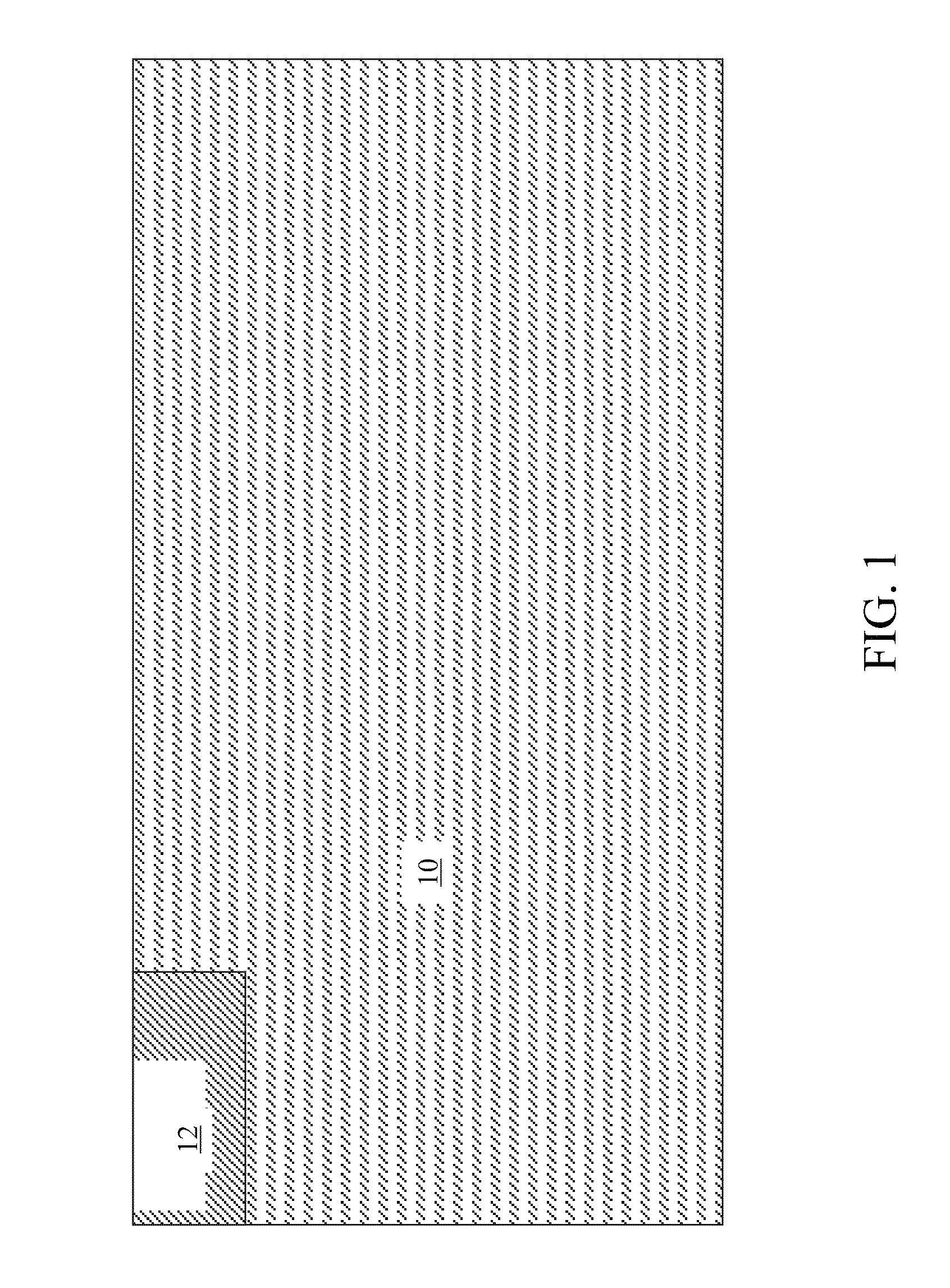

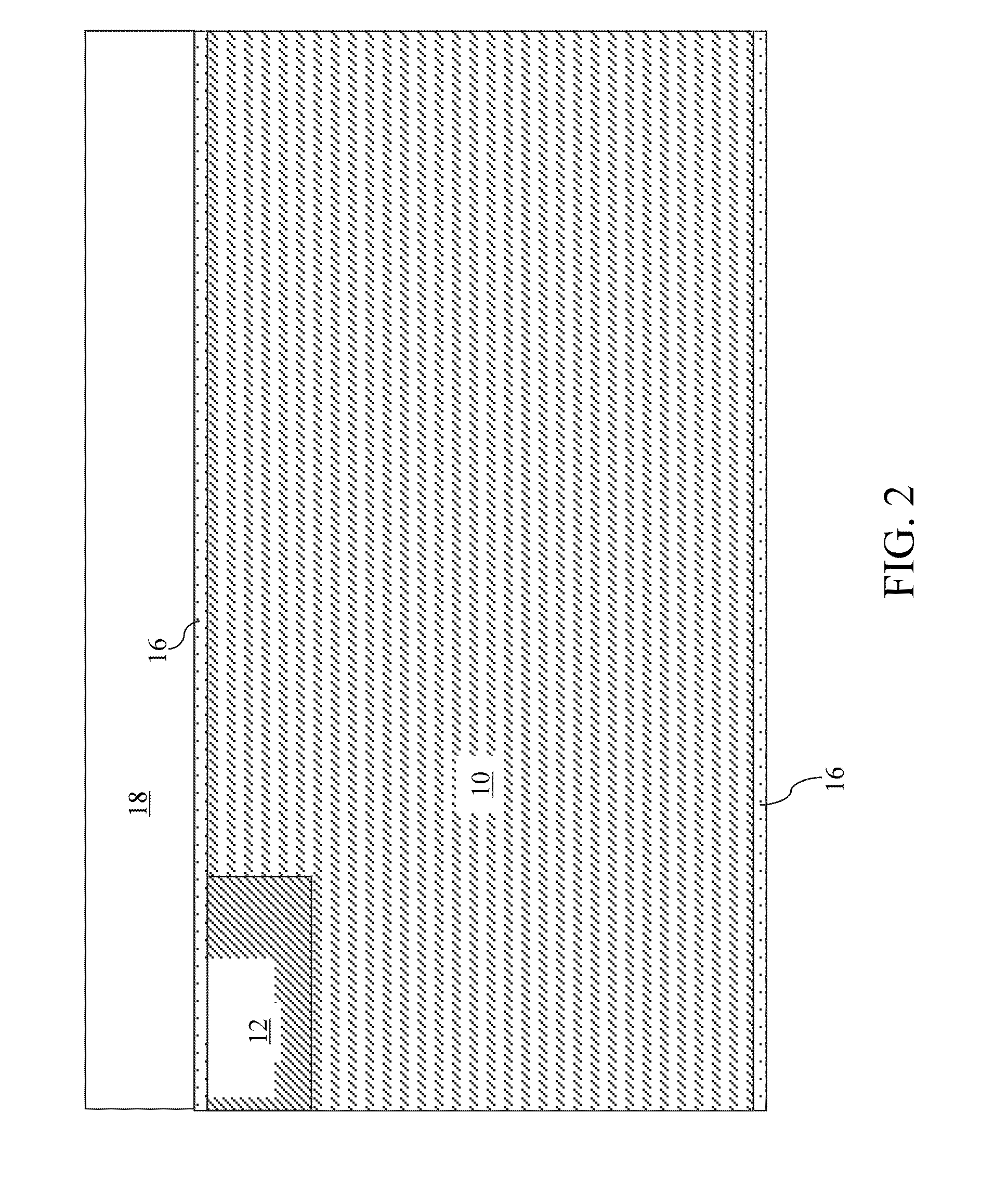

System and method for generating a mask layout file to reduce power supply voltage fluctuations in an integrated circuit

InactiveUS6877144B1Reduce voltage fluctuationsReduce power supply voltage fluctuationCAD circuit designSpecial data processing applicationsEmbedded systemDecoupling capacitor

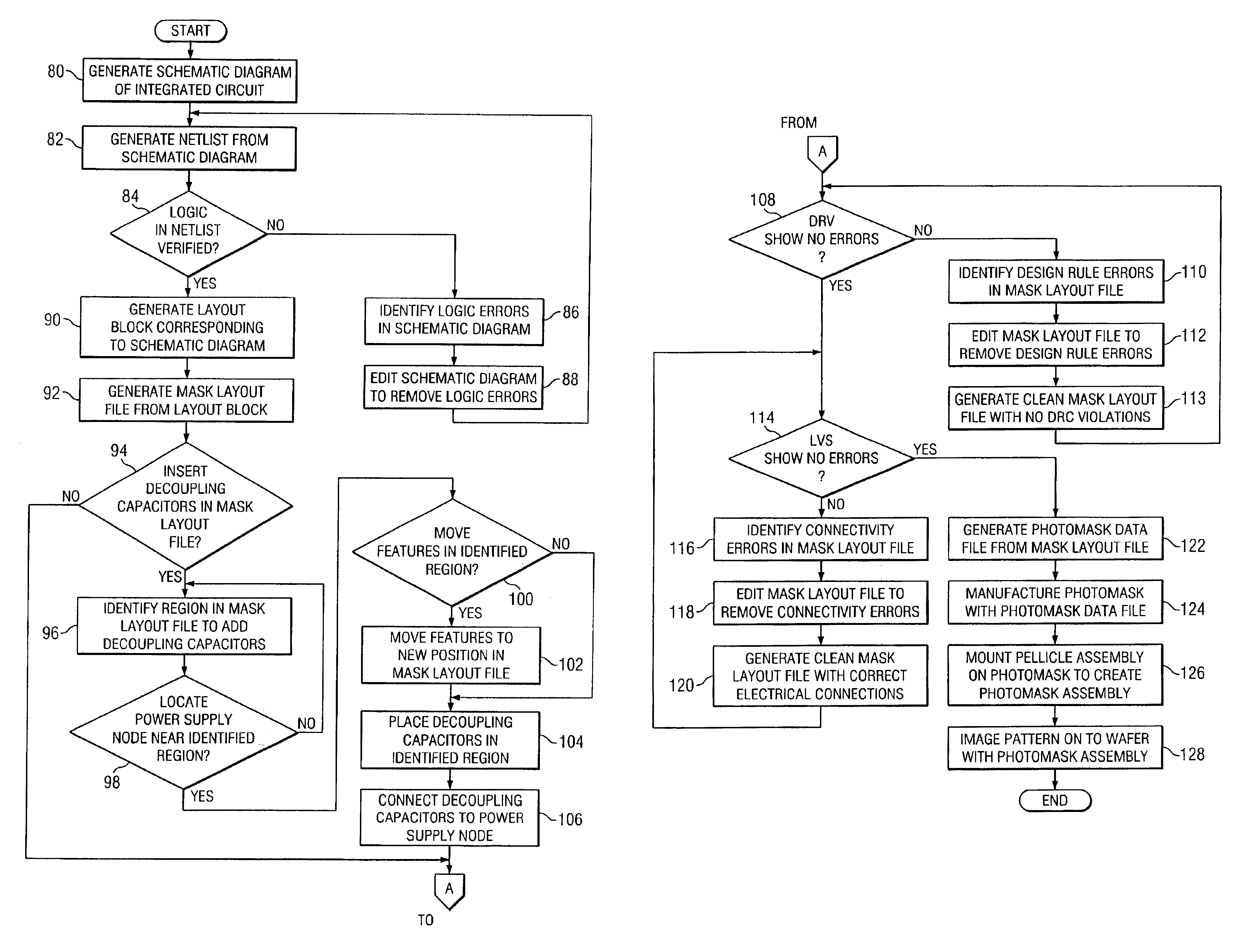

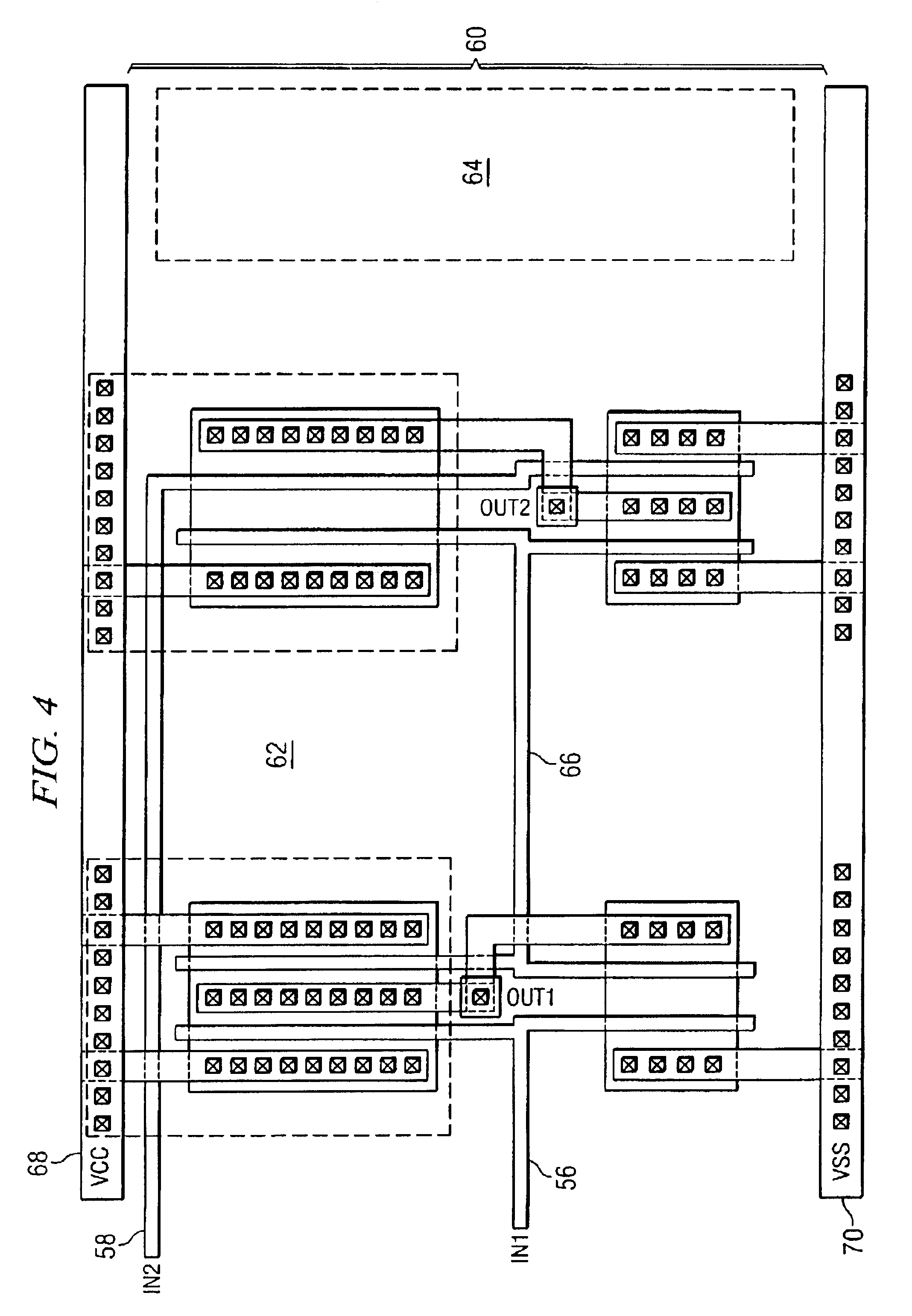

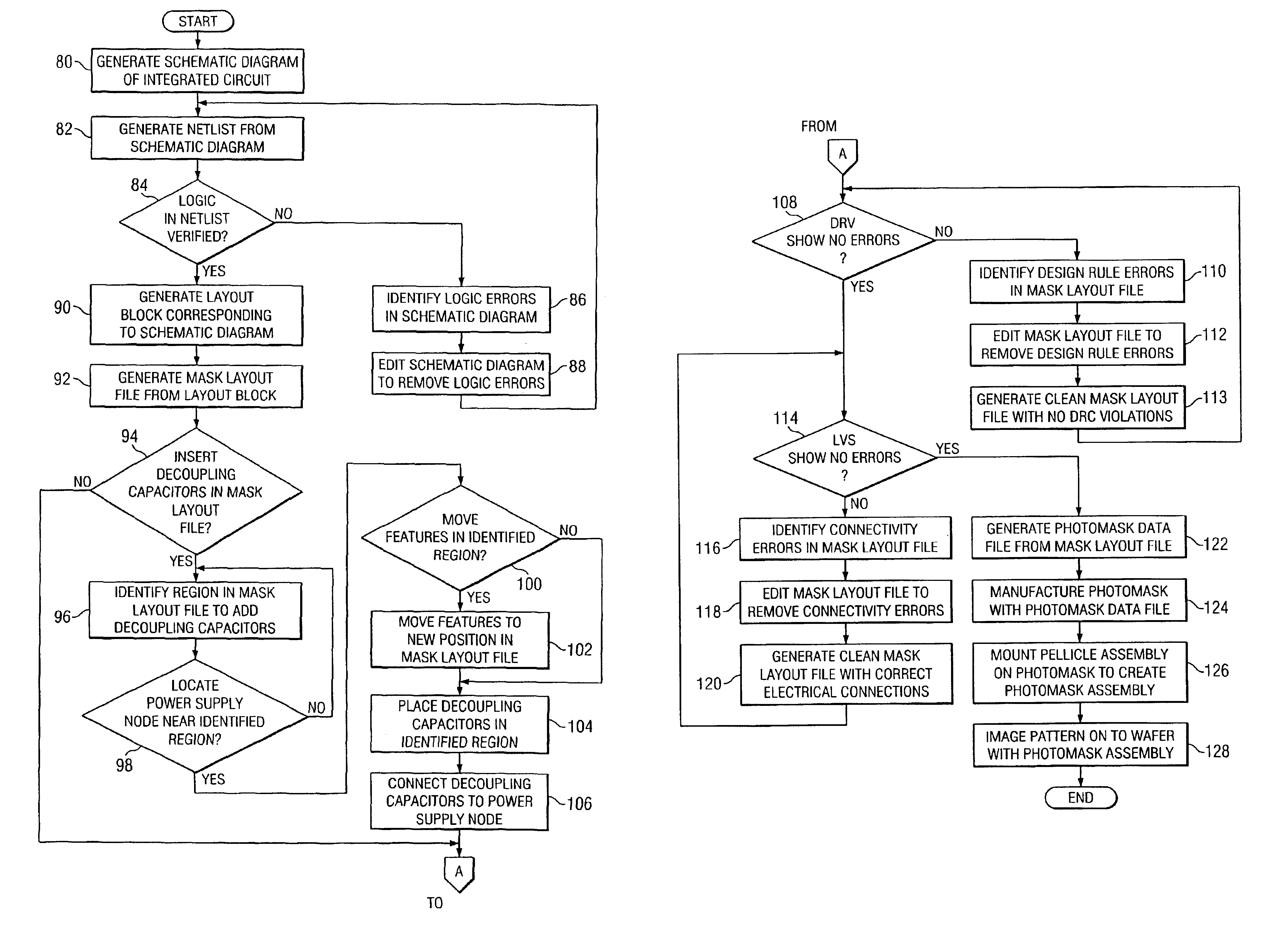

A system and method for generating a mask layout file to reduce power supply voltage fluctuations in an integrated circuit are disclosed. The method includes analyzing a pattern in a mask layout file to identify a region in the pattern to add one or more decoupling capacitors. Once the region is identified, a feature located in the identified region is moved based on a design rule from a first position to a second position in the mask layout file to create a space in the identified region. The decoupling capacitors are automatically placed in the space in the identified region.

Owner:CELERICS TECH

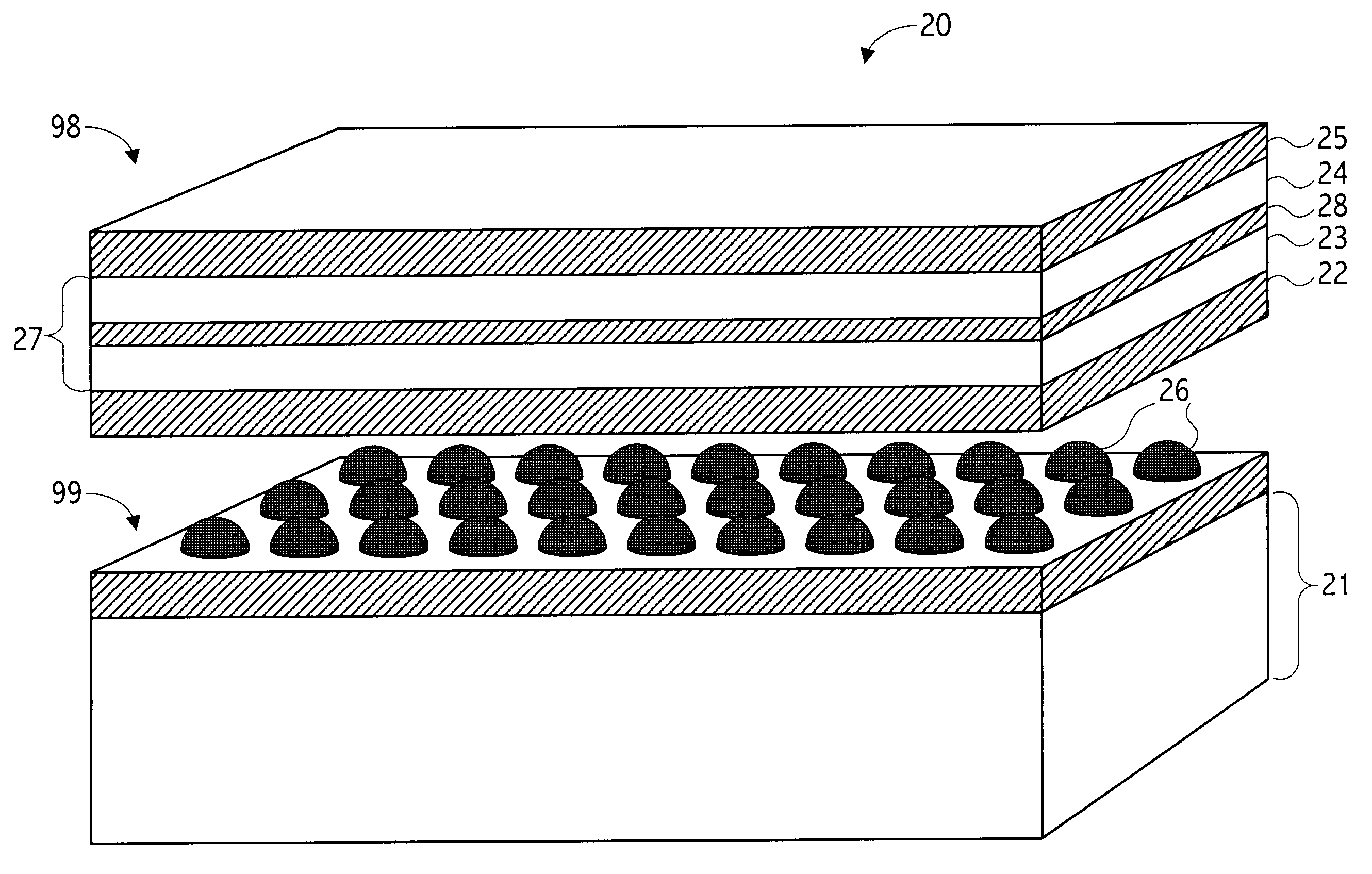

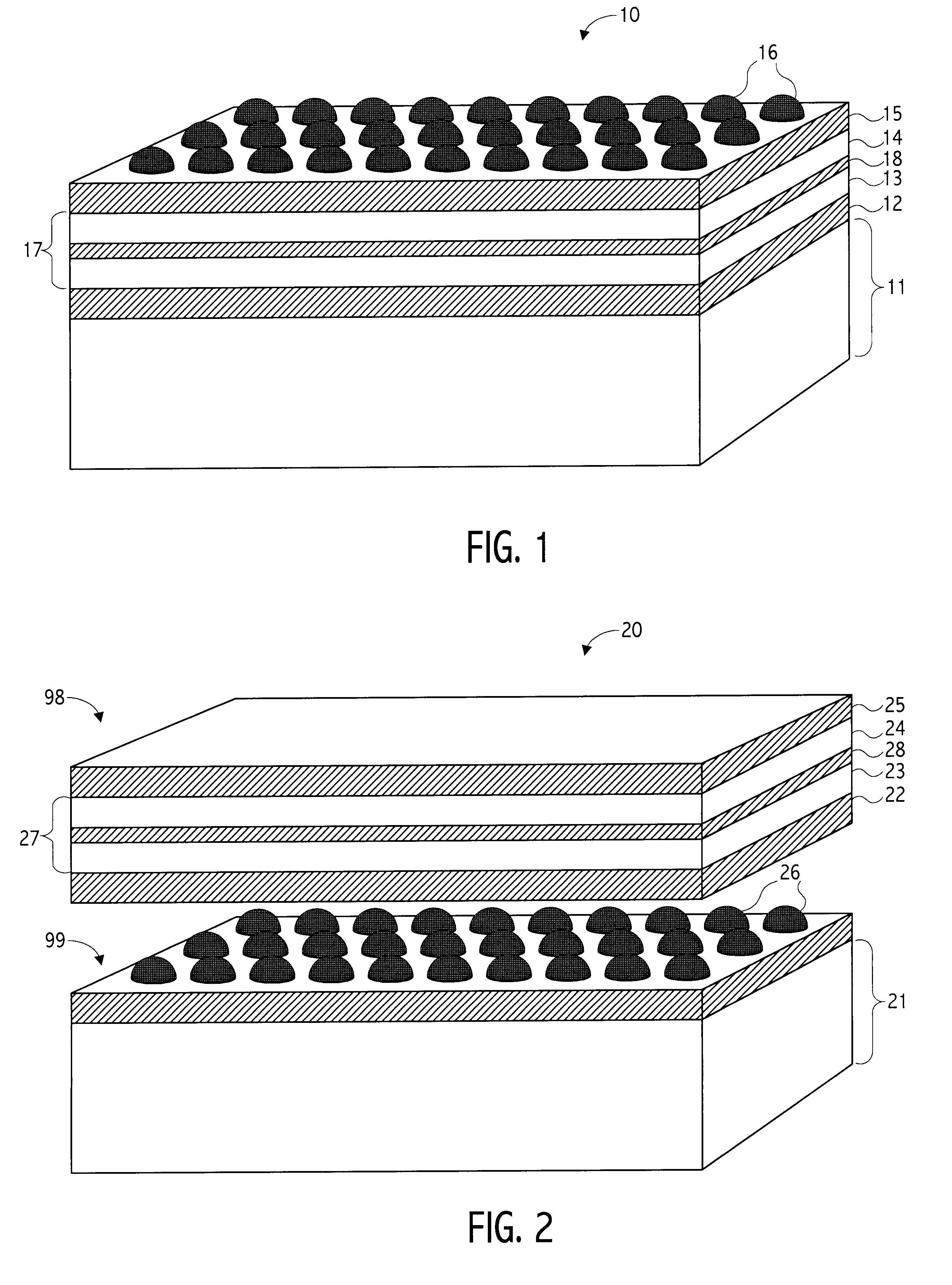

Photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured with the same

InactiveUS6904582B1Shorten the timeShorten cycle timeSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit layoutDecoupling capacitor

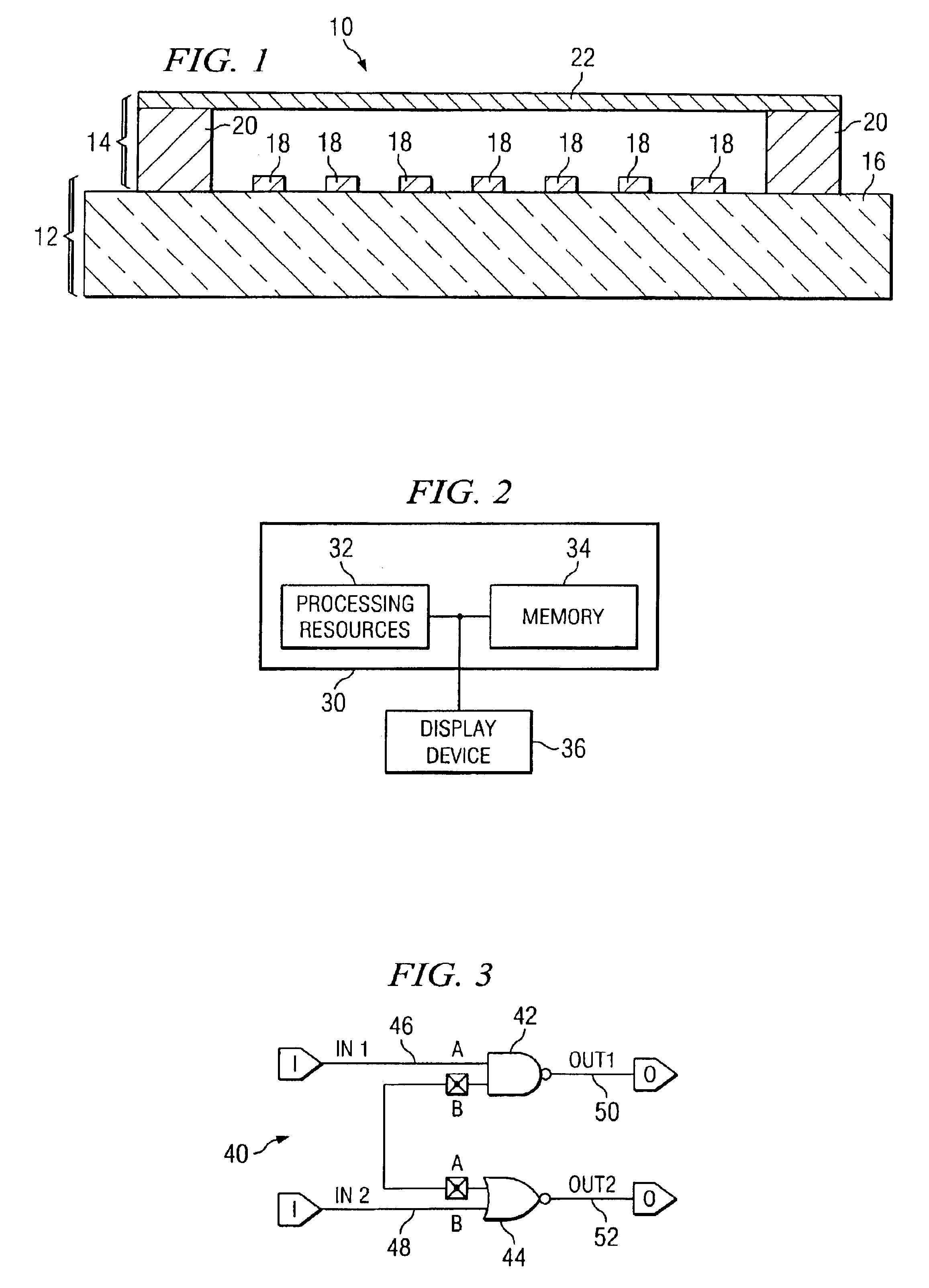

A photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured by the same are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region in the pattern to add one or more decoupling capacitors. Once the region is identified, a feature located in the identified region is moved based on a design rule from a first position to a second position in the mask layout file to create a space in the identified region. The decoupling capacitors are placed in the space in the identified region.

Owner:CELERICS TECH

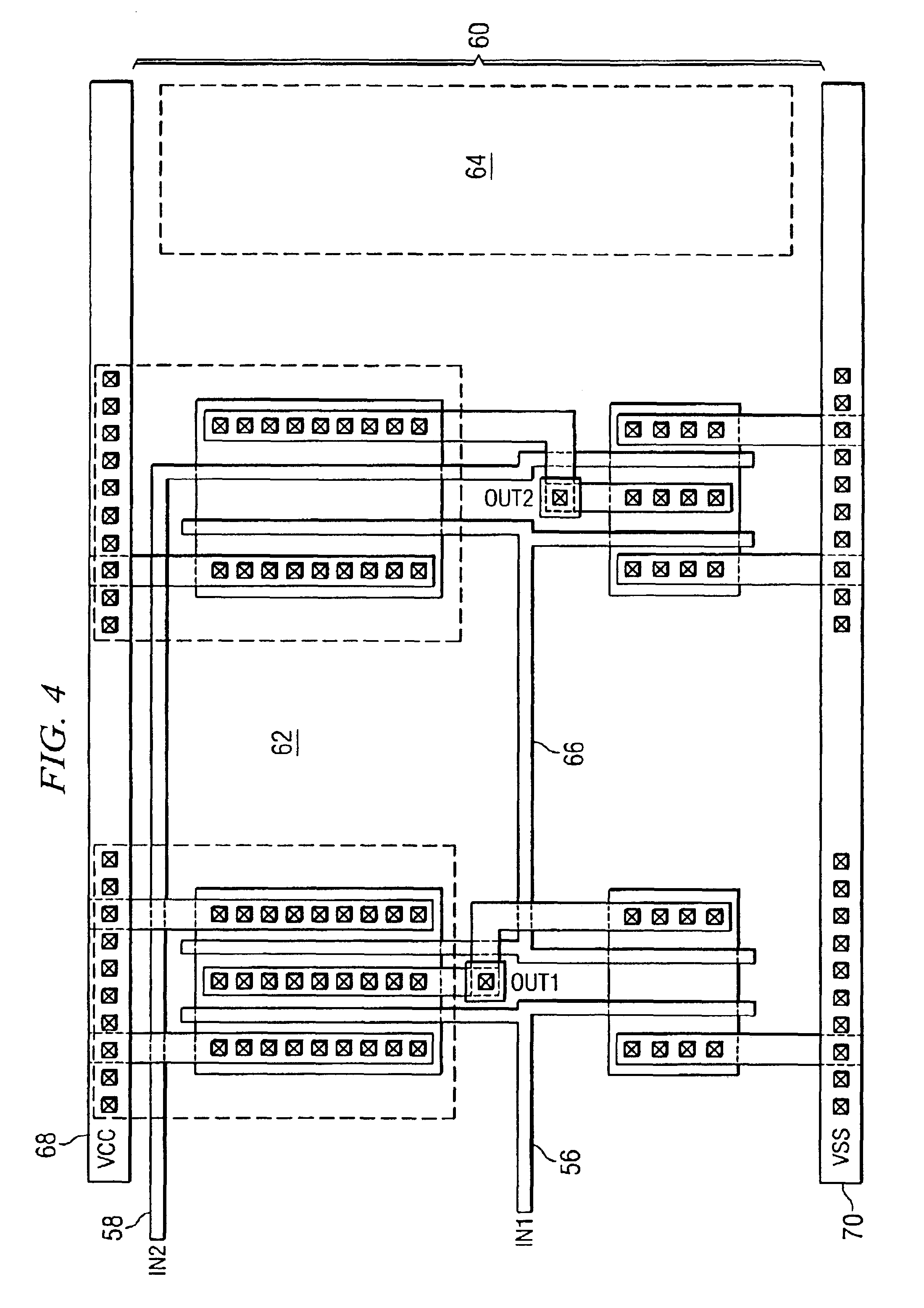

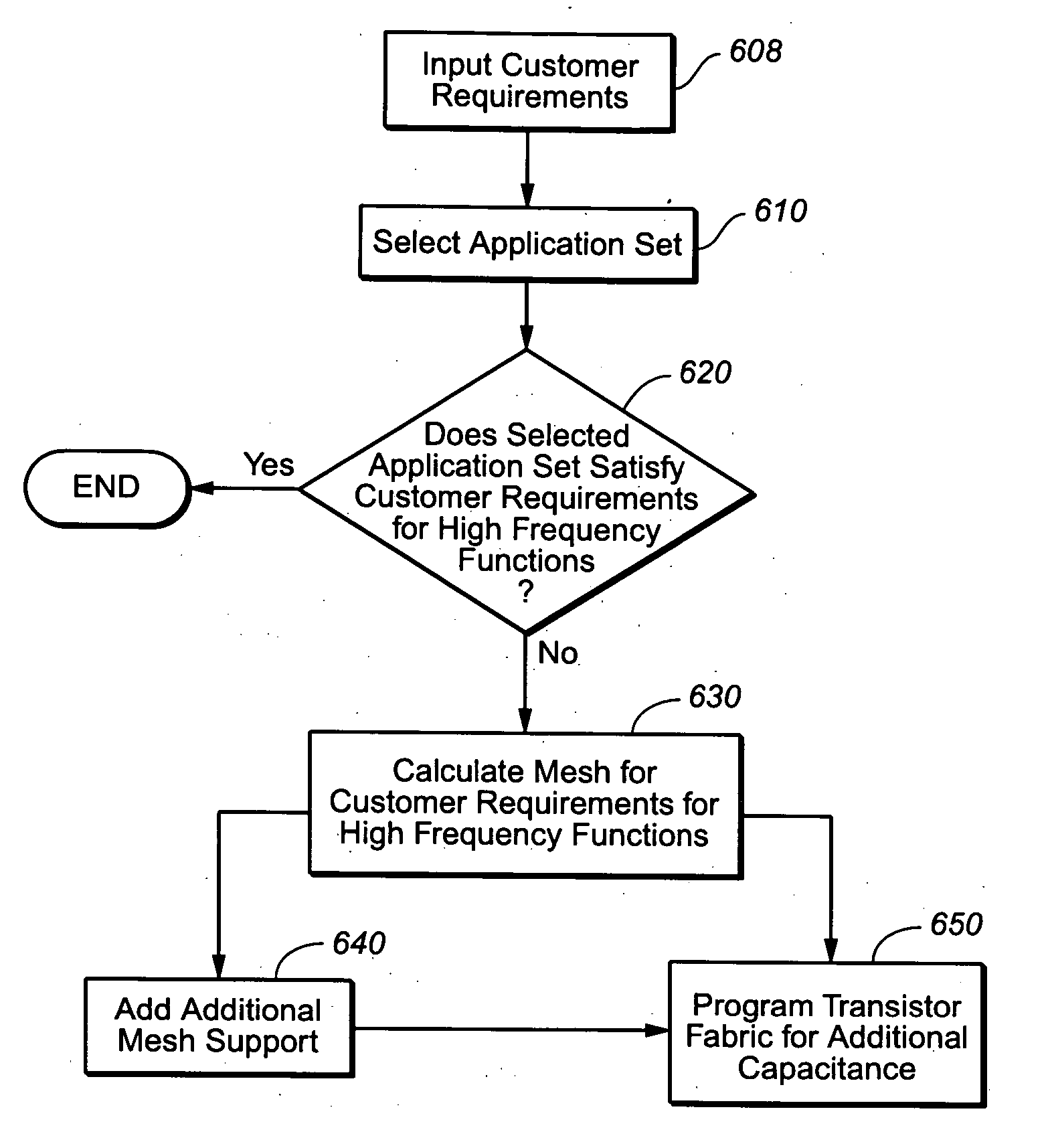

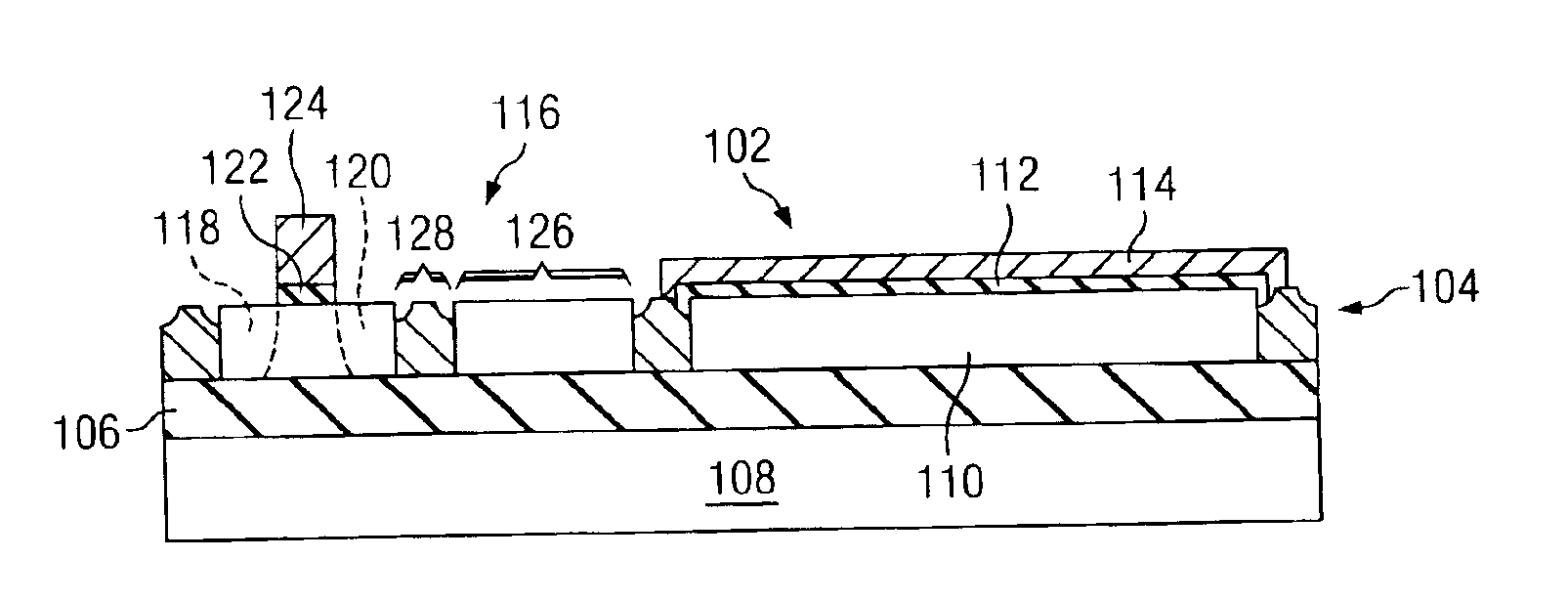

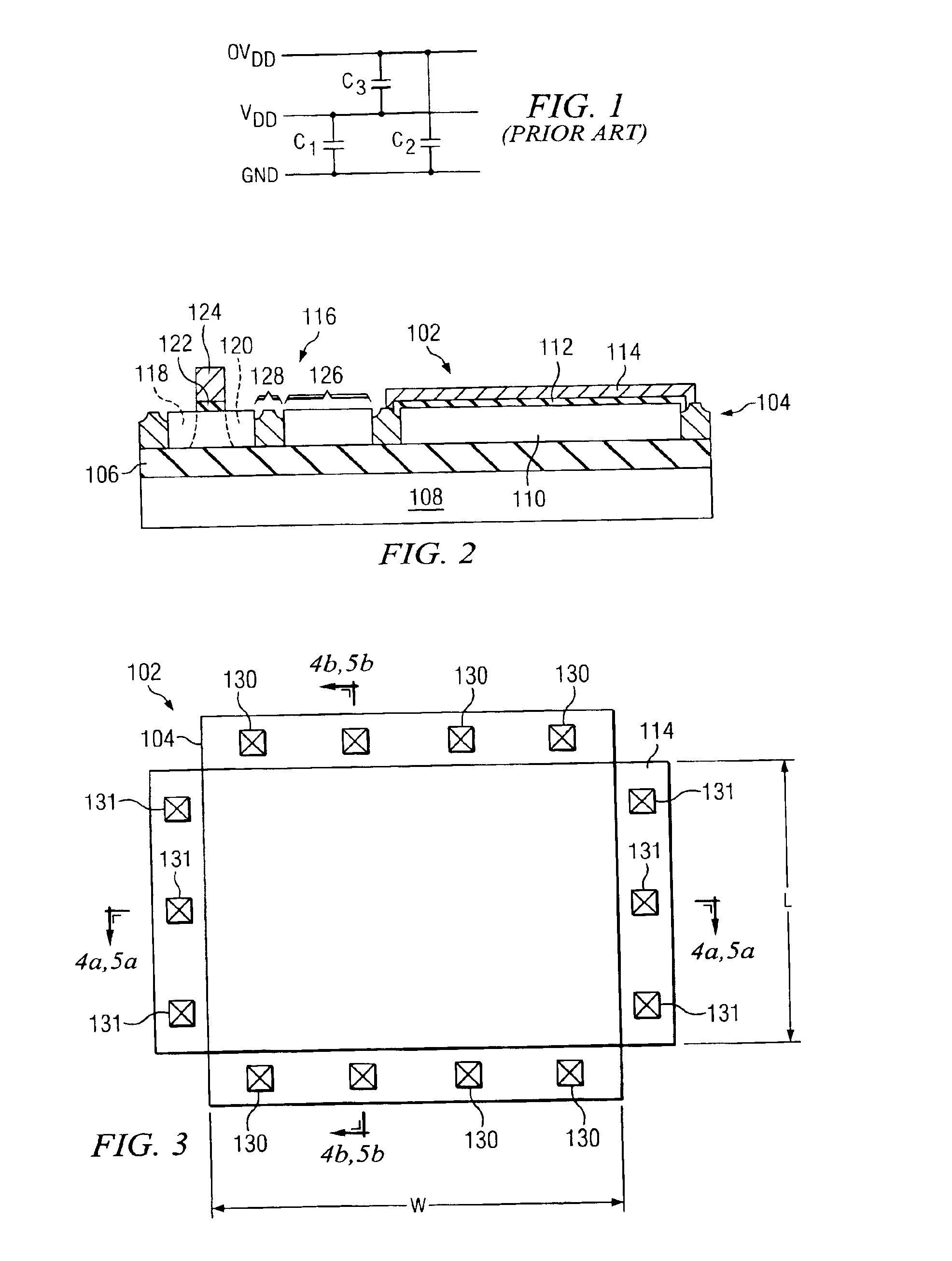

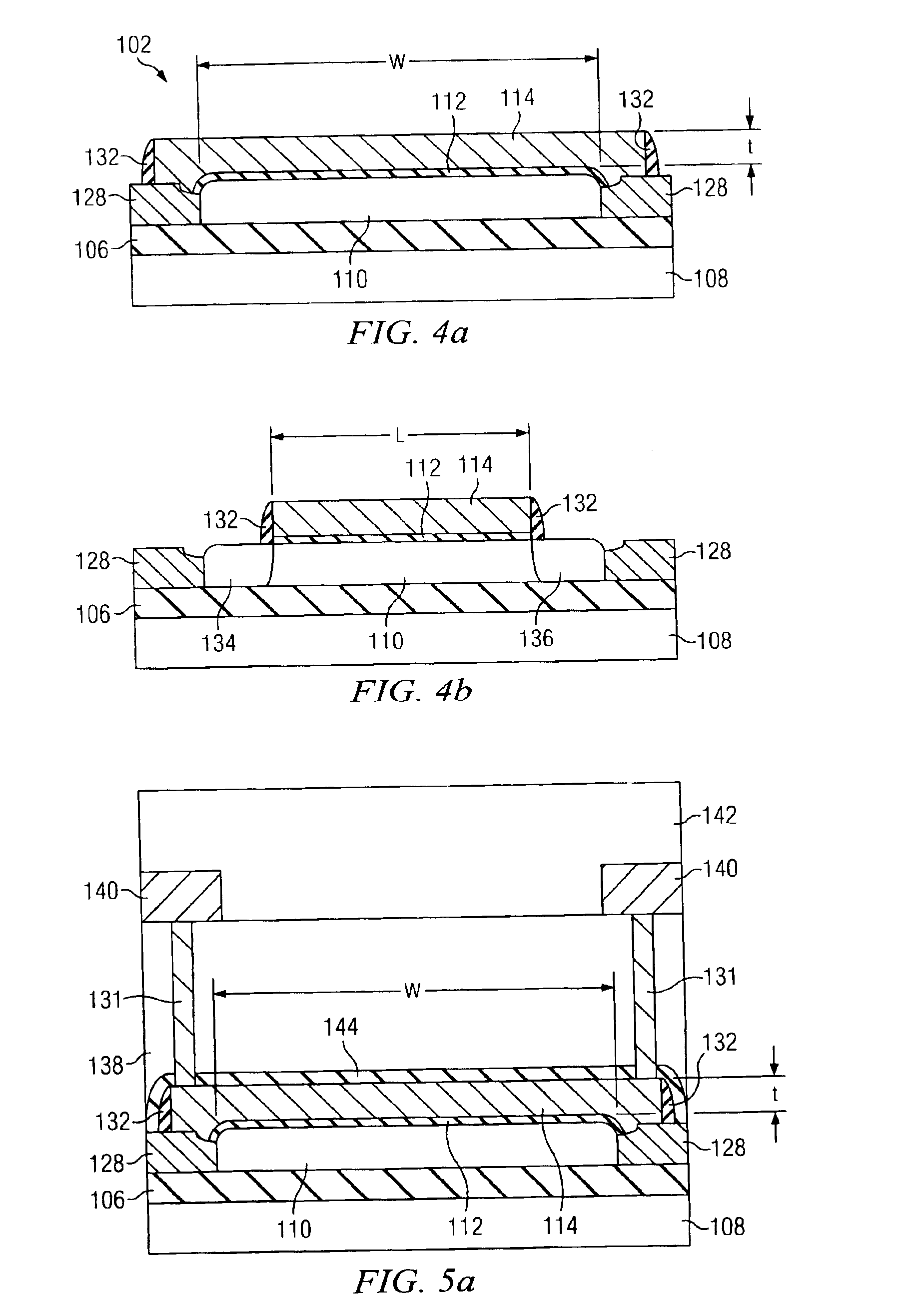

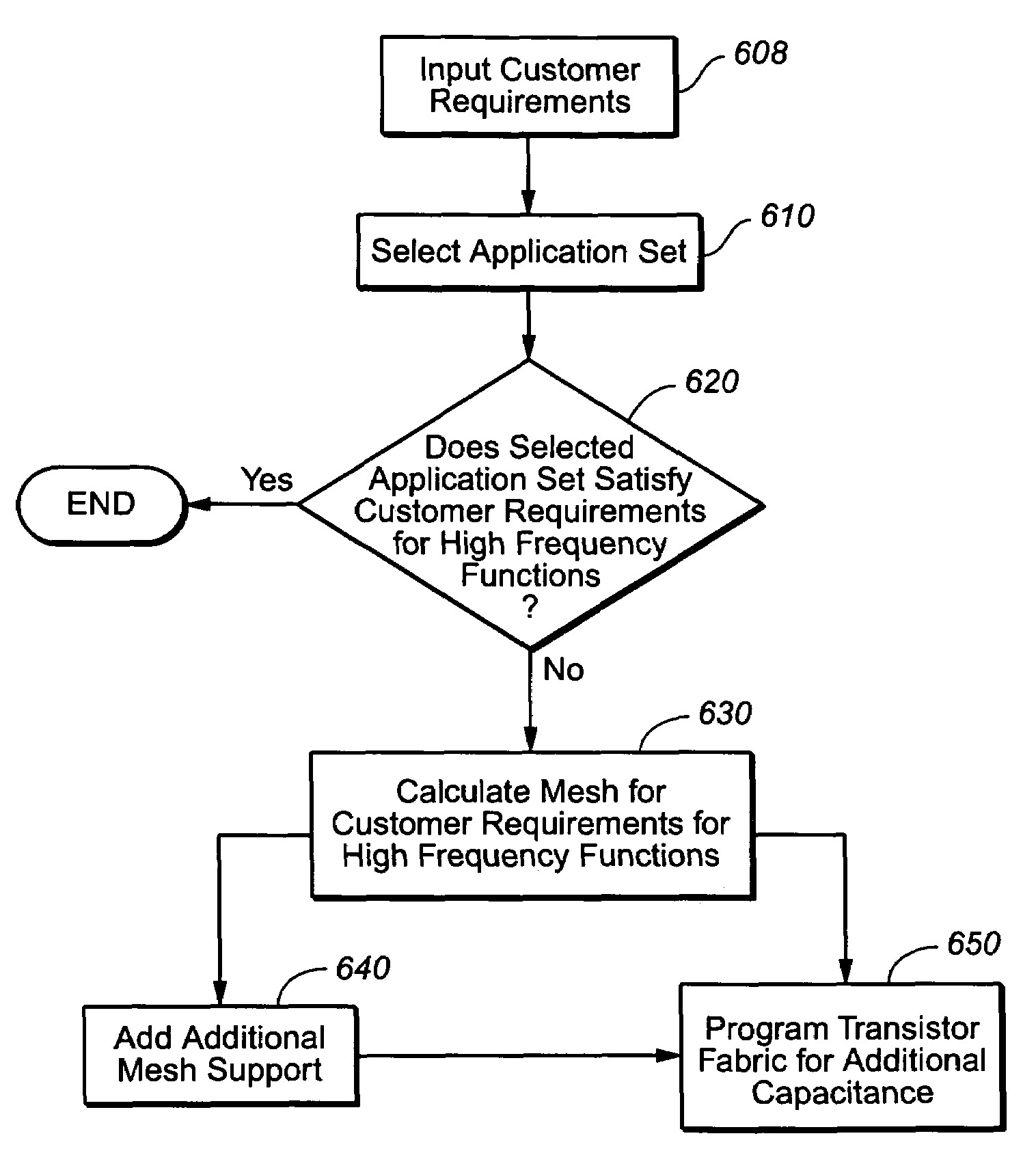

Power mesh for multiple frequency operation of semiconductor products

InactiveUS20060123376A1Decoupling capacitanceIncrease speedComputer programmed simultaneously with data introductionCAD circuit designCapacitanceTransceiver

The design of integrated circuits, i.e., semiconductor products, is made easier with a semiconductor platform having versatile power mesh that is capable of supporting simultaneous operations having different frequencies on the semiconductor product; e.g., higher frequency operations may be embedded as diffused blocks within the lower layers or may be programmed from a configurable transistor fabric above the diffused layers. Preferably the power mesh is located above the layers having the operations requiring the different frequencies, and may be fixed in an application set given to a chip designer or may be configurable by the designer her / himself. For example, to support high speed communications adjacent an embedded high speed data transceiver, the transistor fabric may be programmed as a data link layer having higher performance requirements than the rest of the integrated circuit. The data link layer may be connected to one of the localized grids of the versatile power mesh which may have an increased density and / or wider strap width of a power / ground grid. Additional decoupling capacitance can be embedded in the lower layers of the semiconductor product and / or can be programmed from the configurable transistors fabric.

Owner:AVAGO TECH INT SALES PTE LTD

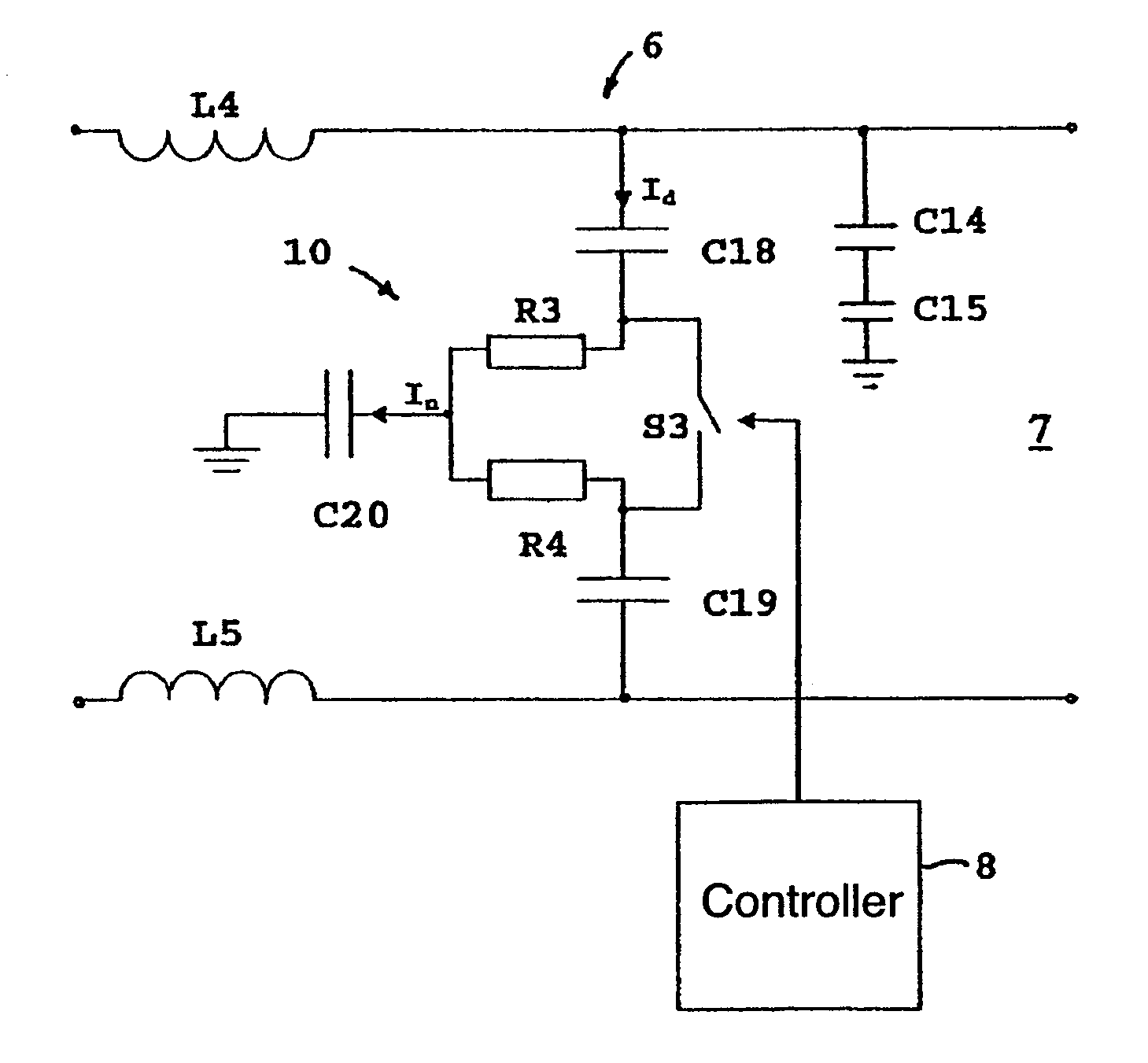

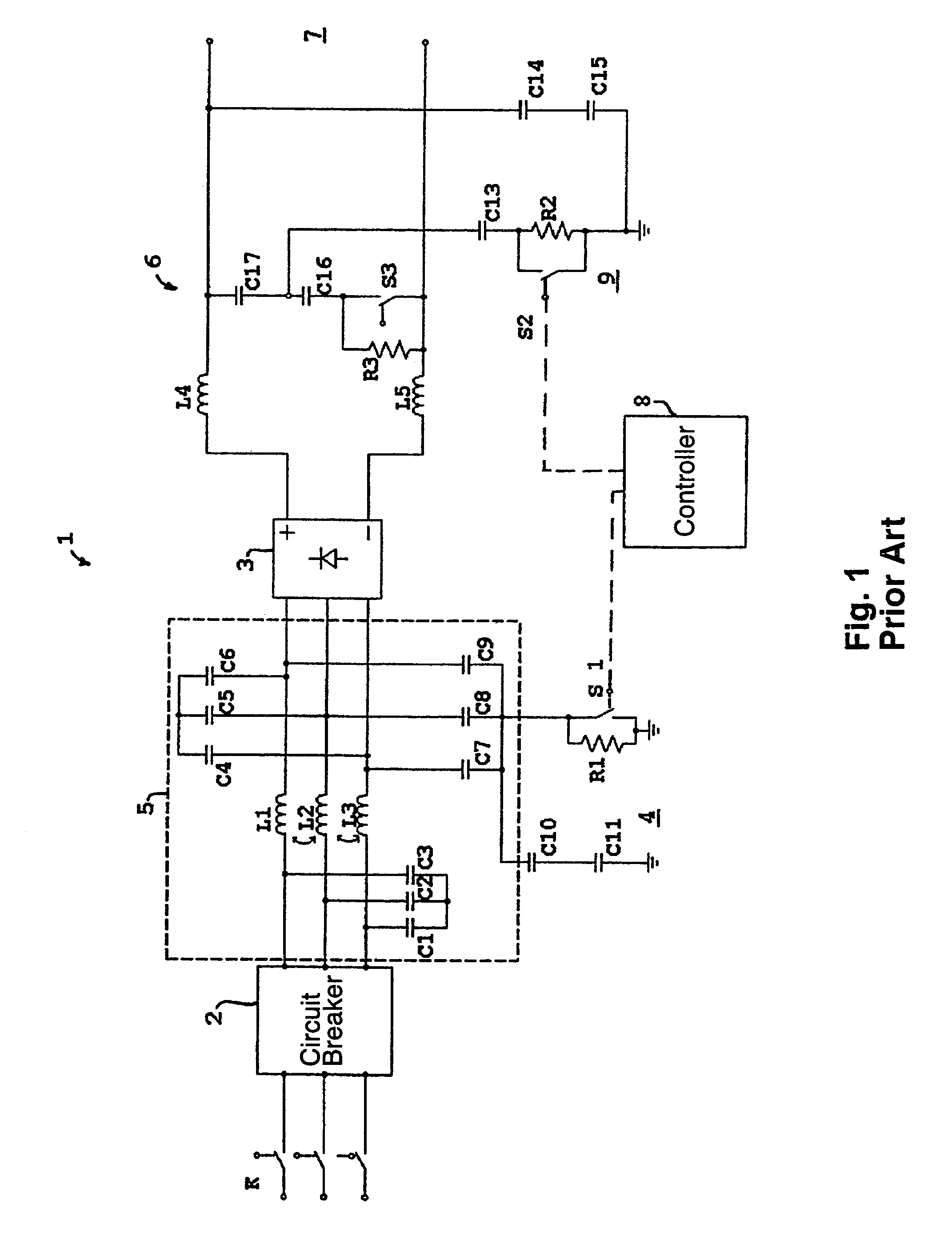

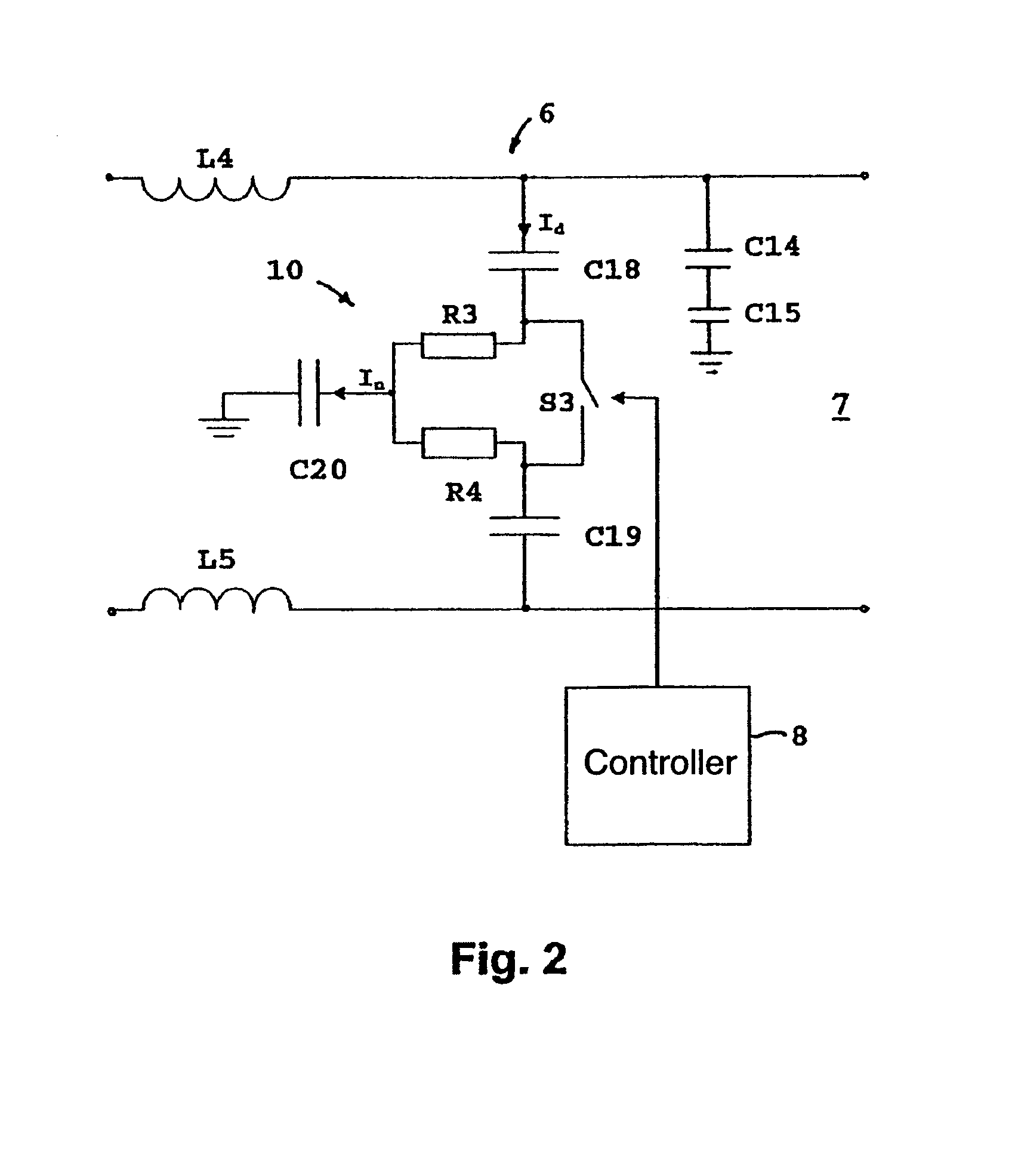

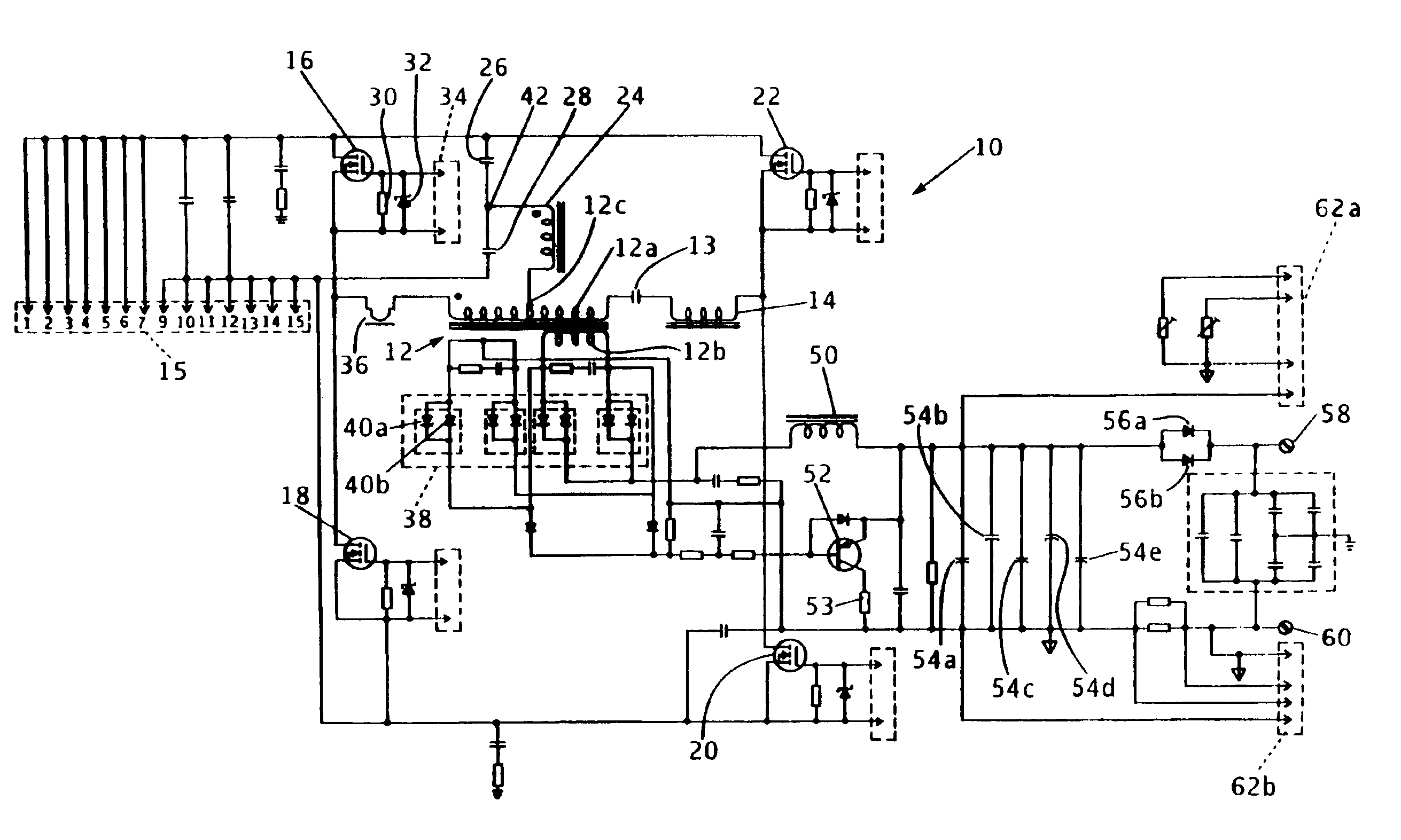

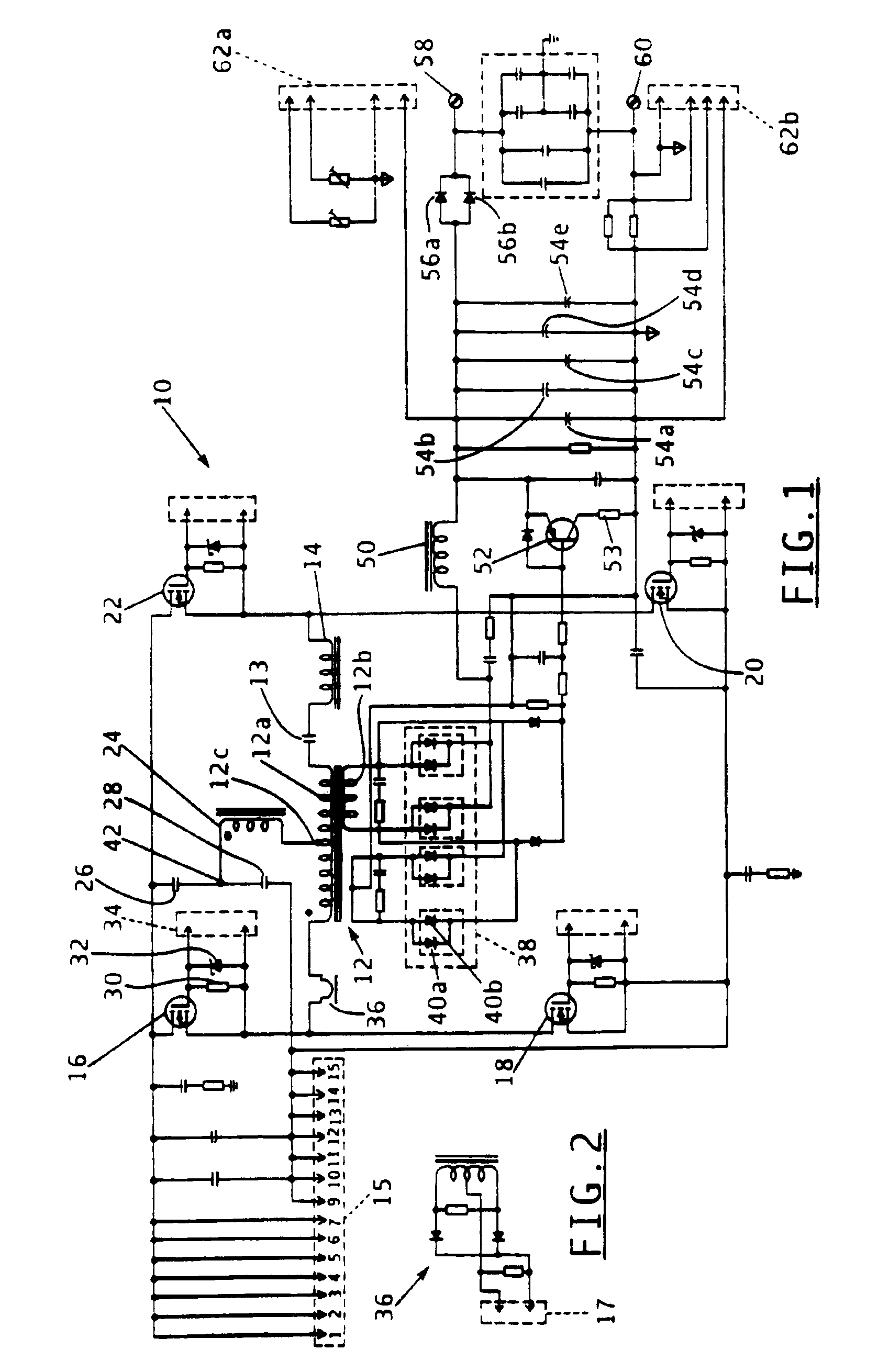

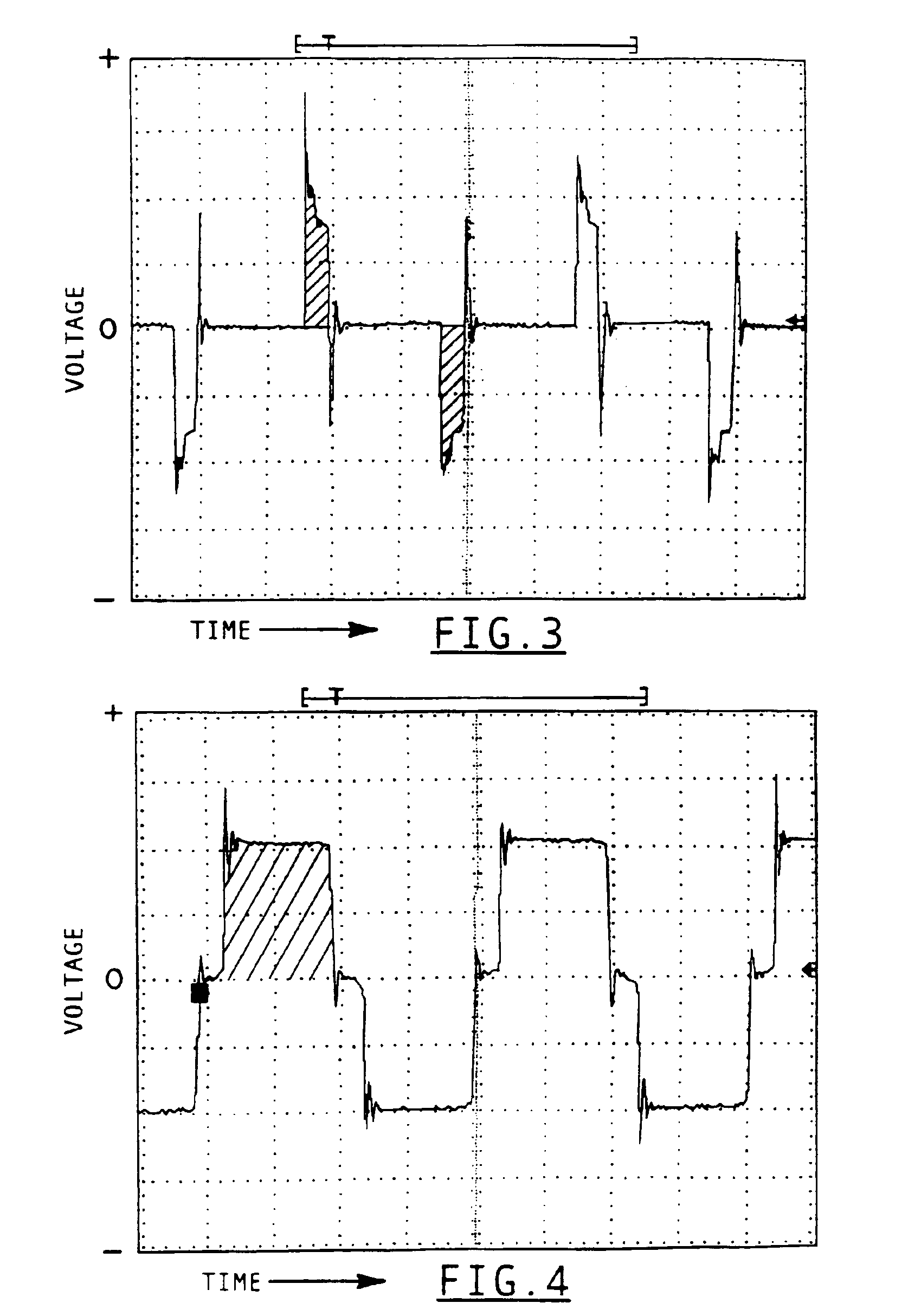

Motor controller incorporating an electronic circuit for protection against inrush currents

InactiveUS7050278B2Minimize the numberConveniently activatedSingle-phase induction motor startersAC motor controlElectrical resistance and conductanceFiltration

Inrush currents in the dc intermediate circuit of a motor controller necessitate the incorporation of protection circuits. These circuits usually take the form of a resistor inserted in series with the intermediate circuit, and the resistor is short-circuited after completion of inrush by a switch positioned in parallel with the resistor. To reduce cable-transmitted electrical noise an earthed noise-decoupling capacitor is added to the intermediate circuit, but it also requires protection against inrush currents. To minimise the number of components, a protection circuit is described which combines noise filtration and inrush protection. According to the invention, the inrush resistor has the form of a resistor network and is connected to a switch which via a controller alters the resistance of the resistor network, so that when the switch is open, the resistance to a differential current is greater than the resistance to a common mode current, and when the switch is closed, there is greater resistance to a common mode current than to the differential current.

Owner:DANFOSS DRIVES

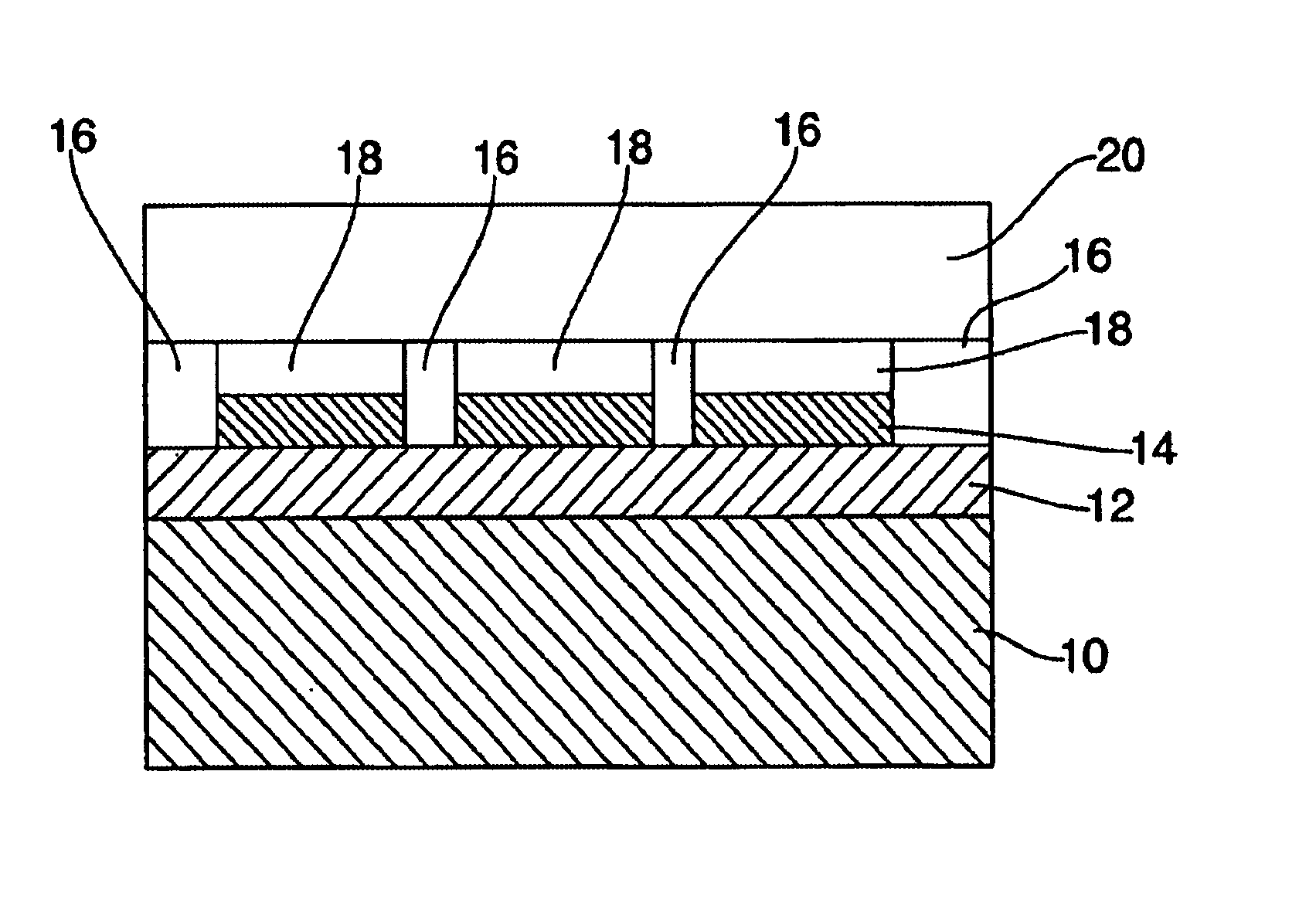

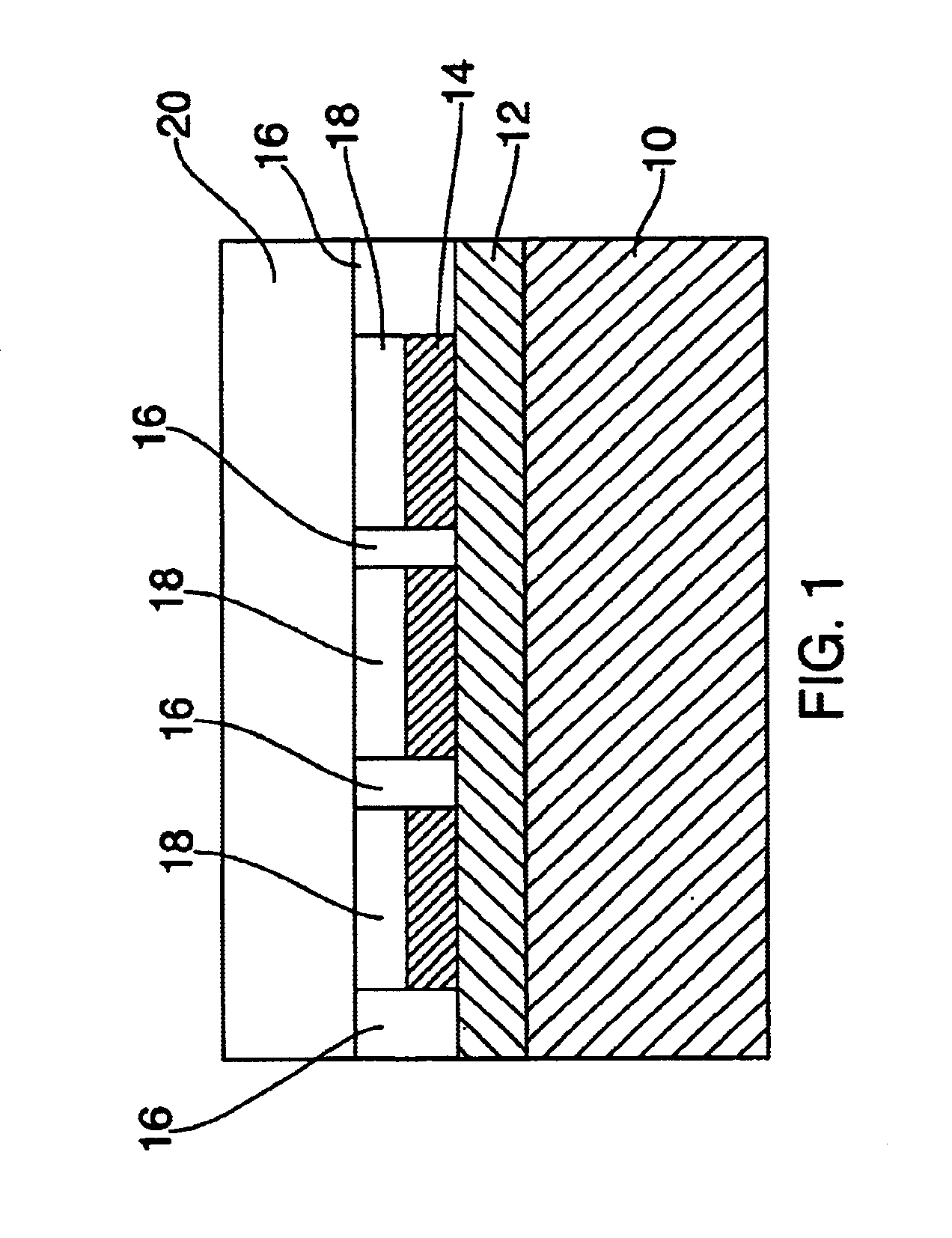

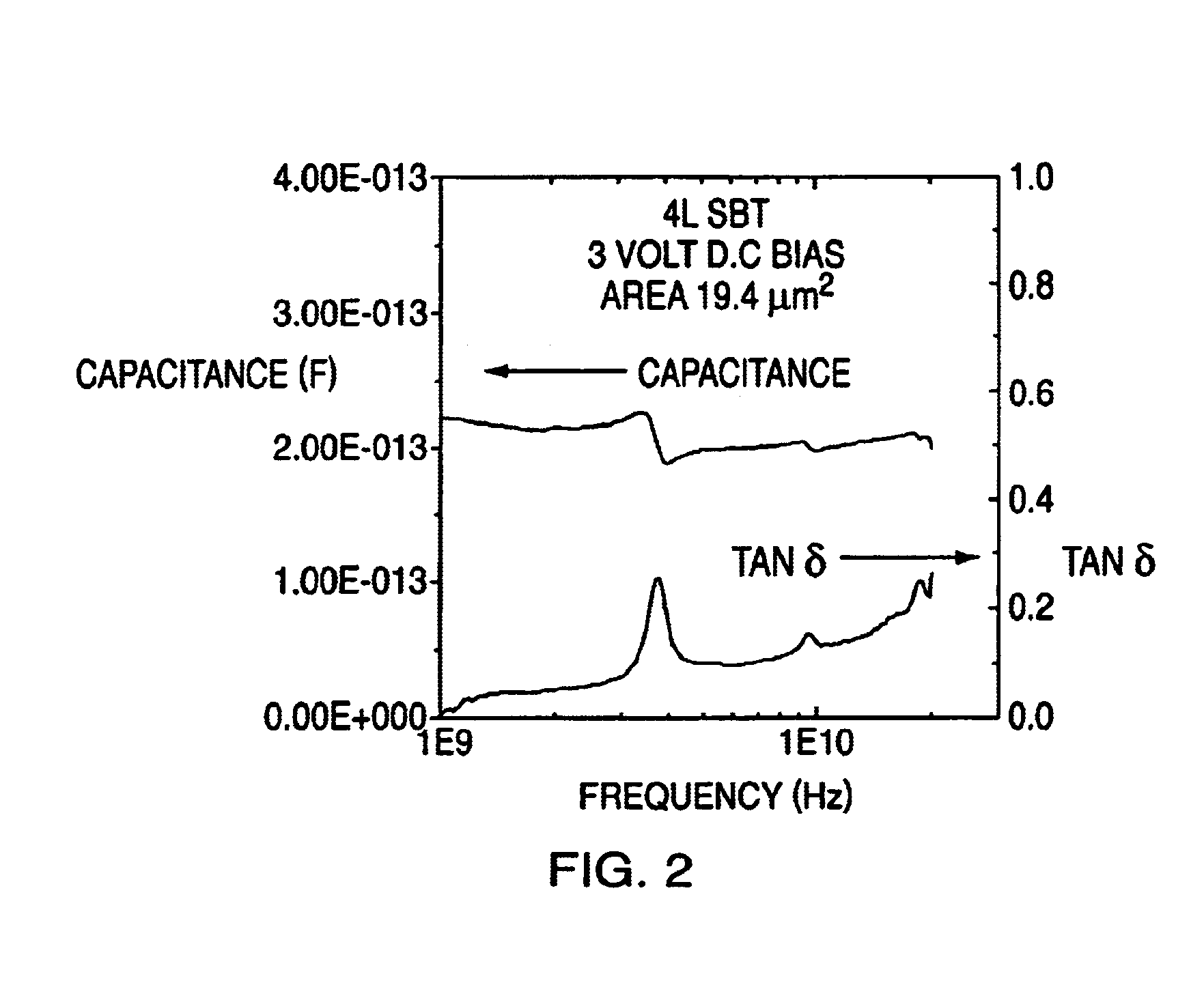

Tuneable ferroelectric decoupling capacitor

InactiveUS6888714B2Big lossLarge dampingSolid-state devicesFixed capacitor terminalsSemiconductorDecoupling capacitor

A voltage supply bypass capacitor for use with a semiconductor integrated circuit chip or module comprising a ferroelectric dielectric having electromechanical properties designed to provide maximum losses at selected frequencies.

Owner:GLOBALFOUNDRIES INC

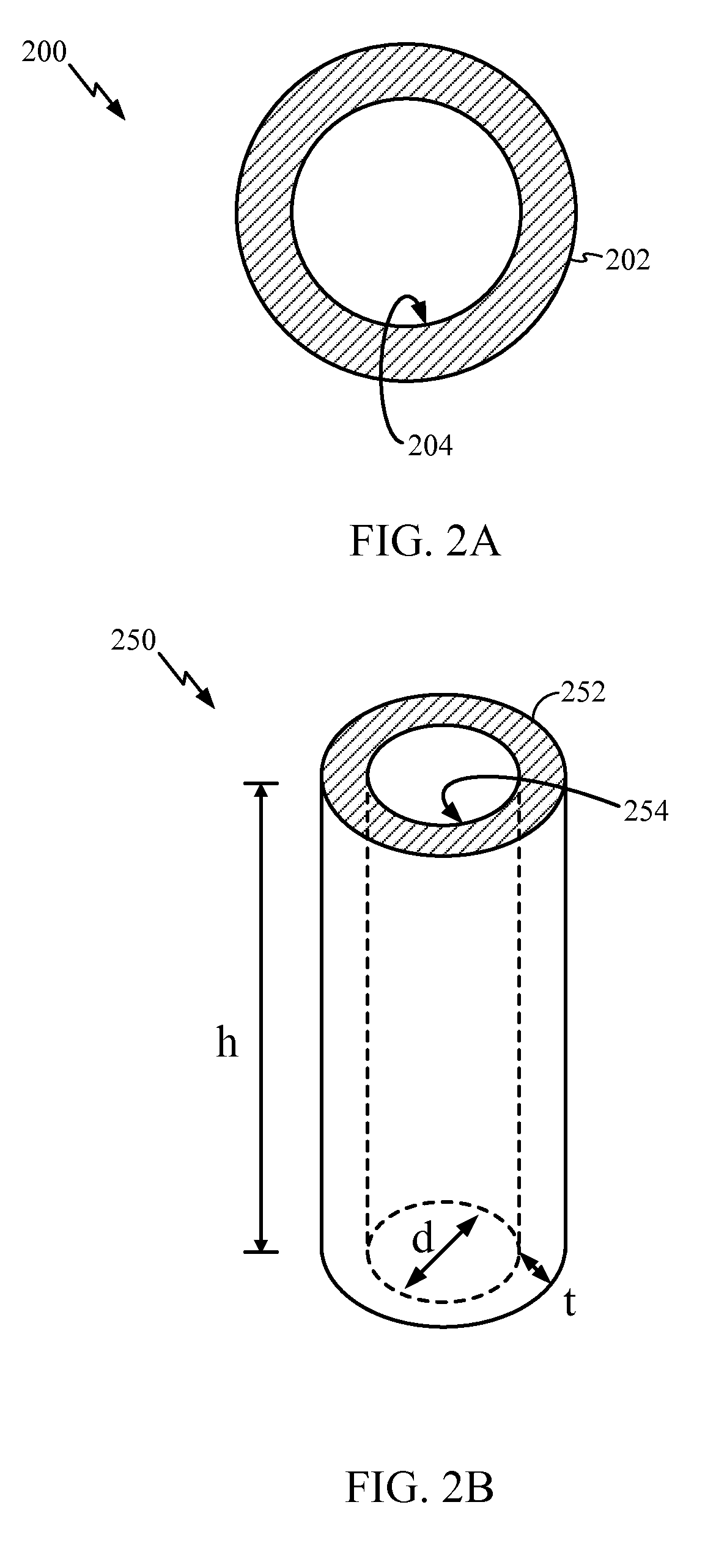

Through Silicon Via With Embedded Decoupling Capacitor

ActiveUS20100308435A1Semiconductor/solid-state device detailsSolid-state devicesDielectricEngineering

A semiconductor die, having a substrate, includes a through silicon via. The through silicon via includes a decoupling capacitor having a first co-axial conductor, a second co-axial conductor, and a co-axial dielectric separating the first co-axial conductor from the second co-axial conductor. The decoupling capacitor is configured to provide local charge storage for components on the semiconductor die.

Owner:QUALCOMM INC

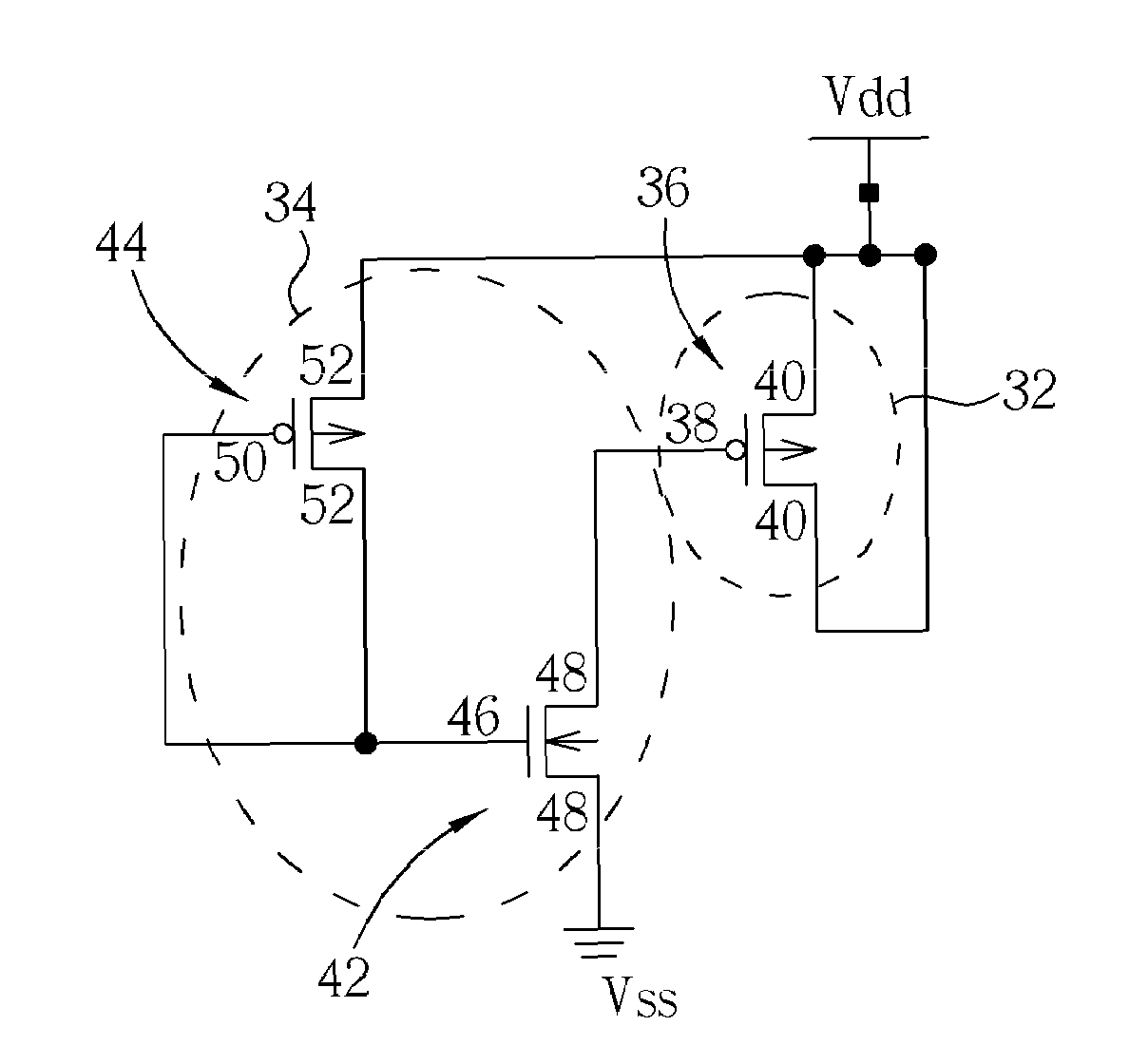

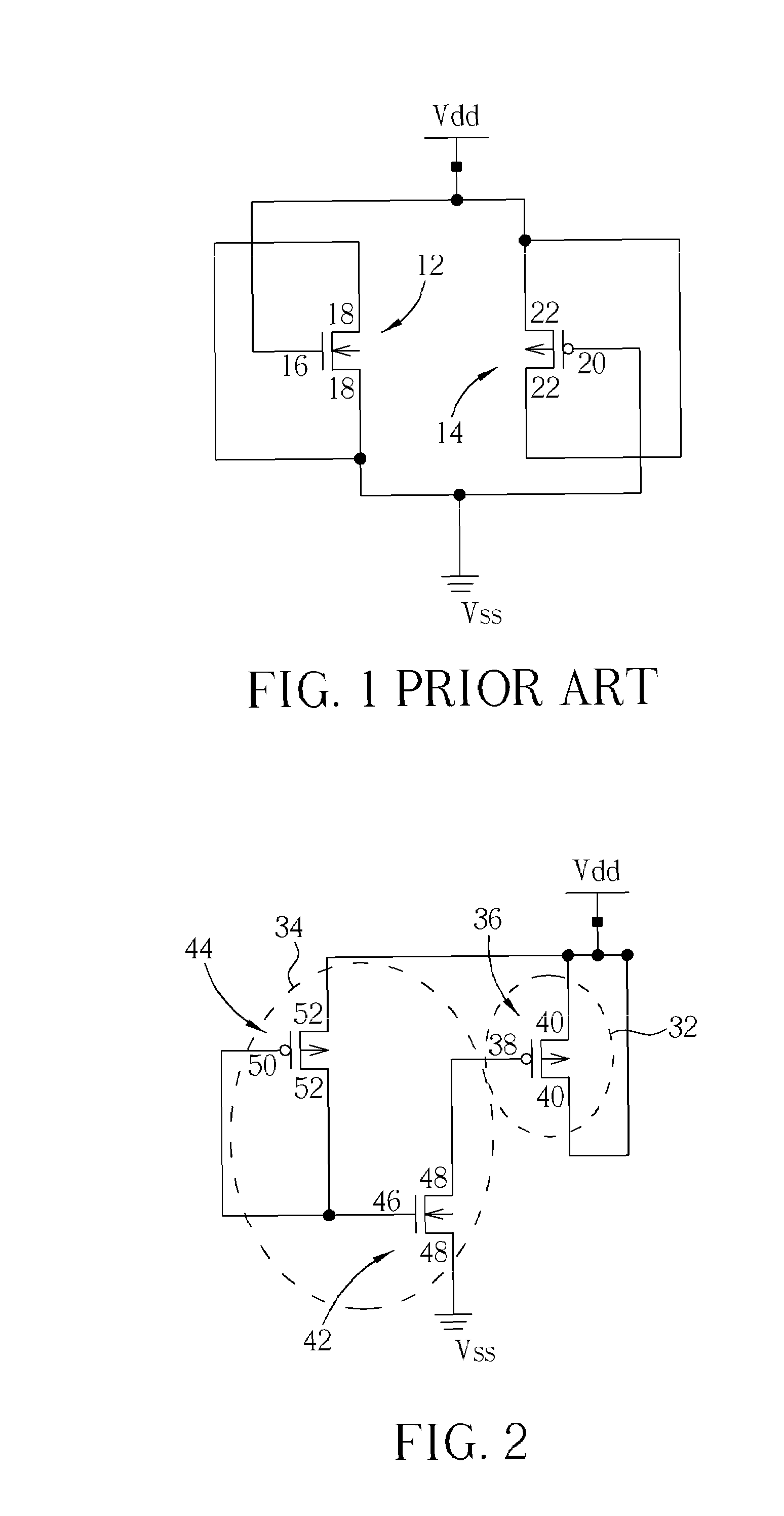

Filler circuit cell

ActiveUS7705666B1Logic circuits characterised by logic functionOscillations generatorsVoltage sourceDecoupling capacitor

A filler circuit cell is disclosed. The filler circuit cell includes a decoupled capacitor, a tie low circuit and a tie high circuit. The decoupled capacitor includes a first NMOS transistor and a first PMOS transistor, in which the source / drain of the first NMOS transistor is connected to a second voltage source and the source / drain of the first PMOS transistor is connected to a first voltage source. The tie low circuit includes a second NMOS transistor and a second PMOS transistor and the tie high circuit includes a third NMOS transistor and a third PMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

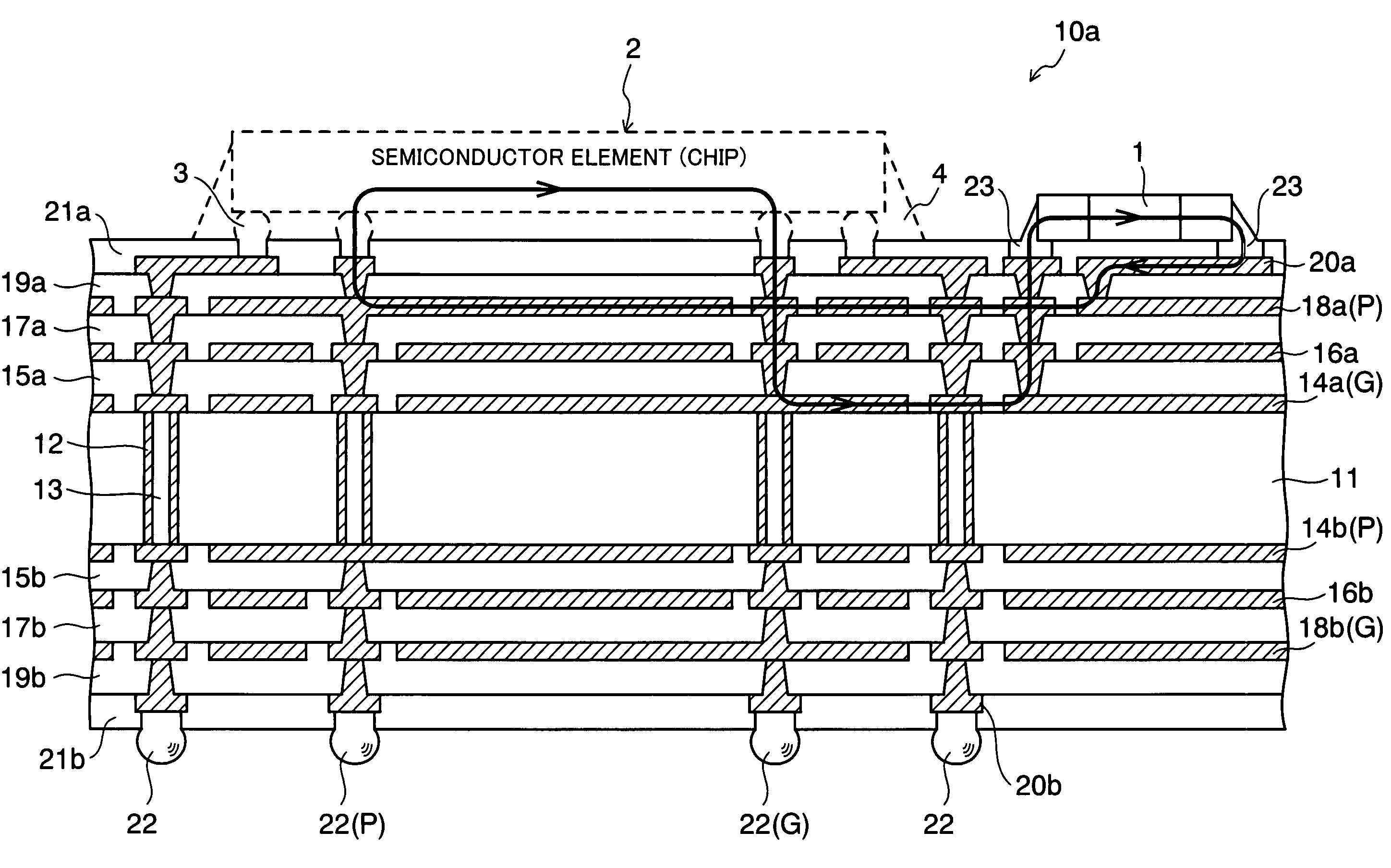

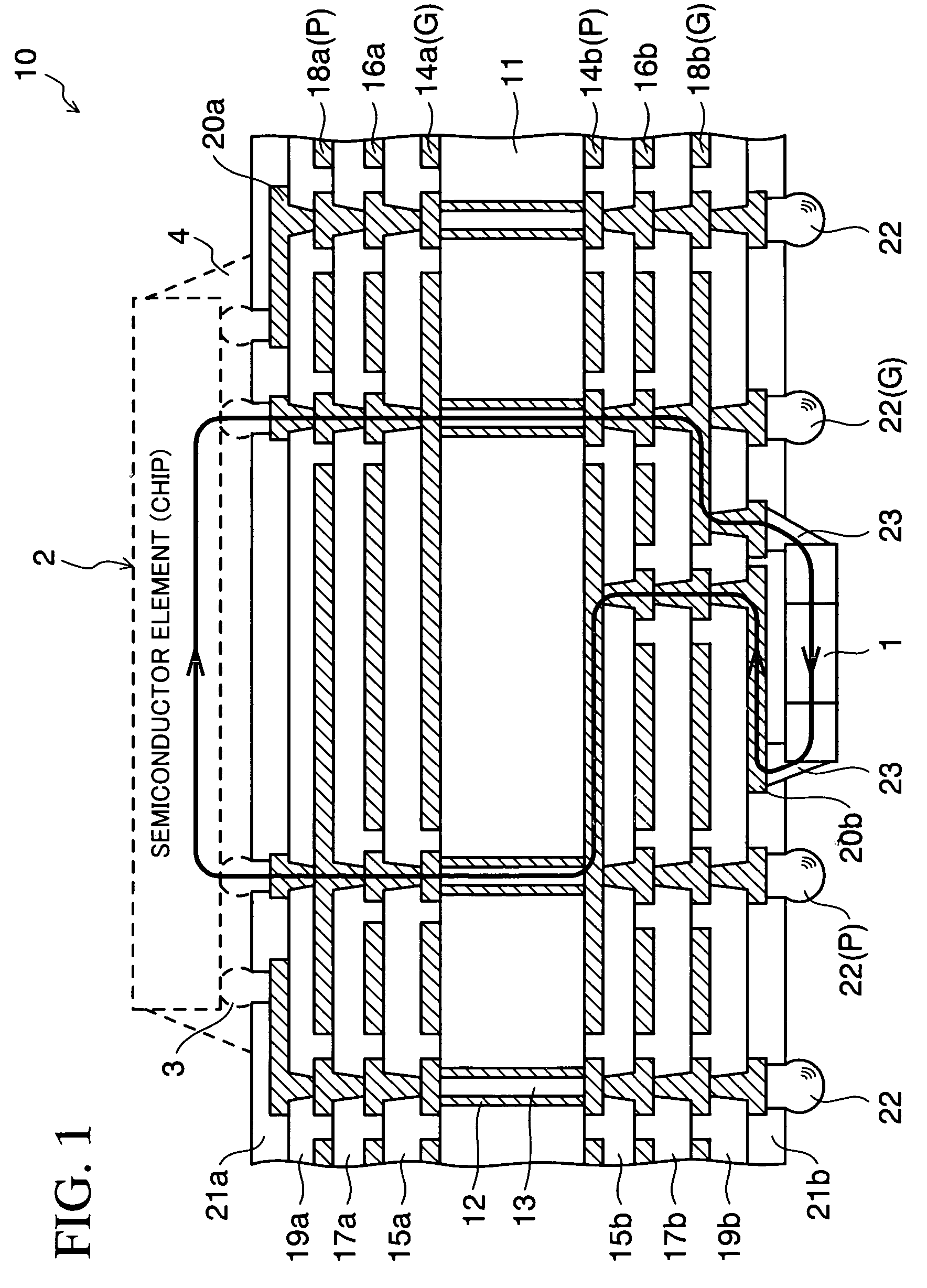

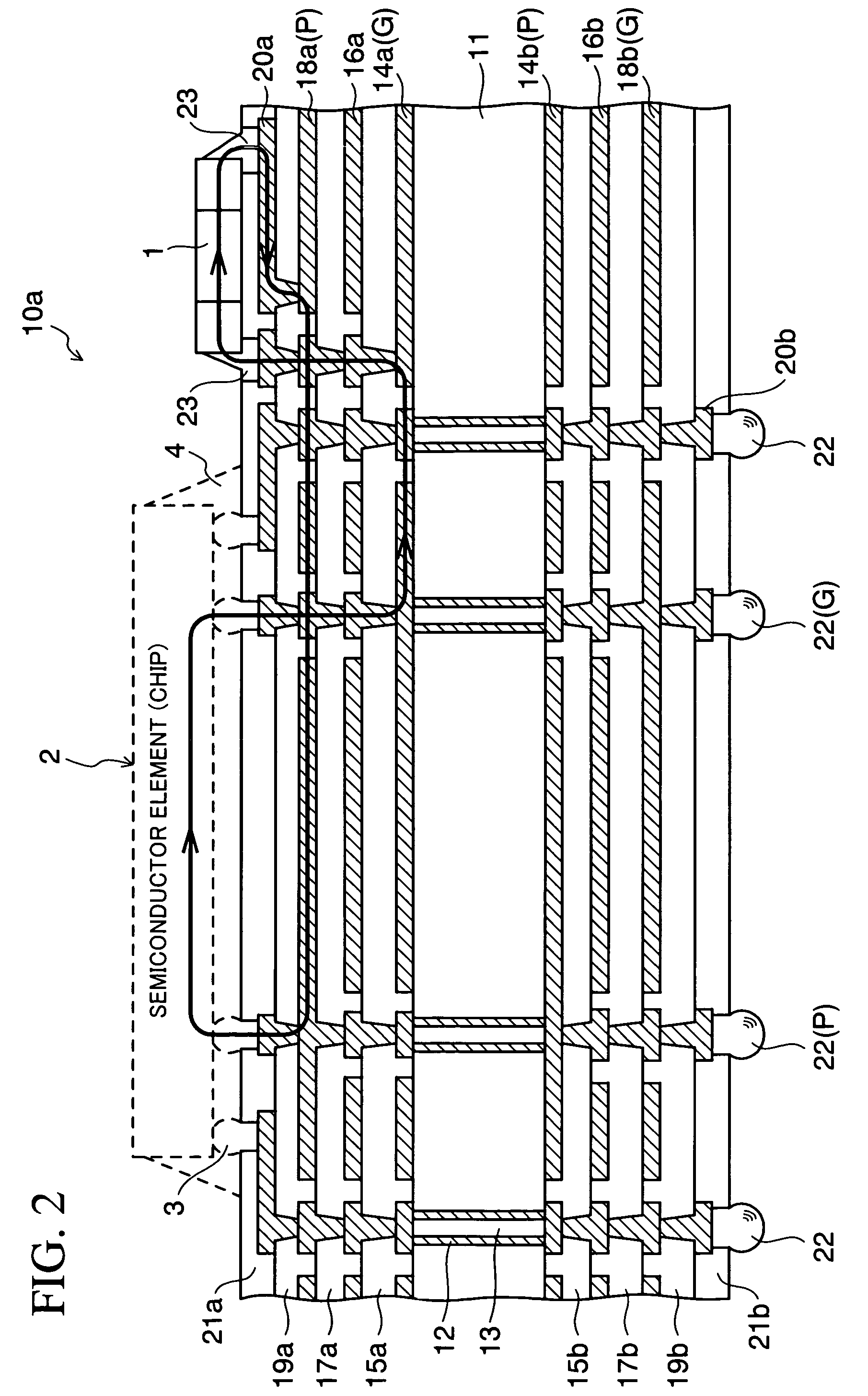

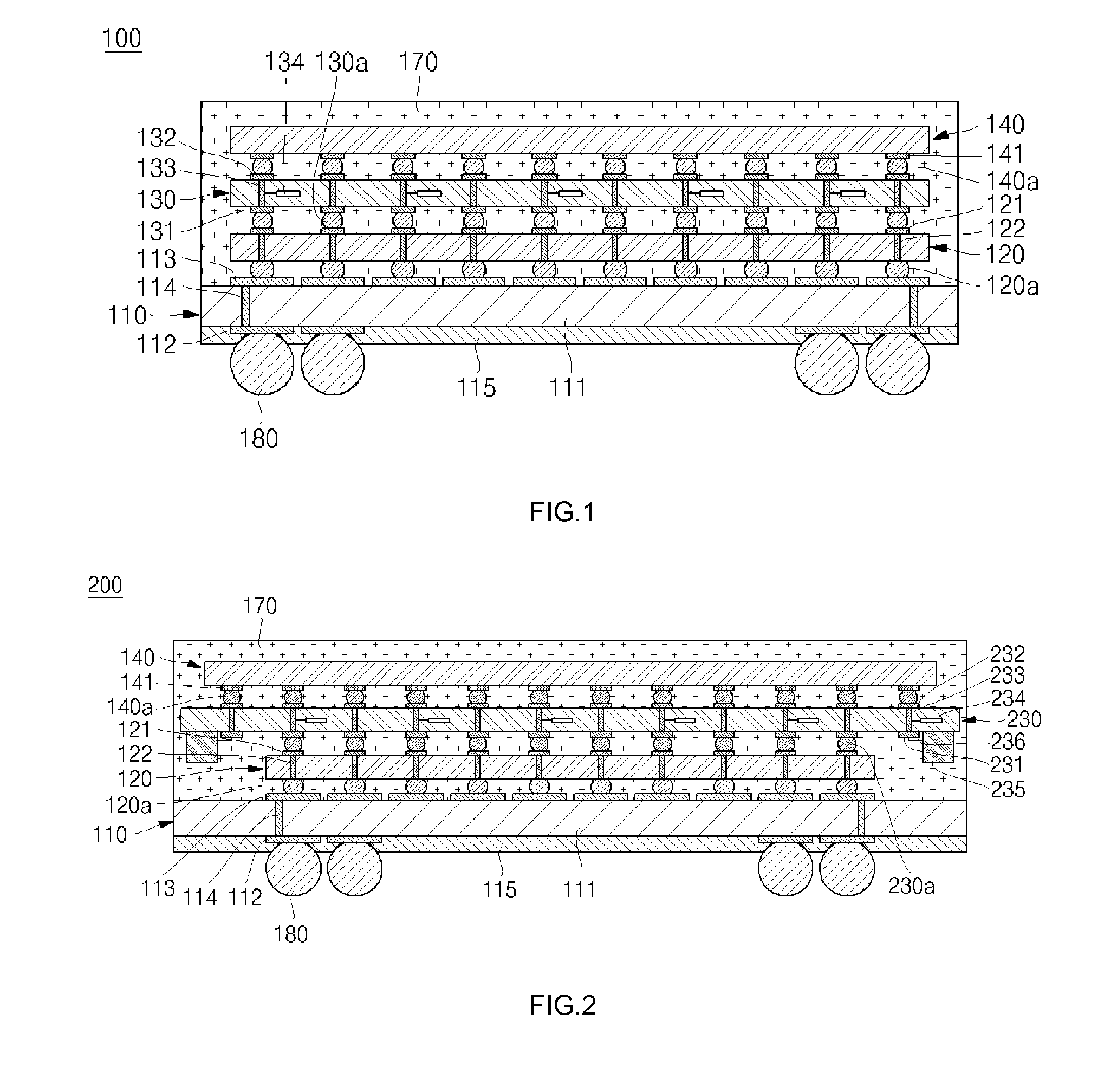

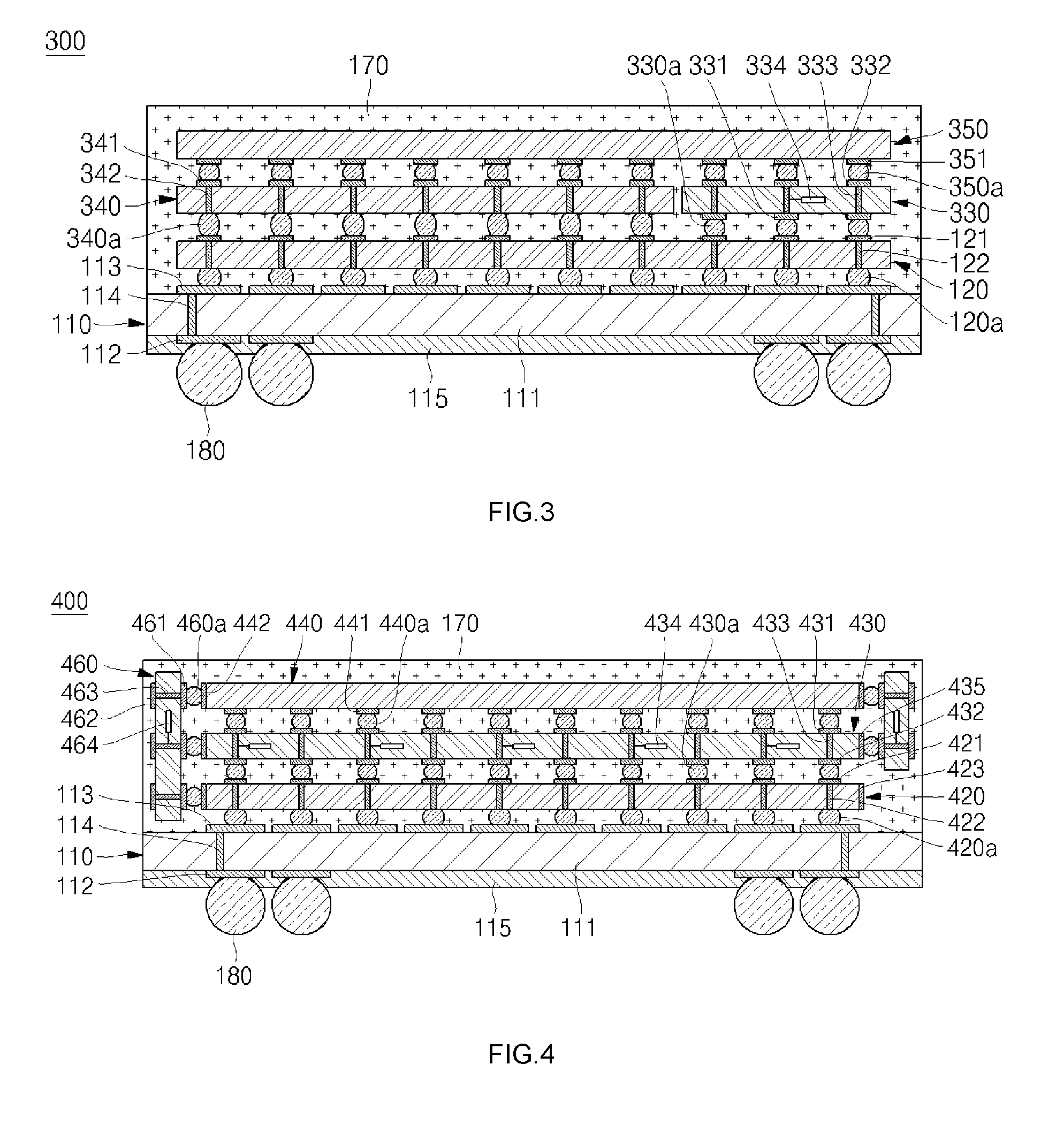

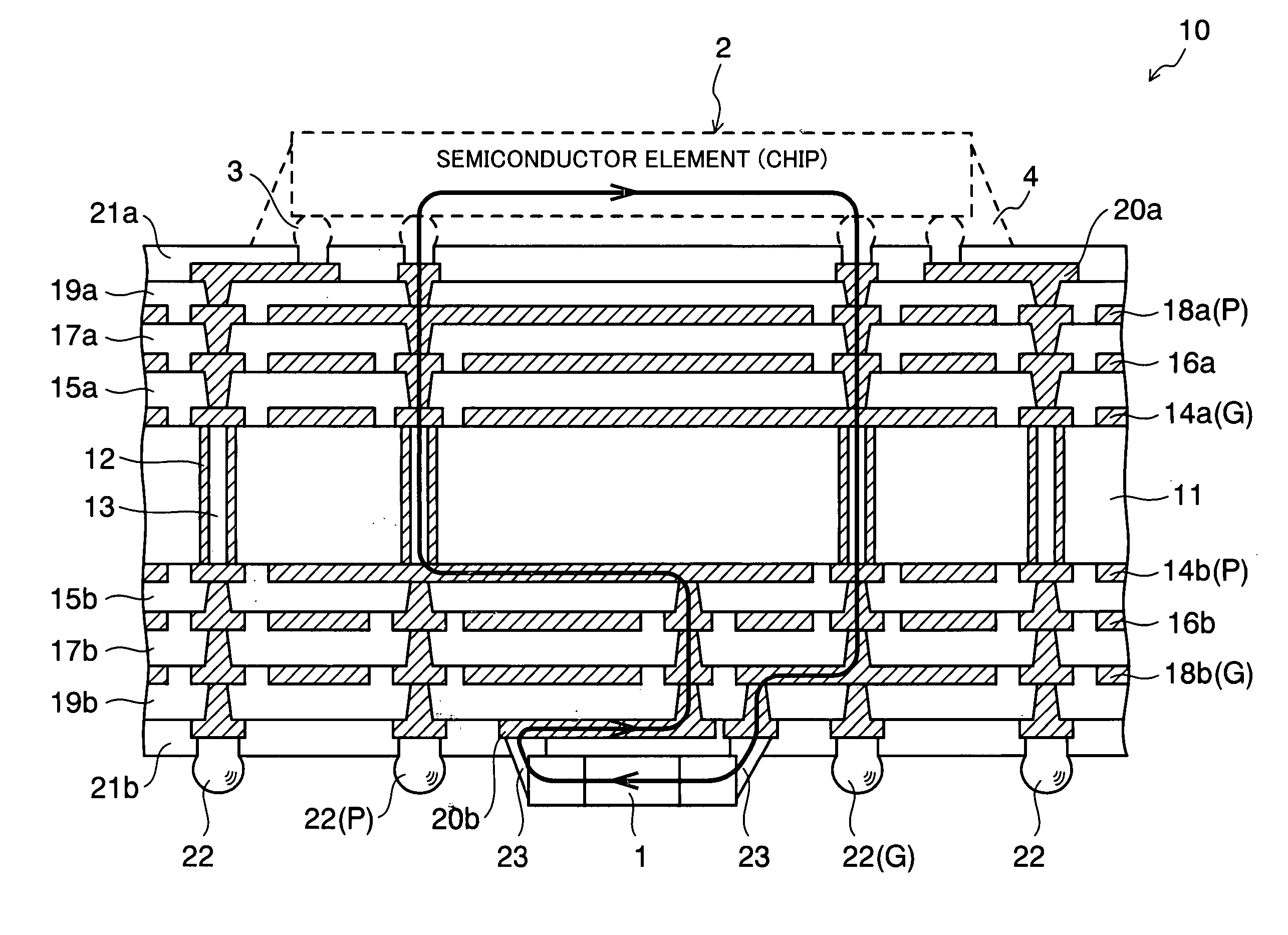

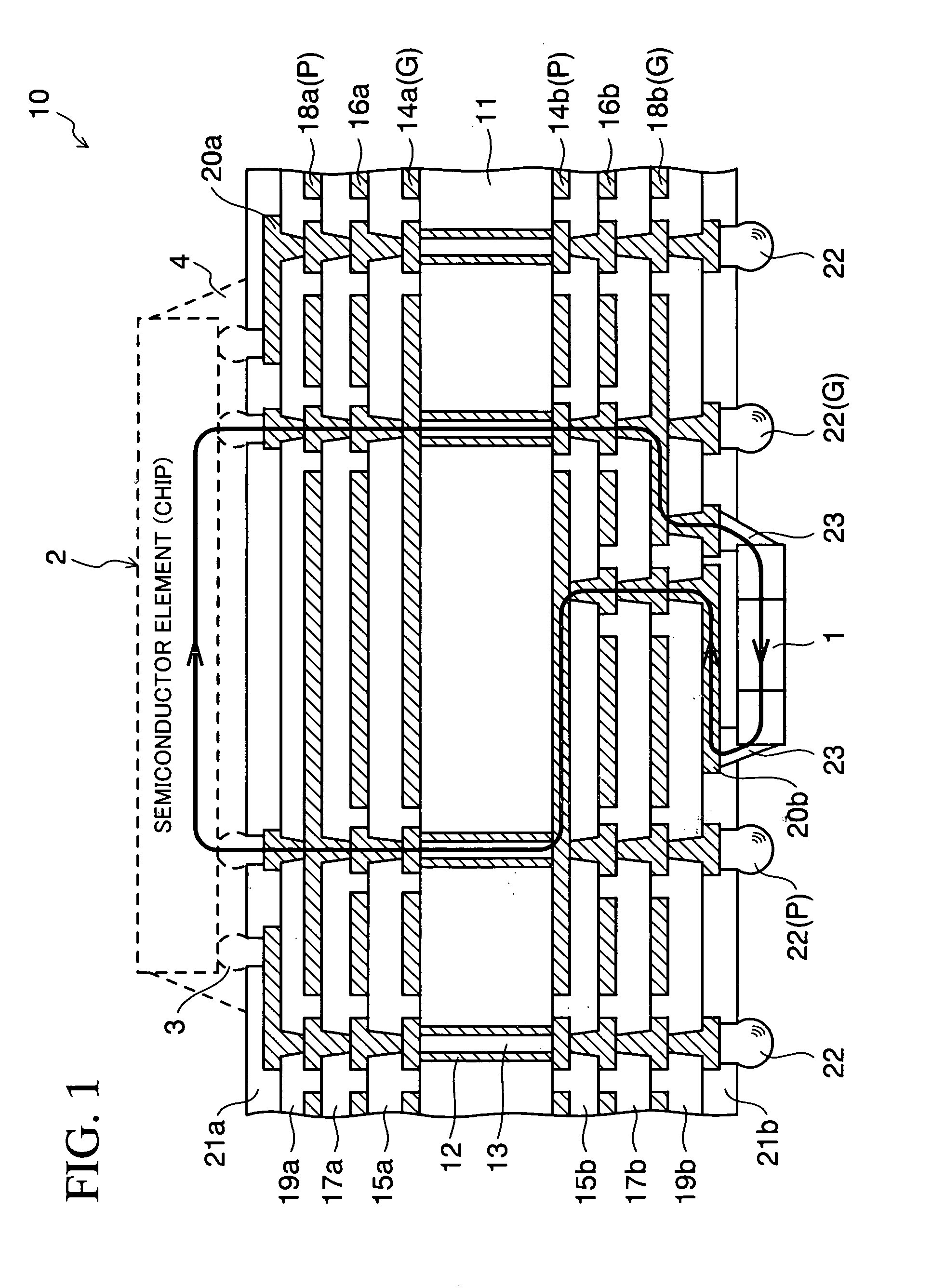

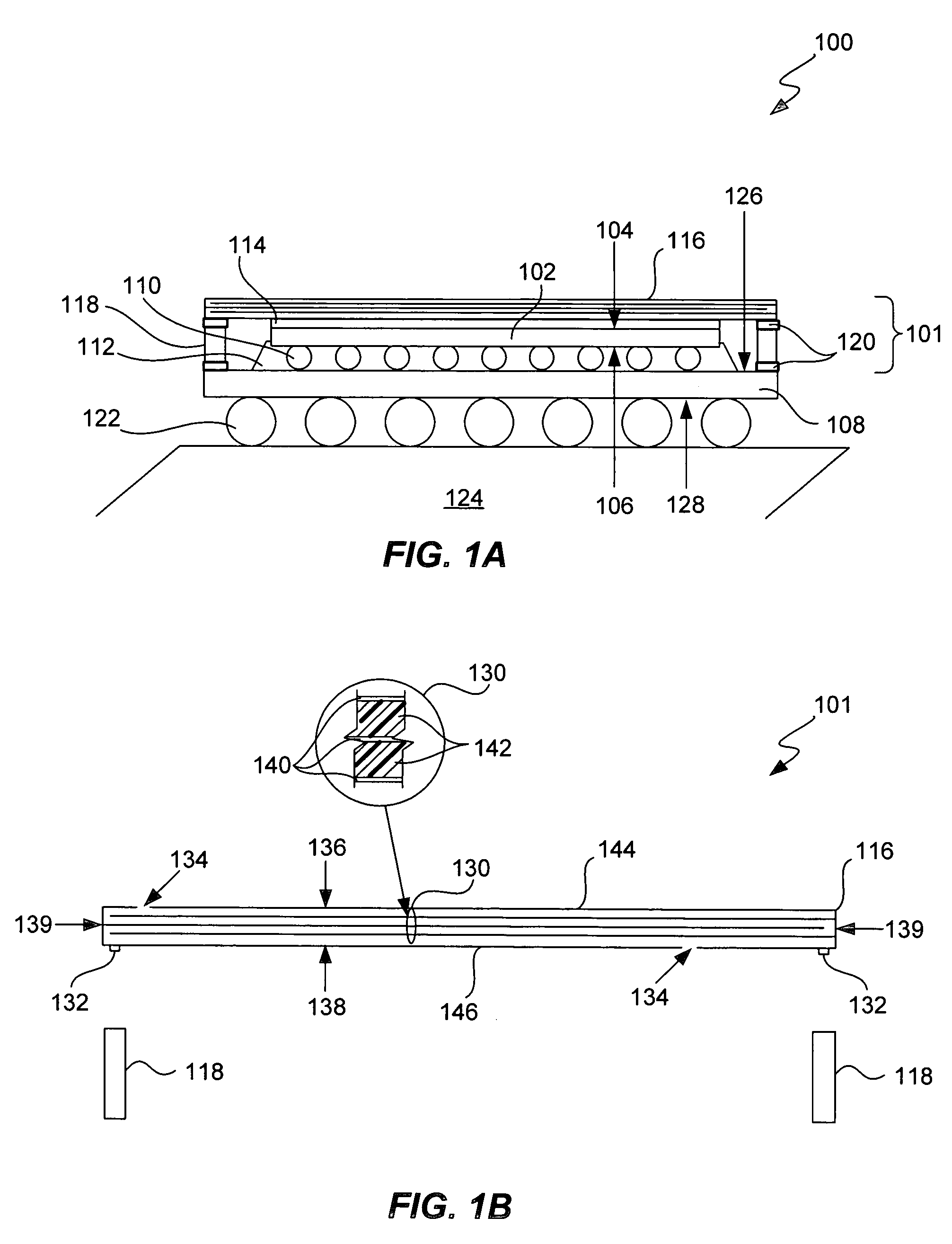

Wiring board mounting a capacitor

ActiveUS7279771B2Guaranteed uptimeEffective decouplingFinal product manufactureSemiconductor/solid-state device detailsElectrical conductorDecoupling capacitor

In a capacitor-mounted wiring board, a plurality of wiring layers each patterned in a required shape are stacked with insulating layers interposed therebetween and are connected to each other via conductors formed to pierce the insulating layers in the direction of thickness. A decoupling capacitor is electrically connected to a wiring layer used as a power supply line or a ground line in the vicinity of the wiring layer, and mounted such that, when a current is passed through the capacitor, the direction of the current is reversed to that of the current flowing through the relevant wiring layer.

Owner:SHINKO ELECTRIC IND CO LTD

Zero-voltage-switched, full-bridge, phase-shifted DC-DC converter with improved light/no-load operation

InactiveUS6909617B1Operation efficiency is highImprove power supply efficiencyEfficient power electronics conversionConversion with intermediate conversion to dcCapacitanceFull bridge

A zero-voltage-switched, full-bridge, phase-shifted DC-DC converter for use in a DC power supply or battery charger includes a power transformer, four switching transistors connected to form a full bridge, and a decoupling capacitor and resonant inductor connected in series to the primary winding of the power transformer. At high loads, i.e., high output voltages, the resonant inductor charges the stray and internal capacitance of the switching transistors. Under light loads or in a no-load condition, with the current through the resonant inductor insufficient to allow the inductor to recharge these capacitances, the combination of a second inductor connected at one end to the central tap of the power transformer's primary winding and at its second opposed end to the middle point of a capacitive voltage divider, permits the second inductor to store enough energy to effectively recharge the stray and internal capacitance of the switching transistors for improved operating efficiency.

Owner:LA MARCHE MFG

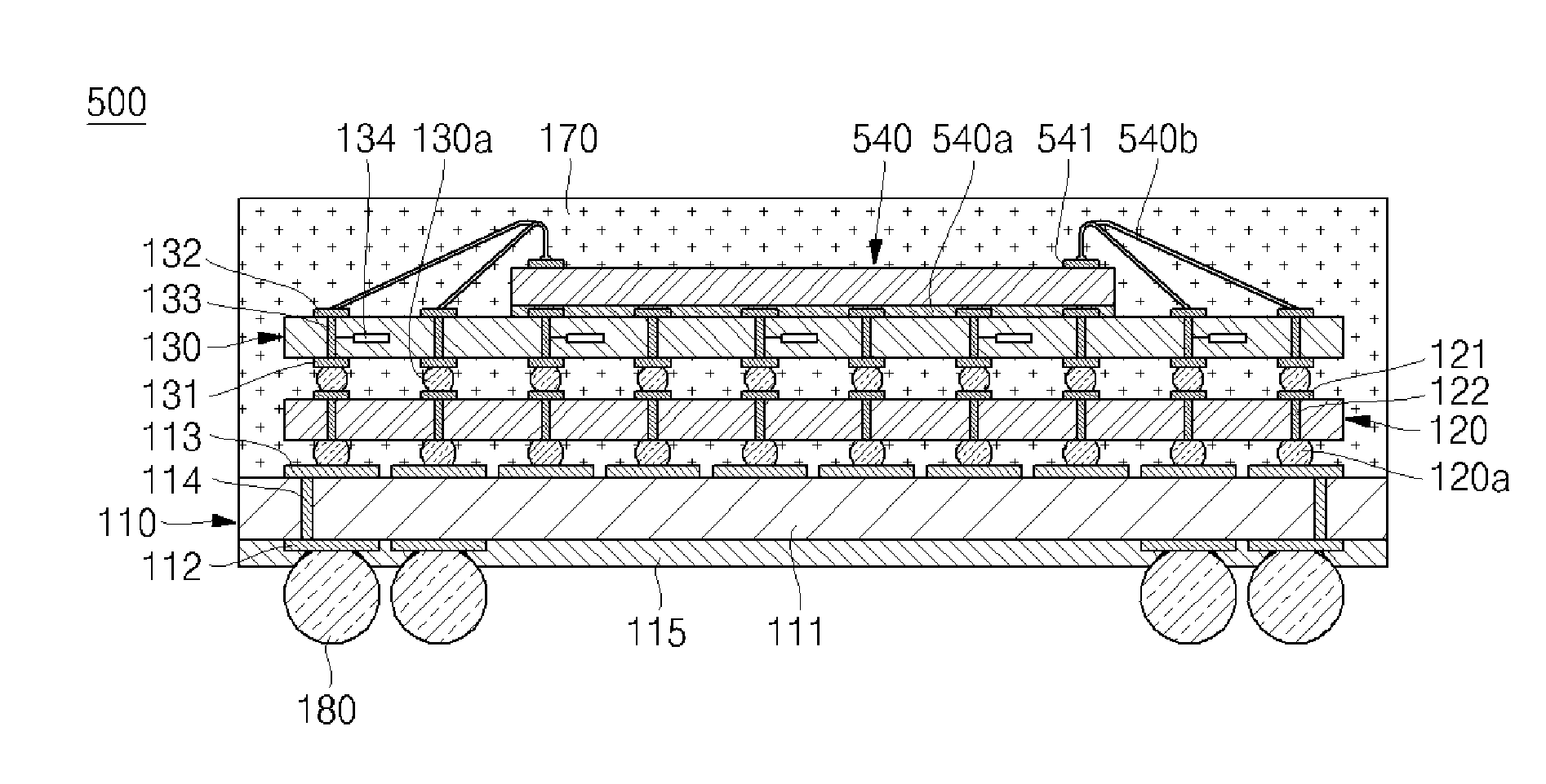

Semiconductor device and fabricating method thereof

ActiveUS20110031598A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A semiconductor device and a method of fabricating the same are disclosed. An interposer used for the semiconductor device includes integrated circuits therein to realize the functions of a decoupling capacitor, an ESD preventing circuit, an impedance matching circuit, and termination. Therefore, it is possible to improve the reliability of the operation of the semiconductor device.

Owner:AMKOR TECH KOREA +1

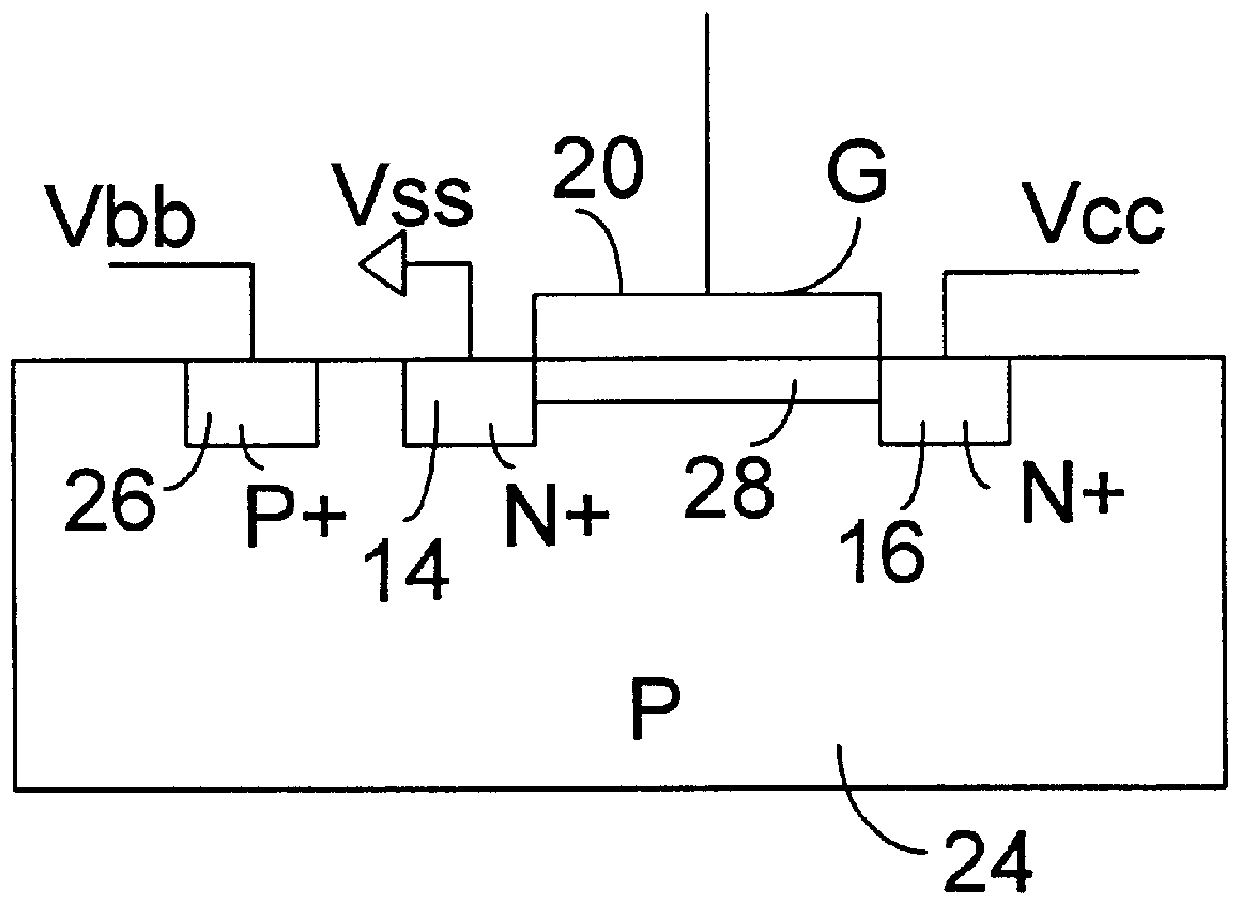

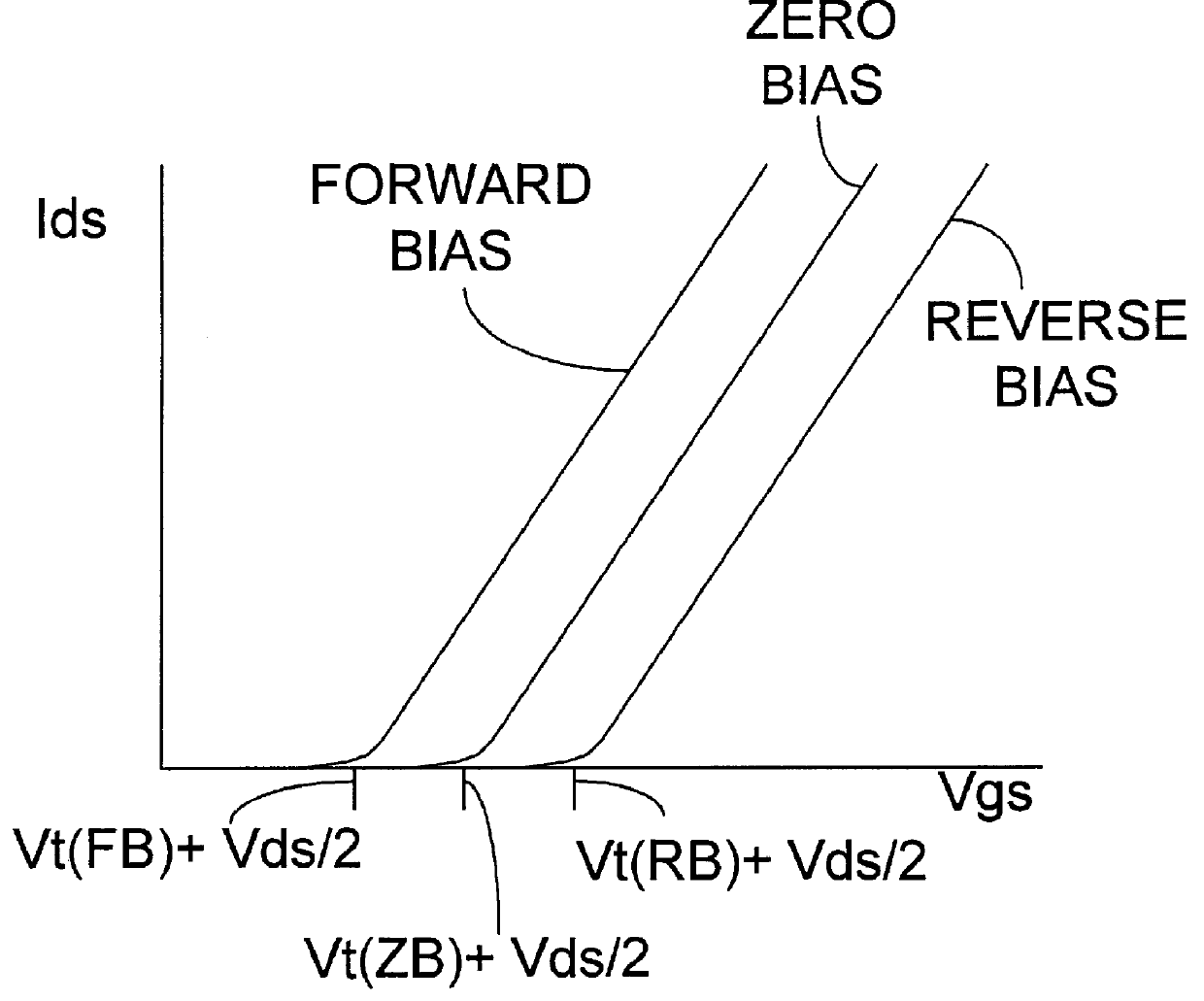

Forward body biased field effect transistor providing decoupling capacitance

In one embodiment of the invention, a semiconductor circuit includes a first group of field effect transistors that are forward body biased and have threshold voltages and a second group of field effect transistors that are not forward body biased and have threshold voltages that are higher than the threshold voltages of the first group of field transistors. In another embodiment of the invention, a semiconductor circuit includes first and second groups of field effect transistors. The circuit includes voltage source circuitry to provide voltage signals to bodies of the first group of field effect transistors to forward body bias the transistors of the first group. When the voltage signals are applied, the transistors of the first group have lower threshold voltages than do the transistors of the second group, except that there may be unintentional variations in threshold voltages due to parameter variations. Other aspects of the invention include forward biased decoupling transistors and a method of testing for leakage.

Owner:INTEL CORP

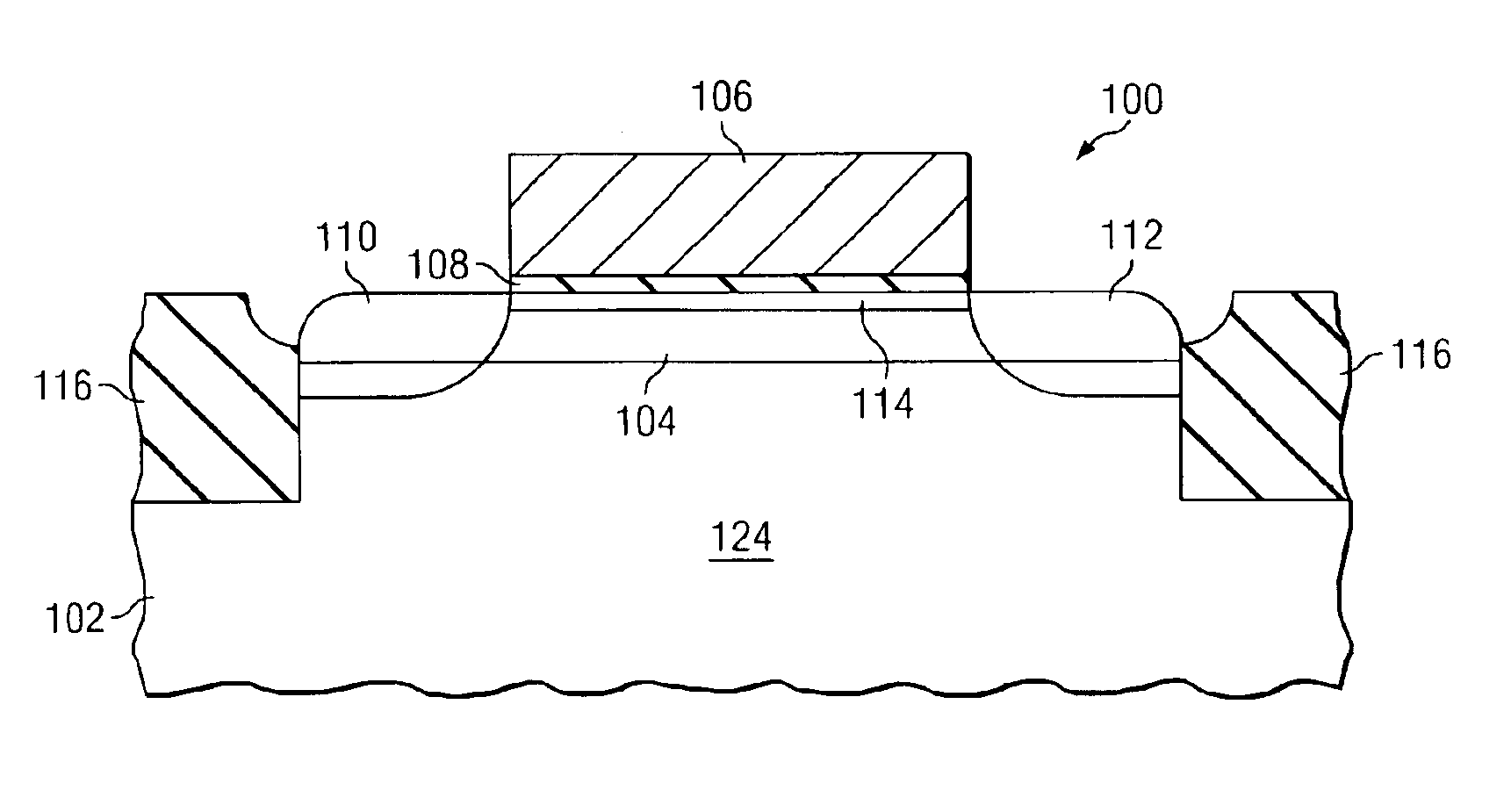

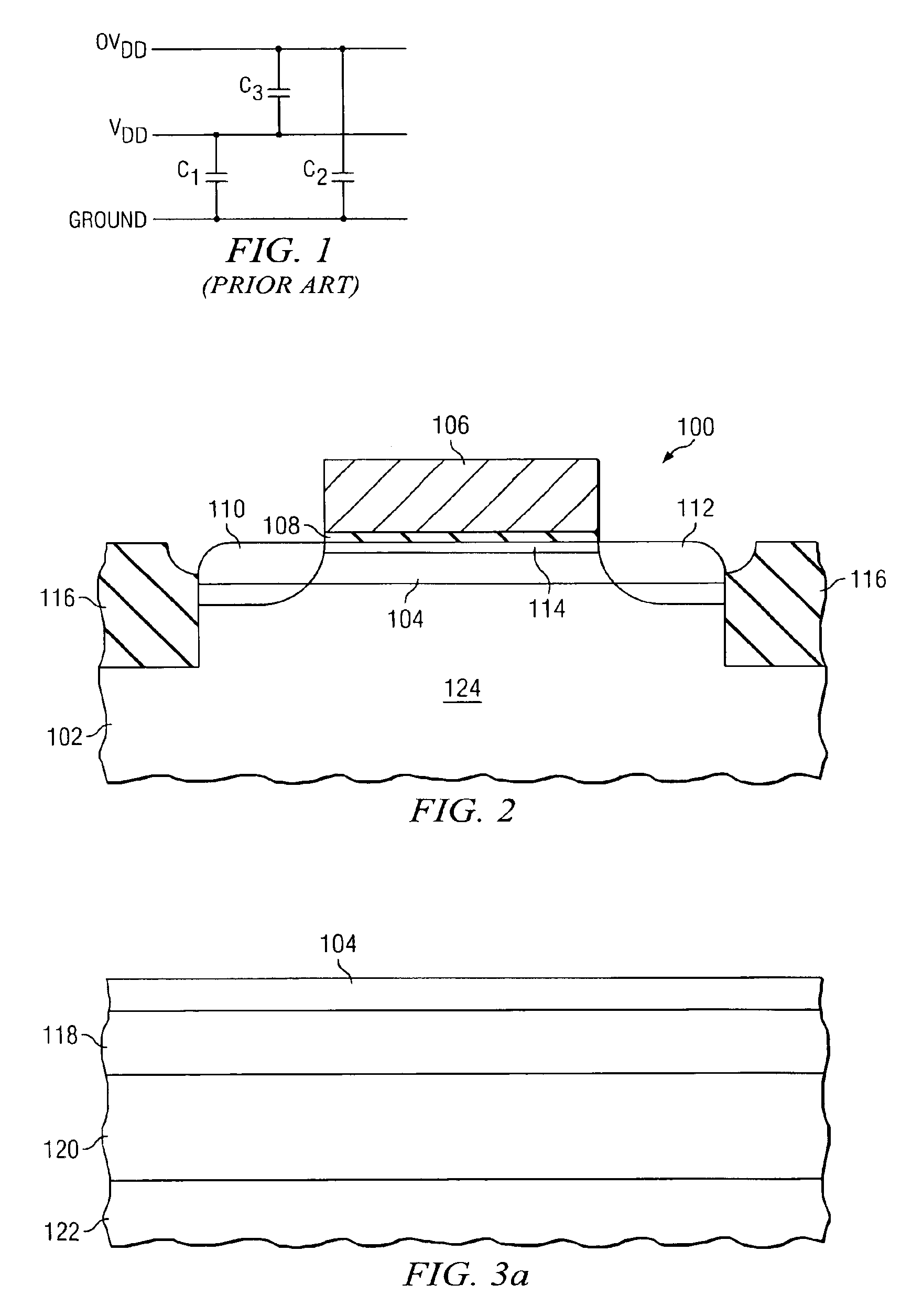

Capacitor that includes high permittivity capacitor dielectric

A decoupling capacitor is formed on a semiconductor substrate that includes a silicon surface layer. A substantially flat bottom electrode is formed in a portion of the semiconductor surface layer. A capacitor dielectric overlies the bottom electrode. The capacitor dielectric is formed from a high permittivity dielectric with a relative permittivity, preferably greater than about 5. The capacitor also includes a substantially flat top electrode that overlies the capacitor dielectric. In the preferred application, the top electrode is connected to a first reference voltage line and the bottom electrode is connected to a second reference voltage line.

Owner:TAIWAN SEMICON MFG CO LTD

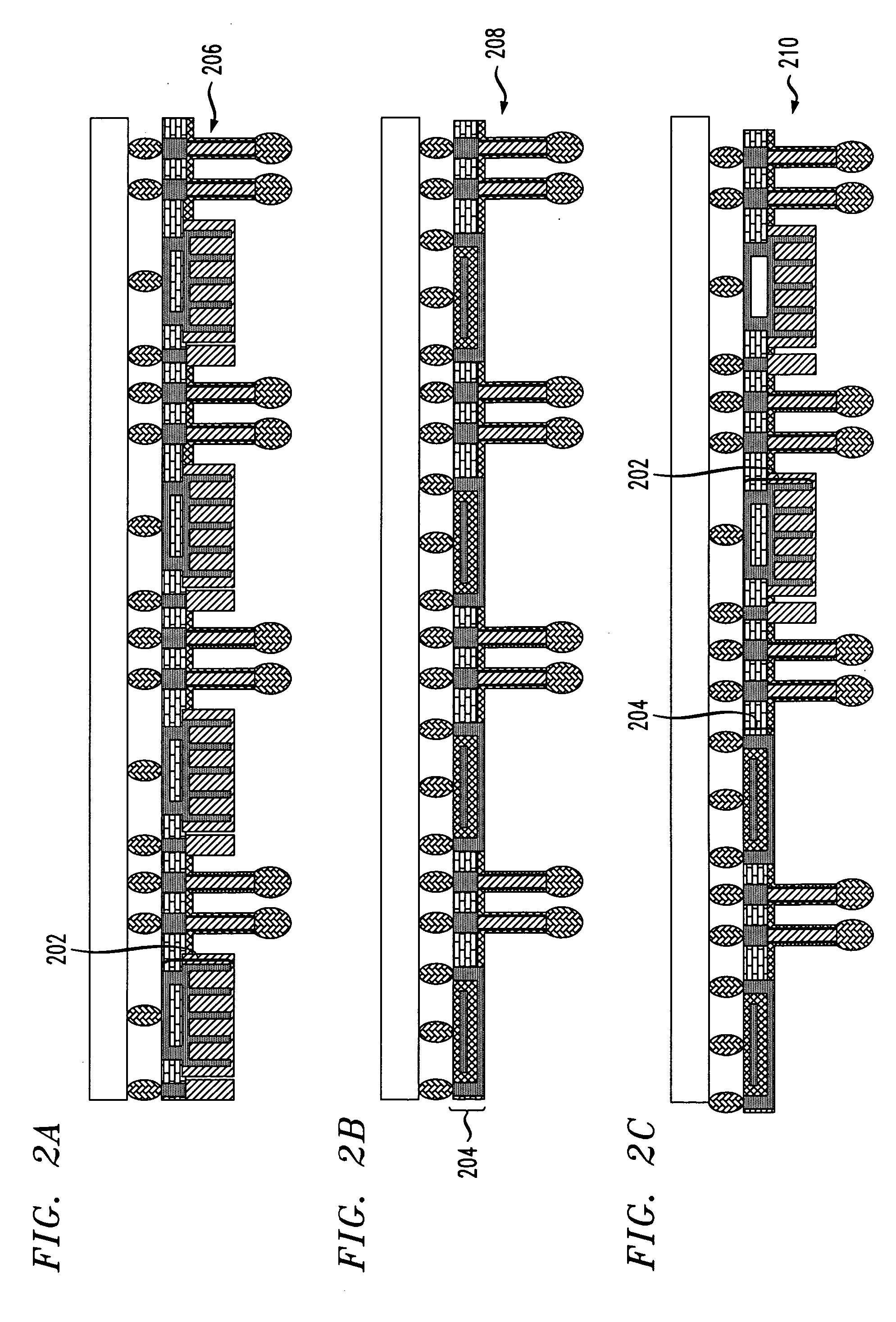

Power mesh for multiple frequency operation of semiconductor products

InactiveUS7424696B2Computer programmed simultaneously with data introductionCAD circuit designCapacitanceTransceiver

The design of integrated circuits, i.e., semiconductor products, is made easier with a semiconductor platform having versatile power mesh that is capable of supporting simultaneous operations having different frequencies on the semiconductor product; e.g., higher frequency operations may be embedded as diffused blocks within the lower layers or may be programmed from a configurable transistor fabric above the diffused layers. Preferably the power mesh is located above the layers having the operations requiring the different frequencies, and may be fixed in an application set given to a chip designer or may be configurable by the designer her / himself. For example, to support high speed communications adjacent an embedded high speed data transceiver, the transistor fabric may be programmed as a data link layer having higher performance requirements than the rest of the integrated circuit. The data link layer may be connected to one of the localized grids of the versatile power mesh which may have an increased density and / or wider strap width of a power / ground grid. Additional decoupling capacitance can be embedded in the lower layers of the semiconductor product and / or can be programmed from the configurable transistors fabric.

Owner:AVAGO TECH INT SALES PTE LTD

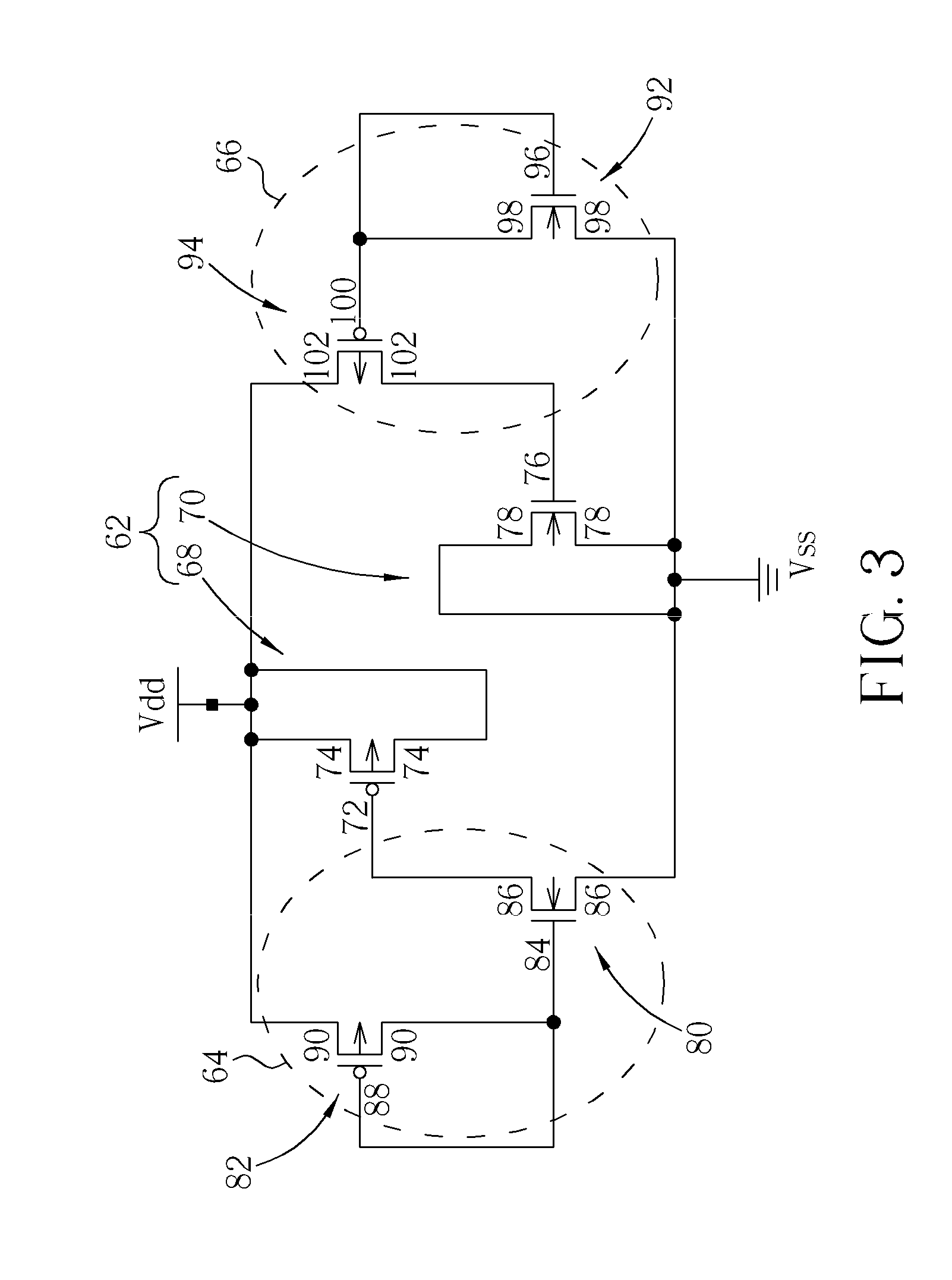

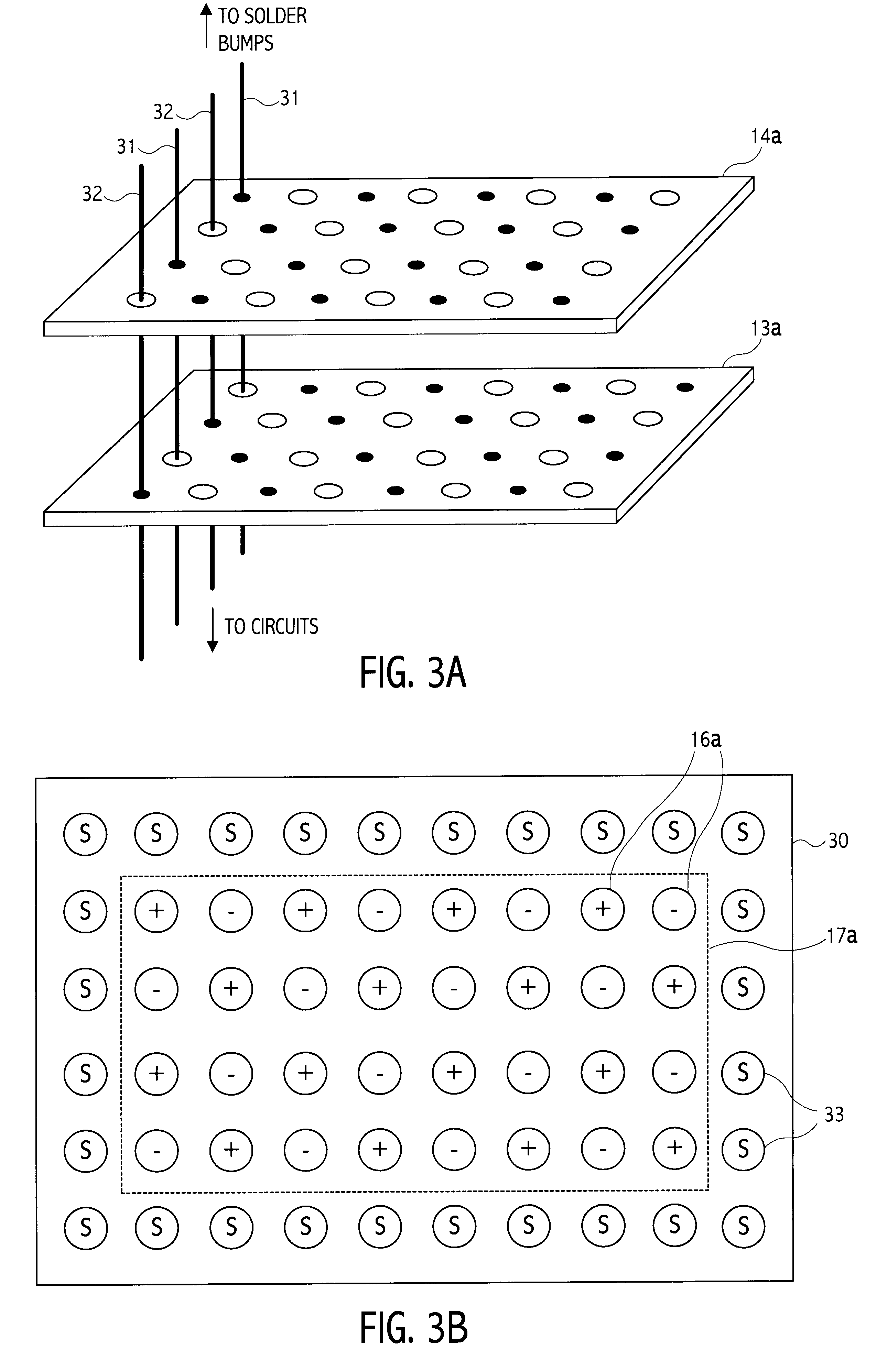

Decoupling capacitor configuration for integrated circuit chip

InactiveUS6191479B1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceElectricity

A decoupling capacitor structure formed integral with an integrated circuit chip and over top of circuitry defined thereon advantageously provides decoupling capacitance in close electrical proximity to switching circuits of the integrated circuit chip without substantially affecting die footprint. In contrast with on-die gate oxide capacitor configurations, a decoupling capacitor structure formed toward the back end of processing, typically after interconnect metal, allows large area capacitor structures without substantial impact on area available for devices and circuitry. Inductance associated with the intervening portion of a power supply loop circuit between switching circuits of the integrated circuit chip and the decoupling capacitor structure can be extremely low in configurations in accordance with the present invention. In some configurations, connection points, e.g., bonding pads and / or solder bumps for conveying power supply voltages, are defined over top of the decoupling capacitor structure.

Owner:GLOBALFOUNDRIES INC

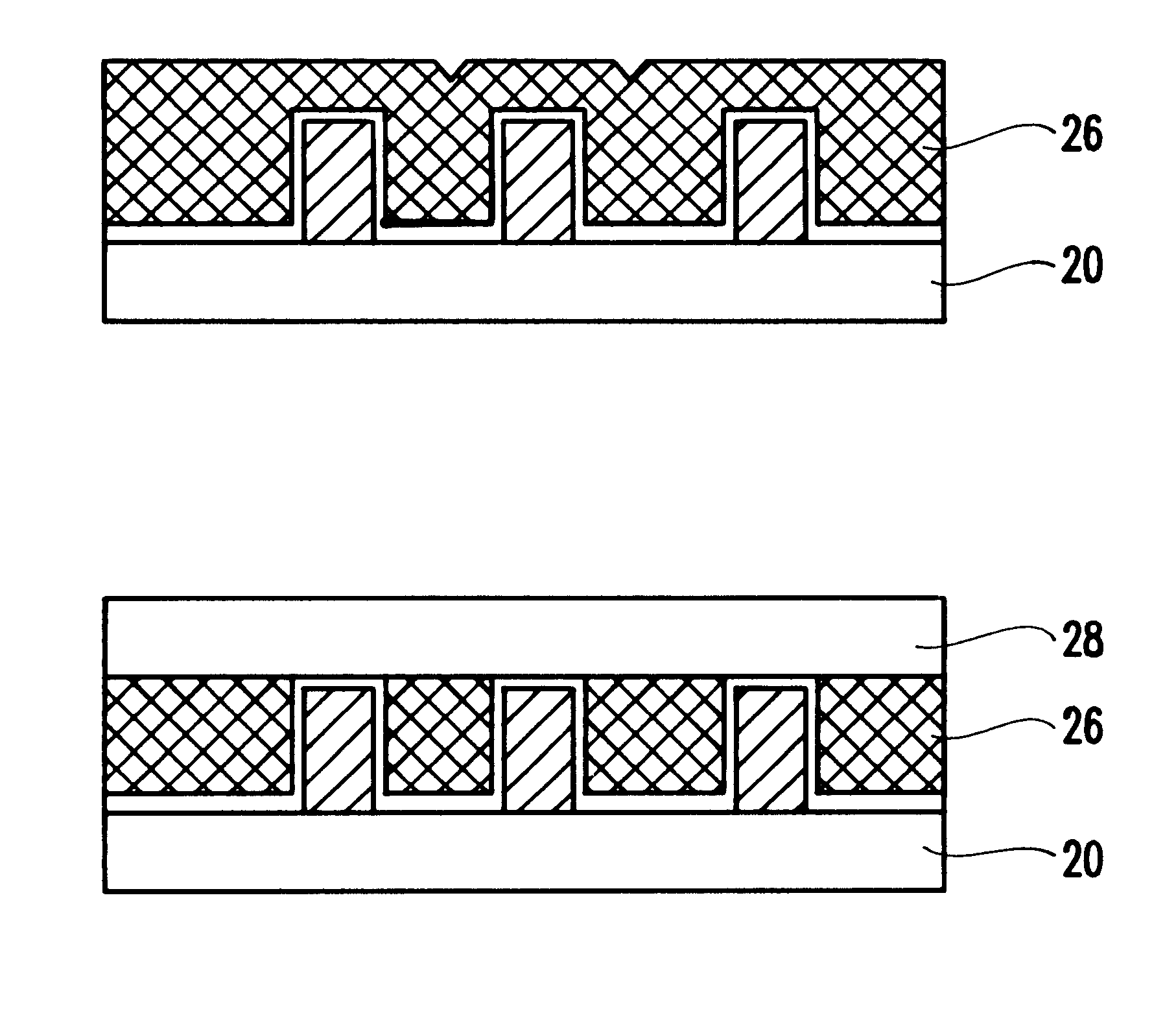

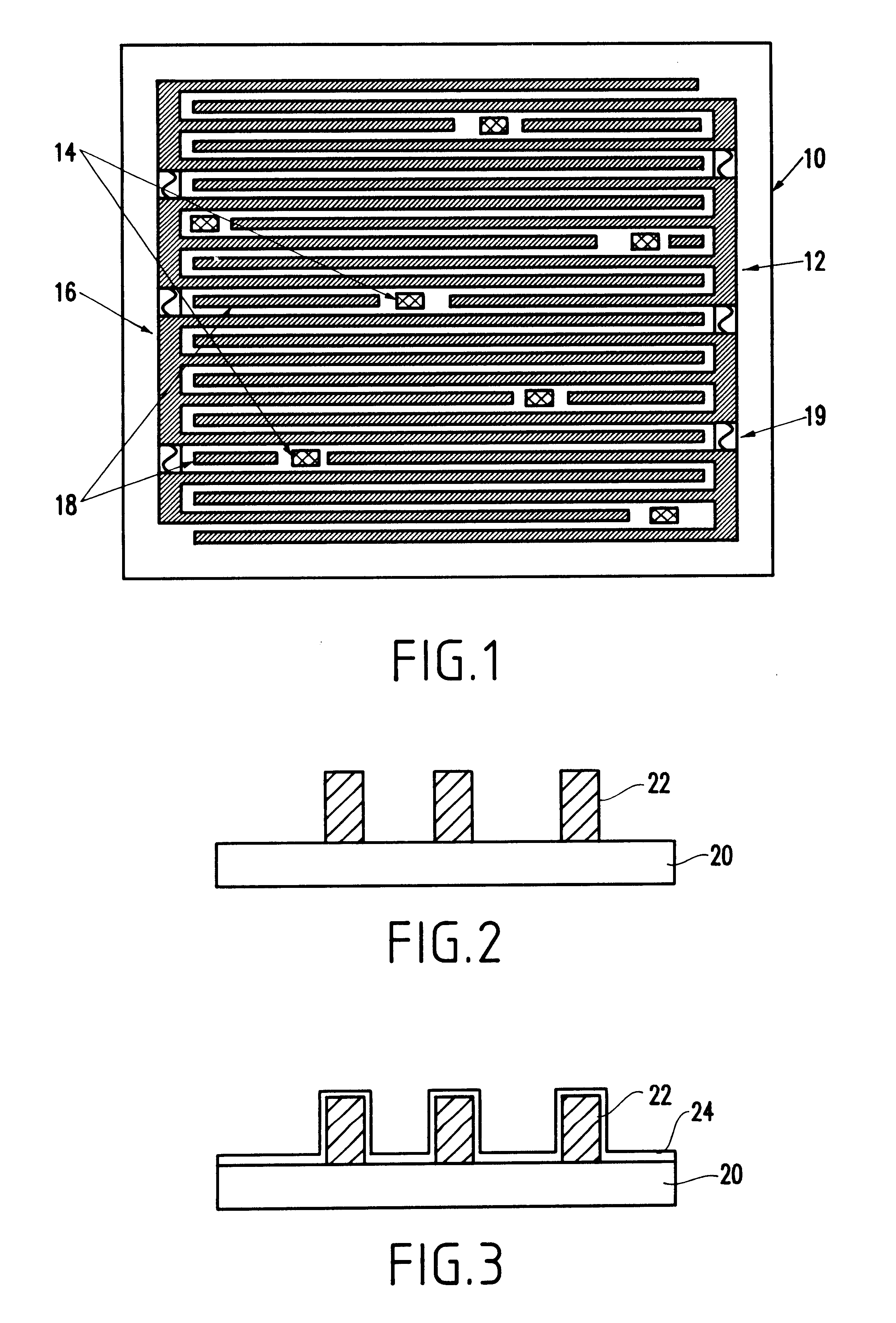

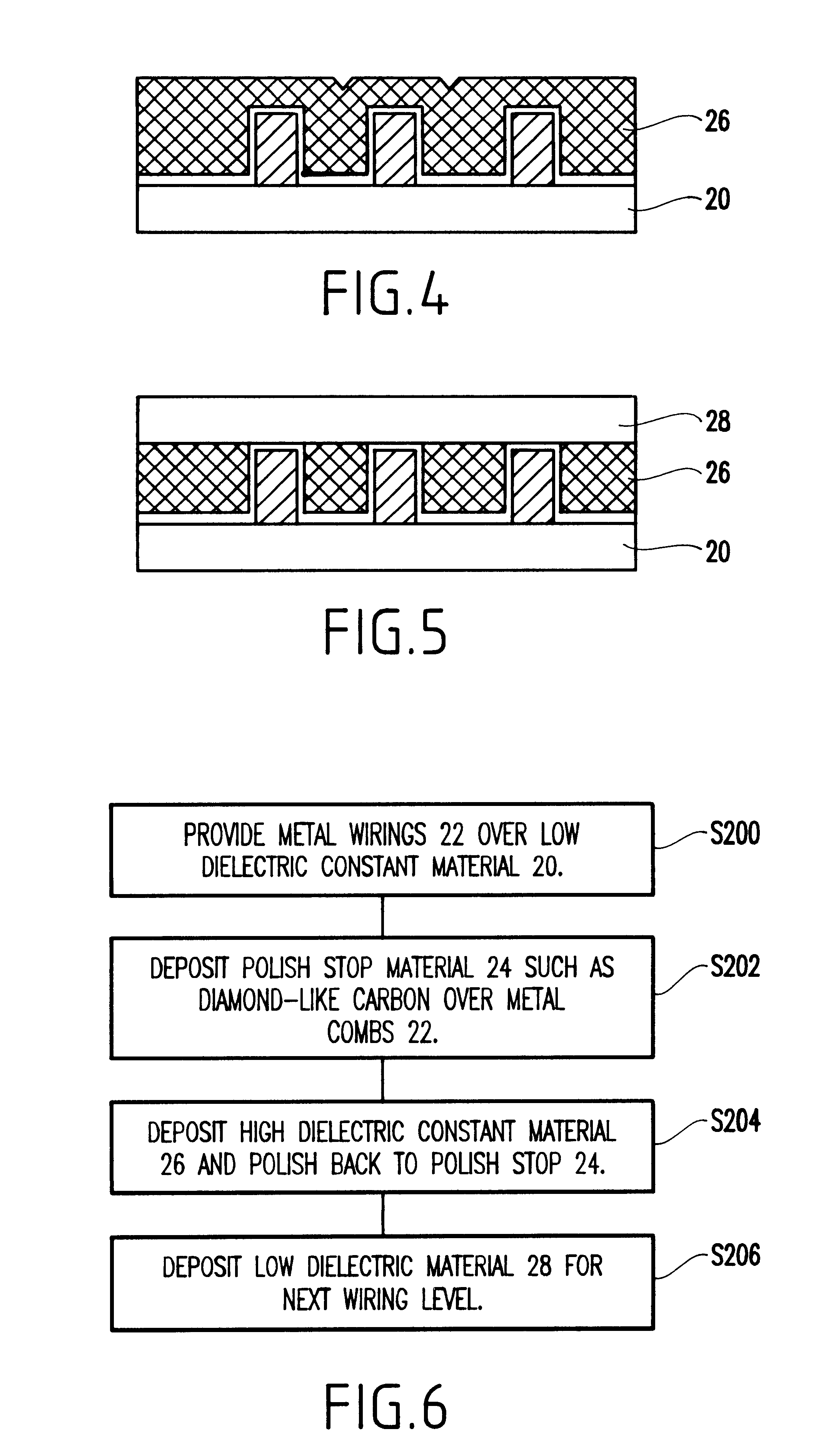

Intralevel decoupling capacitor, method of manufacture and testing circuit of the same

A decoupling capacitor is provided for a semiconductor device and may include a first low dielectric insulator layer and a low resistance conductor formed into at least two interdigitized patterns on the surface of the first low dielectric insulator in a single interconnect plane. A high dielectric constant material may be provided between the two patterns. A circuit for testing a plurality of these capacitors is also provided which includes a charge monitoring circuit, a coupling circuit and a control circuit.

Owner:GLOBALFOUNDRIES INC

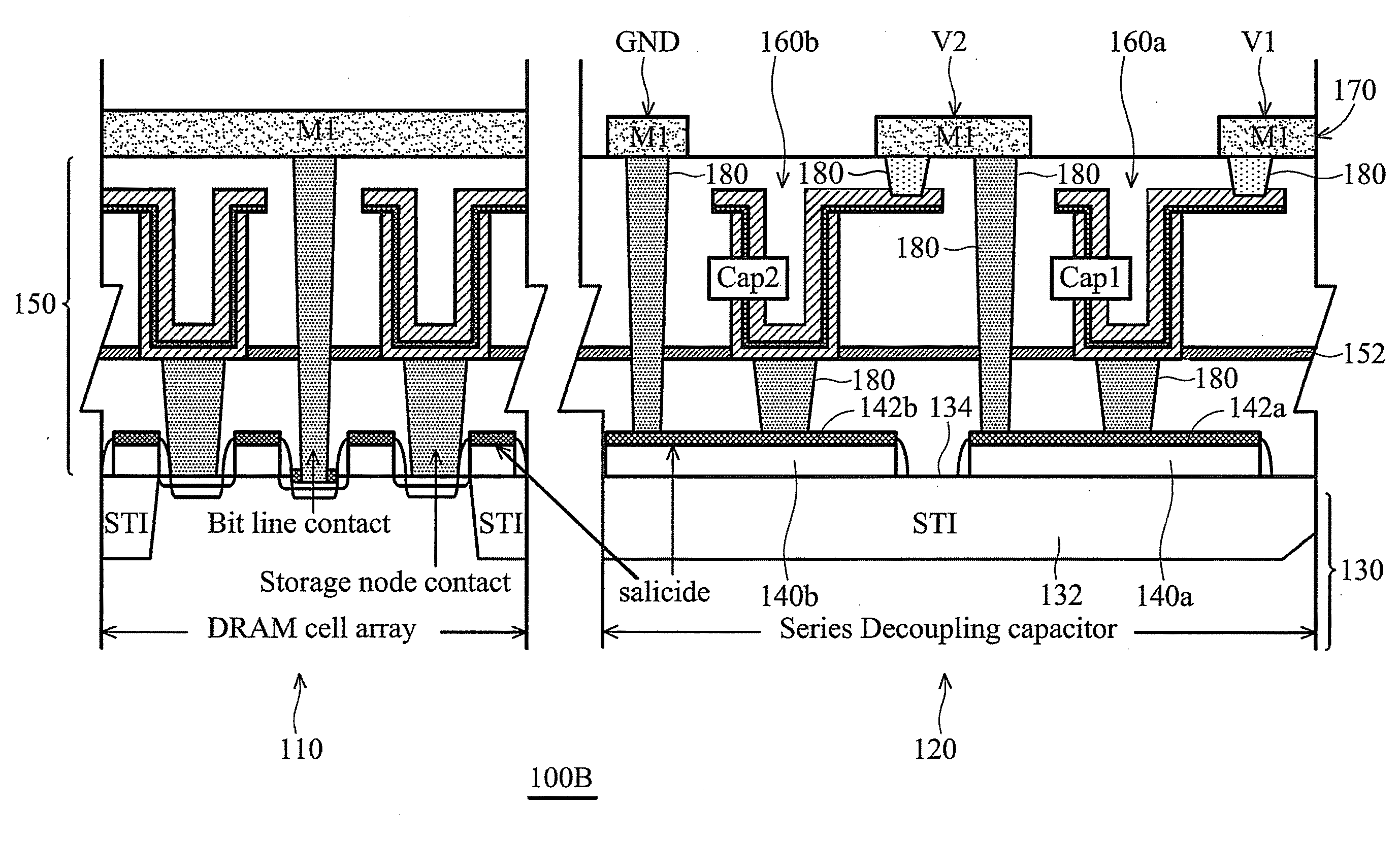

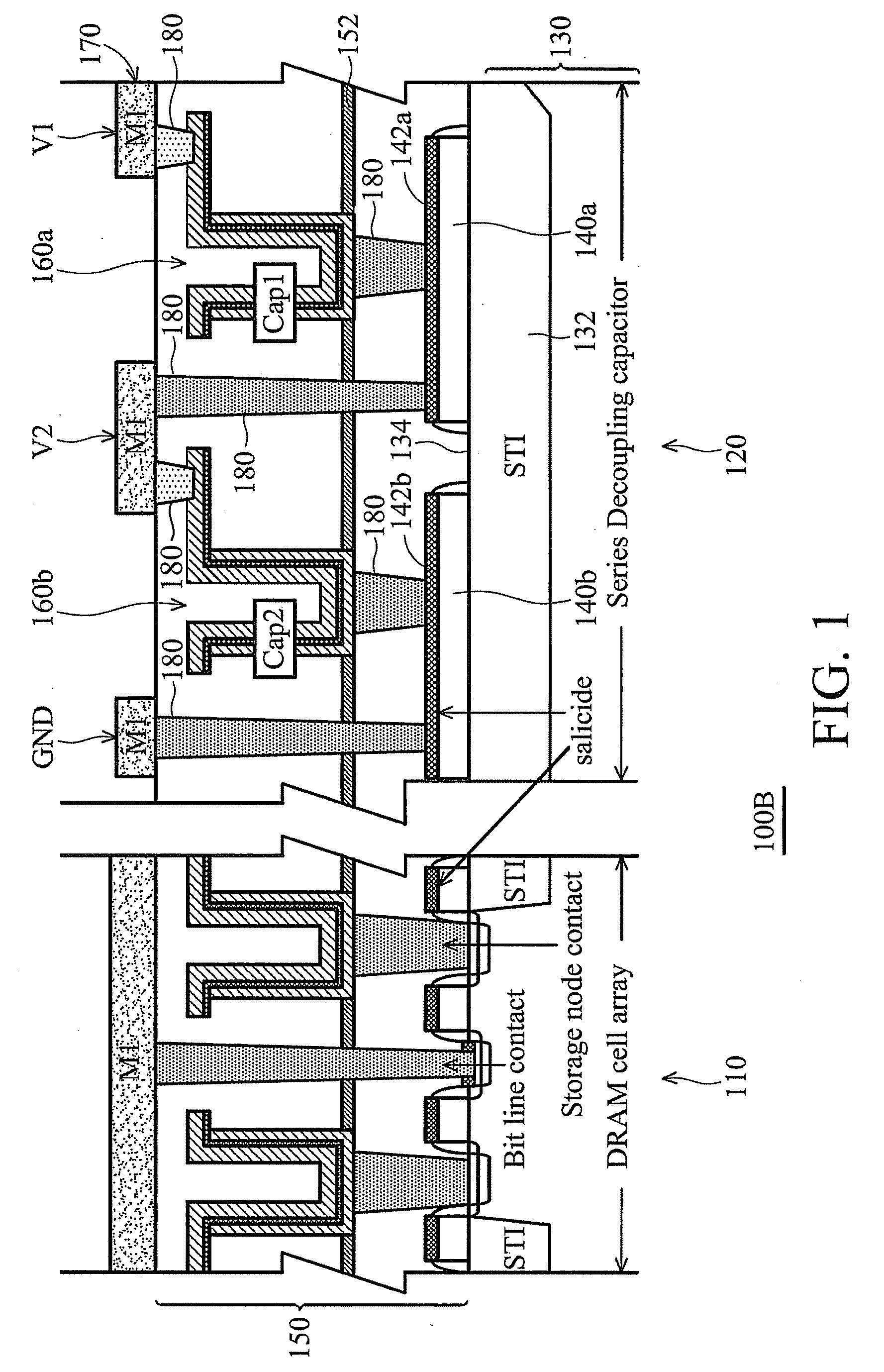

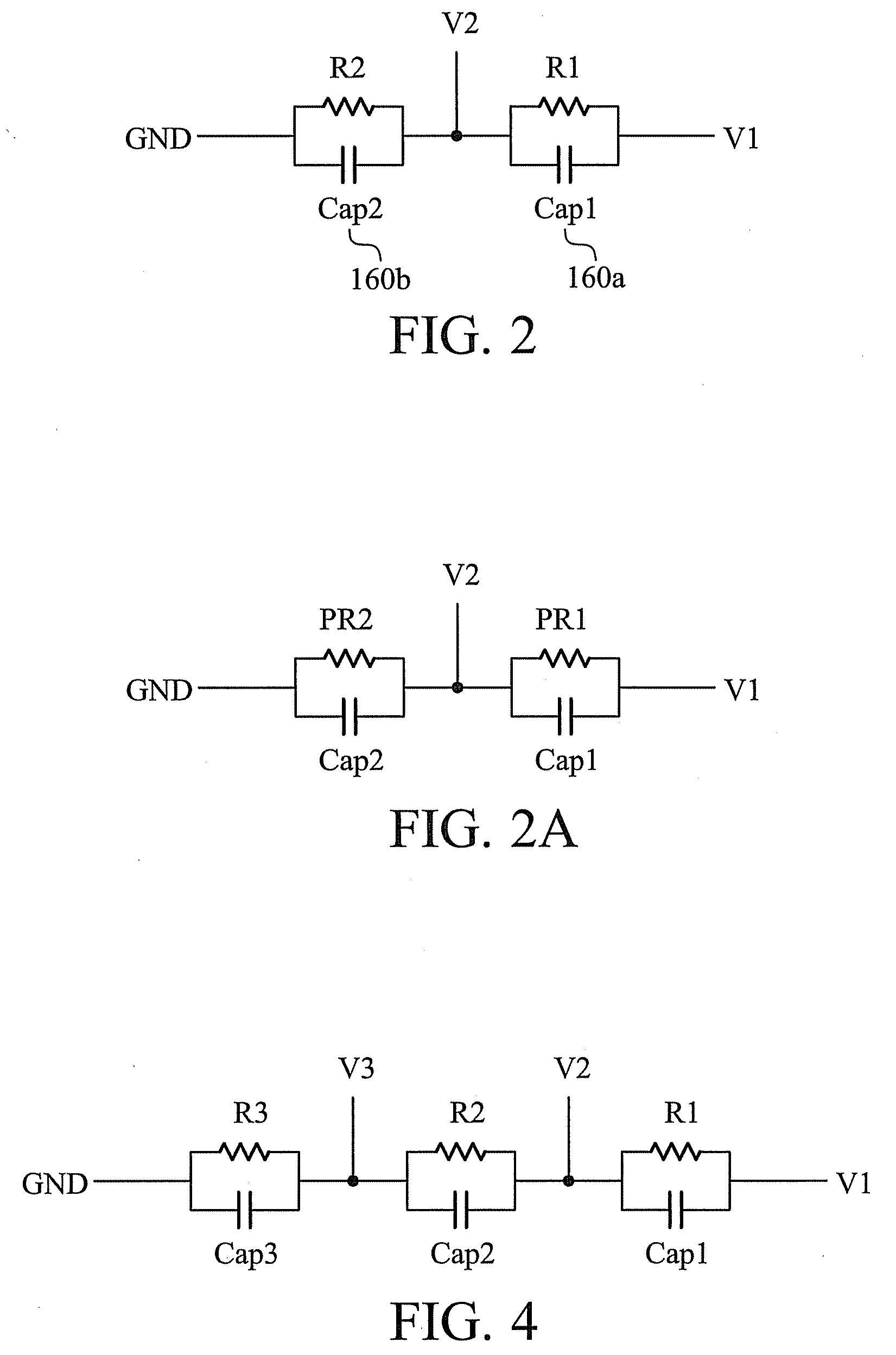

Semiconductor device with decoupling capacitor design

ActiveUS20100065944A1Reduce voltage stressTransistorSemiconductor/solid-state device detailsMetal-insulator-metalCapacitance

An integrated circuit includes a circuit module having a plurality of active components coupled between a pair of supply nodes, and a capacitive decoupling module coupled to the circuit module. The capacitive decoupling module includes a plurality of metal-insulator-metal (MiM) capacitors coupled in series between the pair of supply nodes, wherein a voltage between the supply nodes is divided across the plurality of MiM capacitors, thereby reducing voltage stress on the capacitors.

Owner:TAIWAN SEMICON MFG CO LTD

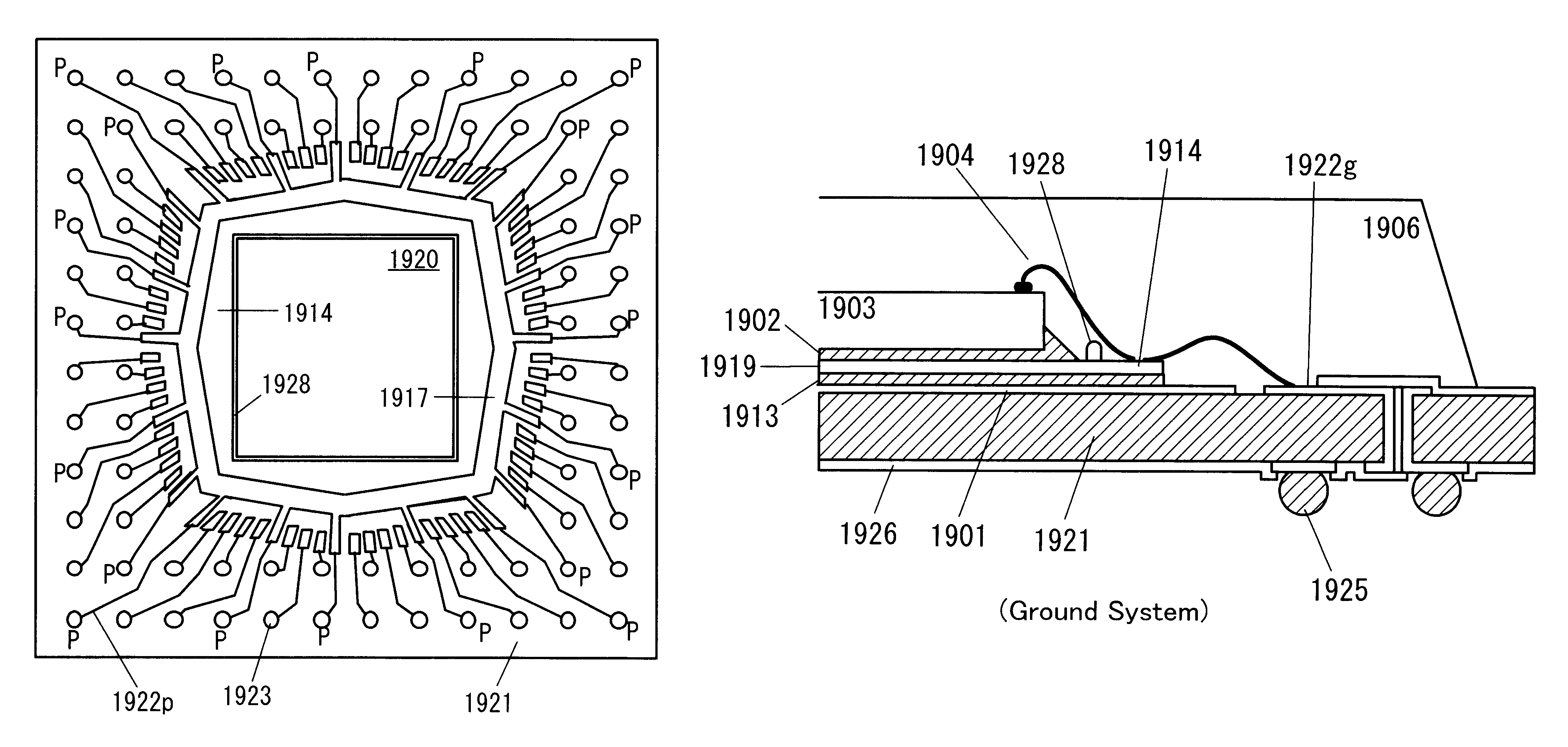

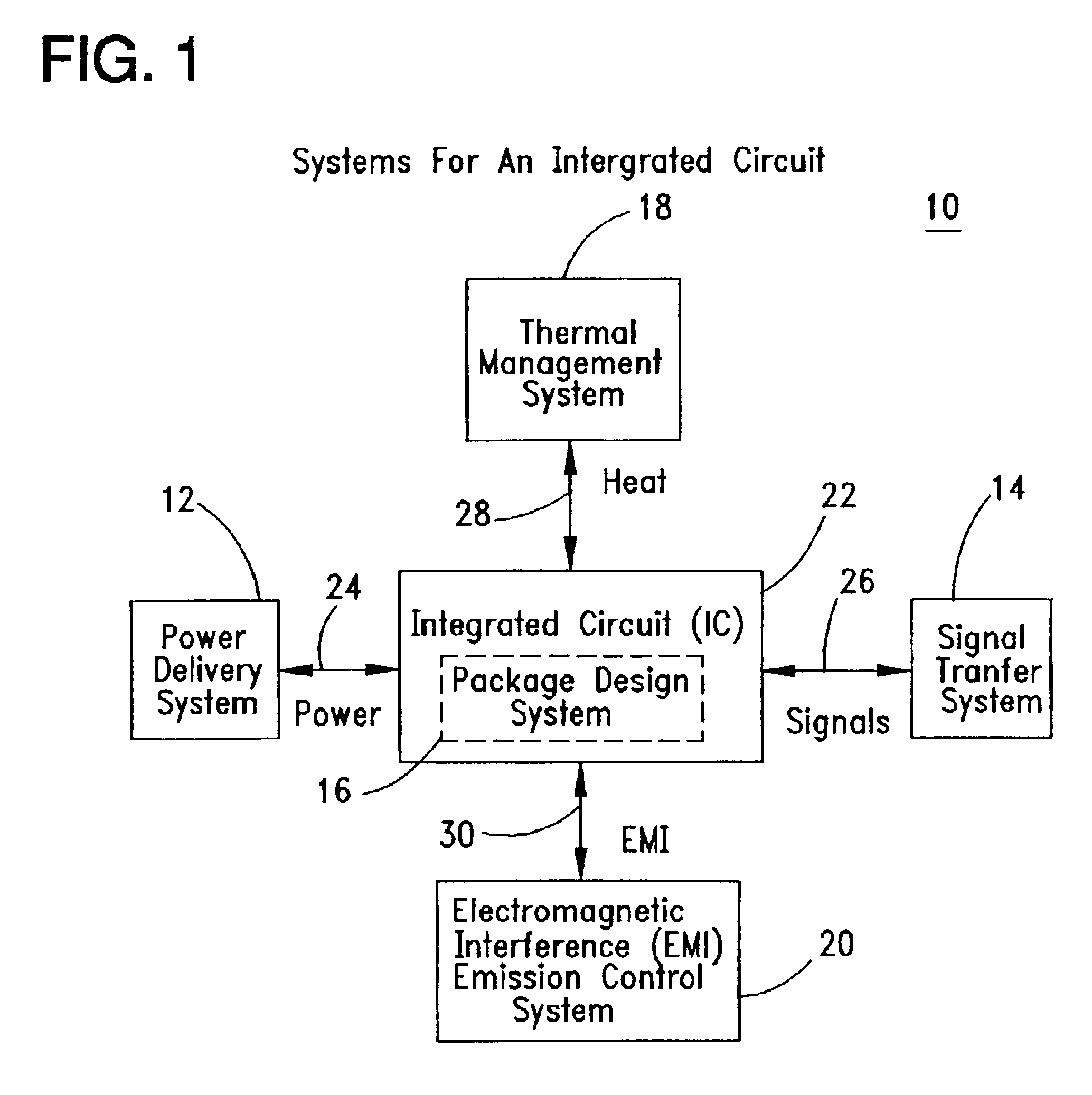

Semiconductor apparatus with decoupling capacitor

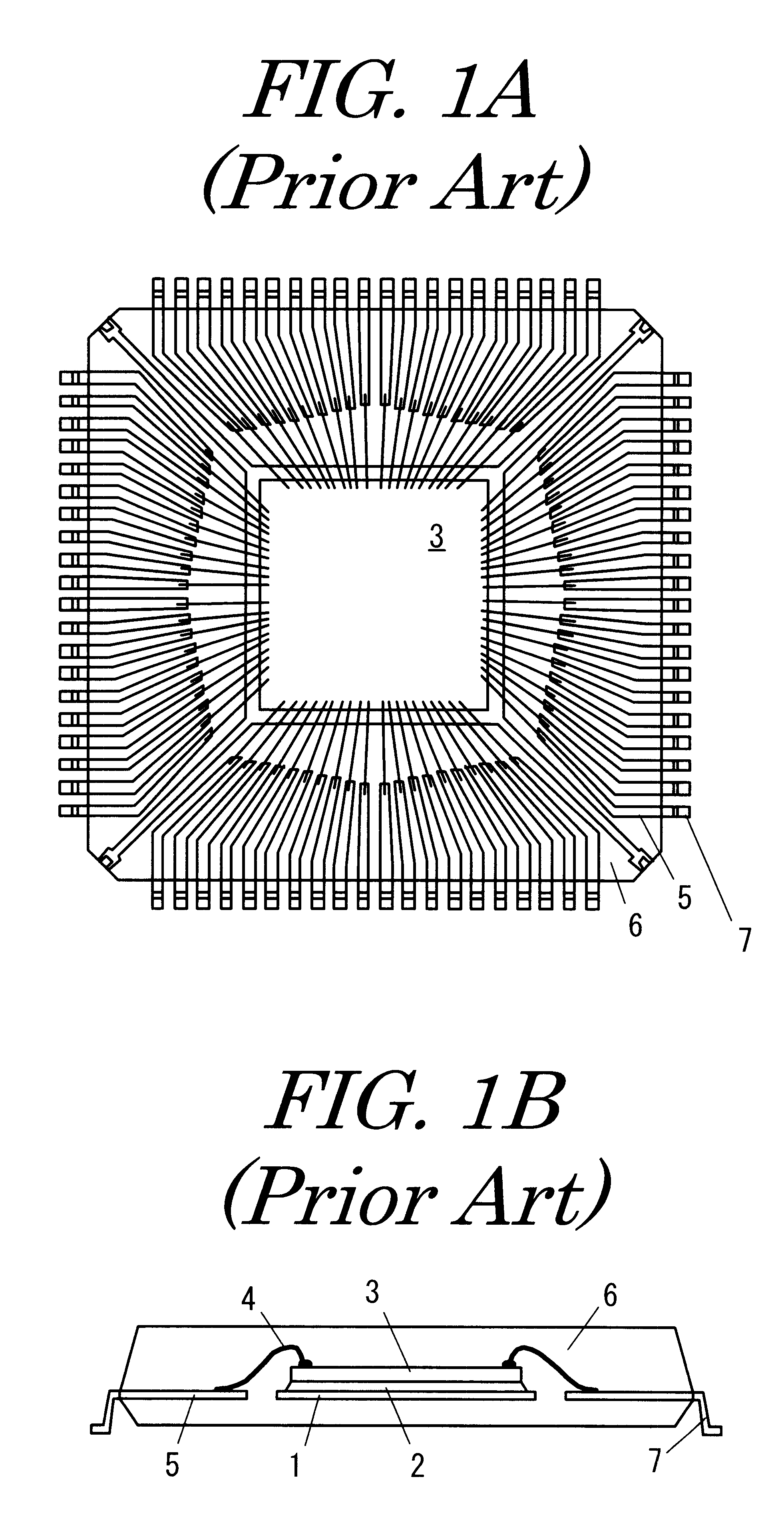

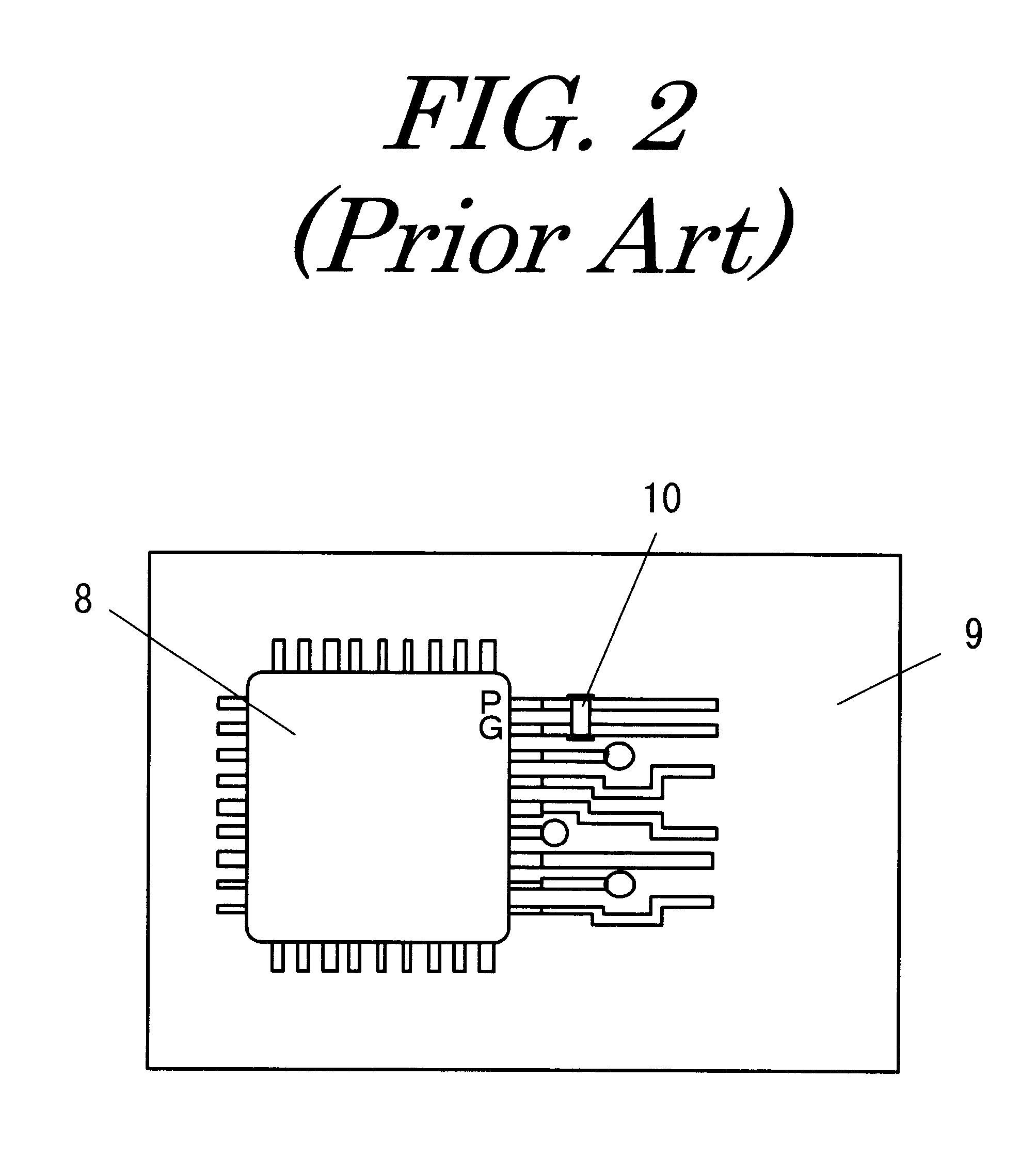

InactiveUS6608375B2Reduce noiseSemiconductor/solid-state device detailsCross-talk/noise/interference reductionSemiconductor chipLead frame

A lead frame type of semiconductor apparatus includes a die pad on which a semiconductor chip is mounted; ground terminals which are to be grounded; power supply terminals which are connected to a power supply; inner leads connected to the ground terminals and power supply terminals, in which a pair of adjacent inner leads for power supply terminal and ground terminal are extended inwardly; a chip capacitor mounting pad which is provided at inner ends of the extended inner leads; and a chip capacitor which is mounted on the chip capacitor mounting pad so that a decoupling capacitor is provided.

Owner:LAPIS SEMICON CO LTD

Capacitor with enhanced performance and method of manufacture

InactiveUS6940705B2Improve performanceAnti-noise capacitorsFixed capacitor electrodesDielectricEngineering

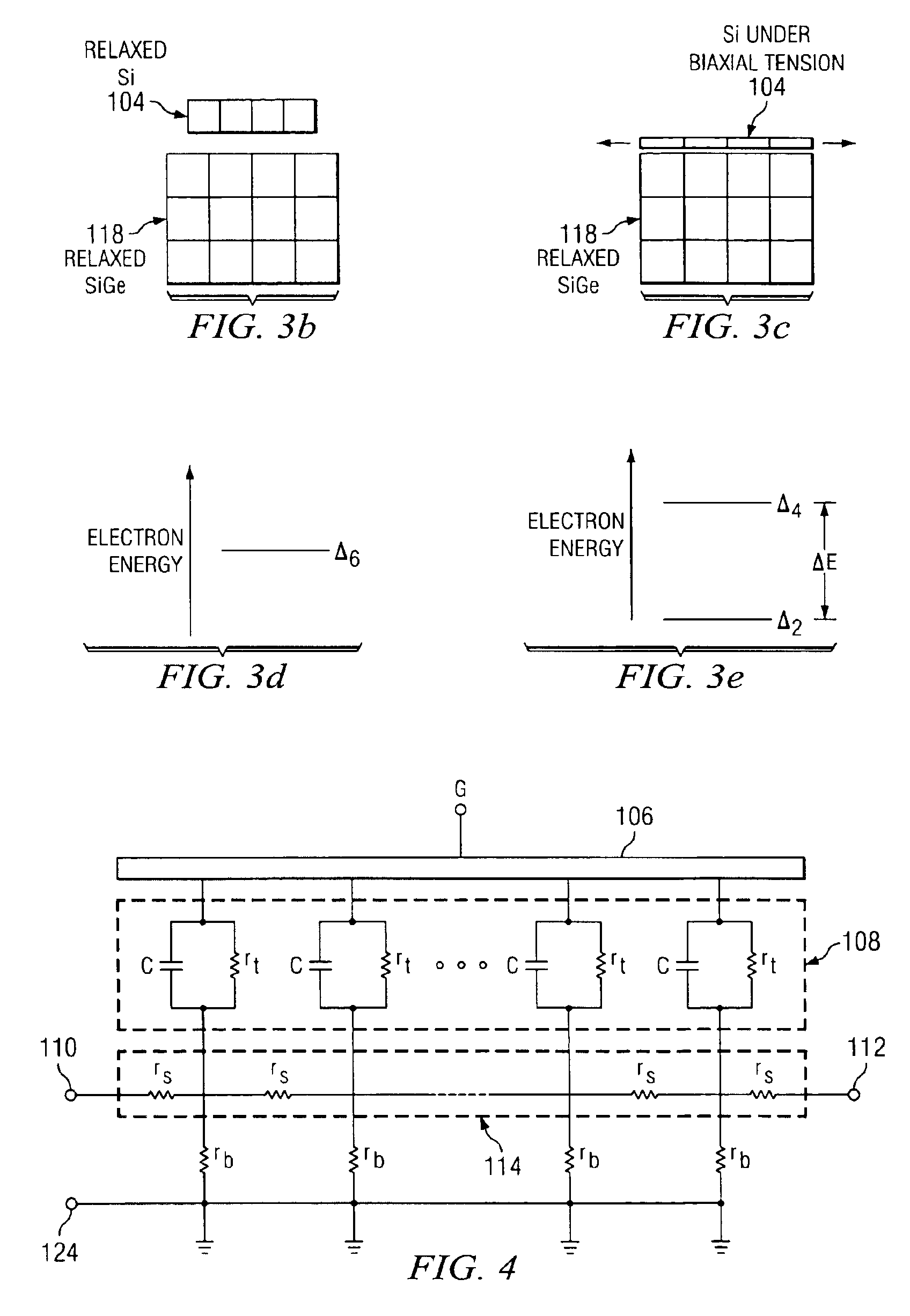

A decoupling capacitor is formed in a semiconductor substrate that includes a strained silicon layer. A substantially flat bottom electrode is formed in a portion of the strained silicon layer and a capacitor dielectric overlying the bottom electrode. A substantially flat top electrode overlies said capacitor dielectric. The top electrode is connected to a first reference voltage line and the bottom electrode is connected to a second reference voltage line.

Owner:TAIWAN SEMICON MFG CO LTD

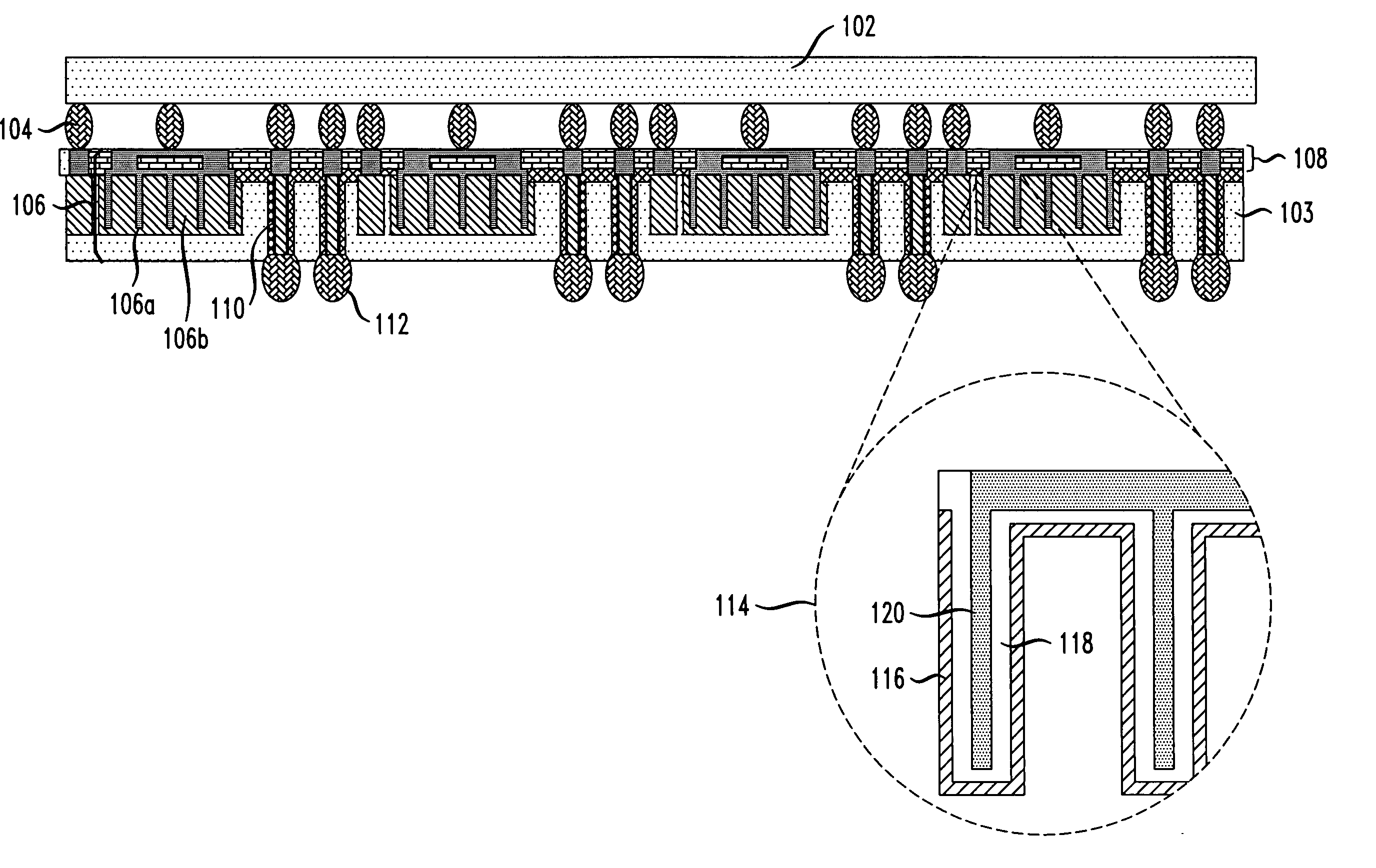

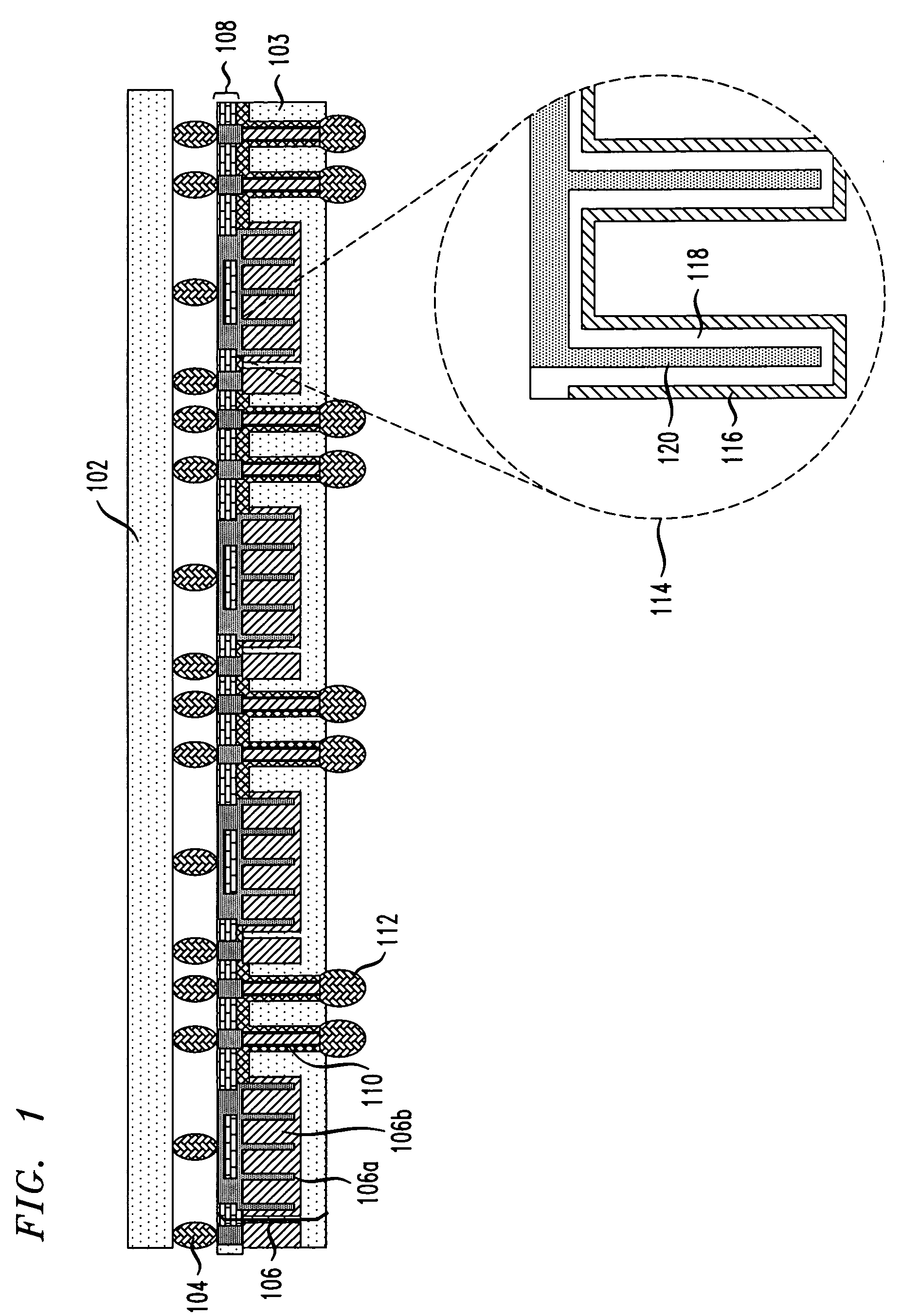

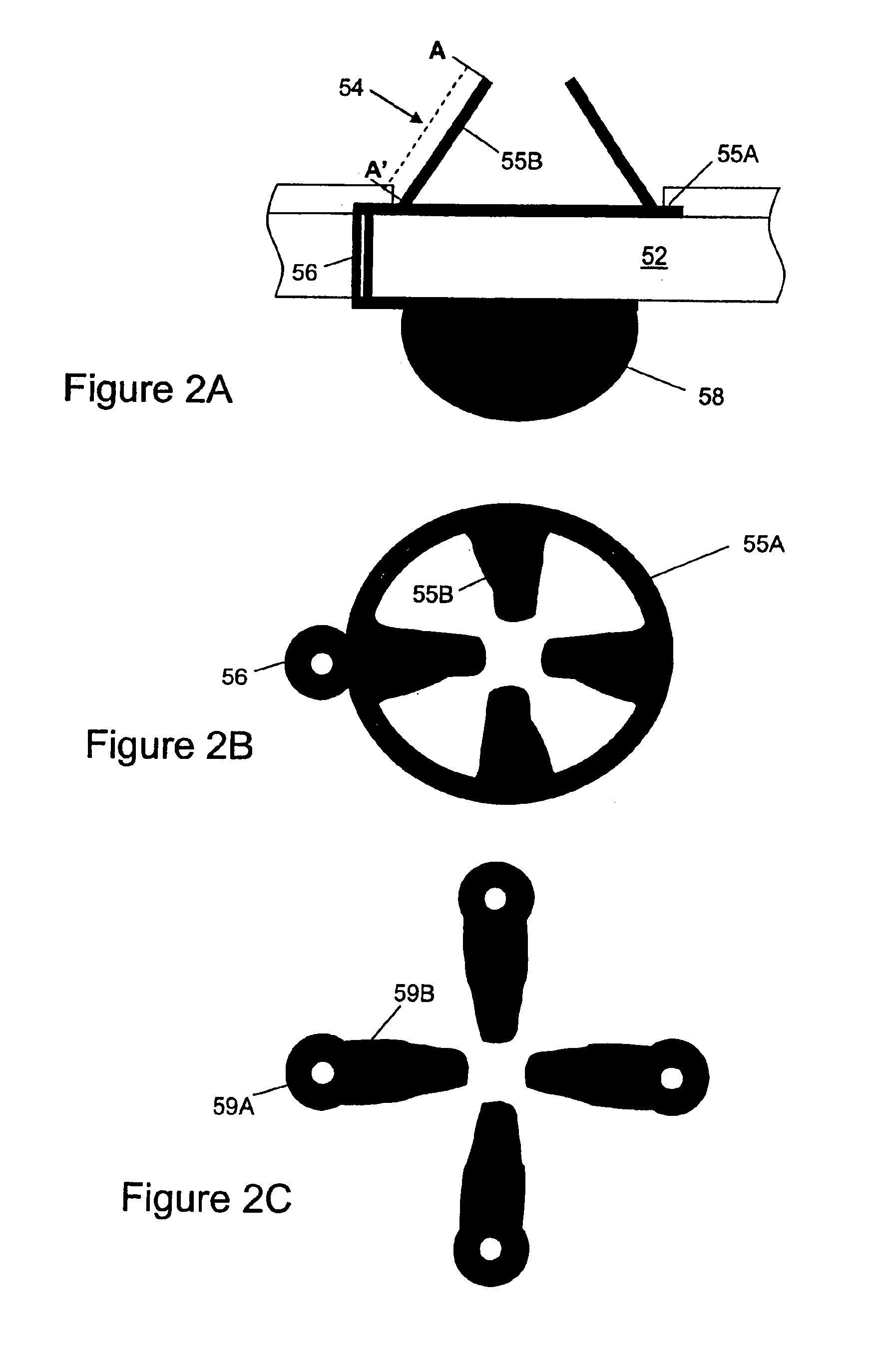

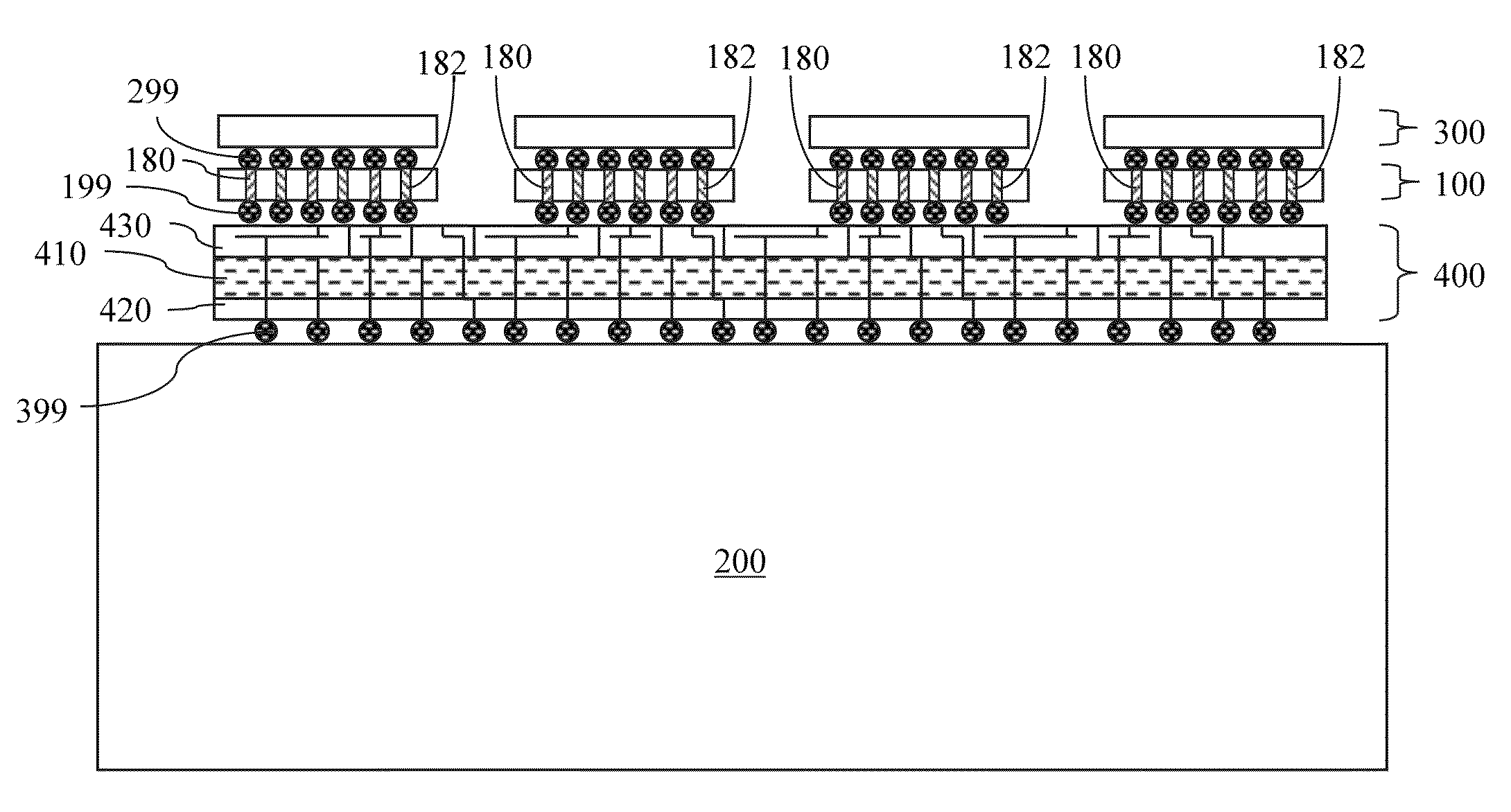

Techniques for providing decoupling capacitance

InactiveUS20070035030A1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceInterposer

Techniques for electronic device fabrication are provided. In one aspect, an electronic device is provided. The electronic device comprises at least one interposer structure having one or more vias and a plurality of decoupling capacitors integrated therein, the at least one interposer structure being configured to allow for one or more of the plurality of decoupling capacitors to be selectively deactivated. In another aspect, a method of fabricating an electronic device comprising at least one interposer structure having one or more vias and a plurality of decoupling capacitors integrated therein comprises the following step. One or more of the plurality of decoupling capacitors are selectively deactivated.

Owner:IBM CORP

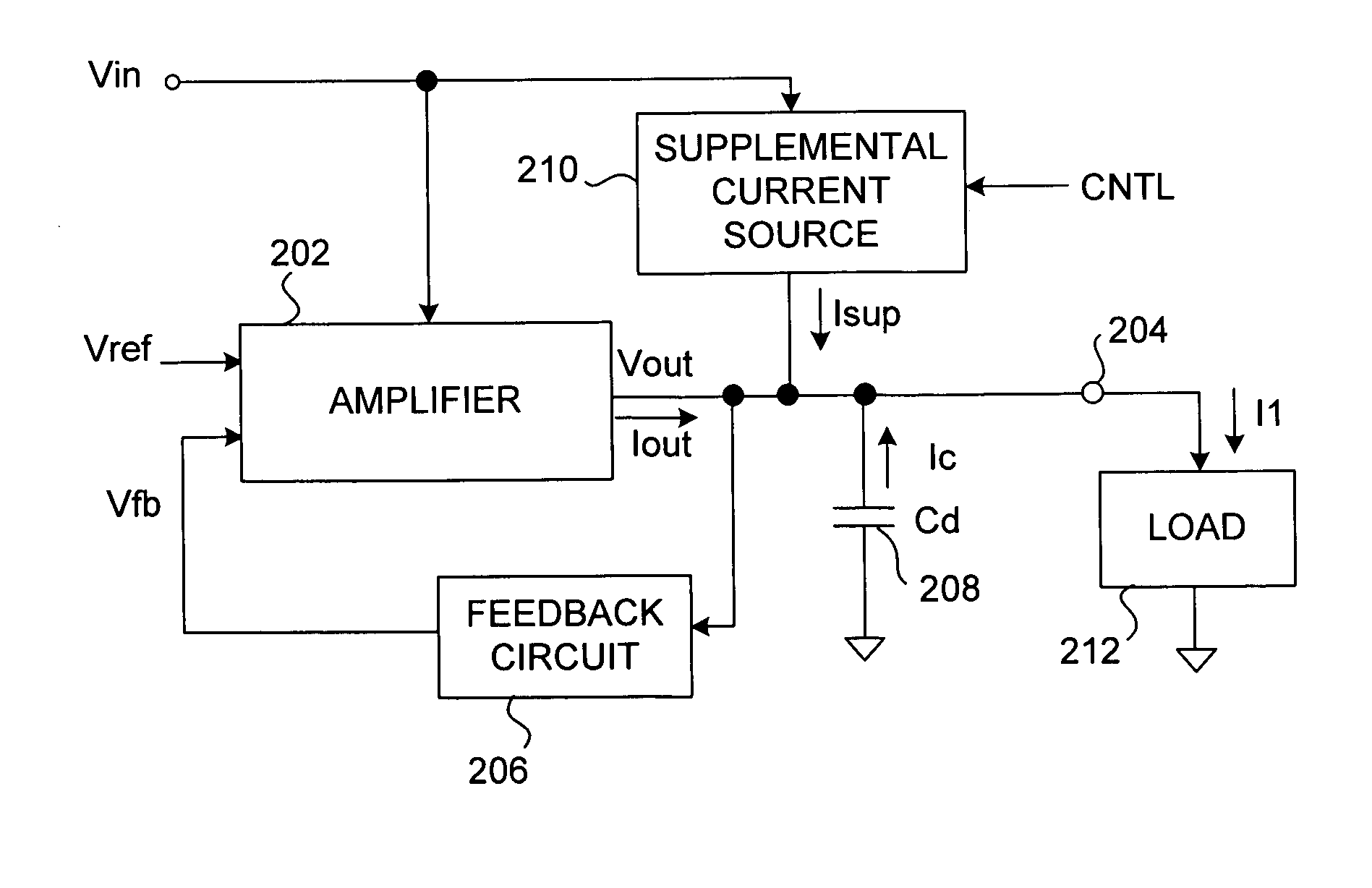

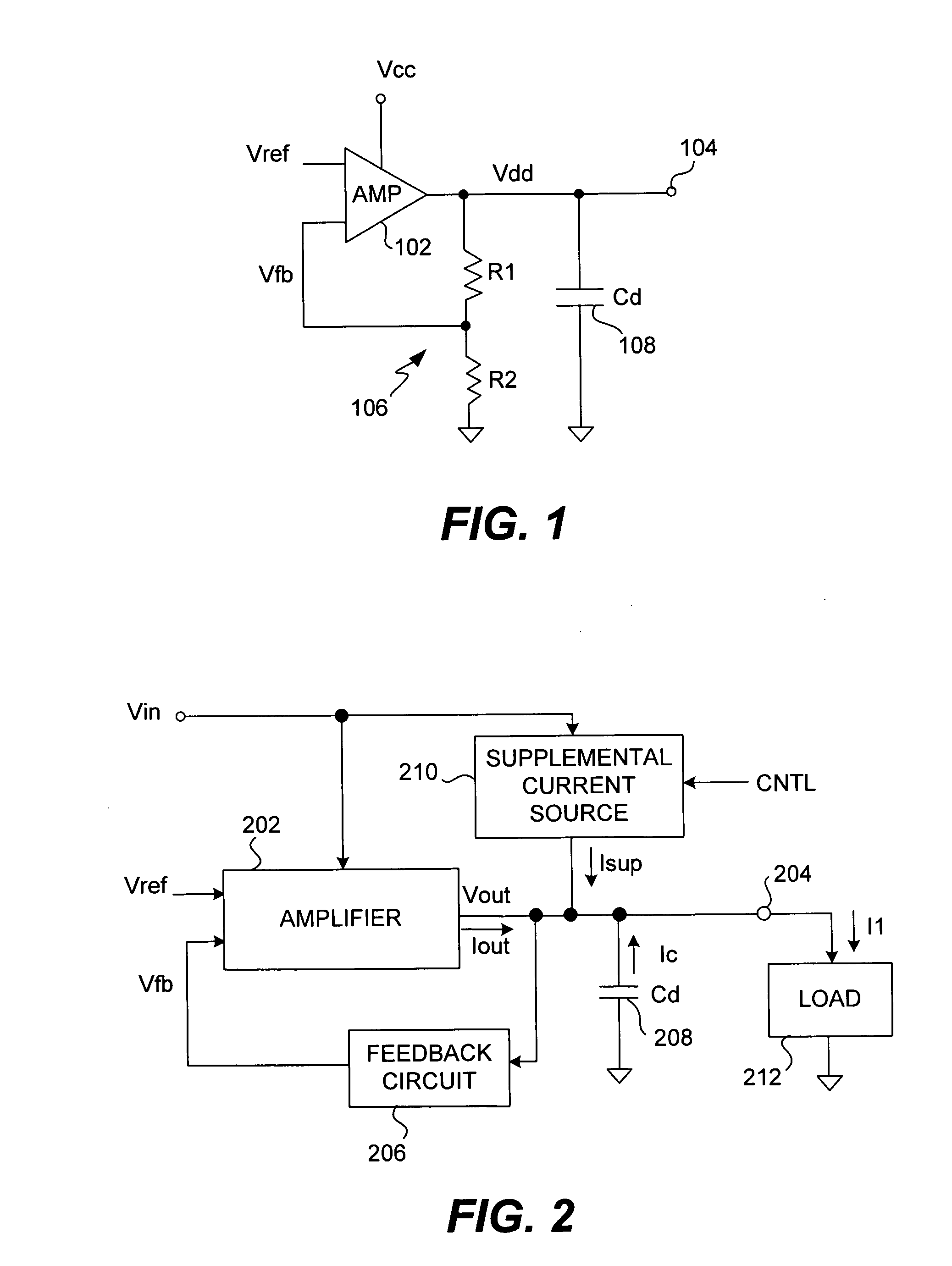

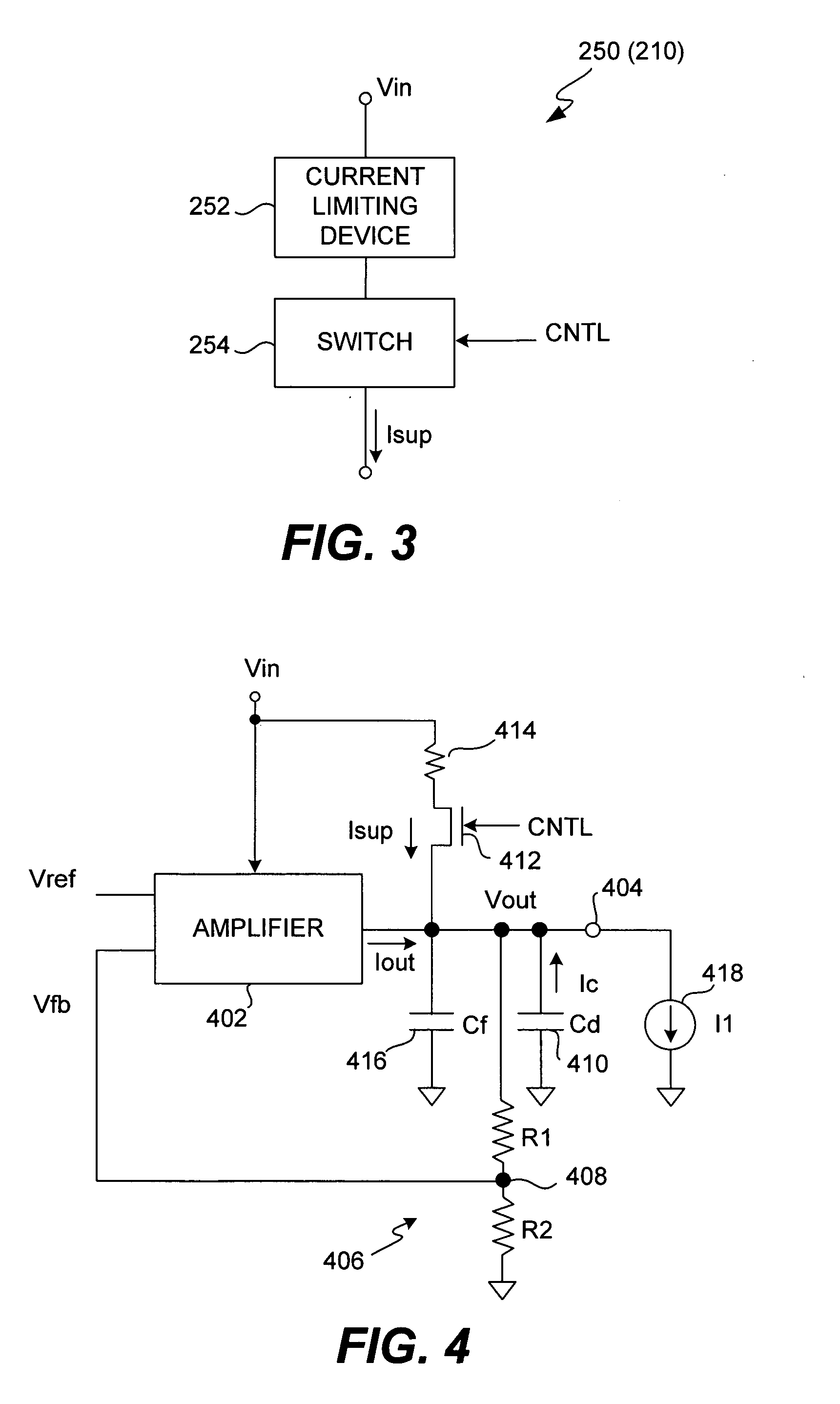

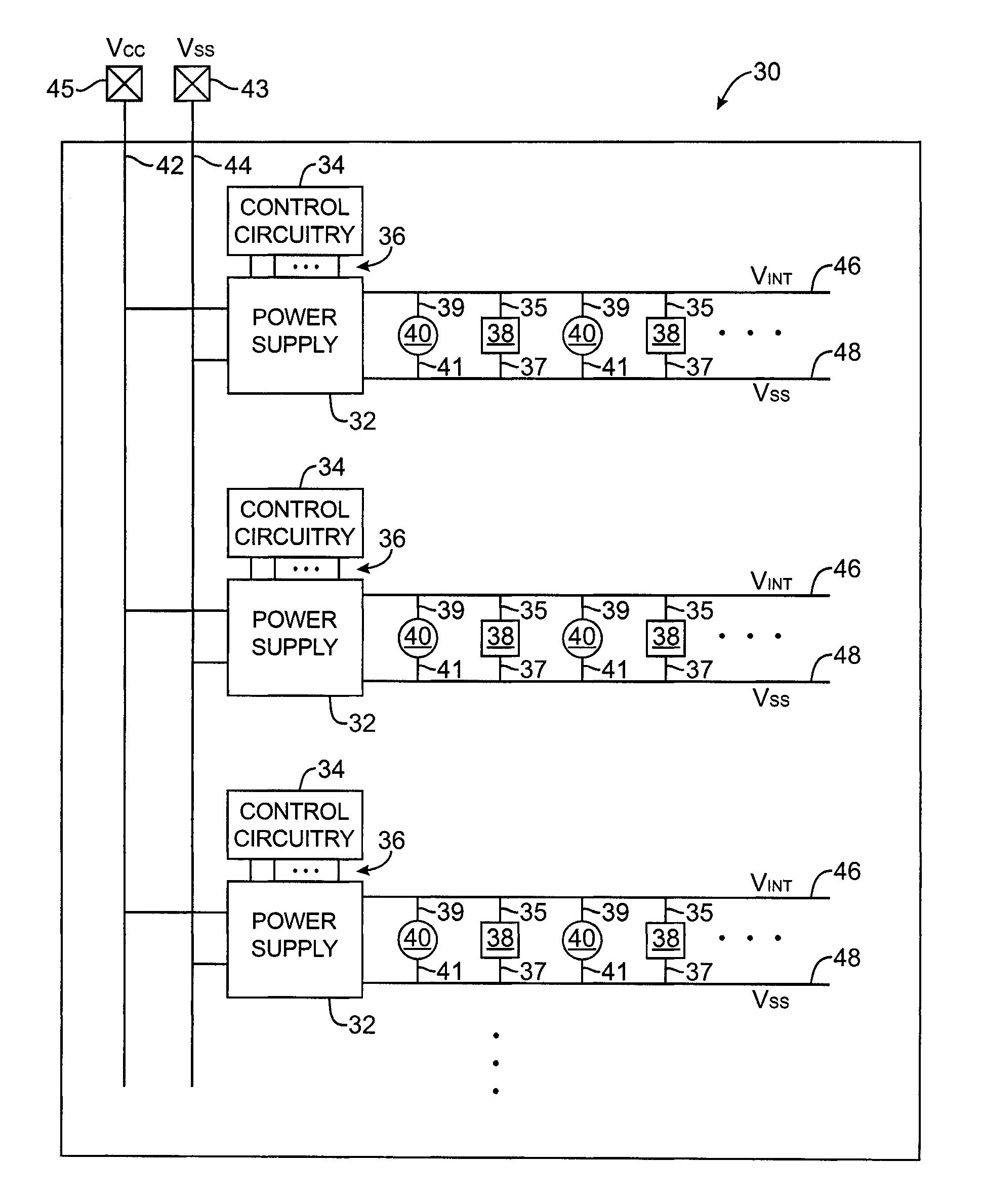

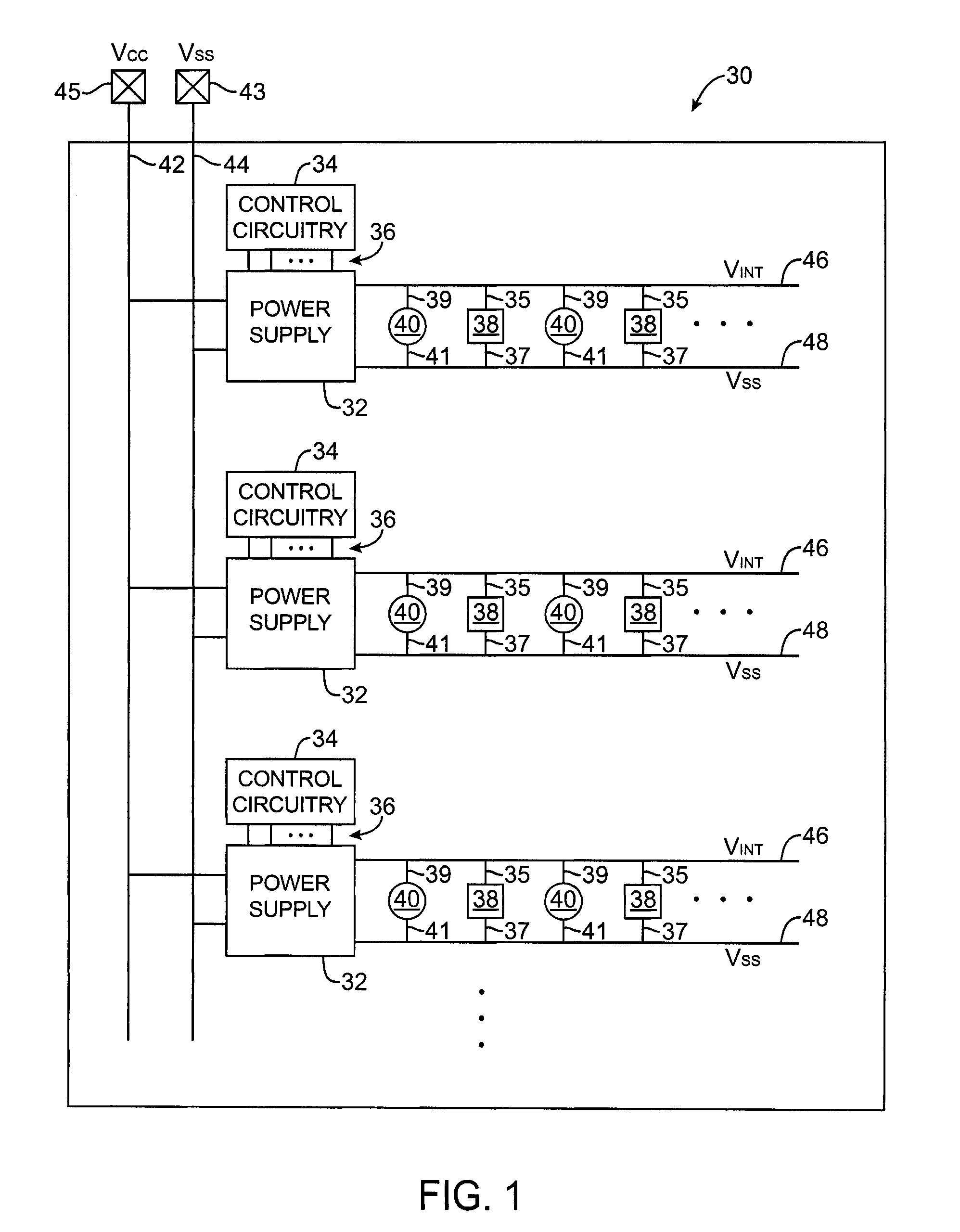

Voltage regulation with active supplemental current for output stabilization

ActiveUS20070139100A1Effective and stableSubstantial die area savingStatic storageElectric variable regulationCapacitanceVoltage regulation

Techniques for efficiently stabilizing an output voltage produced by a voltage regulation circuit are disclosed. One embodiment pertains to a voltage regulation circuit that includes a supplemental current source that can be controllably activated to provide a supplemental current to an output terminal of the voltage regulation circuit. This supplemental current can then assist in stabilizing the output voltage level at the output terminal of the voltage regulation circuit even in the presence of high current surges by a load (i.e., electronic circuitry). Advantageously, given the availability of the supplemental current, the required amount of capacitance for a decoupling capacitor (also coupled to the output terminal of the voltage regulation circuit) can be significantly reduced. In the case of semiconductor electronic devices, the reduction in the needed capacitance yields substantial die area savings with respect to decoupling capacitors.

Owner:SANDISK TECH LLC

Capacitor-mounted wiring board and method of manufacturing the same

ActiveUS20050218502A1Effective decouplingGuaranteed uptimeFinal product manufactureSemiconductor/solid-state device detailsElectrical conductorEngineering

In a capacitor-mounted wiring board, a plurality of wiring layers each patterned in a required shape are stacked with insulating layers interposed therebetween and are connected to each other via conductors formed to pierce the insulating layers in the direction of thickness. A decoupling capacitor is electrically connected to a wiring layer used as a power supply line or a ground line in the vicinity of the wiring layer, and mounted such that, when a current is passed through the capacitor, the direction of the current is reversed to that of the current flowing through the relevant wiring layer.

Owner:SHINKO ELECTRIC IND CO LTD

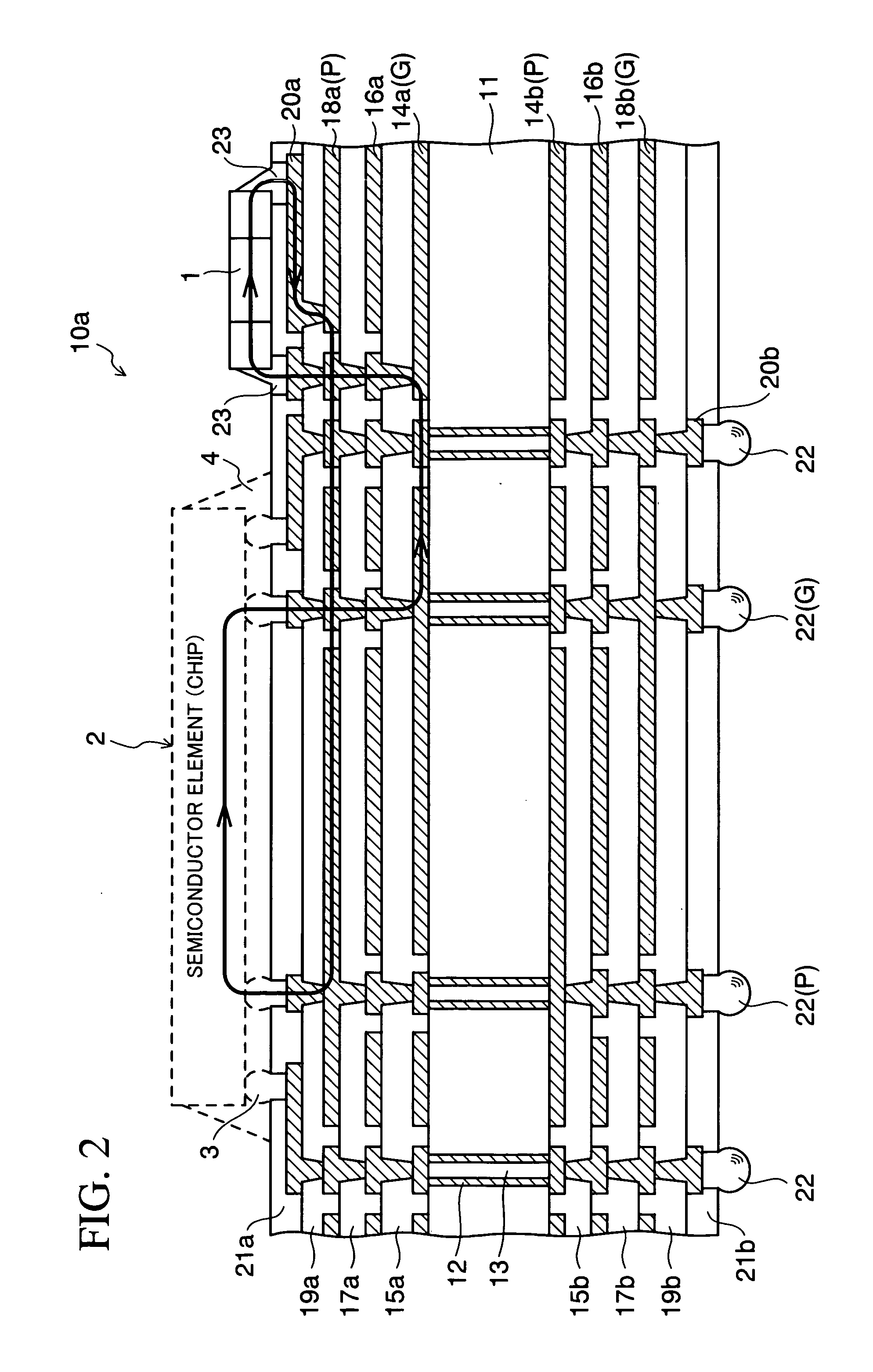

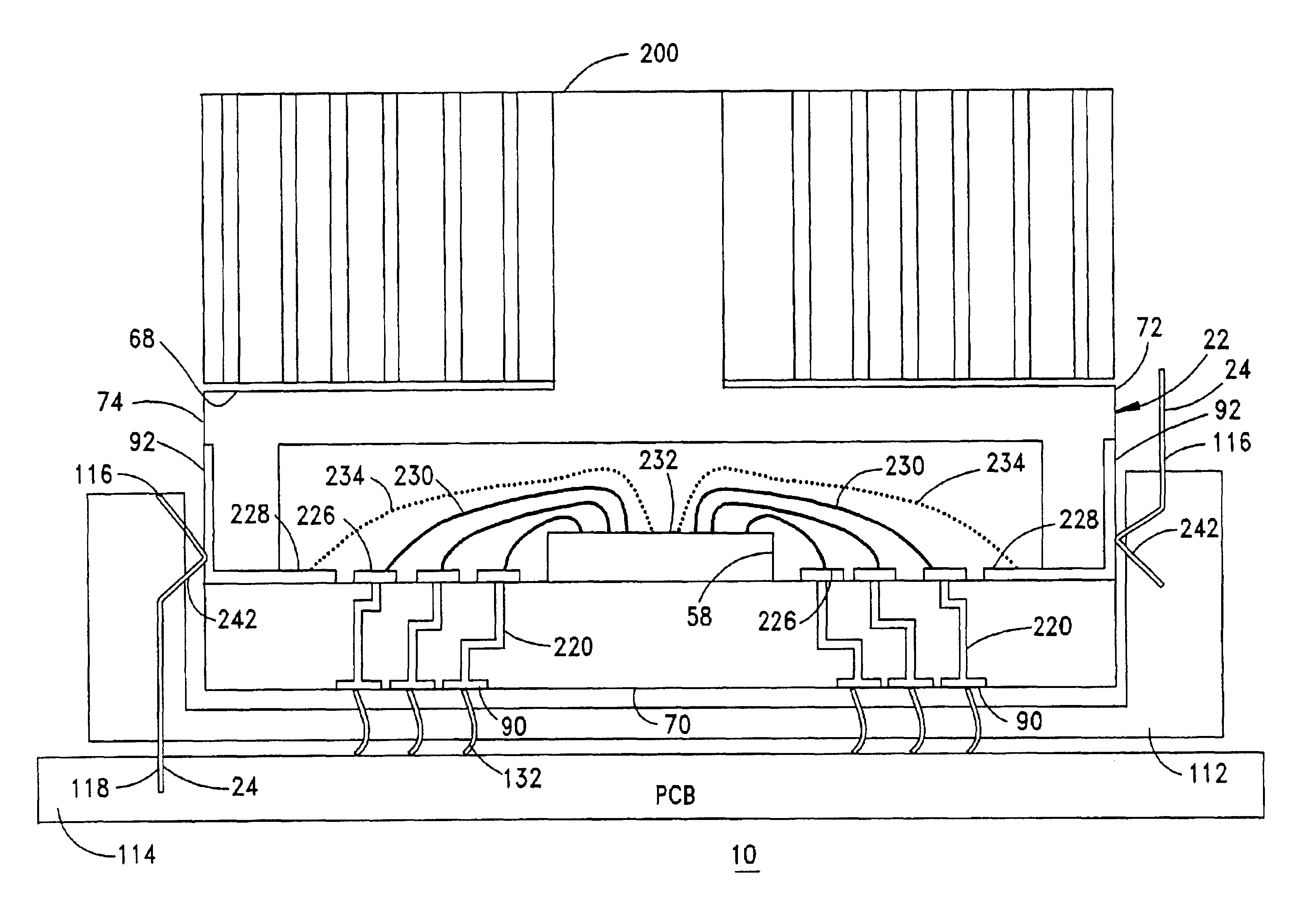

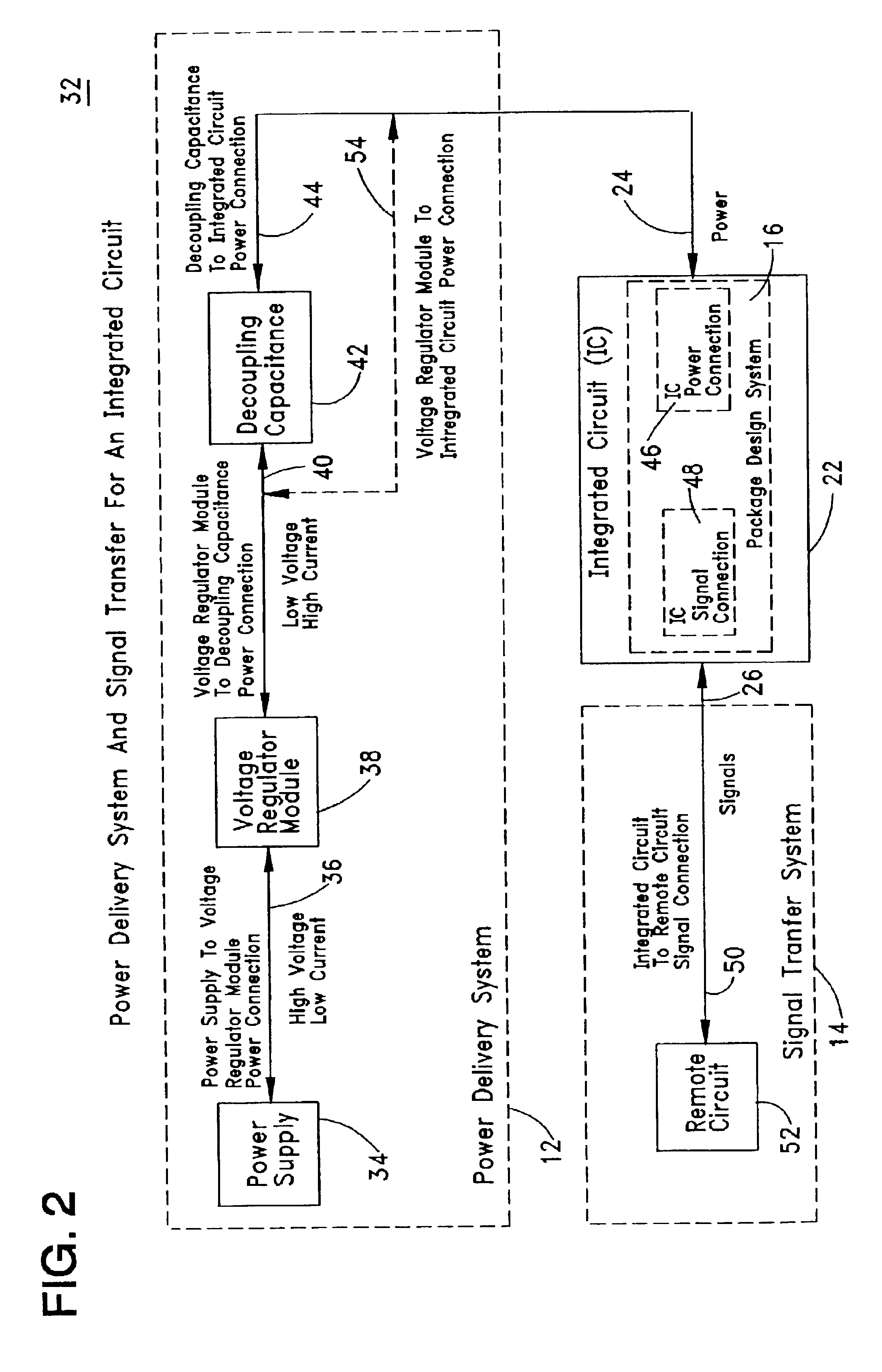

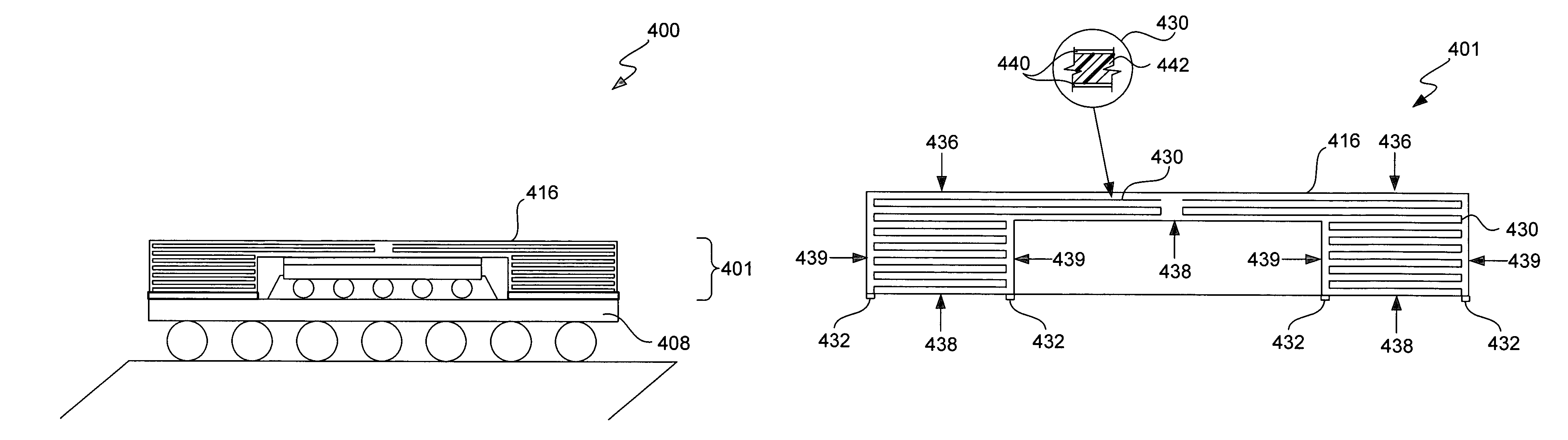

Thermal management of power delivery systems for integrated circuits

InactiveUS6853559B2Less spaceEliminate needSemiconductor/solid-state device detailsSolid-state devicesCapacitanceElectricity delivery

A system for delivering power to an integrated circuit includes a decoupling capacitance located in a connector that is formed as a socket, or frame for the IC. The power delivery system takes the form of a power reservoir that is integrated into a connector, thereby eliminating the need for complex and expensive power traces to be formed in or discrete capacitors mounted on a circuit board to which the IC is connected. The power reservoir is integrated into a cover member that fits over the IC and which contains a recess that accommodates a portion of the IC therein. The cover member includes at least one opening that opens up to a operational surface of the integrated circuit. A heat-dissapating device, such as a finned heat sink or the like is supported by the cover member and extends through its opening into contact with a heat-generating surface of the integrated circuit to cool it during operation.

Owner:MOLEX INC

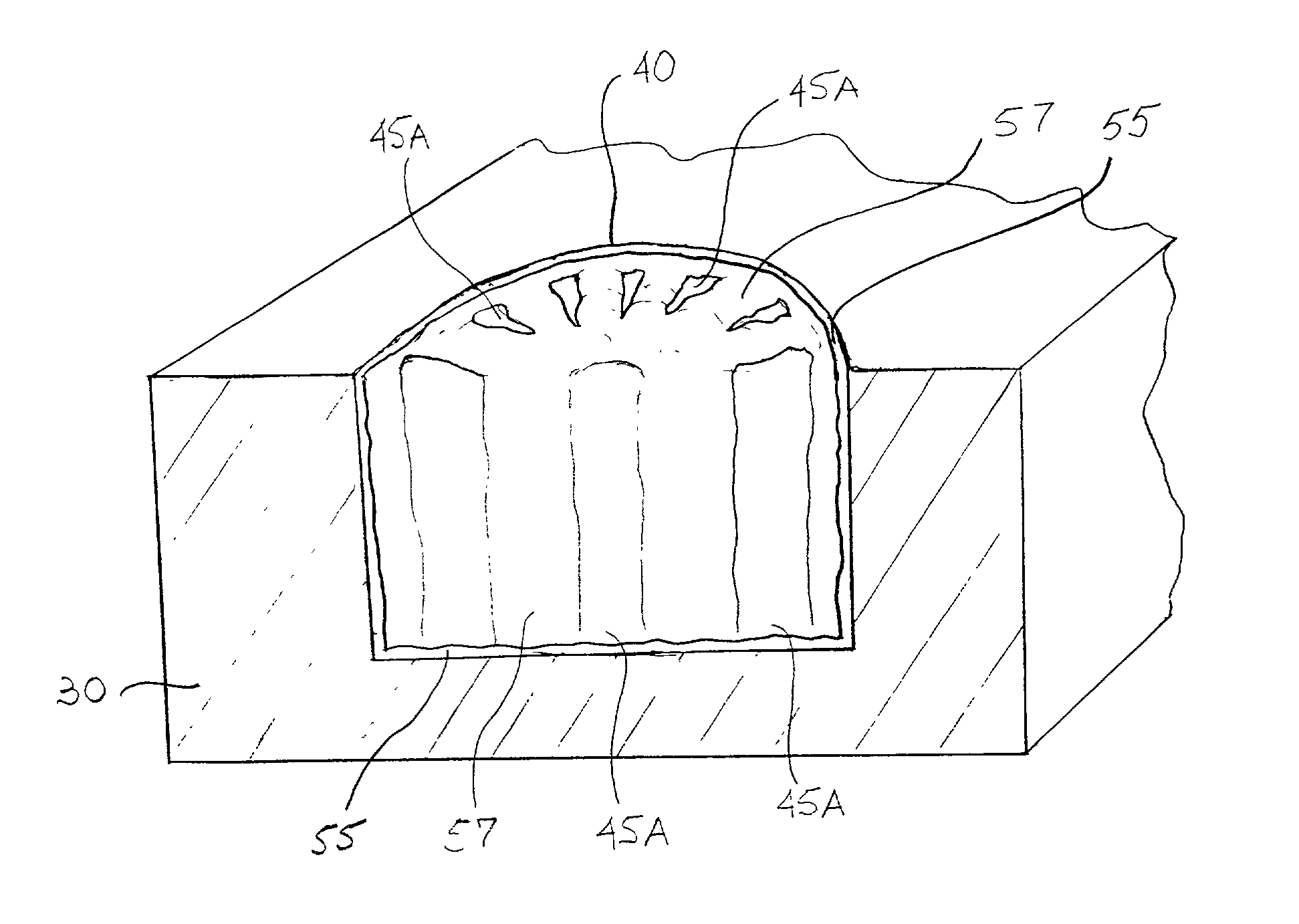

Integrated decoupling capacitors

InactiveUS20020167057A1Reduces undesirable noiseReduce noiseTransistorSolid-state devicesCapacitanceDielectric layer

A method for fabricating buried decoupling capacitors in an integrated circuit is disclosed. The method forms decoupling capacitors by creating an opening within a substrate which has fin-like spacers, depositing a dielectric material over the spacers, depositing an electrode material over the dielectric material, depositing an insulative material over the electrode material, and forming integrated circuit components over the insulative material.

Owner:CONVERSANT INTPROP MANAGEMENT INC

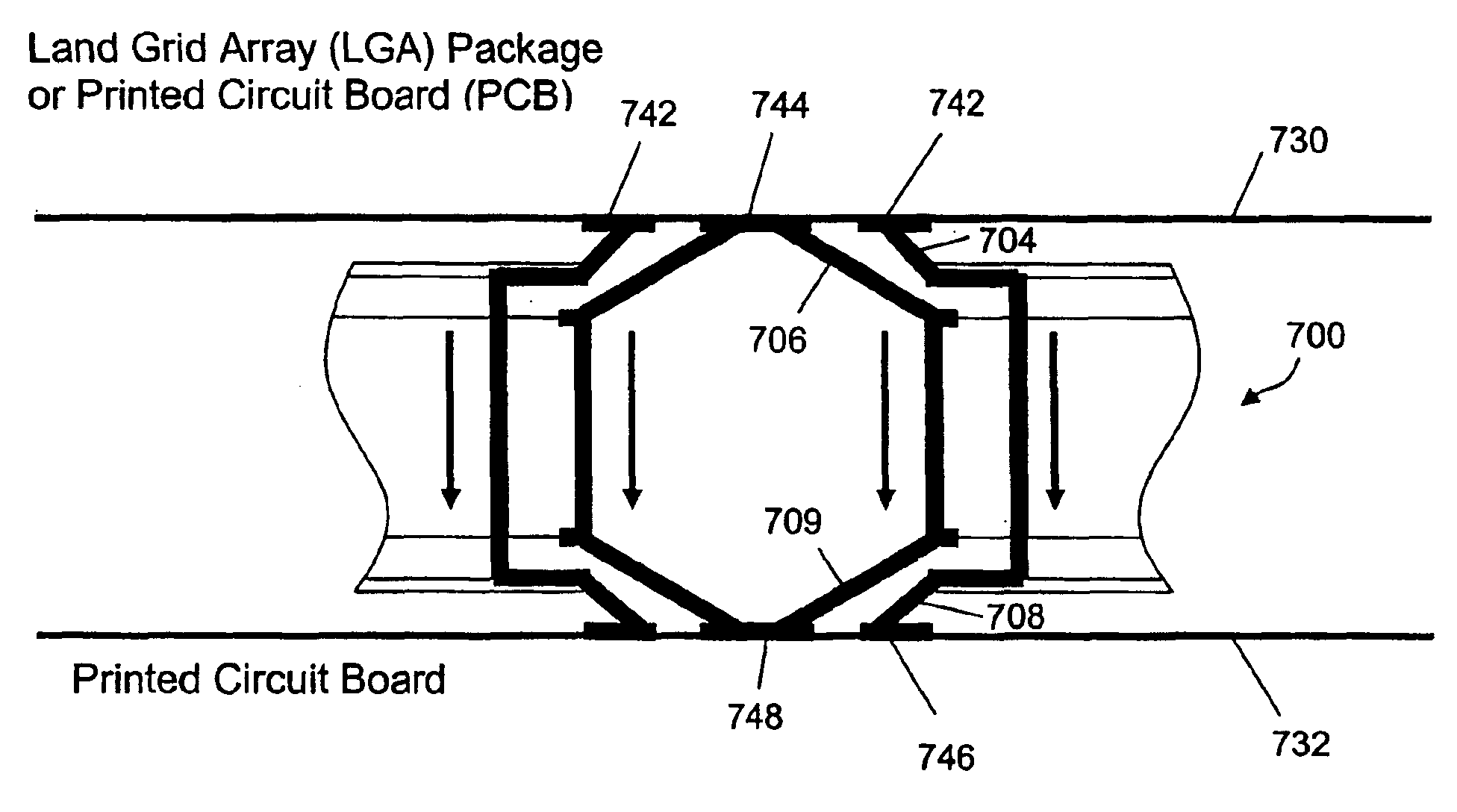

Circuitized connector for land grid array

InactiveUS6869290B2Printed circuit assemblingContact member assembly/disassemblyElectrical connectionEngineering

A connector for electrically connecting to pads of a land grid array formed on an electronic component includes a dielectric layer including opposing first and second surfaces, and a multiple number of contact elements extending above the first surface of the dielectric layer. Each contact element includes a conductive portion disposed to engage a respective pad of the land grid array for providing electrical connection to the land grid array. The connector further includes an electrical circuit formed on or within the dielectric layer. The electrical circuit is electrically connected to at least one of the multiple number of contact elements. In one embodiment, the electrical circuit includes an electrical component, such as a decoupling capacitor. In another embodiment, the electrical circuit operates to connect two contact elements together. For instance, the contact elements connecting to the ground potential can be connected together through the electrical circuit.

Owner:NEOCONIX INC

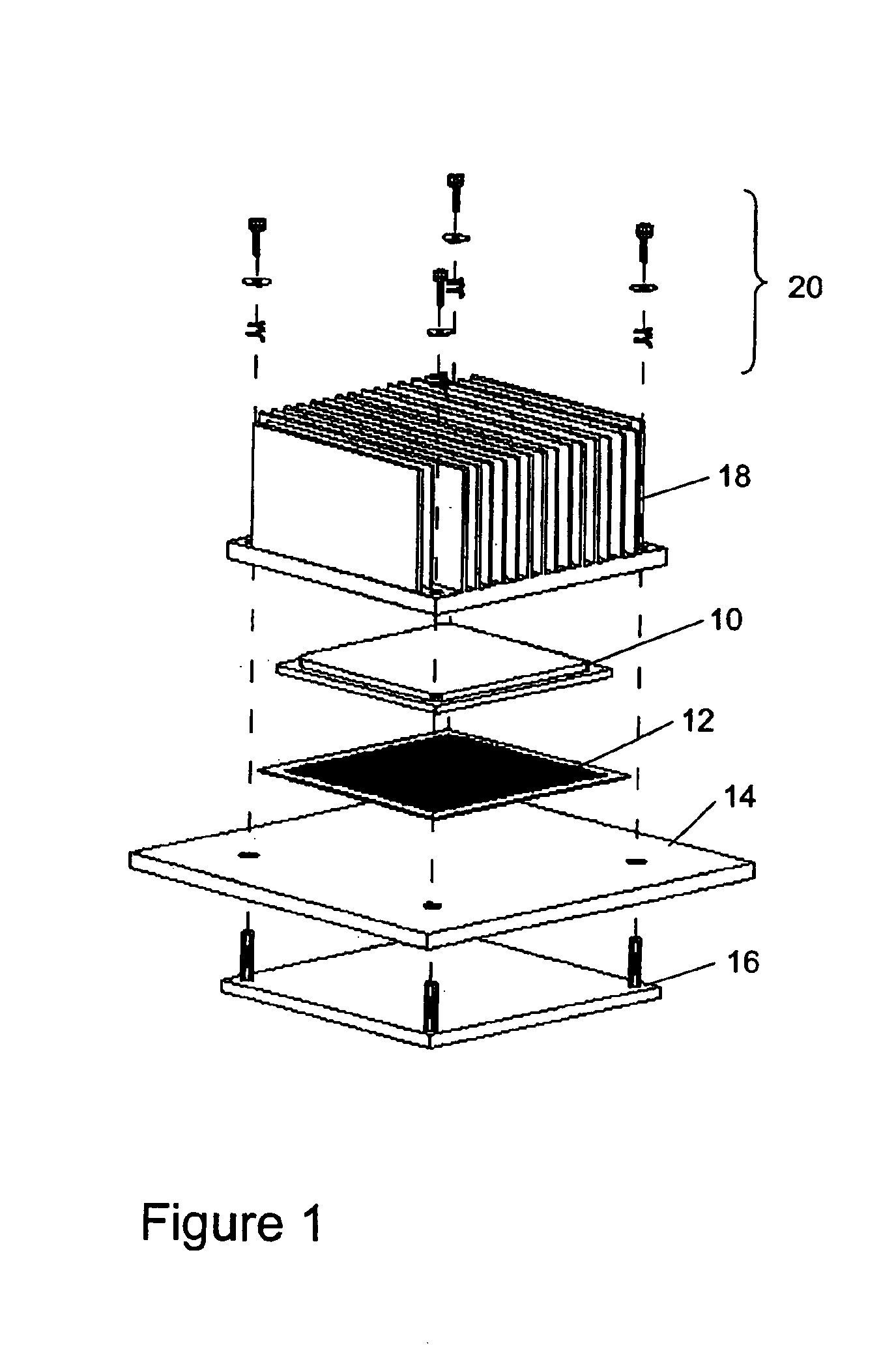

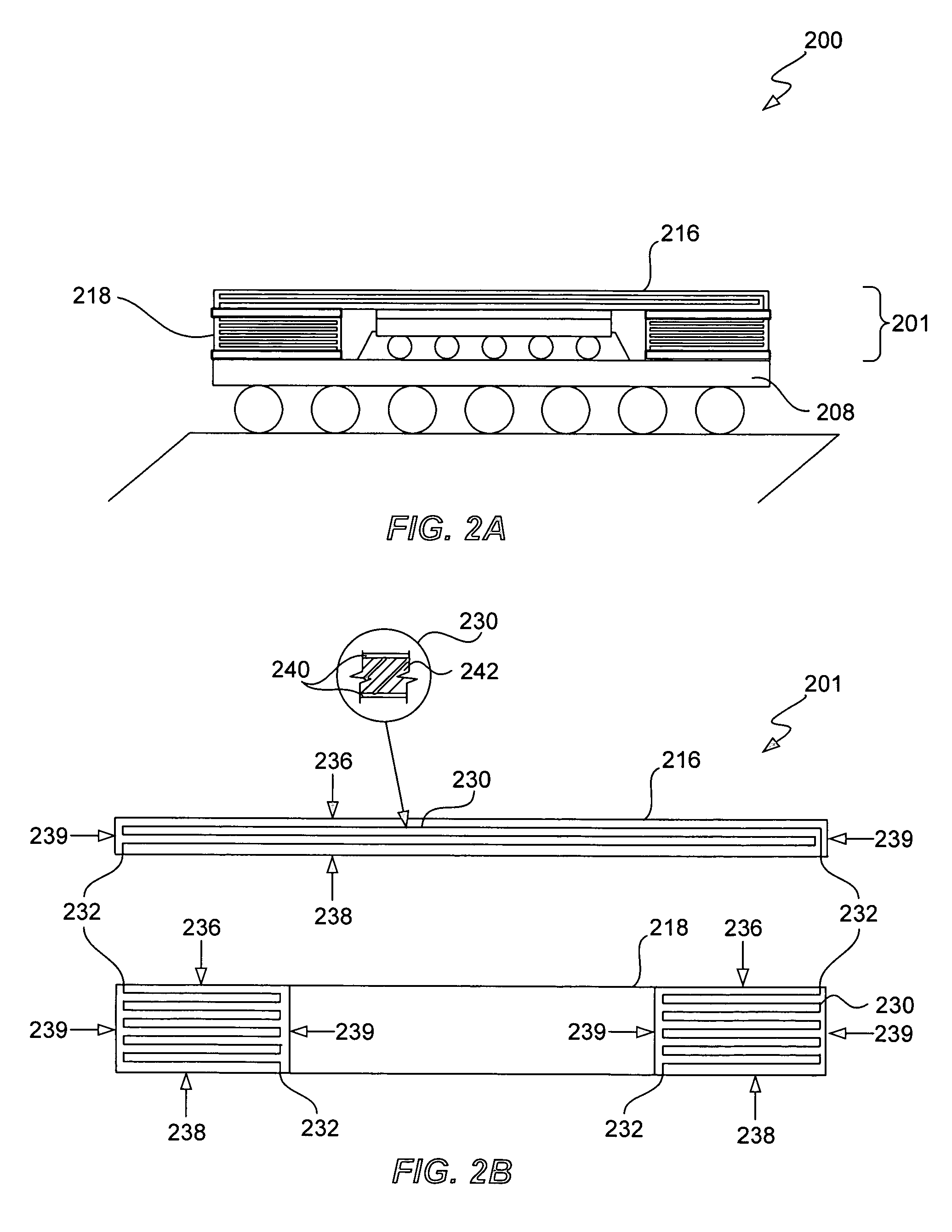

Bypass capacitor embedded flip chip package lid and stiffener

InactiveUS7115988B1Minimize SSNInstant powerElectrolytic capacitorsSemiconductor/solid-state device detailsCapacitanceSemiconductor

The present invention provides a heat spreader with a bypass capacitor to provide substantially instant power and / or to control simultaneous switching noise (SSN). The present invention also provides a semiconductor device package incorporating this heat spreader. In addition, fabrication methods for such heat spreaders and packages are provided. Generally, the heat spreaders and packages of the present invention include an embedded bypass capacitor that can provide decoupling capacitance in order to deliver near instant power to the die and / or minimize SSN. In a preferred embodiment, the embedded bypass capacitor is connected to terminals integrated with the heat spreader (e.g., lid; stiffener) and / or to a package plane (e.g., power plane or ground plane) in the package substrate for connection via the flip chip package's power delivery system to a power source and / or component.

Owner:ALTERA CORP

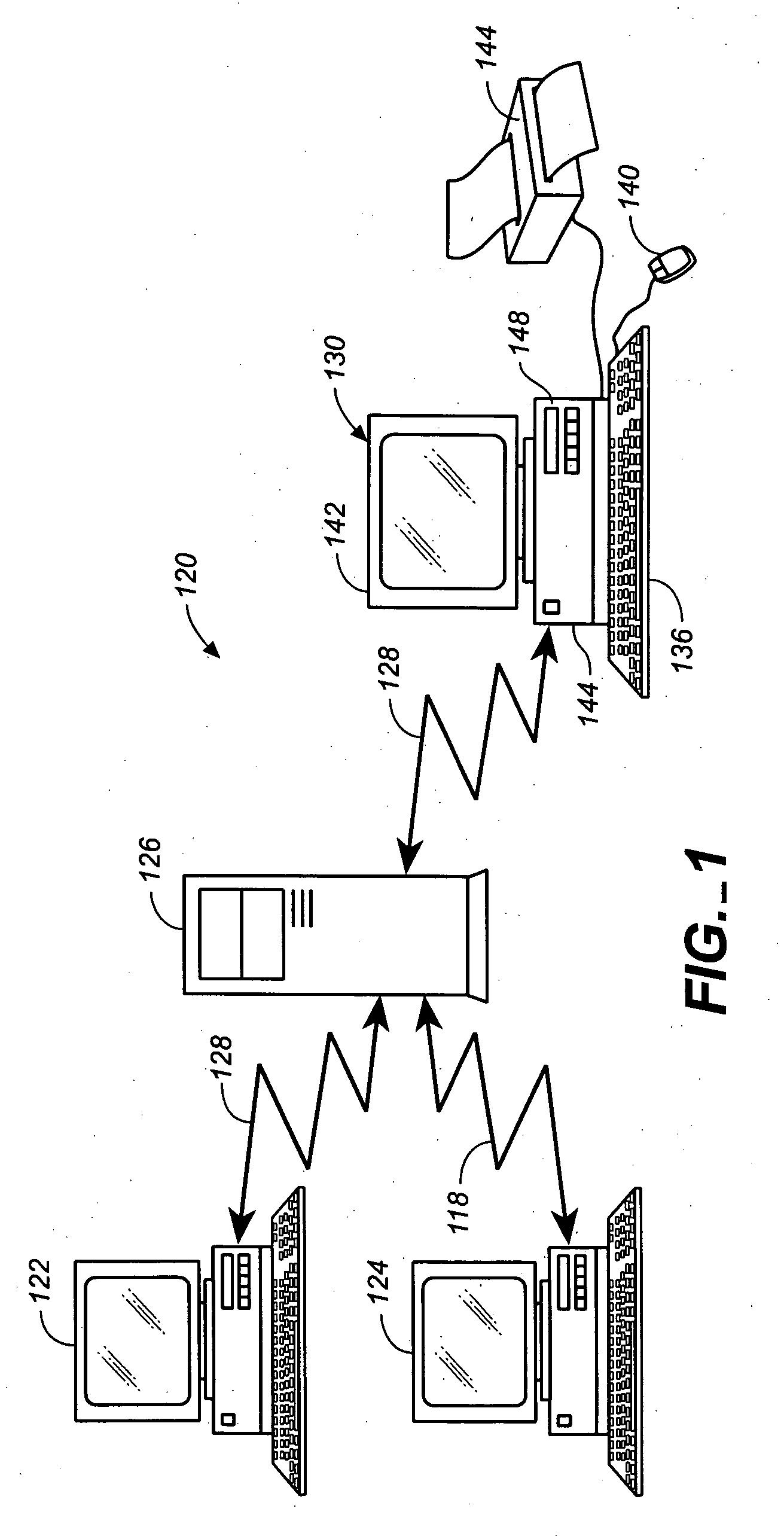

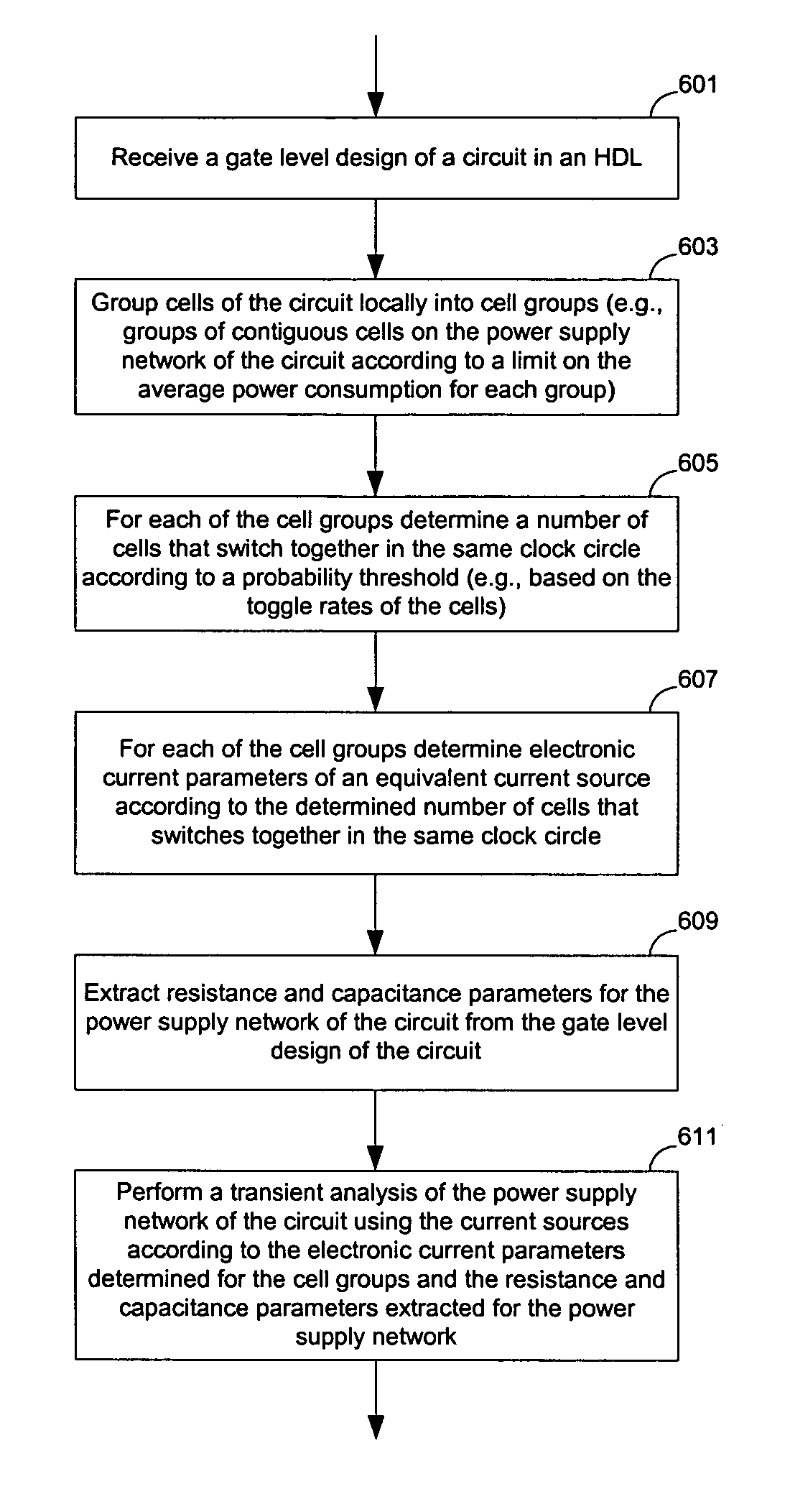

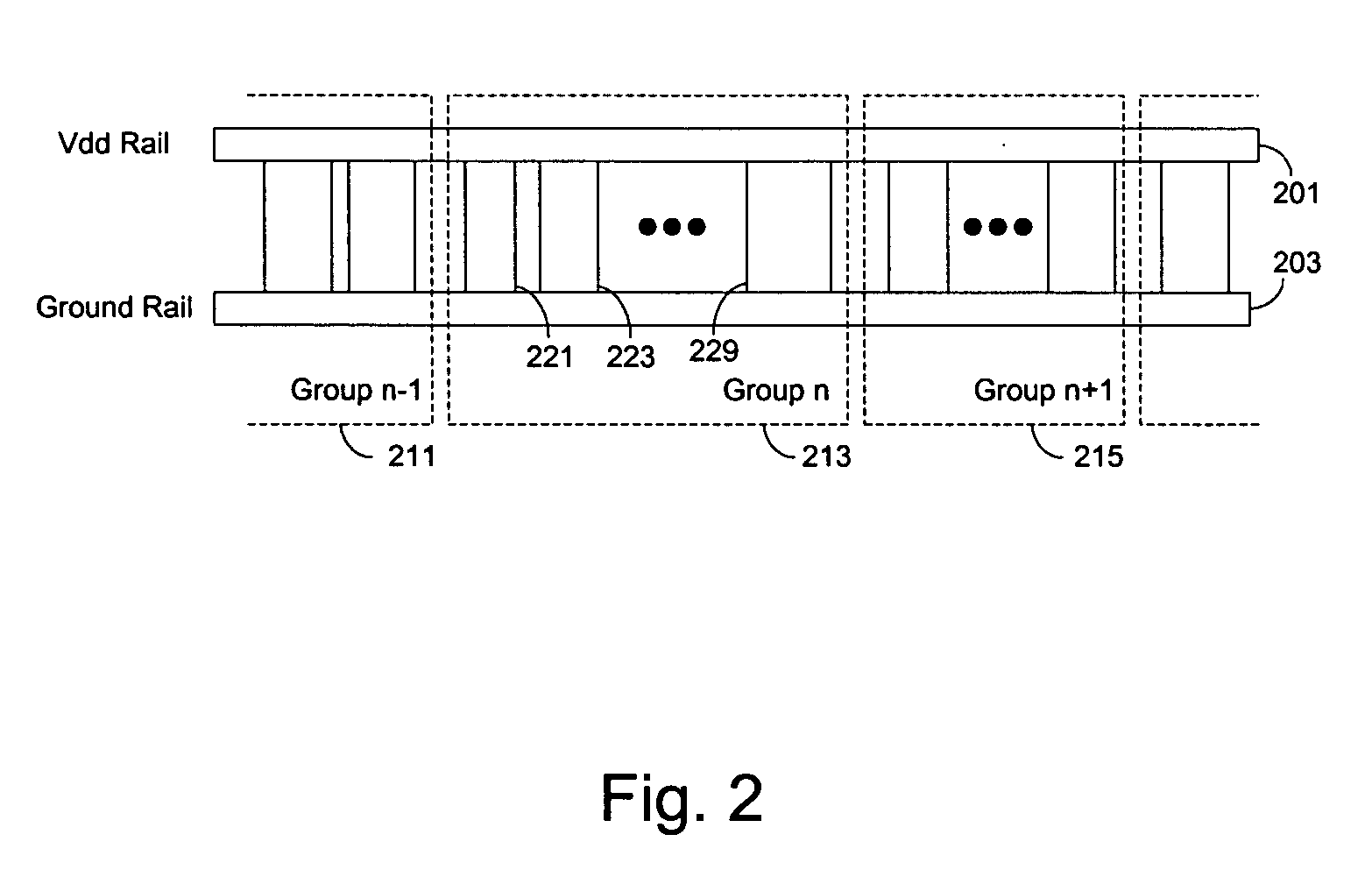

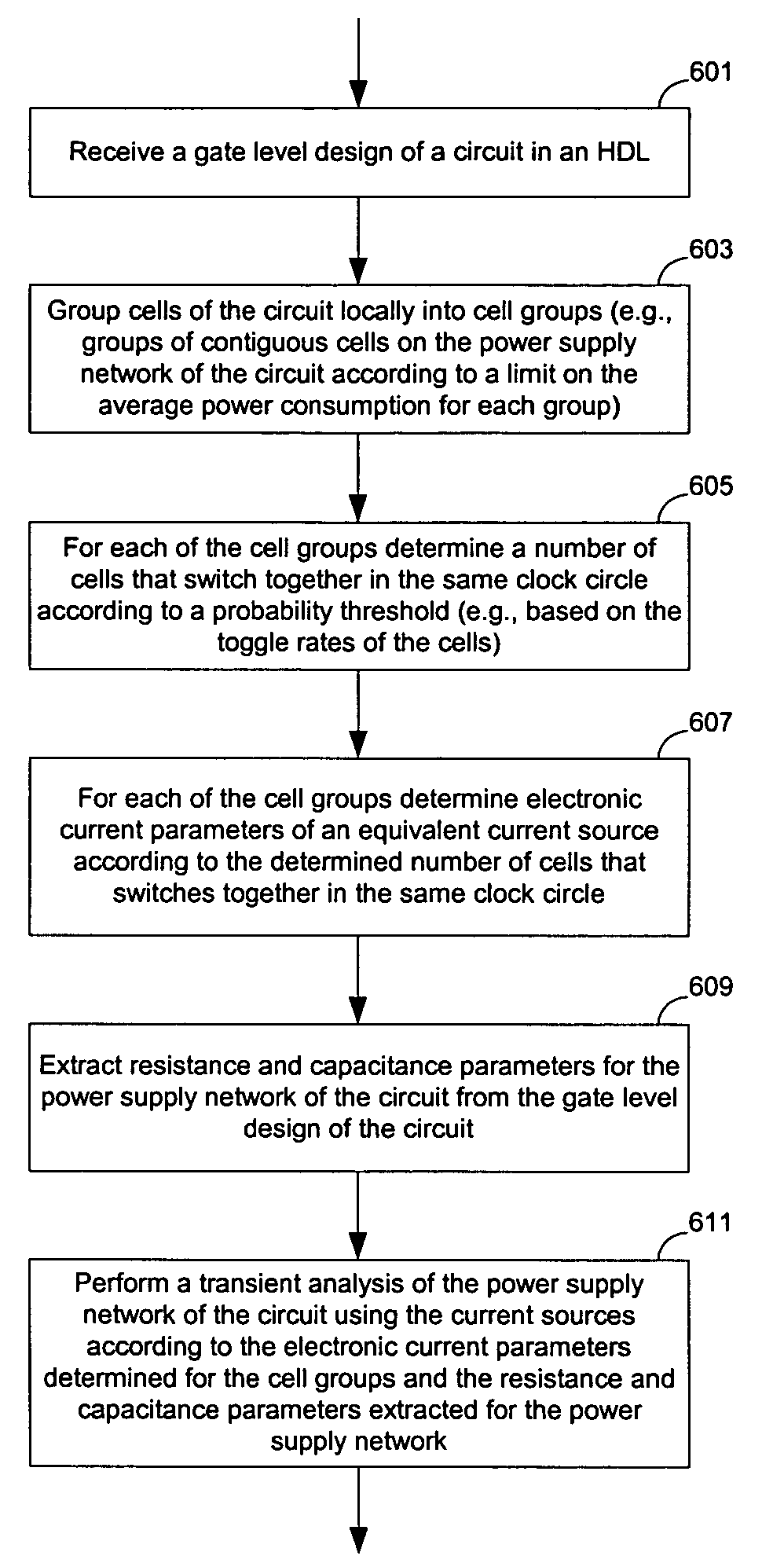

Methods and apparatuses for transient analyses of circuits

ActiveUS20060031795A1Computer aided designSoftware simulation/interpretation/emulationCapacitanceElectrical resistance and conductance

Methods and apparatuses for transient analyses of a circuit using a hierarchical approach. In one embodiment, the cells are grouped locally on the power supply network according to average power dissipation. A time varying current of each cell group is estimated using a probabilistic approach to represent the cell group so that the probability of a more severe waveform for the current of the cell group is under a certain level. For example, the cells in a group are partitioned as switching cells and non-switching cells using cell toggle rates for the determination of the time varying current. The circuit model of the power supply network includes the current sources according to the estimated time varying currents for the cell groups, the power supply wire resistance, the power supply to ground wire capacitance, well capacitance and the de-coupling capacitance from non-switching cells.

Owner:SYNOPSYS INC

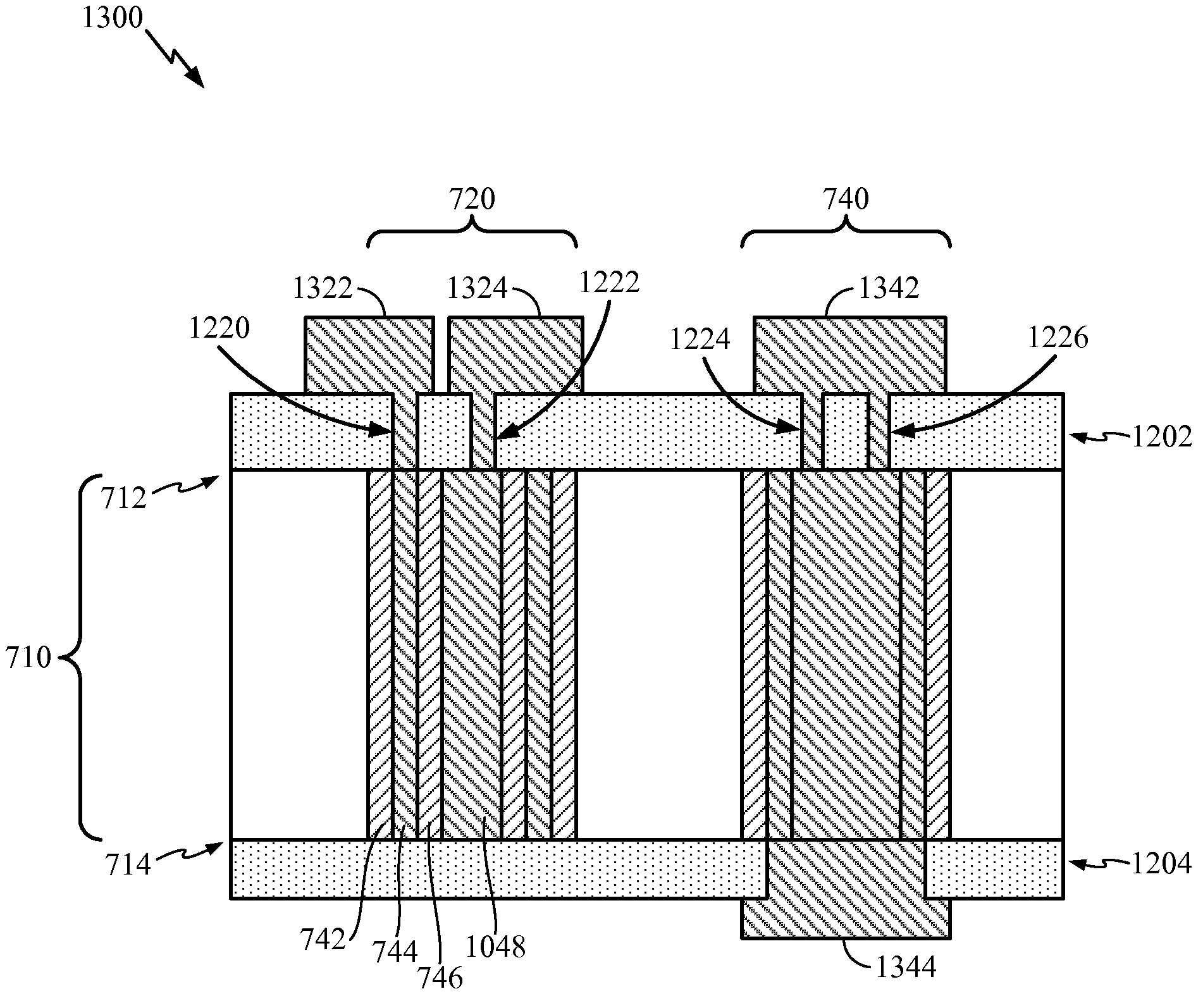

Integrated decoupling capacitor employing conductive through-substrate vias

ActiveUS20110108948A1Reduce inductanceReduce high frequency noiseSemiconductor/solid-state device detailsSolid-state devicesCapacitanceSemiconductor chip

A capacitor in a semiconductor substrate employs a conductive through-substrate via (TSV) as an inner electrode and a columnar doped semiconductor region as an outer electrode. The capacitor provides a large decoupling capacitance in a small area, and does not impact circuit density or a Si3D structural design. Additional conductive TSV's can be provided in the semiconductor substrate to provide electrical connection for power supplies and signal transmission therethrough. The capacitor has a lower inductance than a conventional array of capacitors having comparable capacitance, thereby enabling reduction of high frequency noise in the power supply system of stacked semiconductor chips.

Owner:TESSERA INC

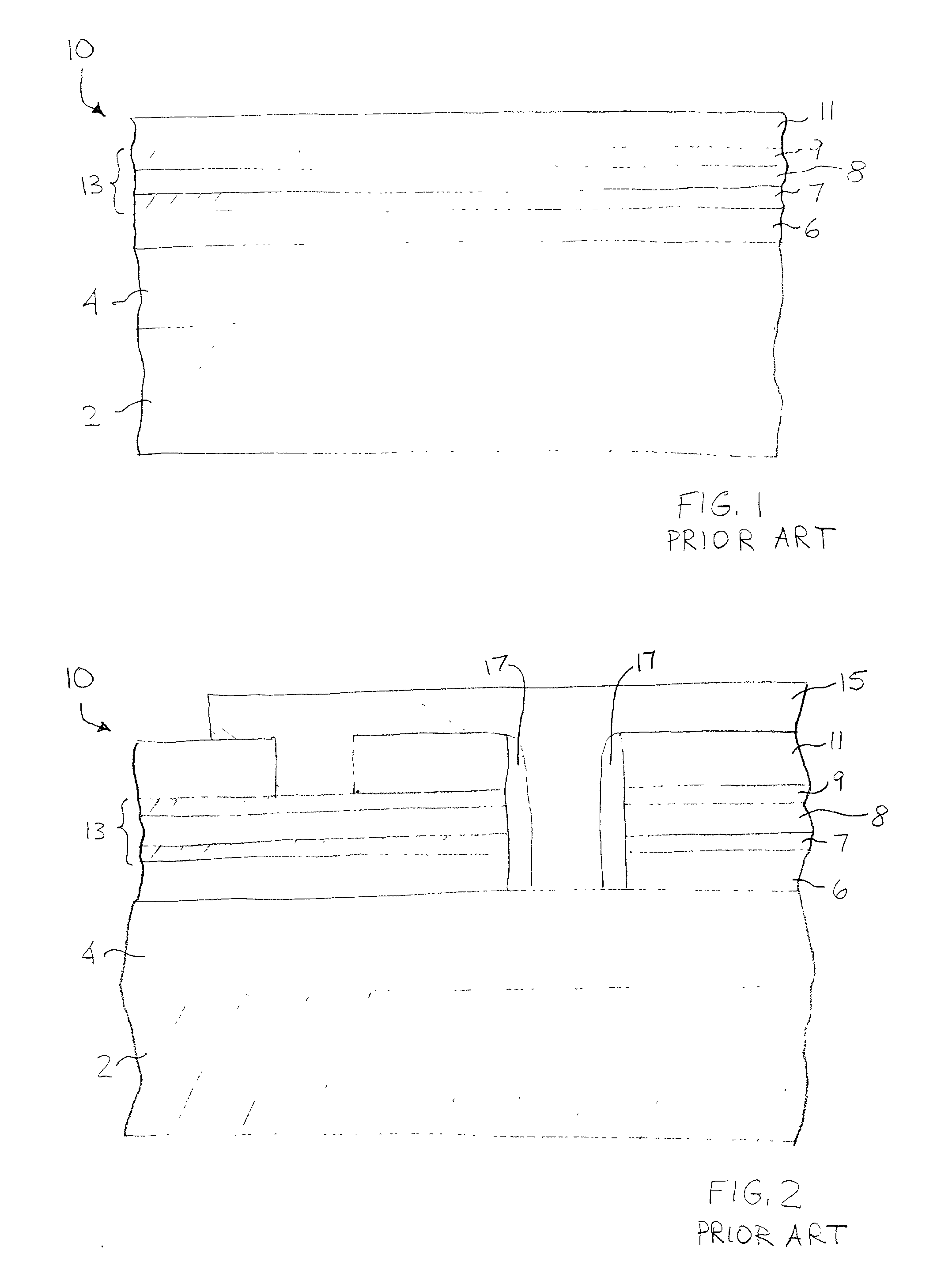

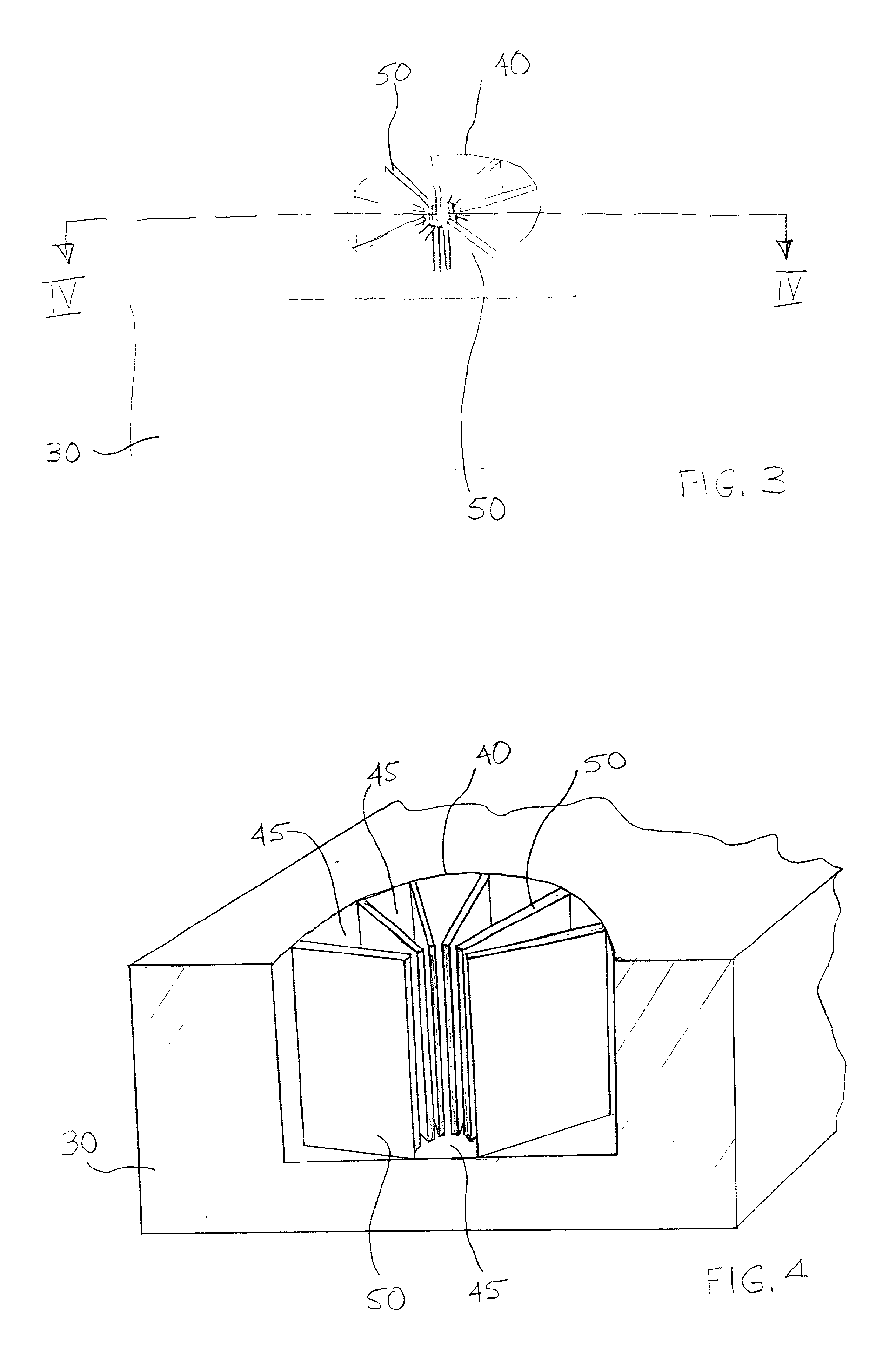

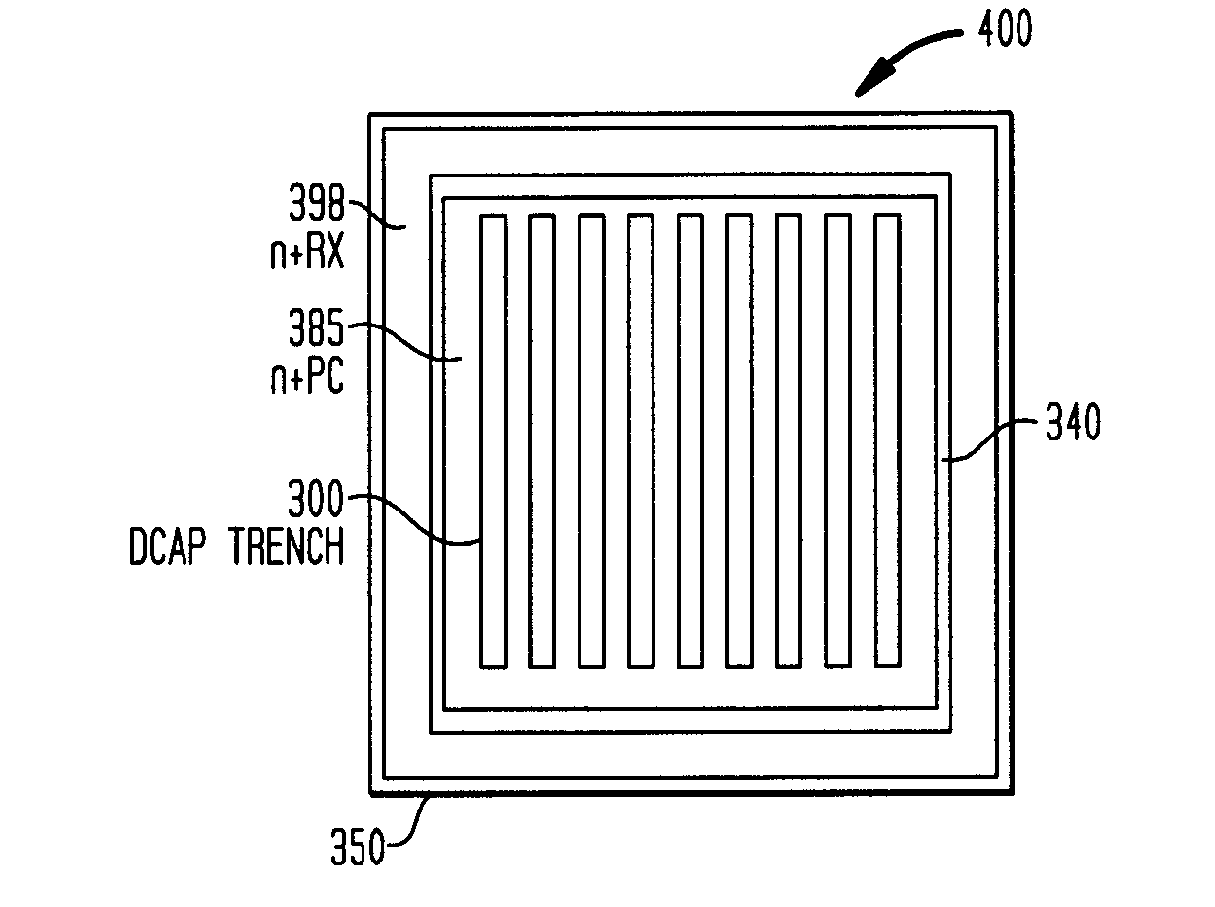

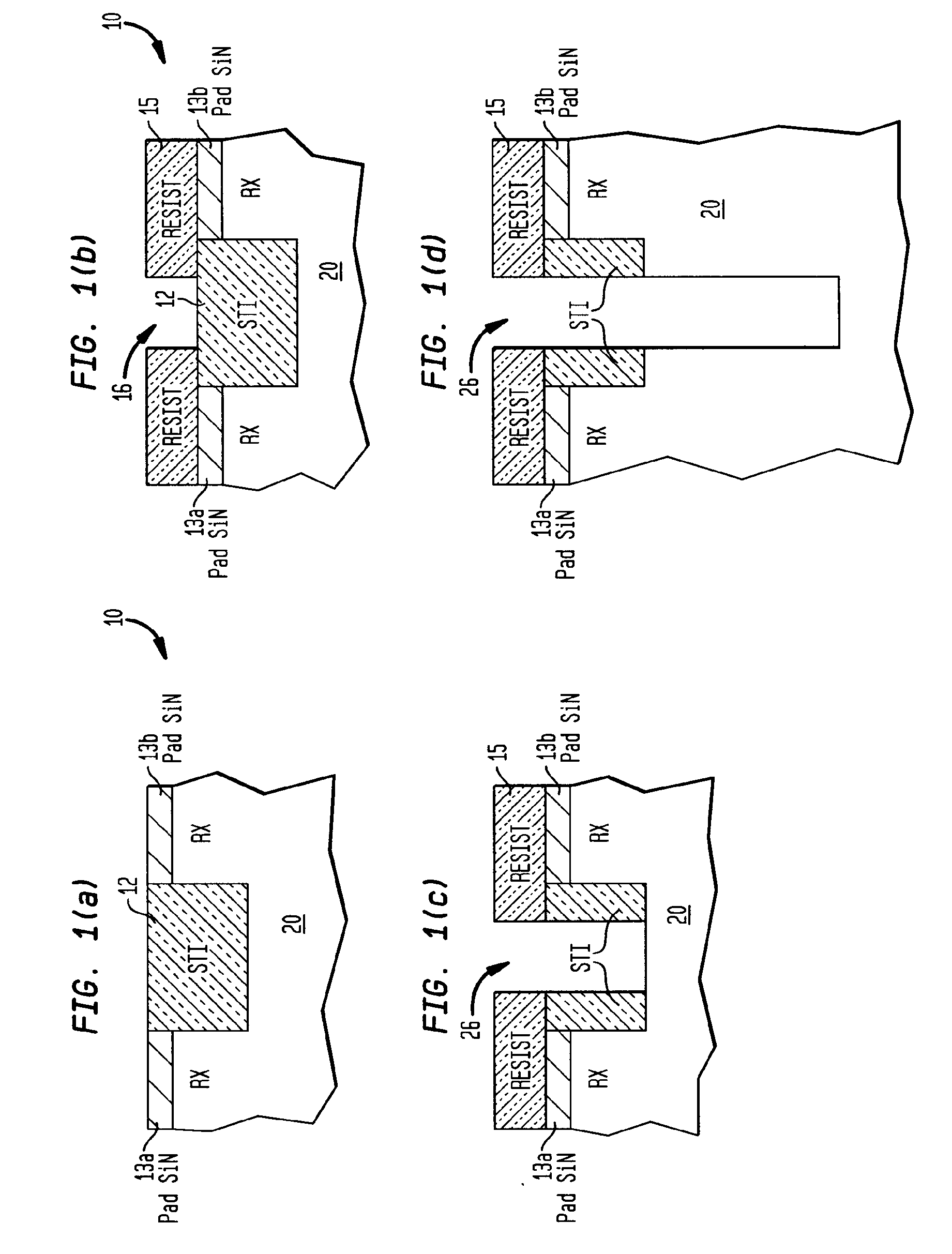

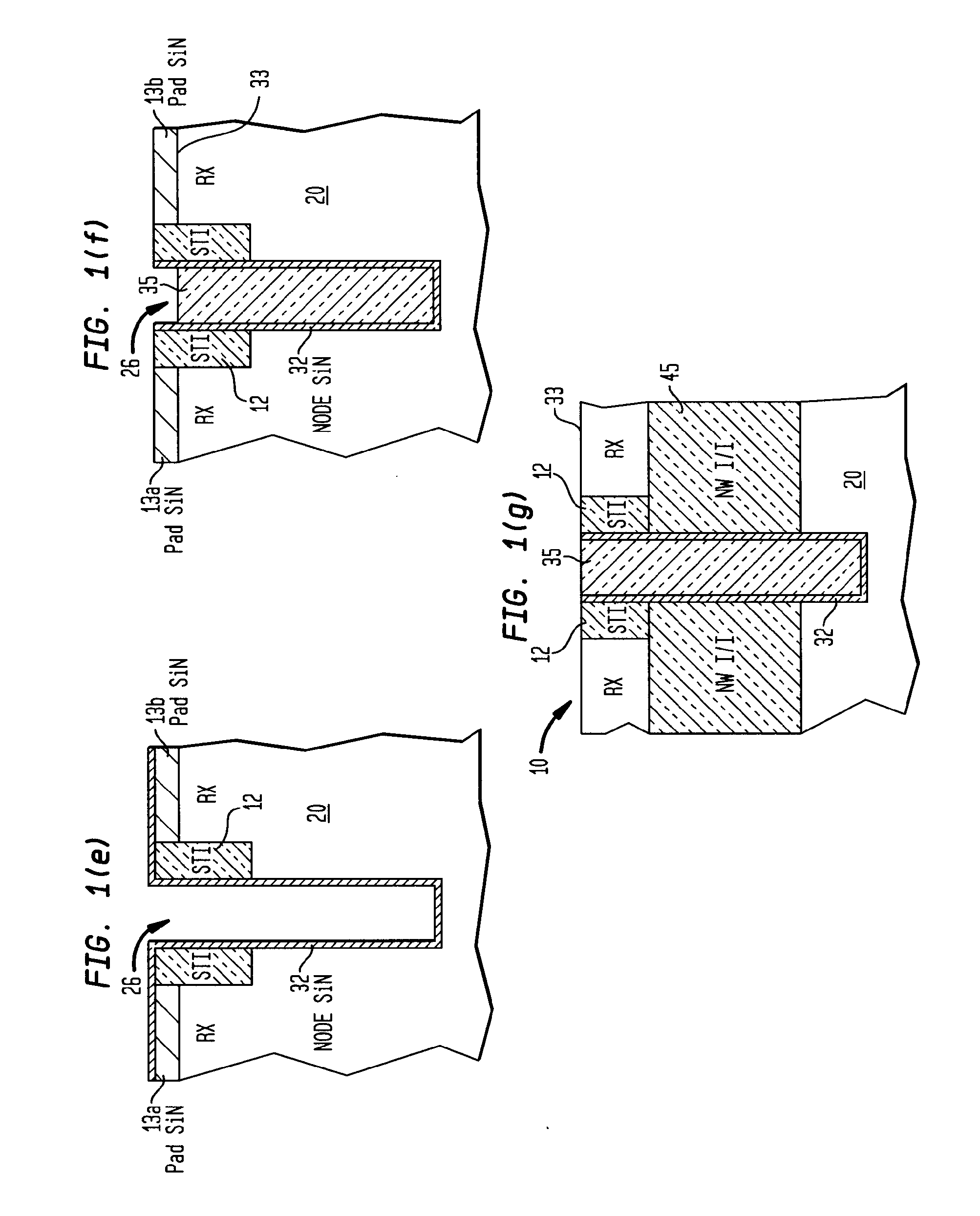

Low-Cost Deep Trench Decoupling Capacitor Device and Process of Manufacture

ActiveUS20060124982A1Avoid less flexibilityIncreases cost of waferTransistorSolid-state devicesCapacitanceManufacturing technology

A novel trench-type decoupling capacitor structure and low-cost manufacturing process to create trench decoupling capacitors (decaps). In a unique aspect, the invention necessitates the addition of only a simplified trench to a base logic design.

Owner:GLOBALFOUNDRIES US INC

Methods and apparatuses for transient analyses of circuits

ActiveUS7278120B2Computer aided designSoftware simulation/interpretation/emulationProbabilistic methodCapacitance

Methods and apparatuses for transient analyses of a circuit using a hierarchical approach. In one embodiment, the cells are grouped locally on the power supply network according to average power dissipation. A time varying current of each cell group is estimated using a probabilistic approach to represent the cell group so that the probability of a more severe waveform for the current of the cell group is under a certain level. For example, the cells in a group are partitioned as switching cells and non-switching cells using cell toggle rates for the determination of the time varying current. The circuit model of the power supply network includes the current sources according to the estimated time varying currents for the cell groups, the power supply wire resistance, the power supply to ground wire capacitance, well capacitance and the de-coupling capacitance from non-switching cells.

Owner:SYNOPSYS INC

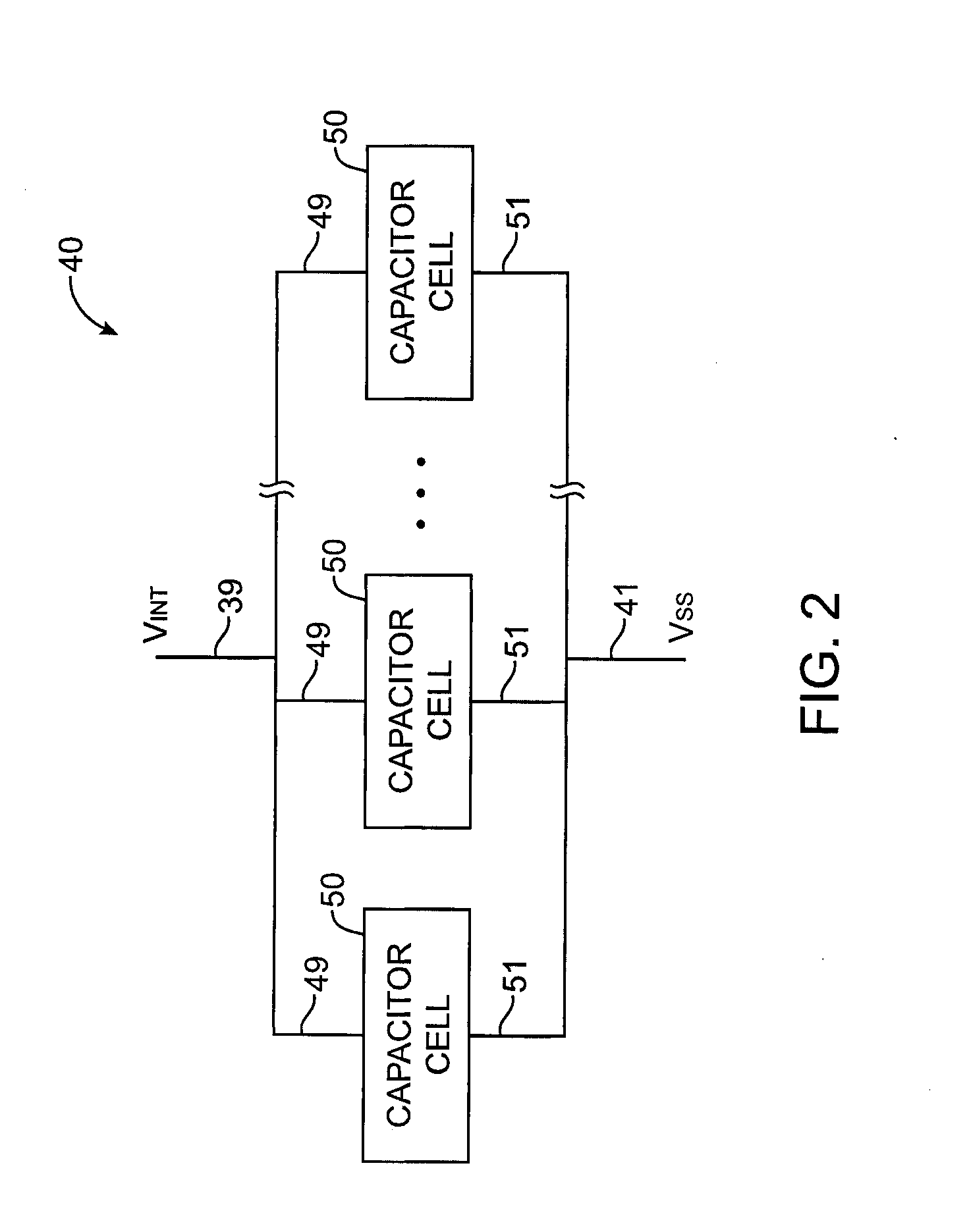

Integrated circuit decoupling capacitors

ActiveUS20100148304A1Control flowReduce the overall decoupling capacitorSemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalEngineering

Power supply decoupling capacitors are provided for integrated circuits. The decoupling capacitors may be distributed in clusters amongst powered circuit components. Each cluster may contain a number of individual capacitor cells that are connected in parallel. Each capacitor cell may contain a capacitor and a resistor connected in series with the capacitor. The capacitors may be metal-insulator-metal (MIM) capacitors. The resistor in each cell may limit the current through an individual capacitor in the event of a short in the capacitor due to a dielectric defect.

Owner:ALTERA CORP