Semiconductor apparatus with decoupling capacitor

a technology of capacitor and semiconductor, applied in the direction of electrical apparatus contruction details, cross-talk/noise/interference reduction, etc., can solve the problem of hard to reduce electromagnetic radiation noise generated in the semiconductor package, the power supply/ground noise inside the semiconductor package cannot be removed sufficiently, and the parasitic inductance is increased. problem, to achieve the effect of sufficiently reducing power supply/ground nois

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first preferred embodiment

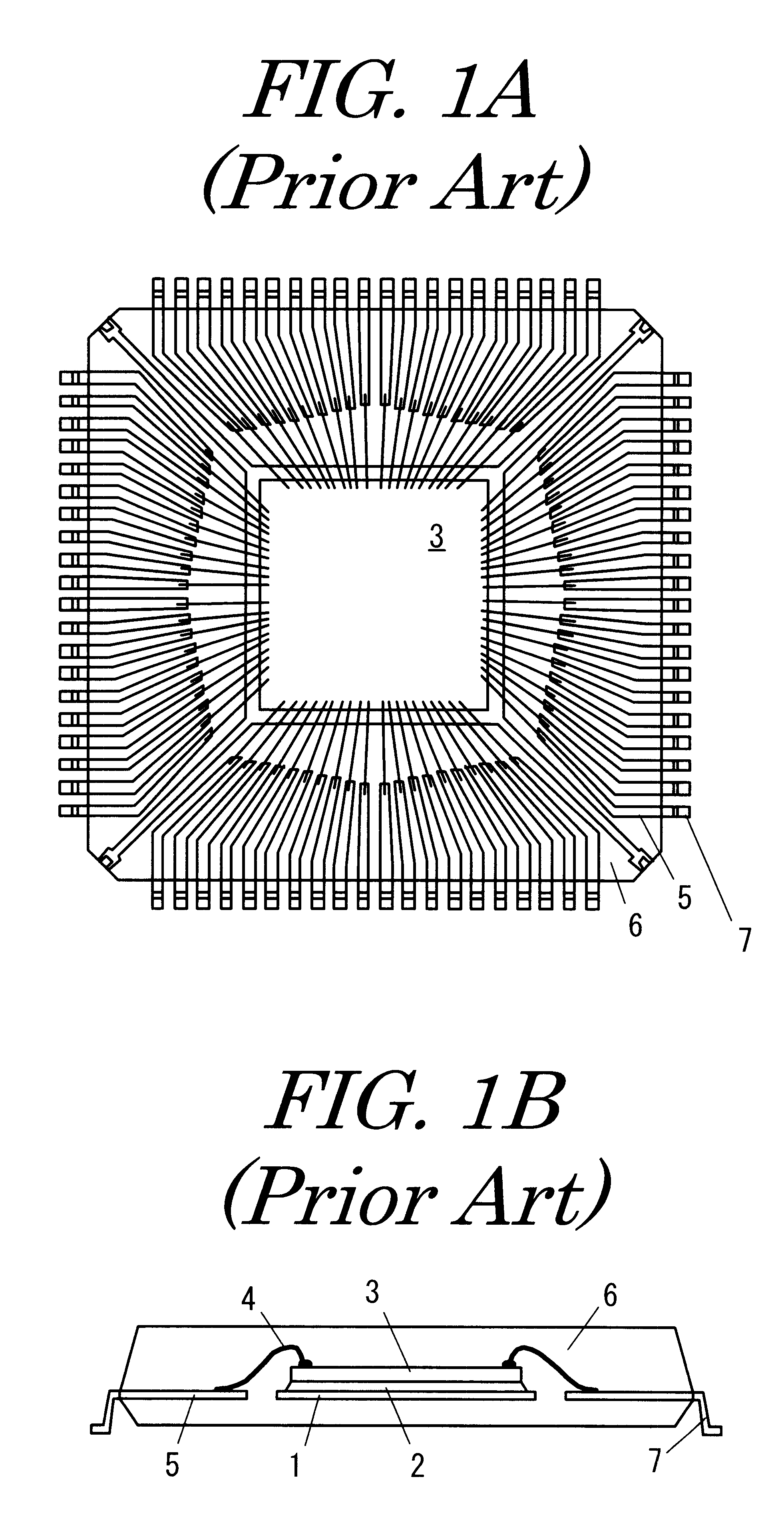

FIG. 3 is a plane view showing an inside of a lead frame type of semiconductor package according to a first preferred embodiment of the present invention. FIG. 4 is a cross-sectional view showing an inside of the semiconductor package, shown in FIG. 3. The semiconductor package according to the first preferred embodiment includes a die pad 101, a semiconductor device (chip) 103; inner leads 105 and a mold resin 106.

The semiconductor chip 103 is mounted on the die pad 101 using conductive paste 102. In the drawings, "P" represents a power supply terminal and "G" represents a ground terminal. The inner leads 105, connected to the power supply terminals P and ground terminals G, are extended inwardly toward the semiconductor chip 103. A chip capacitor mounting pad 111 is formed at the inner ends of the adjacent two extended inner leads 105. A chip capacitor 110 is mounted on each of the chip capacitor mounting pads 111 using conductive adhesives 112, such as silver-epoxy system adhesiv...

second preferred embodiment

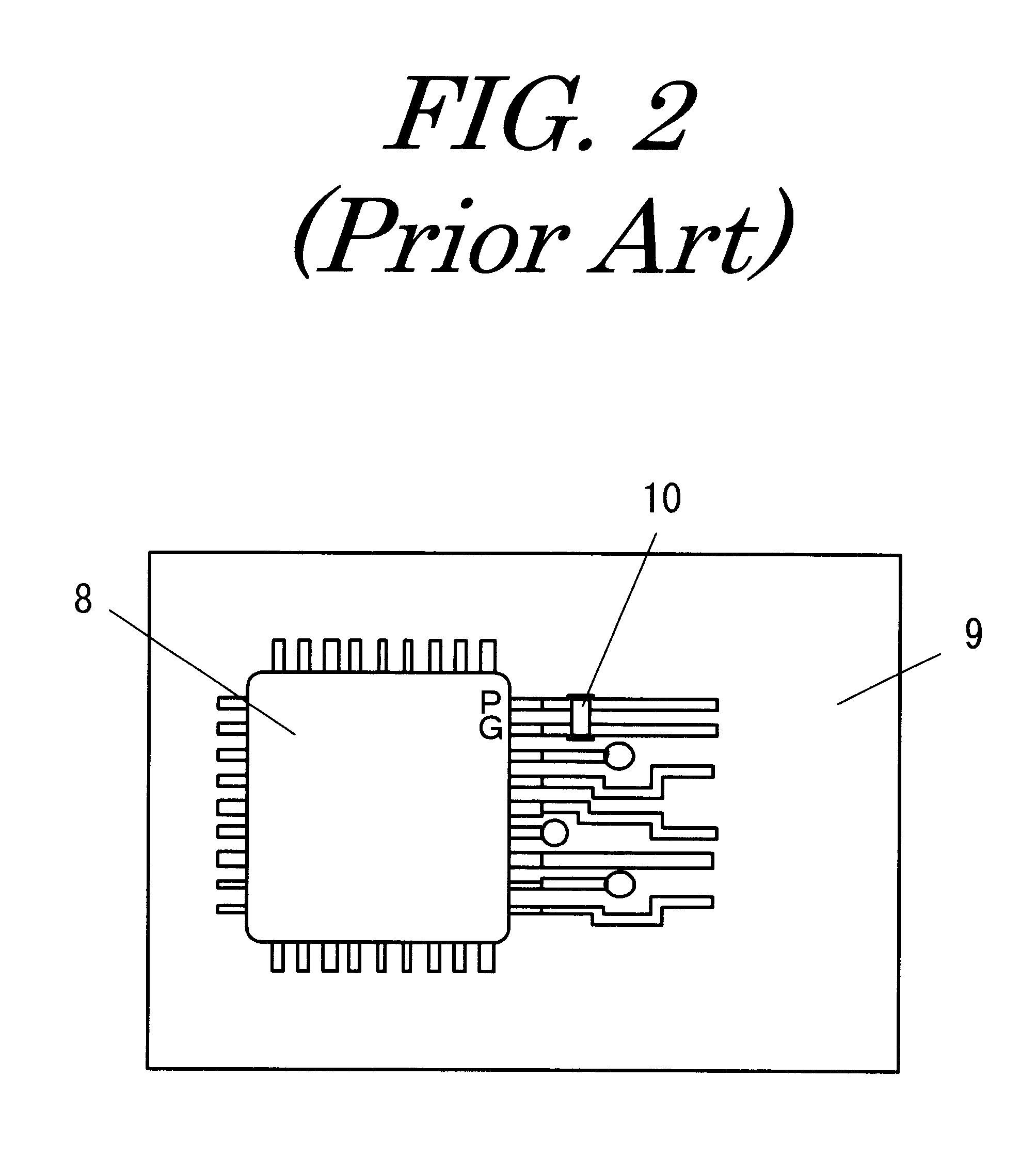

FIG. 5 is a plane view showing an inside of a lead frame type of semiconductor package according to a second preferred embodiment of the present invention. FIG. 6A is a cross-sectional view showing a part of inner leads of the semiconductor package, shown in FIG. 5. FIG. 6B is a cross-sectional view taken on line A-A' of FIG. 6A. The semiconductor package according to the second preferred embodiment includes a semiconductor device (chip) 203, inner leads 205 and outer leads 207. In the drawings, "P" represents a power supply terminal and "G" represents a ground terminal.

In this embodiment, the power supply terminals P and ground terminals G are arranged adjacent or next to each other. High dielectric constant material 213 is arranged between adjacent power supply terminal P and ground terminal G so as to form a decoupling capacitor between those terminals. Surface electrodes on the semiconductor chip 203 are connected to the power supply terminals P, ground terminals G and signal te...

third preferred embodiment

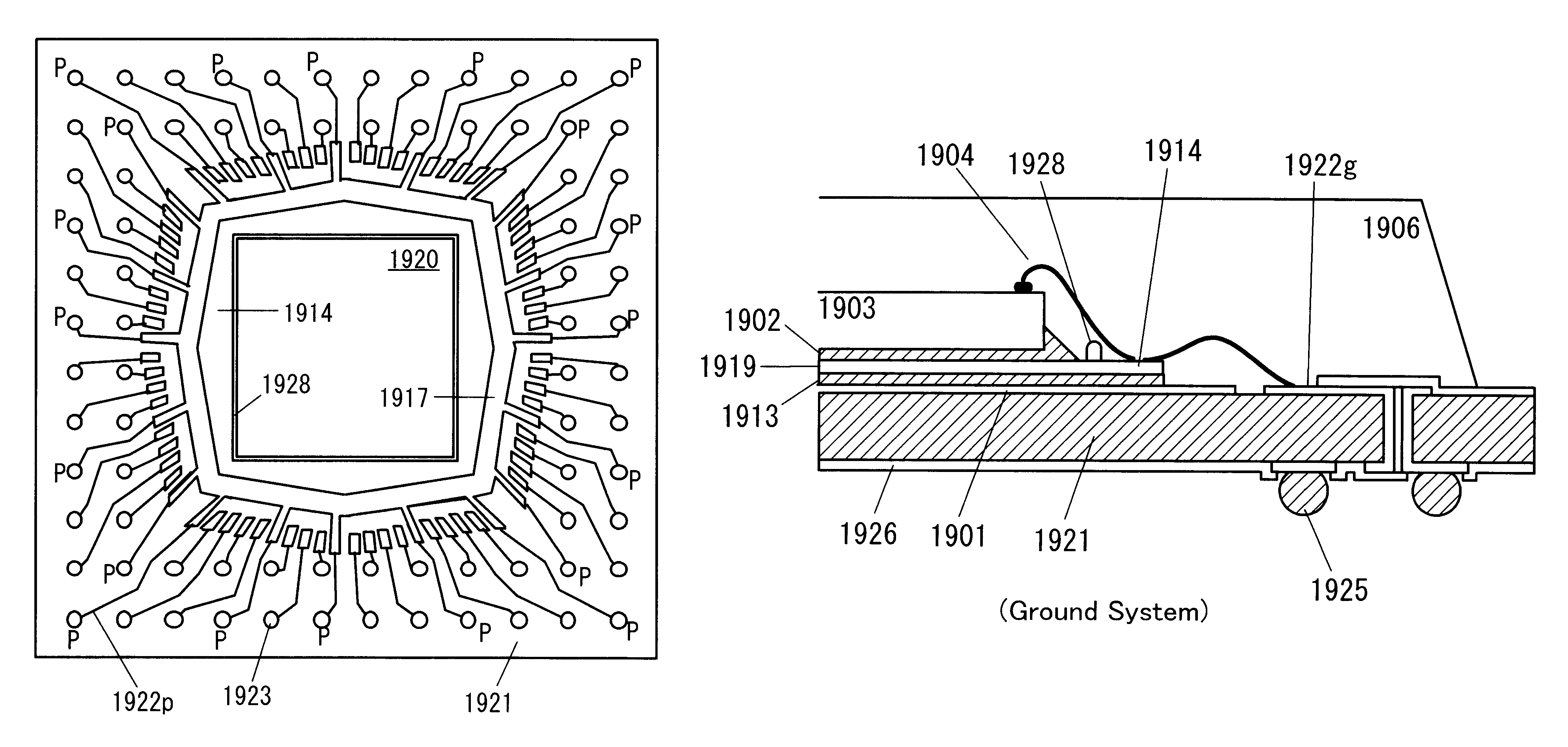

FIG. 7 is a plane view showing an inside of a lead frame type of semiconductor package according to a third preferred embodiment of the present invention. FIG. 8A is a cross-sectional view showing an inside of the semiconductor package, shown in FIG. 7. FIG. 8B is a cross-sectional view showing an inside of the semiconductor package, shown in FIG. 7. The semiconductor package according to the third preferred embodiment includes a die pad 301, a semiconductor device (chip) 303 and inner leads 305. The semiconductor chip 303 is mounted on the die pad 301 using conductive paste 302. In the drawings, "P" represents a power supply terminal and "G" represents a ground terminal.

The die pad 301 is expanded outwardly to form a bonding area 314 for ground. Chip capacitors 310 are arranged between the bonding area 314 and the inner leads 305 for power supply terminals "P". Each of the chip capacitors 310 is connected to the inner leads 305 and bonding area 314 using conductive adhesives 312, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More