Patents

Literature

4510 results about "Solder paste" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Solder paste (or solder cream) is a material used in the manufacture of printed circuit boards to connect surface mount components to pads on the board. It is also possible to solder through hole pin in paste components by printing solder paste in/over the holes. The paste initially adheres components in place by being sticky, it is then heated (along with the rest of the board) melting the paste and forming a mechanical bond as well as an electrical connection. The paste is applied to the board by jet printing, stencil printing or syringe and then the components are put in place by a pick-and-place machine or by hand.

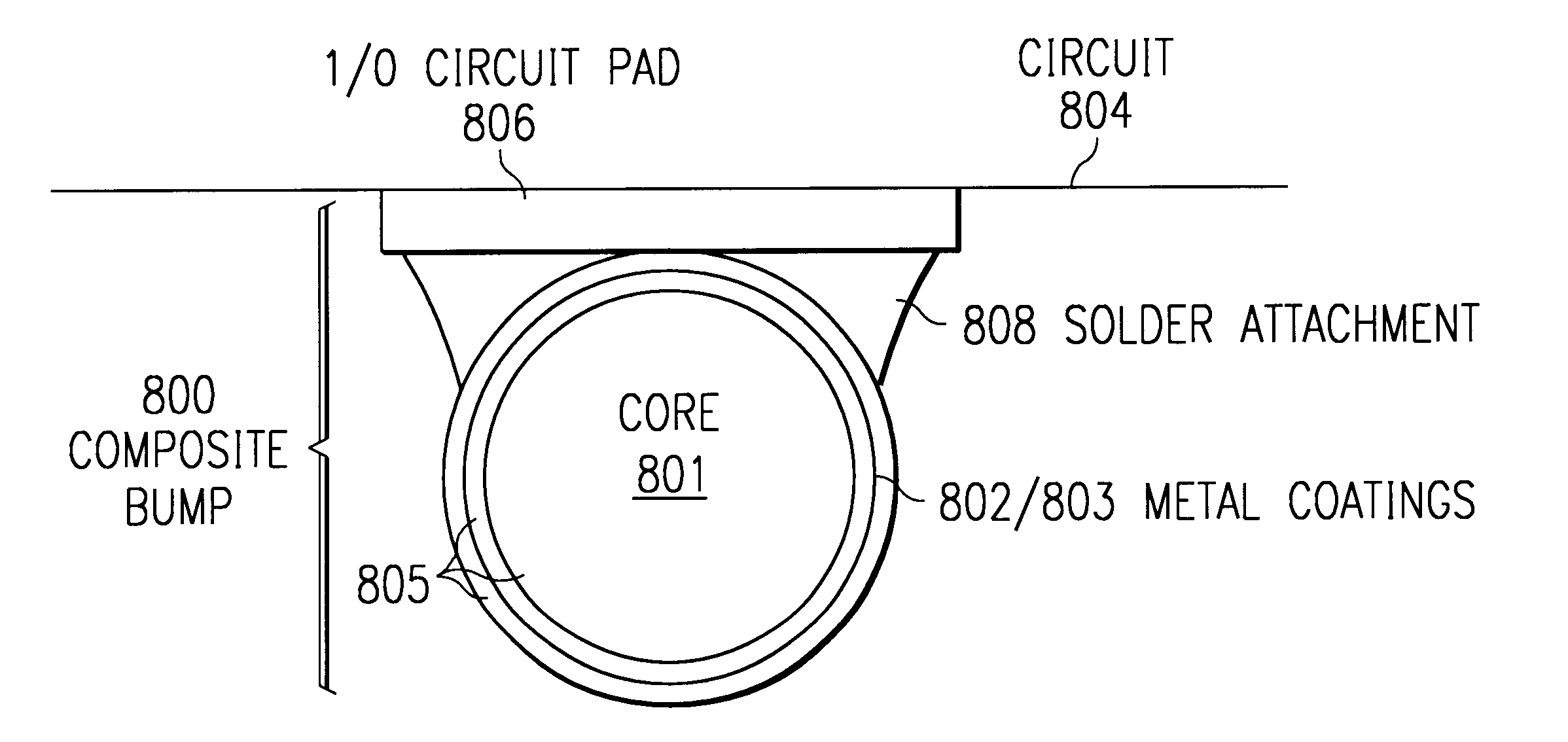

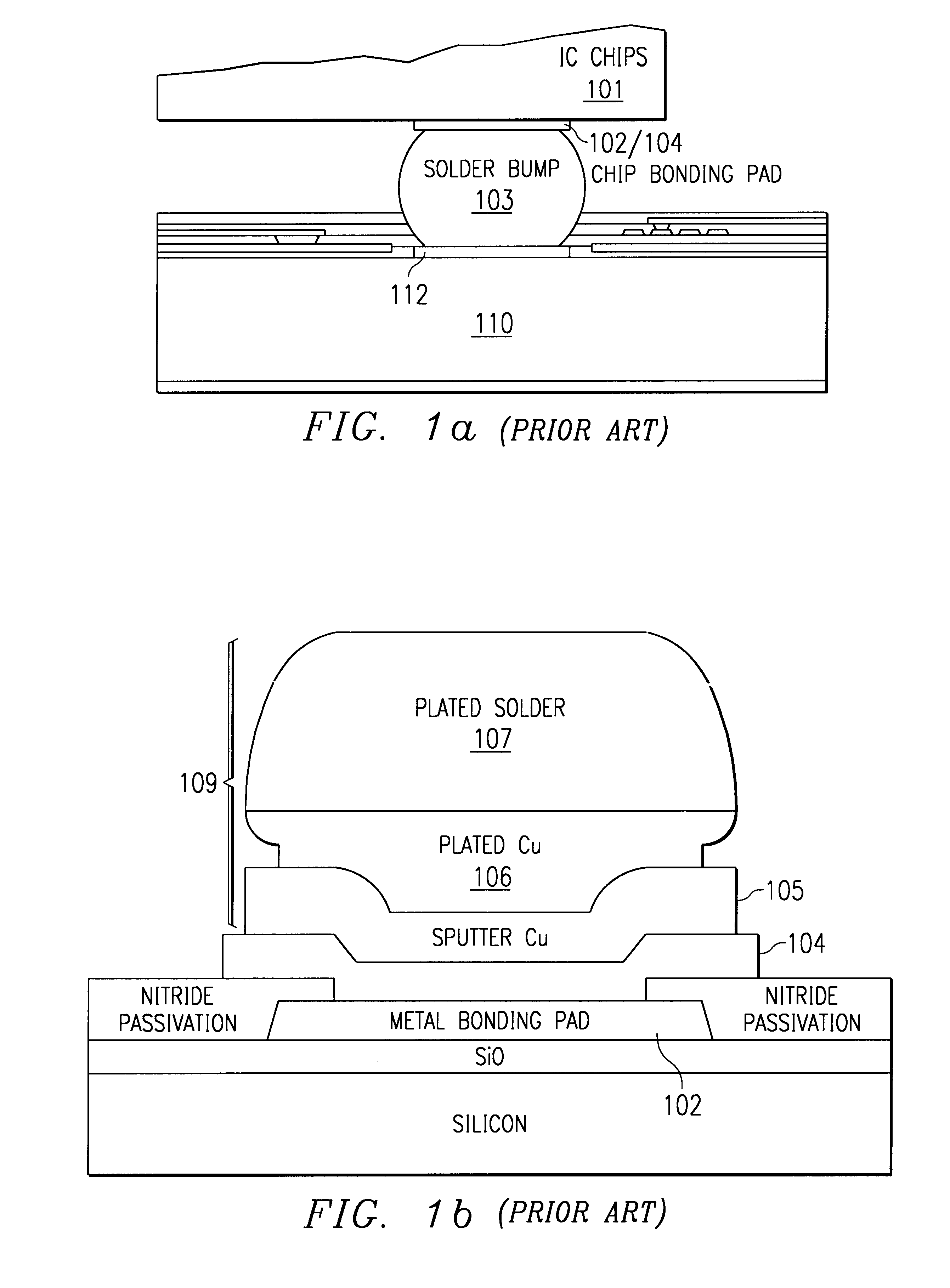

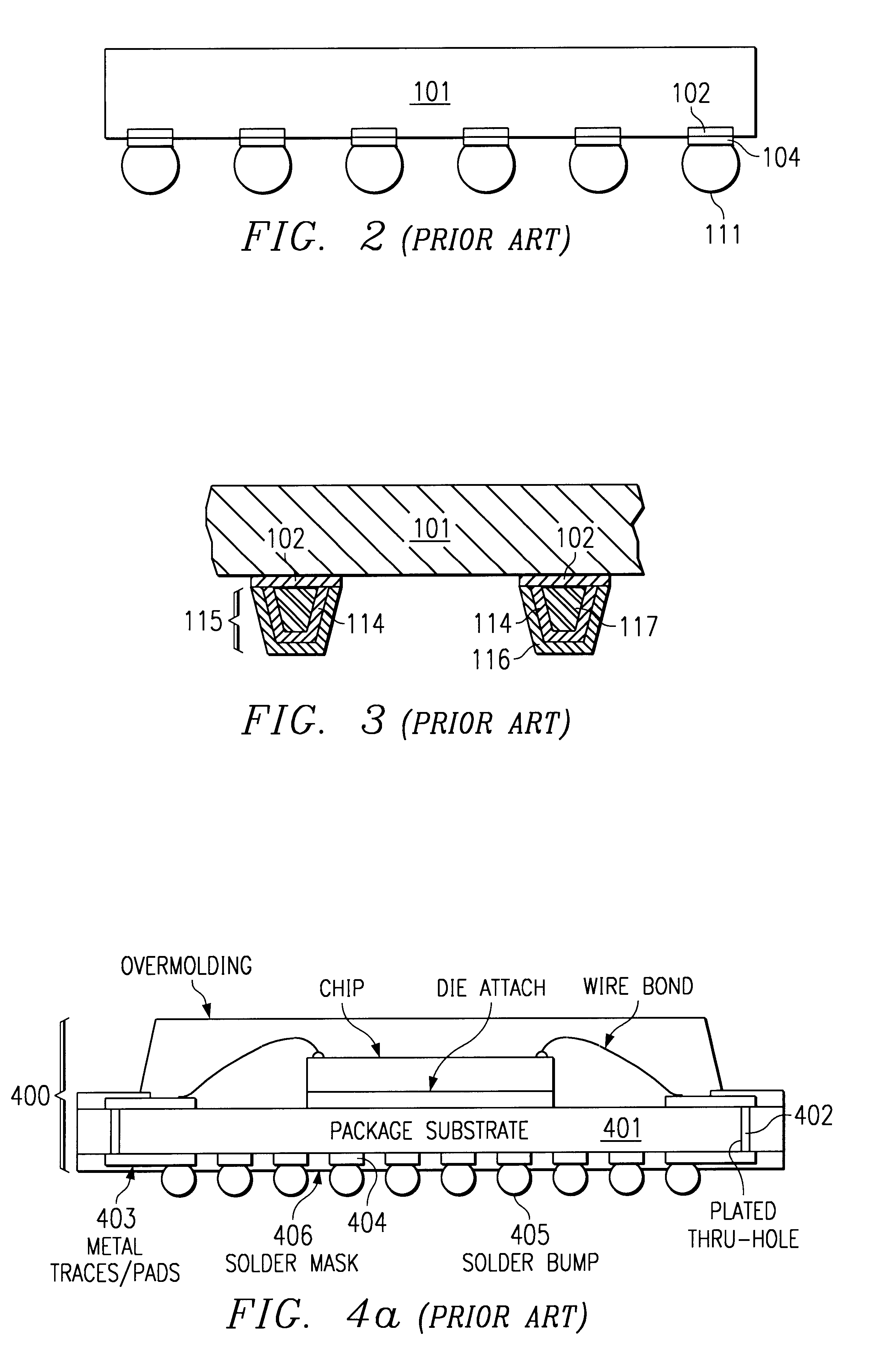

Composite connection structure and method of manufacturing

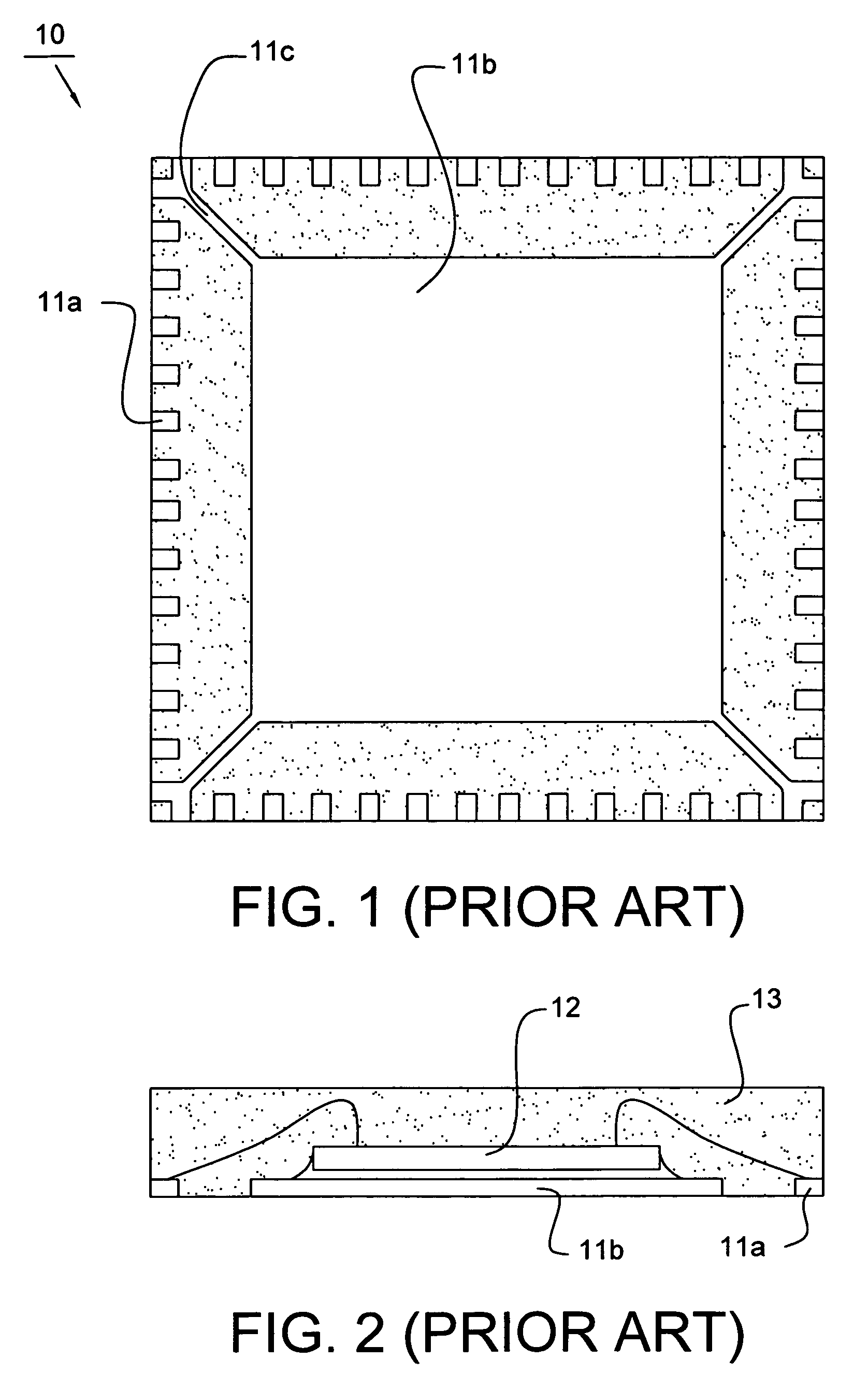

InactiveUS6337445B1Improve reliability and performanceImprove thermal conductivityPrinted circuit assemblingFinal product manufactureContact padSolder paste

A bump connection structure and a method of attachment to integrated circuits or packages is provided which comprises a prefabricated core structure coated with solderable metal layers to form a composite bump. Said composite bump is aligned to contact pads of the chip or package which have been coated with solder paste, and the assembly heated to form a metallurgical bond. The prefabricated core structures are comprised of metal, plastic or ceramic of the size and dictated by package standards. The connection structure is preferably lead free.

Owner:TEXAS INSTR INC

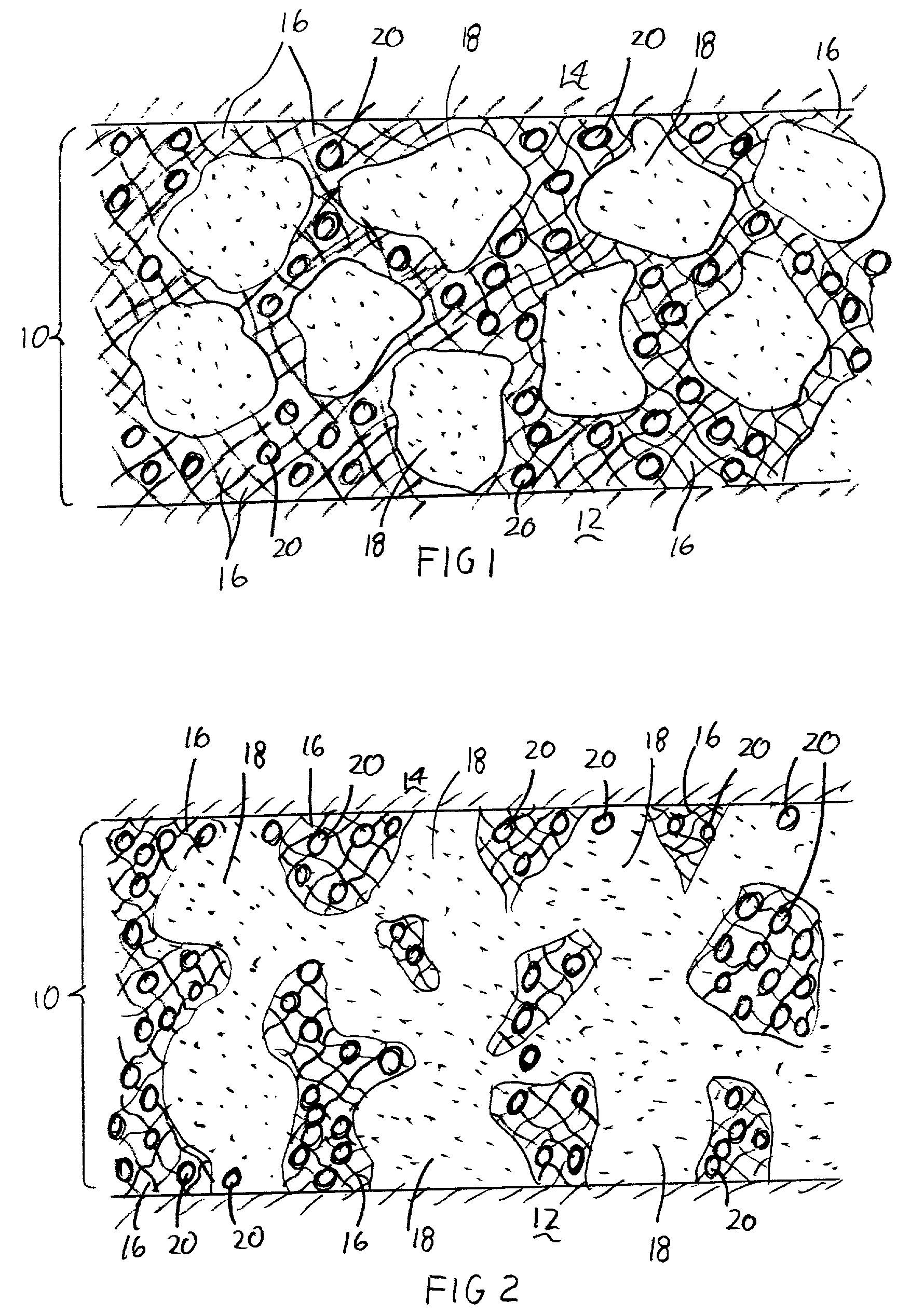

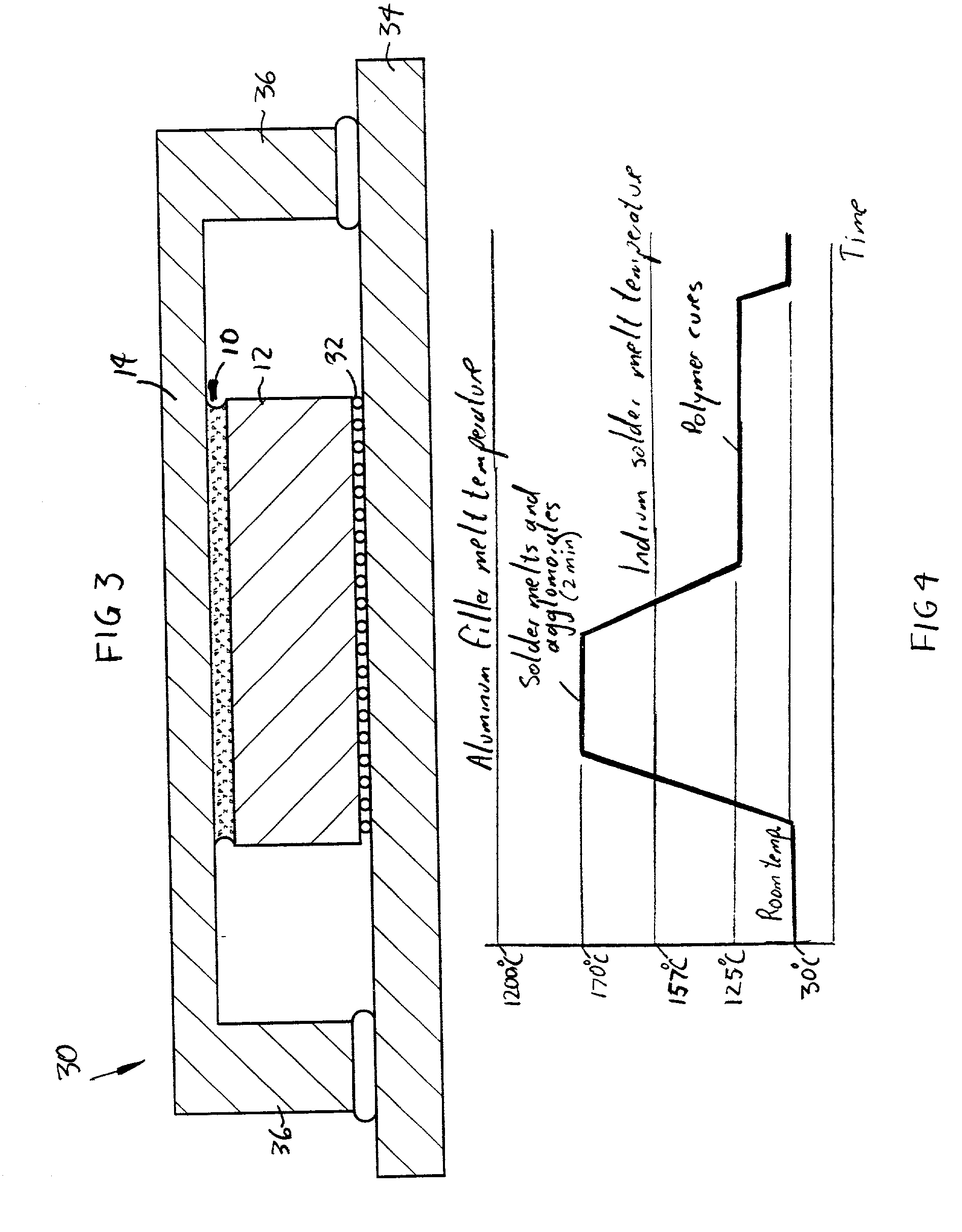

Thermal interface material and electronic assembly having such a thermal interface material

InactiveUS20030077478A1Artificial flowers and garlandsSemiconductor/solid-state device detailsStress conditionsIndium

A thermal interface material is described for thermal coupling of an electronic component to a thermally conductive member. The thermal interface material includes a viscoelastic polymer matrix material, fusible solder particles in the matrix material, and filler particles in the matrix material. The solder particles have a melting temperature below a selected temperature (e.g. 157° C. for indium) and the filler particles have a melting temperature substantially above the selected temperature (e.g. 961° C. for silver). The filler particles keep the thermal interface material intact under adverse thermal and stress conditions.

Owner:INTEL CORP

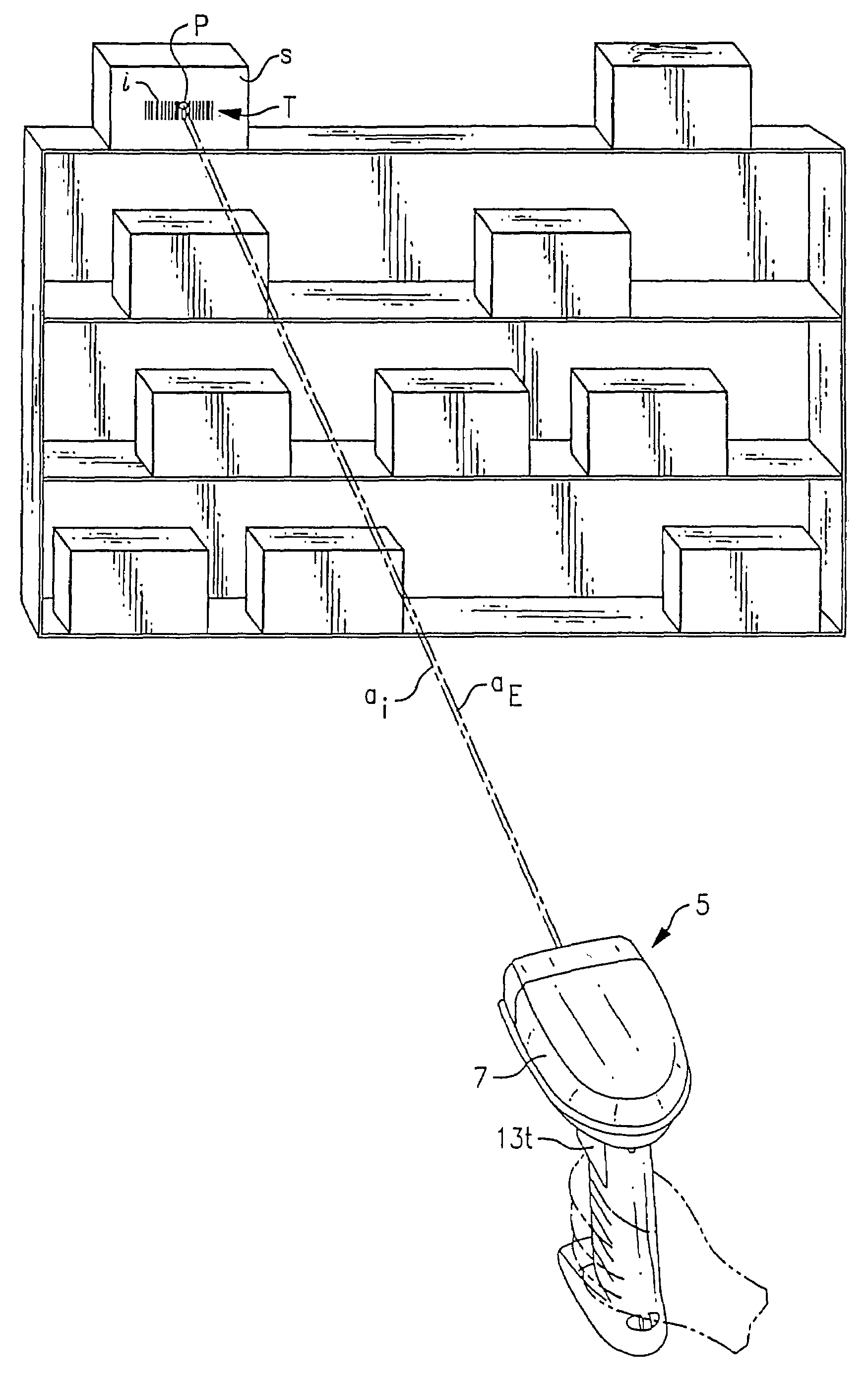

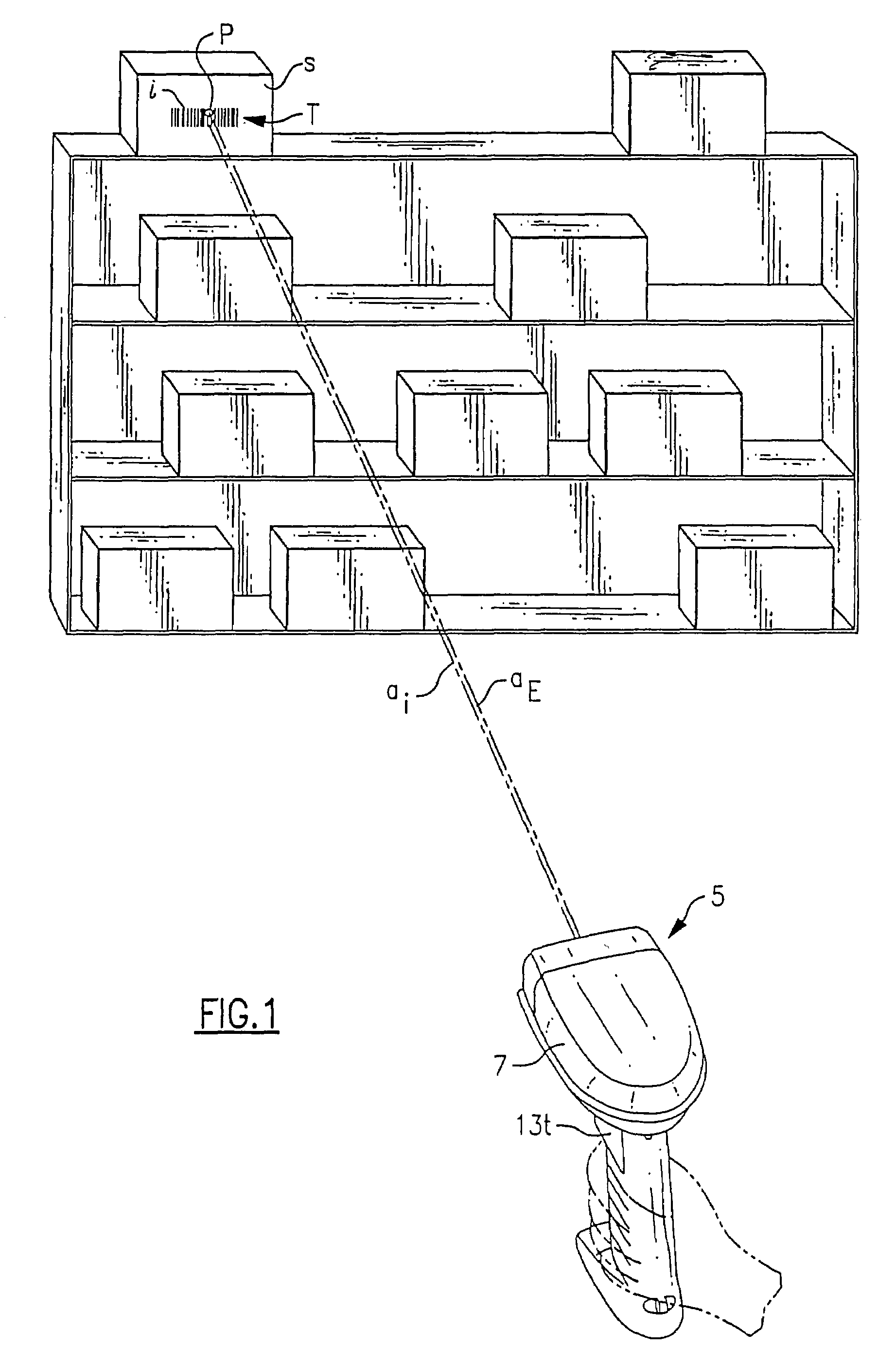

Long range optical reader

InactiveUS7090132B2Increase signal strengthSignal strength (signal to noise ratio) of a long range reader can be enhancedPrinted circuit aspectsElectrical connection printed elementsEngineeringSolder paste

An optical reader in one embodiment can include a substrate defining an opening and solder pads coupled to the substrate proximate the opening. A laser diode including first, second, and third electrical leads can also be coupled to the substrate. First, second and third solder pads can be provided on the substrate and the first, second, and third electrical leads of the laser diode can be coupled to the first, second, and third solder pads. An optical reader in another embodiment can include a substrate having a first surface and a second surface. A laser diode assembly configured to emit a laser beam can be coupled to the first surface and an illumination assembly that can include light emitting diodes can be coupled to the second surface.

Owner:HAND HELD PRODS

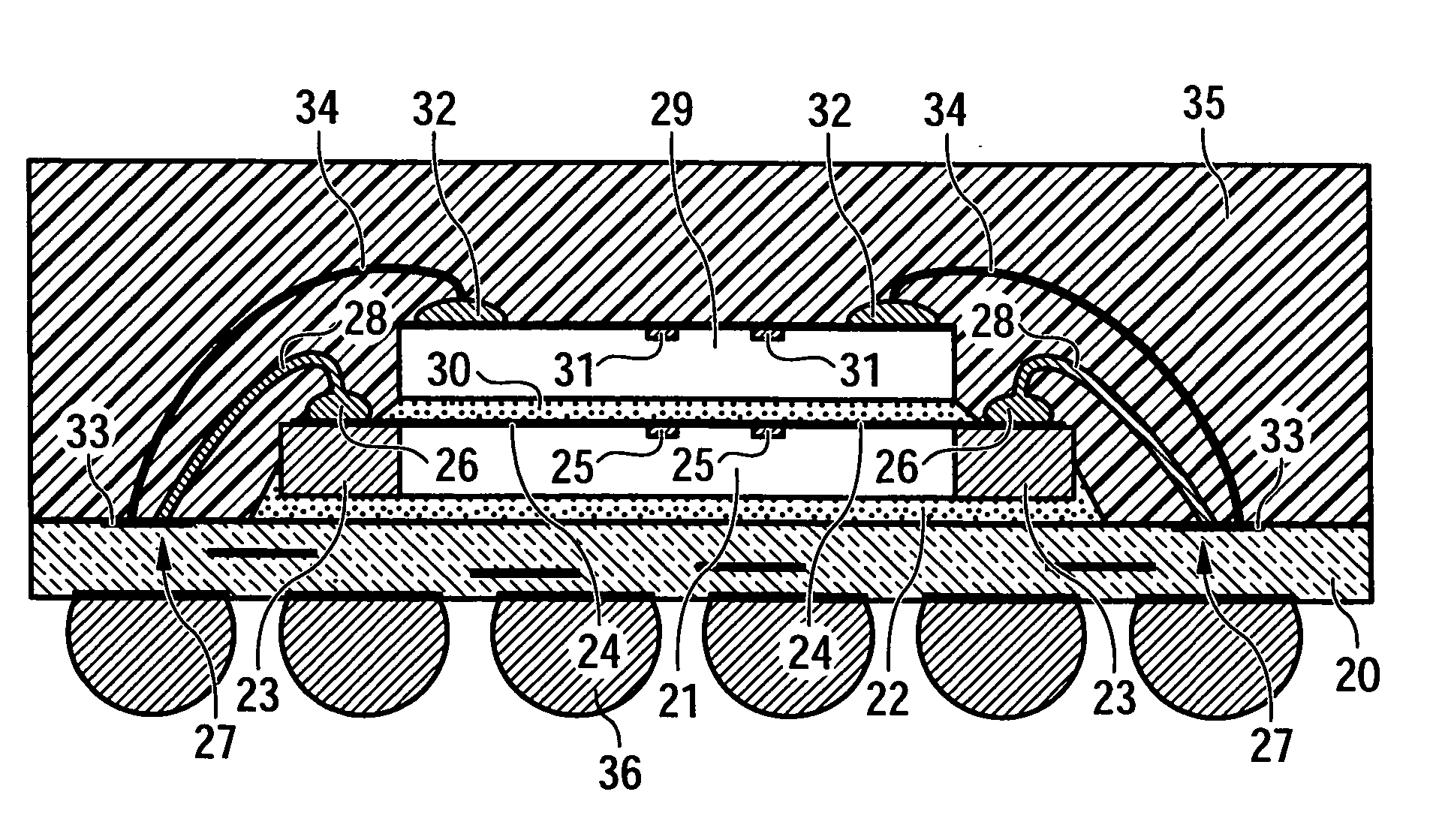

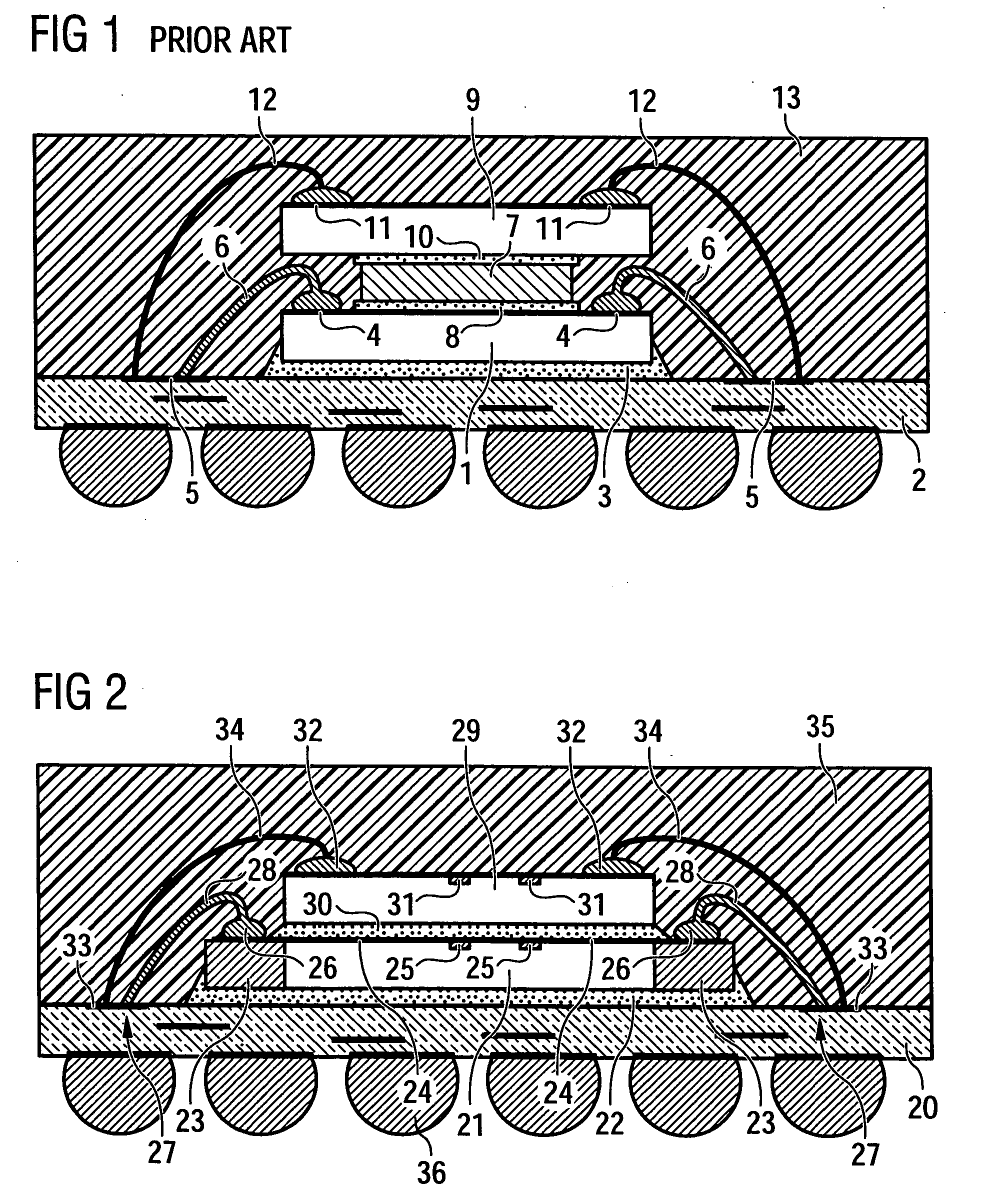

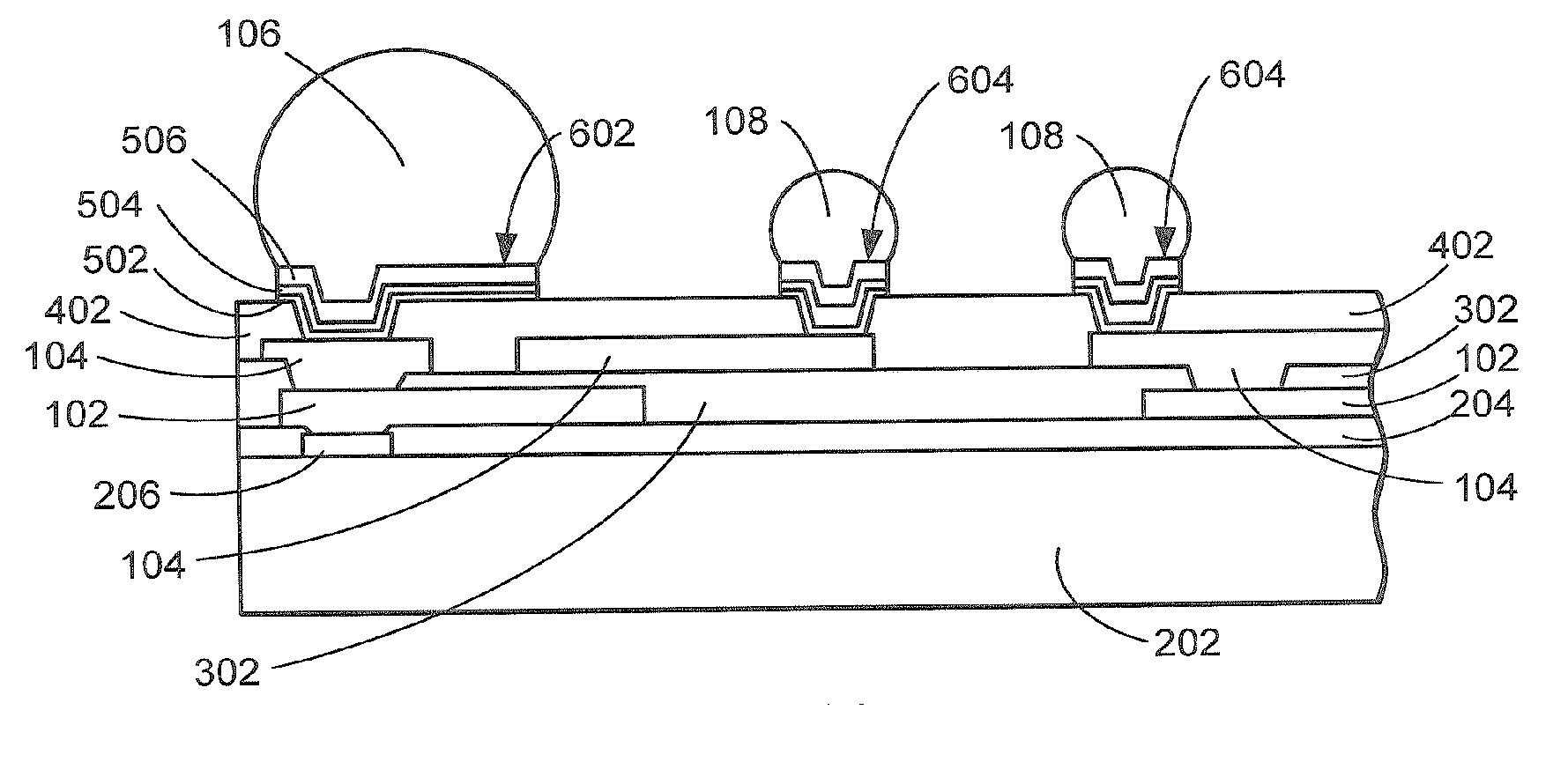

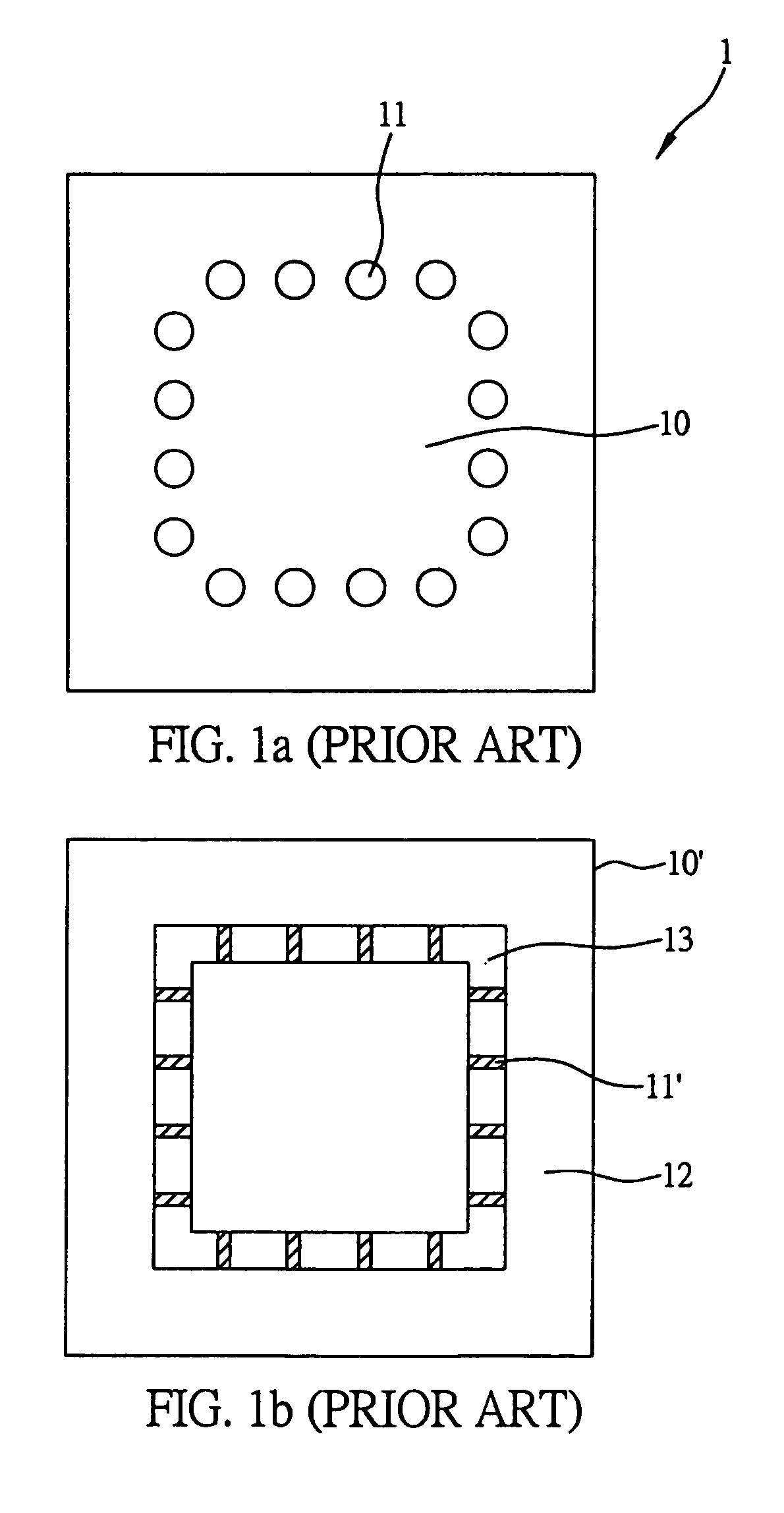

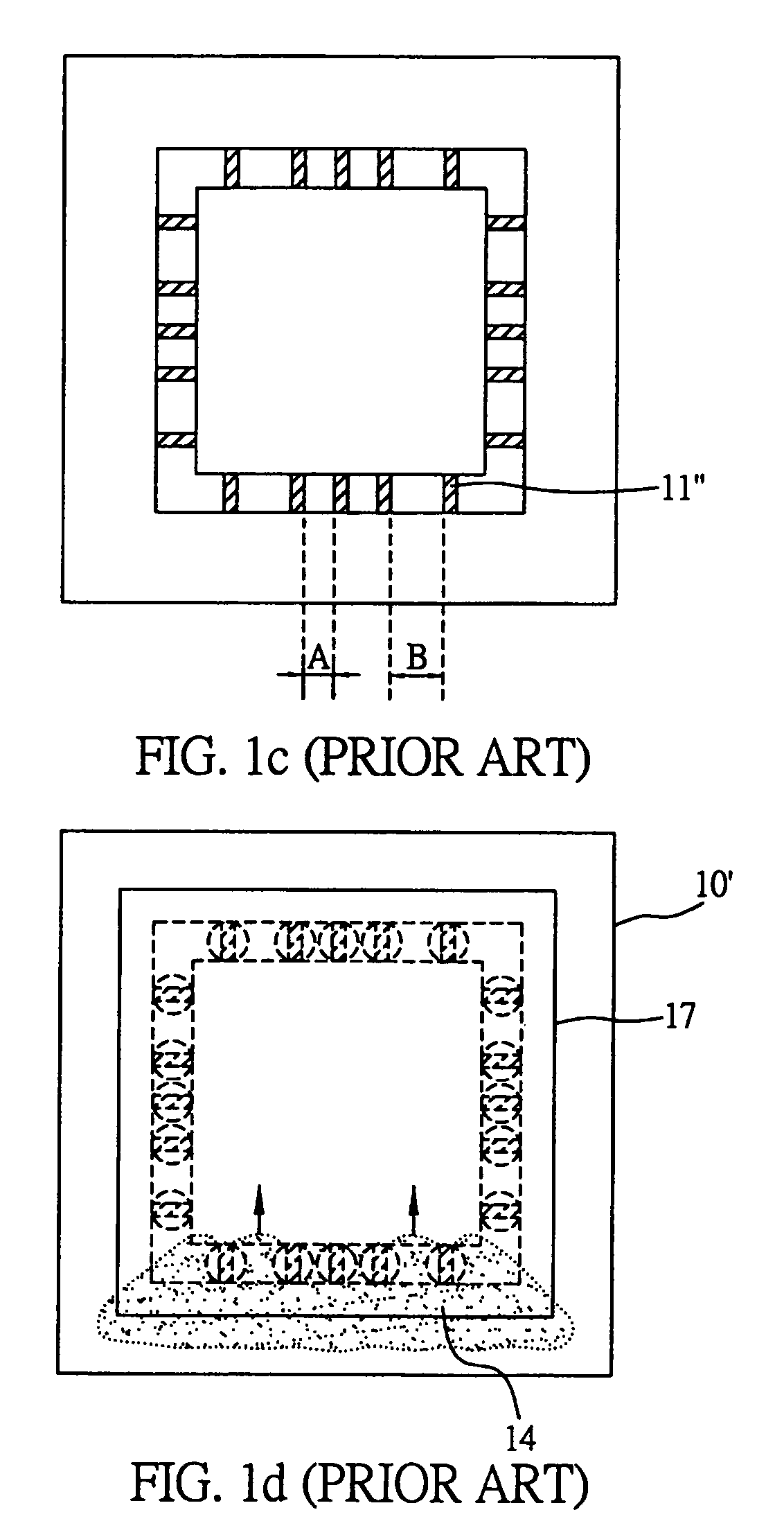

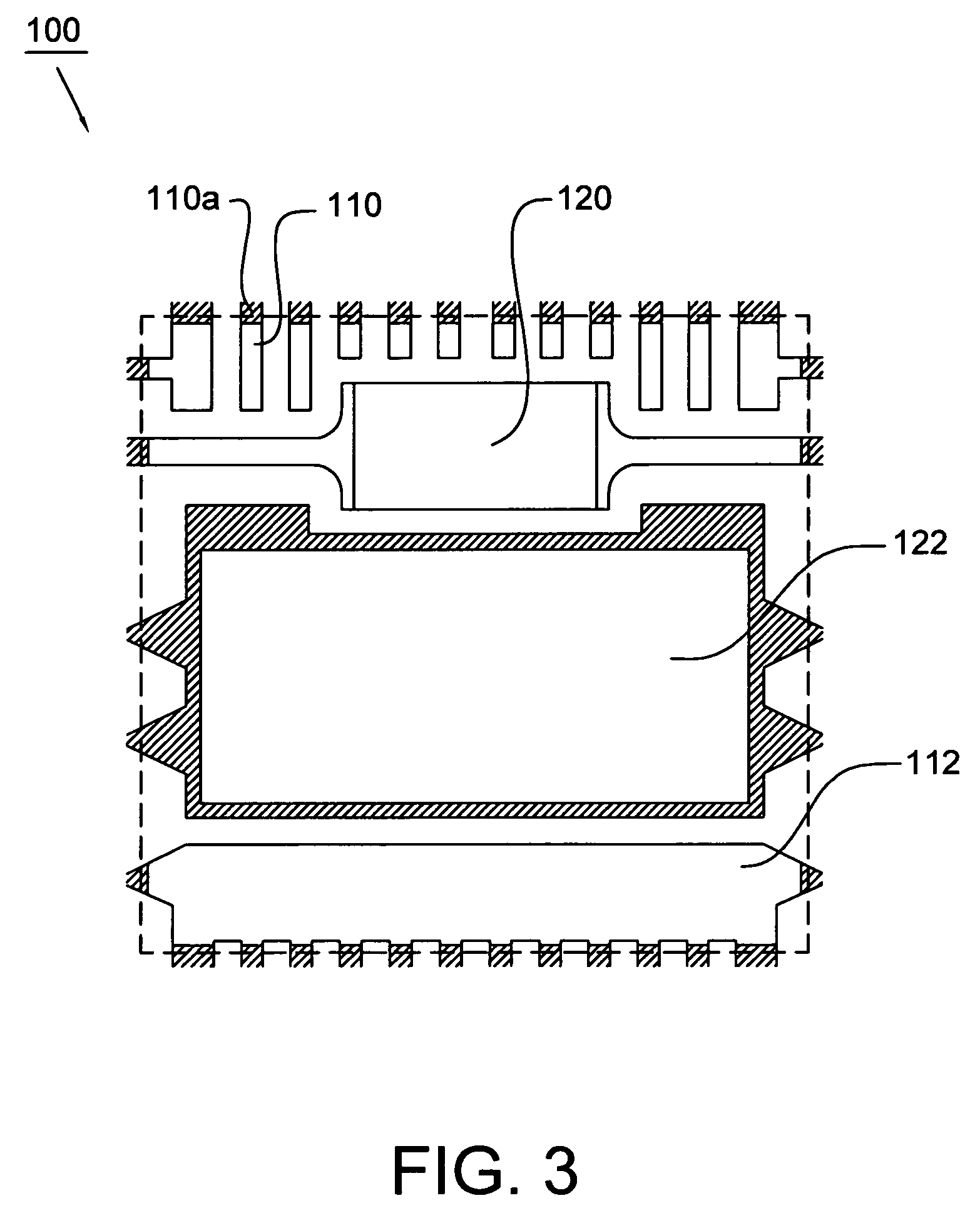

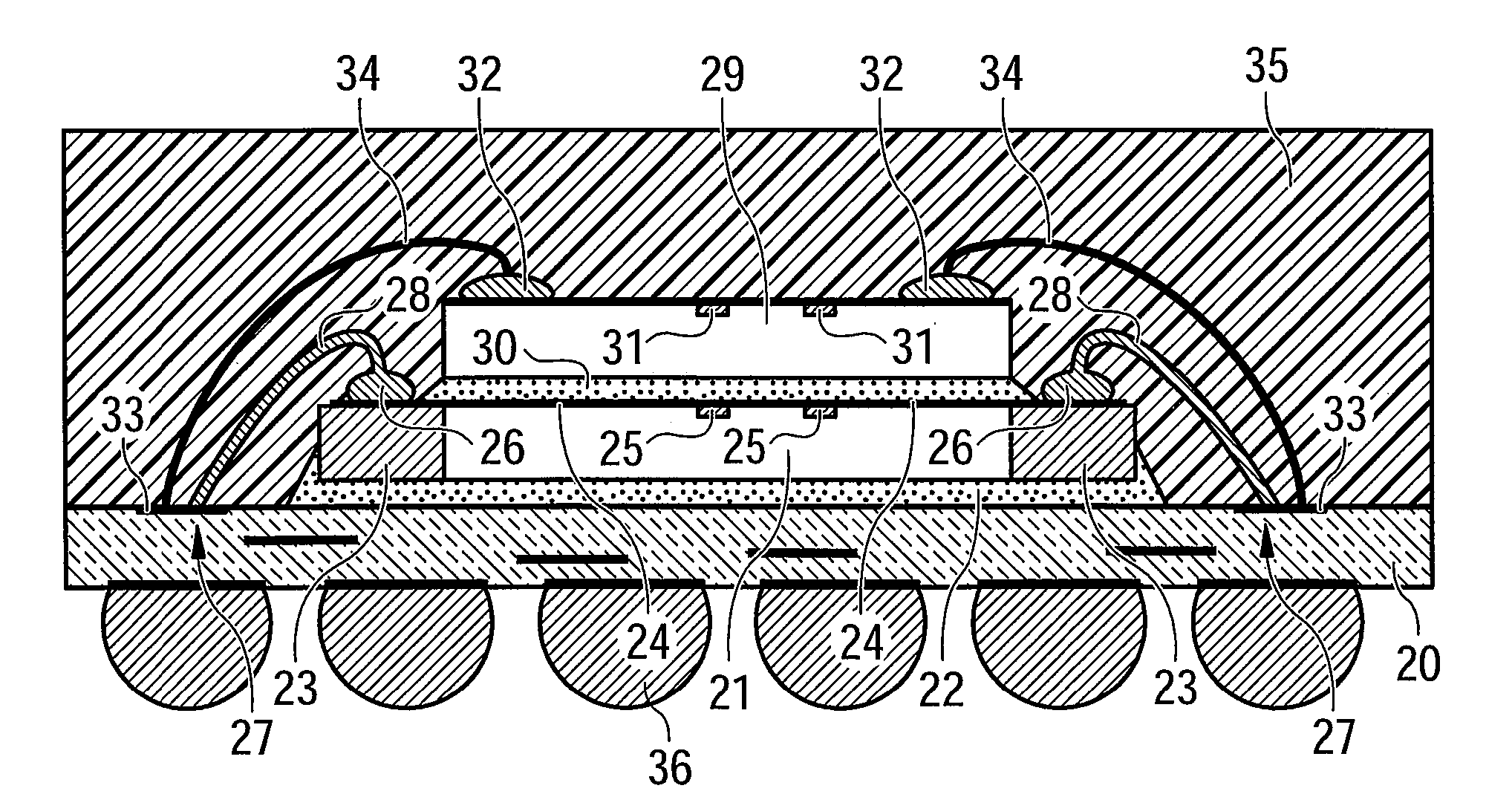

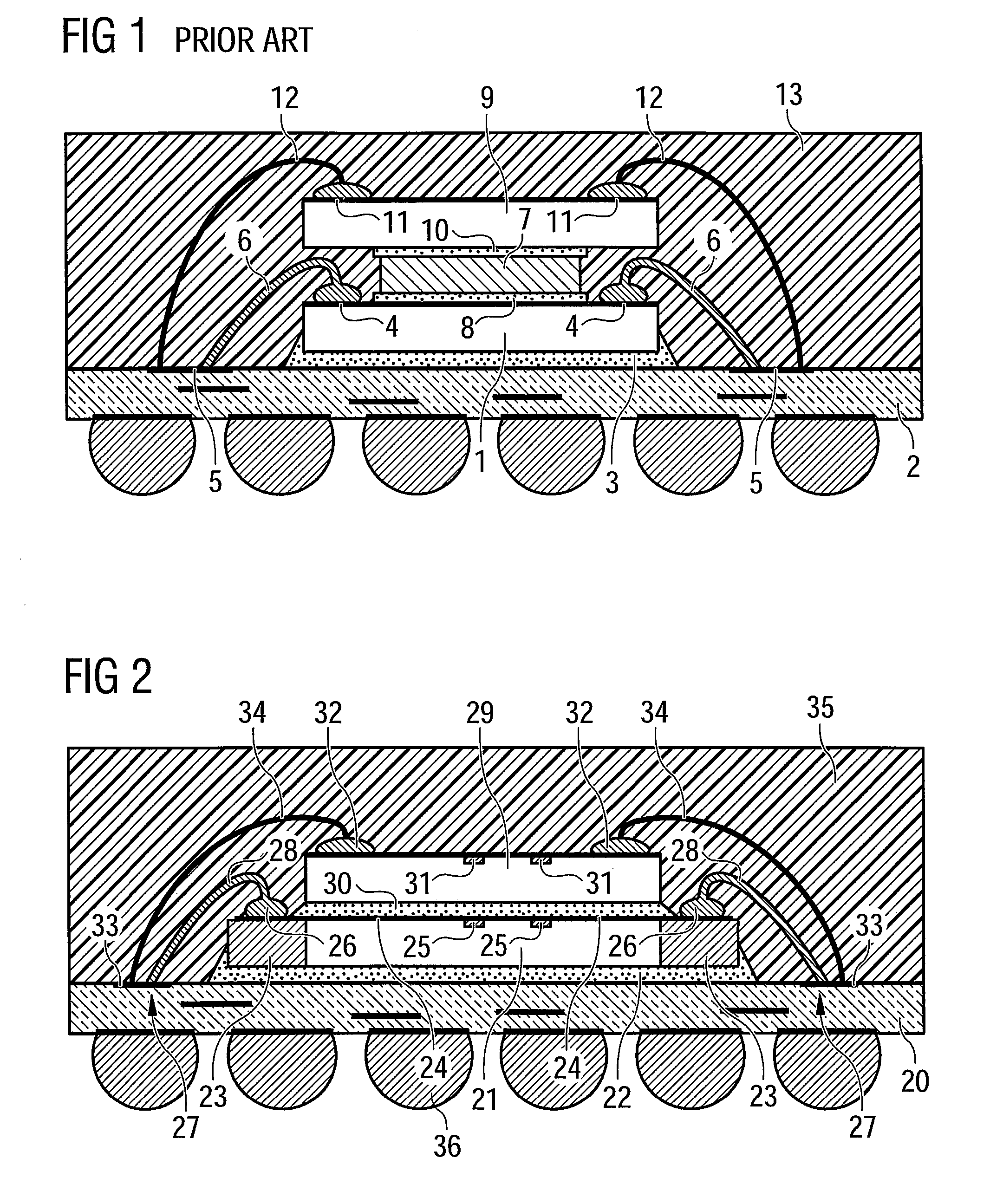

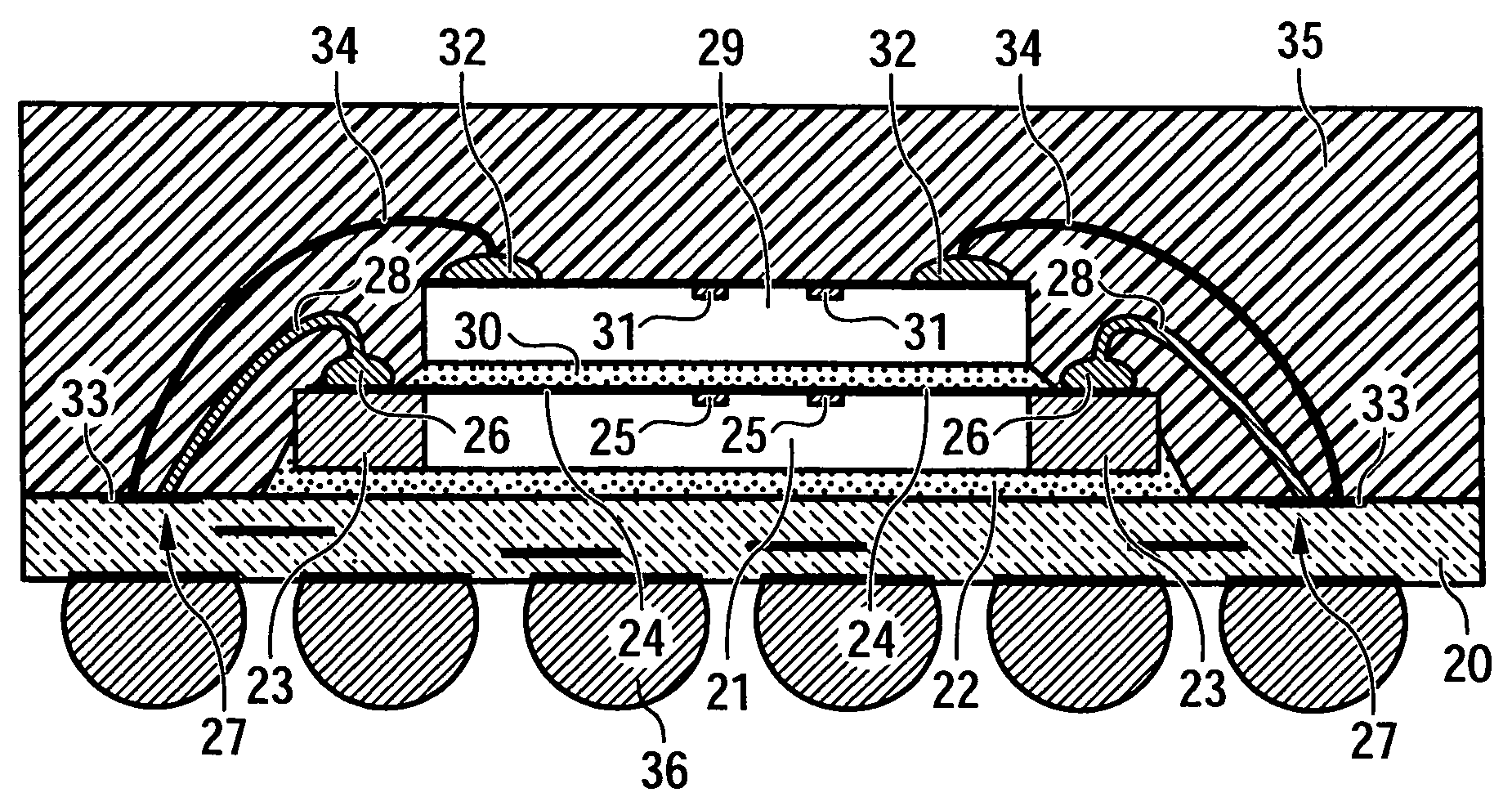

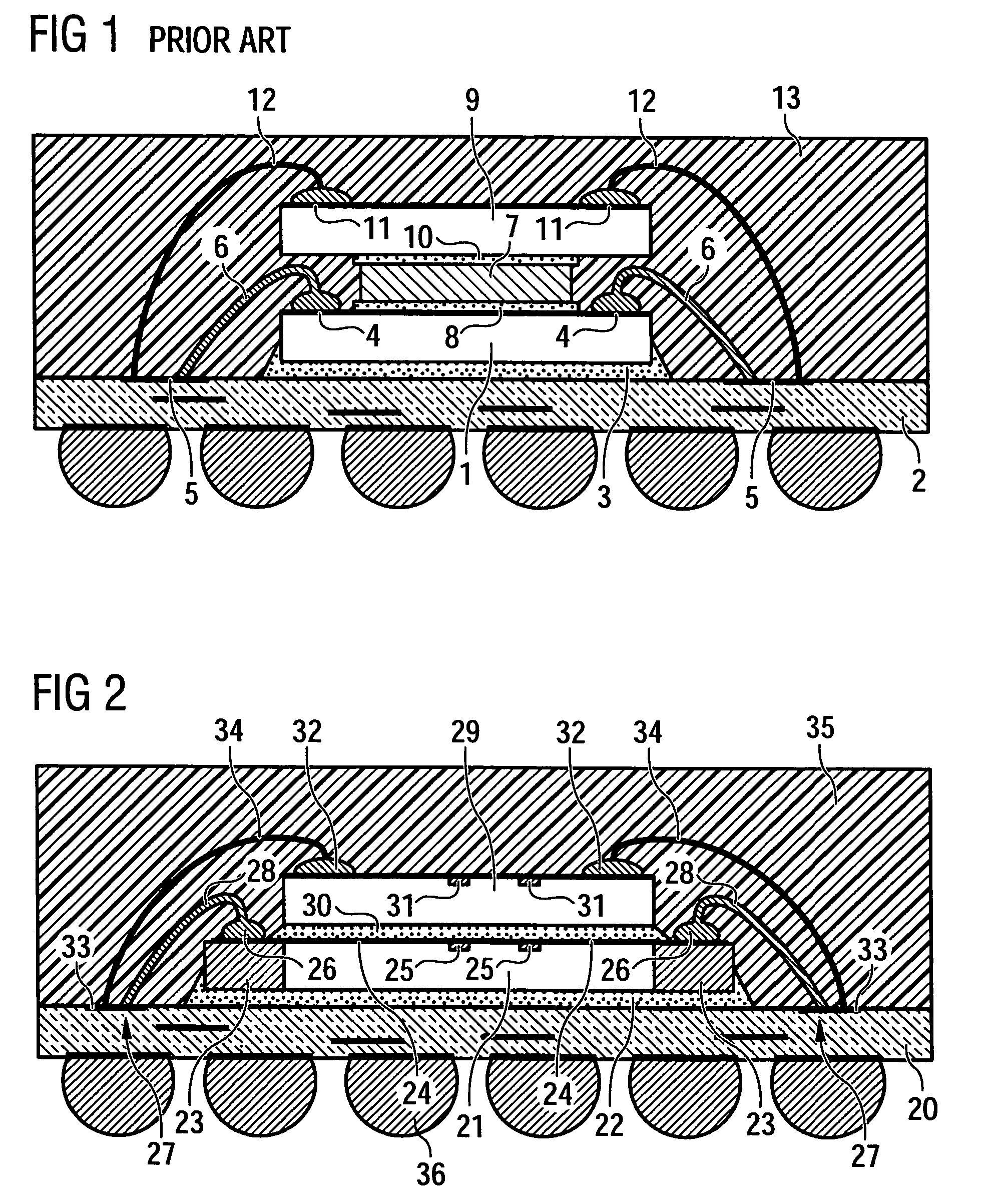

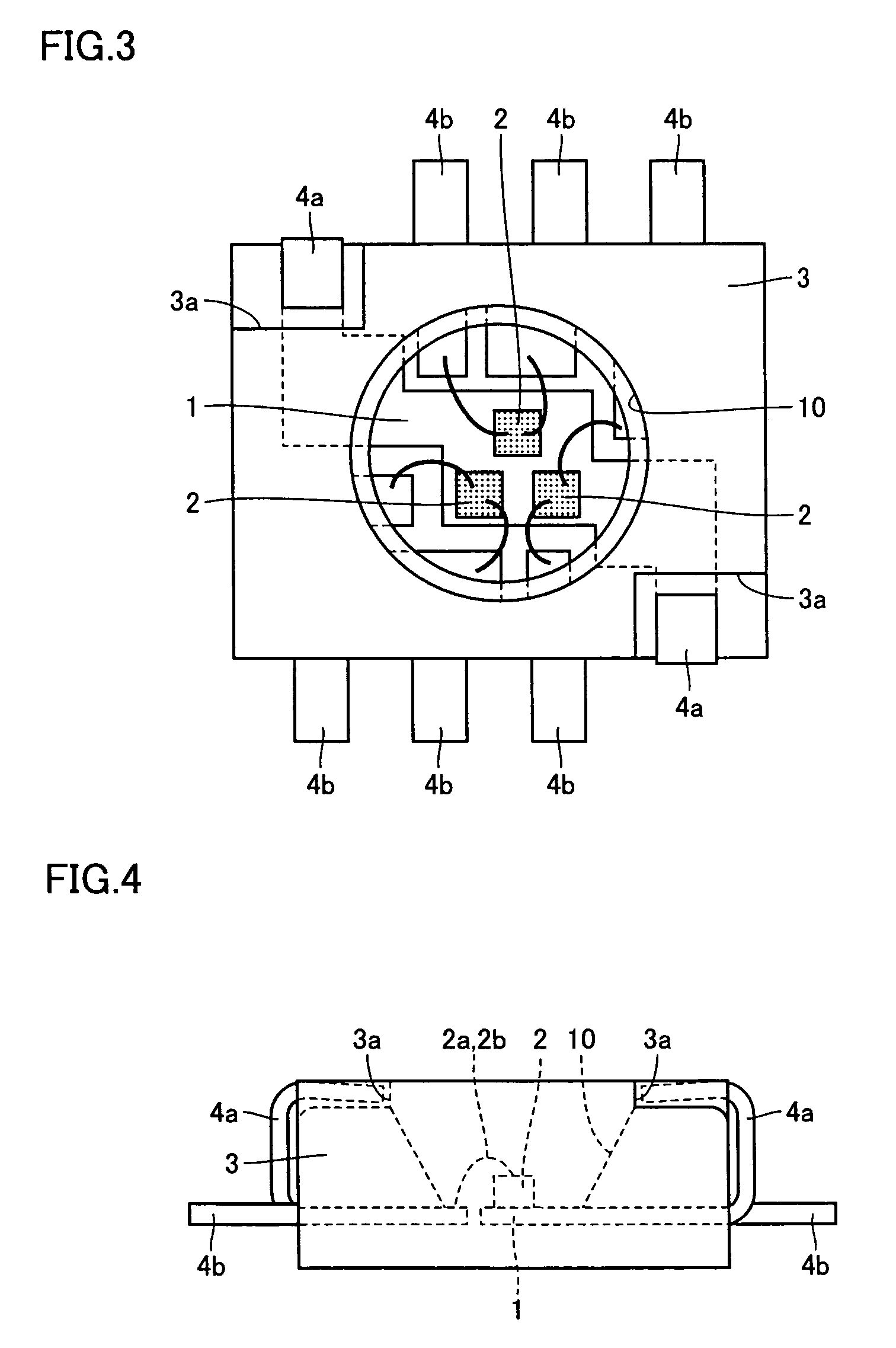

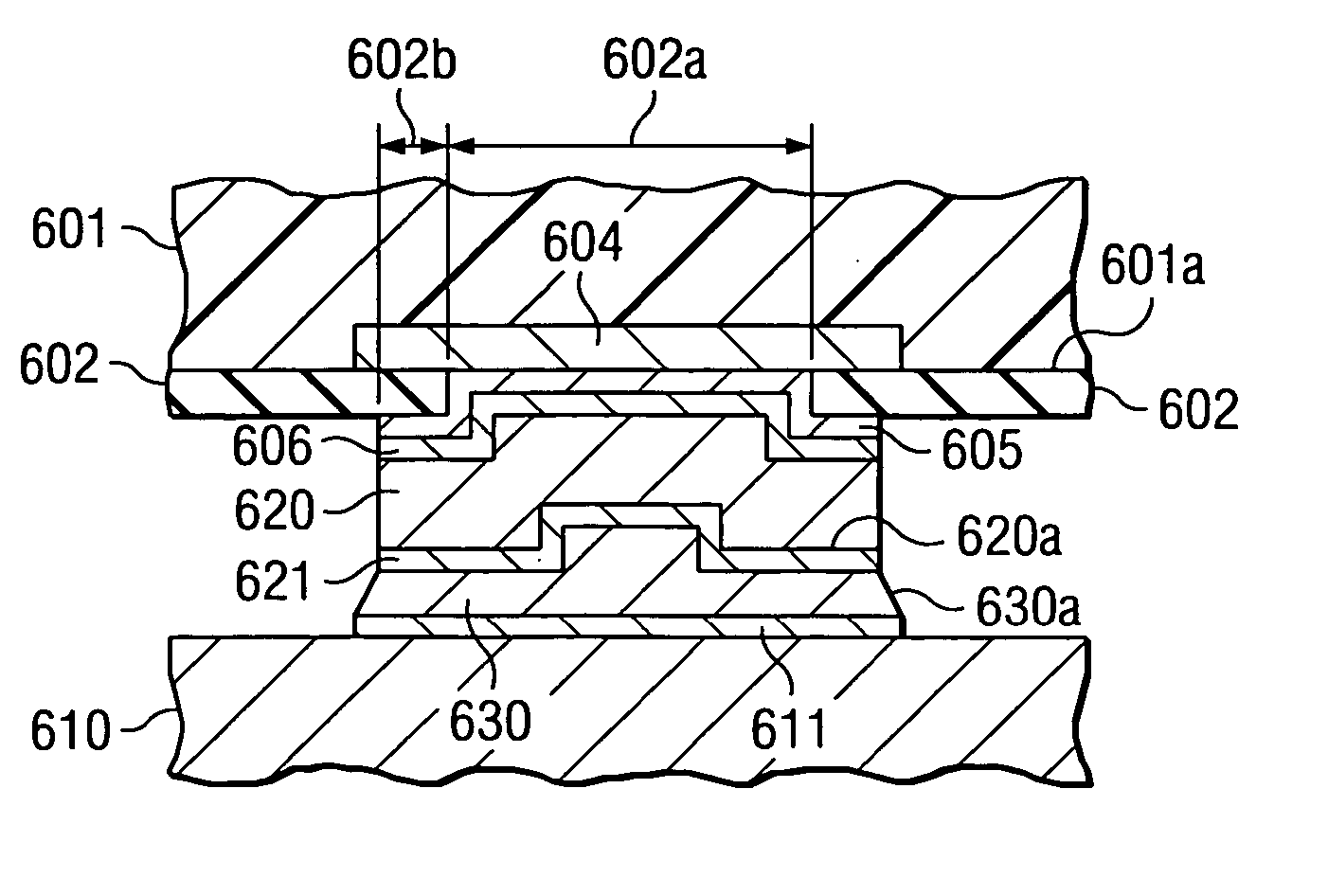

Stacked die package

InactiveUS20060220262A1Add dimensionImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSolder paste

A stacked die package includes a substrate or interposer board that includes a contact area on a top surface and landing pads surrounding the contact area. Solder pads are disposed on an opposite side of the substrate. The solder pads are electrically connected with the landing pads by inner board wiring. A reconstituted die, which includes a die surrounded by a frame, is mounted over the substrate. A top die is mounted over the reconstituted die. Both the reconstituted die and the top die are electrically connected to the substrate, e.g., by wire bonds.

Owner:POLARIS INNOVATIONS

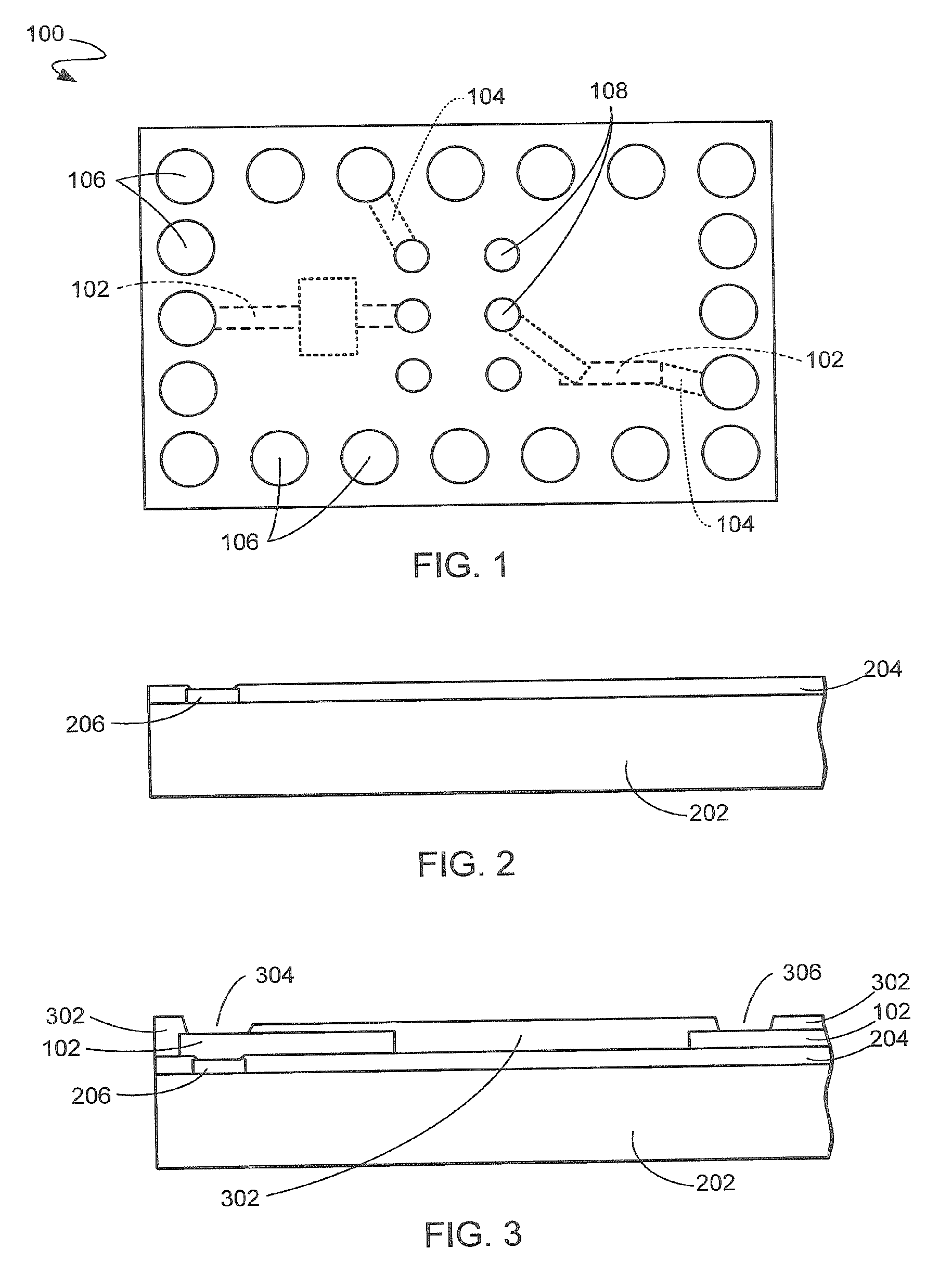

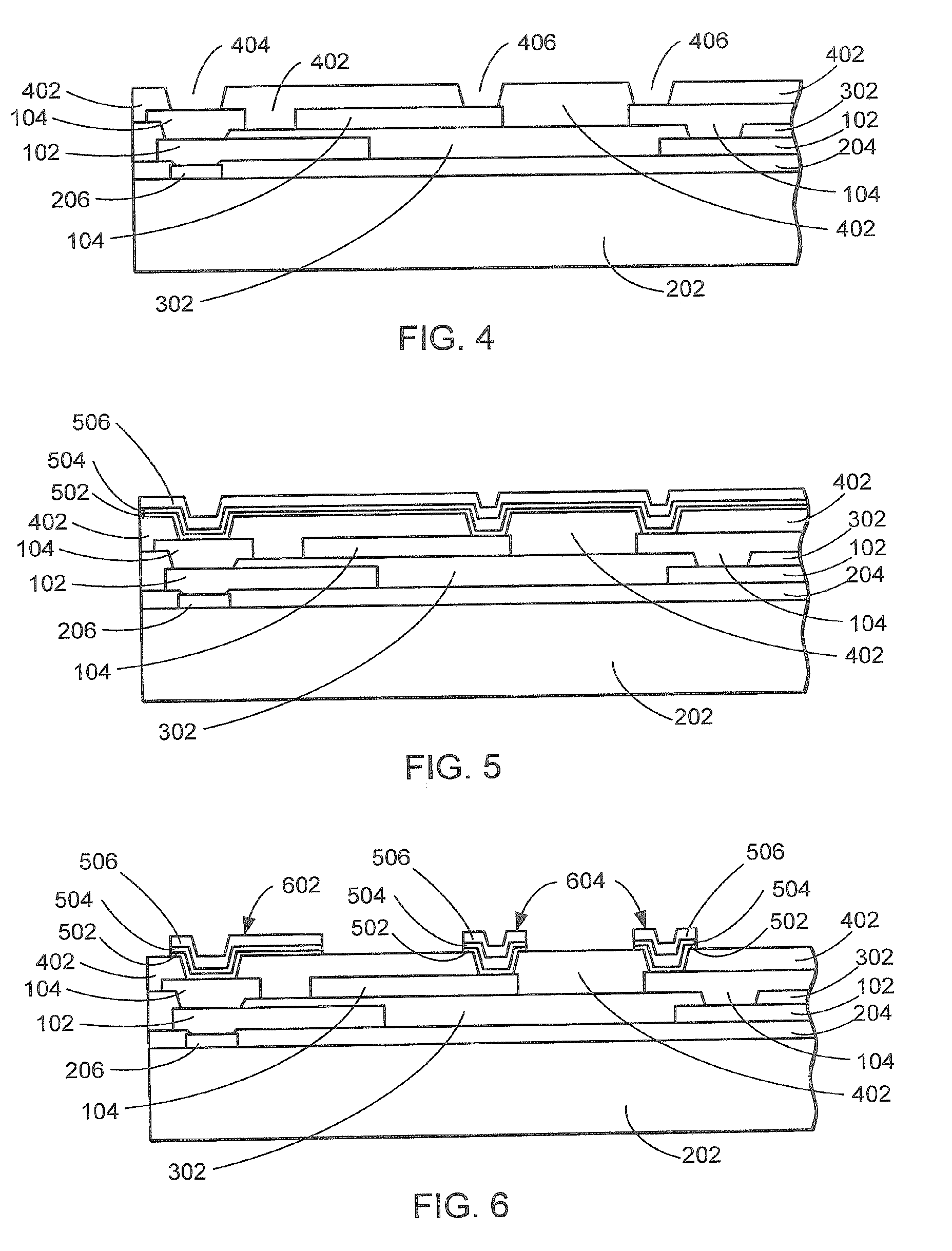

Integrated circuit solder bumping system

ActiveUS20070069346A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerInsulation layer

An integrated circuit solder bumping system provides a substrate and forms a redistribution layer on the substrate. An insulation layer is formed on the redistribution layer. The insulation layer has a plurality of openings therethrough. A first UBM layer of titanium is deposited on the insulation layer and in the openings therethrough. A second UBM layer of chromium / copper alloy is deposited on the first UBM layer. A third UBM layer of copper is deposited on the second UBM layer. UBM pads of at least two different sizes are formed from the UBM layers. Solder paste is printed over at least some of the UBM pads. The solder paste is reflowed to form at least smaller solder bumps on at least some of the UBM pads. Bigger solder bumps are formed on at least some of the UBM pads.

Owner:JCET SEMICON (SHAOXING) CO LTD

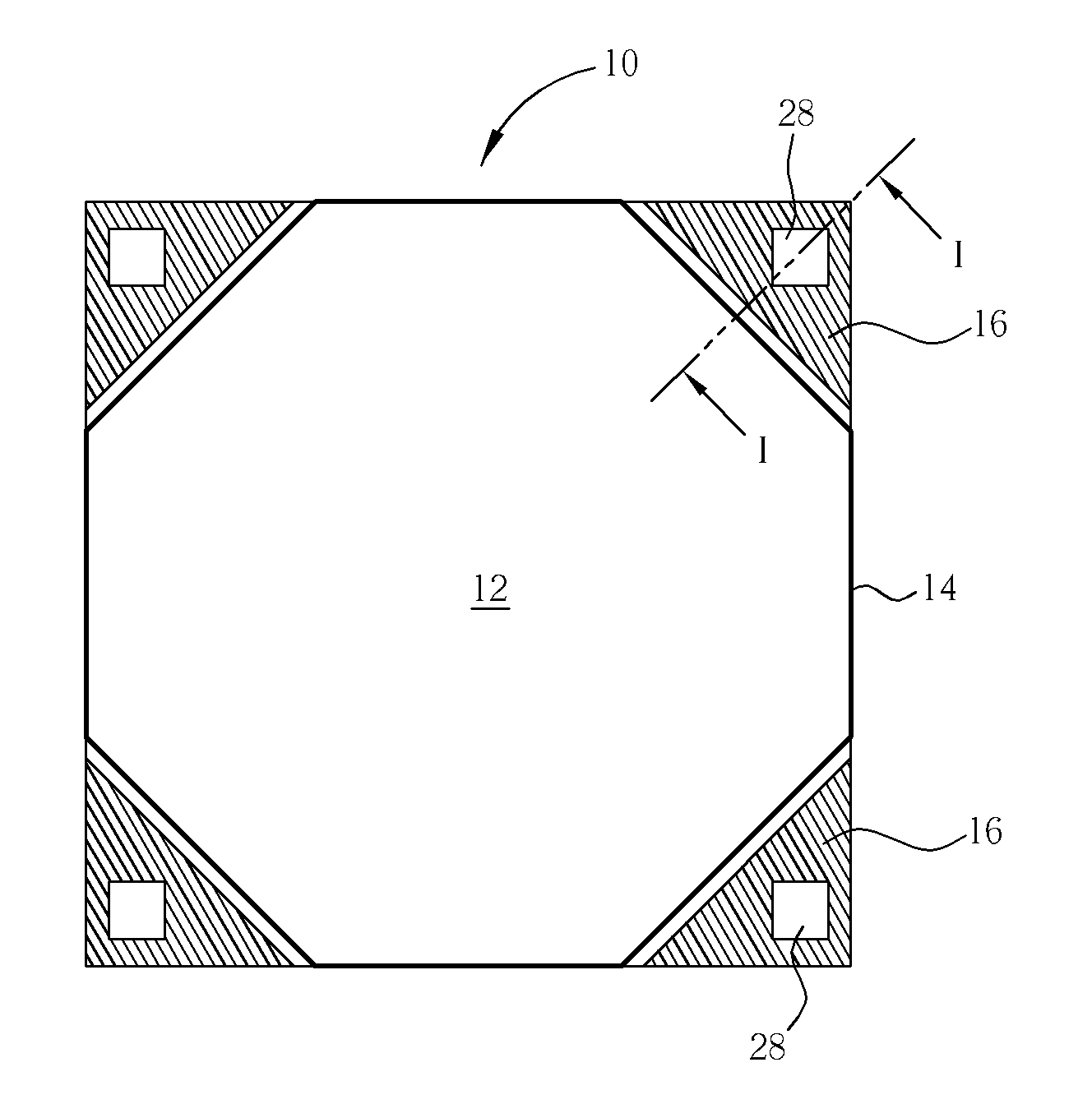

Chip carrier for semiconductor chip

ActiveUS7102239B2Reduce formationInhibition effectSemiconductor/solid-state device detailsSolid-state devicesSolder maskSemiconductor chip

A chip carrier for a semiconductor chip is provided. A plurality of solder pads for bump soldering are formed on a chip mounting surface of the chip carrier, to allow a flip chip to be mounted and electrically connected to the chip carrier. A solder mask layer is formed on the chip carrier, wherein a plurality of openings are provided in the solder mask layer to expose the solder pads, and an outwardly opening extended portion is formed respectively from the openings corresponding to the solder pads having a relatively narrower pitch therebetween, so as to prevent formation of voids during an underfill process for filing a gap between the flip chip and the chip carrier.

Owner:SILICONWARE PRECISION IND CO LTD

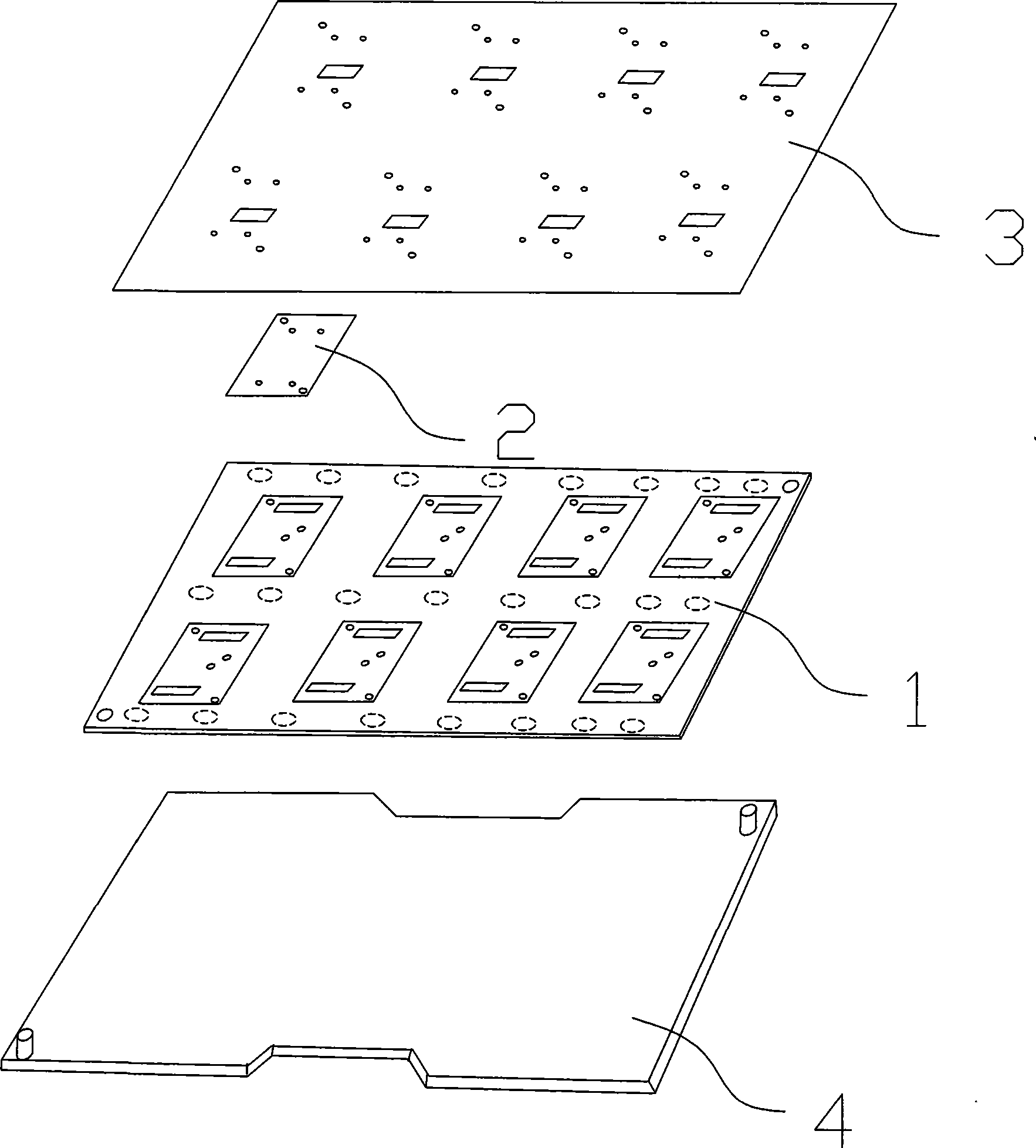

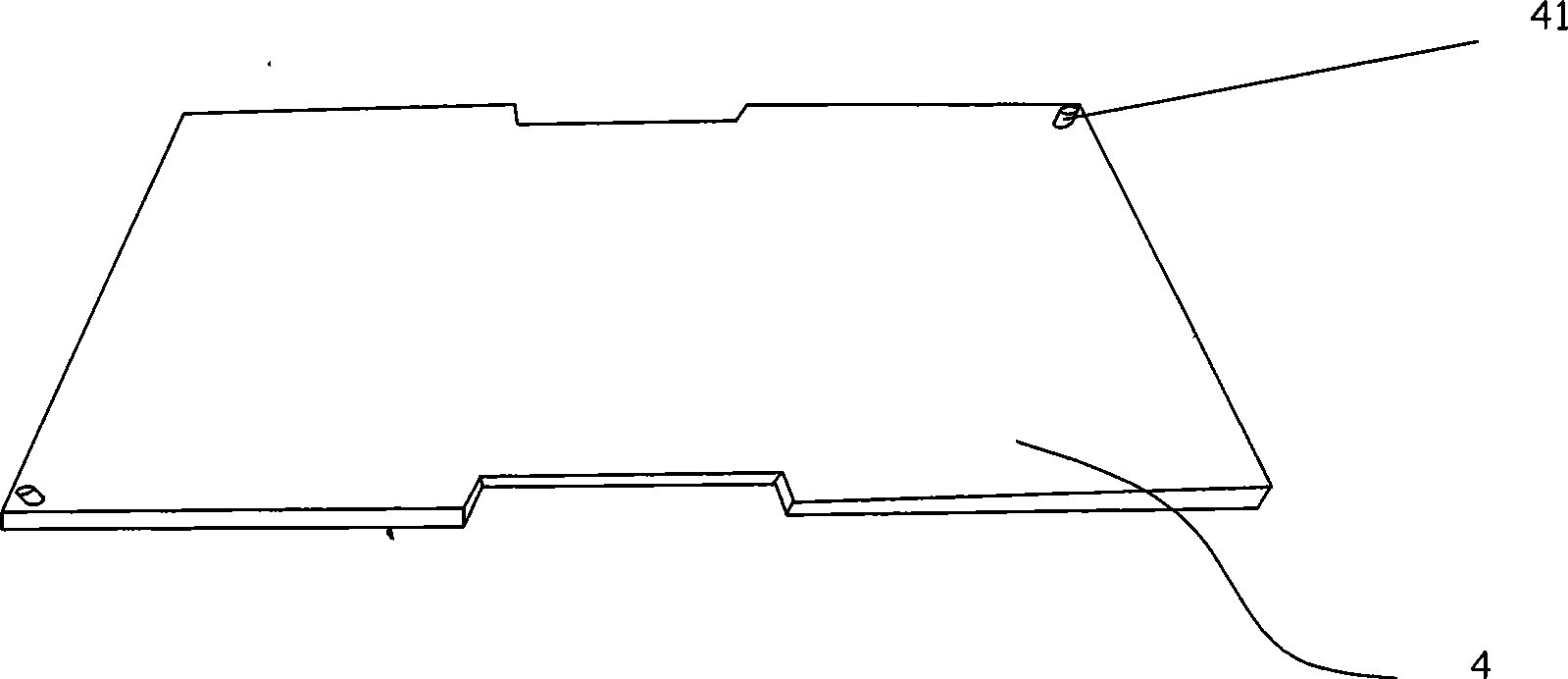

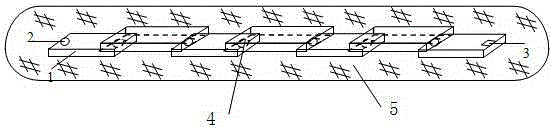

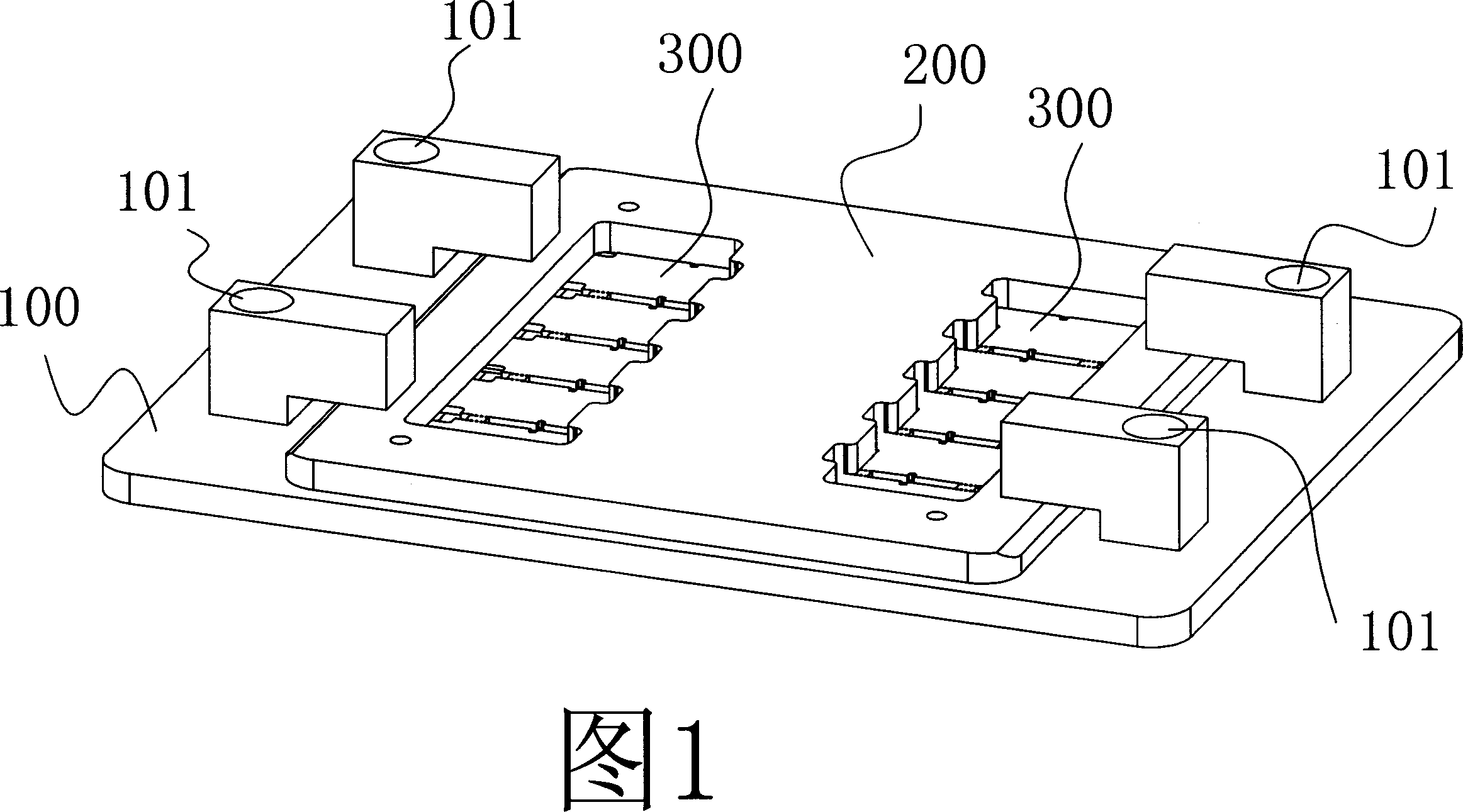

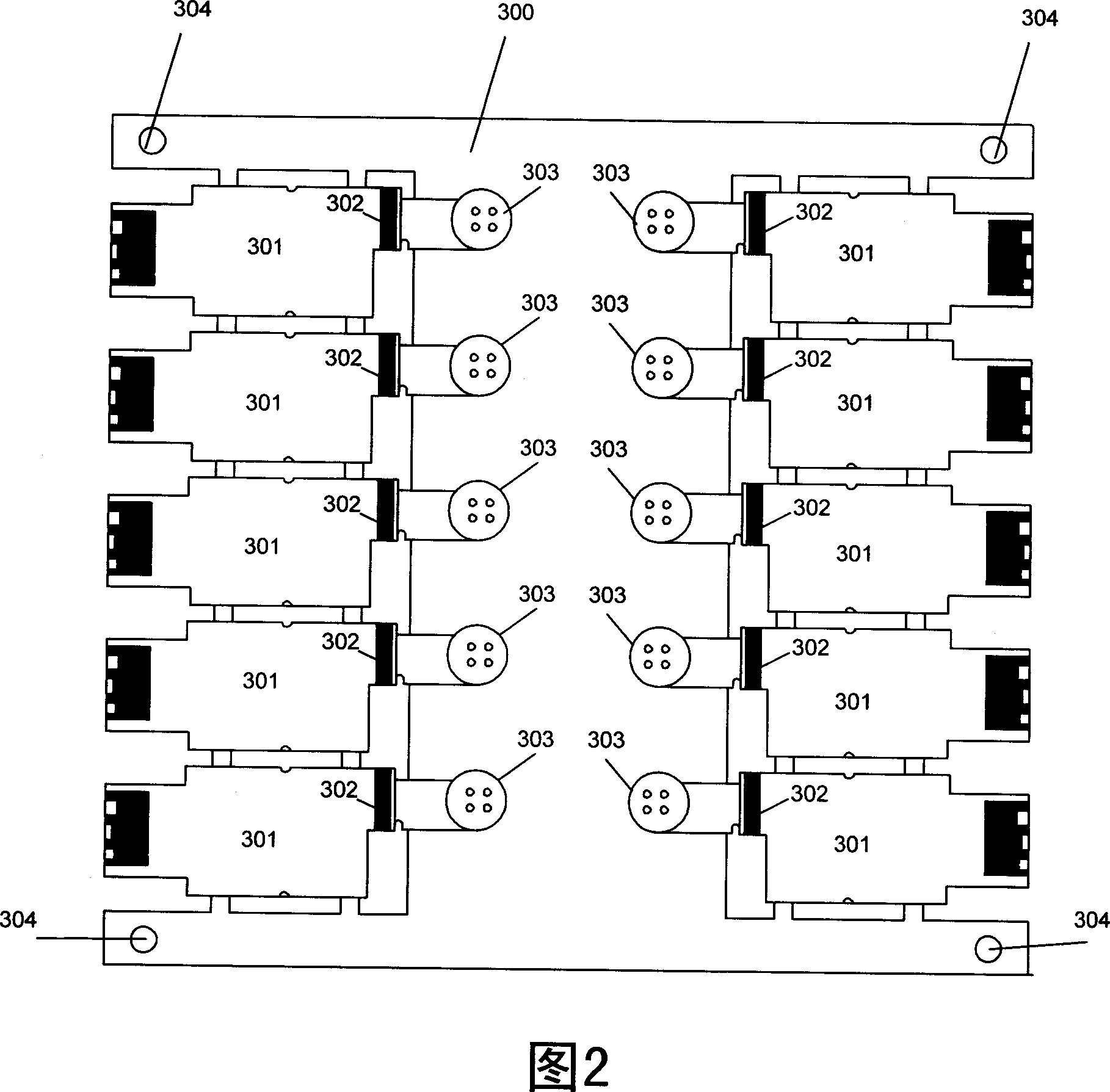

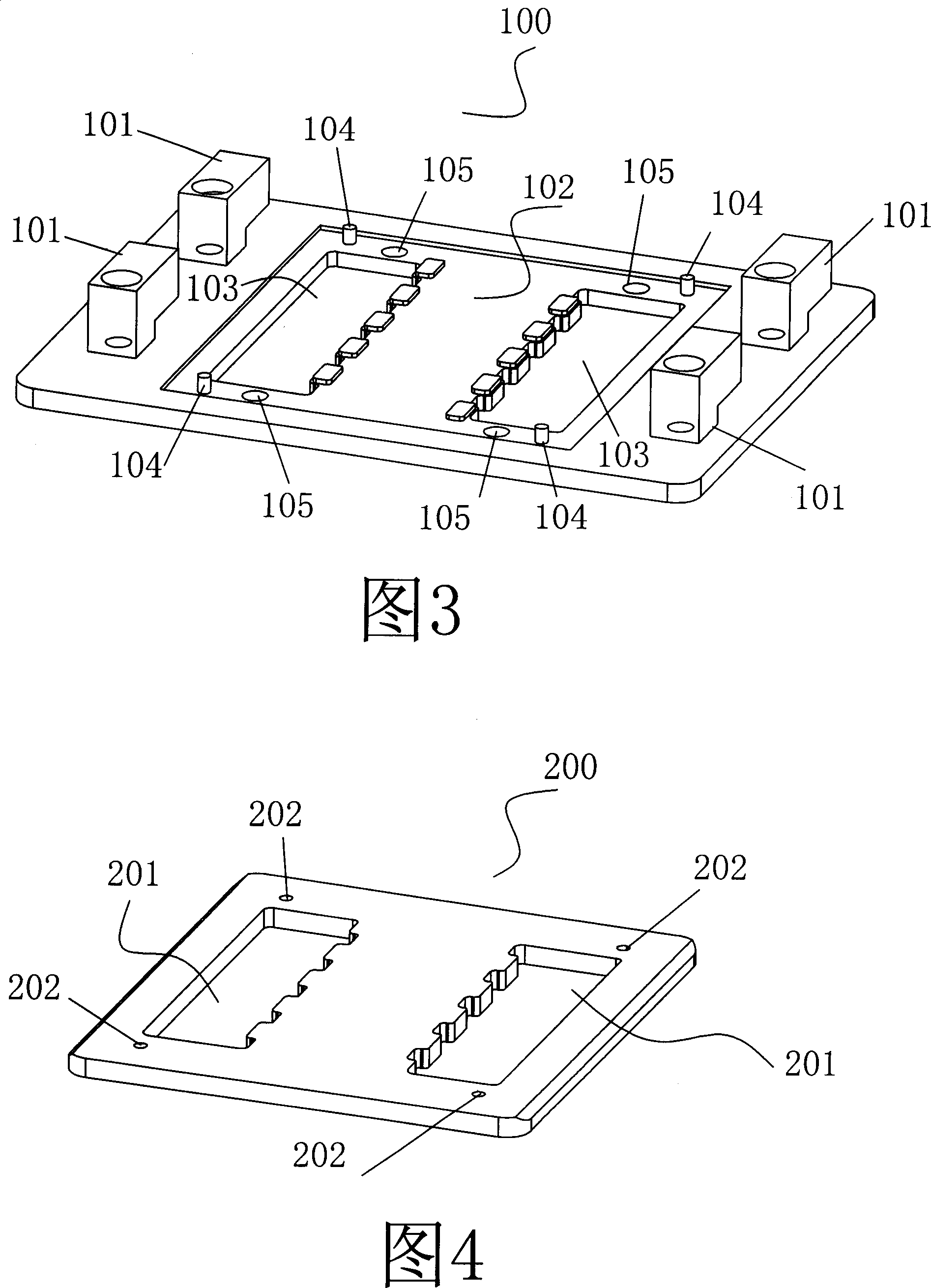

Surface mounting process for flexible circuit board and used magnetic tool and steel mesh

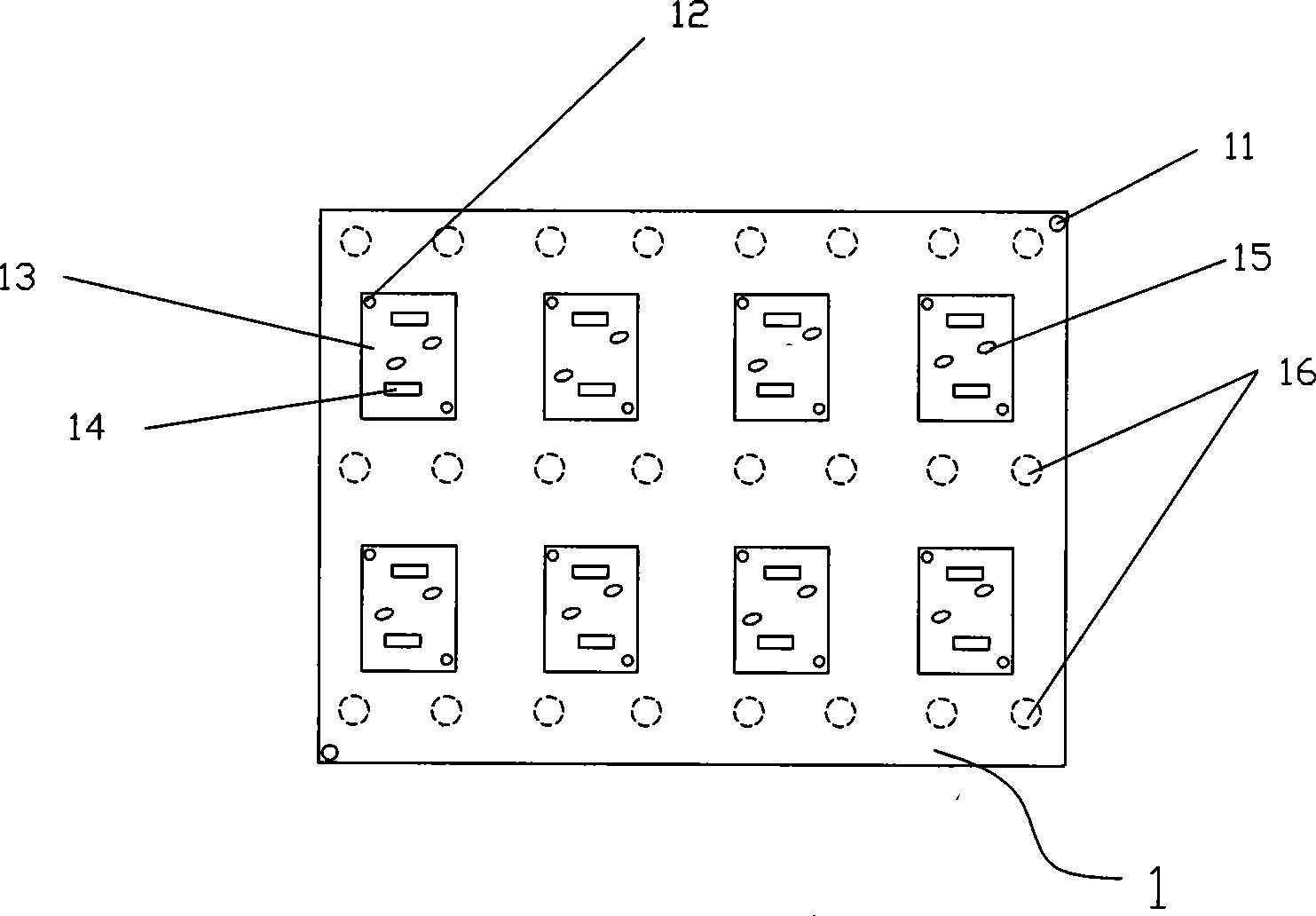

ActiveCN101384136AExtended service lifeLow costPrinted circuit assemblingManufacturing technologyFlexible circuits

The invention relates to the manufacturing technology of printed wiring board, in particular to a flexible printed circuit (FPC) surface mount technology (SMT) as well as a magnetic tool and a steel mesh which are used for the FPCSMT. The magnetic tool comprises a buckle cover board and a magnetic carrying tray, wherein the magnetic carrying tray is a magnetic baseplate, the buckle cover board is a metal sheet which can be attracted by the magnetic baseplate, and the buckle cover board is provided with a slotted hole used for the solder paste printing and the surface mounting of a FPC. The invention is characterized in that the buckle cover board is a steel sheet which can be attracted by the magnetic baseplate, the step layer which is the same as the buckle cover board in shape is etched on the magnetic carrying tray, the depth of the step layer is the same as the thickness of the steel sheet; before the circuit board printing, the magnetic carrying tray is fixed on a positioning base, and then the FPC and the buckle cover board are arranged on the magnetic carrying tray; after the accurate positioning, the FPC and the magnetic tool are taken down the positioning base to conduct the solder paste printing process, the surface mounting process and the reflow soldering process.

Owner:东莞市贞观盛智控科技有限公司

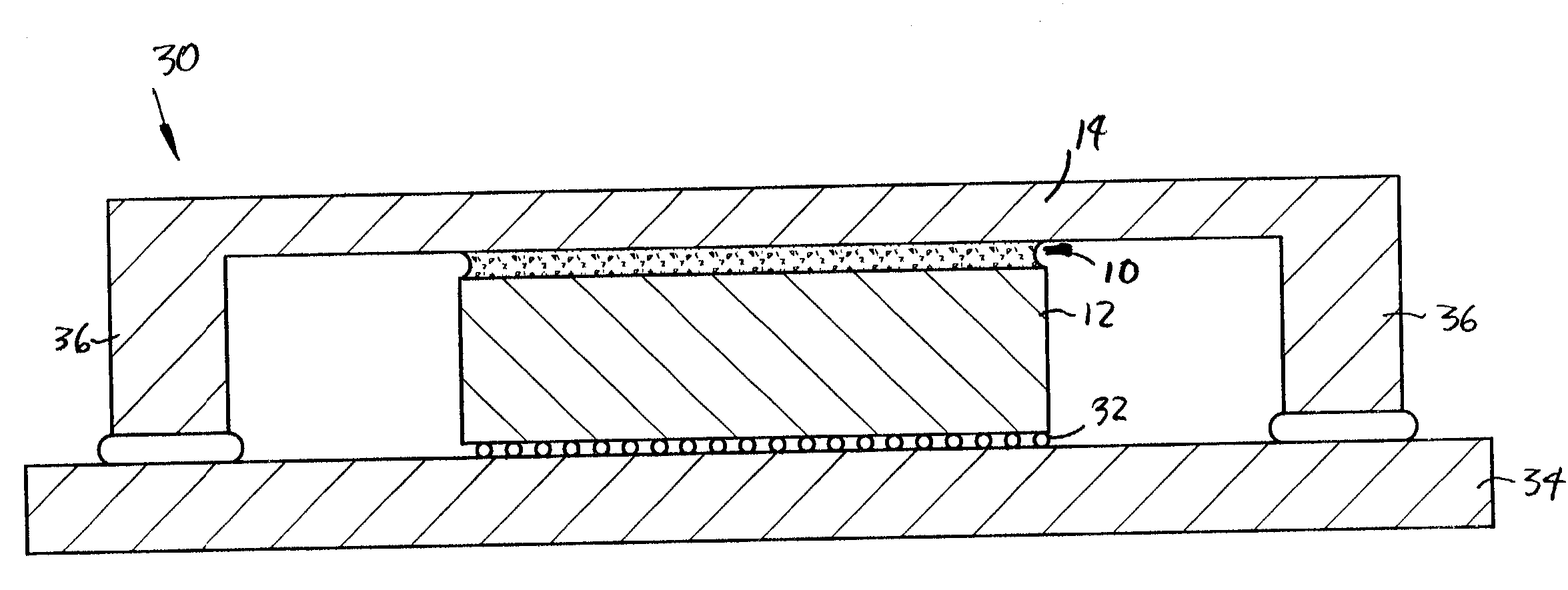

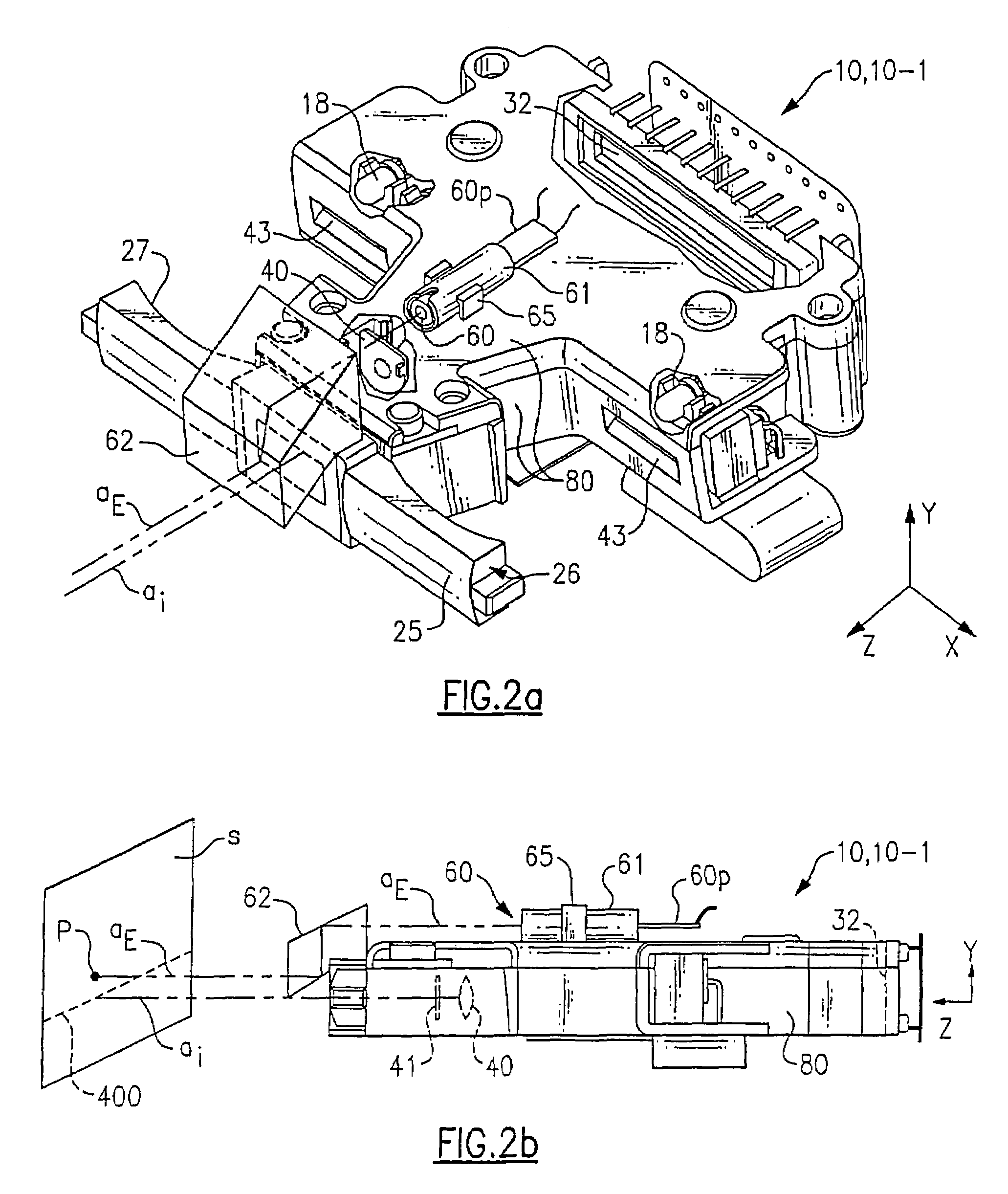

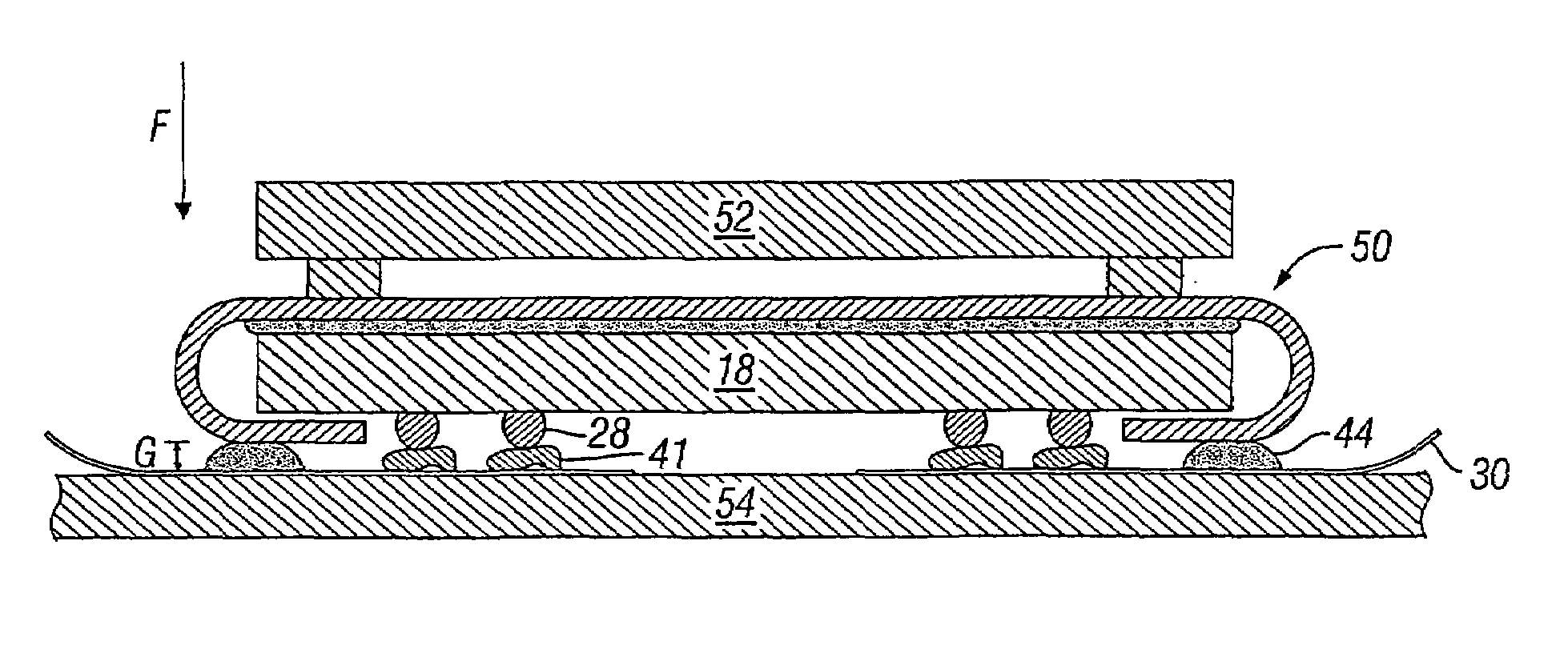

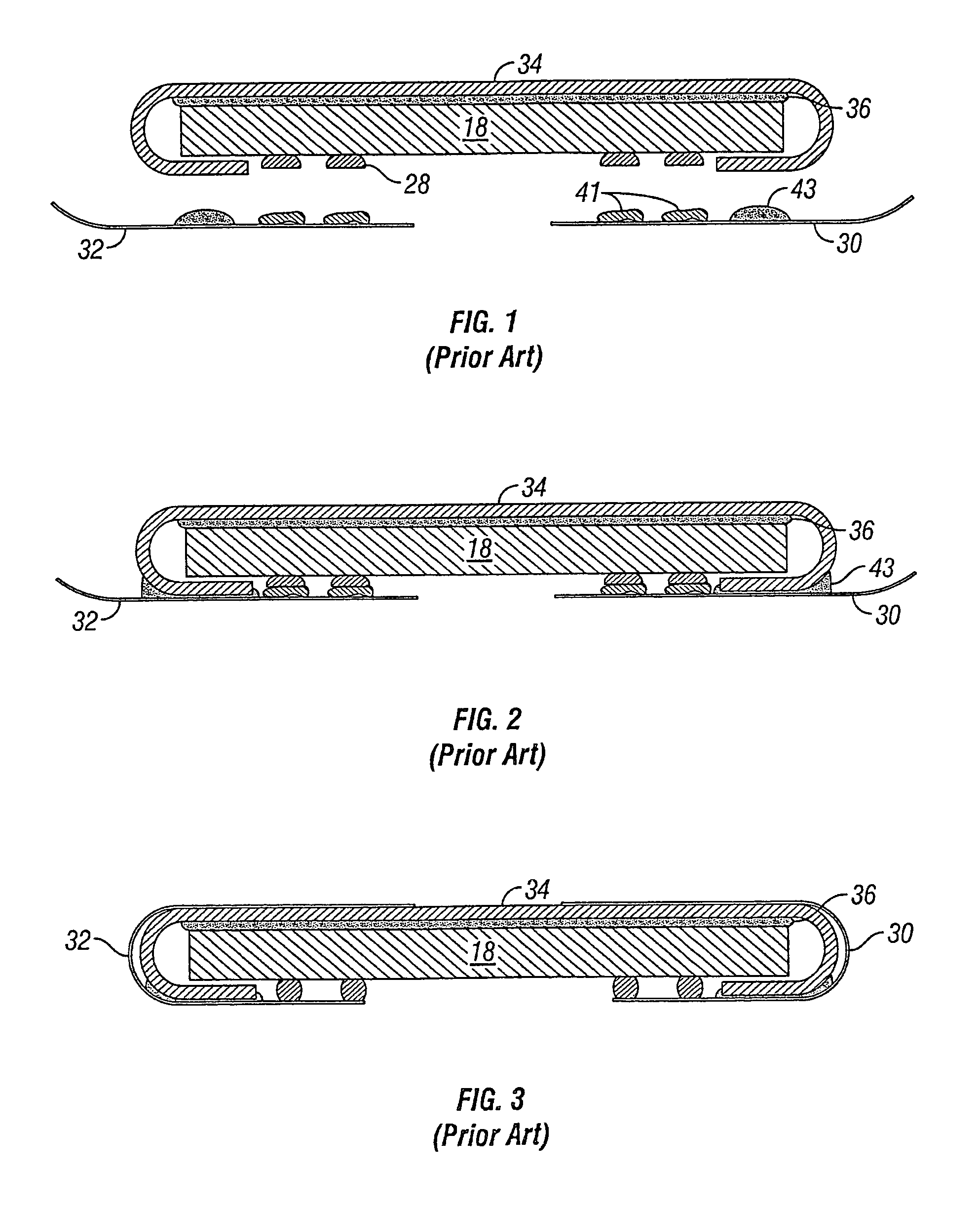

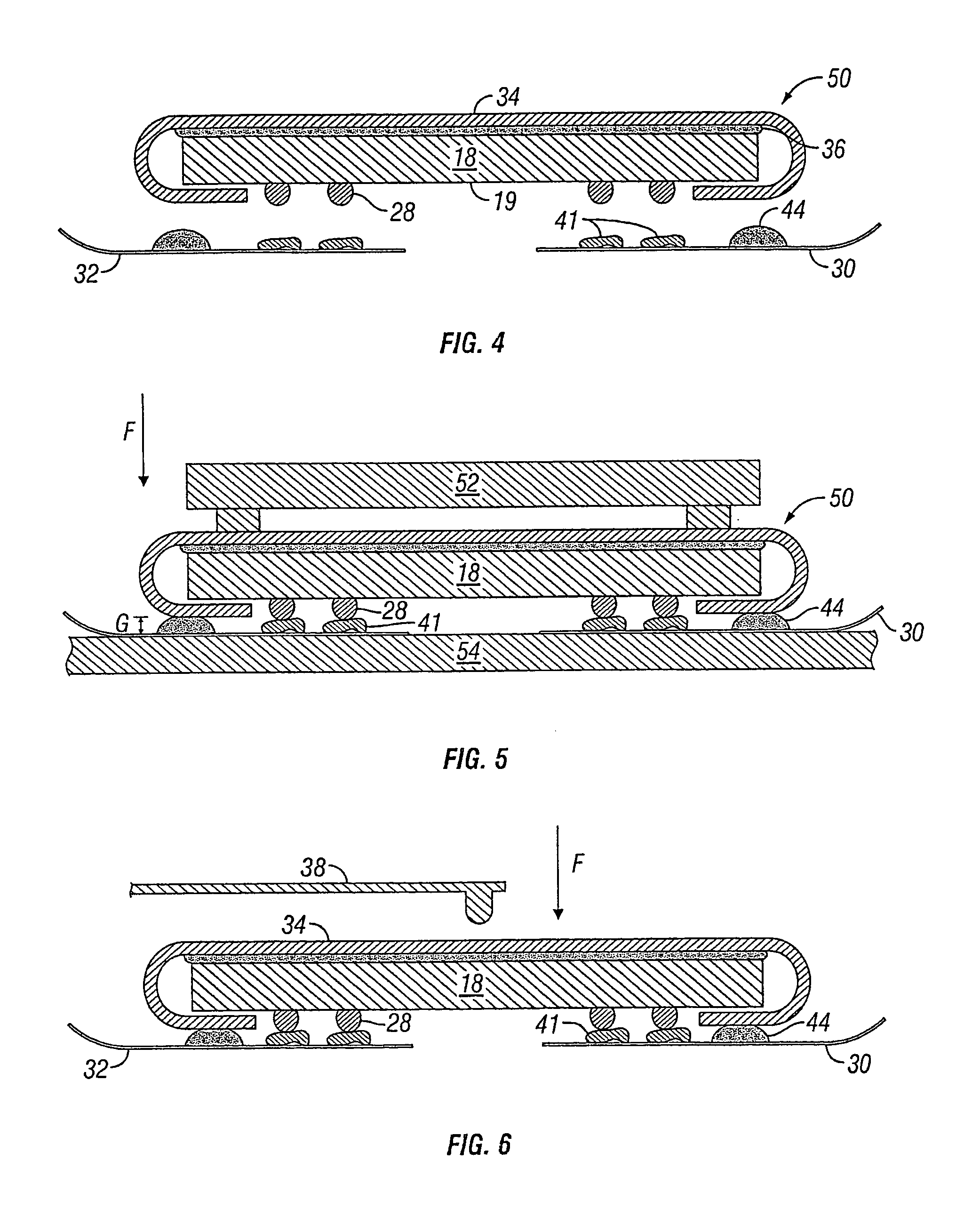

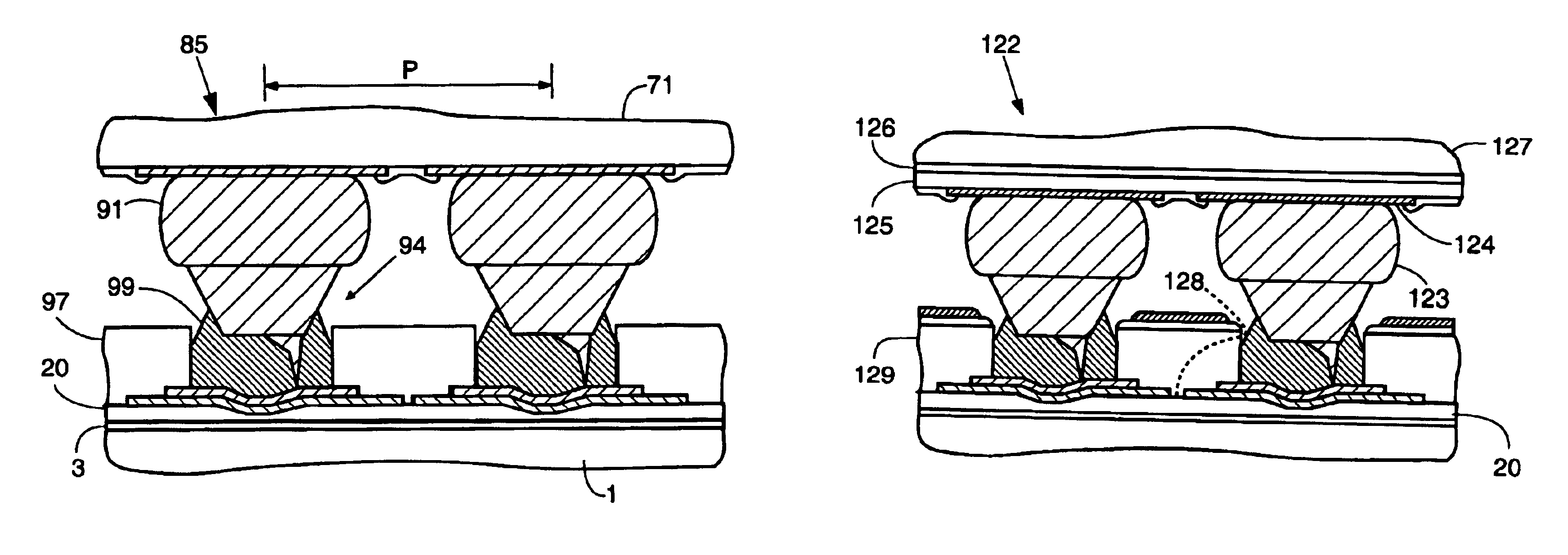

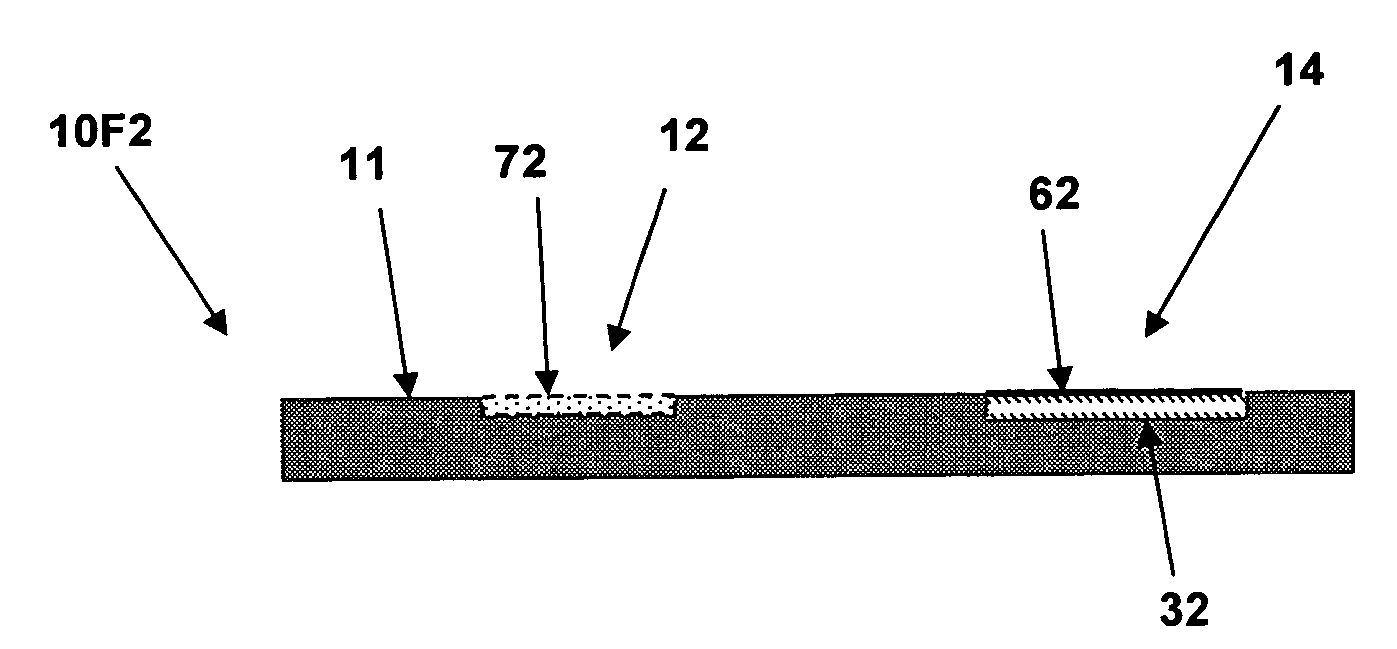

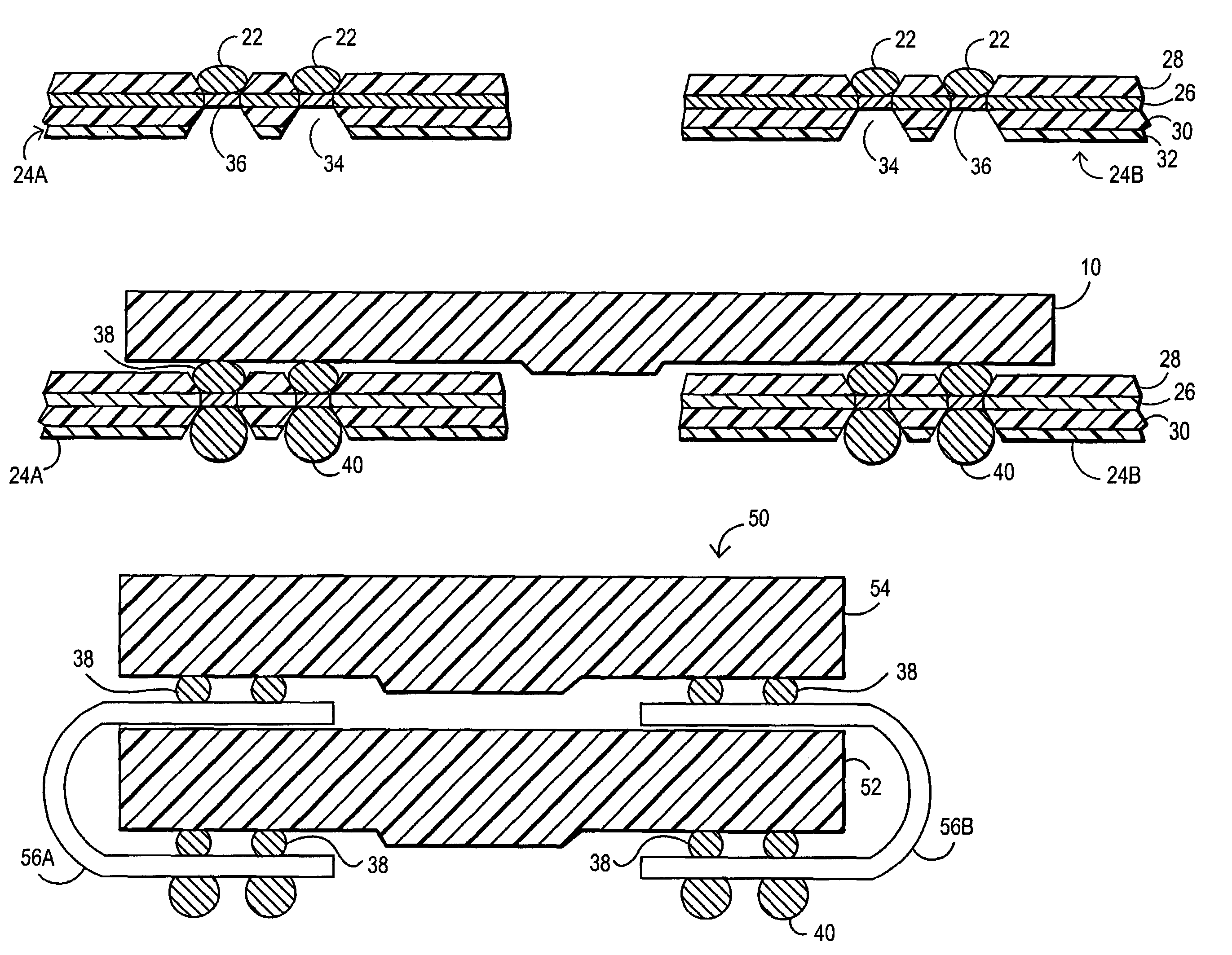

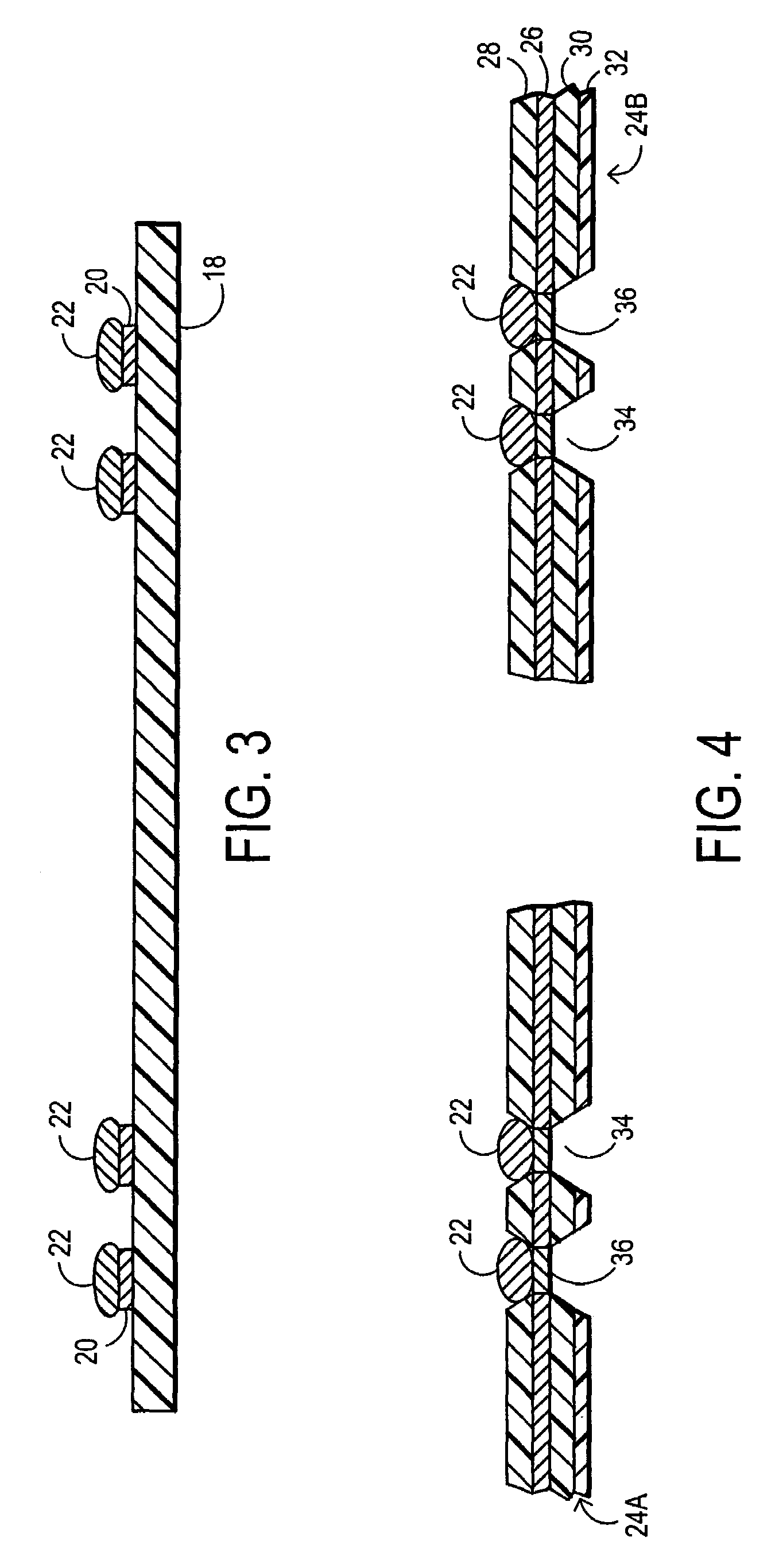

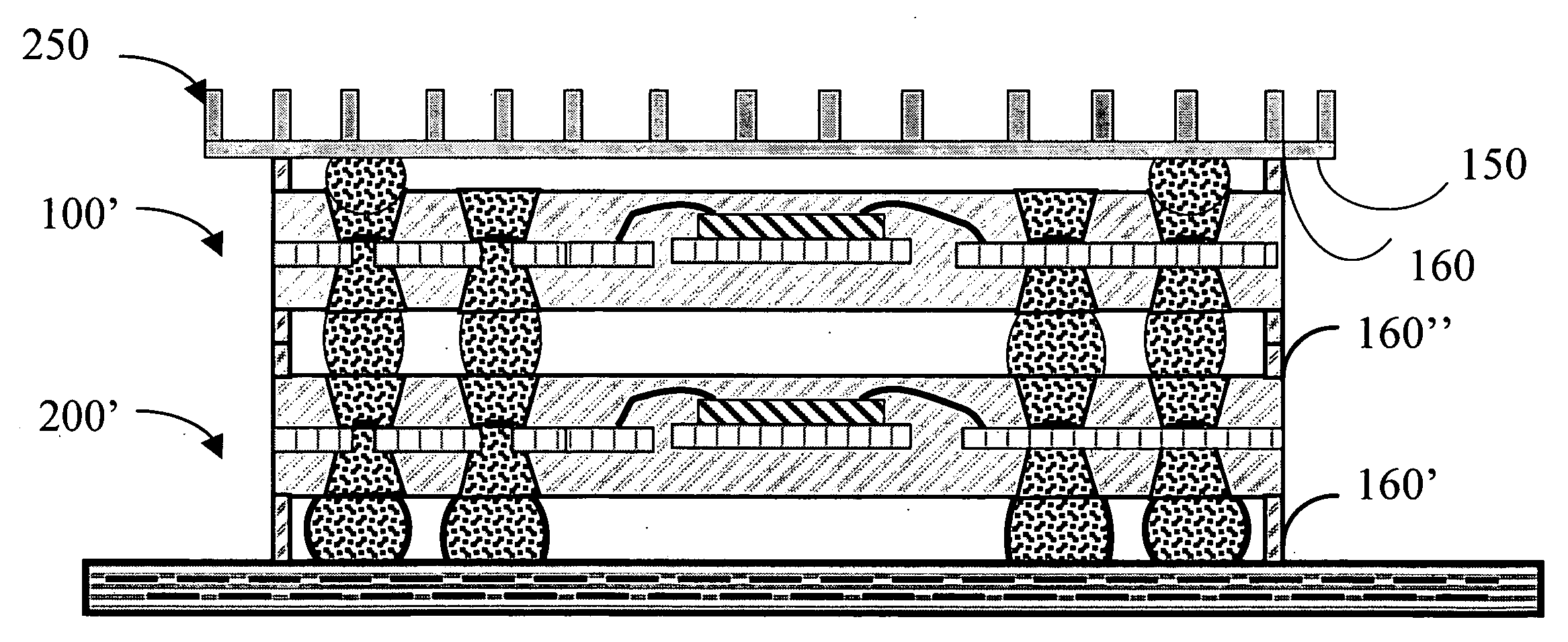

Stacked module systems and method

ActiveUS7033861B1Final product manufactureSemiconductor/solid-state device detailsAdhesiveEngineering

A combination composed from a form standard and a CSP is attached to flex circuitry. Solder paste is applied to first selected locations on the flex circuitry and adhesive is applied to second selected locations on the flex circuitry. The flex circuitry and the combination of the form standard and CSP are brought into proximity with each other. During solder reflow operation, a force is applied that tends to bring the combination and flex circuitry closer together. As the heat of solder reflow melts the contacts of the CSP, the combination collapses toward the flex circuitry displacing the adhesive as the solder paste and contacts merge into solder joints. In a preferred embodiment, the form standard will be devised of heat transference material, a metal, for example, such as copper would be preferred, to improve thermal performance. In other embodiments, the methods of the invention may be used to attach a CSP without a form standard to flex circuitry.

Owner:TAMIRAS PER PTE LTD LLC

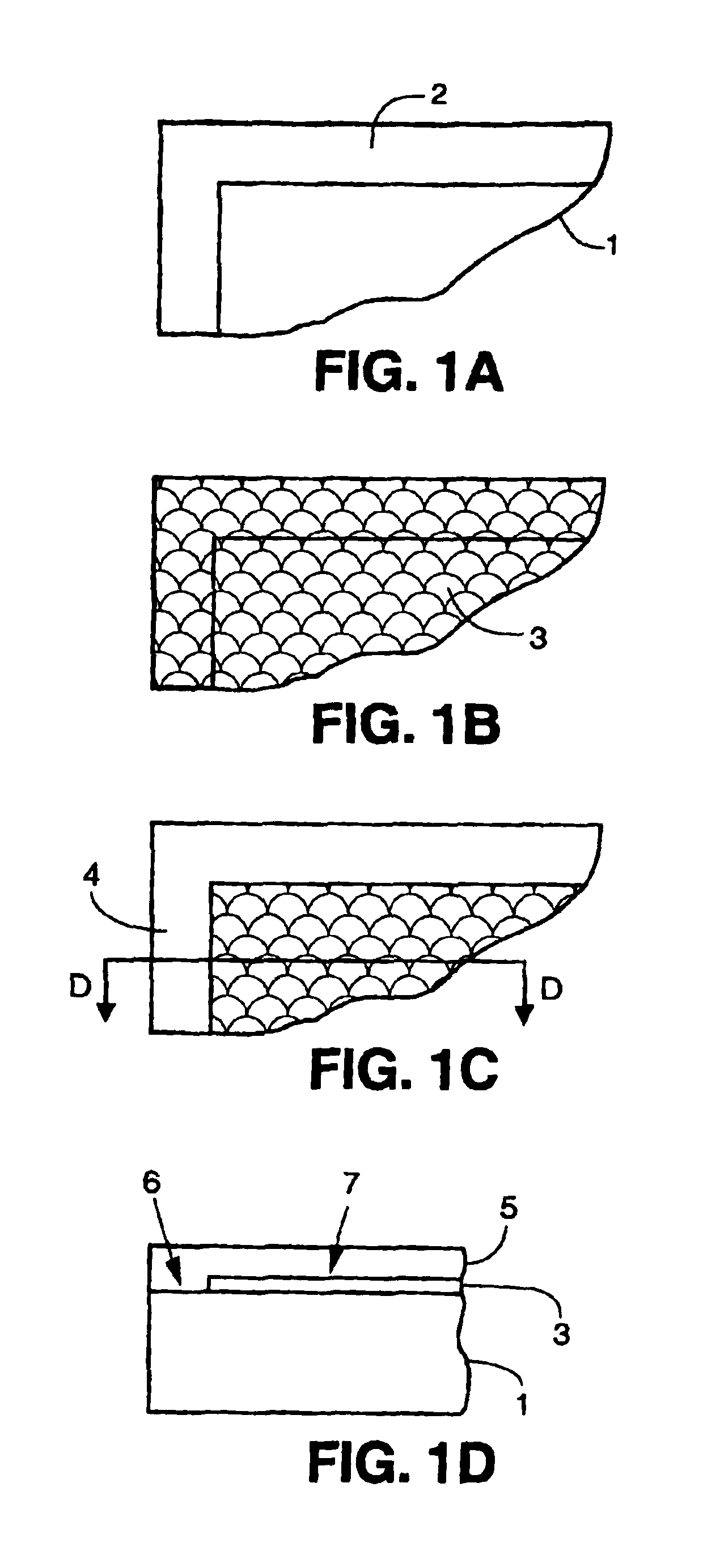

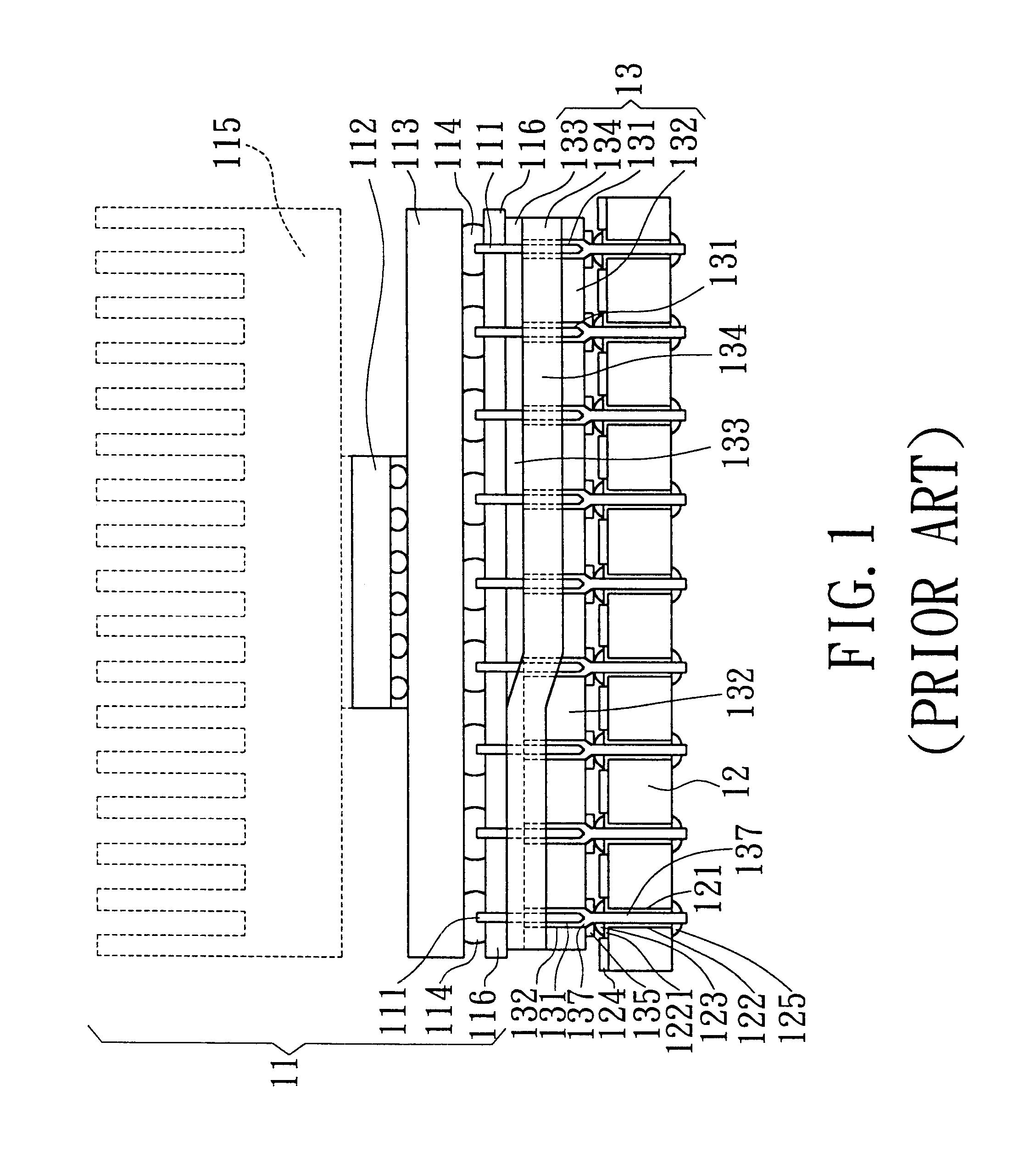

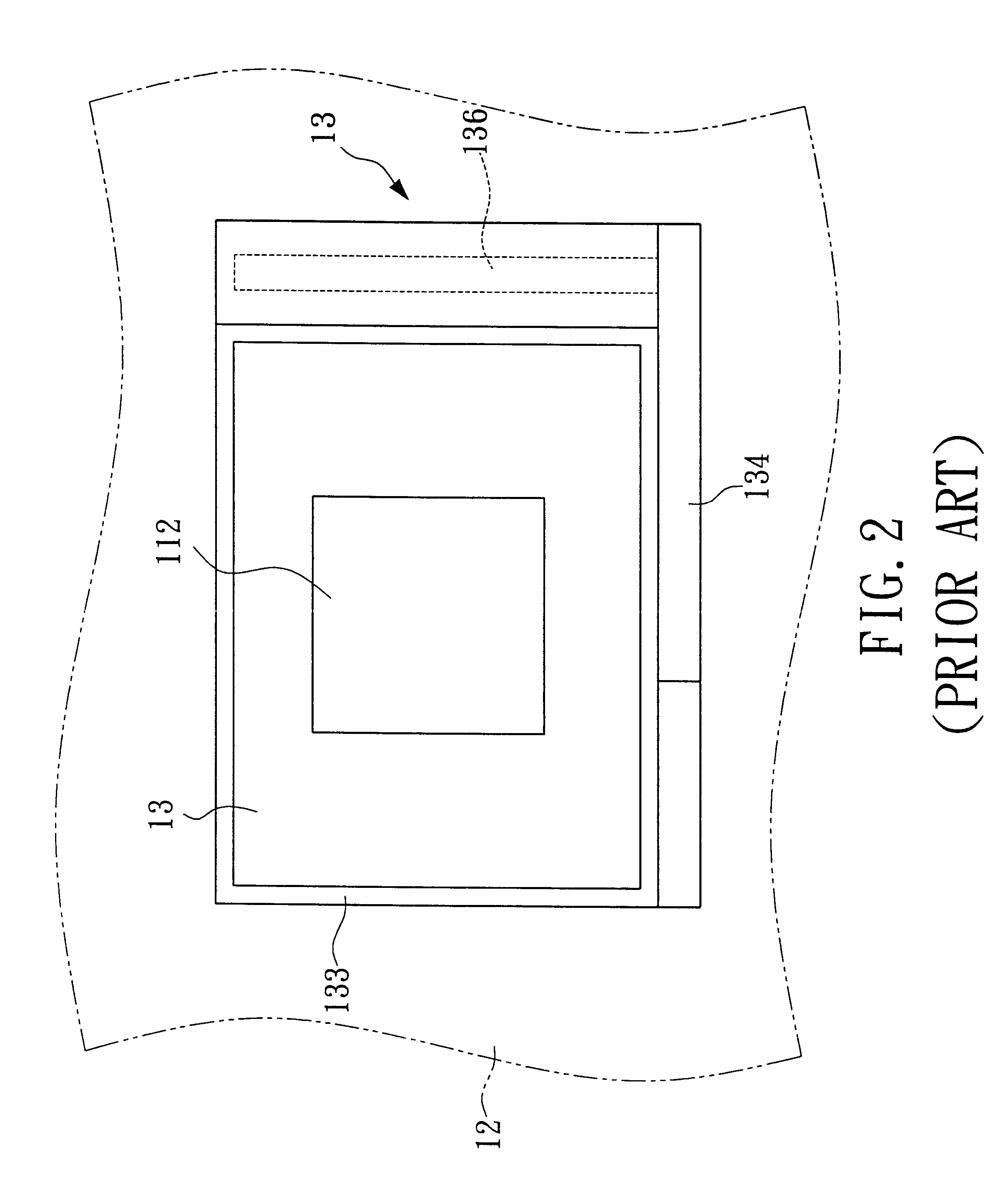

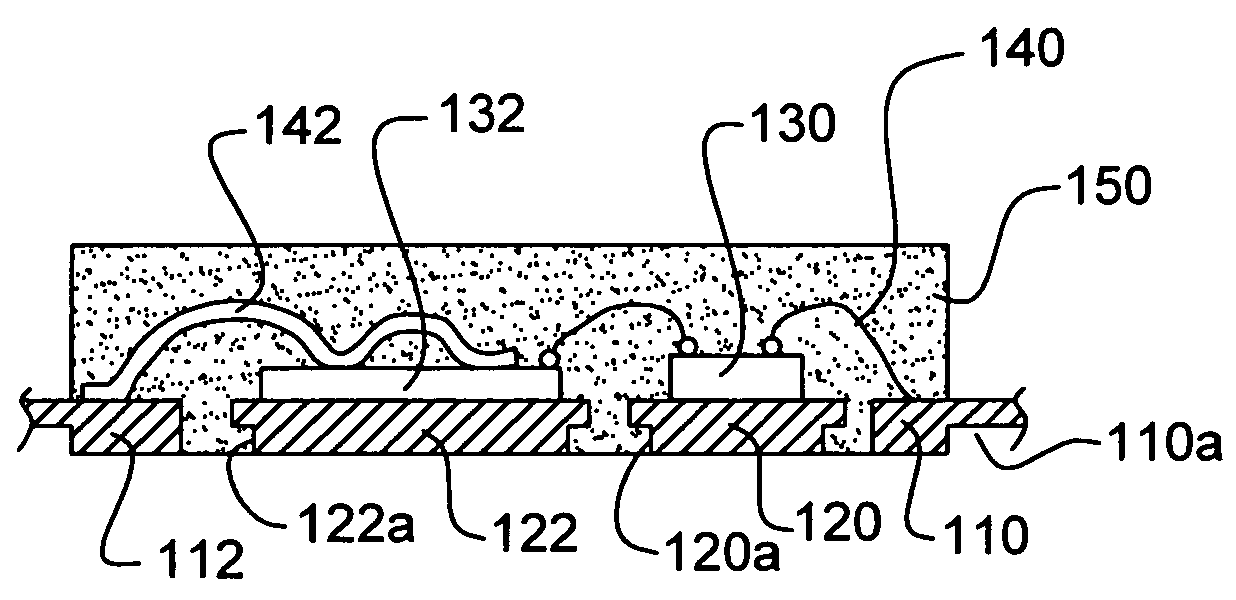

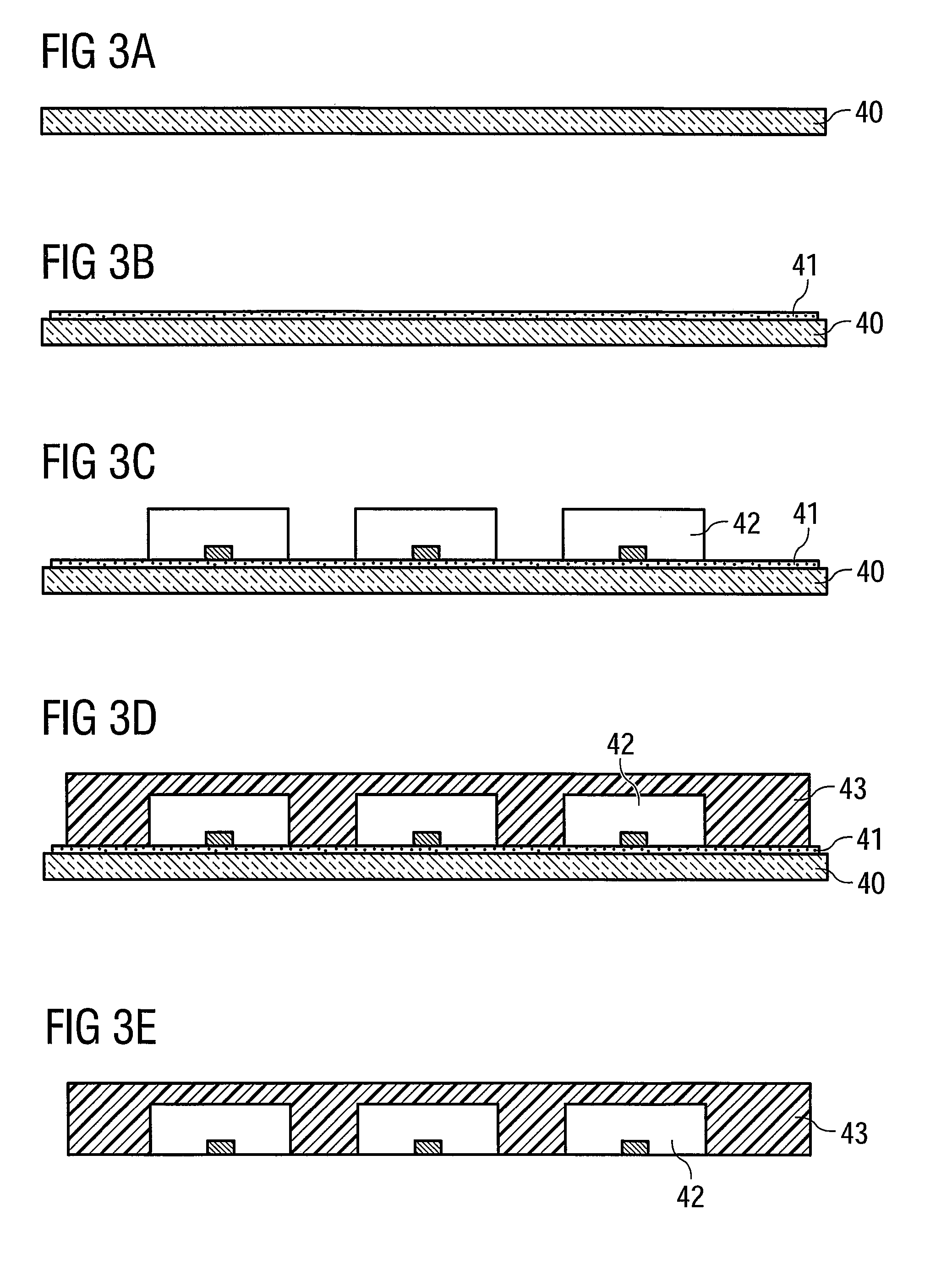

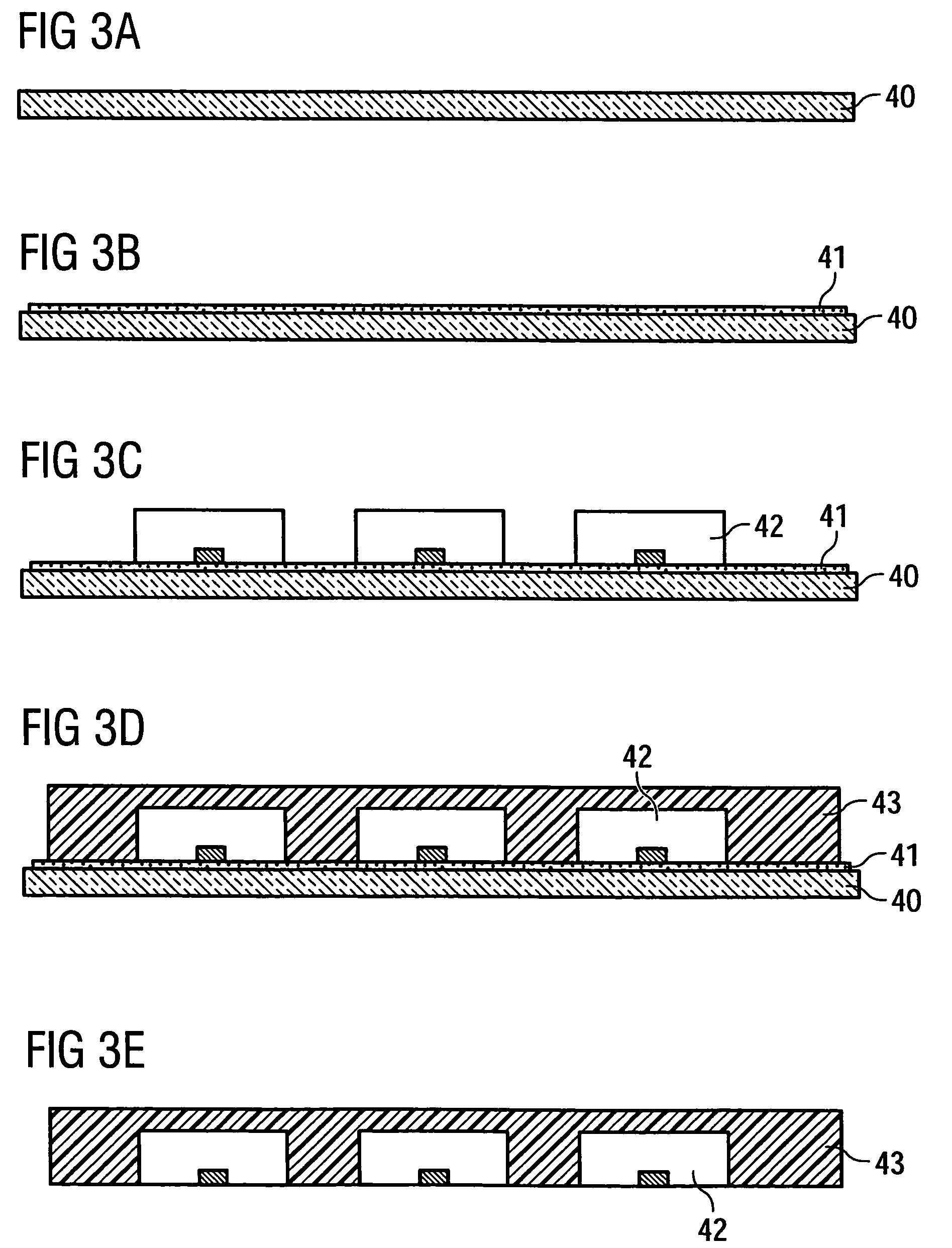

Electronic system modules and method of fabrication

InactiveUS6927471B2Good dimensional stabilityLow costPrinted circuit assemblingFinal product manufactureDielectricEngineering

This specification describes techniques for manufacturing an electronic system module. The module includes flexible multi-layer interconnection circuits with trace widths of 5 microns or less. A glass panel manufacturing facility, similar to those employed for making liquid crystal display, LCD, panels is used to fabricate the interconnection circuits. A polymer base layer is formed on a glass carrier with an intermediate release layer. Alternate layers of metal and dielectric are formed on the base layer, and patterned to create an array of multi-layer interconnection circuits on the glass panel. A thick layer of polymer is deposited on the interconnection circuit, and openings formed at input / output (I / O) pad locations. Solder paste is deposited in the openings to form wells filled with solder. After dicing the glass carrier to form separated interconnection circuits, IC chips are stud bumped and assembled using flip chip bonding, wherein the stud bumps on the components are inserted into corresponding wells on the interconnection circuits. The IC chips are tested and reworked to form tested circuit assemblies. Methods for connecting to testers and to other modules and electronic systems are described. Module packaging layers are provided for hermetic sealing and for electromagnetic shielding. A blade server embodiment is also described.

Owner:SK HYNIX INC

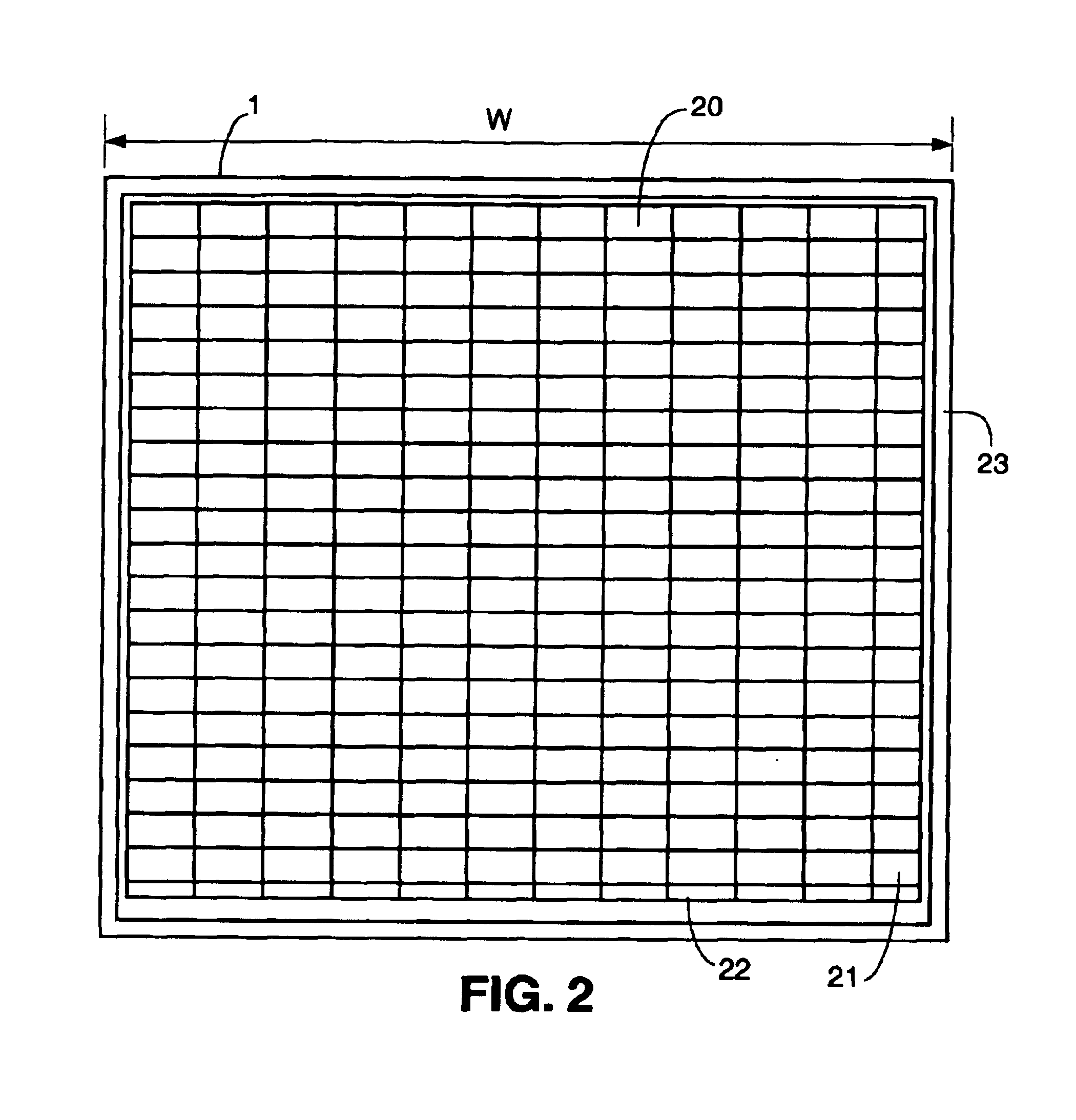

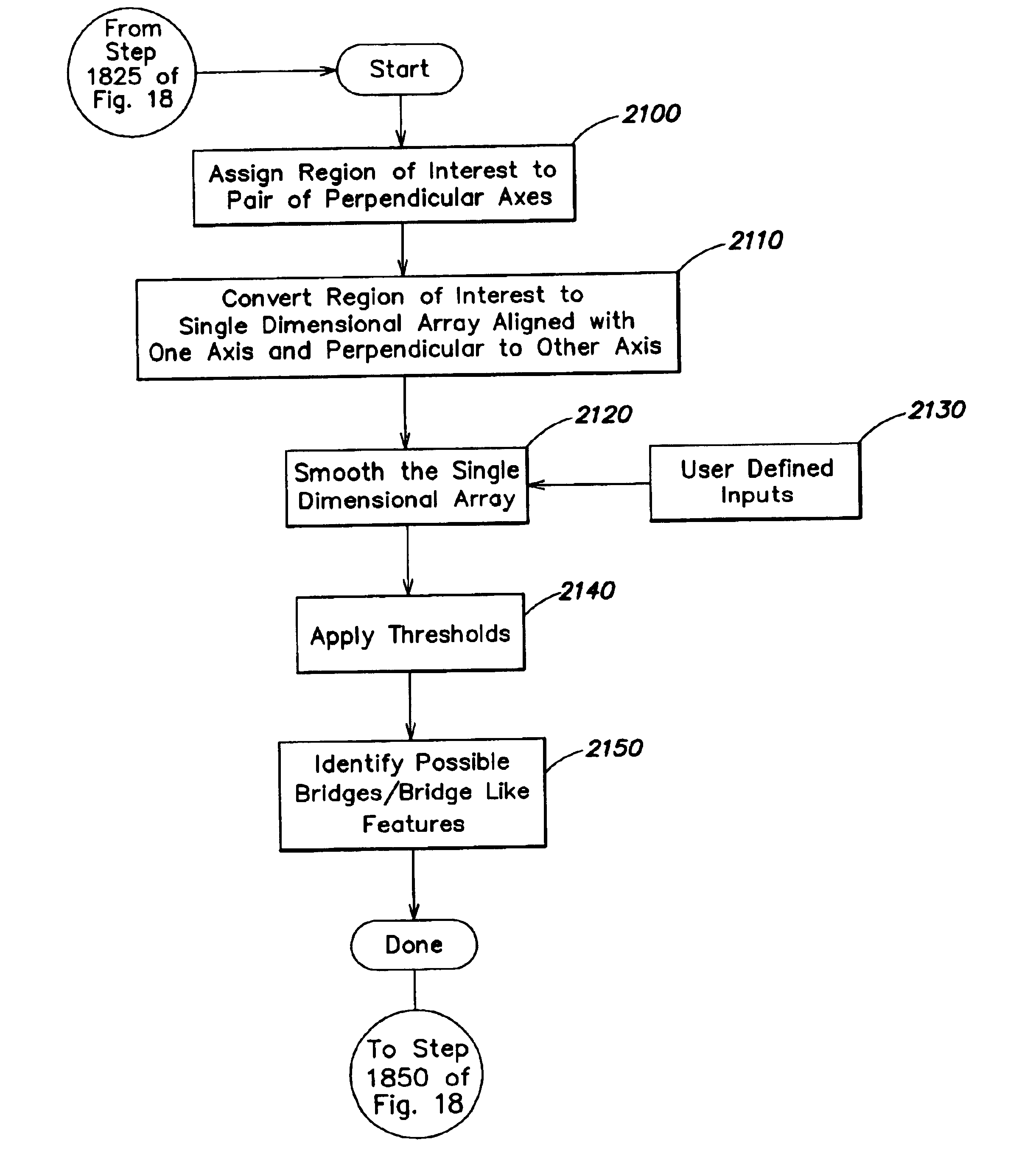

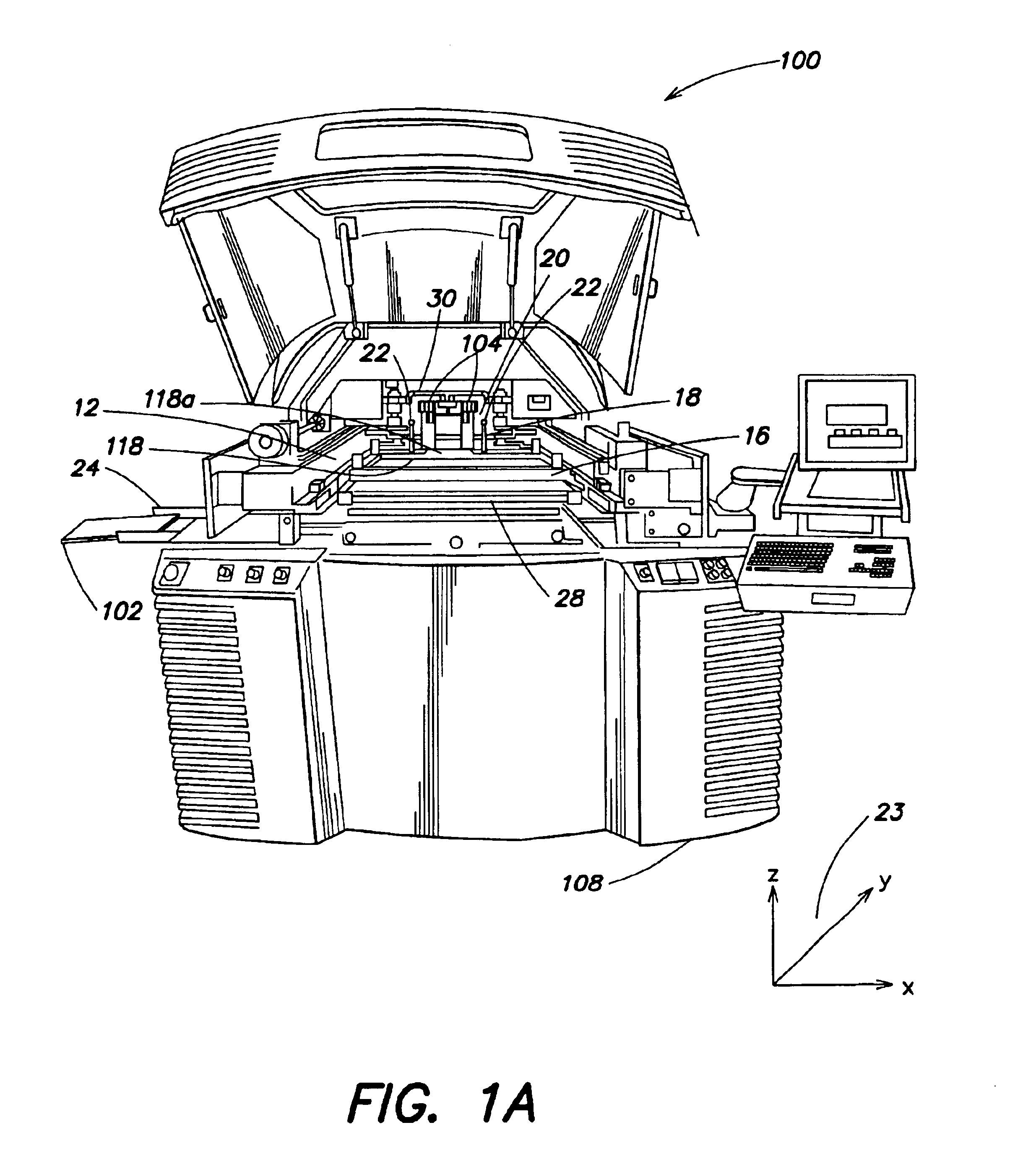

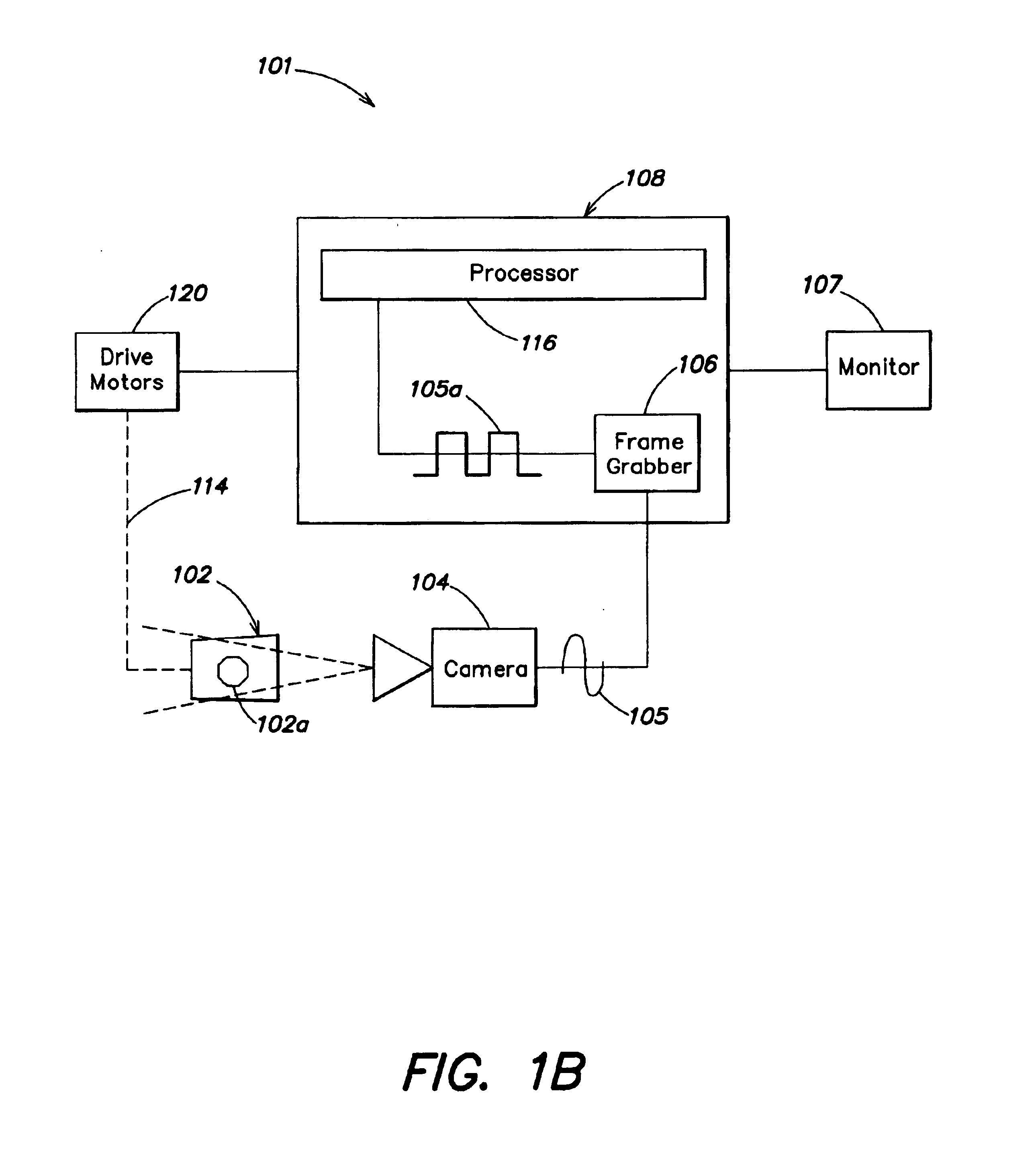

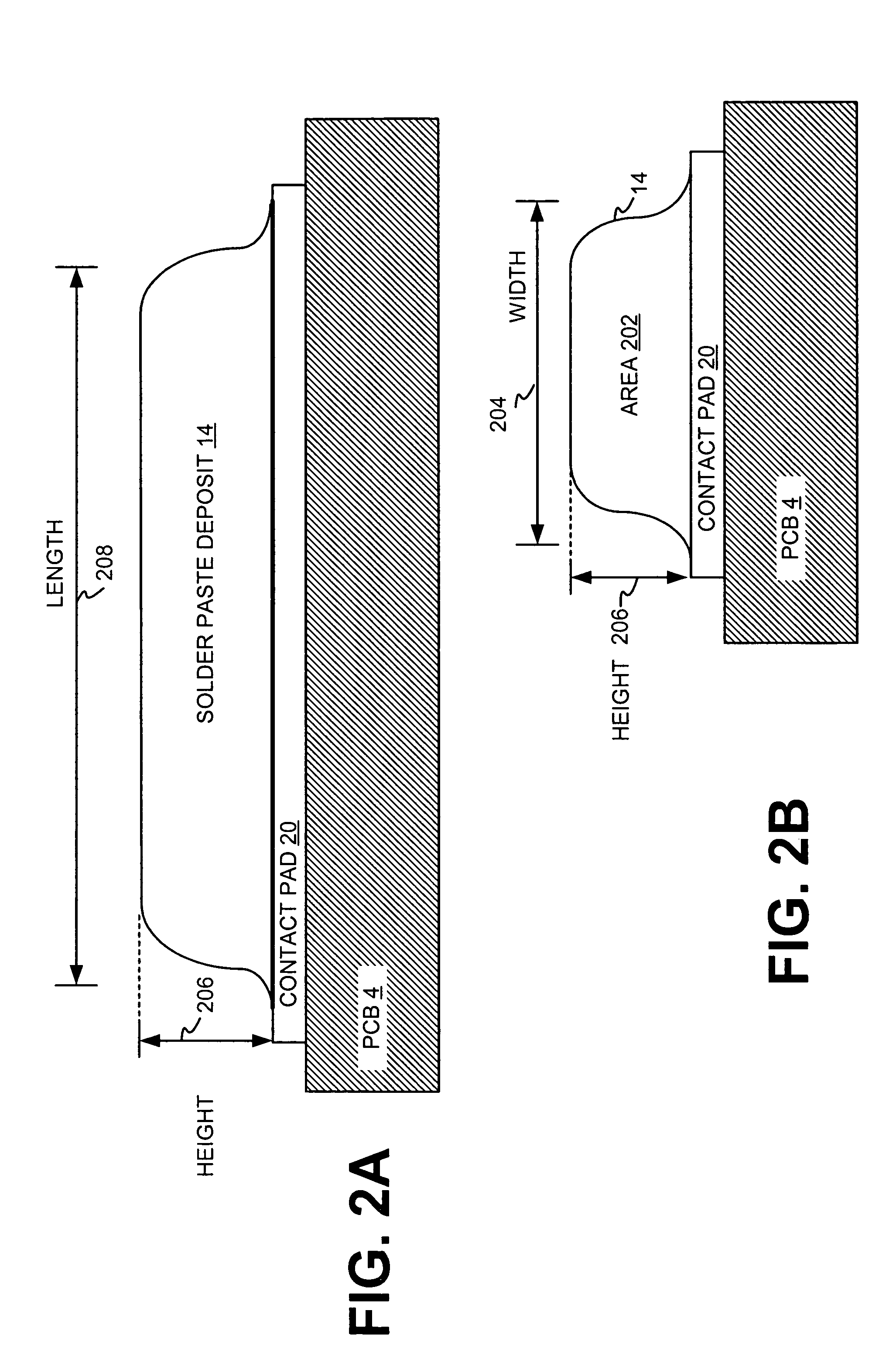

Systems and methods for detecting defects in printed solder paste

InactiveUS6891967B2Easy to detectEasy to controlImage enhancementImage analysisSolder pasteRegion of interest

A method of analyzing an image of a substance deposited onto a substrate, the image comprising a plurality of pixels, includes defining a region of interest in the image, associating the region of interest with first and second perpendicular axis, wherein a set of pixels in the image lie along the first axis, converting the pixels in the region of interest to a single dimensional array aligned with the first axis and projecting along the second axis, and applying at least one threshold to the single dimensional array, the threshold based at least in part on a predetermined limit.

Owner:KPS SPECIAL SITUATIONS FUND II LP

LED lamp filament illuminating strip and preparation method therefor

ActiveCN105161608AImprove yieldImprove uniformitySolid-state devicesSemiconductor devicesFluorescenceLap joint

The invention discloses an LED lamp filament illuminating strip and a preparation method therefor. The illuminating strip comprises LED chips in upper and lower rows, wherein all LED chips in the lower row are distributed at intervals, and all LED chips in the upper row are respectively connected between two adjacent LED chips in the lower row in a lap joint manner. The illuminating surfaces of the LED chips in the upper and lower rows are opposite to each other. The positive and negative electrodes of all LED chips in the upper row are respectively welded with the negative and positive electrodes of two adjacent LED chips, in lap joint connection with the LED chips in the upper row, in the lower row. The preparation method comprises the steps: coating solder paste on the positive and negative electrodes of all LED chips in the lower row; heating the solder paste and enabling the solder paste to be melted, welding the corresponding electrodes, coating the front and back surfaces of chip strips in series connection with fluorescent glue, and solidifying the fluorescent glue. The illuminating strip employs the chips which are not overlapped with each other, and the illuminating surfaces of the chips are arranged oppositely, thereby improving the light-emitting uniformity and facilitating heat dissipation. The wire crossing and tandem among chips is avoided, the packaging cost is reduced, and the yield of finished products is improved.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

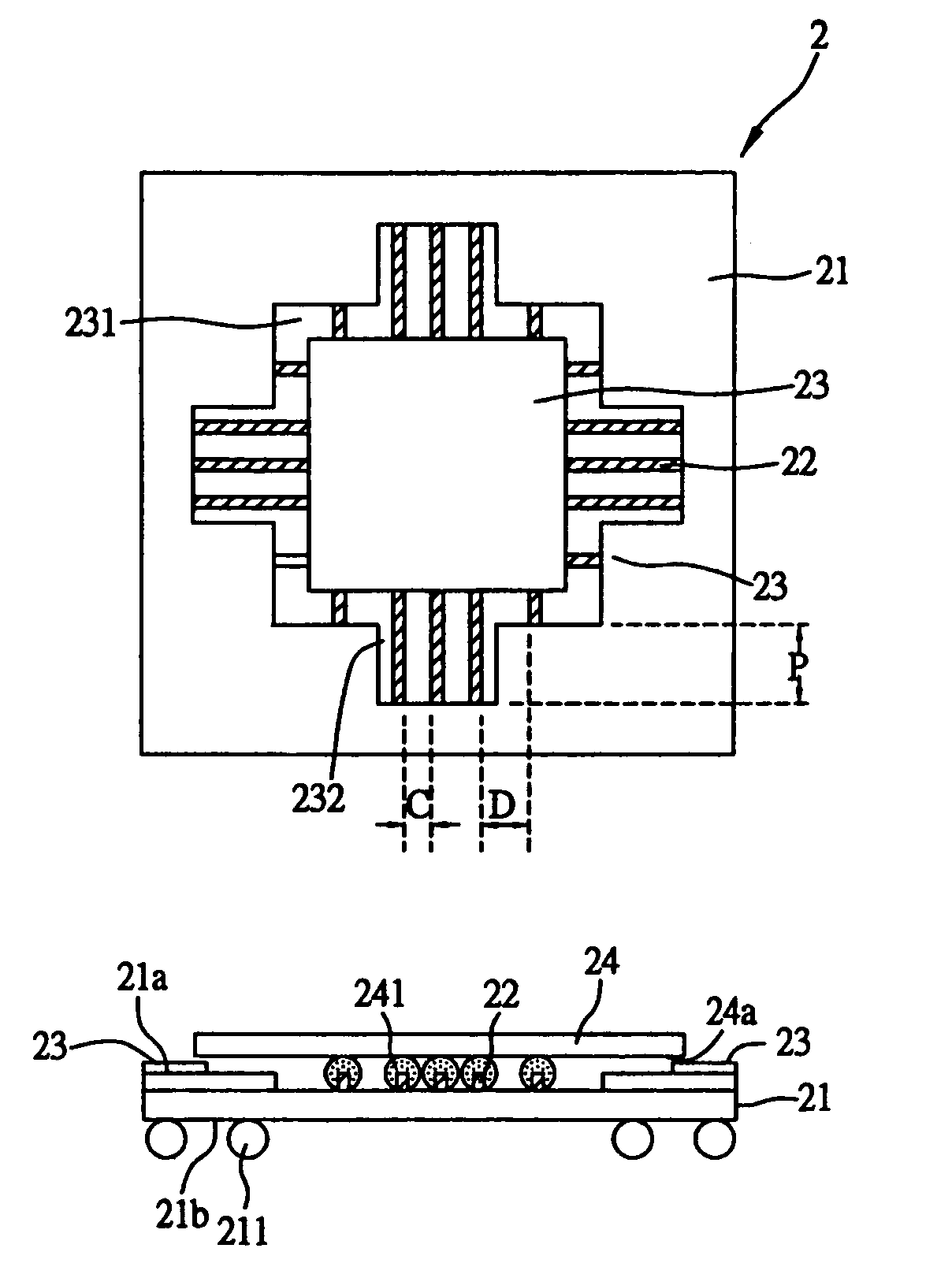

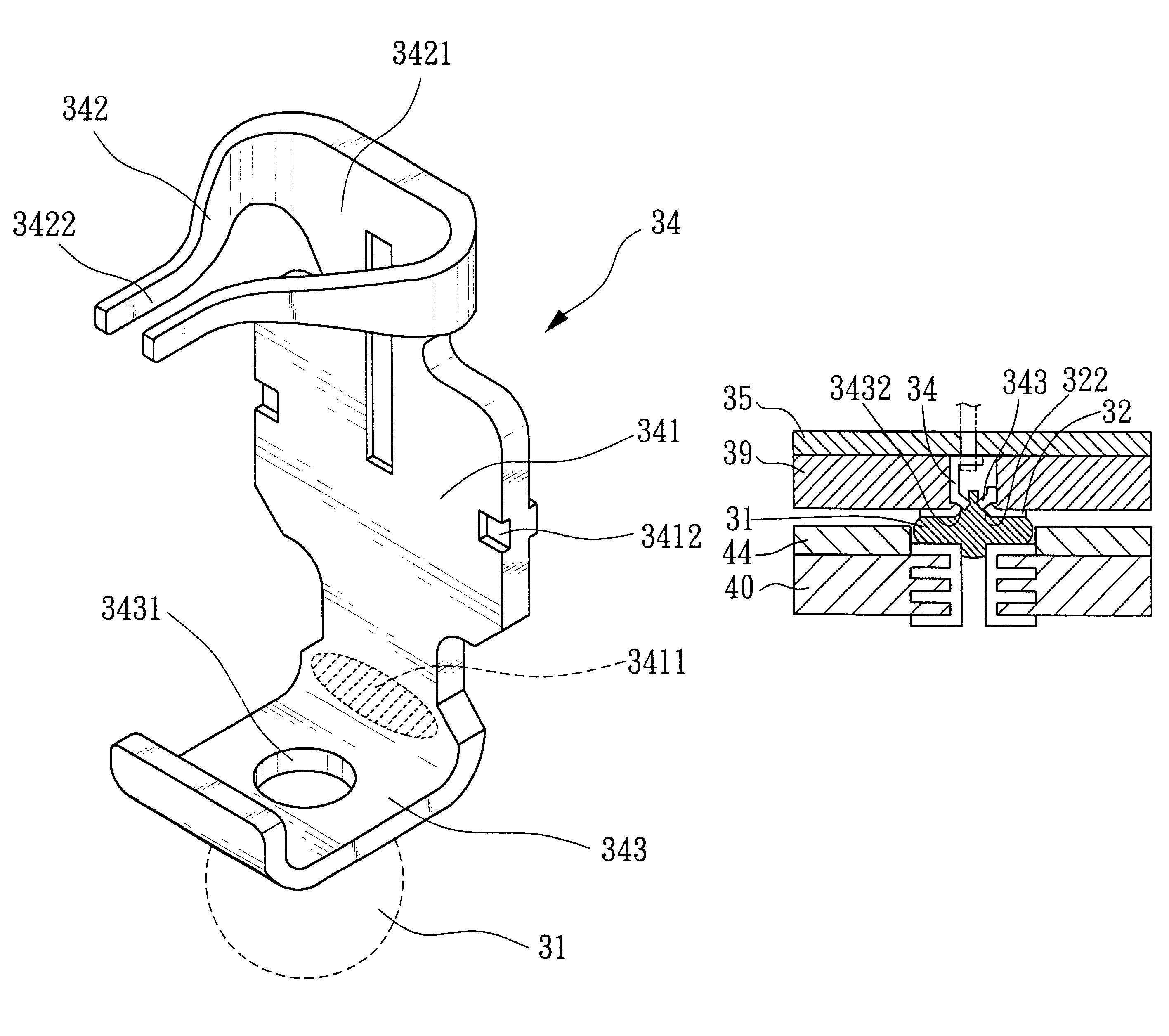

Electrical connection device

InactiveUS6692265B2Printed circuit assemblingFinal product manufactureElectricityElectrical connection

An electrical connection device comprises a socket, a plurality of electrical conducting holder in between, a contact ring and a plurality of solder balls. A plurality of pin holes are placed on the socket to provide the insert function for the pins of a IC package. The electrical conducting holder is placed in the pin holes and comprises an extensional part, a holder on the top of the extension part and a solder pad on the bottom part of the extension part to combine the solder ball. At least one 2D or 3D geometrical structure such as the hole, the convex and concave part or the slope on the bottom surface of the solder pad is formed. The geometrical structure will make the bottom surface of the solder pad not the flat plane. With the geometrical structure and the contact ring, the contact area of the solder pad and the contact ring will be enlarged during the solder reflow process. The coupling effect will be better and meanwhile improve the characteristics of the electricity, the intensity of the structure, the production yield and the characteristics of the co-planarity.

Owner:VIA TECH INC

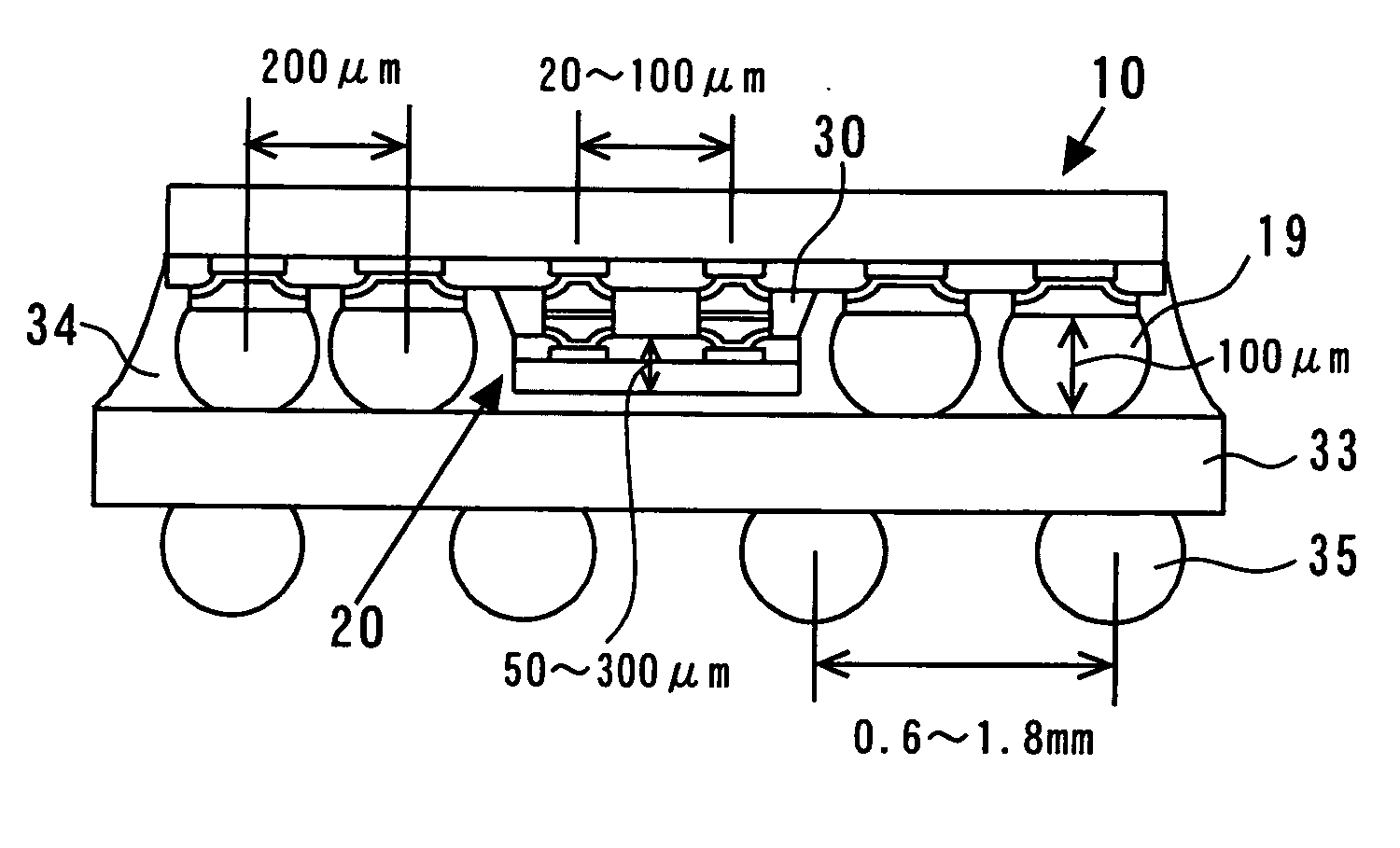

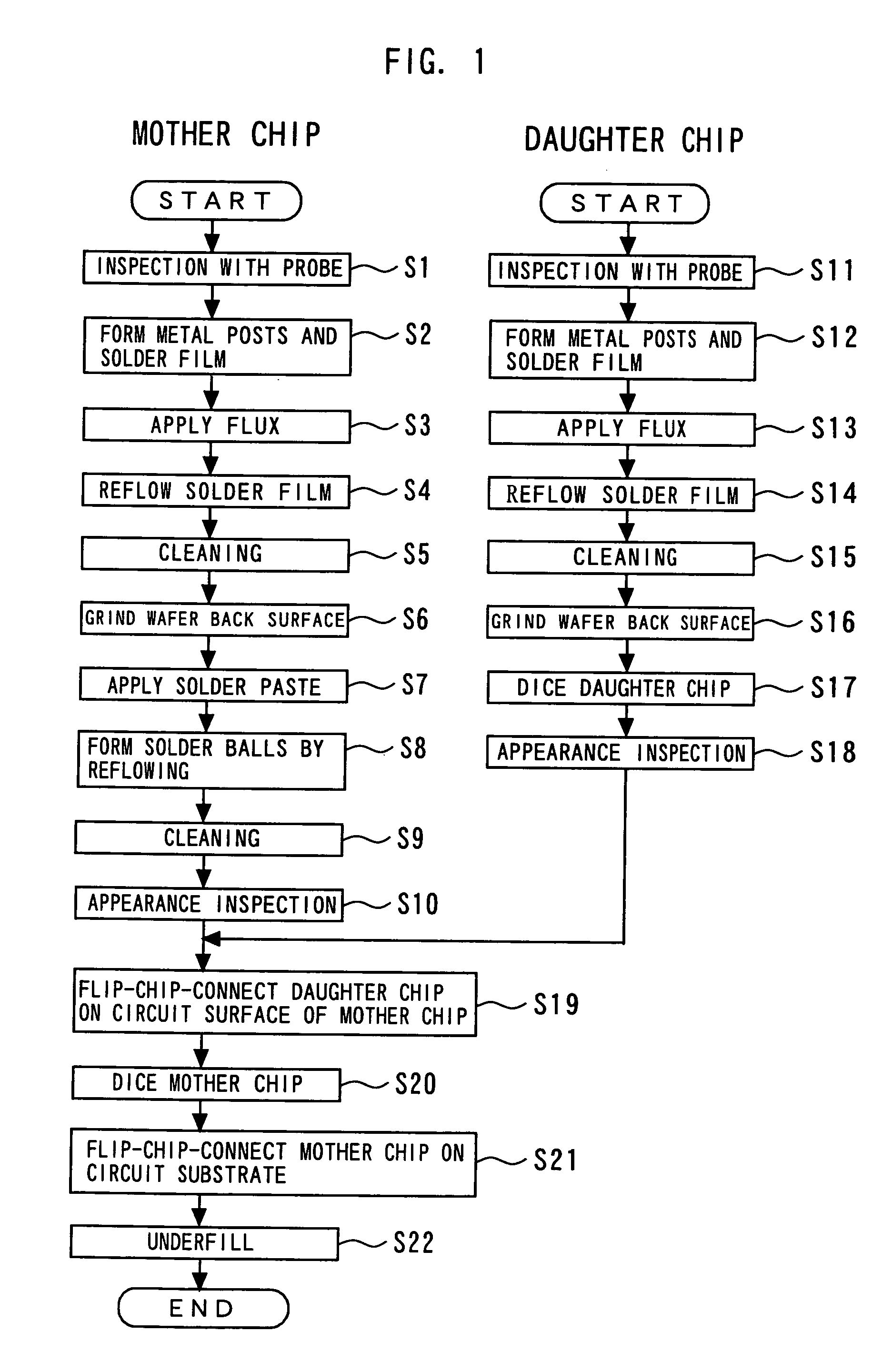

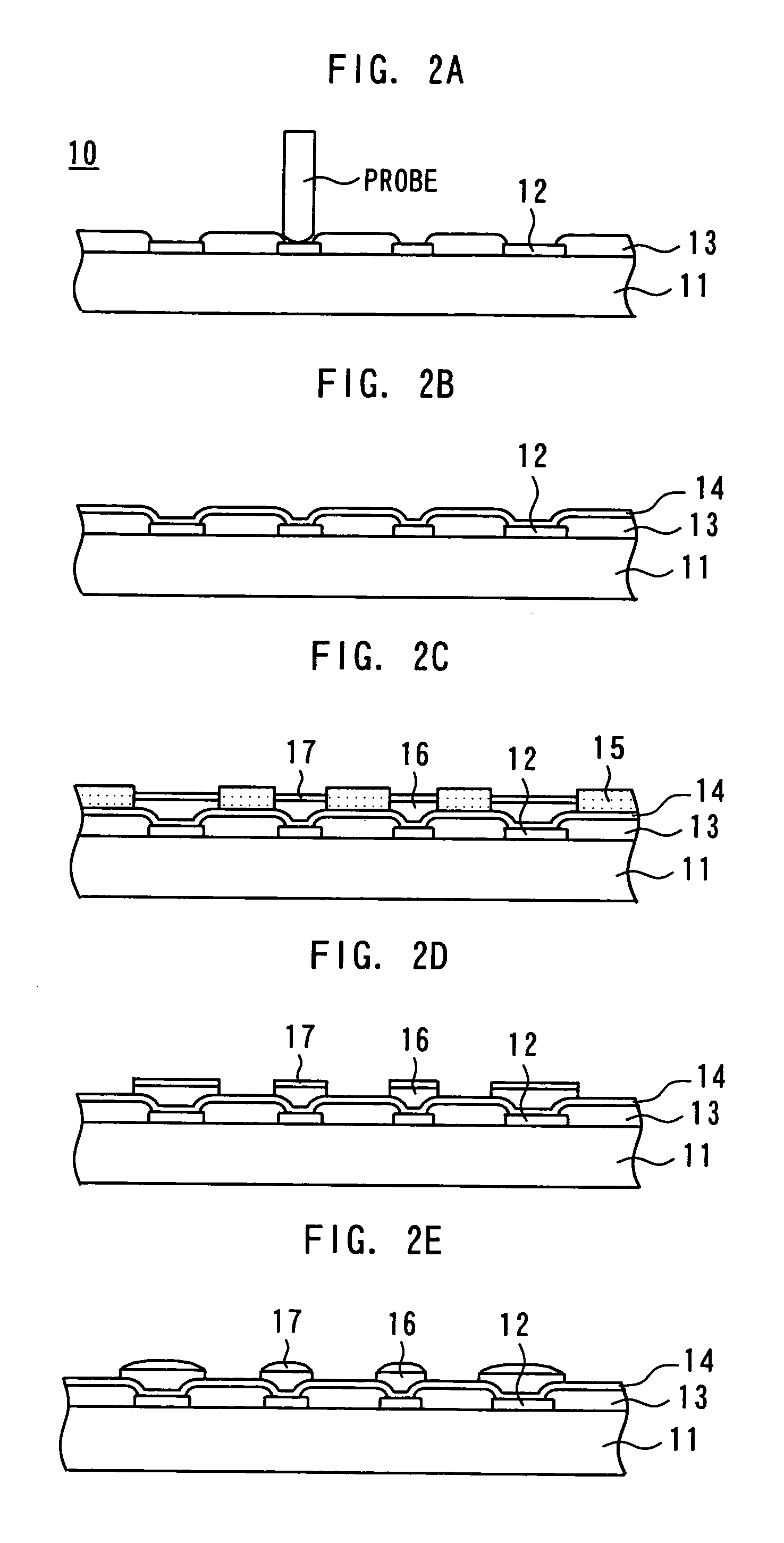

Method of manufacturing semiconductor device

InactiveUS20070141750A1Avoid connection failureSolid-state devicesSemiconductor/solid-state device manufacturingNitrogen atmosphereSolder ball

A method of manufacturing a semiconductor device includes a first step of forming solder film on metal posts of a mother chip, a second step of forming solder balls after the first step by printing a solder paste on the mother chip and heating the mother chip so that the solder paste is ref lowed, a third step of bonding the metal posts of the mother chip and metal posts of a daughter chip to each other in a thermocompression bonding manner by means of the solder film after the second step, and a fourth step of flip-chip-connecting the mother chip on a circuit substrate by using the solder balls. In the second step, the mother chip is heated in a nitrogen atmosphere in which the oxygen concentration is 500 ppm or less.

Owner:RENESAS ELECTRONICS CORP

Leadless semiconductor package and manufacturing method thereof

ActiveUS7053469B2Reduce thermal resistanceLower on-resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A leadless semiconductor package mainly includes a semiconductor device securely attached to an upper surface of a die pad by solder paste and a plurality of leads arranged about the periphery of the die pad. The thickness of the leads and the die pad are within a range of 10 to 20 mils. The semiconductor device is electrically coupled to one of the leads. A package body is formed over the semiconductor device and the leads in a manner that the lower surfaces of the die pad and the leads are exposed through the package body. Preferably, the first semiconductor device is electrically coupled to one of the leads by at least one heavy gauge aluminum wire. The present invention further provides a method of producing the semiconductor package described above.

Owner:ADVANCED SEMICON ENG INC

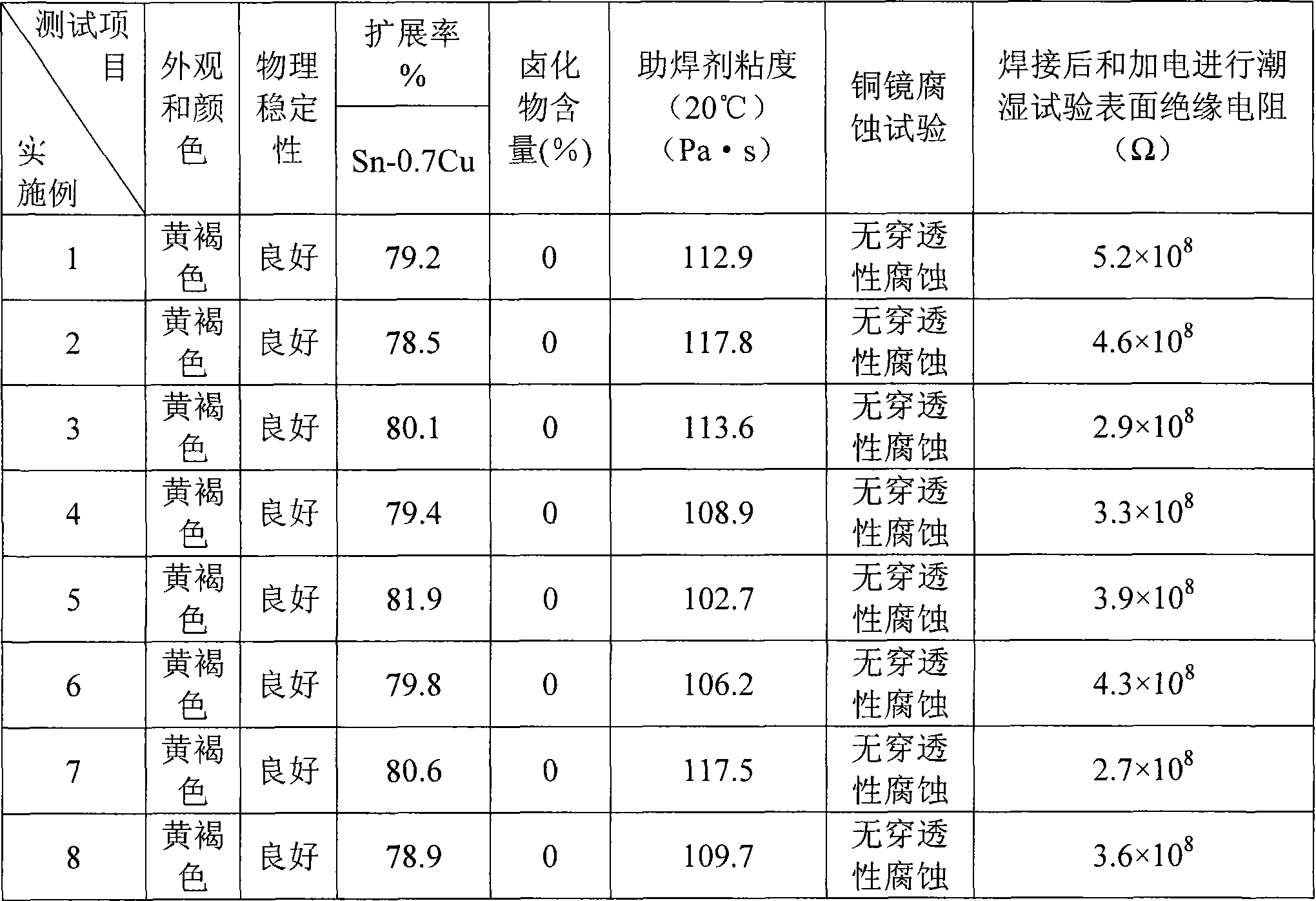

Low-rosin and cleaning-free welding accessory without halogen for lead-free welding grease

InactiveCN101073862AGood print shapeNo viscosity requirementWelding/cutting media/materialsSoldering mediaSolventSolder paste

The invention is concerned with low rosin type halogen-free and cleaning-free flux using for lead-free solder paste, belonging to flux field. About the existing rosin type flux, the leftover after welding is high and the leavings with halogen has cauterization. The matter of this invention is 5 to 20 wt percent of organic acid activator, 10 to 29 wt percent of modified rosin, 1 to 10 wt percent of binder, 0.5 to 6 wt percent of stabilizer, 1 to 6 wt percent of surfactant, 1 to 8 wt percent of corrosion inhibitor, 1 to 10 wt percent of thickener, and the rest is solvent with high boiling point. The copper mirror after welding is not penetration, and this invention without halogen has high insulation resistance and good assistant jointing capability. The viscosity of matched solder paste is advisable to solve the high content of rosin in the flux and great smoke. The leftover after welding is colorless and transparent film and it dose not absorb water with the normal temperature without clearing to fit for the welding demand of common production.

Owner:BEIJING UNIV OF TECH

Stacked Die Package

InactiveUS20080128884A1Improve reliabilityReduce in quantitySemiconductor/solid-state device detailsSolid-state devicesSolder pasteElectrical and Electronics engineering

A stacked die package includes a substrate or interposer board that includes a contact area on a top surface and landing pads surrounding the contact area. Solder pads are disposed on an opposite side of the substrate. The solder pads are electrically connected with the landing pads by inner board wiring. A reconstituted die, which includes a die surrounded by a frame, is mounted over the substrate. A top die is mounted over the reconstituted die. Both the reconstituted die and the top die are electrically connected to the substrate, e.g., by wire bonds.

Owner:POLARIS INNOVATIONS LTD

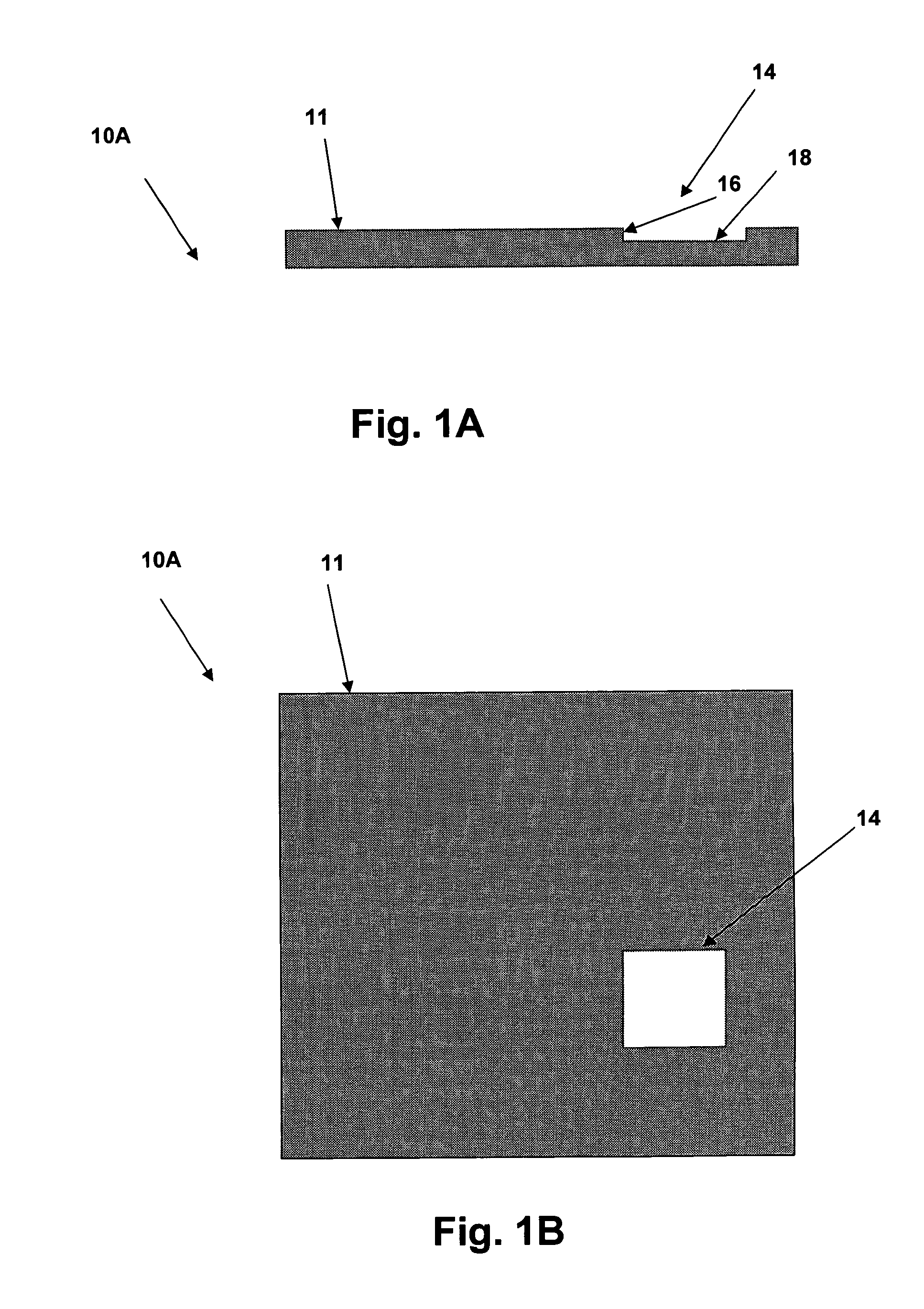

Method for making an integrated circuit substrate having embedded passive components

InactiveUS7334326B1Low incremental costIncremental costPrinted circuit assemblingElectrolytic capacitorsConductive pasteConductive materials

A method for making an integrated circuit substrate having embedded passive components provides a reduced cost and compact package for a die and one or more passive components. An insulating layer of the substrate is embossed or laser-ablated to generate apertures for insertion of a paste forming the body of the passive component. A resistive paste is used to form resistors and a dielectric paste is used for forming capacitors. A capacitor plate may be deposited at a bottom of the aperture by using a doped substrate material and activating only the bottom wall of the aperture, enabling plating of the bottom wall without depositing conductive material on the side walls of the aperture. Vias may be formed to the bottom plate by using a disjoint structure and conductive paste technology. Connection to the passive components may be made by conductive paste-filled channels forming conductive patterns on the substrate.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

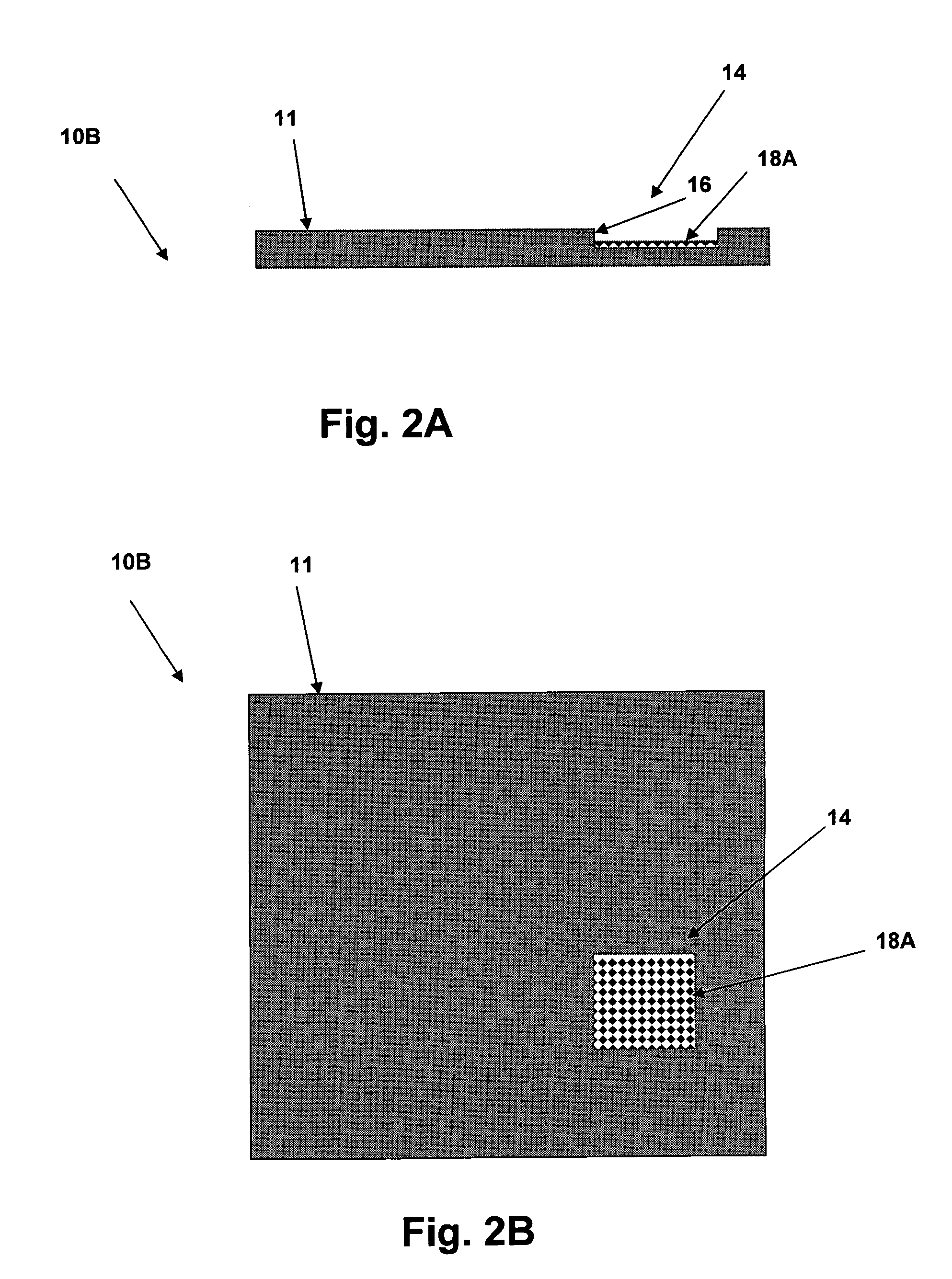

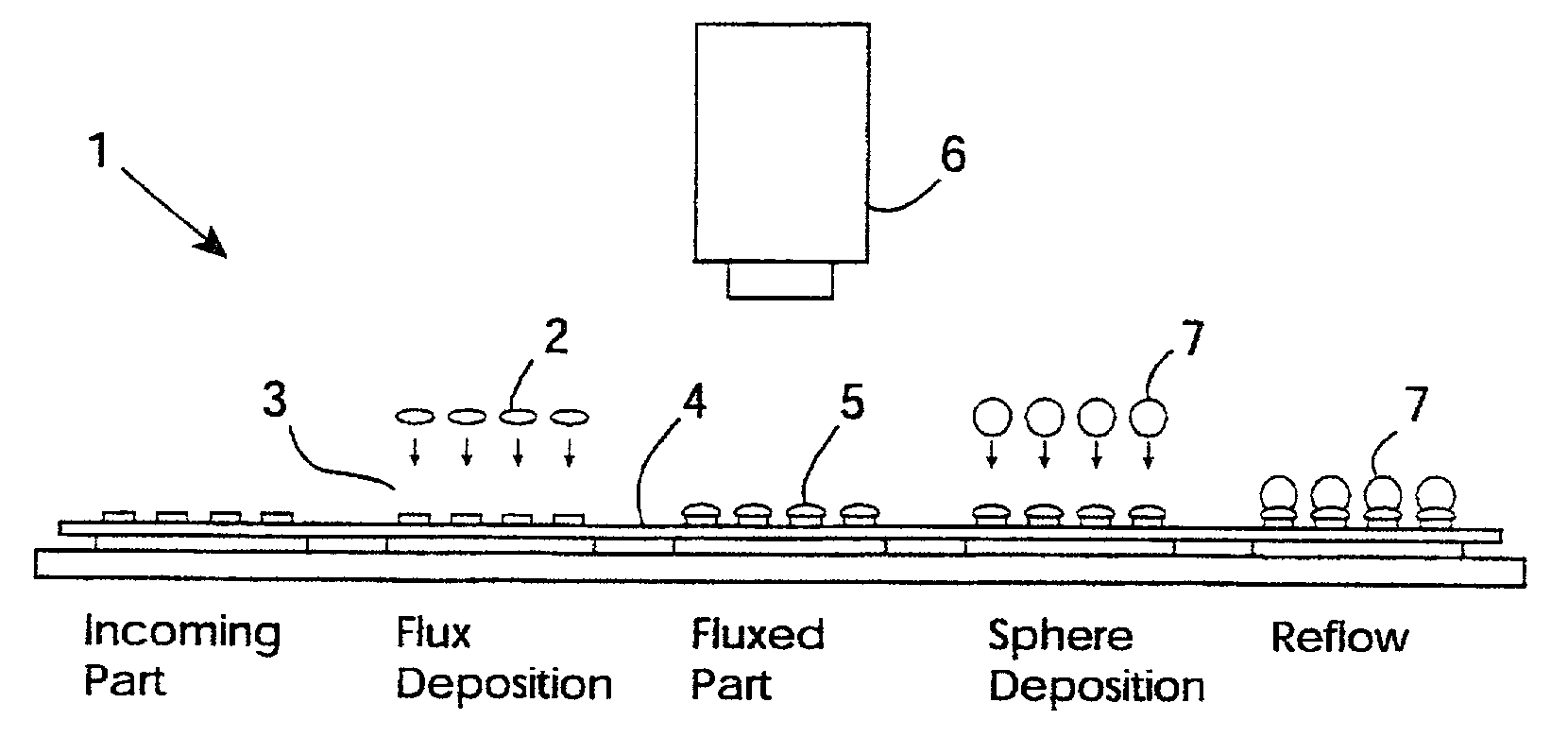

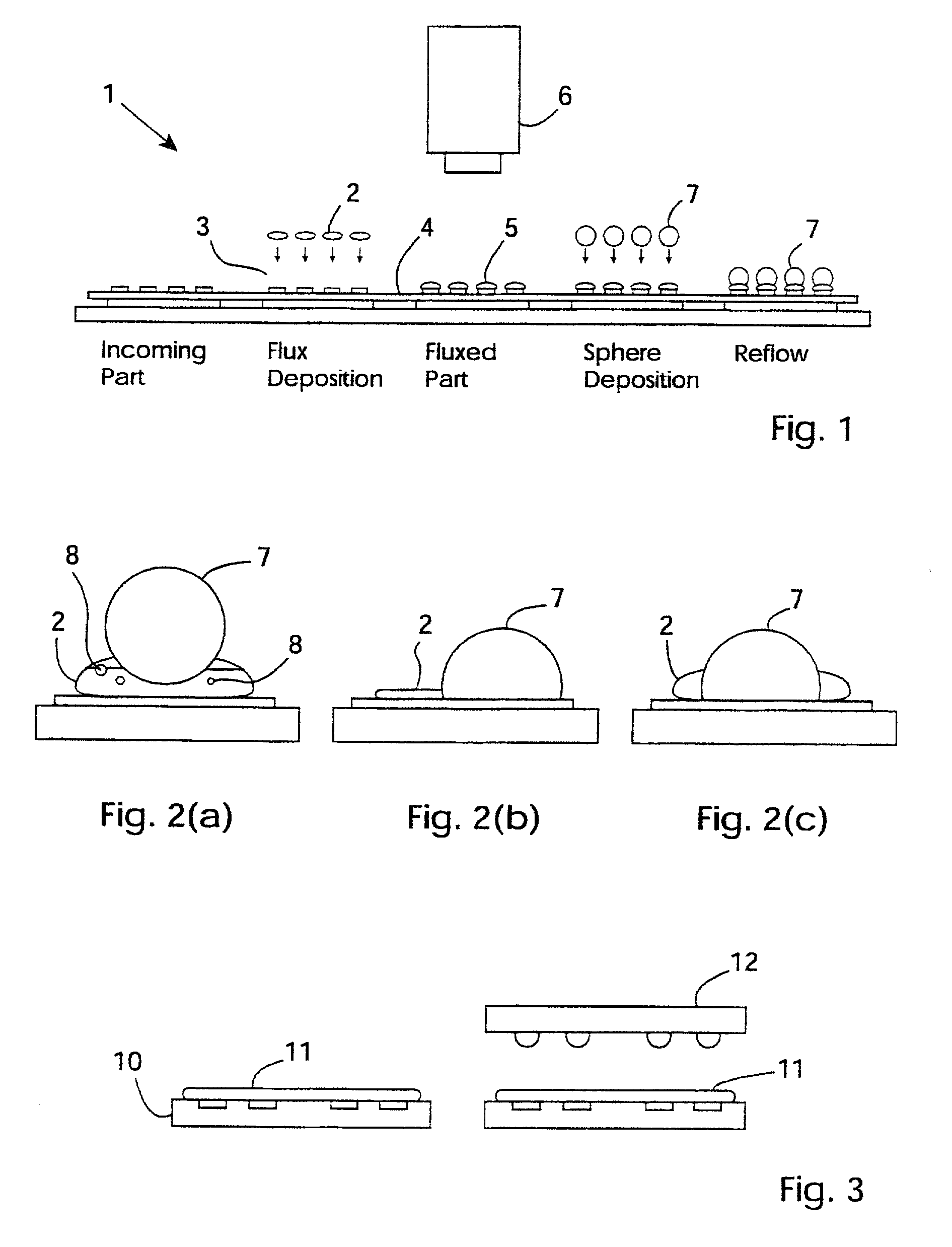

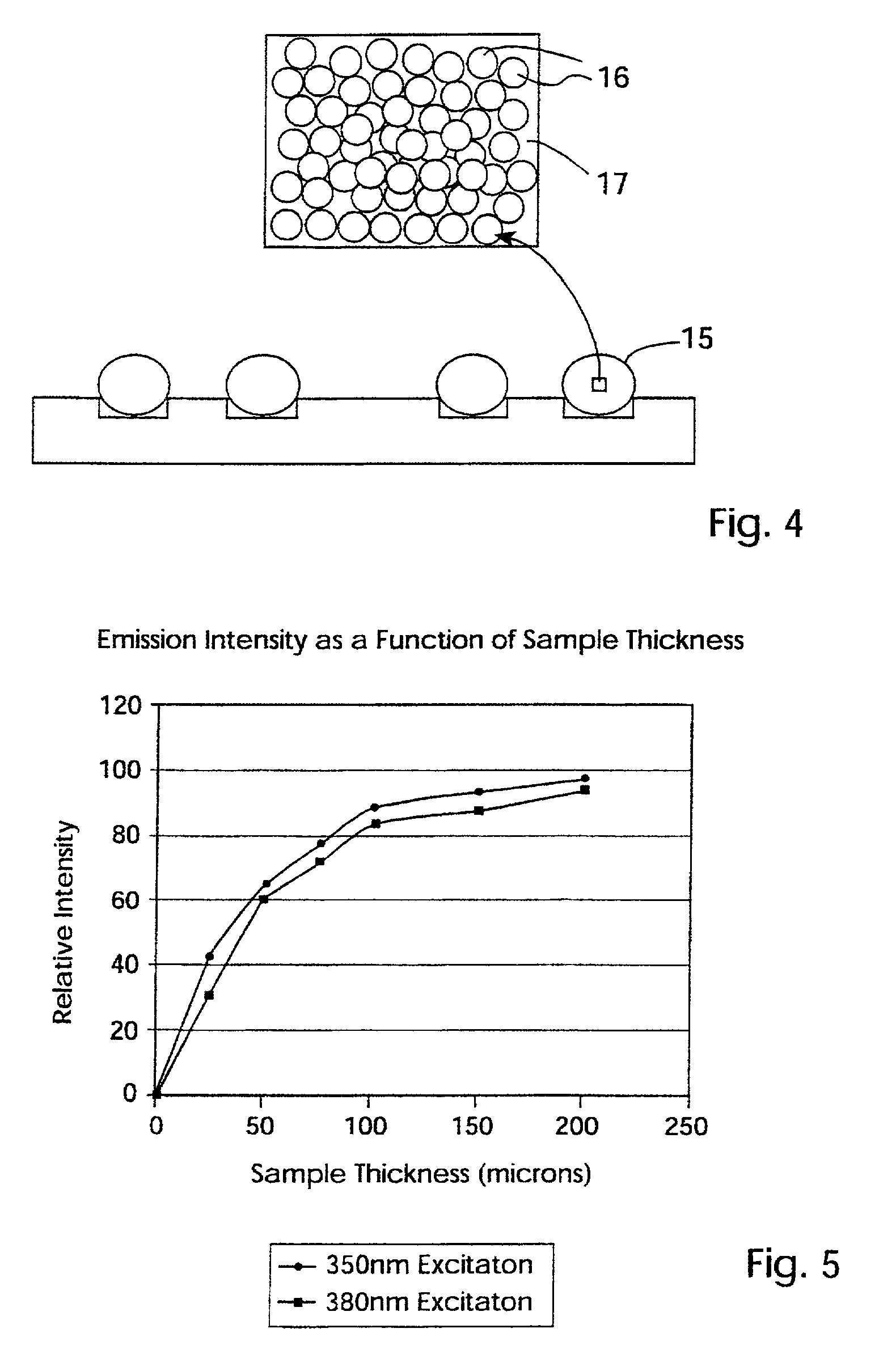

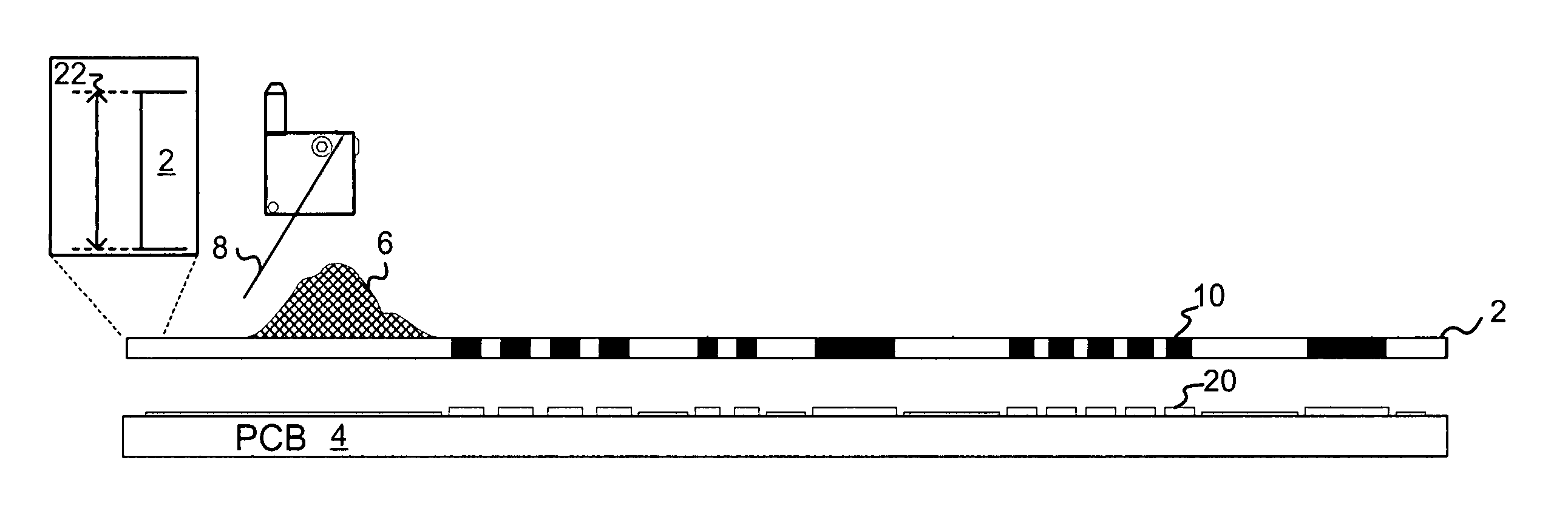

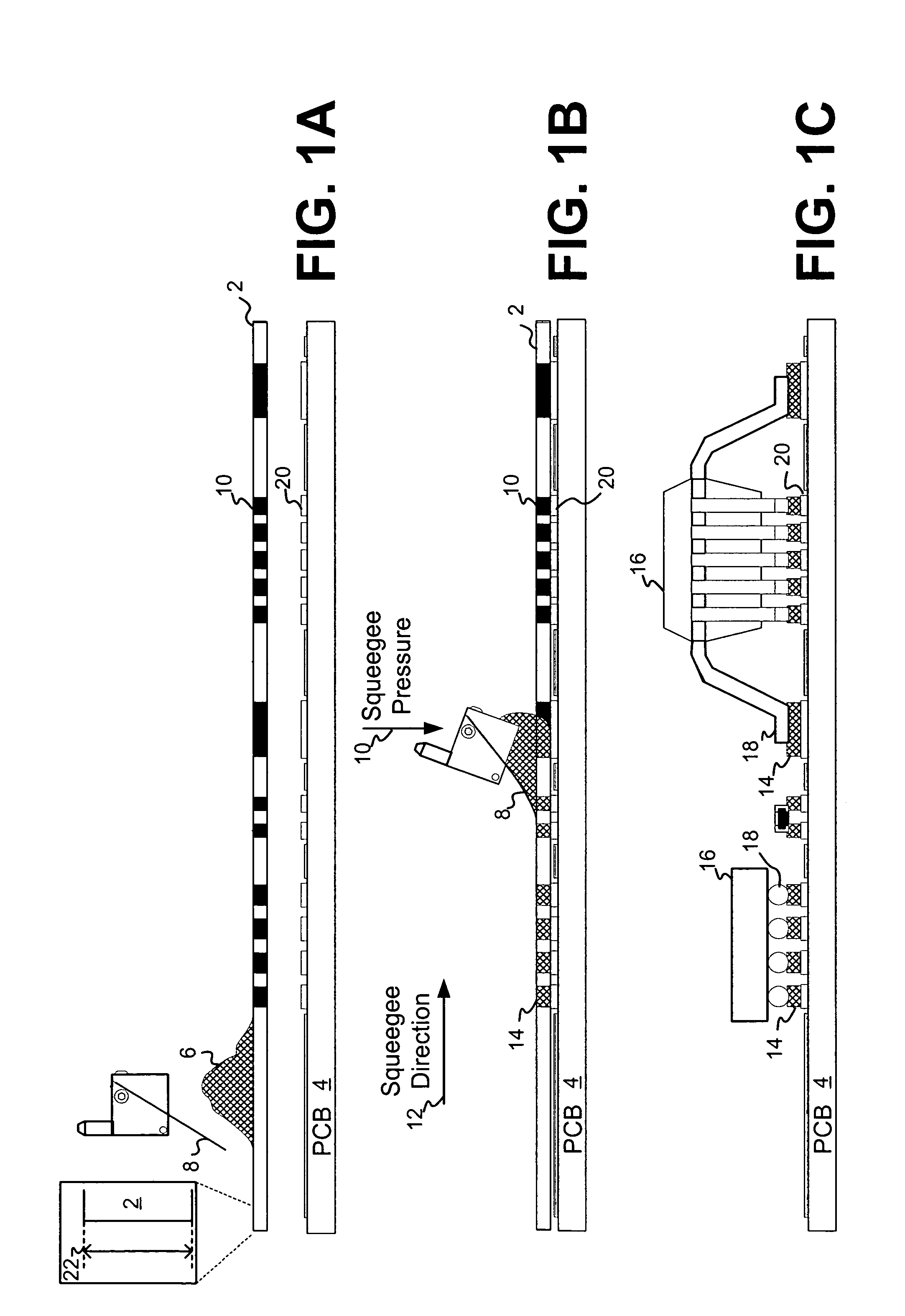

Material inspection

InactiveUS20020053589A1Avoid downstream processing defectMinimize sensationAutomatic control devicesPrecision positioning equipmentDiffuse illuminationFluorescence

An inspection station (6) has a ring of 370 nm LEDs (24) for low-angle diffuse illumination of flux. This stimulates inherent fluorescent emission of the flux without the need for flux additives or pre-treatment. A CCD sensor (20) detects the emission. An image processor generates output data indicating flux volume according to a relationship between emission intensity and volume over the surface of the flux. Intensity non-uniformity indicates either height non-uniformity or hidden voids, both of which give rise to defects after application of solder paste and reflow. The inspection is particularly effective for pre solder application flux inspection.

Owner:AGILENT TECH INC

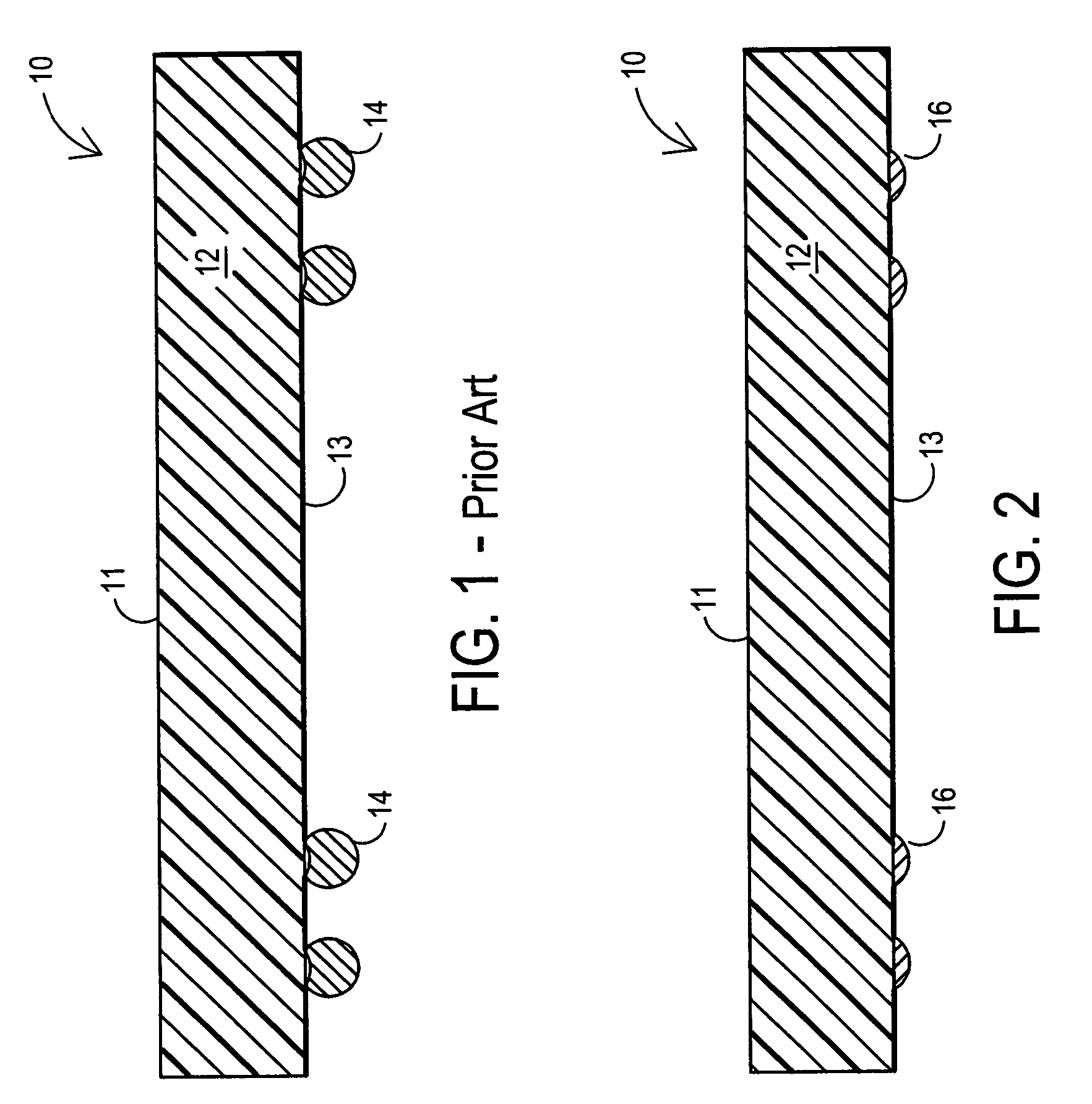

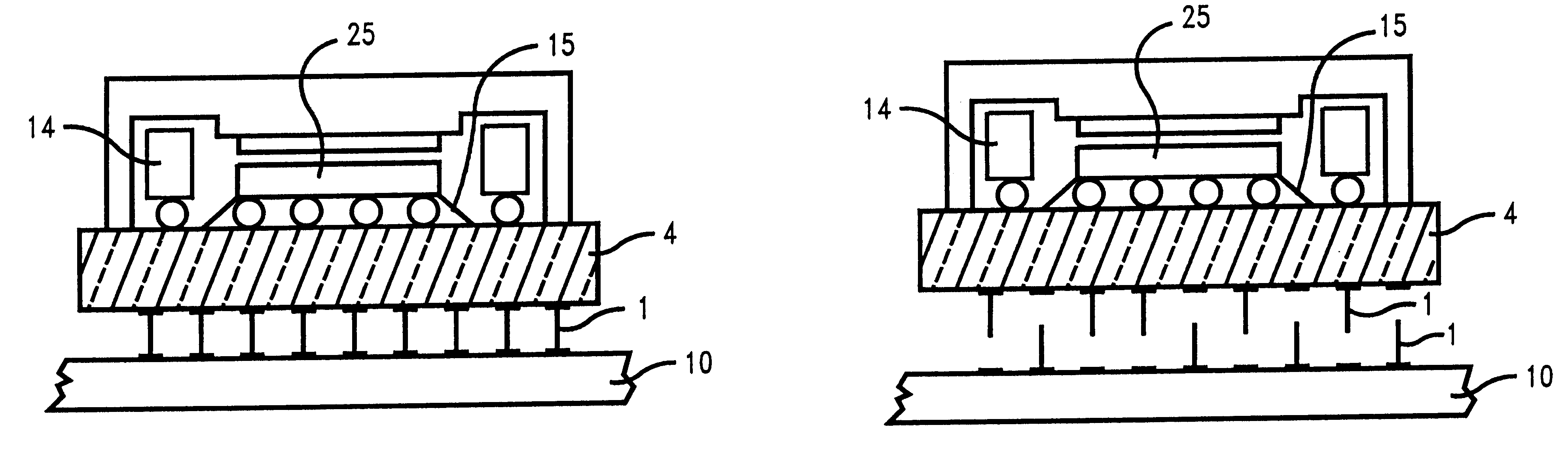

Low profile stacking system and method

InactiveUS7180167B2Printed circuit assemblingSemiconductor/solid-state device detailsContact padAlloy

The present invention provides a system and method that mounts integrated circuit devices onto substrates and a system and method for employing the method in stacked modules. The contact pads of a packaged integrated circuit device are substantially exposed. A solder paste that includes higher temperature solder paste alloy is applied to a substrate or to the integrated circuit device to be mounted. The integrated circuit device is positioned to contact the contacts of the substrate. Heat is applied to create high temperature joints between the contacts of the substrate and the integrated circuit device resulting in a device-substrate assembly with high temperature joints. The formed joints are less subject to re-melting in subsequent processing steps. The method may be employed in devising stacked module constructions such as those disclosed herein as preferred embodiments in accordance with the invention. Typically, the created joints are low in profile.

Owner:OVID DATA CO

Stacked die package

InactiveUS7326592B2Improve reliabilityReduce in quantitySemiconductor/solid-state device detailsSolid-state devicesSolder pasteElectrical and Electronics engineering

A stacked die package includes a substrate or interposer board that includes a contact area on a top surface and landing pads surrounding the contact area. Solder pads are disposed on an opposite side of the substrate. The solder pads are electrically connected with the landing pads by inner board wiring. A reconstituted die, which includes a die surrounded by a frame, is mounted over the substrate. A top die is mounted over the reconstituted die. Both the reconstituted die and the top die are electrically connected to the substrate, e.g., by wire bonds.

Owner:POLARIS INNOVATIONS LTD

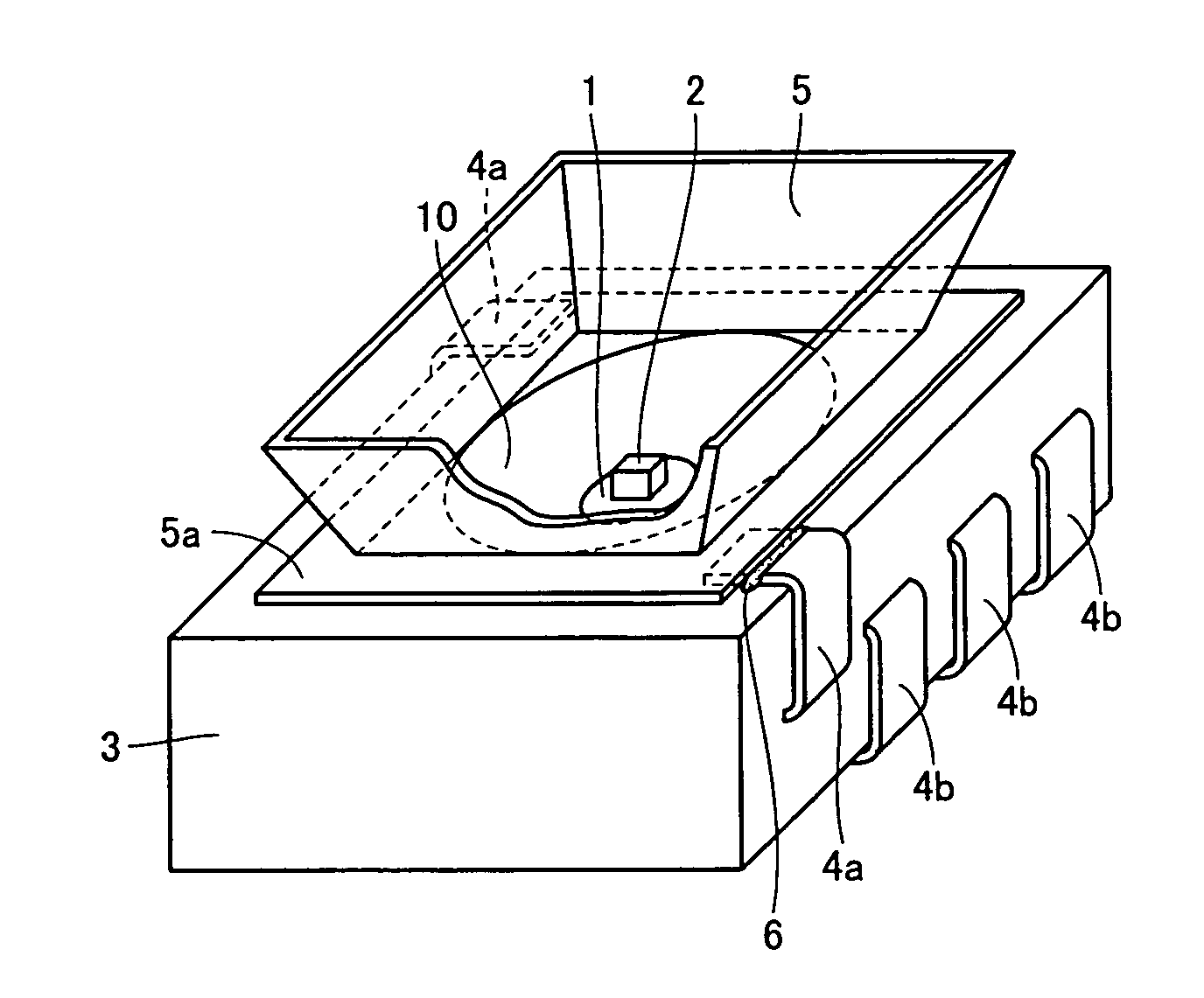

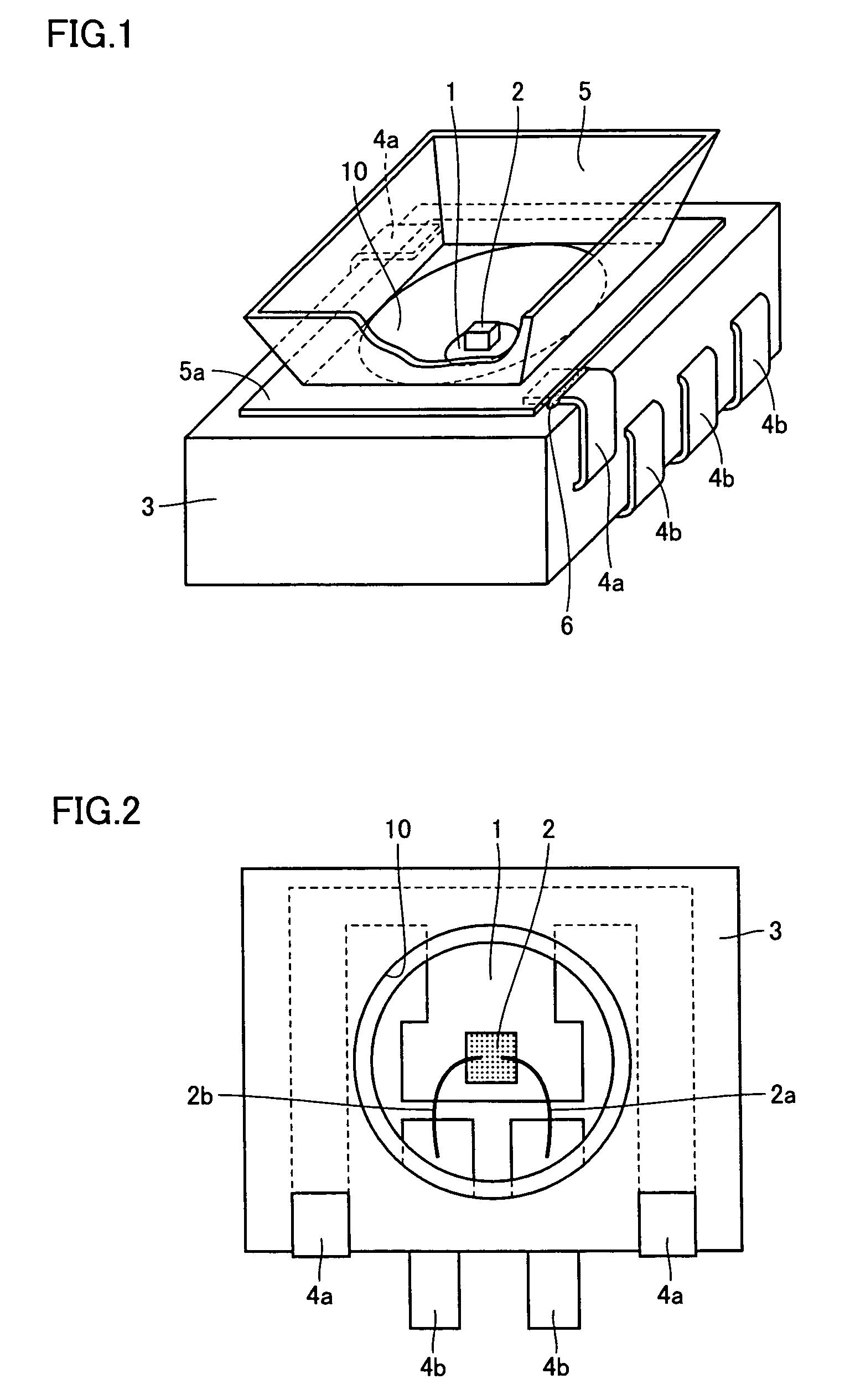

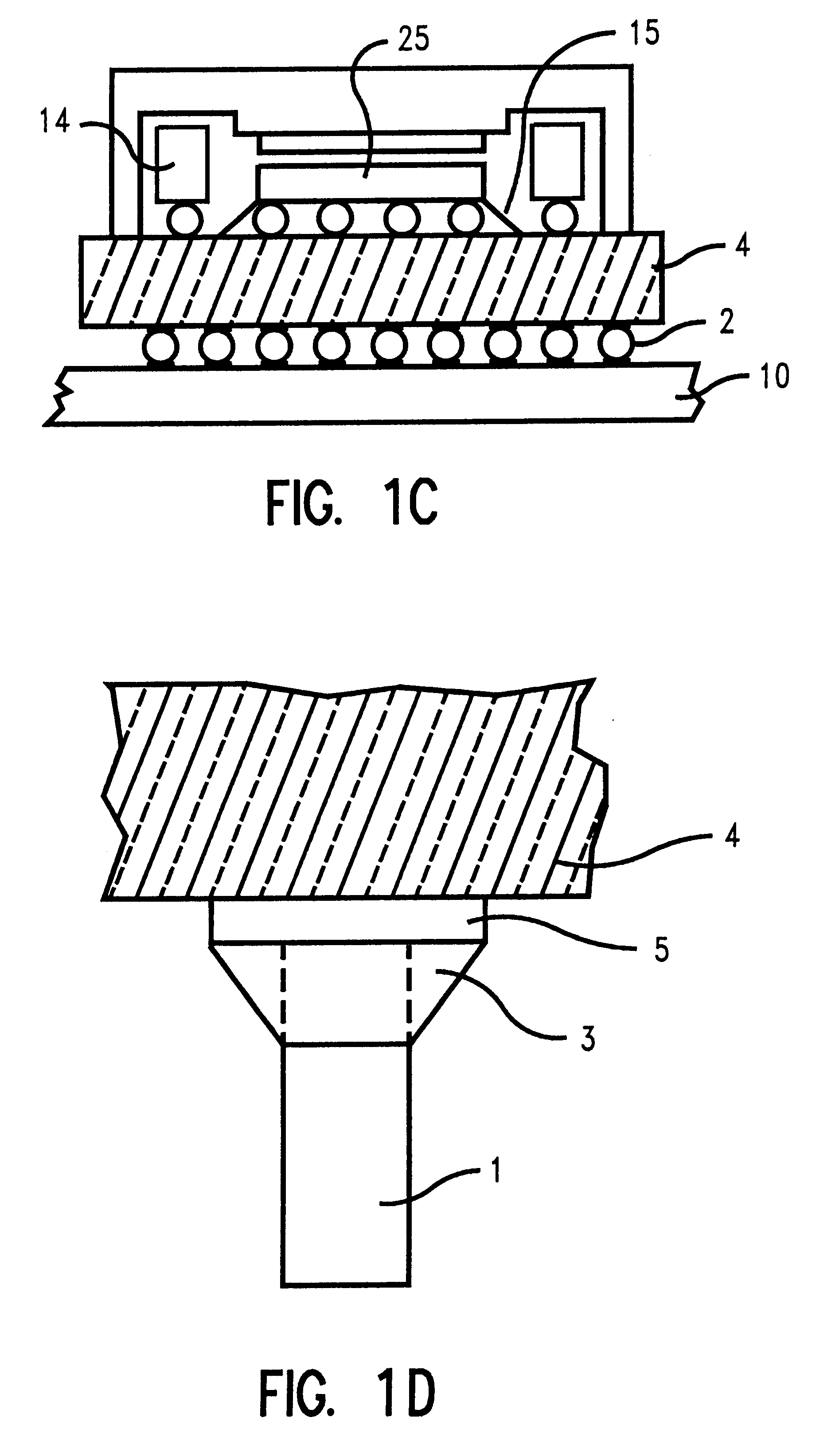

Semiconductor light emitting device

ActiveUS7282740B2Reliable heat conductionEfficient heat dissipationNon-electric lightingPoint-like light sourceEngineeringLead frame

A light emitting element is die-bonded to a portion of a lead frame exposed at the bottom of an opening formed at a top face of a resin package. A reflector to direct light emitted from the light emitting element towards a predetermined direction is attached to the top face of the resin package. Lead terminals are arranged so as to protrude from two opposite side regions of the resin package. A predetermined lead terminal among the plurality of lead terminals, connected to a portion where the light emitting element is die-bonded, is bent upwards, and soldered to the reflector by solder paste.

Owner:SHARP KK

Interconnection structure and process module assembly and rework

An interconnection structure and methods for making and detaching the same are presented for column and ball grid array (CGA and BGA) structures by using a transient solder paste on the electronic module side of the interconnection that includes fine metal powder additives to increase the melting point of the solder bond. The metal powder additives change the composition of the solder bond such that the transient melting solder composition does not completely melt at temperatures below +230° C. and detach from the electronic module during subsequent reflows. A Pb-Sn eutectic with a lower melting point is used on the opposite end of the interconnection structure. In the first method a transient melting solder paste is applied to the I / O pad of an electronic module by a screening mask. Interconnect structures are then bonded to the I / O pad. In a second method, solder preforms in a composition of the transient melting solder paste are wetted onto electronic module I / O pads and interconnect columns or balls are then bonded. Detachment of an electronic module from a circuit card can then be performed by heating the circuit card assembly to a temperature above the eutectic solder melting point, but below the transient solder joint melting point.

Owner:ULTRATECH INT INC

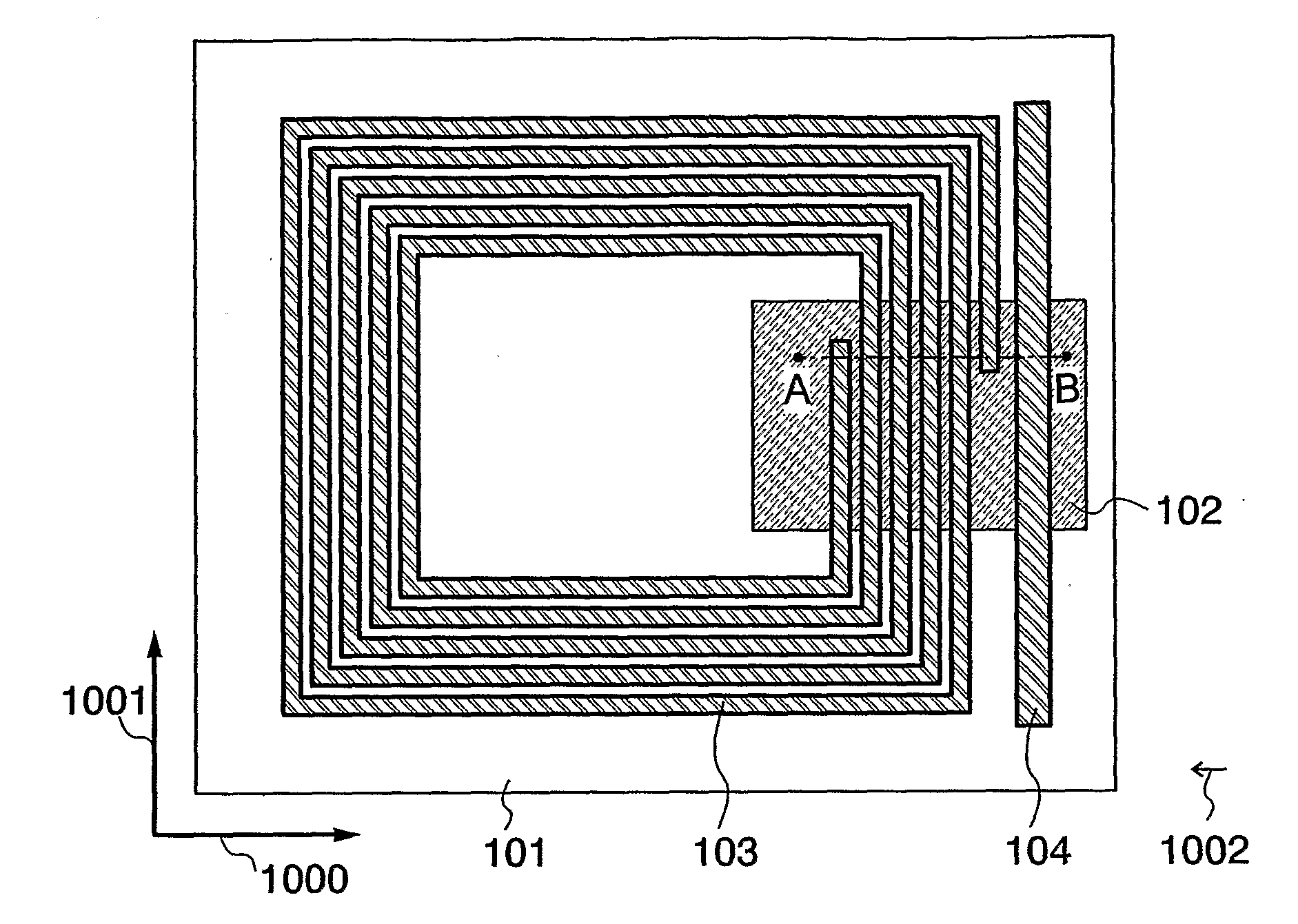

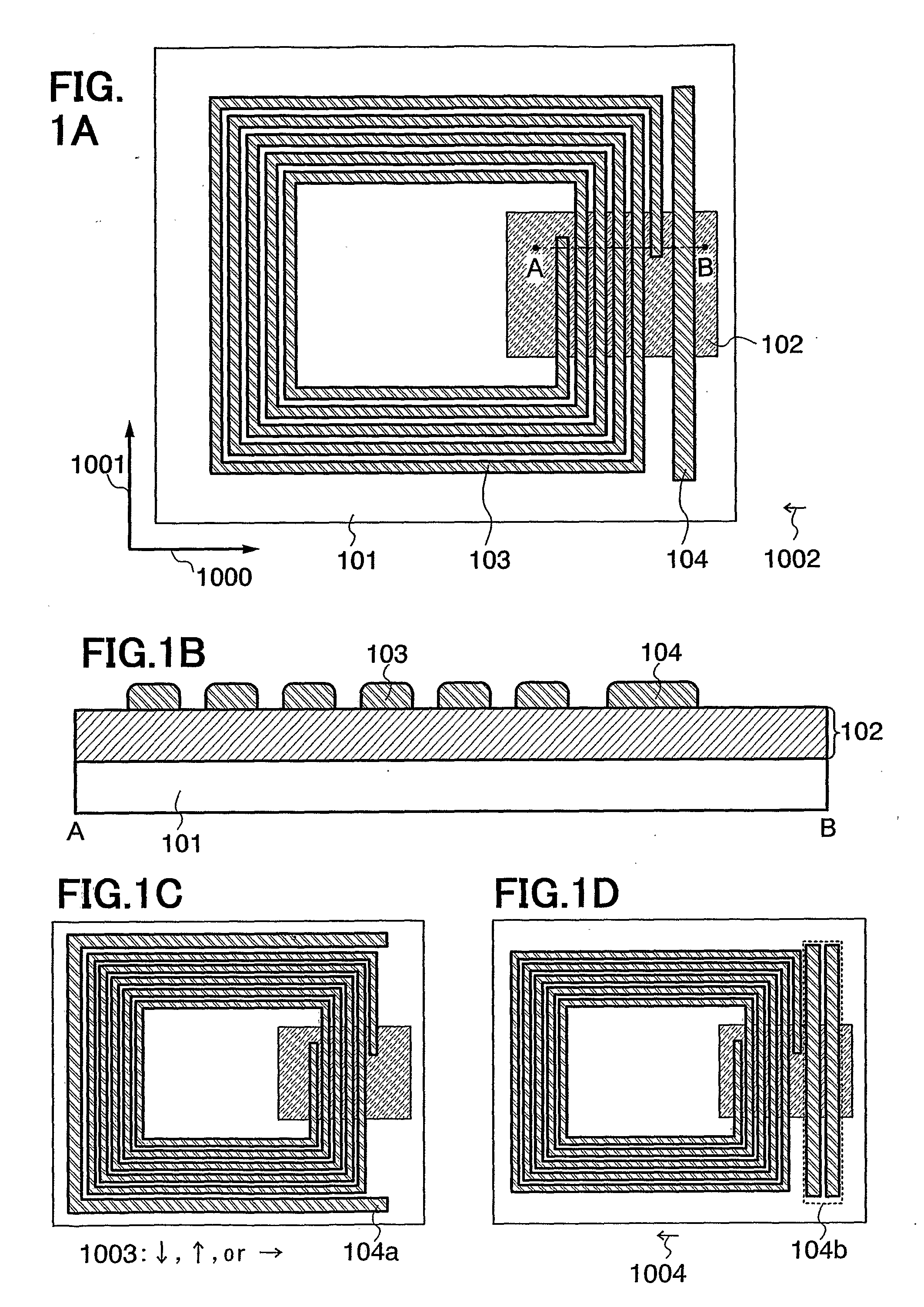

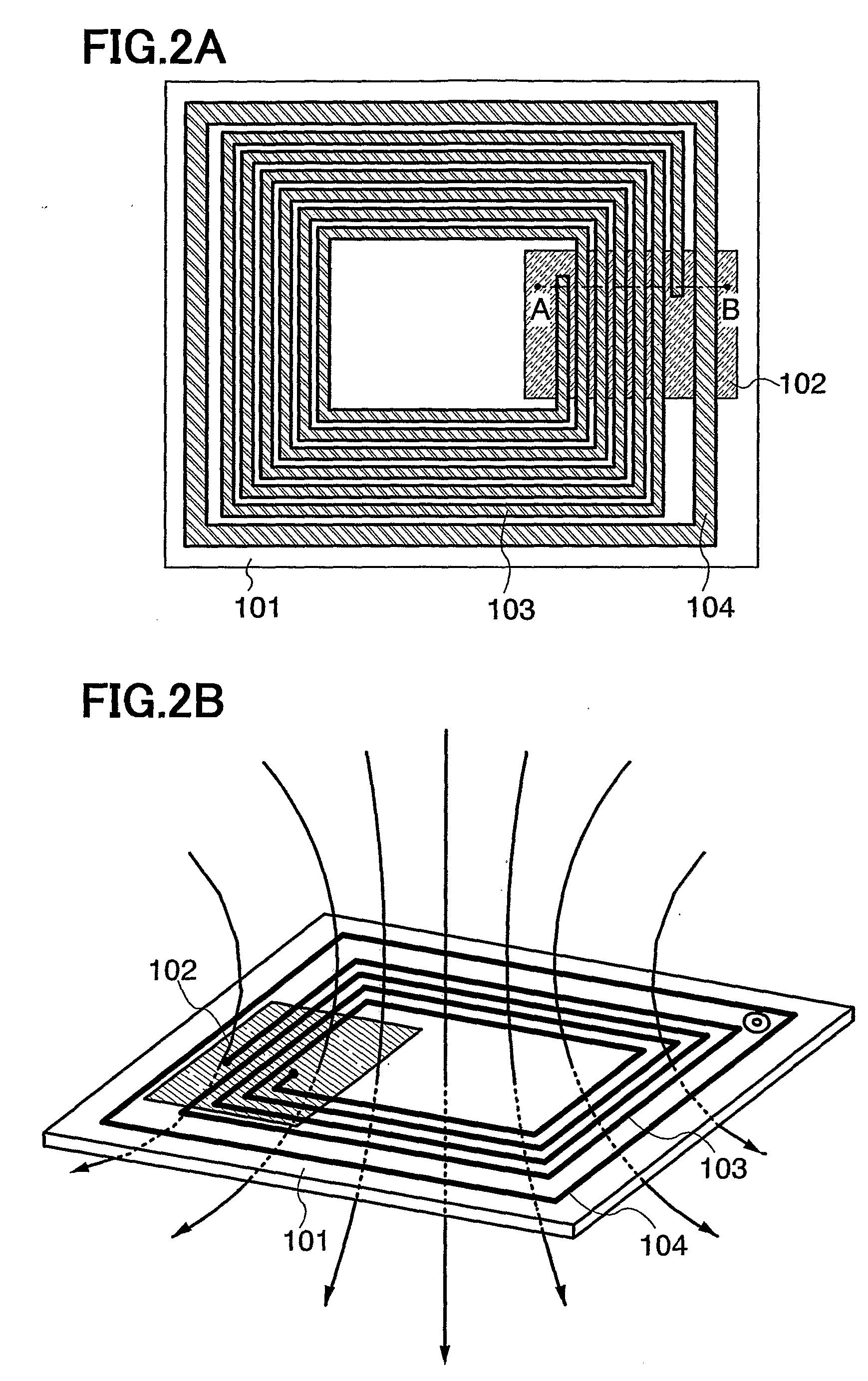

Semiconductor Device, Manufacturing Method Thereof, and Manufacturing Method of Antenna

InactiveUS20090065588A1Increase productionSemiconductor/solid-state device detailsSolid-state devicesEngineeringSolder paste

An element group having a transistor is formed over a substrate and a conductive film to be a dummy pattern is formed over the element group by pushing out a paste including conductive particles from a first opening portion, and then a conductive film functioning as an antenna is formed continuously thereafter so as to electrically connect with the transistor, by pushing out a paste including conductive particles from a second opening portion. Therefore, an element group having a transistor, provided over a substrate; a first conductive film functioning as an antenna provided over the element group and is electrically connected to the transistor; a second conductive film to be a dummy pattern provided to be adjacent to the first conductive film and is not electrically connected to the transistor; are included.

Owner:SEMICON ENERGY LAB CO LTD

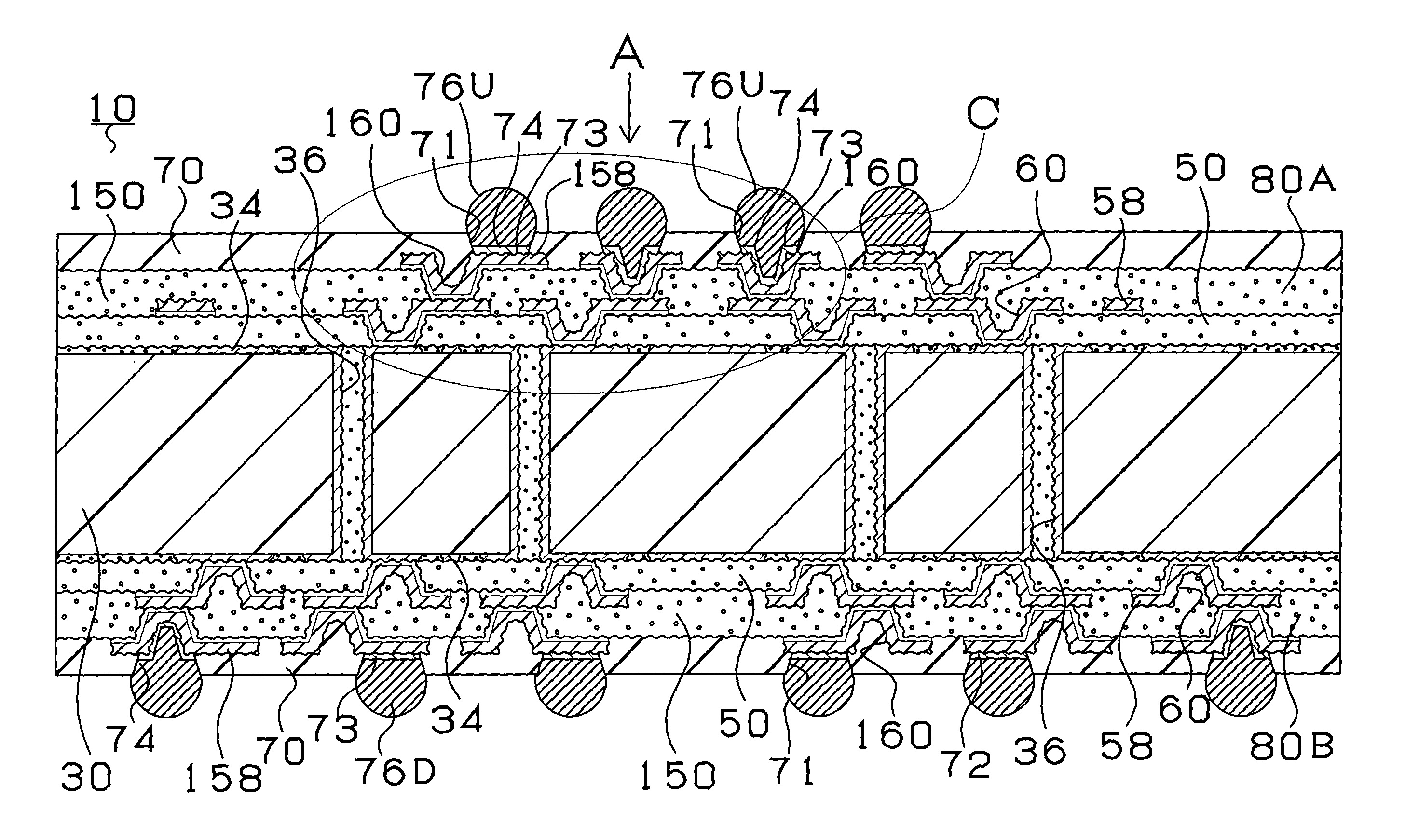

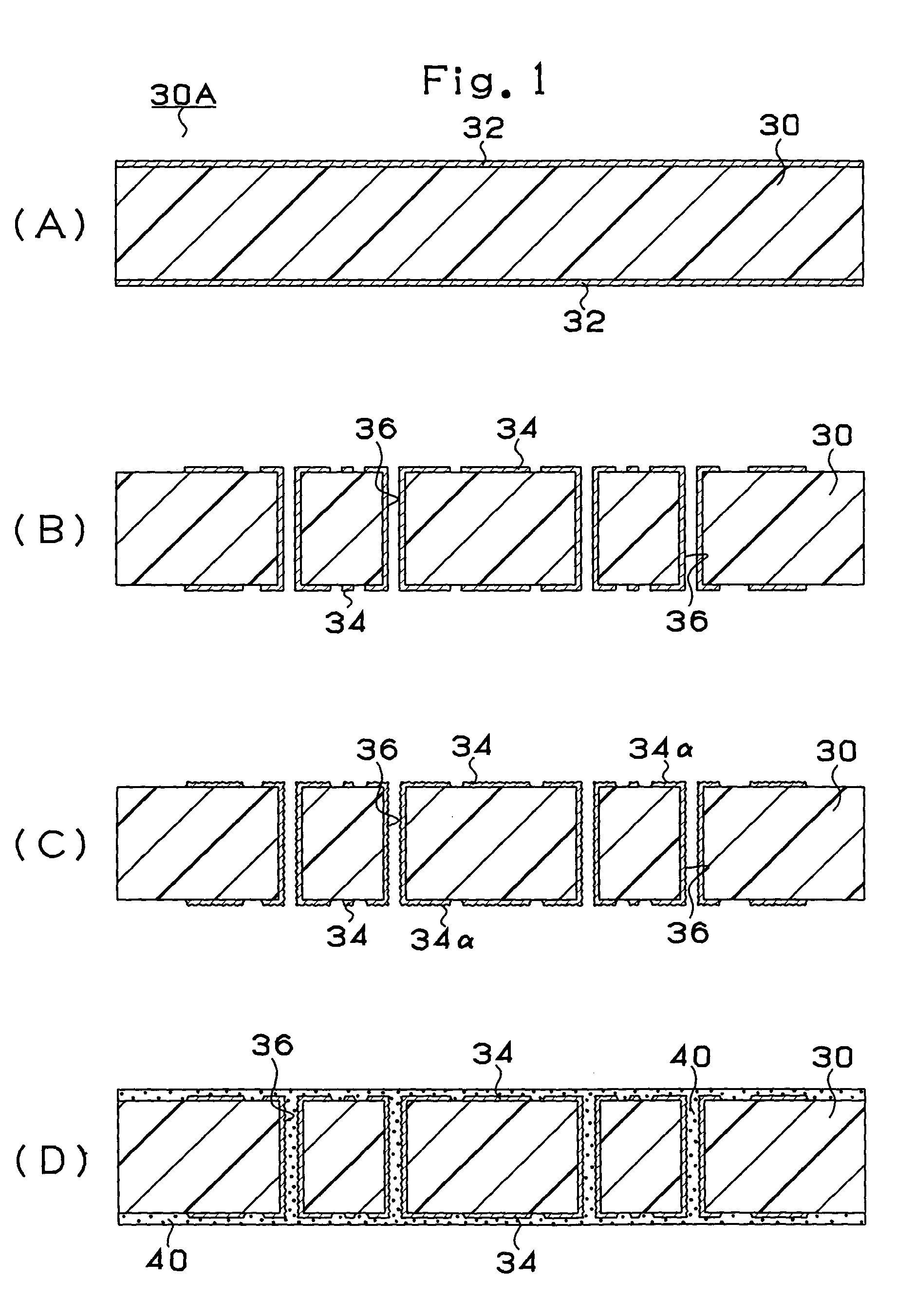

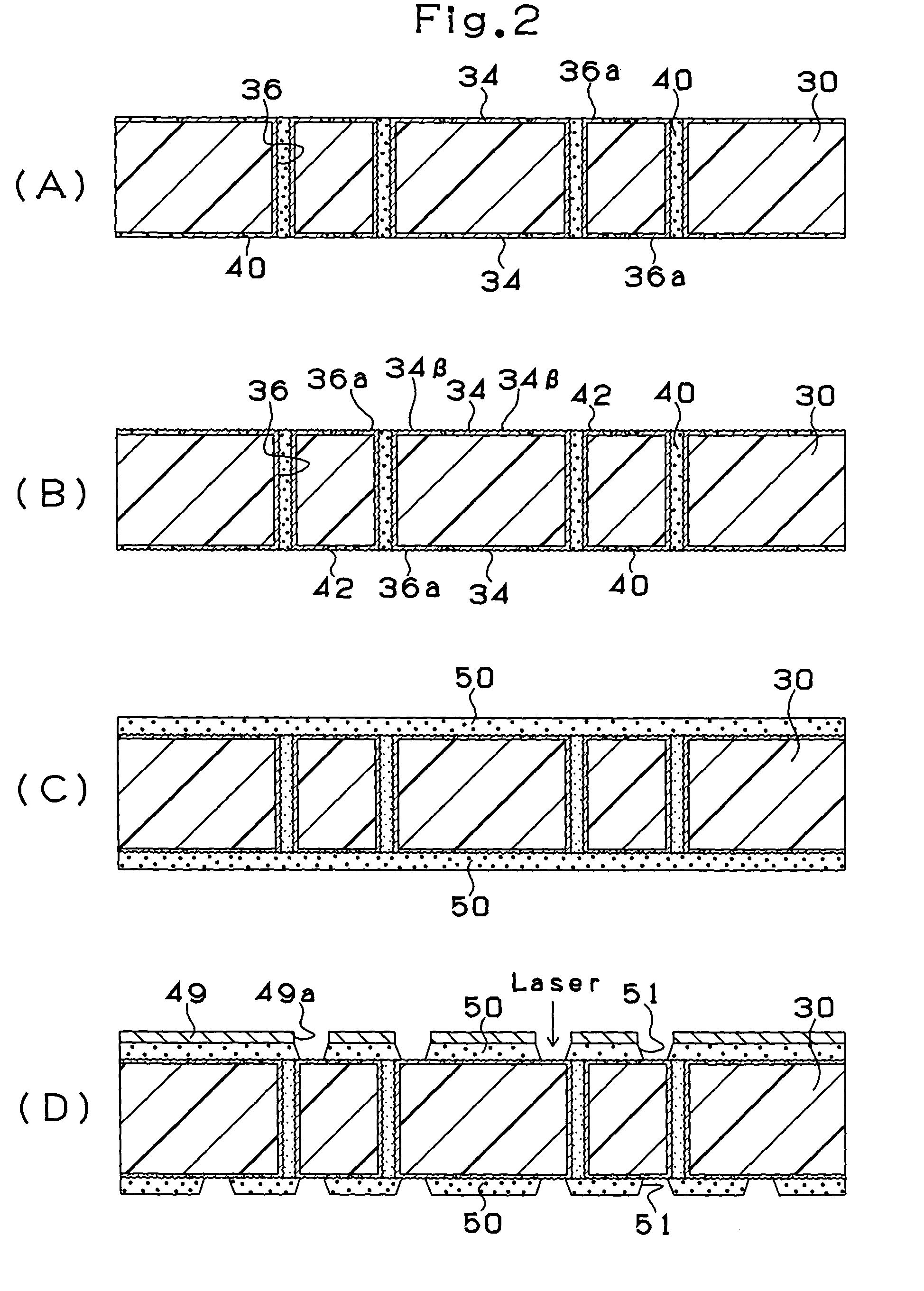

Printed wiring board and production method for printed wiring board

InactiveUS7129158B2Improve adhesionIncrease the propagation speedPrinted circuit assemblingInsulating substrate metal adhesion improvementManufacturing cost reductionElectrical conductor

A printed wiring board including solder pads excellent in frequency characteristic is provided. To do so, each solder pad 73 is formed by providing a single tin layer 74 on a conductor circuit 158 or a via 160. Therefore, a signal propagation rate can be increased, as compared with a printed wiring board of the prior art on which two metal layers are formed. In addition, due to lack of nickel layers, manufacturing cost can be decreased and electric characteristics can be enhanced.

Owner:IBIDEN CO LTD

System and methods for data-driven control of manufacturing processes

Systems and methods for implementing hybrid, closed-loop control that generates control values for processes defined by a limited number of function evaluations and large amounts of process and measurement noise. The described control system is applied to a stencil printing process for applying solder paste to an electronic medium such as a printed circuit board or semiconductor wafer. The control system is defined by a hybrid approach. A first, coarse algorithm is used to rapidly produce the value of a stencil printer control value resulting in a solder paste deposit having a volume within predetermined acceptable limits. After the coarse algorithm no longer produces solder paste deposits closer to a desired volume, a second, more refined estimator is used to fine tune the process. An additional transitional algorithm may be added between the coarse algorithm and refined estimator. The coarse algorithm may be implemented with a constrained-conjugated gradient search, and the refined search may be a implemented using a least-squares affine estimator or a quadratic estimator. The transitional algorithm may be implemented using a block version of a least-squares affine estimator.

Owner:GEORGIA TECH RES CORP

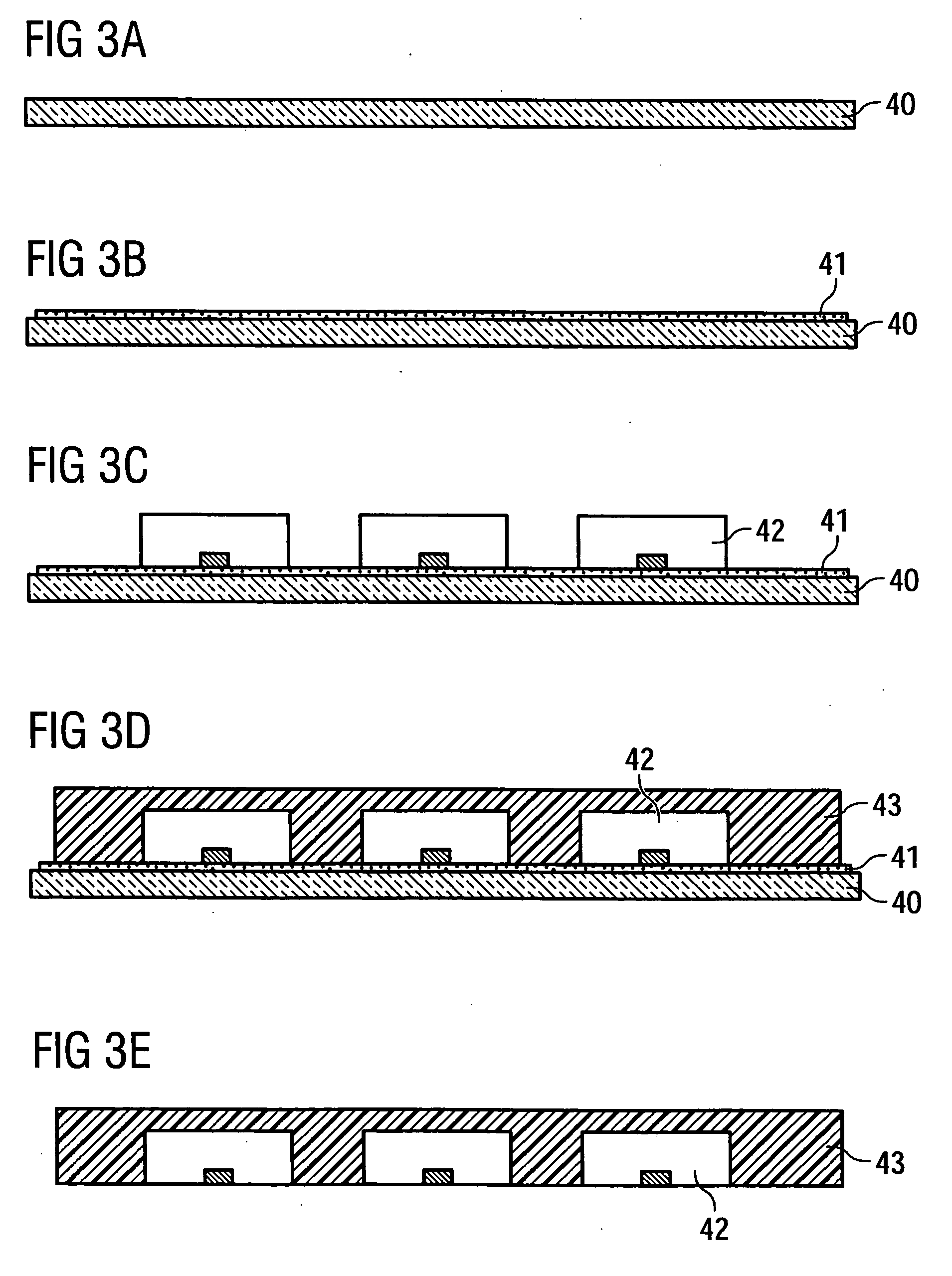

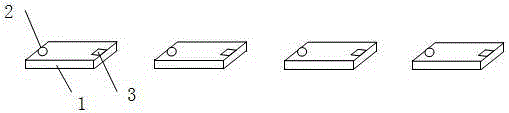

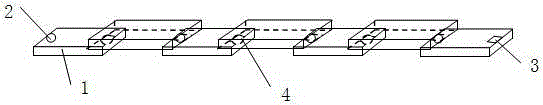

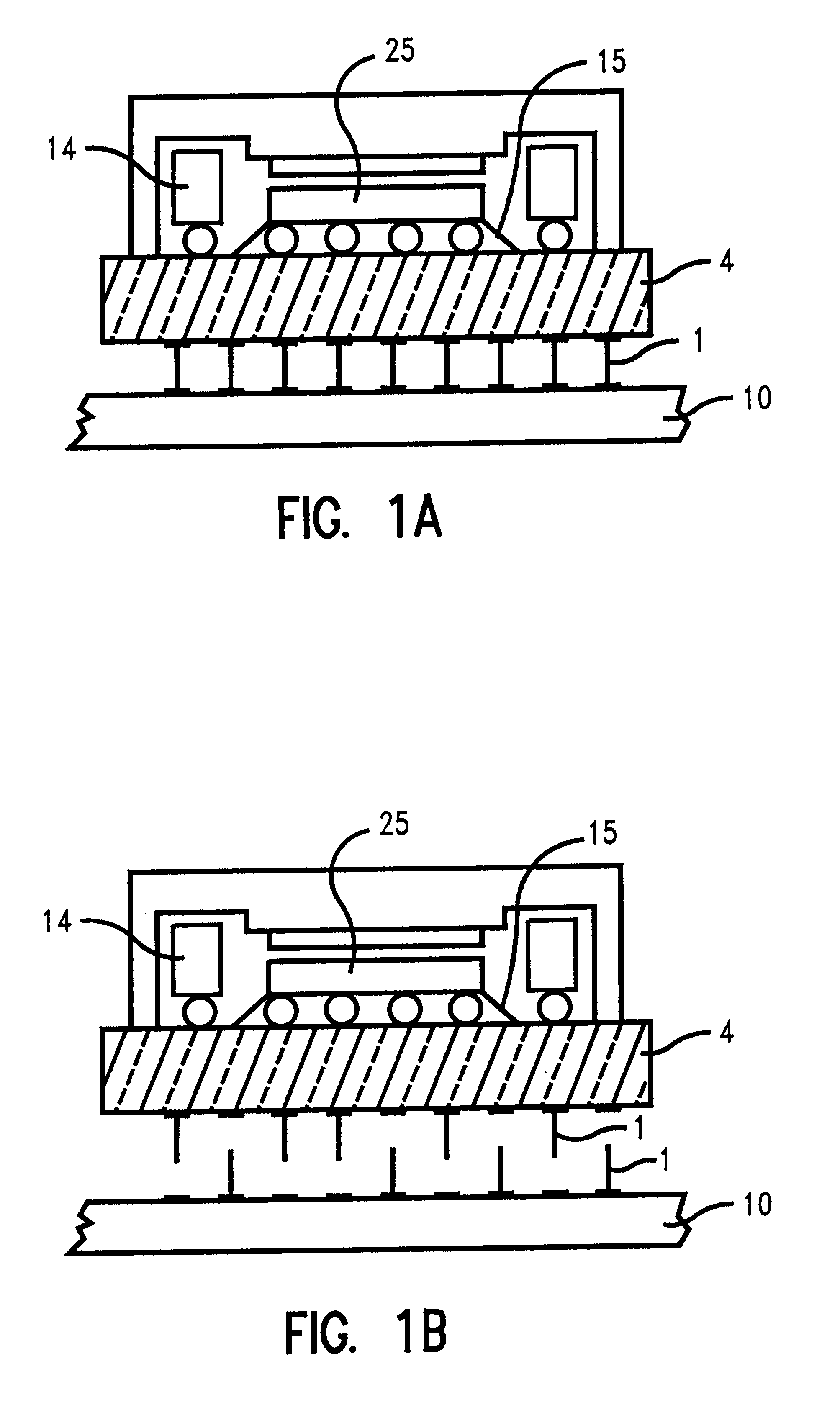

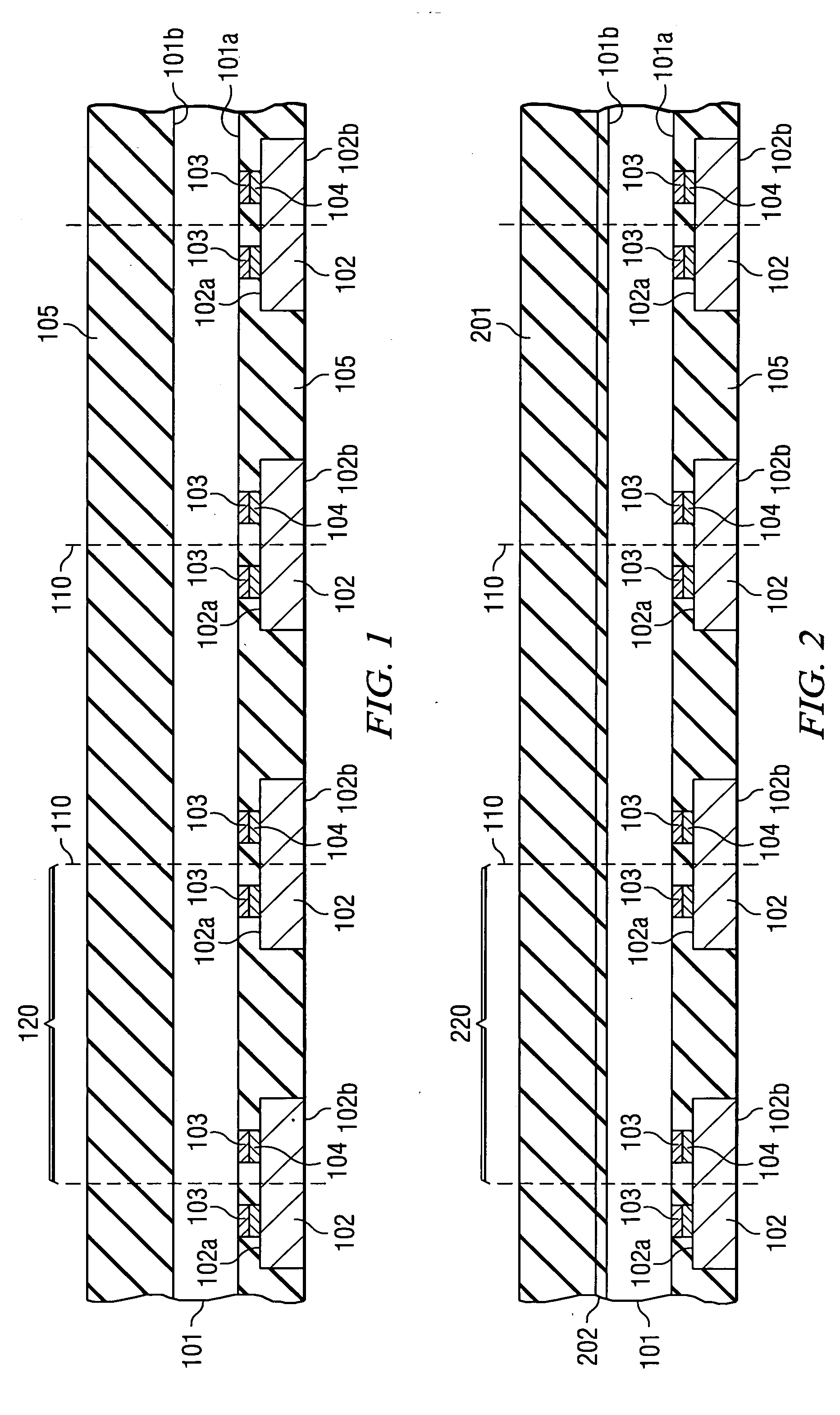

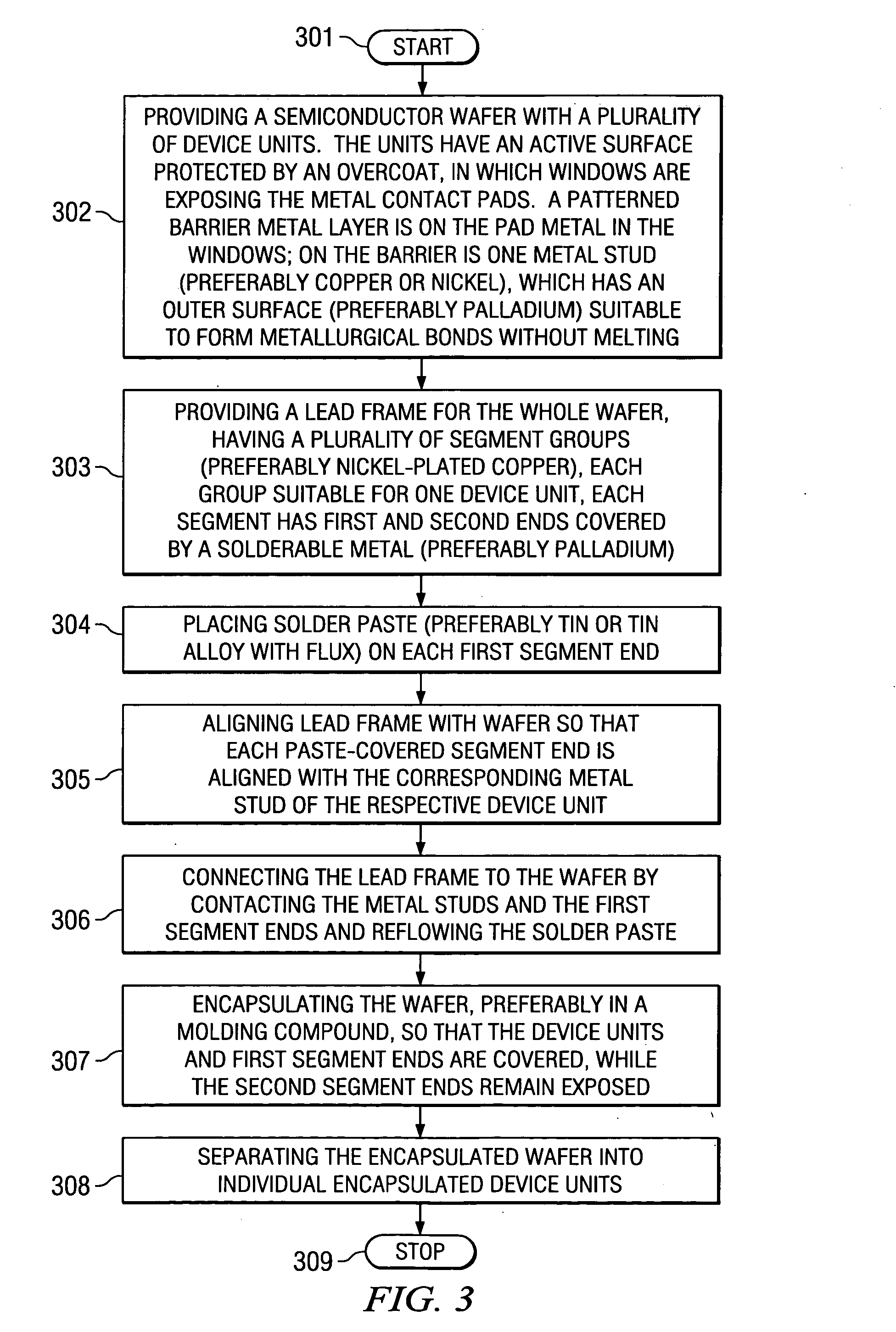

Wafer-level assembly method for chip-size devices having flipped chips

InactiveUS20050151268A1Reduce manufacturing costImprove packaging effectSemiconductor/solid-state device detailsSolid-state devicesContact padChip size

A method for assembling a whole semiconductor wafer (101) with a plurality of device units (120) having metal contact pads. Each contact pad has a patterned barrier metal layer and a metal stud (103, preferably copper or nickel) with an outer surface suitable to form metallurgical bonds without melting. A leadframe suitable for the whole wafer is provided, which has a plurality of segments groups (102), each group suitable for one device unit; each segment has first (102a) and second ends (102b) covered by solderable metal. A predetermined amount of solder paste (104) is placed on each of the first segment ends. The leadframe is then aligned with the wafer so that each of the paste-covered segment ends is aligned with the corresponding metal stud of the respective device unit. The leadframe is connected to the wafer and the whole wafer is encapsulated (105) so that the device units and the first segment ends are covered, while the second segment ends remain exposed. The encapsulated wafer is separated (110) into individual device units (120).

Owner:TEXAS INSTR INC

Package with solder-filled via holes in molding layers

InactiveUS20080036050A1Improve configurationImproved procedureSemiconductor/solid-state device detailsSolid-state devicesShell moldingFlexible circuits

The present invention discloses an electronic package to contain and protect an integrated circuit (IC) chip. The electronic package further includes a leadframe, a flexible circuit or PCB type of substrate. The leadframe, flexible circuit or PCB type substrate further includes solder contacts, which are aligned with via holes in the molding layers on the top and bottom sides of the package. These via holes are for placing solder paste or solder balls from above and below for electrical access to the IC chip. These solder balls provide access for electrical testing after the package is mounted on a motherboard. They also provide the connection points for stacking multiple packages vertically.

Owner:LIN PAUL T +1

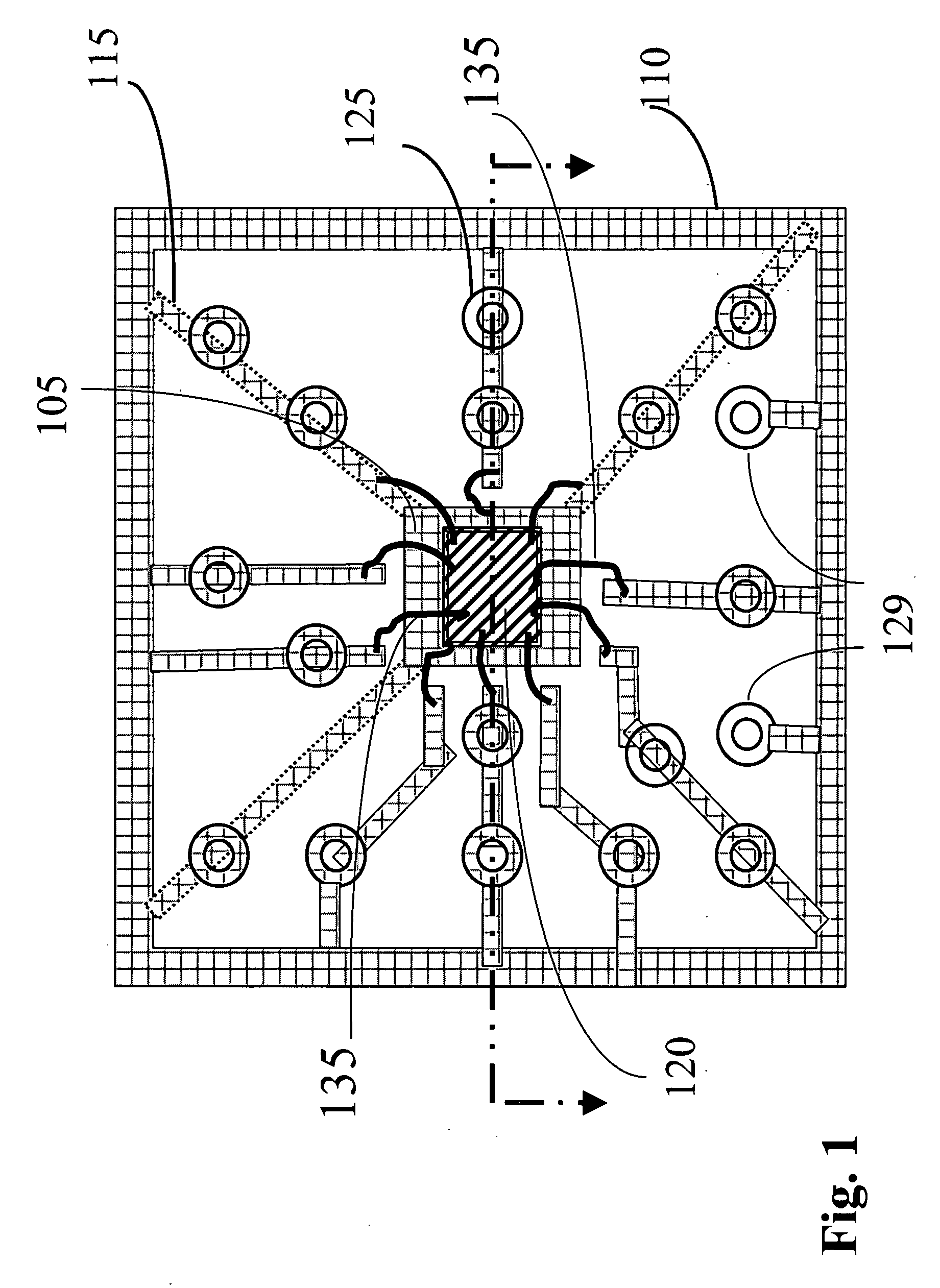

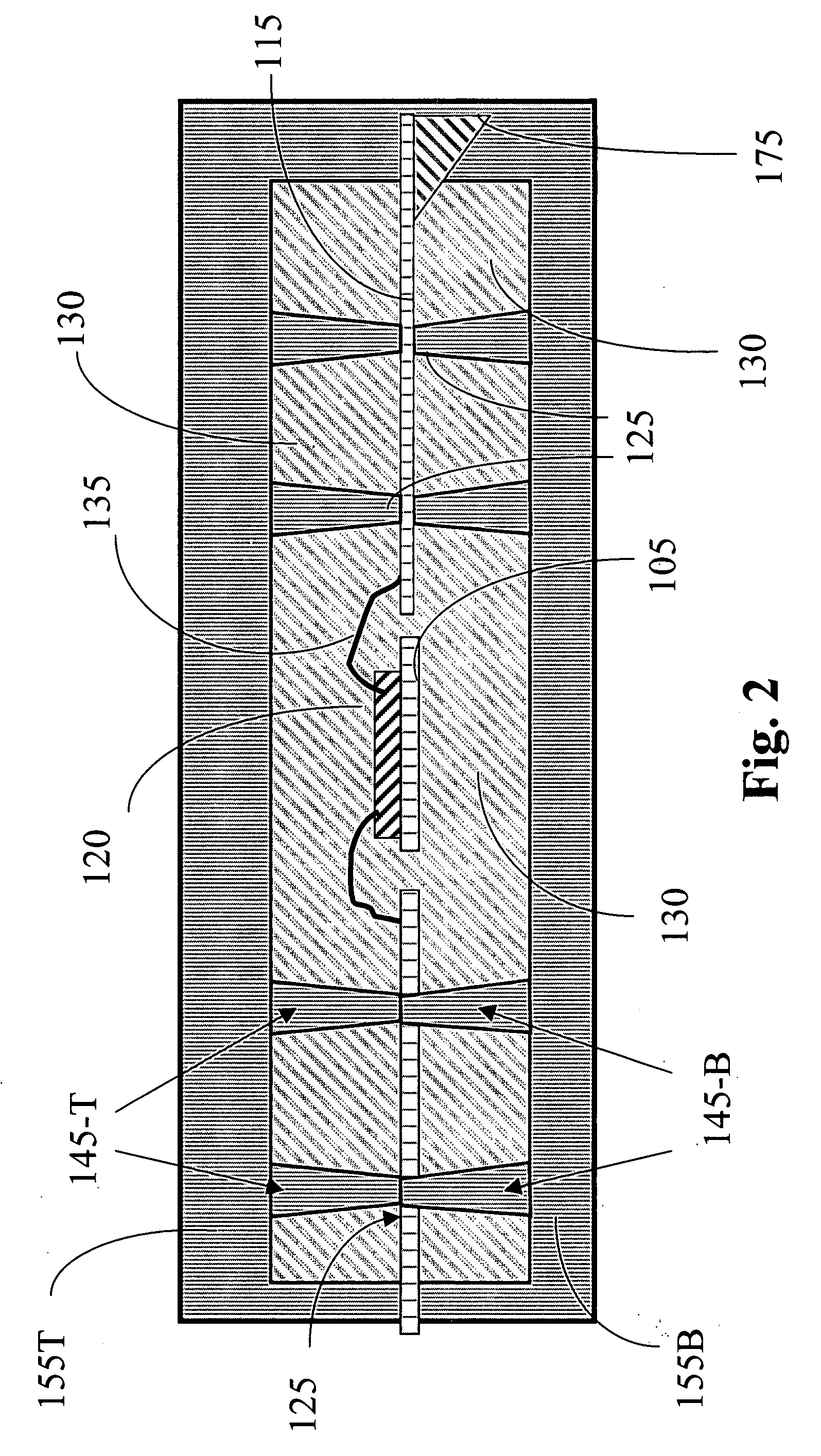

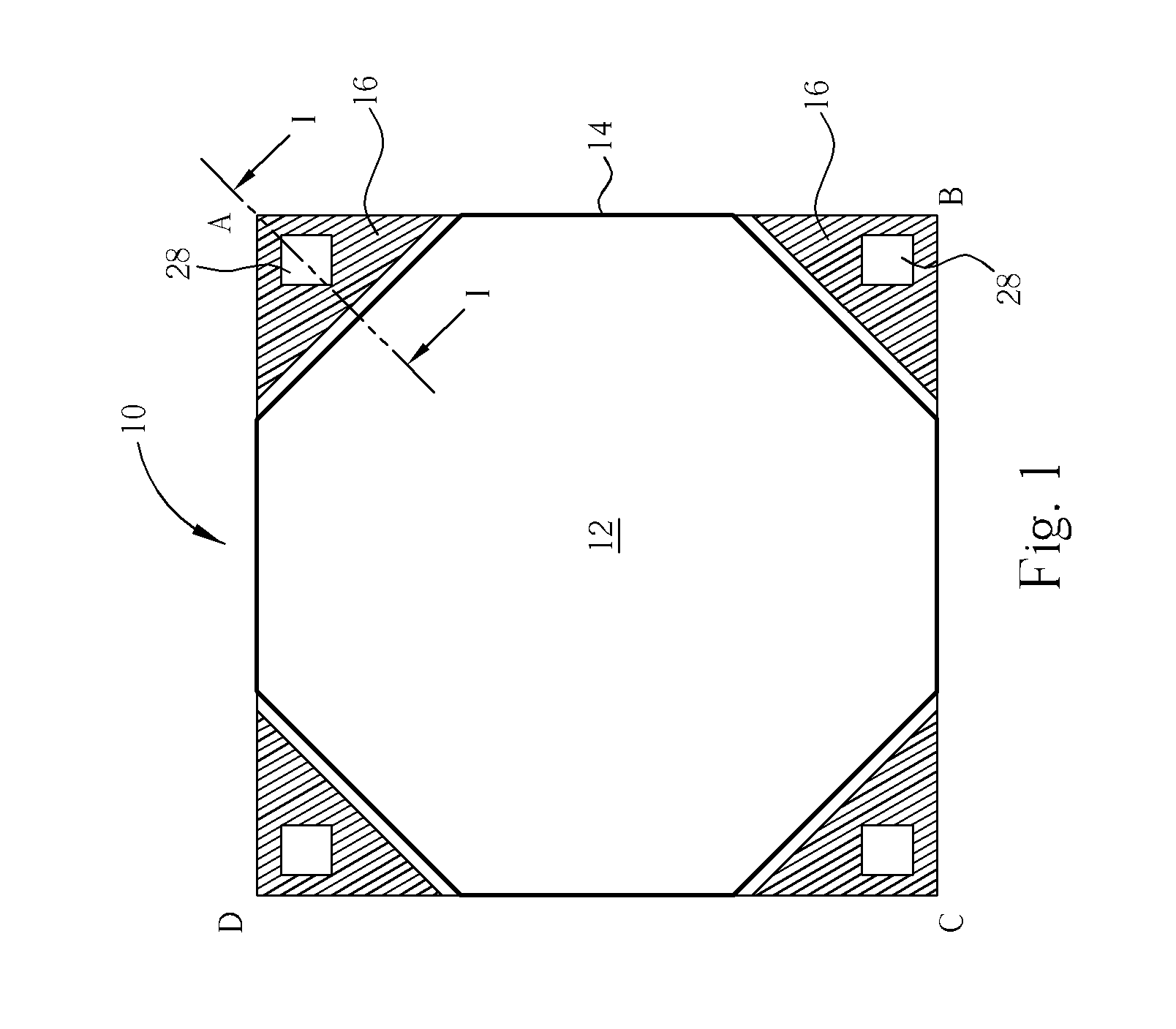

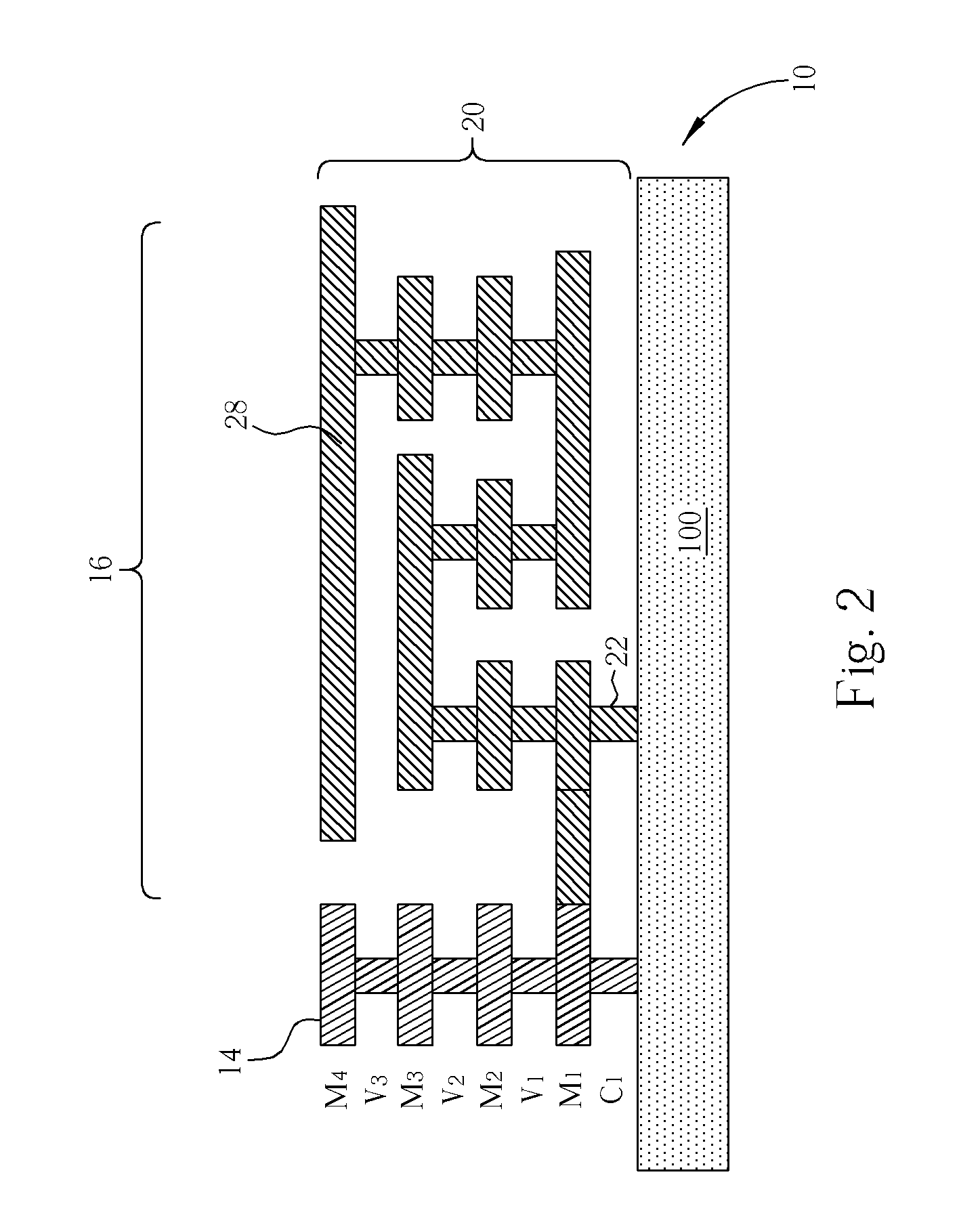

On-chip test circuit for assessing chip integrity

ActiveUS20070023915A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder paste

A semiconductor chip includes an active inner circuit; a die seal ring surrounding the active inner circuit; a first circuit structure fabricated at a first corner of the semiconductor chip outside the die seal ring and electrically connected to the die seal, wherein the first circuit structure has a first solder pad; and a second circuit structure fabricated at a second corner of the semiconductor chip outside the die seal ring and electrically connected to the die seal, wherein the second circuit structure has a second solder pad.

Owner:UNITED MICROELECTRONICS CORP

Method for welding FPC plate with PCB plate and its dedicated clamp

ActiveCN101083878AImprove consistencySmall temperature differencePrinted circuit assemblingEngineeringSolder paste

The present invention offers a method of welding FPC board and PCB board, and the special fixture for this method which includes an upper-template and an under-template. The method includes the following steps: the first step, printing solder paste onto a big-piece PCB board composed of several small-piece PCB boards; the second step, using SMT to compose components onto the PCB board; the third step, fixing the PCB board in the slot of under-template of the fixture for locating; the fourth step, aligning the solder pad zones of FPC board and PCB board; the fifth step, covering the upper-template of the fixture to the upper-surface of the PCB board, and the overlapped area of solder-pad zone is 50%-80%, the under-surface of the upper-template should must maintain horizontal, rotating the block button on the under-template to fasten the upper-template; the sixth step, sending the fastened fixture into enclosed reflow oven for refluxing weld; the seventh step, taking off the template, checking the welding state between FPC board and PCB board. As the said welding method is less in steps and simple in its special fixture, the productive efficiency is high, and the cost is low.

Owner:SHENZHEN NEOPHOTONICS TECH

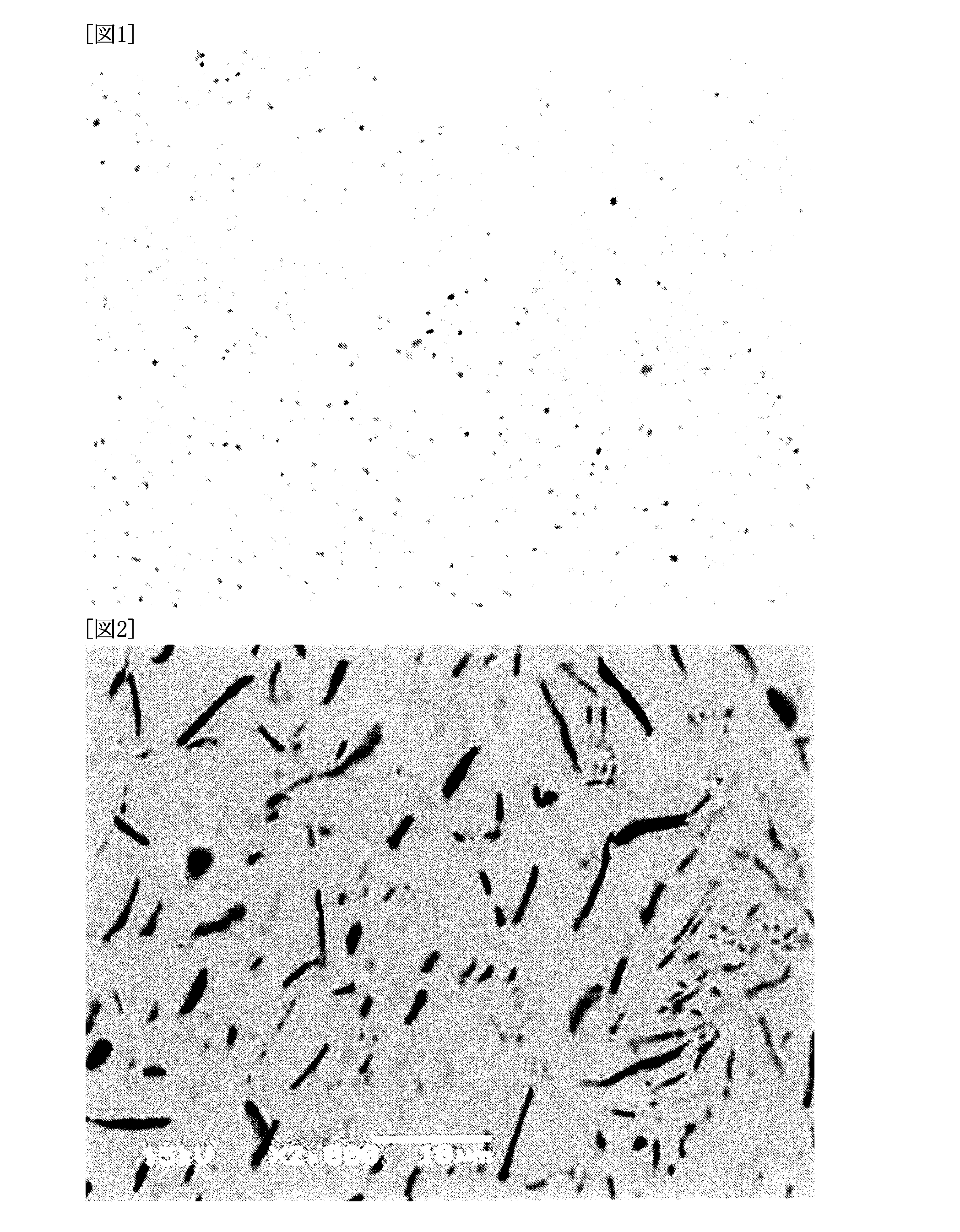

Lead-free solder paste

ActiveUS20090301606A1Reduced strengthImprove heat resistancePrinted circuit aspectsPrinted circuit manufactureAlloySolder paste

In a conventional Sn—Zn based lead-free solder, Zn crystallized to a large size of several tens of micrometers, and it was difficult to suppress the formation of coarse crystallizates and to increase the bonding strength without changing the soldering temperature. There were alloys which improved strength by the addition of a minute amount of a Group 1B metal, but the alloys had an increased melting temperature so that reflow could not be performed with the same temperature profile as for Sn—Pb, so the alloys had advantages and disadvantages.By using a solder paste formed by mixing an ethanol solution containing nanoparticles having a particle diameter of 5-300 nm and containing at least one of Ag, Au, and Cu with a flux and solder powder for an Sn—Zn based lead-free solder paste, the formation of an alloy of Au, Au, or Cu with Zn occurs during soldering, thereby forming fine clusters in the resulting liquid phase of molten solder, and a fine solder structure is obtained following melting.

Owner:SENJU METAL IND CO LTD