Patents

Literature

14205results about "Electrical connection printed elements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

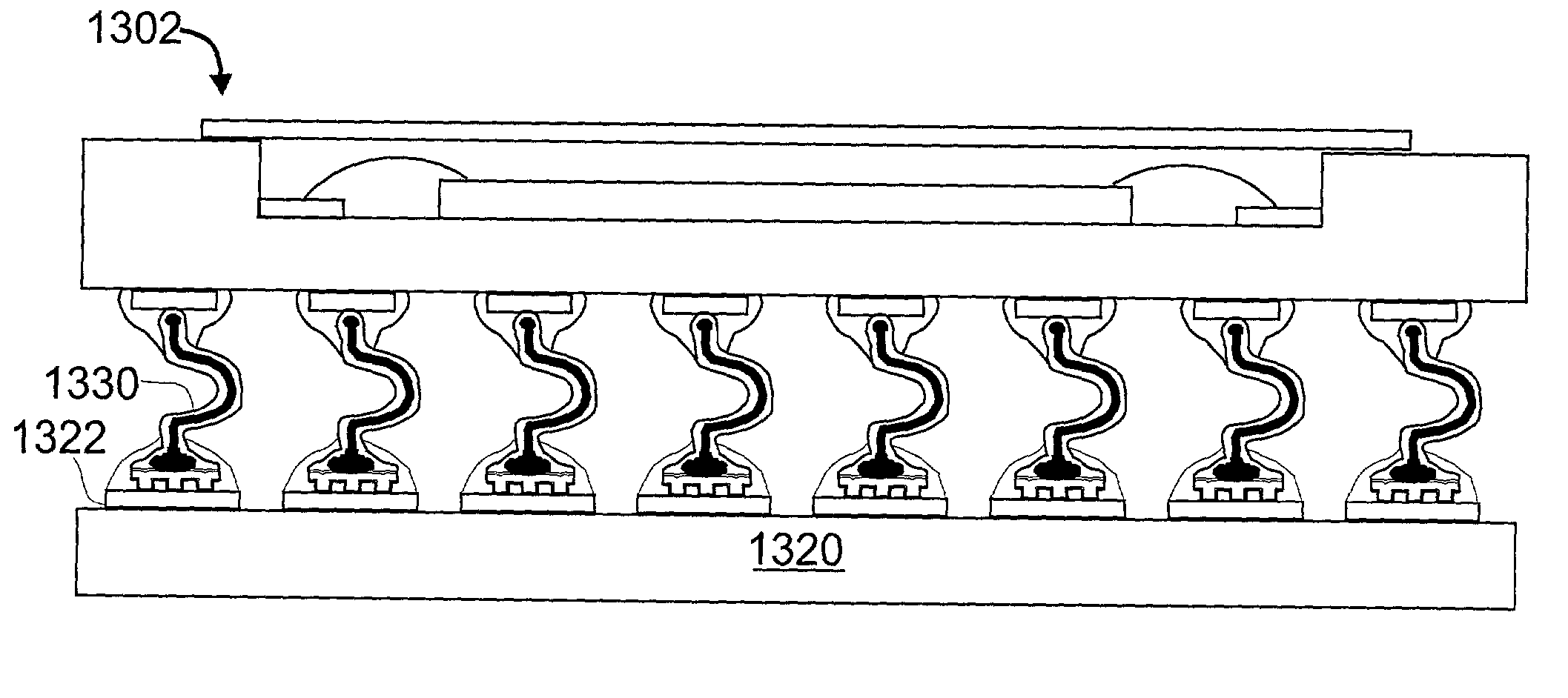

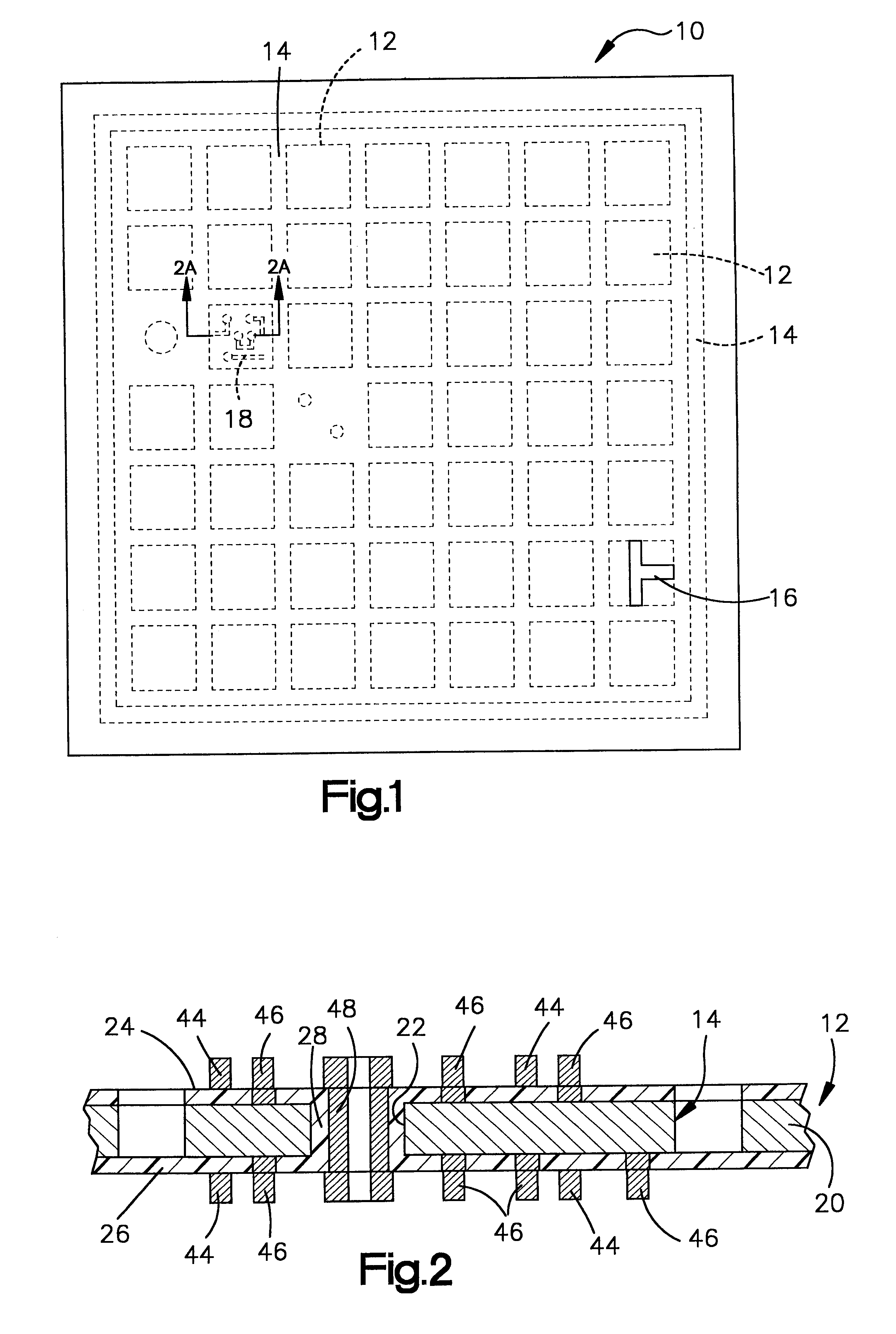

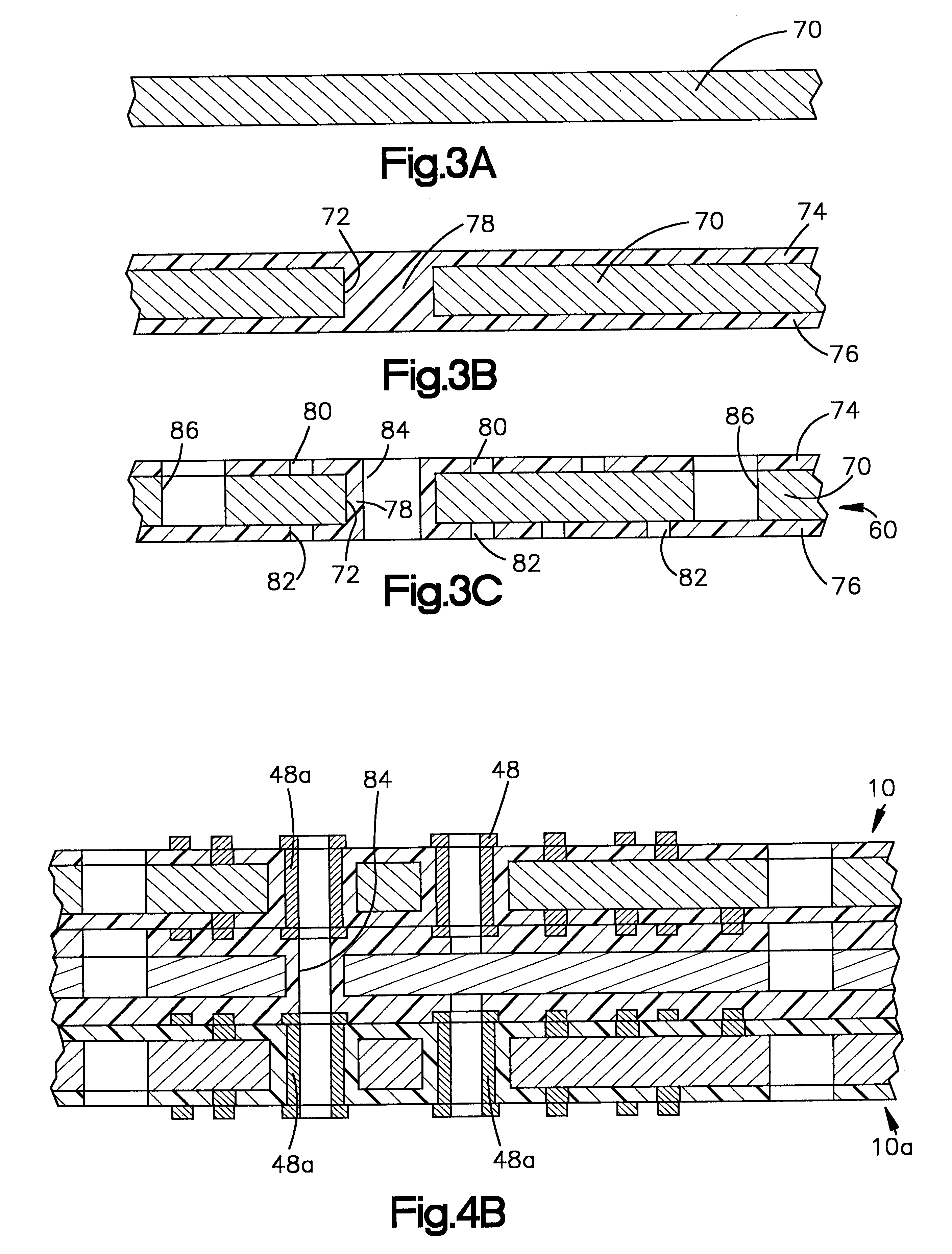

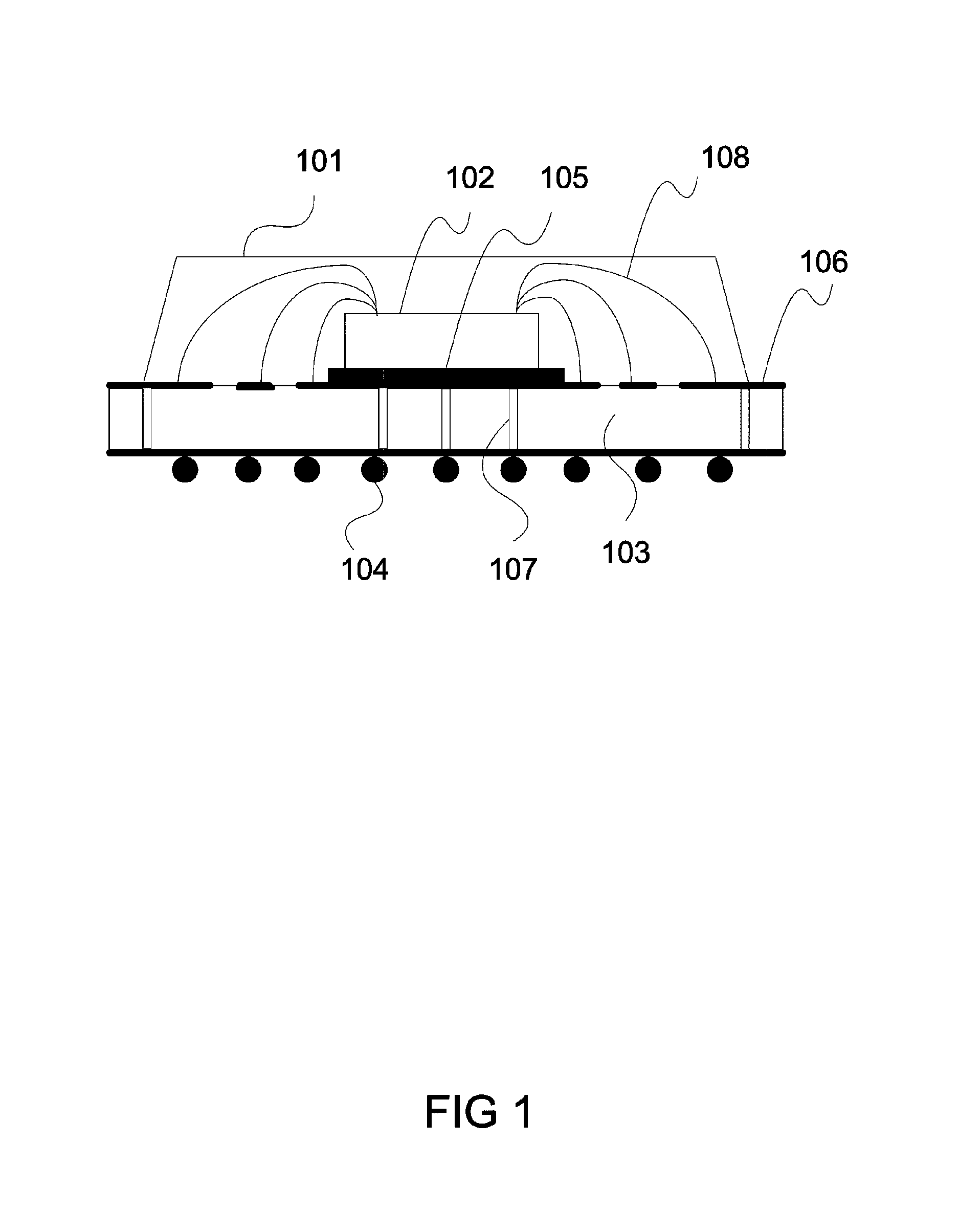

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

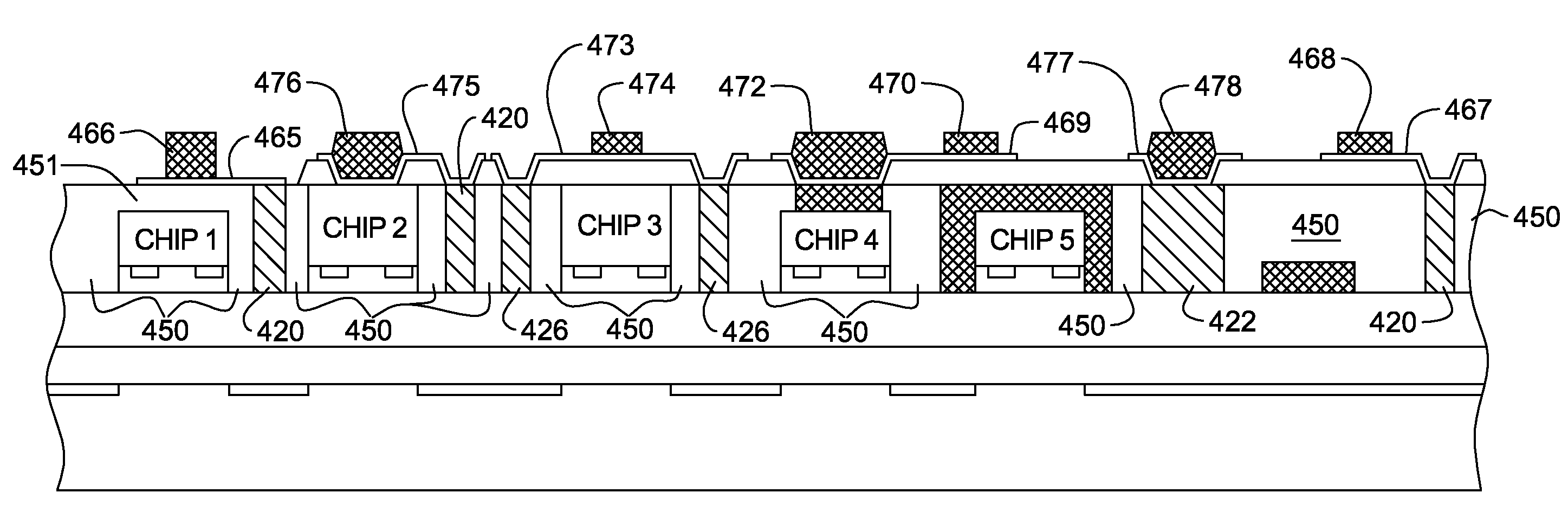

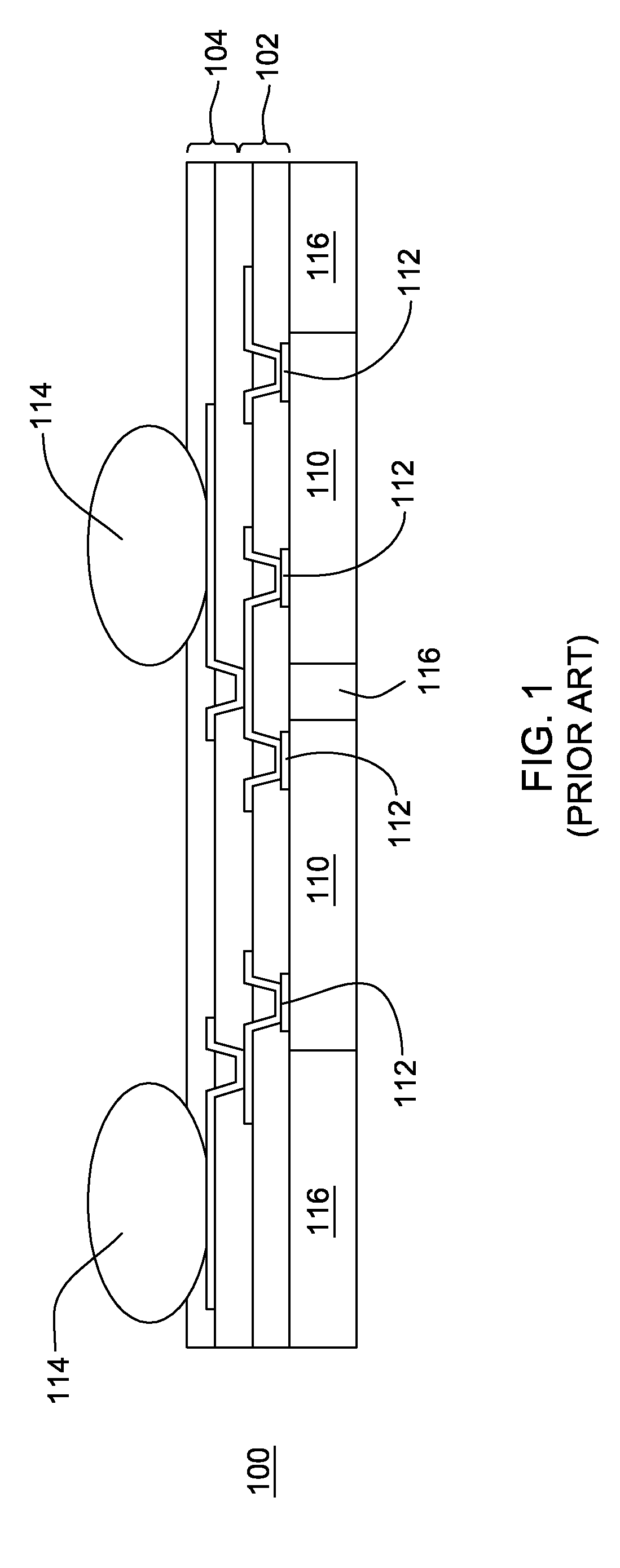

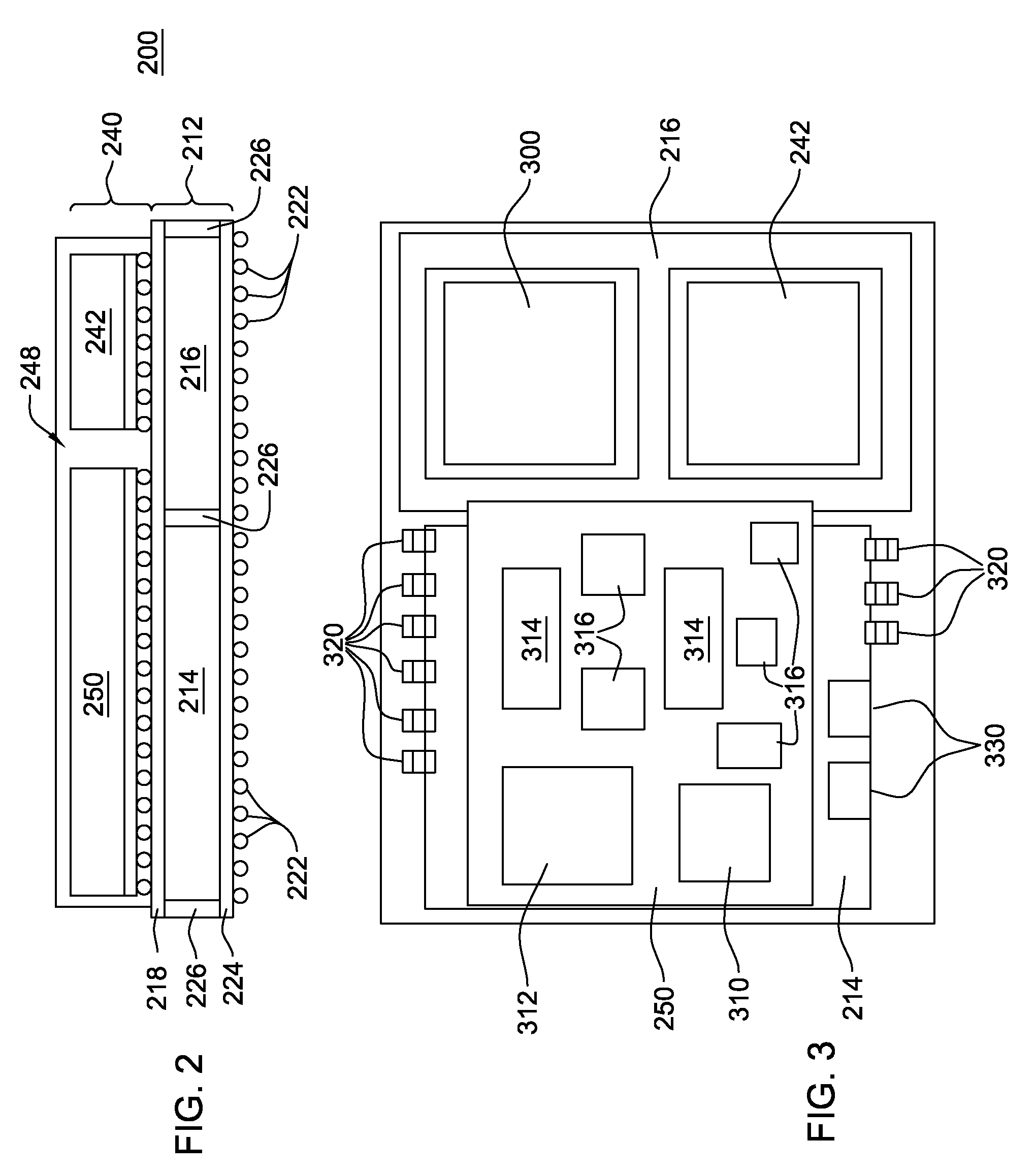

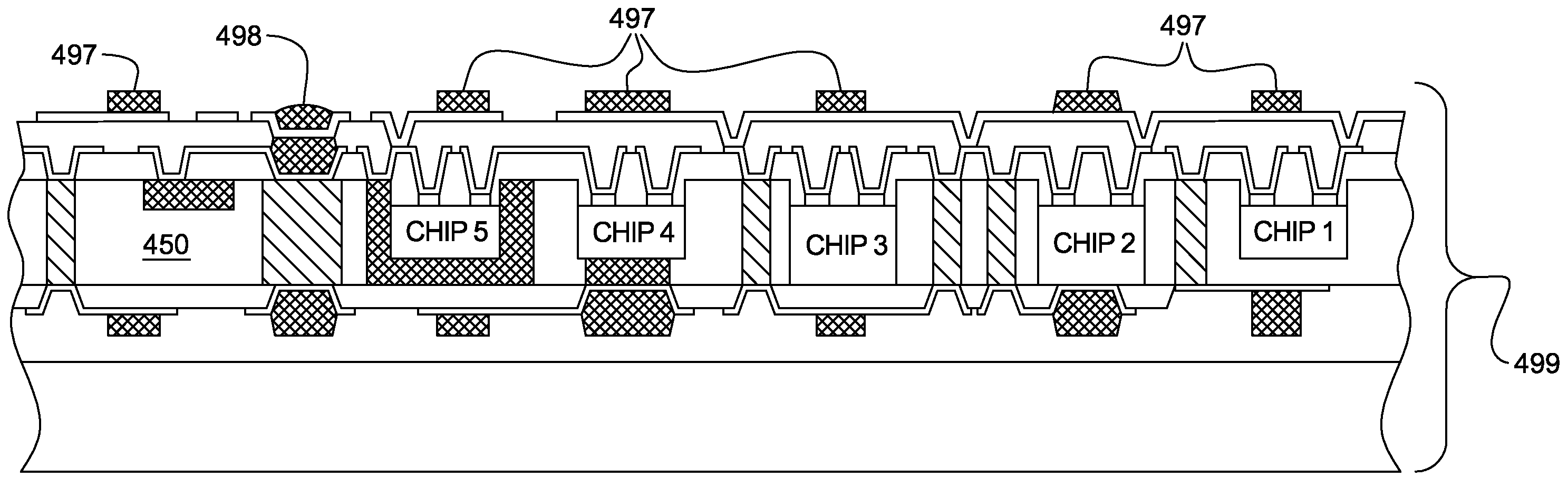

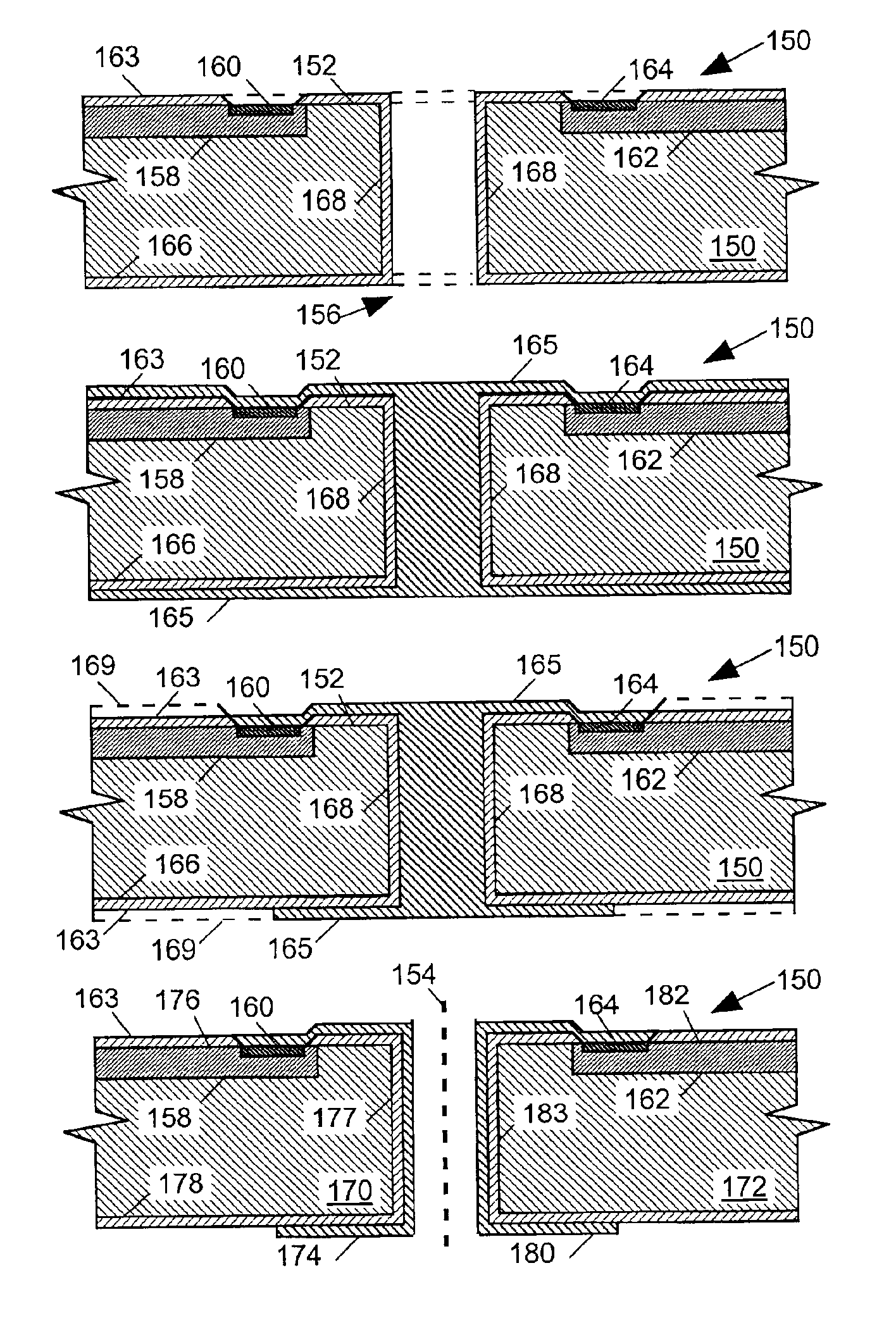

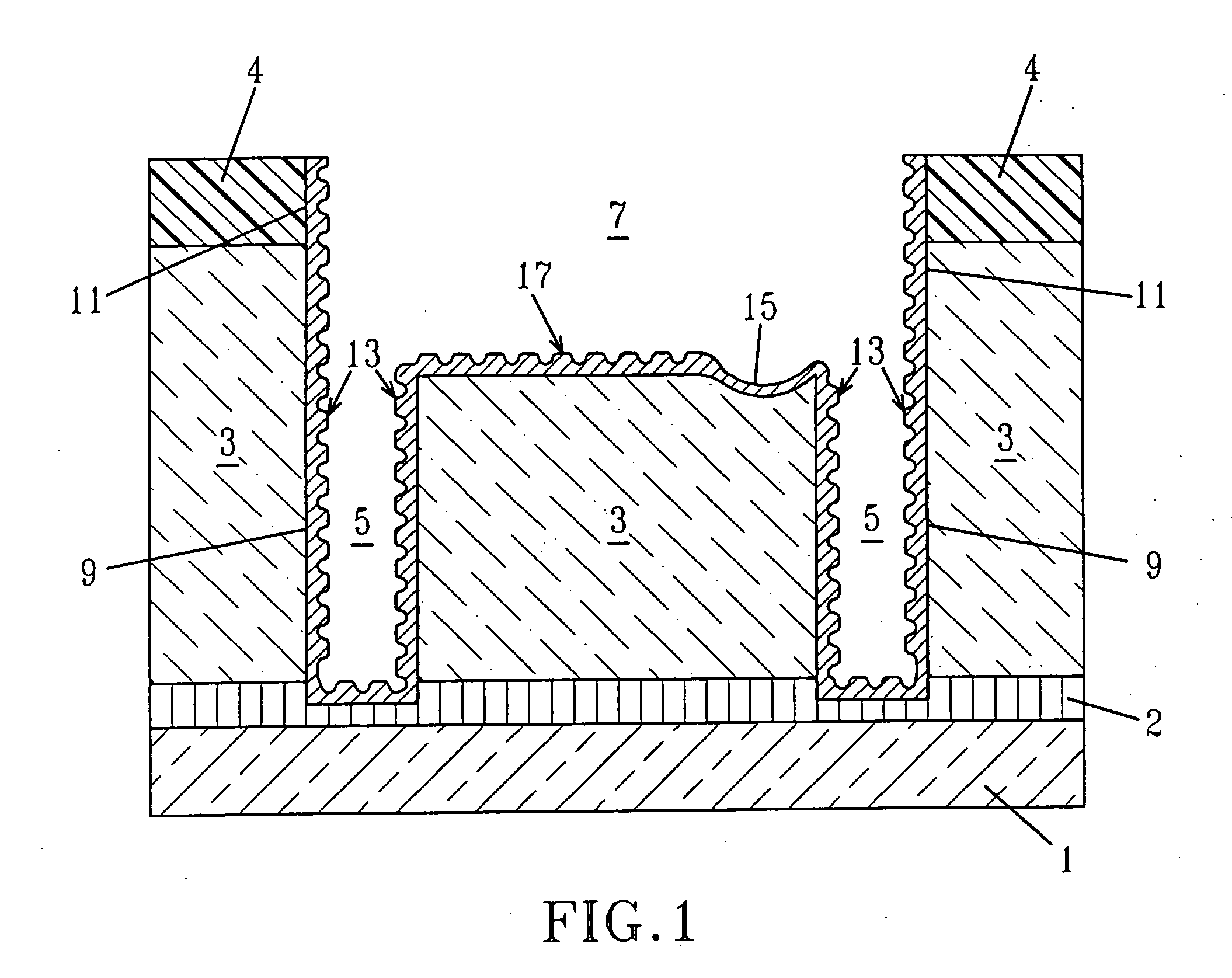

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

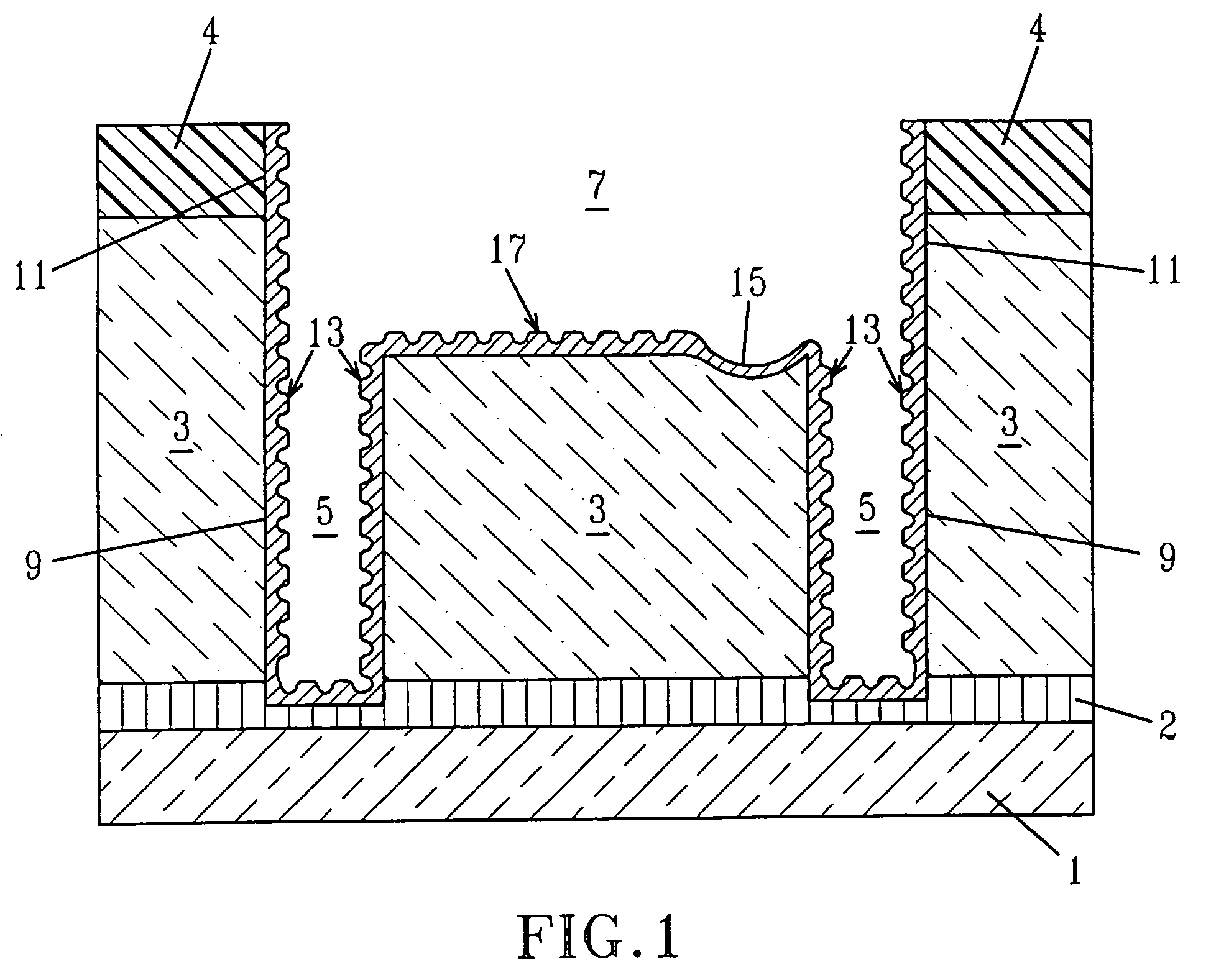

Structures and methods for integration of ultralow-k dielectrics with improved reliability

ActiveUS7088003B2Semiconductor/solid-state device detailsSolid-state devicesBiological activationDielectric layer

An improved back end of the line (BEOL) interconnect structure comprising an ultralow k (ULK) dielectric is provided. The structure may be of the single or dual damascene type and comprises a dense thin dielectric layer (TDL) between a metal barrier layer and the ULK dielectric. Disclosed are also methods of fabrication of BEOL interconnect structures, including (i) methods in which a dense TDL is provided on etched opening of a ULK dielectric and (ii) methods in which a ULK dielectric is placed in a process chamber on a cold chuck, a sealing agent is added to the process chamber, and an activation step is performed.

Owner:GLOBALFOUNDRIES U S INC

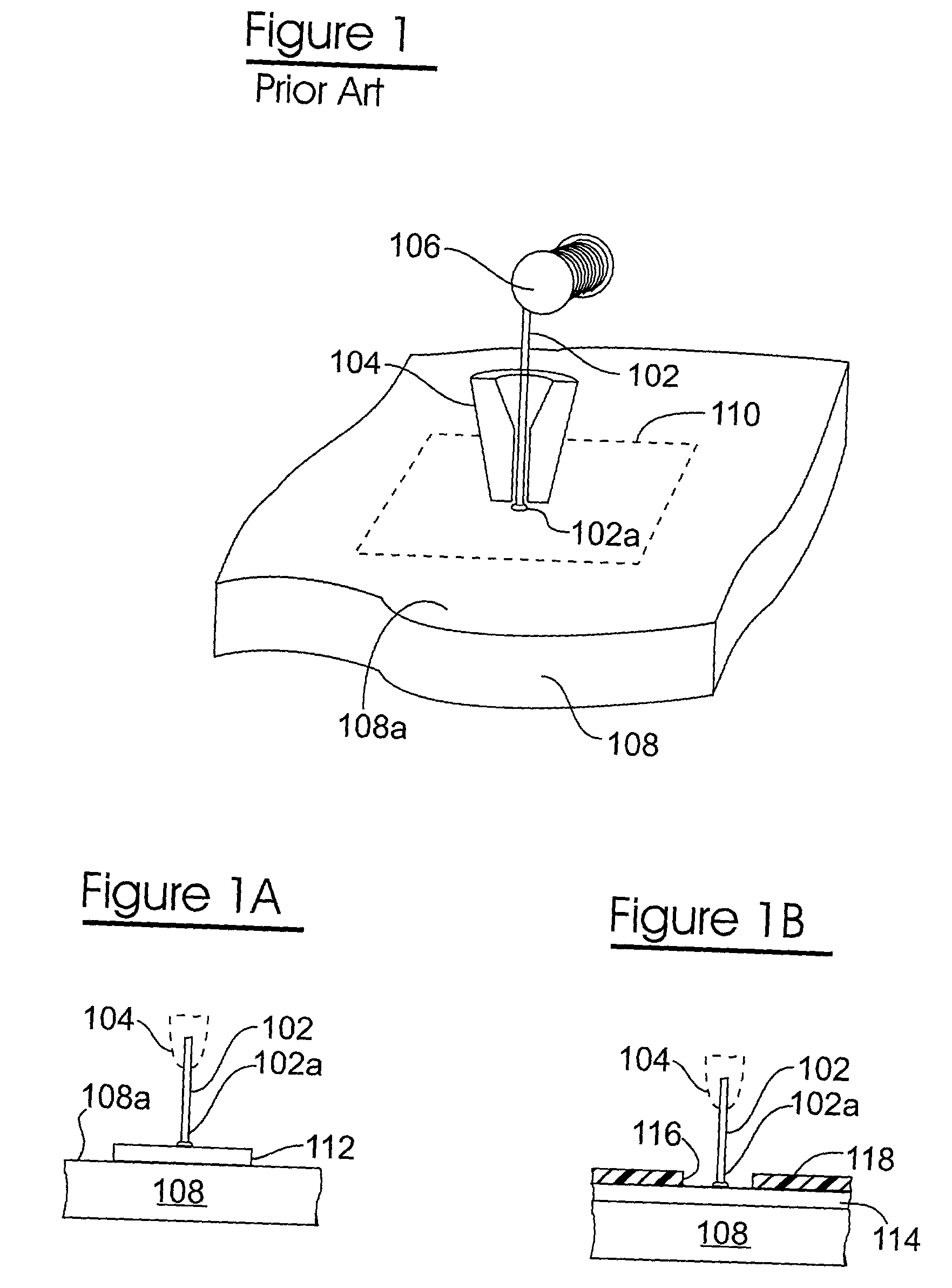

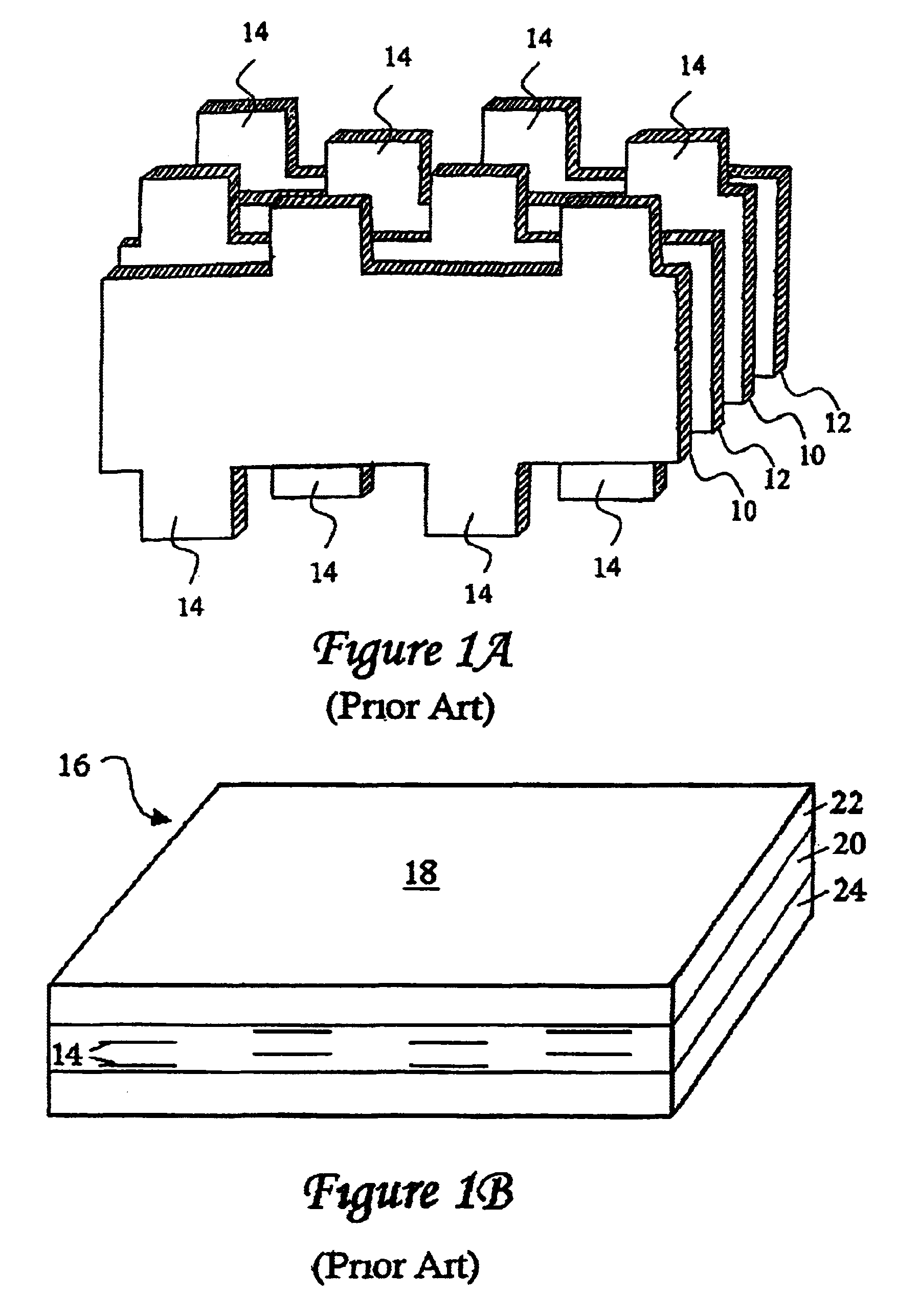

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

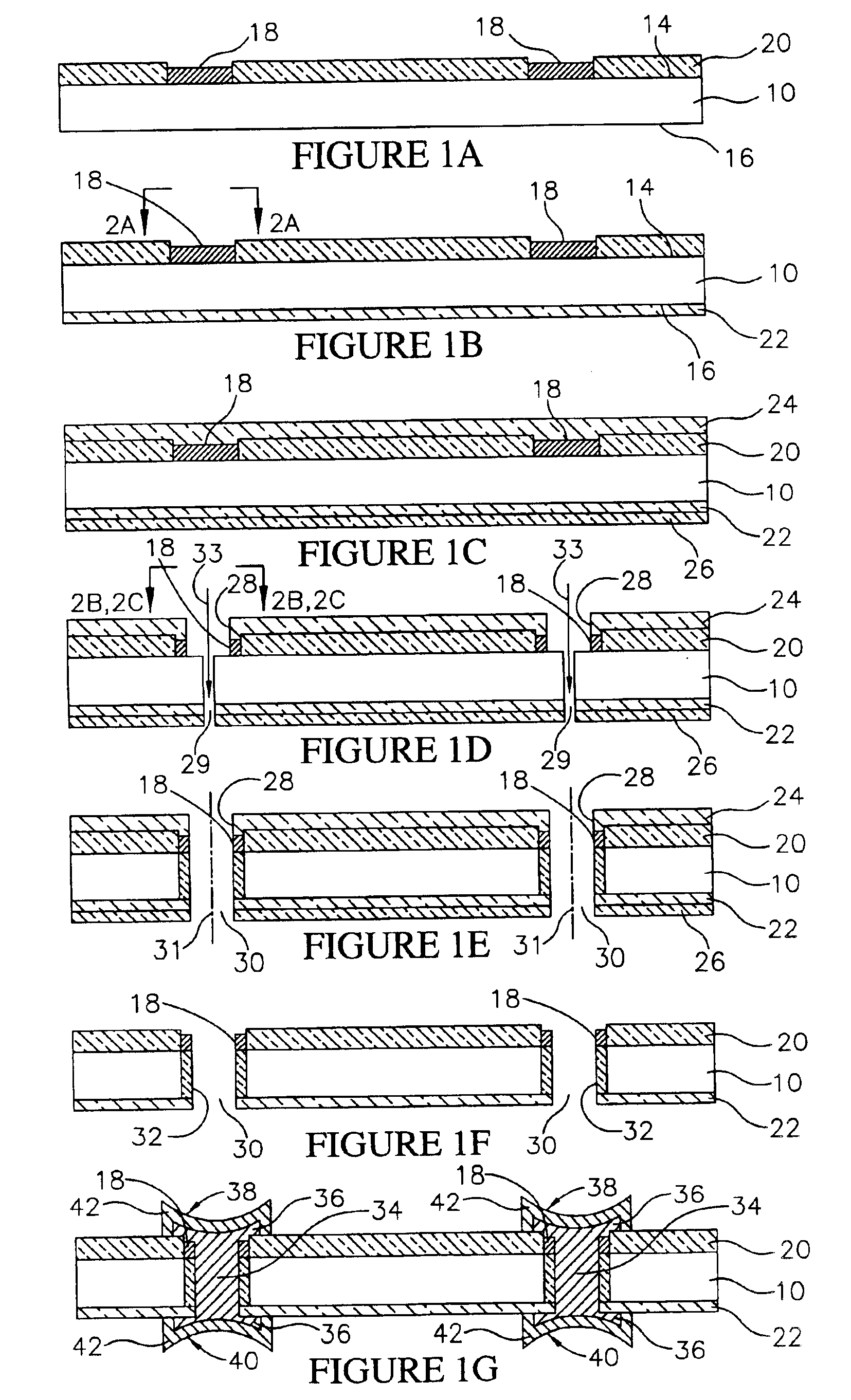

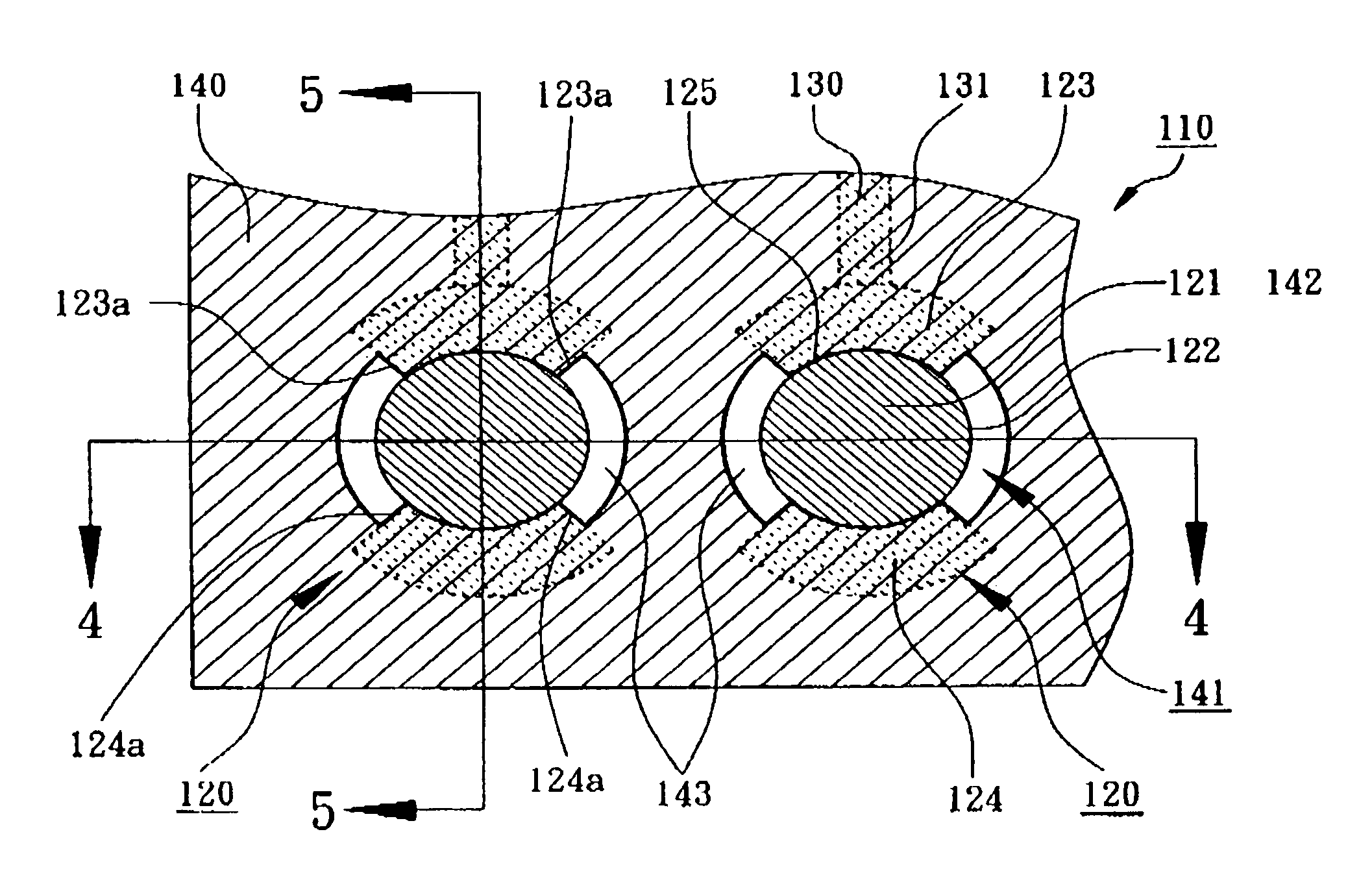

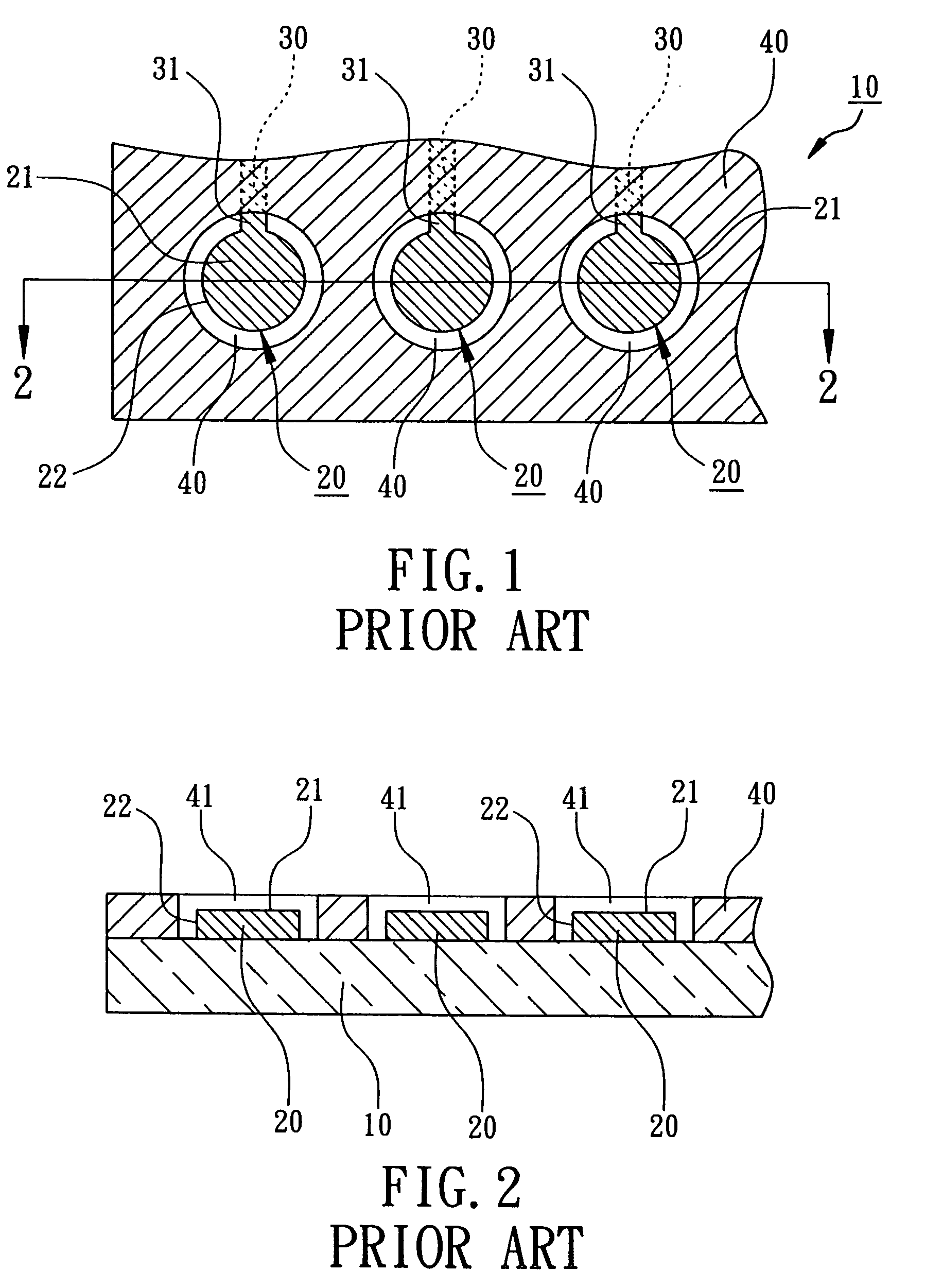

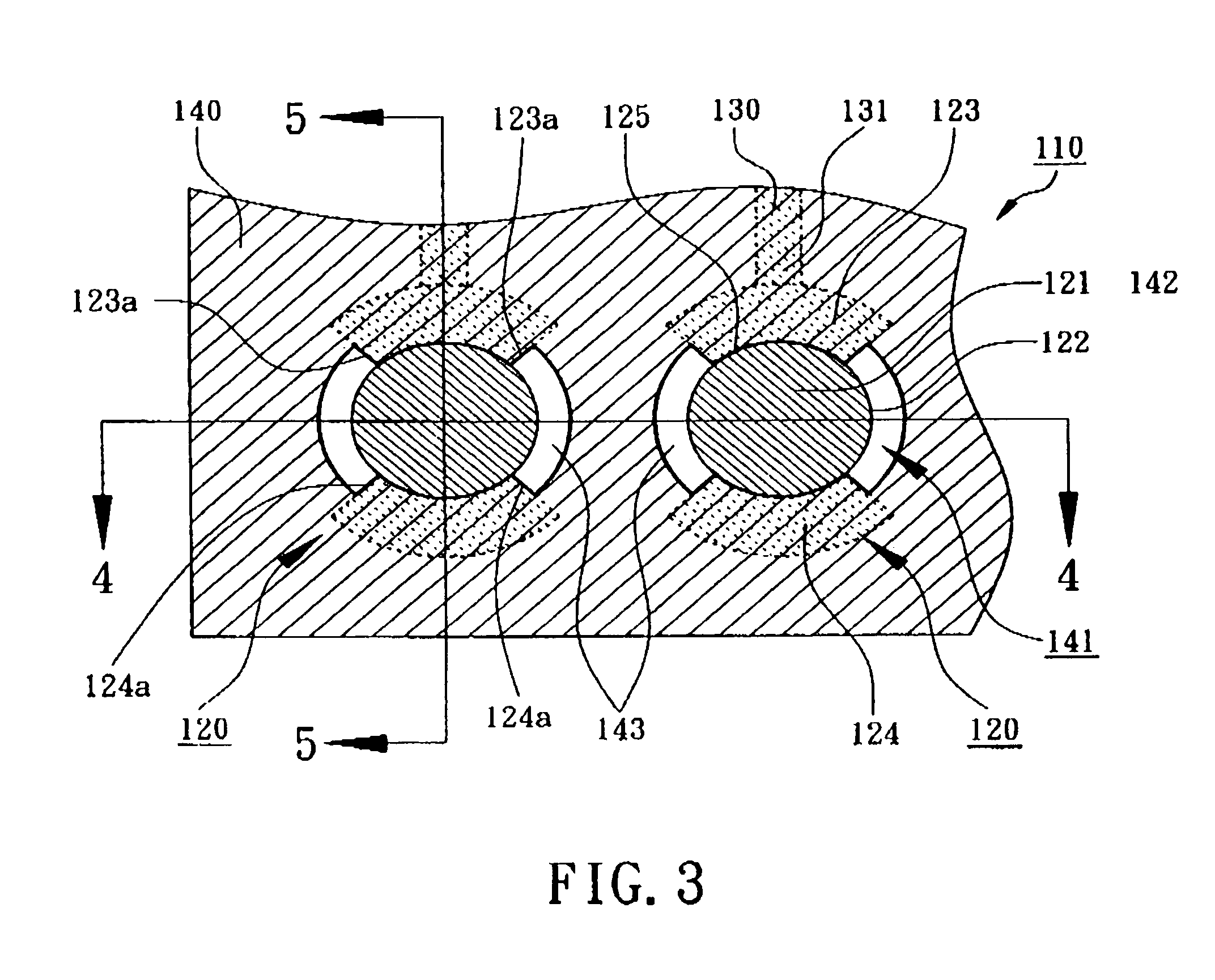

Semiconductor component and interconnect having conductive members and contacts on opposing sides

InactiveUS6903443B2Easy to manufactureSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectronic assemblies

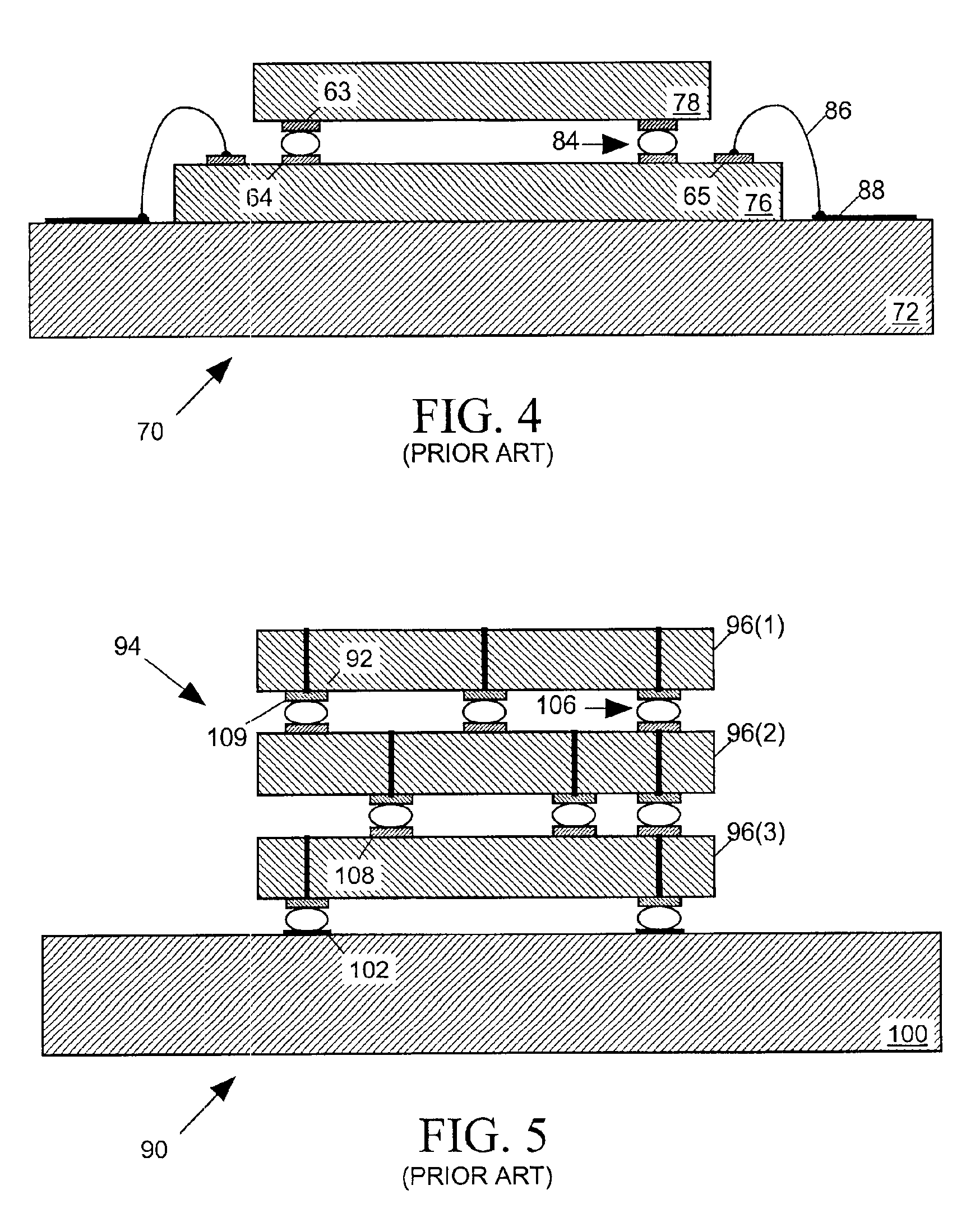

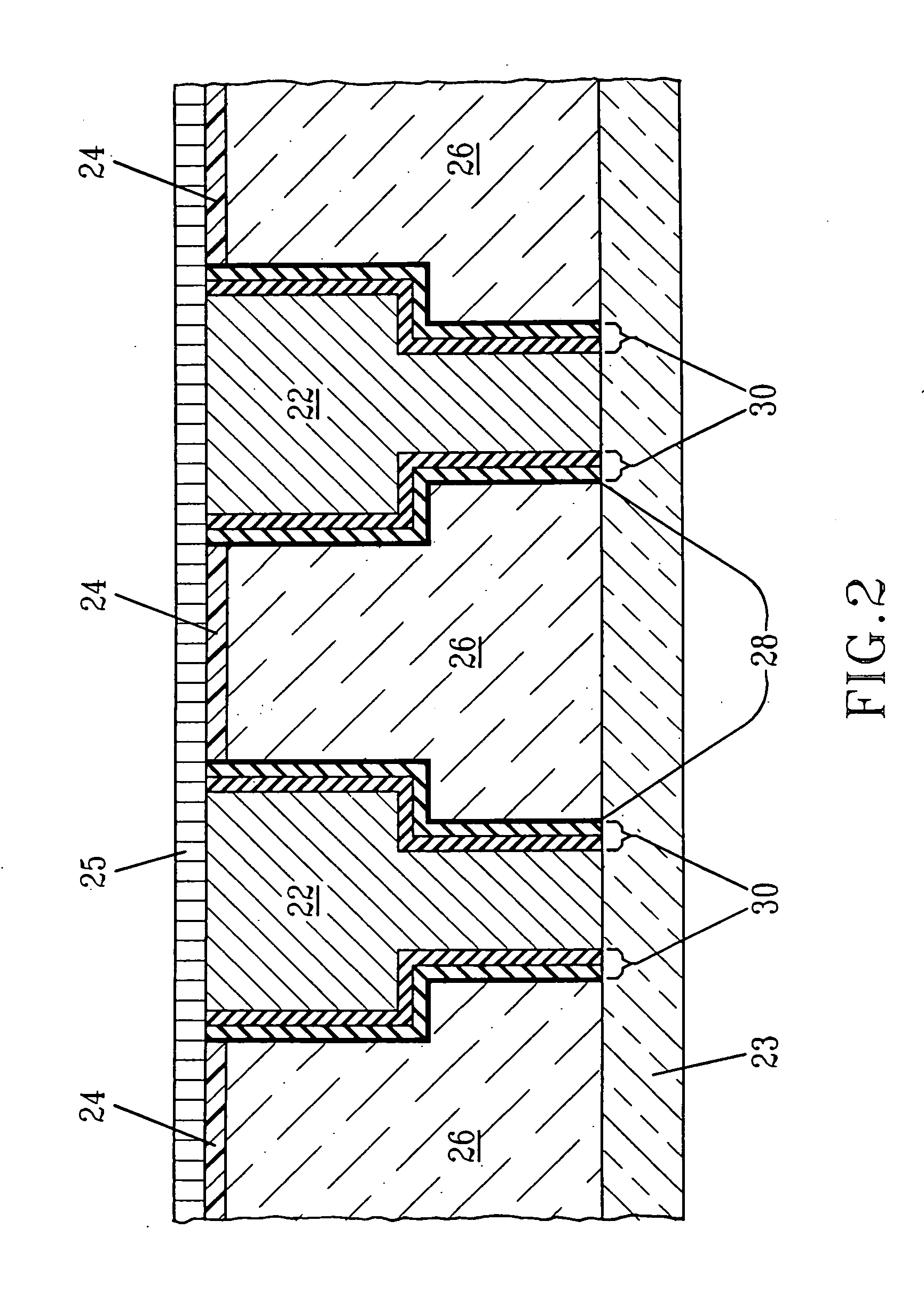

A method for fabricating semiconductor components and interconnects includes the steps of providing a substrate, such as a semiconductor die, forming external contacts on opposing sides of the substrate by laser drilling vias through the substrate, and forming conductive members in the vias. The conductive members include enlarged terminal portions that are covered with a non-oxidizing metal. The method can be used to fabricate stackable semiconductor packages having integrated circuits in electrical communication with the external contacts. The method can also be used to fabricate interconnects for electrically engaging packages, dice and wafers for testing or for constructing electronic assemblies.

Owner:ROUND ROCK RES LLC

Integrated circuit substrate having laser-embedded conductive patterns and method therefor

InactiveUS6930256B1Printed electric component incorporationSemiconductor/solid-state device detailsScreen printingHigh density

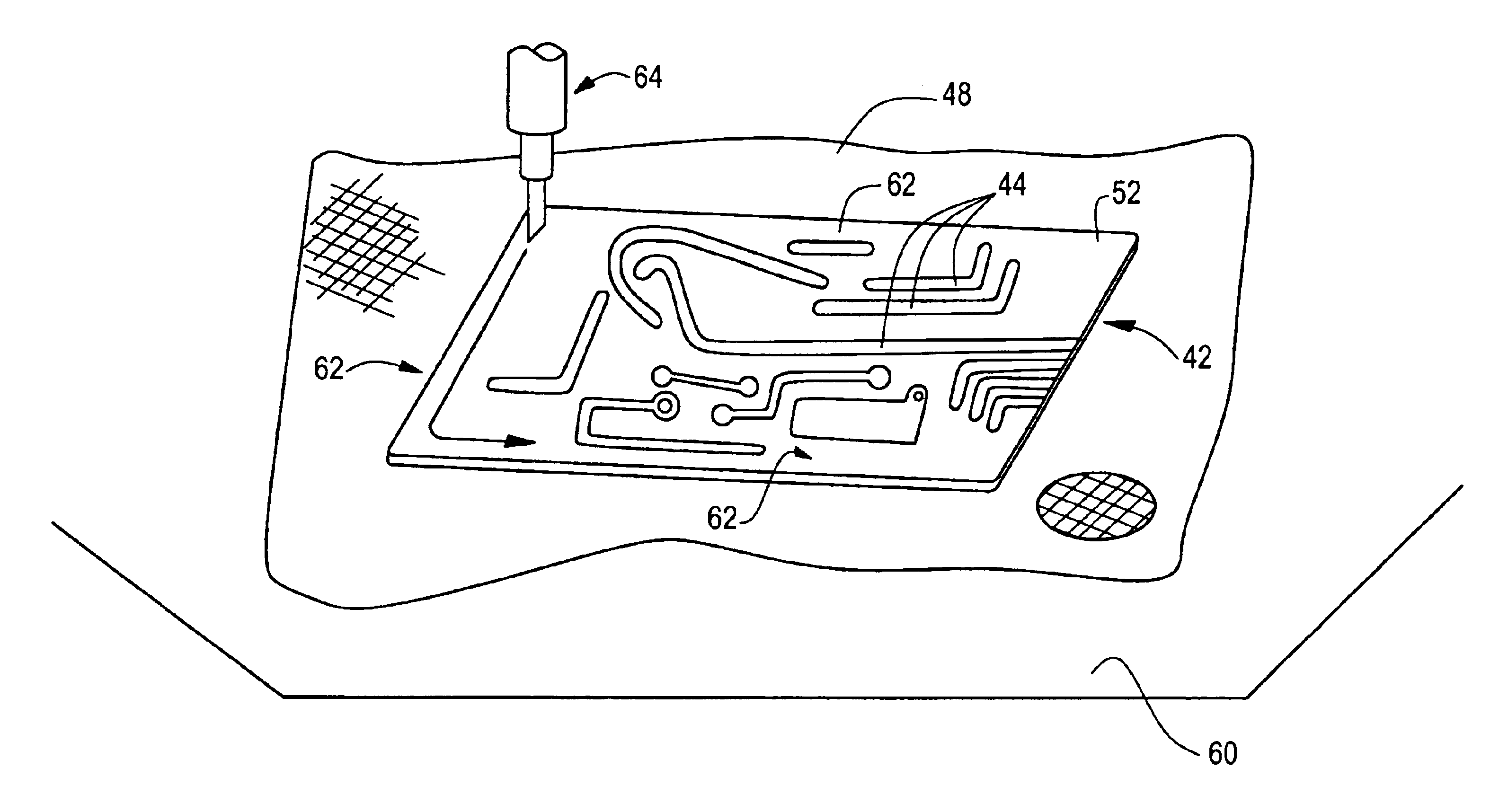

An integrated circuit substrate having laser-embedded conductive patterns provides a high-density mounting and interconnect structure for integrated circuits. Conductive patterns within channels on the substrate provide interconnects that are isolated by the channel sides. A dielectric material is injection-molded or laminated over a metal layer that is punched or etched. The metal layer can provide one or more power planes within the substrate. A laser is used to ablate channels on the surfaces of the outer dielectric layer for the conductive patterns. The conductive patterns are electroplated or paste screen-printed and an etchant-resistive material is applied. Finally, a plating material can be added to exposed surfaces of the conductive patterns. An integrated circuit die and external terminals can then be attached to the substrate, providing an integrated circuit having a high-density interconnect.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

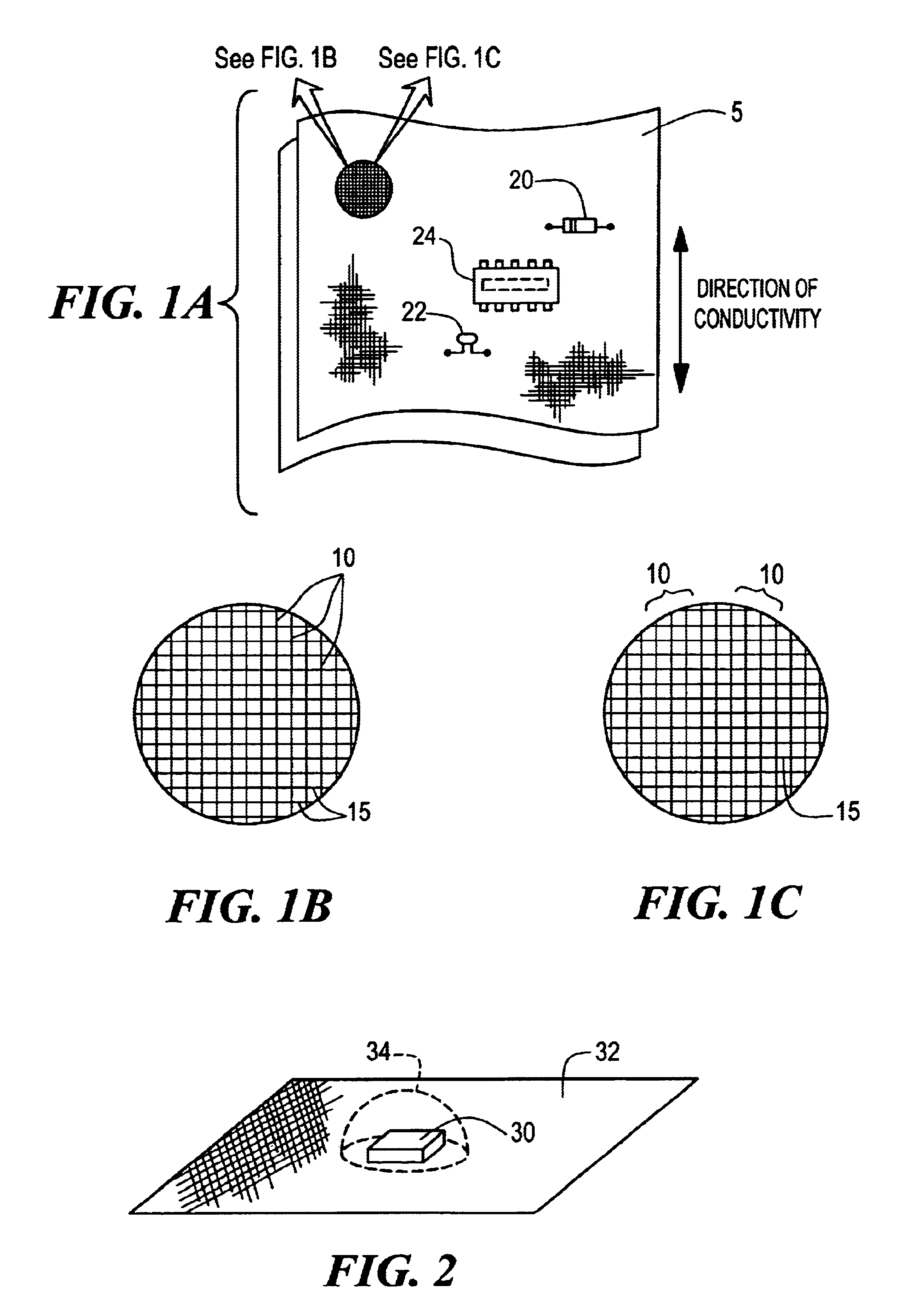

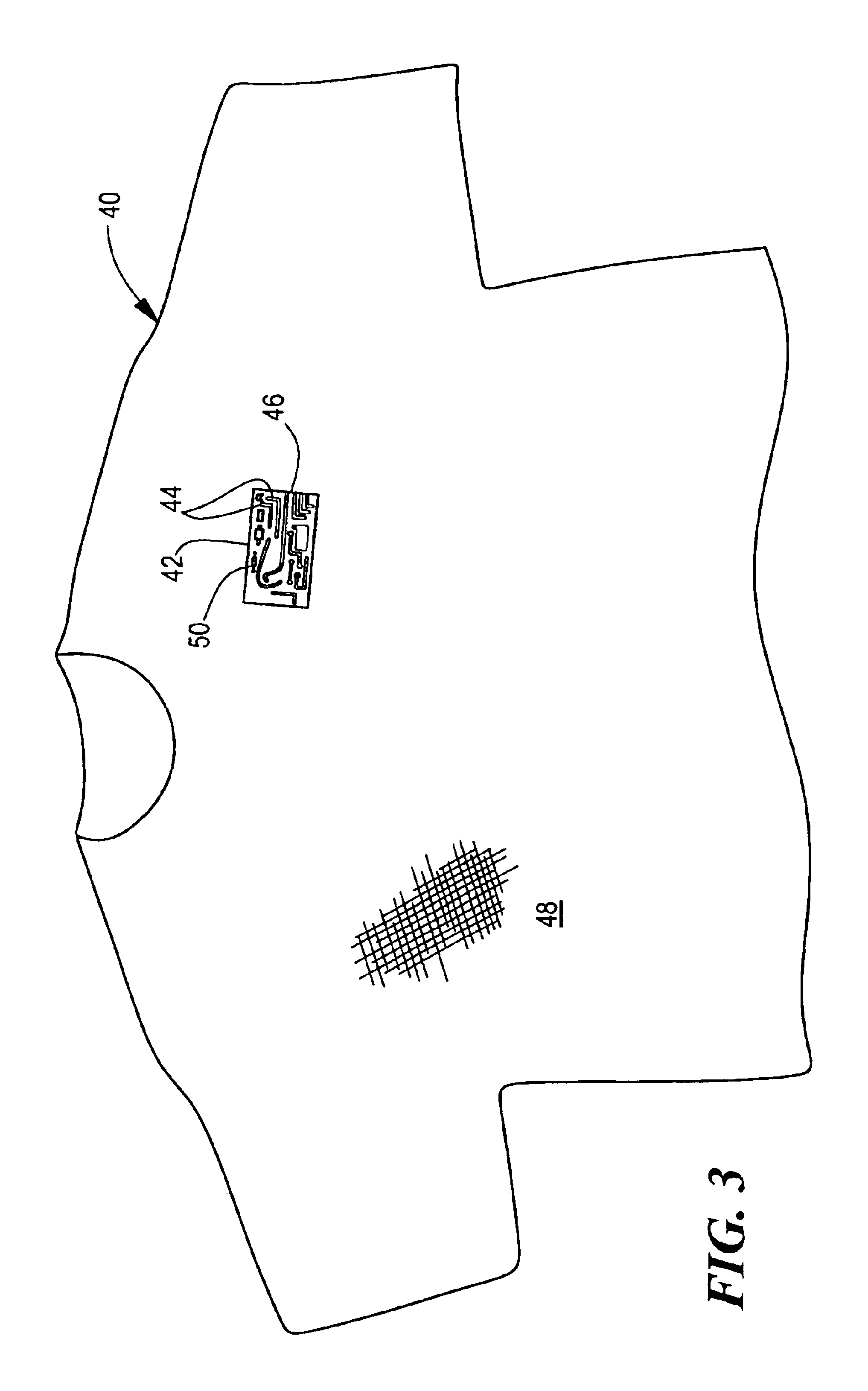

Appendage Mountable Electronic Devices COnformable to Surfaces

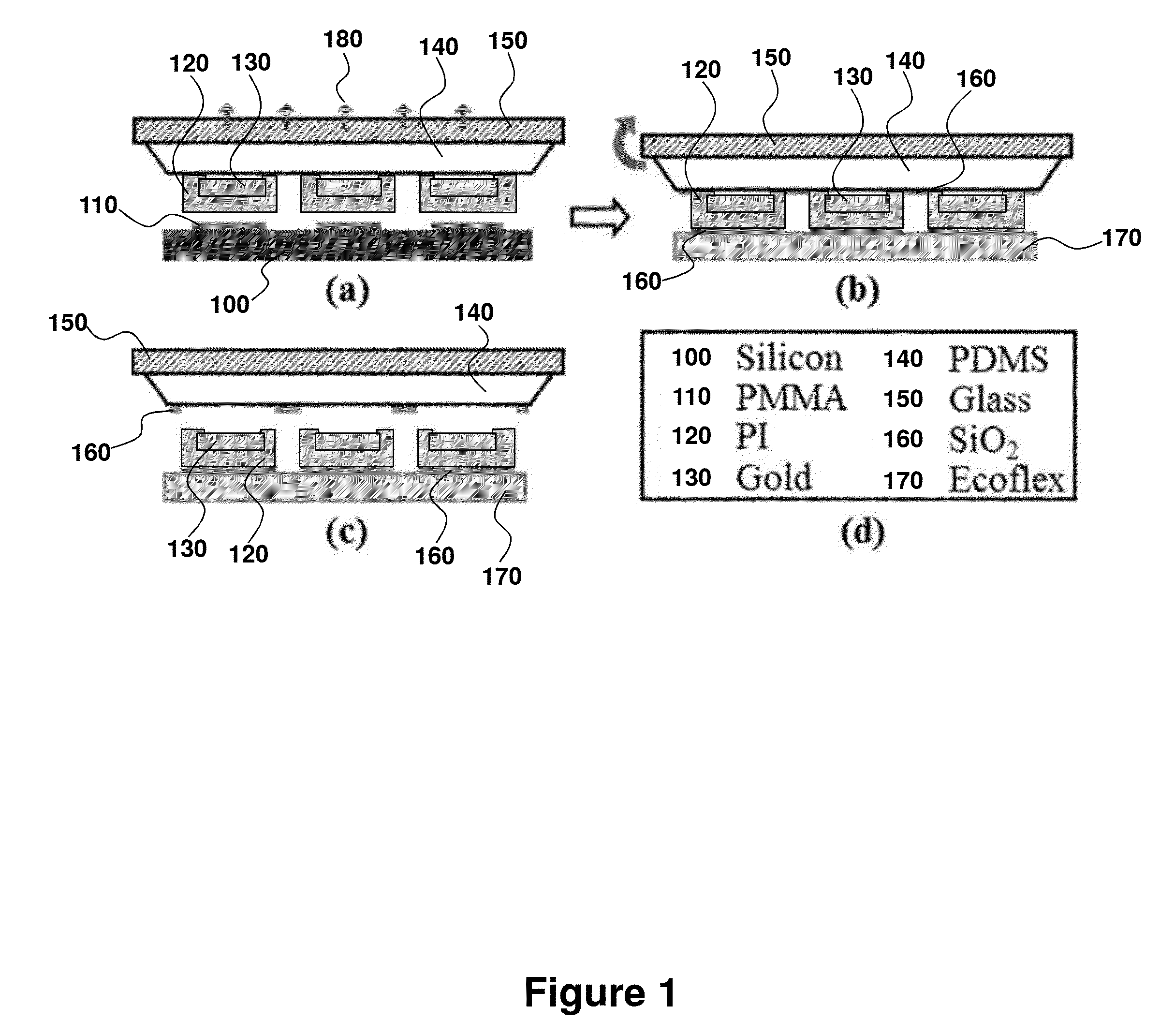

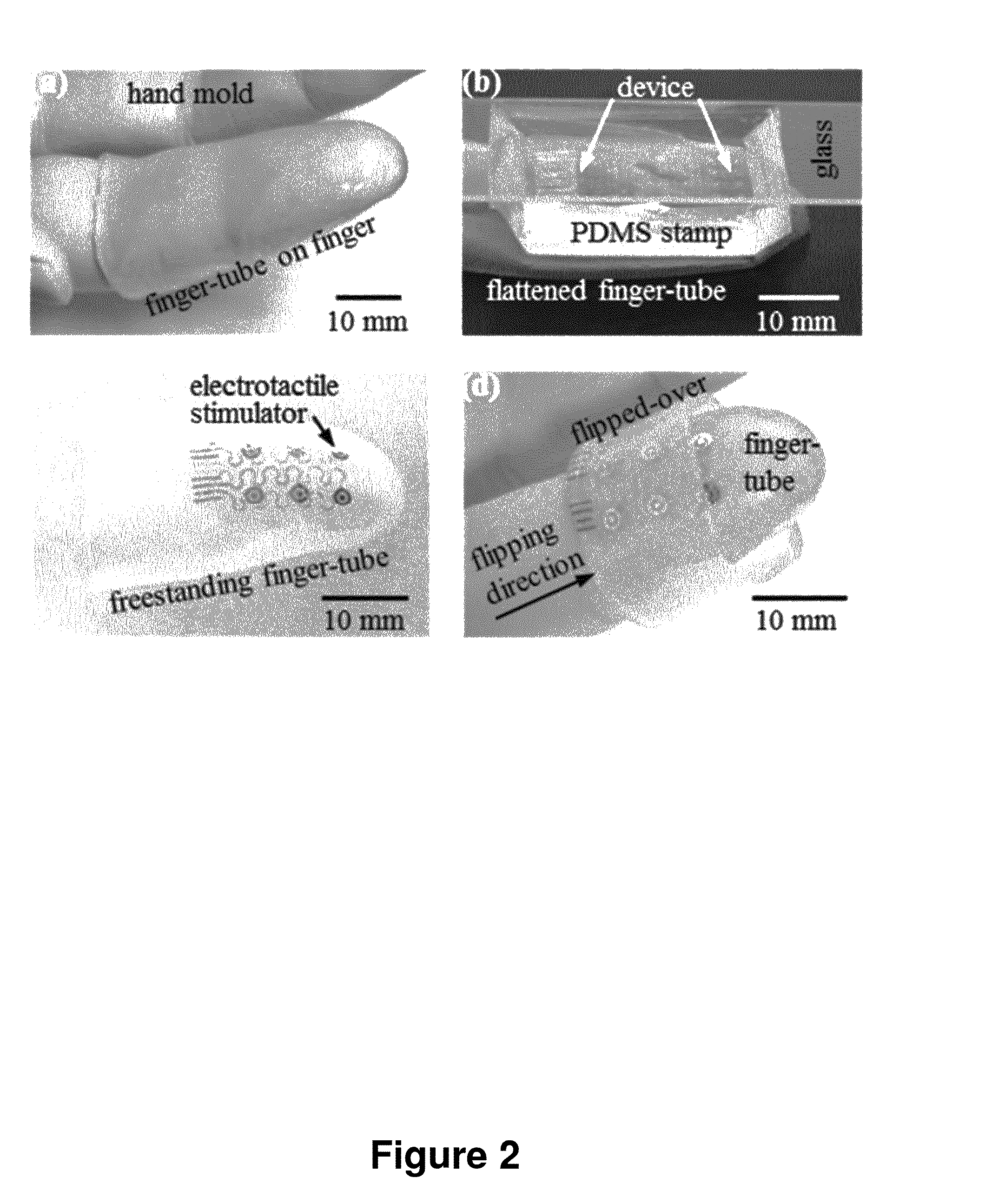

ActiveUS20130333094A1Lower the volumeReduce the overall diameterDigital data processing detailsSolid-state devicesSensor arrayElectronic systems

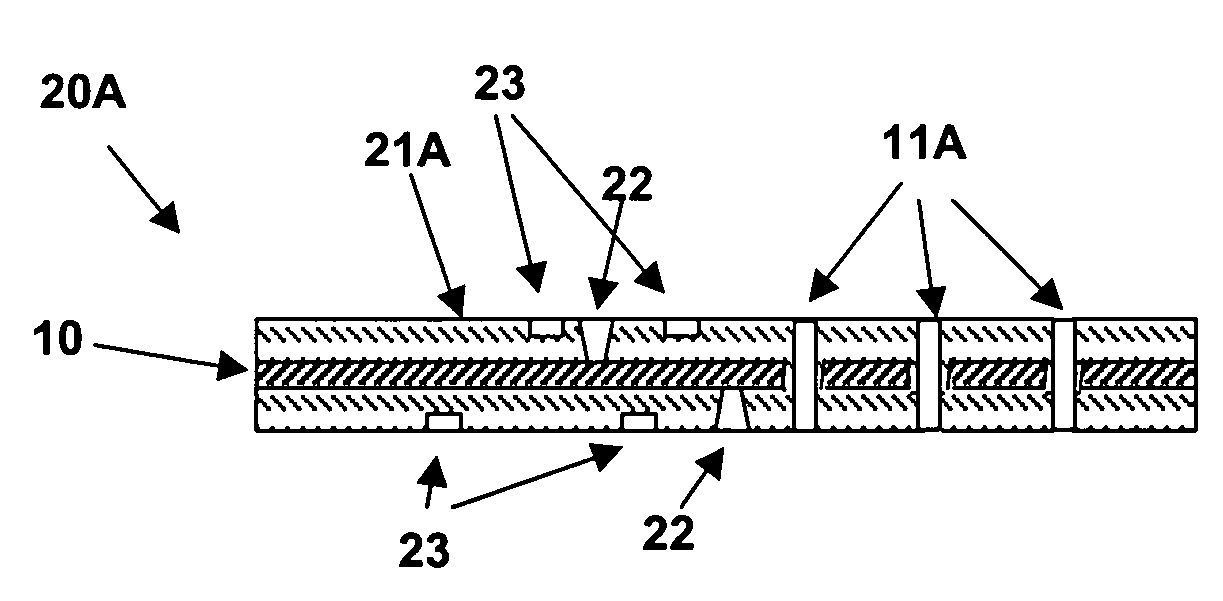

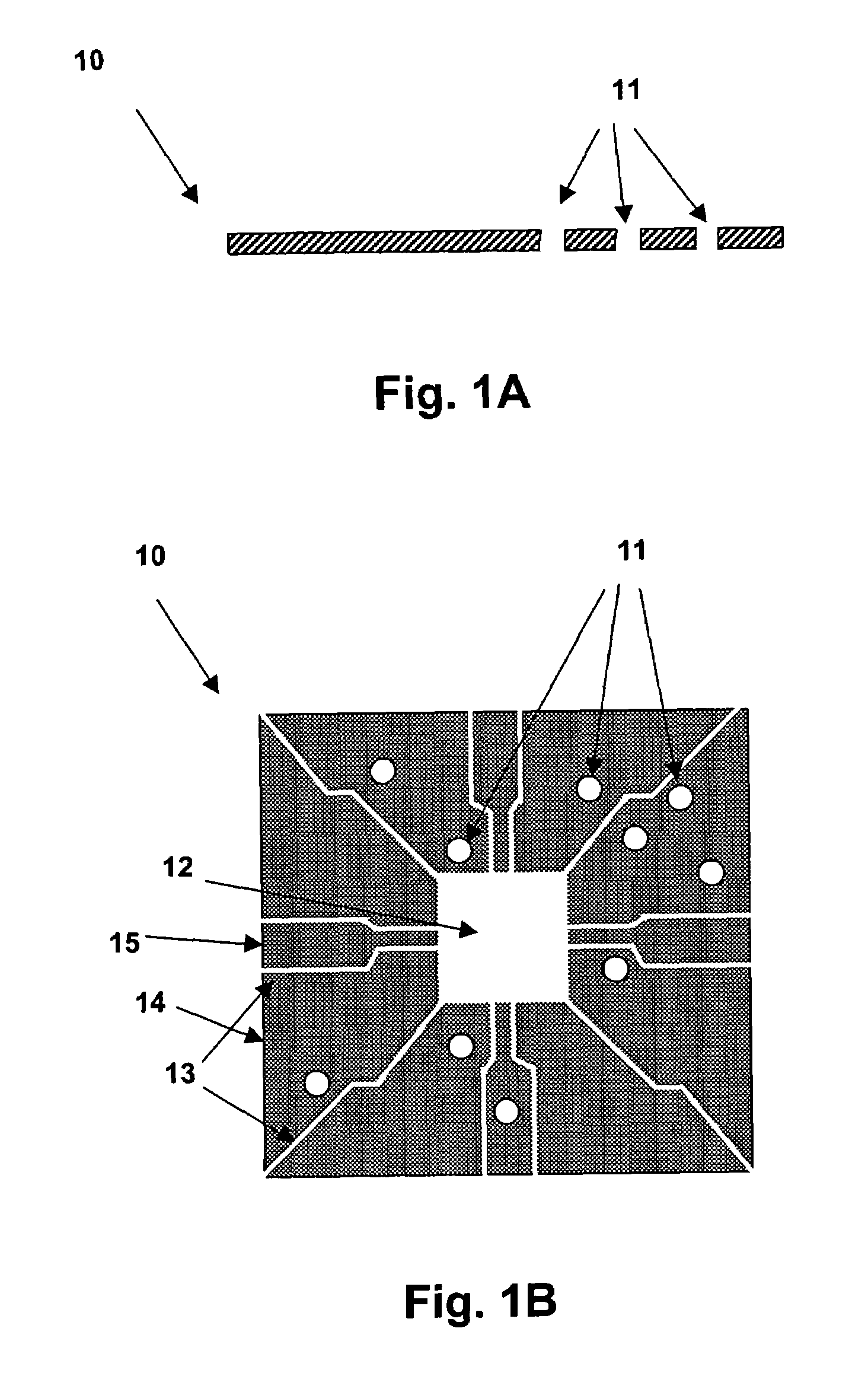

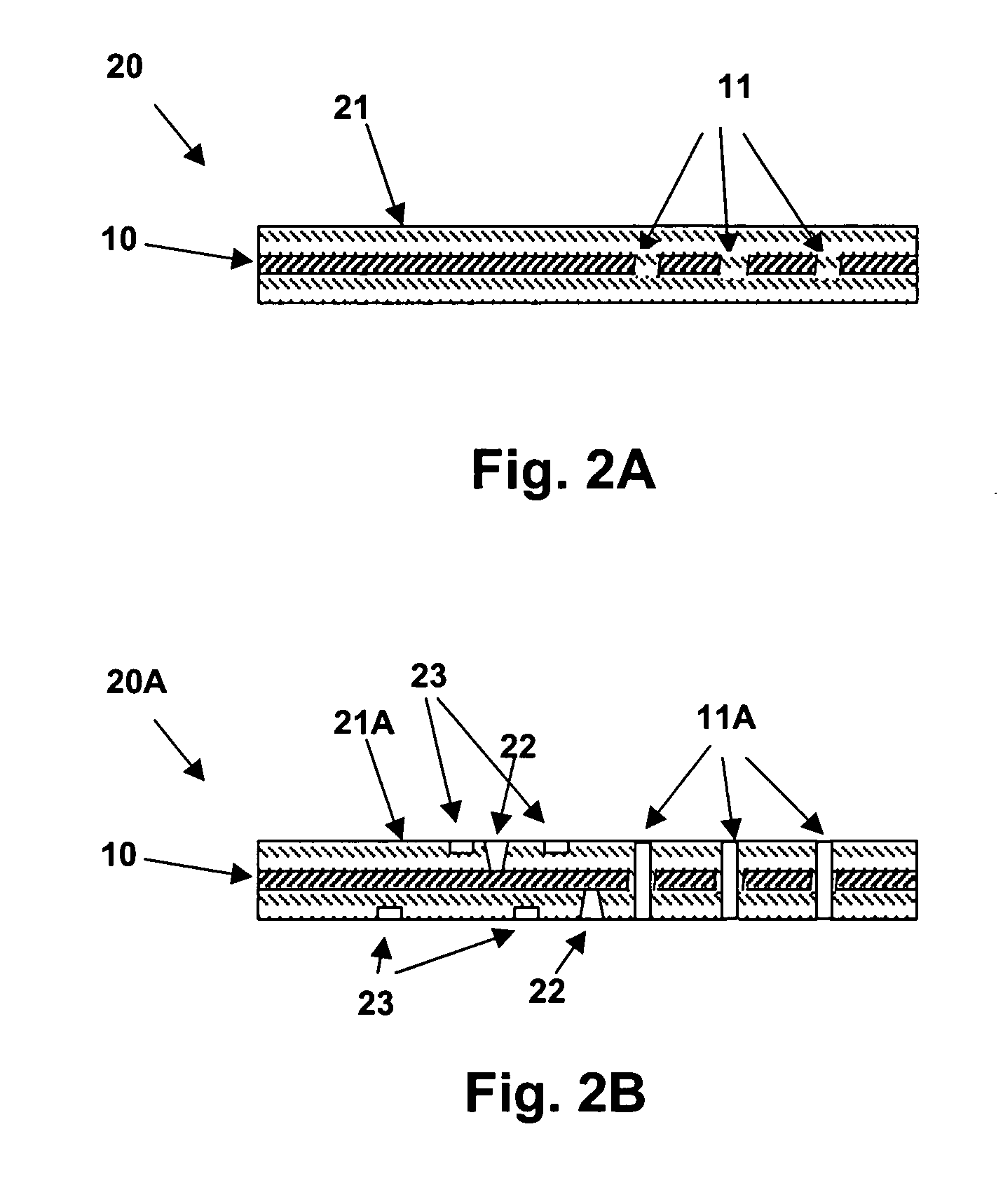

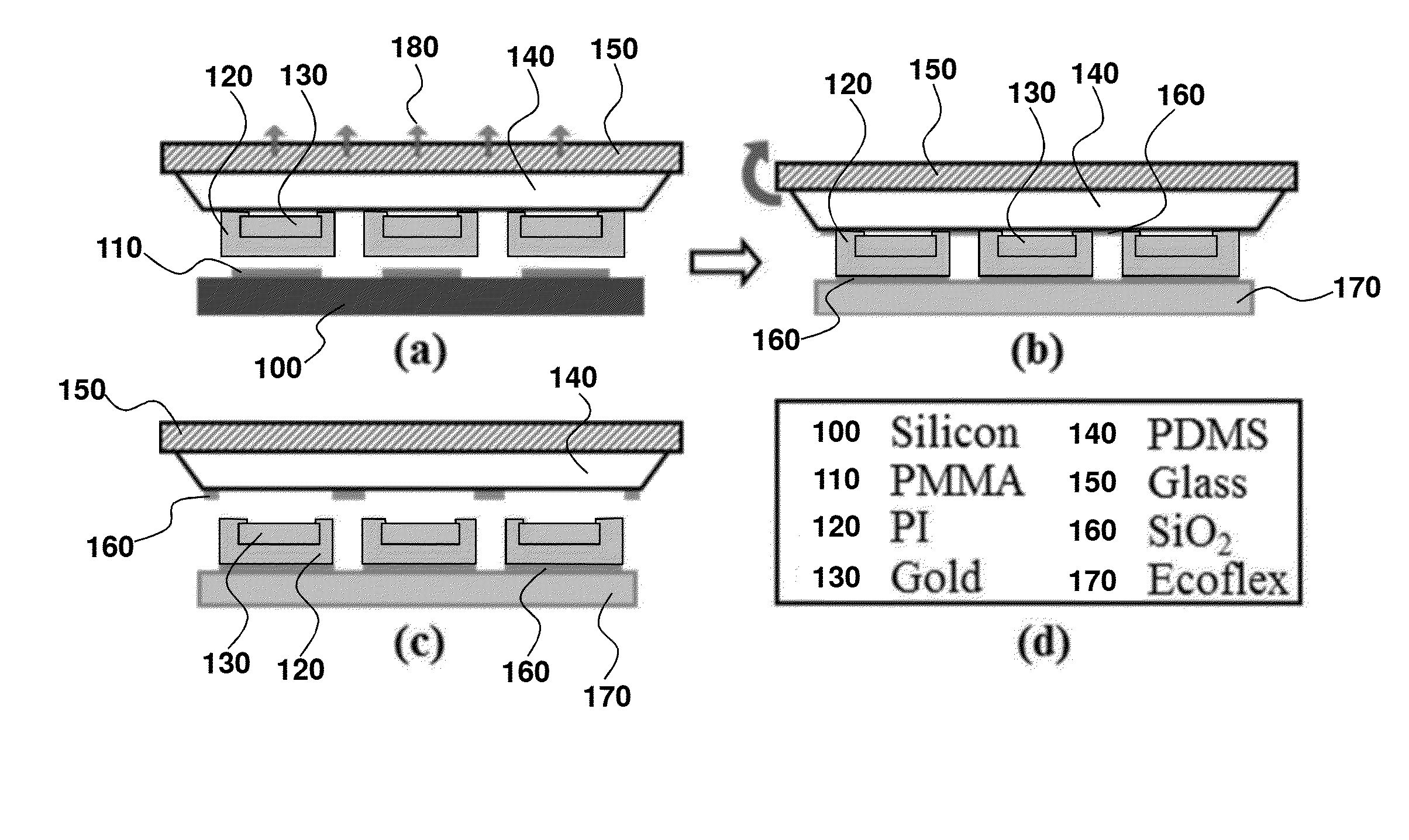

Disclosed are appendage mountable electronic systems and related methods for covering and conforming to an appendage surface. A flexible or stretchable substrate has an inner surface for receiving an appendage, including an appendage having a curved surface, and an opposed outer surface that is accessible to external surfaces. A stretchable or flexible electronic device is supported by the substrate inner and / or outer surface, depending on the application of interest. The electronic device in combination with the substrate provides a net bending stiffness to facilitate conformal contact between the inner surface and a surface of the appendage provided within the enclosure. In an aspect, the system is capable of surface flipping without adversely impacting electronic device functionality, such as electronic devices comprising arrays of sensors, actuators, or both sensors and actuators.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

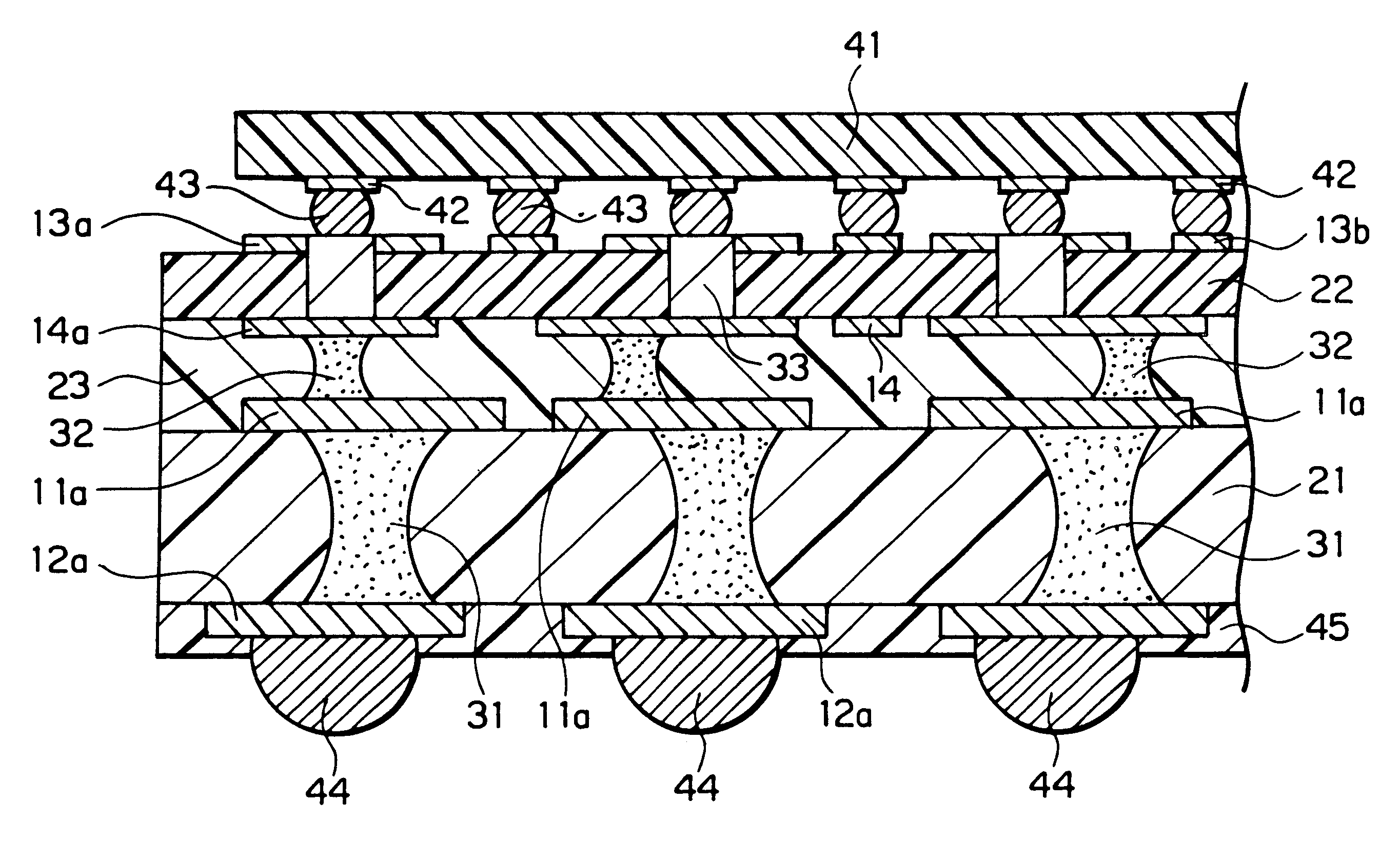

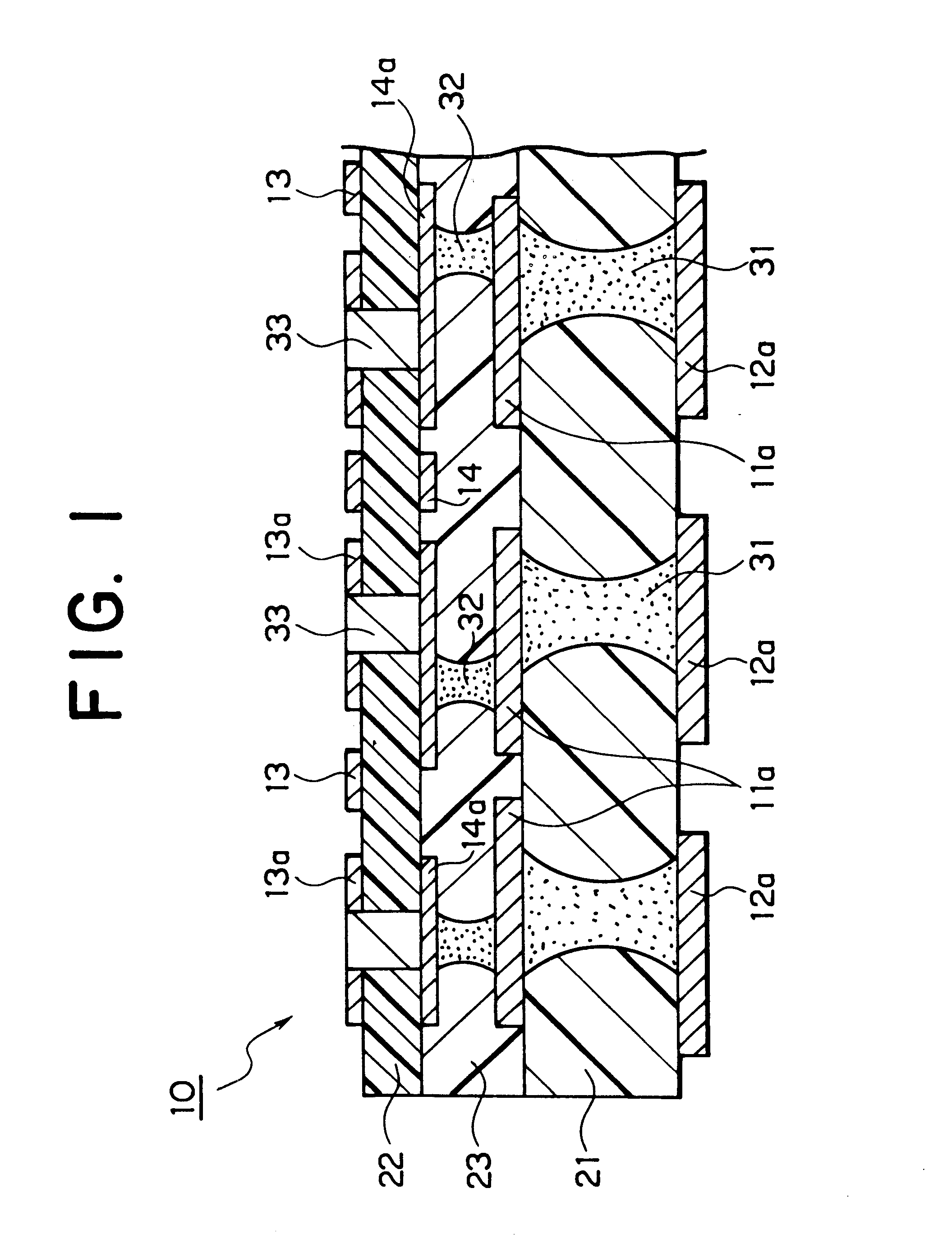

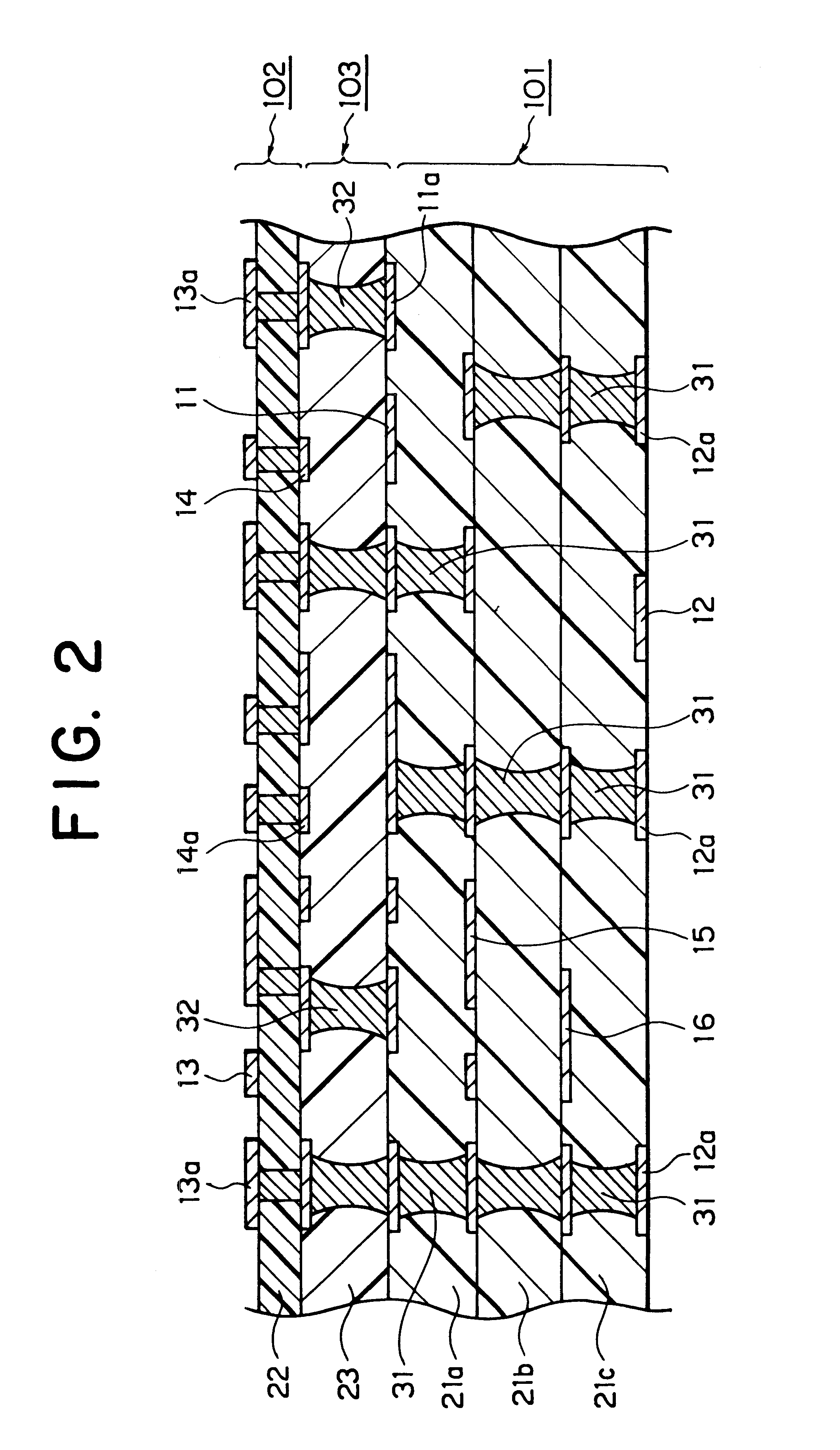

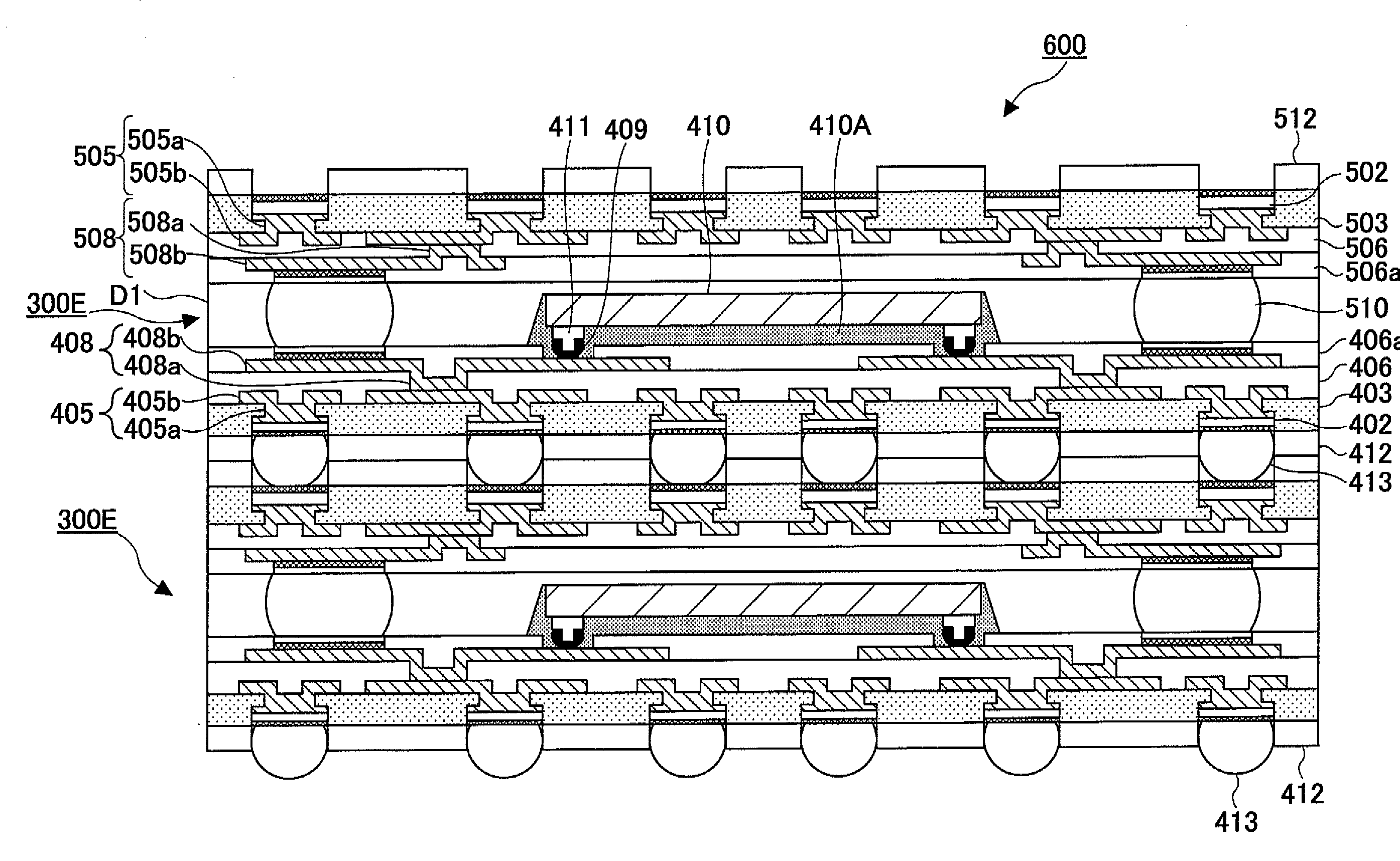

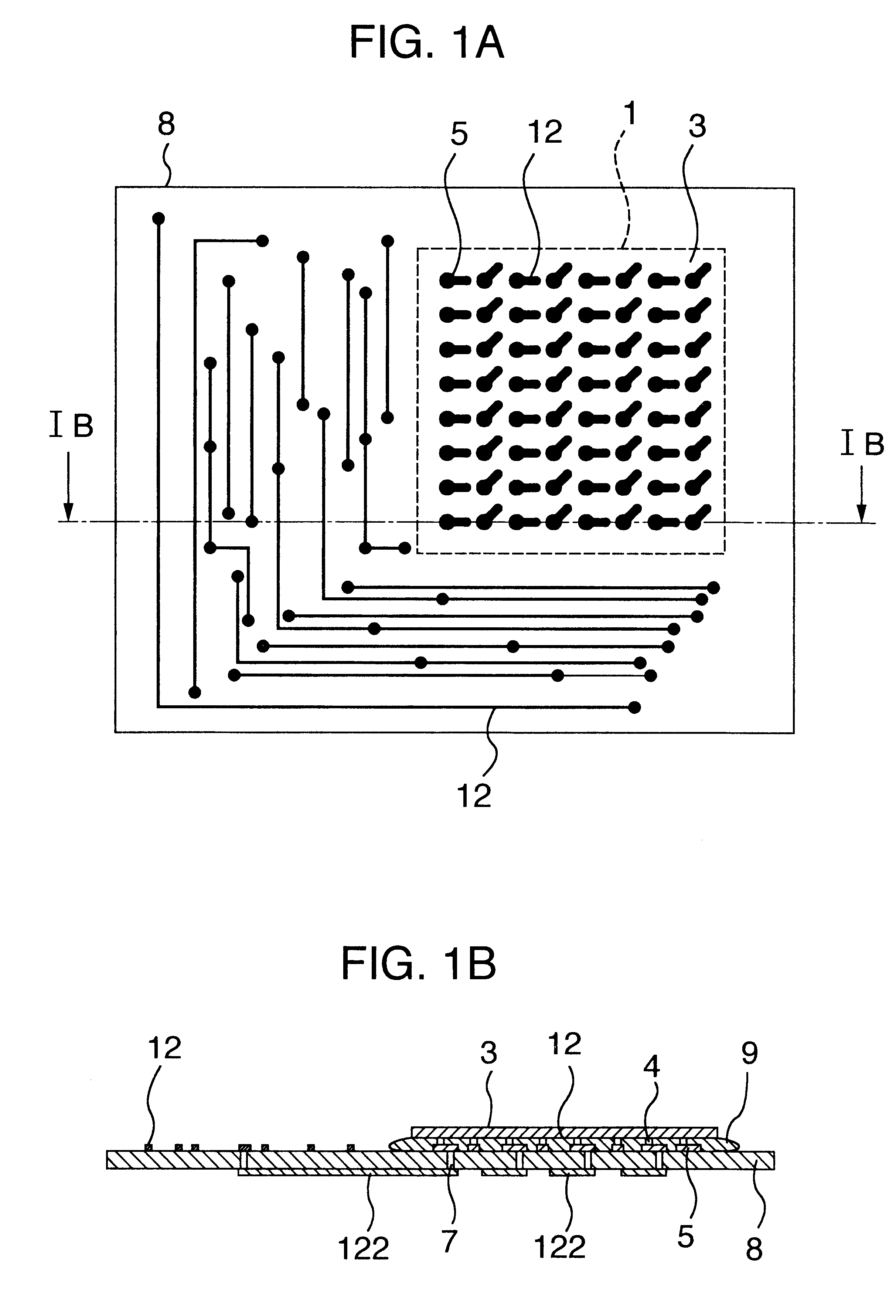

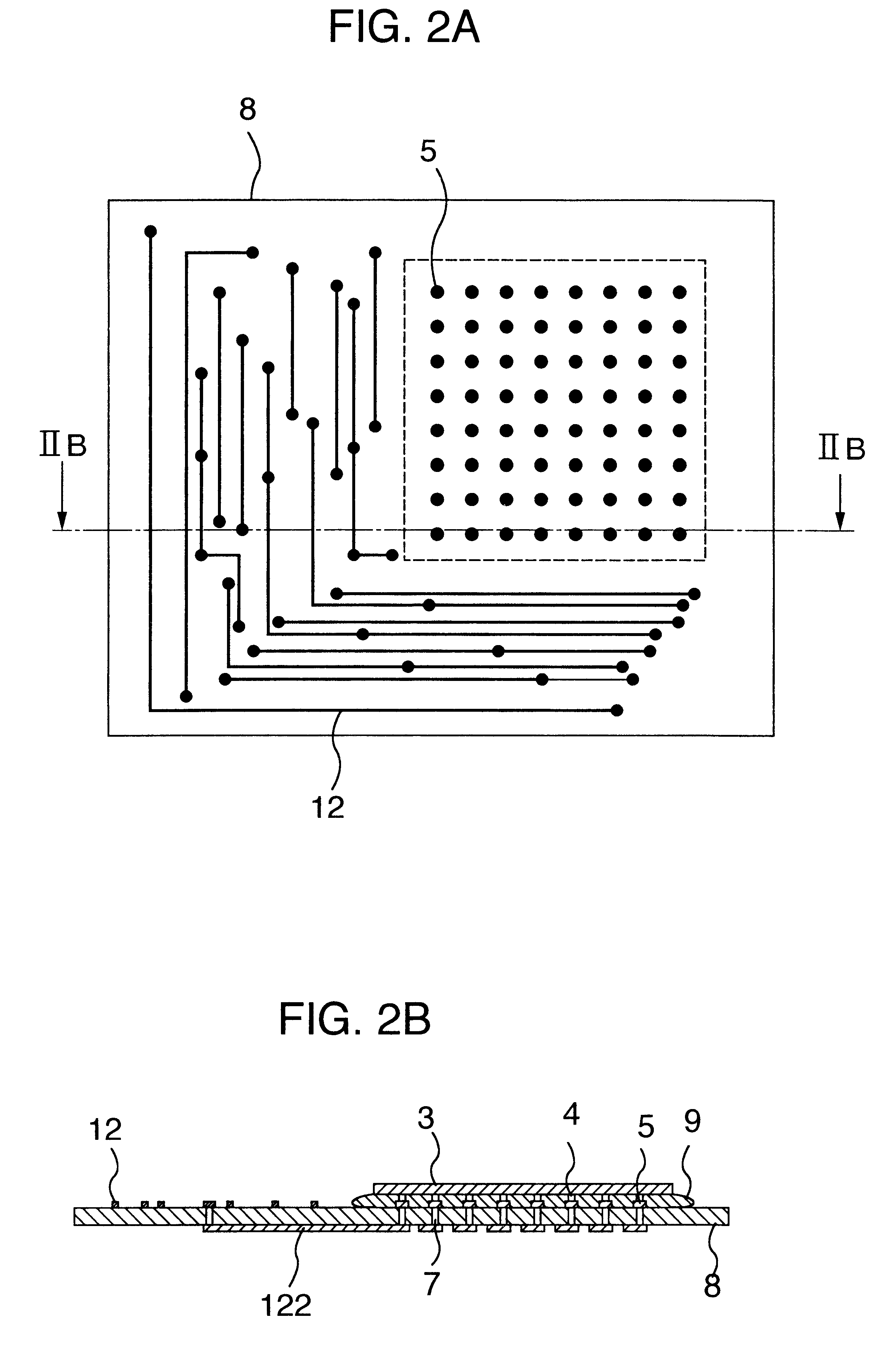

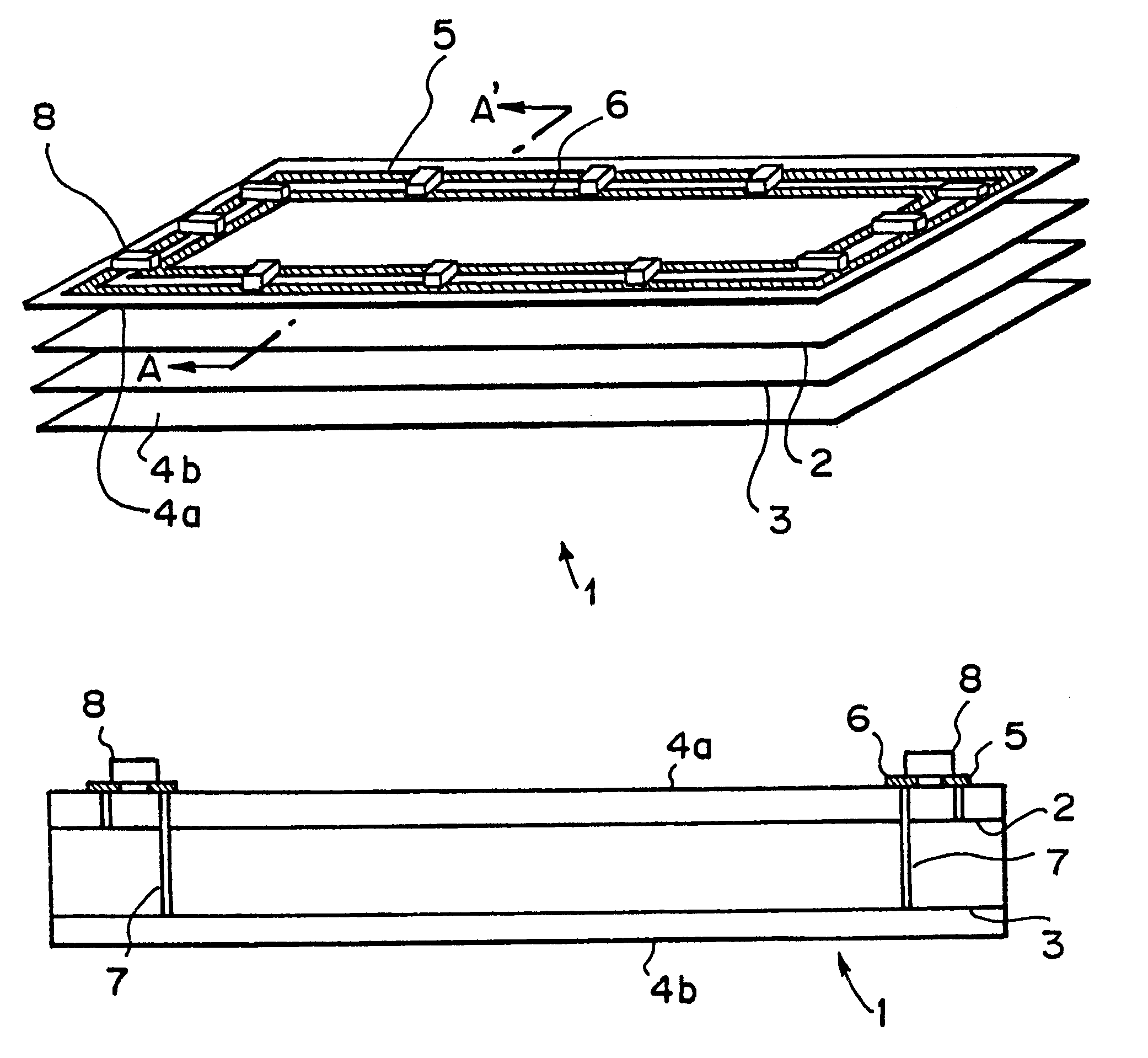

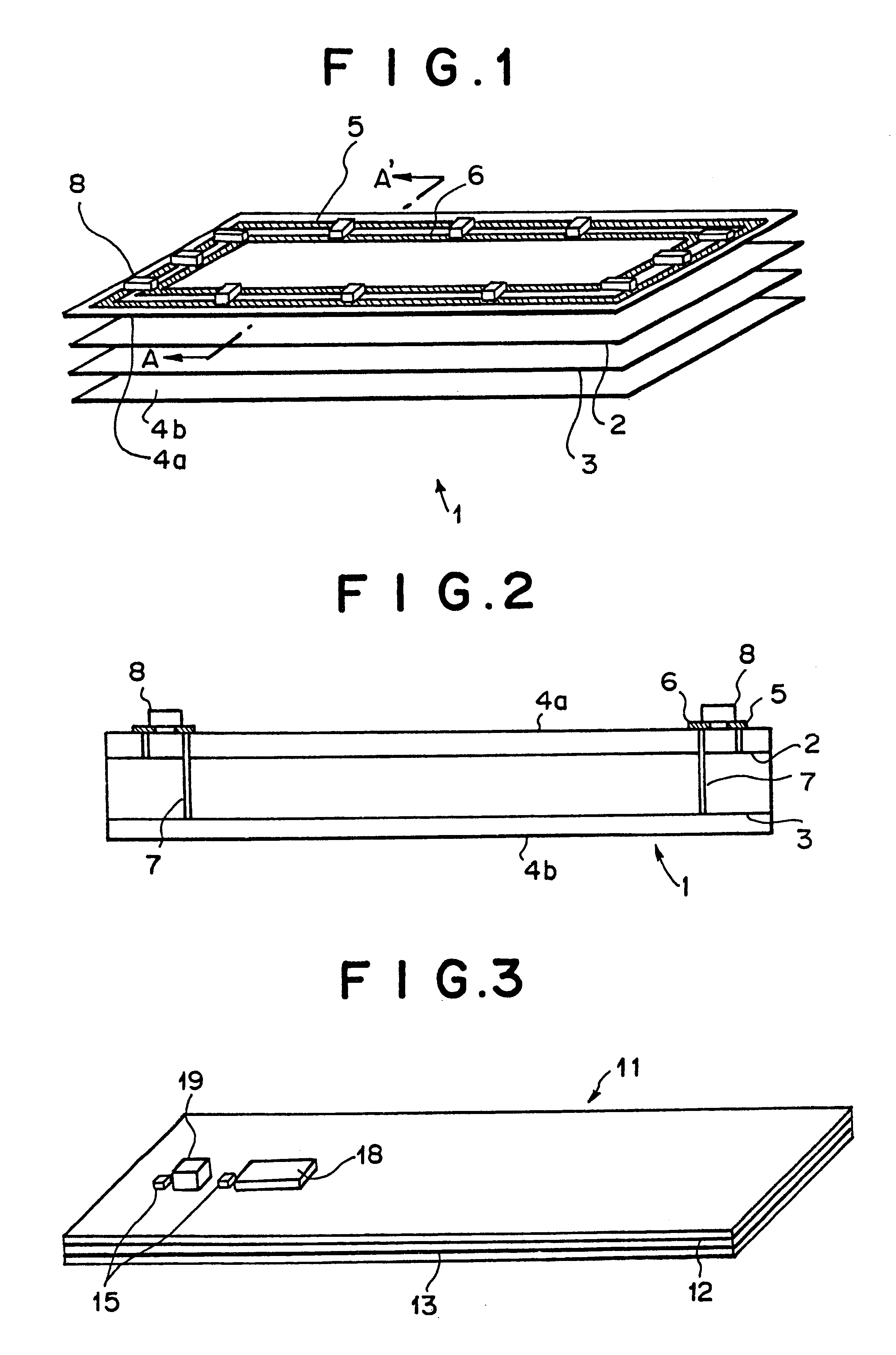

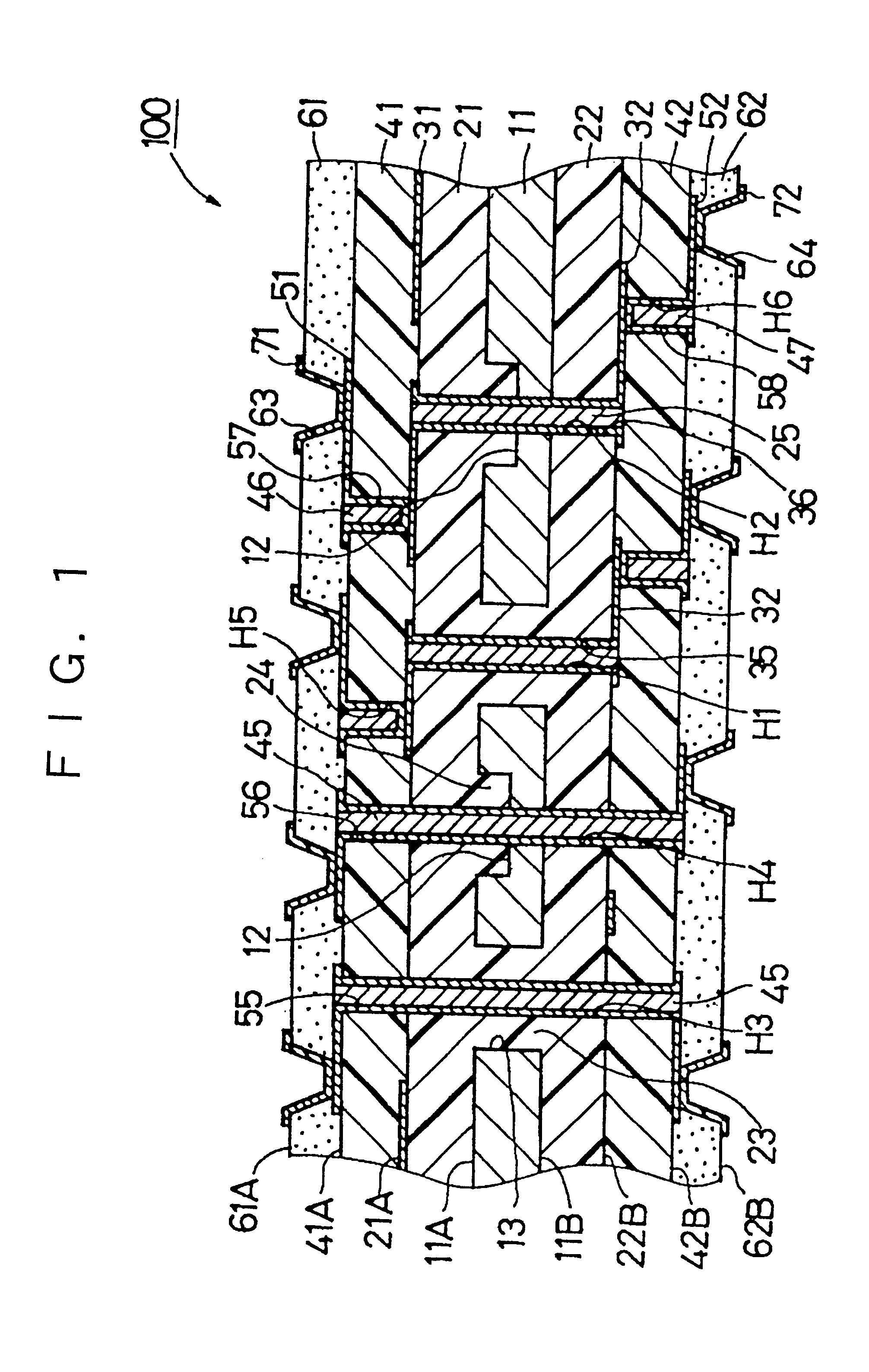

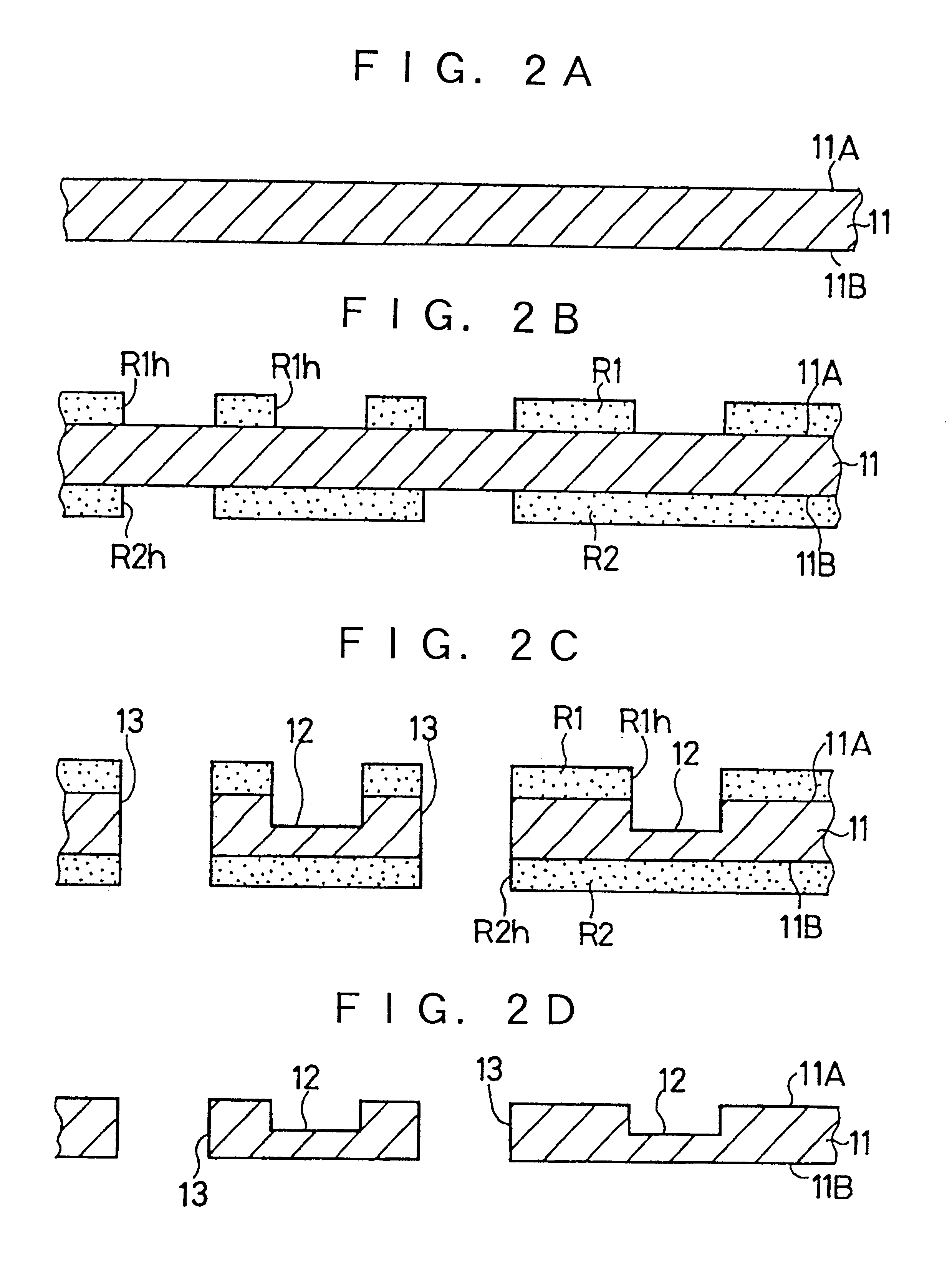

Hybrid wiring board, semiconductor apparatus, flexible substrate, and fabrication method of hybrid wiring board

InactiveUS6329610B1Semiconductor/solid-state device detailsPrinted electric component incorporationInsulation layerEngineering

A first via land of a wiring layer on a first surface of a first insulation layer that is a rigid layer and a second via land of a wiring layer on a second surface of a second insulation layer that is a flexible layer are electrically and mechanically connected with a conductive pillar pierced through a third insulation layer disposed between the first insulation layer and the second insulation layer. In such a structure, a wiring board that can mount a highly integrated semiconductor device, that is small and thin, and that has high reliability can be accomplished.

Owner:KK TOSHIBA

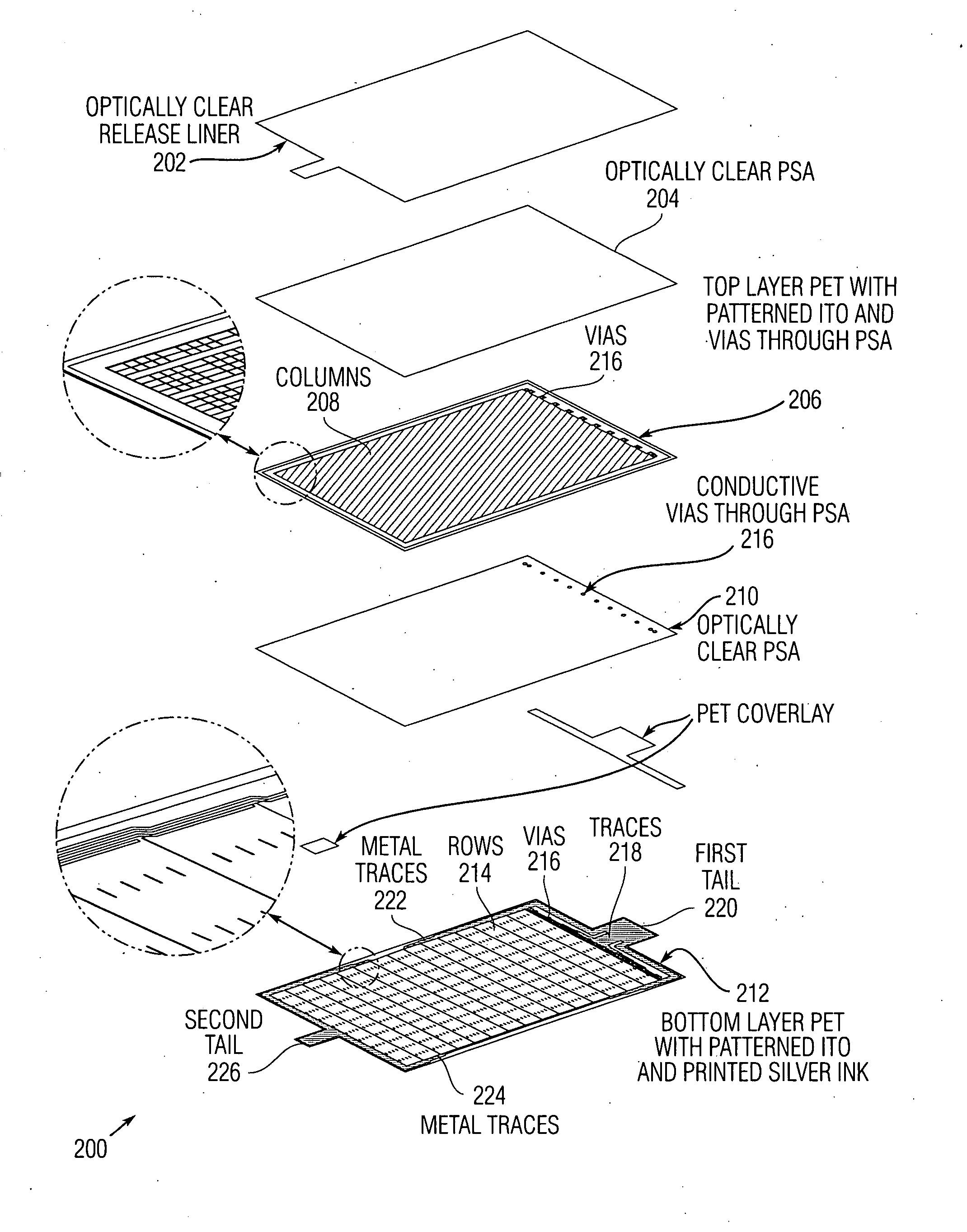

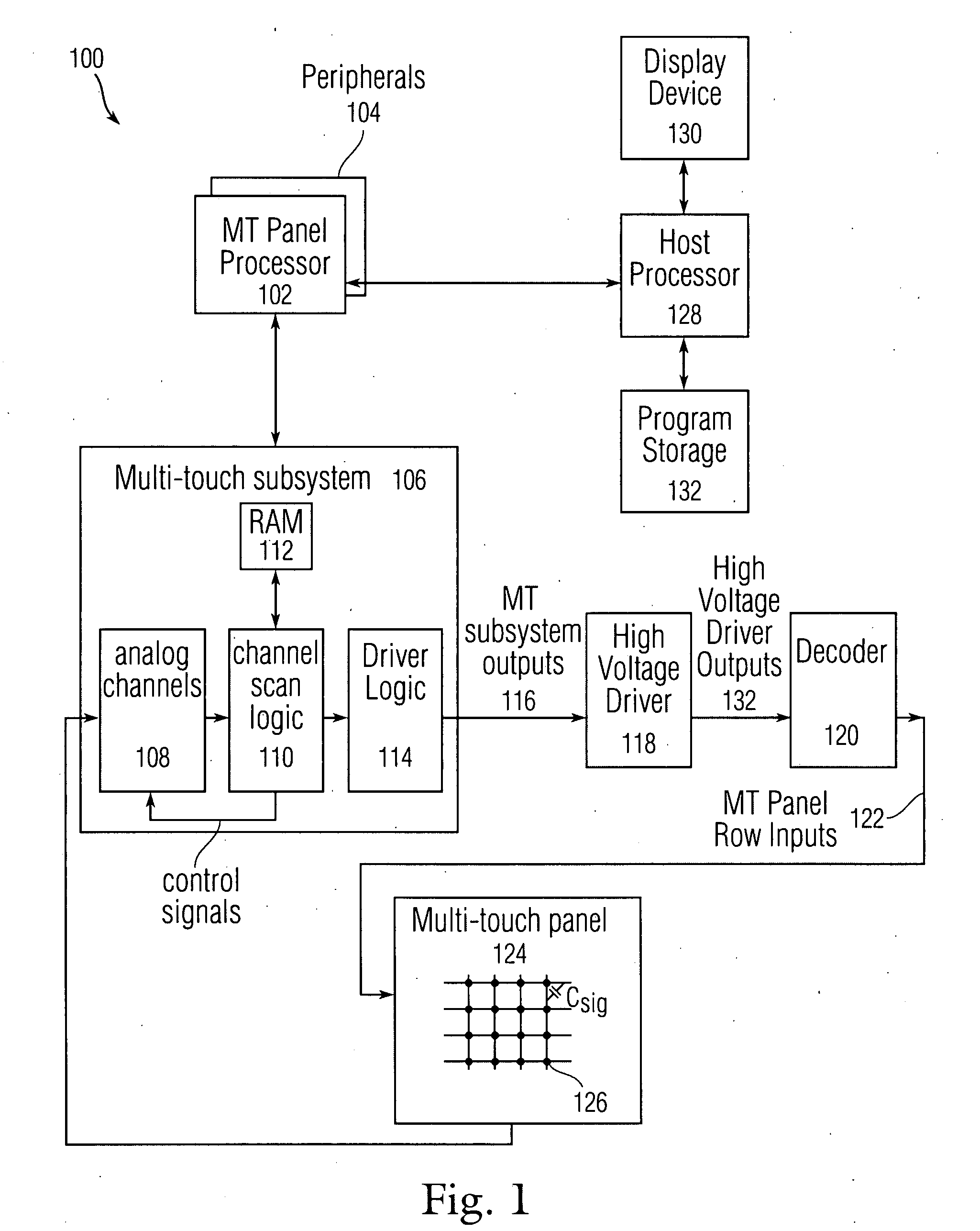

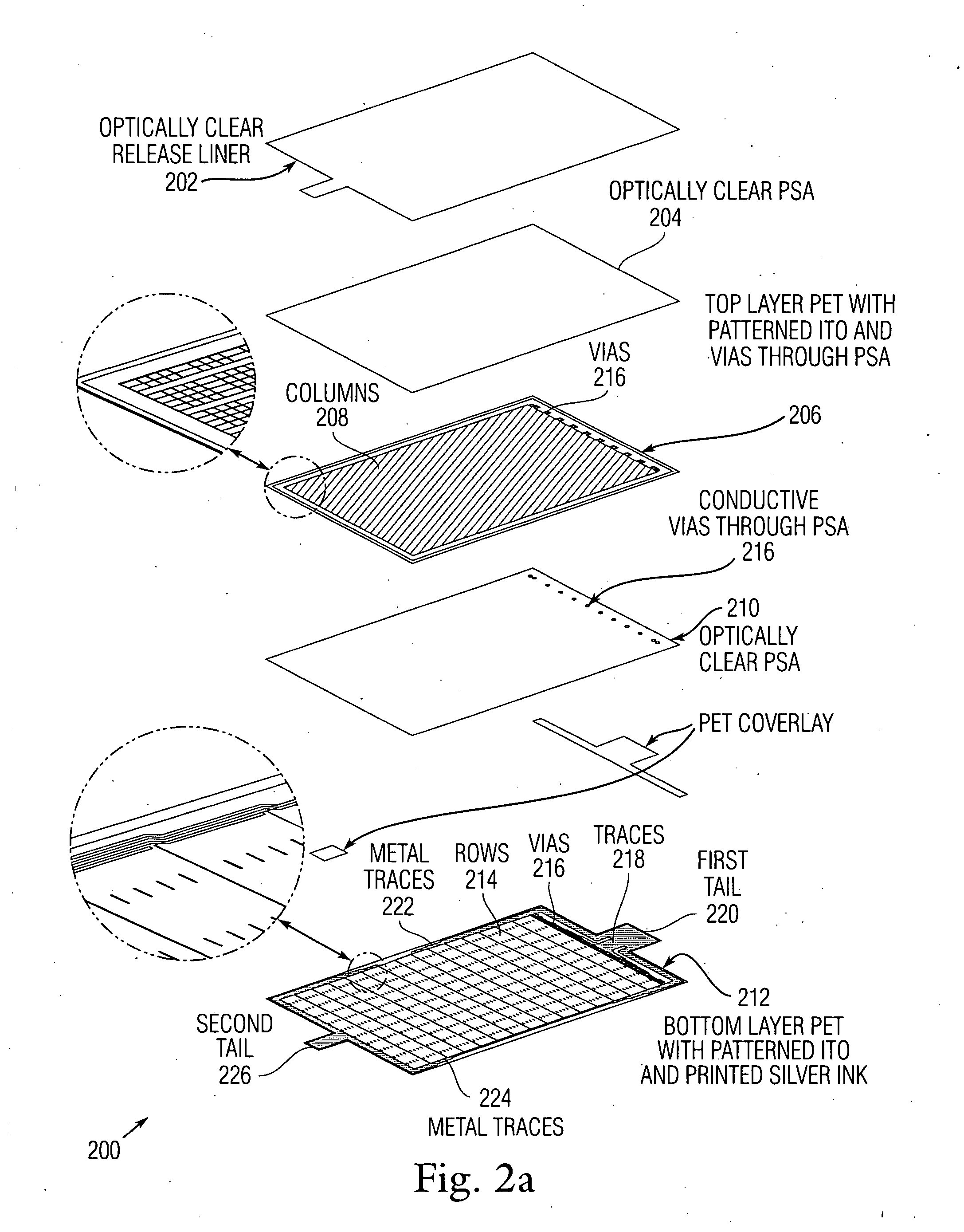

Pet-based touch pad

ActiveUS20080143683A1Avoid less flexibilityMinimized in sizeTransparent dielectricsConductive pattern formationAdhesiveEngineering

A space-efficient substantially transparent mutual capacitance touch sensor panel can be created by forming columns made of a substantially transparent conductive material on one side of a first substantially transparent substrate, forming rows made of the substantially transparent conductive material on one side of a second substantially transparent substrate, adhering the two substrates together with a substantially transparent adhesive, bringing column connections down to the second substrate using vias, and routing both the column and row connections to a single connection area on the second substrate. In addition, in some embodiments some of the row connections can be routed to a second connection area on the second substrate to minimize the size of the sensor panel.

Owner:APPLE INC

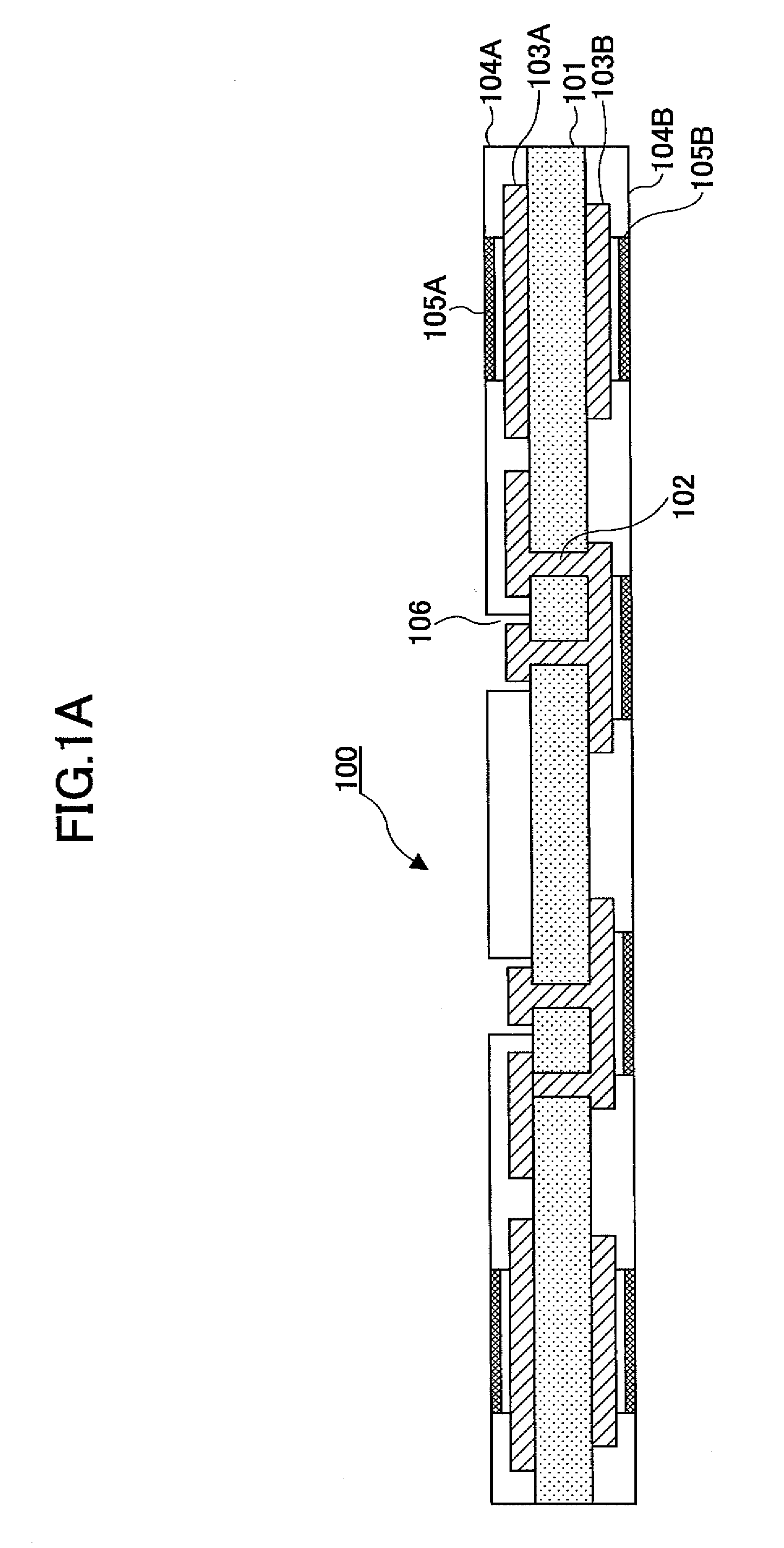

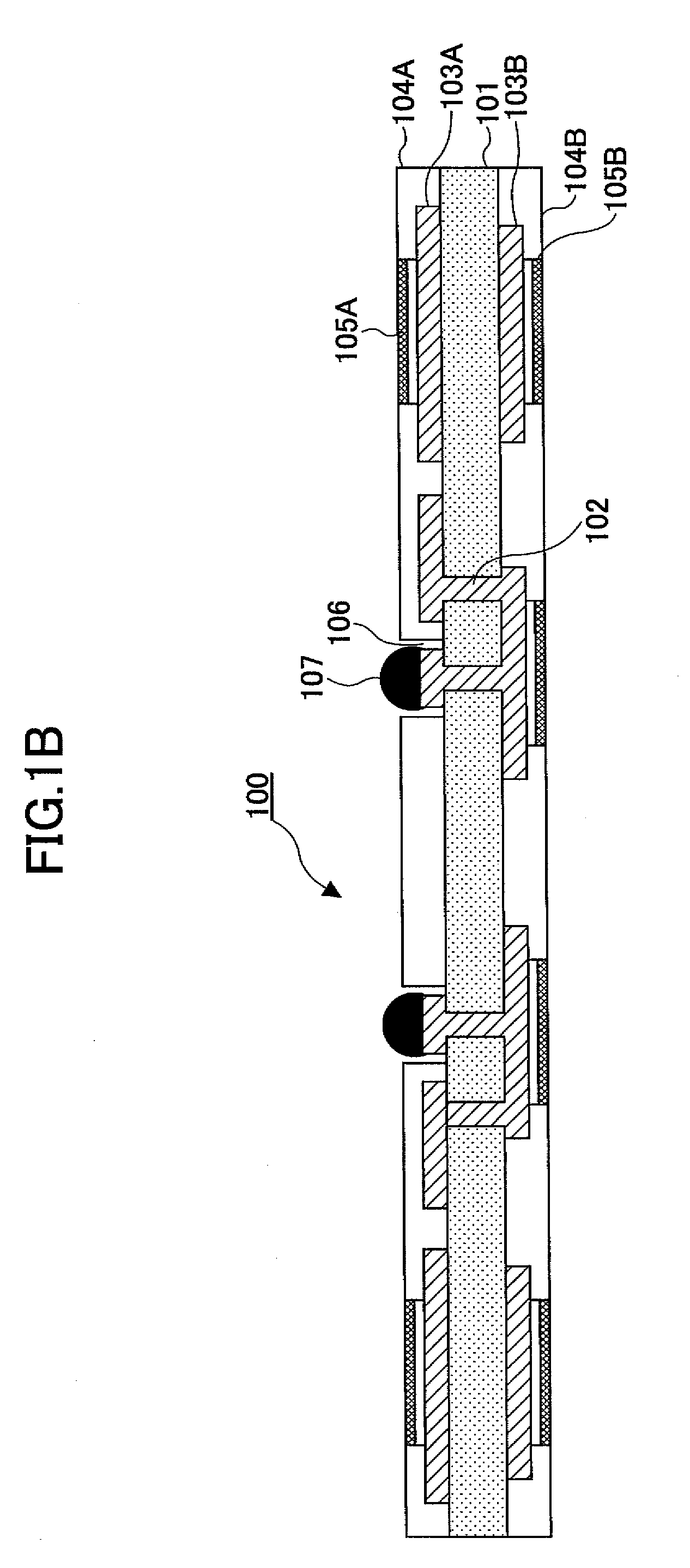

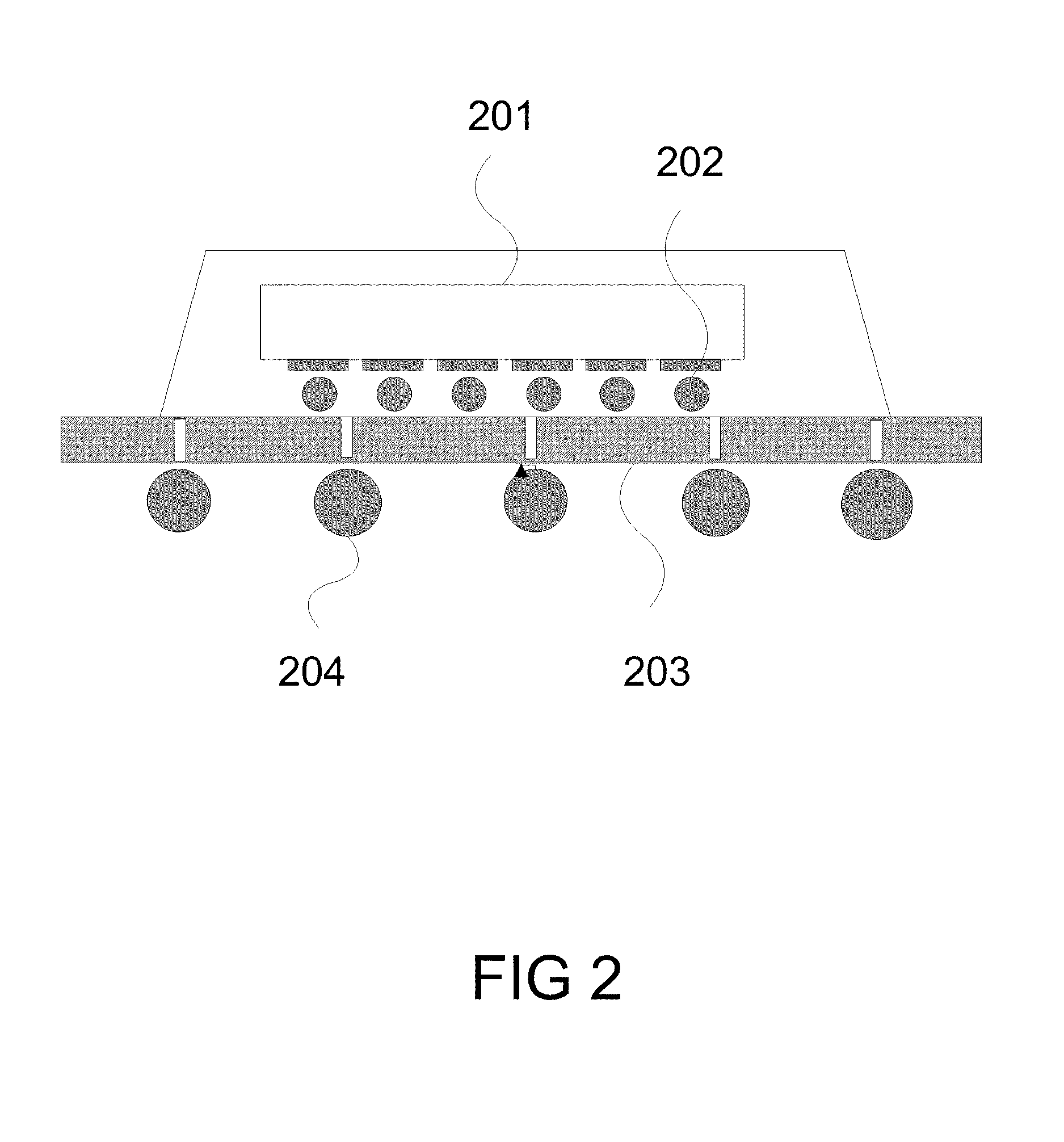

Chip embedded substrate and method of producing the same

ActiveUS20090008765A1Improve production yieldHigh reliability in electrical connectionPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

A method of producing a chip embedded substrate is disclosed. This method comprises a first step of mounting a semiconductor chip on a first substrate on which a first wiring is formed; and a second step of joining the first substrate with a second substrate on which a second wiring is formed. In the second step, the semiconductor chip is encapsulated between the first substrate and the second substrate and electrical connection is made between the first wiring and the second wiring so as to form multilayered wirings connected to the semiconductor chip.

Owner:SHINKO ELECTRIC IND CO LTD

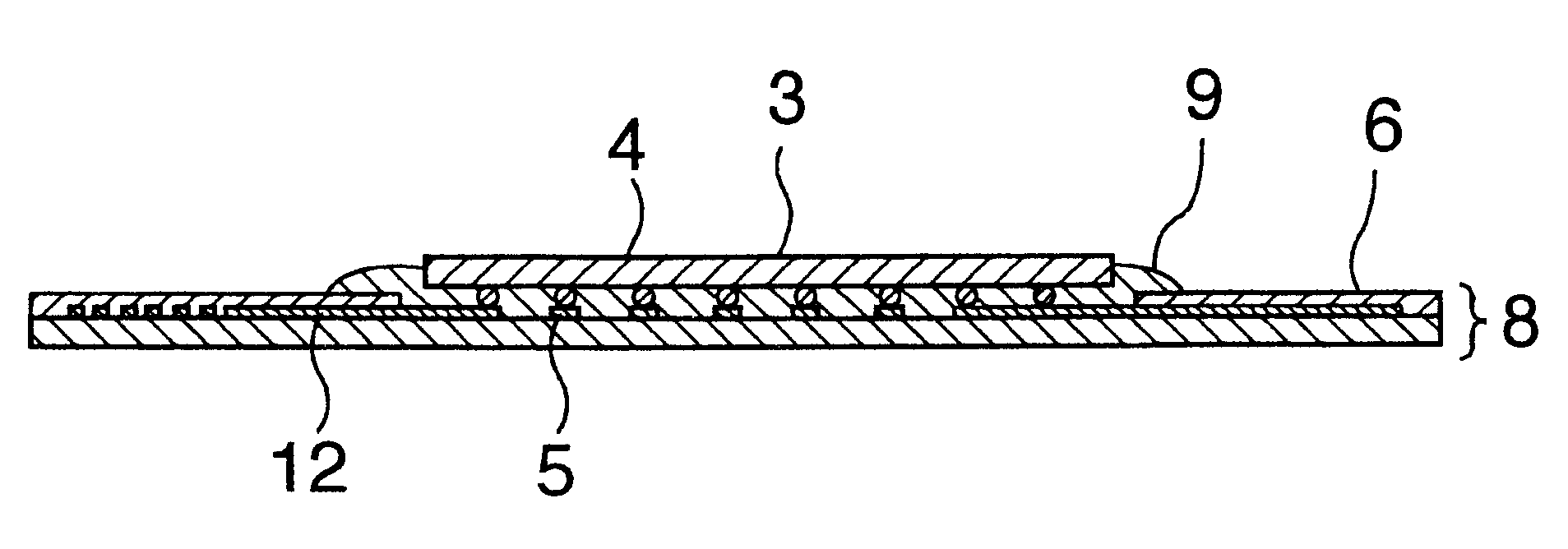

Substrate for mounting semiconductor chips

InactiveUS6281450B1Improve connection reliabilityImprove batch productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical conductor

A substrate for mounting a semiconductor chip having bumps using an adhesive thereon, said substrate being, for instance, provided with an insulating coating having an opening in the semiconductor chip mounting area so that the wiring conductors will not be exposed to the substrate surface near the boundary of the semiconductor chip mounting area, is improved in connection reliability and has high mass productivity.

Owner:HITACHI CHEM CO LTD

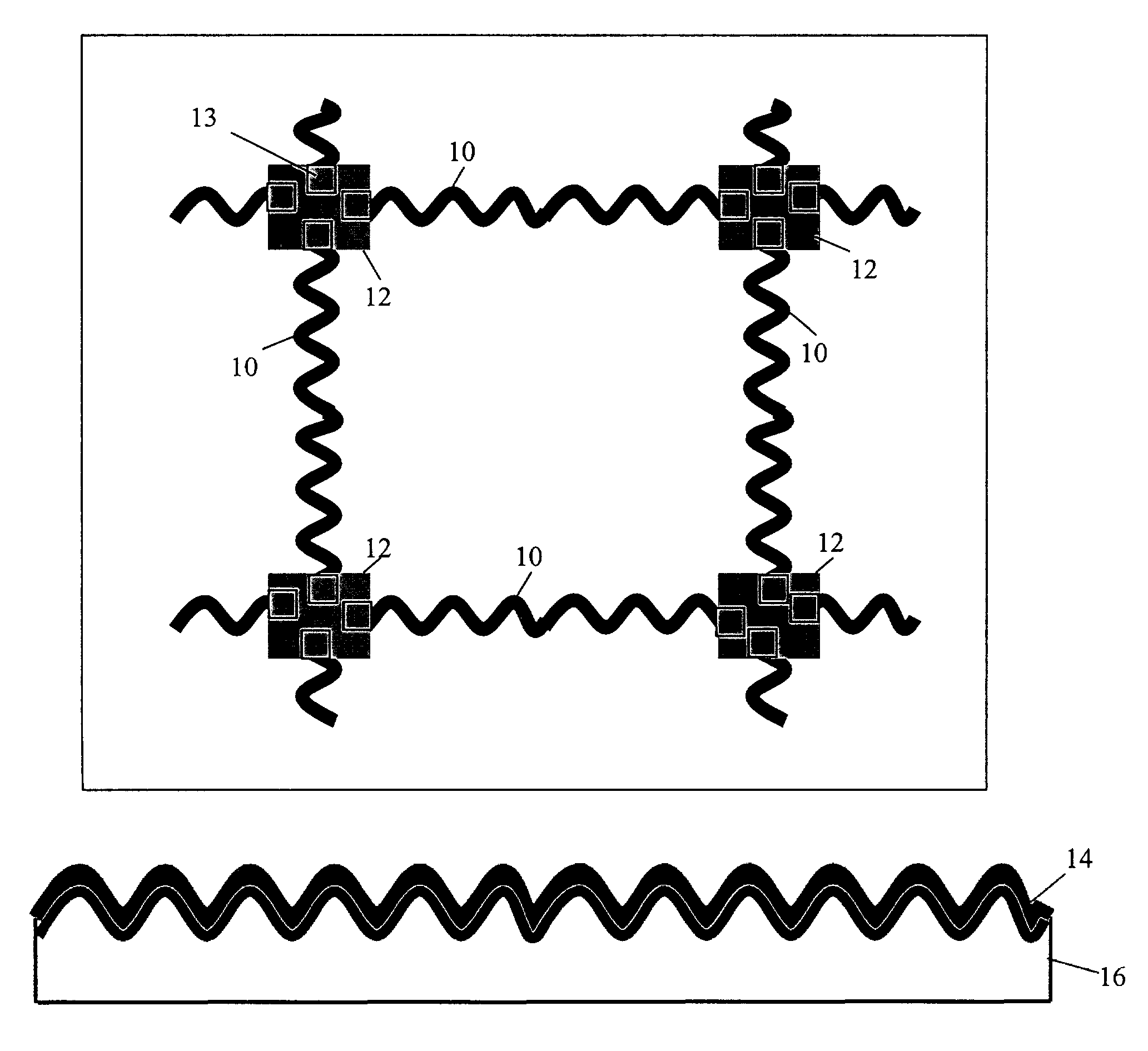

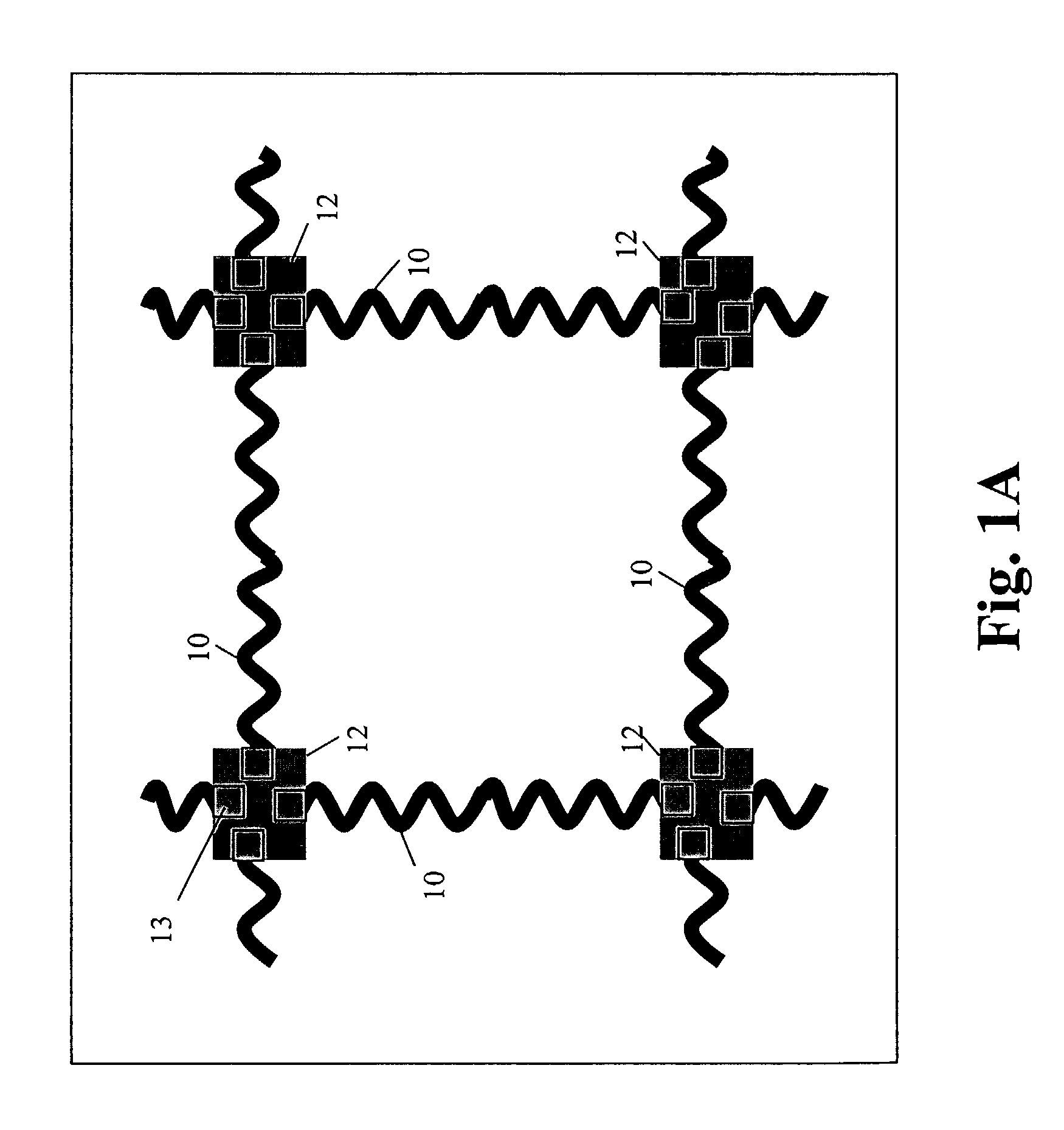

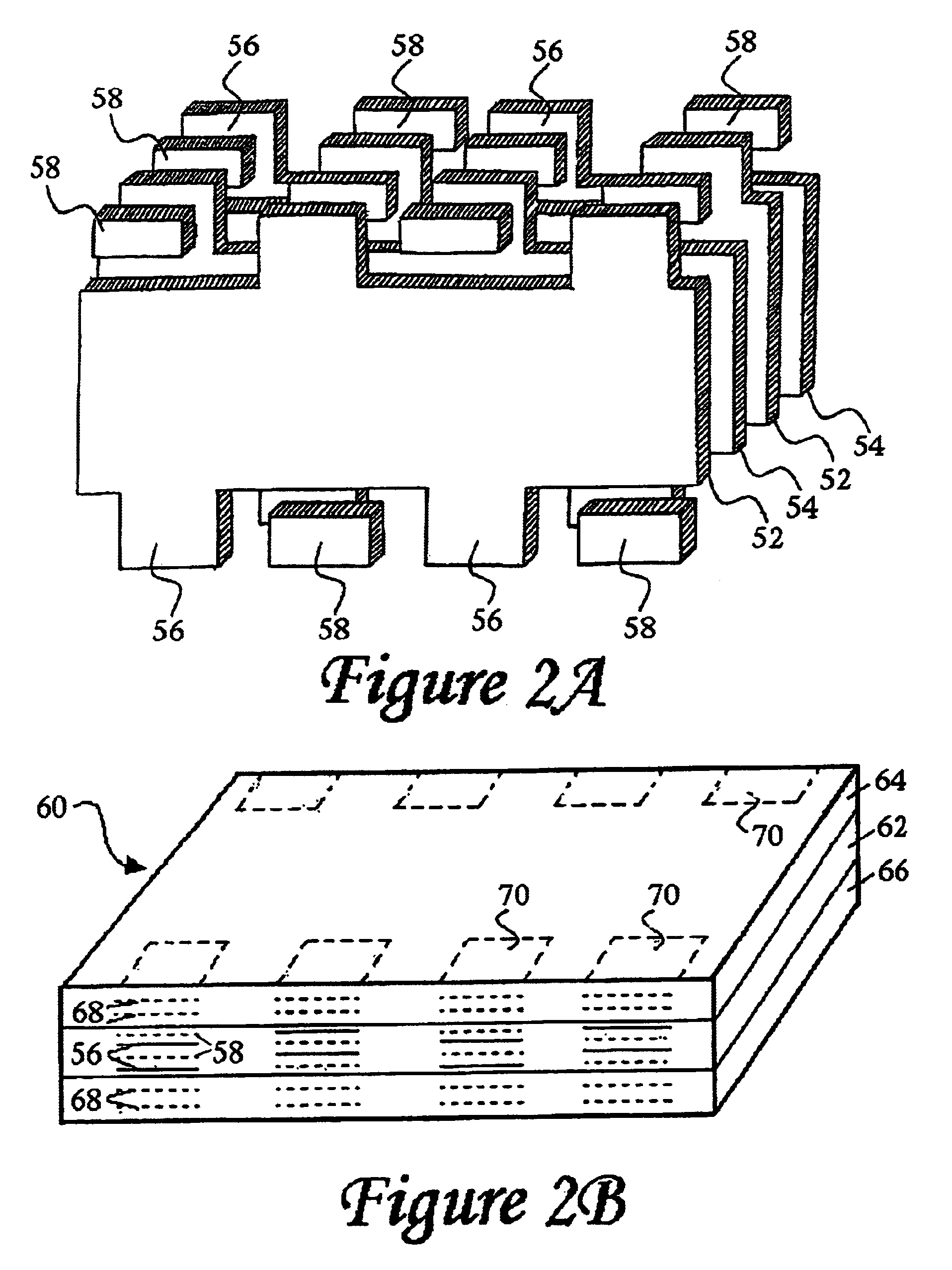

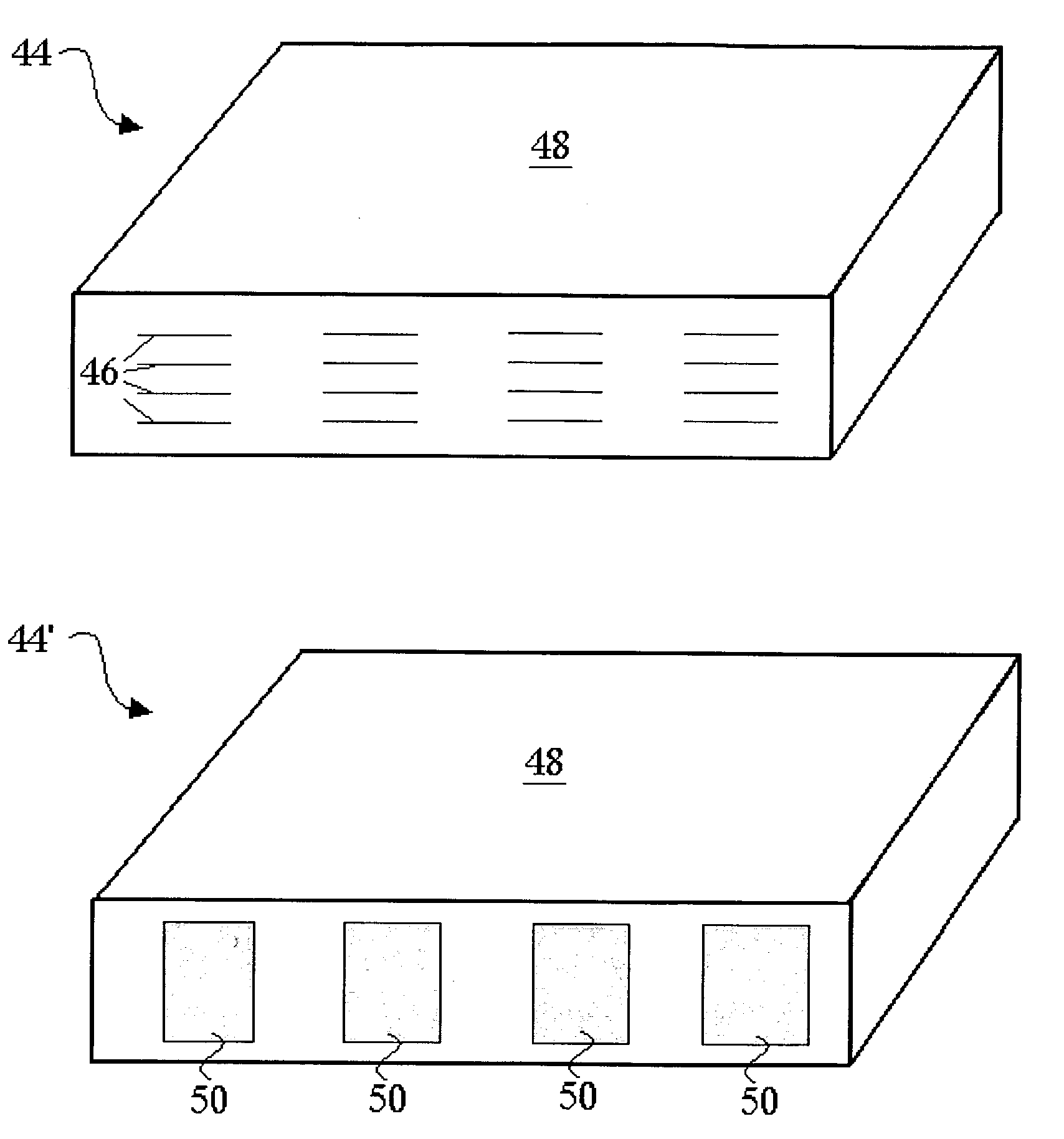

Stretchable and elastic interconnects

InactiveUS7491892B2Reduce mechanical stressSave spaceCircuit bendability/stretchabilityTwo-part coupling devicesElastomerPlastic materials

The present invention relates to stretchable interconnects which can be made in various geometric configurations, depending on the intended application. The stretchable interconnects can be formed of an electrically conducting film or an elastomer material to provide elastic properties in which the interconnects can be reversibly stretched in order to stretch and relax the elastomer material to its original configuration. Alternatively, stretchable interconnects can be formed of an electrically conducting film or a plastic material to provide stretching of the material to a stretched position and retaining the stretched configuration. The stretchable interconnect can be formed of a flat 2-dimensional conductive film covering an elastomeric or plastic substrate. When this structure is stretched in one or two dimensions, it retains electrical conduction in both dimensions. Alternatively, the stretchable and / or elastic interconnects can be formed of a film or stripe that is formed on an elastomeric or plastic substrate such that it is buckled randomly, or organized in waves with long-range periodicity. The buckling or waves can be induced by various techniques, including: release of built-in stress of the conductive film or conductive stripe; pre-stretching the substrate prior to the fabrication of the conductive film or conductive stripe; and patterning of the surface of the substrate prior to the fabrication of the metal film. The stretchable interconnect can be formed of a plurality of conductive films or conductive stripes embedded between a plurality of layers of a substrate formed of an elastomer or plastic.

Owner:PRINCETON UNIV

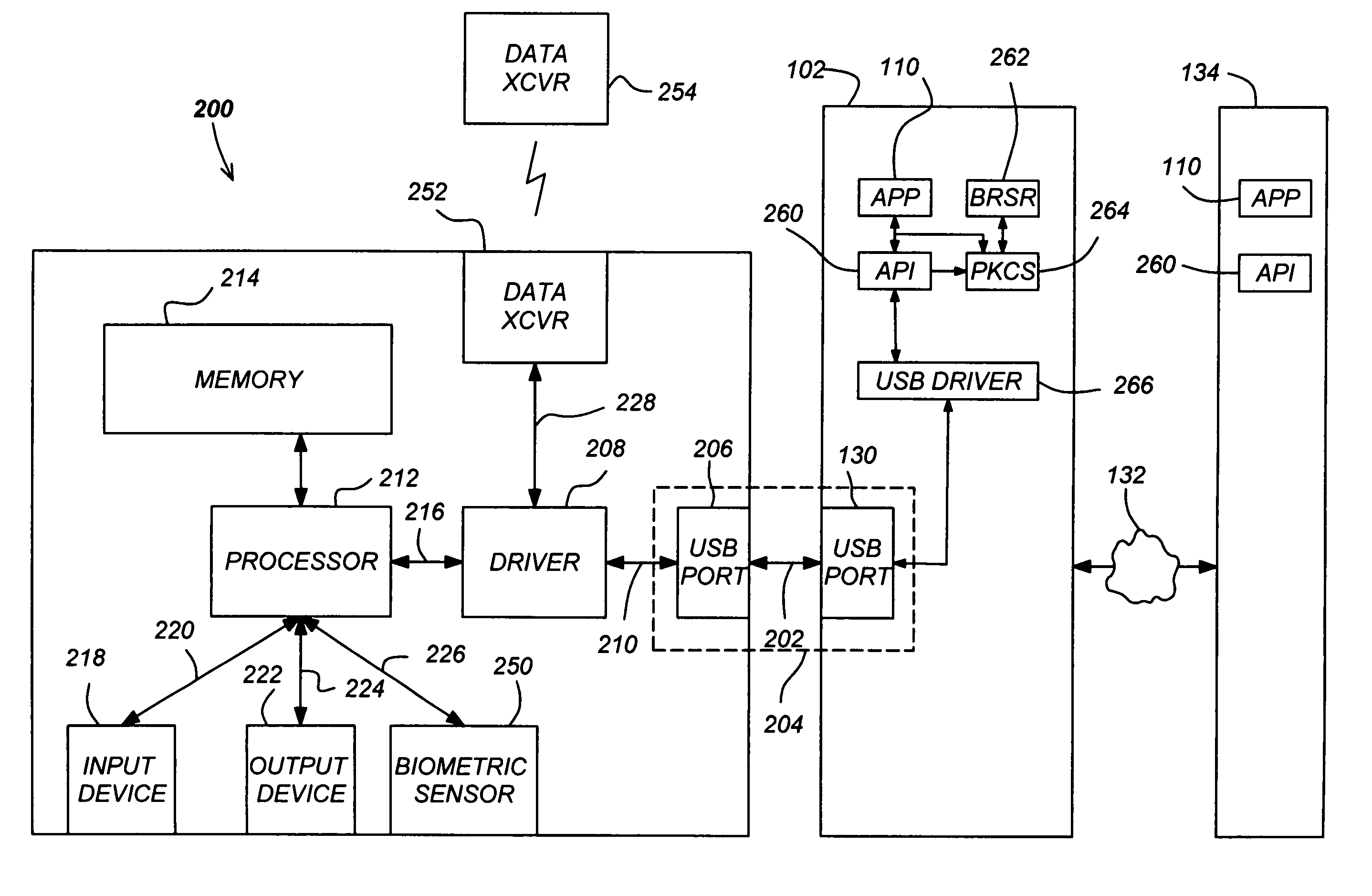

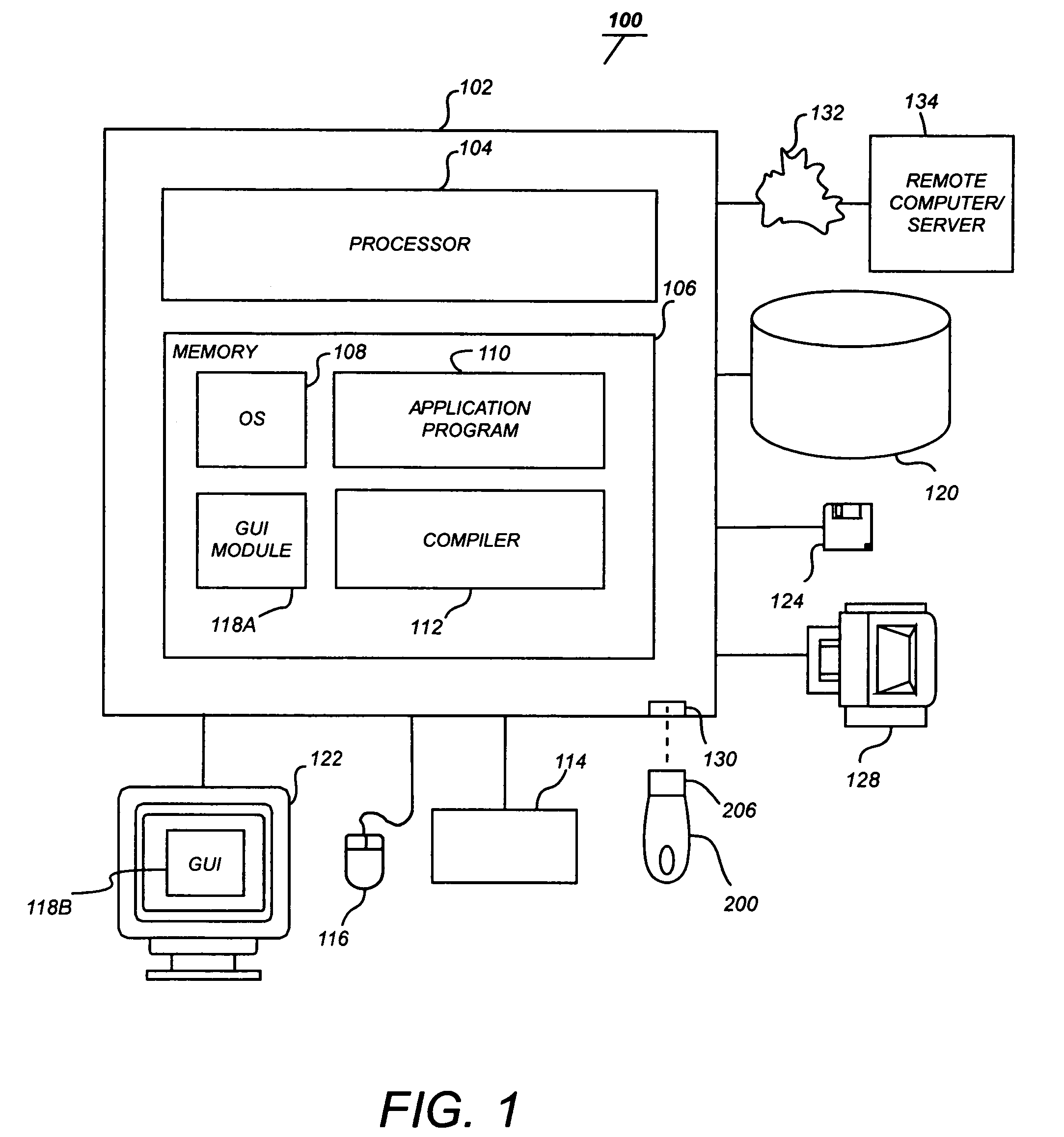

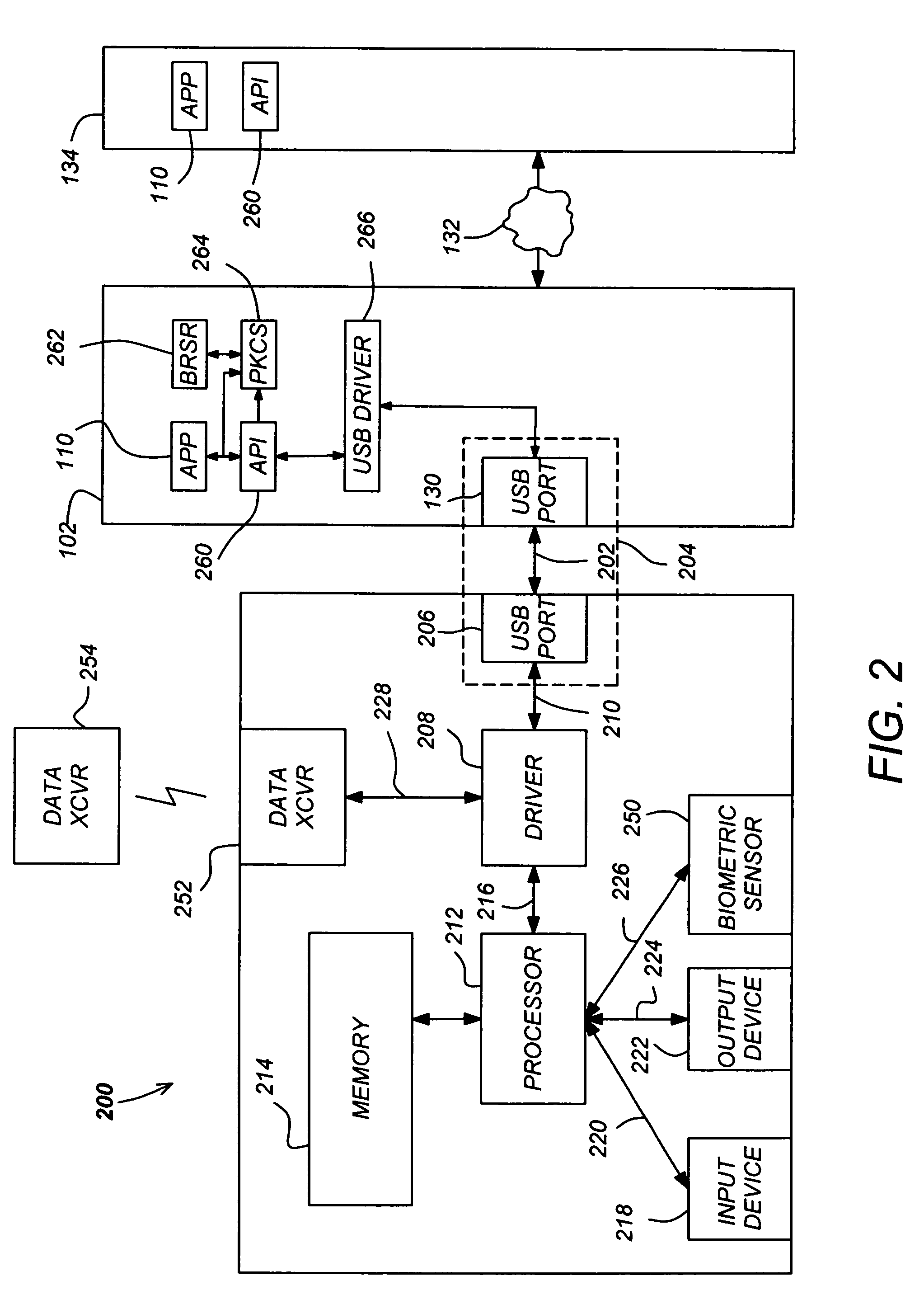

USB-compliant personal key with integral input and output devices

InactiveUS7272723B1Prevent copyingPrevent unauthorized useDigital data processing detailsUser identity/authority verificationUser inputConditional access

A compact, self-contained, personal key is disclosed. The personal key comprises a USB-compliant interface releaseably coupleable to a host processing device; a memory; and a processor. The processor provides the host processing device conditional access to data storable in the memory as well as the functionality required to manage files stored in the personal key and for performing computations based on the data in the files. In one embodiment, the personal key also comprises an integral user input device and an integral user output device. The input and output devices communicate with the processor by communication paths which are independent from the USB-compliant interface, and thus allow the user to communicate with the processor without manifesting any private information external to the personal key.

Owner:SAFENET

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS20080316714A1Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

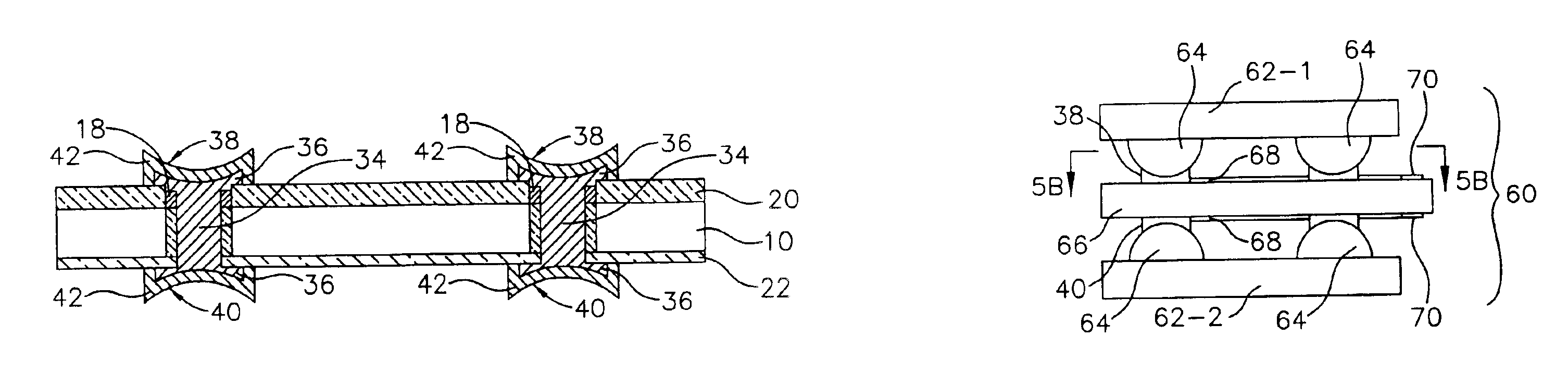

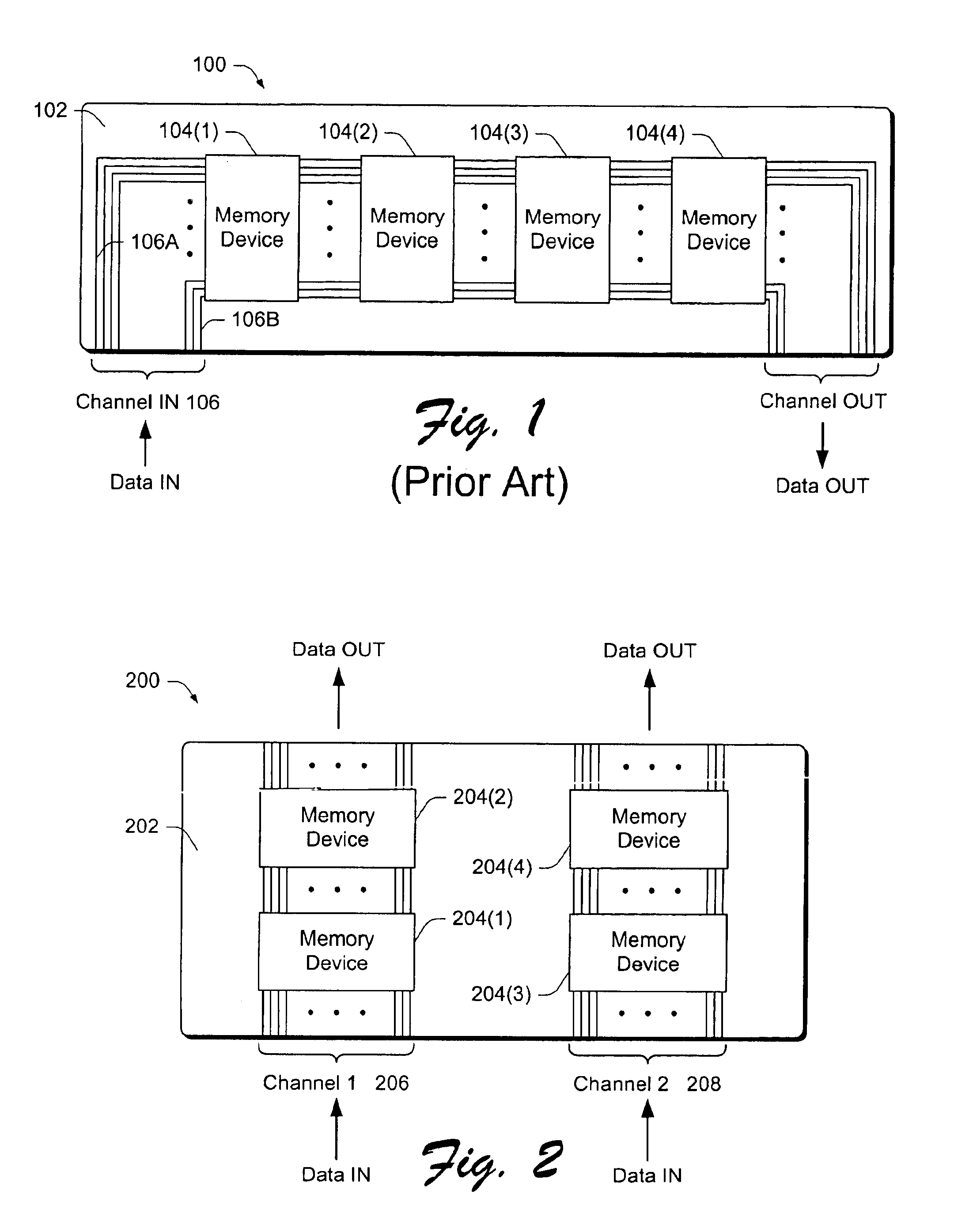

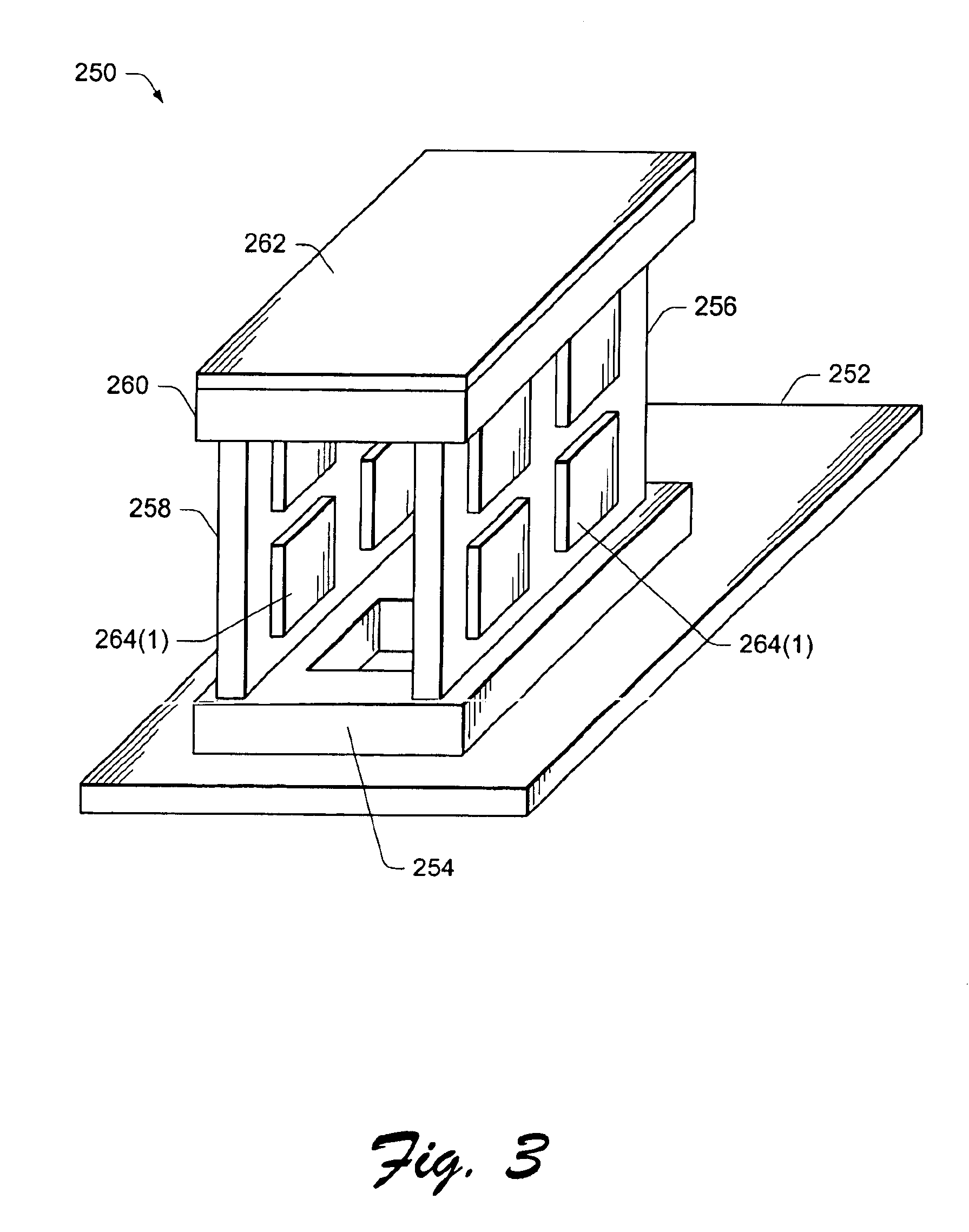

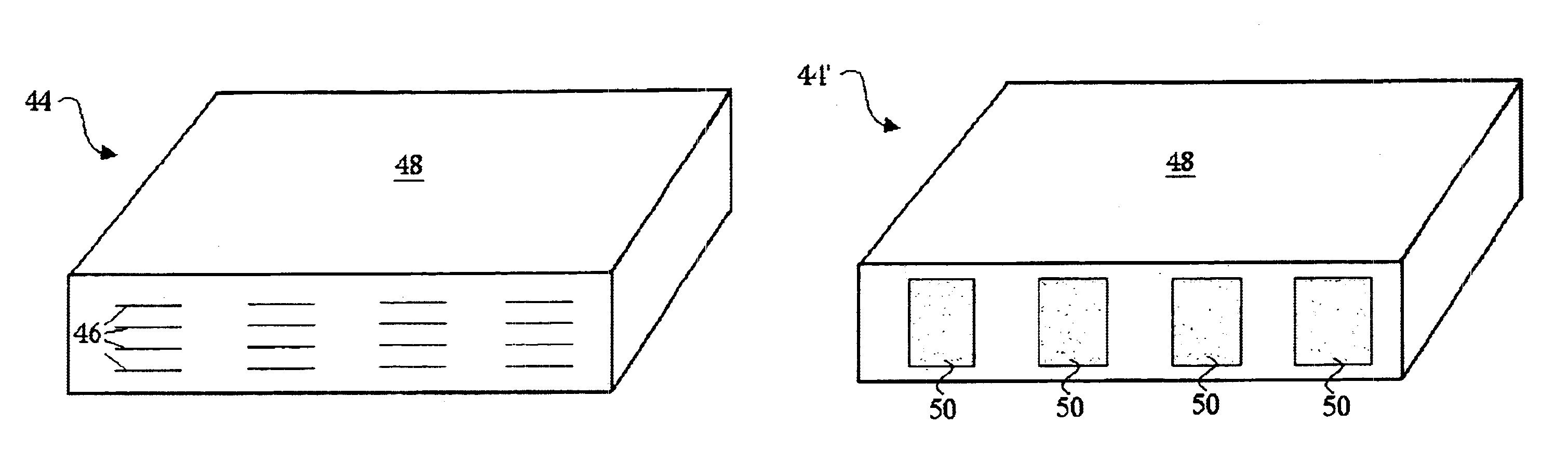

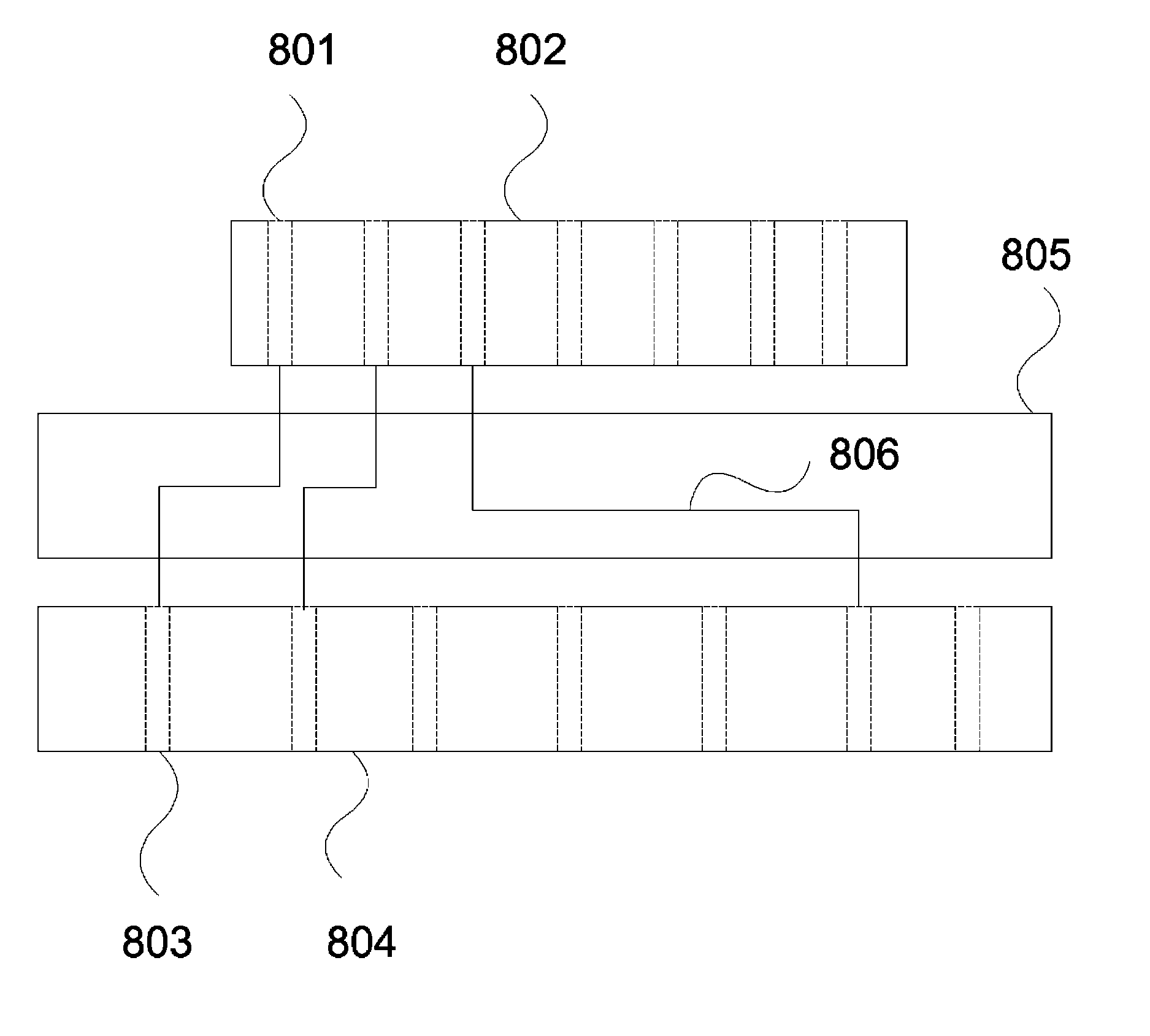

Multi-channel memory architecture

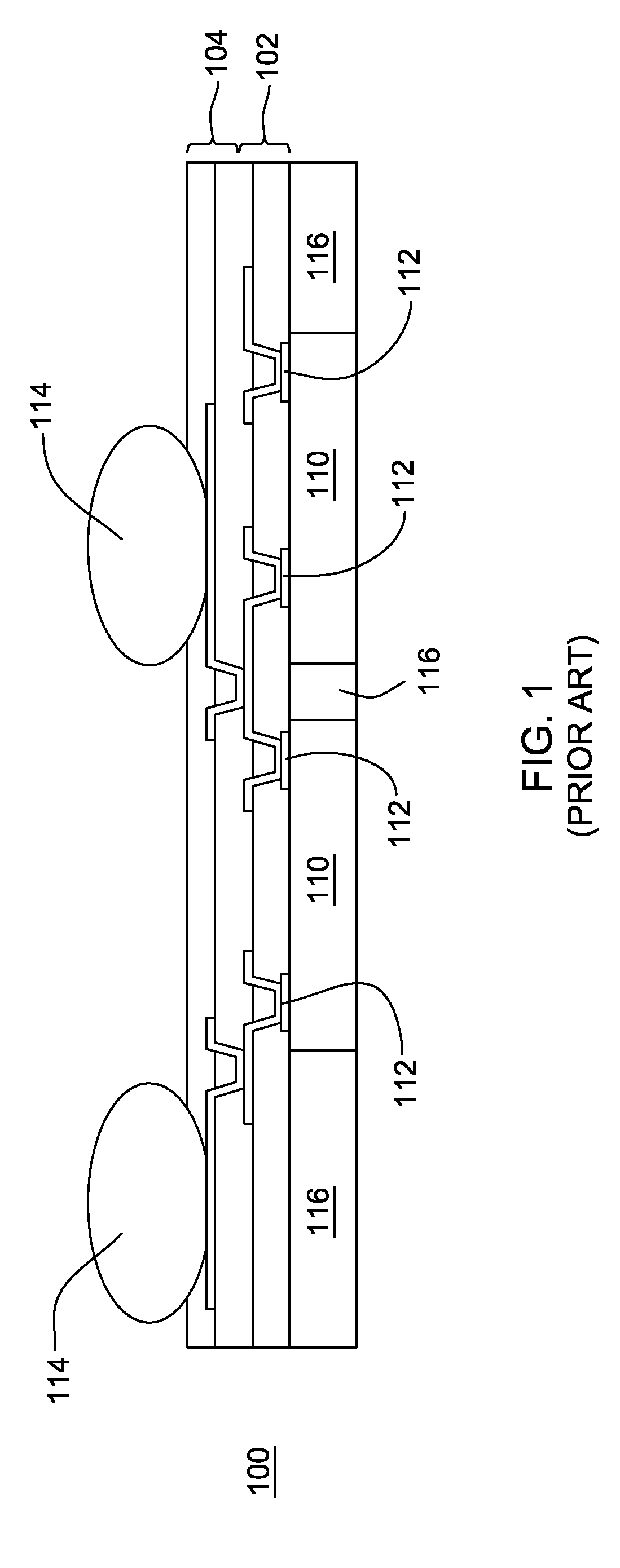

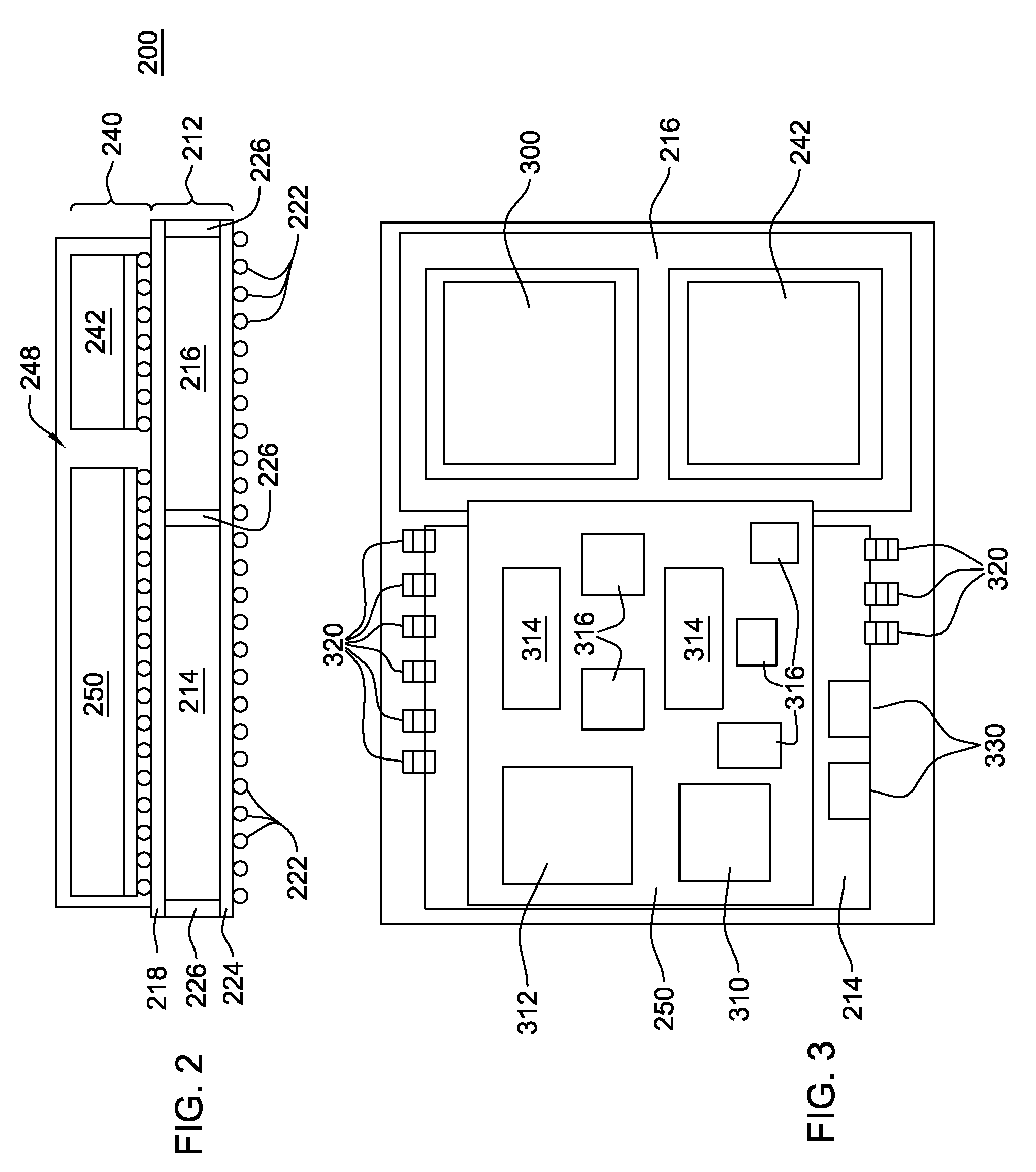

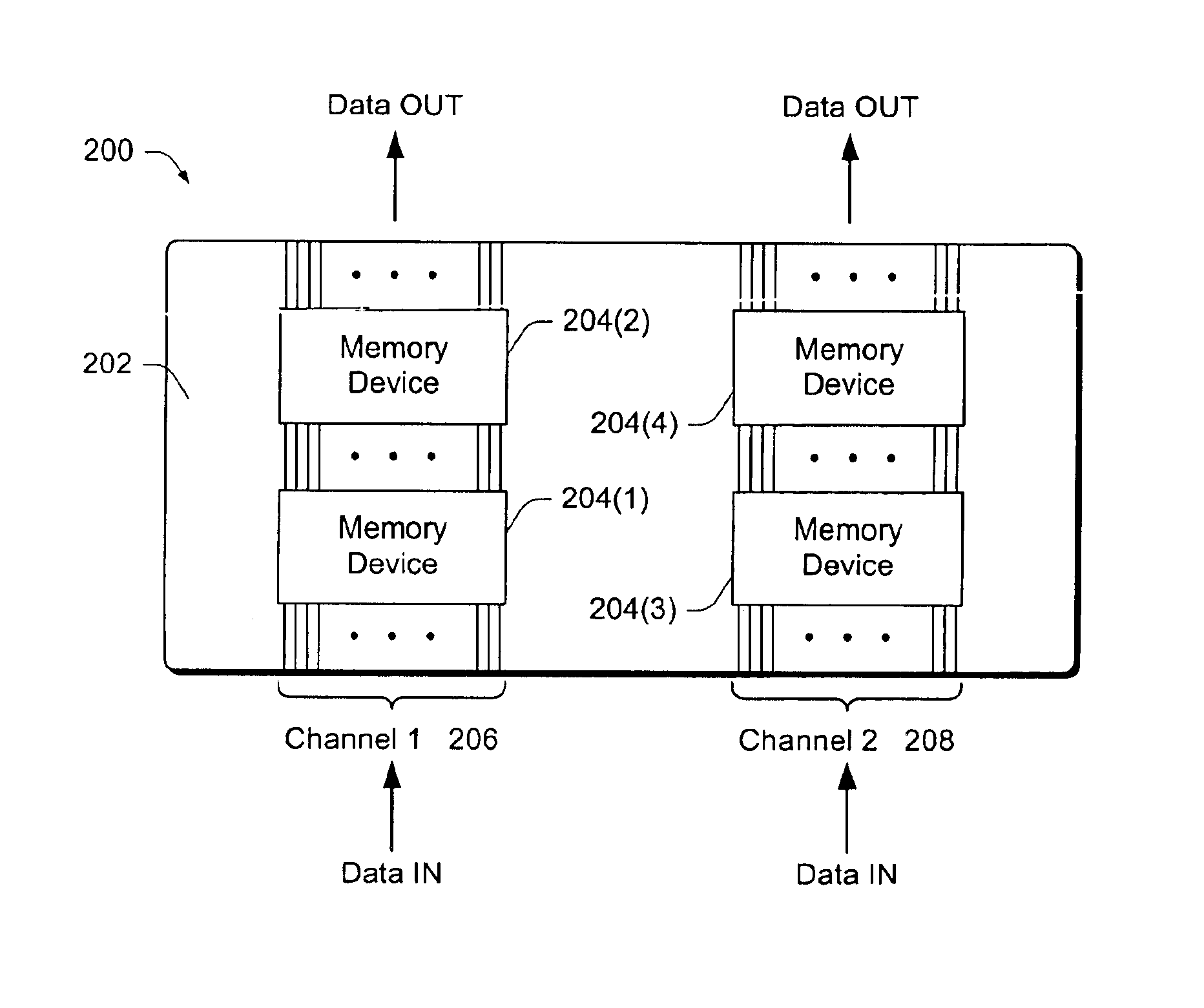

InactiveUS6853557B1Circuit arrangements on support structuresPrinted circuit aspectsElectrical conductorEngineering

A memory architecture includes a first substrate containing multiple memory devices and a first channel portion extending across the first substrate. The architecture further includes a second substrate containing multiple memory devices and a second channel portion extending across the second substrate. A connector couples the first channel portion to the second channel portion to form a single channel. The connector includes a first slot that receives an edge of the first substrate and a second slot that receives an edge of the second substrate. Another connector has a pair of slots that receive opposite edges of the first and second substrates. The channel portions extend across the substrates in a substantially linear path. Each channel portion includes multiple conductors having lengths that are approximately equal.

Owner:RAMBUS INC

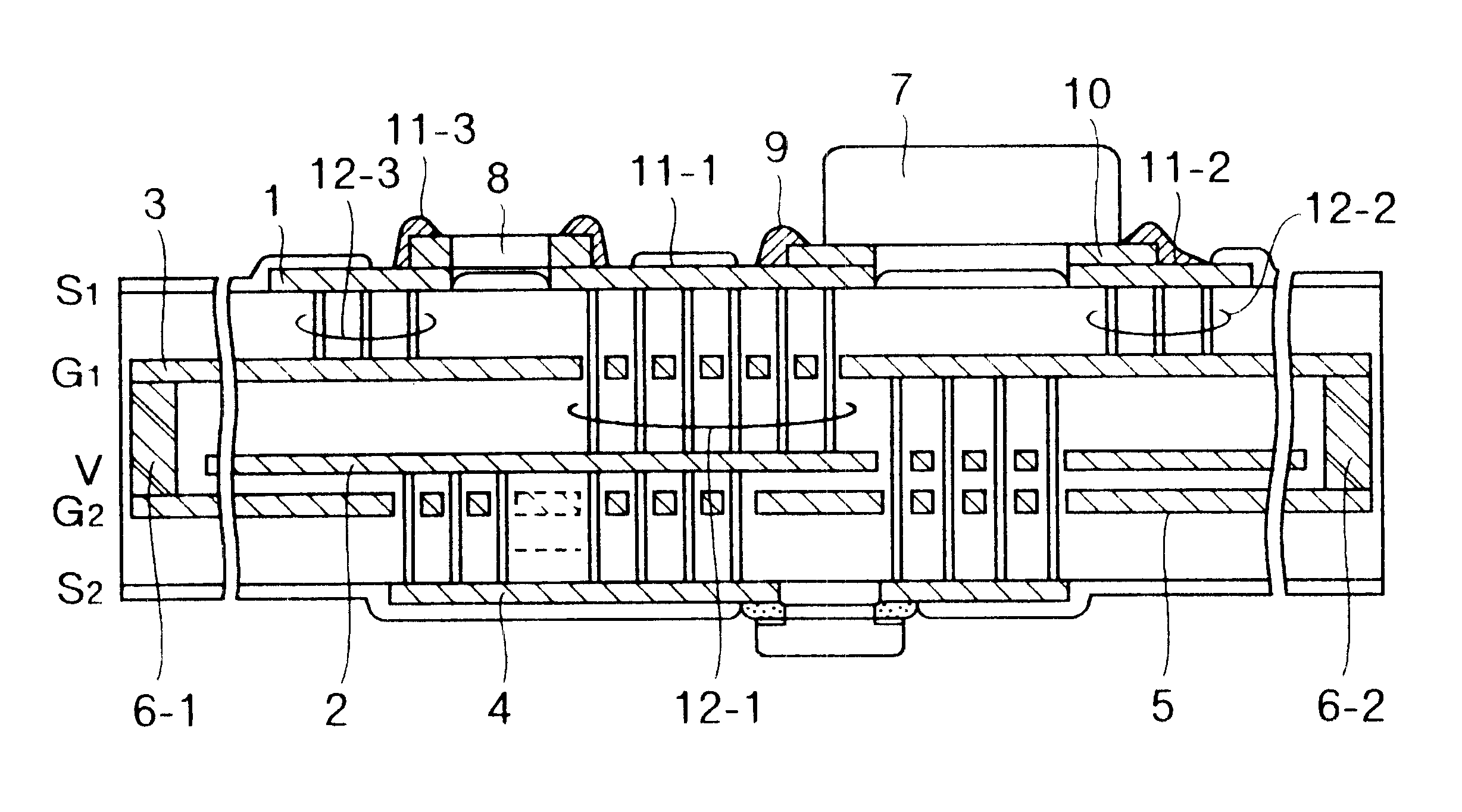

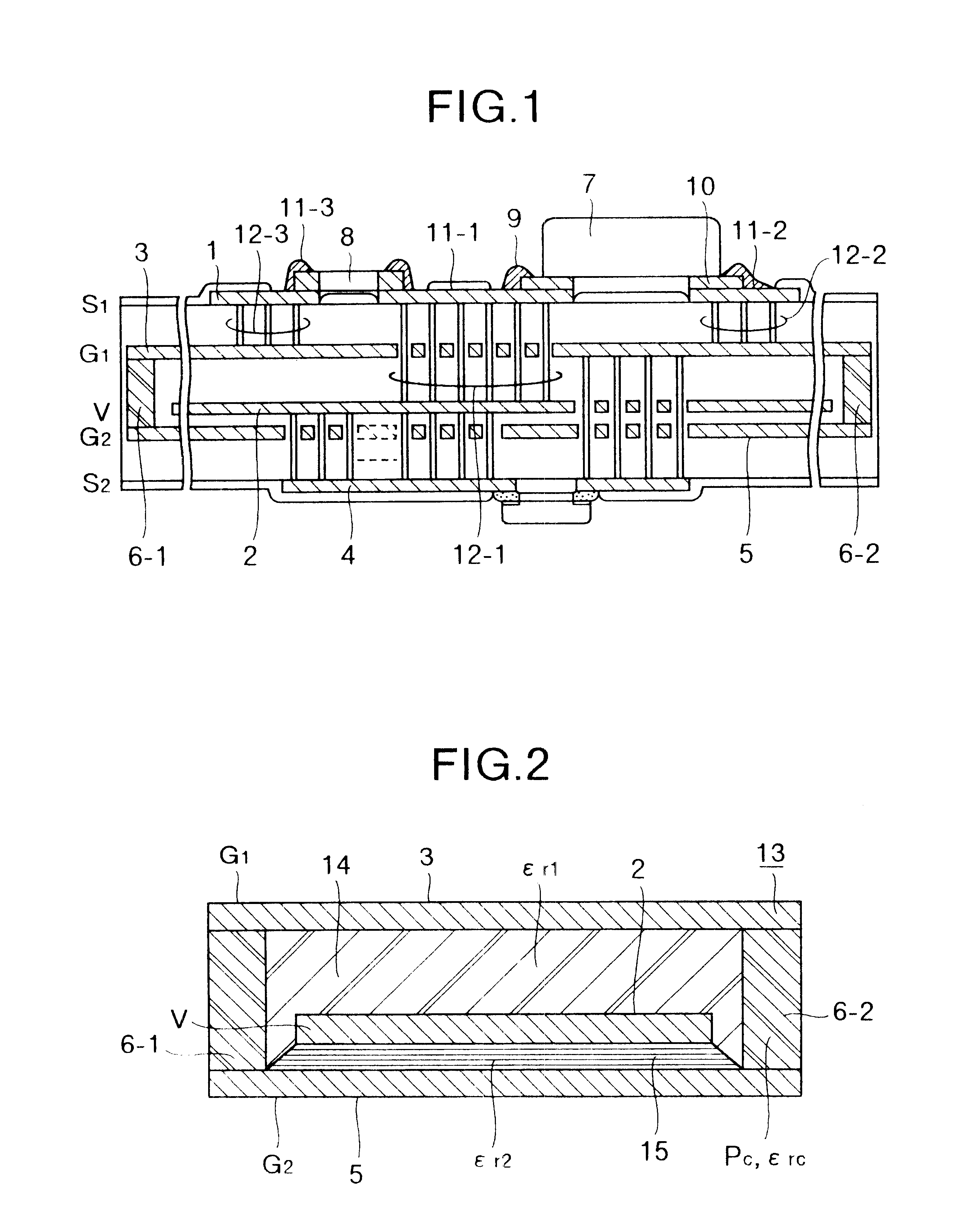

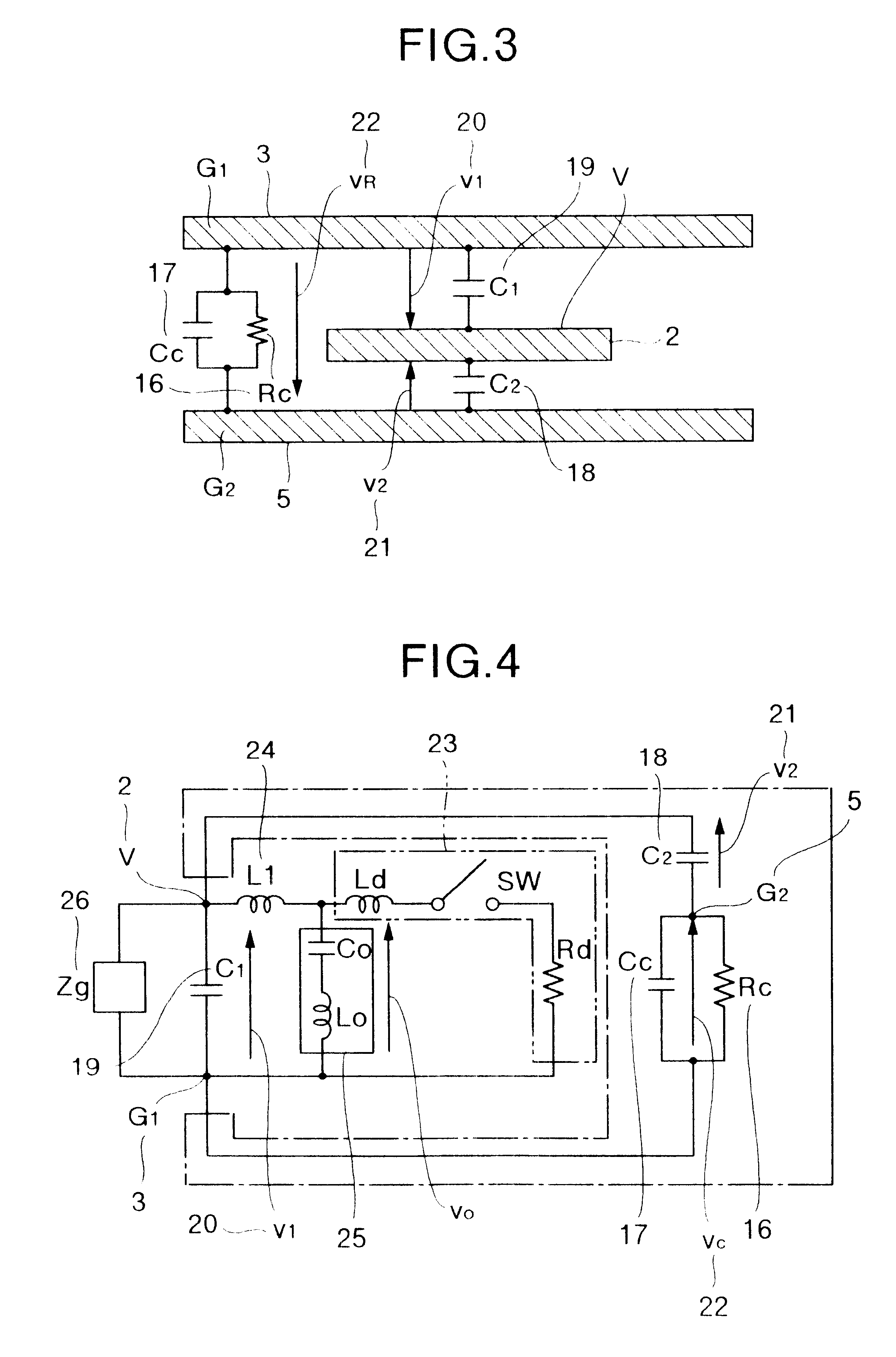

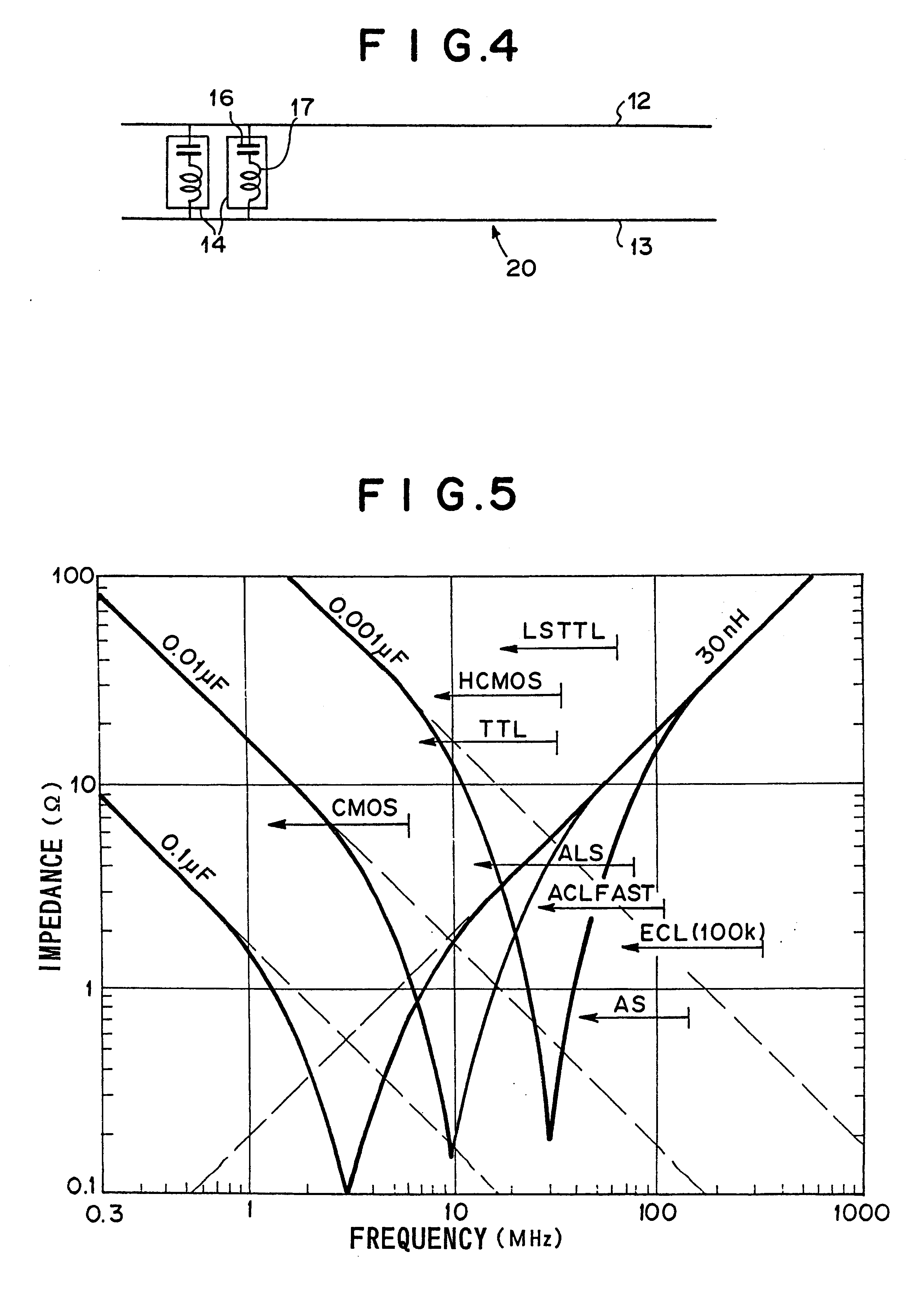

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

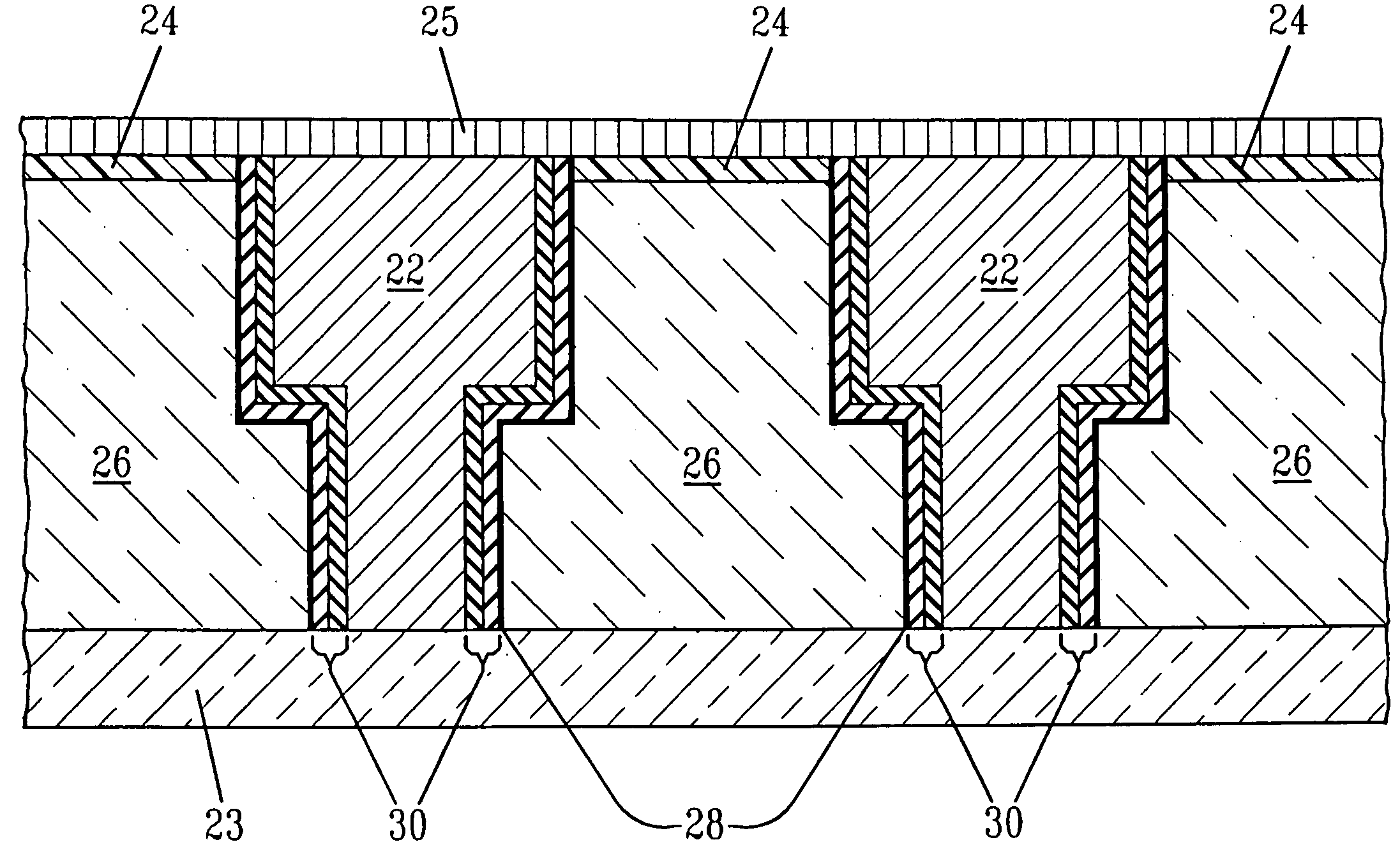

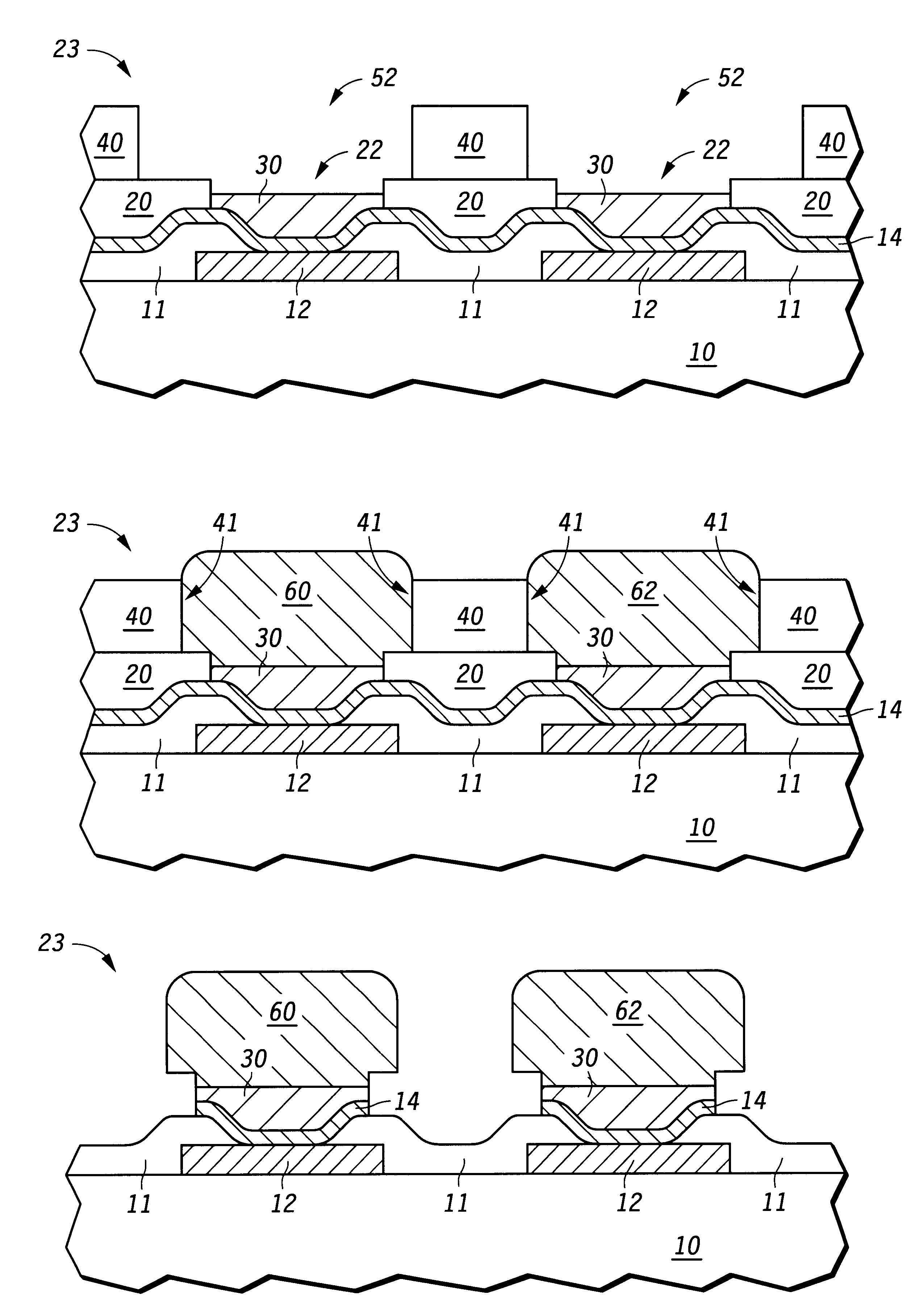

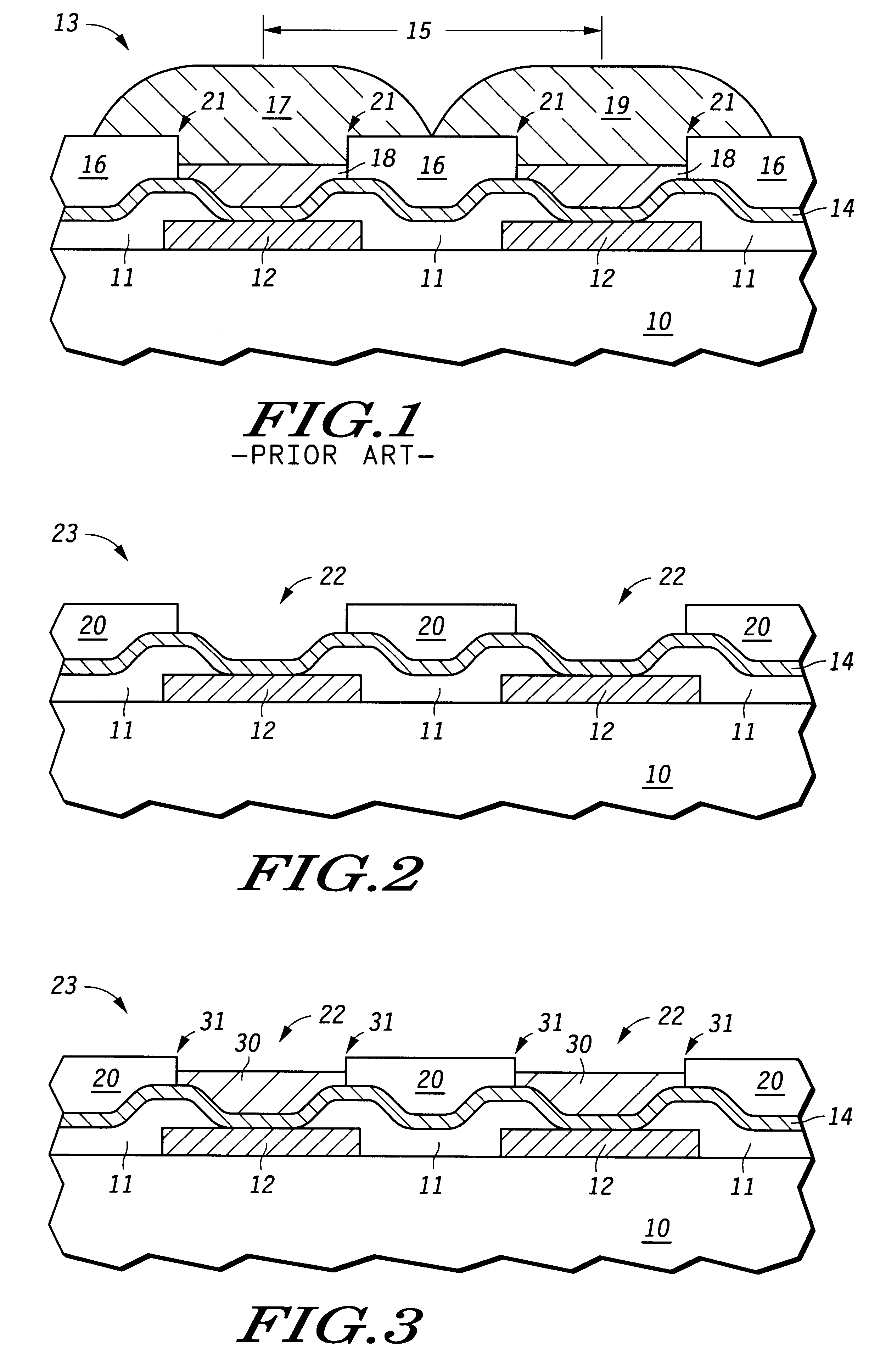

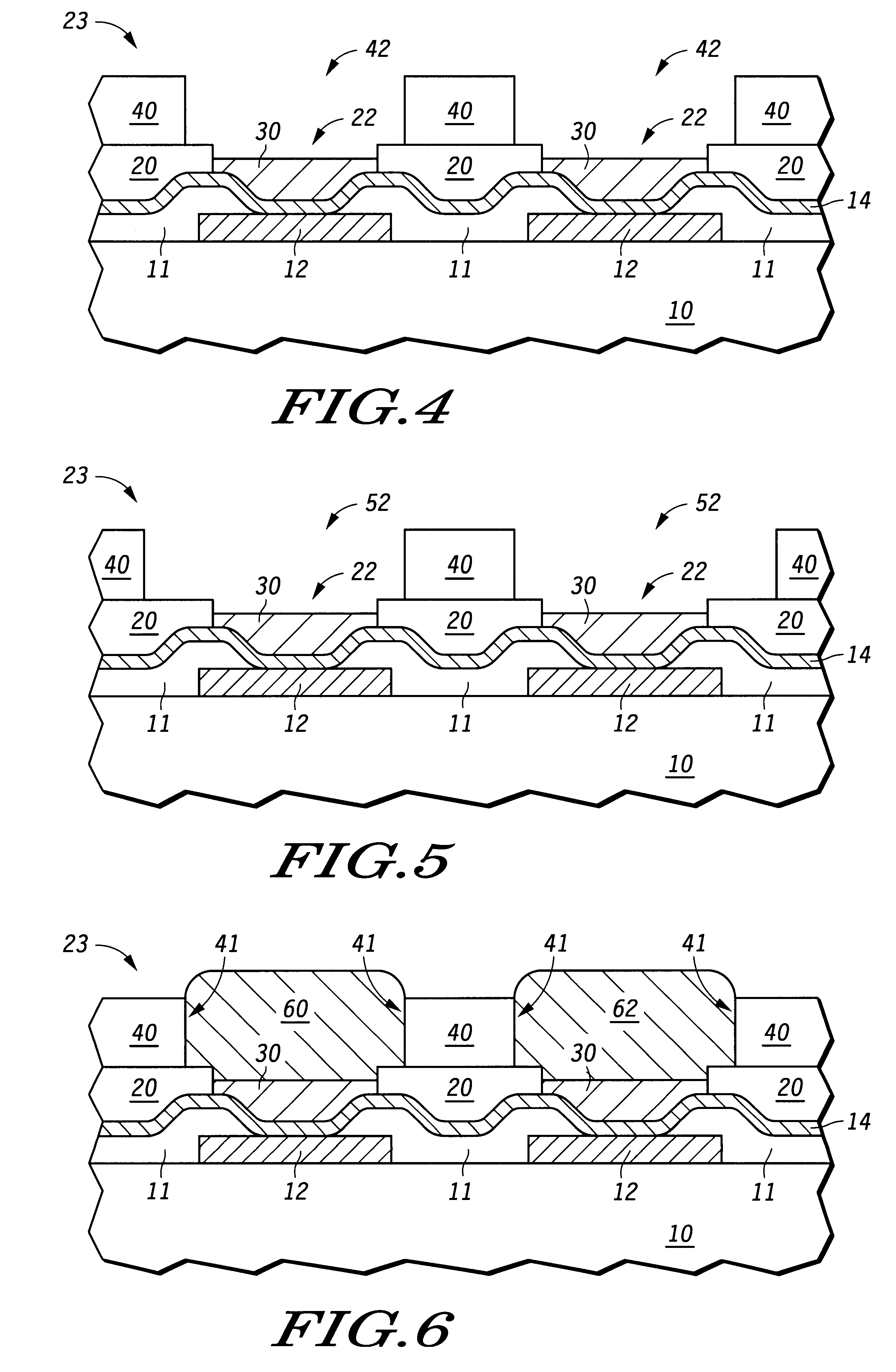

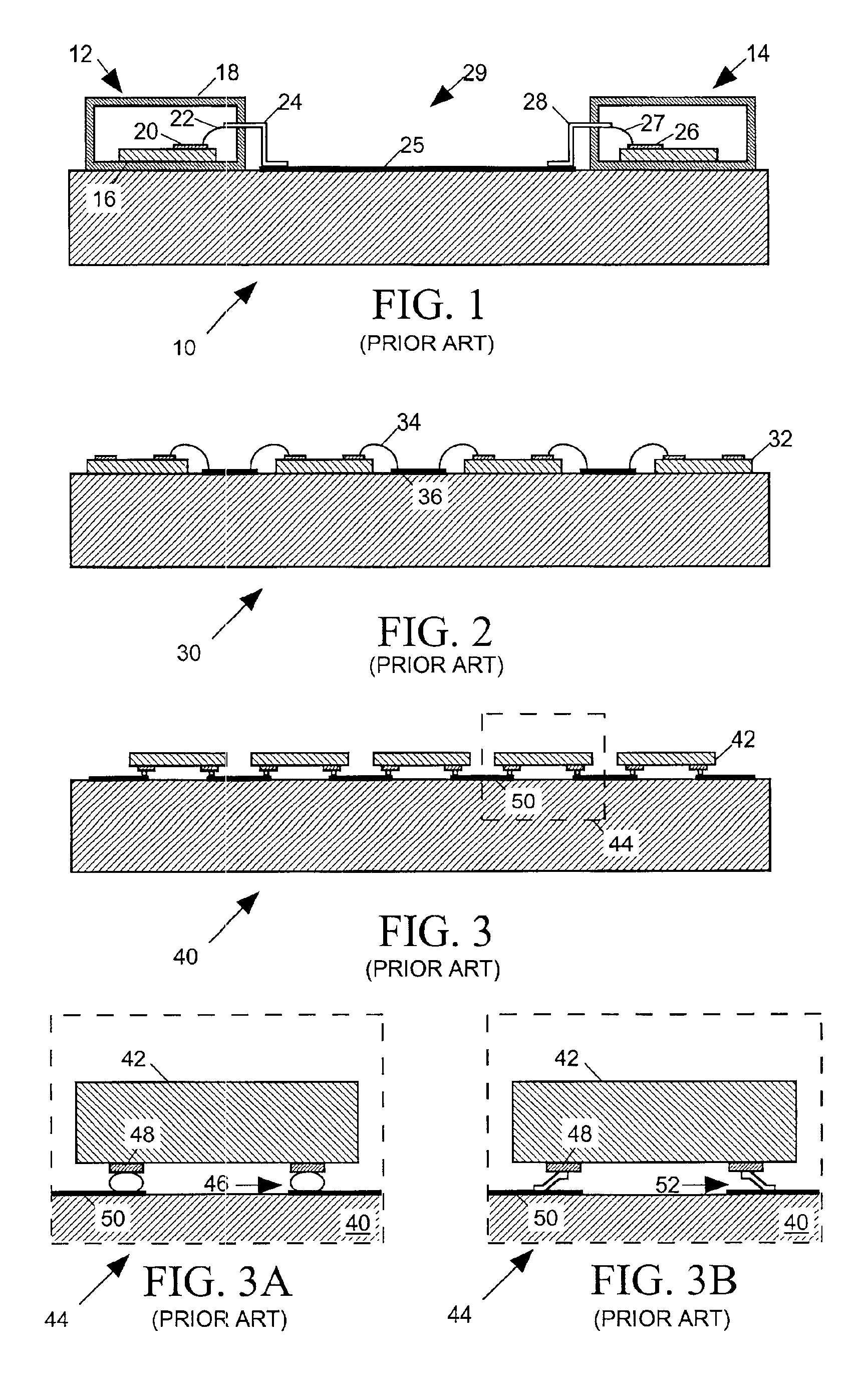

Fine pitch bumping with improved device standoff and bump volume

Embodiments of the present invention relate generally to solder bump formation and semiconductor device assemblies. One embodiment related to a method for forming a bump structure includes providing a semiconductor device (10) having a bond pad (12), and forming a first masking layer (20) overlying the bond pad (12). The first masking layer (20) is patterned to form a first opening (22) overlying at least a portion of the bond pad (12). A second masking layer (40) is formed overlying the first masking layer (20), and the second masking layer (40) is patterned to form a second opening (42) overlying at least a portion of the first opening (22). The method further includes forming a stud (30) at least within the first opening (22) and a solder bump (60) at least within the second opening (42).

Owner:NORTH STAR INNOVATIONS

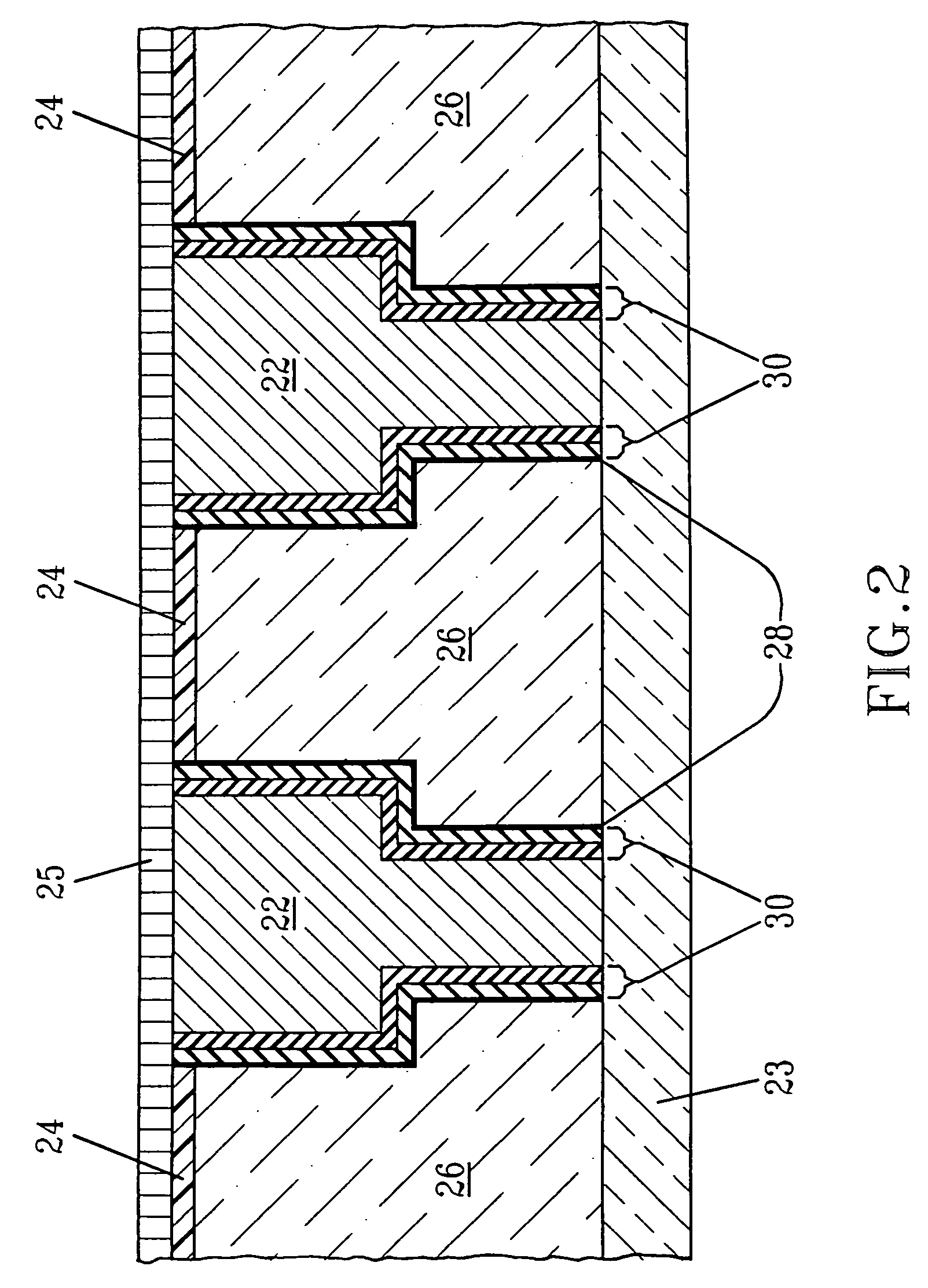

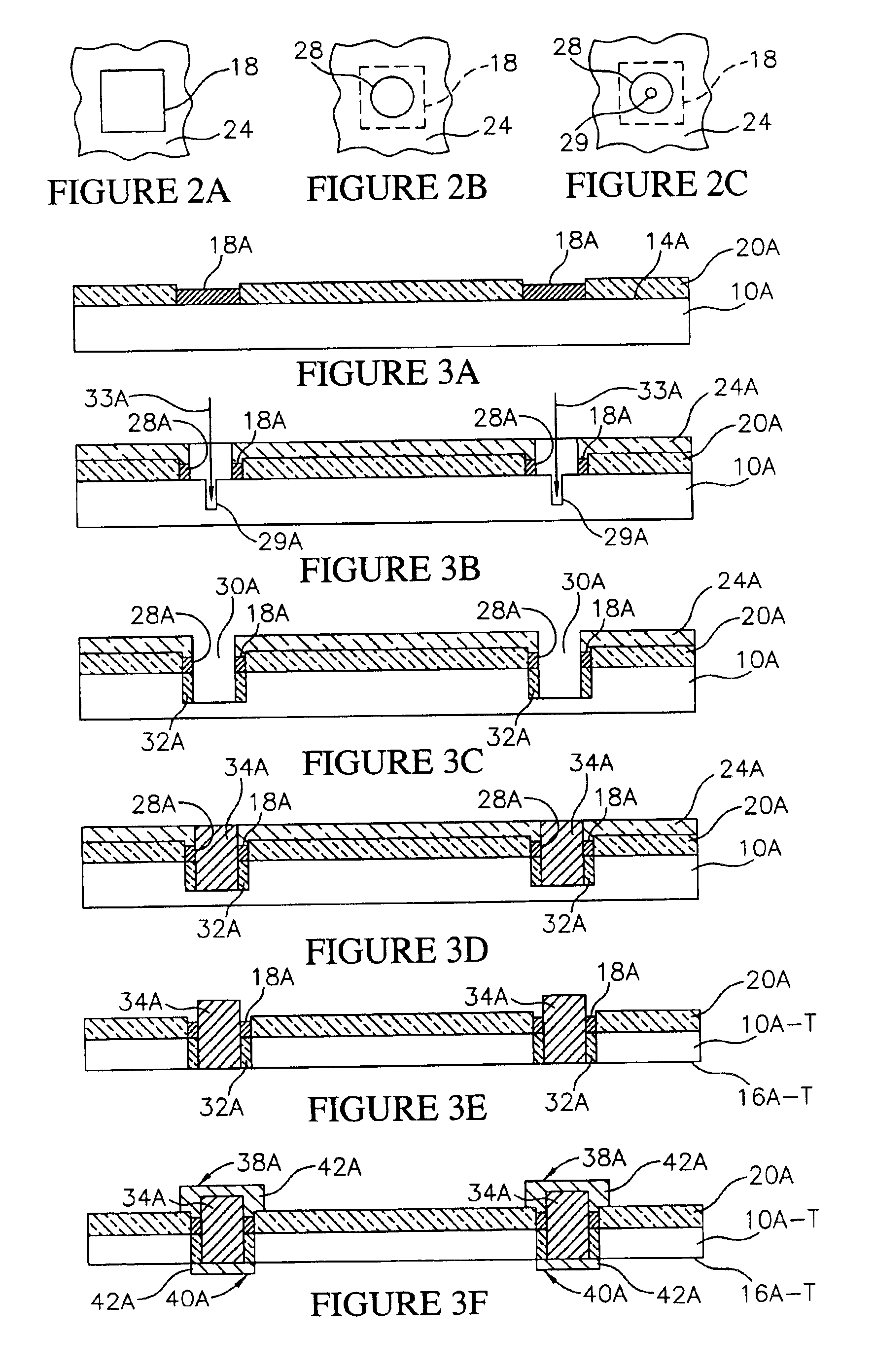

Method for fabricating an IC interconnect system including an in-street integrated circuit wafer via

InactiveUS6910268B2Inexpensively formedSemiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

Vertical holes are created in streets separating individual integrated circuit (IC) dies formed on a semiconductor wafer, the holes spanning saw-lines along which the wafer is to be later cut to separate the IC die from one another to form individual IC chips. The holes are then filled with conductive material. After the wafer is cut along the saw-lines, portions of the conductive material on opposing sides of the saw-lines remain on peripheral edges of the IC chip to form signal paths between the upper and lower surfaces of the IC chips.

Owner:FORMFACTOR INC

Method of manufacturing a fabric article to include electronic circuitry and an electrically active textile article

InactiveUS6729025B2Low-profileEliminate needLayered productsSemiconductor/solid-state device detailsEngineeringElectron

A method of manufacturing a fabric article to include electronic circuitry in which a flex circuit is assembled to include conductive traces and pads on a flexible substrate, a fabric article is placed on a rigid surface, and the substrate of the flex circuit is secured to the fabric article. Also disclosed is a fabric article which includes electronic circuitry and an electrically active textile article.

Owner:FOSTER-MILLER

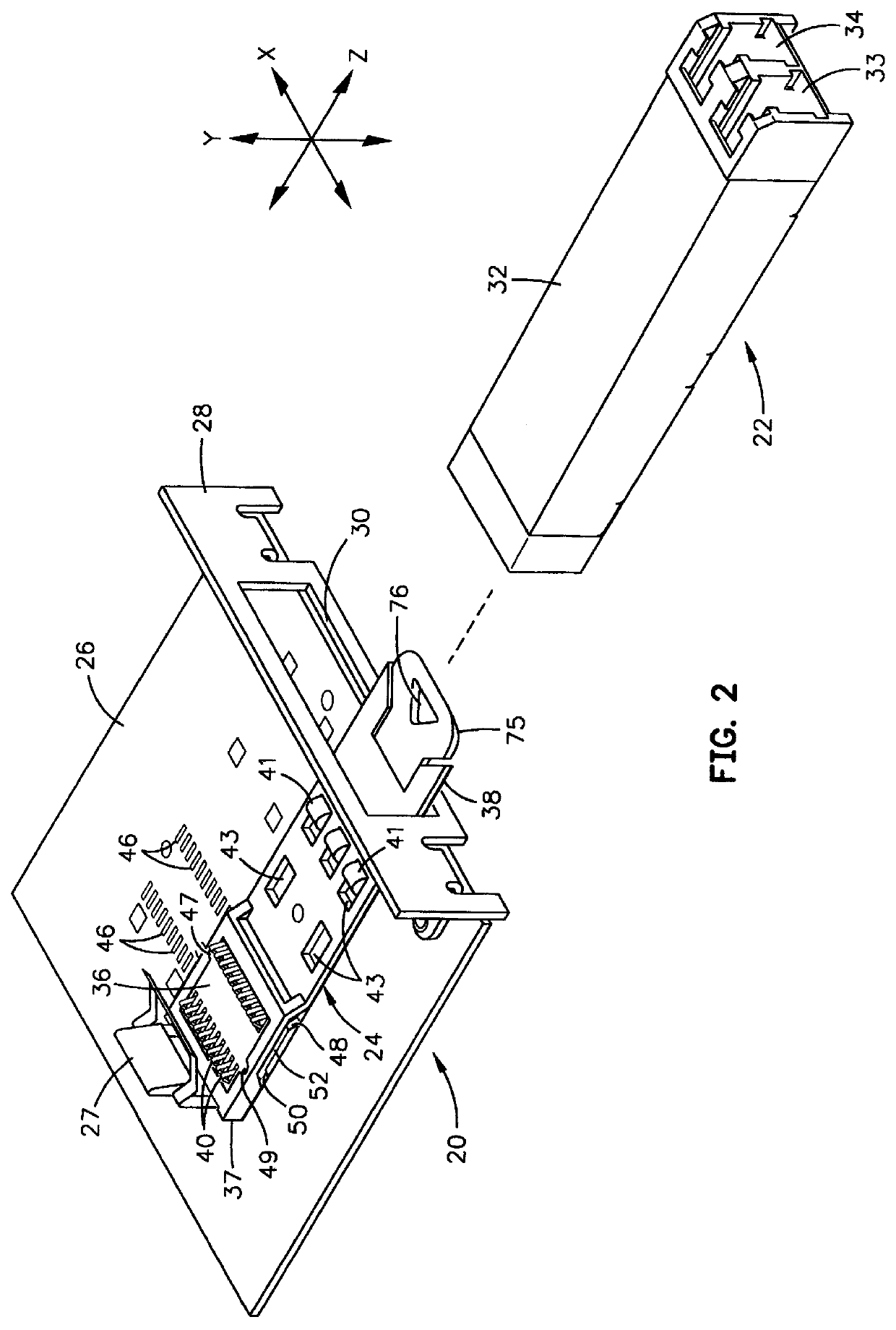

Guide rail and cam system with integrated connector for removable transceiver

InactiveUS6142802AEngagement/disengagement of coupling partsPrinted circuit aspectsGround contactTransceiver

An electrical connector system has two connectors, one of which is included in a module mateable with the other connector in a pluggable manner. The other connector includes an elongated guide rail and a connector block in which are retained two or more electrical contacts. Signal connections can be made in a predetermined sequence when the module is plugged into the other connector because the contact pads of the module are of different lengths. For example, sequencing the connection of power and ground signals with respect to data signals provides hot-pluggability. Also, a grounding contact on the module is engaged by a spring clip on the other connector to provide an additional or alternative grounding path.

Owner:LUMENTUM OPERATIONS LLC

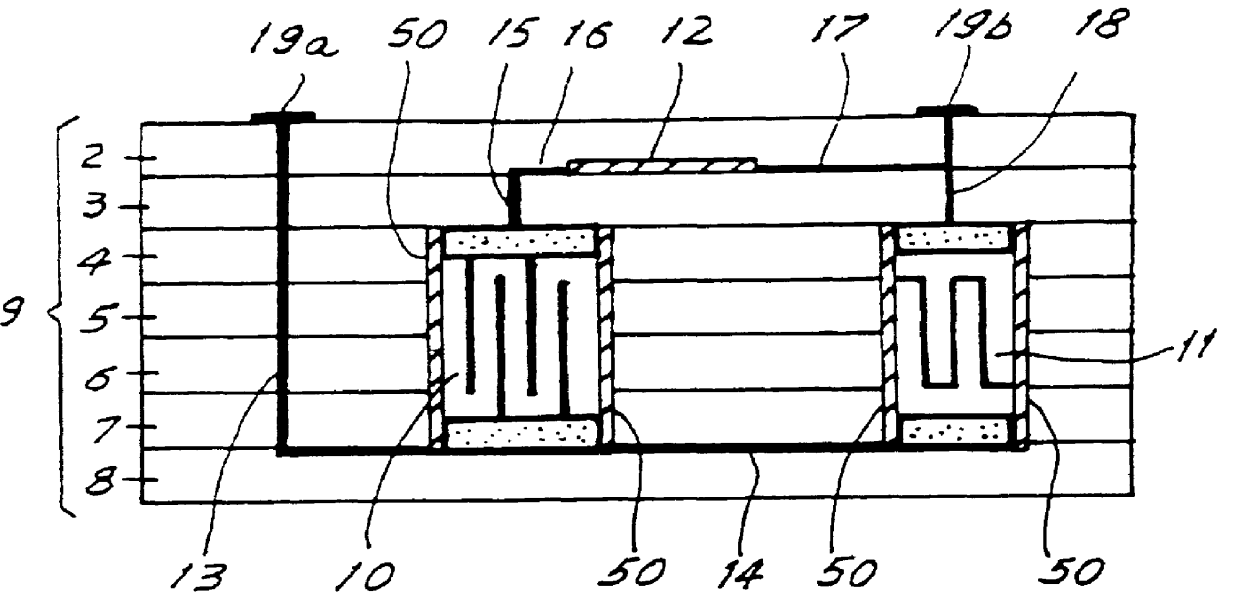

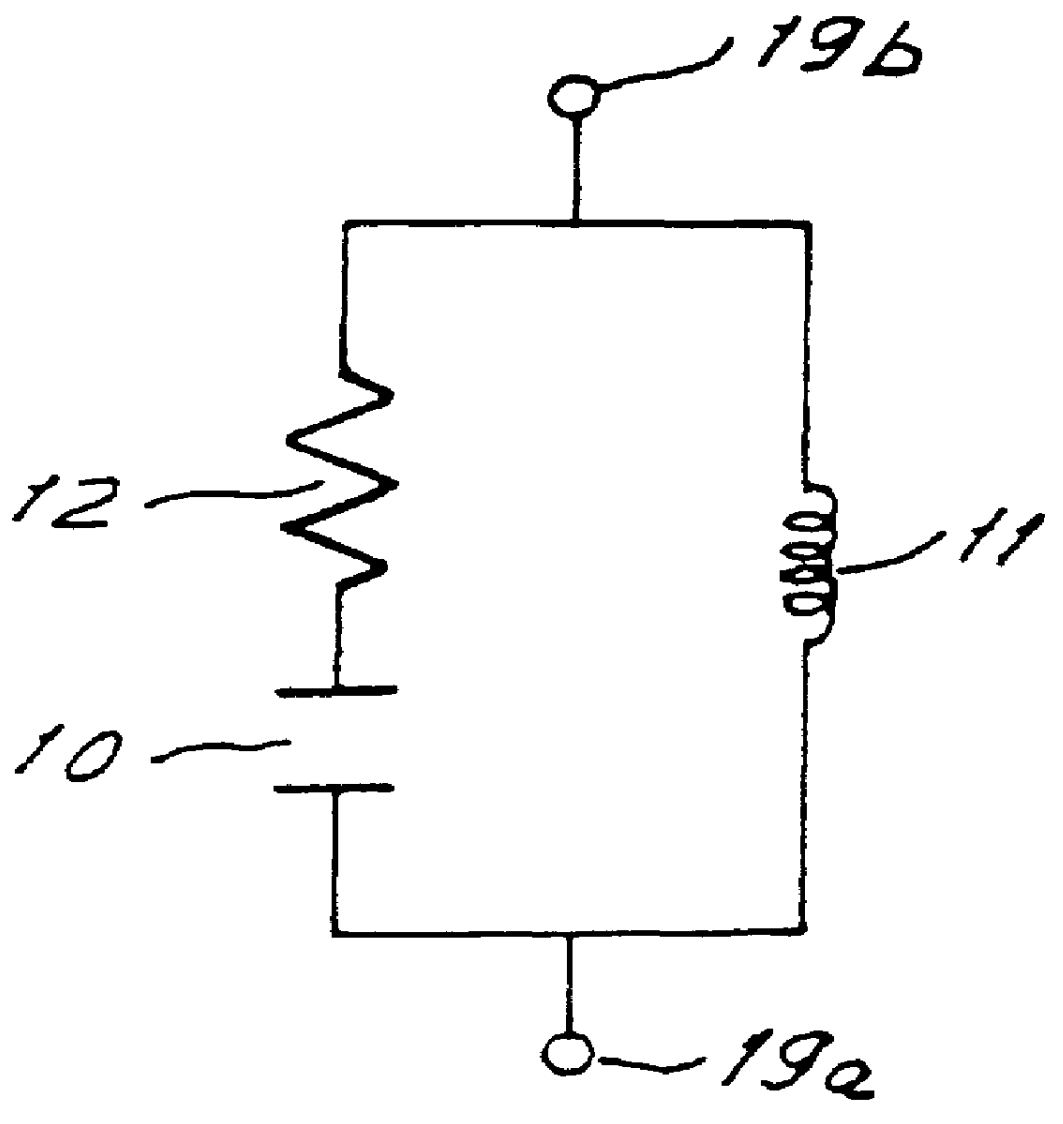

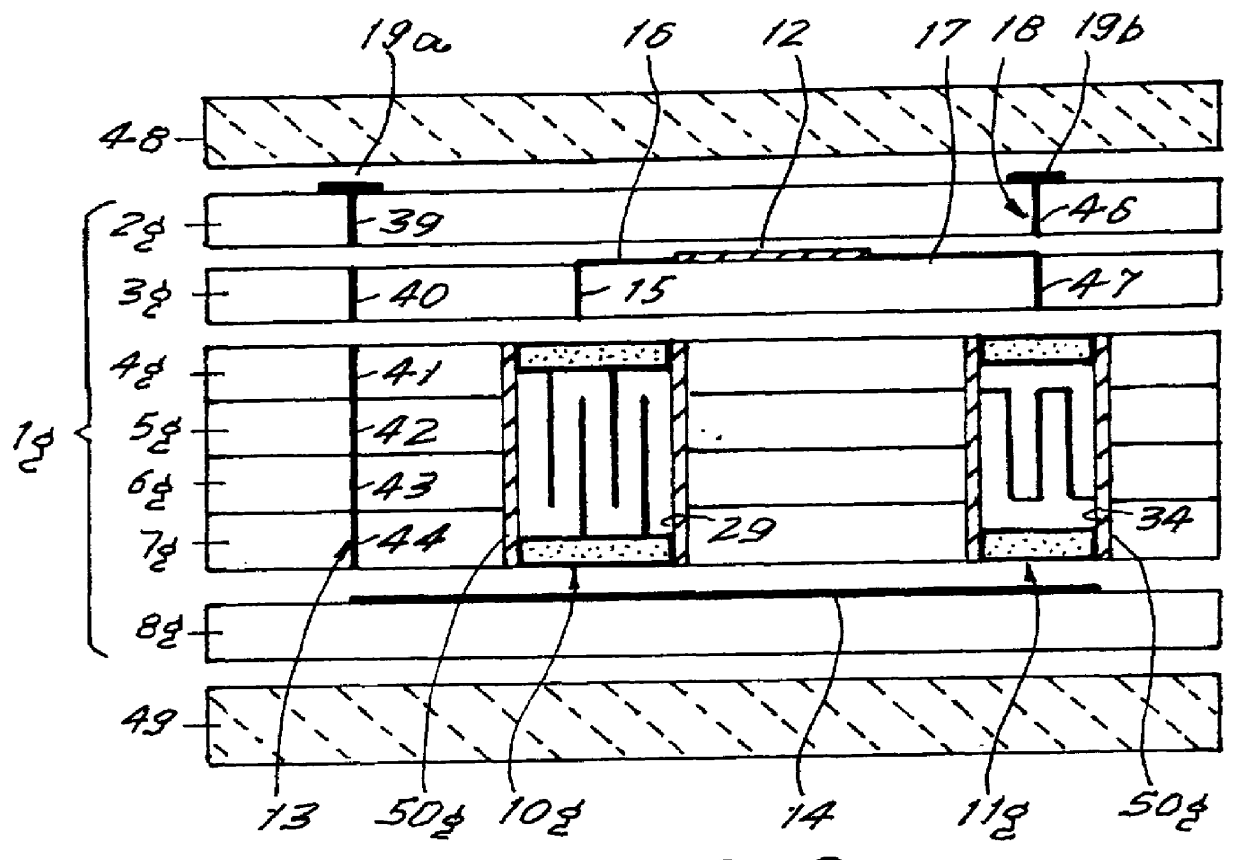

Multi-layer ceramic substrate and method for producing the same

InactiveUS6153290AFinal product manufactureSemiconductor/solid-state device detailsHigh densityInductor

The present invention provides a method for producing a high-density multi-layer ceramic substrate with stable characteristics, the substrate incorporating therein a passive component such as a high-precision capacitor or inductor. The method comprises the steps of providing compact blocks containing a green ceramic functional material to form the passive components; providing a composite green laminate having a plurality of ceramic green sheets comprising a ceramic insulating material and in which the compact blocks are built in pre-disposed spaces and a paste containing a metal inducing, during firing, oxidation reaction accompanied by expansion is provided in space between inside walls of the spaces and the compact blocks; firing the composite green laminate in a state in which the laminate is sandwiched by the sheet-like supports formed of green ceramics that cannot be sintered at the sintering temperature, so as to prevent shrinkage of the laminate; and removing the unsintered sheet-like supports.

Owner:MURATA MFG CO LTD

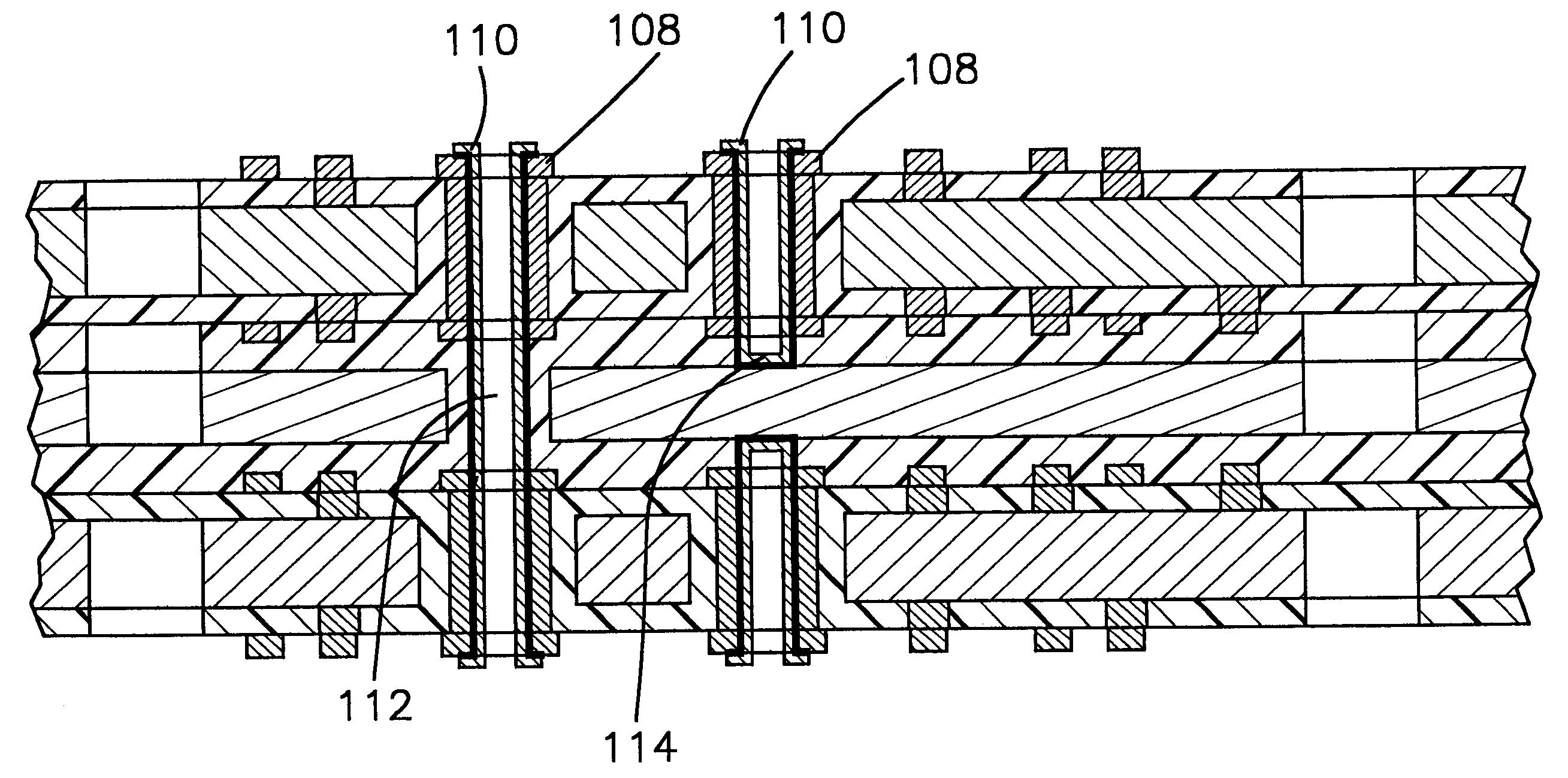

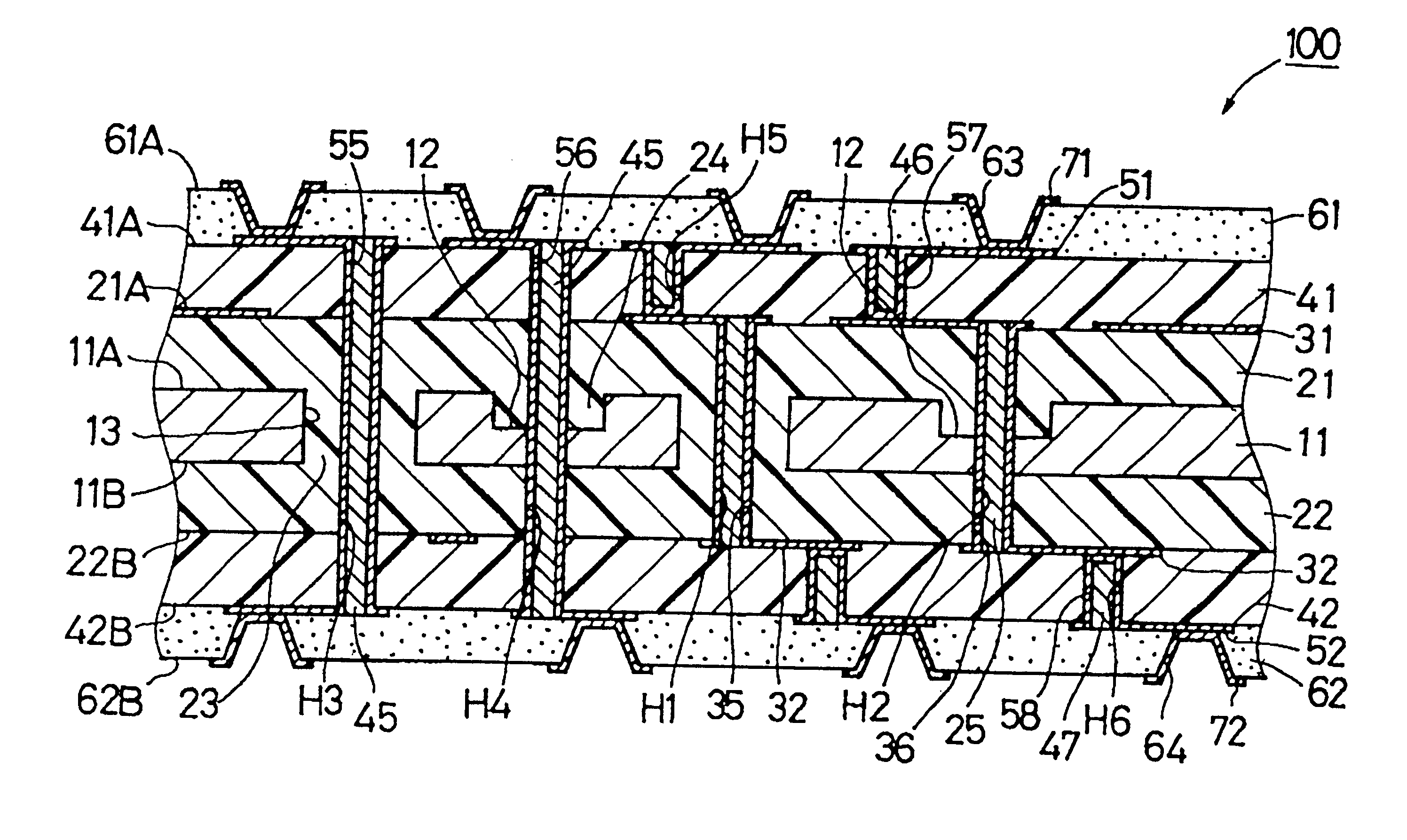

Composite laminate circuit structure and method of forming the same

InactiveUS6175087B1Printed circuit aspectsElectrical connection printed elementsComposite laminatesConductive materials

A method forming a composite laminate structure includes providing first and second circuit board element each having circuitry on at least one face thereof and plated through holes. A voltage plane element is provided having at least one voltage plane having opposite faces with layers of partially cured photodielectric material on each face. At least one hole is photopatterned and etched through the voltage plane element but completely isolated from the voltage plane. Each through hole in the voltage plane element is aligned with a plated through hole in each of the circuit board elements to provide a surface on the voltage plane element communicating with the plated through holes. The voltage plane is laminated between the circuit board elements and the photoimageable material on the voltage plane is fully cured. The surfaces of the voltage plane element communicating with the plated through holes in the circuit board elements are plated with a conducting material to establish a connection between the circuitry on the first and second circuit board elements.

Owner:GLOBALFOUNDRIES INC

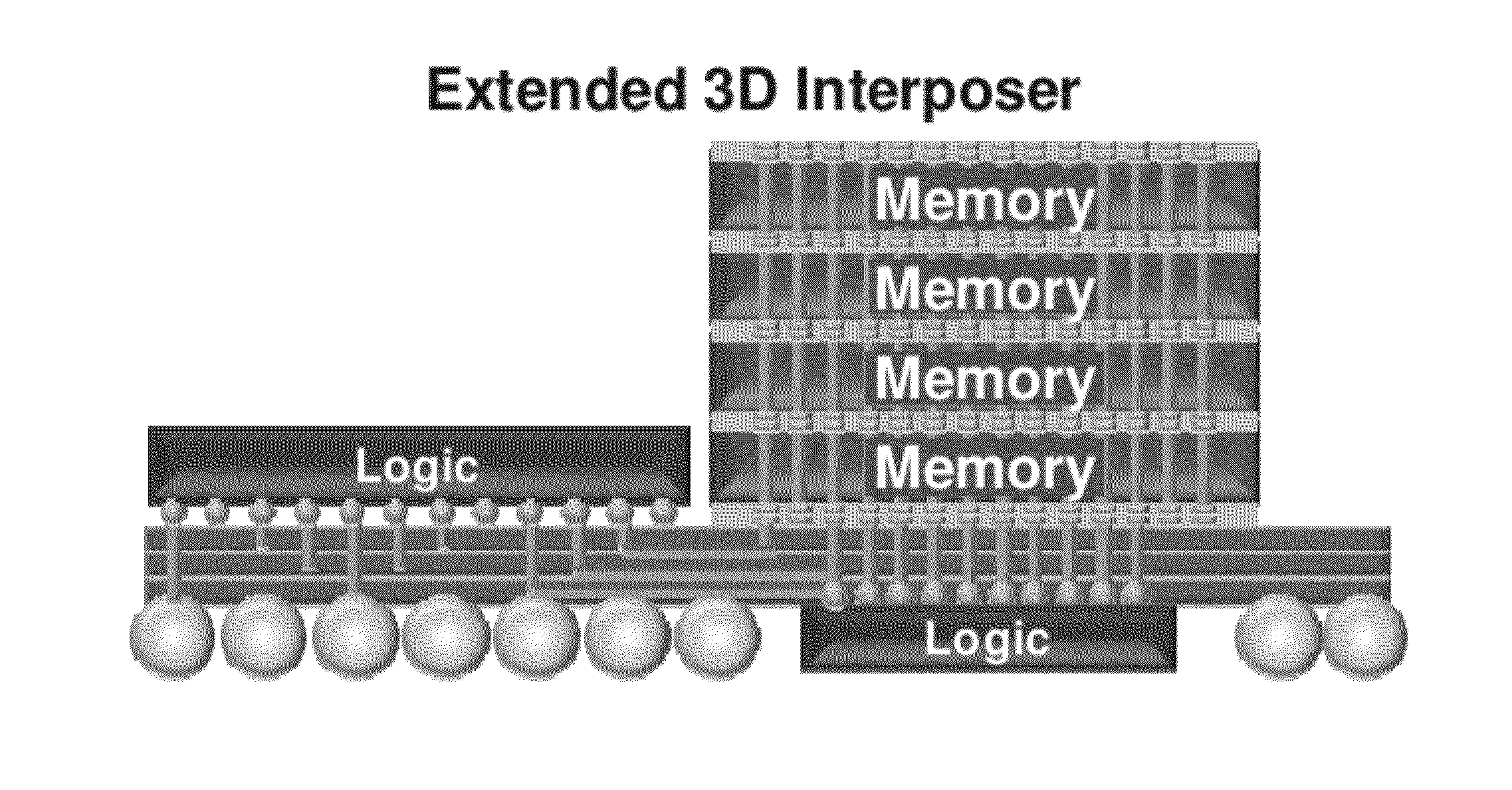

Ultra-thin interposer assemblies with through vias

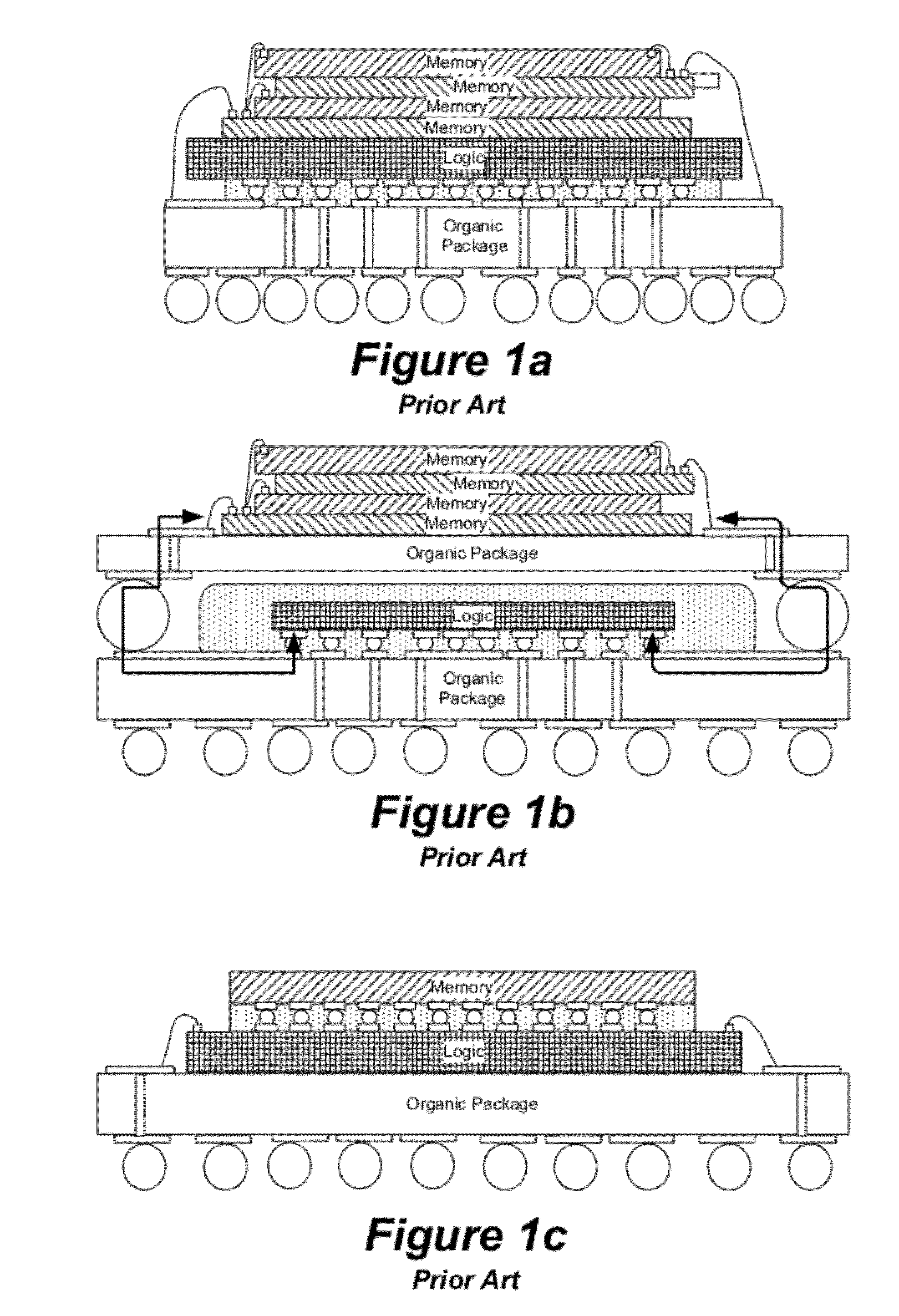

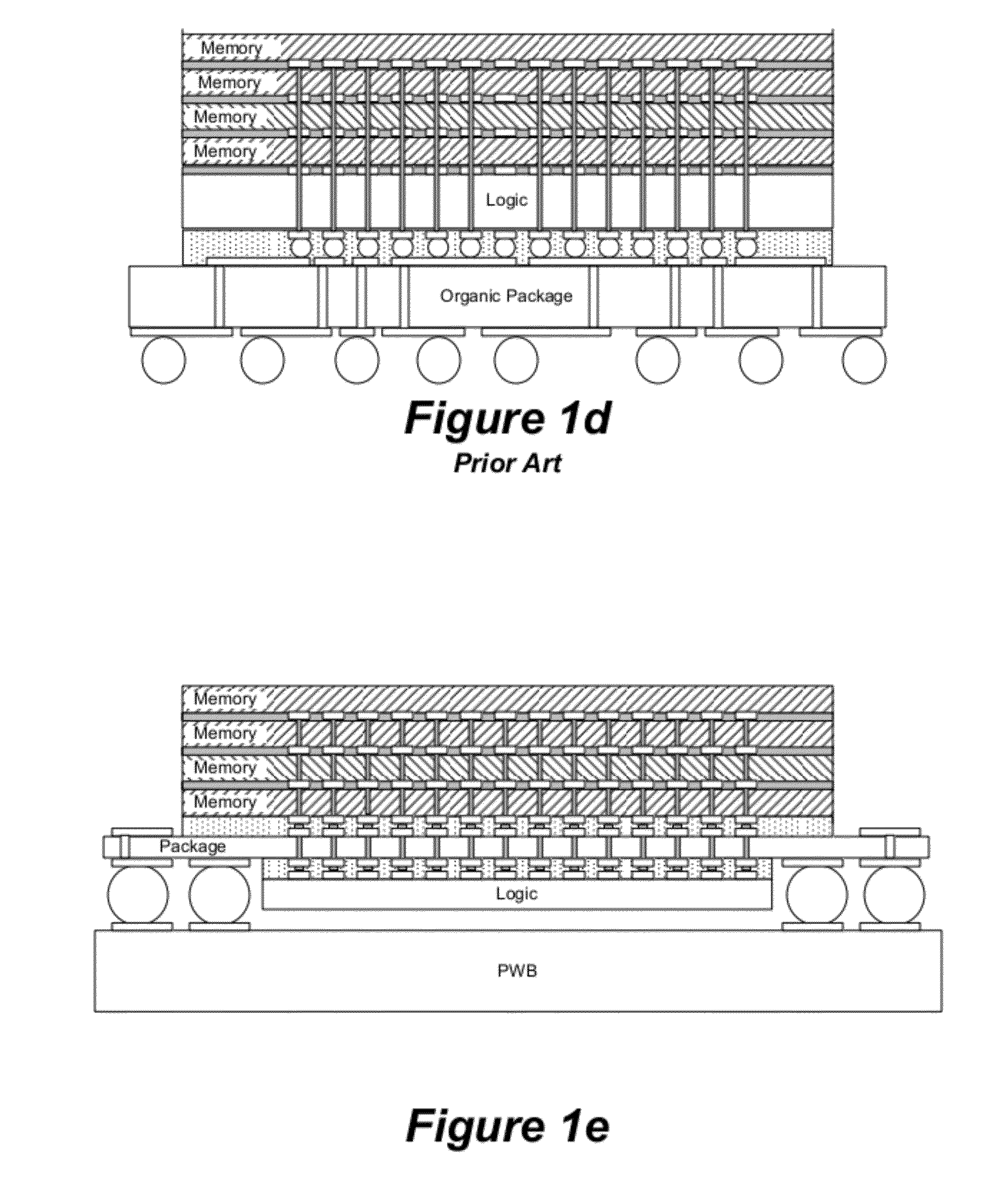

ActiveUS20120106117A1Semiconductor/solid-state device detailsPrinted circuit aspectsGraphicsElectricity

A 3D interconnect structure comprising an ultra-thin interposer having a plurality of ultra-high density of through-via interconnections defined therein. The 3D interposer electrically connects first and second electronic devices in vertical dimension and has the same or similar through-via density as the first or second electronic devices it connects. The various embodiments of the interconnect structure allows 3D ICs to be stacked with or without TSVs and increases bandwidth between the two electronic devices as compared to other interconnect structures of the prior art. Further, the interconnect structure of the present invention is scalable, testable, thermal manageable, and can be manufactured at relatively low costs. Such a 3D structure can be used for a wide variety of applications that require a variety of heterogeneous ICs, such as logic, memory, graphics, power, wireless and sensors that cannot be integrated into single ICs.

Owner:GEORGIA TECH RES CORP

Printed circuit board with capacitors connected between ground layer and power layer patterns

InactiveUS6198362B1Magnetic/electric field screeningCurrent interference reductionEngineeringGround pattern

A printed circuit board is disclosed. A top layer power supply pattern and a top layer ground pattern are formed. The top layer power supply pattern and the top layer ground pattern are connected to a power supply layer and a ground layer through a plurality of viaholes, respectively. A plurality of capacitors or a plurality of capacitor resistor series circuits are disposed at predetermined intervals between the top layer power supply pattern and the top layer ground pattern.

Owner:NEC CORP

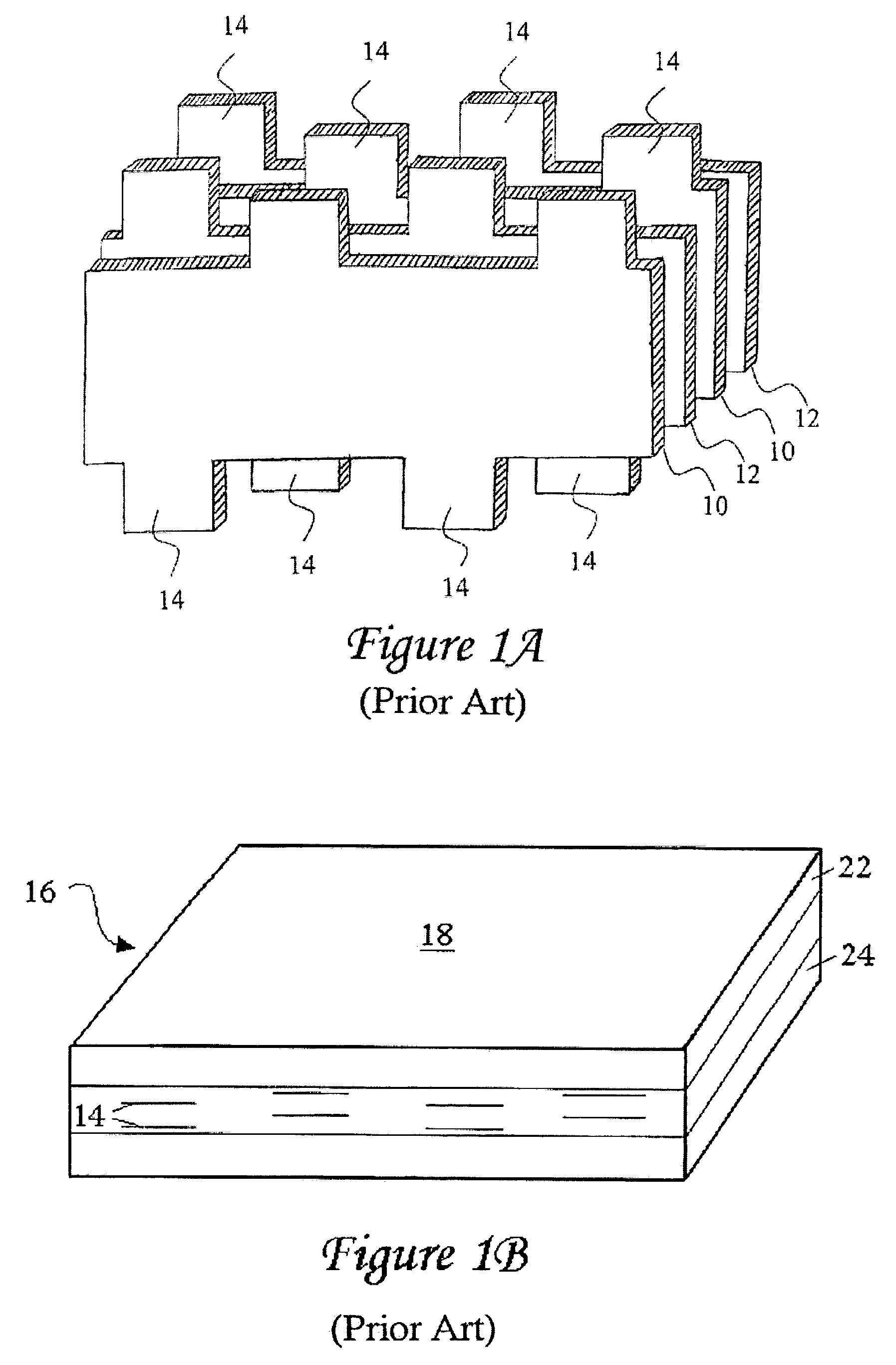

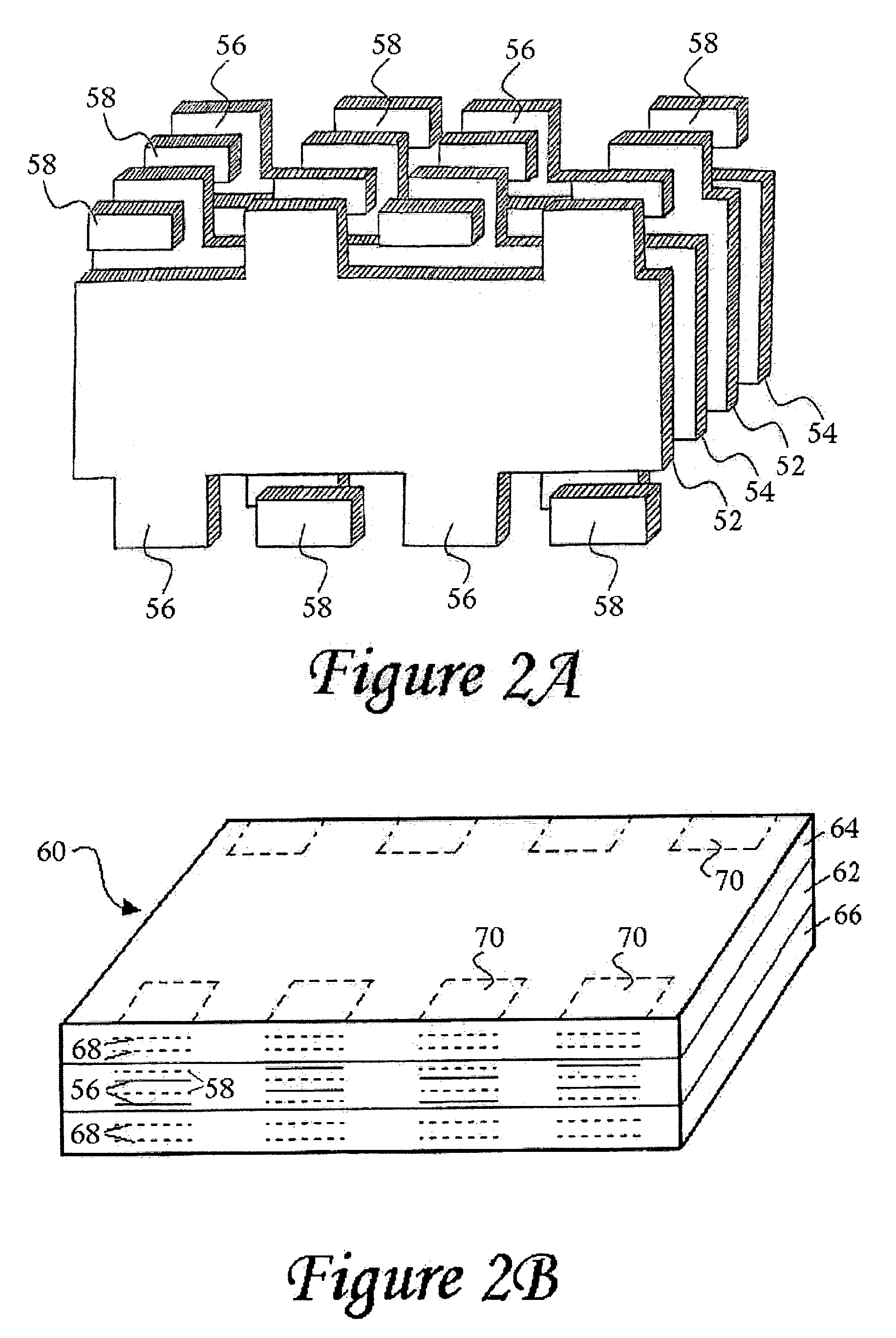

Plated terminations

InactiveUS6960366B2Improved termination featureEliminate and greatly simplifyResistor terminals/electrodesFinal product manufactureTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on one or both of top and bottom surfaces of a monolithic structure can facilitate the formation of selective wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

Stacking integrated circuits containing serializer and deserializer blocks using through silicon via

ActiveUS8014166B2Efficiently routedReduce and eliminate and capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

Metal core multilayer resin wiring board with thin portion and method for manufacturing the same

InactiveUS6323439B1Improve rigidityFirmly connectedElectrically conductive connectionsPrinted circuit aspectsEngineeringMachining

A multilayer resin wiring board includes a metal core substrate having a first main surface and a second main surface; a plurality of wiring layers located on the first and second main surfaces of the metal core substrate; a plurality of insulating resin layers, each intervening between the metal core substrate and the wiring layers and between the metal core substrate and the wiring layers and between the wiring layers; and a via formed on the wall of a through hole for connection to the metal core substrate extending through the insulating resin layers and the metal core substrate so as to establish electrical conductivity to the metal core substrate. The metal core substrate has a thin portion which is thinner than the remaining portion of the metal core substrate. The through hole for connection to the metal core substrate is formed through the thin portion by laser machining.

Owner:NGK SPARK PLUG CO LTD

Substrate with reinforced contact pad structure

ActiveUS7005750B2Improve positional stabilitySimple structurePrinted circuit assemblingFinal product manufactureSolder maskContact pad

A substrate with reinforced contact pad structure includes a metal wiring layer and a solder mask formed over its surface. The metal wiring layer includes at least a NSMD (Non-Solder Mask Defined) type contact pad, a trace and an extension. The extension connects the contact pad and the trace, and has an upper surface which is covered by the solder mask so as to enhance the connecting strength between the trace and the contact pad and to improve the position stability of the NSMD type contact pad on the substrate. In an embodiment, the contact pad is circular for bonding a bump or a solder ball. The first extension is fan-shaped. The extension also has a sidewall exposed out of the solder mask.

Owner:ASE SHANGHAI

Method for forming plated terminations

InactiveUS7152291B2Improved termination featureEliminate or greatly simplify thick-film stripesElectrolytic capacitorsSemiconductor/solid-state device detailsTermination problemEngineering

Improved method steps for terminating multilayer electronic components are disclosed. Monolithic components are formed with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. Electrode and dielectric layers are provided in an interleaved arrangement and selected portions of the electrode layers are exposed. Electrically isolated anchor tabs may optionally be provided and exposed in some embodiments. Termination material is then plated to the exposed portions of the electrode layers until exposed portions of selected such portions thereof are connected. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

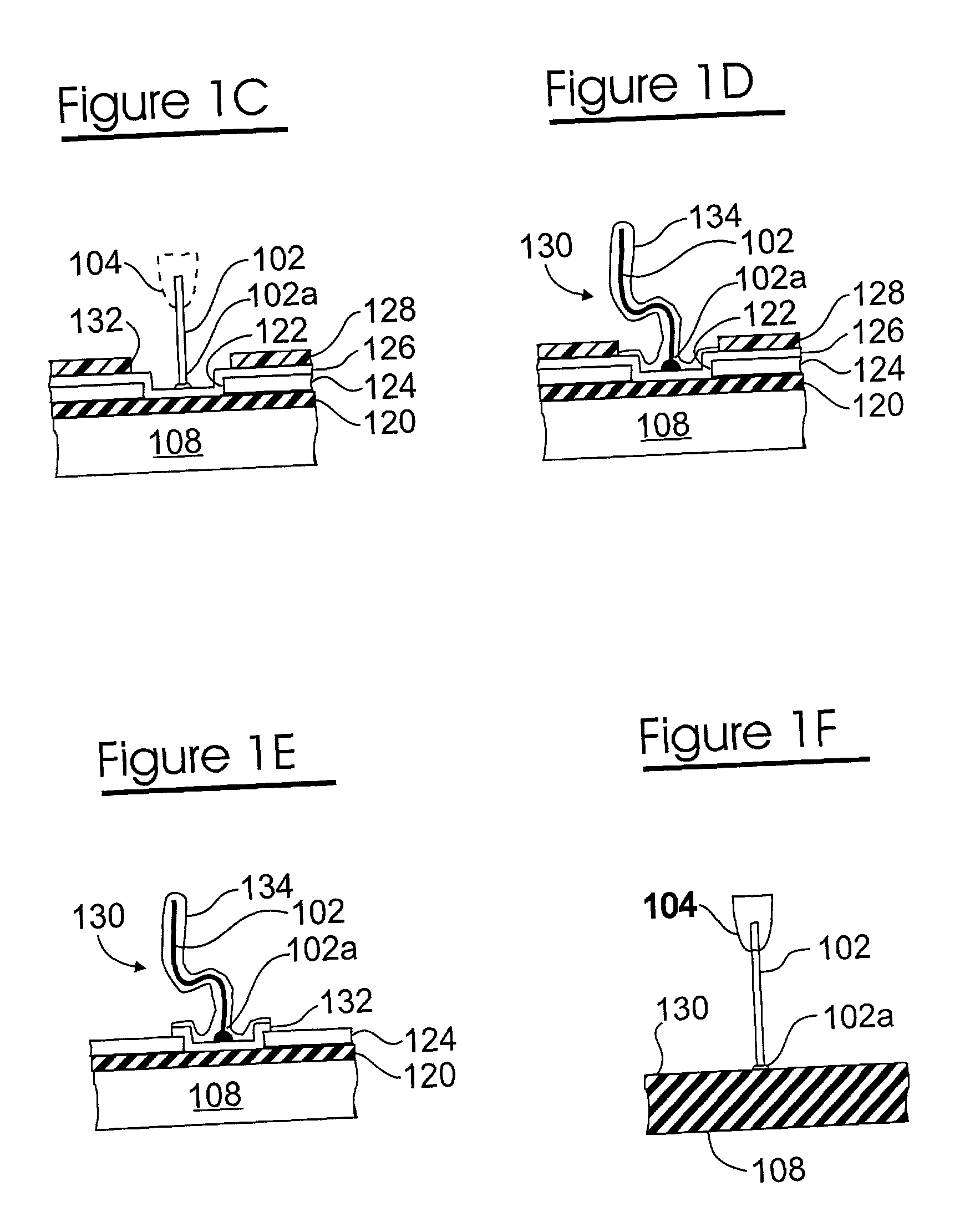

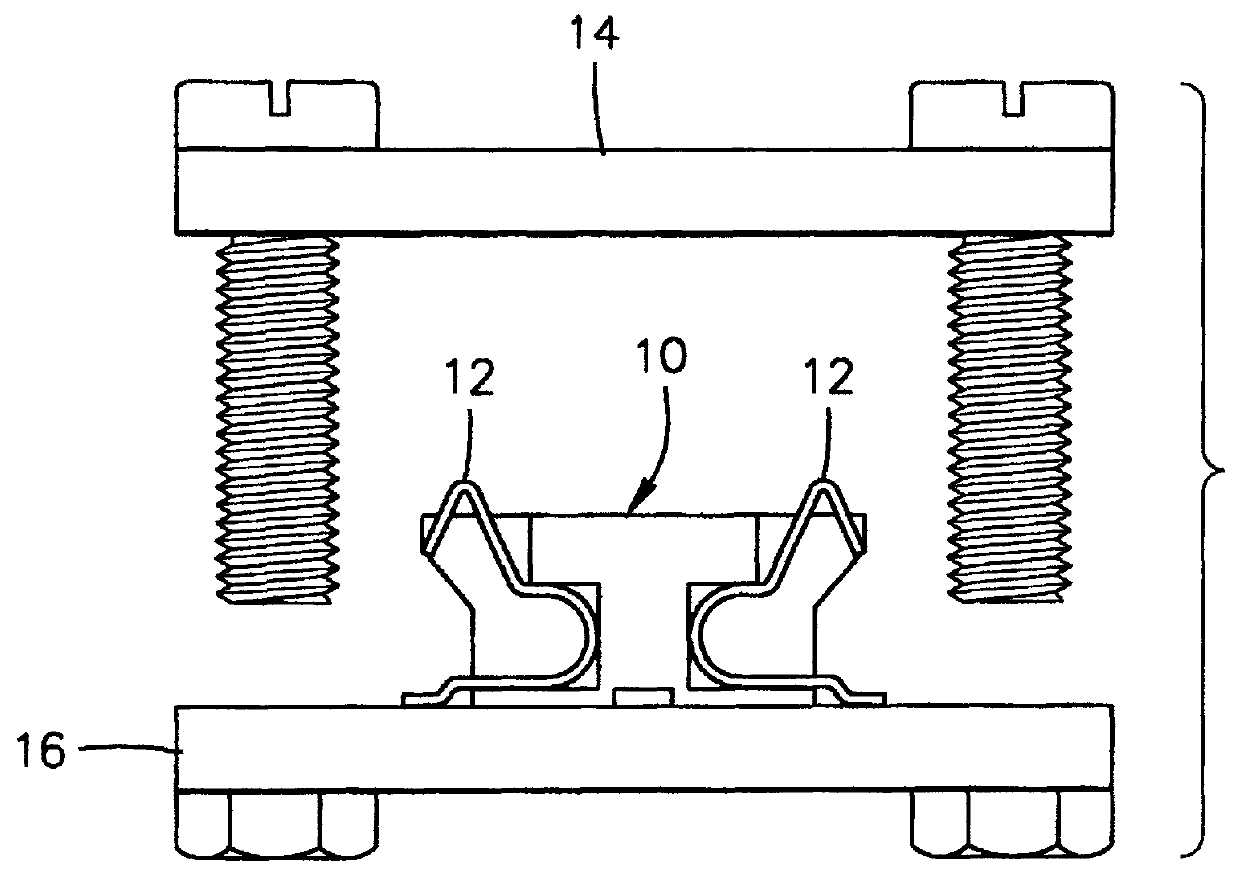

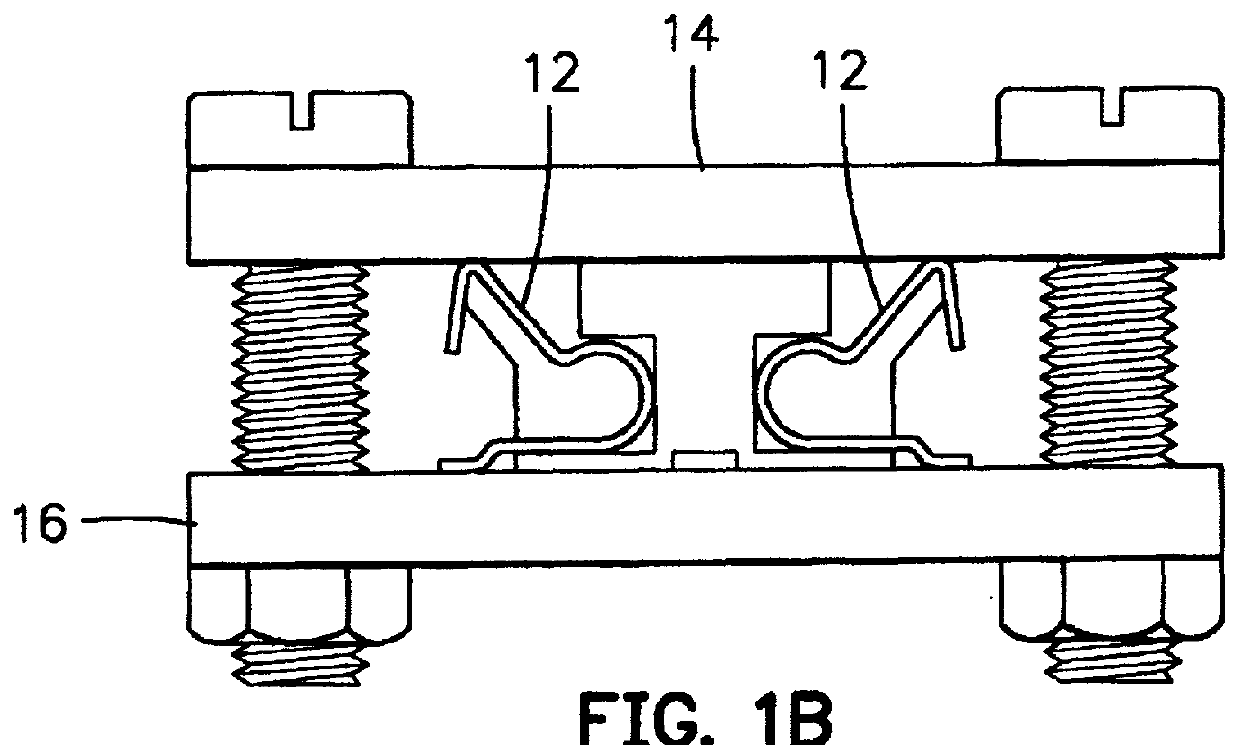

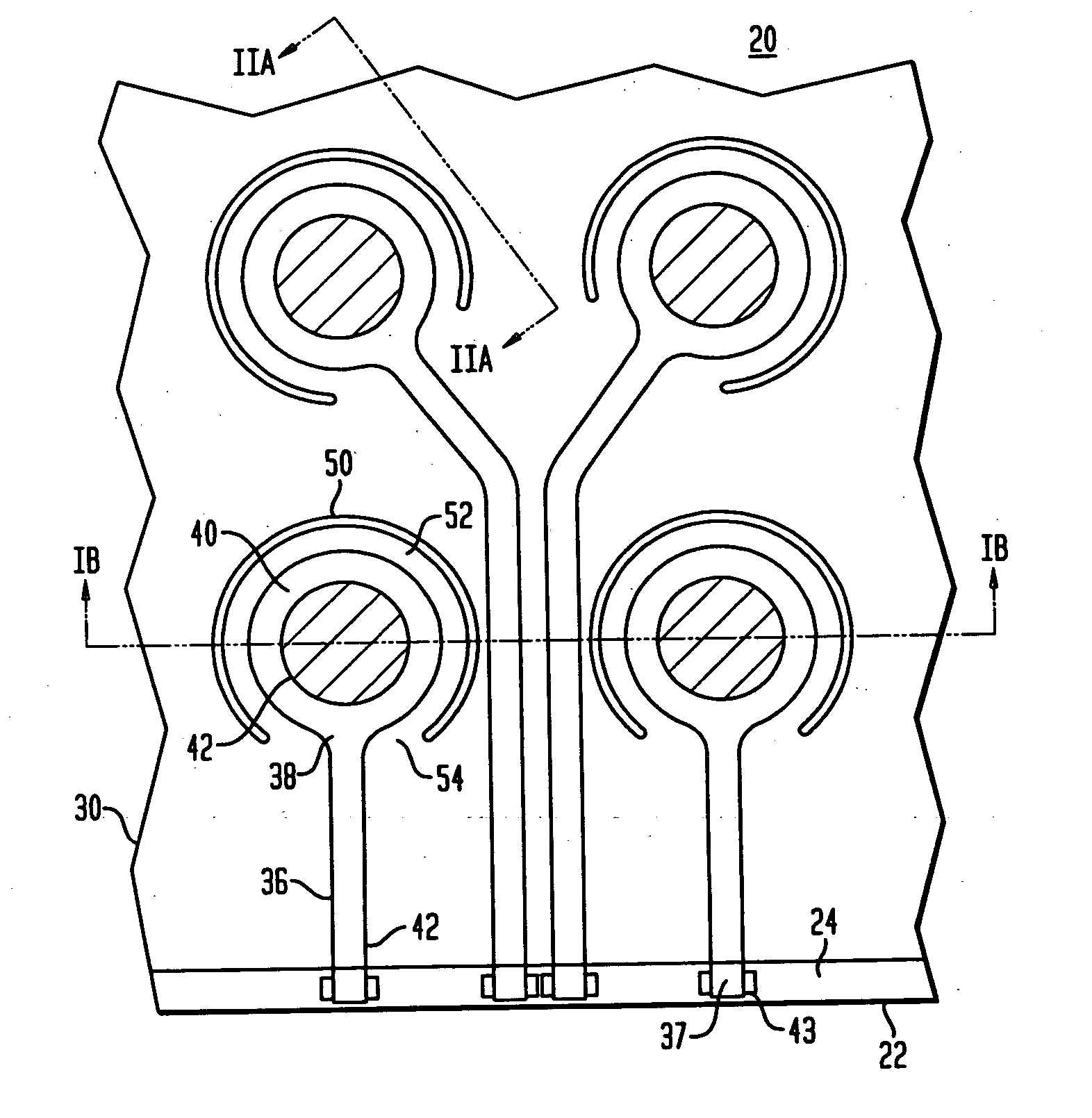

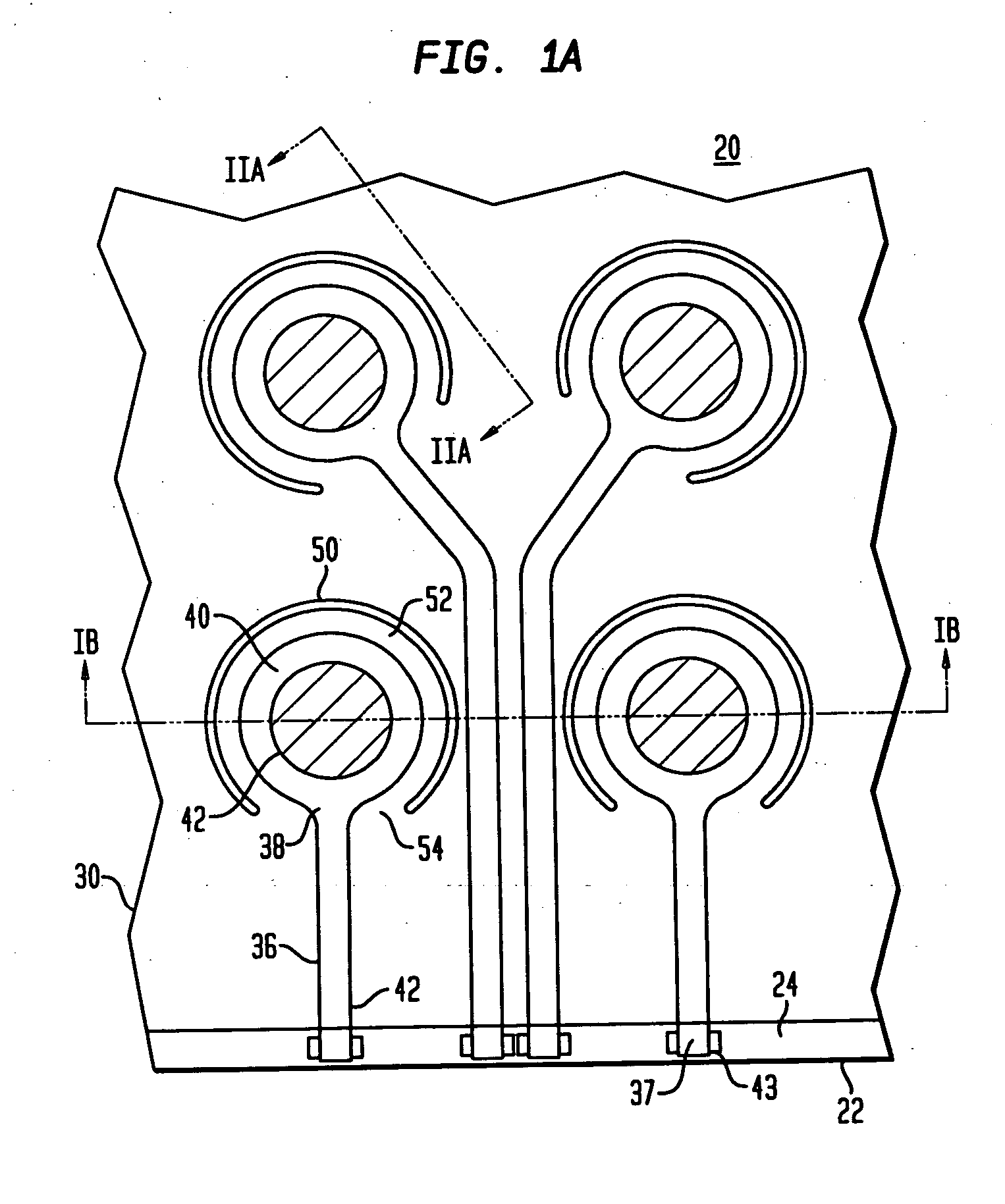

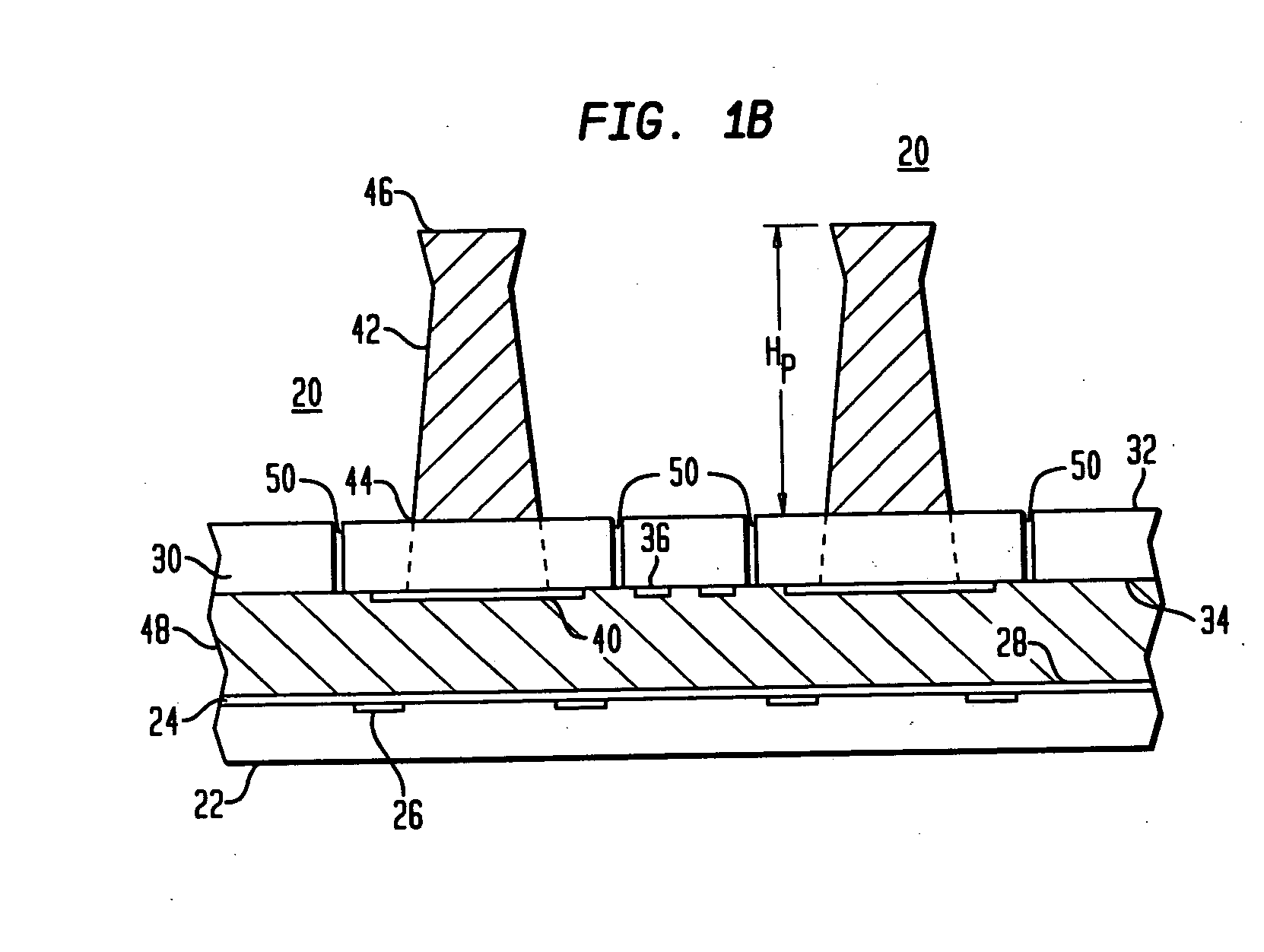

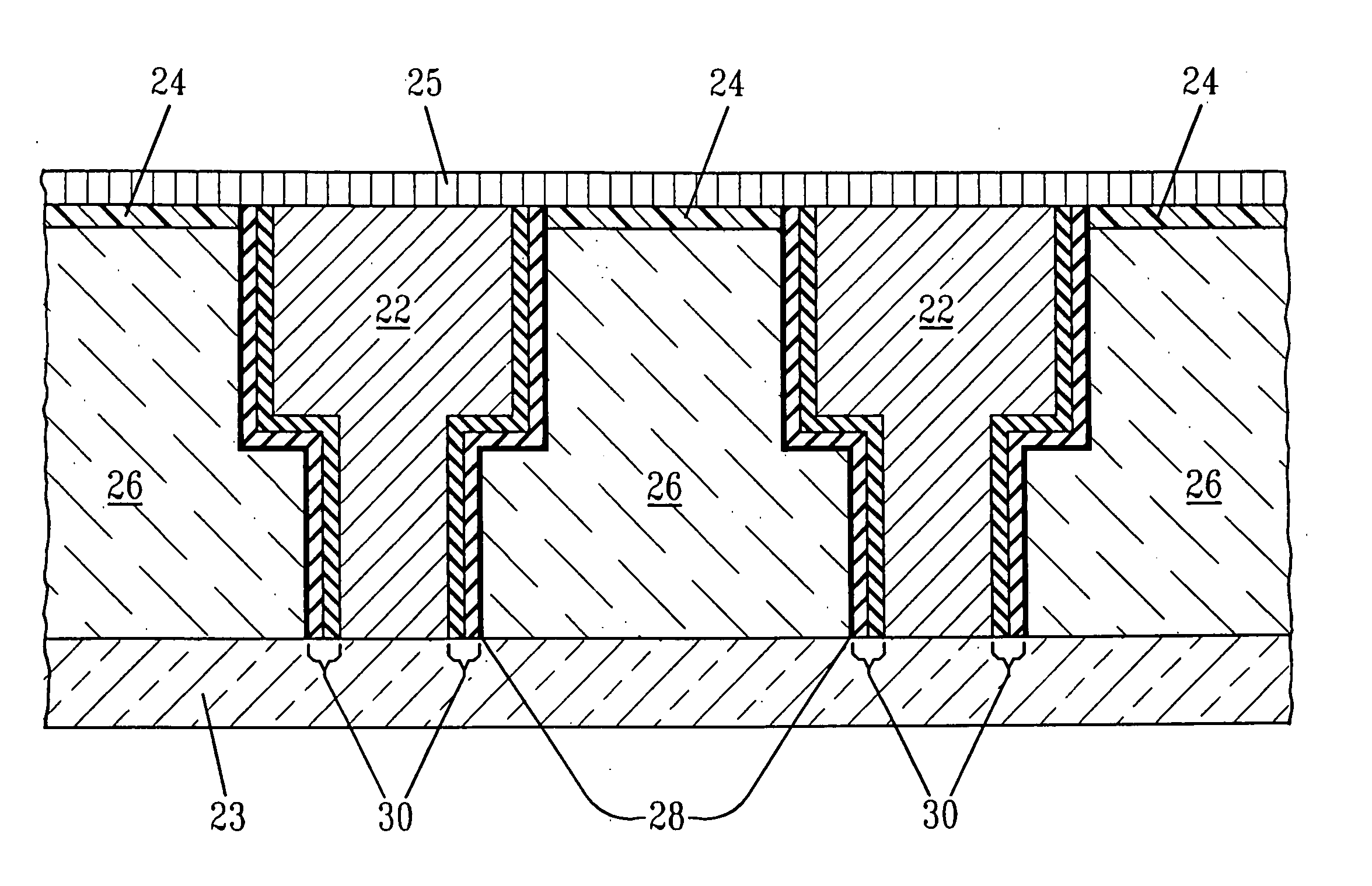

Micro pin grid array with pin motion isolation

InactiveUS20050173805A1Promote sportsFacilitates flexing of the substratePrinted circuit assemblingSemiconductor/solid-state device detailsPin grid arrayPartial alignment

A microelectronic package includes a microelectronic element having faces and contacts, a flexible substrate overlying and spaced from a first face of the microelectronic element, and a plurality of conductive terminals exposed at a surface of the flexible substrate. The conductive terminals are electrically interconnected with the microelectronic element and the flexible substrate includes a gap extending at least partially around at least one of the conductive terminals. In certain embodiments, the package includes a support layer, such as a compliant layer, disposed between the first face of the microelectronic element and the flexible substrate. In other embodiments, the support layer includes at least one opening that is at least partially aligned with one of the conductive terminals.

Owner:TESSERA INC

Structures and methods for intergration of ultralow-k dielectrics with improved reliability

ActiveUS20050184397A1Semiconductor/solid-state device detailsSolid-state devicesBiological activationDielectric layer

An improved back end of the line (BEOL) interconnect structure comprising an ultralow k (ULK) dielectric is provided. The structure may be of the single or dual damascene type and comprises a dense thin dielectric layer (TDL) between a metal barrier layer and the ULK dielectric. Disclosed are also methods of fabrication of BEOL interconnect structures, including (i) methods in which a dense TDL is provided on etched opening of a ULK dielectric and (ii) methods in which a ULK dielectric is placed in a process chamber on a cold chuck, a sealing agent is added to the process chamber, and an activation step is performed.

Owner:GLOBALFOUNDRIES US INC

Popular searches

Semiconductor/solid-state device manufacturing Electrical apparatus contructional details Printed circuits structural associations Semiconductor devices Cross-talk/noise/interference reduction Printed circuit non-printed electric components association Circuit thermal arrangements Printed circuit manufacture Metallic pattern materials Electrical testing