Patents

Literature

6490results about How to "Improve production yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

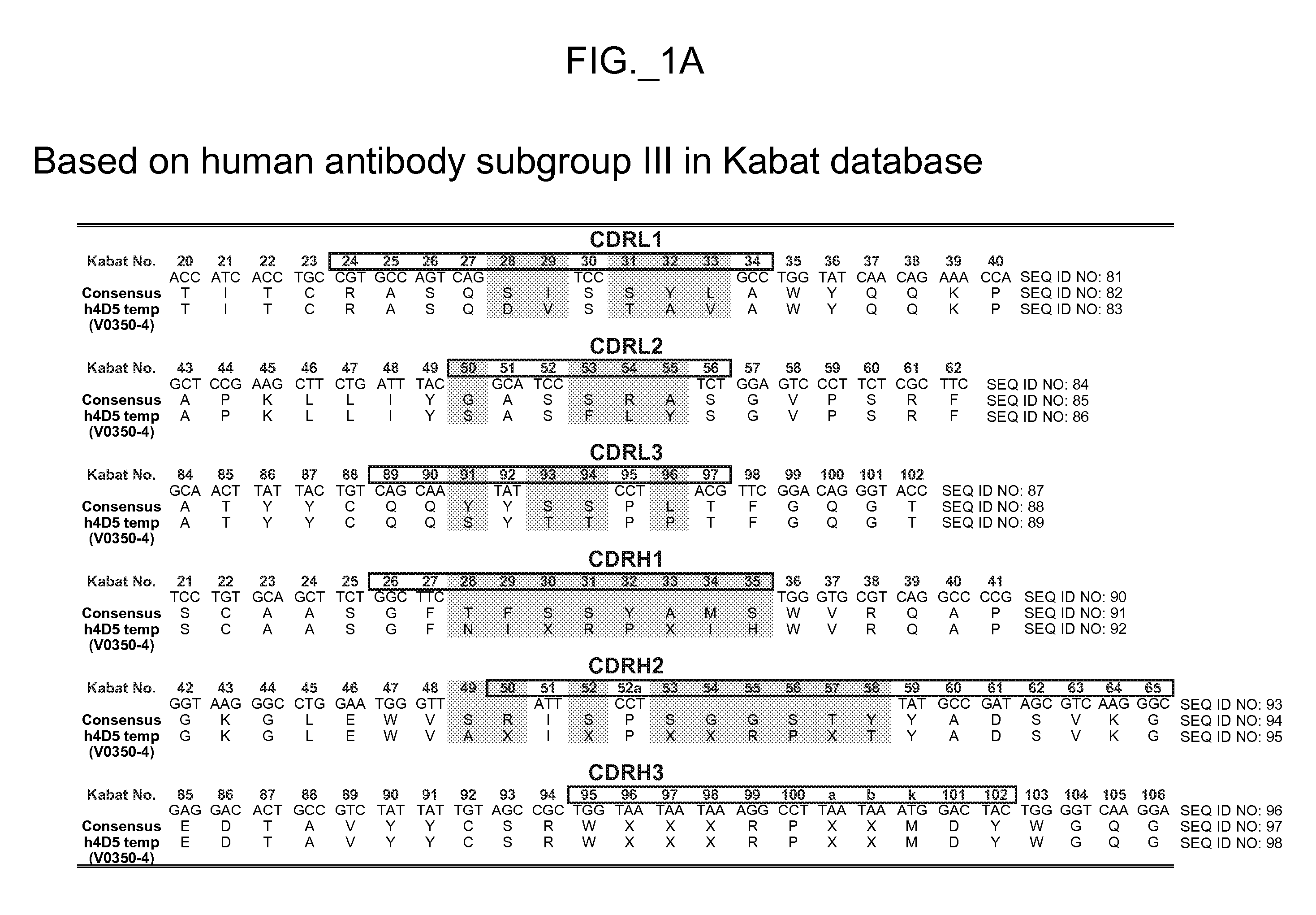

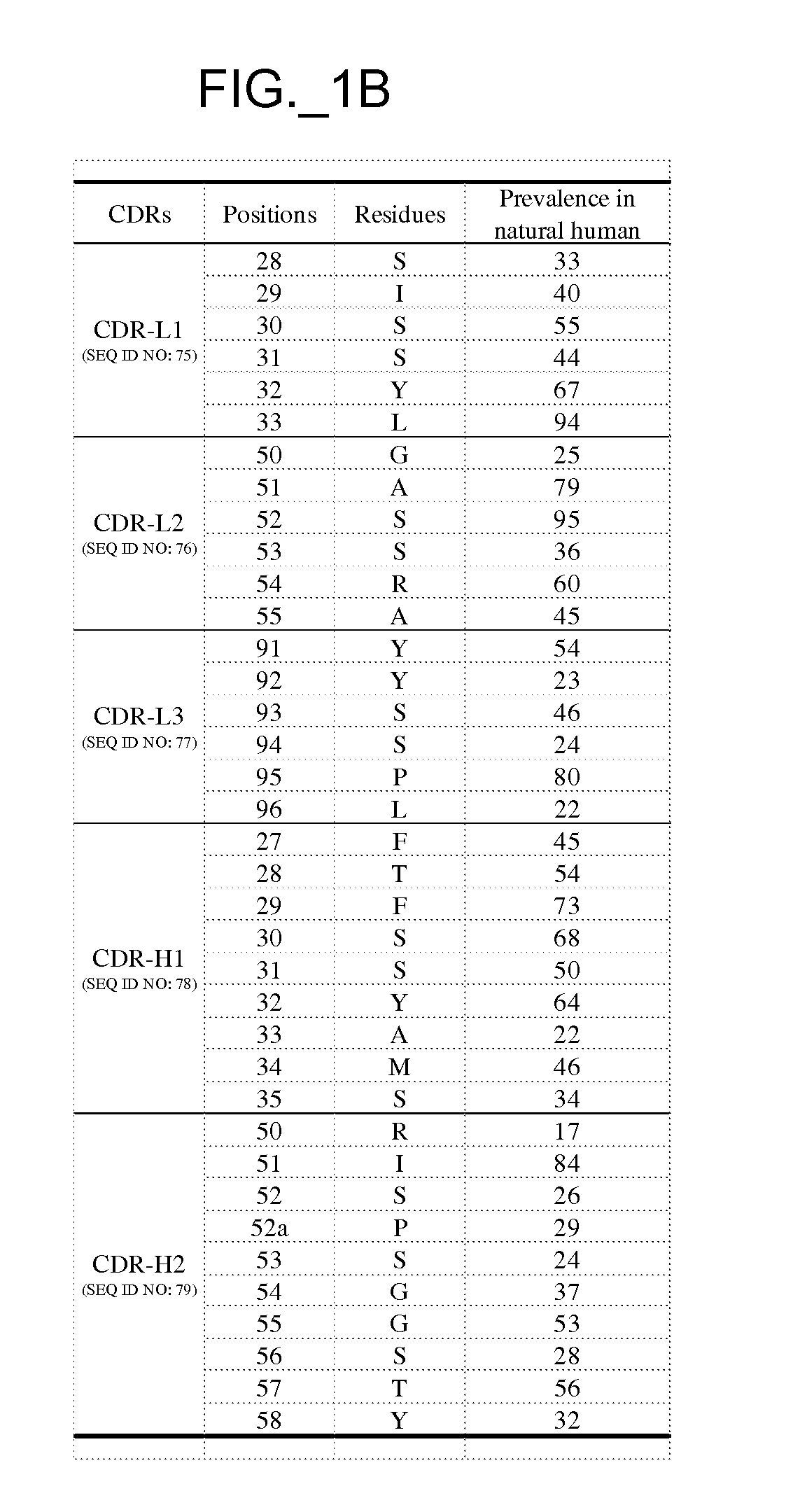

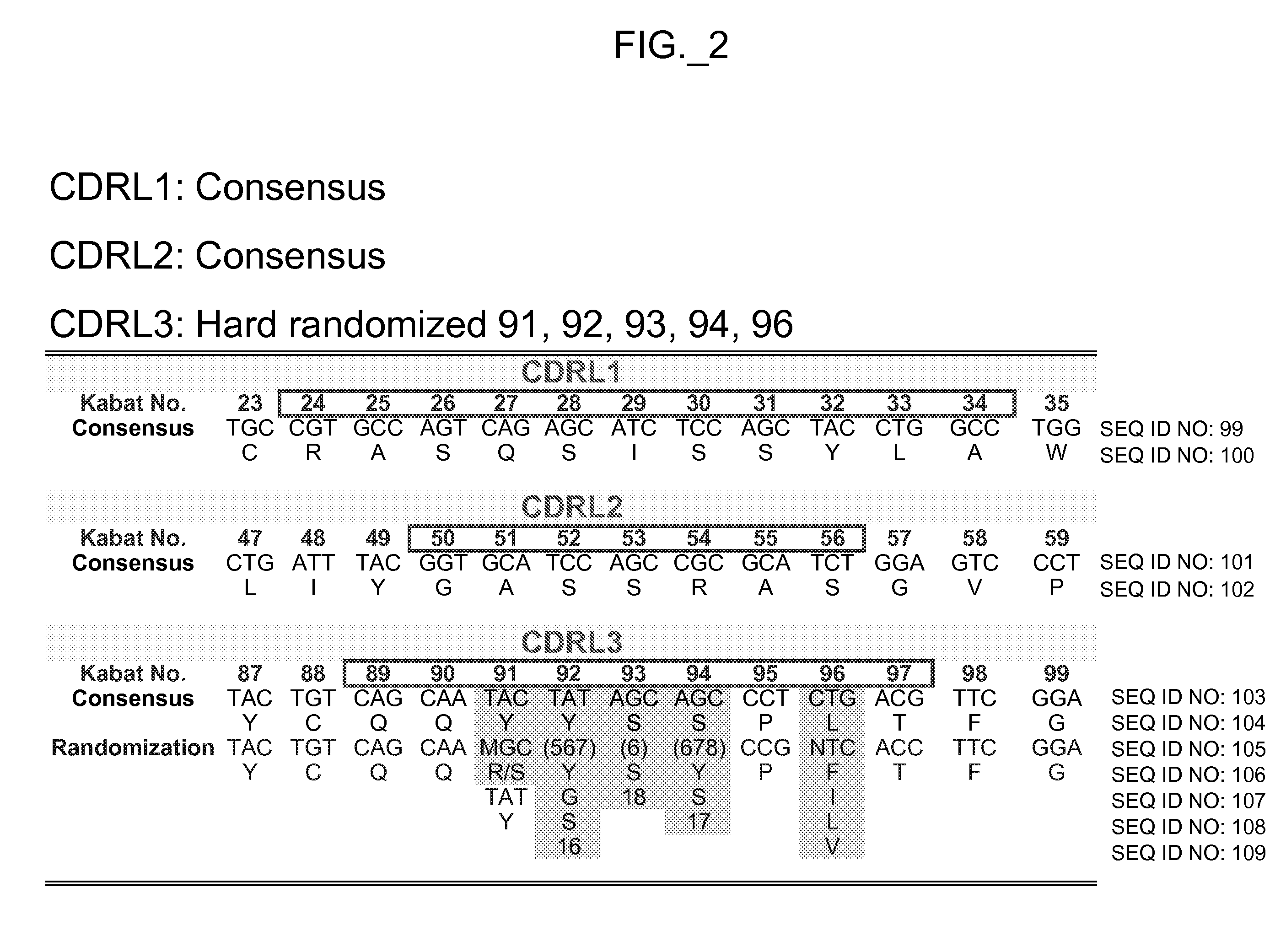

Binding polypeptides with diversified and consensus vh/vl hypervariable sequences

ActiveUS20070160598A1Raise the possibilitySmall sizeAnimal cellsSugar derivativesAntibody hypervariable regionBioinformatics

The invention provides variant hypervariable regions comprising selected amino acid sequence diversity. Libraries comprising a plurality of these polypeptides are also provided. In addition, methods of and compositions for generating and using these polypeptides and libraries are provided.

Owner:GENENTECH INC

Liquid crystal display device

InactiveUS20060066793A1Low costImprove production yieldLiquid crystal compositionsNon-linear opticsChemistryCompound (substance)

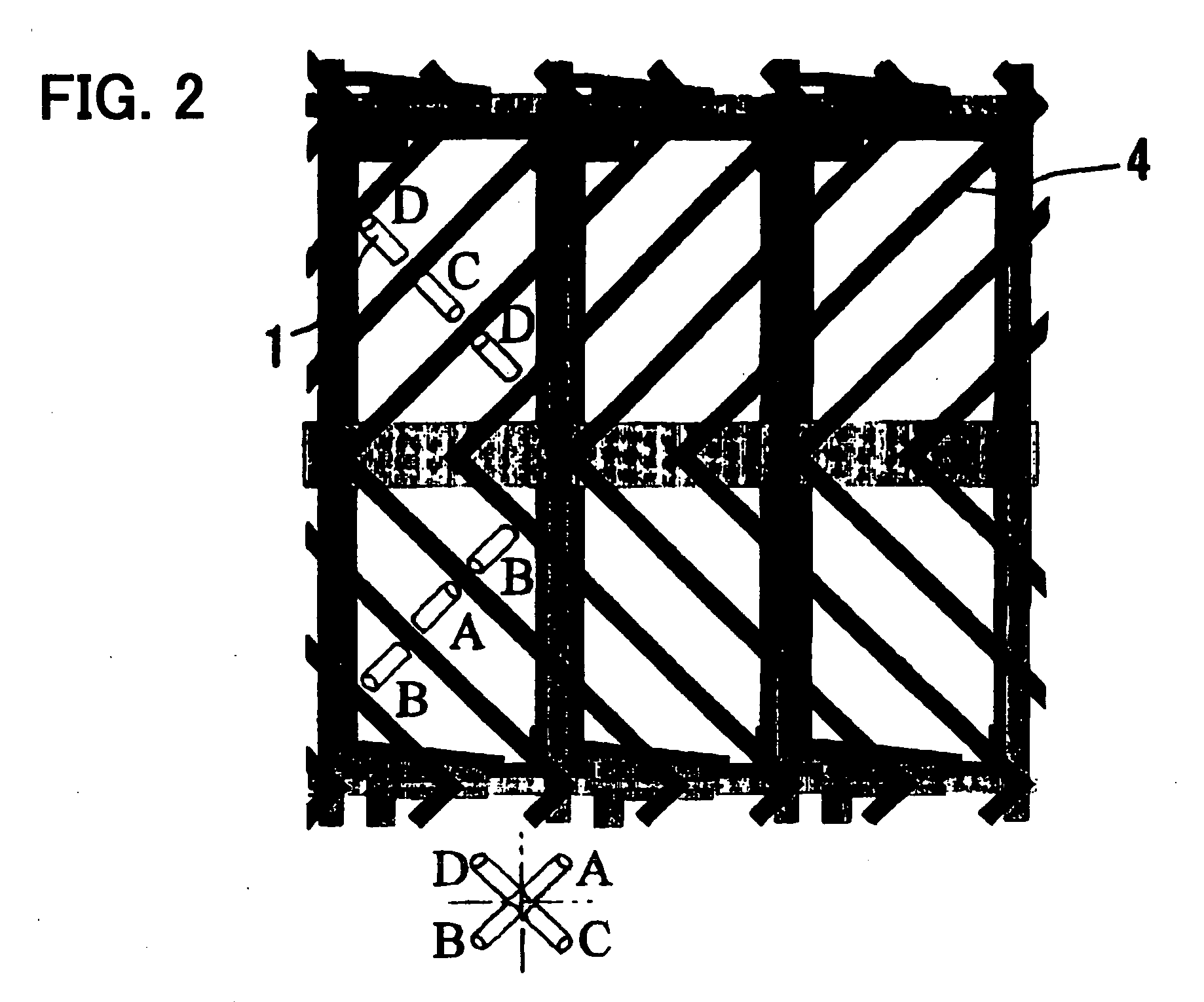

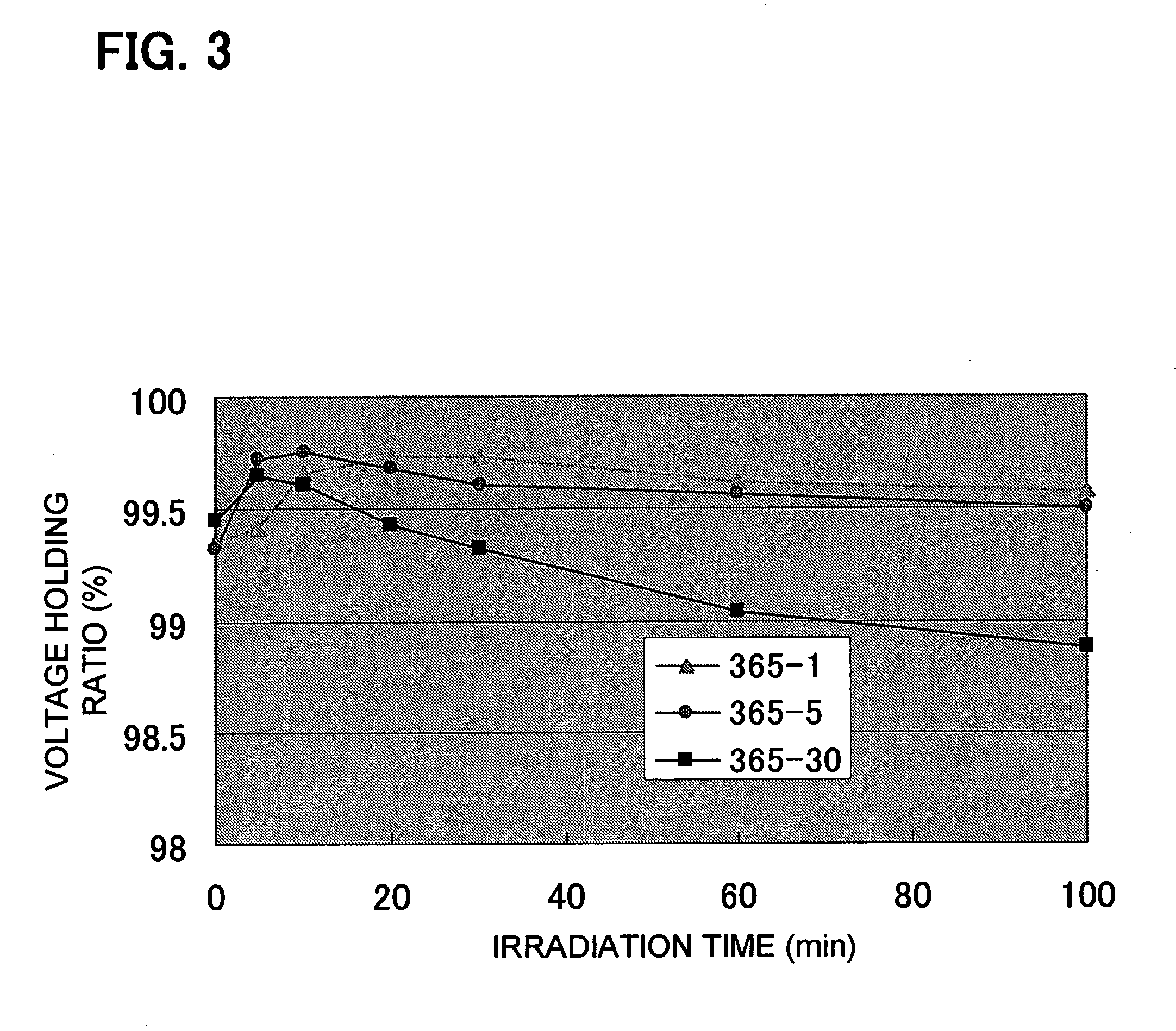

A high-performance liquid crystal display device is provided that can be manufactured at a low cost and a high production yield. In this liquid crystal display device, a liquid crystal composition comprising liquid crystal molecules and a polymerizable compound that can be polymerized by ultraviolet rays or by a combination of ultraviolet rays and heat is disposed between a pair of substrates; the polymerizable compound is polymerized, forming a liquid crystal layer, by an operation including irradiation of ultraviolet rays that do not contain wavelength components of not higher than 313 nm; and uneven portions are installed on the liquid crystal layer contacting surface, or a slit pattern is installed in an electrode, or uneven portions are installed on the liquid crystal layer contacting surface, and a slit pattern is installed in the electrode.

Owner:SHARP KK

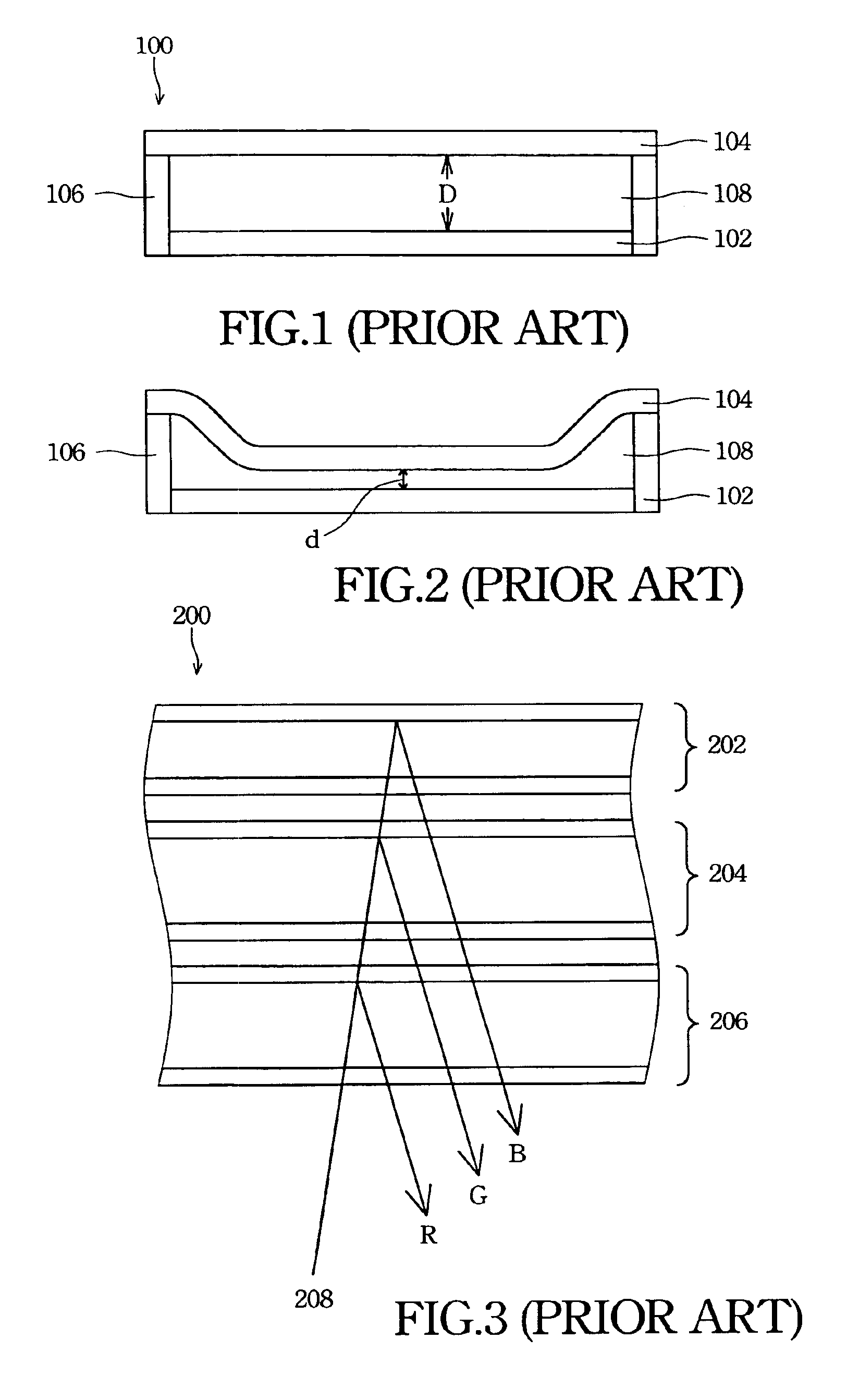

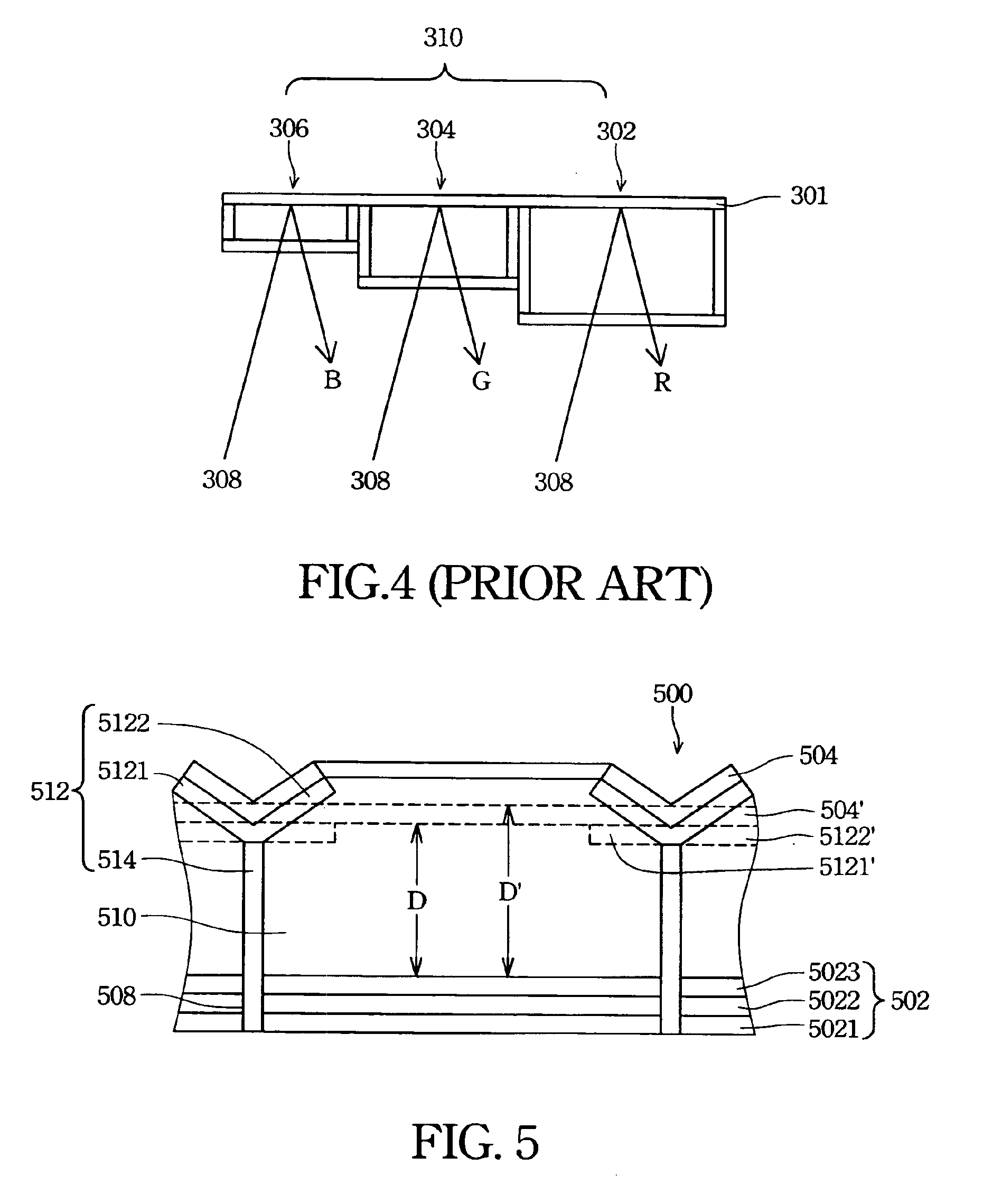

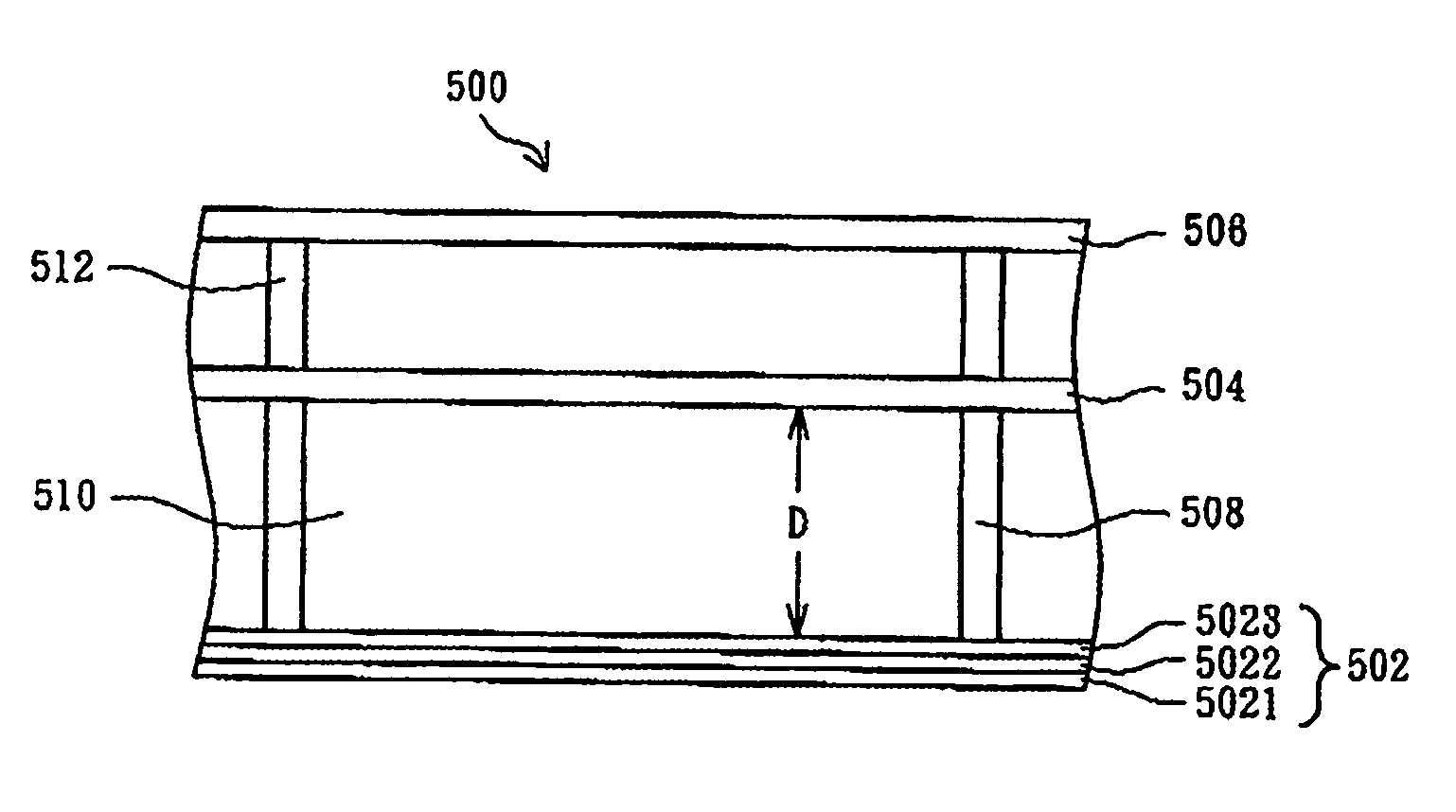

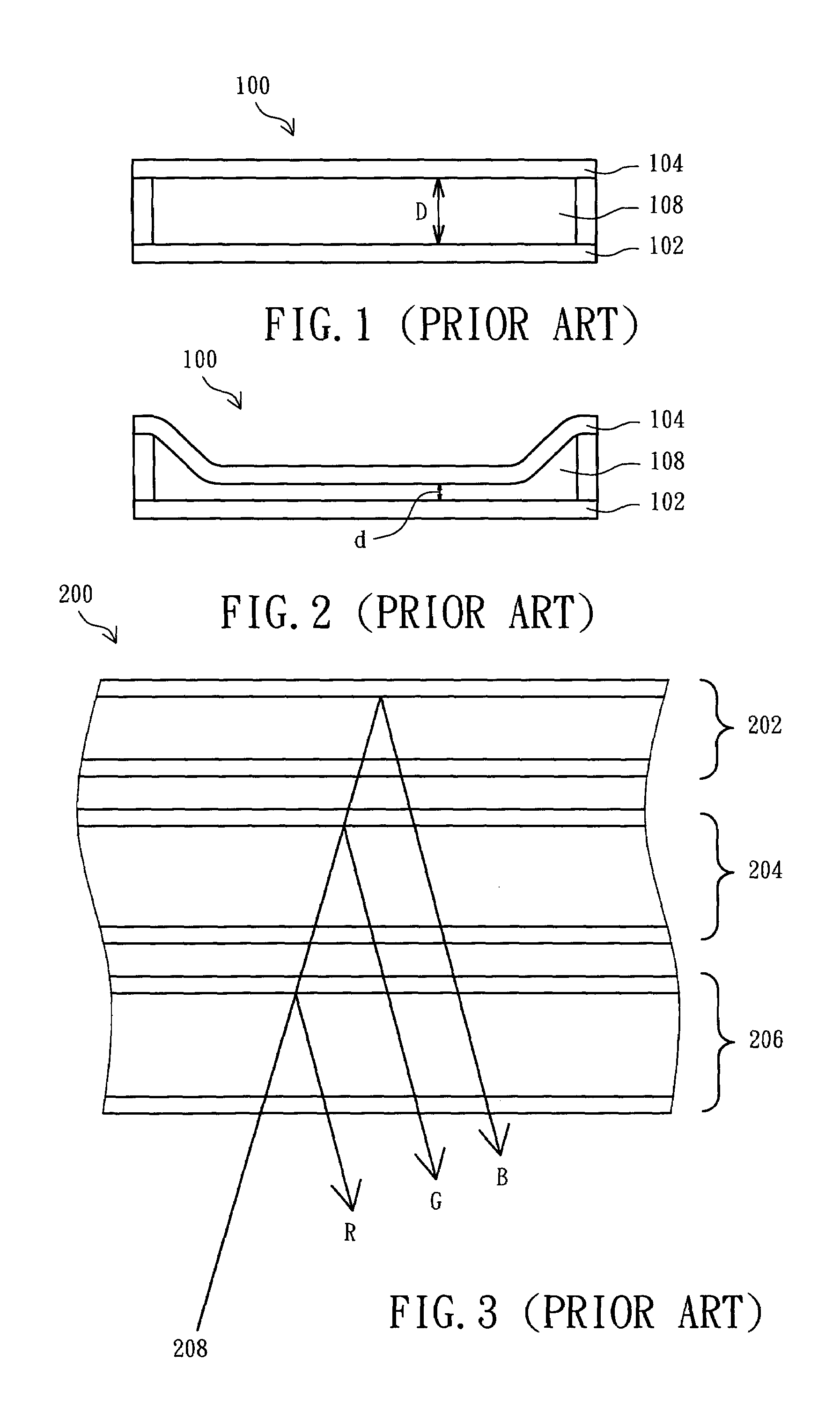

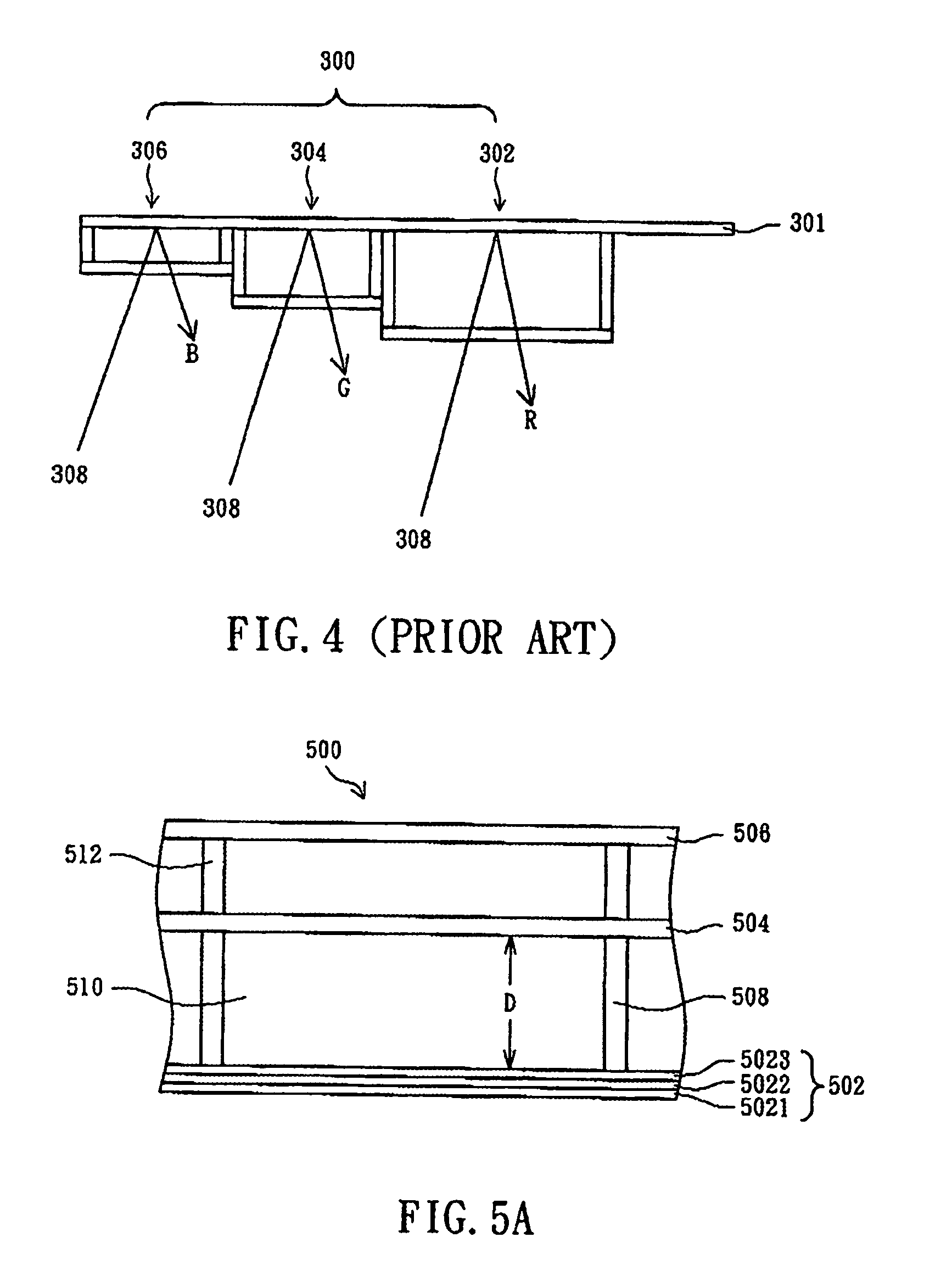

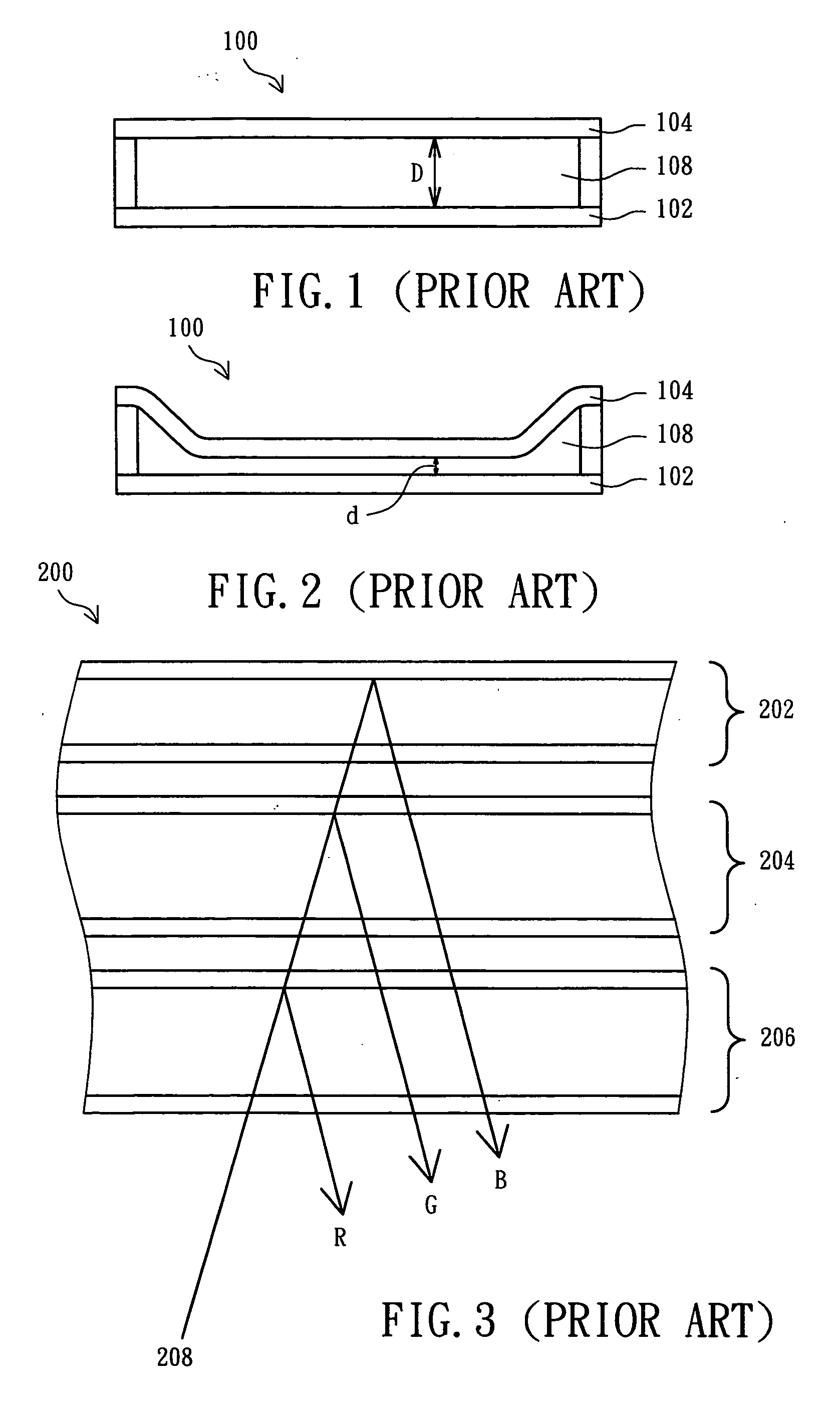

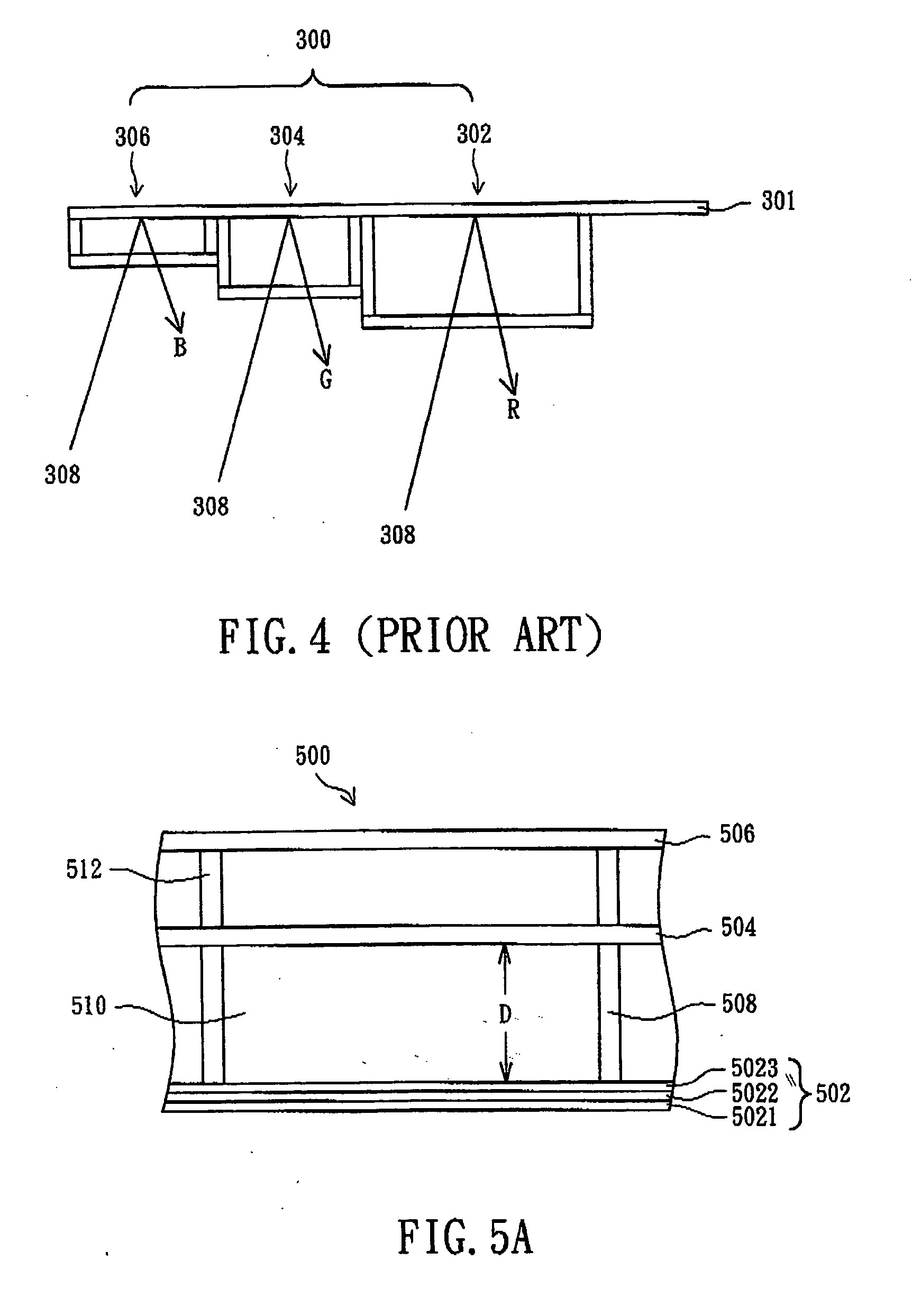

Structure of an optical interference display cell

A structure of an interference display cell is provided. The cell comprises a first plate and a second plate, wherein a support is located between the first plate and the second plate. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The support has at least one arm. The arm's stress makes the arm hiking upward or downward. The distance between the first plate and the second plate is also changed. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

Color changeable pixel

InactiveUS6982820B2Increase brightnessHigh resolutionNon-linear opticsOptical elementsOptoelectronicsVoltage

Owner:SNAPTRACK

Programmable Resistive RAM and Manufacturing Method

ActiveUS20070158690A1Low costReduce the numberSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceReduced size

Programmable resistive RAM cells have a resistance that depends on the size of the programmable resistive elements. Manufacturing methods and integrated circuits for programmable resistive elements with uniform resistance are disclosed that have a cross-section of reduced size compared to the cross-section of the interlayer contacts.

Owner:MACRONIX INT CO LTD

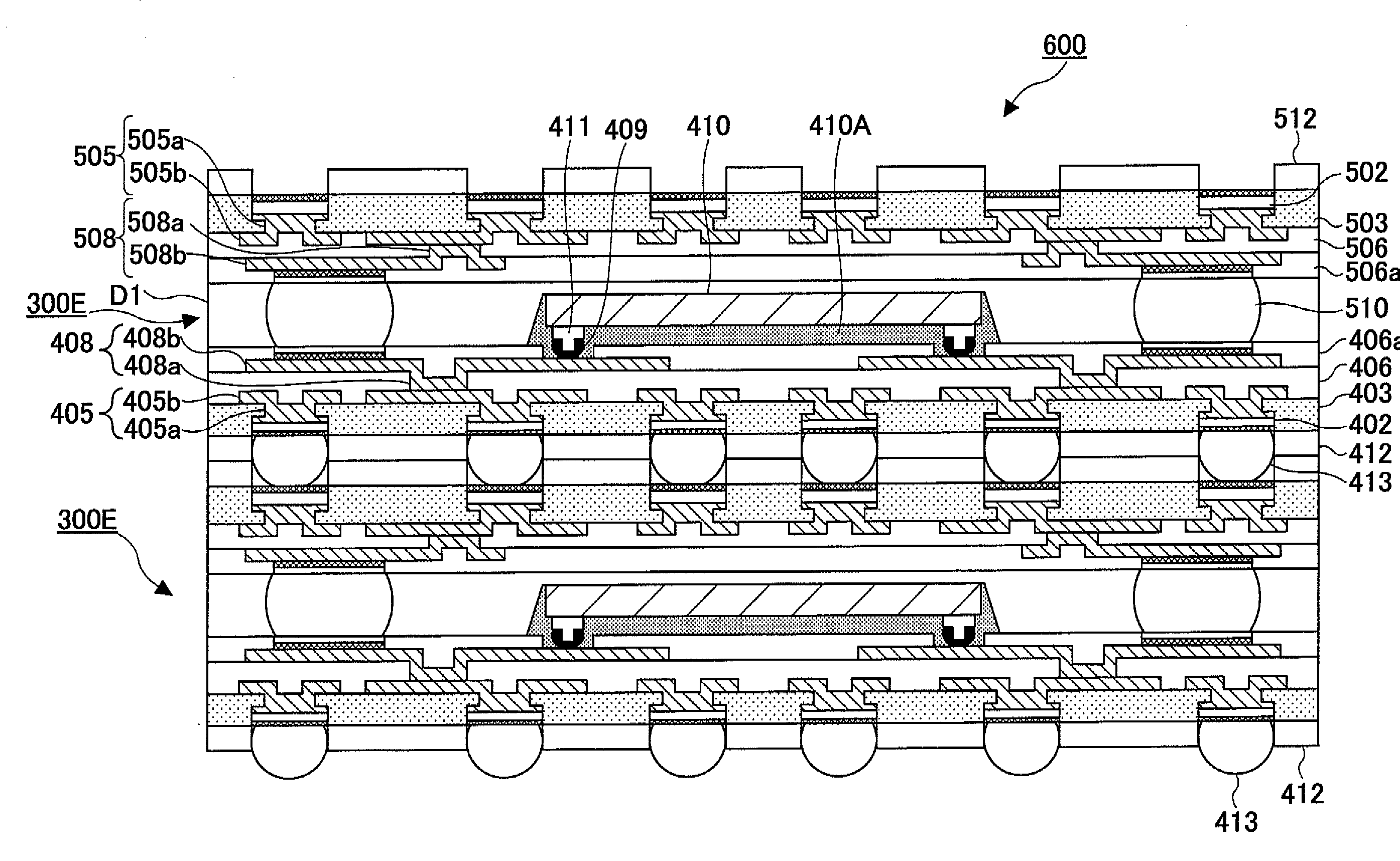

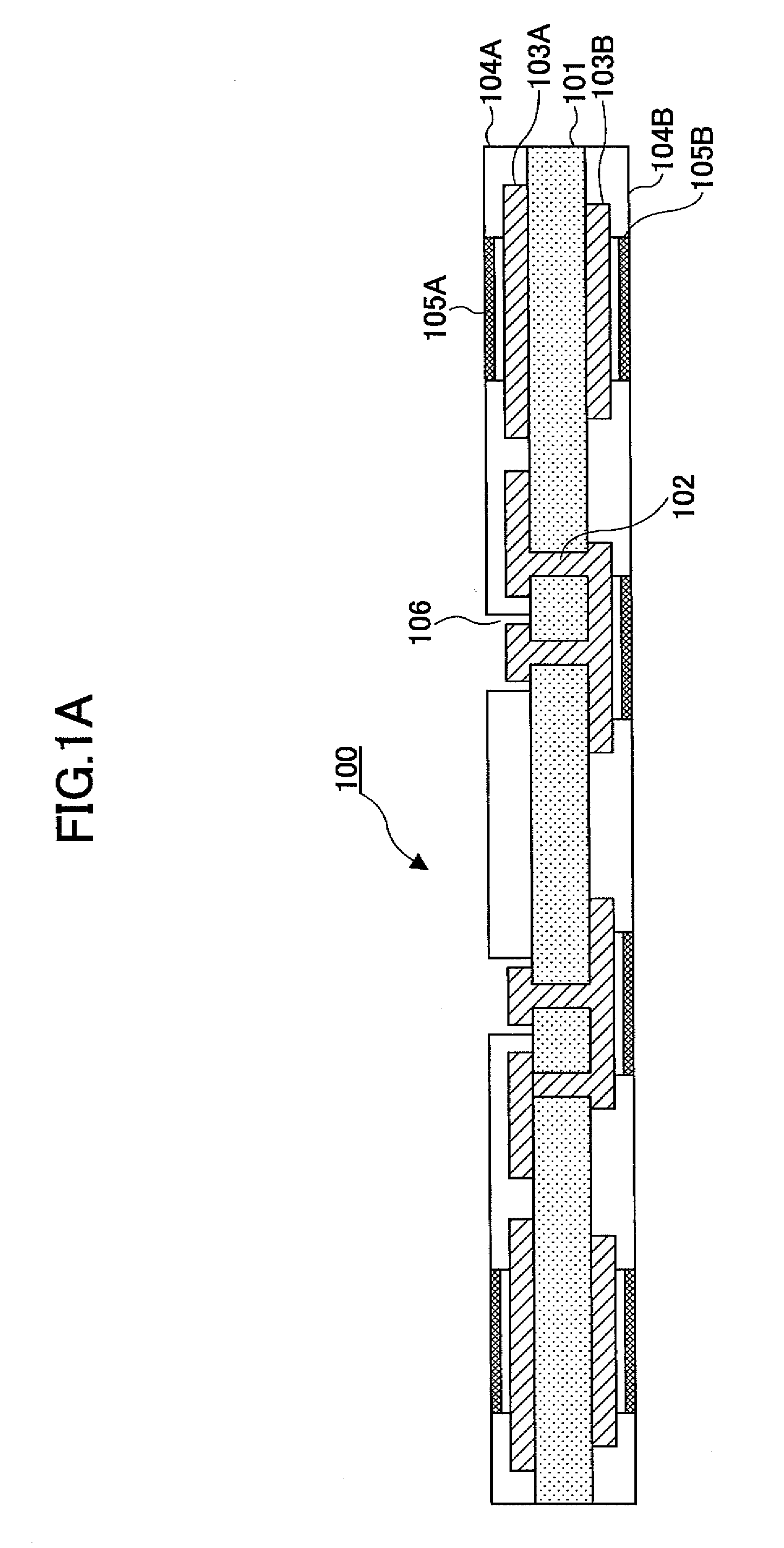

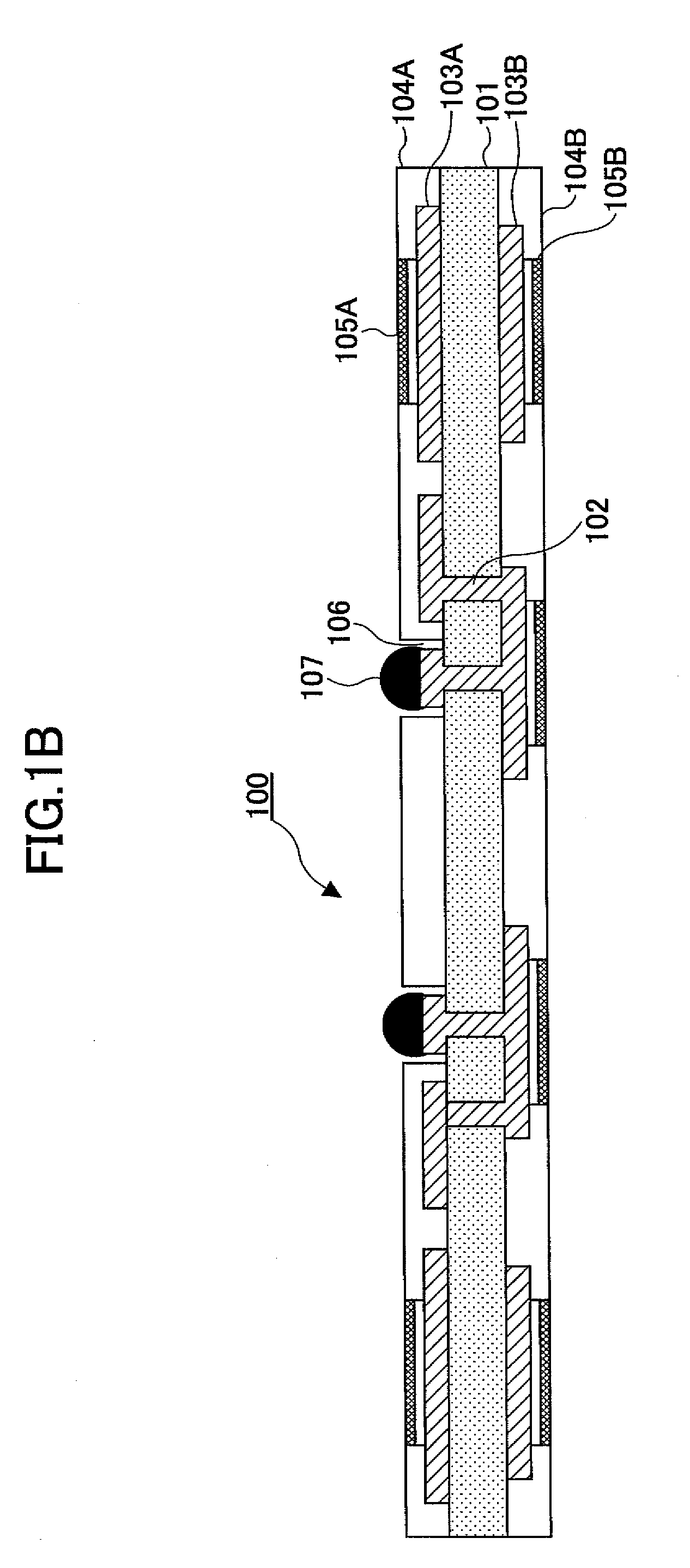

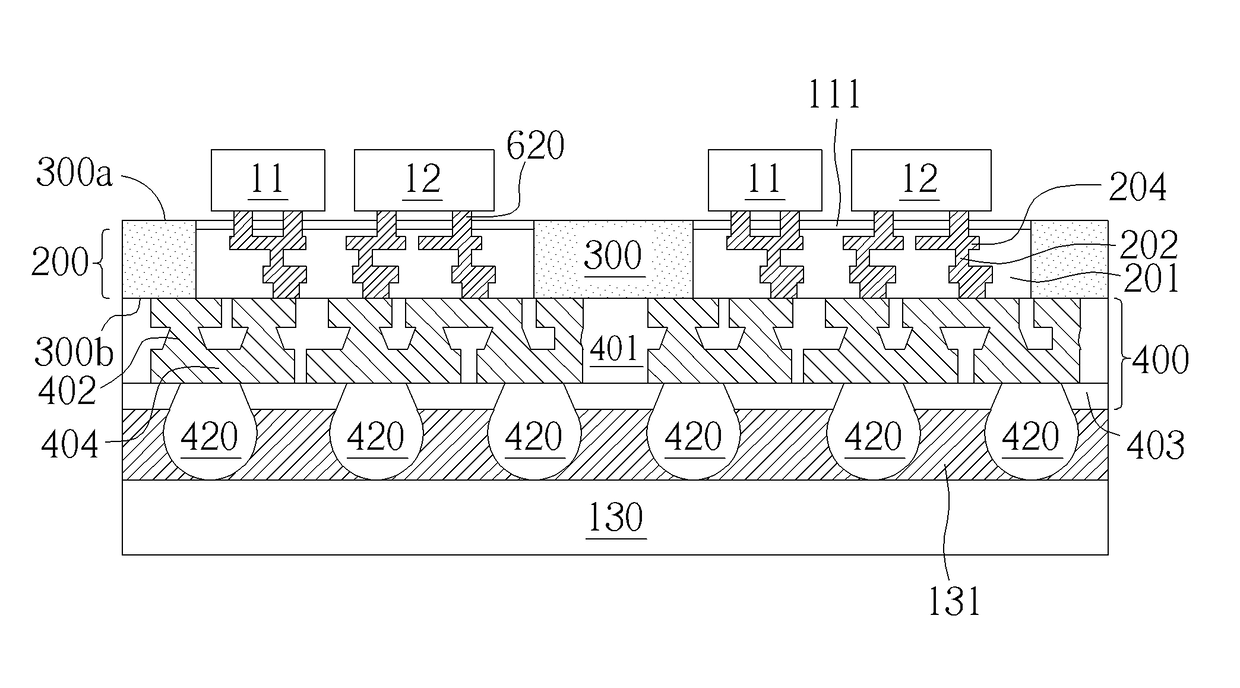

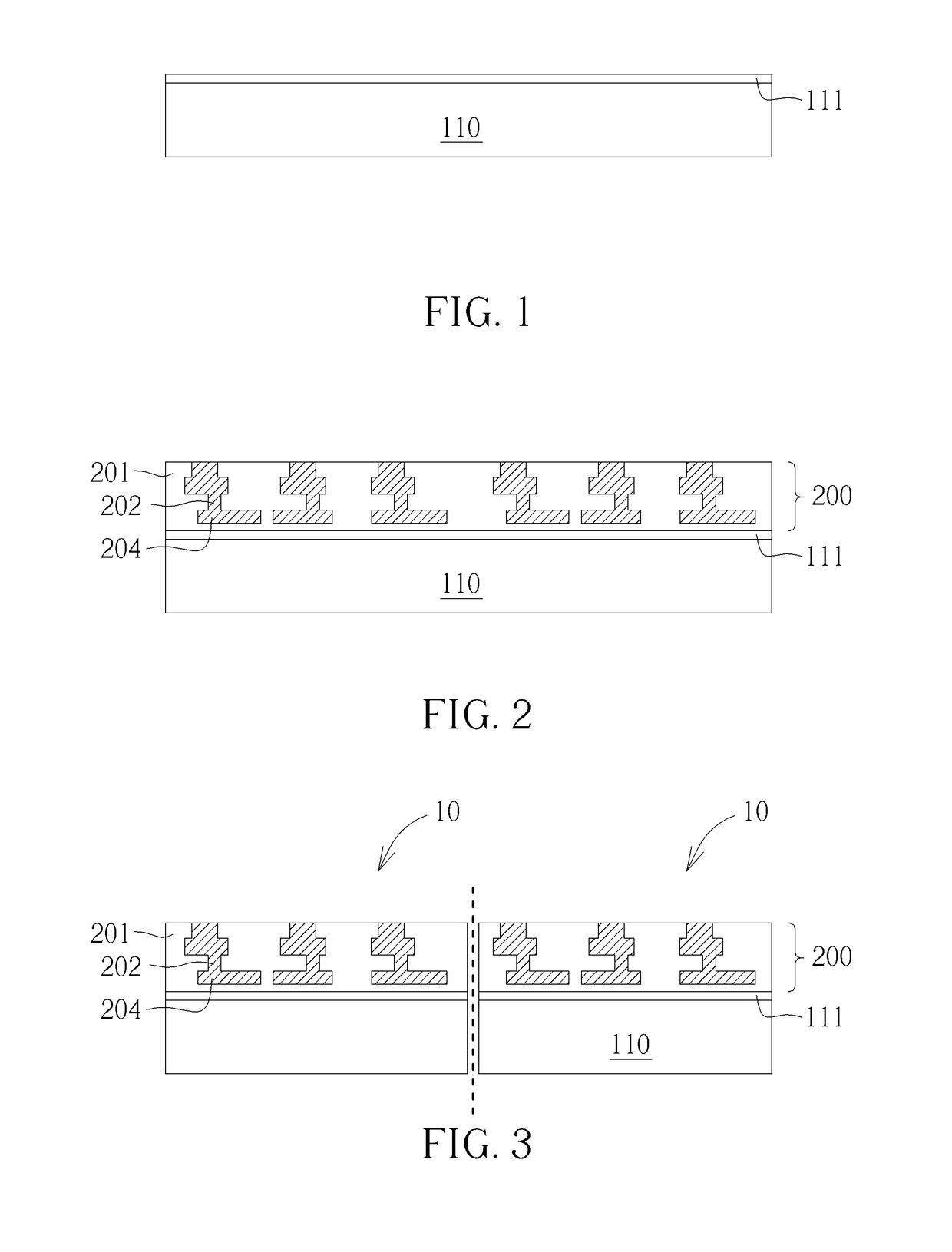

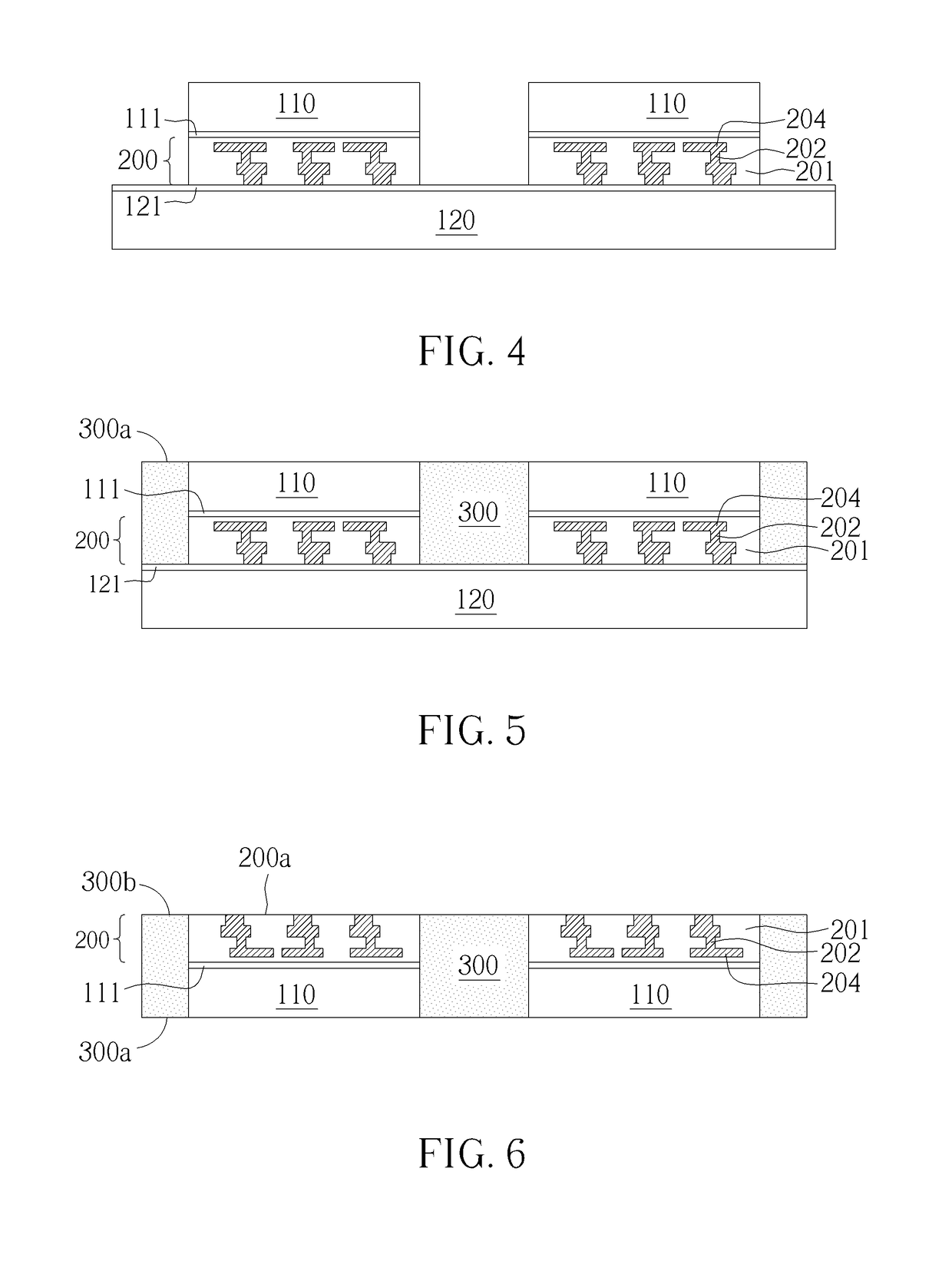

Chip embedded substrate and method of producing the same

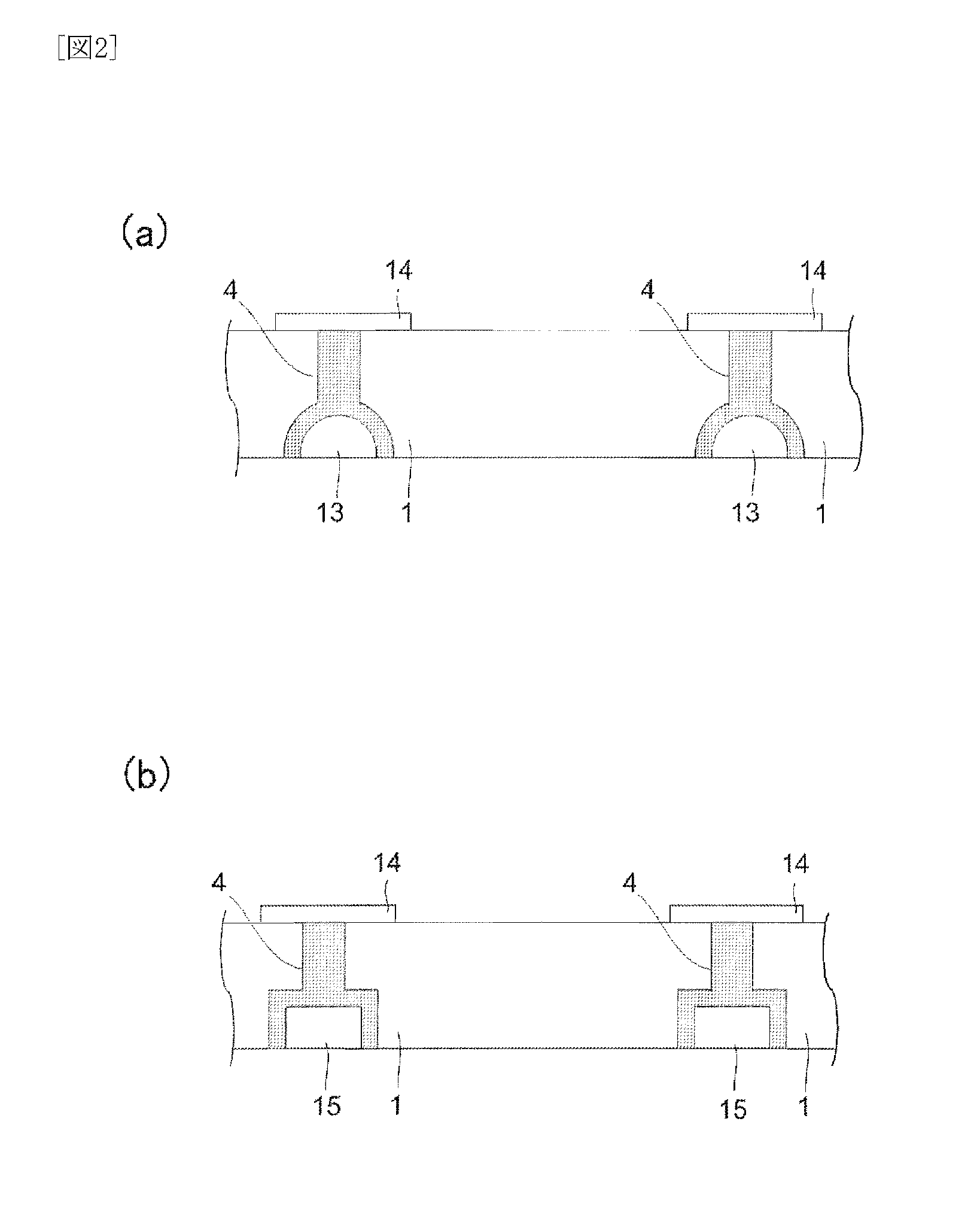

ActiveUS20090008765A1Improve production yieldHigh reliability in electrical connectionPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

A method of producing a chip embedded substrate is disclosed. This method comprises a first step of mounting a semiconductor chip on a first substrate on which a first wiring is formed; and a second step of joining the first substrate with a second substrate on which a second wiring is formed. In the second step, the semiconductor chip is encapsulated between the first substrate and the second substrate and electrical connection is made between the first wiring and the second wiring so as to form multilayered wirings connected to the semiconductor chip.

Owner:SHINKO ELECTRIC IND CO LTD

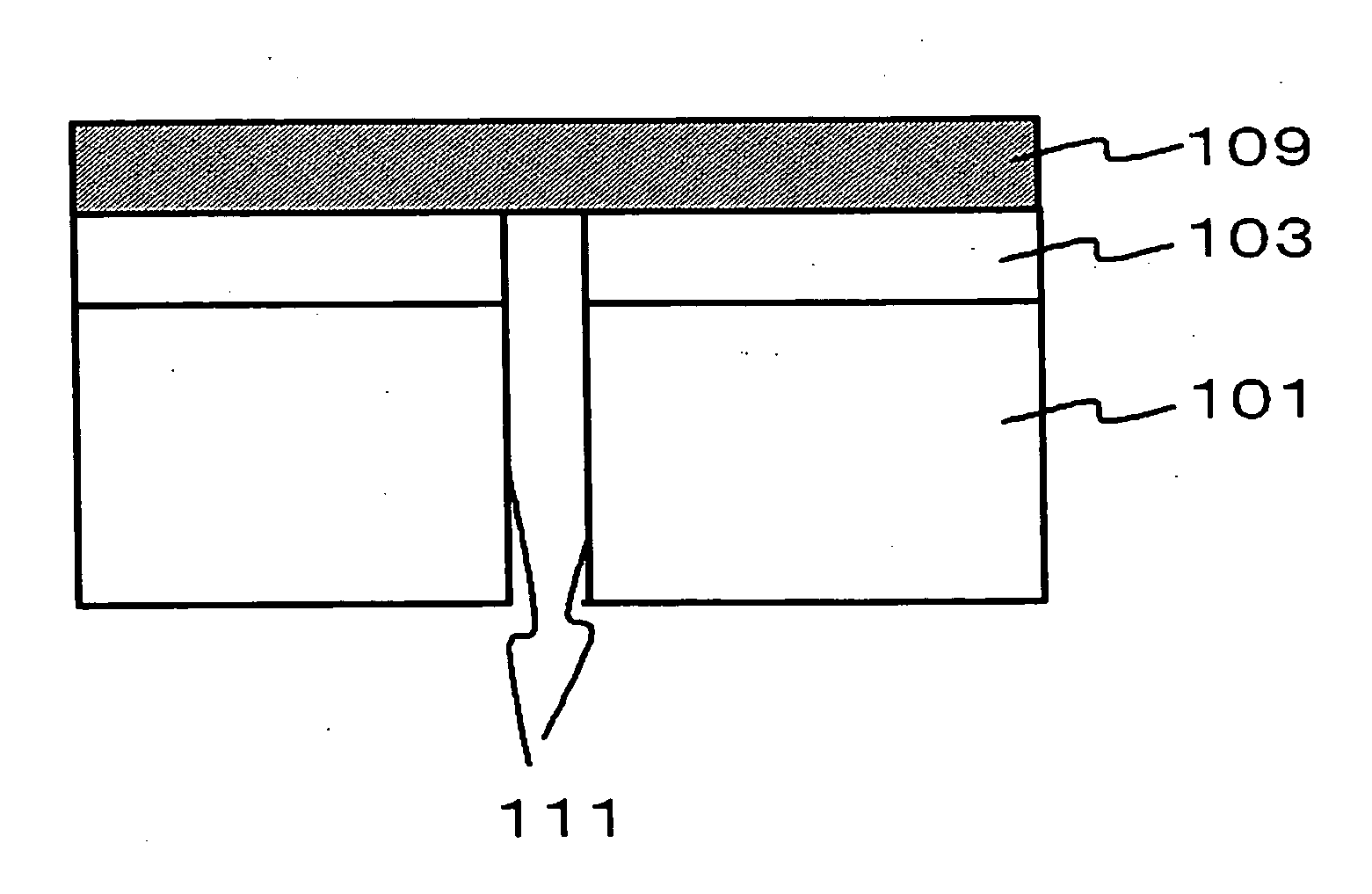

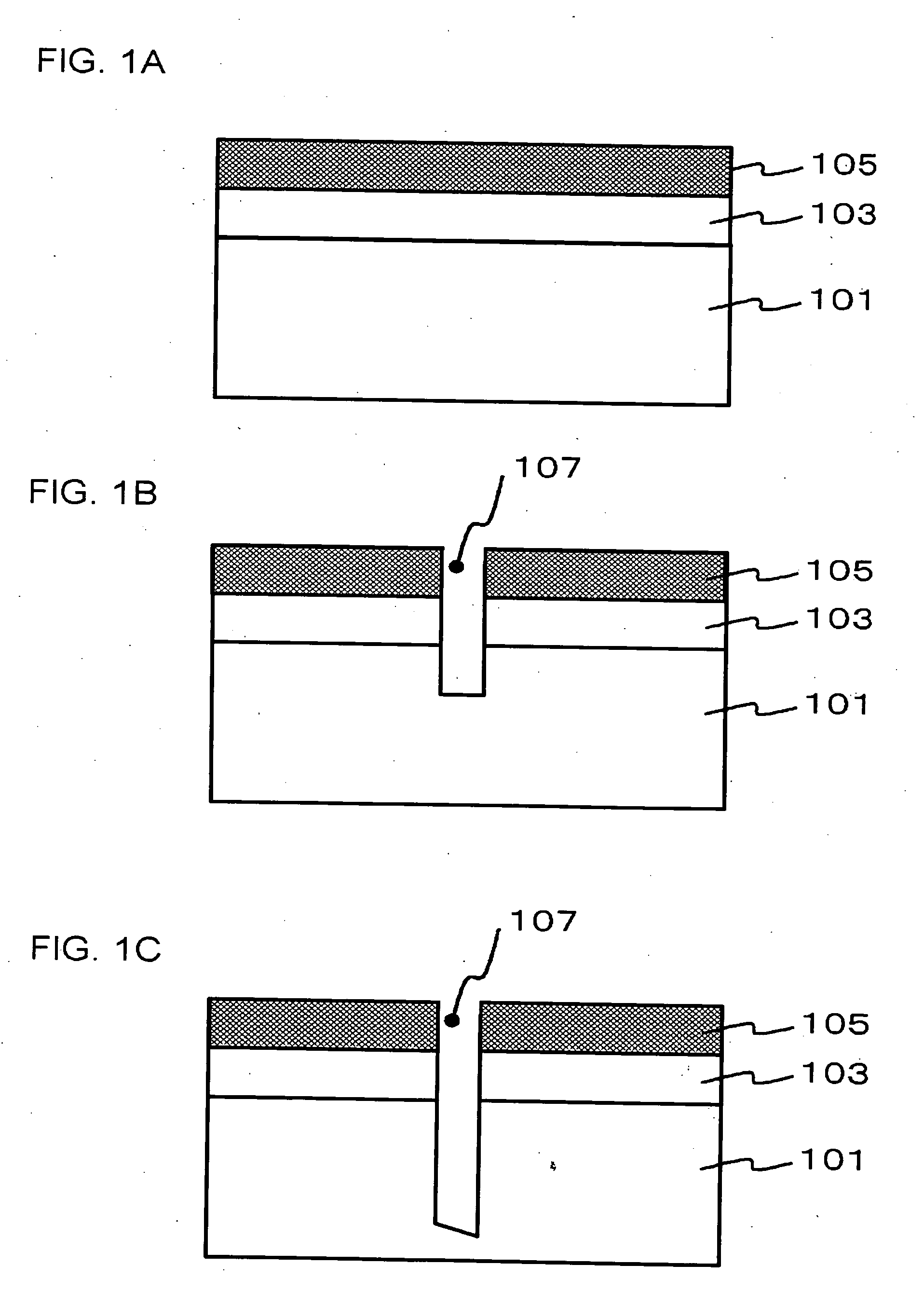

Method for manufacturing semiconductor device

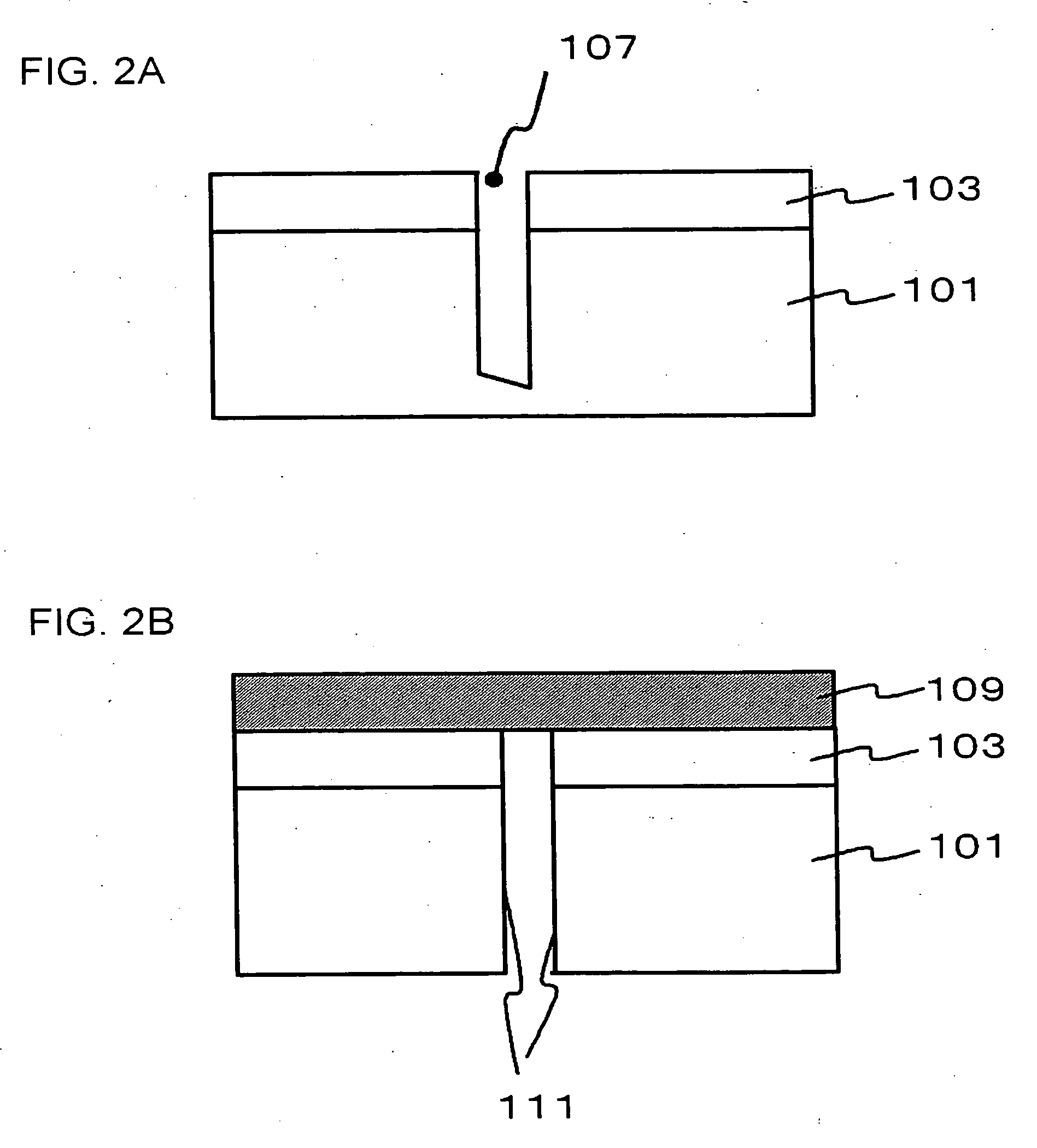

InactiveUS20060205182A1Reduce widthRate of the processing for providing the trenched portion can beSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialDevice form

A method of dicing a semiconductor wafer includes providing an interconnect layer providing a protective film on the interconnect layer on the side of a device-forming surface of a silicon wafer, irradiating the protective film with a laser beam to provide a trenched portion that extends through the interconnect layer from the protective film and reaches to an inside of the silicon wafer, removing a portion of the silicon wafer selectively in a depth direction from a bottom of the trenched portion, after irradiating with the laser beam to provide the trenched portion and dividing the silicon wafer along the portion where the trenched portion is provided into respective pieces of the silicon wafer, after removing a portion of the silicon wafer 101 selectively in the depth direction.

Owner:NEC ELECTRONICS CORP

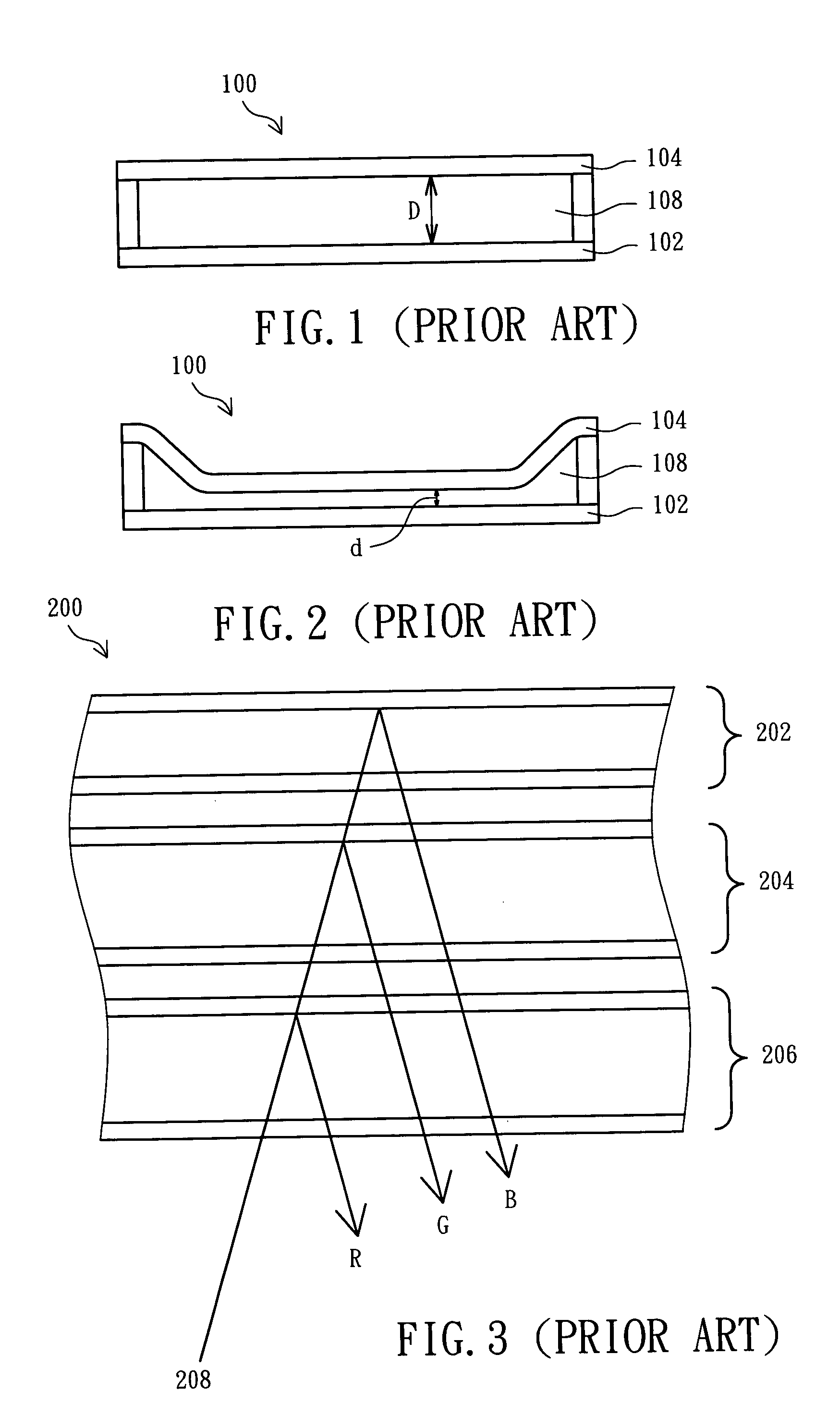

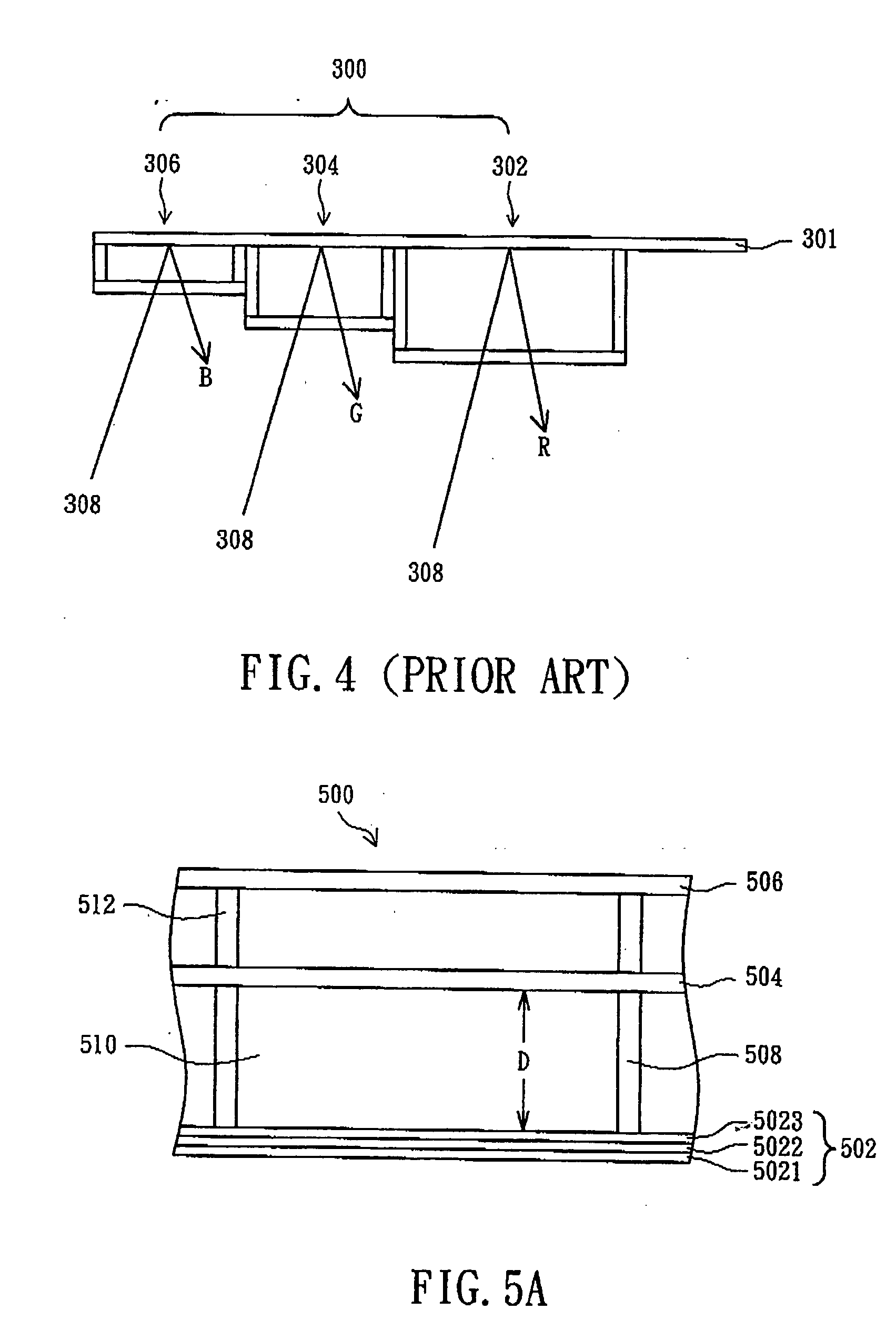

Color changeable pixel

InactiveUS20050068605A1Increase brightnessHigh resolutionNon-linear opticsOptical elementsOptoelectronicsVoltage

A color changeable pixel comprises a first plate, a second plate and a third plate. The three plates are settled in parallel. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The second plate shifts by the voltage added on the third plate to change the distance between the first plate and the second plate. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

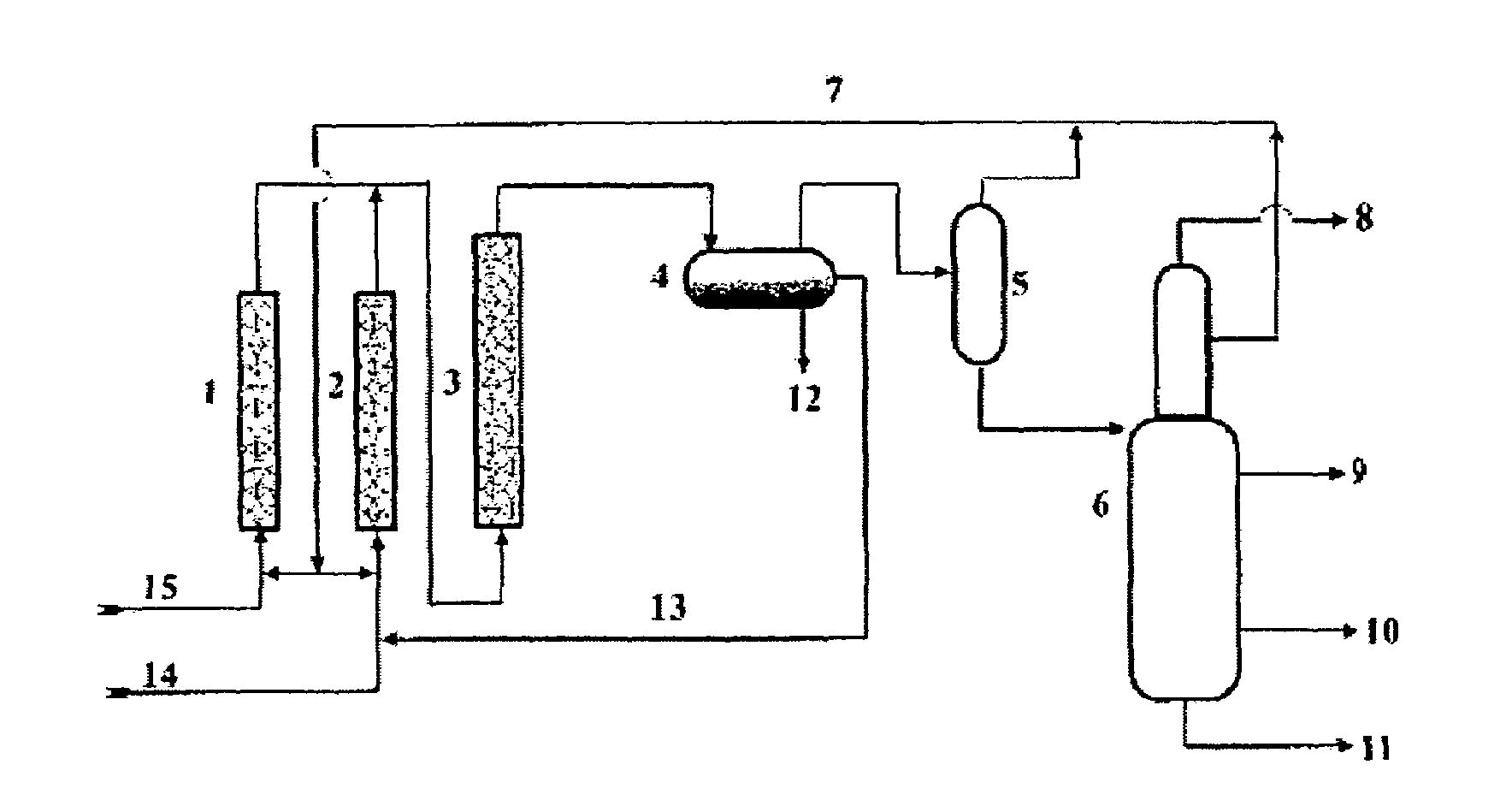

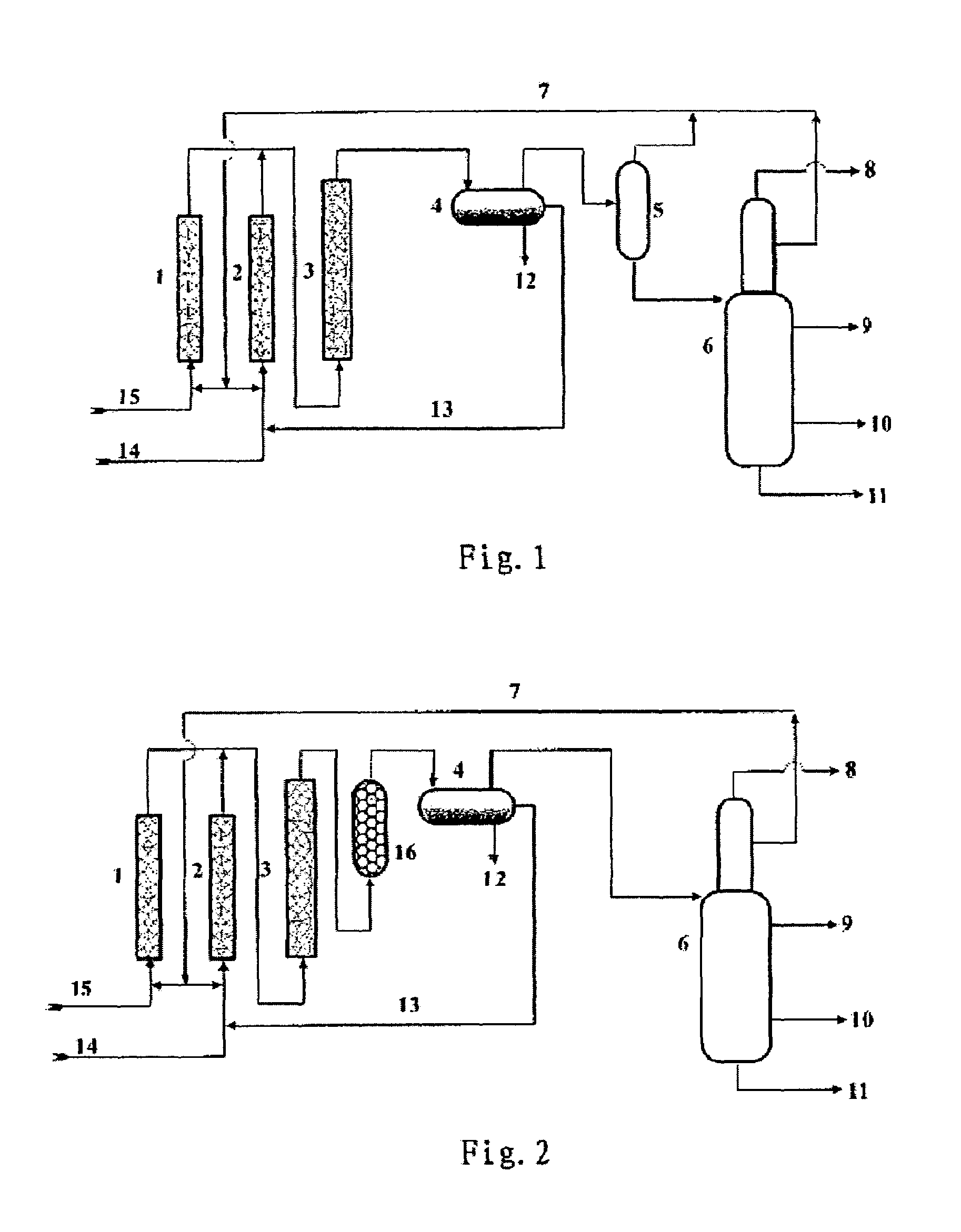

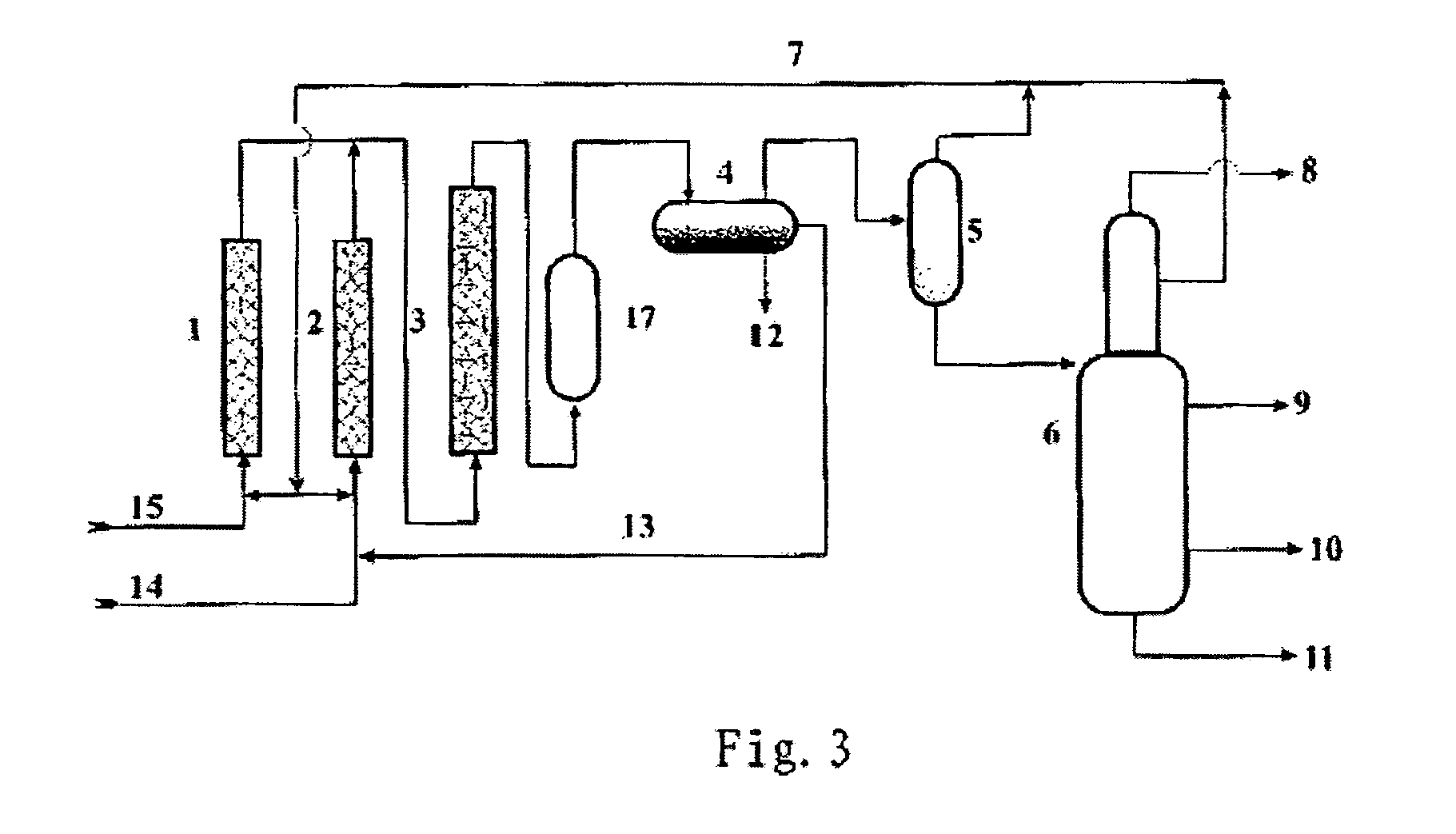

Method for manufacturing alkylate oil with composite ionic liquid used as catalyst

ActiveUS7285698B2High selectivityImprove production yieldOrganic chemistry methodsLiquid hydrocarbon mixtures productionAlkaneIonic liquid

The present invention pertains to a method for manufacturing alkylate oil using a composite ionic liquid as catalyst. A mixture of isobutane and C4 olefins is used as the raw material, and a composite ionic liquid is used as catalyst to carry out an alkylation reaction. The alkane / olefin ratio in the raw material is higher than 1:1. In the composition of the aforementioned composite ionic liquid catalyst, the cations come from a hydrohalide of an alkyl-containing amine or pyridine, while the anions are composite coordinate anions coming from two or more metal compounds. One of the metal compounds is an aluminum compound, while other metal compounds are compounds of Group IB and Group IIB elements of the Periodic Table and the transition metals. The present invention also provides a design of static mixer reaction apparatus that can realize the aforementioned manufacturing method. The method of the present invention increases the selectivity of the alkylation reaction to give the alkylation product a relatively high octane number and further increase the product yield. Also, the manufacturing operation is simplified, and the cost can be reduced. This method is an environmentally friendly method that will not pollute the environment.

Owner:CHINA UNIV OF PETROLEUM (BEIJING)

Color changeable pixel

InactiveUS20050068606A1Increase brightnessHigh resolutionNon-linear opticsReflectorsVoltageOptoelectronics

A color changeable pixel comprises a first plate, a second plate and a third plate. The three plates are settled in parallel. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The second plate shifts by the voltage added on the third plate to change the distance between the first plate and the second plate. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

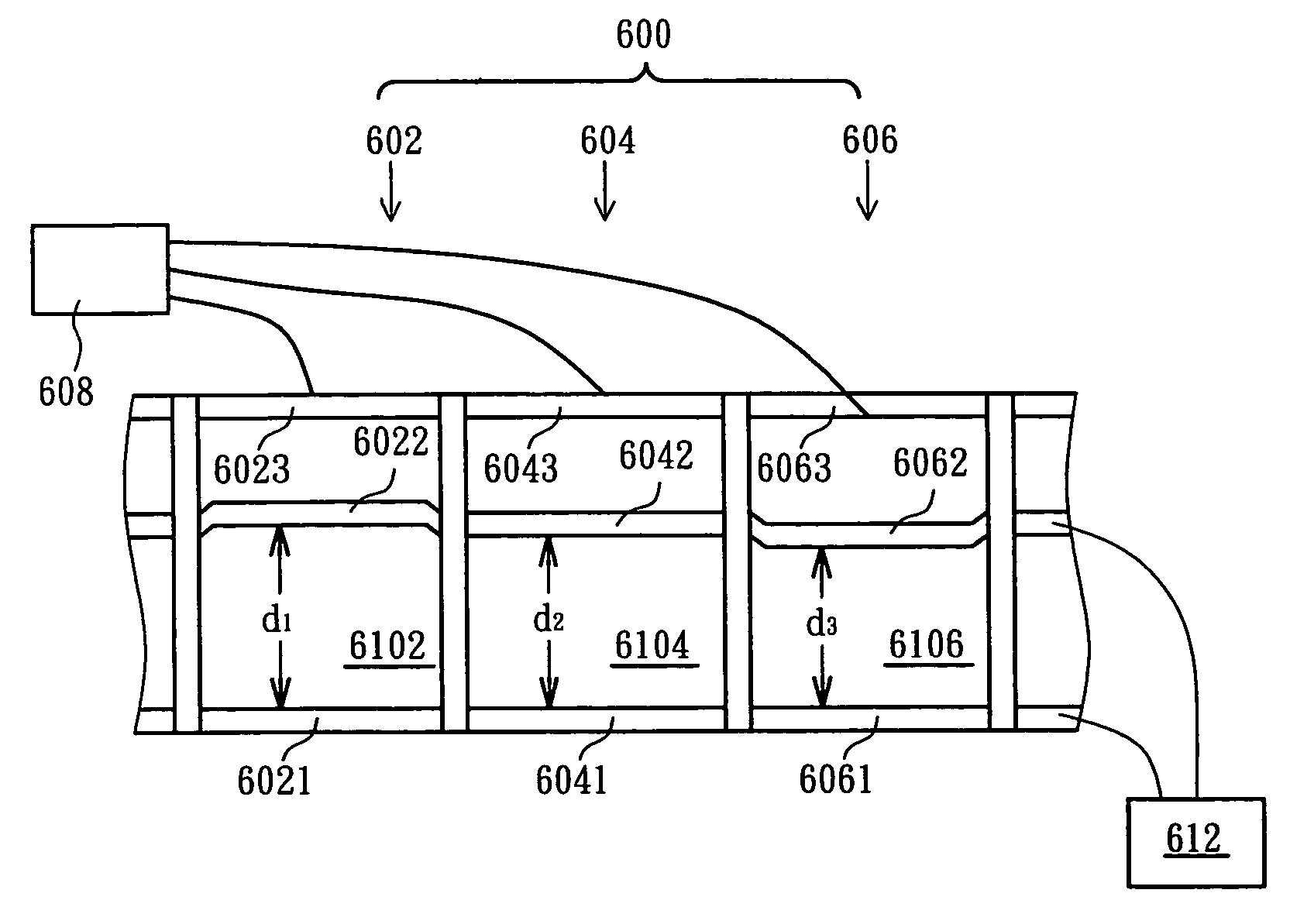

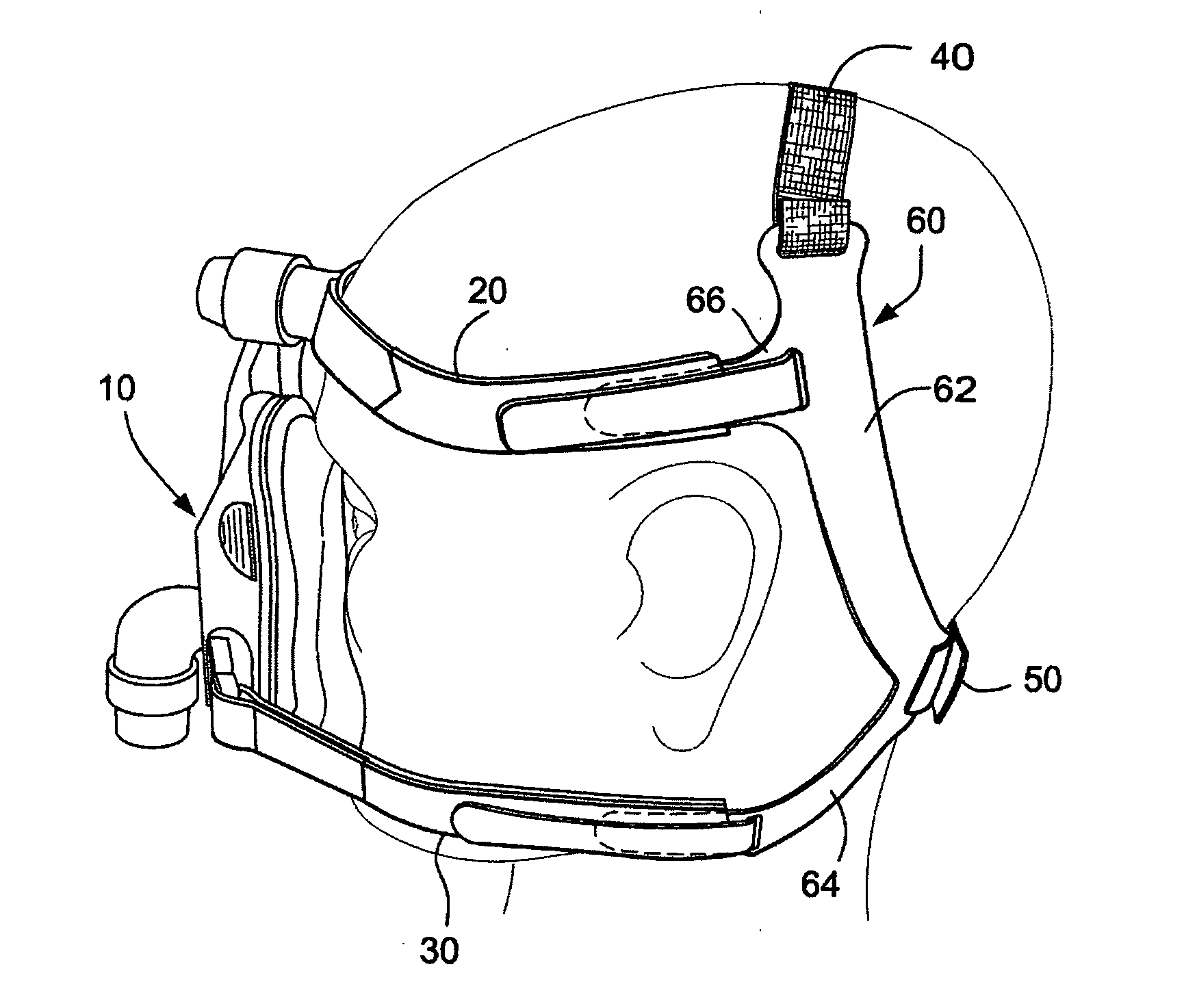

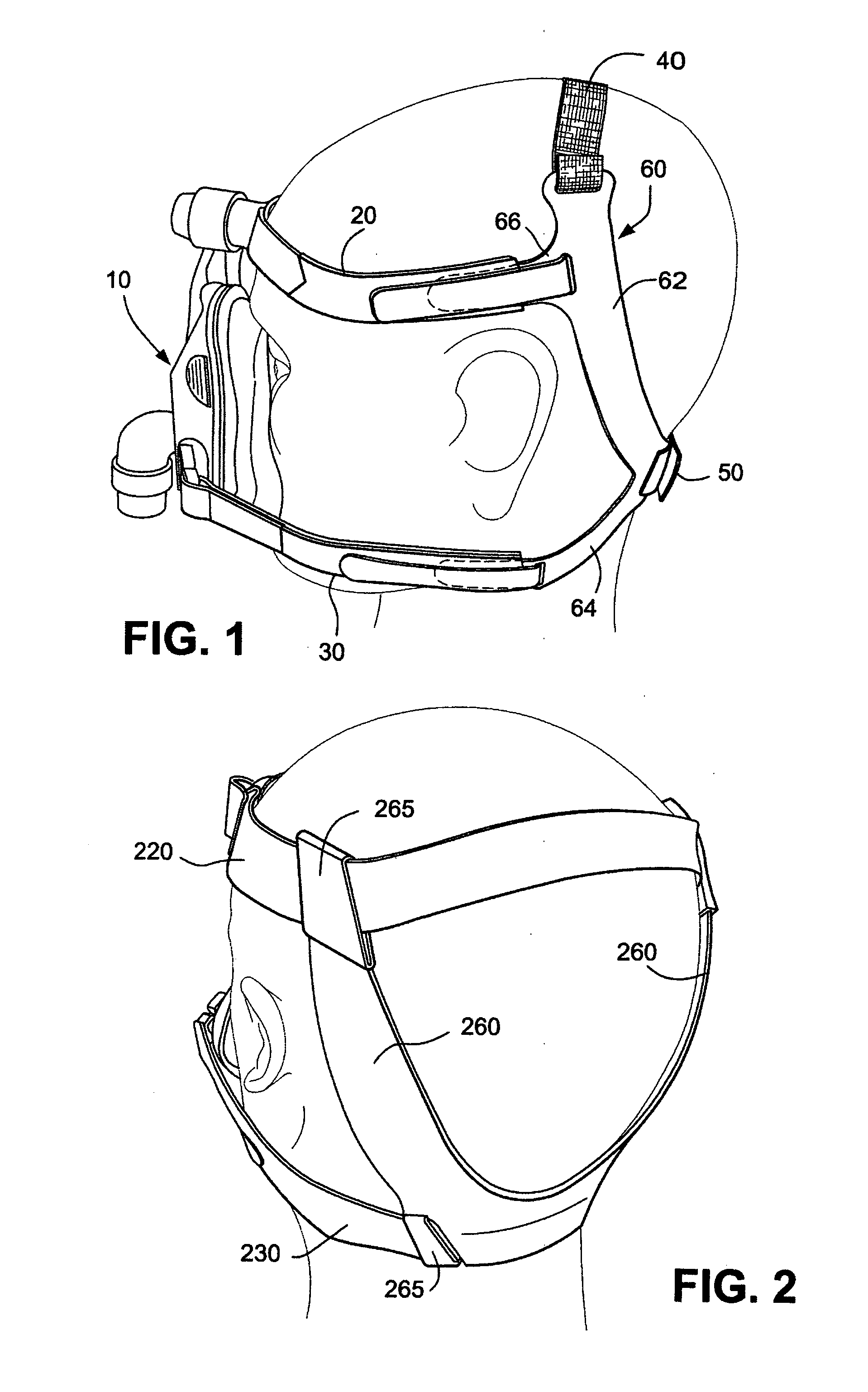

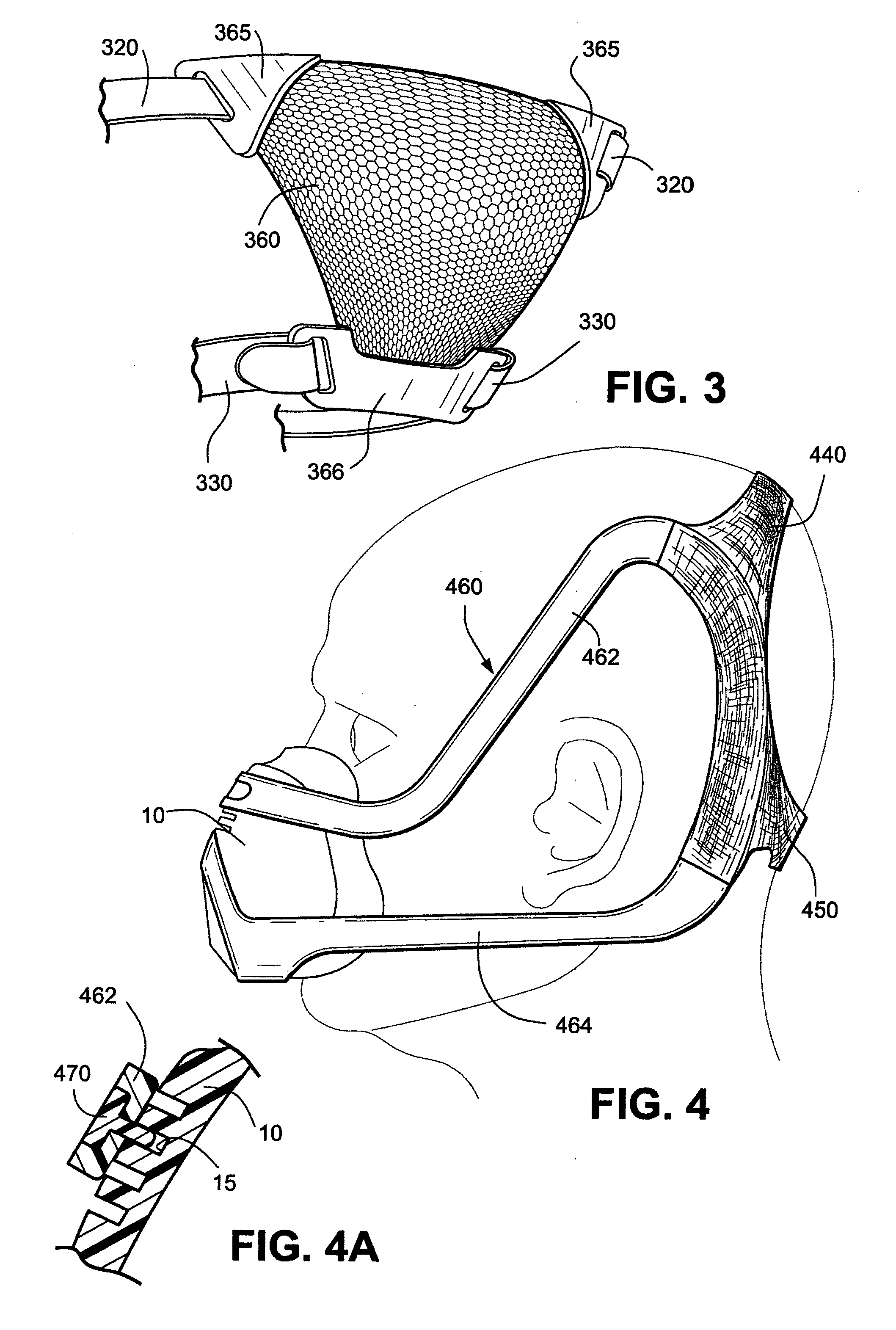

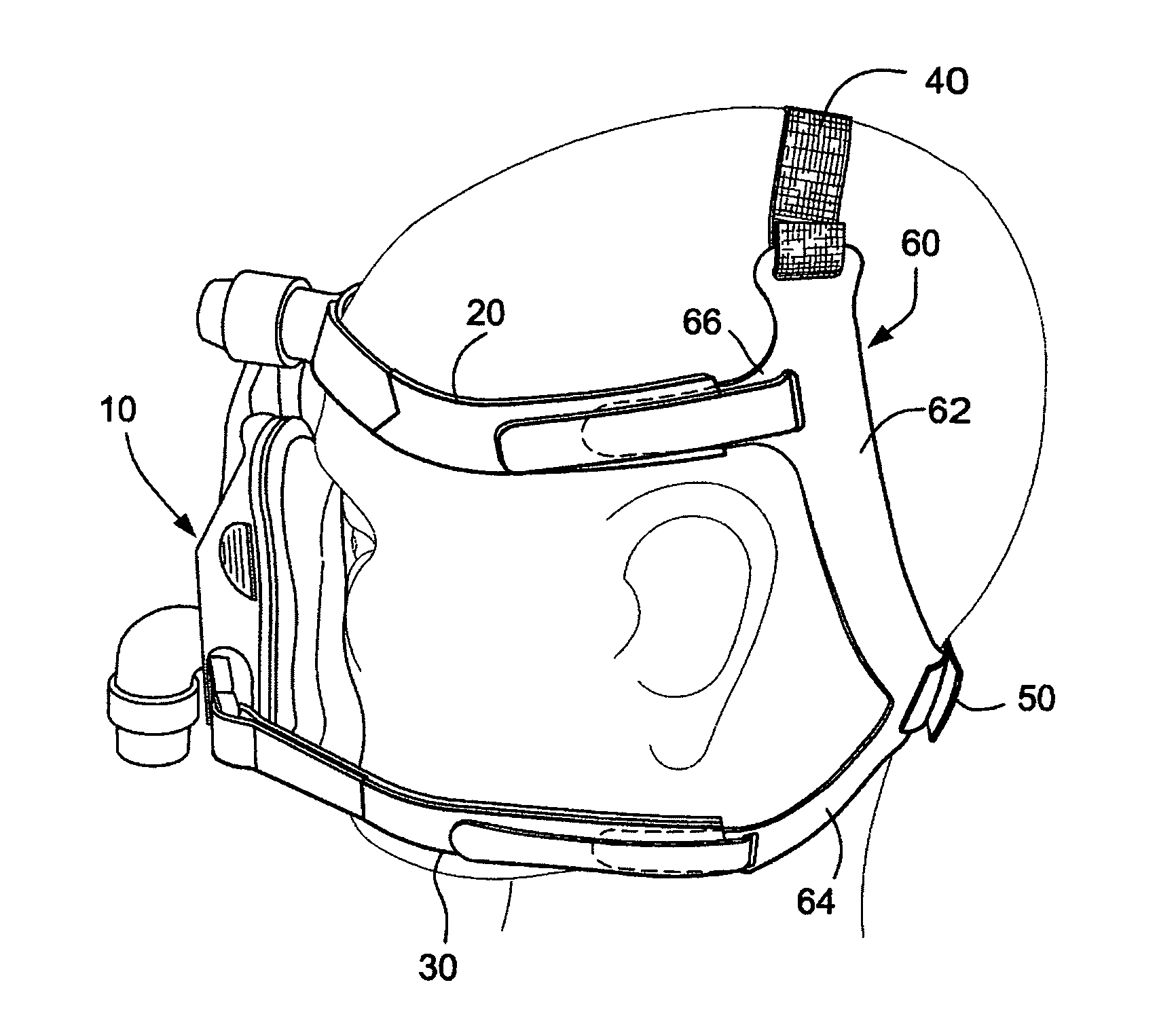

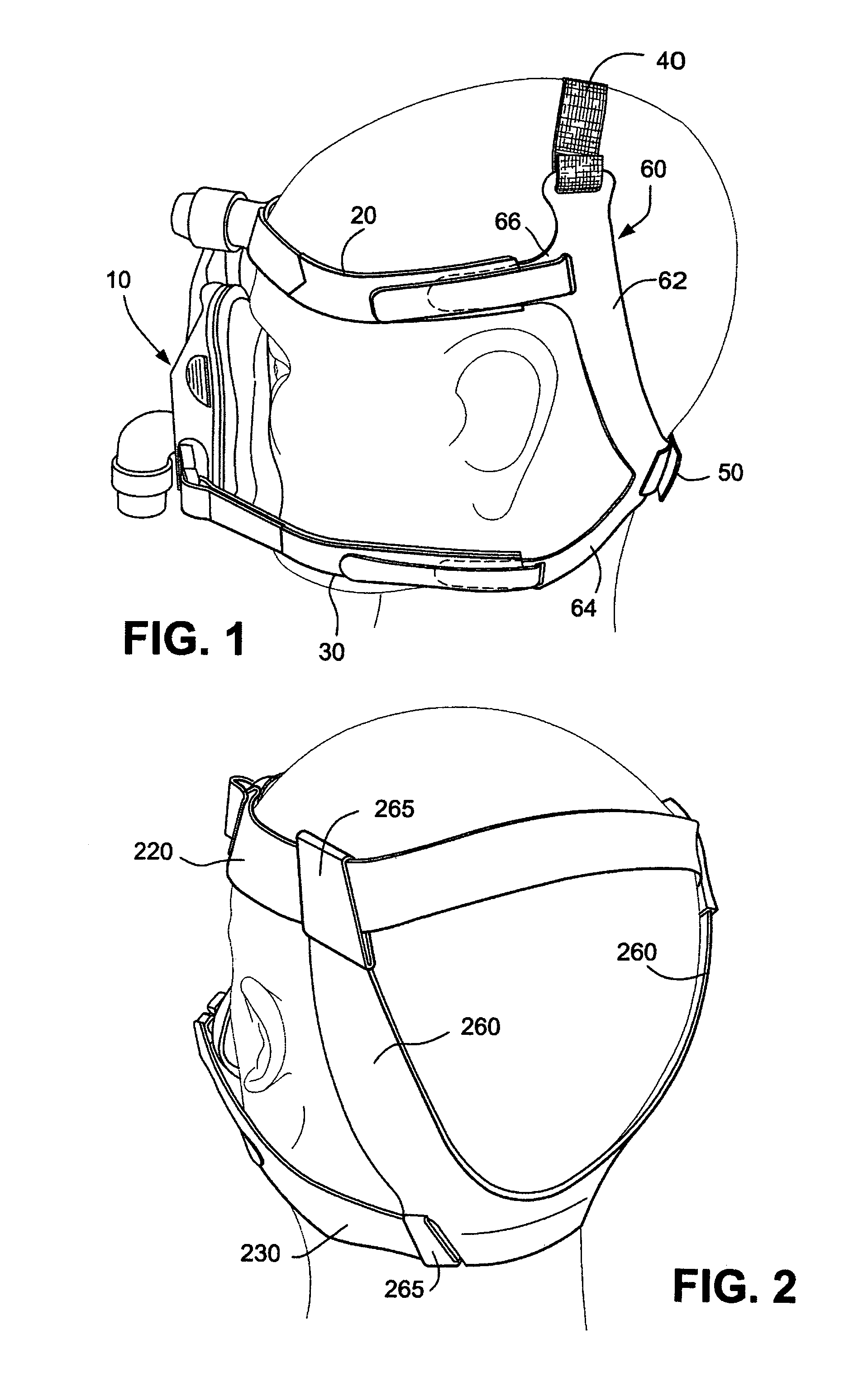

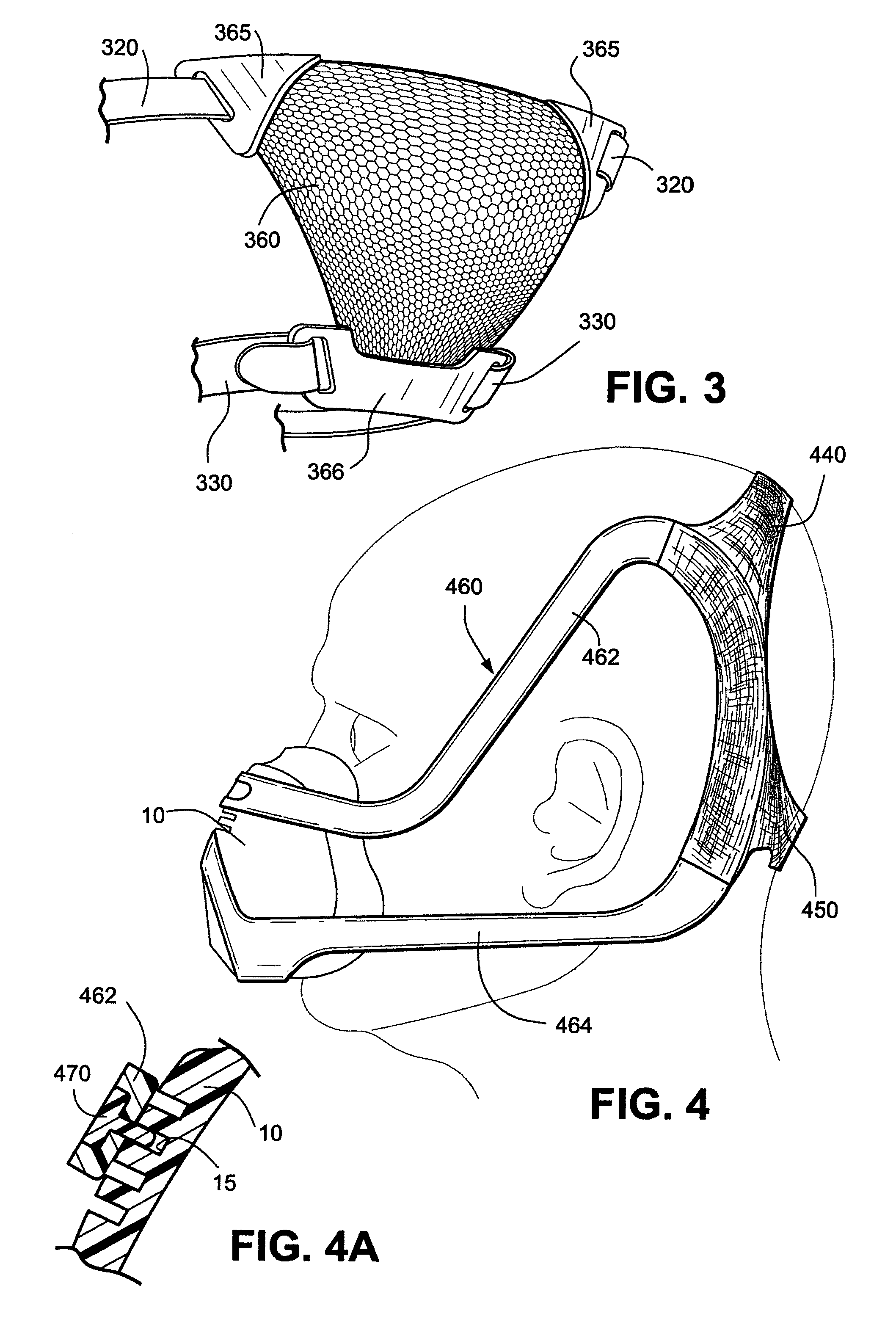

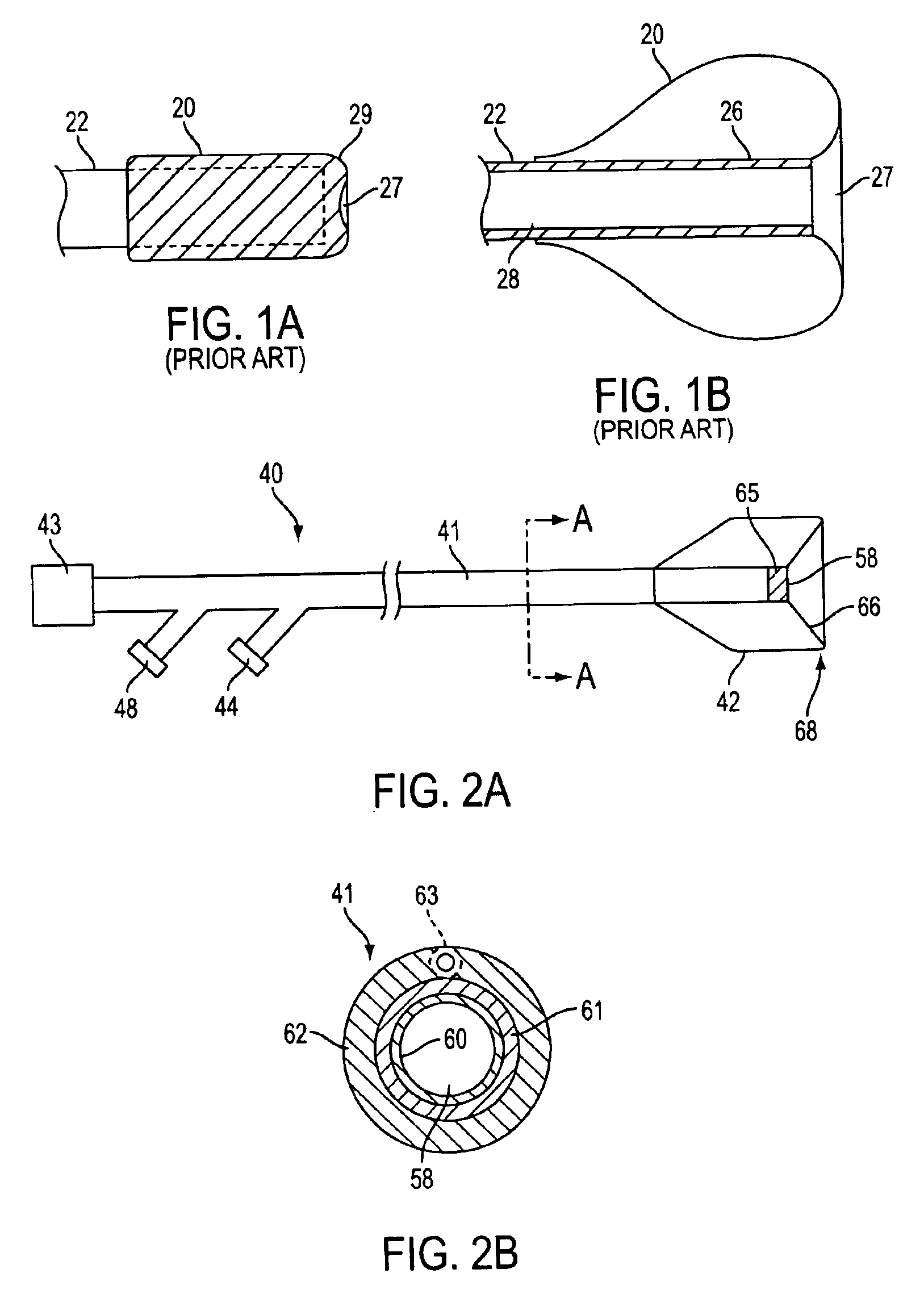

Headgear for masks

ActiveUS20110197341A1Low costEasy to useBreathing masksMedical devicesPhysical medicine and rehabilitationEngineering

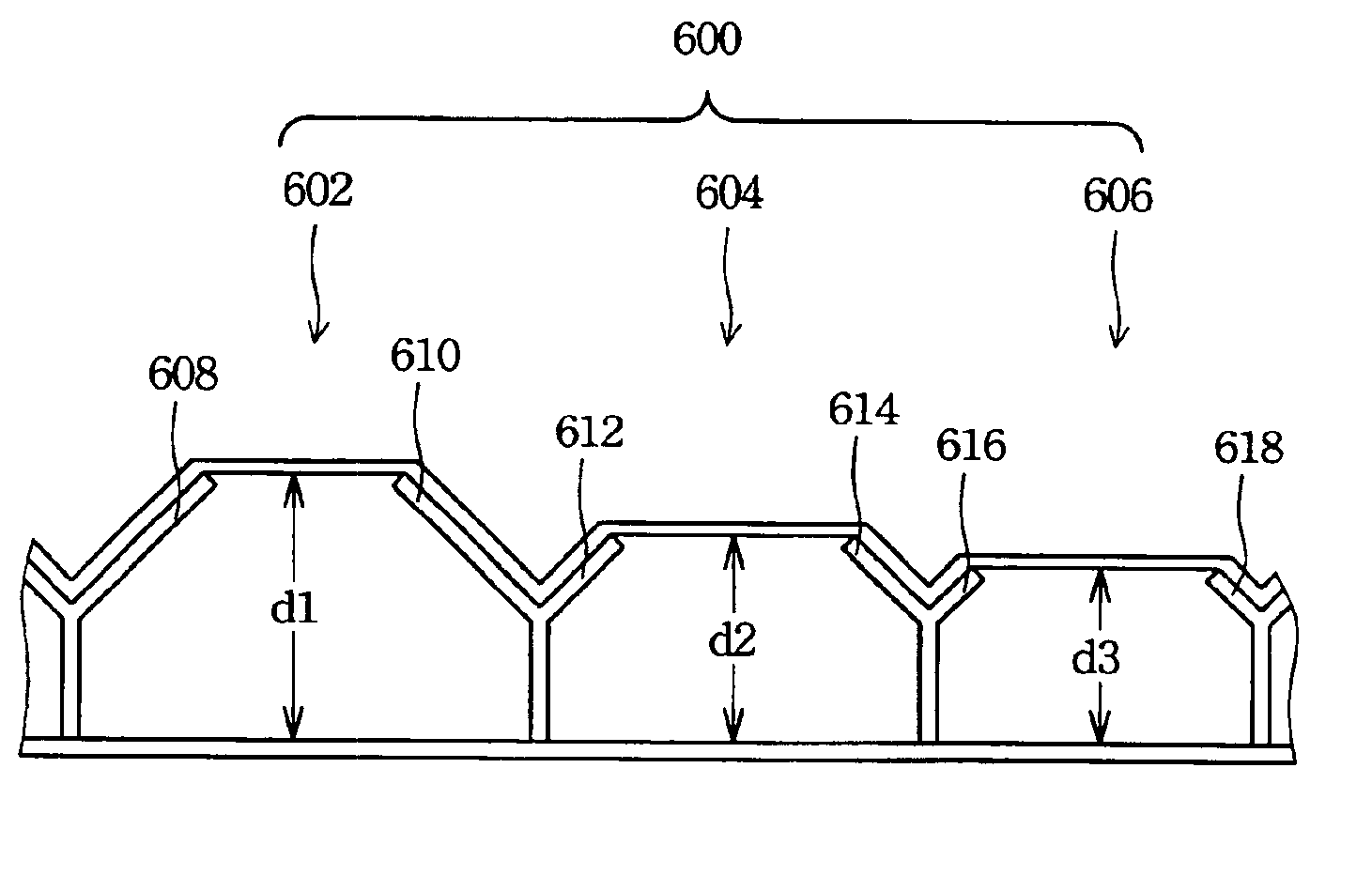

A headgear for use with a mask includes a first strap (660) being configured to engage a back of a patient's head and extend on either side of the patient's parietal bone behind the patient's ears and assume, in use, a substantially circular or oval shape. At least a portion of the first strap is substantially inextensible. The headgear also includes at least one second strap (620, 630) configured to removably connect the first strap to the mask. The second strap may be more extensible than the first strap. At least a portion of the first strap is self-supporting such that the headgear maintains a three dimensional shape when not in use. The substantially inextensible portion of the first strap is constructed to resiliently return to a predetermined shape when not in use. The arcuate region includes a first portion that may be arranged to align substantially parallel with a top of the patient's head and a second portion being arranged to align substantially to a rear surface of the patient's head.

Owner:RESMED LTD

Headgear for masks

ActiveUS8950404B2Low costEasy to useProtective equipmentRespiratory masksMedicineThree dimensional shape

A headgear for use with a mask includes a first strap (660) being configured to engage a back of a patient's head and extend on either side of the patient's parietal bone behind the patient's ears and assume, in use, a substantially circular or oval shape. At least a portion of the first strap is substantially inextensible. The headgear also includes at least one second strap (620, 630) configured to removably connect the first strap to the mask. The second strap may be more extensible than the first strap. At least a portion of the first strap is self-supporting such that the headgear maintains a three dimensional shape when not in use. The substantially inextensible portion of the first strap is constructed to resiliently return to a predetermined shape when not in use. The arcuate region includes a first portion that may be arranged to align substantially parallel with a top of the patient's head and a second portion being arranged to align substantially to a rear surface of the patient's head.

Owner:RESMED LTD

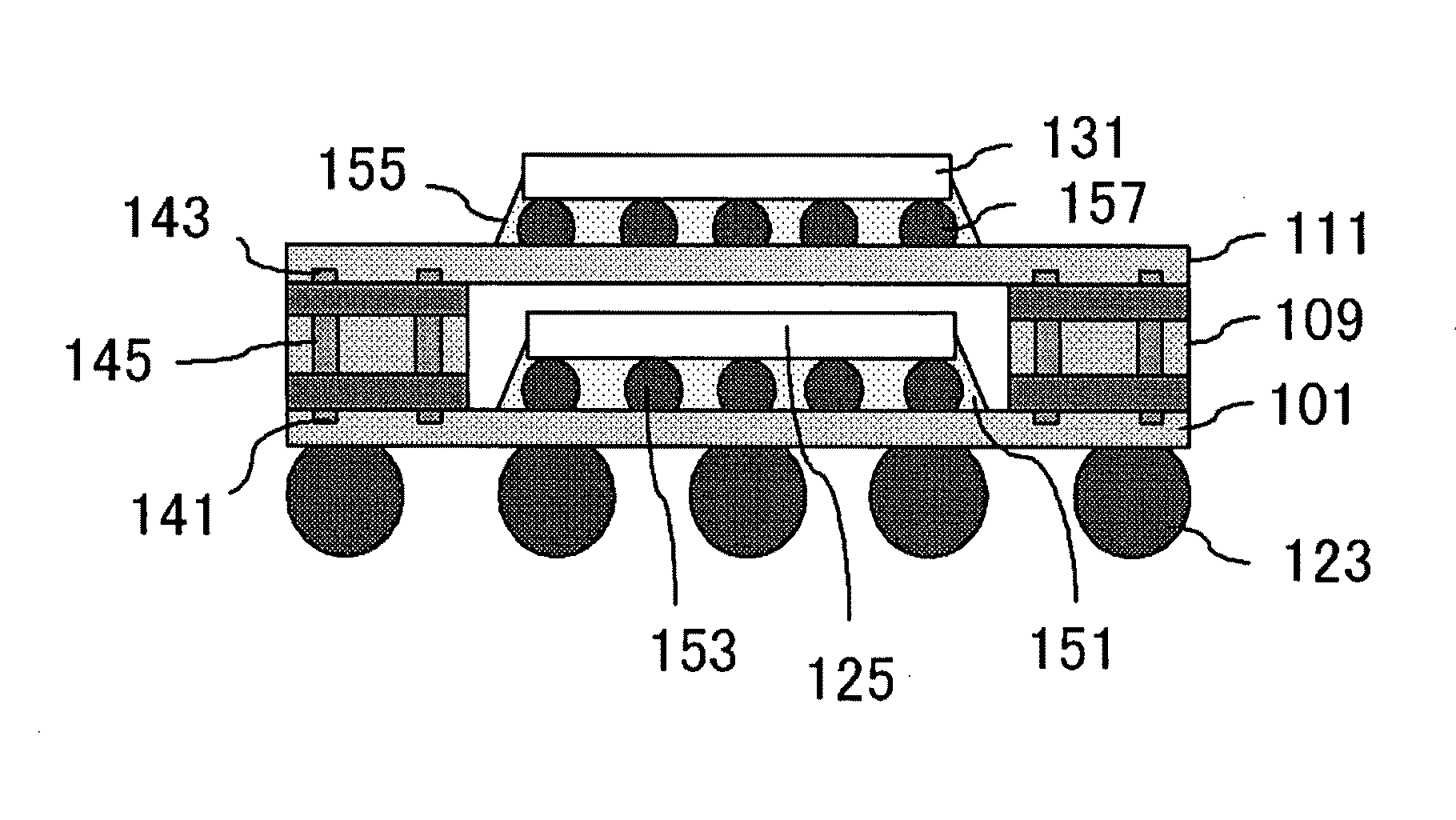

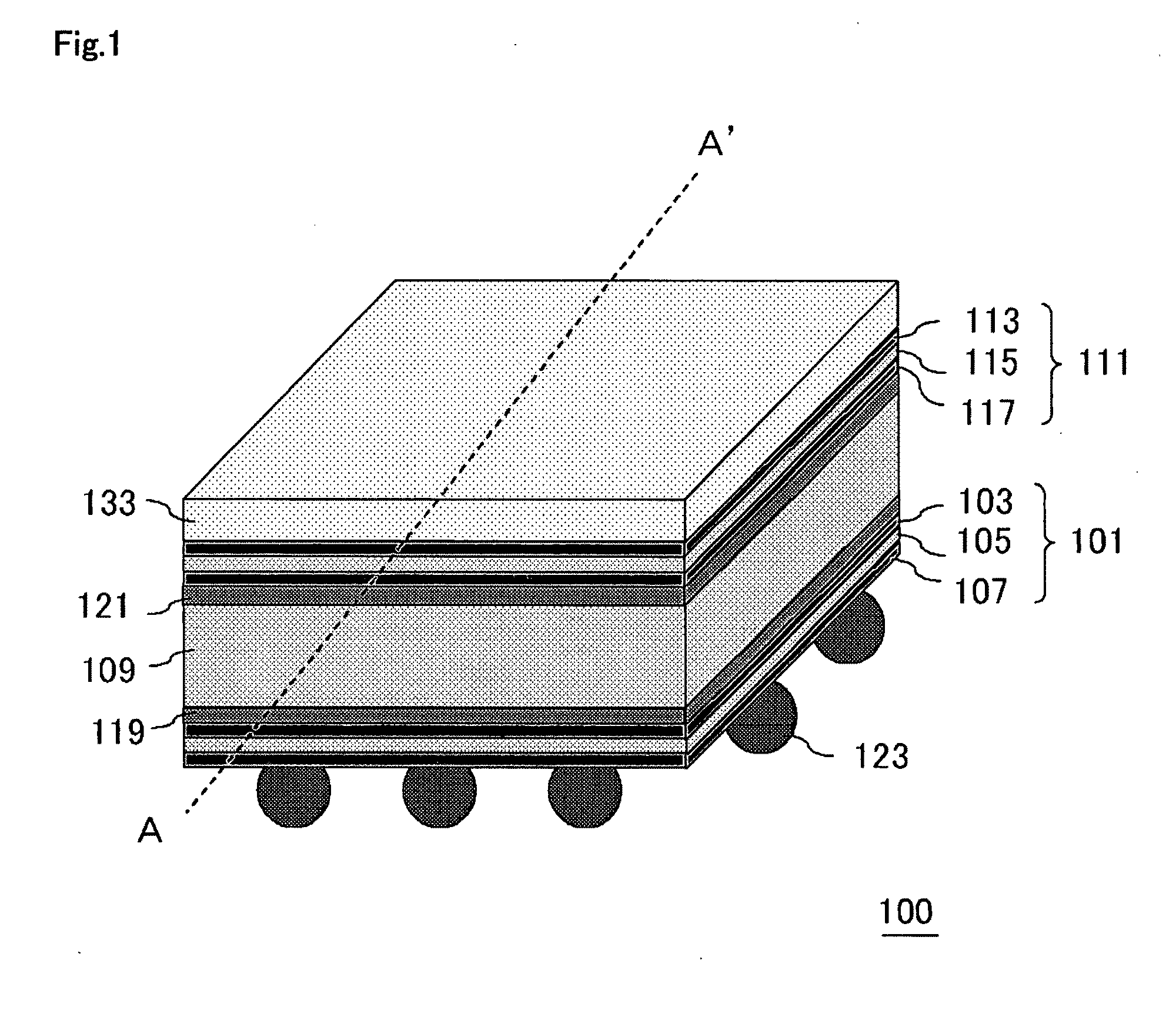

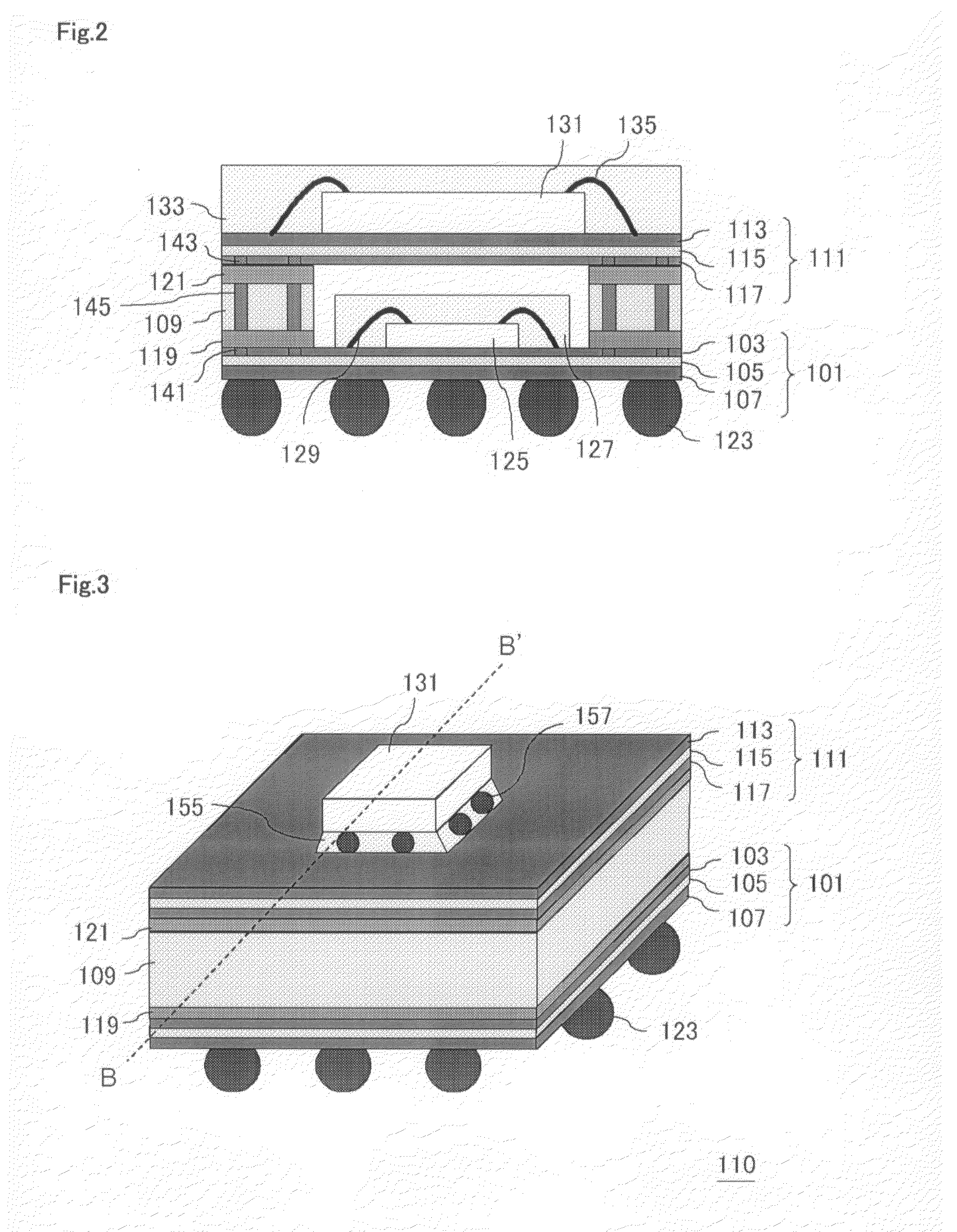

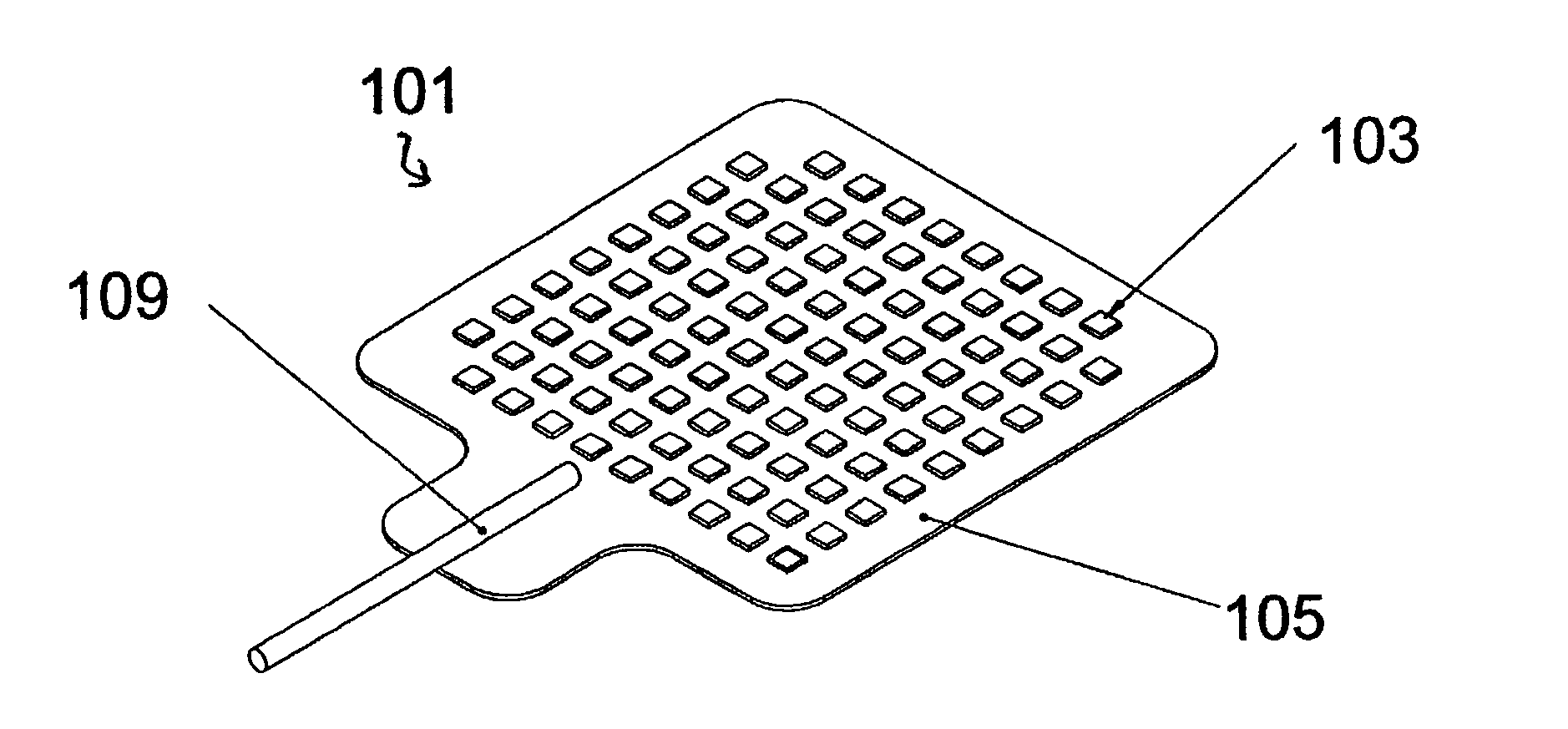

Semiconductor Device and Method for Manufacturing Semiconductor Device

InactiveUS20090243065A1Improve joint reliabilityLower elastic modulusSemiconductor/solid-state device detailsSolid-state devicesSurface mountingSemiconductor chip

A semiconductor device (100) comprises a first resin substrate (101) on which a first semiconductor chip (125) is mounted a surface thereof; a second resin substrate (111) on which a second semiconductor chip (131) is mounted on a surface thereof; and a resin base material (109), joined to a front surface of the first resin substrate (101) and to a back surface of the second resin substrate (111), so that these surfaces are electrically connected. The resin base material (109) is disposed in a circumference of the first resin substrate (101) in the surface of the first resin substrate (101). Further, the first semiconductor chip (125) is disposed in a space section provided among the first resin substrate (101), the second resin substrate (111) and the resin base material (109) in the surface of the first resin substrate (101).

Owner:SUMITOMO BAKELITE CO LTD

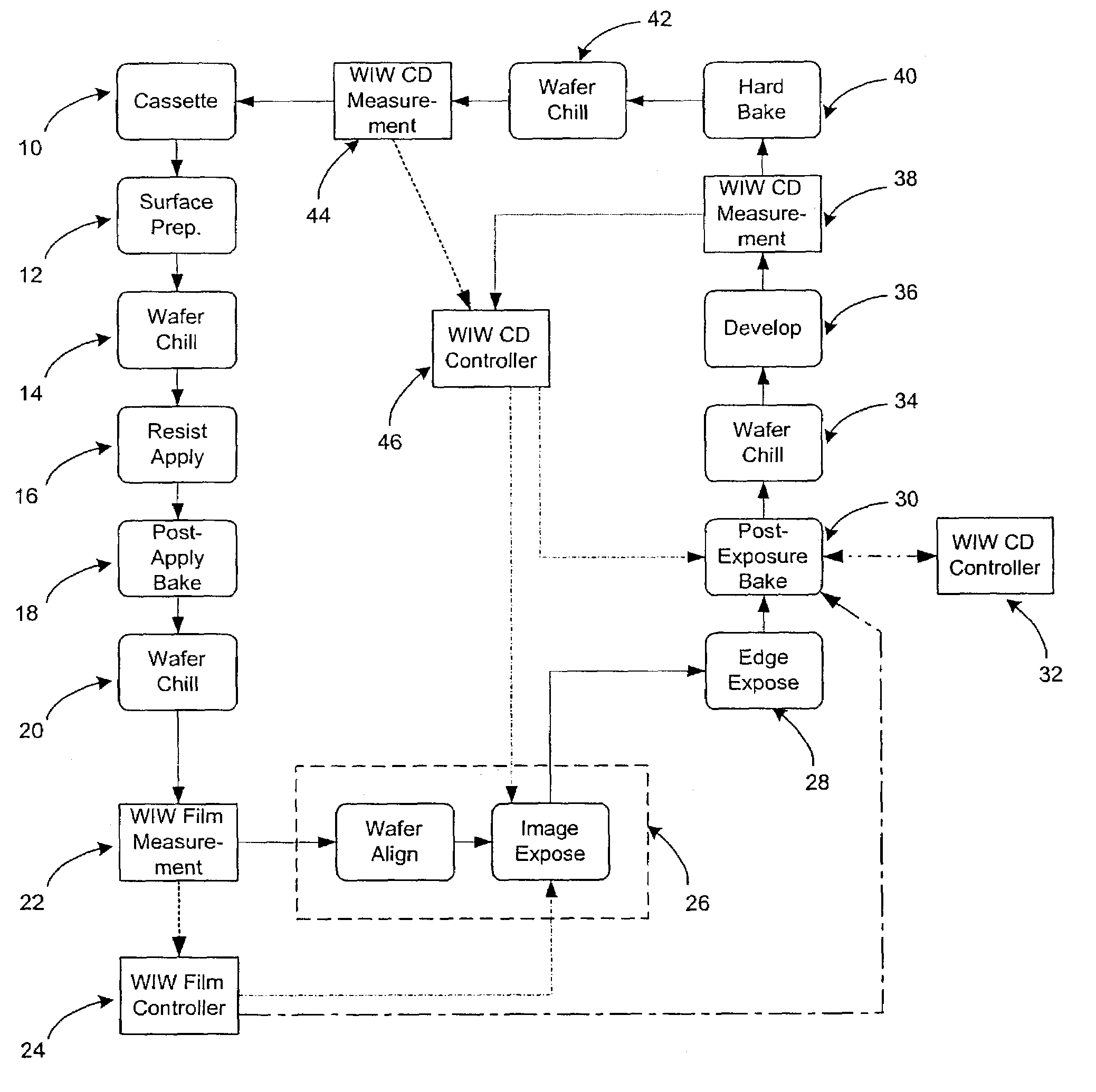

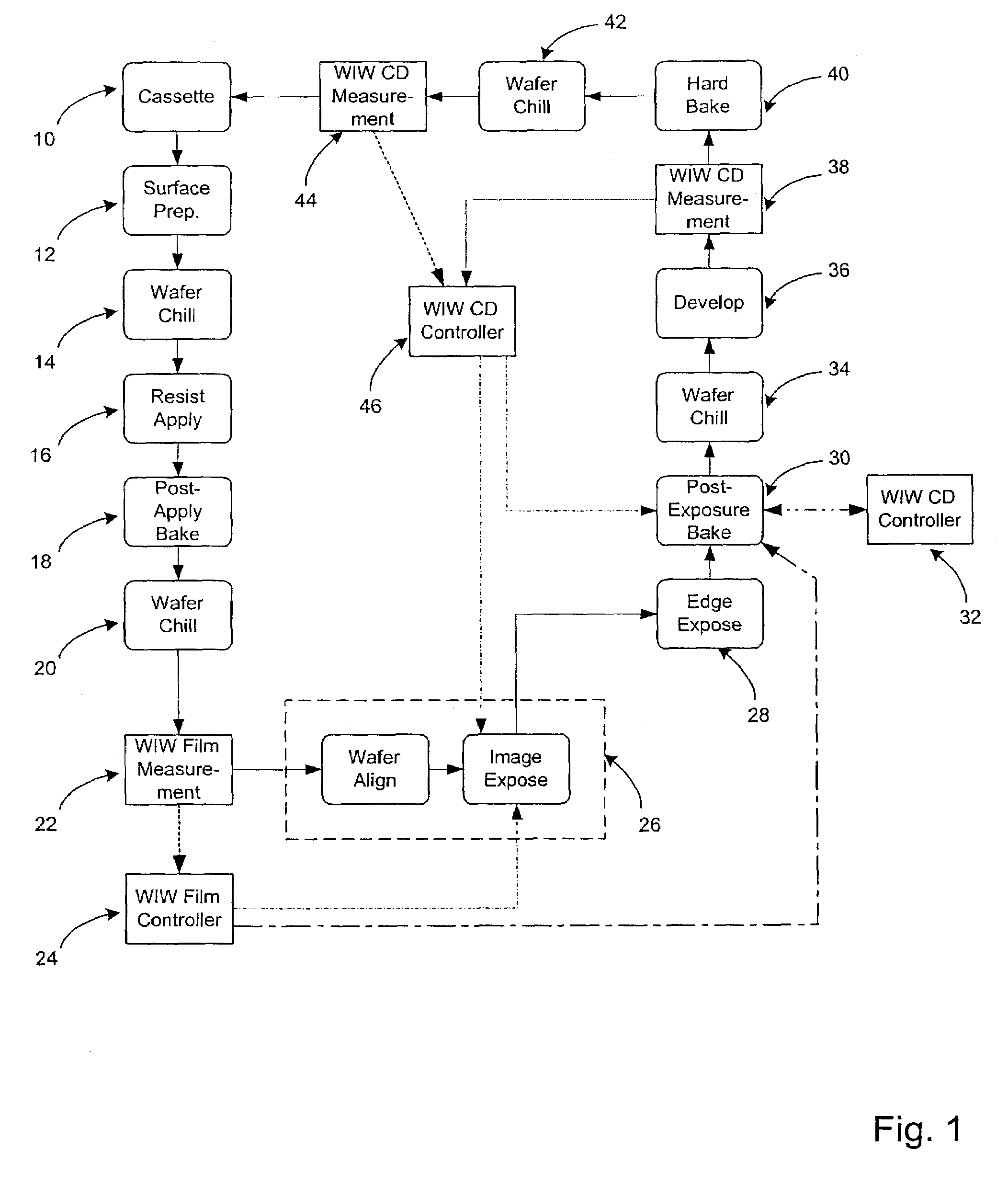

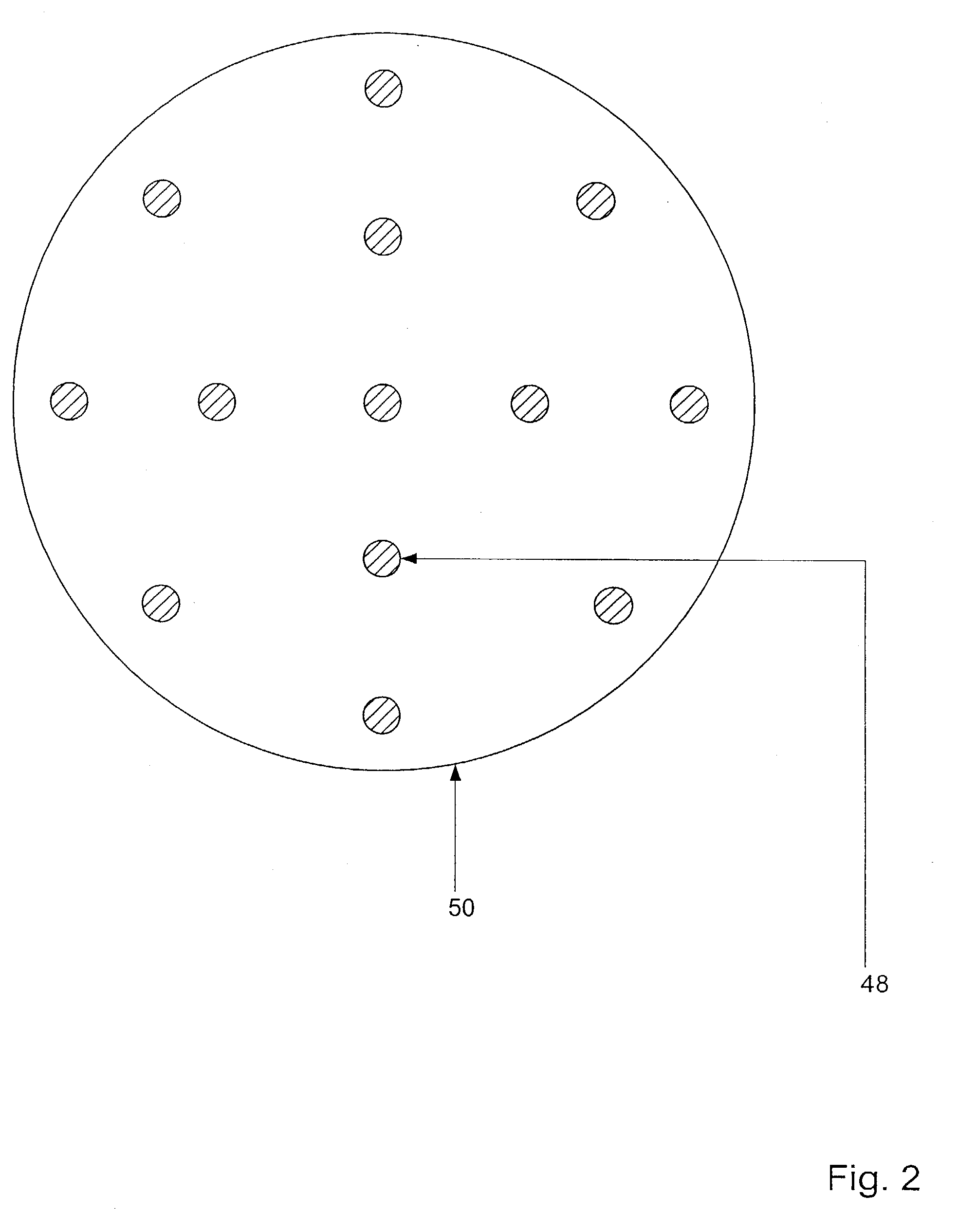

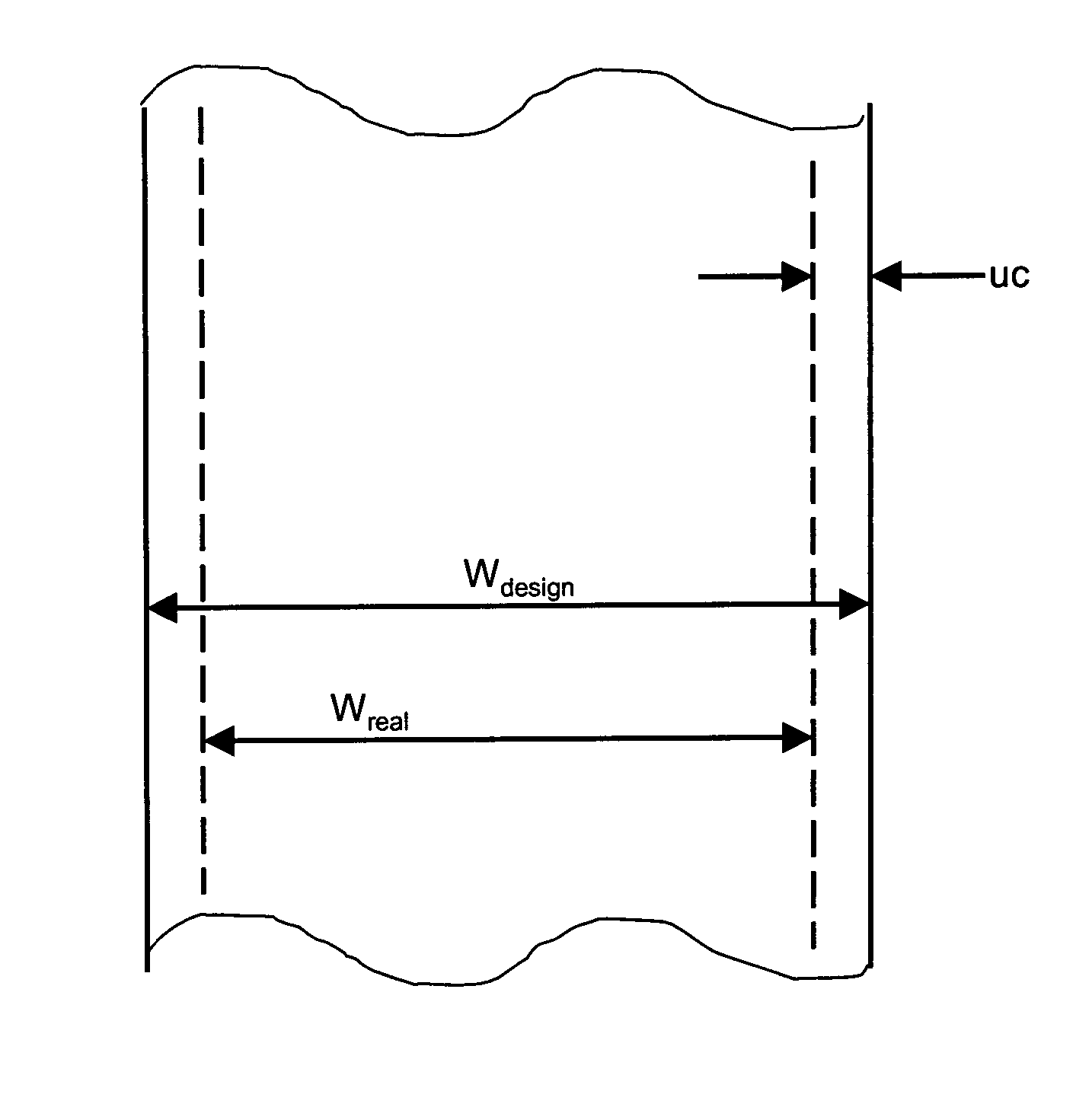

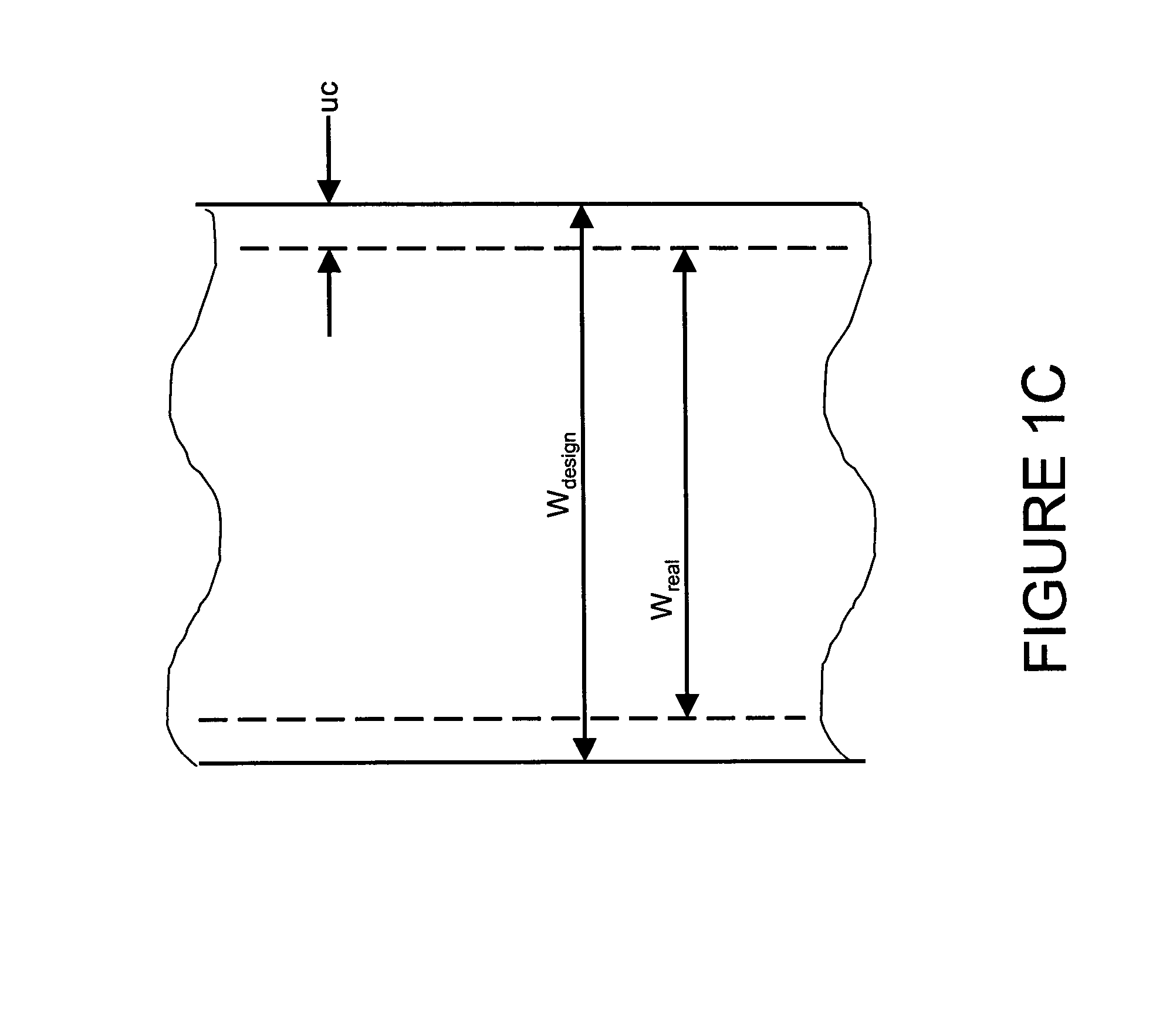

Methods and systems for lithography process control

InactiveUS6987572B2High performance bin distributionReduce yieldSemiconductor/solid-state device testing/measurementSolid-state devicesLithography processProcess module

Methods and systems for evaluating and controlling a lithography process are provided. For example, a method for reducing within wafer variation of a critical metric of a lithography process may include measuring at least one property of a resist disposed upon a wafer during the lithography process. A critical metric of a lithography process may include, but may not be limited to, a critical dimension of a feature formed during the lithography process. The method may also include altering at least one parameter of a process module configured to perform a step of the lithography process to reduce within wafer variation of the critical metric. The parameter of the process module may be altered in response to at least the one measured property of the resist.

Owner:KLA TENCOR TECH CORP

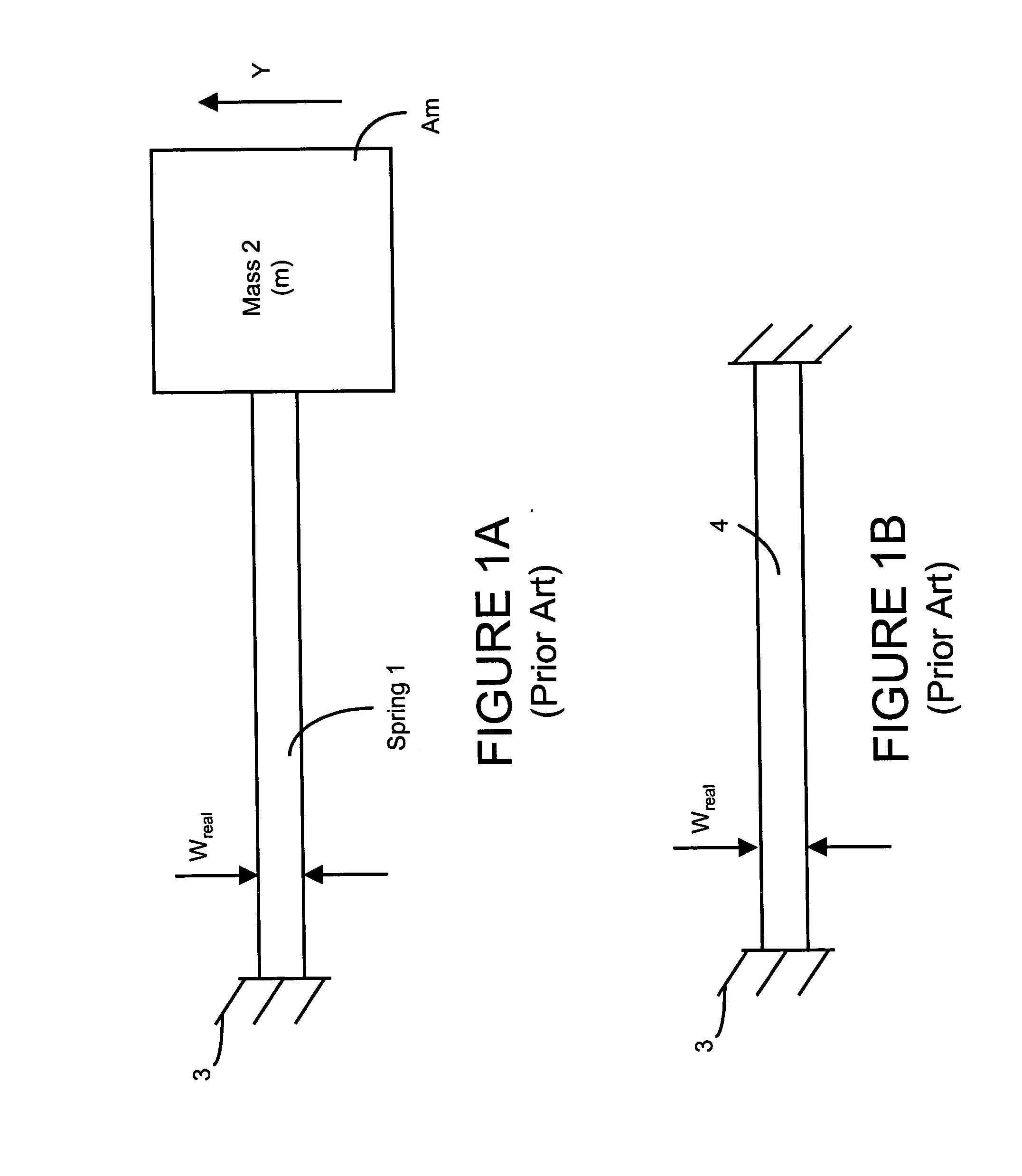

Frequency compensated oscillator design for process tolerances

InactiveUS20050073078A1Improve immunityImprove production yieldPortable framesImpedence networksEngineeringMass element

A continuous or distributed resonator geometry is defined such that the fabrication process used to form a spring mechanism also forms an effective mass of the resonator structure. Proportional design of the spring mechanism and / or mass element geometries in relation to the fabrication process allows for compensation of process-tolerance-induced fabrication variances. As a result, a resonator having increased frequency accuracy is achieved.

Owner:ROBERT BOSCH GMBH

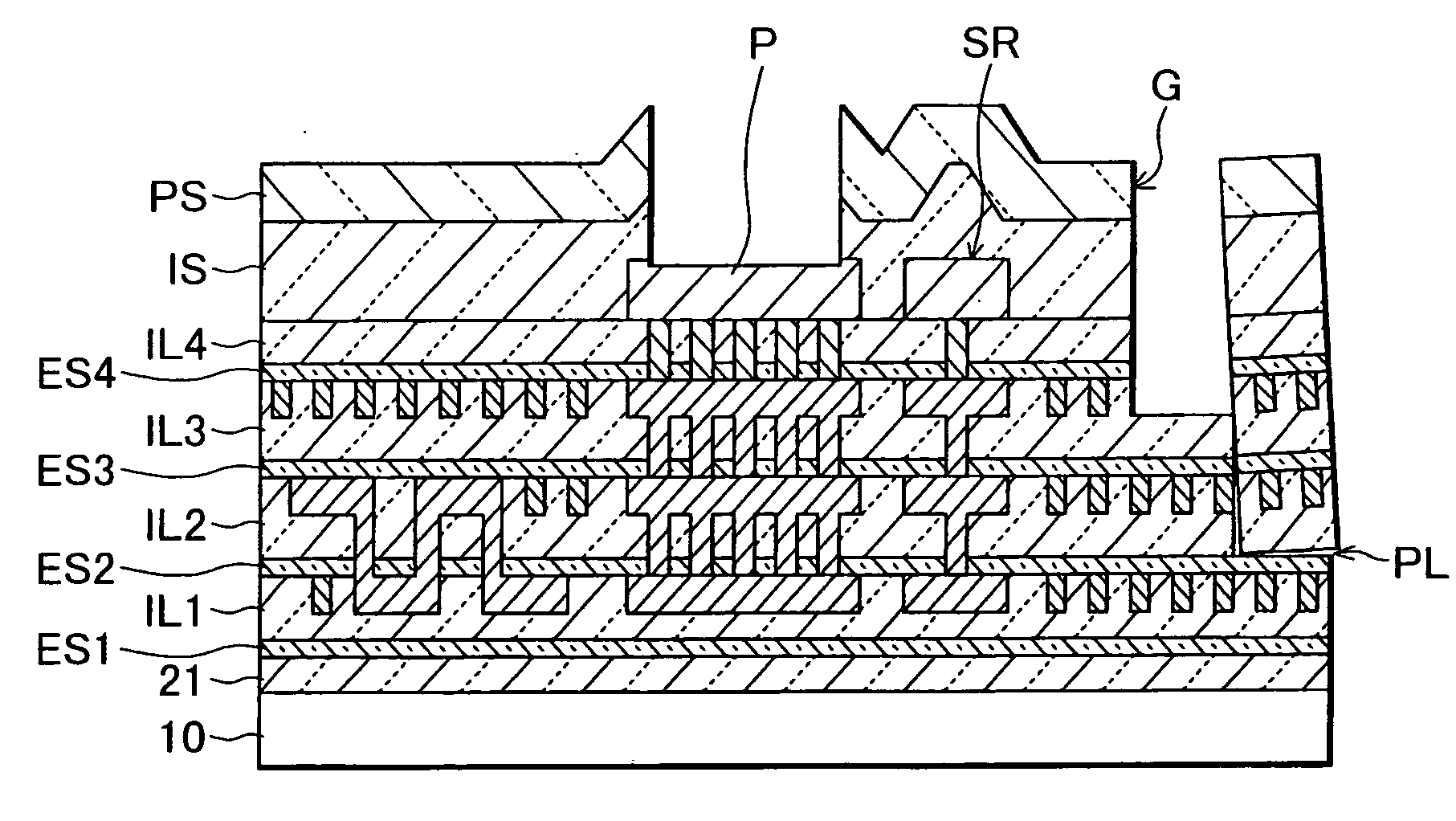

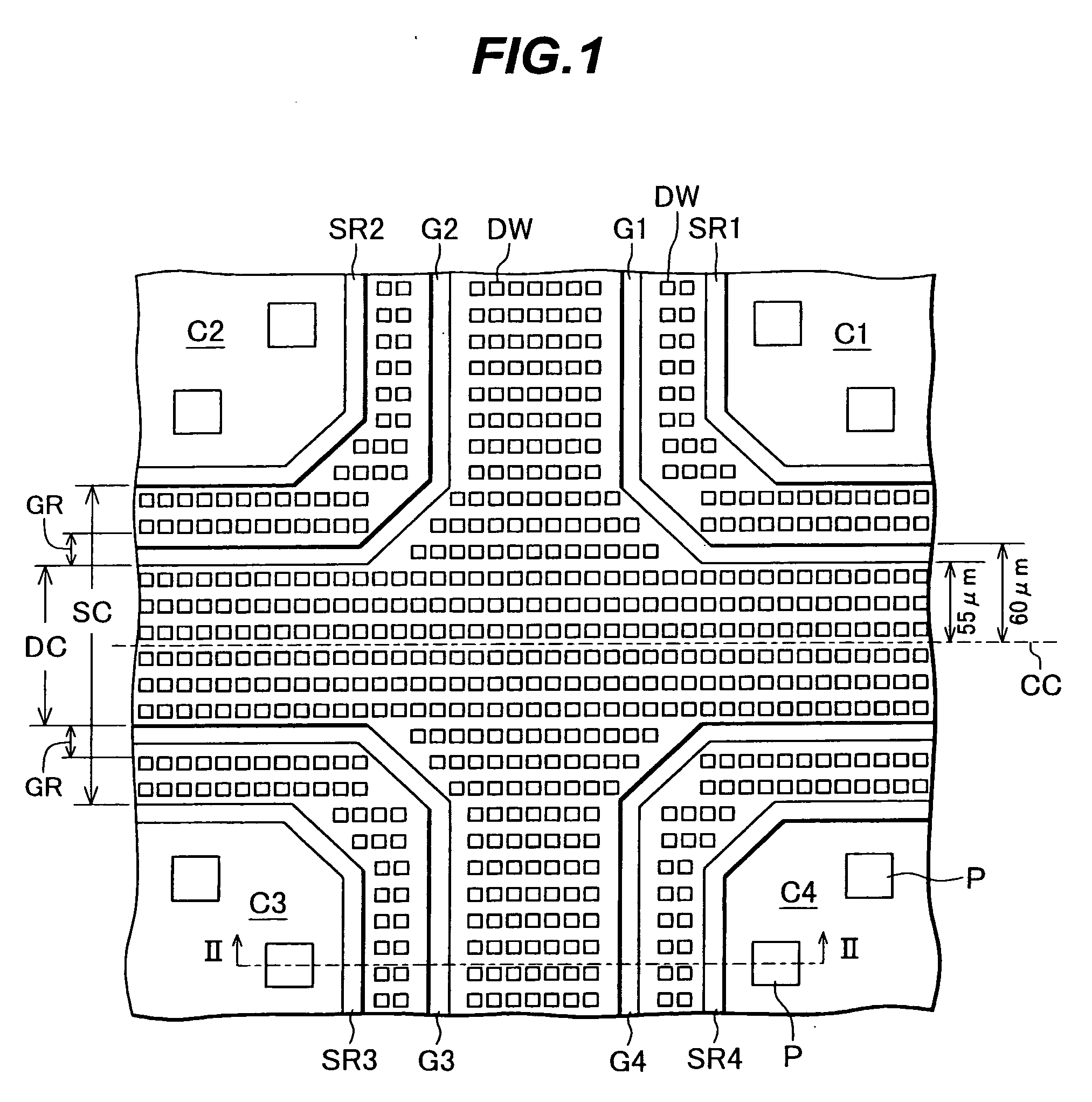

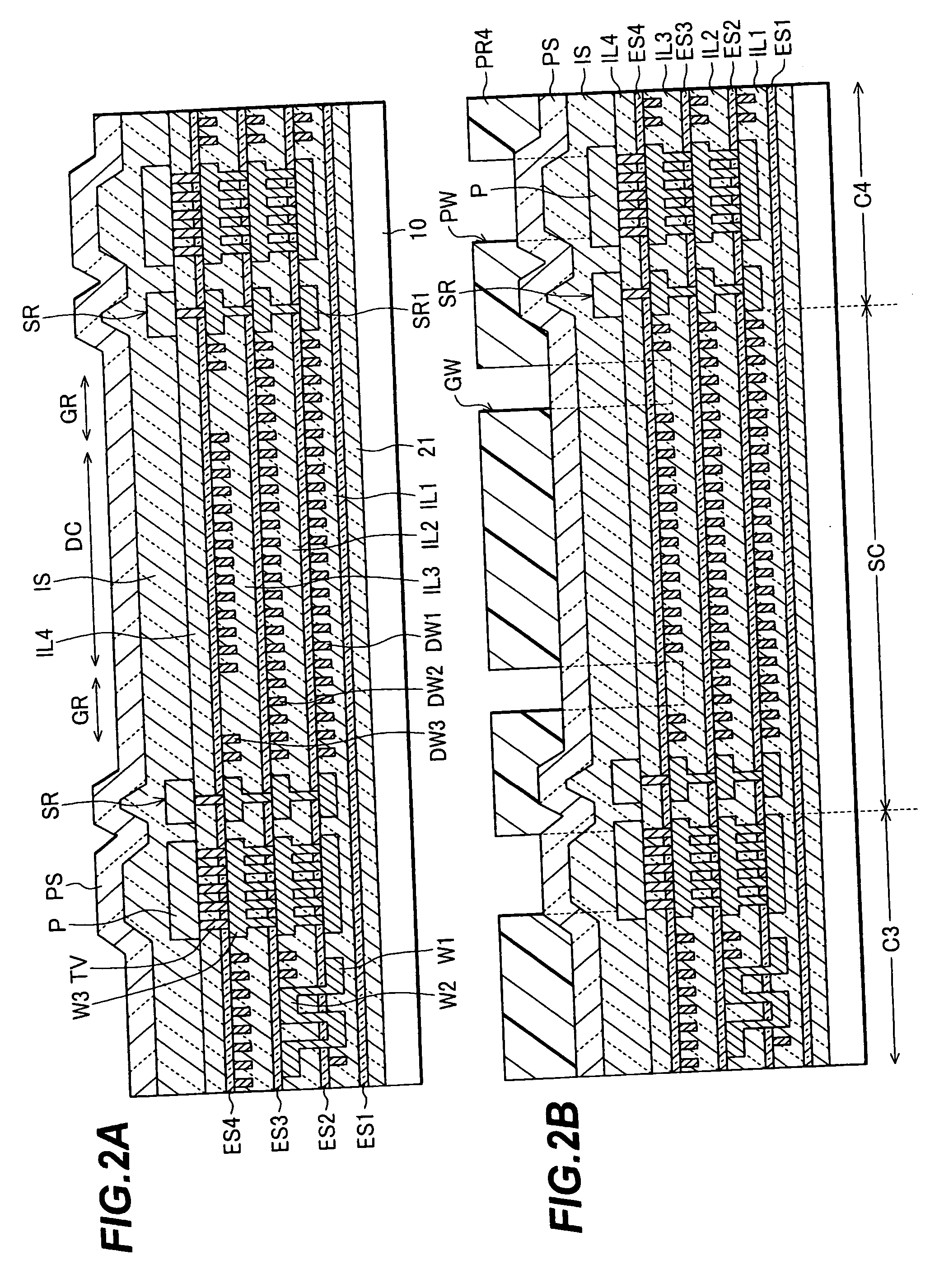

Method for fabricating semiconductor device capable of scribing chips with high yield

ActiveUS20050269702A1Improve production yieldSpeed up preparationSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

A method for fabricating a semiconductor device in which a scribe area can be diced with high yield. The method for fabricating a semiconductor device comprises (a) a step for providing a semiconductor wafer having a plurality of chip areas in which semiconductor elements are formed, and a scribe area for separating the plurality of chip areas and including dicing areas with groove forming areas being defined to surround each chip area on the outer side of the dicing area in the scribe area, (b) a step for arranging a multilayer interconnection structure where interlayer insulation films and interconnection layers are formed alternately above the semiconductor wafer along with dummy lines, (c) a step for forming a cover layer covering the multilayer interconnection structure and including a passivation layer, and (d) a step for forming a groove surrounding each of the plurality of chip areas and penetrating at least the passivation layer from above in the groove forming area.

Owner:FUJITSU LTD

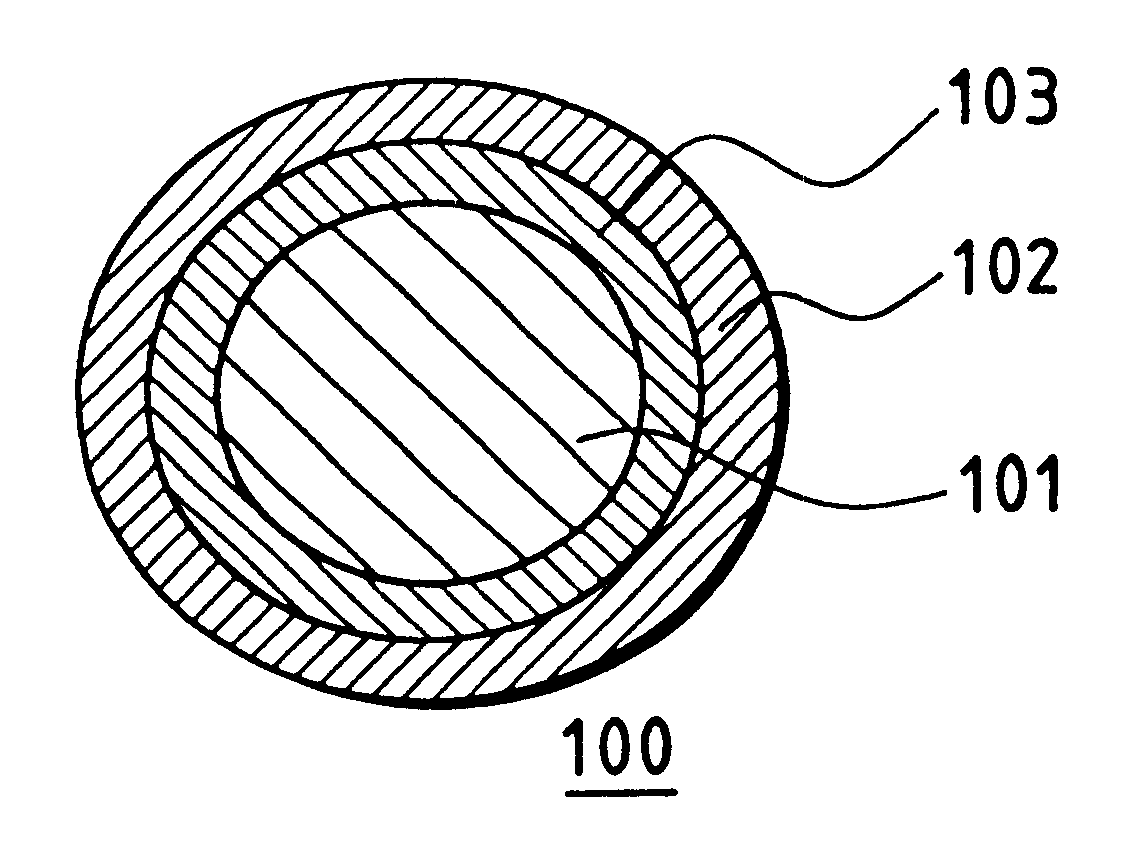

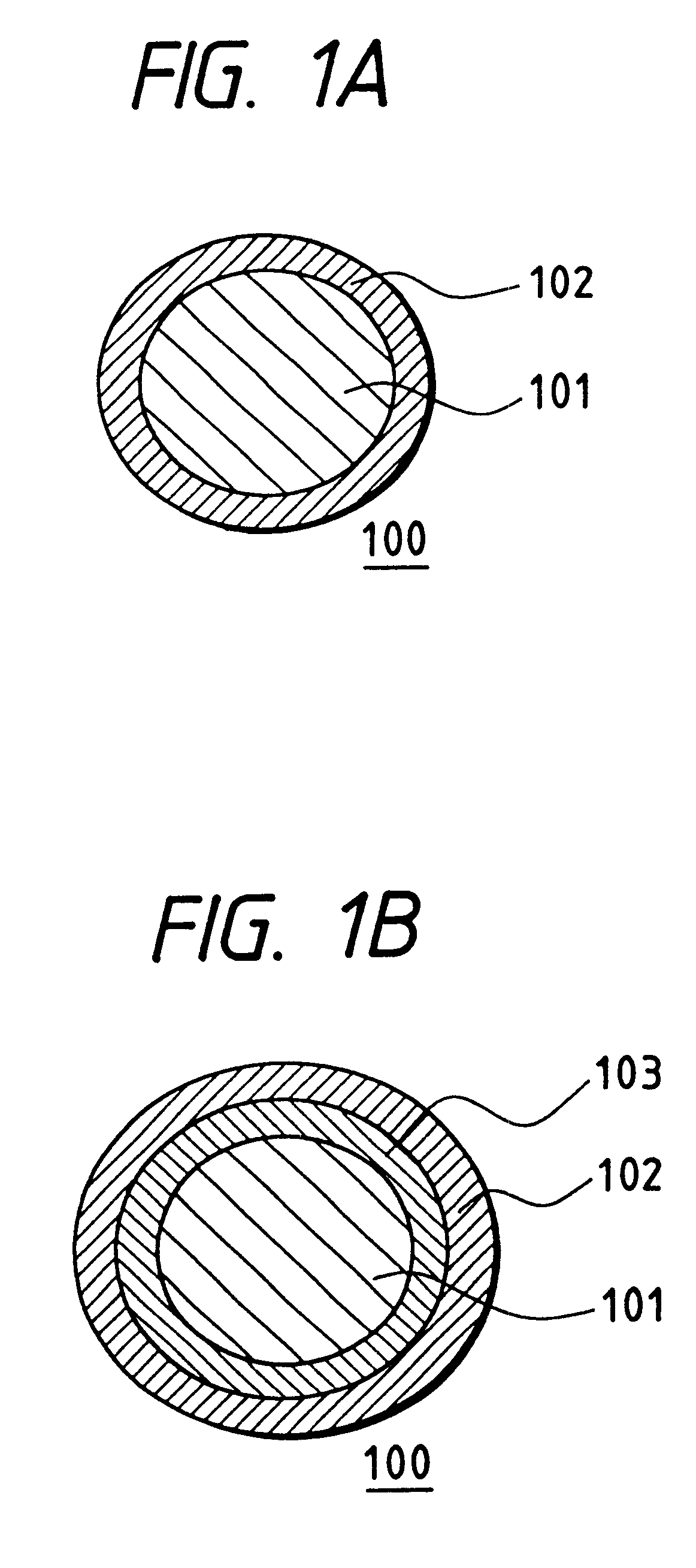

Photovoltaic element and method for producing the same

InactiveUS6472594B1Improve adhesionHigh initial characteristicPhotovoltaic energy generationSemiconductor devicesAdhesiveEngineering

A photovoltaic element comprising an electrode comprising an electrically conductive core member which is coated with a conductive adhesive fixed on the light incident surface of a photoactive semiconductor layer, via the conductive adhesive, is disclosed.The conductive adhesive is composed of at least two layers. The softening point of the conductive adhesive layer nearer to the core member is higher than the highest temperature encountered in the manufacture of the photovoltaic element.

Owner:CANON KK

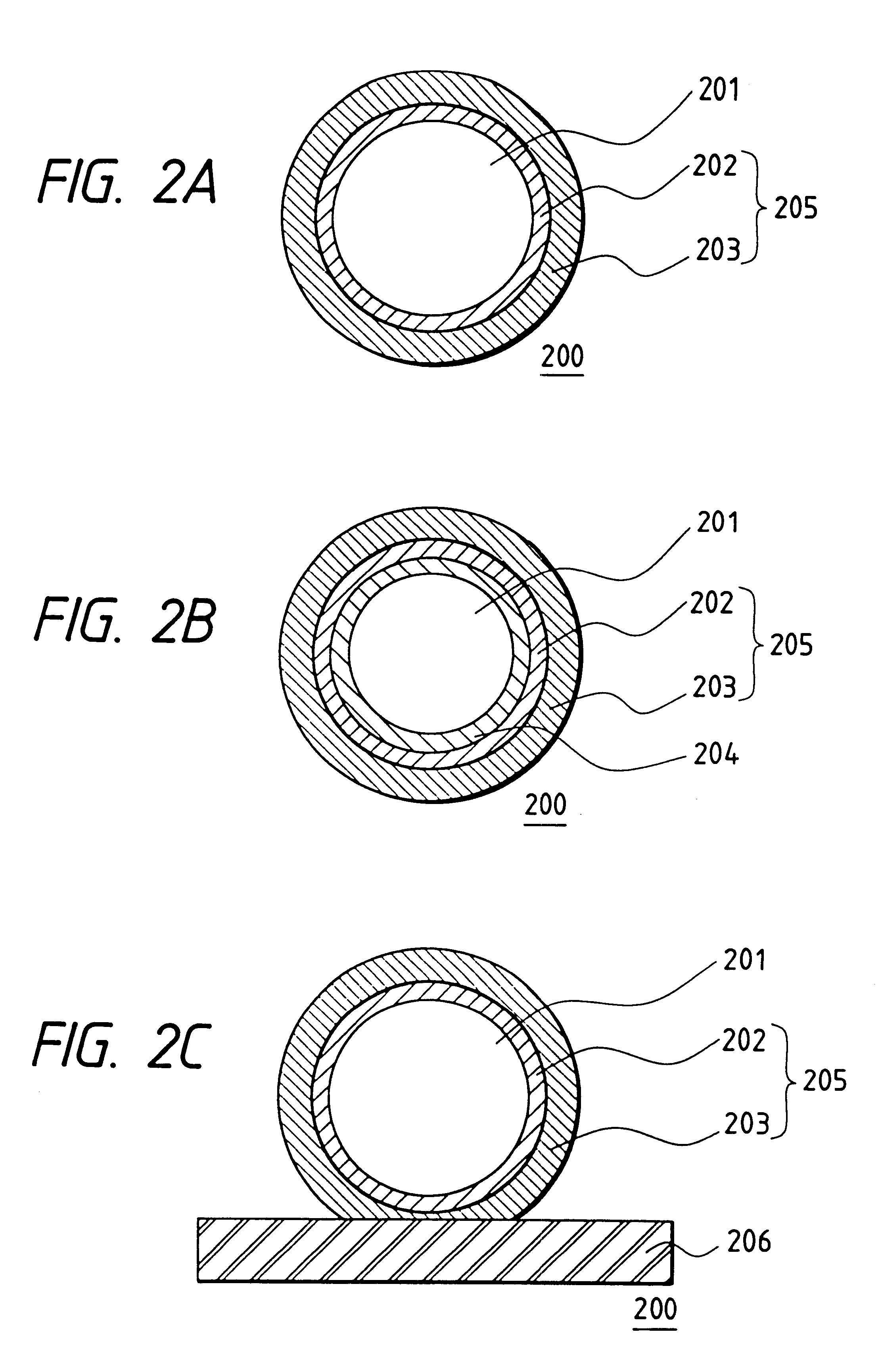

Touch screen

InactiveUS20120162099A1Improve production yieldReduce processing timeInput/output processes for data processingTouchscreenComputer science

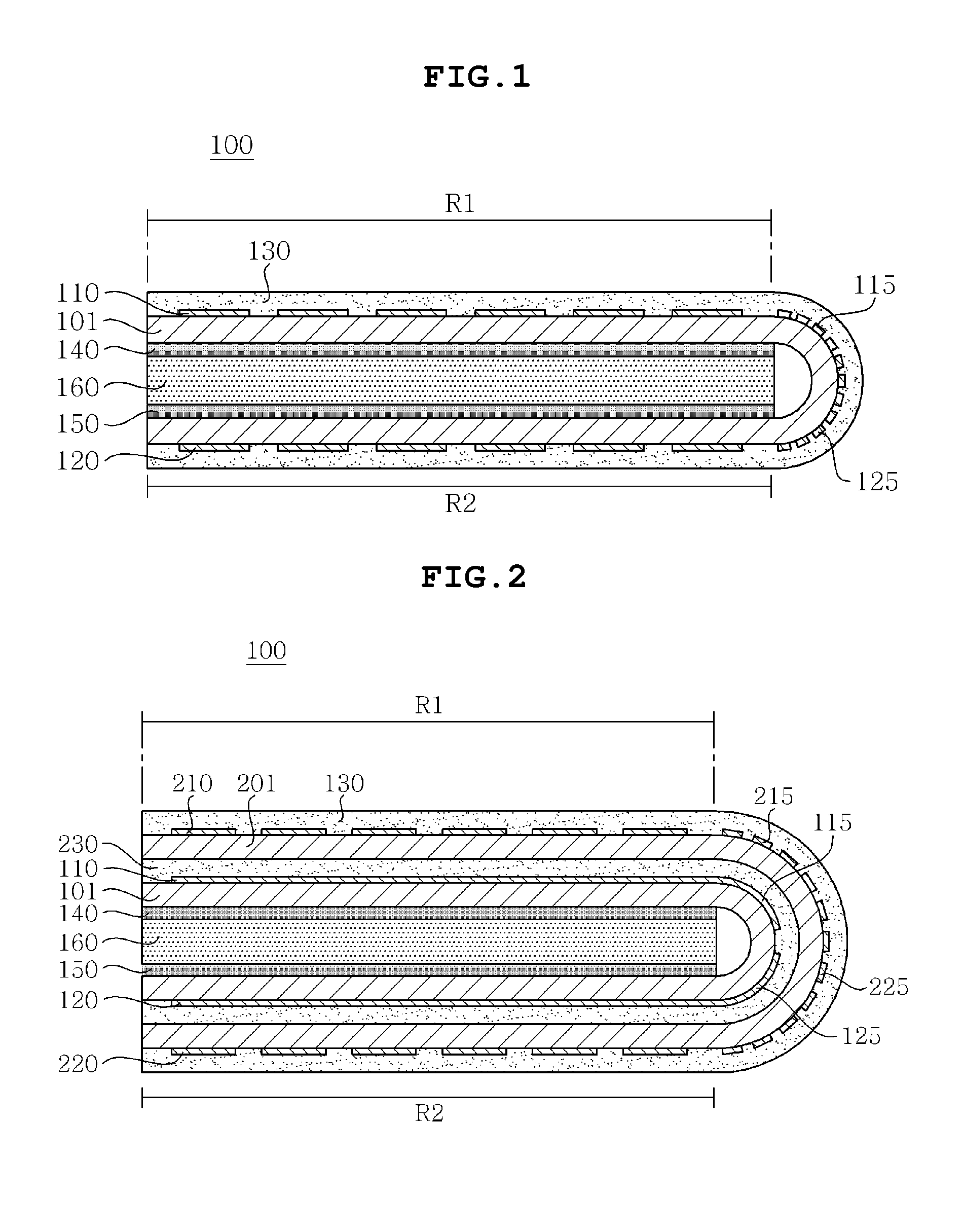

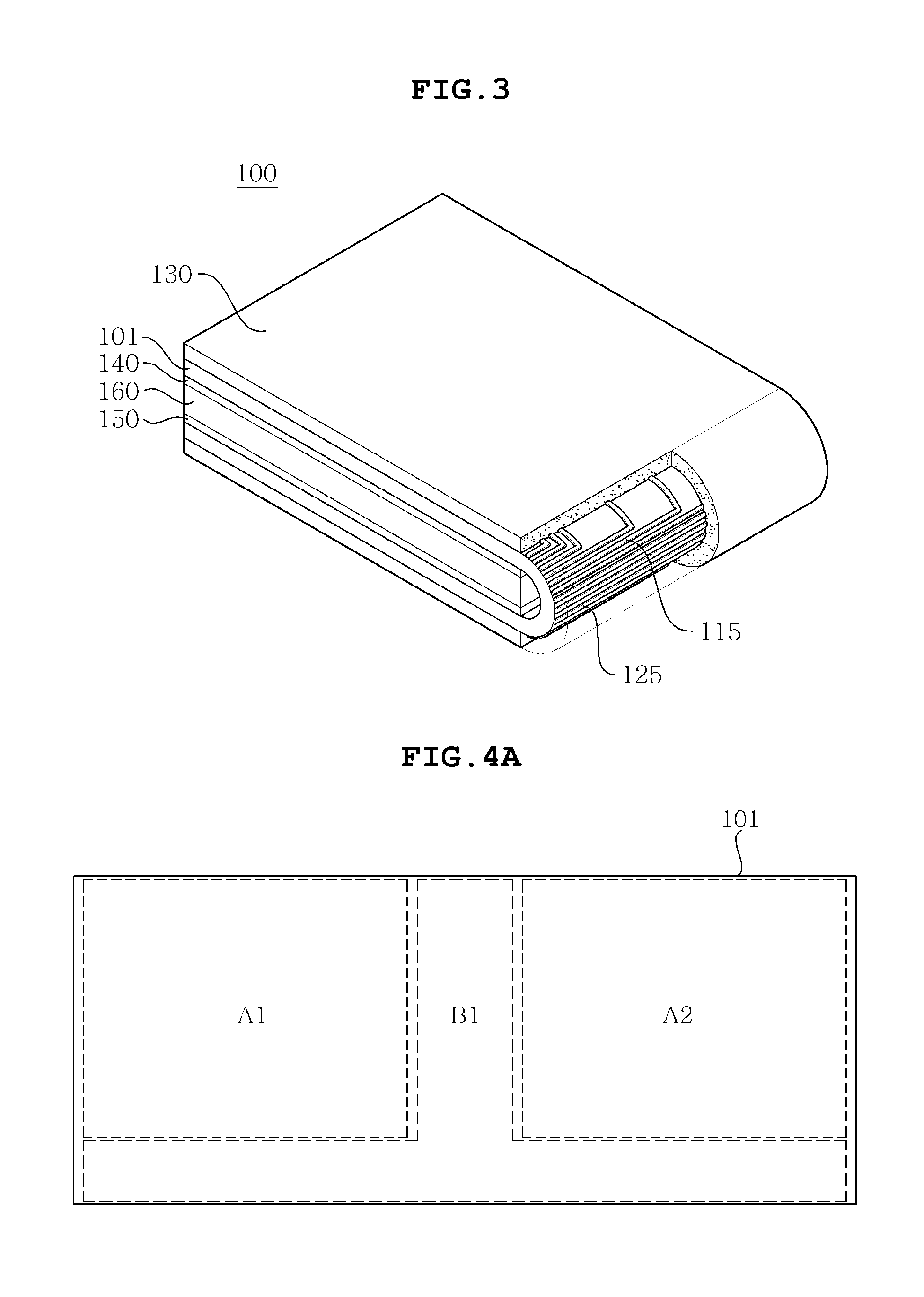

Disclosed herein is a touch screen 100 designed to control an image displayed on image display units 140 and 150 on both-sides of the touch screen. The touch screen 100 according to the present invention may overcome an obscured screen problem caused by an input device, increase production yield while reducing a process time of the touch screen 100 by simultaneously forming transparent electrodes and electrode wires on a transparent substrate and, after forming an image display unit and an active region on the transparent substrate, folding the transparent substrate, and minimize an area of a bezel region.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

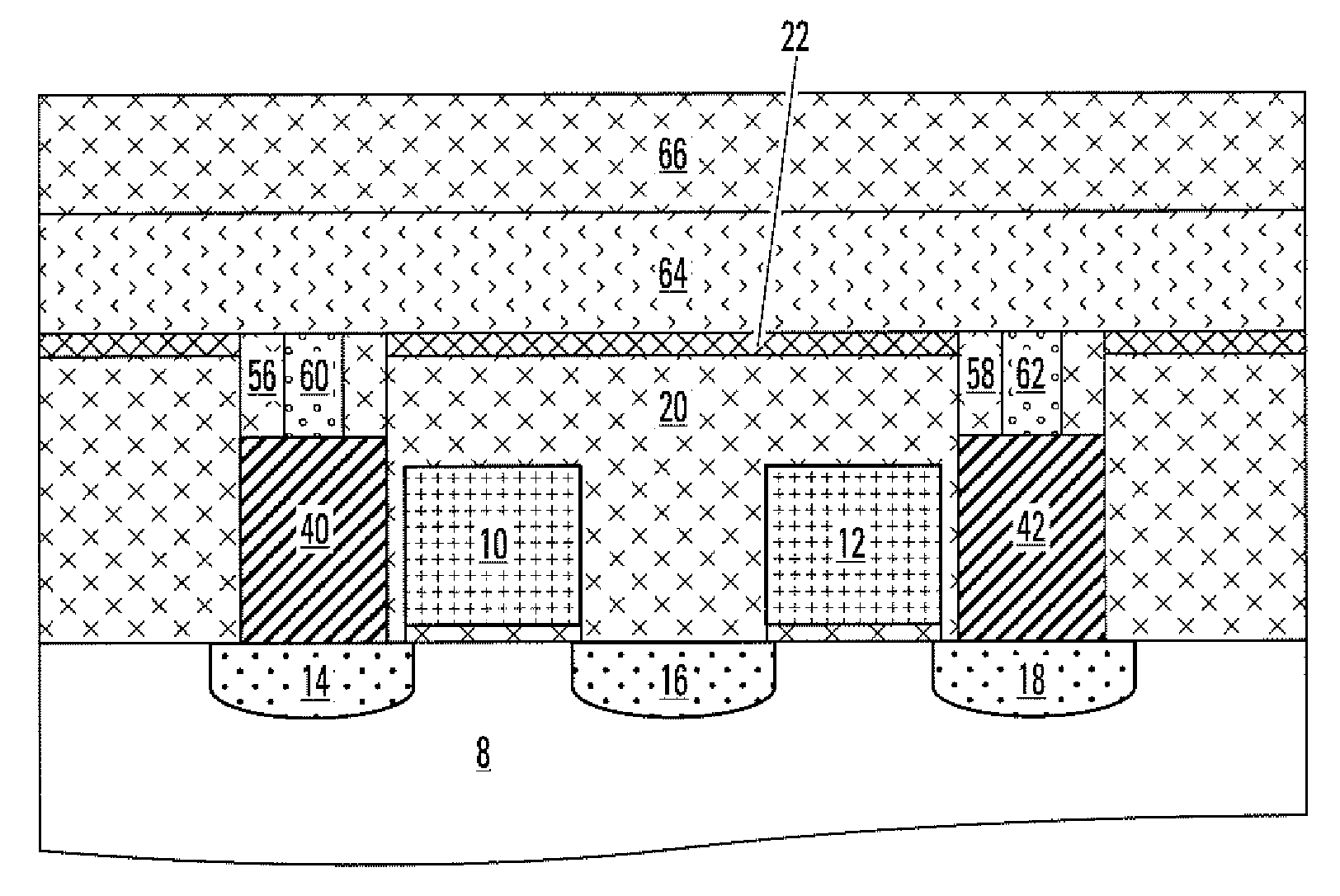

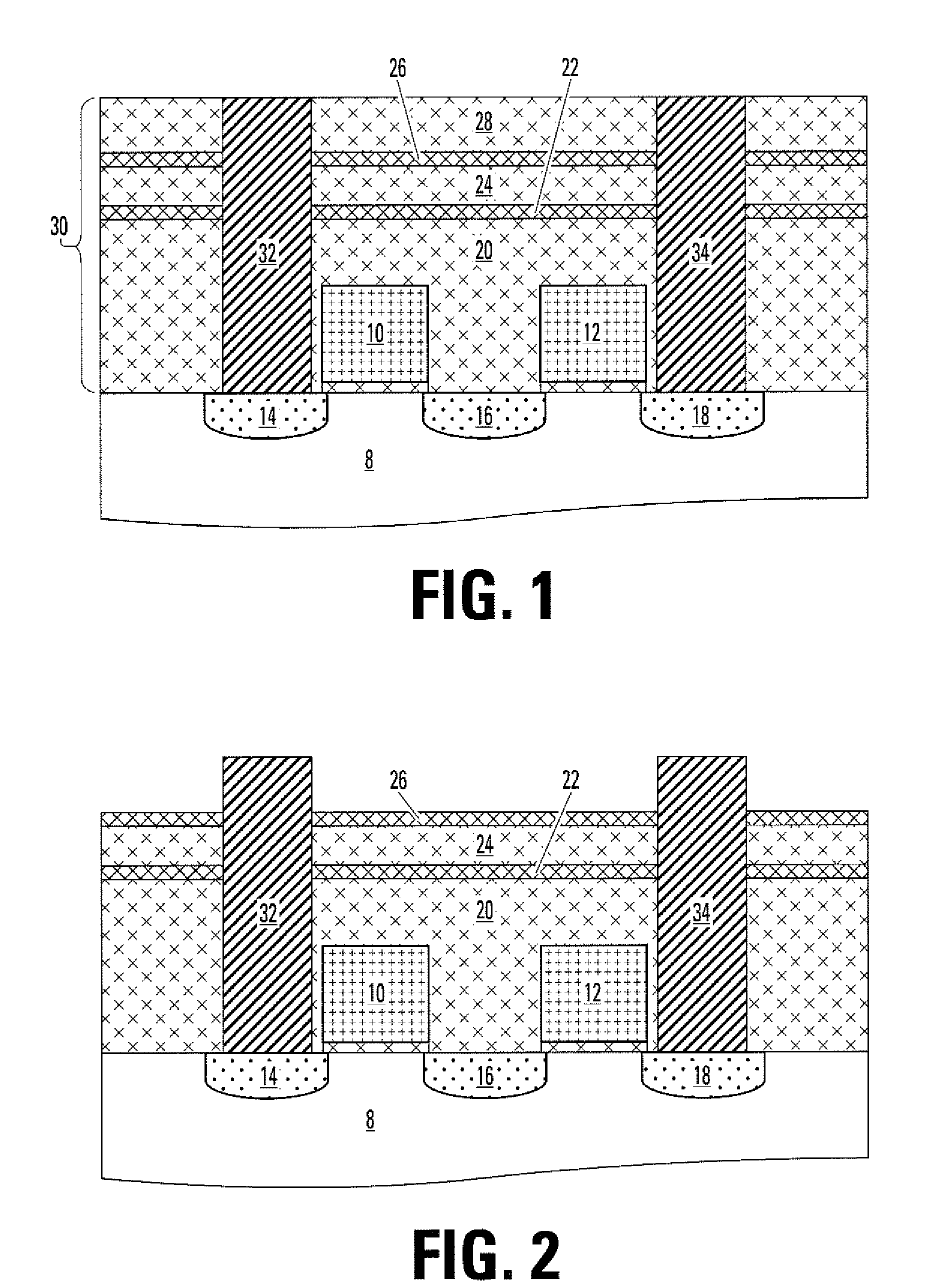

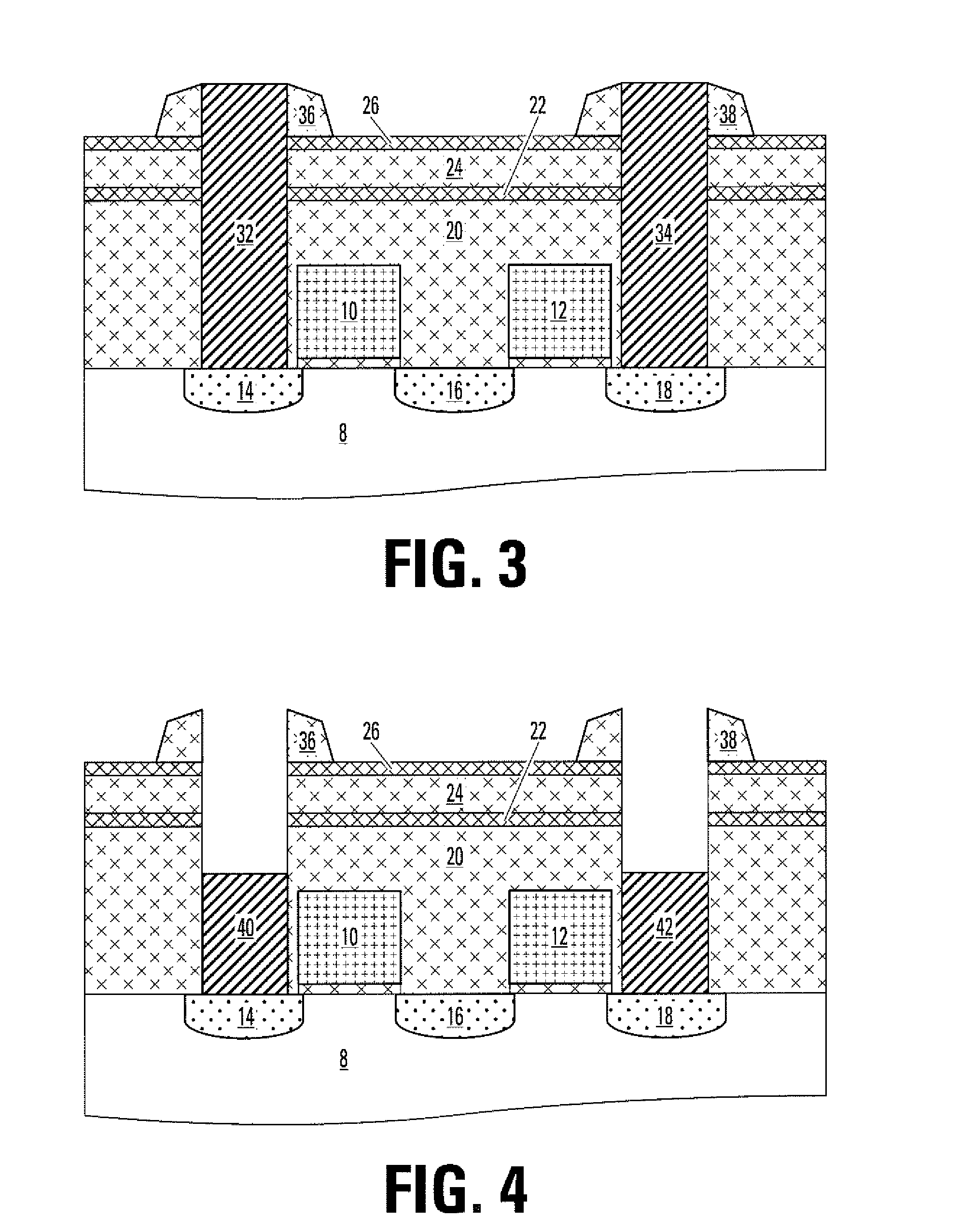

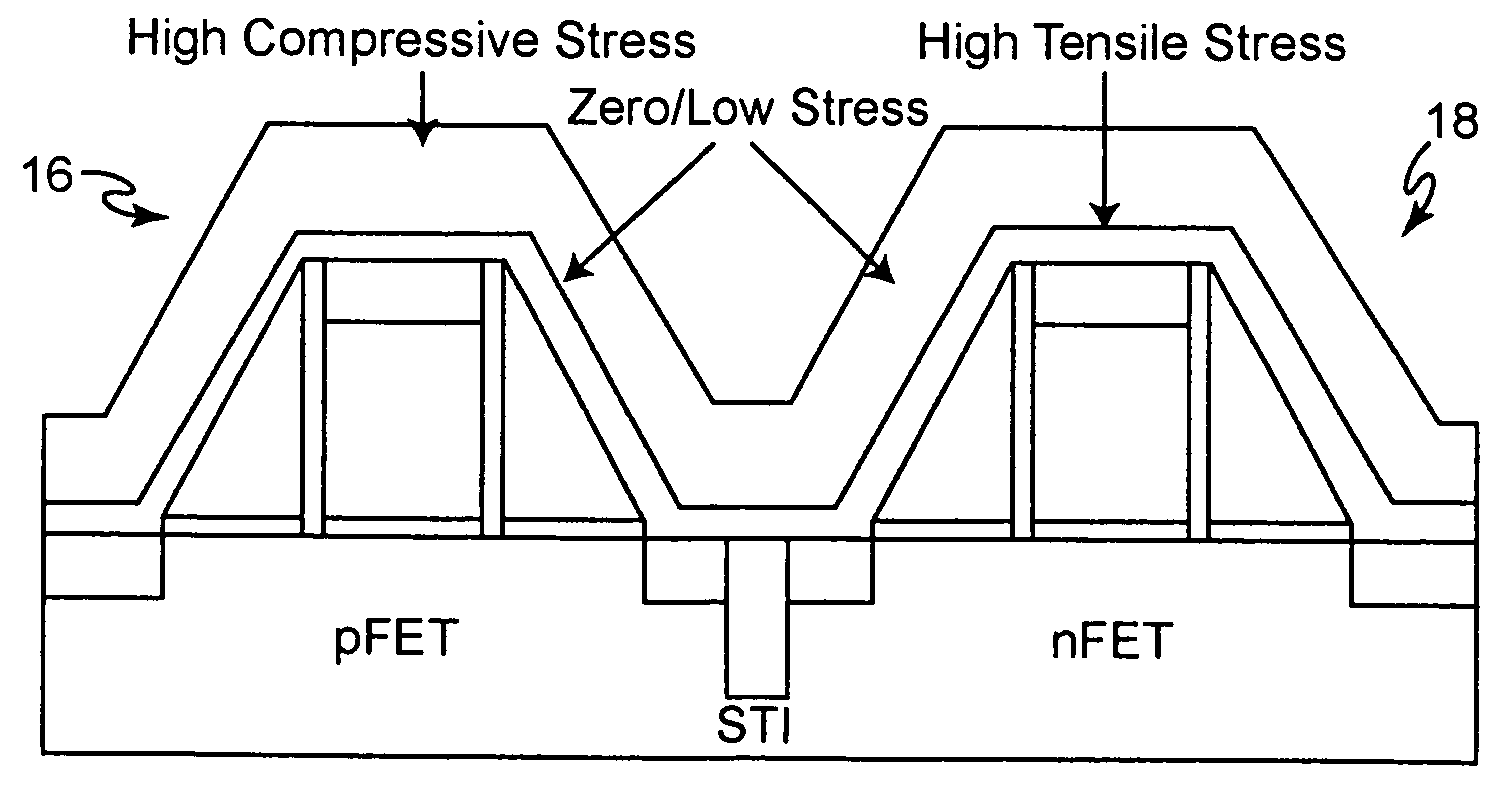

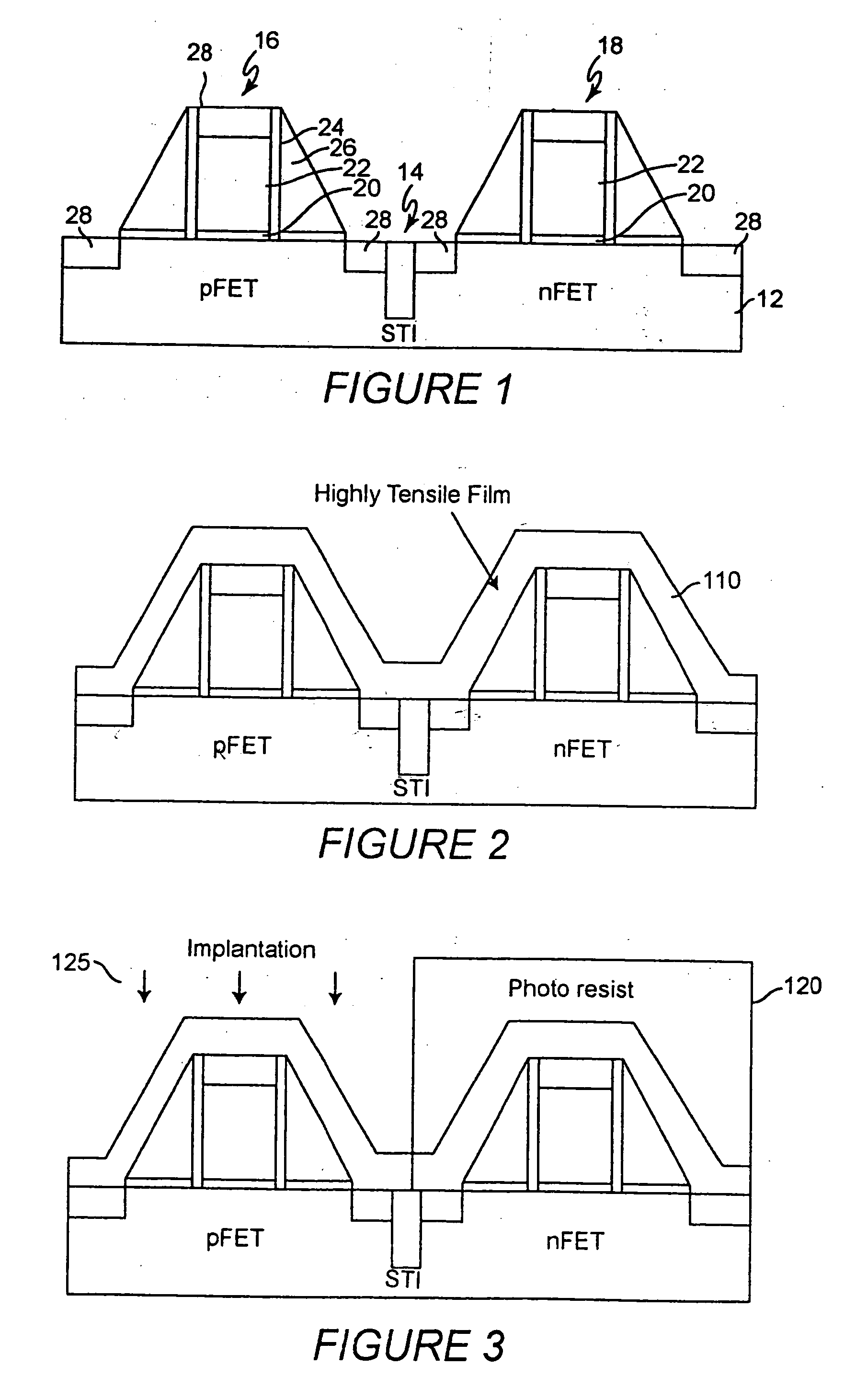

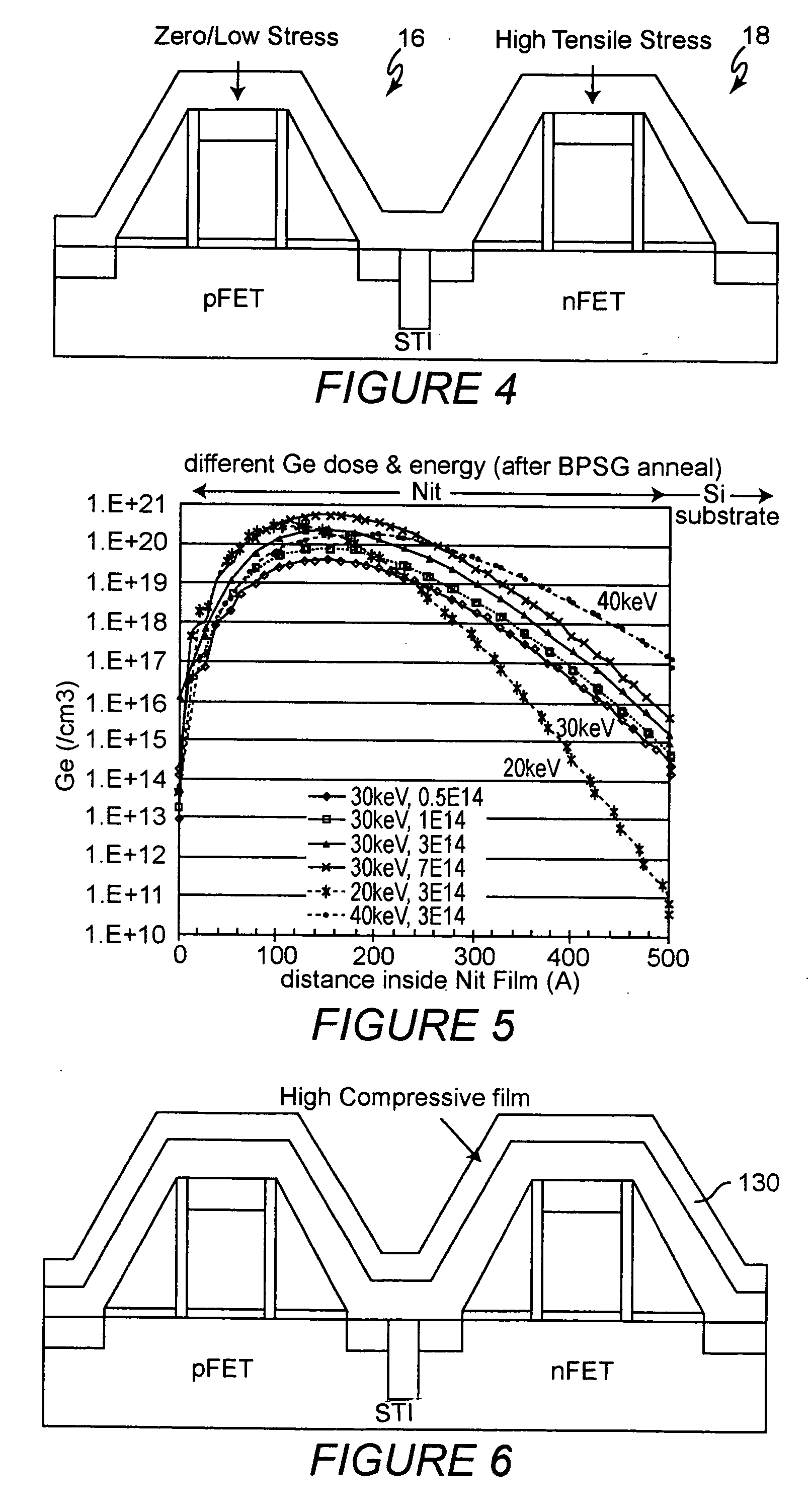

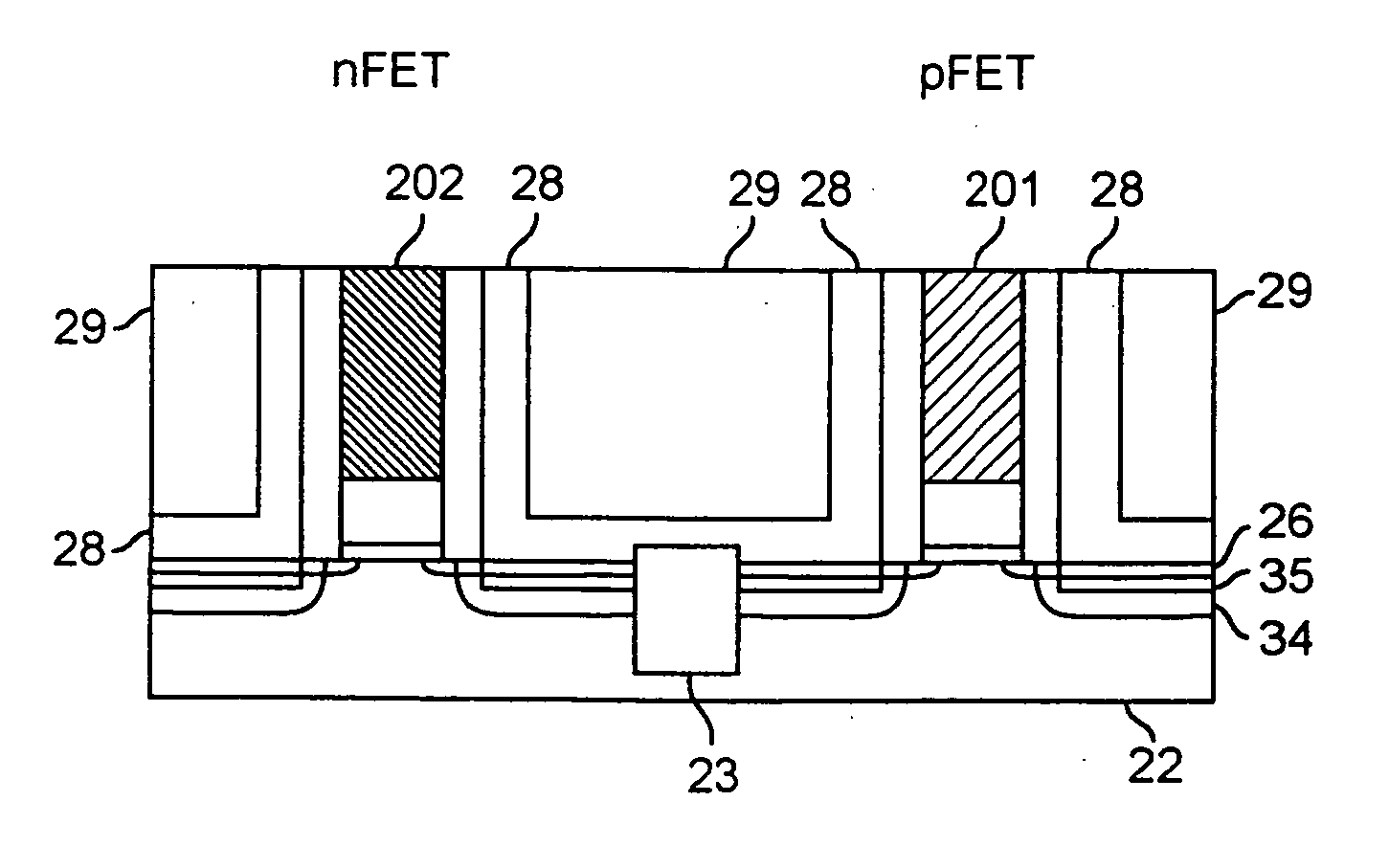

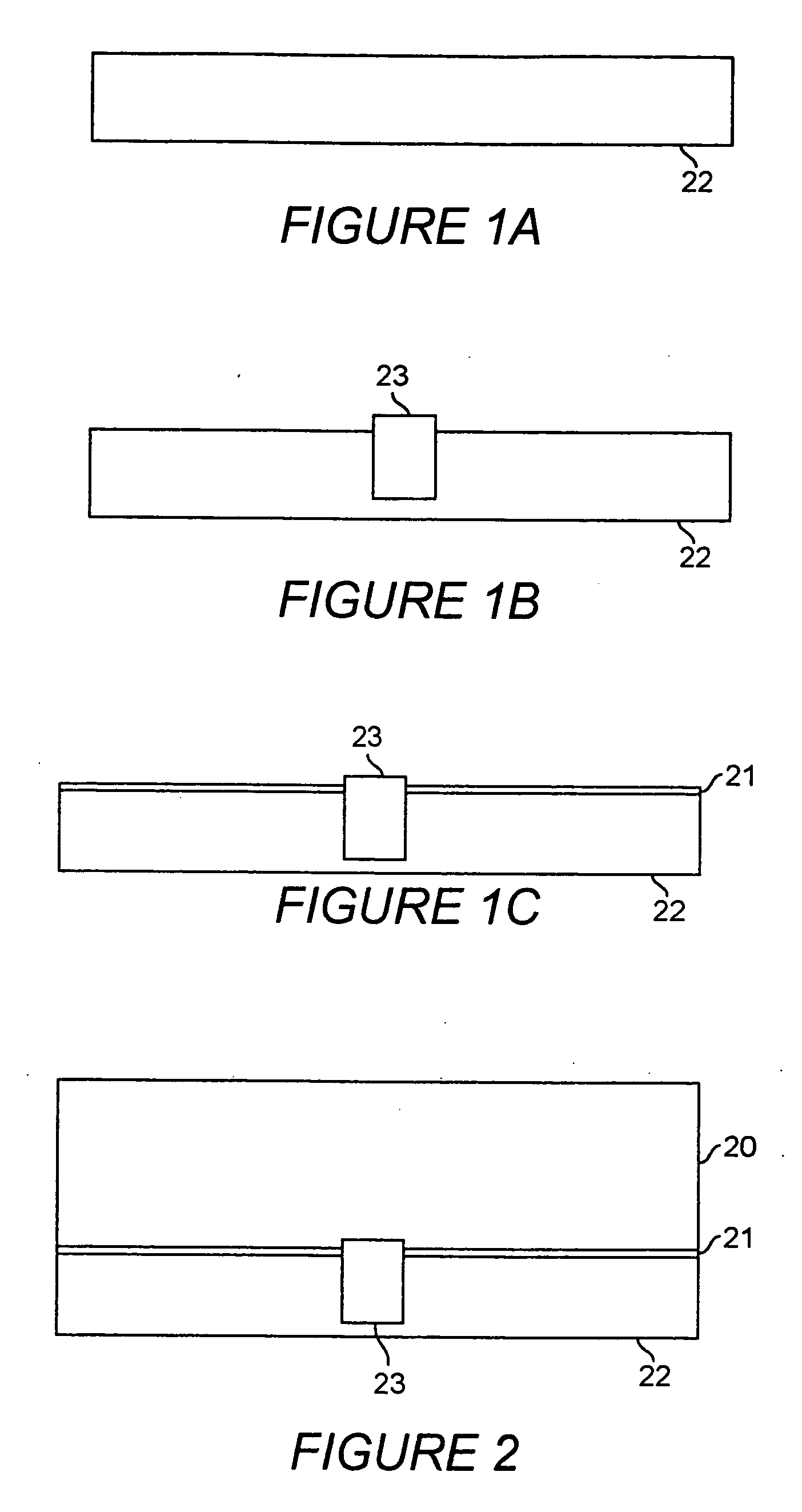

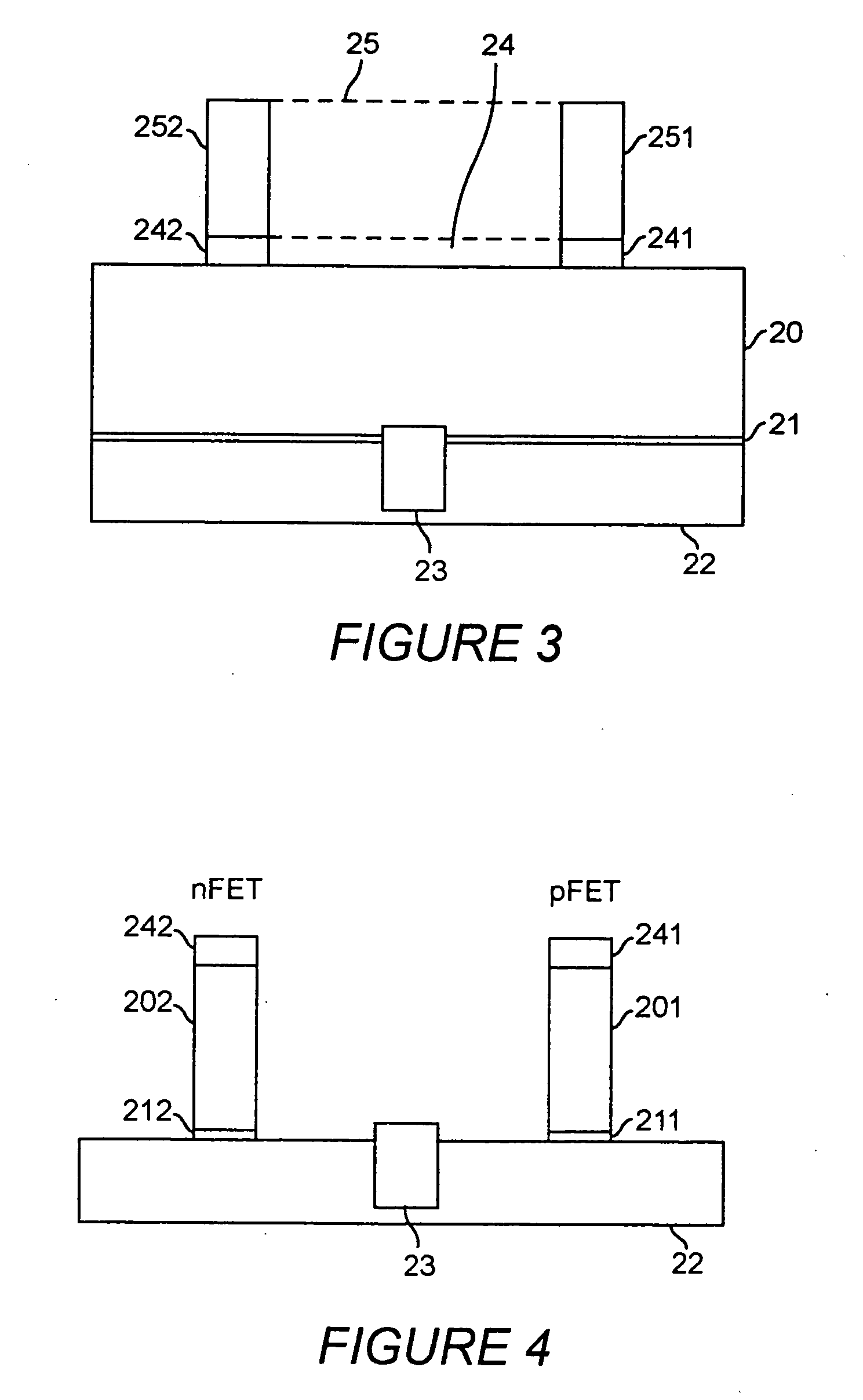

Increasing carrier mobility in NFET and PFET transistors on a common wafer

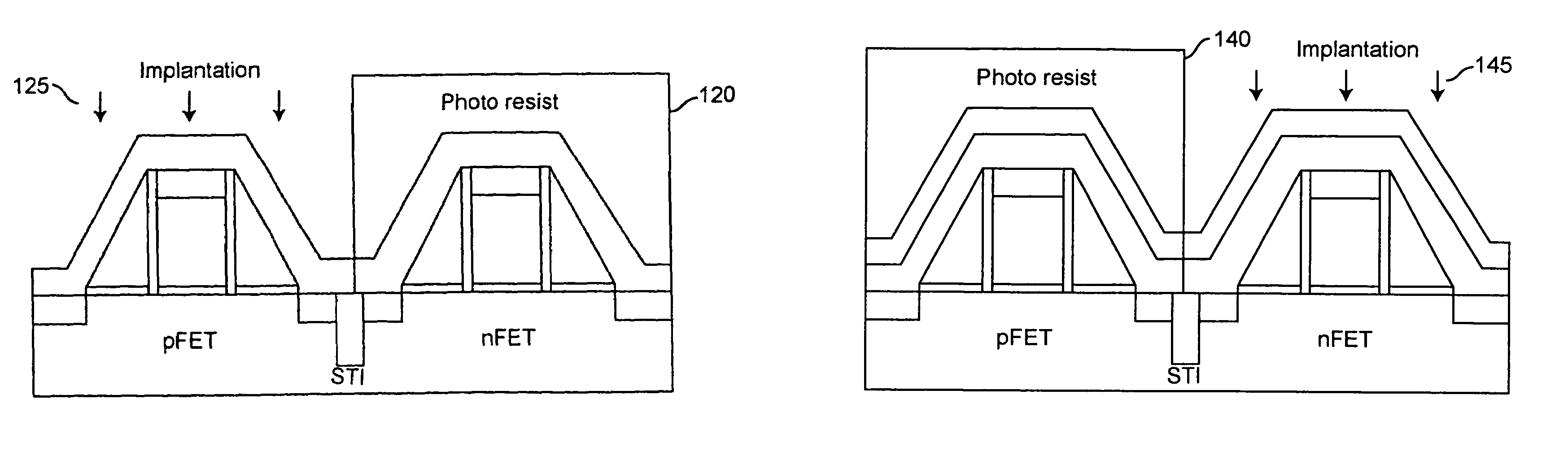

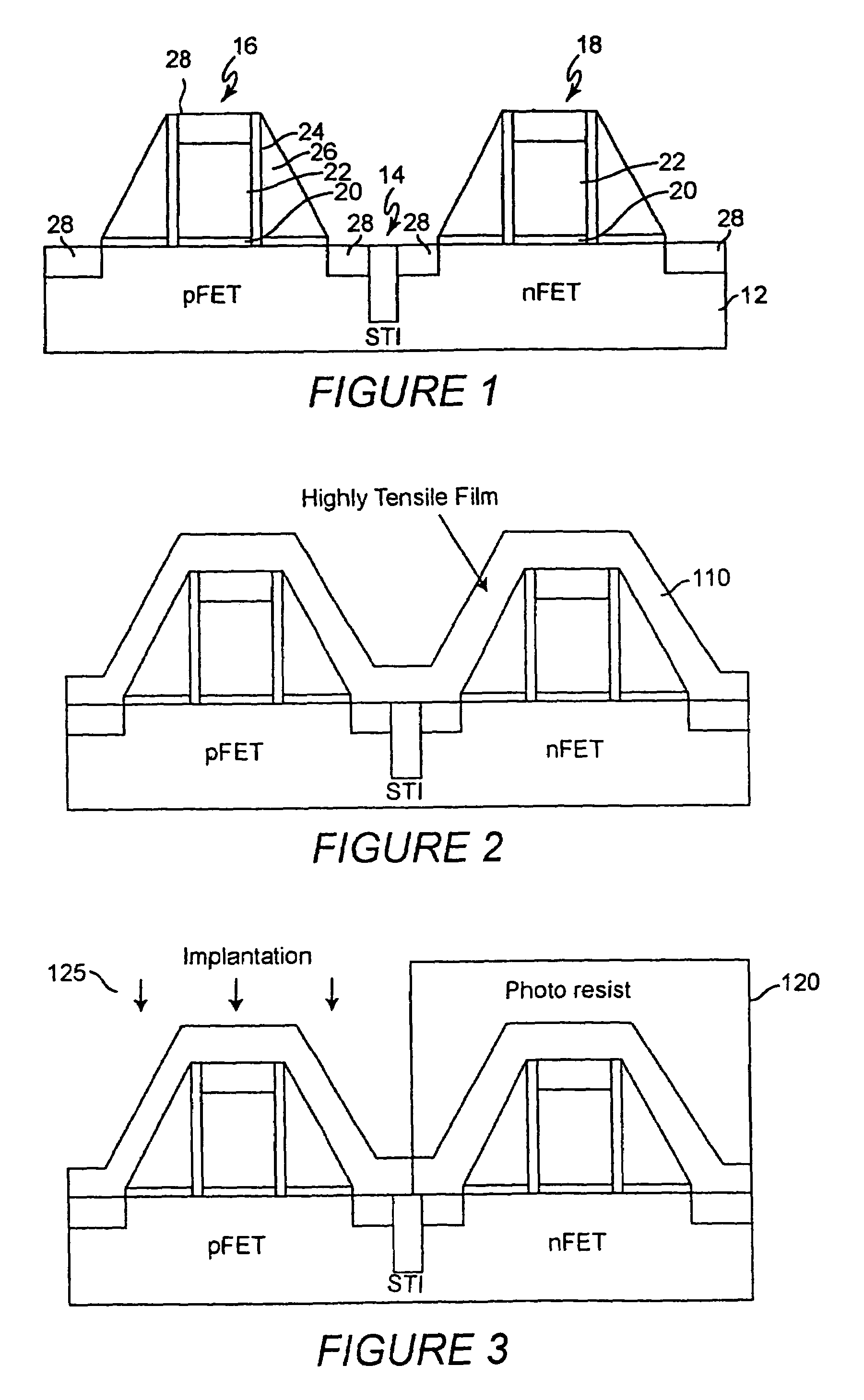

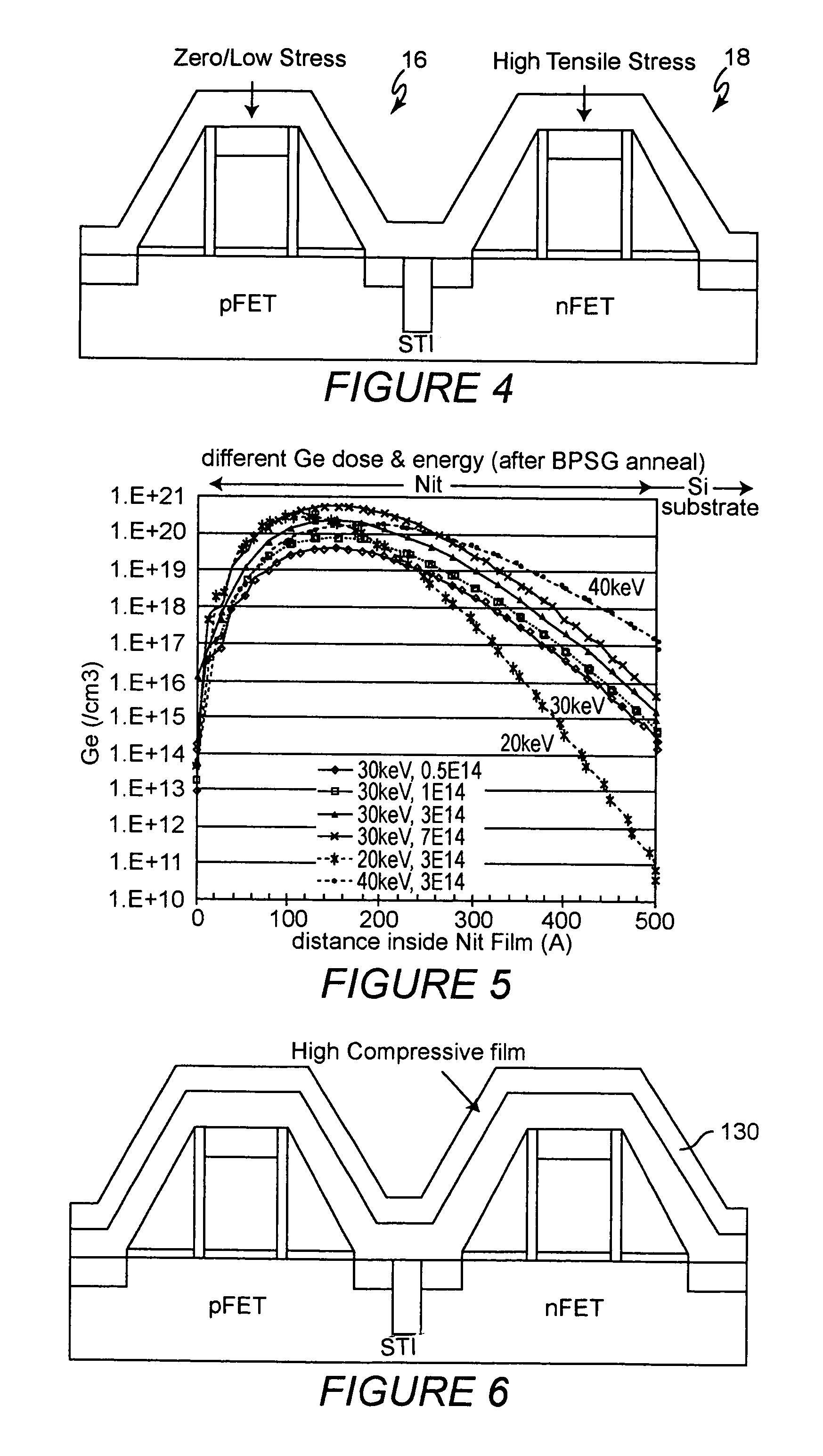

ActiveUS20050093078A1Easily and repeatably formedImprove production yieldTransistorSemiconductor/solid-state device manufacturingIndiumCharge carrier mobility

Enhanced carrier mobility in transistors of differing (e.g. complementary) conductivity types is achieved on a common chip by provision of two or more respective stressed layers, such as etch stop layers, overlying the transistors with stress being wholly or partially relieved in portions of the respective layers, preferably by implantations with heavy ions such as germanium, arsenic, xenon, indium, antimony, silicon, nitrogen oxygen or carbon in accordance with a block-out mask. The distribution and small size of individual areas of such stressed structures also prevents warping or curling of even very thin substrates.

Owner:IBM CORP

Structure and method to improve channel mobility by gate electrode stress modification

InactiveUS20050245017A1Easily and repeatably formedImprove production yieldTransistorSolid-state devicesCMOSCharge carrier mobility

Owner:GLOBALFOUNDRIES INC

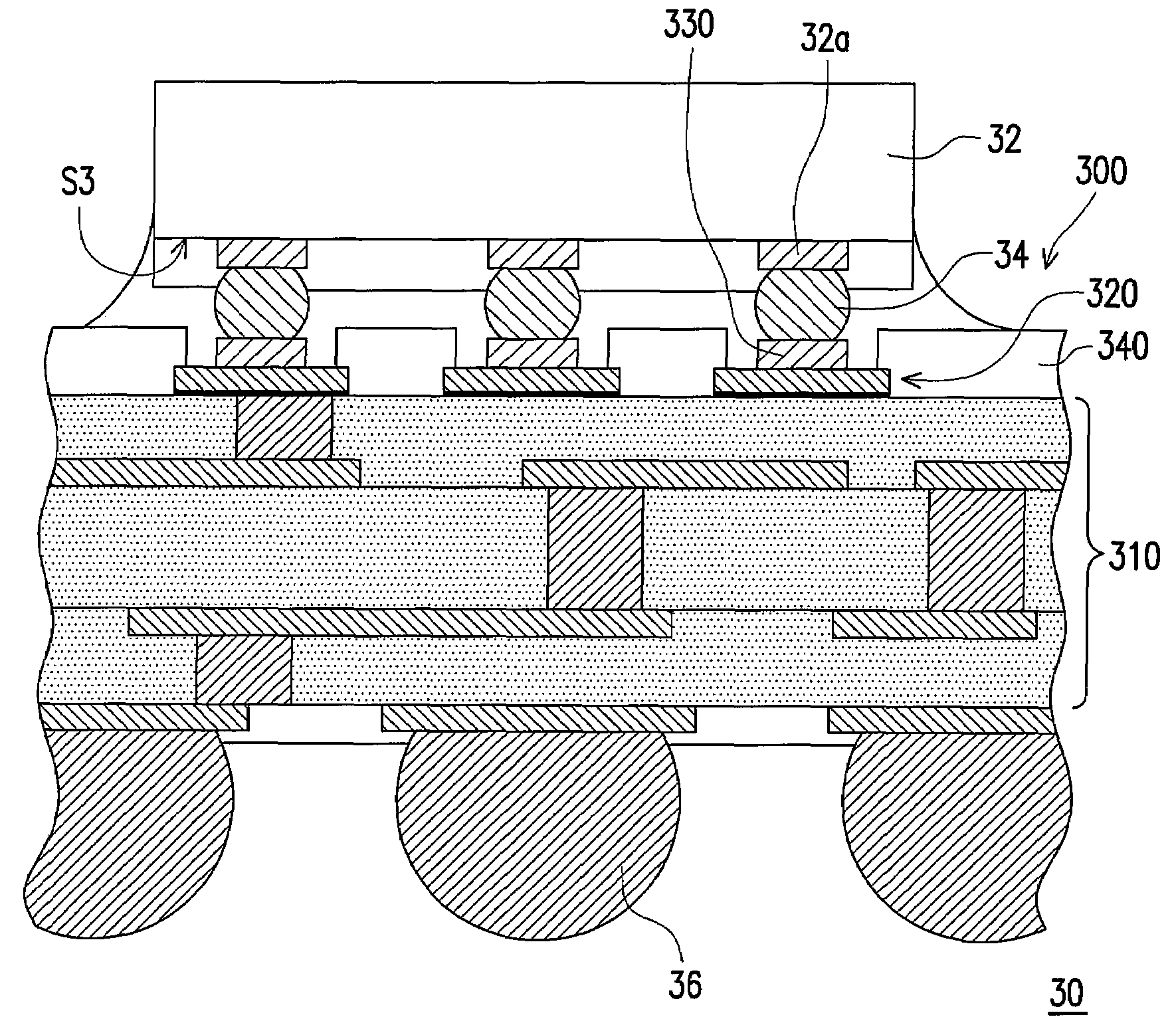

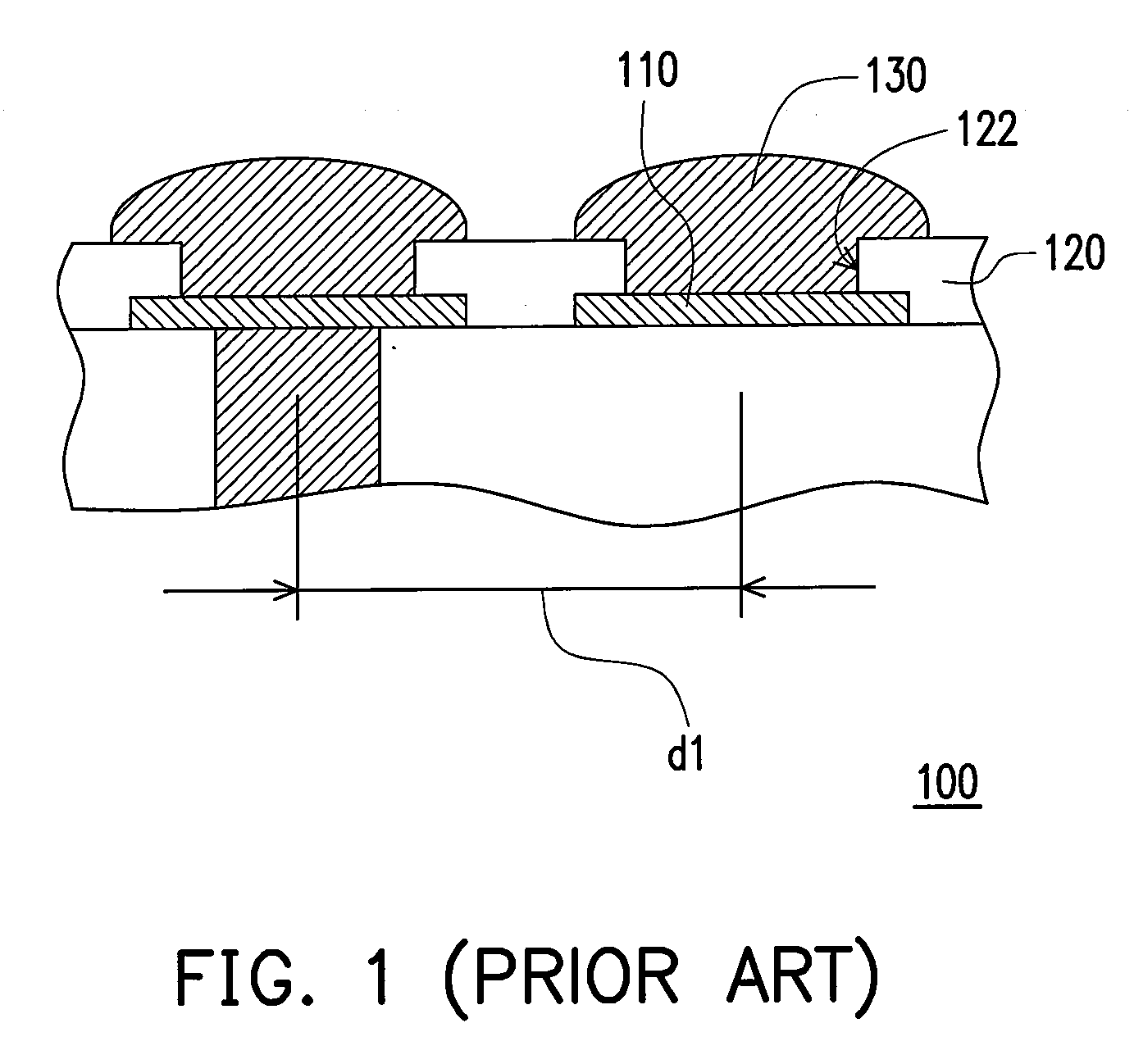

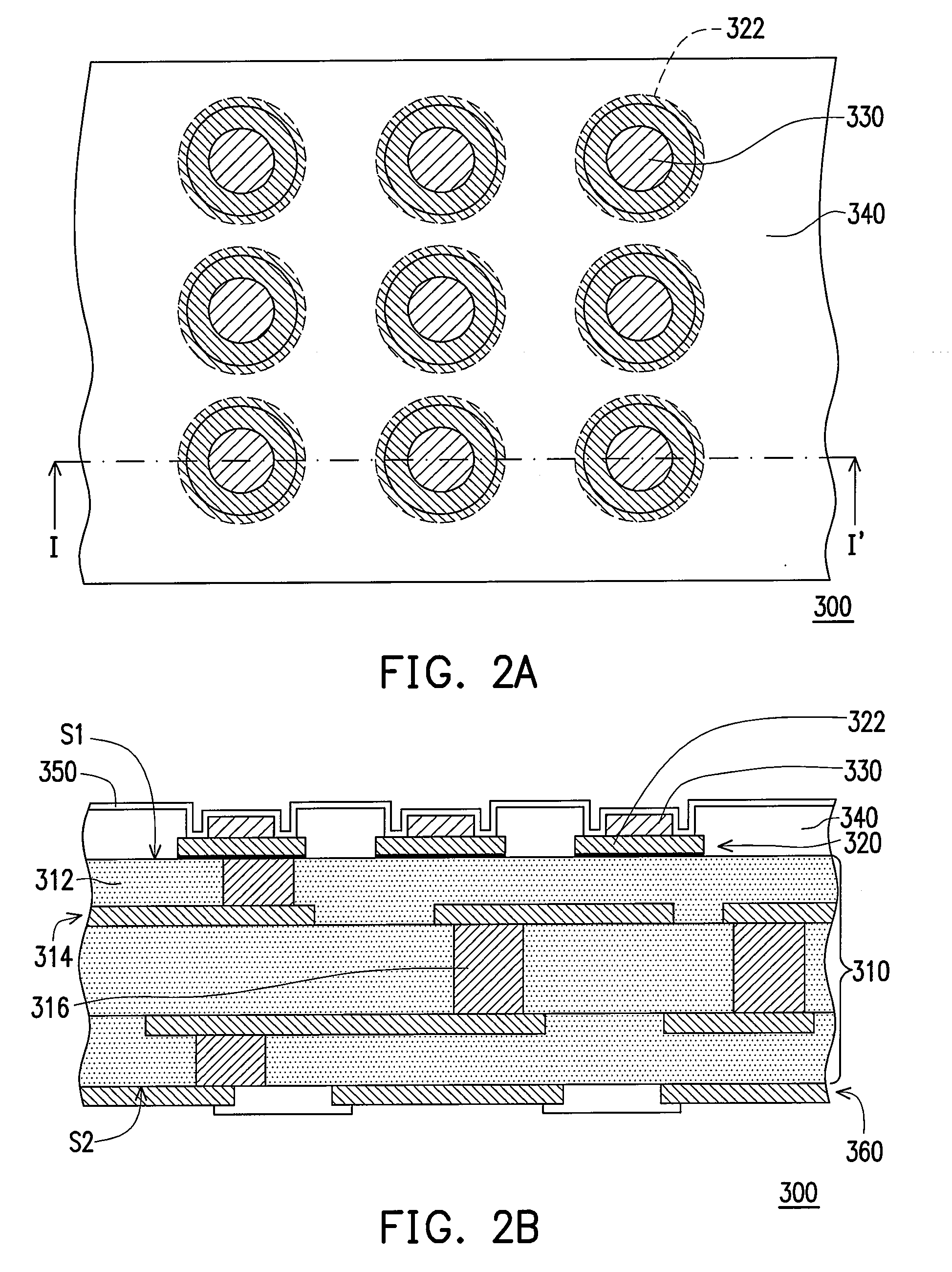

Package substrate, method of fabricating the same and chip package

InactiveUS20080179740A1Improve chip reliabilityIncrease distribution densitySemiconductor/solid-state device detailsStacked resist layersSolder maskEngineering

A package substrate, including a base layer, a surface circuit layer, a plurality of conductive bumps, and a patterned solder mask layer, is provided. The surface circuit layer having a plurality of bonding pads is disposed on a surface of the base layer. The conductive bumps are disposed on the bonding pads individually. The patterned solder mask layer is disposed on the surface of the base layer and outside a corresponding region occupied by the conductive bumps, so as to expose the conductive bumps. In addition, a method of fabricating the package substrate and a chip package structure employing the package substrate are also provided.

Owner:ADVANCED SEMICON ENG INC

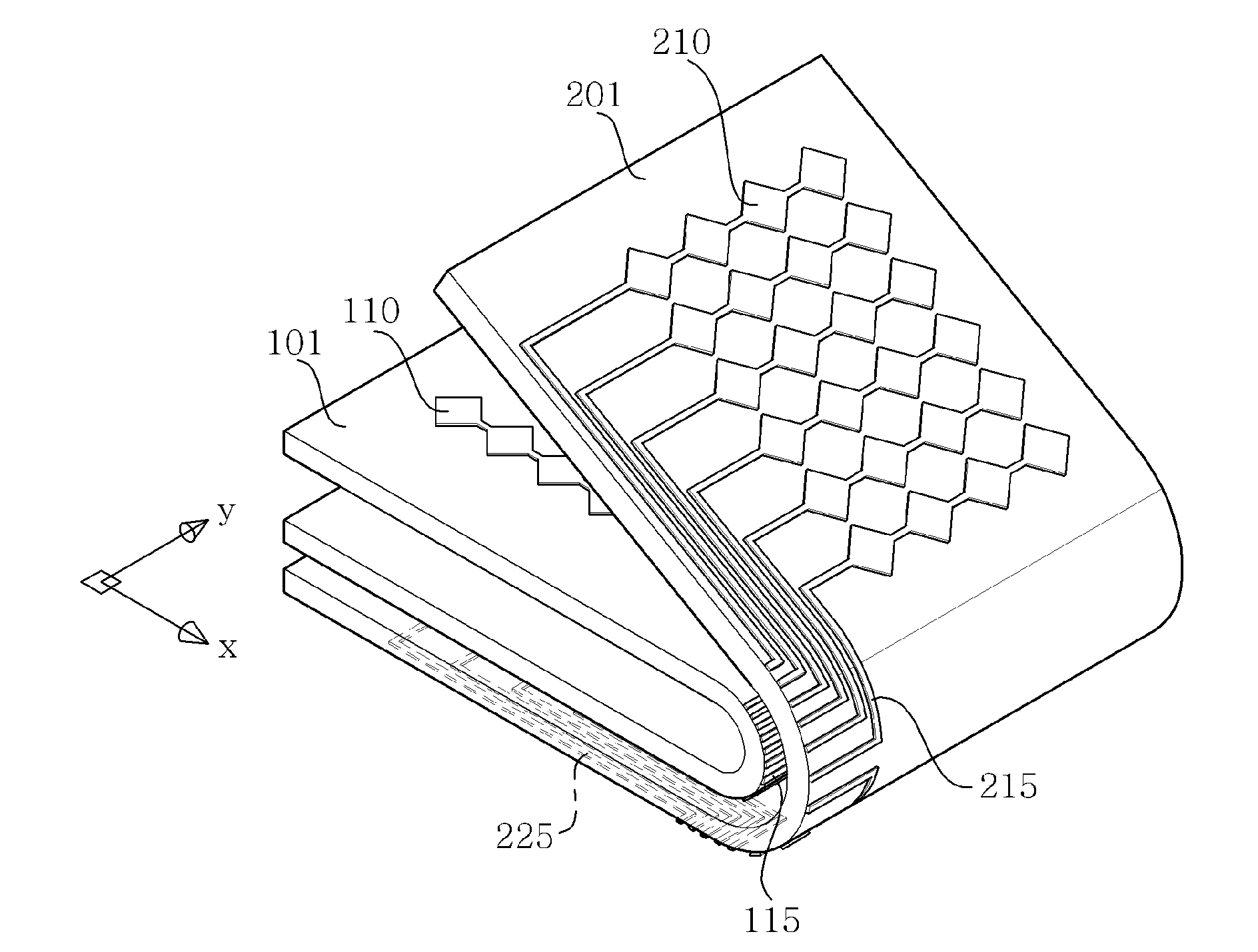

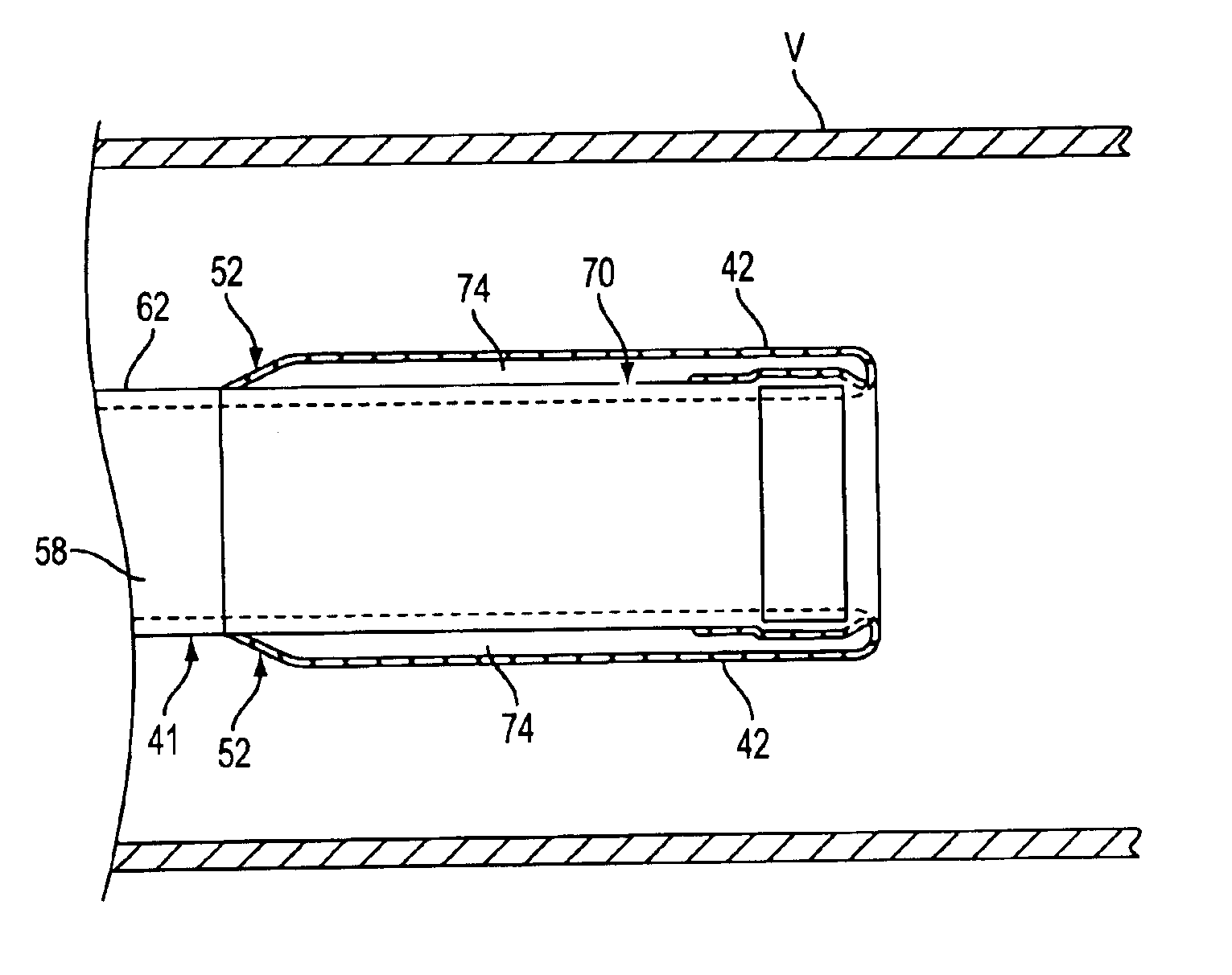

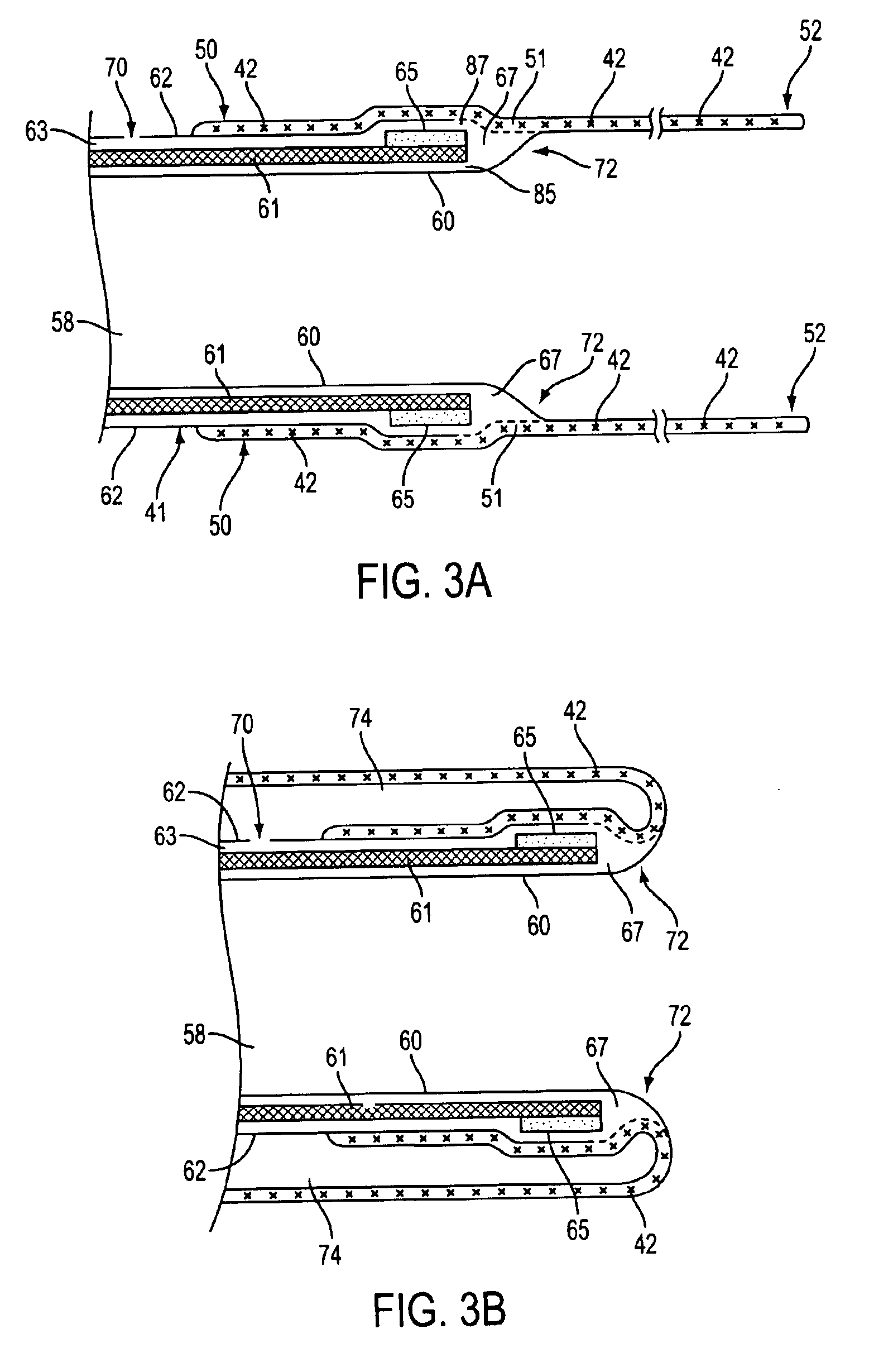

Catheter having a funnel-shaped occlusion balloon of uniform thickness and methods of manufacture

InactiveUS6960222B2Improve manufacturabilityReduce manufacturing costStentsBalloon catheterPercutaneous angioplastySurgical department

Methods and apparatus are provided for removing emboli during an angioplasty, stenting or surgical procedure comprising a catheter having a funnel-shaped occlusion balloon of uniform thickness disposed on a distal end of the catheter. The occlusion balloon is fused to the distal end so that it provides a substantially seamless flow transition into a working lumen of the catheter. Additionally, a distal edge of the occlusion balloon is configured to be in close proximity with an inner wall of a vessel to facilitate blood flow into the catheter and efficiently remove emboli.

Owner:WL GORE & ASSOC INC

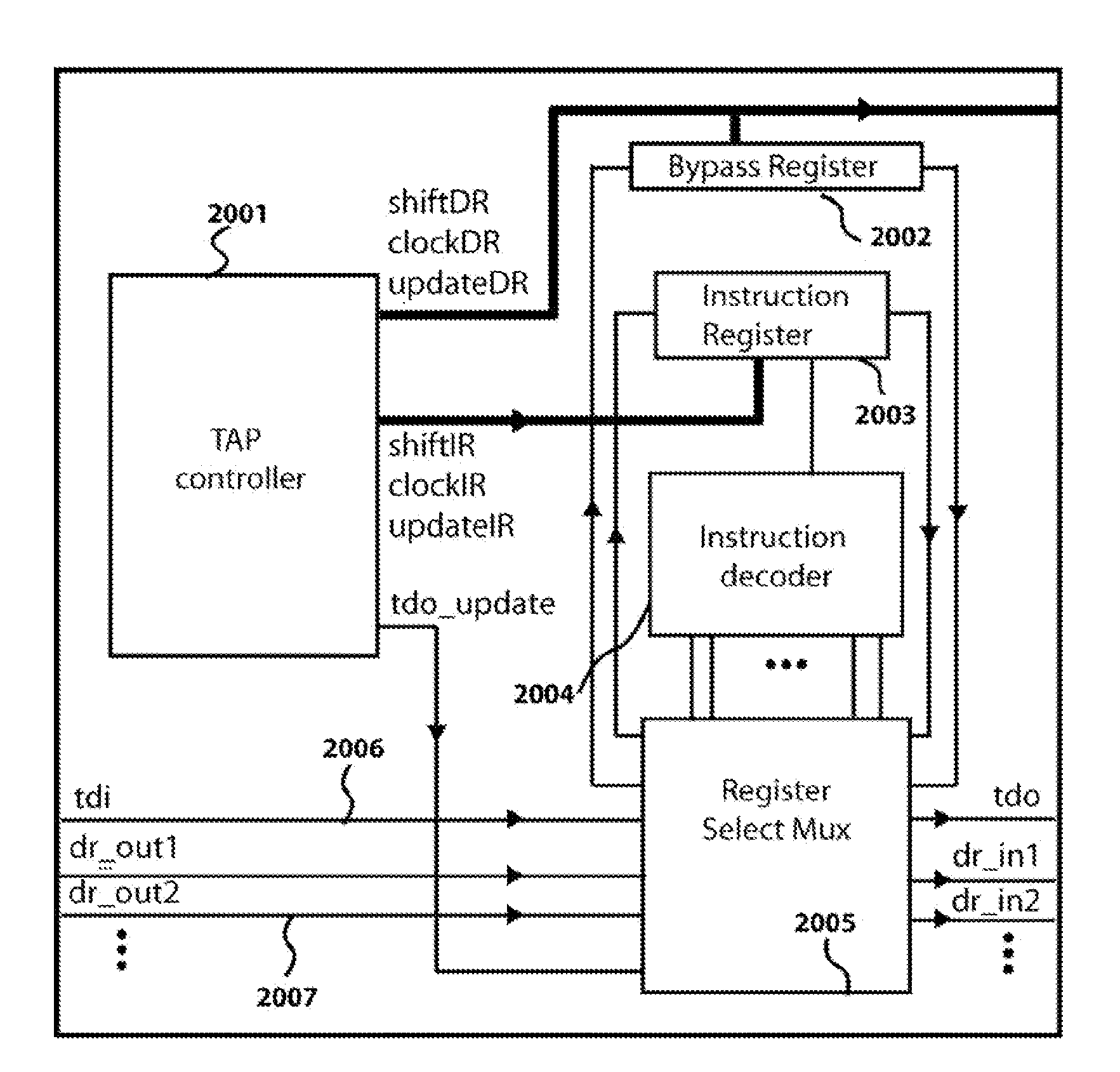

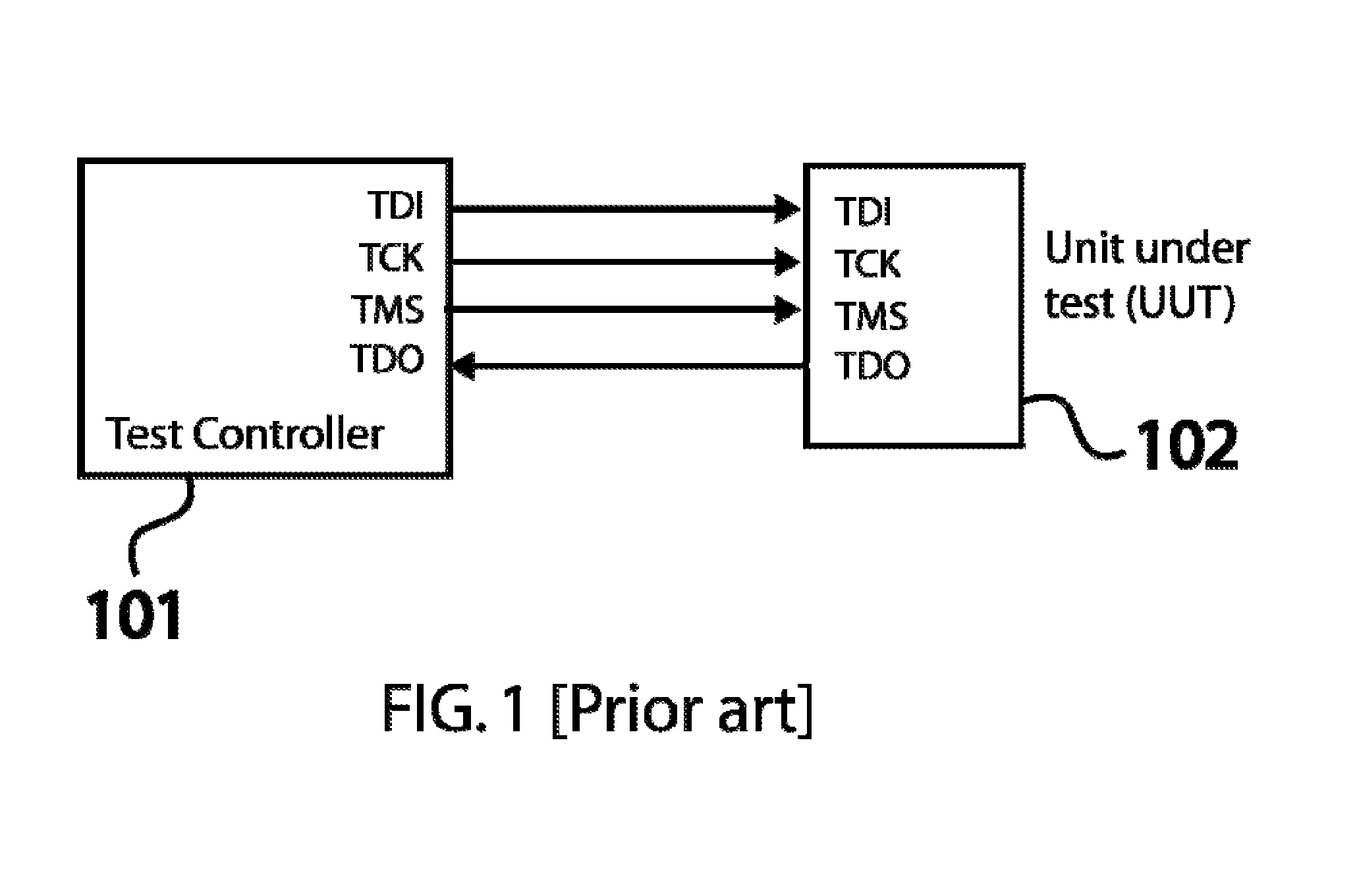

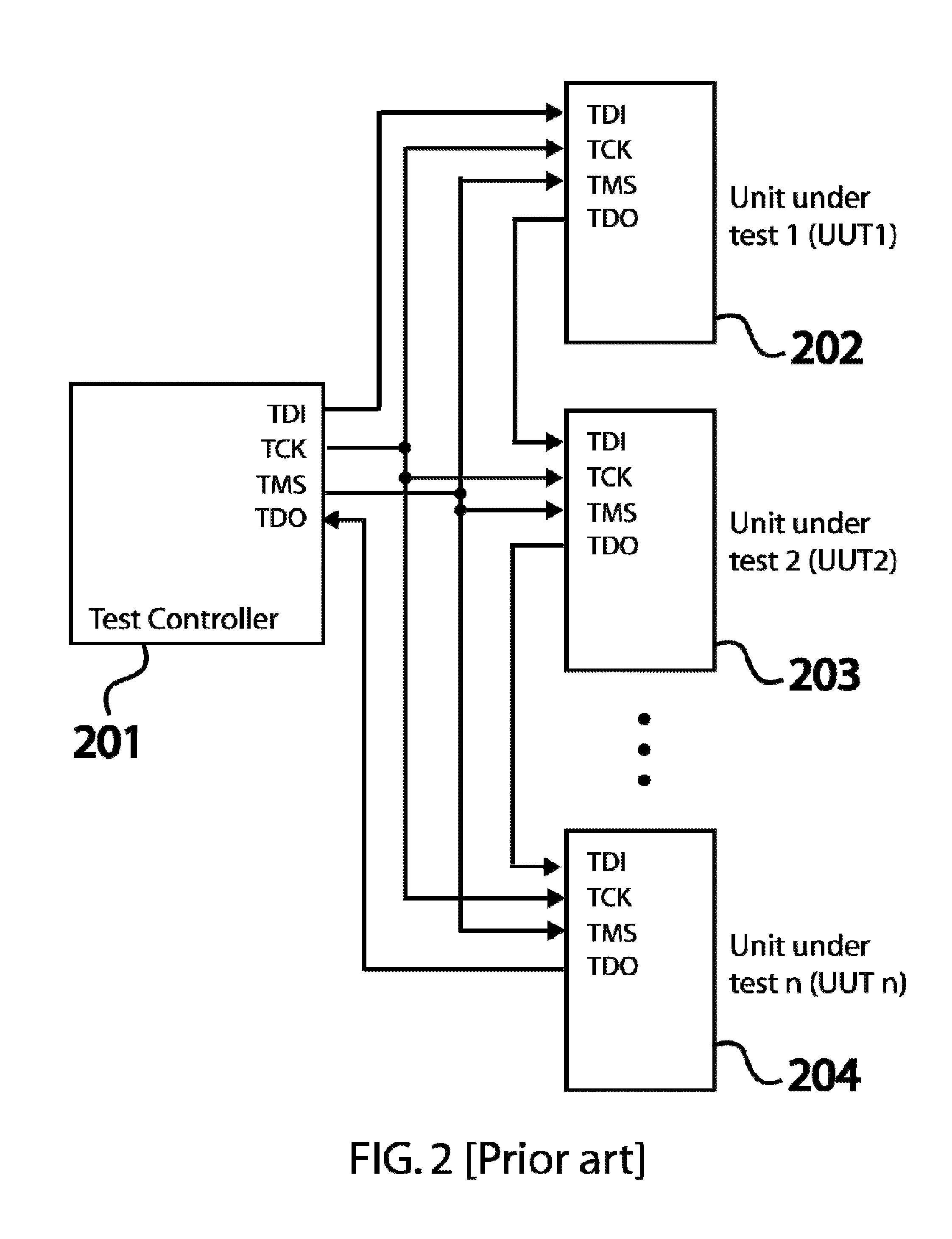

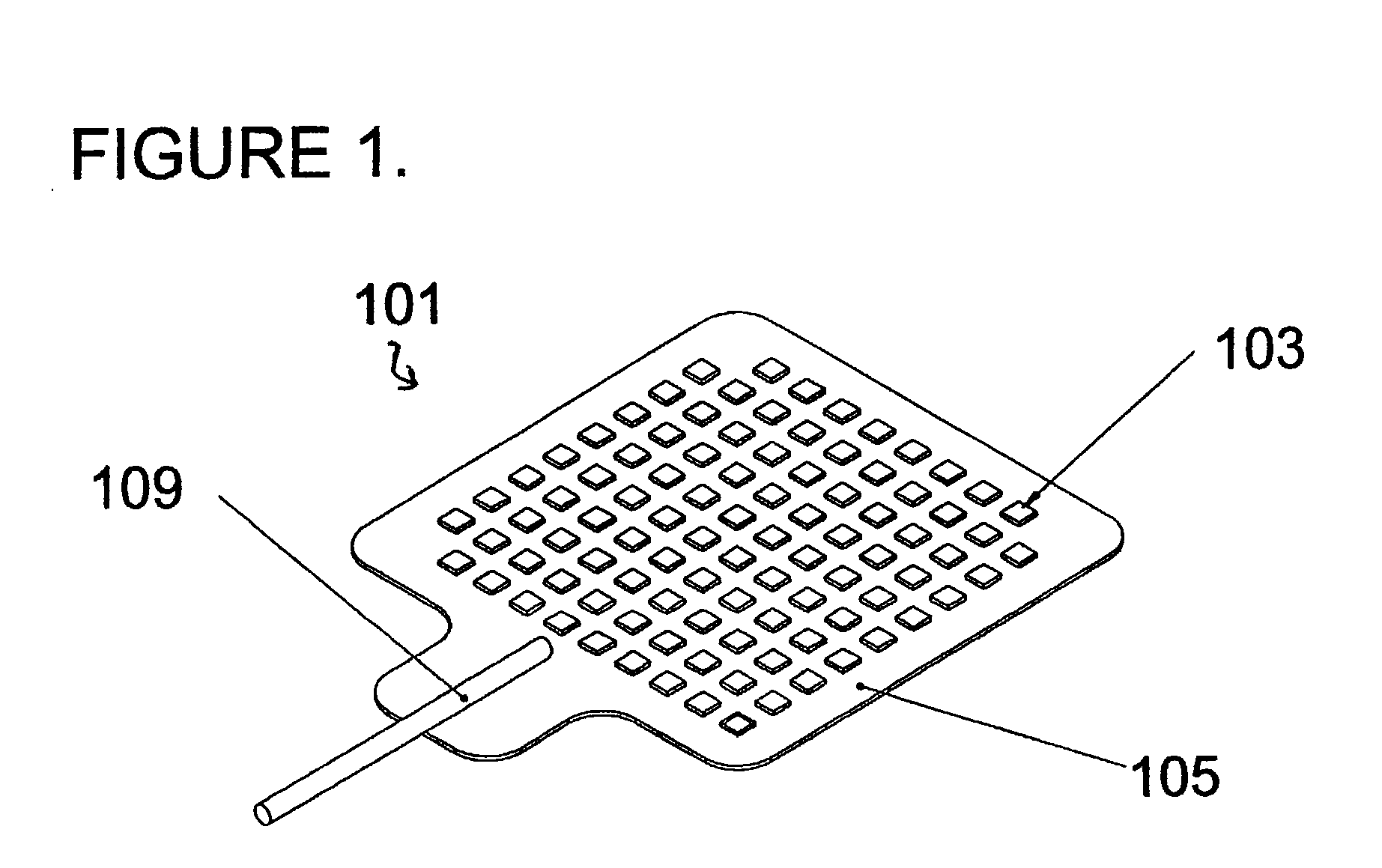

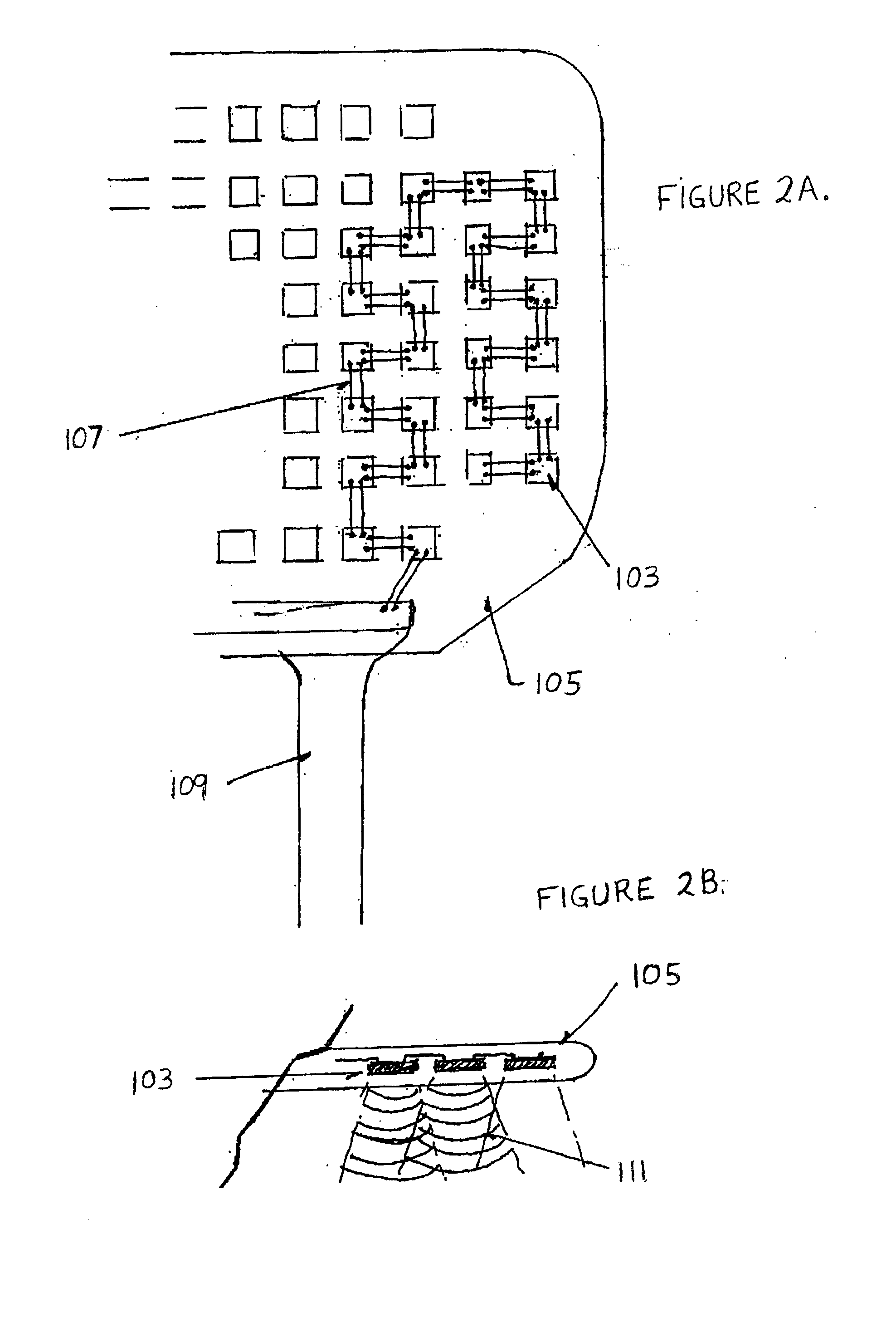

Methods, apparatus and system to support large-scale micro- systems including embedded and distributed power supply, thermal regulation, multi-distributedsensors and electrical signal propagation

InactiveUS20130285739A1Improve production yieldReduce mechanical stressPrinted circuit assemblingSemiconductor/solid-state device detailsStructure of Management InformationEngineering

The present invention relates to technologies for integrated circuits and Large Area Integrated Circuits (LAICs), which are integrated circuits made from photo-repetition of one or several reticle image fields, stitched together on at least one lithographic process layer. It also relates to a specific class of LAIC that can connect to the contacts of other ICs placed on its surface, where specific contact detection algorithms means are disclosed. The innovations include means for defect tolerance of serial communication links, means for efficient diagnosis of short and stuck-at faults in regular reconfigurable network, means for a programmable interposer for rapid prototyping of 3D stacked chips, means to build efficient large area micro-system devices (LAMS), with distributed and configurable hierarchical structures for power supply, thermal regulation and signal propagation, means to reduce mechanical / thermal / thermo-mechanical issues in LAMS devices, means to propagate analog signal on a configurable digital network, means to predict thermo-mechanical stress peaks.

Owner:TRANSFERT PLUS S E C +2

Semiconductor package and fabrication method thereof

ActiveUS9786586B1Improve production yieldHigh product yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor package

A semiconductor package includes an interconnect component surrounded by a molding compound. The interconnect component comprises a first RDL structure. A second RDL structure is disposed on the interconnect component. A plurality of first connecting elements is disposed on the second RDL structure. A polish stop layer covers a surface of the interconnect component. A plurality of second connecting elements is disposed on and in the polish stop layer. At least one semiconductor die is mounted on the second connecting elements.

Owner:MICRON TECH INC

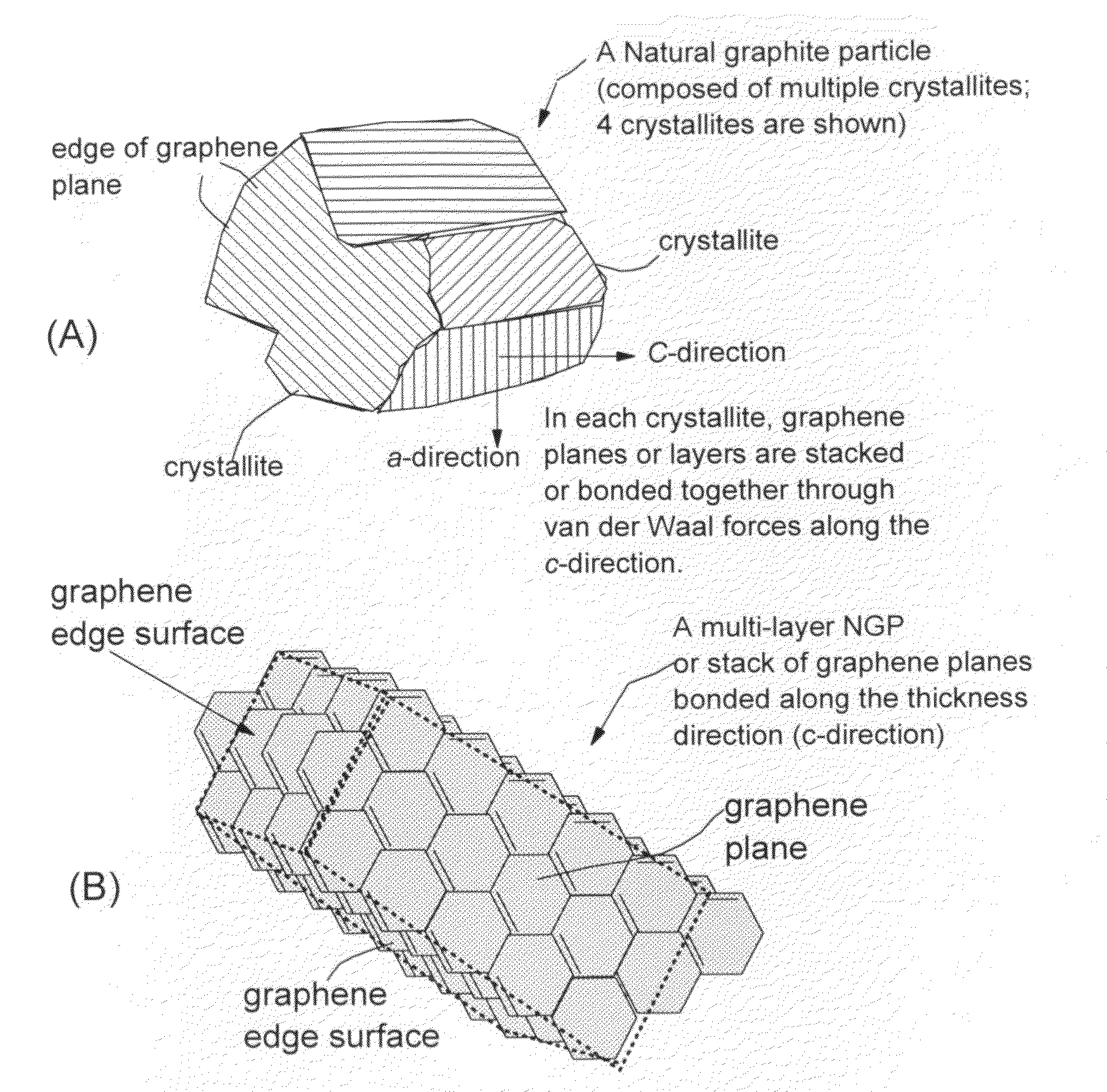

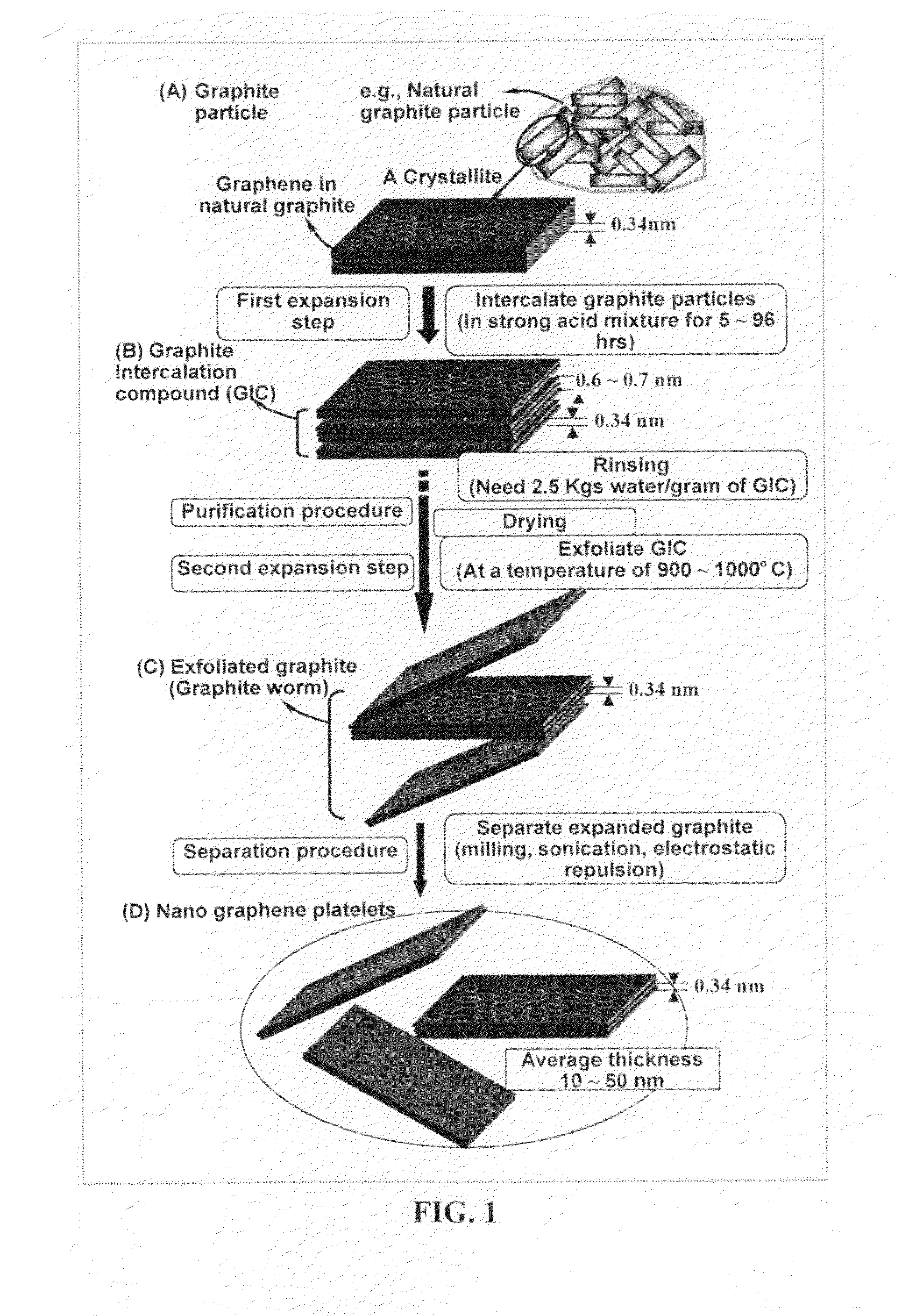

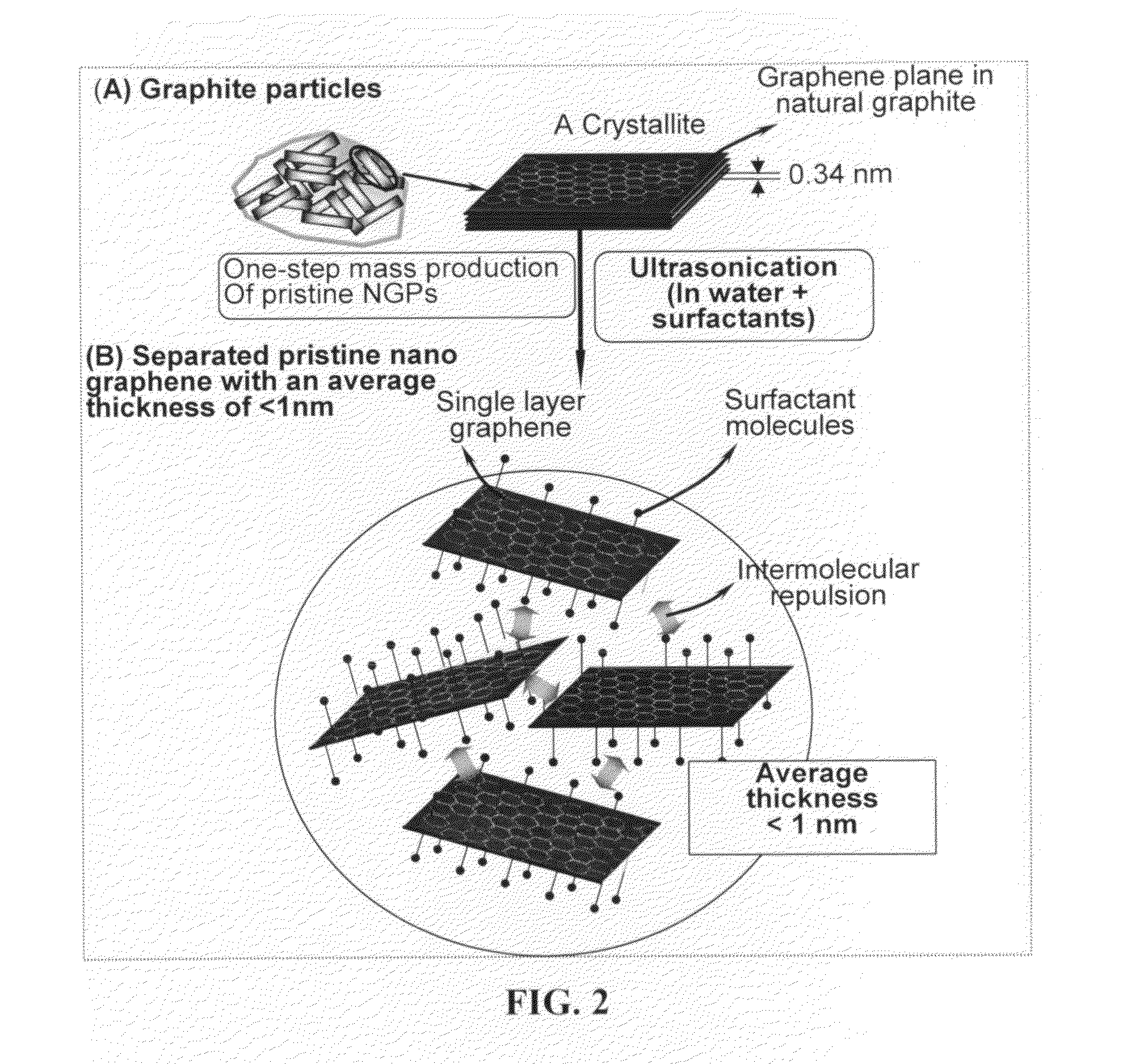

Mass production of pristine nano graphene materials

ActiveUS20110017585A1Reduce surface tensionImprove production yieldMaterial nanotechnologyGrapheneLiquid mediumDisplay device

The present invention provides a method of producing pristine or non-oxidized nano graphene platelets (NGPs) that are highly conductive. The method comprises: (a) providing a pristine graphitic material comprising at least a graphite crystallite having at least a graphene plane and an edge surface; (b) dispersing multiple particles of the pristine graphitic material in a liquid medium containing therein no surfactant to produce a suspension, wherein the multiple particles in the liquid have a concentration greater than 0.1 mg / mL and the liquid medium is characterized by having a surface tension that enables wetting of the liquid on a graphene plane exhibiting a contact angle less than 90 degrees; and (c) exposing the suspension to direct ultrasonication at a sufficient energy or intensity level for a sufficient length of time to produce the NGPs. Pristine NGPs can be used as a conductive additive in transparent electrodes for solar cells or flat panel displays (e.g., to replace expensive indium-tin oxide), battery and supercapacitor electrodes, and nanocomposites for electromagnetic wave interference (EMI) shielding, static charge dissipation, and fuel cell bipolar plate applications.

Owner:GLOBAL GRAPHENE GRP INC

Biological Cell Acoustic Enhancement and Stimulation

InactiveUS20080045882A1Improve efficiencyAccelerate patient recoverySonopheresisUltrasound therapyBiological cellAcoustic energy

A method for enhancing the uptake of a therapeutic biological agent by treated cells. A low-power, unfocused field of acoustic energy is directed at the treated cells after the delivery of the therapeutic agent to the treated cells. A related method for stimulating either neural cells or cells in a cell culture. A portable sized device provides the field, and may include either an array of emitters or a scanable emitter.

Owner:FINSTERWALD P MICHAEL

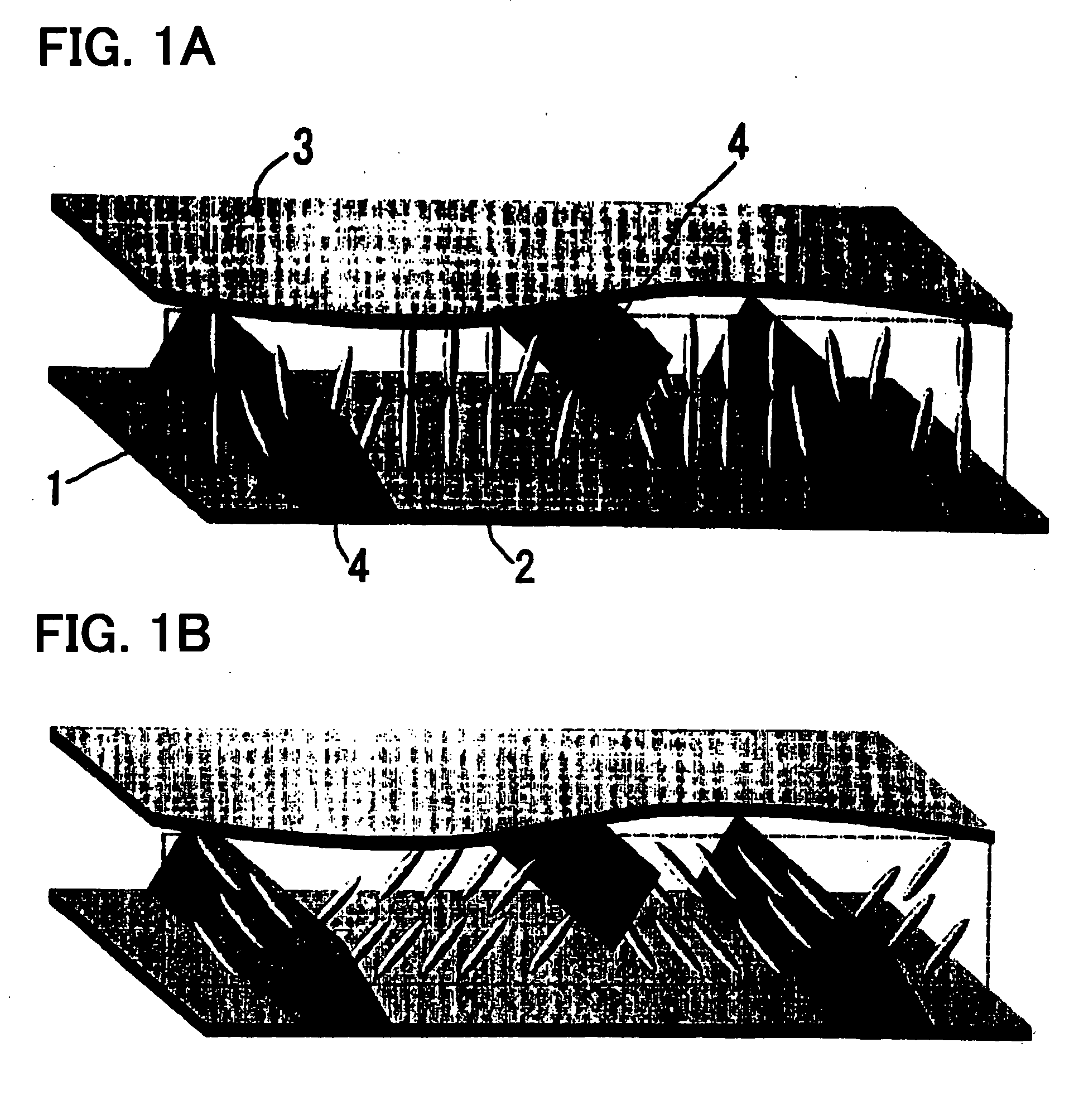

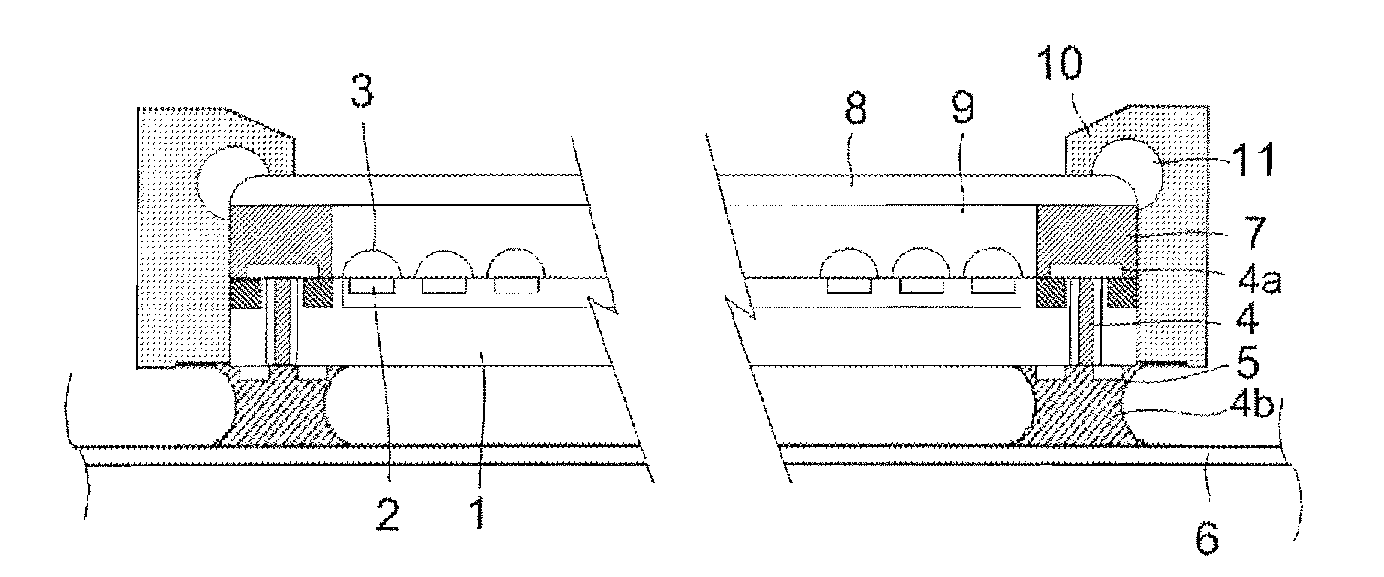

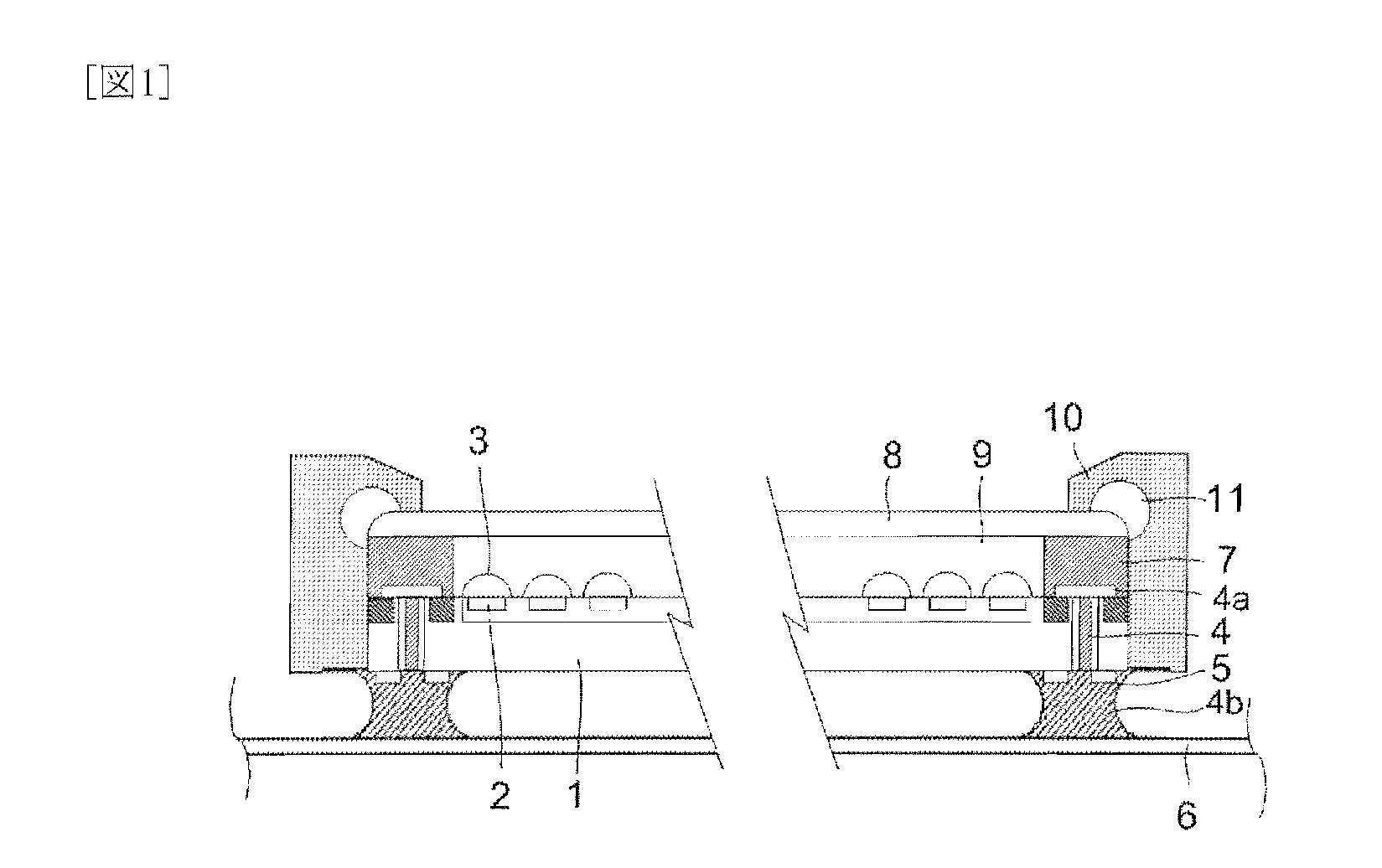

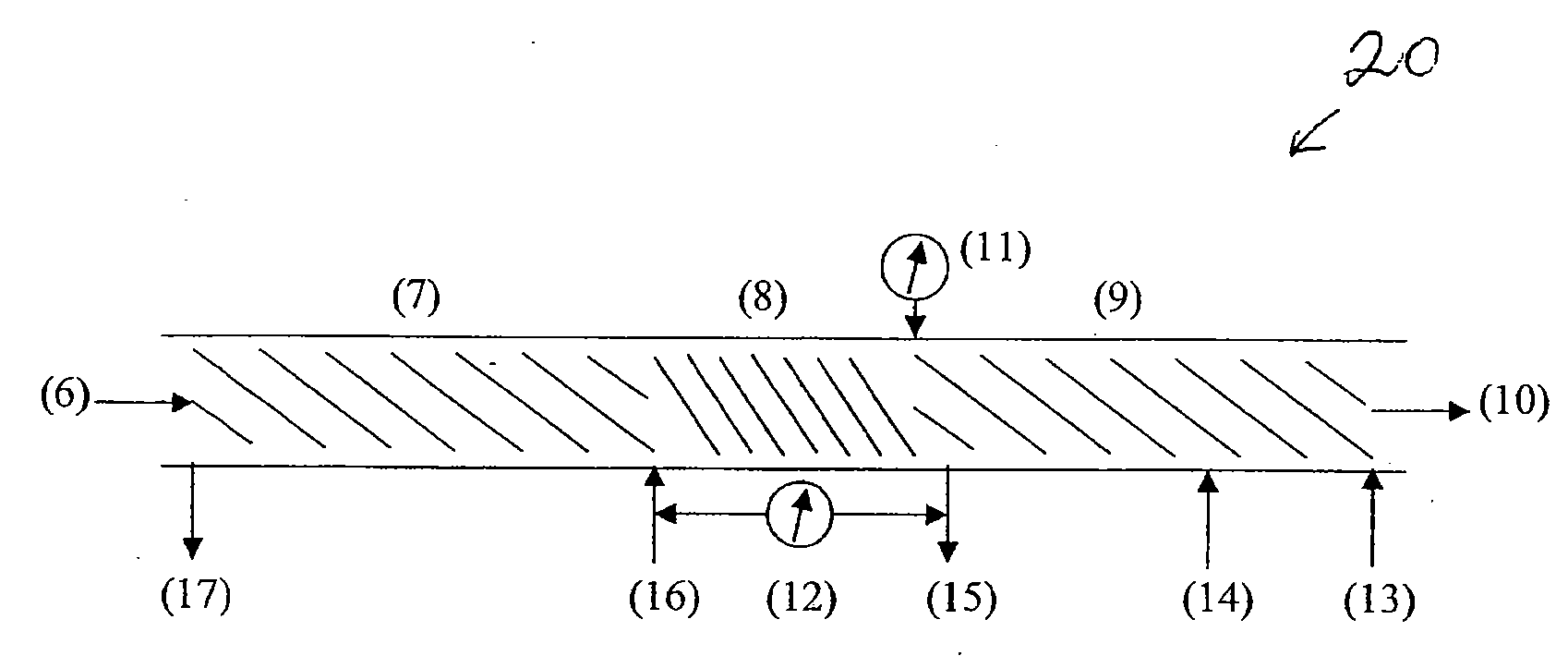

Solid-Stated Image Pickup Device And Method For Manufacturing Same

ActiveUS20080042227A1Reliability of device can be ensuredImprove production yieldTelevision system detailsSolid-state devicesEngineeringOptical glass

There are provided image pickup devices capable of significantly increasing production yield and ensuring long-term reliability and a method for manufacturing the image pickup devices. This invention is characterized in that it has a large number of light-receiving portions 2 formed at a surface portion of a wafer 1 and a microlens 3 formed for each of the light-receiving portions, through electrodes 4 for performing supply of power to the light-receiving portions 2 and passing and reception of an electrical signal are provided all over the periphery of the wafer 1, one end of each through electrode 4 is connected to an electrode pad 4a which is connected to a wire leading to a light-receiving element at the surface portion of the wafer 1, the other end is connected to a wire through a back electrode 5, a rib 7 which serves as a partition portion arranged to surround the microlenses 3 on four sides is provided on the surface of the wafer 1, a transparent plate 8 of optical glass or the like is bonded to an upper surface of the rib 7 with adhesive, and a protective frame 10 is provided at a junction between the rib 7 and the transparent plate 8.

Owner:AAC ACOUSTIC TECH (SHENZHEN) CO LTD +1

Increasing carrier mobility in NFET and PFET transistors on a common wafer

InactiveUS6939814B2Easily and repeatably formedImprove production yieldTransistorSolid-state devicesIndiumCharge carrier mobility

Enhanced carrier mobility in transistors of differing (e.g. complementary) conductivity types is achieved on a common chip by provision of two or more respective stressed layers, such as etch stop layers, overlying the transistors with stress being wholly or partially relieved in portions of the respective layers, preferably by implantations with heavy ions such as germanium, arsenic, xenon, indium, antimony, silicon, nitrogen oxygen or carbon in accordance with a block-out mask. The distribution and small size of individual areas of such stressed structures also prevents warping or curling of even very thin substrates.

Owner:IBM CORP

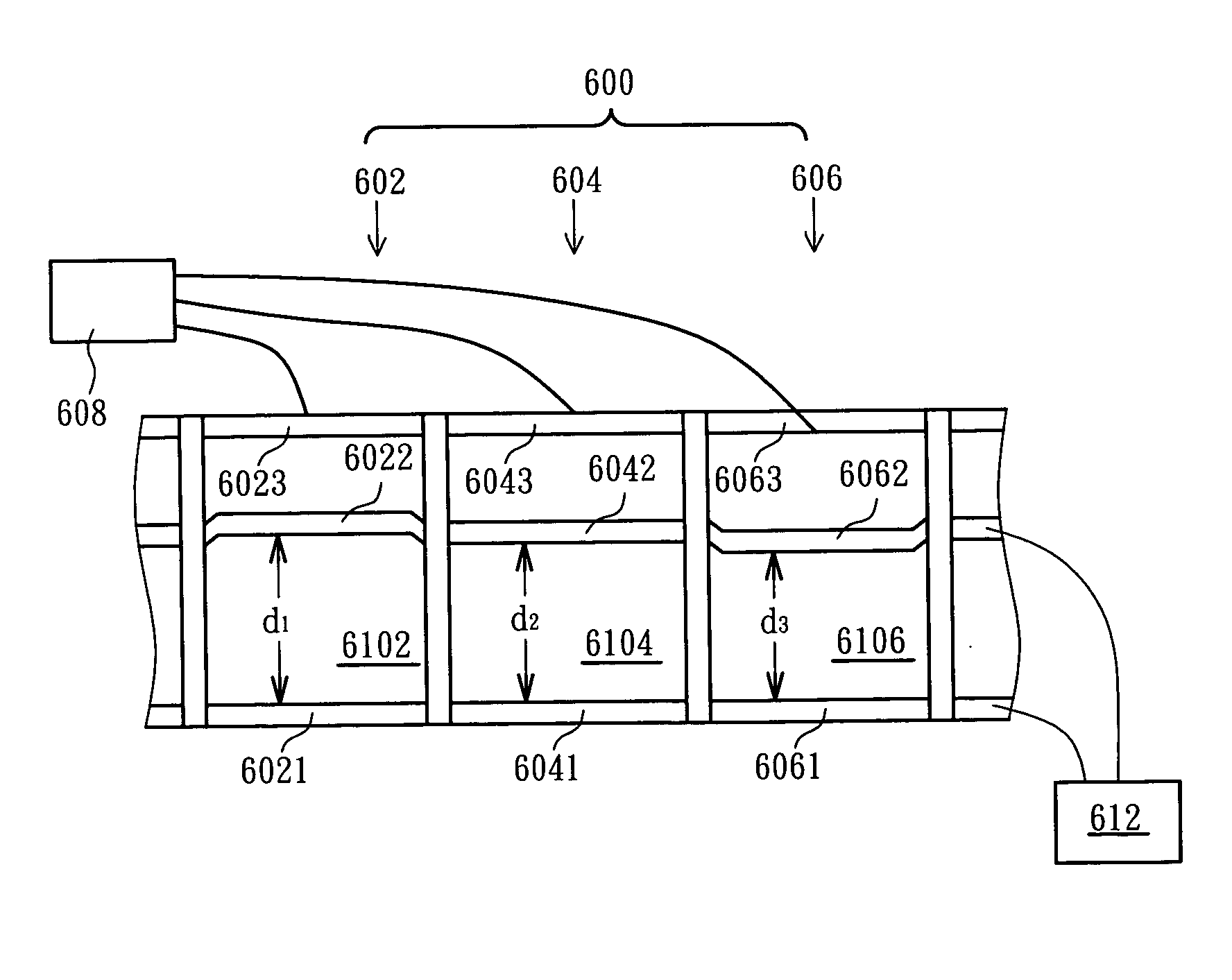

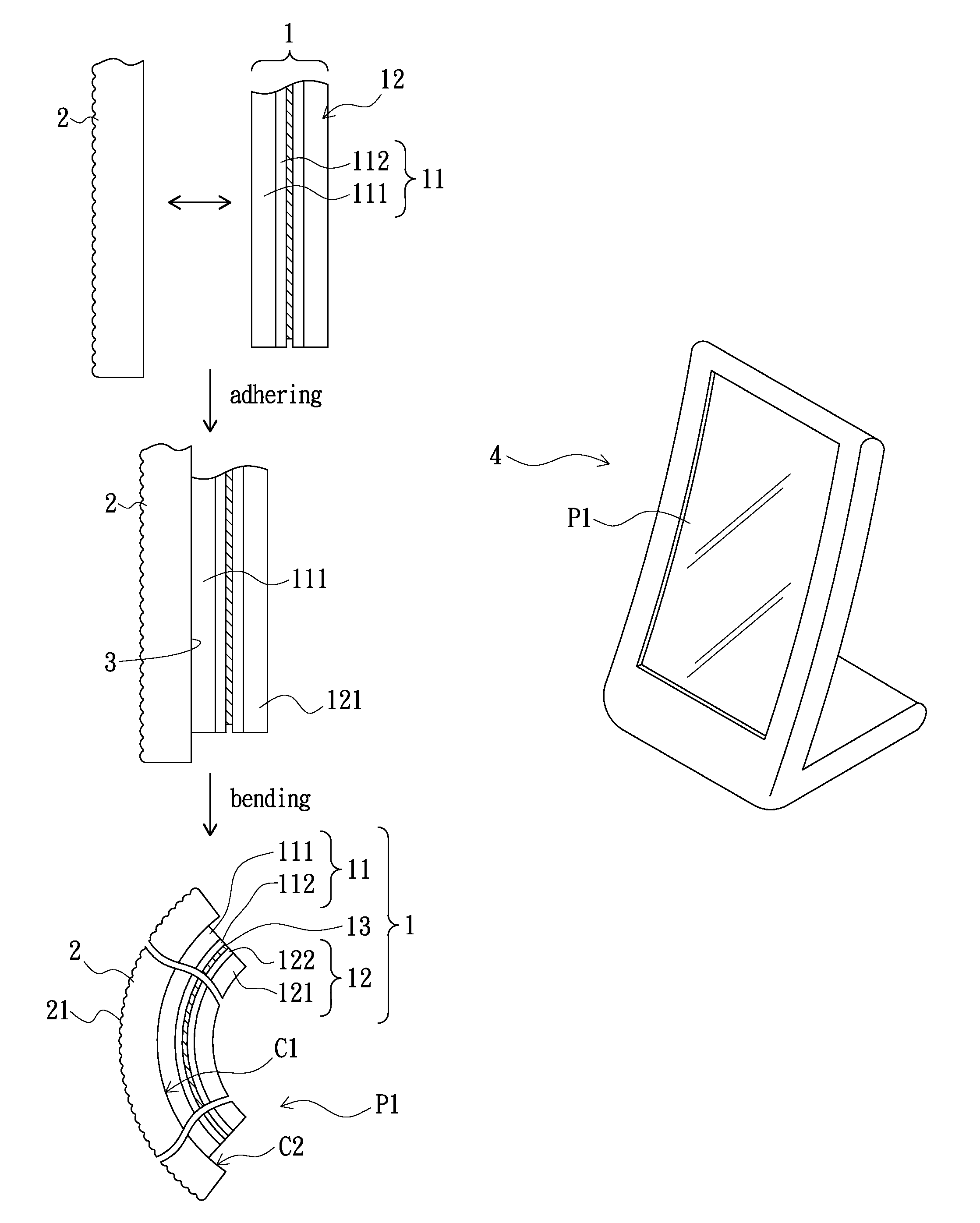

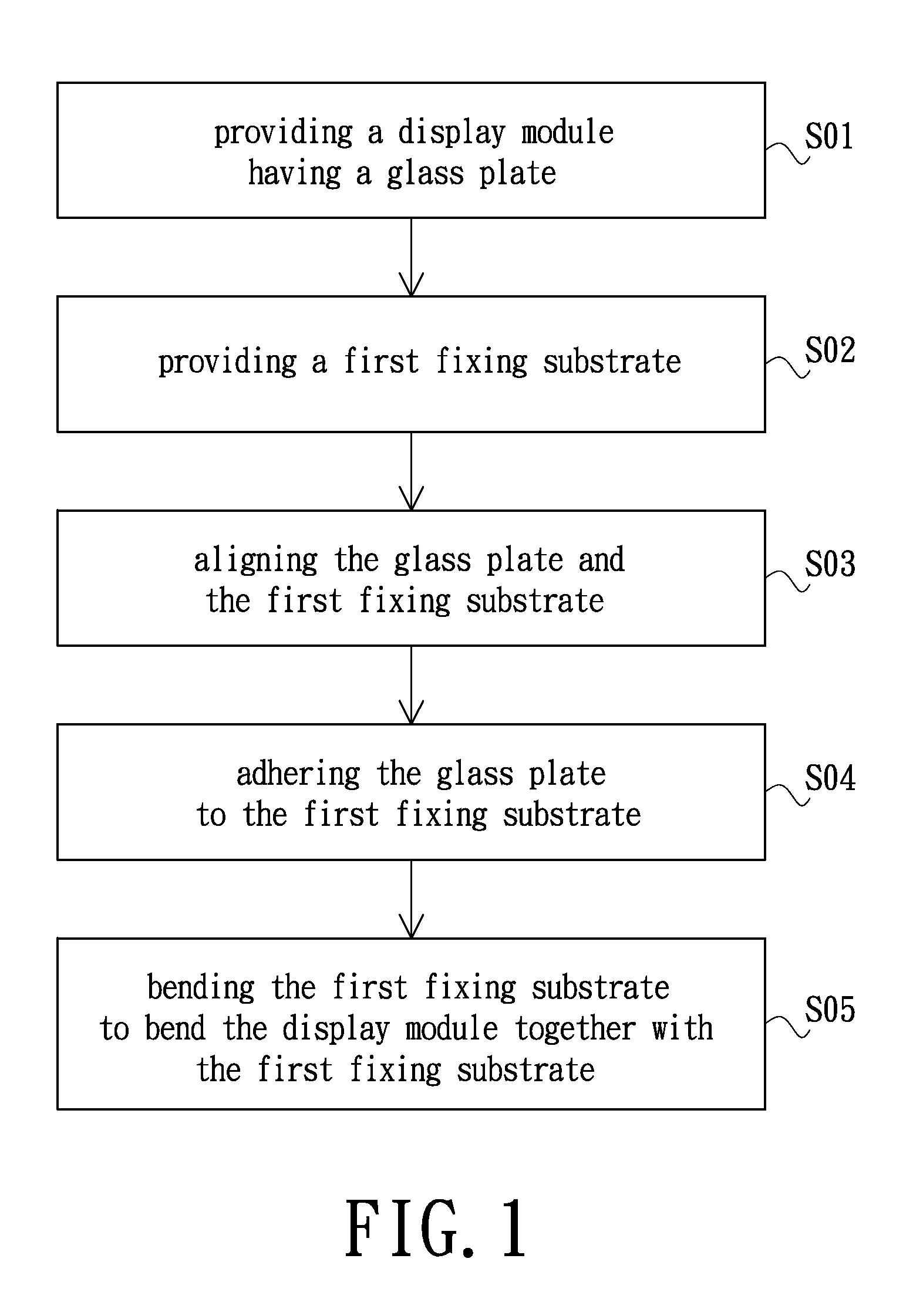

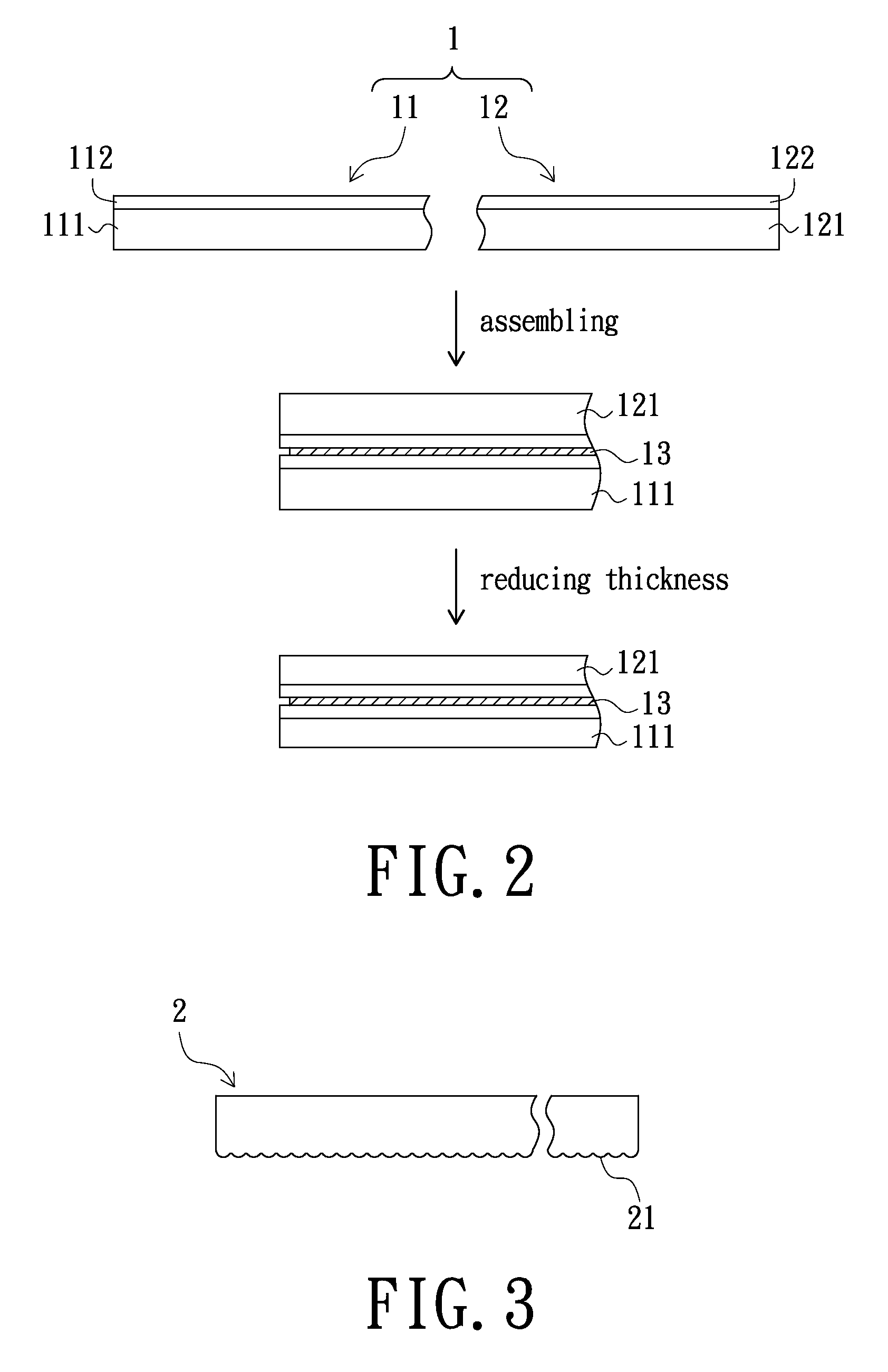

Curved display panel and method for manufacturing the same

ActiveUS8305743B2Improve production yieldIncrease stickinessDisposition/mounting of recording headsDigital data processing detailsEngineeringGlass sheet

Owner:OPTRONIC SCI LLC

Moving bed biomass fractionation system and method

InactiveUS20080029233A1Improve production yieldIncrease pressureWashing/displacing pulp-treating liquorsDigestersChemical reactionFiltration

Countercurrent extraction of lignocellulosic biomass such as trees, grasses, shrubs, and agricultural residues or waste involves the separation of cellulose fibers from other constituents, for subsequent use in the manufacture of paper, plastics, ethanol, and other industrial chemicals. Systems and methods involve continuous, multiple processing steps that may include chemical reactions with mixing at elevated temperature and / or pressure, efficient reagent or solvent utilization, filtration at elevated temperature and / or pressure, controlled discharge of liquid and solid products, and energy recuperation.

Owner:PUREVISION TECH