Patents

Literature

1579results about How to "High product yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

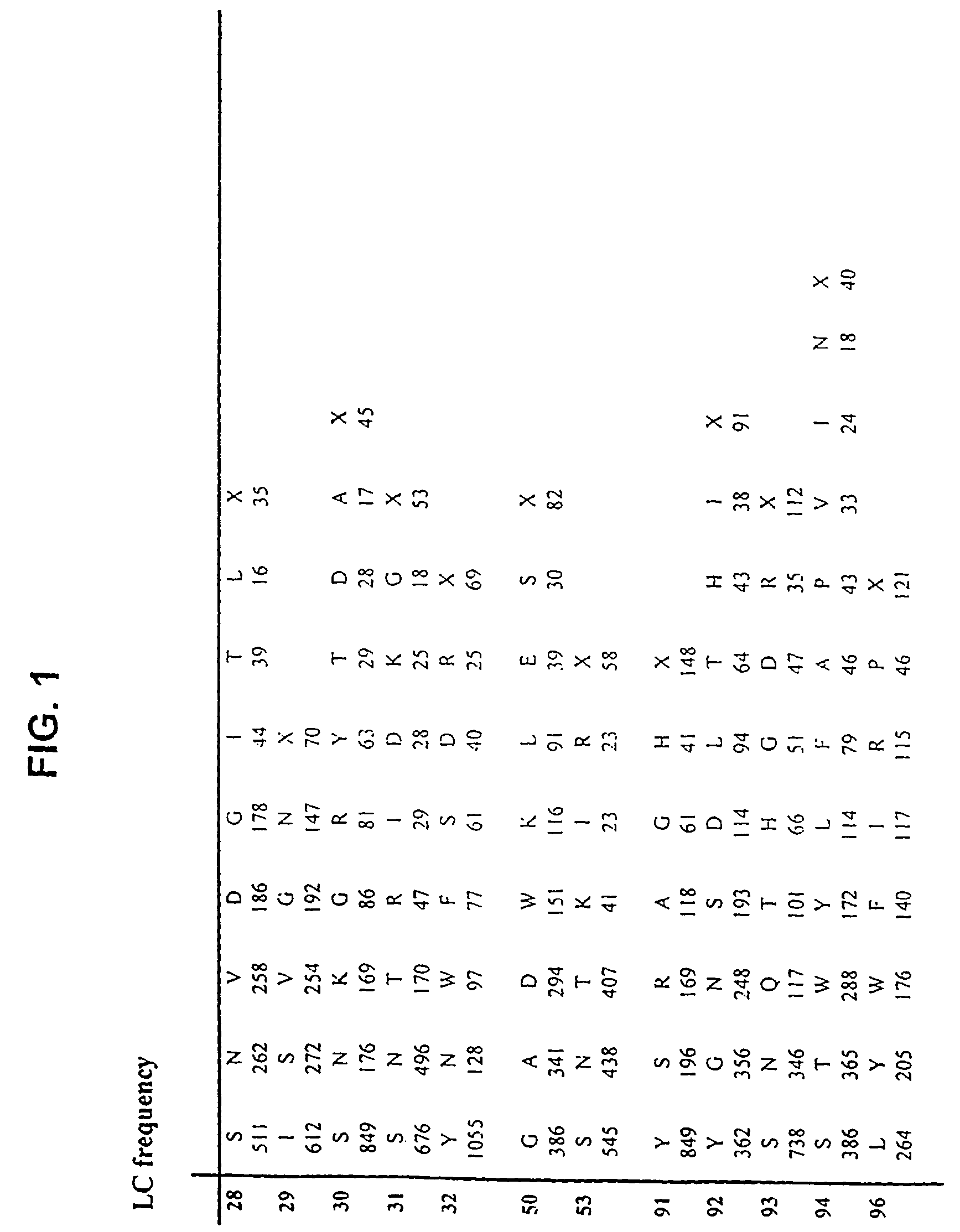

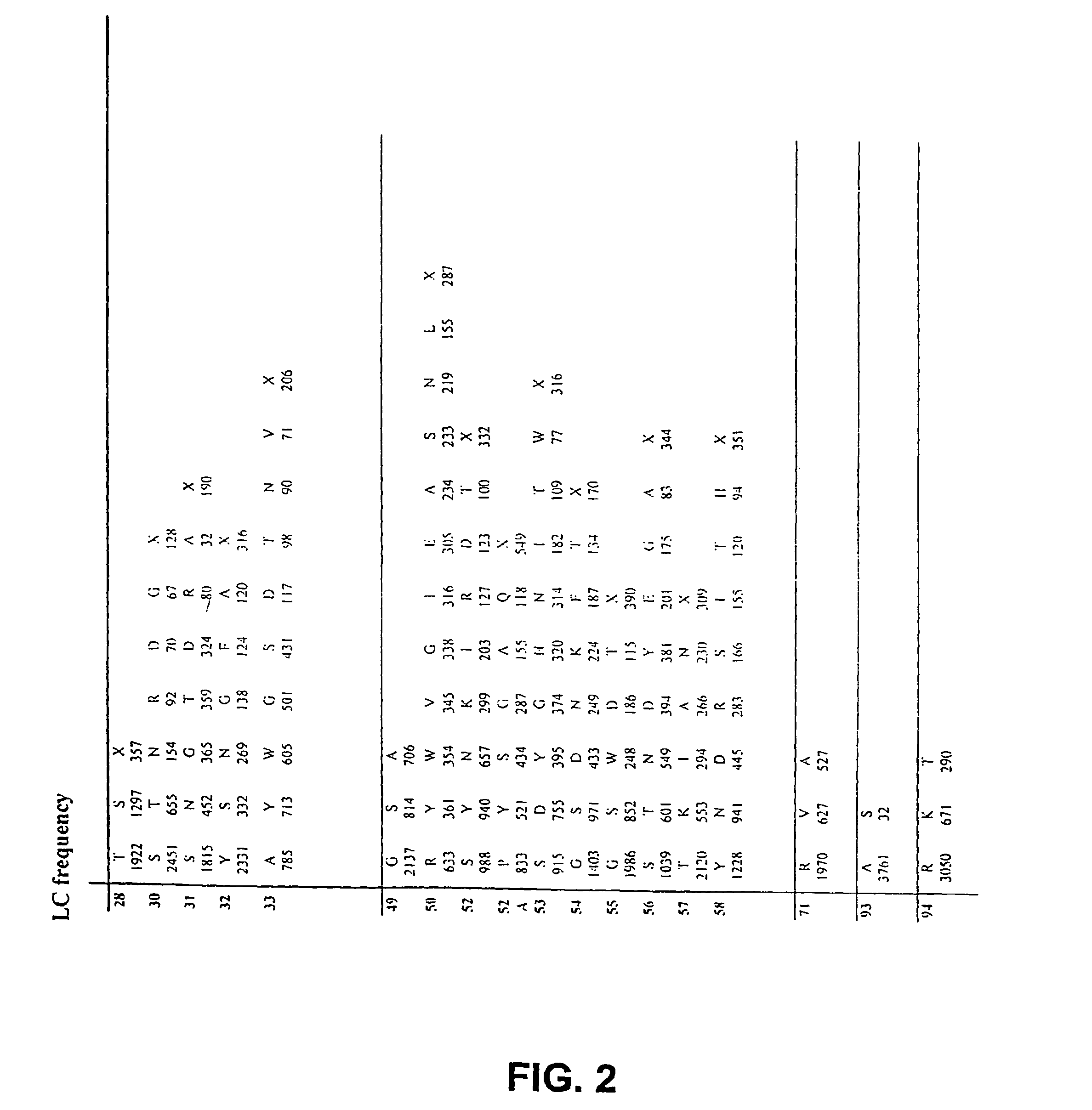

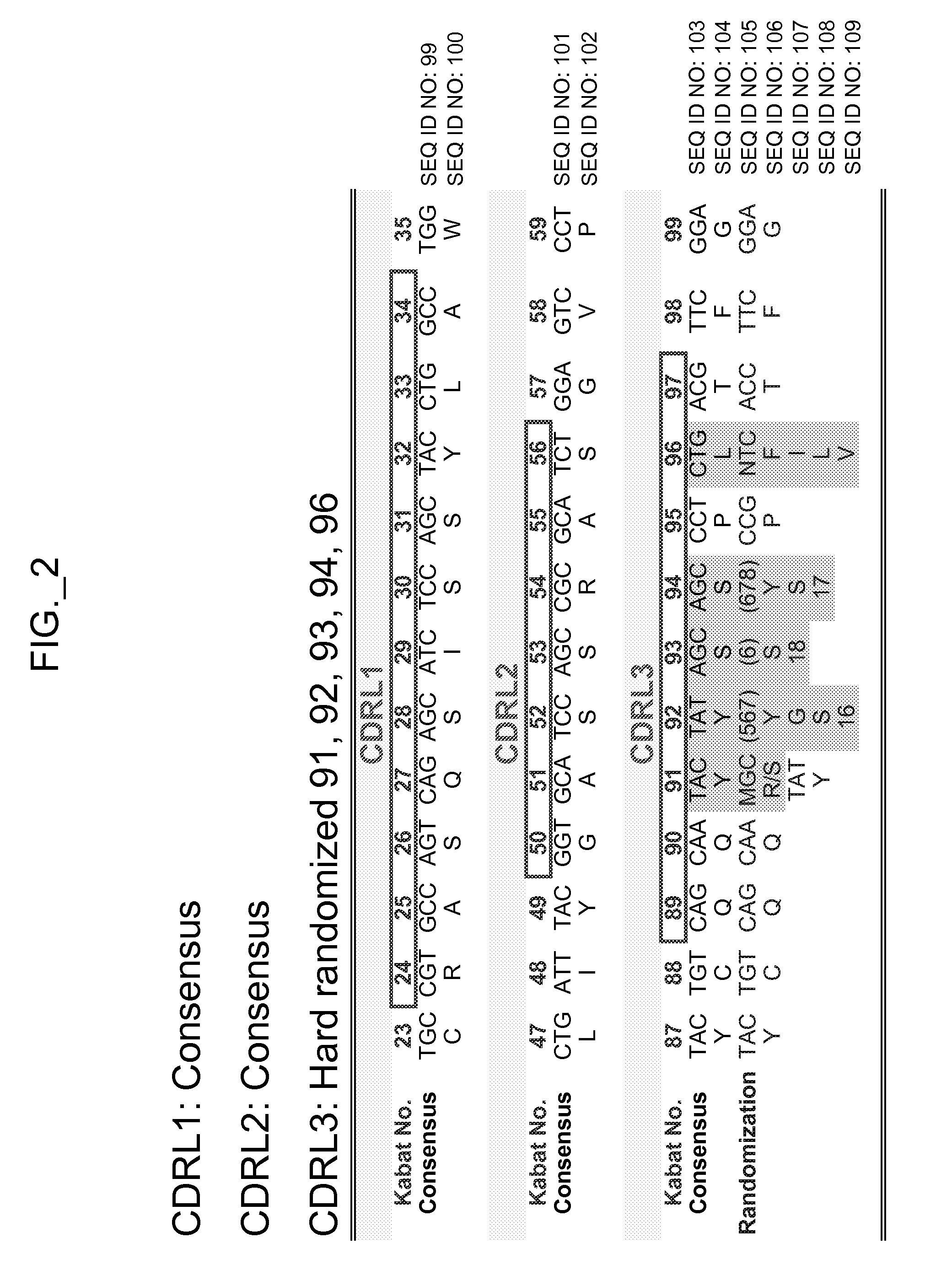

Binding polypeptides with restricted diversity sequences

InactiveUS20070237764A1Small sizeHigh-quality target binding characteristicFermentationVector-based foreign material introductionHeterologousAntigen binding

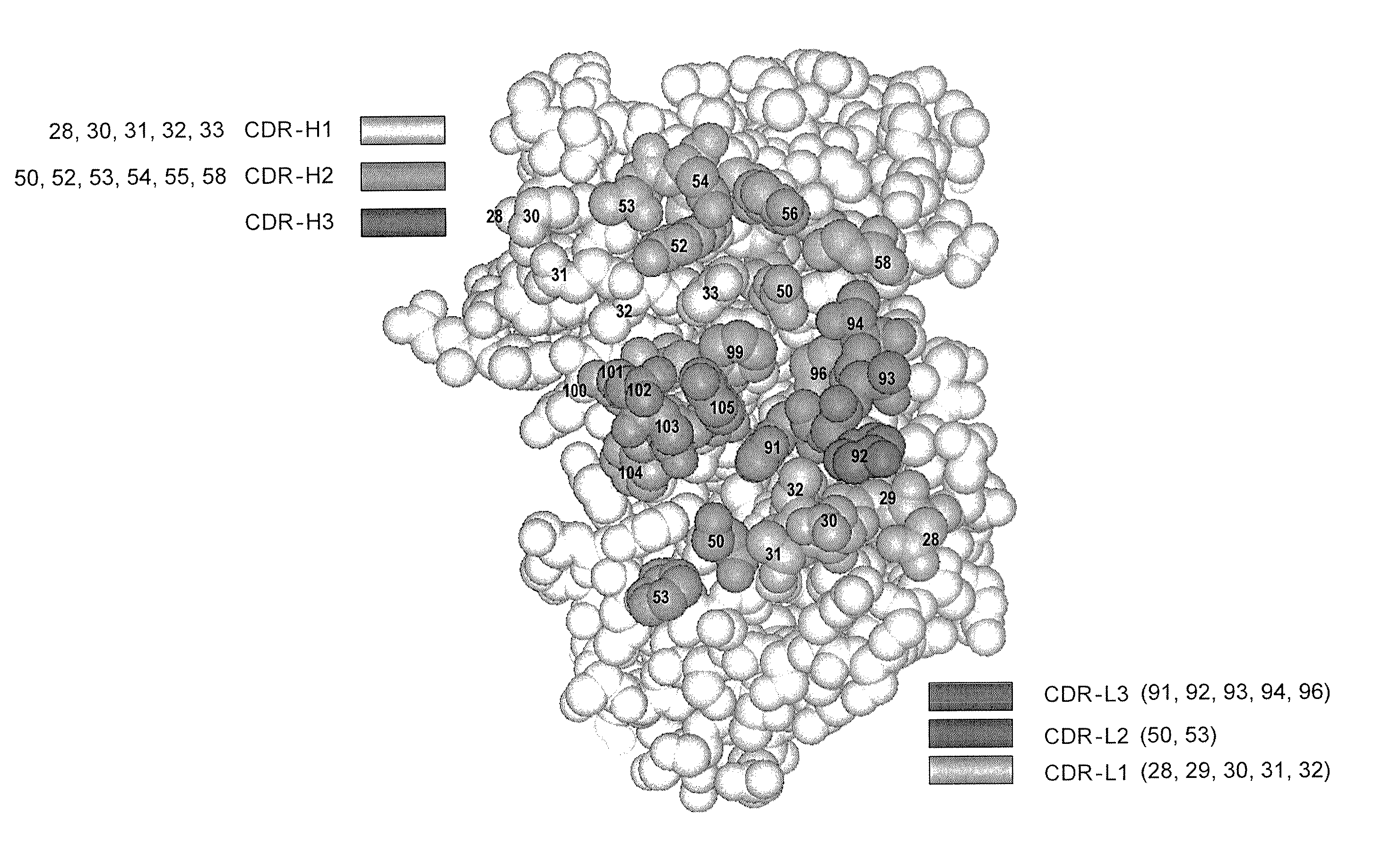

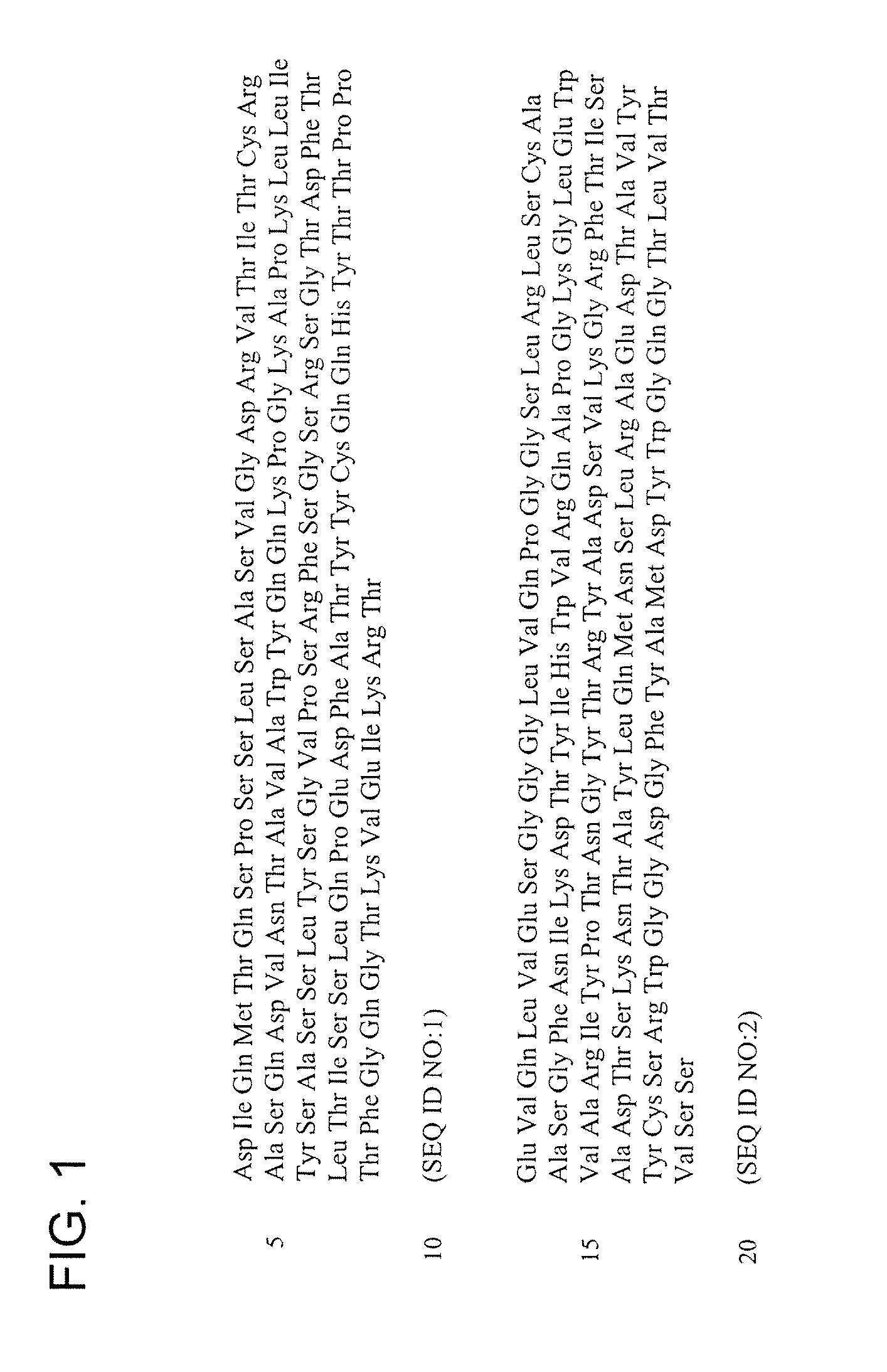

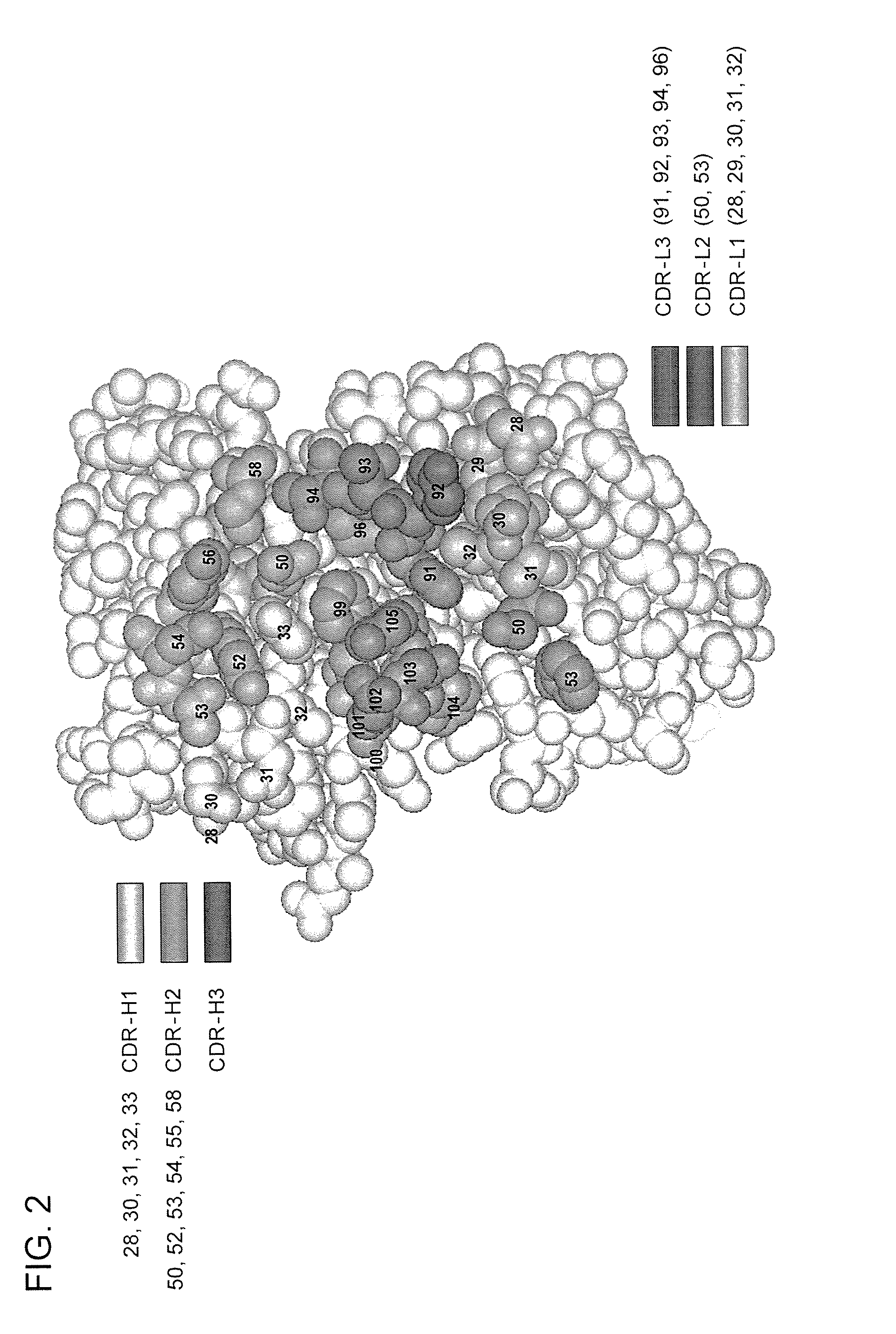

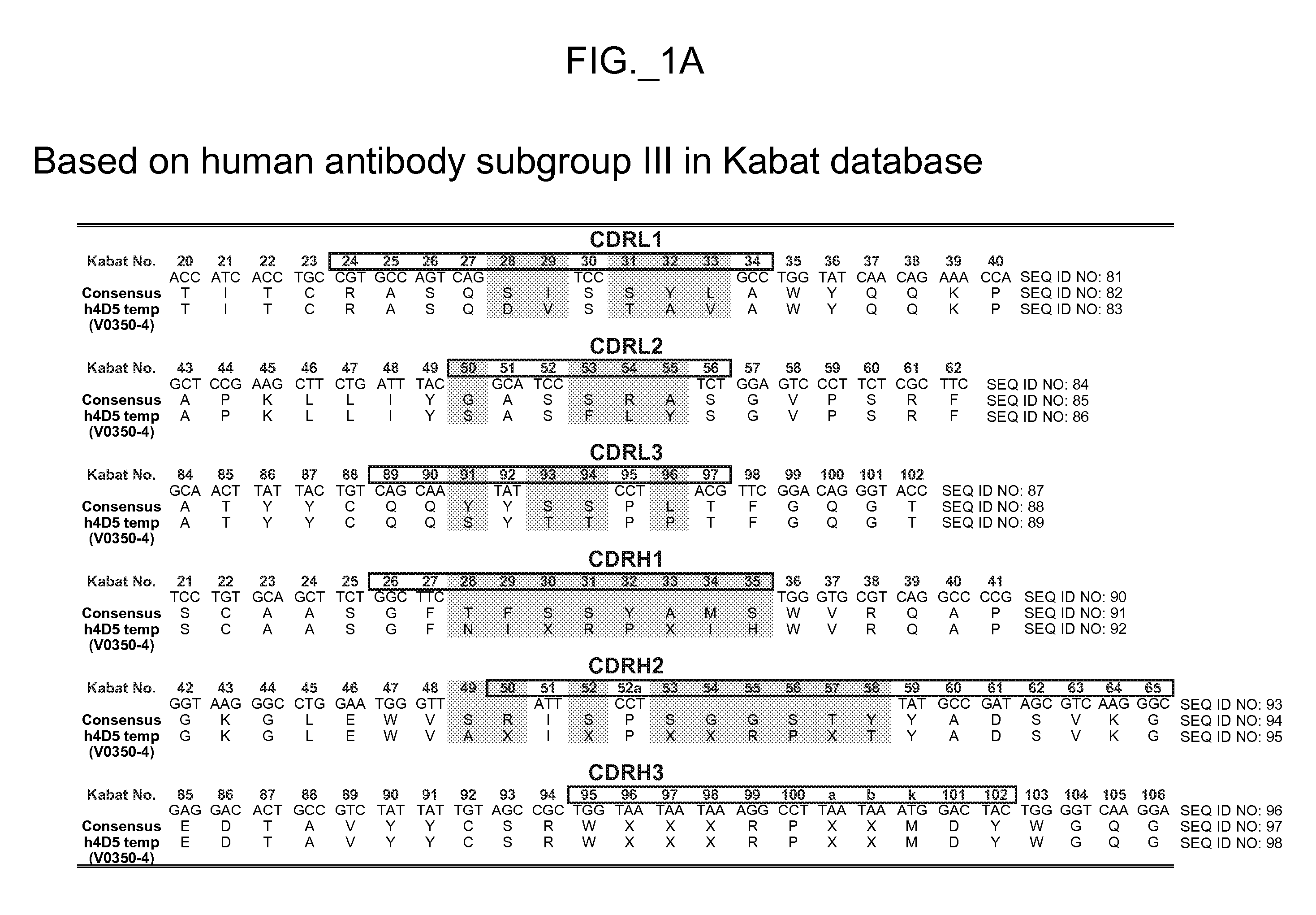

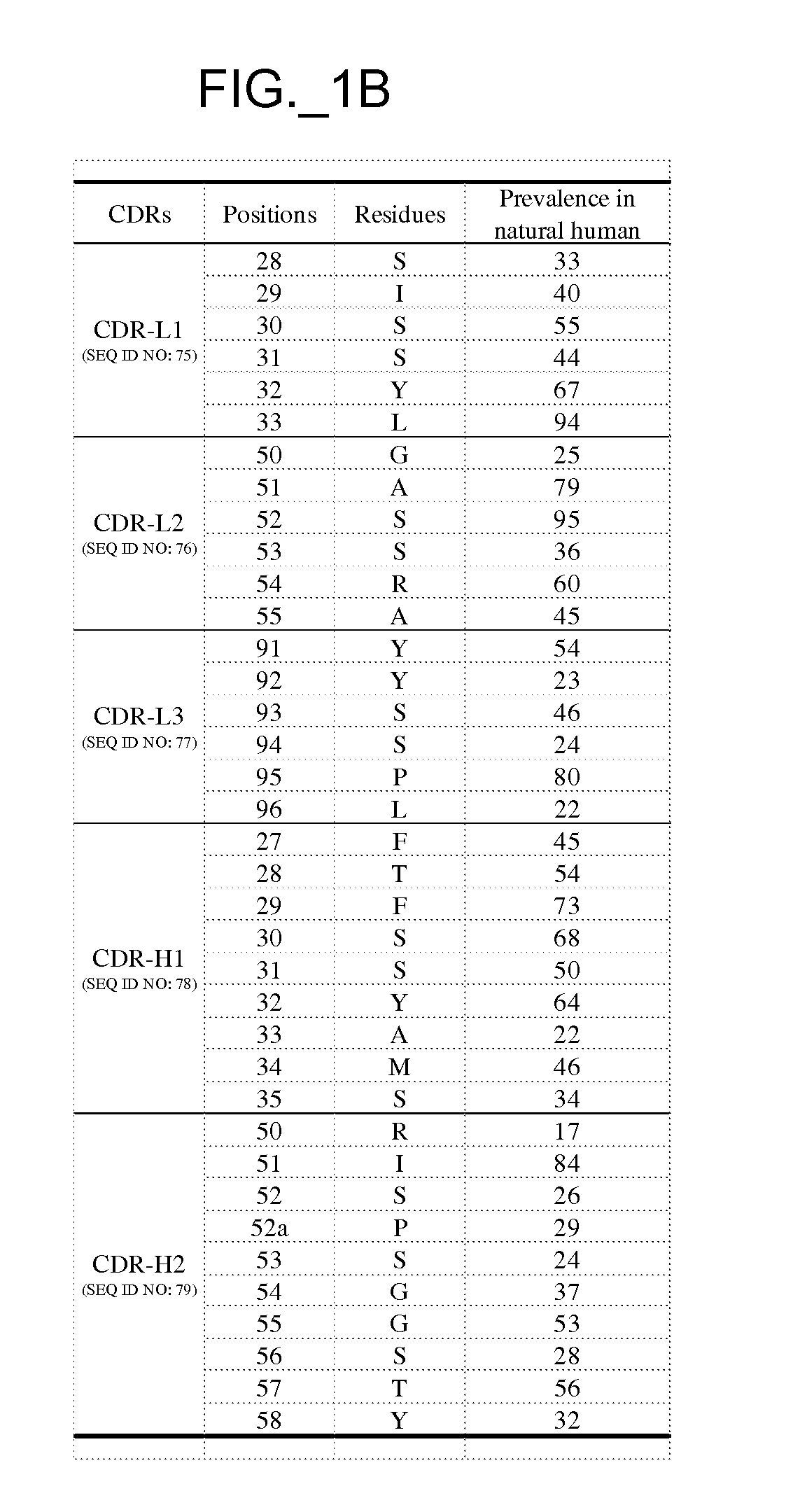

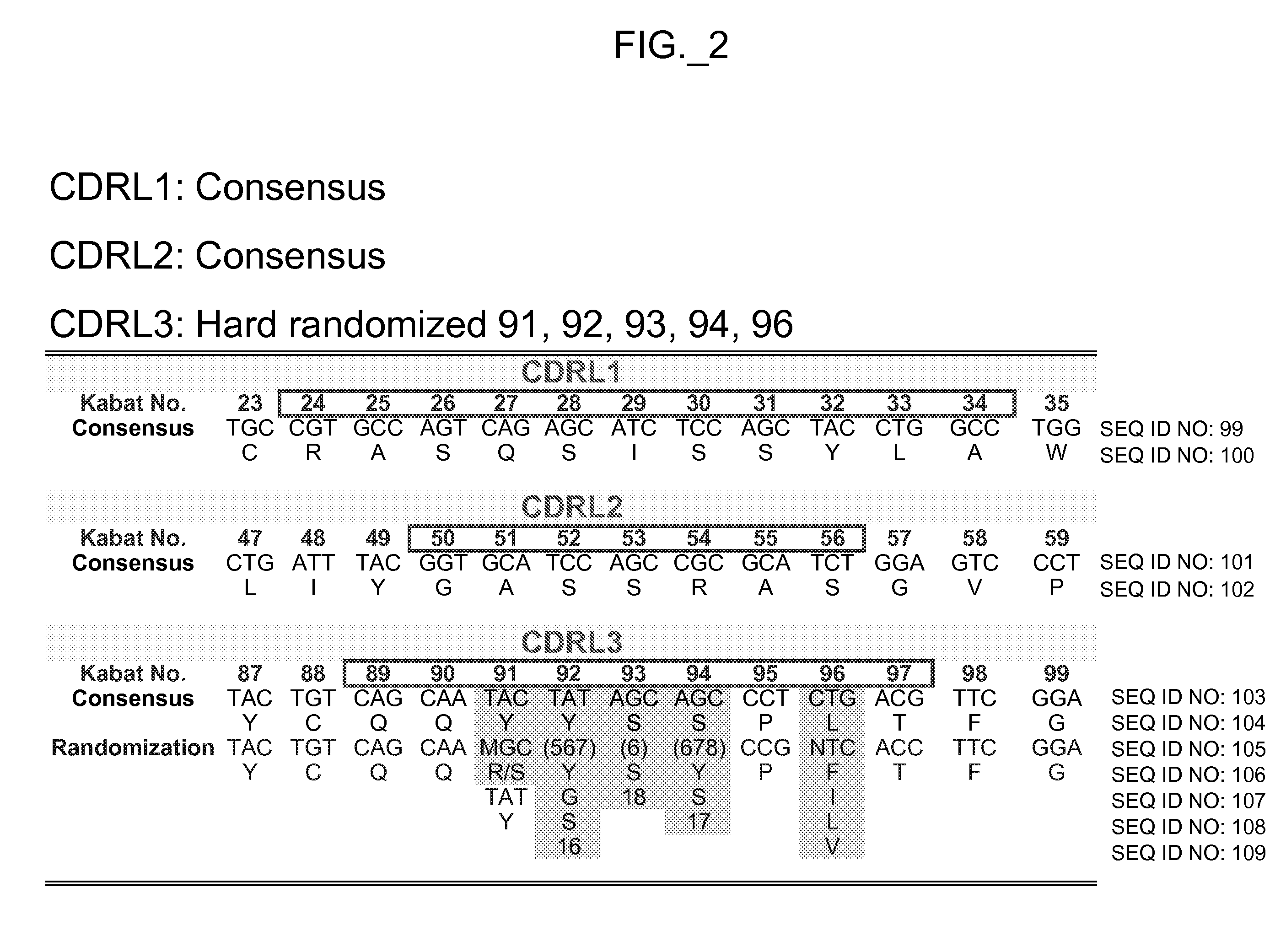

The invention provides variant CDRs comprising highly restricted amino acid sequence diversity. These polypeptides provide a flexible and simple source of sequence diversity that can be used as a source for identifying novel antigen binding polypeptides. The invention also provides these polypeptides as fusion polypeptides to heterologous polypeptides such as at least a portion of phage or viral coat proteins, tags and linkers. Libraries comprising a plurality of these polypeptides are also provided. In addition, methods of and compositions for generating and using these polypeptides and libraries are provided.

Owner:GENENTECH INC

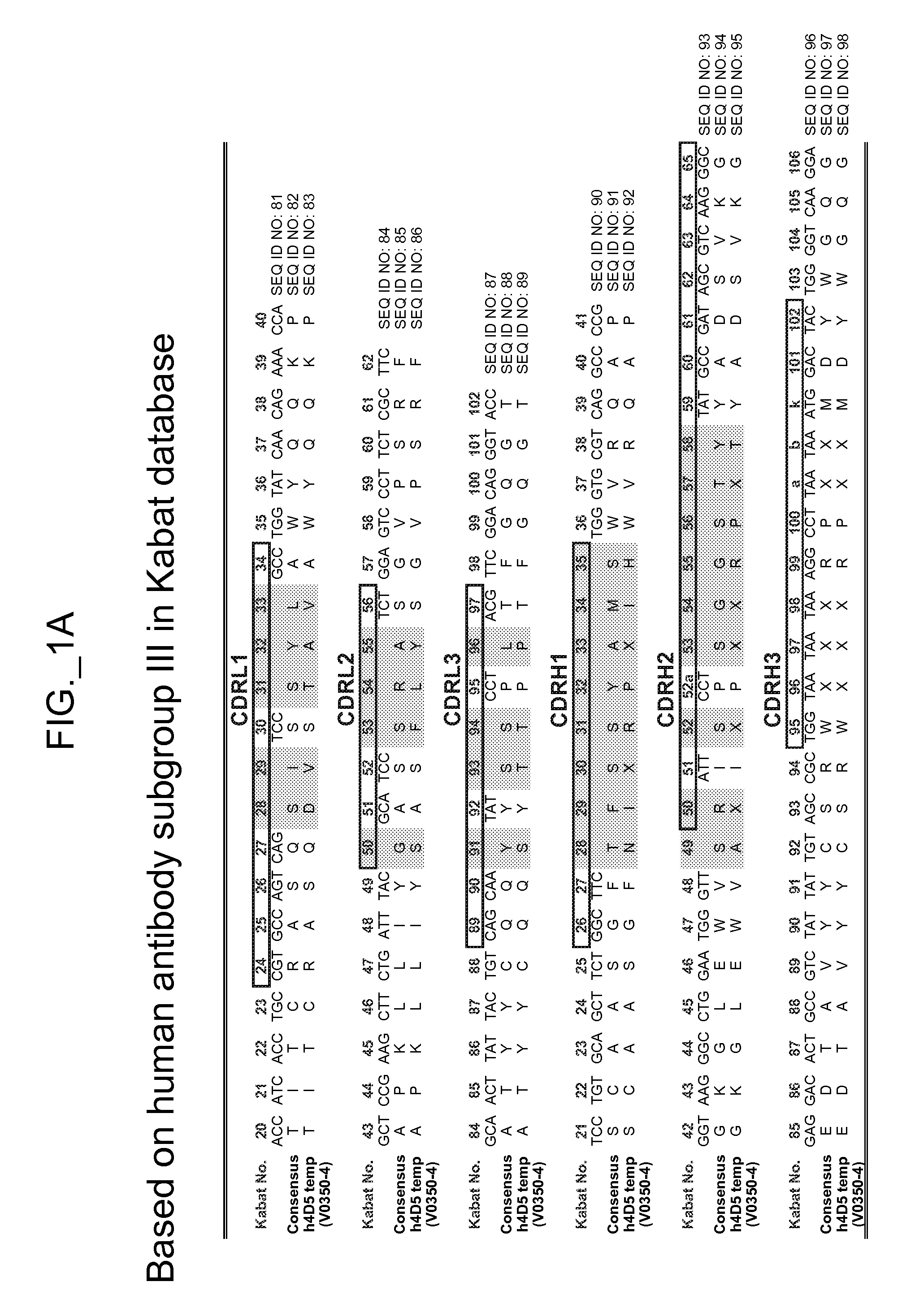

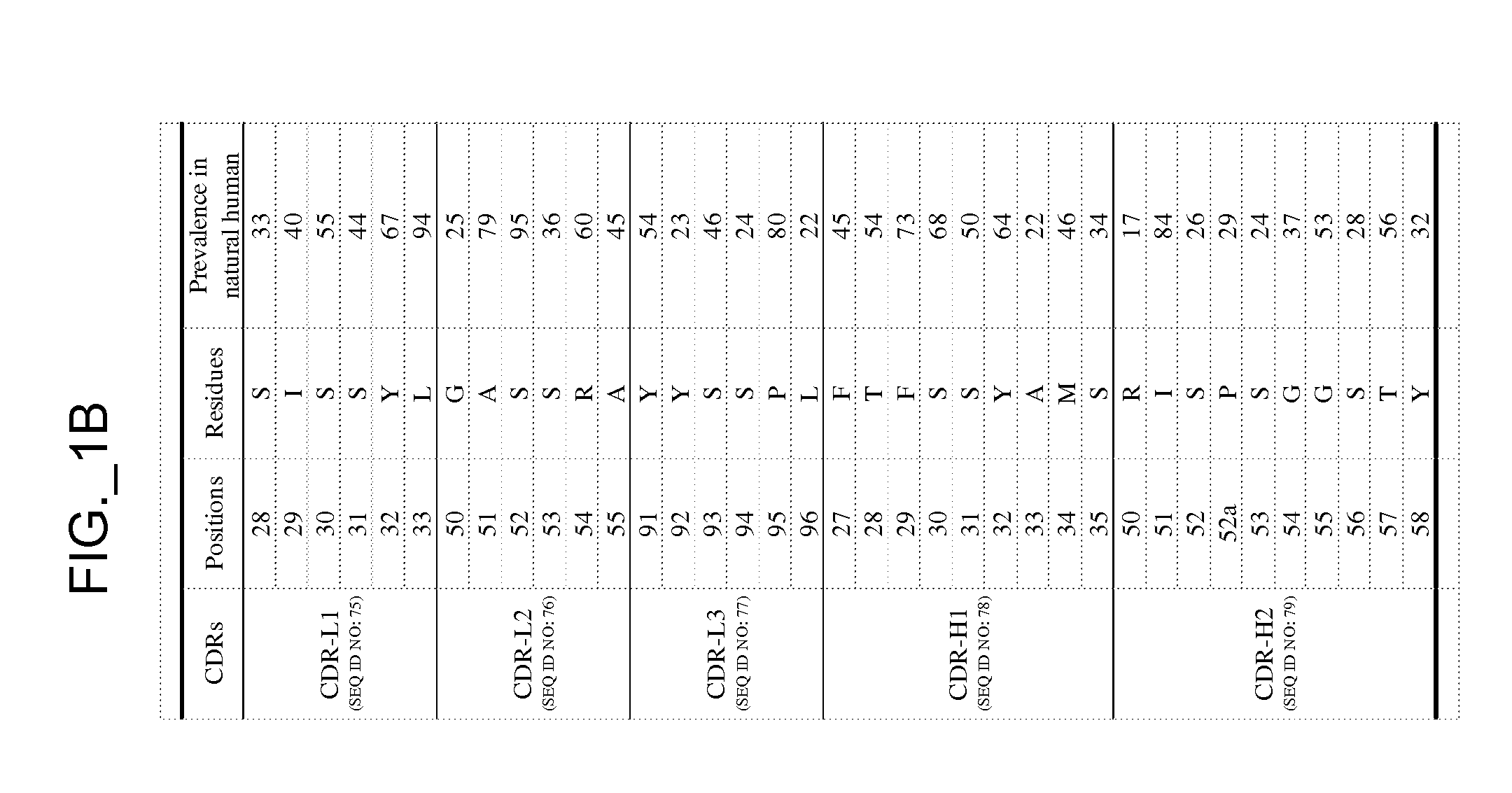

Binding polypeptides with diversified and consensus vh/vl hypervariable sequences

ActiveUS20070160598A1Raise the possibilitySmall sizeAnimal cellsSugar derivativesAntibody hypervariable regionBioinformatics

The invention provides variant hypervariable regions comprising selected amino acid sequence diversity. Libraries comprising a plurality of these polypeptides are also provided. In addition, methods of and compositions for generating and using these polypeptides and libraries are provided.

Owner:GENENTECH INC

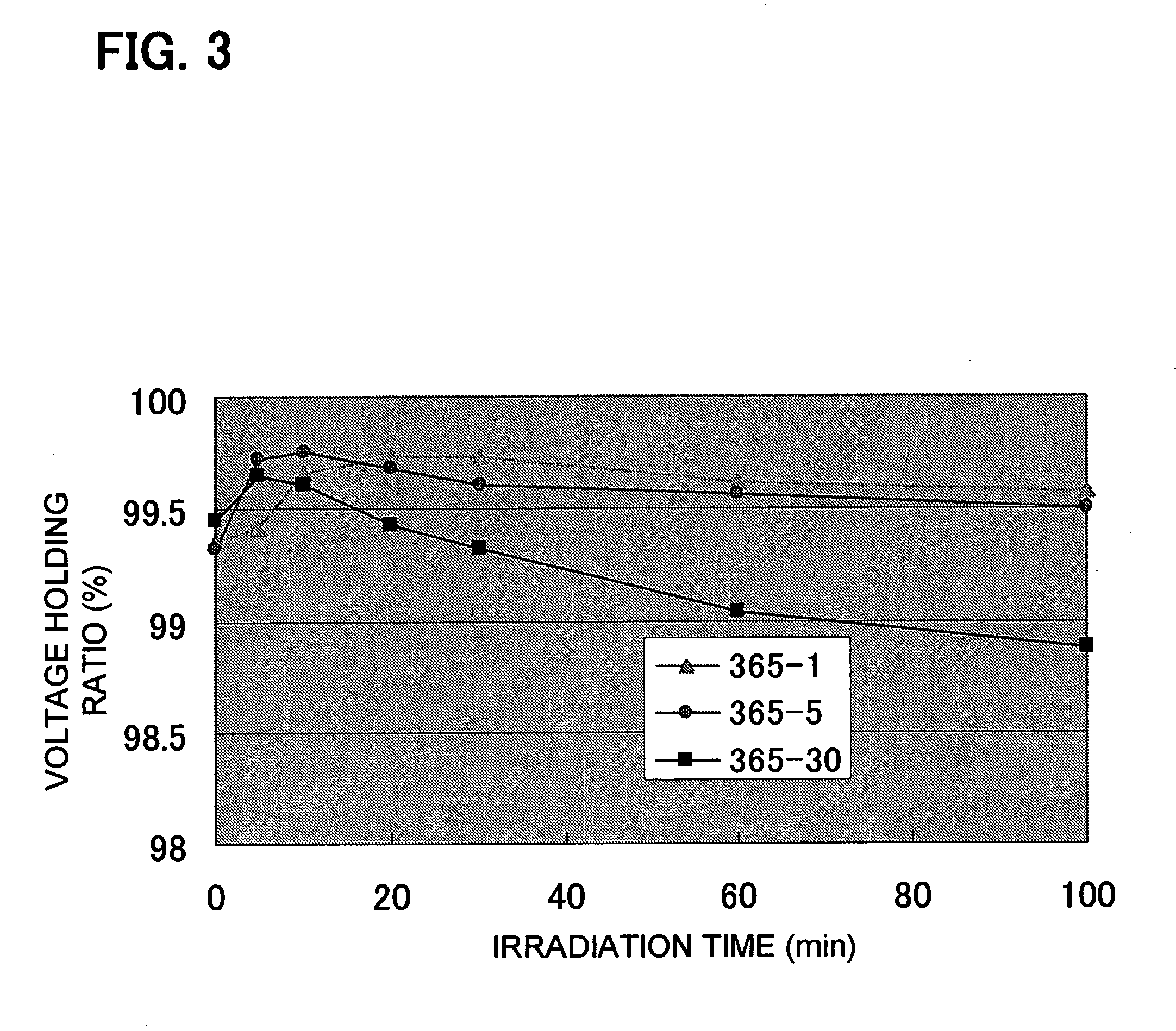

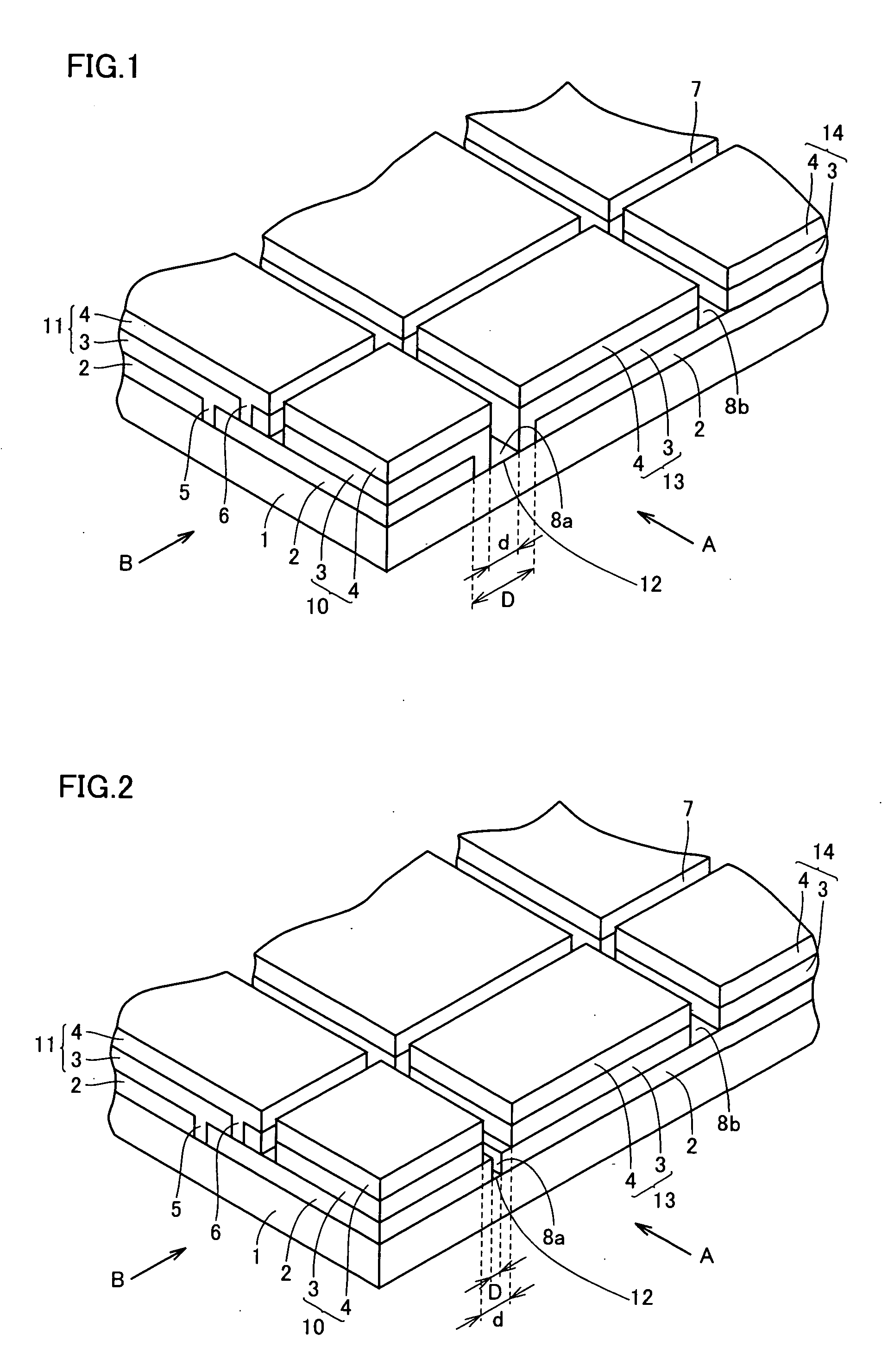

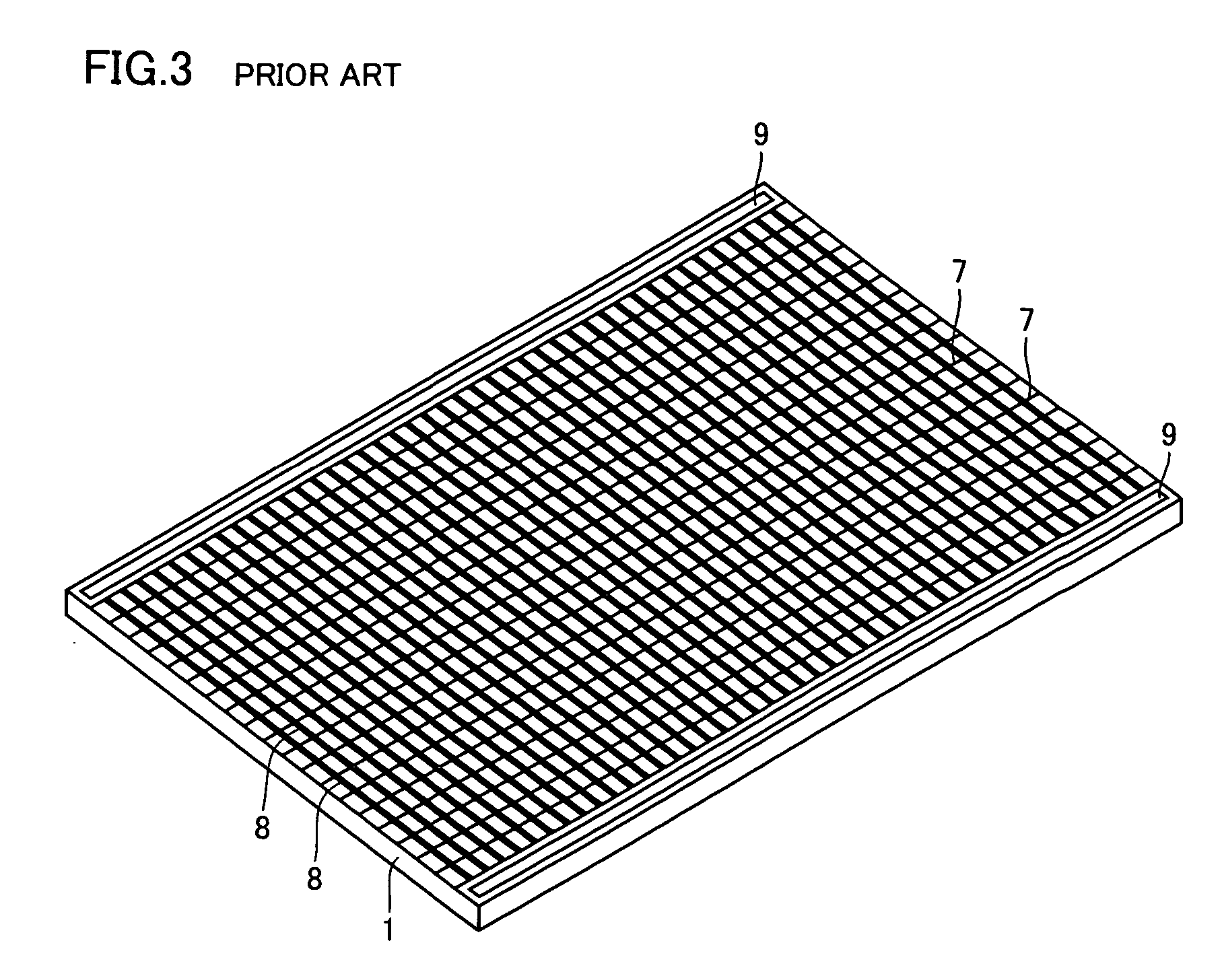

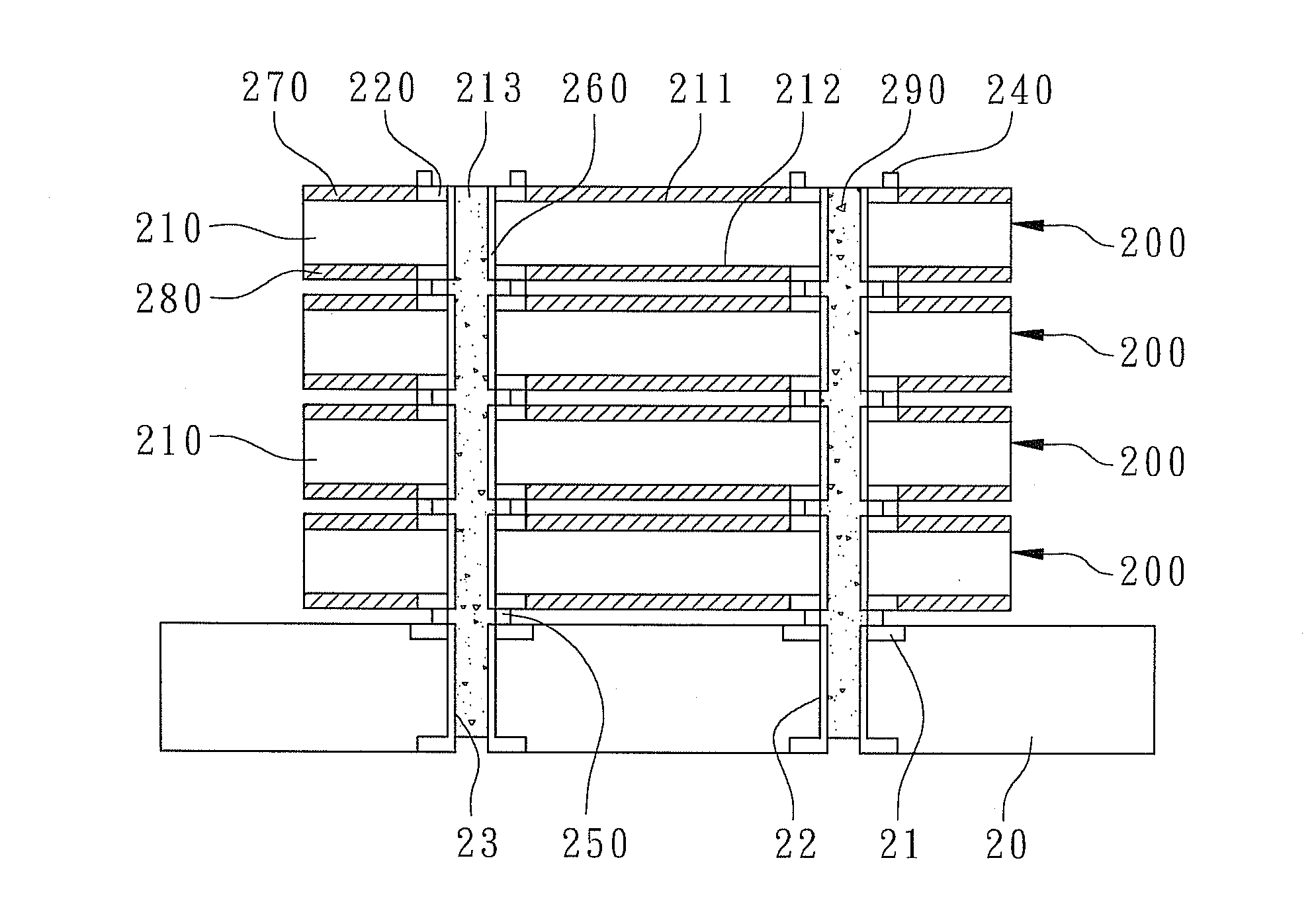

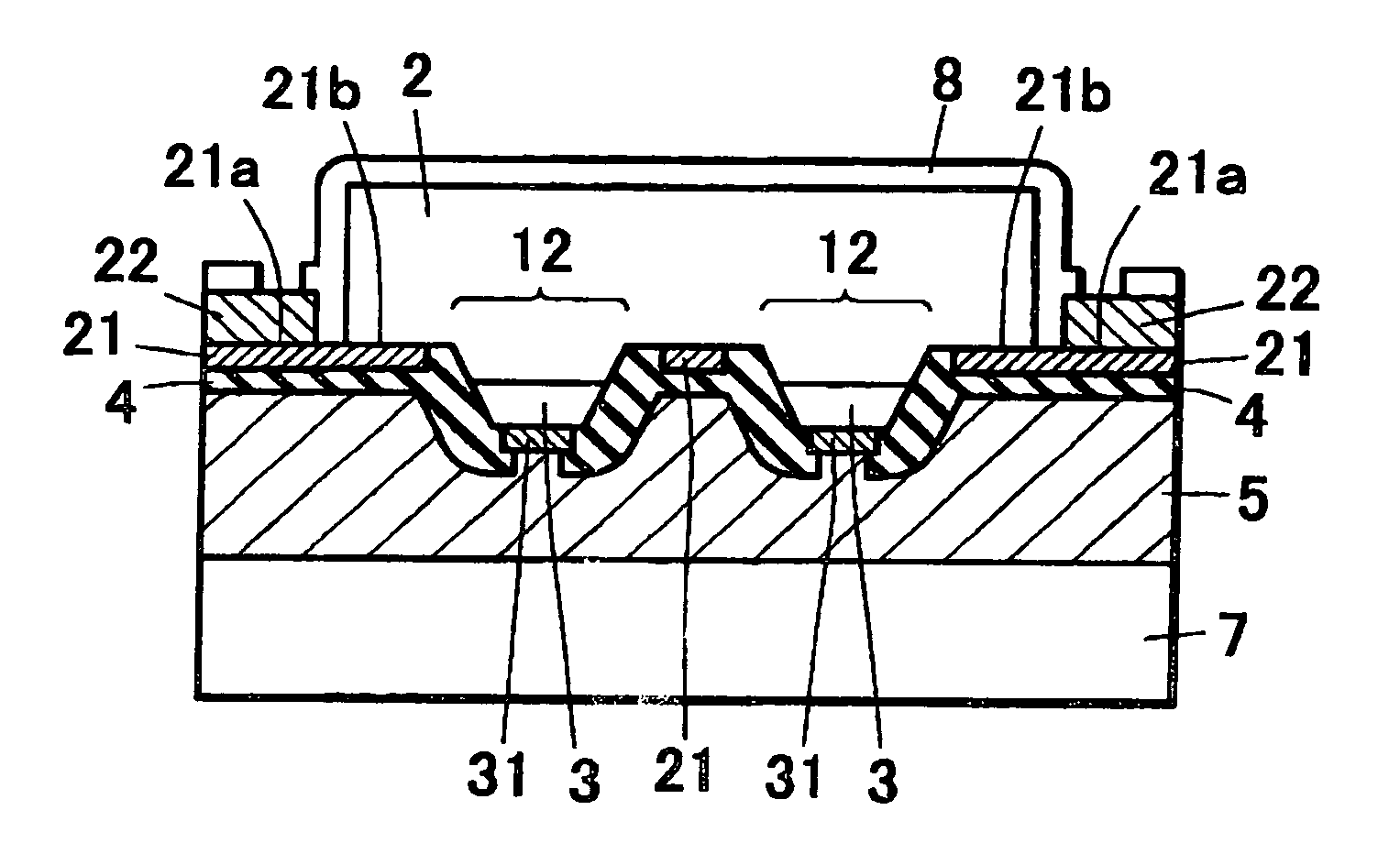

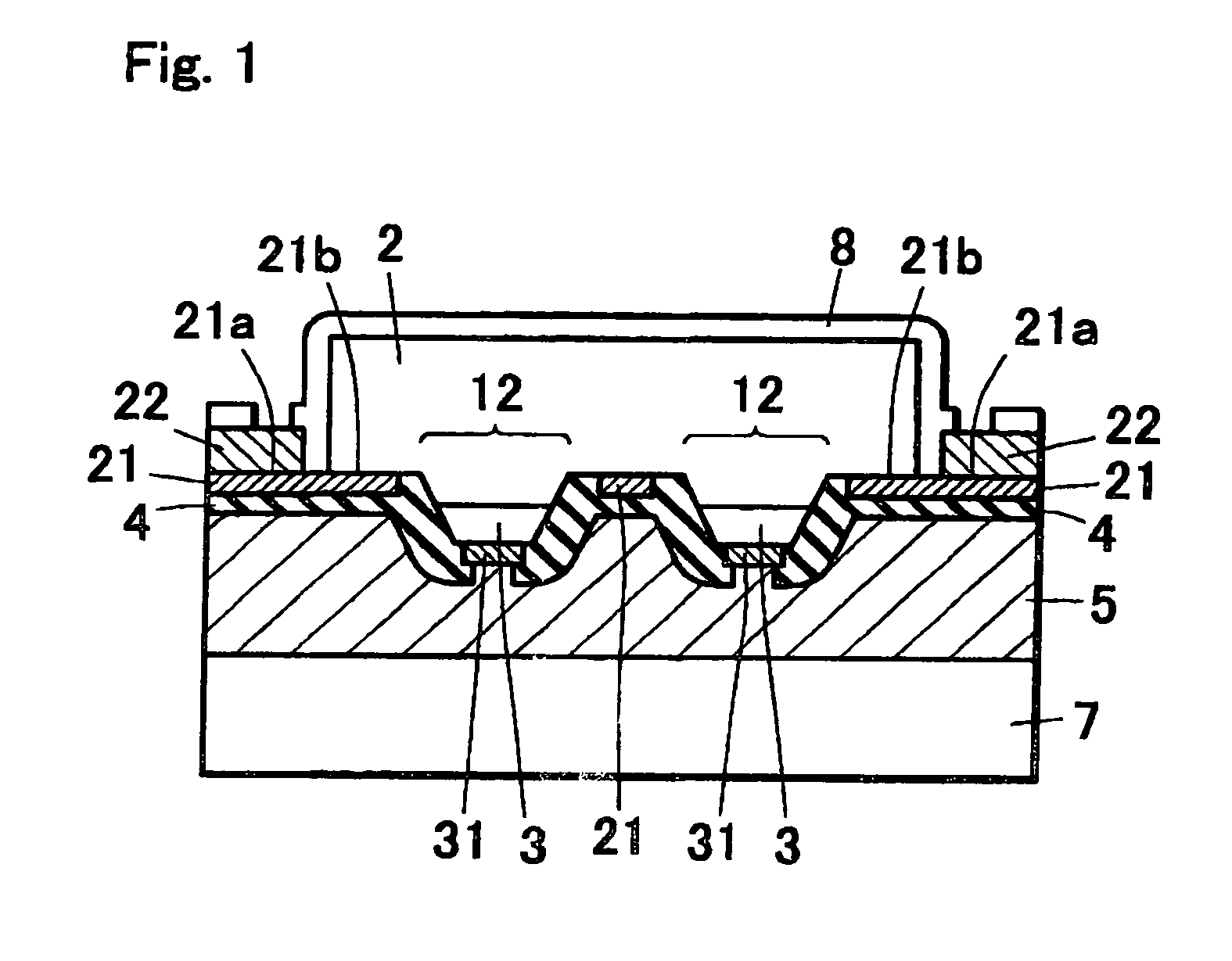

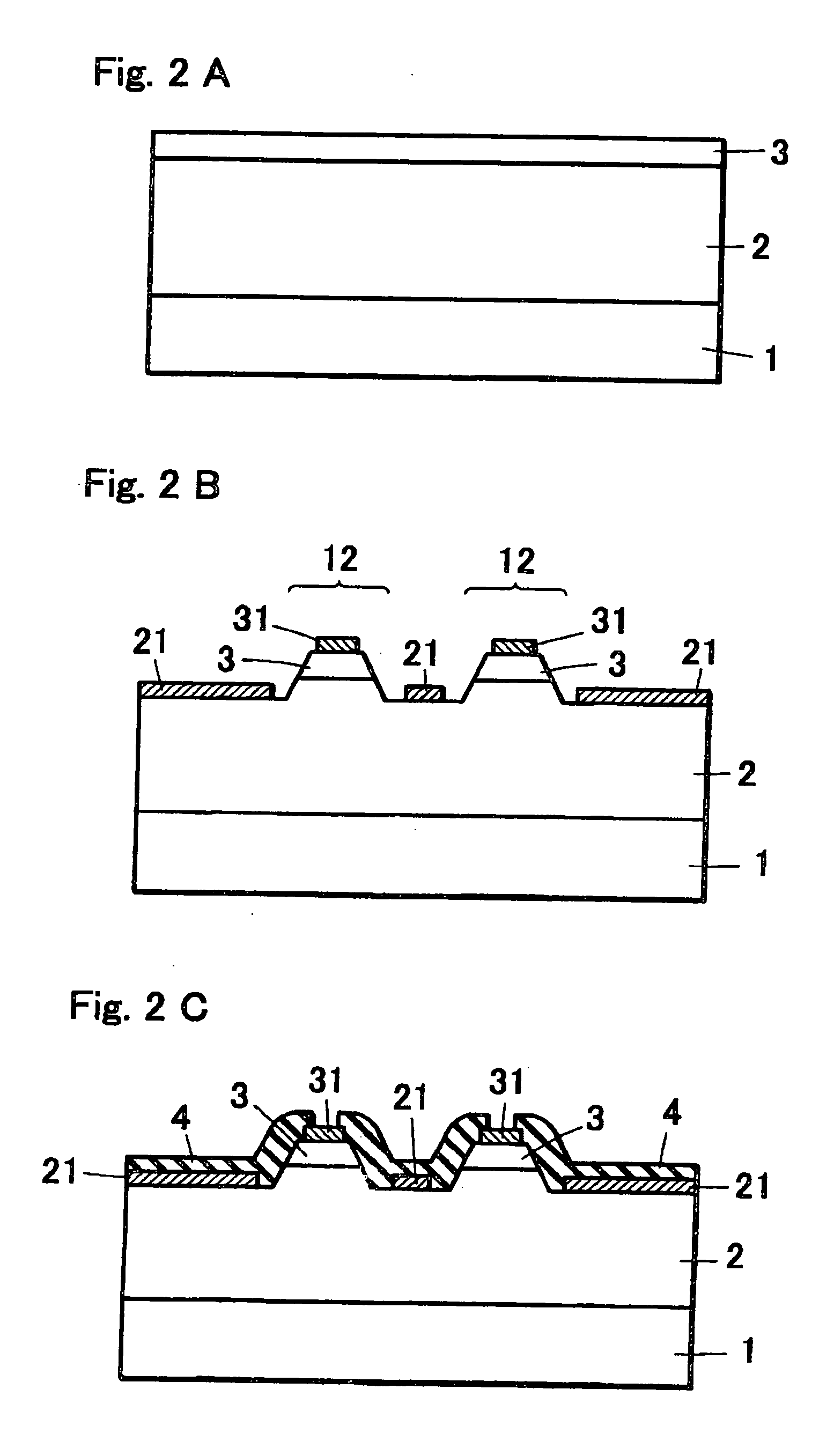

Liquid crystal display device

InactiveUS20060066793A1Low costImprove production yieldLiquid crystal compositionsNon-linear opticsChemistryCompound (substance)

A high-performance liquid crystal display device is provided that can be manufactured at a low cost and a high production yield. In this liquid crystal display device, a liquid crystal composition comprising liquid crystal molecules and a polymerizable compound that can be polymerized by ultraviolet rays or by a combination of ultraviolet rays and heat is disposed between a pair of substrates; the polymerizable compound is polymerized, forming a liquid crystal layer, by an operation including irradiation of ultraviolet rays that do not contain wavelength components of not higher than 313 nm; and uneven portions are installed on the liquid crystal layer contacting surface, or a slit pattern is installed in an electrode, or uneven portions are installed on the liquid crystal layer contacting surface, and a slit pattern is installed in the electrode.

Owner:SHARP KK

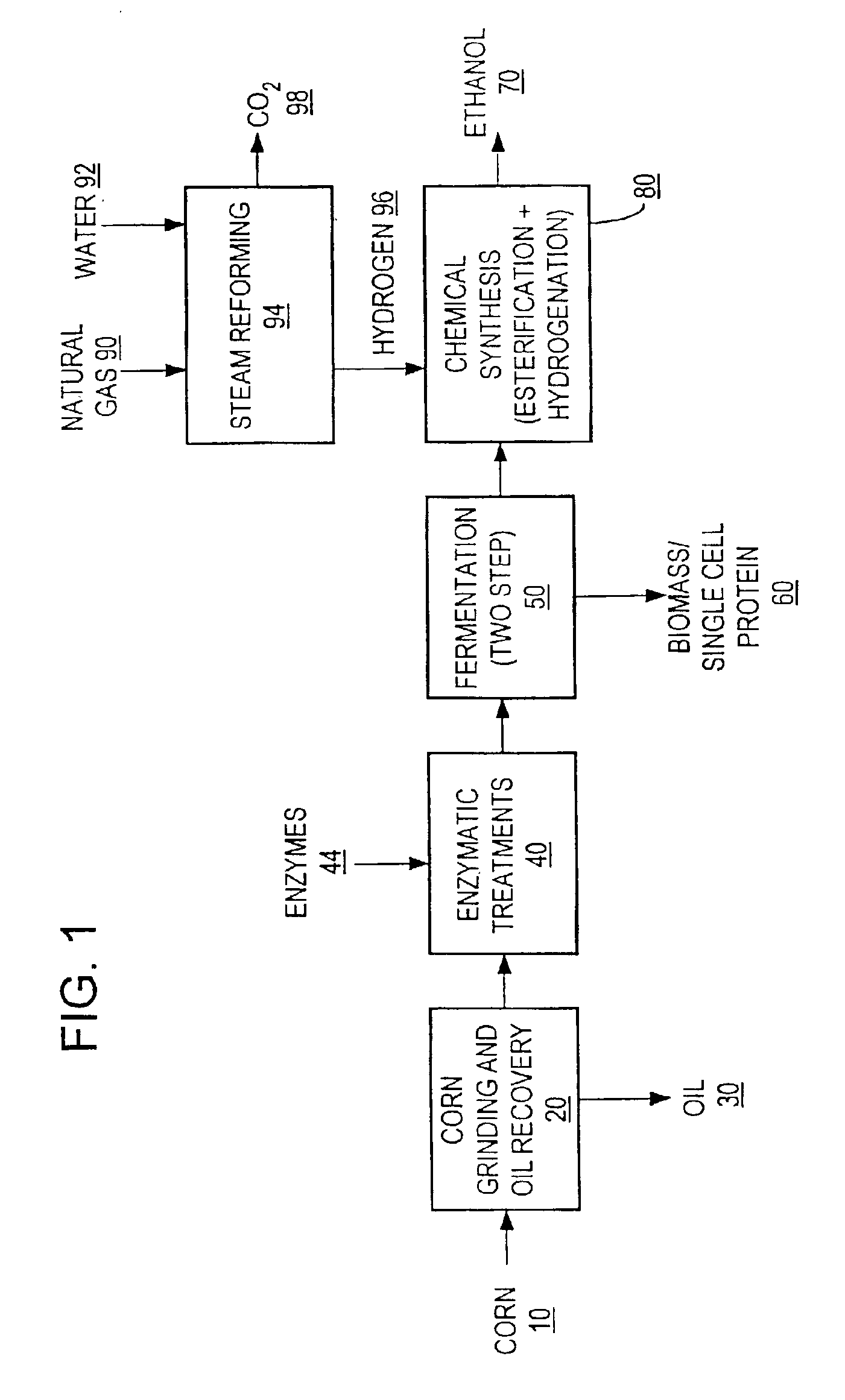

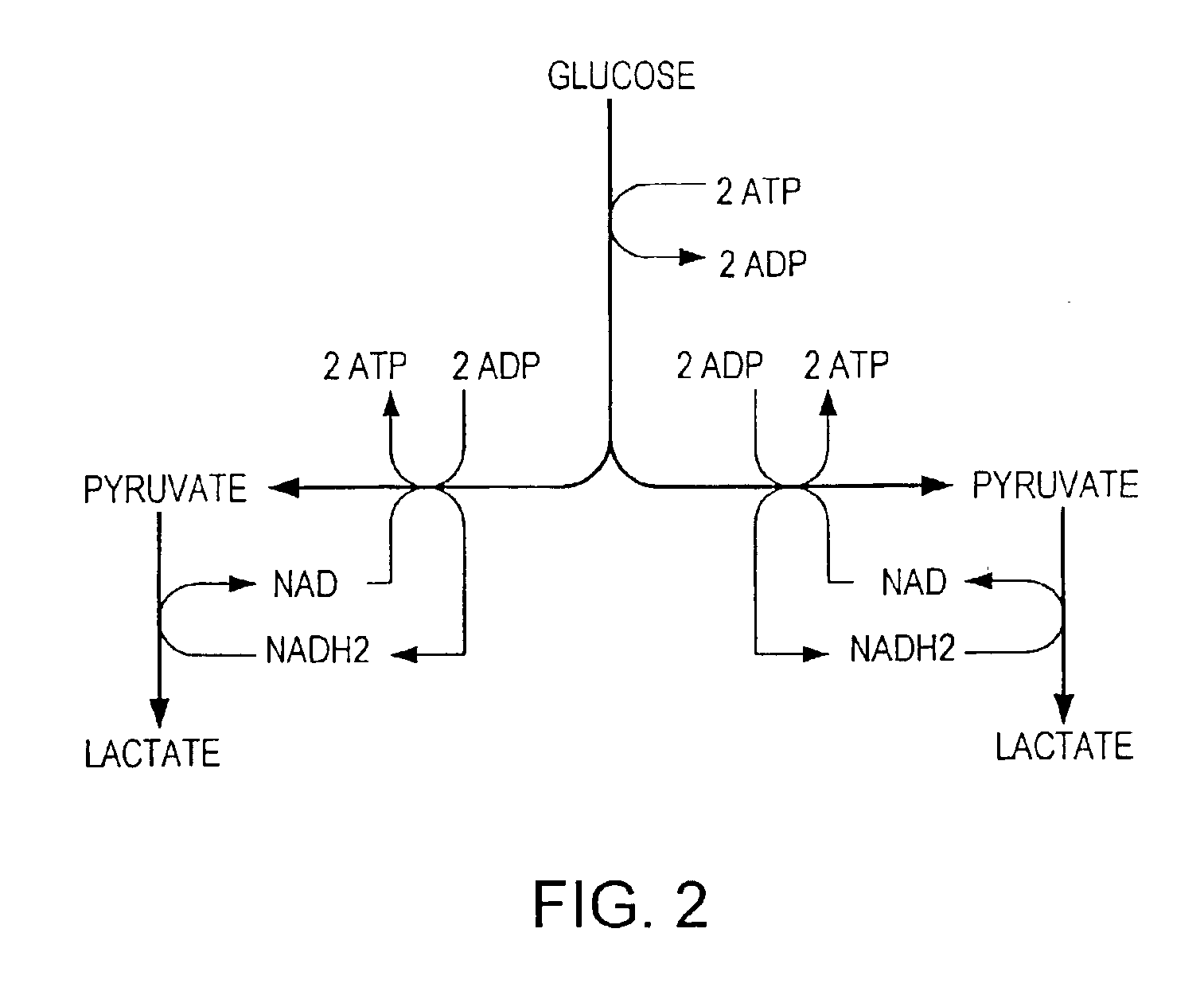

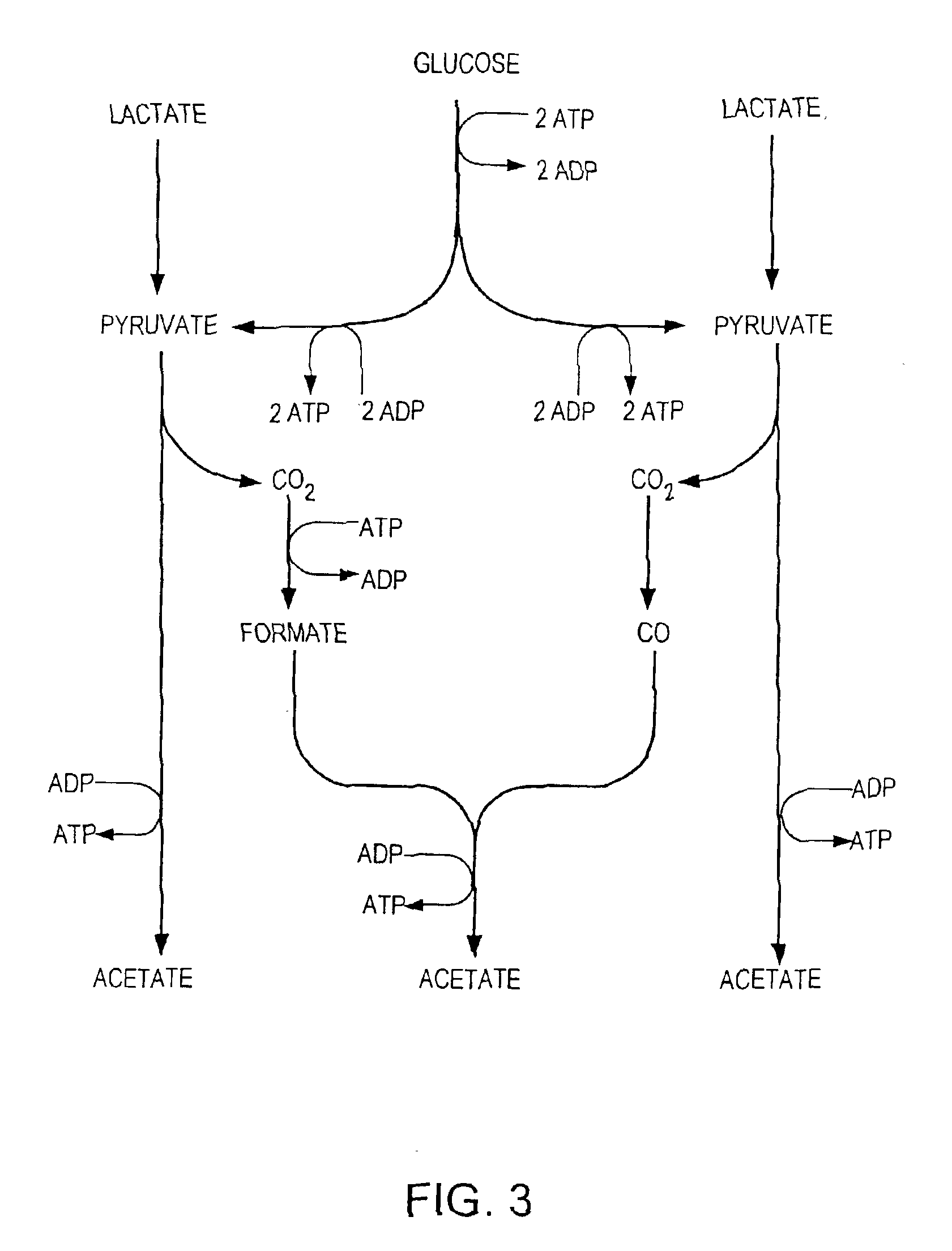

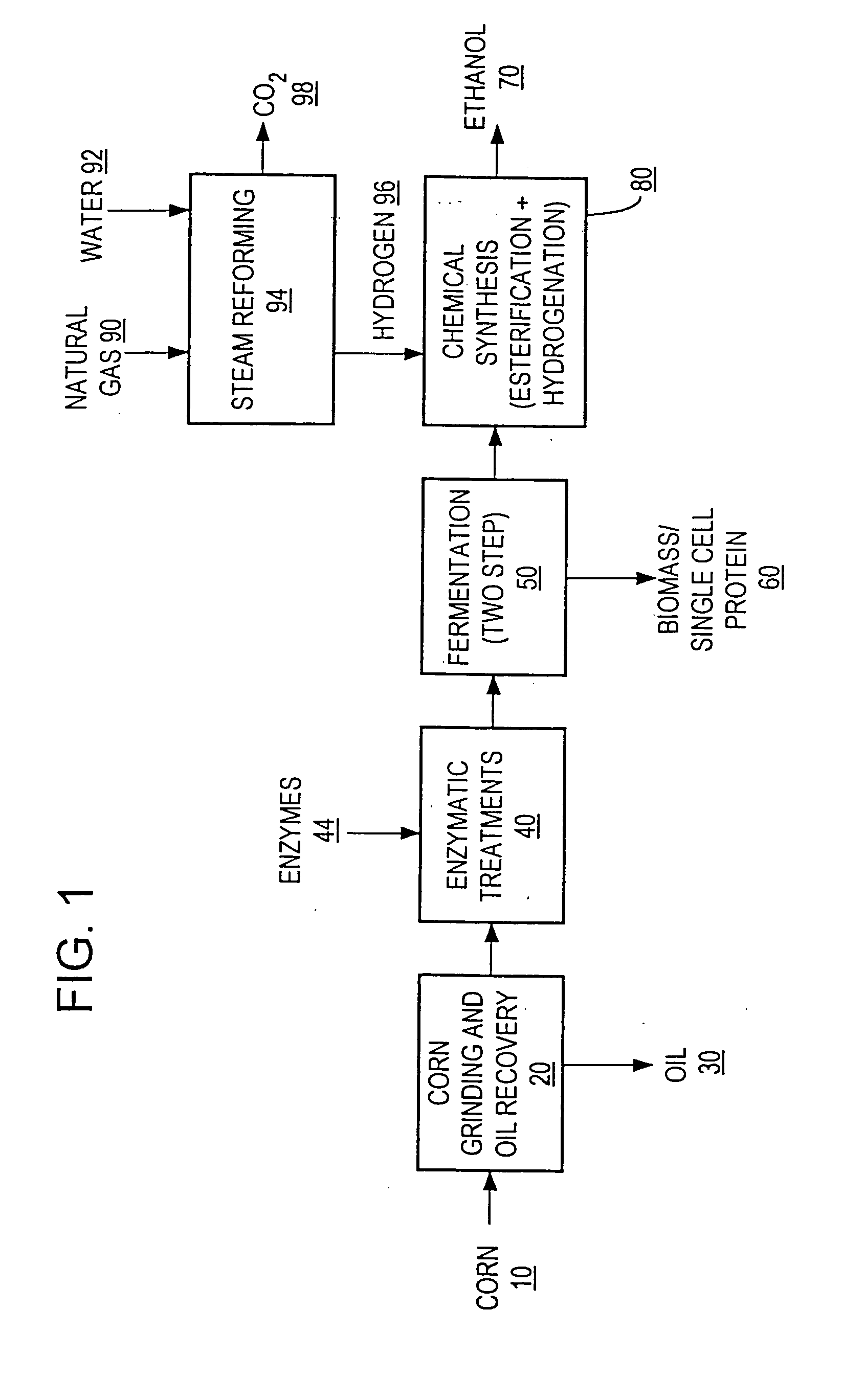

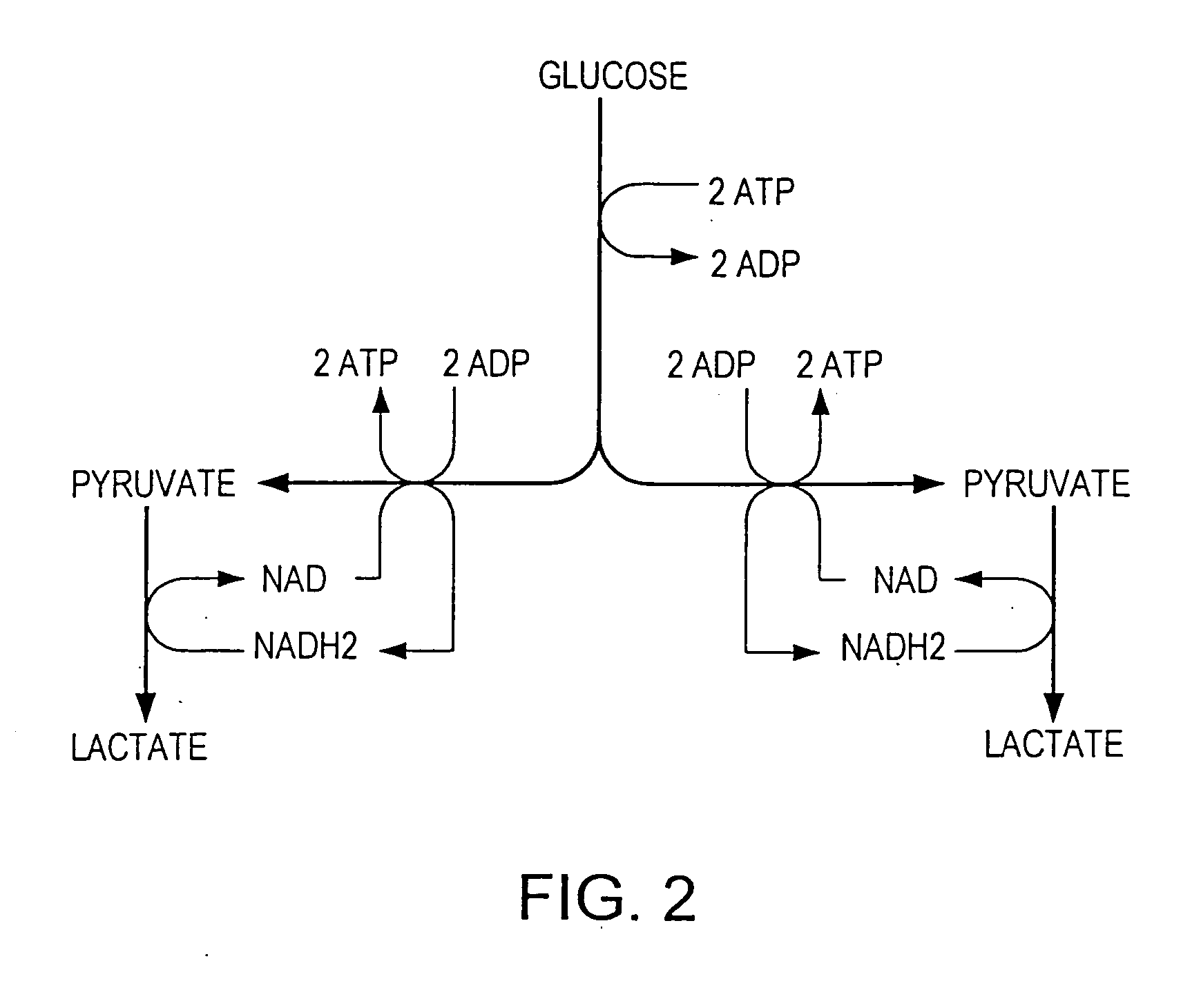

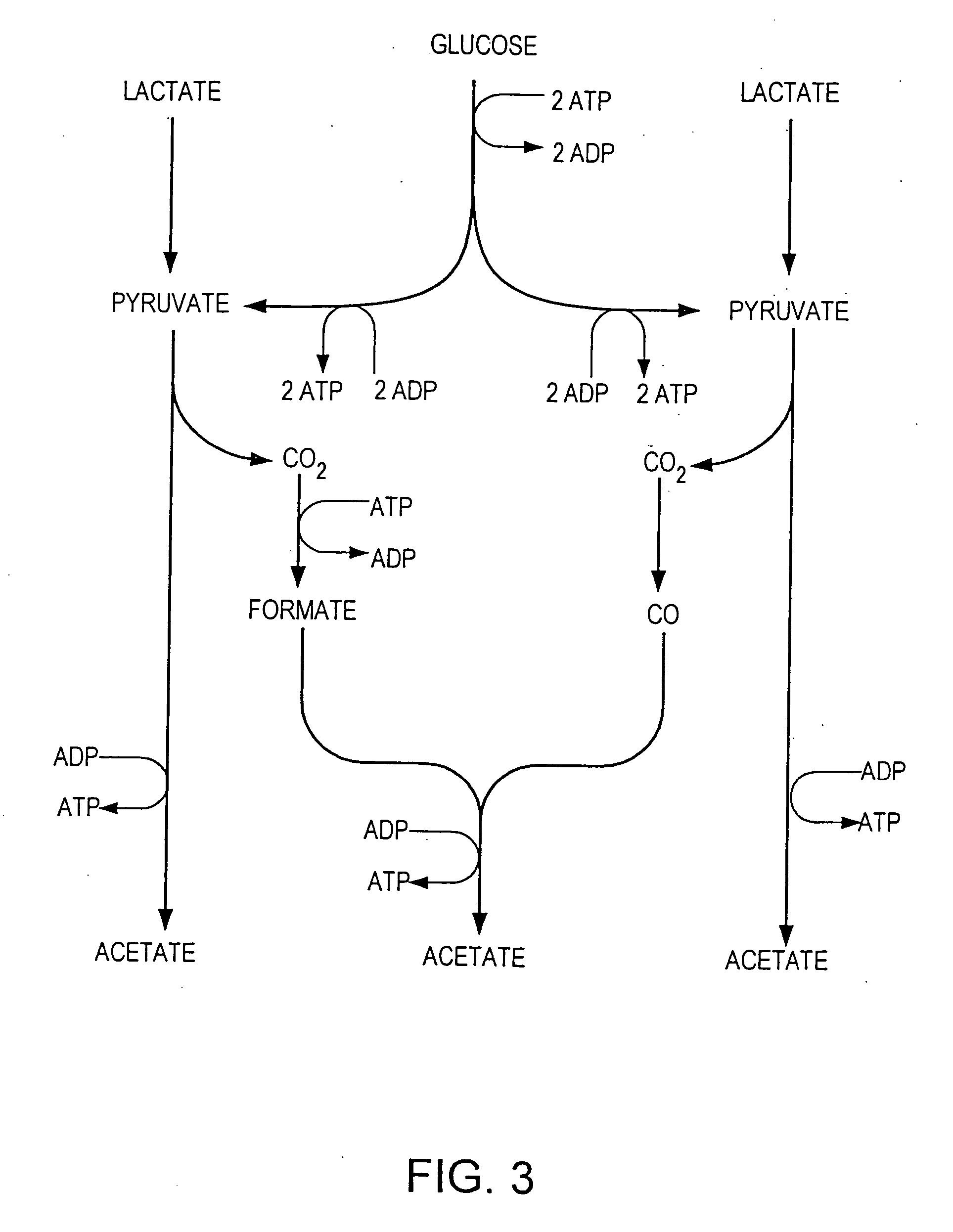

Process for producing ethanol

InactiveUS6927048B2High carbon yieldHigh protein concentrationOrganic compound preparationCarboxylic acid esters preparationAcetic acidHydrogenation reaction

A process for producing ethanol including a combination of biochemical and synthetic conversions results in high yield ethanol production with concurrent production of high value coproducts. An acetic acid intermediate is produced from carbohydrates, such as corn, using enzymatic milling and fermentation steps, followed by conversion of the acetic acid into ethanol using esterification and hydrogenation reactions. Coproducts can include corn oil, and high protein animal feed containing the biomass produced in the fermentation.

Owner:ZEACHEM

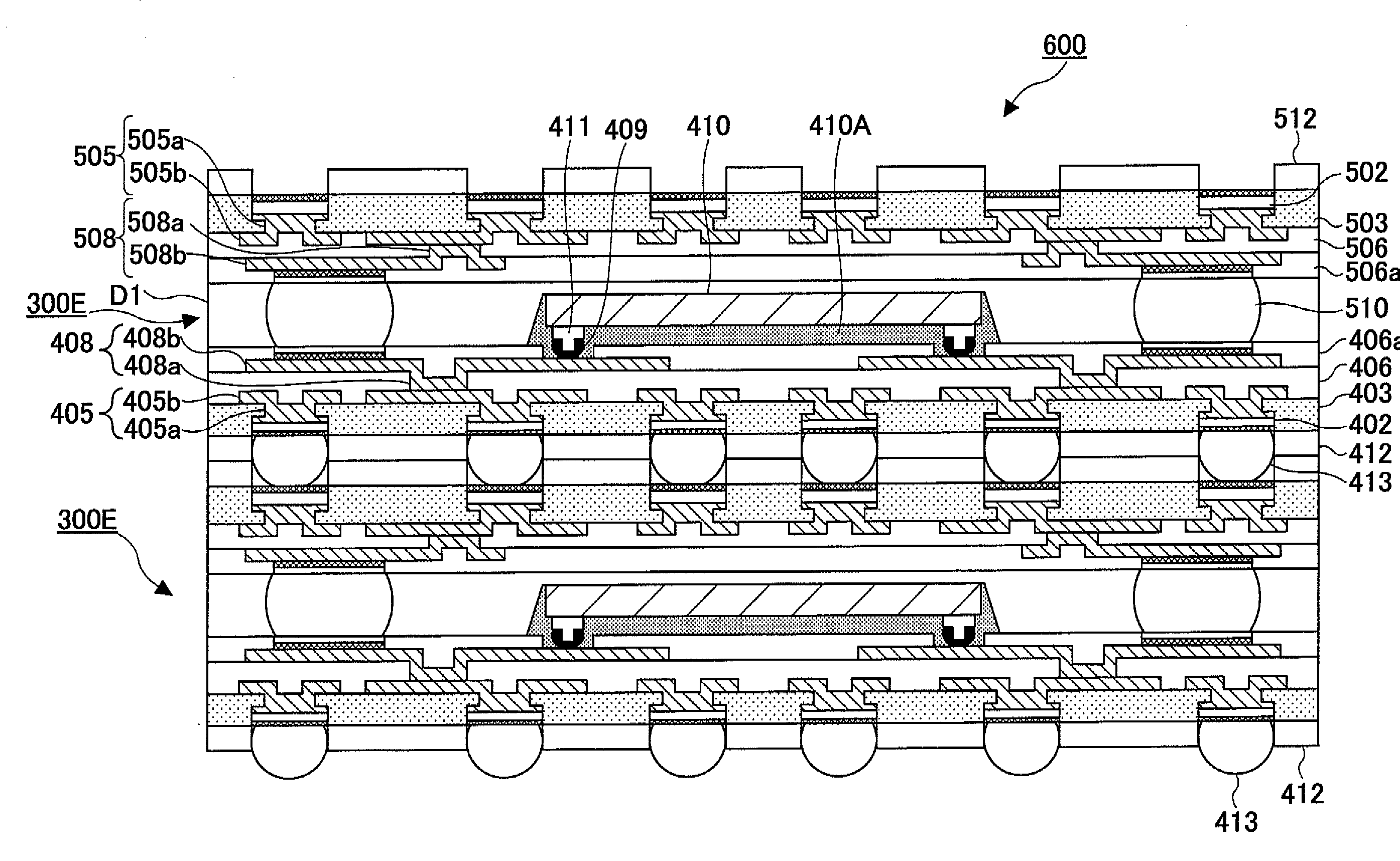

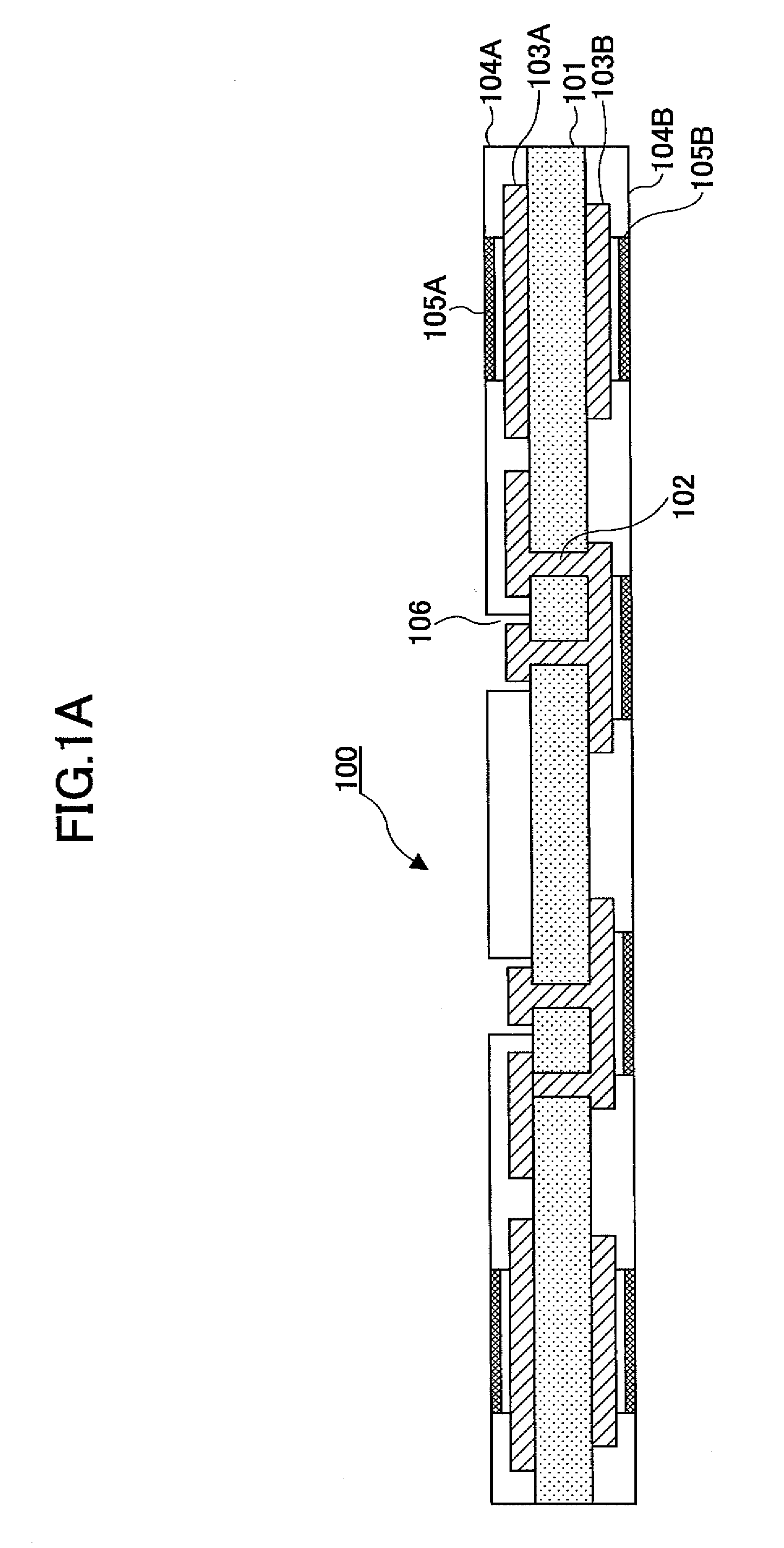

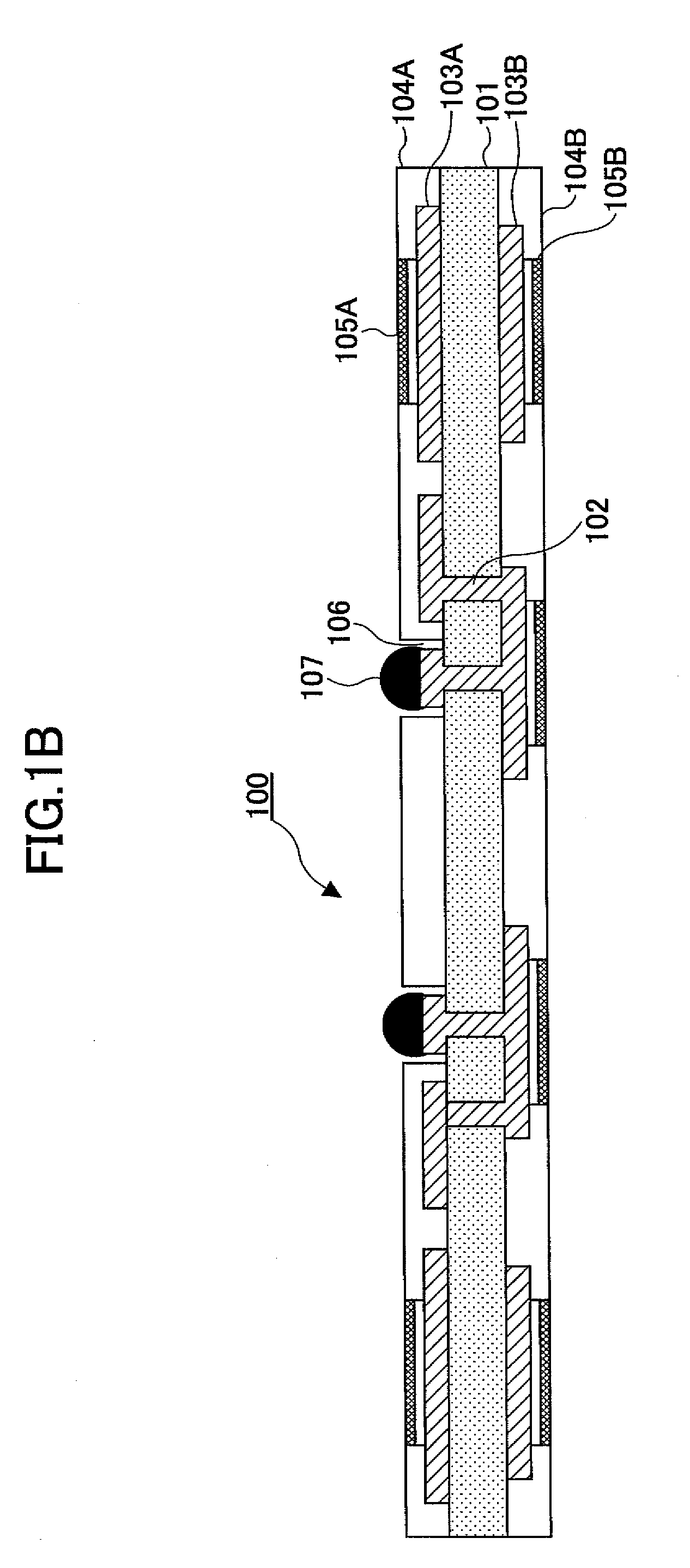

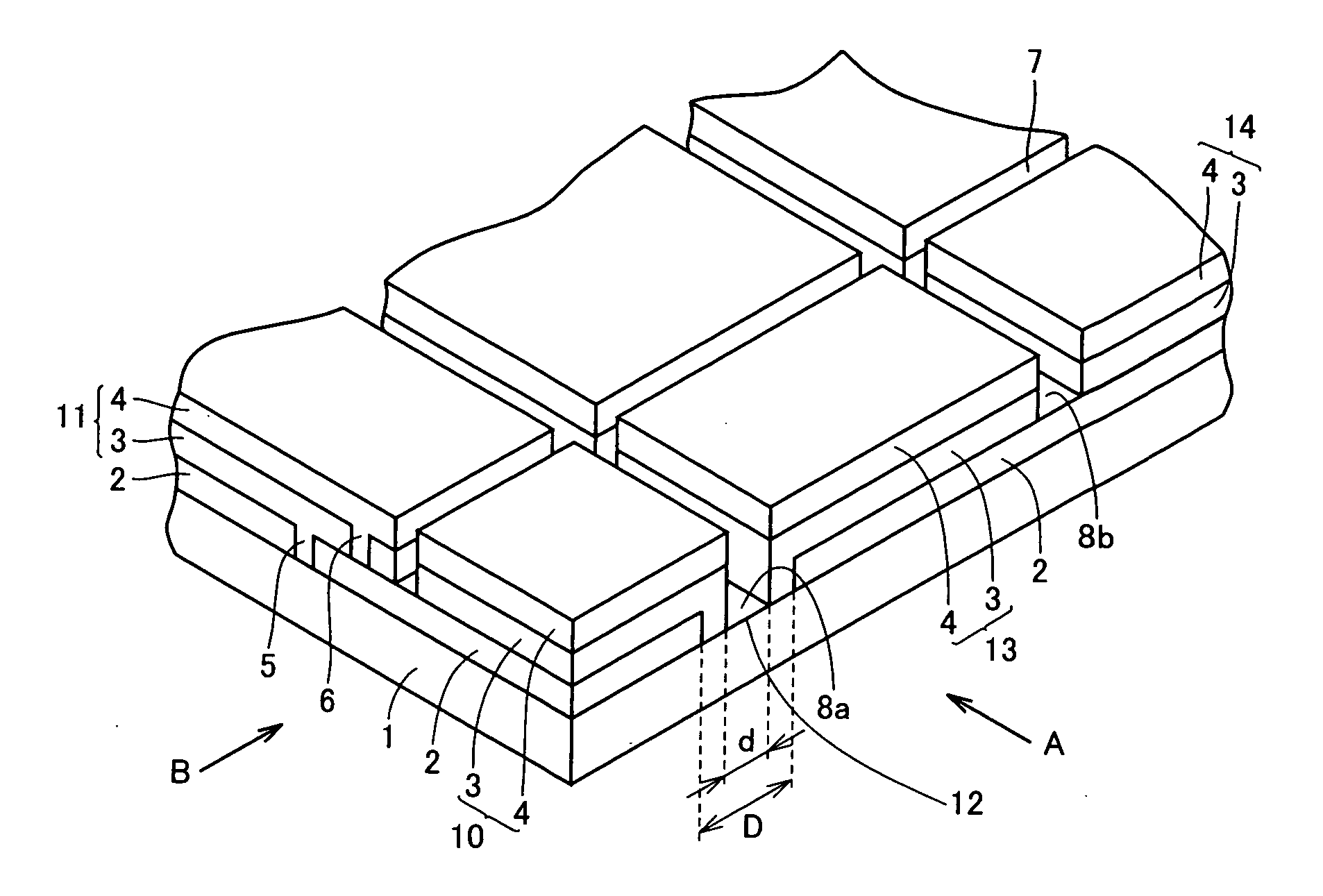

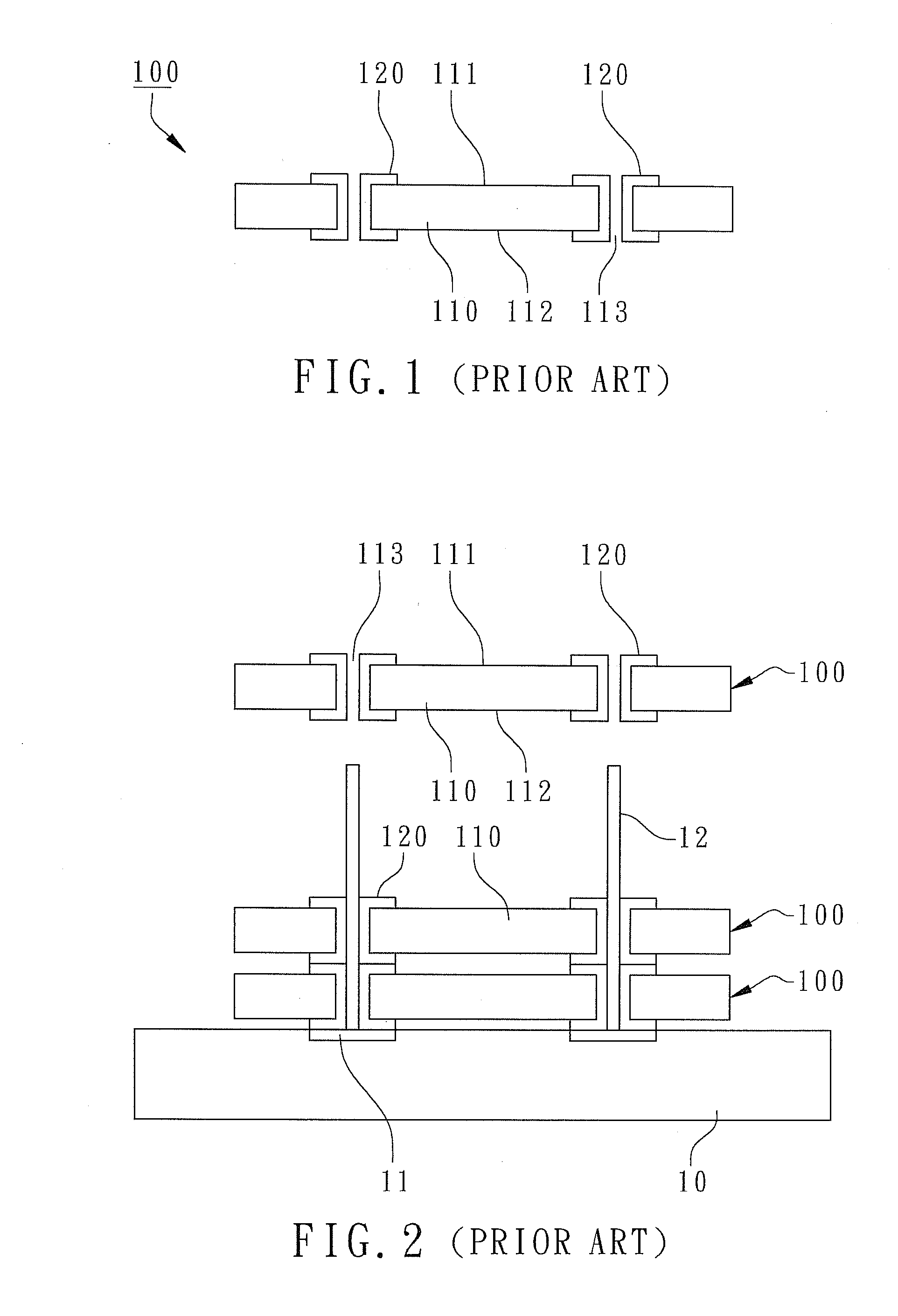

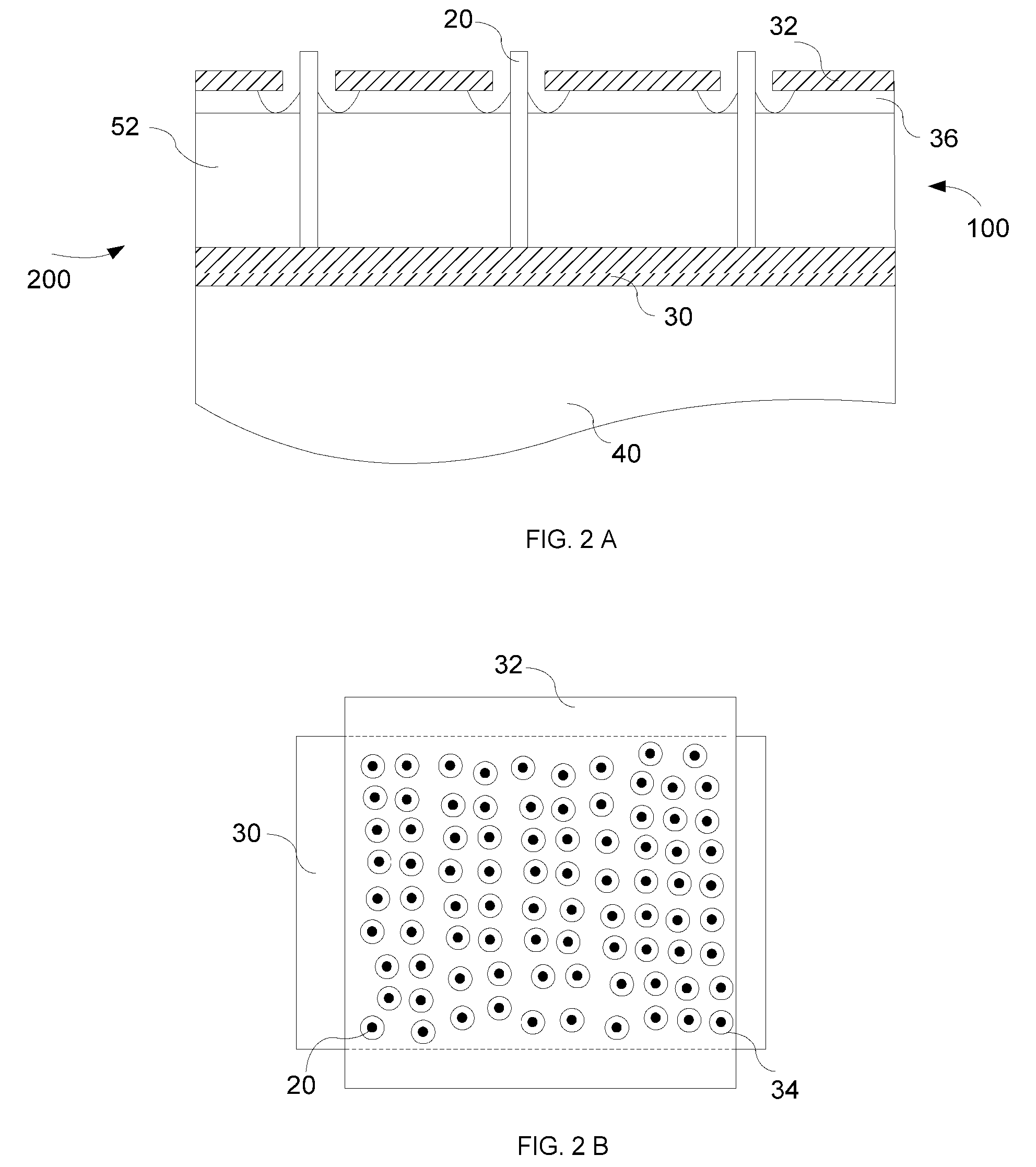

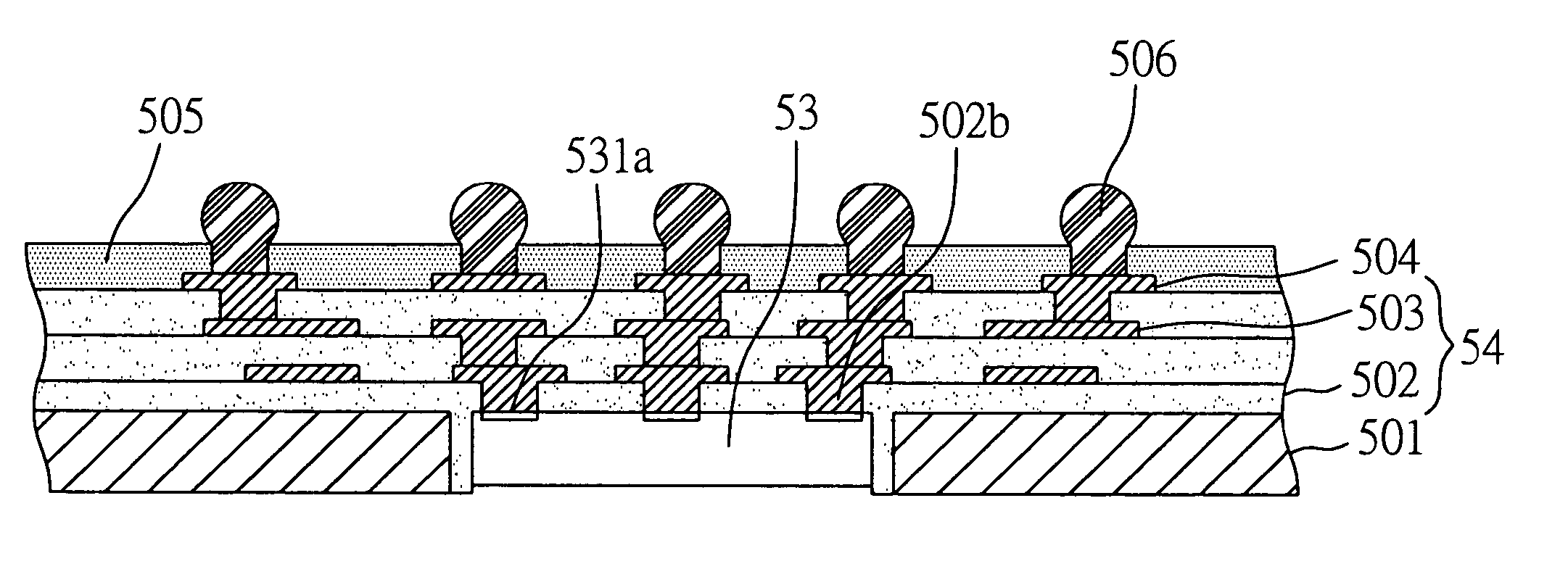

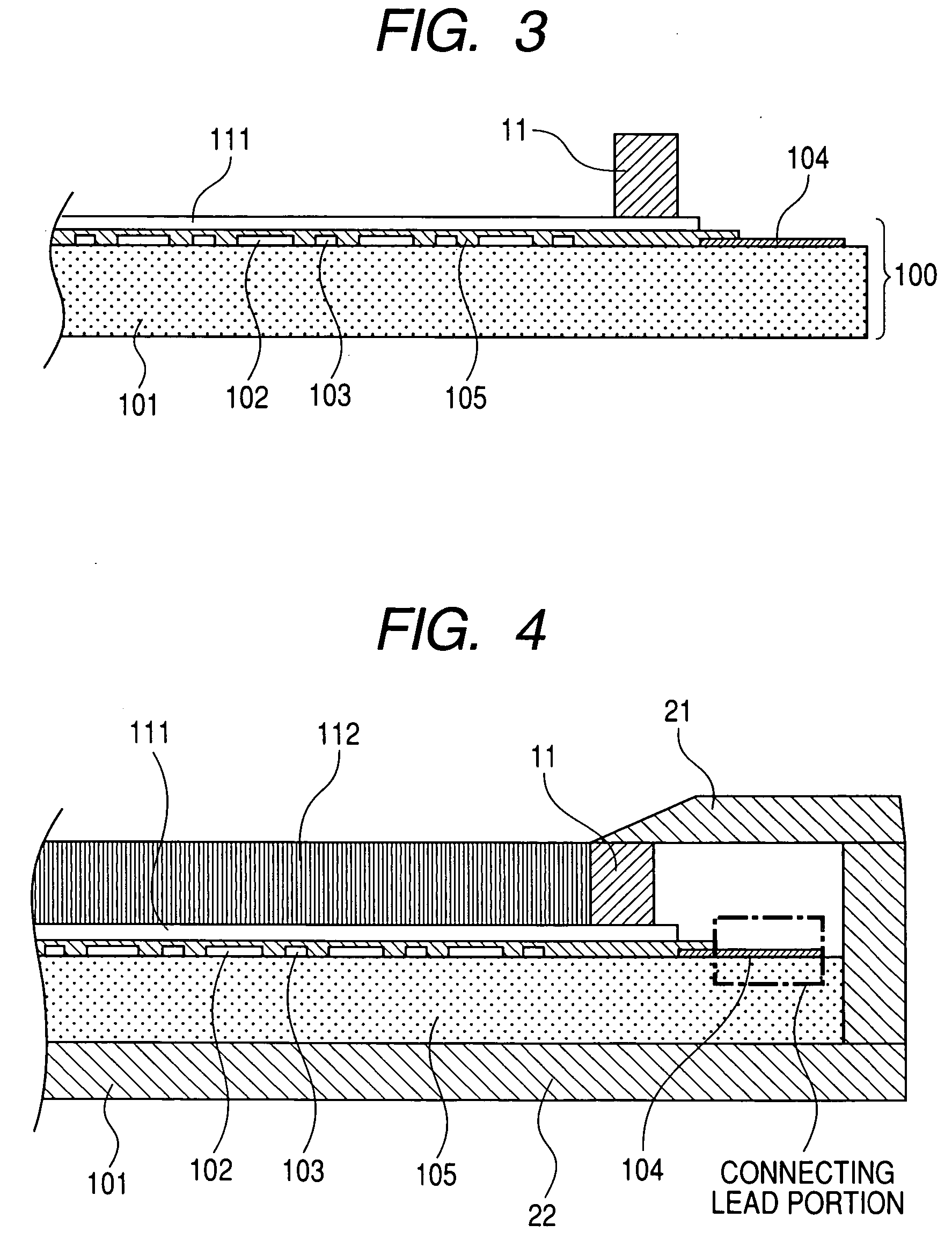

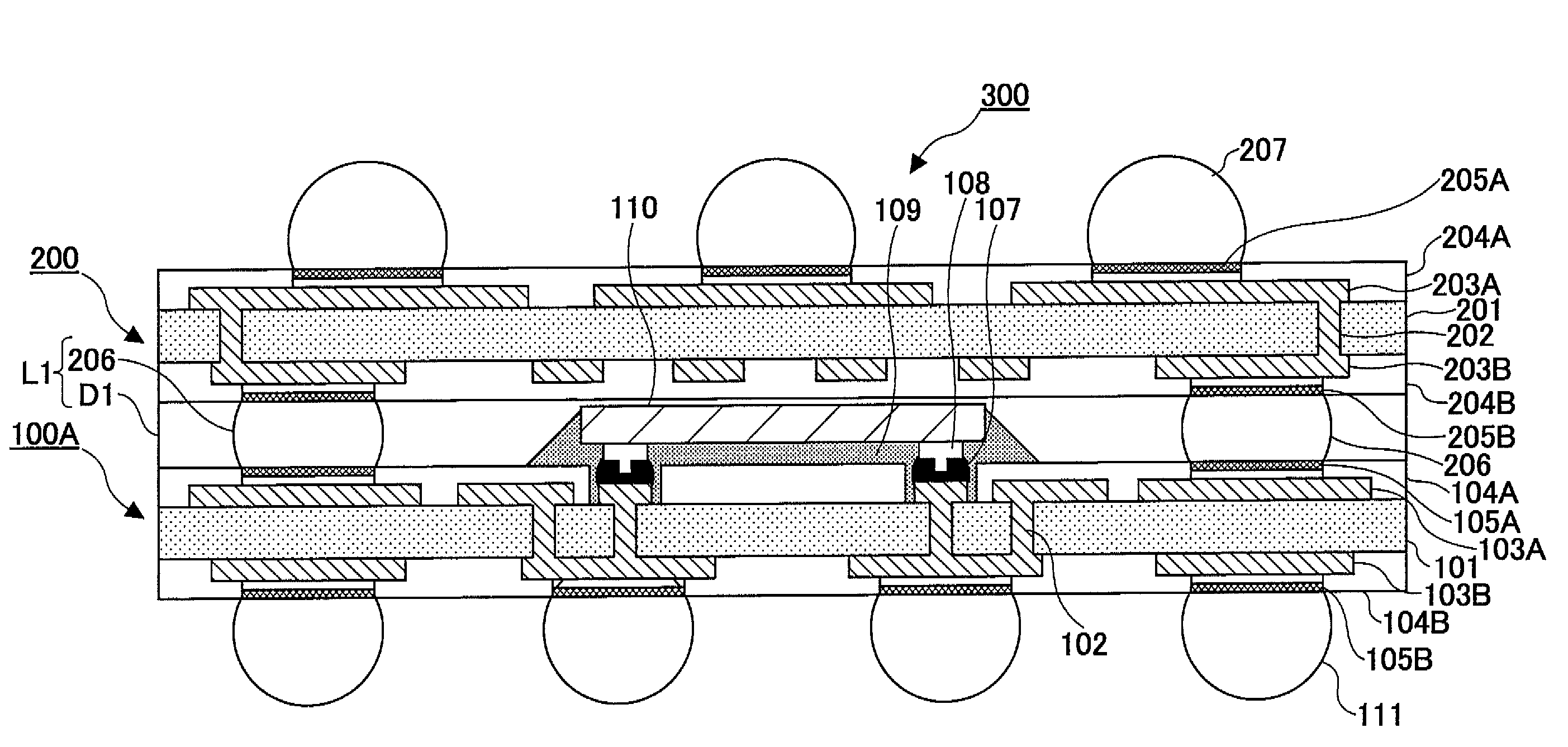

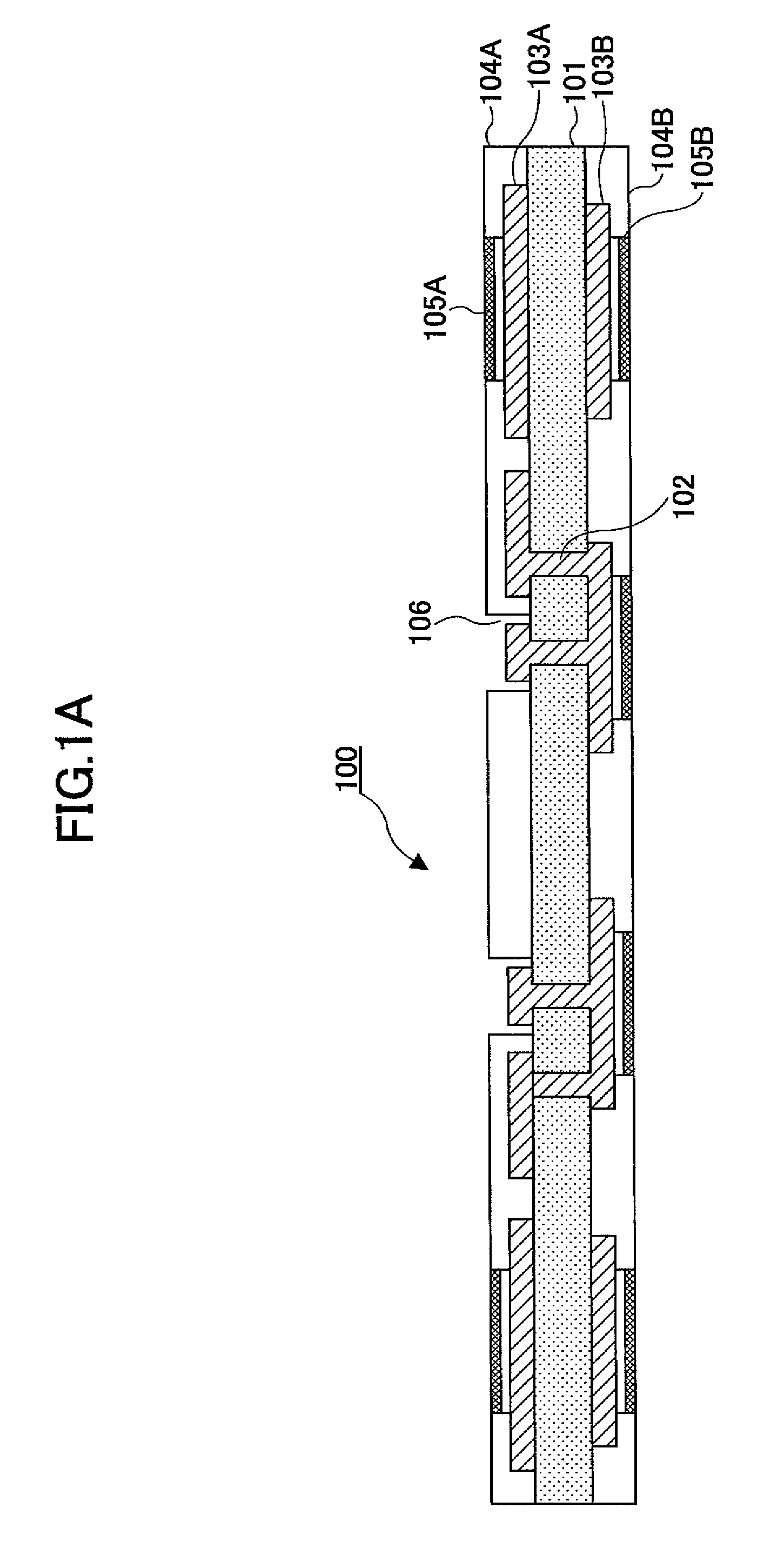

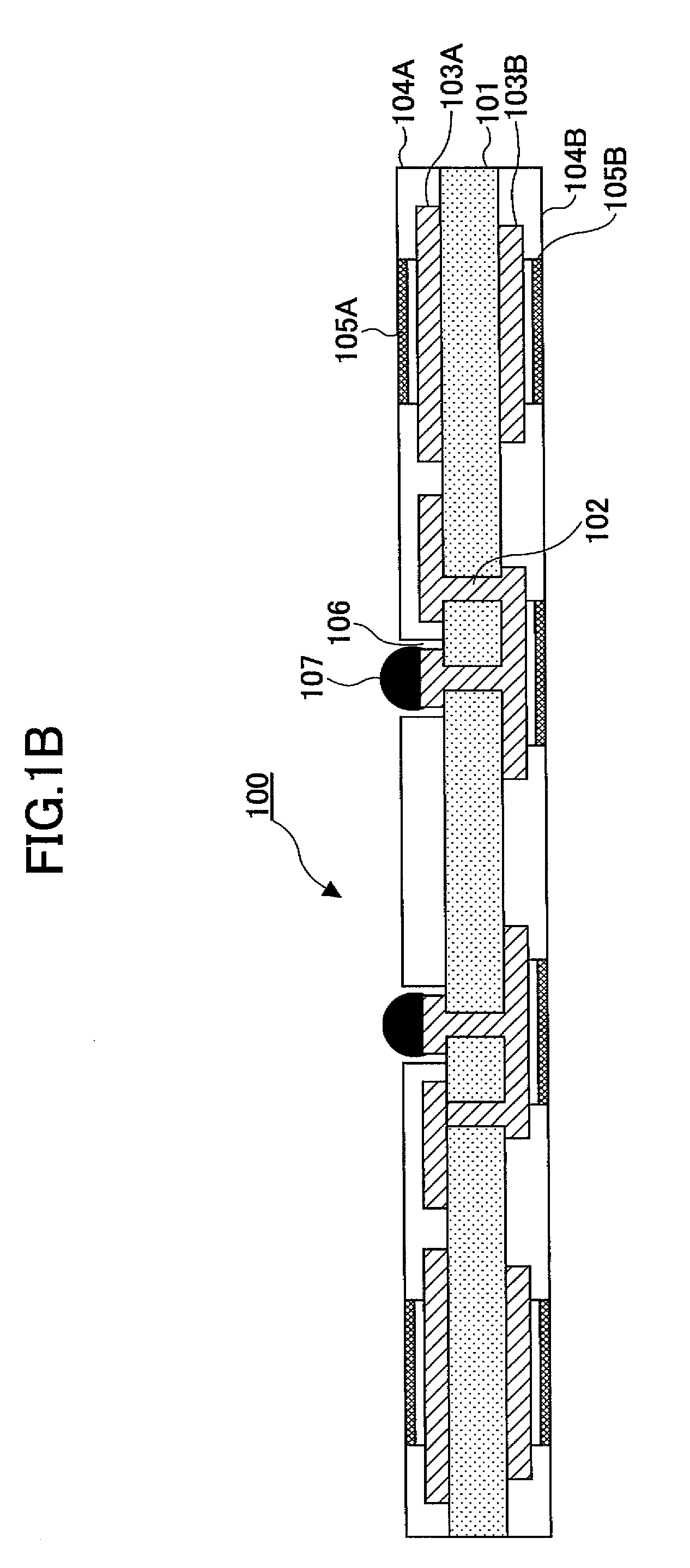

Chip embedded substrate and method of producing the same

ActiveUS20090008765A1Improve production yieldHigh reliability in electrical connectionPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

A method of producing a chip embedded substrate is disclosed. This method comprises a first step of mounting a semiconductor chip on a first substrate on which a first wiring is formed; and a second step of joining the first substrate with a second substrate on which a second wiring is formed. In the second step, the semiconductor chip is encapsulated between the first substrate and the second substrate and electrical connection is made between the first wiring and the second wiring so as to form multilayered wirings connected to the semiconductor chip.

Owner:SHINKO ELECTRIC IND CO LTD

Process for producing ethanol

InactiveUS20060019360A1High carbon yieldHigh protein concentrationOrganic compound preparationChemical industryAcetic acidHydrogenation reaction

A process for producing ethanol including a combination of biochemical and synthetic conversions results in high yield ethanol production with concurrent production of high value coproducts. An acetic acid intermediate is produced from carbohydrates, such as corn, using enzymatic milling and fermentation steps, followed by conversion of the acetic acid into ethanol using esterification and hydrogenation reactions. Coproducts can include corn oil, and high protein animal feed containing the biomass produced in the fermentation.

Owner:ZEACHEM

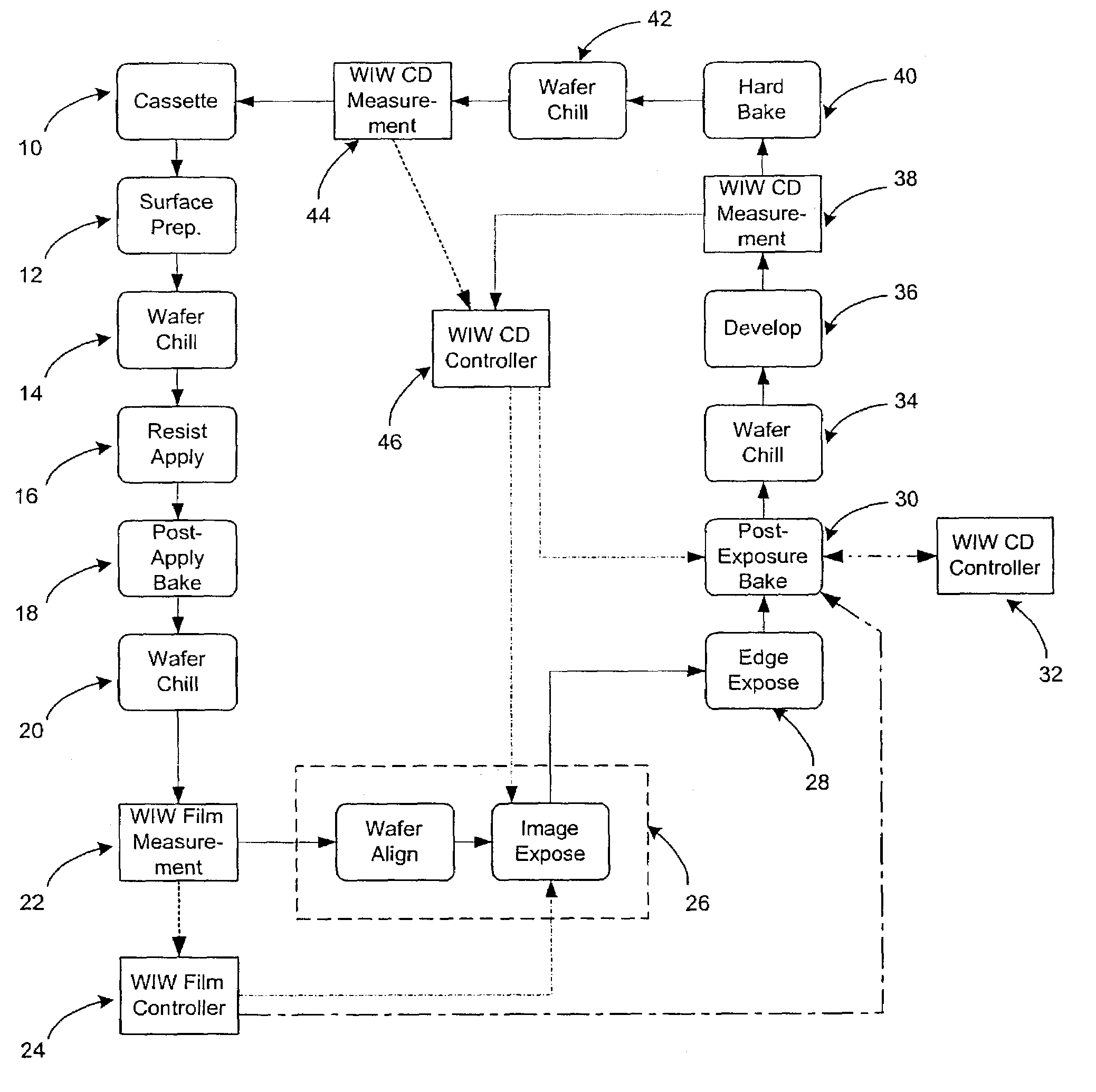

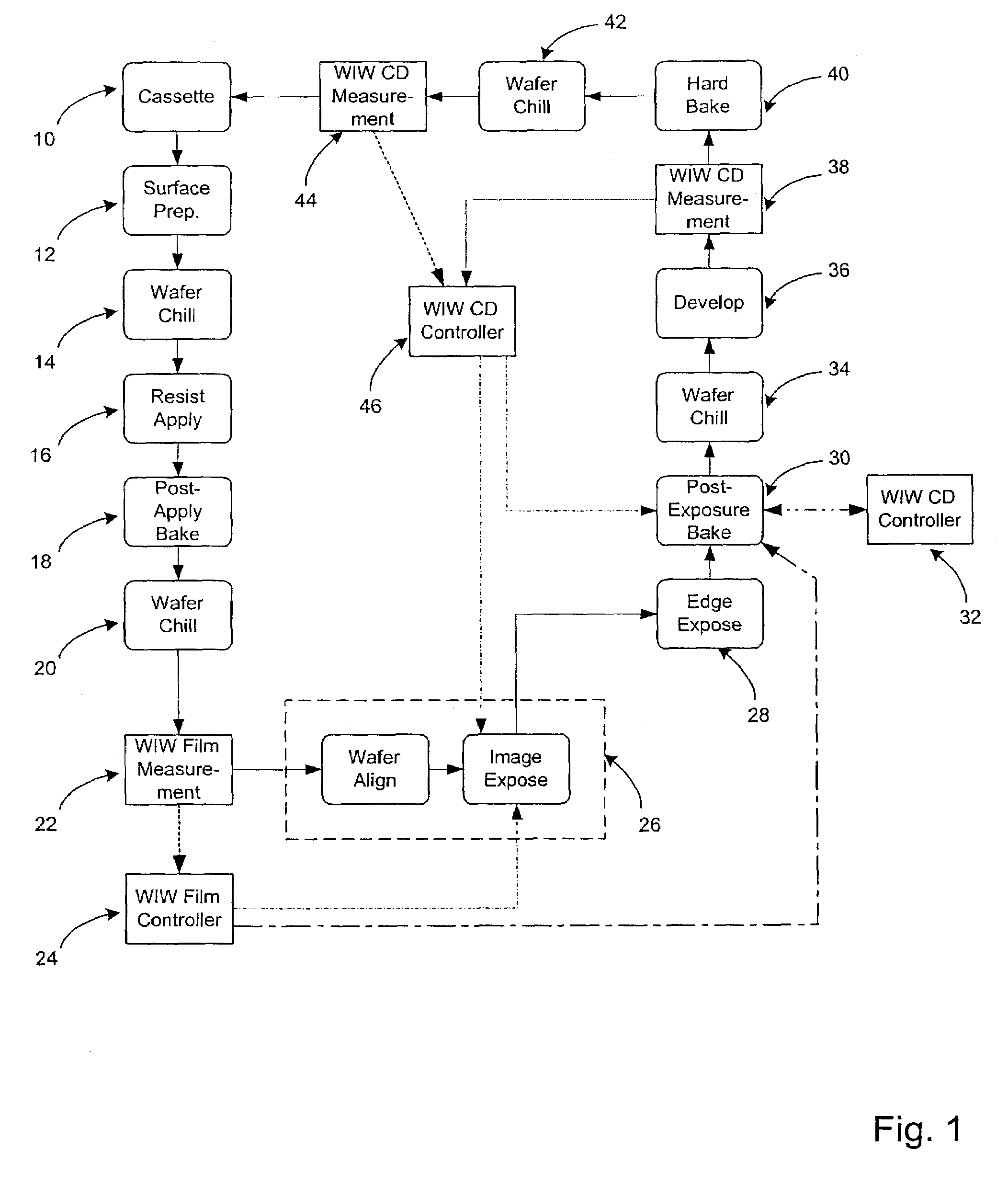

Methods and systems for lithography process control

InactiveUS6987572B2High performance bin distributionReduce yieldSemiconductor/solid-state device testing/measurementSolid-state devicesLithography processProcess module

Methods and systems for evaluating and controlling a lithography process are provided. For example, a method for reducing within wafer variation of a critical metric of a lithography process may include measuring at least one property of a resist disposed upon a wafer during the lithography process. A critical metric of a lithography process may include, but may not be limited to, a critical dimension of a feature formed during the lithography process. The method may also include altering at least one parameter of a process module configured to perform a step of the lithography process to reduce within wafer variation of the critical metric. The parameter of the process module may be altered in response to at least the one measured property of the resist.

Owner:KLA TENCOR TECH CORP

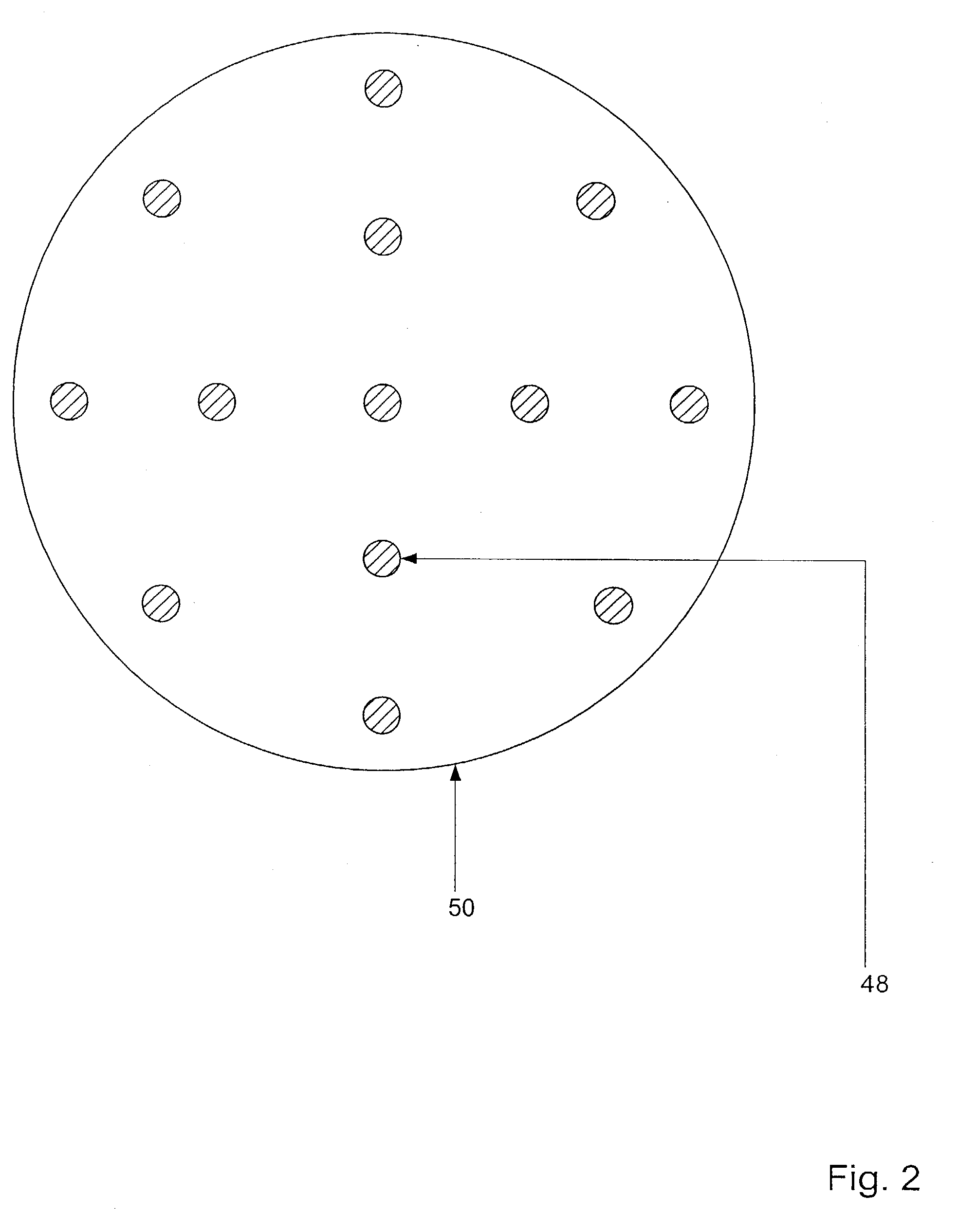

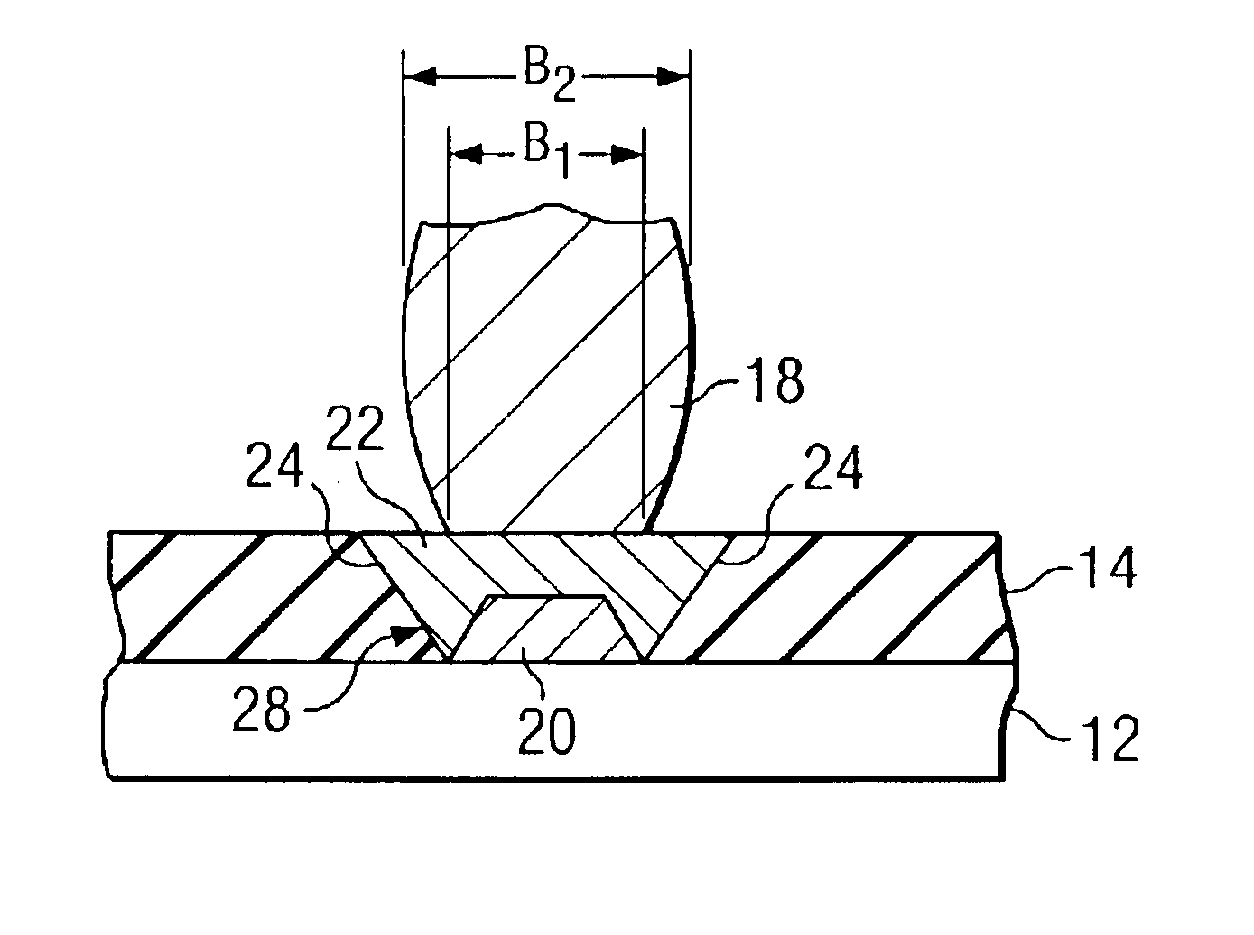

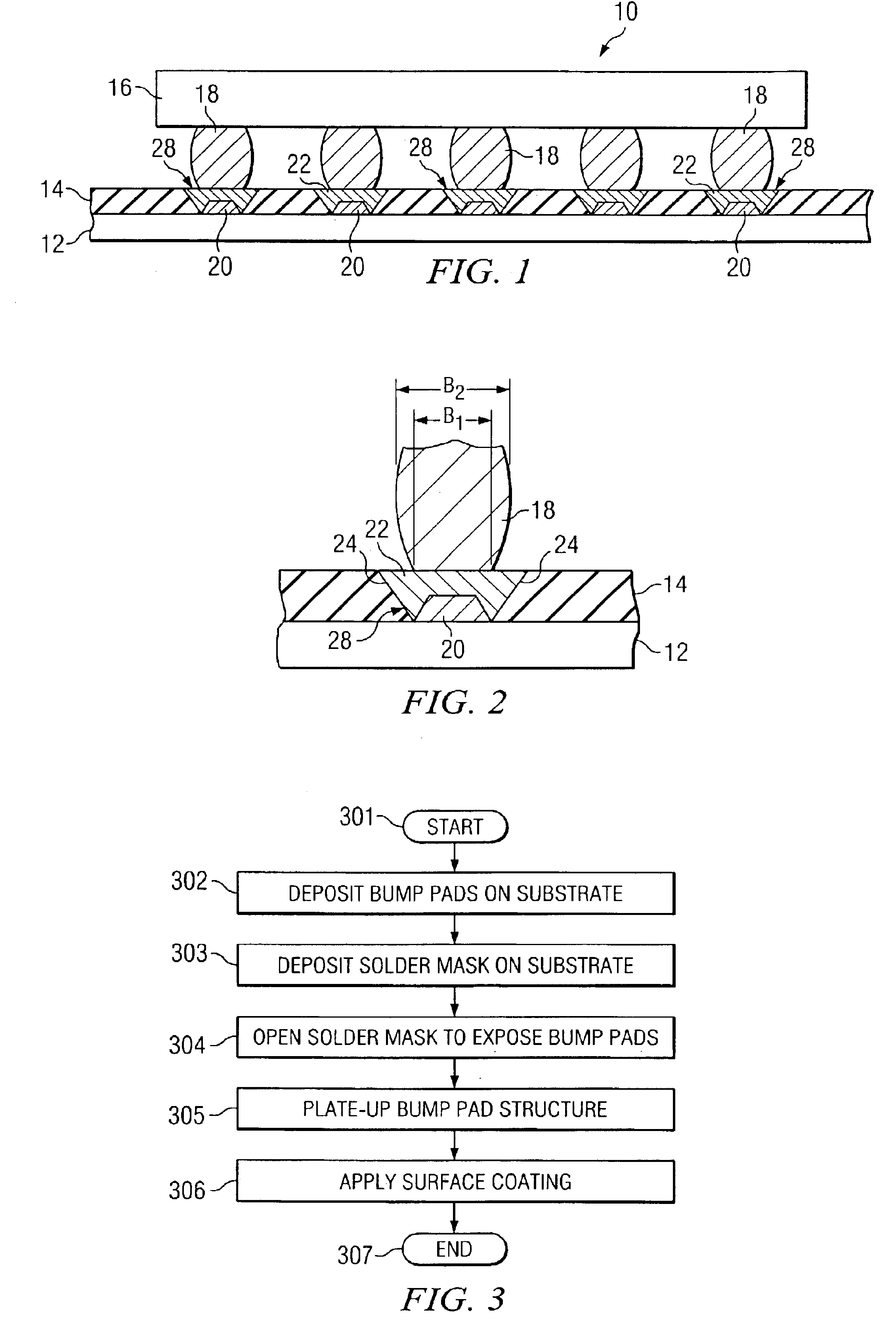

Built-up bump pad structure and method for same

InactiveUS6888255B2Reduce thicknessLess sensitivePrinted circuit assemblingFinal product manufactureSolder maskConductive materials

In accordance with the present invention, a built-up bump pad structure and method for the same are provided. The bump pad structure includes a substrate, a bump pad disposed upon the substrate, a solder mask disposed upon the substrate defining an opening around the bump pad, and a conductive material deposited upon the bump pad such that the conductive material at least partially fills the opening around the bump pad.

Owner:TEXAS INSTR INC

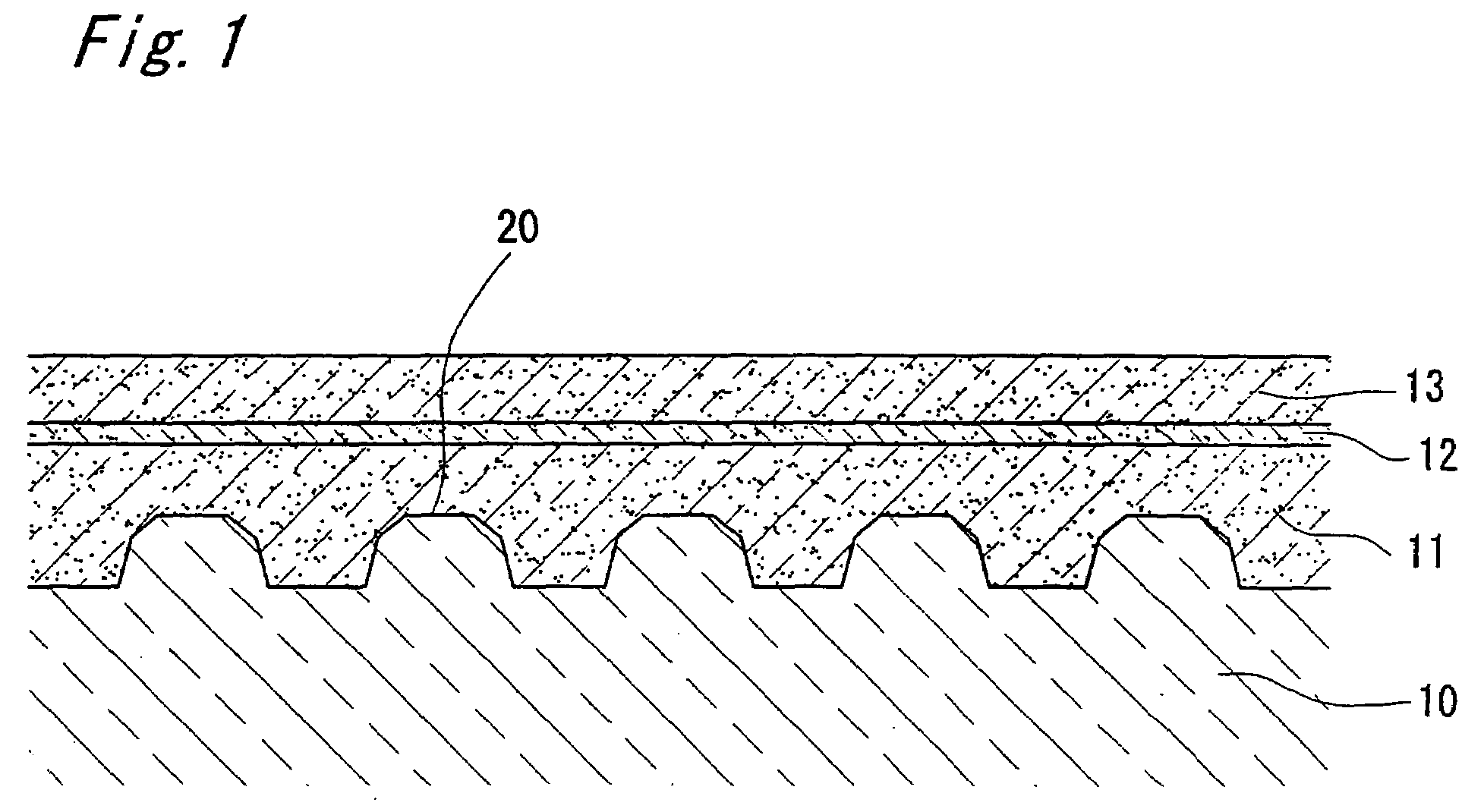

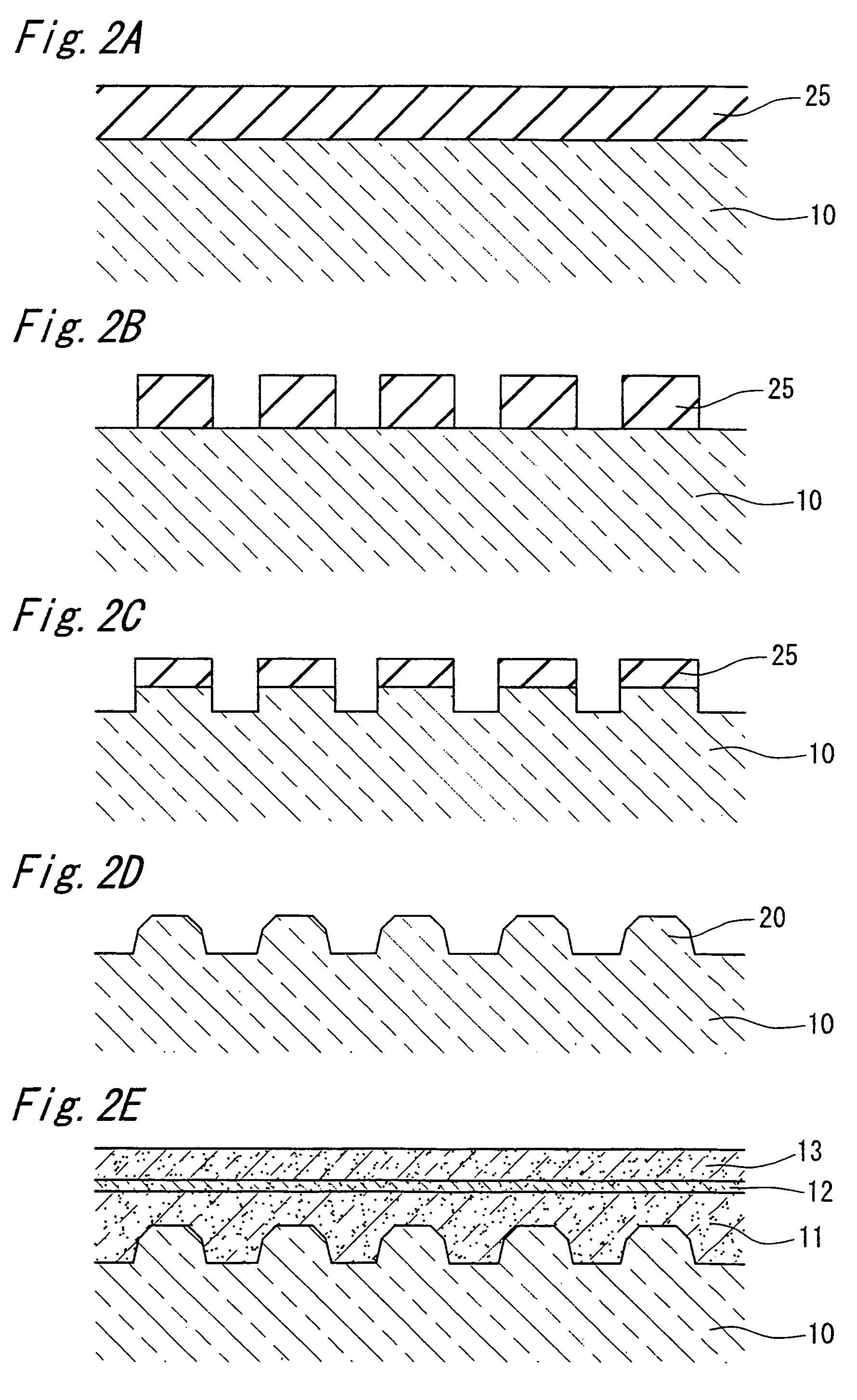

Thin film solar cell and manufacturing method thereof

InactiveUS20060196536A1Improve production yieldPrevent degradationPV power plantsSolid-state devicesTransparent conducting filmEngineering

A thin film solar cell includes: a transparent conductive film arranged on a translucent insulating substrate; first and second separation trenches orthogonal to each other on the translucent insulating substrate and separating the transparent conductive film; and a first opening trench parallel to the first separation trench and second opening trenches parallel to said second separation trench, orthogonal to each other on the translucent insulating substrate; wherein solar cells formed on the translucent insulating substrate are arranged at adjacent positions with said first opening trench positioned therebetween and at adjacent positions with said second opening trench positioned therebetween; pairs of said solar cells adjacent to each other with said first opening trench positioned therebetween are electrically connected, and among pairs of solar cells positioned adjacent to each other with the second opening trench in between, some are electrically connected to each other, and others are electrically insulated from each other. Method of manufacturing the thin film solar cell is also provided.

Owner:SHARP KK

Synthetic antibody phage libraries

The invention provides comprising variant amino acids in CDRs of antibody variable domains. These polypeptides provide a source of great sequence diversity that can be used as a source for identifying novel antigen binding polypeptides. The invention also provides these polypeptides as fusion polypeptides to heterologous polypeptides such as at least a portion of phage or viral coat proteins, tags, and linkers. Libraries comprising a plurality of these polypeptides are also provided. In addition, methods of and compositions for generating and using these polypeptides and libraries are provided.

Owner:GENENTECH INC

Semiconductor package and fabrication method thereof

ActiveUS9786586B1Improve production yieldHigh product yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor package

A semiconductor package includes an interconnect component surrounded by a molding compound. The interconnect component comprises a first RDL structure. A second RDL structure is disposed on the interconnect component. A plurality of first connecting elements is disposed on the second RDL structure. A polish stop layer covers a surface of the interconnect component. A plurality of second connecting elements is disposed on and in the polish stop layer. At least one semiconductor die is mounted on the second connecting elements.

Owner:MICRON TECH INC

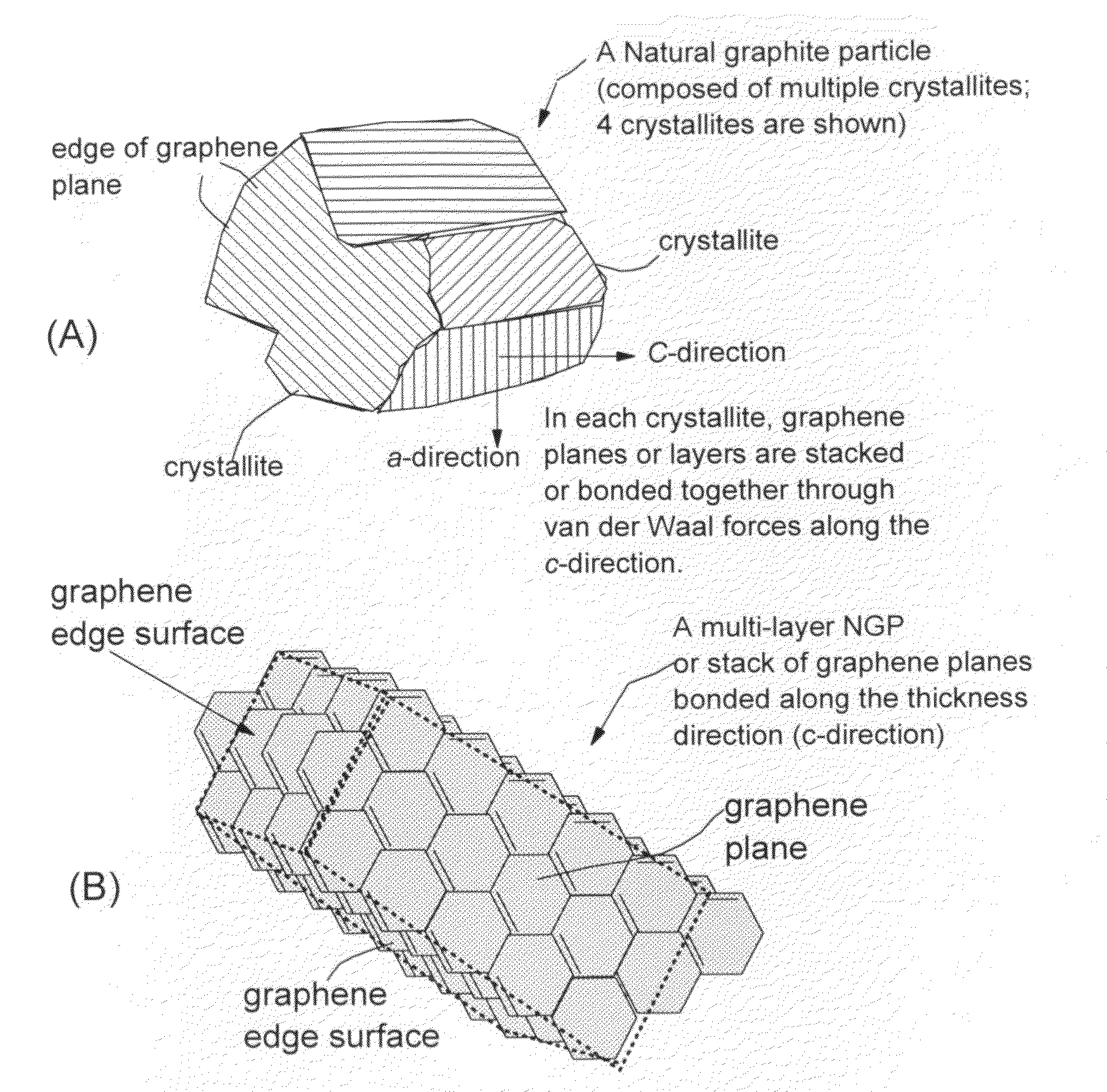

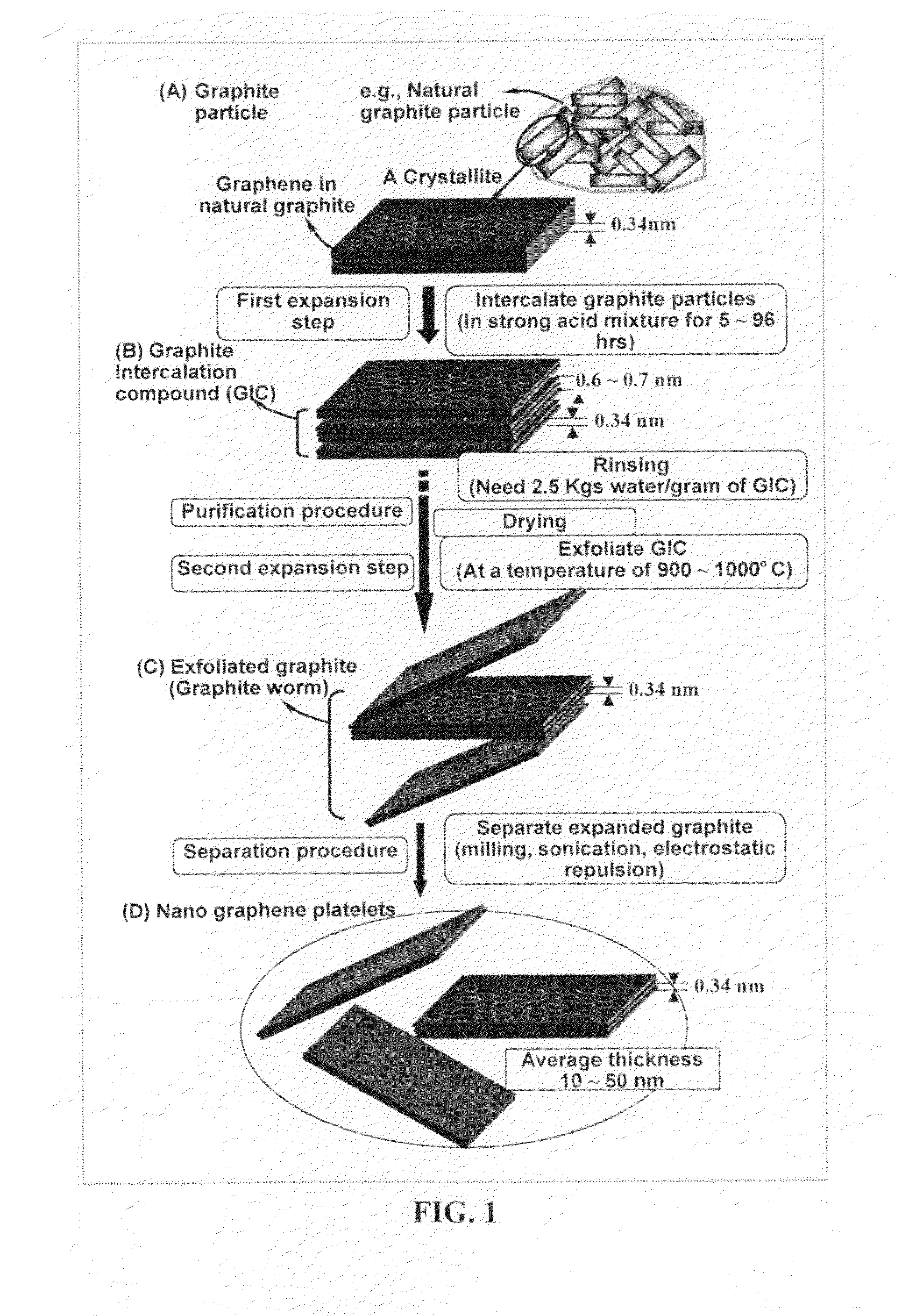

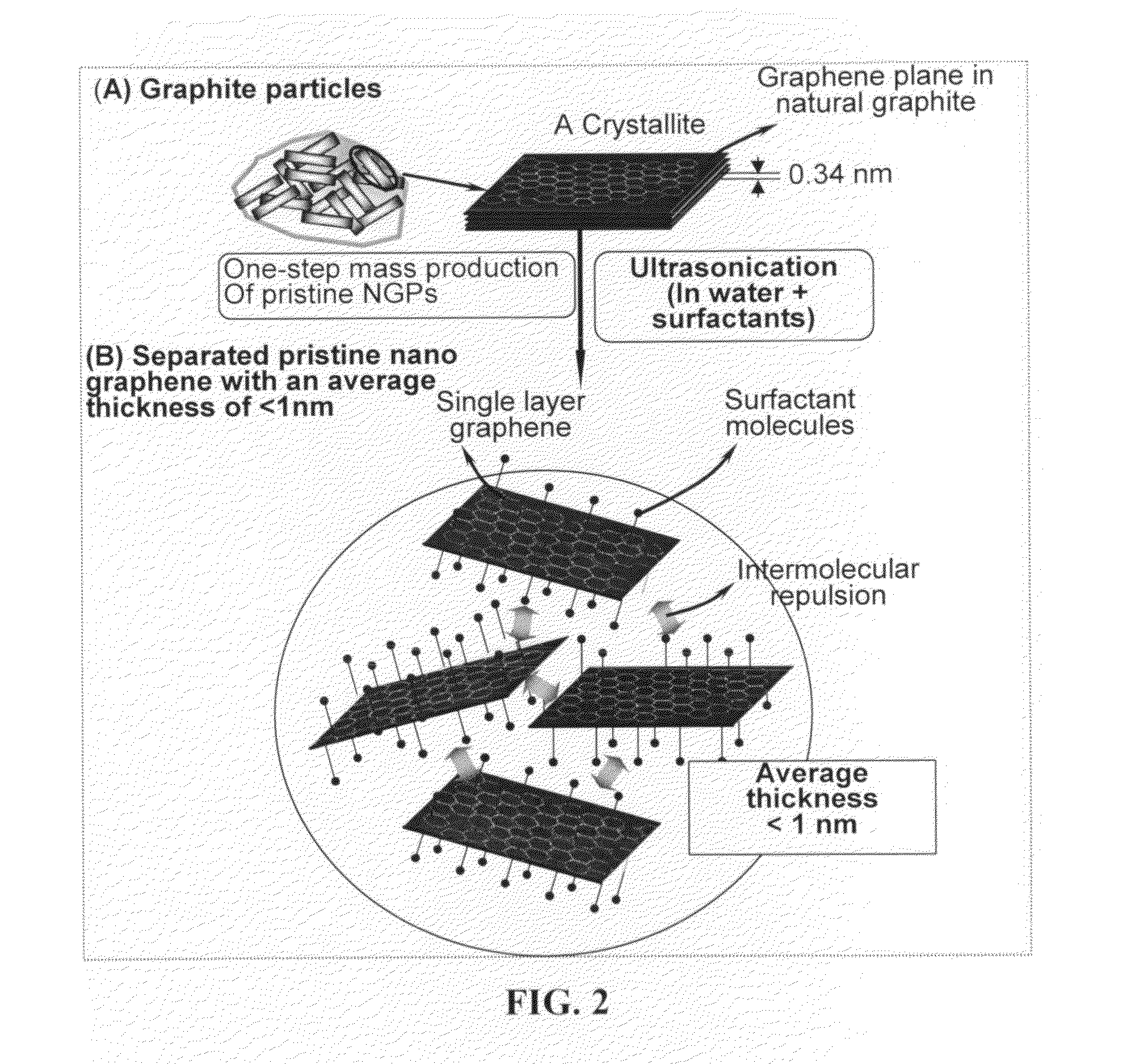

Mass production of pristine nano graphene materials

ActiveUS20110017585A1Reduce surface tensionImprove production yieldMaterial nanotechnologyGrapheneLiquid mediumDisplay device

The present invention provides a method of producing pristine or non-oxidized nano graphene platelets (NGPs) that are highly conductive. The method comprises: (a) providing a pristine graphitic material comprising at least a graphite crystallite having at least a graphene plane and an edge surface; (b) dispersing multiple particles of the pristine graphitic material in a liquid medium containing therein no surfactant to produce a suspension, wherein the multiple particles in the liquid have a concentration greater than 0.1 mg / mL and the liquid medium is characterized by having a surface tension that enables wetting of the liquid on a graphene plane exhibiting a contact angle less than 90 degrees; and (c) exposing the suspension to direct ultrasonication at a sufficient energy or intensity level for a sufficient length of time to produce the NGPs. Pristine NGPs can be used as a conductive additive in transparent electrodes for solar cells or flat panel displays (e.g., to replace expensive indium-tin oxide), battery and supercapacitor electrodes, and nanocomposites for electromagnetic wave interference (EMI) shielding, static charge dissipation, and fuel cell bipolar plate applications.

Owner:GLOBAL GRAPHENE GRP INC

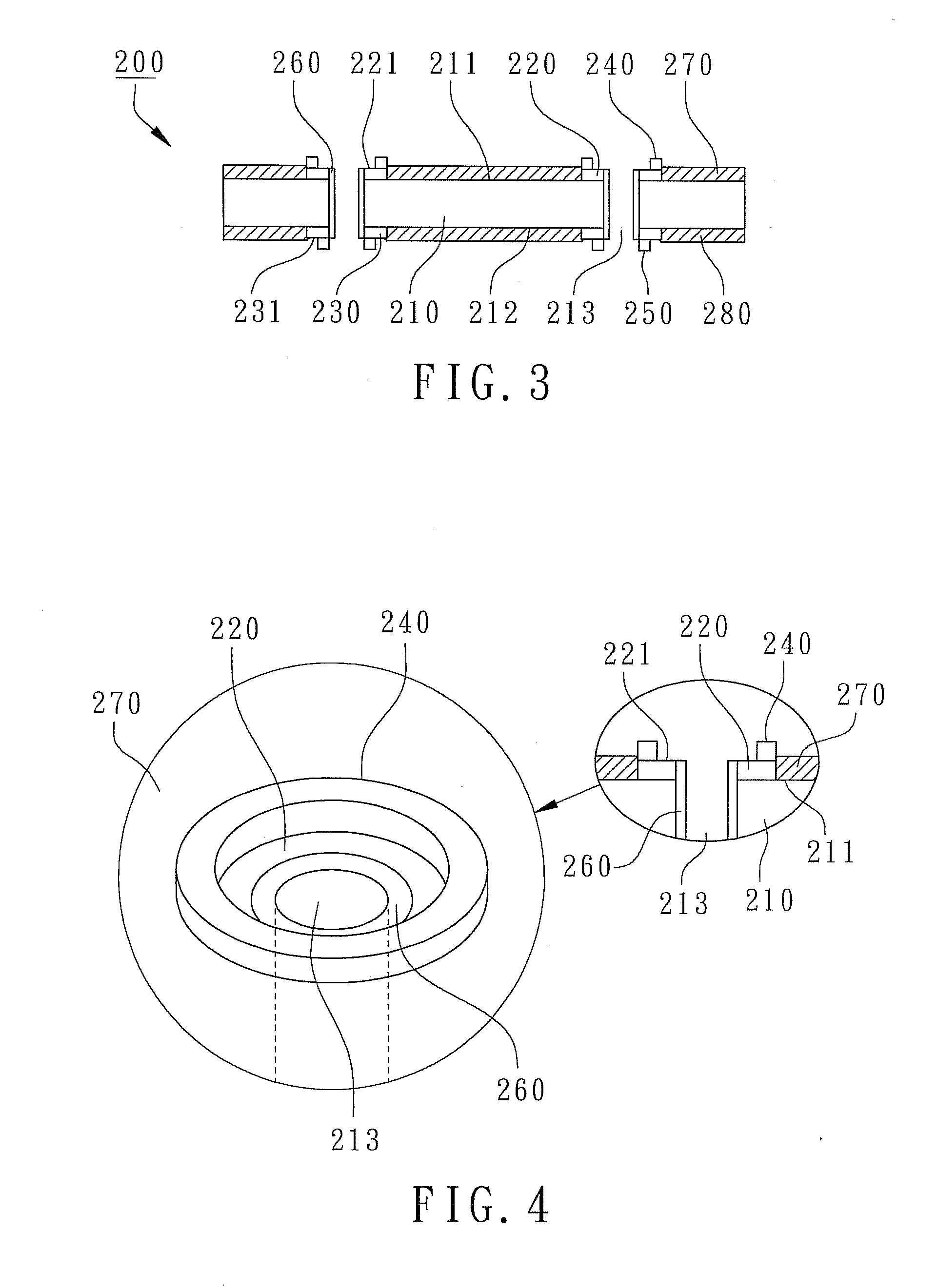

Semiconductor chip having TSV (through silicon via) and stacked assembly including the chips

InactiveUS20090267194A1Precise alignmentReduce the overall heightSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip having through silicon vias (TSV) and a stacked assembly including the chip are revealed. The chip has a plurality of first and second bonding pads disposed on two opposing surfaces of a semiconductor substrate respectively. Through hole vertically penetrate through the semiconductor substrate and the first and second bonding pads. By forming first extruded ring, the first bonding pad has a first contact surface located between the first extruded ring and the through hole. By forming second extruded ring, the second bonding pad has a second contact surface located outside and adjacent to the second extruded rings to encircle the second extruded ring. The second extruded ring has a proper dimension to fit in the first extruded ring. Accordingly, a plurality of semiconductor chip can be stacked each other with accurate alignment without shifting to effectively reduce the stacked assembly height, moreover, chip stacking processes are accomplished by vertically stacking a plurality of chips first then filling conductive material into the through holes without electrical short between the adjacent bonding pads due to overflow of conductive material to meet the fine-pitch requirements of TSV. The process flow for the stacked assembly is simplified with higher production yields.

Owner:POWERTECH TECHNOLOGY

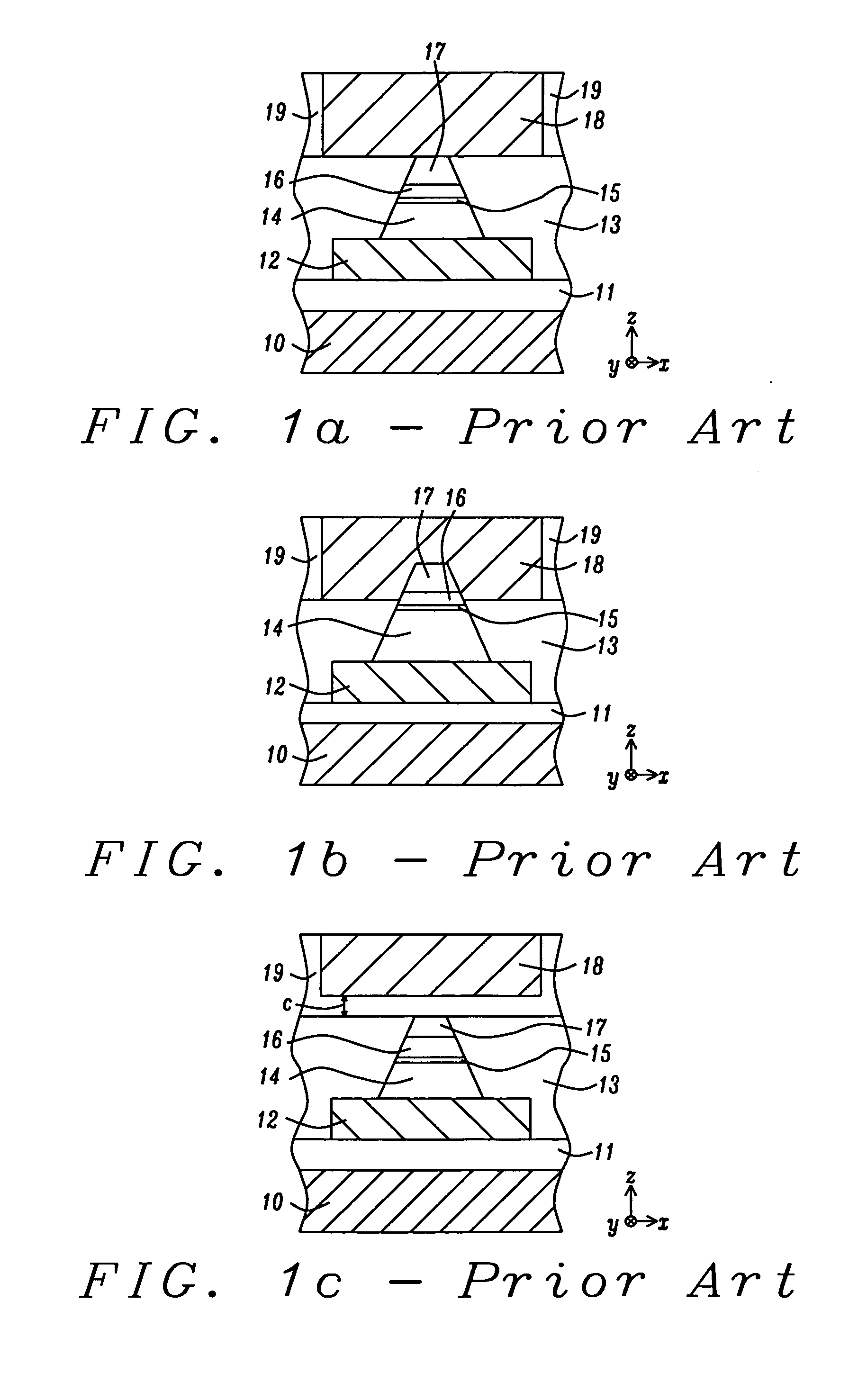

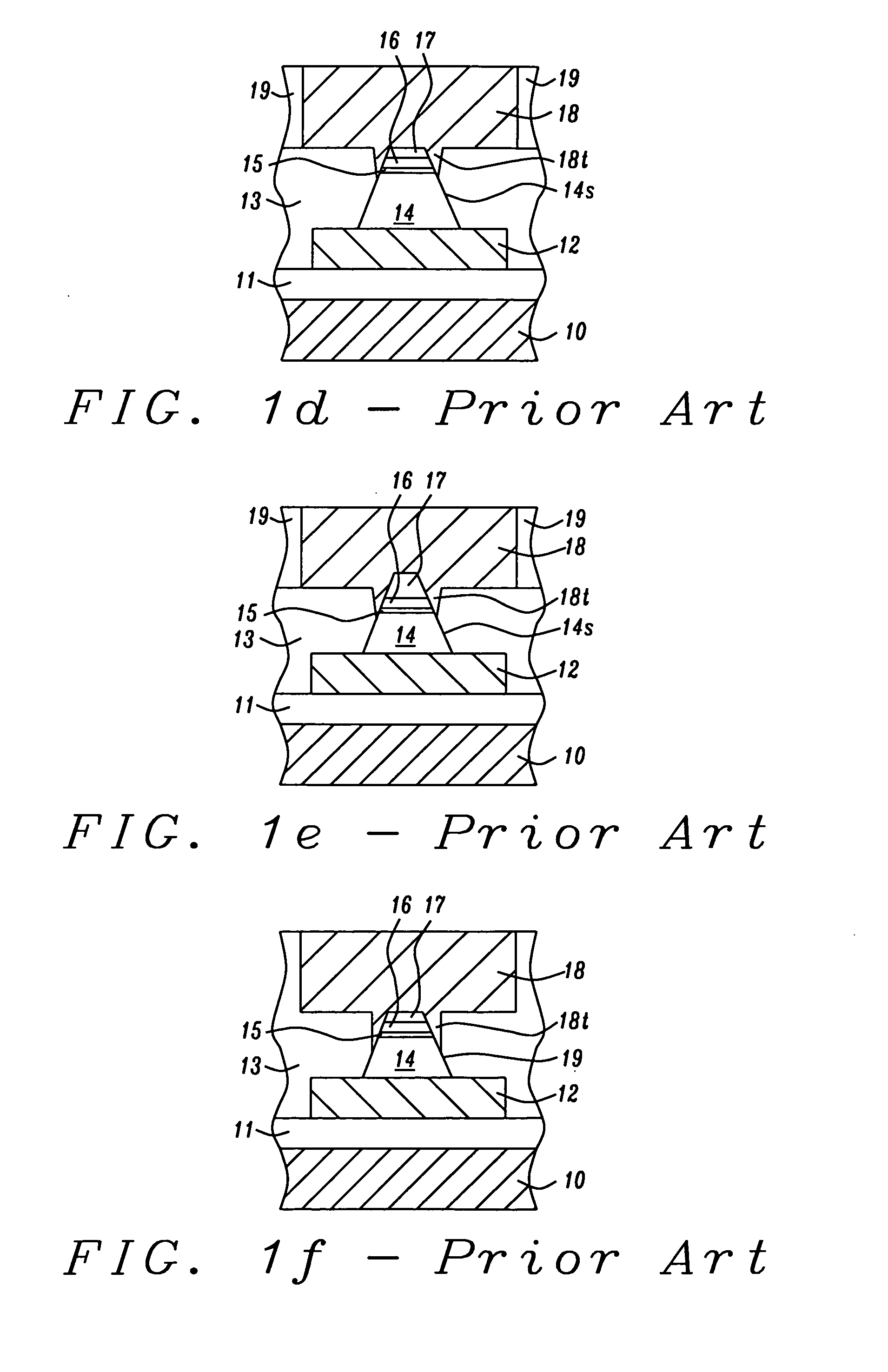

Low voltage electron source with self aligned gate apertures, fabrication method thereof, and luminous display using the electron source

InactiveUS20050127351A1Narrow diameterHigh densityNanoinformaticsThermionic cathodesHigh current densityHigh energy

An electron source include a first cathode electrode disposed over a substrate and terminated to provide electrons; an emitter layer disposed over the cathode electrode and formed from one or plurality vertically aligned and mono-dispersed nano-structures that are truncated to the same length, embedded in a solid matrix and protruding above the surface for emitting electrons; an insulator disposed over the emitter layer and having one or plurality of apertures, each is self-aligned with and exposes one nano-structure in the emitter layer; and a second gate electrode disposed over the insulator, having one or plurality of apertures self-aligned with the apertures in the insulator and terminated to extract electrons from the exposed nano-structures through the apertures. The gate aperture is substantially less than one micrometer and the gated nano-structures can have a density on the order of 108 / cm2. Such an electron source can be modulated with an extra low voltage, emits electrons with high current density and high uniformity, and operates with high energy-efficiency and long lifetime.

Owner:TOLT ZHIDAN LI

Binding polypeptides with diversified and consensus VH/VL hypervariable sequences

ActiveUS8679490B2Small sizeImprove efficiencyAnimal cellsSugar derivativesAntibody hypervariable regionAmino acid

The invention provides variant hypervariable regions comprising selected amino acid sequence diversity. Libraries comprising a plurality of these polypeptides are also provided. In addition, methods of and compositions for generating and using these polypeptides and libraries are provided.

Owner:GENENTECH INC

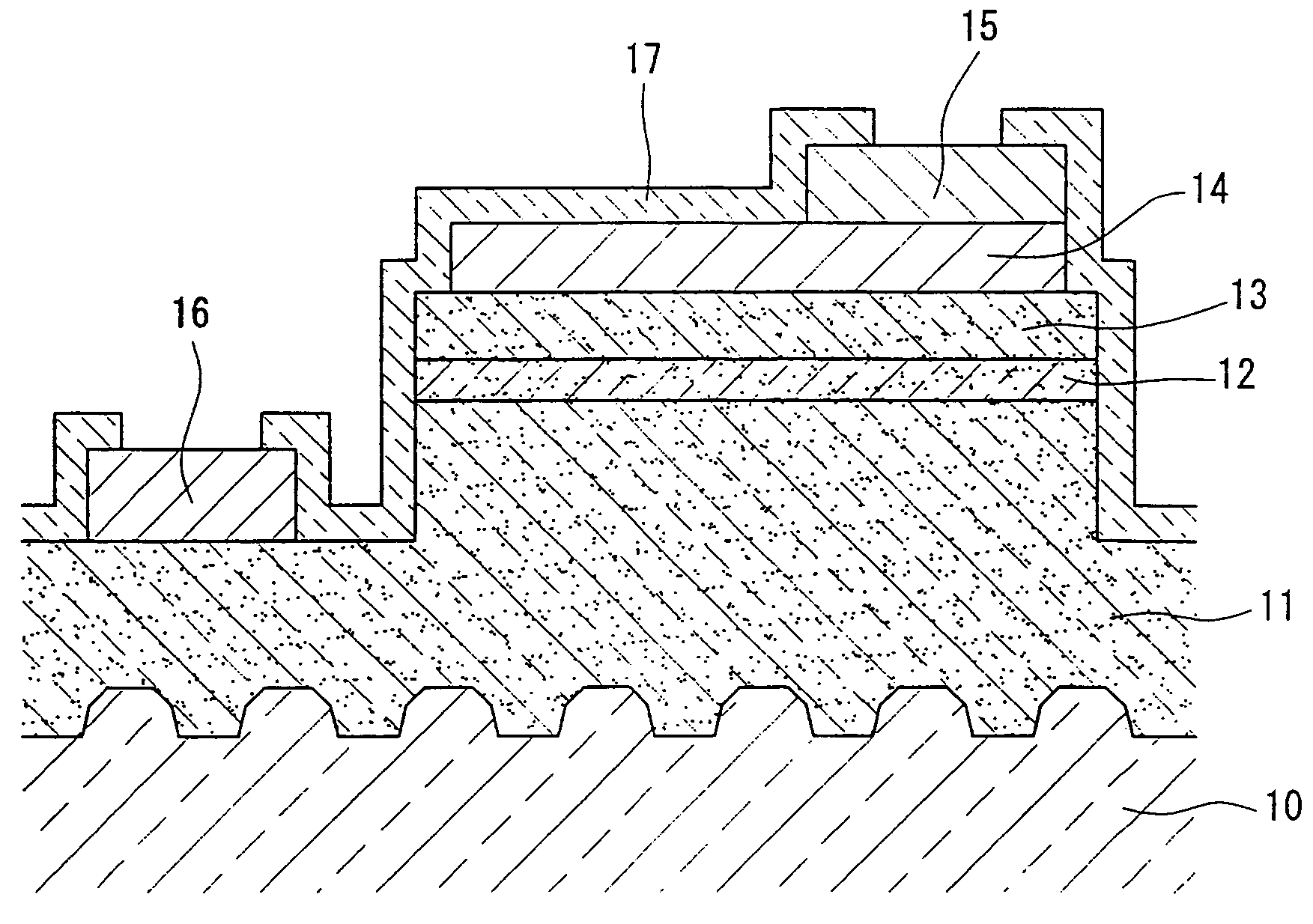

Semiconductor light emitting device with protrusions to improve external efficiency and crystal growth

ActiveUS7683386B2Easy to produceReduce crystallinitySemiconductor/solid-state device detailsSolid-state devicesCrystallographic defectActive layer

Owner:NICHIA CORP

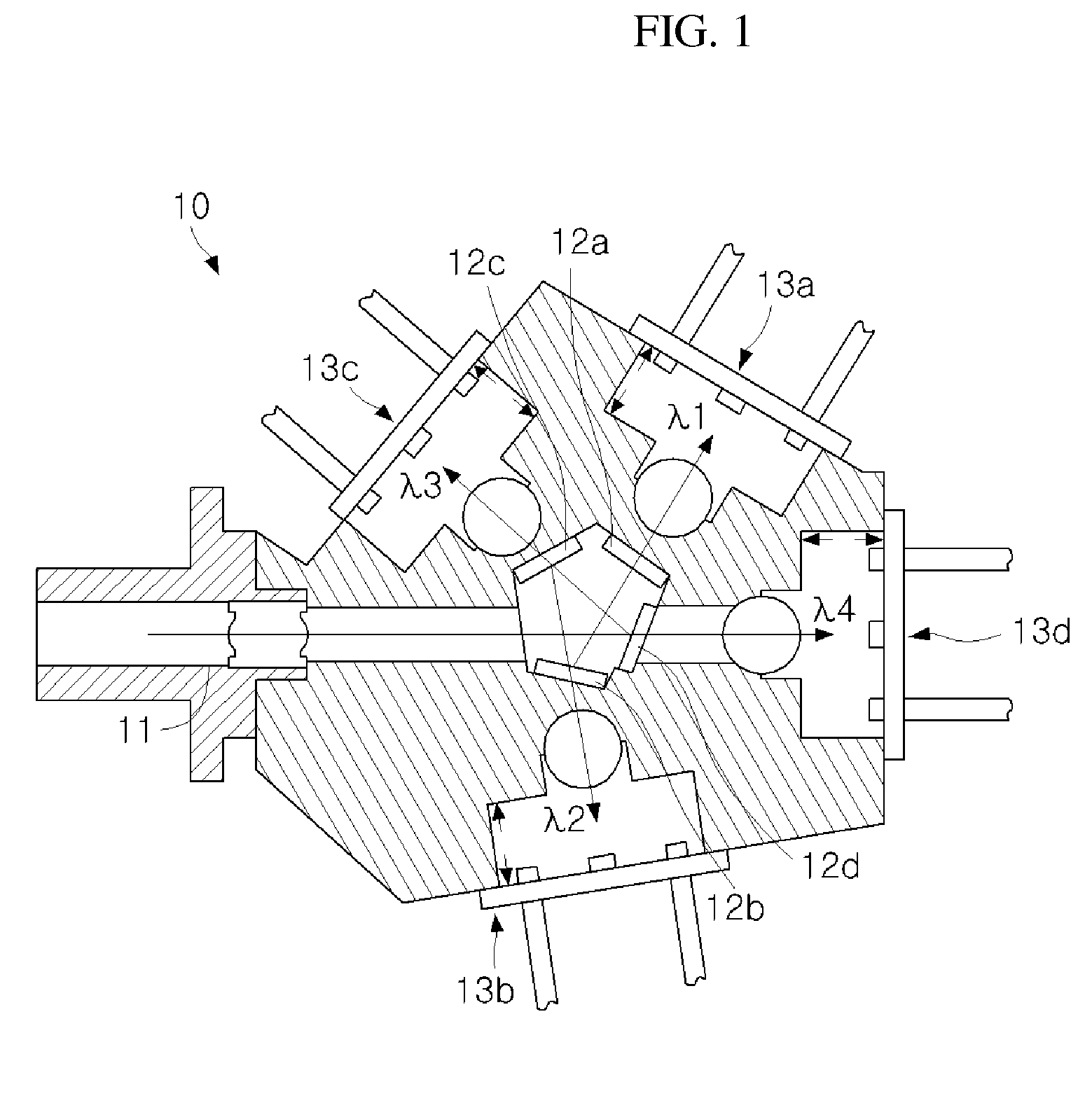

Multi-wavelength optical transmitting and receiving modules

ActiveUS20110058771A1Easy alignmentImprove production yieldCoupling light guidesMultiplexingCoupling

A multi-wavelength optical transmitting module includes a housing, an optical output block, an optical transmitting block, and an optical multiplexer (MUX) block. The housing has a first coupling hole and a second coupling hole respectively formed in opposite surfaces thereof. The optical output block is coupled to the first coupling hole of the housing, is connected to an optical signal connector, and includes a first lens. The optical transmitting block is coupled to the second coupling hole of the housing and is connected to an electrical signal connector. In addition, the optical transmitting block includes a plurality of transmitting devices which respectively output light having different wavelengths and are arranged parallel to the optical output block, and a plurality of second lenses which are arranged on a light output side of the transmitting devices to correspond respectively to the transmitting devices. The optical multiplexer (MUX) block is disposed within the housing, multiplexes optical signals of multiple wavelengths, which were output from the transmitting devices and passed through the second is lenses, and transmits the multiplexed optical signals to the optical output block.

Owner:ELECTRONICS & TELECOMM RES INST

Semiconductor light emitting device and method for manufacturing the same

ActiveUS20060124954A1Highly structuredImprove accuracySolid-state devicesSemiconductor devicesElectrical conductorLight emitting device

A semiconductor light emitting device having a semiconductor stacking structure bonded onto the support member and having excellent characteristics is provided by a preferable electrode structure. The semiconductor light emitting device comprising; a semiconductor stacking structure having a first semiconductor layer and a second semiconductor layer of conductivity types different from each other, a first electrode connected to the first semiconductor layer, and a second electrode connected to the second semiconductor layer, wherein one principal surface of the first electrode has a portion that makes contact with the first semiconductor layer so as to establish electrical continuity and an external connection section.

Owner:NICHIA CORP

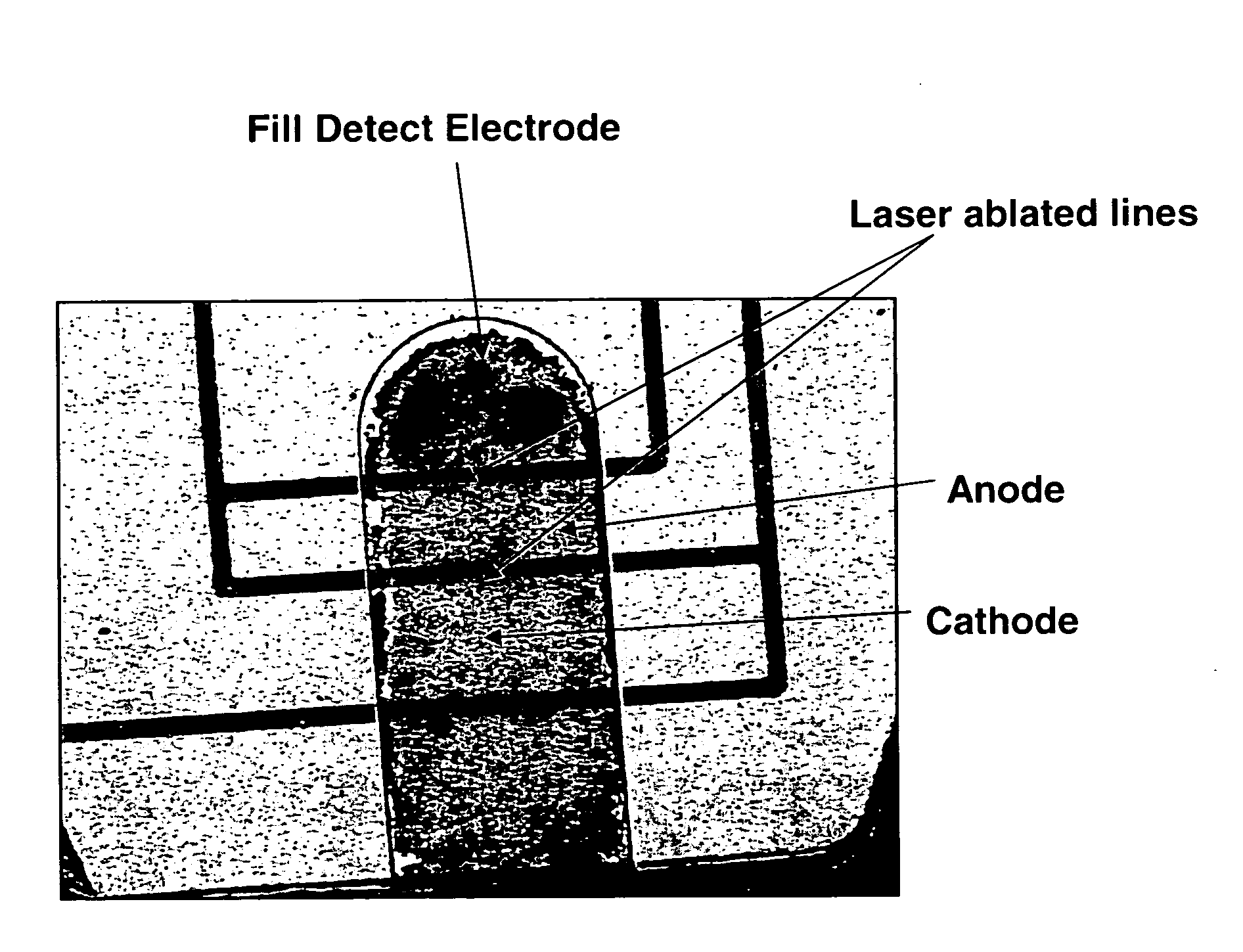

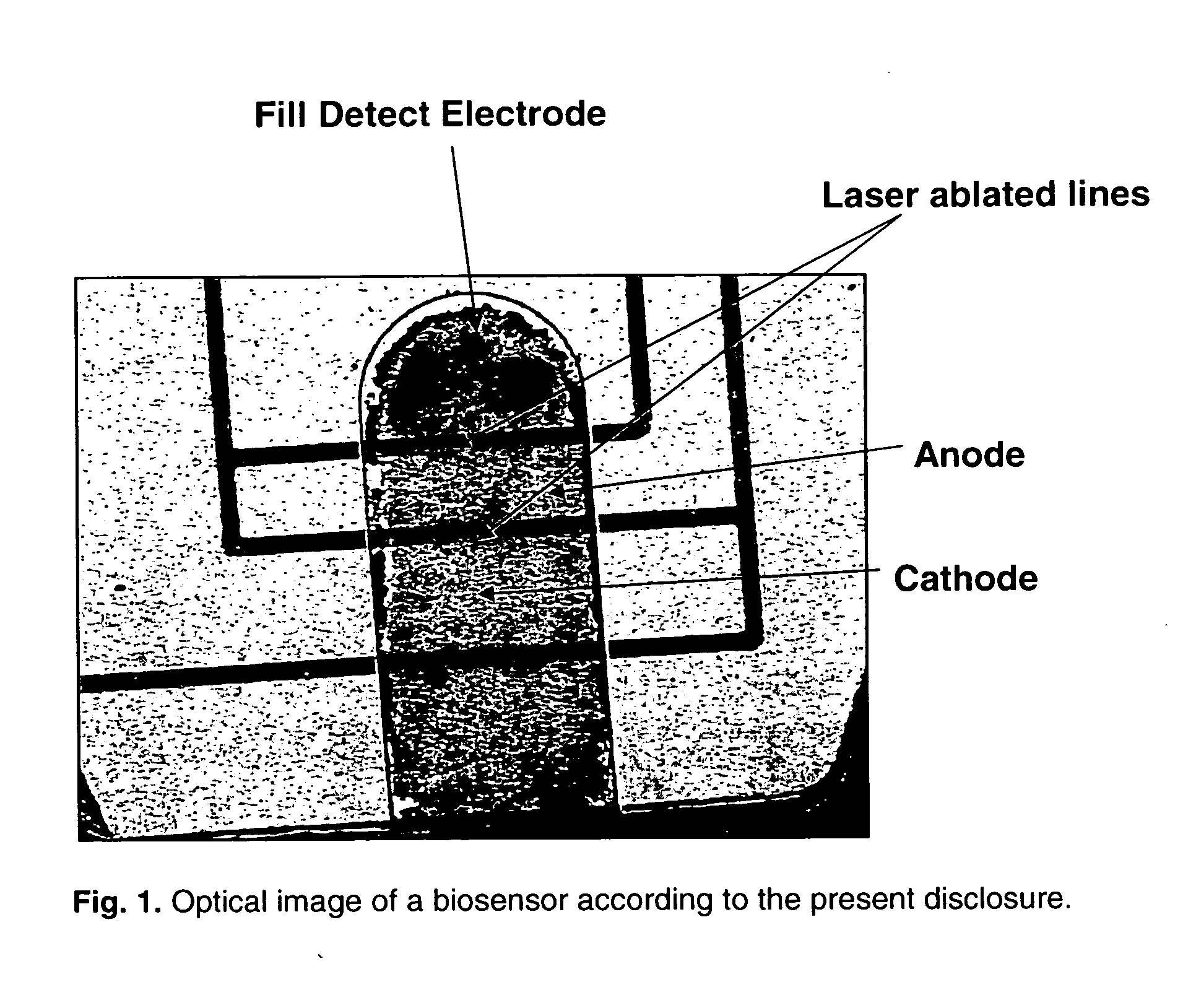

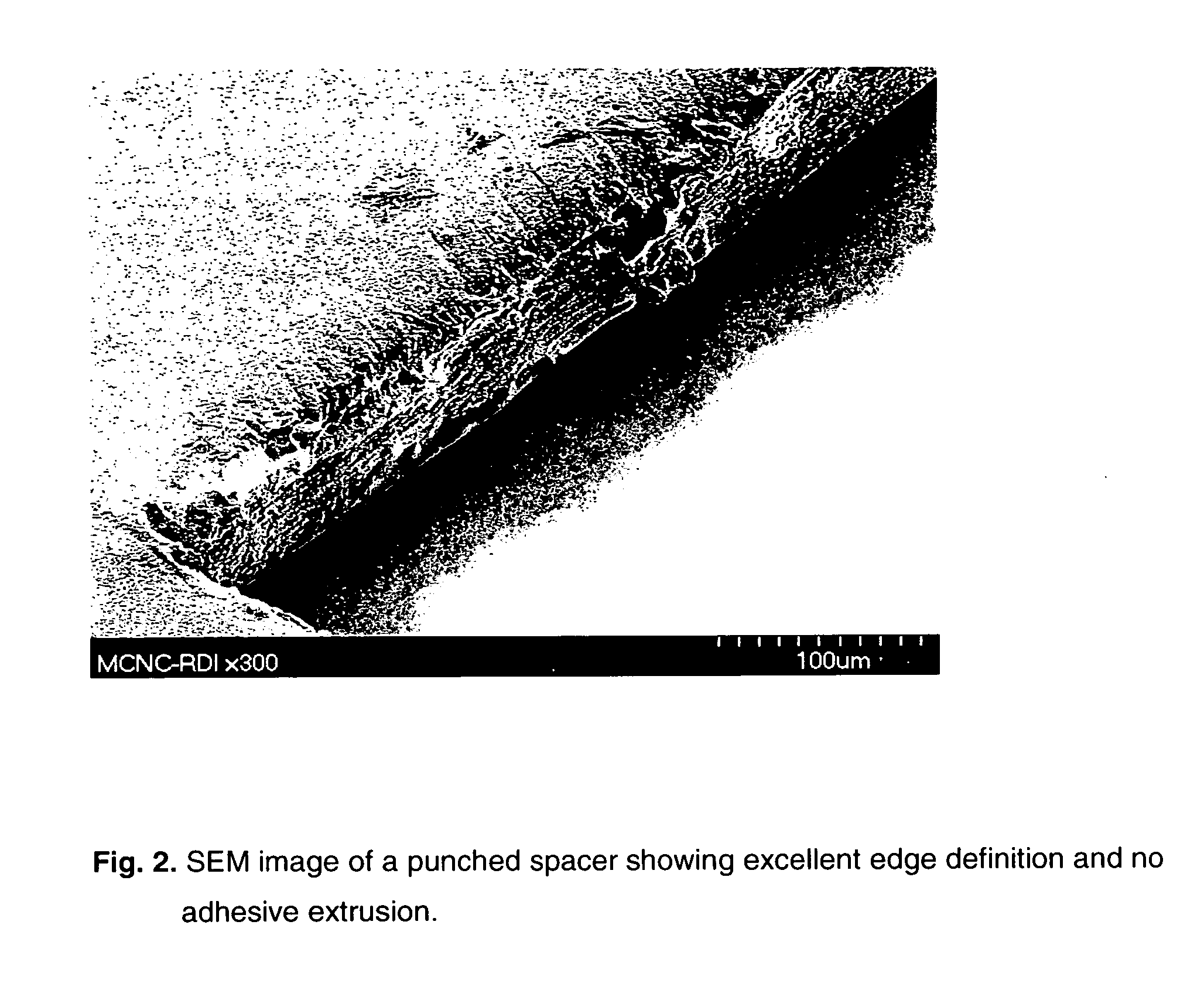

Biosensors comprising heat sealable spacer materials

InactiveUS20070240984A1Improve edge qualityLess-painful lancingImmobilised enzymesBioreactor/fermenter combinationsAnalyteOrganic layer

Disclosed herein is a biosensor for measuring analyte in a fluid that comprises a substrate layer having disposed thereon at least one each of an electrode, cathode, anode, and a novel spacer material. The spacer material according to the present disclosure comprises a heat sealable organic layer that covers at least a portion of the anode and defines at least one edge of the anode, wherein the spacer material has at least one hole punched through it and defines a cavity or well for accepting chemistry. Also disclosed is a method of making such biosensors.

Owner:NIPRO DIAGNOSTICS INC

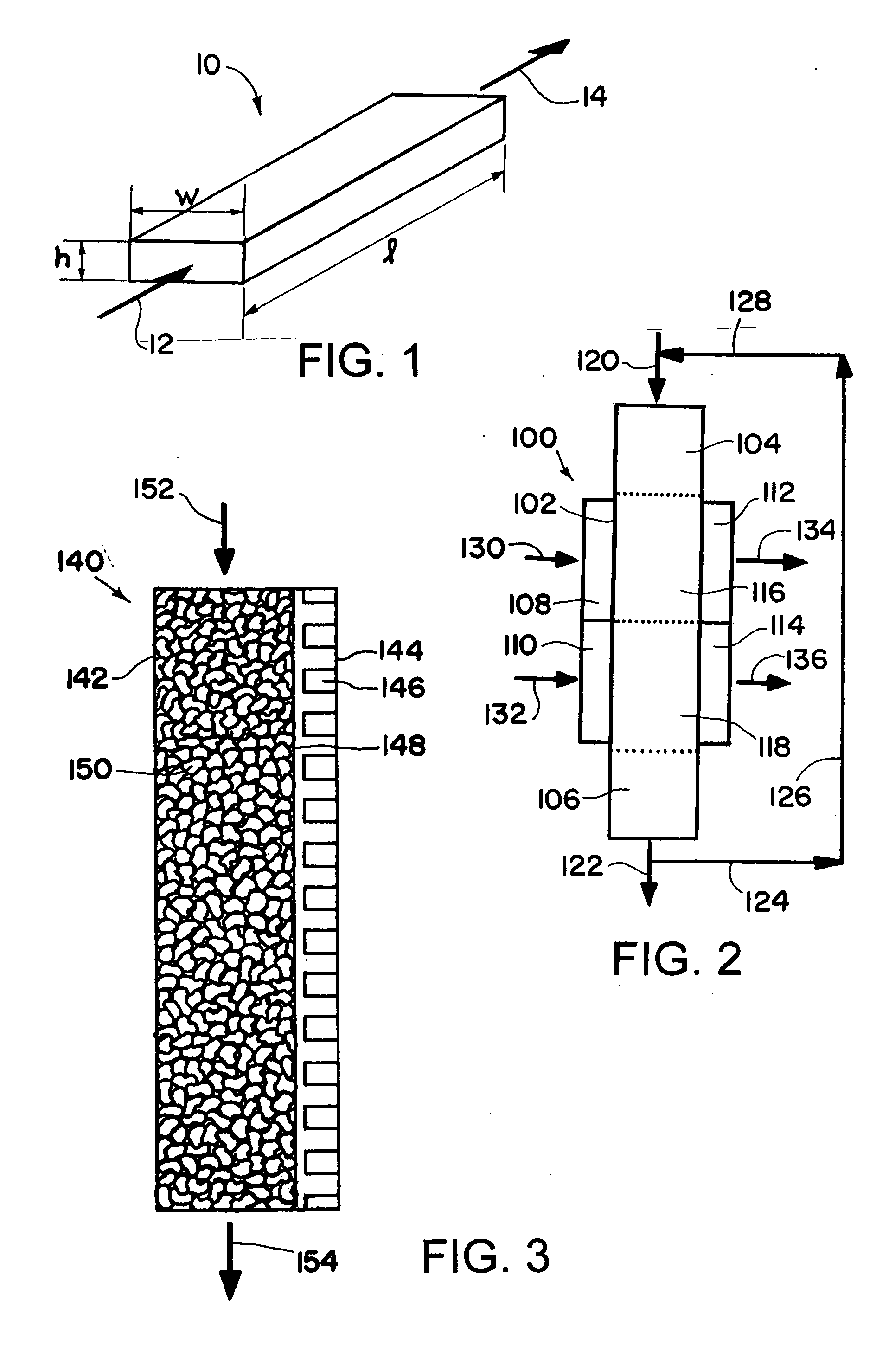

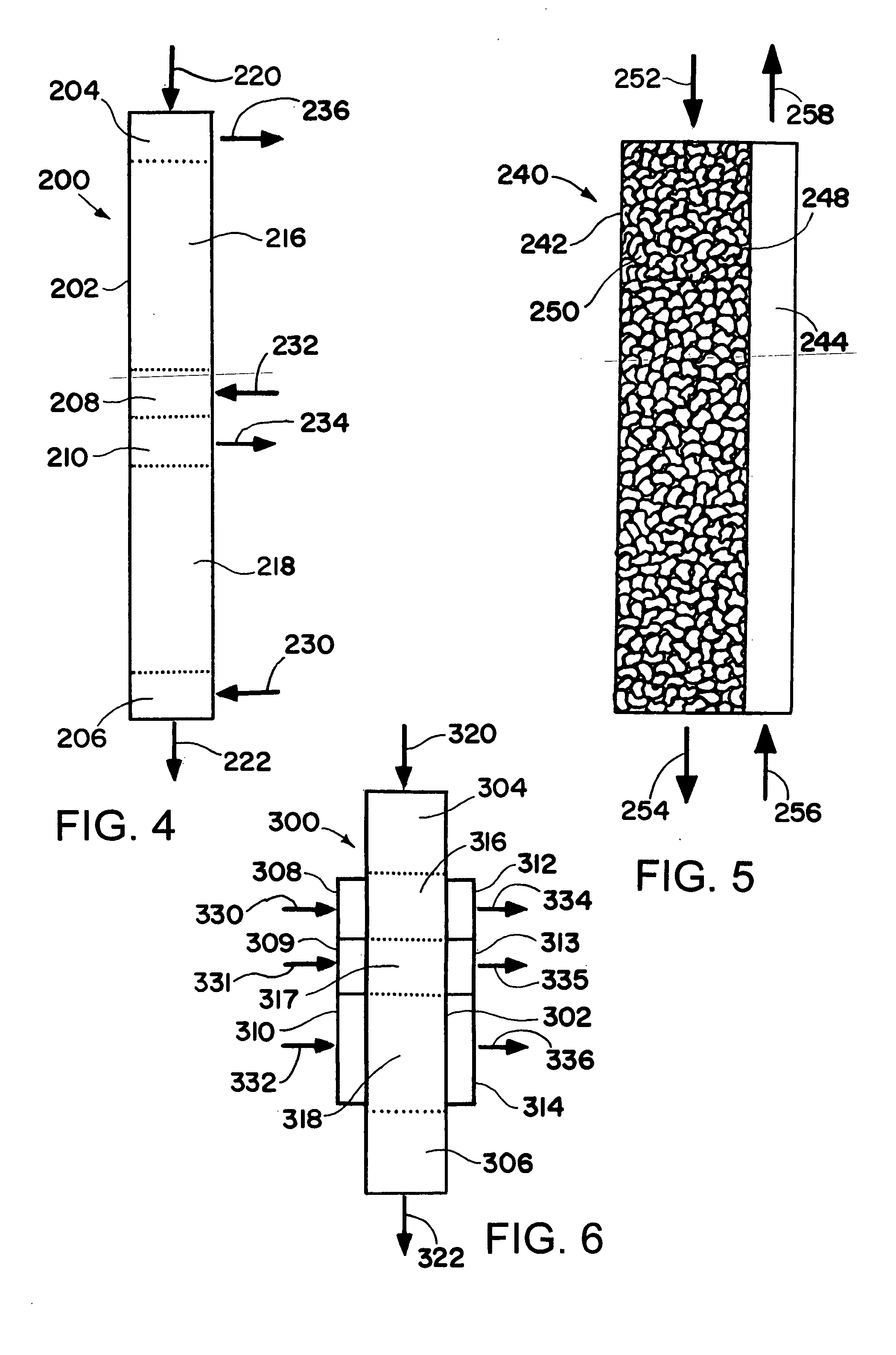

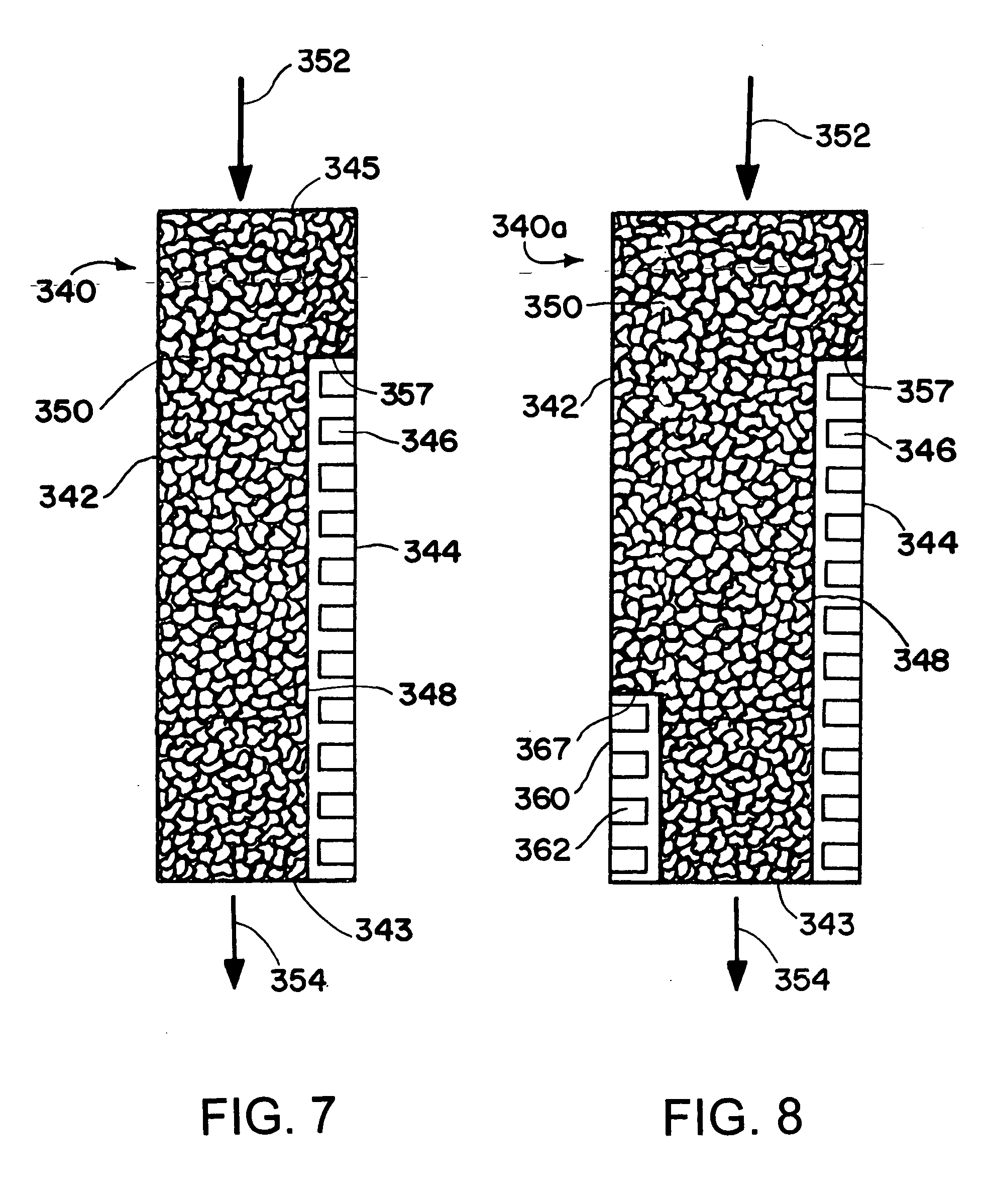

Process for conducting an equilibrium limited chemical reaction using microchannel technology

InactiveUS20050176832A1Large specific surface areaIncrease heatOrganic compounds purification/separation/stabilisationOrganic compound preparationChemical reactionDimethyl ether

The disclosed invention relates to a process for conducting an equilibrium limited chemical reaction in a microchannel reactor. The process involves the use of active heat exchange and is suitable for conducting exothermic and endothermic reactions. The process is particularly suitable for synthesizing methanol and dimethyl ether.

Owner:VELOCYS CORPORATION

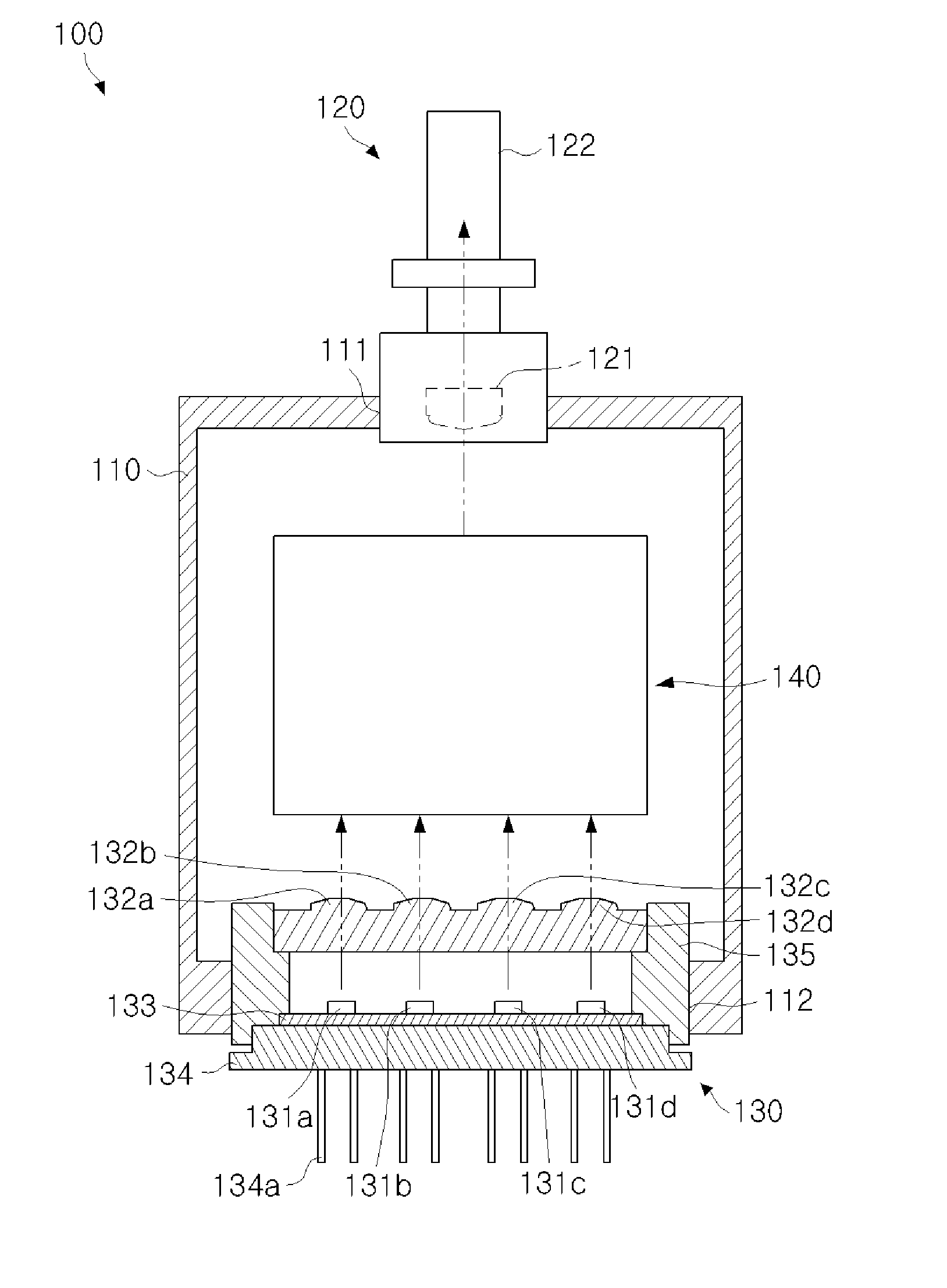

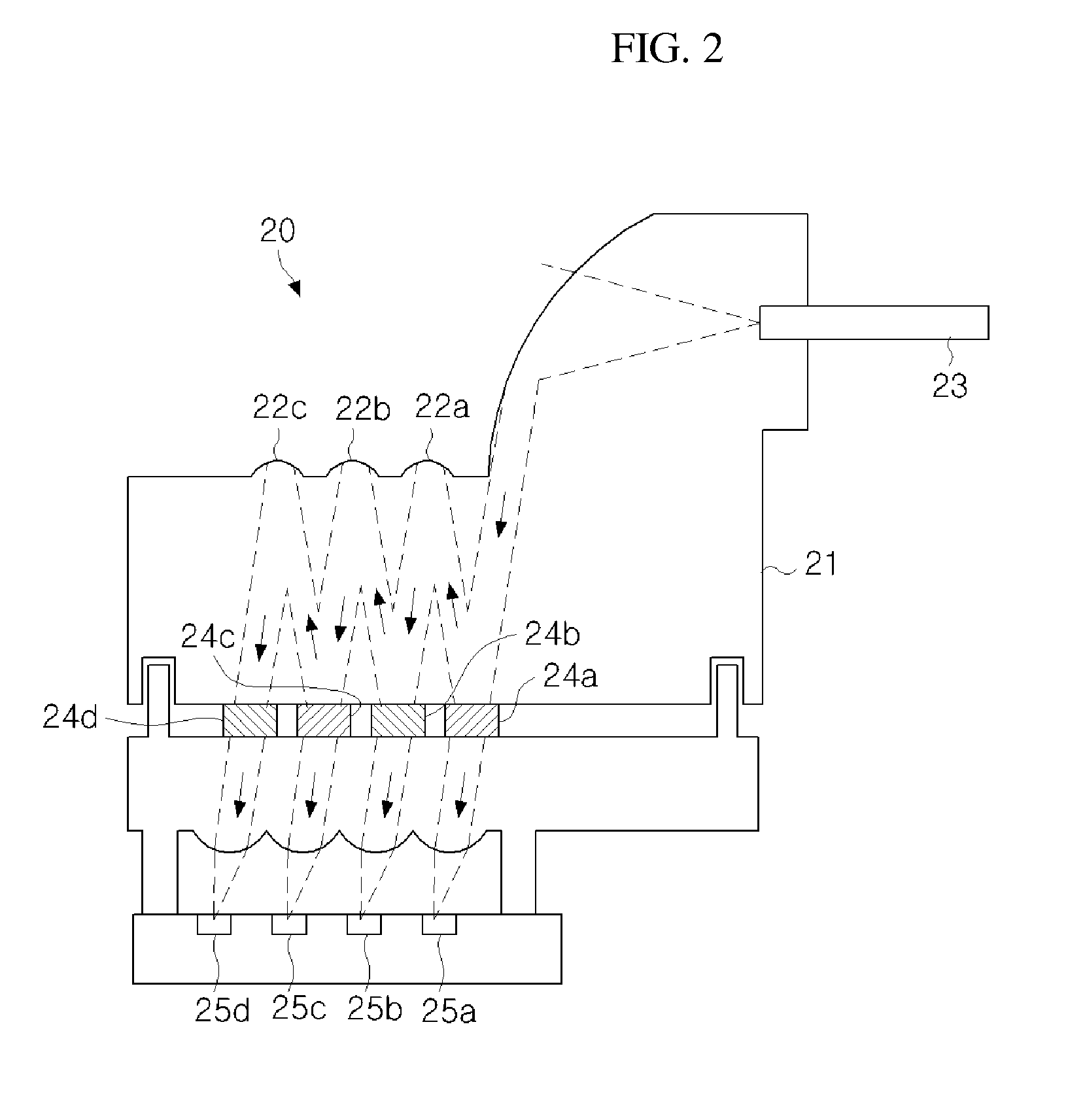

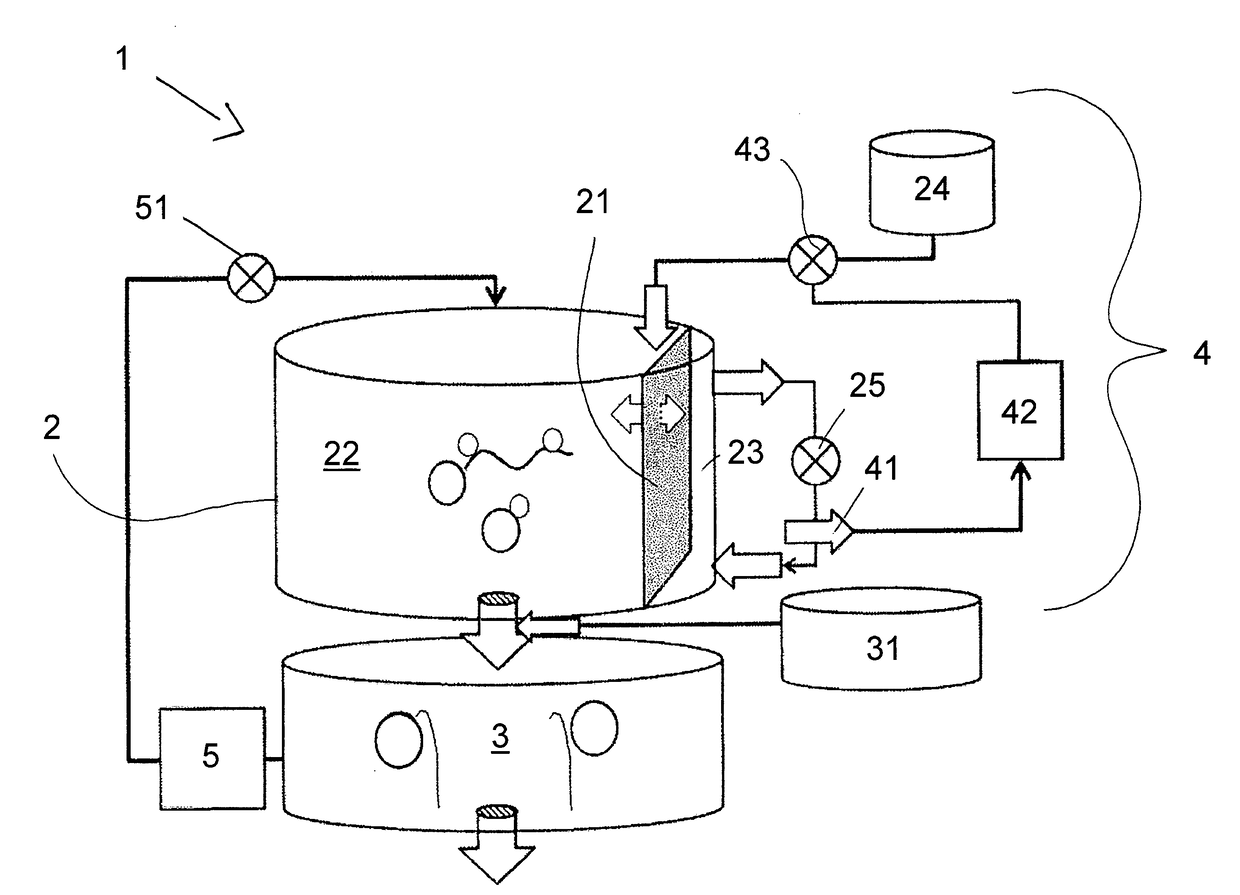

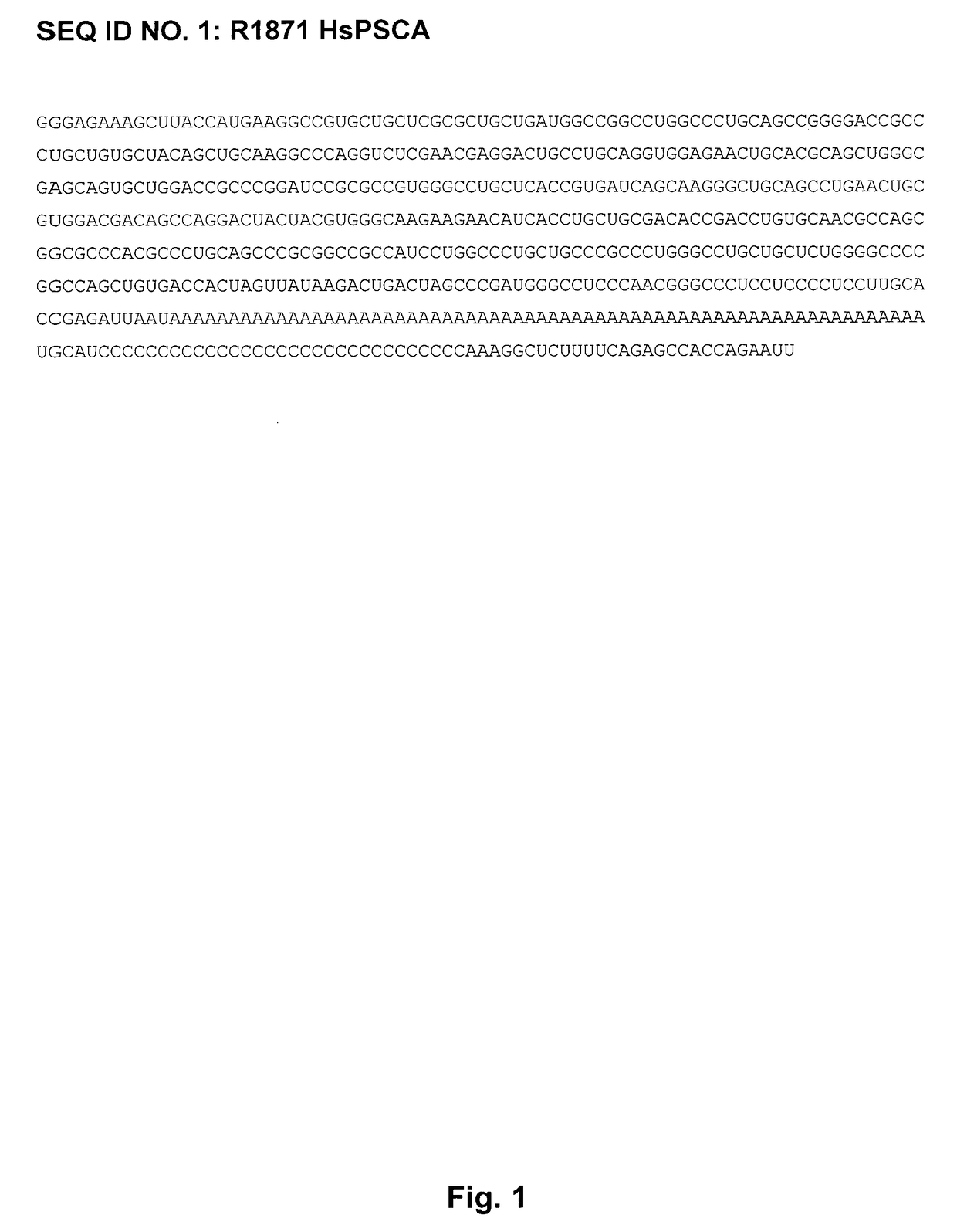

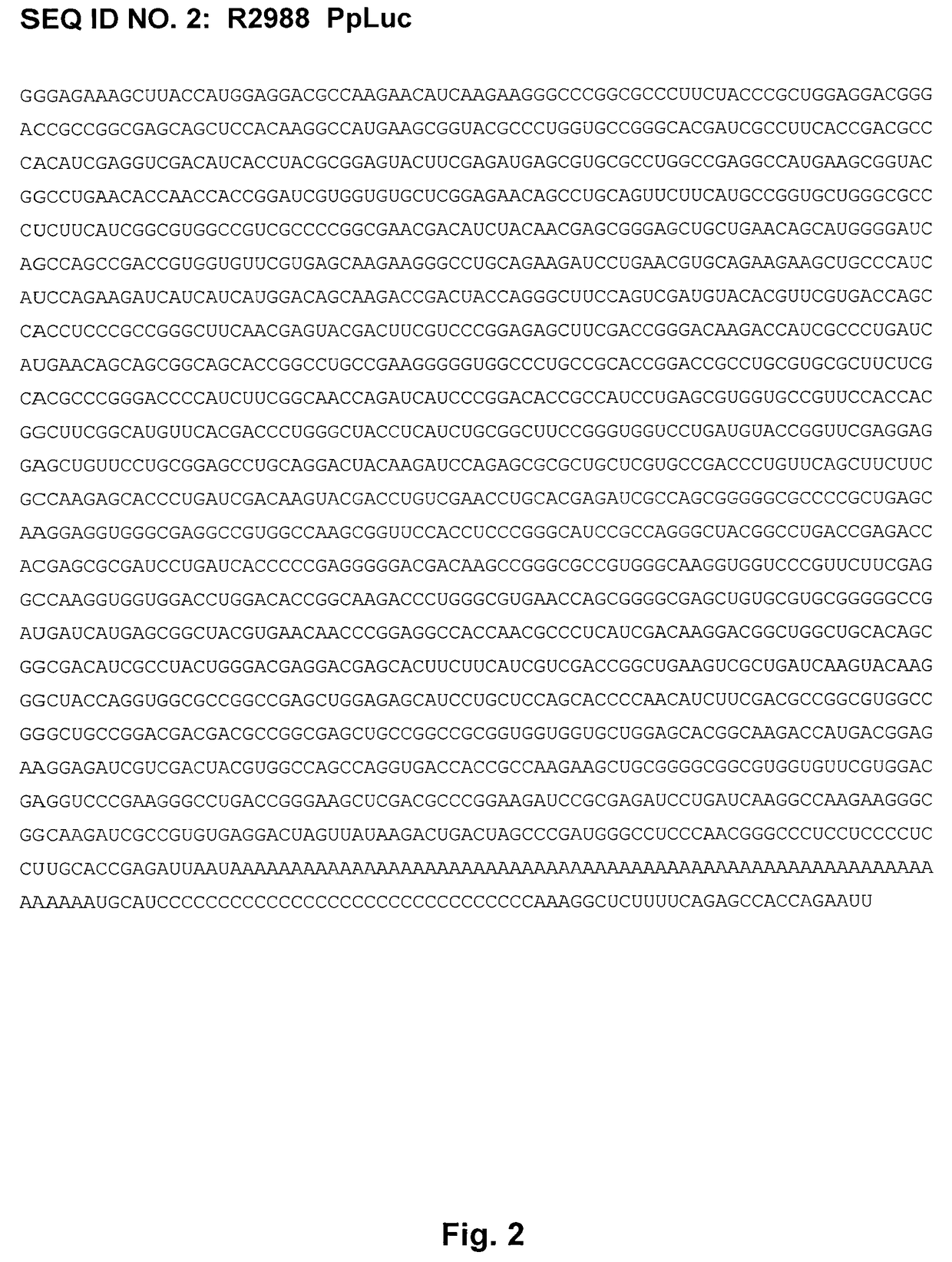

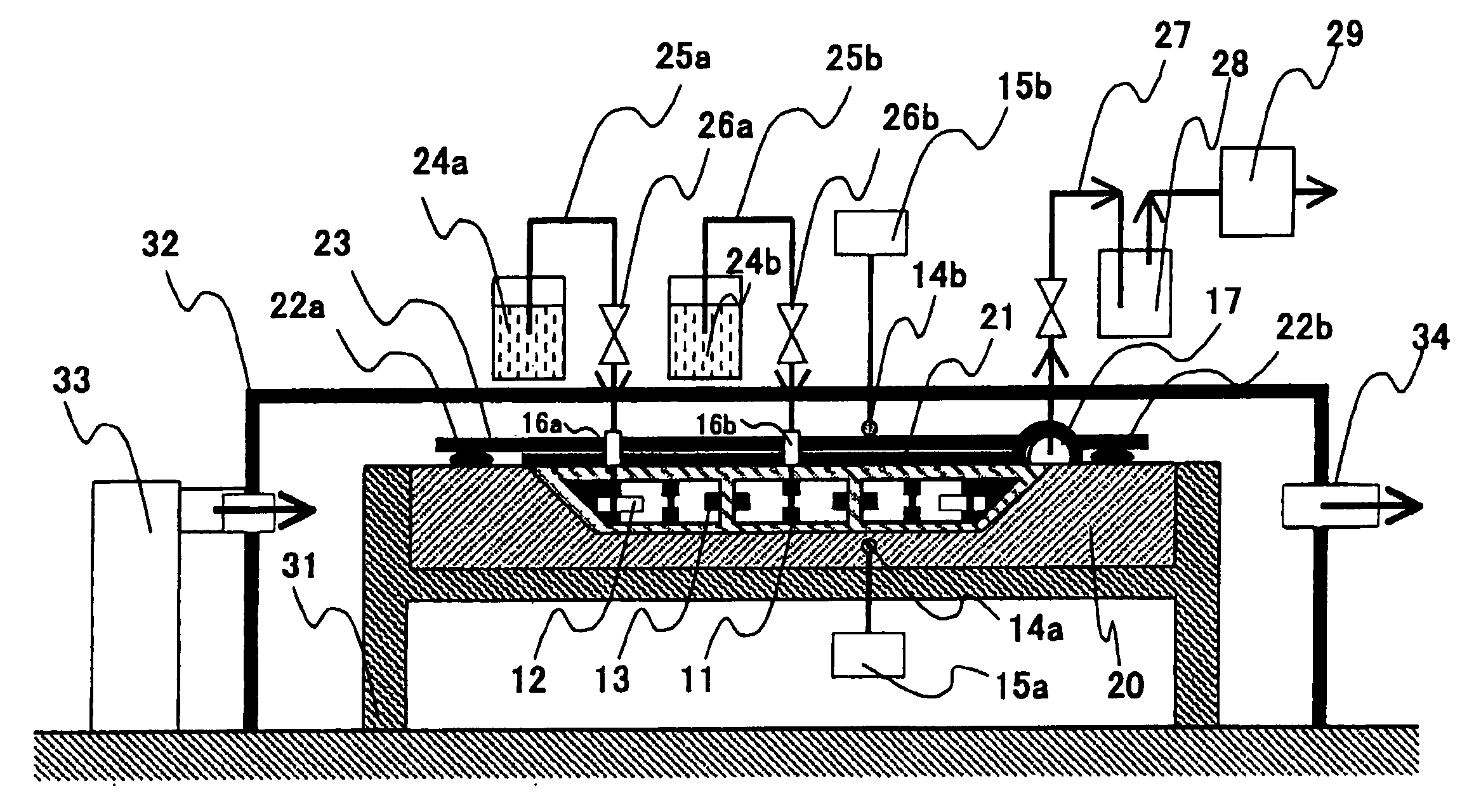

Methods and means for enhancing RNA production

ActiveUS20170114378A1Improved and economical meanImproved and economical and methodBioreactor/fermenter combinationsBiological substance pretreatmentsRibonucleosideFiltration membrane

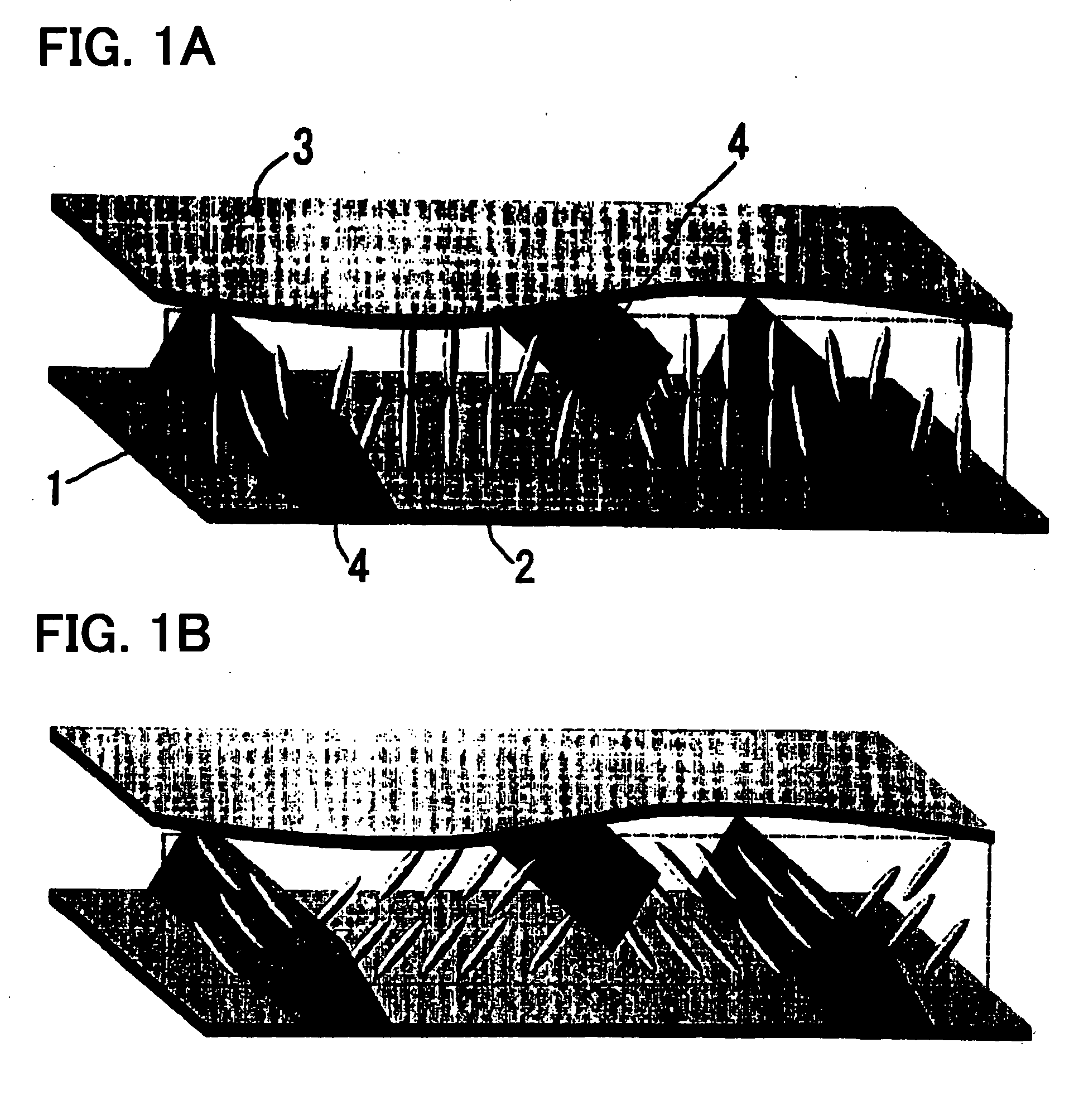

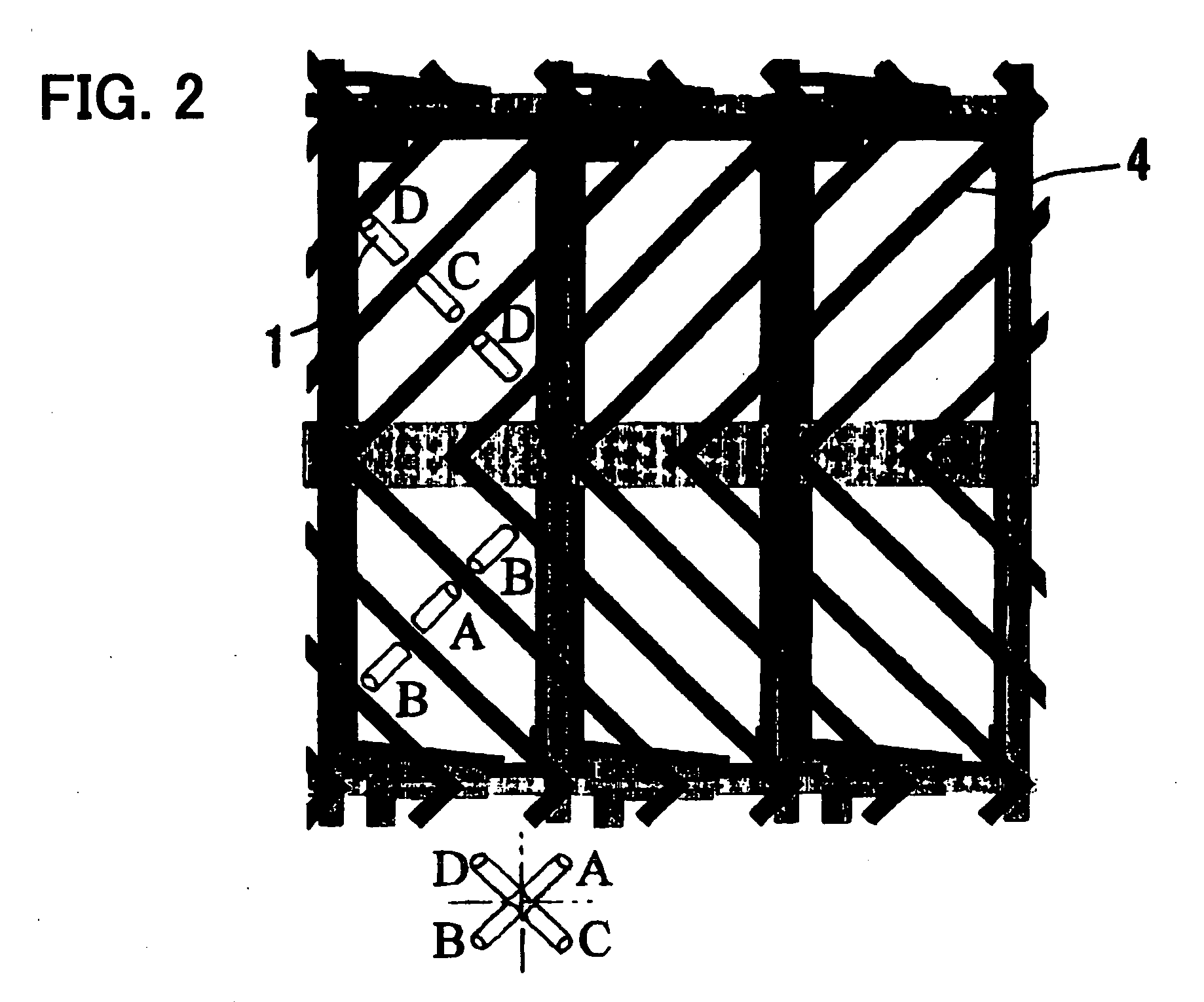

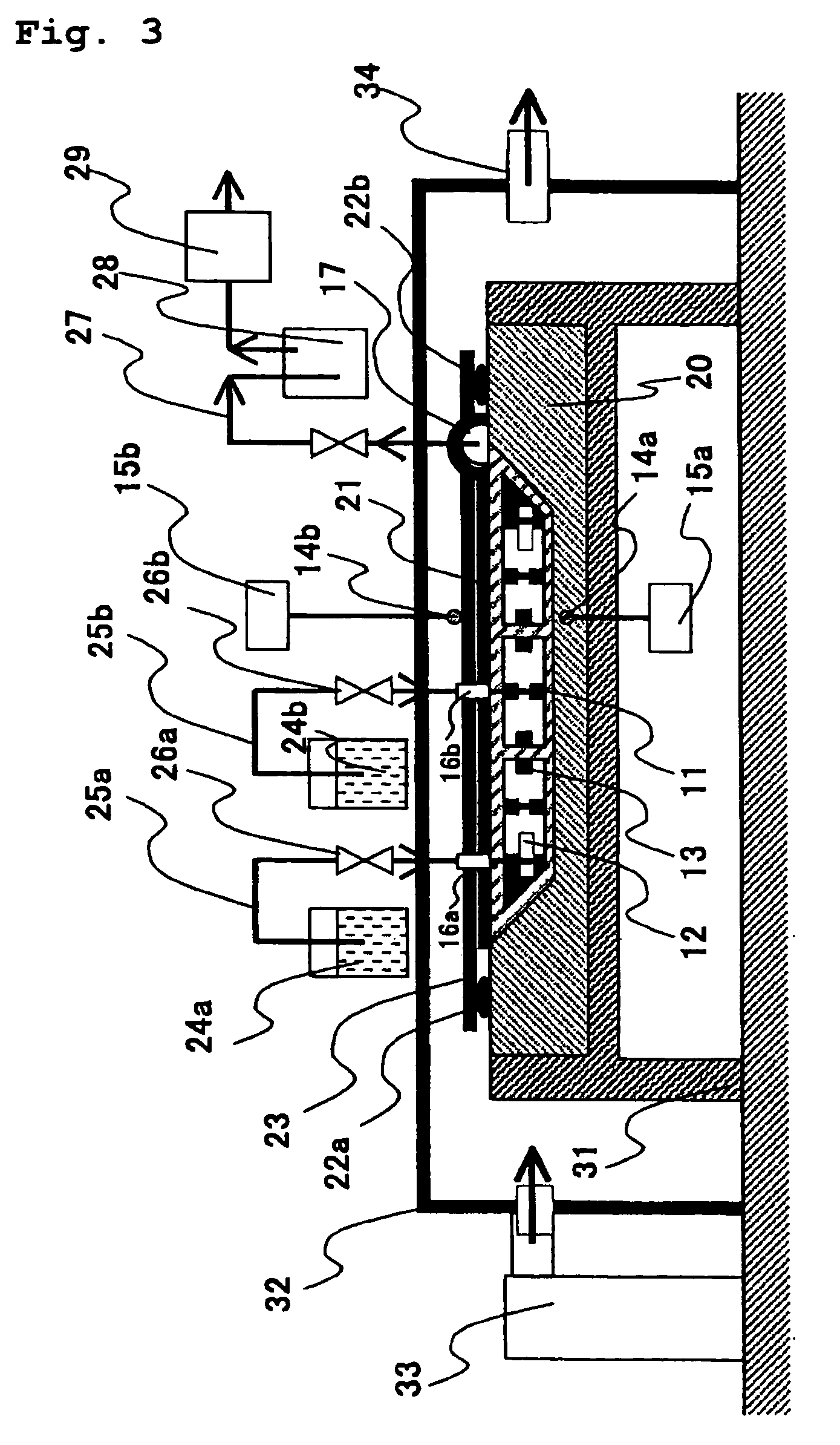

The present invention relates to a method for synthesizing an RNA molecule of a given sequence, comprising the step of determining the fraction (1) for each of the four nucleotides G, A, C and U in said RNA molecule, and the step of synthesizing said RNA molecule by in vitro transcription in a sequence-optimized reaction mix, wherein said sequence-optimized reaction mix comprises the four ribonucleoside triphosphates GTP, ATP, CTP and UTP, wherein the fraction (2) of each of the four ribonucleoside triphosphates in the sequence-optimized reaction mix corresponds to the fraction (1) of the respective nucleotide in said RNA molecule, a buffer, a DNA template, and an RNA polymerase. Further, the present invention relates to a bioreactor (1) for synthesizing RNA molecules of a given sequence, the bioreactor (1) having a reaction module (2) for carrying out in vitro RNA transcription reactions in a sequence-optimized reaction mix, a capture module (3) for temporarily capturing the transcribed RNA molecules, and a control module (4) for controlling the infeed of components of the sequence-optimized reaction mix into the reaction module (2), wherein the reaction module (2) comprises a filtration membrane (21) for separating nucleotides from the reaction mix, and the control of the infeed of components of the sequence-optimized reaction mix by the control module (4) is based on a measured concentration of separated nucleotides.

Owner:CUREVAC REAL ESTATE GMBH

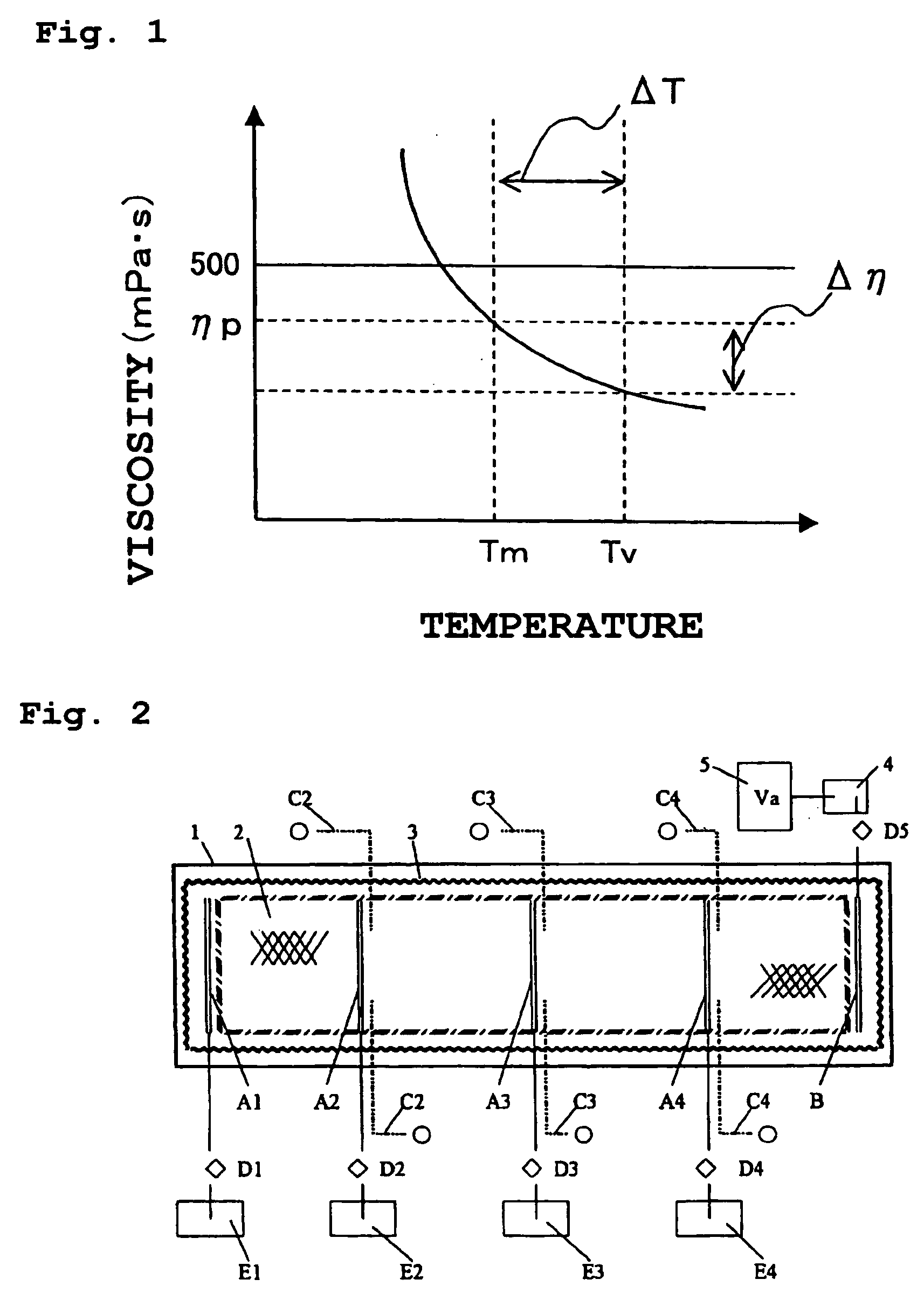

Method for producing upsized frp member

InactiveUS20040130072A1Improve mass productionReduce manufacturing costLamination ancillary operationsLaminationAir cycleFiber

The present invention relates to a method for manufacturing a large FRP member and has the following structure. The method for manufacturing a large FRP member, comprising the following steps (A) to (F). They are: setting step (A) of disposing a preform containing a reinforcing fiber base material on a surface of a molding die; sealing step (B) of covering a molding portion with a bagging material or a mold and providing at least one suction port and at least one resin injection port for sealing; evacuating step (C) of evacuating the molding portion through the suction port; hot-air heating step (D) of heating the molding portion by hot air; resin injection step (E) of injecting a thermosetting resin from the resin injection port for impregnating the reinforcing fiber base material with the resin while a temperature Tm of the molding die and a temperature Tv of the bagging material or the mold are both set to room temperature or more, and a difference DeltaT in temperature between the Tm and the Tv is set to 10° C. or less; and curing step (F) of curing the resin by maintaining the molding portion at a predetermined temperature Tpc which is equal to or more than room temperature. Preferably, the preform described above includes the reinforcing fiber base material and a resin distribution medium. In addition, it is preferable that in the hot-air heating step (D), the molding die be placed in a sealed chamber which is heat insulated with a heat insulating material, the hot air be circulated and supplied, and timing of starting the injection of the resin from a plurality of the resin injection ports be controlled in accordance with signals supplied from resin detection sensors provided in the molding die. The present invention provides a method for manufacturing a large FRP member having superior quality at an inexpensive cost and with high production yield, in which non-impregnated portions and voids are unlikely to be formed.

Owner:TORAY IND INC

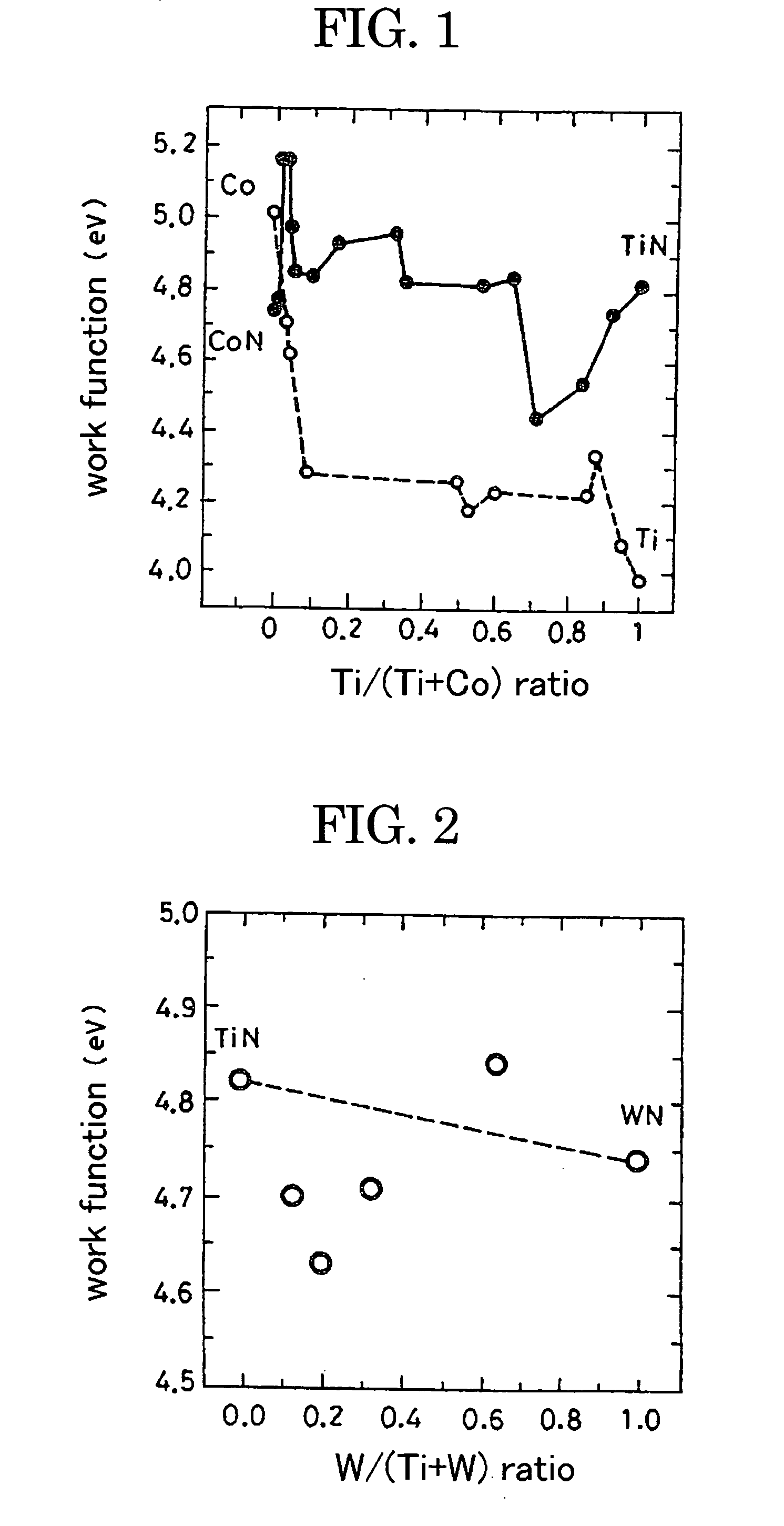

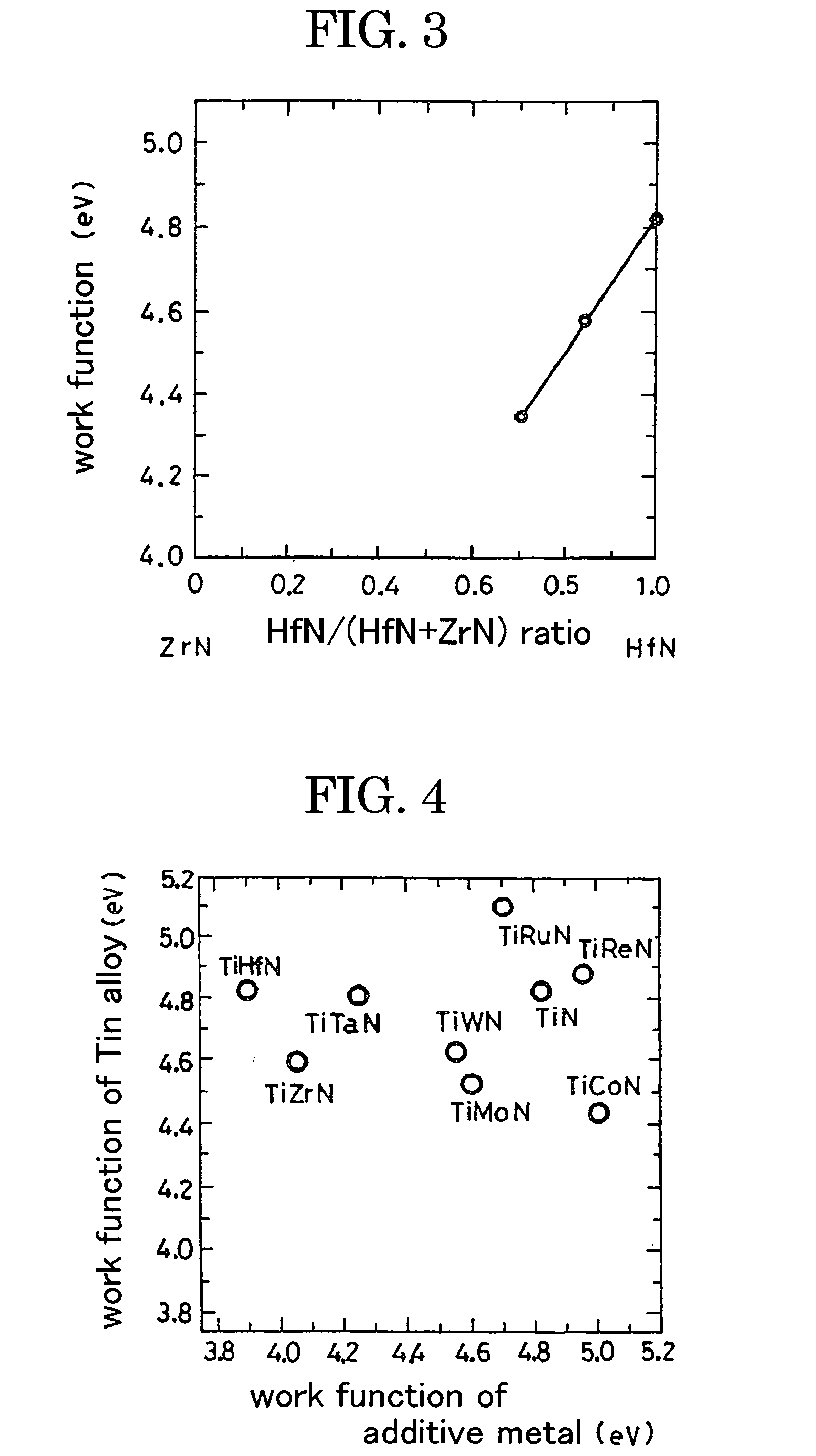

Semiconductor device and its manufacturing method

ActiveUS20050110098A1Lower threshold voltageReduce manufacturing costTransistorSolid-state devicesDevice materialEngineering

A method for manufacturing a semiconductor device wherein both the threshold voltages of an N-type MISFET and a P-type MISFET are low, device can be easily manufactured at a lower cost and a higher product yield, and the reliability of the gate insulation film is higher. The gate insulation film is formed on the surface of a silicon substrate 1 in N-type MISFET forming region and the P-type MISFET forming region, and metal gates 4 and 5 are provided thereon. The metal gate 4 is made from a TiCoN film, and the work function thereof is set at 4.0 to 4.8 eV suited to the gate electrode material of the N-type MISFET. The metal gate 5 is formed from a portion of the TiCoN film by ion-implantation of oxygen into the TiCoN film configuring the gate electrode 4 at a dosage of 1013 to 1014 (ions / cm2) to raise the work function by around 0.2 to 0.8 eV.

Owner:GK BRIDGE 1

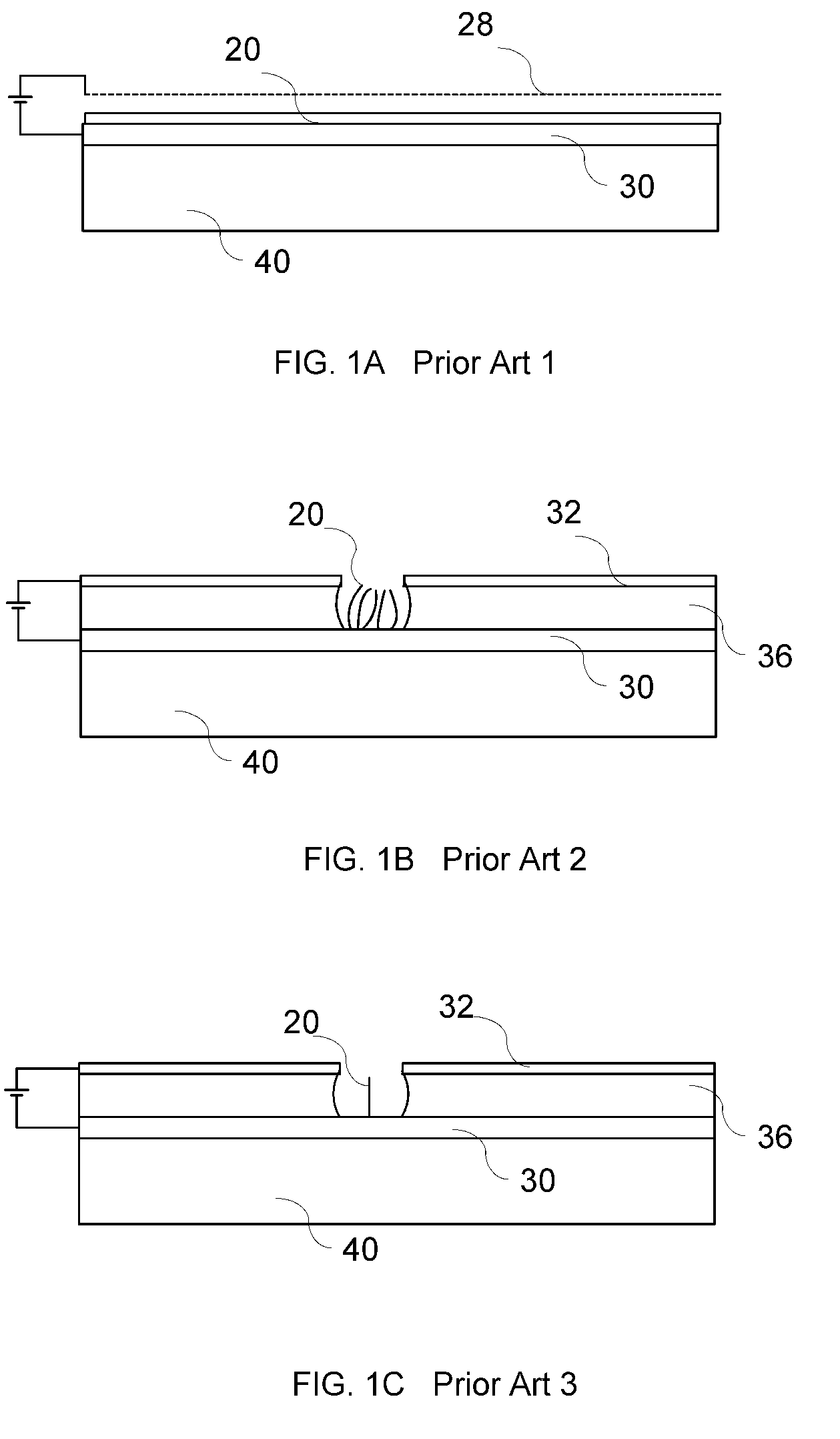

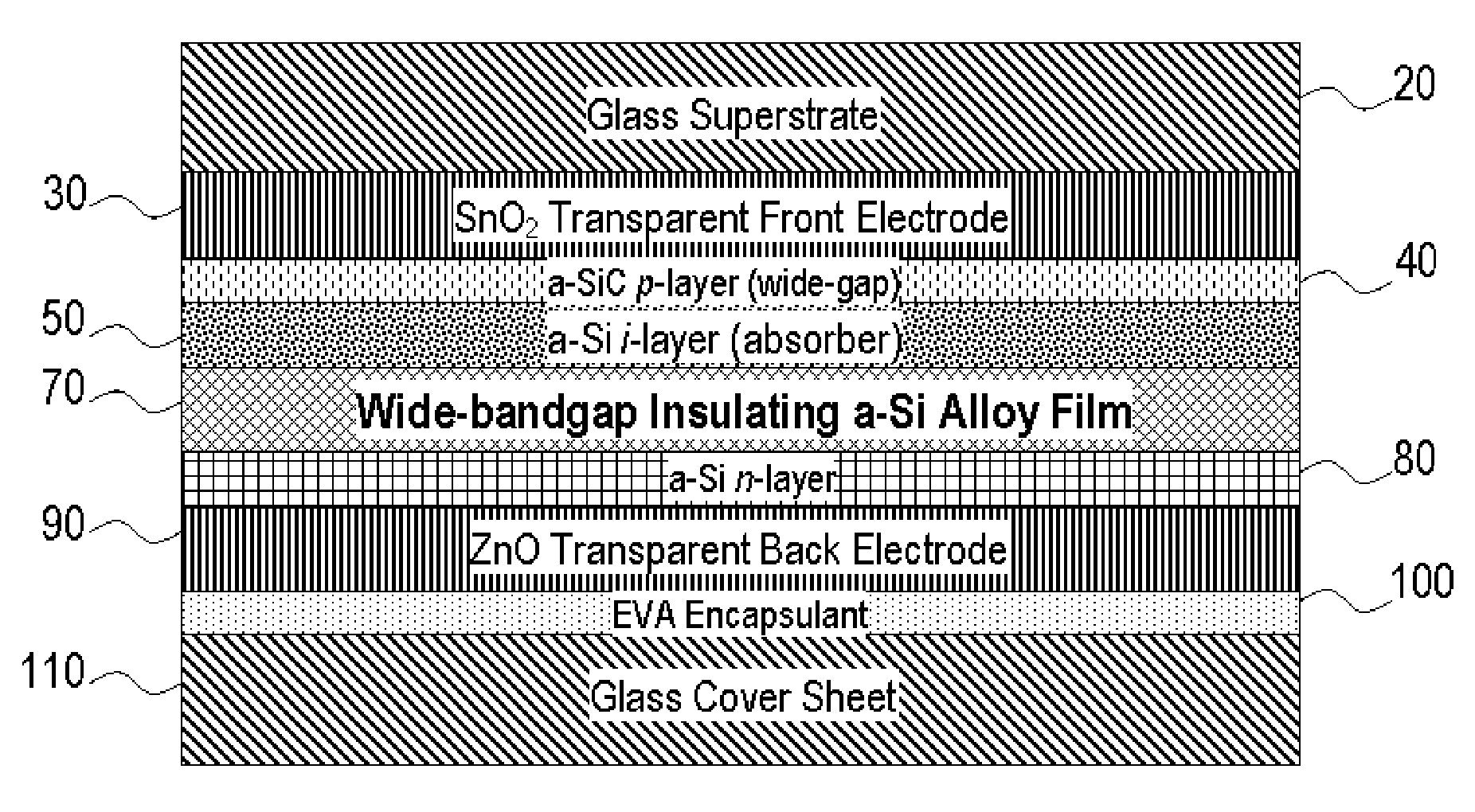

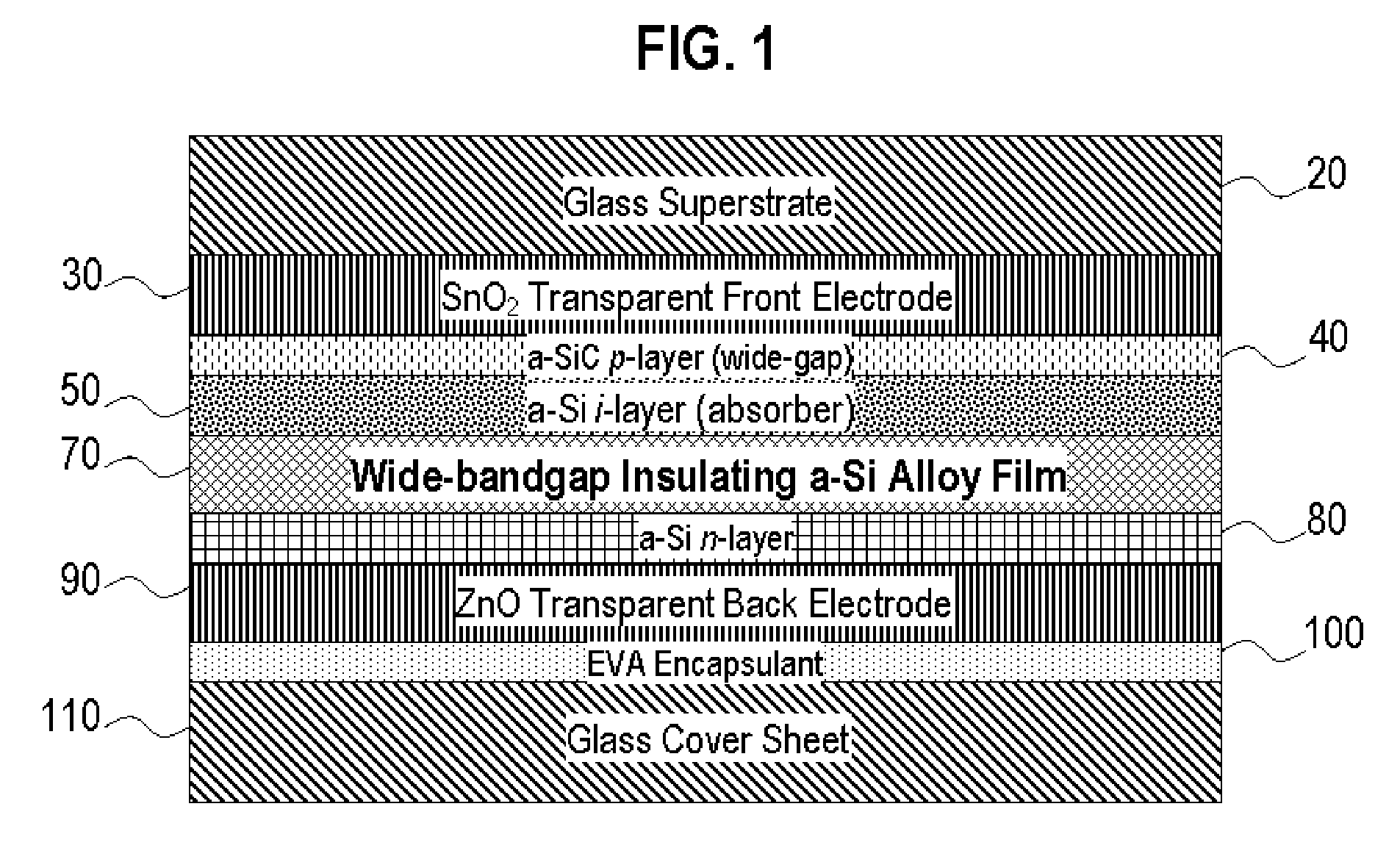

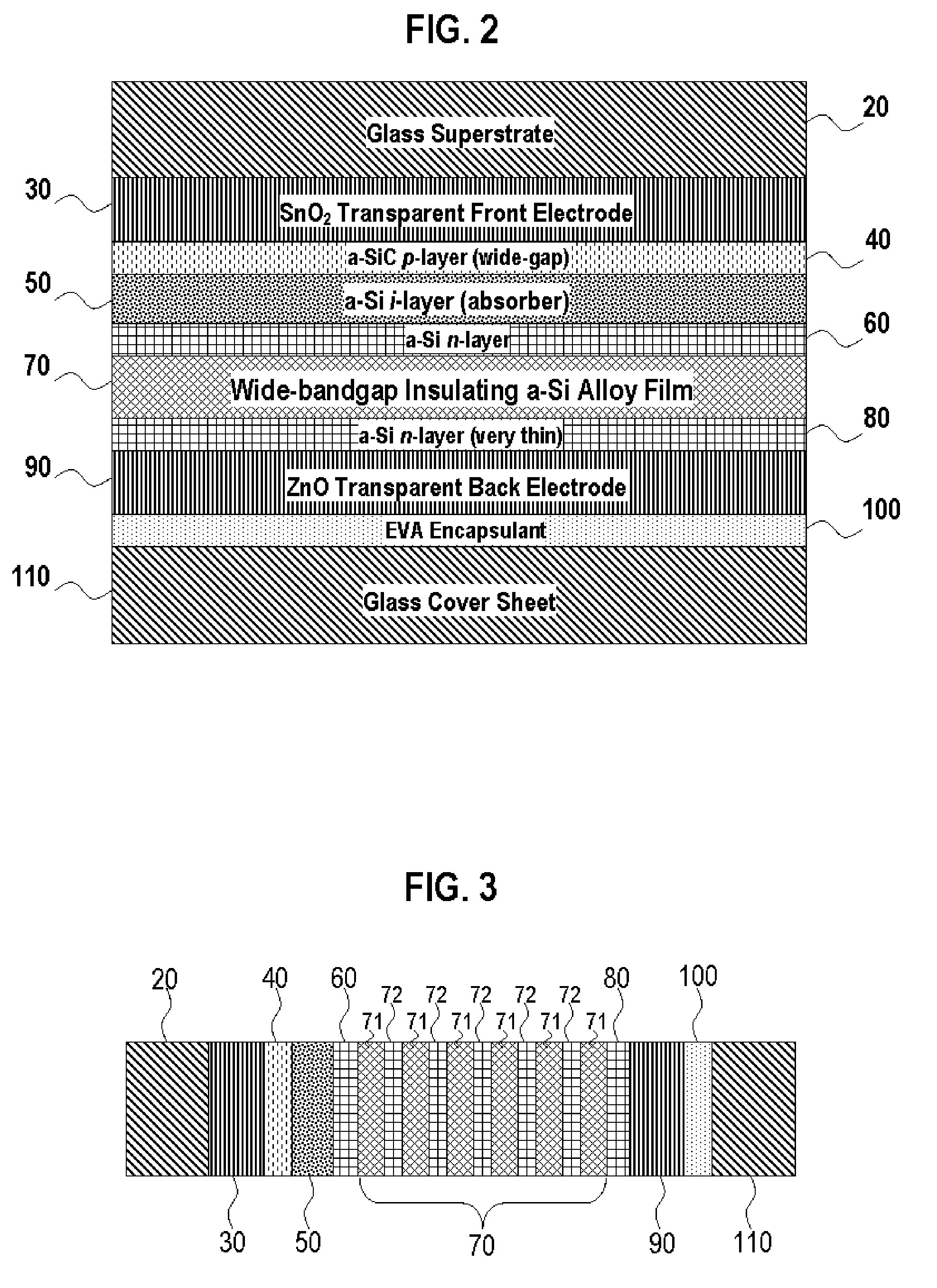

Shunt Passivation Method for Amorphous Silicon Thin Film Photovoltaic Modules

InactiveUS20070068571A1Electrical shunting defectIncrease output powerClimate change adaptationPhotovoltaic energy generationOptical transparencyEngineering

A method for reducing shunt-related defects is described for hydrogenated amorphous silicon (a-Si:H) thin film photovoltaic modules with thin active a-Si:H absorber as required by building integrated photovoltaic windows and sun-roofs with adequate transmission of sunlight. Without shunt-passivation, p-i-n type large area photovoltaic modules with very thin a-Si:H i-layer will suffer excessive performance, yield, and reliability losses due to electrical shorting through i-layer defects. Wide-bandgap a-Si:H based alloy films of sufficient resistivity are deposed between the active solar cell and the conductive back electrode to provide a barrier to leakage current flow. Such a-Si:H based barrier films of high optical transparency are dummy films that do not directly contribute to energy conversion. The shunt-passivation films are entirely produced by the same conventional manufacturing process for a-Si:H photovoltaic devices without invoking complicated or exotic materials or procedures proposed in prior arts.

Owner:TERRA SOLAR GLOBAL

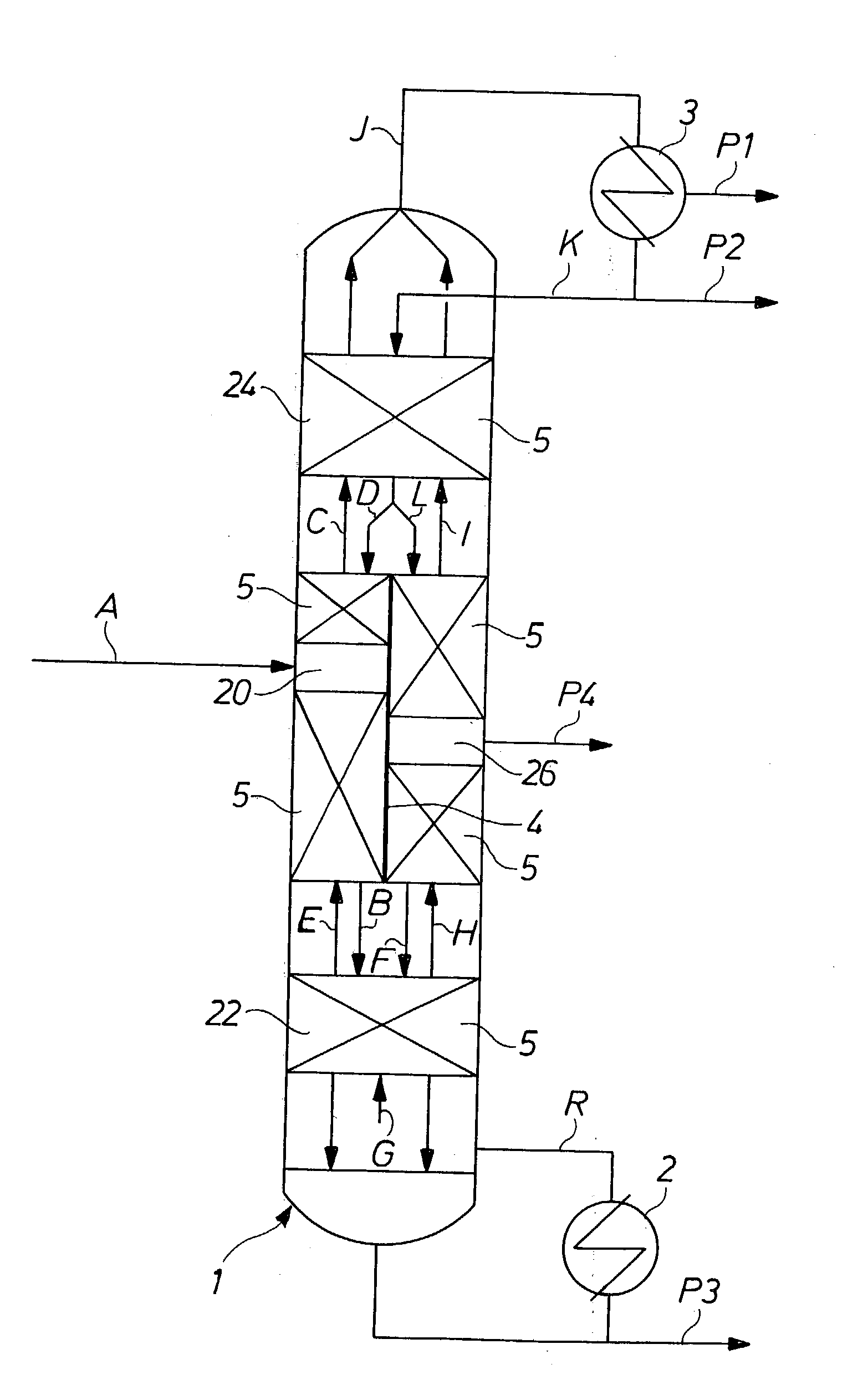

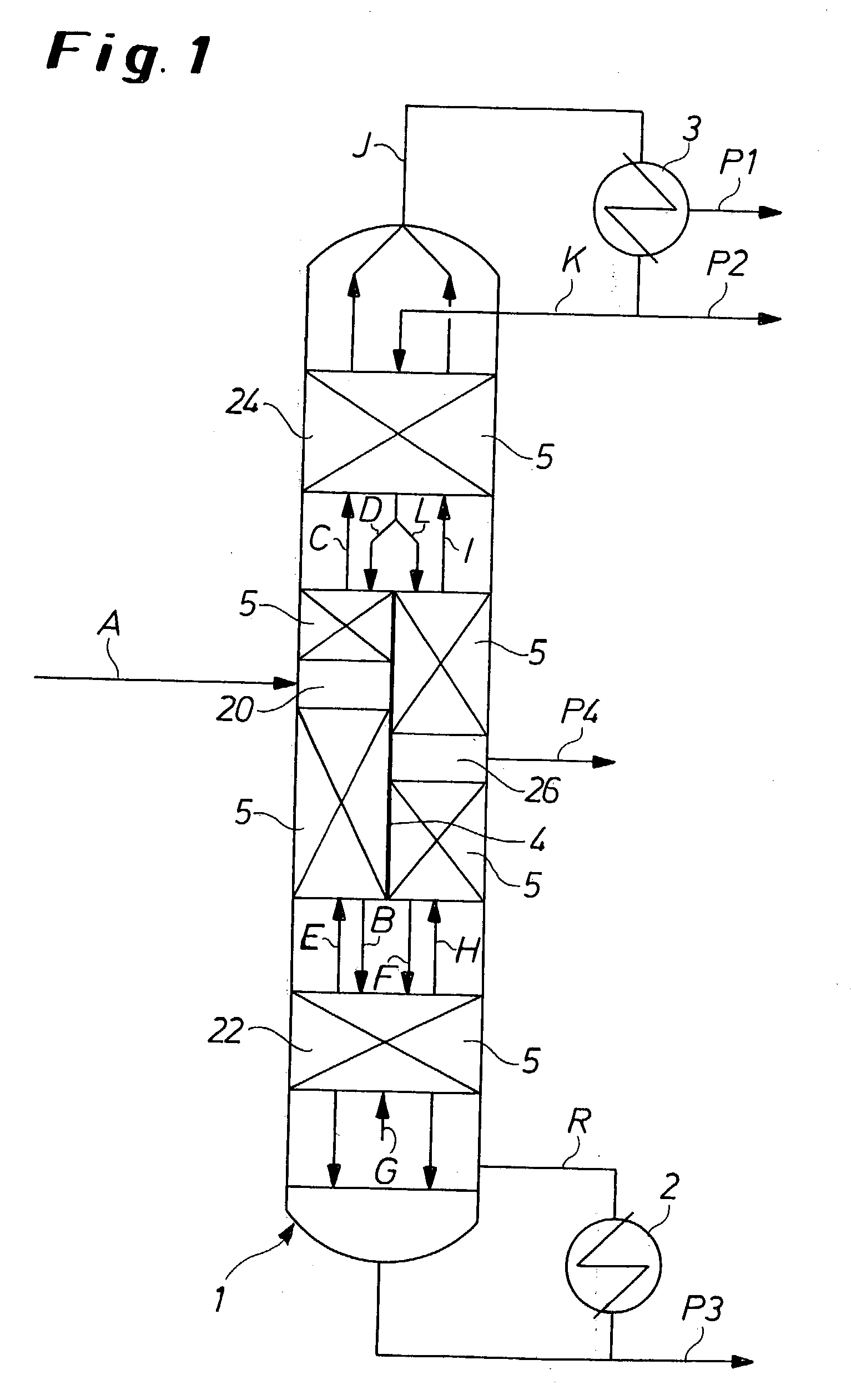

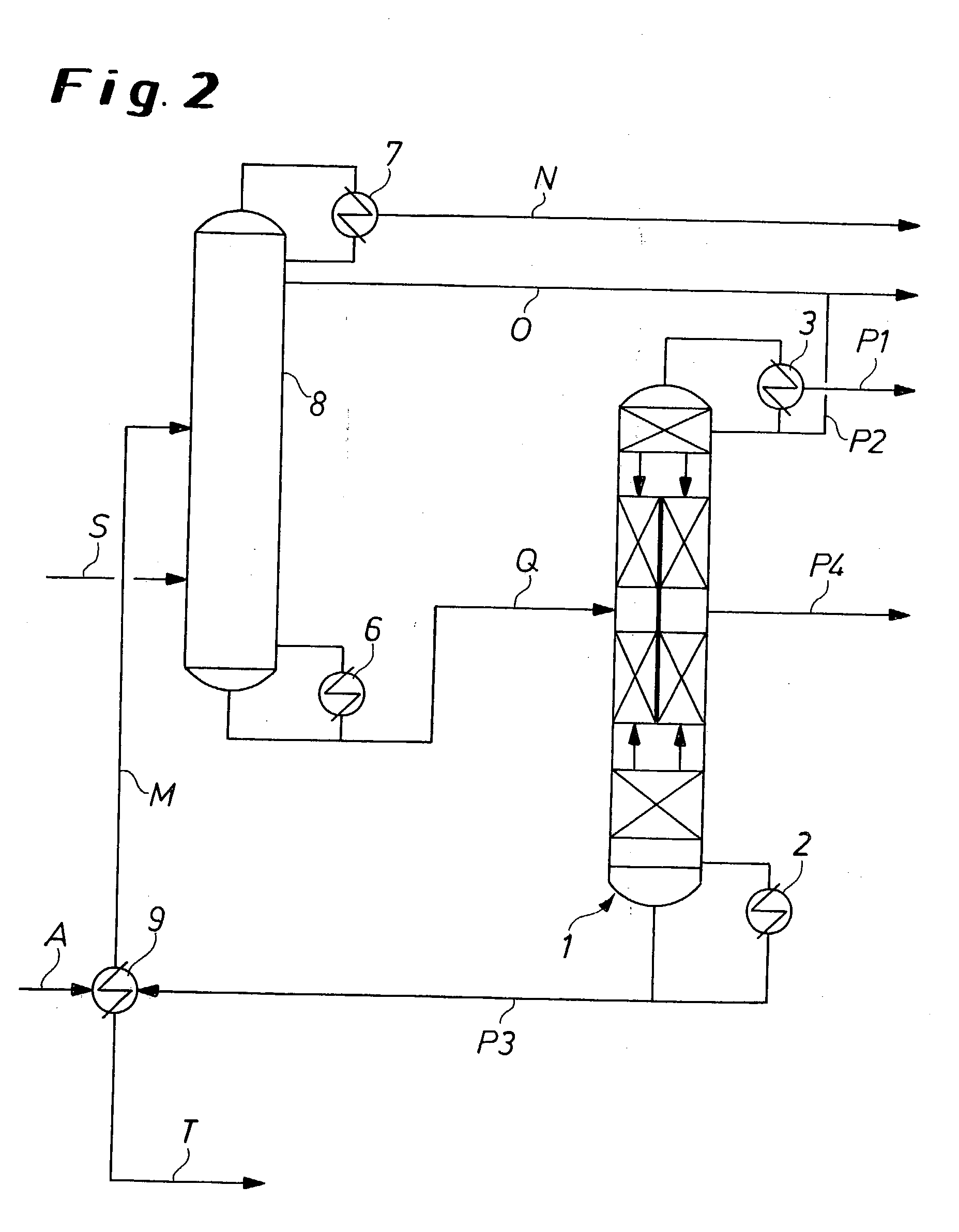

Process for the purification of mixtures of toluenediisocyanate incorporating a dividing-wall distillation column

InactiveUS20030230476A1Weaken energyLow investment costThermal non-catalytic crackingOrganic compound preparationPurification methodsOrganic solvent

Process for the purification of toluenediisocyanate from a crude distillation feed comprising toluenediisocyanate, an organic solvent and less than 2% by weight phosgene by separating the crude distillation feed in a dividing-wall distillation column into at least four product fractions P1-P4. P1 is a phosgene enriched low-boiler product, P2 is a solvent-enriched product, P3 is a high boiler enriched bottoms and P4 is a toluenediisocyanate product stream.

Owner:COVESTRO DEUTSCHLAND AG

Semiconductor package having pre-plated leads and method of manufacturing the same

InactiveUS20070013038A1Improve conductivityEasy accessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A quad flat non-lead (QFN) package at least comprises a die, a lead frame and a molding compound. The lead frame comprises a plurality of L-shaped leads for electrically connecting the die. Two pre-plated conductive layers, formed on a bottom portion and a top portion of each L-shaped lead, are exposed to a bottom surface and a top surface of the package, respectively. The molding compound is formed for encapsulating the die and the L-shaped leads.

Owner:ADVANCED SEMICON ENG INC

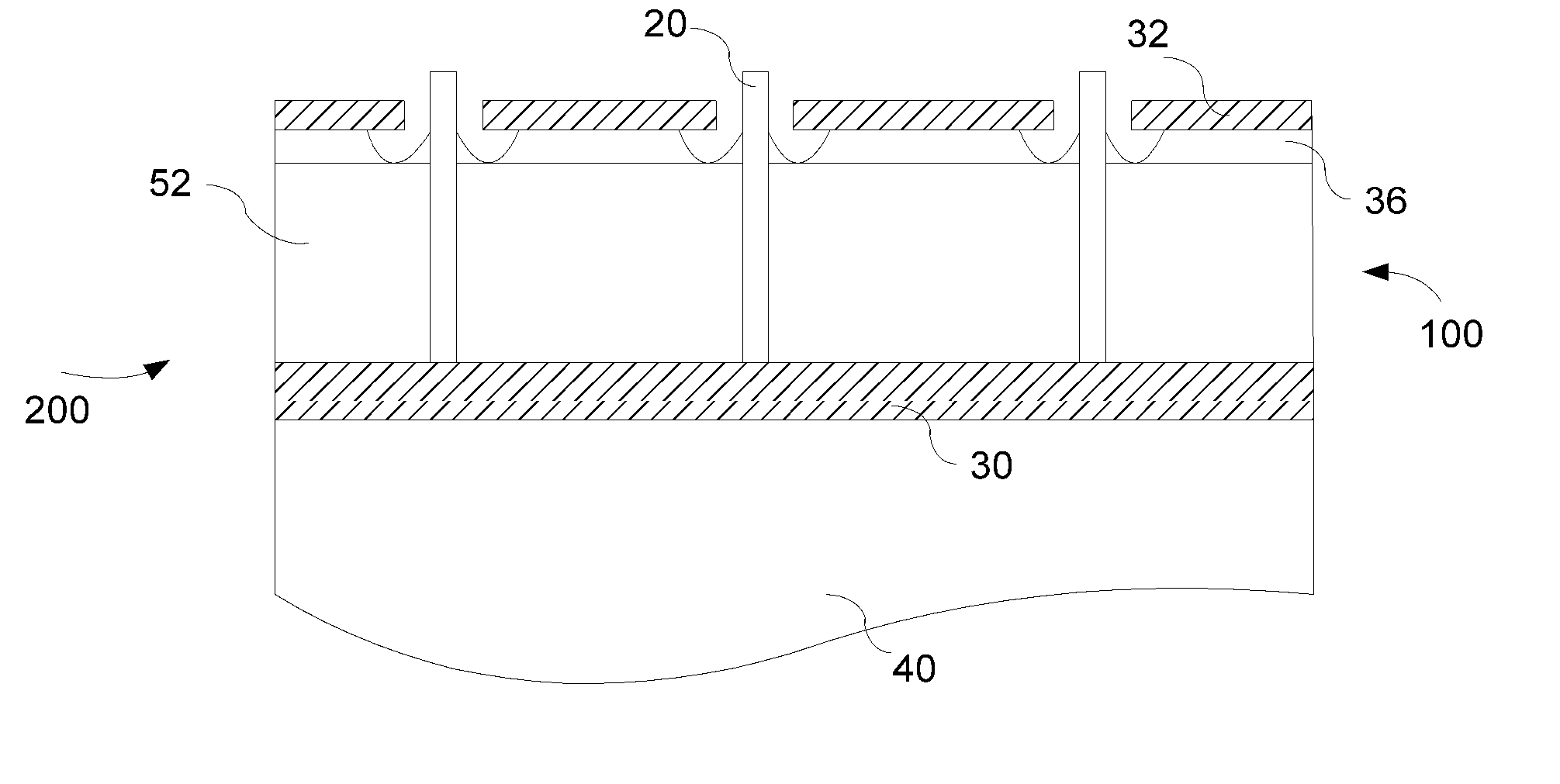

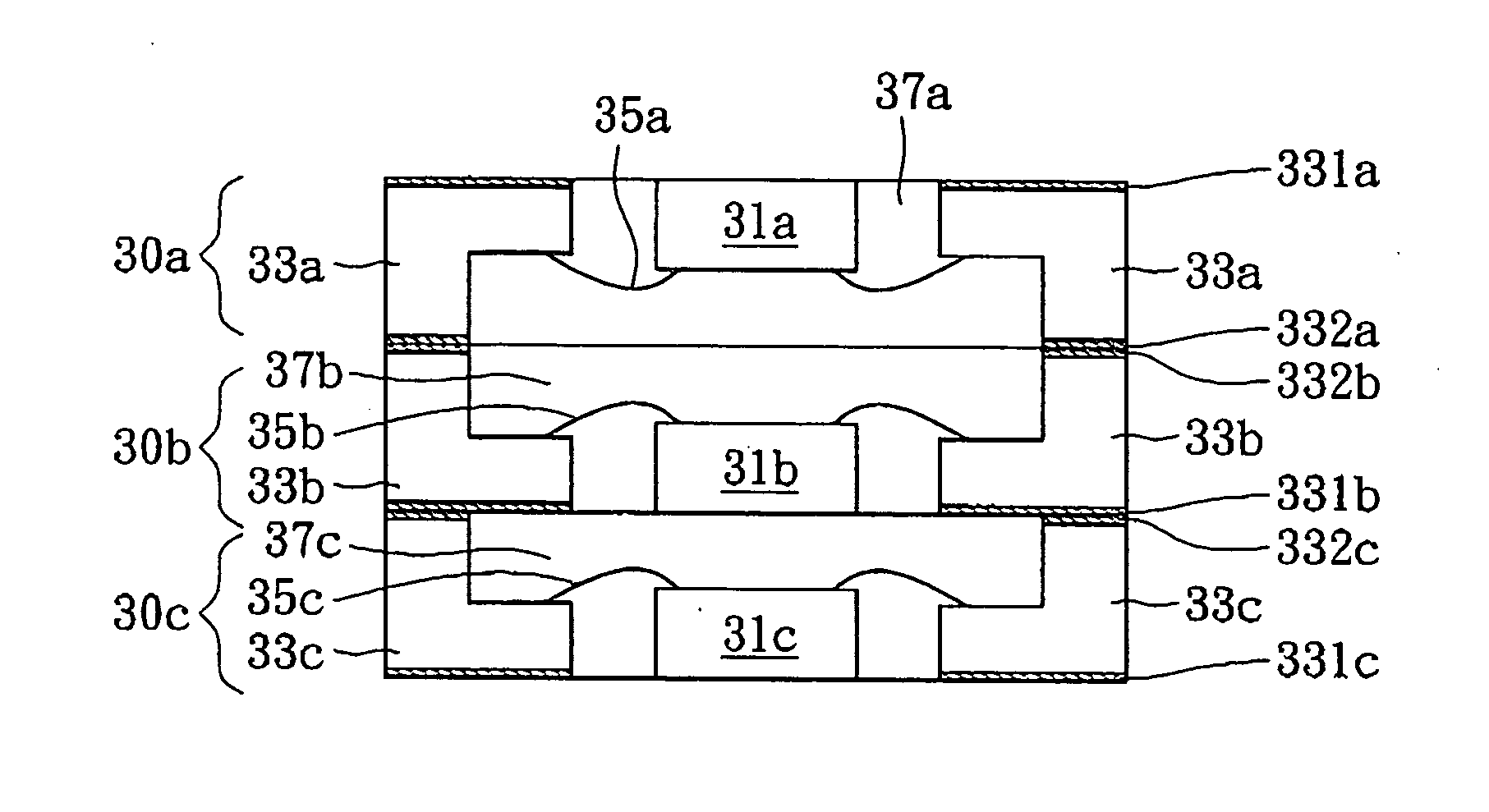

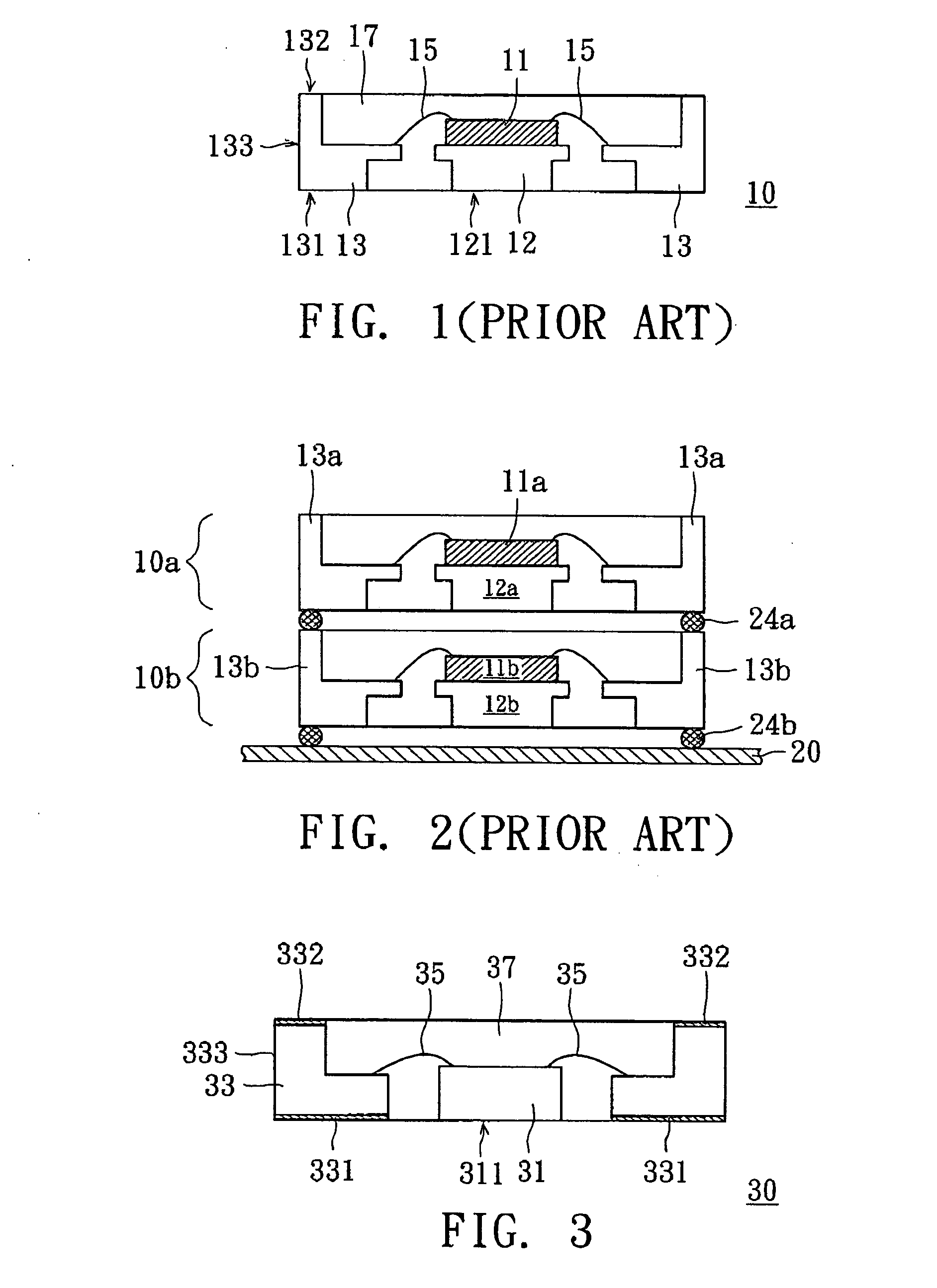

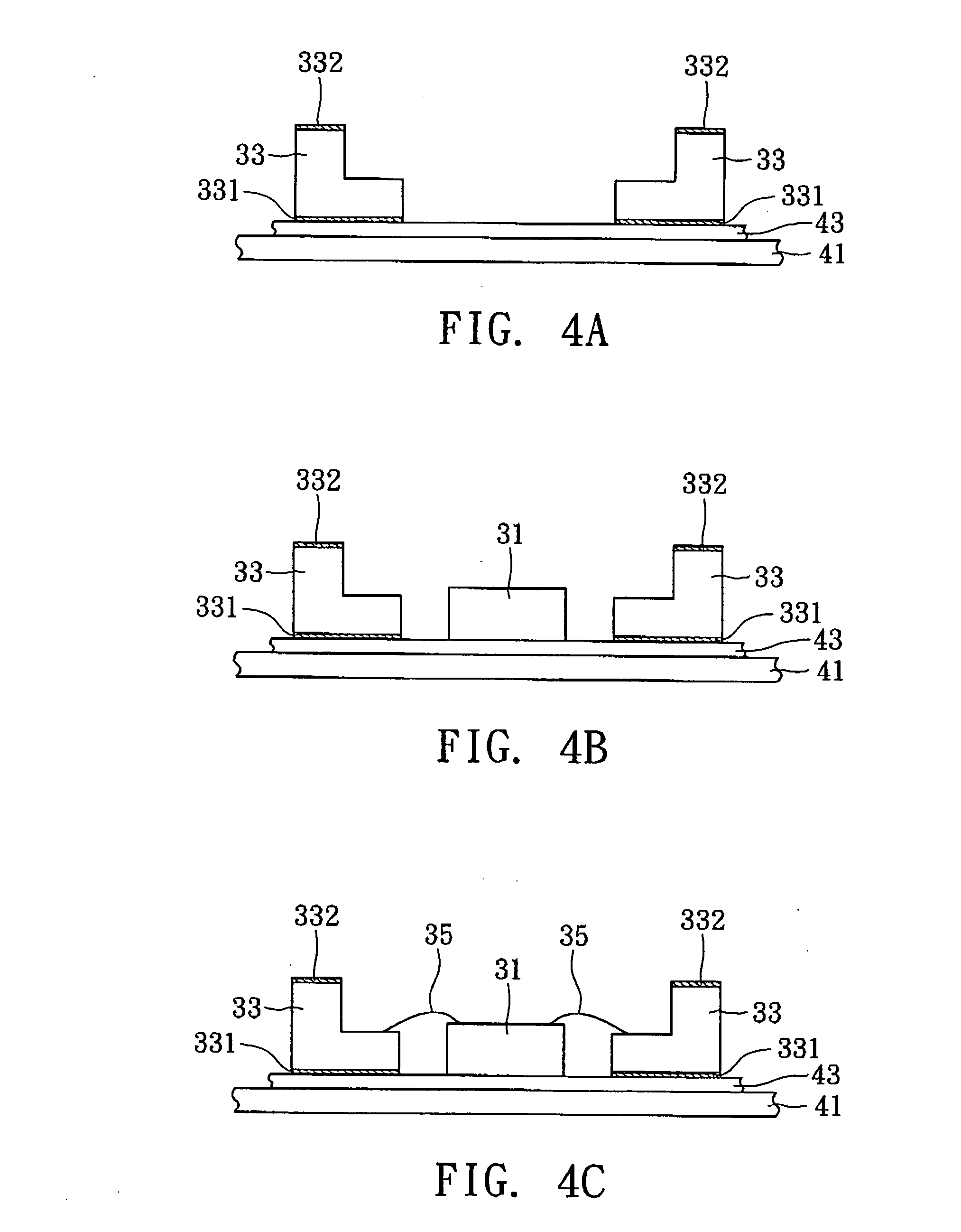

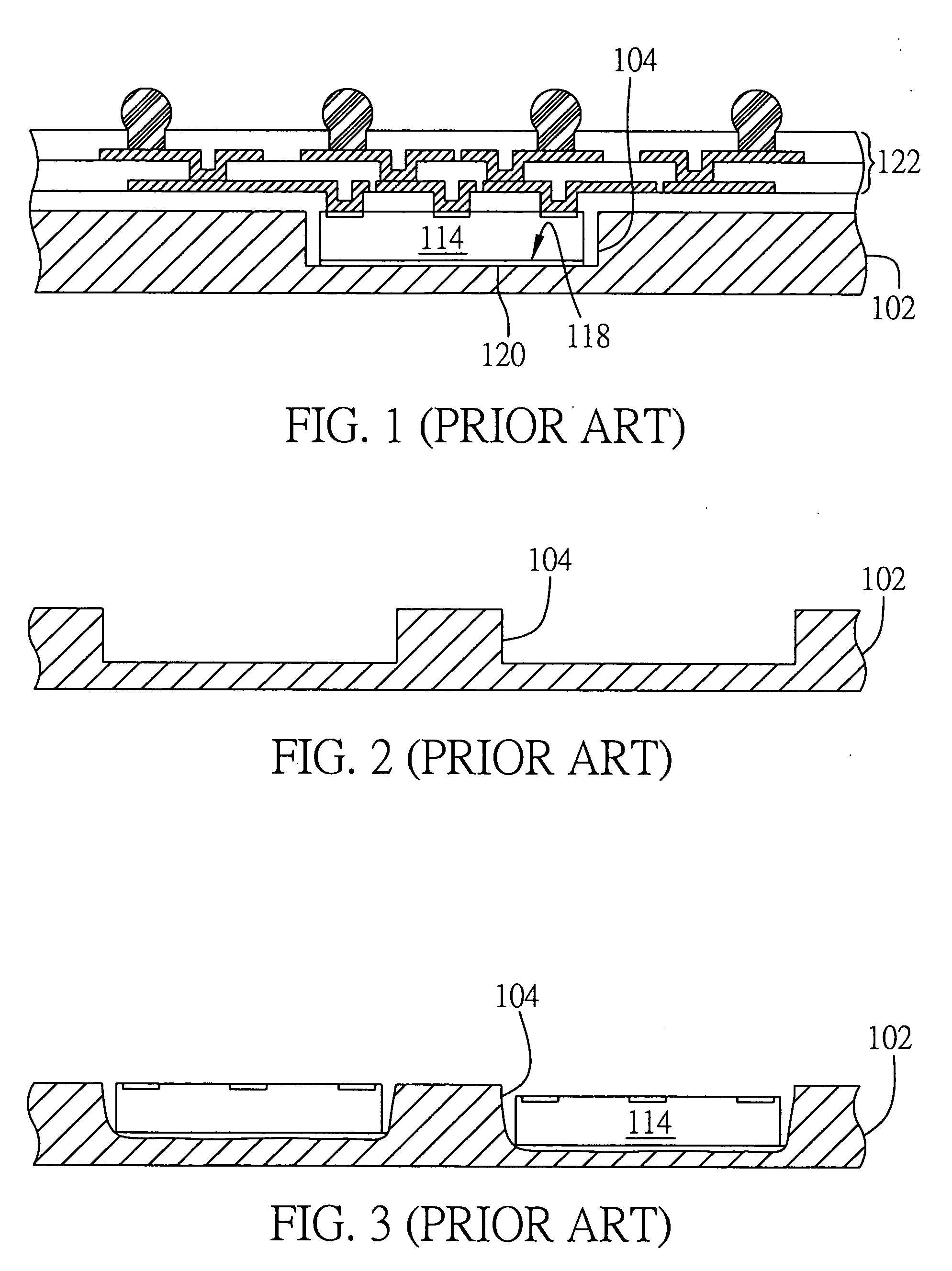

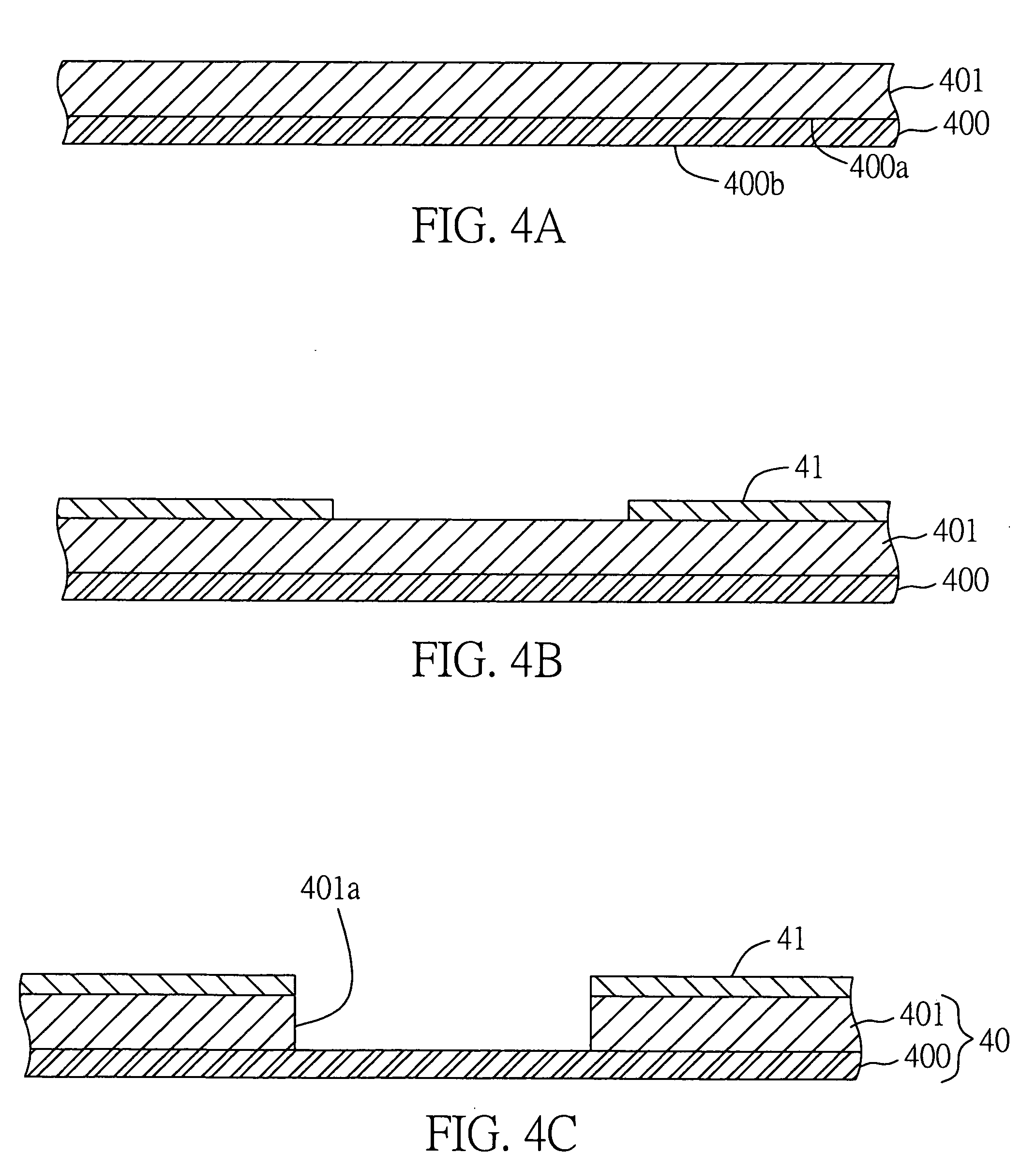

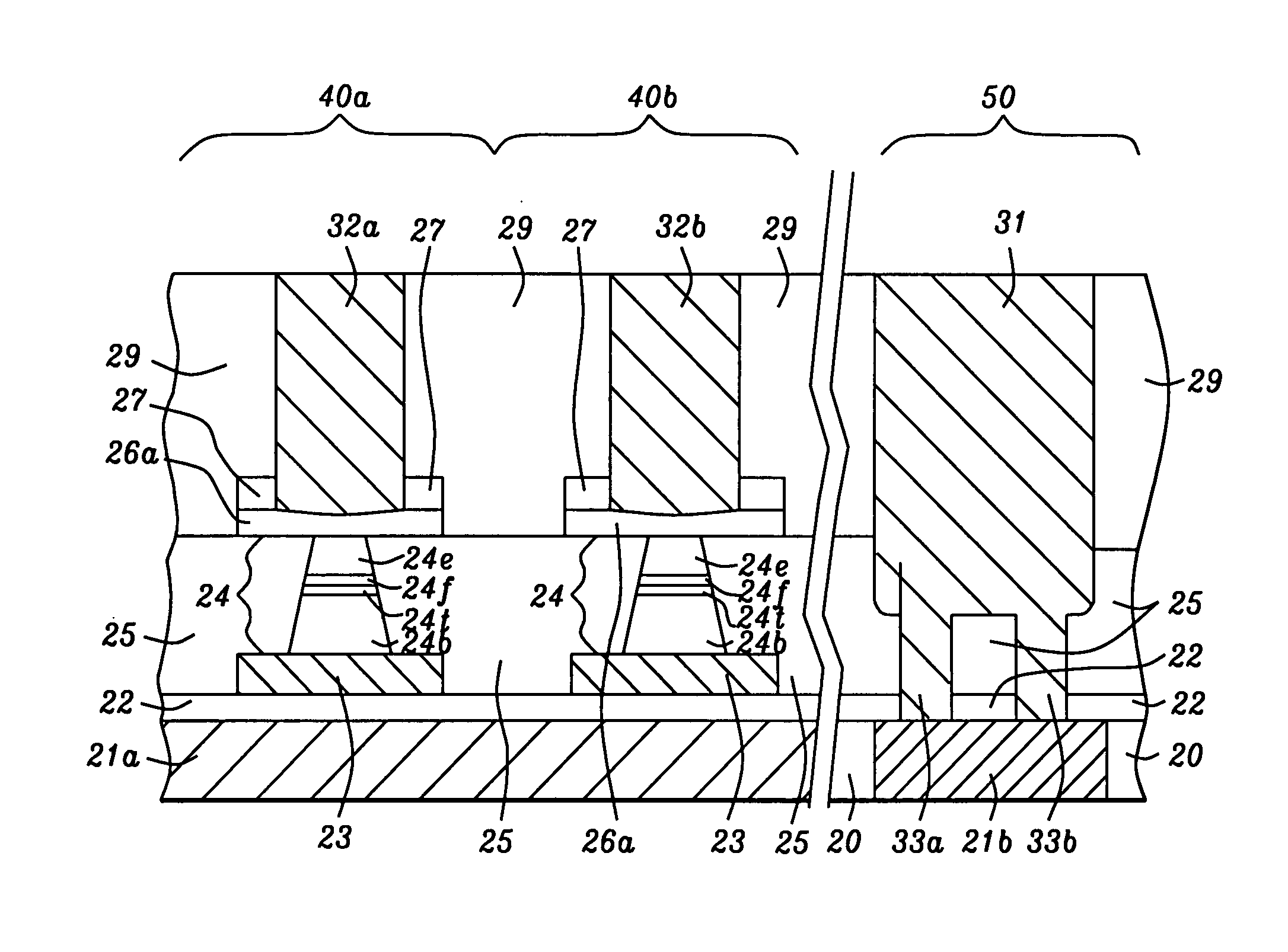

Substrate structure with embedded chip of semiconductor package and method for fabricating the same

InactiveUS20060087037A1Maintain consistencyImprove production yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A substrate structure with embedded chips of a semiconductor package and a method for fabricating the same are proposed. First of all, a carrier structure having a first carrier plate and a second carrier plate being directly formed on the first carrier plate is provided. The second carrier plate is provided with at least an opening. Then, a non-active surface of at least a semiconductor chip is mounted onto the first carrier plate and embedded in the opening of the second carrier plate. A dielectric layer is subsequently formed on a surface of the chip and the second carrier plate, and the material of the dielectric layer is filled in the opening of the second carrier plate. Afterwards, a plurality of vias is formed penetrating through the dielectric layer to expose conductive pads located on an active surface of the chip. A circuit layer and conductive vias are then respectively formed on a surface and penetrating through the dielectric layer, such that the circuit layer can be electrically connected to the conductive pad located on the chip by the means of the conductive via. Finally, conductive elements are provided on a surface of the circuit layer, so that the semiconductor chip embedded in the carrier plate can be electrically connected to an external device.

Owner:PHOENIX PRECISION TECH CORP

Novel bit line preparation method in MRAM fabrication

ActiveUS20110089507A1Easy to controlHigh product yieldSolid-state devicesSemiconductor/solid-state device manufacturingElectricityEtching

A MRAM structure is disclosed that includes a metal contact bridge (MCB) which provides an electrical connection between a MTJ top electrode and an overlying bit line. The MCB has a width greater than a MTJ top electrode and serves as an etch stop during bit line etching to prevent sub-trenches from forming adjacent to the top electrode and causing shorts. MCBs also prevent insufficient etching that causes open circuits. A MCB is preferably a metal, metal compound, or alloy such as Ta with low resistivity and high conductivity. The MCB layer is patterned prior to using a dual damascene process to form a bit line contacting each MCB and a bit line pad connection to a word line pad. MCB thickness is thin enough to allow a strong bit line magnetic field for switching a free layer and large enough to function as an efficient oxide etch stop.

Owner:TAIWAN SEMICON MFG CO LTD

Radiation detecting apparatus, producing method therefor and radiation image pickup system

InactiveUS20060033031A1Stable productionHigh product yieldElectroluminescent light sourcesMaterial analysis by optical meansFluorescenceOpto electronic

A radiation detection apparatus including a sensor panel, having a photoreceiving unit constituted of plural photoelectric converting elements two-dimensionally arranged on a substrate and electrical connecting portions provided in an external portion of the photoreceiving unit and electrically connected to the photoelectric converting elements of respective rows or columns of the photoreceiving unit, a phosphor layer provided at least on the photoreceiving unit for converting a radiation into a light detectable by the photoelectric converting element, and a phosphor protective member covering the phosphor layer and in contact with the sensor panel, characterized in that the phosphor protective member includes a frame member provided between the phosphor layer and the electric connecting portion on the sensor panel, and a phosphor protective layer covering an upper surface of the phosphor layer and provided in close contact with an upper surface of the frame member. This configuration allows to prevent a discharge of an electrostatic charge accumulated on the sensor panel, thereby providing a stable radiation detection apparatus with a high production yield.

Owner:CANON KK

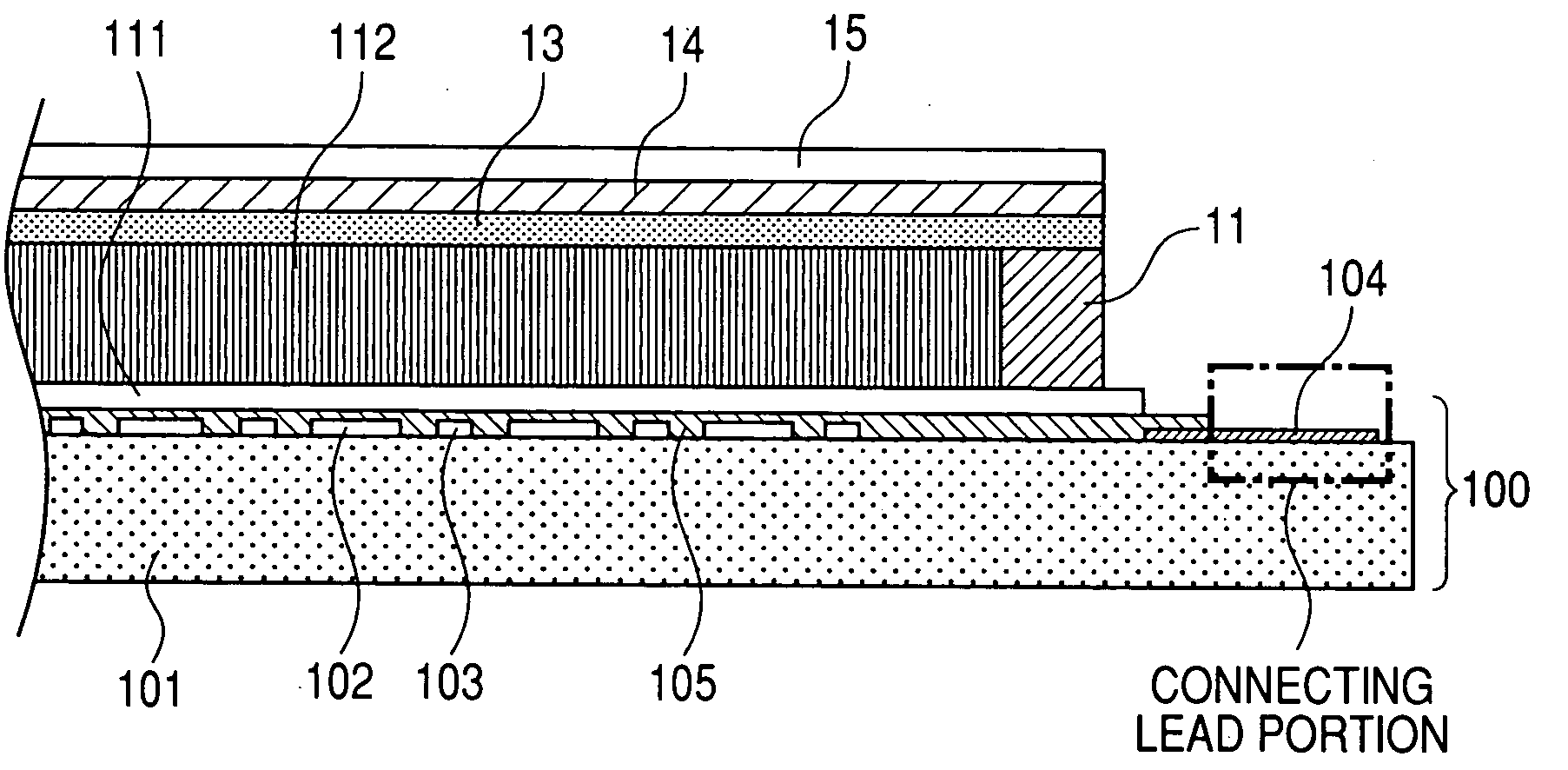

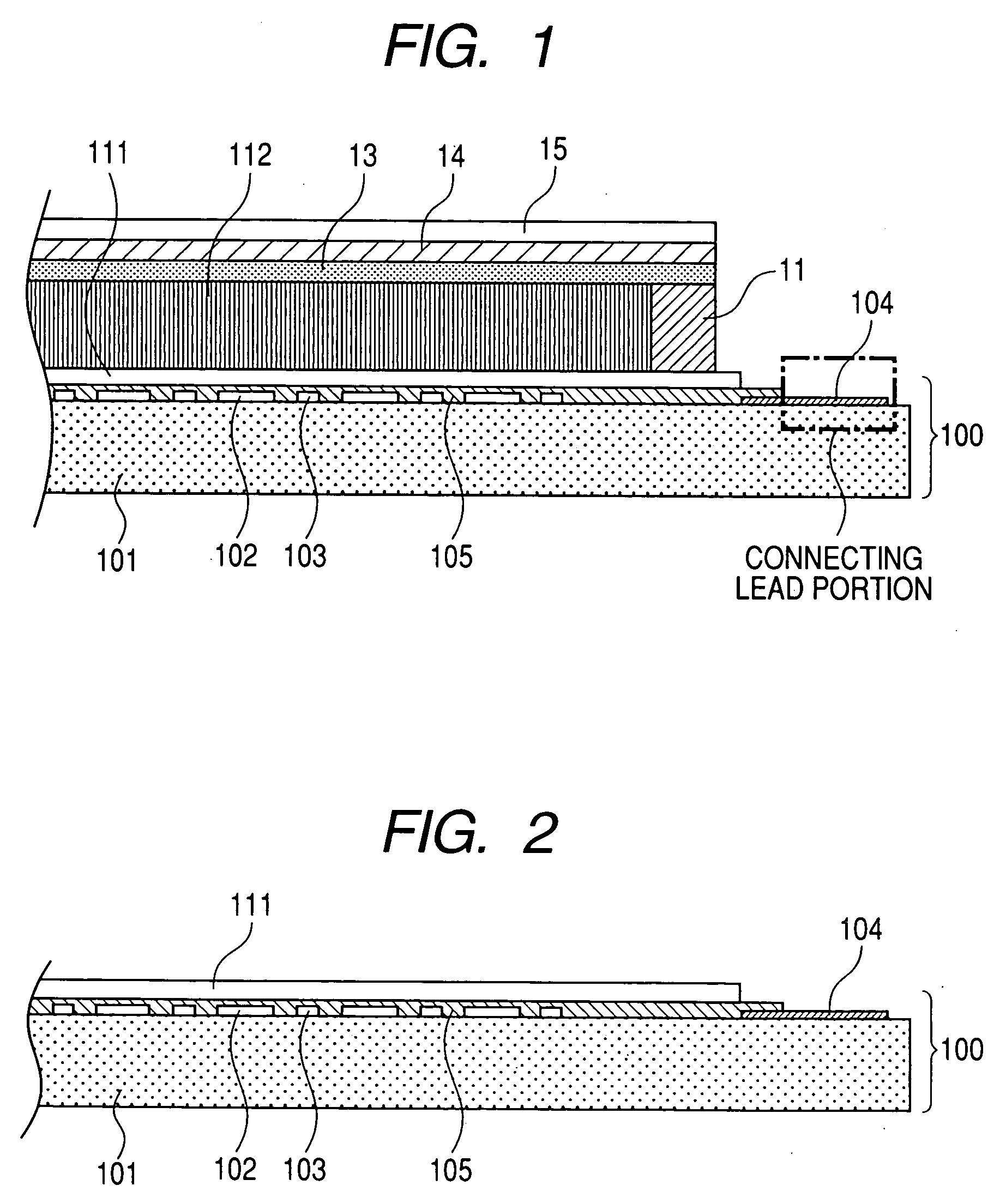

Chip embedded substrate and method of producing the same

ActiveUS7989707B2High product yieldHigh reliability in electrical connectionPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

A method of producing a chip embedded substrate is disclosed. This method comprises a first step of mounting a semiconductor chip on a first substrate on which a first wiring is formed; and a second step of joining the first substrate with a second substrate on which a second wiring is formed. In the second step, the semiconductor chip is encapsulated between the first substrate and the second substrate and electrical connection is made between the first wiring and the second wiring so as to form multilayered wirings connected to the semiconductor chip.

Owner:SHINKO ELECTRIC IND CO LTD