Patents

Literature

4752results about How to "Reduce yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

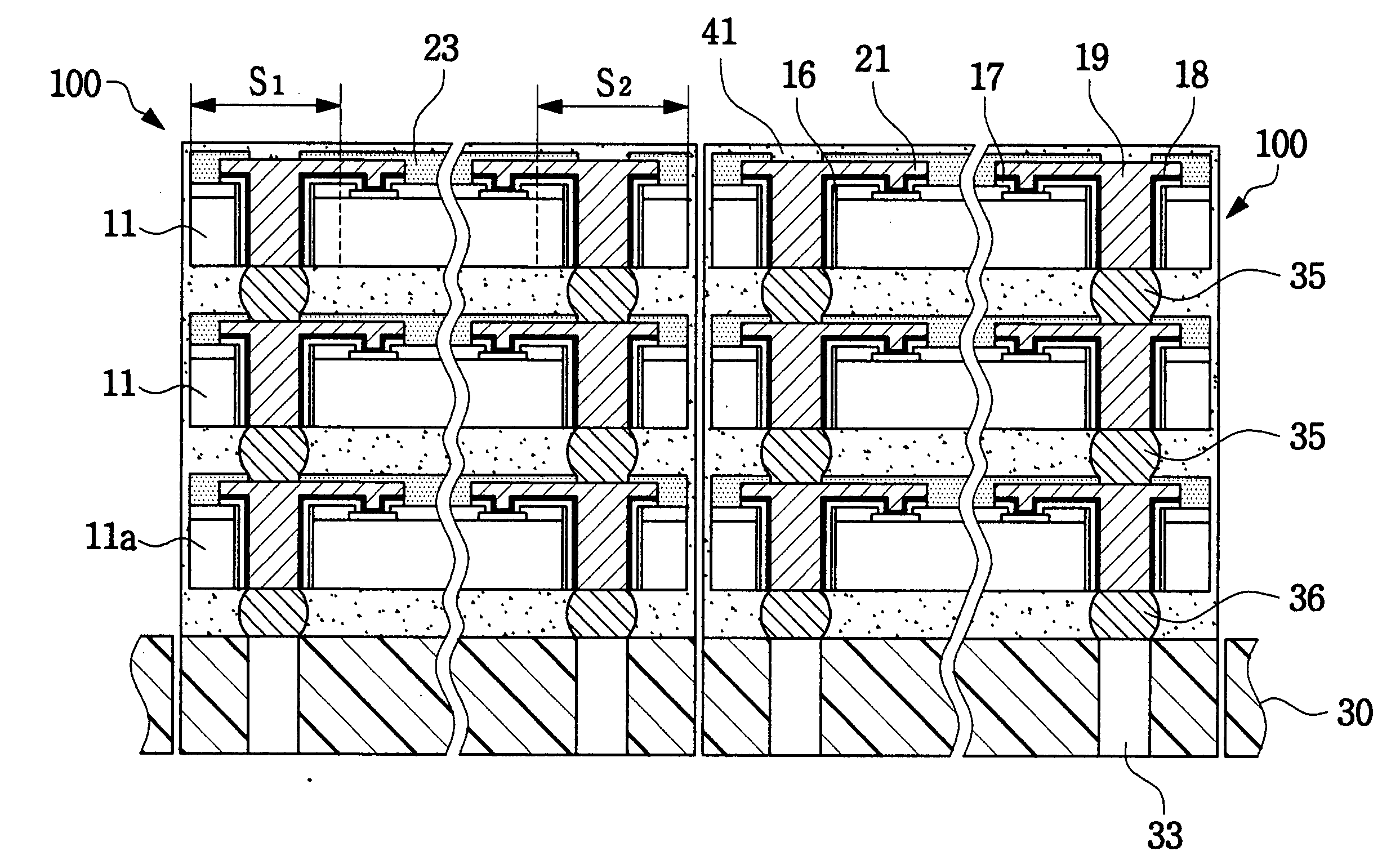

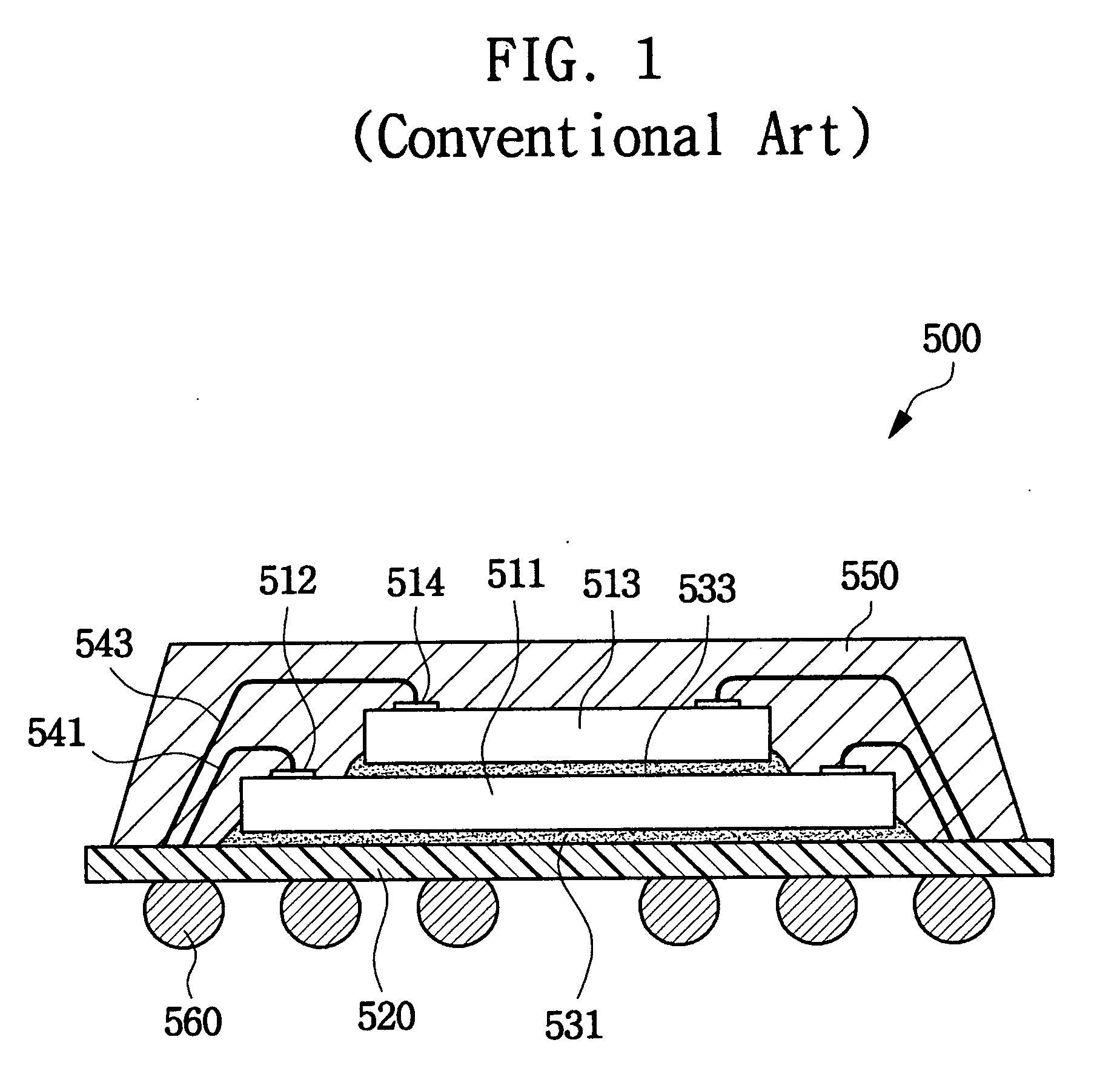

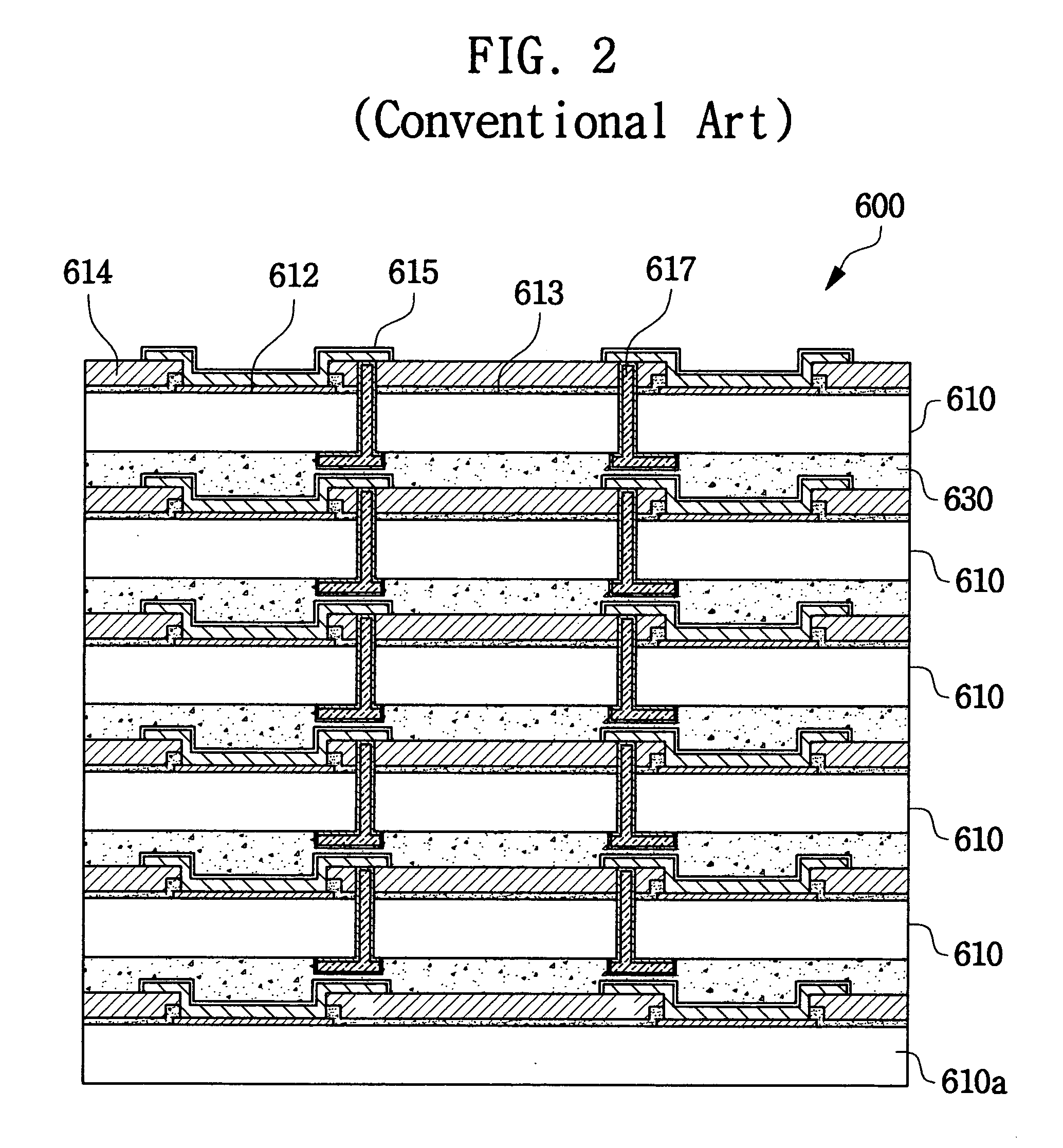

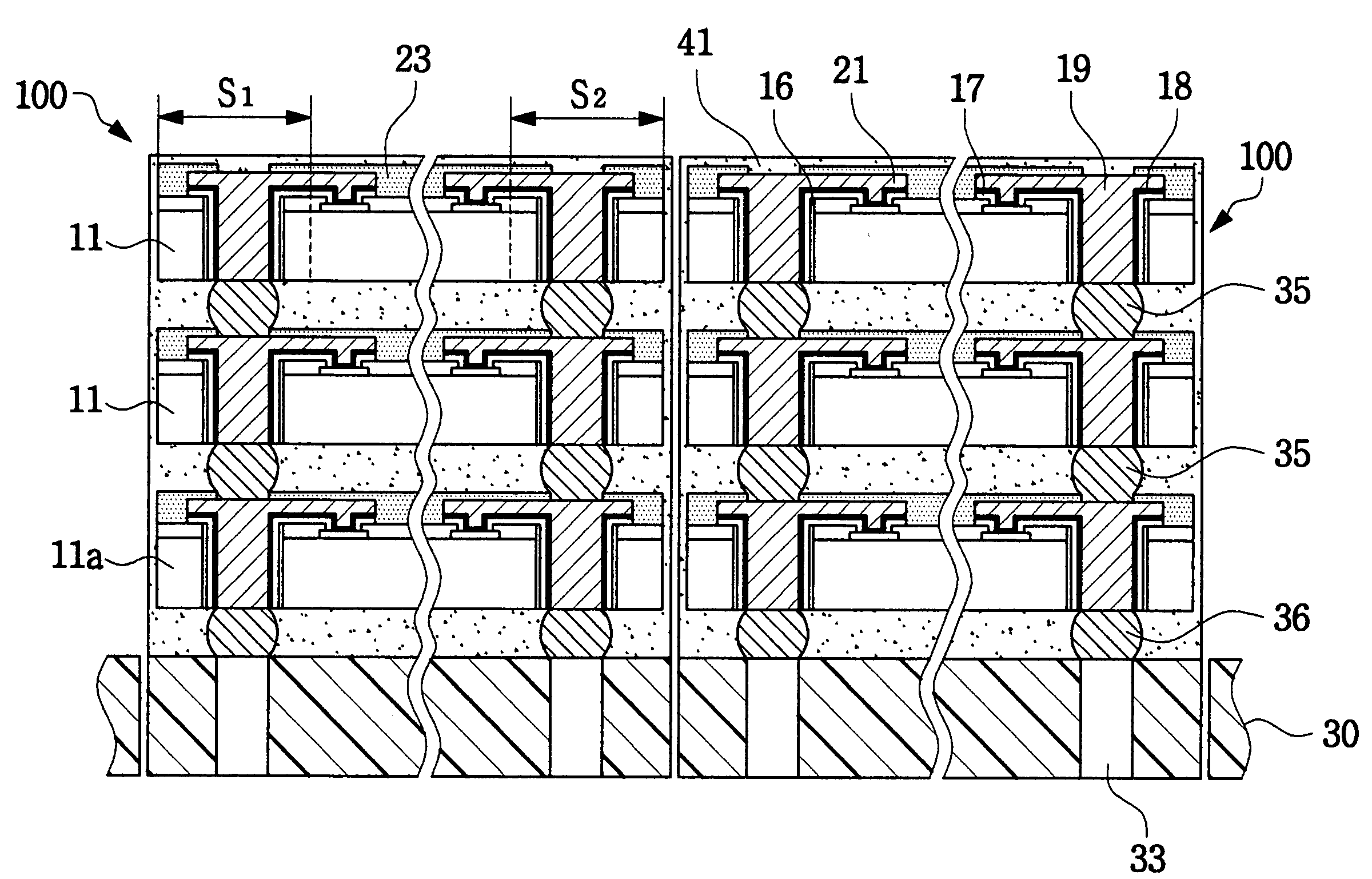

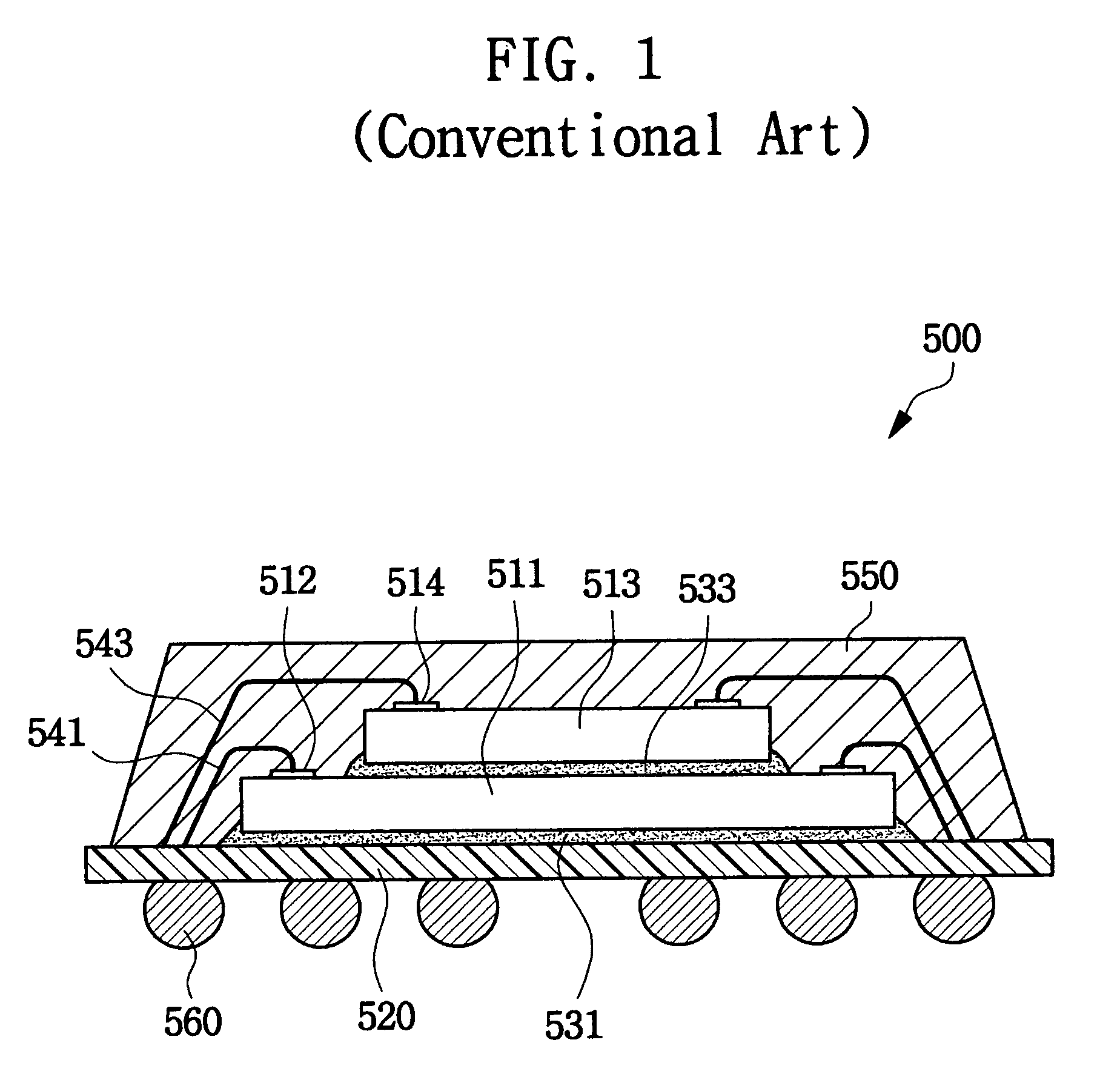

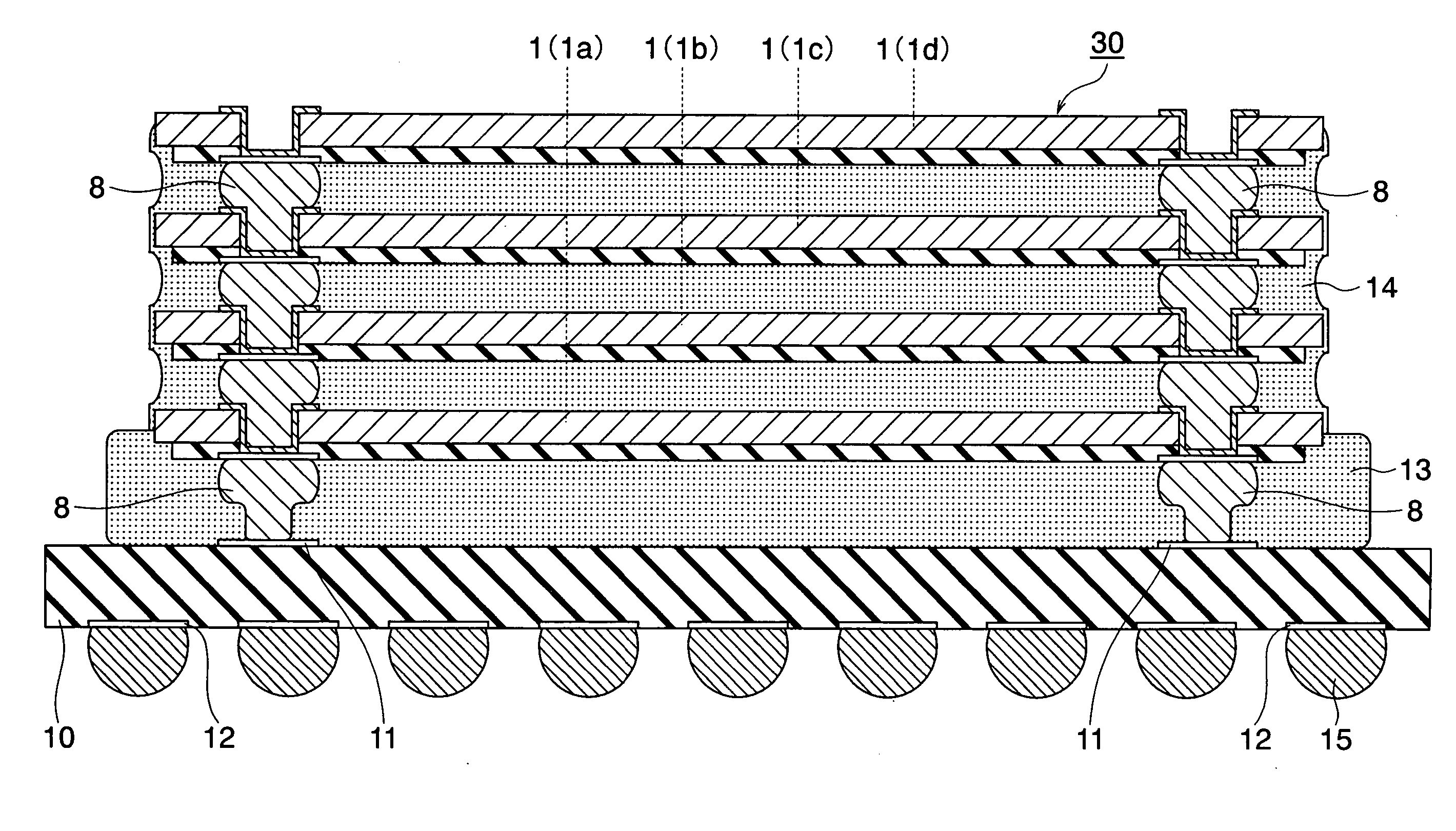

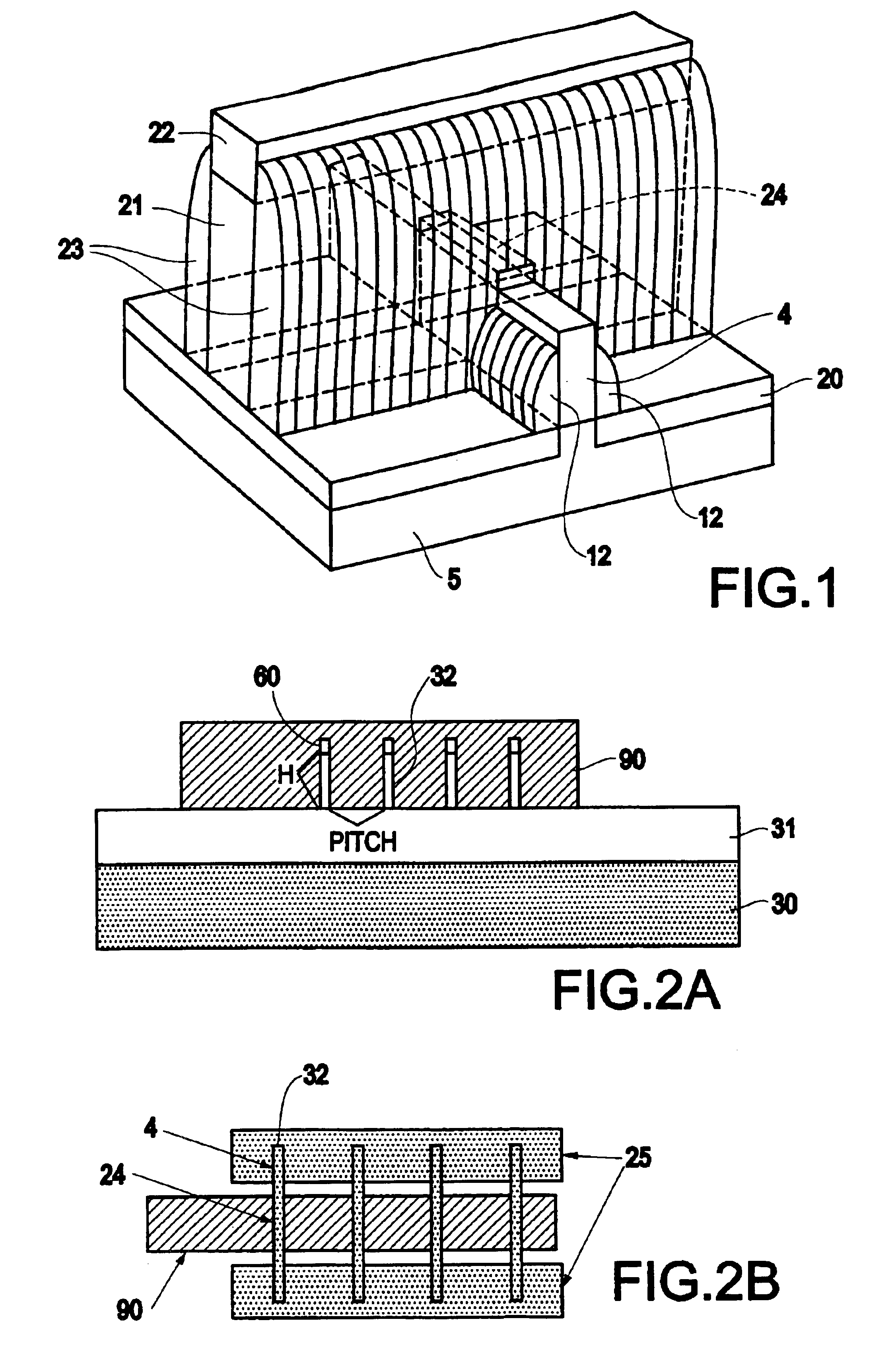

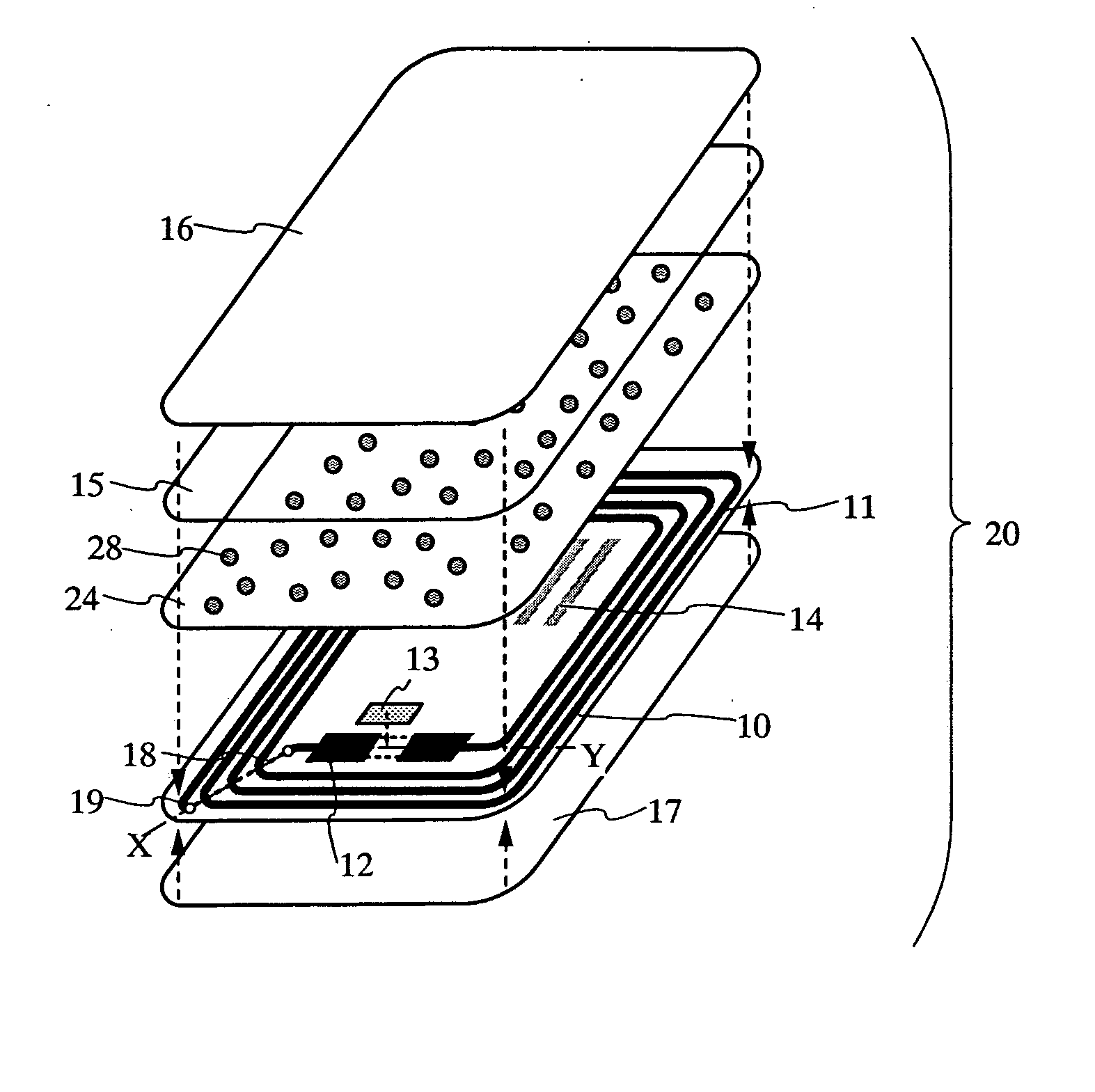

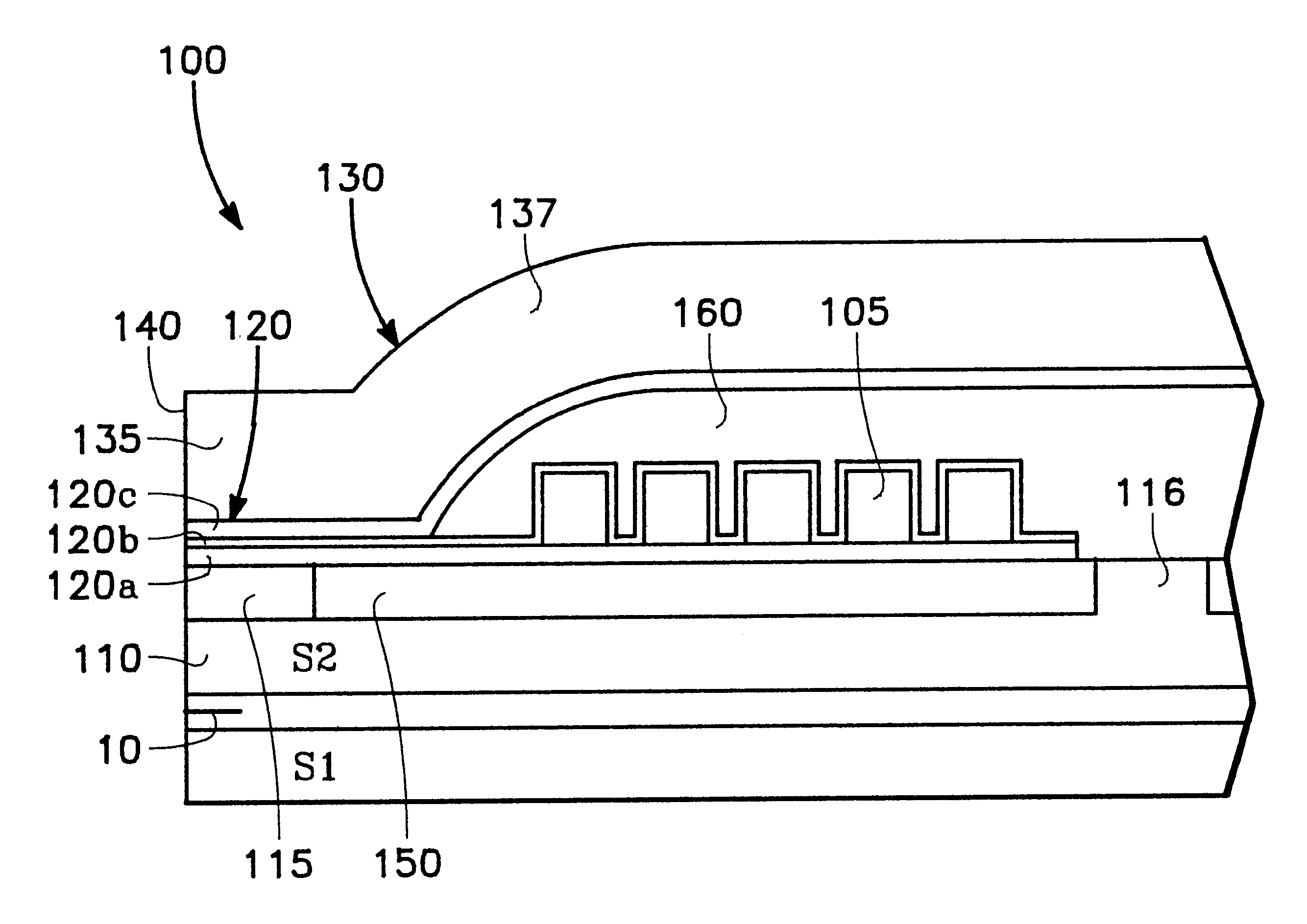

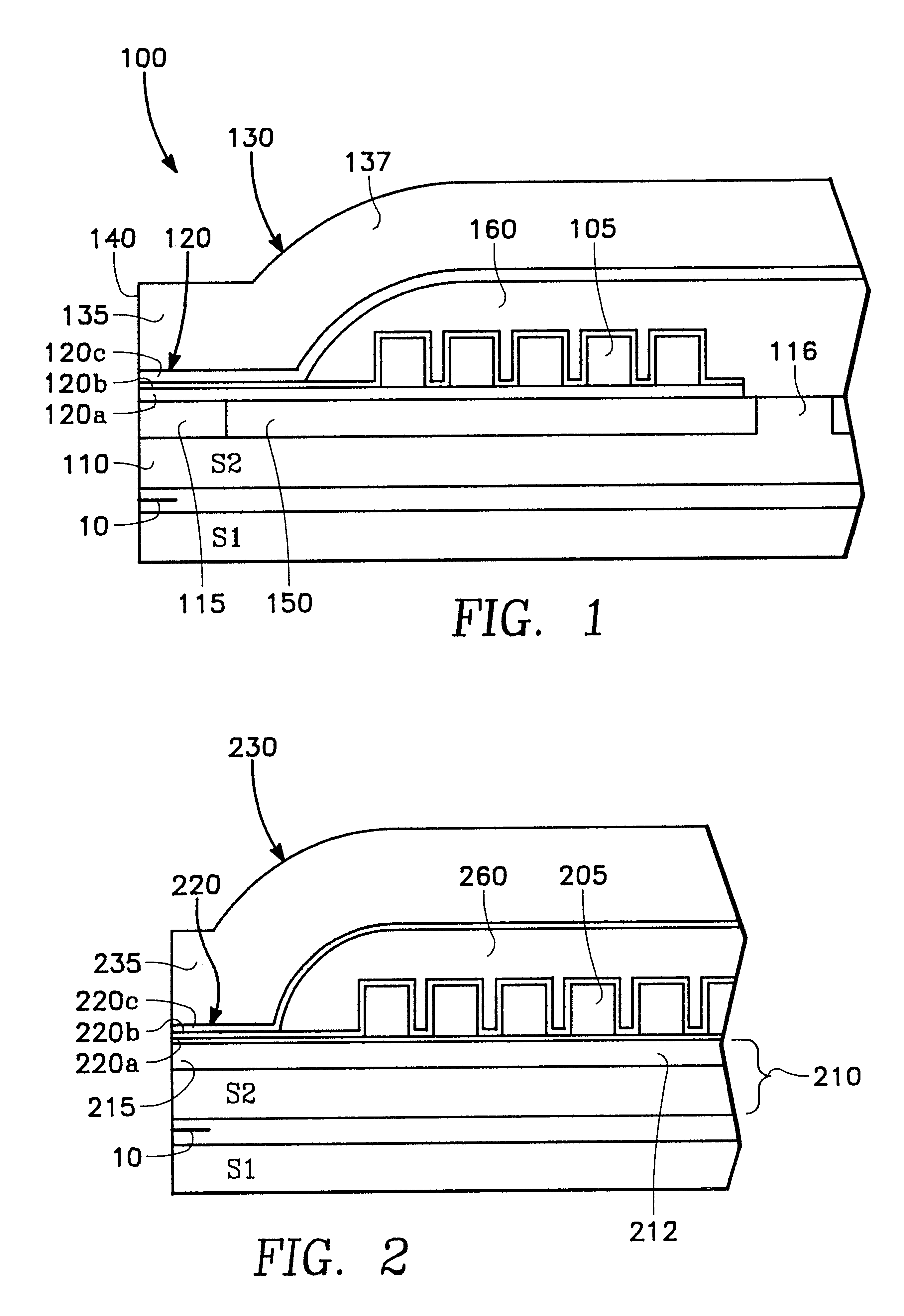

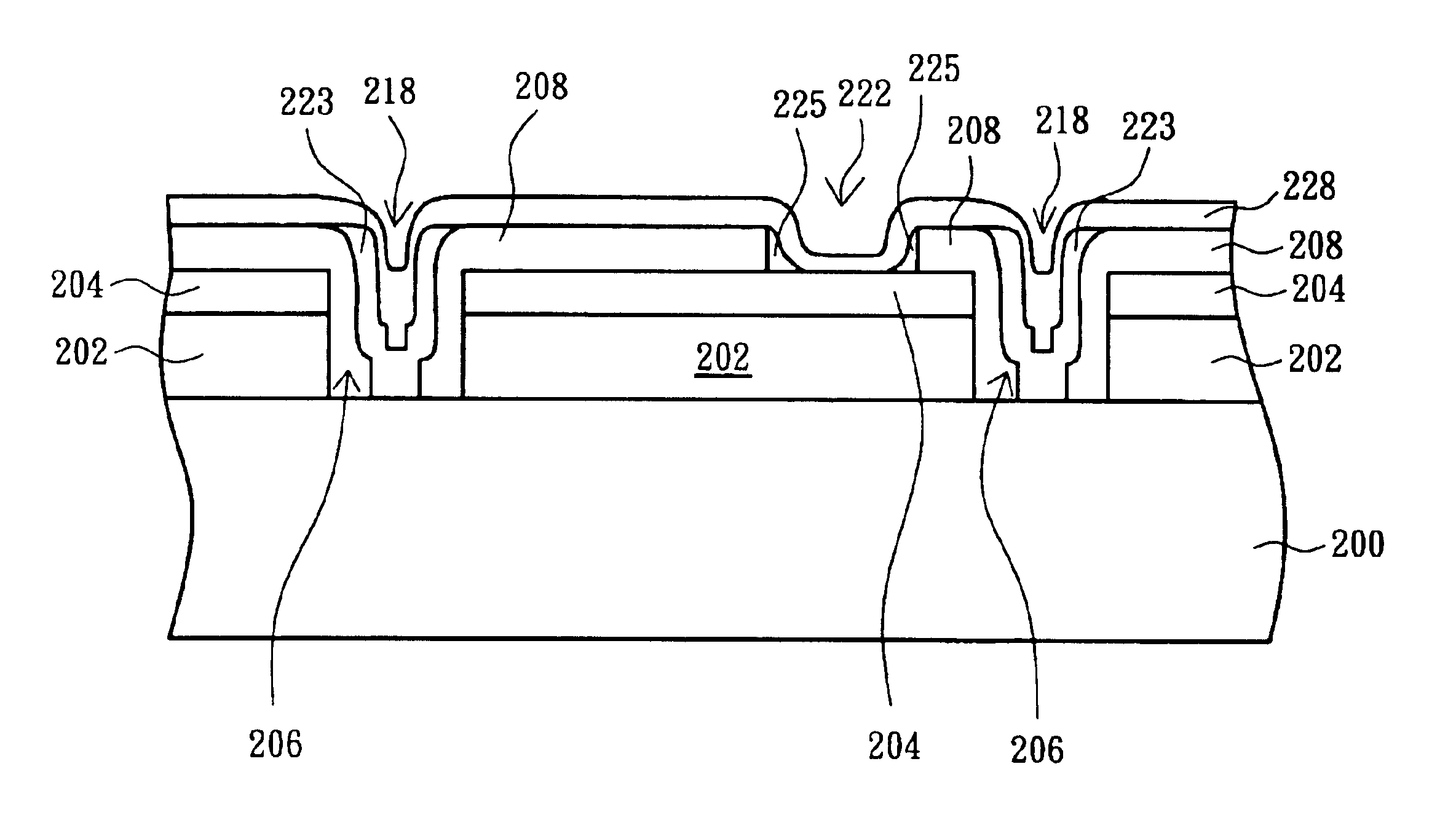

Chip stack package and manufacturing method thereof

ActiveUS20050046002A1Reduce manufacturing costReduce time costSemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical connection

A chip stack package is manufactured at a wafer level by forming connection vias in the scribe lanes adjacent the chips and connecting the device chip pads to the connection vias using rerouting lines. A lower chip is then attached and connected to a substrate, which may be a test wafer, and an upper chip is attached and connected to the lower chip, the electrical connections being achieved through their respective connection vias. In addition to the connection vias, the chip stack package may include connection bumps formed between vertically adjacent chips and / or the lower chip and the substrate. The preferred substrate is a test wafer that allows the attached chips to be tested, and replaced if faulty, thereby ensuring that each layer of stacked chips includes only “known-good die” before the next layer of chips is attached thereby increasing the production rate and improving the yield.

Owner:SAMSUNG ELECTRONICS CO LTD

Chip stack package and manufacturing method thereof

ActiveUS7276799B2Low costShorten the timeSemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical connection

A chip stack package is manufactured at a wafer level by forming connection vias in the scribe lanes adjacent the chips and connecting the device chip pads to the connection vias using rerouting lines. A lower chip is then attached and connected to a substrate, which may be a test wafer, and an upper chip is attached and connected to the lower chip, the electrical connections being achieved through their respective connection vias. In addition to the connection vias, the chip stack package may include connection bumps formed between vertically adjacent chips and / or the lower chip and the substrate. The preferred substrate is a test wafer that allows the attached chips to be tested, and replaced if faulty, thereby ensuring that each layer of stacked chips includes only “known-good die” before the next layer of chips is attached thereby increasing the production rate and improving the yield.

Owner:SAMSUNG ELECTRONICS CO LTD

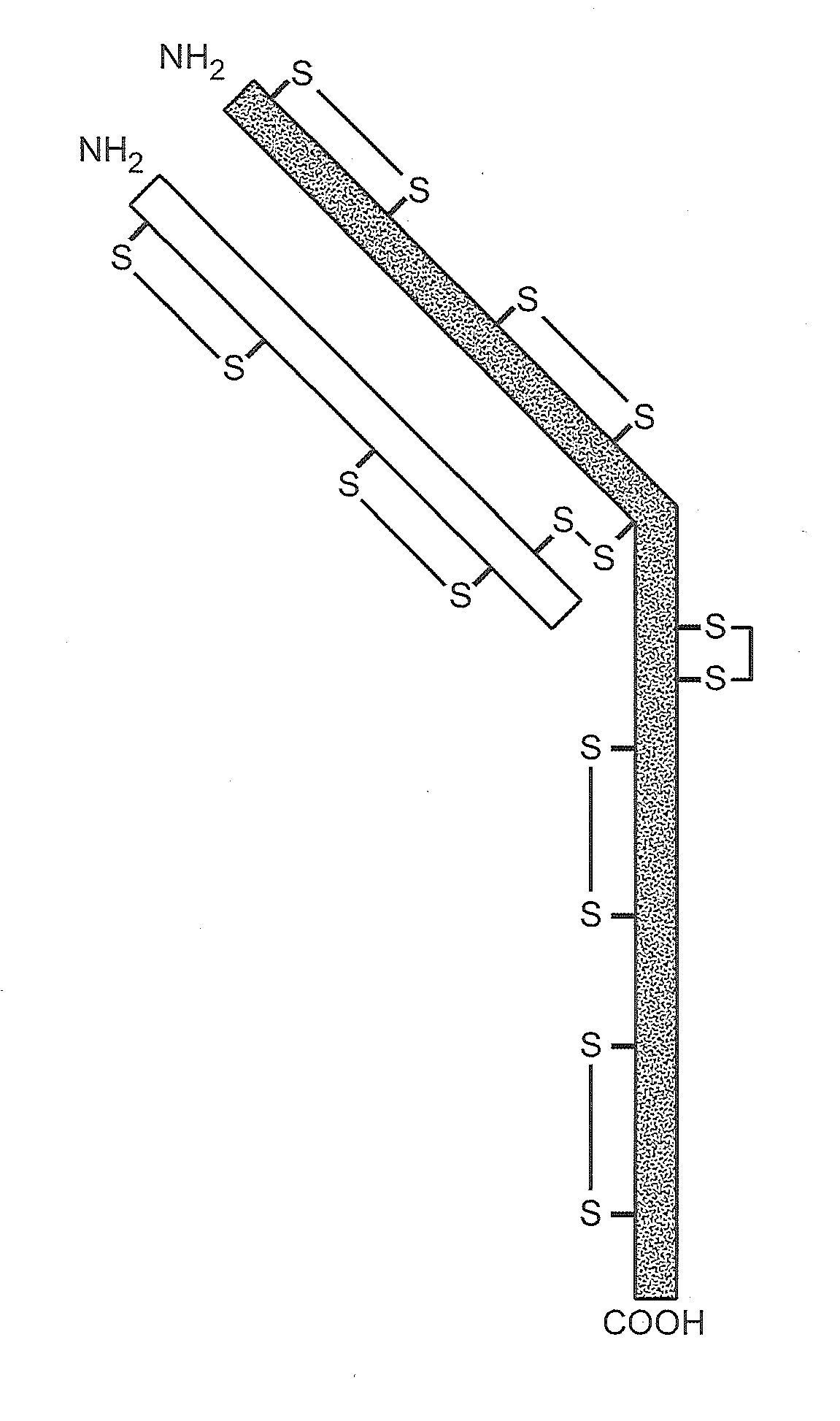

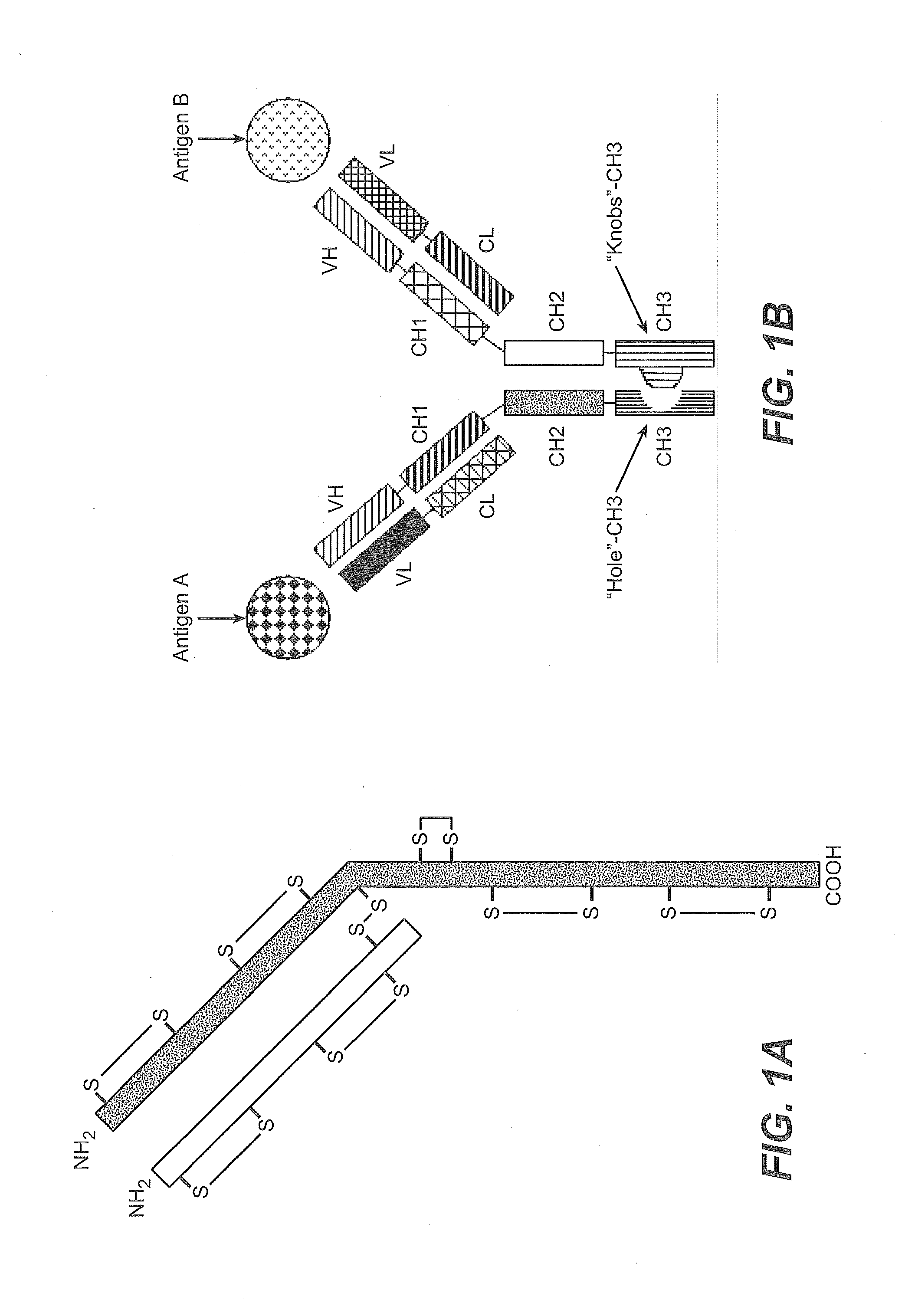

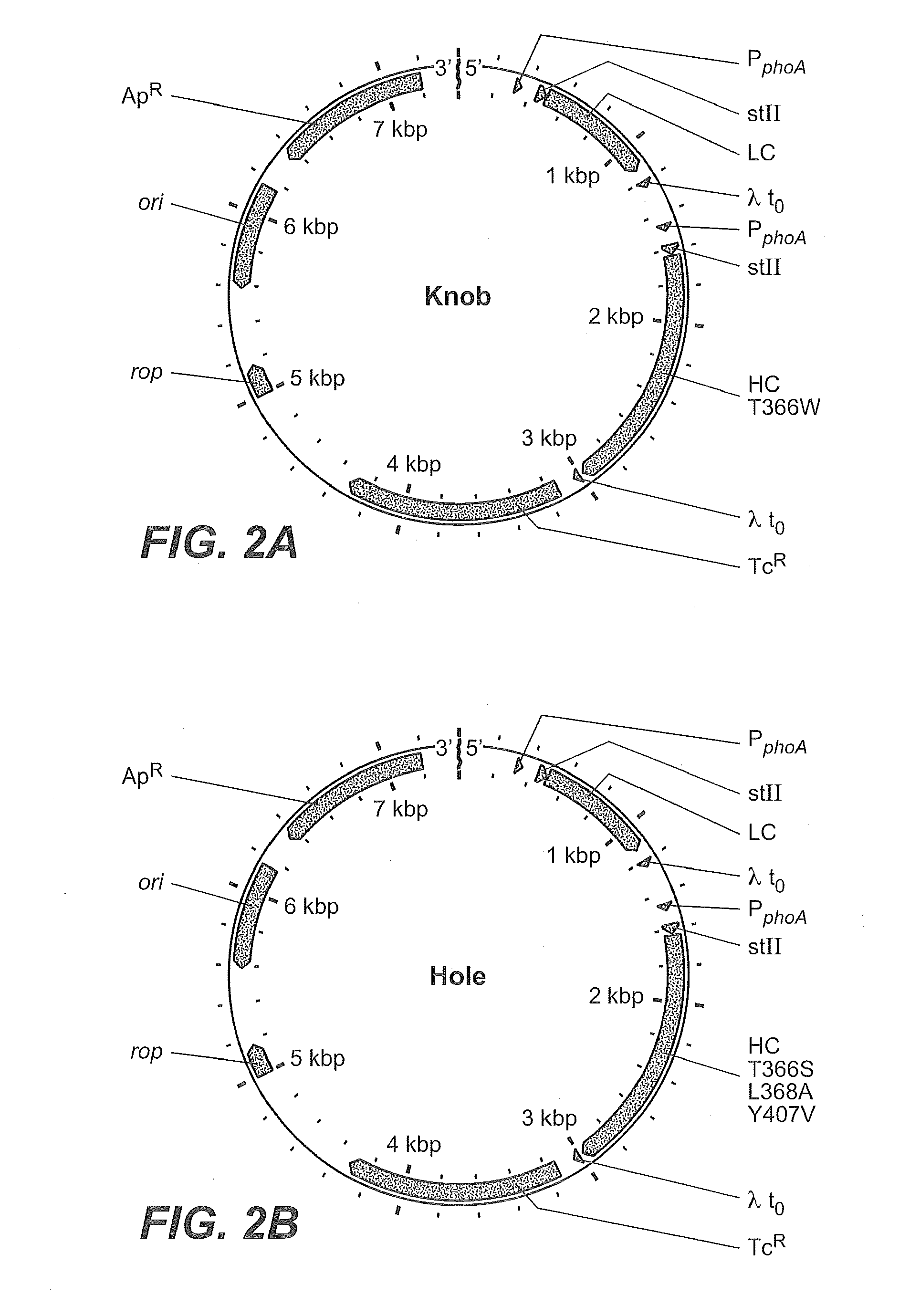

Production of Heteromultimeric Proteins

ActiveUS20110287009A1Reduction in yieldDecreased/elimination of effector functionAntipyreticAnalgesicsEpitopeBiochemistry

Described herein are methods for the efficient production of antibodies and other multimeric protein complexes (collectively referred to herein as heteromultimeric proteins) capable of specifically binding to more than one target. The targets may be, for example, different epitopes on a single molecule or located on different molecules. The methods combine efficient, high gene expression level, appropriate assembly, and ease of purification for the heteromultimeric proteins. The invention also provides methods of using these heteromultimeric proteins, and compositions, kits and articles of manufacture comprising these antibodies.

Owner:F HOFFMANN LA ROCHE & CO AG

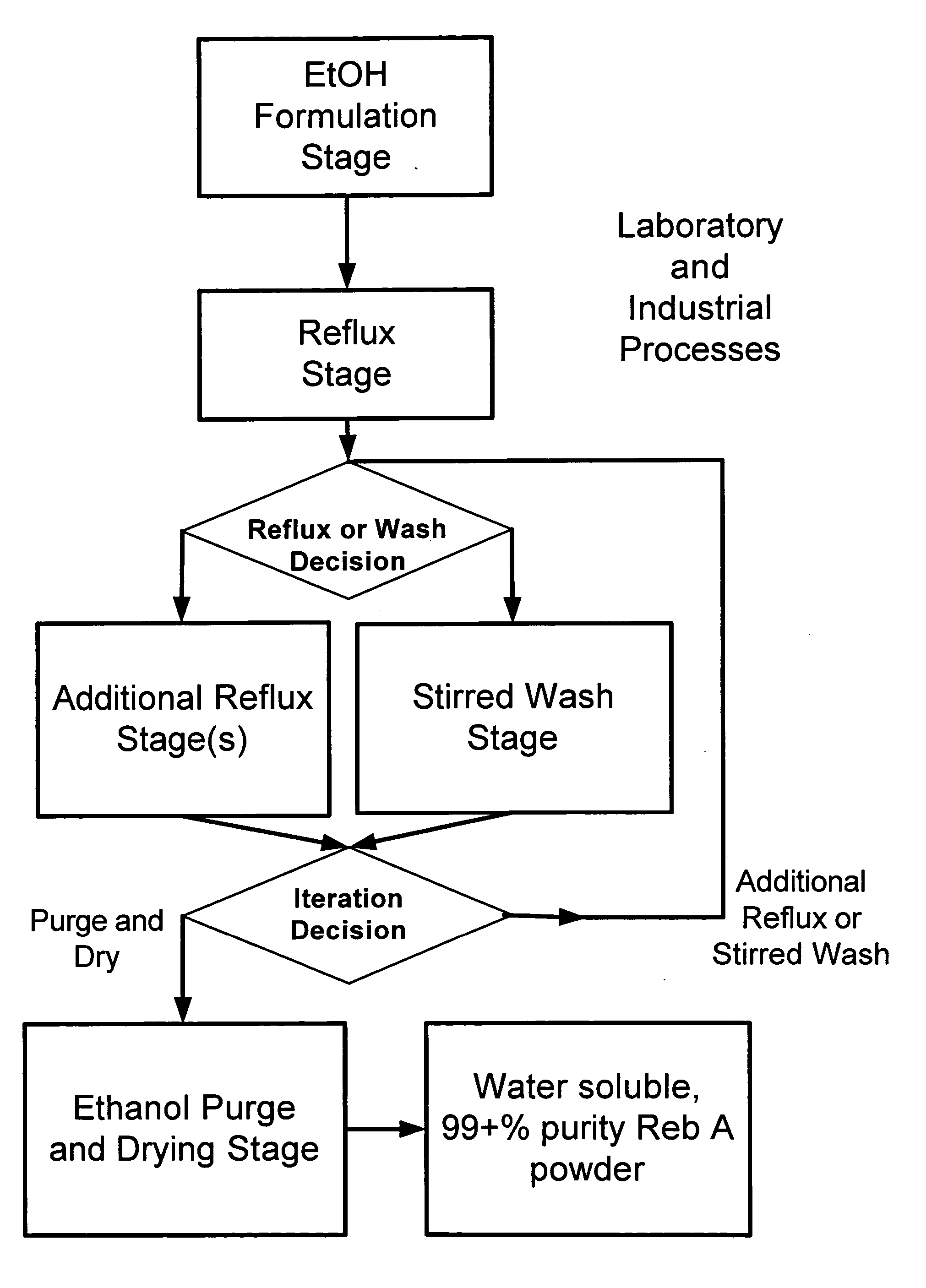

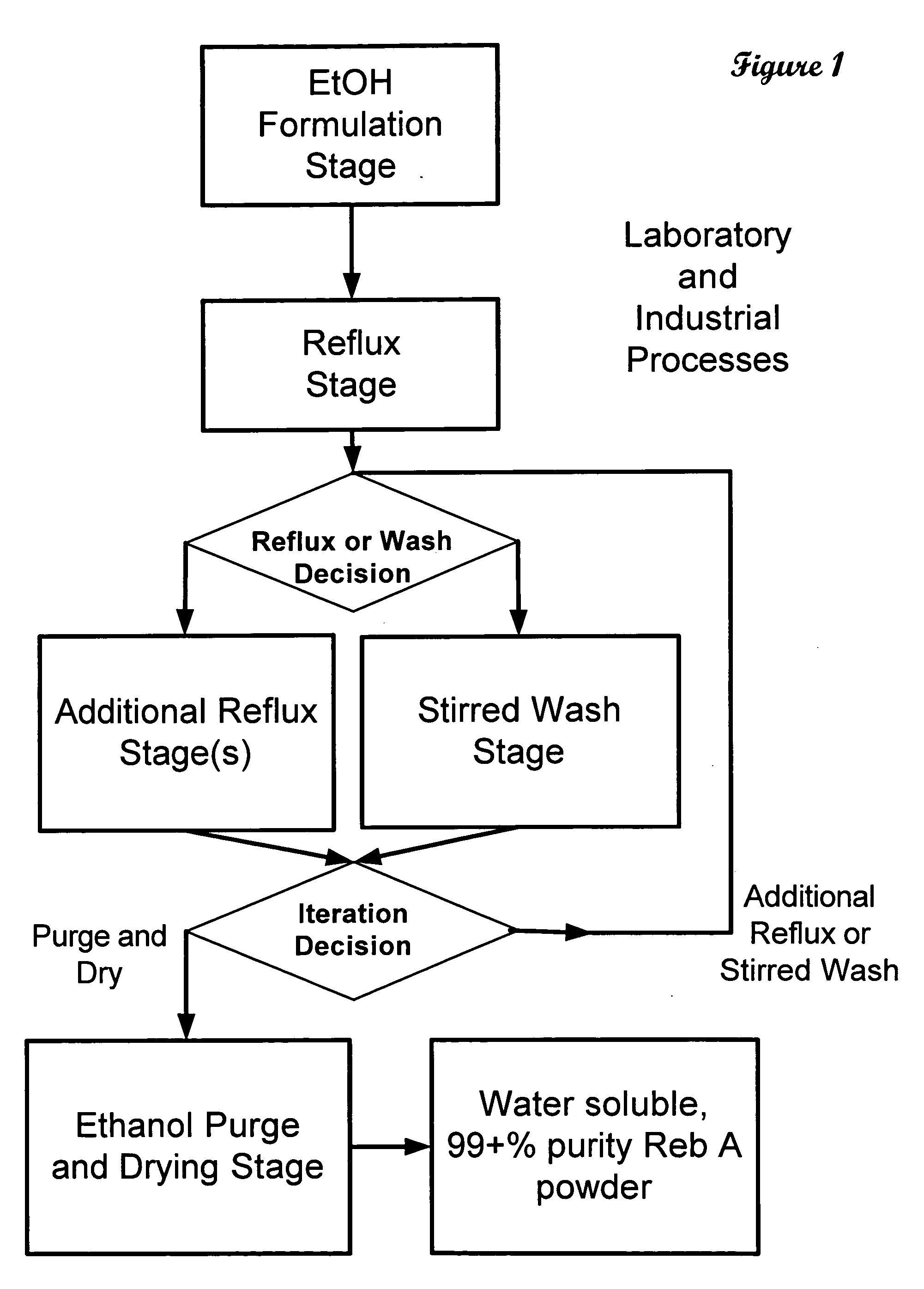

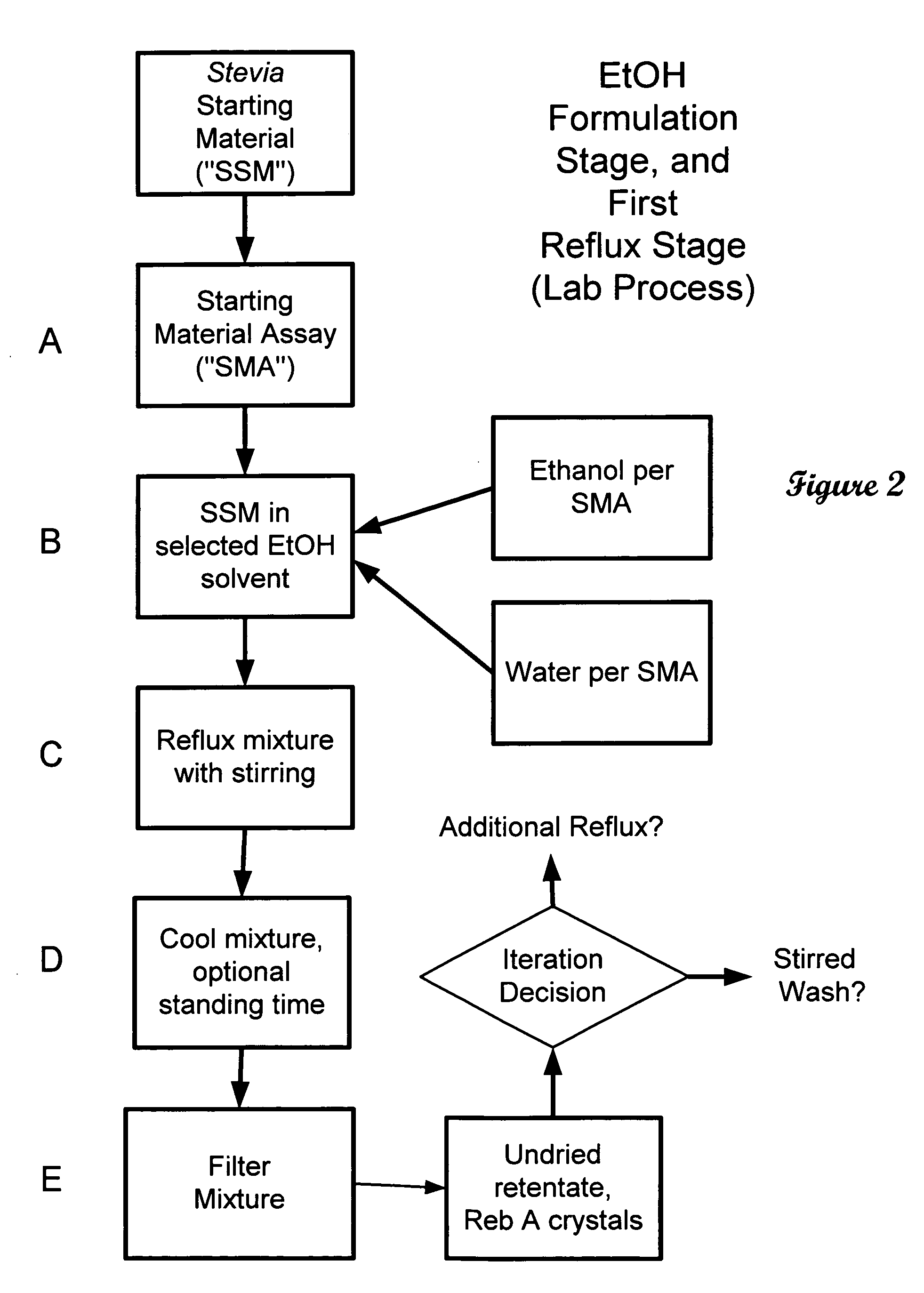

High yield method of producing pure rebaudioside A

ActiveUS20060083838A1Reduction in yieldQuality improvementSugar derivativesMetabolism disorderSolubilityAdditive ingredient

The invention provides a high throughput, high purity, high yield system and method of isolating and purifying rebaudioside A (“Reb A”), with acceptable water solubility for all commercial uses, from commercially available Stevia rebaudiana starting material. The invention also provides a means of maximizing yields of 99+% purity Reb A based on the attributes of a given batch of Stevia starting material. The Reb A produced by the invention is water soluble, devoid of bitterness heretofore associated with rebaudioside sweeteners, non-caloric, and suitable for use as a reagent and as an ingredient in orally consumed products, e.g., as a sweetener, flavor enhancer, and flavor modifier.

Owner:SWEET GREEN FIELDS INT CO LTD

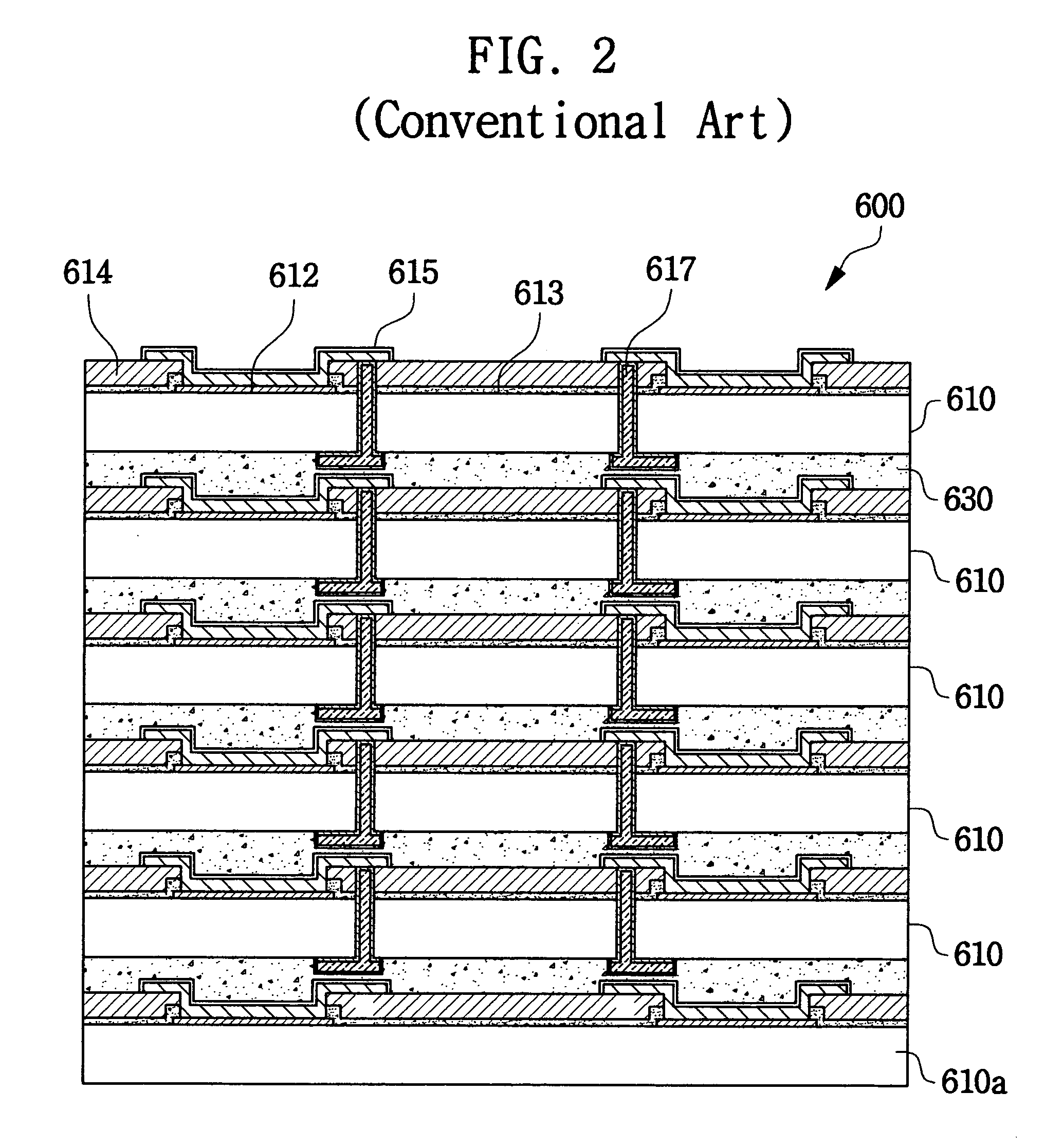

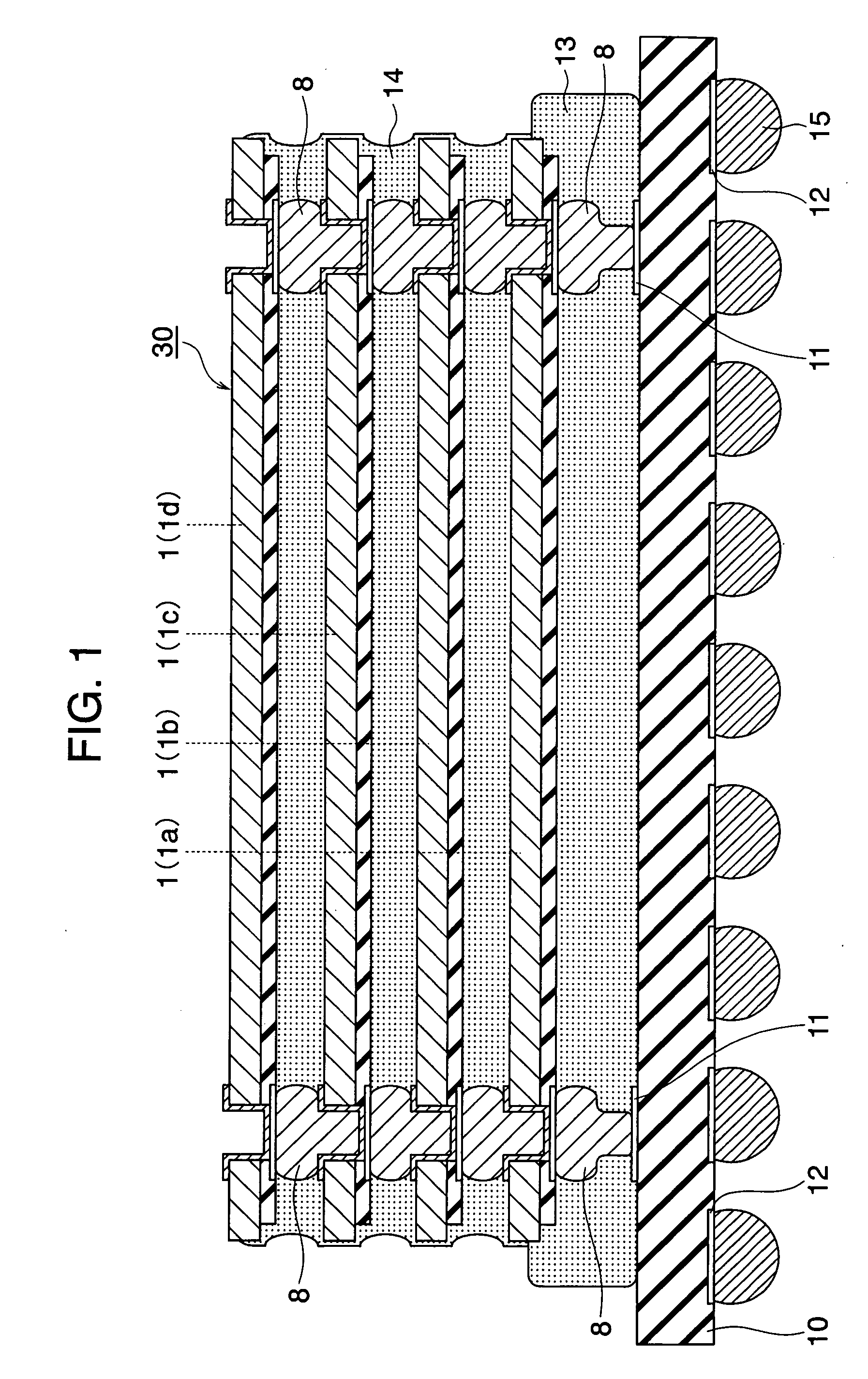

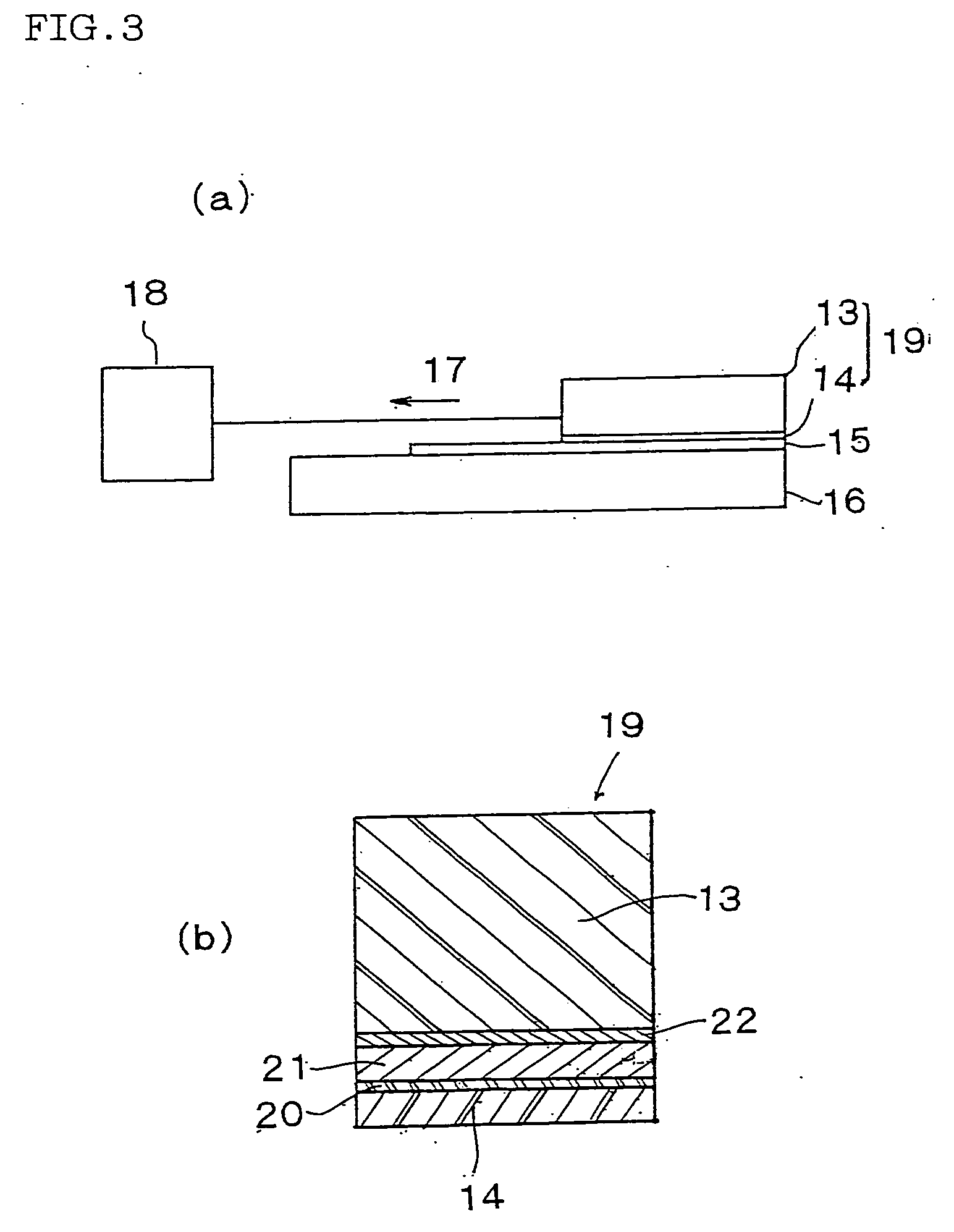

Semiconductor device and manufacturing process therefor

InactiveUS20050263869A1Improve reliabilityHigh practicabilitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologySurface layer

To provide a very-low-cost and short-TAT connection structure superior in connection reliability in accordance with a method for three-dimensionally connecting a plurality of semiconductor chips at a shortest wiring length by using a through-hole electrode in order to realize a compact, high-density, and high-function semiconductor system. The back of a semiconductor chip is decreased in thickness up to a predetermined thickness through back-grinding, a hole reaching a surface-layer electrode is formed at a back position corresponding to a device-side external electrode portion through dry etching, a metallic deposit is applied to the sidewall of the hole and the circumference of the back of the hole, a metallic bump (protruded electrode) of another semiconductor chip laminated on the upper side is deformation-injected into the through-hole by compression bonding, and the metallic bump is geometrically caulked and electrically connected to the inside of a through-hole formed in an LSI chip. It is possible to realize a unique connection structure having a high reliability in accordance with the caulking action using the plastic flow of a metallic bump in a very-low-cost short-TAT process and provide a three-dimensional inter-chip connection structure having a high practicability.

Owner:RENESAS TECH CORP

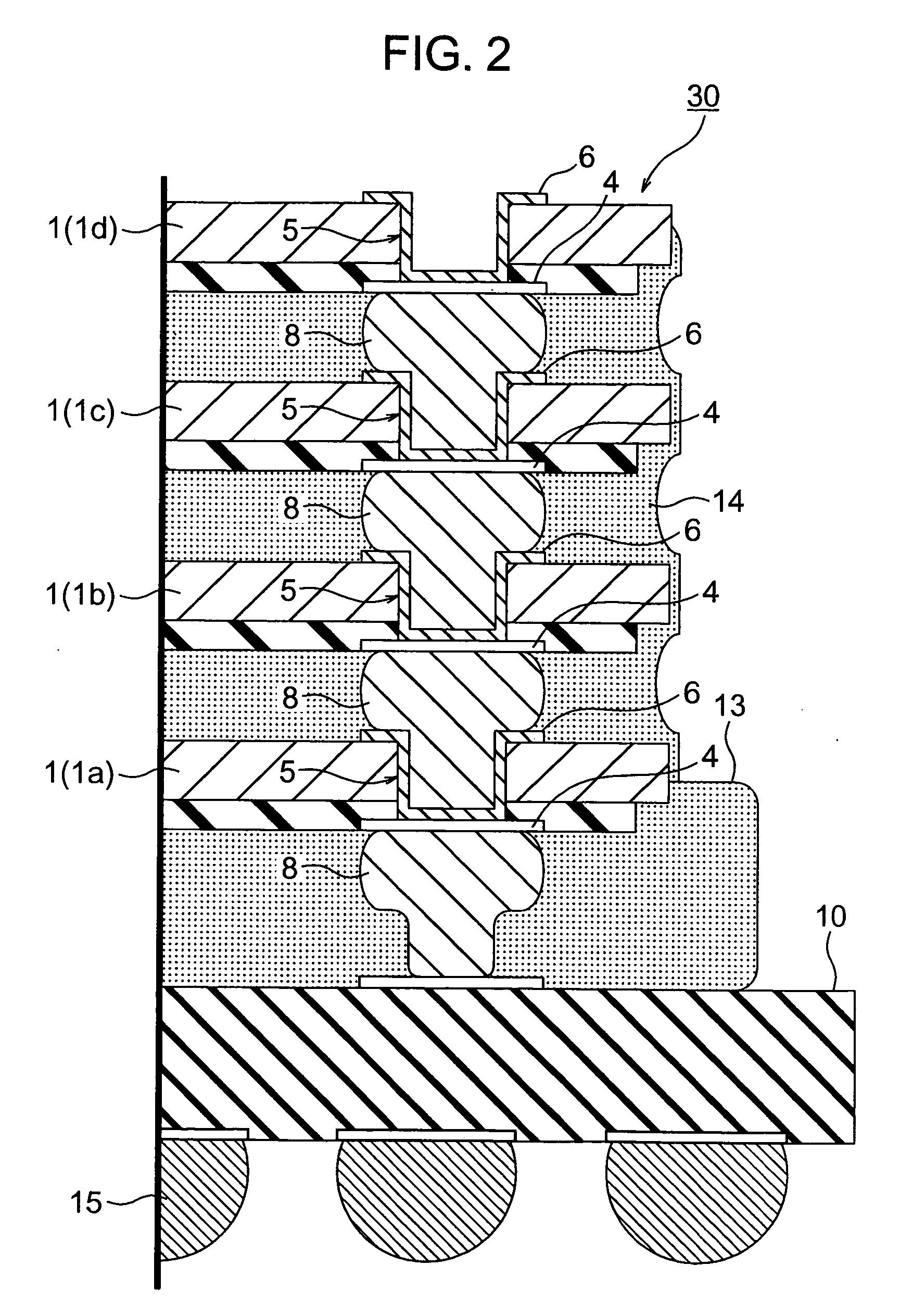

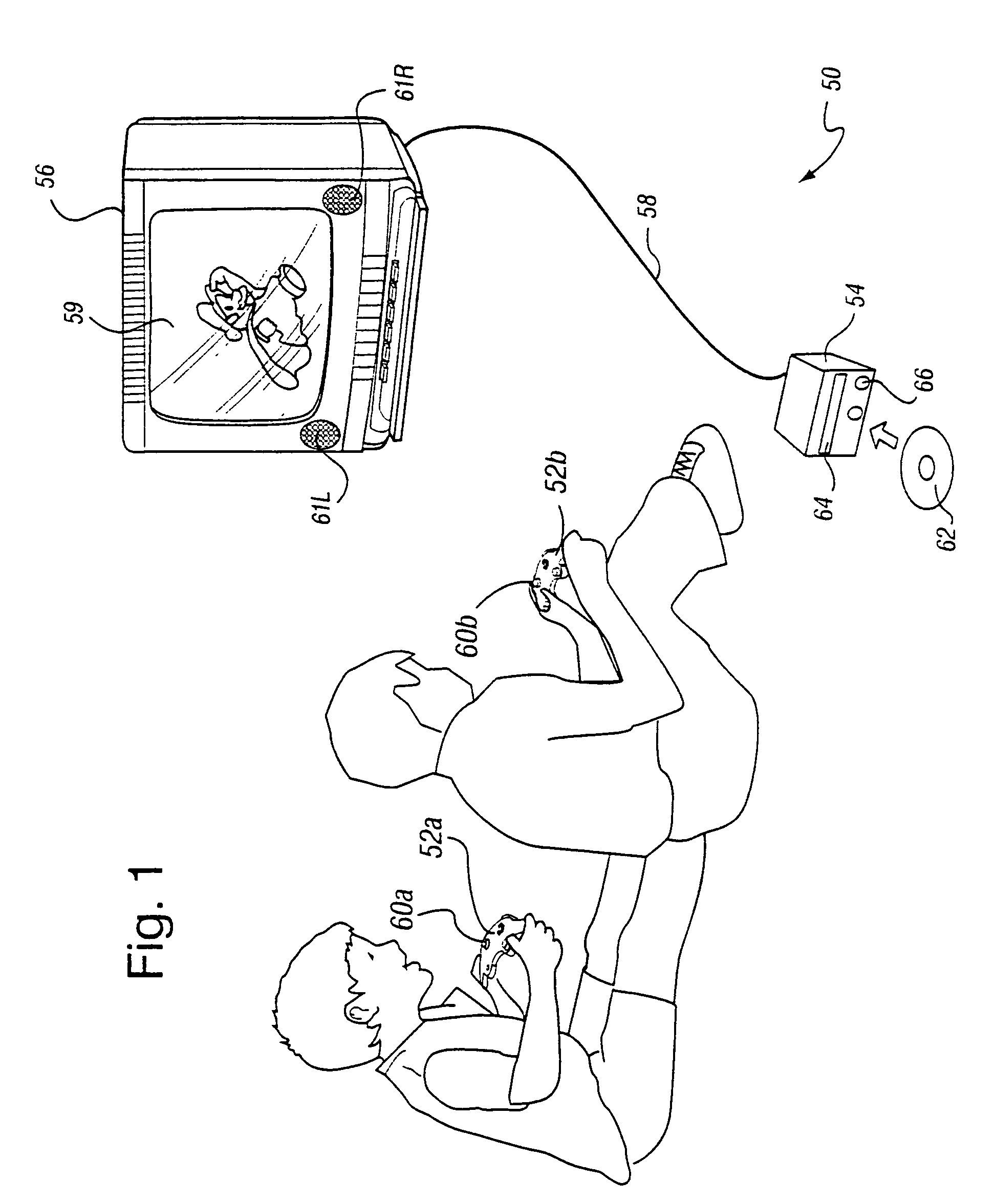

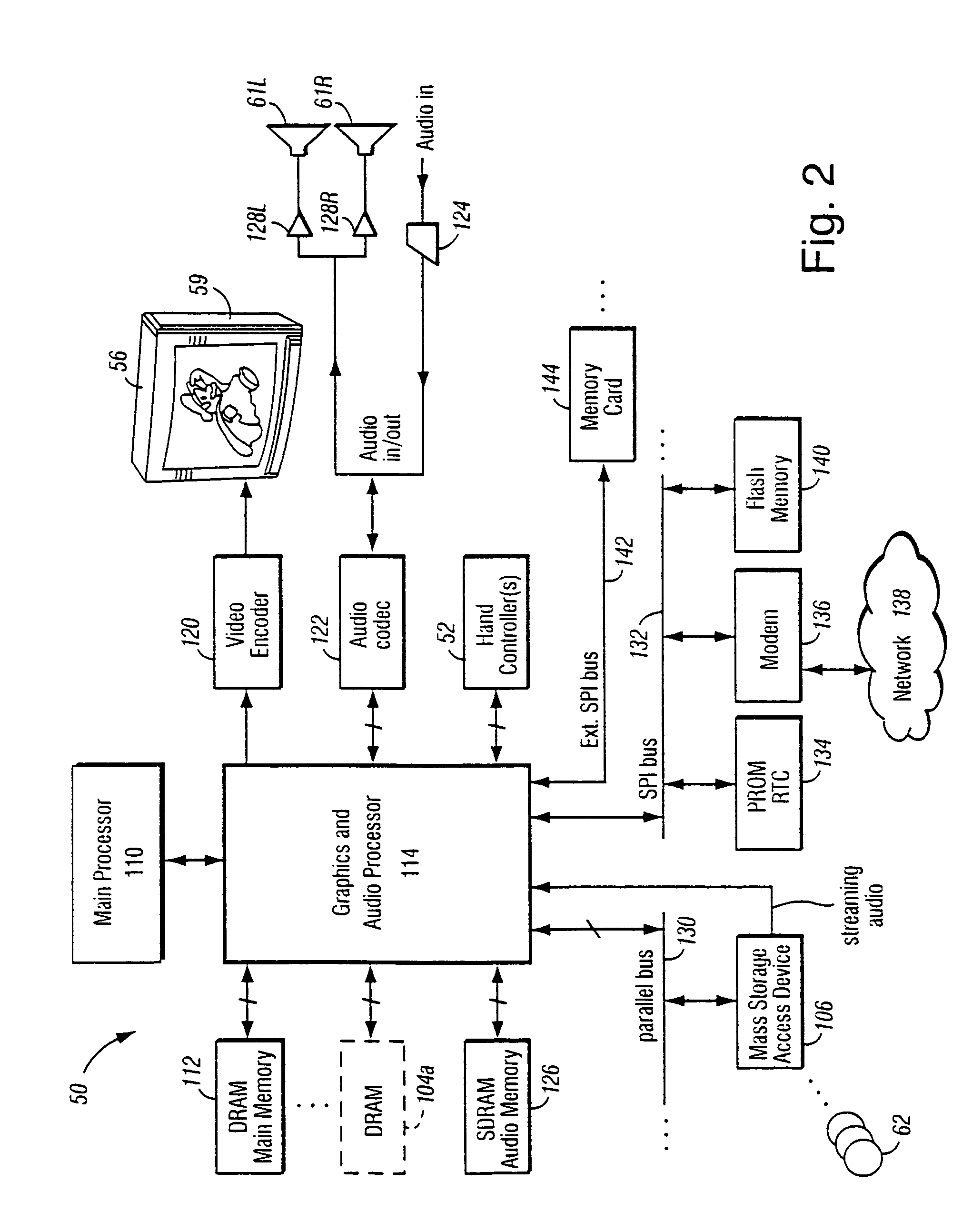

Method and apparatus for interleaved processing of direct and indirect texture coordinates in a graphics system

InactiveUS7002591B1Efficient implementationIncrease in texture mapping hardware complexityCathode-ray tube indicators3D-image renderingPattern recognitionProcessing

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics pipeline renders and prepares images for display at least in part in response to polygon vertex attribute data and texel color data stored as a texture images in an associated memory. An efficient texturing pipeline arrangement achieves a relatively low chip-footprint by utilizing a single texture coordinate / data processing unit that interleaves the processing of logical direct and indirect texture coordinate data and a texture lookup data feedback path for “recirculating” indirect texture lookup data retrieved from a single texture retrieval unit back to the texture coordinate / data processing unit. Versatile indirect texture referencing is achieved by using the same texture coordinate / data processing unit to transform the recirculated texture lookup data into offsets that may be added to the texture coordinates of a direct texture lookup. A generalized indirect texture API function is provided that supports defining at least four indirect texture referencing operations and allows for selectively associating one of at least eight different texture images with each indirect texture defined. Retrieved indirect texture lookup data is processed as multi-bit binary data triplets of three, four, five, or eight bits. The data triplets are multiplied by a 3×2 texture coordinate offset matrix before being optionally combined with regular non-indirect coordinate data or coordinate data from a previous cycle / stage of processing. Values of the offset matrix elements are variable and may be dynamically defined for each cycle / stage using selected constants. Two additional variable matrix configurations are also defined containing element values obtained from current direct texture coordinates. Circuitry for optionally biasing and scaling retrieved texture data is also provided.

Owner:NINTENDO CO LTD

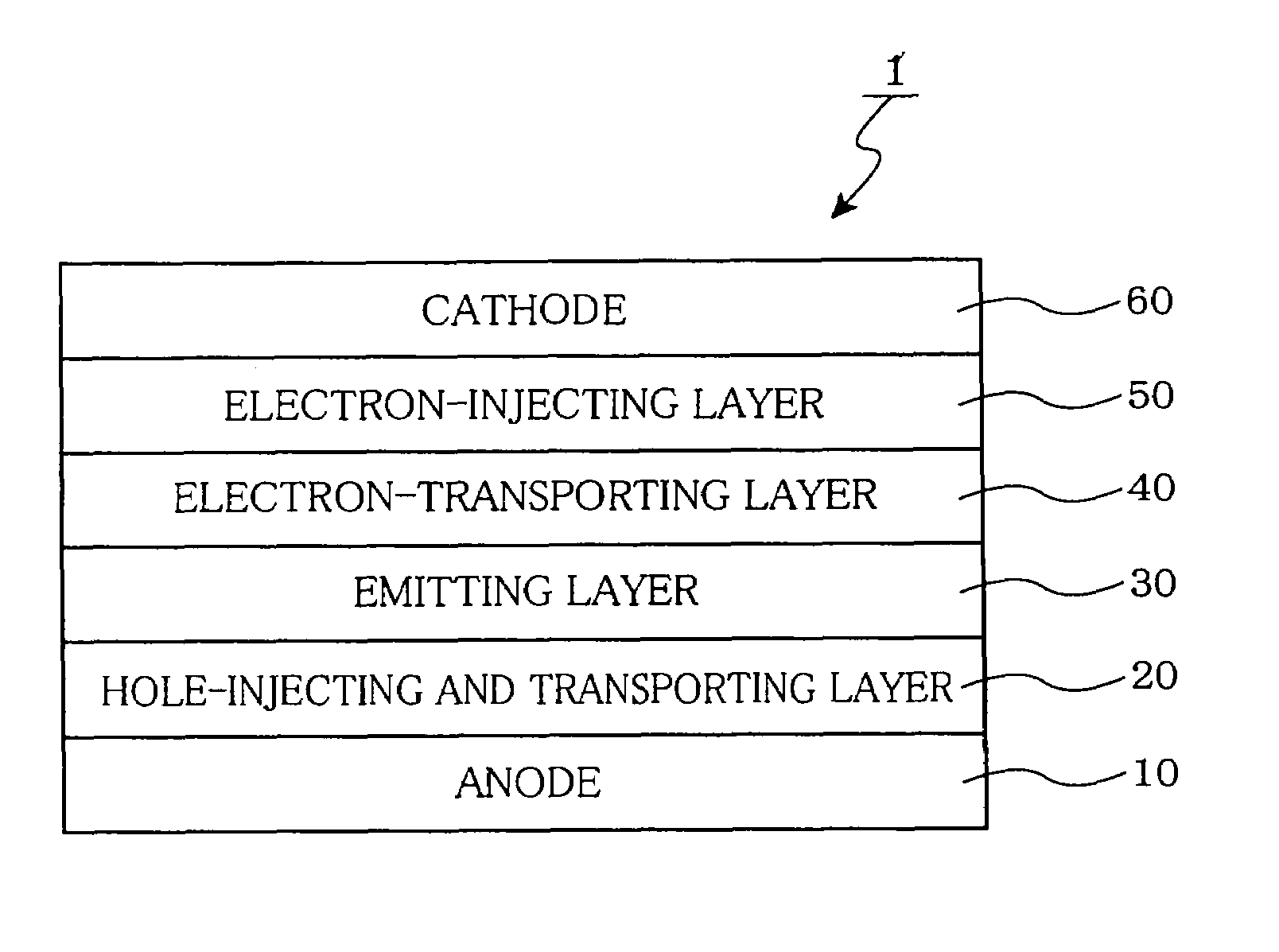

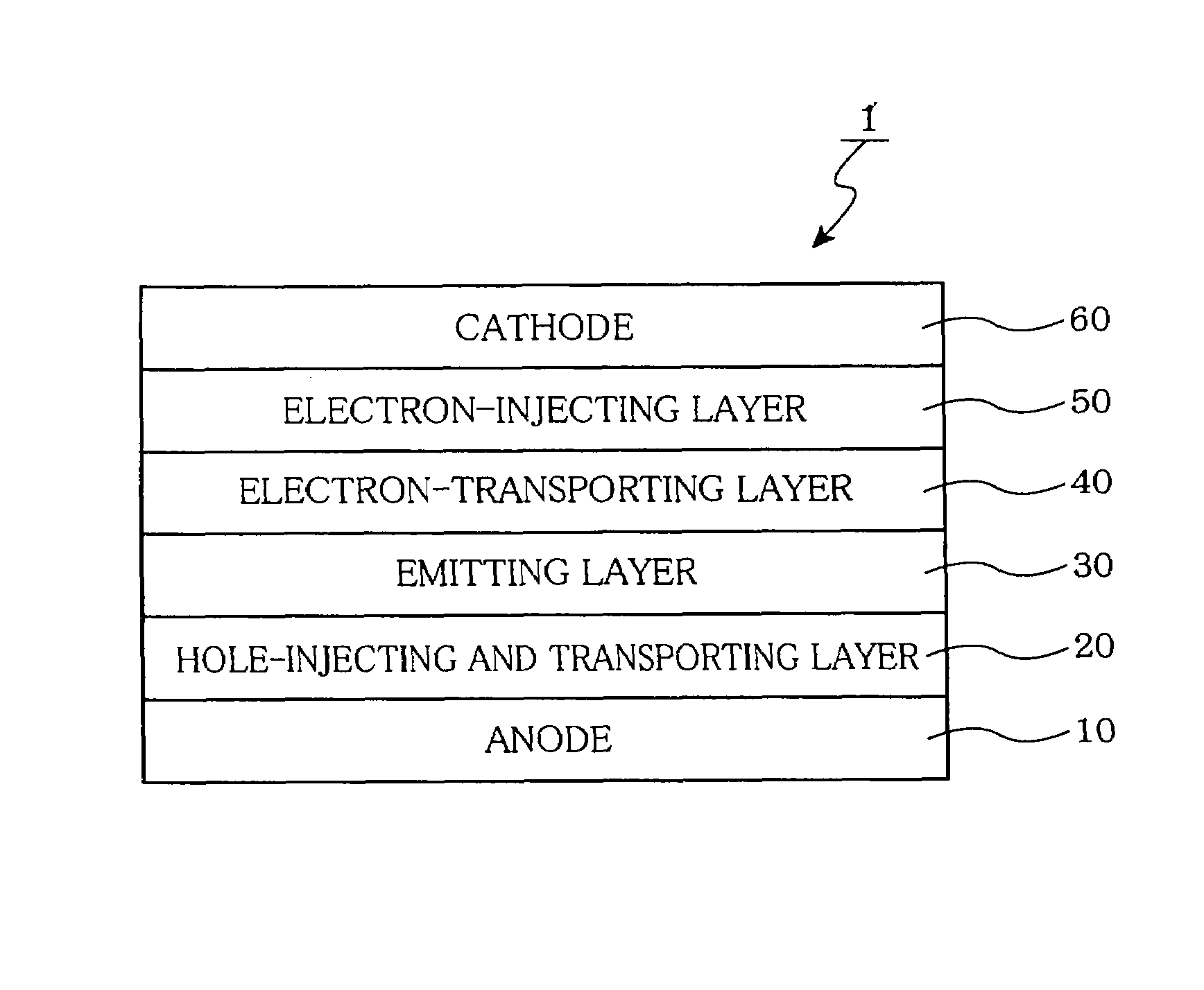

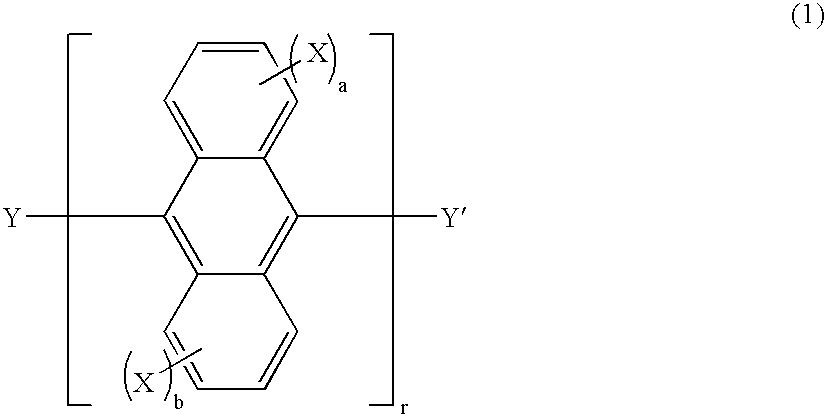

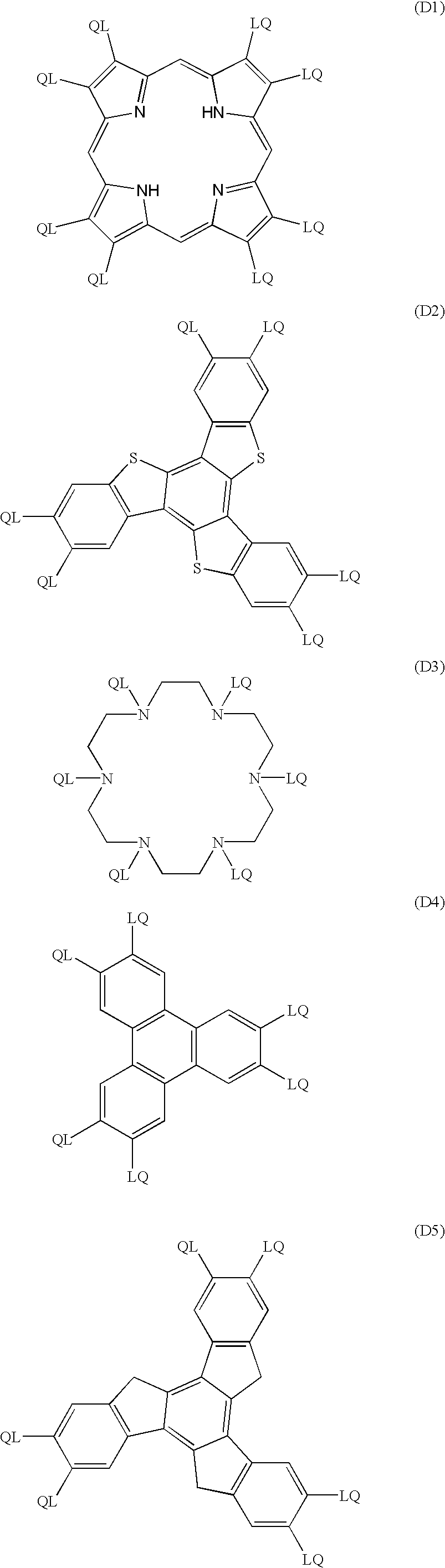

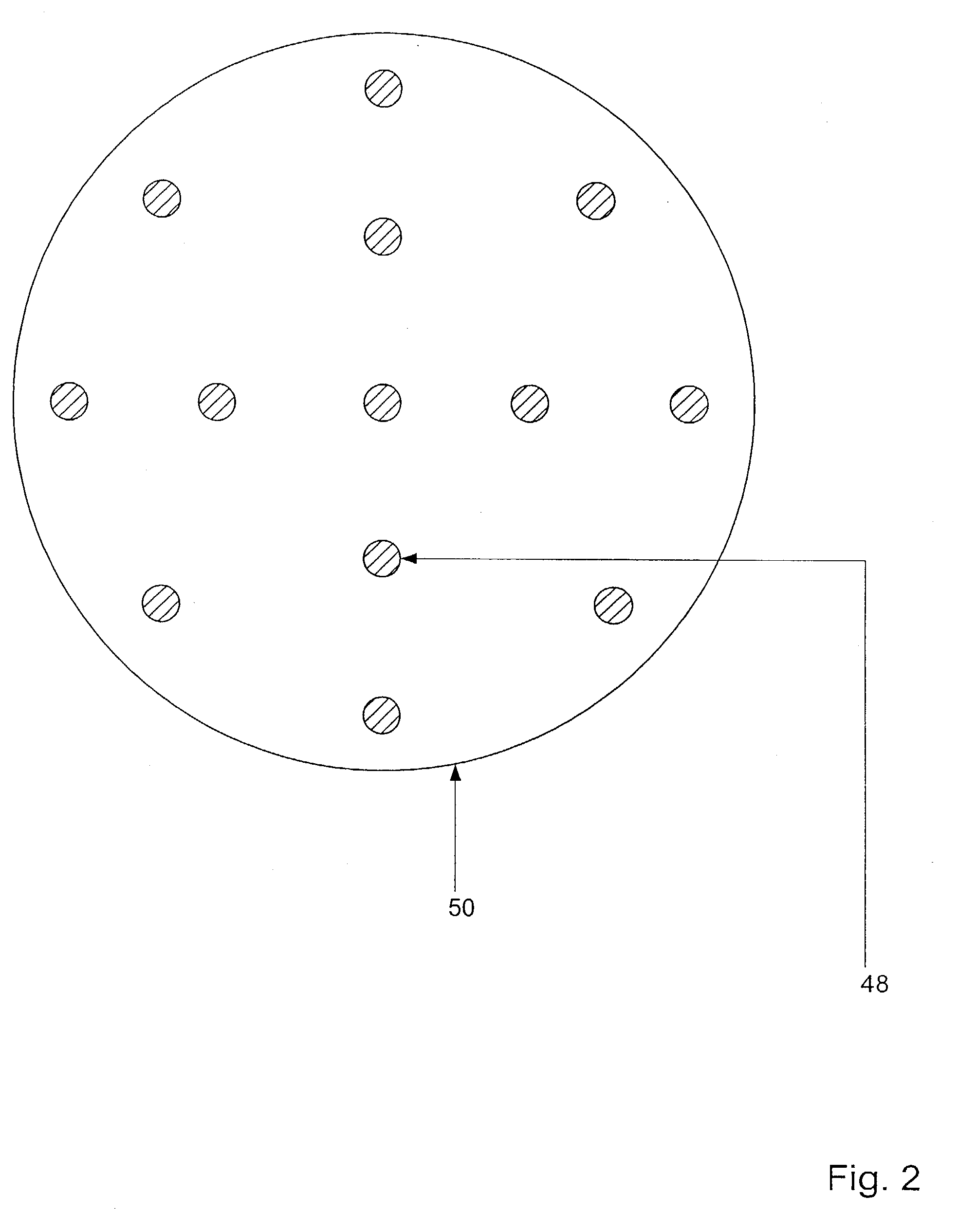

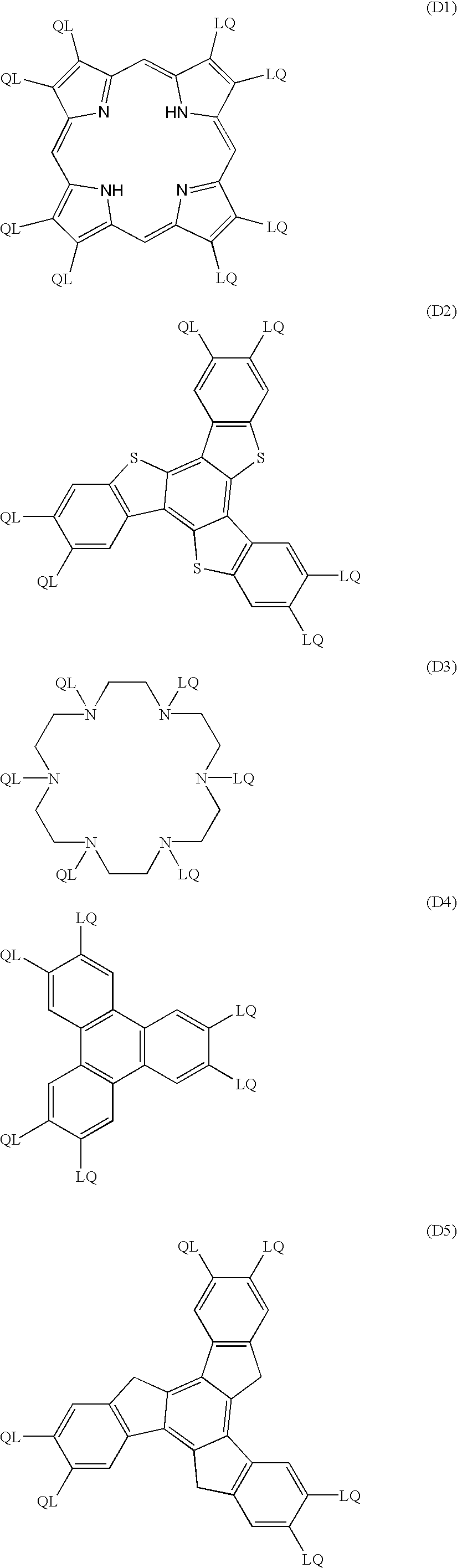

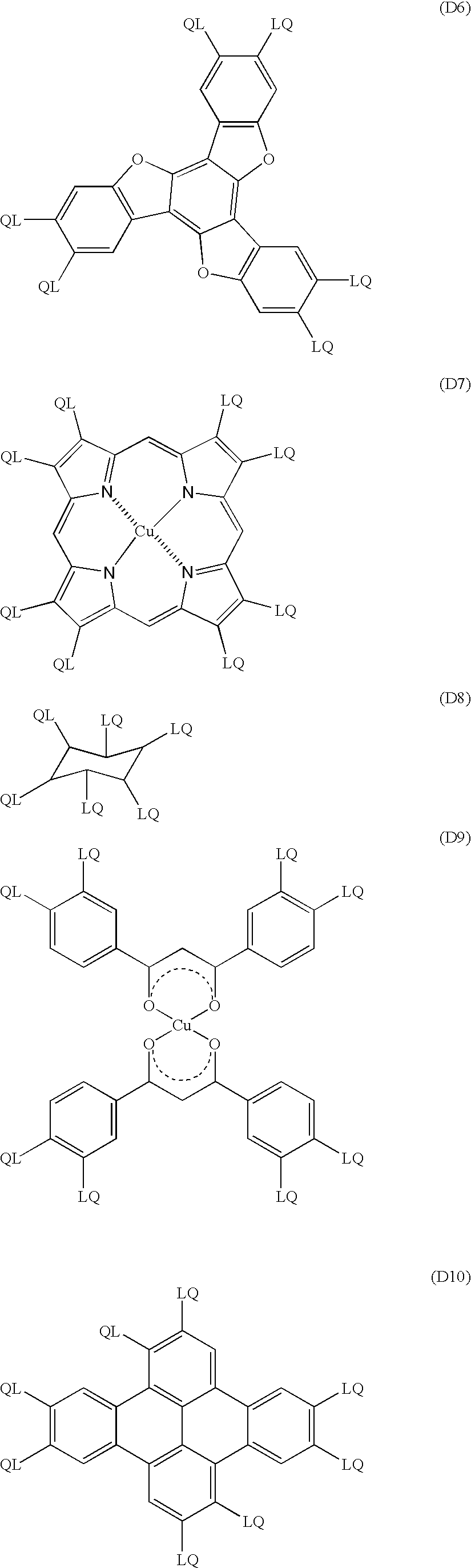

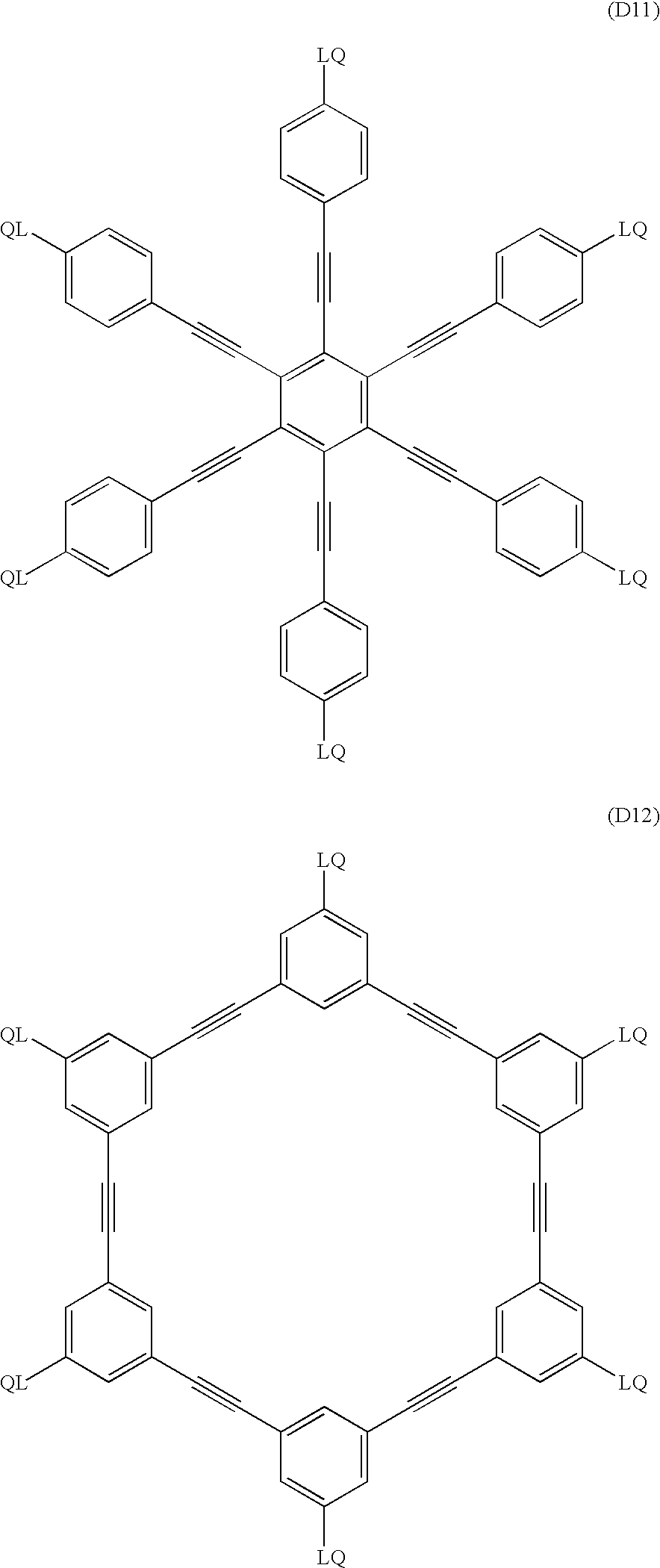

Organic electroluminescent device

InactiveUS20080193796A1High efficiencyLong lifeOrganic chemistryDischarge tube luminescnet screensOrganic electroluminescenceQuantum yield

An organic electroluminescent device including: an anode, a cathode, and at least an emitting layer, an electron-transporting layer and an electron-injecting layer interposed between the anode and the cathode; the emitting layer containing a host material which is a pyrene derivative, a chrysene derivative, a fluorene derivative or an anthracene derivative; the electron-transporting layer containing an electron-transporting material which is a pyrene derivative, a chrysene derivative, a fluorene derivative or an anthracene derivative, the anthracene derivative containing no heterocyclic ring, and has a heterocyclic ring and having a fluorescence quantum yield which is smaller than that of the host material contained in the emitting layer; and the electron-injecting layer containing a non-complex compound having a nitrogen-containing five-membered heterocyclic structure.

Owner:IDEMITSU KOSAN CO LTD

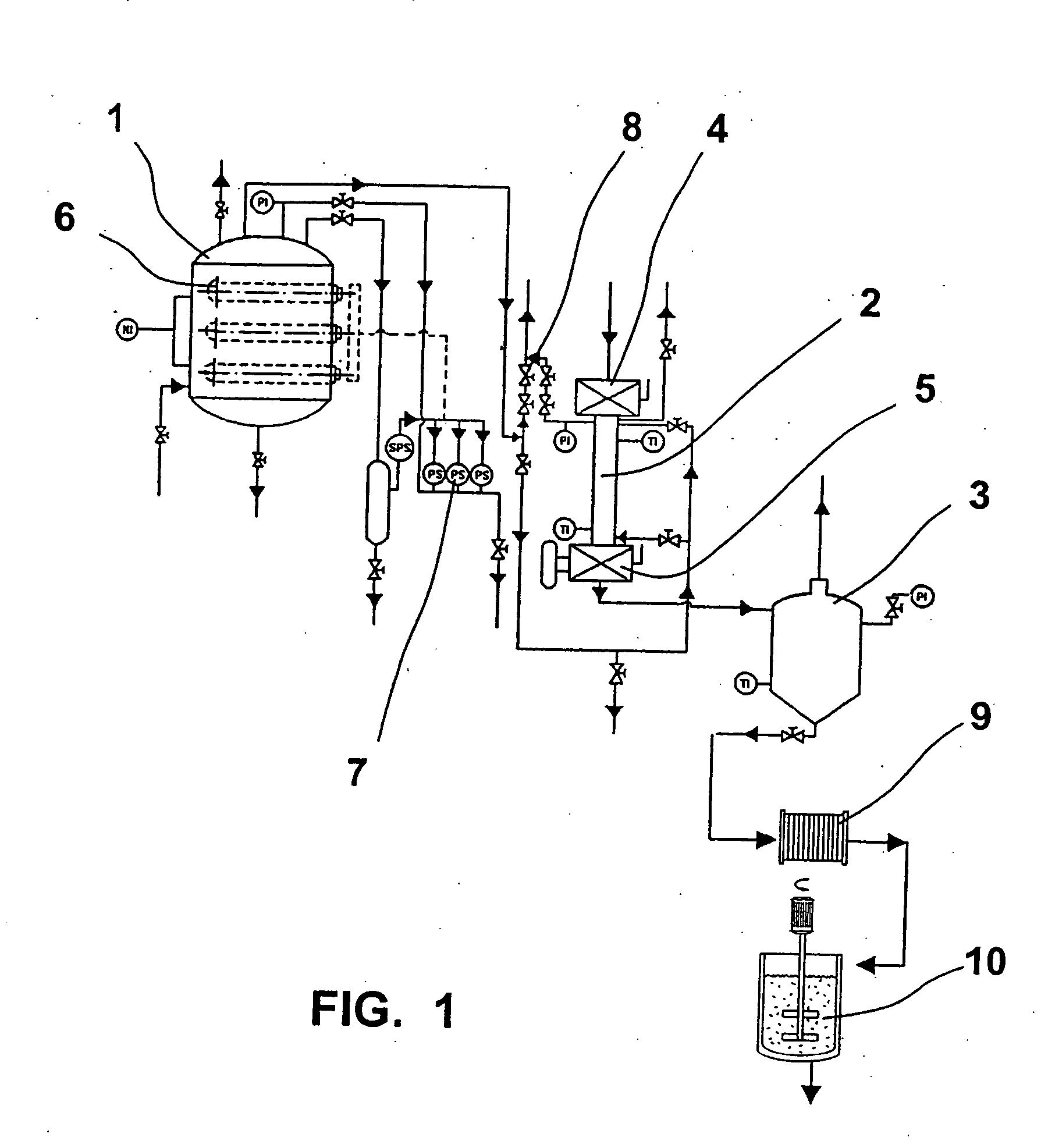

Procedure for the production of ethanol from lignocellulosic biomass using a new heat-tolerant yeast

InactiveUS20050069998A1Low conversion rateReduce yieldFungiBiological substance pretreatmentsFiltrationSolid fraction

It includes the stages of grinding the lignocellulosic biomass to a size of 15-30 mm, subjecting the product obtained to steam explosion pre-treatment at a temperature of 190-230° C. for between 1 and 10 minutes in a reactor (2), collecting the pre-treated material in a cyclone (3) and separating the liquid and solid fractions by filtration in a filter press (9), introducing the solid fraction in a fermentation deposit (10), adding a cellulase at a concentration of 15 UFP per gram of cellulose and 12.6 International Units of β-glucosidase enzyme dissolved in citrate buffer pH 4.8, inoculating the fermentation deposit (10) with a culture of the heat-tolerant bacteria Kluyveromyces marxianus CECT 10875, obtained by chemical mutagenesis from strain DER-26 of Kluyveromyces marxianus and shaking the mixture for 72 hours at 42° C.

Owner:CENT DE INVESTIGACIONES ENERGETICAS MEDIO AMBIENTALLES Y TECNOLOGICAS (C I E M A T)

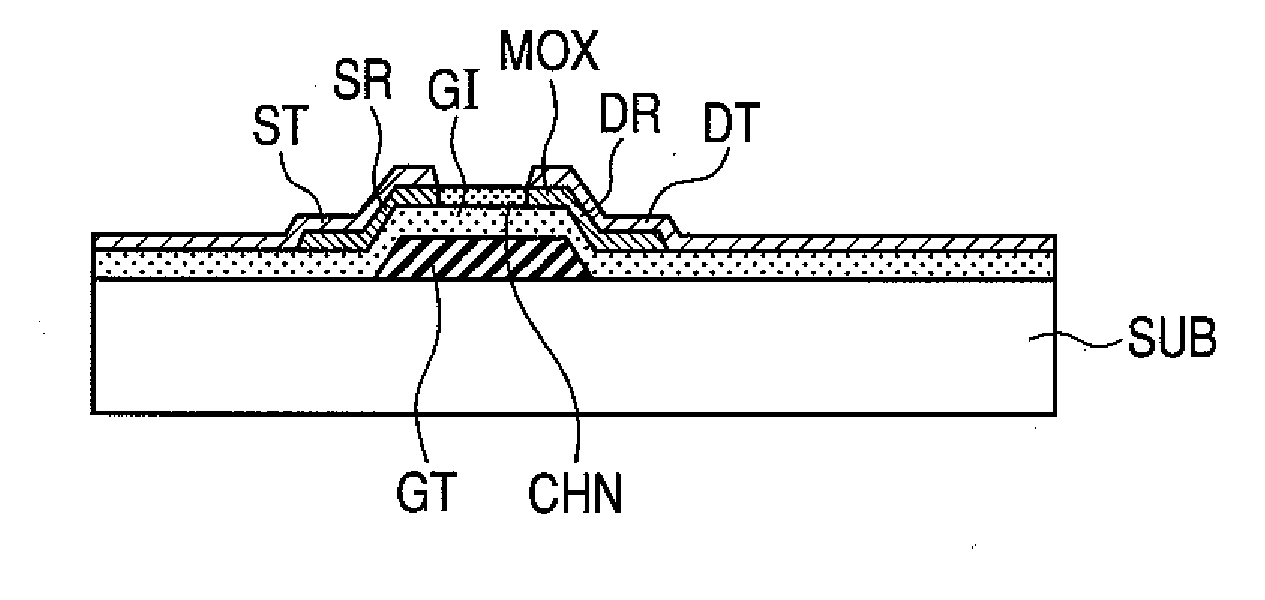

Semiconductor device and method for manufacturing the same

InactiveUS20090261325A1Improve featuresReduce allocationTransistorSolid-state devicesOxygen contentField-effect transistor

A metallic oxide semiconductor device with high performance and small variations. It is a field effect transistor using a metallic oxide film for the channel, which includes a channel region and a source region and comprises a drain region with a lower oxygen content than the channel region in the metallic oxide, in which the channel region exhibits semiconductor characteristics and the oxygen content decreases with depth below the surface.

Owner:HITACHI LTD

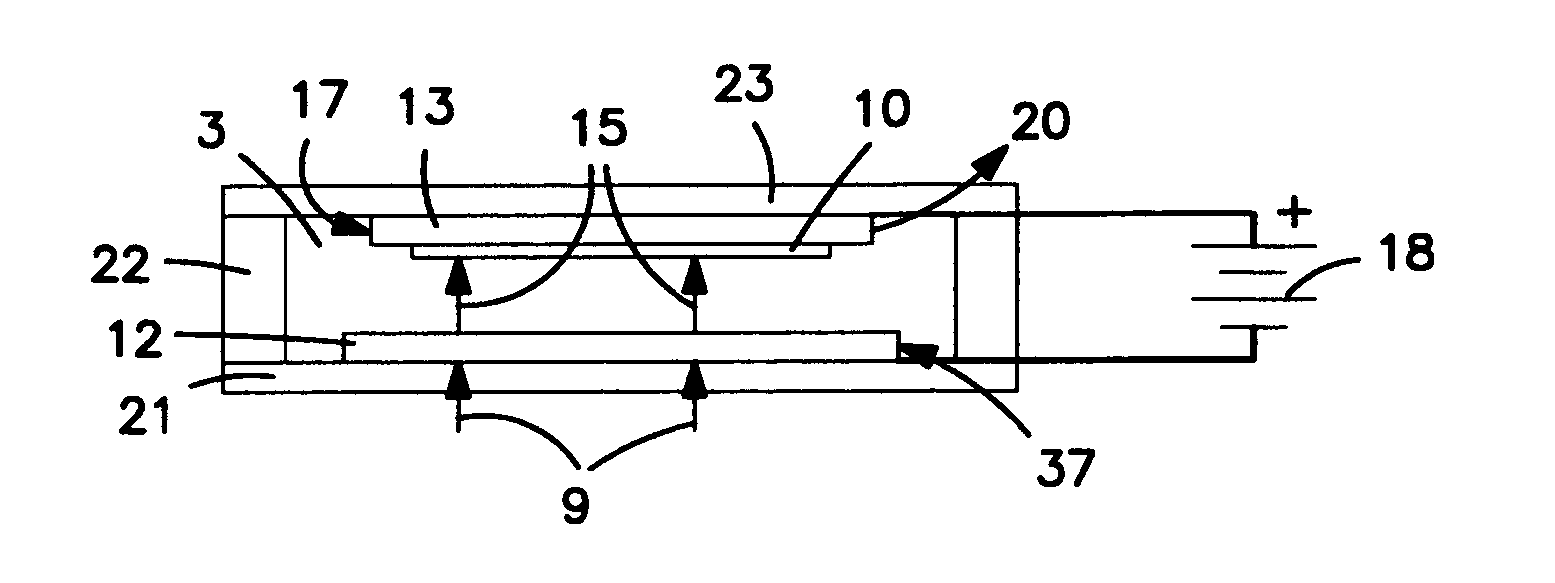

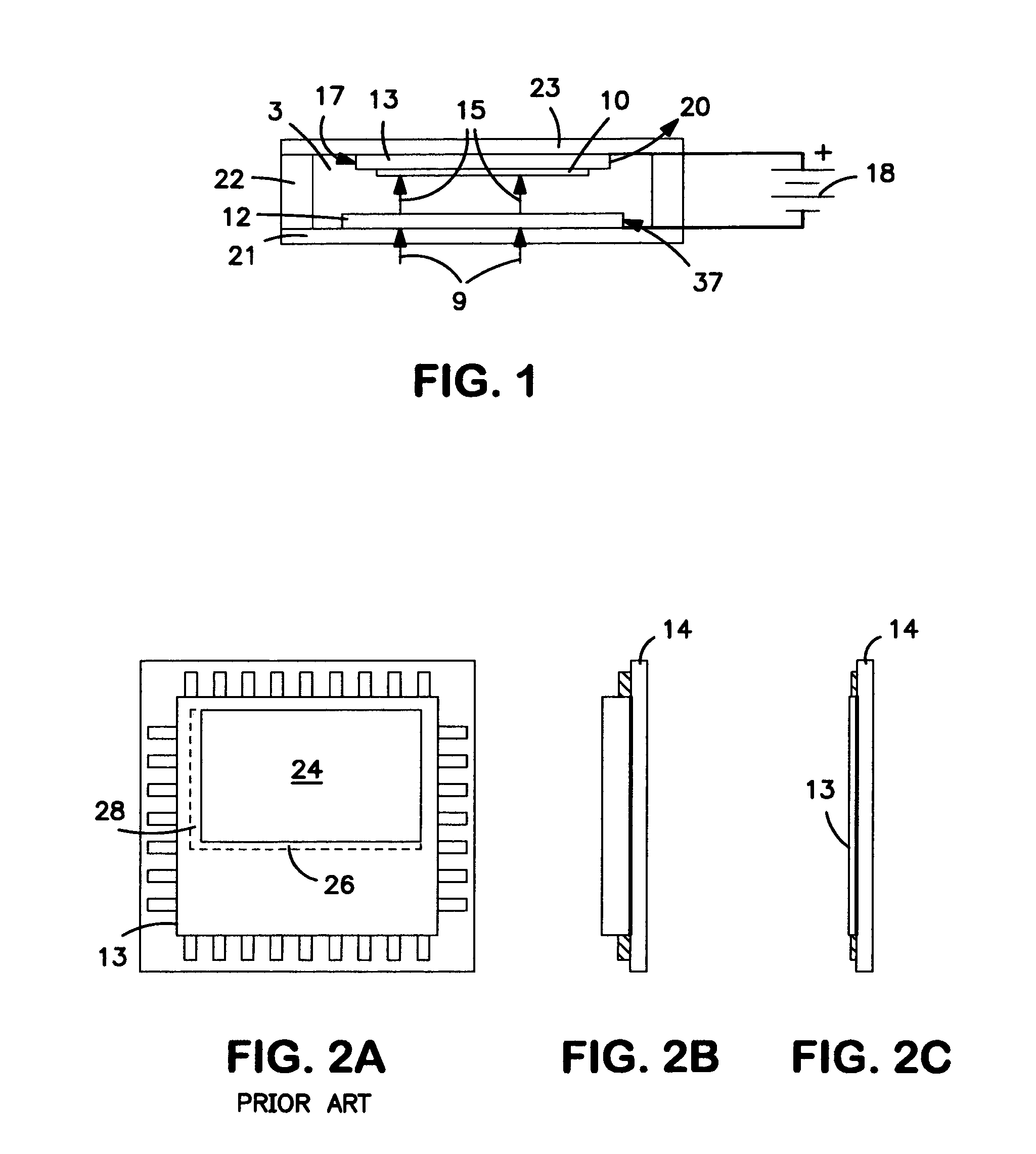

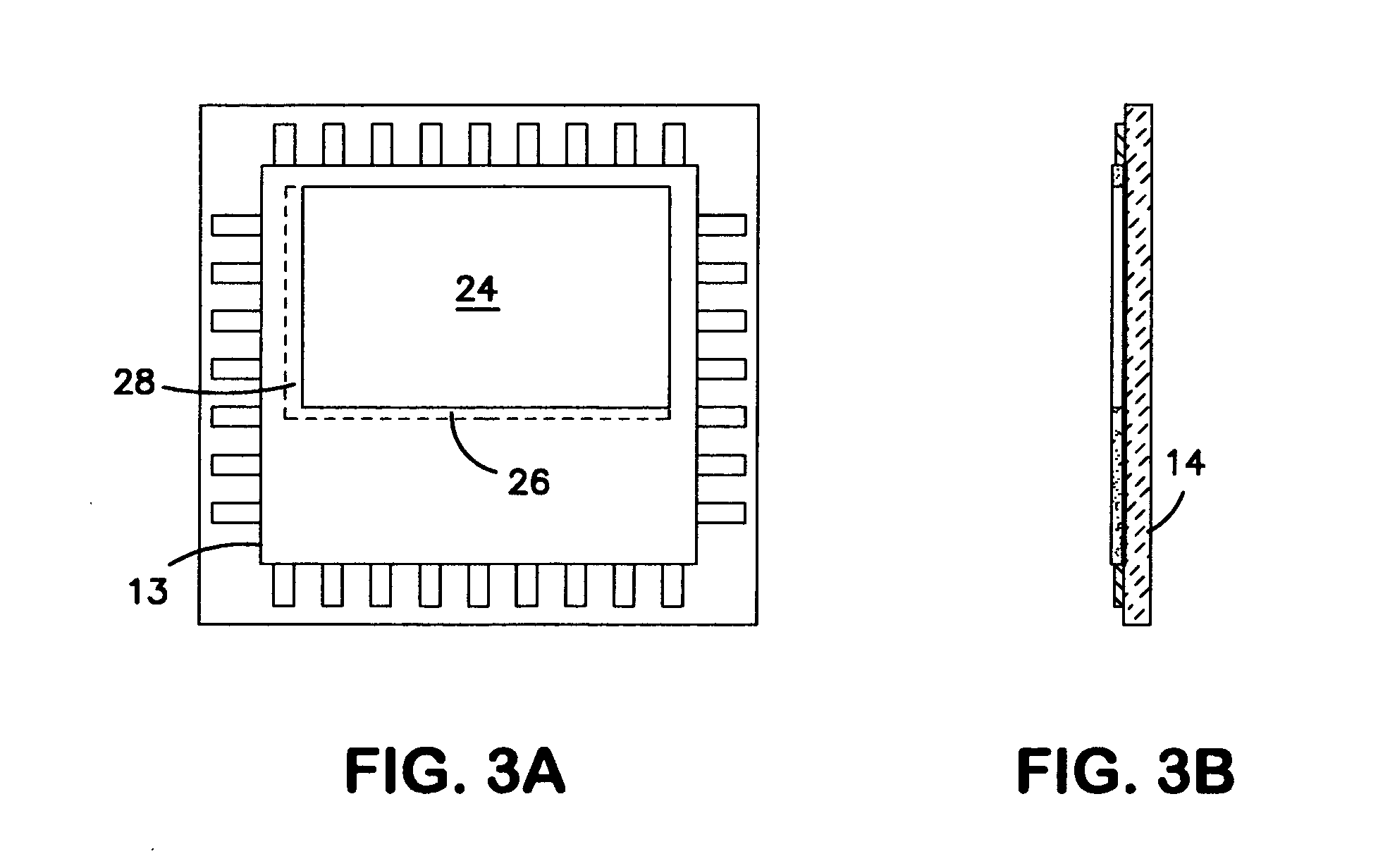

Backside imaging through a doped layer

ActiveUS20060138322A1Improve imaging effectImprove device yieldSolid-state devicesMaterial analysis by optical meansCMOSImage resolution

Backthinning in an area selective manner is applied to CMOS imaging sensors 12 for use in electron bombarded active pixel array devices. A further arrangement results in an array of collimators 51 aligned with pixels 42 or groups of pixels of an active pixel array providing improved image contrast of such image sensor. Provision of a thin P-doped layer 52 on the illuminated rear surface provides both a diffusion barrier resulting in improved resolution and a functional shield for reference pixels. A gradient in concentration of P-doped layer 52 optimizes electron collection at the pixel array.

Owner:EOTECH LLC

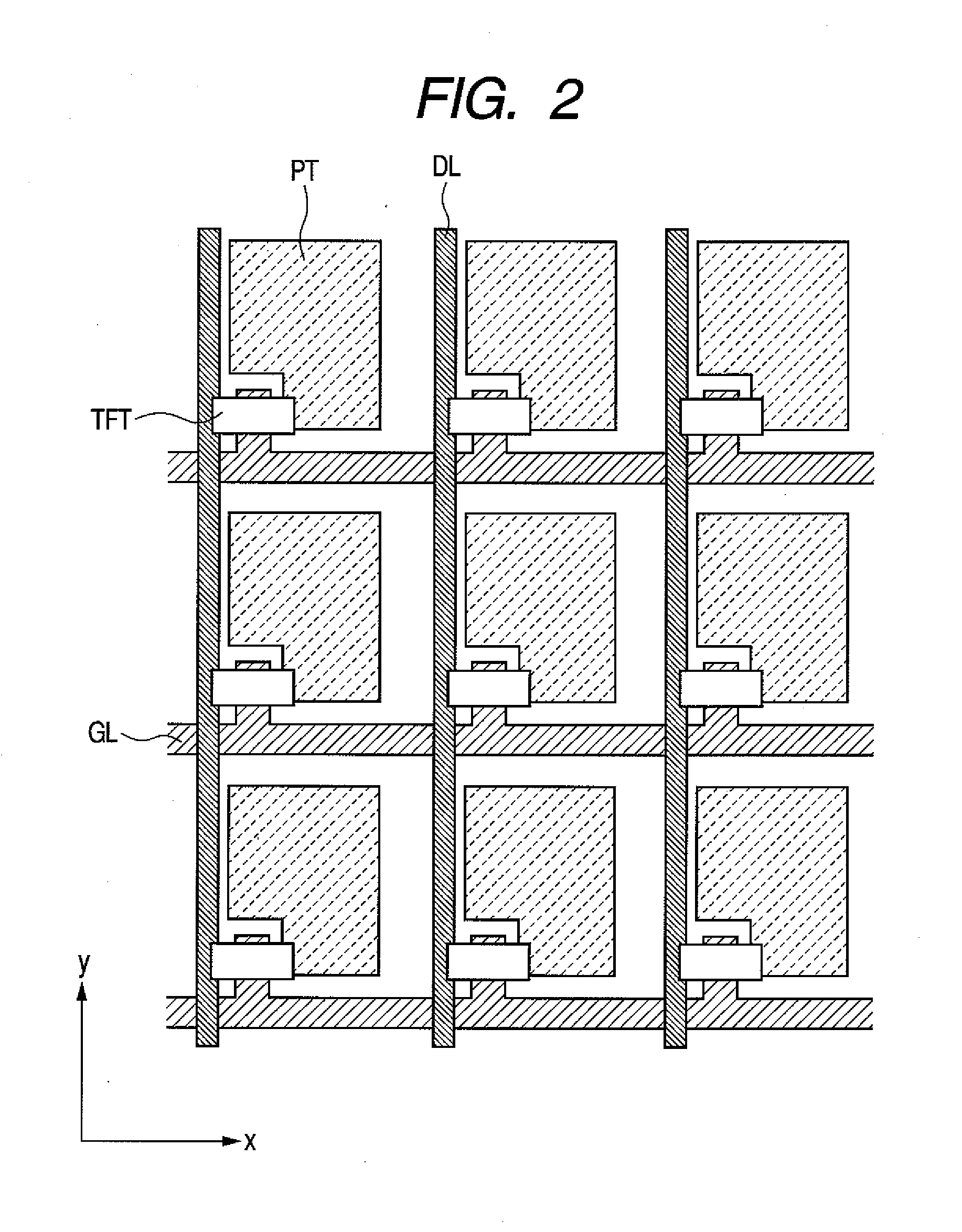

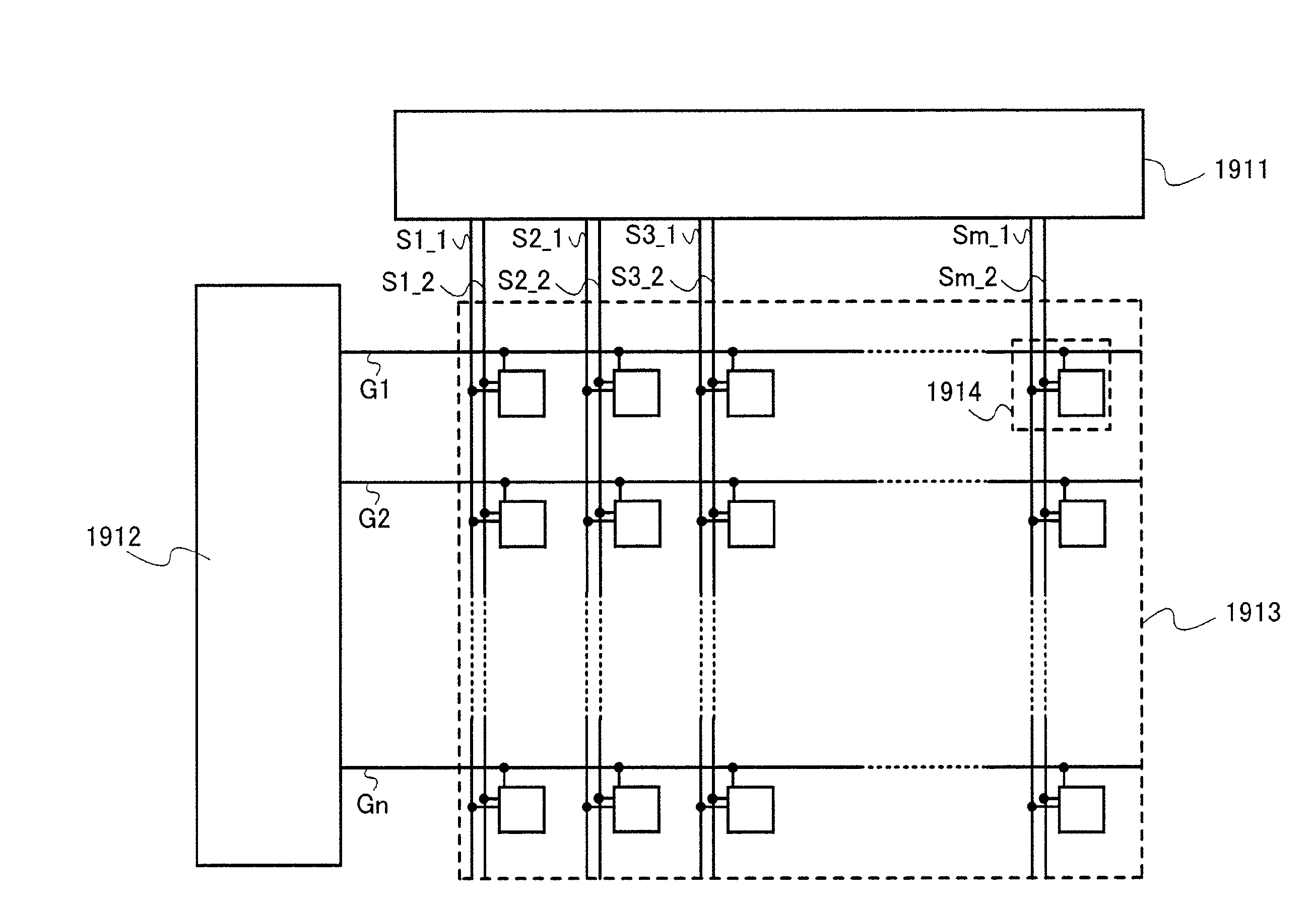

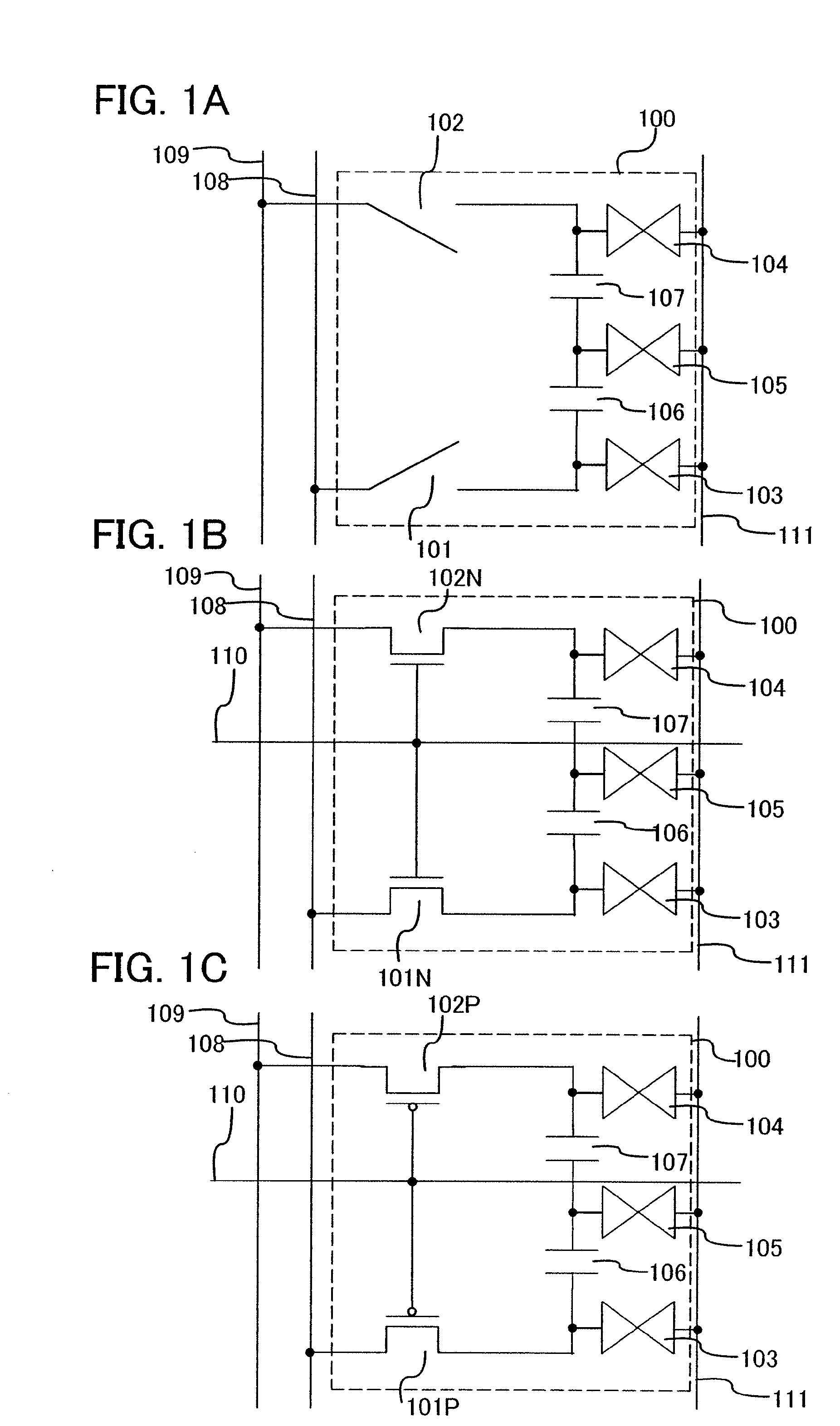

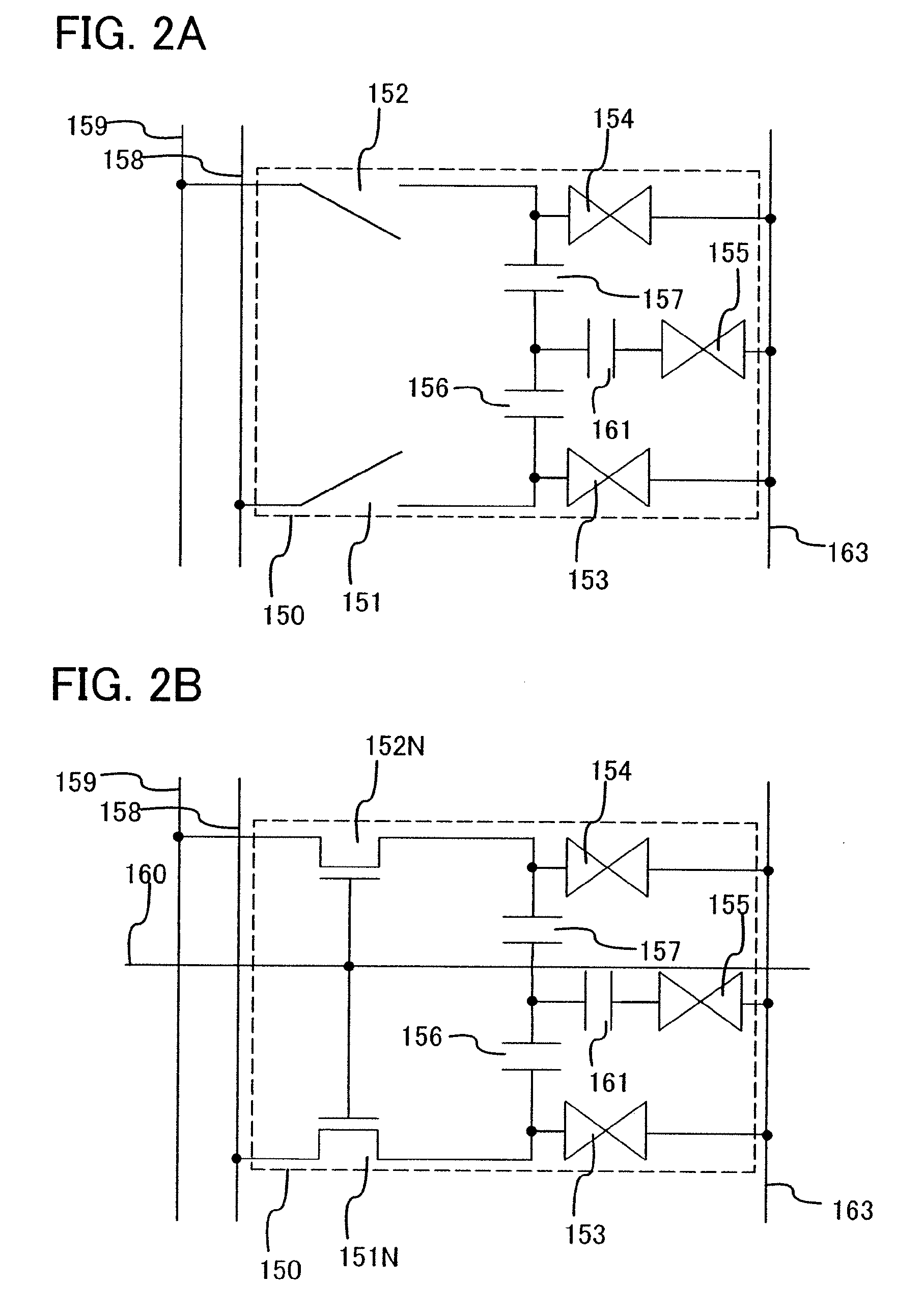

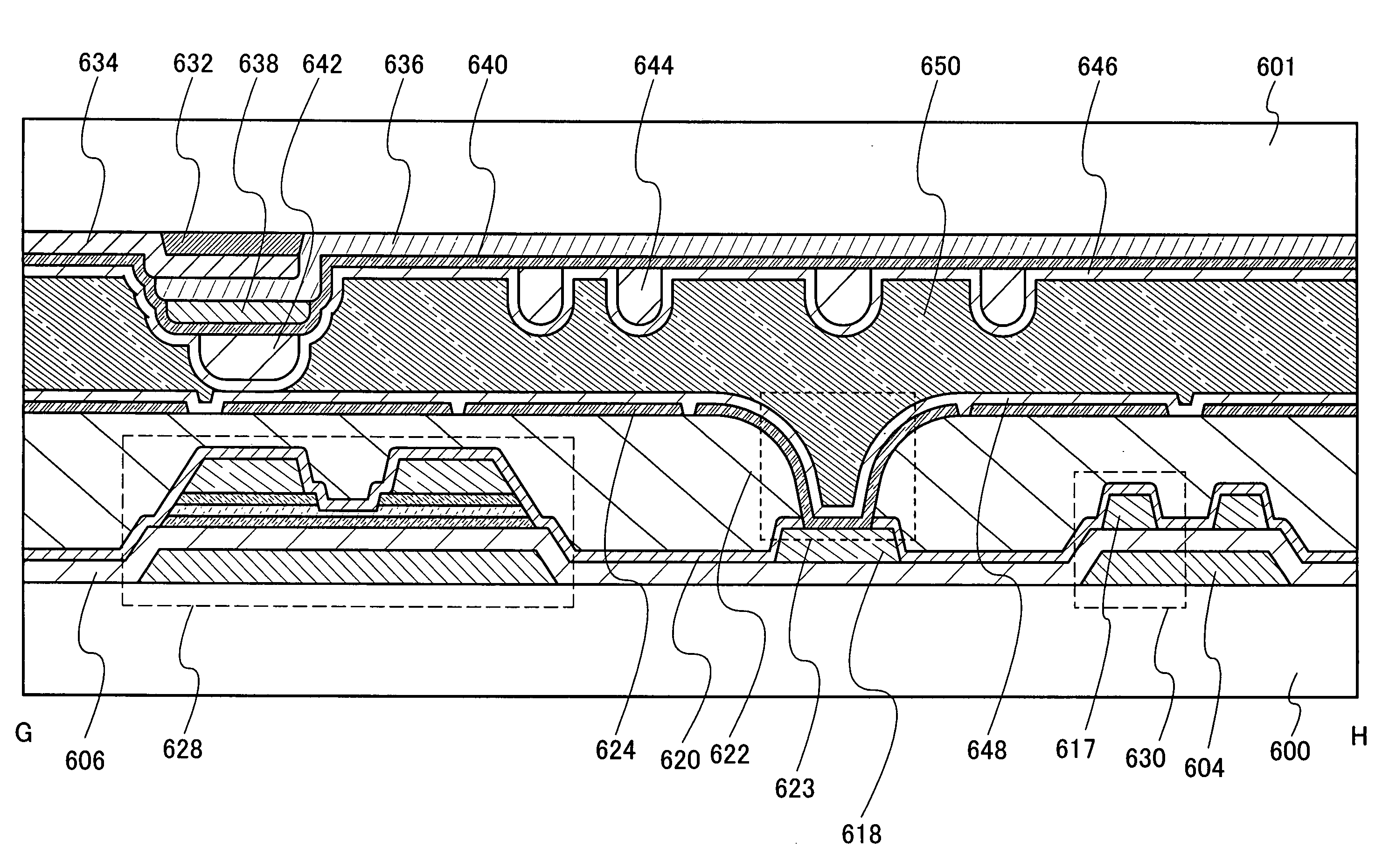

Liquid crystal display device

ActiveUS20080284929A1Reliable display deviceReduce power consumptionStatic indicating devicesSolid-state devicesLiquid-crystal displayLiquid crystal

To improve viewing angle characteristics by varying voltage which is applied between liquid crystal elements. A liquid crystal display device in which one pixel is provided with three or more liquid crystal elements and the level of voltage which is applied is varied between the liquid crystal elements is varied. In order to vary the level of the voltage which is applied between the liquid crystal elements, an element which divides the applied voltage is provided. In order to vary the level of the applied voltage, a capacitor, a resistor, a transistor, or the like is used. Viewing angle characteristics can be improved by varying the level of the voltage which is applied between the liquid crystal elements.

Owner:SEMICON ENERGY LAB CO LTD

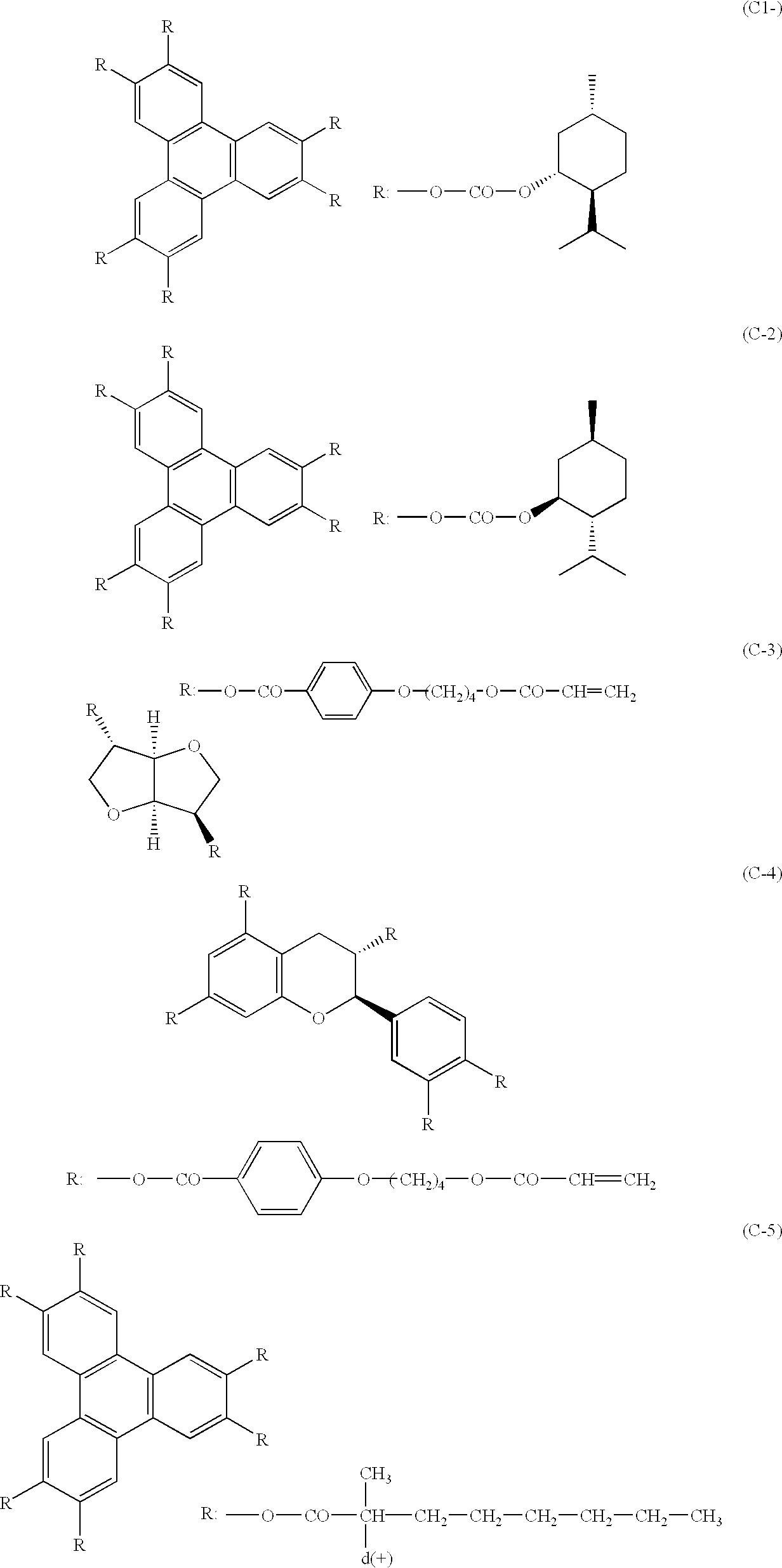

Quarter wave plate comprising two optically anisotropic layers

InactiveUS20020159005A1Improve adhesionReduce yieldPolarising elementsNon-linear opticsOptical propertyLength wave

A circularly polarizing plate comprises a linearly polarizing membrane and a quarter wave plate. The quarter wave plate comprises an optically anisotropic layer A and an optically anisotropic layer B. The quarter wave plate has such an optical characteristic that a retardation value essentially is a quarter of a wavelength when the retardation value is measured at the wavelength of 450 nm, 550 nm and 650 nm. One of the optically anisotropic layers A and B is a layer made from liquid crystal molecules, and the other is a polymer film or a layer made from liquid crystal molecules.

Owner:FUJIFILM CORP

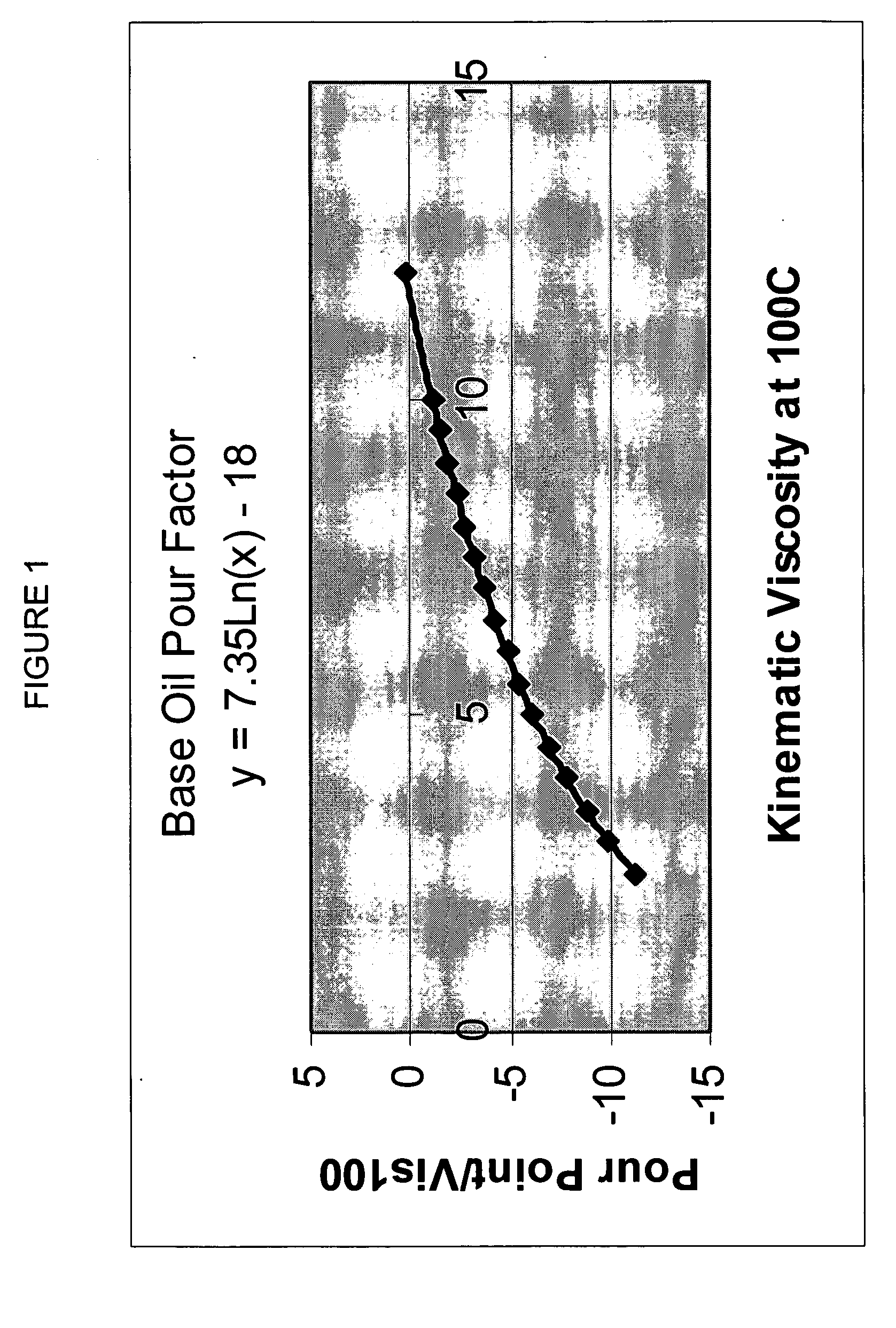

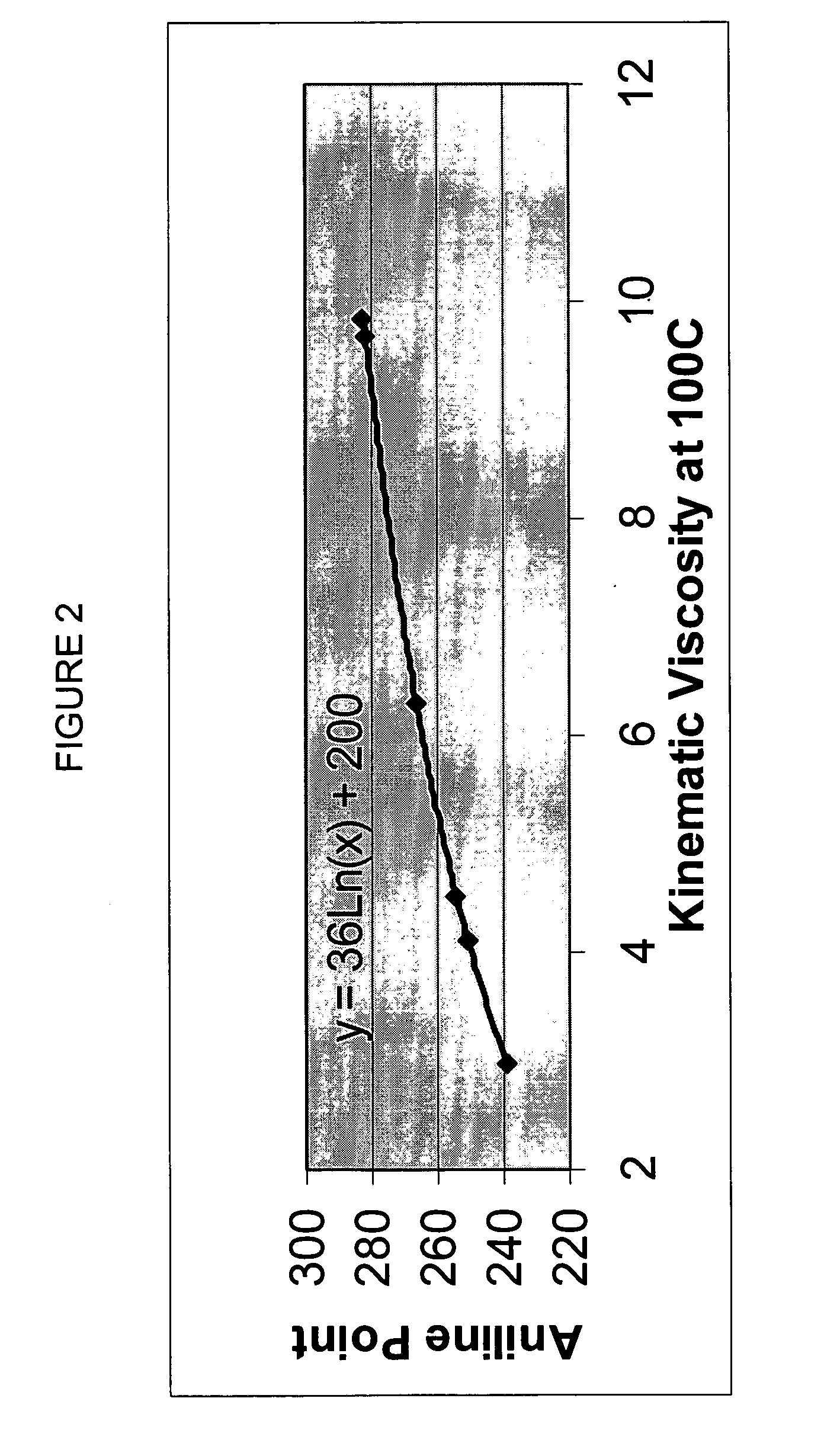

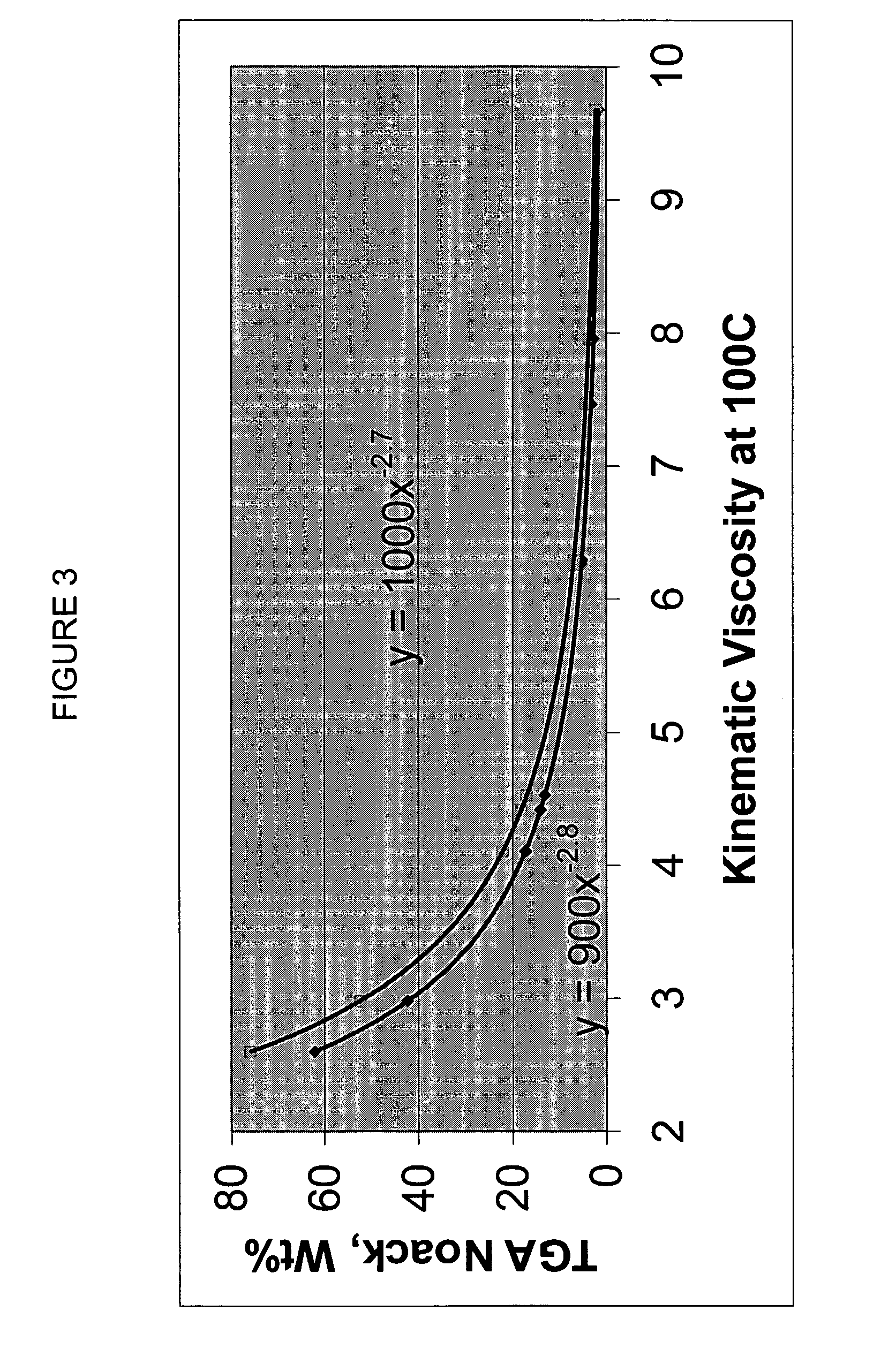

Process for manufacturing lubricating base oil with high monocycloparaffins and low multicycloparaffins

InactiveUS20050133409A1Improve Oxidation StabilityHigh viscosity indexTreatment with hydrotreatment processesAdditivesSyngasMolecular sieve

A process for manufacturing a lubricating base oil by: a) performing Fischer-Tropsch synthesis on syngas to provide a product stream; b) isolating from said product stream a substantially paraffinic wax feed having less than about 30 ppm total nitrogen and sulfur, and less than about 1 wt % oxygen; c) dewaxing said feed by hydroisomerization dewaxing using a shape selective intermediate pore size molecular sieve comprising a noble metal hydrogenation component, wherein the hydroisomerization temperature is between about 600° F. (315° C.) and about 750° F. (399° C.), to produce an is dimerized oil; and d) hydrofinishing said isomerized oil to produce a lubricating base oil having specific desired properties.

Owner:CHEVROU USA INC

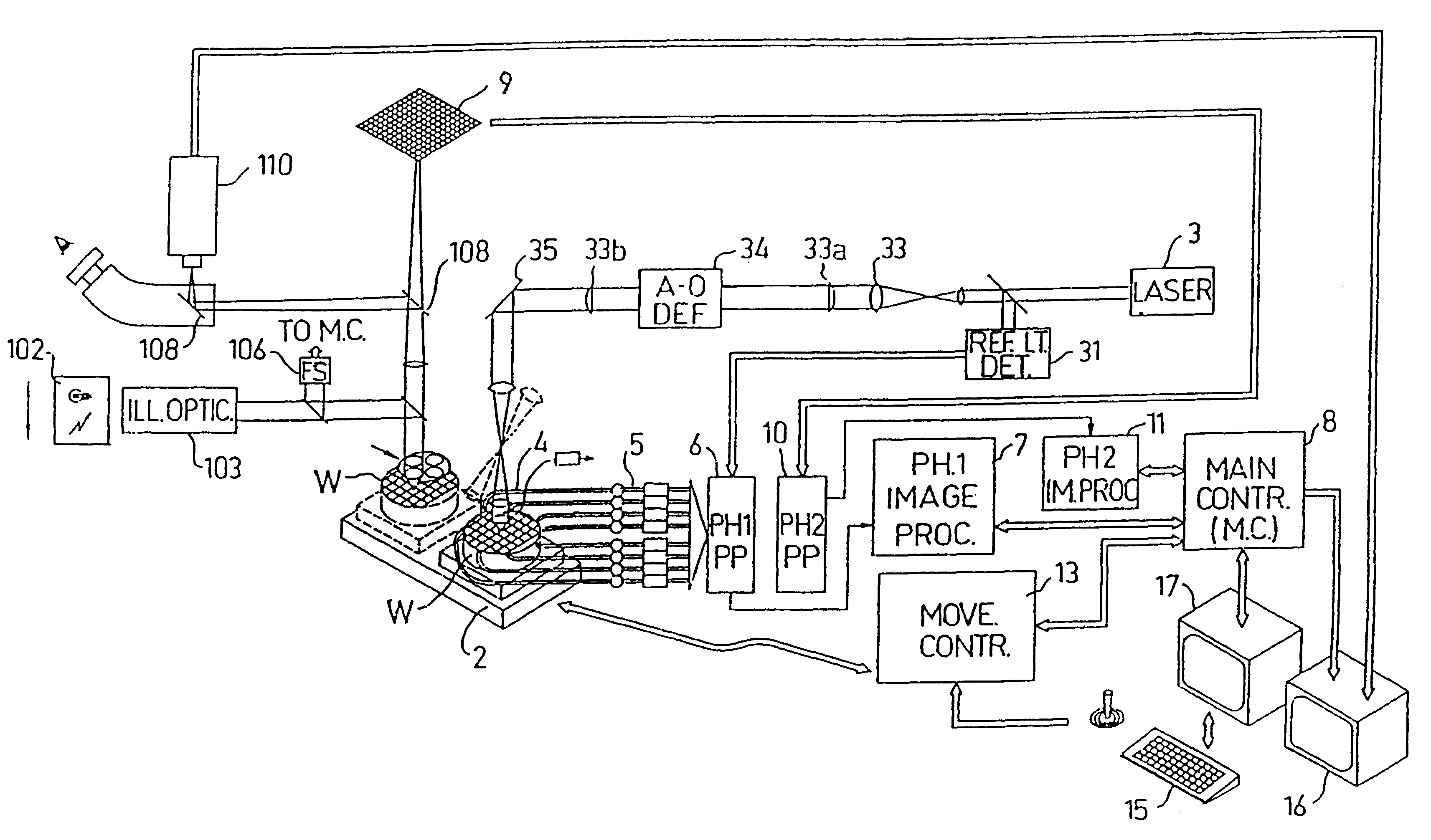

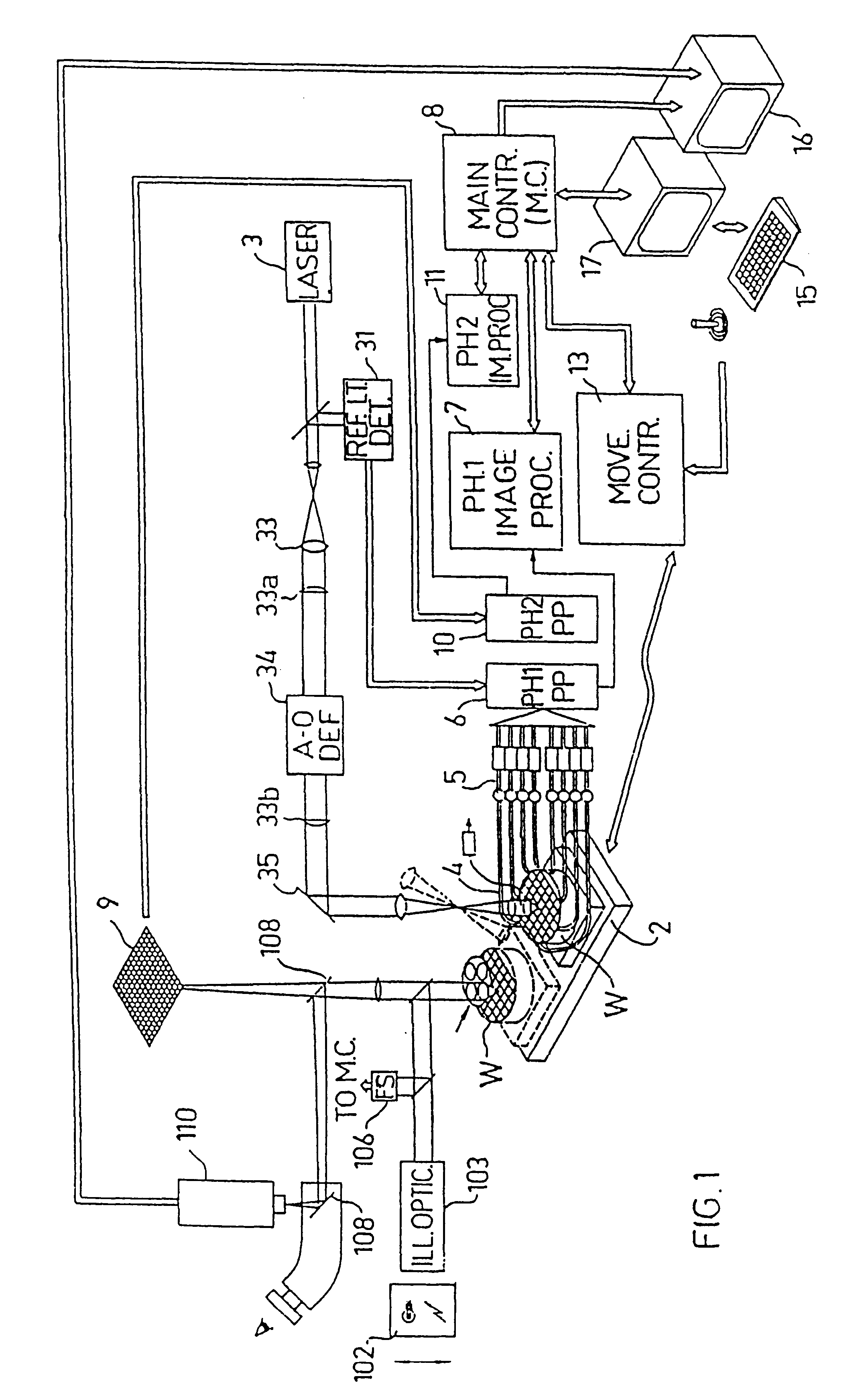

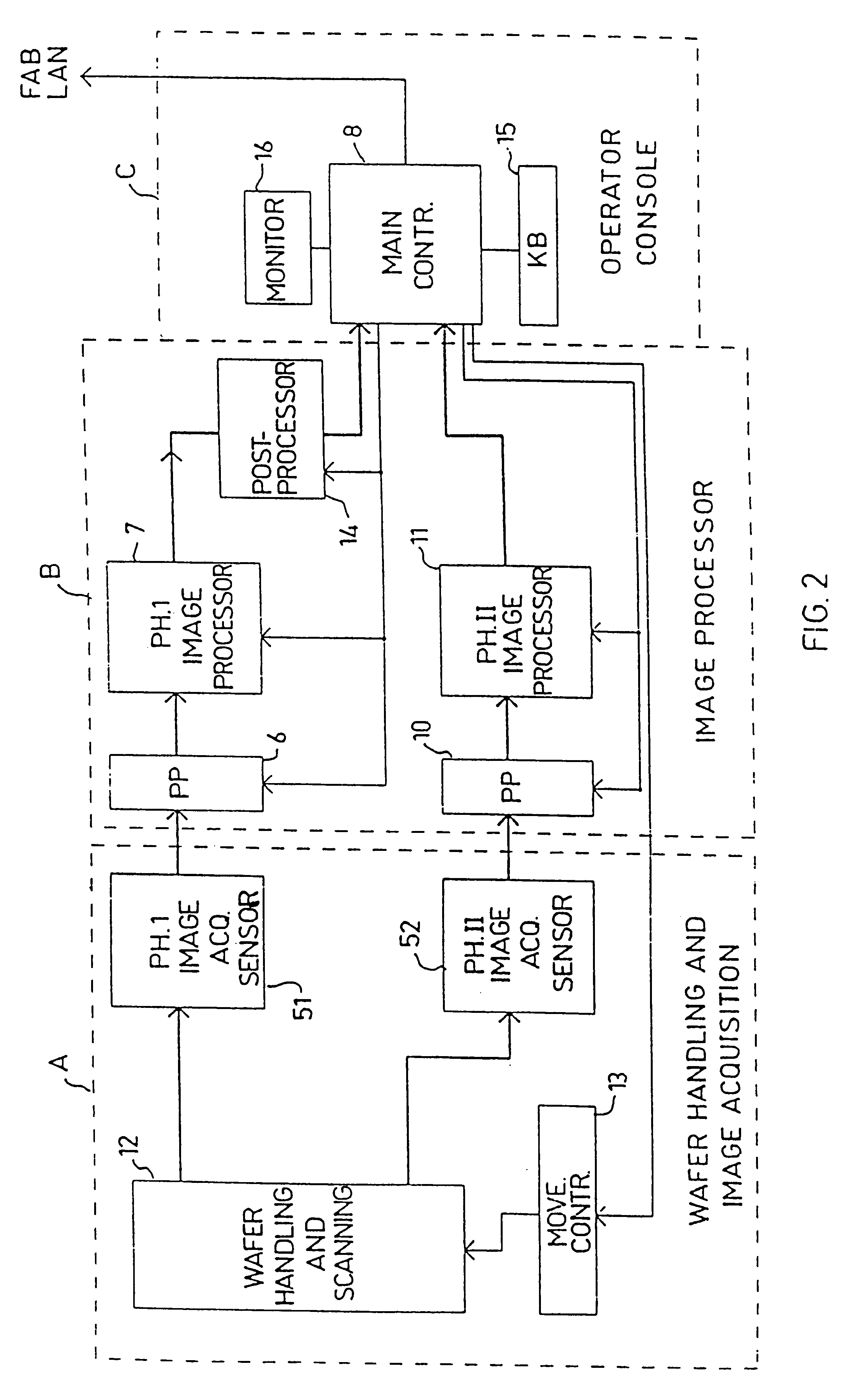

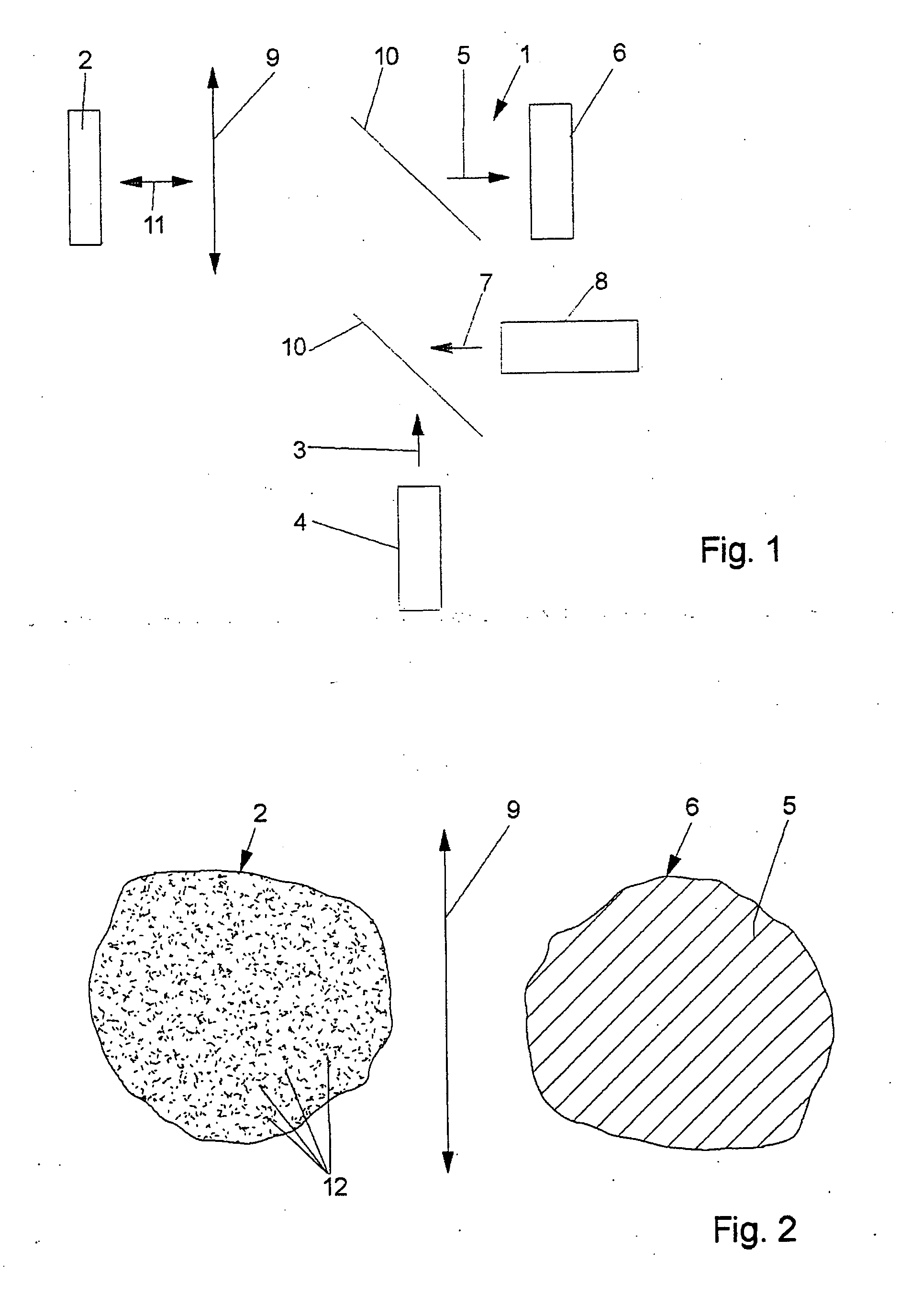

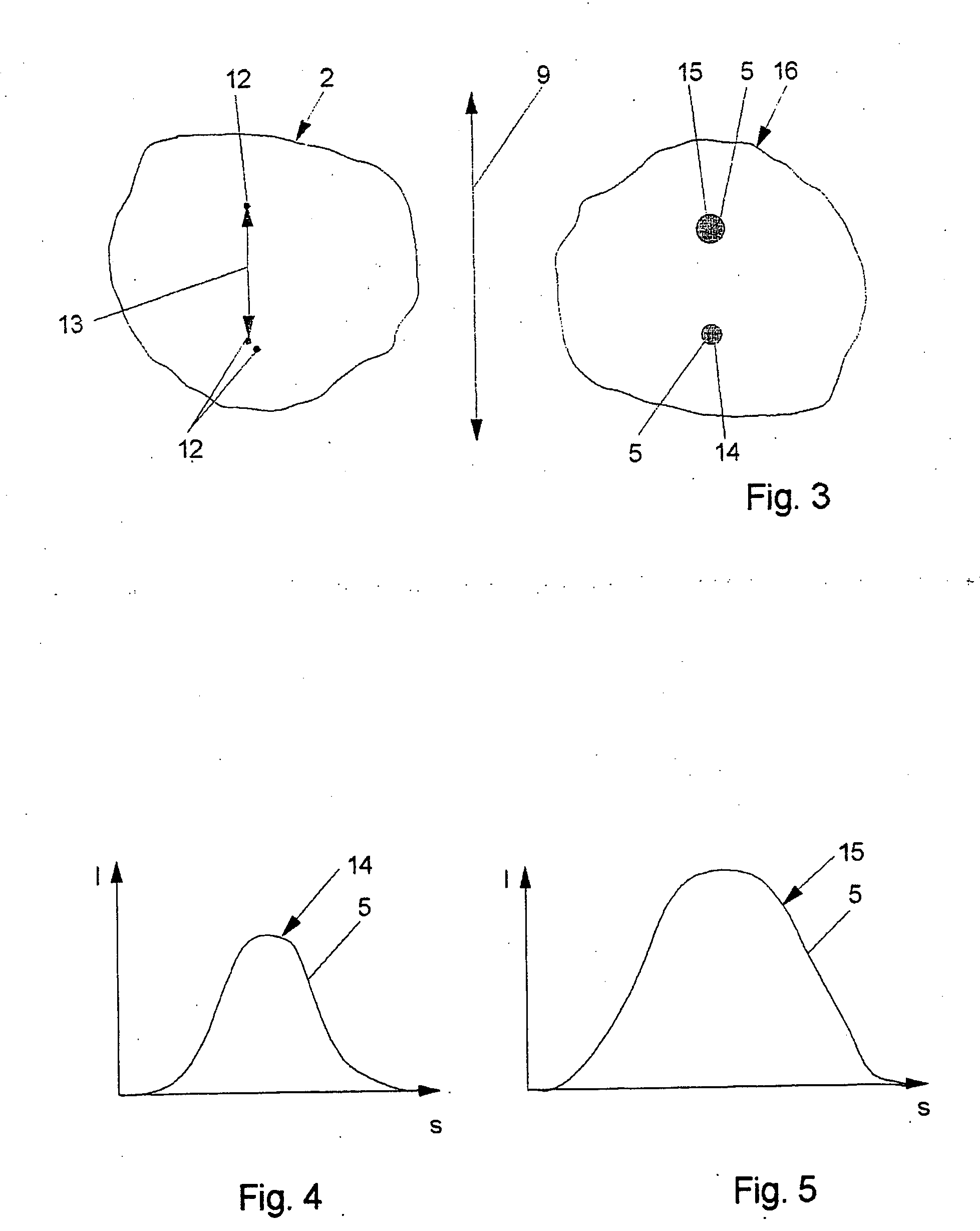

Substrate inspection method and apparatus

InactiveUS6178257B1High throughputIncrease sensitivityCharacter and pattern recognitionOptically investigating flaws/contaminationImage resolutionHigh spatial resolution

A method and apparatus for inspecting the surface of articles, such as chips and wafers, for defects, includes a first phase of optically examining the complete surface of the article inspected at a relatively high speed and with a relatively low spatial resolution, and a second phase of optically examining with a relatively high spatial resolution only the suspected locations for the presence or absence of a defect therein.

Owner:APPLIED MATERIALS INC

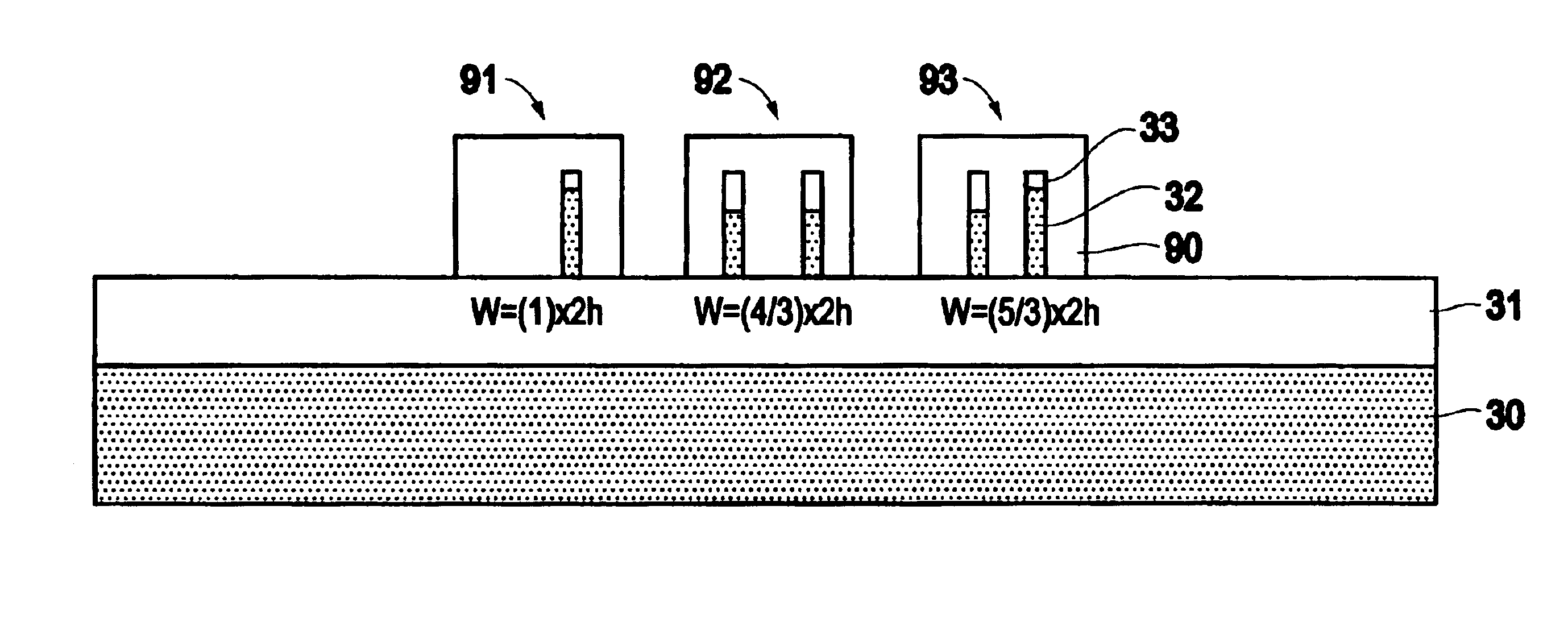

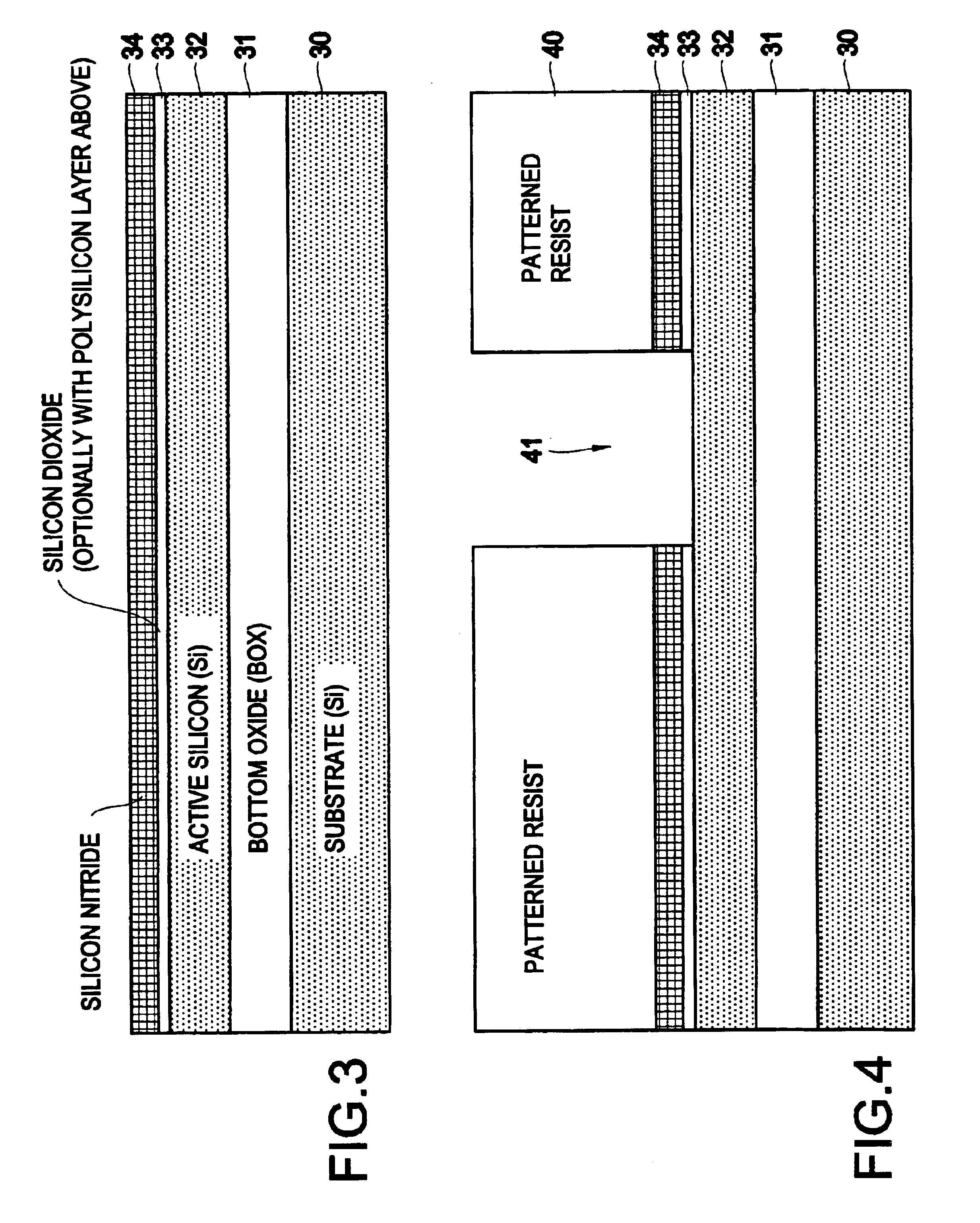

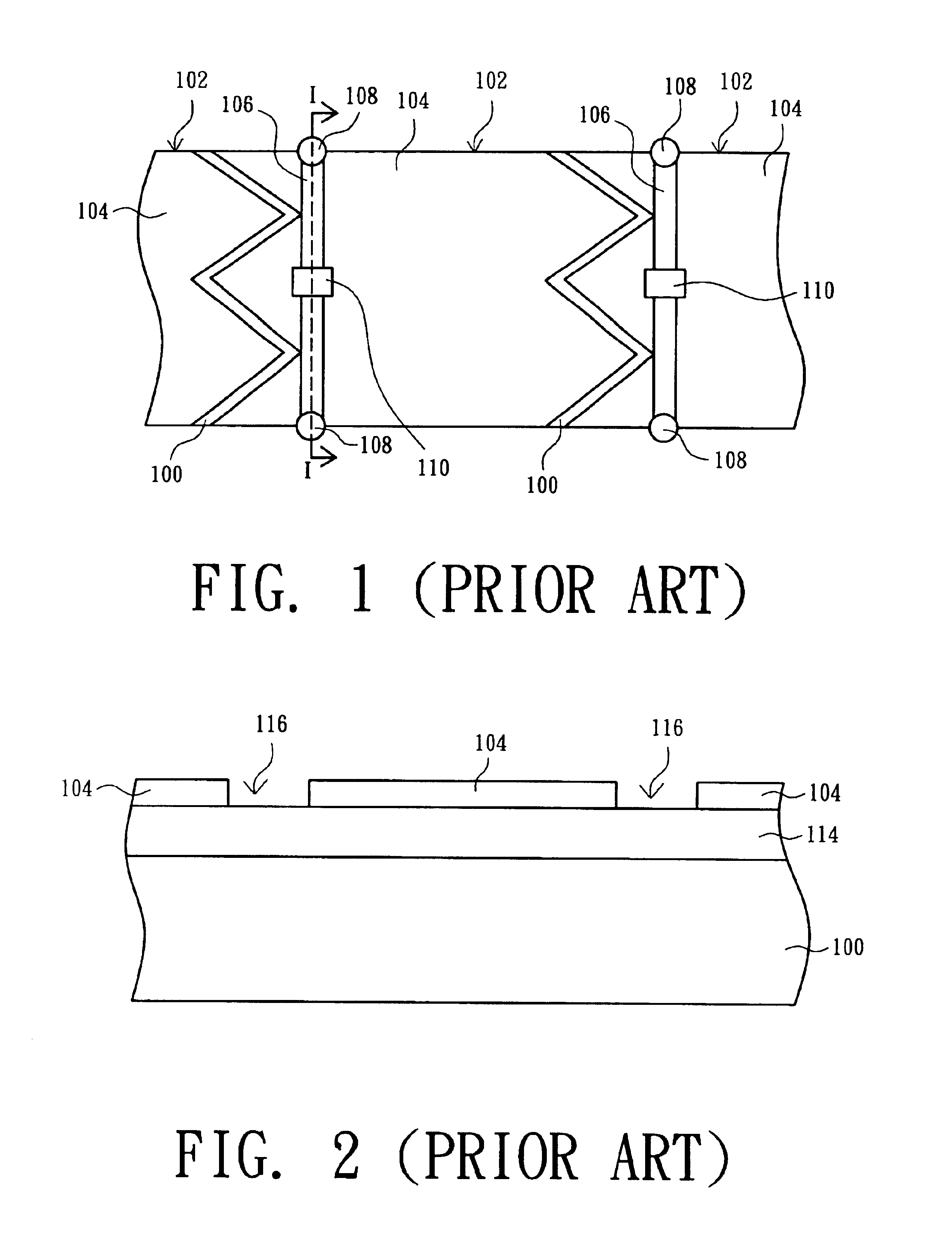

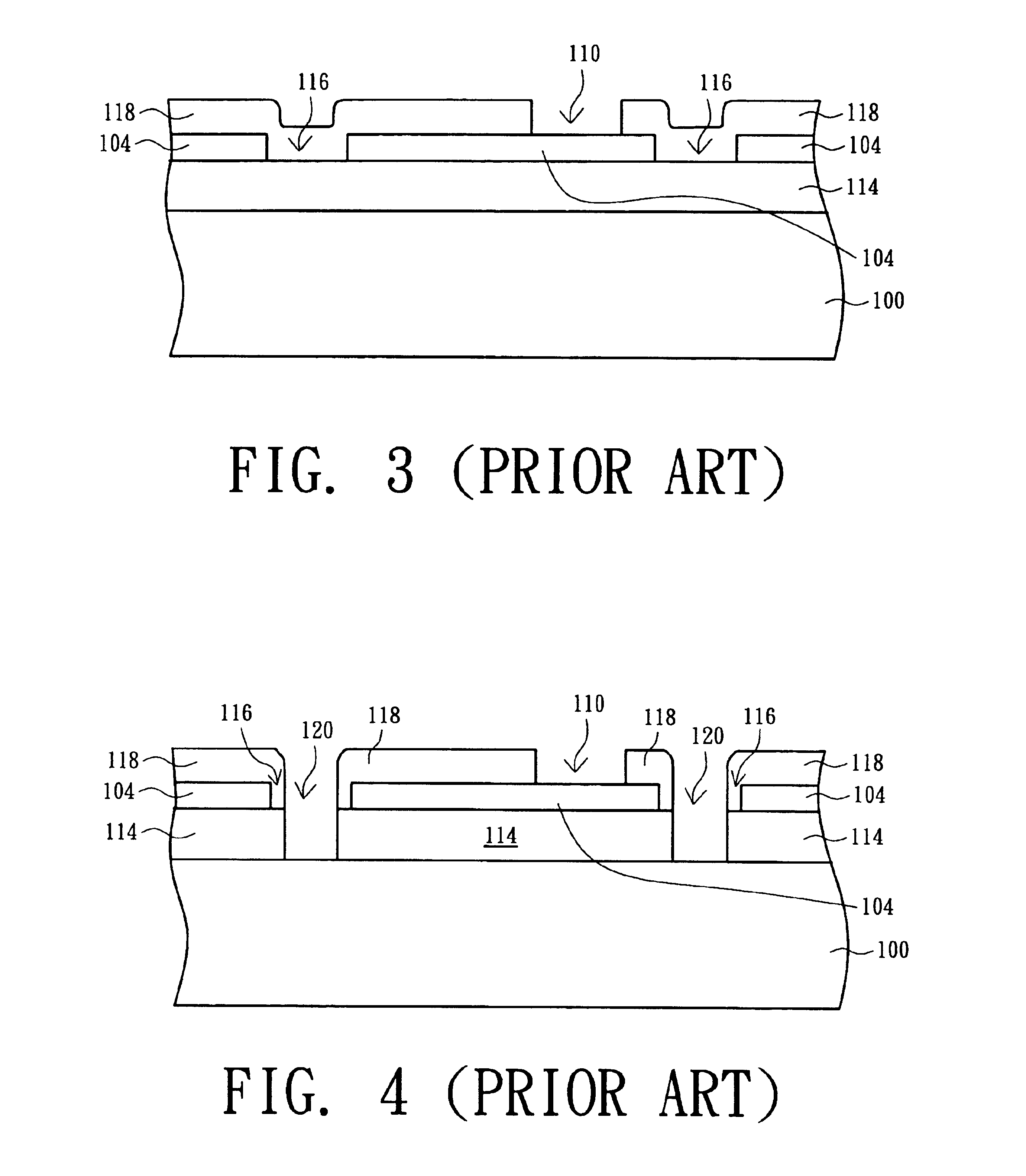

Multi-height FinFETS

InactiveUS6909147B2Raise the ratioReduce yieldTransistorSolid-state devicesElectrical conductorChannel width

The present invention provides a FinFET device that has a first fin and a second fin. Each fin has a channel region and source and drain regions that extend from the channel region. The fins have different heights. The invention has a gate conductor positioned adjacent the fins. The gate conductor runs perpendicular to the fins and crosses the channel region of each of the first fin and second fin. The fins are parallel to one another. The ratio of the height of the first fin to the height of the second fin comprises a ratio of one to 2 / 3. The ratio is used to tune the performance of the transistor and determines the total channel width of the transistor.

Owner:AURIGA INNOVATIONS INC

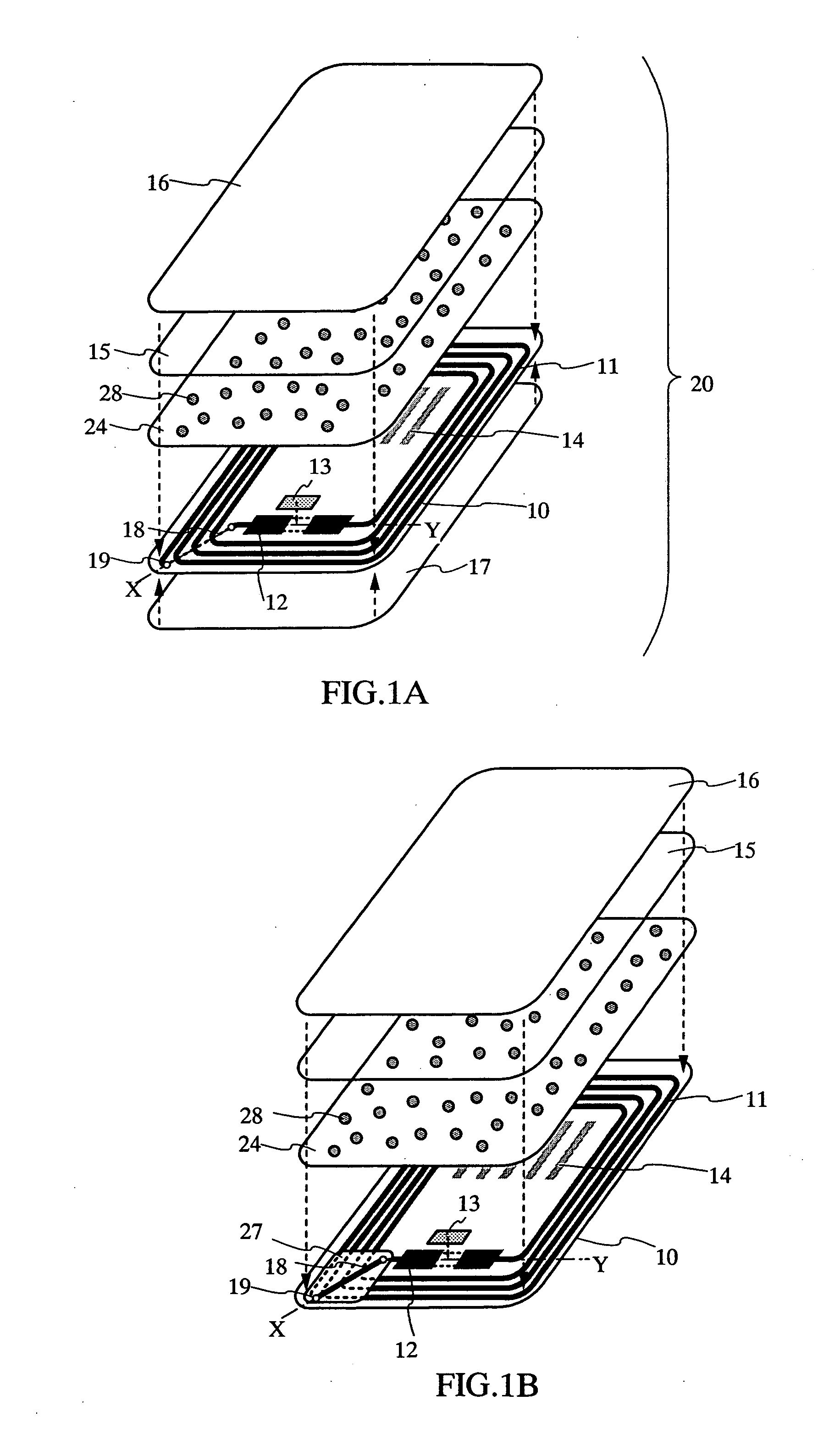

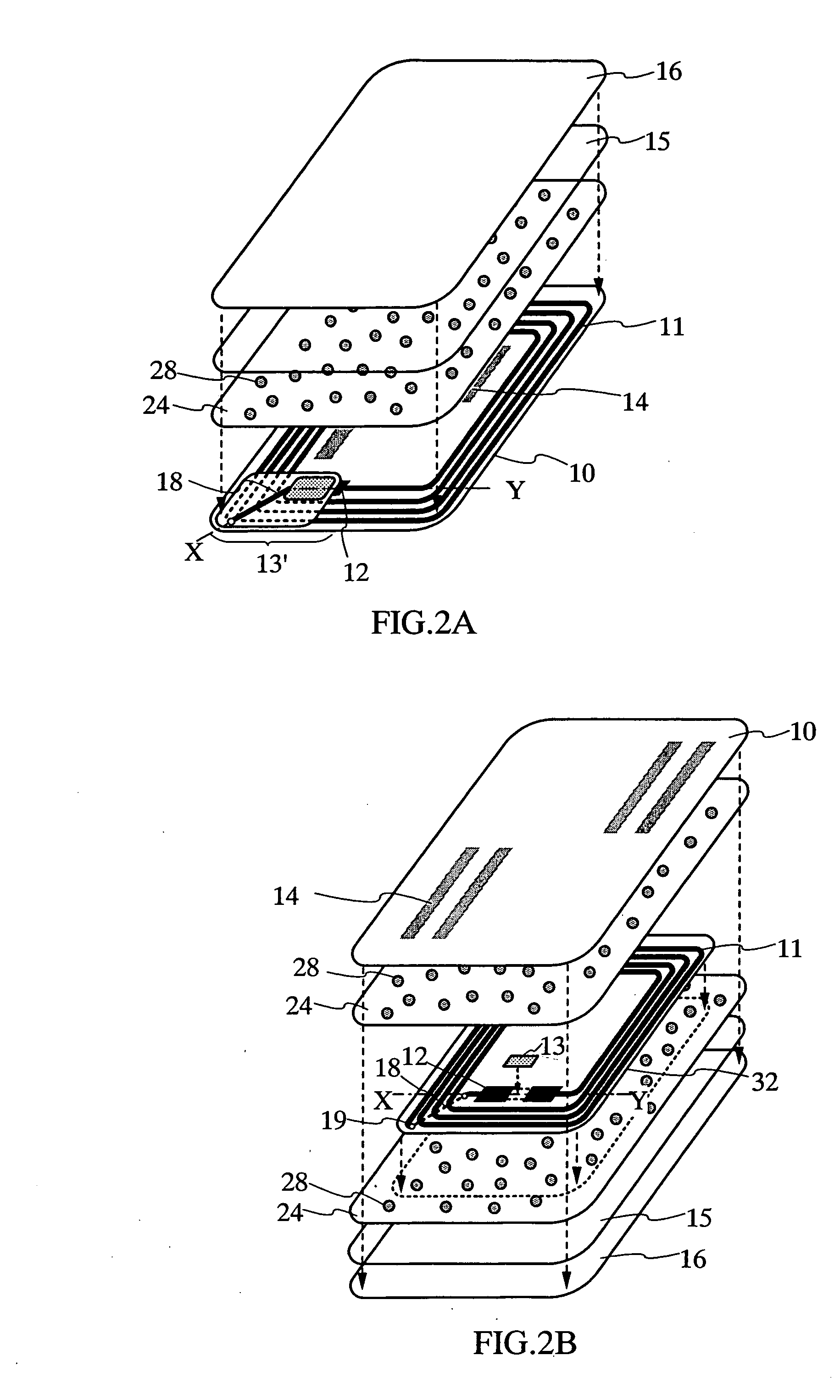

ID label, ID tag, and ID card

InactiveUS20050168339A1Lower Reliability RequirementsReduce yieldRecord carriers used with machinesBurglar alarm by hand-portable articles removalEngineeringThermal expansion

In commercial products to which a non-contact type or contact type ID label or ID tag is attached and ID cards, there is fear that, due to a difference between coefficients of thermal expansion between an antenna for communication and a resin provided around the antenna, stress is applied to the resin with the larger coefficient of thermal expansion to break the resin. This contributes to decrease in manufacturing yield, lifetime, and reliability of an ID label or the like. In an article such as an ID label, an ID tag, and an ID card according to the present invention, a filler is included in a filling layer provided around an antenna forming an ID label, an ID tag, and an ID card so that the difference in coefficient of thermal expansion between the antenna and the filling layer can be reduced. This makes it possible to ease generation of stress due to the difference in coefficient of thermal expansion and prevent peeling and cracks of the filling layer.

Owner:SEMICON ENERGY LAB CO LTD

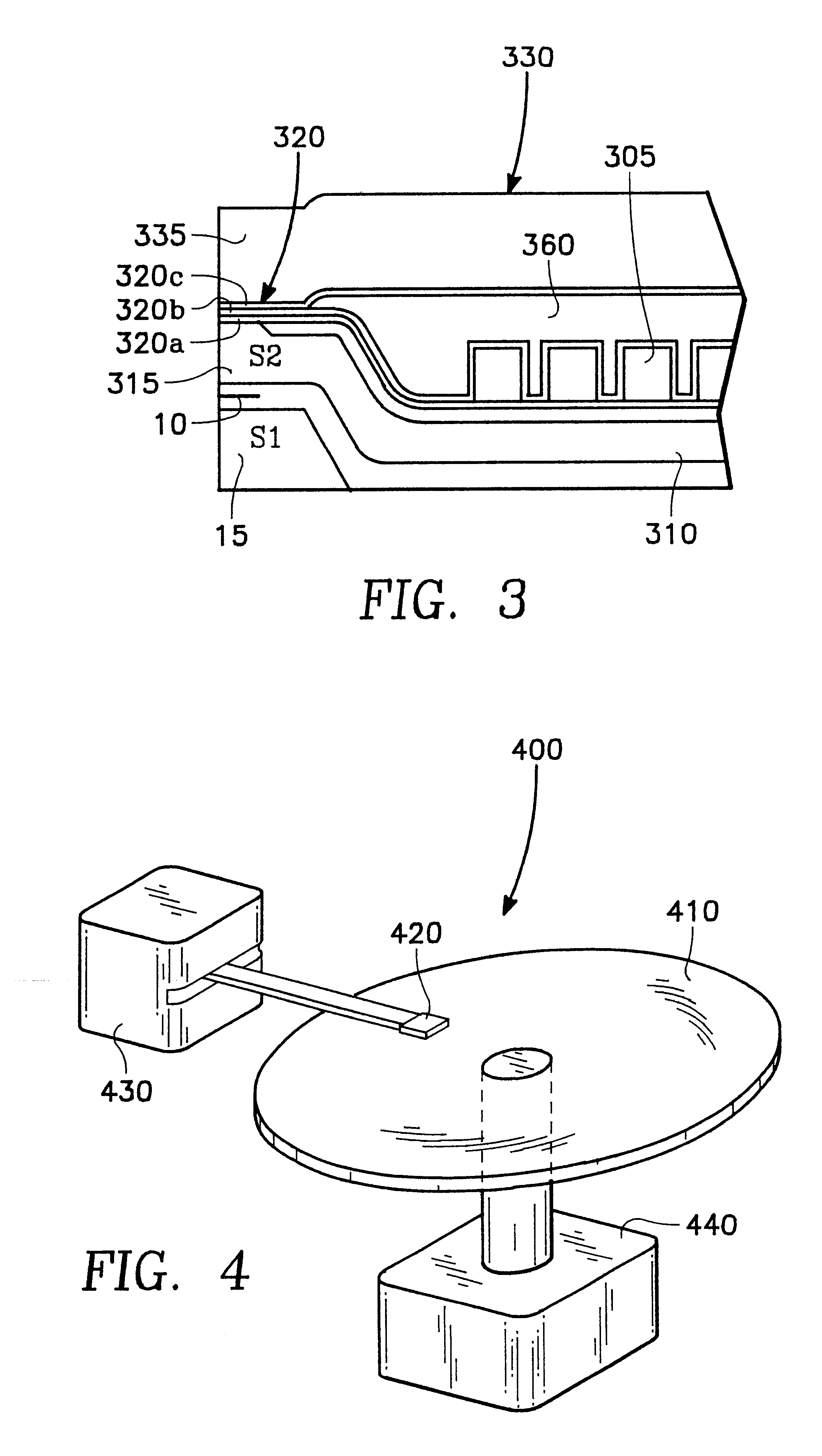

Thin film writer with multiplayer write gap

InactiveUS6724569B1Easy to controlControl performanceConstruction of head windingsManufacture head surfaceElectrical conductorLower pole

Embodiments in accordance with the thin film write head of the present invention have a lower pole structure, an upper pole structure, and a multilayer write gap extending from an air bearing surface between the upper and lower pole structures. In preferred embodiments, the write gap comprises at least two of: (a) a first layer covering a lower pole tip portion of the lower pole structure, (b) a second layer covering turns of a semiconductor winding, or (c) a third layer covering a winding insulation stack. In more preferred embodiments, the write gap is formed of the first, the second, and the third write gap layers. An advantage of a write head with a multilayer write gap is that it allows better control of write gap thickness. As such, loss of write gap thickness can be compensated for by deposition of the second write gap layers, or by deposition of the third write gap layer. Some embodiments have one or more additional advantages in providing increased corrosion prevention, improving the integrity of conductor insulation, and / or improving the top pole magnetic material characteristics.

Owner:WESTERN DIGITAL TECH INC

Method for manufacturing reflective spatial light modulator mirror devices

InactiveUS6841081B2Increased process reliabilityHigh yieldSemiconductor/solid-state device manufacturingOptical articlesSpatial light modulatorUltimate tensile strength

A method for manufacturing reflective spatial light modulator mirror devices is disclosed. In the method, a portion of a mirror layer and a first sacrificial layer beneath the portion of the mirror layer are removed simultaneously to expose the substrate while defining a pattern of the mirror layer. Then, a second sacrificial layer is deposited conformally, and substrate contact openings and a mirror layer contact opening are defined in the second sacrificial layer at the same time. Subsequently, a support material layer is deposited conformally and etched back, so as to form supporting posts of the mirror layer in the substrate contact openings. Before the support material layer is etched back, the substrate contact openings can be filled with a photoresist material first, so as to maintain the support material layer in the substrate contact openings and increase the structural intensity of the supporting posts.

Owner:TAIWAN SEMICON MFG CO LTD

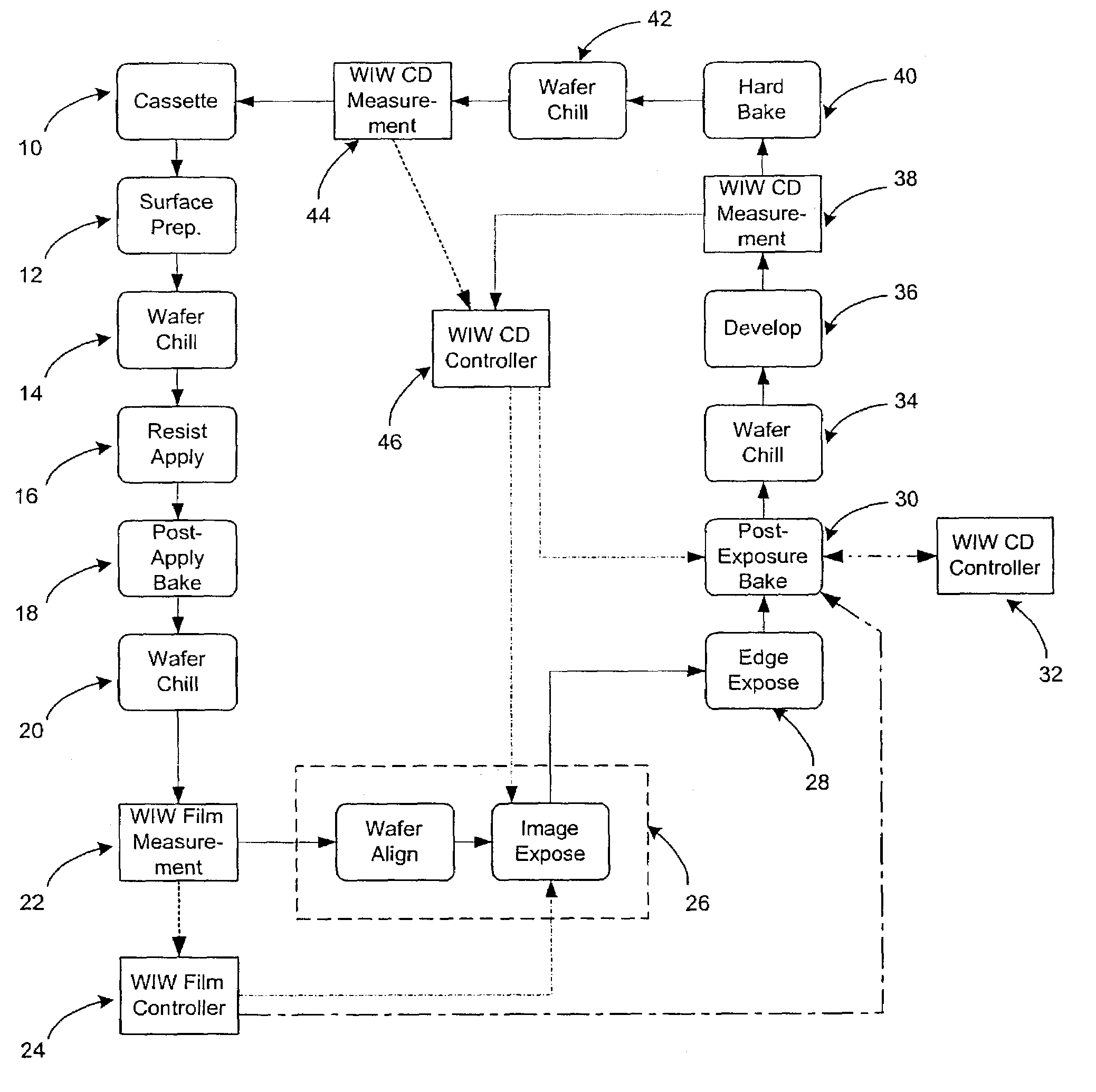

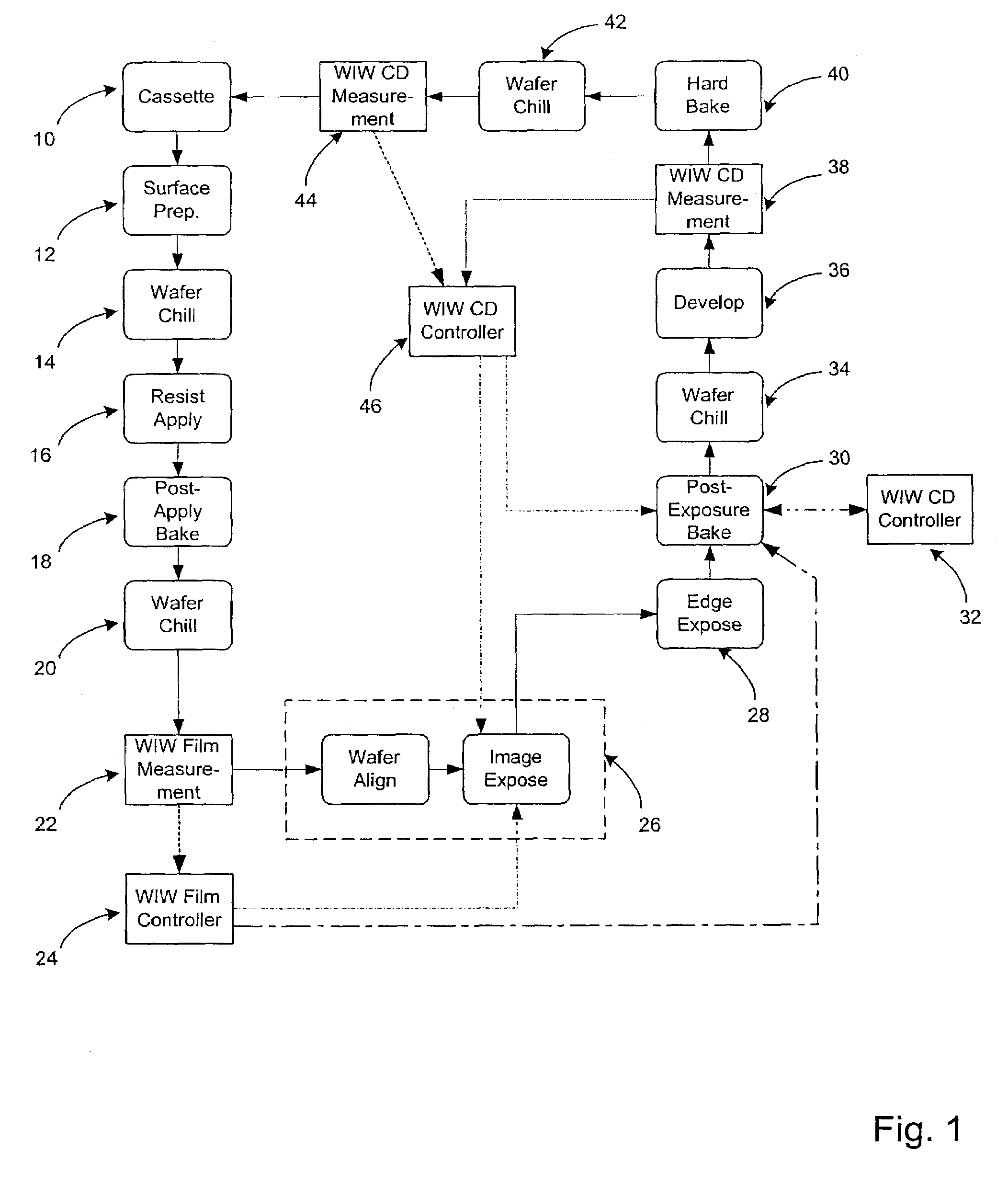

Methods and systems for lithography process control

InactiveUS6987572B2High performance bin distributionReduce yieldSemiconductor/solid-state device testing/measurementSolid-state devicesLithography processProcess module

Methods and systems for evaluating and controlling a lithography process are provided. For example, a method for reducing within wafer variation of a critical metric of a lithography process may include measuring at least one property of a resist disposed upon a wafer during the lithography process. A critical metric of a lithography process may include, but may not be limited to, a critical dimension of a feature formed during the lithography process. The method may also include altering at least one parameter of a process module configured to perform a step of the lithography process to reduce within wafer variation of the critical metric. The parameter of the process module may be altered in response to at least the one measured property of the resist.

Owner:KLA TENCOR TECH CORP

Quarter wave plate comprising two optically anisotropic layers

InactiveUS6593984B2Reduce yieldEasy to preparePolarising elementsNon-linear opticsOptical propertyLength wave

A circularly polarizing plate comprises a linearly polarizing membrane and a quarter wave plate. The quarter wave plate comprises an optically anisotropic layer A and an optically anisotropic layer B. The quarter wave plate has such an optical characteristic that a retardation value essentially is a quarter of a wavelength when the retardation value is measured at the wavelength of 450 nm, 550 nm and 650 nm. One of the optically anisotropic layers A and B is a layer made from liquid crystal molecules, and the other is a polymer film or a layer made from liquid crystal molecules.

Owner:FUJIFILM CORP

Hydrogenation process for hydrocarbon resins

InactiveUS20030150778A1Improve productivityIncrease volumePreparation by oxo-reaction and reductionCatalyst activation/preparationProduction rateHalogen

This invention provides a process for hydrotreating hydrocarbon resins, which process comprises contacting a feedstock comprising a hydrocarbon resin or rosin, under suitable hydrotreating conditions, with a bulk multimetallic catalyst comprised of at least one Group VIII non-noble metal and at least two Group VIB metals and wherein the ratio of Group VIB metal to Group VIII non-noble metal is from about 10:1 to about 1:10. The process accord invention can achieve increased hydrocarbon resin productivity through increase in throughput volumes and effective catalyst lifetimes. The process of the invention is desirably practiced with a bulk catalyst consisting of only the combination of the metal species with the active metal components. The absence of carrier substrates largely removes the possibility of halogen accumulation on substrate surfaces that, in turn, can acidify metal catalysts such that additional, progressive cracking of the hydrocarbon resin molecules occurs.

Owner:EXXONMOBIL CHEM PAT INC

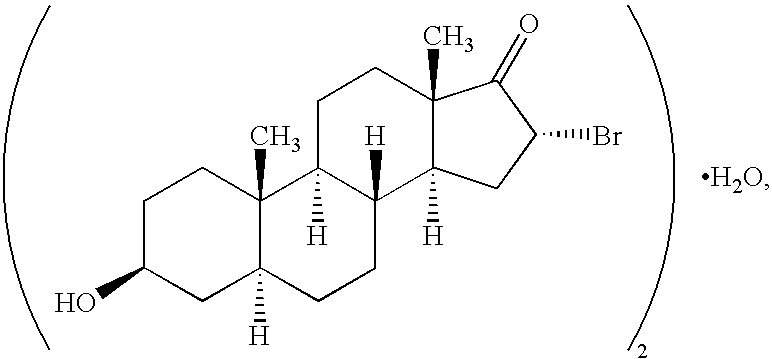

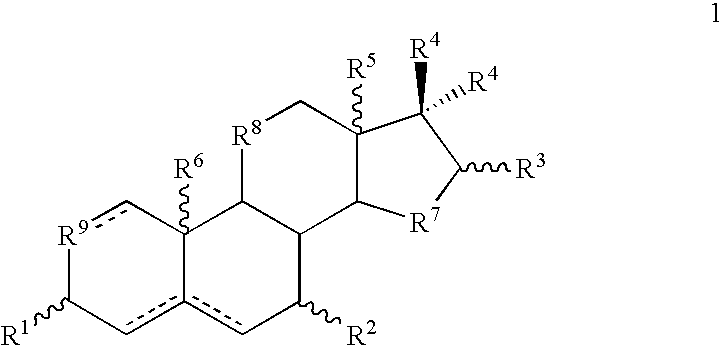

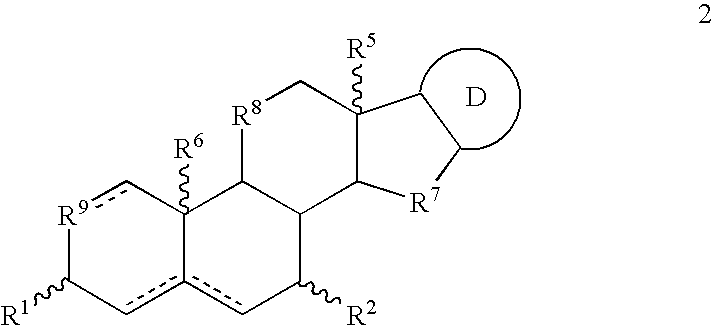

Pharmaceutical compositions and treatment methods

InactiveUS6667299B1Efficient transportReduce yieldAntibacterial agentsOrganic active ingredientsRegimenKetone

The invention provides compositions comprising, 16alpha-bromo-3beta-hydroxy-5alpha-androstan-17-one hemihydrate and one or more excipients, typically wherein the composition comprises less than about 3% water. The compositions are useful to make improved pharmaceutical formulations. The invention also provides methods of intermittent dosing of steroid compounds such as analogs of 16alpha-bromo-3beta-hydroxy-5alpha-androstan-17-one and compositions useful in such dosing regimens. The invention further provides compositions and methods to inhibit pathogen (viral) replication, ameliorate symptoms associated with immune dysregulation and to modulate immune responses in a subject using certain steroids and steroid analogs. The invention also provides methods to make and use these immunomodulatory compositions and formulations.

Owner:NEURMEDIX +2

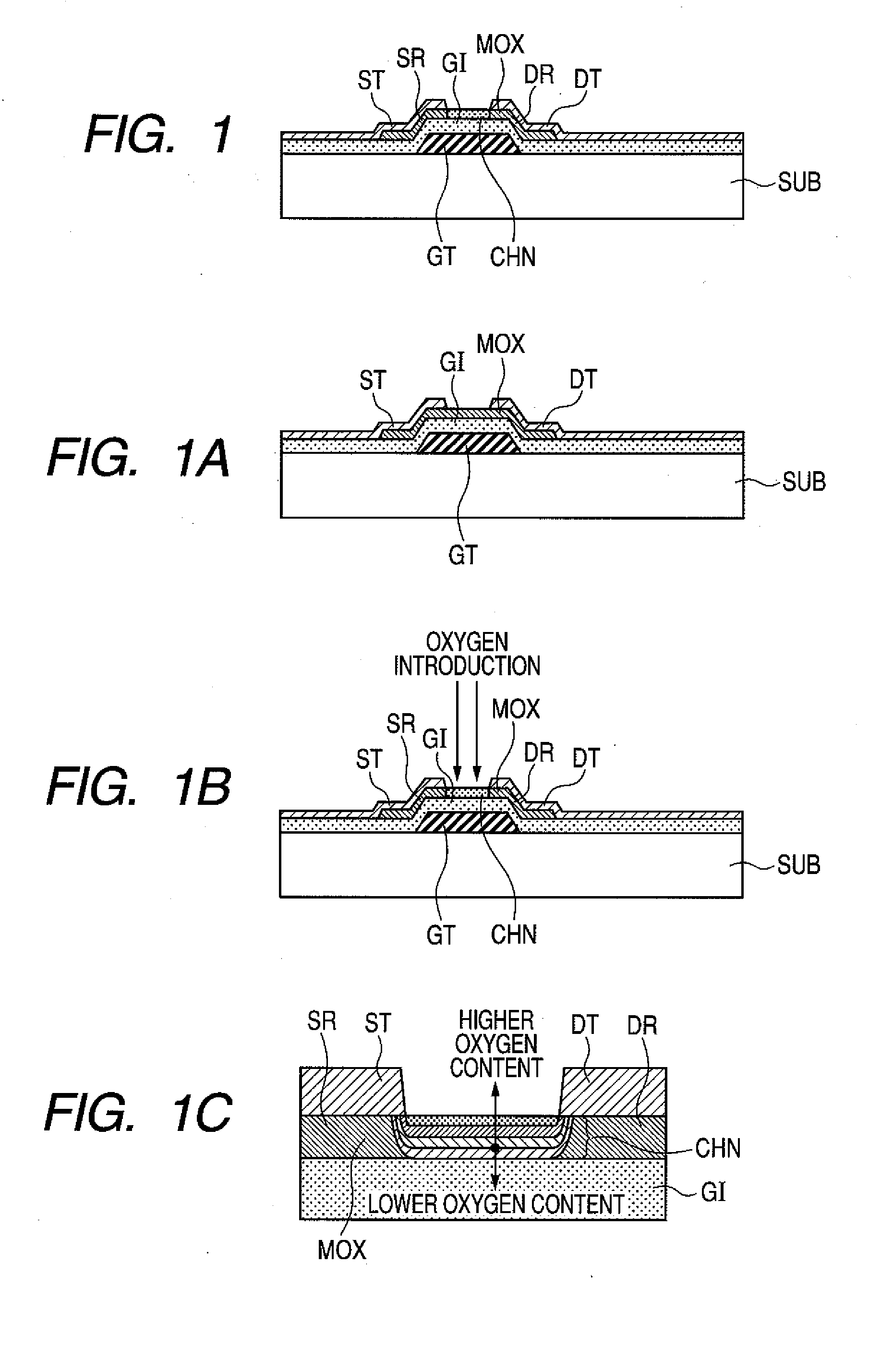

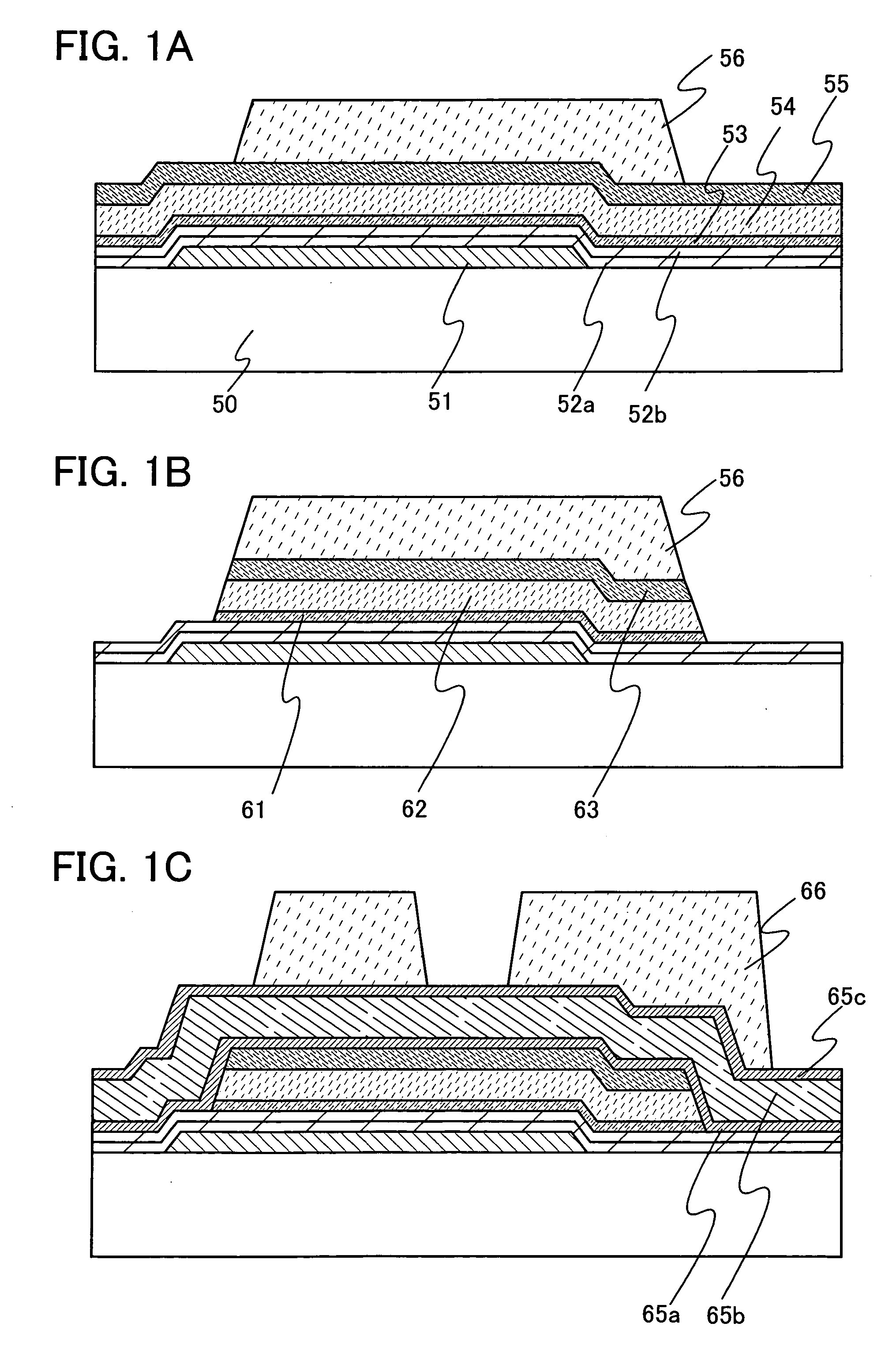

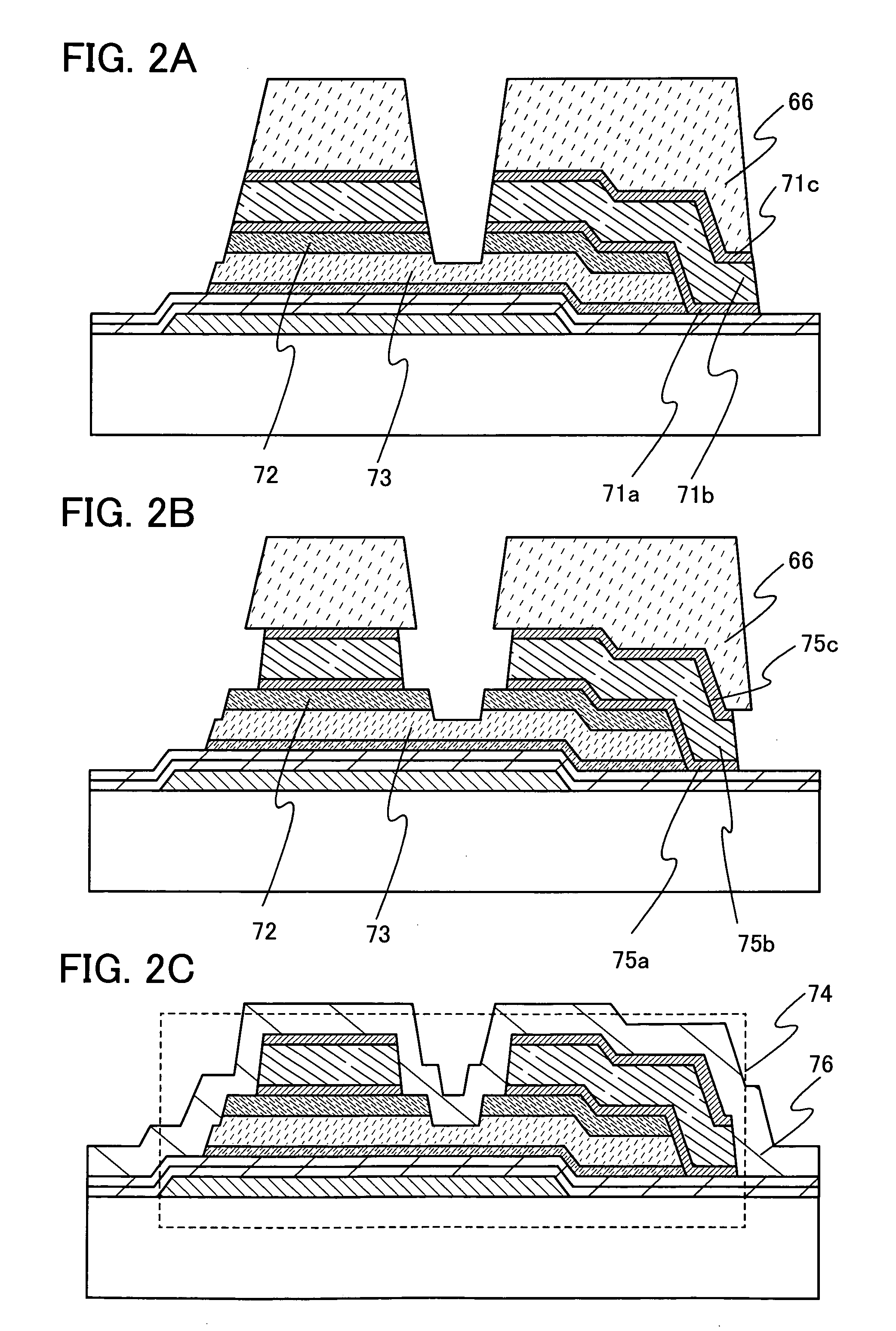

Liquid crystal display device

InactiveUS20090002591A1Improve batch productivityHighly reliable electric characteristicSemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayEngineering

An object is to propose a method of manufacturing, with high mass productivity, liquid crystal display devices having thin film transistors with highly reliable electric characteristics. In a liquid crystal display device having an inverted staggered thin film transistor, the inverted staggered thin film transistor is formed as follows: a gate insulating film is formed over a gate electrode; a microcrystalline semiconductor film which functions as a channel formation region is formed over the gate insulating film; a buffer layer is formed over the microcrystalline semiconductor film; a pair of source and drain regions are formed over the buffer layer; and a pair of source and drain electrodes are formed in contact with the source and drain regions so as to expose a part of the source and drain regions.

Owner:SEMICON ENERGY LAB CO LTD

Method for fabricating semiconductor device

ActiveUS20090162993A1Small sizeLower manufacturing yieldSemiconductor/solid-state device manufacturingFine working devicesSemiconductorSemiconductor device

An object is to provide a technology capable of improving a manufacturing yield of semiconductor devices by preventing scattering of irregular-shaped scraps formed at the time of dicing. To achieve the above object, for dicing lines, by which an irregular-shaped outer periphery may possibly be cut off, among a plurality of dicing lines, formation of the dicing lines starts from an outside of a semiconductor wafer, and after the semiconductor wafer is cut off partway, formation of the dicing lines is ended before reaching the irregular-shaped outer periphery formed on a outer periphery of the semiconductor wafer. For other dicing lines, formation of the dicing lines starts from the outside of the semiconductor wafer, and after the semiconductor wafer is cut off, is ended outside the semiconductor wafer.

Owner:RENESAS ELECTRONICS CORP

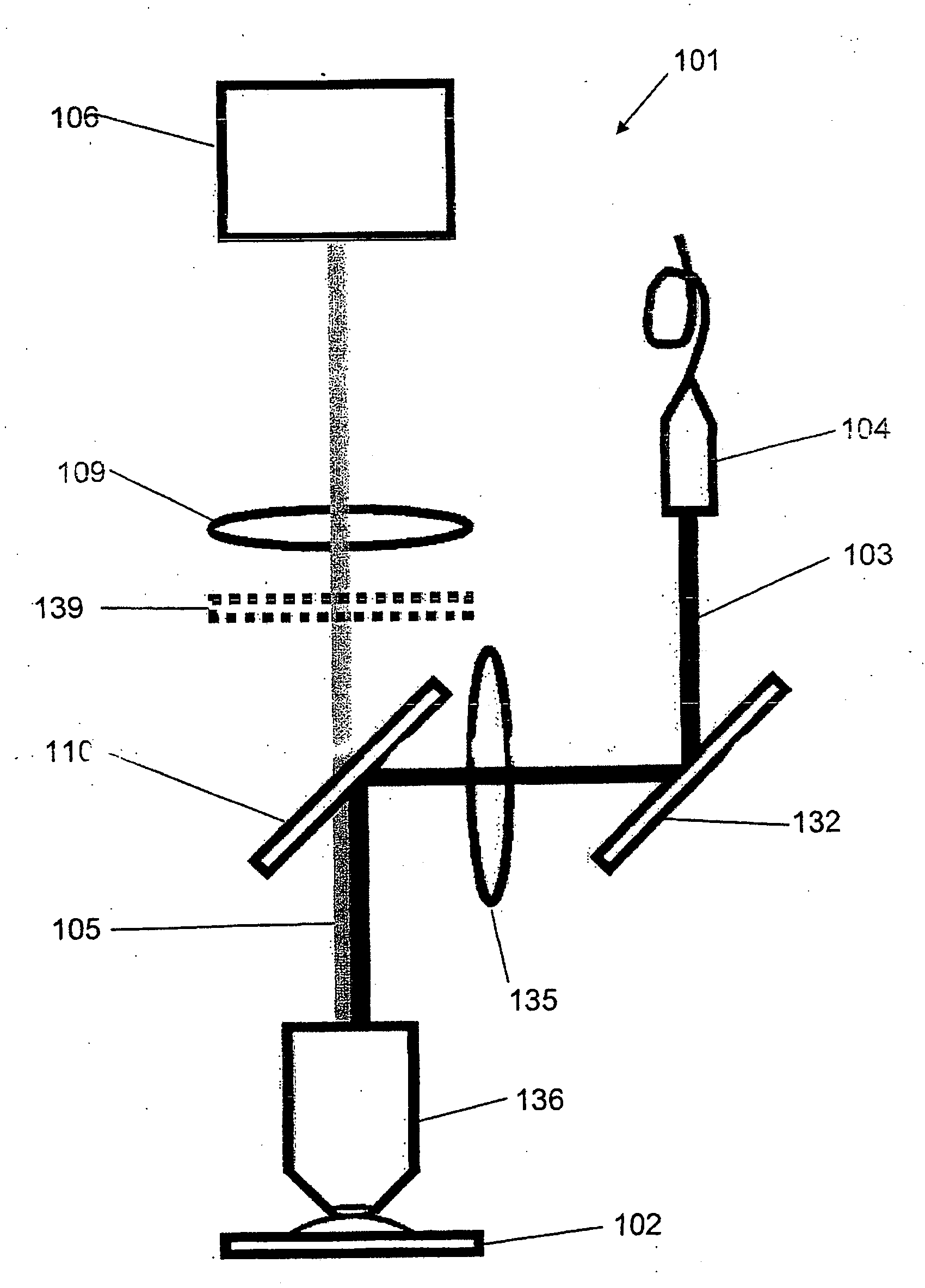

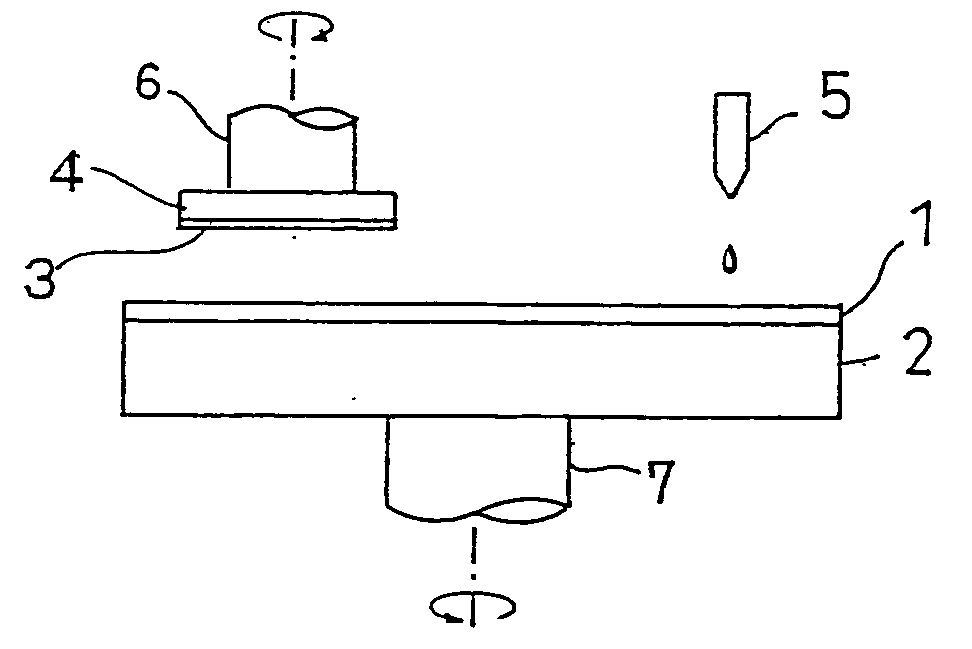

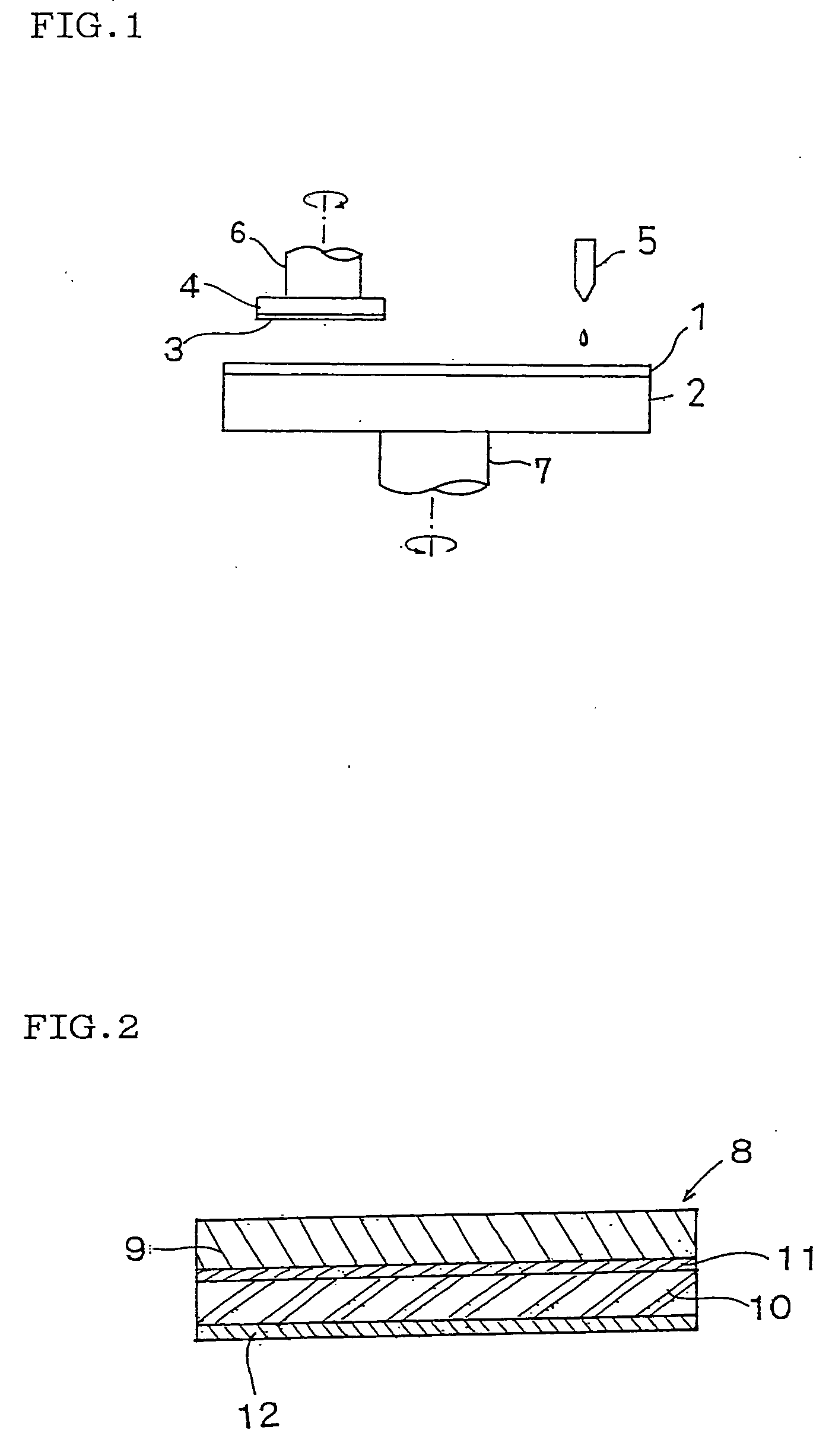

High spatial resolution imaging of a structure of interest in a specimen

ActiveUS20090134342A1Reduces yield of fluorescent lightHigh resolutionMicrobiological testing/measurementPreparing sample for investigationSensor arrayFluorescence

For the high spatial resolution imaging of a structure of interest in a specimen, a substance is selected from a group of substances which have a fluorescent first state and a nonfluorescent second state; which can be converted fractionally from their first state into their second state by light which excites them into fluorescence, and which return from their second state into their first state; the specimen's structure of interest is imaged onto a sensor array, a spatial resolution limit of the imaging being greater (i.e. worse) than an average spacing between closest neighboring molecules of the substance in the specimen; the specimen is exposed to light in a region which has dimensions larger than the spatial resolution limit, fractions of the substance alternately being excited by the light to emit fluorescent light and converted into their second state, and at least 10% of the molecules of the substance that are respectively in the first state lying at a distance from their closest neighboring molecules in the first state which is greater than the spatial resolution limit; and the fluorescent light, which is spontaneously emitted by the substance from the region, is registered in a plurality of images recorded by the sensor array during continued exposure of the specimen to the light.

Owner:MAX PLANCK GESELLSCHAFT ZUR FOERDERUNG DER WISSENSCHAFTEN EV

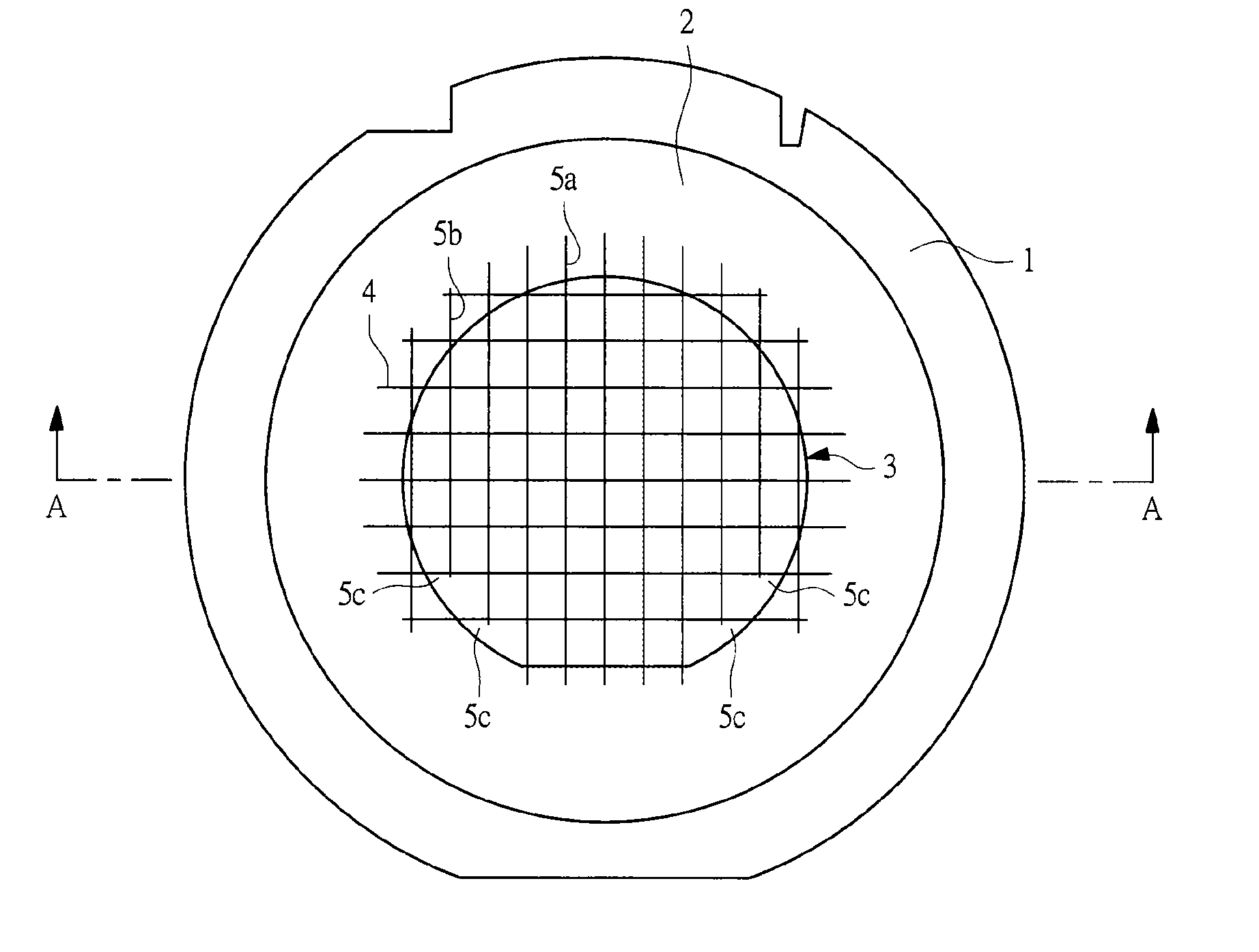

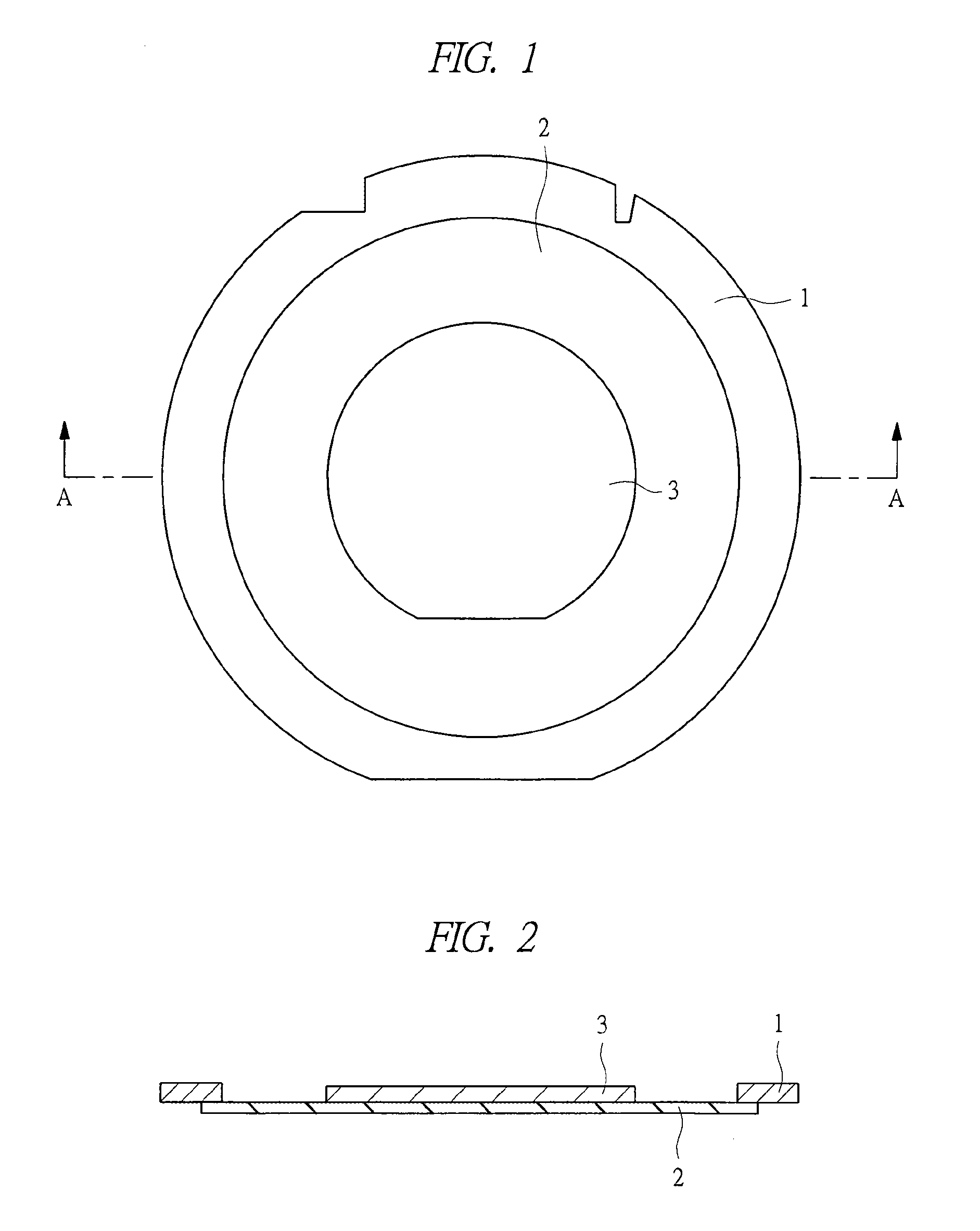

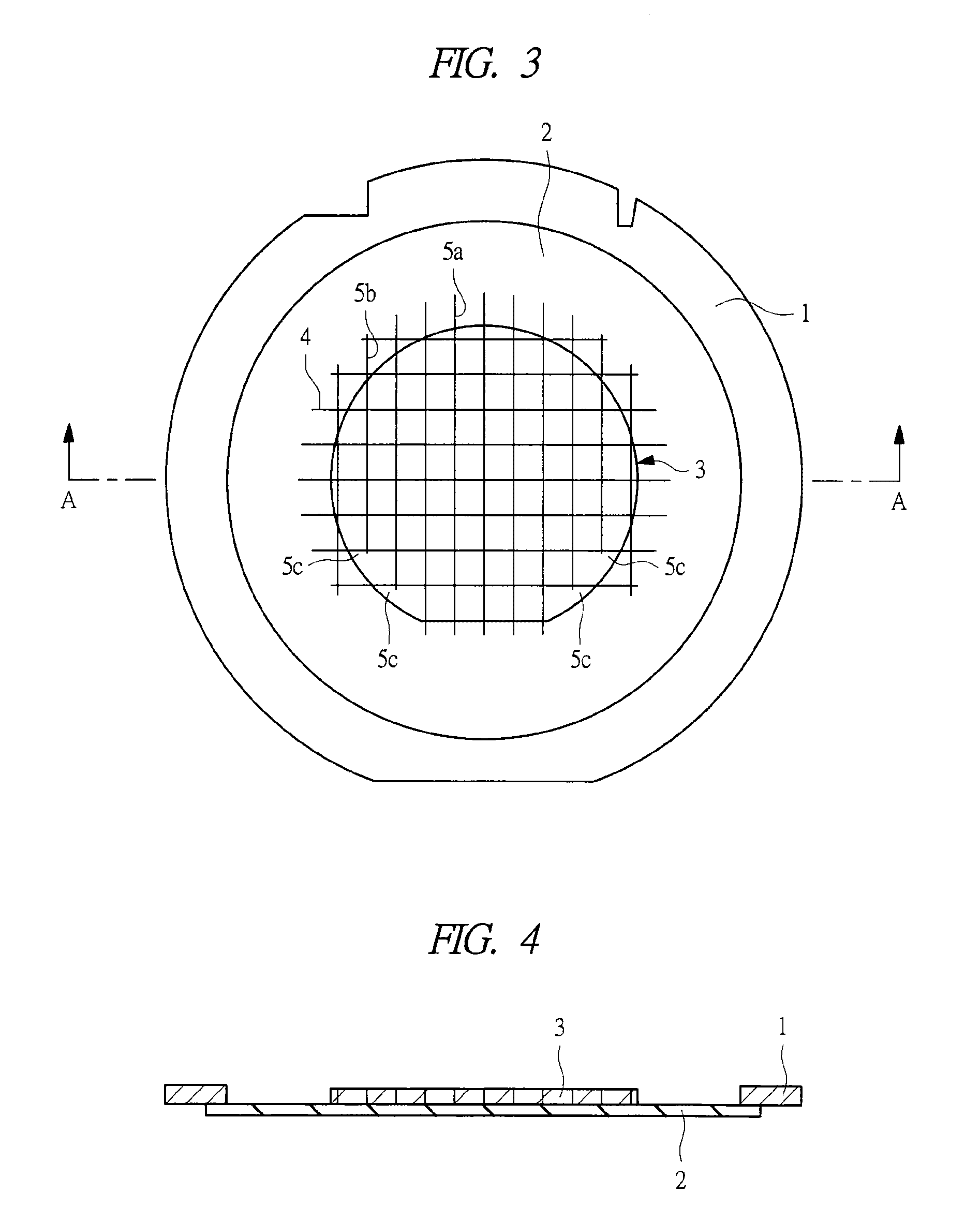

Grinding pad and method of producing the same

InactiveUS20050064709A1Reduce rateReduce hardnessLayered productsAbrasion apparatusAluminum substrateSemiconductor

The invention provides a polishing pad by which optical materials such as lenses, reflecting mirrors etc., or materials requiring a high degree of surface planarity, as in the polishing of silicone wafers, glass substrates or aluminum substrates for hard disks, or general metal polishing, can be flattened with stability and high polishing efficiency. The invention also provides a polishing pad for semiconductor wafers, which is superior in planarizing characteristic, is free from scratches and can be produced at low cost. There is provided a polishing pad which is free from dechucking error so that neither damage to wafers nor decrease in operating efficiency occurs. There is provided a polishing pad which is satisfactory in planarity, within wafer uniformity, and polishing rate and produces less change in polishing rate. There is provided a polishing pad which can make planarity improvement and scratch decrease compatible.

Owner:ROHM & HAAS ELECTRONICS MATERIALS CMP HLDG INC

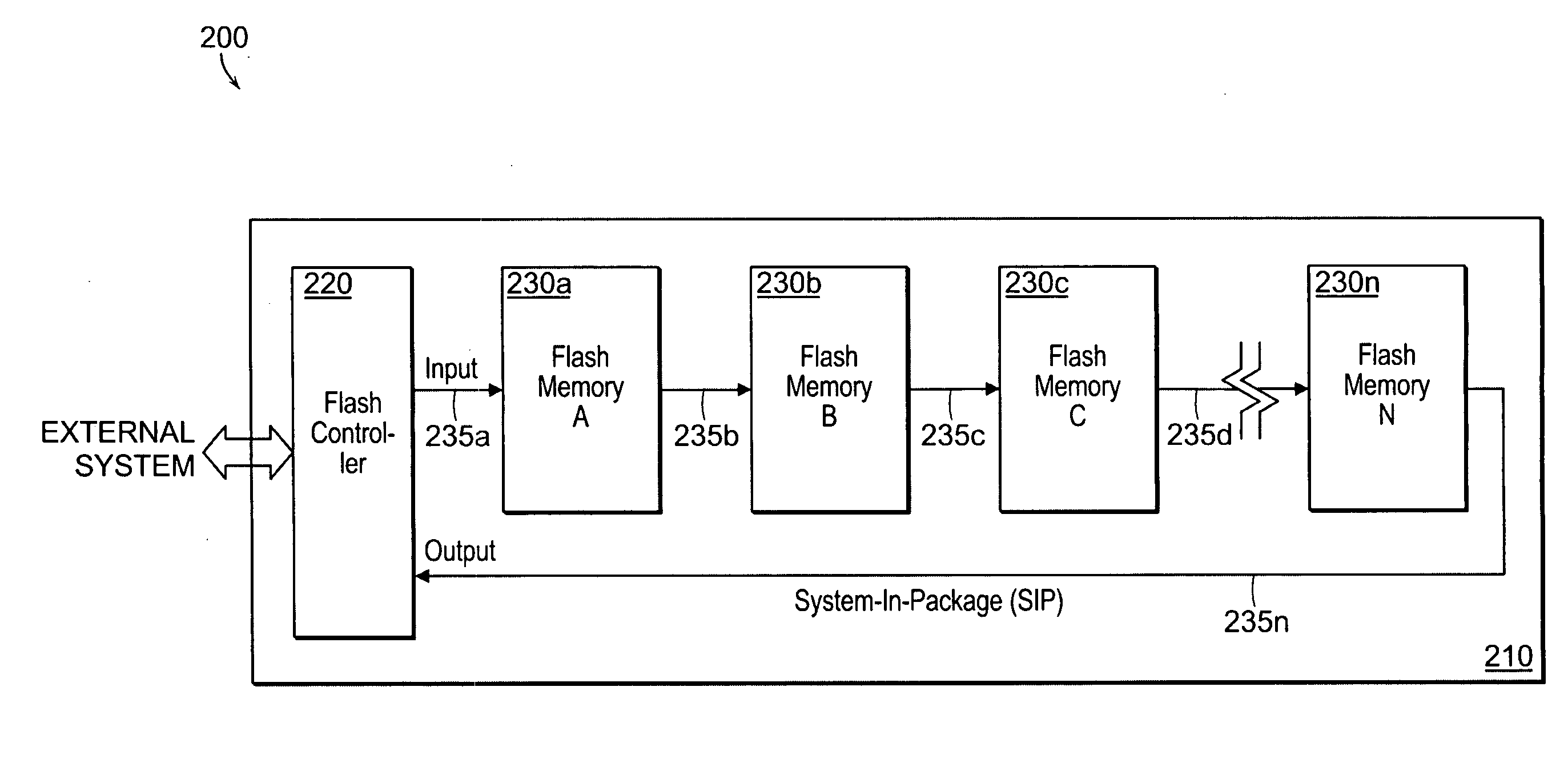

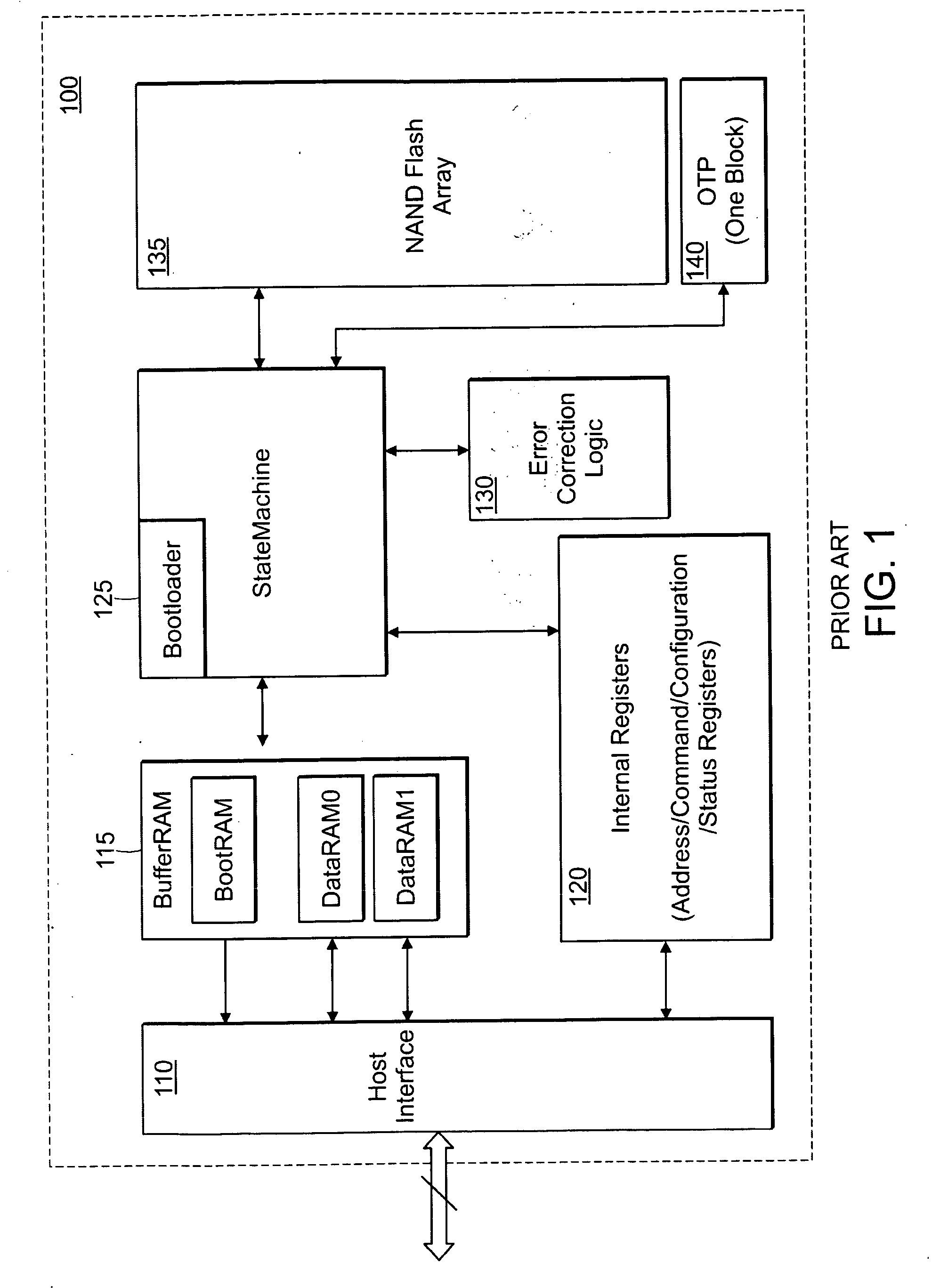

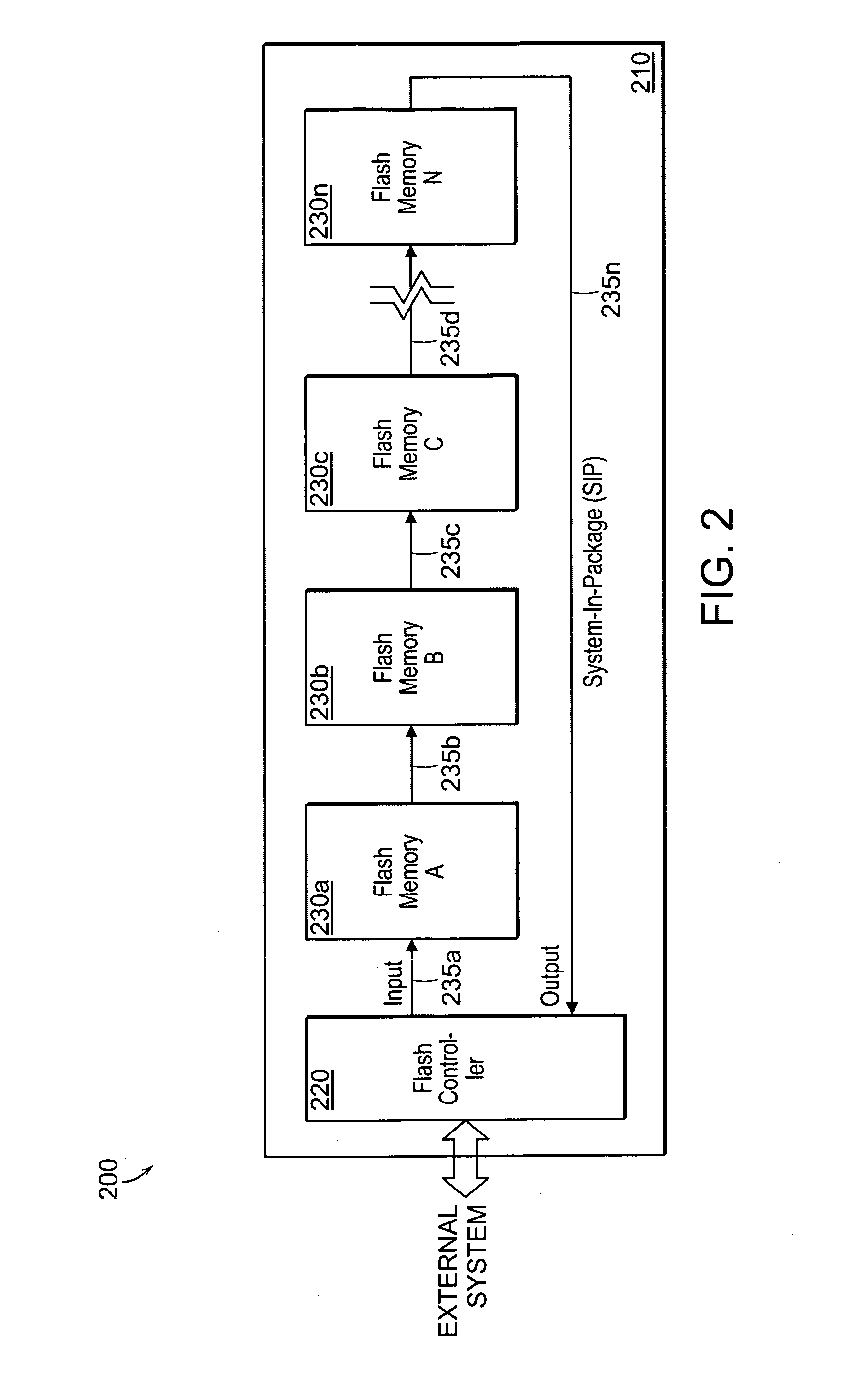

Nonvolatile memory system

InactiveUS20070165457A1Increase memory capacitySignificant overheadSolid-state devicesRead-only memoriesDaisy chainFlash memory controller

A Flash memory system is implemented in a system-in-package (SIP) enclosure, the system comprising a Flash memory controller and a plurality Flash memory devices. An SIP relates to a single package or module comprising a number of integrated circuits (chips). The Flash memory controller is configured to interface with an external system and a plurality of memory devices within the SIP. The memory devices are configured in a daisy chain cascade arrangement, controlled by the Flash memory controller through commands transmitted through the daisy chain cascade.

Owner:CONVERSANT INTPROP MANAGEMENT INC

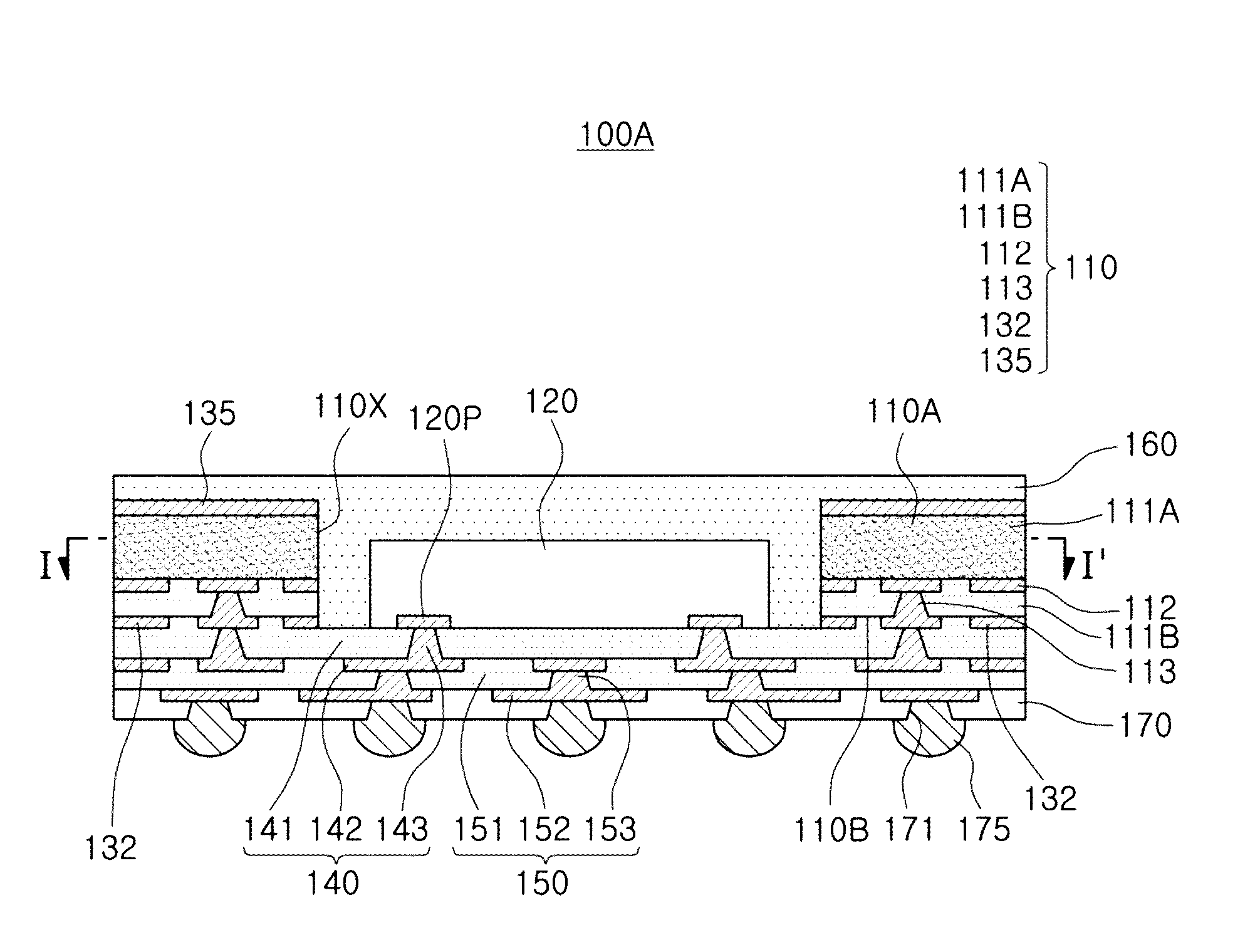

Electronic component package and method of manufacturing the same

ActiveUS20160338202A1Reduce yieldPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringElectronic component

An electronic component package and a method of manufacturing the same are provided. The electronic component package includes a frame having a through-hole, an electronic component disposed in the through-hole of the frame, and a redistribution part disposed at one side of the frame and the electronic component. One or more first wiring layers of the frame are electrically connected to the electronic component through the redistribution part.

Owner:SAMSUNG ELECTRONICS CO LTD

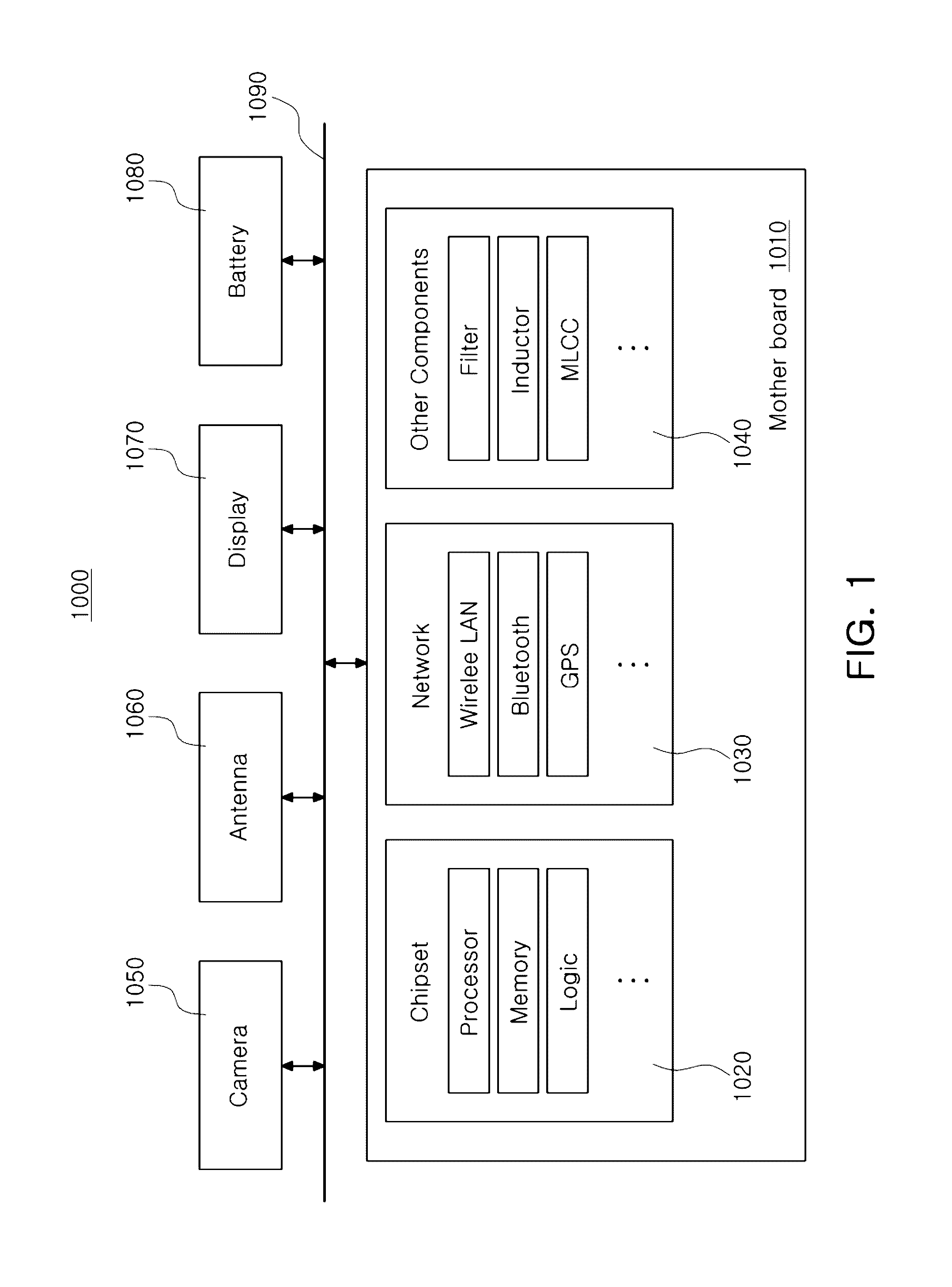

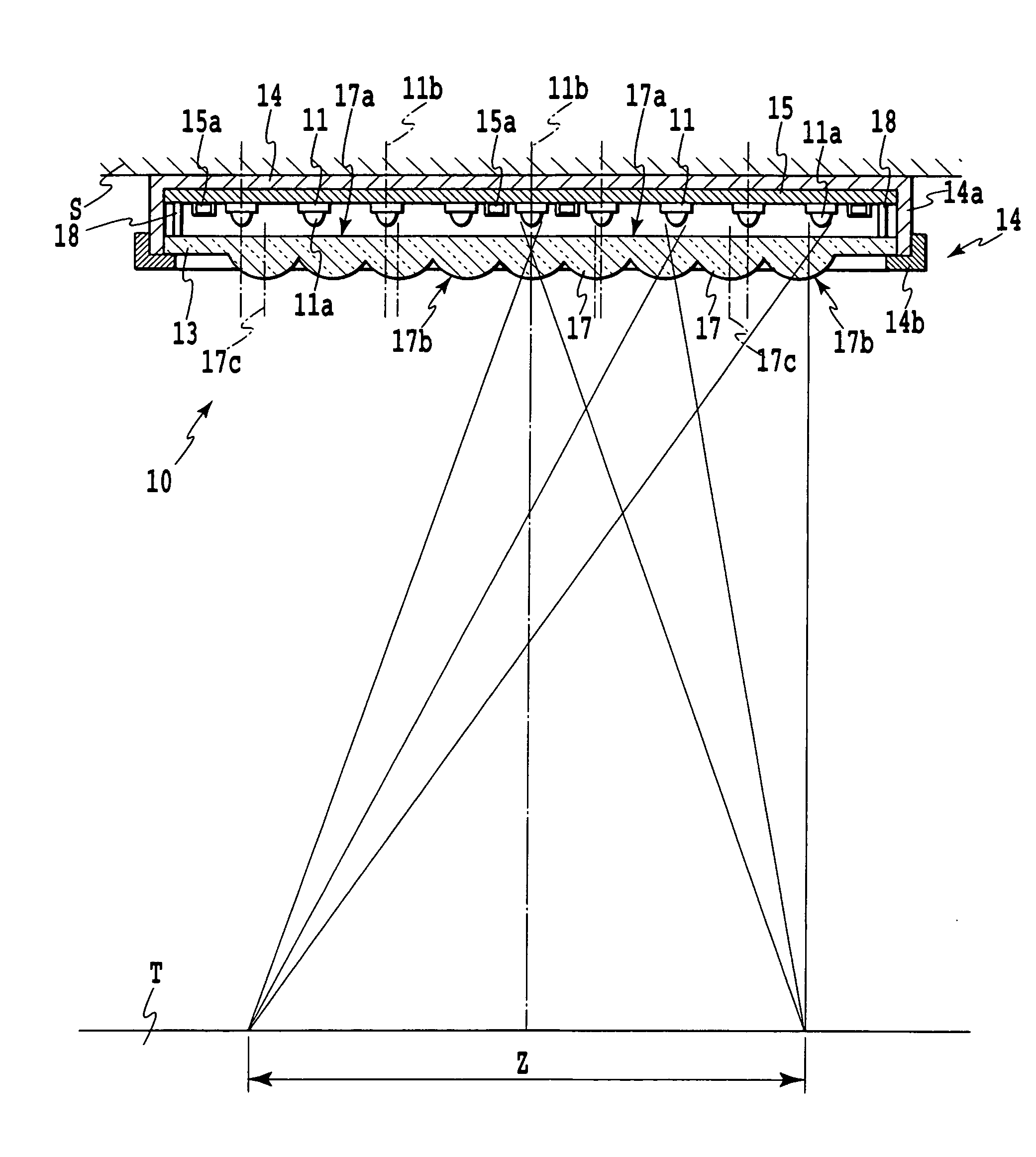

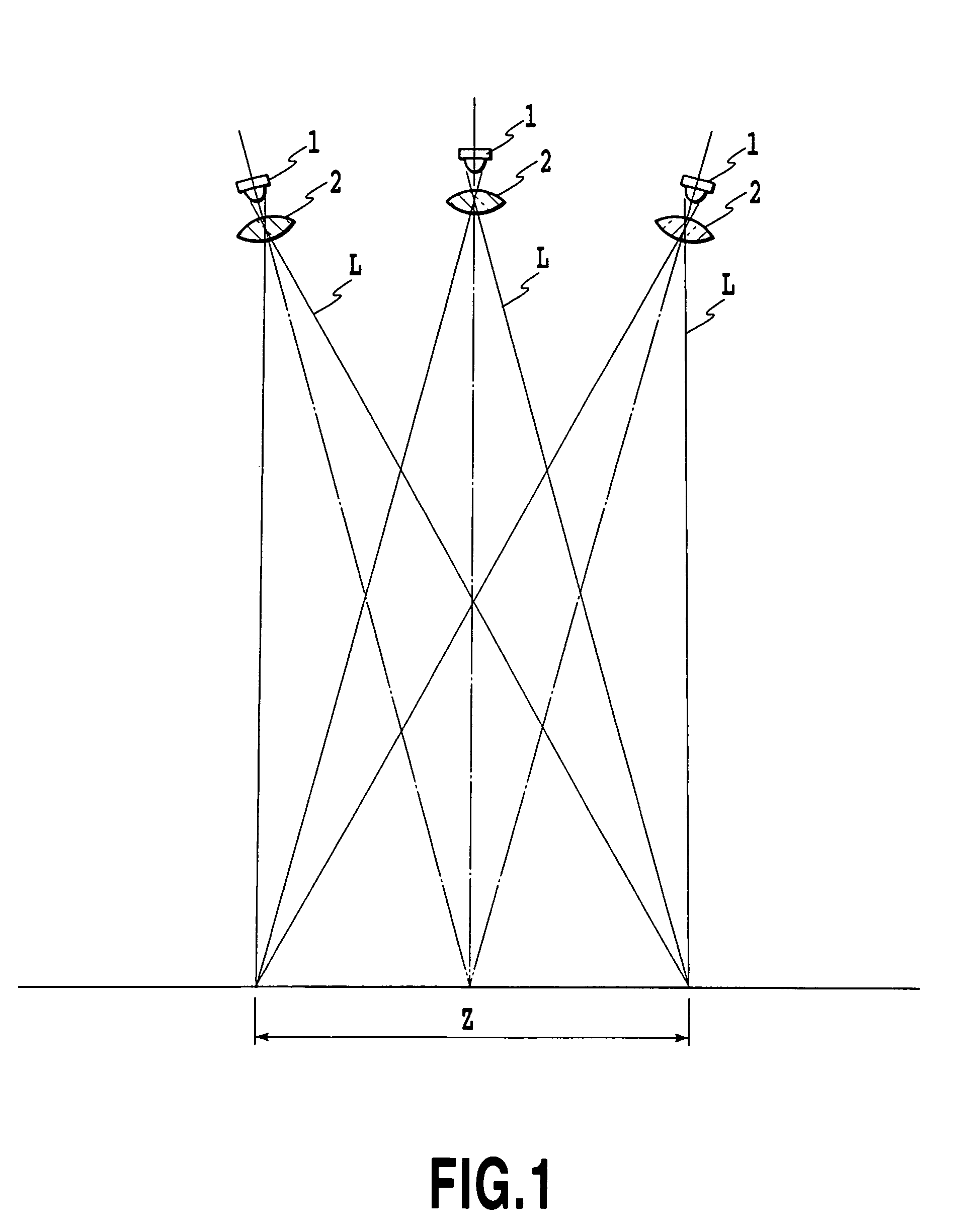

Lighting system

InactiveUS20080084693A1Facilitate cleaningQuick and easyPlanar light sourcesMechanical apparatusLighting systemEngineering

The lighting system according to the present invention includes an electrical wiring substrate in which a connector to a power source is formed, a plurality of LED chips mounted in a predetermined array pattern on the electrical wiring substrate, a deflection lens array disposed in proximity to the LED chips between the LED chip and the predetermined illumination region and a housing for receiving the electrical wiring substrate and the deflection lens array. A plurality of deflection lenses are integrally molded in the deflection lens array to lead lights from the LED chips to the predetermined illumination region in a state where the lights from the LED chips are superposed with each other. The lights emitted from the LED chips are collected in a state where they all are superposed in a common, single illumination region through the deflection lenses.

Owner:YANCHERS CORP

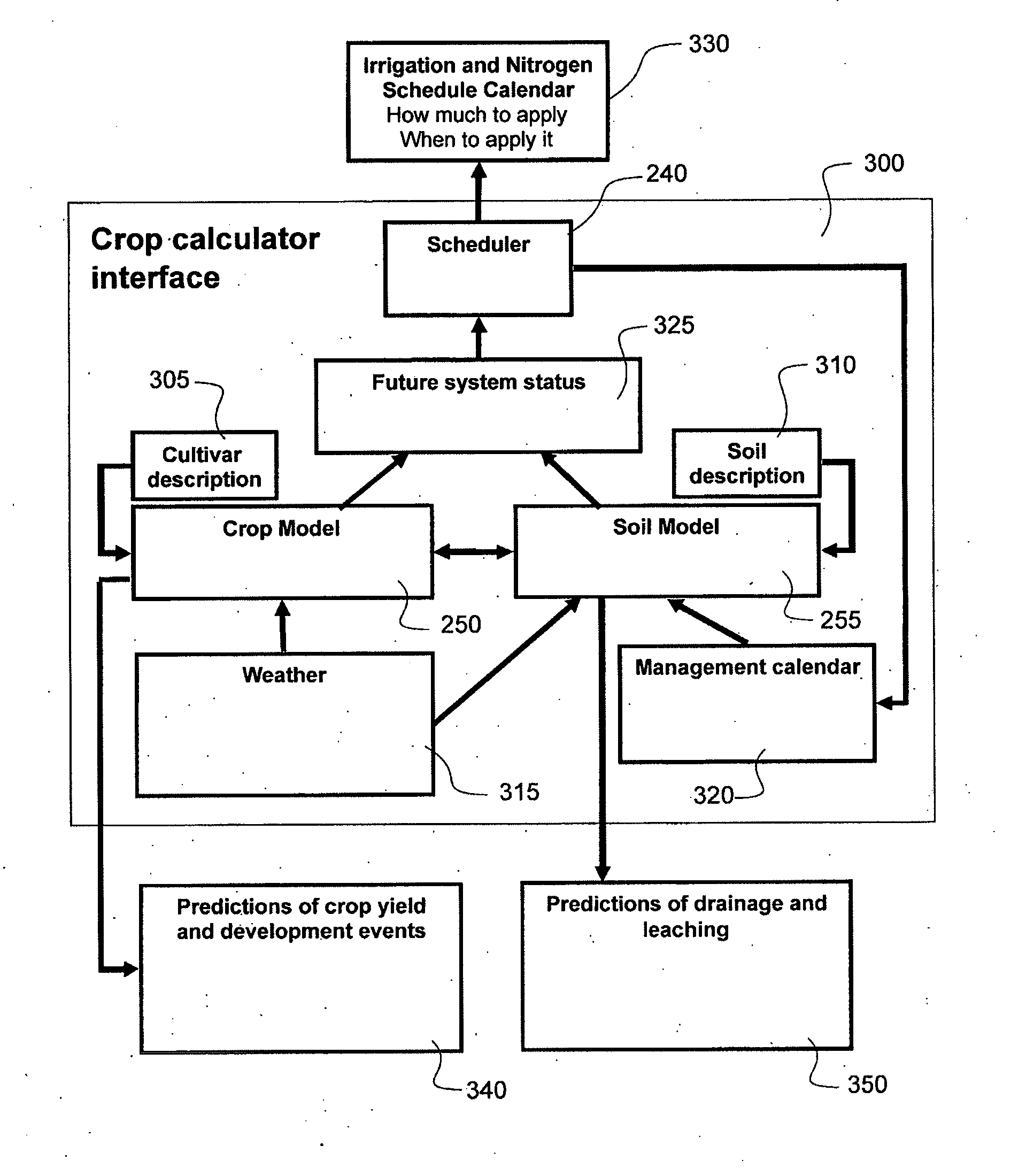

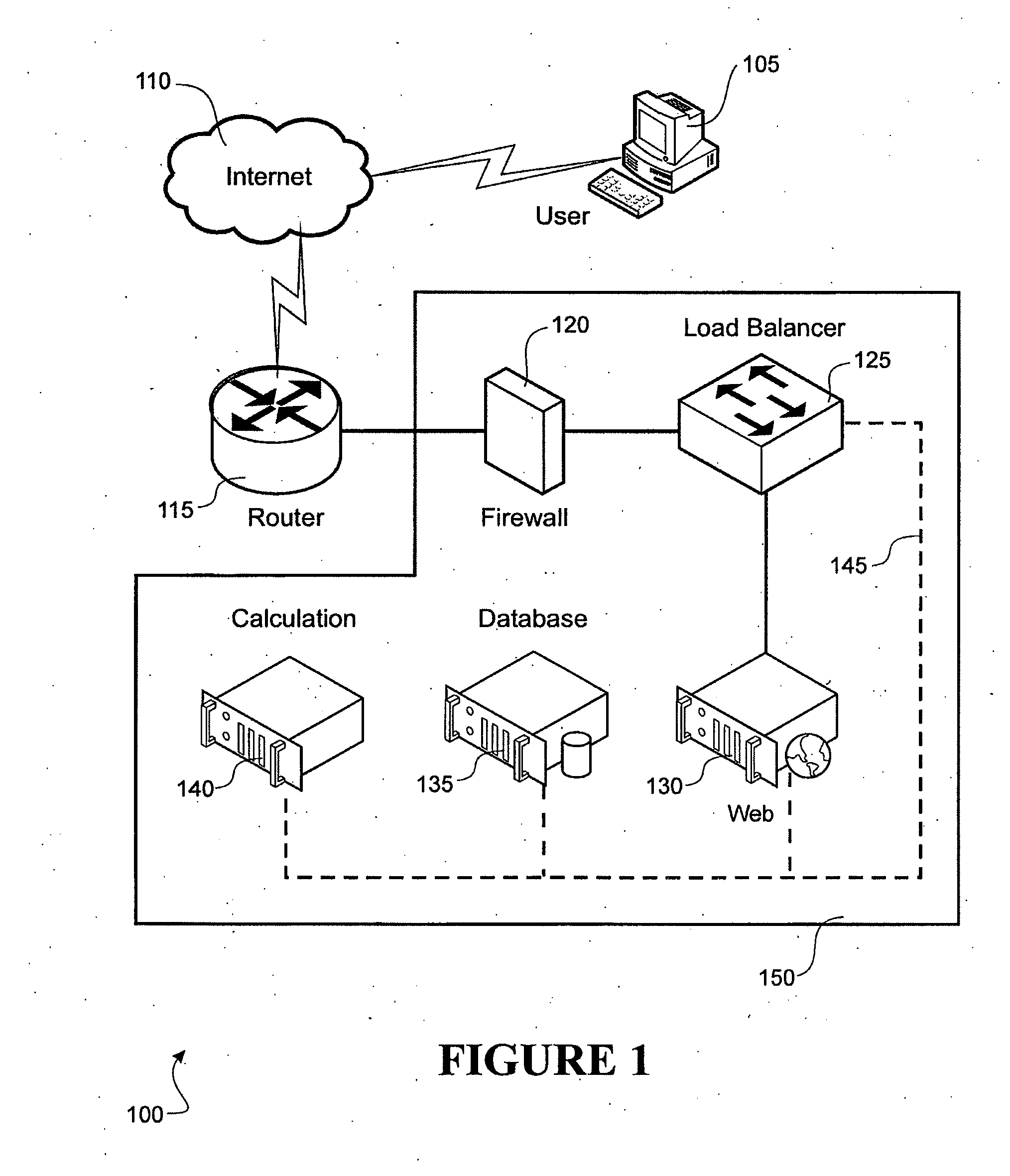

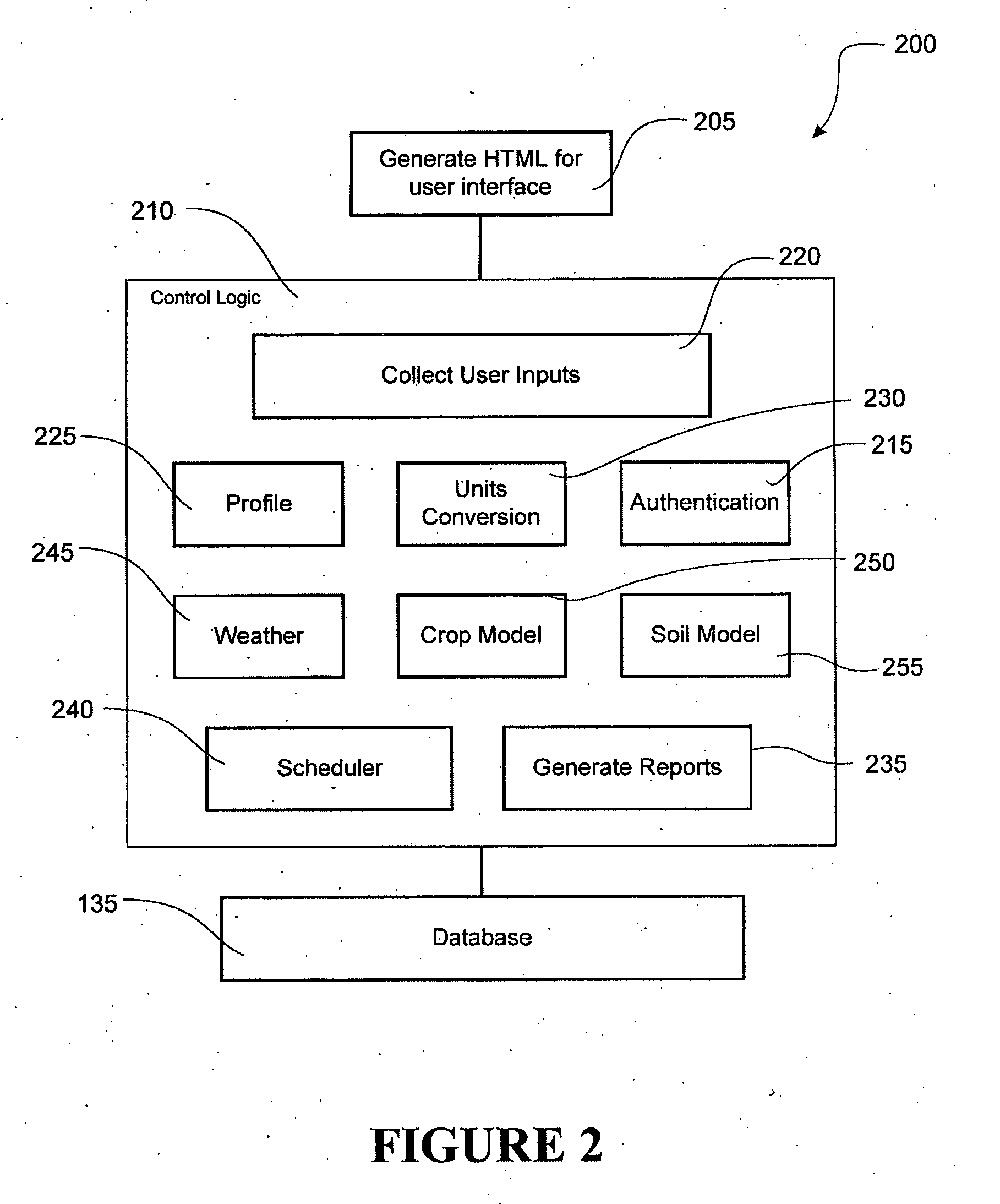

System and method for managing and predicting crop performance

ActiveUS20100306012A1Reduction in yieldReduce yieldWatering devicesCultivating equipmentsFertilizerWeather data

The invention provides a method of managing fertiliser and irrigation inputs for a crop, the method comprising obtaining management data for the crop, the management data including a planting date for the crop; obtaining weather data representative of the geographic area of the crop; obtaining soil description data representative of the geographic area of the crop; calculating an emergence date at least partly from the planting date; calculating a plurality of nitrogen deficit values at least partly from the emergence date and the soil description data, the nitrogen deficit values associated with respective dates each later than the emergence date; calculating a plurality of water deficit values at least partly from the emergence date and the weather data, the water deficit values associated with respective dates each later than the emergence date; and presenting on a display a schedule of recommended nitrogen application values, irrigation values and application dates, the schedule calculated at least partly from the nitrogen deficit values and the water deficit values.

Owner:NEW ZEALAND INST FOR CROP & FOOD RES