Patents

Literature

371 results about "Graphics pipeline" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

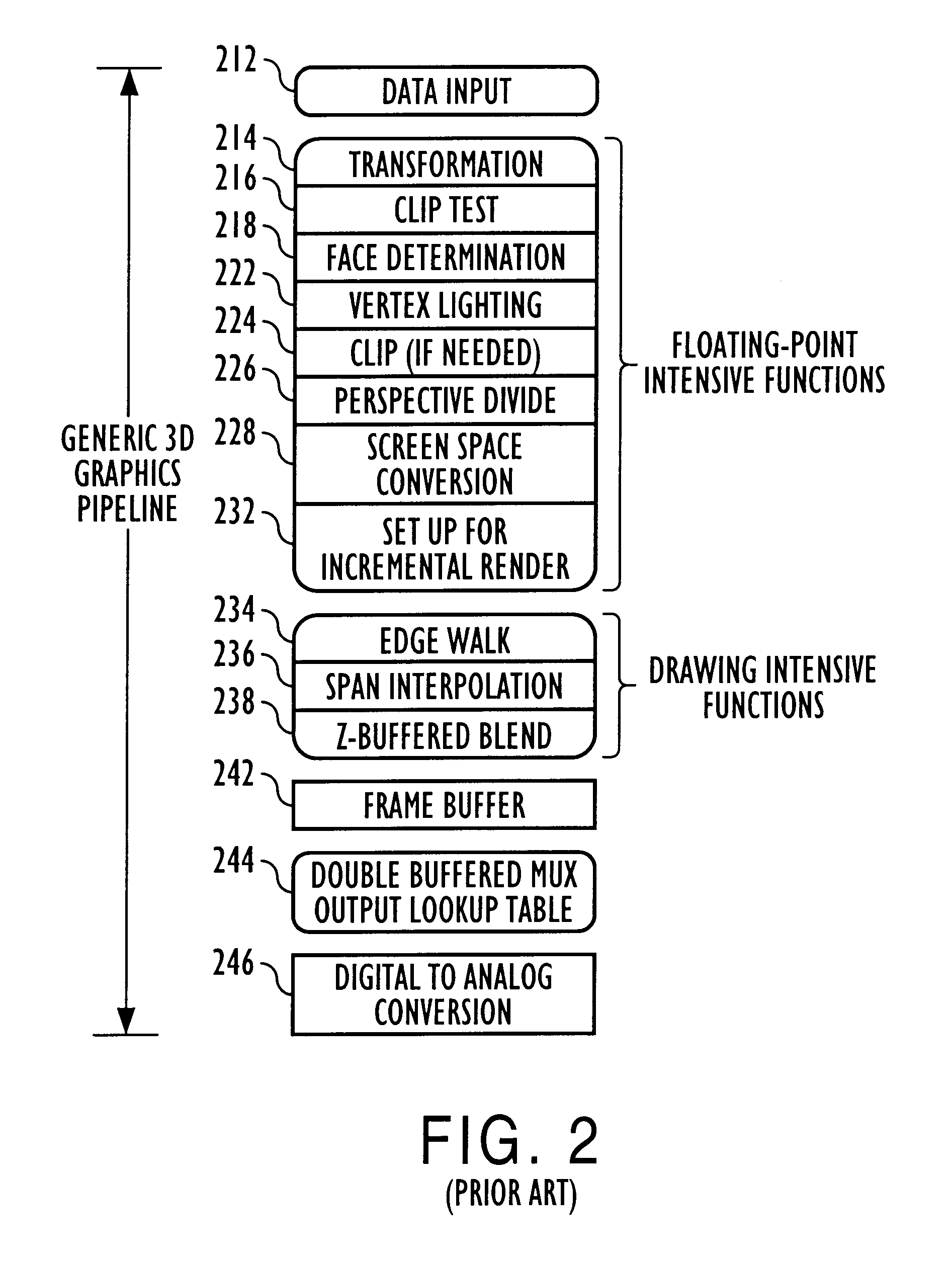

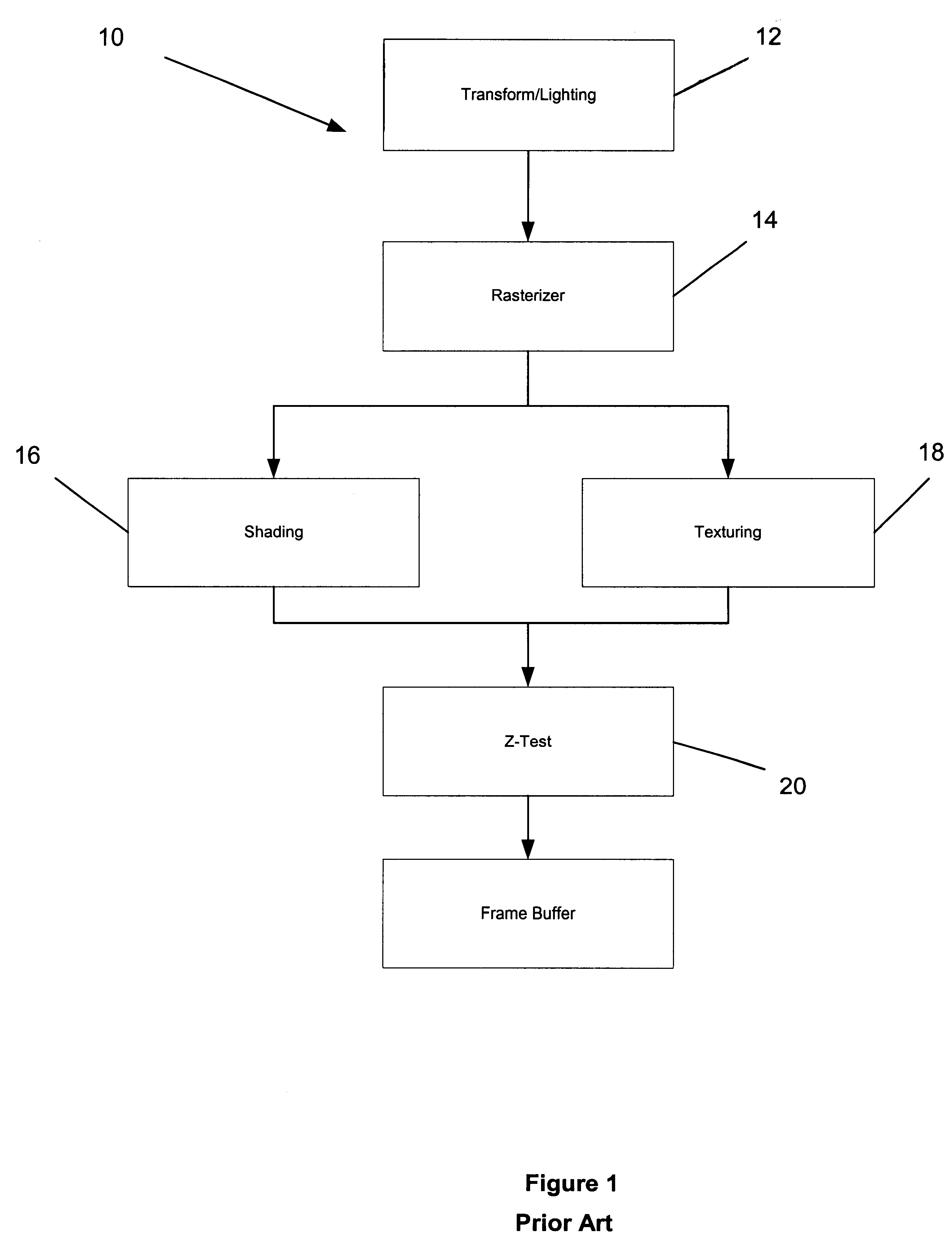

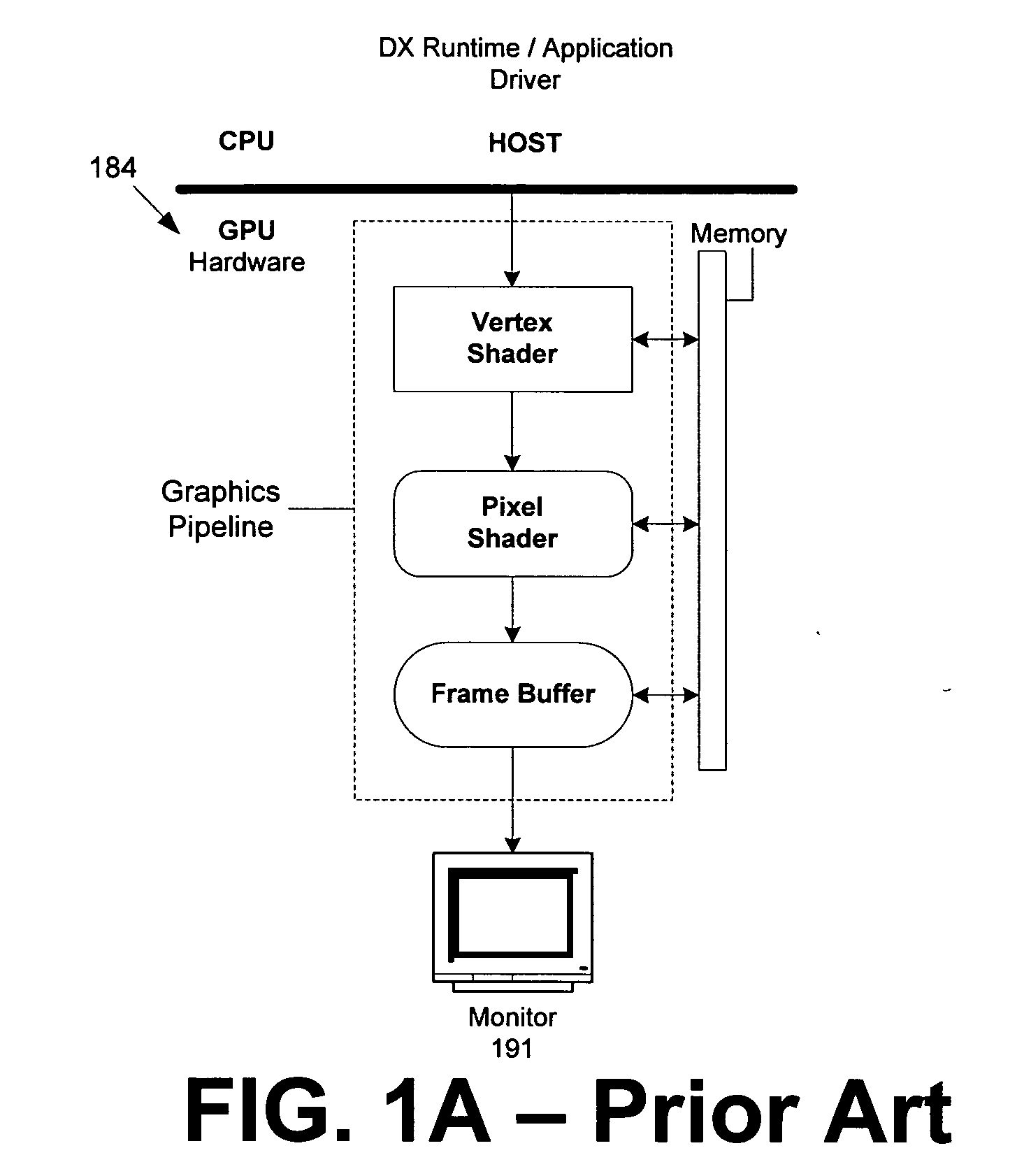

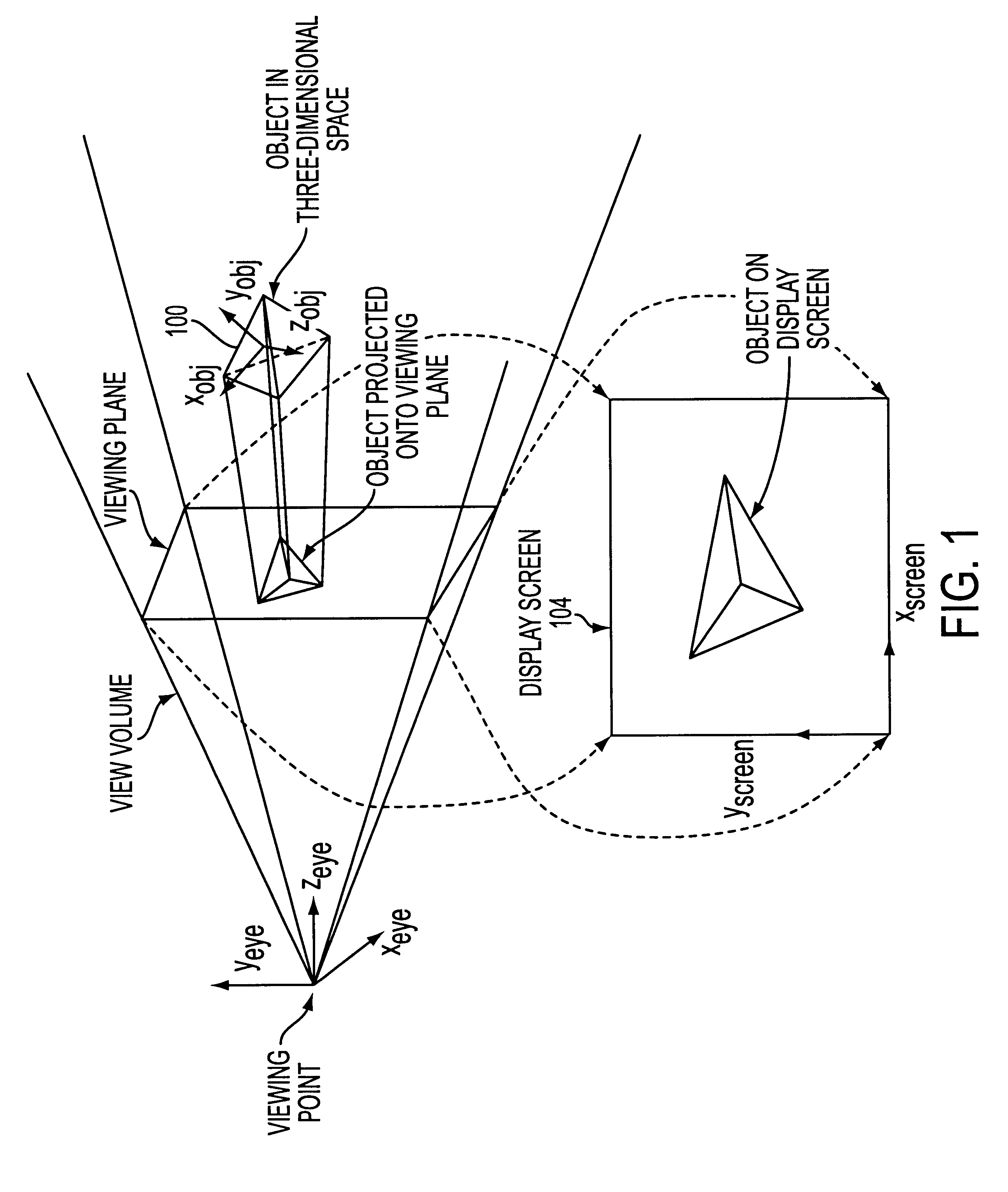

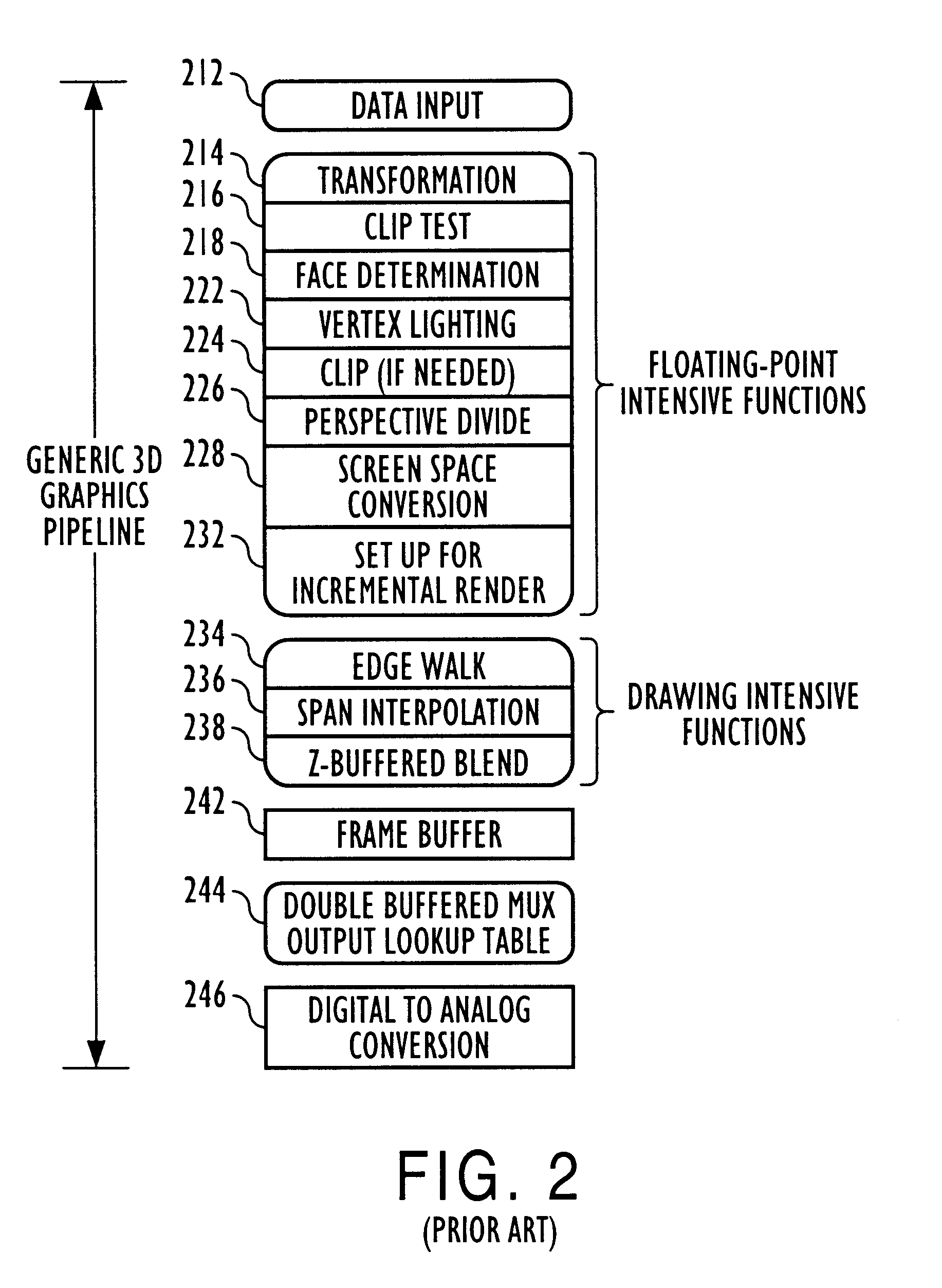

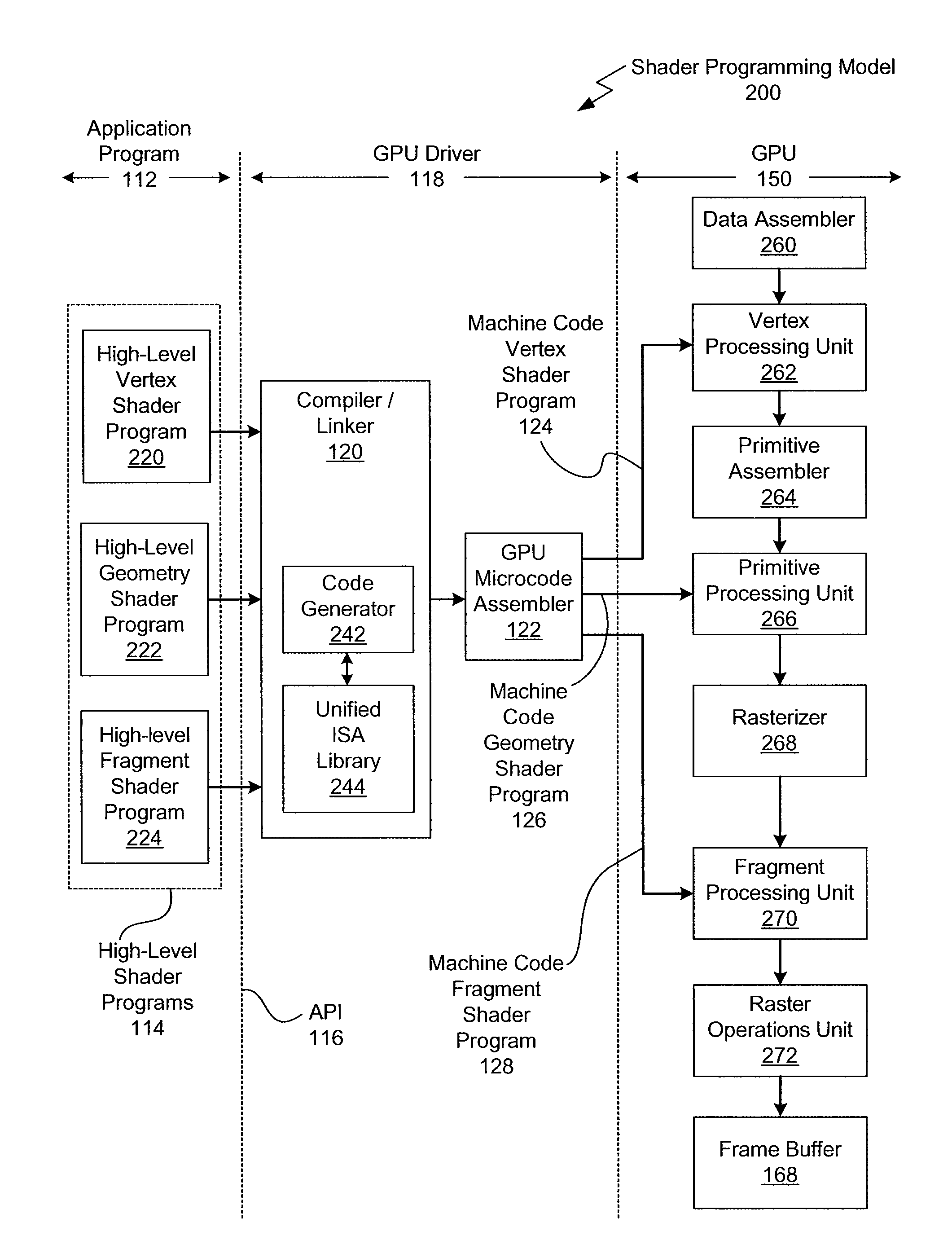

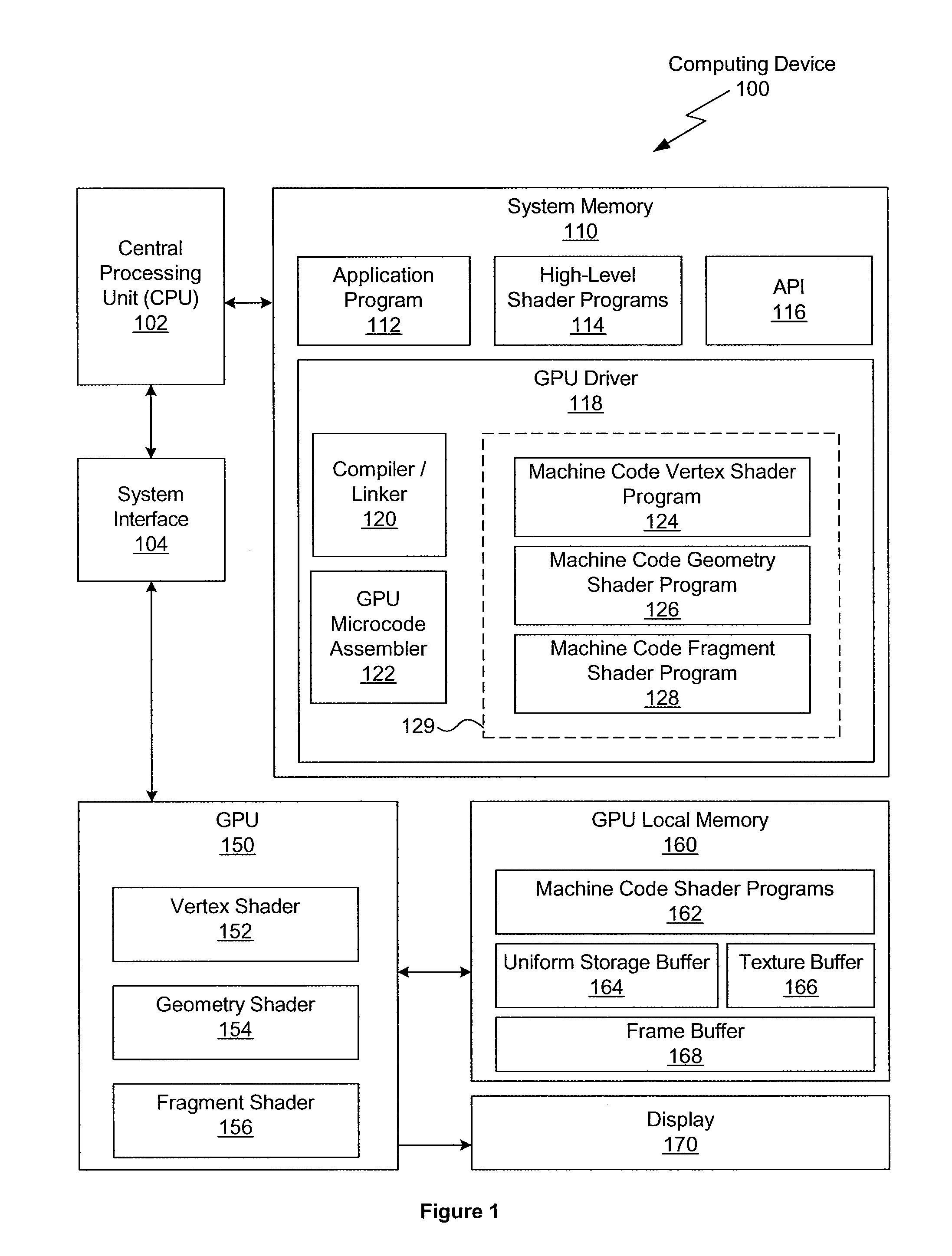

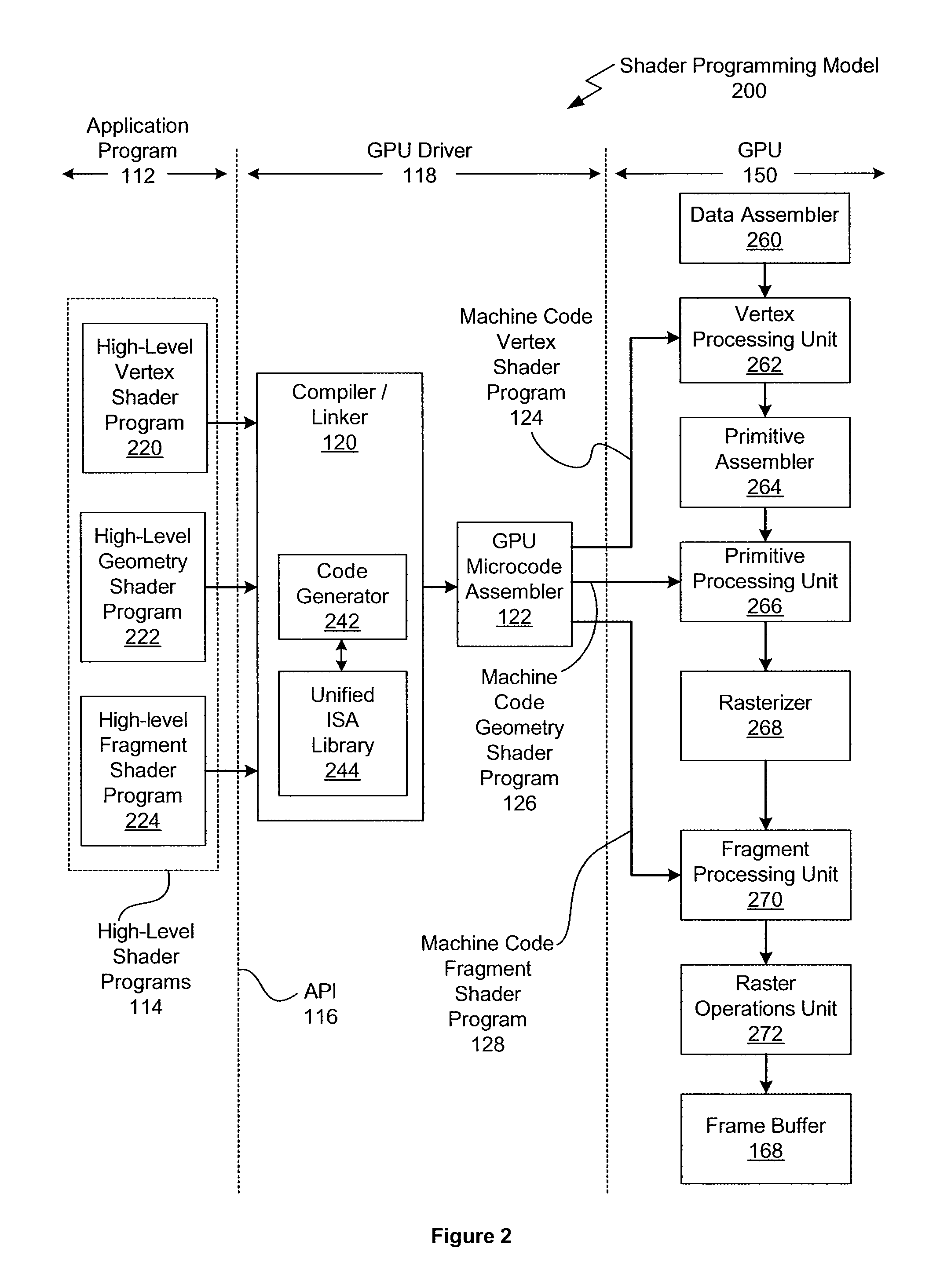

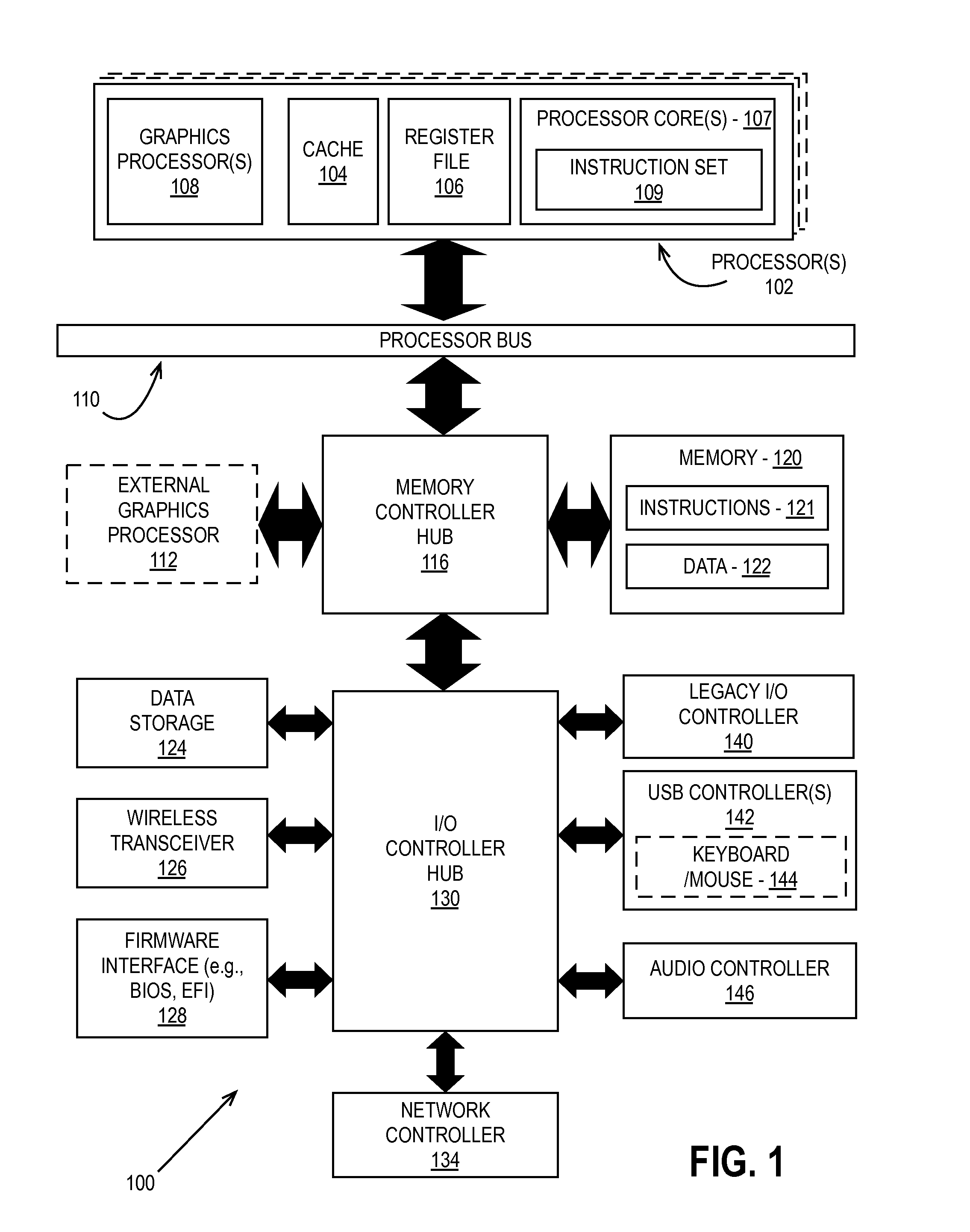

In computer graphics, a computer graphics pipeline, rendering pipeline or simply graphics pipeline, is a conceptual model that describes what steps a graphics system needs to perform to render a 3D scene to a 2D screen. Once a 3D model has been created, for instance in a video game or any other 3D computer animation, the graphics pipeline is the process of turning that 3D model into what the computer displays. Because the steps required for this operation depend on the software and hardware used and the desired display characteristics, there is no universal graphics pipeline suitable for all cases. However, graphics application programming interfaces (APIs) such as Direct3D and OpenGL were created to unify similar steps and to control the graphics pipeline of a given hardware accelerator. These APIs abstract the underlying hardware and keep the programmer away from writing code to manipulate the graphics hardware accelerators (AMD/Intel/NVIDIA etc.).

Method, system, and computer program product for implementing derivative operators with graphics hardware

InactiveUS6717599B1Cathode-ray tube indicatorsImage generationApplication programming interfaceTheoretical computer science

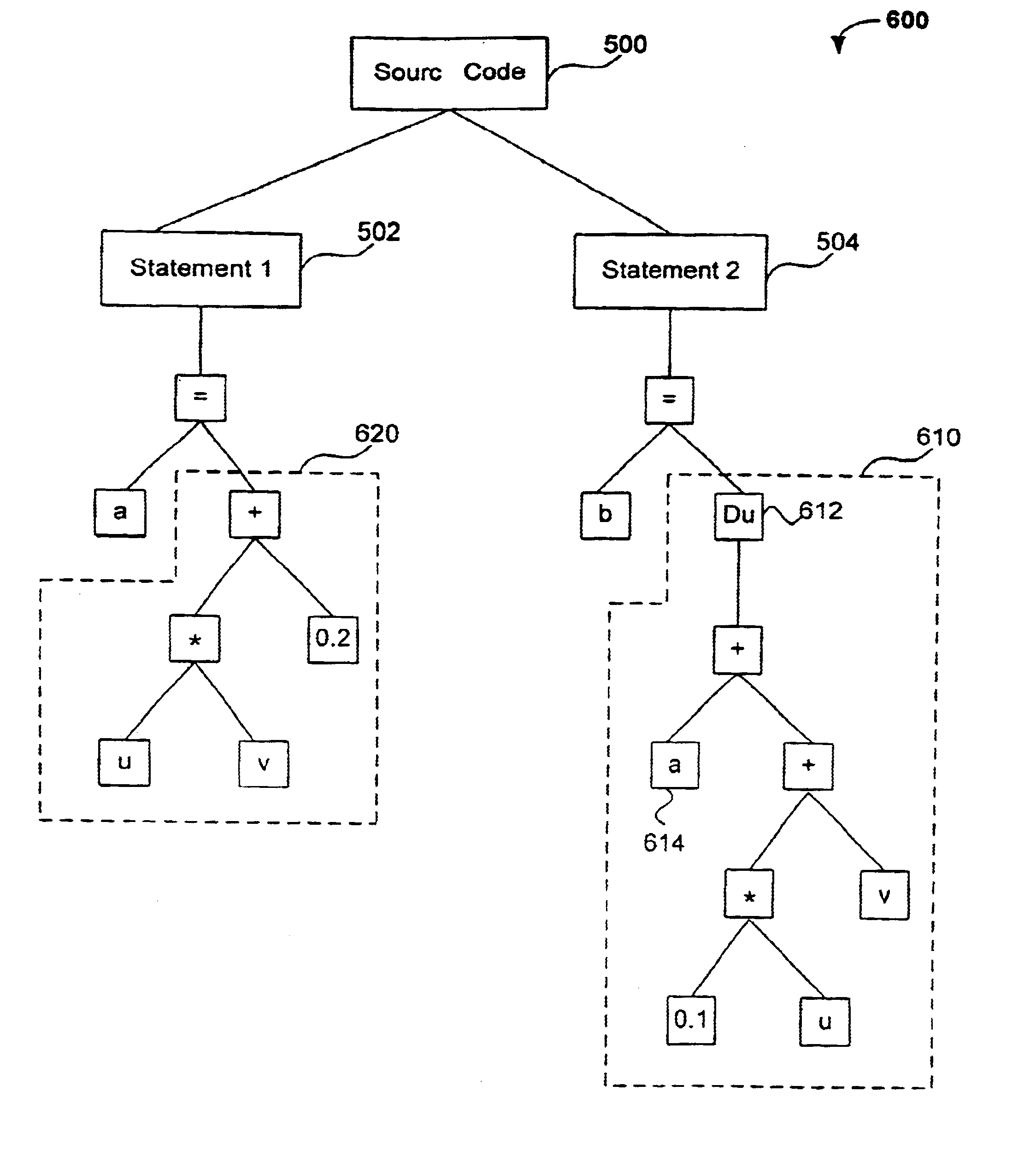

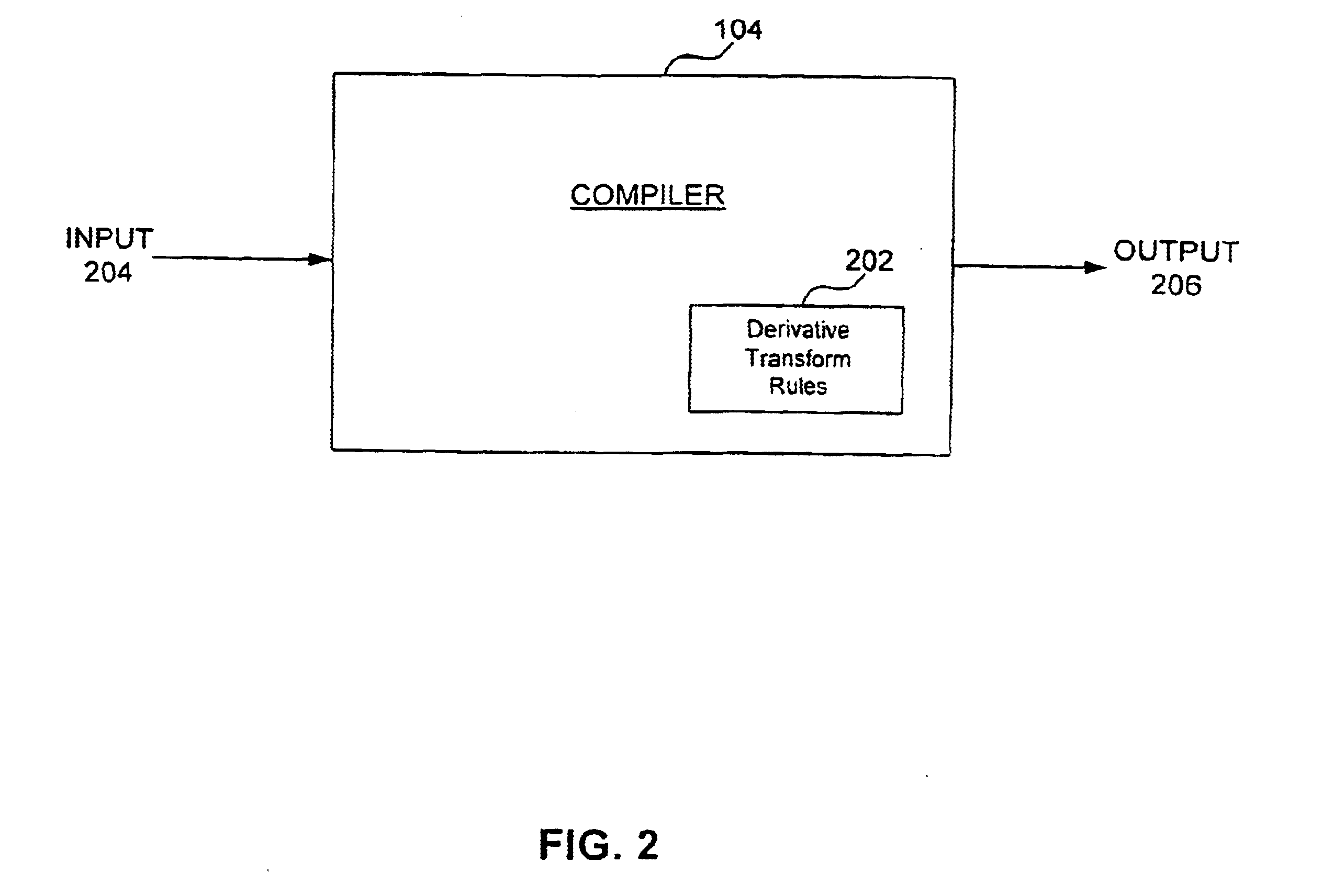

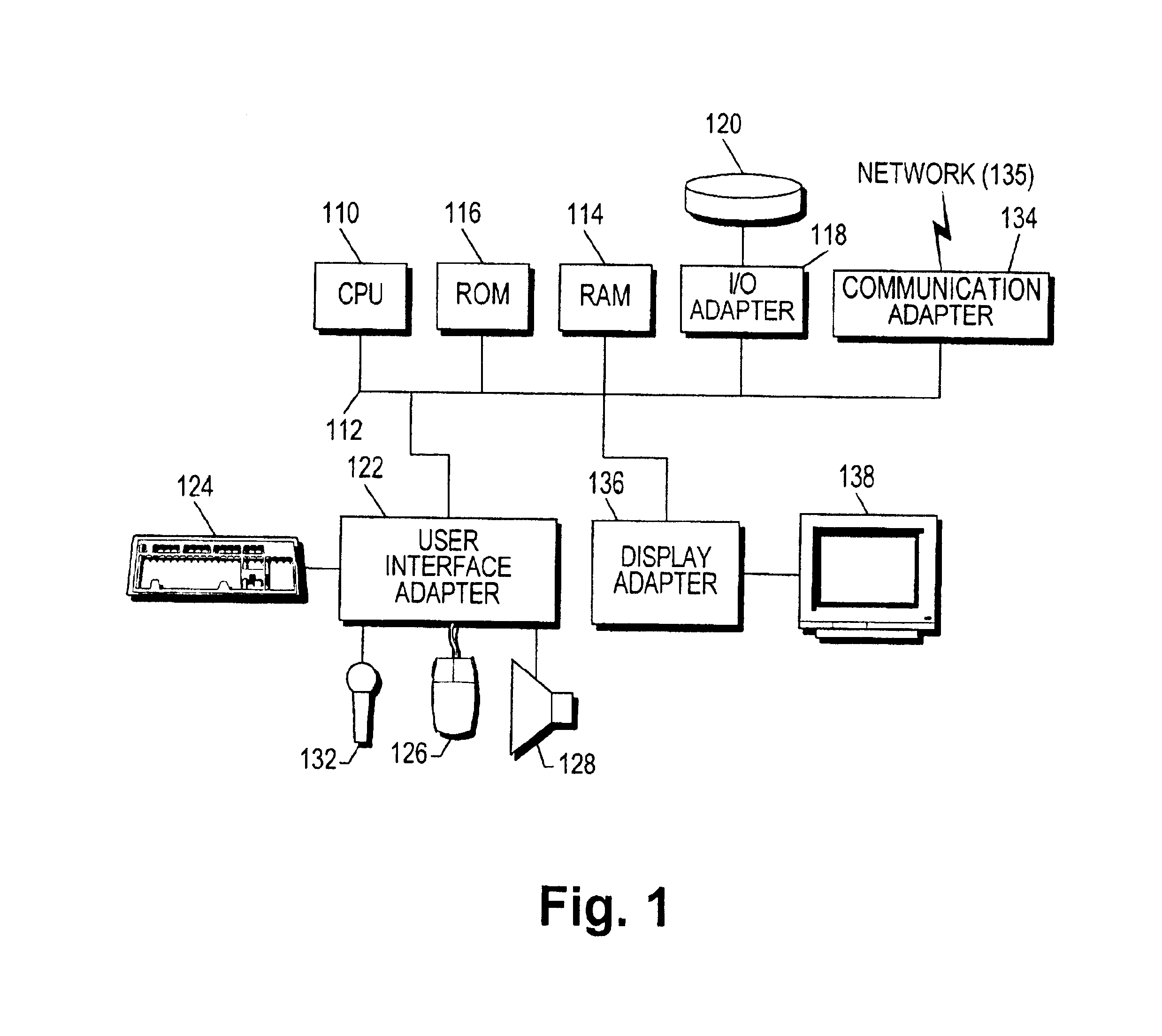

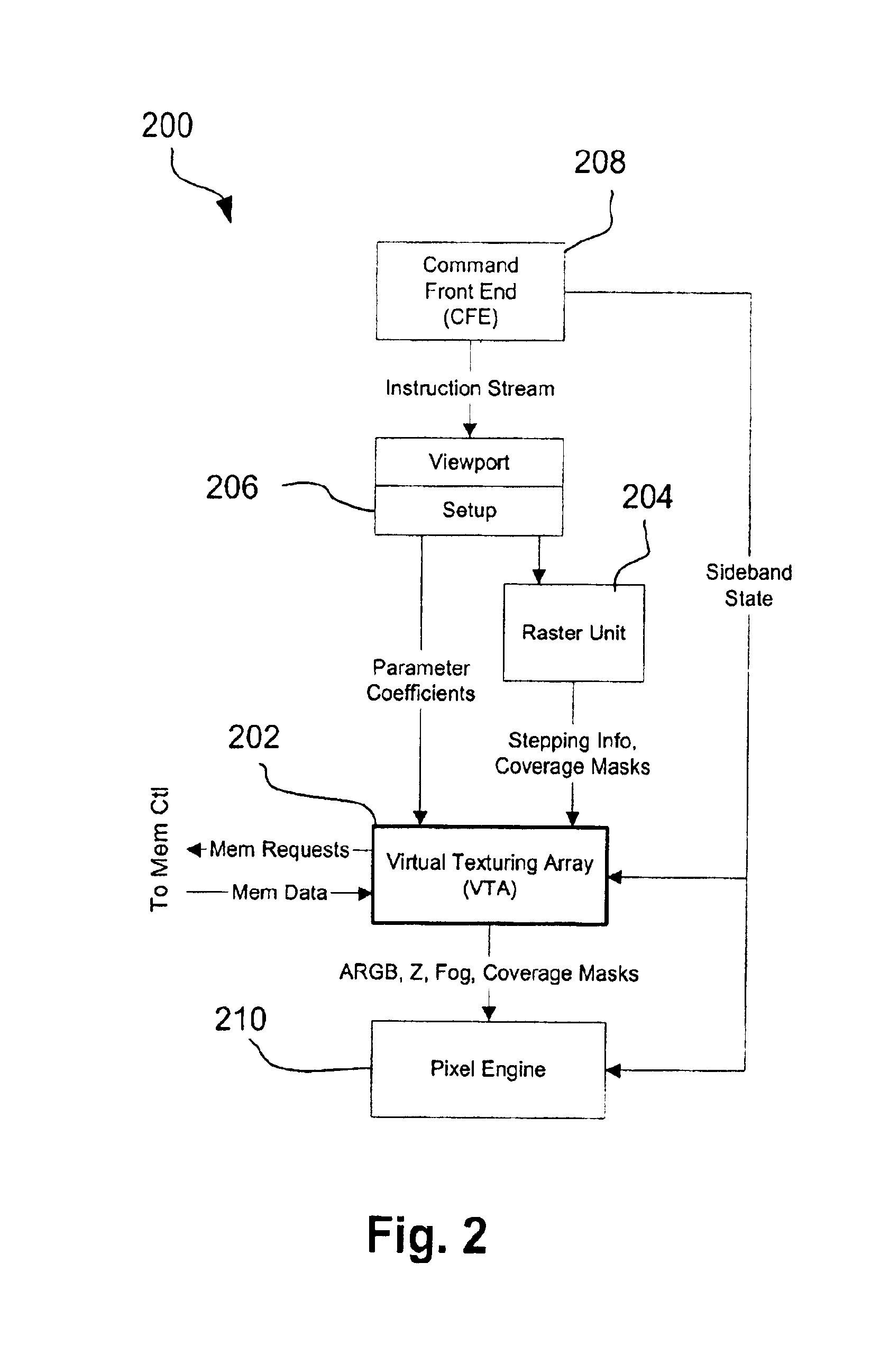

Method, system, and computer program product for implementing derivative operators at an interactive rate in computer graphics systems. In an embodiment, a data structure representing the operation of one or more computer program statements is received by a compiler and transformed into a tree data structure. Nodes of the tree data structure that determine derivative information are marked, and a transform rule is applied to the marked nodes to transform the tree data structure into a data structure that can be implemented with graphics hardware interface program statements. In one embodiment of the invention, the compiler transforms shading language statements into graphics application programming interface statements that can be implemented with multiple passes through a graphics pipeline. It is a feature of the present invention that it can be implemented on a wide range of computer graphics systems.

Owner:MICROSOFT TECH LICENSING LLC

Method and apparatus for interleaved processing of direct and indirect texture coordinates in a graphics system

InactiveUS7002591B1Efficient implementationIncrease in texture mapping hardware complexityCathode-ray tube indicators3D-image renderingPattern recognitionProcessing

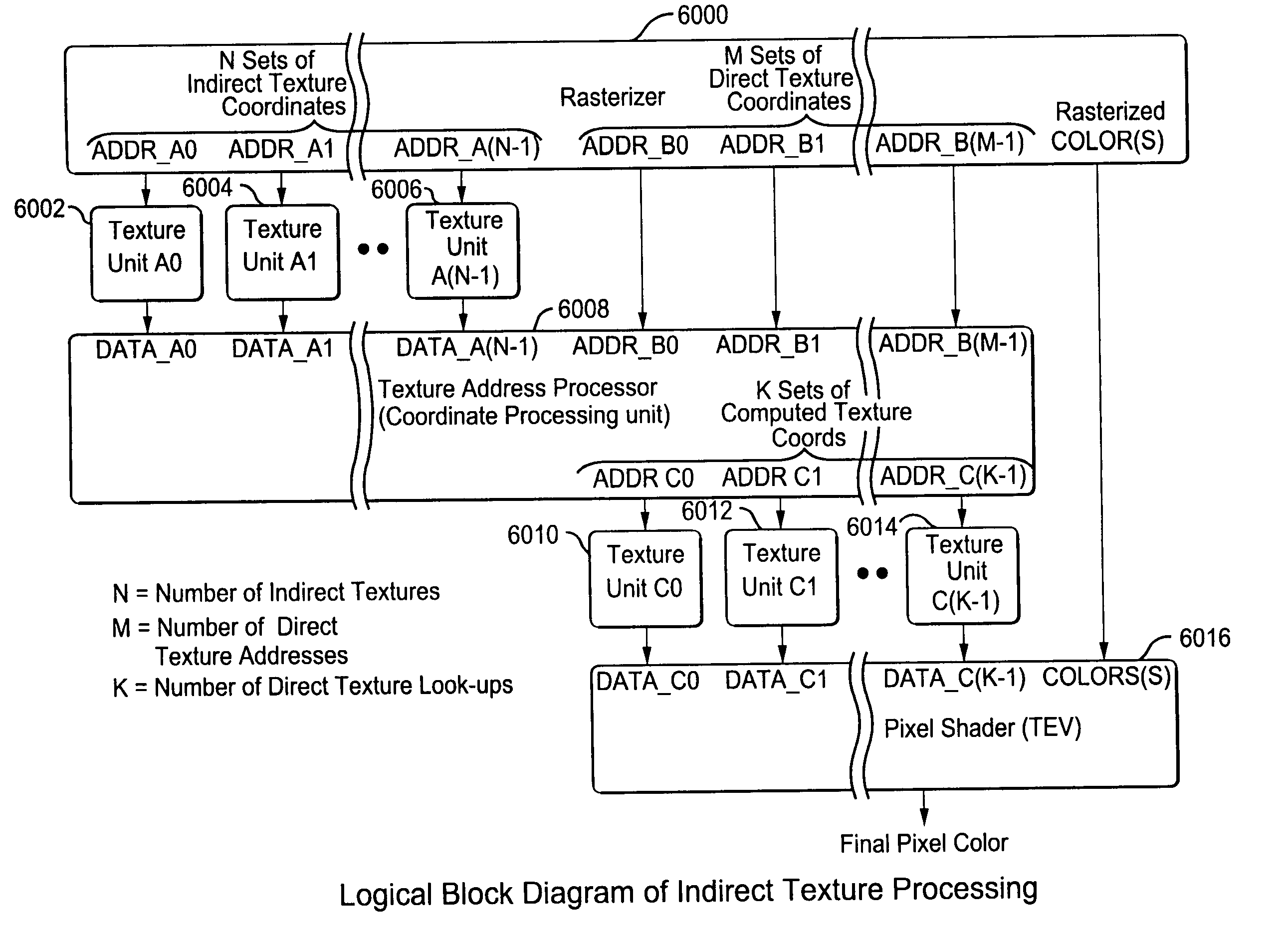

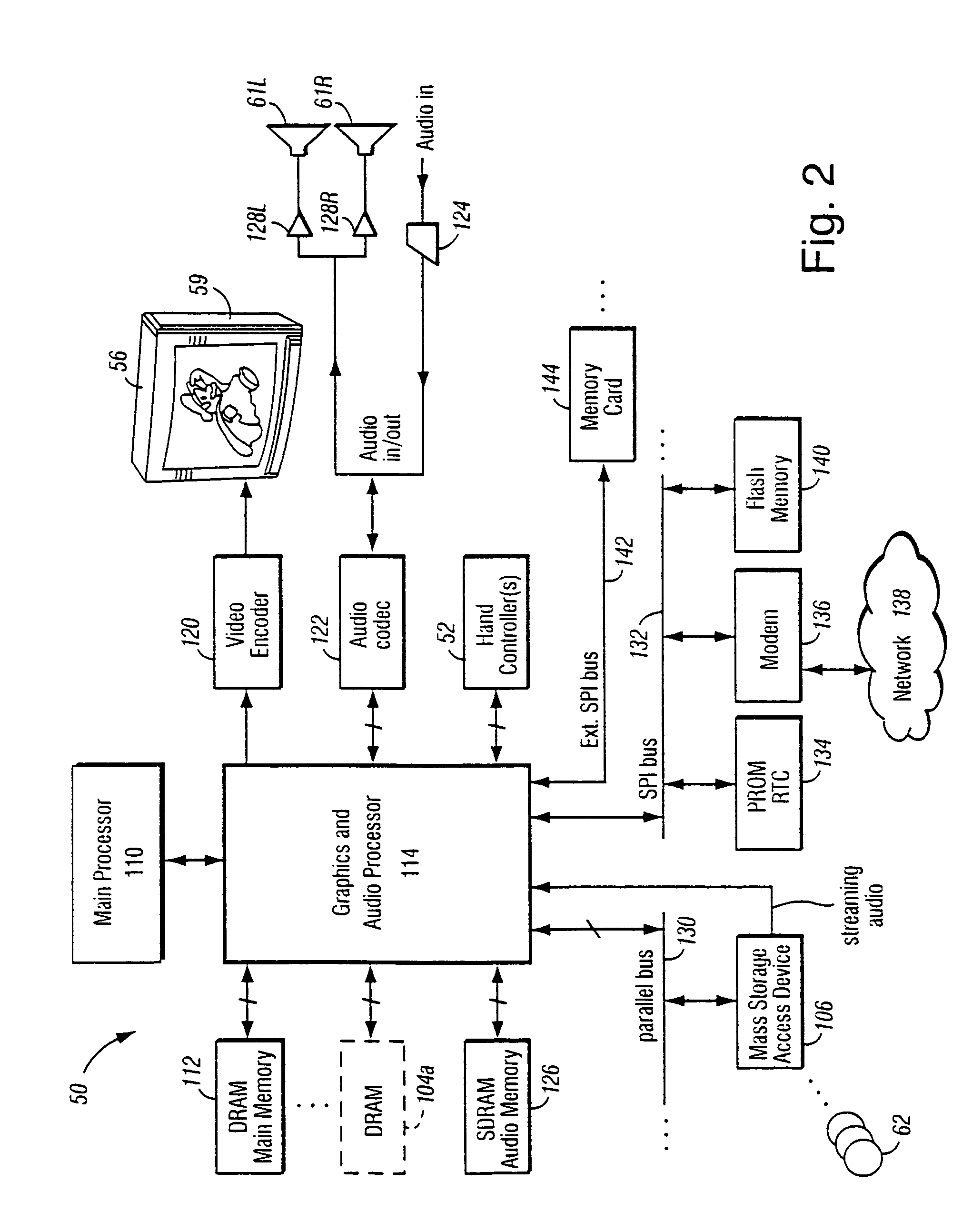

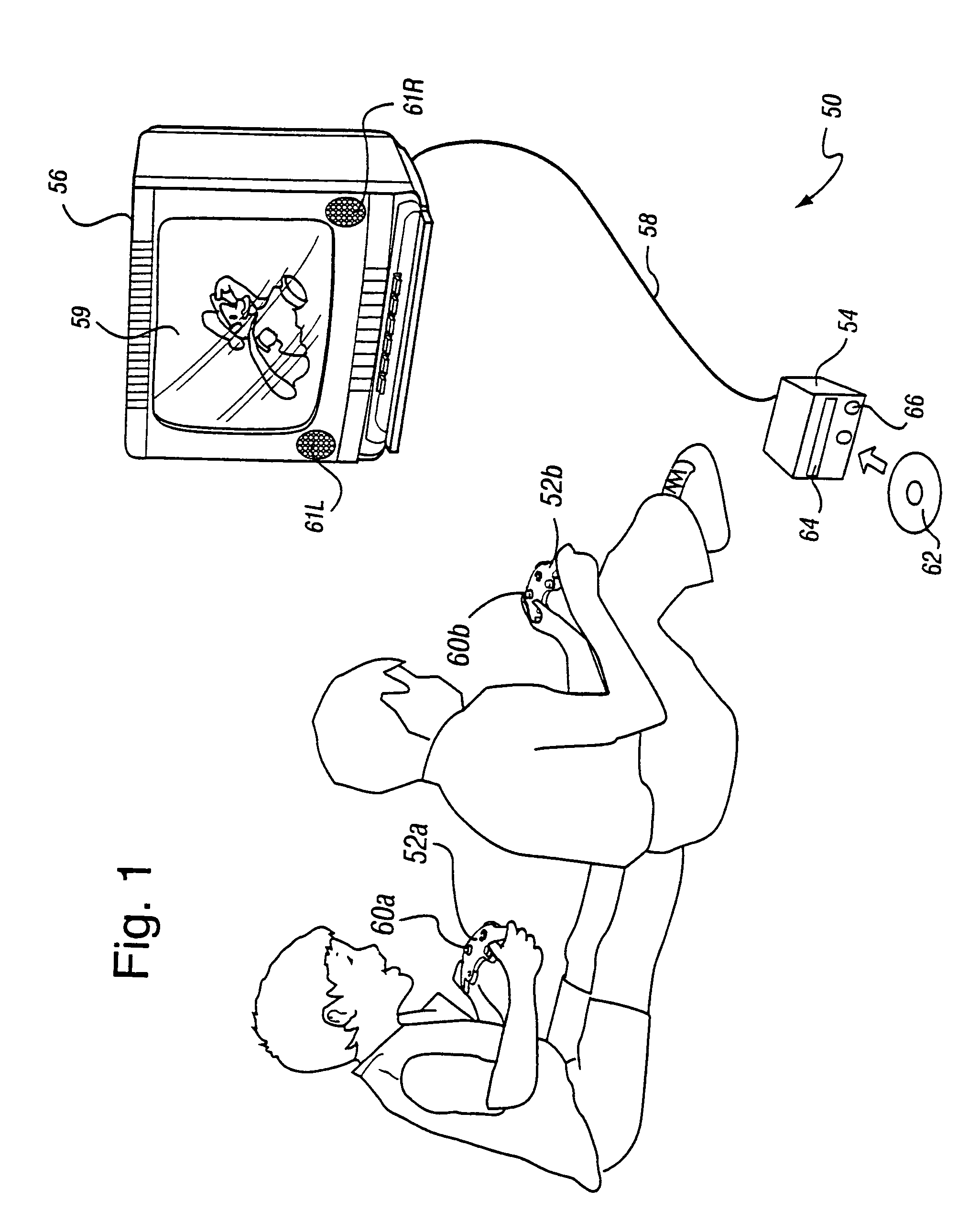

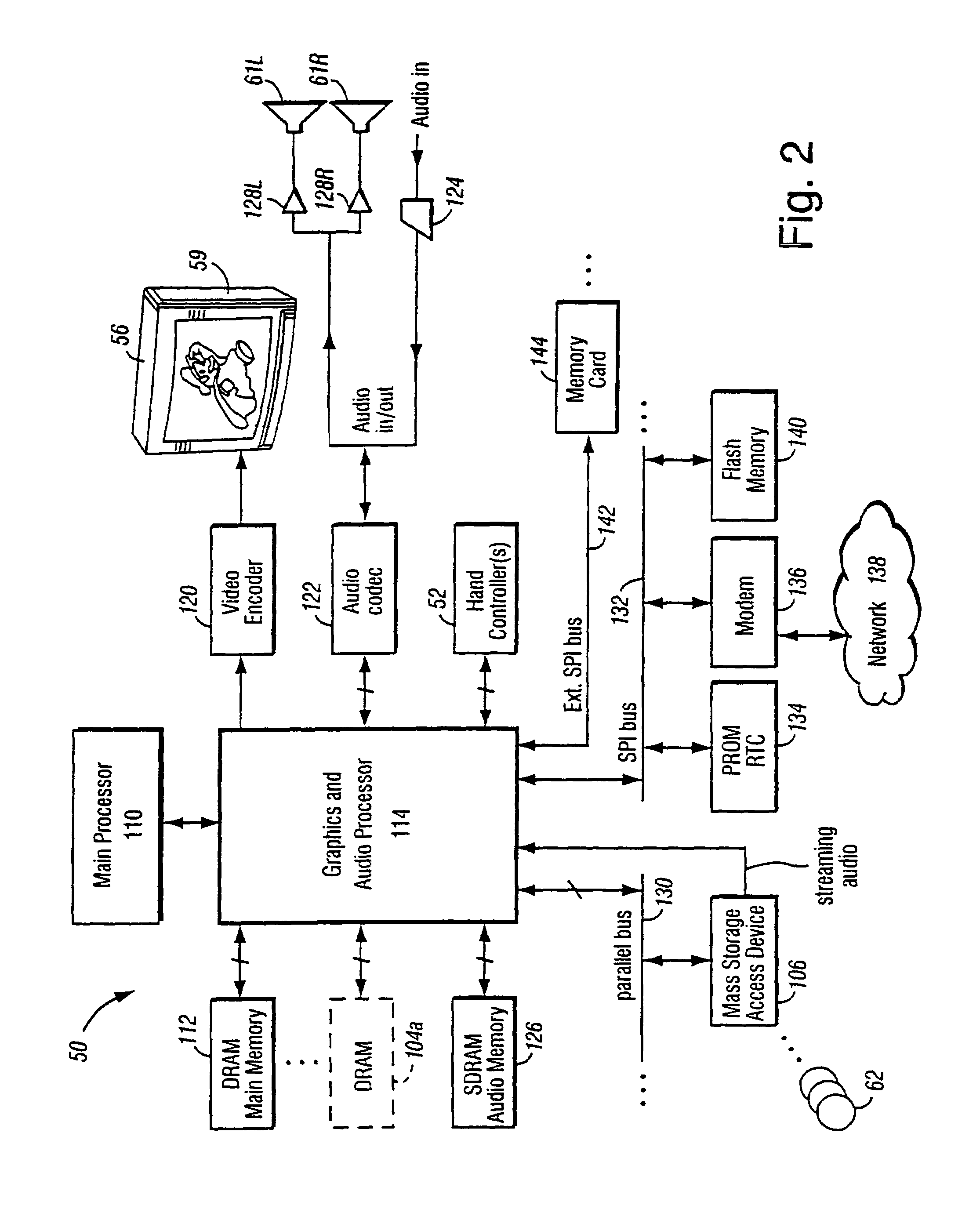

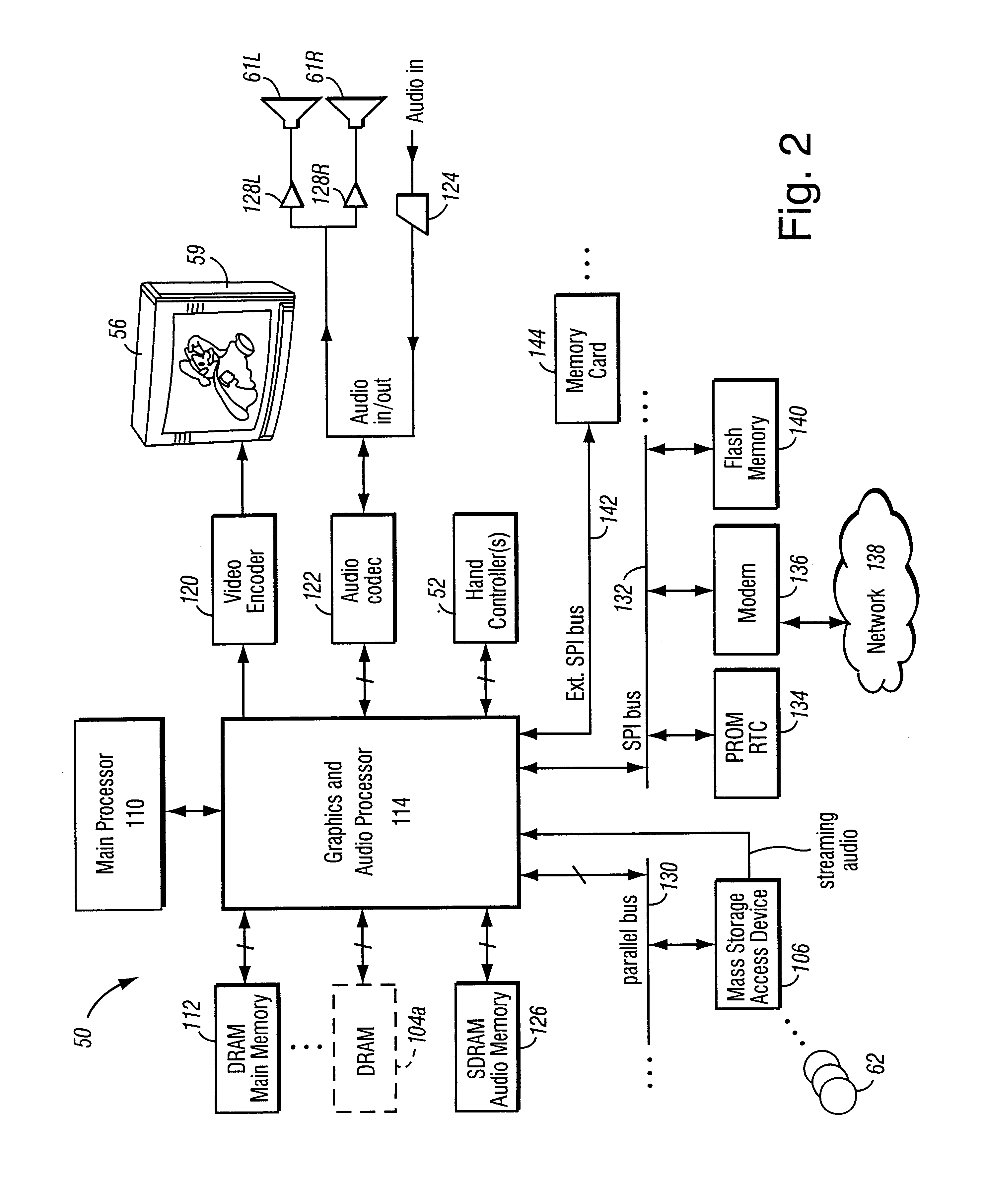

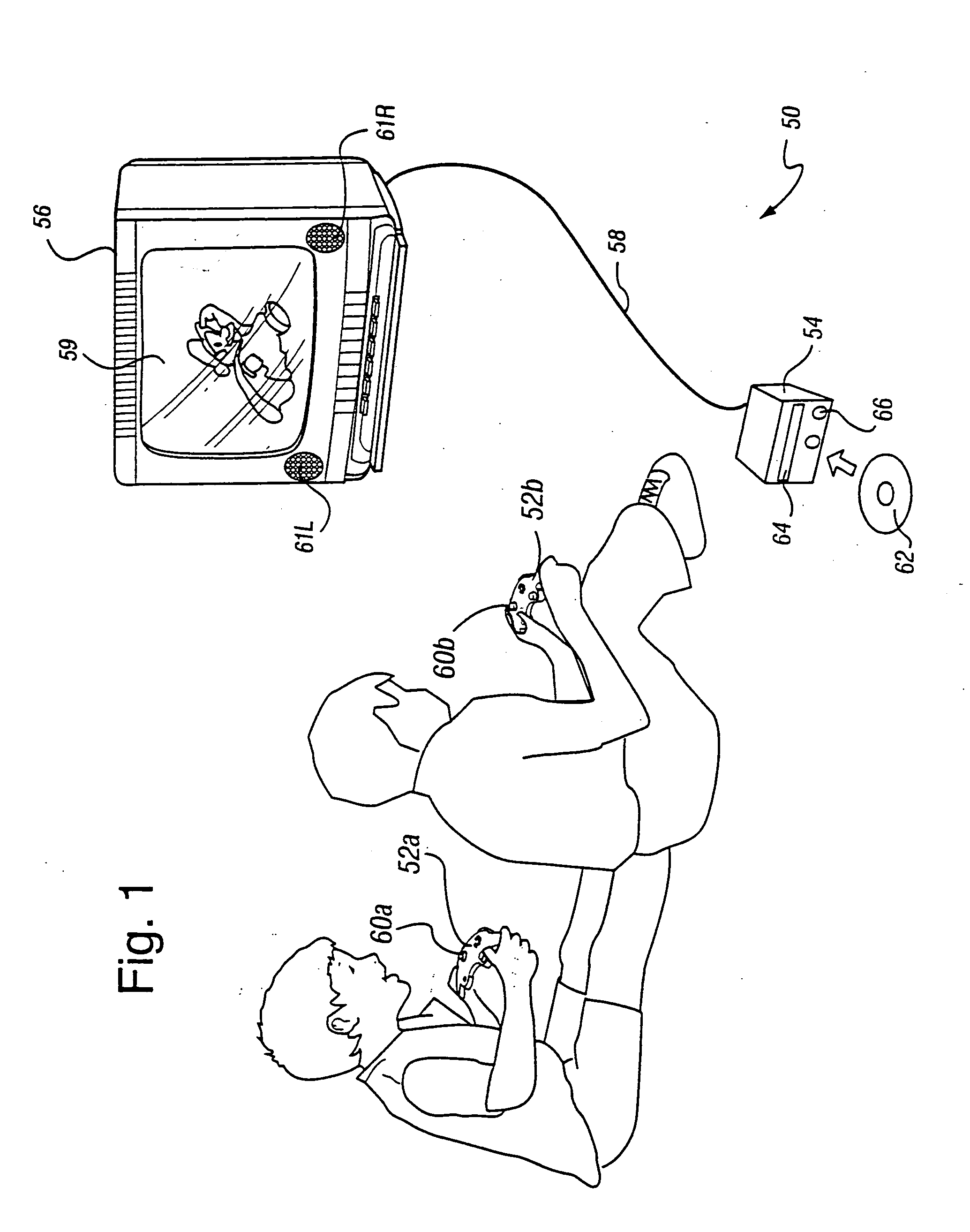

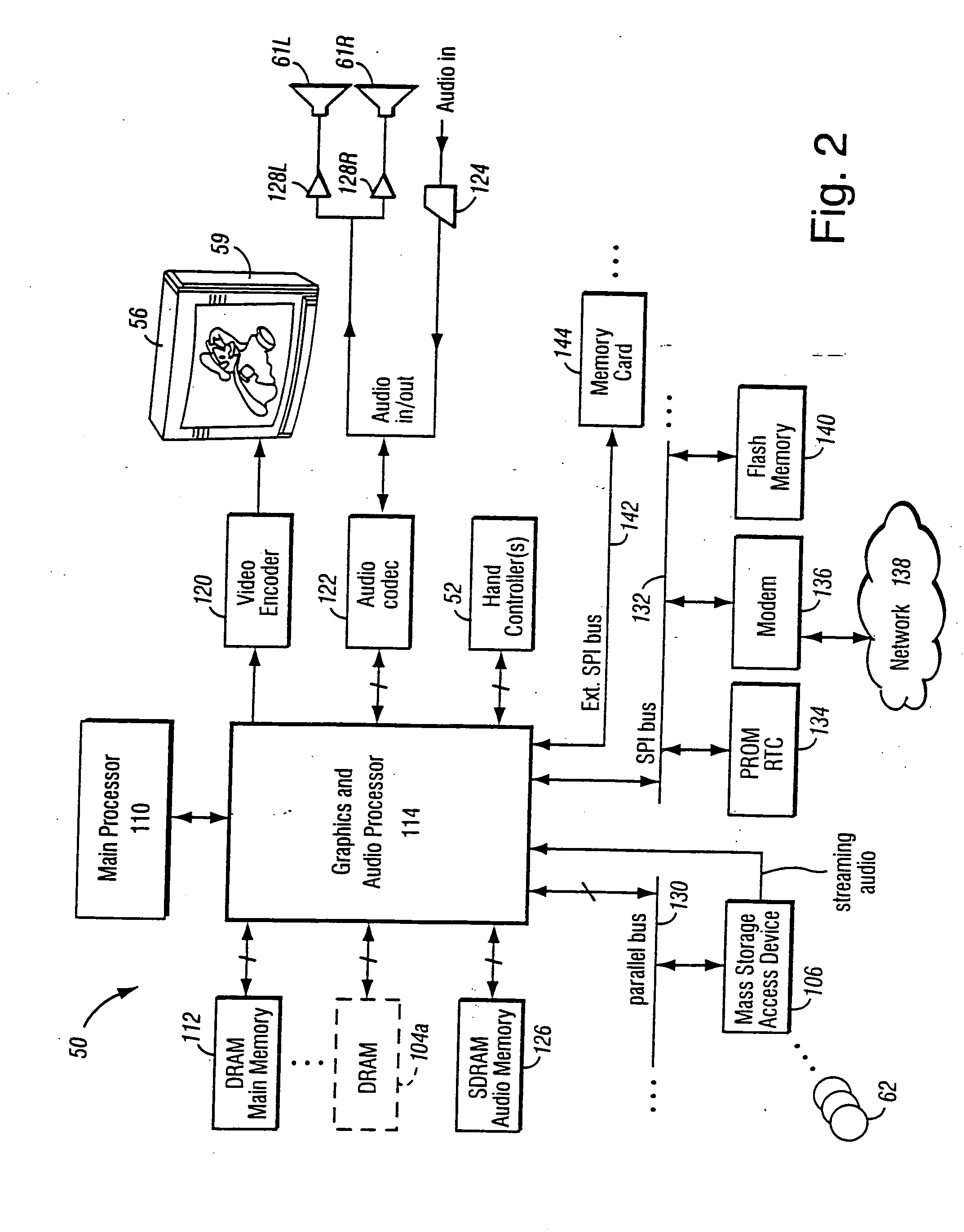

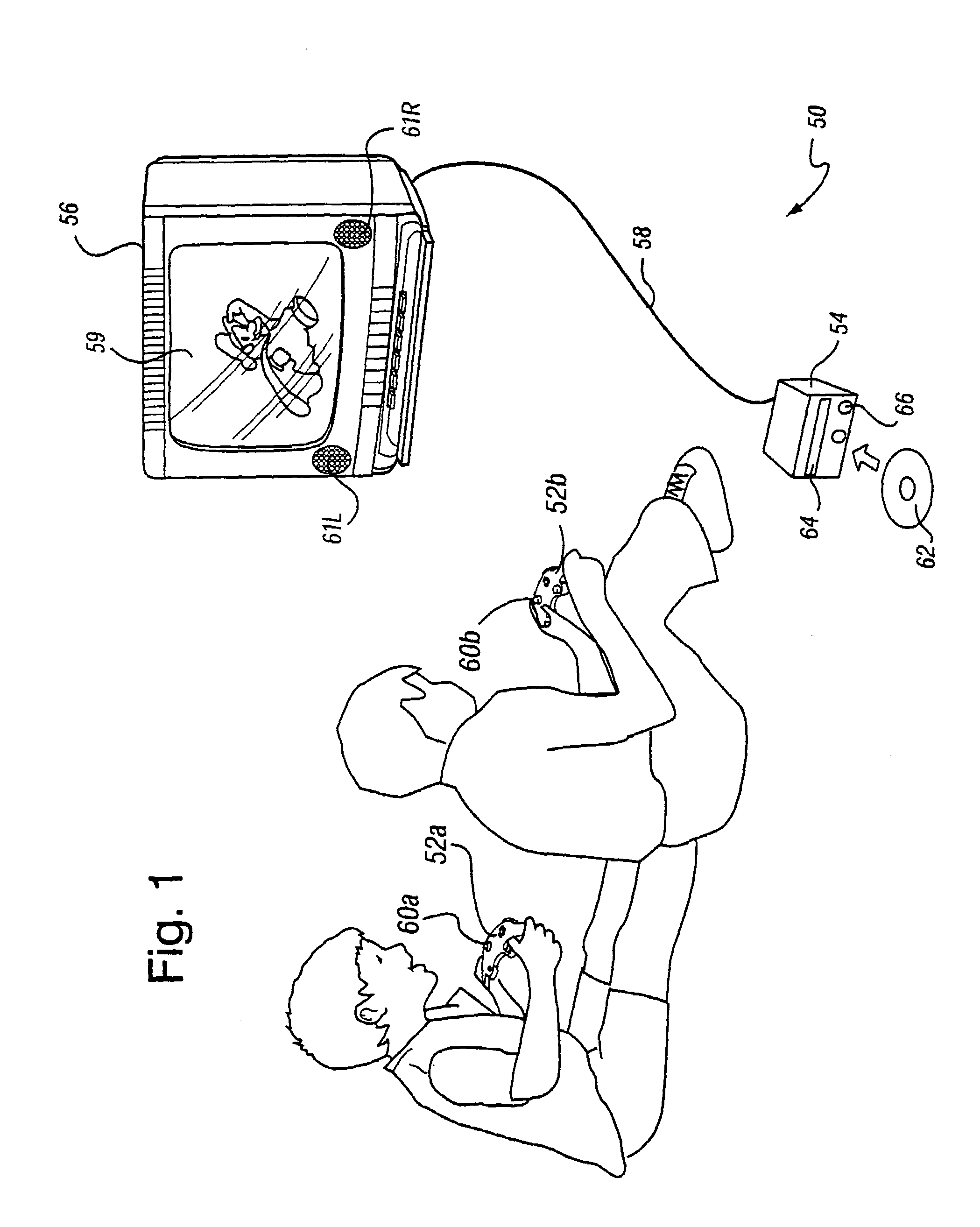

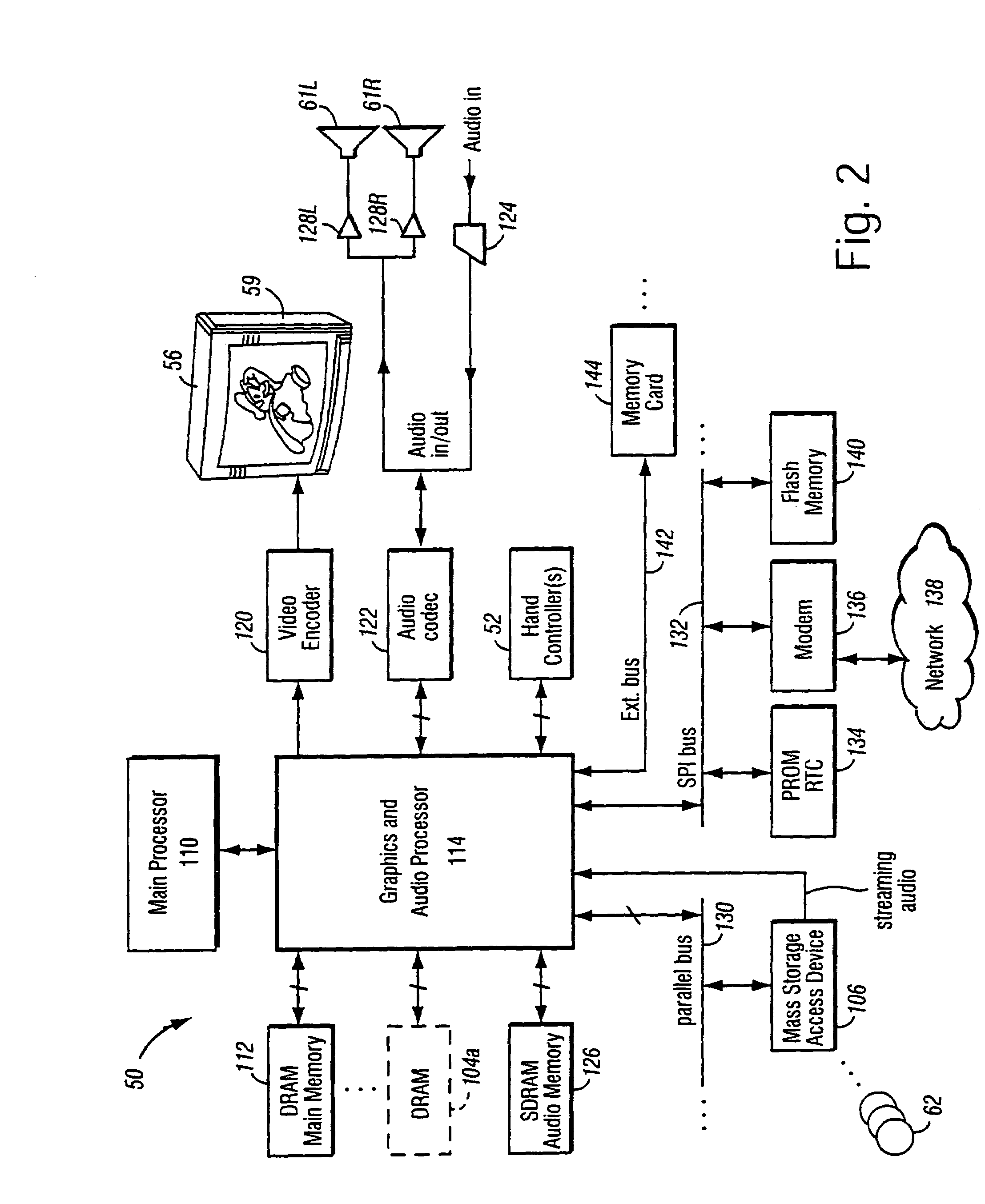

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics pipeline renders and prepares images for display at least in part in response to polygon vertex attribute data and texel color data stored as a texture images in an associated memory. An efficient texturing pipeline arrangement achieves a relatively low chip-footprint by utilizing a single texture coordinate / data processing unit that interleaves the processing of logical direct and indirect texture coordinate data and a texture lookup data feedback path for “recirculating” indirect texture lookup data retrieved from a single texture retrieval unit back to the texture coordinate / data processing unit. Versatile indirect texture referencing is achieved by using the same texture coordinate / data processing unit to transform the recirculated texture lookup data into offsets that may be added to the texture coordinates of a direct texture lookup. A generalized indirect texture API function is provided that supports defining at least four indirect texture referencing operations and allows for selectively associating one of at least eight different texture images with each indirect texture defined. Retrieved indirect texture lookup data is processed as multi-bit binary data triplets of three, four, five, or eight bits. The data triplets are multiplied by a 3×2 texture coordinate offset matrix before being optionally combined with regular non-indirect coordinate data or coordinate data from a previous cycle / stage of processing. Values of the offset matrix elements are variable and may be dynamically defined for each cycle / stage using selected constants. Two additional variable matrix configurations are also defined containing element values obtained from current direct texture coordinates. Circuitry for optionally biasing and scaling retrieved texture data is also provided.

Owner:NINTENDO CO LTD

Deferred shading graphics pipeline processor

InactiveUS6229553B1Lower communication bandwidthAttenuation bandwidthTexturing/coloringImage memory managementPhong shadingDeferred shading

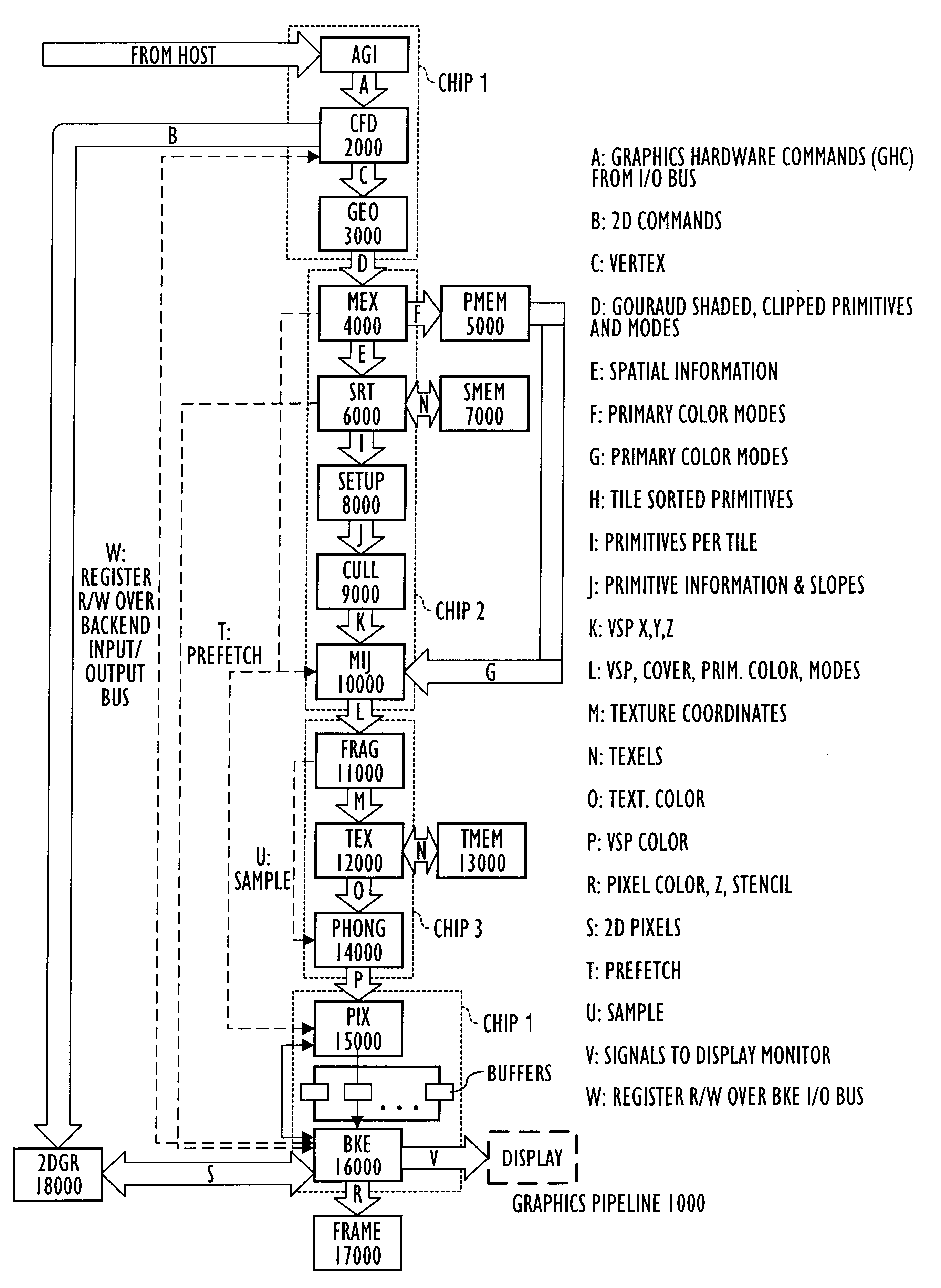

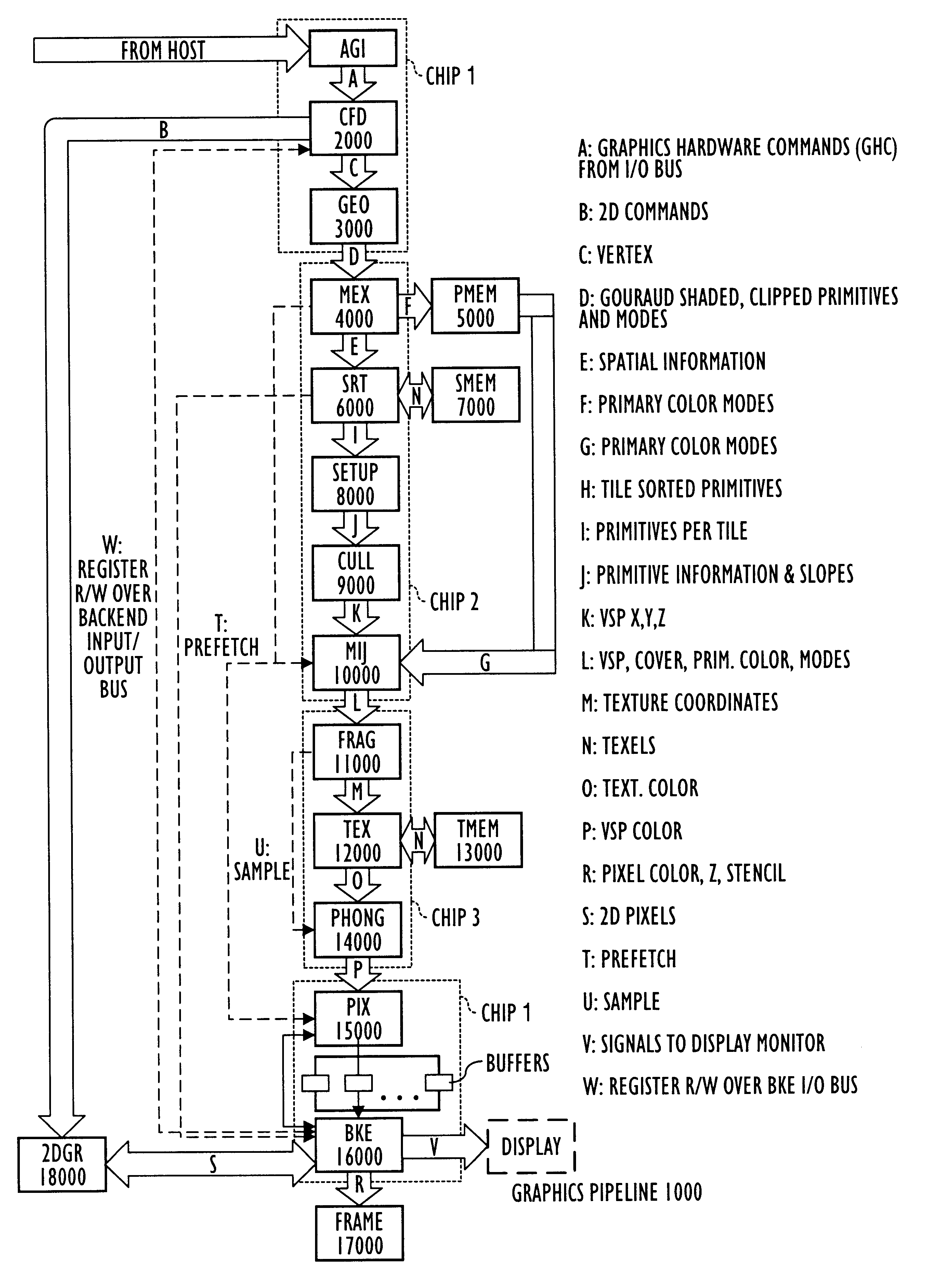

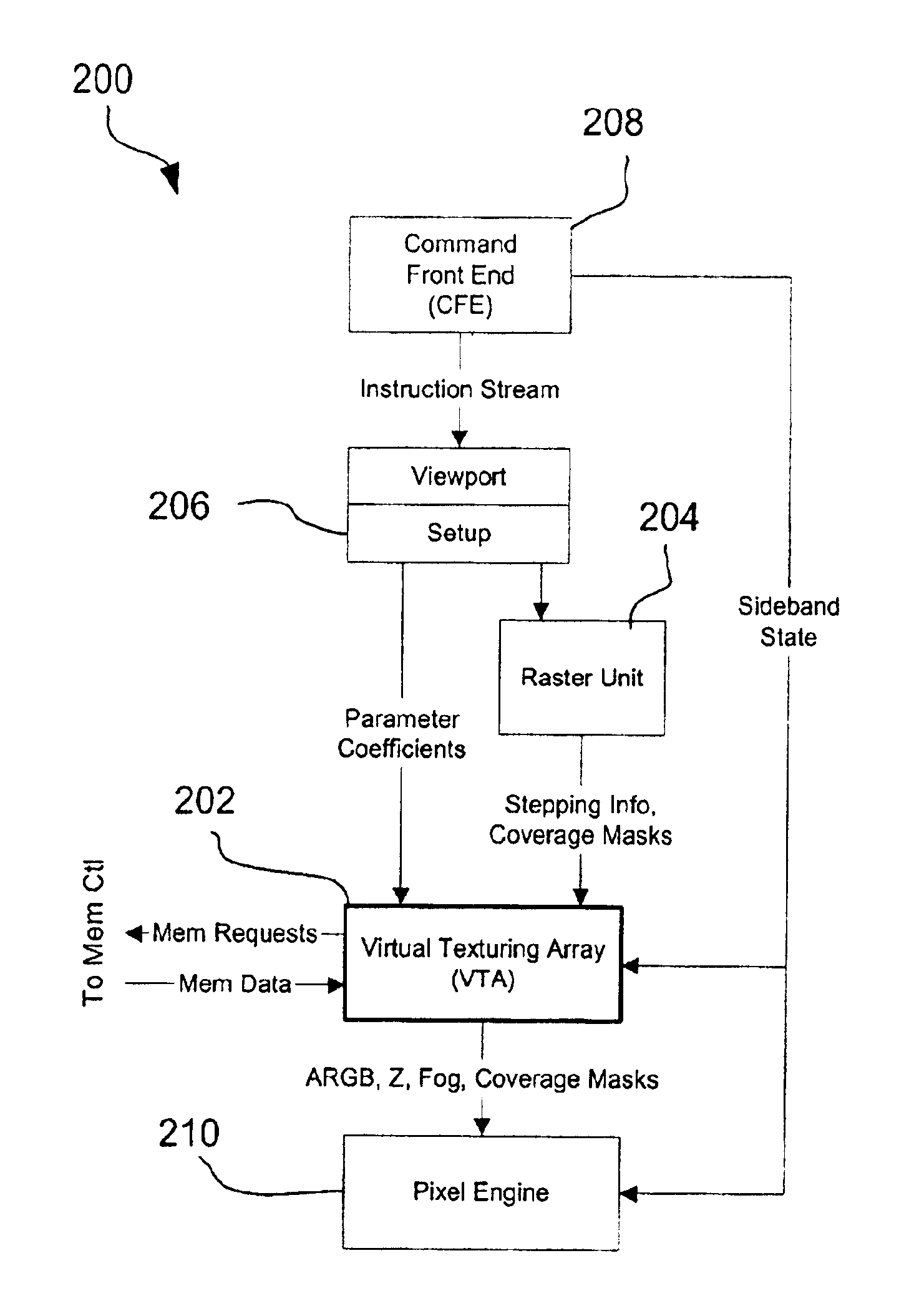

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

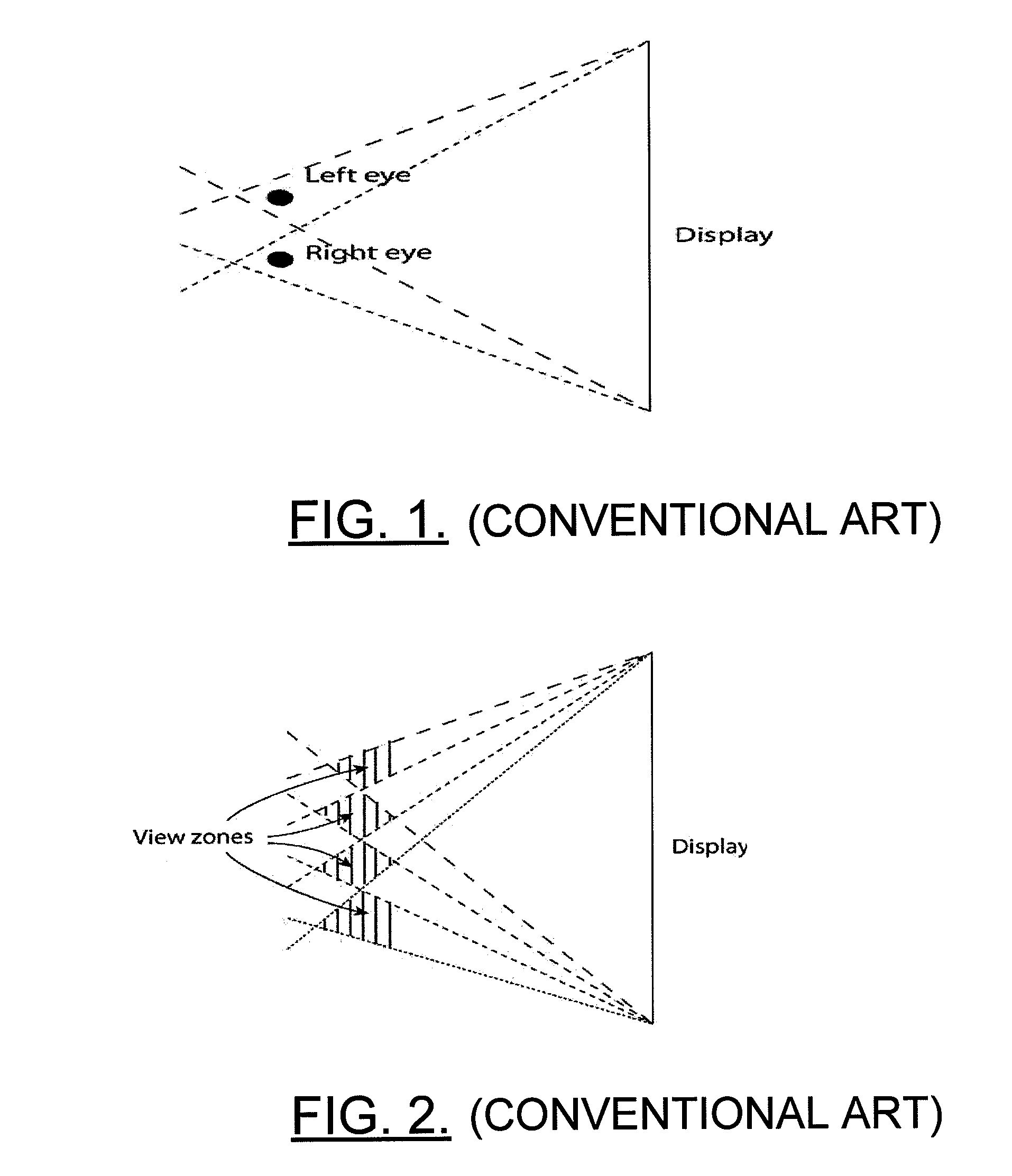

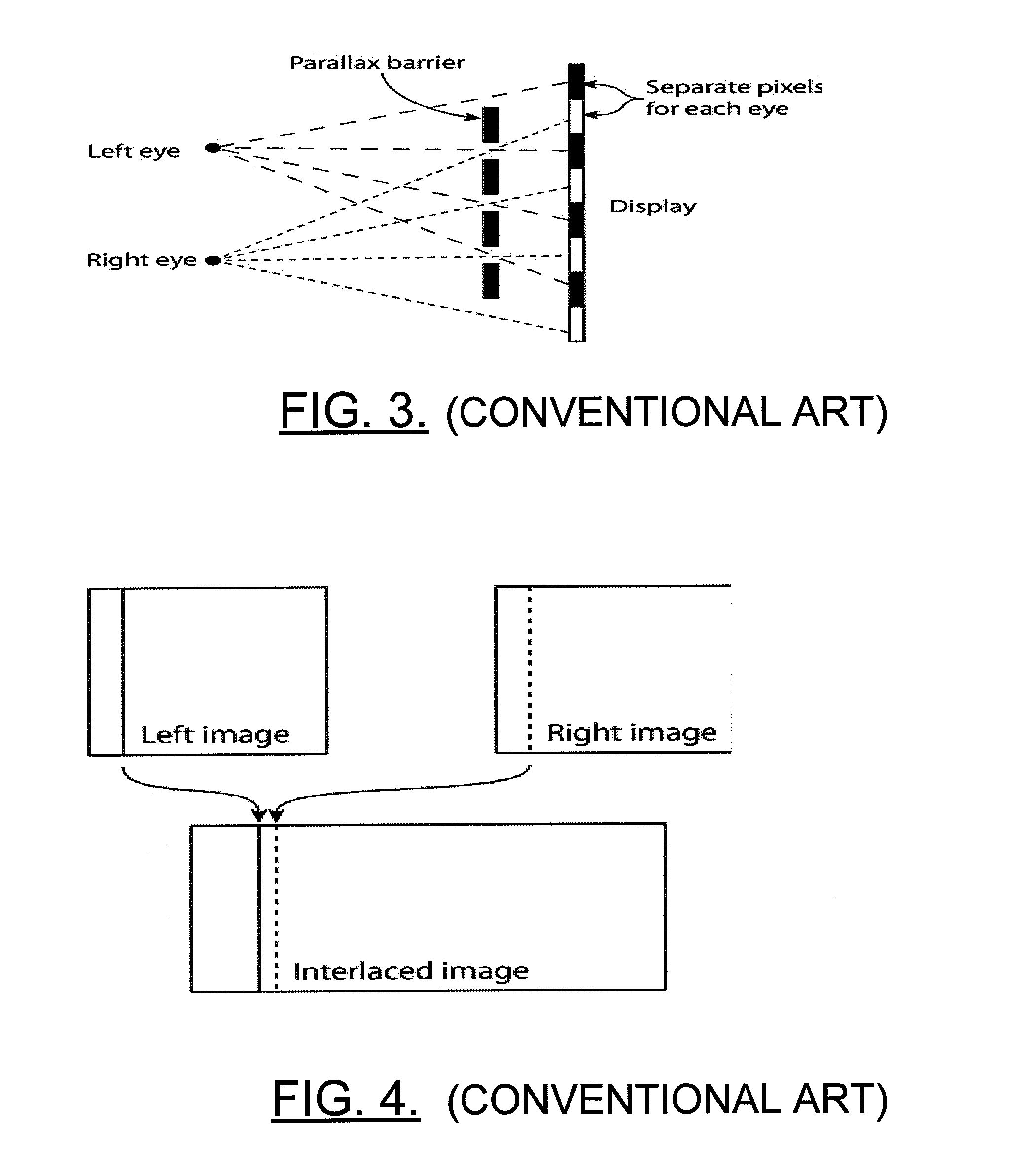

Apparatus, method and a computer program product for providing a unified graphics pipeline for stereoscopic rendering

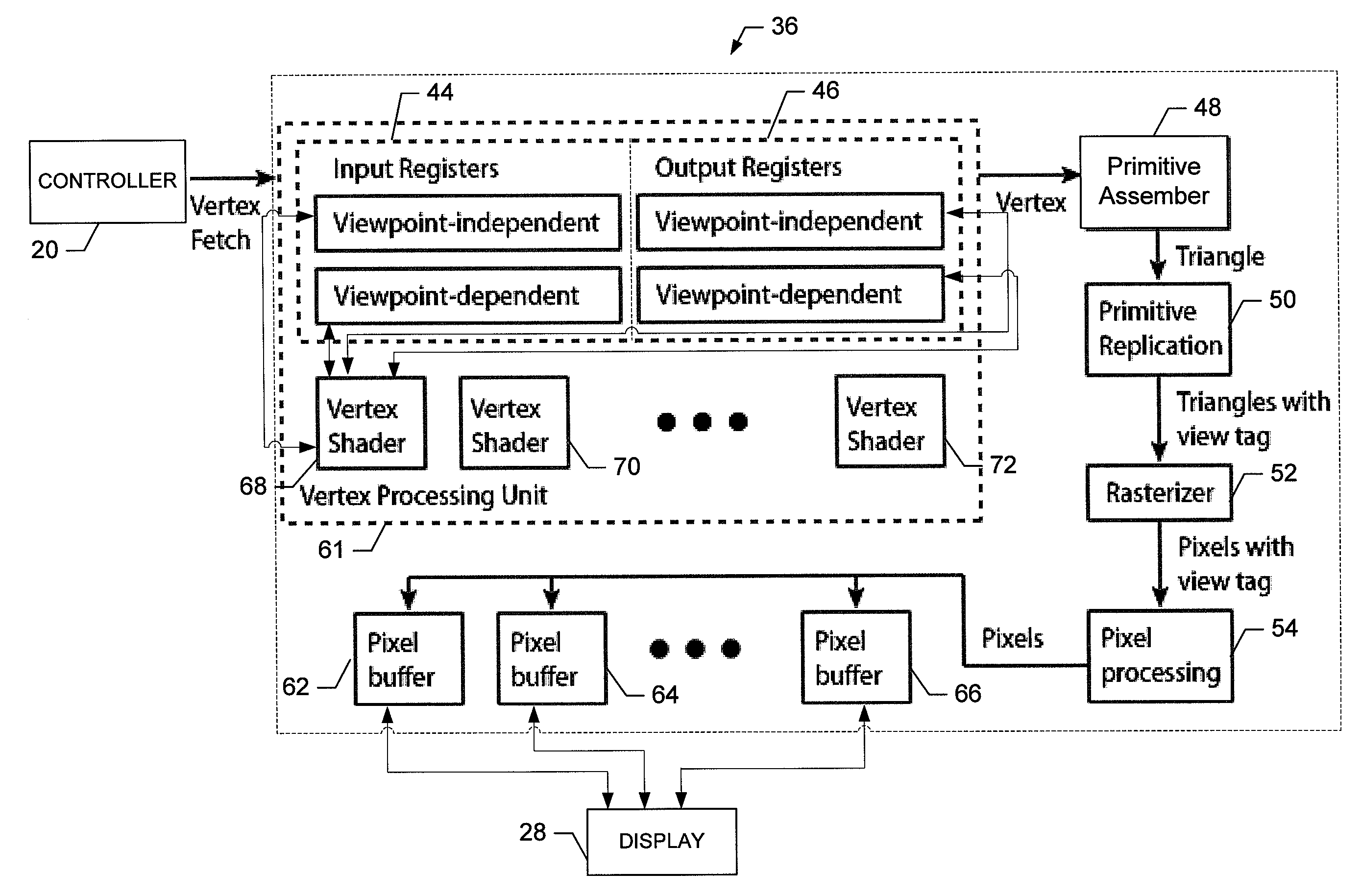

InactiveUS20080007559A1Reduce computationReduce power consumptionDigital computer detailsImage data processing detailsDisplay deviceMultiple viewpoint

A device for rendering to multiple viewpoints of a stereoscopic display is provided. The device includes vertex shaders which receive vertices corresponding to primitives and process viewpoint dependent information. The device also includes a primitive replication unit which replicates primitives according to a number of viewpoints supported by the stereoscopic display. The primitive replication unit adds unique view tags to each of the primitives which identify the viewpoint that the respective primitive is destined for. Each replicated primitive is processed by a rasterizer and converted into pixels. The rasterizer adds a view tag to the rasterized pixels so that the pixels identify a respective primitive and identify a respective pixel buffer that the pixel is destined for. The pixels can then be processed by a pixel processing unit and written to a pixel buffer corresponding to a respective viewpoint. The pixels are subsequently output to the stereoscopic display.

Owner:WSOU INVESTMENTS LLC

Graphics system with copy out conversions between embedded frame buffer and main memory

InactiveUS7184059B1Improve system flexibilityEasy to useImage memory managementCathode-ray tube indicatorsGraphic systemGraphics processing unit

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics processor includes an embedded frame buffer for storing frame data prior to sending the frame data to an external location, such as main memory. A copy pipeline is provided which converts the data from one format to another format prior to writing the data to the external location. The conversion may be from one RGB color format to another RGB color format, from one YUV format to another YUV format, from an RGB color format to a YUV color format, or from a YUV color format to an RGB color format. The formatted data is either transferred to a display buffer, for use by the video interface, or to a texture buffer, for use as a texture by the graphics pipeline in a subsequent rendering process.

Owner:NINTENDO CO LTD

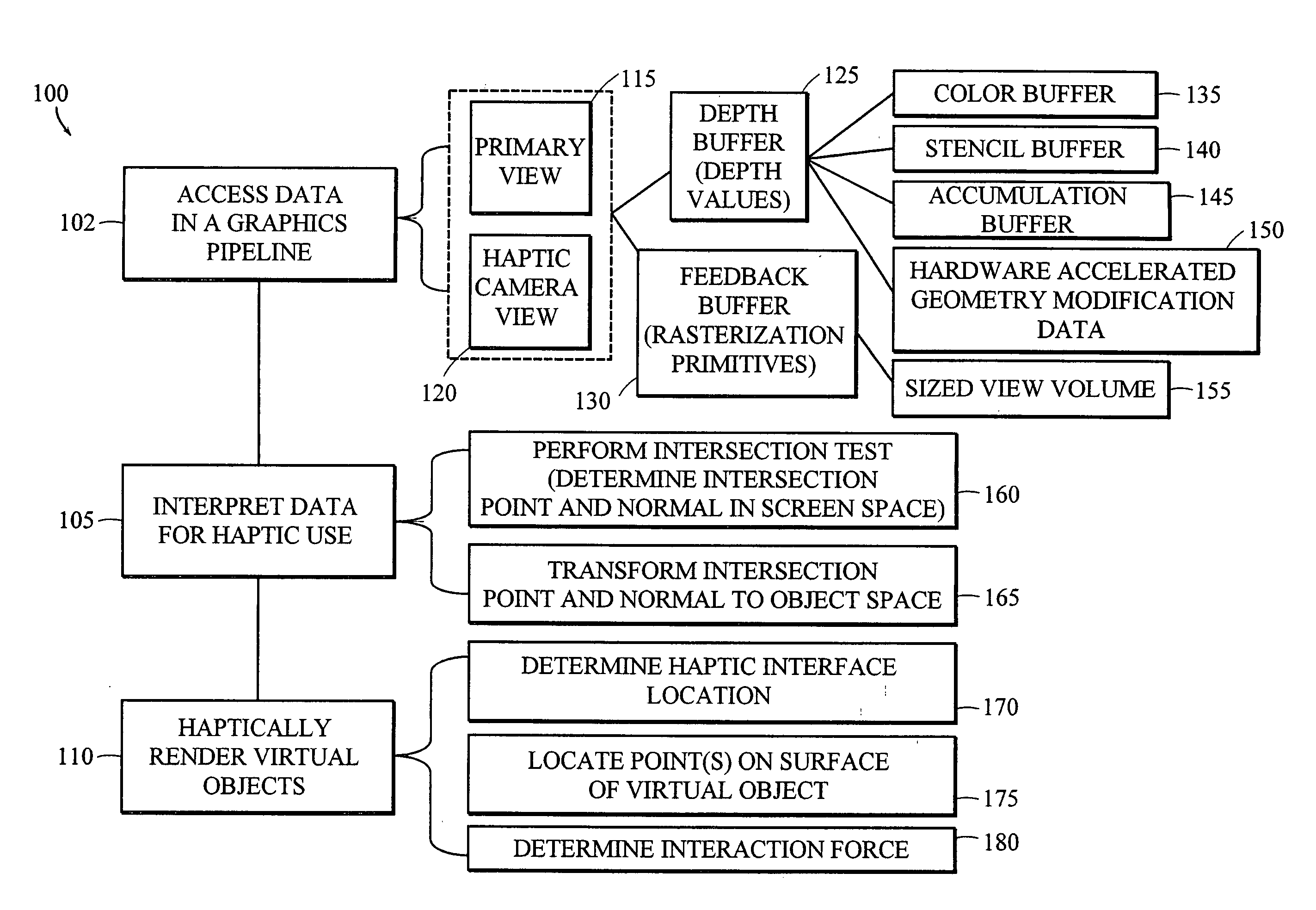

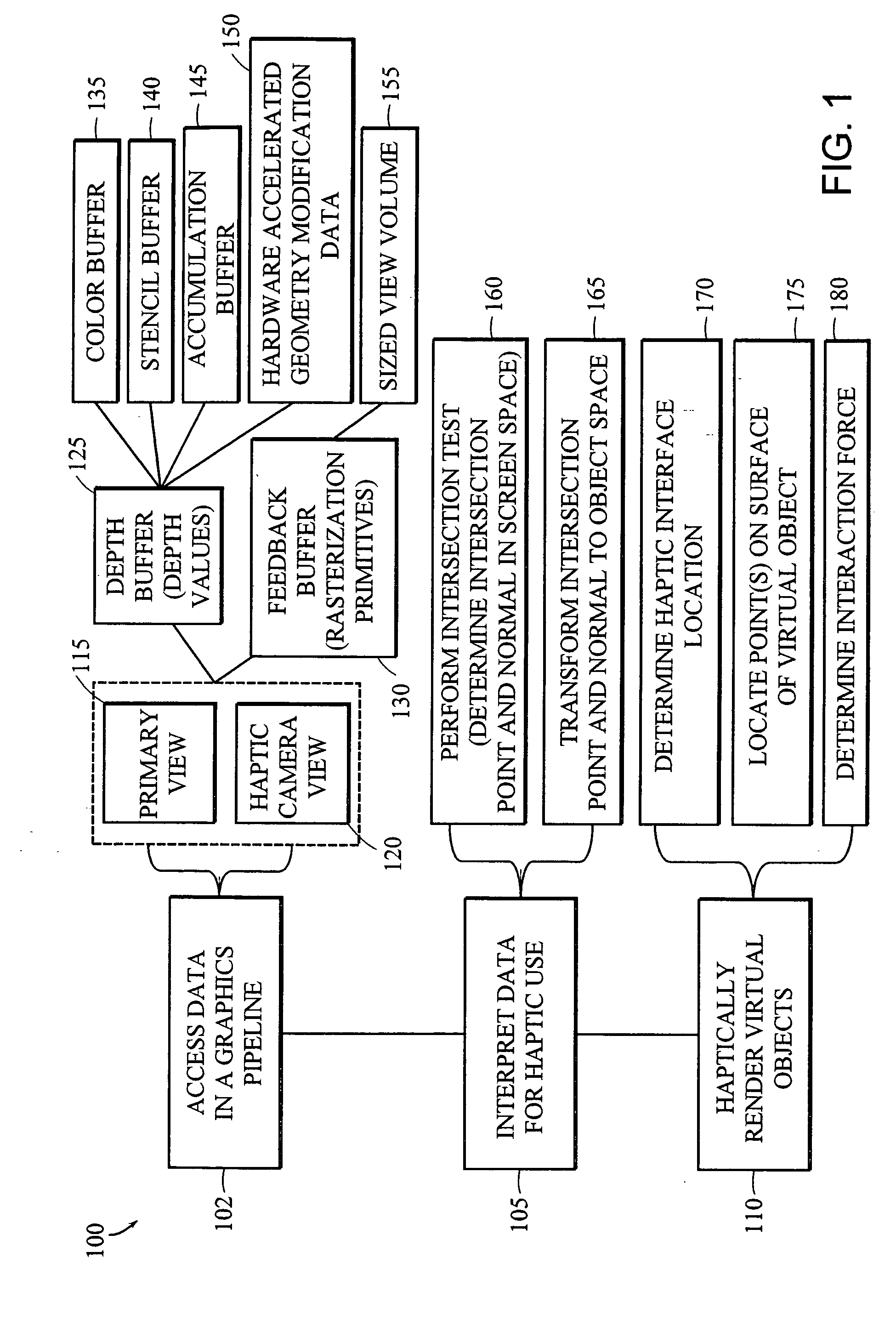

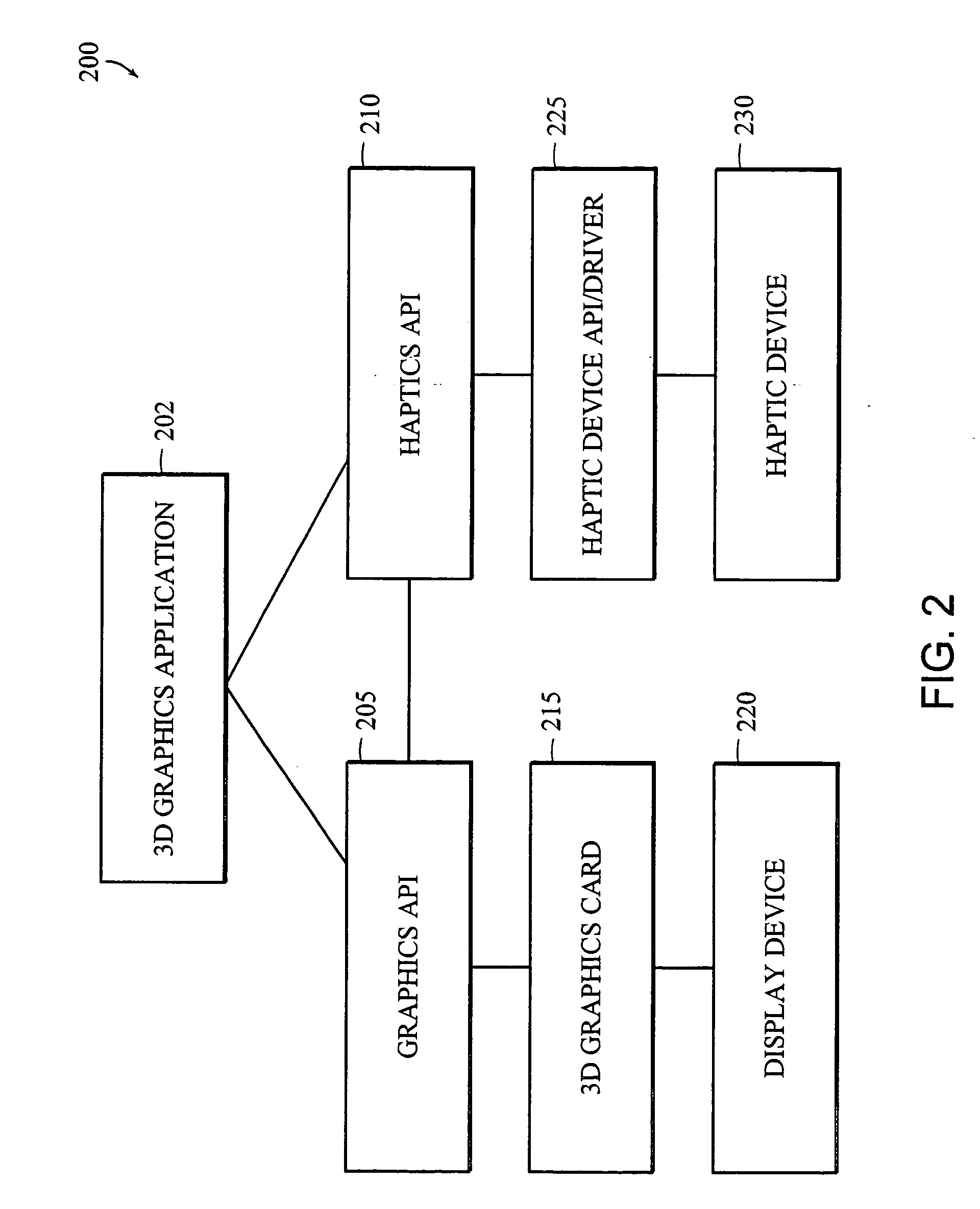

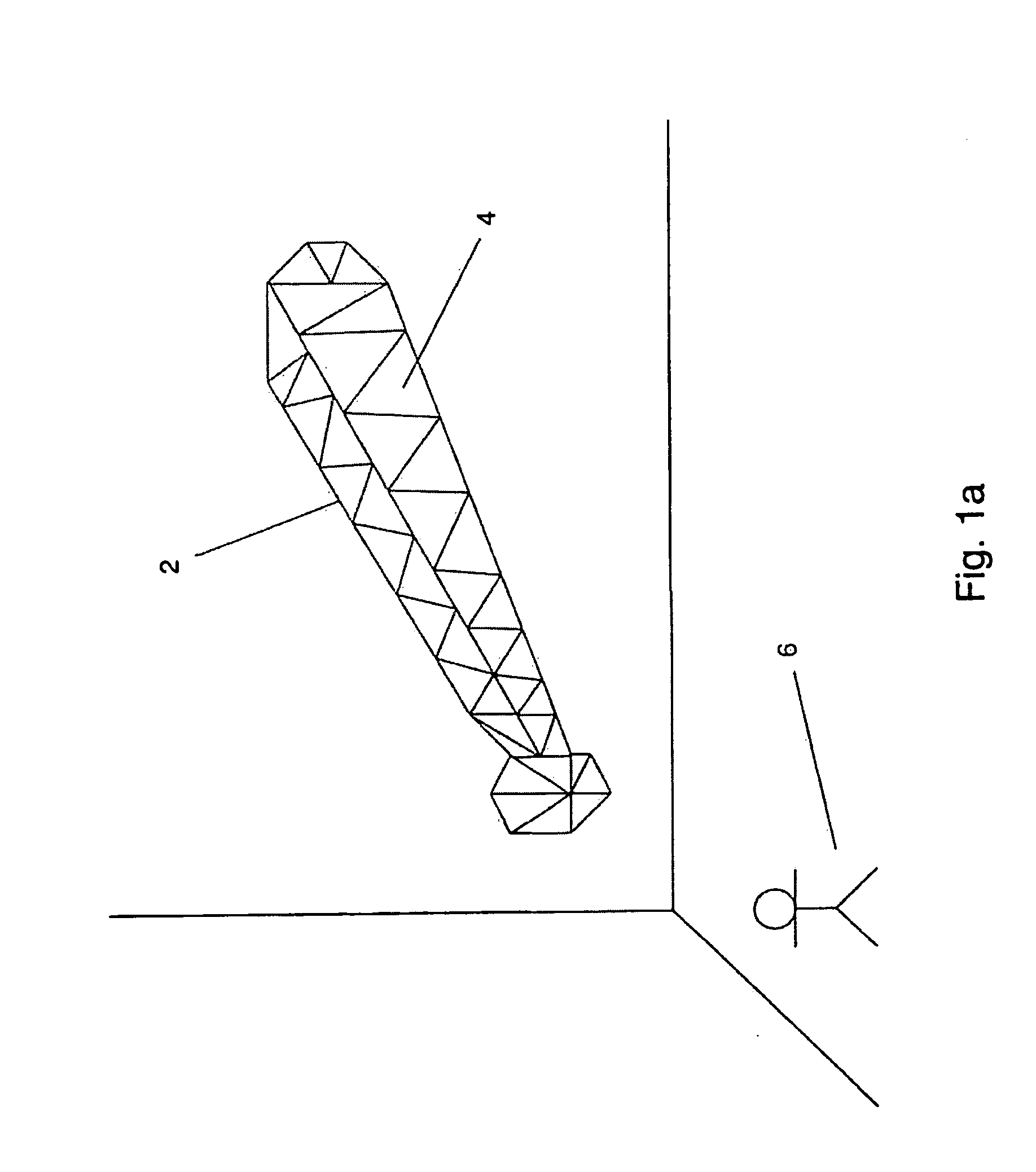

Apparatus and methods for haptic rendering using data in a graphics pipeline

ActiveUS20060109266A1Unleash processing performanceQuick fixGearworksMusical toysGraphicsLine tubing

The invention provides methods for leveraging data in the graphics pipeline of a 3D graphics application for use in a haptic rendering of a virtual environment. The invention provides methods for repurposing graphical information for haptic rendering. Thus, at least part of the work that would have been performed by a haptic rendering process to provide touch feedback to a user is obviated by work performed by the graphical rendering process.

Owner:3D SYST INC

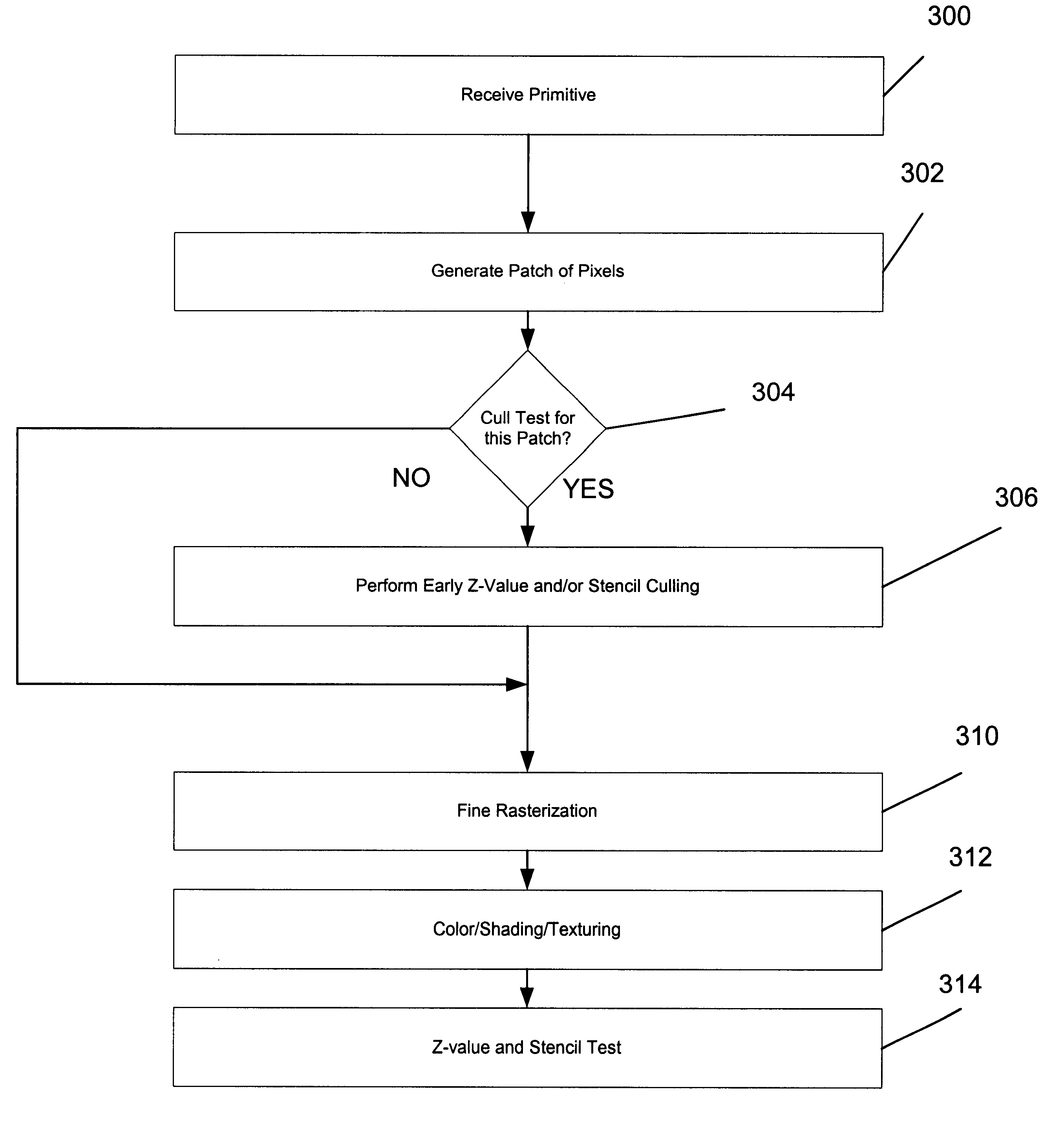

System, method and article of manufacture for Z-value and stencil culling prior to rendering in a computer graphics processing pipeline

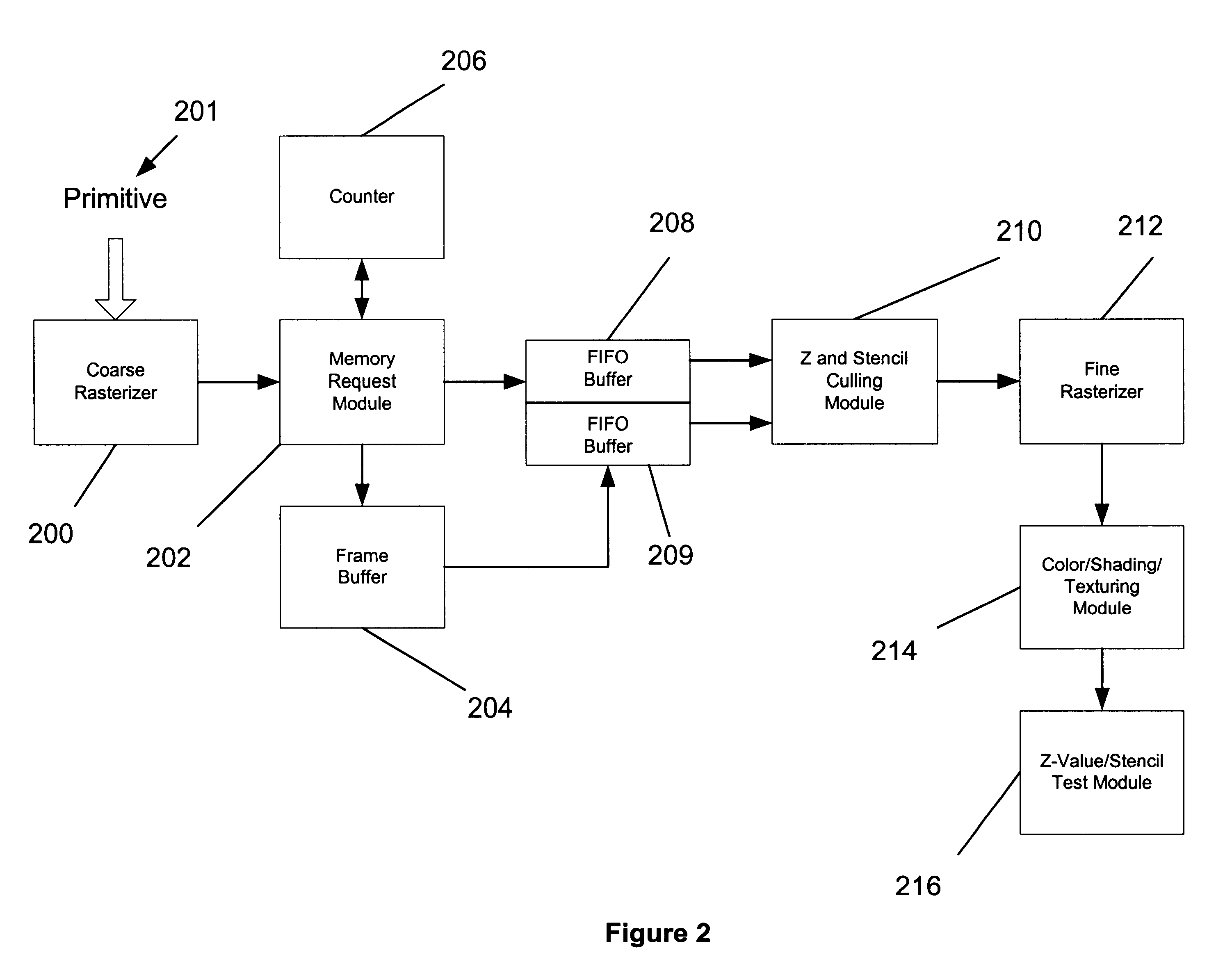

ActiveUS7068272B1Solve many processesReduce processing steps3D-image rendering3D modellingGraphicsGraphics pipeline

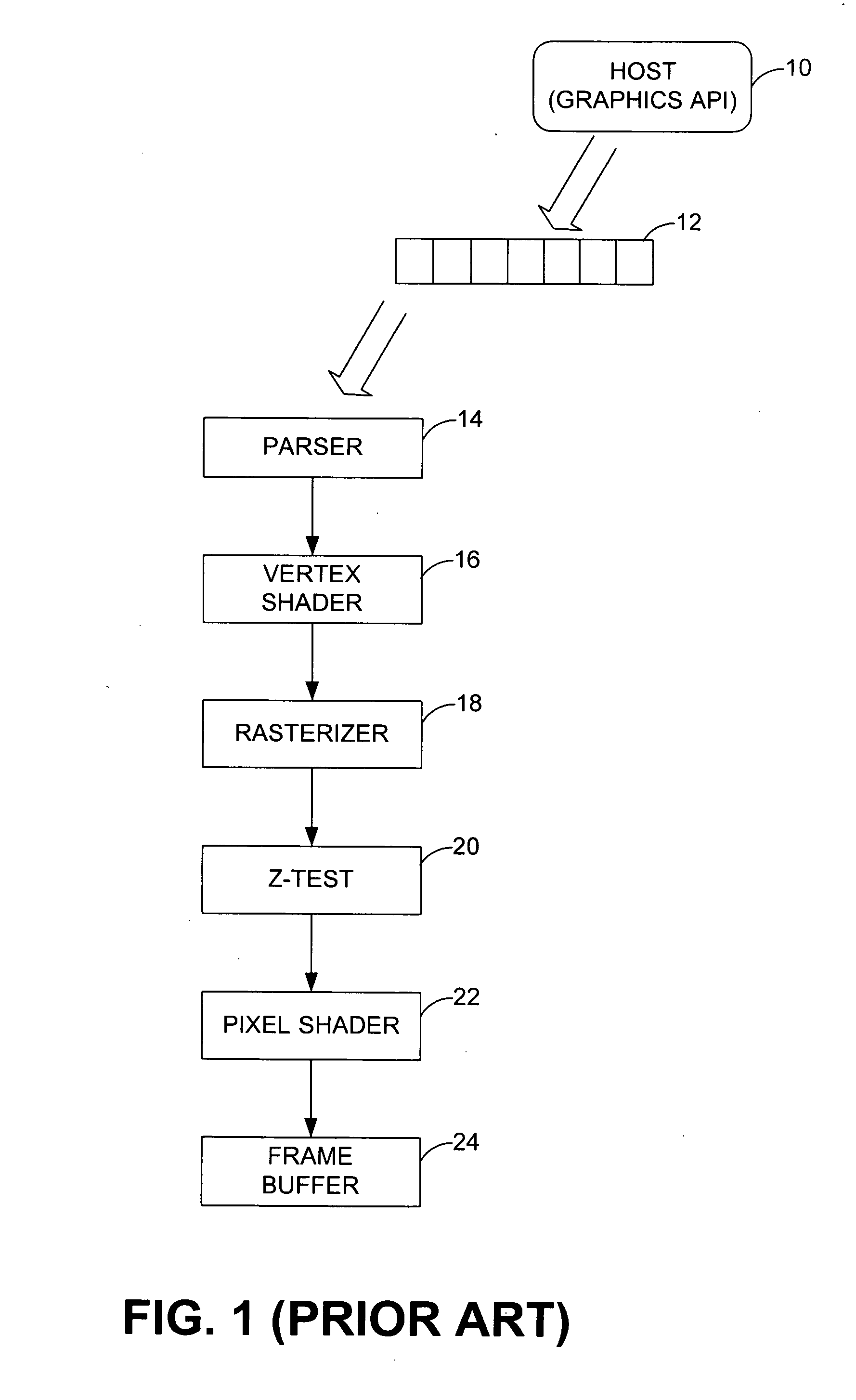

A system, method and article of manufacture are provided for early Z-value based culling prior to pixel rendering in a graphics pipeline. In initial stages of processing, Z-value culling is performed on at least one pixel. Thereafter, the pixel is conditionally rendered. Whether the pixel is rendered or not is conditioned on results of the Z-value culling. By culling, or removing, the pixels that do not meet certain criteria prior to rendering, much processing is avoided in the rendering portion of the graphics pipeline.

Owner:NVIDIA CORP

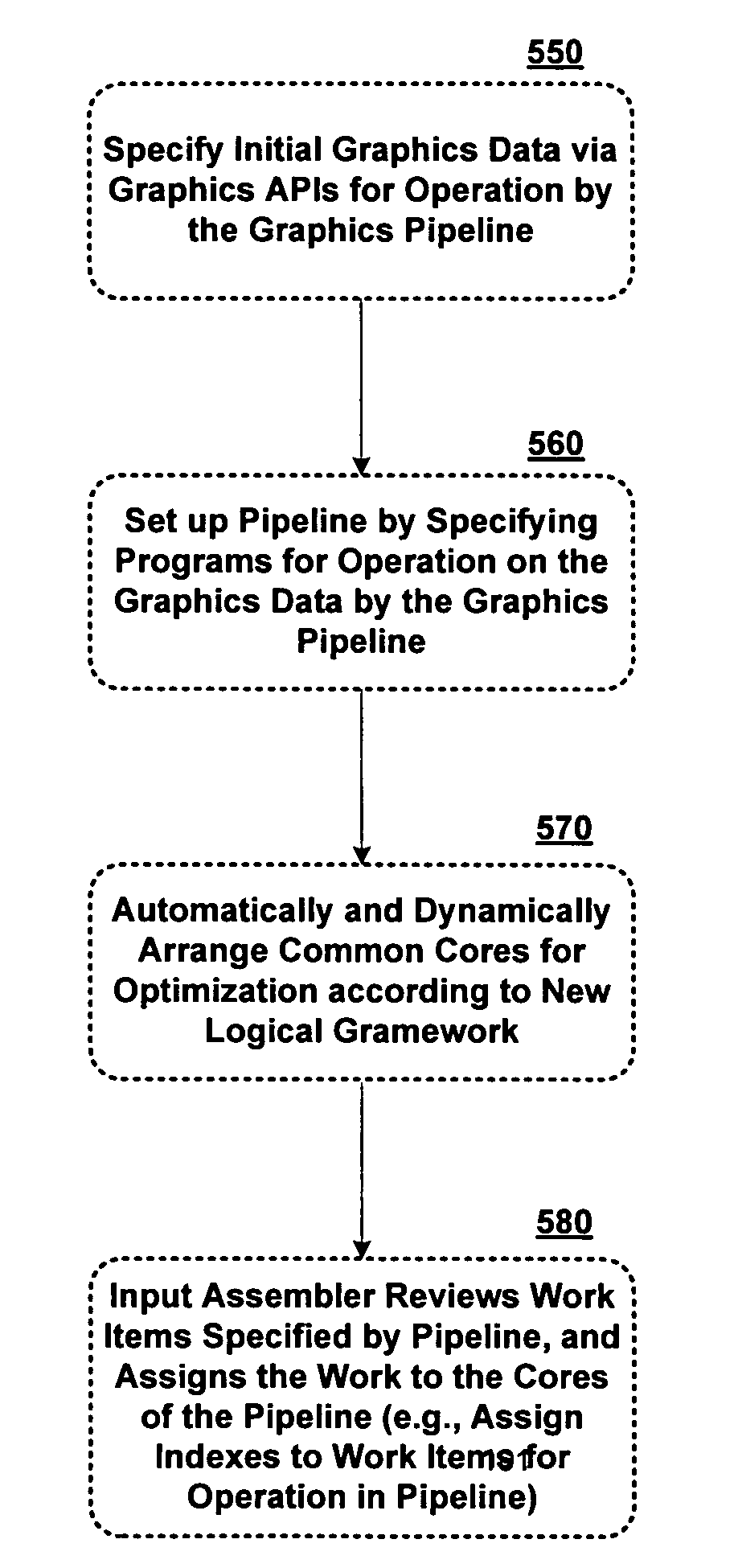

Systems and methods for providing an enhanced graphics pipeline

An enhanced graphics pipeline is provided that enables common core hardware to perform as different components of the graphics pipeline, programmability of primitives including lines and triangles by a component in the pipeline, and a stream output before or simultaneously with the rendering a graphical display with the data in the pipeline. The programmer does not have to optimize the code, as the common core will balance the load of functions necessary and dynamically allocate those instructions on the common core hardware. The programmer may program primitives using algorithms to simplify all vertex calculations by substituting with topology made with lines and triangles. The programmer takes the calculated output data and can read it before or while it is being rendered. Thus, a programmer has greater flexibility in programming. By using the enhanced graphics pipeline, the programmer can optimize the usage of the hardware in the pipeline, program vertex, line or triangle topologies altogether rather than each vertex alone, and read any calculated data from memory where the pipeline can output the calculated information.

Owner:MICROSOFT TECH LICENSING LLC

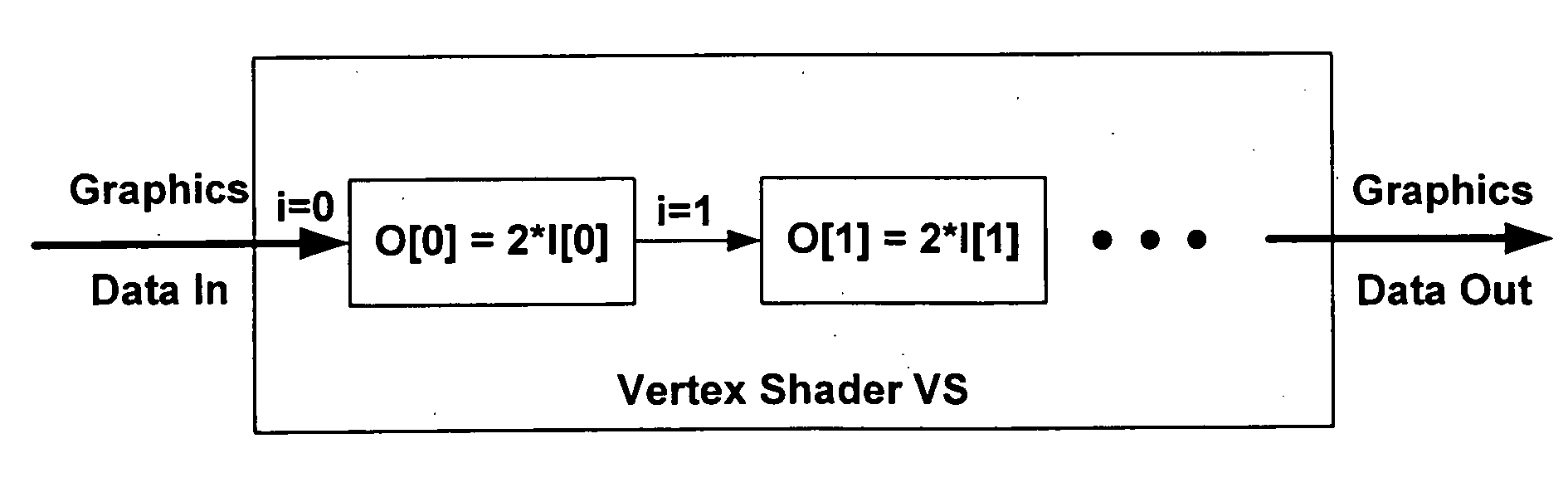

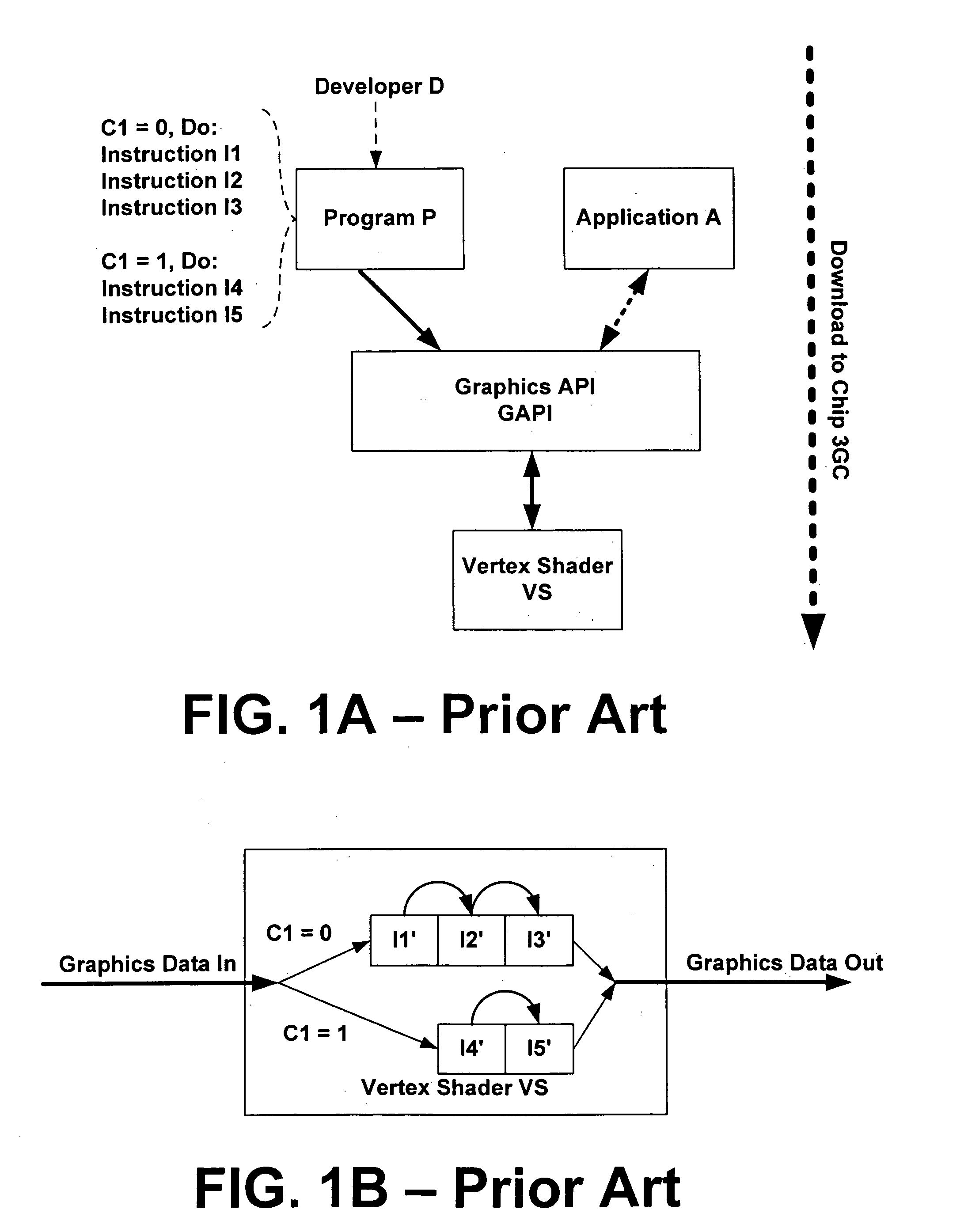

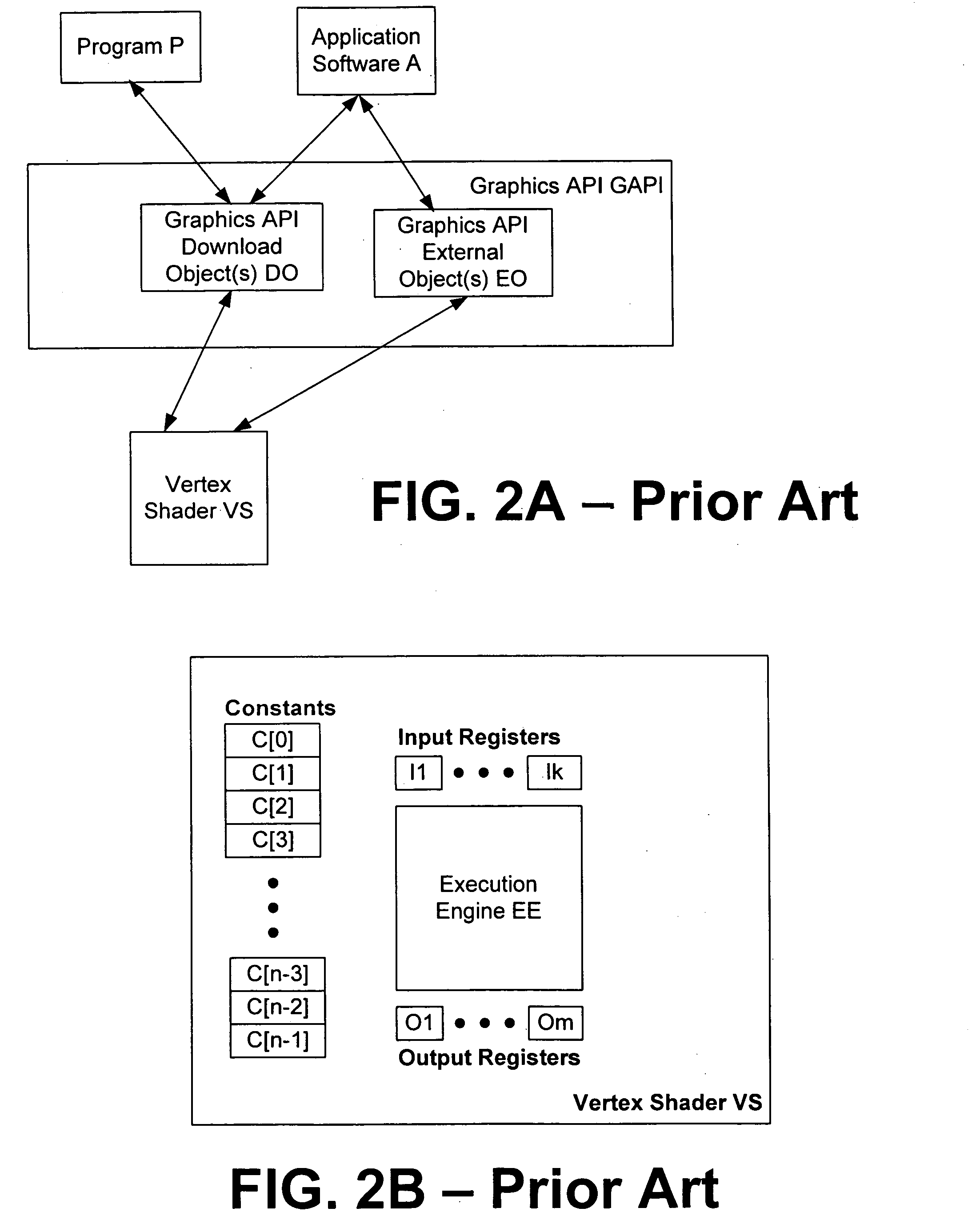

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122330A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

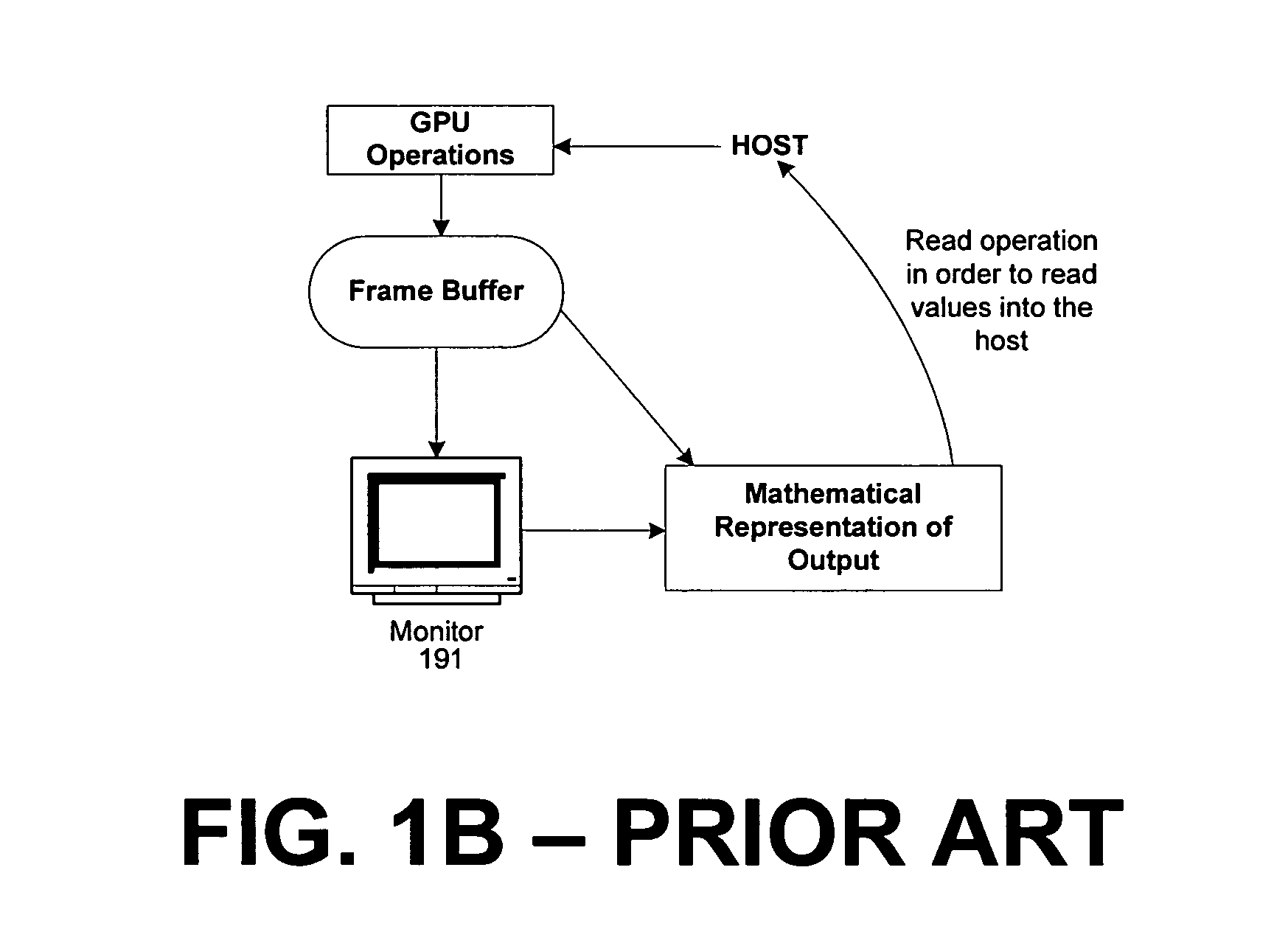

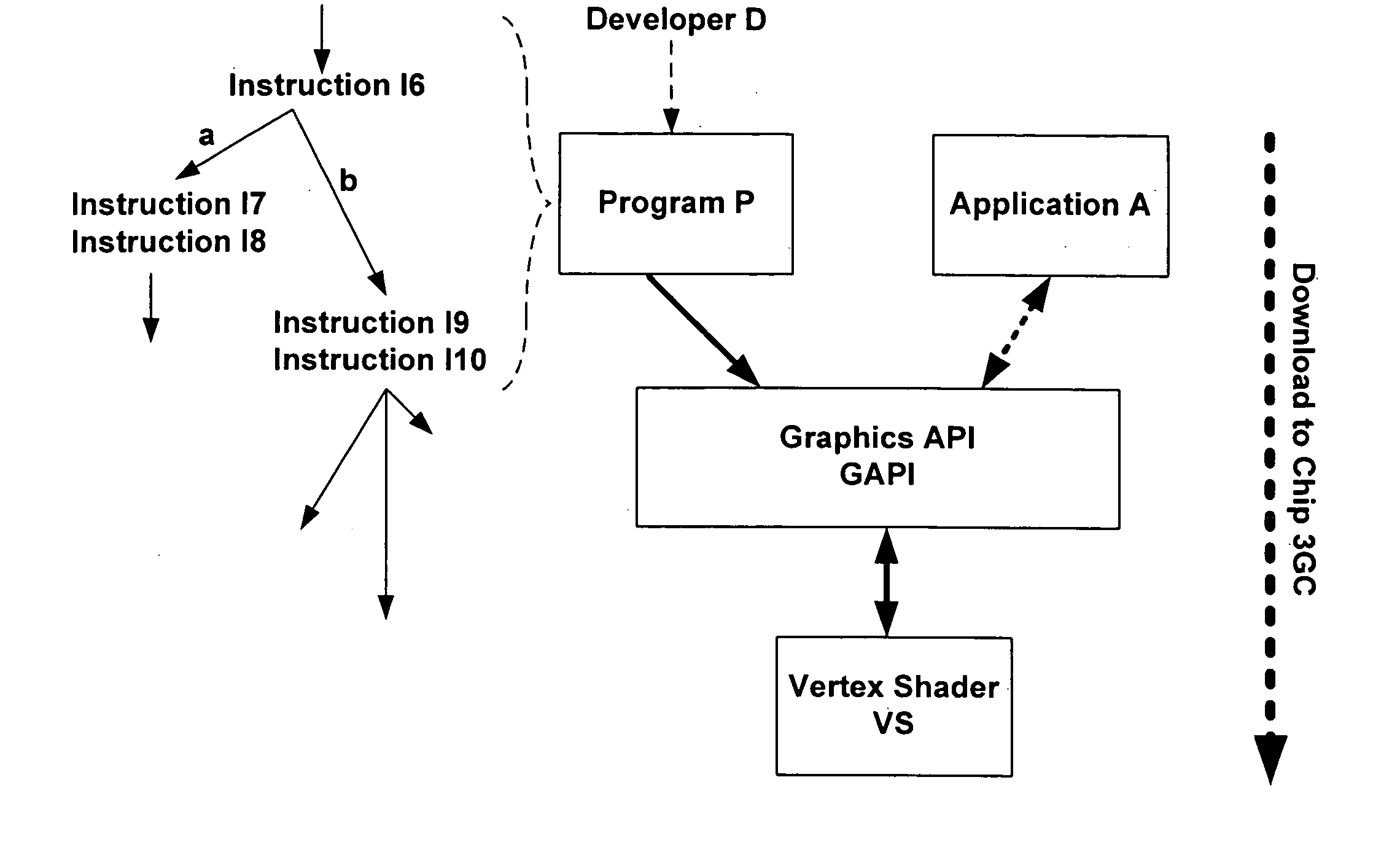

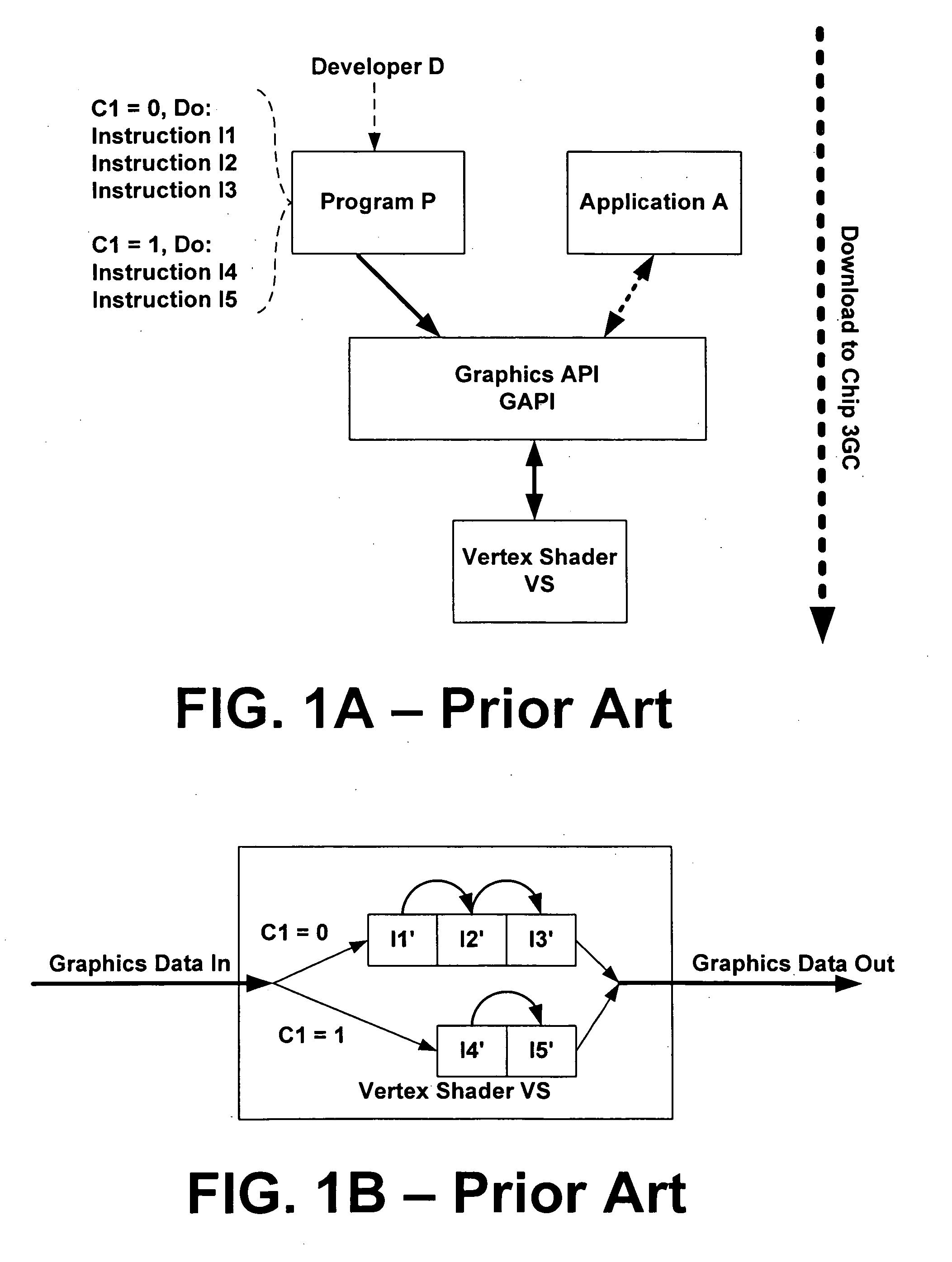

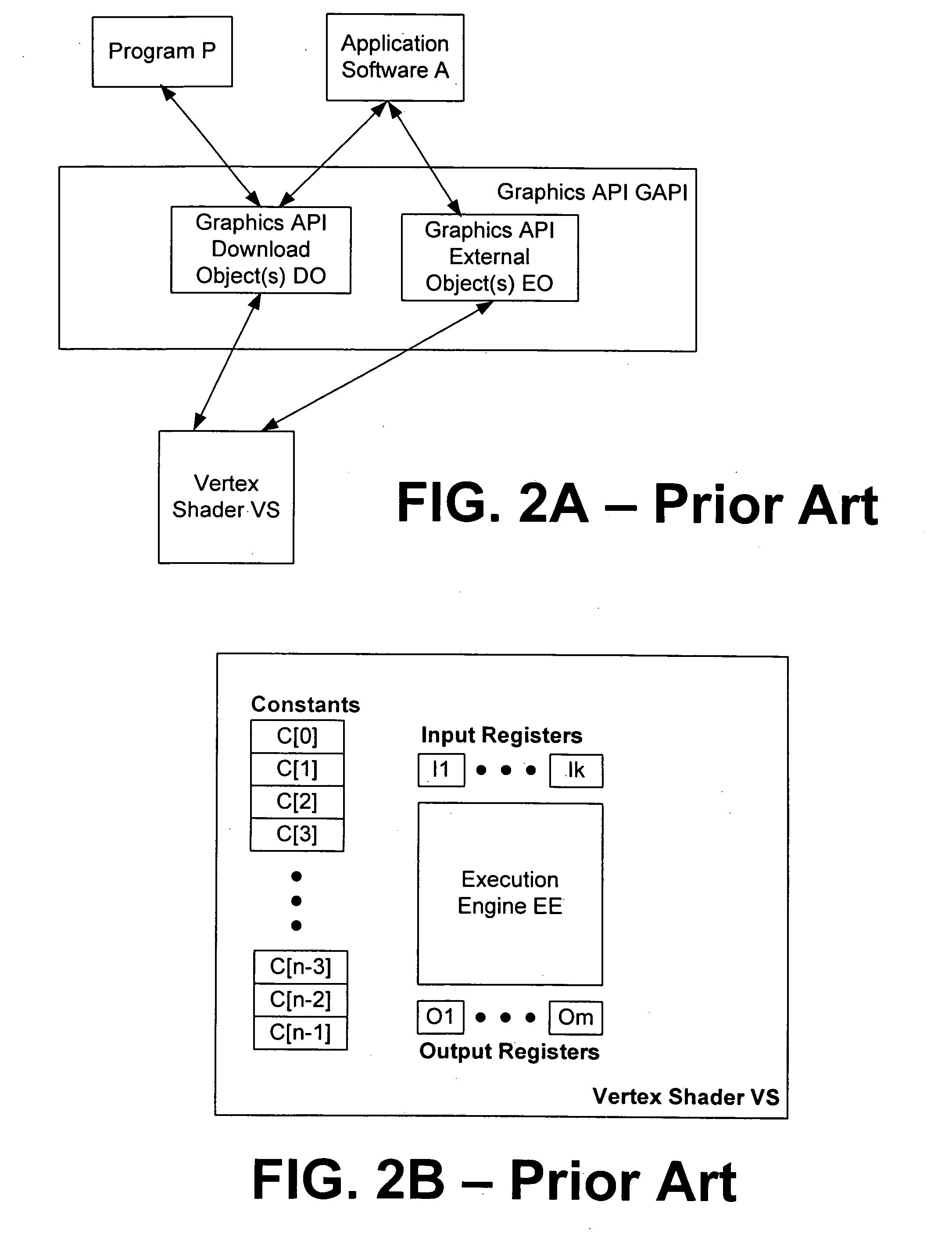

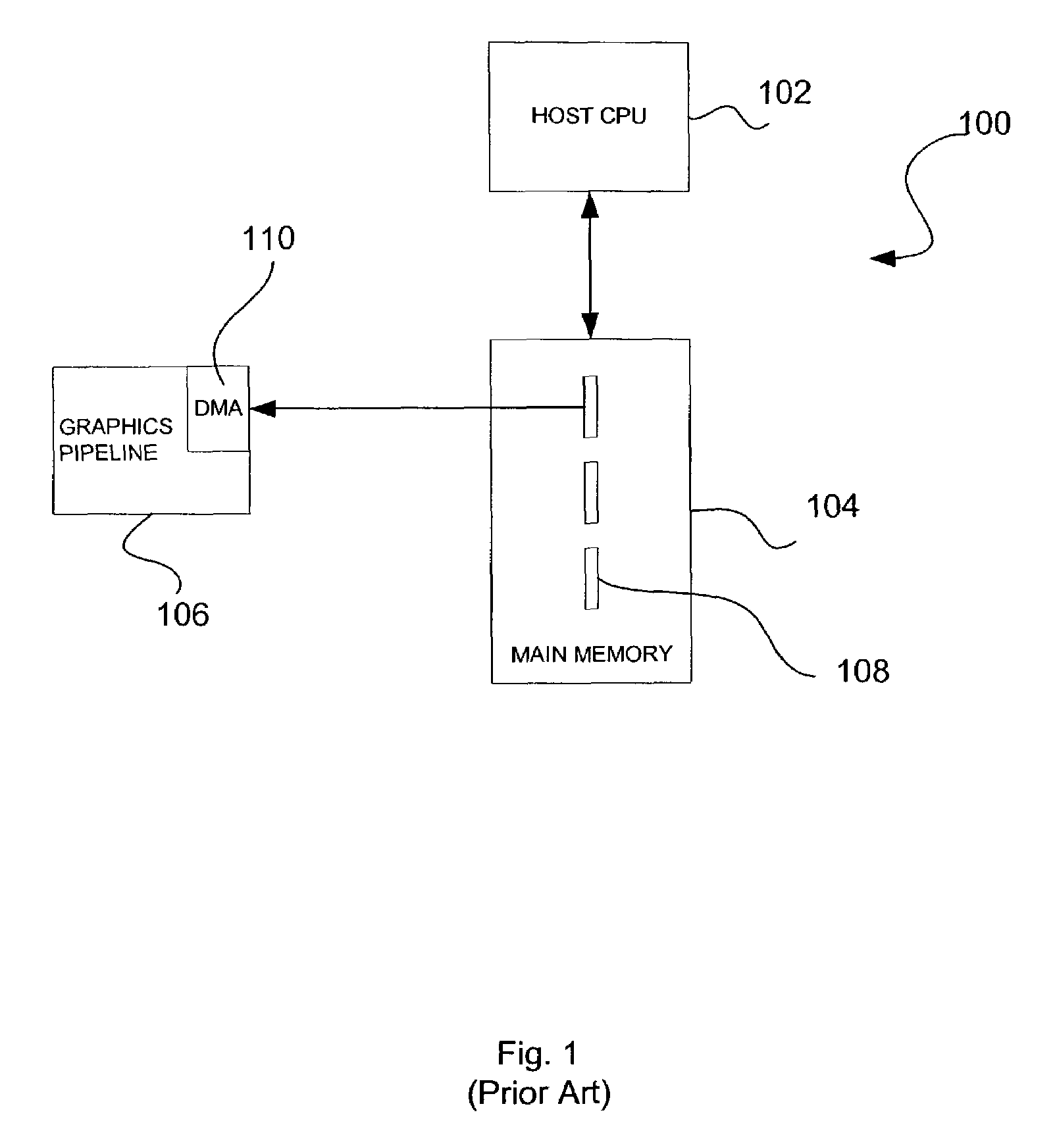

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

Deferred shading graphics pipeline processor

InactiveUS6268875B1Attenuation bandwidthTexturing/coloringImage memory managementPhong shadingComputer graphics (images)

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is a Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch & decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

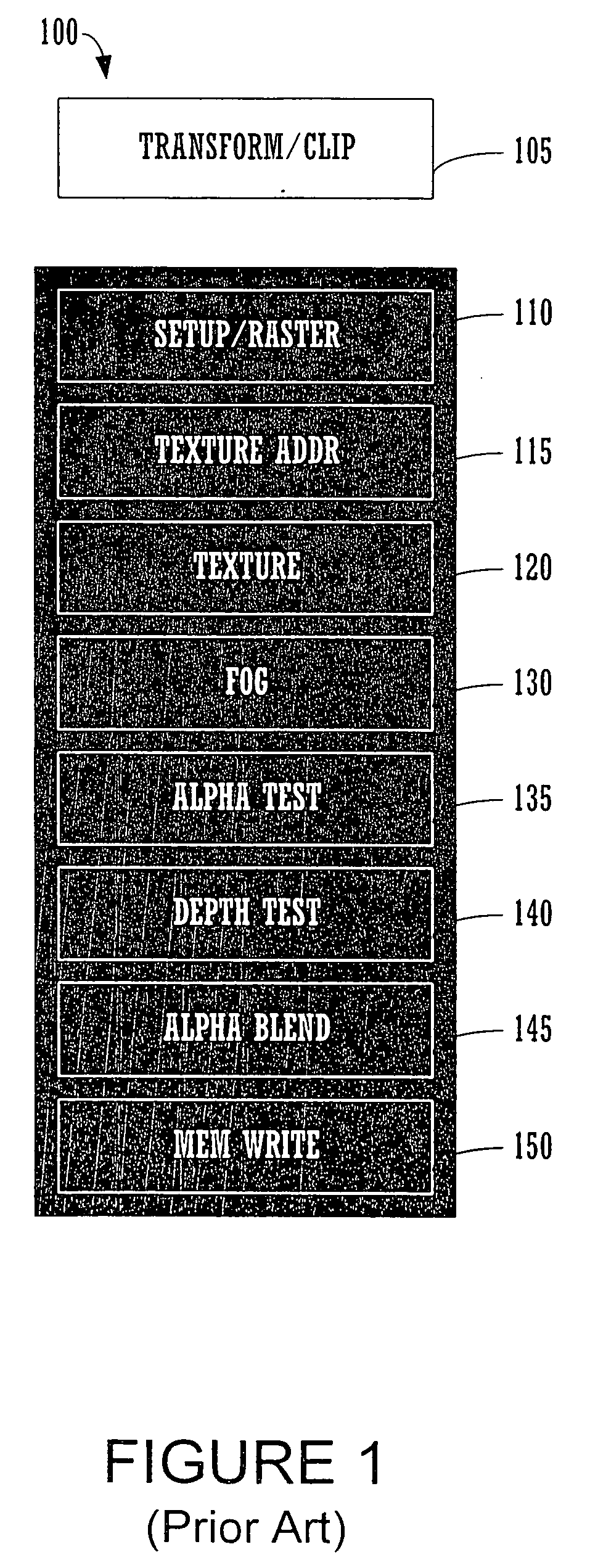

Efficient graphics pipeline with a pixel cache and data pre-fetching

InactiveUS6801203B1Mask inherent latencyImage memory managementMultiple digital computer combinationsGraphicsHigh bandwidth

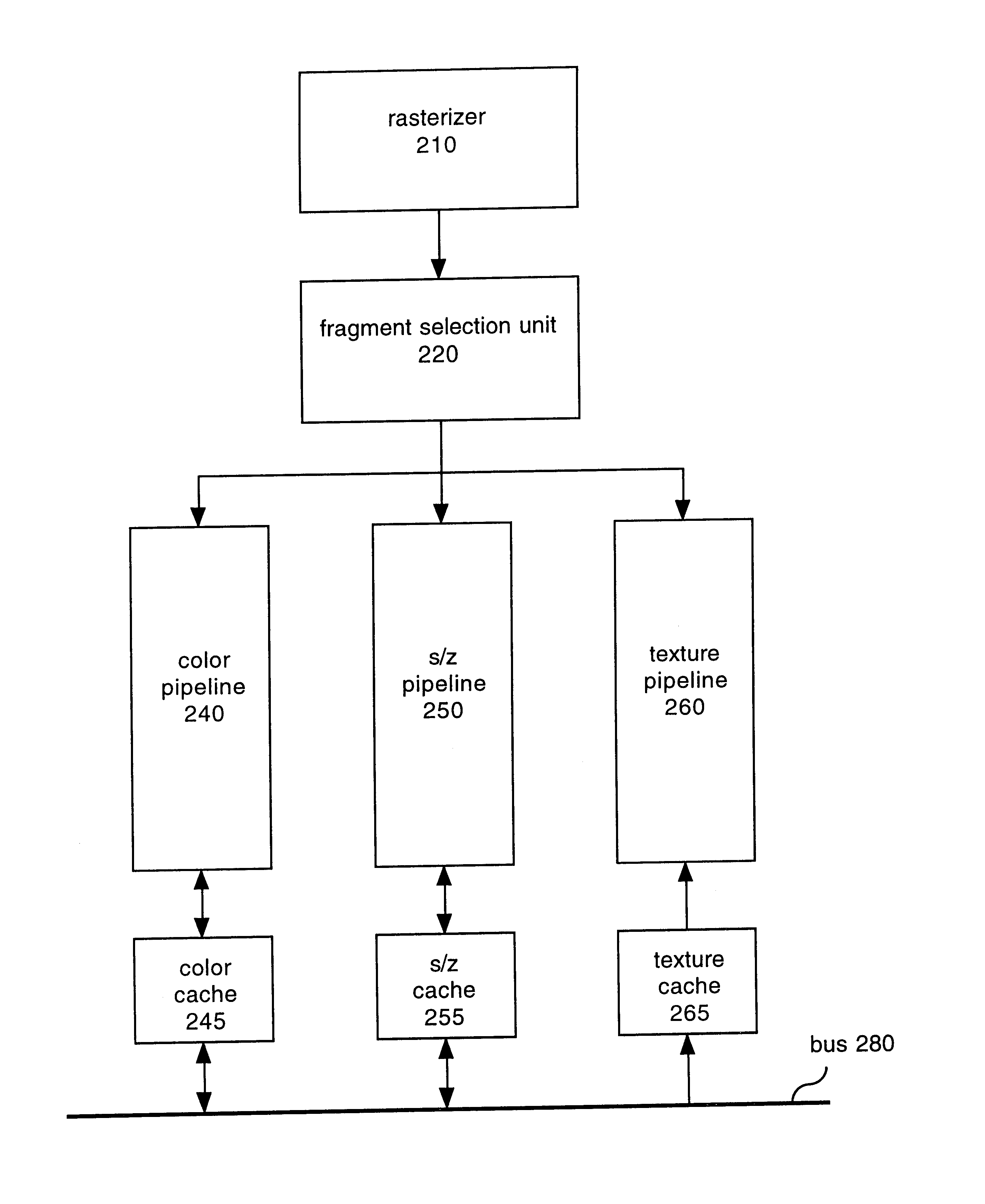

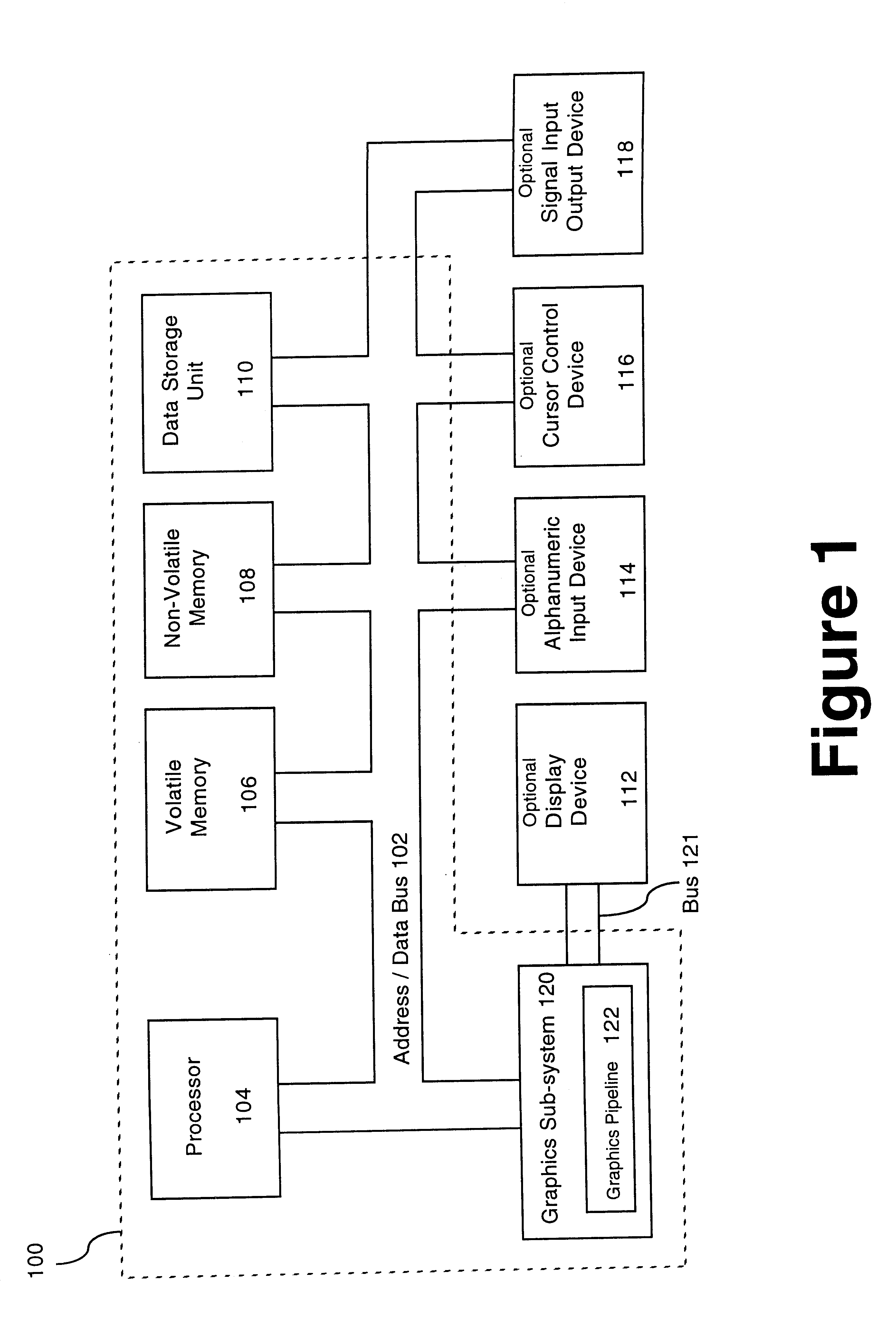

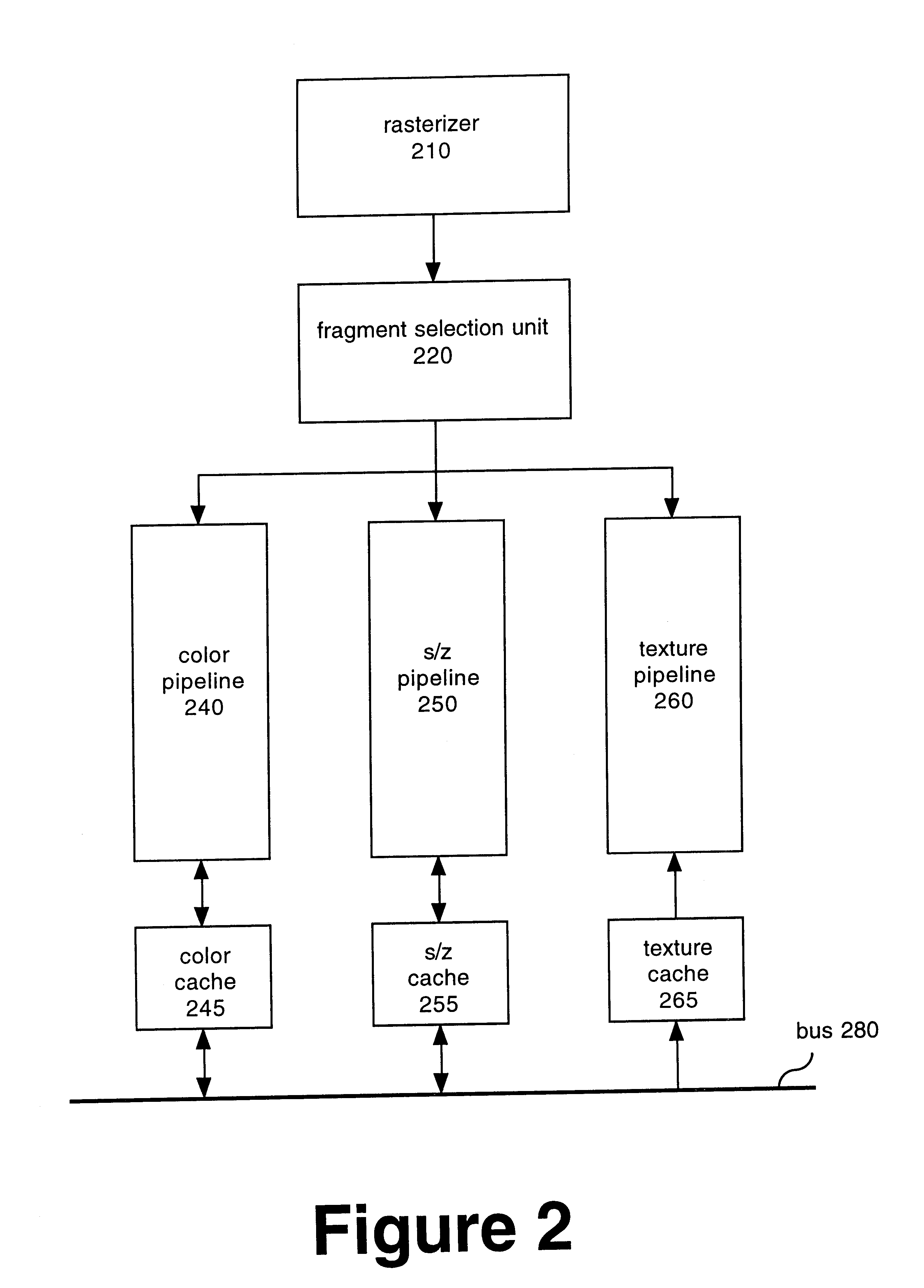

An efficient graphics pipeline with a pixel cache and data pre-fetching. By combining the use of a pixel cache in the graphics pipeline and the pre-fetching of data into the pixel cache, the graphics pipeline of the present invention is able to take best advantage of the high bandwidth of the memory system while effectively masking the latency of the memory system. More particularly, advantageous reuse of pixel data is enabled by caching, which when combined with pre-fetching masks the memory latency and delivers high throughput. As such, the present invention provides a novel and superior graphics pipeline over the prior art in terms of more efficient data access and much greater throughput. In one embodiment, the present invention is practiced within a computer system having a processor for issuing commands; a memory sub-system for storing information including graphics data; and a graphics sub-system for processing the graphics data according to the commands from the processor. The graphics sub-system comprises a rasterizer for traversing graphics primitives of the graphics data to generate pixel coordinates for pixels corresponding to the graphics primitives; a graphics pipeline for processing the graphics data of the pixels; and a pixel cache for caching the pixel data. In this embodiment, he graphics sub-system masks the inherent latency of the memory sub-system by pre-fetching the graphics data and storing the graphics data within the pixel cache.

Owner:MICROSOFT TECH LICENSING LLC

Graphics pipeline token synchronization

InactiveUS6867781B1Problem is complicatedMultiple digital computer combinationsProcessor architectures/configurationGraphicsGraphic system

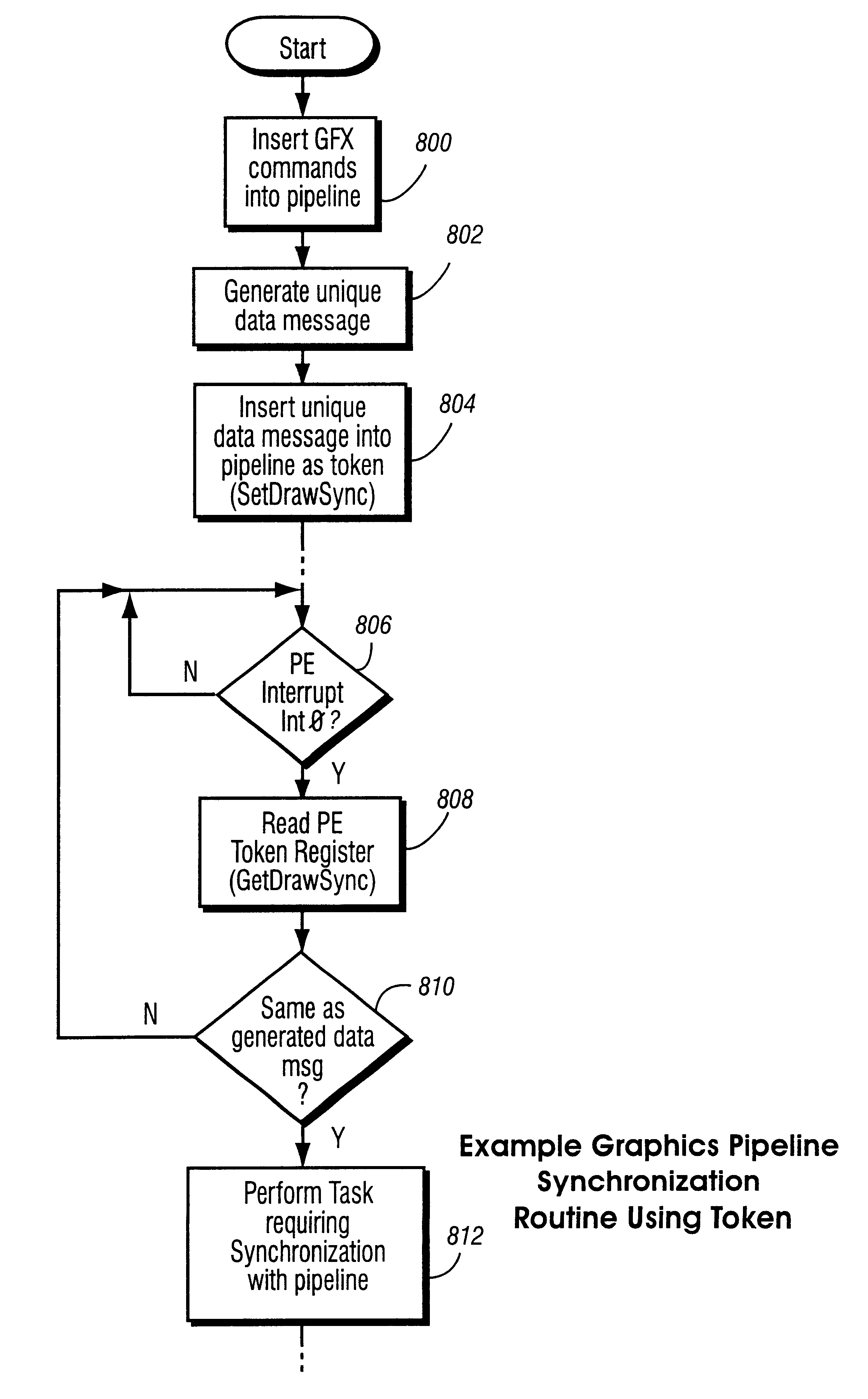

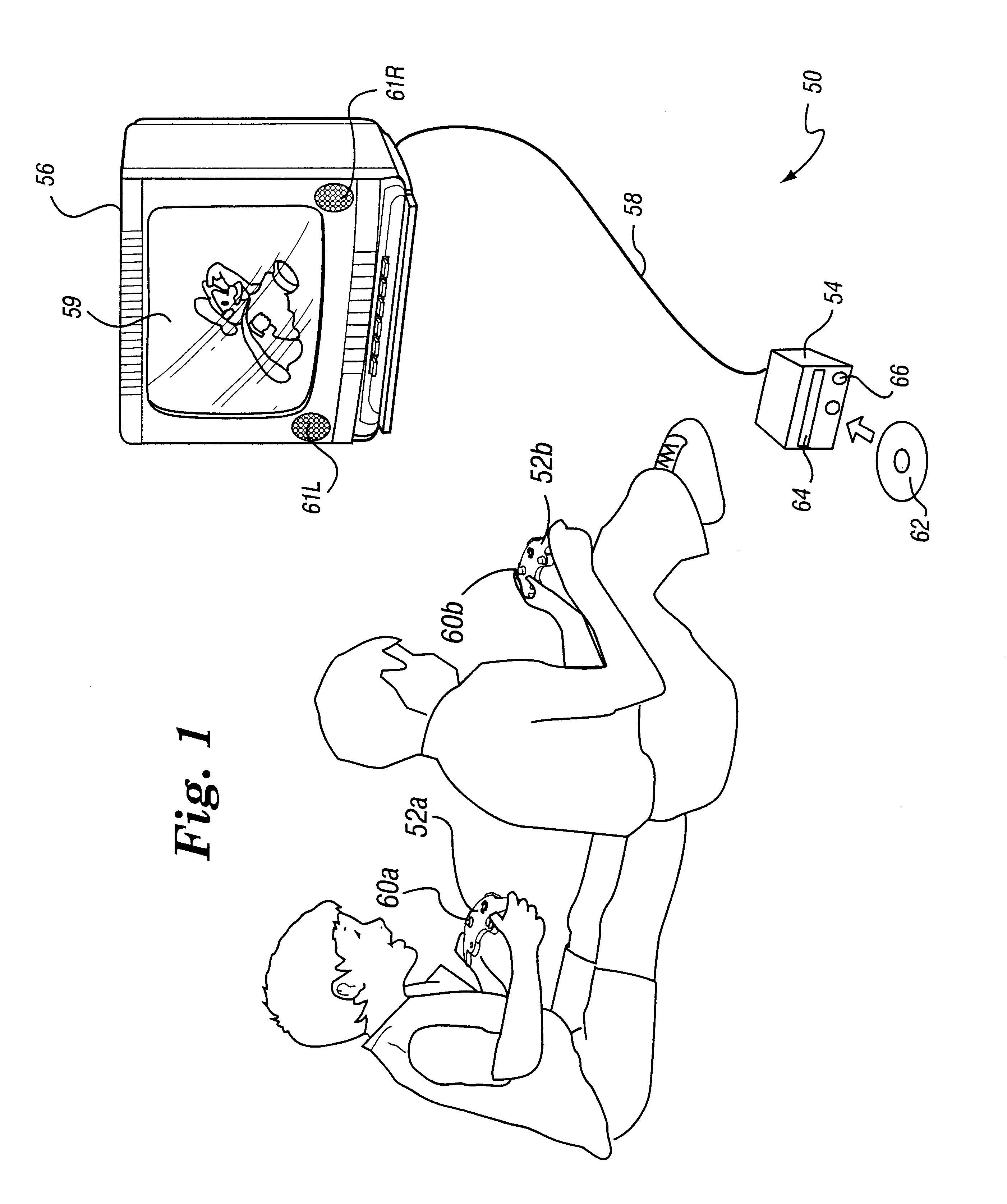

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics pipeline processes graphics commands at different rates depending upon the type of operation being performed. This makes it difficult to synchronize pipeline operations with external operations (e.g., a graphics processor with a main processor). To solve this problem, a synchronization token including a programmable data message is inserted into a graphics command stream sent to a graphics pipeline. At a predetermined point near the bottom of the pipeline, the token is captured and a signal is generated indicated the token has arrived. The graphics command producer can look at the captured token to determine which of multiple possible tokens has been captured, and can use the information to synchronize a task with the graphics pipeline. Applications include maintaining memory coherence in memory shared between the 3D graphics pipeline and a graphics command producer.

Owner:NINTENDO CO LTD

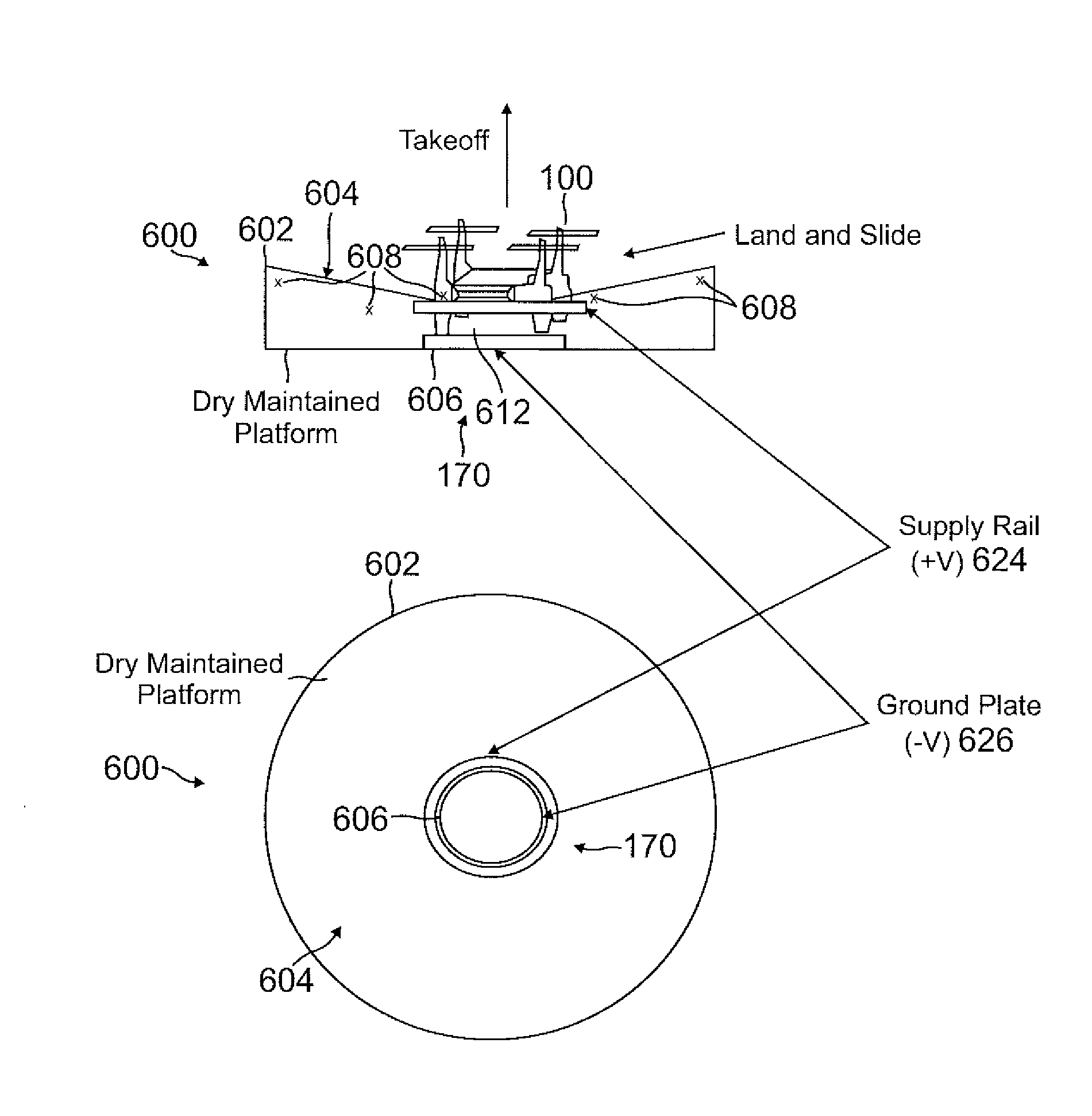

Vertical takeoff and landing (VTOL) small unmanned aerial system for monitoring oil and gas pipelines

Owner:MOHAMADI FARROKH

Apparatus and method for rendering graphics primitives using a multi-pass rendering approach

InactiveUS20050122338A1Cathode-ray tube indicatorsProcessor architectures/configurationComputational scienceGraphics

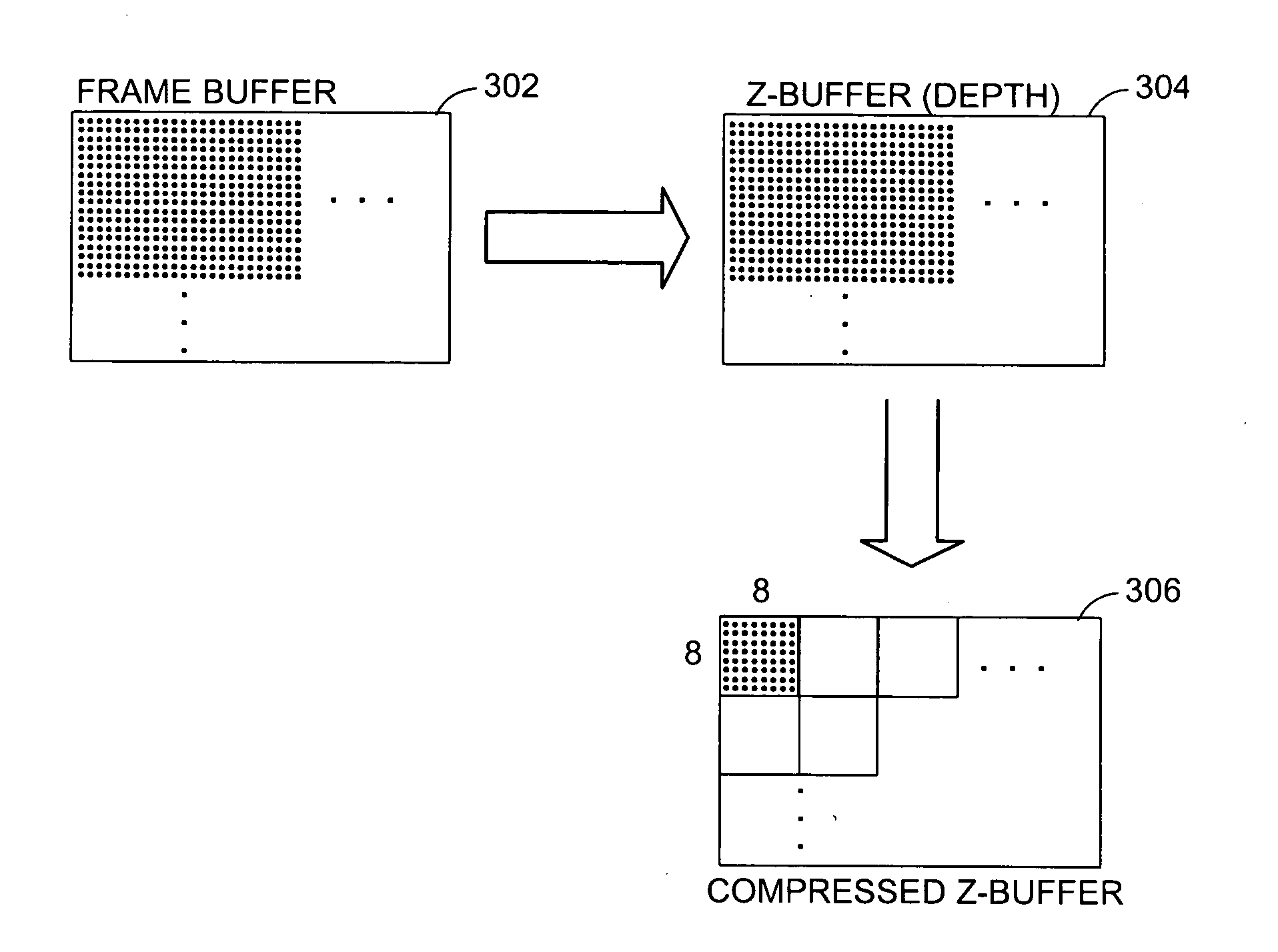

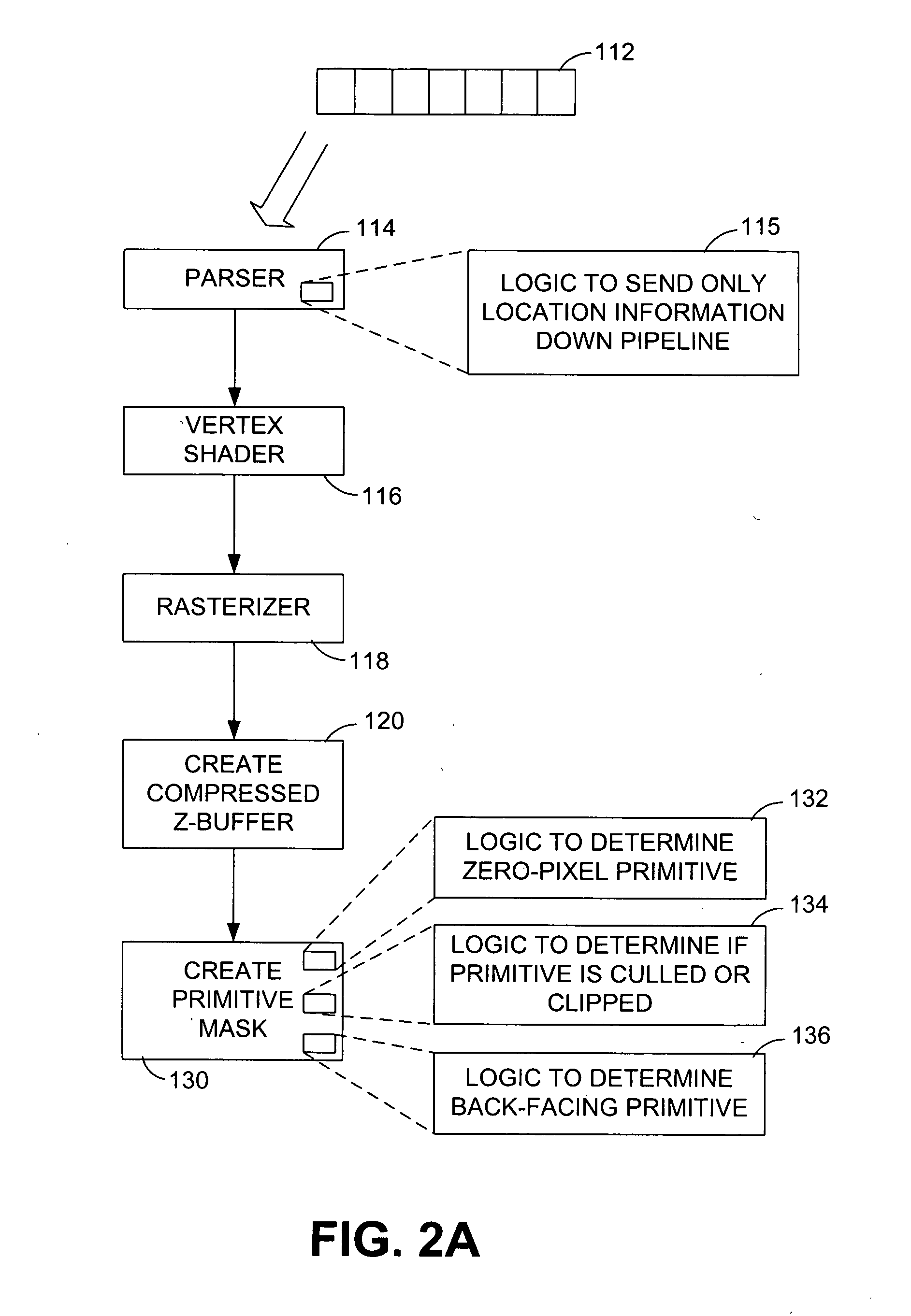

The present invention is generally directed to a multi-pass rendering system and method. In one embodiment, in first pass of a graphics primitive data through a graphics pipeline, a compressed z-buffer is generated for the primitive. A primitive mask is also generated, which indicates whether all pixels of the primitive are hidden from view. In a second pass, graphics data for a given primitive is passed through the pipeline, only if the primitive mask for that primitive indicates that some portion of the primitive is visible. Thereafter, a two-level z-test is performed on that primitive. In the two-level z-test, a first level comparison is made on groups of pixels at a time, using the compressed z-buffer created in the first pass.

Owner:VIA TECH INC

Efficient 2-d and 3-d graphics processing

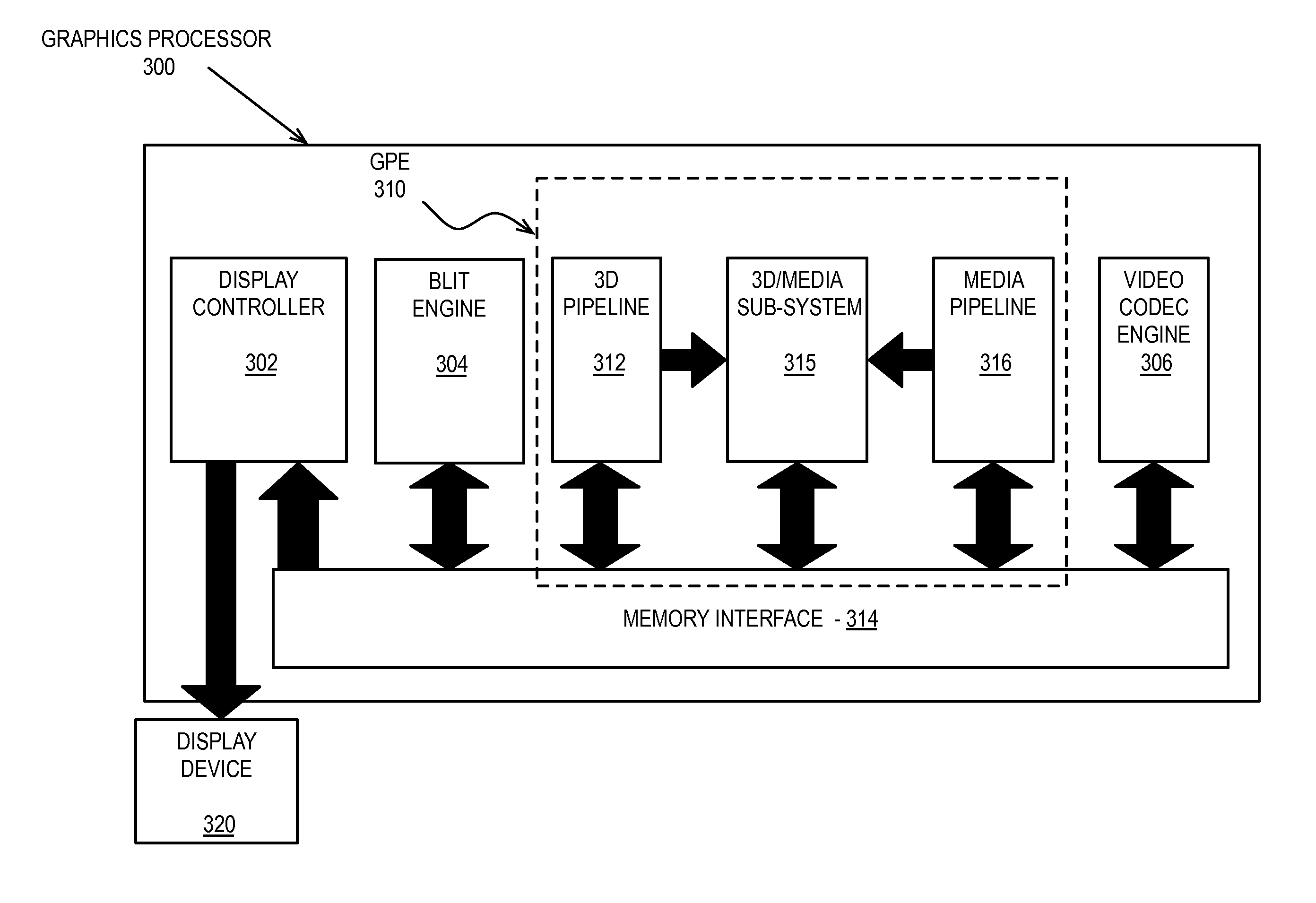

ActiveUS20080198168A1Easy to useEffective supportDigital computer detailsCathode-ray tube indicatorsComputational scienceGraphics processing unit

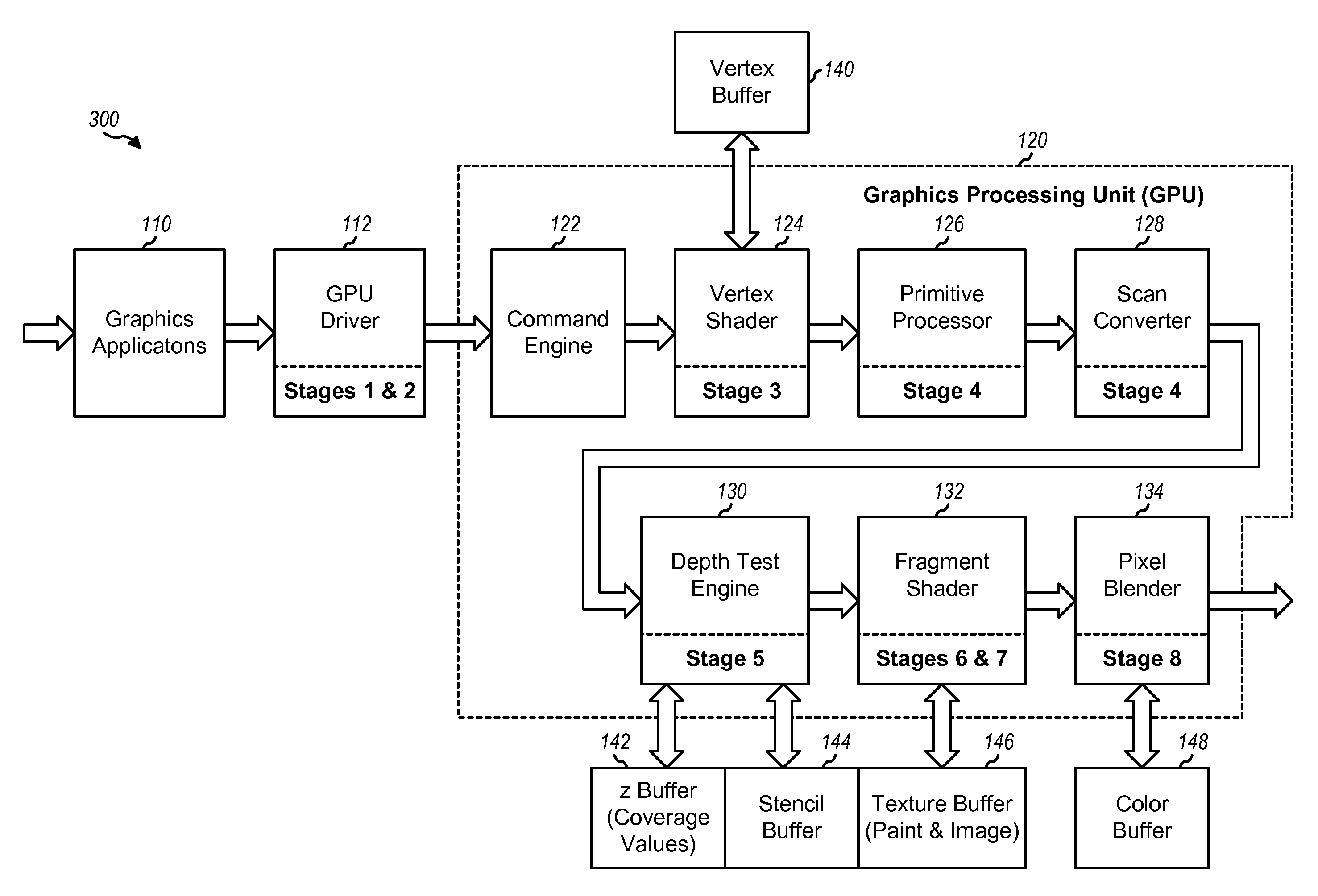

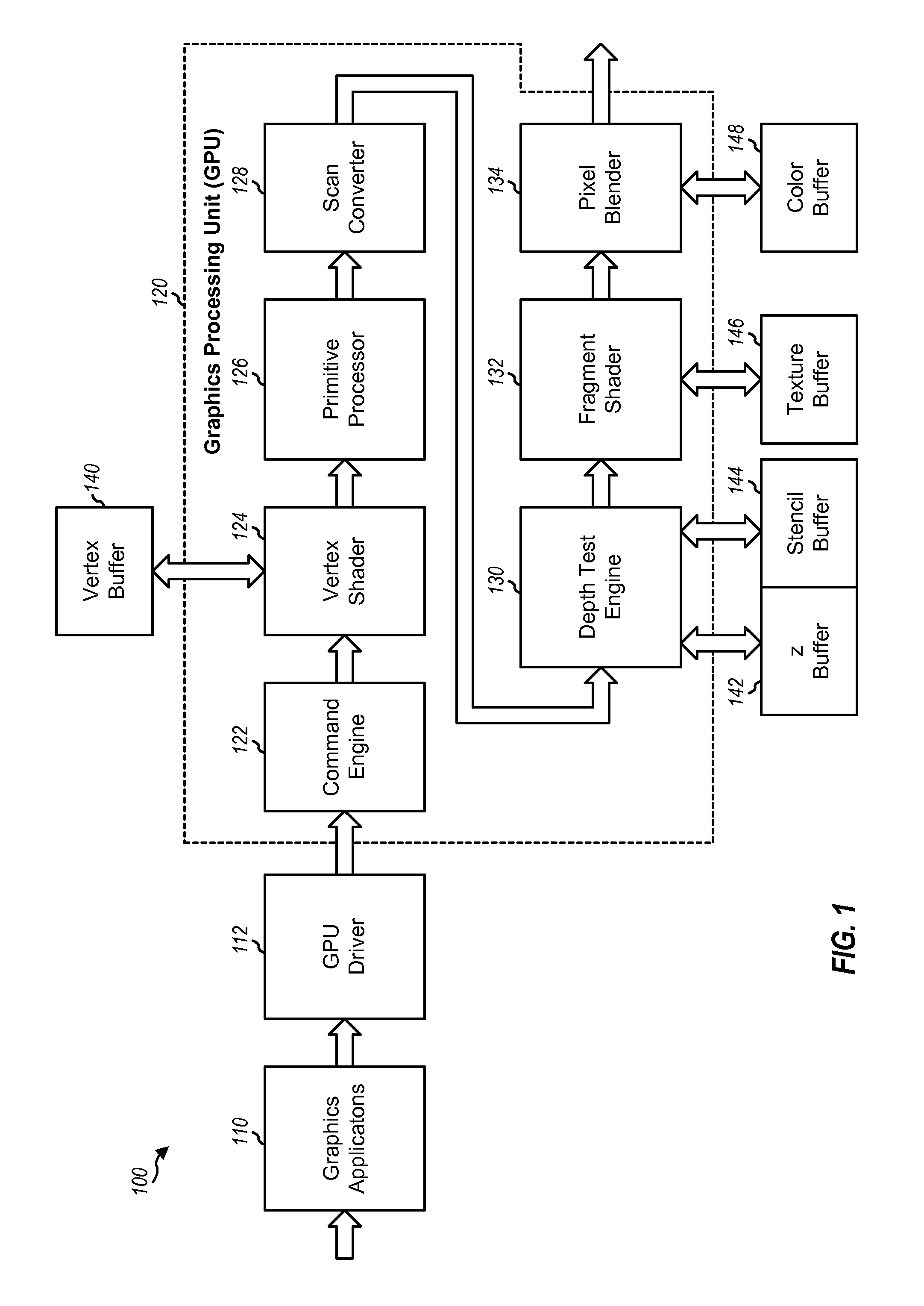

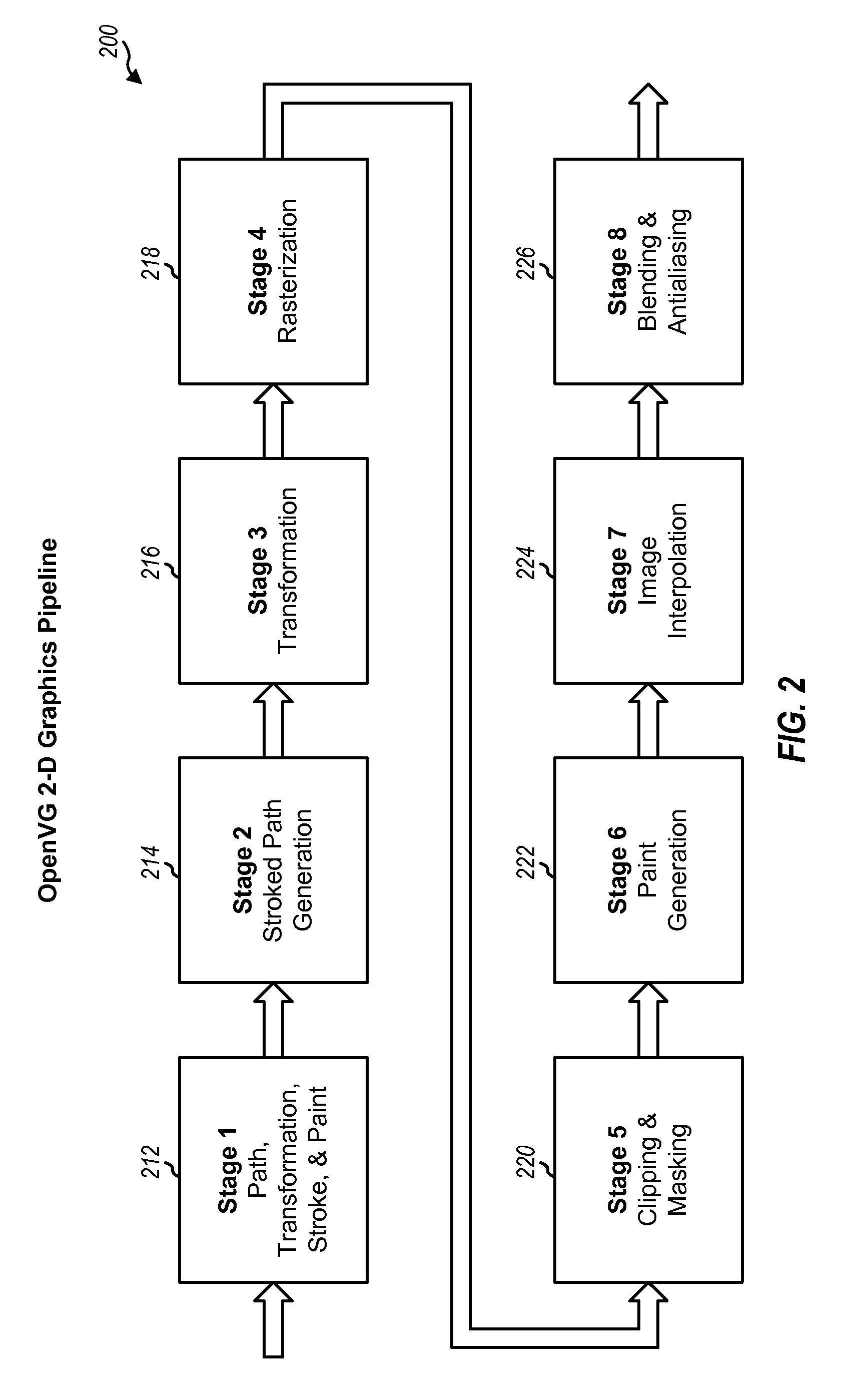

Techniques for supporting both 2-D and 3-D graphics are described. A graphics processing unit (GPU) may perform 3-D graphics processing in accordance with a 3-D graphics pipeline to render 3-D images and may also perform 2-D graphics processing in accordance with a 2-D graphics pipeline to render 2-D images. Each stage of the 2-D graphics pipeline may be mapped to at least one stage of the 3-D graphics pipeline. For example, a clipping, masking and scissoring stage in 2-D graphics may be mapped to a depth test stage in 3-D graphics. Coverage values for pixels within paths in 2-D graphics may be determined using rasterization and depth test stages in 3-D graphics. A paint generation stage and an image interpolation stage in 2-D graphics may be mapped to a fragment shader stage in 3-D graphics. A blending stage in 2-D graphics may be mapped to a blending stage in 3-D graphics.

Owner:QUALCOMM INC

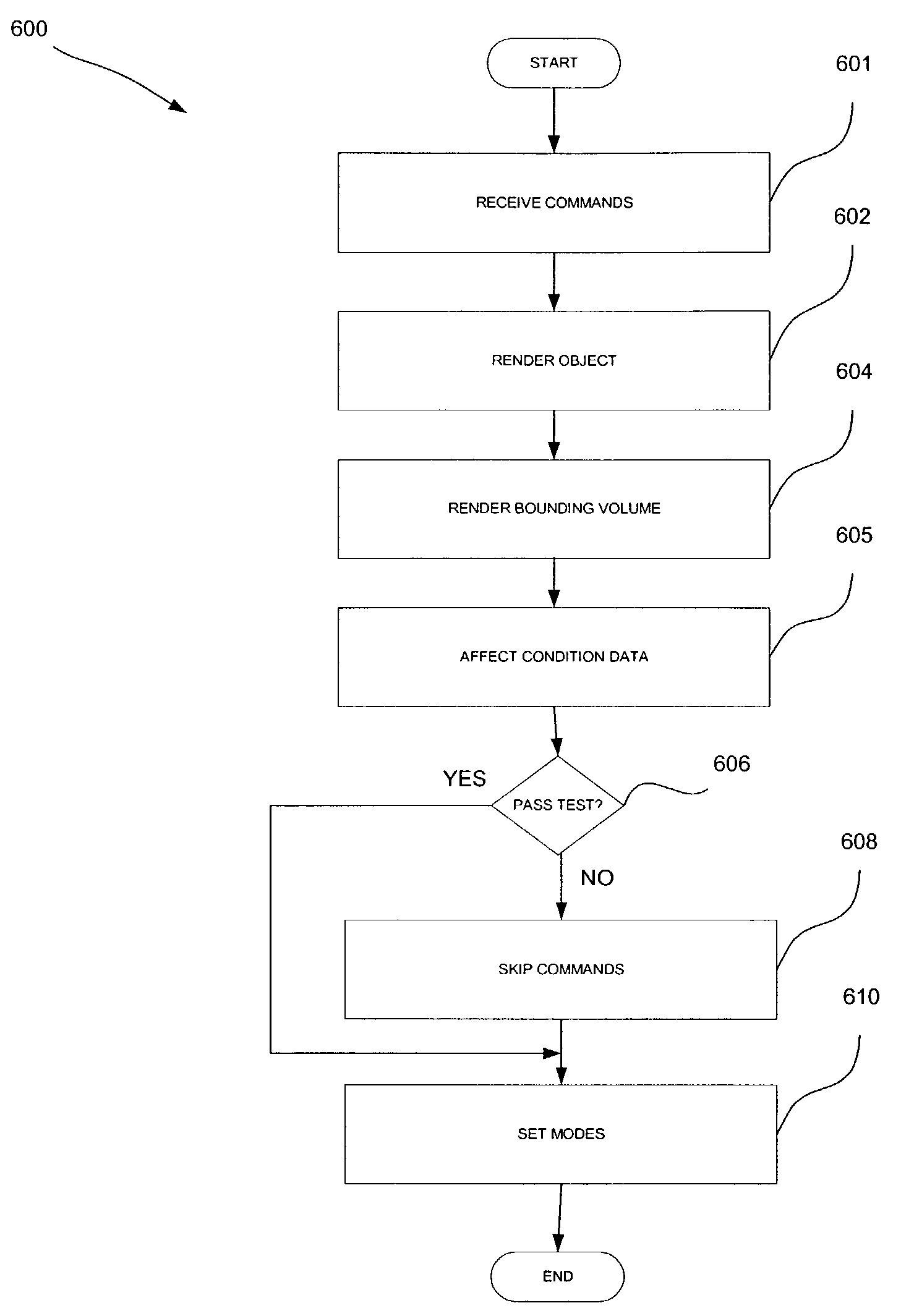

System and method for display list occlusion branching

A system and method are provided for conditional branching in a hardware graphics pipeline. Initially, a plurality of graphics commands is received. Condition data is then affected based on at least some of the graphics commands utilizing the hardware graphics pipeline. At least one of the graphics commands is then conditionally skipping based on the condition data in response to another graphics command utilizing the hardware graphics pipeline.

Owner:NVIDIA CORP

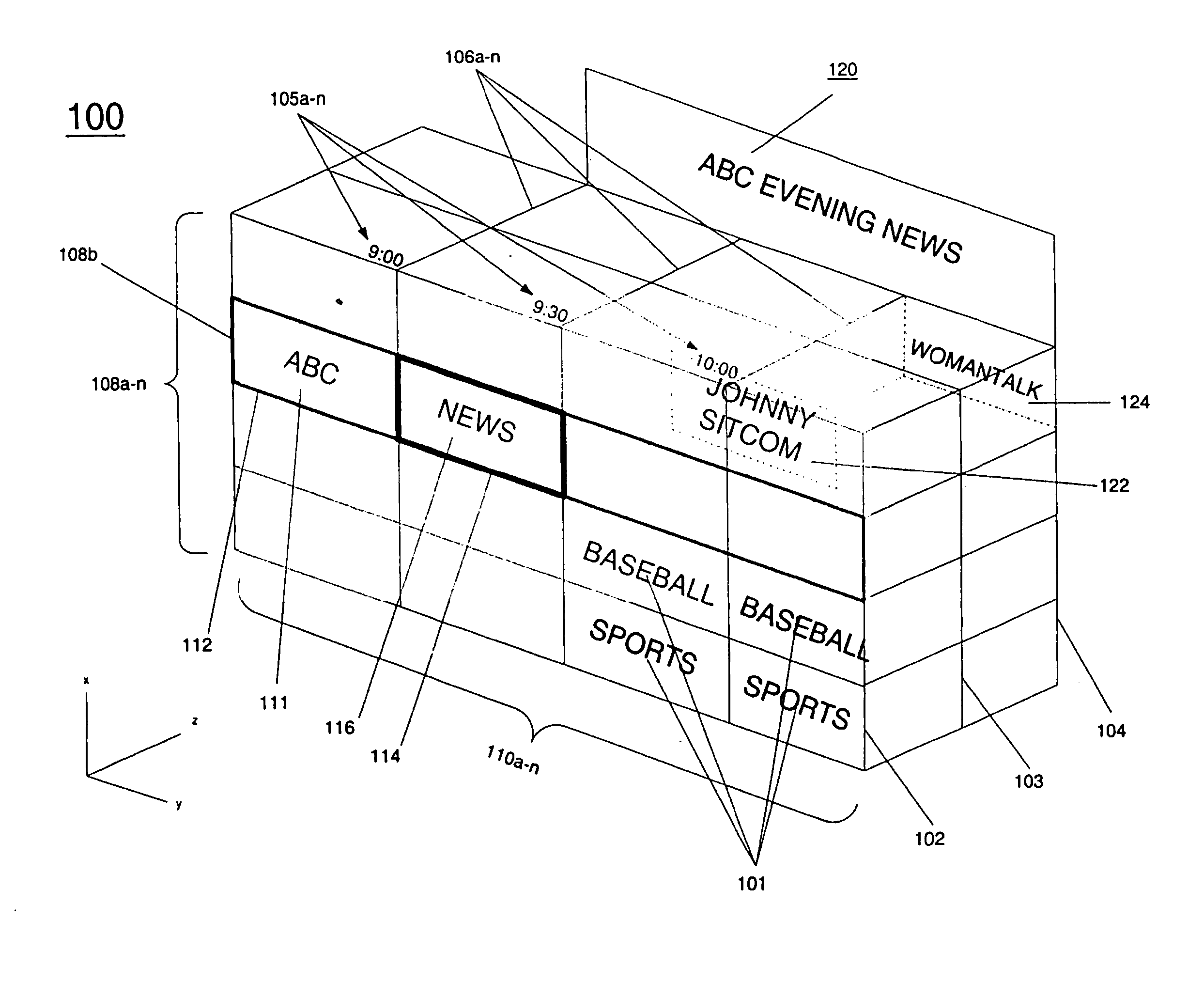

Three dimensional light electronic programming guide

InactiveUS20050097603A1Reduced graphic hardware requirementLow hardware requirementsTelevision system detailsDrawing from basic elementsThree dimensional graphicsHardware acceleration

A method and apparatus of displaying an Electronic Programming Guide (EPG). In one embodiment, an EPG is displayed in a three dimensional virtual mesh, in which independent objects representing television programs are situated. The simplified nature of the three dimensional EPG reduces the amount of processing necessary to display it. In addition, the virtual mesh may be displayed isometrically, so that hardware requirements are further reduced and it may be possible to use a software only three dimensional graphics pipeline. If a user has a set top box (STB) with a hardware accelerated graphics pipeline, the EPG may be displayed in a full three dimensional perspective view. A user can navigate the mesh to find television programs that they wish to view. A user can assign values to types of television programs that they prefer, and these programs will be displayed more prominently.

Owner:JLB VENTURES LLC

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122334A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

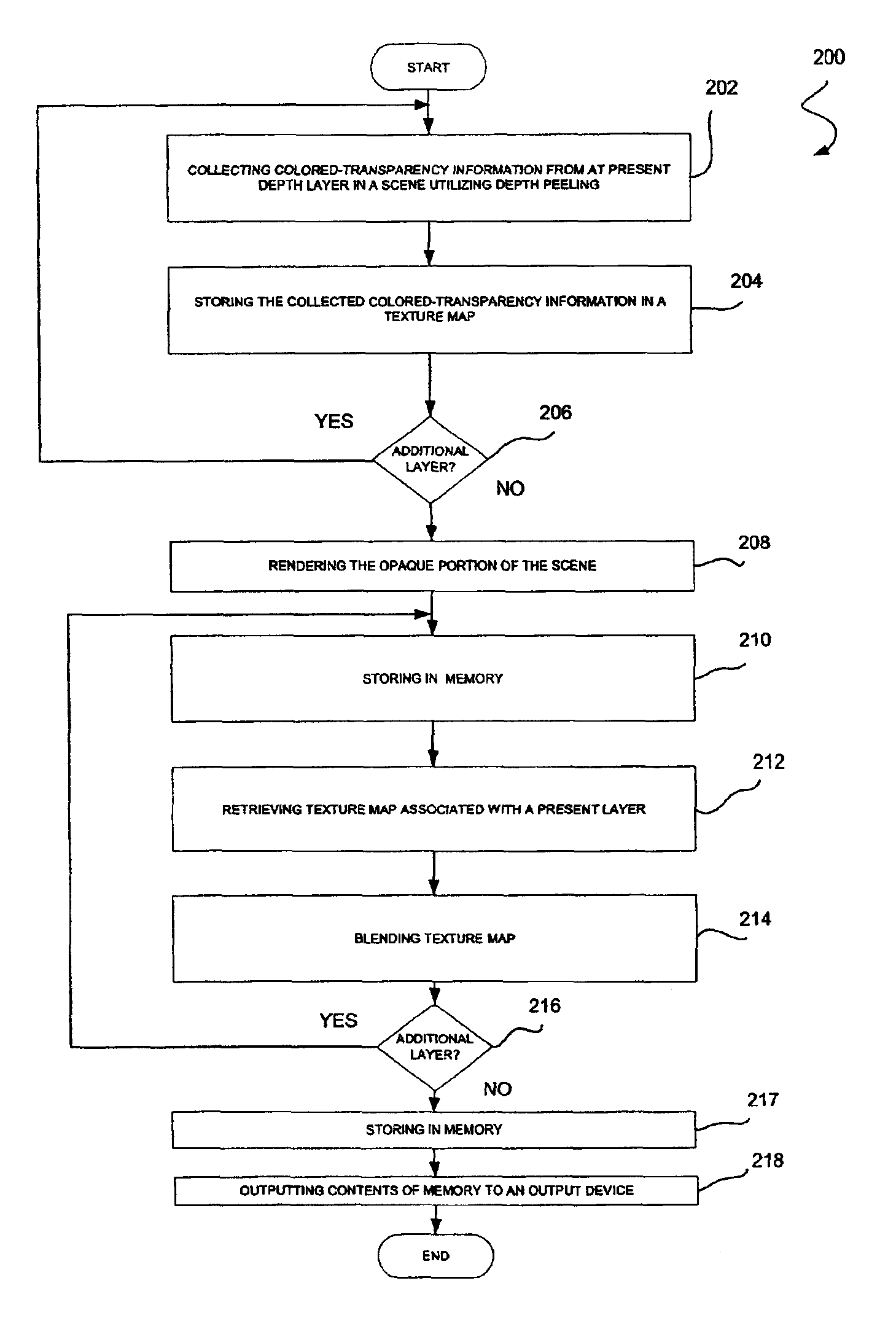

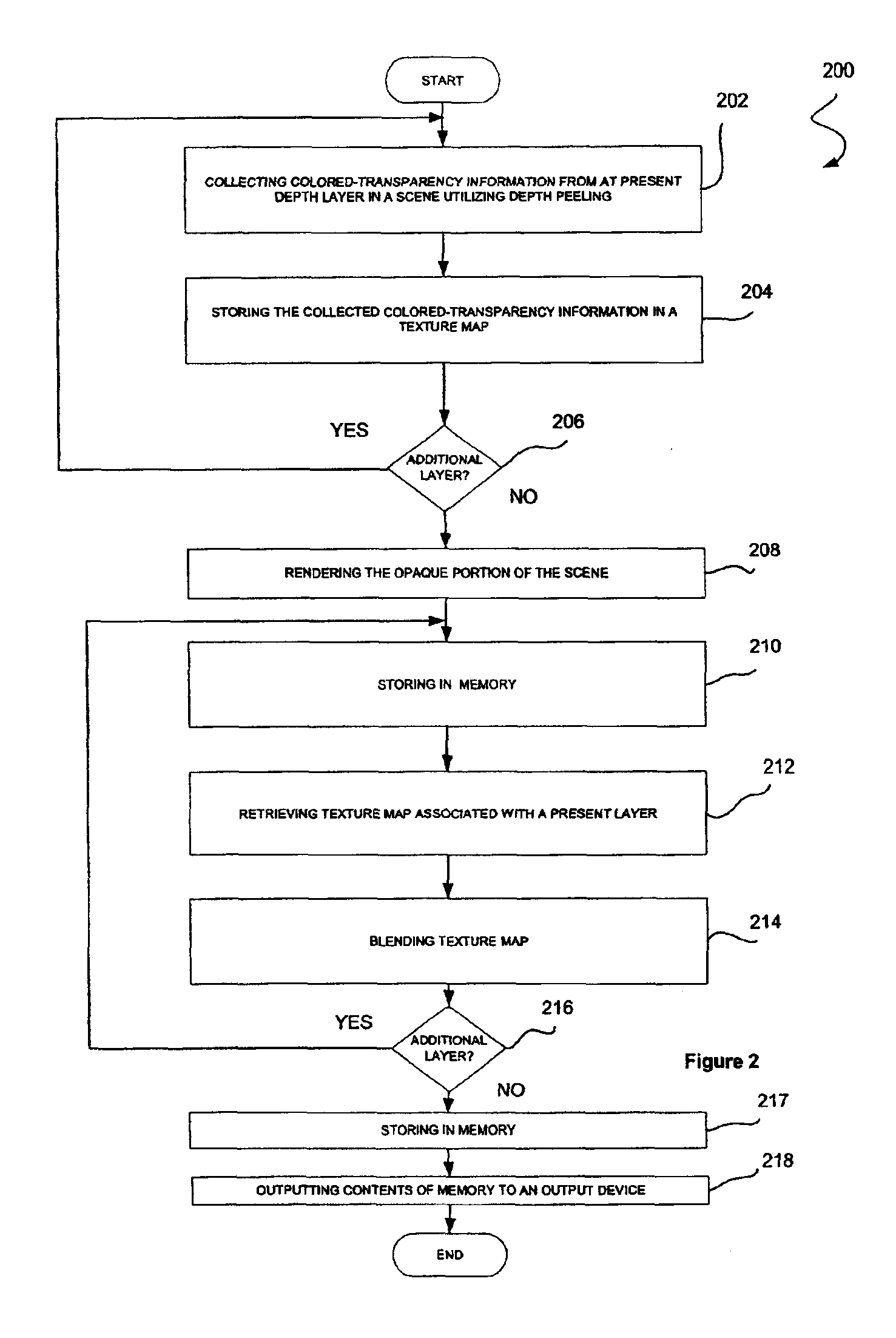

Order-independent transparency rendering system and method

InactiveUS6989840B1Easy to collectCathode-ray tube indicators3D-image renderingGraphicsColor transparency

A system, method and computer program product are provided for transparency rendering in a graphics pipeline. Initially, colored-transparency information is collected from a plurality of depth layers (i.e. colored-transparency layers, etc.) in a scene to be rendered. The collected colored-transparency information is then stored in memory. The colored-transparency information from the depth layers may then be blended in a predetermined order.

Owner:NVIDIA CORP

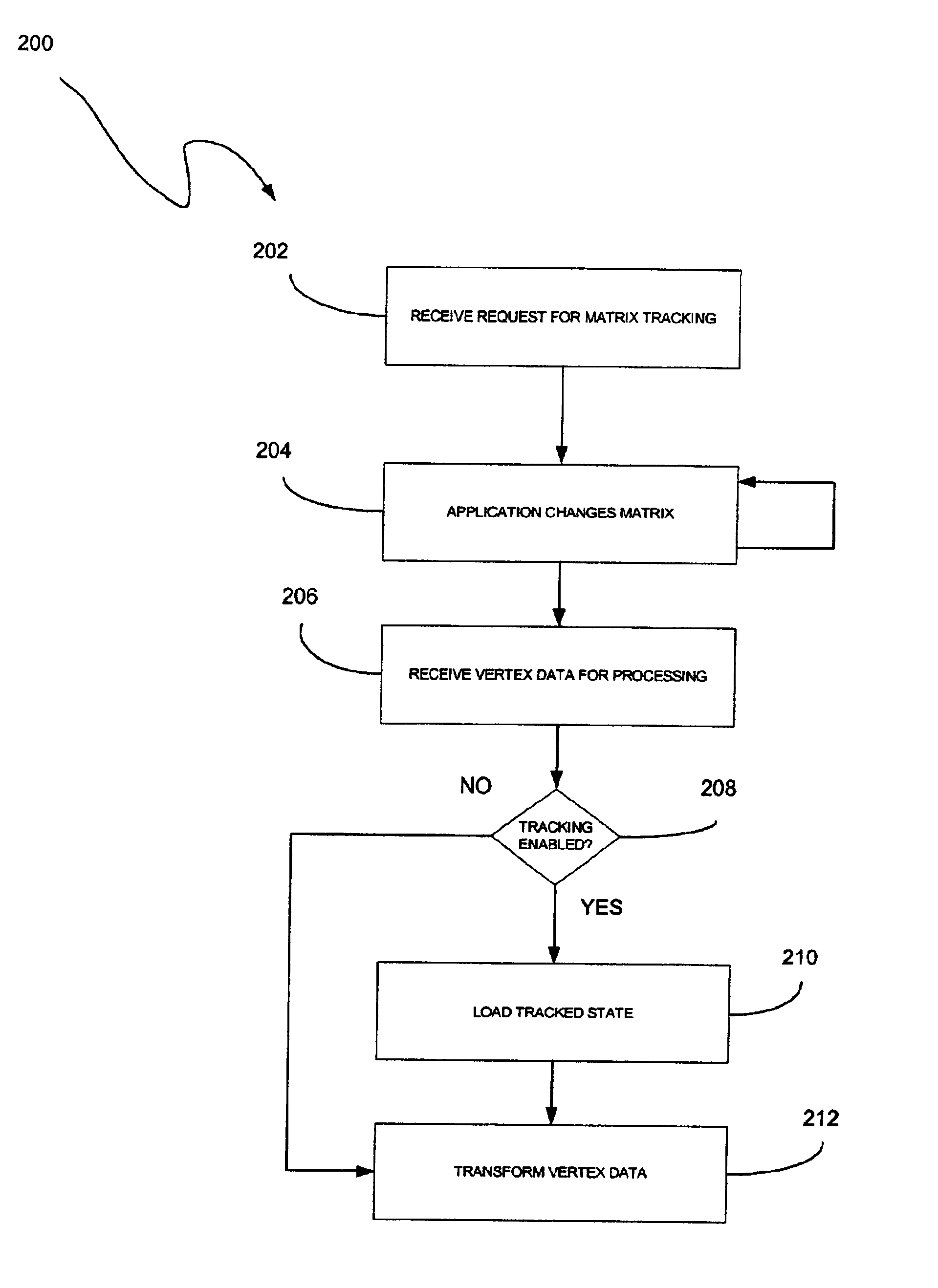

System, method and computer program product for vertex attribute aliasing in a graphics pipeline

A system, method and article of manufacture are provided for aliasing vertex attributes during vertex processing. Initially, a plurality of identifiers are each mapped to one of a plurality of parameters associated with vertex data. Thereafter, the vertex data is processed by calling the parameters utilizing a vertex program capable of referencing the parameters using the identifiers.

Owner:NVIDIA CORP

Integer-based functionality in a graphics shading language

One embodiment of the present invention sets forth a technique for improving the flexibility and programmability of a graphics pipeline by adding application programming interface (API) extensions to the OpenGL Shading Language (GLSL) that provide native support for integer data types and operations. The integer API extensions span from the API to the hardware execution units within a graphics processing unit (GPU), thereby providing native integer support throughout the graphics pipeline.

Owner:NVIDIA CORP

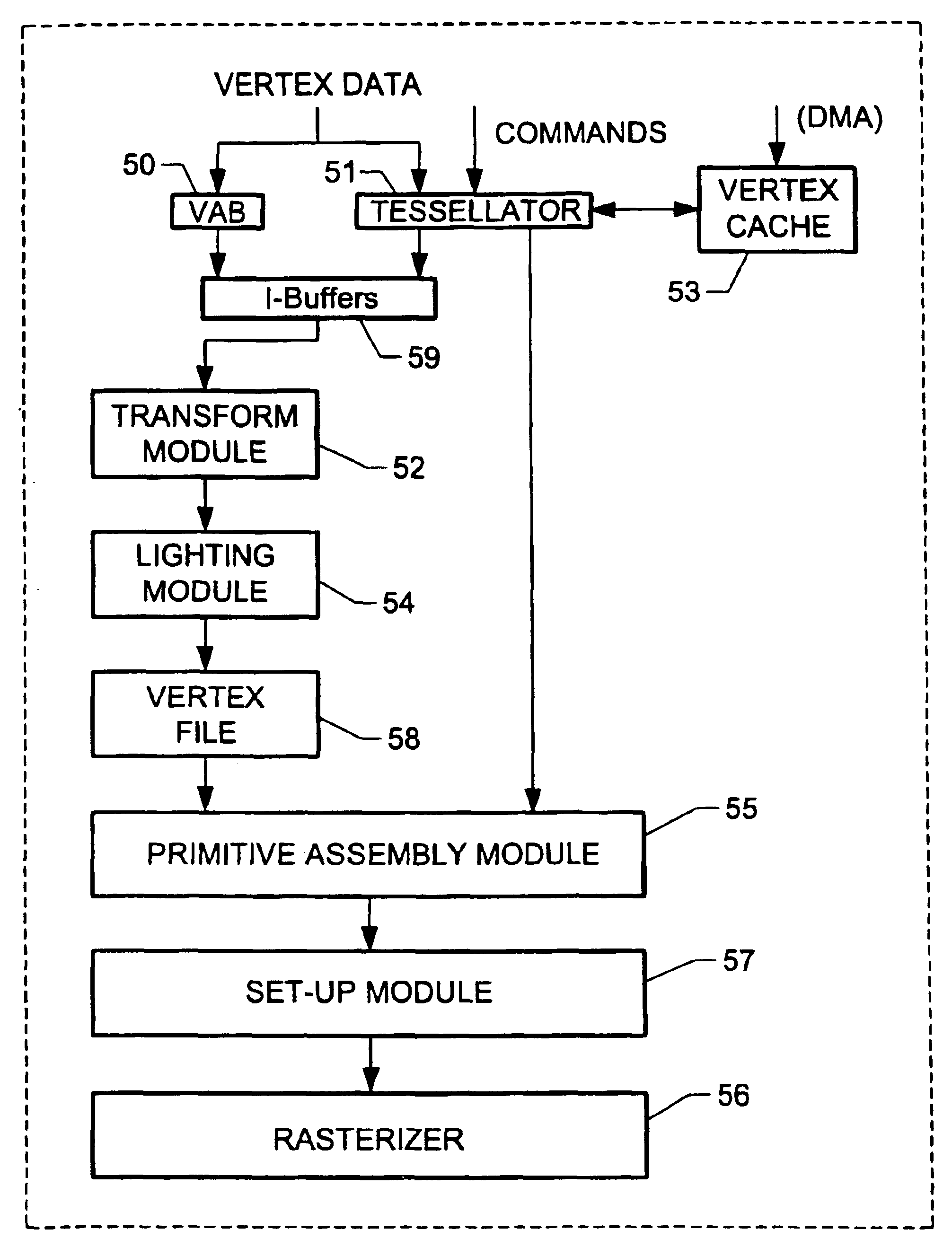

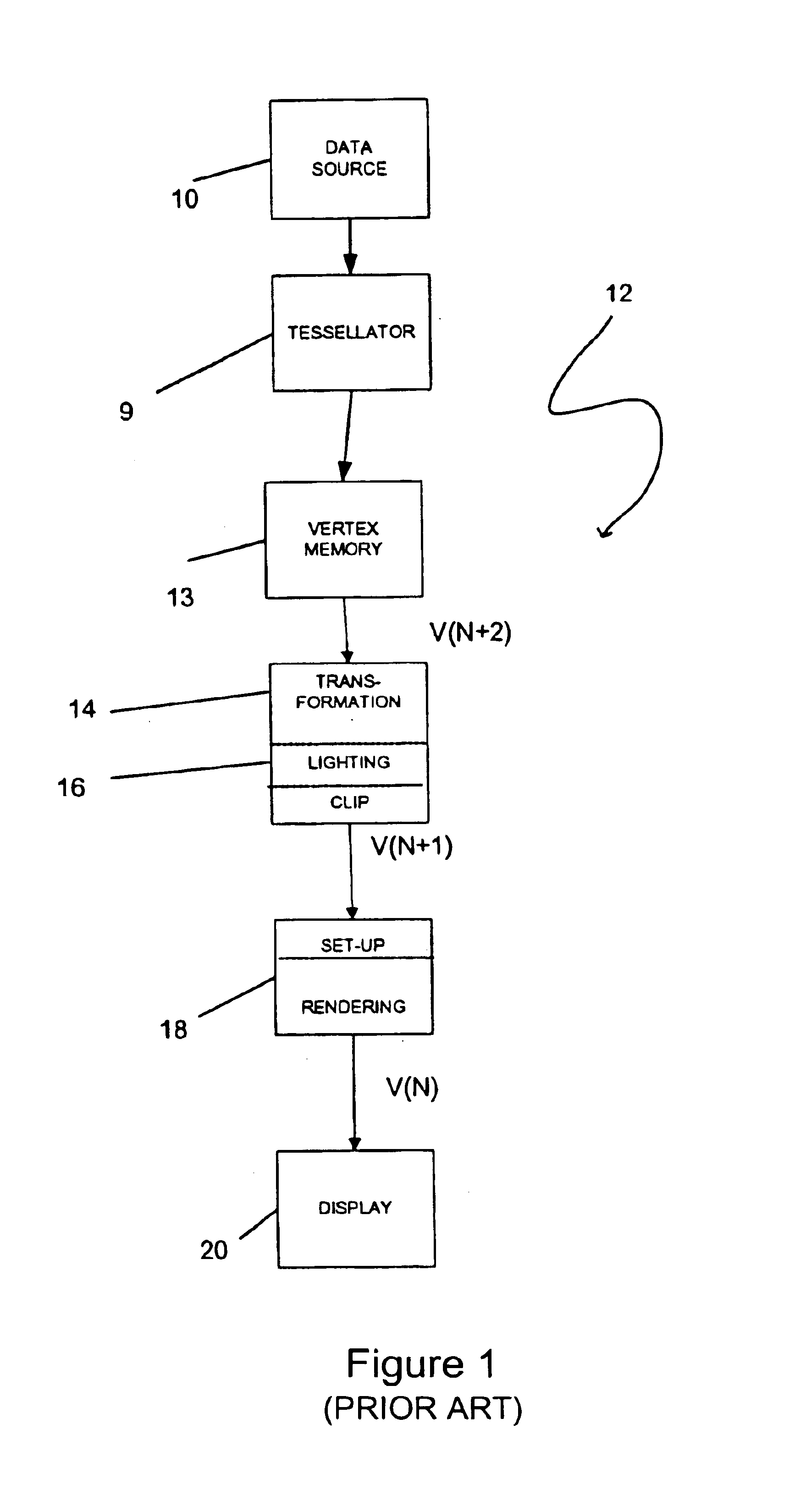

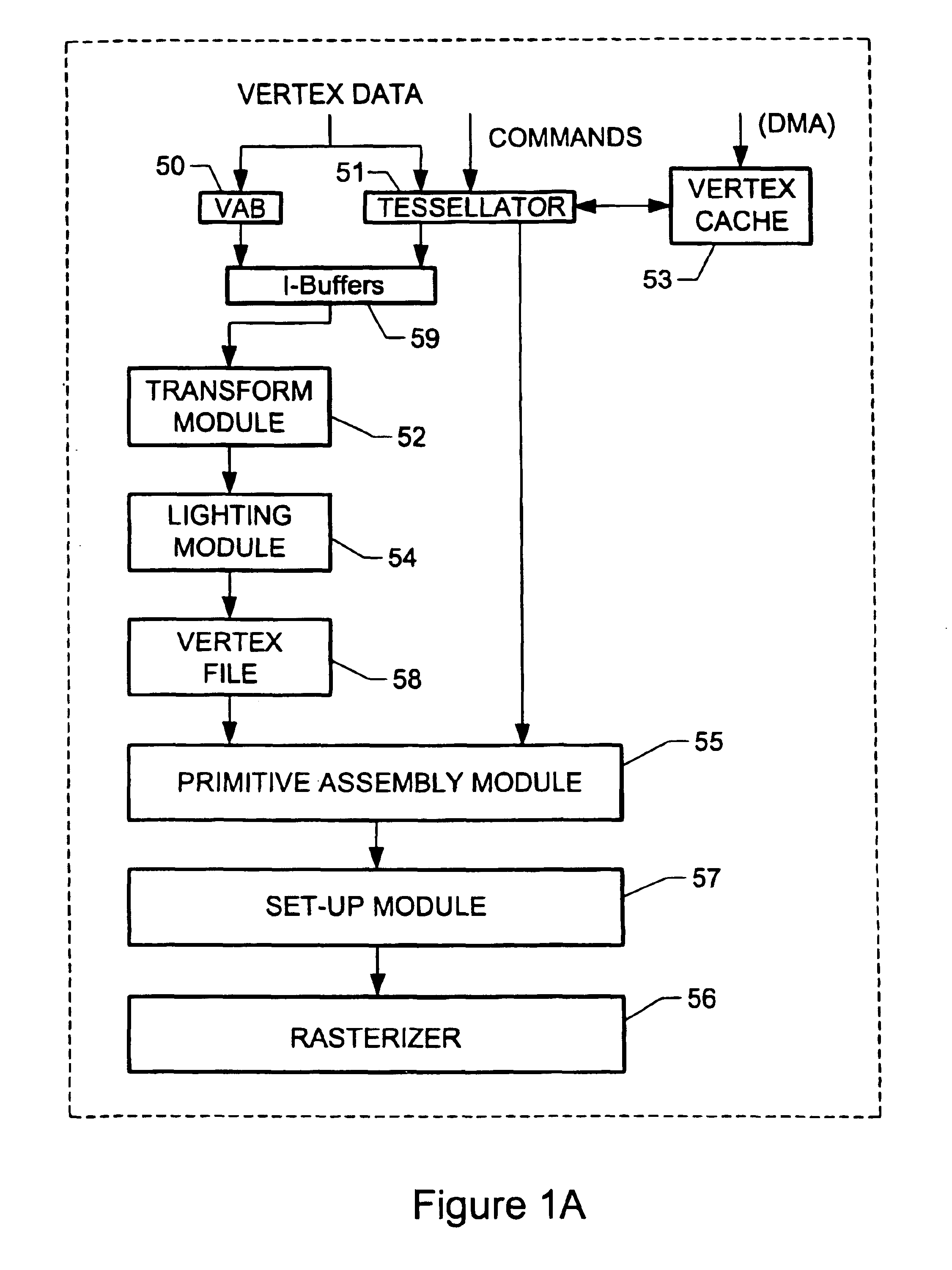

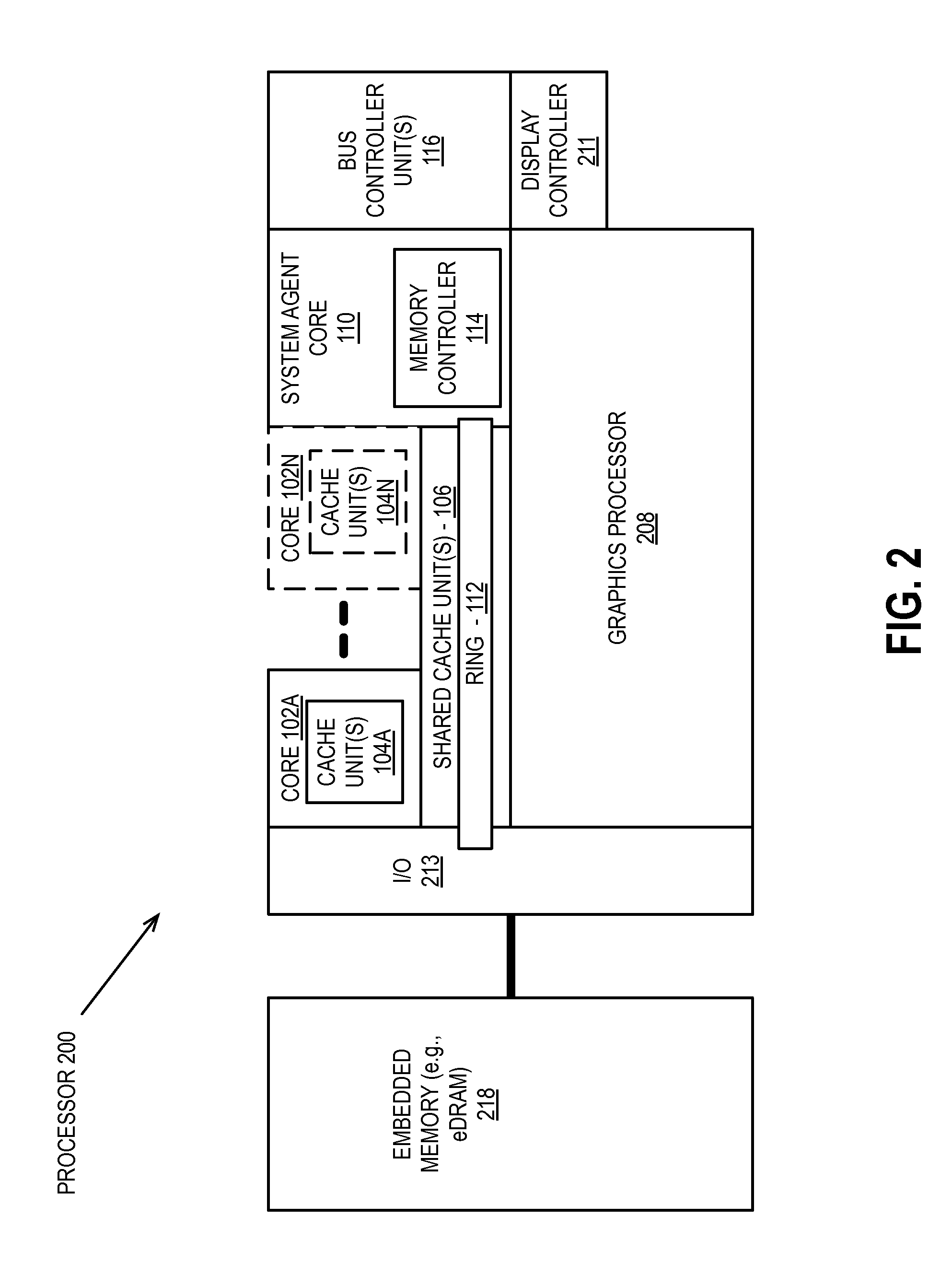

Integrated tessellator in a graphics processing unit

InactiveUS6906716B2Improve performanceQuality improvementProcessor architectures/configurationElectric digital data processingGraphicsSemiconductor

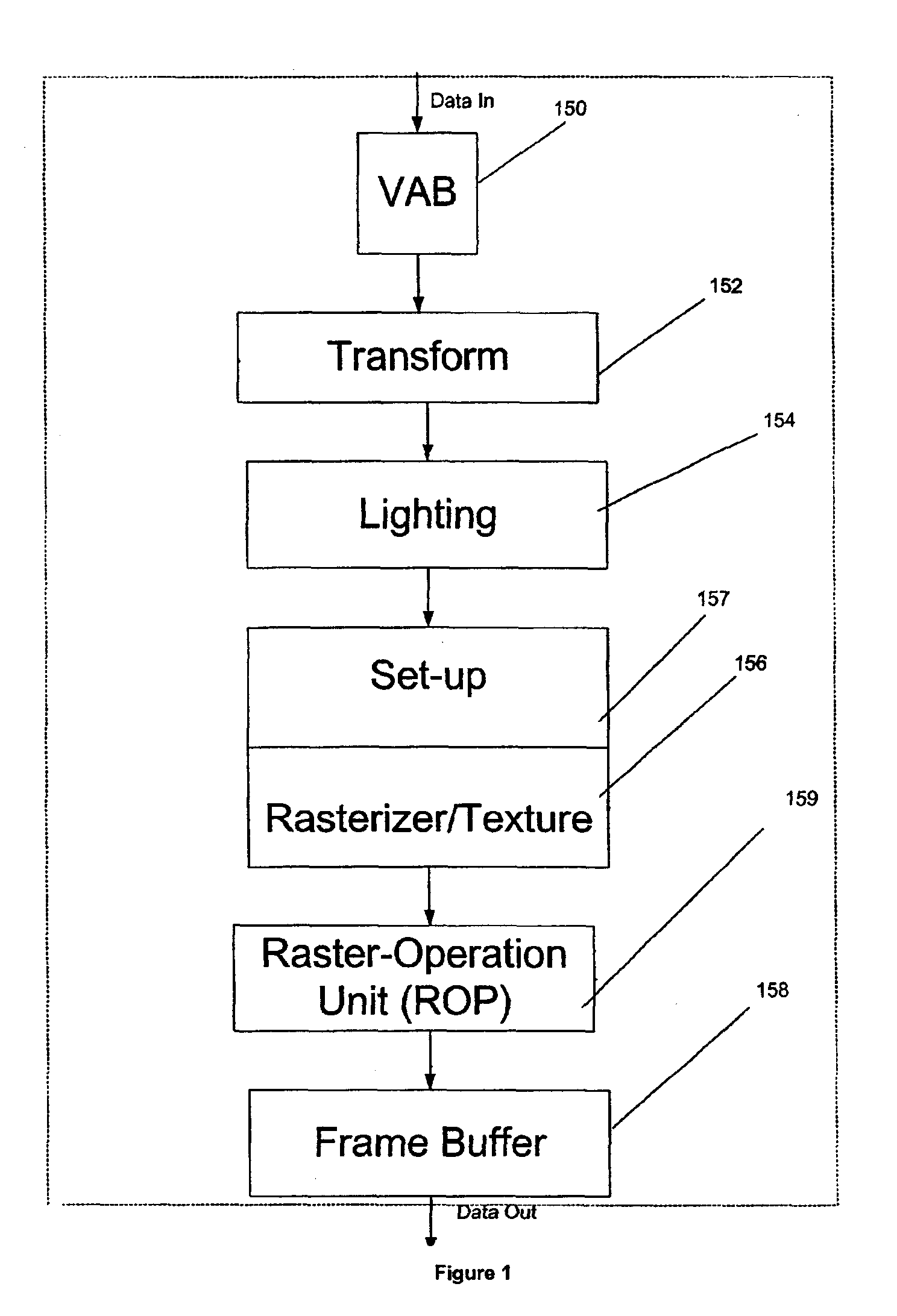

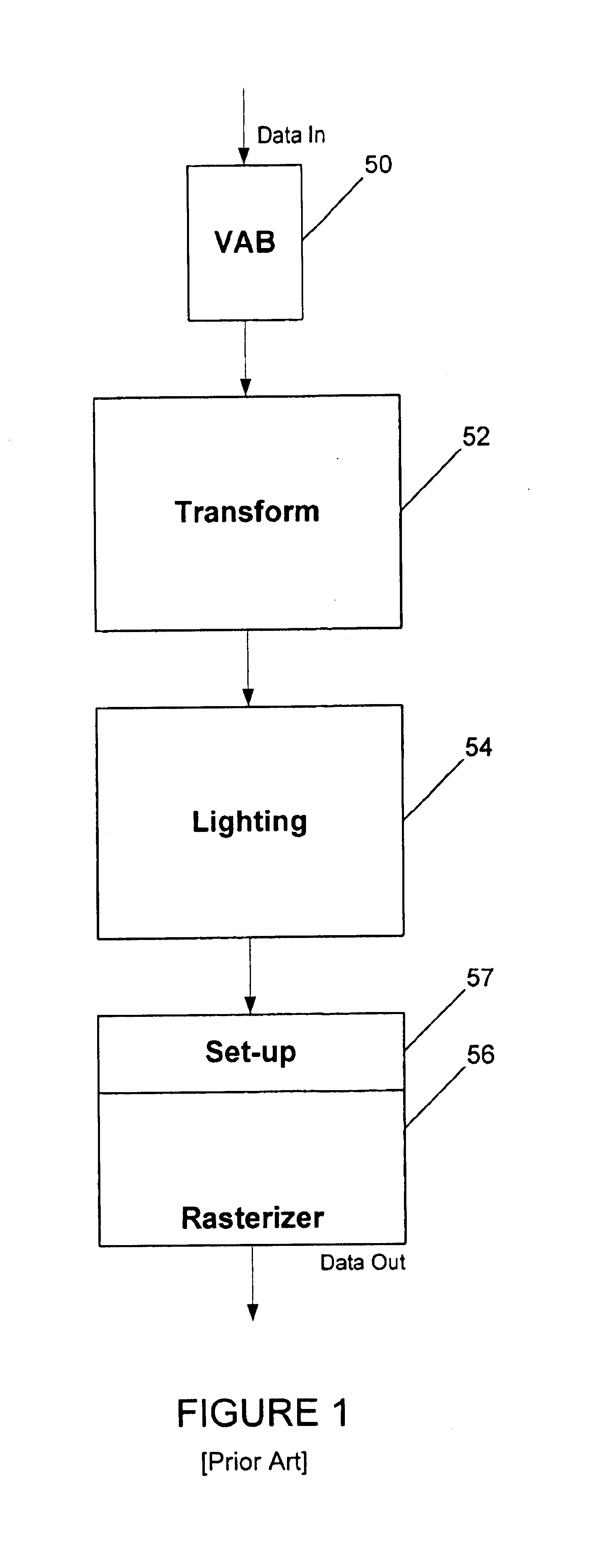

An integrated graphics pipeline system is provided for graphics processing. Such system includes a tessellation module that is positioned on a single semiconductor platform for receiving data for tessellation purposes. Tessellation refers to the process of decomposing either a complex surface such as a sphere or surface patch into simpler primitives such as triangles or quadrilaterals, or a triangle into multiple smaller triangles. Also included on the single semiconductor platform is a transform module adapted to transform the tessellated data from a first space to a second space. Coupled to the transform module is a lighting module which is positioned on the single semiconductor platform for performing lighting operations on the data received from the transform module. Also included is a rasterizer coupled to the lighting module and positioned on the single semiconductor platform for rendering the data received from the lighting module.

Owner:NVIDIA CORP

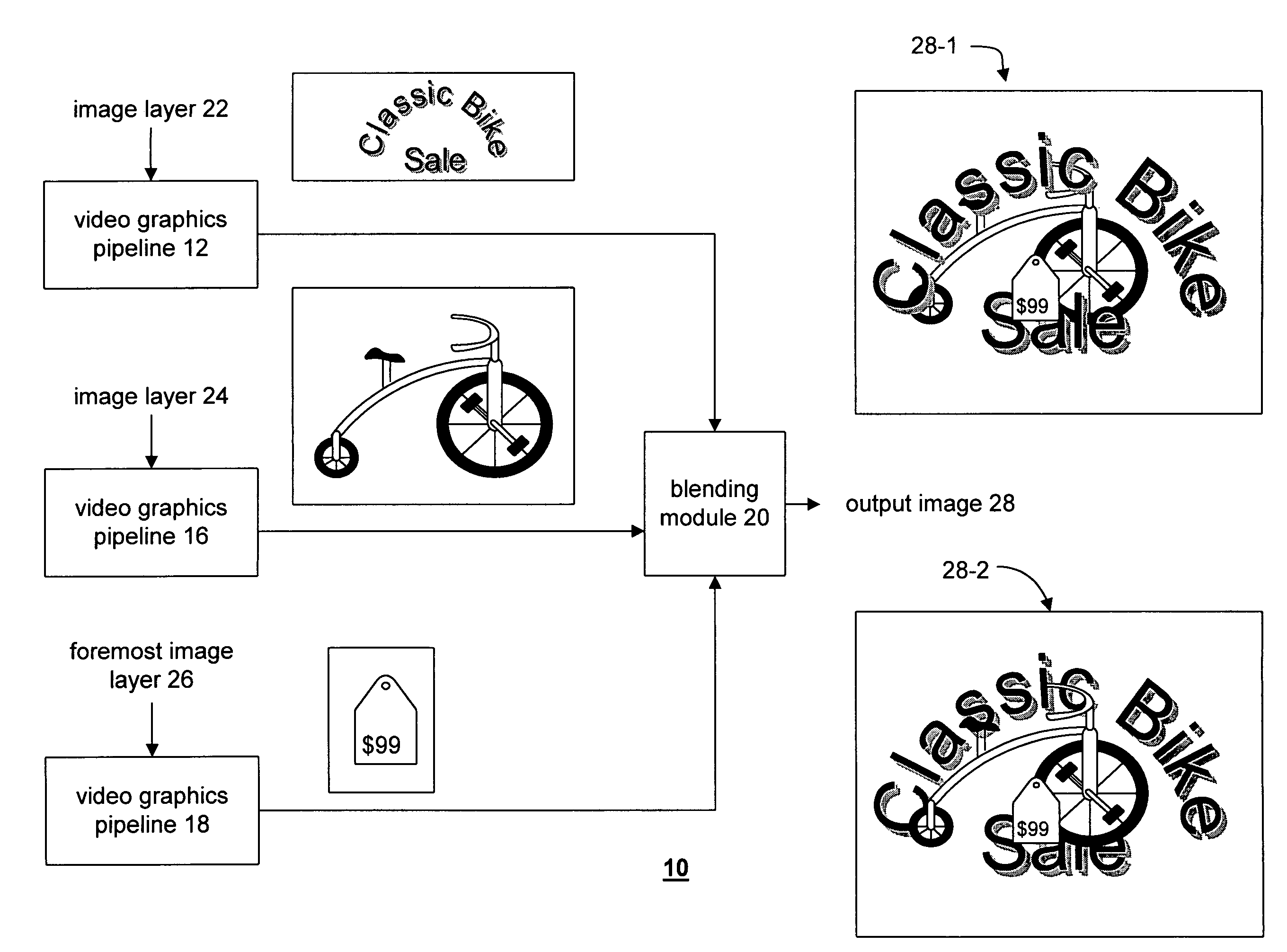

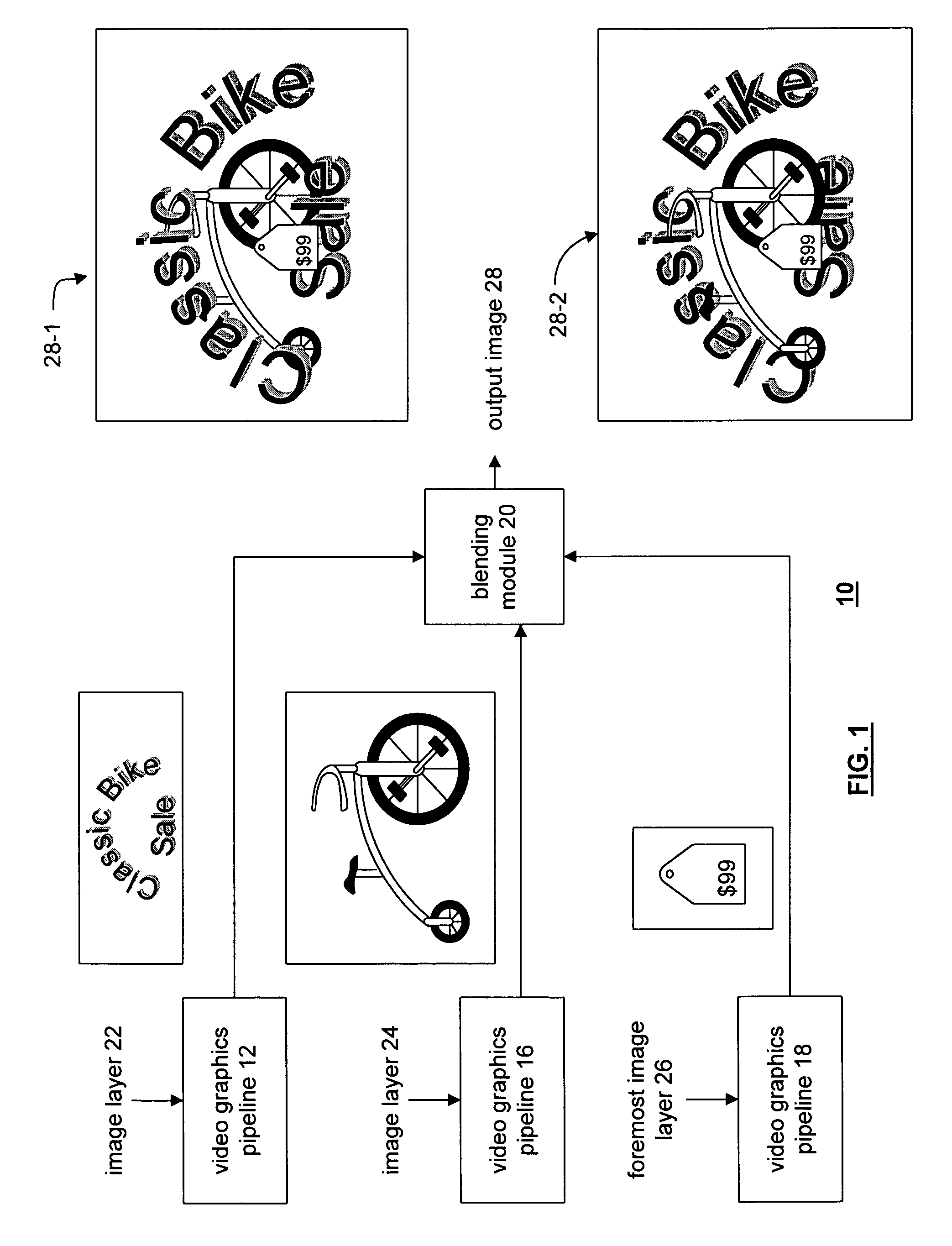

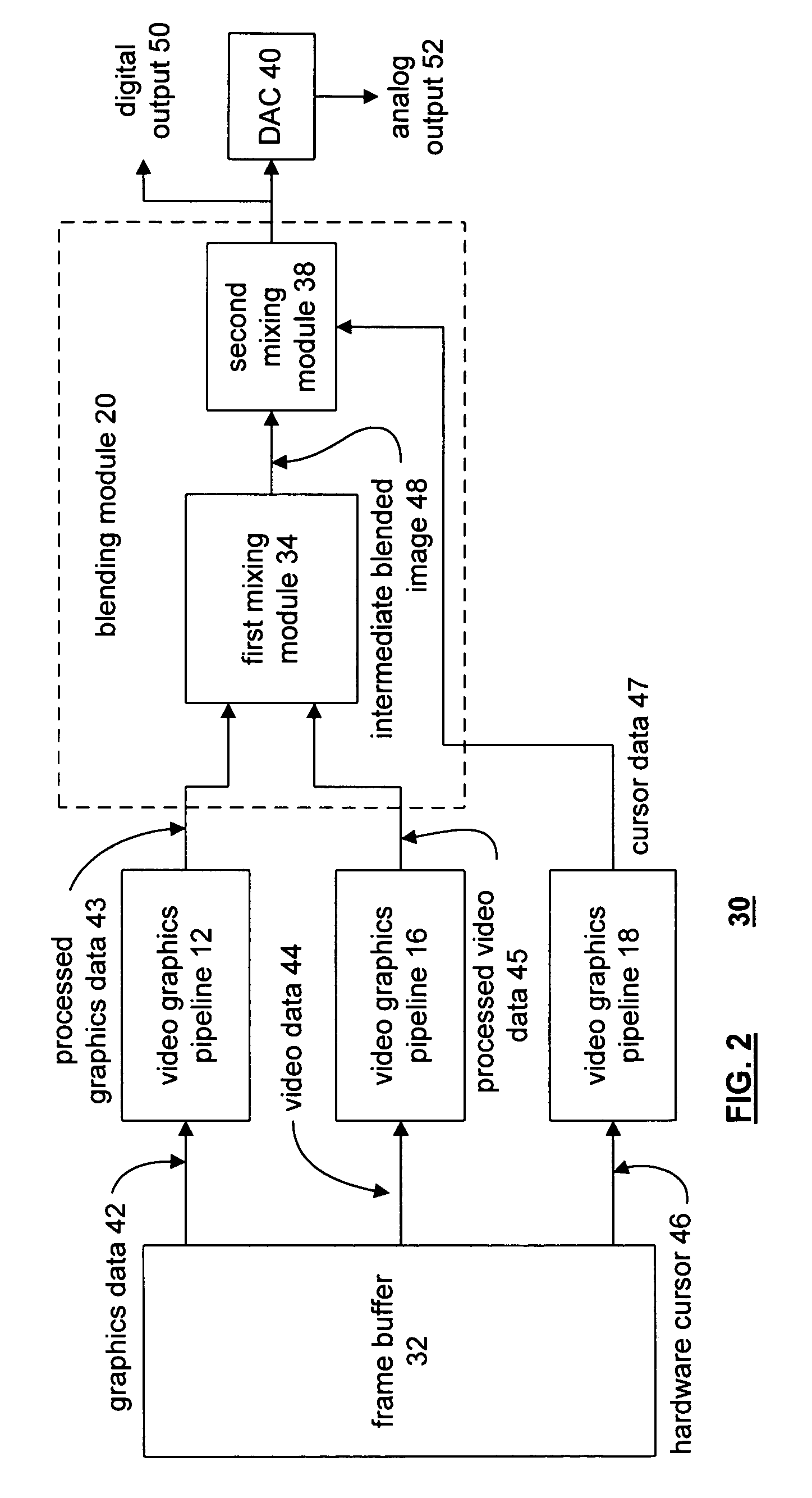

Video graphics module capable of blending multiple image layers

A video graphics module capable of blending multiple image layers includes a plurality of video graphic pipelines, each of which is operable to process a corresponding image layer. One of the video graphic pipelines processes a foremost image layer. For example, the foremost image layer may be a hardware cursor. The video graphics module also includes a blending module that is operably coupled to the plurality of video graphic pipelines. The blending module blends, in accordance with a blending convention (e.g., AND / Exclusive OR blending and / or alpha blending), the corresponding image layers of each pipeline in a predetermined blending order to produce an output image. The blending module blends the foremost image layer such that it appears in a foremost position with respect to the other image layers.

Owner:ATI TECH INC

System, method and computer program product for texture address operations based on computations involving other textures

A system, method and computer program product are provided for texture sampling in a graphics pipeline. Initially, texture information is retrieved using texture coordinates. Thereafter, the texture information is utilized to generate results. Next, the texture information and the results are utilized to generate further results. The foregoing operation may optionally be repeated, and the results outputted.

Owner:NVIDIA CORP

Method and apparatus for filtered coarse pixel shading

An apparatus and method for performing coarse pixel shading (CPS). For example, one embodiment of a method comprises: A method for coarse pixel shading (CPS) comprising: pre-processing a graphics mesh by creating a tangent-plane parameterization of desired vertex attributes for each vertex of the mesh; and performing rasterization of the mesh in a rasterization stage of a graphics pipeline using the tangent-plane parameterization.

Owner:INTEL CORP

Graphics system with embedded frame buffer having reconfigurable pixel formats

InactiveUS20060197768A1Improve system flexibilityEasy to useCathode-ray tube indicators3D-image renderingGraphic systemSignal processing

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics system has a graphics processor includes an embedded frame buffer for storing frame data prior to sending the frame data to an external location, such as main memory. The embedded frame buffer is selectively configurable to store the following pixel formats: point sampled RGB color and depth, super-sampled RGB color and depth, and YUV (luma / chroma). Graphics commands are provided which enable the programmer to configure the embedded frame buffer for any of the pixel formats on a frame-by-frame basis.

Owner:NINTENDO CO LTD

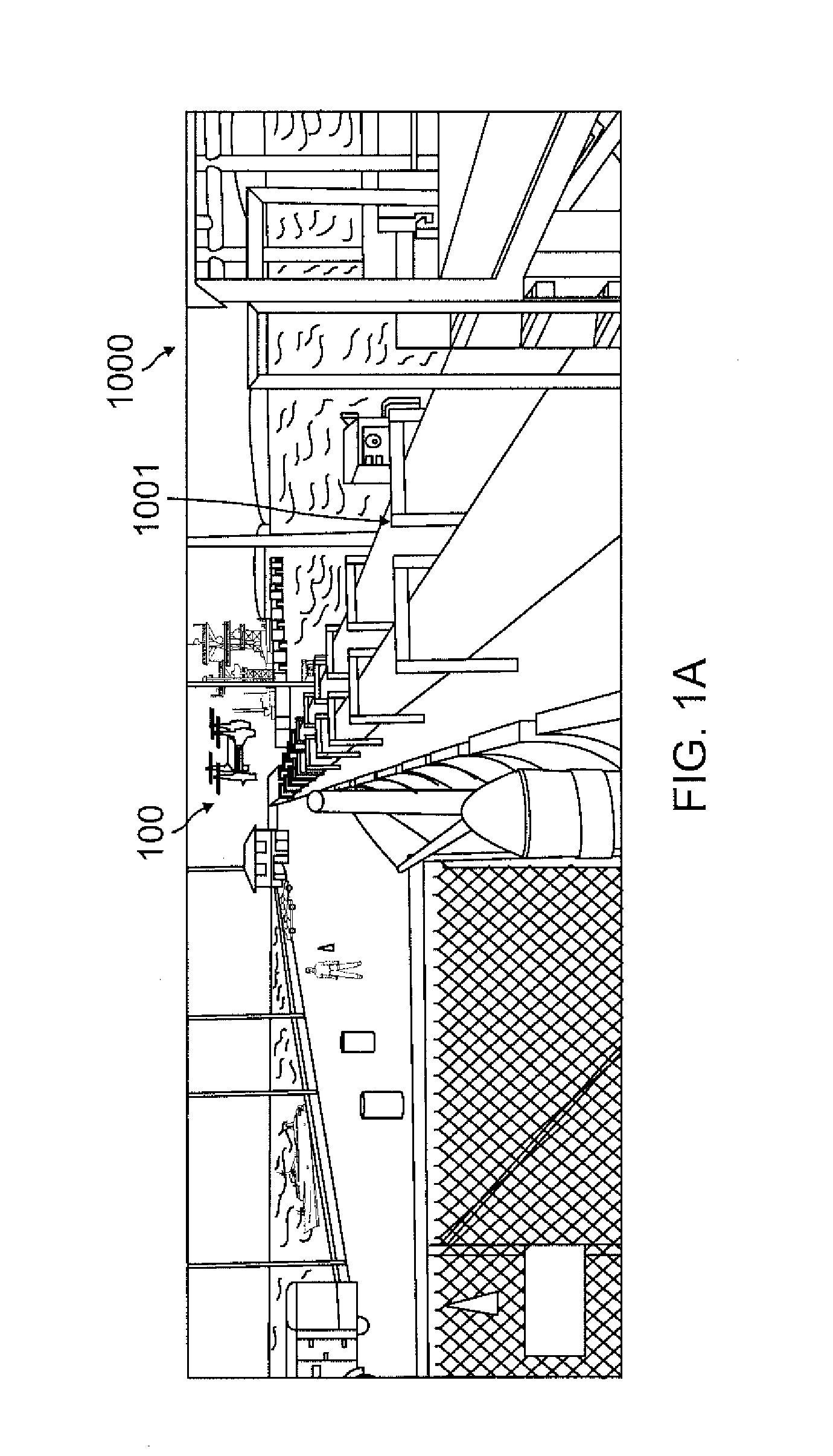

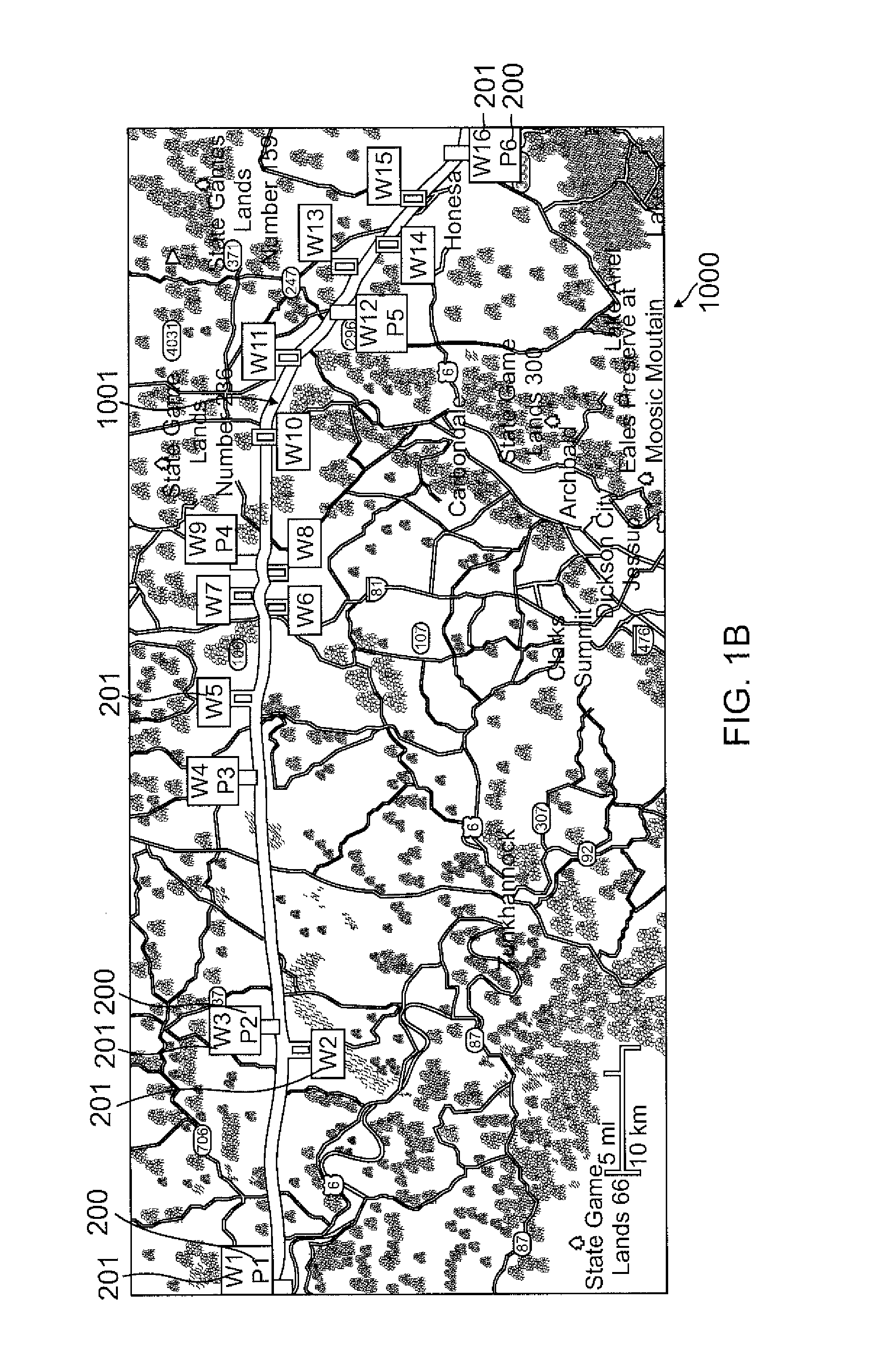

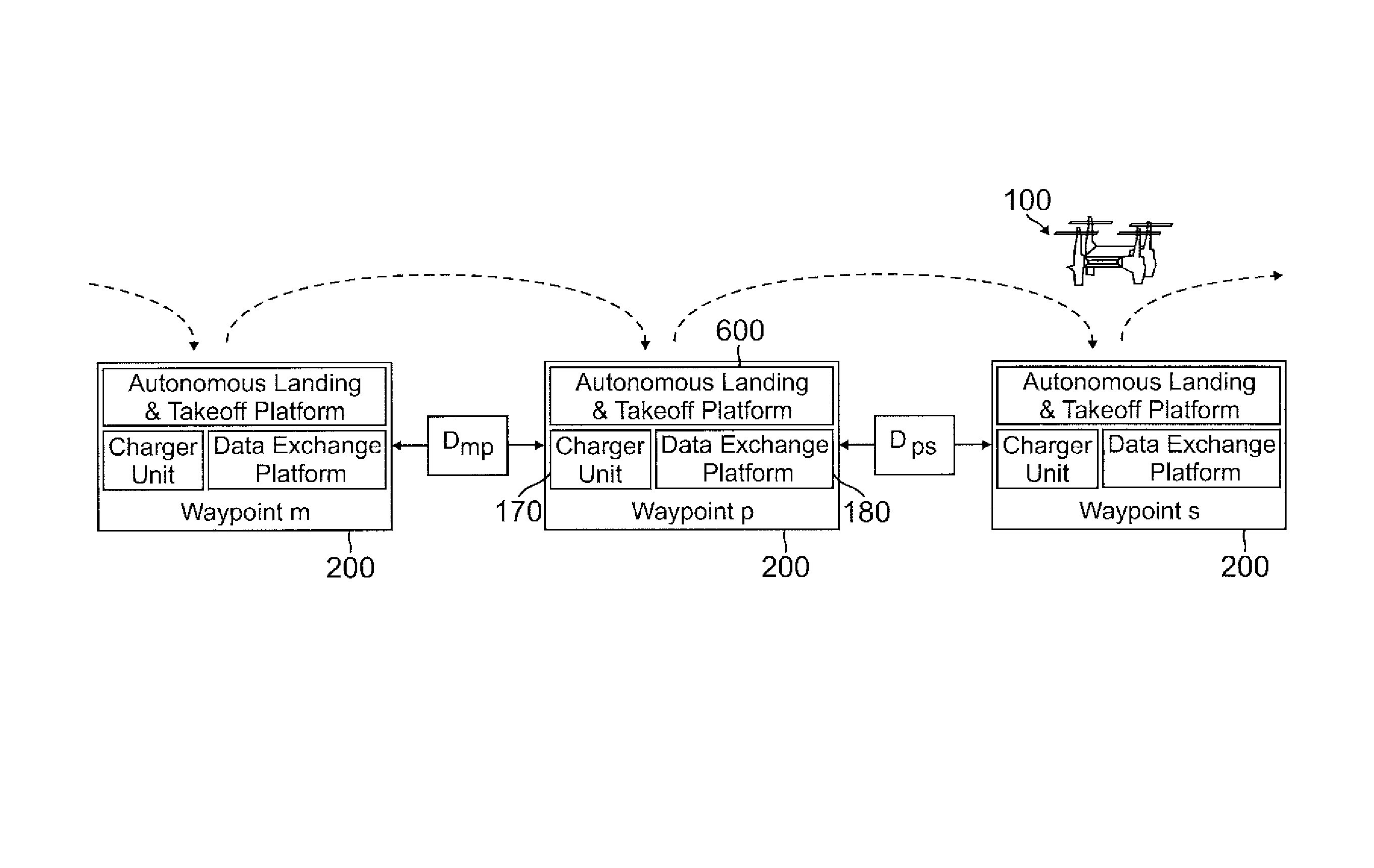

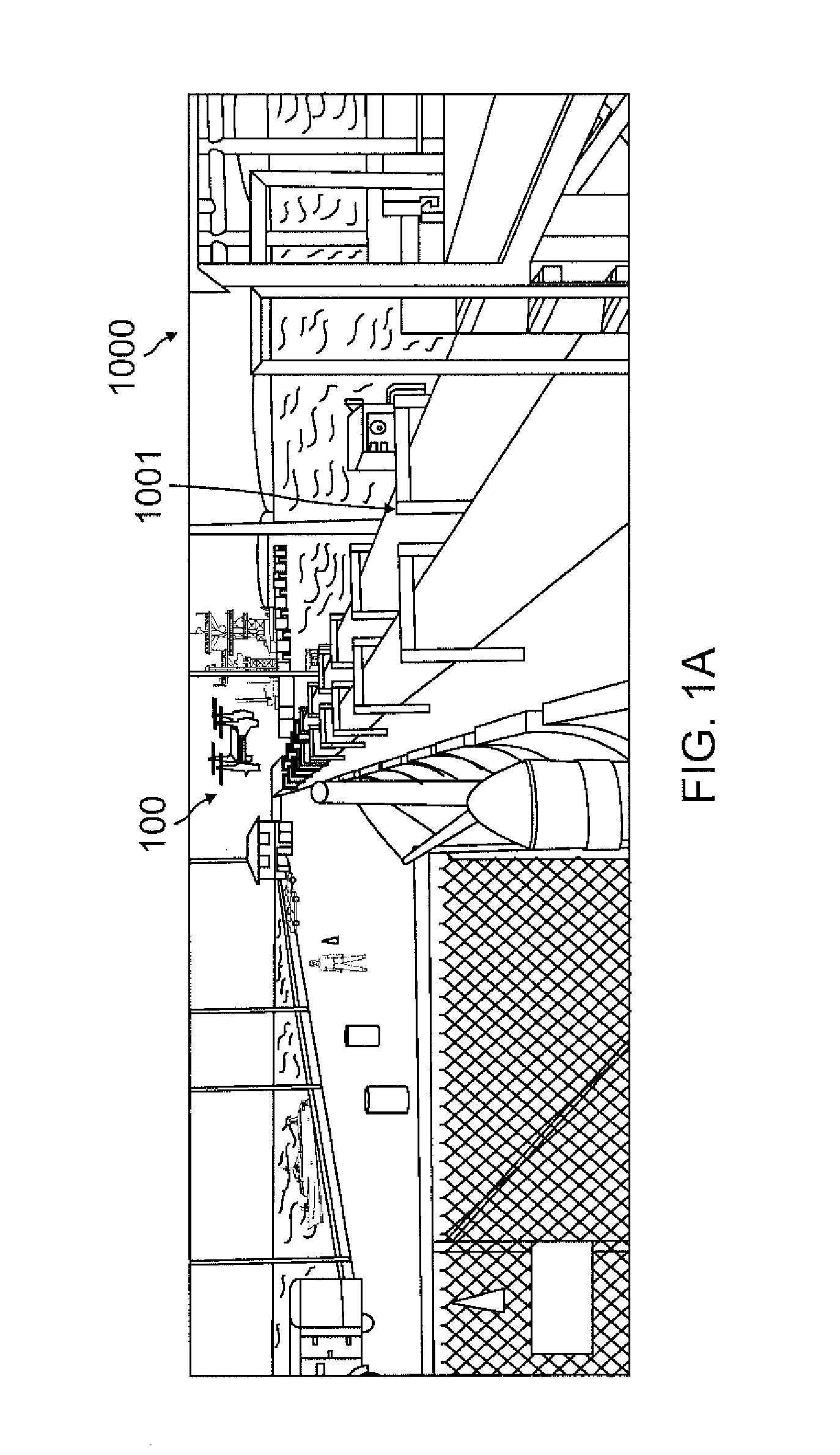

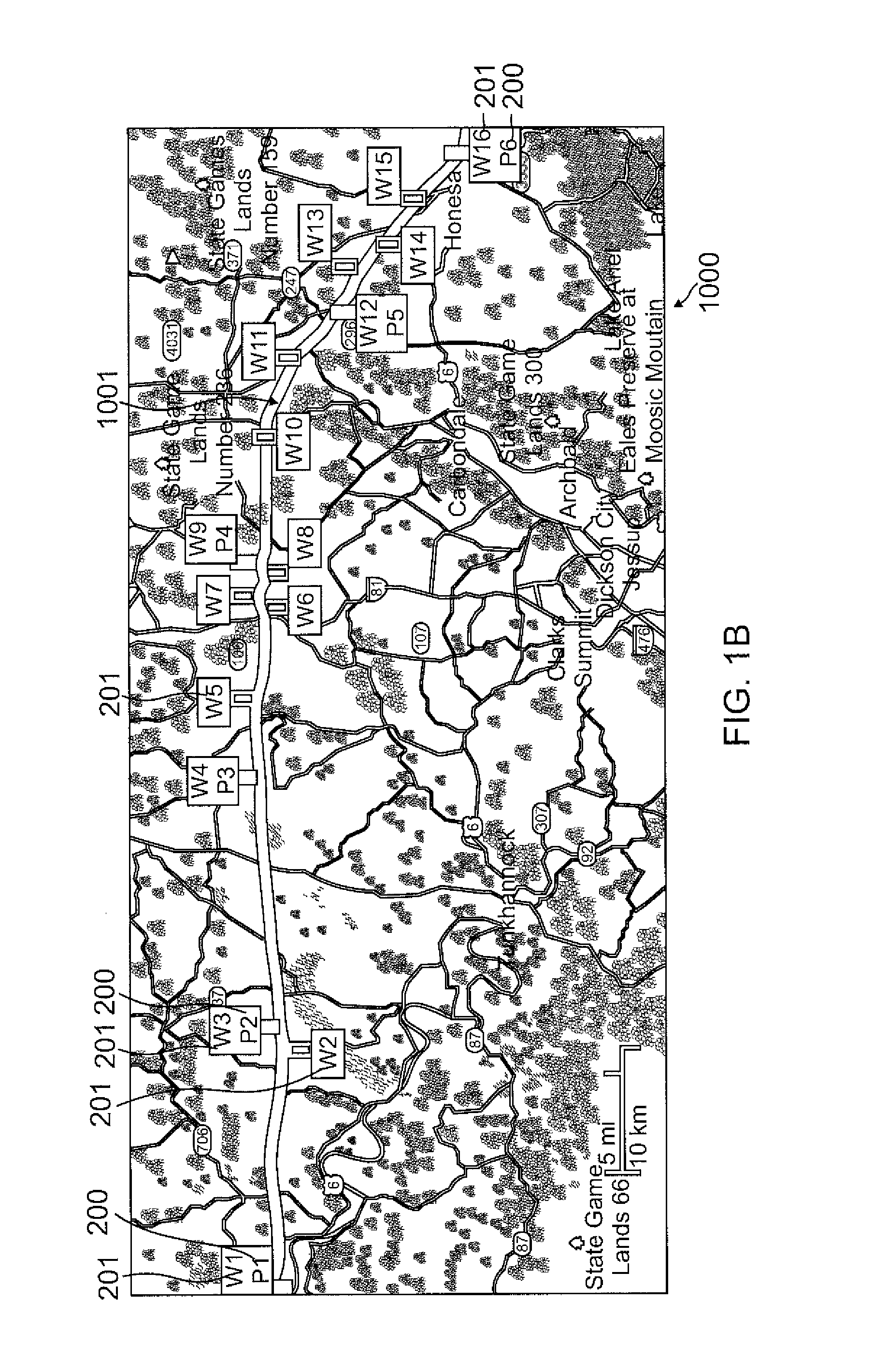

Vertical takeoff and landing (VTOL) small unmanned aerial system for monitoring oil and gas pipelines

ActiveUS8880241B2Analogue computers for vehiclesDigital data processing detailsJet aeroplaneUncrewed vehicle

Extended-range monitoring and surveillance of facilities and infrastructure—such as oil, water, and gas pipelines and power lines—employs autonomous vertical take-off and landing (VTOL) capable, small unmanned aerial system (sUAS) aircraft and docking platforms for accommodating the sUAS aircraft. Monitoring and surveillance of facilities using one or more embodiments may be performed continually by the sUAS flying autonomously along a pre-programmed flight path. The sUAS aircraft may have an integrated gas collector and analyzer unit, and capability for downloading collected data and analyzer information from the sUAS aircraft to the docking platforms. The gas collector and analyzer unit may provide remote sensing and in-situ investigation of leaks and other environmental concerns as part of a “standoff” (e.g., remote from operators of the system or the facilities) survey that can keep field operators out of harm's way and monitor health of the environment.

Owner:MOHAMADI FARROKH

Method and system for implementing multiple high precision and low precision interpolators for a graphics pipeline

ActiveUS20060268005A1Reduce total powerMeet cutting requirementsCathode-ray tube indicatorsFilling planer surface with attributesComputational scienceGraphics

A rasterizer stage configured to implement multiple interpolators for graphics pipeline. The rasterizer stage includes a plurality of simultaneously operable low precision interpolators for computing a first set of pixel parameters for pixels of a geometric primitive and a plurality of simultaneously operable high precision interpolators for computing a second set of pixel parameters for pixels of the geometric primitive. The rasterizer stage also includes an output mechanism coupled to the interpolators for routing computed pixel parameters into a memory array. Parameters may be programmably assigned to the interpolators and the results thereof may be programmably assigned to portions of a pixel packet.

Owner:NVIDIA CORP

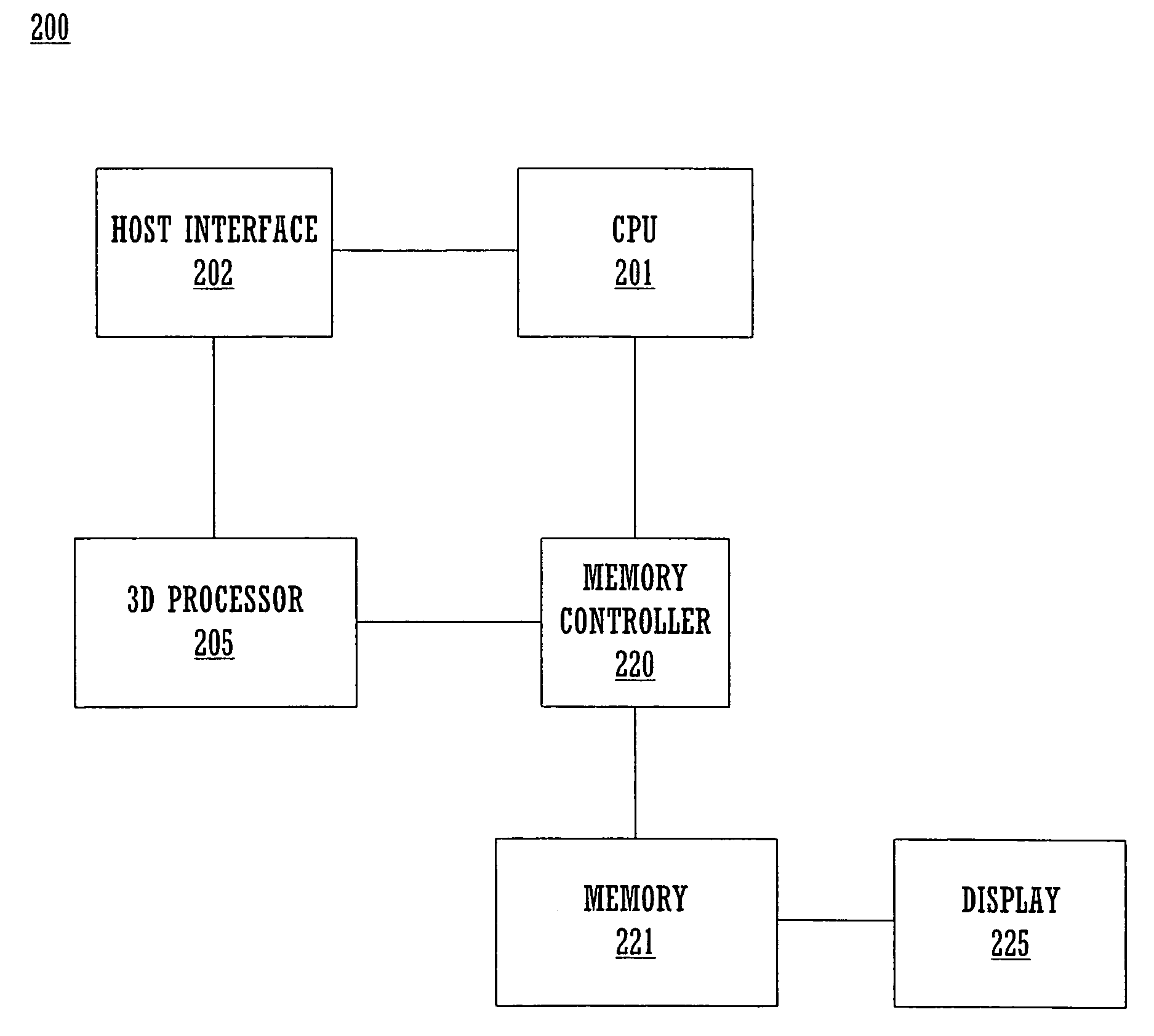

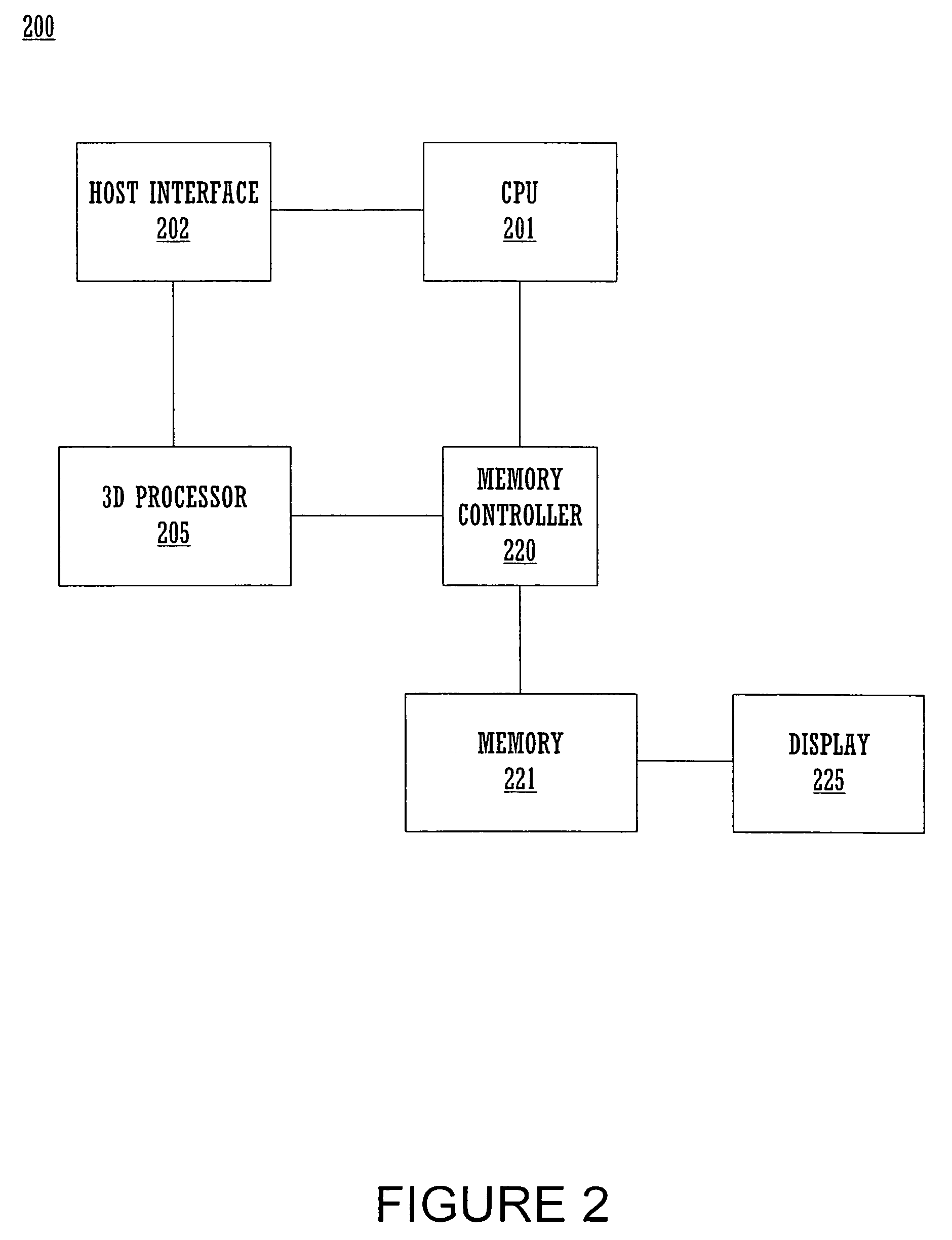

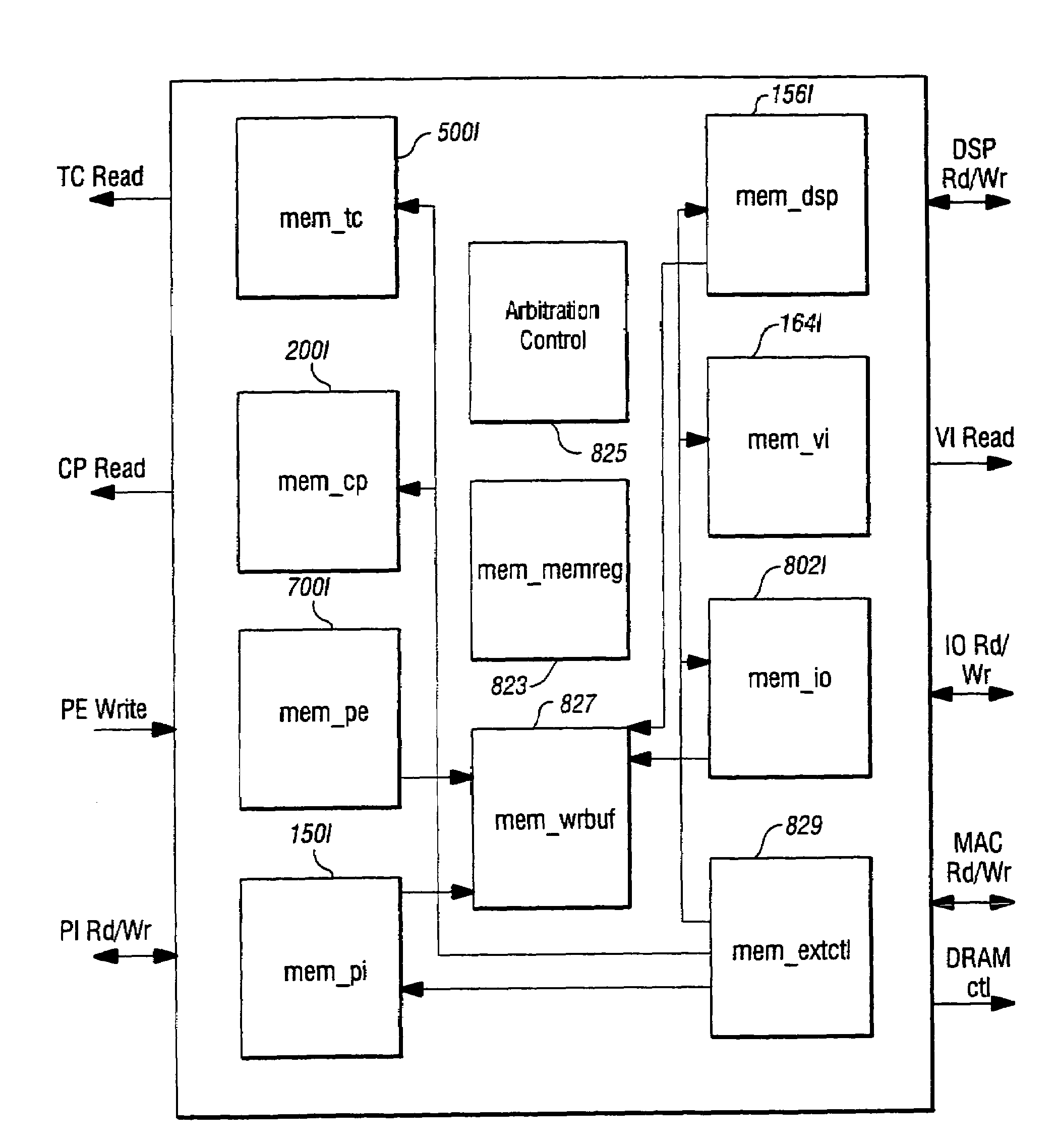

Graphics processing system with enhanced memory controller

ActiveUS7538772B1Effective flushingMinimize switchingImage memory managementCathode-ray tube indicatorsParallel computingConsistency problem

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. A memory controller performs a wide range of memory control related functions including arbitrating between various competing resources seeking access to main memory, handling memory latency and bandwidth requirements of the resources requesting memory access, buffering writes to reduce bus turn around, refreshing main memory, and protecting main memory using programmable registers. The memory controller minimizes memory read / write switching using a “global” write queue which queues write requests from various diverse competing resources. In this fashion, multiple competing resources for memory writes are combined into one resource from which write requests are obtained. Memory coherency issues are addressed both within a single resource that has both read and write capabilities and among different resources by efficiently flushing write buffers associated with a resource.

Owner:NINTENDO CO LTD

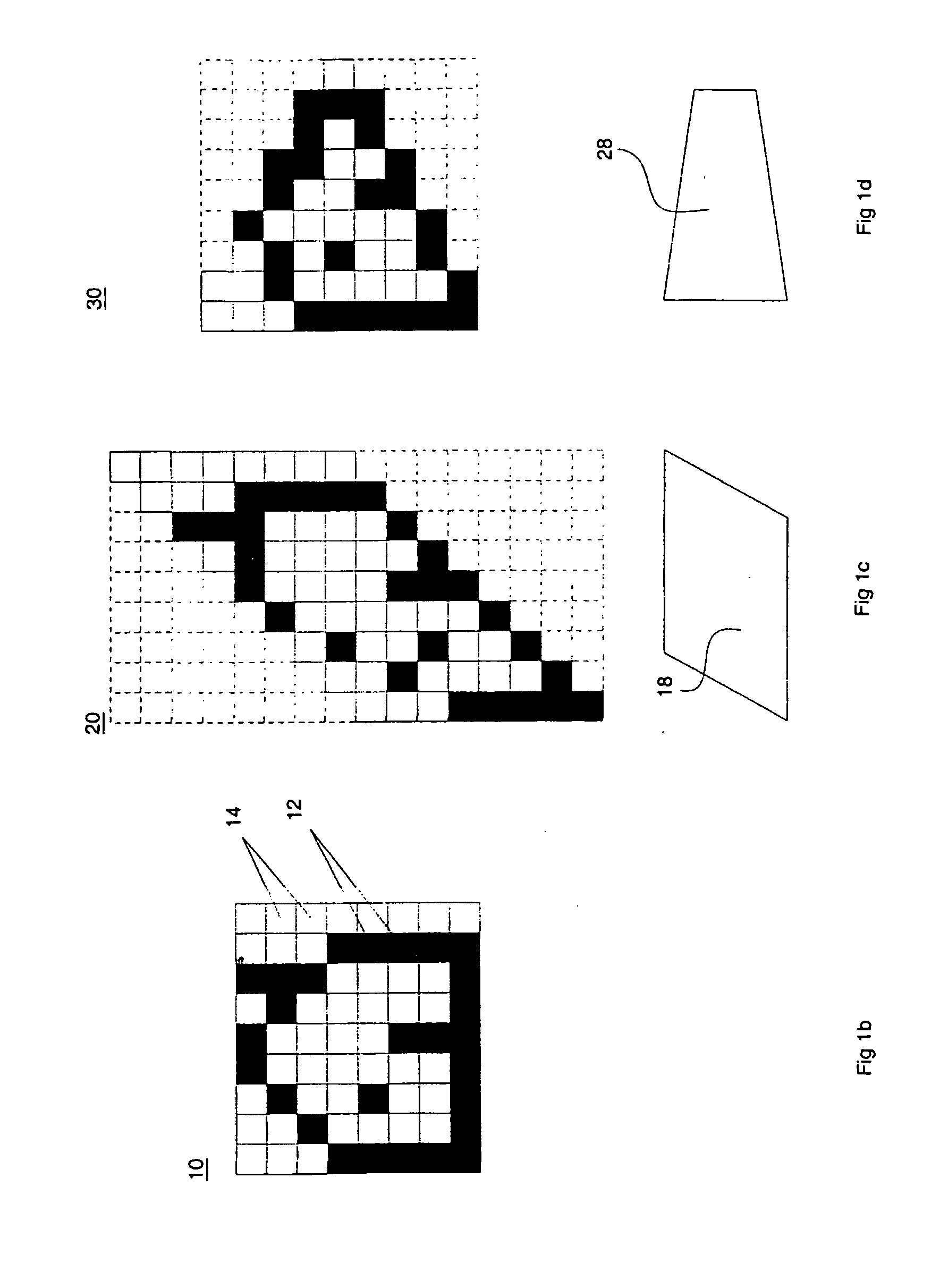

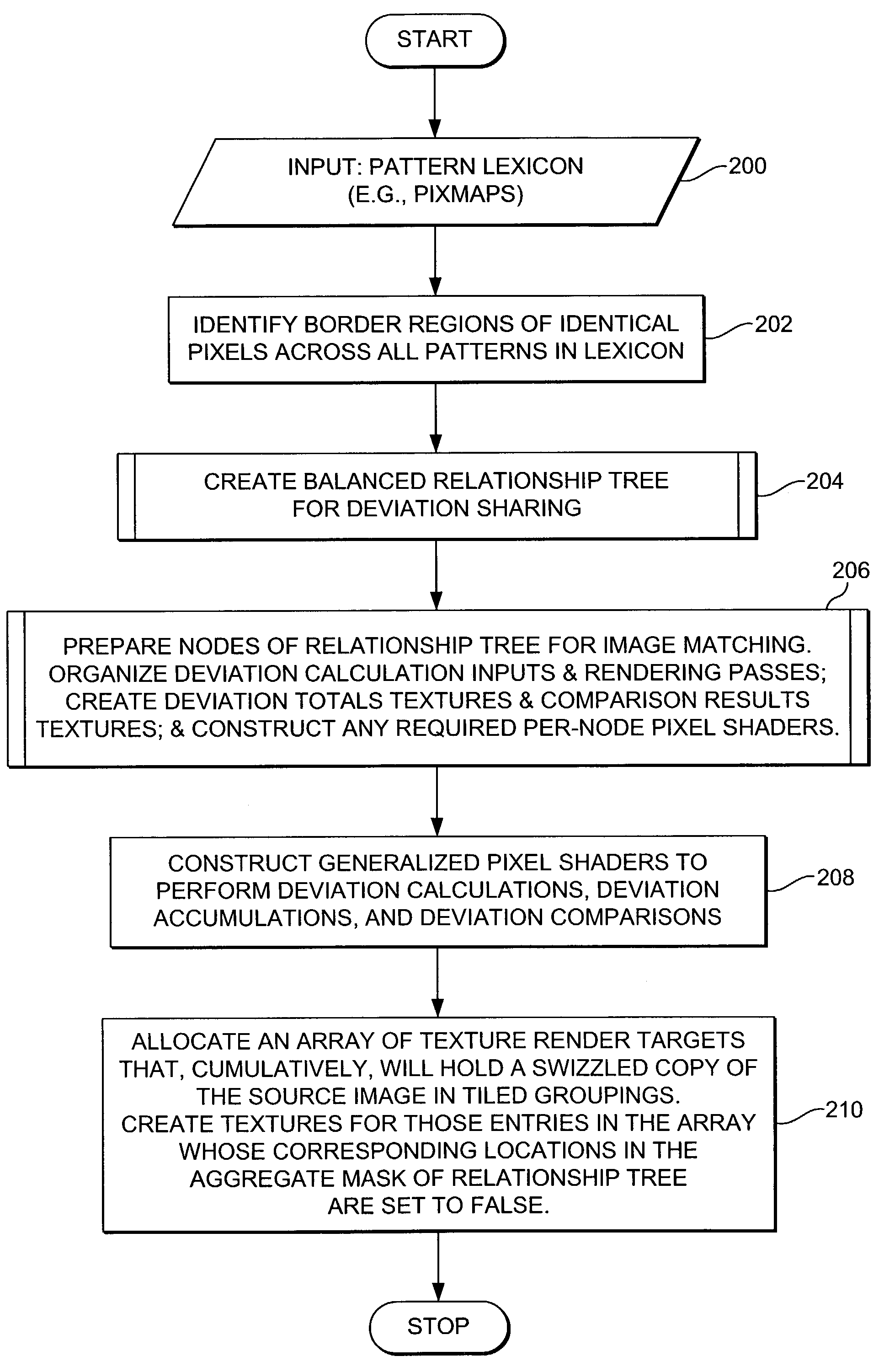

Real time data matching

InactiveUS7130467B1Minimize the numberAccess useCharacter and pattern recognitionDigital video signal modificationGraphicsReal-time data

Representing source data with predefined data patterns, or identifying predefined data patterns in source data, where each data pattern includes a unique combination of pattern elements, without comparing every pattern element of each data pattern to the source data. A hierarchical structure of relationships between the data patterns is predetermined in an initialization stage by comparing the data patterns to identify identical pattern elements among groups of the data patterns. Selected node elements in a resulting relationship tree are compared to the source data to determined deviations. The deviations are propagated and accumulated throughout the relationship structure of the tree, and data patterns having the minimum deviation are selected to represent corresponding source data cells. A graphics pipeline preferably is used to determine the deviations and select data patterns in real time.

Owner:MICROSOFT TECH LICENSING LLC