Patents

Literature

7924results about "Processor architectures/configuration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

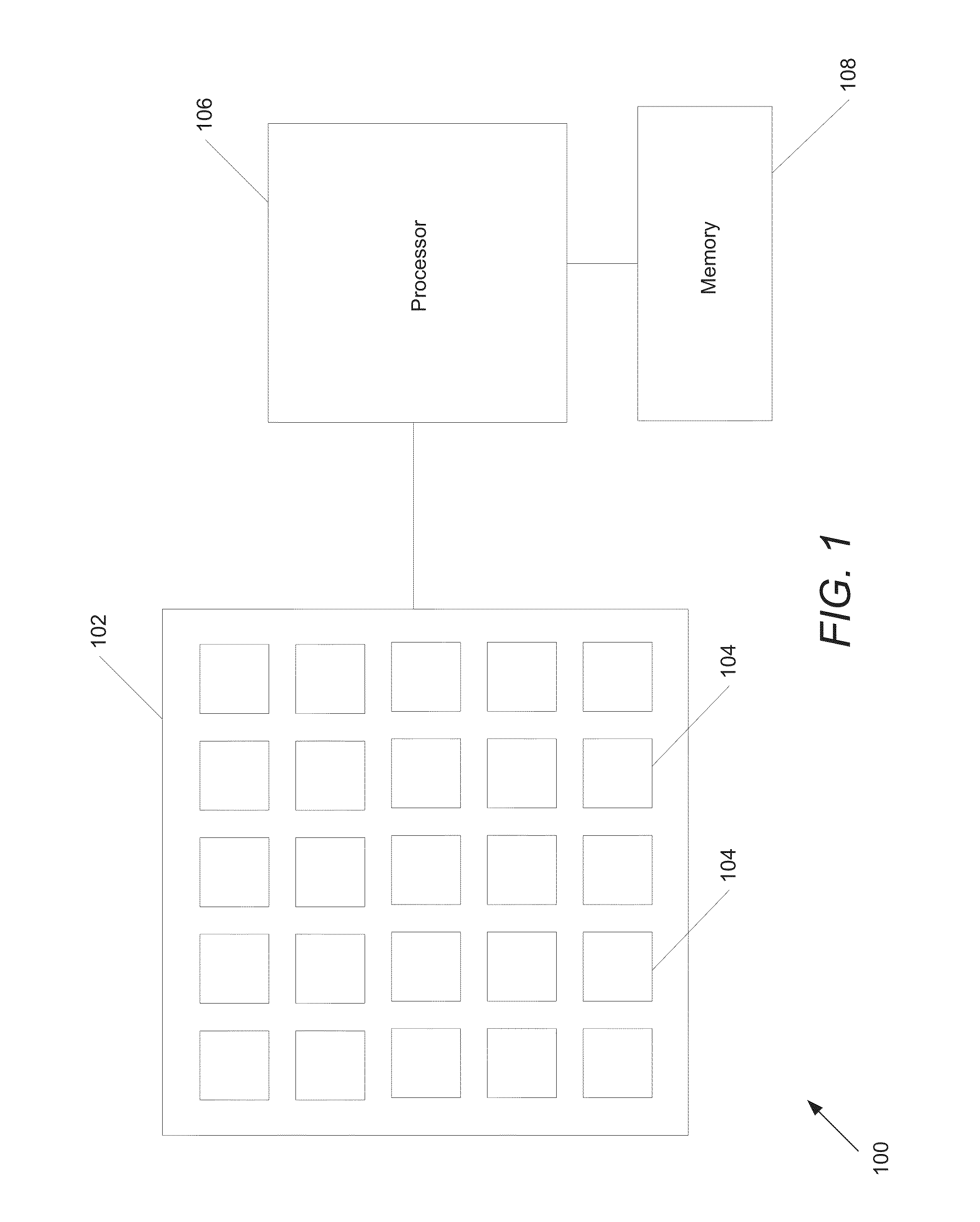

Data processing system and method

InactiveUS6215898B1Reduce overheadHigh sensitivityImage enhancementImage analysisStatic random-access memoryHigh memory

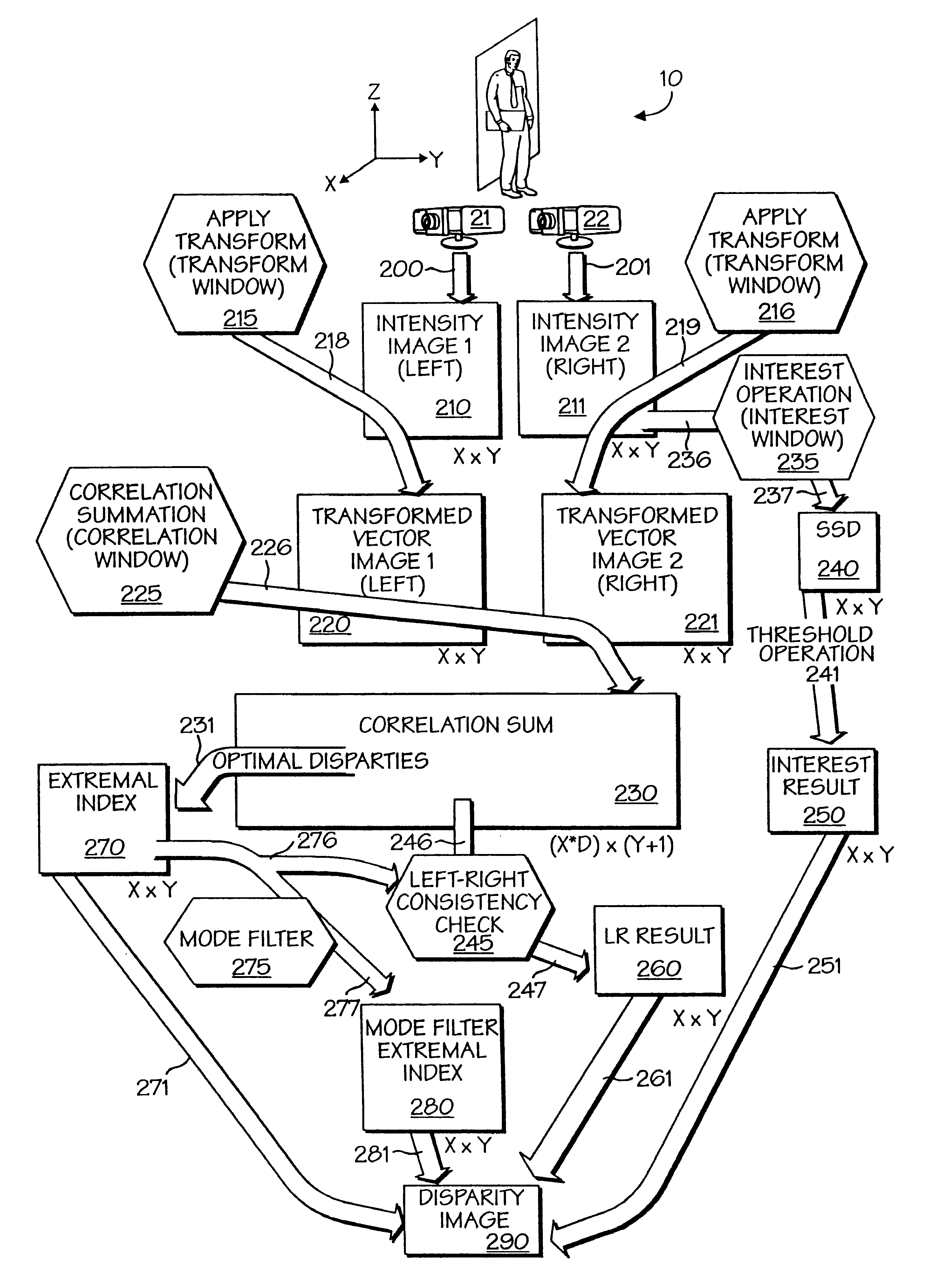

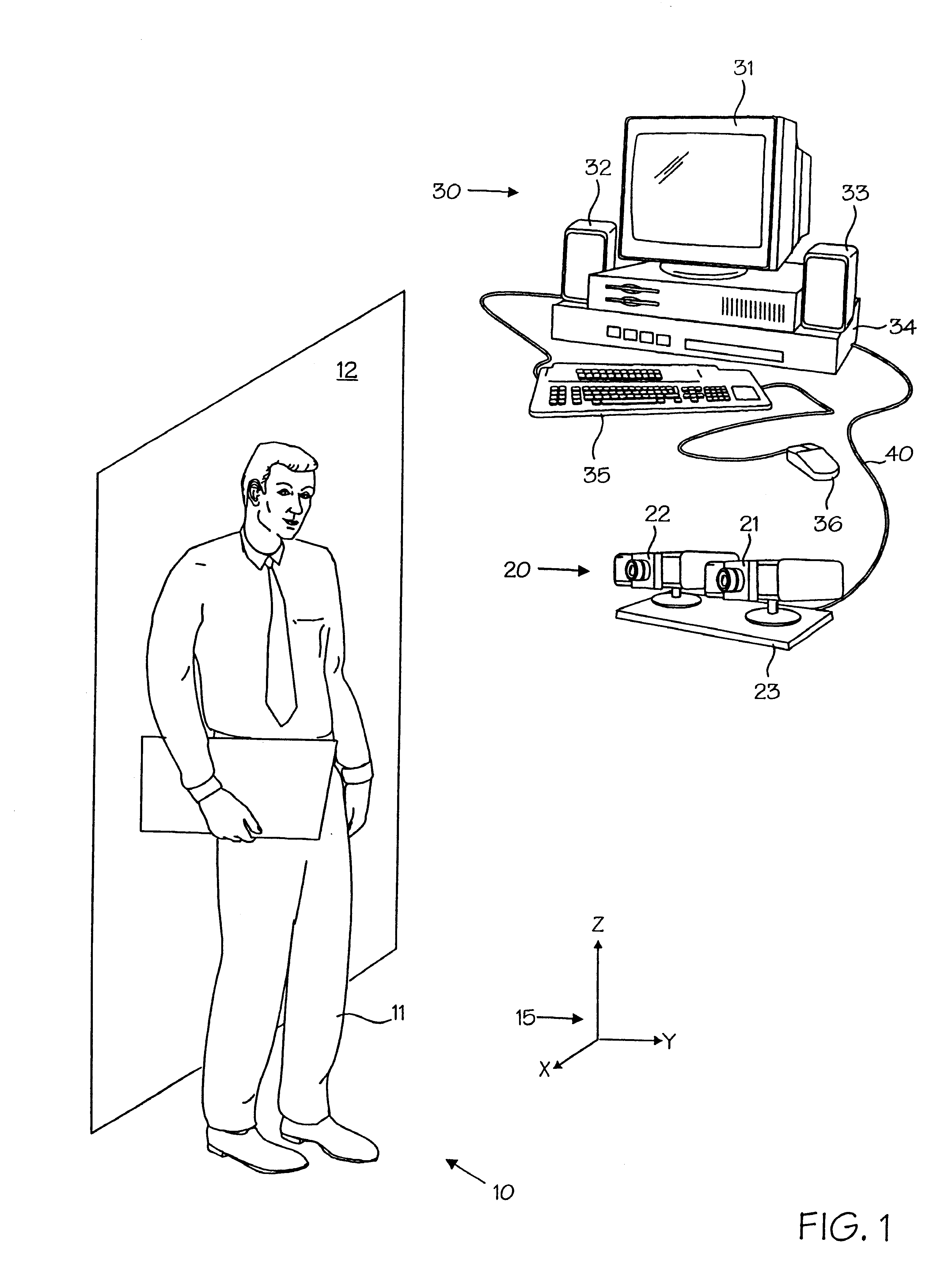

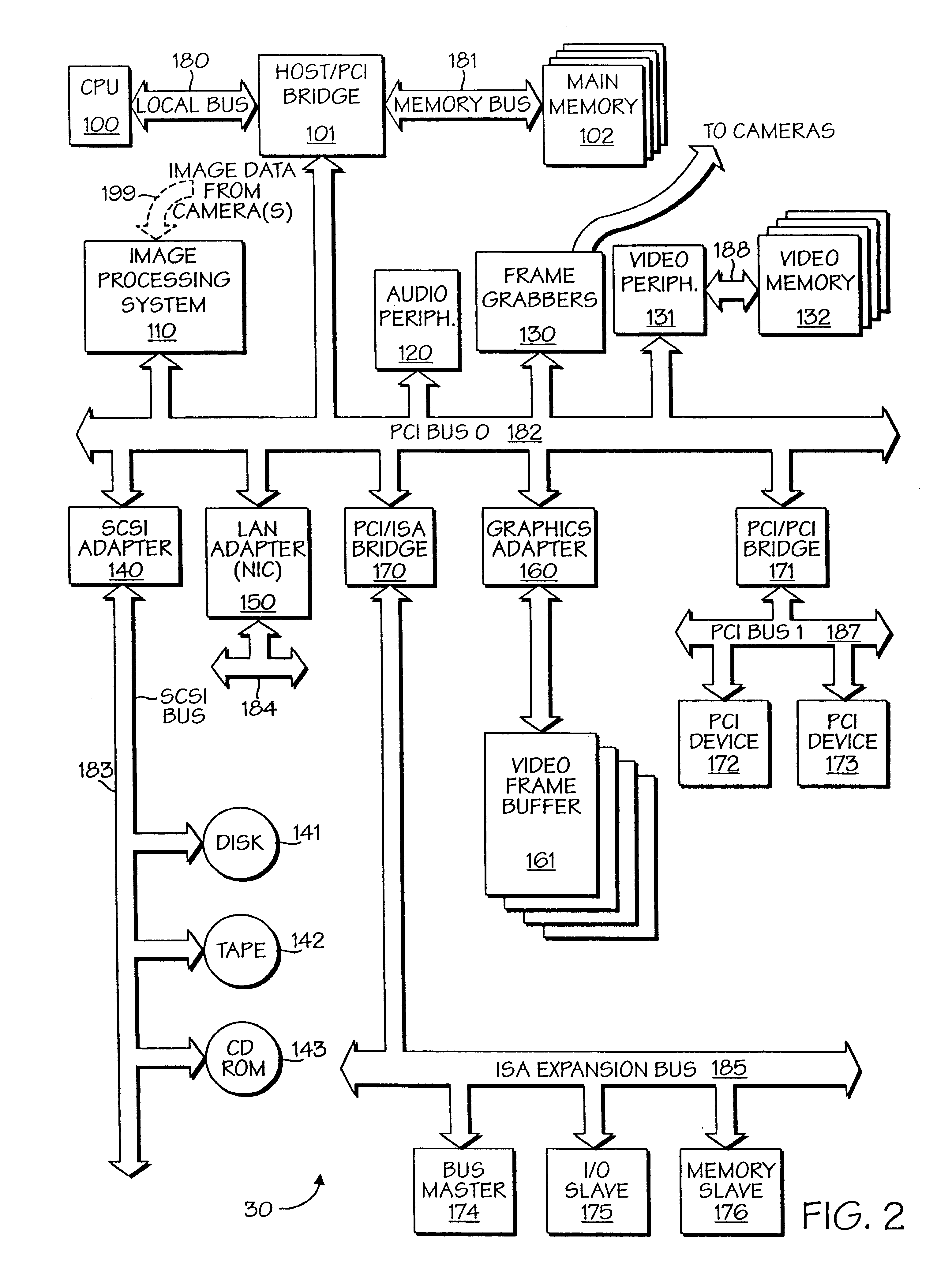

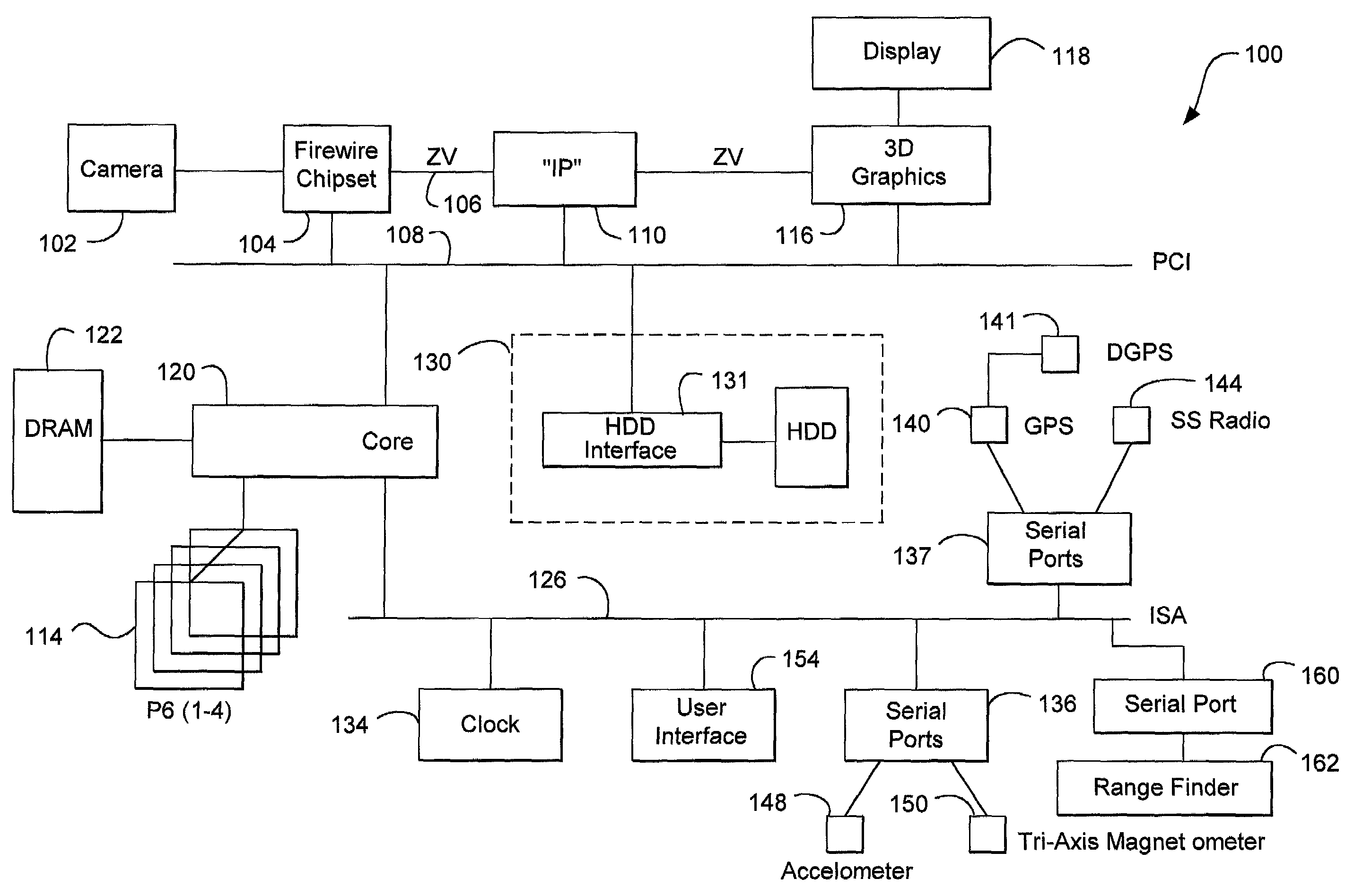

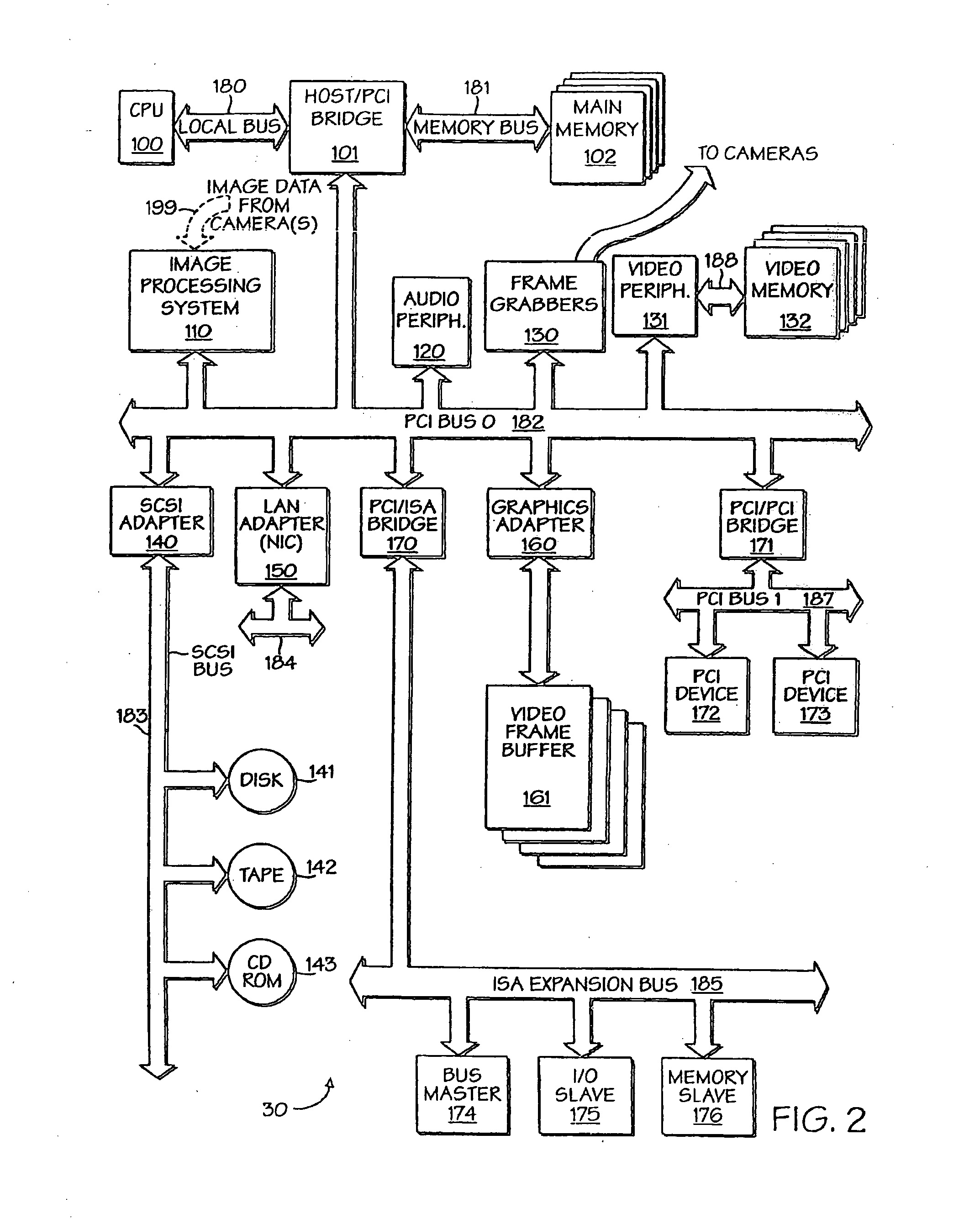

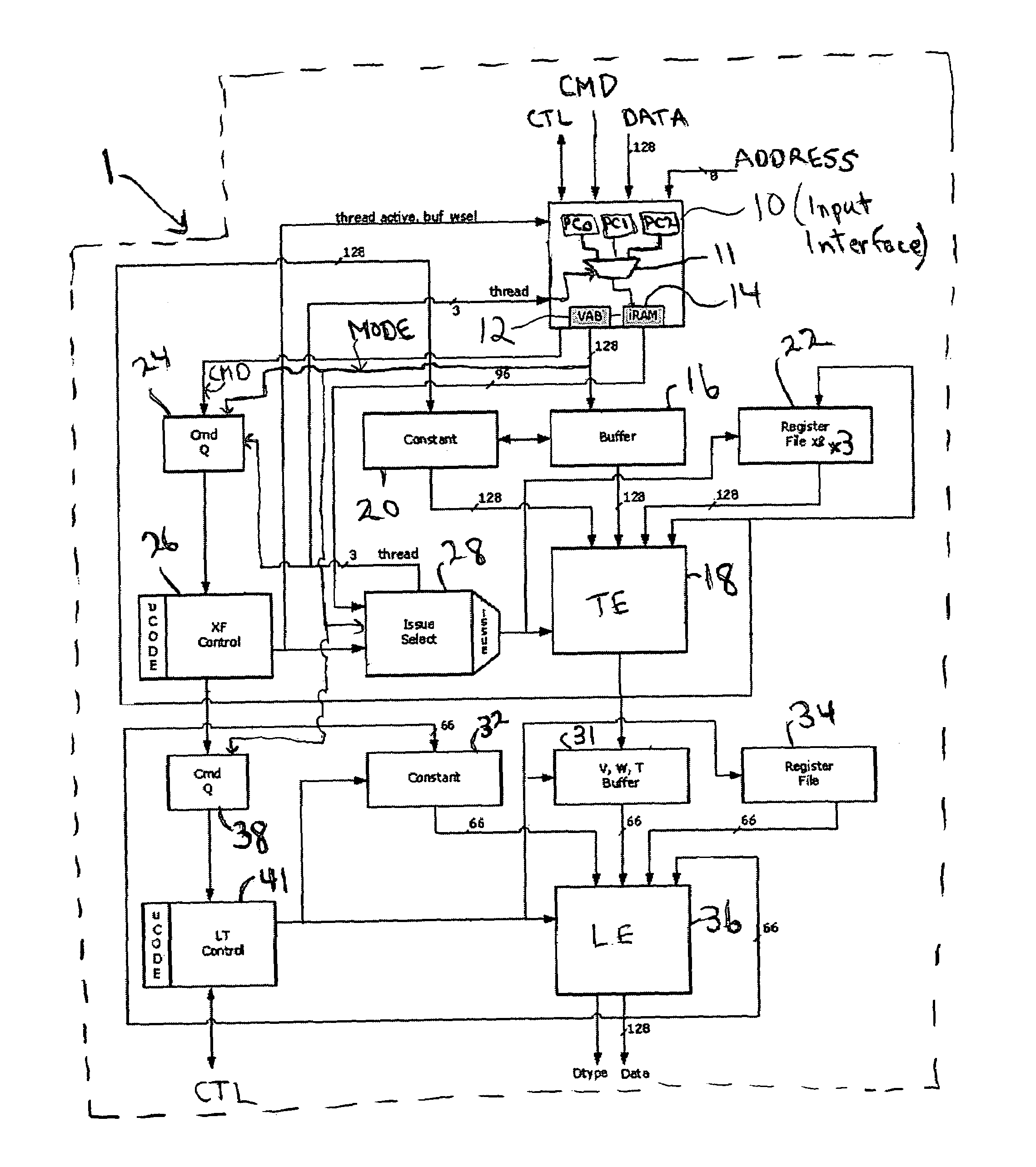

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

Distributed sensing techniques for mobile devices

ActiveUS20050093868A1Input/output for user-computer interactionServices signallingHuman–computer interactionMobile device

Methods and apparatus of the invention allow the coordination of resources of mobile computing devices to jointly execute tasks. In the method, a first gesture input is received at a first mobile computing device. A second gesture input is received at a second mobile computing device. In response, a determination is made as to whether the first and second gesture inputs form one of a plurality of different synchronous gesture types. If it is determined that the first and second gesture inputs form the one of the plurality of different synchronous gesture types, then resources of the first and second mobile computing devices are combined to jointly execute a particular task associated with the one of the plurality of different synchronous gesture types.

Owner:MICROSOFT TECH LICENSING LLC

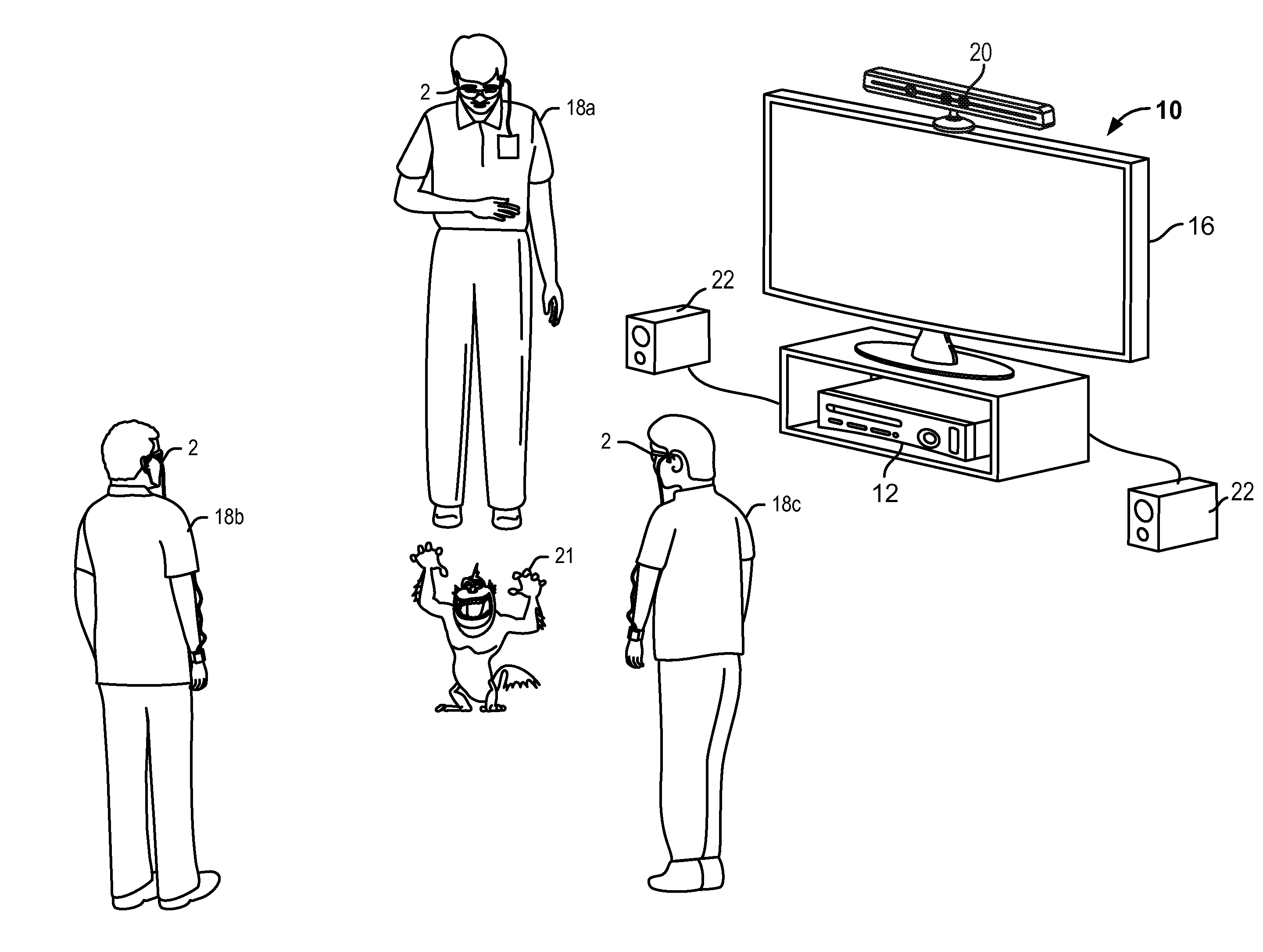

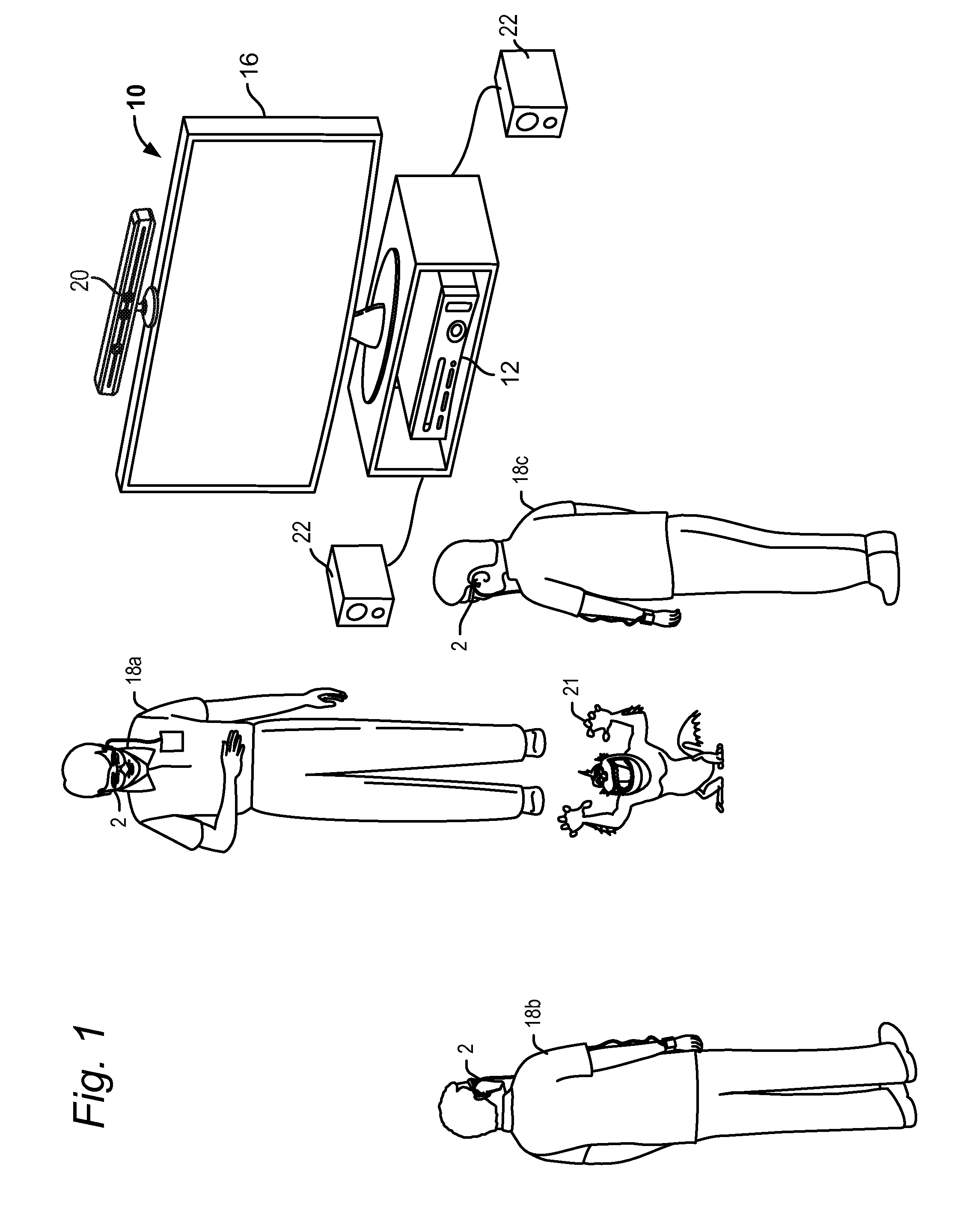

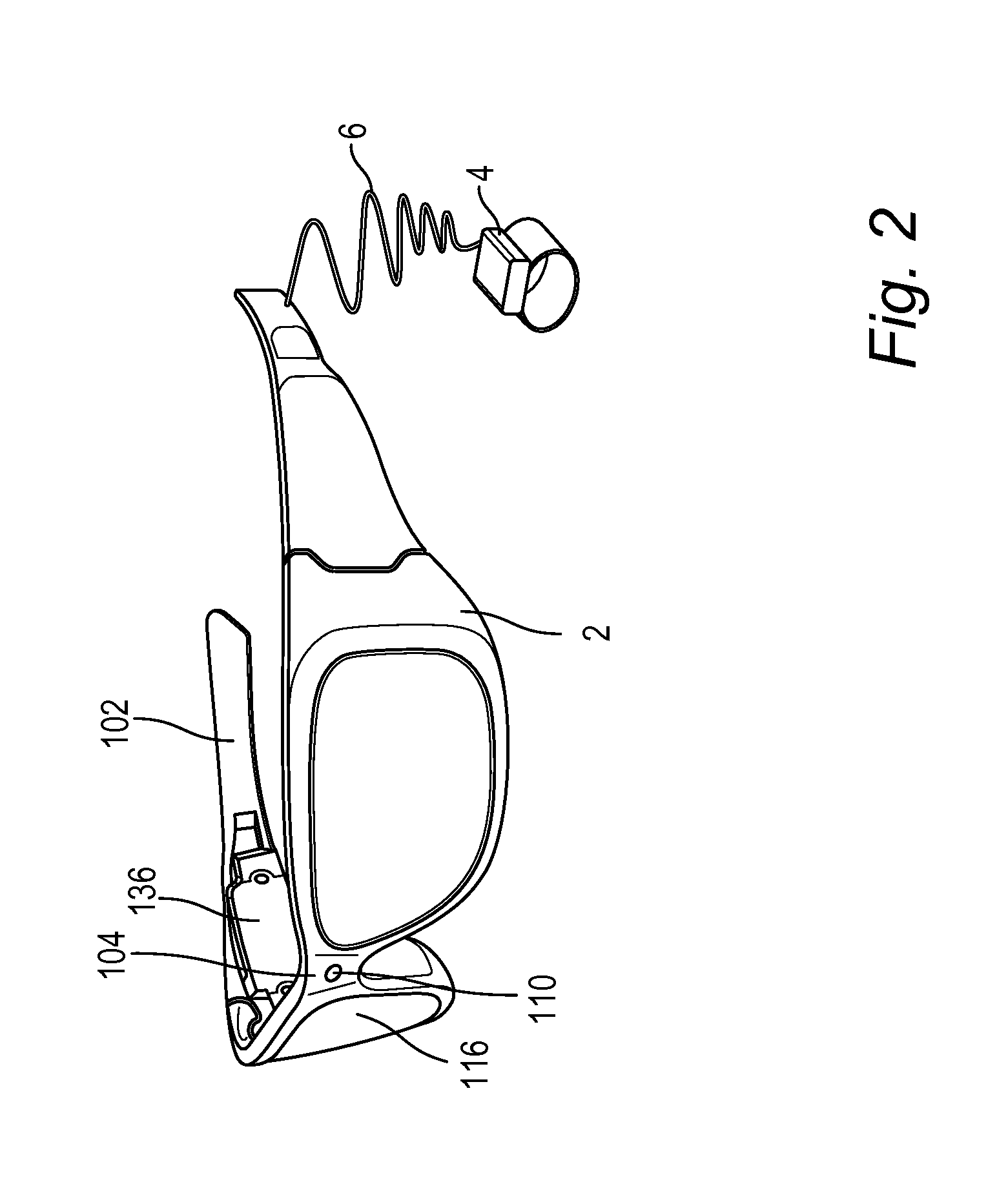

Low-latency fusing of virtual and real content

ActiveUS20120105473A1Introduce inherent latencyImage analysisCathode-ray tube indicatorsMixed realityLatency (engineering)

A system that includes a head mounted display device and a processing unit connected to the head mounted display device is used to fuse virtual content into real content. In one embodiment, the processing unit is in communication with a hub computing device. The processing unit and hub may collaboratively determine a map of the mixed reality environment. Further, state data may be extrapolated to predict a field of view for a user in the future at a time when the mixed reality is to be displayed to the user. This extrapolation can remove latency from the system.

Owner:MICROSOFT TECH LICENSING LLC

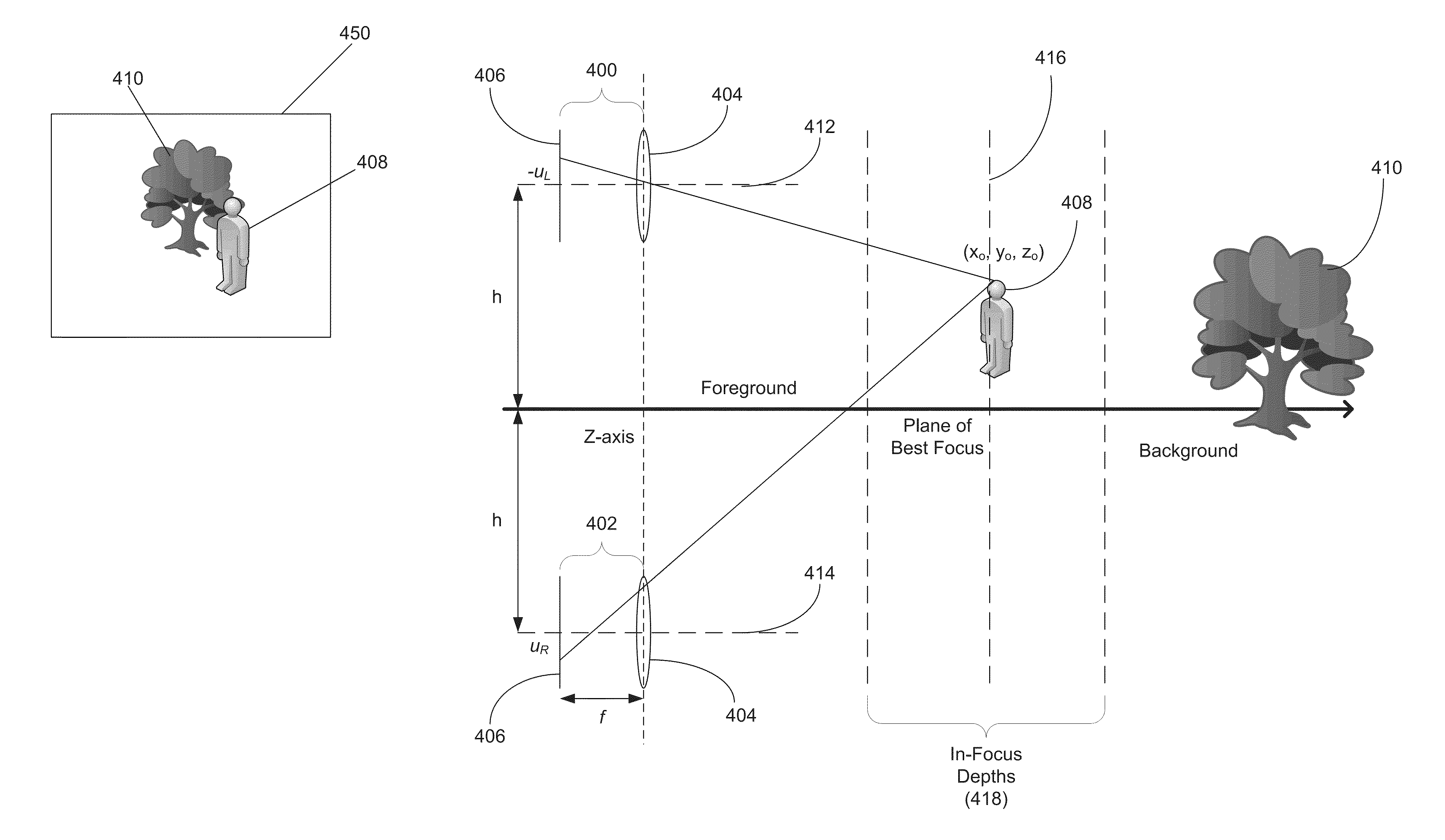

Systems and Methods for Synthesizing Images from Image Data Captured by an Array Camera Using Restricted Depth of Field Depth Maps in which Depth Estimation Precision Varies

ActiveUS20140267243A1Great depth estimation precisionHigh depth estimateImage enhancementImage analysisImaging processingViewpoints

Systems and methods are described for generating restricted depth of field depth maps. In one embodiment, an image processing pipeline application configures a processor to: determine a desired focal plane distance and a range of distances corresponding to a restricted depth of field for an image rendered from a reference viewpoint; generate a restricted depth of field depth map from the reference viewpoint using the set of images captured from different viewpoints, where depth estimation precision is higher for pixels with depth estimates within the range of distances corresponding to the restricted depth of field and lower for pixels with depth estimates outside of the range of distances corresponding to the restricted depth of field; and render a restricted depth of field image from the reference viewpoint using the set of images captured from different viewpoints and the restricted depth of field depth map.

Owner:FOTONATION LTD

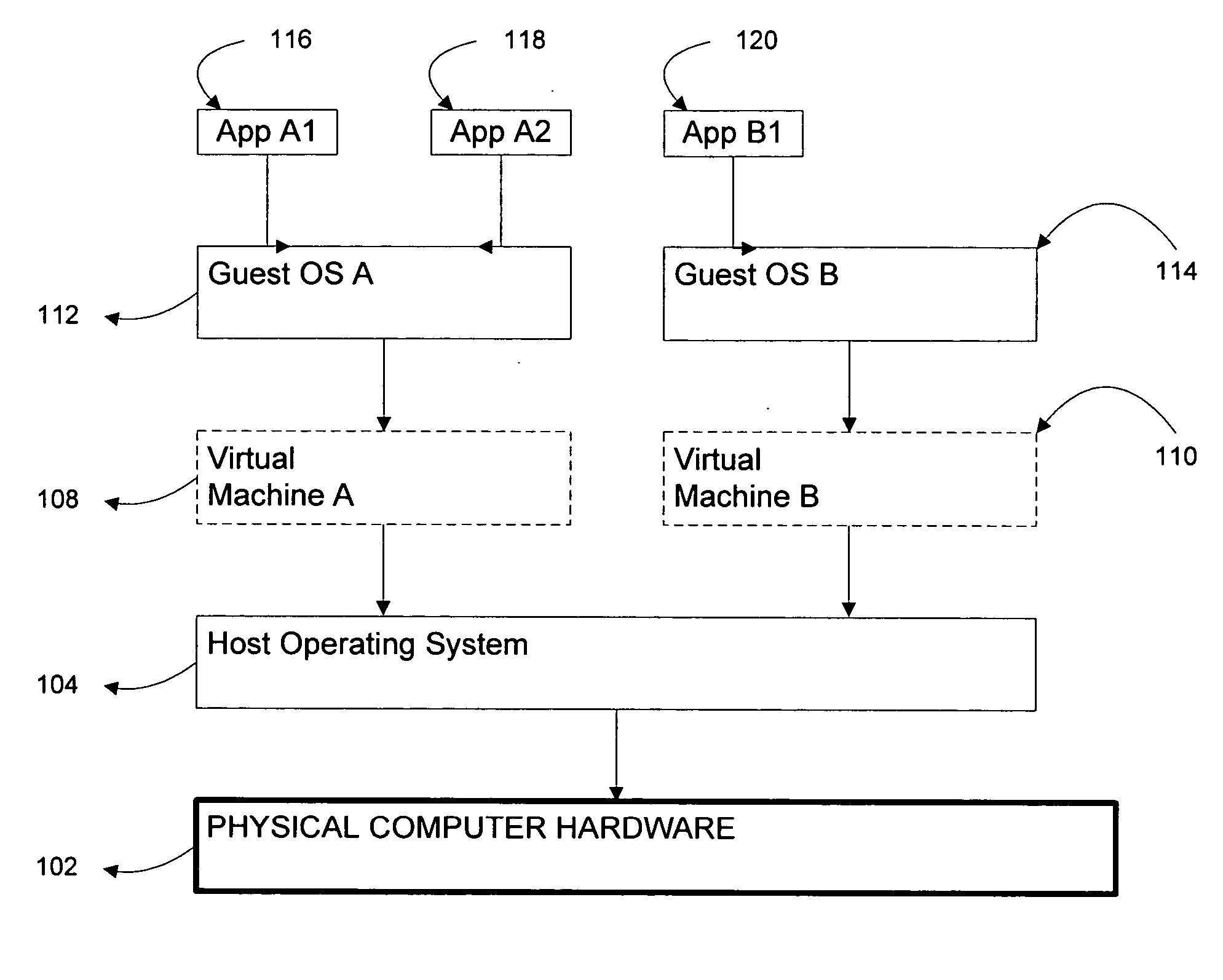

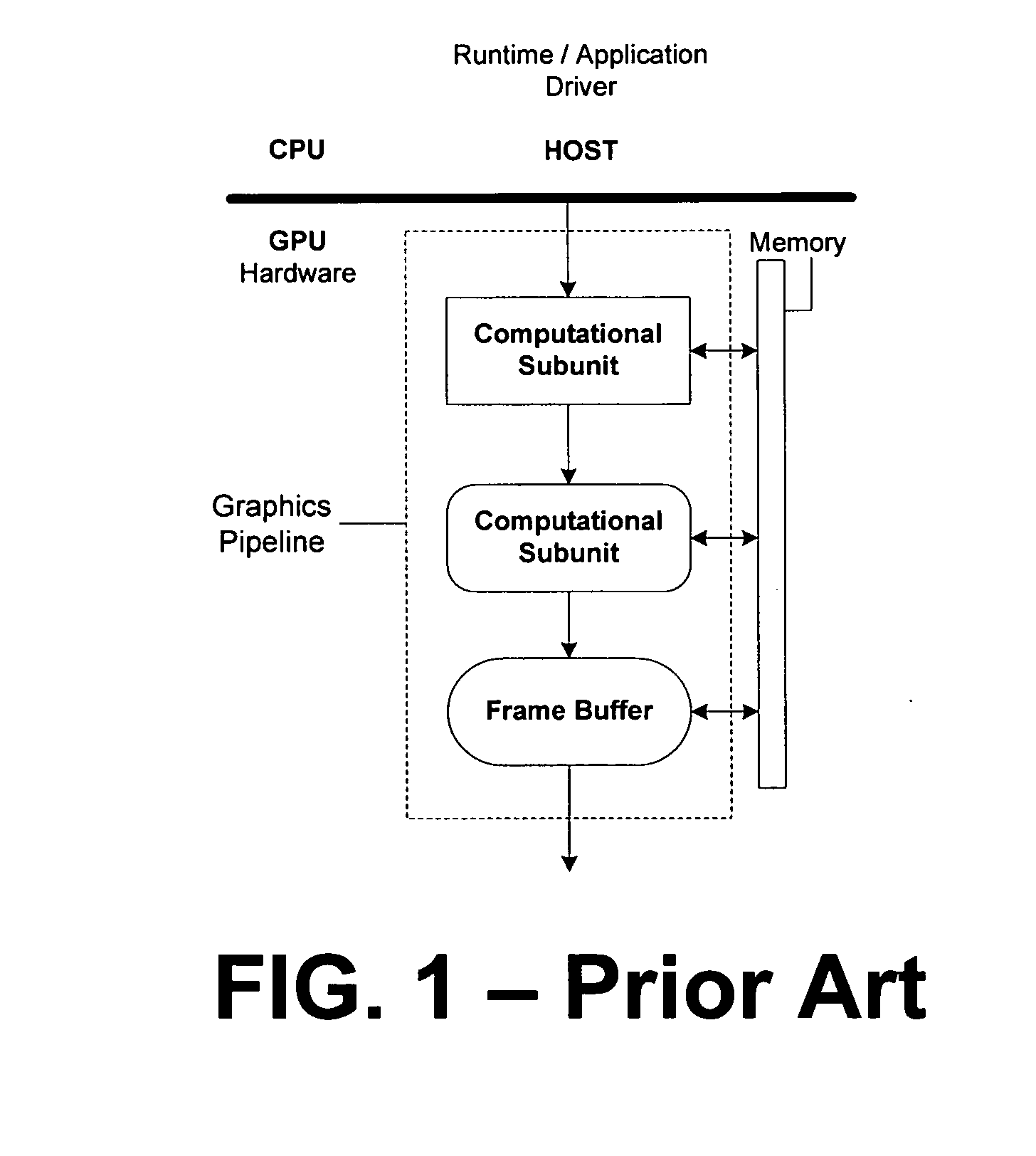

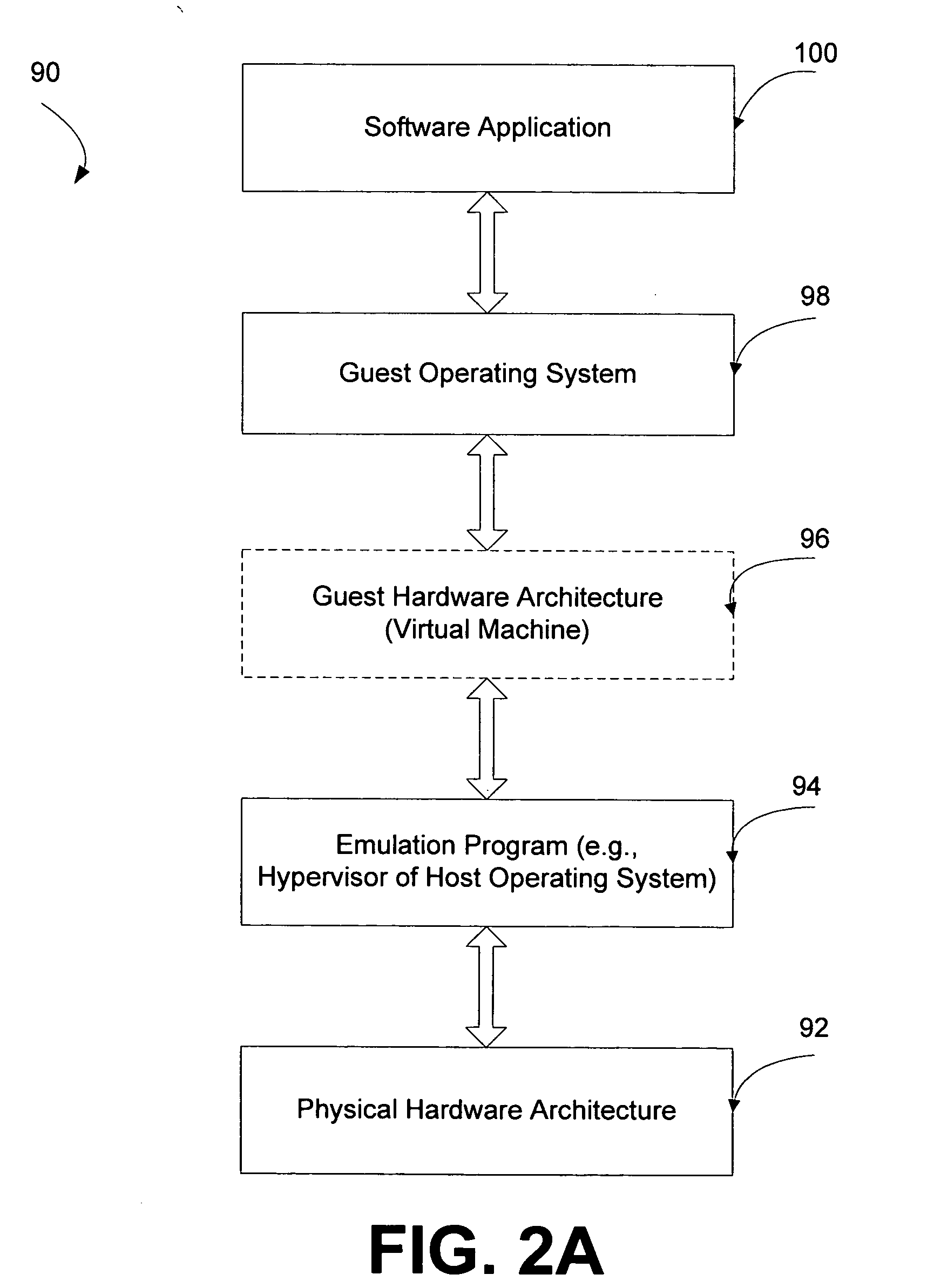

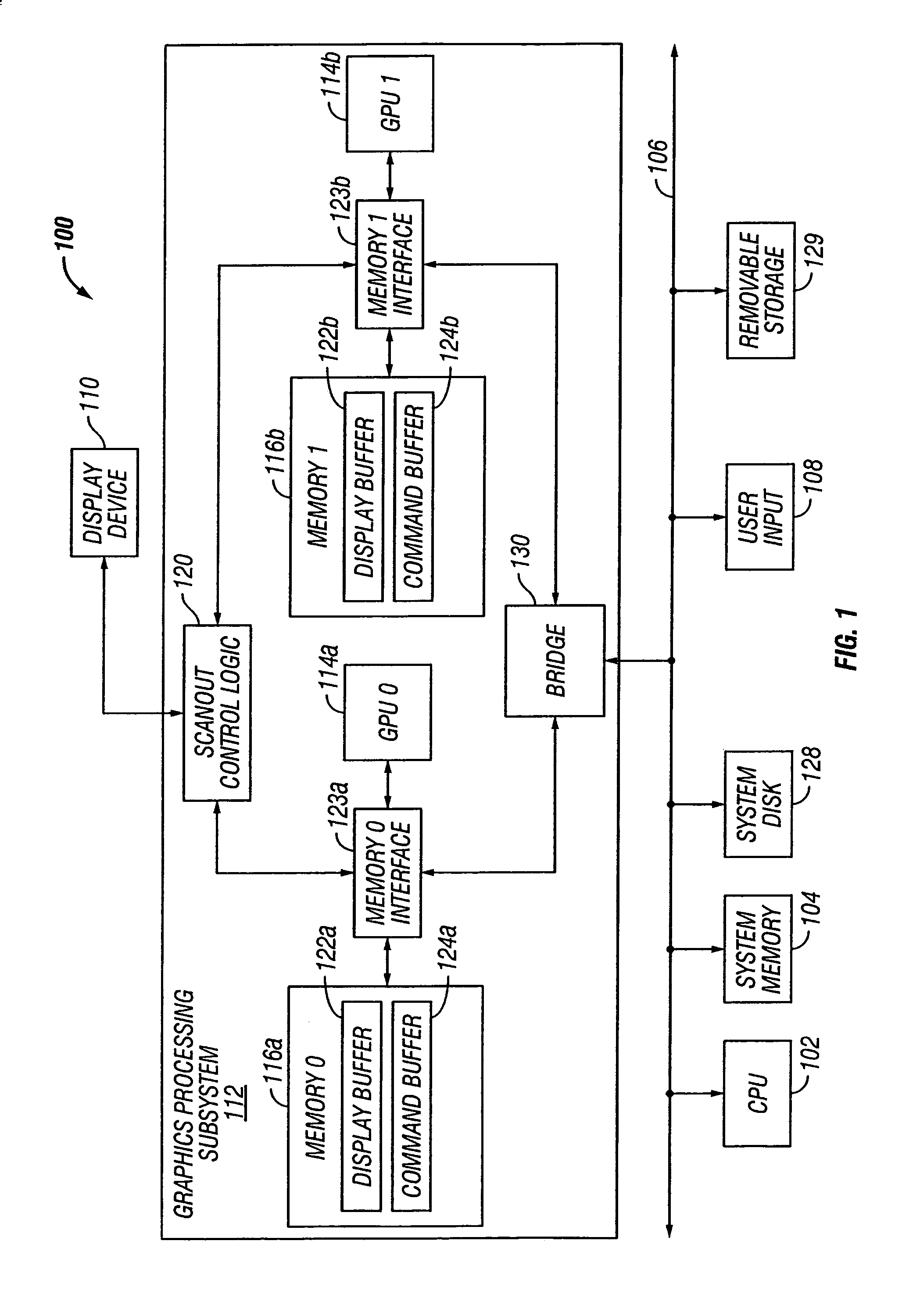

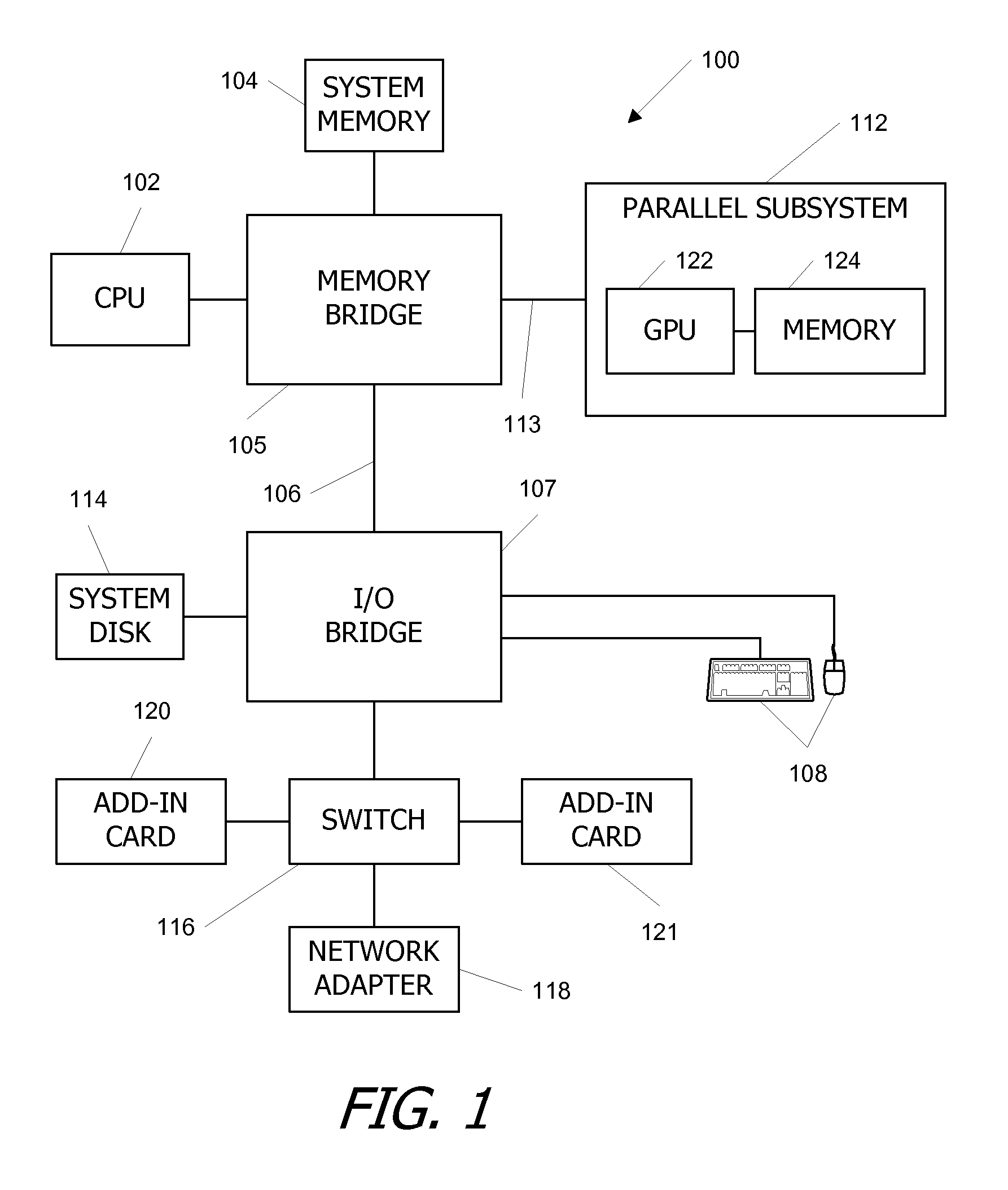

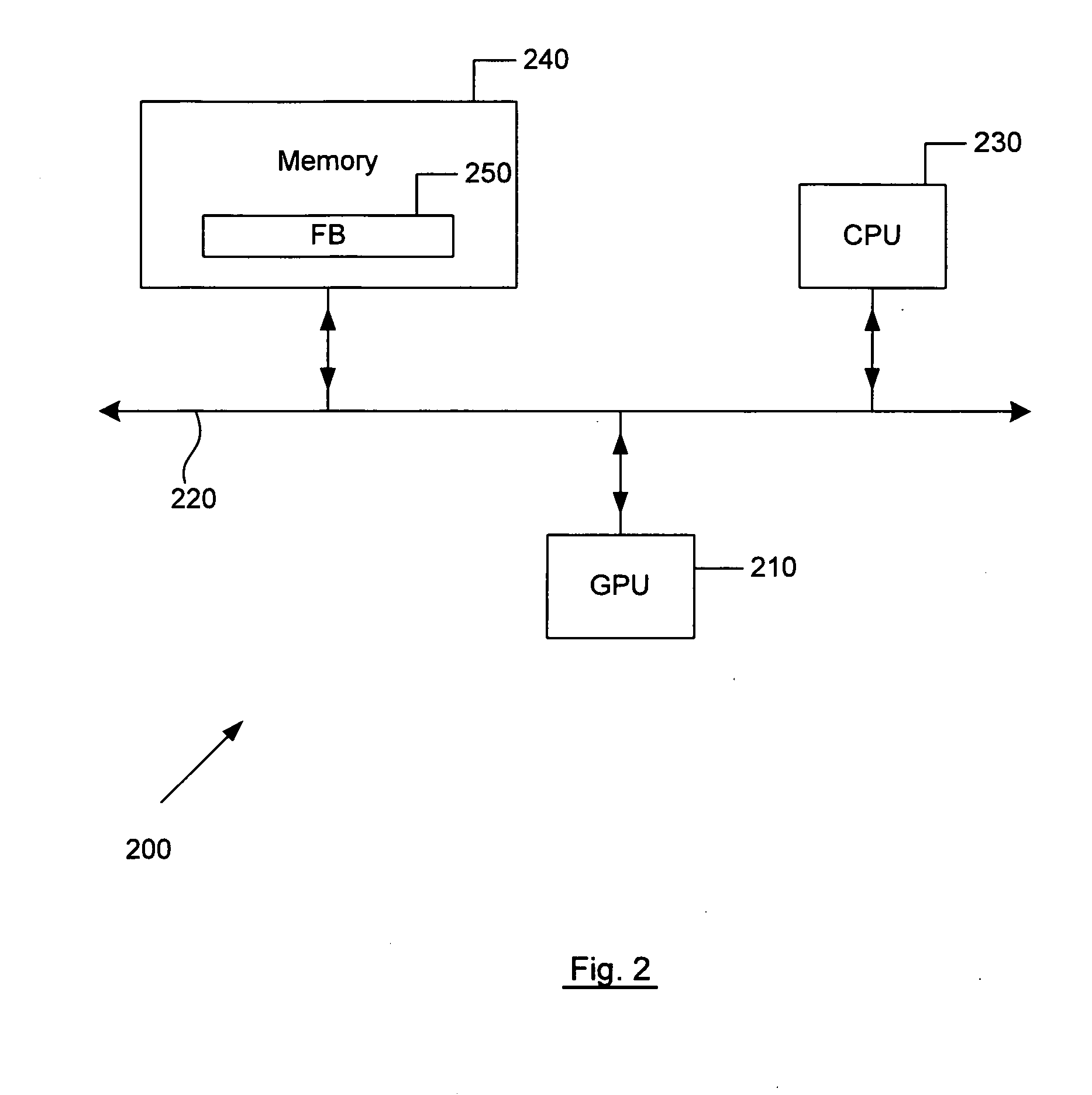

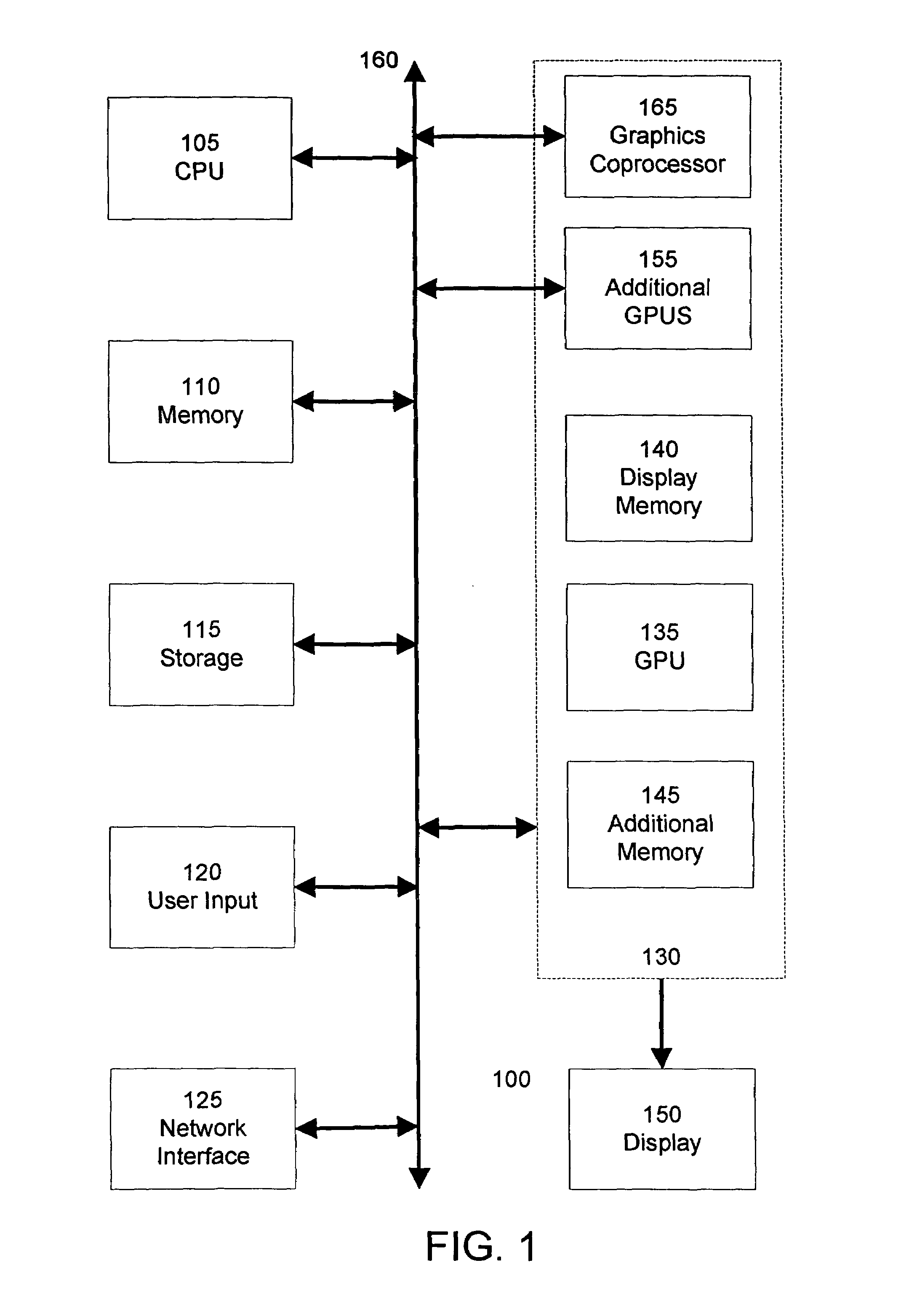

Systems and methods for virtualizing graphics subsystems

ActiveUS20060146057A1Program control using stored programsProcessor architectures/configurationVirtualizationOperational system

Systems and methods for applying virtual machines to graphics hardware are provided. In various embodiments of the invention, while supervisory code runs on the CPU, the actual graphics work items are run directly on the graphics hardware and the supervisory code is structured as a graphics virtual machine monitor. Application compatibility is retained using virtual machine monitor (VMM) technology to run a first operating system (OS), such as an original OS version, simultaneously with a second OS, such as a new version OS, in separate virtual machines (VMs). VMM technology applied to host processors is extended to graphics processing units (GPUs) to allow hardware access to graphics accelerators, ensuring that legacy applications operate at full performance. The invention also provides methods to make the user experience cosmetically seamless while running multiple applications in different VMs. In other aspects of the invention, by employing VMM technology, the virtualized graphics architecture of the invention is extended to provide trusted services and content protection.

Owner:MICROSOFT TECH LICENSING LLC

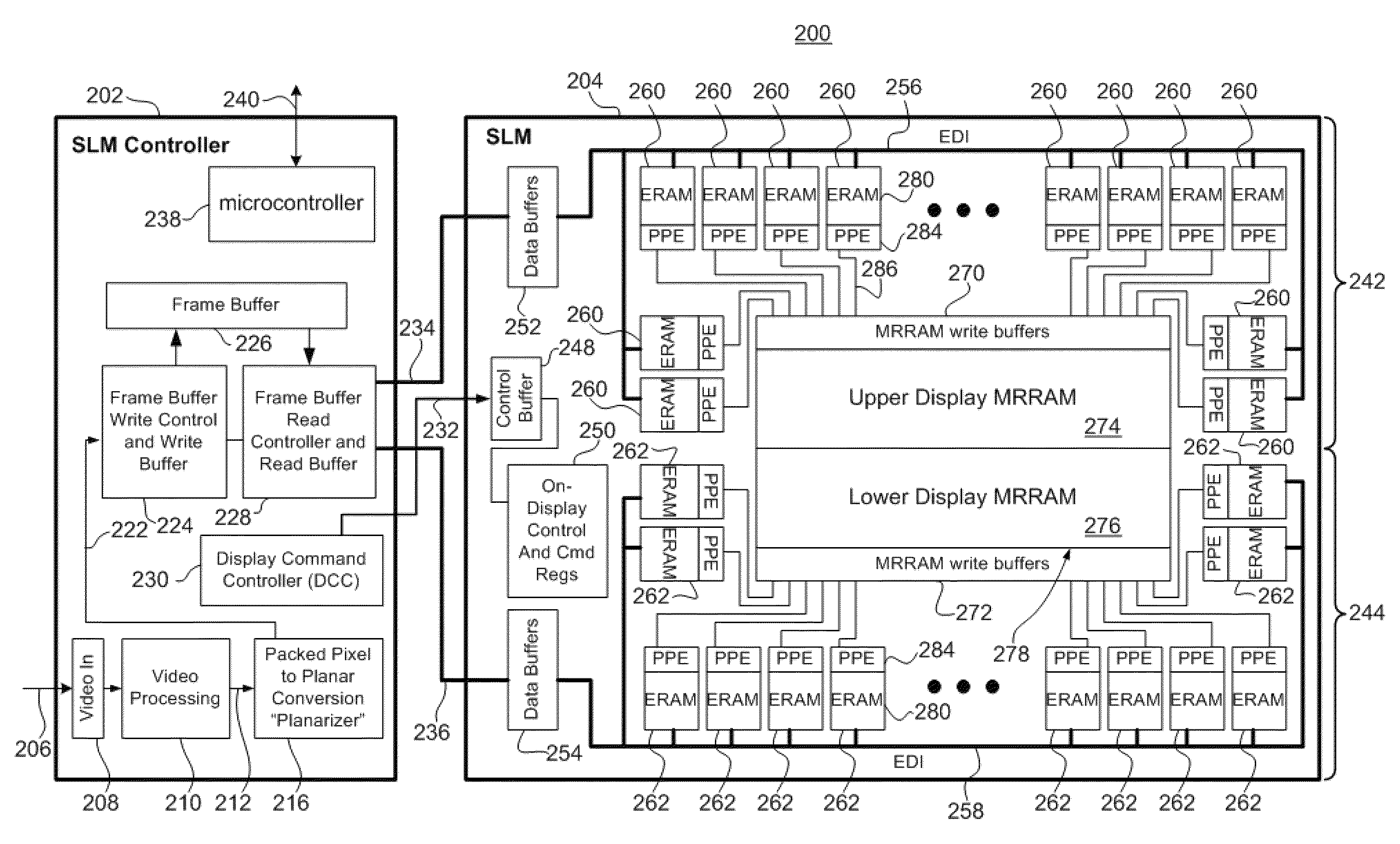

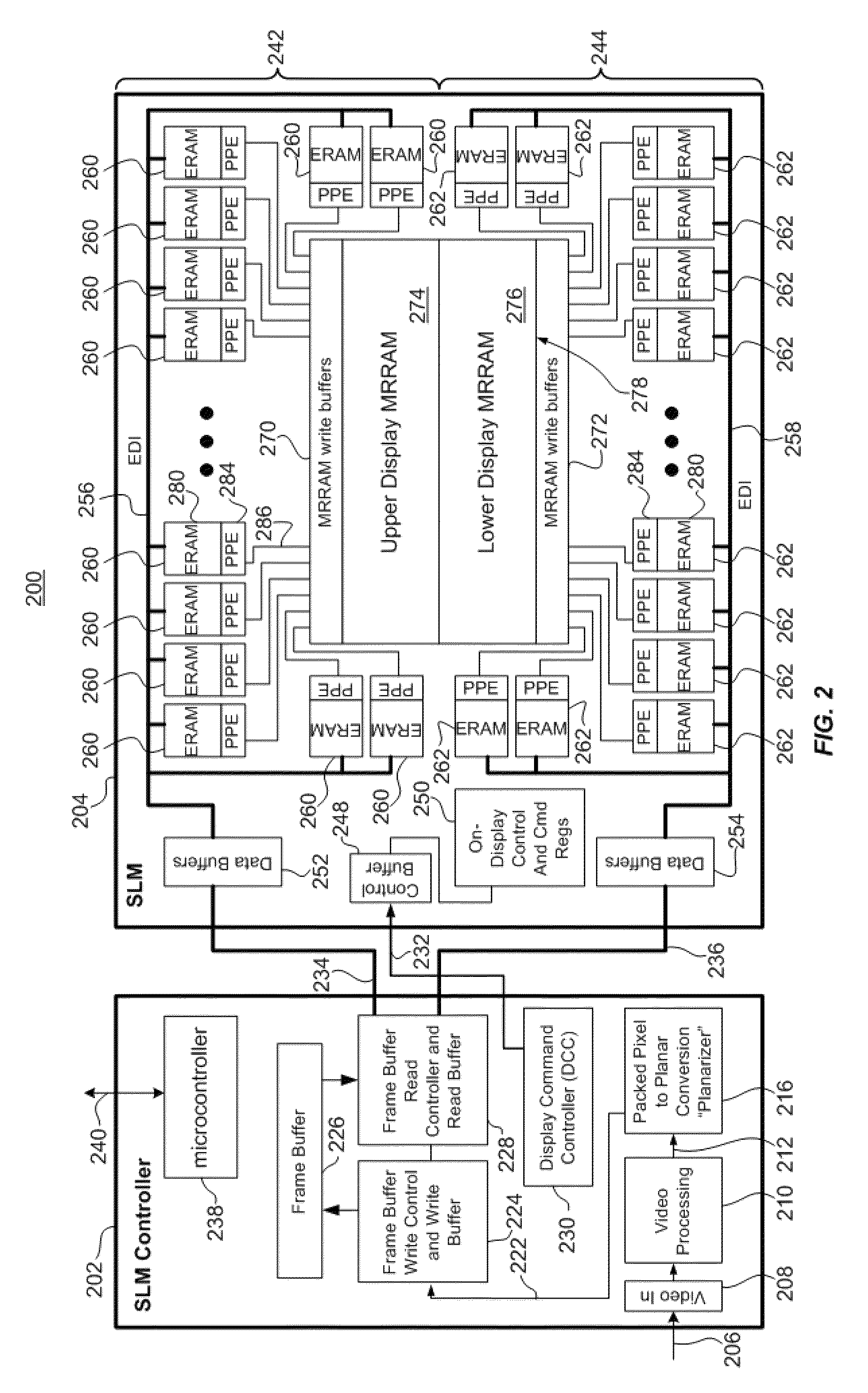

Spatial light modulator with masking-comparators

ActiveUS8605015B2Cathode-ray tube indicatorsProcessor architectures/configurationSpatial light modulatorEngineering

Described is a device comprising a spatial light modulator comprising a plurality of comparators for computing a respective drive for each pixel of a plurality of pixels.

Owner:SYNDIANT

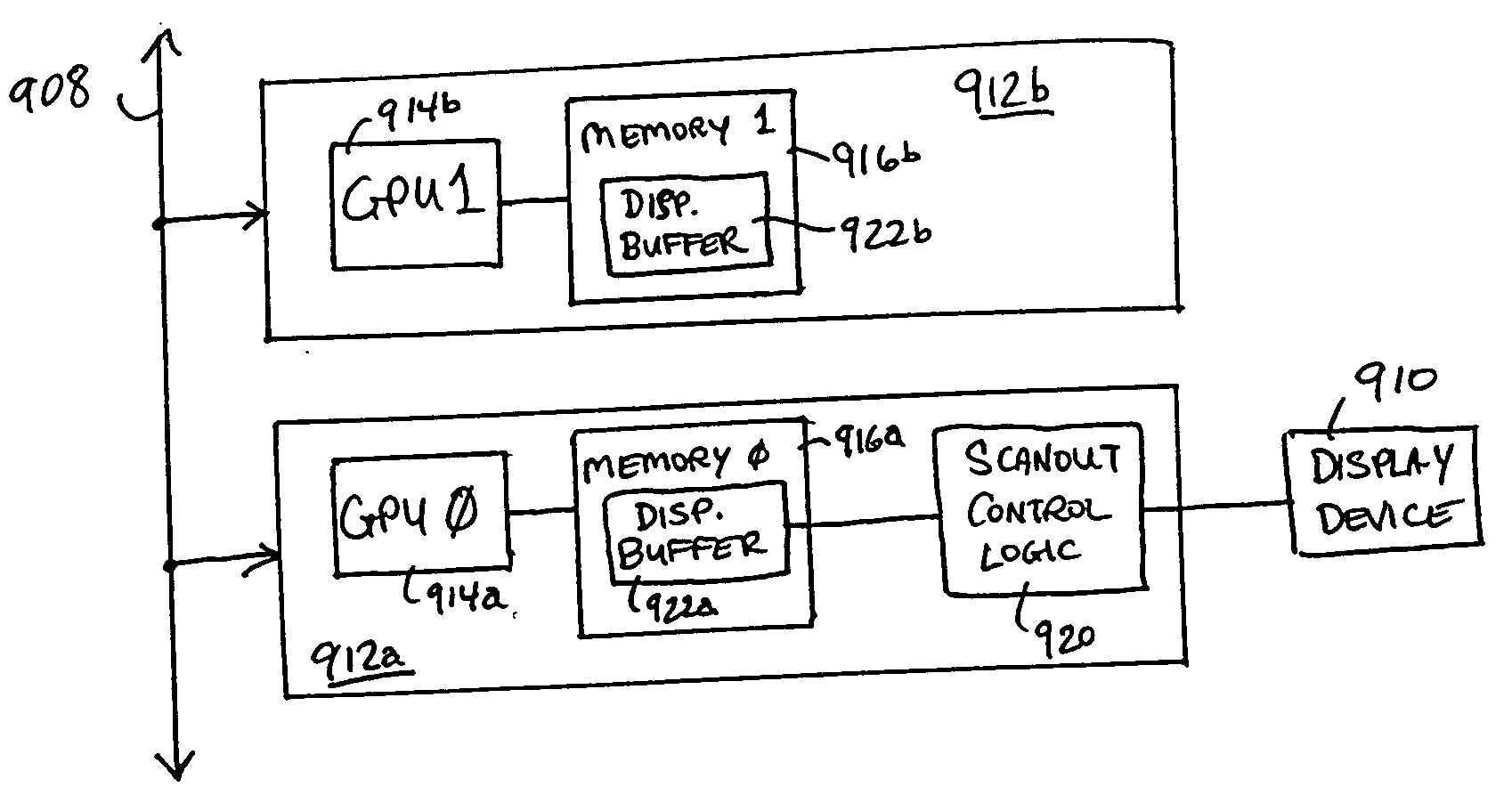

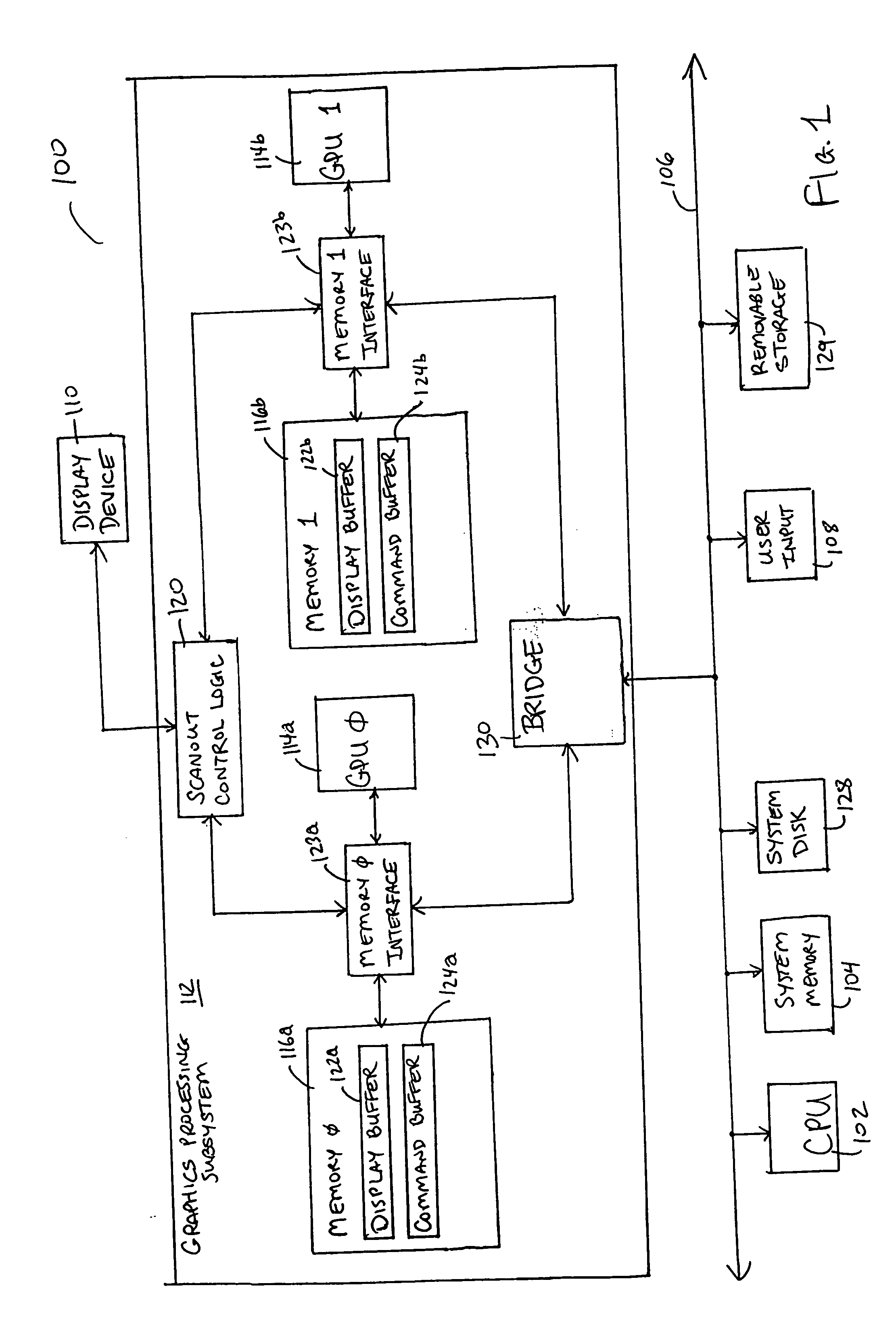

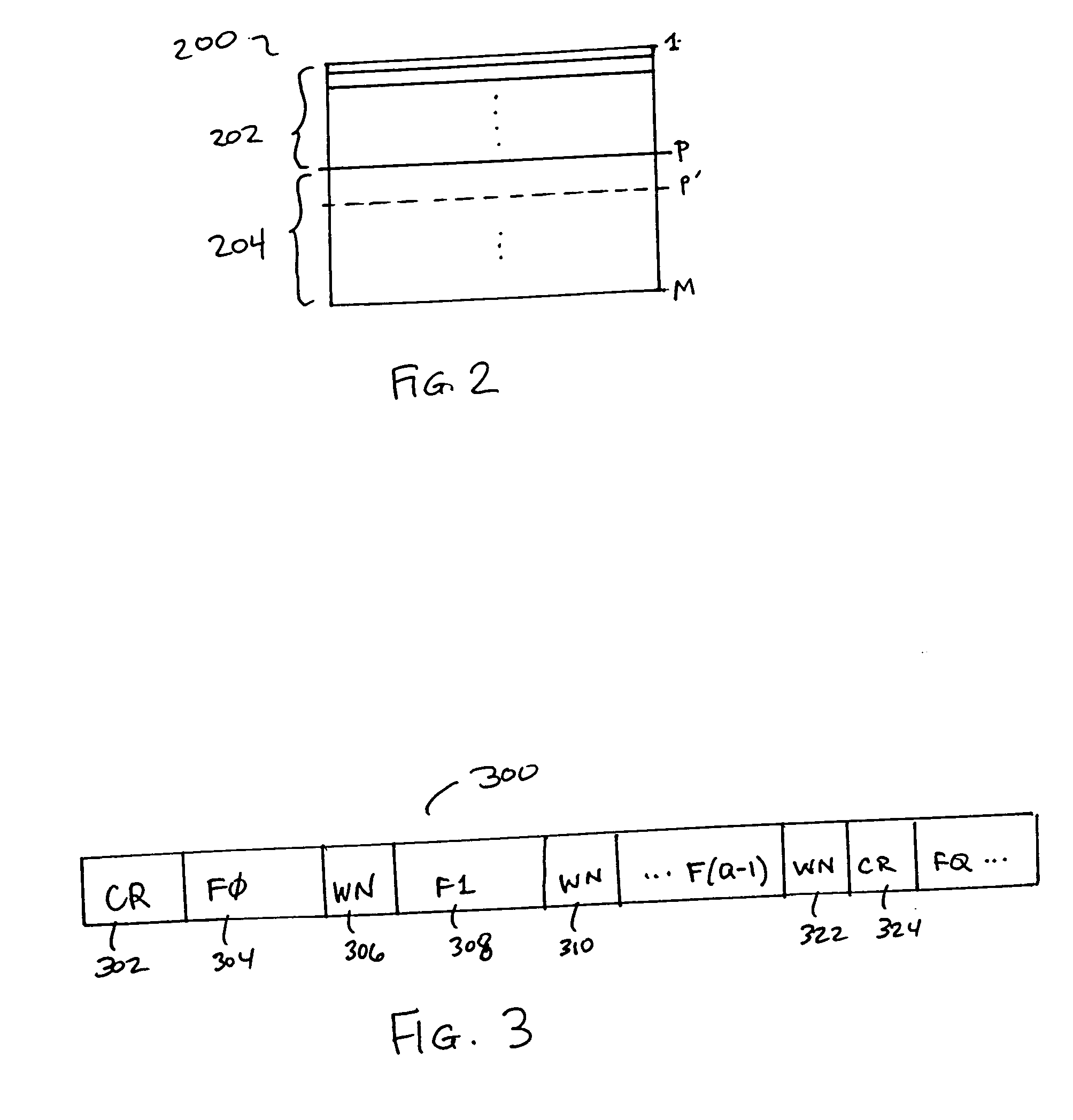

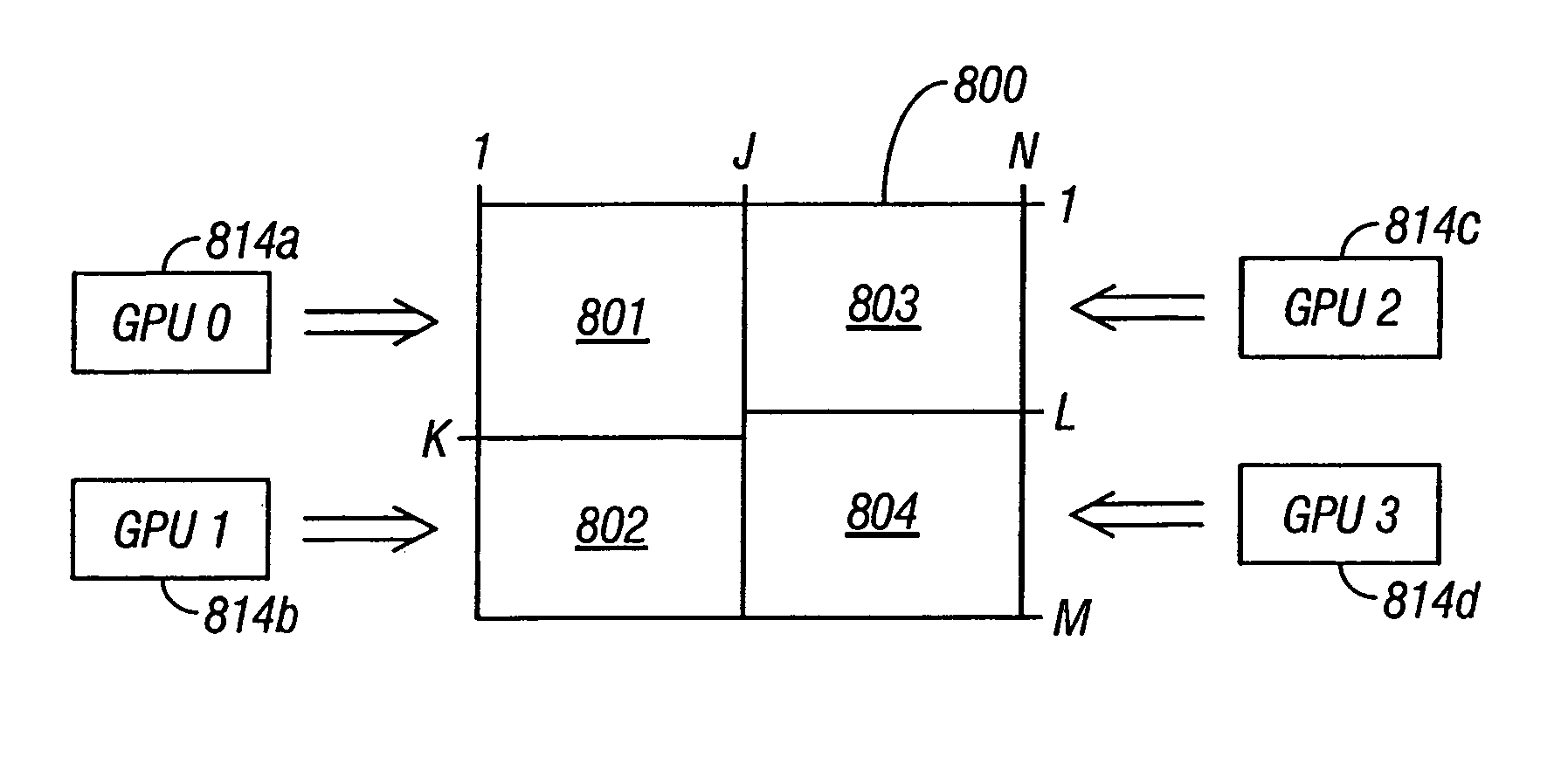

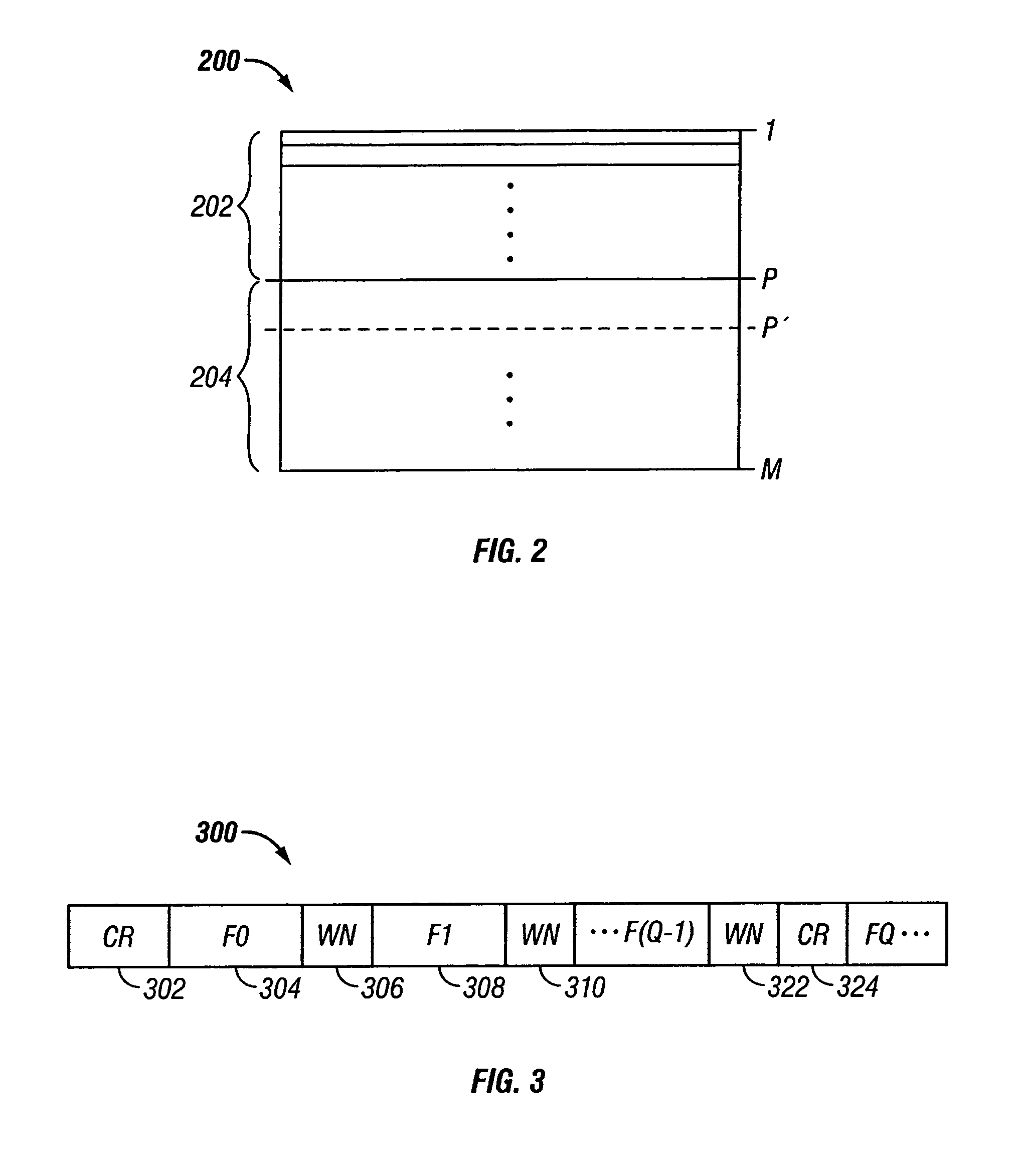

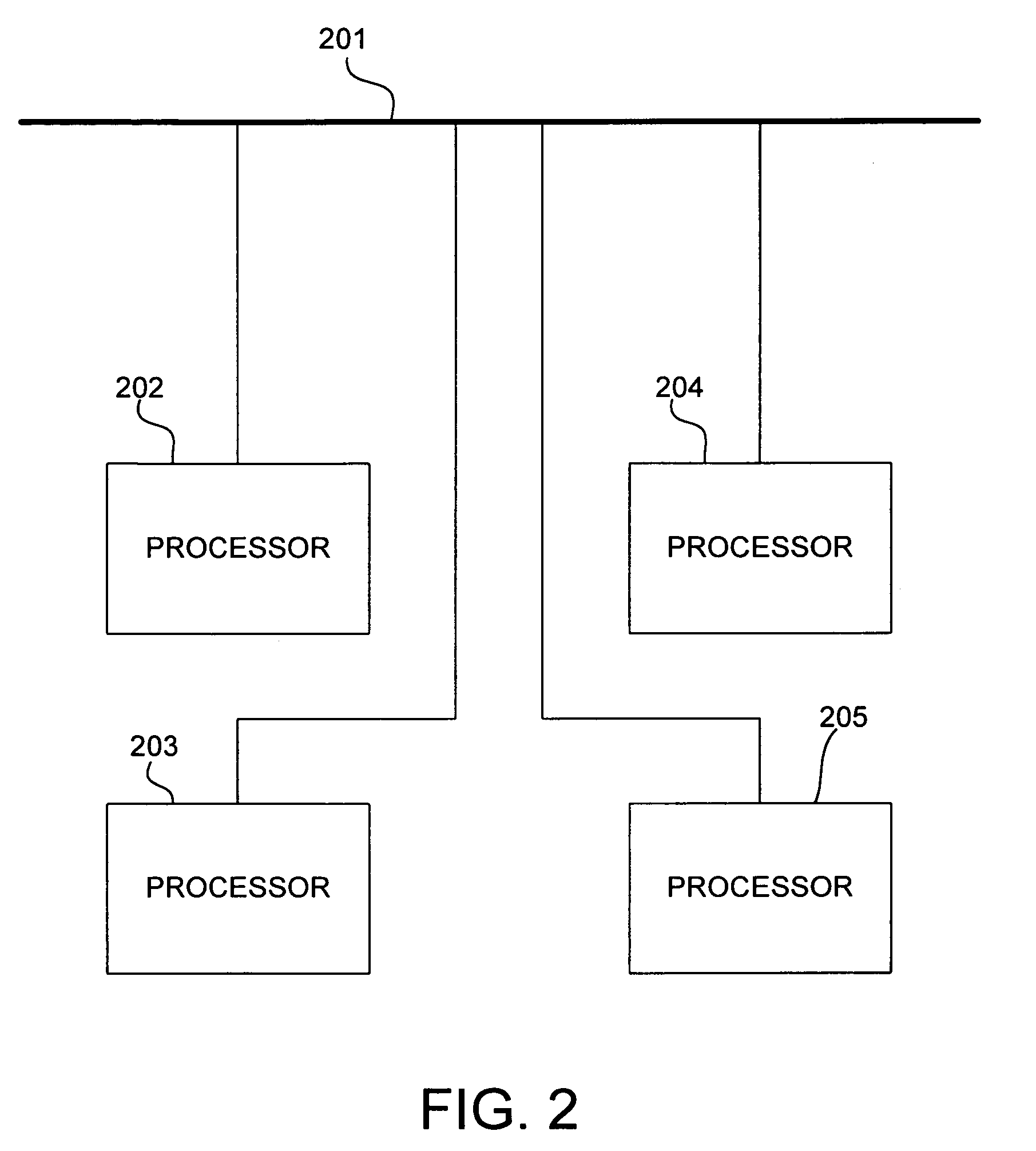

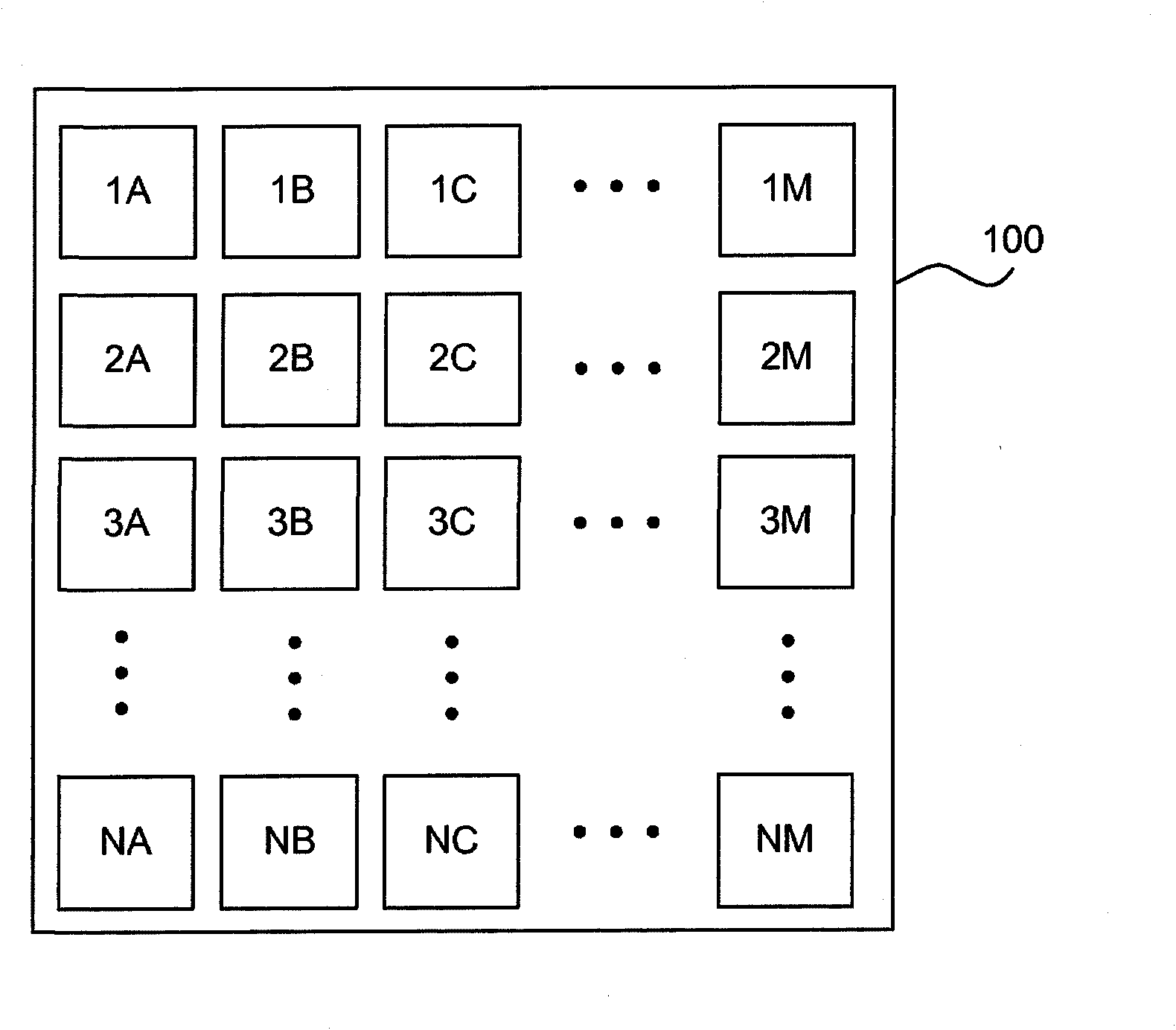

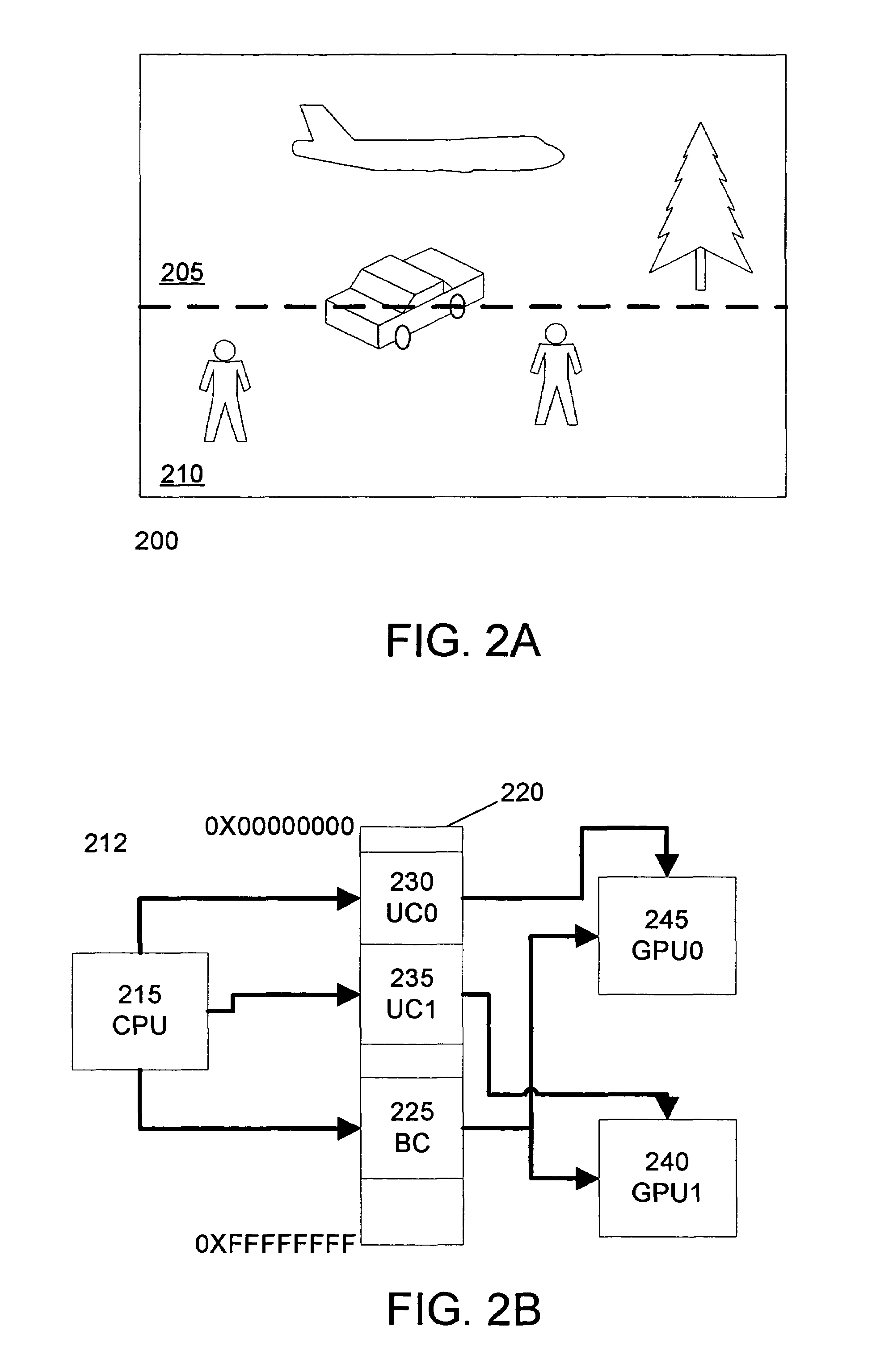

Adaptive load balancing in a multi-processor graphics processing system

ActiveUS20050041031A1Increase in sizeSmall sizeCathode-ray tube indicatorsMultiple digital computer combinationsGraphicsMulti processor

Systems and methods for balancing a load among multiple graphics processors that render different portions of a frame. A display area is partitioned into portions for each of two (or more) graphics processors. The graphics processors render their respective portions of a frame and return feedback data indicating completion of the rendering. Based on the feedback data, an imbalance can be detected between respective loads of two of the graphics processors. In the event that an imbalance exists, the display area is re-partitioned to increase a size of the portion assigned to the less heavily loaded processor and to decrease a size of the portion assigned to the more heavily loaded processor.

Owner:NVIDIA CORP

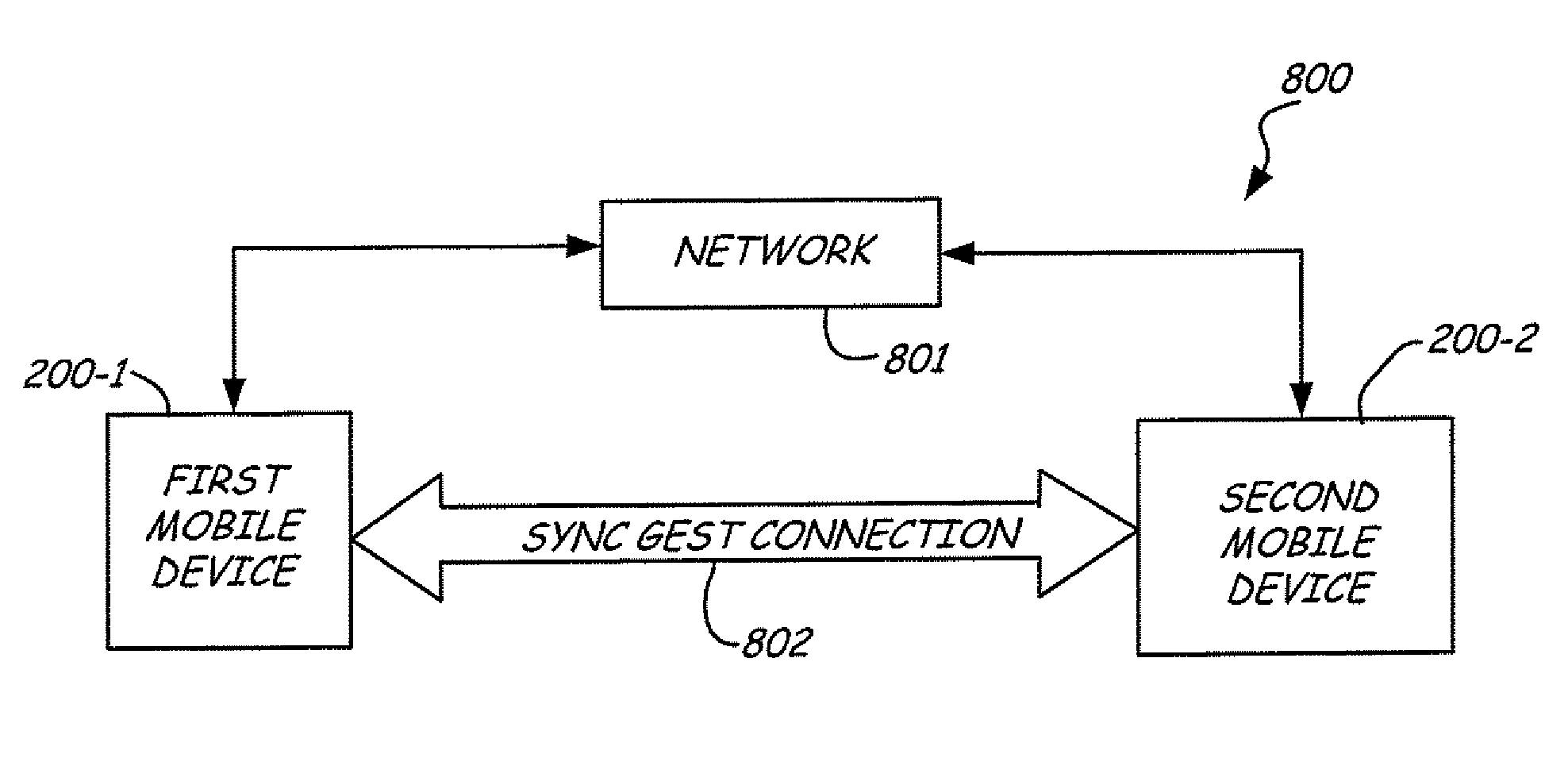

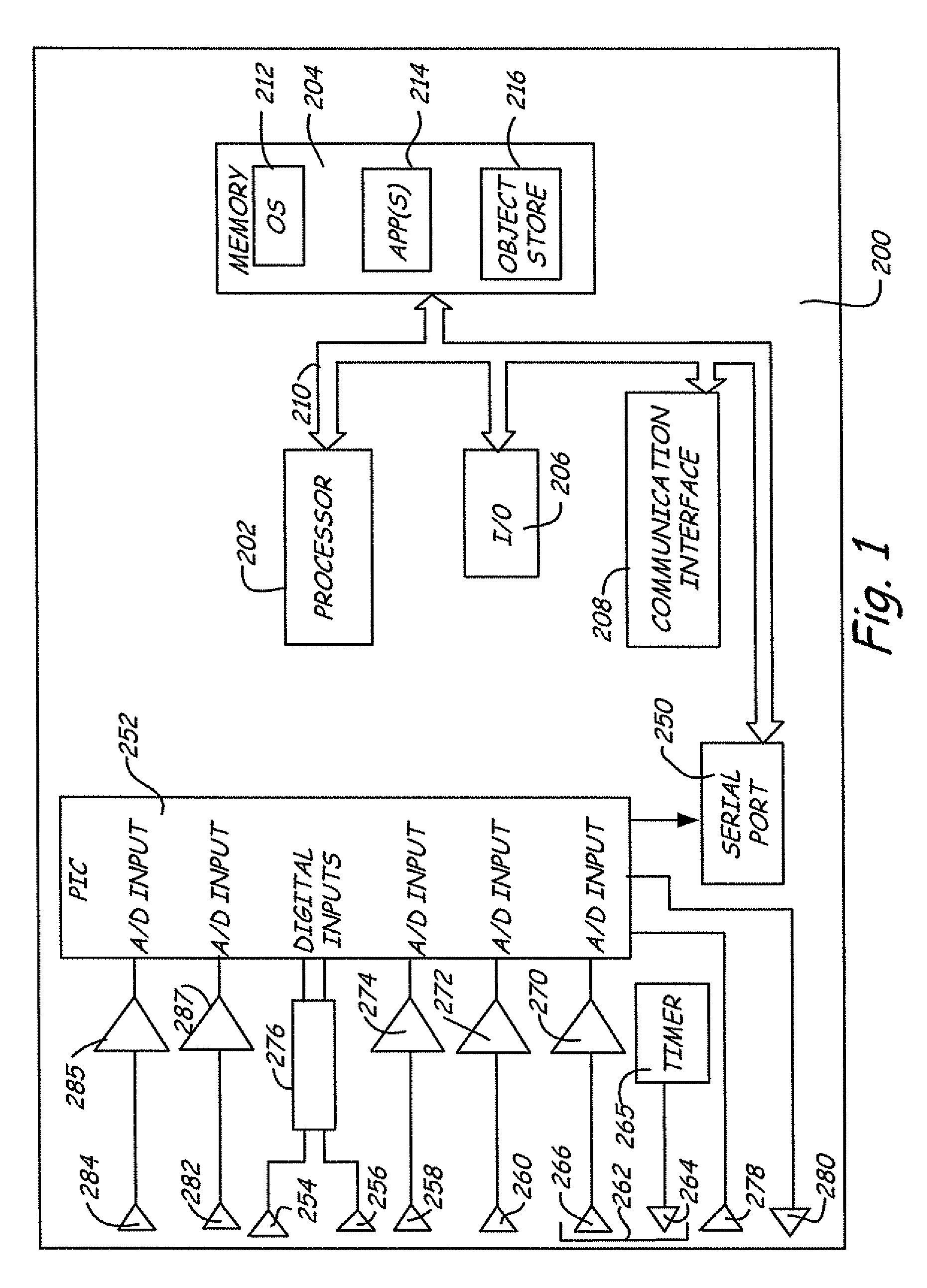

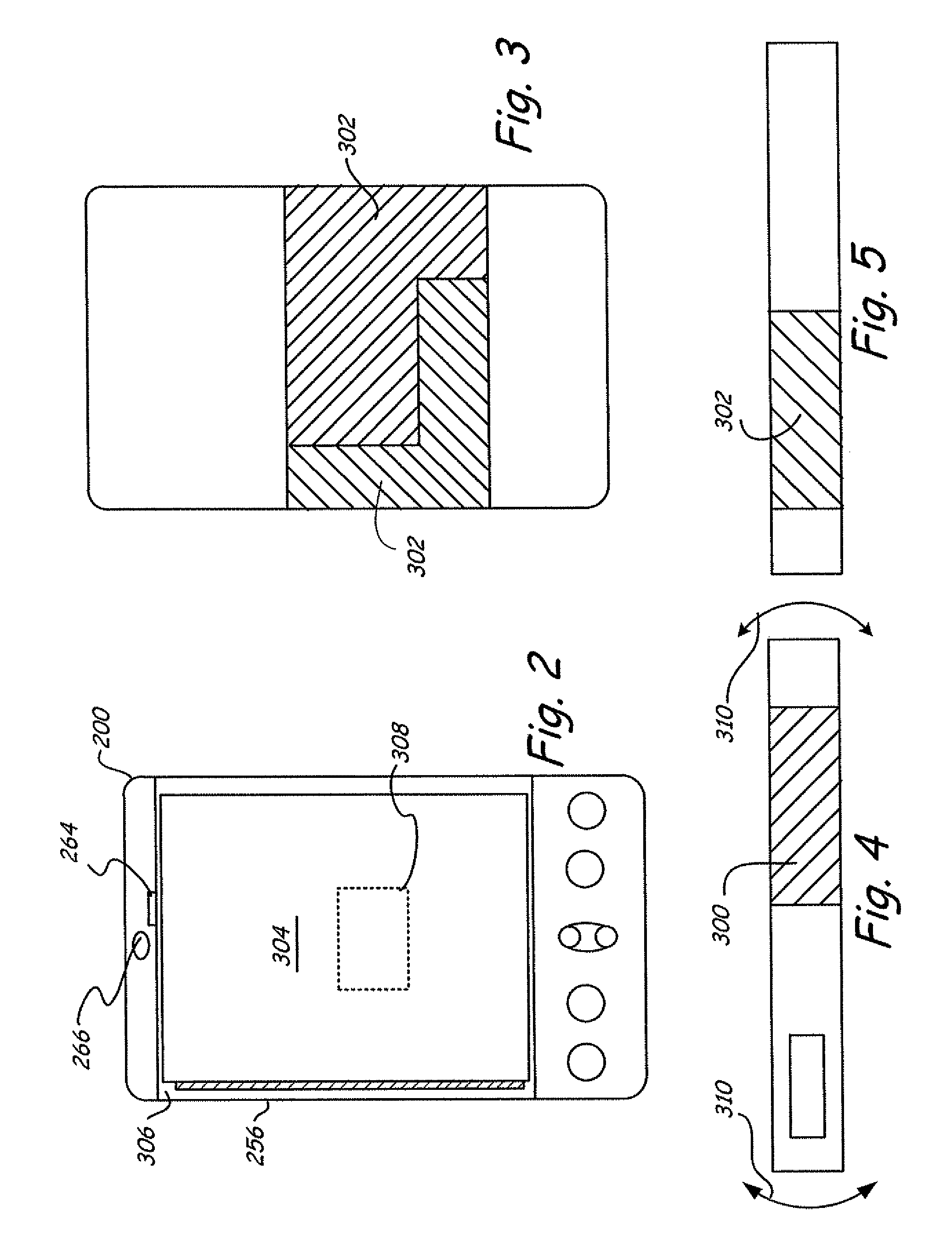

Distributed sensing techniques for mobile devices

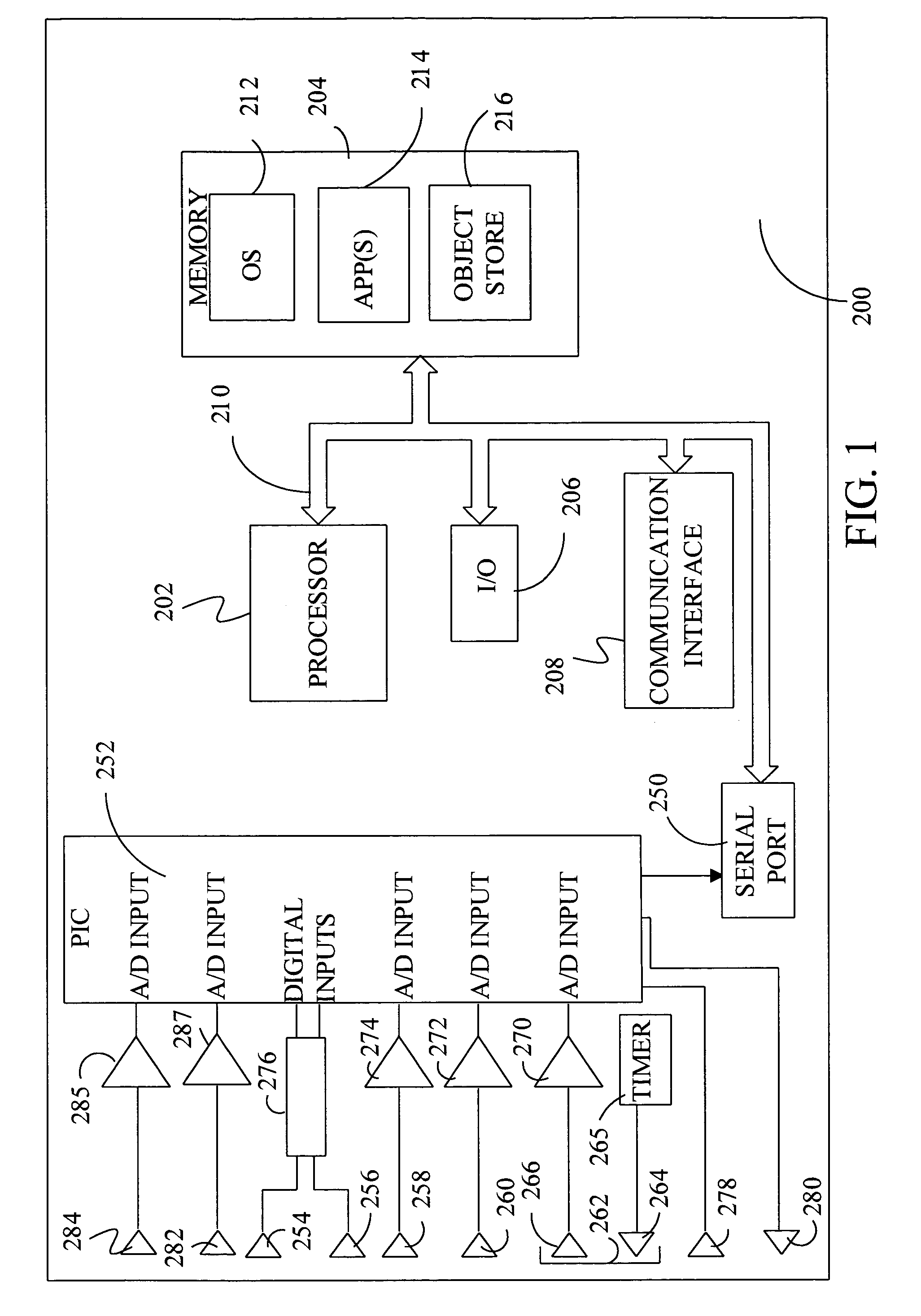

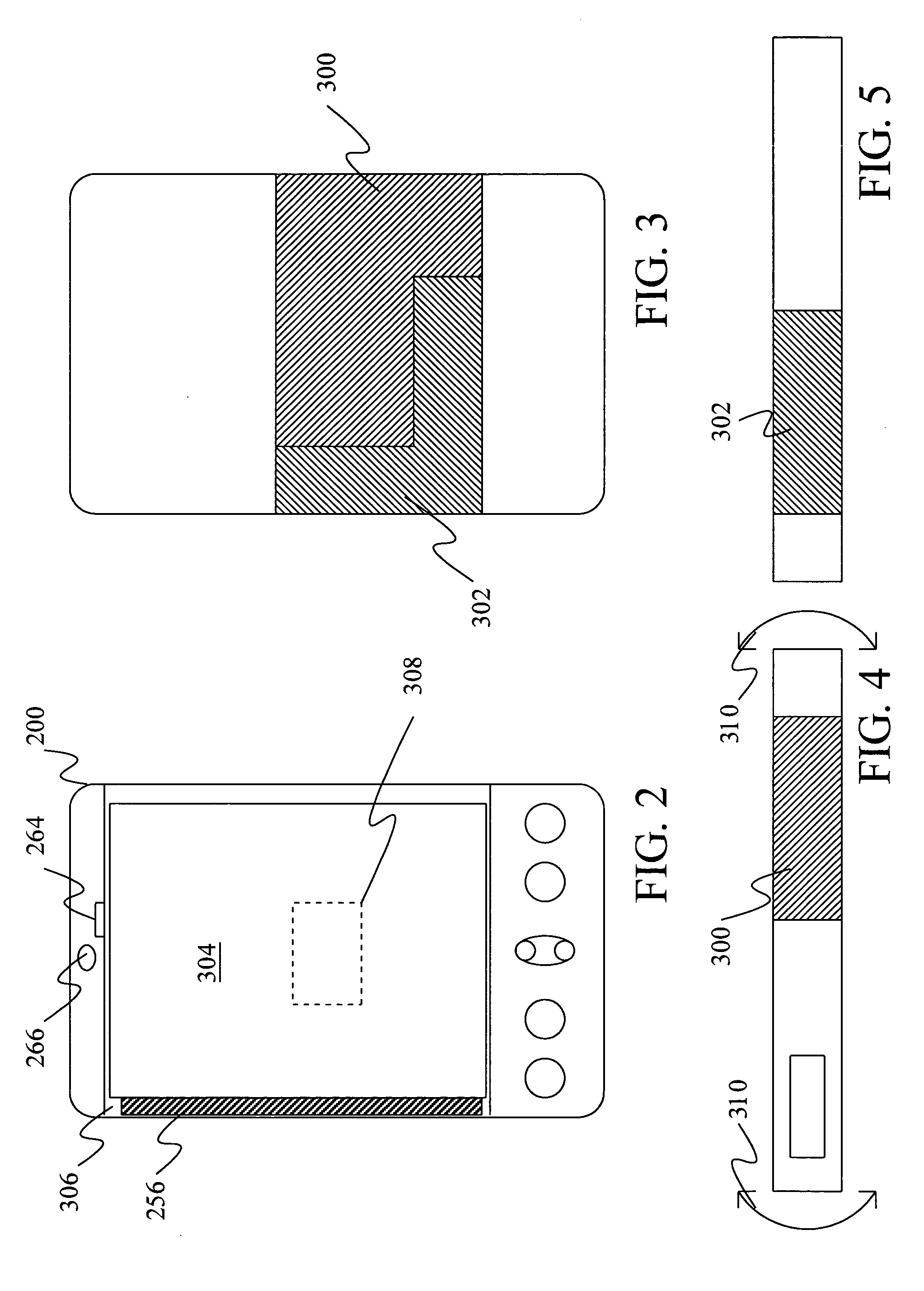

ActiveUS7532196B2Input/output for user-computer interactionServices signallingHuman–computer interactionMobile device

Methods and apparatus of the invention allow the coordination of resources of mobile computing devices to jointly execute tasks. In the method, a first gesture input is received at a first mobile computing device. A second gesture input is received at a second mobile computing device. In response, a determination is made as to whether the first and second gesture inputs form one of a plurality of different synchronous gesture types. If it is determined that the first and second gesture inputs form the one of the plurality of different synchronous gesture types, then resources of the first and second mobile computing devices are combined to jointly execute a particular task associated with the one of the plurality of different synchronous gesture types.

Owner:MICROSOFT TECH LICENSING LLC

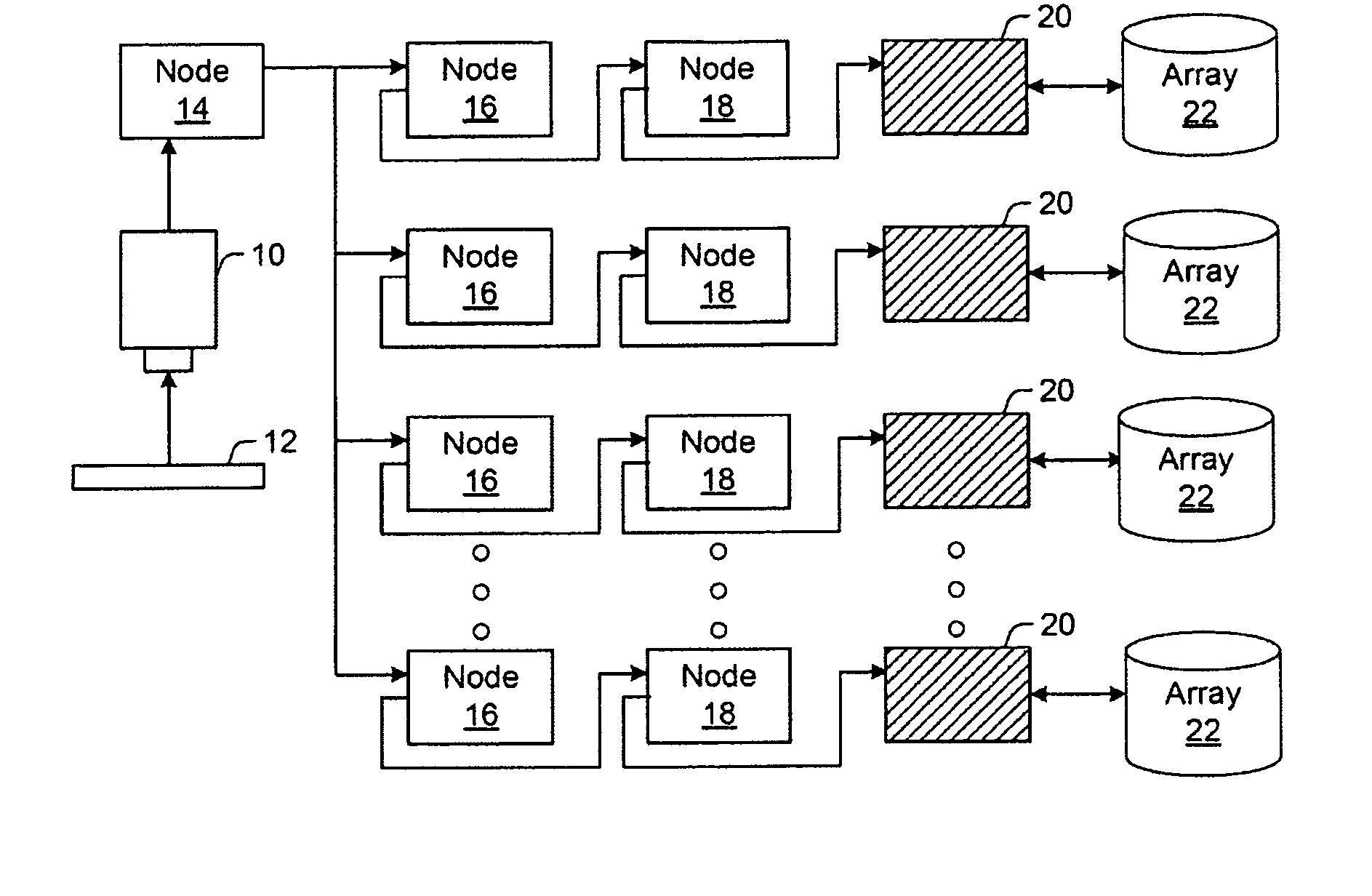

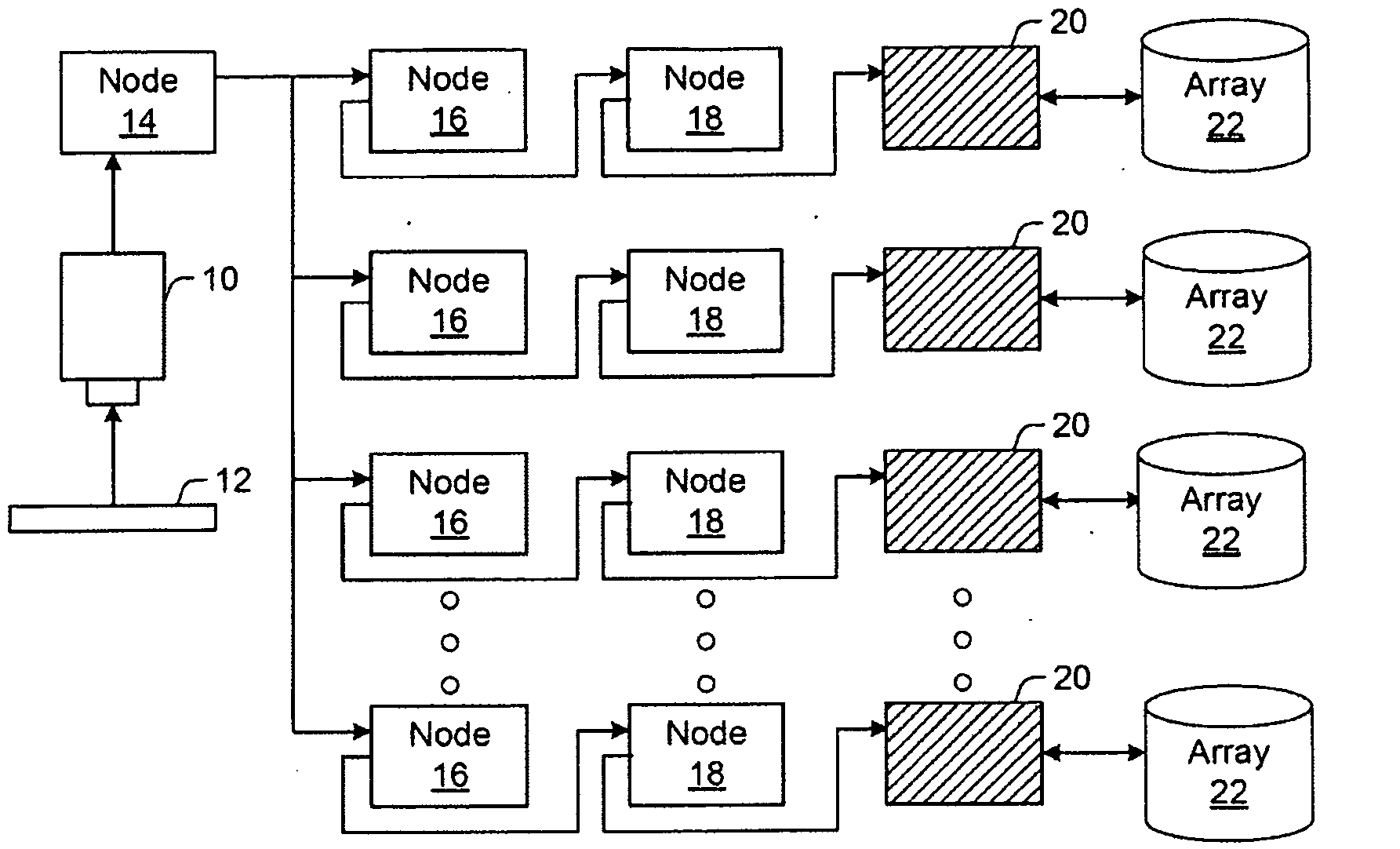

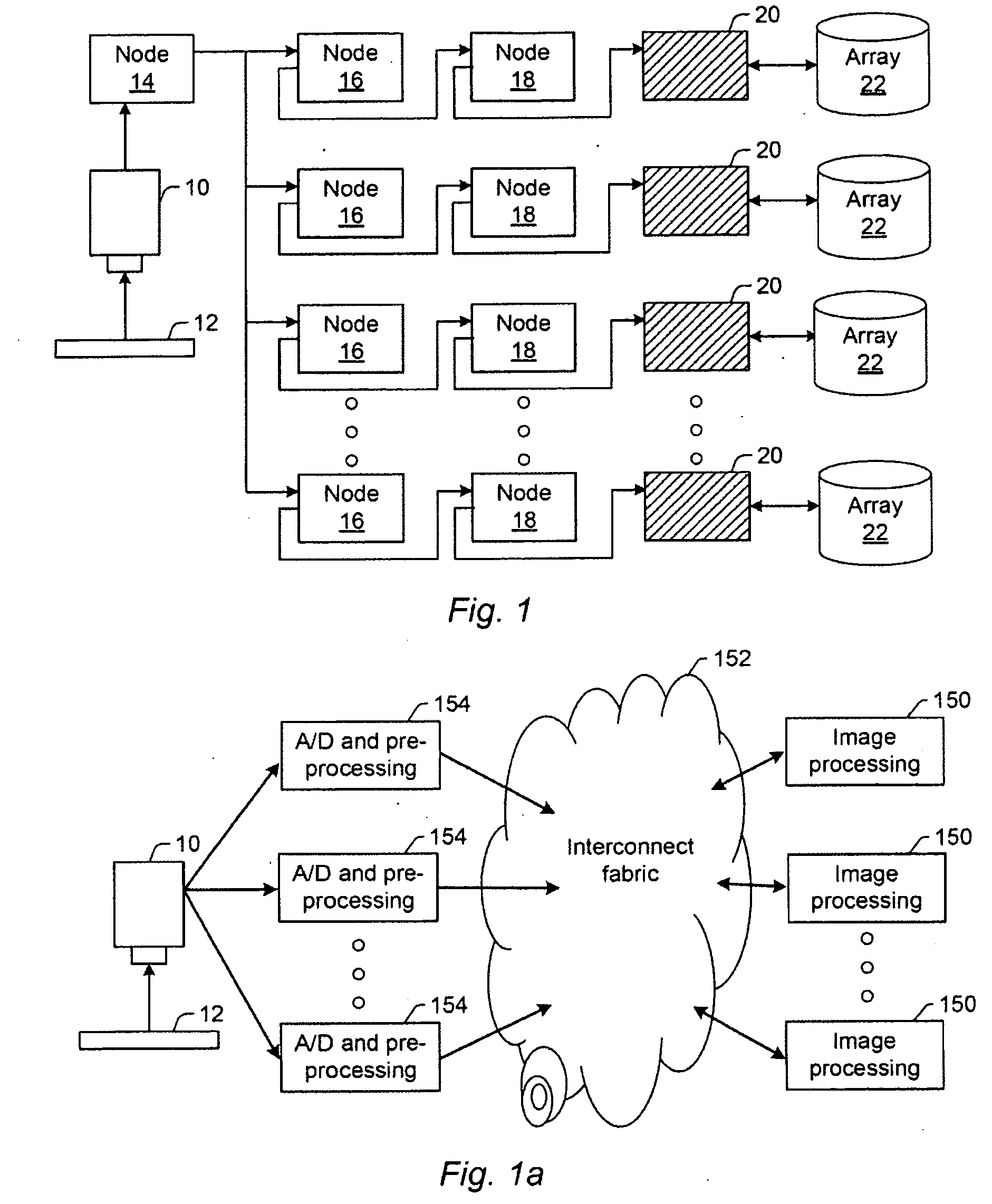

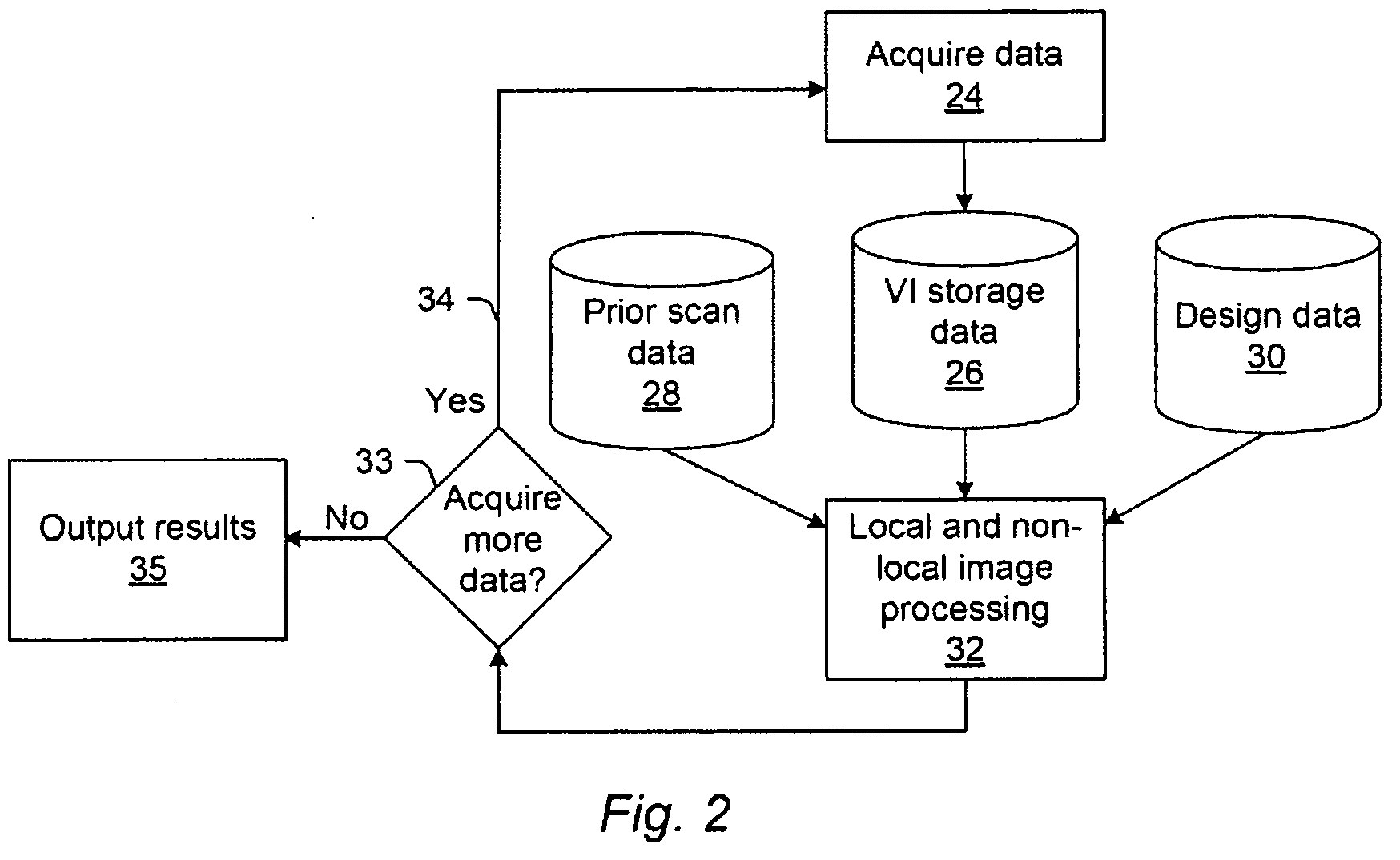

Systems and methods for creating persistent data for a wafer and for using persistent data for inspection-related functions

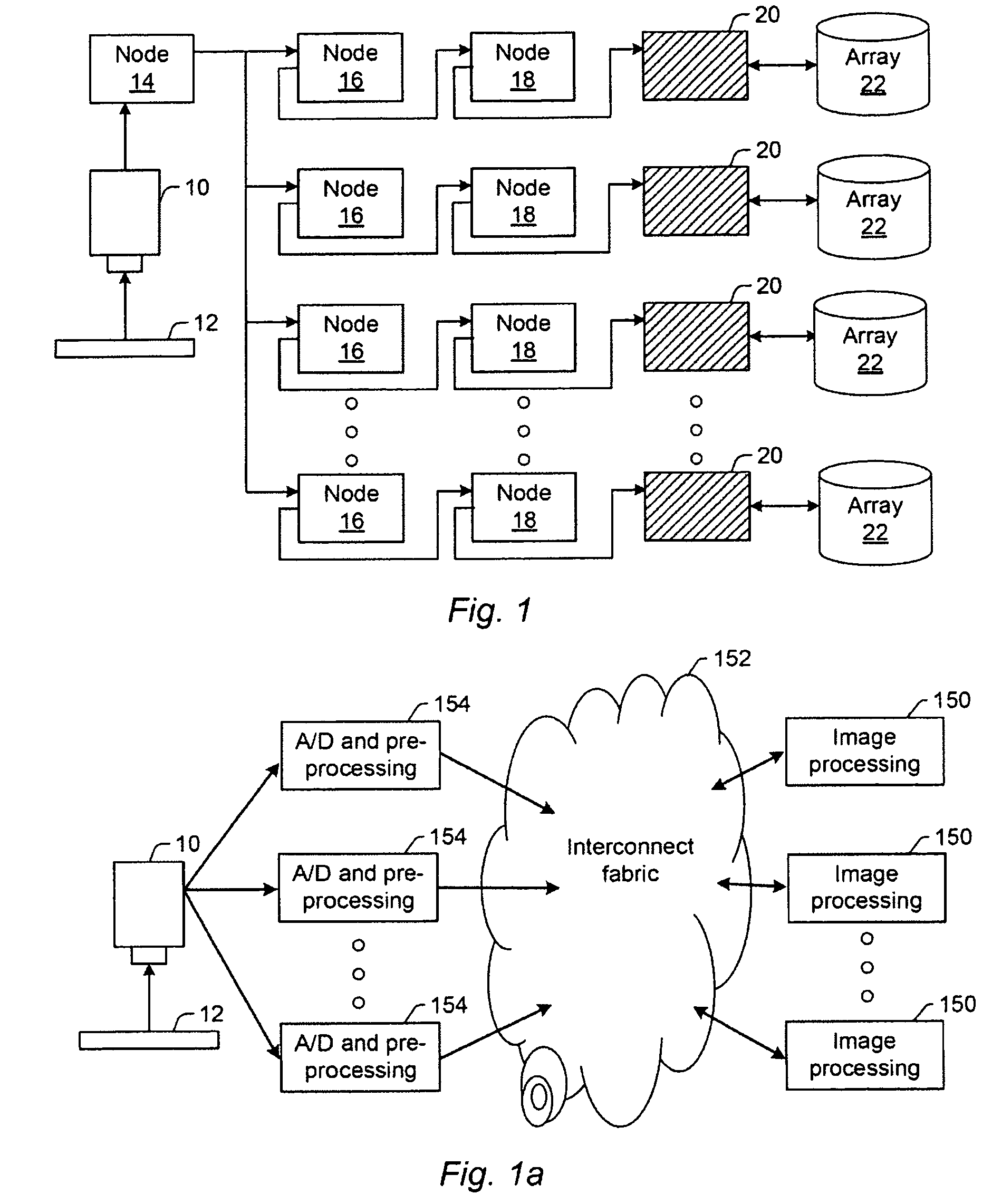

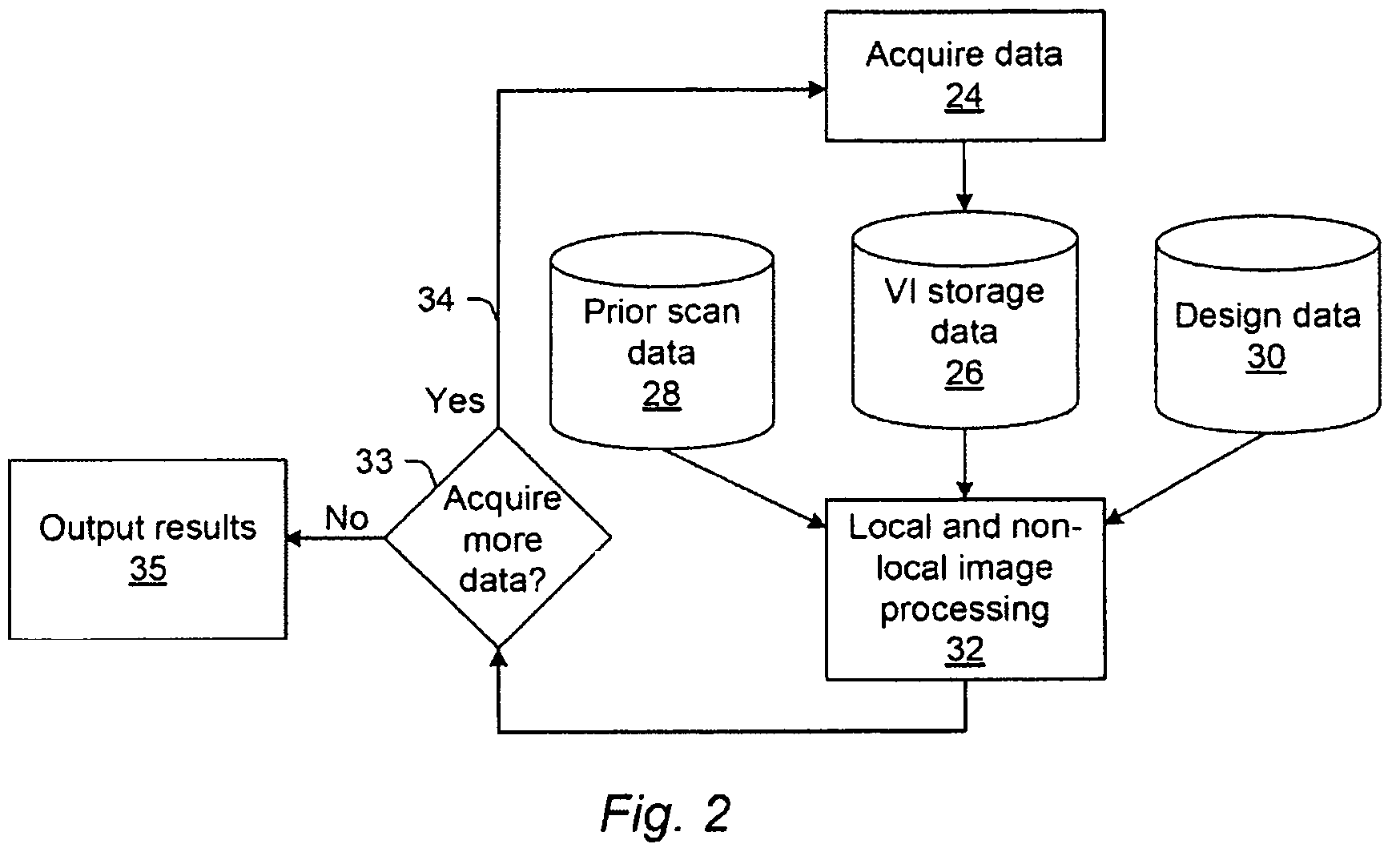

Various systems and methods for creating persistent data for a wafer and using persistent data for inspection-related functions are provided. One system includes a set of processor nodes coupled to a detector of an inspection system. Each of the processor nodes is configured to receive a portion of image data generated by the detector during scanning of a wafer. The system also includes an array of storage media separately coupled to each of the processor nodes. The processor nodes are configured to send all of the image data or a selected portion of the image data received by the processor nodes to the arrays of storage media such that all of the image data or the selected portion of the image data generated by the detector during the scanning of the wafer is stored in the arrays of the storage media.

Owner:KLA CORP

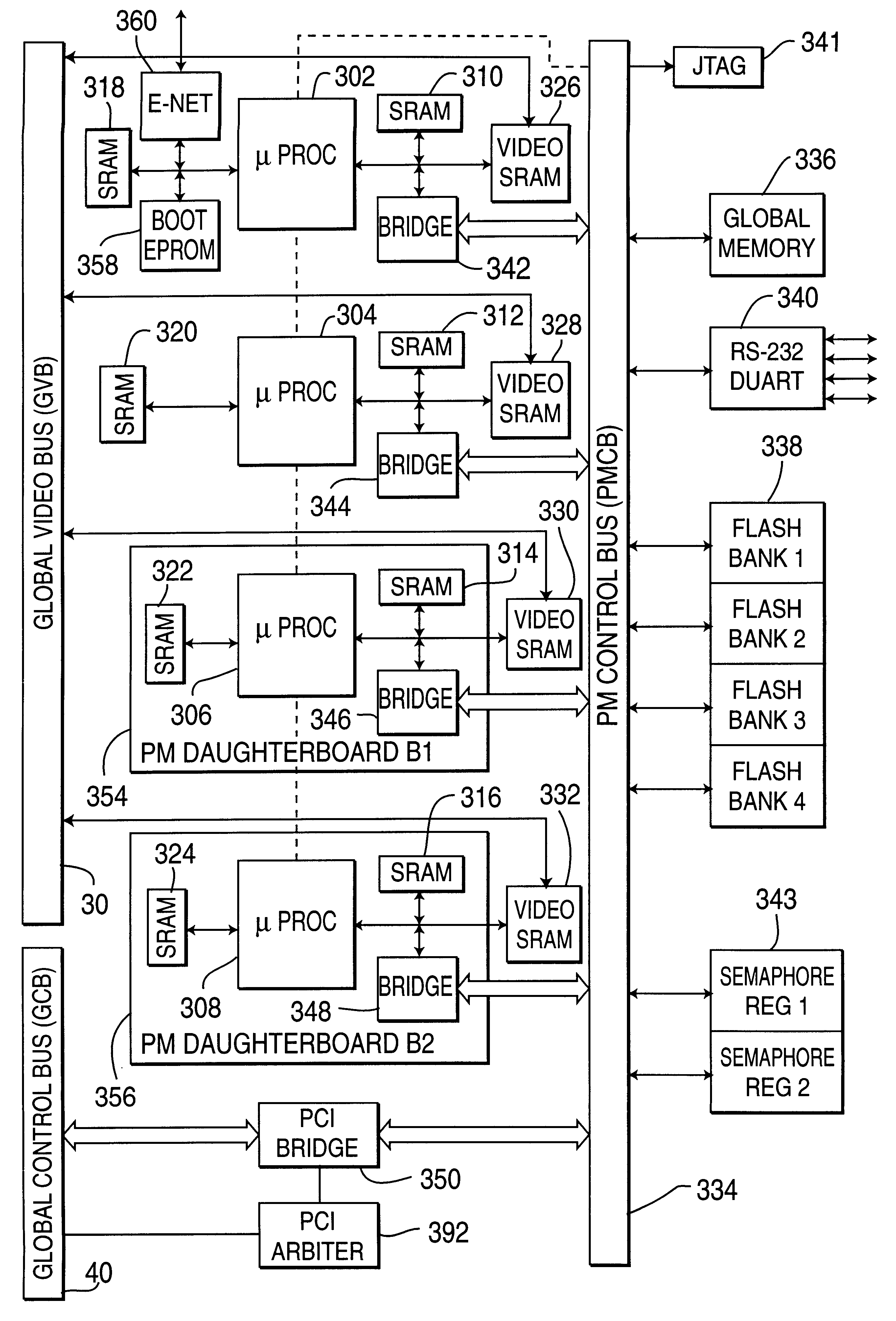

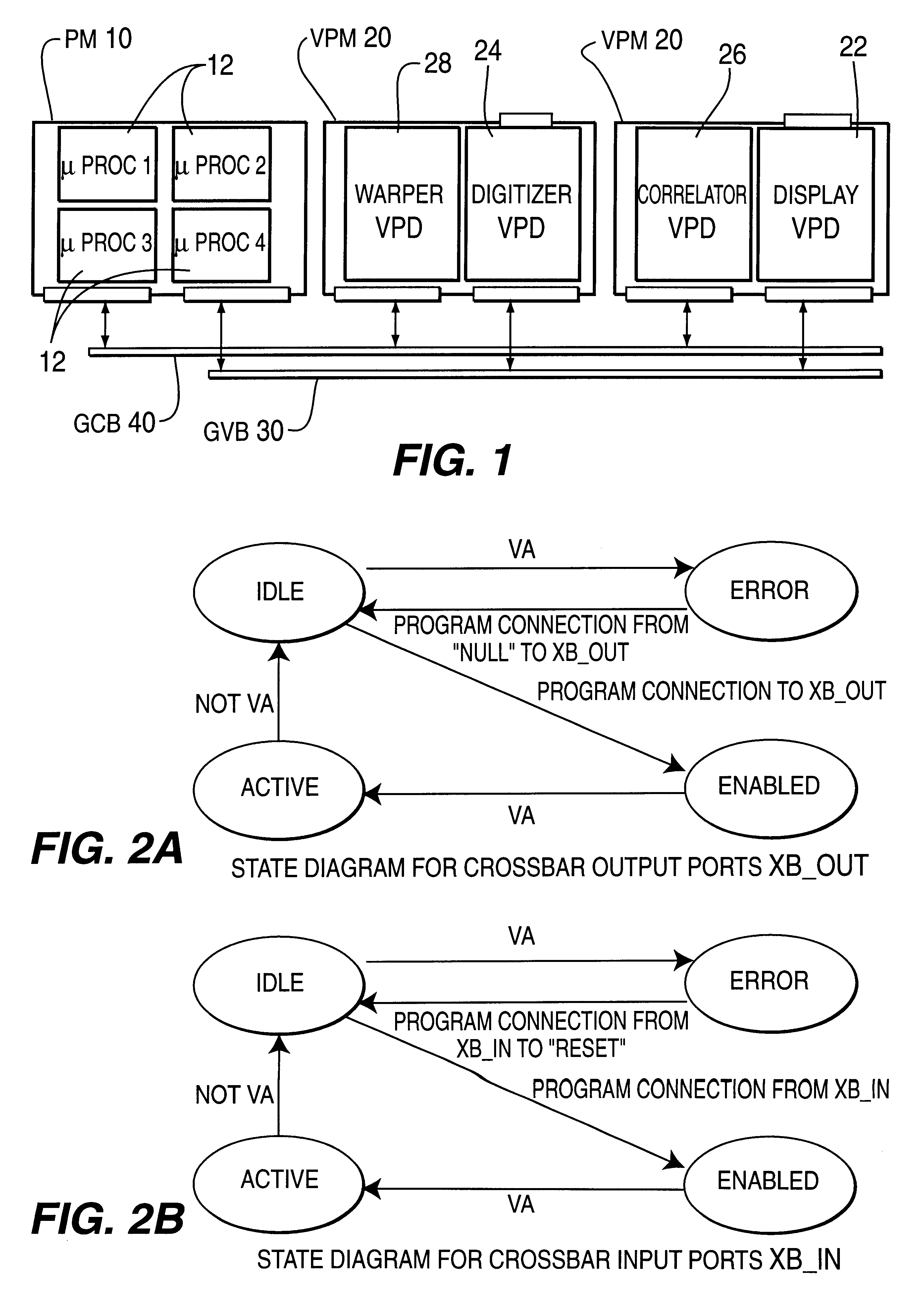

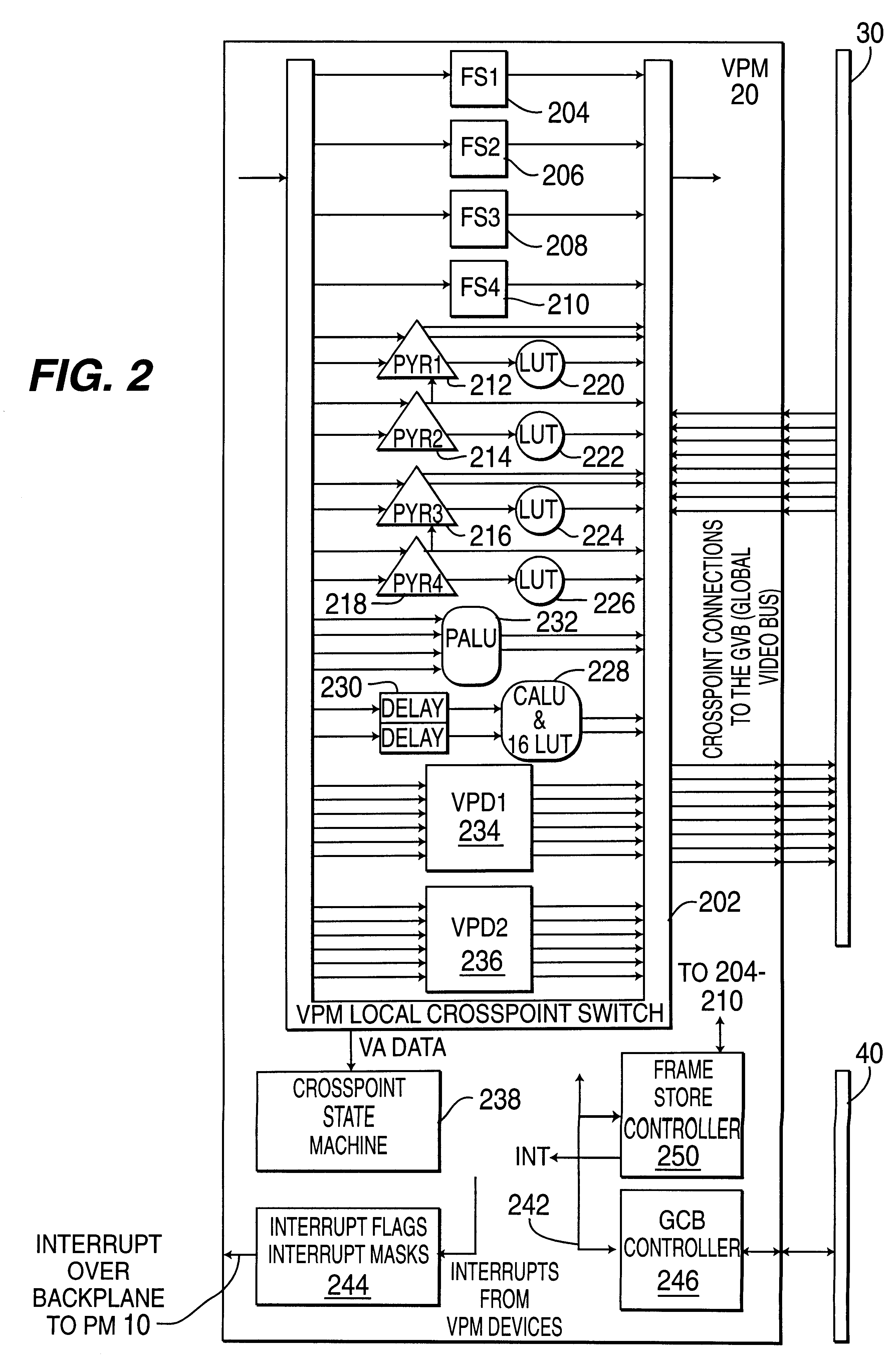

Modular parallel-pipelined vision system for real-time video processing

InactiveUS6188381B1Easy to operateReduce control overheadTelevision system detailsColor signal processing circuitsProcess moduleHandling system

A real-time modular video processing system (VPS) which can be scaled smoothly from relatively small systems with modest amounts of hardware to very large, very powerful systems with significantly more hardware. The modular video processing system includes a processing module containing at least one general purpose microprocessor which controls hardware and software operation of the video processing system using control data and which also facilitates communications with external devices. One or more video processing modules are also provided, each containing parallel pipelined video hardware which is programmable by the control data to provide different video processing operations on an input stream of video data. Each video processing module also contains one or more connections for accepting one or more daughterboards which each perform a particular image processing task. A global video bus routes video data between the processing module and each video processing module and between respective processing modules, while a global control bus provides the control data to / from the processing module from / to the video processing modules separate from the video data on the global video bus. A hardware control library loaded on the processing module provides an application programming interface including high level C-callable functions which allow programming of the video hardware as components are added and subtracted from the video processing system for different applications.

Owner:SARNOFF CORP

Adaptive load balancing in a multi-processor graphics processing system

ActiveUS7075541B2Increase in sizeSmall sizeCathode-ray tube indicatorsMultiple digital computer combinationsGraphicsMulti processor

Systems and methods for balancing a load among multiple graphics processors that render different portions of a frame. A display area is partitioned into portions for each of two (or more) graphics processors. The graphics processors render their respective portions of a frame and return feedback data indicating completion of the rendering. Based on the feedback data, an imbalance can be detected between respective loads of two of the graphics processors. In the event that an imbalance exists, the display area is re-partitioned to increase a size of the portion assigned to the less heavily loaded processor and to decrease a size of the portion assigned to the more heavily loaded processor.

Owner:NVIDIA CORP

Methods and apparatuses for load balancing between multiple processing units

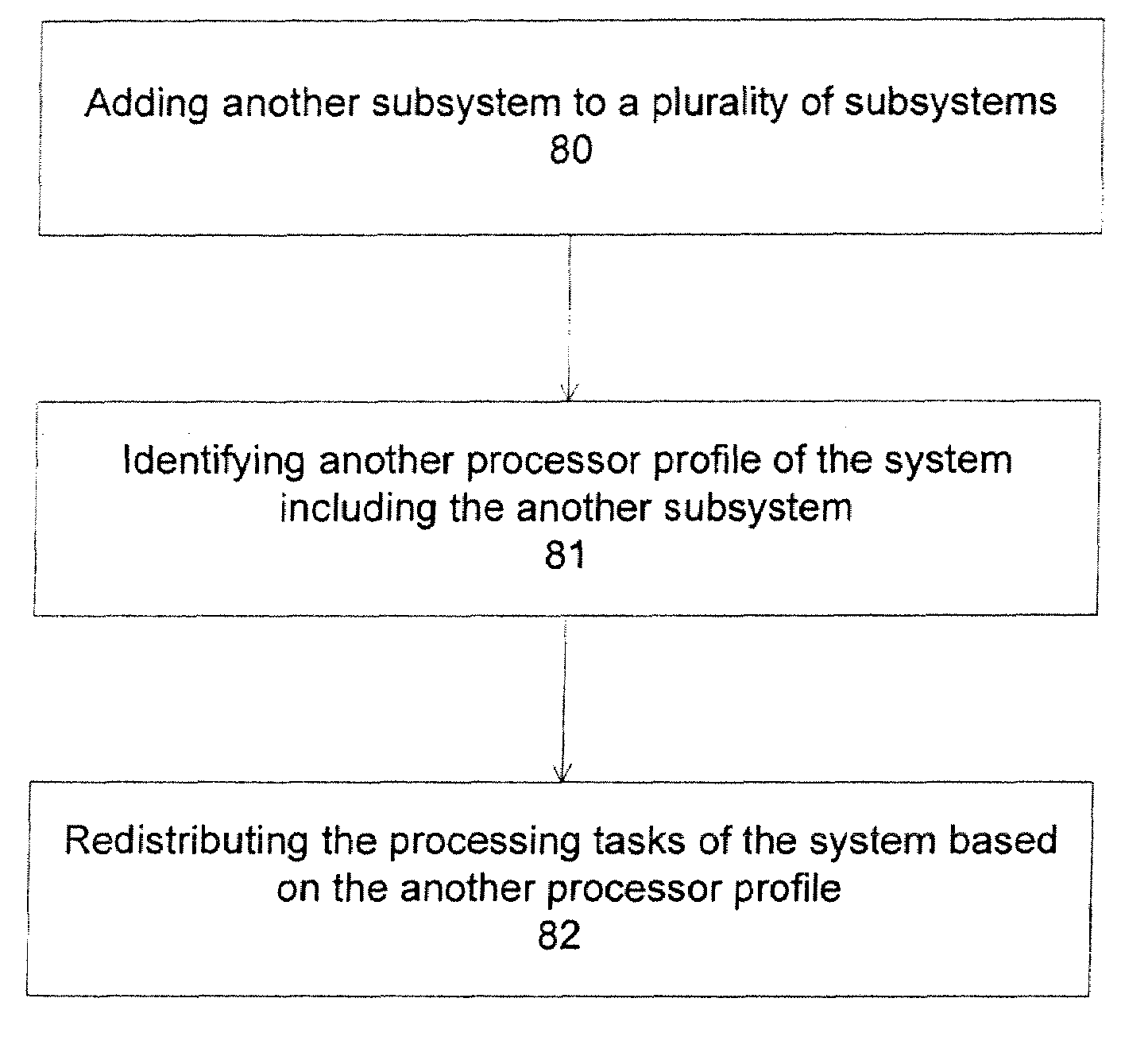

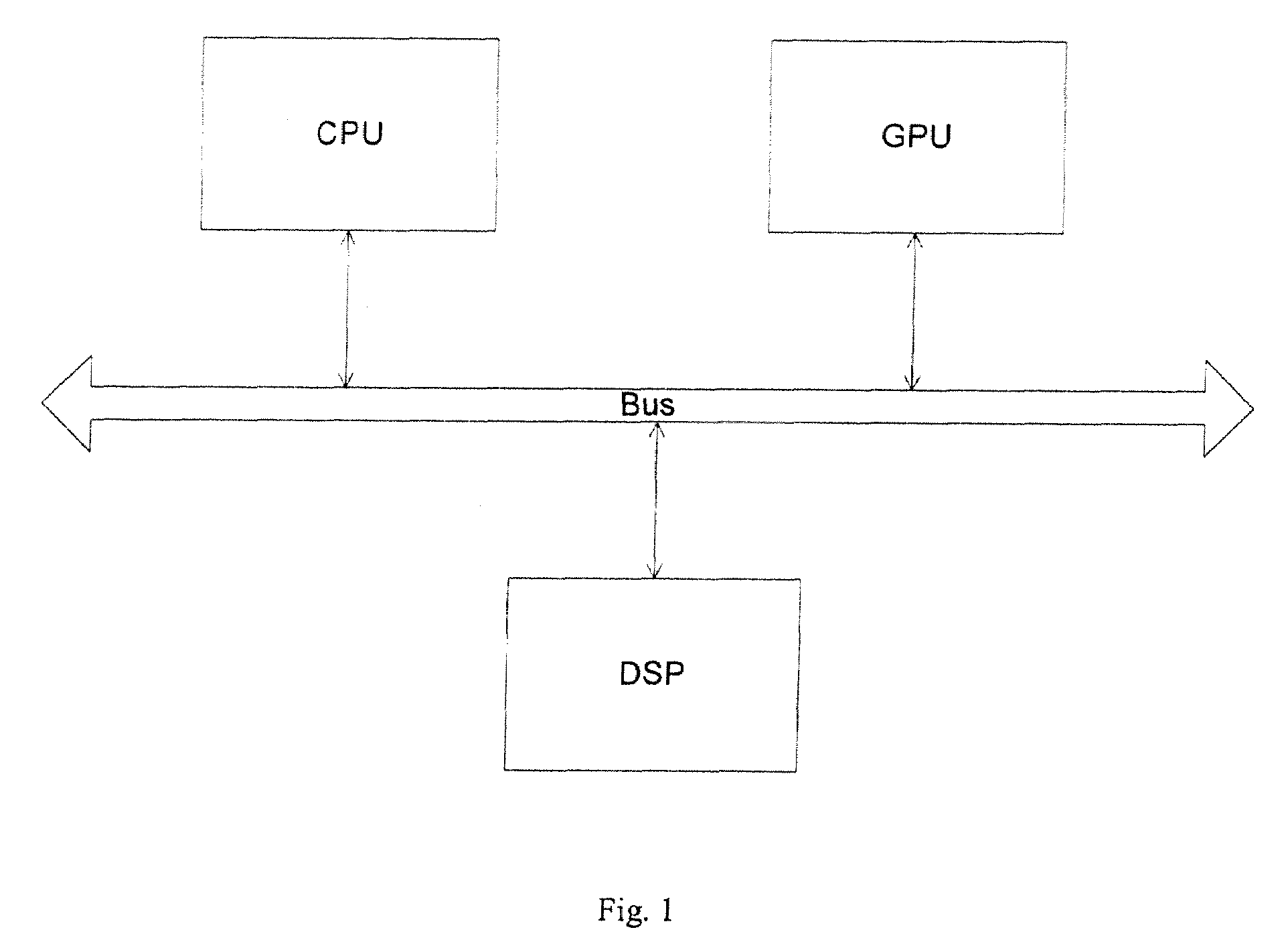

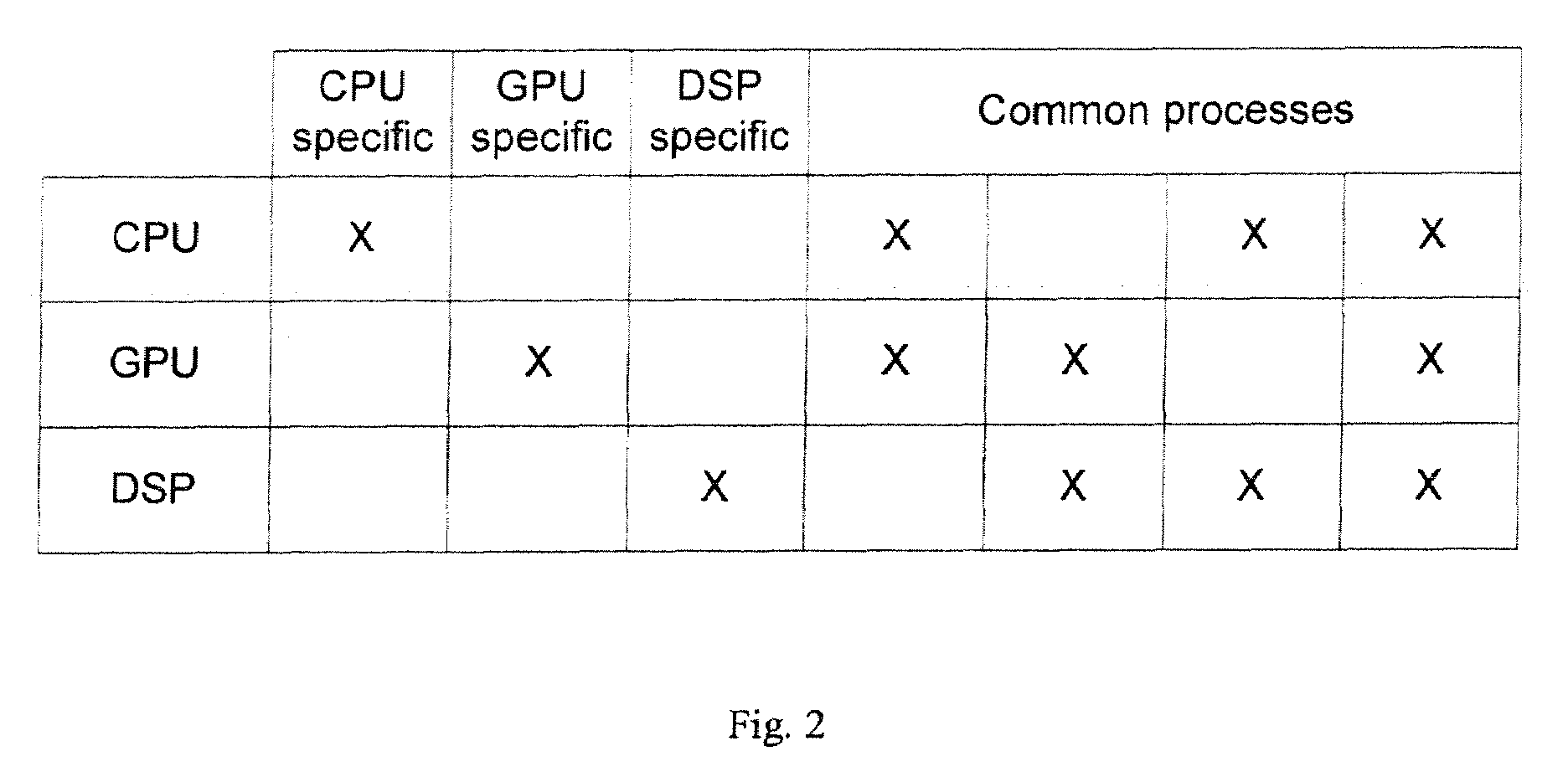

ActiveUS20090109230A1PerformanceProcessingEnergy efficient ICTDigital data processing detailsDigital signal processingGraphics

Exemplary embodiments of methods and apparatuses to dynamically redistribute computational processes in a system that includes a plurality of processing units are described. The power consumption, the performance, and the power / performance value are determined for various computational processes between a plurality of subsystems where each of the subsystems is capable of performing the computational processes. The computational processes are exemplarily graphics rendering process, image processing process, signal processing process, Bayer decoding process, or video decoding process, which can be performed by a central processing unit, a graphics processing units or a digital signal processing unit. In one embodiment, the distribution of computational processes between capable subsystems is based on a power setting, a performance setting, a dynamic setting or a value setting.

Owner:APPLE INC

Systems and methods for creating persistent data for a wafer and for using persistent data for inspection-related functions

Various systems and methods for creating persistent data for a wafer and using persistent data for inspection-related functions are provided. One system includes a set of processor nodes coupled to a detector of an inspection system. Each of the processor nodes is configured to receive a portion of image data generated by the detector during scanning of a wafer. The system also includes an array of storage media separately coupled to each of the processor nodes. The processor nodes are configured to send all of the image data or a selected portion of the image data received by the processor nodes to the arrays of storage media such that all of the image data or the selected portion of the image data generated by the detector during the scanning of the wafer is stored in the arrays of the storage media.

Owner:KLA TENCOR CORP

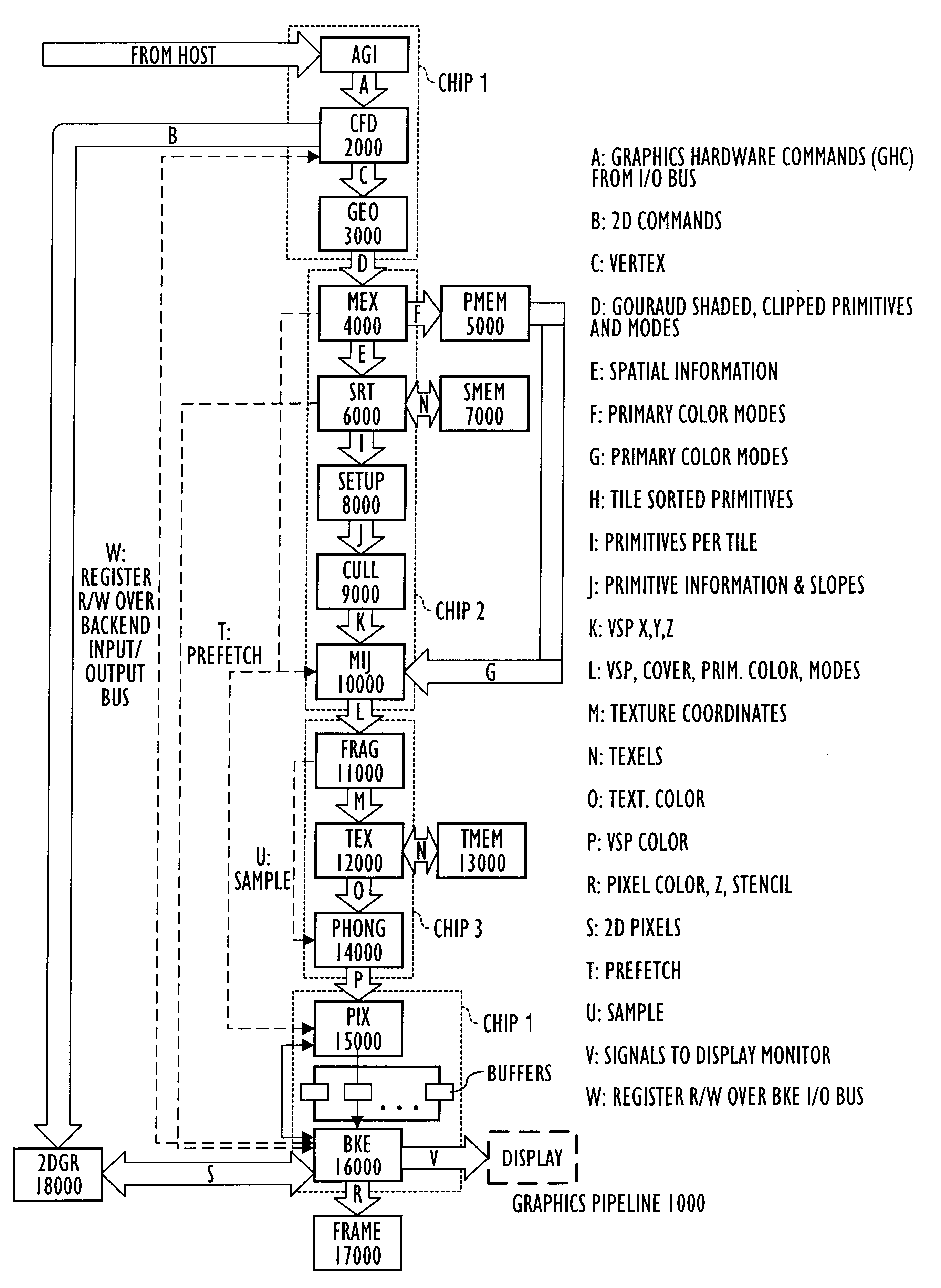

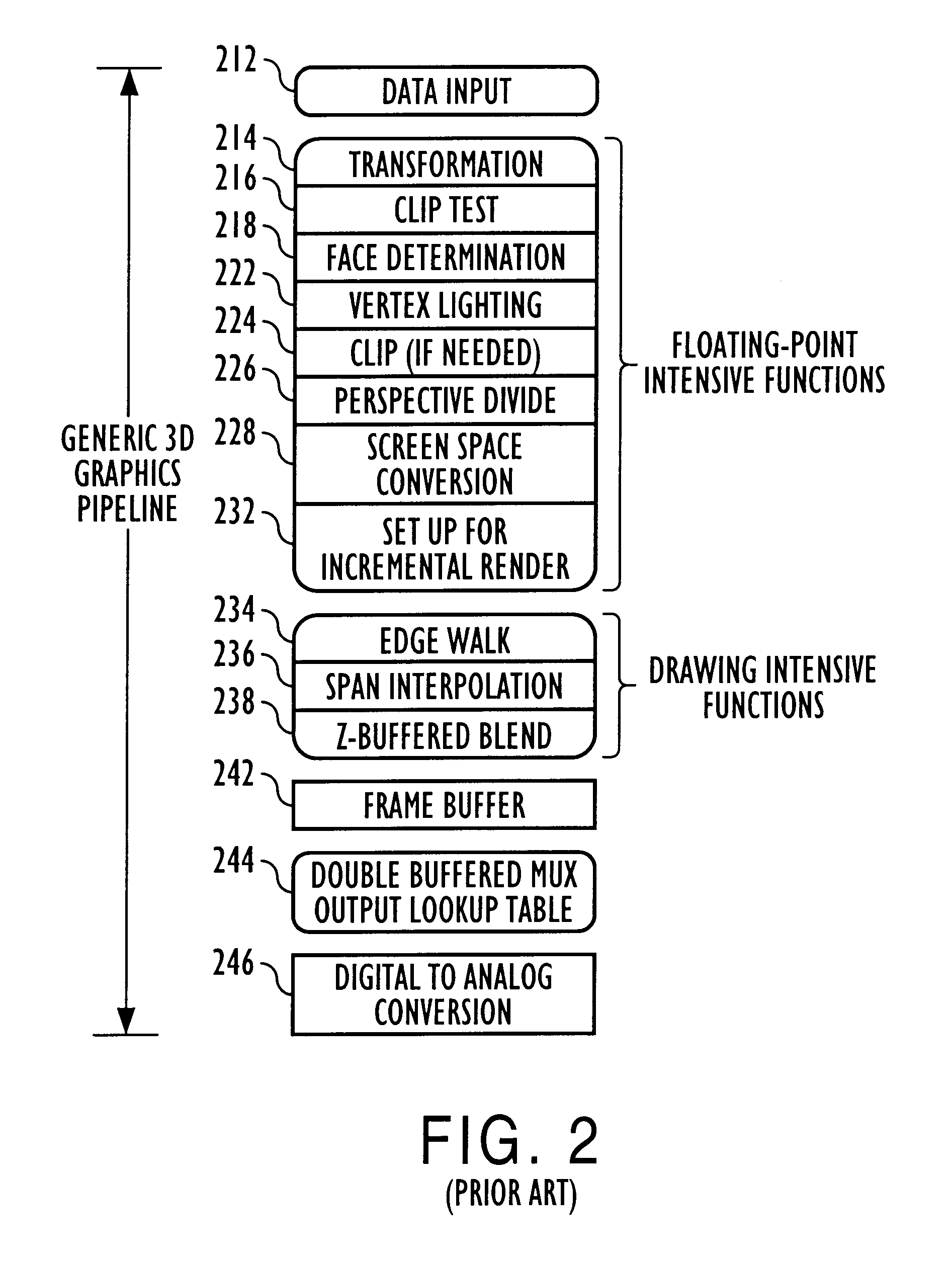

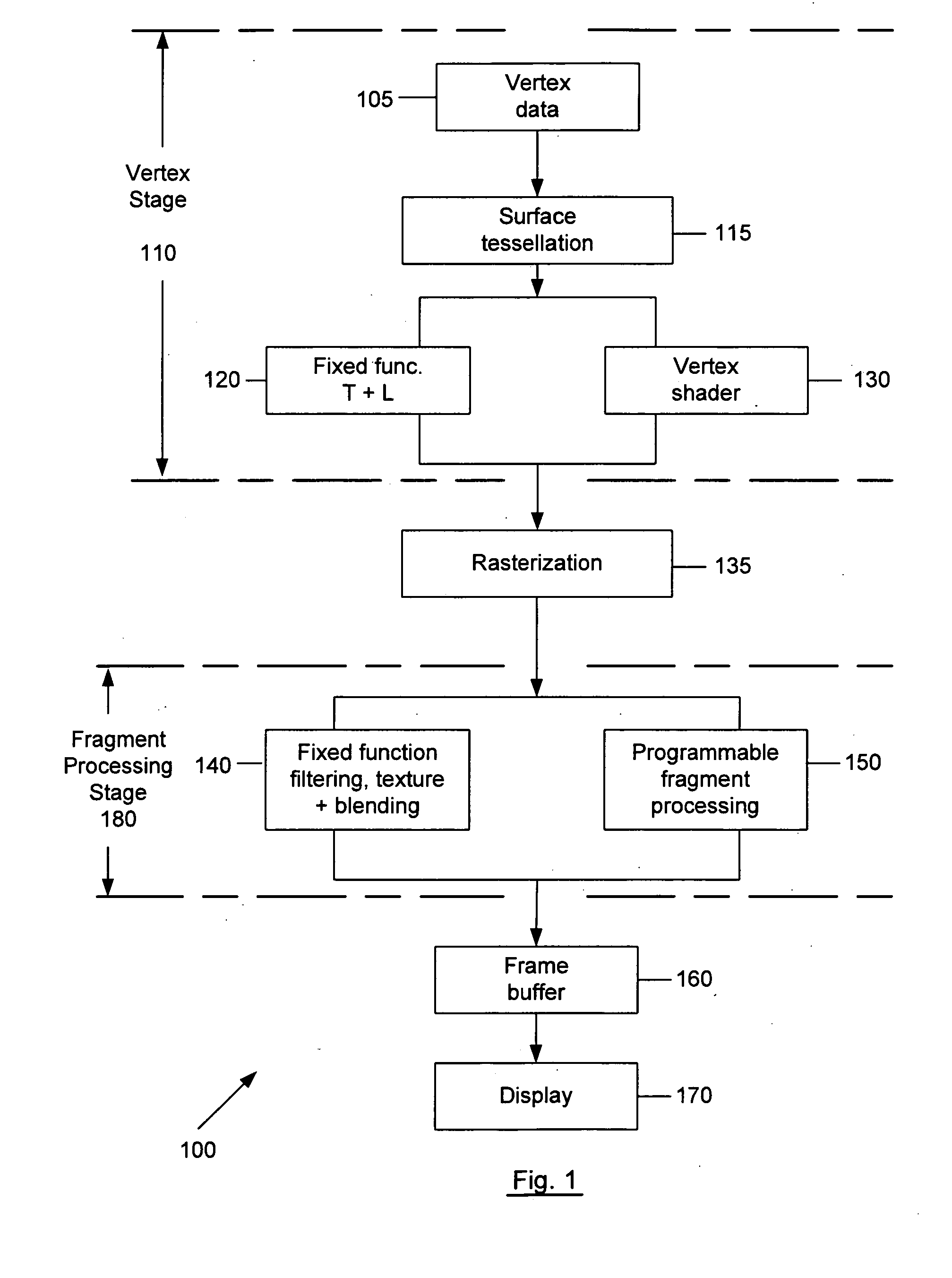

Deferred shading graphics pipeline processor

InactiveUS6229553B1Lower communication bandwidthAttenuation bandwidthTexturing/coloringImage memory managementPhong shadingDeferred shading

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

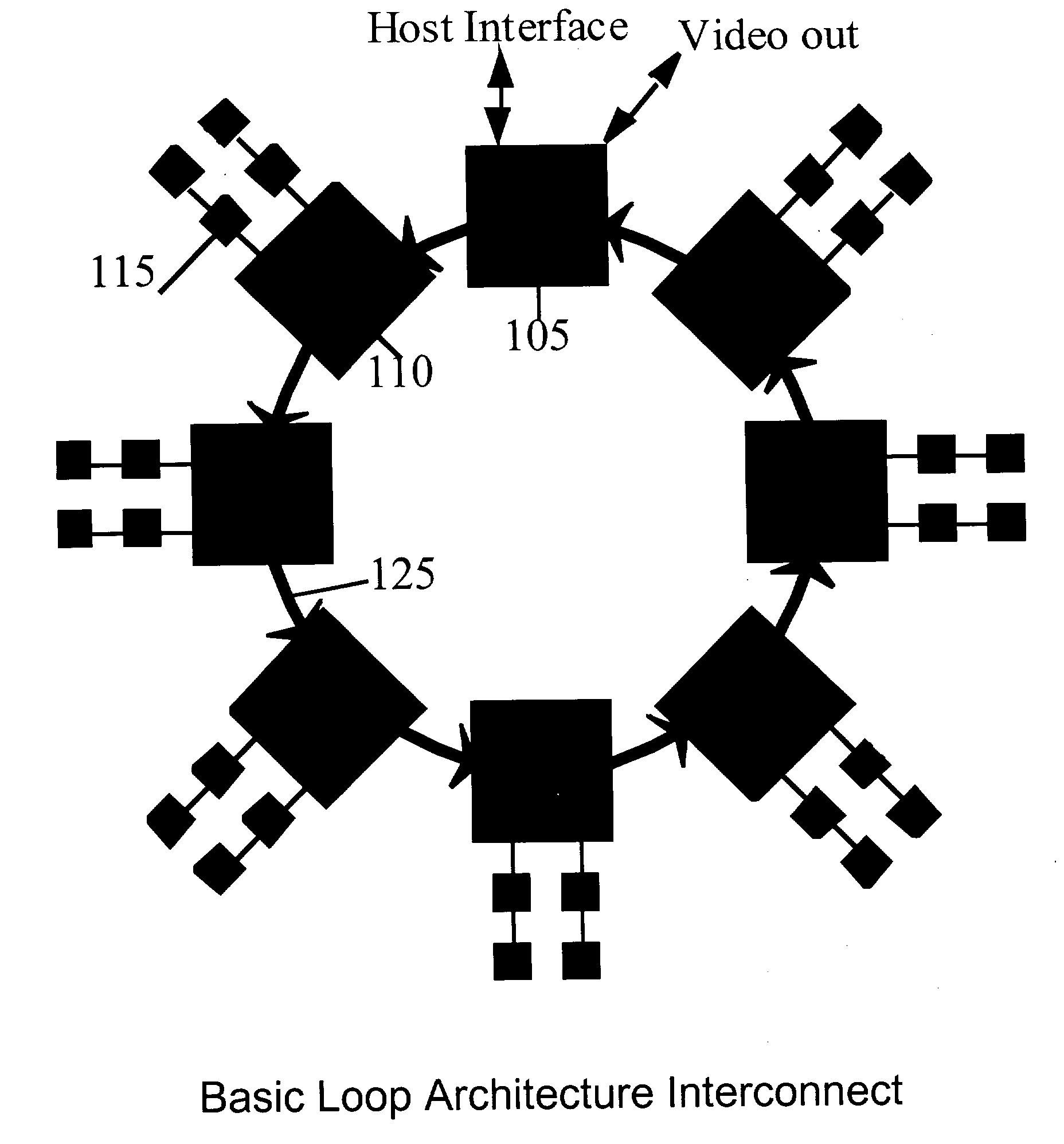

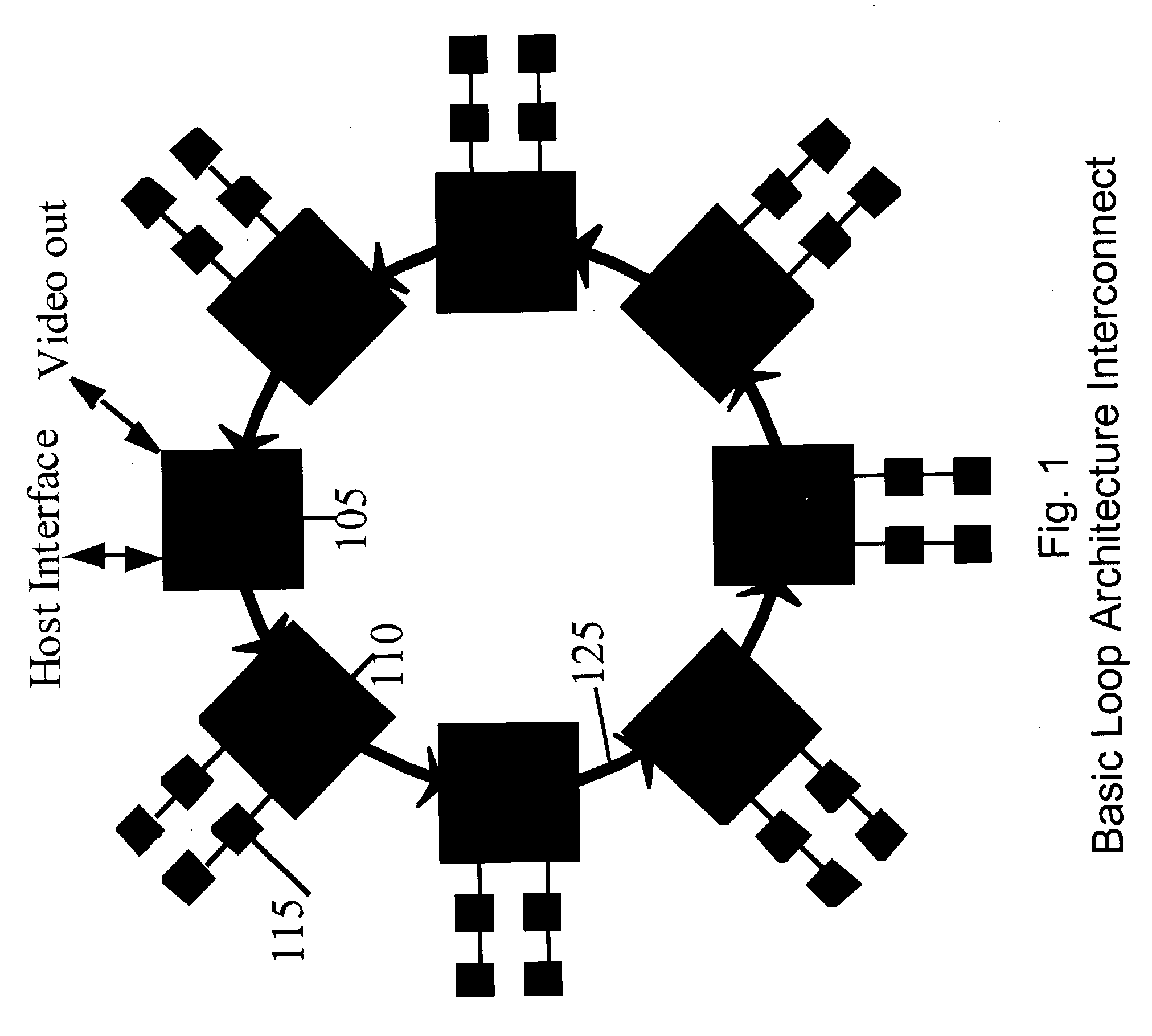

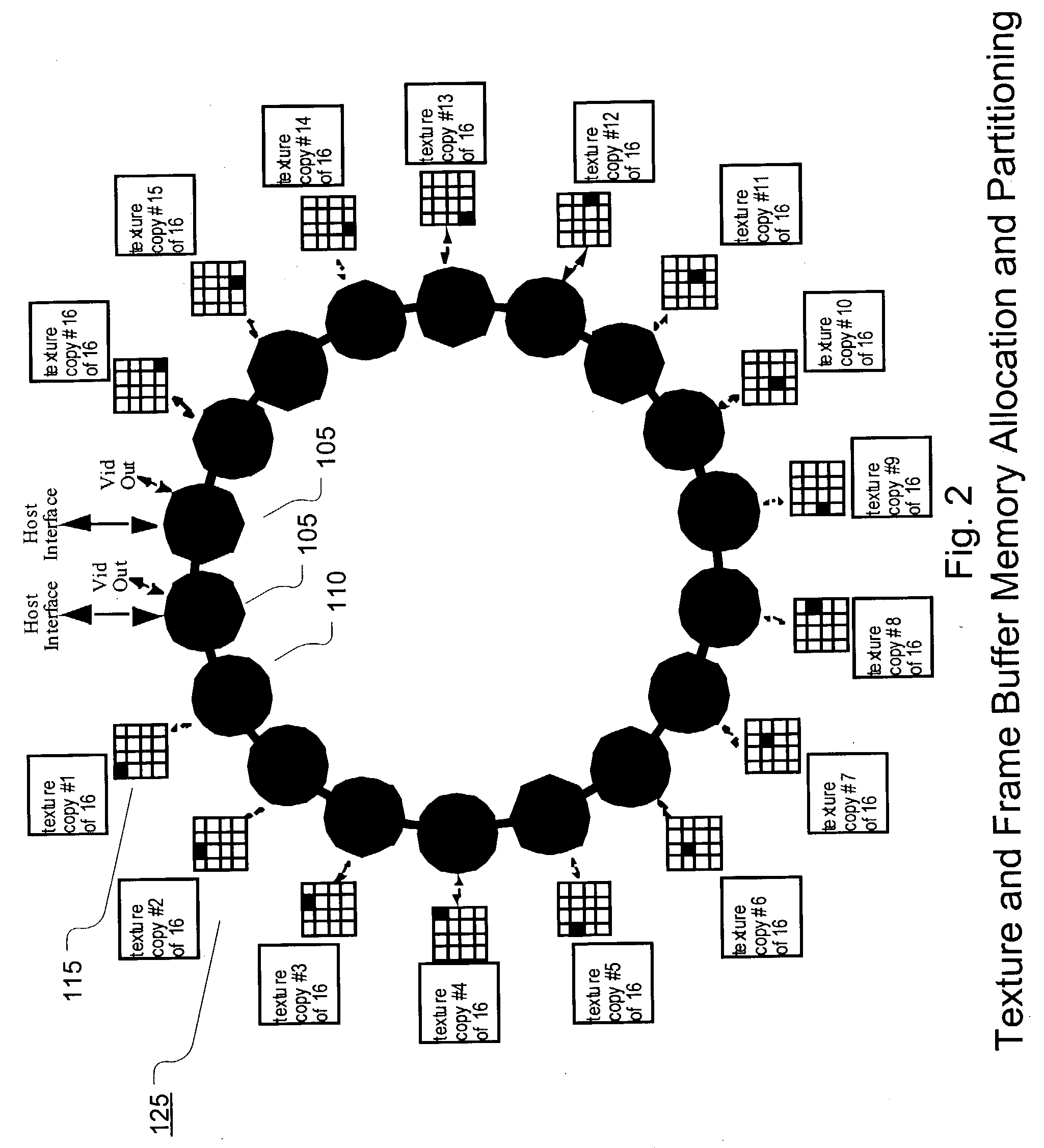

Scalable high performance 3d graphics

InactiveUS20040012600A1Minimizes cost and riskEasy to scaleImage enhancementImage memory managementGraphicsHigh bandwidth

A high-speed ring topology. In one embodiment, two base chip types are required: a "drawing" chip, LoopDraw, and an "interface" chip, LoopInterface. Each of these chips have a set of pins that supports an identical high speed point to point unidirectional input and output ring interconnect interface: the LoopLink. The LoopDraw chip uses additional pins to connect to several standard memories that form a high bandwidth local memory sub-system. The LoopInterface chip uses additional pins to support a high speed host computer host interface, at least one video output interface, and possibly also additional non-local interconnects to other LoopInterface chip(s).

Owner:DEERING MICHAEL F +2

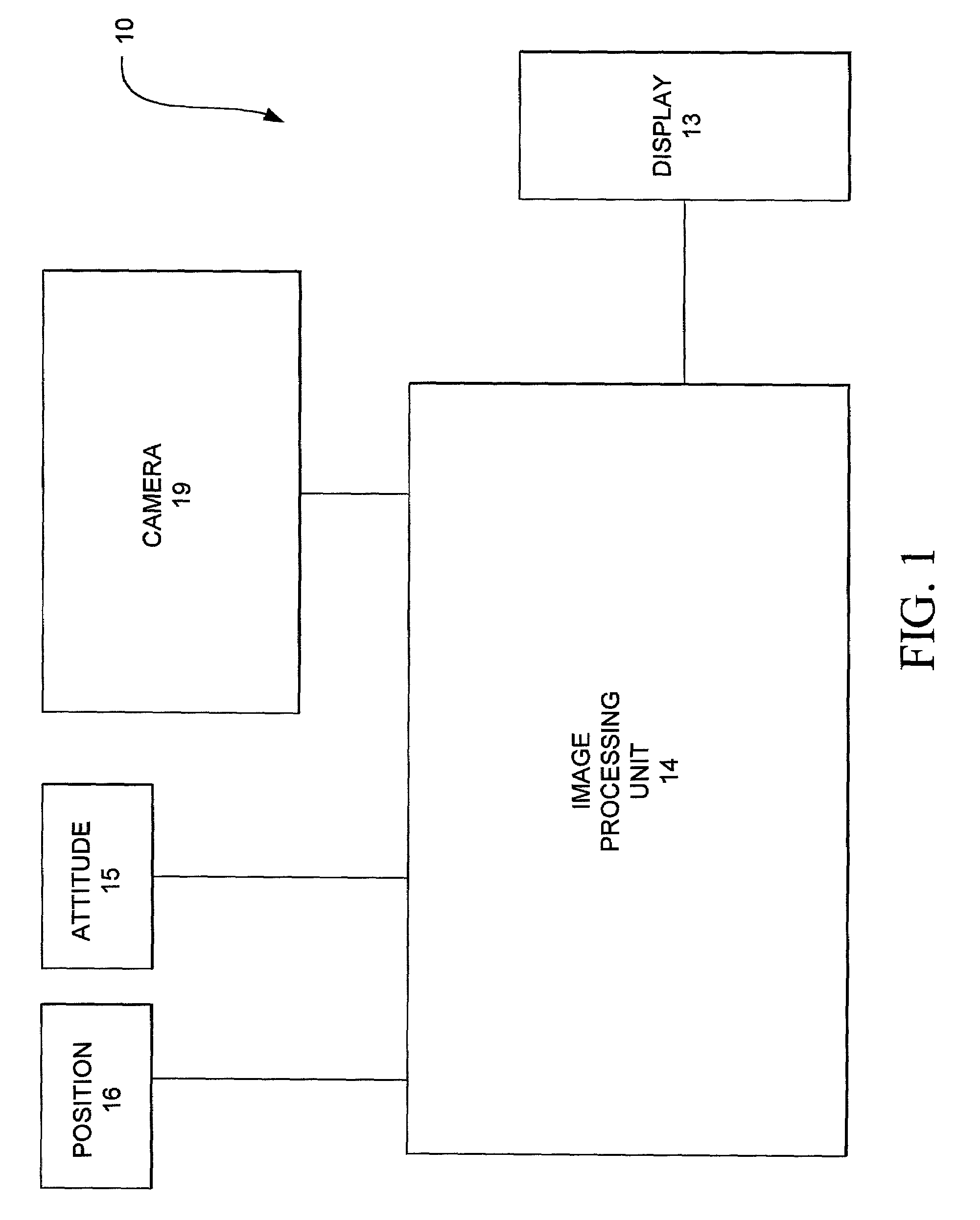

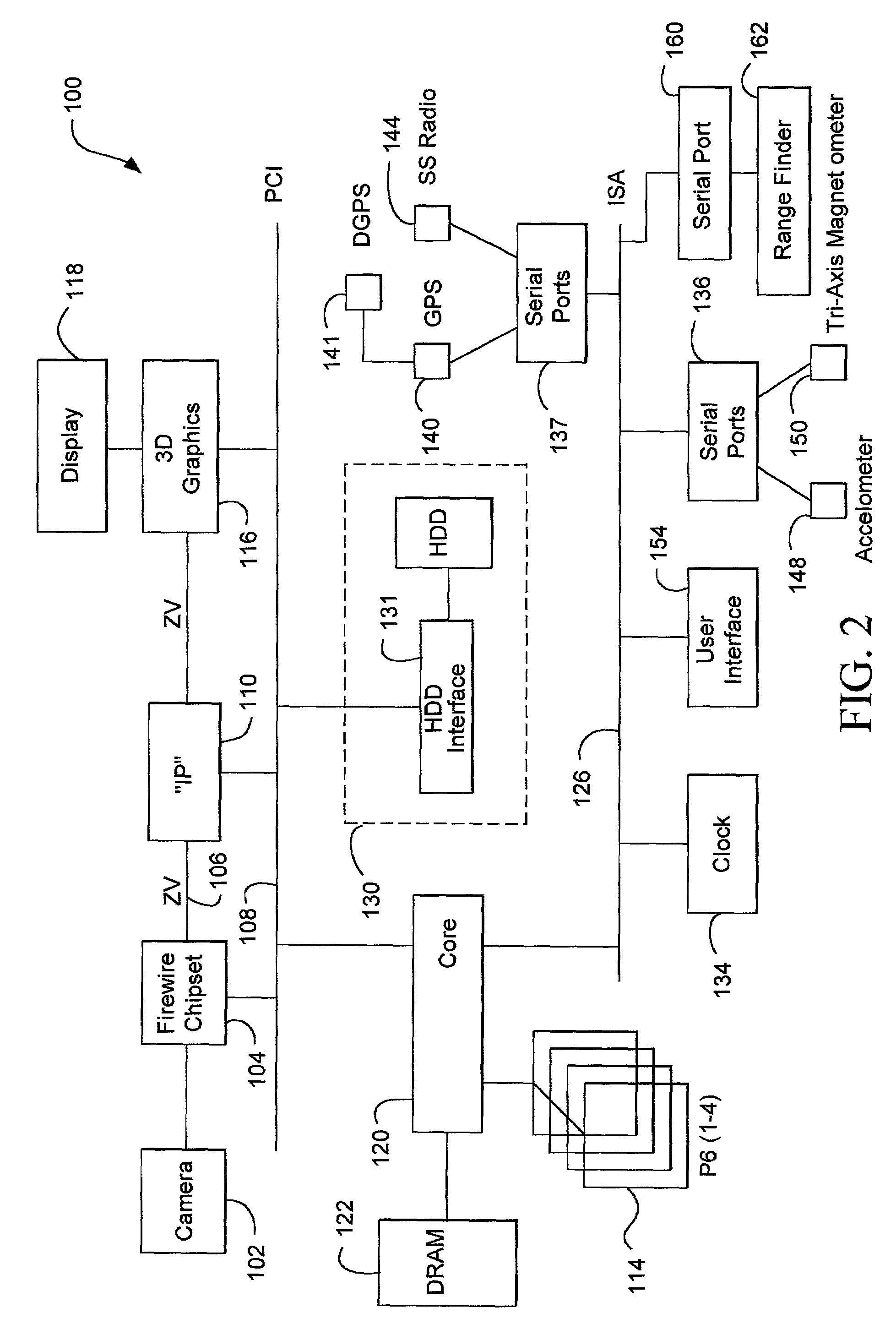

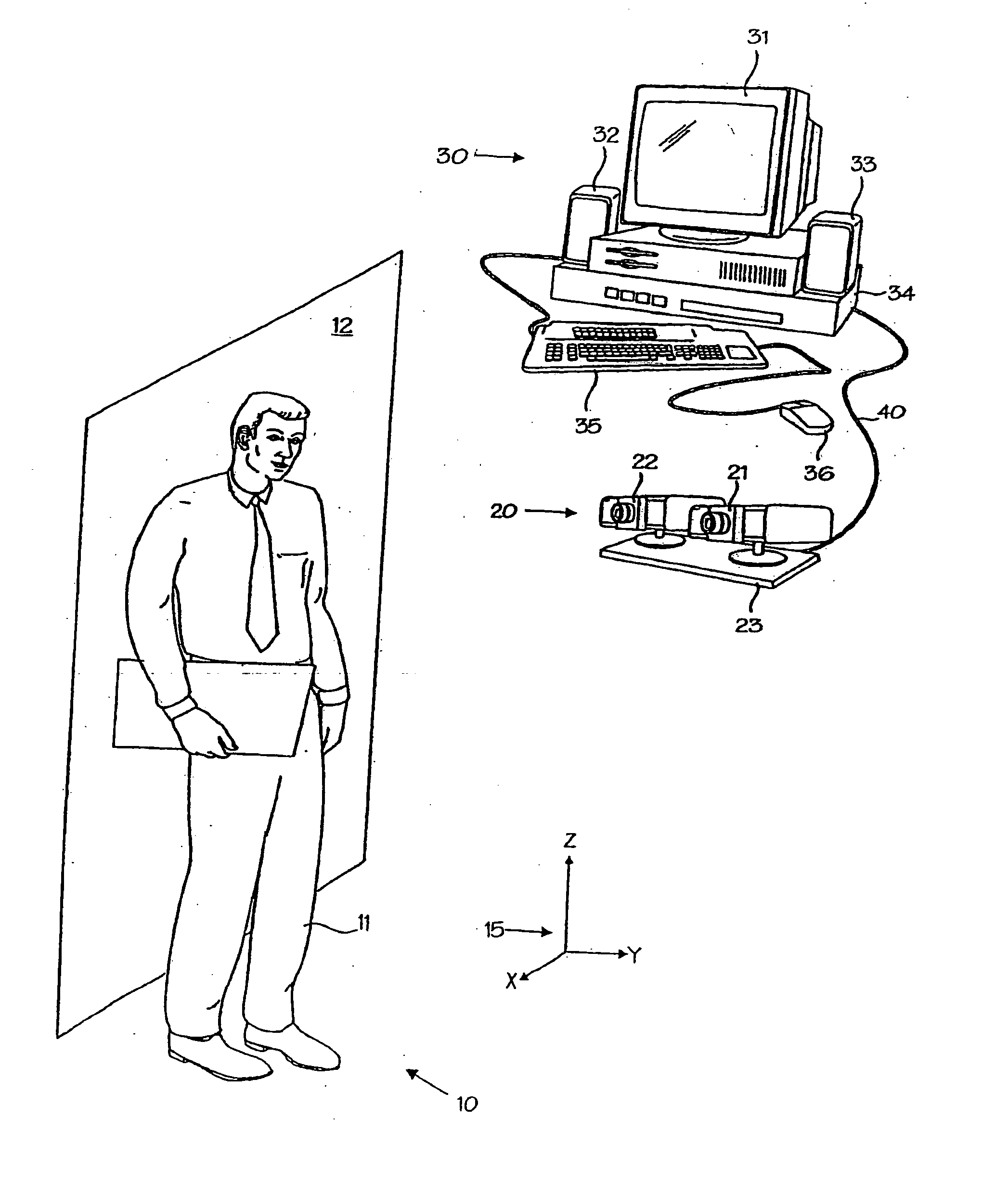

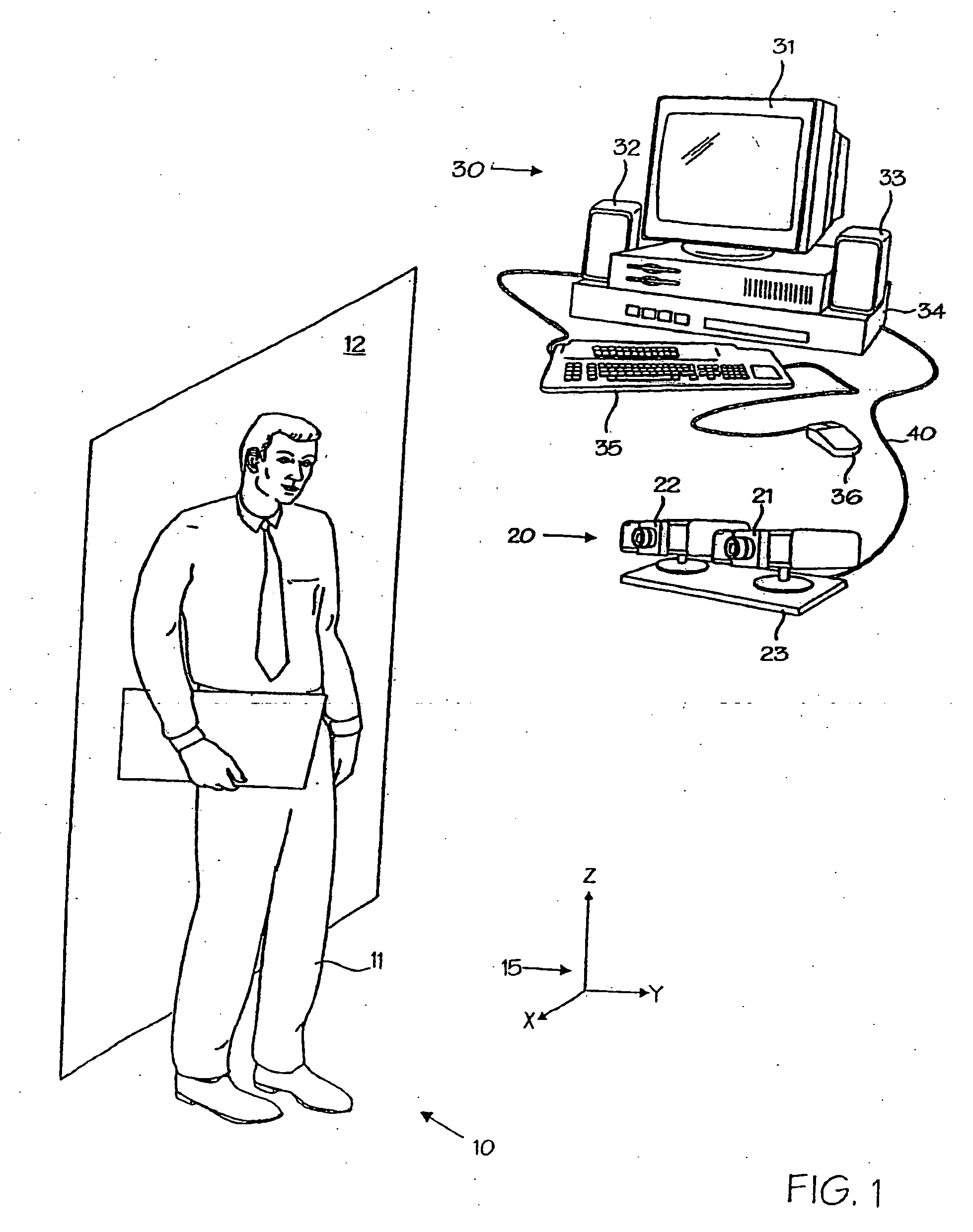

Electro-optic vision systems

InactiveUS7301536B2Programme controlNavigational calculation instrumentsGraphicsSynthetic vision system

An image processing system for delivering real scene information to a data processor. The system includes the data processor, an image-delivery mechanism, an information delivery mechanism, and a graphic processor.

Owner:GEOVECTOR

Data processing system and method

InactiveUS20060013473A1Eliminate informationImage enhancementImage analysisStatic random-access memoryHigh memory

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

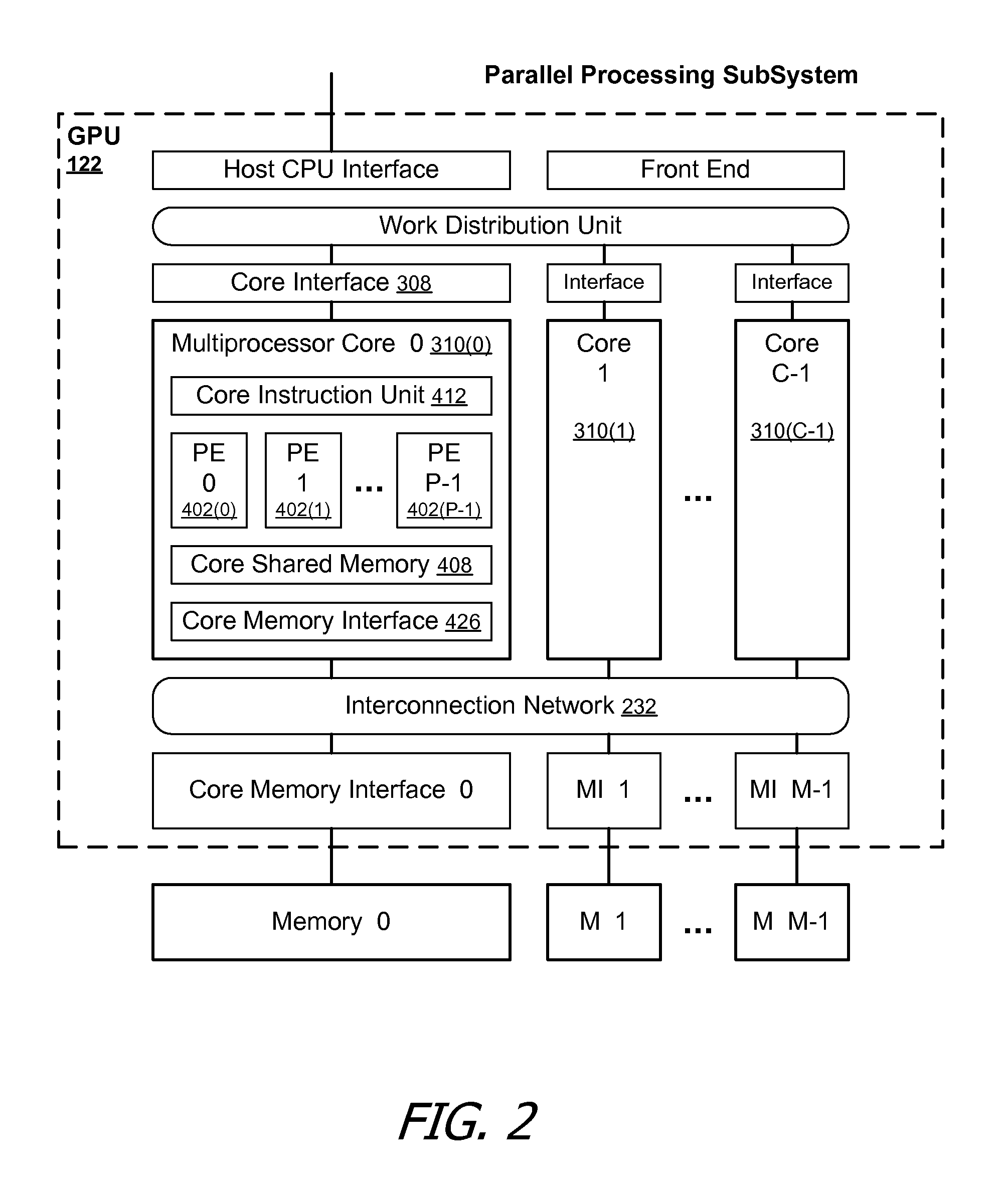

Atomic memory operators in a parallel processor

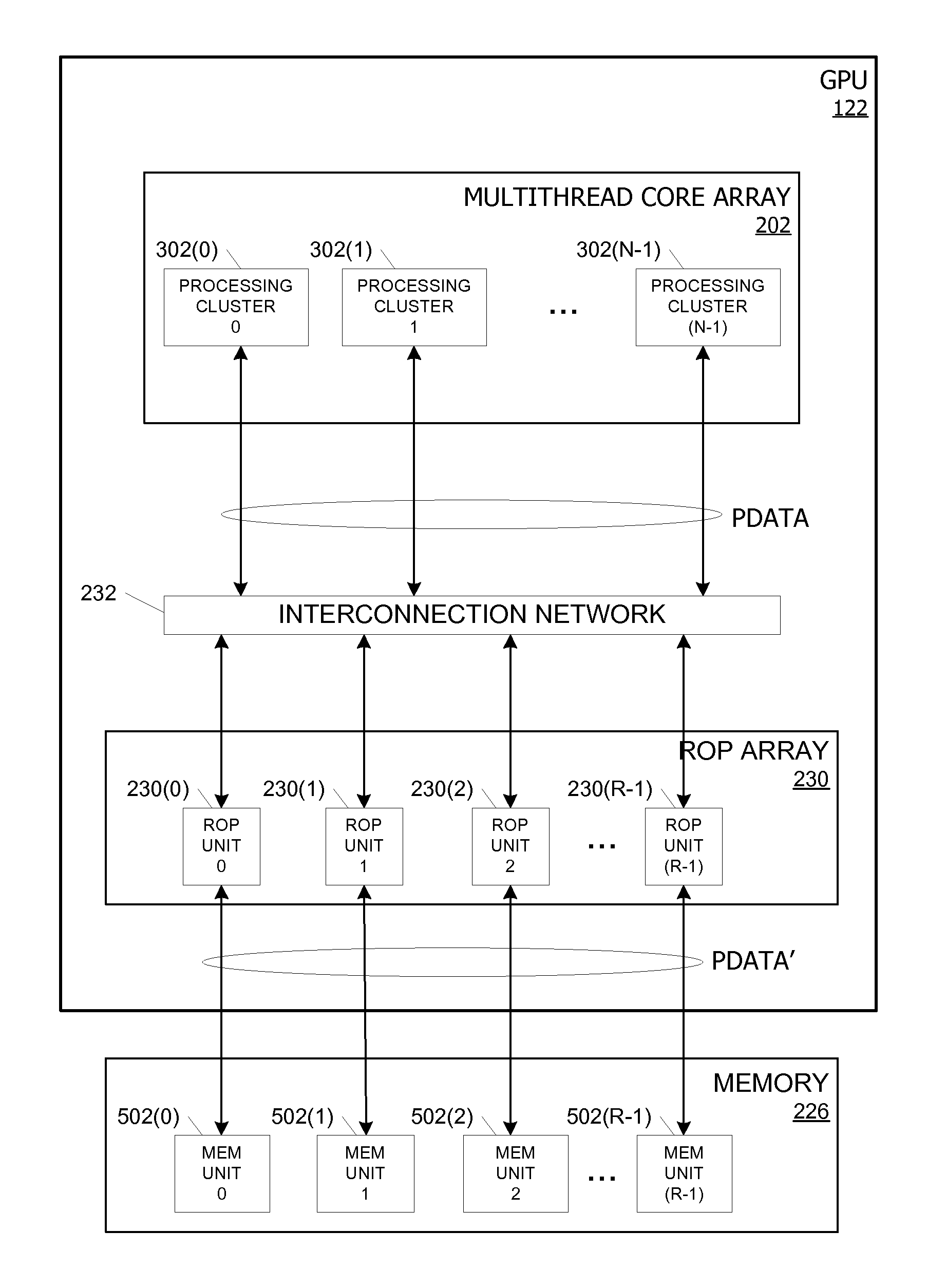

ActiveUS7627723B1Direct performanceLower performance requirementsCathode-ray tube indicatorsProcessor architectures/configurationMachine instructionParallel processing

Owner:NVIDIA CORP

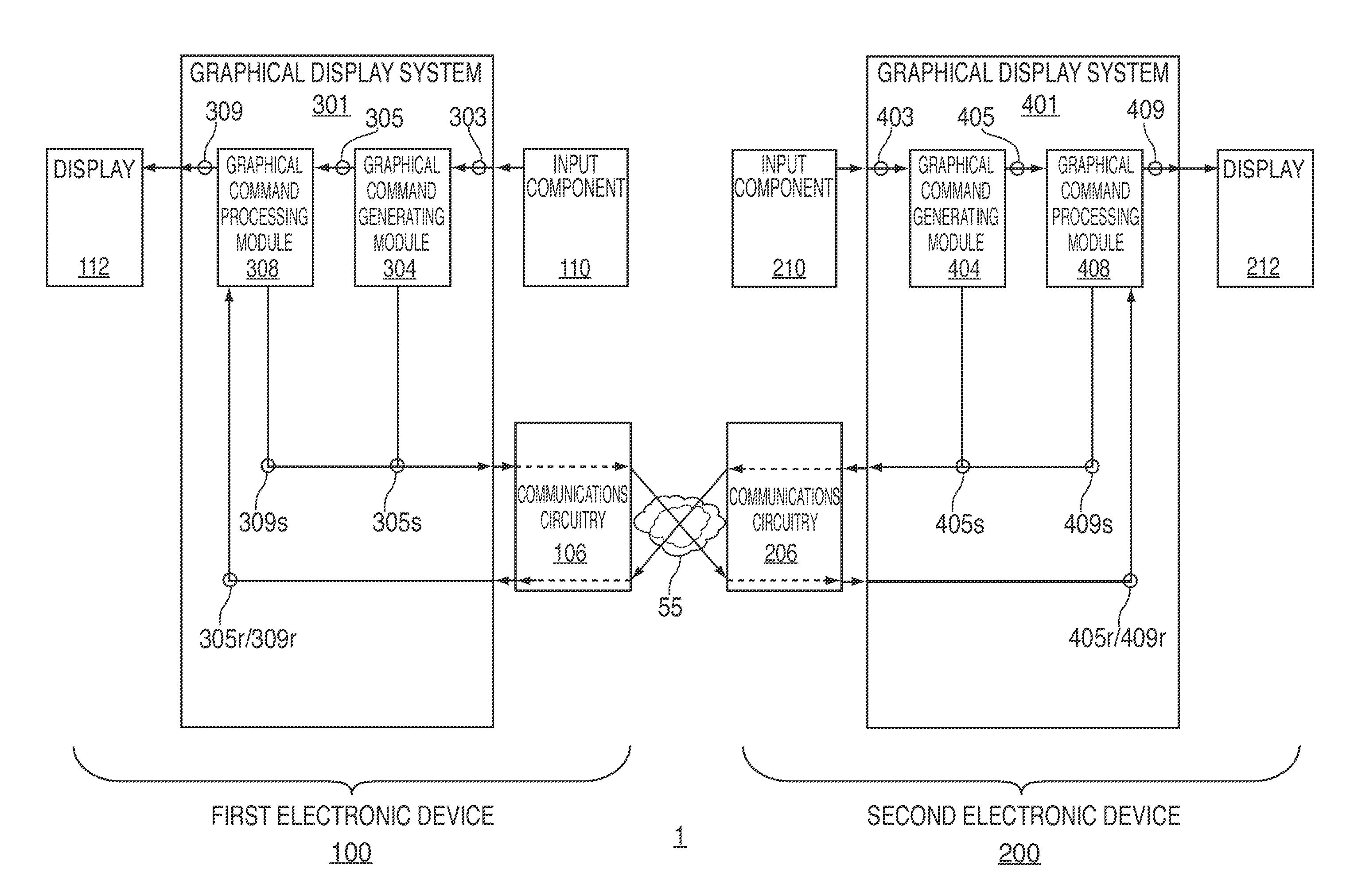

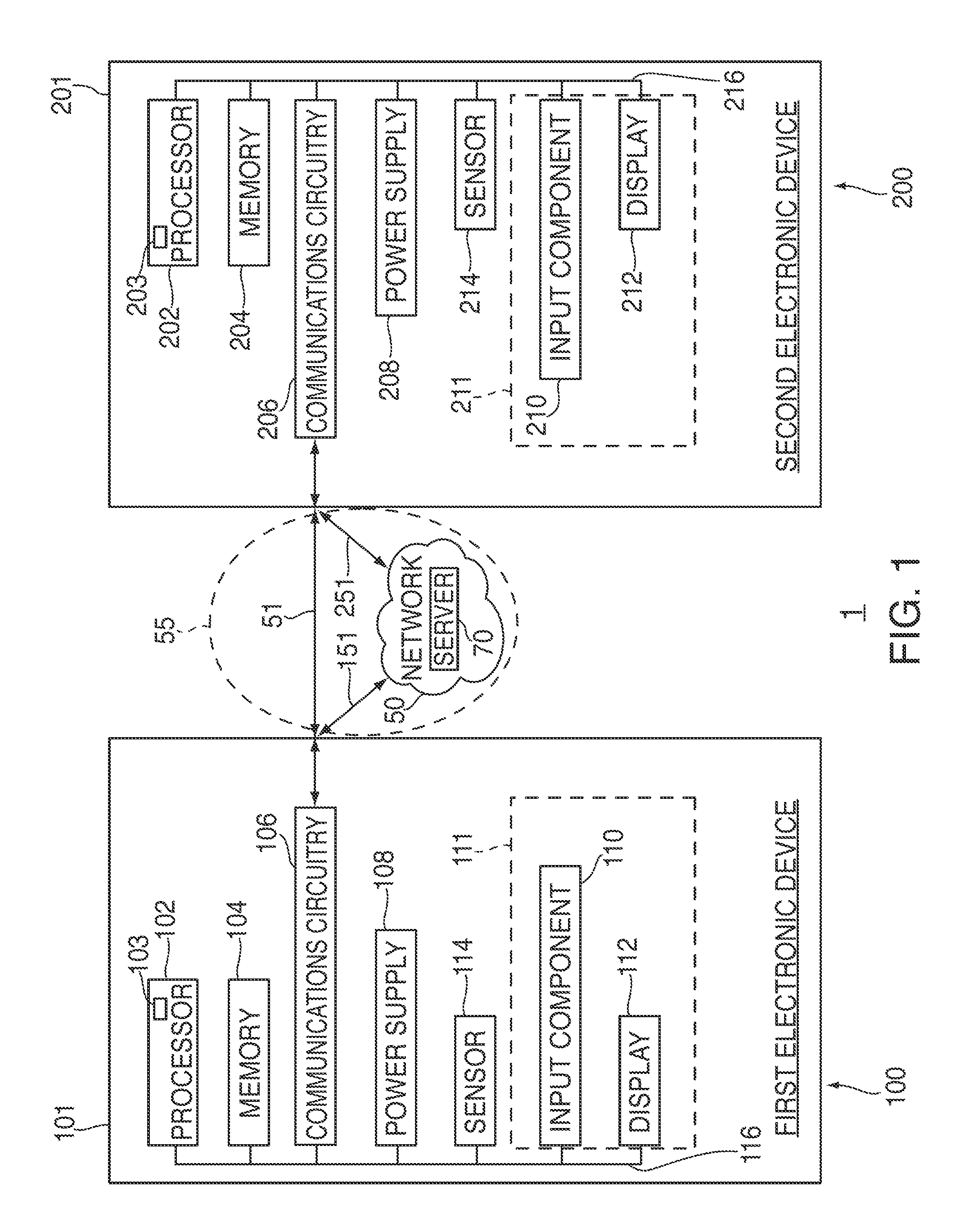

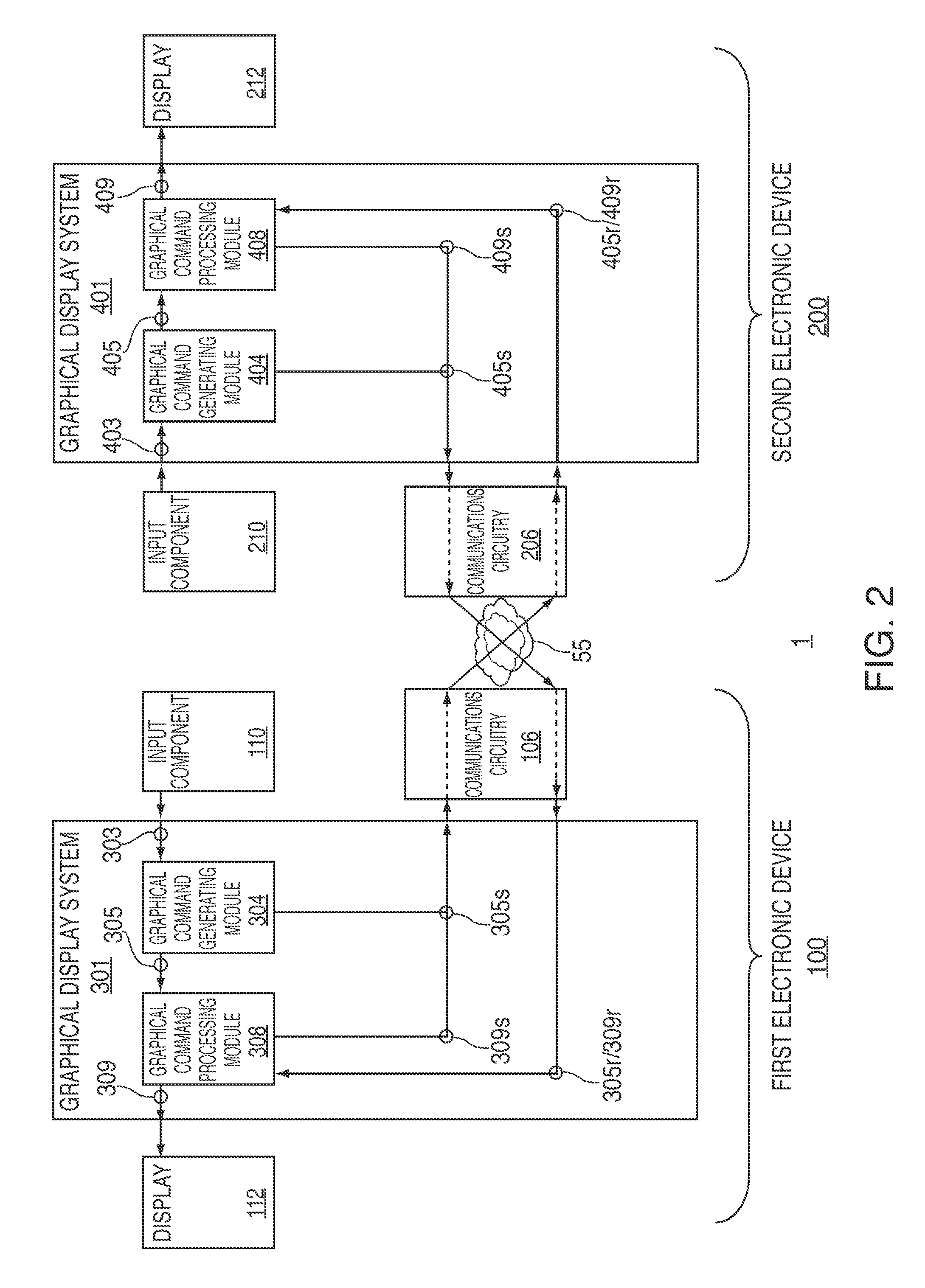

Systems, methods, and computer-readable media for managing collaboration on a virtual work of art

Systems, methods, and computer-readable media for managing collaboration on a virtual work of art between multiple electronic devices are provided. A first graphical display system of a first device may generate an input command in response to receiving user information through a user interface of the first device, and may then share this input command with a second graphical display system of a second device. The first graphical display system may process the shared input command to generate pixel array data in a canvas of the first device while the second graphical display system may process the shared input command to generate pixel array data in a canvas of the second device. By sharing input commands rather than pixel array data, system latency may be reduced. Despite operating on the same artwork, the user interfaces and graphical processing capabilities of each device may vary, thereby providing the user greater expressiveness.

Owner:APPLE INC

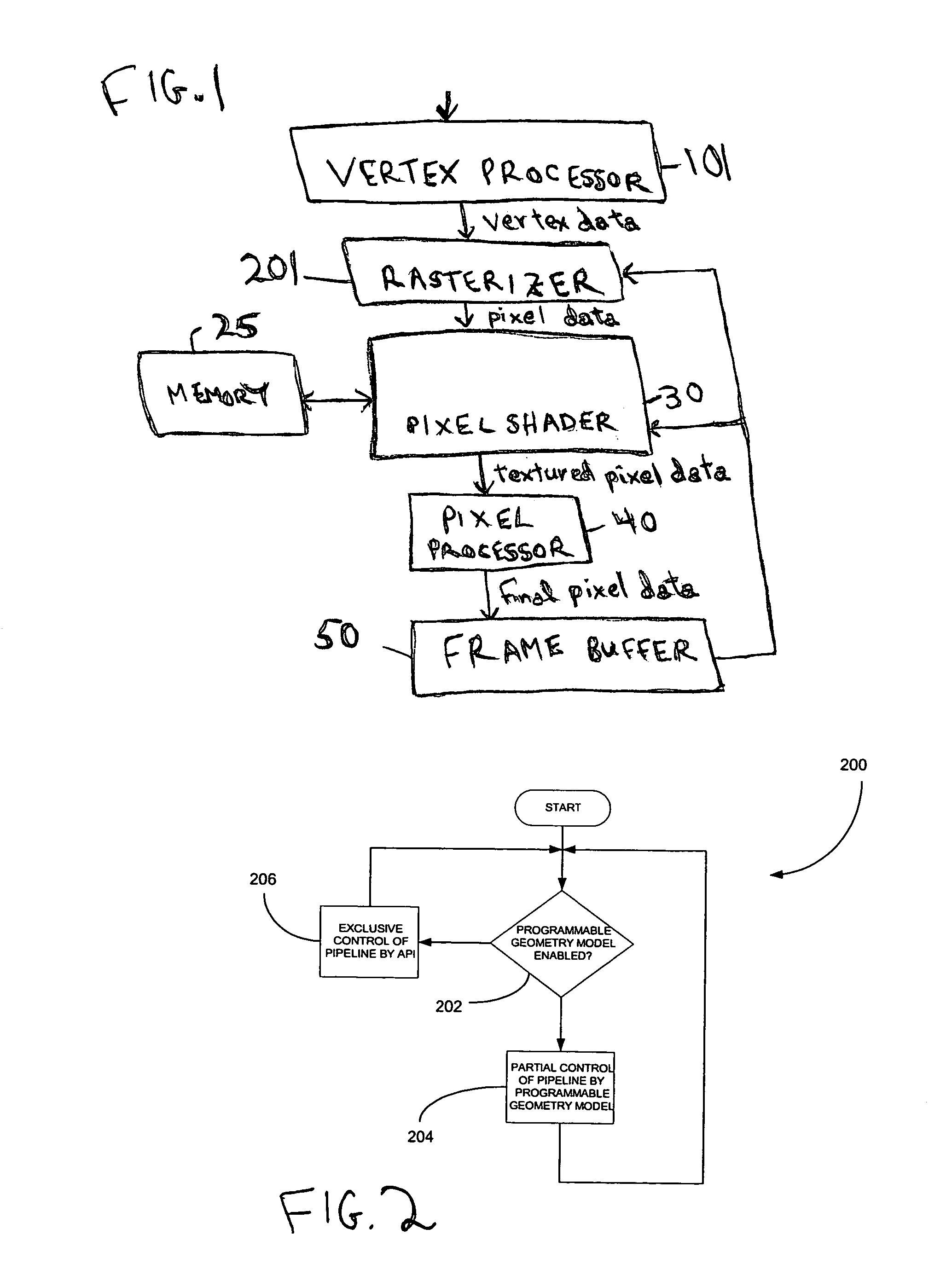

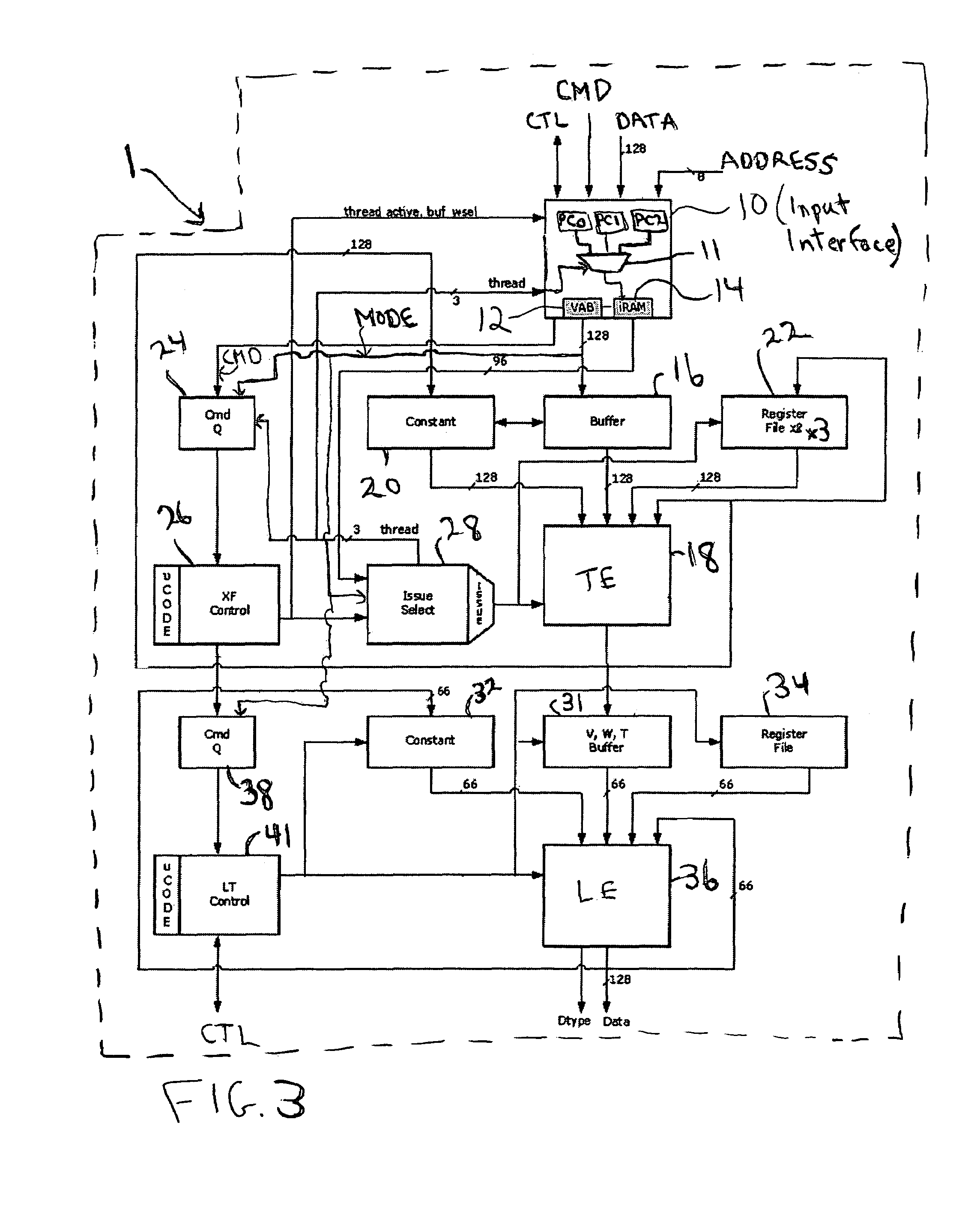

Method and system for programmable pipelined graphics processing with branching instructions

InactiveUS6947047B1Avoid confictMultiple digital computer combinationsProcessor architectures/configurationGraphicsMode control

A programmable, pipelined graphics processor (e.g., a vertex processor) having at least two processing pipelines, a graphics processing system including such a processor, and a pipelined graphics data processing method allowing parallel processing and also handling branching instructions and preventing conflicts among pipelines. Preferably, each pipeline processes data in accordance with a program including by executing branch instructions, and the processor is operable in any one of a parallel processing mode in which at least two data values to be processed in parallel in accordance with the same program are launched simultaneously into multiple pipelines, and a serialized mode in which only one pipeline at a time receives input data values to be processed in accordance with the program (and operation of each other pipeline is frozen). During parallel processing mode operation, mode control circuitry recognizes and resolves branch instructions to be executed (before processing of data in accordance with each branch instruction starts) and causes the processor to operate in the serialized mode when (and preferably only for as long as) necessary to prevent any conflict between the pipelines due to branching. In other embodiments, the processor is operable in any one of a parallel processing mode and a limited serialized mode in which operation of each of a sequence of pipelines (or pipeline sets) pauses for a limited number of clock cycles. The processor enters the limited serialized mode in response to detecting a conflict-causing instruction that could cause a conflict between resources shared by the pipelines during parallel processing mode operation.

Owner:NVIDIA CORP

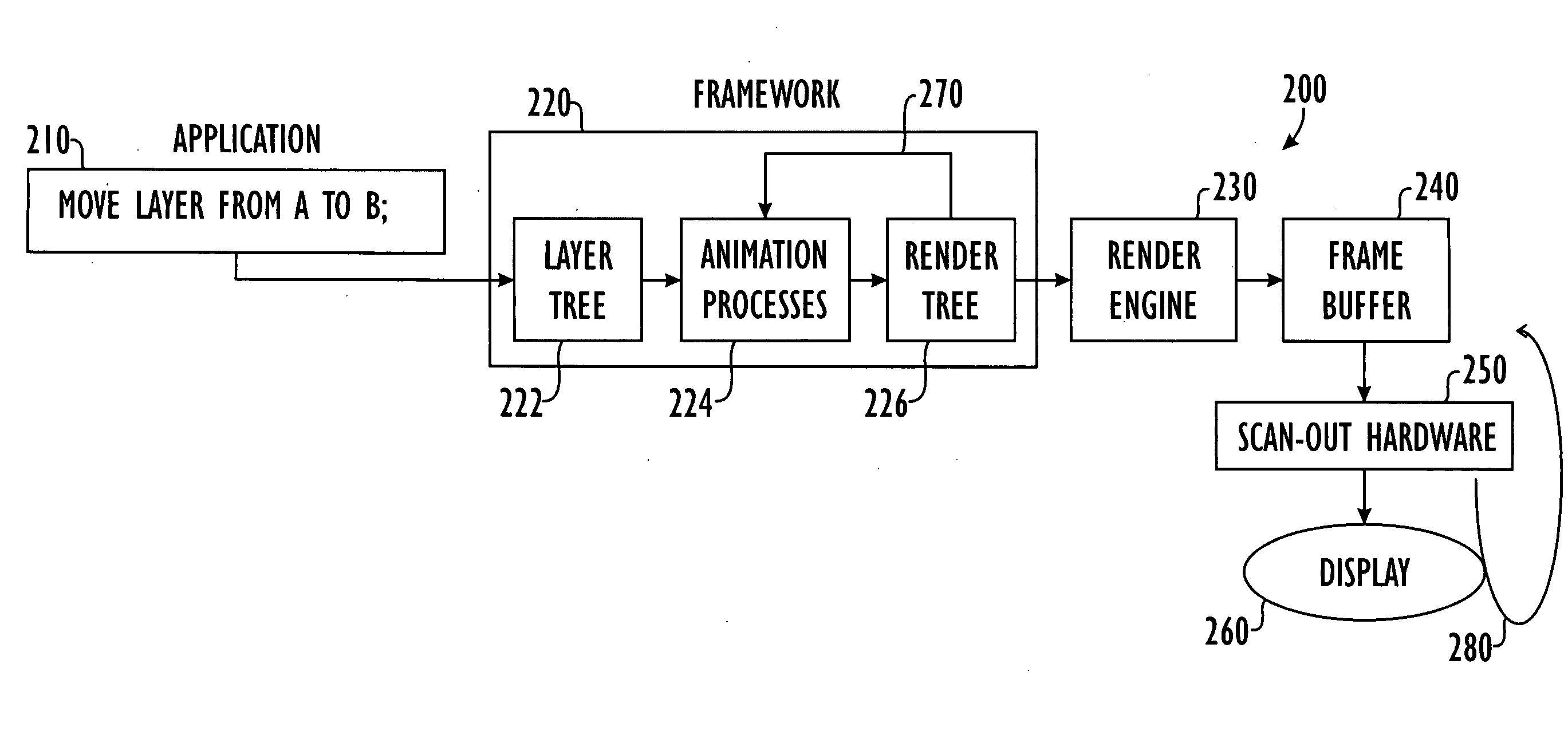

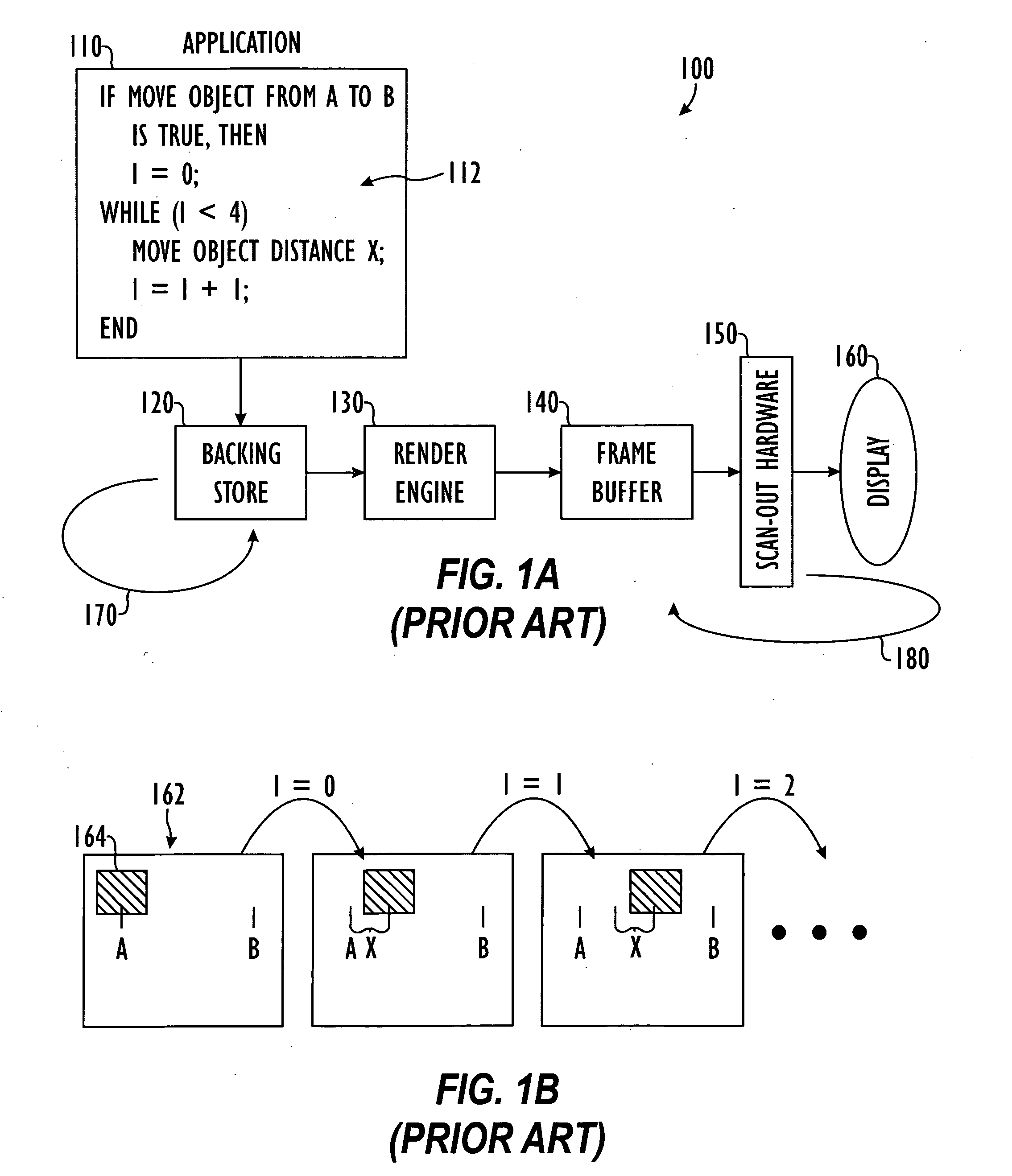

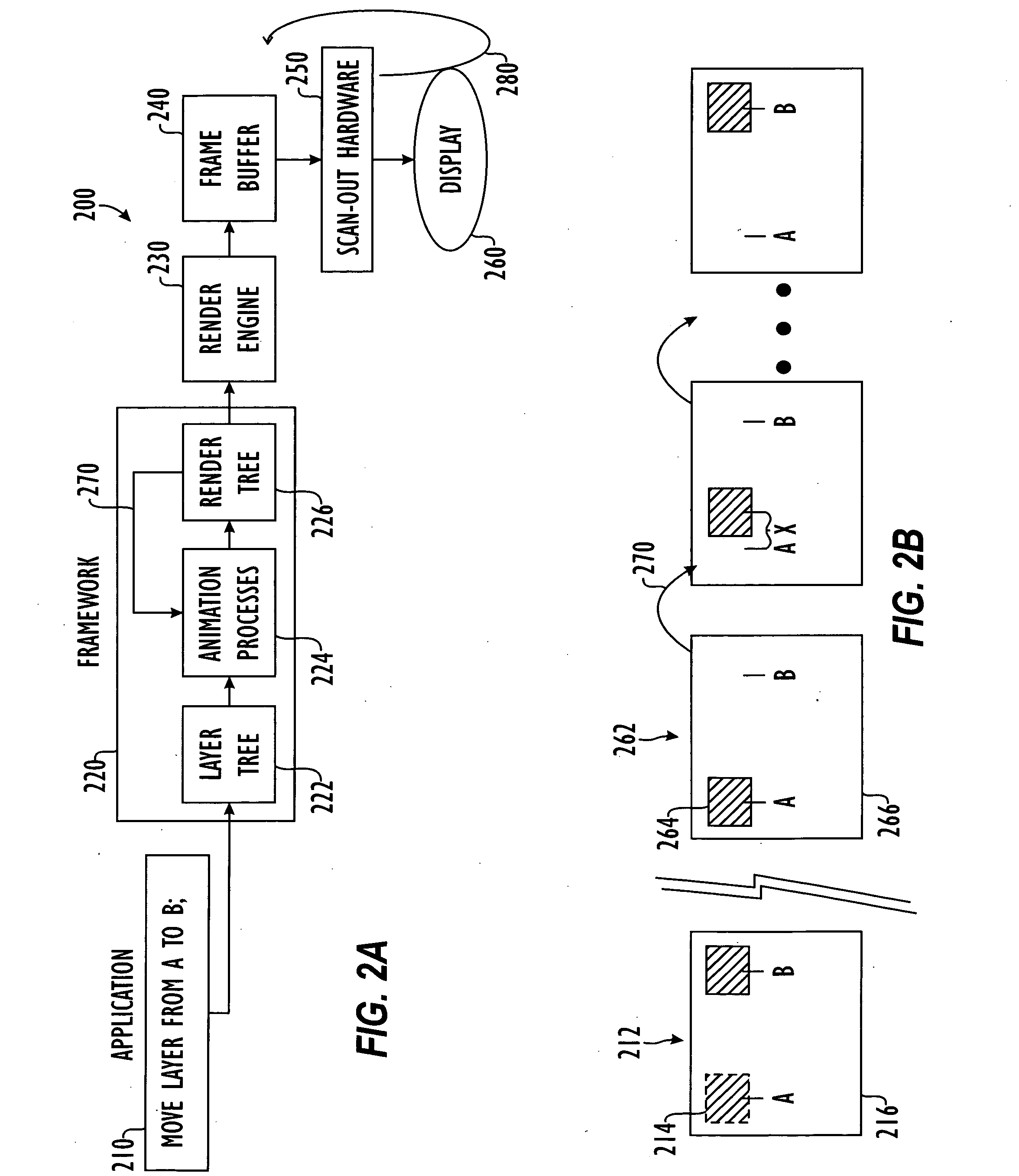

Framework for graphics animation and compositing operations

ActiveUS20080034292A1Improve resource utilizationAnimationProcessor architectures/configurationGraphicsVisibility

A framework for performing graphics animation and compositing operations has a layer tree for interfacing with the application and a render tree for interfacing with a render engine. Layers in the layer tree can be content, windows, views, video, images, text, media, or any other type of object for a user interface of an application. The application commits change to the state of the layers of the layer tree. The application does not need to include explicit code for animating the changes to the layers. Instead, an animation is determined for animating the change in state. In determining the animation, the framework can define a set of predetermined animations based on motion, visibility, and transition. The determined animation is explicitly applied to the affected layers in the render tree. A render engine renders from the render tree into a frame buffer for display on the computer system. Those portions of the render tree that have changed relative to prior versions can be tracked to improve resource management.

Owner:APPLE INC

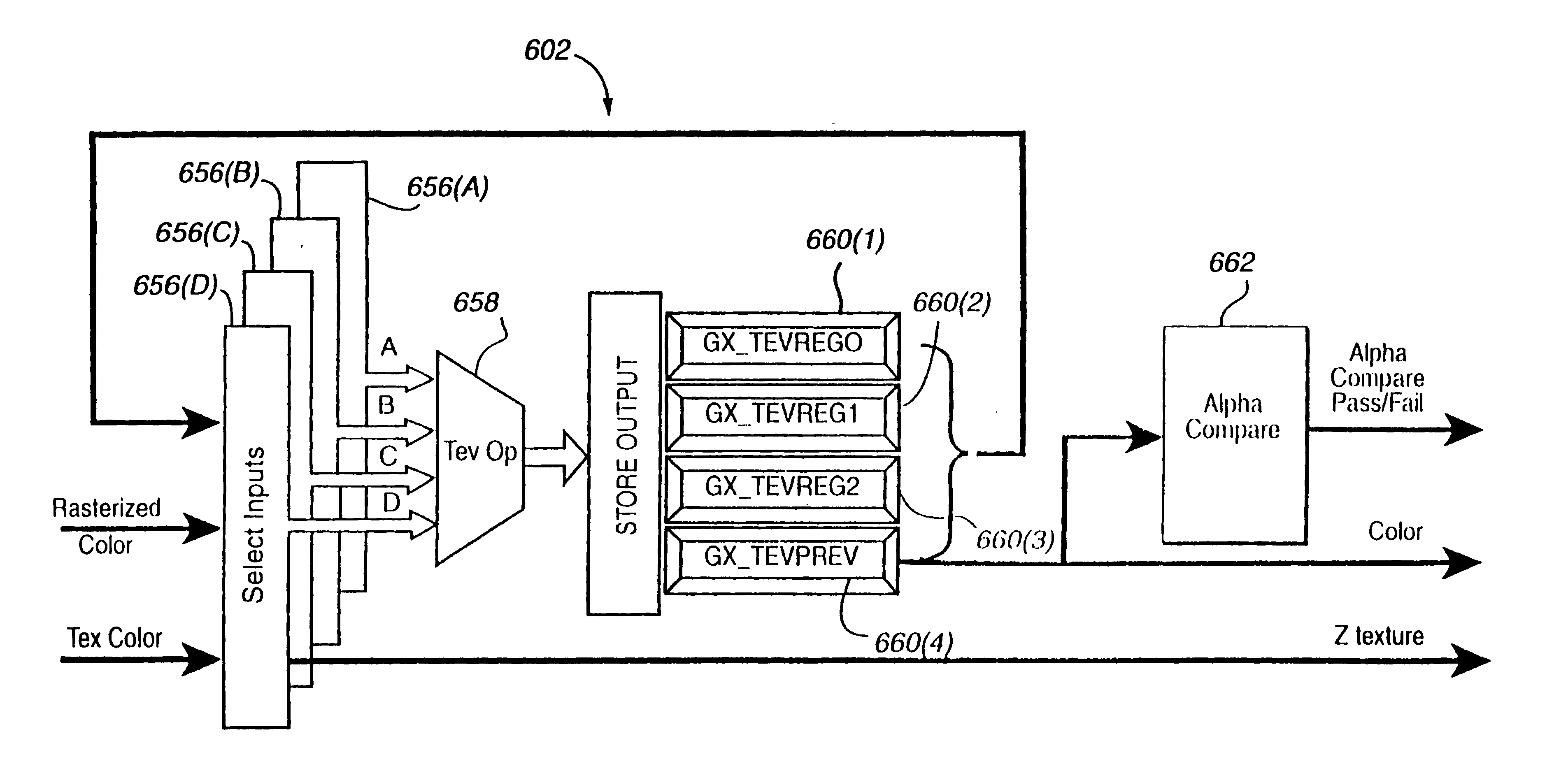

Recirculating shade tree blender for a graphics system

InactiveUS7034828B1Good flexibilityReduce in quantityCathode-ray tube indicatorsProcessor architectures/configurationGraphic systemComputer science

A hardware-accelerated recirculating programmable texture blender / shader arrangement circulates computed color and alpha data over multiple texture blending / shading cycles (stages) to provide multi-texturing and other effects. Up to sixteen independently programmable consecutive stages, forming a chain of blending operations, are supported for applying multiple textures to a single object in a single rendering pass.

Owner:NINTENDO CO LTD

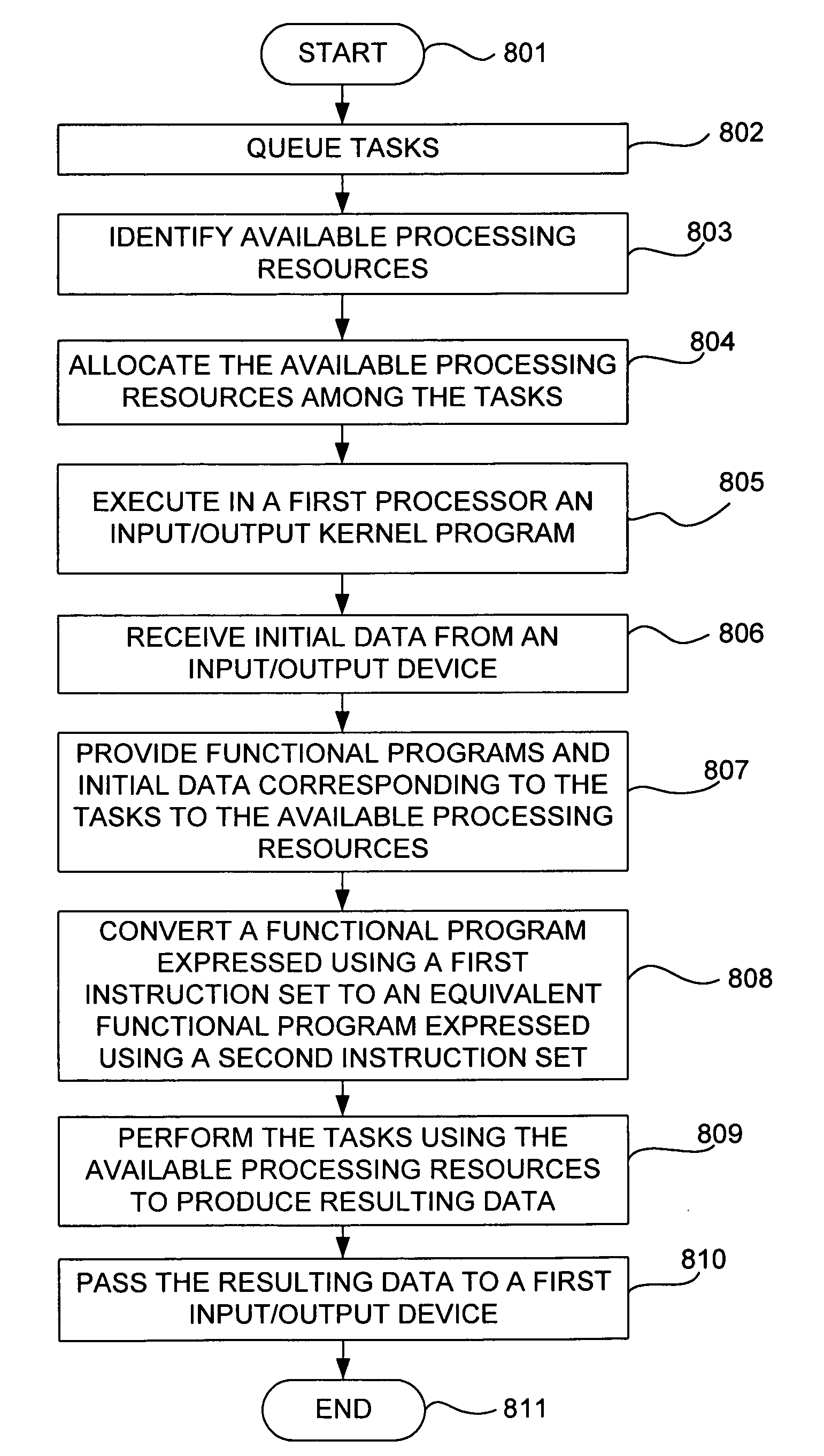

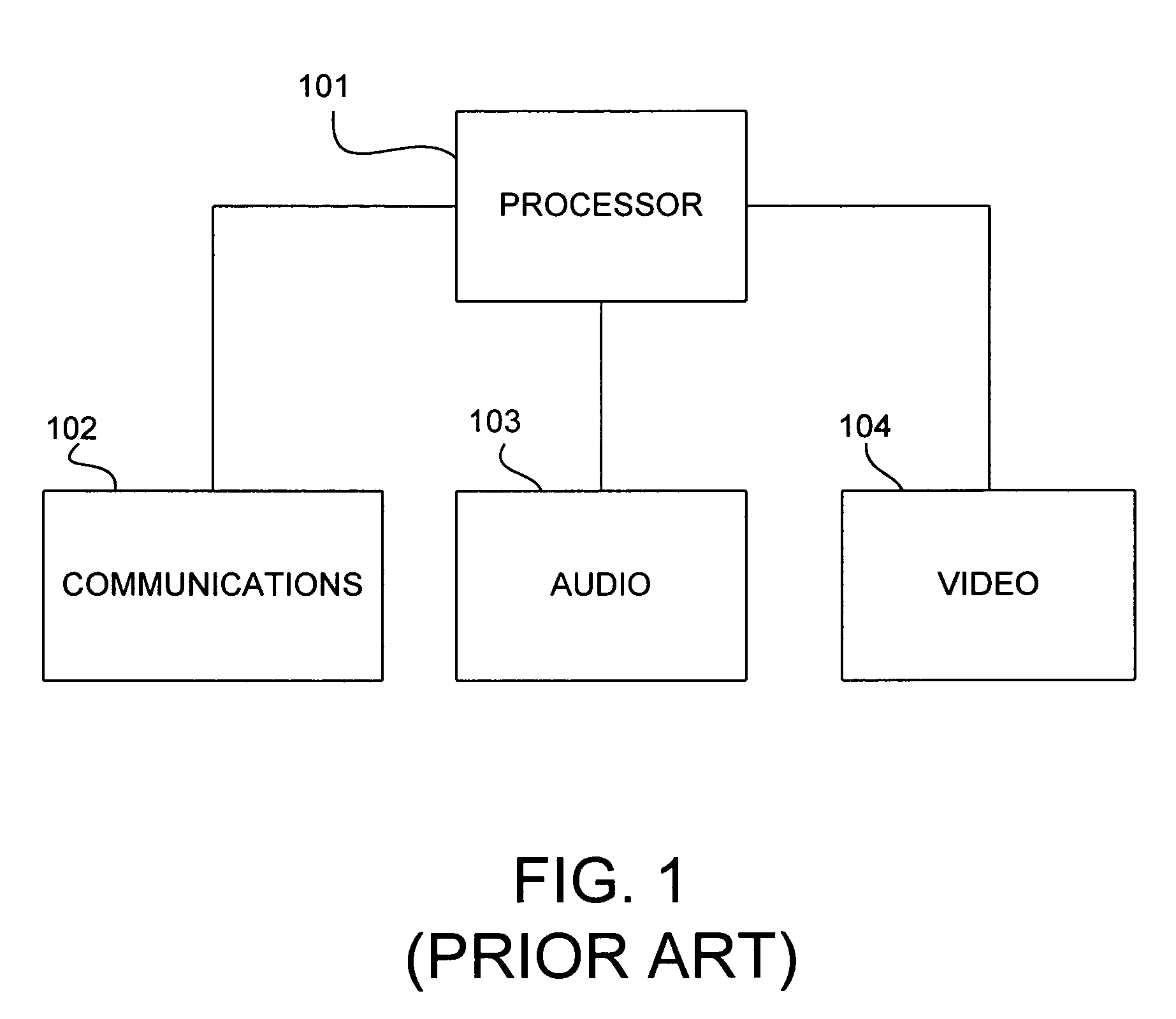

Method and apparatus for dynamic allocation of processing resources

InactiveUS7661107B1Digital data processing detailsGeneral purpose stored program computerComputer architectureOutput device

A method and apparatus for dynamic allocation of processing resources and tasks, including multimedia tasks. Tasks are queued, available processing resources are identified, and the available processing resources are allocated among the tasks. The available processing resources are provided with functional programs corresponding to the tasks. The tasks are performed using the available processing resources to produce resulting data, and the resulting data is passed to an input / output device.

Owner:ADVANCED MICRO DEVICES INC

Load balancing

ActiveUS20060059494A1Multiprogramming arrangementsMultiple digital computer combinationsComputational scienceGraphics

Embodiments of methods, apparatuses, devices, and / or systems for load balancing two processors, such as for graphics and / or video processing, for example, are described.

Owner:NVIDIA CORP

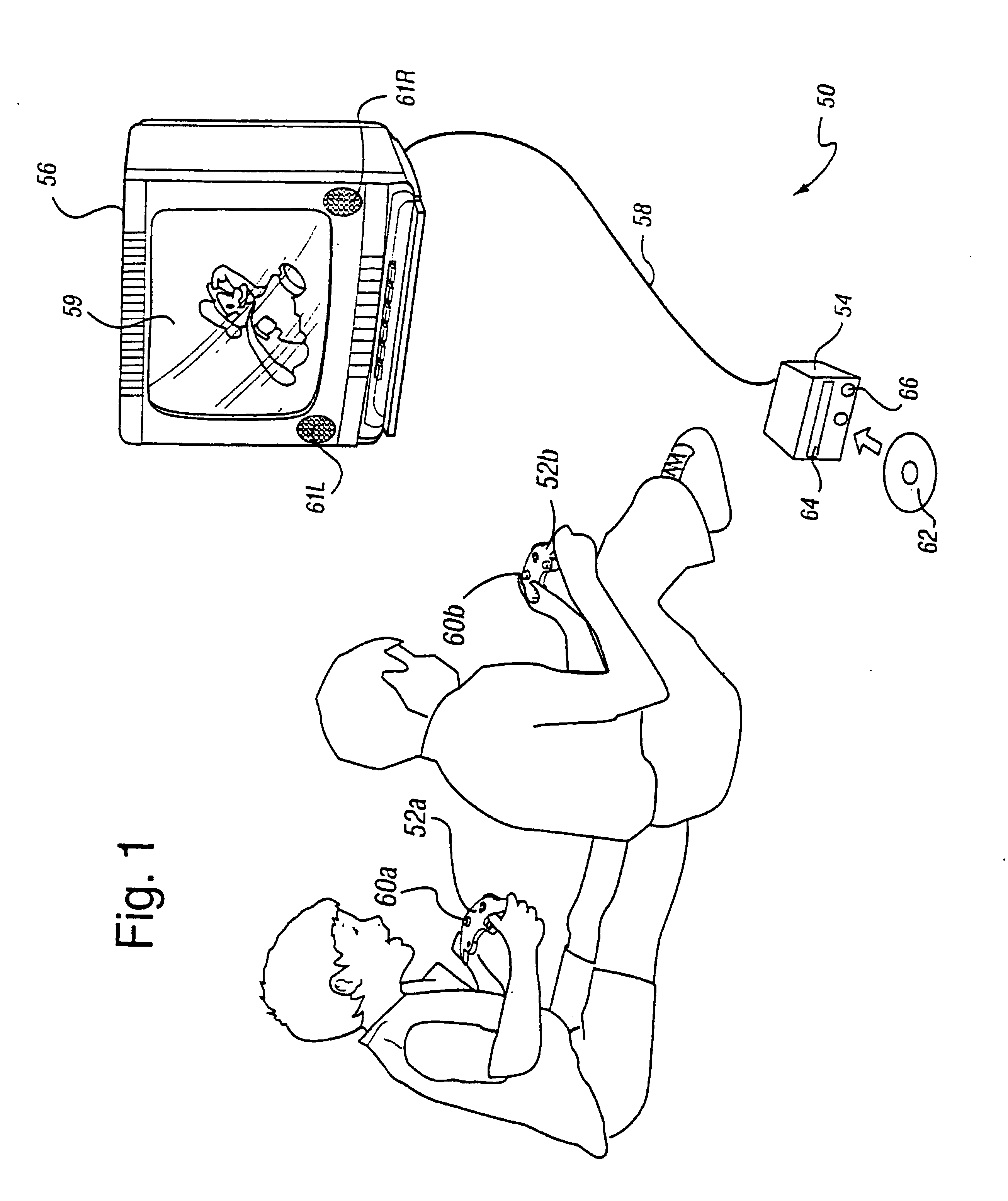

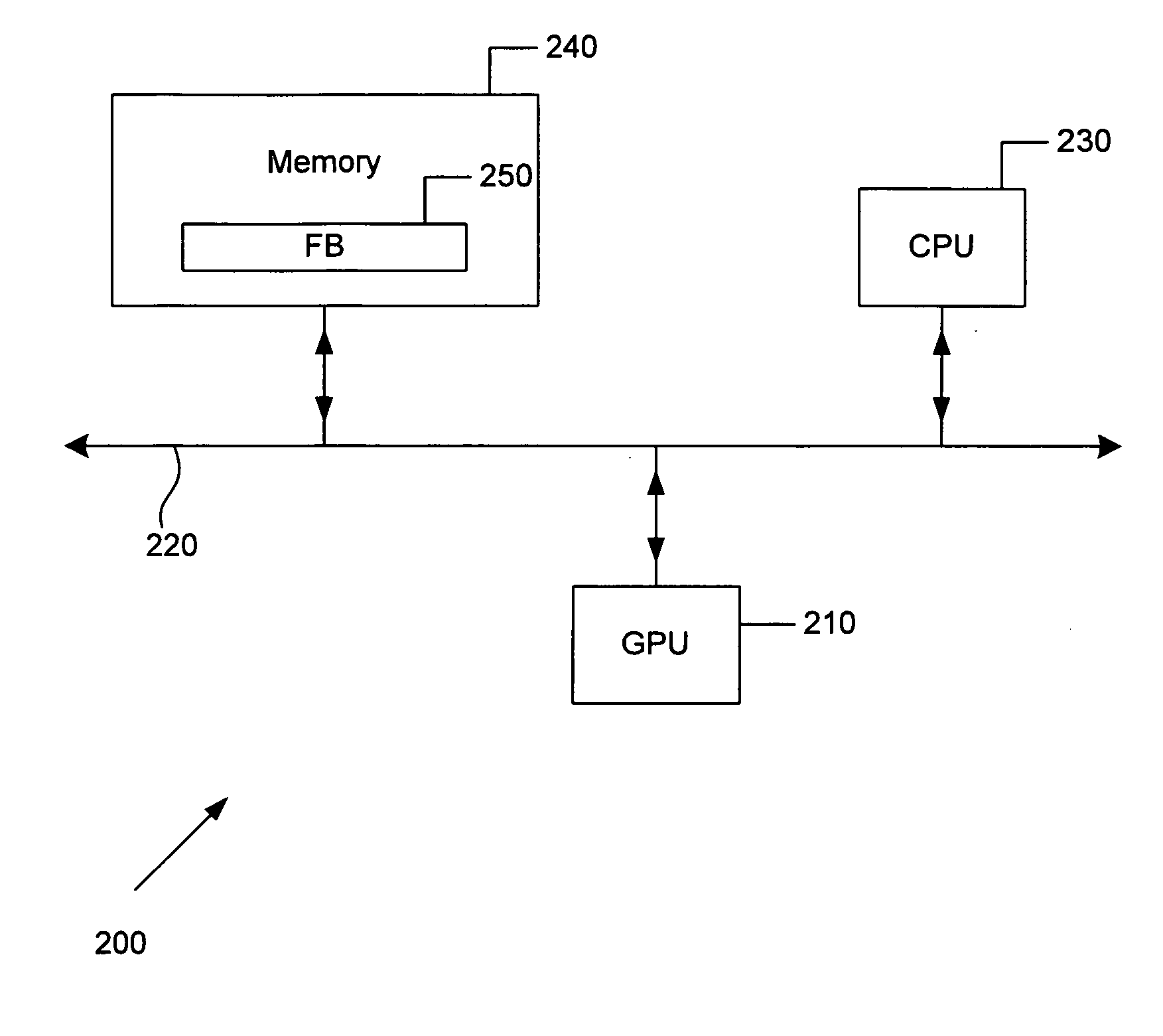

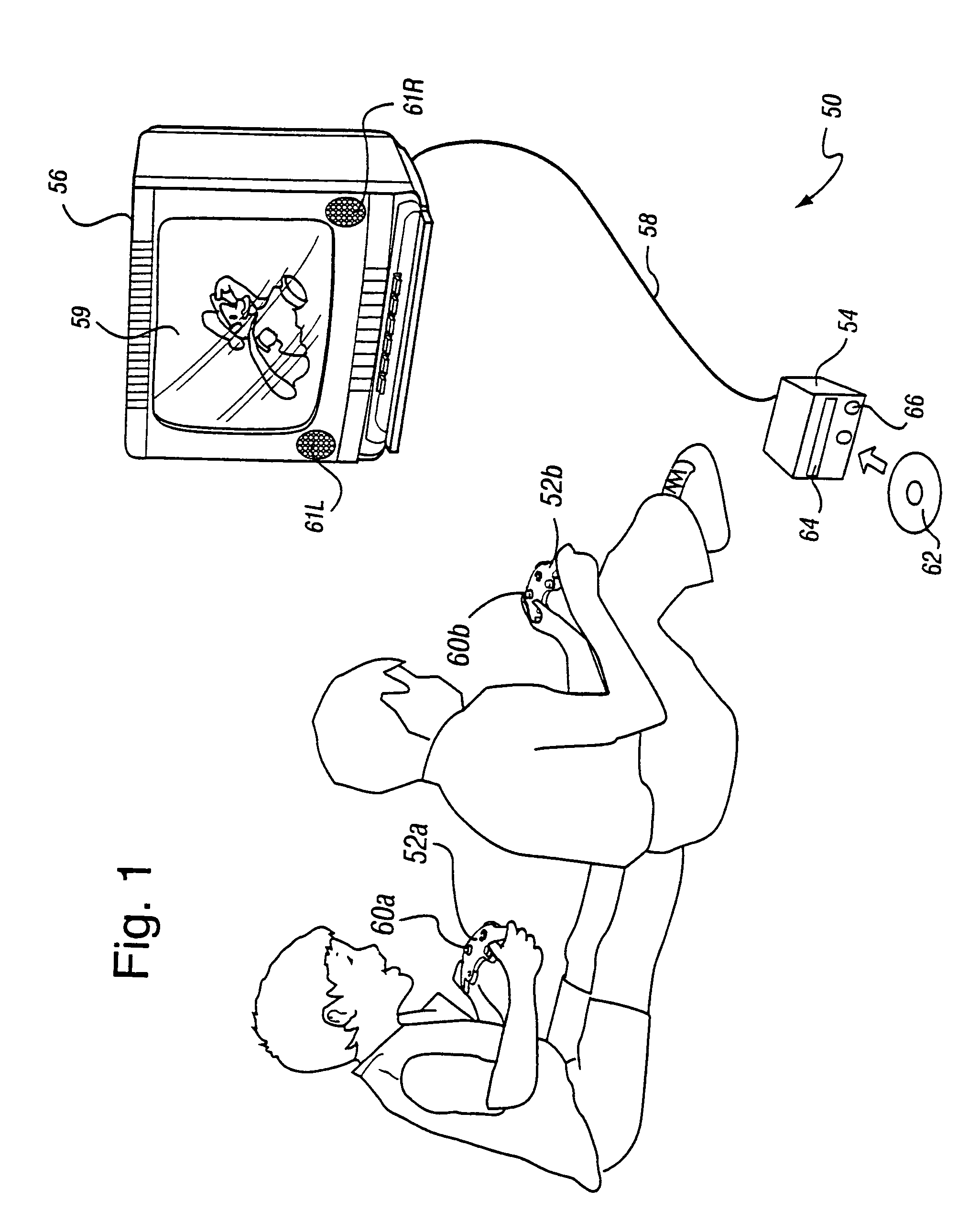

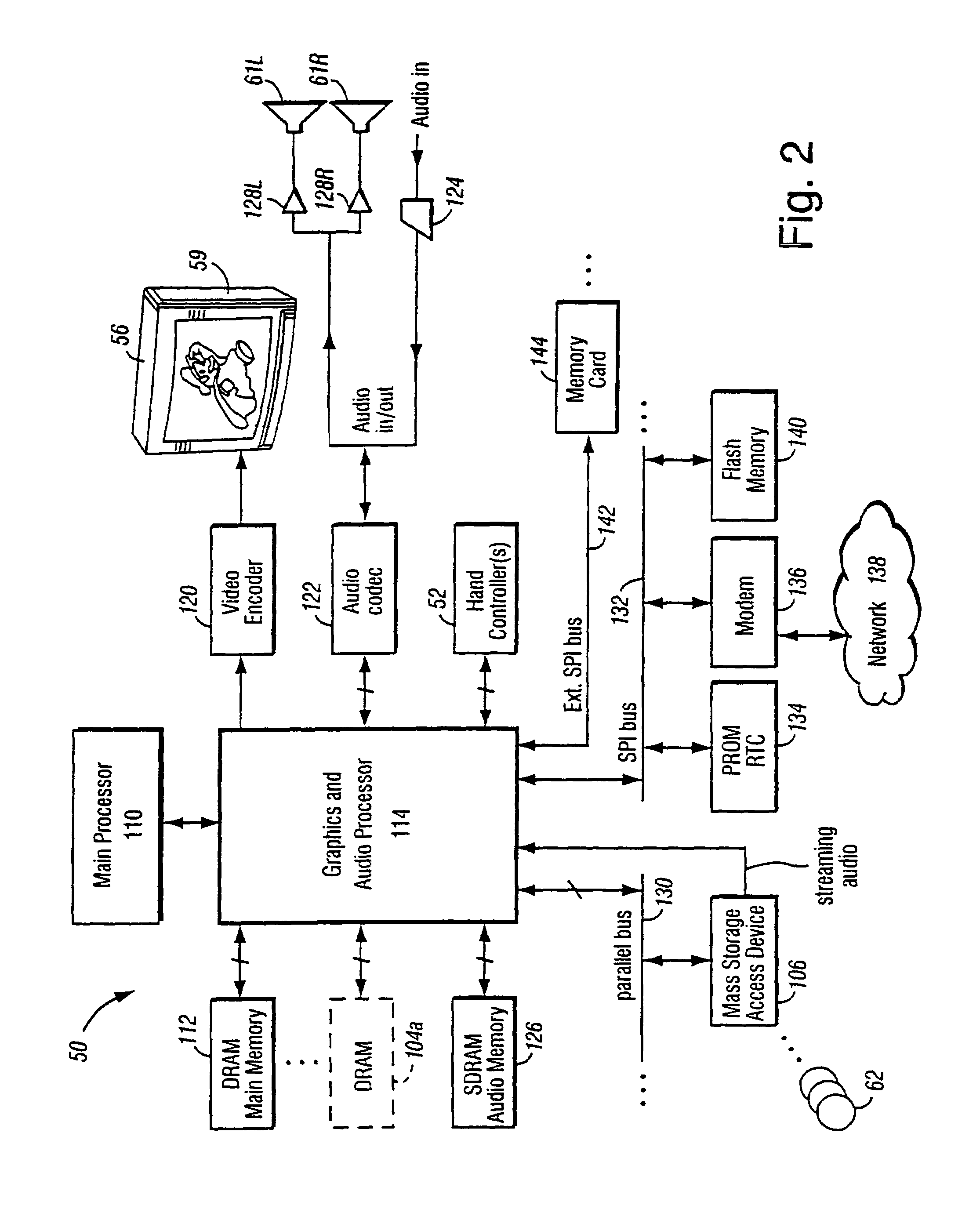

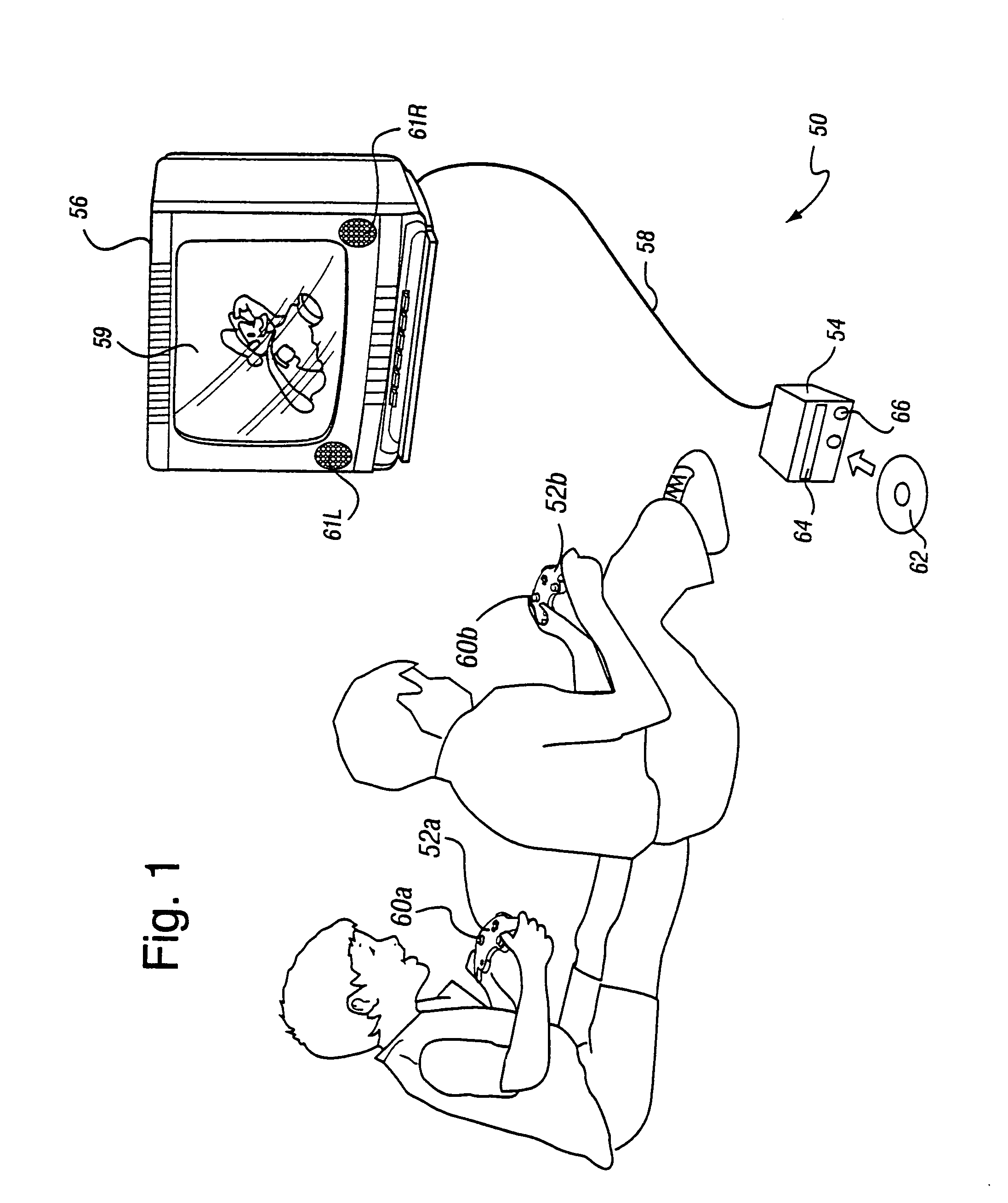

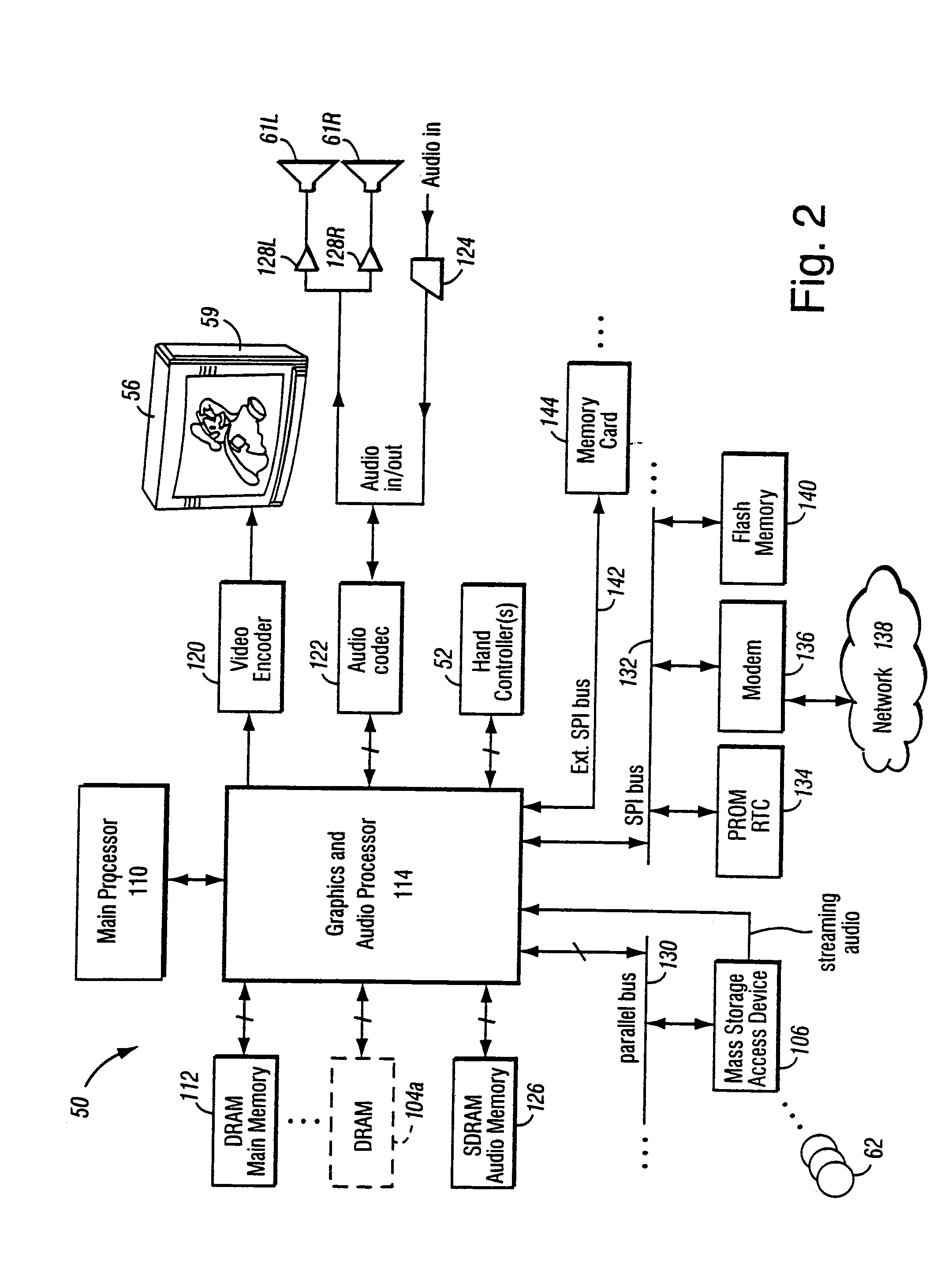

Graphics system with copy out conversions between embedded frame buffer and main memory

InactiveUS7184059B1Improve system flexibilityEasy to useImage memory managementCathode-ray tube indicatorsGraphic systemGraphics processing unit

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics processor includes an embedded frame buffer for storing frame data prior to sending the frame data to an external location, such as main memory. A copy pipeline is provided which converts the data from one format to another format prior to writing the data to the external location. The conversion may be from one RGB color format to another RGB color format, from one YUV format to another YUV format, from an RGB color format to a YUV color format, or from a YUV color format to an RGB color format. The formatted data is either transferred to a display buffer, for use by the video interface, or to a texture buffer, for use as a texture by the graphics pipeline in a subsequent rendering process.

Owner:NINTENDO CO LTD

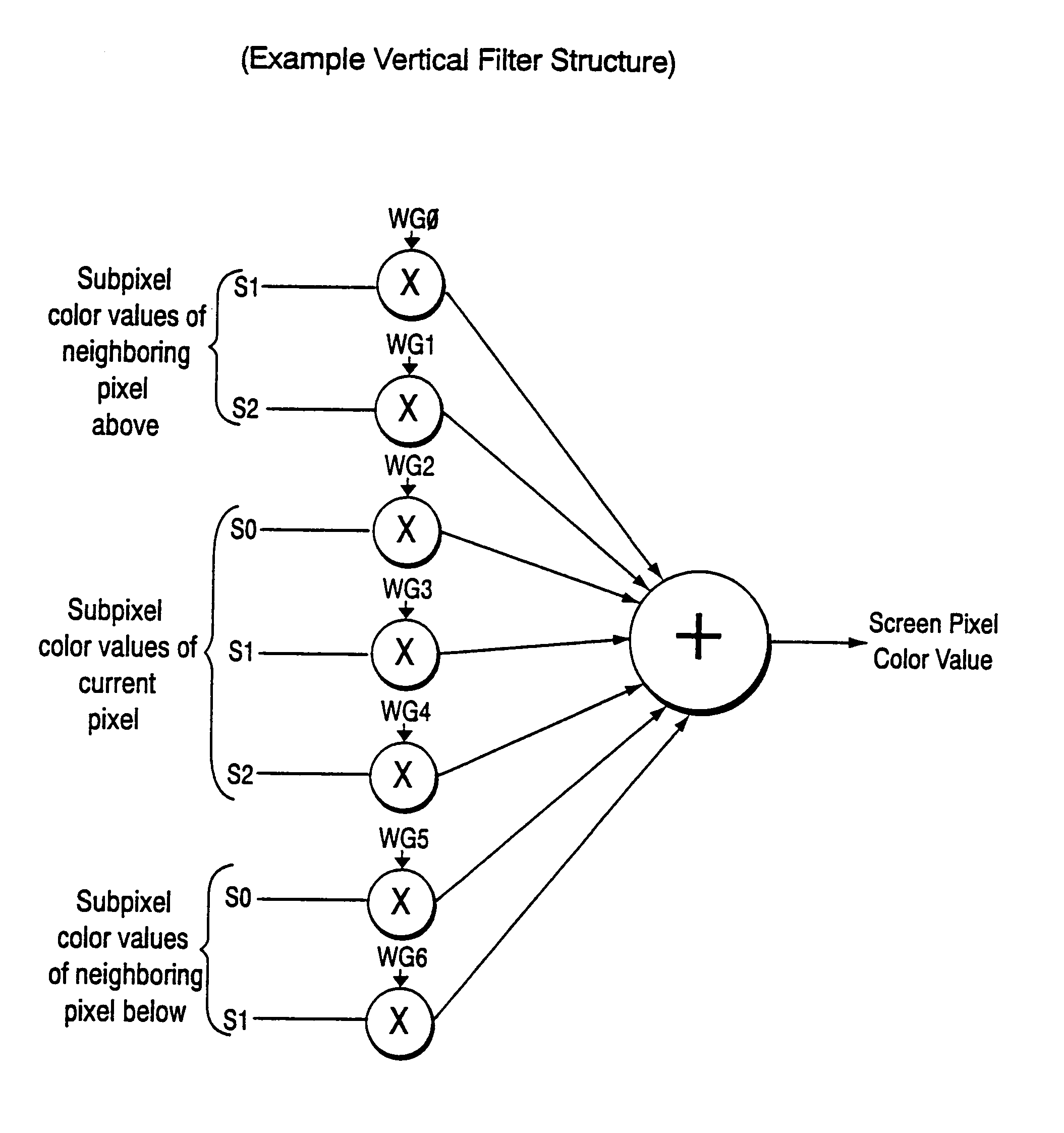

Method and apparatus for anti-aliasing in a graphics system

InactiveUS6999100B1Low costHigh cost-effectiveImage enhancementCathode-ray tube indicatorsInterlaced videoAnti-aliasing

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The system achieves highly efficient full-scene anti-aliasing by implementing a programmable-location super-sampling arrangement and using a selectable-weight vertical-pixel support area blending filter. For a 2×2 pixel group (quad), the locations of three samples within each super-sampled pixel are individually selectable. A twelve-bit multi-sample coverage mask is used to determine which of twelve samples within a pixel quad are enabled based on the portions of each pixel occupied by a primitive fragment and any pre-computed z-buffering. Each super-sampled pixel is filtered during a copy-out operation from a local memory to an external frame buffer using a pixel blending filter arrangement that combines seven samples from three vertically arranged pixels. Three samples are taken from the current pixel, two samples are taken from a pixel immediately above the current pixel and two samples are taken from a pixel immediately below the current pixel. A weighted average is then computed based on the enabled samples to determine the final color for the pixel. The weight coefficients used in the blending filter are also individually programmable. De-flickering of thin one-pixel tall horizontal lines for interlaced video displays is also accomplished by using the pixel blending filter to blend color samples from pixels in alternate scan lines.

Owner:NINTENDO CO LTD

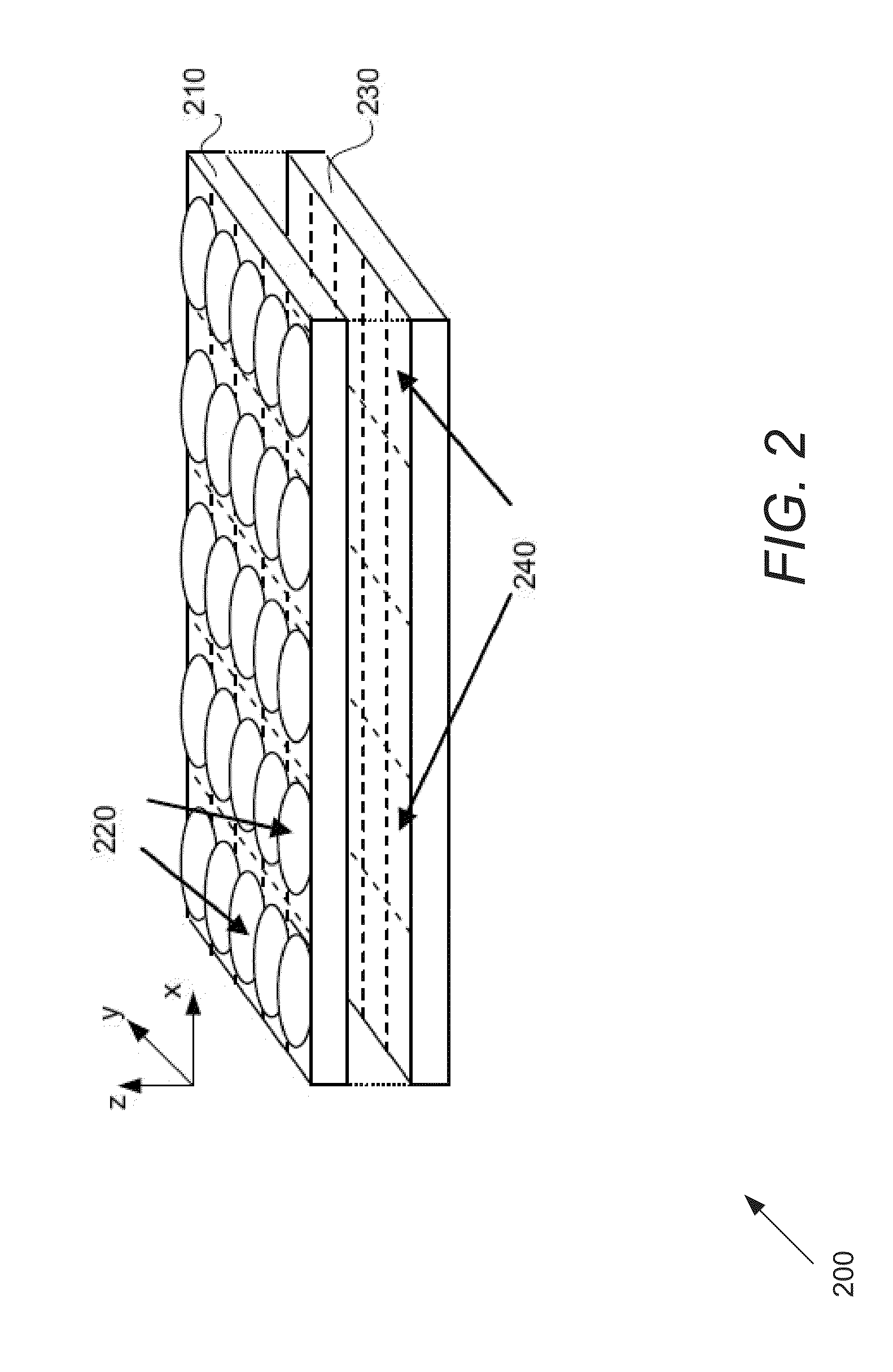

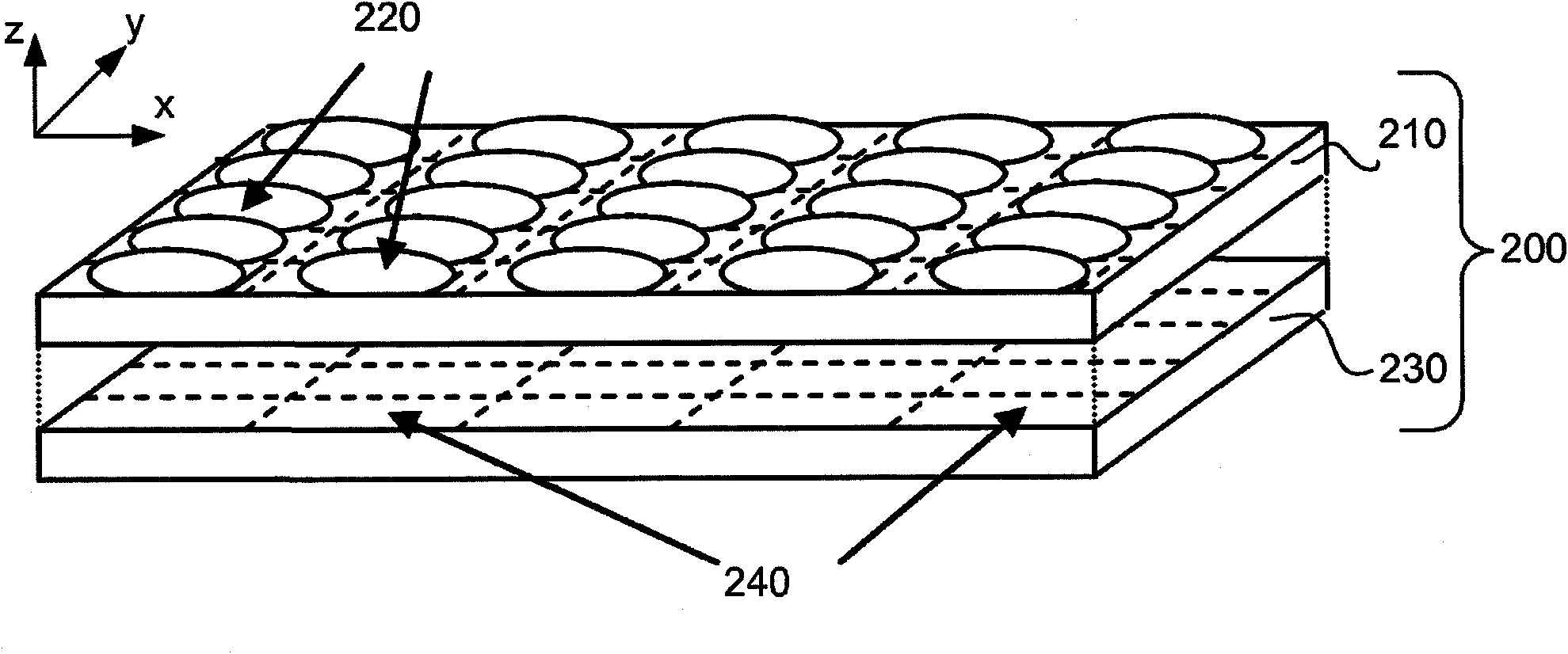

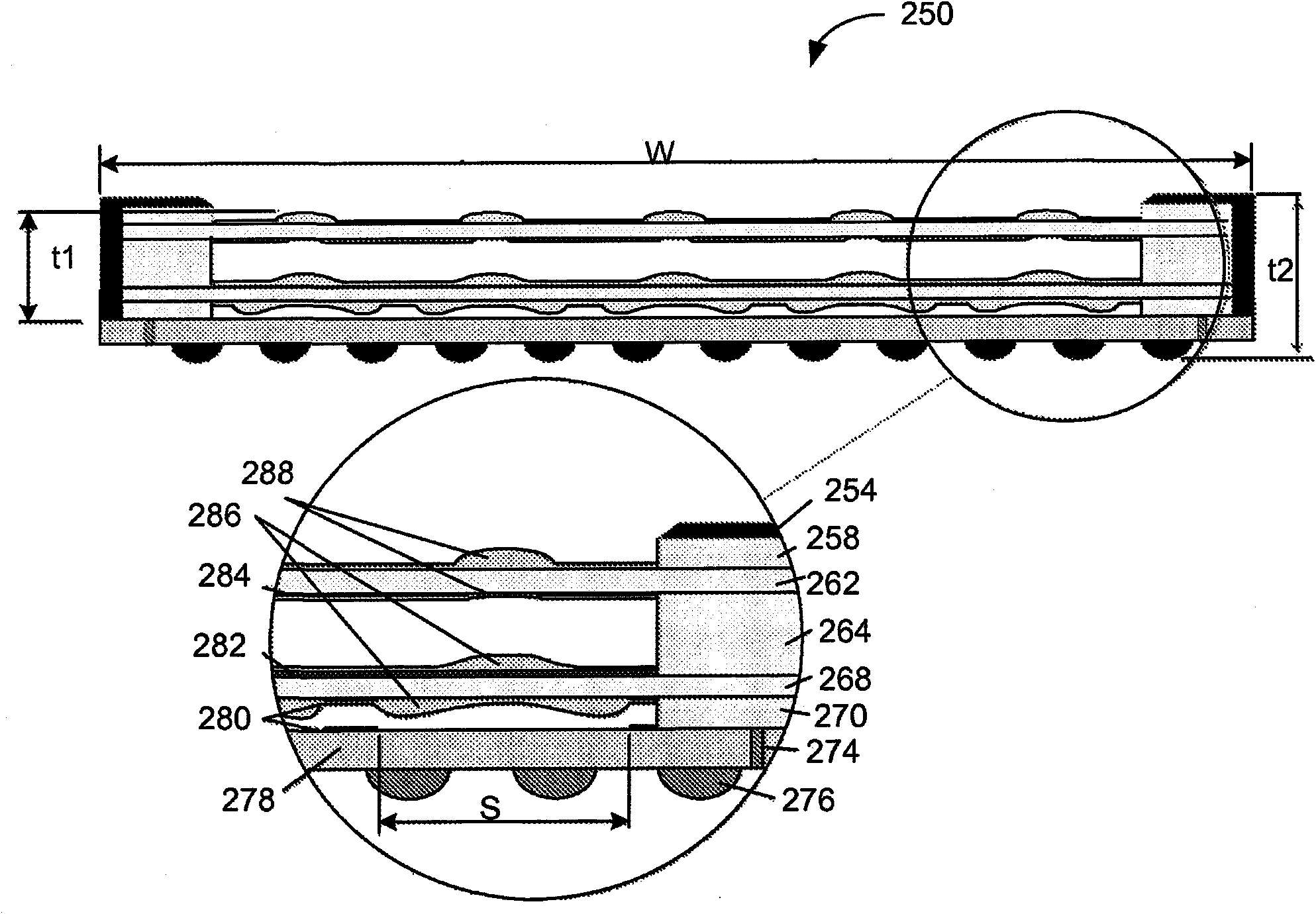

Capturing and processing of images using monolithic camera array with hetergeneous imagers

A camera array, an imaging device and / or a method for capturing image that employ a plurality of imagers fabricated on a substrate is provided. Each imager includes a plurality of pixels. The plurality of imagers include a first imager having a first imaging characteristics and a second imager having a second imaging characteristics. The images generated by the plurality of imagers are processed to obtain an enhanced image compared to images captured by the imagers. Each imager may be associated with an optical element fabricated using a wafer level optics (WLO) technology.

Owner:FOTONATION LTD

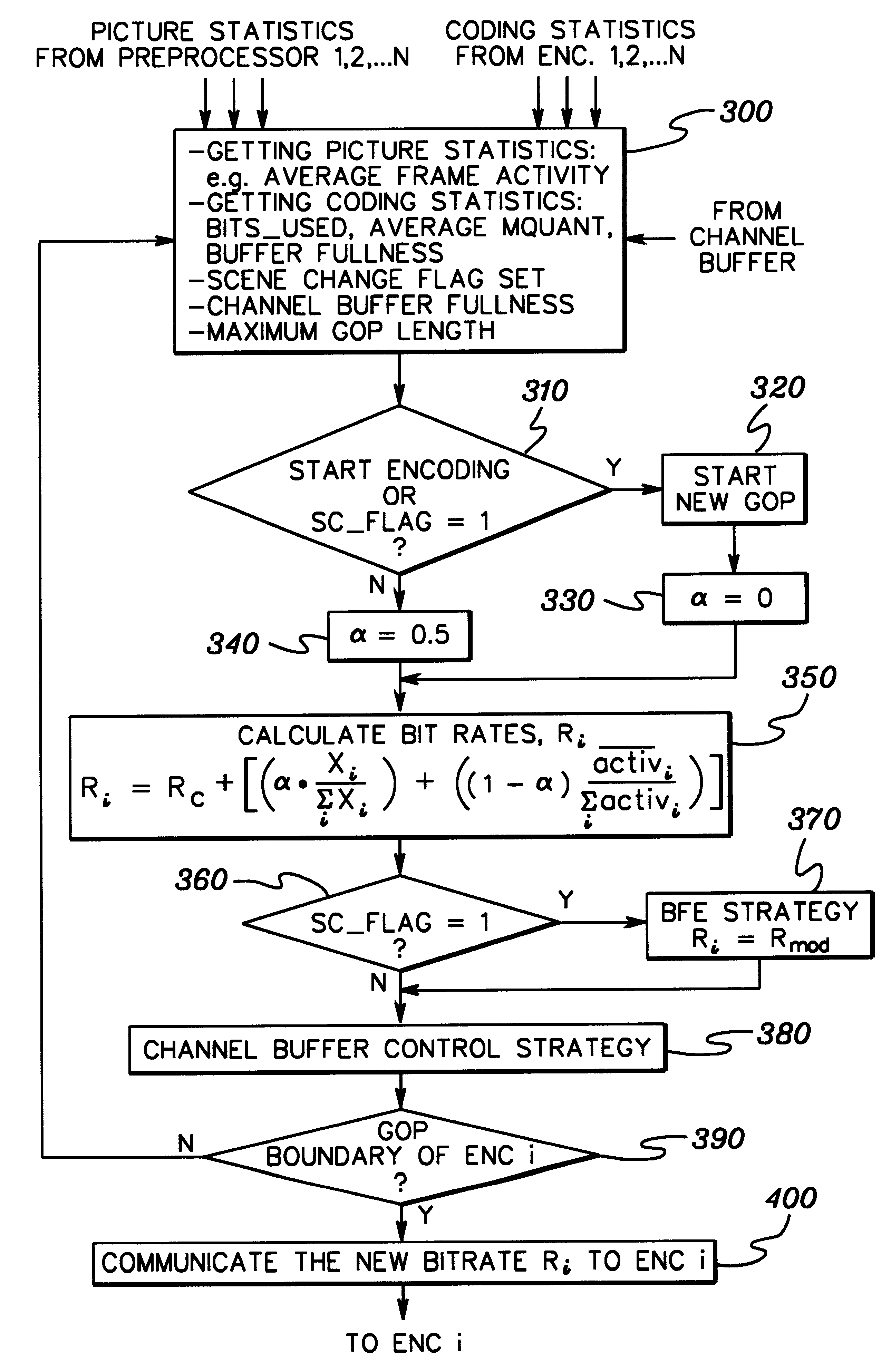

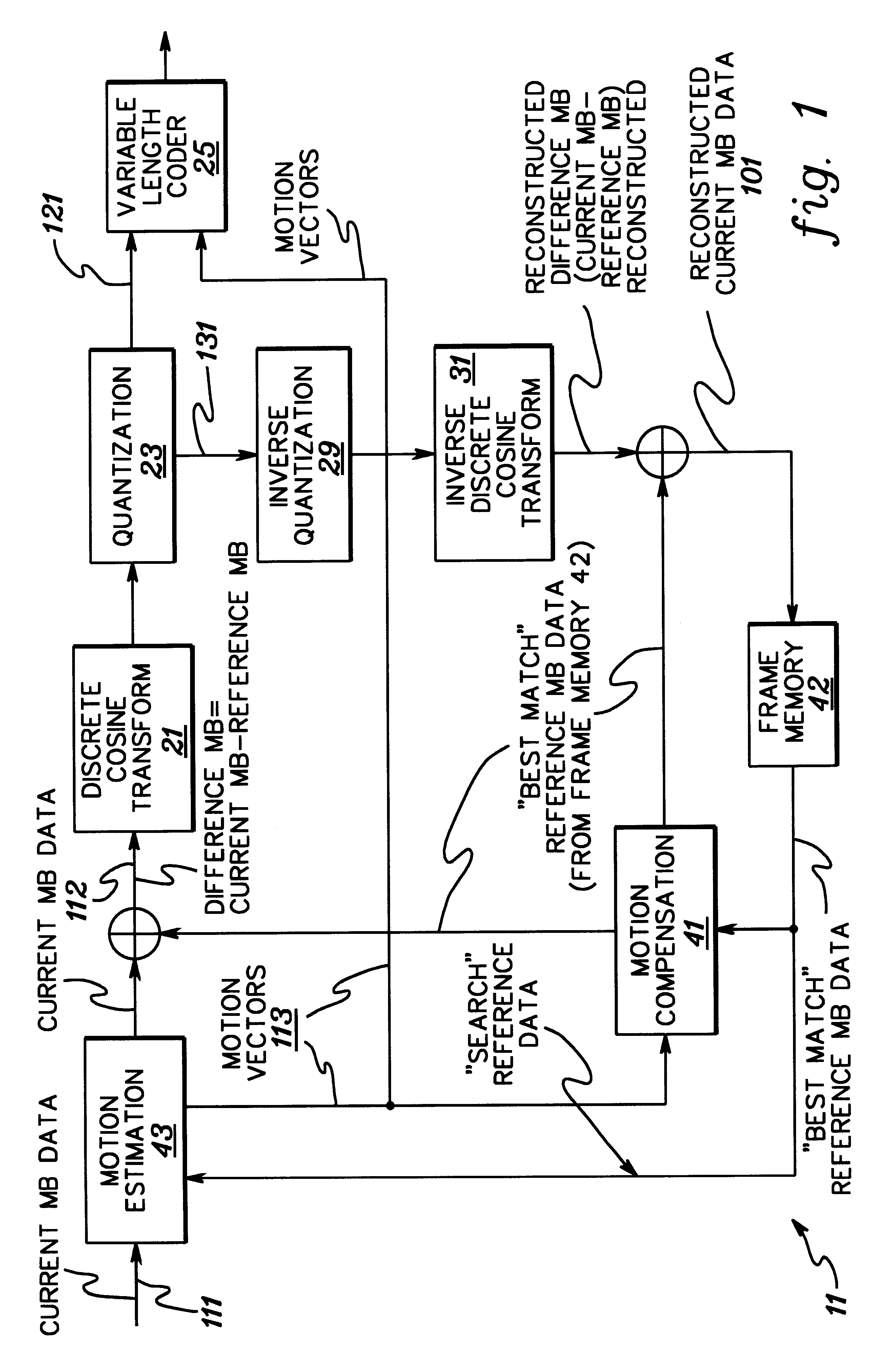

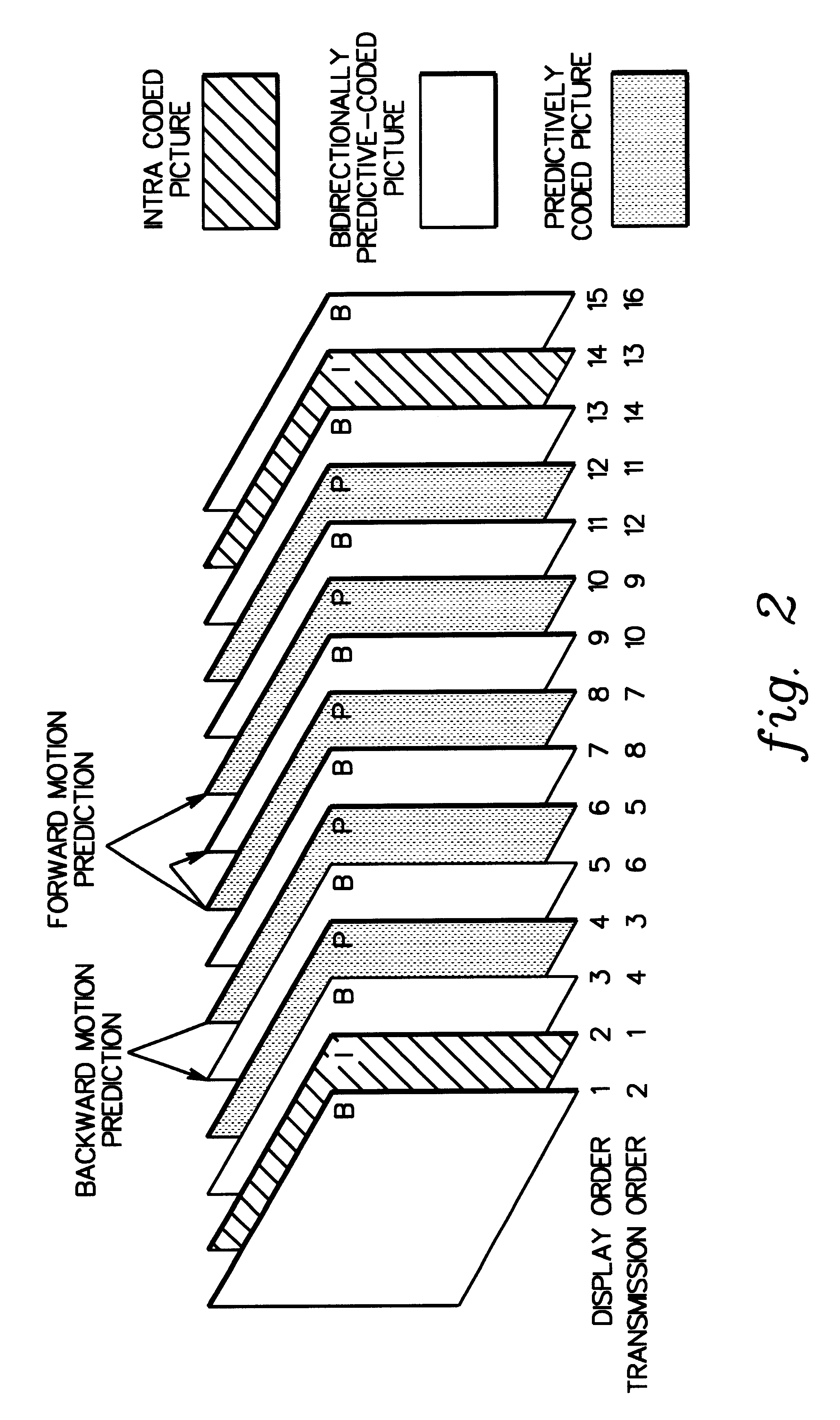

Adaptively encoding multiple streams of video data in parallel for multiplexing onto a constant bit rate channel

InactiveUS6859496B1Configuration highRapid responsePulse modulation television signal transmissionPicture reproducers using cathode ray tubesMultiplexingFrame based

A control strategy is provided for dynamically encoding multiple streams of video data in parallel for multiplexing onto a constant bit rate channel. The control strategy allows individual encode bit rates to be dynamically adjusted for each video data stream based in part on relative complexity of the multiple streams of video data, as well as fullness of compressed video data buffers and a channel buffer coupled between the encoders and the constant bit rate channel. The control strategy includes analyzing the multiple streams of video to determine relative complexity thereof, encoding the multiple streams of video frames in parallel, and dynamically adapting encoding of at least one stream of the video frames based on the relative complexity of the video frames. The bit rate for each stream of video frames is only changed at GOP boundaries, or if a scene change occurs. The calculated bit rate is preferably further modified based upon buffer fullness.

Owner:IBM CORP

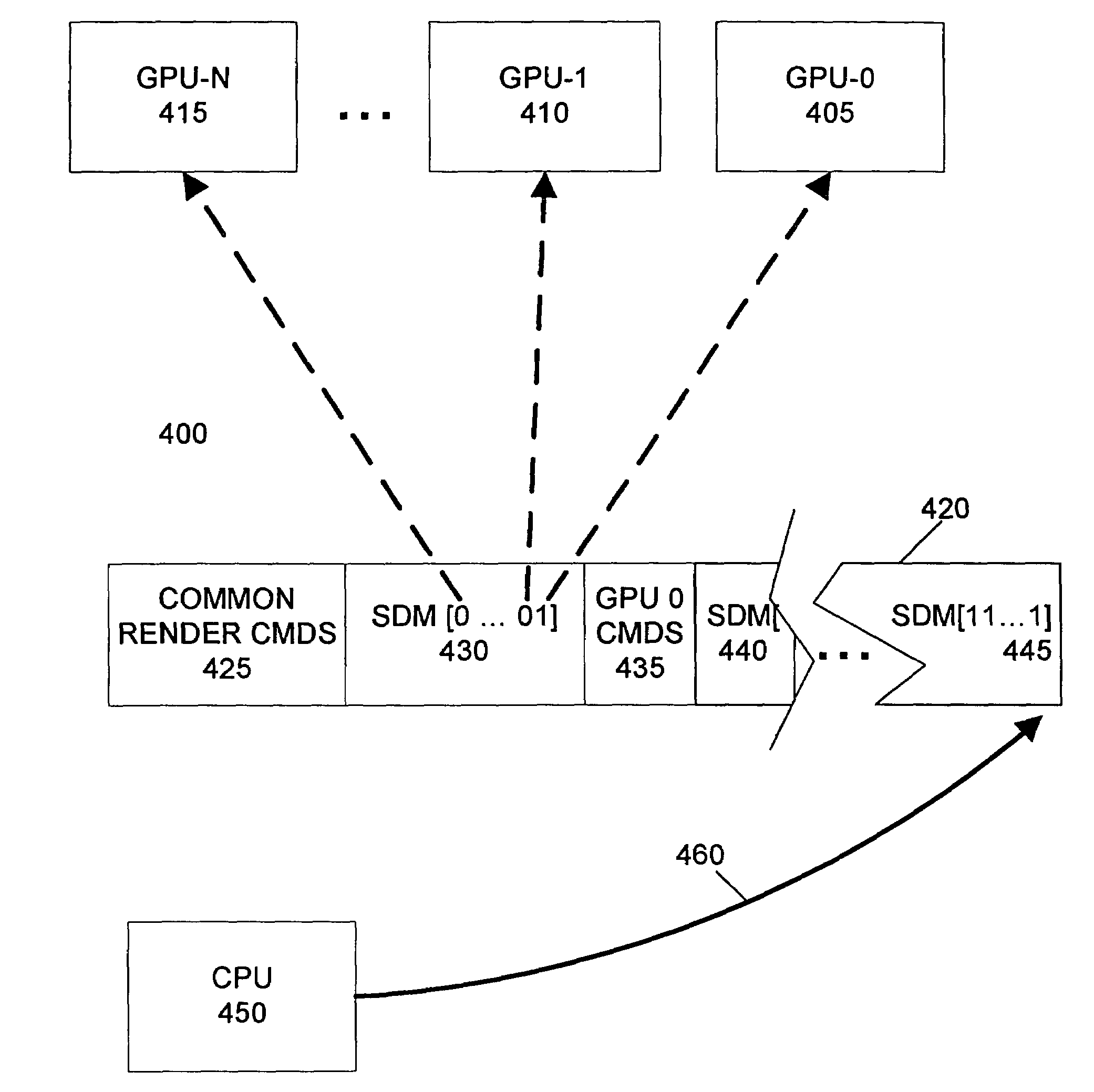

Programming multiple chips from a command buffer

ActiveUS7015915B1Keep in syncSingle instruction multiple data multiprocessorsProcessor architectures/configurationGraphicsCoprocessor

A CPU selectively programs one or more graphics devices by writing a control command to the command buffer that designates a subset of graphics devices to execute subsequent commands. Graphics devices not designated by the control command will ignore the subsequent commands until re-enabled by the CPU. The non-designated graphics devices will continue to read from the command buffer to maintain synchronization. Subsequent control commands can designate different subsets of graphics devices to execute further subsequent commands. Graphics devices include graphics processing units and graphics coprocessors. A unique identifier is associated with each of the graphics devices. The control command designates a subset of graphics devices according to their respective unique identifiers. The control command includes a number of bits. Each bit is associated with one of the unique identifiers and designates the inclusion of one of the graphics devices in the first subset of graphics devices.

Owner:NVIDIA CORP

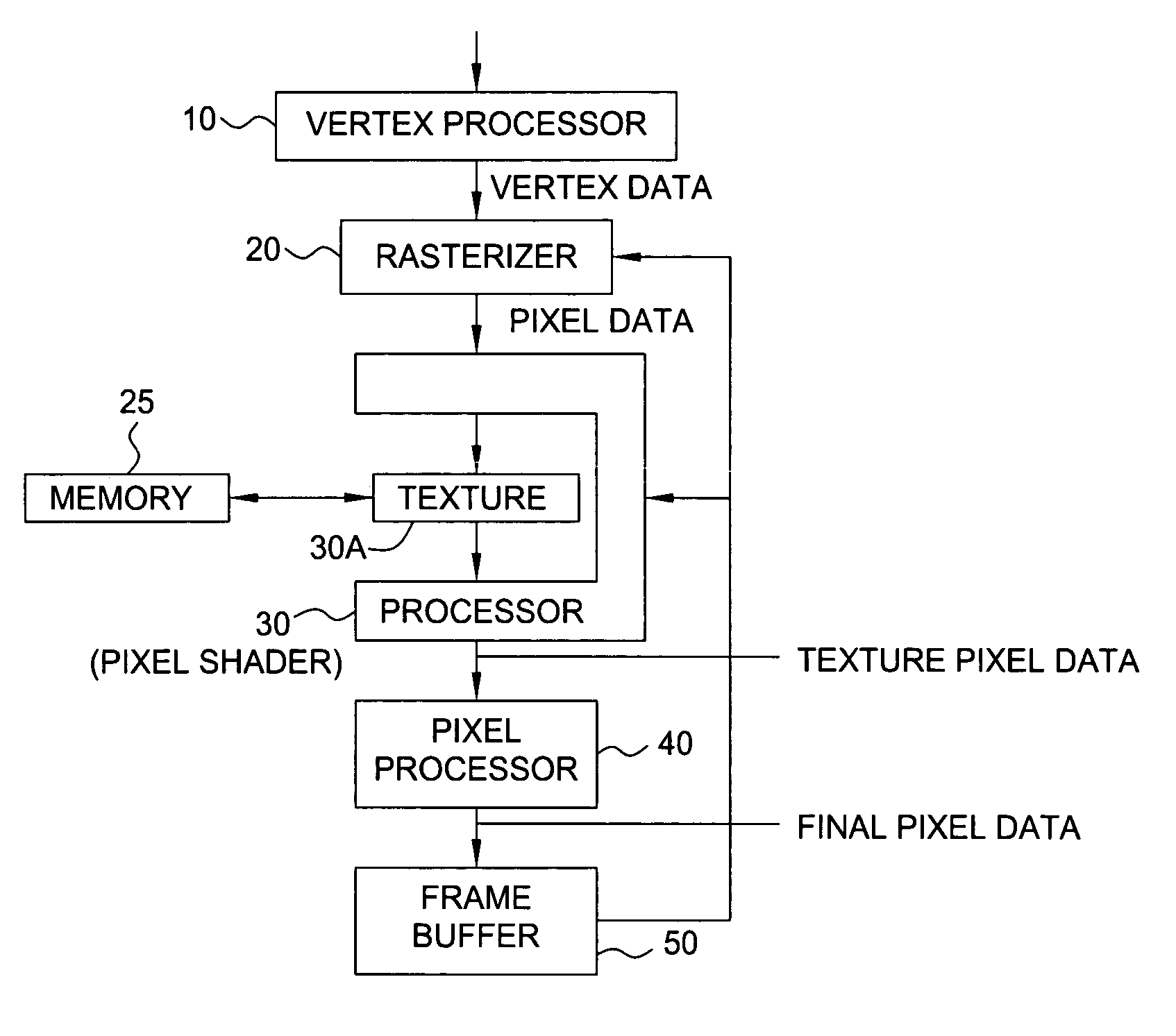

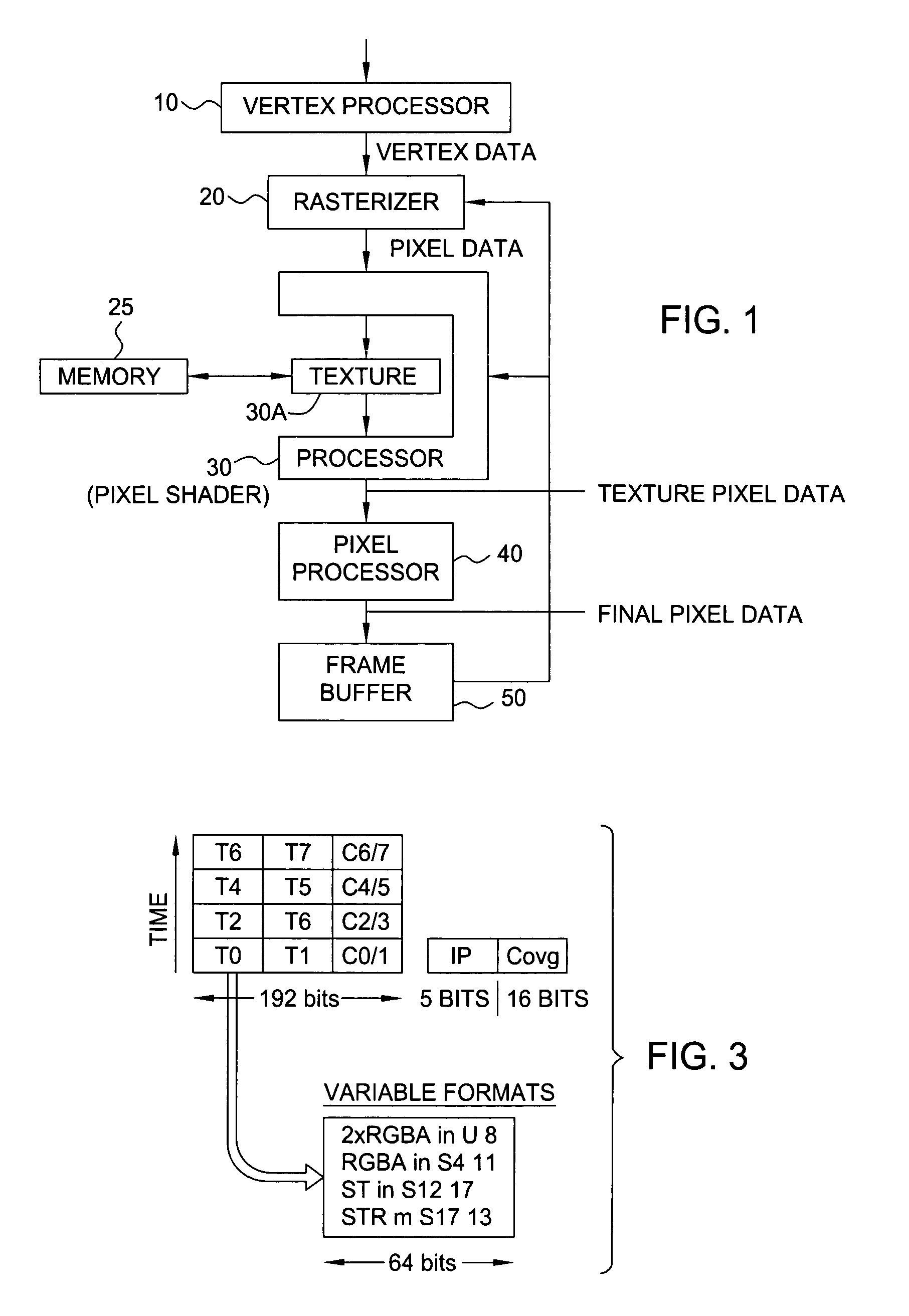

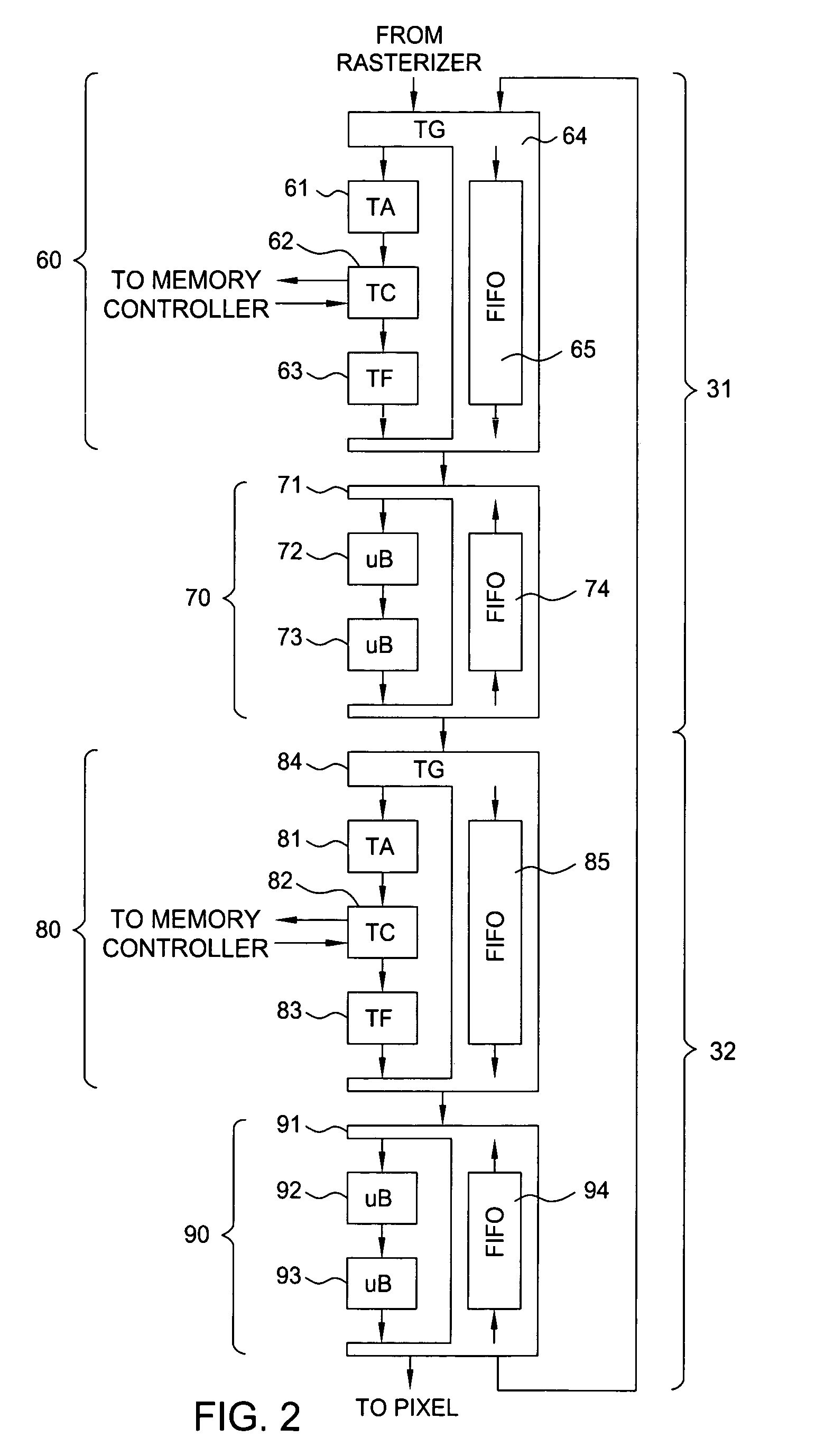

Method and system for scalable, dataflow-based, programmable processing of graphics data

ActiveUS6980209B1Improve system performanceLess system performanceCathode-ray tube indicatorsProcessor architectures/configurationArray data structureNetwork packet

A scalable pipelined pixel shader that processes packets of data and preserves the format of each packet at each processing stage. Each packet is an ordered array of data values, at least one of which is an instruction pointer. Each member of the ordered array can be indicative of any type of data. As a packet progresses through the pixel shader during processing, each member of the ordered array can be replaced by a sequence of data values indicative of different types of data (e.g., an address of a texel, a texel, or a partially or fully processed color value). Information required for the pixel shader to process each packet is contained in the packet, and thus the pixel shader is scalable in the sense that it can be implemented in modular fashion to include any number of identical pipelined processing stages and can execute the same program regardless of the number of stages. Preferably, each processing stage is itself scalable, can be implemented to include an arbitrary number of identical pipelined instruction execution stages known as microblenders, and can execute the same program regardless of the number of microblenders. The current value of the instruction pointer (IP) in a packet determines the next instruction to be executed on the data contained in the packet. Any processing unit can change the instruction that will be executed by a subsequent processing unit by modifying the IP (and / or condition codes) of a packet that it asserts to the subsequent processing unit. Other aspects of the invention include graphics processors (each including a pixel shader configured in accordance with the invention), methods and systems for generating packets of data for processing in accordance with the invention, and methods for pipelined processing of packets of data.

Owner:PVC CONTAINER CORP +1