Patents

Literature

2604 results about "Datapath" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A datapath is a collection of functional units such as arithmetic logic units or multipliers, that perform data processing operations, registers, and buses. Along with the control unit it composes the central processing unit (CPU). A larger datapath can be made by joining more than one number of datapaths using multiplexer.

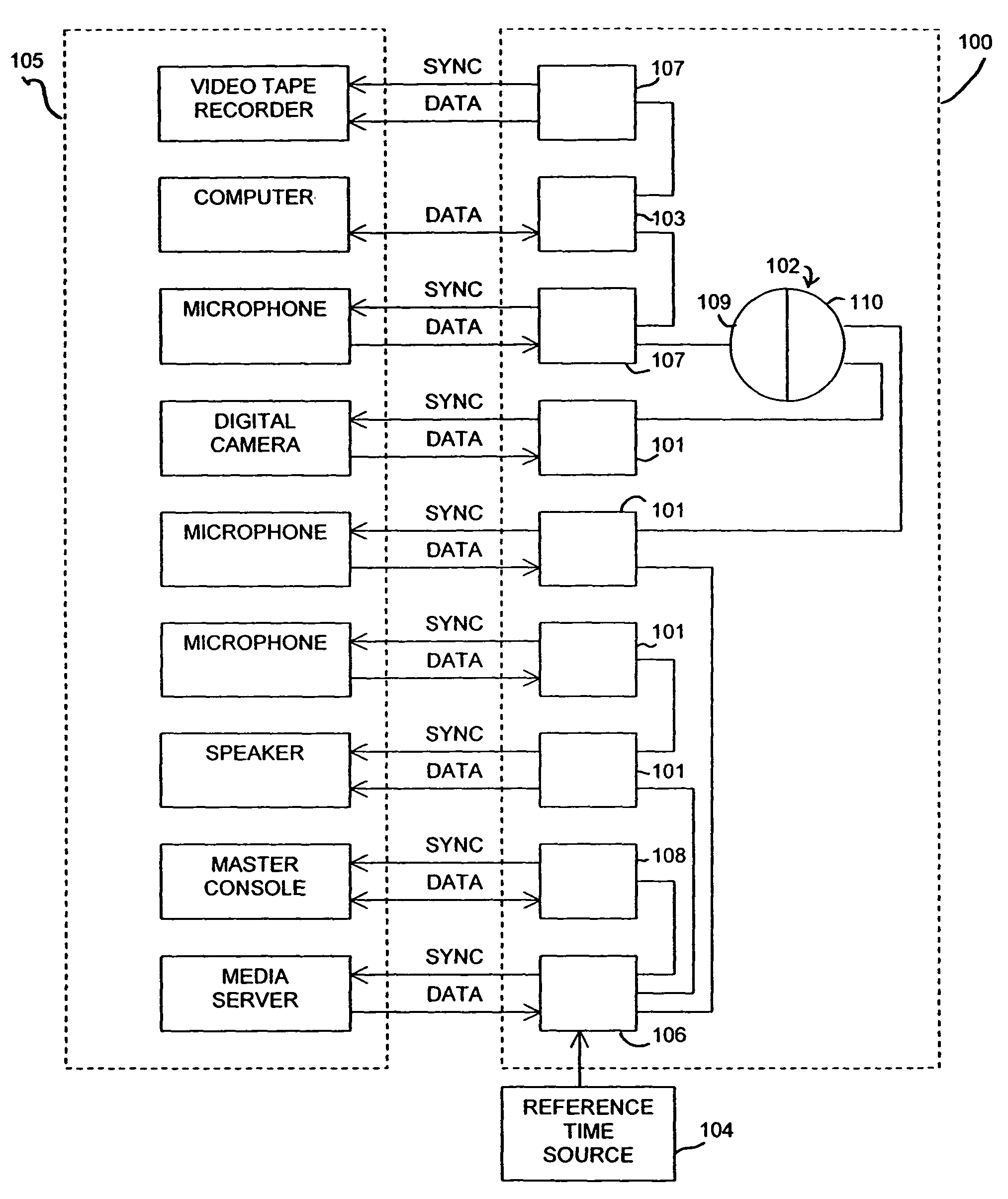

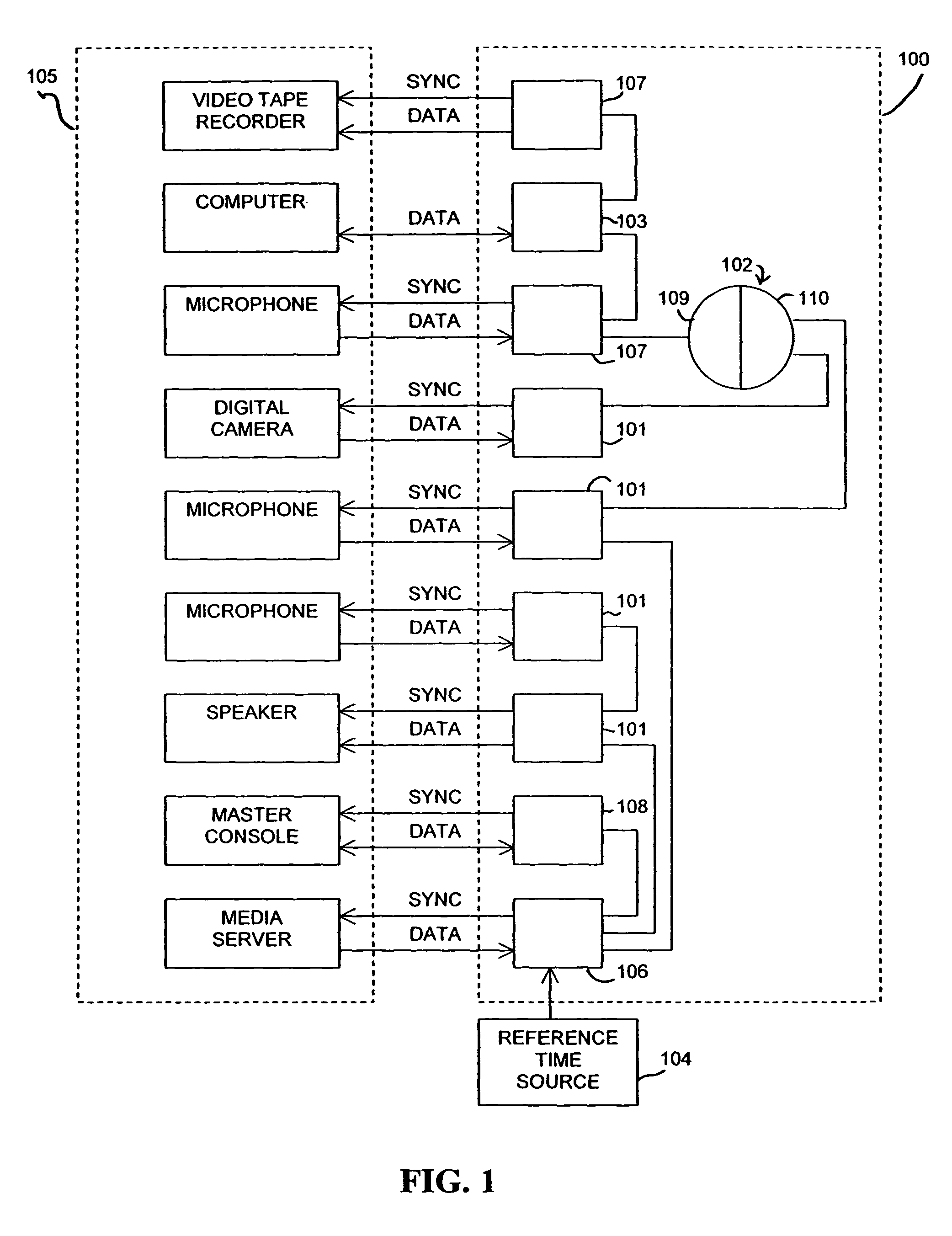

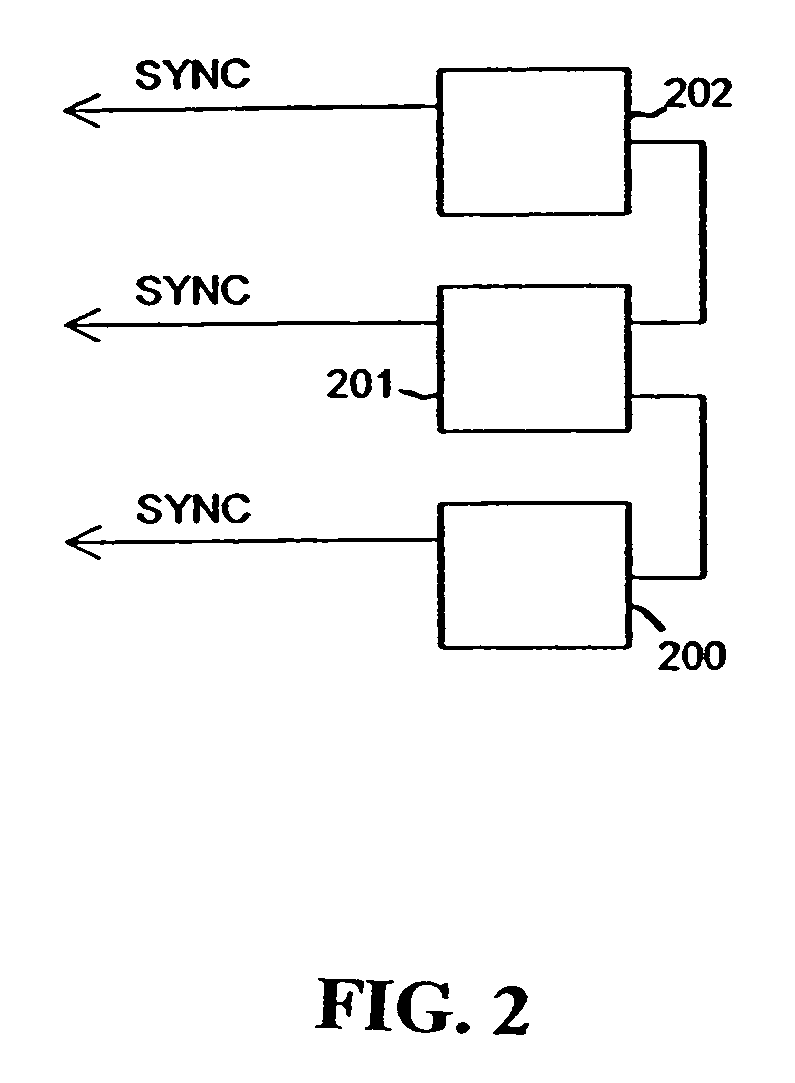

Reference time distribution over a network

InactiveUS8014423B2Time-division multiplexGenerating/distributing signalsTime informationData stream

A reference time distribution system and method use a data transmission network having a plurality of nodes to distribute the House Sync signal. A network-wide time signal is generated using a reference time generator, and the network-wide time signal is then distributed over the network to the plurality of nodes. At each node, the network-wide time signal is converted to a local synchronization signal for use in performing synchronization of the timing of each node. Either network-inherent timing and / or additional time signaling is used to provide the nodes attached to this network with a network-wide notion of time. The time information is converted locally into synchronization signals or time information as required by a respective application. When data is transported over the network, delay compensation is performed to simultaneously output different data streams that have been synchronously input into the network, regardless of the data path.

Owner:POLARIS POWERLED TECH LLC

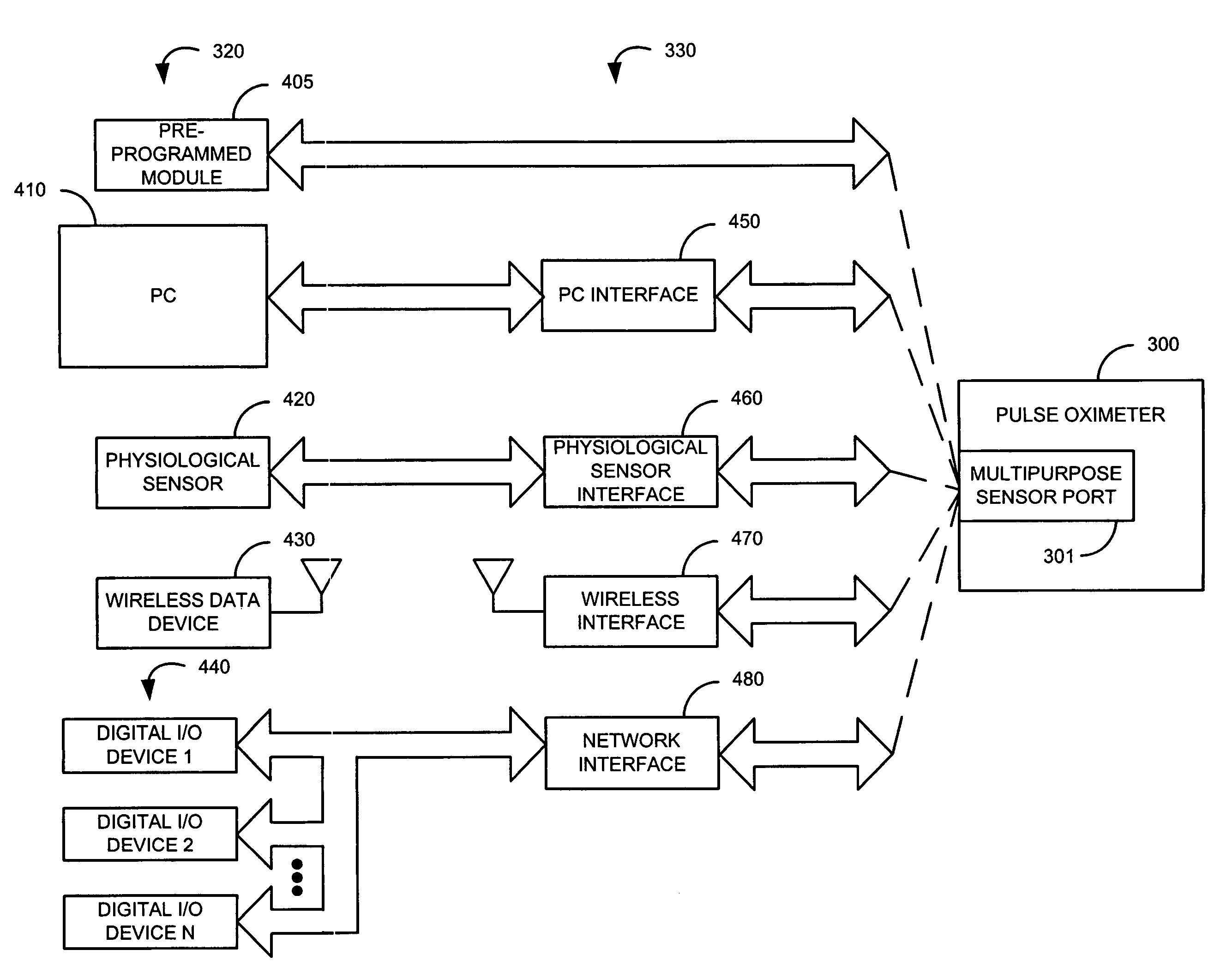

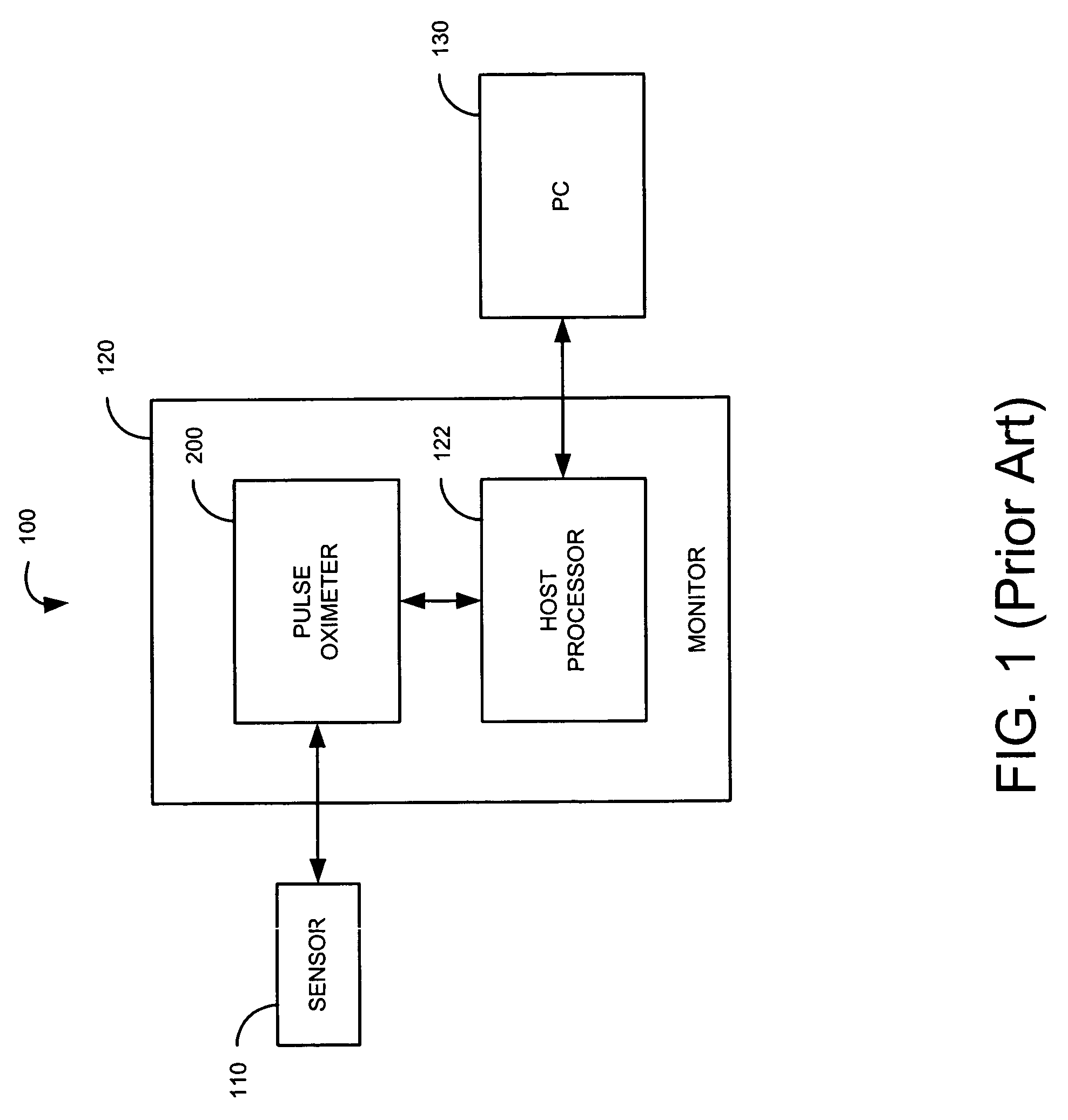

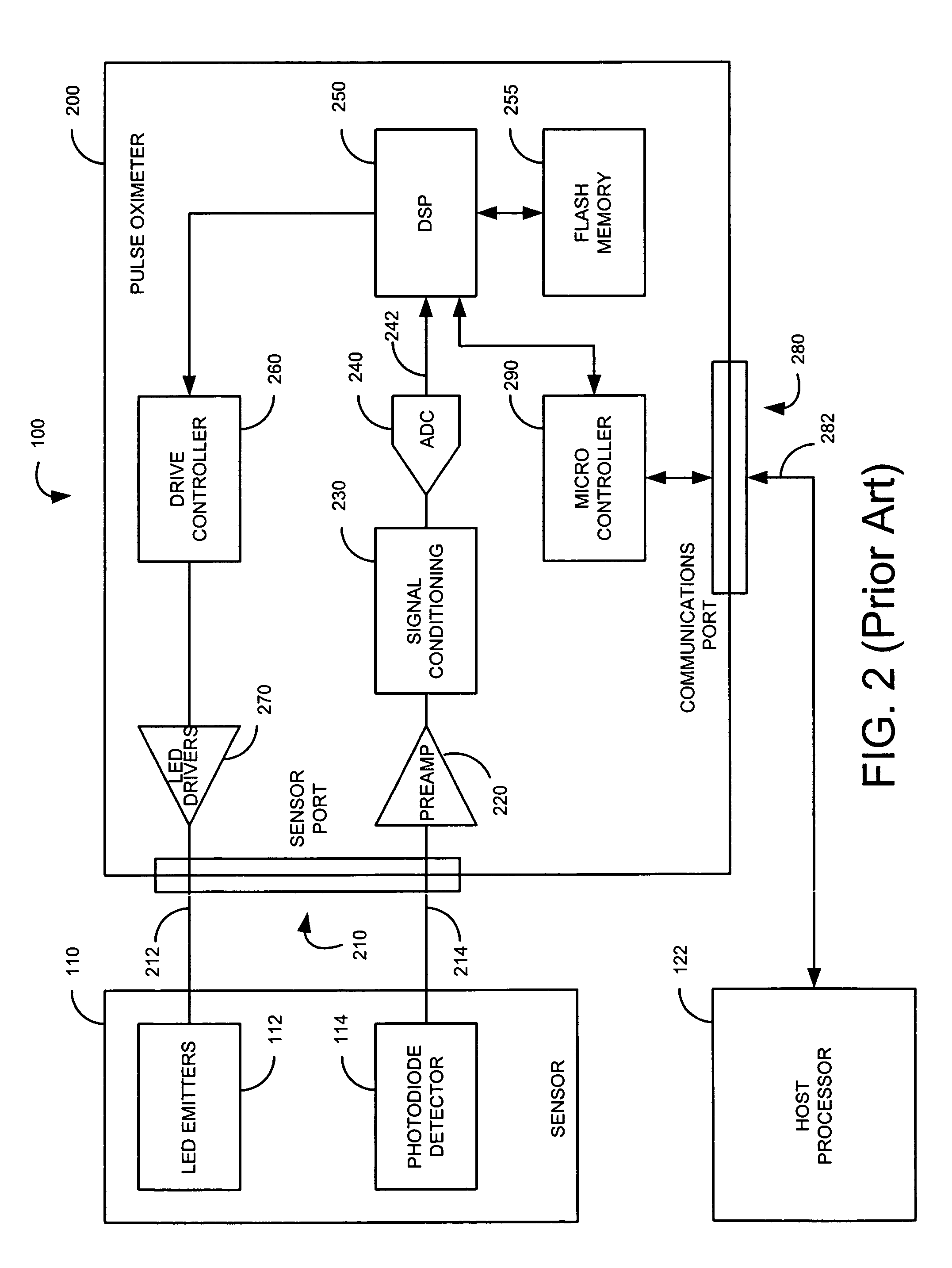

Multipurpose sensor port

A sensor port is adapted to connect to either a sensor or a data source. A reader is configured to identify which of the sensor and the data source is connected to the sensor port. A data path is configured to communicate an analog signal associated with the sensor and digital data associated with the data source to a signal processor according to the identification made by the reader.

Owner:JPMORGAN CHASE BANK NA

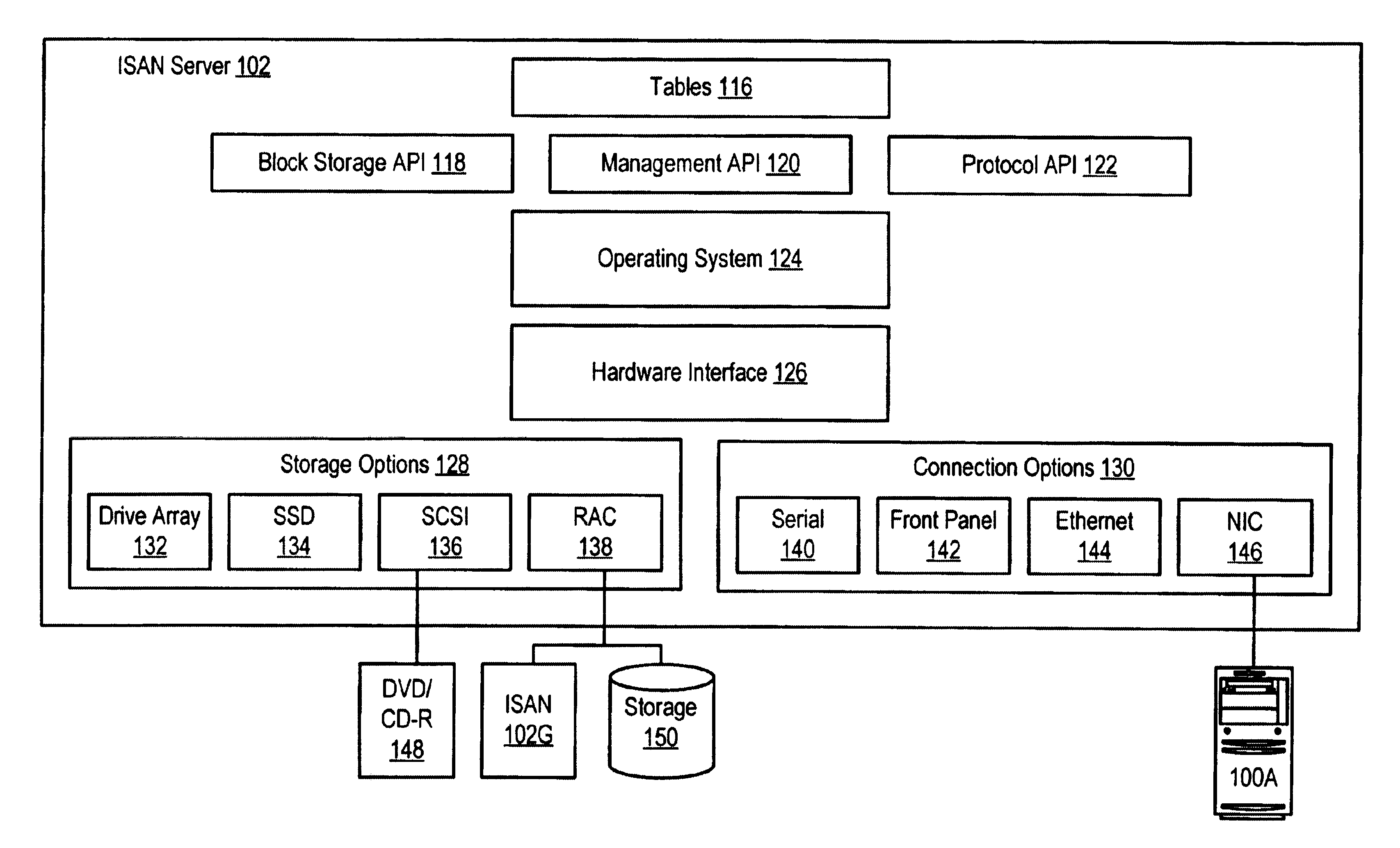

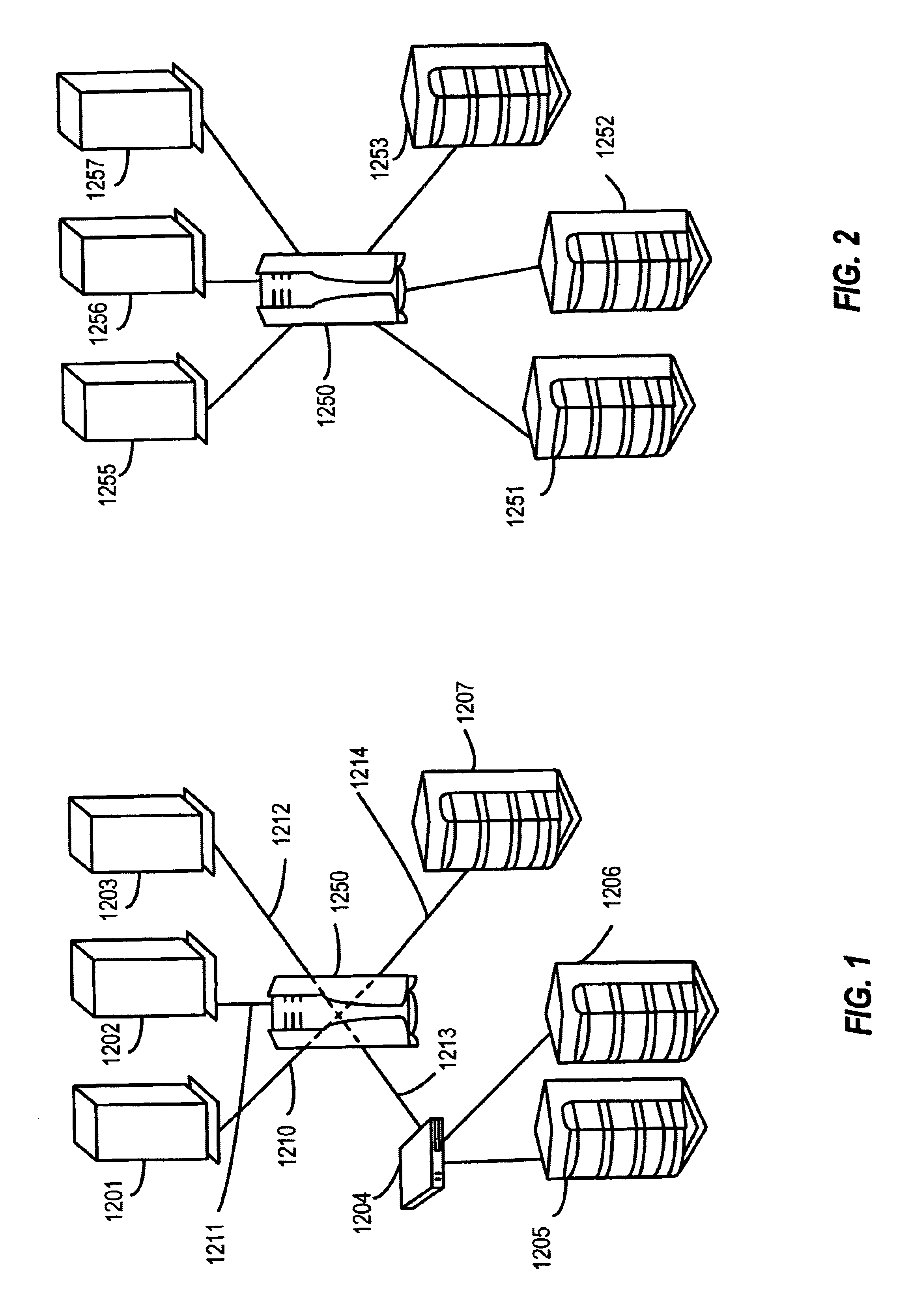

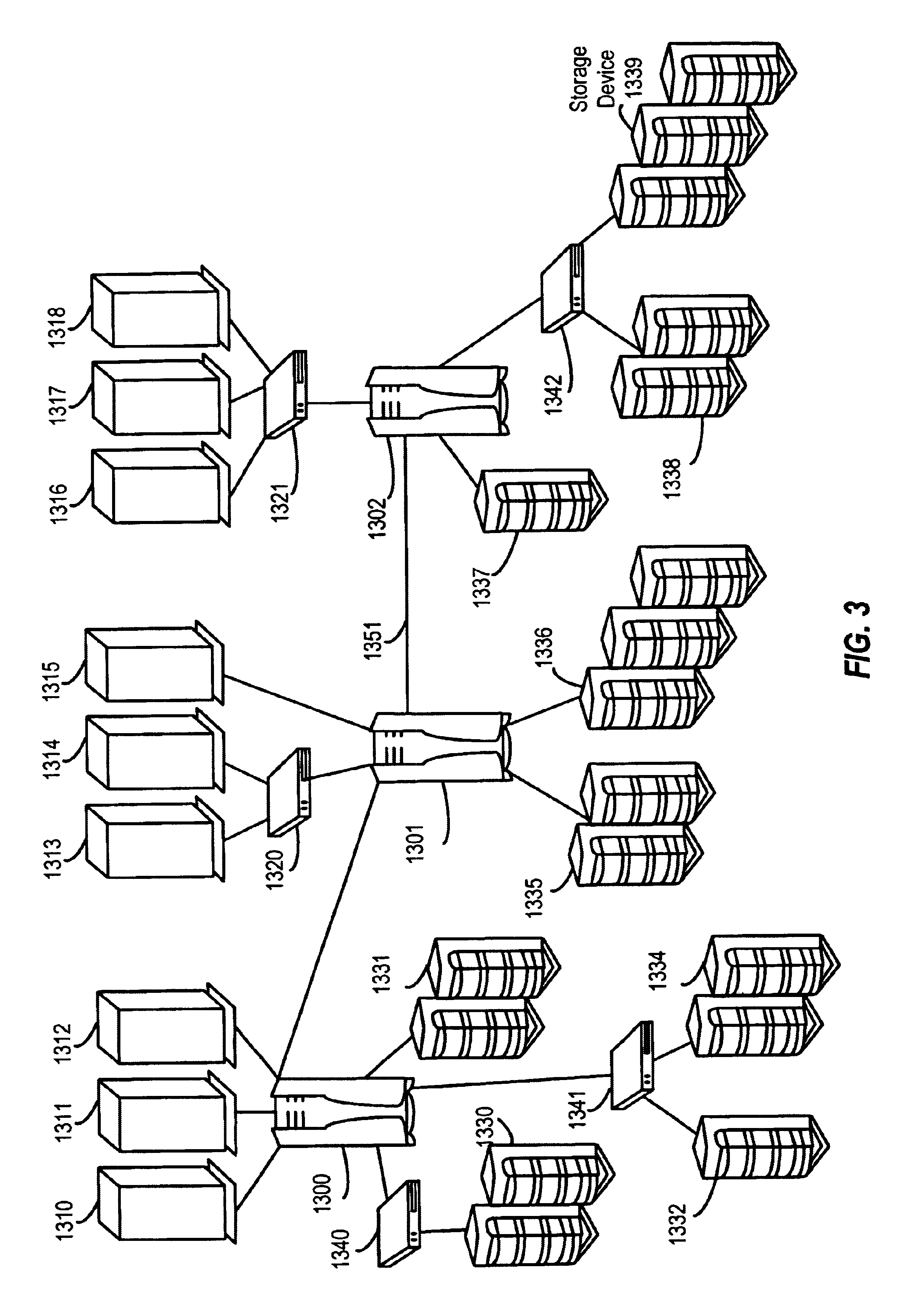

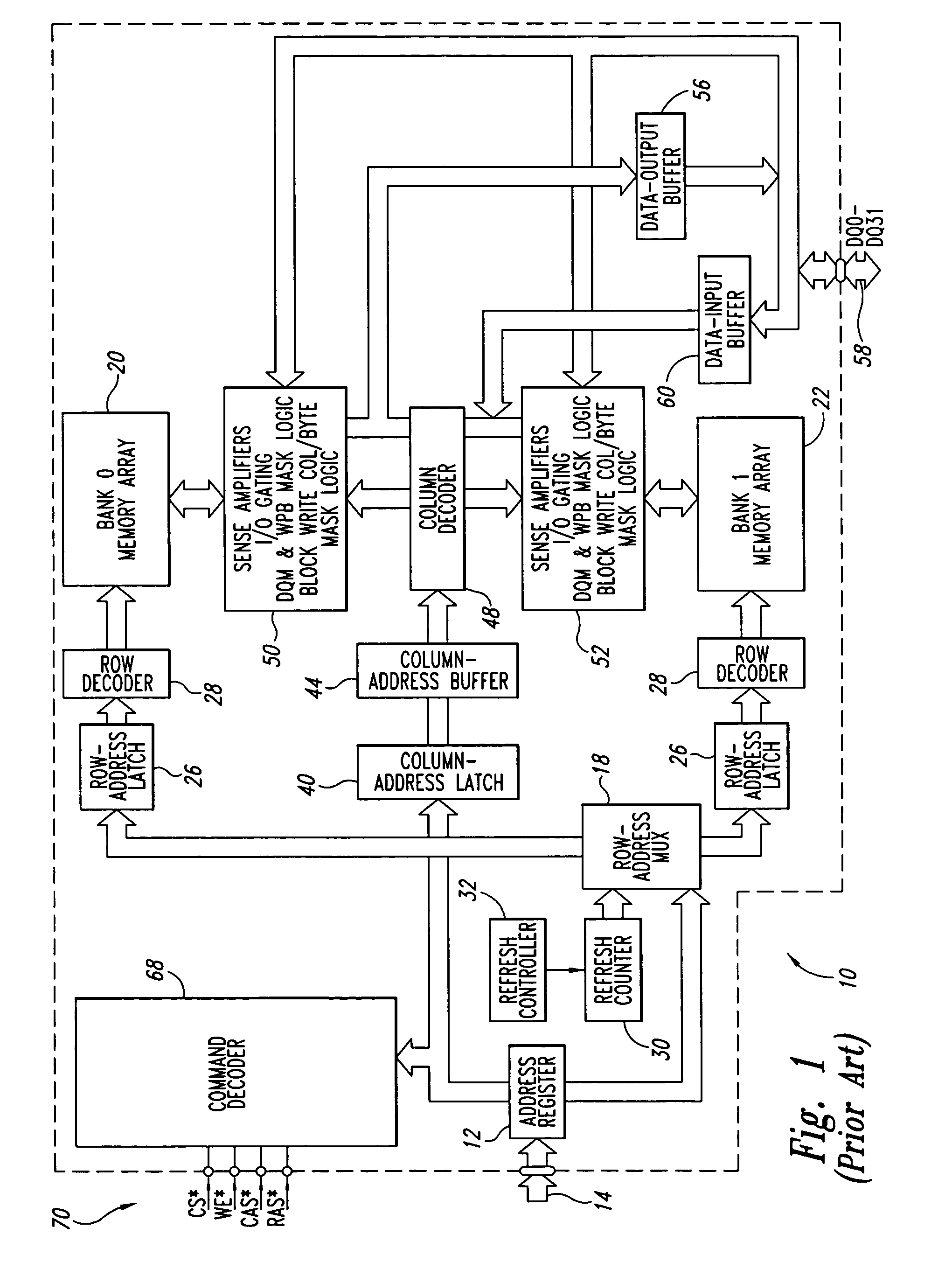

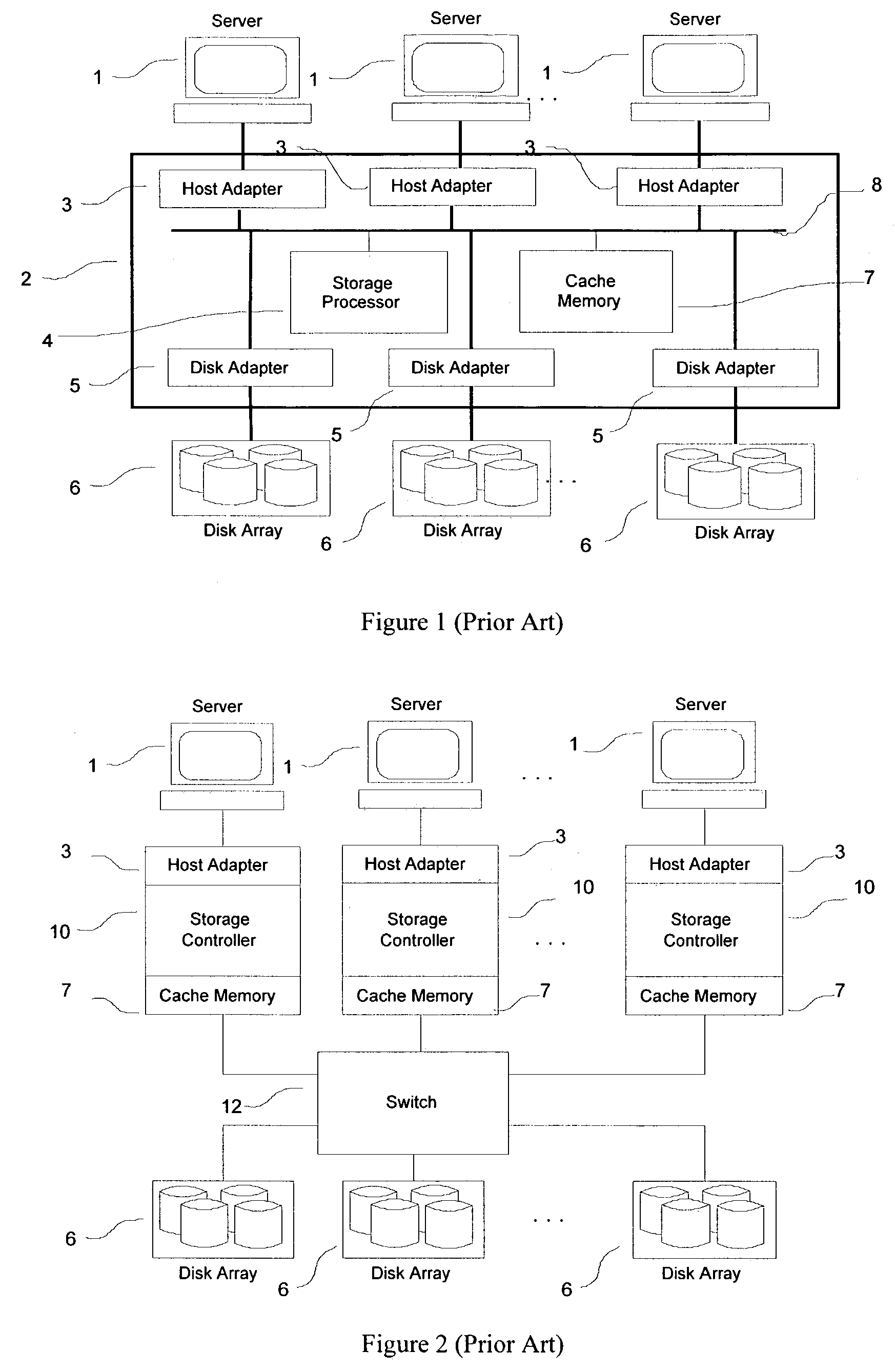

Method for configuration and management of storage resources in a storage network

InactiveUS6640278B1Improve performanceInput/output to record carriersData processing applicationsCommunication interfaceStorage area network

A storage domain management system supports storage domains. The storage server includes a plurality of communication interfaces. A first set of communication interfaces in the plurality is adapted for connection to all kinds of users of data. A second set of communication interfaces in the plurality is adapted for connection to respective devices in a pool of storage devices for use in a storage domain. Data processing resources in the server are coupled to the plurality of communication interfaces for transferring data among the interfaces. The data processing resources comprise a plurality of driver modules and configurable logic linking driver modules into data paths. Each configured data path acts as a virtual circuit that includes a set of driver modules selected from the plurality of driver modules. A data storage transaction which is received at a communication interface is mapped to one of the configured data paths. A display and a user input device are included with data processing structures to manage images displayed on the display.

Owner:DELL PROD LP

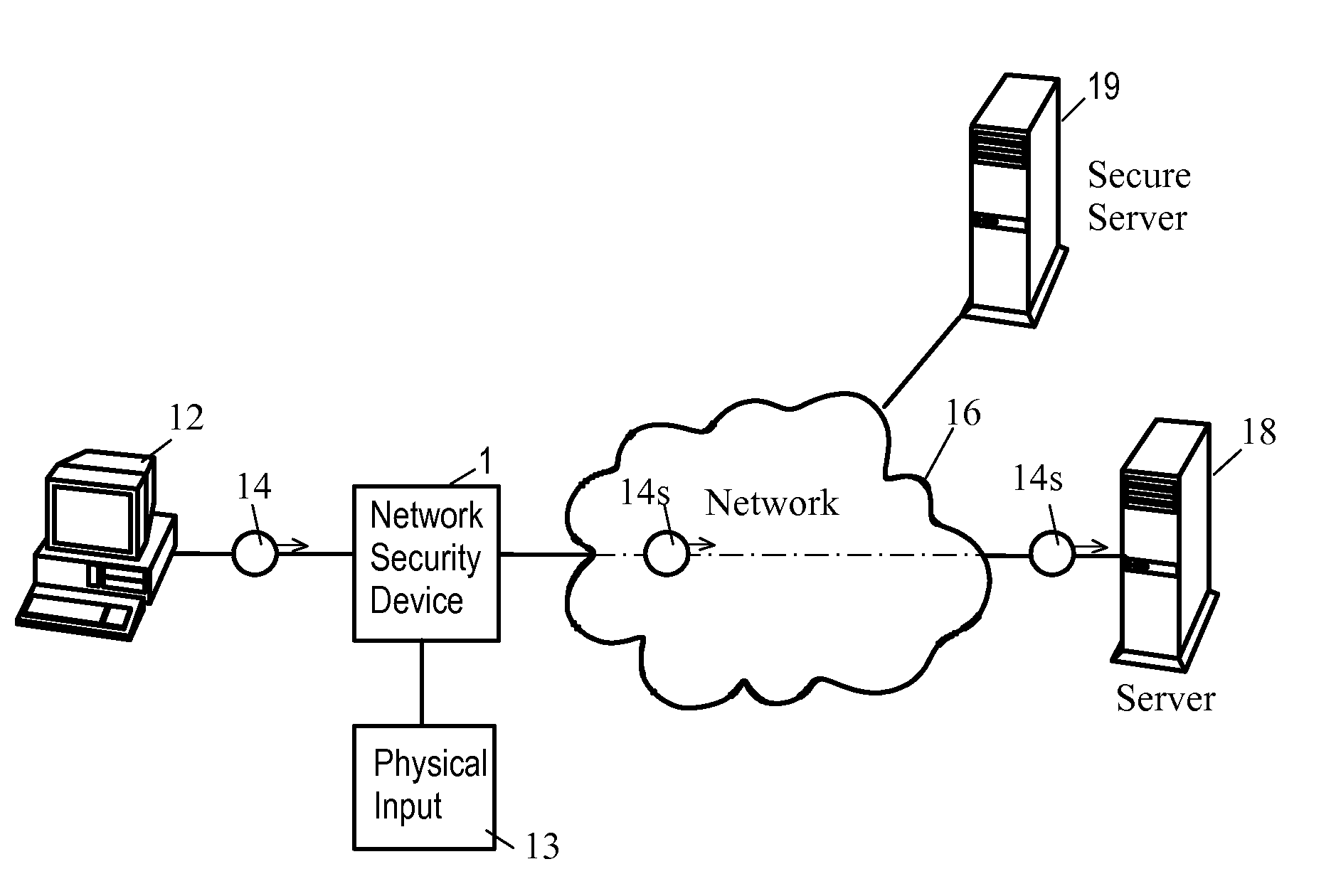

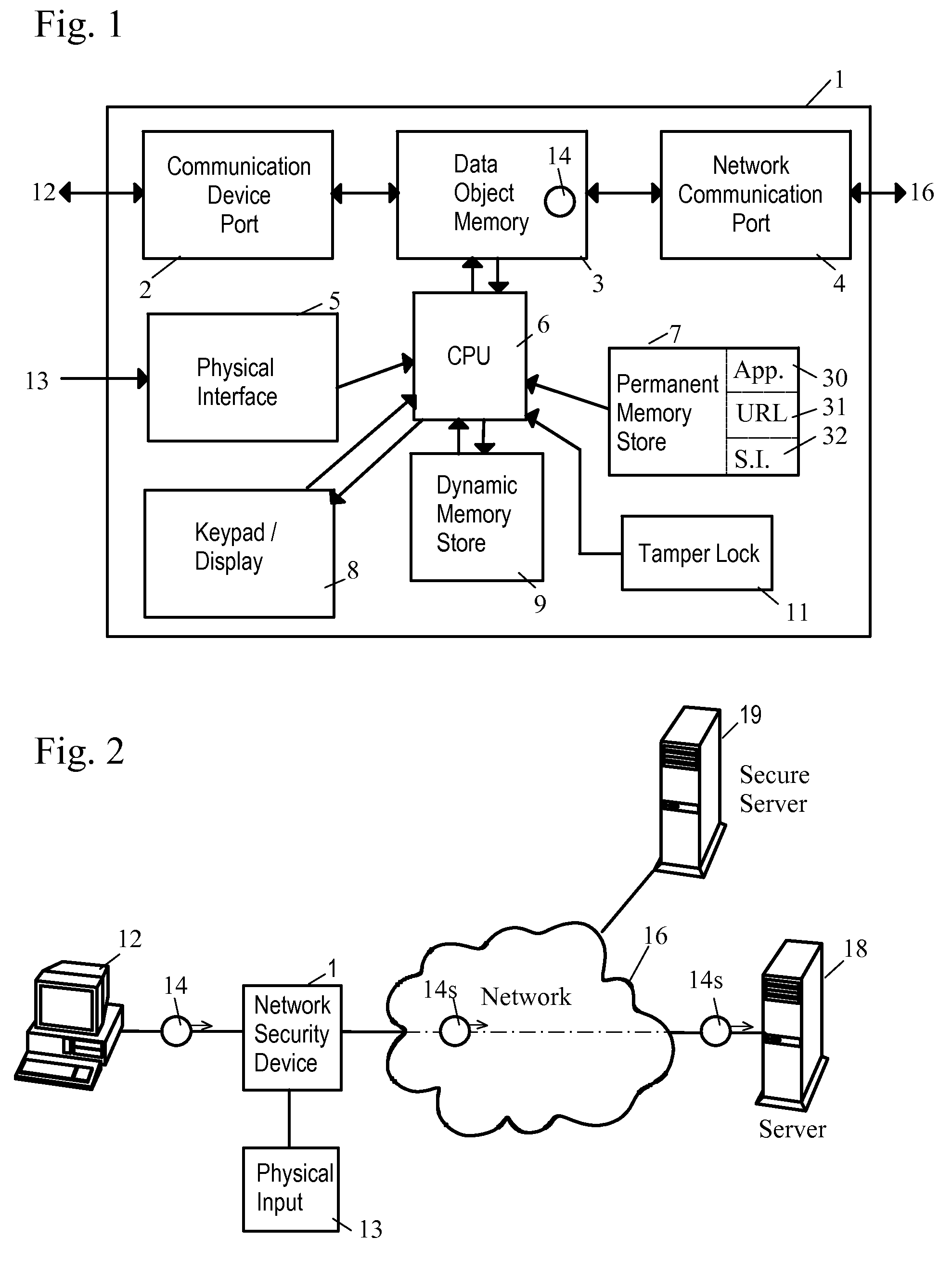

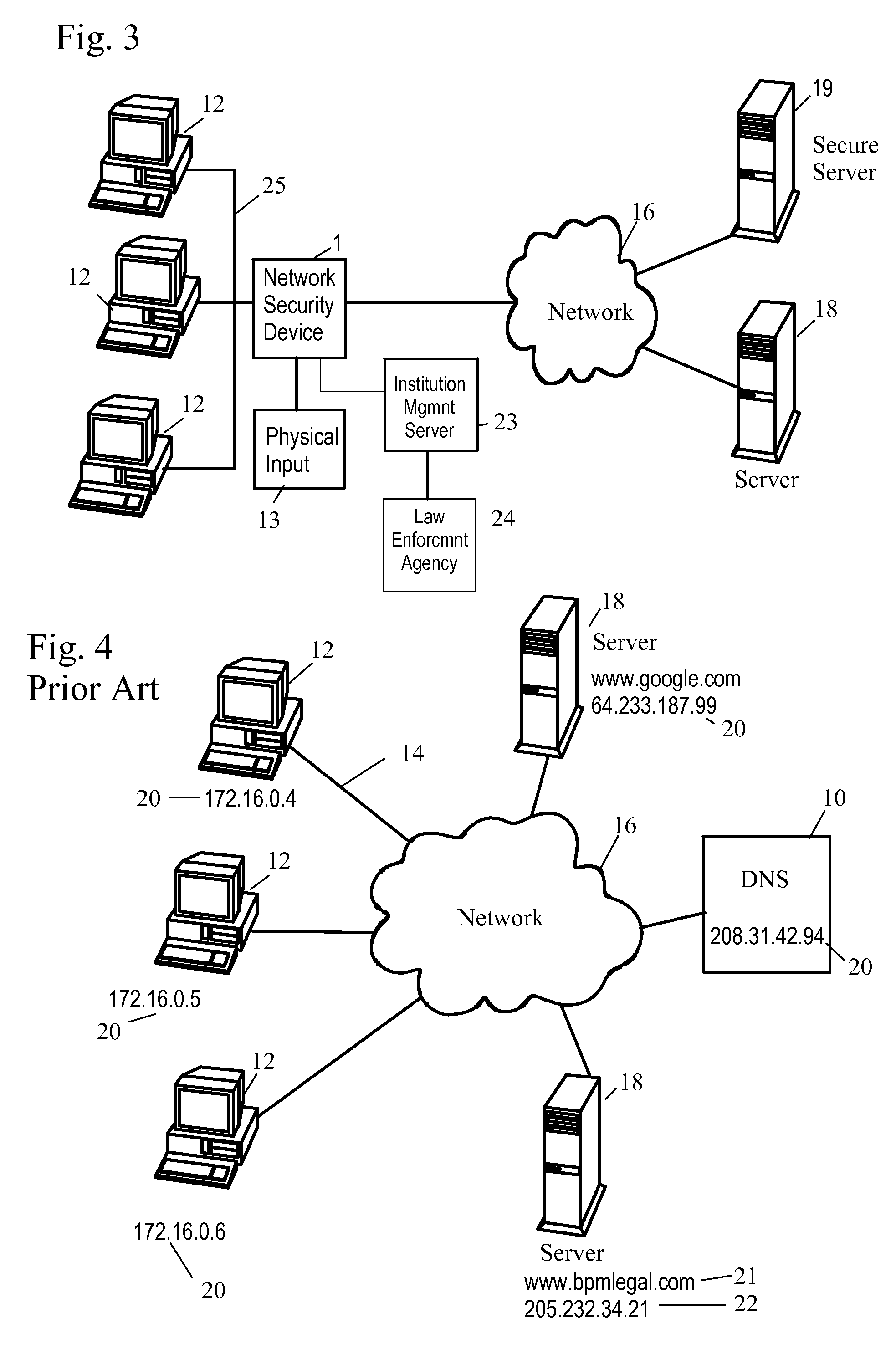

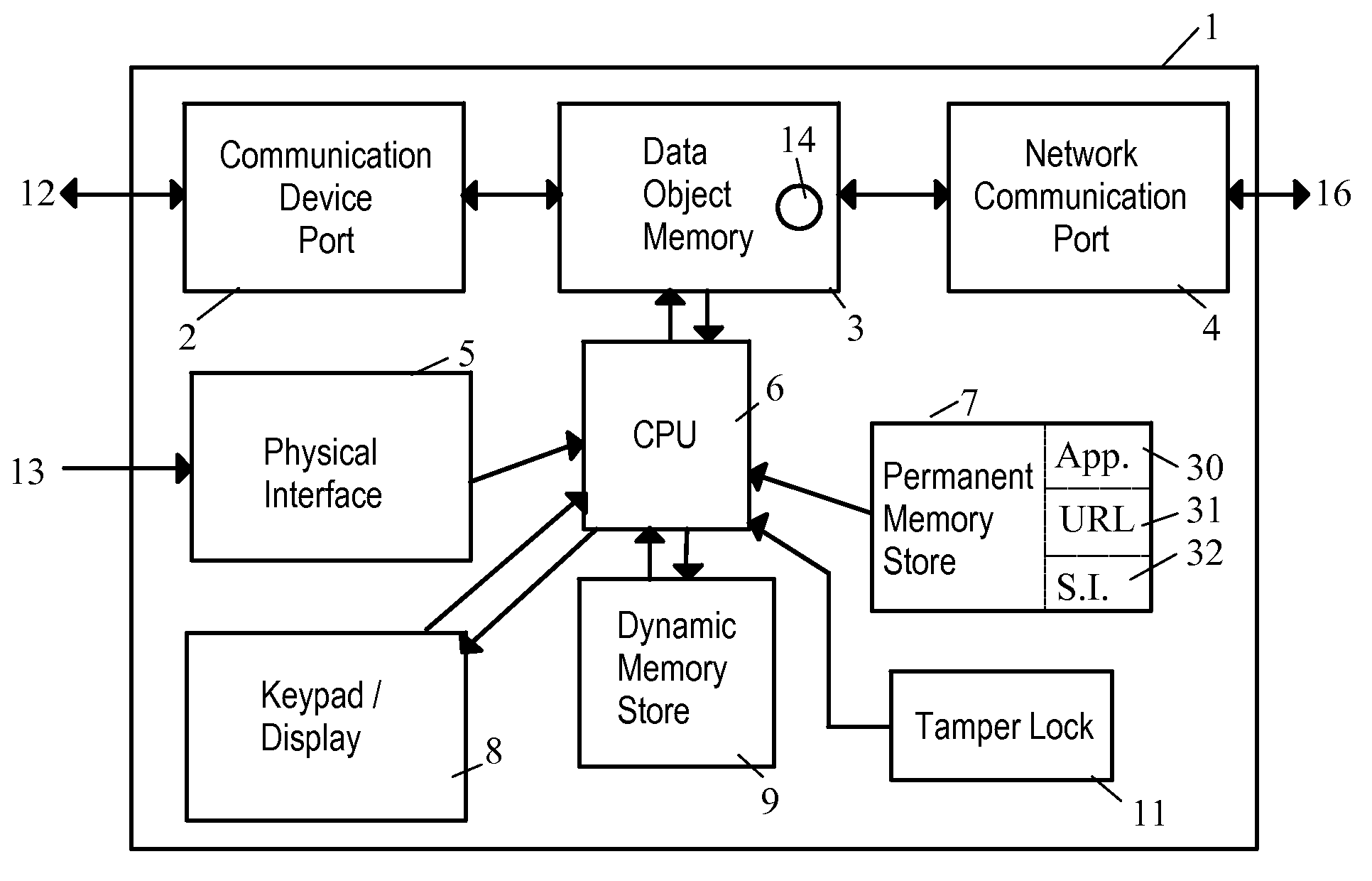

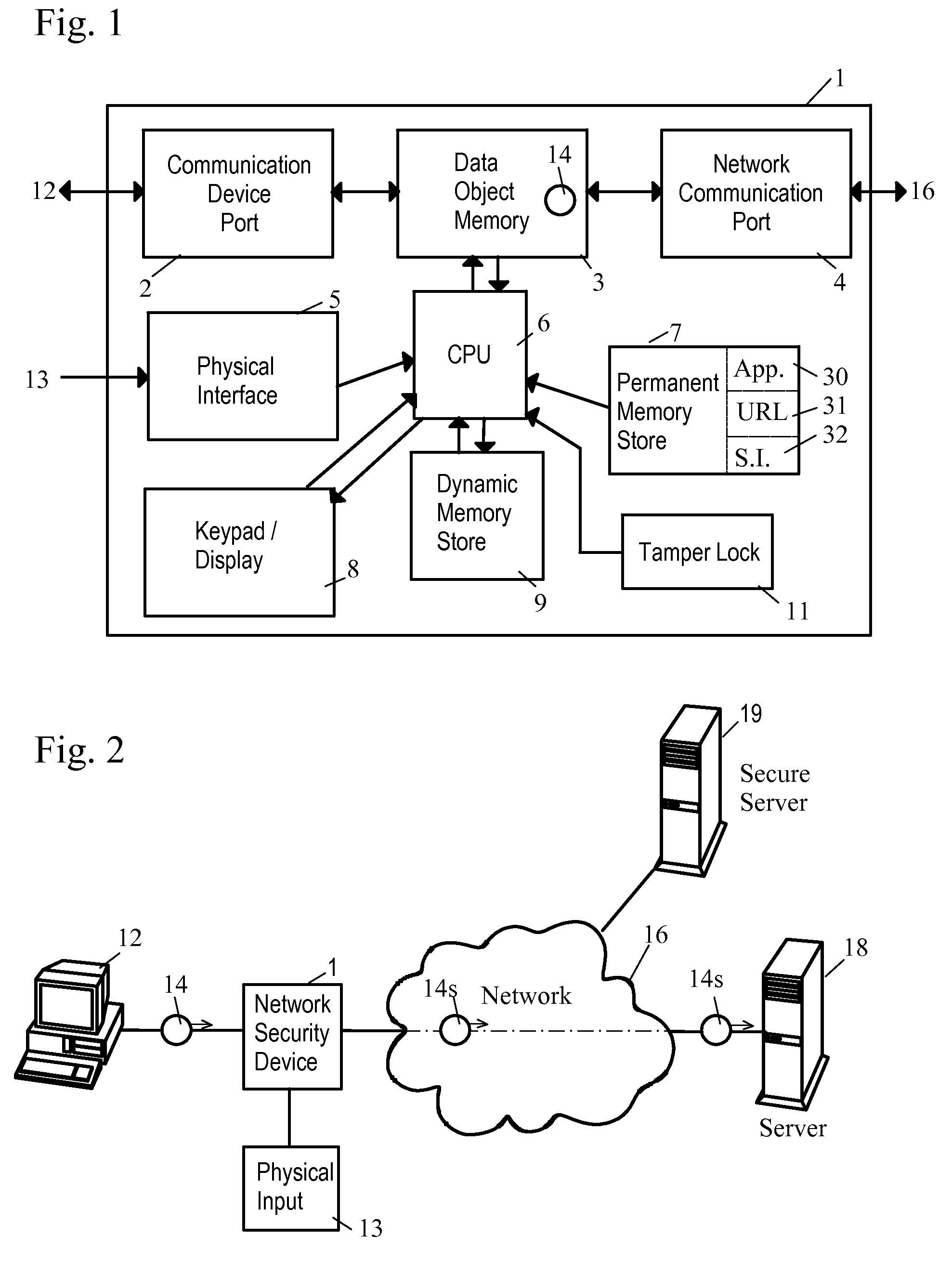

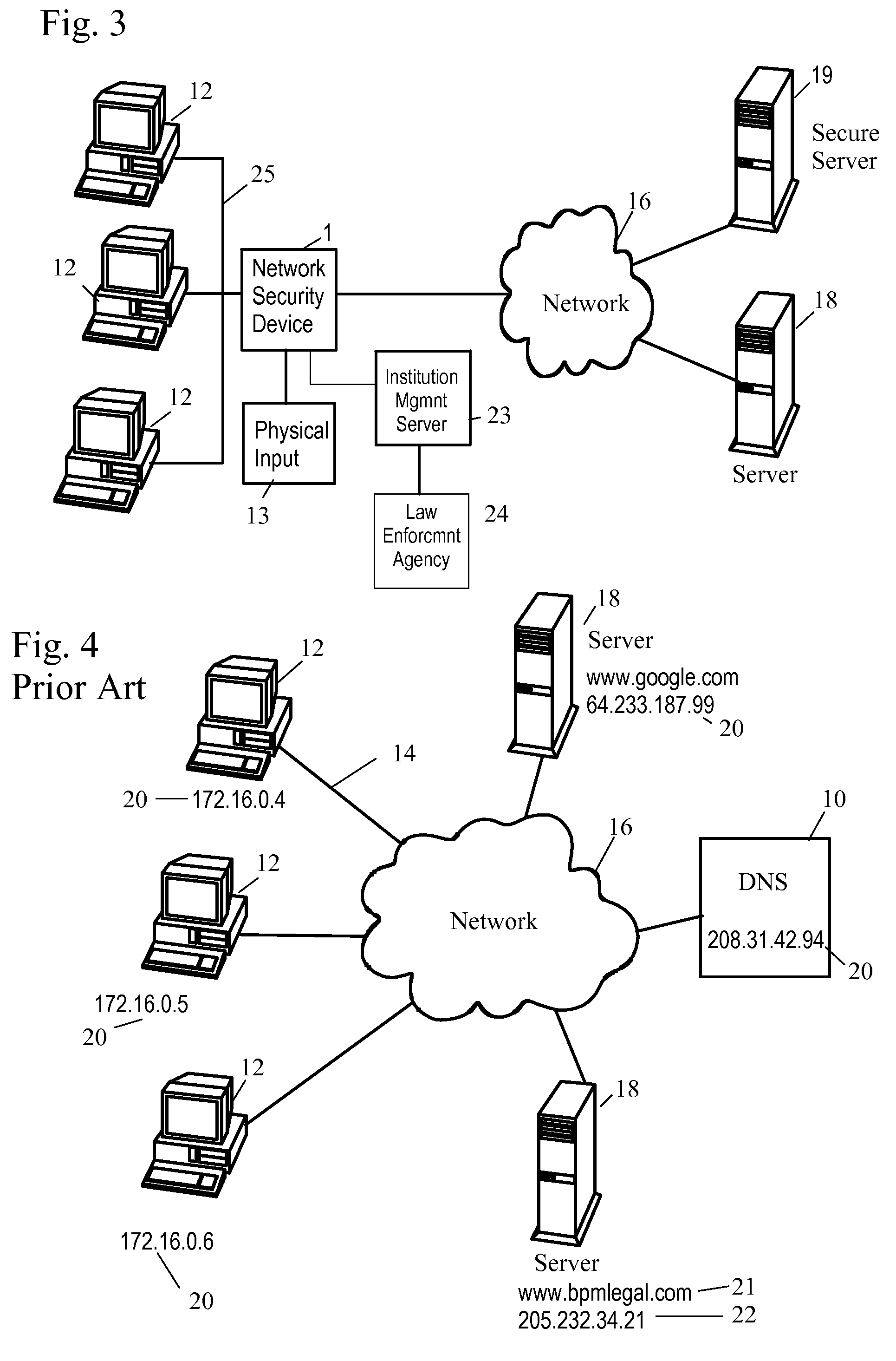

Network Security Device

ActiveUS20070261112A1Function providedFacilitate law enforcement effortDigital data processing detailsUser identity/authority verificationNetwork packetDatapath

A network security device which acts as an “airlock” for traffic between a communications device and a network. Data is screened using rules based analysis by the security device to counter various threats, including viruses, phishing, attempts to “hijack” communications, communications with known malicious addresses or unknown addresses, and transmission of sensitive information. Data packets can be reassembled into files for screening, and decoded or expanded as necessary, but is never executed. The data path for the data being screened is kept separate from the operations of the network security device itself, so that the device is incorruptible—its programming cannot be compromised from outside sources. Updates for rules and entry of sensitive data for screening, etc., must be done through a physical interface, not via the normal data communications channel. The device is invisible—it cannot be “seen” by the network, and thus cannot be attacked.

Owner:ELECTRO GUARD CORP

Method and apparatus for regulating data flow between a communications device and a network

ActiveUS7890612B2Digital data processing detailsComputer security arrangementsTraffic capacityData stream

A network security device which acts as an “airlock” for traffic between a communications device and a network. Data is screened using rules based analysis by the security device to counter various threats, including viruses, phishing, attempts to “hijack” communications, communications with known malicious addresses or unknown addresses, and transmission of sensitive information. Data packets can be reassembled into files for screening, and decoded or expanded as necessary, but is never executed. The data path for the data being screened is kept separate from the operations of the network security device itself, so that the device is incorruptible—its programming cannot be compromised from outside sources. Updates for rules and entry of sensitive data for screening, etc., must be done through a physical interface, not via the normal data communications channel. The device is invisible—it cannot be “seen” by the network, and thus cannot be attacked.

Owner:ELECTRO GUARD CORP

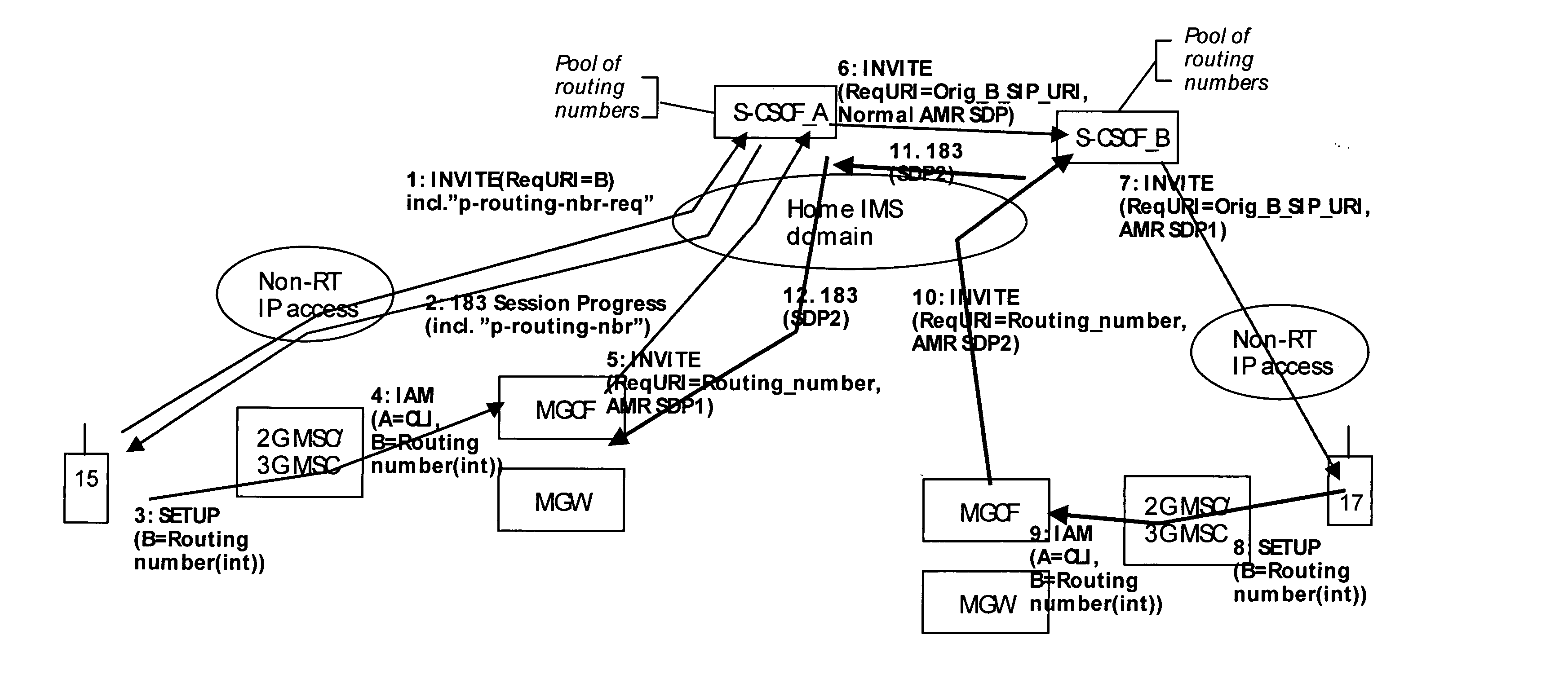

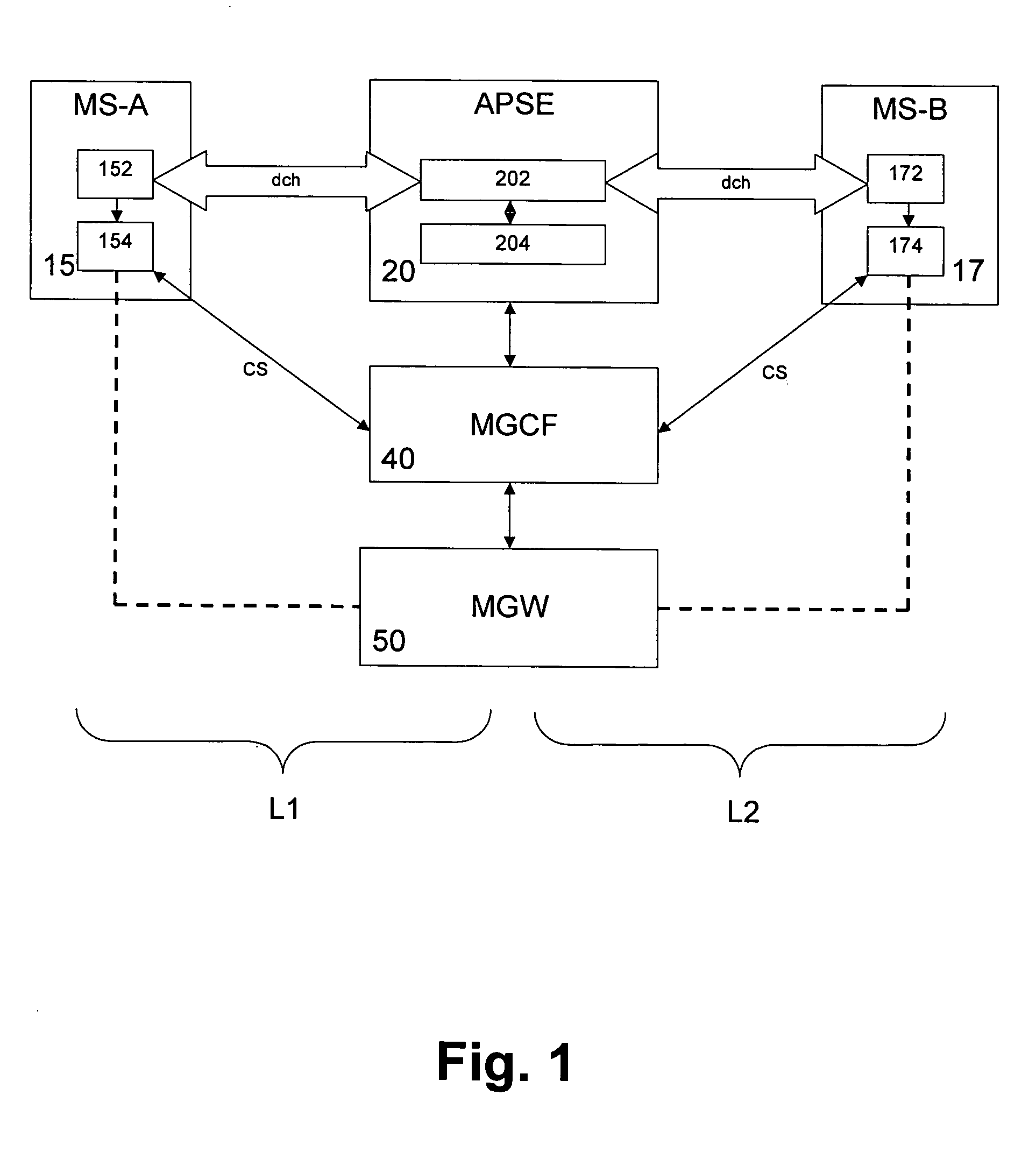

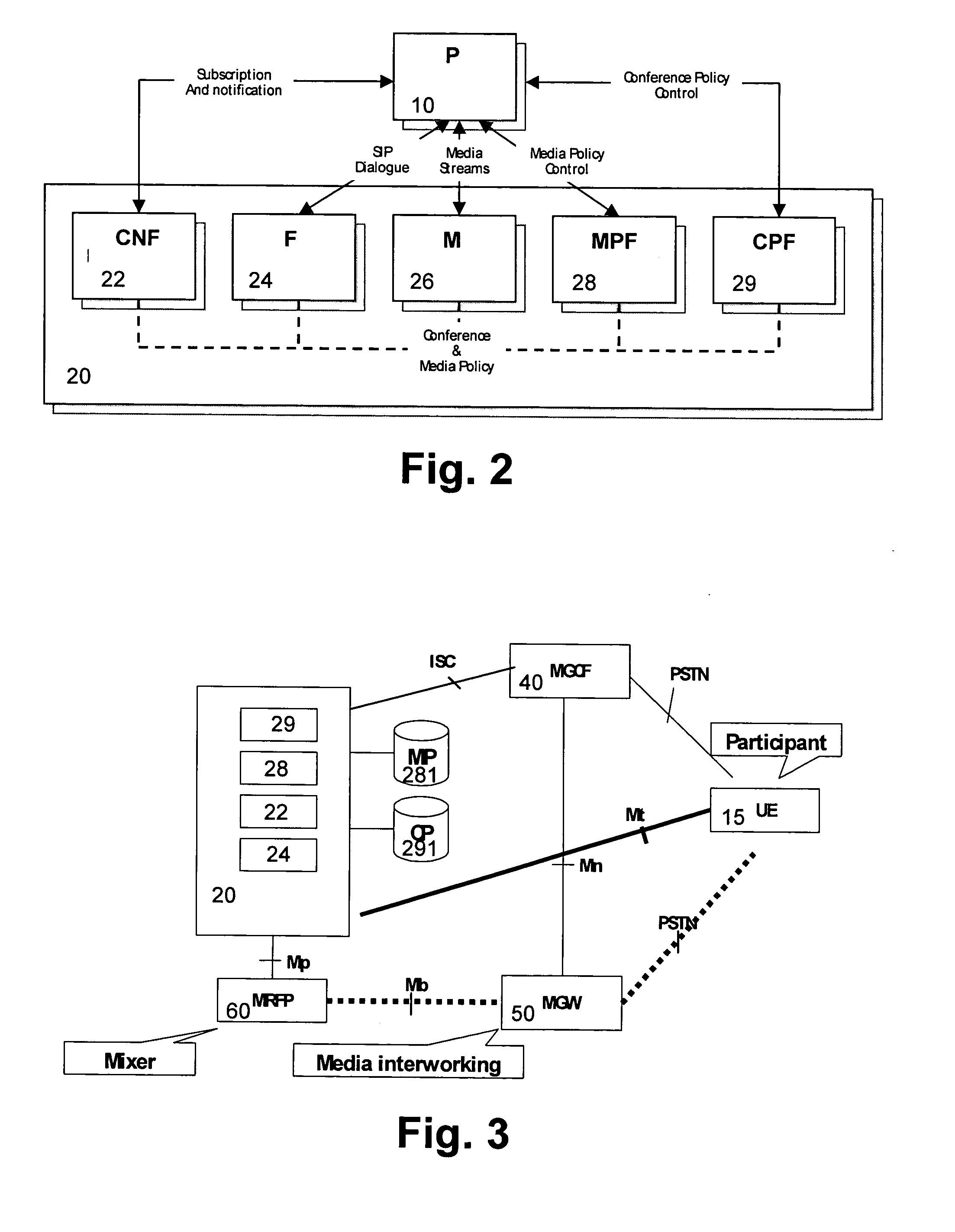

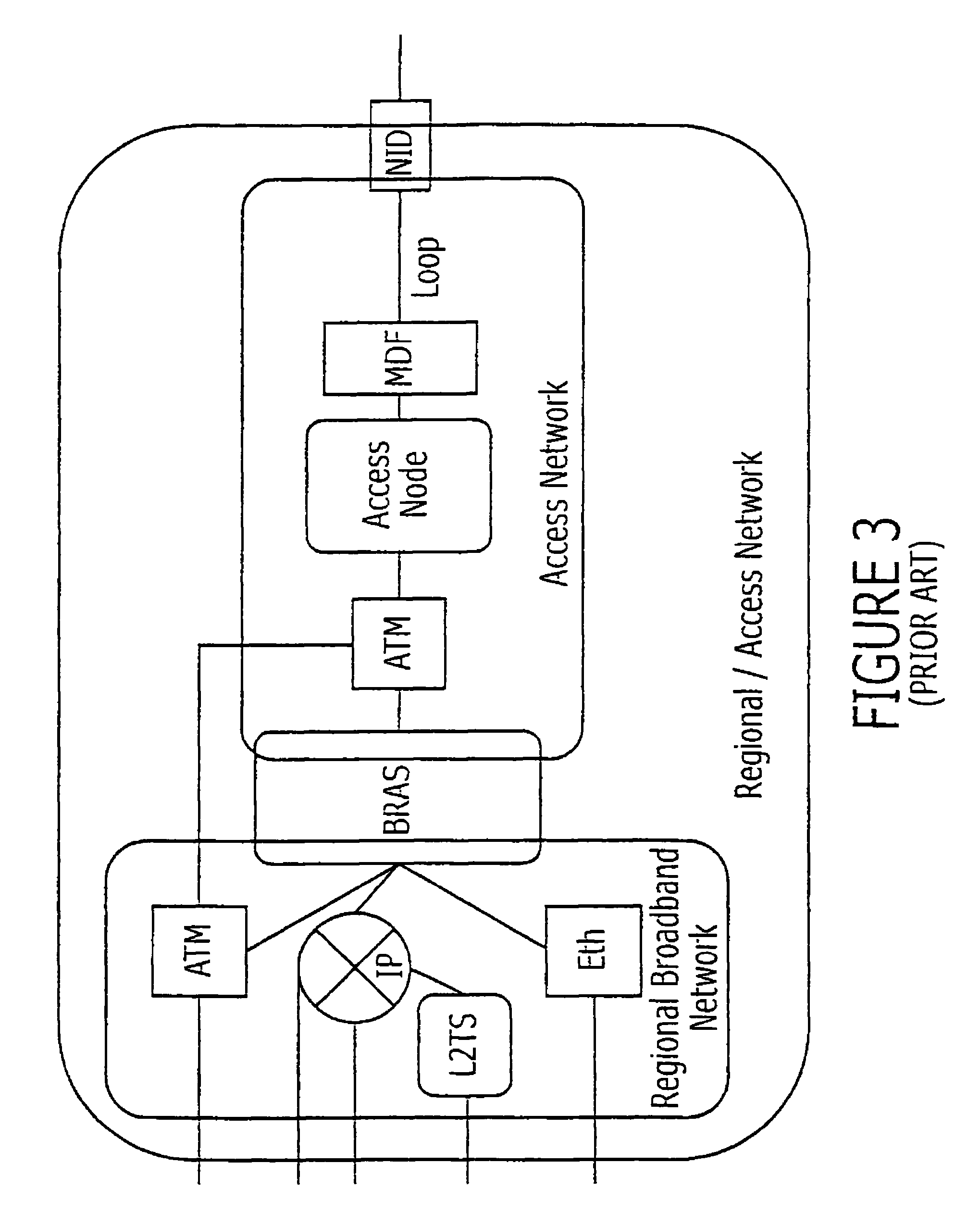

IP-based services for circuit-switched networks

ActiveUS20050058125A1Multiplex system selection arrangementsInterconnection arrangementsRadio access networkVoice over IP

A mechanism for providing a connection from an IP-based network to a circuit-switched network, such as a GSM network is disclosed. A temporary routing number for the circuit-switched network, such as an E.164 number, is delivered to a user terminal, and a circuit-switched call leg is established from the user terminal to the IP-based network using the routing number. Thereby, IMS-services are provided for end users which are located in the radio access network not having sufficient QoS required for voice over IP. In the example of a conference call service, a request for a conference call may forwarded via a data channel or data path to an application server which provides that conference call service. The application server then selects a conference routing number and returns the routing number to the conference host terminal via the data channel. Using the received conference routing number, the conference host terminal can then set up a circuit-switched connection as a call leg of the conference call.

Owner:NOKIA TECHNOLOGLES OY

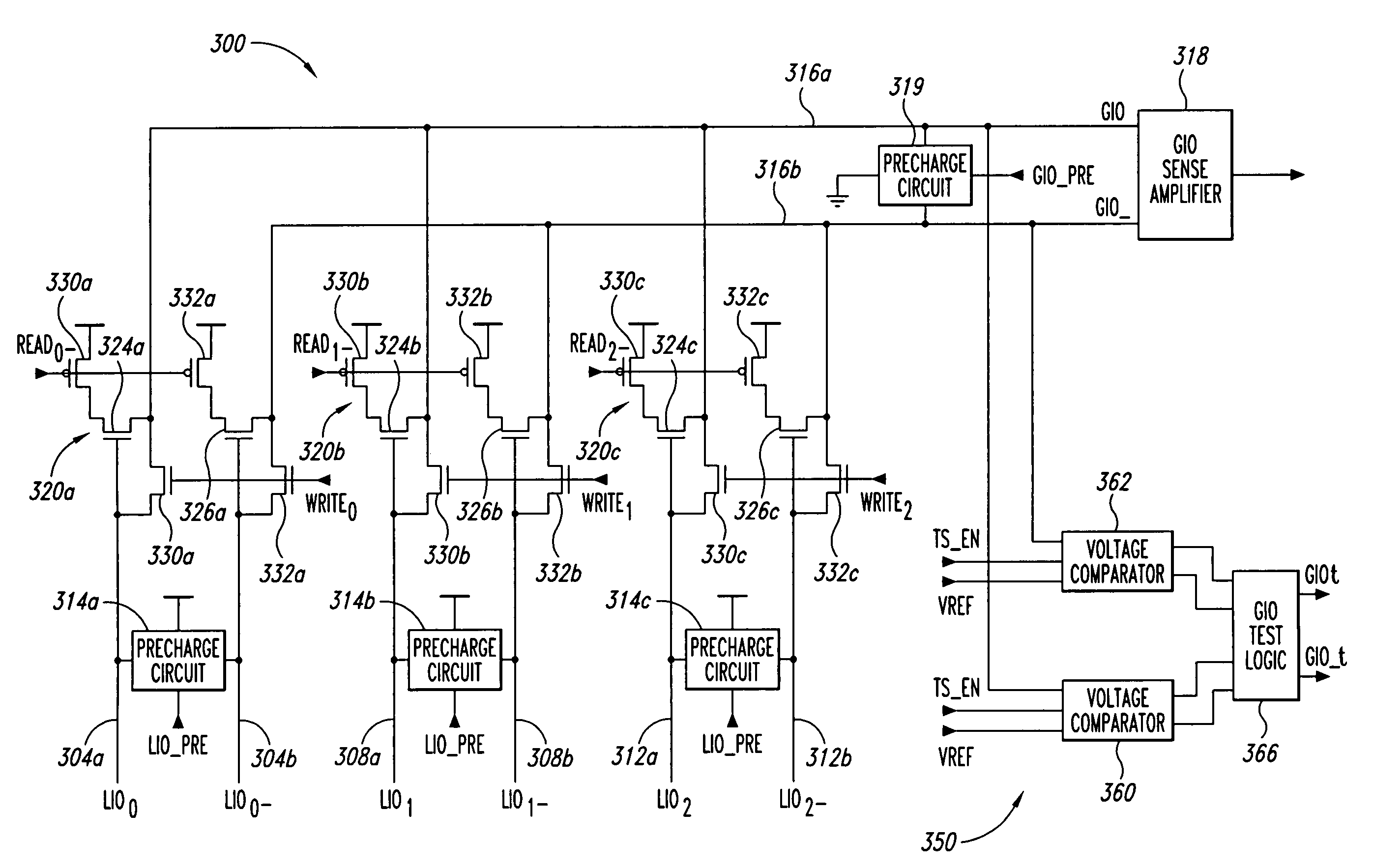

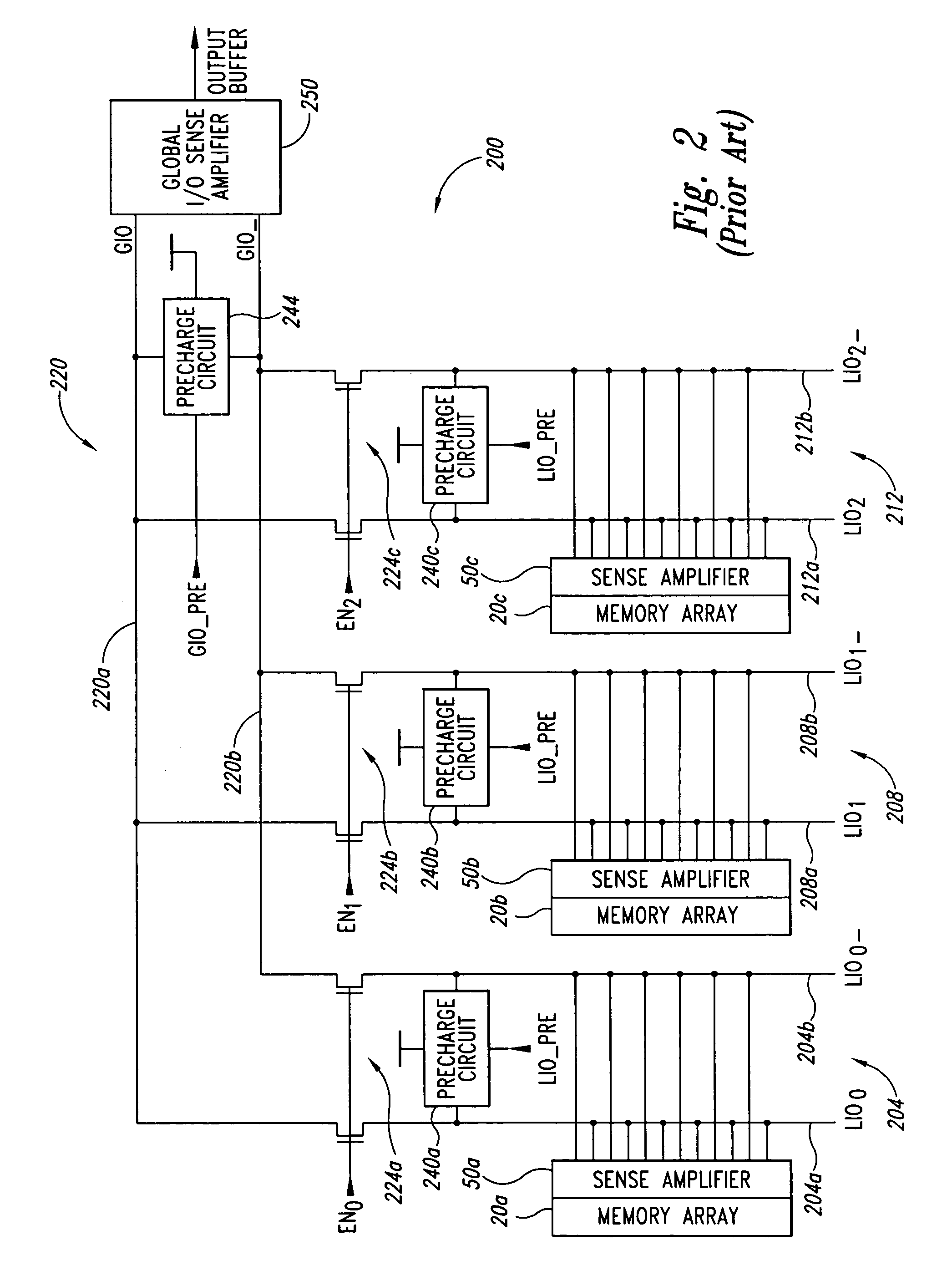

Data path having grounded precharge operation and test compression capability

A data path for coupling data between a memory cell and an input / output (IO) line sense amplifier. An IO line coupling circuit is coupled to a pair of global data lines and a pair of local data lines to couple and decouple each of the global data lines to and from a voltage supply based on the voltage levels of the local data lines for the memory read operation. For the memory write operation, the IO line coupling circuit couples and decouples each of the global data lines to and from a respective one of the local data lines. The data path also includes a first precharge circuit coupled to the global data lines to couple the global data lines to ground to precharge the signal lines prior to a memory read or write operation, and can further include a test compression circuit coupled to the global data lines.

Owner:MOSAID TECH

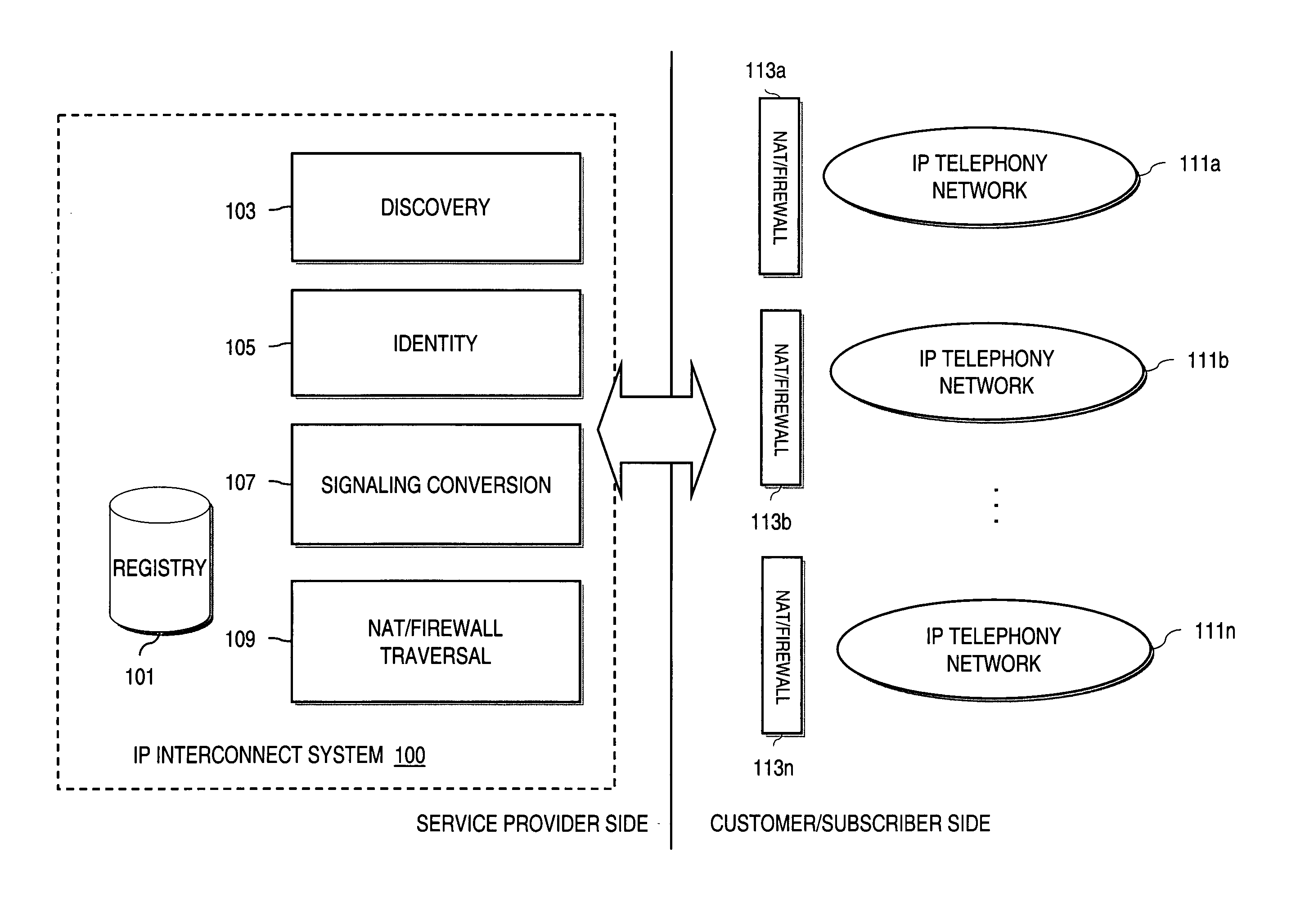

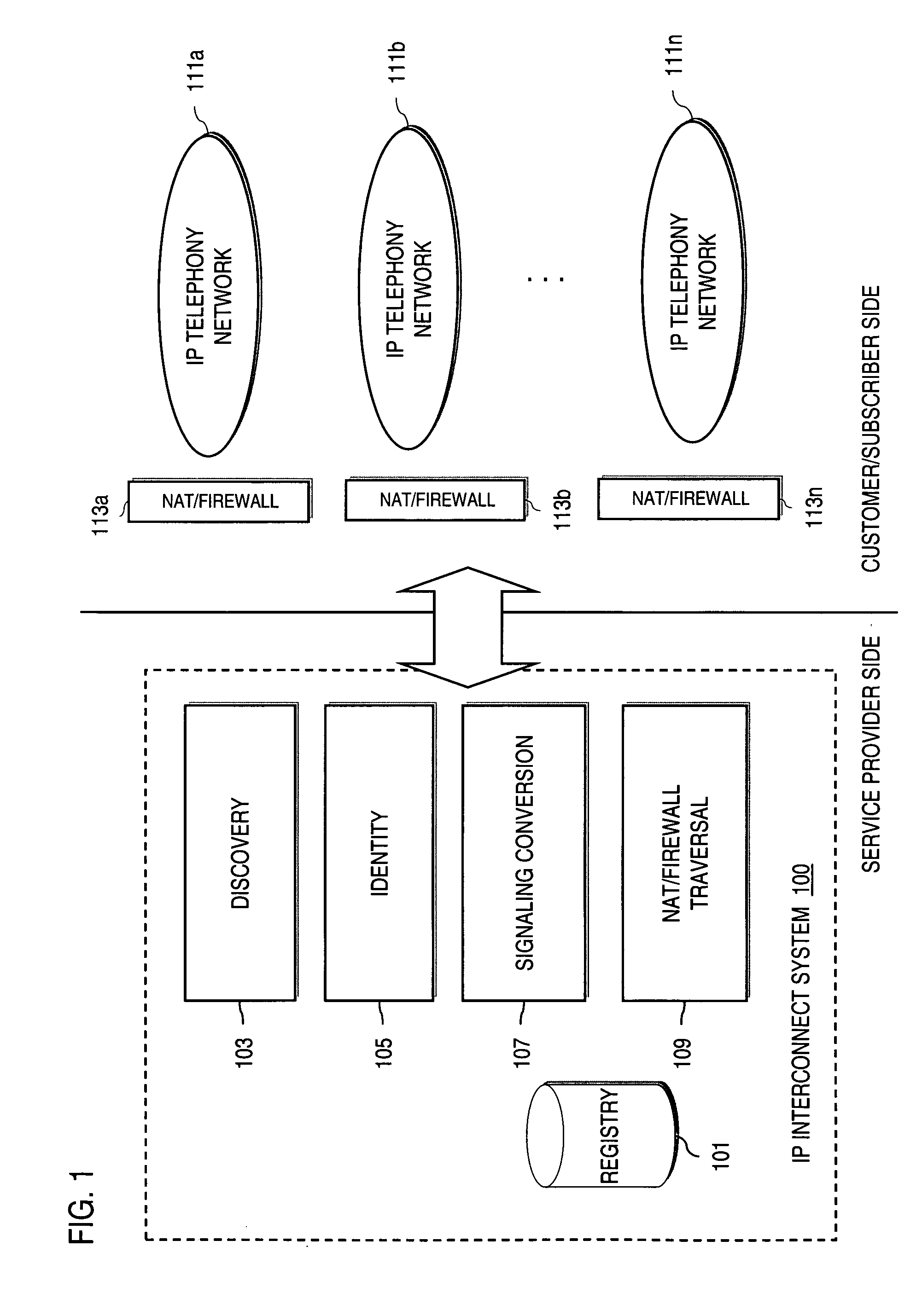

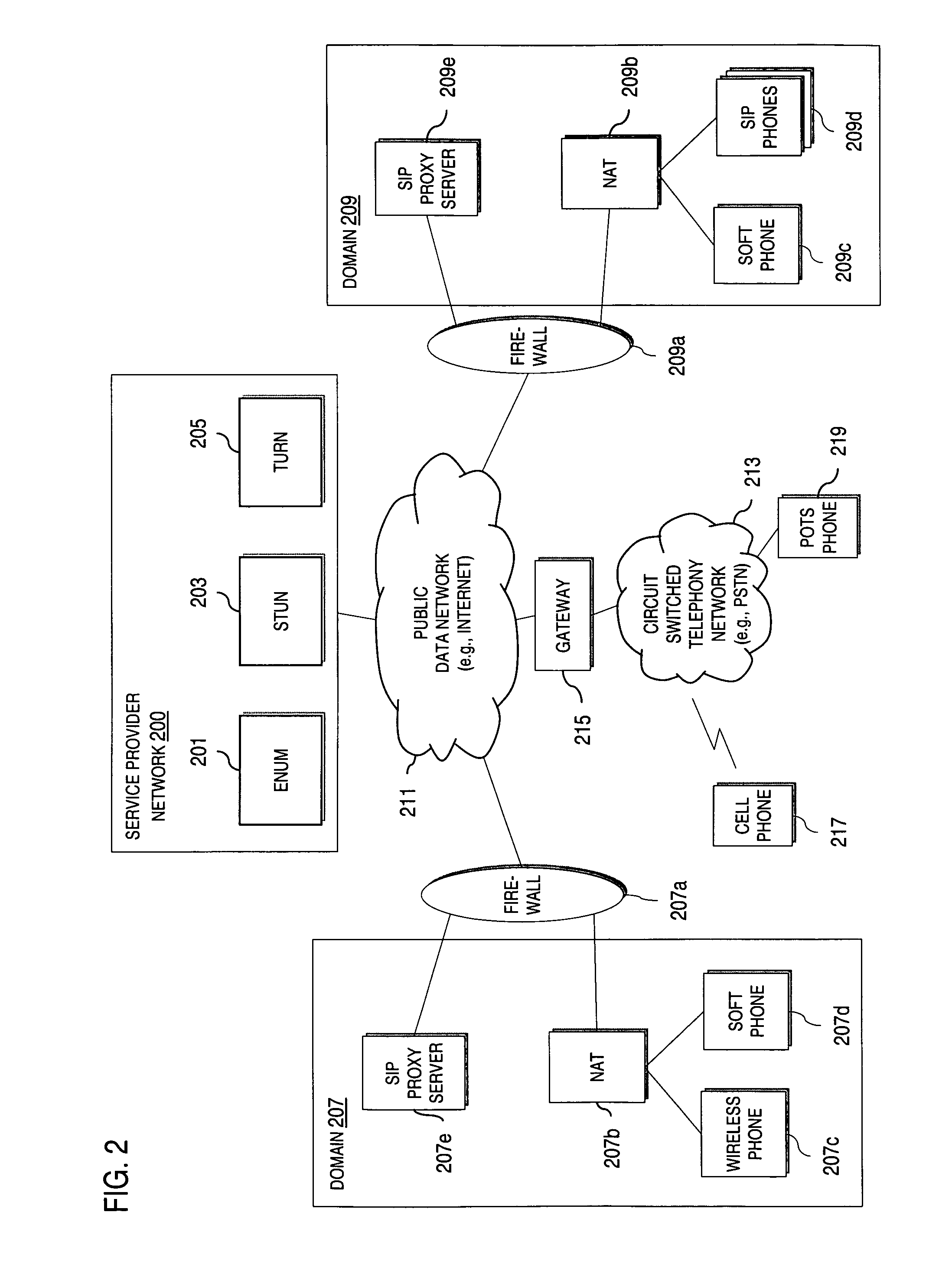

Method and system for providing voice over IP managed services utilizing a centralized data store

ActiveUS20070036143A1Interconnection arrangementsData switching by path configurationVoice over IPData memory

An approach provides interdomain traversal to support packetized voice transmissions. A centralized data store, maintained by a service provider, stores one or more user identifiers and an associated directory number. The centralized data store also stores routing information including one or more communication paths corresponding to the user identifier, wherein the routing information includes a data path or a circuit-switched path for establishing a call to the user. In response to a request for establishing the call to the directory number, the data store retrieves the routing information for use to establish the call.

Owner:VERIZON PATENT & LICENSING INC

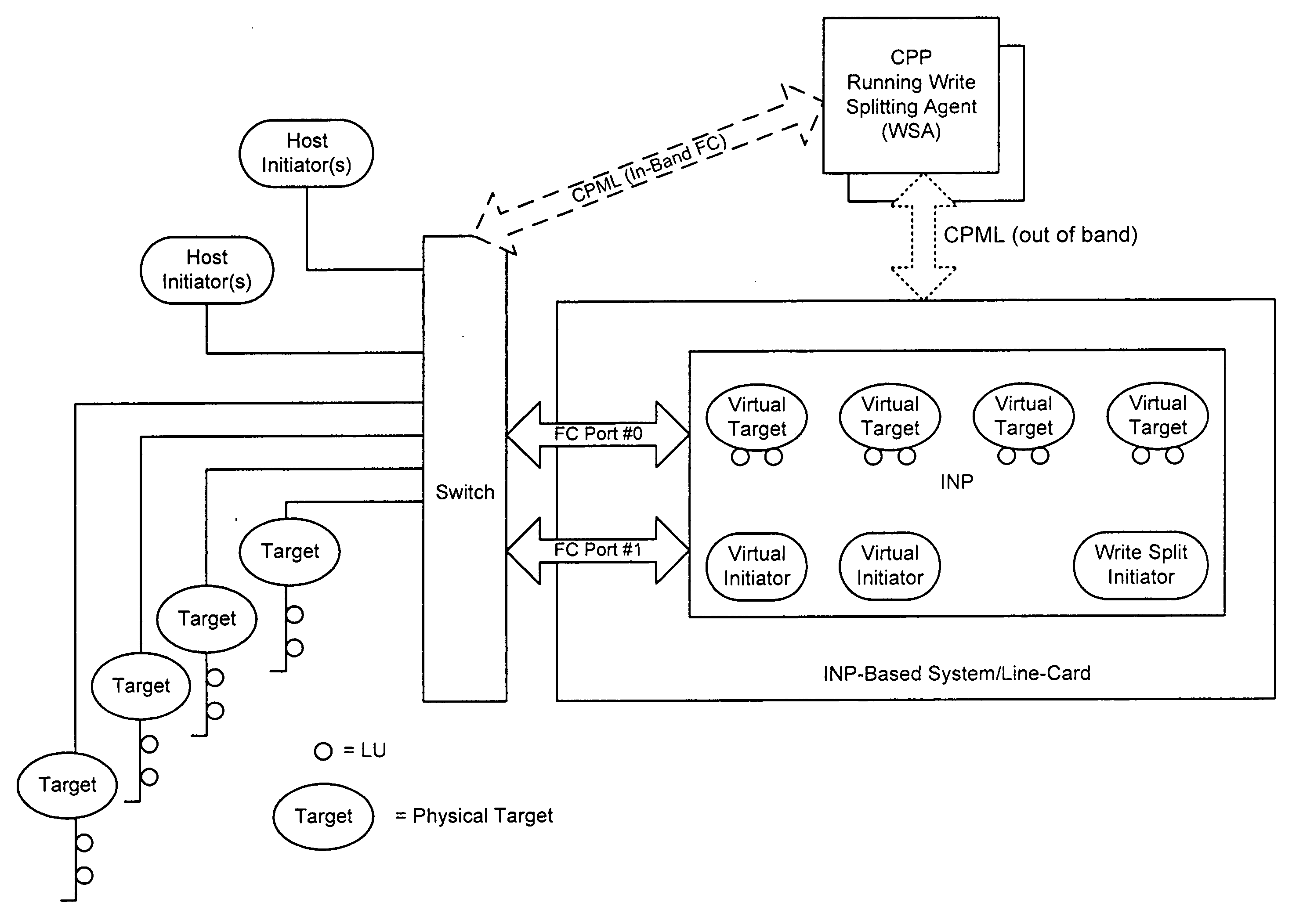

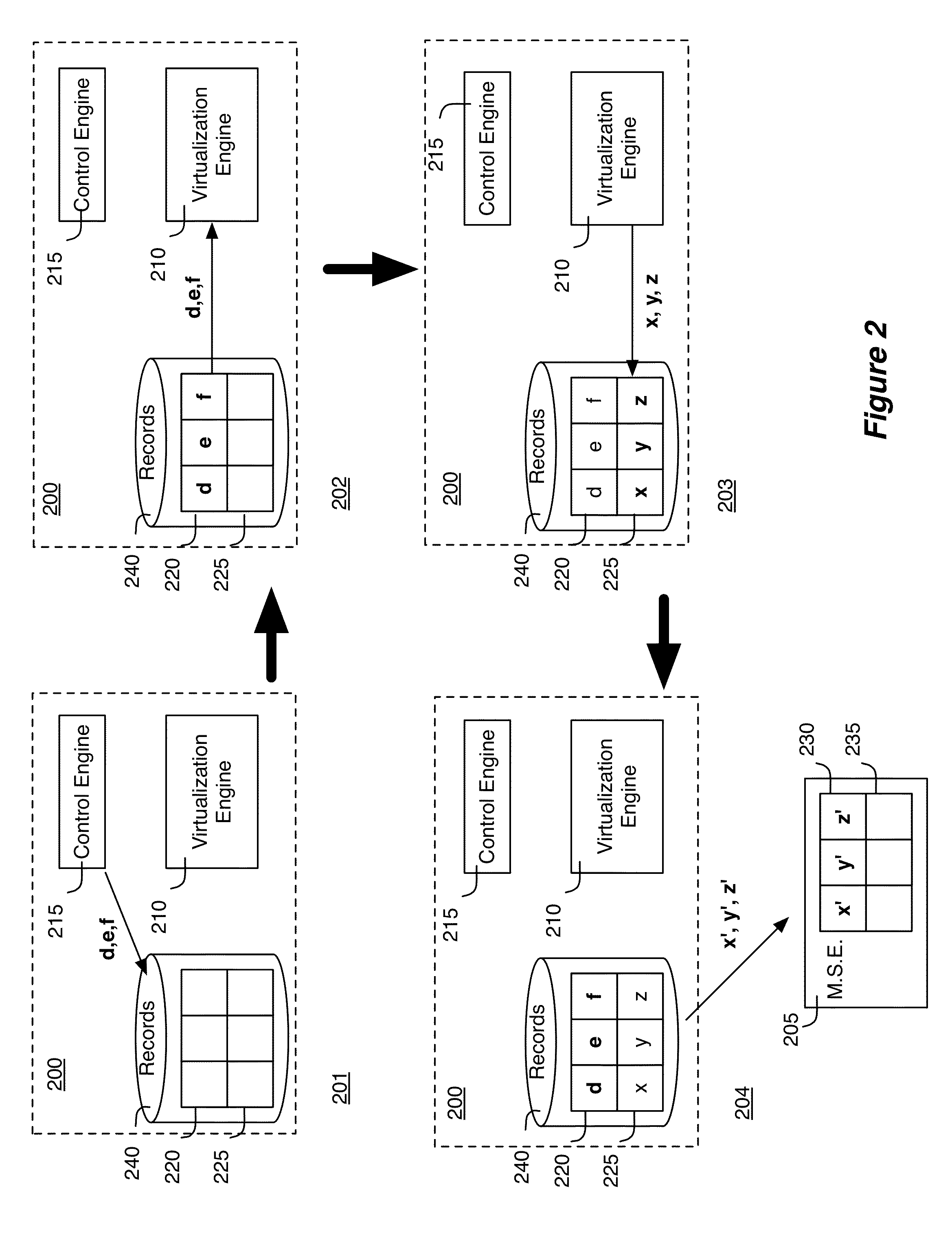

Apparatus for performing storage virtualization

ActiveUS20070239944A1Simplify writingIncrease overheadError detection/correctionMemory adressing/allocation/relocationVirtual targetData management

The splitting of storage applications and functions into a control path (CP) component and a data path (DP) component is disclosed. Reads and writes may be handled primarily in the DP. The CP may be responsible for discovery, configuration, and exception handling. The CP can also be enabled for orchestrating complex data management operations such as snapshots and migration. Storage virtualization maps a virtual I / O to one or more physical I / O. A virtual target (vTarget) in the virtual domain is associated with one physical port in the physical domain. Each vTarget may be associated with one or more virtual LUNs (vLUNs). Each vLUN includes one or more vExtents. Each vExtent may point to a region table, and each entry in the region table may contain a pointer to a region representing a portion of a pExtent, and attributes (e.g. read / write, read only, no access) for that region.

Owner:AVAGO TECH INT SALES PTE LTD

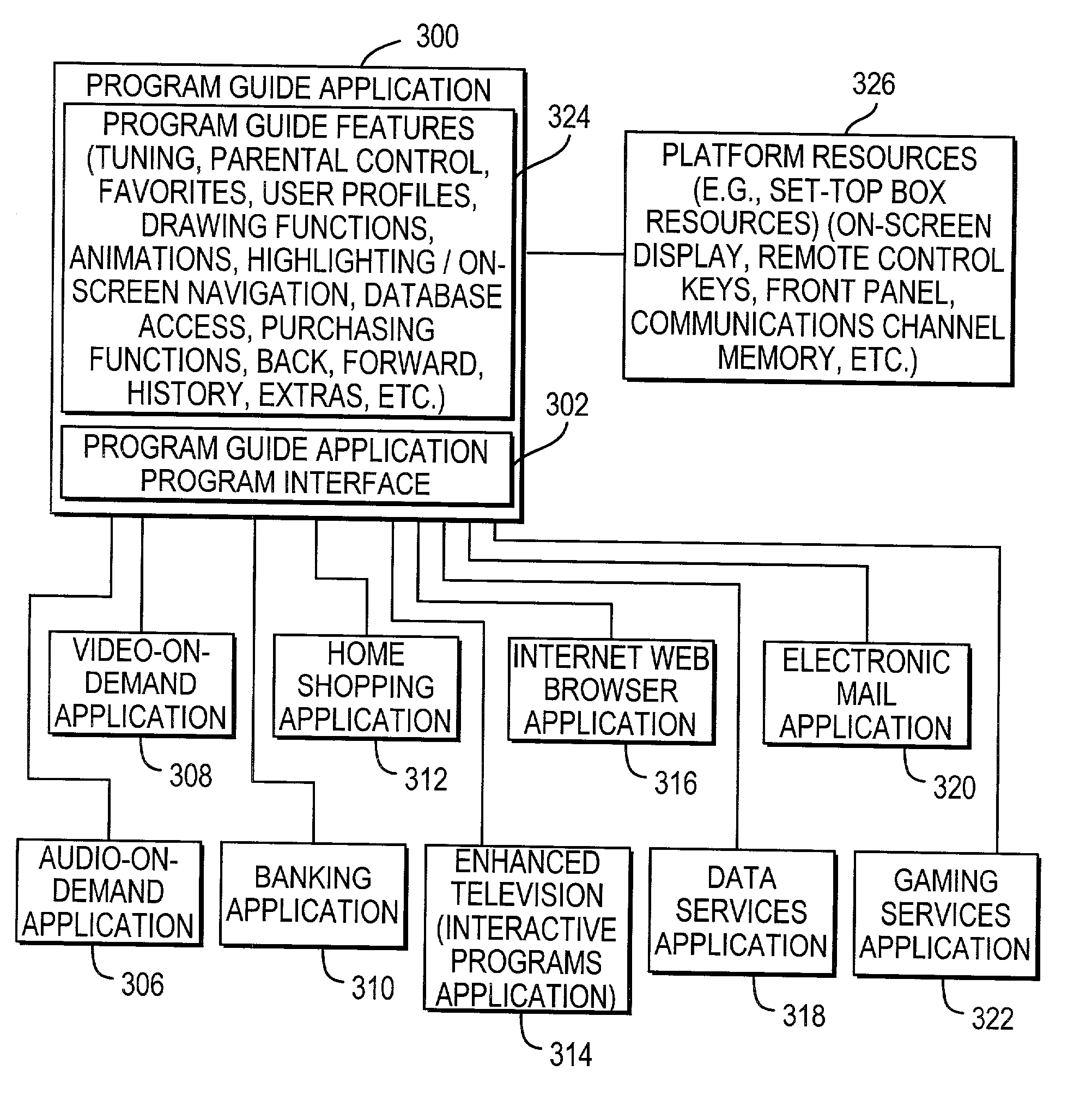

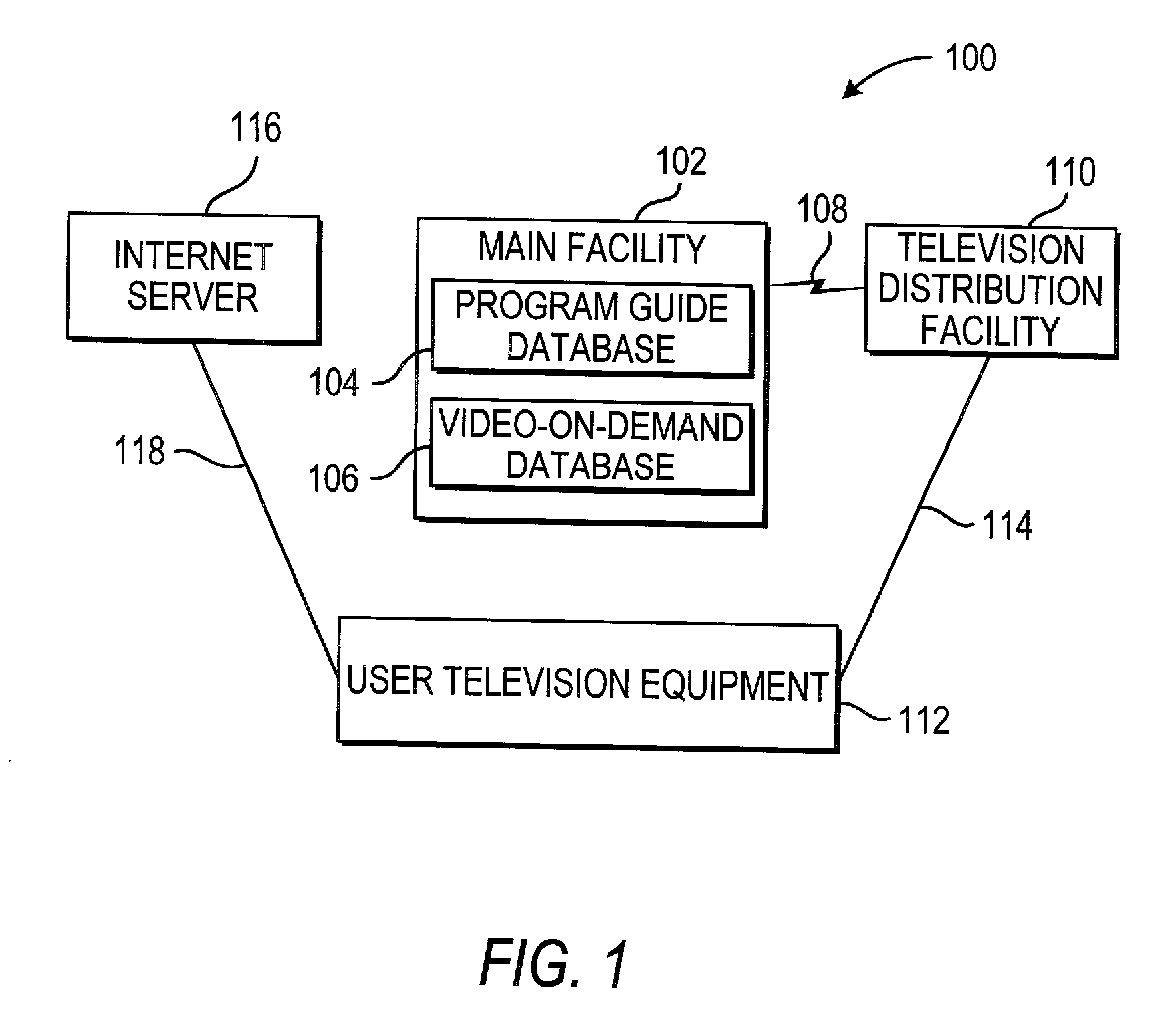

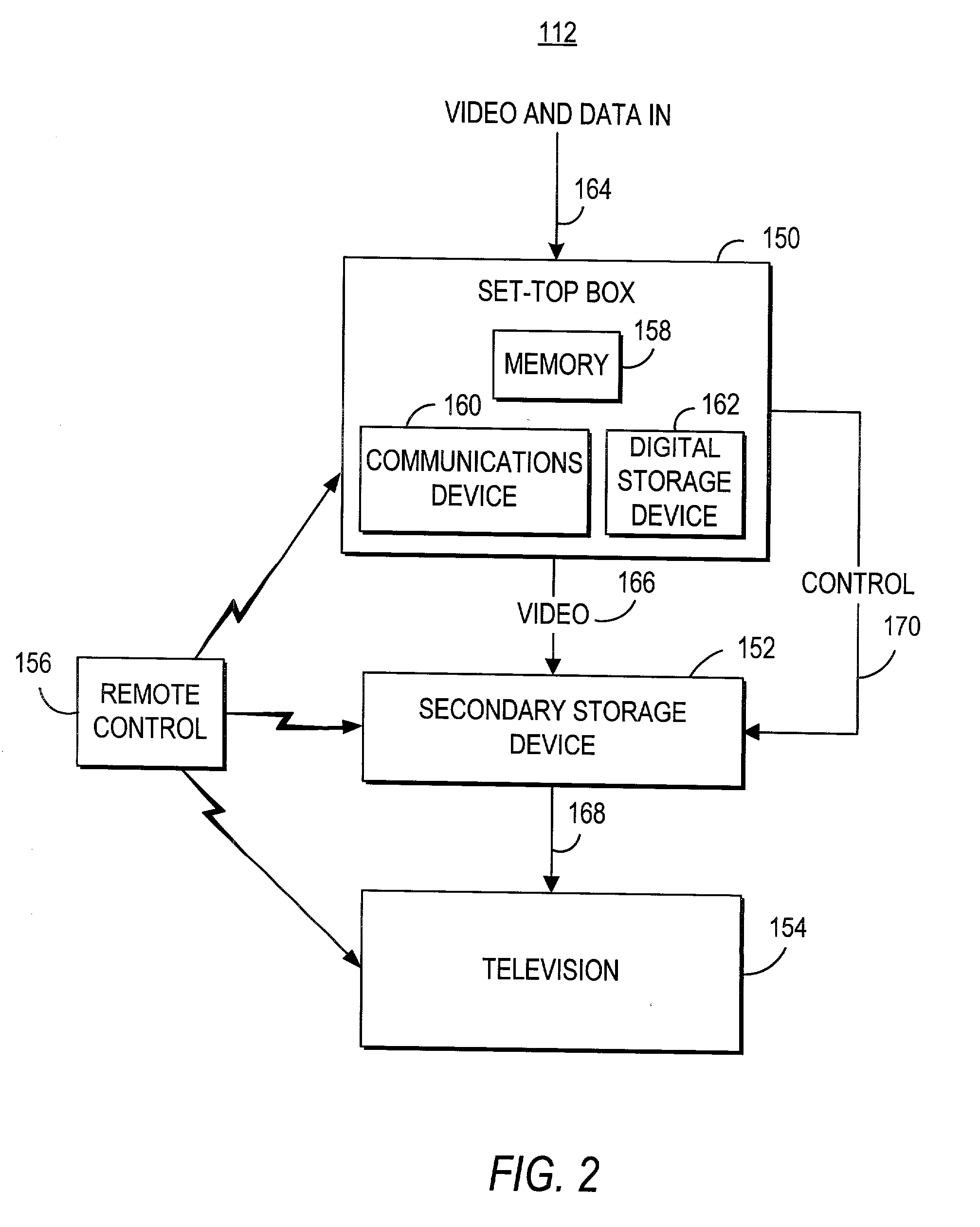

Features for use with advanced set-top applications on interactive television systems

InactiveUS20050235319A1Television system detailsAnalogue secracy/subscription systemsTelevision systemInteractive television

Advanced features for interactive television applications are described, including a back feature, a forward feature, a history feature, a go to feature, an extras feature, a reminder feature, a favorites feature, a parental control feature, and a search feature. Features may be inter-resource. Support for multiple data paths, Internet access, interactive services, and user profiles are also described.

Owner:UNITED VIDEO PROPERTIES

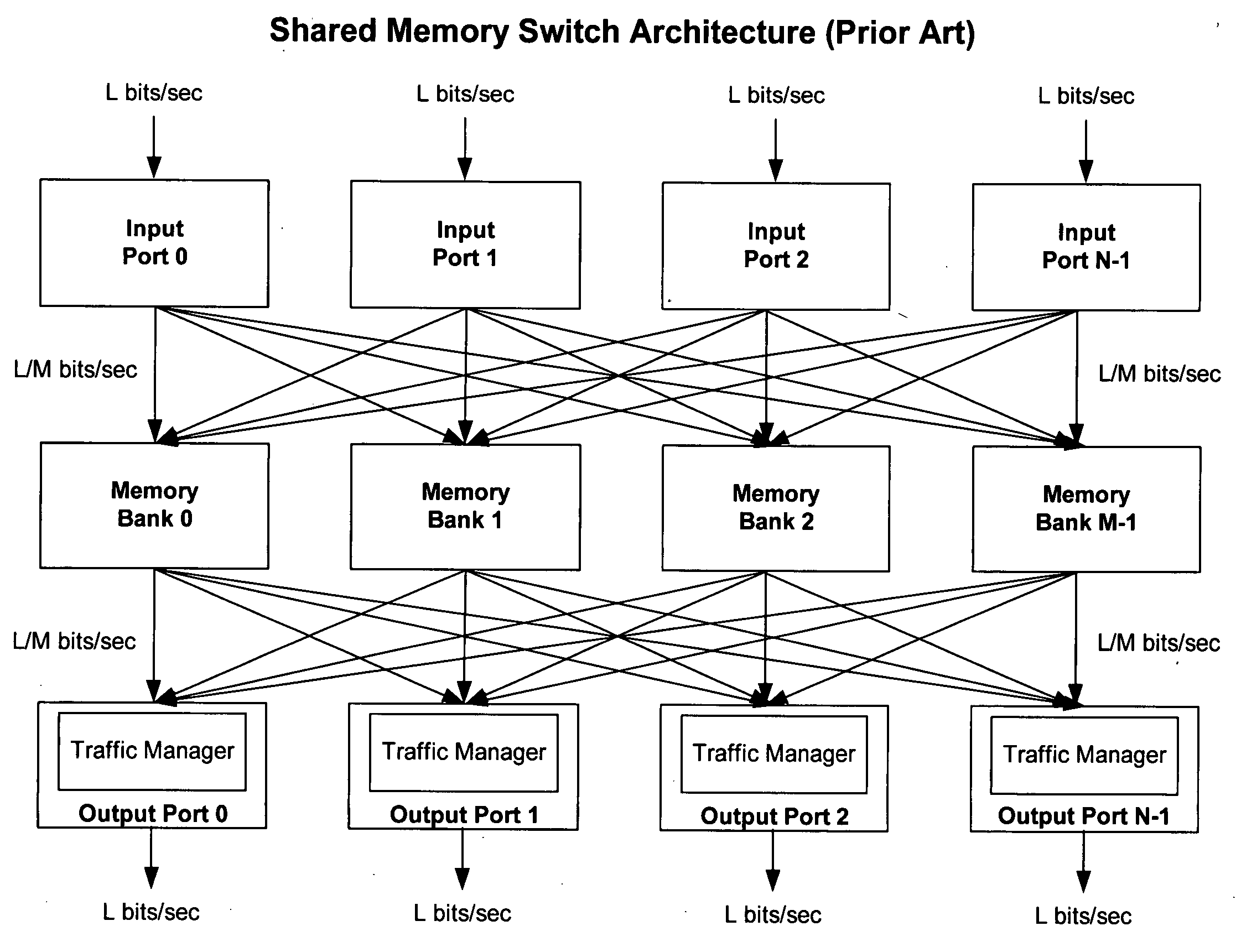

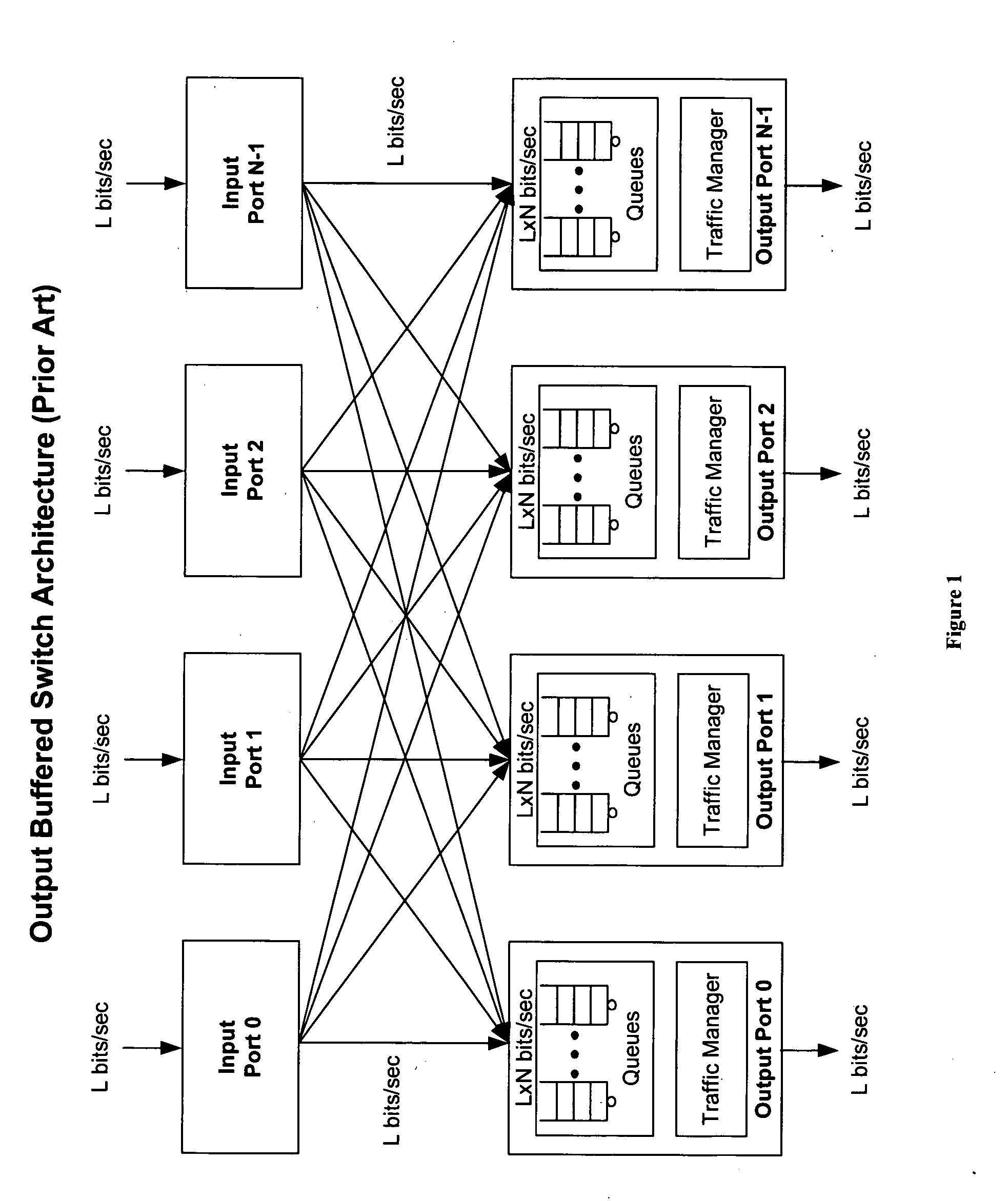

Method of and system for physically distributed, logically shared, and data slice-synchronized shared memory switching

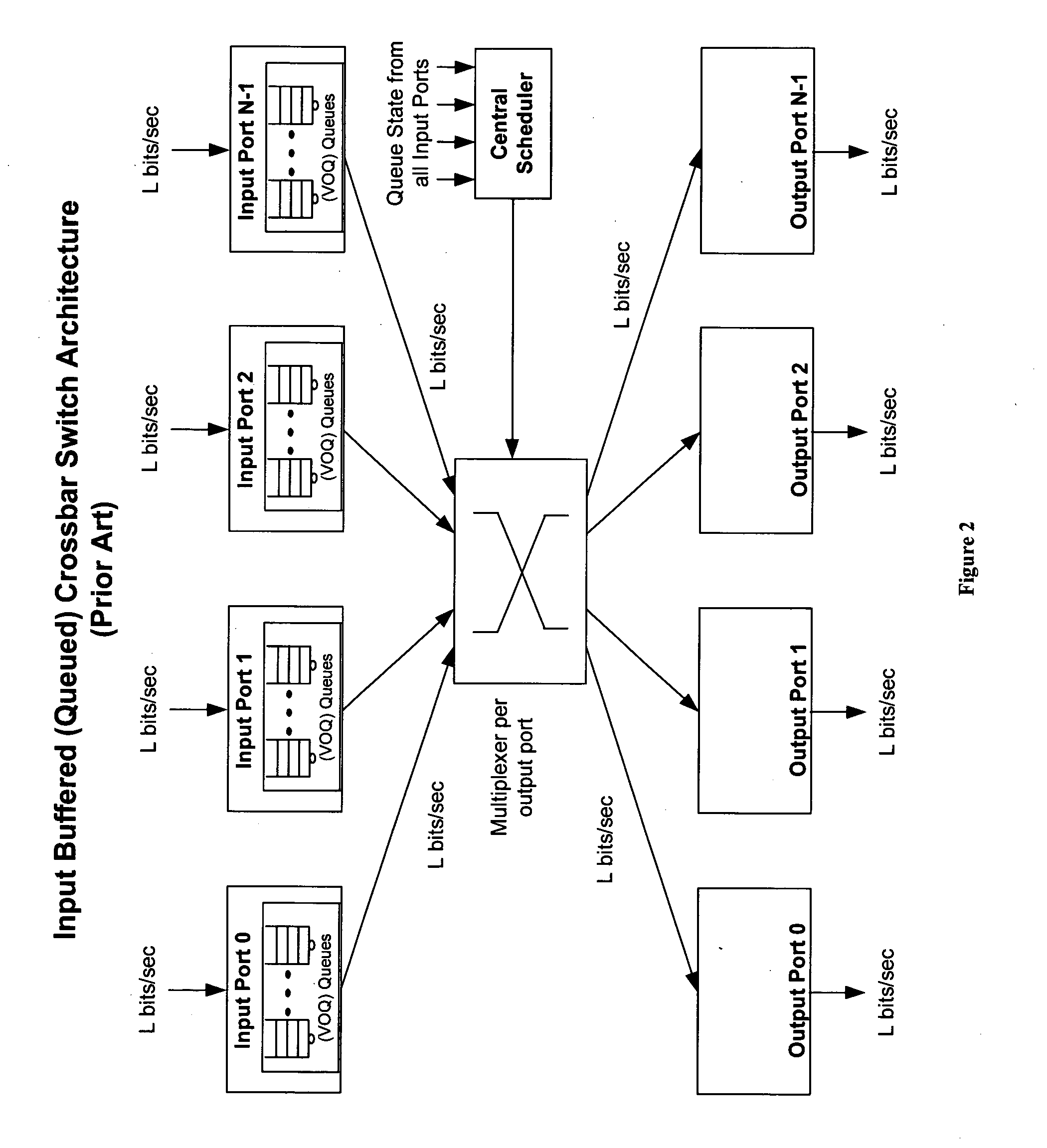

An improved data networking technique and apparatus using a novel physically distributed but logically shared and data-sliced synchronized shared memory switching datapath architecture integrated with a novel distributed data control path architecture to provide ideal output-buffered switching of data in networking systems, such as routers and switches, to support the increasing port densities and line rates with maximized network utilization and with per flow bit-rate latency and jitter guarantees, all while maintaining optimal throughput and quality of services under all data traffic scenarios, and with features of scalability in terms of number of data queues, ports and line rates, particularly for requirements ranging from network edge routers to the core of the network, thereby to eliminate both the need for the complication of centralized control for gathering system-wide information and for processing the same for egress traffic management functions and the need for a centralized scheduler, and eliminating also the need for buffering other than in the actual shared memory itself,—all with complete non-blocking data switching between ingress and egress ports, under all circumstances and scenarios.

Owner:QOS LOGIX

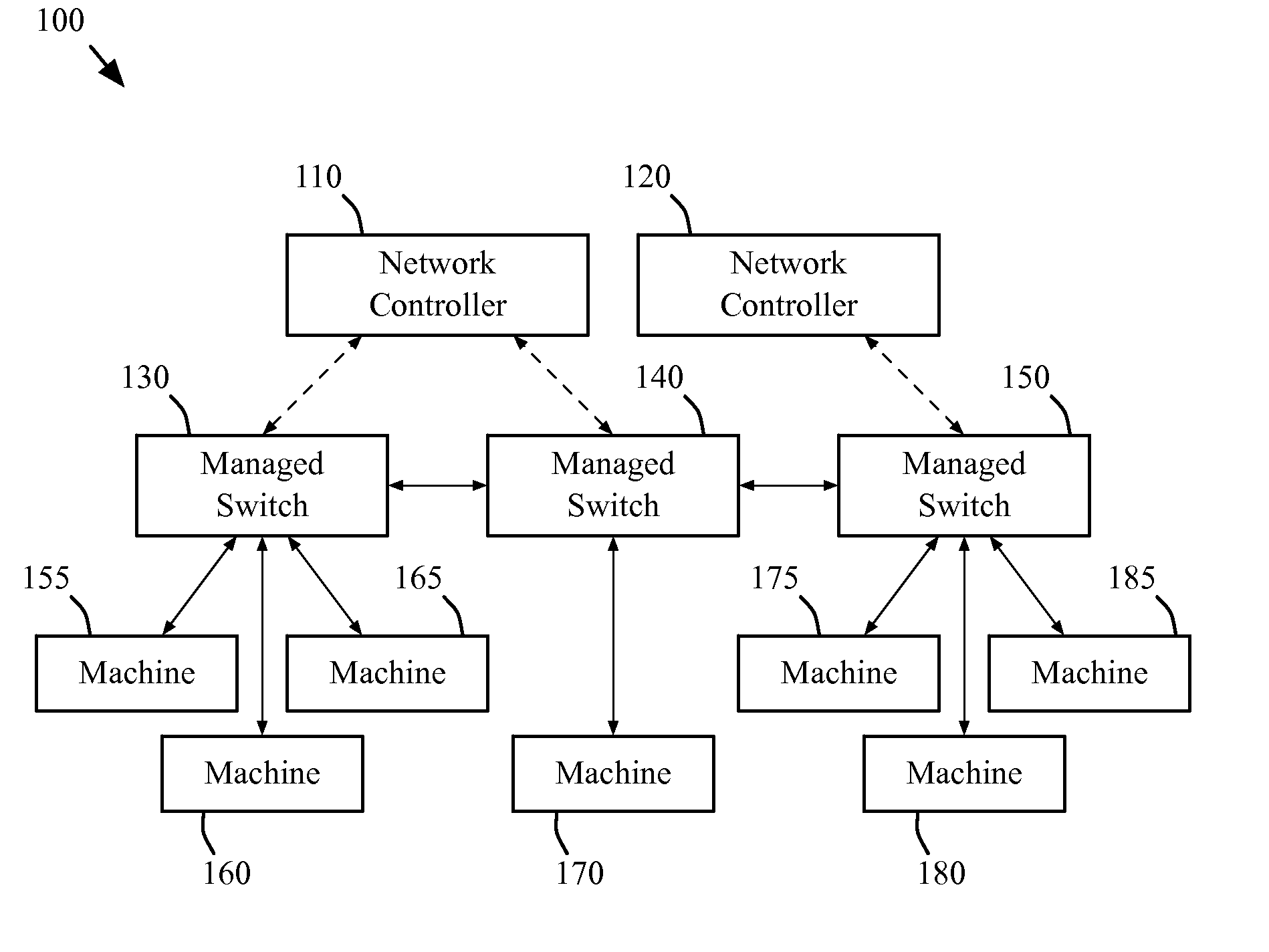

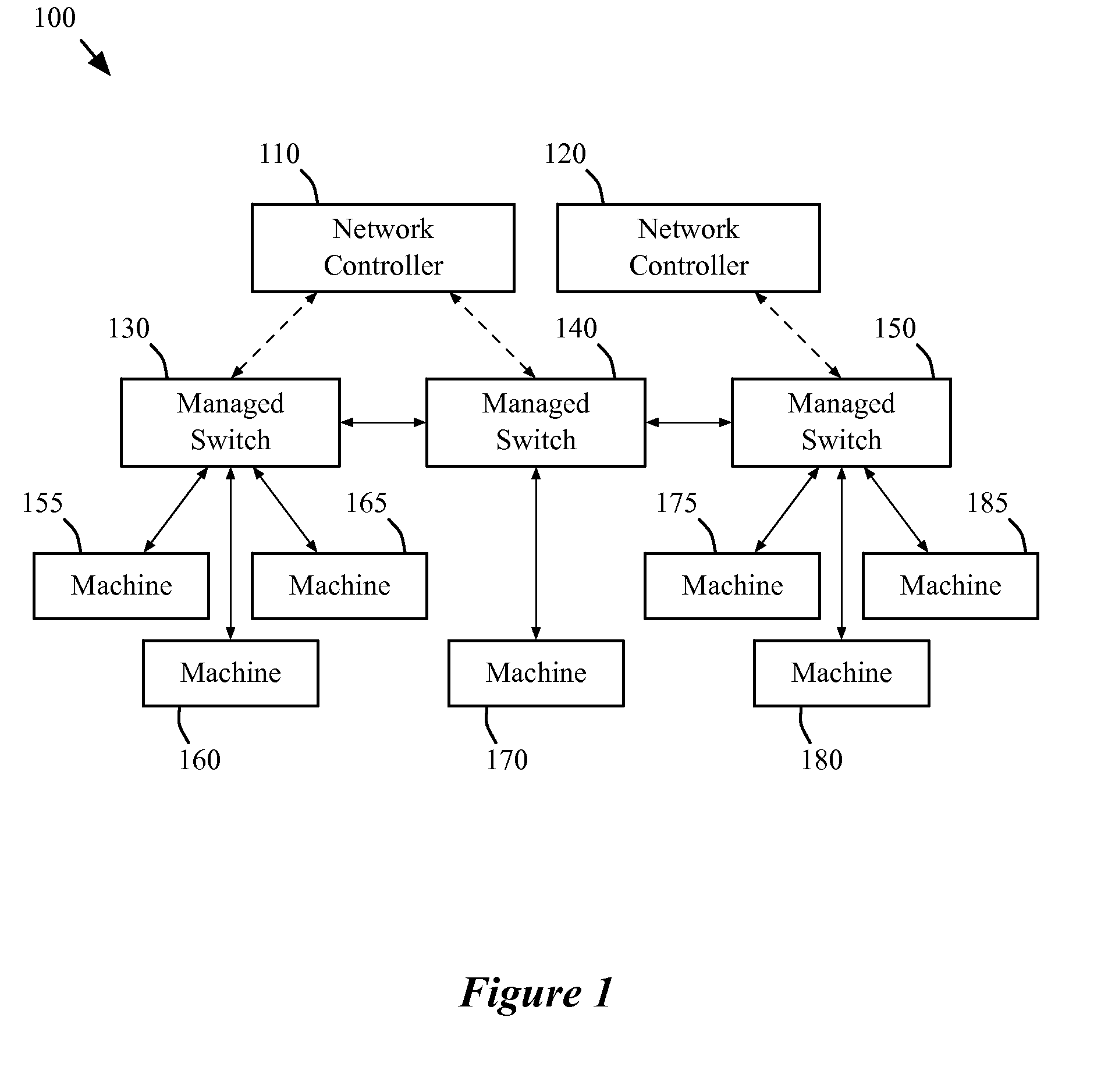

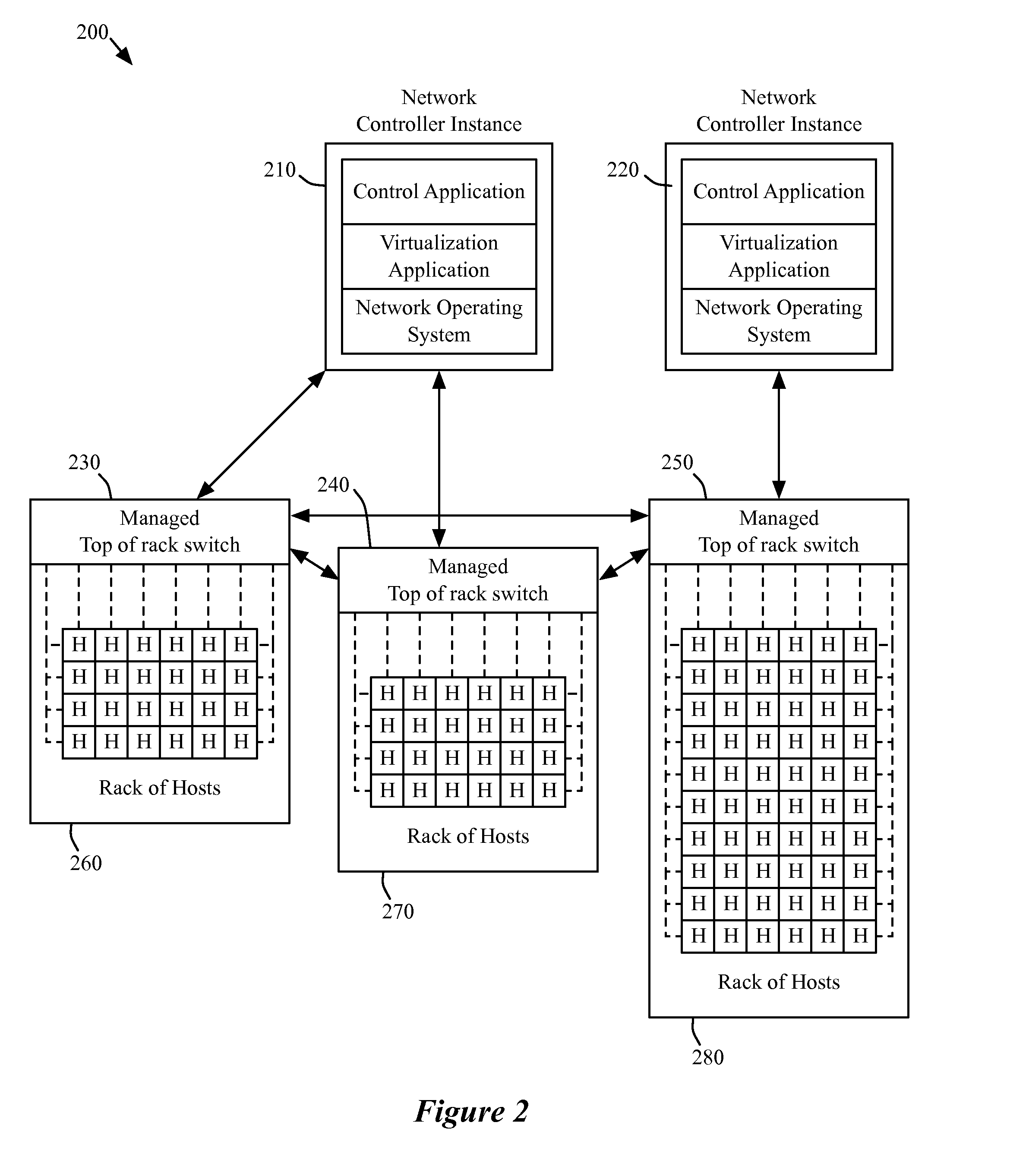

Chassis controller

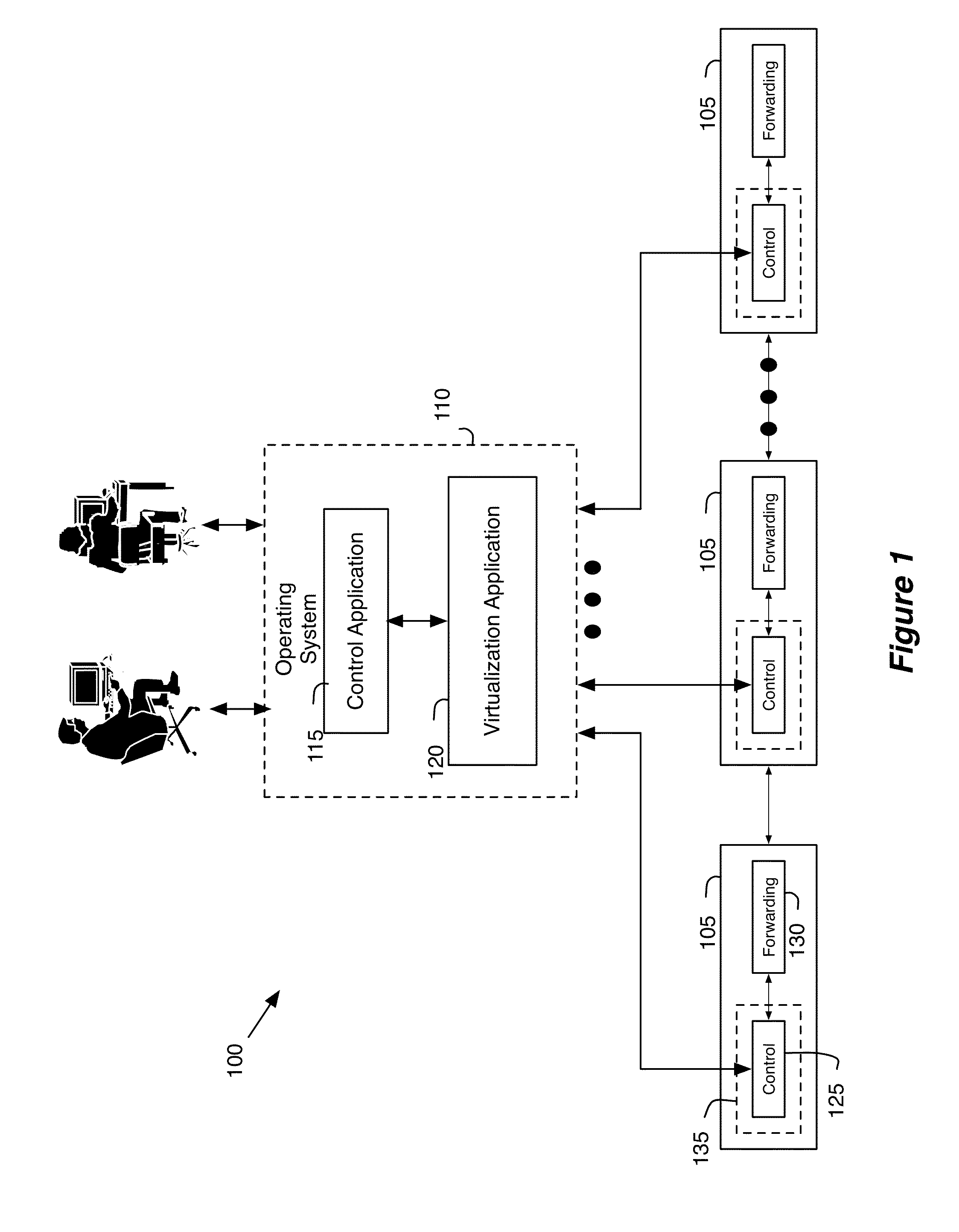

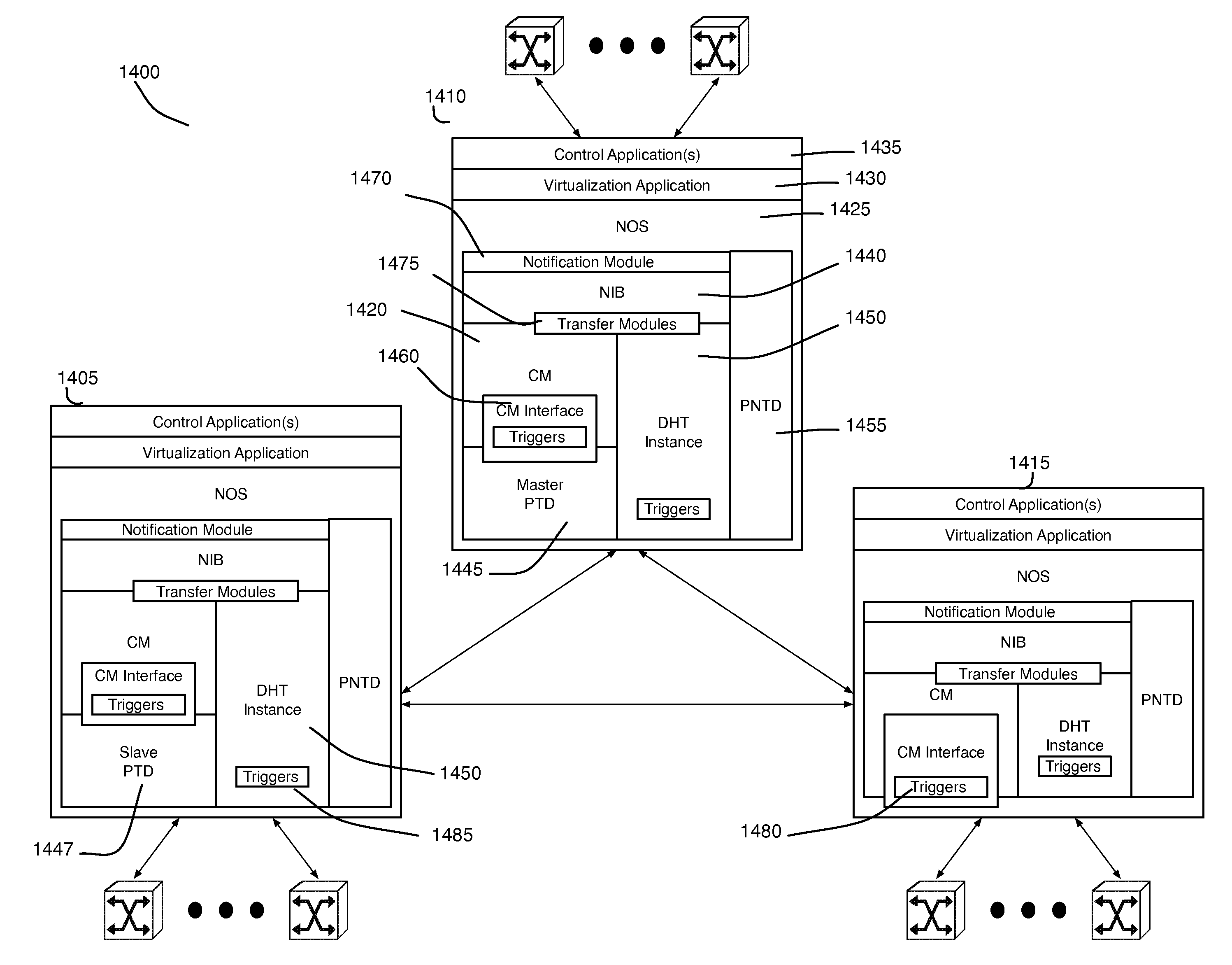

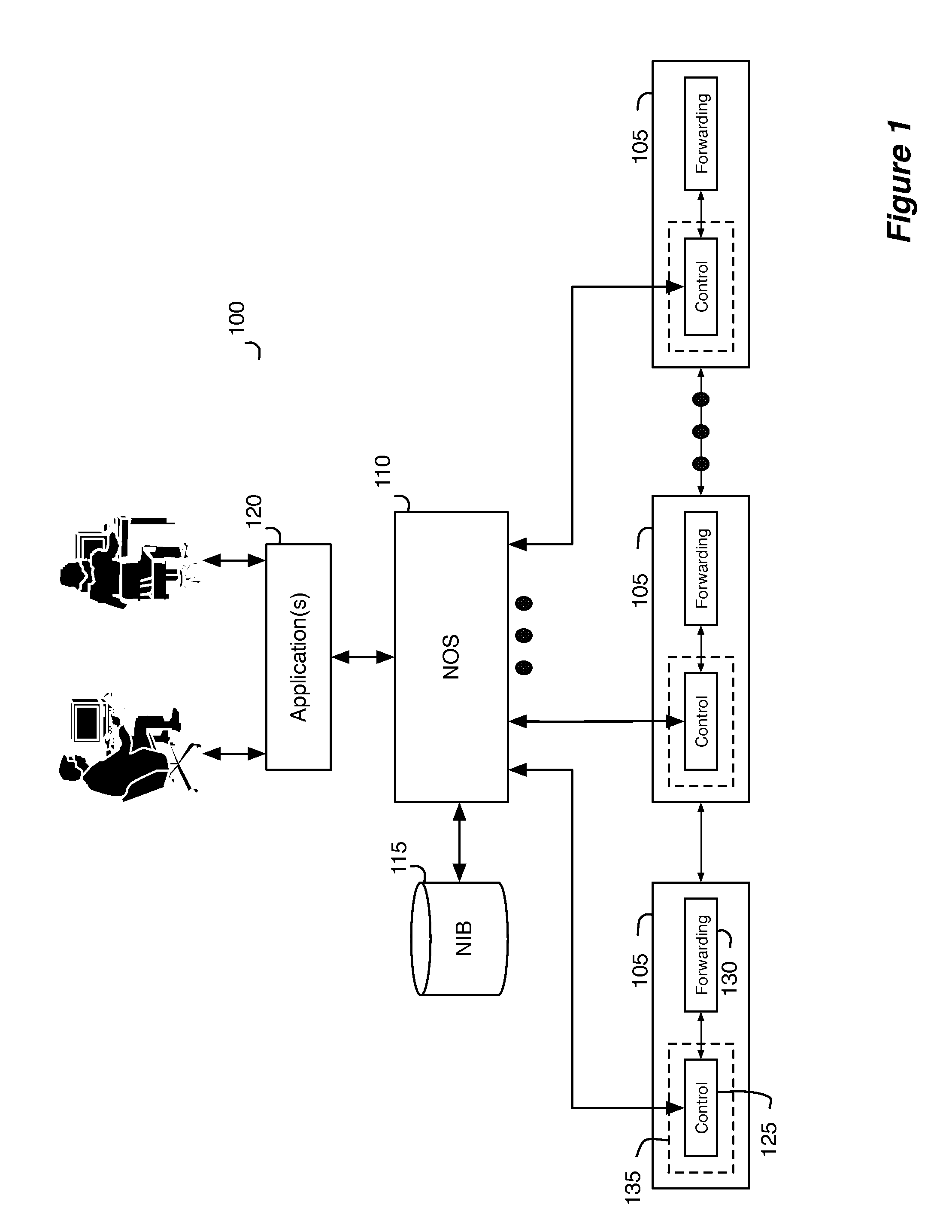

ActiveUS20130103817A1Avoid becoming scalability bottleneckControl volumeDigital computer detailsElectric controllersNetwork controlDatapath

A network control system for generating physical control plane data for managing first and second managed forwarding elements that implement forwarding operations associated with a first logical datapath set is described. The system includes a first controller instance for converting logical control plane data for the first logical datapath set to universal physical control plane (UPCP) data. The system further includes a second controller instance for converting UPCP data to customized physical control plane (CPCP) data for the first managed forwarding element but not the second managed forwarding element. The system further includes a third controller instance for receiving UPCP data generated by the first controller instance, identifying the second controller instance as the controller instance responsible for generating the CPCP data for the first managed forward element, and supplying the received UPCP data to the second controller instance.

Owner:NICIRA

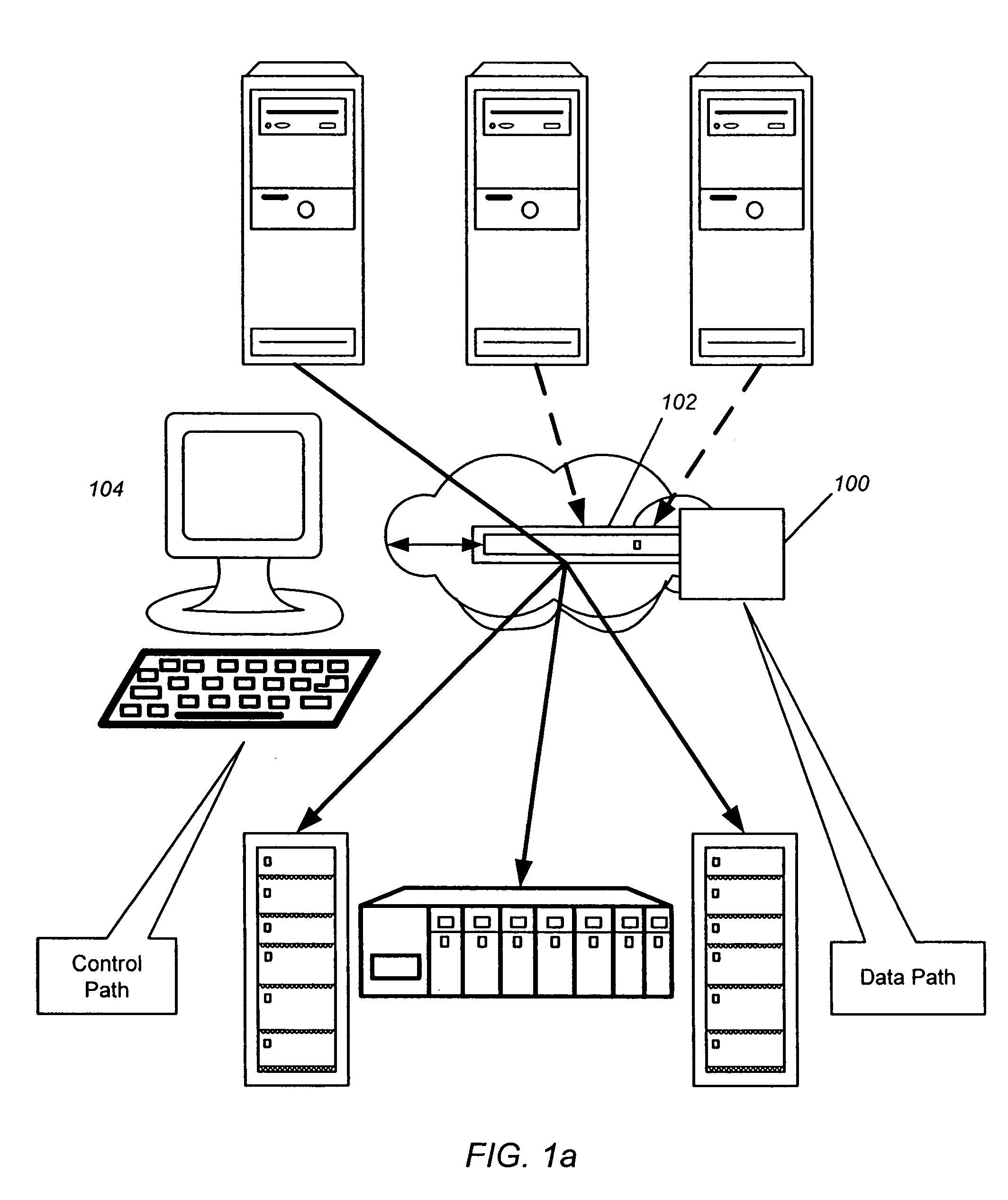

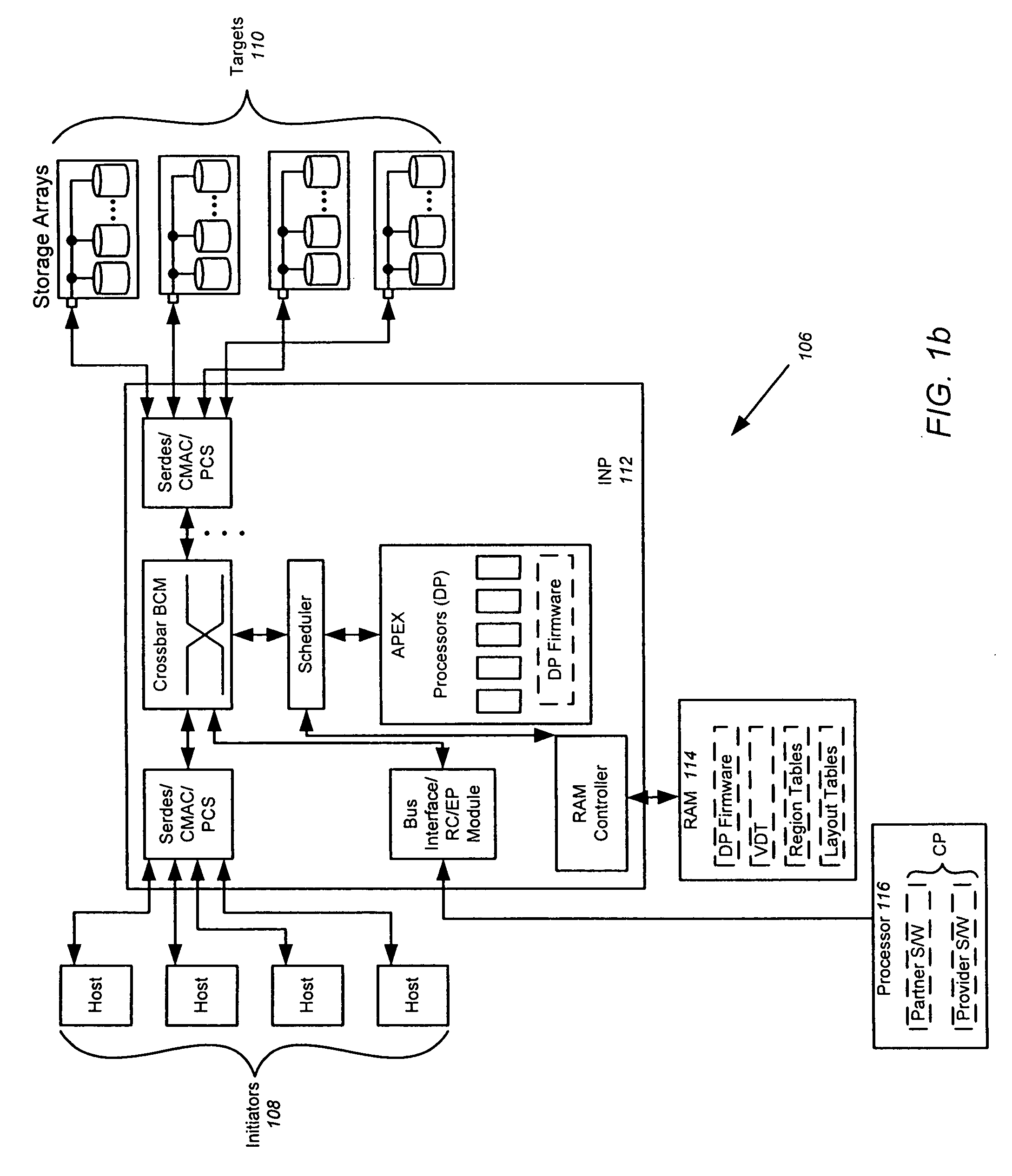

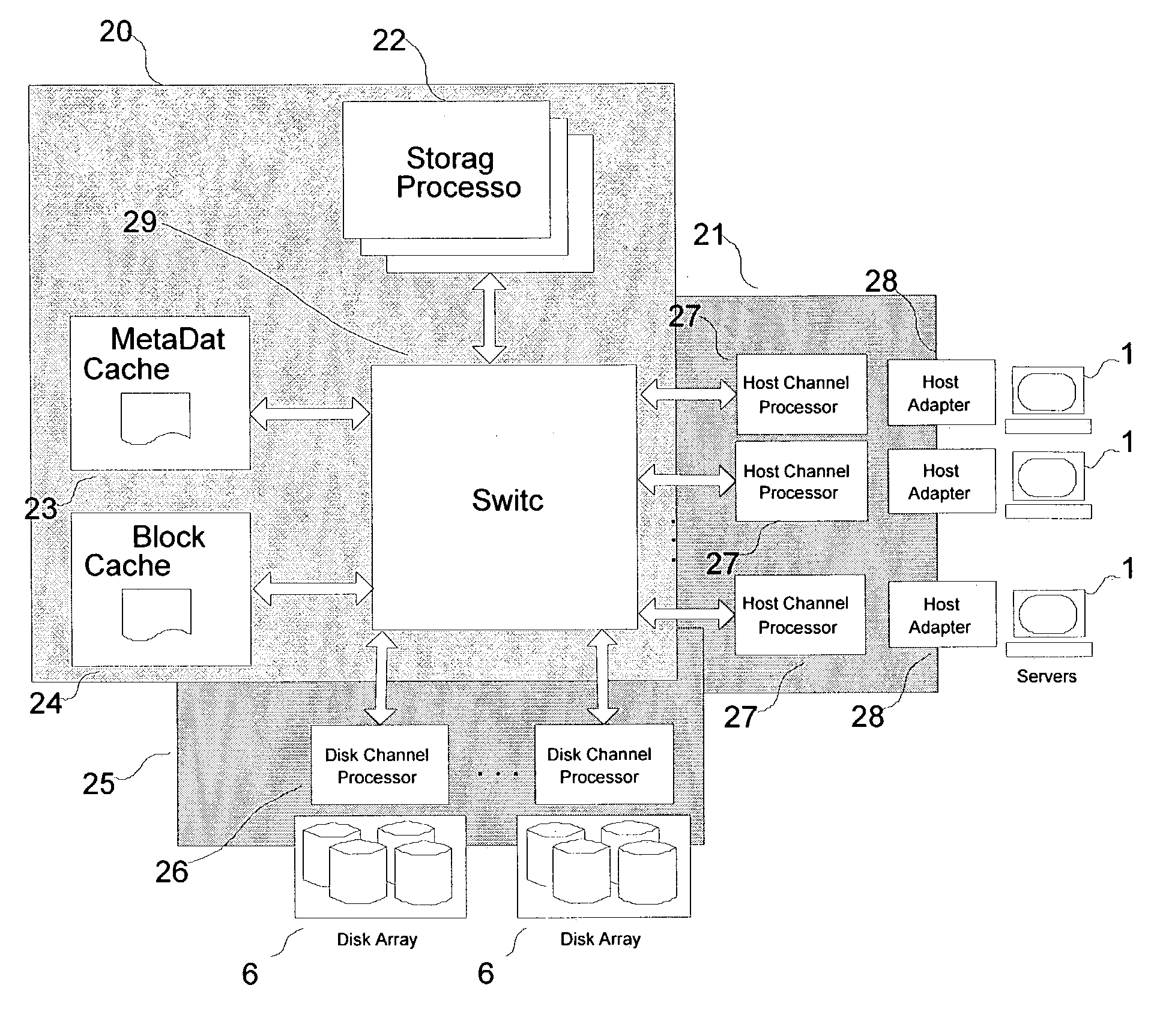

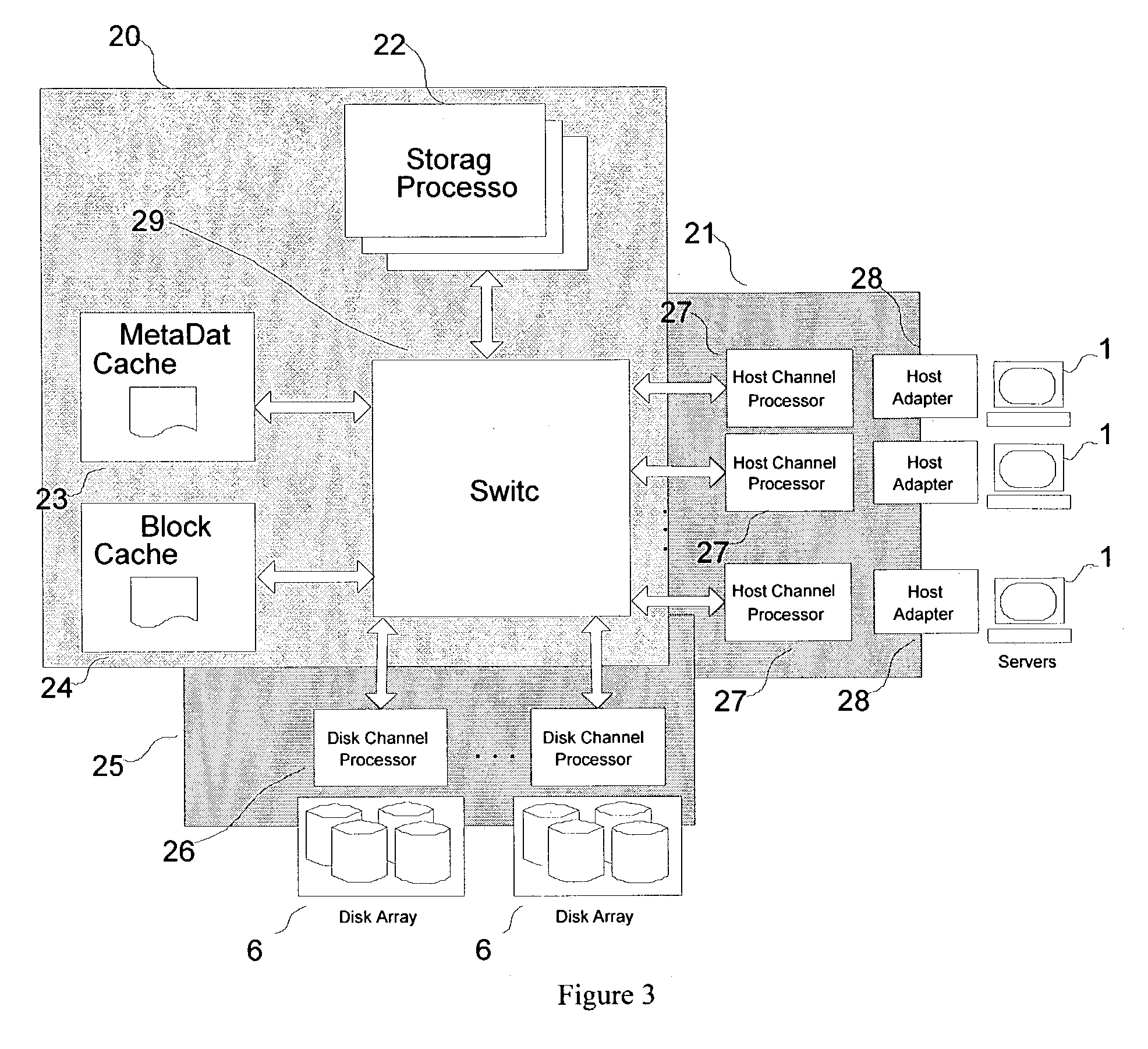

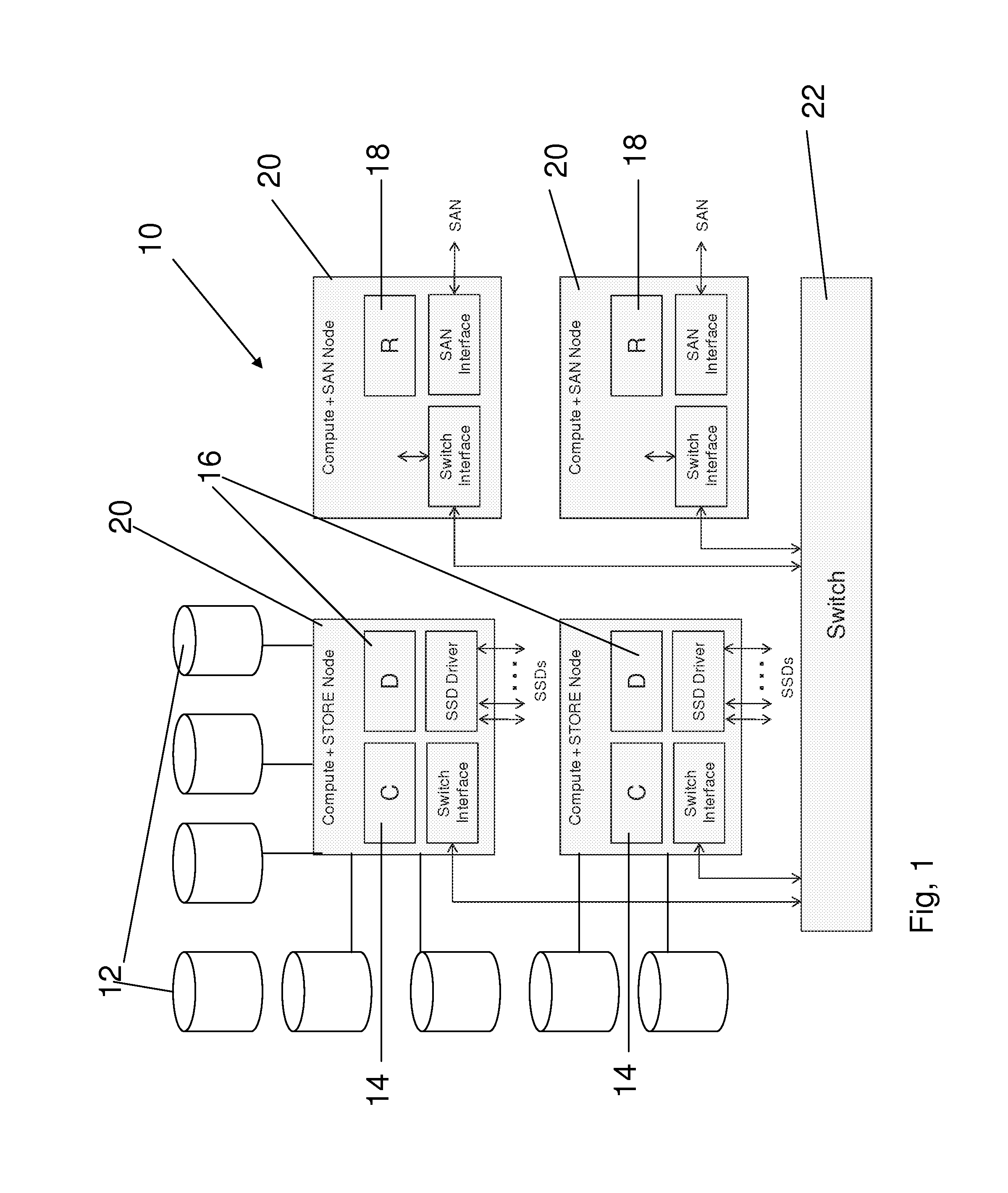

Method and apparatus for efficient scalable storage management

ActiveUS7181578B1Improve performanceSolve the lack of spaceMemory systemsInput/output processes for data processingHandling systemDatapath

A hybrid centralized and distributed processing system includes a switching device that connects a storage processor to one or more servers through a host channel processor. The switching device also connects the storage processor to one or more storage devices such as disk drive arrays, and to a metadata cache and a block data cache memory. The storage processor processes access request from one or more servers in the form of a logical volume or logical block address and accesses the metadata cache to determine the physical data address. The storage processor monitors the performance of the storage system and performs automatic tuning by reallocating the logical volume, load balancing, hot spot removal, and dynamic expansion of storage volume. The storage processor also provides fault-tolerant access and provides parallel high performance data paths for fail over. The storage processor also provides faster access by providing parallel data paths for, making local copies and providing remote data copies, and by selecting data from a storage device that retrieves the data the earliest.

Owner:COPAN SYST INC +1

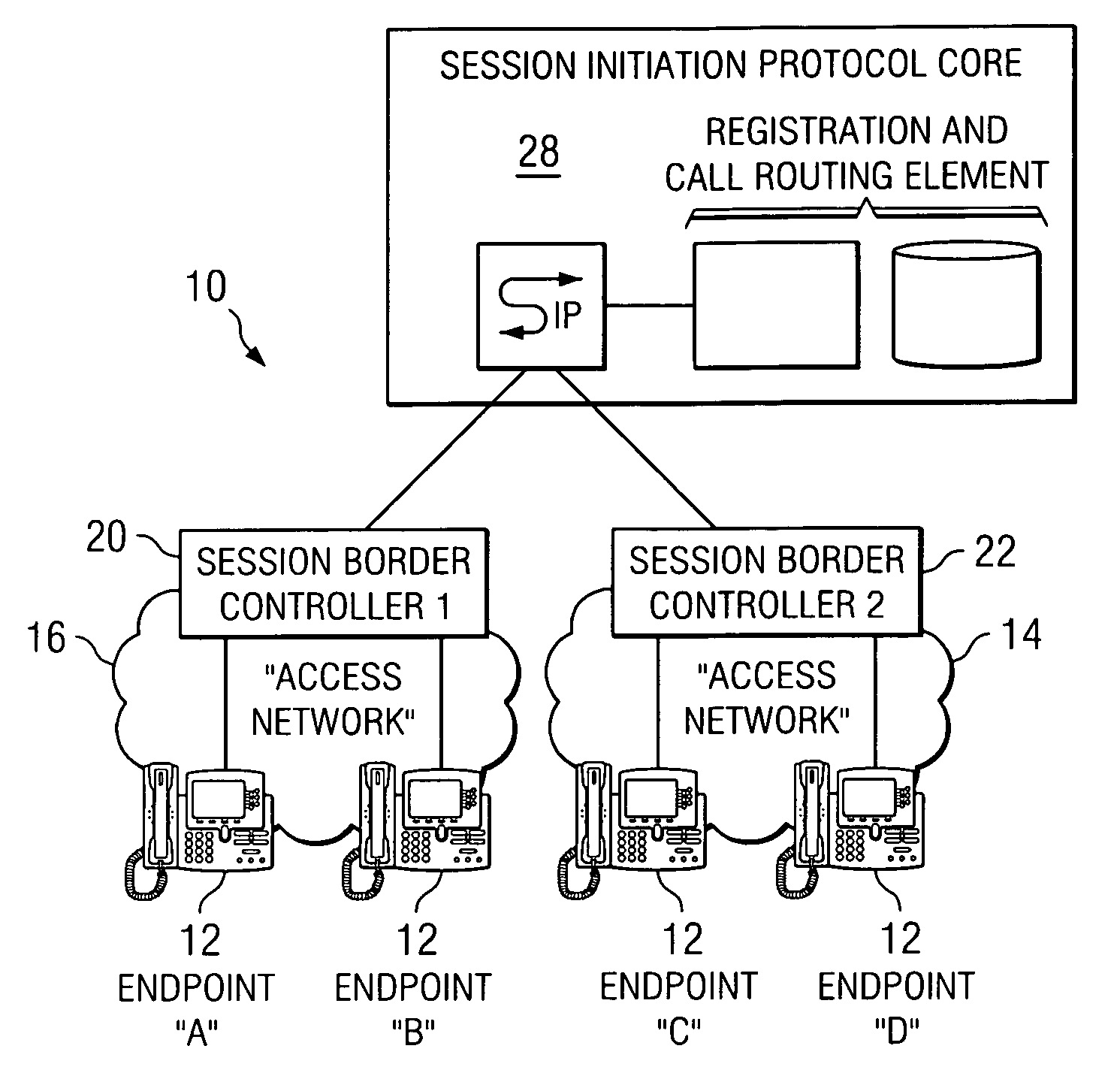

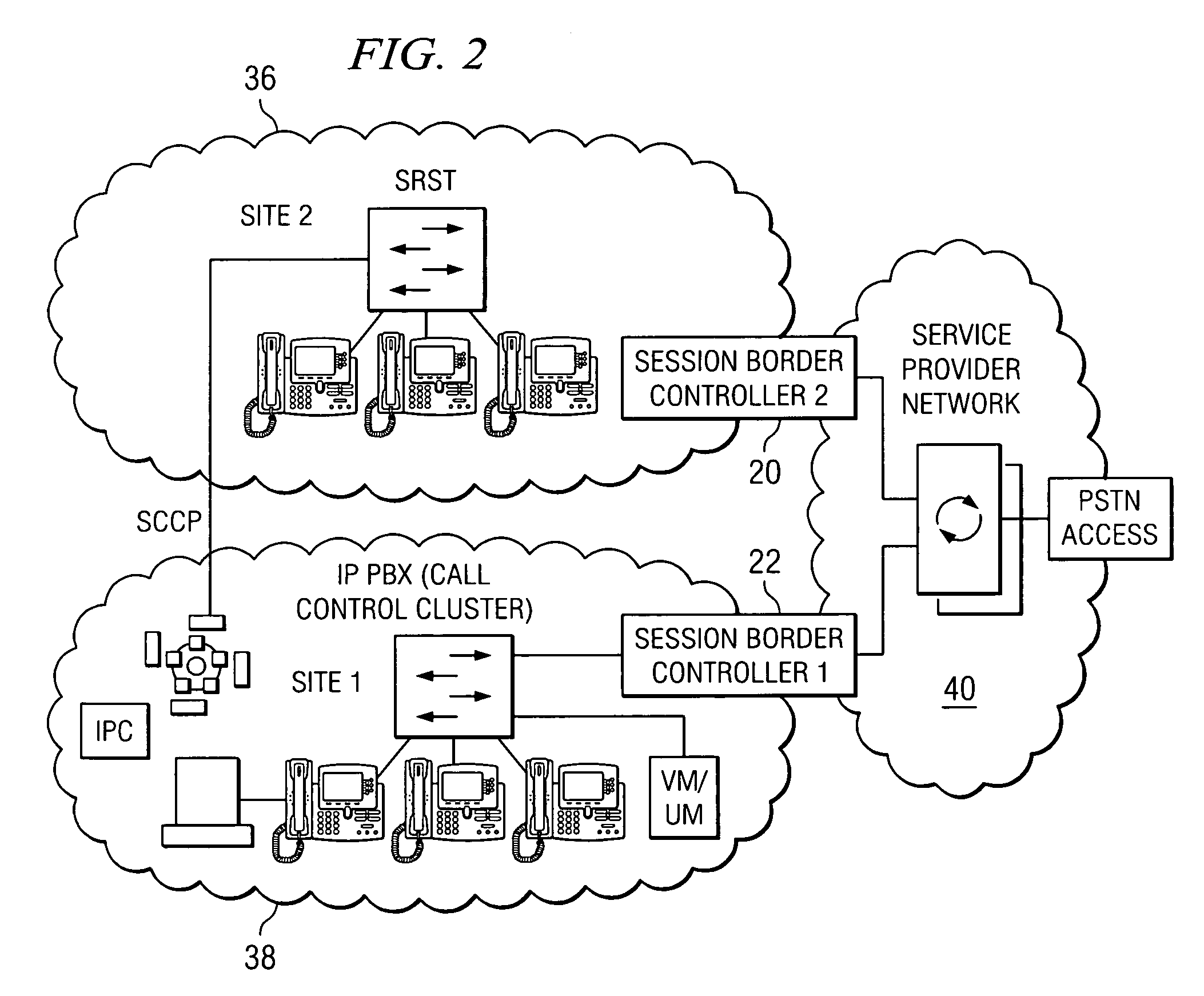

System and method for optimizing communications between session border controllers and enpoints in a network environment

ActiveUS20070019619A1Reduce disadvantagesReduce problemsMultiplex system selection arrangementsSpecial service provision for substationDatapathSession border controller

An apparatus for optimizing communications between session border controllers in a network environment is provided that includes a session border controller (SBC) operable to communicate with a first endpoint and a second endpoint. The SBC is also operable to communicate with a data path border element (DBE) and a signaling path border element (SBE). The DBE is operable to provide a media relay for a communication session involving the endpoints, the media relay being invoked by either of the endpoints using a traversal using relay network address translation (TURN) protocol, which allows the SBC to operate in either of two modes depending on protocol support present in the endpoints.

Owner:CISCO TECH INC

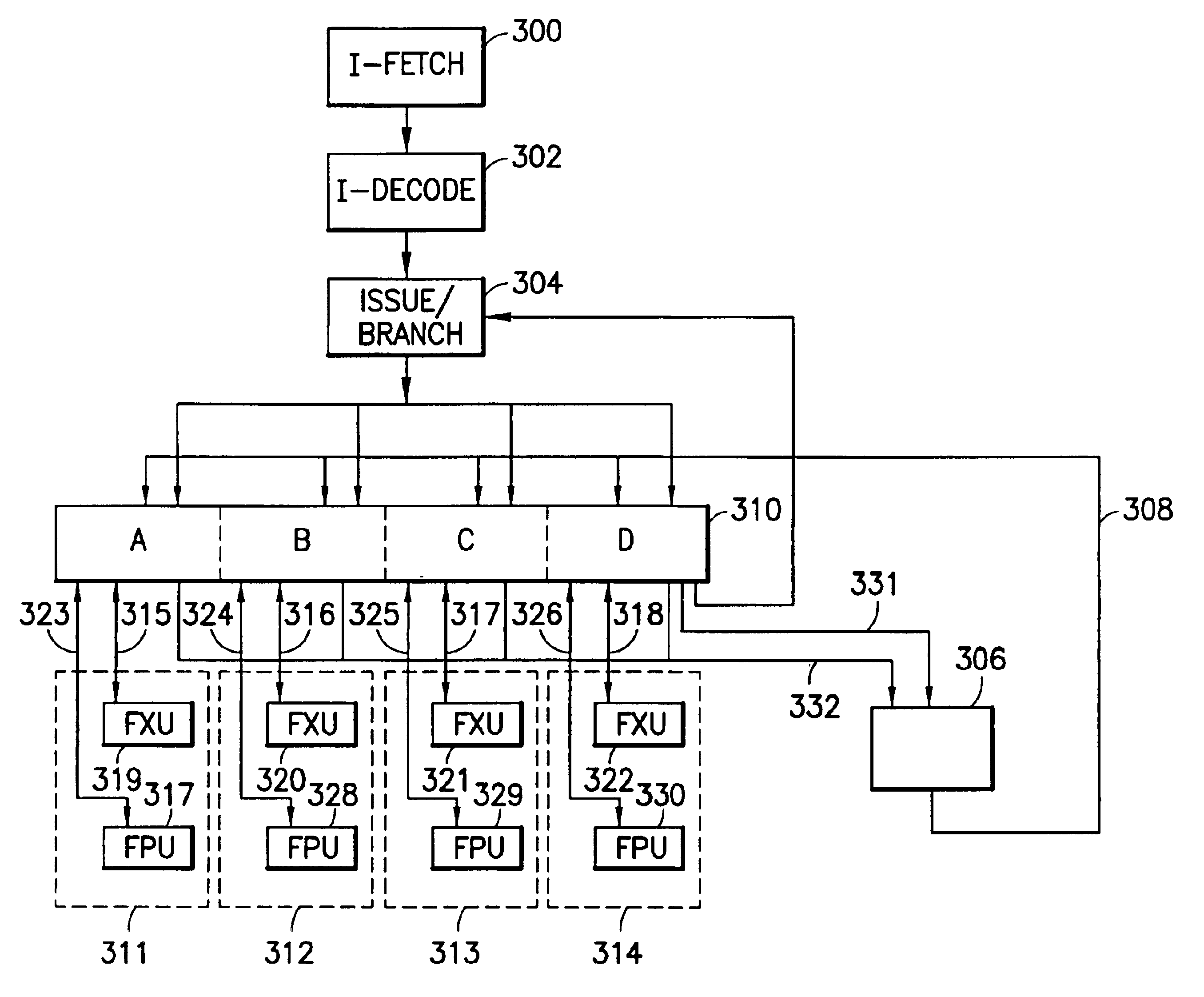

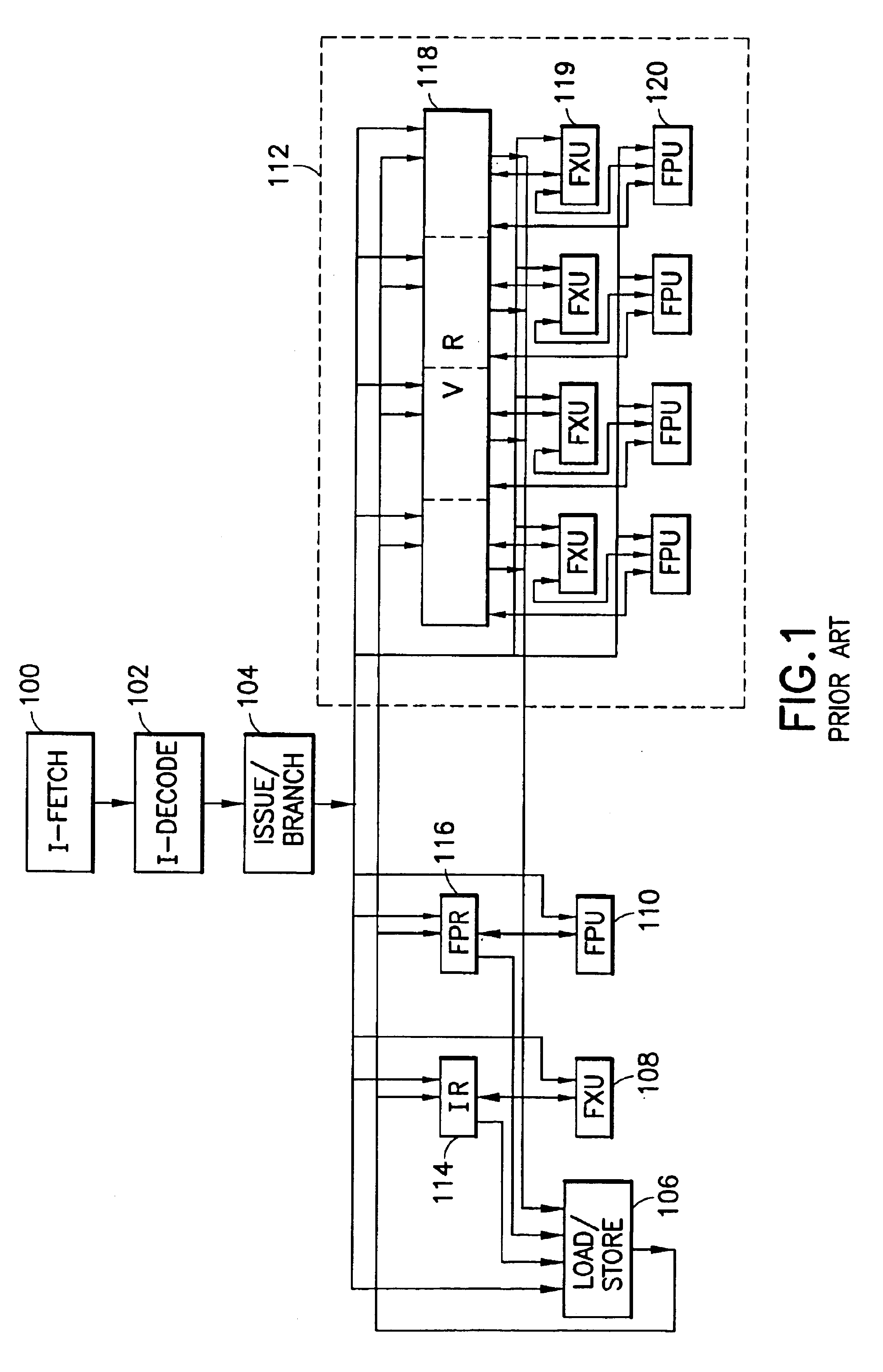

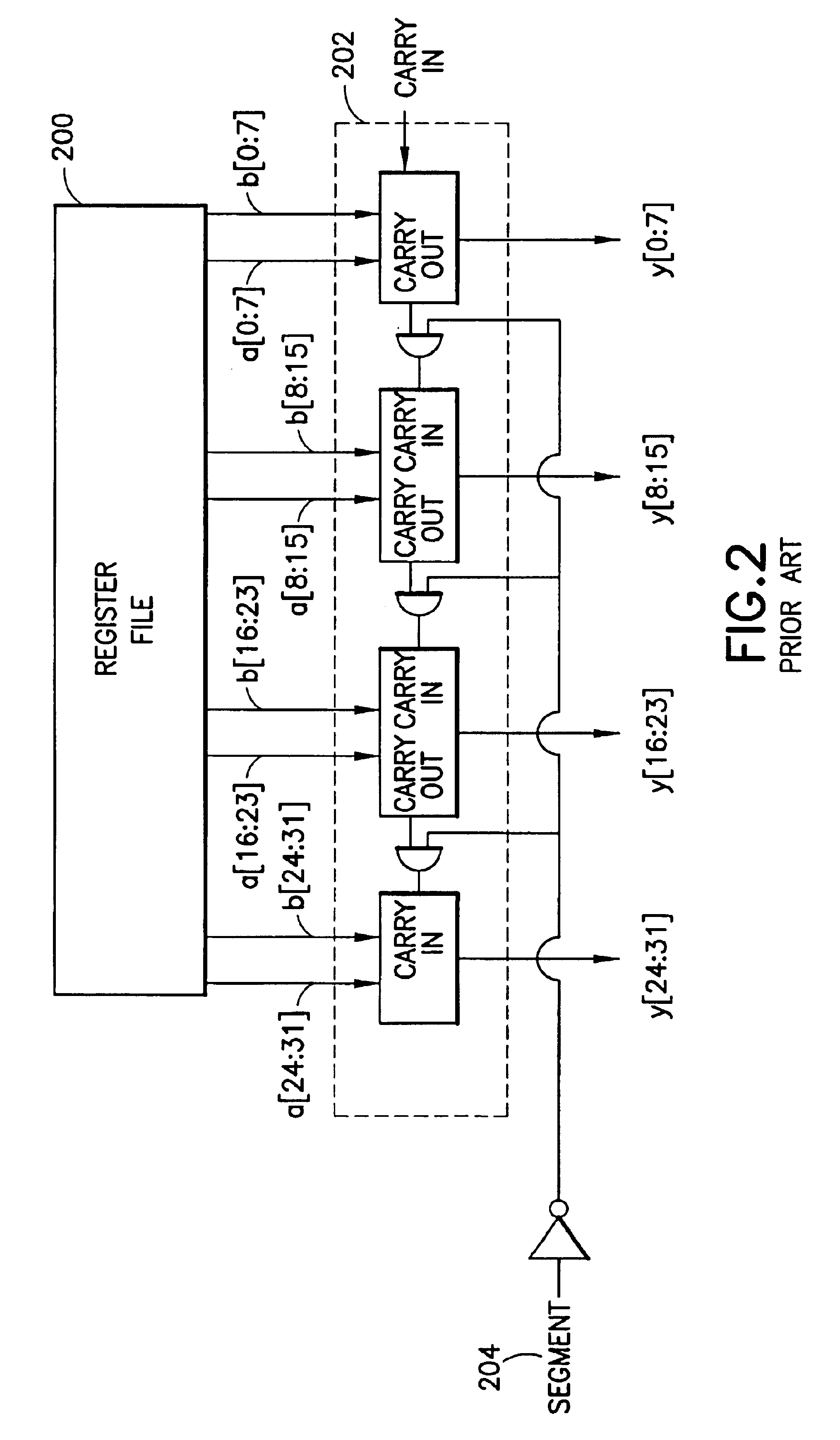

SIMD datapath coupled to scalar/vector/address/conditional data register file with selective subpath scalar processing mode

InactiveUS6839828B2Not compromise SIMD data processing performanceReduce consumptionRegister arrangementsDigital data processing detailsProcessor registerOperation mode

There is provided a processor designed to operate in a plurality of modes for processing vector and scalar instructions. Register files are each for storing scalar and vector data and address information. A parallel vector unit, coupled to the register files, includes functional units configurable to operate in a vector operation mode and a scalar operation mode. The vector unit includes an apparatus for tightly coupling the functional units to perform an operation specified by a current instruction. Under a vector operation mode, the vector unit performs, in parallel, a single vector operation on a plurality of data elements. The operations performed on the plurality of data elements are each performed by a different functional unit of the vector unit. Under a scalar operation mode, the vector unit performs a scalar operation on a data element received from the register files in a functional unit within the vector unit.

Owner:INTEL CORP

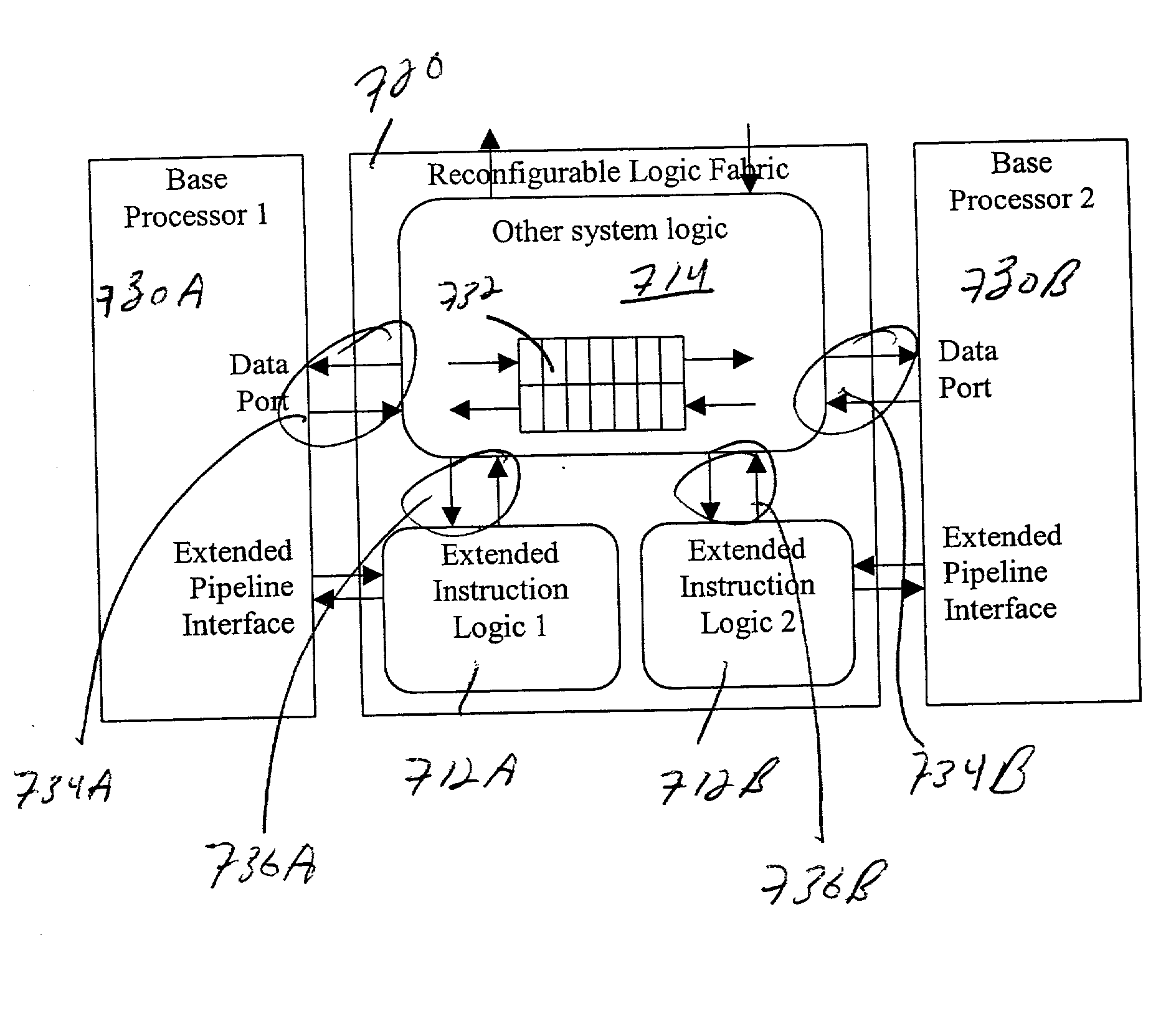

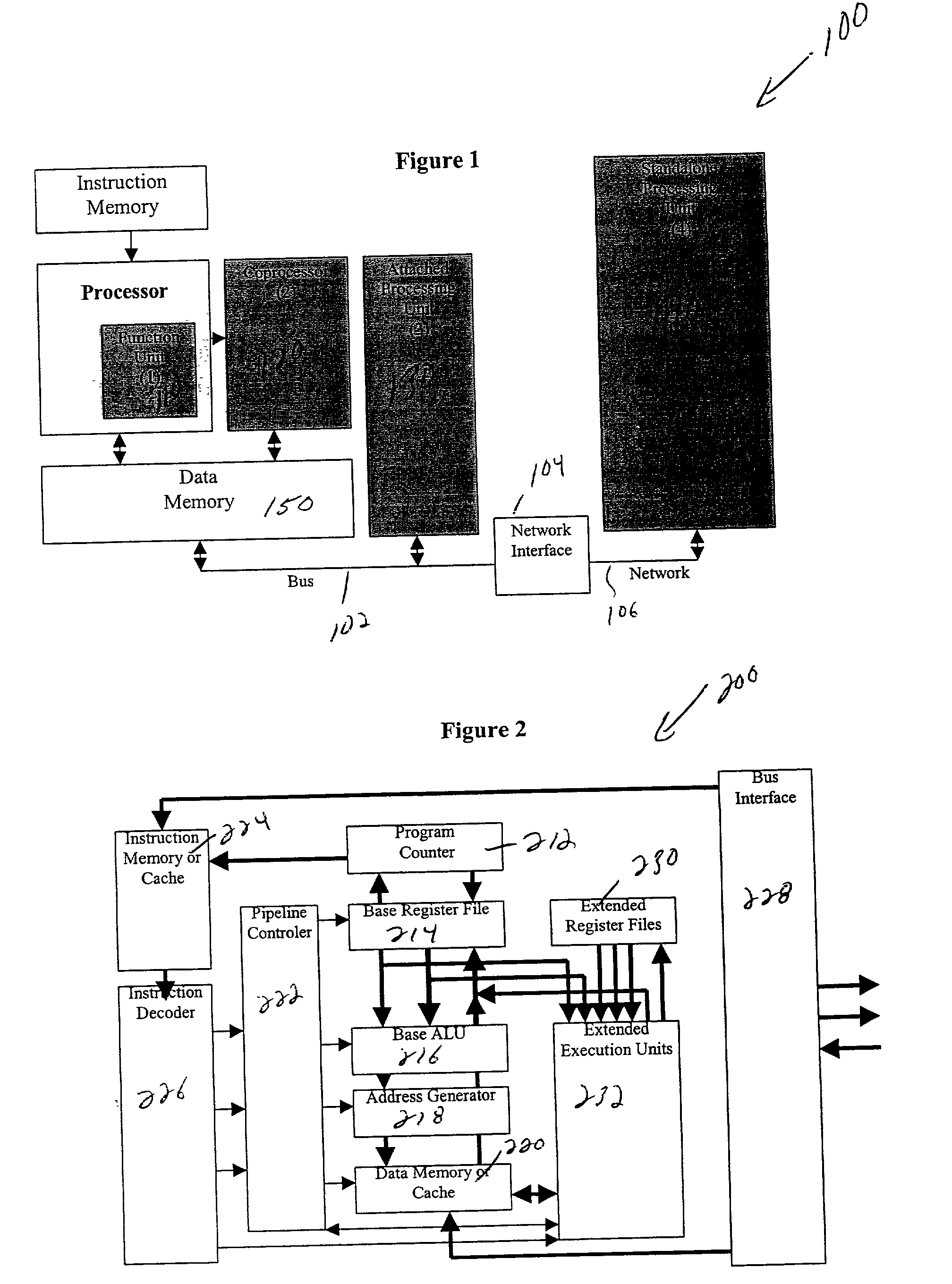

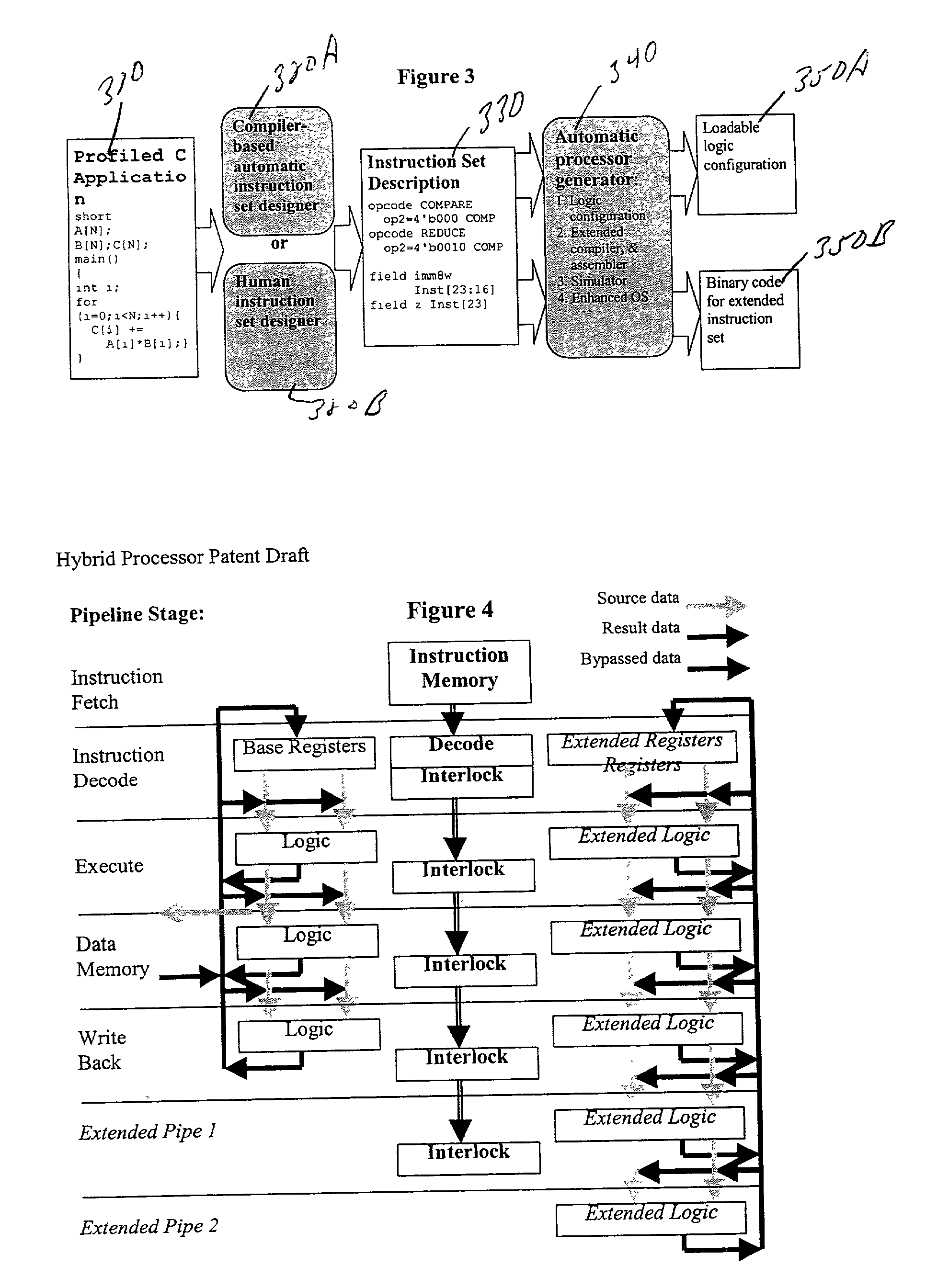

High-performance hybrid processor with configurable execution units

InactiveUS20050166038A1High bandwidthFlexibilityInstruction analysisConcurrent instruction executionHigh bandwidthLatency (engineering)

A new general method for building hybrid processors achieves higher performance in applications by allowing more powerful, tightly-coupled instruction set extensions to be implemented in reconfigurable logic. New instructions set configurations can be discovered and designed by automatic and semi-automatic methods. Improved reconfigurable execution units support deep pipelining, addition of additional registers and register files, compound instructions with many source and destination registers and wide data paths. New interface methods allow lower latency, higher bandwidth connections between hybrid processors and other logic.

Owner:TENSILICA

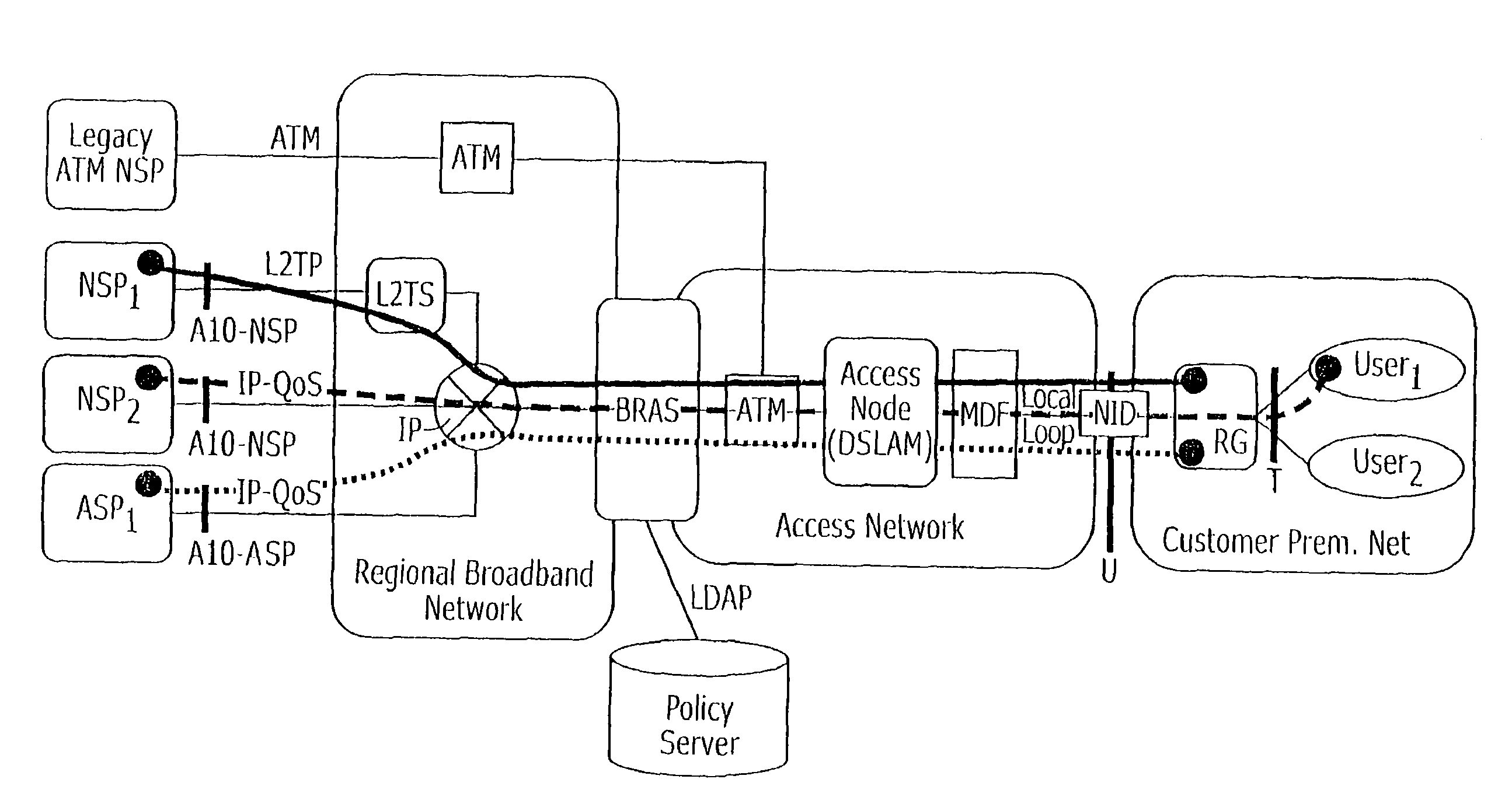

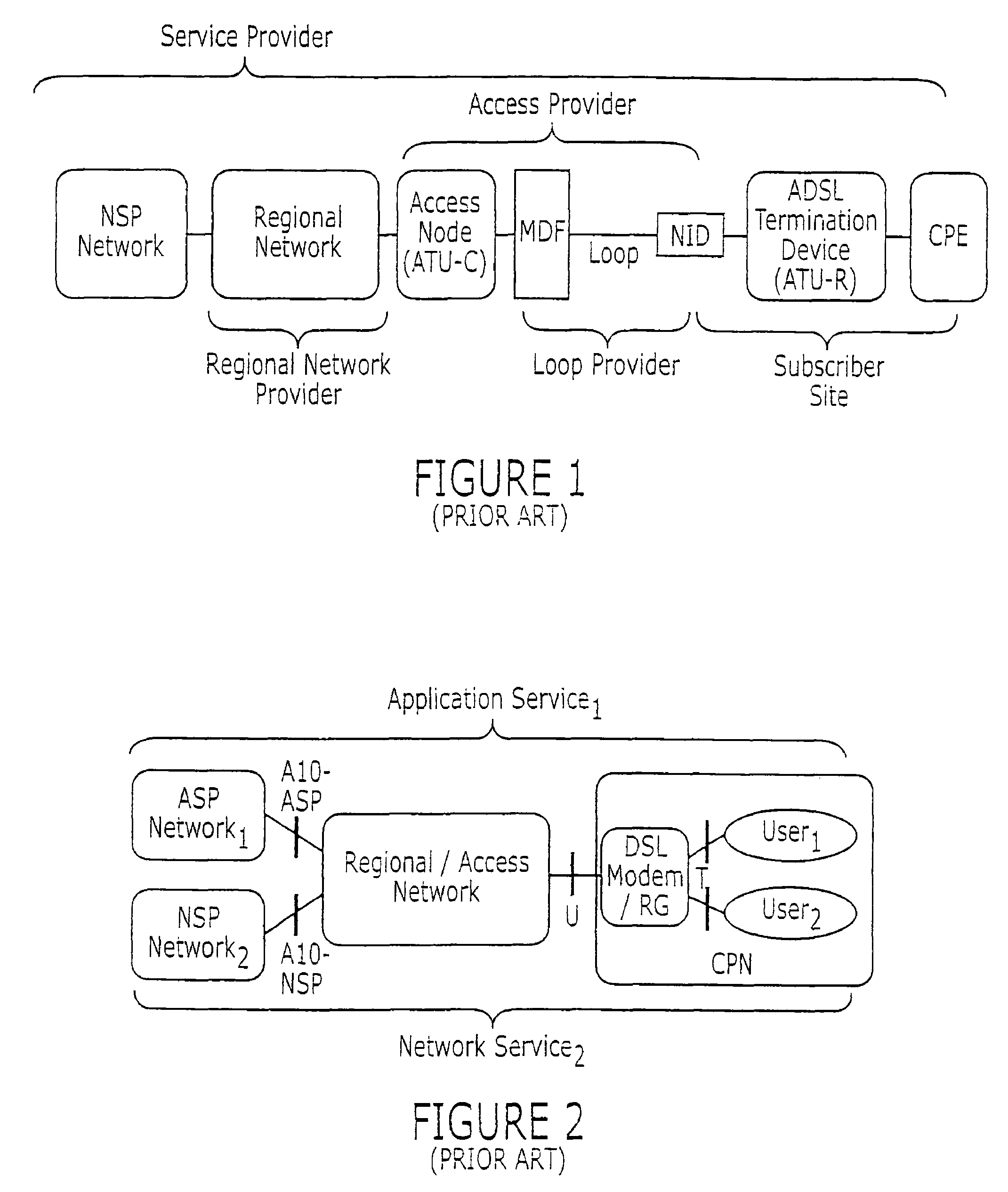

Methods of implementing dynamic QoS and/or bandwidth provisioning and related data networks, data service providers, routing gateways, and computer program products

Owner:AT&T INTPROP I LP

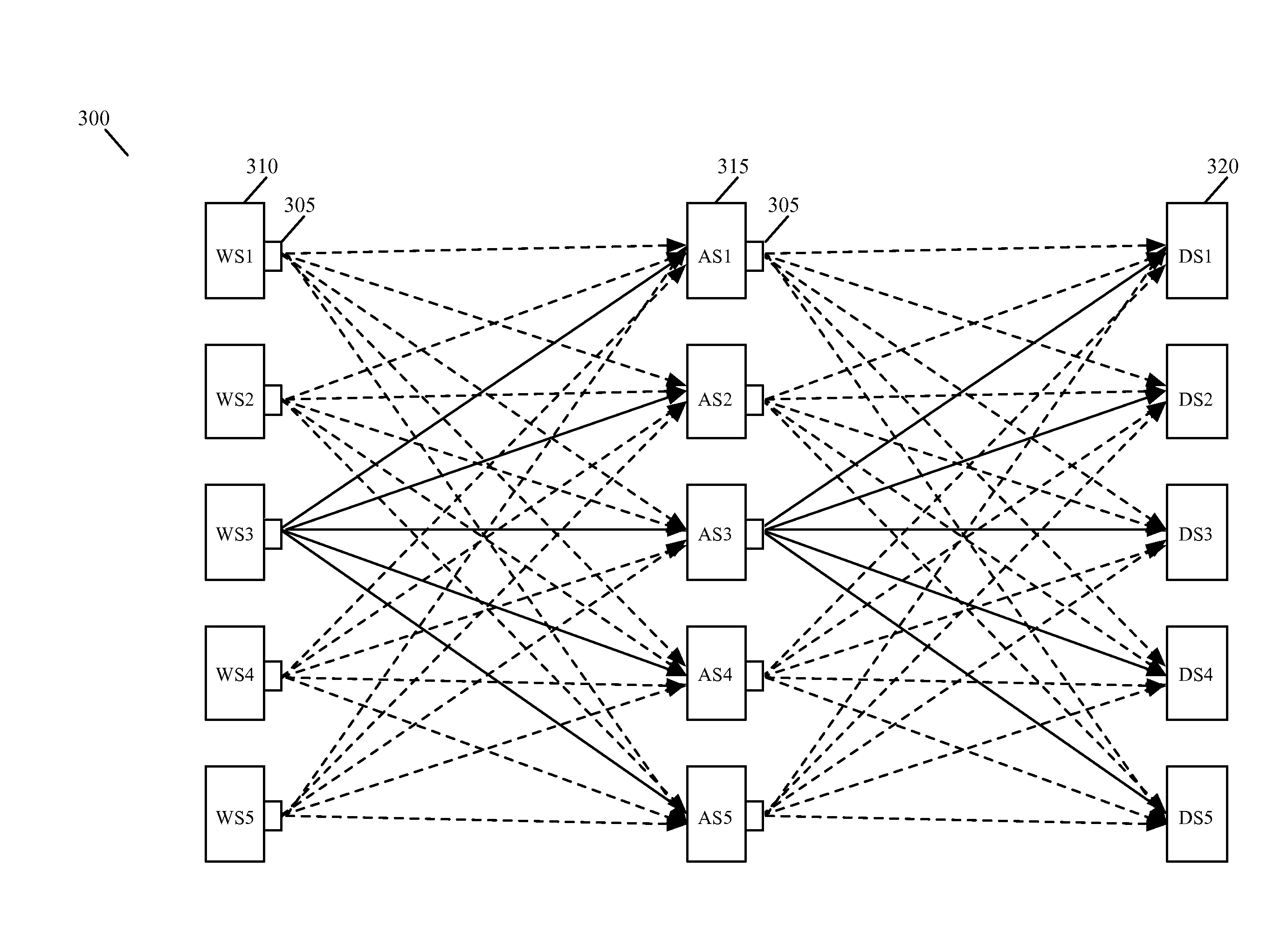

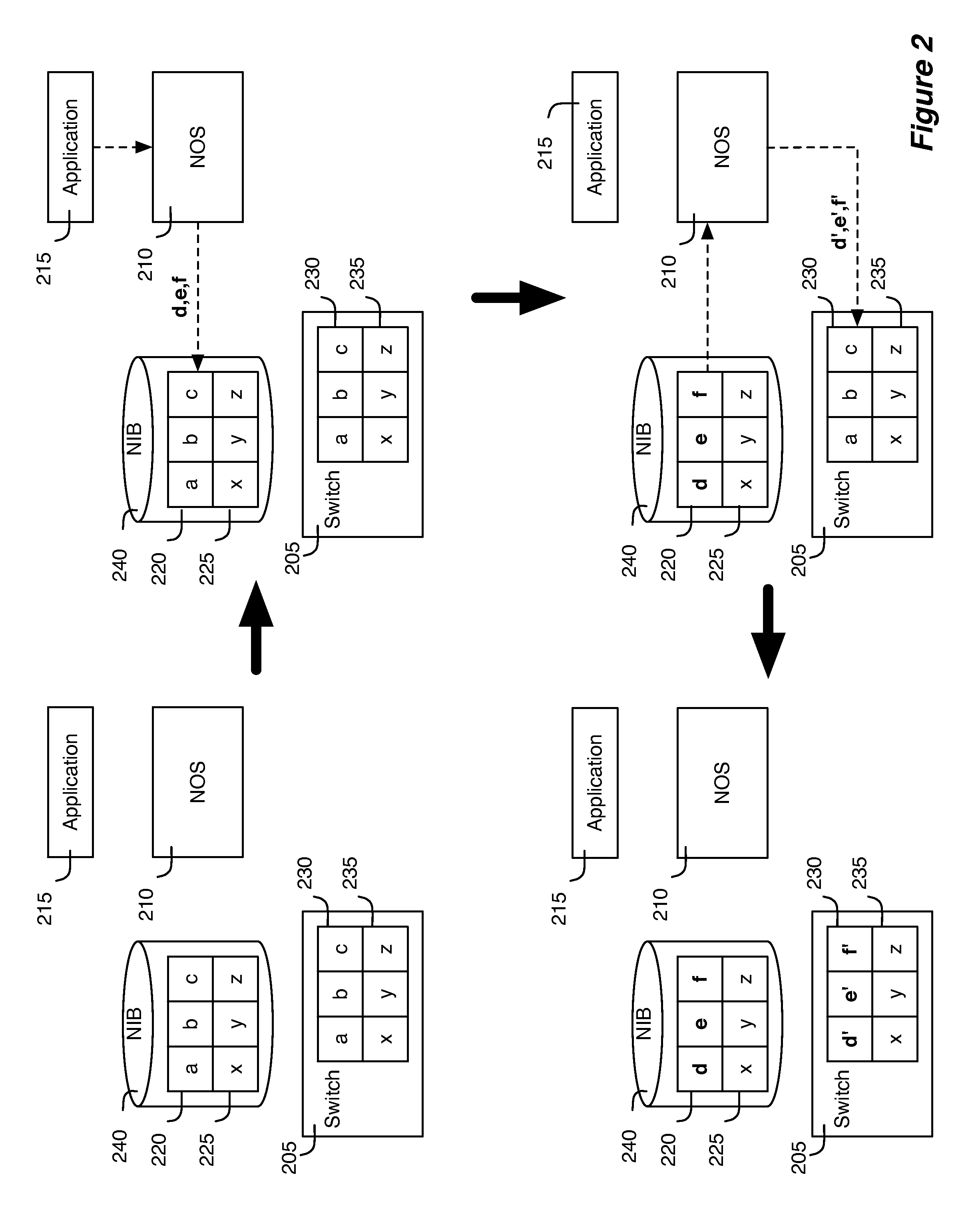

Packet processing for logical datapath sets

Some embodiments provide a method that processes network data through a network. The method receives a packet destined for a network host associated with a logical datapath set implemented by a set of managed edge switching elements and a set of managed non-edge switching elements in the network. The method determines whether the packet is a known packet. When the packet is a known packet, the method forwards the packet to a managed switching element in the set of managed edge switching elements for forwarding to the network host. When the packet is not a known packet, the method forwards the packet to a managed switching element in the set of managed non-edge switching elements for further processing.

Owner:NICIRA

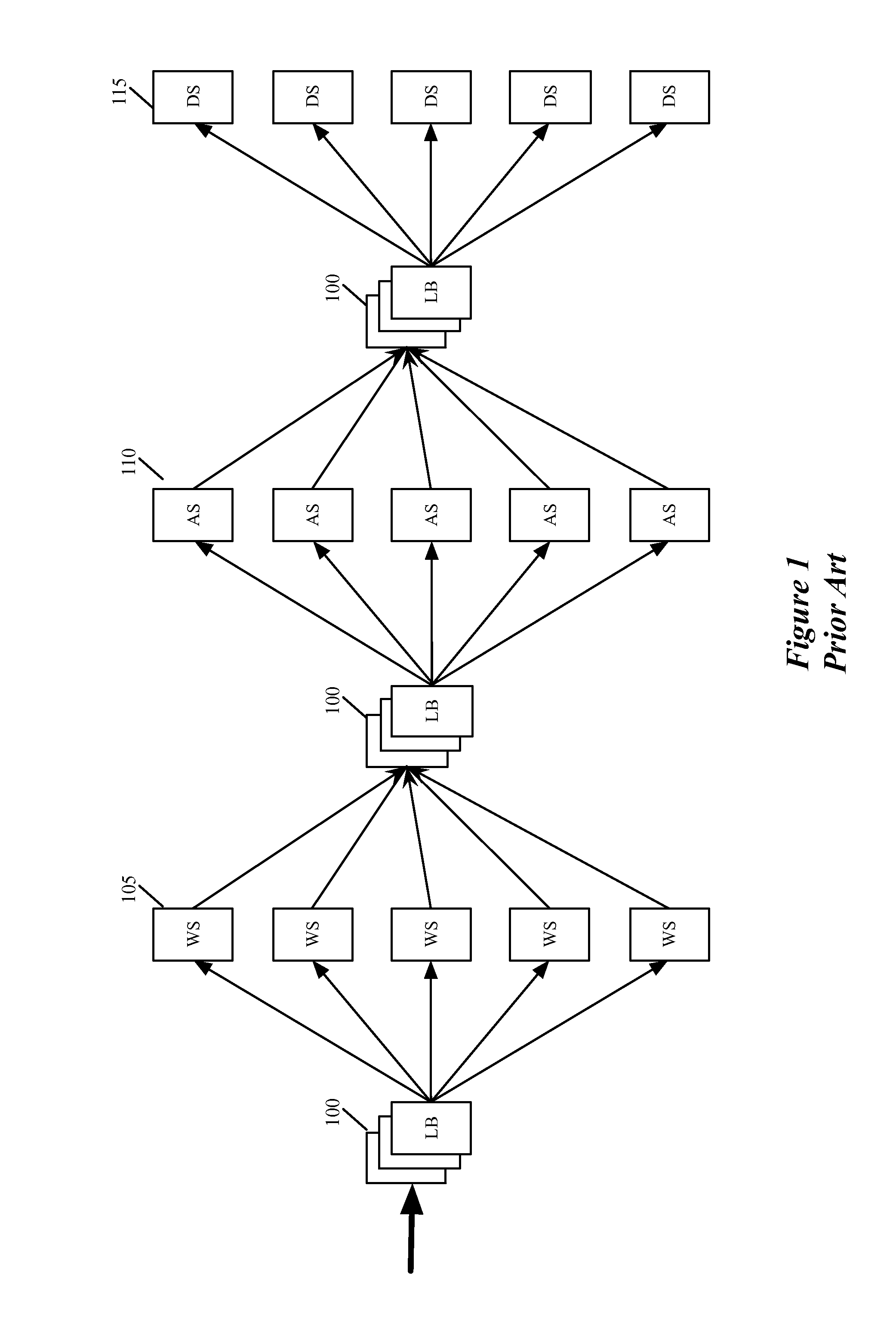

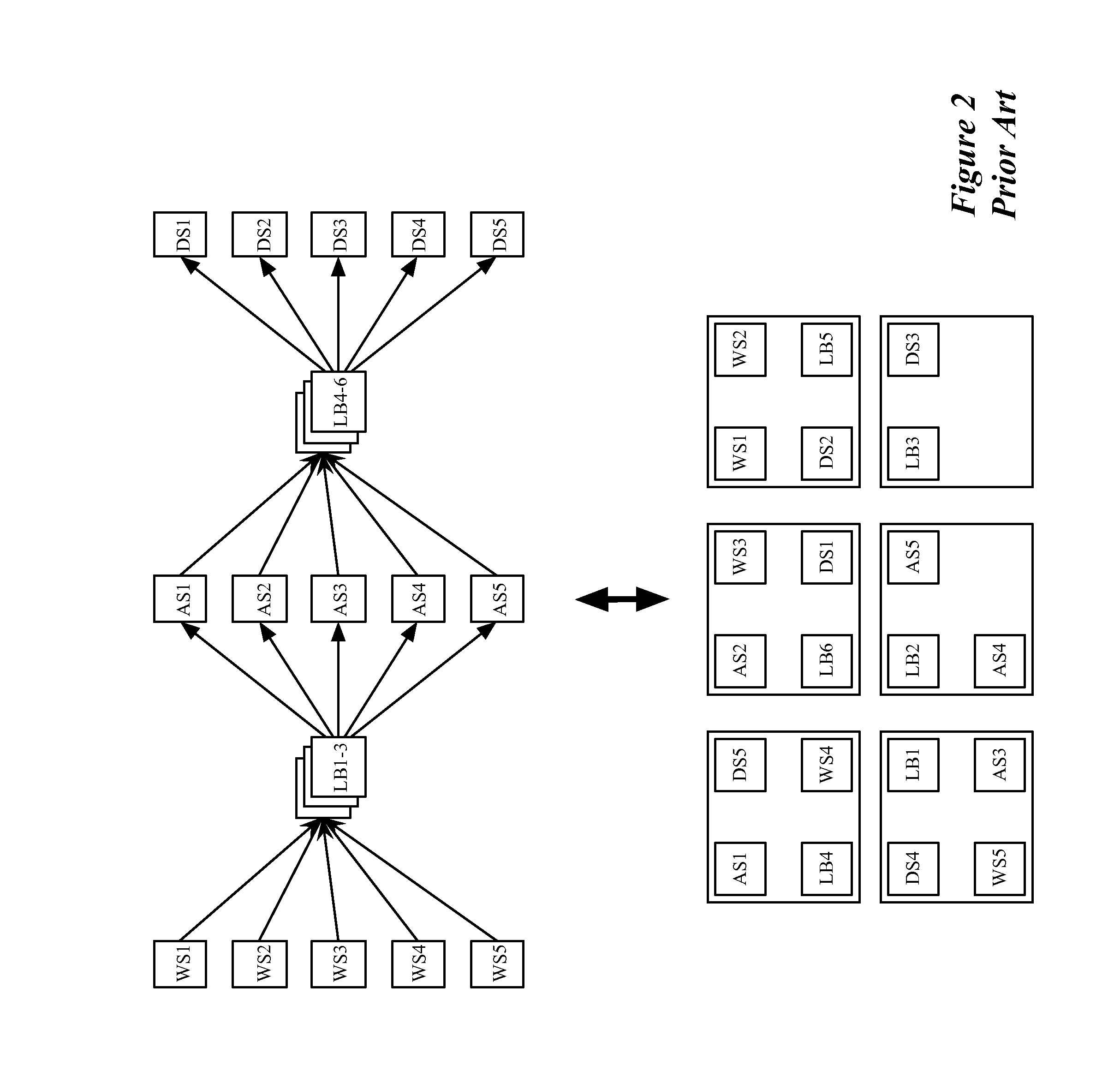

Method and system for remote load balancing in high-availability networks

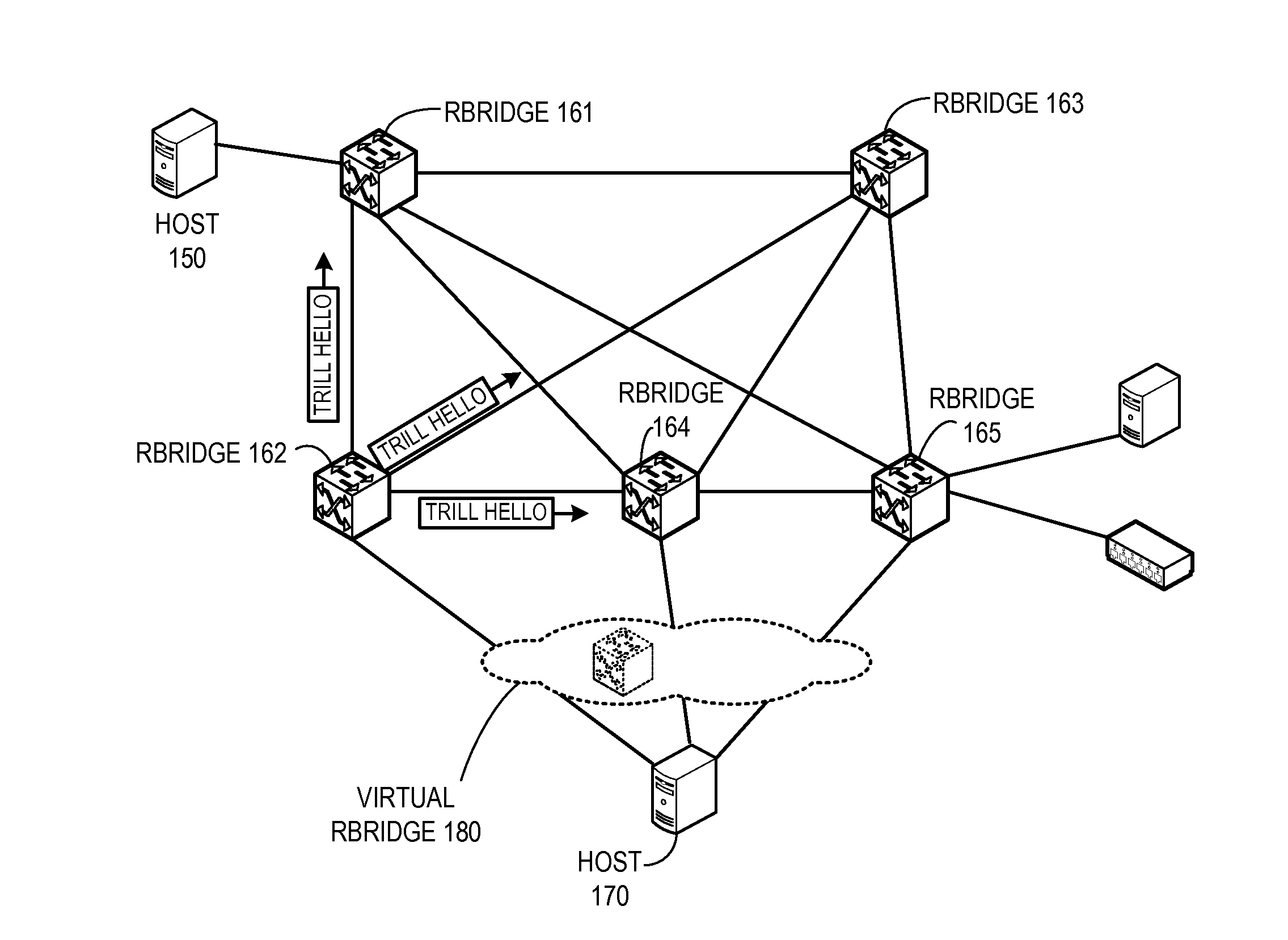

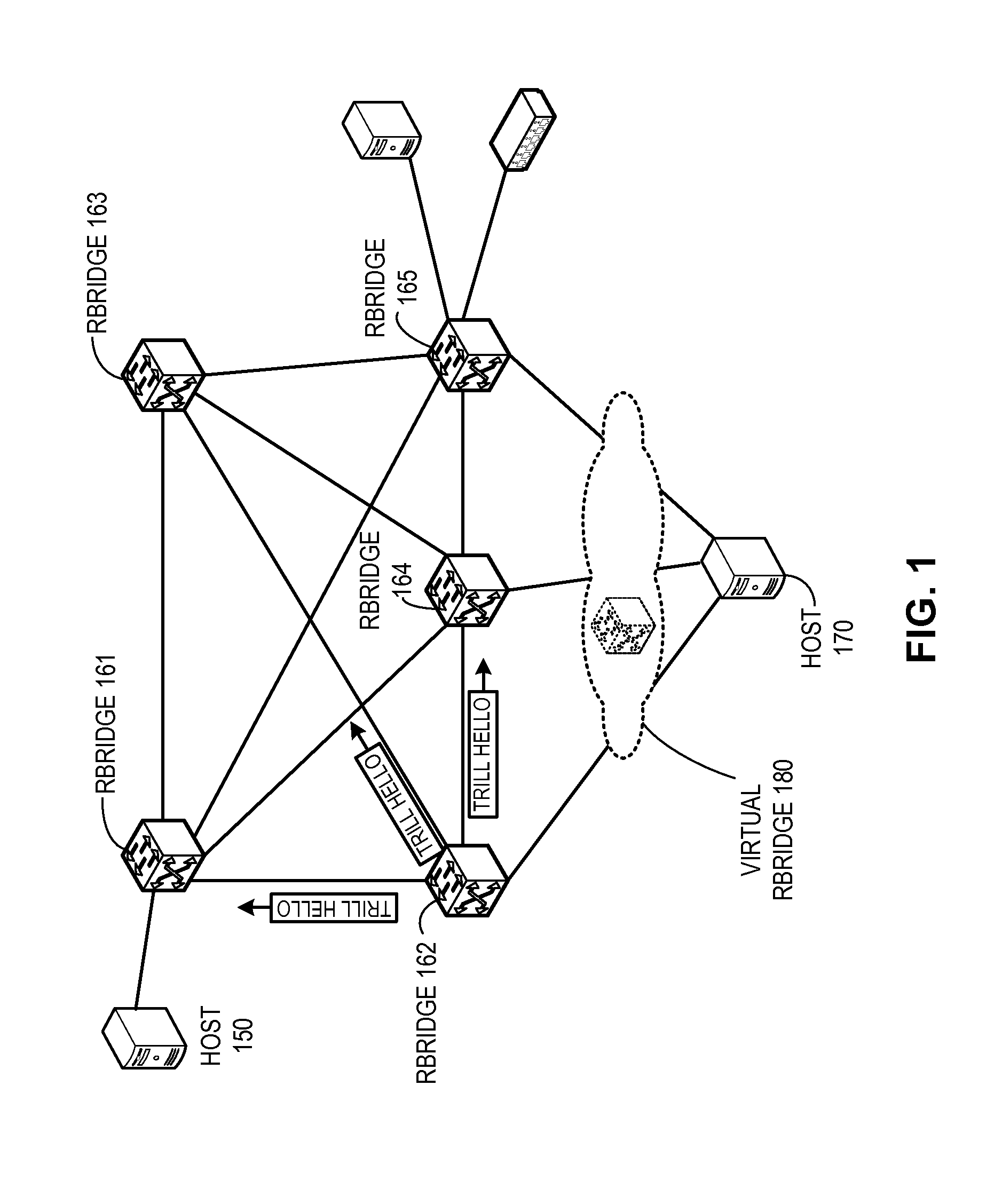

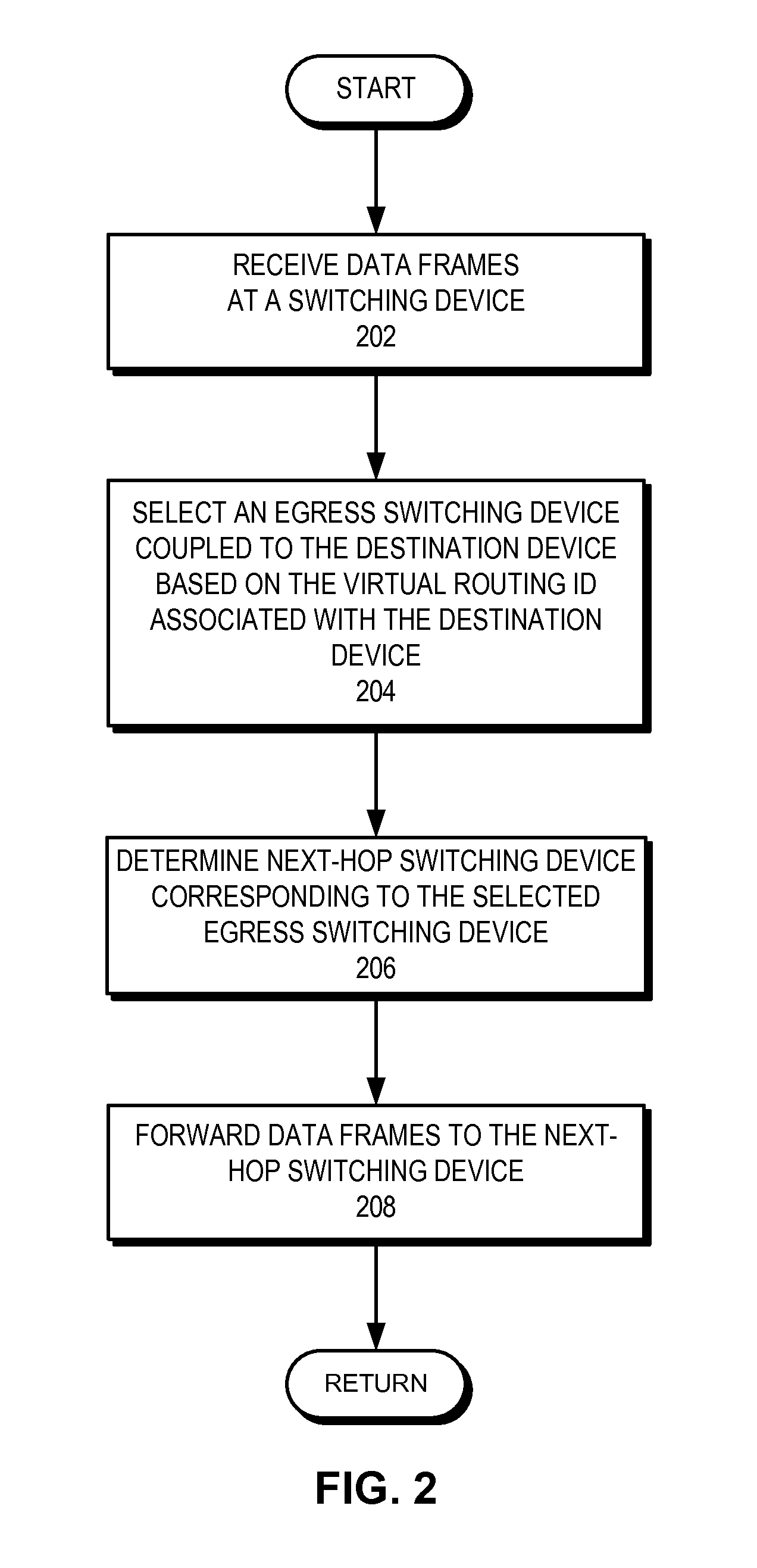

InactiveUS20120163164A1To achieve load balancingFacilitating remote load balancingError preventionFrequency-division multiplex detailsHigh availabilityDatapath

A system is provided for facilitating remote load balancing in a high-availability network. During operation, the system receives a plurality of data frames destined for a destination device, wherein the destination device is coupled to a network via a trunk link, the trunk link coupling the destination device to at least two separate egress switching devices. The system then forwards the data frames via at least two data paths, each of which leads to a respective egress switching device.

Owner:AVAGO TECH INT SALES PTE LTD

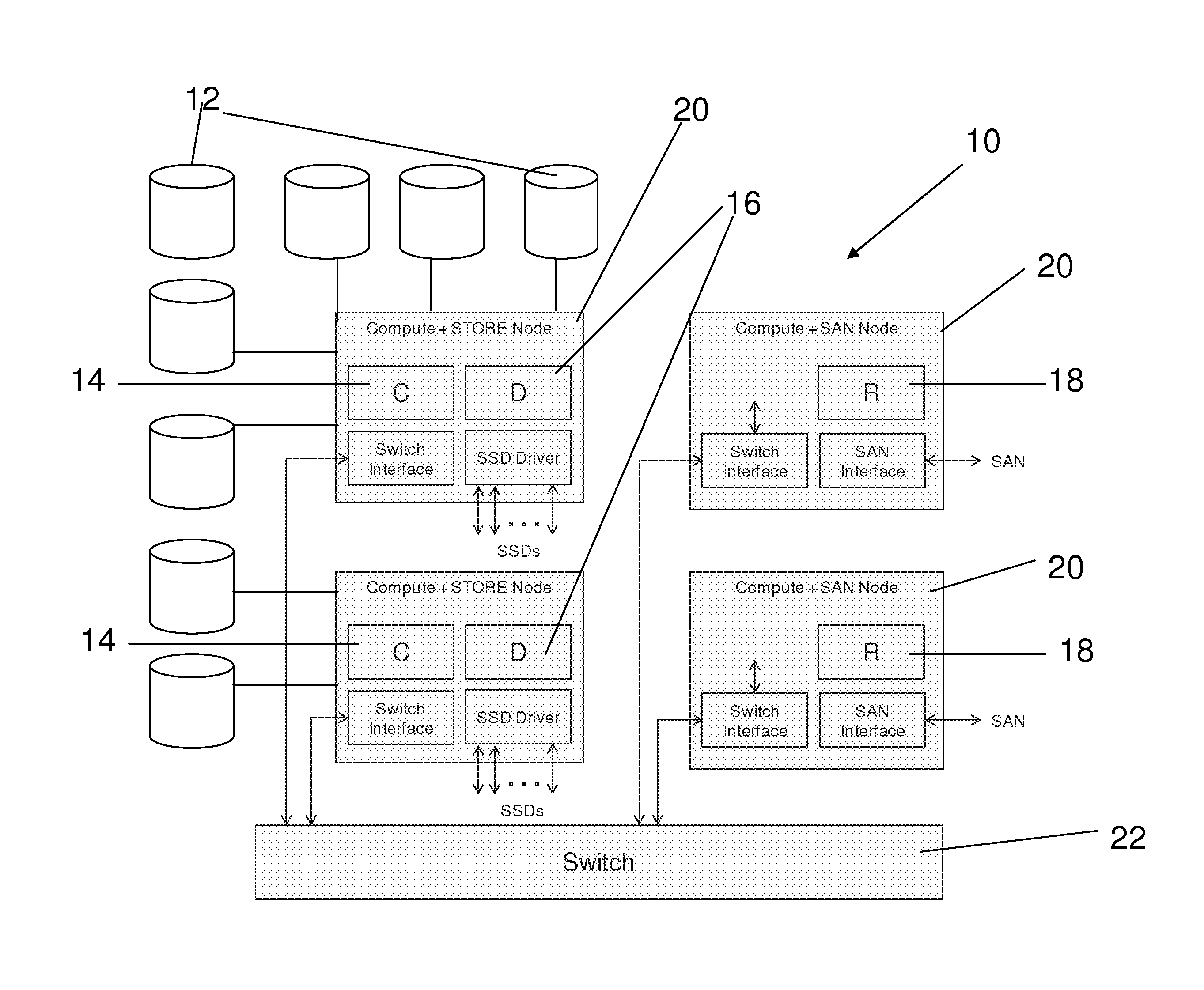

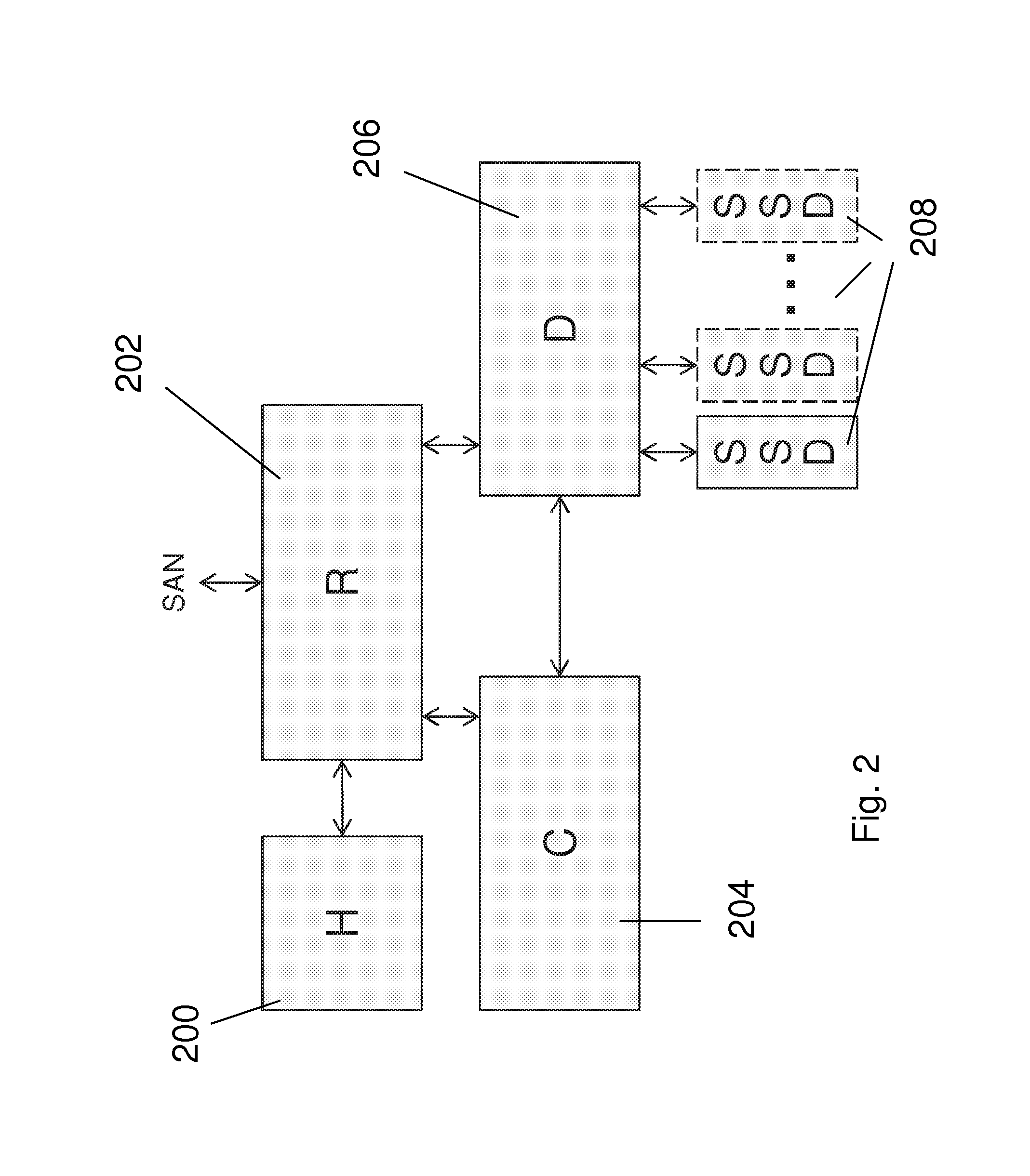

Scalable block data storage using content addressing

ActiveUS9104326B2Unlimited in capacityUnlimited in performanceInput/output to record carriersMemory systemsComputer moduleDatapath

A device for scalable block data storage and retrieval uses content addressing. Data storage devices store data blocks, and are connected over a network to computing modules. The modules comprise control modules and data modules and carry out content addressing for both storage and retrieval. The network defines separate control paths via the control modules and data paths via the data modules.

Owner:EMC IP HLDG CO LLC

Dynamically adjusting load balancing

ActiveUS20160094643A1Facilitate DLB operationReduce loadDigital computer detailsProgram controlIp addressDatapath

Some embodiments provide a novel method for load balancing data messages that are sent by a source compute node (SCN) to one or more different groups of destination compute nodes (DCNs). In some embodiments, the method deploys a load balancer in the source compute node's egress datapath. This load balancer receives each data message sent from the source compute node, and determines whether the data message is addressed to one of the DCN groups for which the load balancer spreads the data traffic to balance the load across (e.g., data traffic directed to) the DCNs in the group. When the received data message is not addressed to one of the load balanced DCN groups, the load balancer forwards the received data message to its addressed destination. On the other hand, when the received data message is addressed to one of load balancer's DCN groups, the load balancer identifies a DCN in the addressed DCN group that should receive the data message, and directs the data message to the identified DCN. To direct the data message to the identified DCN, the load balancer in some embodiments changes the destination address (e.g., the destination IP address, destination port, destination MAC address, etc.) in the data message from the address of the identified DCN group to the address (e.g., the destination IP address) of the identified DCN.

Owner:NICIRA

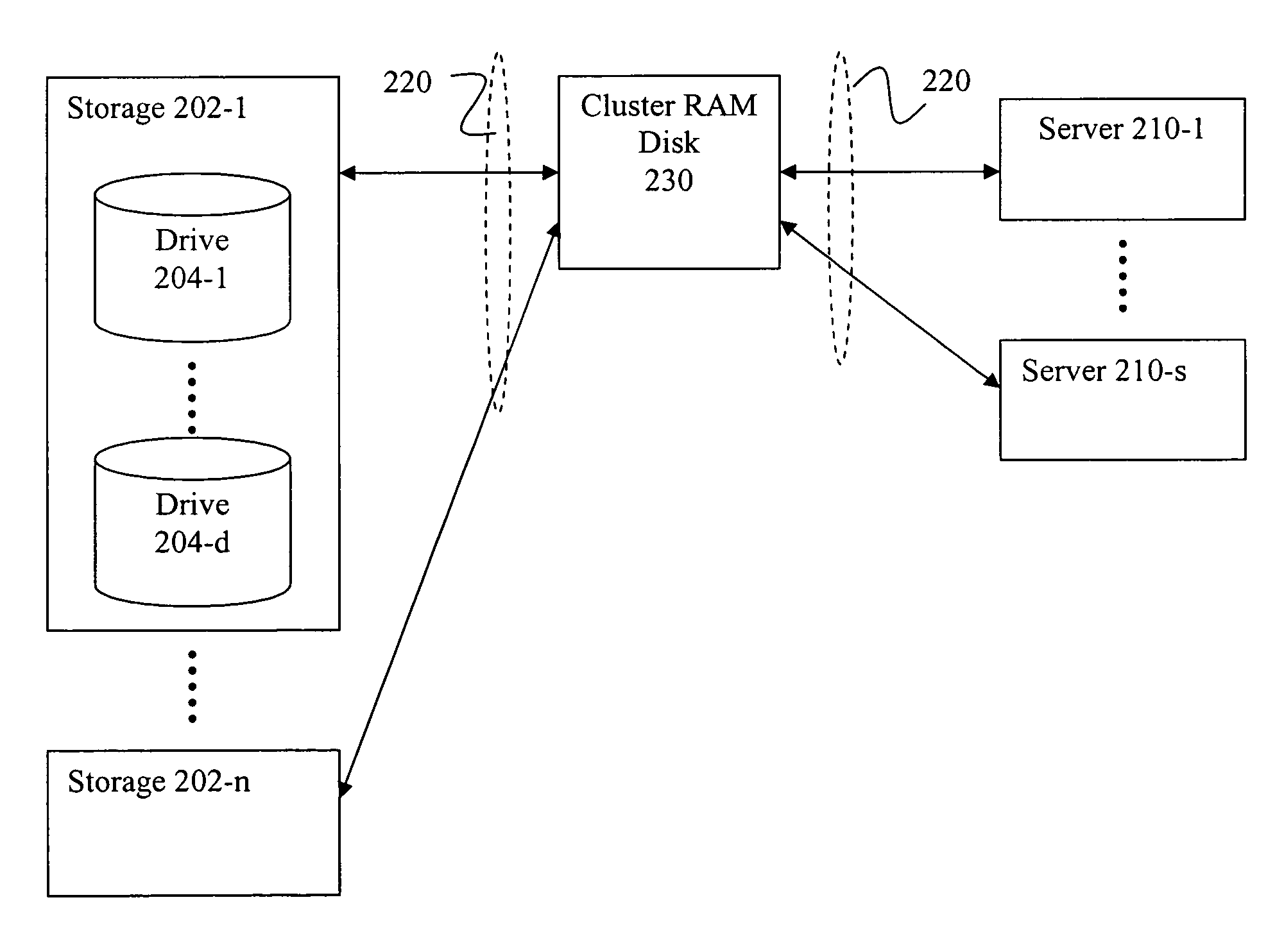

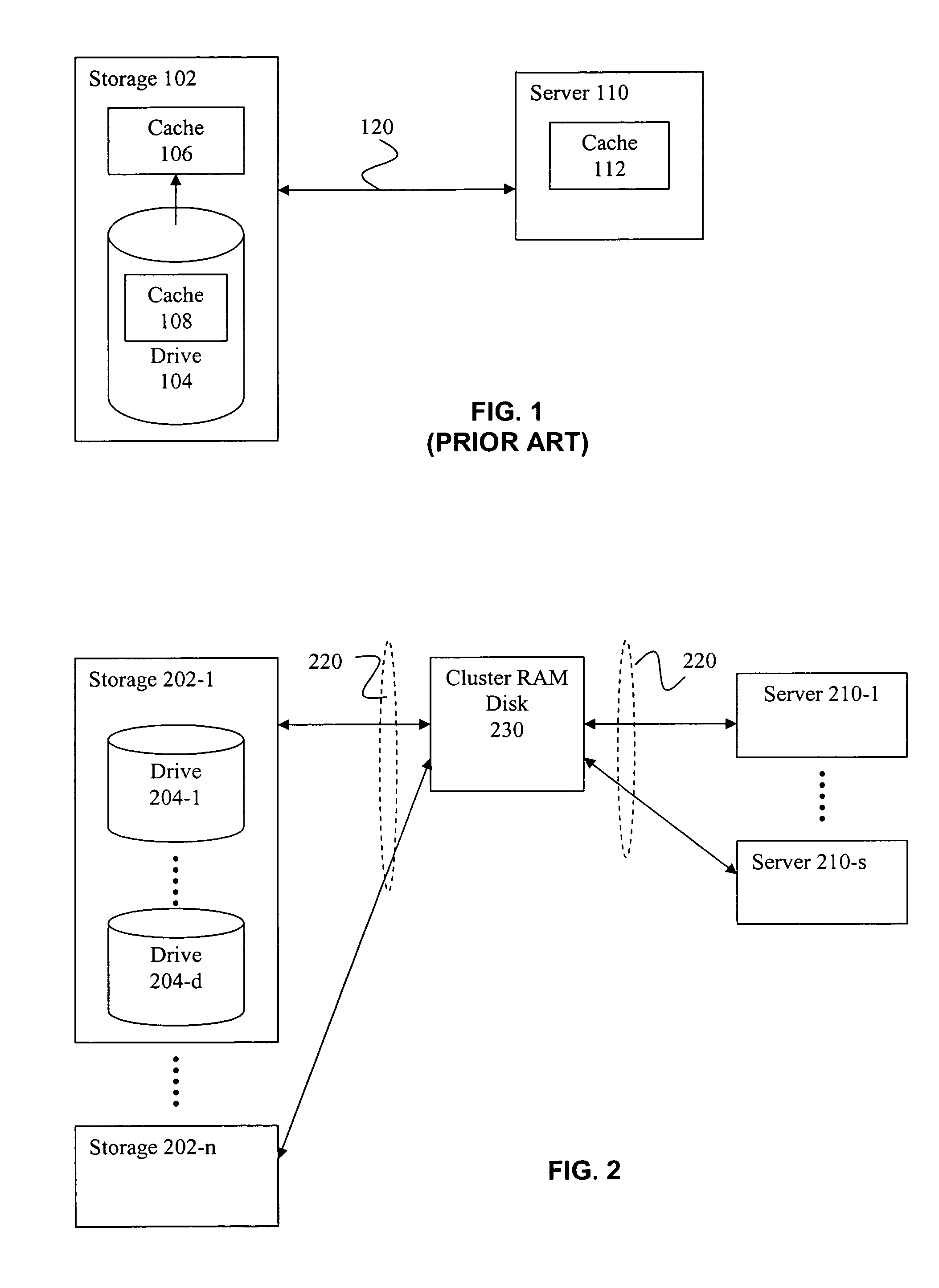

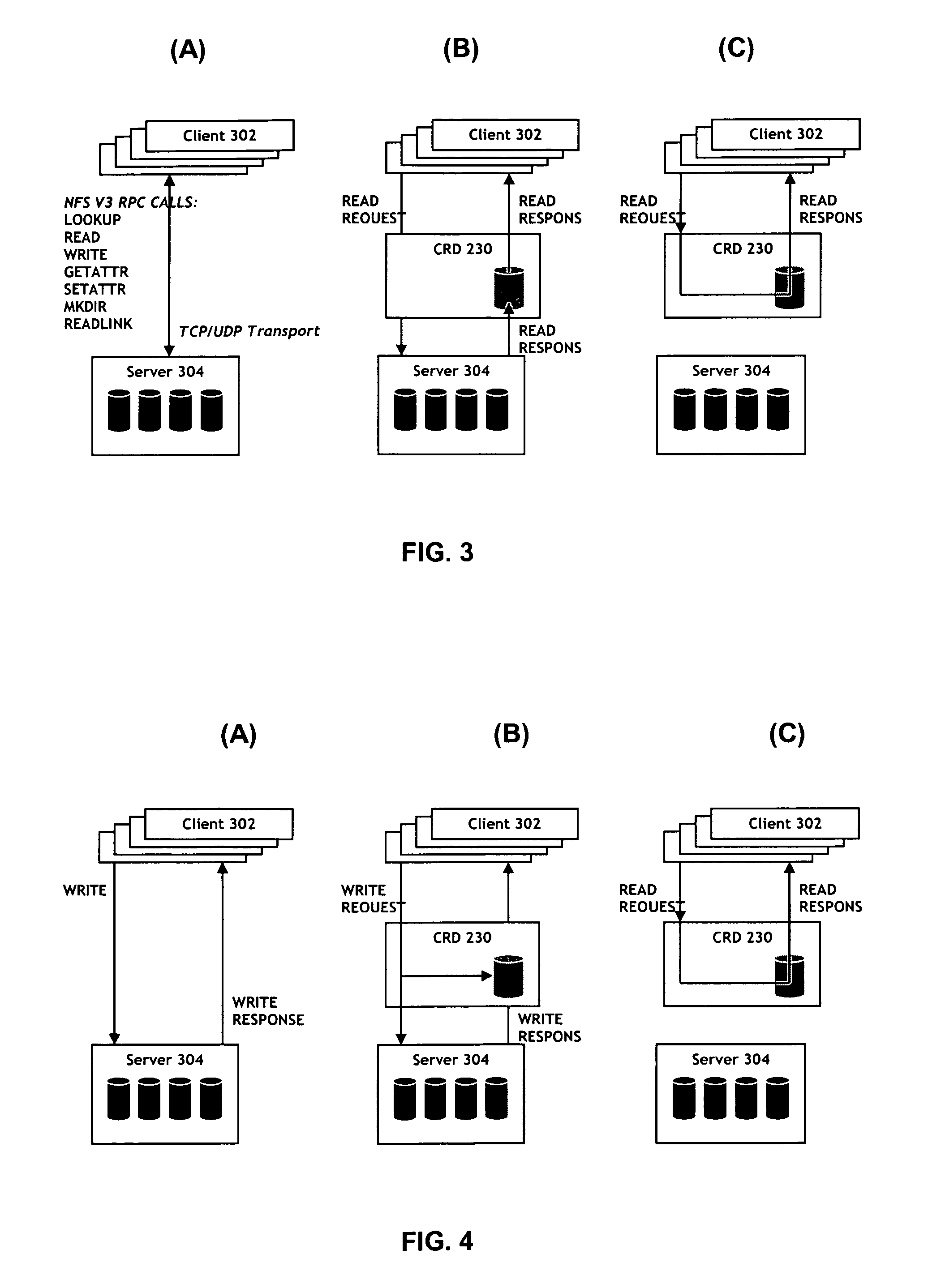

Method and apparatus for providing high-performance and highly-scalable storage acceleration

ActiveUS9390019B2Memory architecture accessing/allocationMemory adressing/allocation/relocationLatency (engineering)Datapath

A method and apparatus of providing high performance and highly scalable storage acceleration includes a cluster node-spanning RAM disk (CRD) interposed in the data path between a storage server and a computer server. The CRD addresses performance problems with applications that need to access large amounts of data and are negatively impacted by the latency of classic disk-based storage systems. It solves this problem by placing the data the application needs into a large (with respect to the server's main memory) RAM-based cache where it can be accessed with extremely low latency, hence improving the performance of the application significantly. The CRD is implemented using a novel architecture which has very significant cost and performance advantages over existing or alternative solutions.

Owner:INNOVATIONS IN MEMORY LLC

Reconfigurable processing

ActiveUS20070198971A1Reduce signal delayReduce areaEnergy efficient ICTSoftware engineeringPathPingComputer architecture

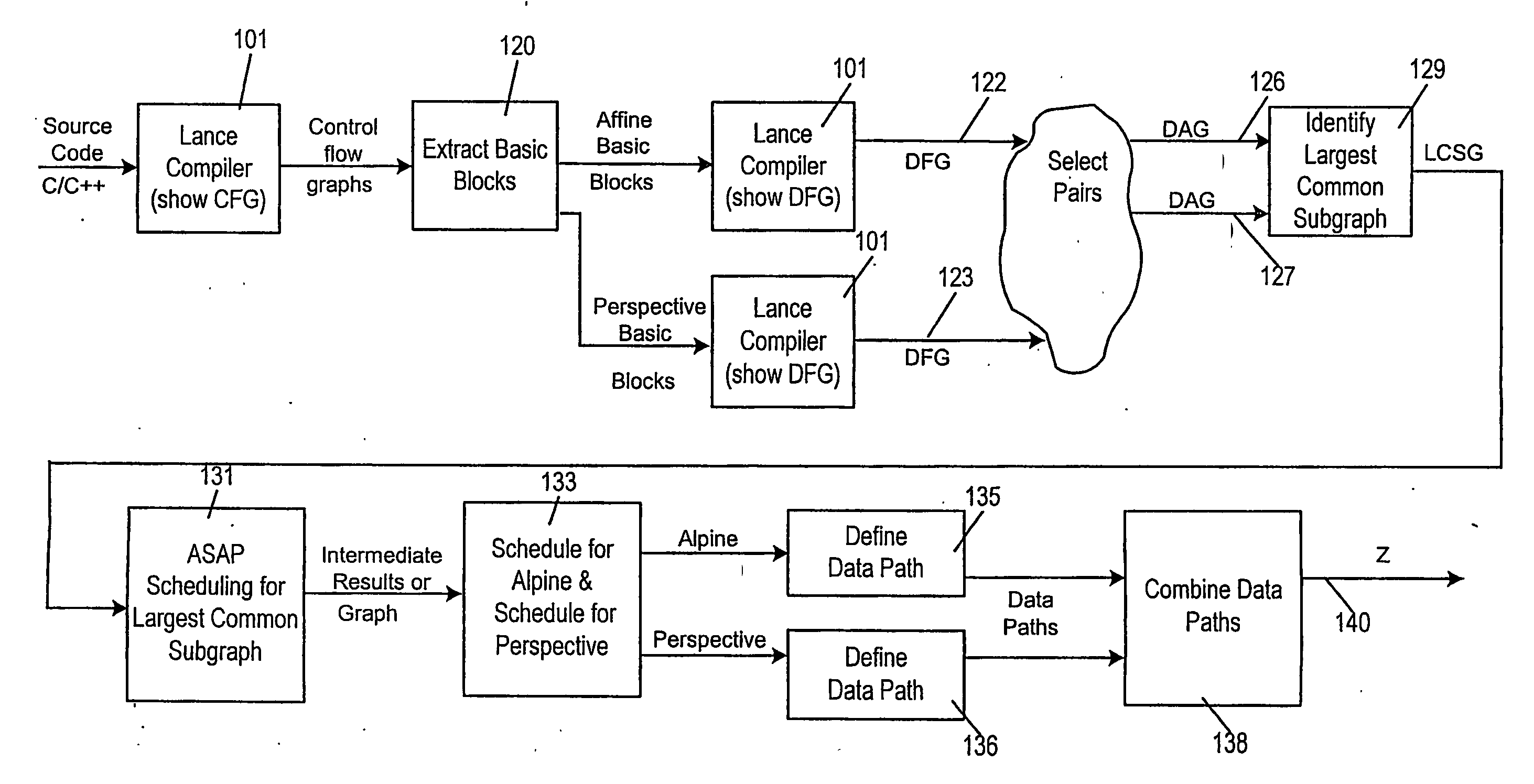

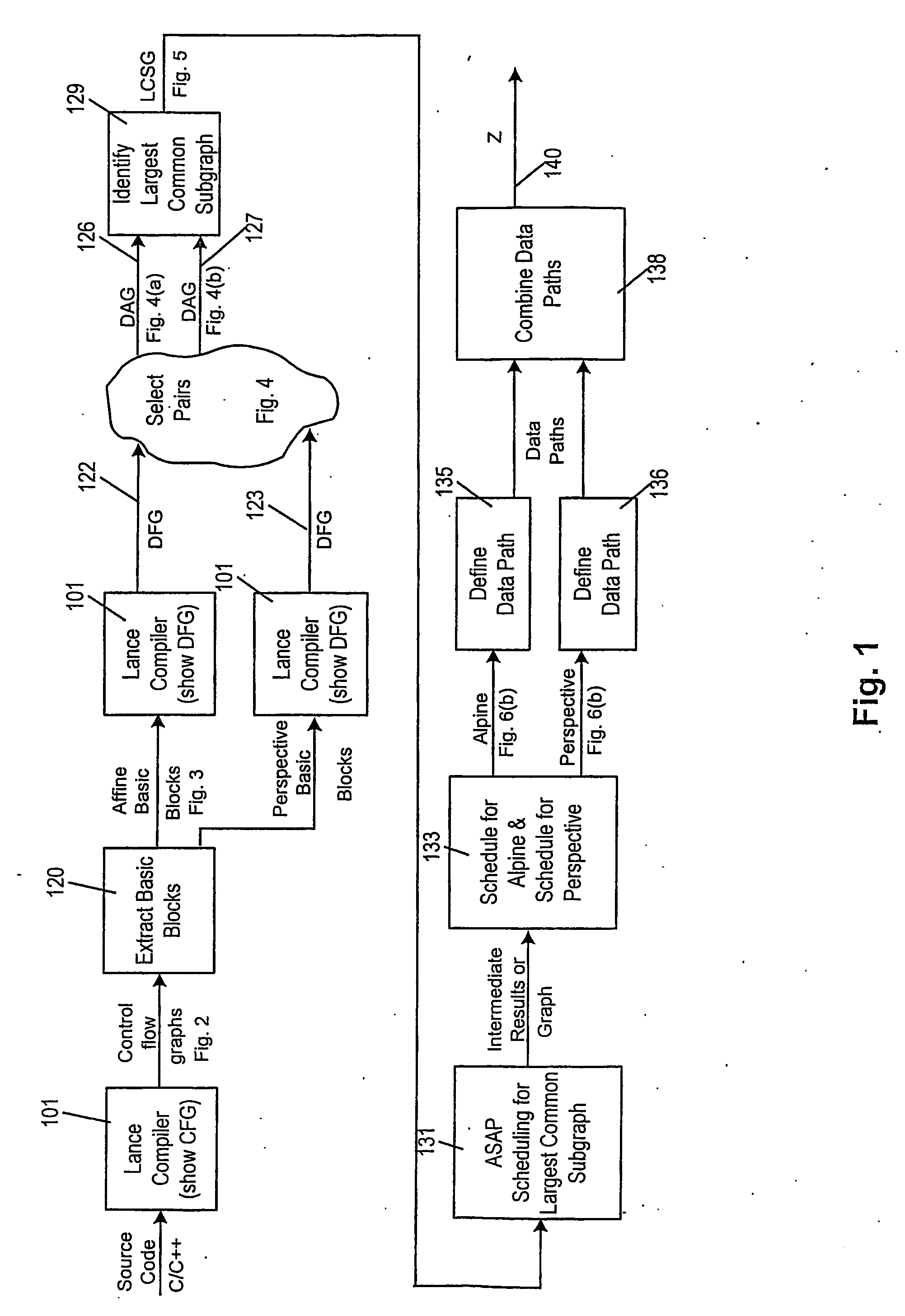

A method of producing a reconfigurable circuit device for running a computer program of moderate complexity such as multimedia processing. Code for the application is compiled into Control Flow Graphs representing distinct parts of the application to be run. From those Control Flow Graphs are extracted basic blocks. The basic blocks are converted to Data Flow Graphs by a compiler utility. From two or more Data Flow Graphs, a largest common subgraph is determined. The largest common subgraph is ASAP scheduled and substituted back into the Data Flow Graphs which also have been scheduled. The separate Data Flow Graphs containing the scheduled largest common subgraph are converted to data paths that are then combined to form code for operating the application. The largest common subgraph is effected in hardware that is shared among the parts of the application from which the Data Flow Graphs were developed. Scheduling of the overall code is effected for sequencing, providing fastest run times and the code is implemented in hardware by partitioning and placement of processing elements on a chip and design of the connective fabric for the design elements.

Owner:ARIZONA STATE UNIVERSITY

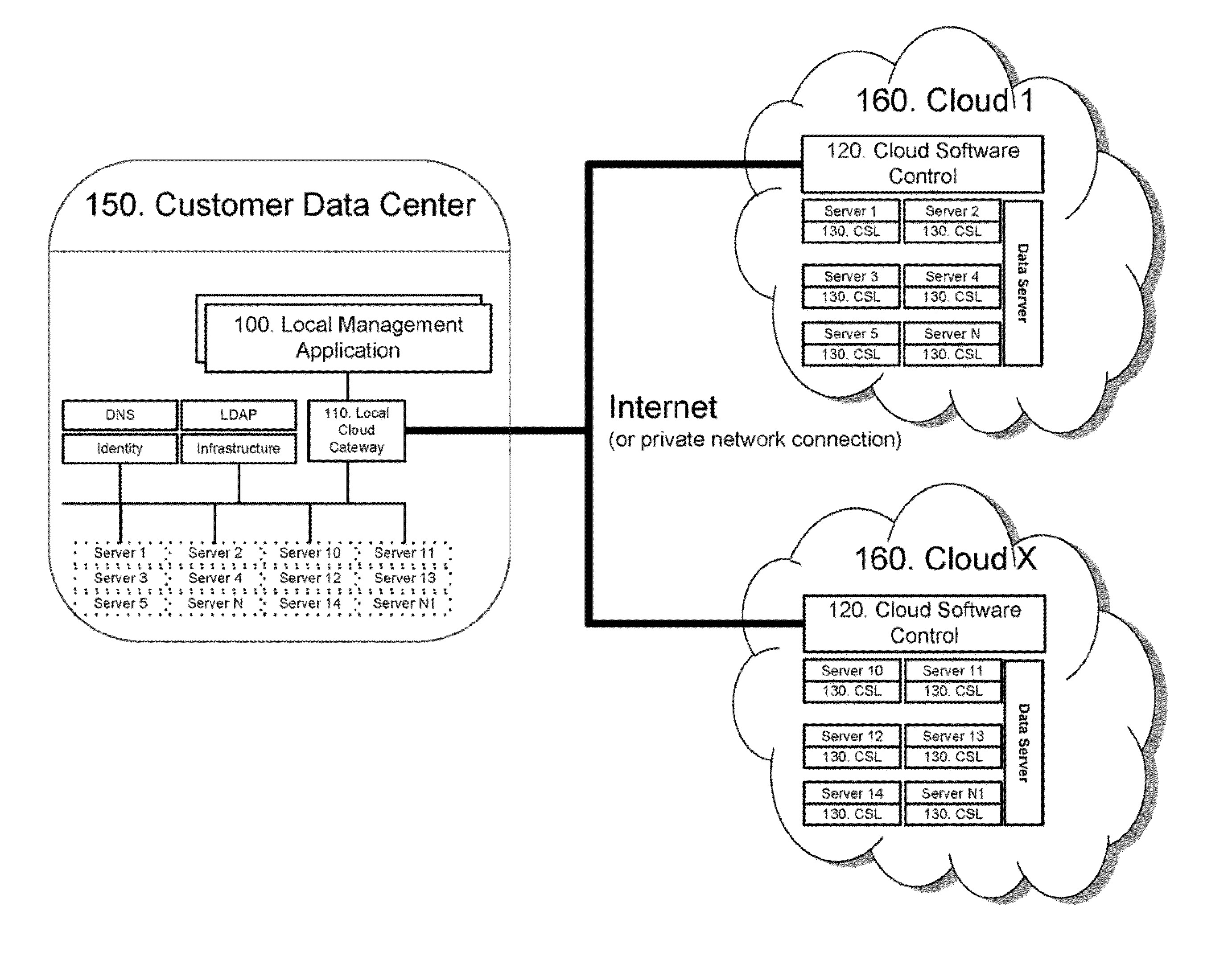

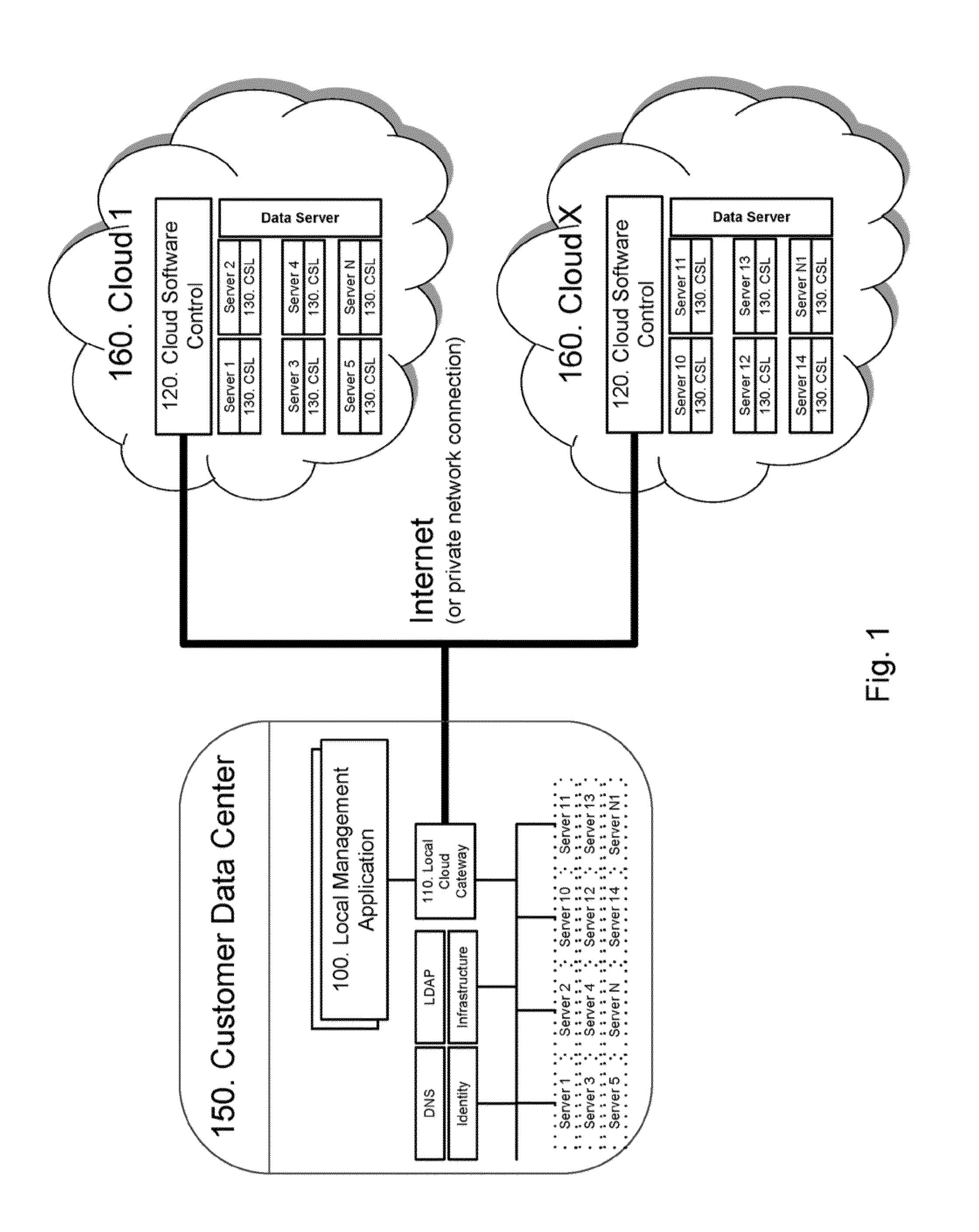

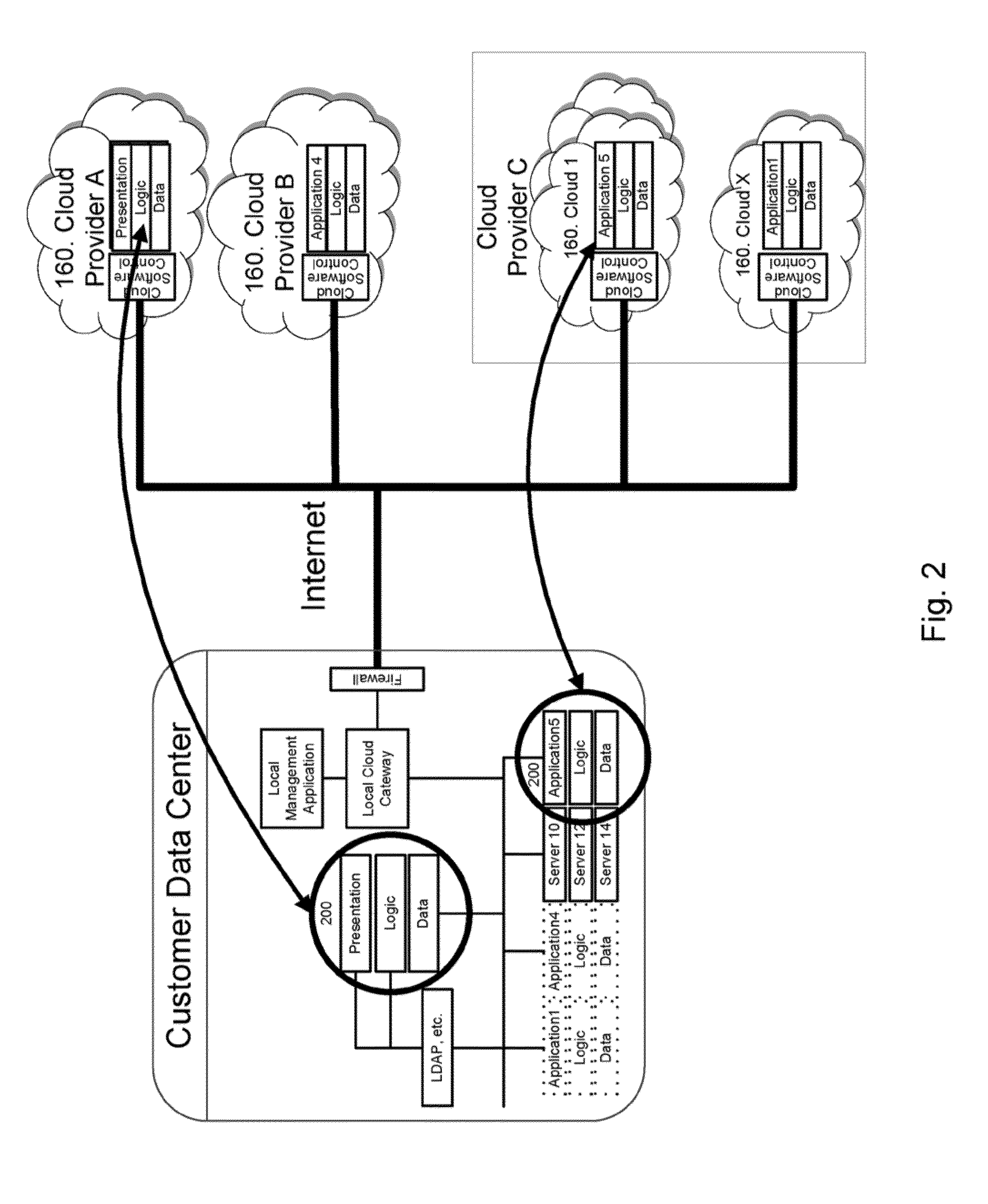

Environment preserving cloud migration and management

ActiveUS8417938B1Maximise its operationProtect environmentProgram controlTransmissionData centerIsolation layer

A system and method of operation is disclosed describing migration, management, and operation of applications and servers from customer data centers to cloud computing platforms without modification to existing environments or user access procedures. A cloud isolation layer operates as a virtual layer on the cloud platform, enabling server operation in a virtual environment that appears the same as the prior local environment. A cloud software image and a local cloud gateway act to redirect existing addressing from the local environment to the cloud implementation through secure network and data paths. A local management application provides a control interface and maps and manages the local environment and utilized cloud resources.

Owner:RAKUTEN GRP INC

Network control apparatus and method for populating logical datapath sets

For a network control system that receives, from a user, logical datapath sets that logically express desired forwarding behaviors that are to be implemented by a set of managed switching elements, a controller for managing several managed switching elements that forward data in a network that includes the managed switching elements is described. The controller includes a set of modules for detecting a change in one or more managed switching elements and for updating logical datapath set based on the detected change. The logical datapath set is for subsequent translation into a set of physical forwarding behaviors of the managed switching elements.

Owner:NICIRA

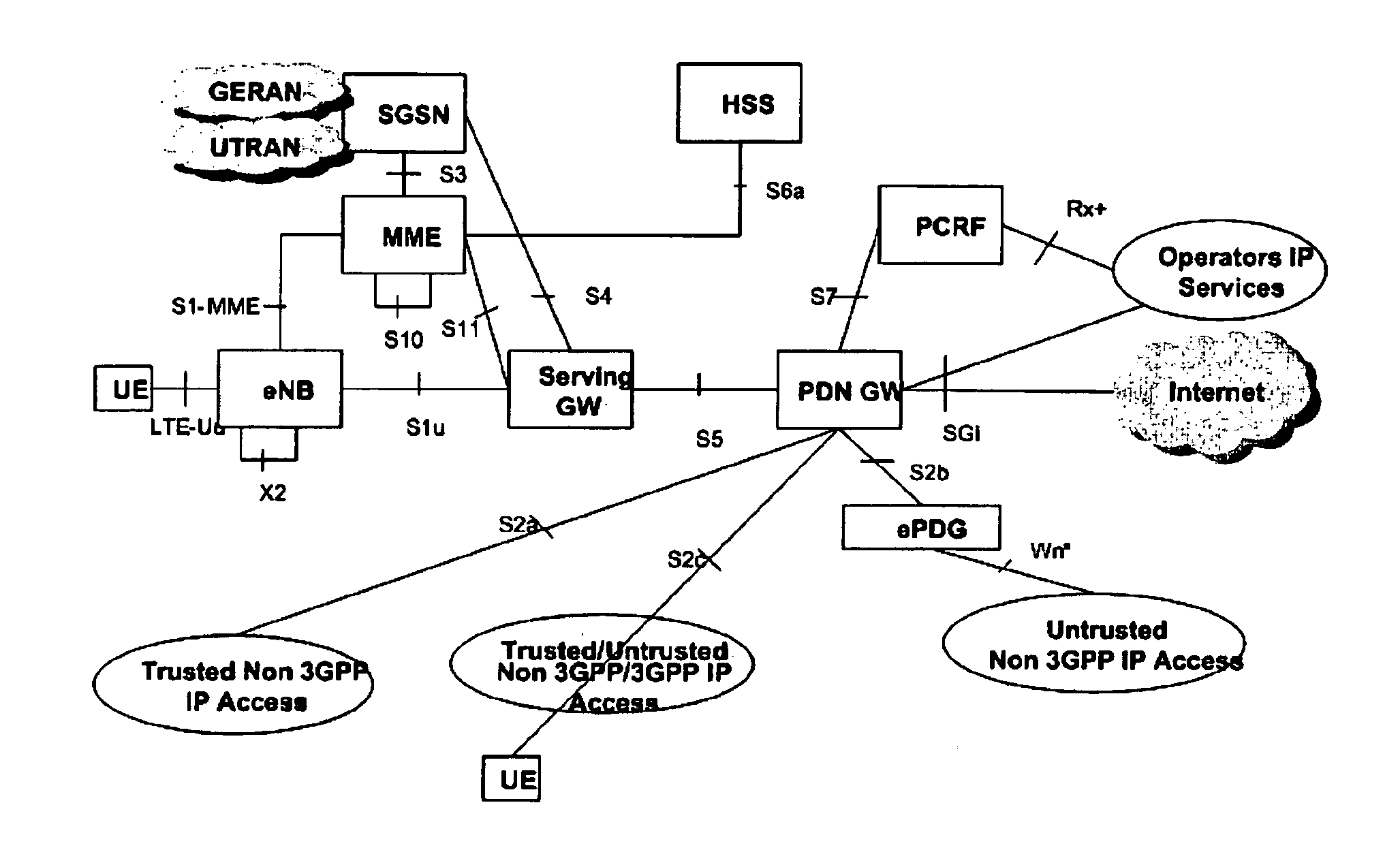

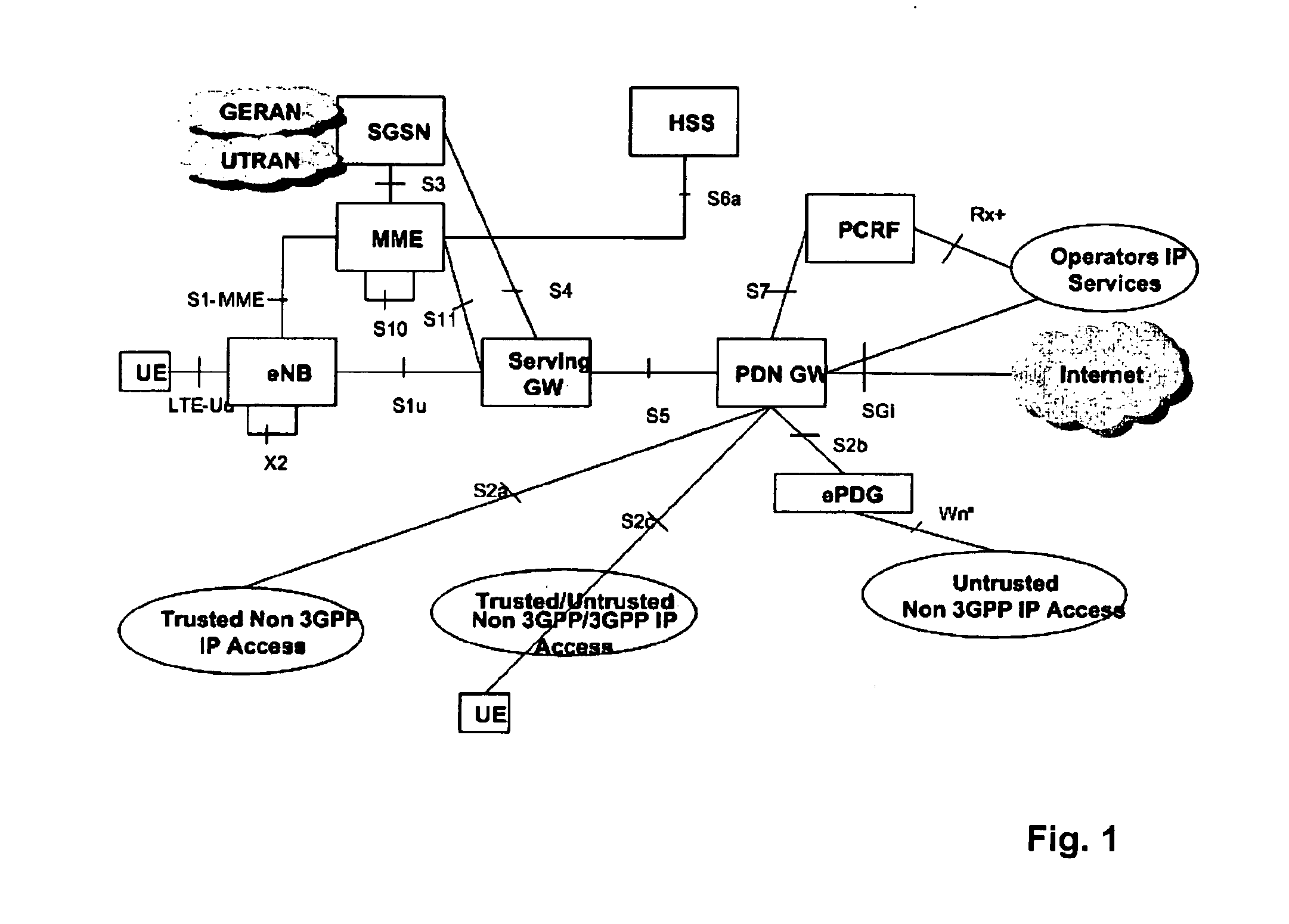

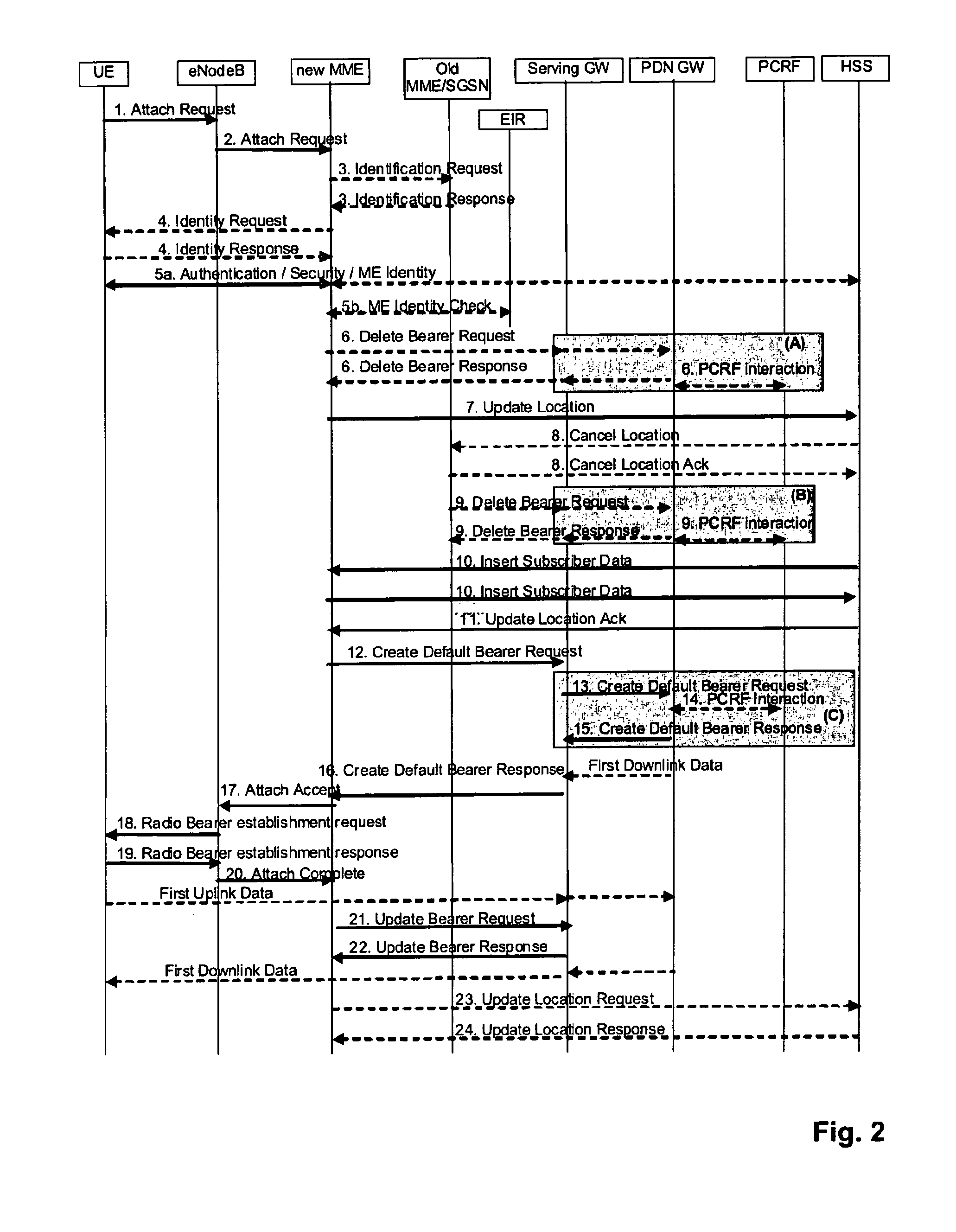

Non-3gpp to 3gpp network handover optimizations

ActiveUS20100323700A1Raise the possibilityReduce signal strengthWireless communicationDatapathHandover

The invention relates to a method for a handover of a mobile node from a non-3GPP to a 3GPP network, and of a mobile node, which is located in a non-3GPP / 3GPP network. The handover is improved by discovering an appropriate MME and registering the mobile node at the discovered MME, in advance. This includes to first determine the location of the mobile node in the non-3GPP network, so as to be able to detect an MME in the vicinity of the mobile node's location. The 3GPP contexts are then transmitted to the new MME before the handover is performed. Moreover, the invention teaches to change the Serving-Gateway in the 3GPP network before performing a handover, thereby accelerating the handover. When a handover gets likely, the mobile node's location is determined and a new Serving-Gateway is selected. The data path is changed to go via the new Serving-Gateway.

Owner:SUN PATENT TRUST

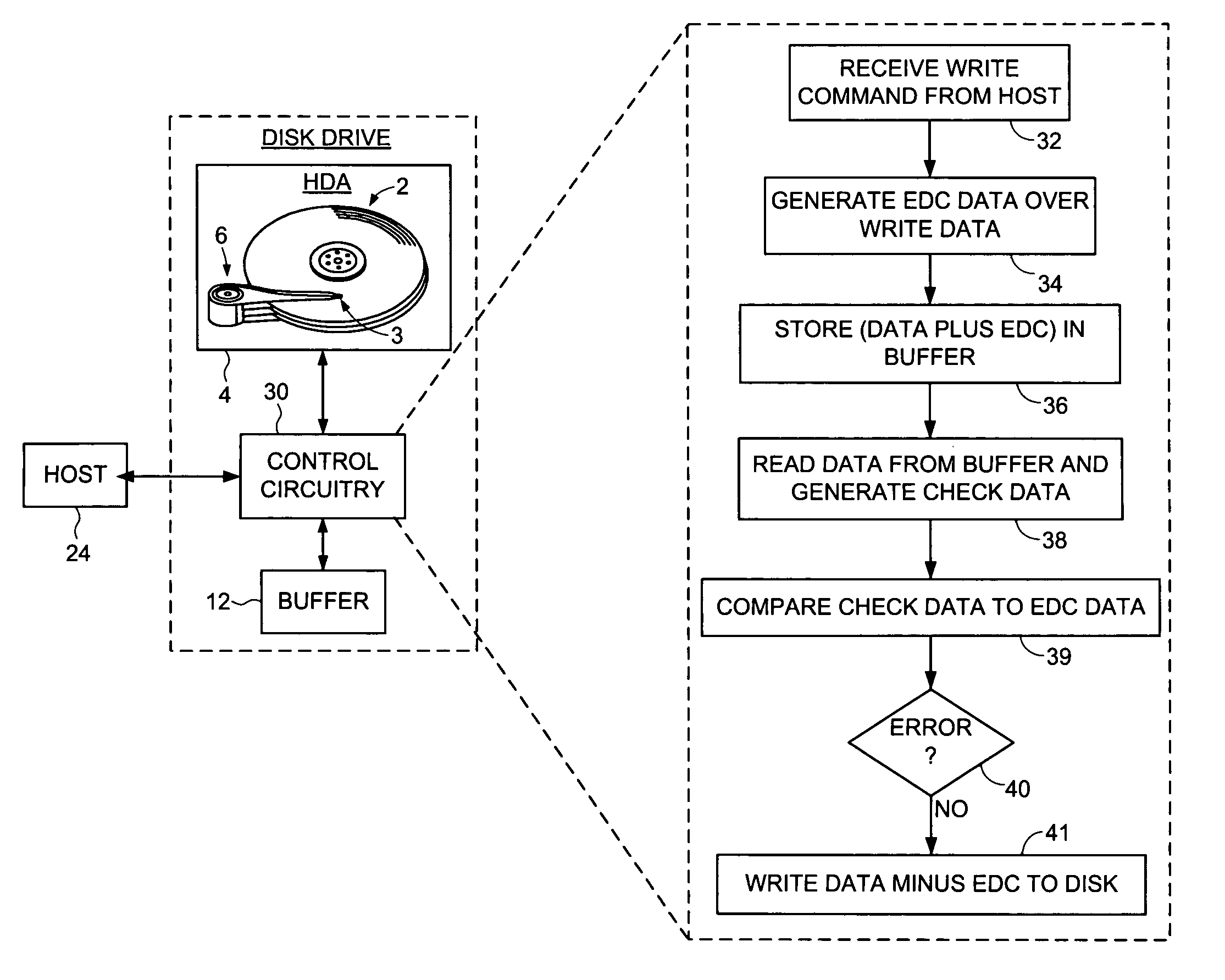

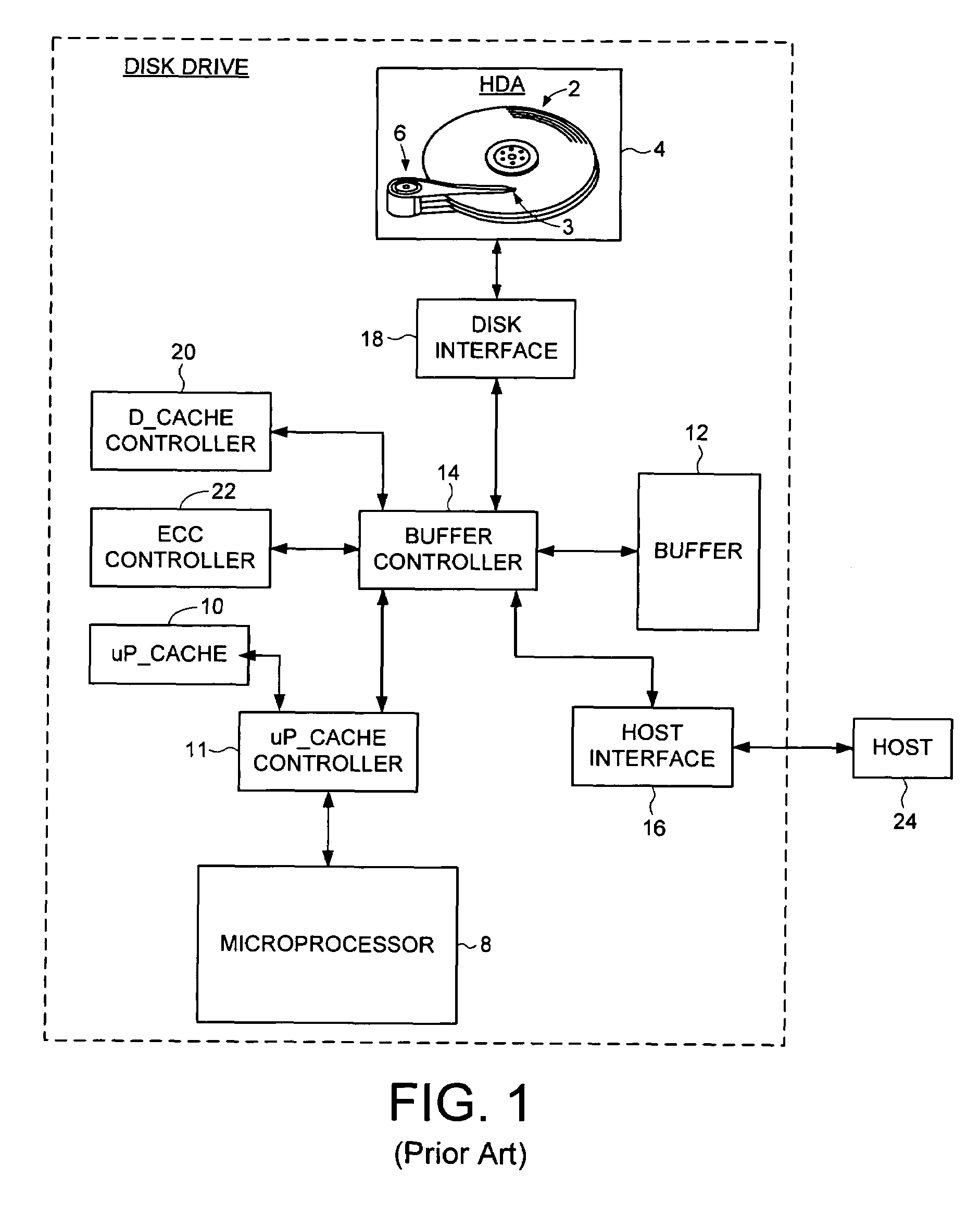

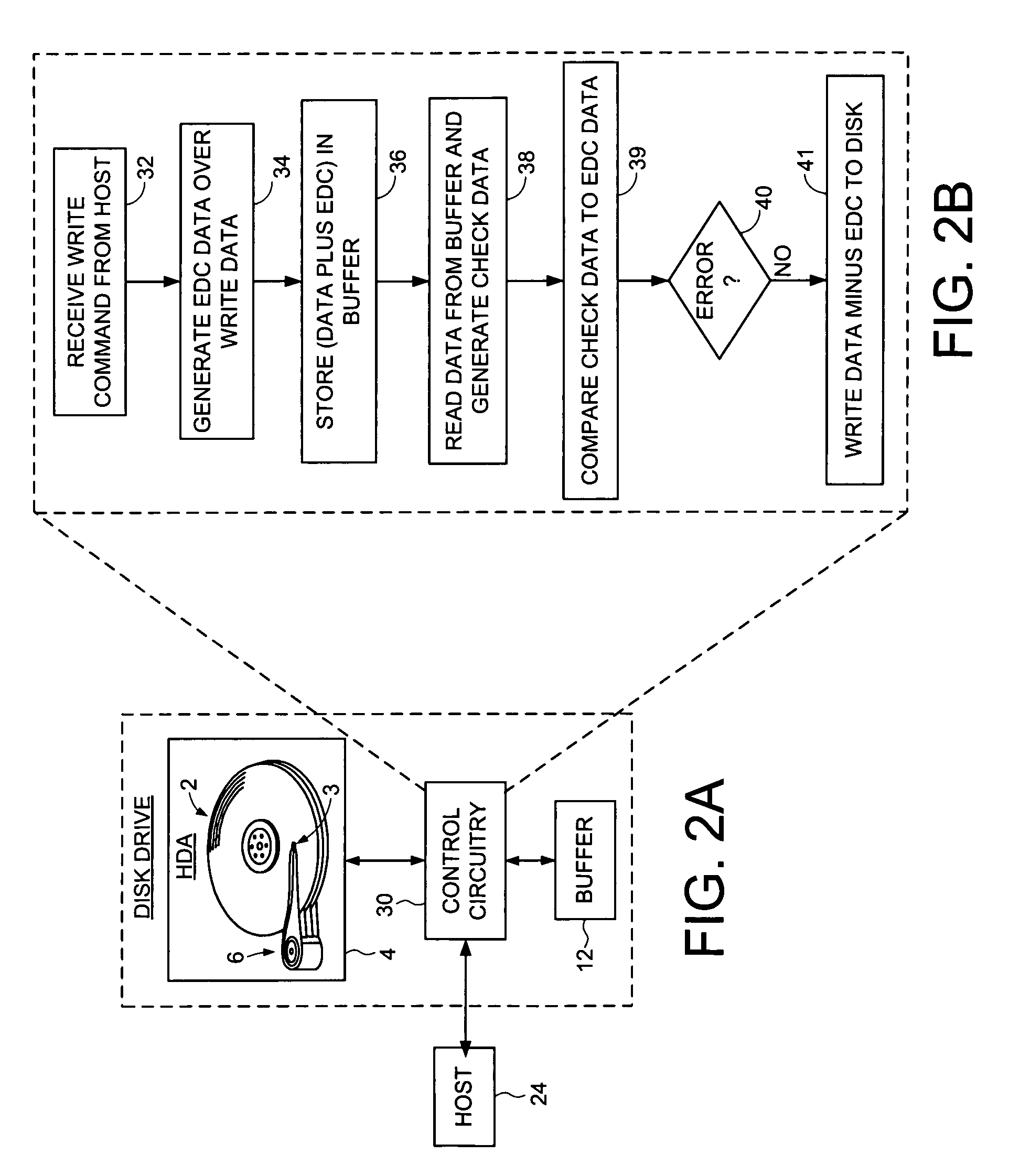

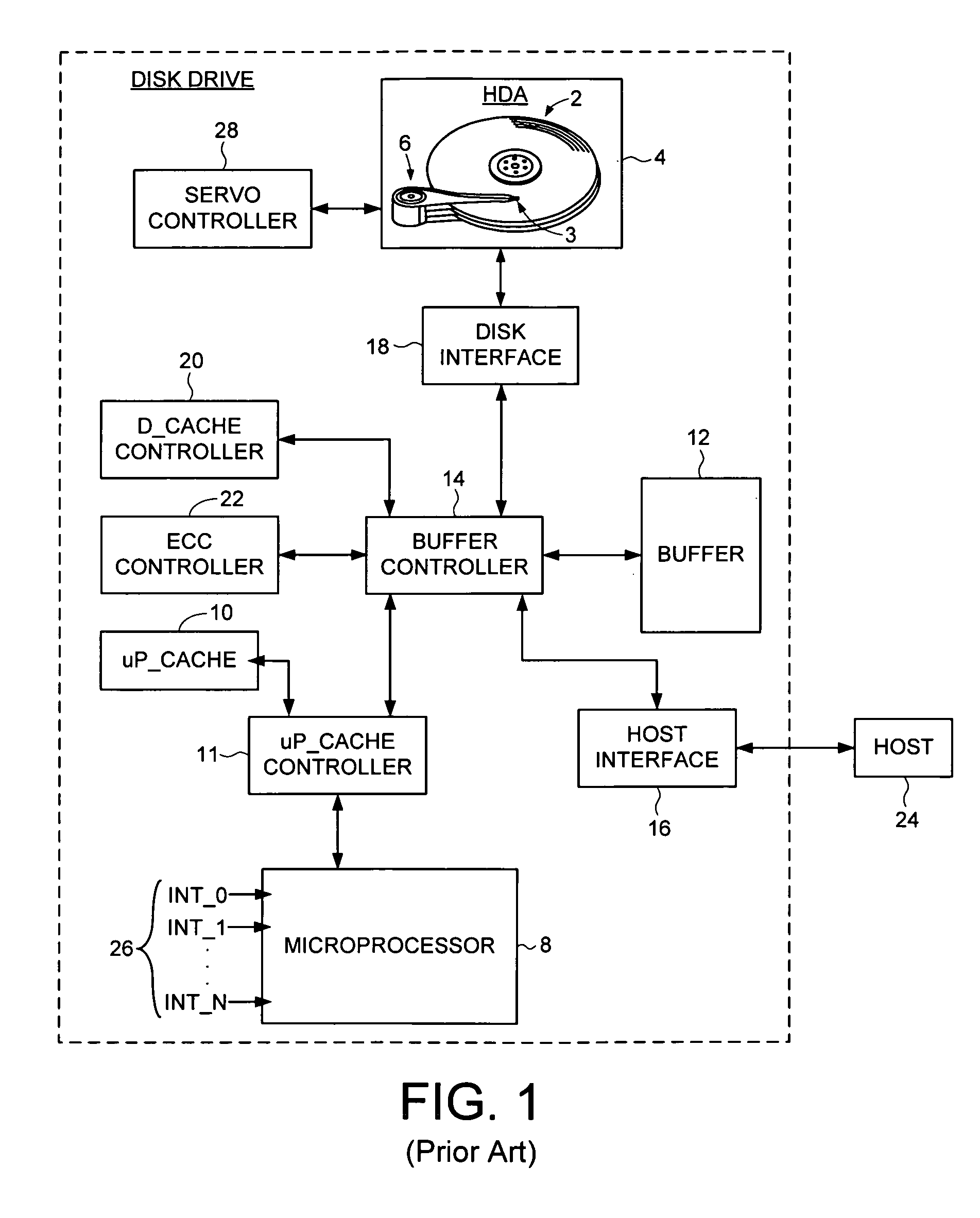

Disk drive implementing data path protection without writing the error detection code data to the disk

Owner:WESTERN DIGITAL TECH INC

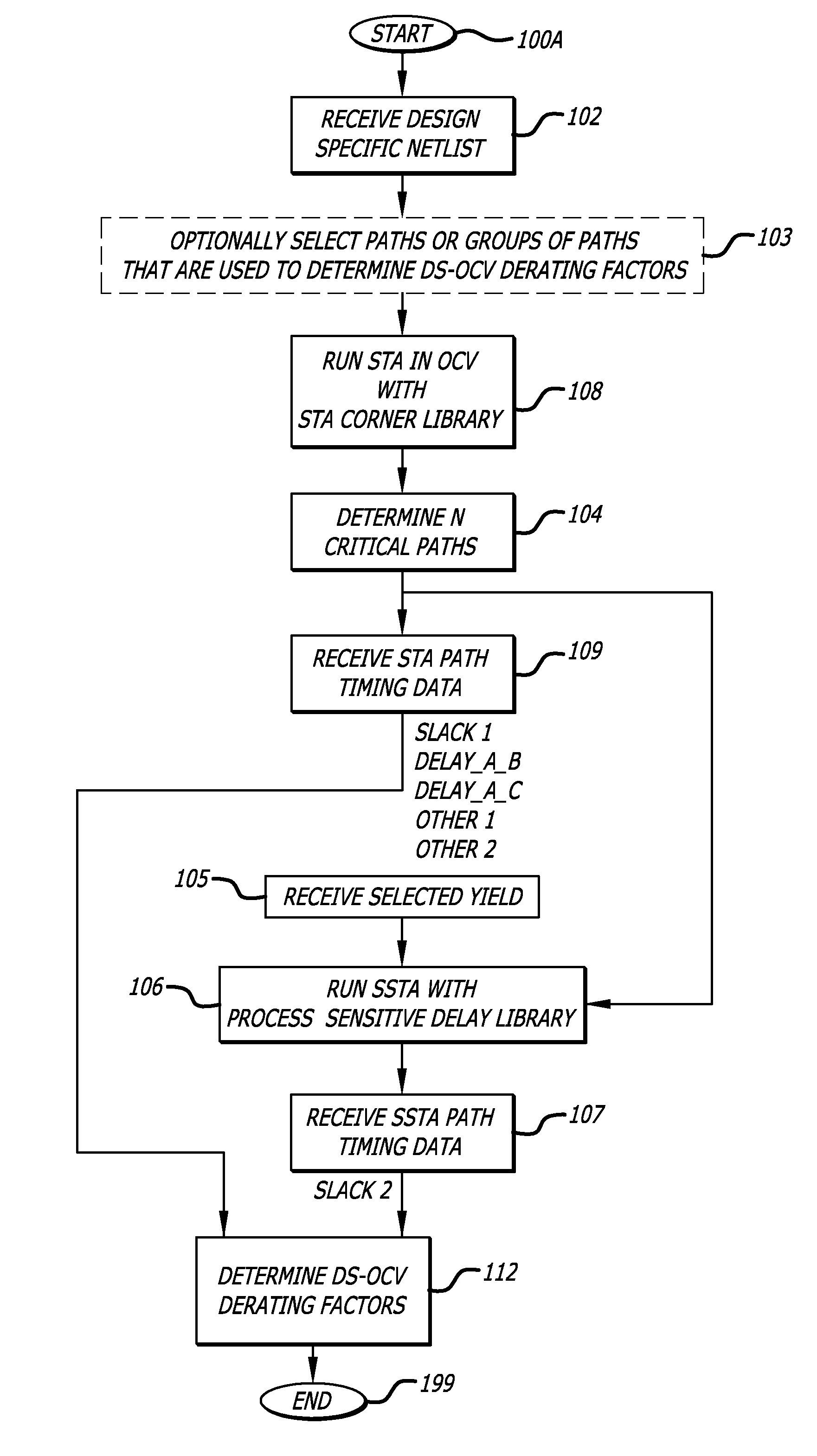

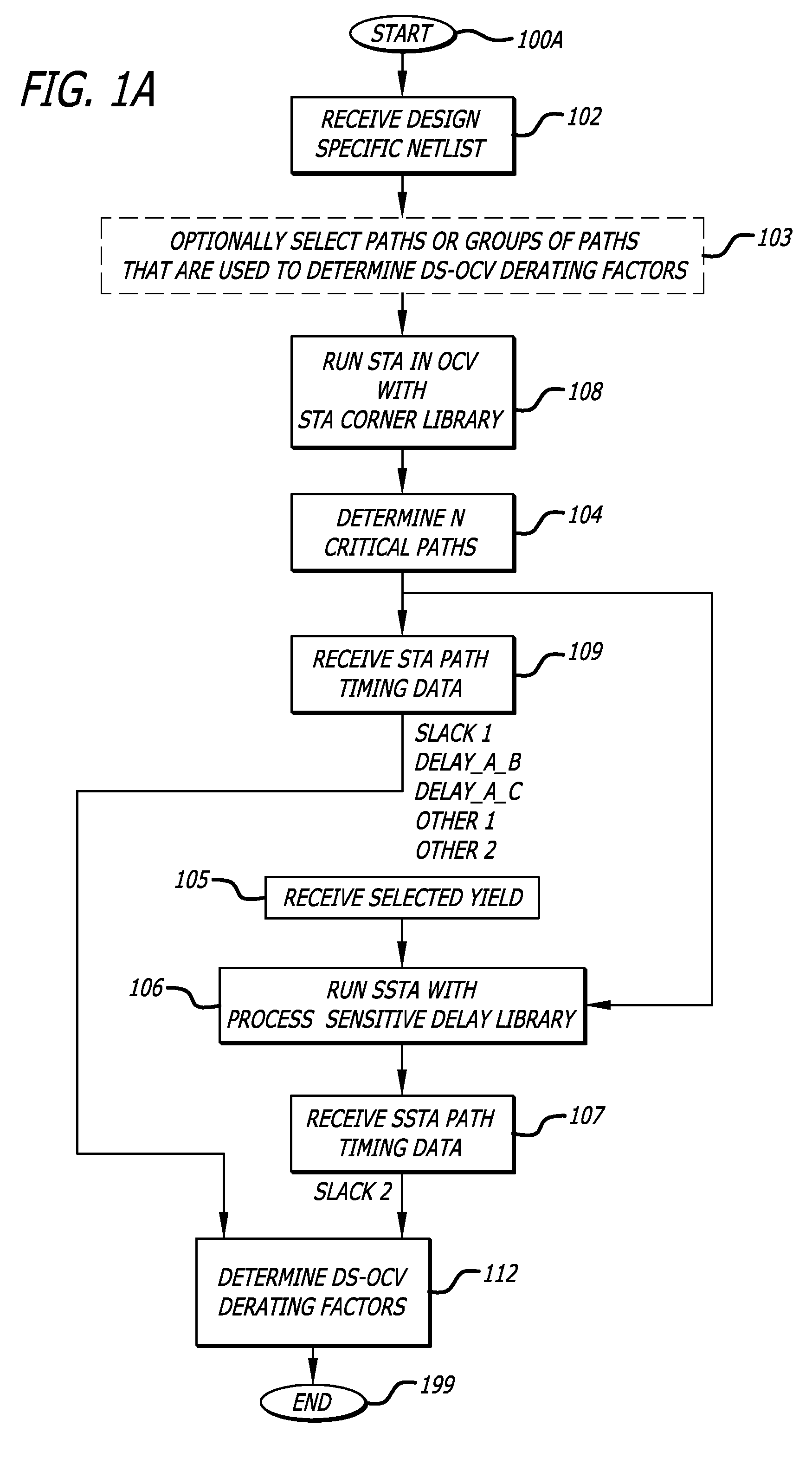

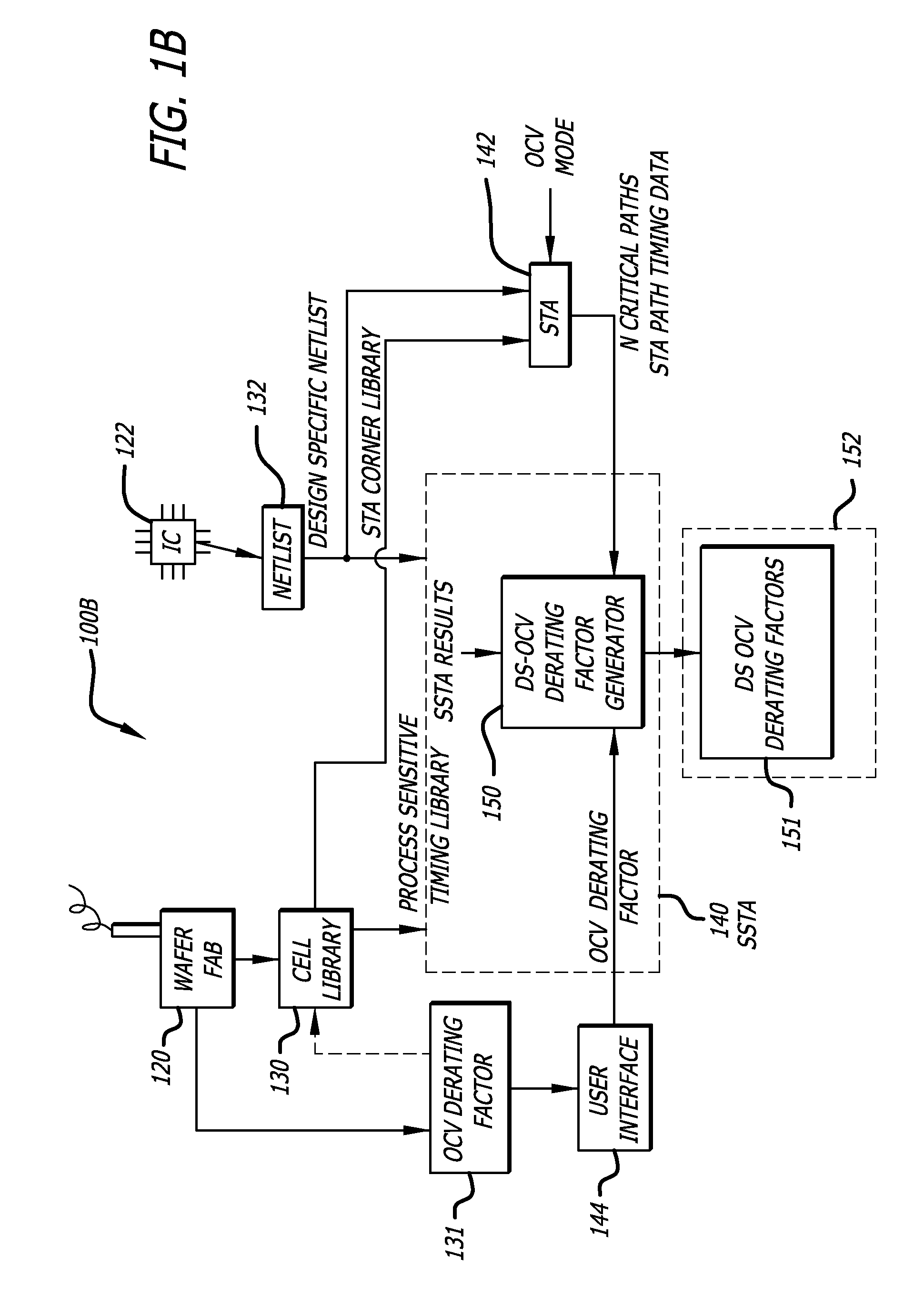

Design-specific on chip variation de-rating factors for static timing analysis of integrated circuits

InactiveUS8336010B1Reduce running timeDesign specificationComputer aided designSoftware simulation/interpretation/emulationTime informationDying processes

In one embodiment of the invention, a method of analysis of a circuit design with respect to within-die process variation is disclosed to generate a design-specific on chip variation (DS-OCV) de-rating factor. The method includes executing a static timing analysis (STA) in an on-chip variation mode using a process corner library. Collecting timing information of the top N critical timing paths. Executing a statistical static timing analysis (SSTA) on the N critical timing paths using timing models characterized for SSTA with sensitivities of delays to process variables. Compare the two timing results and deriving DS-OCV de-rating factors for the clock / data paths to be used in a STA OCV timing analysis to correctly account for the effects of process variations. A user may select to specify DS-OCV de-rating factors for paths or groups of paths and achieve an accurate timing analysis report in a reduced amount of run-time.

Owner:CADENCE DESIGN SYST INC

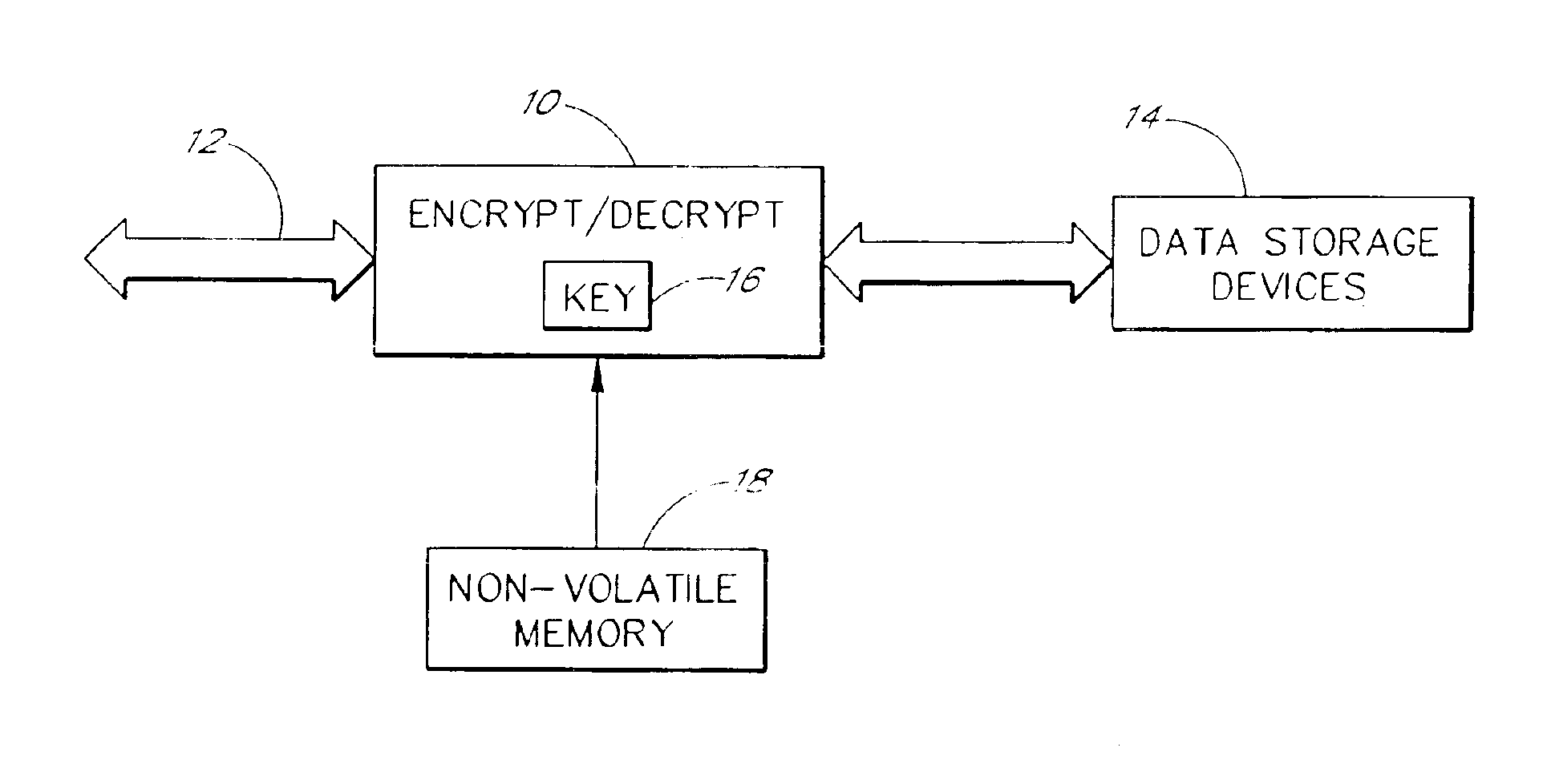

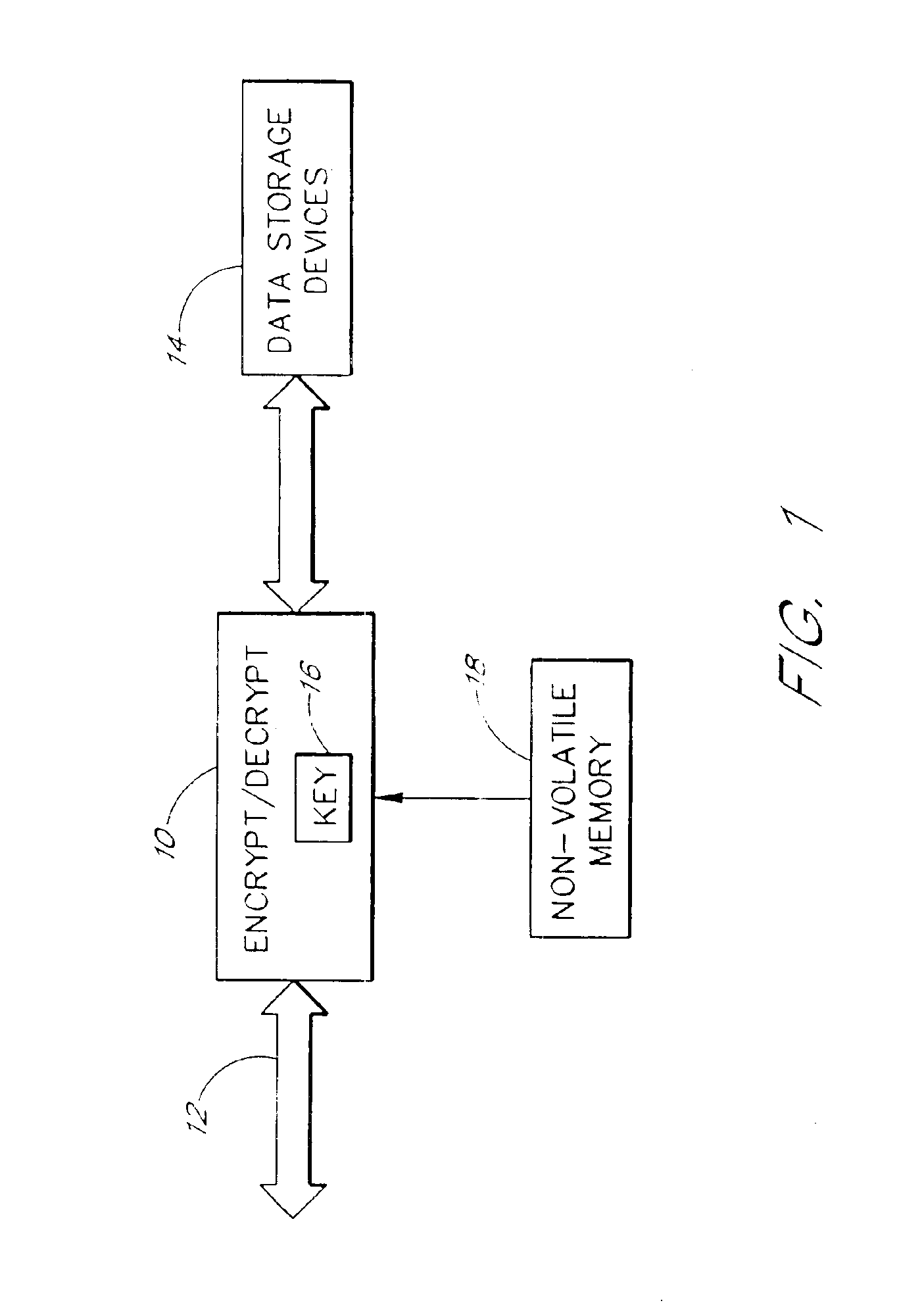

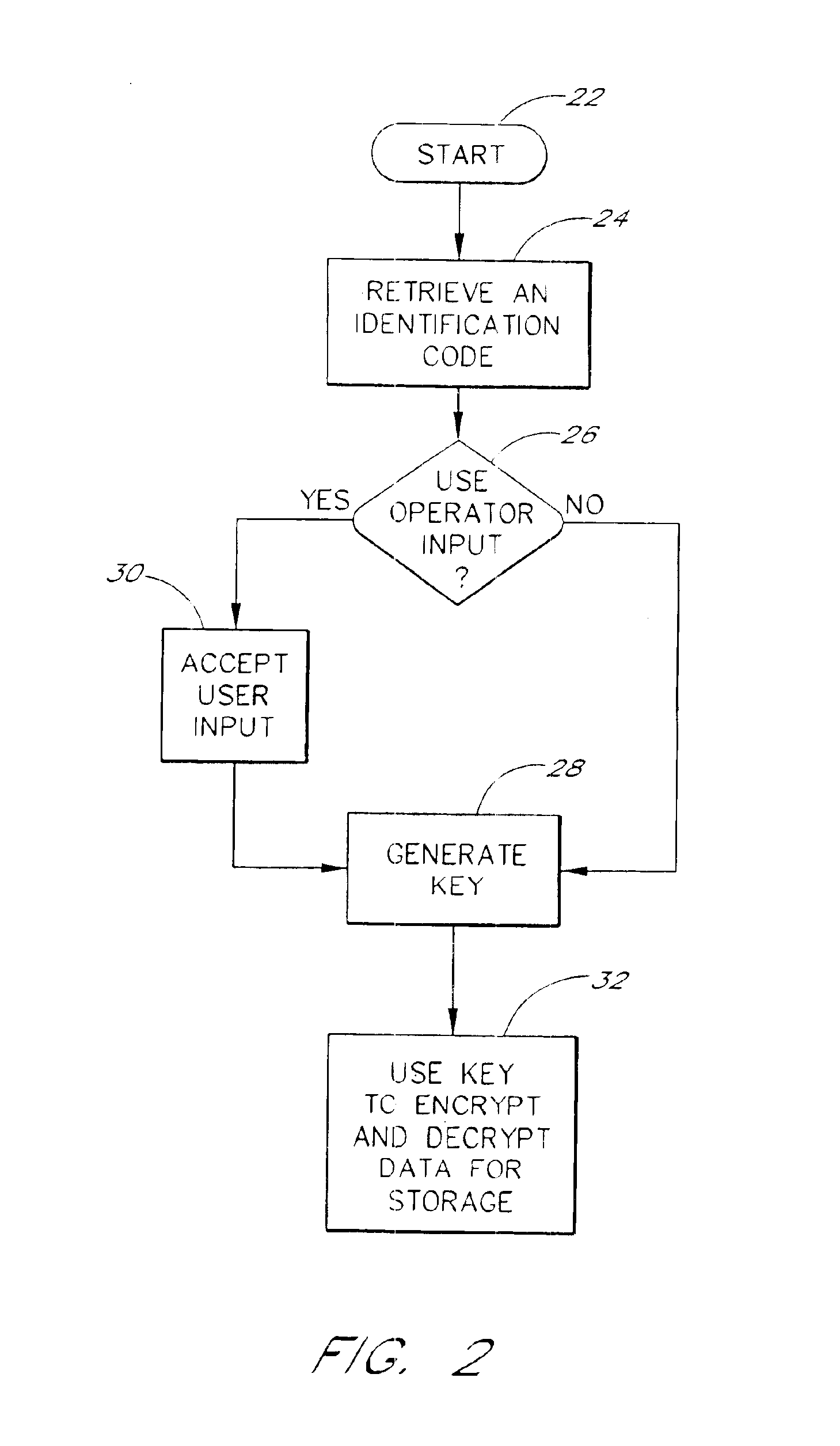

Data security for digital data storage

InactiveUS6857076B1Key distribution for secure communicationUnauthorized memory use protectionUser inputData source

A computing system includes data encryption in the data path between a data source and data storage devices. The data encryption may utilize a key which is derived at least in part from an identification code stored in a non-volatile memory. The key may also be derived at least in part from user input to the computer.

Owner:ROUND ROCK RES LLC

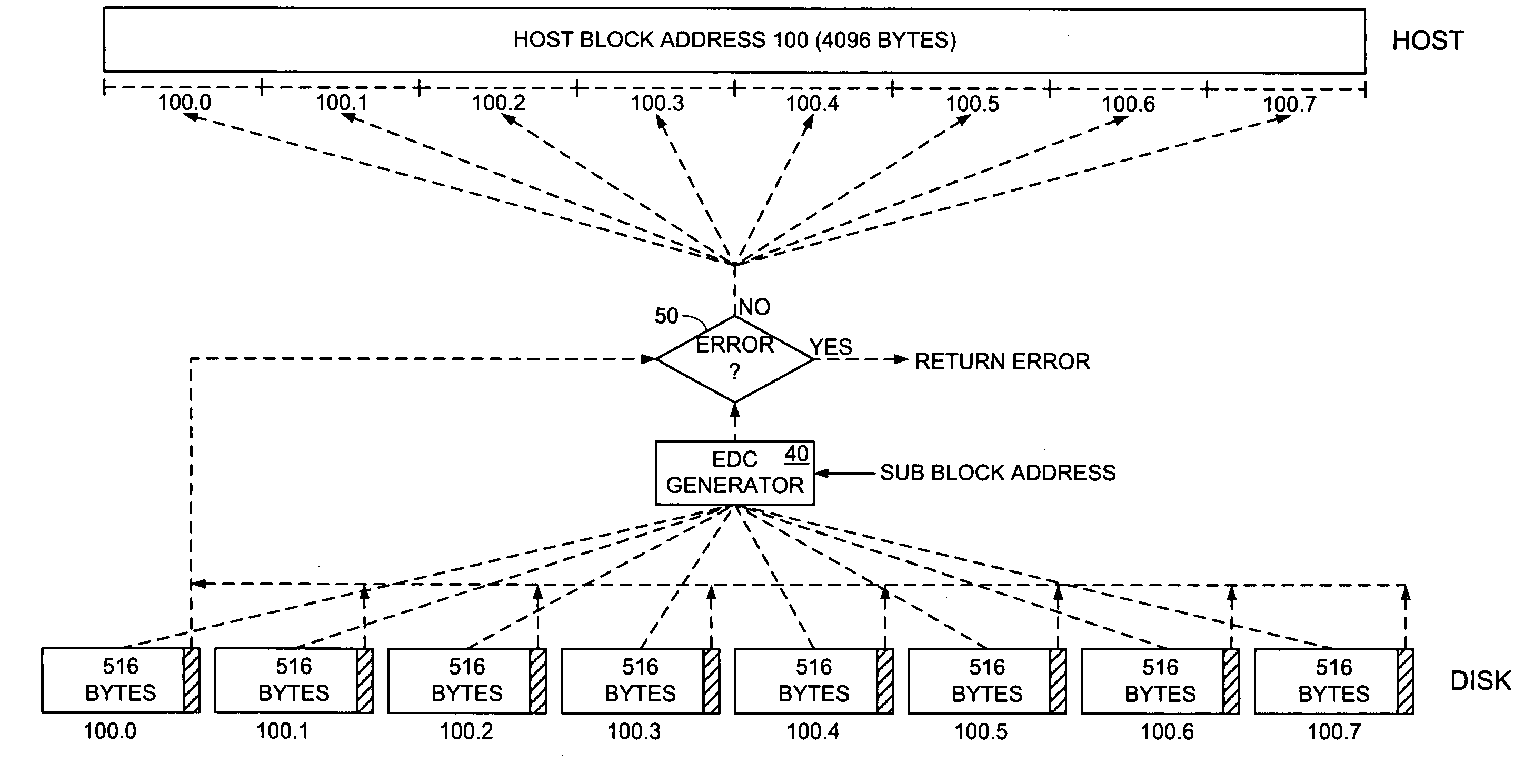

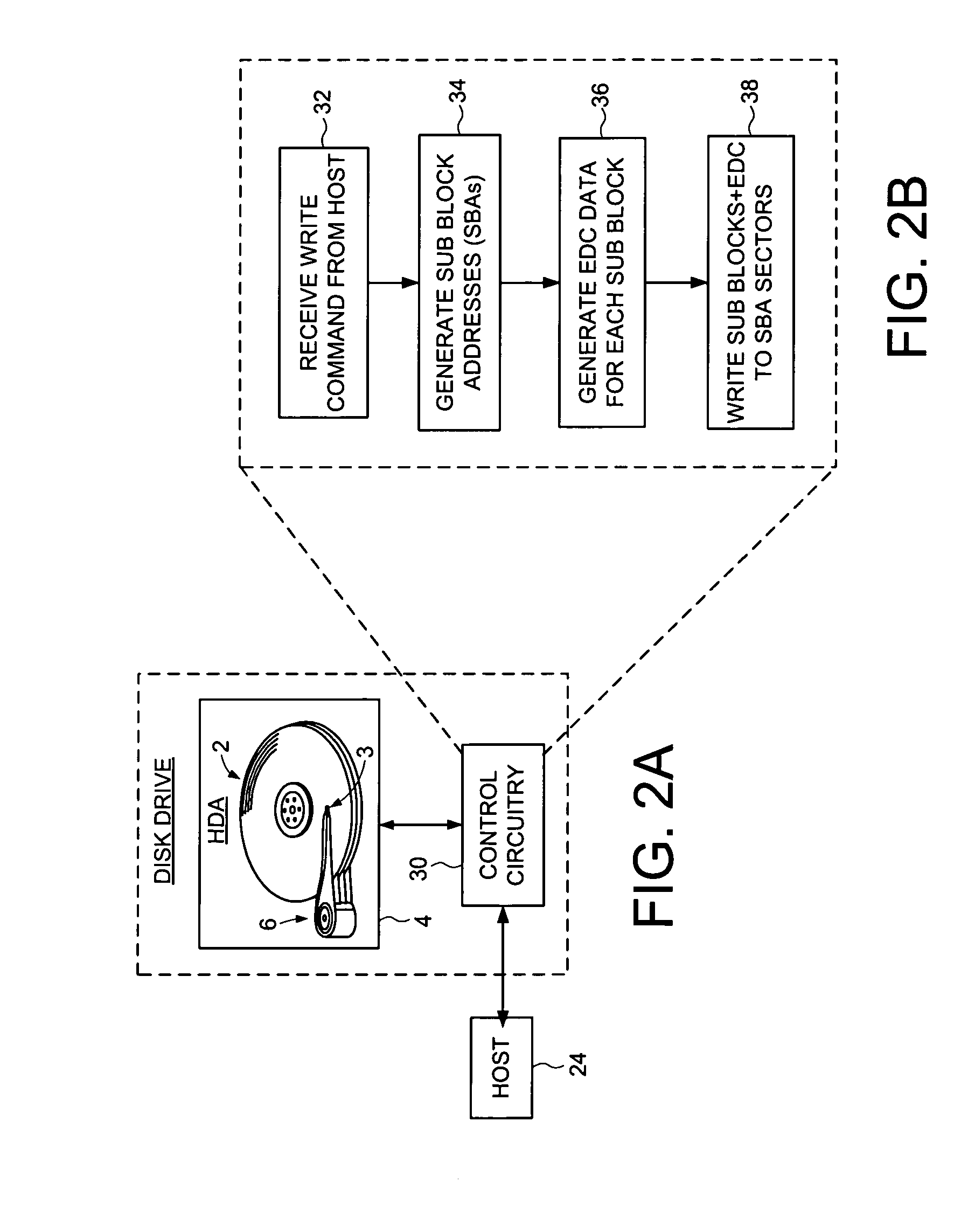

Disk drive implementing data path protection by encoding large host blocks into sub blocks

A disk drive is disclosed including a disk having a plurality of data tracks, wherein each data track includes a plurality of data sectors. A head is actuated over the disk for accessing the data sectors. A write command is received from a host, wherein the write command includes a host block and corresponding host block address. The host block is partitioned into a plurality of sub blocks, and a plurality of sub block addresses are generated in response to the host block address, wherein each sub block address corresponds to one of the sub blocks. Error detection code (EDC) data is generated for each sub block in response to the sub block and corresponding sub block address. Each sub block and corresponding EDC data are combined to generate a plurality of partial codewords that are written to the data sectors corresponding to the sub block addresses.

Owner:WESTERN DIGITAL TECH INC