Patents

Literature

382 results about "Error detection code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

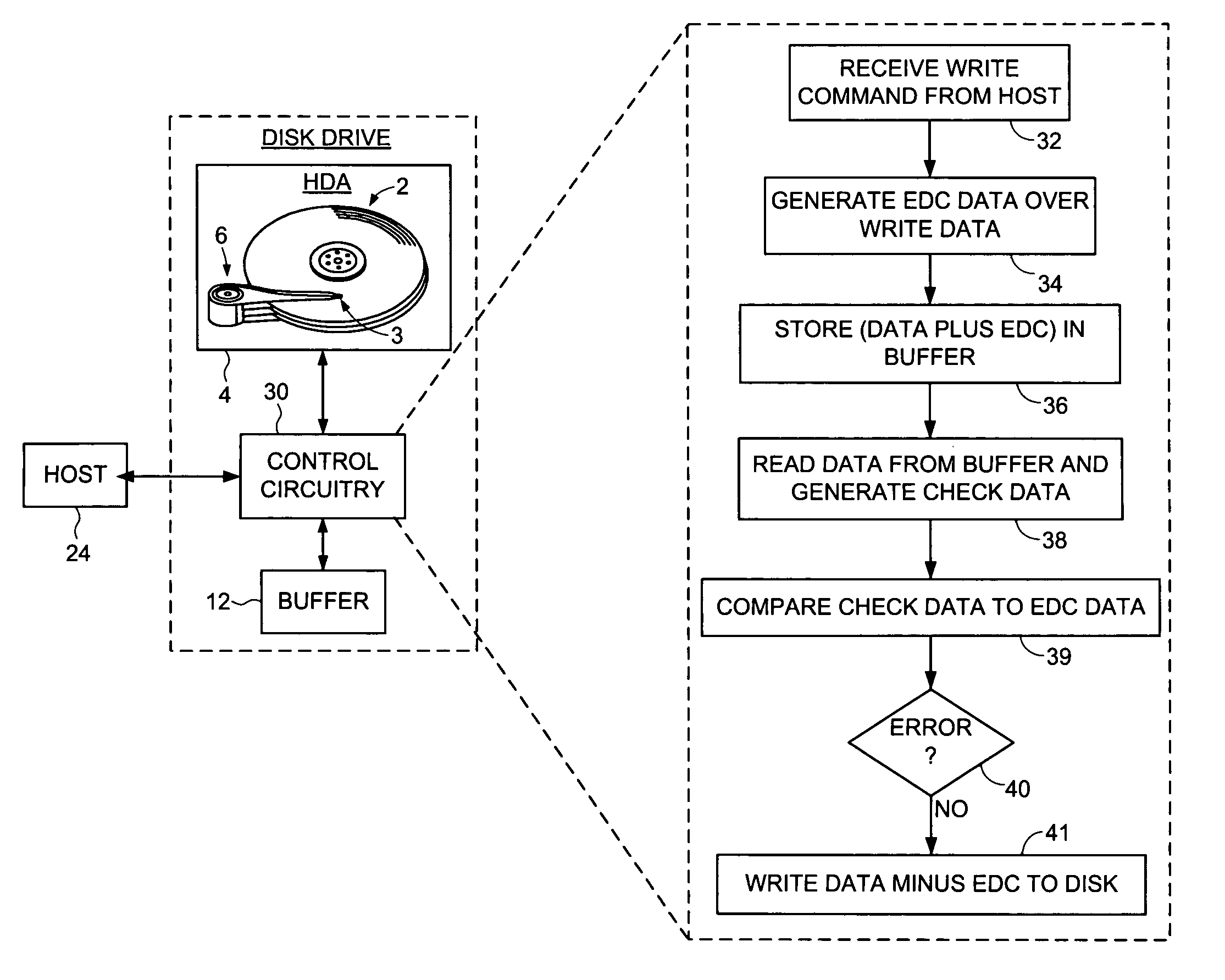

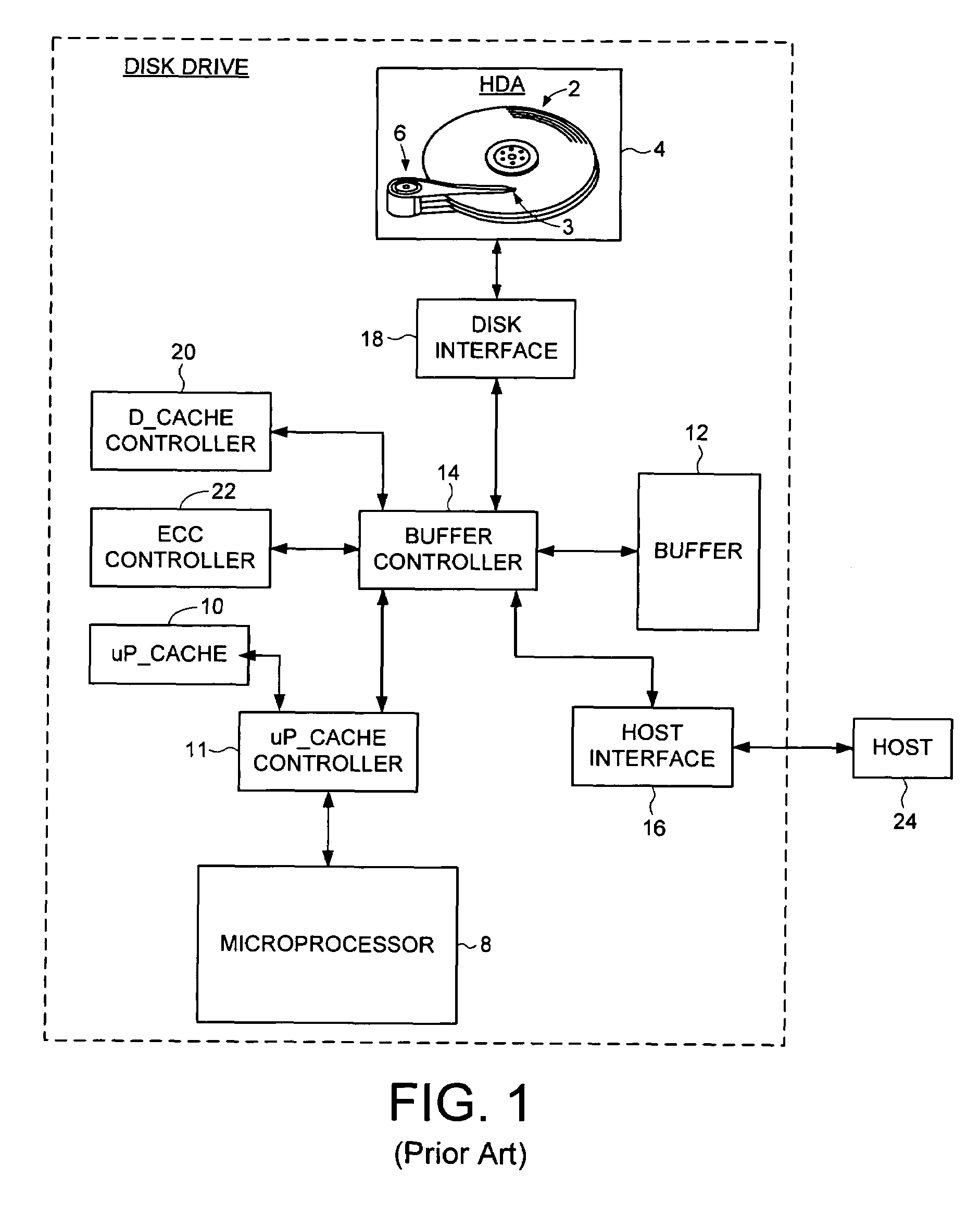

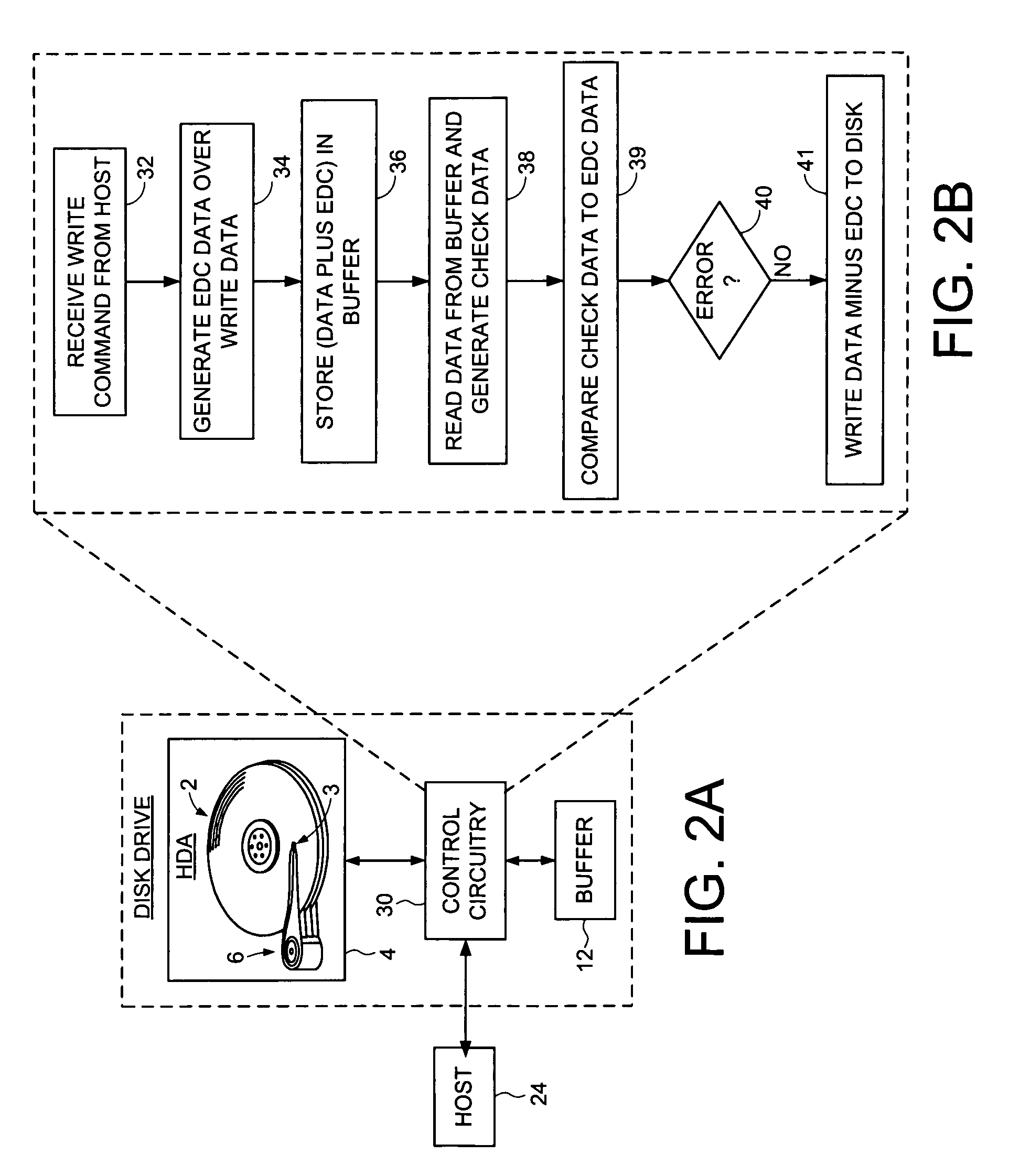

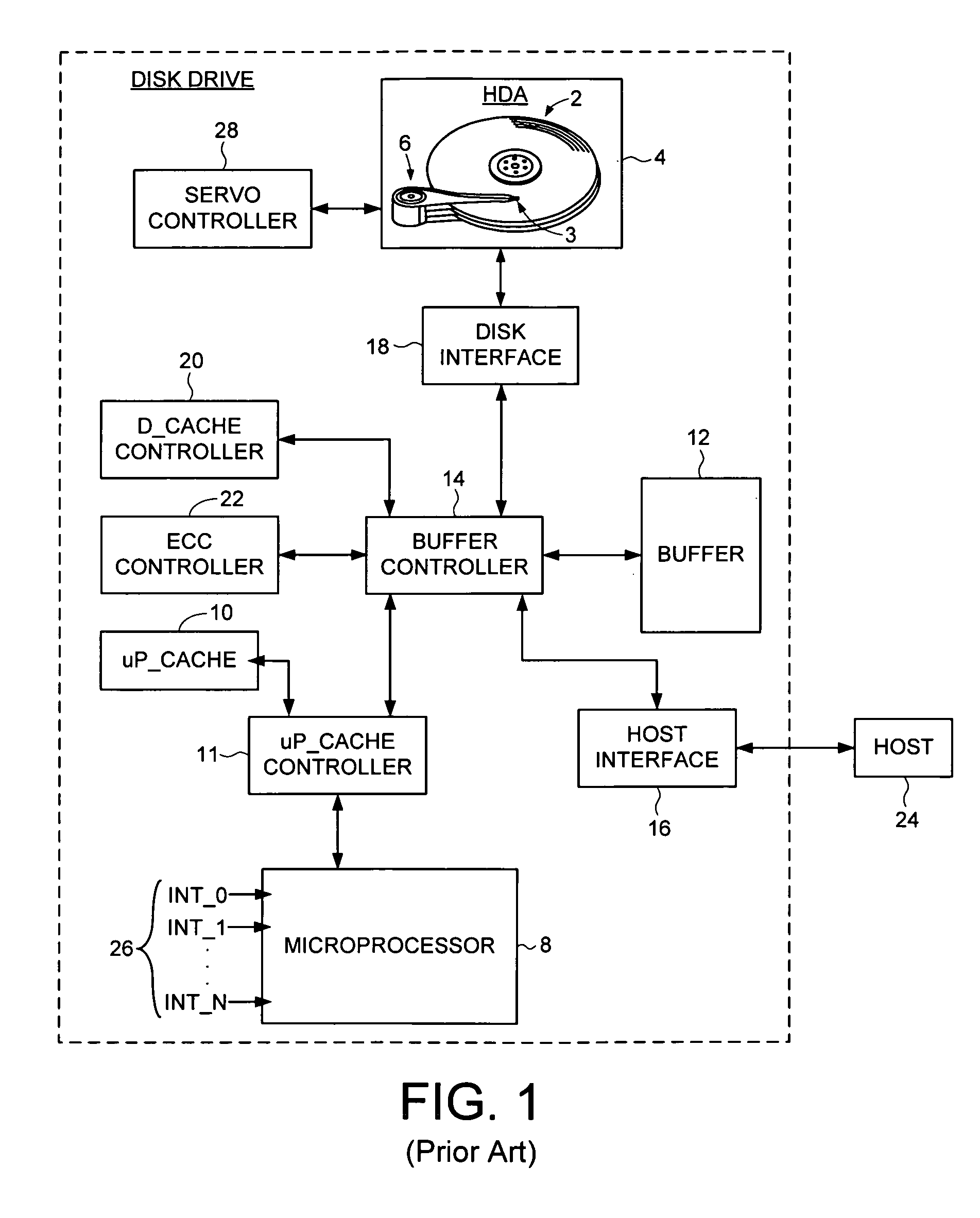

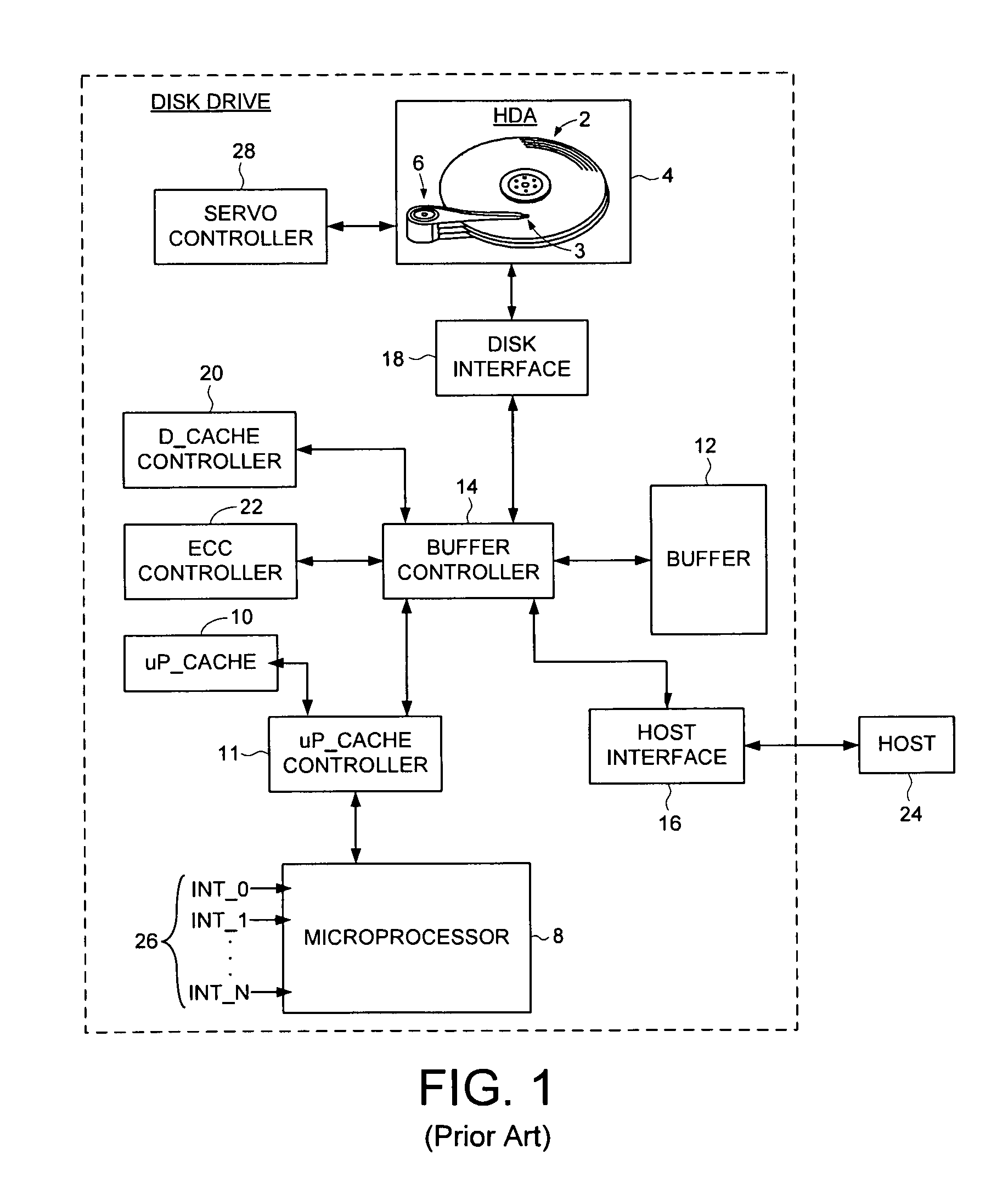

Disk drive implementing data path protection without writing the error detection code data to the disk

Owner:WESTERN DIGITAL TECH INC

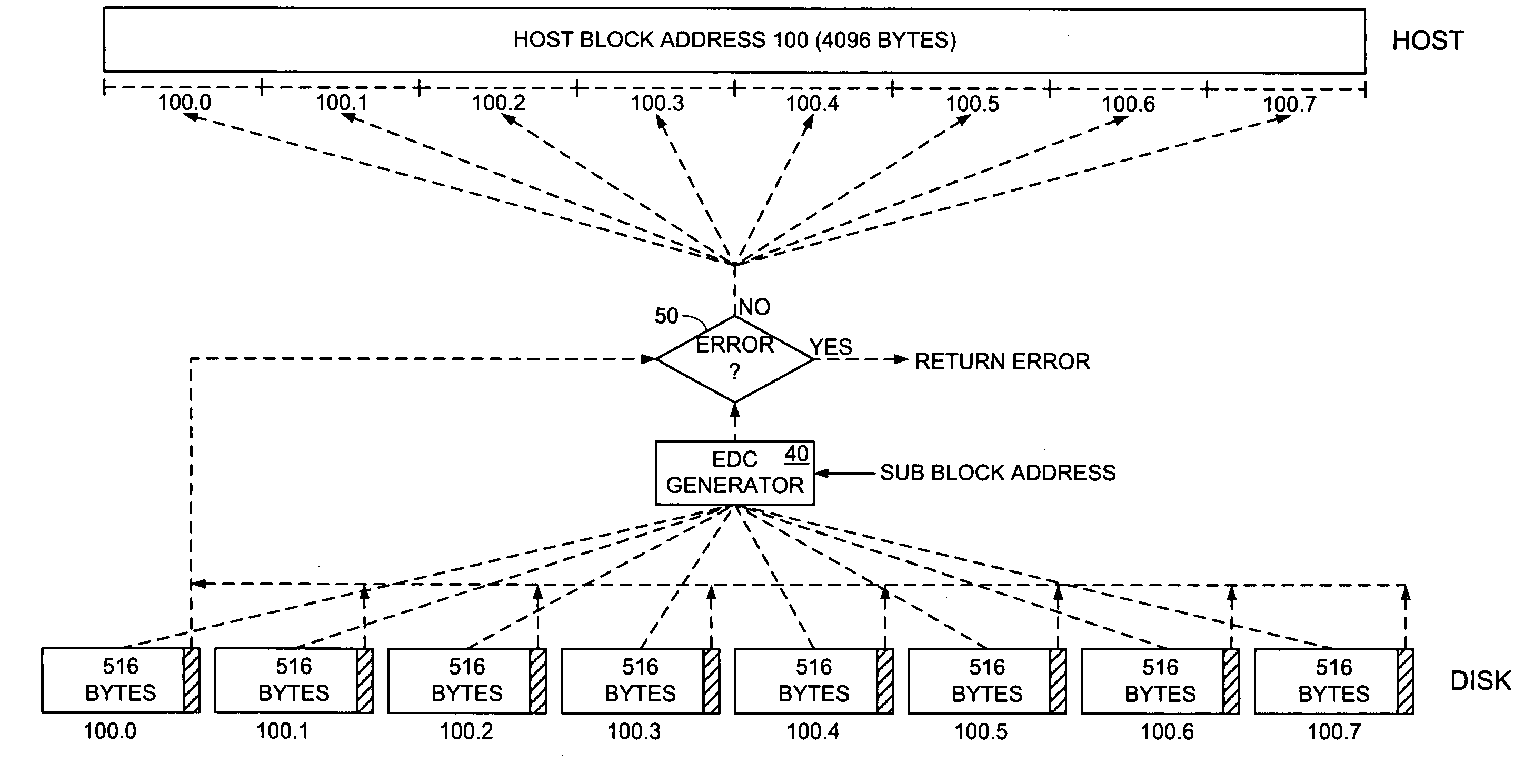

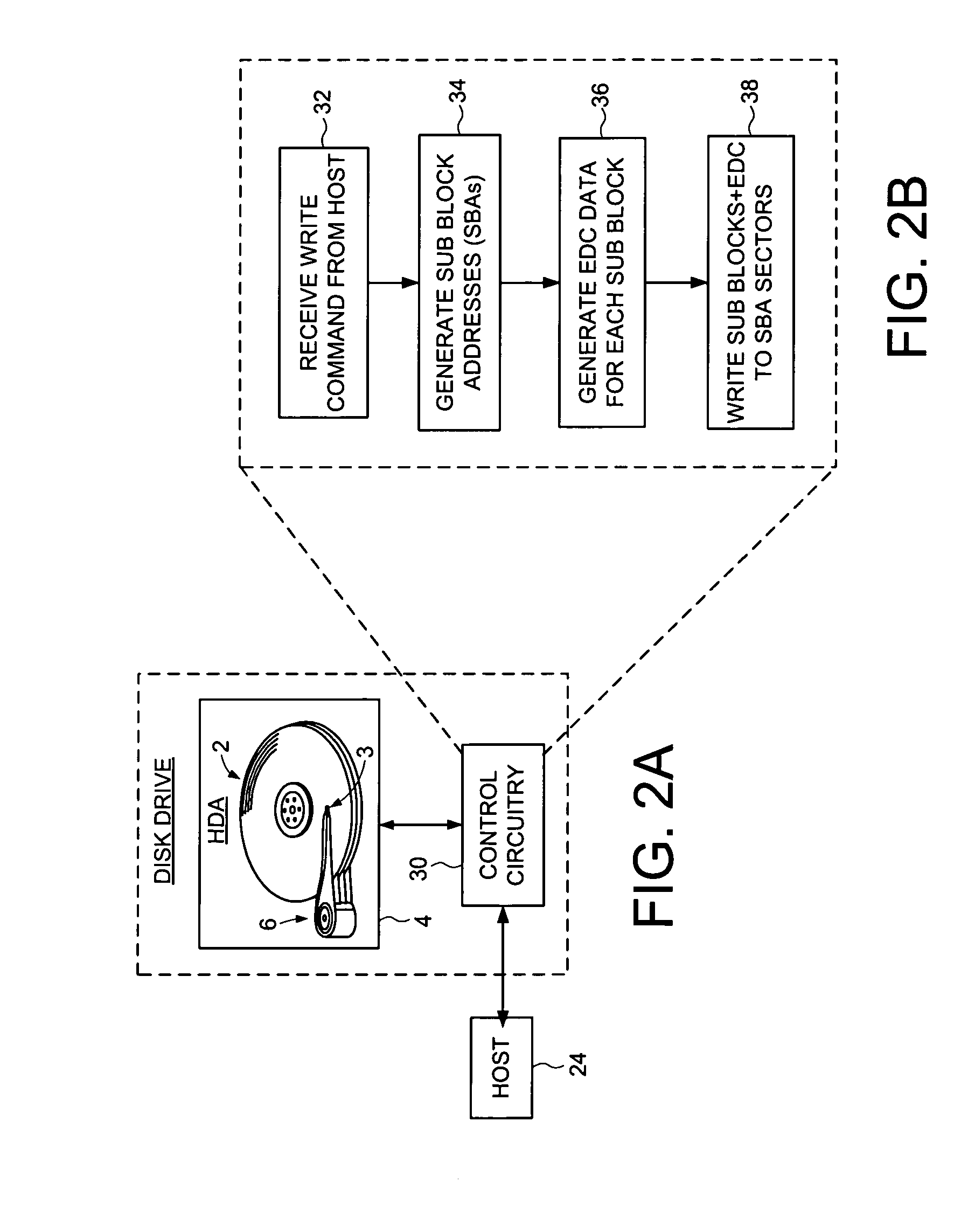

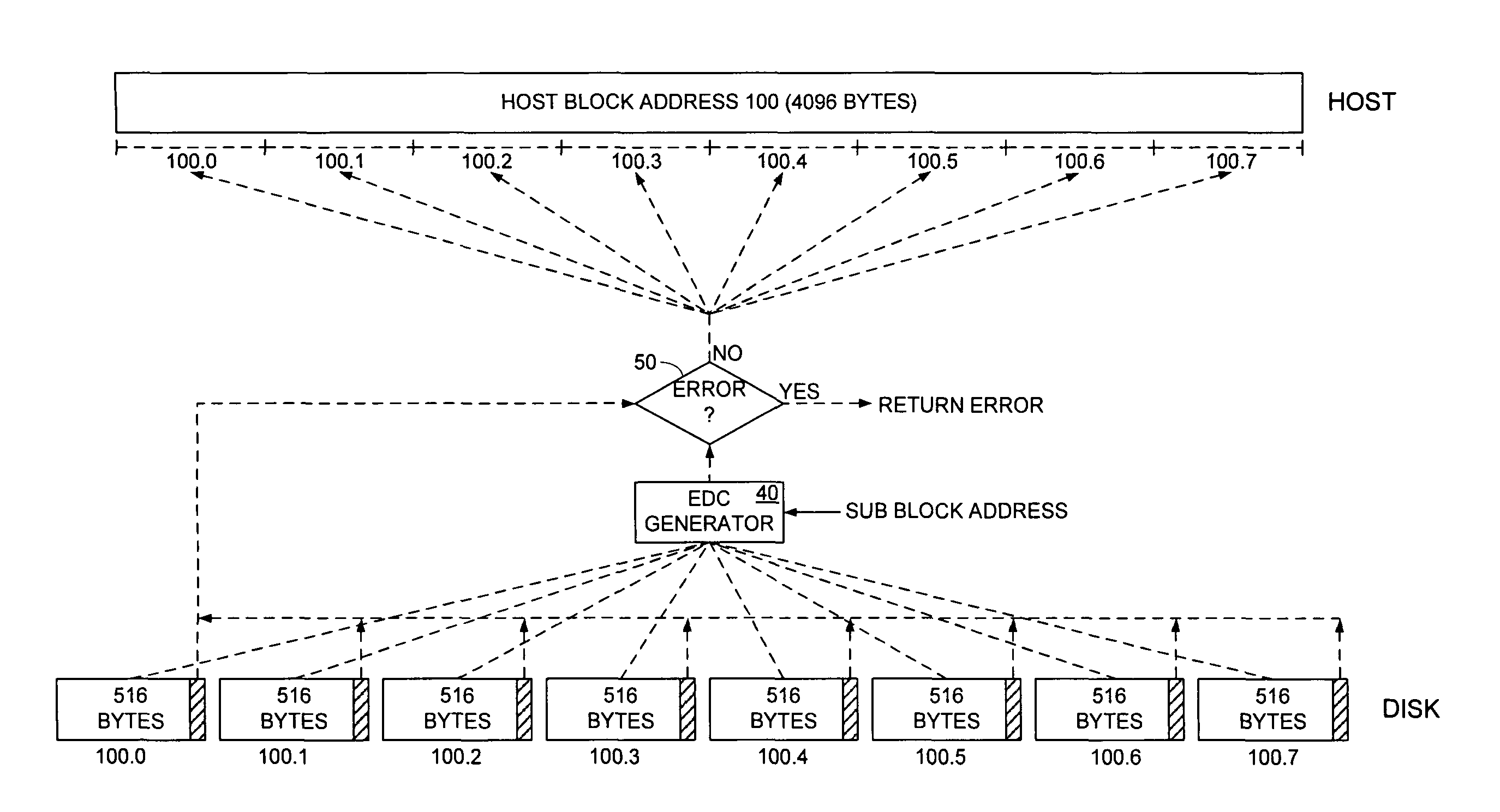

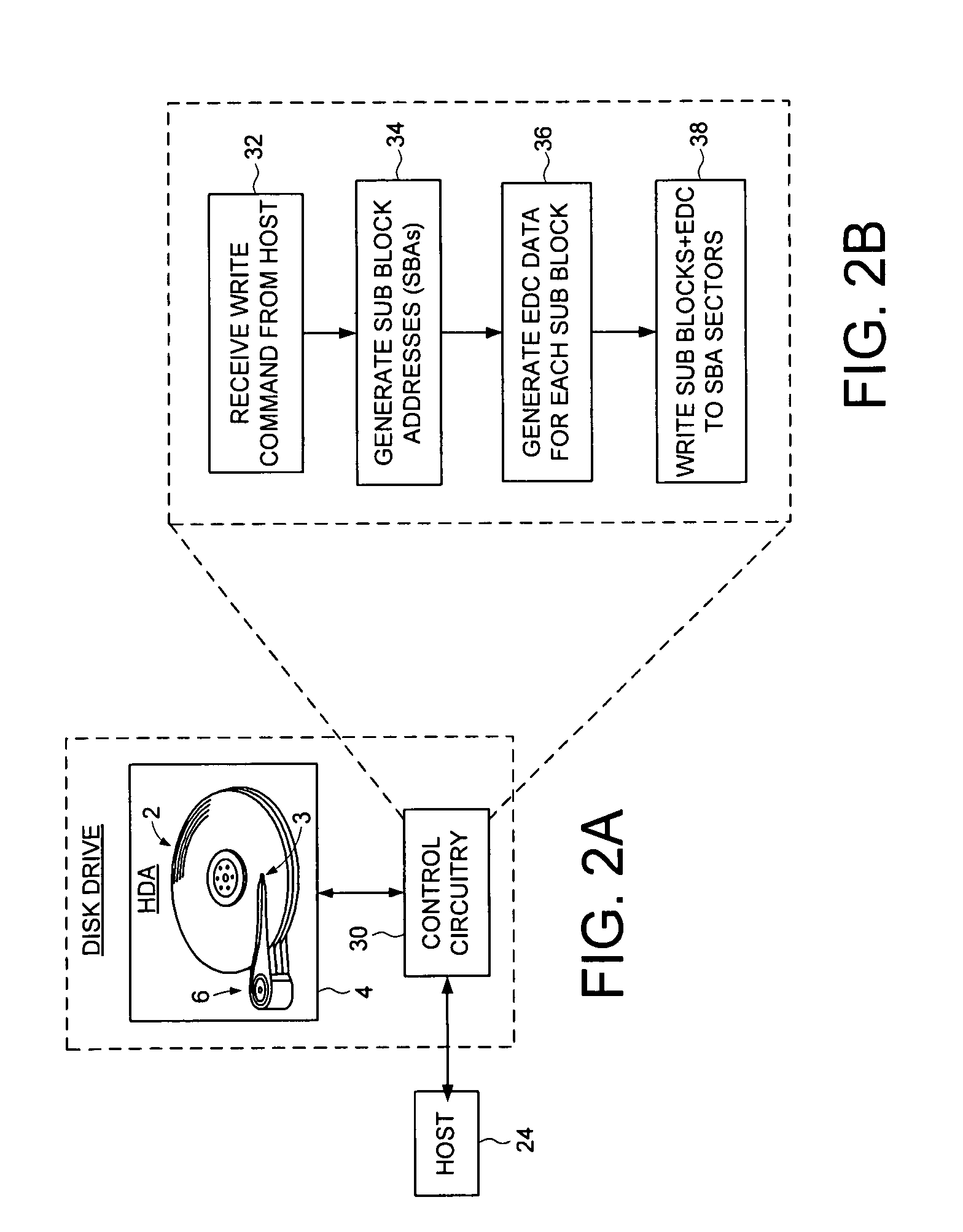

Disk drive implementing data path protection by encoding large host blocks into sub blocks

A disk drive is disclosed including a disk having a plurality of data tracks, wherein each data track includes a plurality of data sectors. A head is actuated over the disk for accessing the data sectors. A write command is received from a host, wherein the write command includes a host block and corresponding host block address. The host block is partitioned into a plurality of sub blocks, and a plurality of sub block addresses are generated in response to the host block address, wherein each sub block address corresponds to one of the sub blocks. Error detection code (EDC) data is generated for each sub block in response to the sub block and corresponding sub block address. Each sub block and corresponding EDC data are combined to generate a plurality of partial codewords that are written to the data sectors corresponding to the sub block addresses.

Owner:WESTERN DIGITAL TECH INC

Storage device implementing data path protection by encoding large host blocks into sub blocks

ActiveUS8433977B1Input/output to record carriersRecord information storageControl circuitComputer science

A storage device is disclosed comprising control circuitry. A write command is received from a host, wherein the write command comprises a host block and corresponding host block address. The host block is partitioned into a plurality of sub blocks, and a plurality of sub block addresses are generated in response to the host block address, wherein each sub block address corresponds to one of the sub blocks. Error detection code (EDC) data is generated for each sub block in response to the sub block and corresponding sub block address. Each sub block and corresponding EDC data are combined to generate a plurality of partial codewords that are written to one or more data sectors corresponding to the sub block addresses.

Owner:WESTERN DIGITAL TECH INC

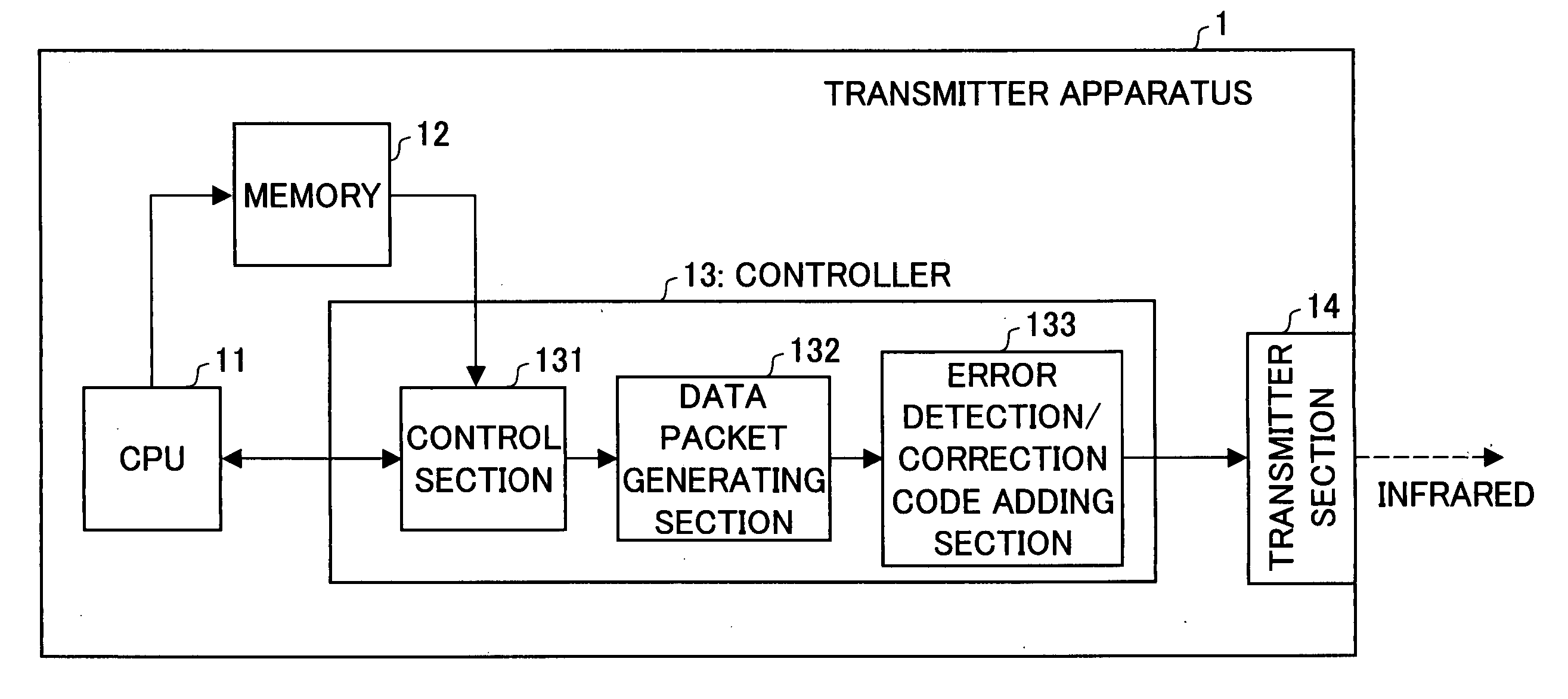

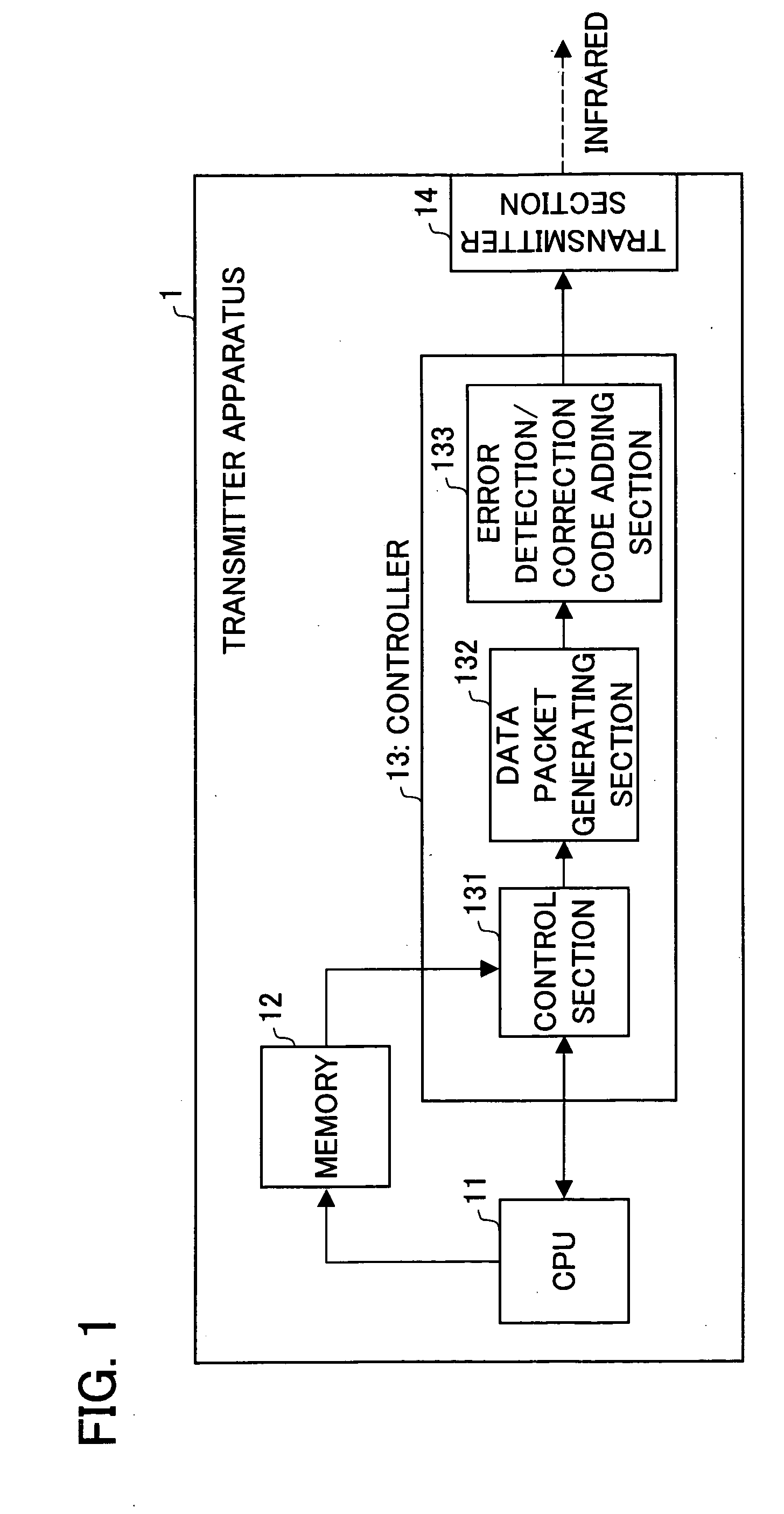

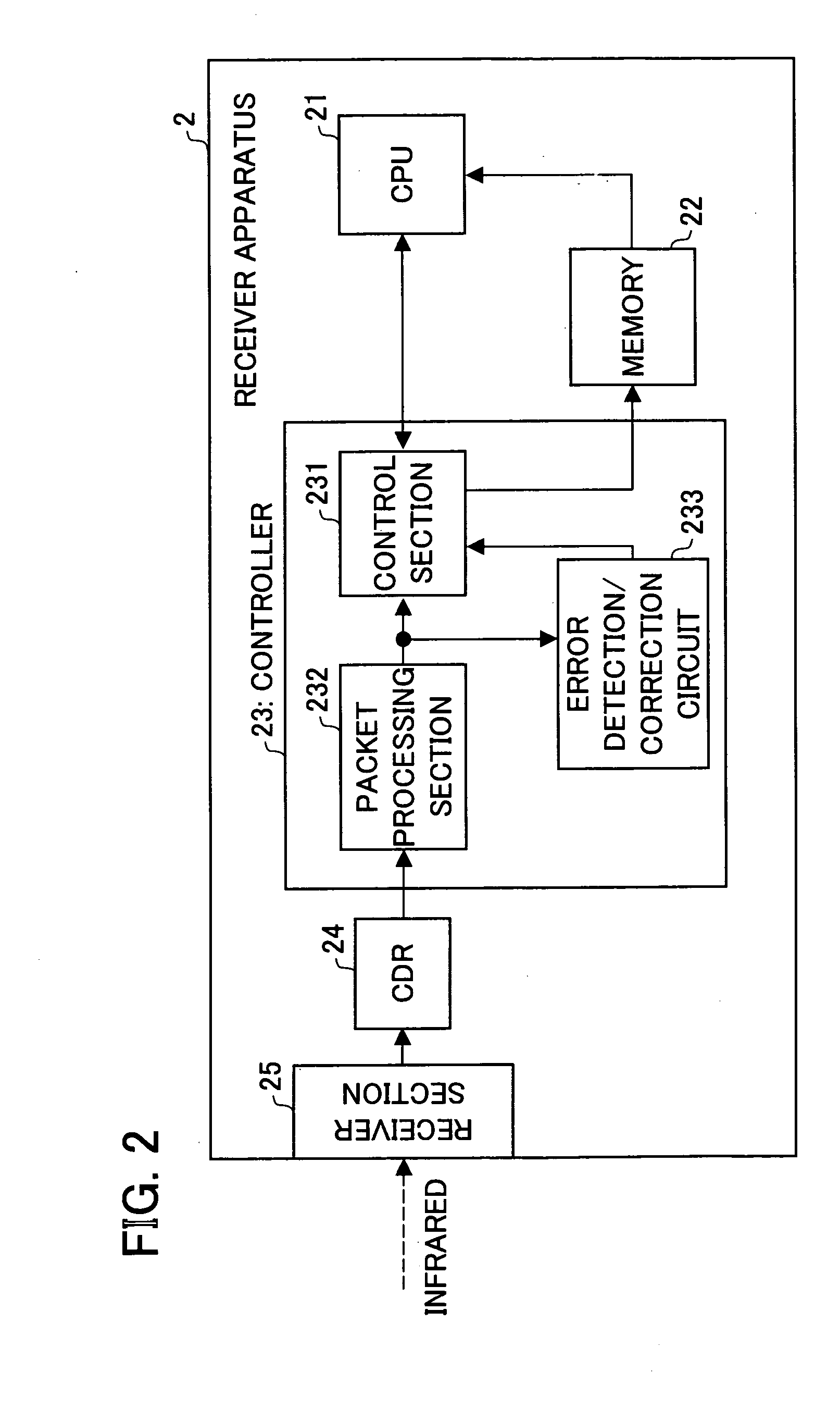

Transmitter, receiver, data transfer system, transmission method, reception method, computer program for transmission, computer program for reception, and recording medium

InactiveUS20050254456A1Reliable and quick data transferImprove reliabilityError preventionError detection/correctionData packData set

A transmitter apparatus 1 transmits transfer data having a predetermined amount to a receiver apparatus. The apparatus 1 includes: a data packet generating section 132 dividing the transfer data into multiple divisional data sets; an error detection / correction code adding section 133 adding an error detection code (error detection information) by which an error in the divisional data sets is detected to each of the divisional data sets; and a transmitter section 14 transmitting the multiple divisional data sets to which the error detection code is added all together. Thus, data transfer is very reliable. It takes less time to transfer data.

Owner:SHARP KK

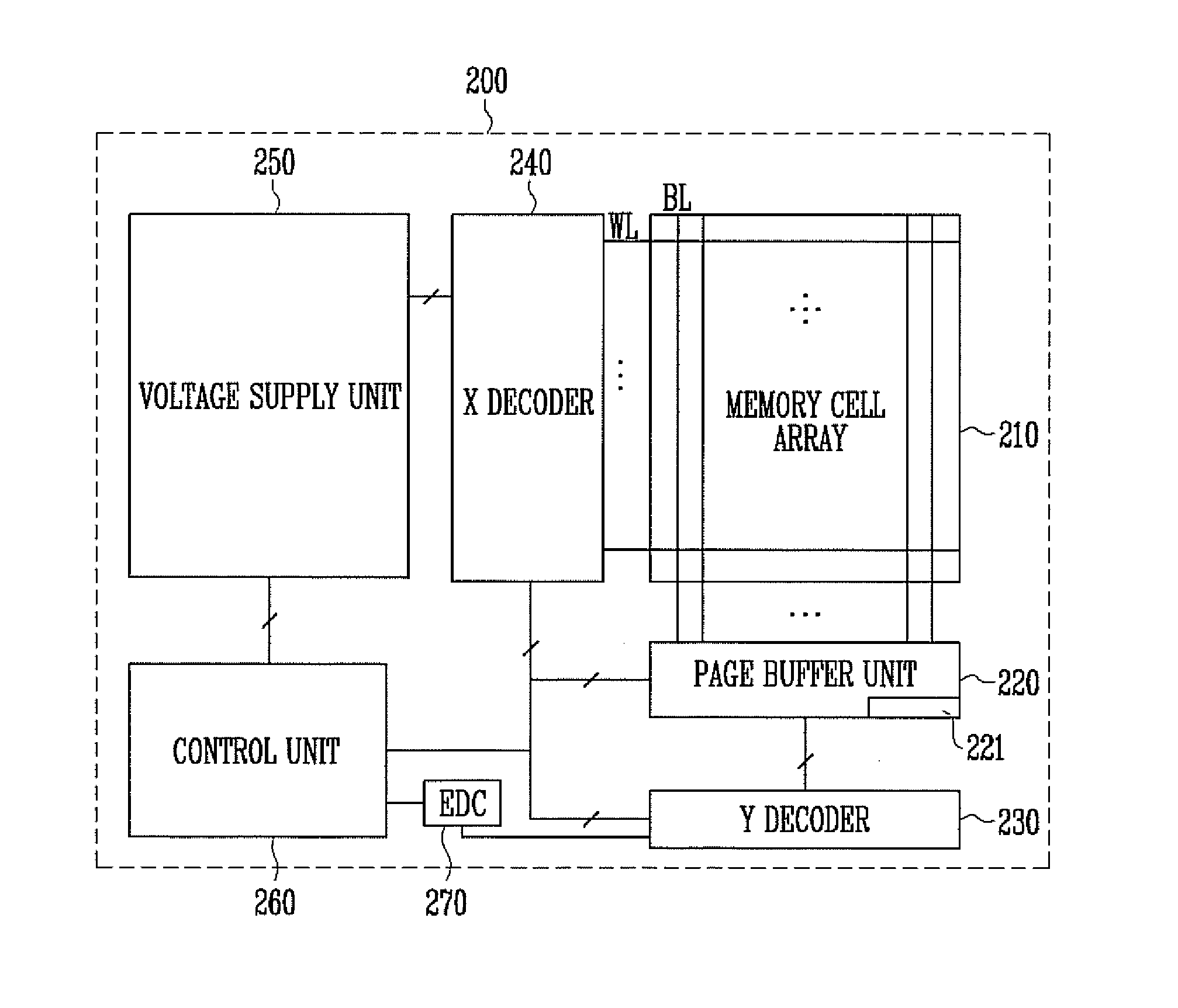

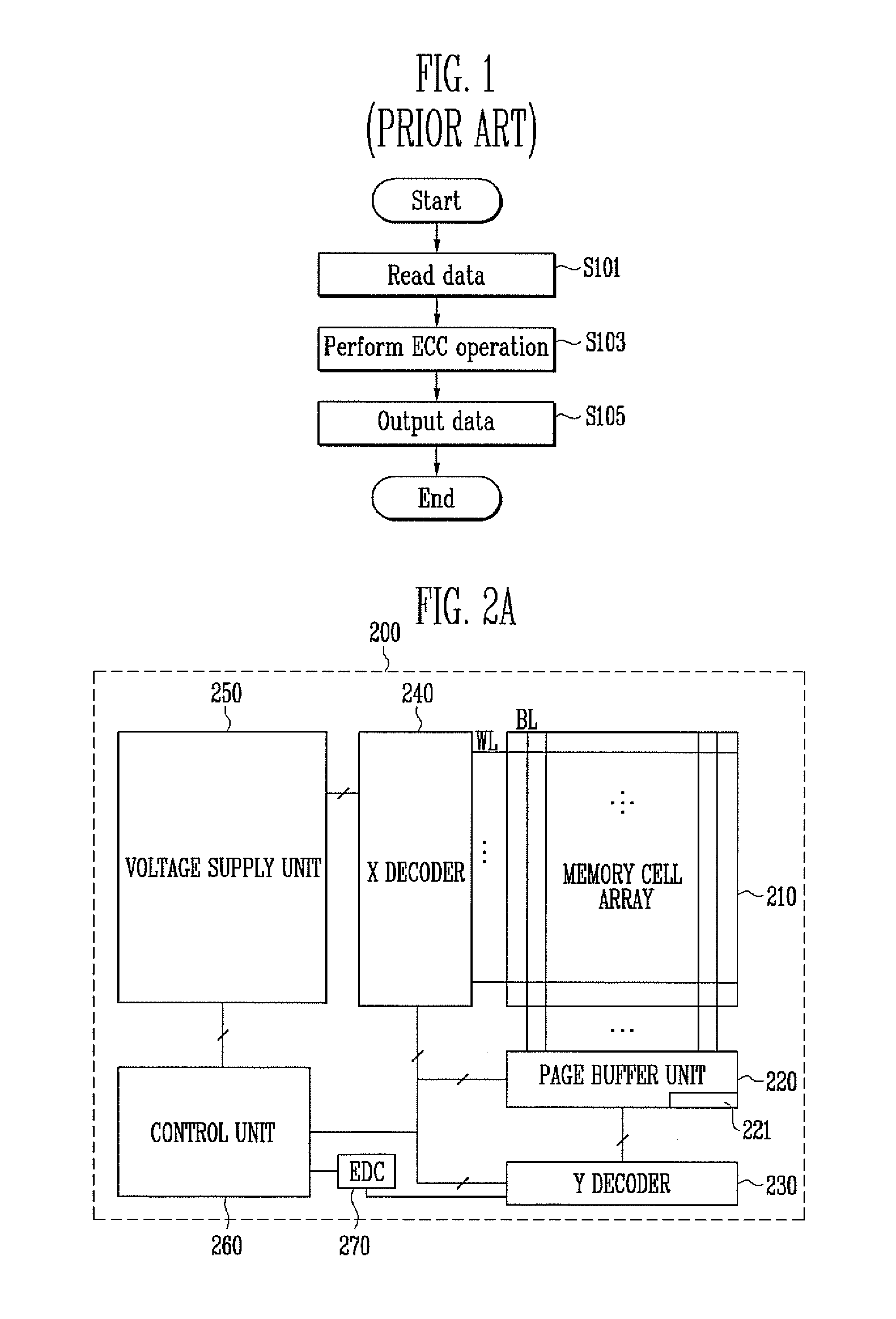

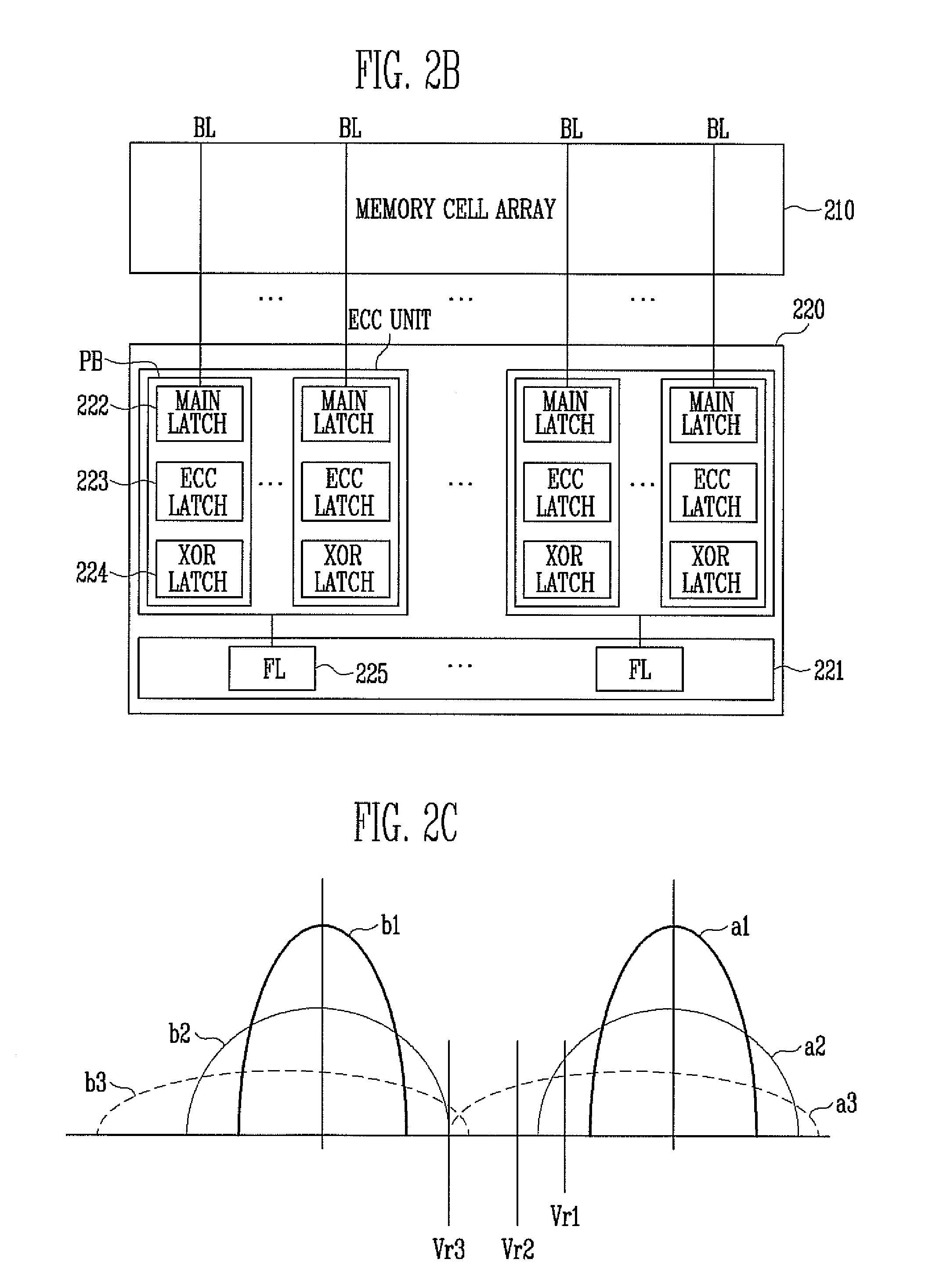

Nonvolatile memory device and method of operating the same

ActiveUS20100199138A1Correction errorError preventionTransmission systemsLogical operationsError detection coding

A nonvolatile memory device includes a memory cell array configured to comprise memory cells coupled by bit lines and word lines, a page buffer unit configured to comprise page buffers and flag latches, wherein the page buffers, coupled to one or more of the bit lines, each are configured to comprise a plurality of latches for storing logic operation results for error correction and configured to store data read using a read voltage, and the flag latches each are configured to classify the page buffers into some page buffer groups each having a predetermined number and to store flag information indicating whether an error has occurred in each group, and an error detection code (EDC) checker configured to determine whether an error has occurred in each of the page buffer groups.

Owner:SK HYNIX INC

System and method for in-line consistency checking of packetized data

ActiveUS20060059400A1Reduce dataLower latencyError preventionCode conversionError detection codingError detection code

A system and method for efficiently detecting and correcting transmission errors in packet-based communications by using cumulative error detection codes. The system may comprise a transmitting unit, which transmits one or more data packets. Each of the transmitted packets may comprise a plurality of transmission subunits. The transmitting unit preferably generates a cumulative error detection code (e.g., cumulative CRC code) for each of the transmission subunits of a packet. The system may further comprise a receiving unit to receive each of the transmission subunits of the packet. The receiving unit preferably generates a new cumulative error detection code for each of the received transmission subunits. The new cumulative error detection code is compared to the received cumulative error detection code to determine if any errors occurred in the transmission of the transmission subunit.

Owner:NATIONAL INSTRUMENTS

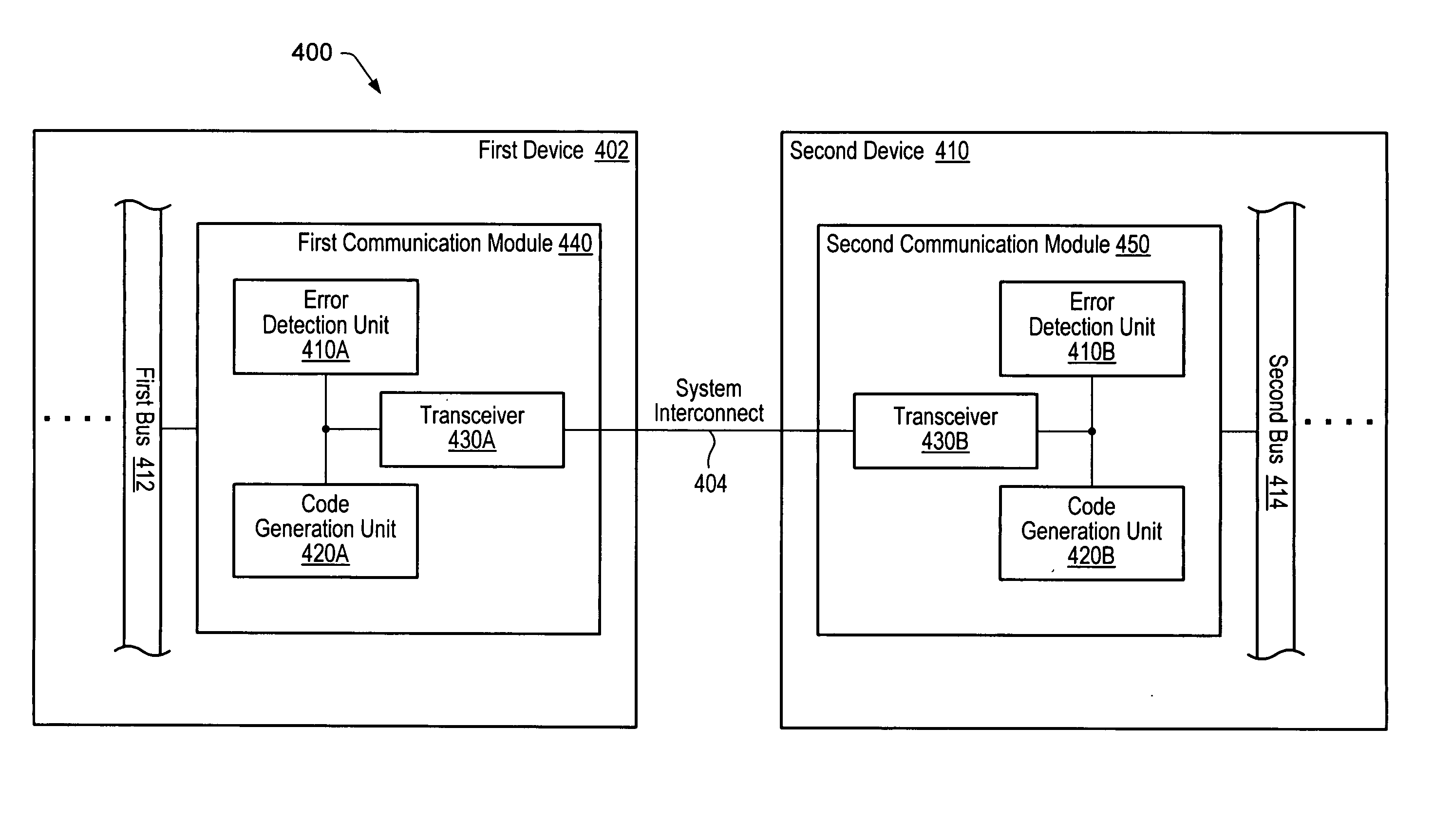

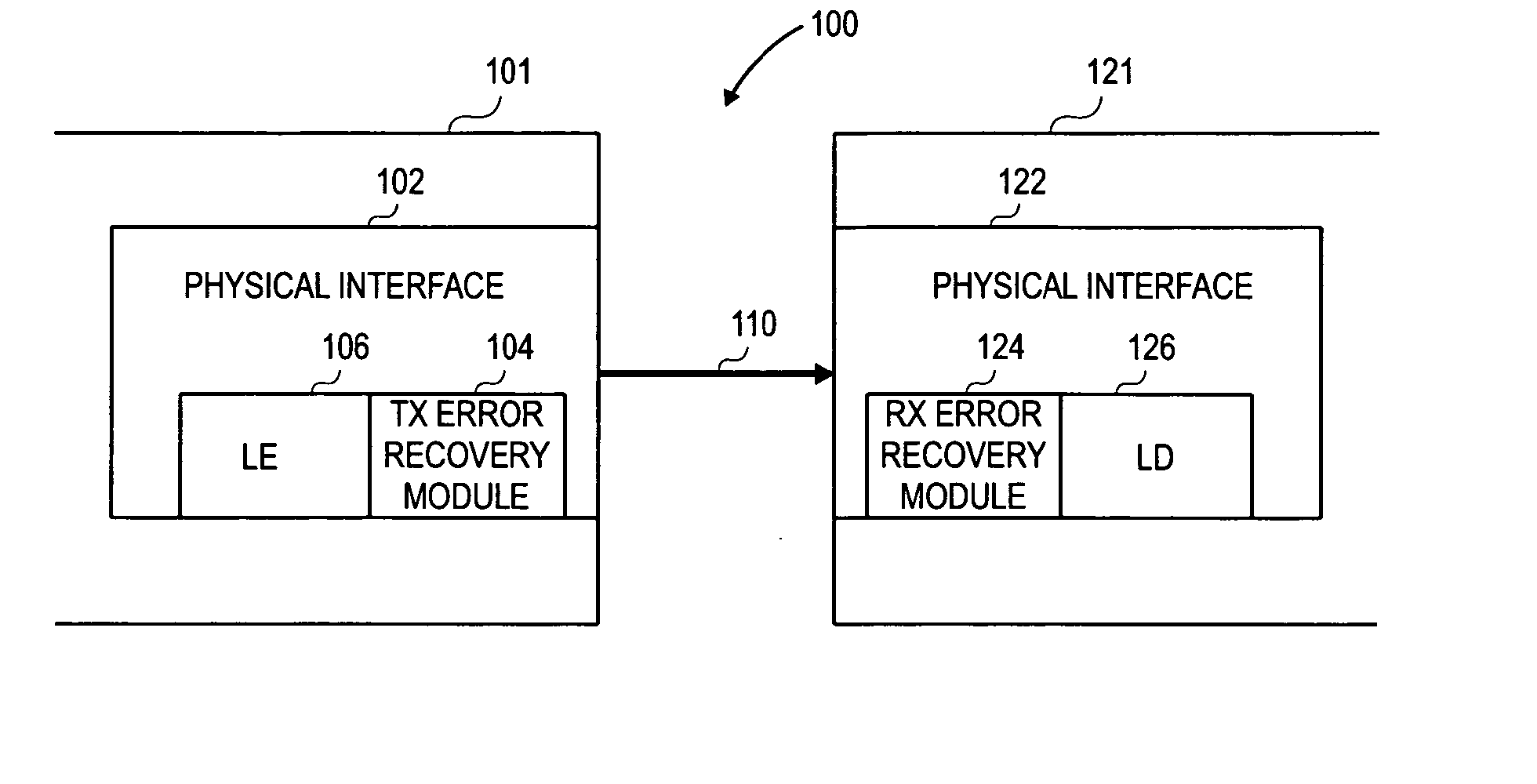

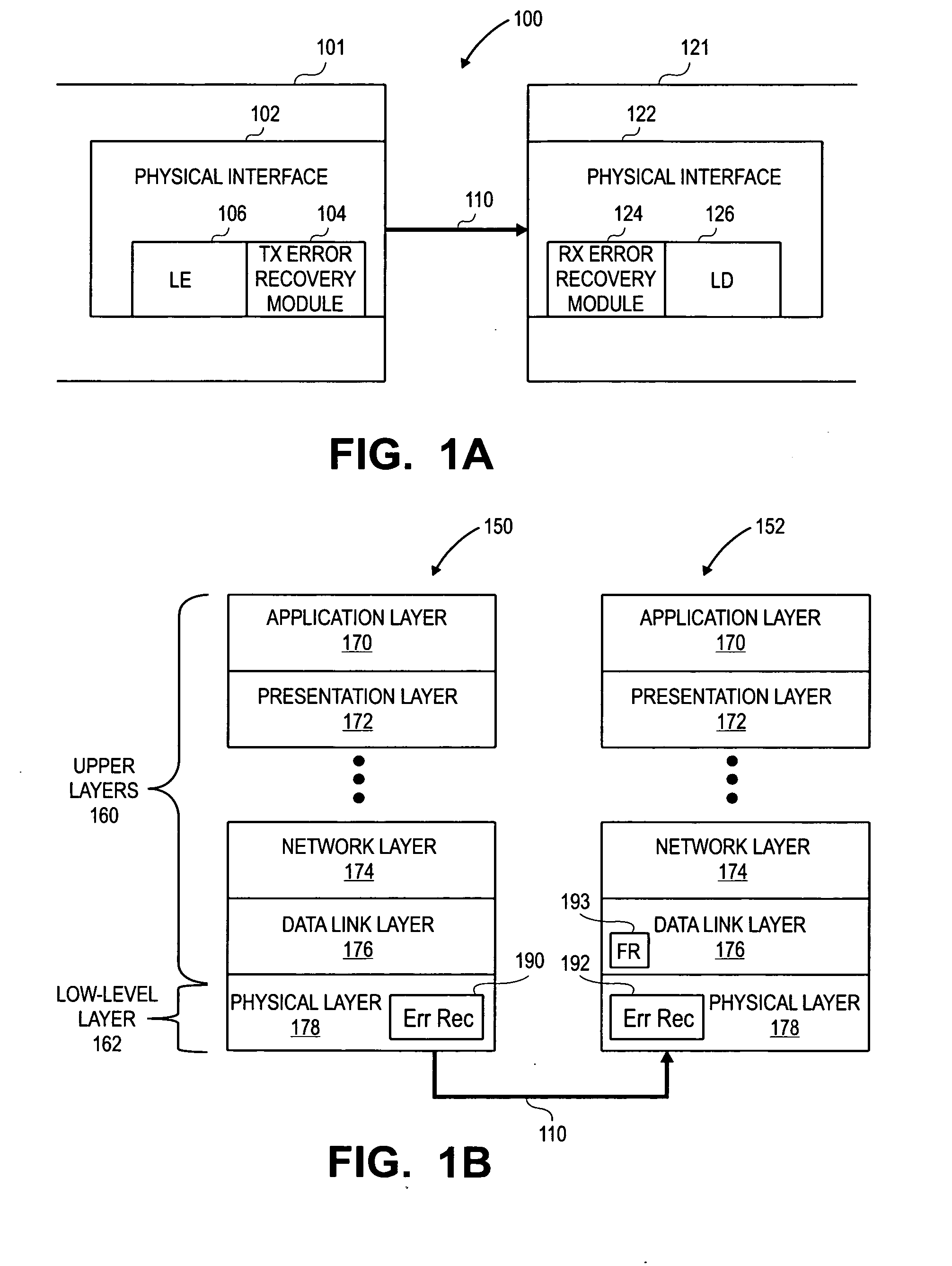

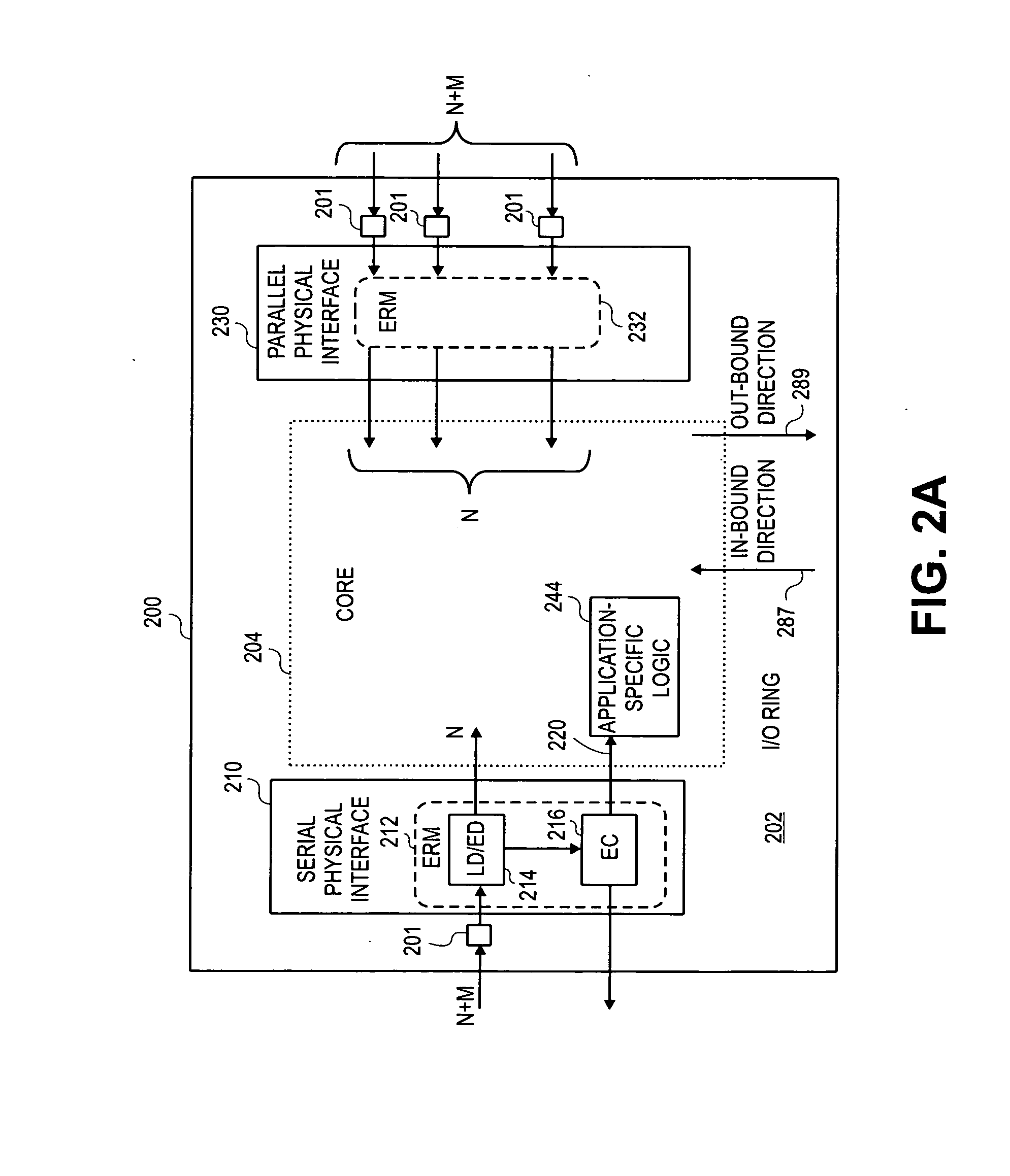

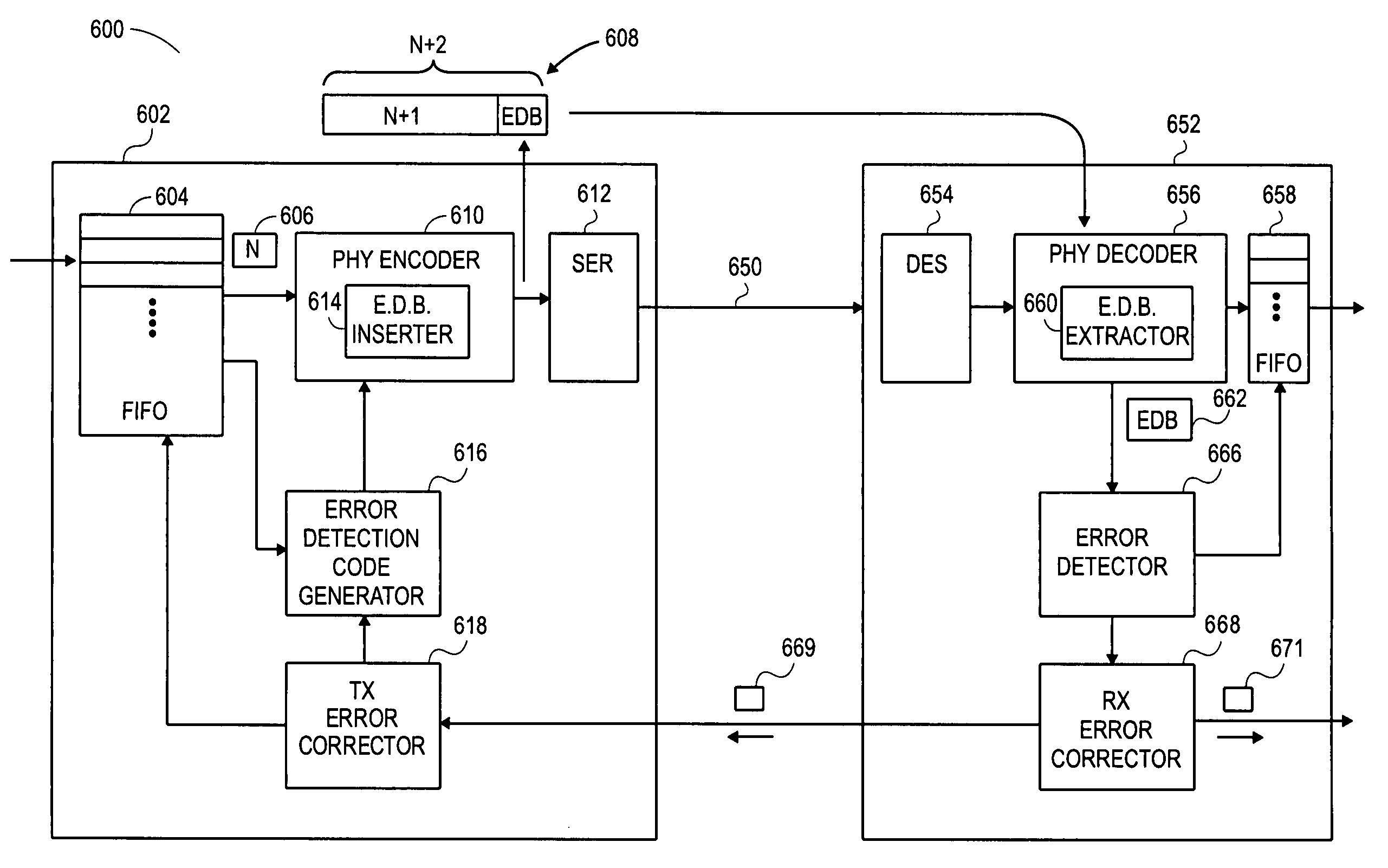

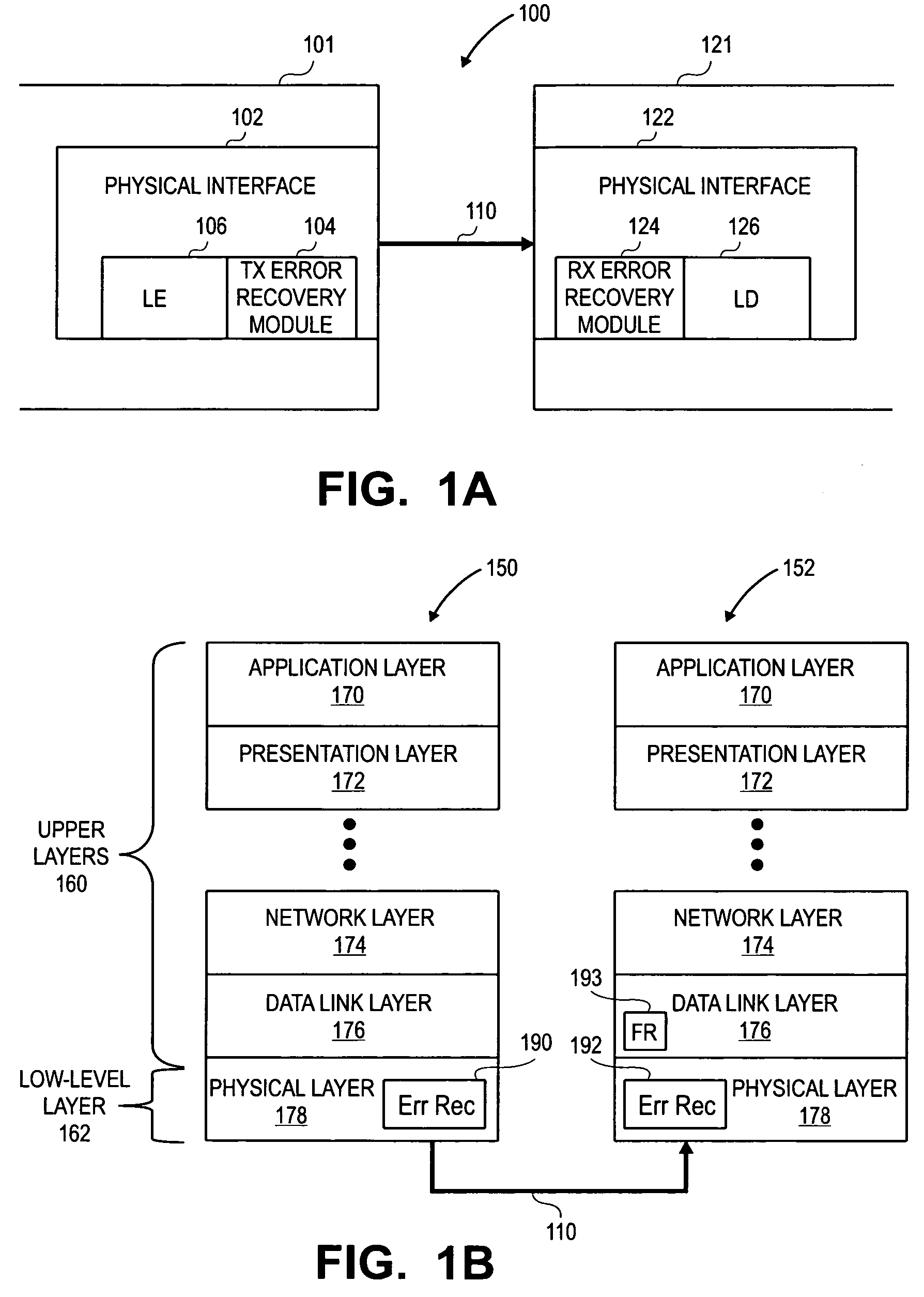

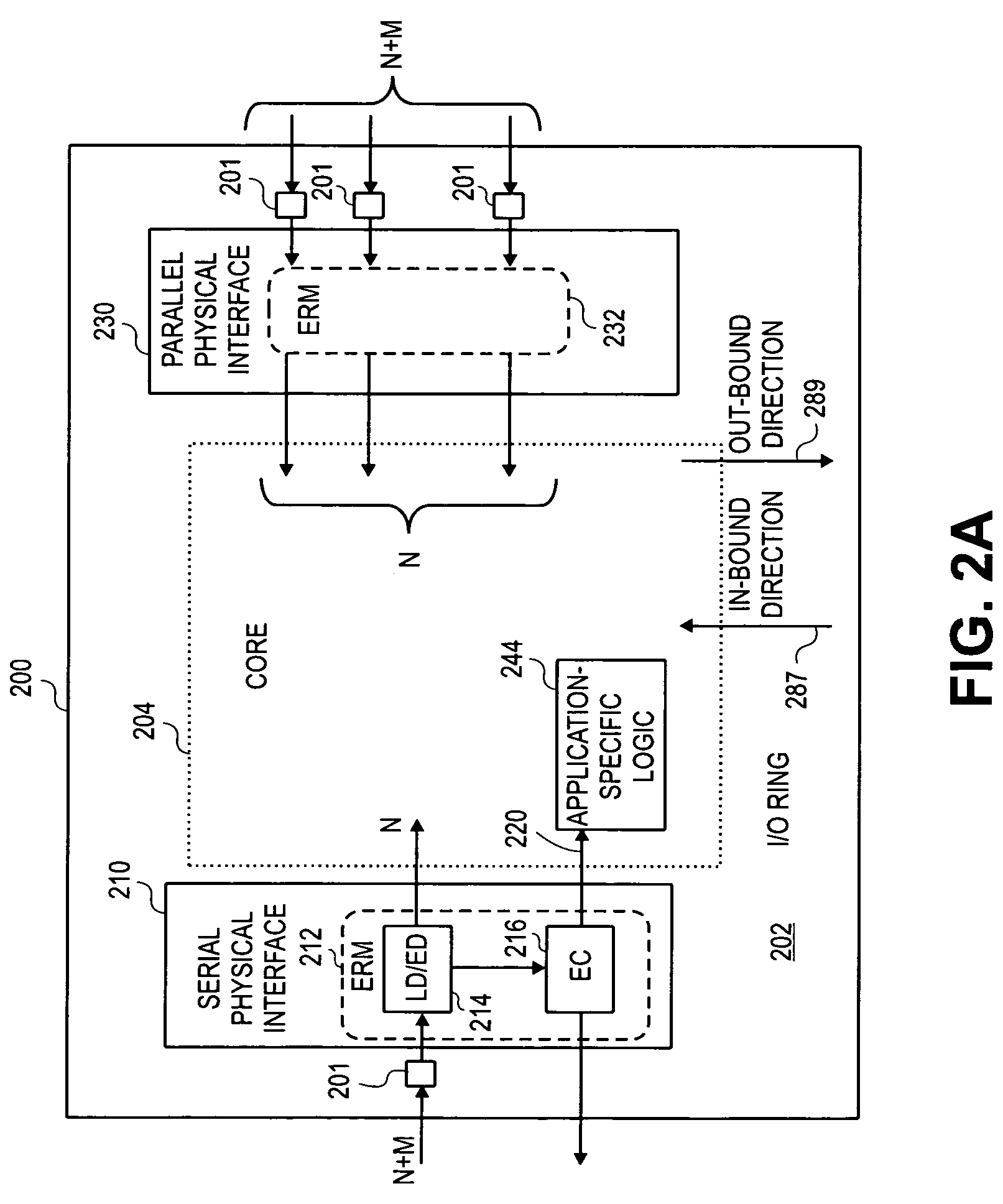

Error detection in physical interfaces for point-to-point communications between integrated circuits

ActiveUS20070260965A1Shorten the timeTransmission systemsError detection/correctionPhysical layerError detection coding

An apparatus, system and method for detecting errors in a physical interface during the transmission and / or receipt of data communications between integrated circuits (“ICs”) are disclosed. In one embodiment, an apparatus is configured to operate as or within a receiving physical interface. The apparatus includes a decoder configured to decode a subset of encoded data bits to yield decoded data bits. It also includes a physical interface (“PI”) error detection bit extractor configured to extract a physical interface error detection bit from the decoded data bits. As such, the apparatus uses the physical interface error detection bit to determine whether the encoded data bits include at least one erroneous data bit as an error. In some embodiments, the apparatus includes an error detector configured to operate within a physical layer. In at least one embodiment, the apparatus efficiently transmits error detection codes within, for example, an NB / (N+1)B line coder.

Owner:LATTICE SEMICON CORP

Error detection in physical interfaces for point-to-point communications between integrated circuits

ActiveUS7694204B2Shorten the timeTransmission systemsError detection/correctionPhysical layerError detection coding

An apparatus, system and method for detecting errors in a physical interface during the transmission and / or receipt of data communications between integrated circuits (“ICs”) are disclosed. In one embodiment, an apparatus is configured to operate as or within a receiving physical interface. The apparatus includes a decoder configured to decode a subset of encoded data bits to yield decoded data bits. It also includes a physical interface (“PI”) error detection bit extractor configured to extract a physical interface error detection bit from the decoded data bits. As such, the apparatus uses the physical interface error detection bit to determine whether the encoded data bits include at least one erroneous data bit as an error. In some embodiments, the apparatus includes an error detector configured to operate within a physical layer. In at least one embodiment, the apparatus efficiently transmits error detection codes within, for example, an NB / (N+1)B line coder.

Owner:LATTICE SEMICON CORP

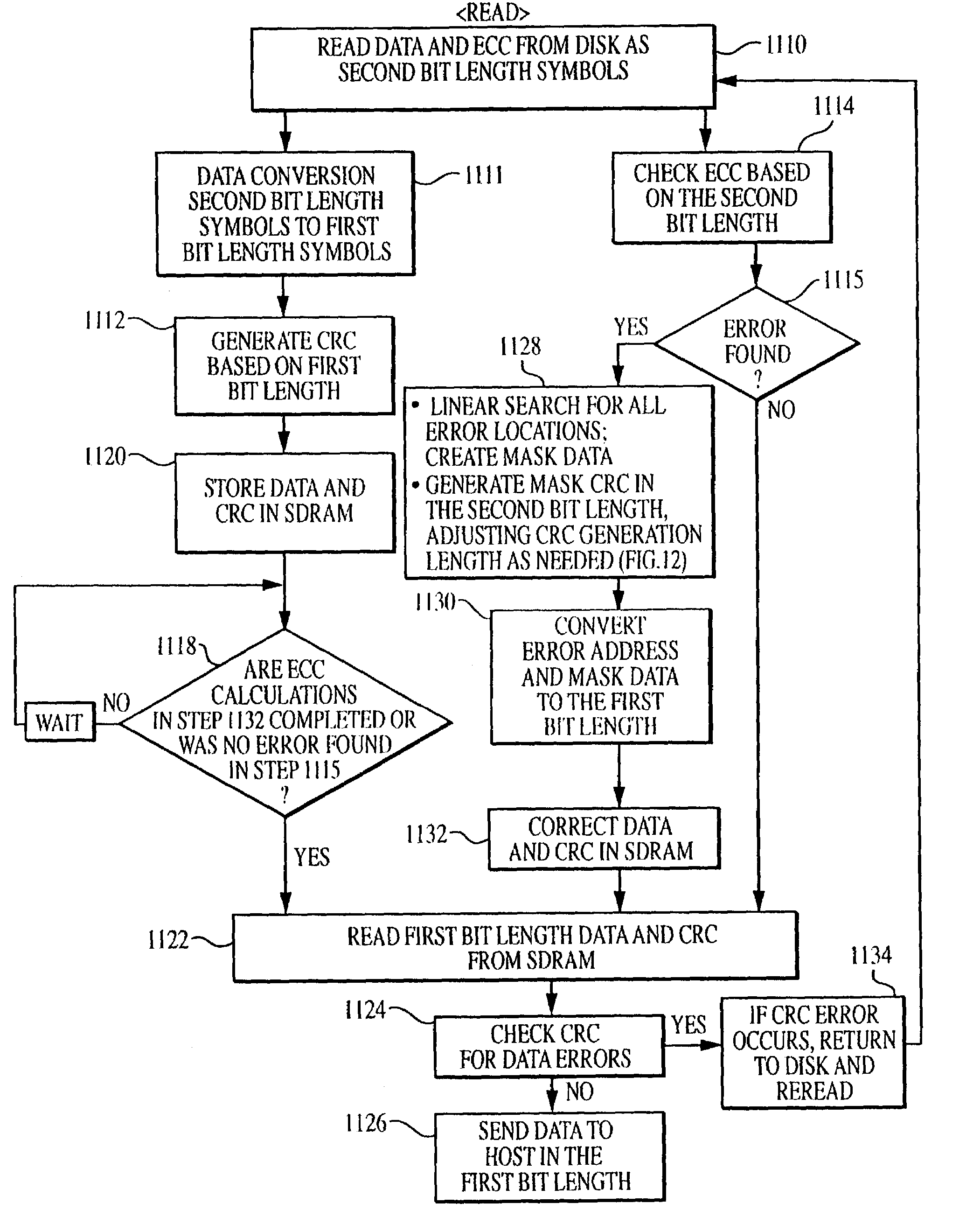

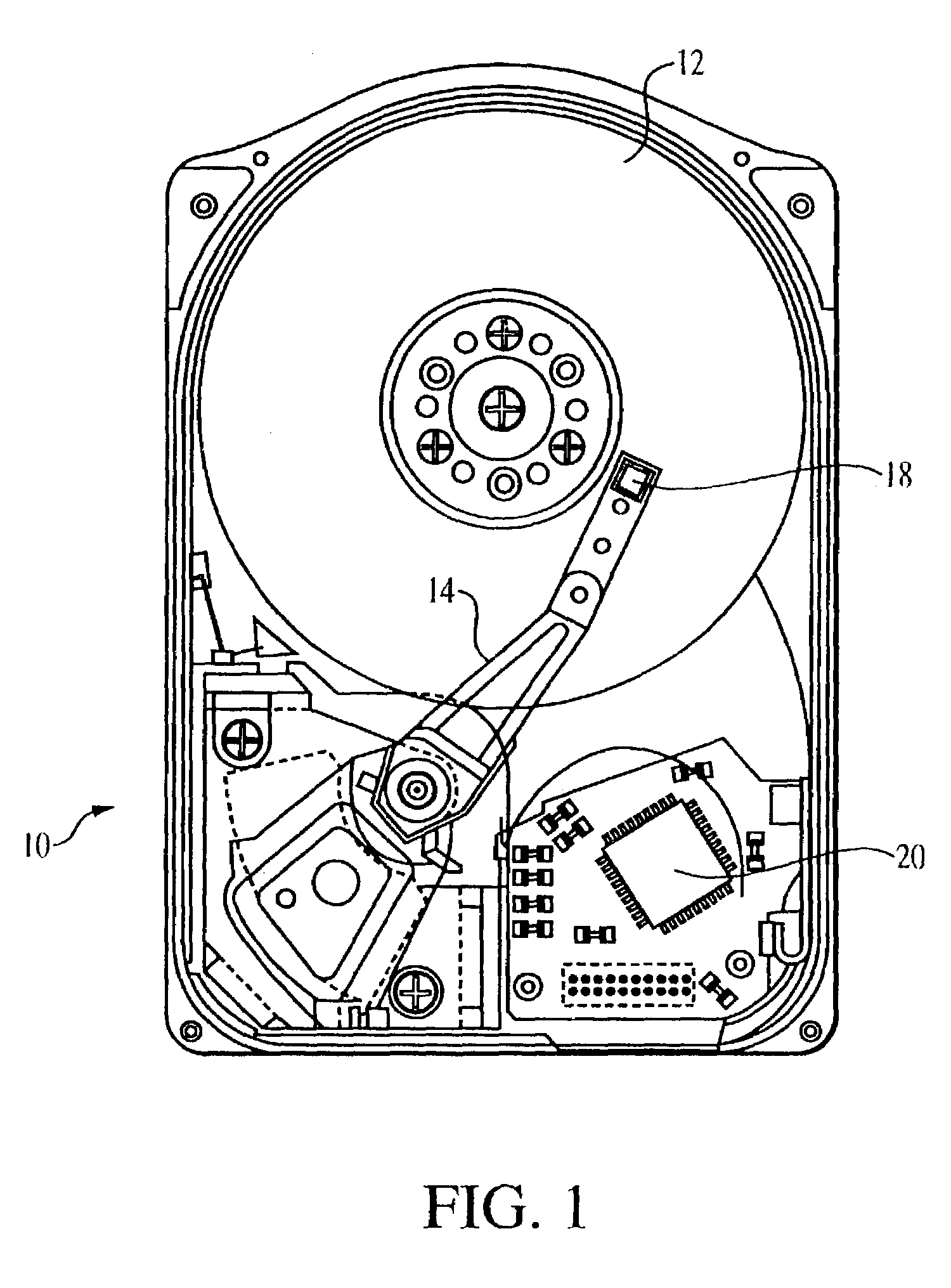

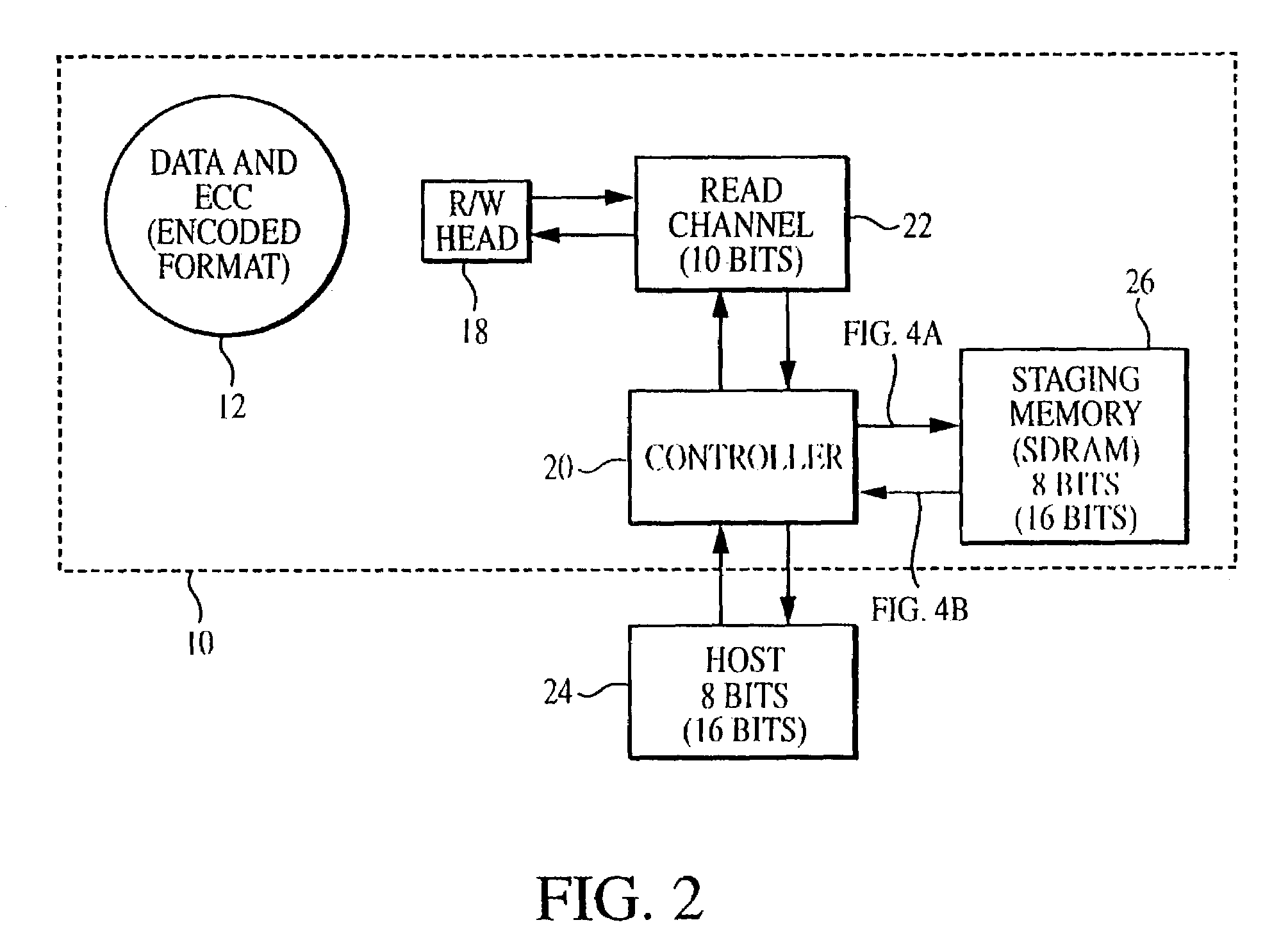

Methods and apparatus for correcting data and error detection codes on the fly

When data is read from a disk and stored in volatile memory, check bits are generated and stored in the memory using an algorithm such as cyclical redundancy check (CRC). The CRC algorithm operates on the basis of the bit length in which the data is organized, such as 8 bits. If the data has errors, an error correction code (ECC) algorithm is used to correct the data errors, but the ECC algorithm operates on the basis of symbols having a different bit length, such as 10 bits. To avoid having to re-read the data from the volatile memory to adjust the CRC value, the CRC algorithm is executed on selected mask data developed by the ECC algorithm, the CRC algorithm being executed on the basis of the second bit length to generate a CRC mask. The CRC mask corrects the stored CRC value.

Owner:TOSHIBA STORAGE DEVICE CORP

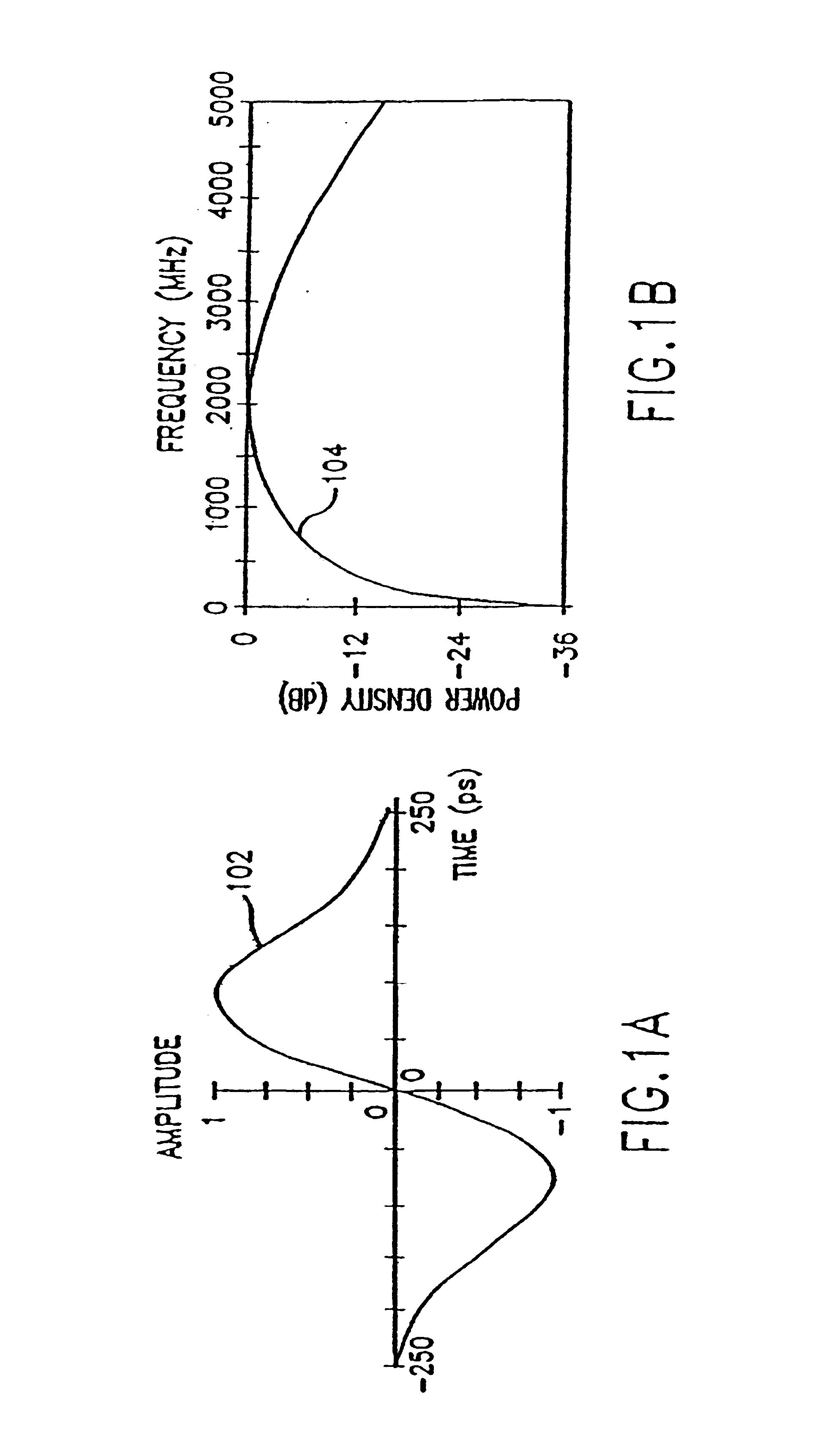

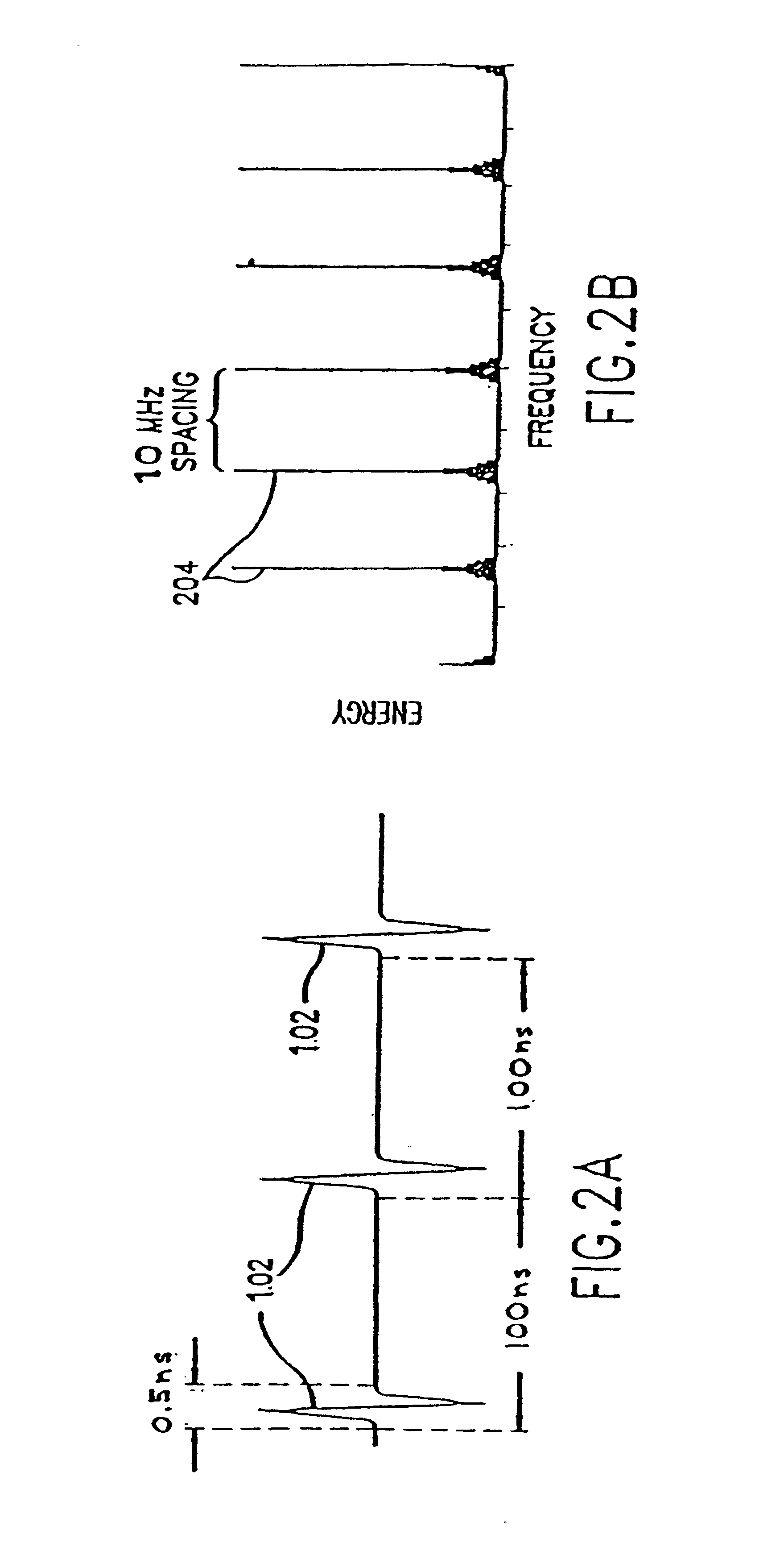

Method for mitigating effects of interference in impulse radio communication

InactiveUS6823022B1Error preventionLine-faulsts/interference reductionError detection codingError detection code

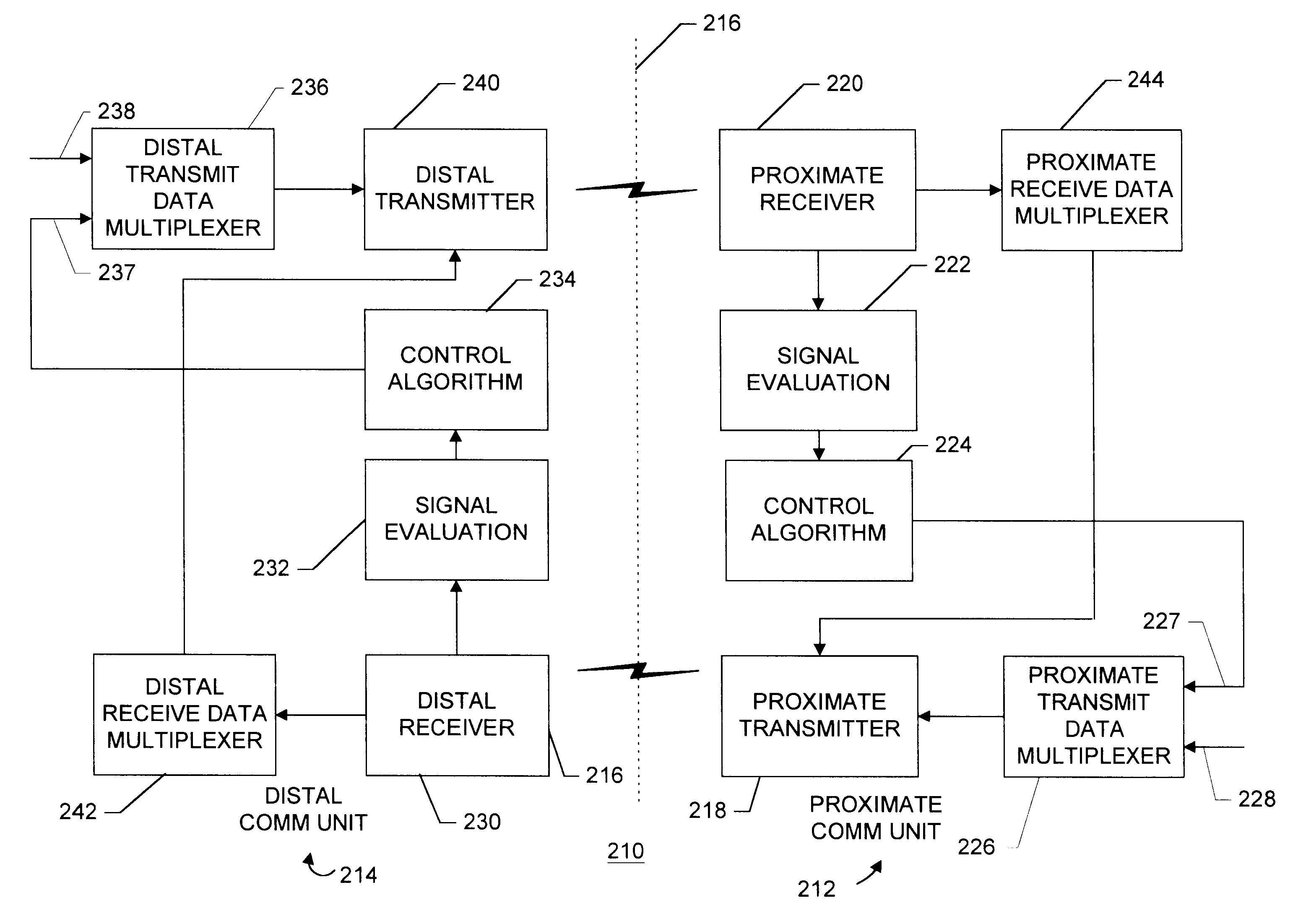

A method for mitigating interference in impulse radio communication conveying a message from a transmitting station to a receiving station. The method comprises the steps of: (a) conveying the message in packets; (b) repeating conveyance of selected packets to make up a repeat package; and (c) conveying the repeat package a plurality of times at a repeat period greater than twice the occurrence period of the interference. The communication may convey a message from a proximate transmitter to a distal receiver, and receive a message by a proximate receiver from a distal transmitter. In such a system, the method comprises the steps of: (a) providing interference indications by the distal receiver to the proximate transmitter; (b) using the interference indications to determine predicted noise periods; and (c) operating the proximate transmitter to convey the message according to at least one of the following: (1) avoiding conveying the message during noise periods; (2) conveying the message at a higher power during noise periods; (3) varying error detection coding in the message during noise periods; (4) retransmitting the message following noise periods; (5) avoiding conveying the message when interference is greater than a first strength; (6) conveying the message at a higher power when the interference is greater than a second strength; (7) varying error detection coding in the message when the interference is greater than a third strength; and (8) retransmitting a portion of the message after interference has subsided to less than a predetermined strength.

Owner:TIME DOMAIN

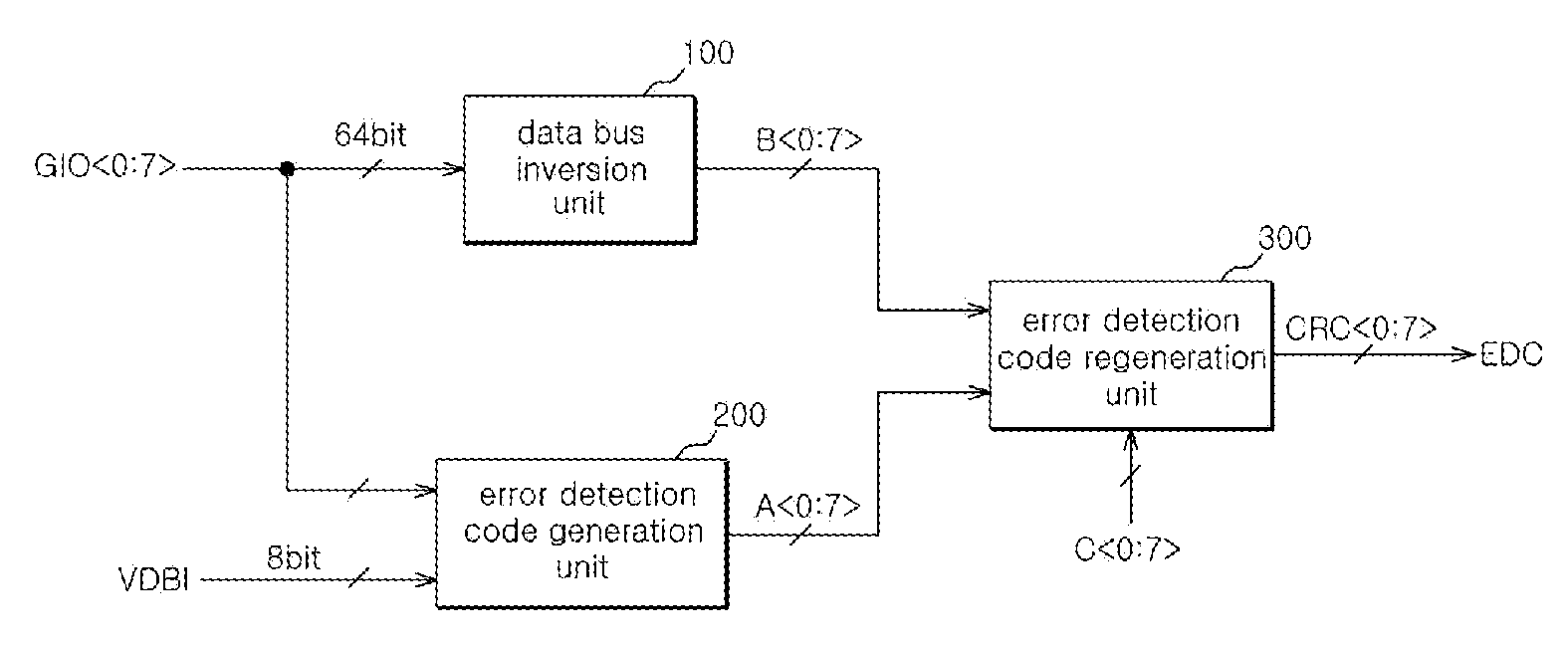

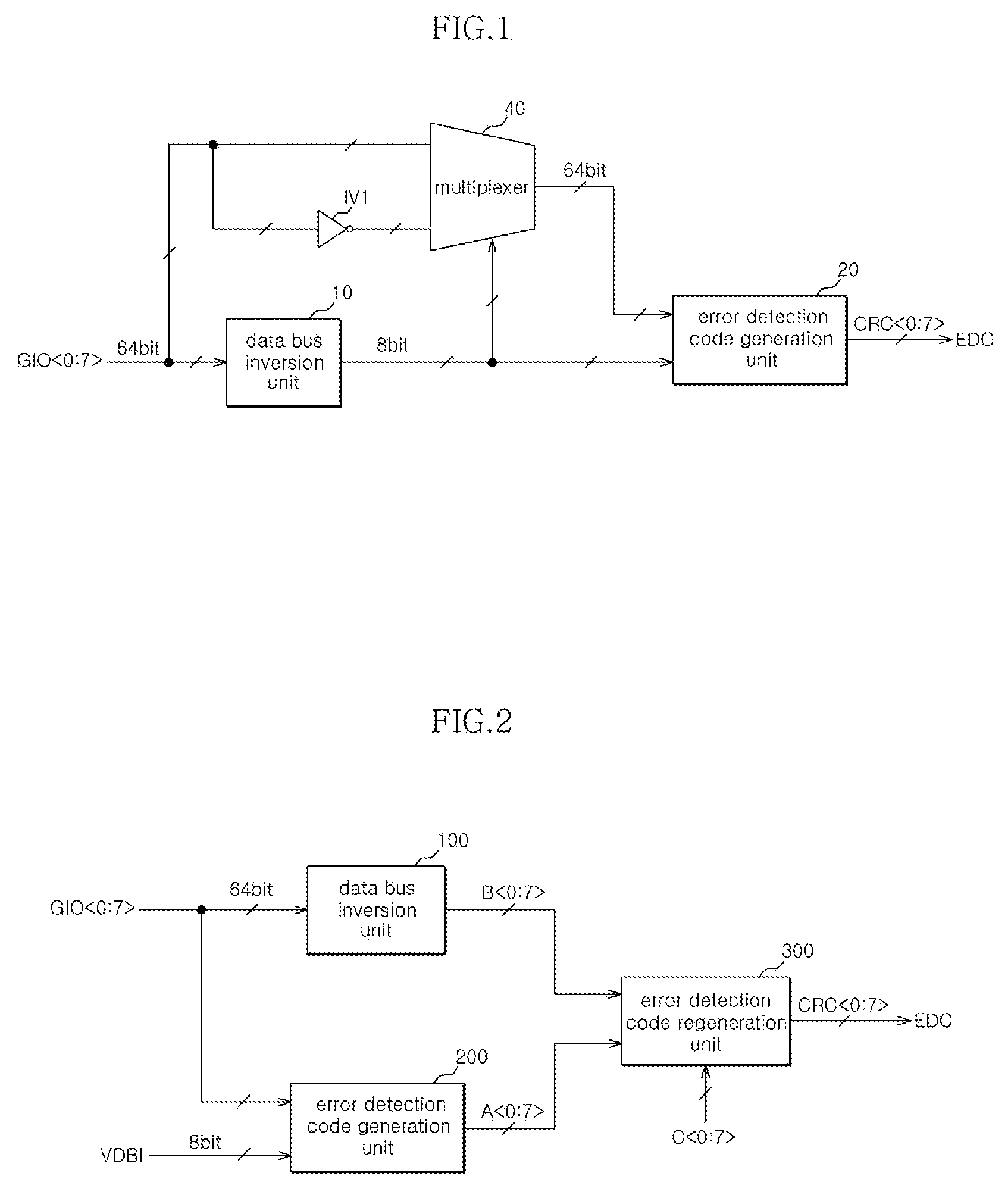

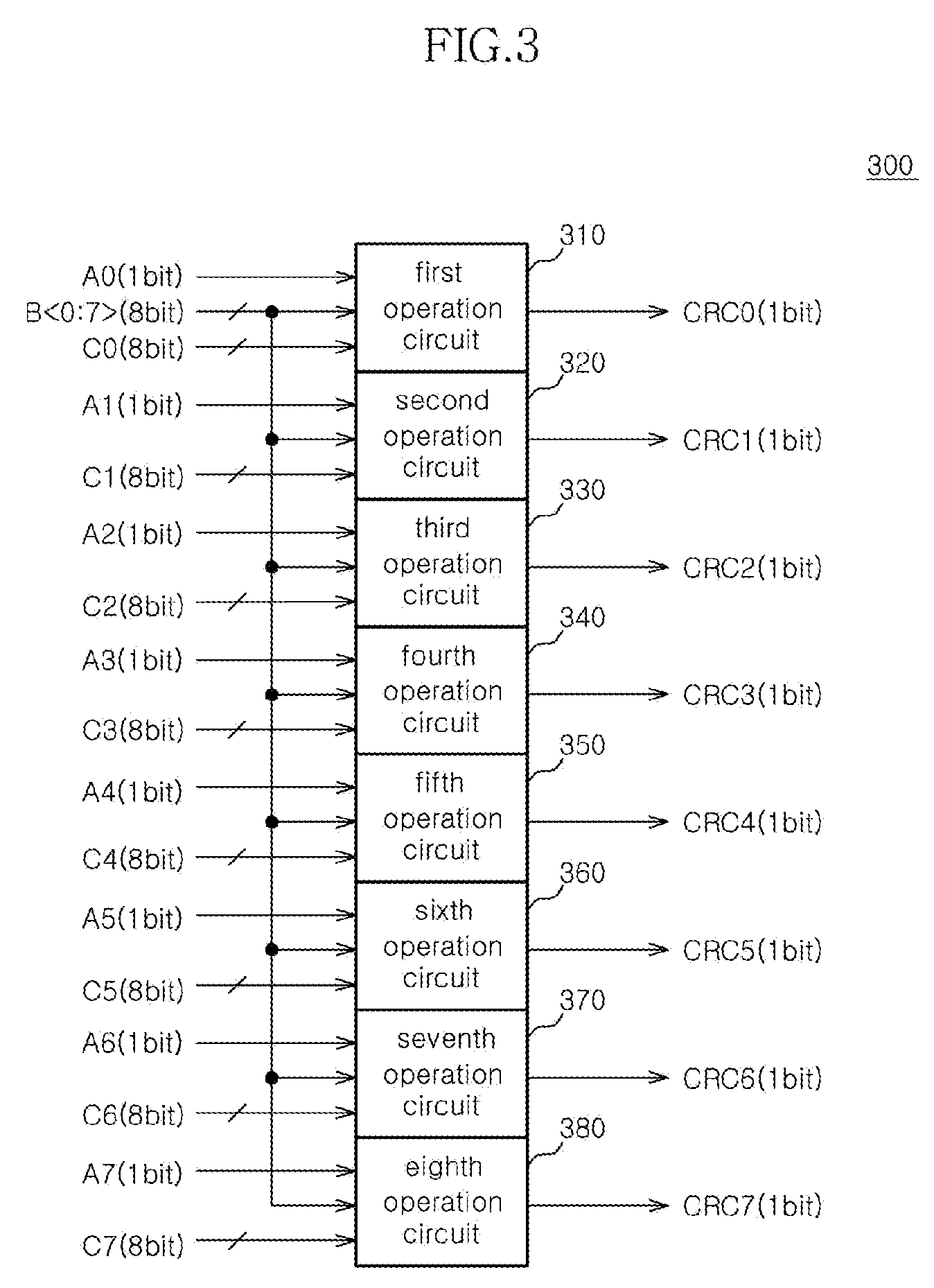

Apparatus and method for generating error detection codes

ActiveUS20090019344A1Shorten the timeCode conversionCoding detailsComputer hardwareError detection coding

An apparatus for generating error detection codes can include an error detection code generation unit configured to generate virtual error detection codes using virtual DBI information and data, and an error detection code regeneration unit configured to generate error detection codes using even and odd number information which define whether the number of data associated with the generation of the error detection codes is even or odd, DBI information associated with the even and odd number information, and the virtual error detection codes.

Owner:SK HYNIX INC

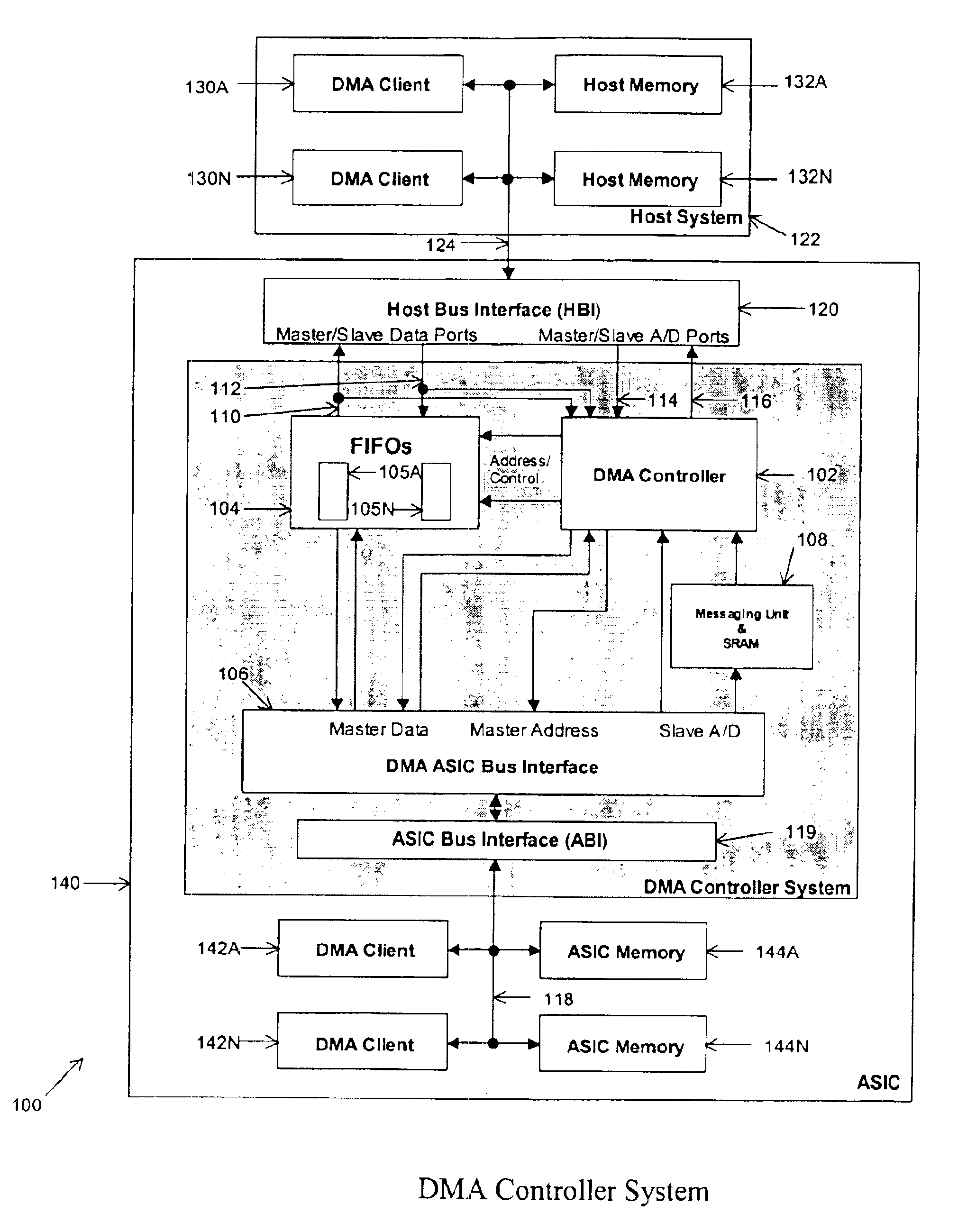

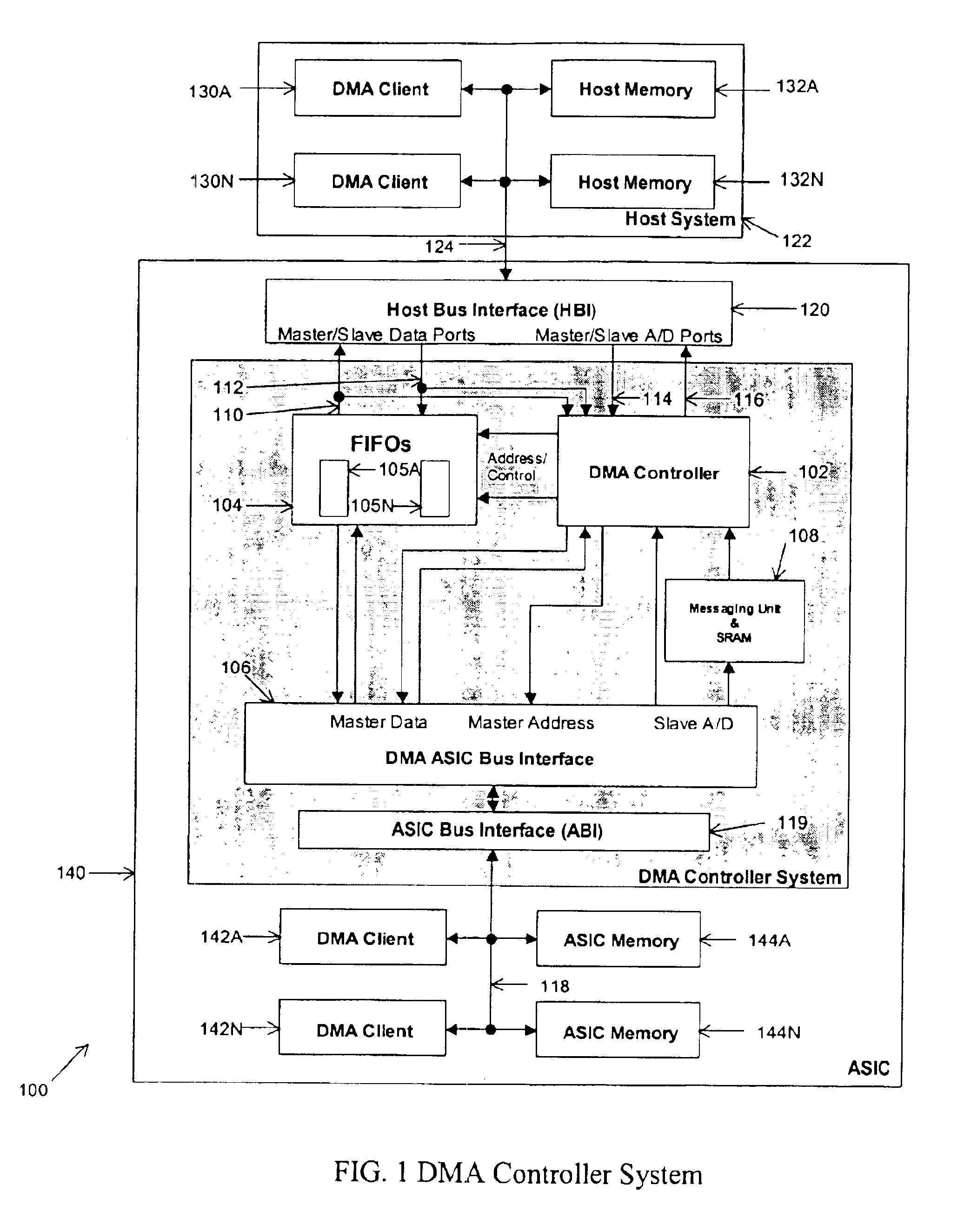

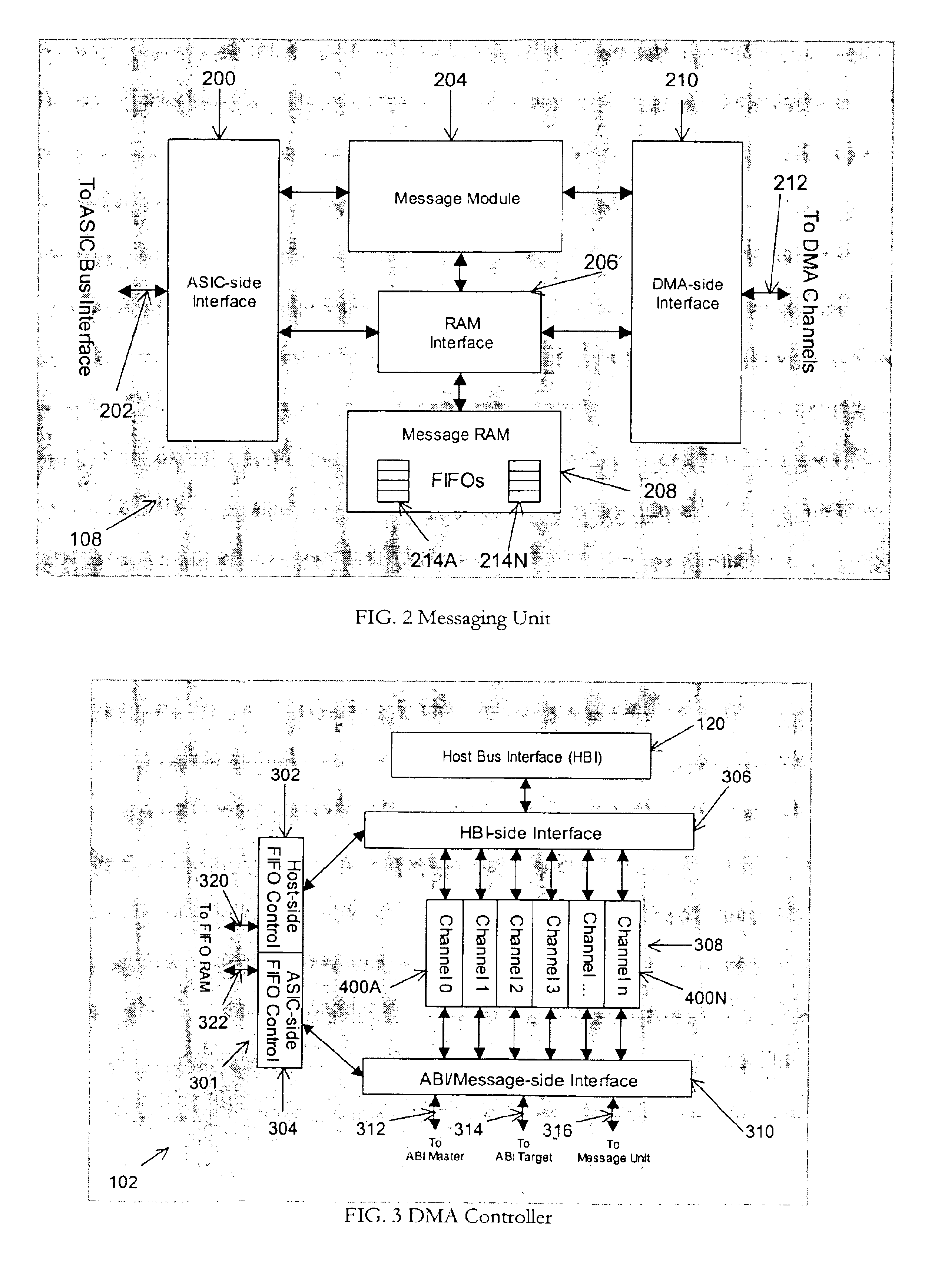

Direct memory access controller system with message-based programming

InactiveUS6874054B2Performance advantageEasy to operateProgram initiation/switchingRedundant data error correctionDirect memory accessTransfer system

A data transfer system comprising a first bus interface, a second bus interface, a first-in-first-out memory, a controller and a message unit. The message unit is operable to queue a plurality of data transfer request messages from the first bus interface and the second bus interface. The controller is operable to process each data transfer request message and transfer data between the first bus interface, the first-in-first-out memory and the second bus interface. The controller is configured to calculate error detection codes (EDCs) and chain EDC values.

Owner:AVAGO TECH INT SALES PTE LTD

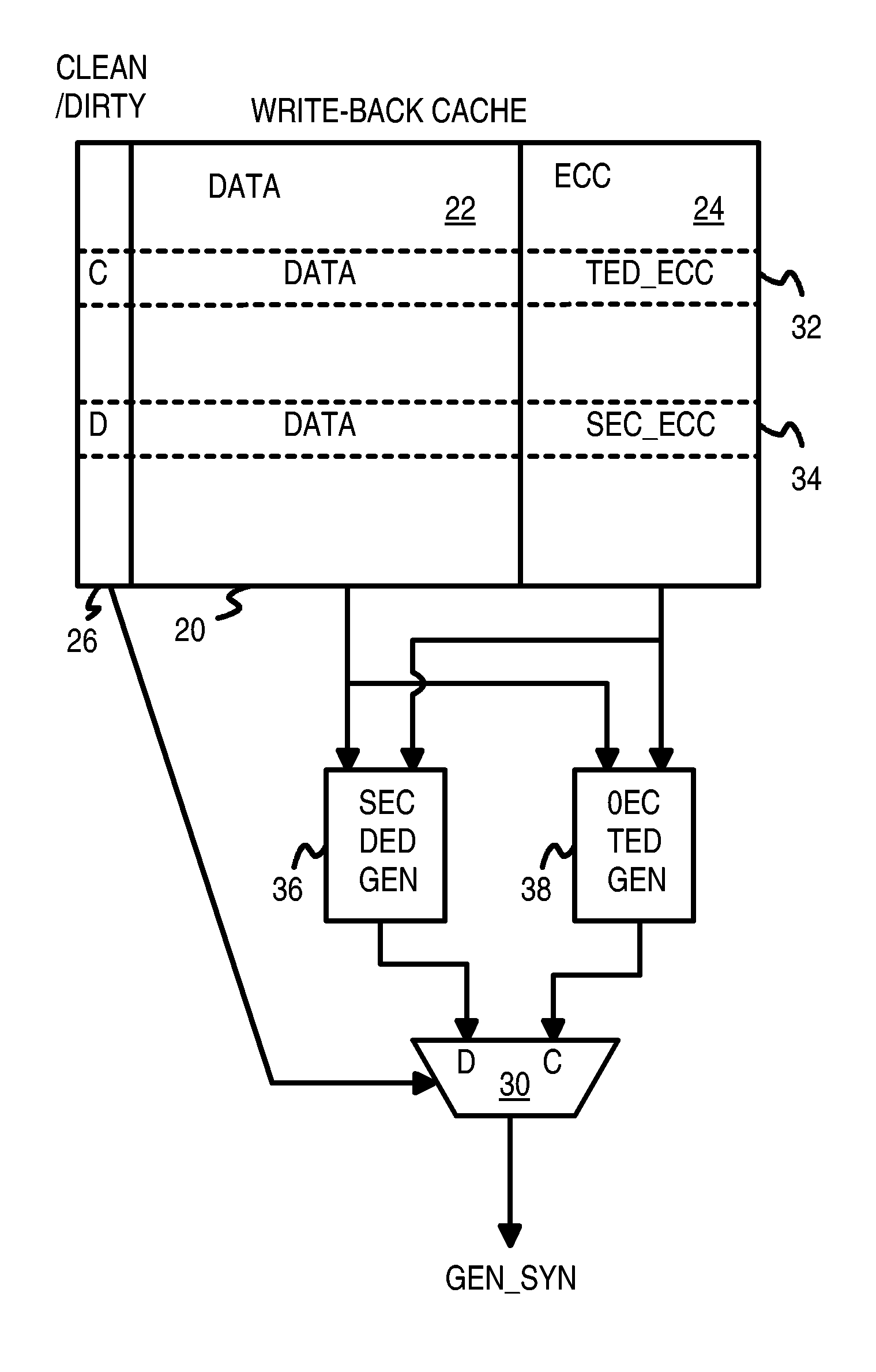

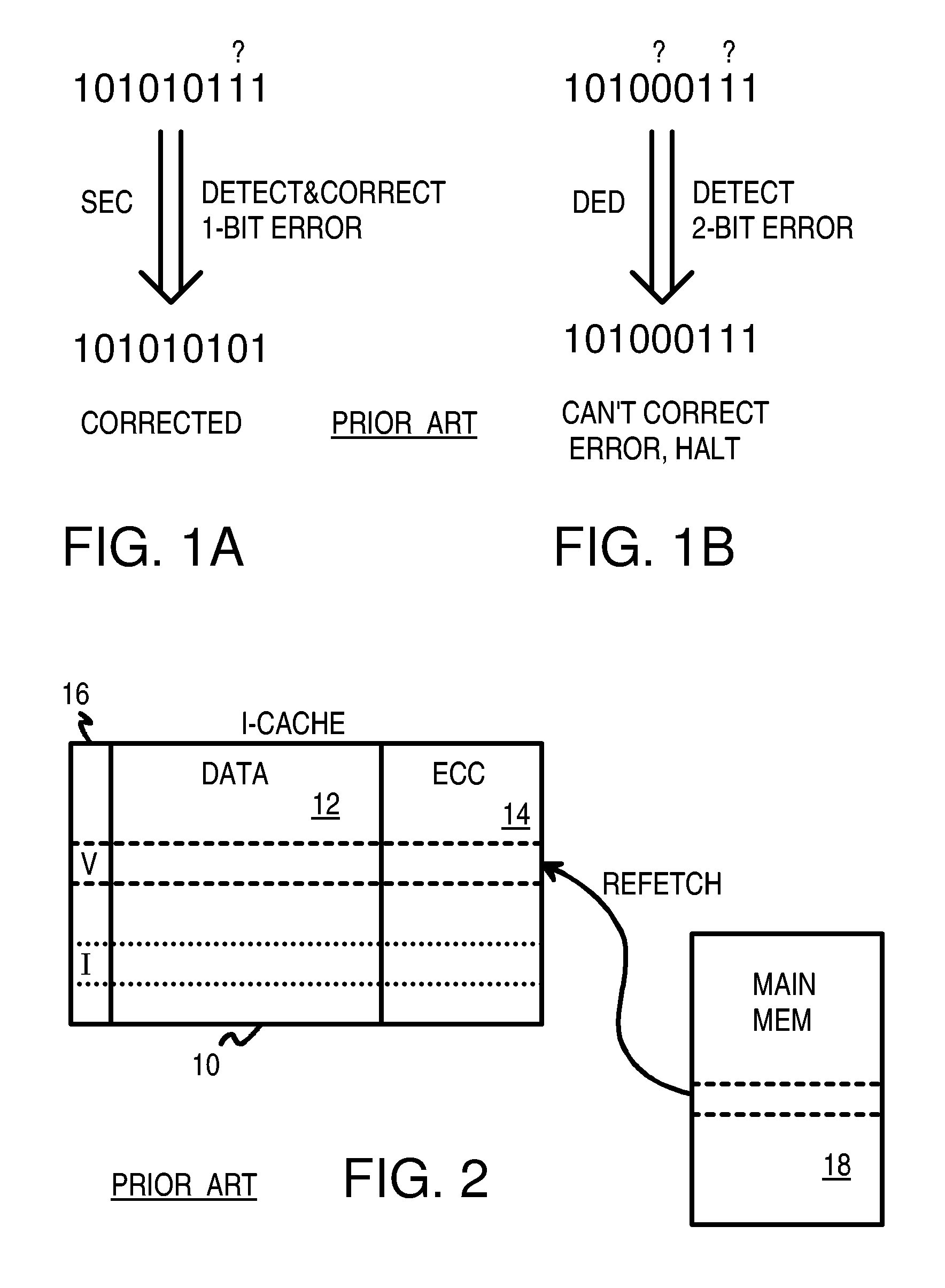

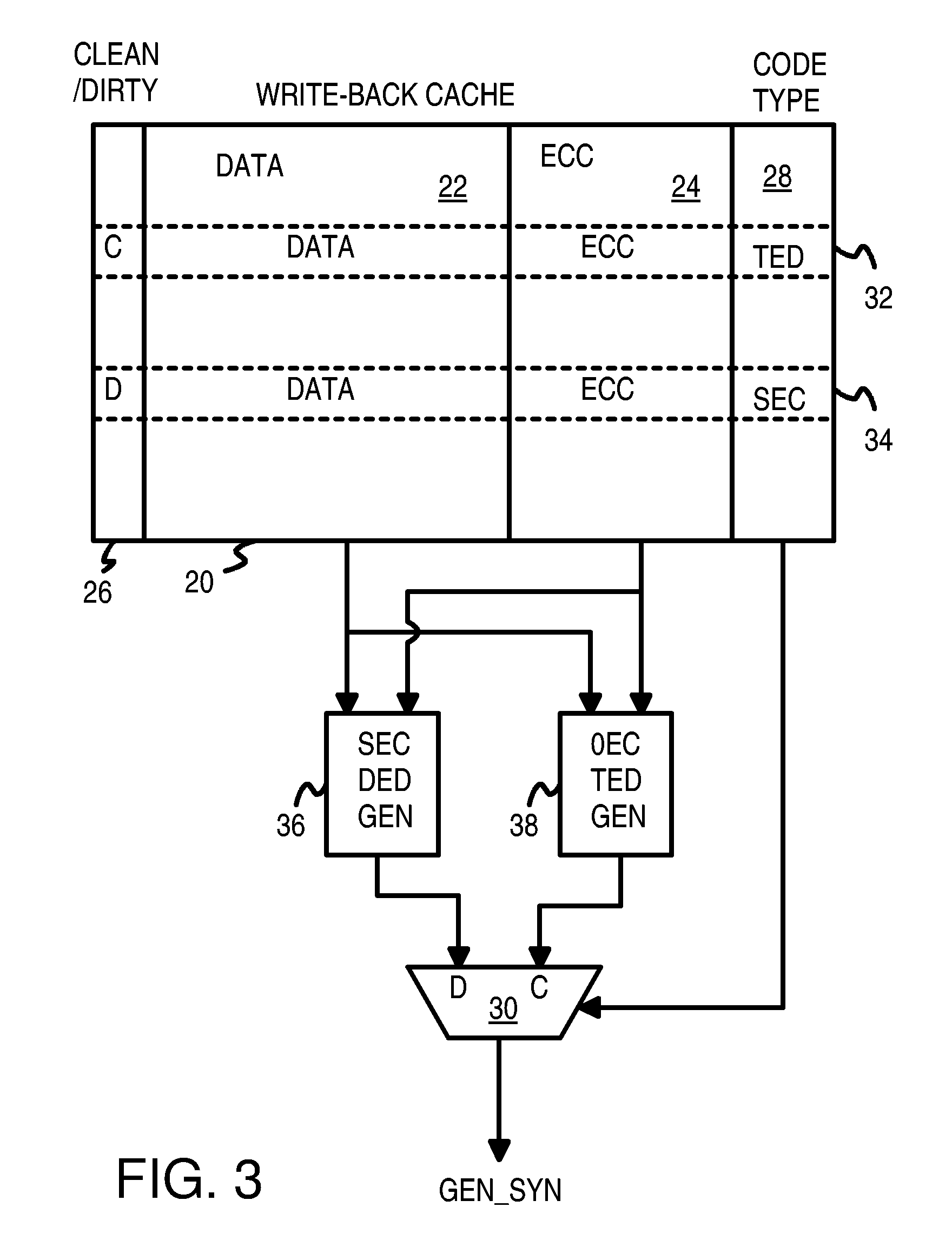

Write-back cache with different ECC codings for clean and dirty lines with refetching of uncorrectable clean lines

ActiveUS7437597B1Static storageRedundant data error correctionParallel computingError detection coding

A write-back cache has error-correction code (ECC) fields storing ECC bits for cache lines. Clean cache lines are re-fetched from memory when an ECC error is detected. Dirty cache lines are corrected using the ECC bits or signal an uncorrectable error. The type of ECC code stored is different for clean and dirty lines. Clean lines use an error-detection code that can detect longer multi-bit errors than the error correction code used by dirty lines. Dirty lines use a correction code that can correct a bit error in the dirty line, while the detection code for clean lines may not be able to correct any errors. Dirty lines' ECC is optimized for correction while clean lines' ECC is optimized for detection. A single-error-correction, double-error-detection (SECDED) code may be used for dirty lines while a triple-error-detection code is used for clean lines.

Owner:AZUL SYSTEMS

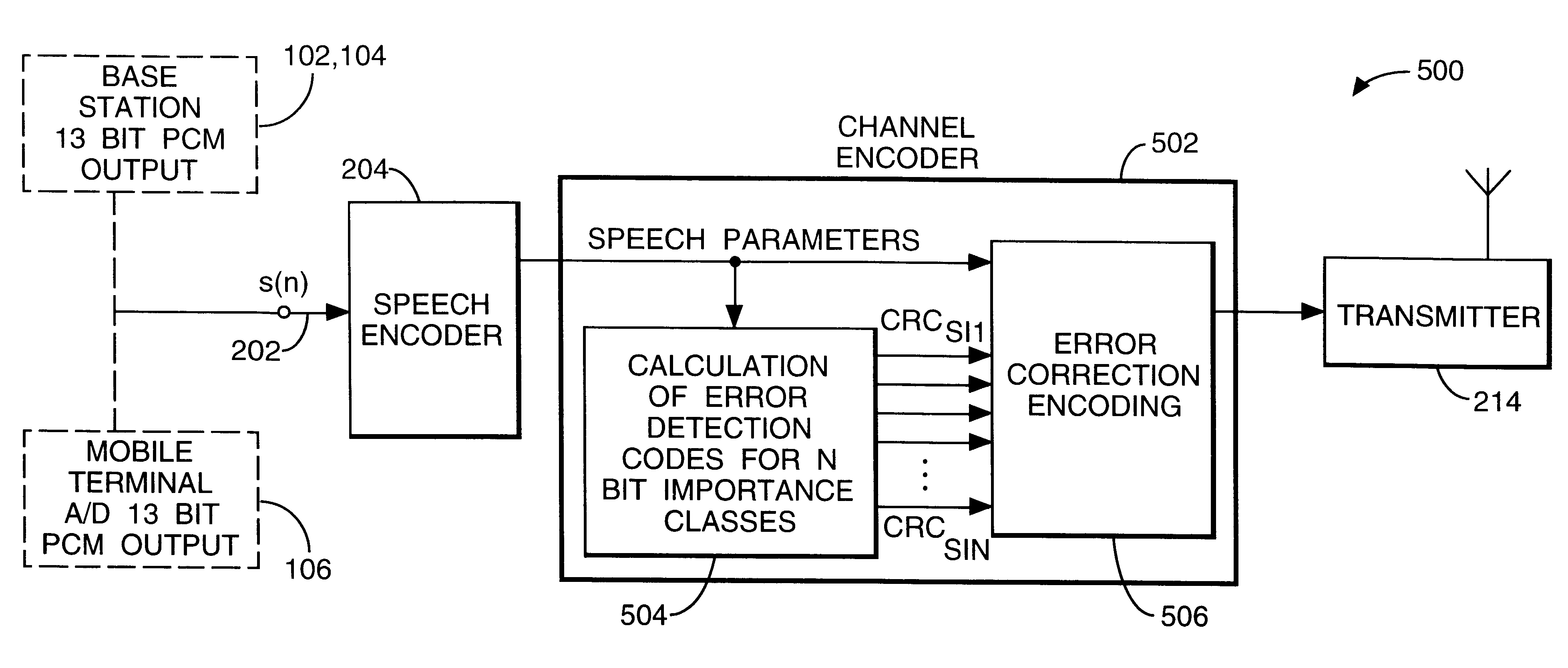

Method and apparatus for error detection in digital communications

InactiveUS6170073B1Accurate detectionImprove voice qualityError preventionOther error detection/correction/protectionData qualityComputer science

An encoder encodes digital signals representative of data by classifying the digital signals into first and second classes indicative of their influence on data quality and subjects them to error detection encoding capable of generating at least two error detection codes which respectively correspond to the first and second classes. A decoder receives the encoded digital signals classified into first and second digital signal classes, decodes the error detection codes, and generates error signals, corresponding to the respective digital signal classes, from which the quality of the received digital signals is estimated and the utility of the received digital signals is determined.

Owner:INTELLECTUAL VENTURES I LLC

Code calculating device

A code computing apparatus with an error detection code (CRC) generating function and an elliptic curve cryptography (ECC) function, comprising a matrix element computation part 30 for generating matrix elements from parameter values set in first and second registers 201 and 202, a matrix element register 51 for holding the matrix elements generated by the matrix element computation part, and an inner product calculation part 40 for executing inner product calculation between the matrix elements held by the matrix element register and data set in a third register. The matrix element computation part selectively generates matrix elements for error detection and matrix elements for encryption by changing the parameters to be set in the first and second registers, and the inner product calculation part is shared to error control code generation and data encryption by altering the matrix elements to be held in the matrix element register.

Owner:HITACHI LTD

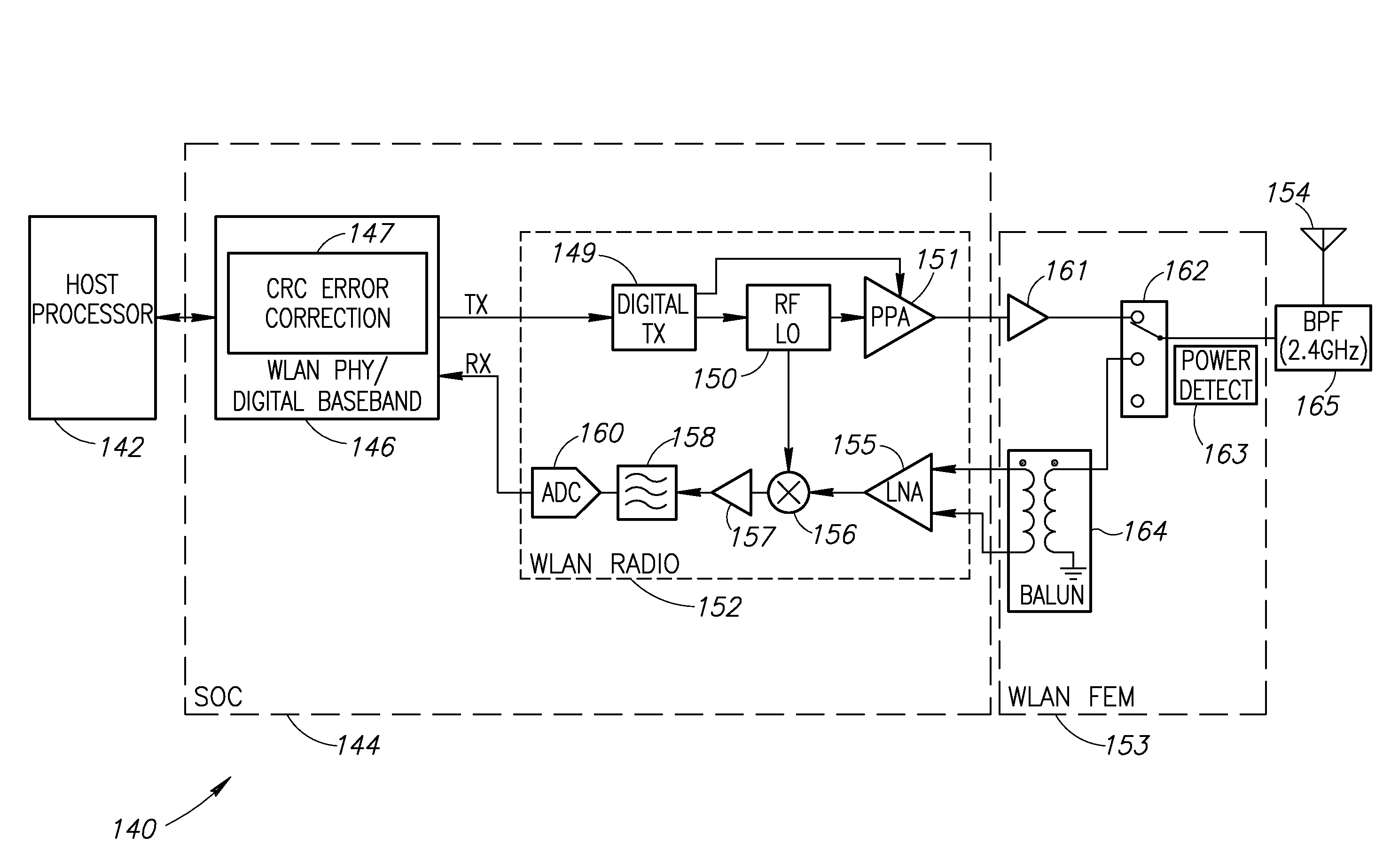

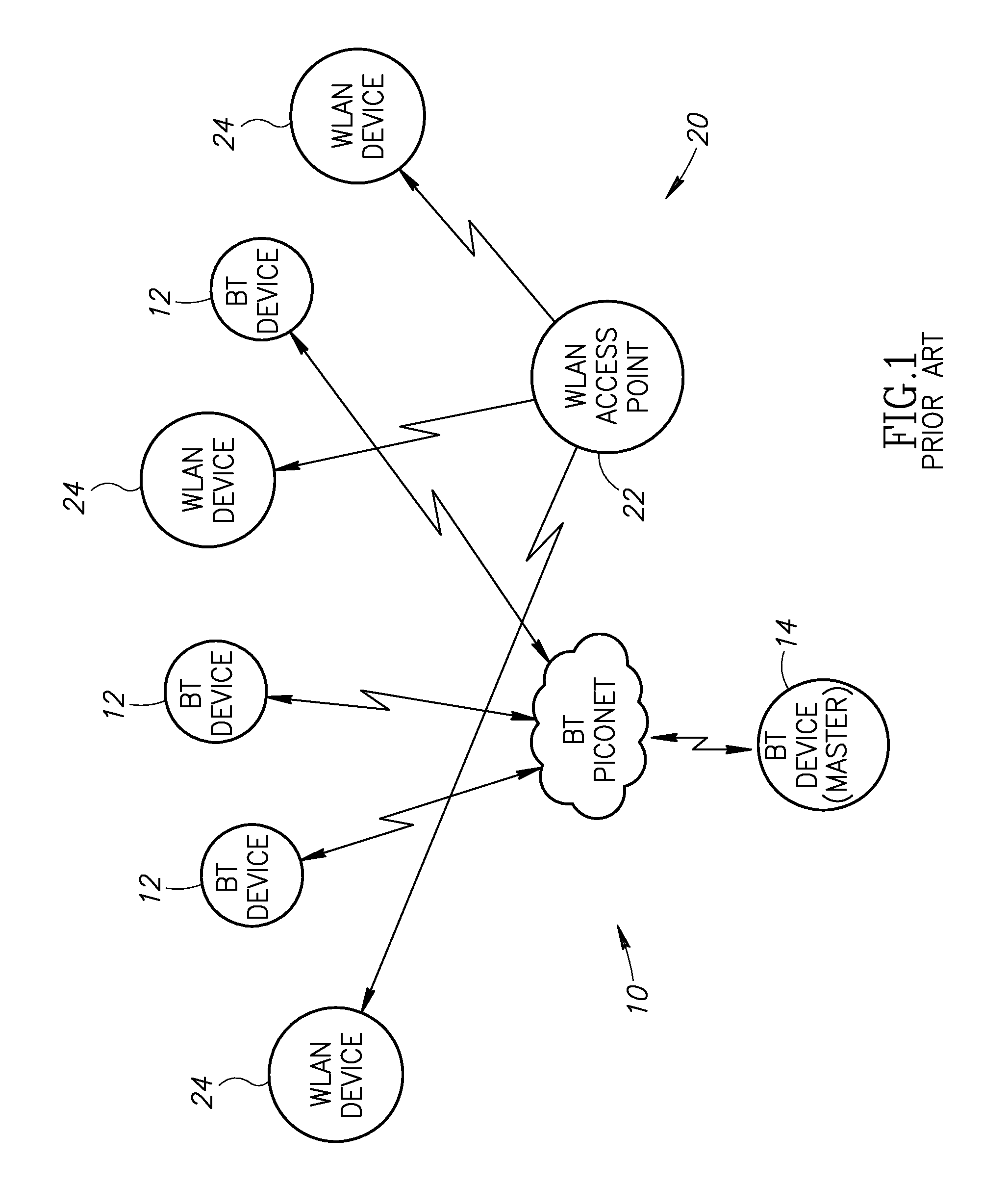

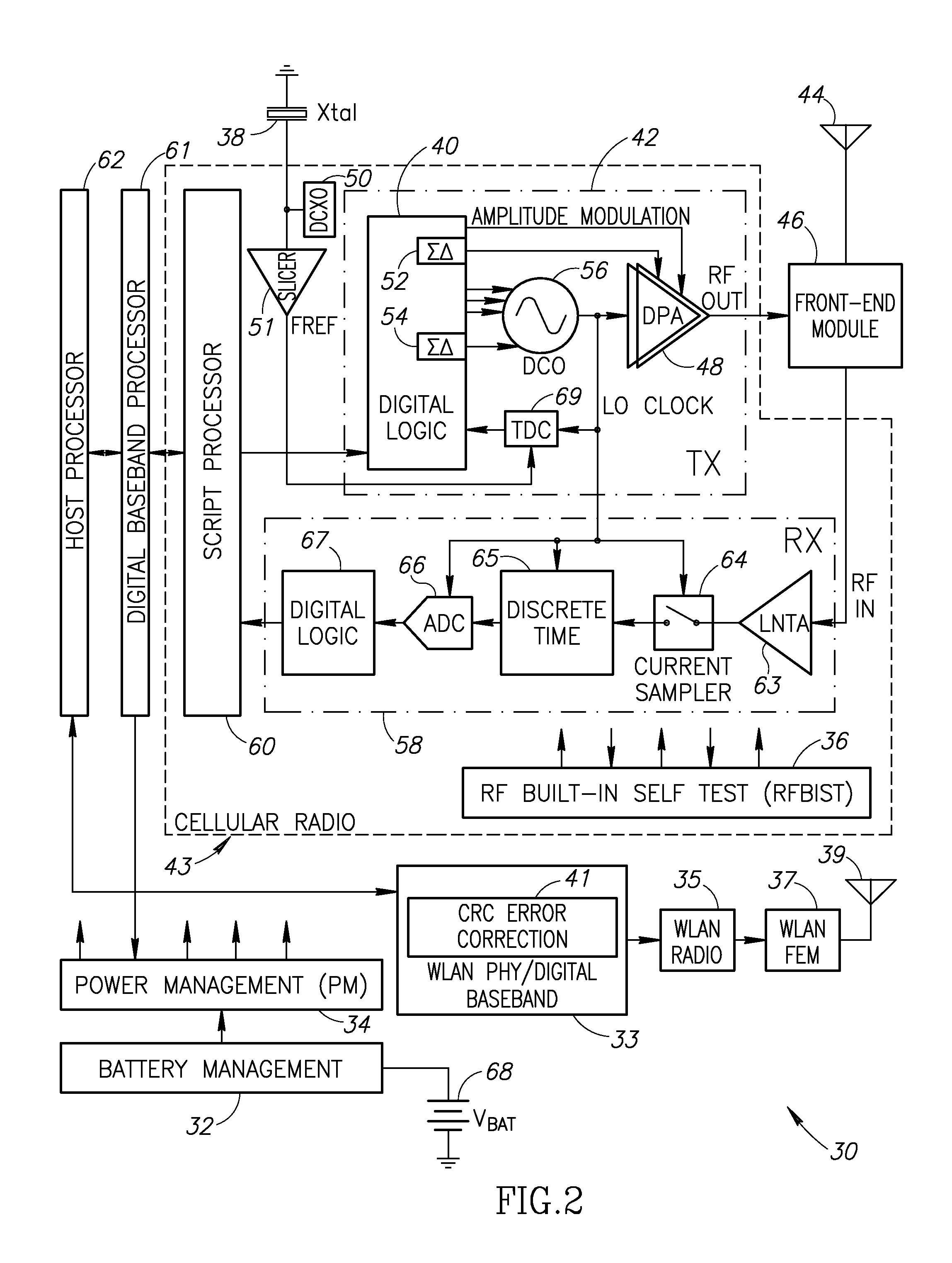

Range Extension and Noise Mitigation For Wireless Communication Links Utilizing a CRC Based Single and Multiple Bit Error Correction Mechanism

ActiveUS20080288845A1Increase the probability of receivingDetecting errorError prevention/detection by using return channelTransmission systemsComputer hardwareTelecommunications link

A novel and useful range extension and in-band noise mitigation mechanism that uses conventional CRC error detection codes to correct single and multiple bit errors in packets received over a communications link. The CRC error correction mechanism of the invention is particularly suitable for use with communication protocols with weak error correction capabilities. The mechanism uses the linearity property of the CRC calculation to detect the existence of errors in the received packet. The entire received packet is searched for single bit errors and are corrected in a single cycle. If no single bit errors are found, the mechanism then searches for multiple bit errors. Packet retransmissions are used to detect and mark the location of multiple bit errors. Multiple bit errors are corrected by trying a plurality of hypotheses of single bit error corrections. Each hypotheses pattern is investigated to find matching CRC patterns for correction using the single bit, single cycle CRC error correction method.

Owner:TEXAS INSTR INC

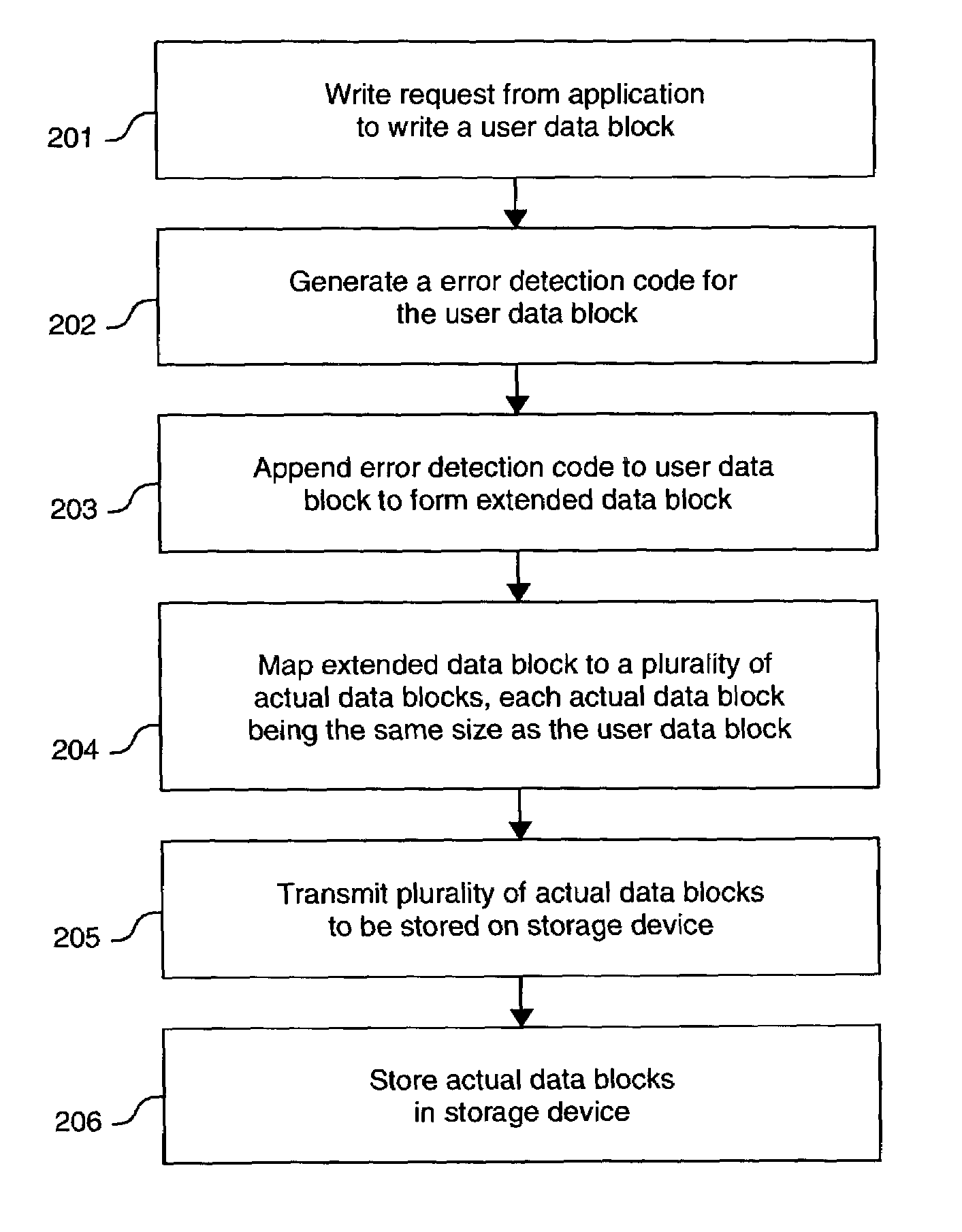

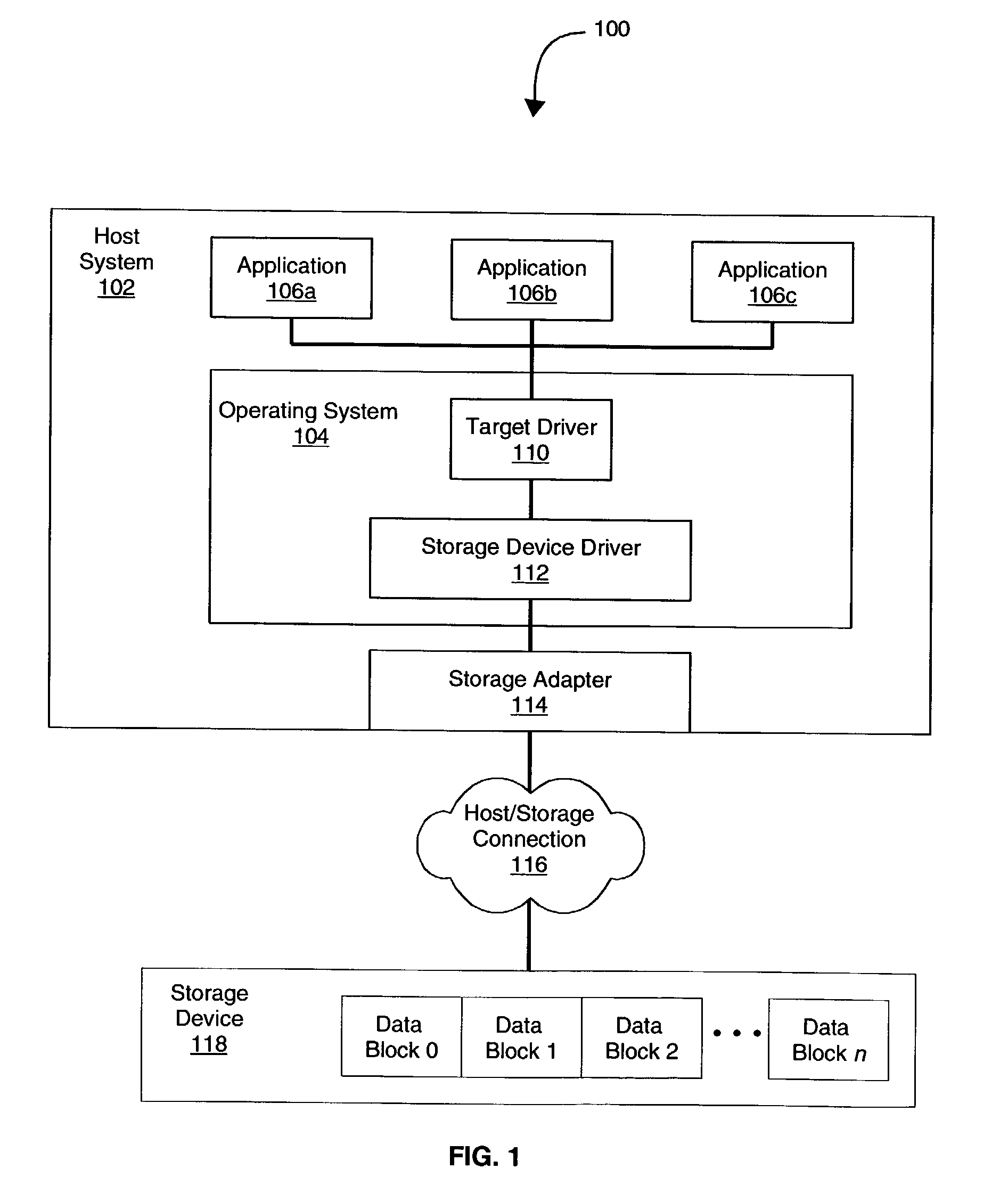

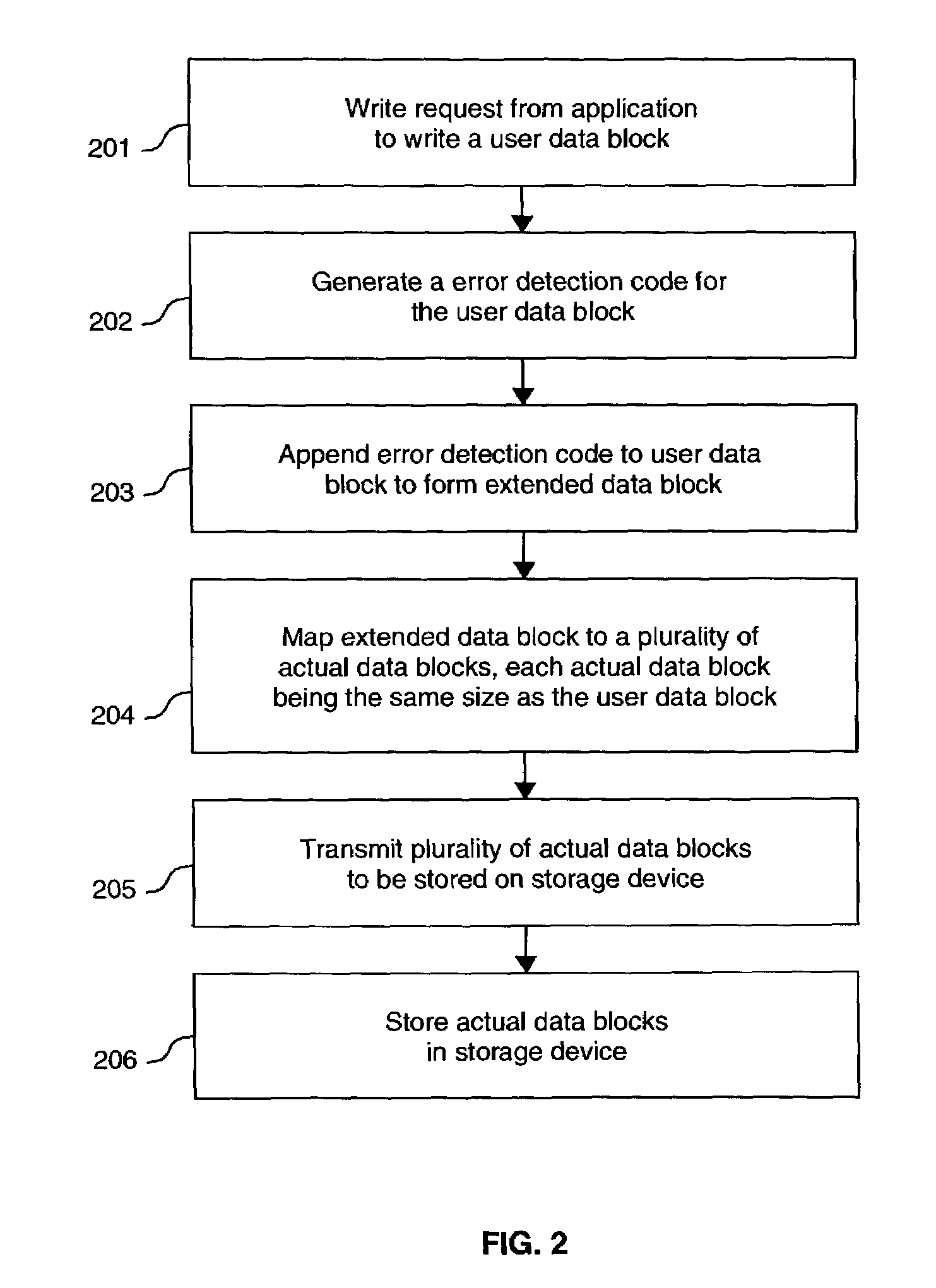

Error detection using data block mapping

ActiveUS7036066B2Code conversionRecord information storageError detection codingError detection code

Error detection using data block mapping is provided. One method includes receiving a write request to write a user data block having a first block size, generating an error detection code for the user data block, appending the error detection code to the user data block to form an extended data block, and mapping the extended data block to a plurality of actual data blocks, each actual data block having a block size equal to the first block size.

Owner:ORACLE INT CORP

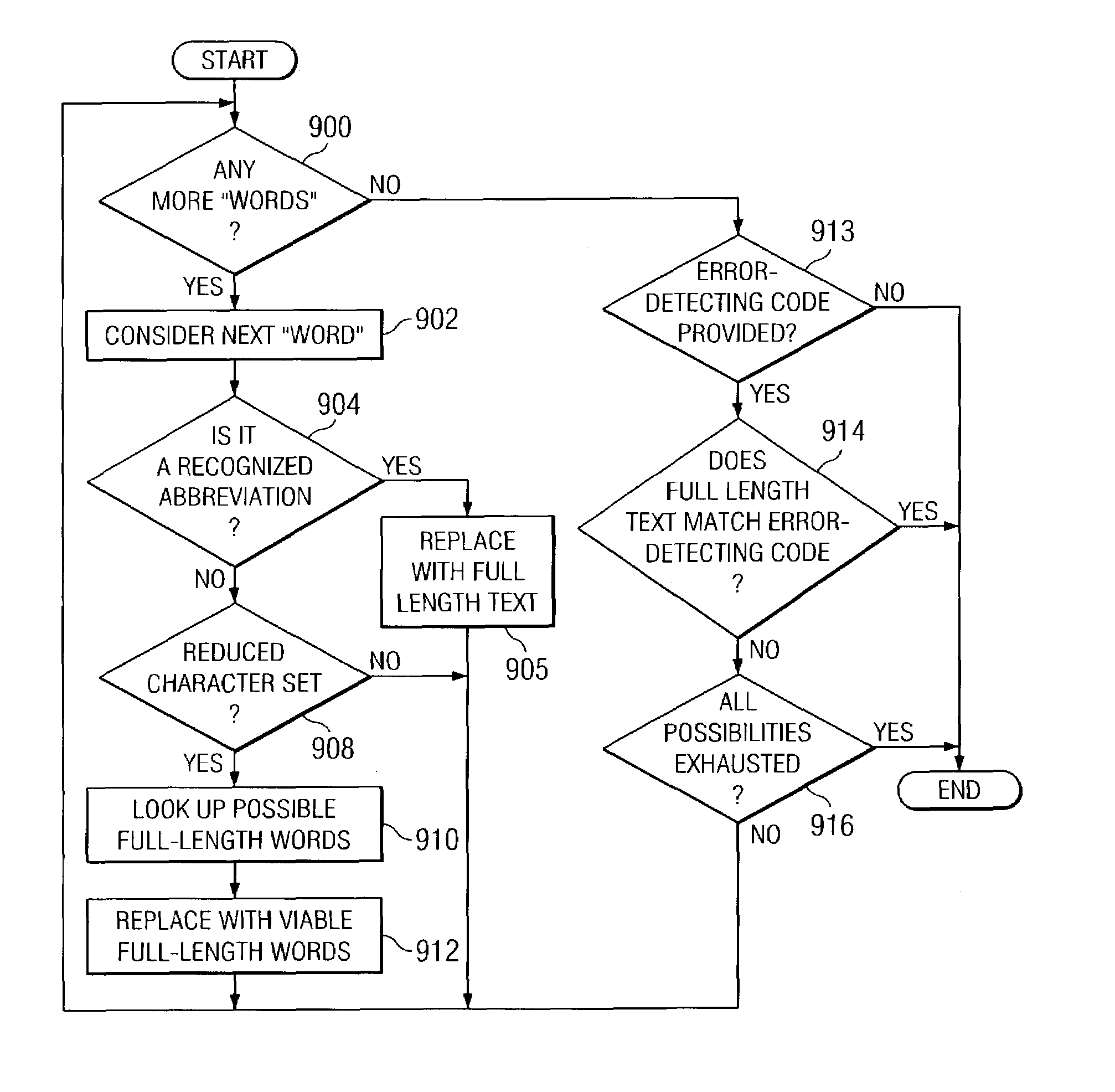

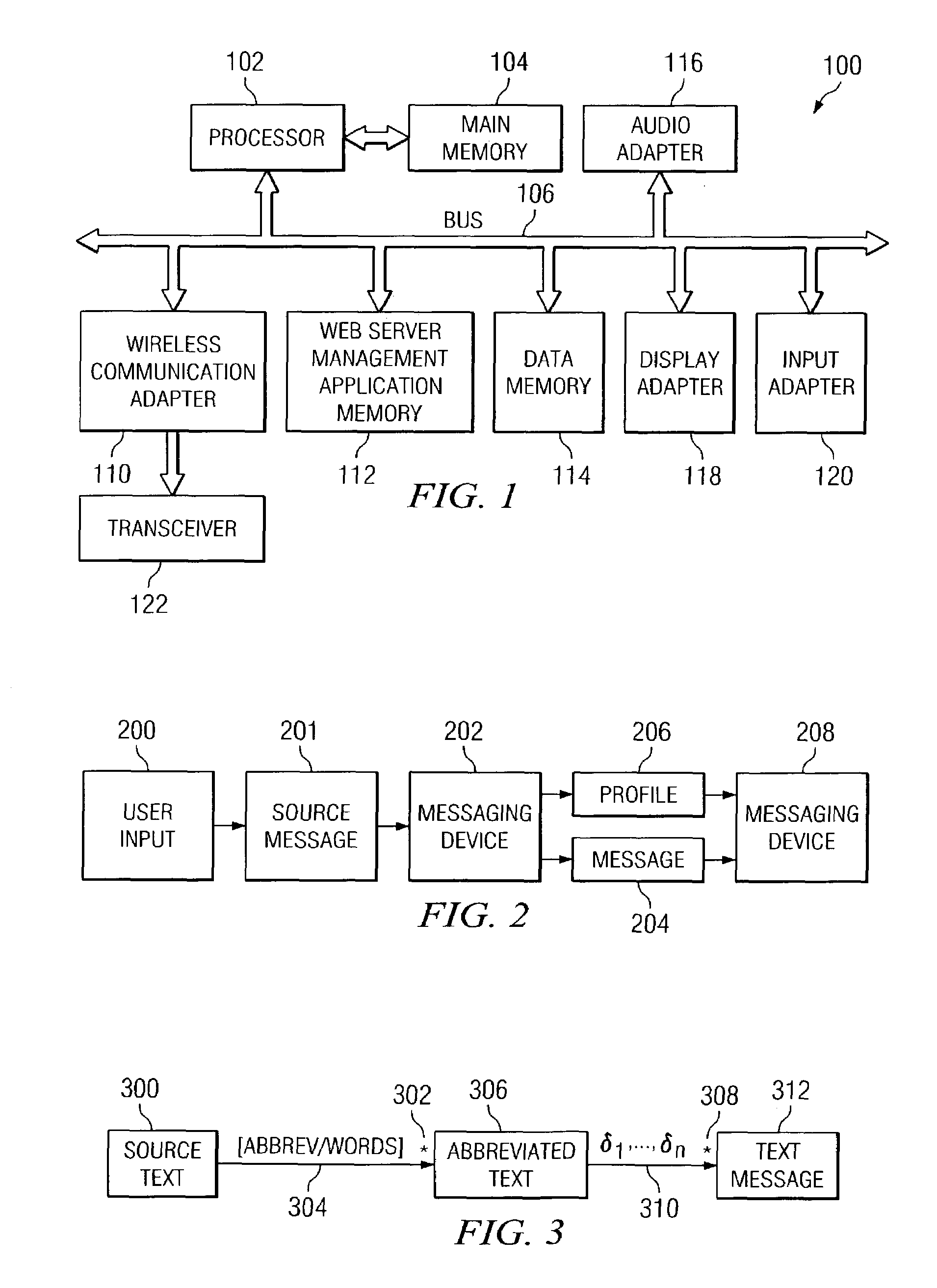

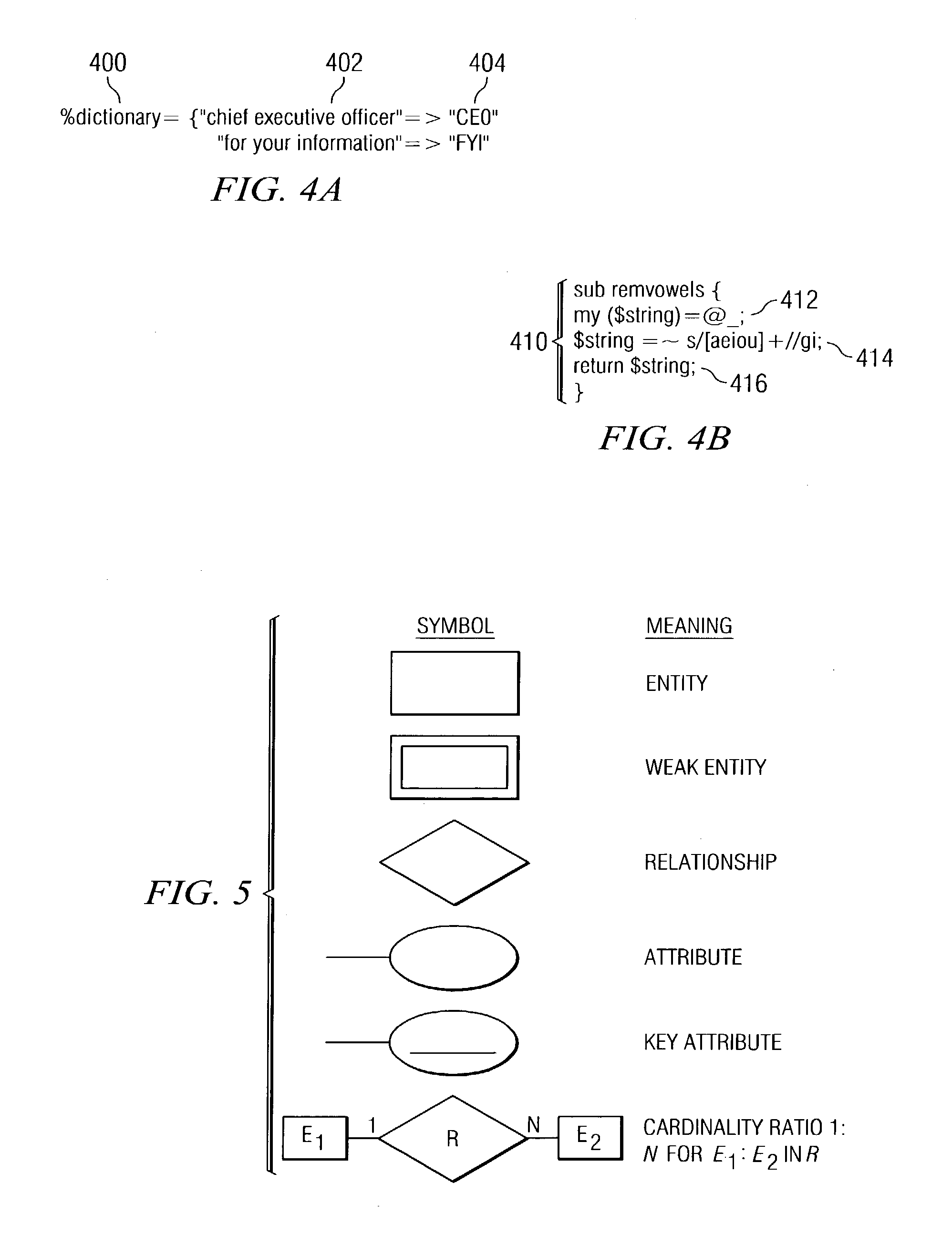

Compression and abbreviation for fixed length messaging

InactiveUS7315902B2Data processing applicationsNatural language data processingMessage lengthData treatment

A method, computer program product, and data processing system for compressing and abbreviating text messages at a first text messaging device for transport and subsequent interpretation at a second text messaging device is disclosed. A user-defined message length reduction profile for producing human-readable compressed text is associated with a source text message at a first text messaging device. The source text message is then shortened using abbreviations and transformation rules in the profile. The shortened text message can then be transmitted to a second text messaging device. In addition, the compression provided by the present invention, although intended to be human-readable, can be complemented with decompression software to expand the compressed and abbreviated text to its full length and verifying, using a checksum or other error detecting code, that the expanded version corresponds to the original text.

Owner:IBM CORP

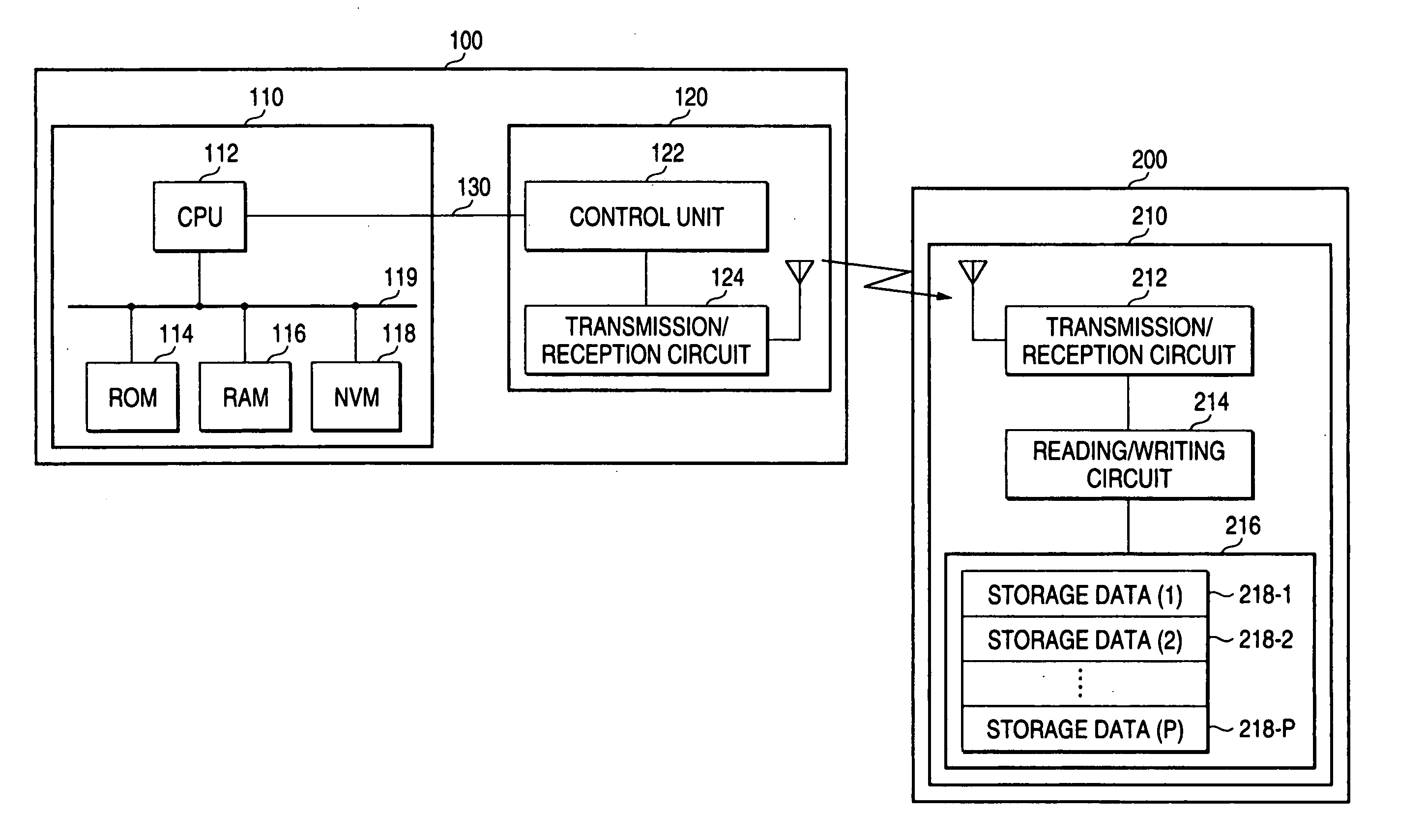

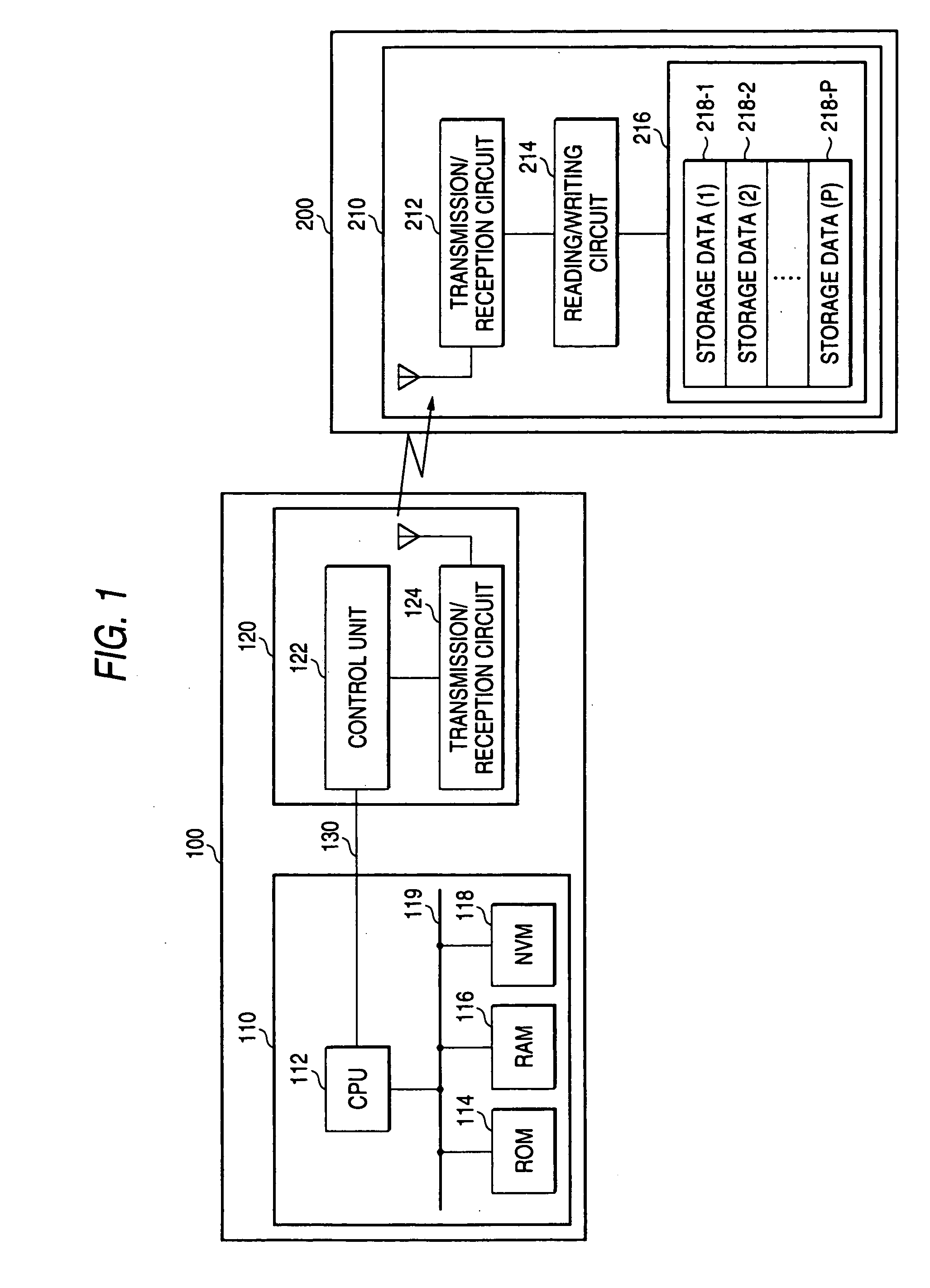

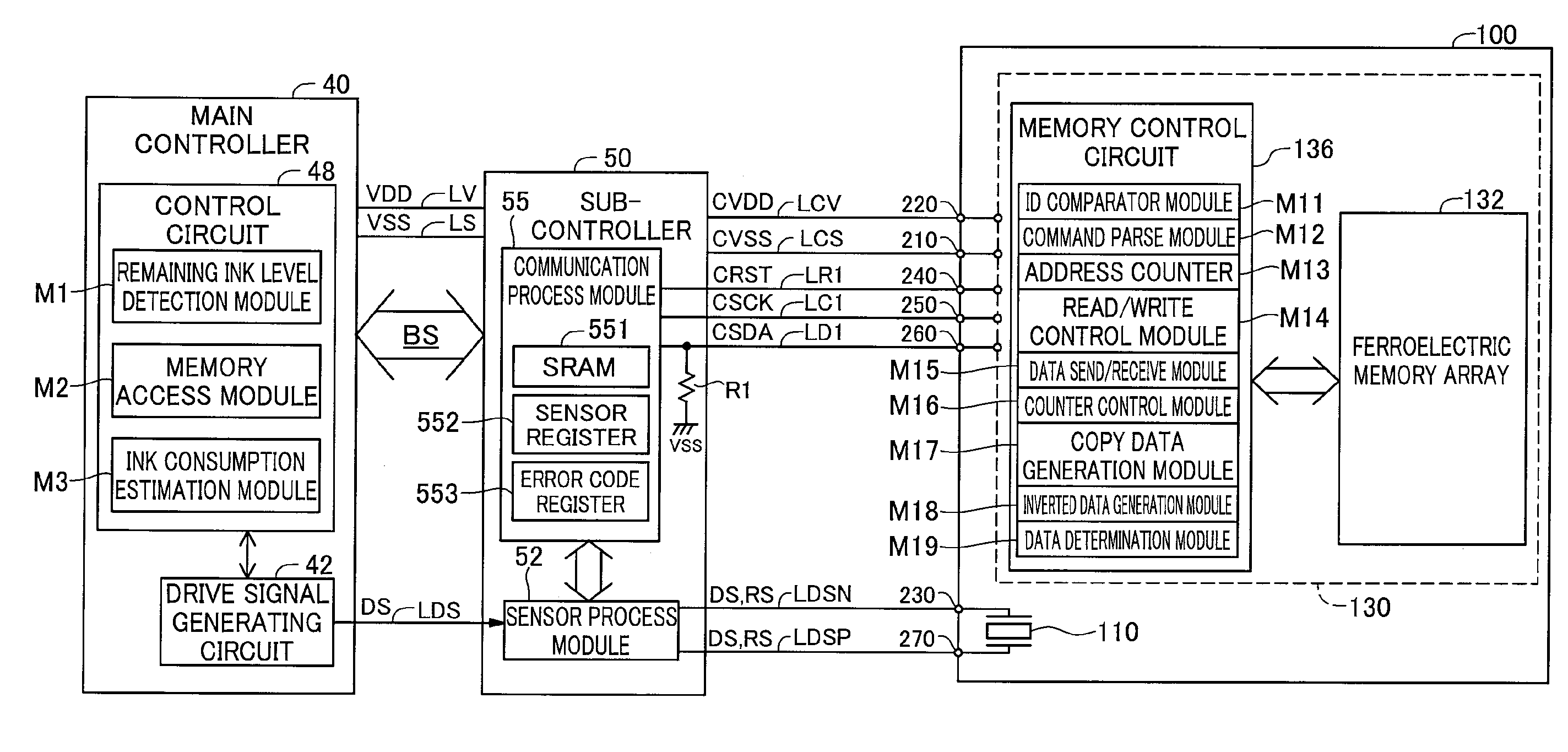

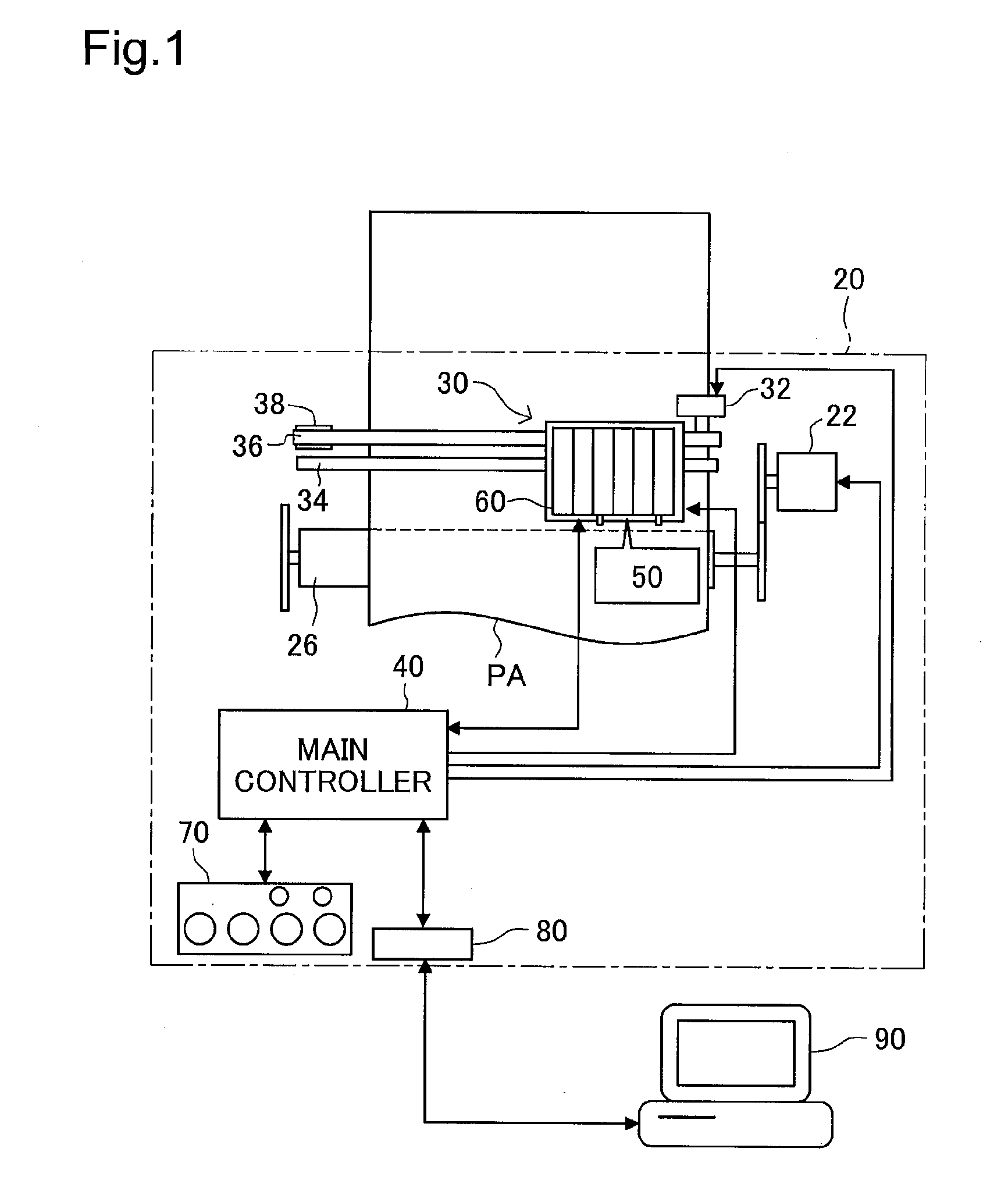

Image forming apparatus and control method of an image forming apparatus

InactiveUS20050120260A1Reduce frequencyError detection/correctionCo-operative working arrangementsImage formationExecution control

An image forming apparatus is mounted with a replacement component having a storage device and includes a processing unit that controls operation of the image forming apparatus by executing a control program and a reading / writing device that writes and reads data to and from the storage device under control of the processing unit. The processing unit generates a command with an error detection code to be transmitted to the storage device and supplies the generated command with the error detection code to the reading / writing device. The reading / writing device performs an error detecting operation on the command with the error detection code received from the processing unit, and informs the processing unit of detection of an error if detecting the error by the error detecting operation and sends the received command with the error detection code to the storage device if not detecting an error by the error detecting operation.

Owner:FUJIFILM BUSINESS INNOVATION CORP

MIMO multiple transmission device and method

InactiveUS20060209813A1Little dataLittle workMultiplex system selection arrangementsModulated-carrier systemsData streamComputer science

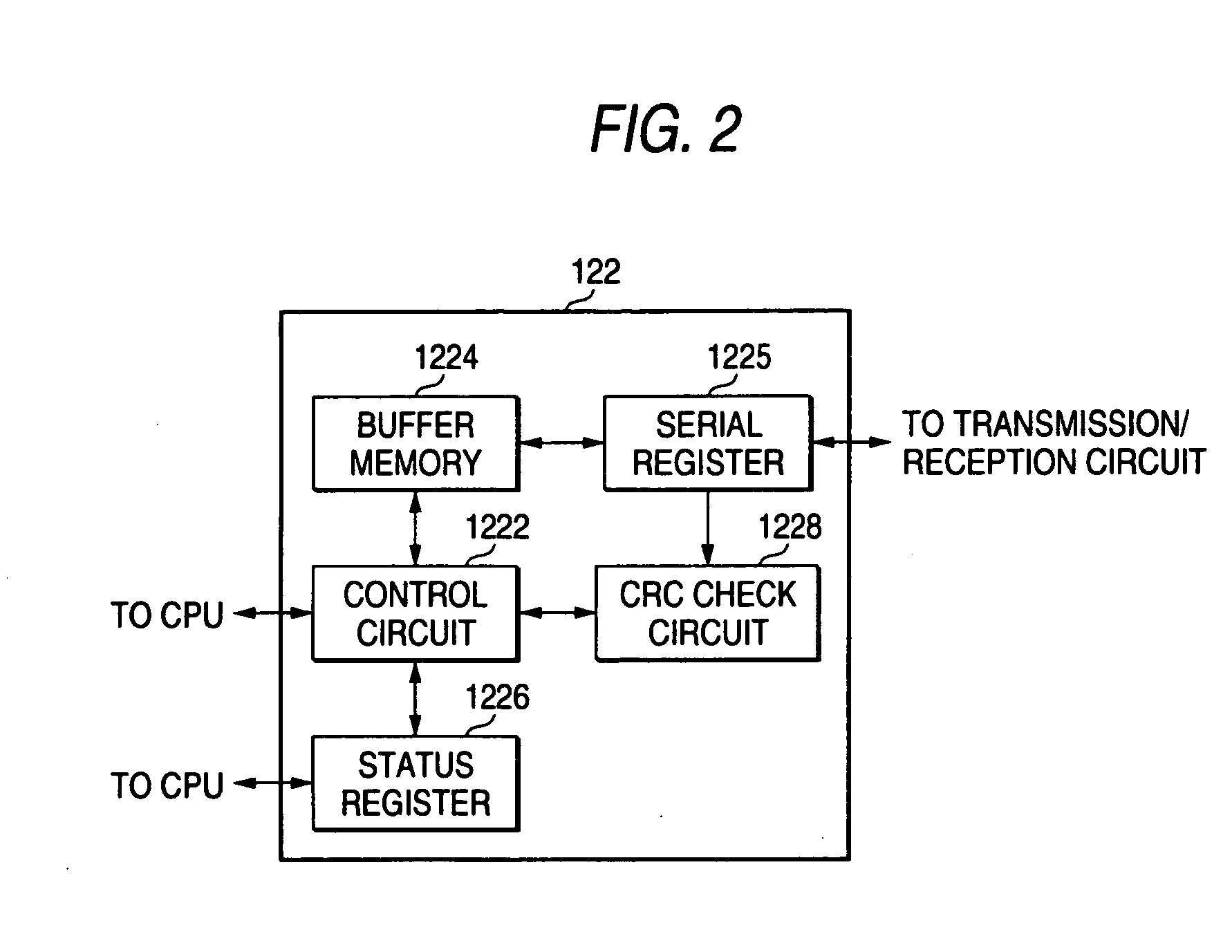

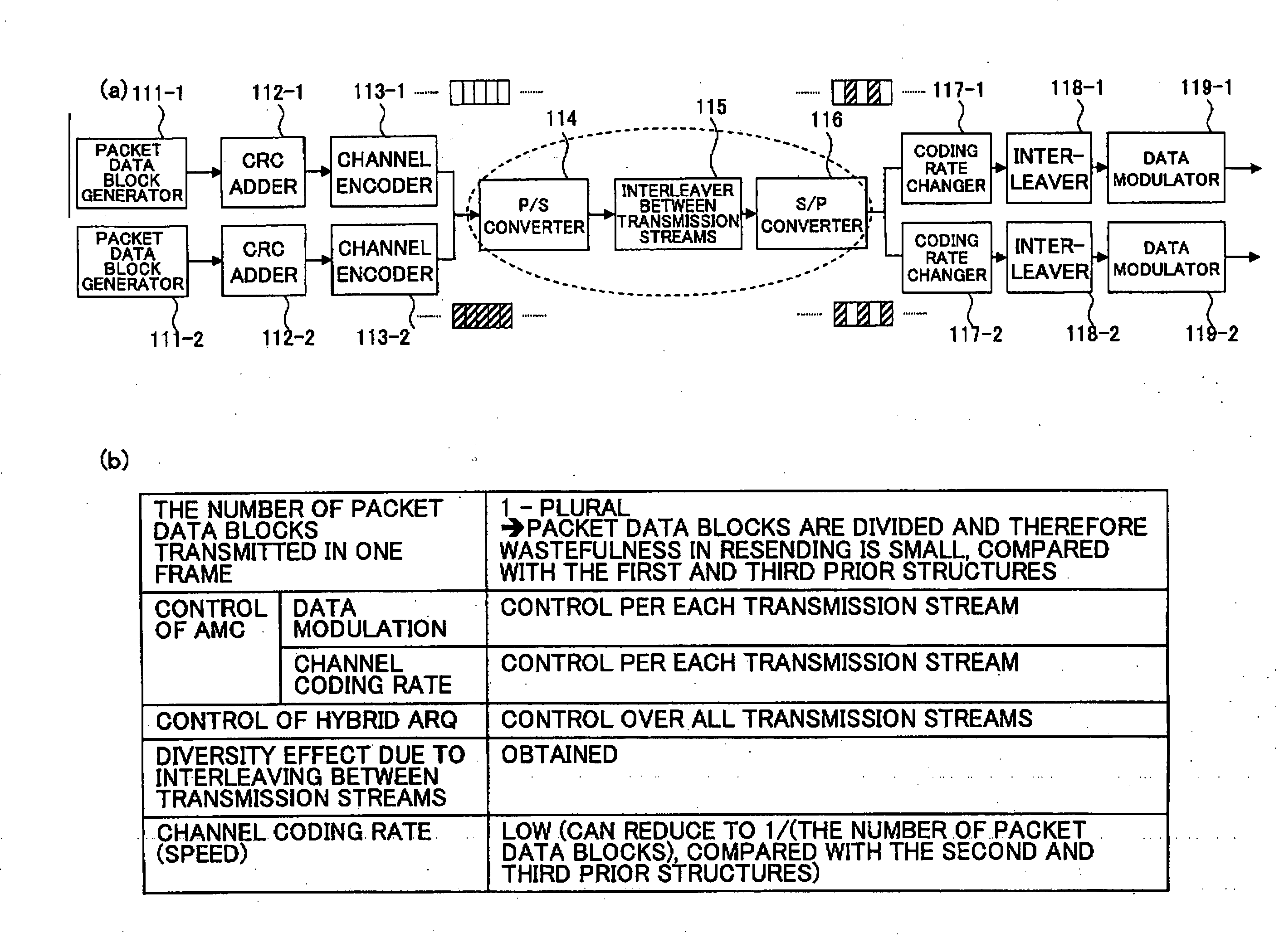

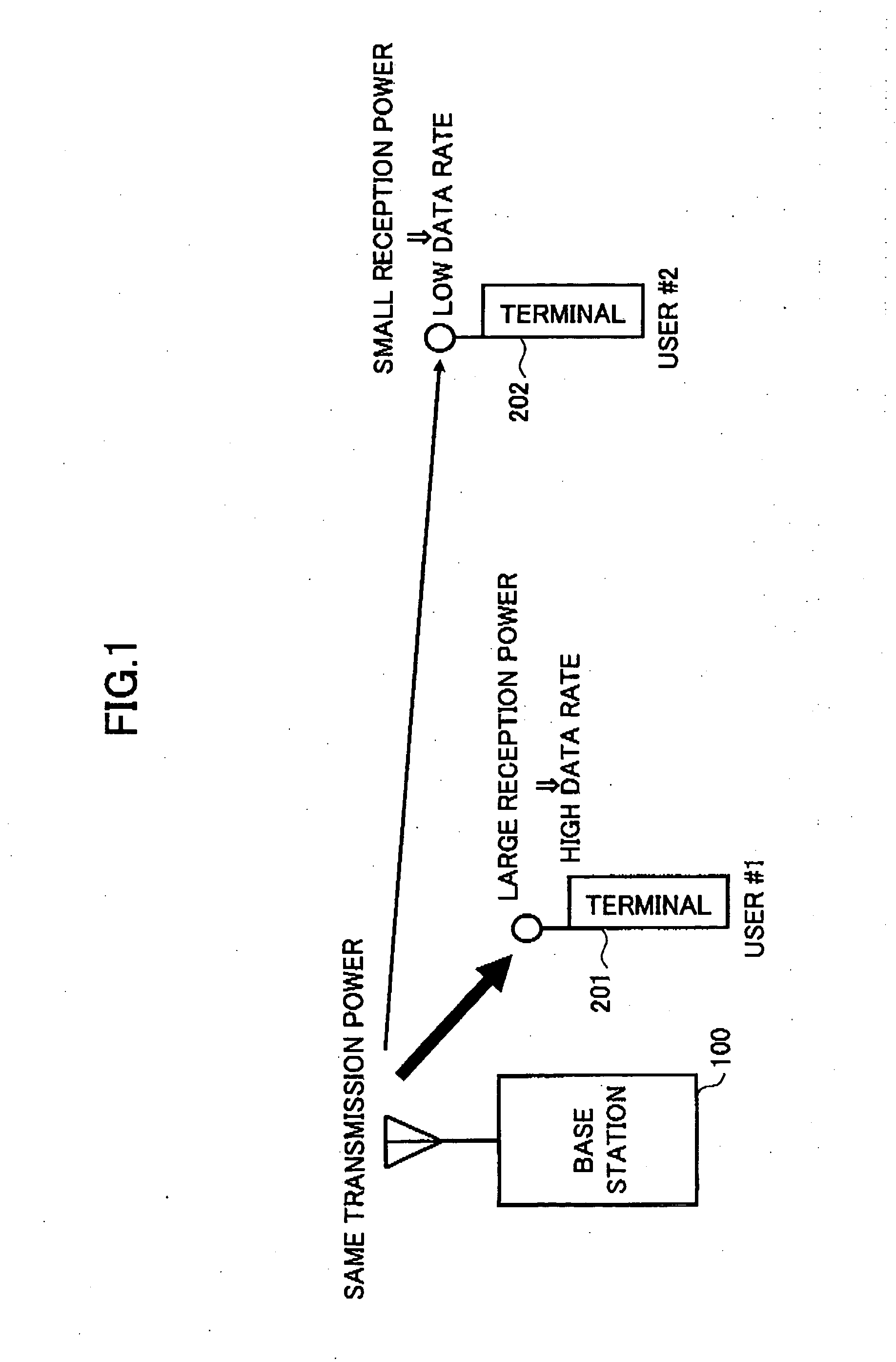

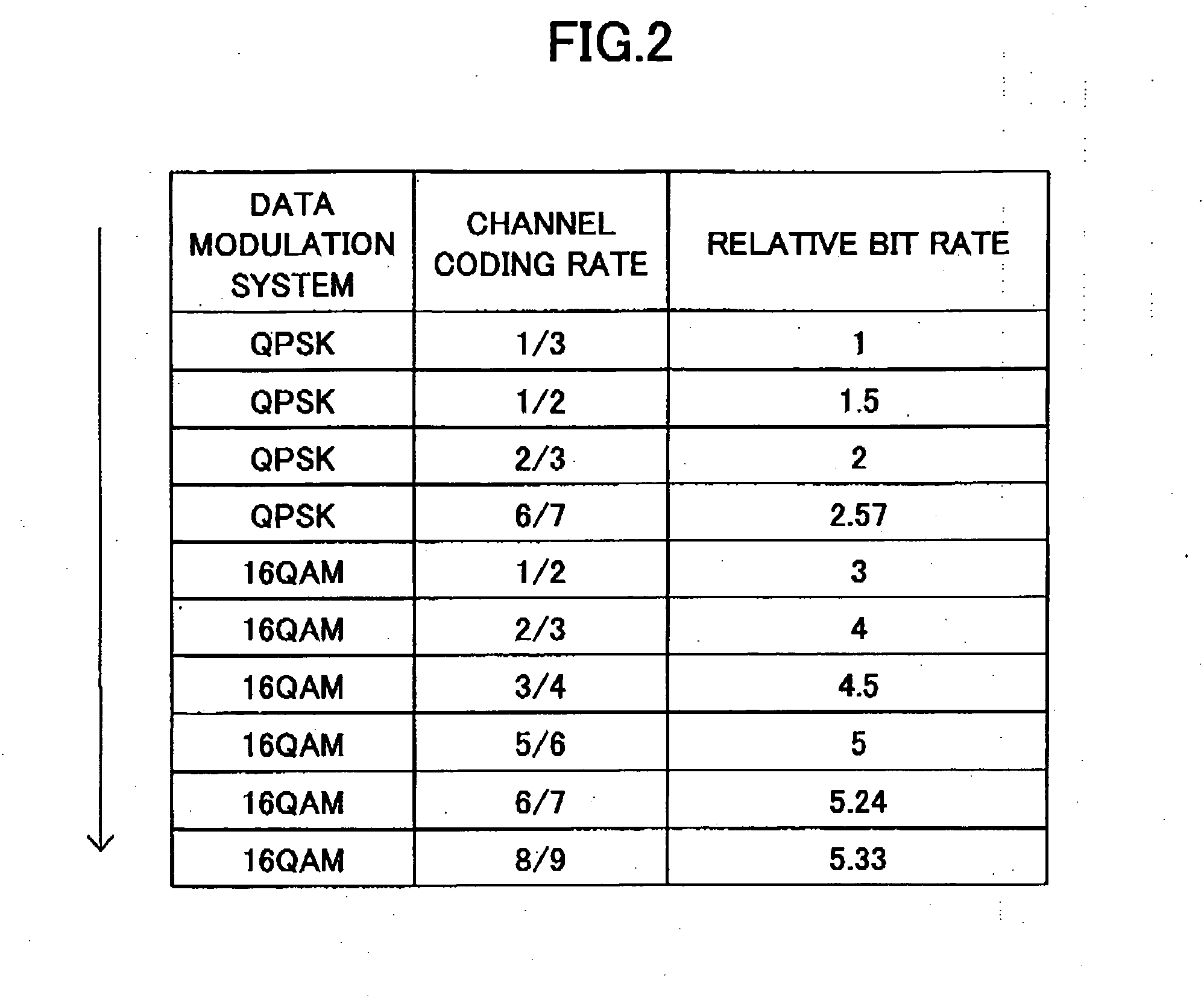

A MIMO multiple transmission device, comprising a packet data block generator (111) for generating a packet data block as a resent unit for hybrid ARQ; a CRC adder (112) for adding an error detection code; a channel encoder (113) for performing channel encoding, the packet data block generator, the CRC adder and the channel encoder being coupled in series in one or more data streams; a parallel-to-serial converter (114) for converting output of the channel encoder to serial form; an interleaver between transmission streams (115) for performing interleaving between transmission streams on outputs from the parallel-to-serial converter; a serial-to-parallel converter (116) for converting outputs from the interleaver between transmission streams to parallel form; a coding rate changer (117) for changing a coding rate; and a data modulator (119) for modulating data, the coding rate changer and the data modulator being connected in series in plural data streams divided by the serial-to-parallel converter.

Owner:NTT DOCOMO INC

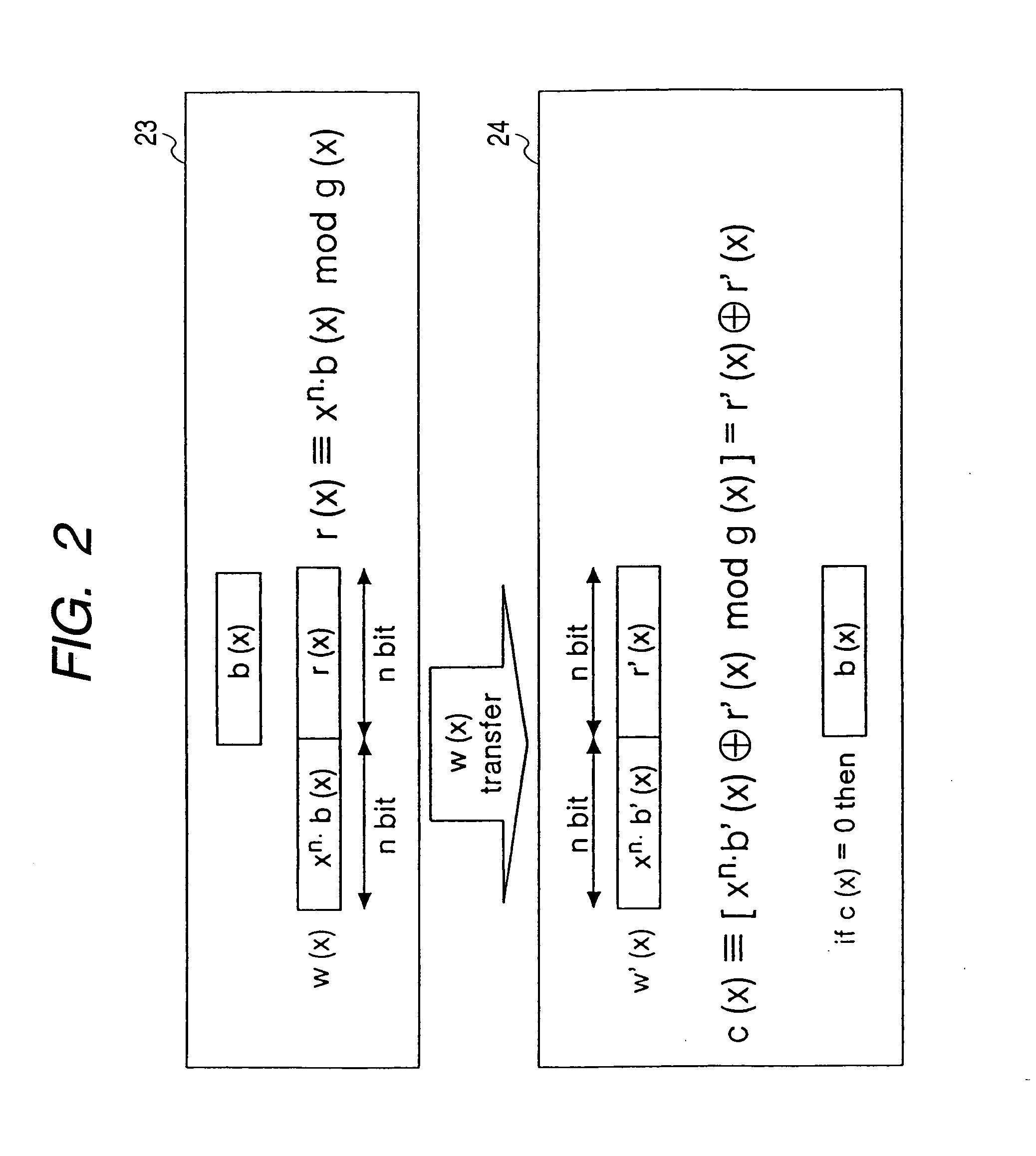

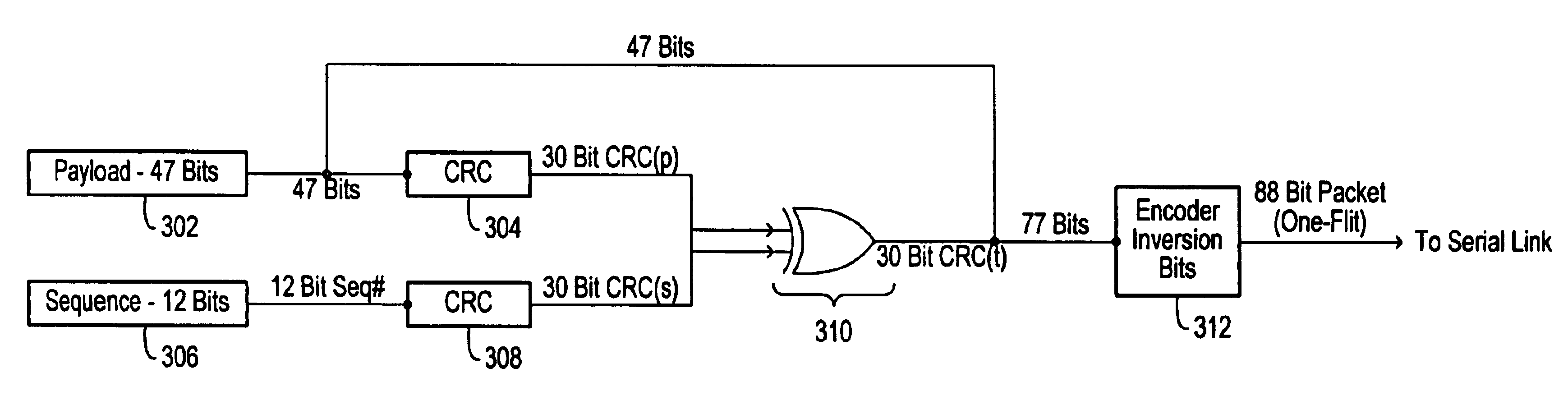

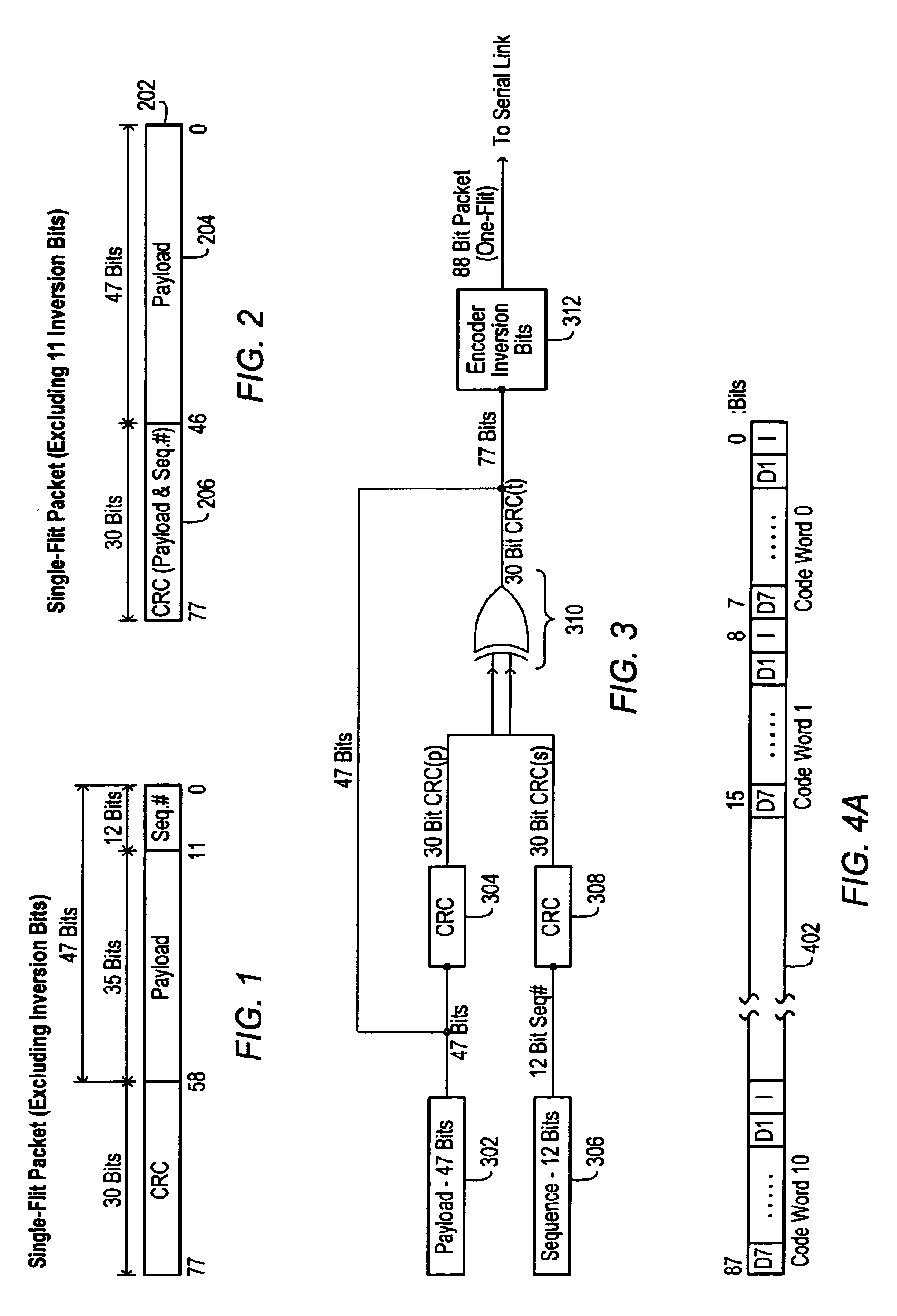

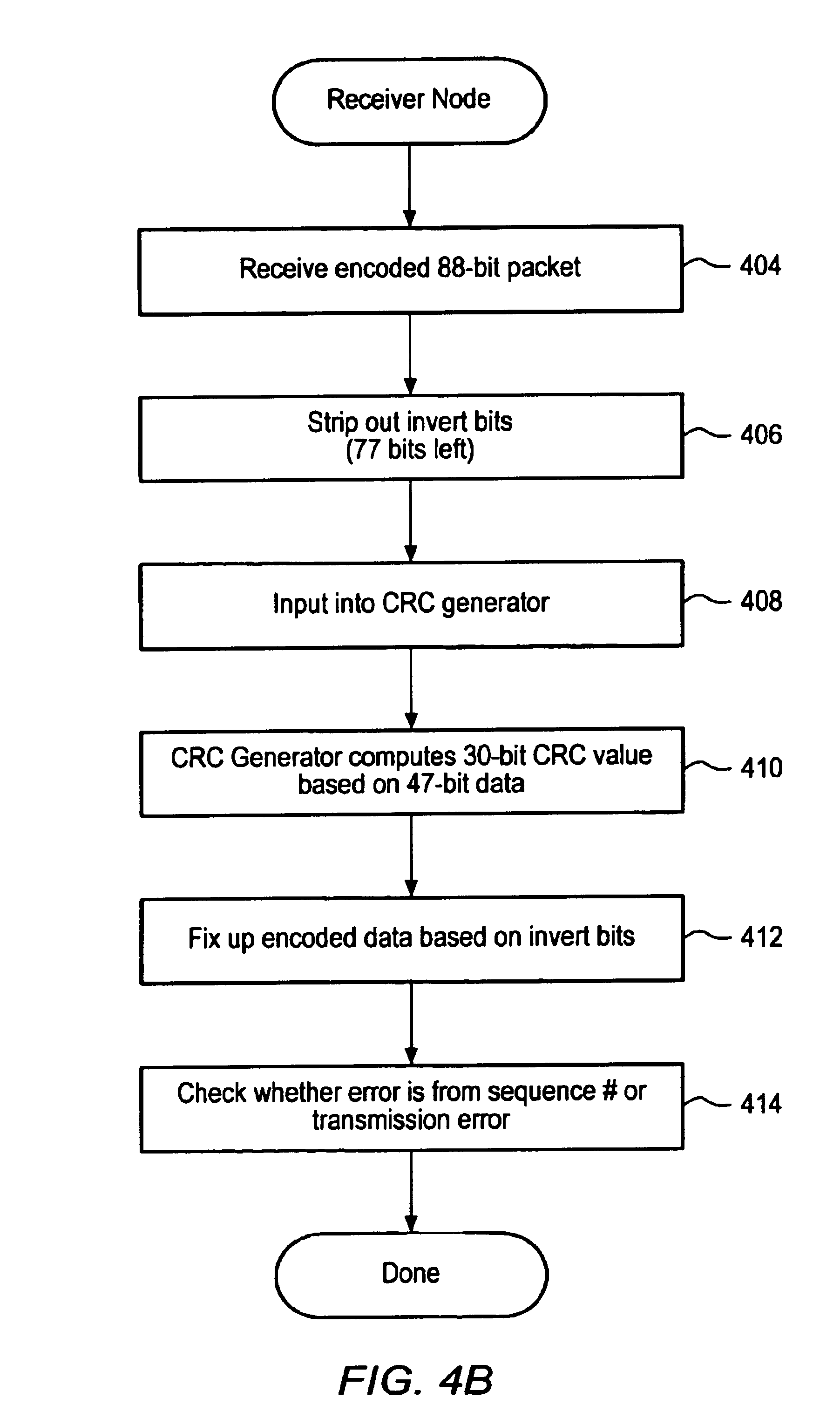

Method for superimposing a sequence number in an error detection code in a data network

A system and method for superimposing a sequence number of a packet into the CRC segment of the packet thereby allowing more bandwidth in the payload portion of the packet for carrying data is described. Also described is a method of acquiring additional information on the type of error in a packet, e.g., data transmission errors or sequence errors, from analyzing a CRC error. For example, a reported CRC error can be the result of the receipt of a packet with a sequence number the receiver is not expecting (which is a normal occurrence on transmission links due to transmitters resending packets that a receiver has already accepted) or can result from a real error in the transmission of a packet. A first error code check (CRC) value is calculated for the payload segment of a data packet. A second CRC value is calculated for the sequence number of the data packet. The first CRC value and the second CRC value are combined thereby creating a third CRC value. The third CRC value is then combined with the payload segment of the data packet thereby creating a data packet that can be transmitted across the link.

Owner:ORACLE INT CORP

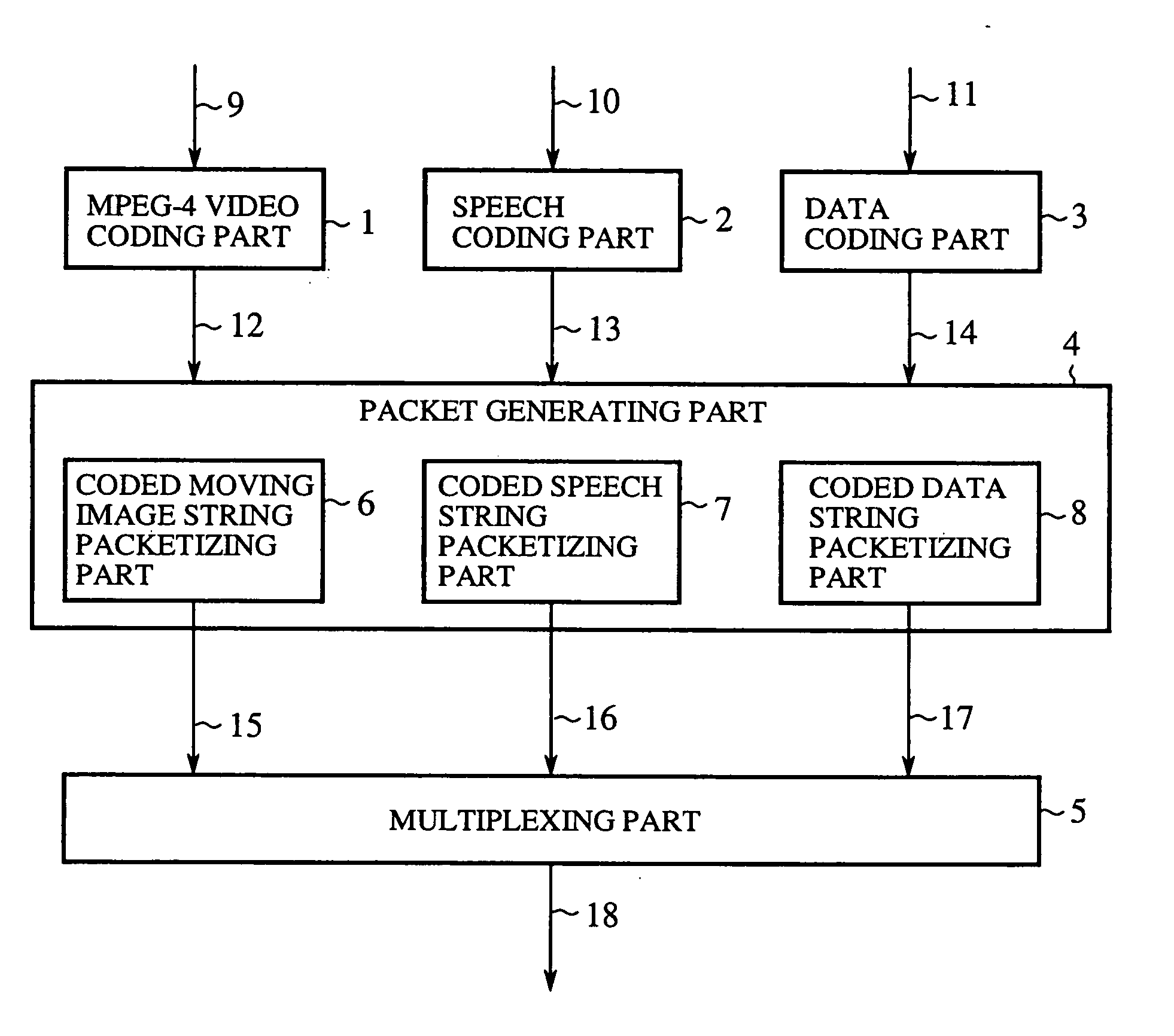

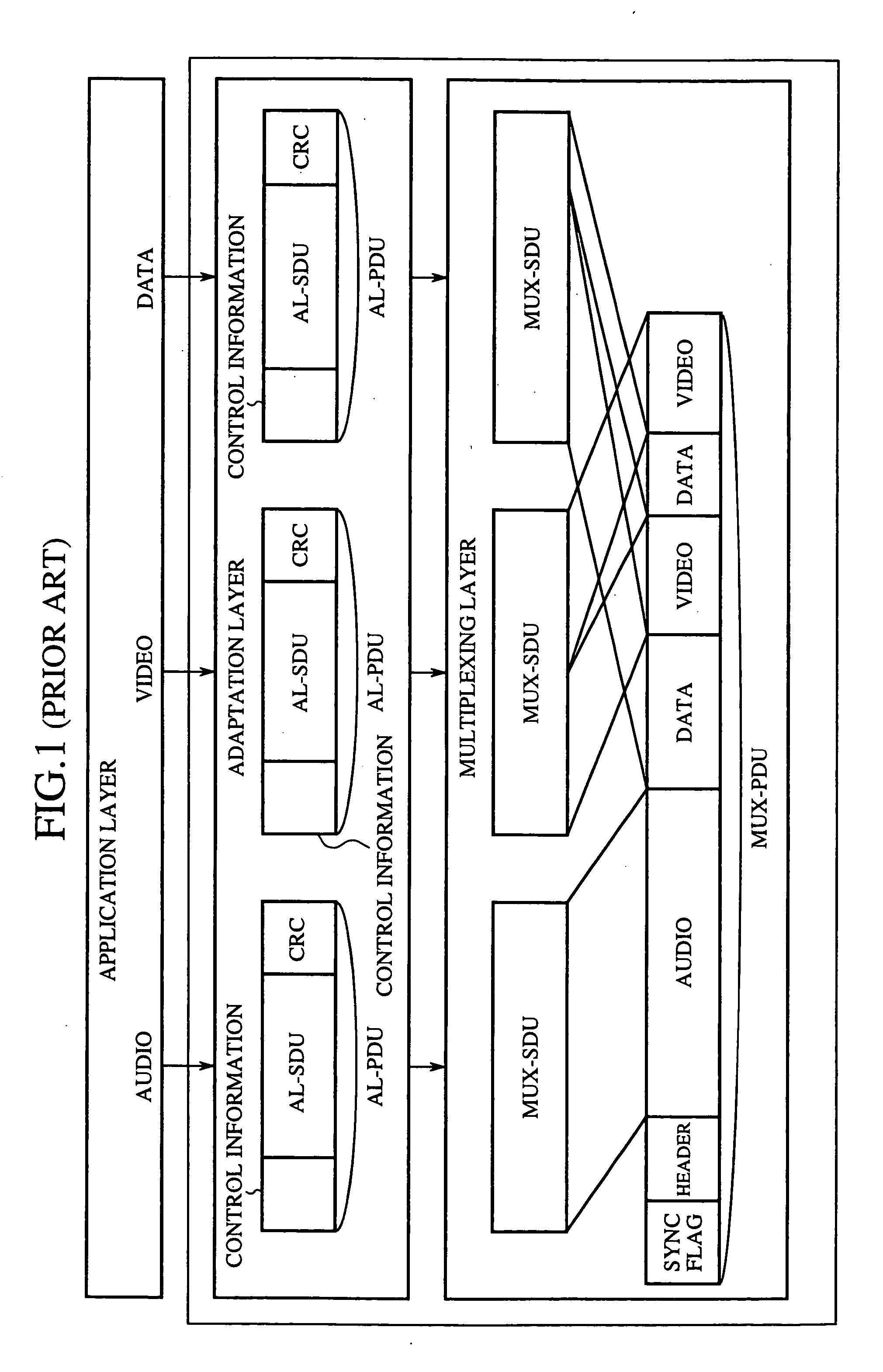

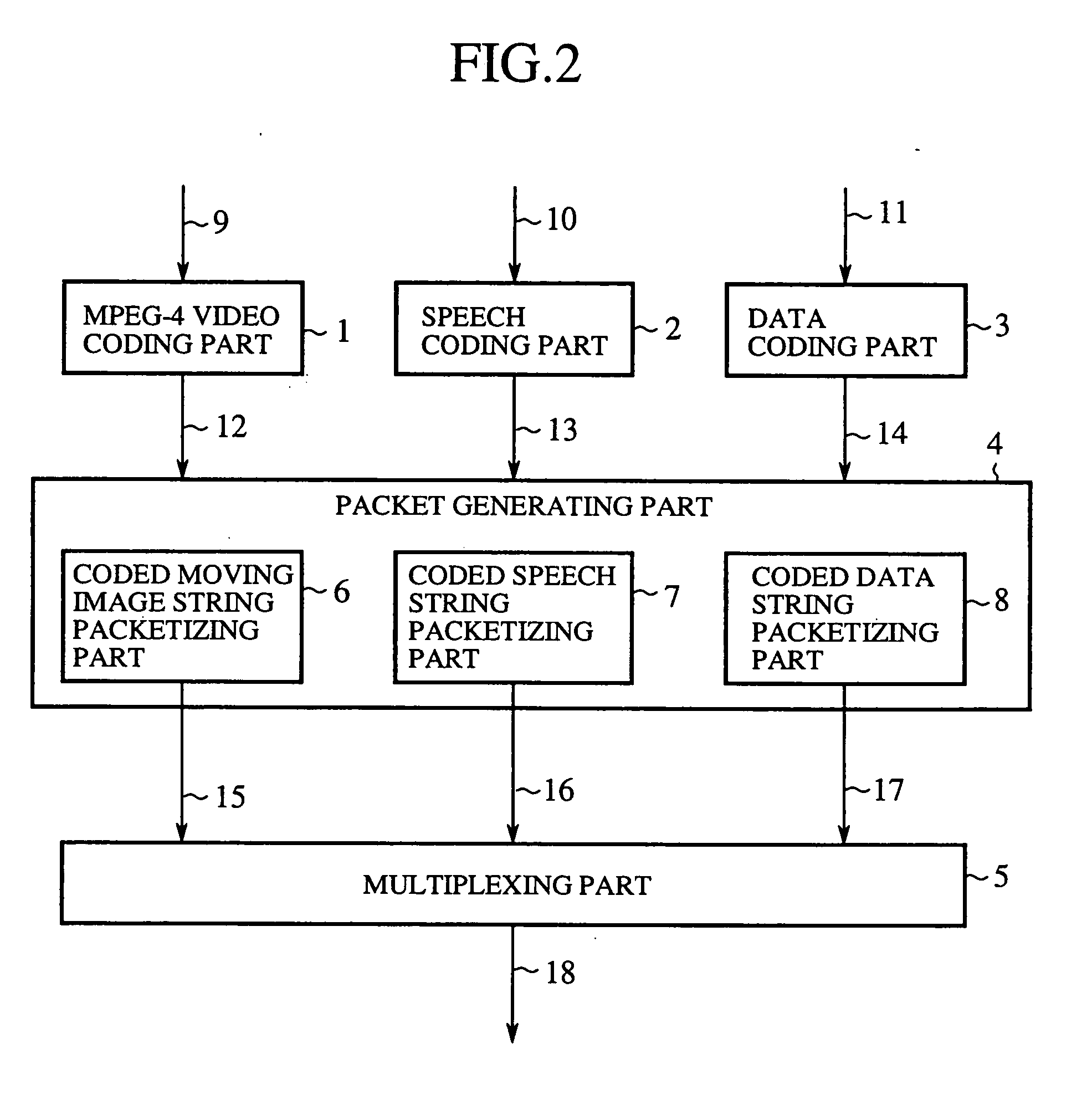

Packet generating method, video decoding method, media multiplexer, media demultiplexer, multimedia communication system and bit stream converter

InactiveUS20060013321A1Promote recoveryEfficient conversionColor television with pulse code modulationColor television with bandwidth reductionMultiplexingCommunications system

A moving image coded string is mapped with a set of information areas as one packet, and each packet is added with an error code and control information in a multiplexing part so that it is decided at the receiving side, from the result of error detection by decoding the error detection code, whether an error has occurred in each information area of the packet.

Owner:MITSUBISHI ELECTRIC CORP

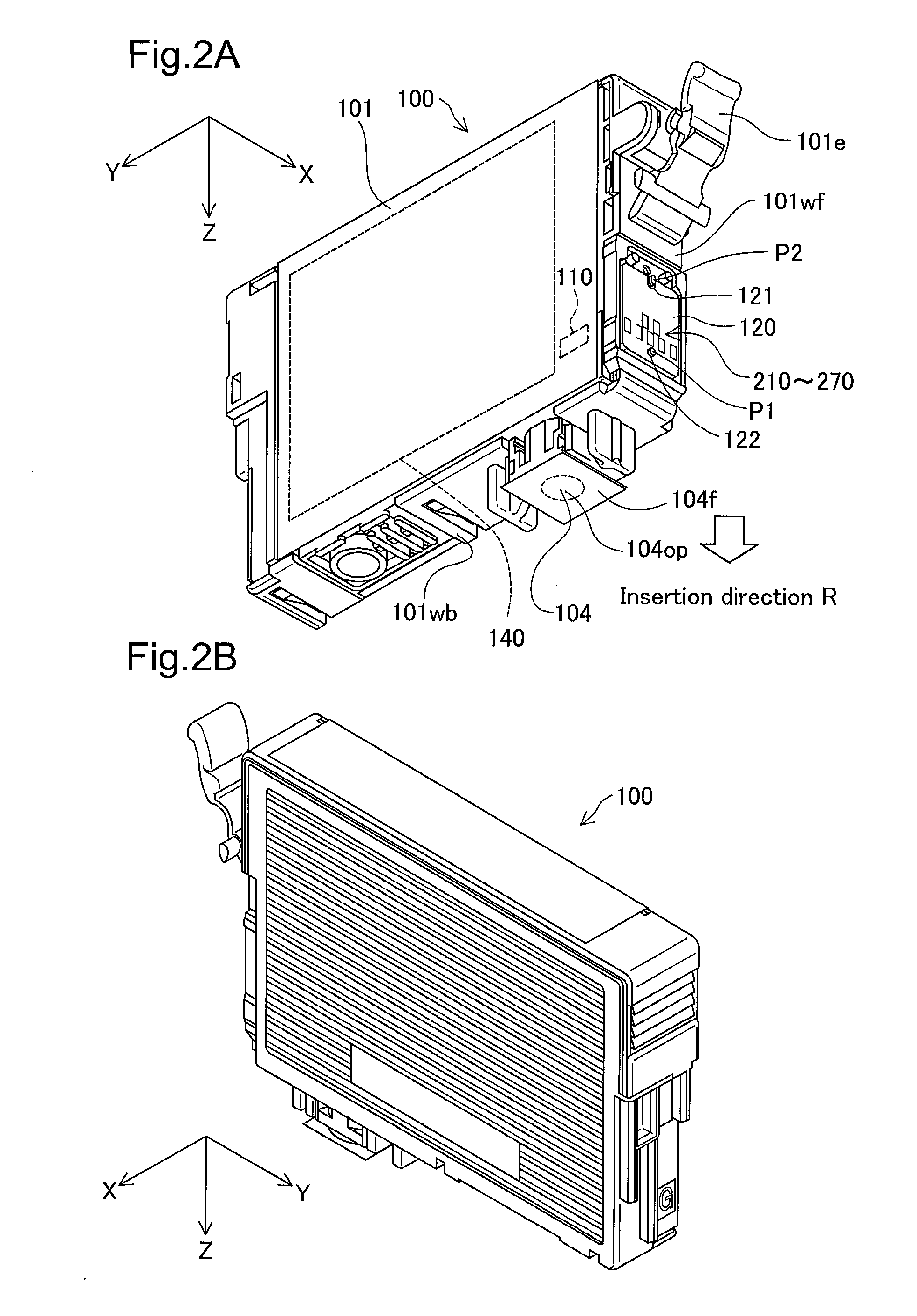

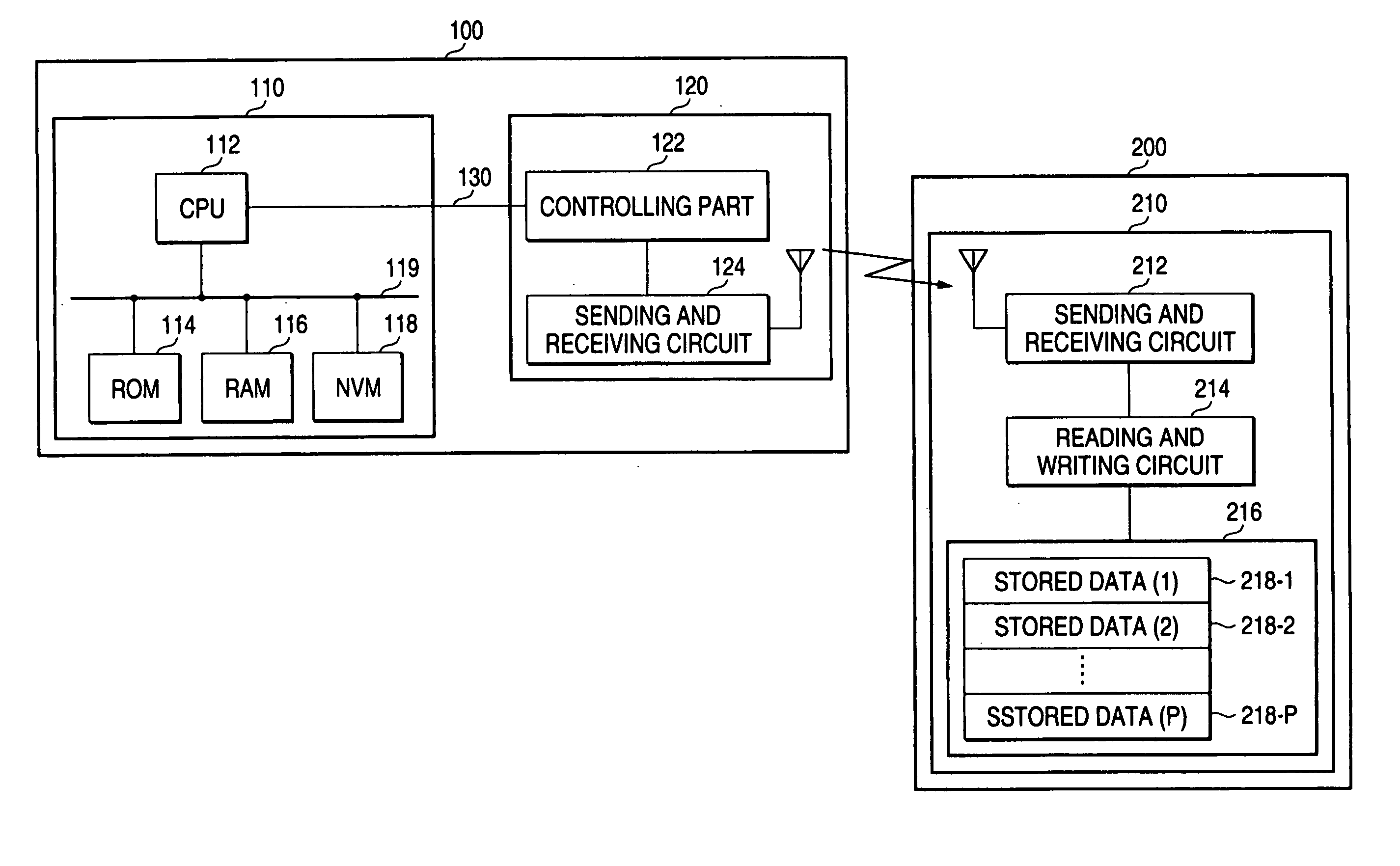

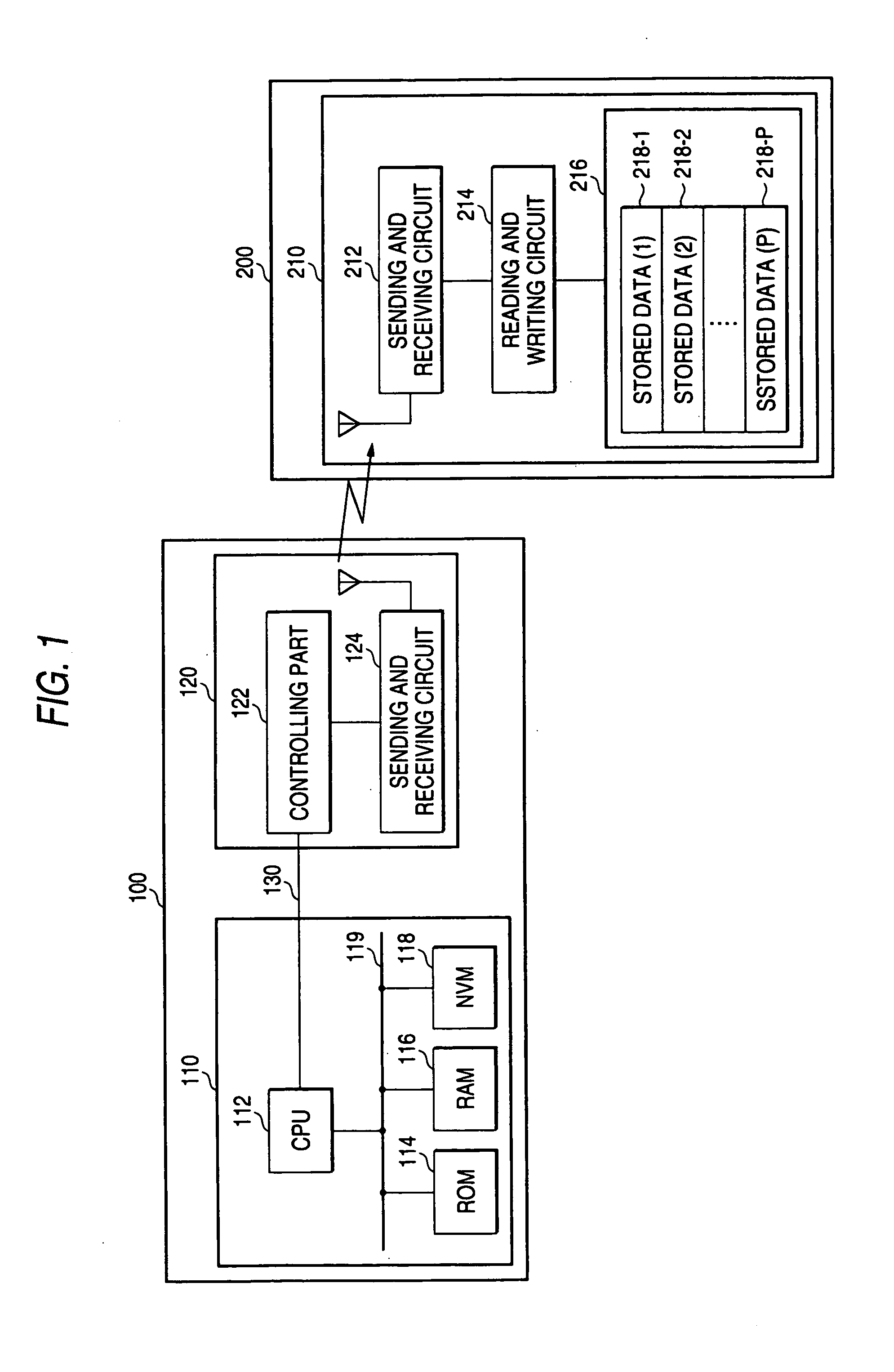

Memory device and system including a memory device electronically connectable to a host circuit

ActiveUS20100257327A1Improve reading efficiencyImprove writing efficiencyError preventionTransmission systemsControl circuitError detection coding

A memory includes a nonvolatile memory cell array, and a memory control circuit which carries out writing of data to and reading of data from the memory cell array in access units of N bits where N is an integer equal to 2 or greater. The memory cell array includes a rewritable area in which both writing of data and reading of data are permissible, and a read-only area in which writing of data is prohibited and reading of data is permissible. The rewritable area is configured so that the N bits constituting one access unit contain both actual data and an error detection code. The read-only area is divided between an actual data area in which the N bits constituting one access unit contain actual data, and an error detection code area in which the N bits constituting one access unit contain error detection codes.

Owner:SEIKO EPSON CORP

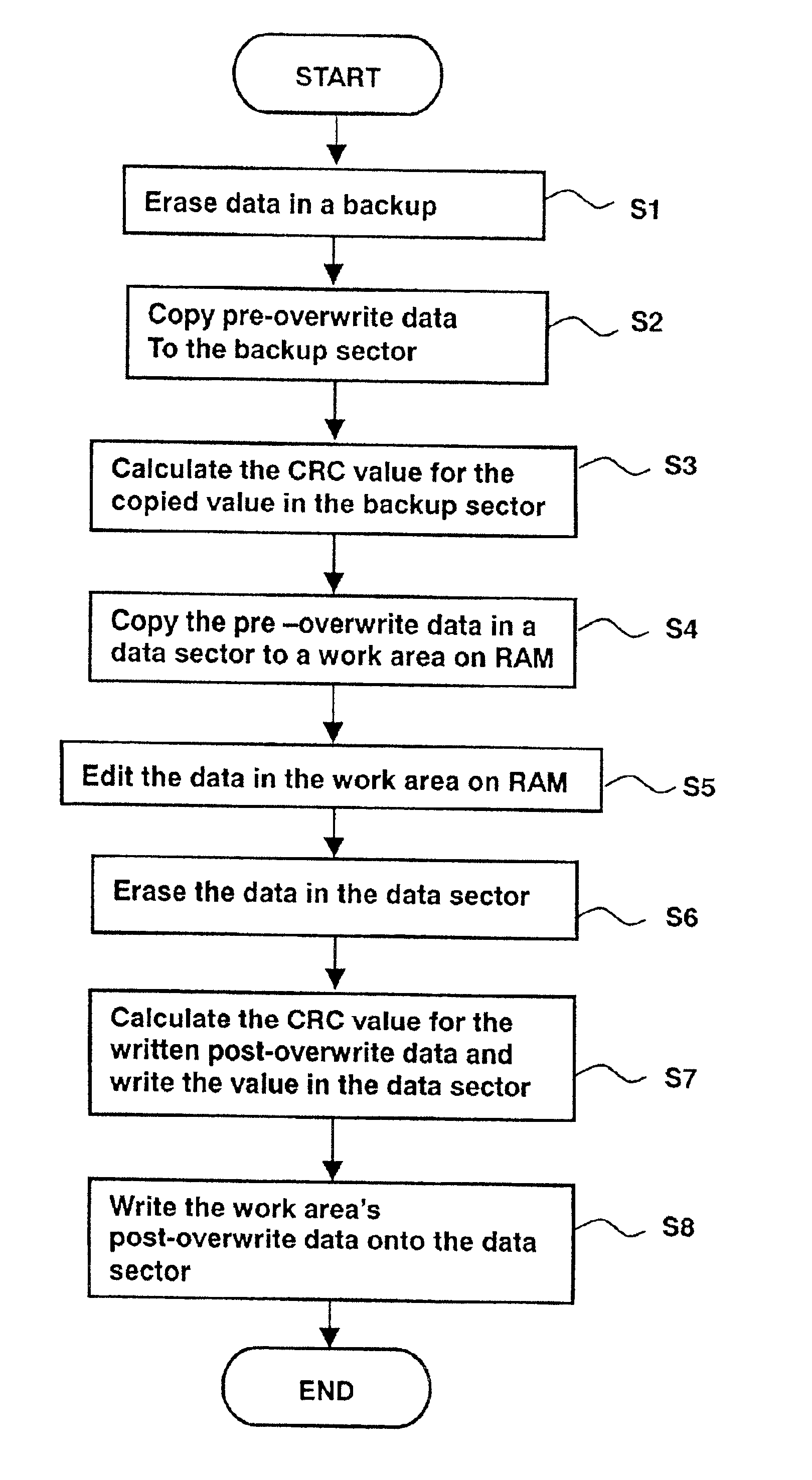

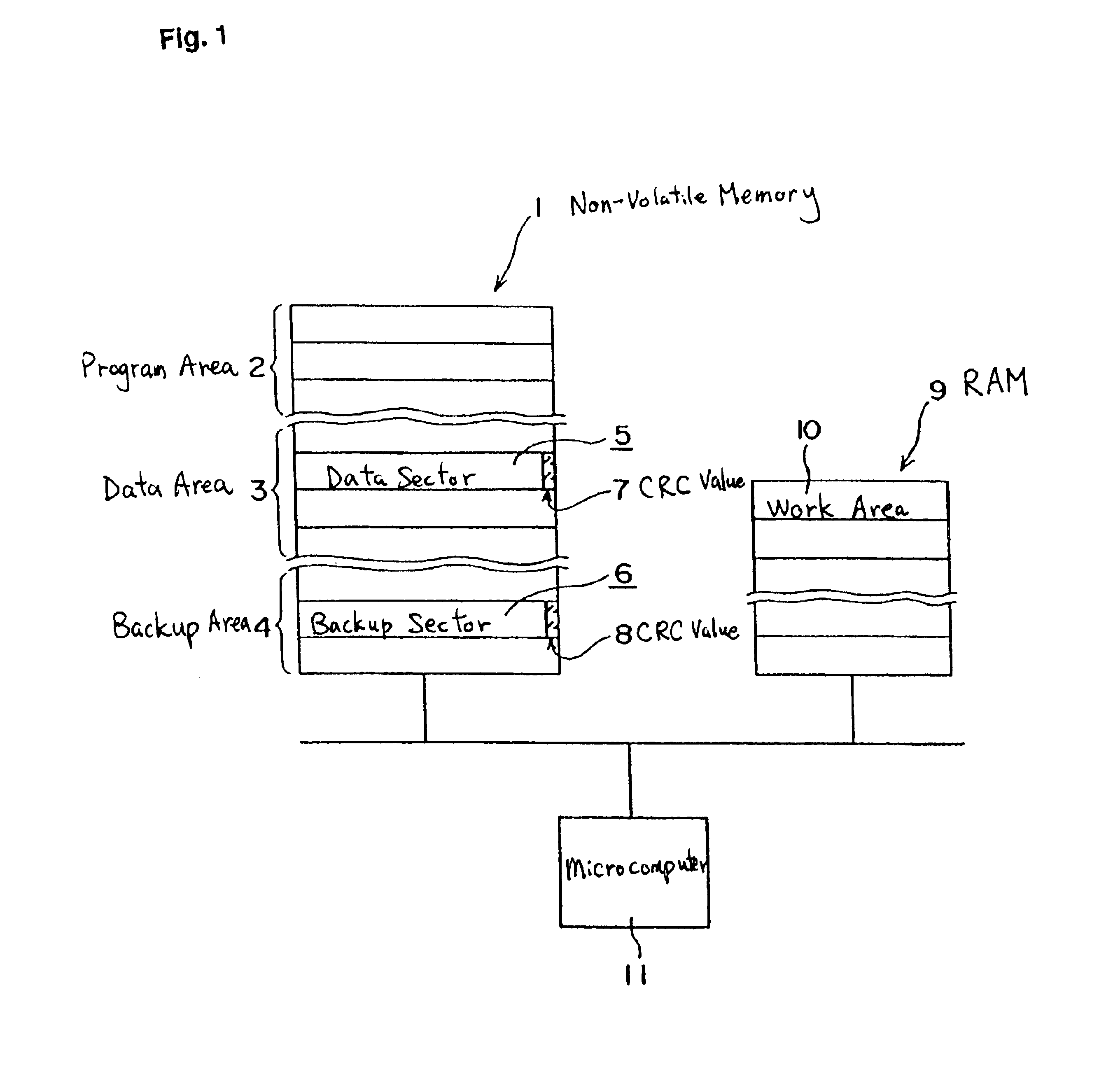

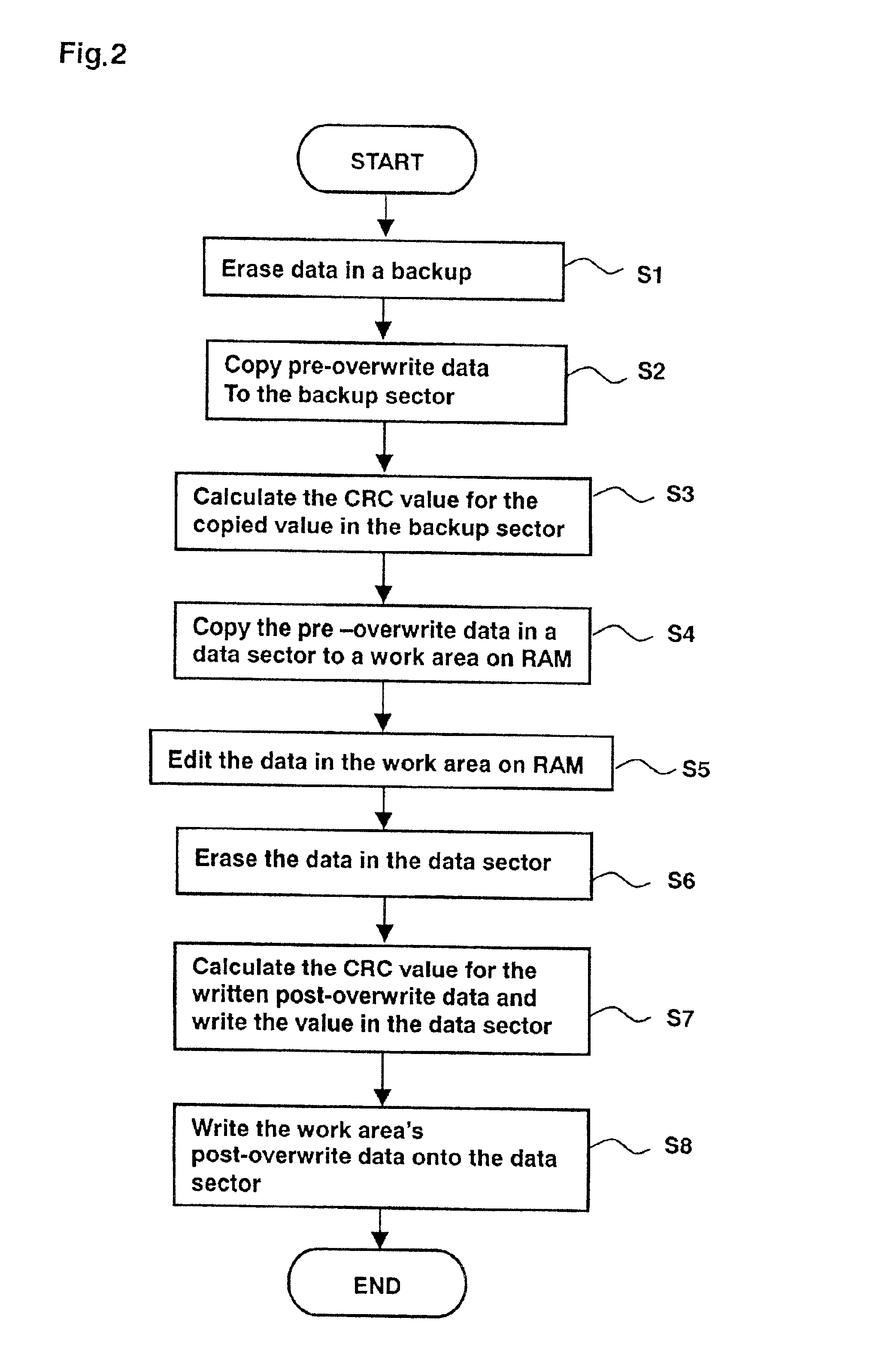

Method of overwriting data in nonvolatile memory and a control apparatus used for the method

In a nonvolatile memory such as flash memory where data is stored sector by sector, a method of overwriting a data sector is provided. The old data to be overwritten in a data sector along with its error detection code are initially saved to a backup region which is also in a non-volatile area. The old data in the data sector is then erased and new data along with its own error detection code are written into the same data sector where the old data was previously stored. When a power outage occurs during the overwrite process, error checking is performed to determine whether the data in the data sector is valid using the associated error detection code. Because the old data is saved in a non-volatile area, even if such unexpected power outage occurs during the overwrite process and the data in the data sector is determined to be invalid, at least the old data can be recovered from the non-volatile backup region which is not affected by the power outage.

Owner:DIGITAL CACHE LLC

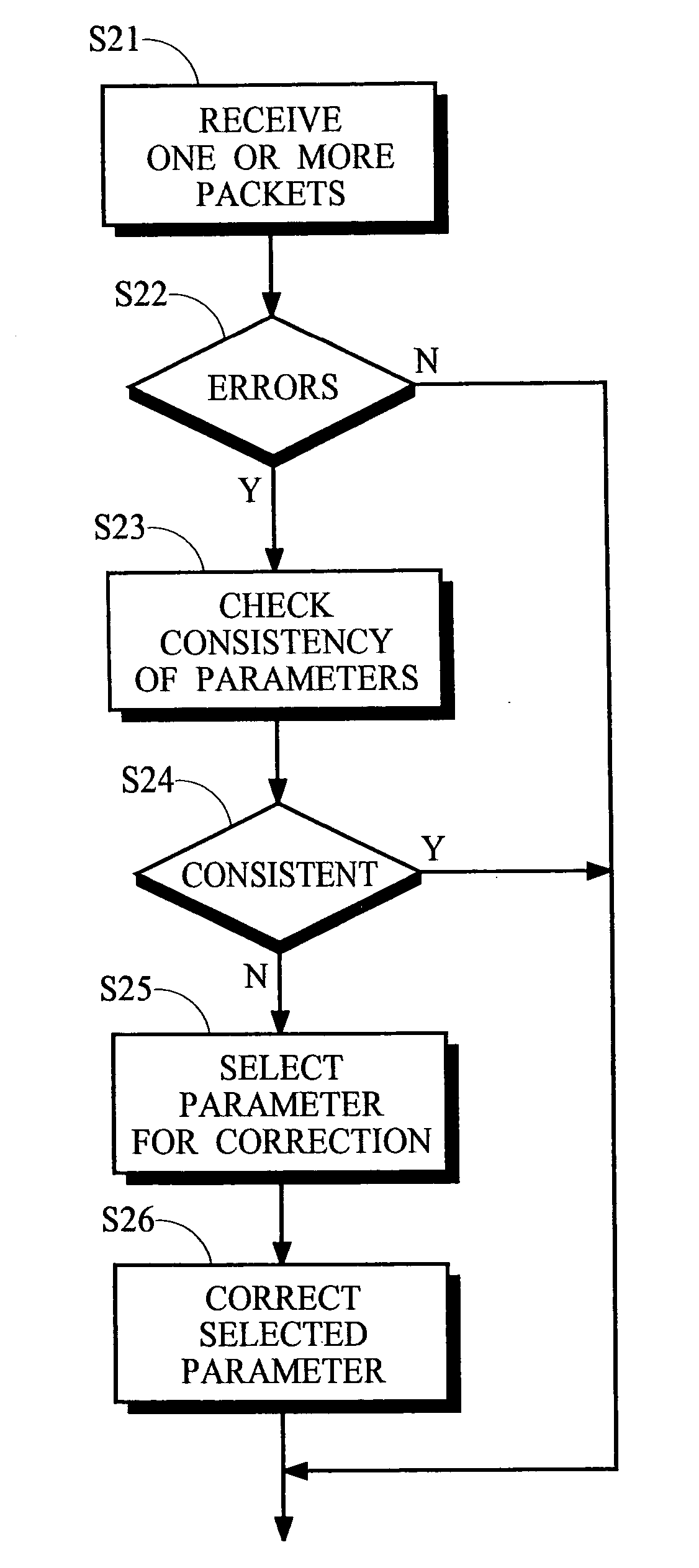

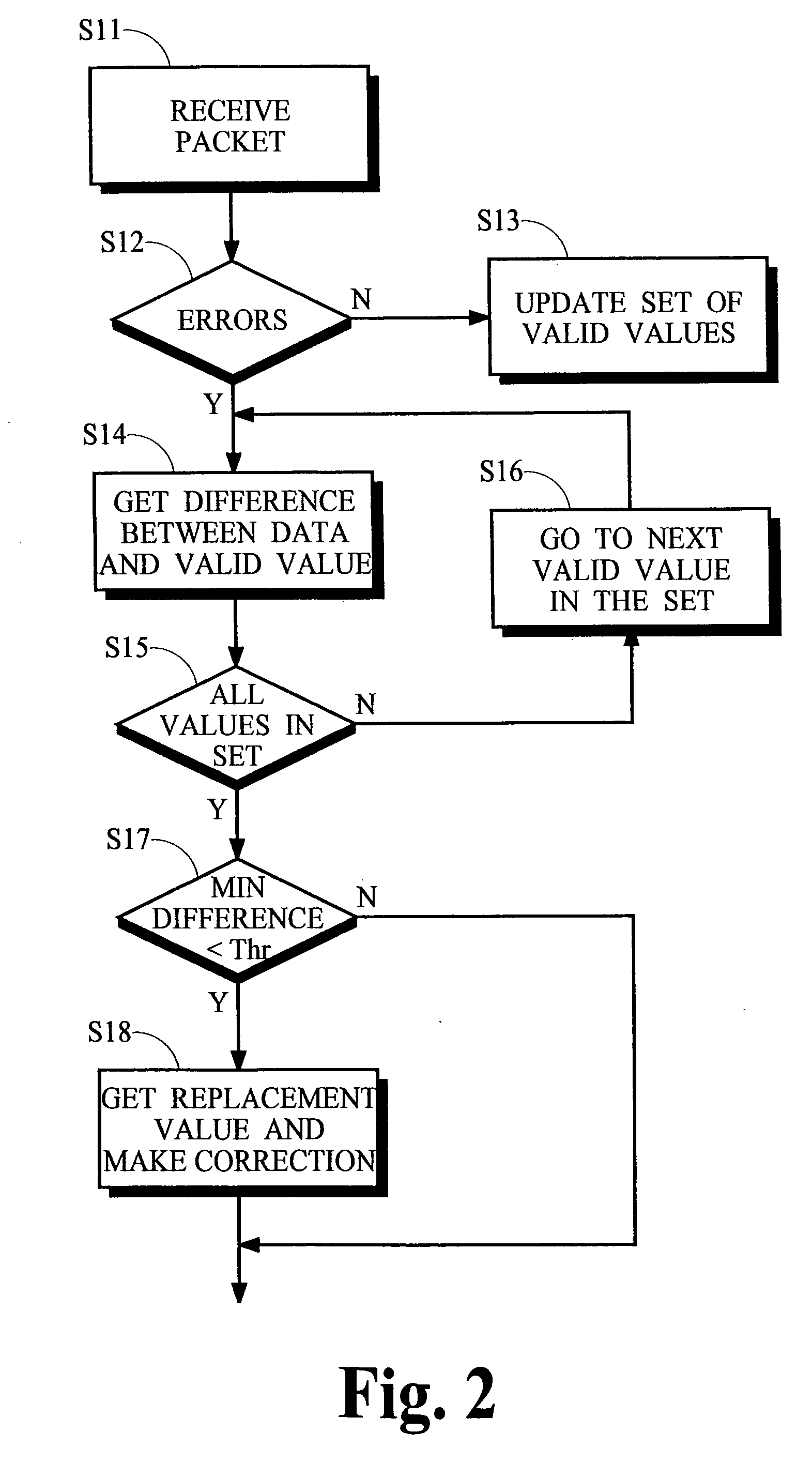

Error correction in packet-based communication networks using data consistency checks

InactiveUS20070089037A1Not be addError prevention/detection by using return channelCode conversionValid ValueError detection coding

Bit errors in packets of data that are communicated in a network such as a wireless network can be corrected by processes that do not require any overhead in the data such as conventional error-detection codes or redundant information such as conventional error-correction codes. A validation-set process compares corrupted data against values in a set of known valid values and selects one of the known valid values to replace the corrupted data. A consistency-check process uses data correlation characteristics of two or more parameters to determine if values obtained from a packet are consistent with one another. If not, values are changed to make them consistent.

Owner:DOLBY LAB LICENSING CORP

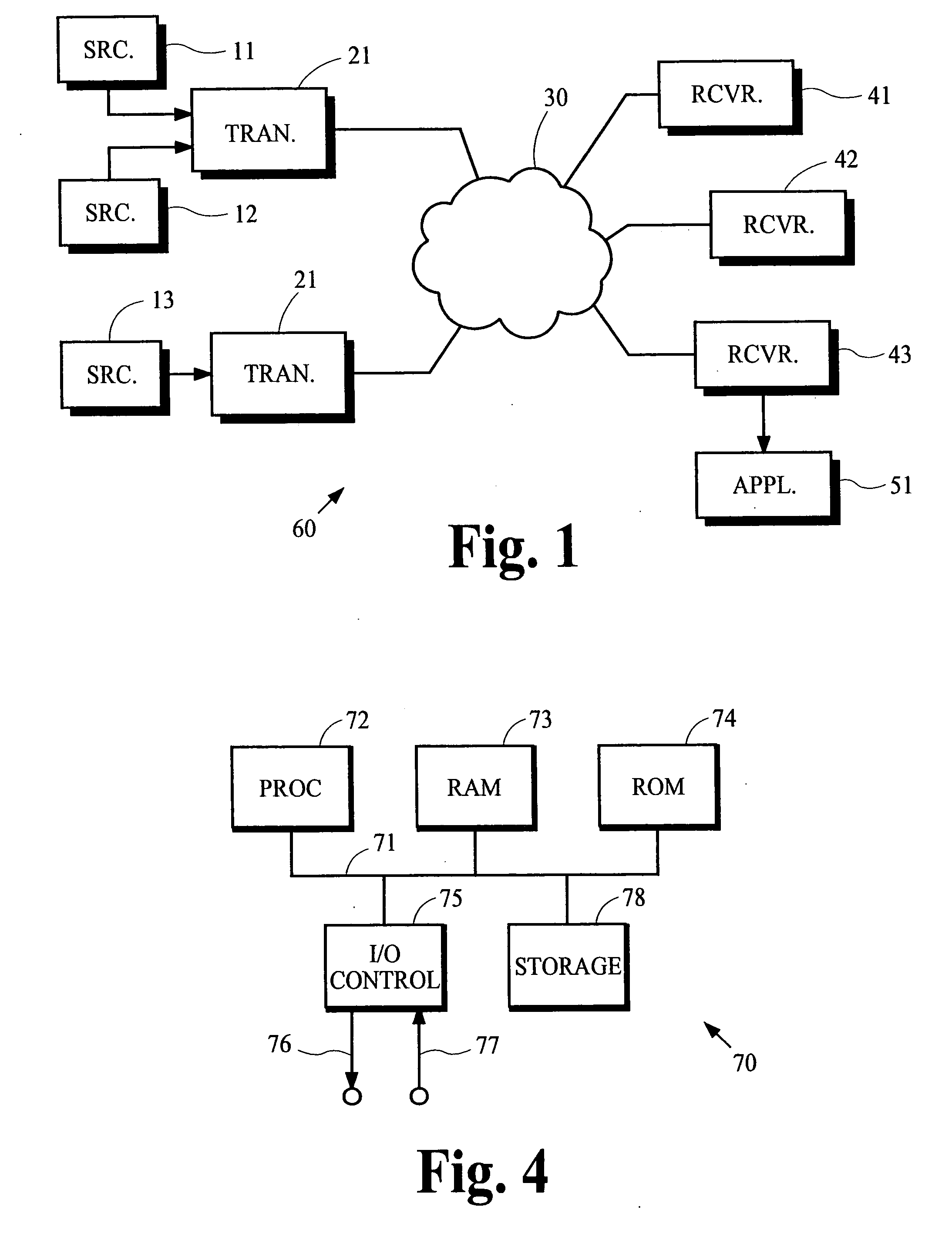

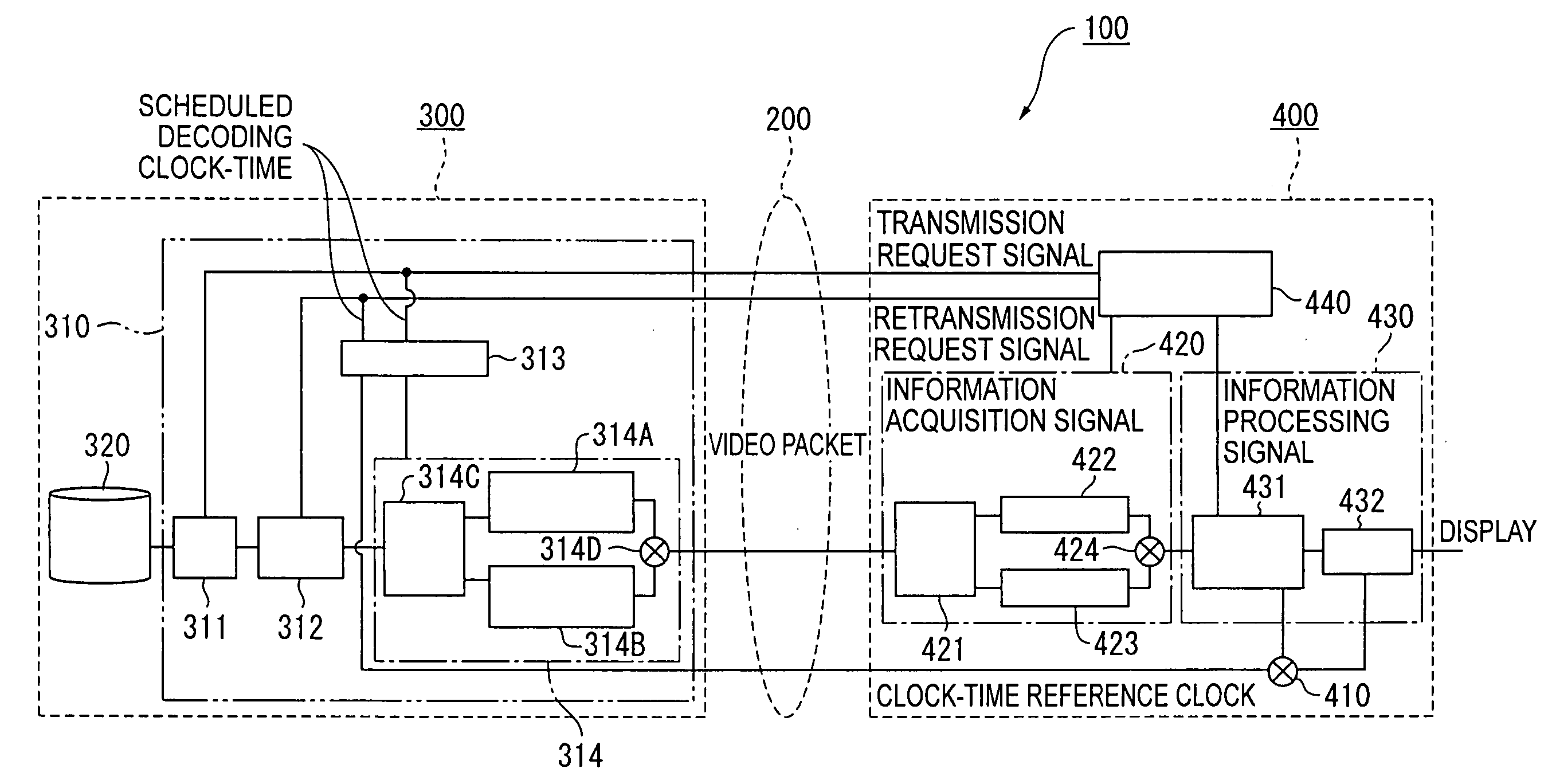

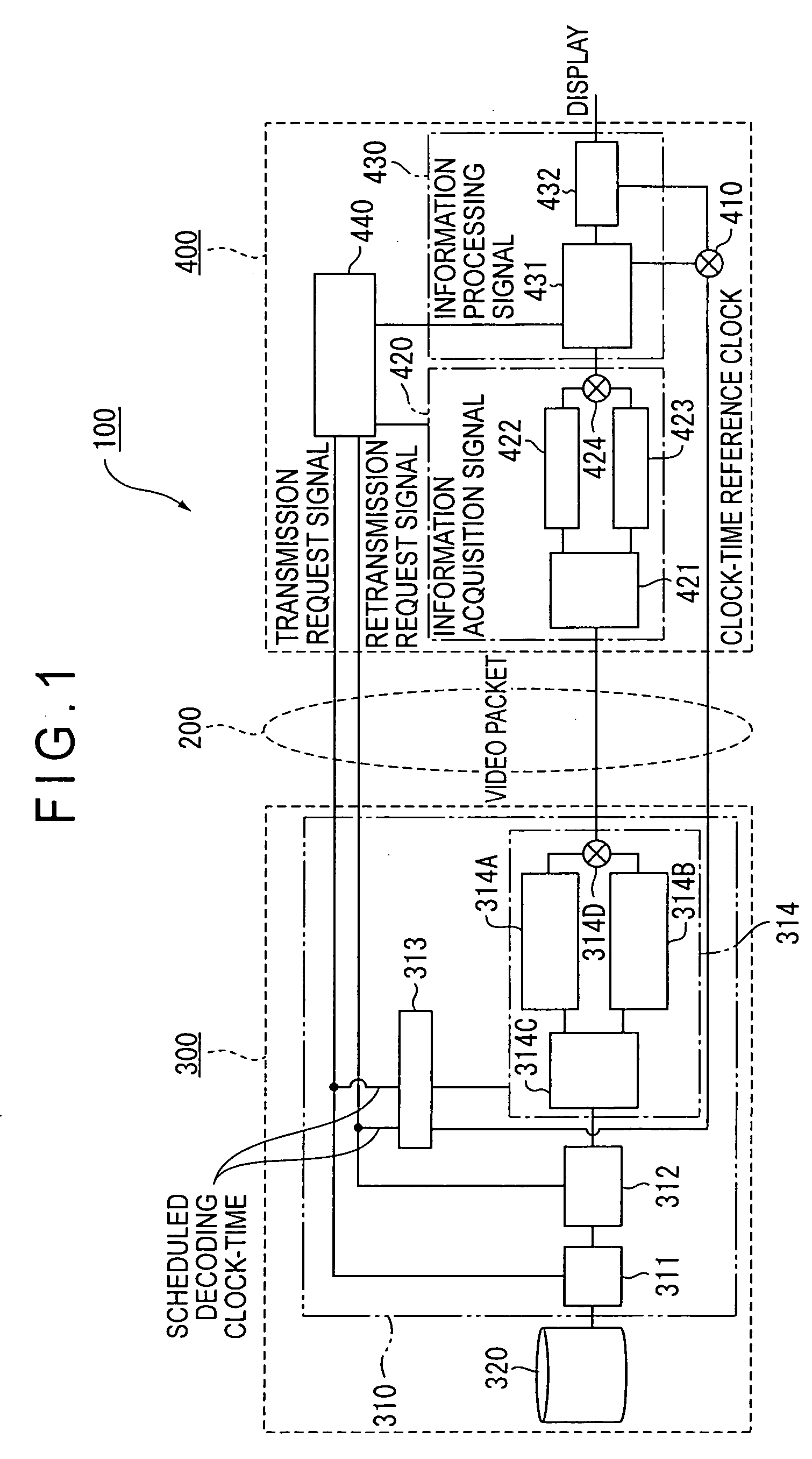

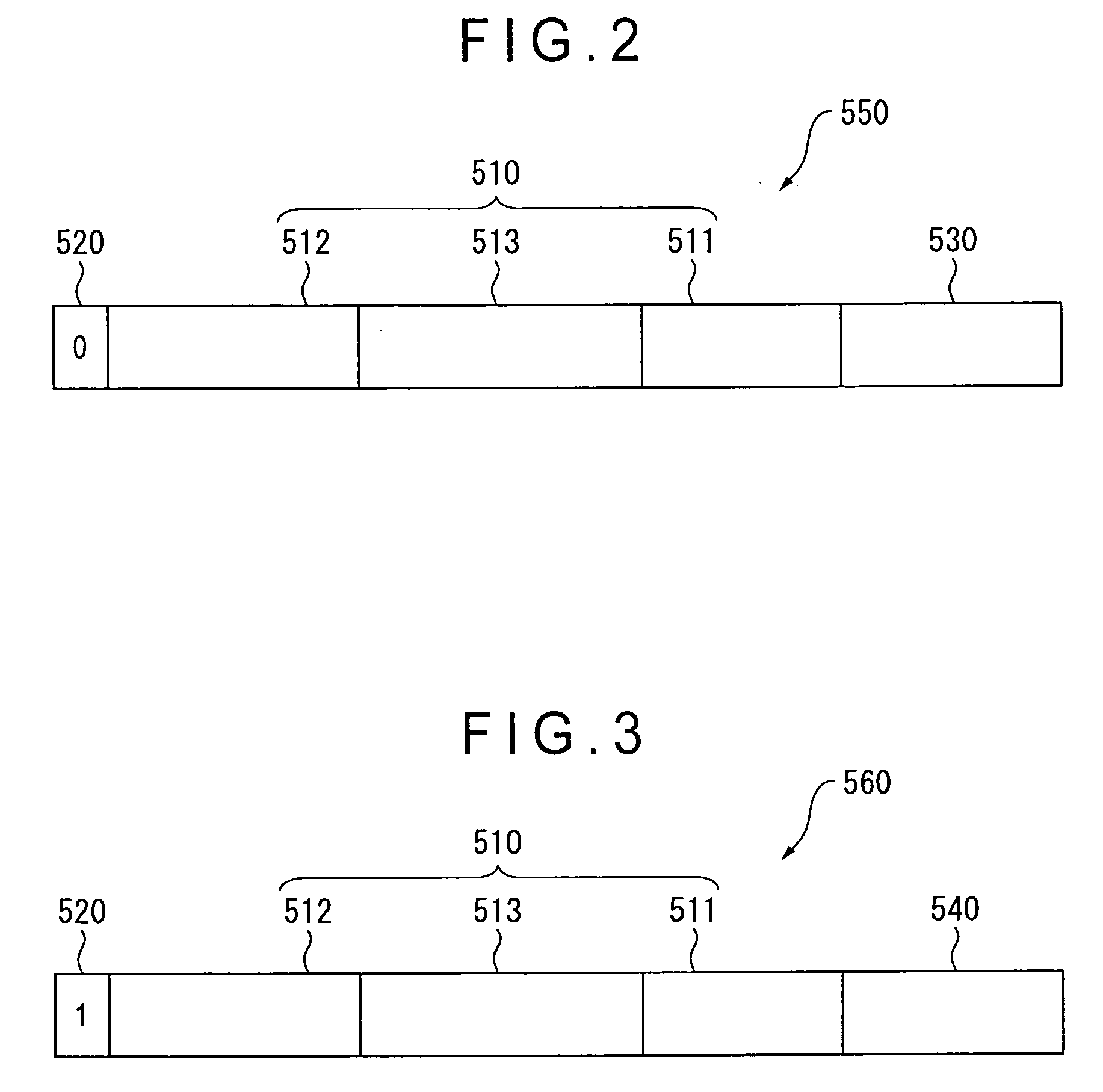

Information processing device, its system, its method, its program, and recording medium storing the program

InactiveUS20050050424A1Receive information efficientlyTransmit information efficientlyError prevention/detection by using return channelTransmission systemsTemporal informationClock time

In a server unit (300), a clock-time comparator (313) acquires the scheduled decoding clock-time information for decoding a video packet and RTT for transferring the video packet to a client unit (400) via a network and computes the time necessary for retransmitting the video packet on the basis of RTT. If the clock-time comparator (313) determines that it cannot meet the scheduled decoding clock-time information when the video packet is retransmitted, a processing unit (314) adds an error correction code to the video packet and transmits it. If, on the other hand, the clock-time comparator (313) determines that it can meet the scheduled decoding clock-time information, the processing unit (314) adds an error detection code to the video packet and transmits it. Thus, either way can be selected depending on the status of transmission and hence it is possible to reduce the load of transmitting video data in order to output video data on a stable basis and improve the processing efficiency.

Owner:PIONEER CORP

Image forming apparatus, method for controlling writing data from the same to storage device, method for controlling reading data from storage device to the same, and replacement part therefor

InactiveUS20050108559A1Detecting falsificationError preventionMultiple keys/algorithms usageComputer hardwareImage formation

Owner:FUJIFILM BUSINESS INNOVATION CORP

Packet communication method and packet communication device

InactiveUS20060280204A1Detection errorError prevention/detection by using return channelNetwork traffic/resource managementComputer hardwarePacket communication

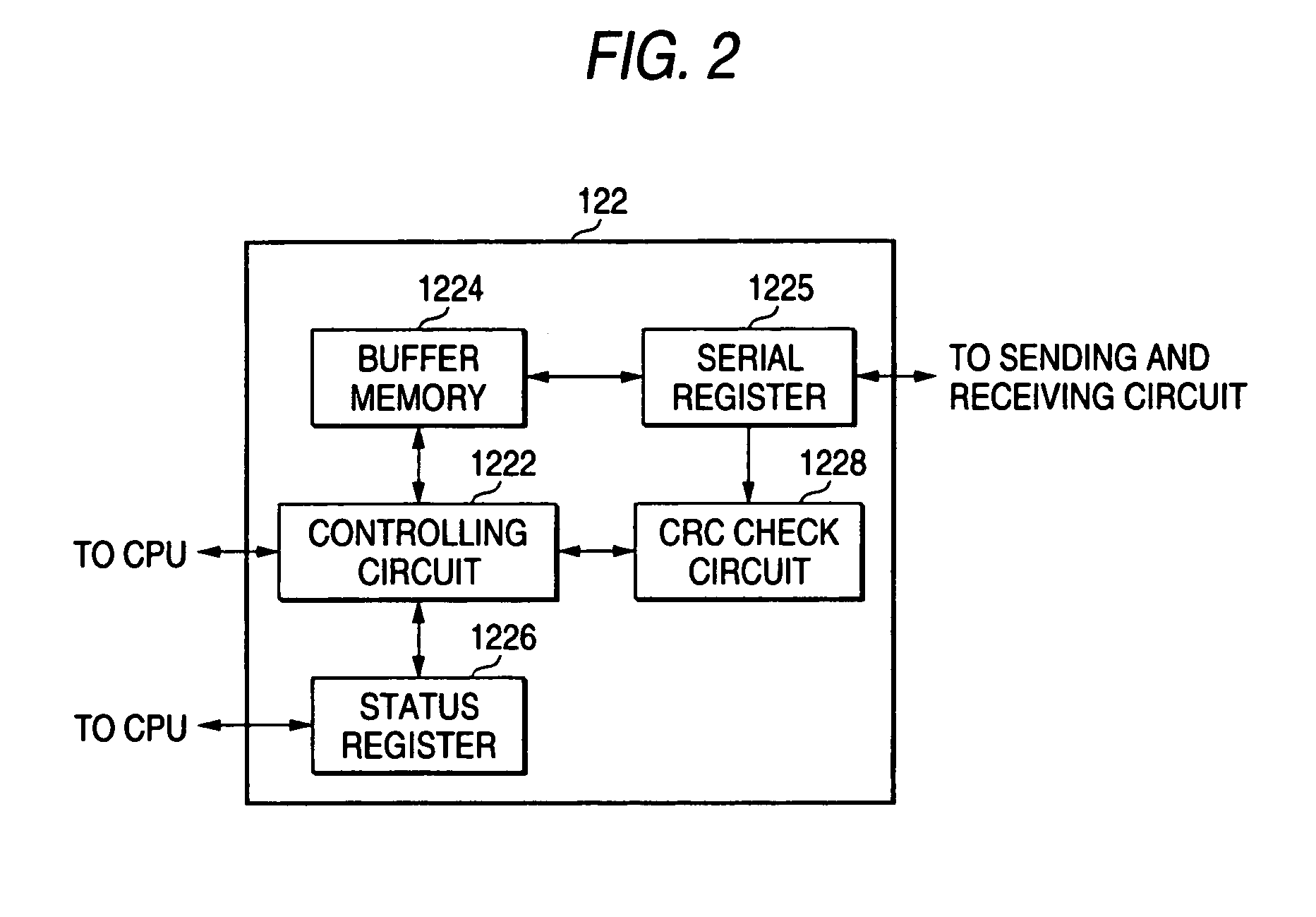

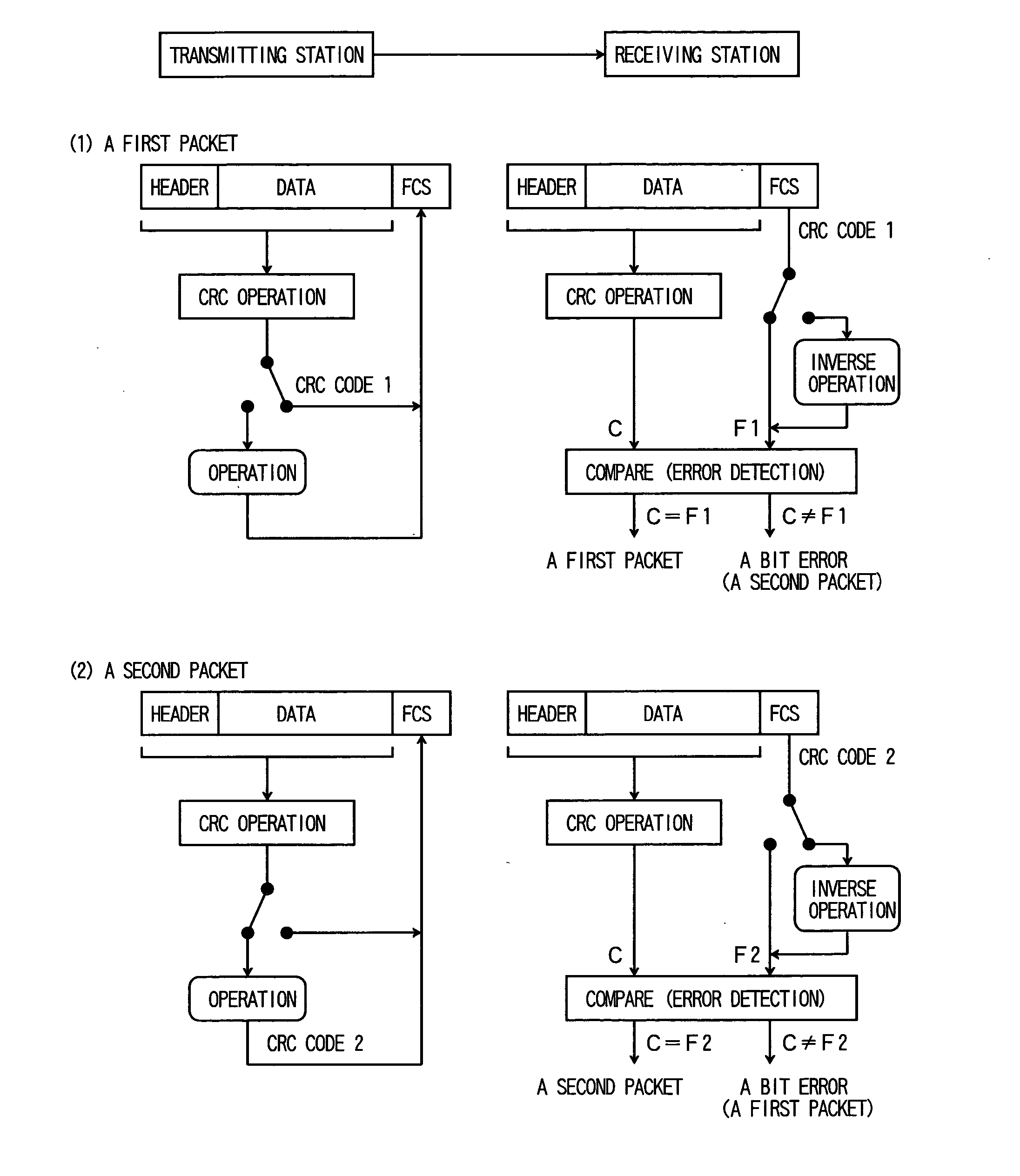

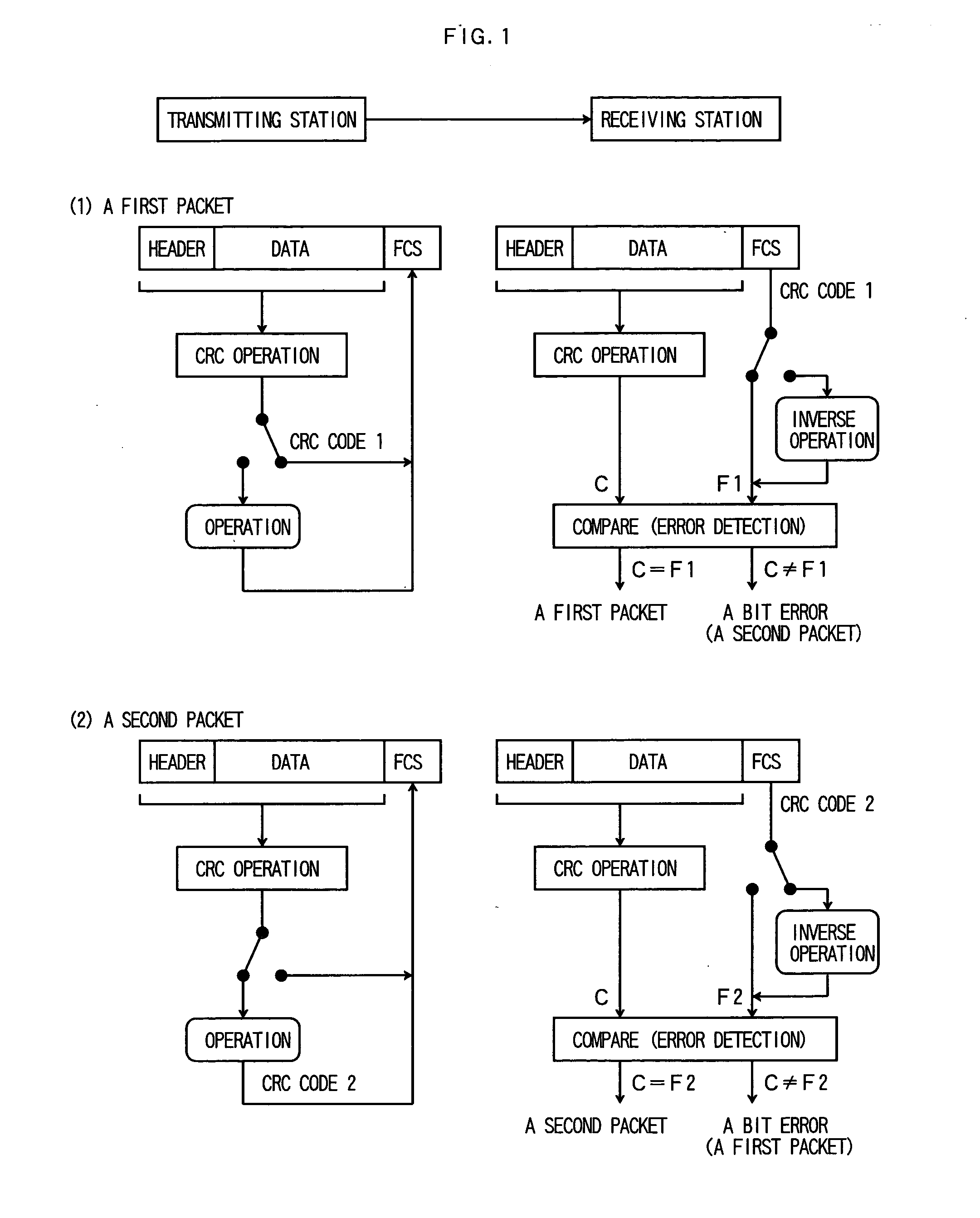

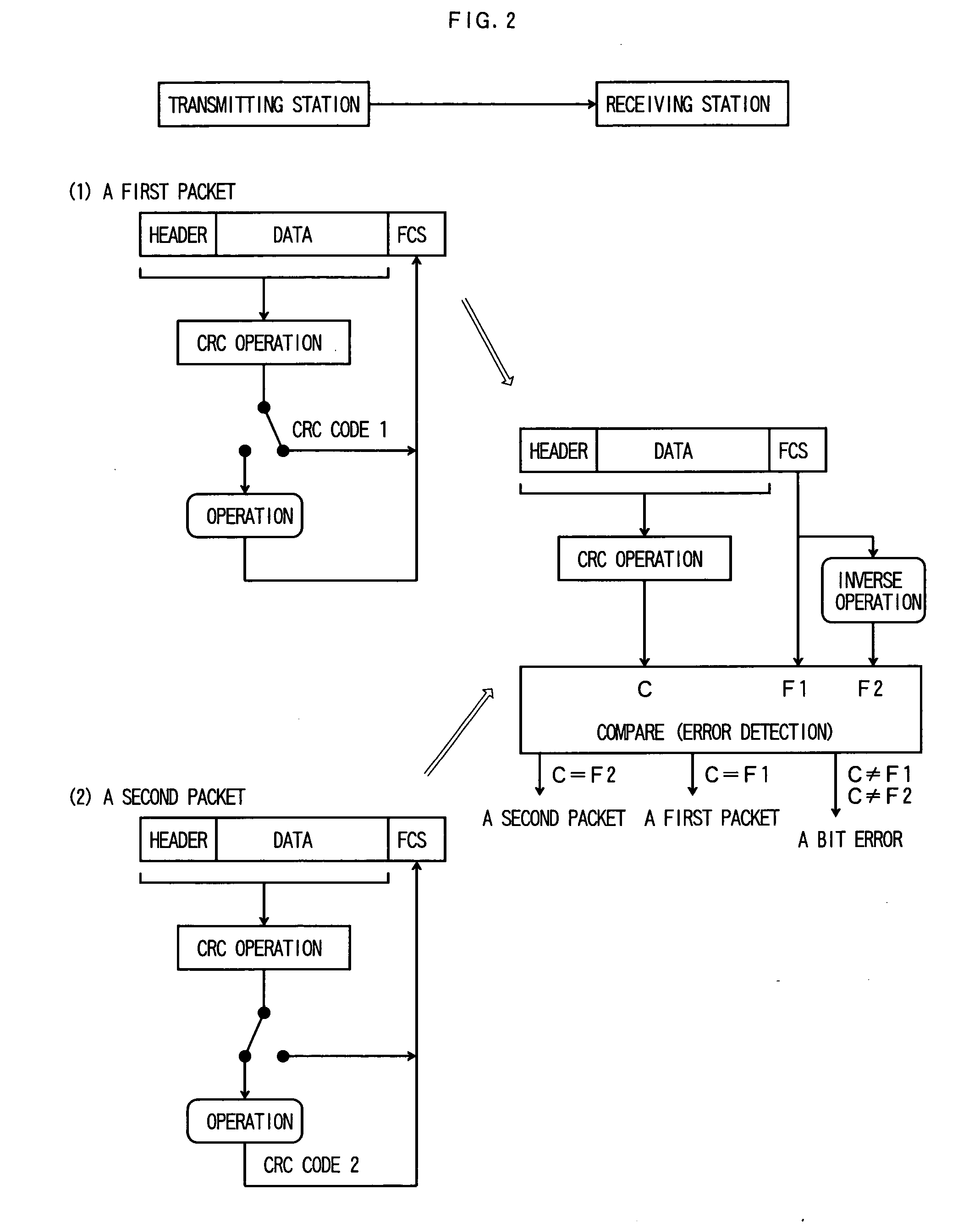

A first communication node, which transmits a packet including a data field and an FCS field, selectively transmits, to a second communication node, a first packet containing, in the FCS field, a first error detection code generated by performing a prescribed error detection code operation on a transmission packet or a second packet containing, in the FCS field, a second error detection code obtained by performing a prescribed operation on the first error detection code. The second communication node compares an error detection code C generated by performing the prescribed error detection code operation on a received packet with an error detection code F1 contained in the FCS field of the received packet, performs reception processing on the received packet with the understanding that it is classified as the first packet if the error detection codes C and F1 coincide with each other, compares the error detection code C generated by performing the prescribed error detection code operation on the received packet with an error detection code F2 obtained by performing an inverse operation for returning a result of the prescribed operation to an original on the error detection code F1 contained in the FCS field of the received packet, and performs reception processing on the received packet with the understanding that it is classified as the second packet if the error detection codes C and F2 coincide with each other.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

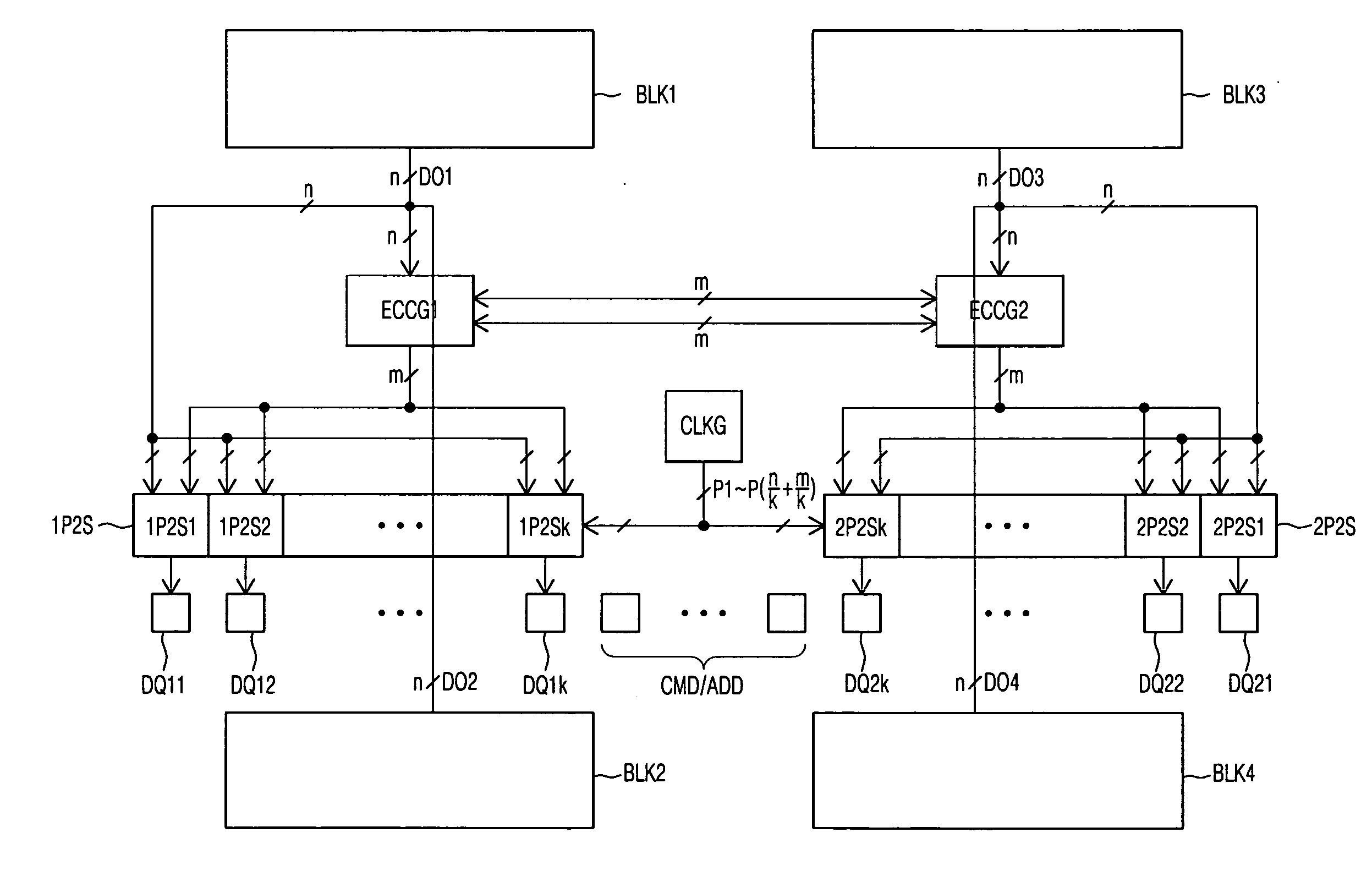

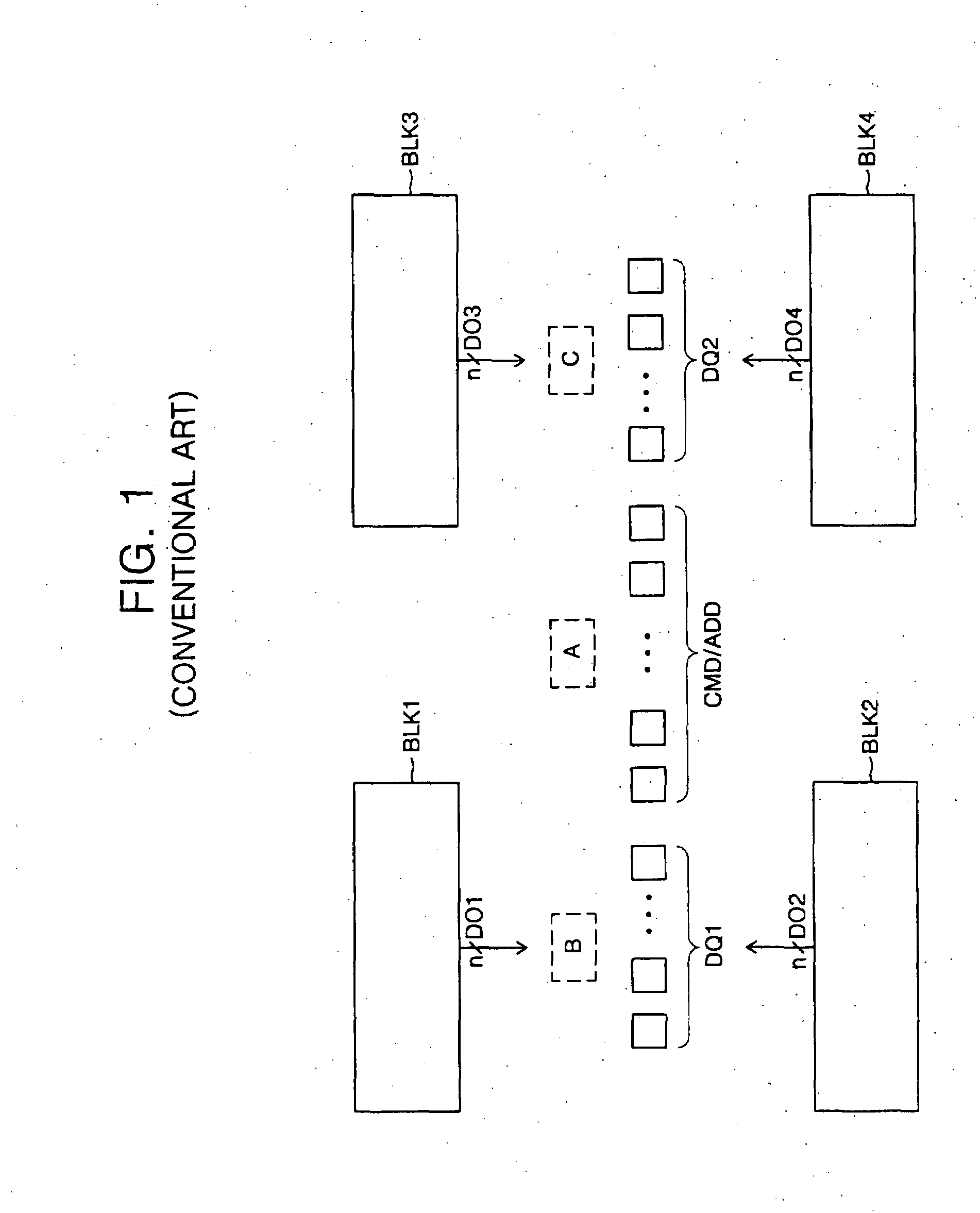

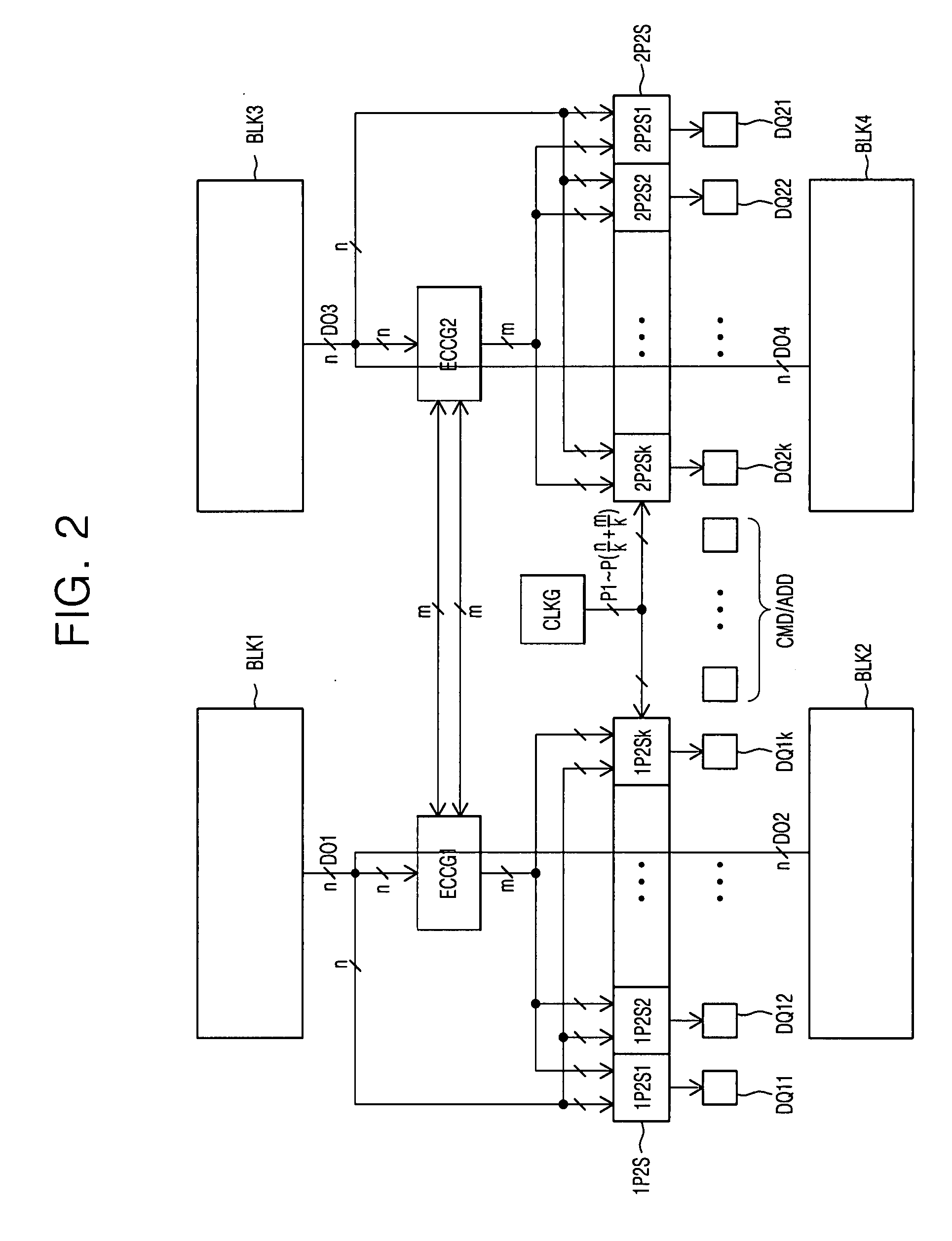

Semiconductor memory device and memory system including the same

ActiveUS20070204199A1Increase layout areaCode conversionMaterial strength using tensile/compressive forcesError detection codingSemiconductor

A semiconductor memory device and a memory system including the same are provided. The semiconductor memory device may include a first memory cell array block generating first data, a second memory cell array block generating second data, and first and second error detection code generators. The first error detection code generator may generate a first error detection code and may combine a portion of bits of the first error detection code with a portion of bits of a second error detection code to generate a first final error detection signal. The second error detection code generator may generate the second error detection code and may combine the remaining bits other than the portion of bits of the second error detection code with the remaining bits other than the portion of bits of the first error detection code to generate a second final error detection signal.

Owner:SAMSUNG ELECTRONICS CO LTD

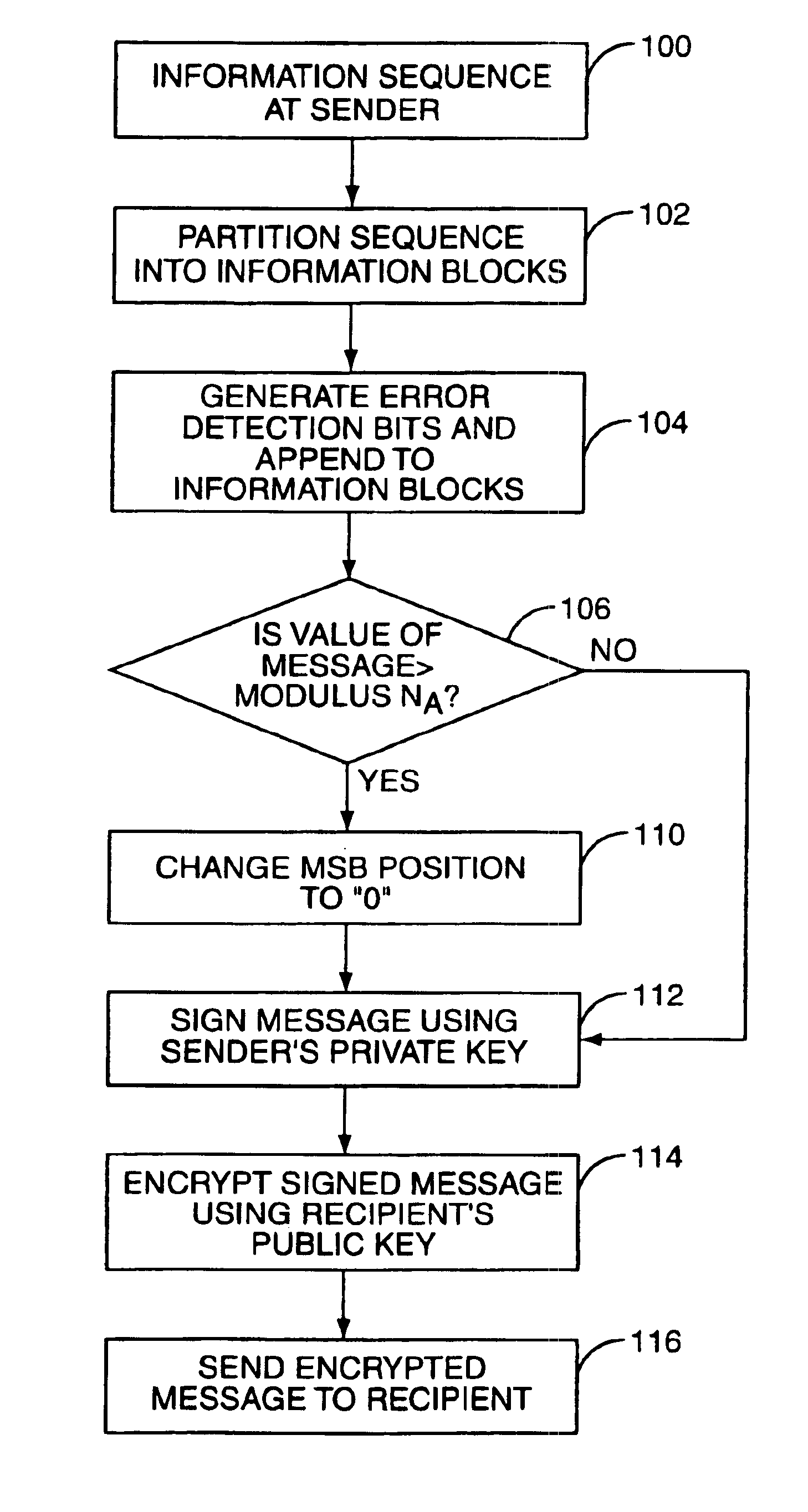

Cryptographic method and system for double encryption of messages

InactiveUS6904150B1Reduce the valuePublic key for secure communicationCode conversionComputer hardwareError detection coding

A method and system for encrypting and decrypting a message. A message is created by appending an error detection code to an information block. The binary value of the resulting message is then compared to the sender's encryption modulus. If the binary value of the message is greater than or equal to the sender's encryption modulus, at least one bit of the error detection code is altered to reduce the binary value of the message below the sender's encryption modulus. The potentially modified message is then encrypted once using the sender's private key to generate a once encrypted message referred to herein as the signed message. The signed message is then encrypted using the recipient's public key to produce a doubly encrypted bitstring. The recipient deciphers and decodes the doubly encrypted bitstring. If an decoding failure occurs, the recipient assumes that the error is due to an intentional bit change by the sender and attempts to restore the presumably altered bit or bits to their presumed original value.

Owner:ERICSSON INC