Patents

Literature

667 results about "Single cycle" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

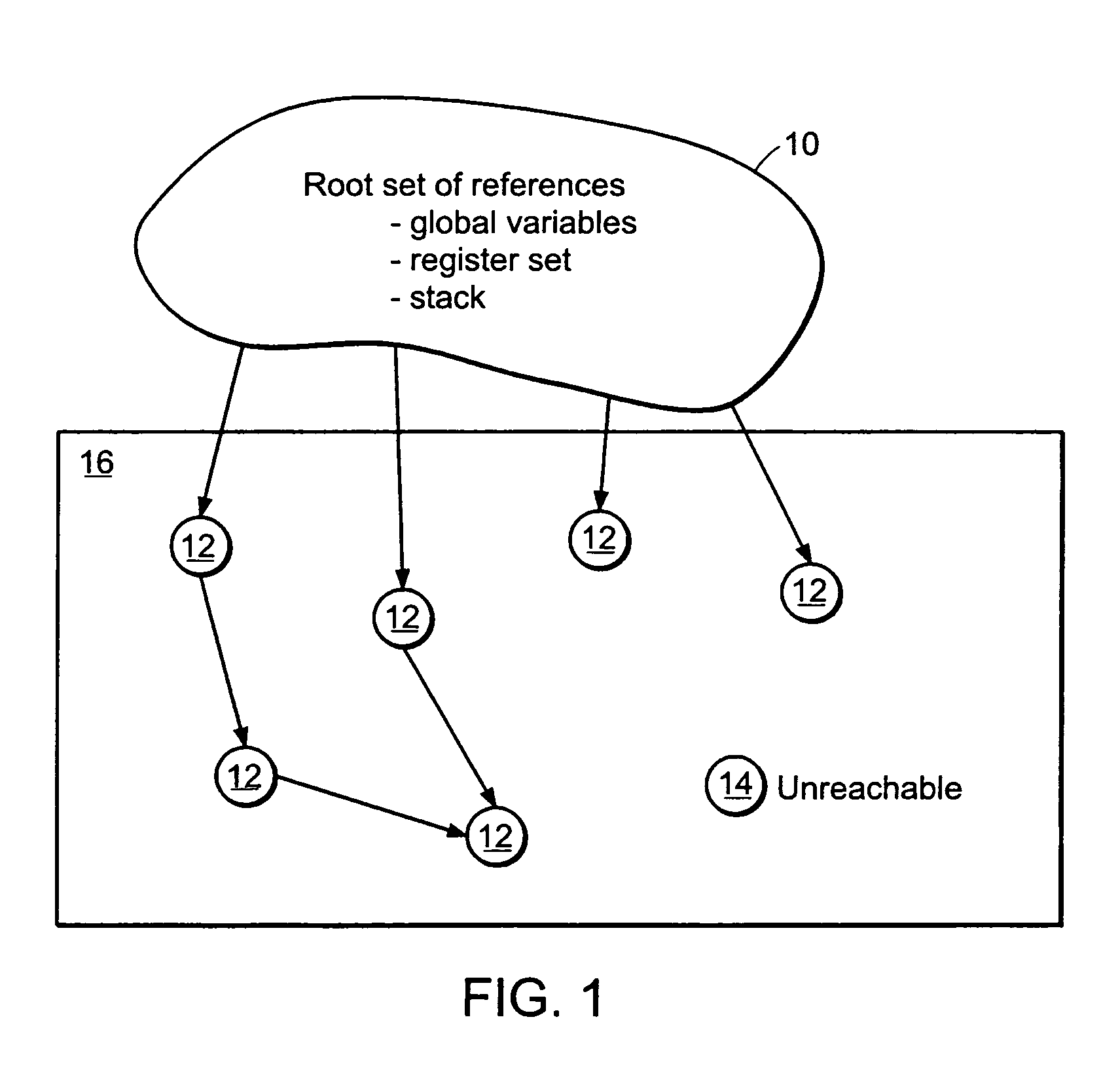

A single cycle processor is a processor that carries out one instruction in a single Clock cycle. MIPS architecture, MIPS-32 architecture. DLX, a very similar architecture designed by John L. Hennessy (creator of MIPS) for teaching purposes.

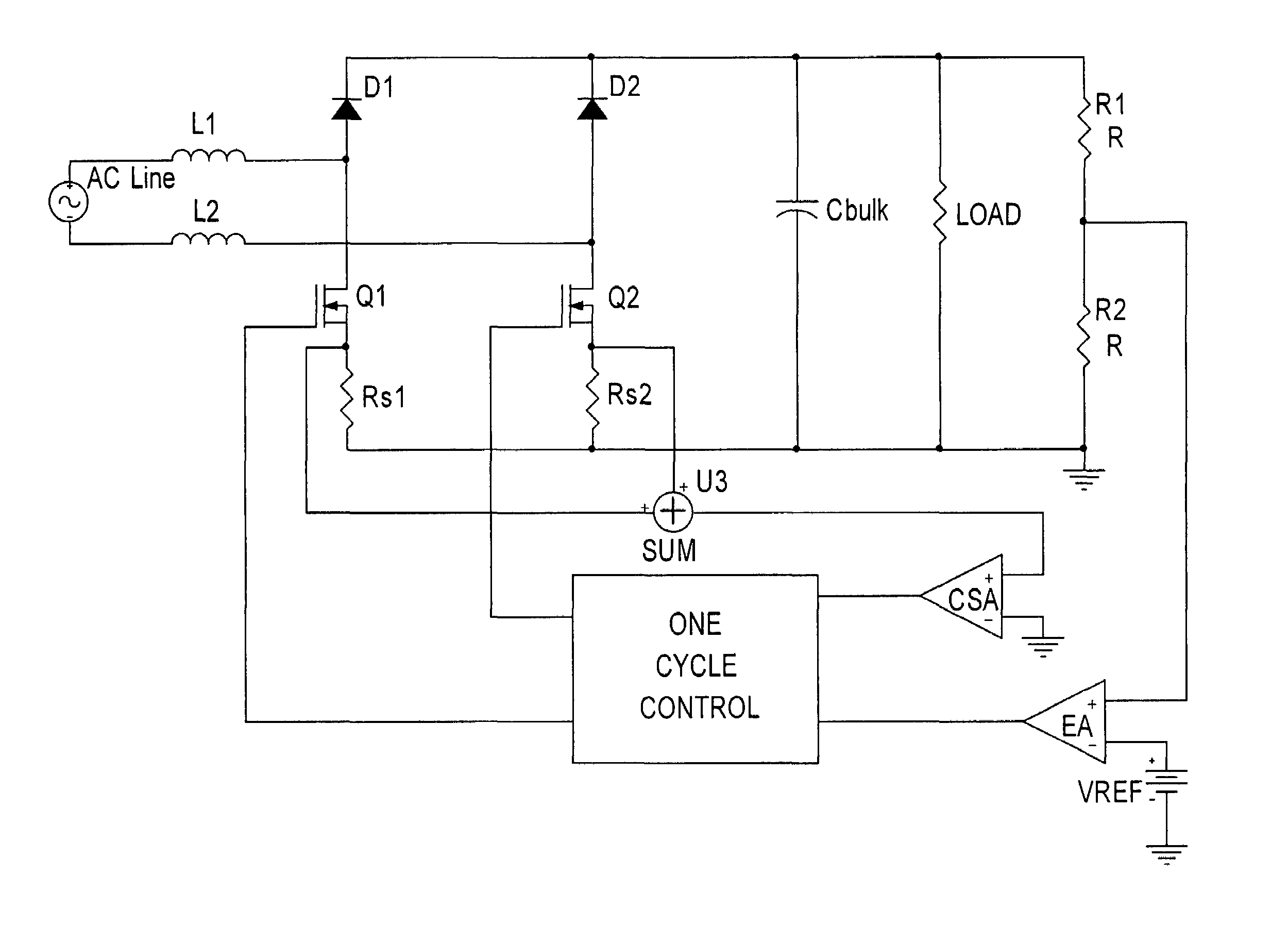

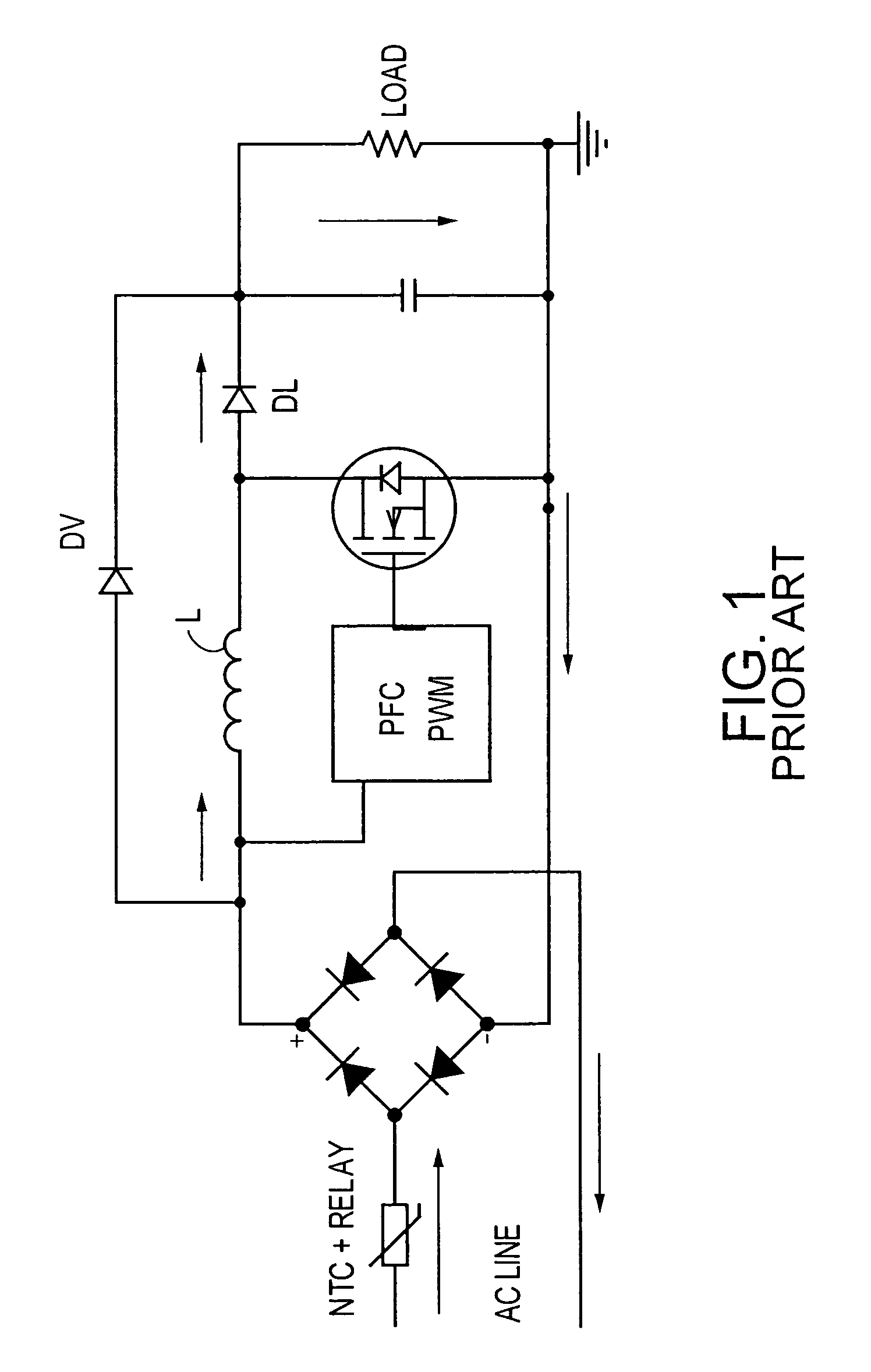

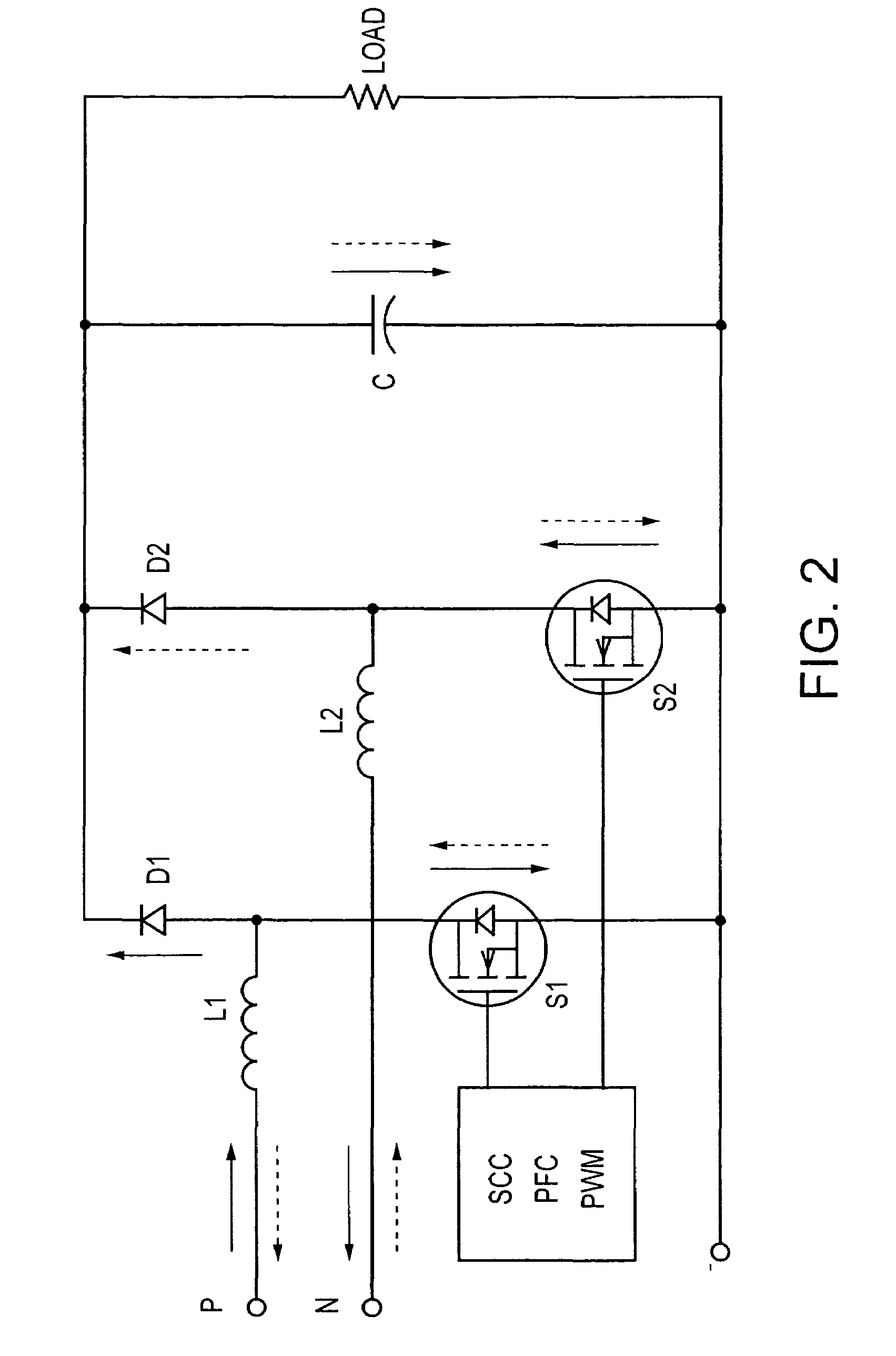

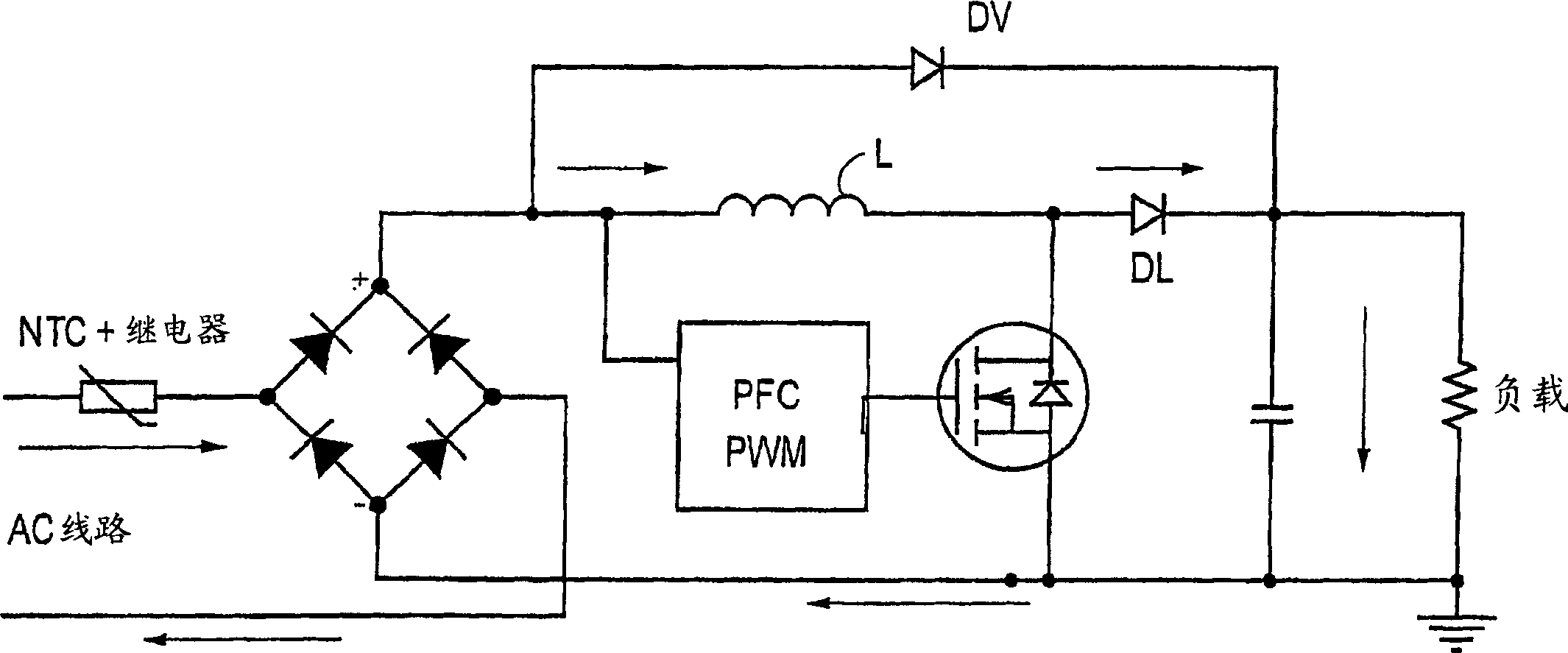

Bridge-less boost (BLB) power factor correction topology controlled with one cycle control

InactiveUS7164591B2Ac-dc conversion without reversalEfficient power electronics conversionCycle controlEngineering

The bridgeless boost topology reduces the power dissipation, cost, and size of prior PFC systems by eliminating the intrinsic loss of the input rectifier bridge. Sensing of the input line voltage by the controller is unnecessary. The use of One Cycle Control (also known as Single Cycle Control) allows the Power Factor Correction function to be performed without complex rectification networks to obtain the AC line voltage reference. The use of bi-directional switches makes it possible to control inrush current (the startup over-current due to the charging of the output bulk capacitor), which allows elimination of over-current limiting devices and reduction of the diode surge capability requirements. Moving the boost inductor to the system input adds an additional filtering function, reducing the cost of input EMI filtering.

Owner:INTERNATIONAL RECTIFIER COEP

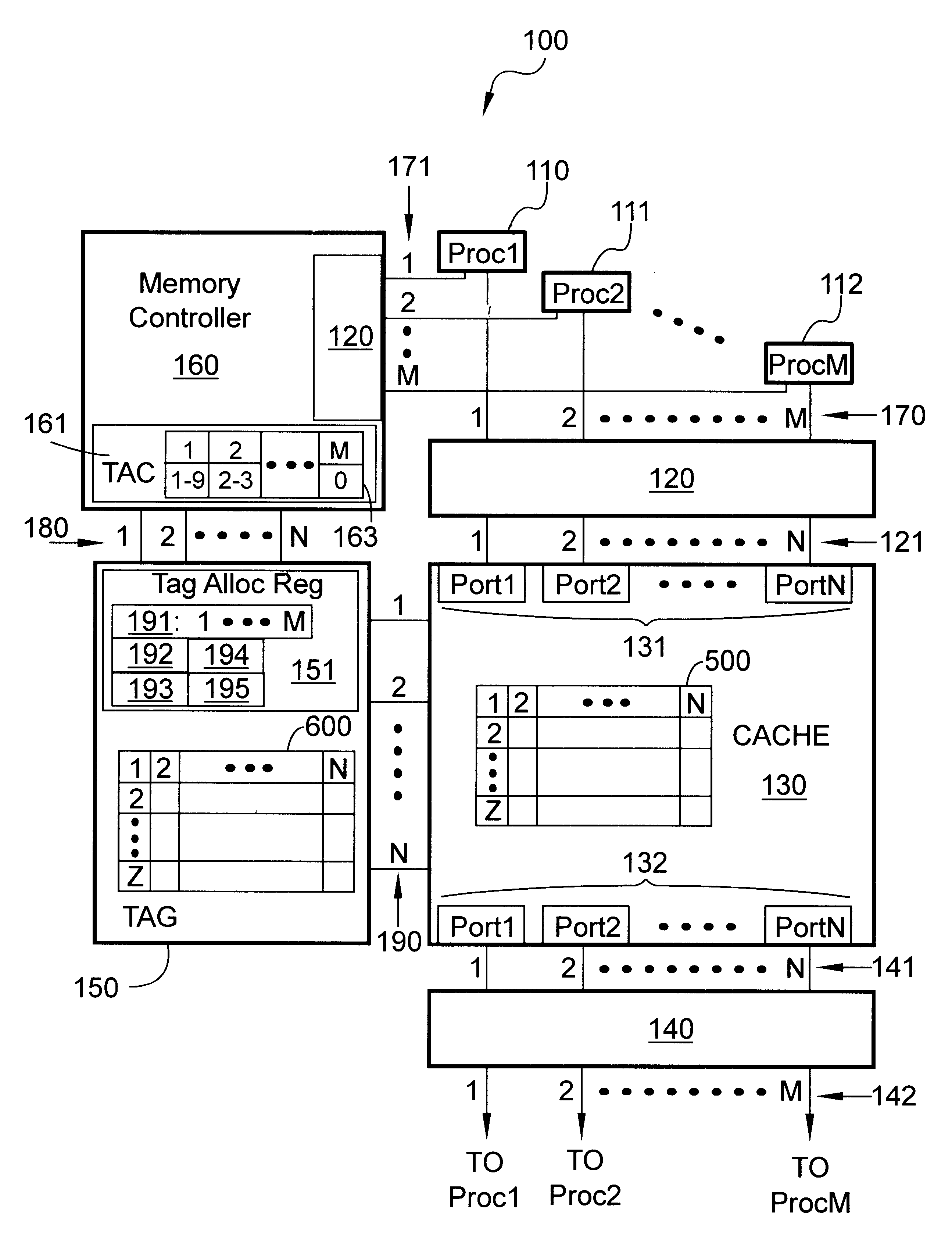

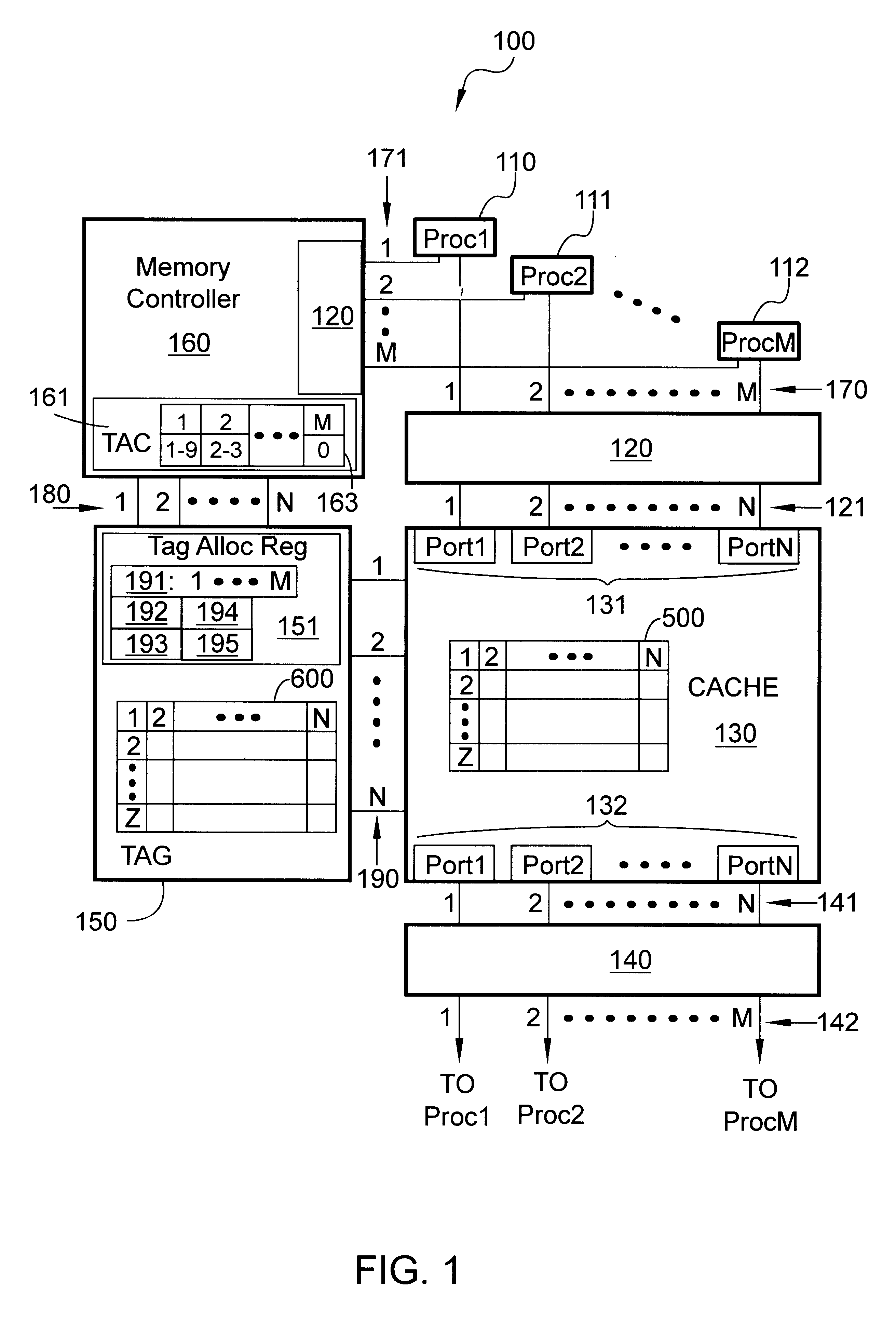

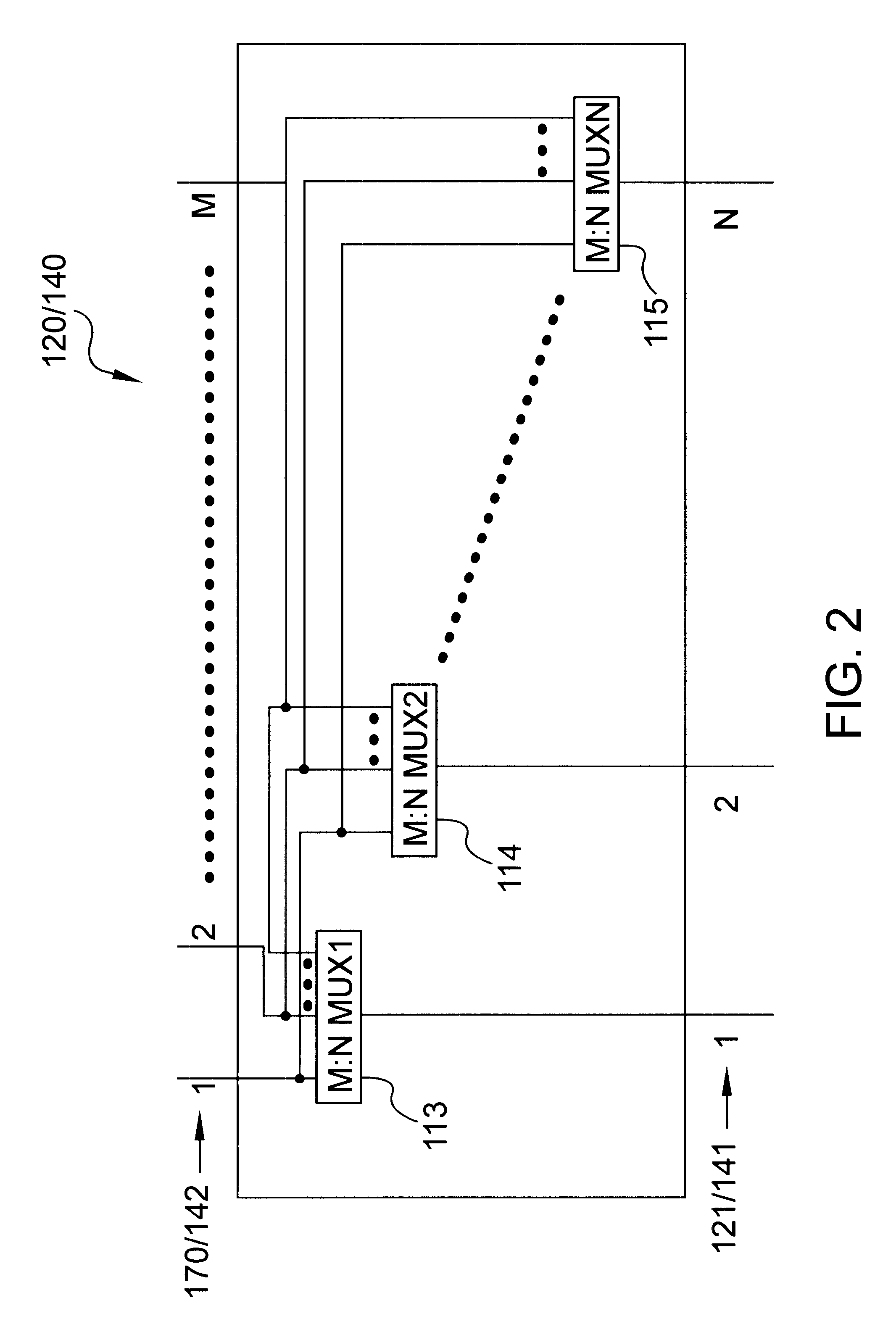

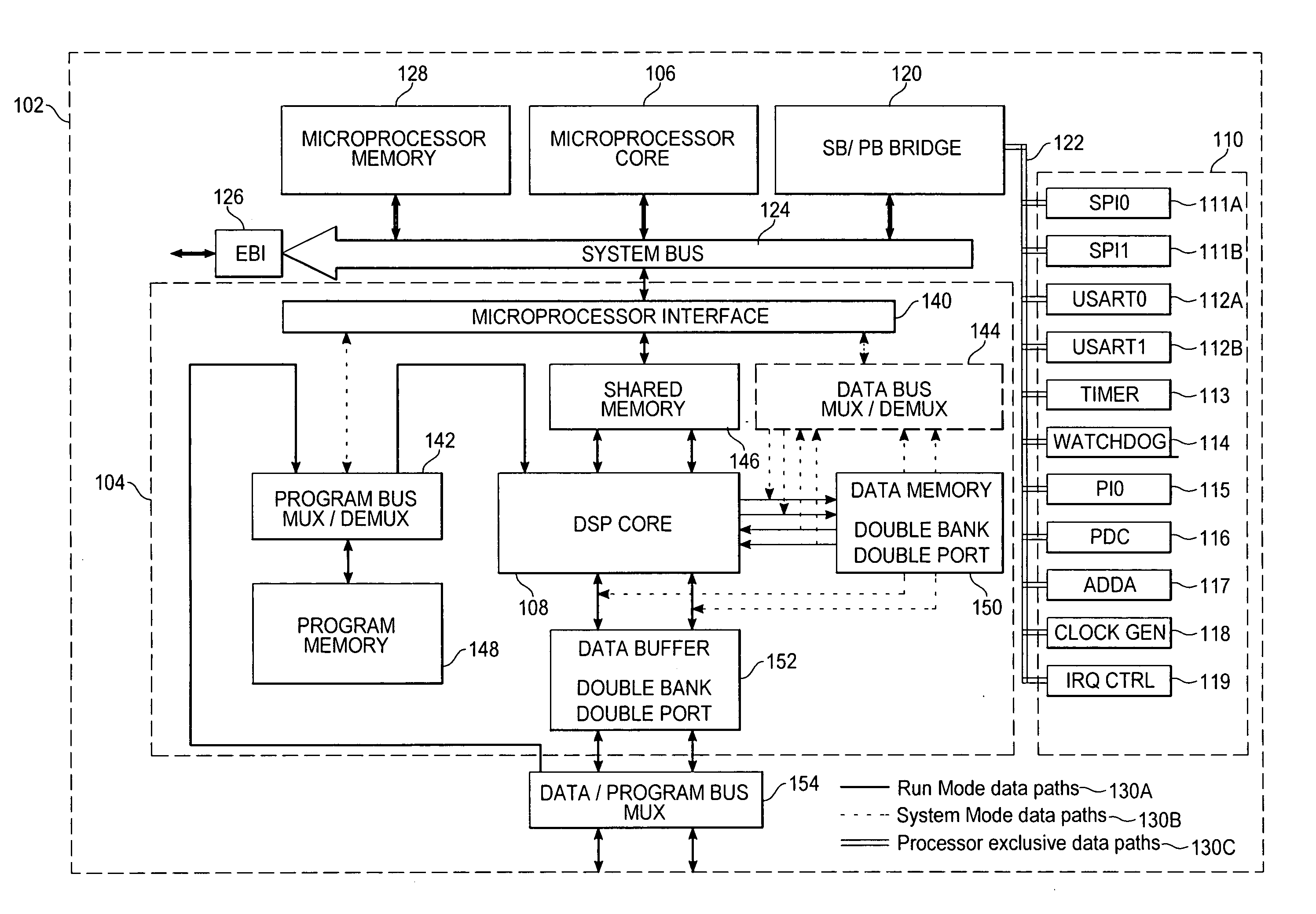

Performance based system and method for dynamic allocation of a unified multiport cache

InactiveUS6604174B1Memory architecture accessing/allocationMemory adressing/allocation/relocationCache accessParallel computing

The present invention provides a performance based system and method for dynamic allocation of a unified multiport cache. A multiport cache system is disclosed that allows multiple single-cycle look ups through a multiport tag and multiple single-cycle cache accesses from a multiport cache. Therefore, multiple processes, which could be processors, tasks, or threads can access the cache during any cycle. Moreover, the ways of the cache can be allocated to the different processes and then dynamically reallocated based on performance. Most preferably, a relational cache miss percentage is used to reallocate the ways, but other metrics may also be used.

Owner:GOOGLE LLC

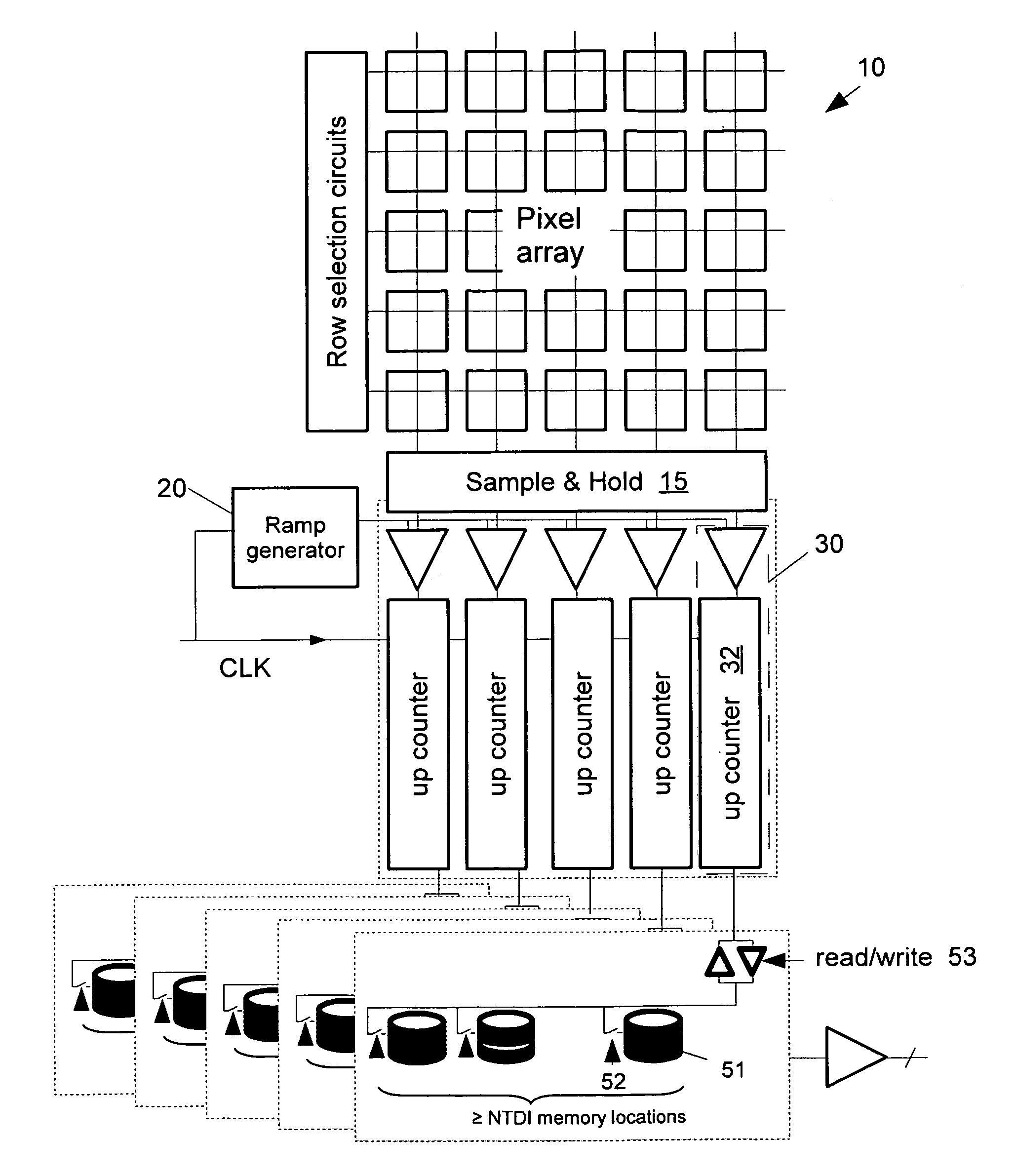

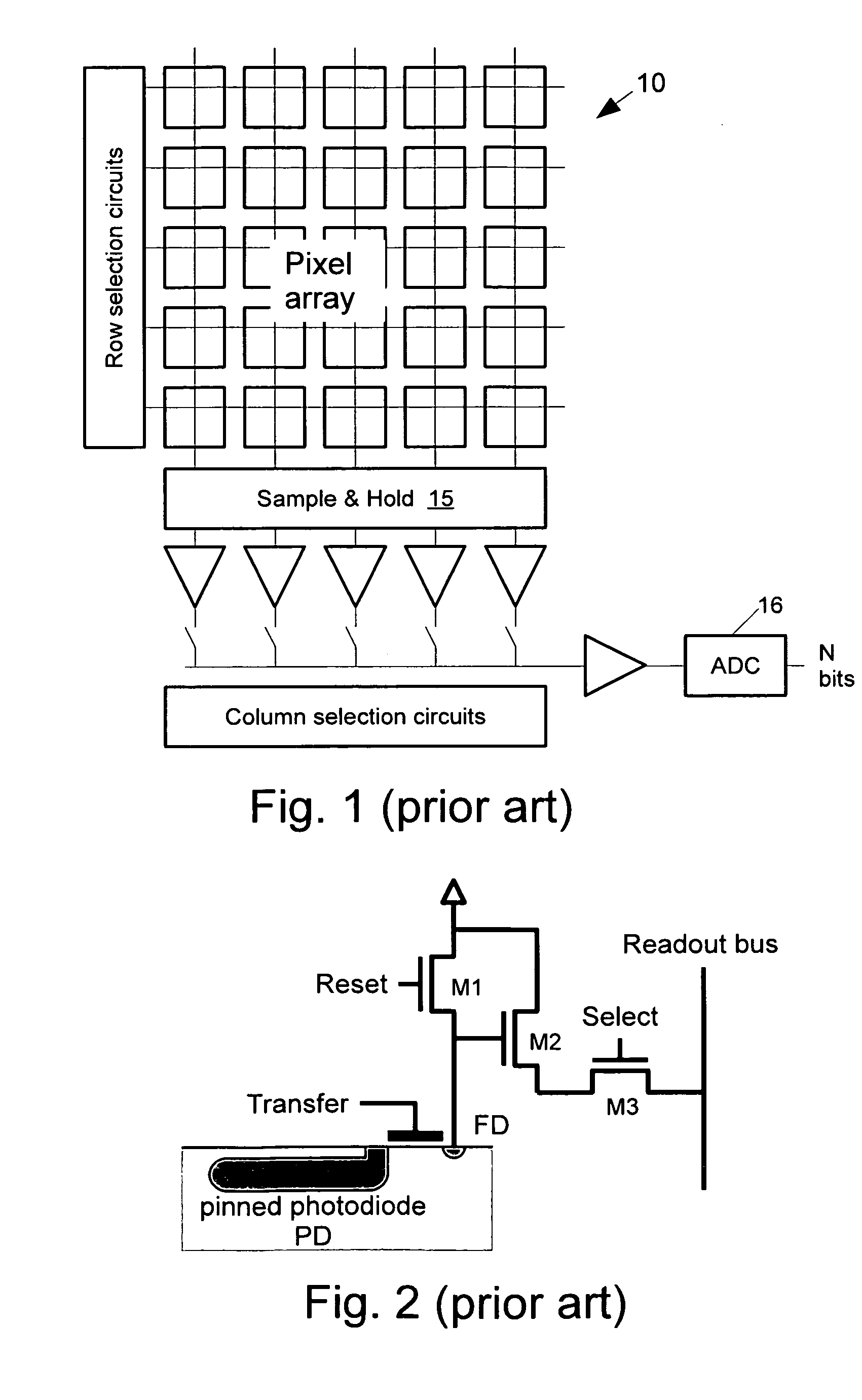

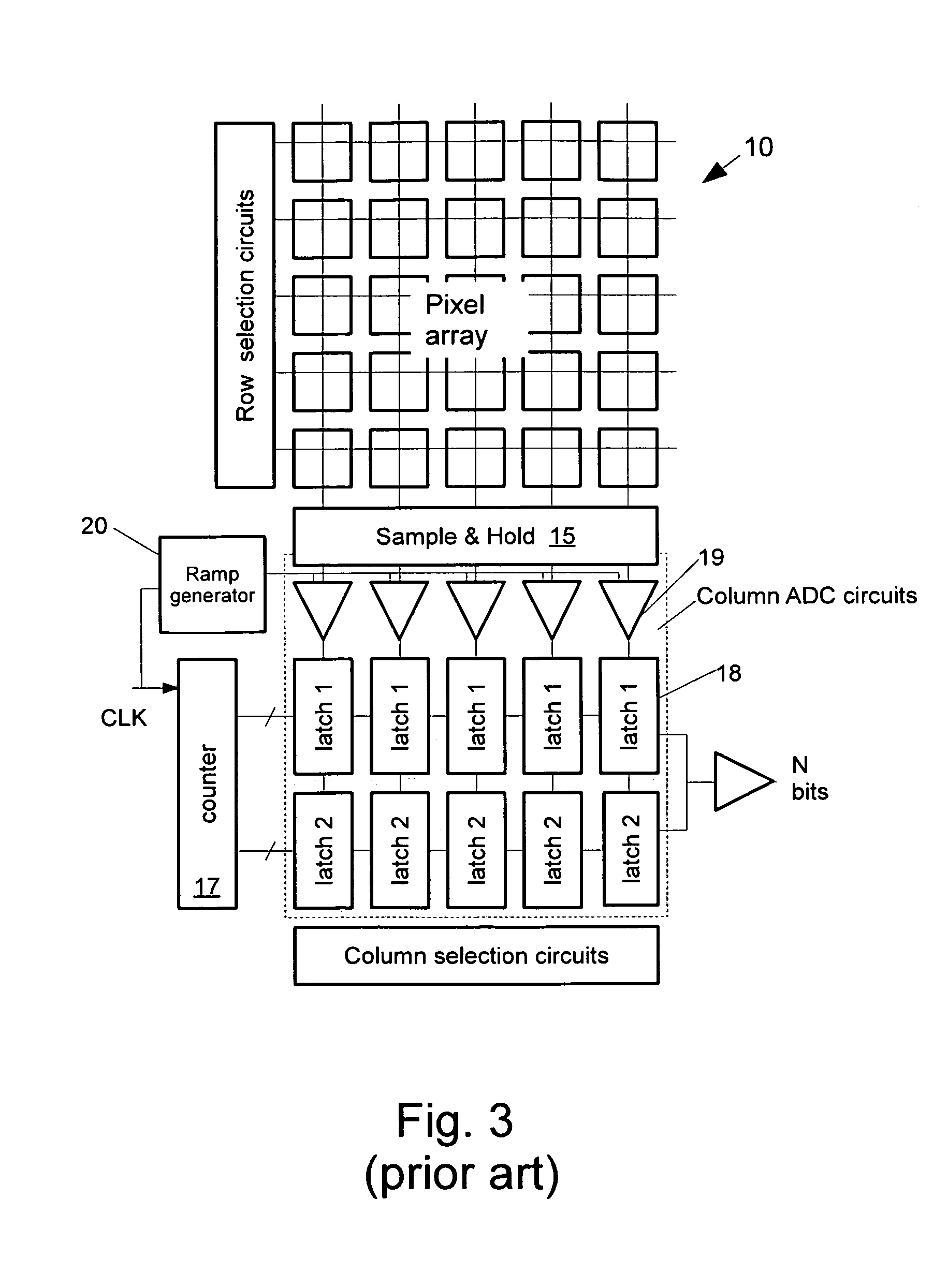

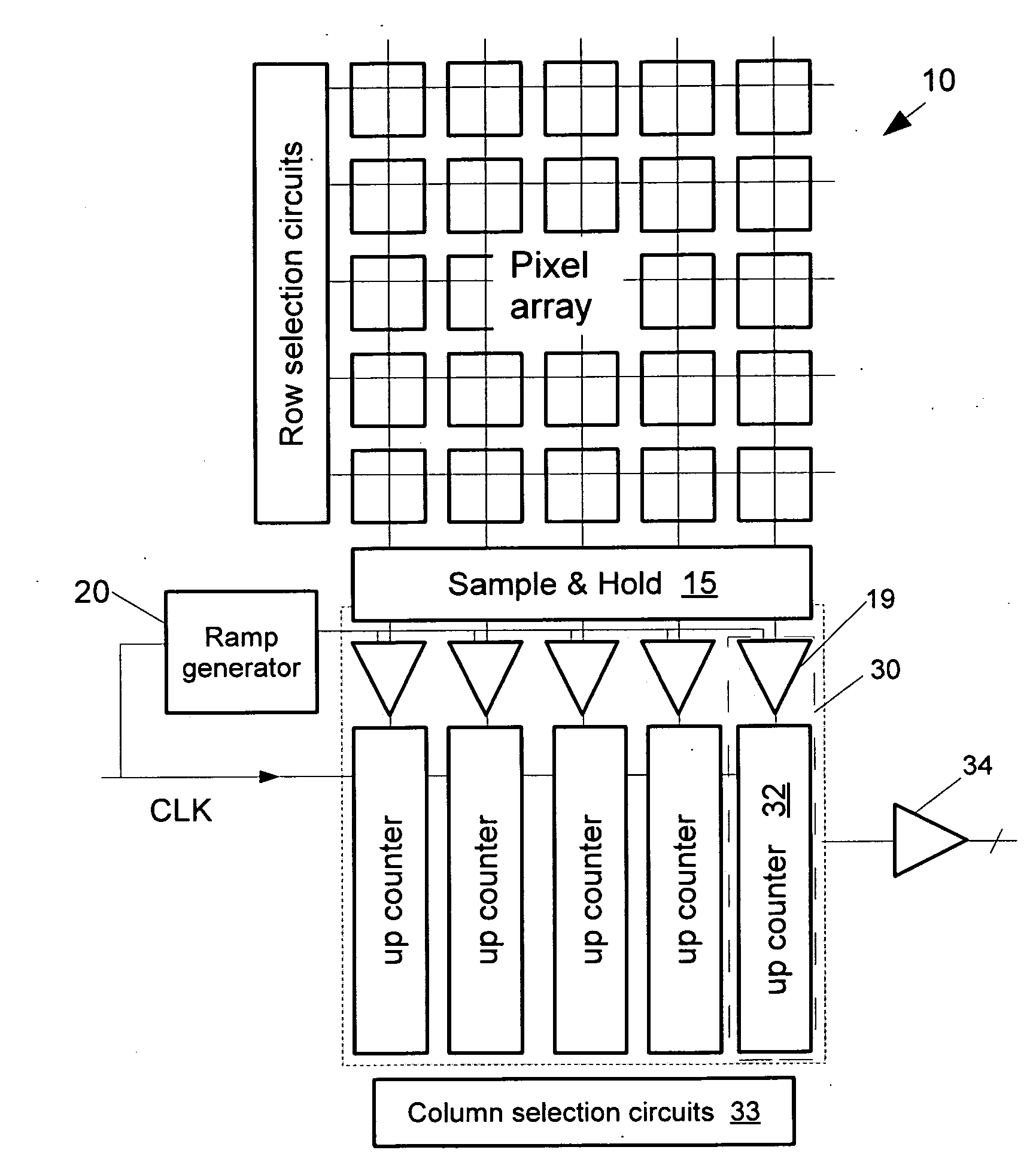

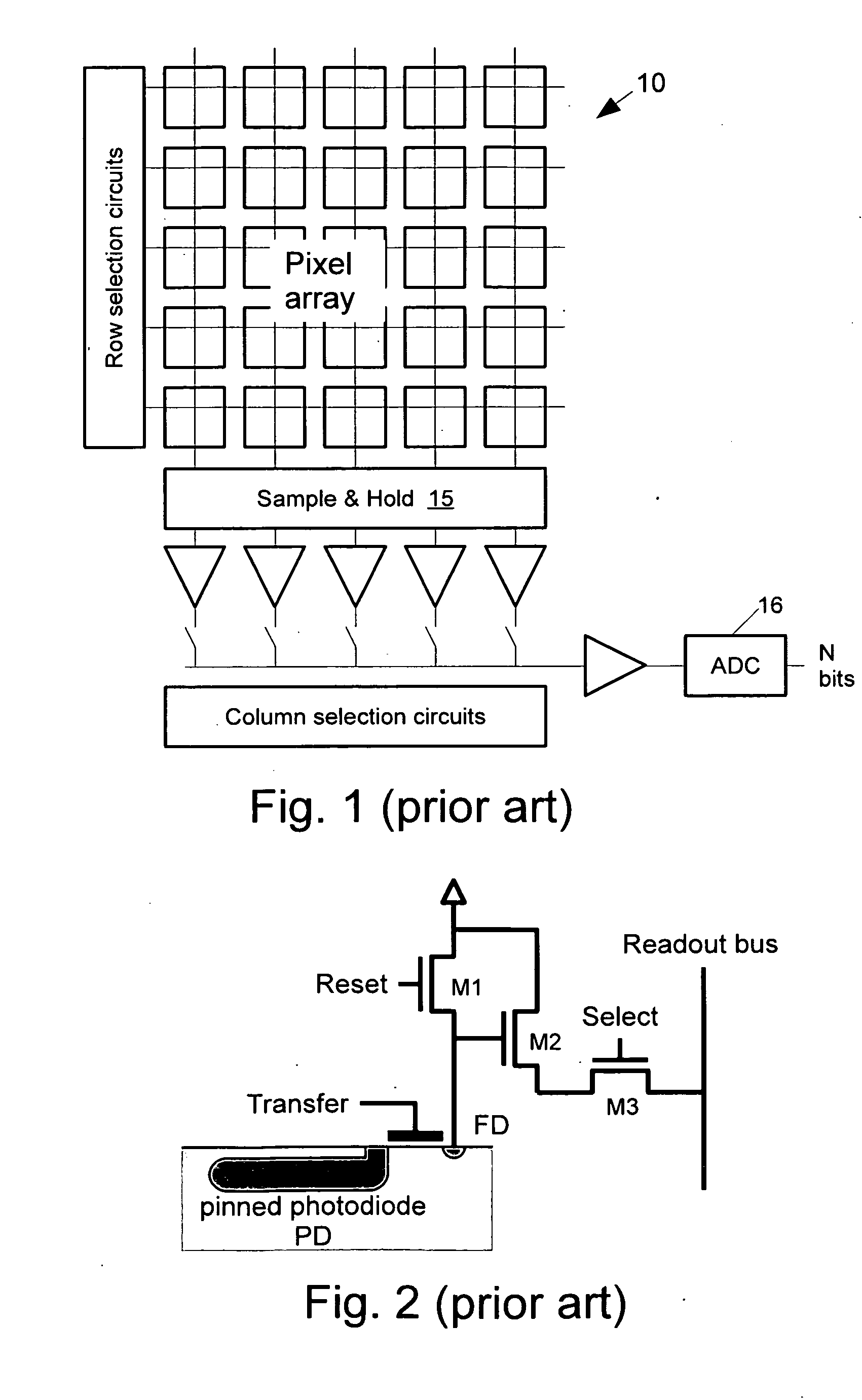

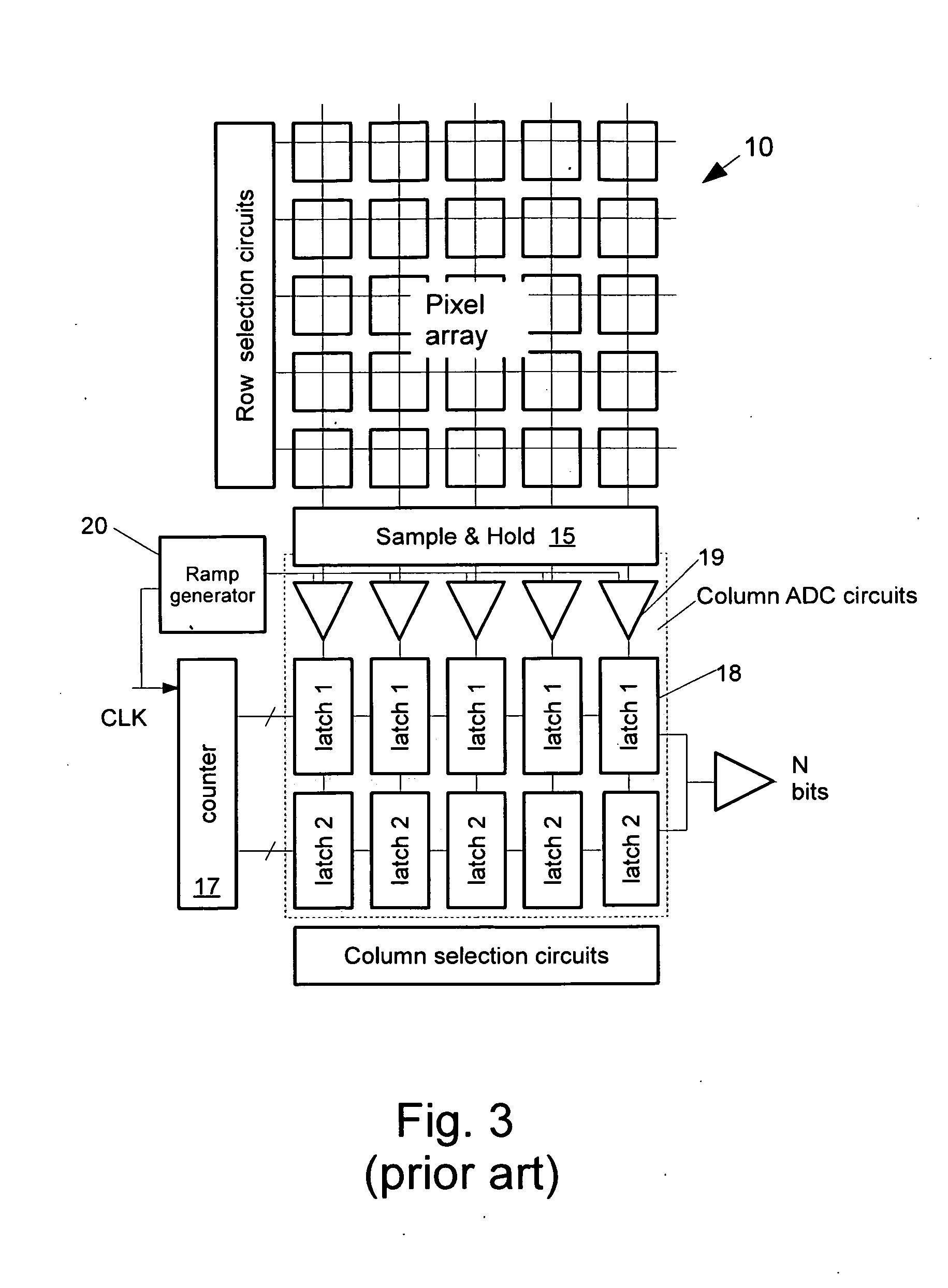

Analog-to-digital conversion in pixel arrays

ActiveUS7880662B2Improve accuracyAvoid the needAnalogue/digital conversionTelevision system detailsExposure periodAnalog signal

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

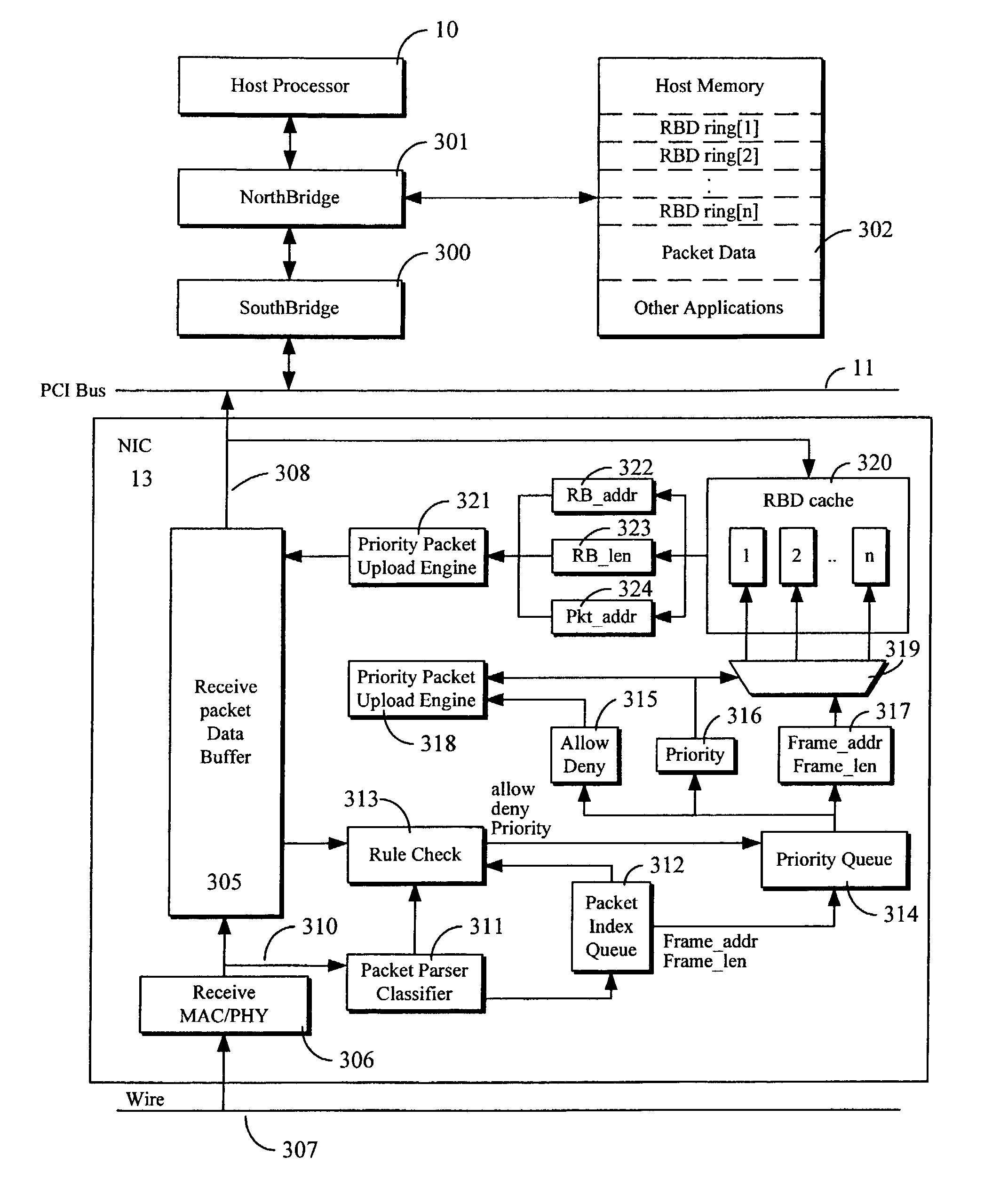

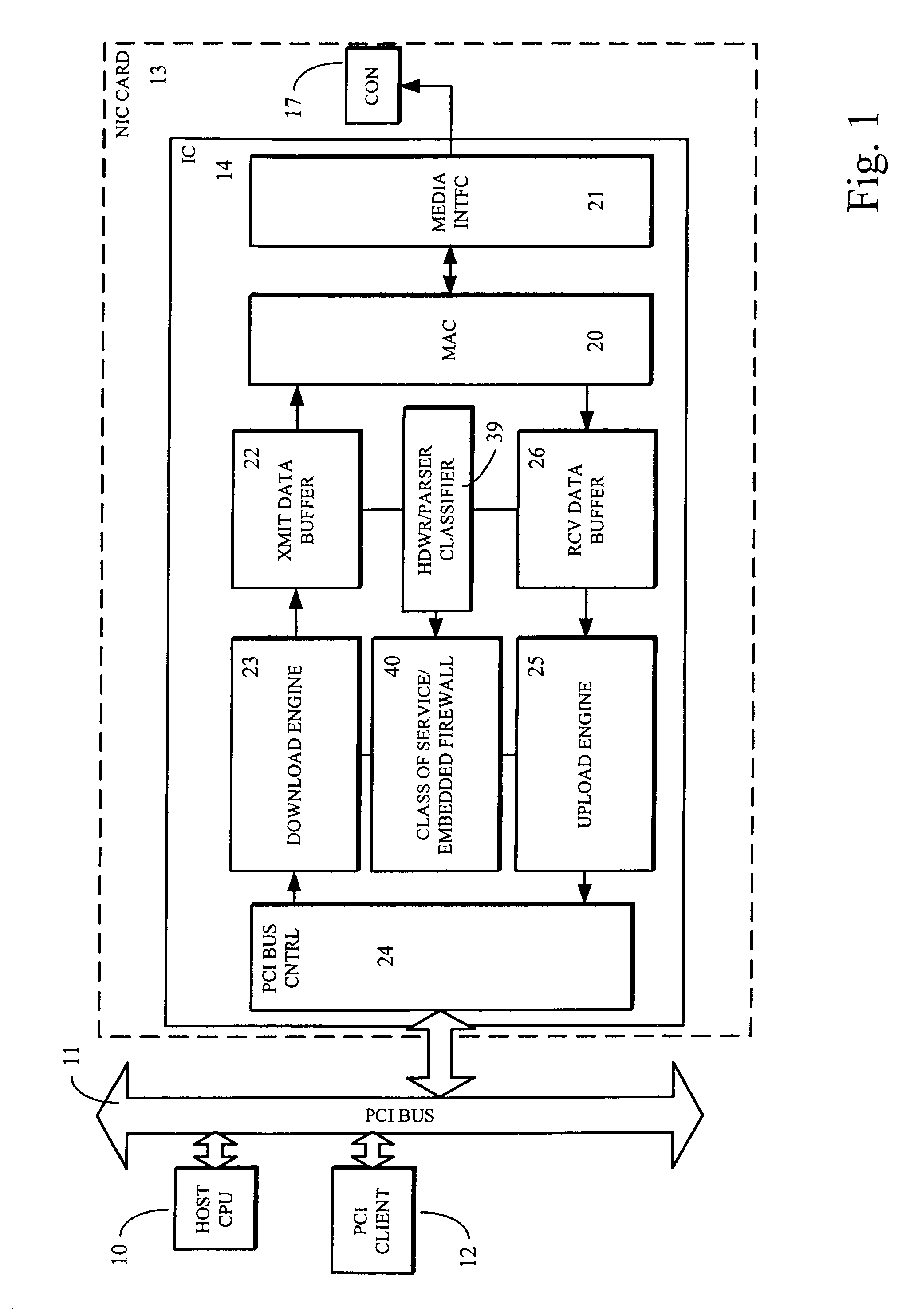

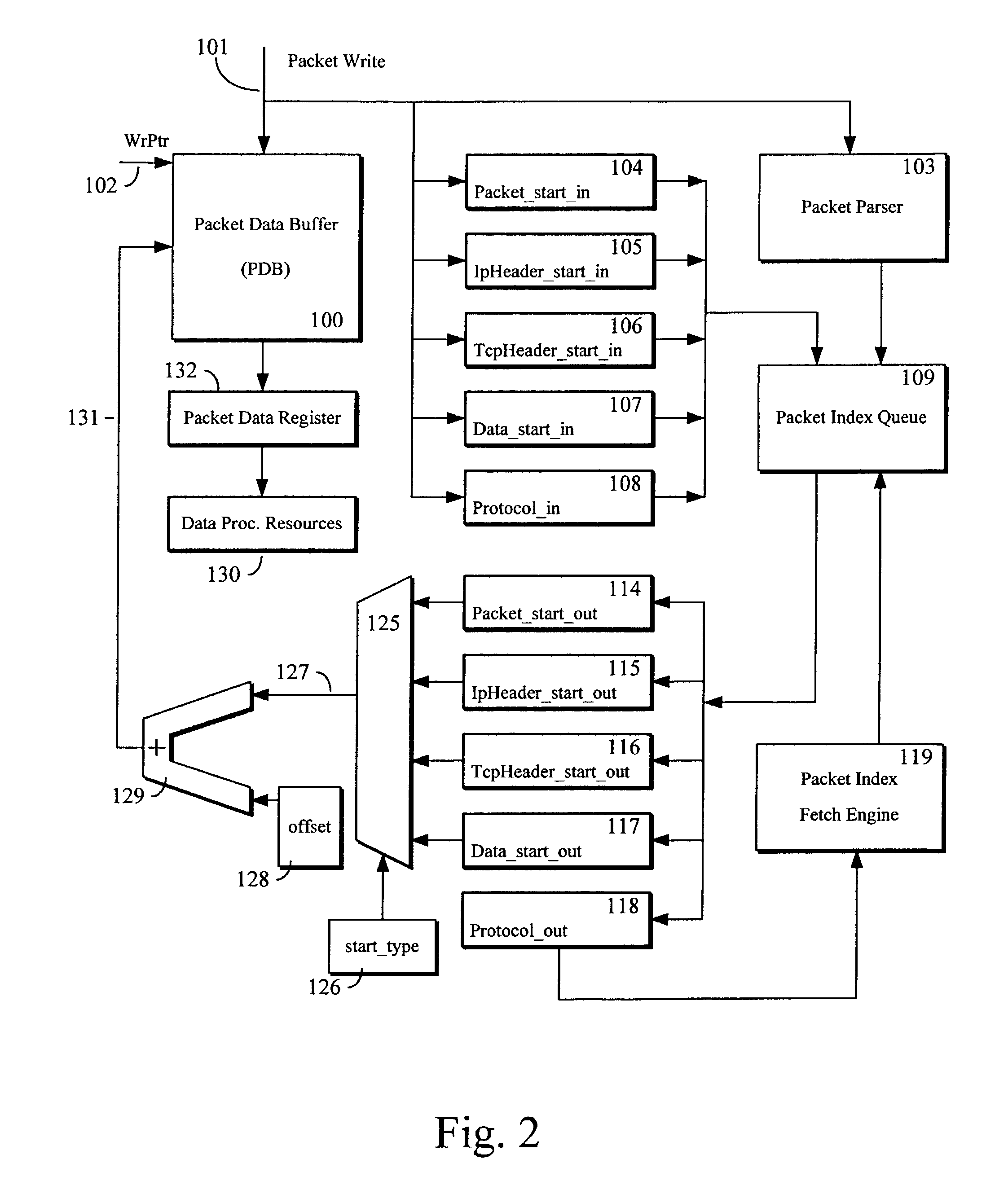

Computer system and network interface supporting class of service queues

ActiveUS7724740B1Increase data rateIncrease speedDigital computer detailsTime-division multiplexClass of serviceData field

A data processing system adapted for high-speed network communications, a method for managing a network interface and a network interface for such system, are provided, in which processing of packets received over the network is achieved by embedded logic at the network interface level. Incoming packets on the network interface are parsed and classified as they are stored in a buffer memory. Functional logic coupled to the buffer memory on the network interface is enabled to access any data field within a packet in a single cycle, using pointers and packet classification information produced by the parsing and classifying step. Results of operations on the data fields in the packets are available before the packets are transferred out of the buffer memory. A data processing system, a method for management of a network interface and a network interface are also provided by the present invention that include an embedded firewall at the network interface level of the system, which protects against inside and outside attacks on the security of data processing system. Furthermore, a data processing system, a method for management of a network interface and a network interface are a provided by the present invention that support class of service management for packets incoming from the network, by applying priority rules at the network interface level of the system.

Owner:VALTRUS INNOVATIONS LTD +1

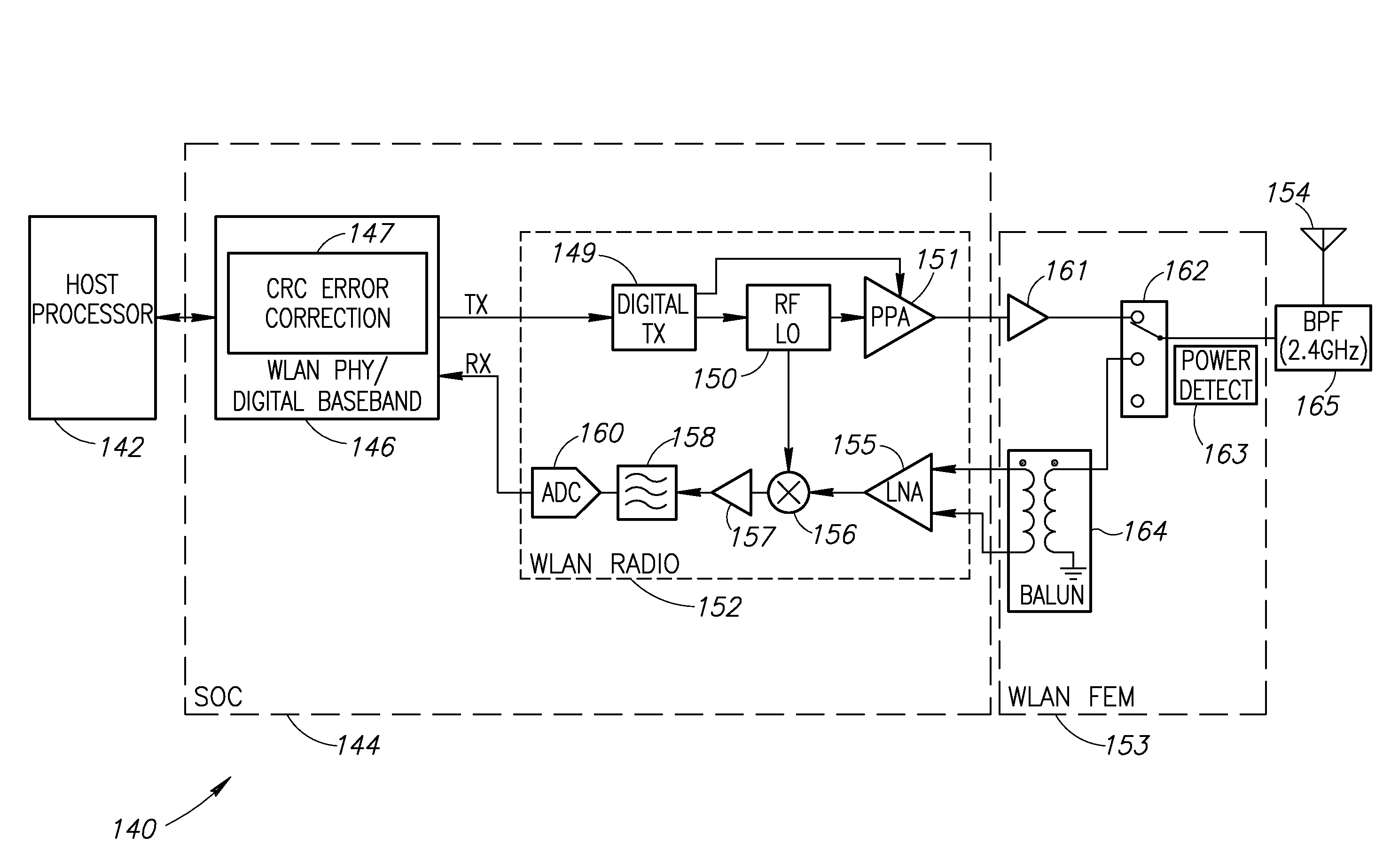

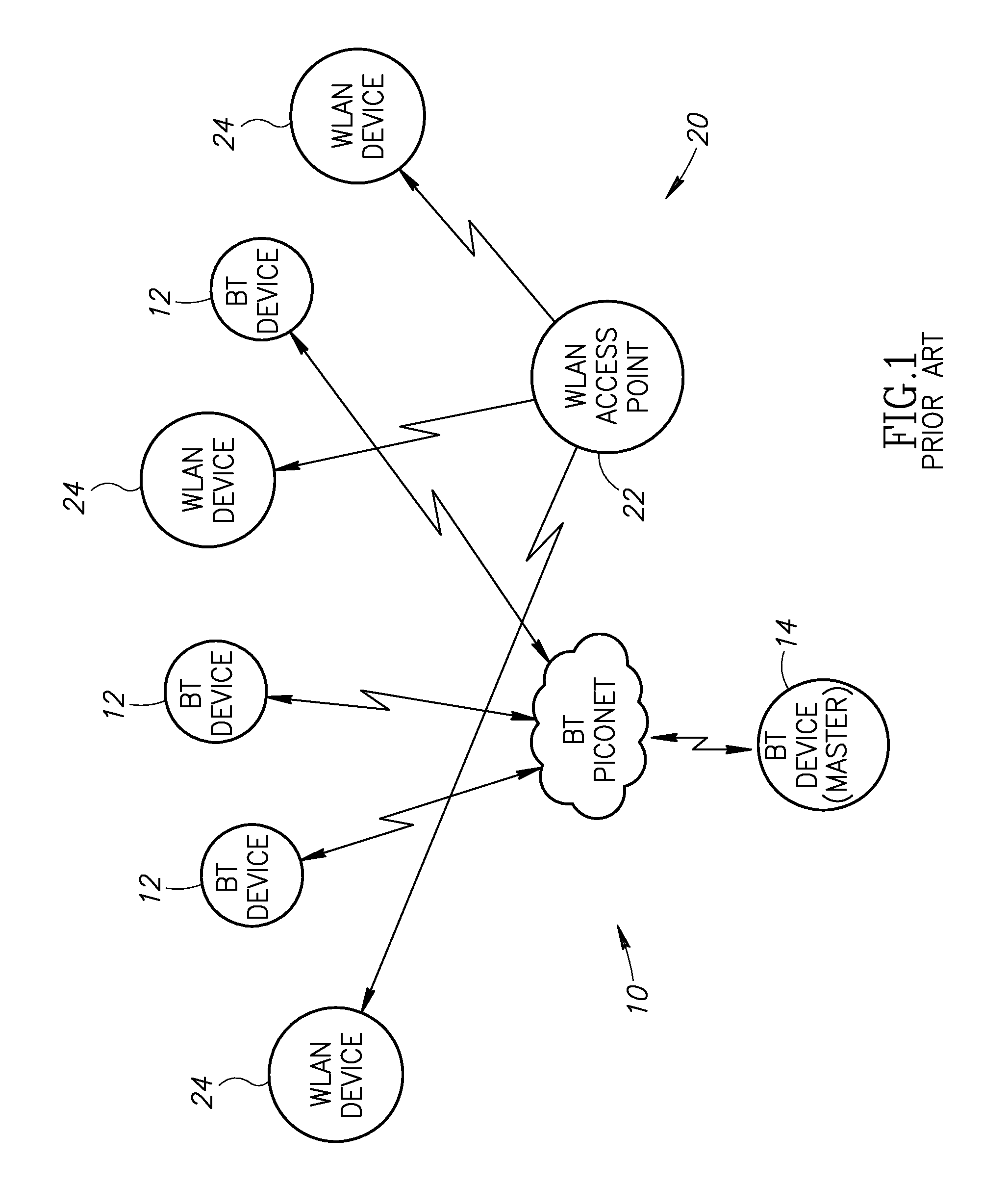

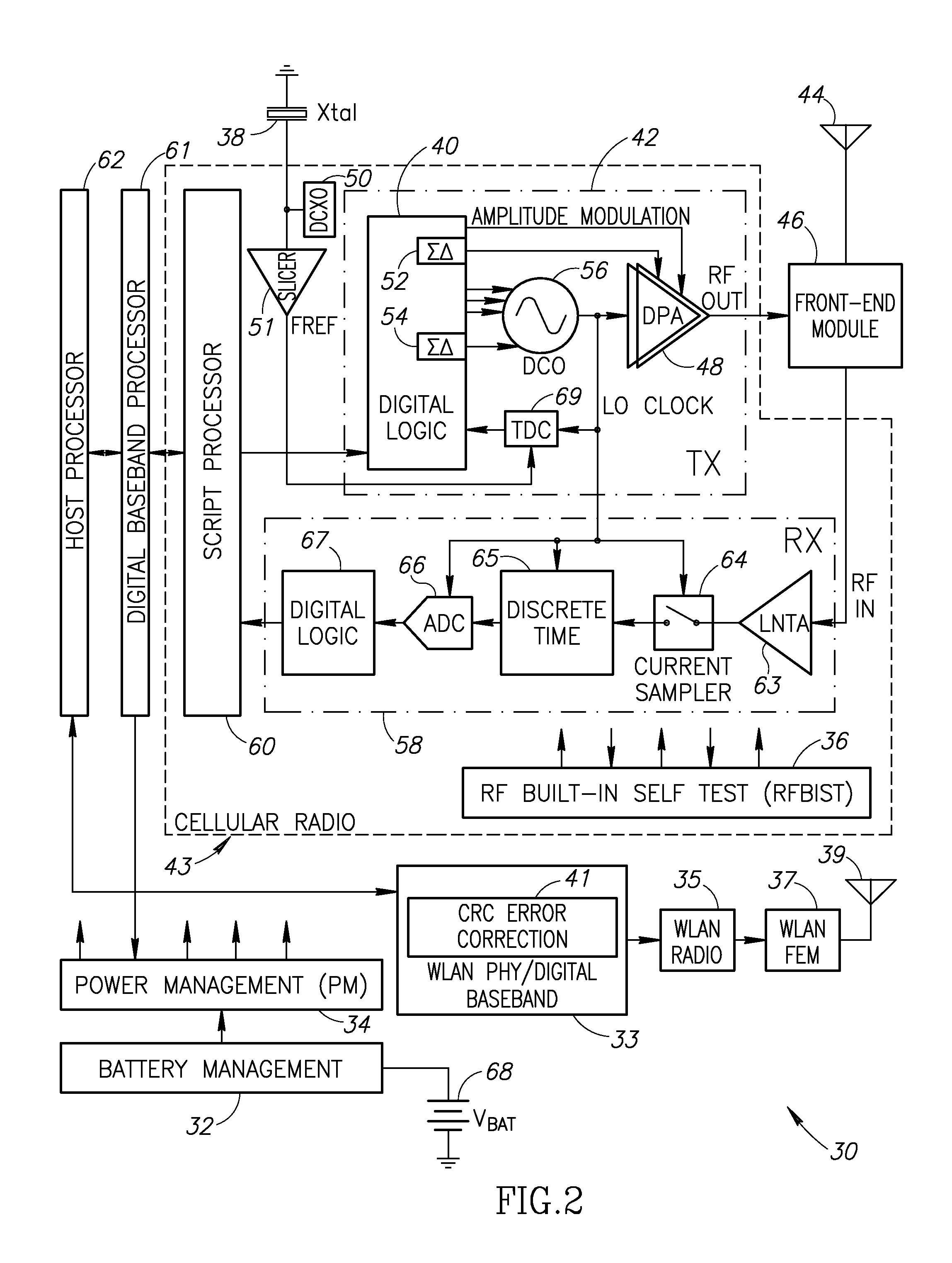

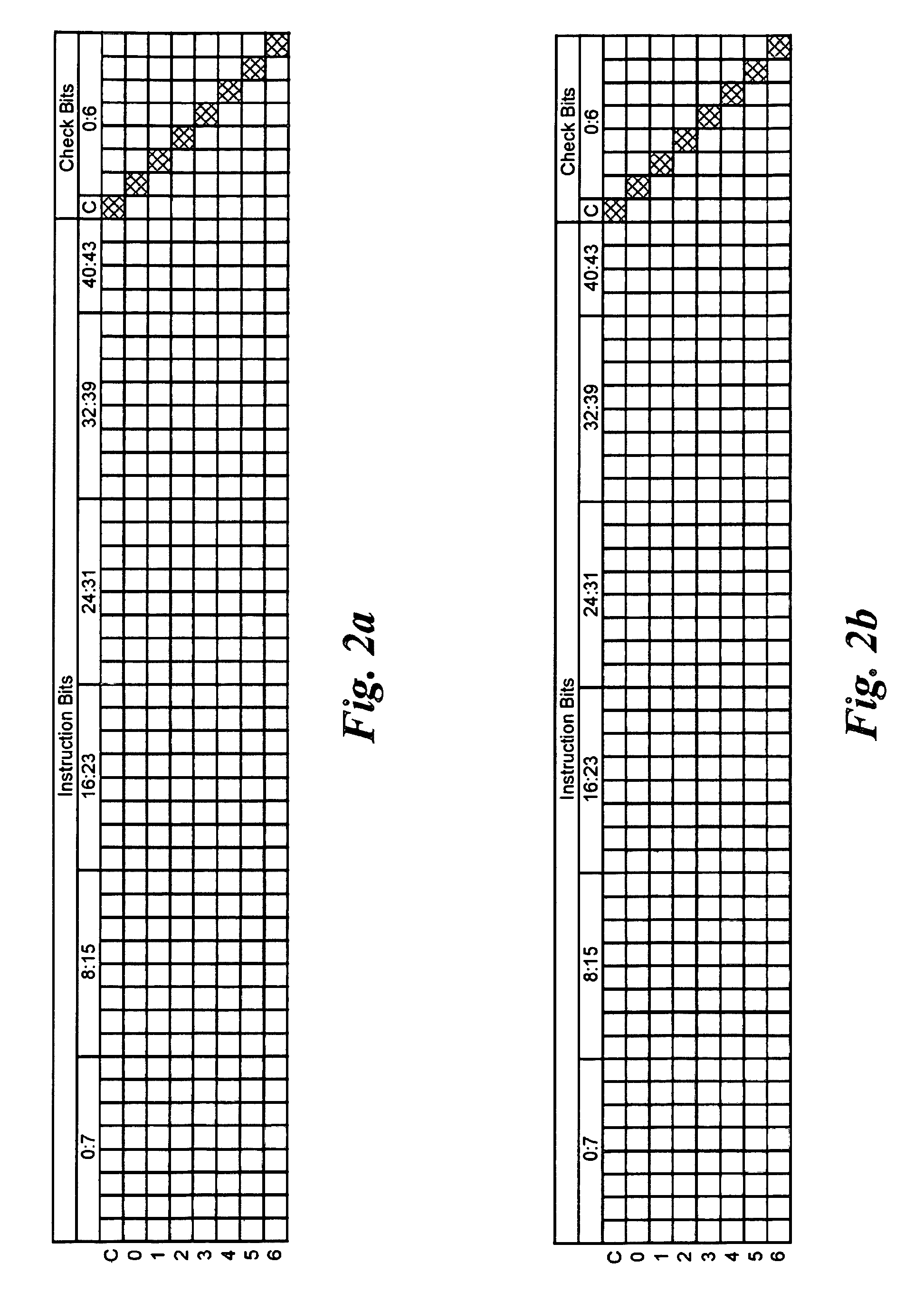

Range Extension and Noise Mitigation For Wireless Communication Links Utilizing a CRC Based Single and Multiple Bit Error Correction Mechanism

ActiveUS20080288845A1Increase the probability of receivingDetecting errorError prevention/detection by using return channelTransmission systemsComputer hardwareTelecommunications link

A novel and useful range extension and in-band noise mitigation mechanism that uses conventional CRC error detection codes to correct single and multiple bit errors in packets received over a communications link. The CRC error correction mechanism of the invention is particularly suitable for use with communication protocols with weak error correction capabilities. The mechanism uses the linearity property of the CRC calculation to detect the existence of errors in the received packet. The entire received packet is searched for single bit errors and are corrected in a single cycle. If no single bit errors are found, the mechanism then searches for multiple bit errors. Packet retransmissions are used to detect and mark the location of multiple bit errors. Multiple bit errors are corrected by trying a plurality of hypotheses of single bit error corrections. Each hypotheses pattern is investigated to find matching CRC patterns for correction using the single bit, single cycle CRC error correction method.

Owner:TEXAS INSTR INC

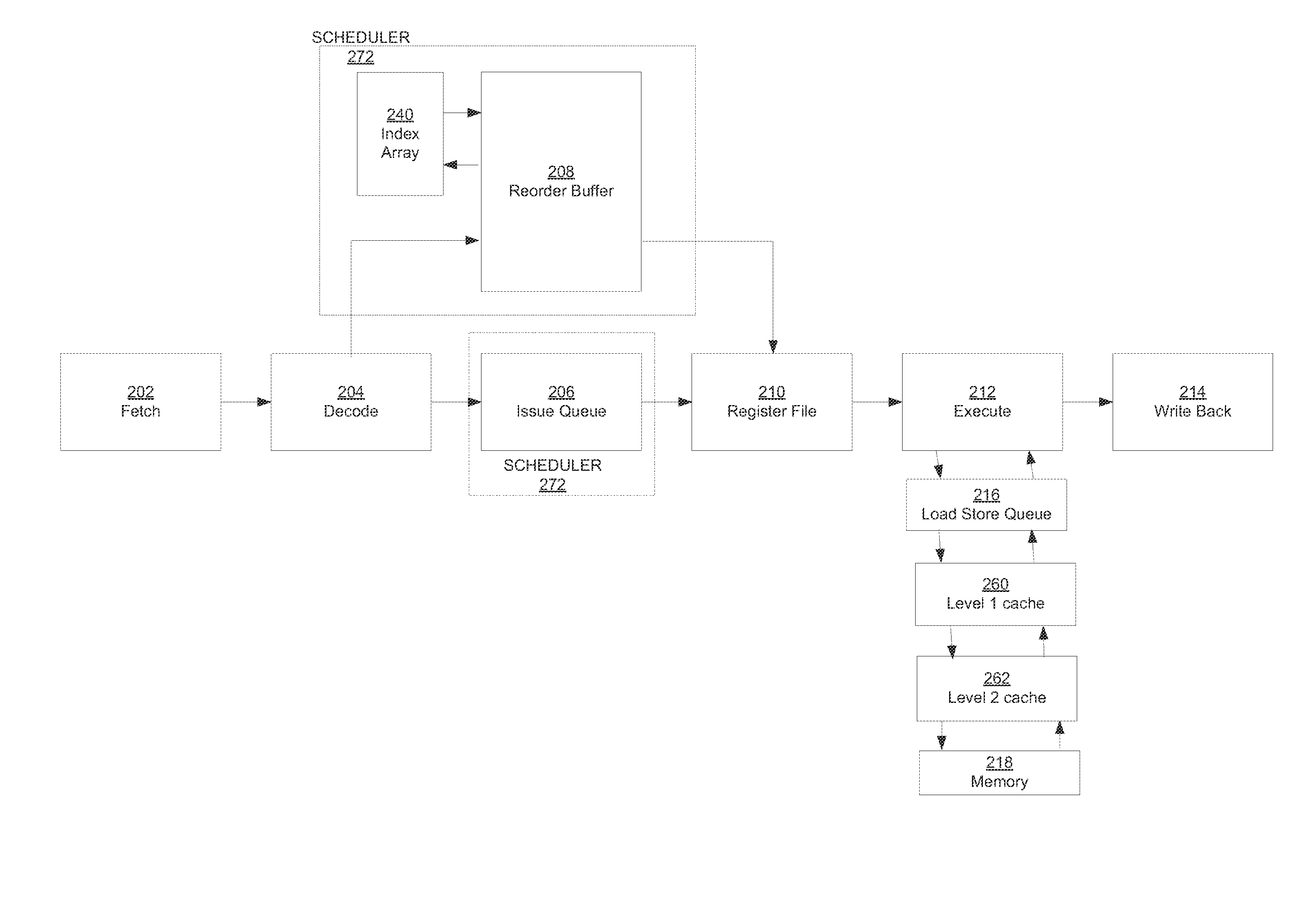

Method and apparatus for supporting a plurality of load accesses of a cache in a single cycle to maintain throughput

A method for supporting a plurality of requests for access to a data cache memory (“cache”) is disclosed. The method comprises accessing a first set of requests to access the cache, wherein the cache comprises a plurality of blocks. Further, responsive to the first set of requests to access the cache, the method comprises accessing a tag memory that maintains a plurality of copies of tags for each entry in the cache and identifying tags that correspond to individual requests of the first set. The method also comprises performing arbitration in a same clock cycle as the accessing and identifying of tags, wherein the arbitration comprises: (a) identifying a second set of requests to access the cache from the first set, wherein the second set accesses a same block within the cache; and (b) selecting each request from the second set to receive data from the same block.

Owner:INTEL CORP

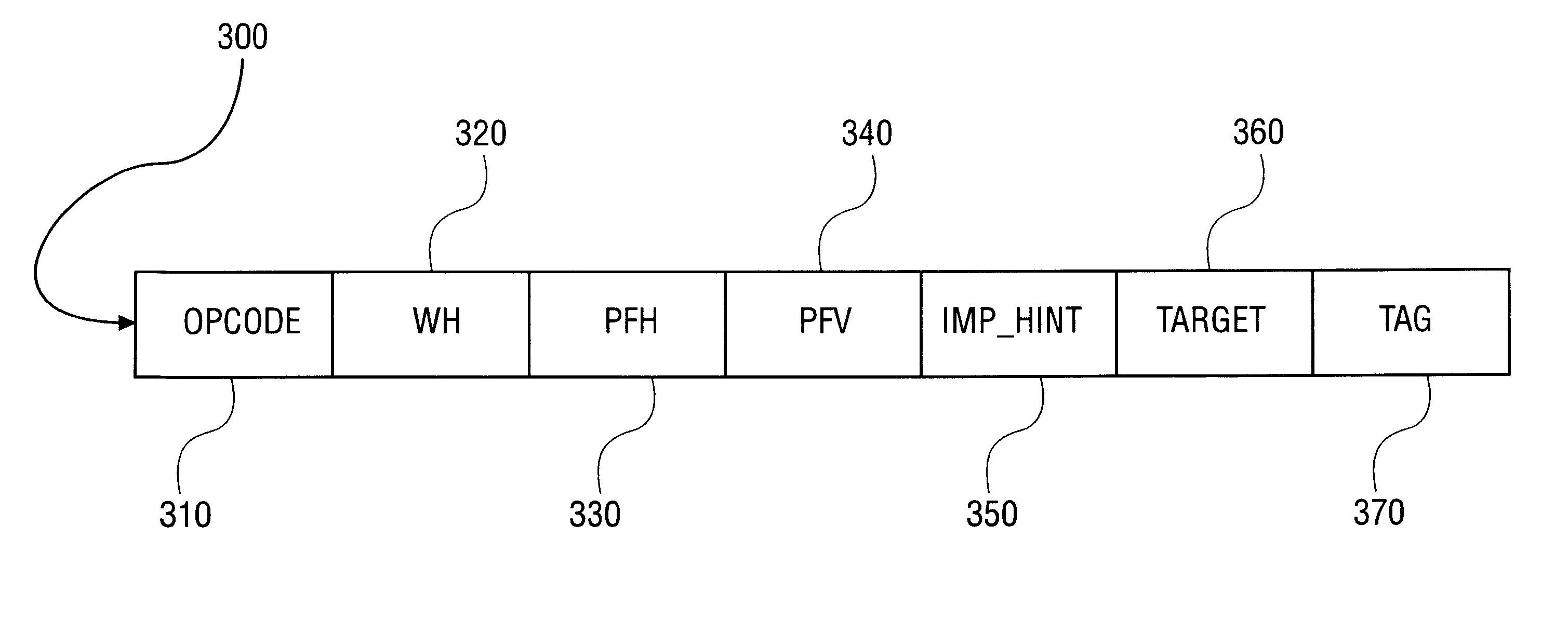

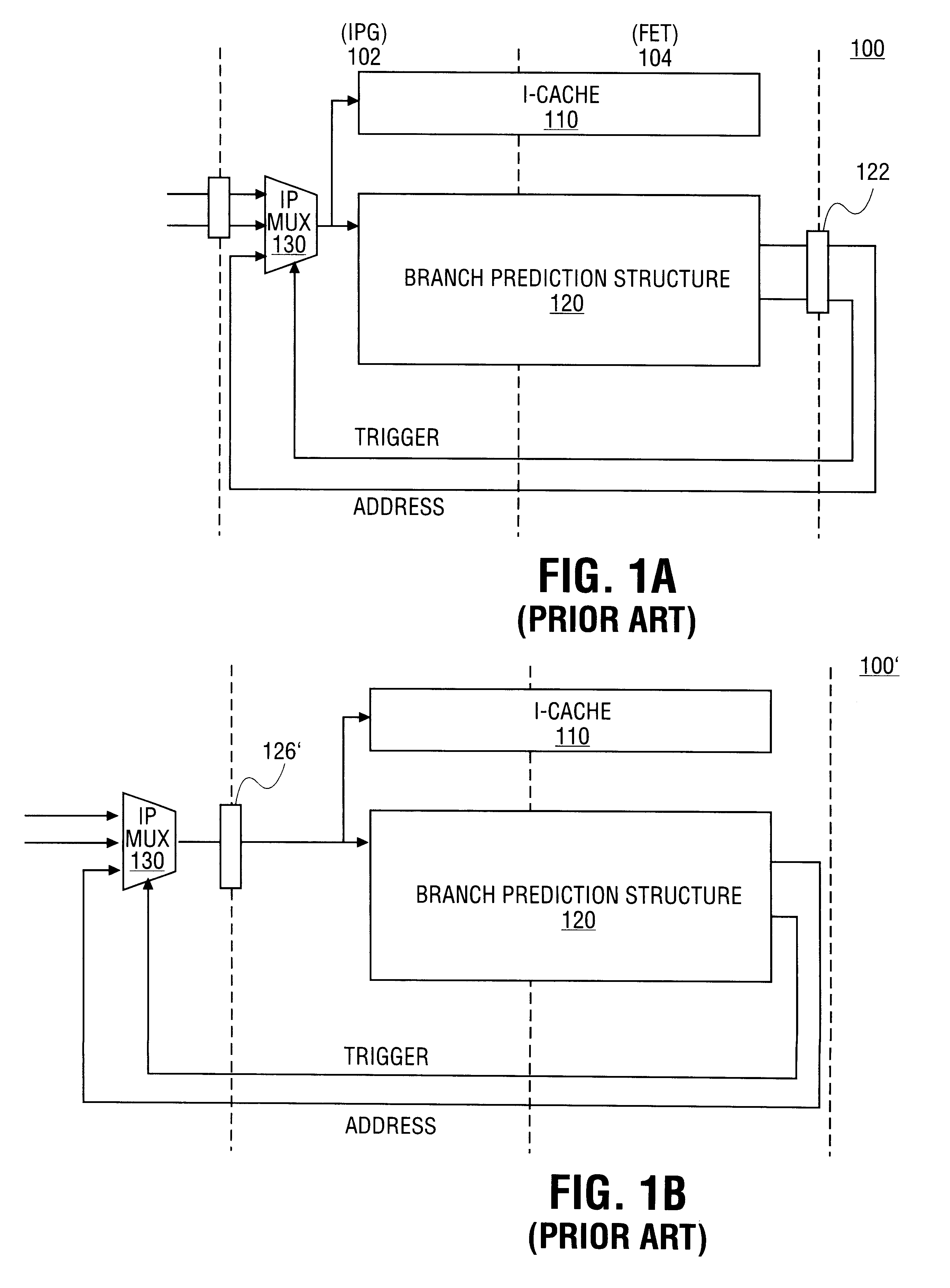

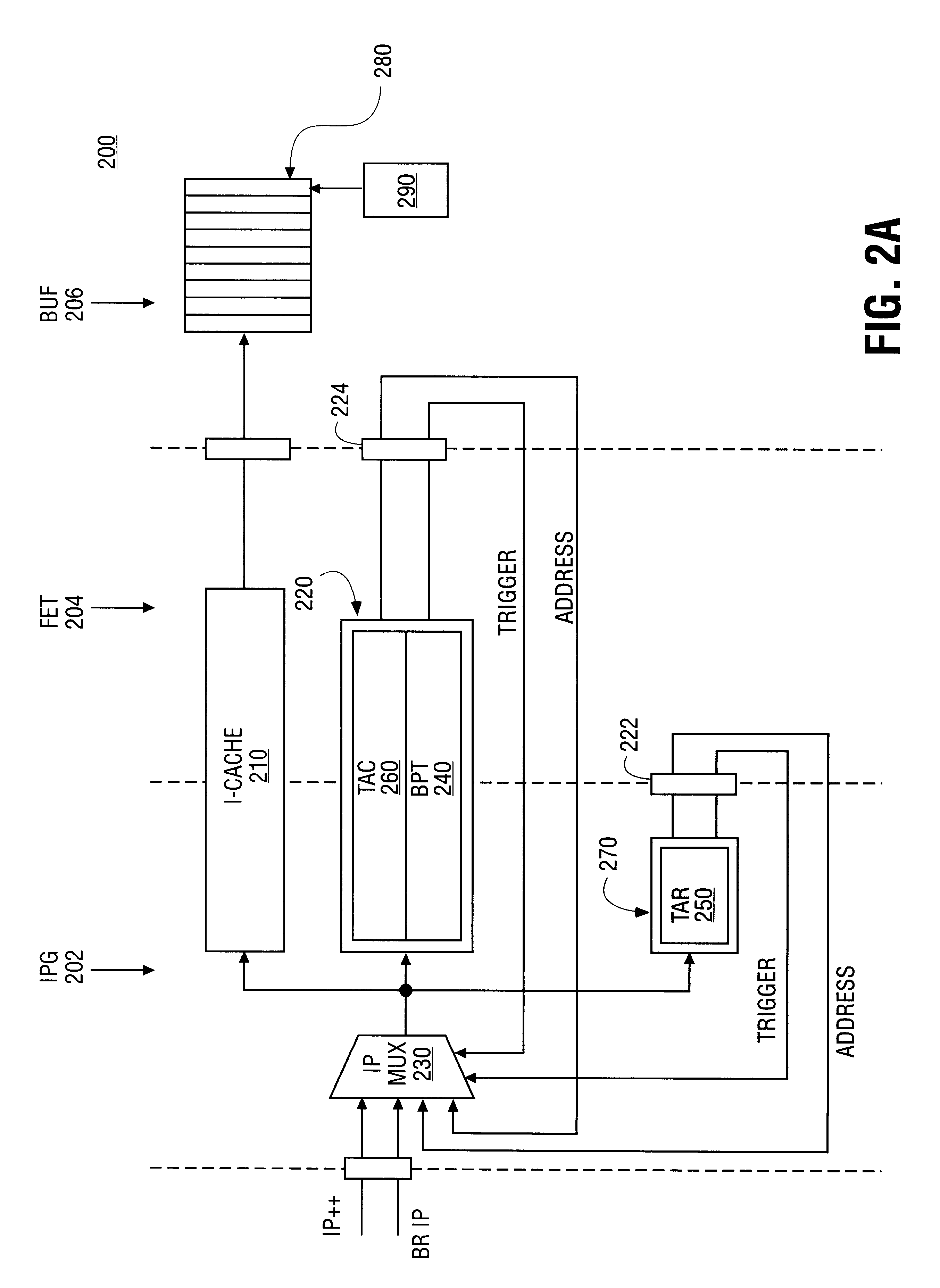

Storing predicted branch target address in different storage according to importance hint in branch prediction instruction

InactiveUS6178498B1Digital computer detailsConcurrent instruction executionTheoretical computer scienceSingle cycle

A branch prediction instruction is provided that includes hint information for indicating a storage location for associated branch prediction information in a hierarchy of branch prediction storage structures. When the hint information is in a first state, branch prediction information is stored in a first structure that provides single cycle access to the stored information. When the hint information is in a second state, the branch prediction information is stored in a second structure that provides slower access to the stored information.

Owner:INTEL CORP

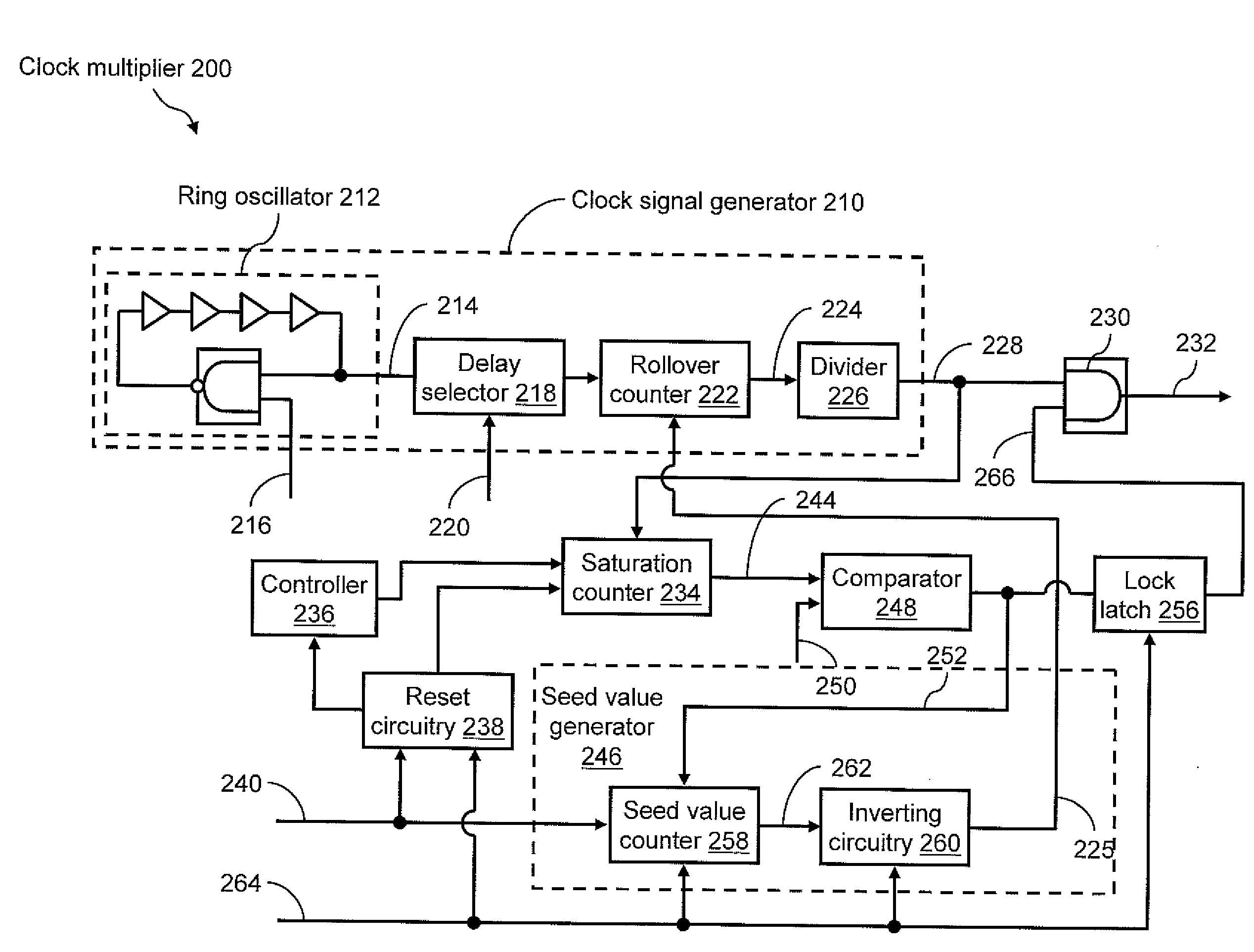

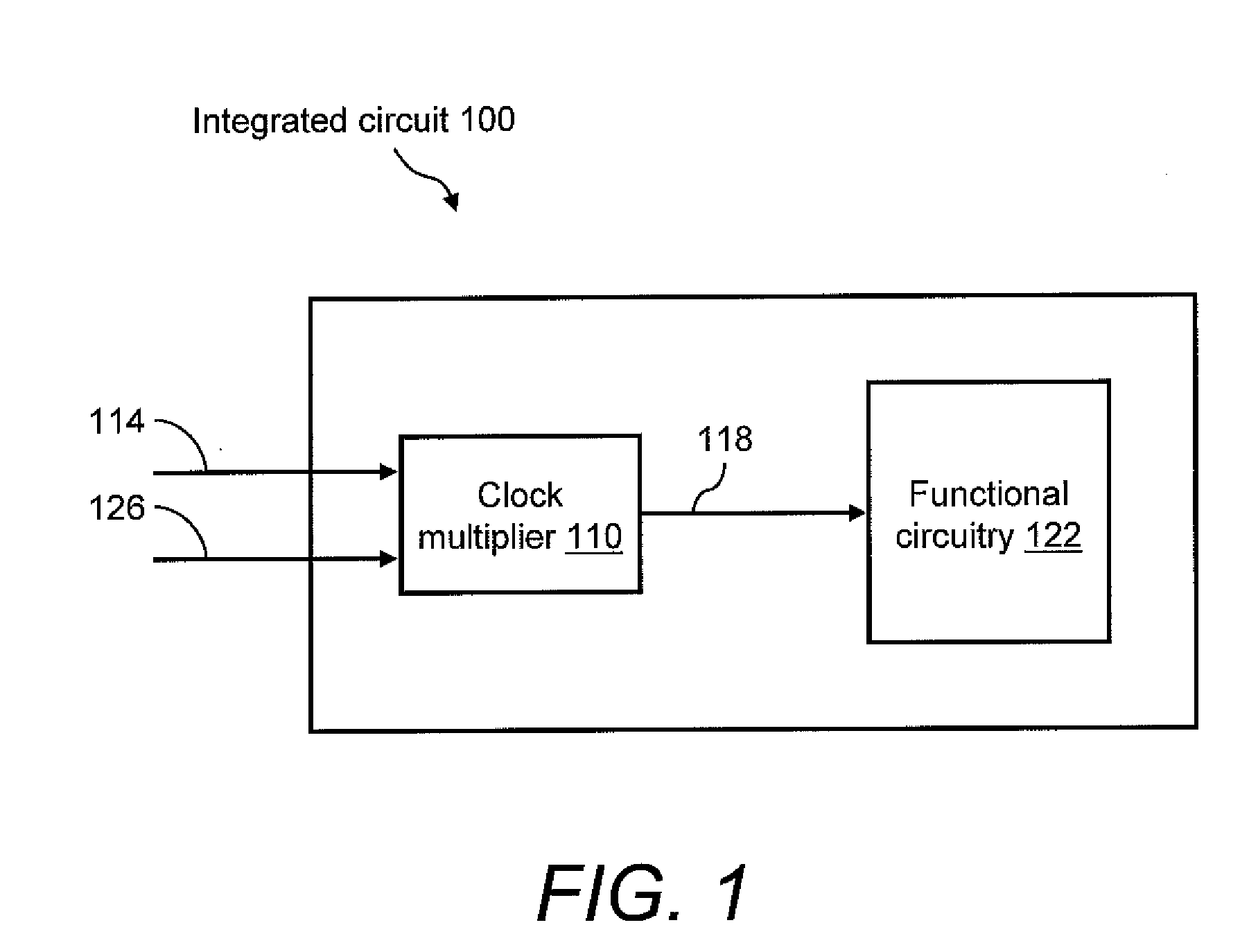

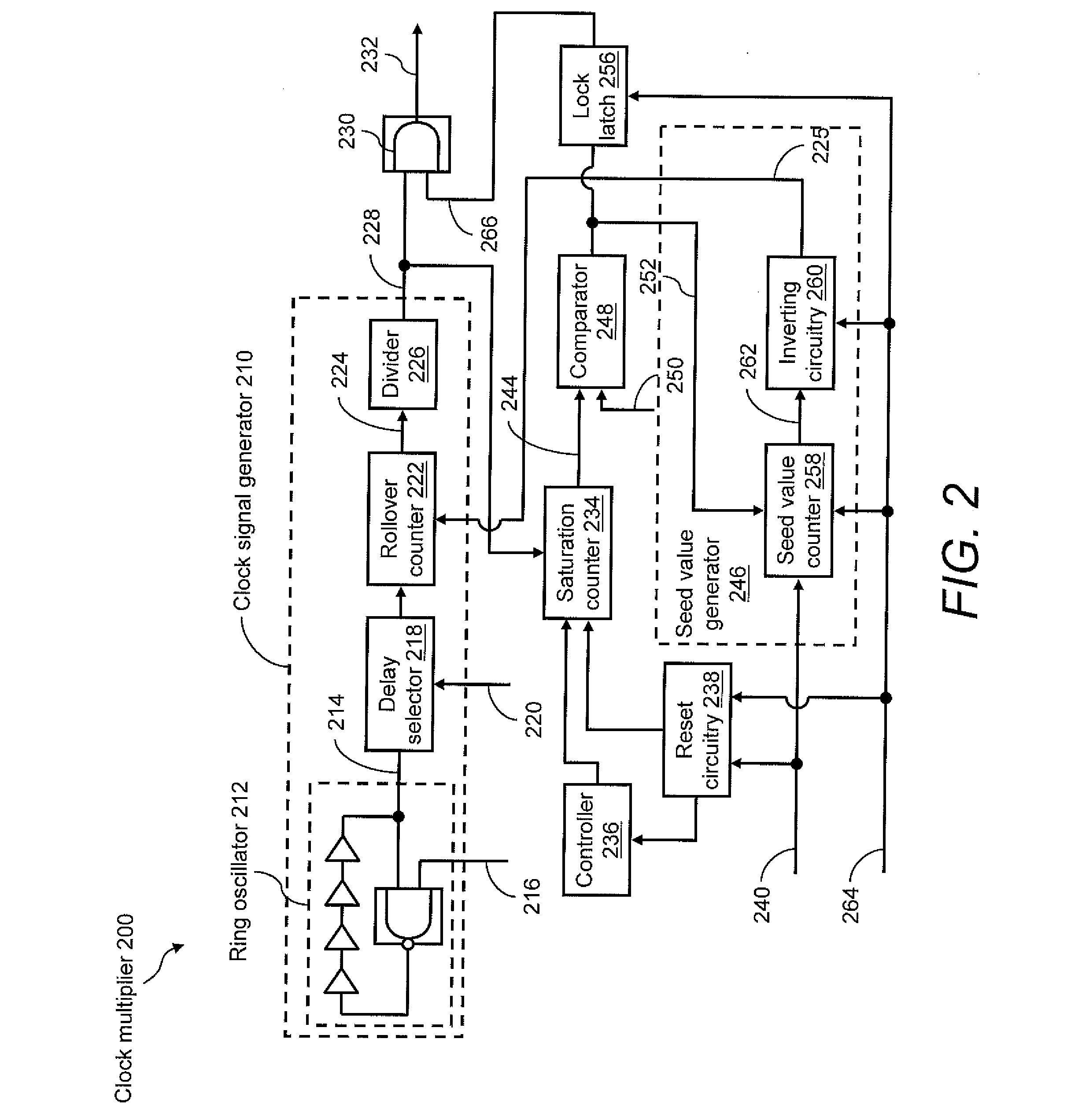

Small scale clock multiplier circuit for fixed speed testing

InactiveUS20080224742A1Counting chain pulse countersComputations using pulse rate multipliers/dividersRolloverClock rate

An on-chip clock multiplier for outputting a fast clock that is approximately a predetermined multiple n of a slow clock. The multiplier utilizing a high-speed oscillator to generate a high-frequency base signal. A lower frequency signal is generated using the high-frequency base signal as a function of the output of a rollover counter that counts from a seed value to a terminal value. A saturation counter is used to determine whether no more than n pulses of the lower frequency signal occur within a single cycle of the slow clock. If not, the lower frequency signal is iteratively slowed by changing the seed value until no more than n pulses of the lower frequency signal occur within a single cycle of the slow clock. When this iteration is done, the fast clock having a frequency that is approximately n times the frequency of the slow clock is output.

Owner:IBM CORP

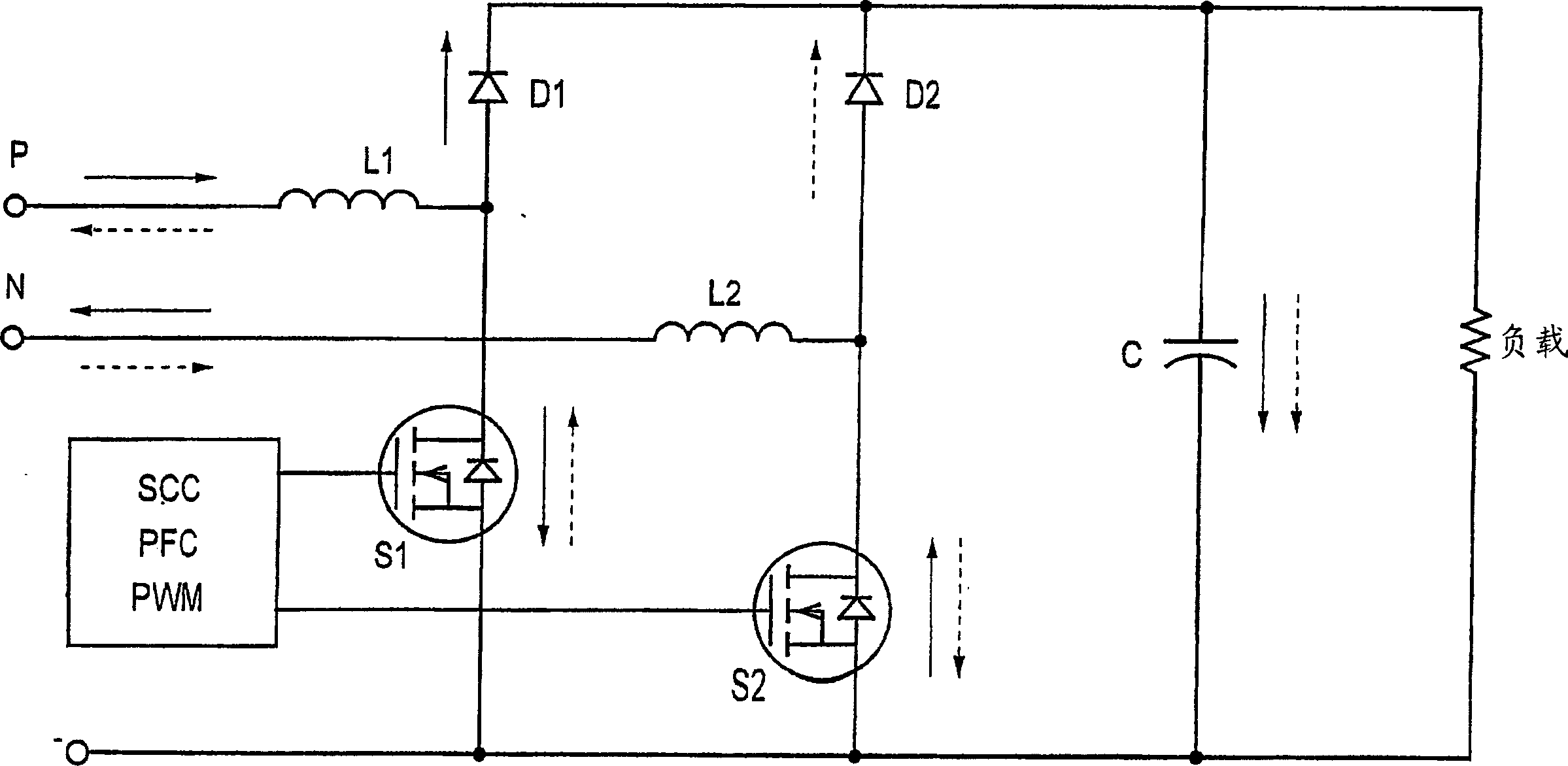

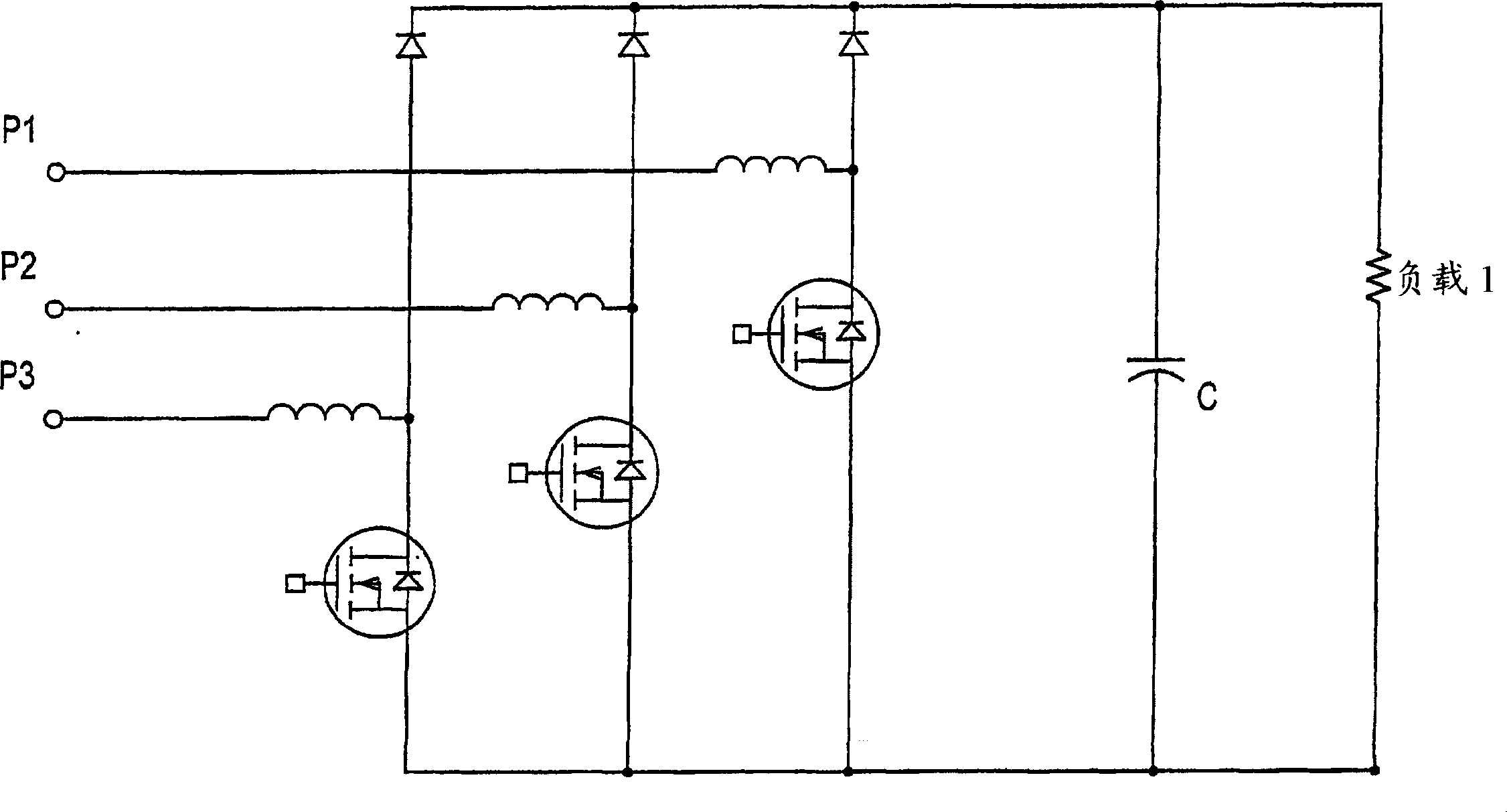

Bridgeless boost converter with pfc circuit

InactiveCN1864319AAvoid restrictionsReduce overload capacity requirementsDc-dc conversionElectric variable regulationCapacitanceCycle control

The bridgeless boost topology reduces the power dissipation, cost, and size of prior PFC systems by eliminating the intrinsic loss of the input rectifier bridge. Sensing of the input line voltage by the controller is unnecessary. The use of One Cycle Control (also known as Single Cycle Control) allows the Power Factor Correction function to be performed without complex rectification networks to obtain the AC line voltage reference. The use of bi-directional switches makes it possible to control inrush current (the startup over-current due to the charging of the output bulk capacitor), which allows elimination of over-current limiting devices and reduction of the diode surge capability requirements. Moving the boost inductor to the system input adds an additional filtering function, reducing the cost of input EMI filtering.

Owner:INTERNATIONAL RECTIFIER COEP

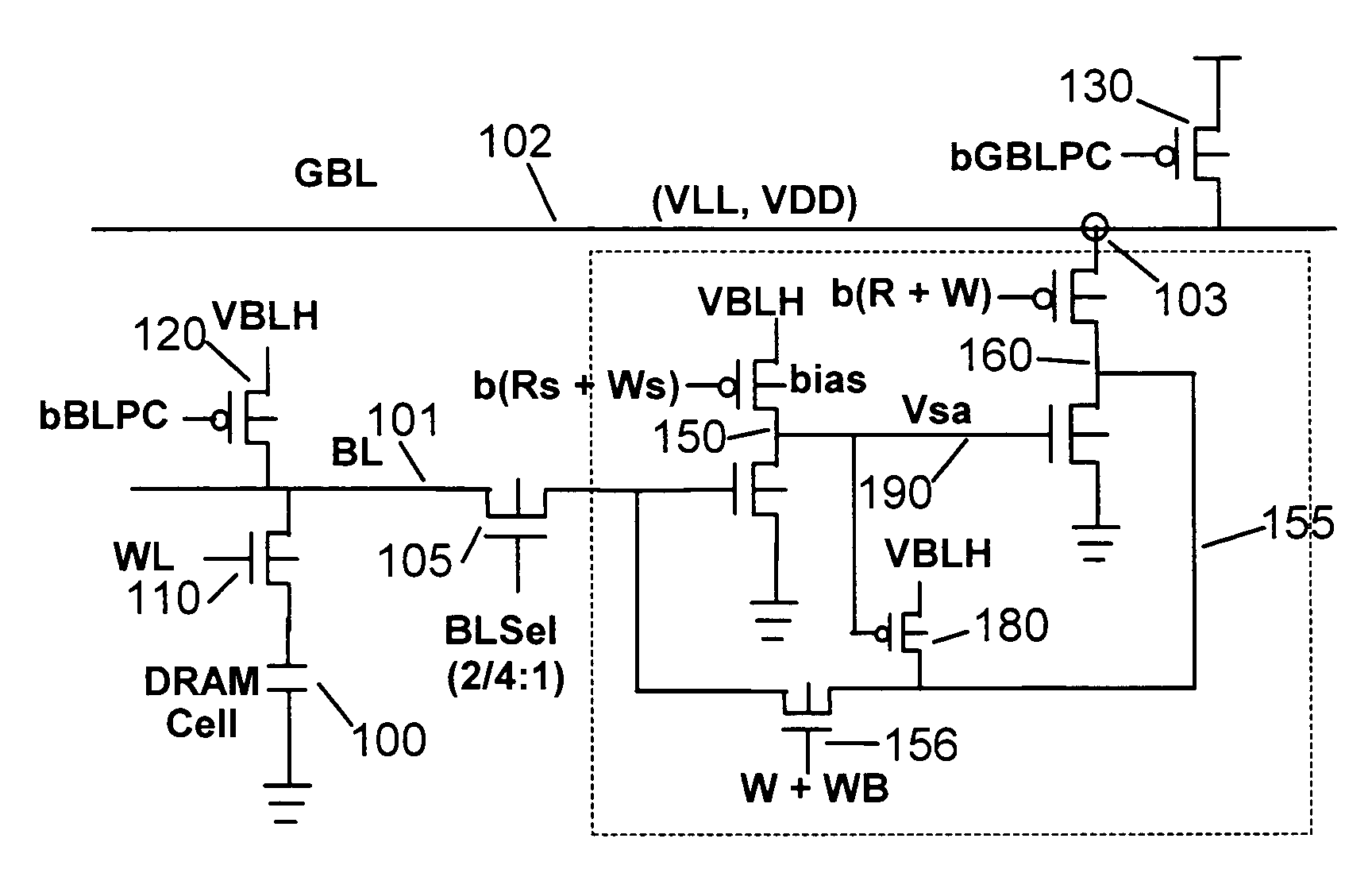

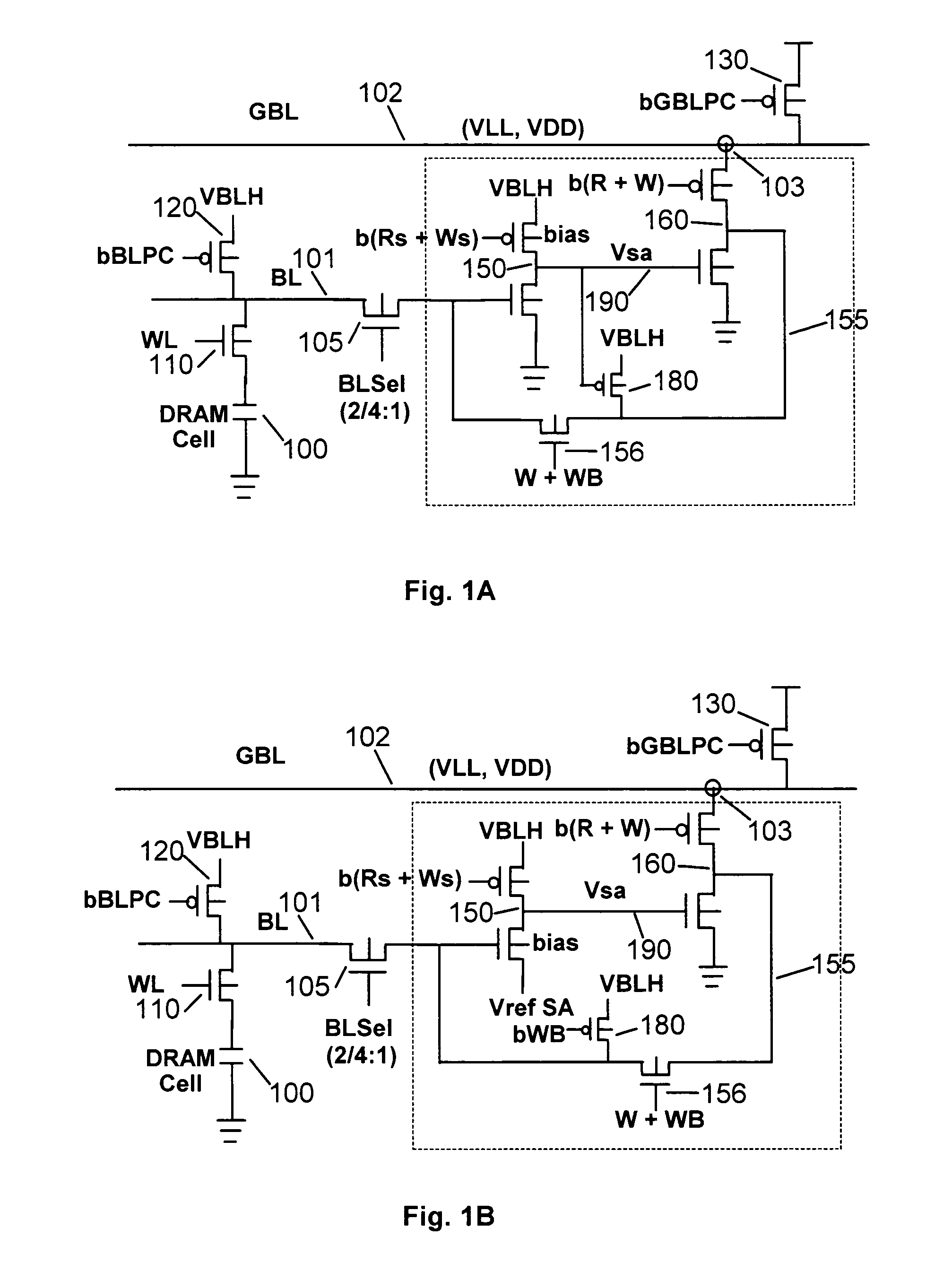

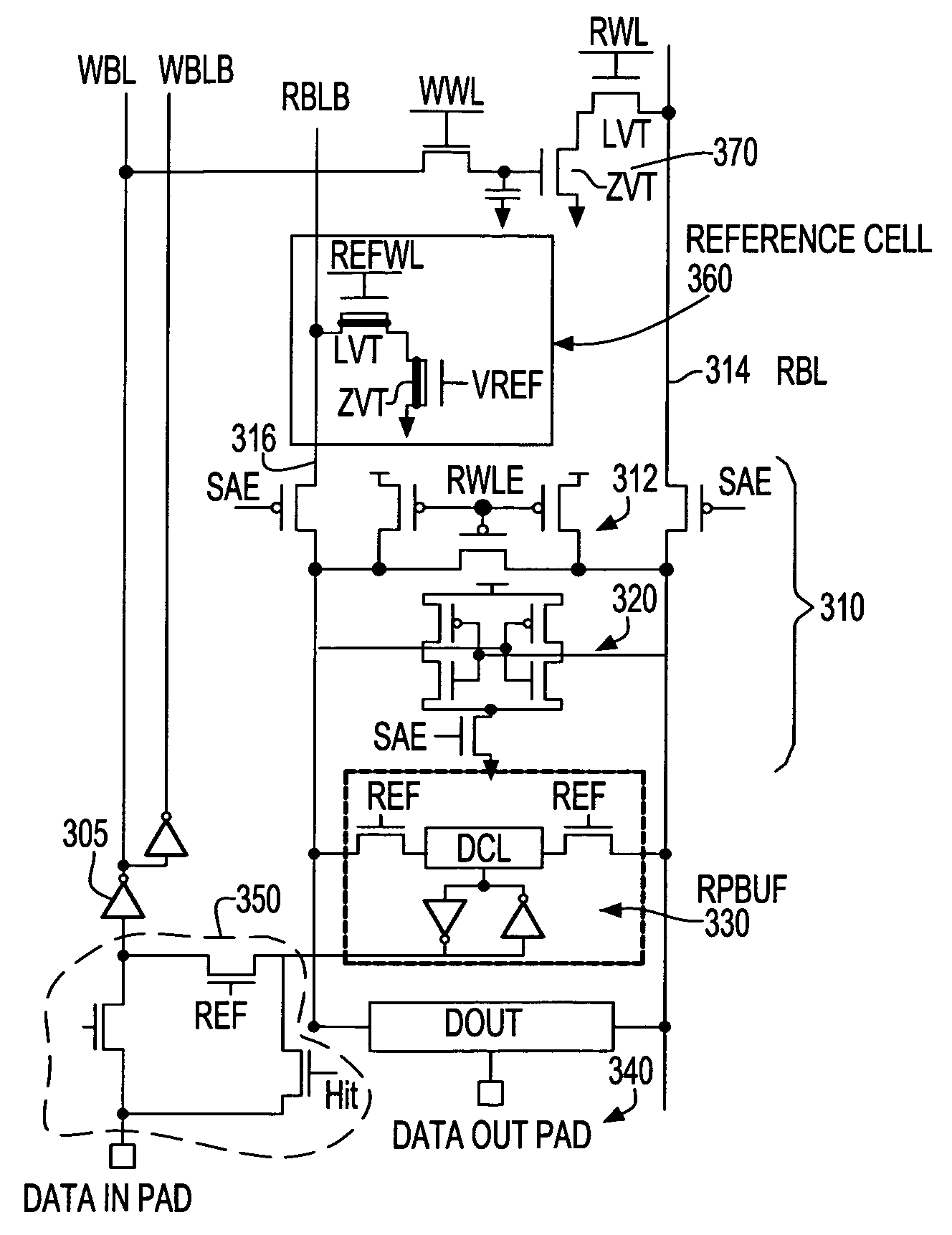

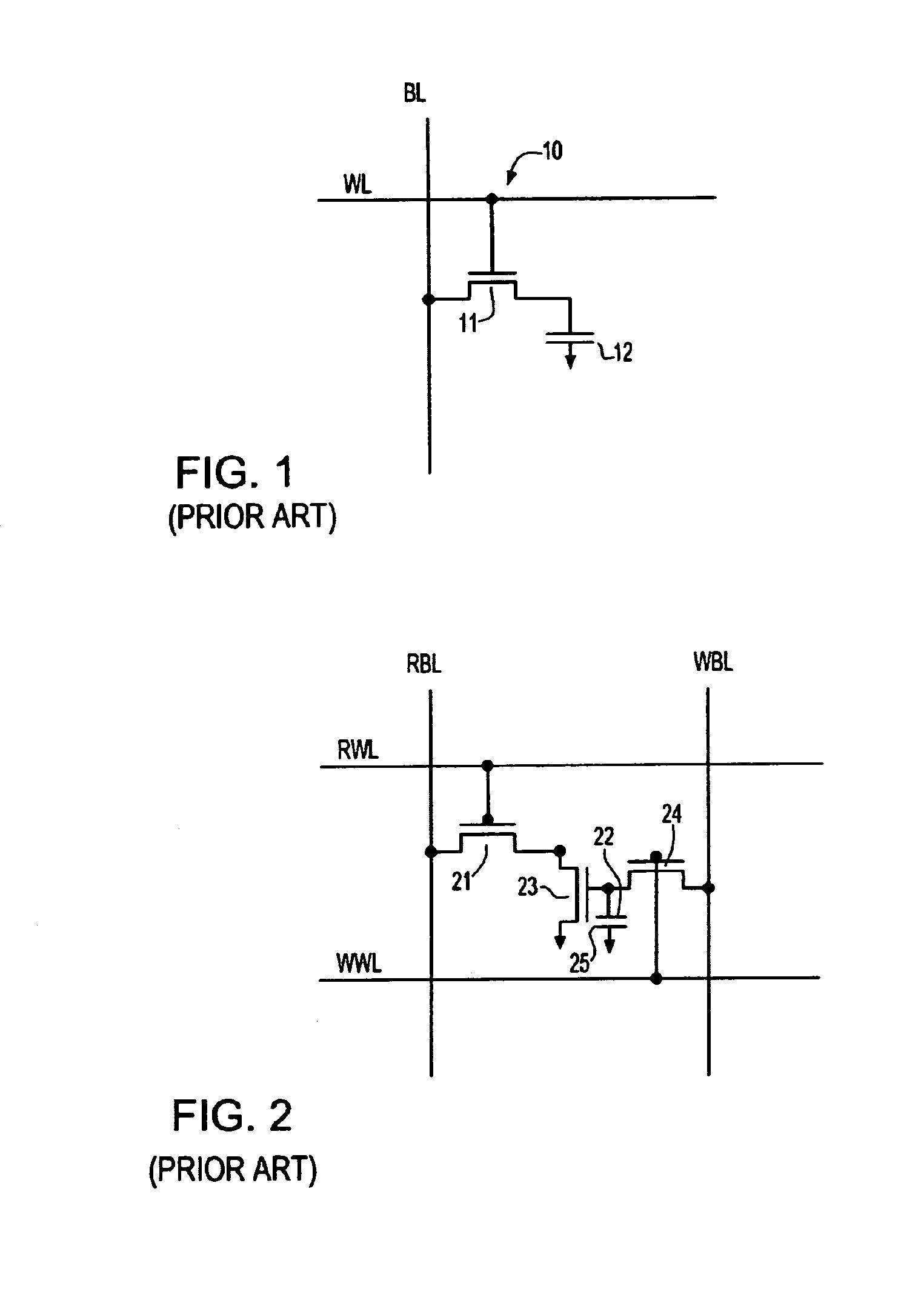

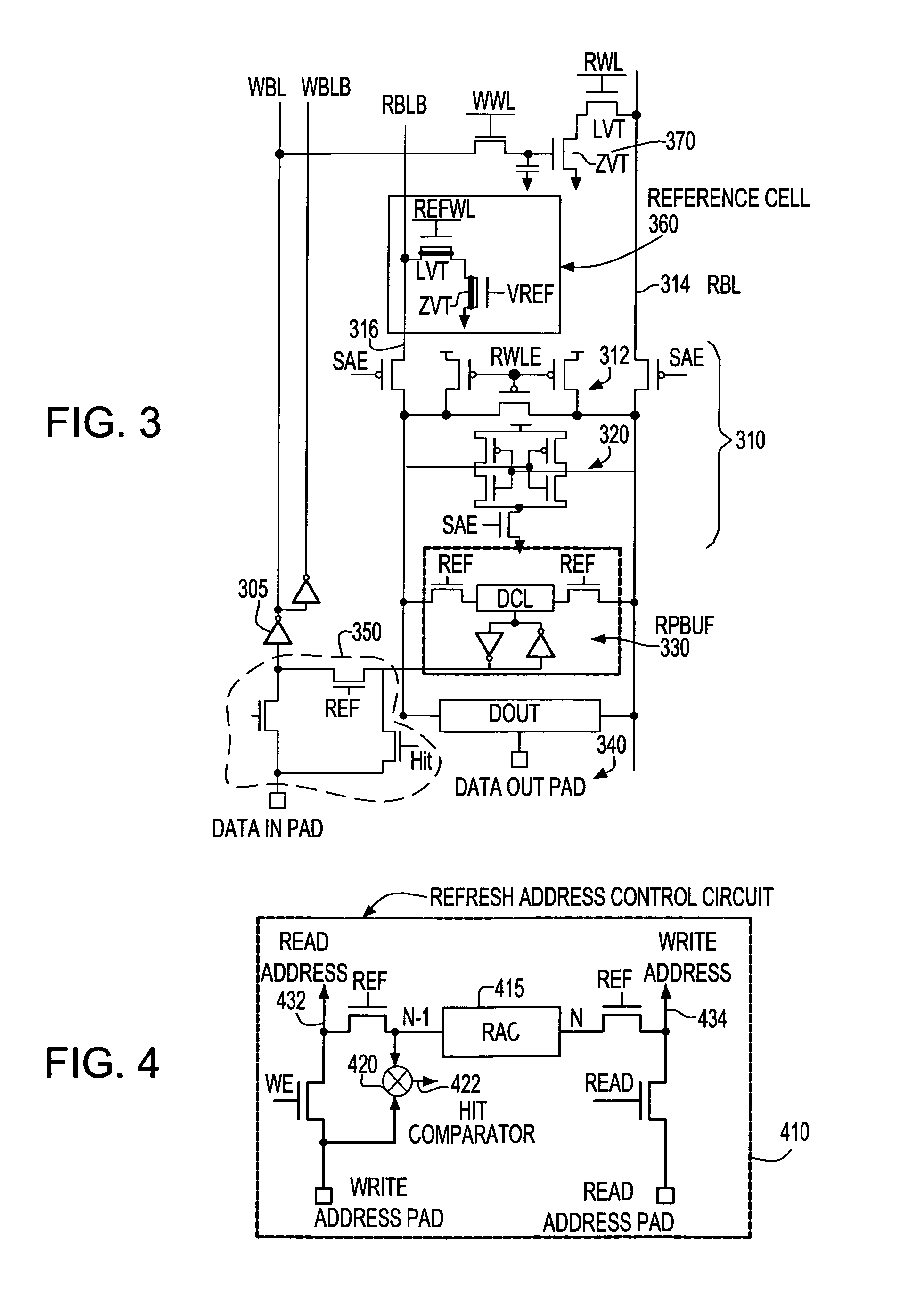

Single cycle read/write/writeback pipeline, full-wordline I/O DRAM architecture with enhanced write and single ended sensing

InactiveUS7099216B2Reduce active powerReduce noise couplingDigital storageComputer architectureAudio power amplifier

A DRAM is disclosed which includes a single ended bitline structure, a single ended global bitline structure, primary sense amplifiers with data storage and data write-back capability and with capability to decouple from the global bitlines, a full-wordline I / O structure where essentially all memory cell that belong to the same wordline are being operated on, and a pipelined architecture. The DRAM further includes a small voltage swing design. The primary sense amplifiers can include more than one amplification stages. Such a DRAM is suitable for applications in conjunction with processors as an embedded DRAM.

Owner:GLOBALFOUNDRIES INC

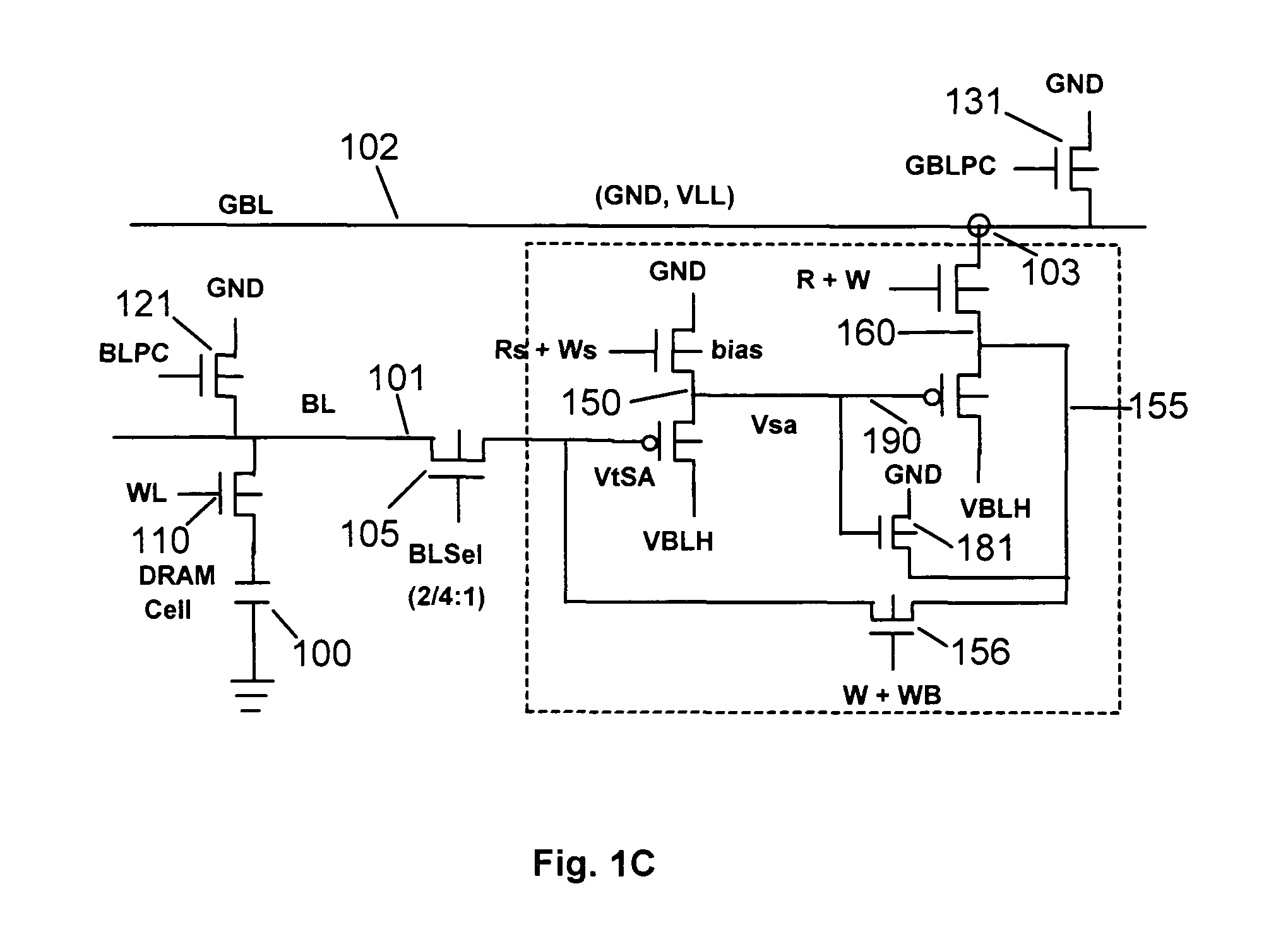

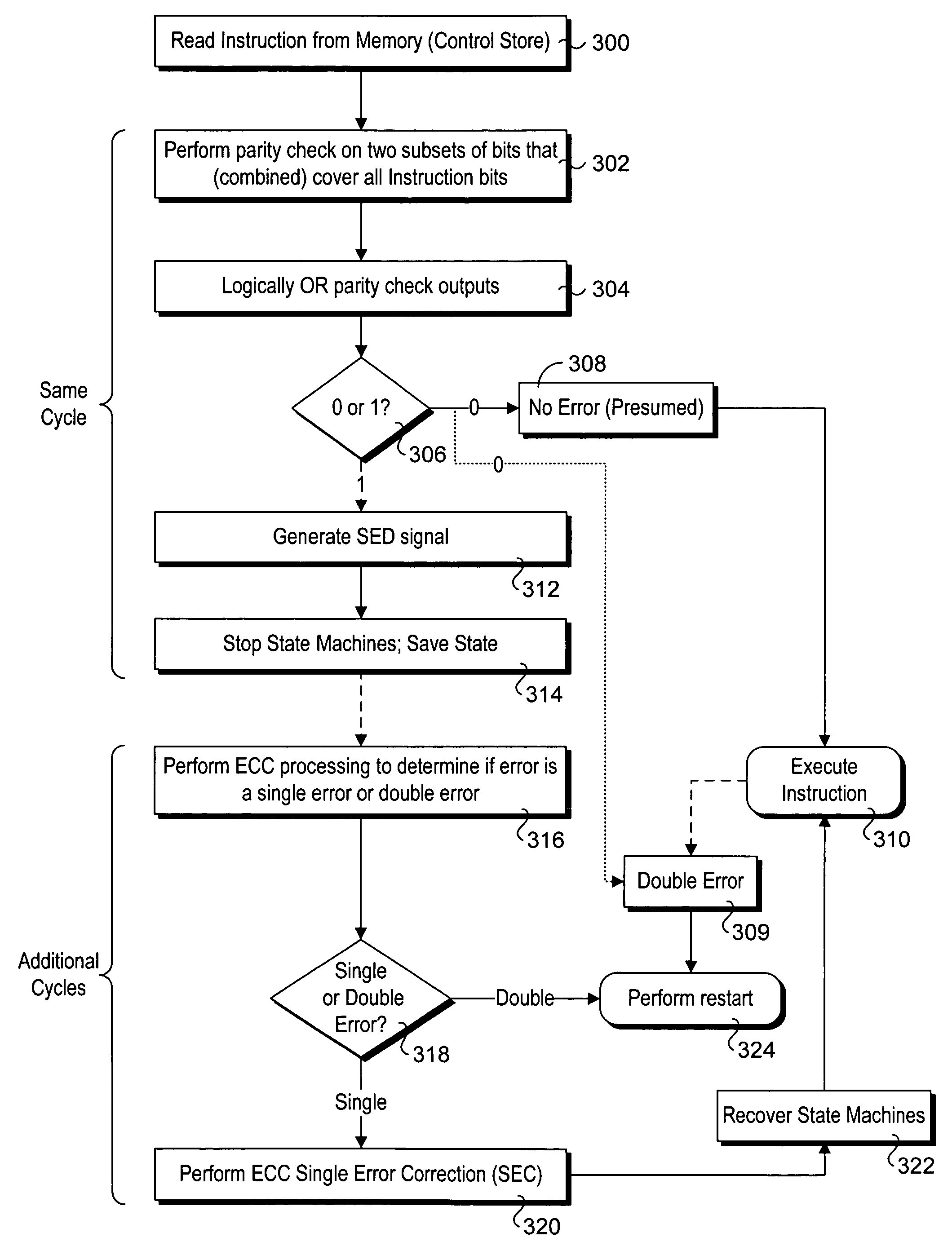

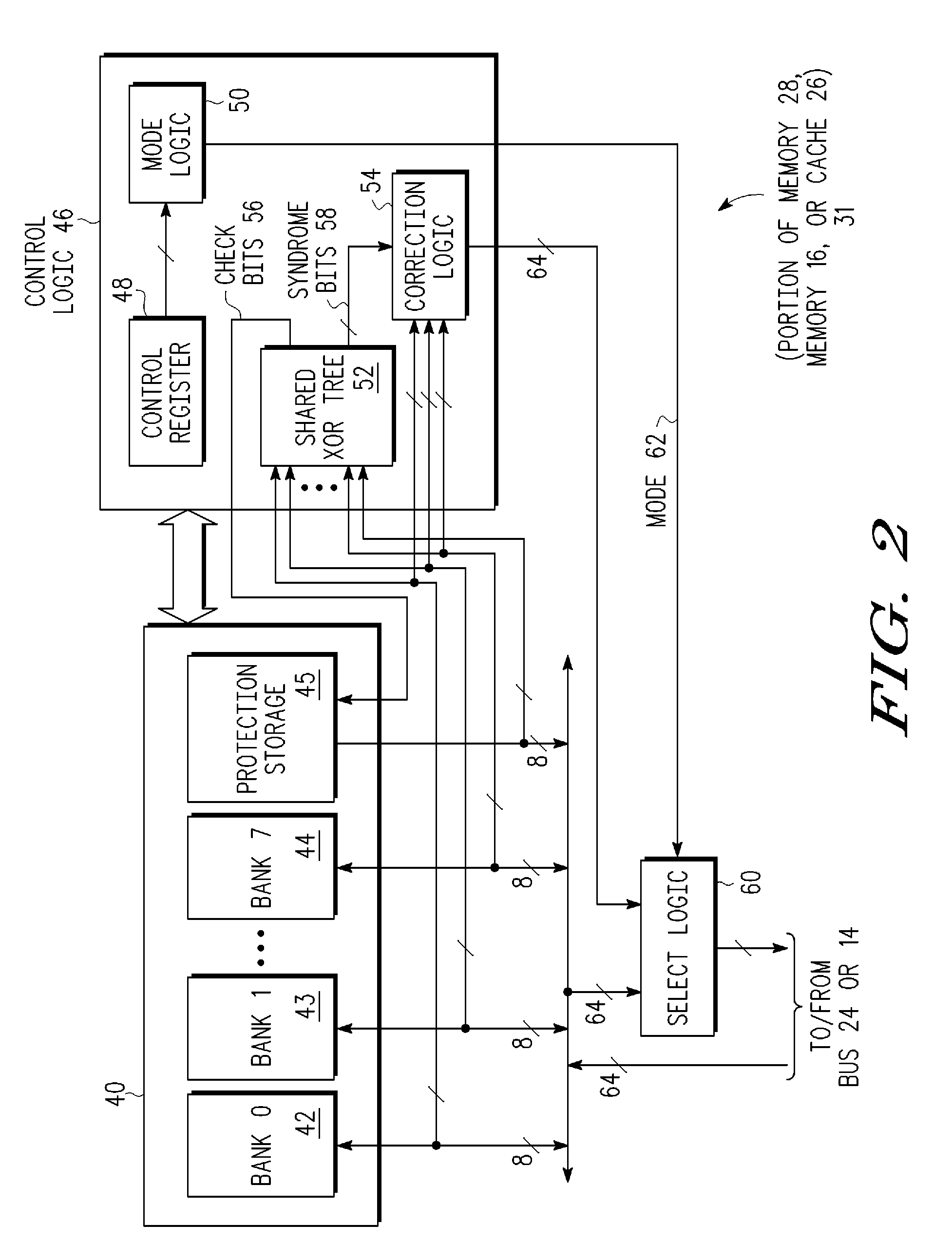

ECC coding for high speed implementation

Methods and apparatus for performing error correction code (ECC) coding techniques for high-speed implementations. The ECC code word is structured to facilitate a very fast single-error-detect (SED) that allows state machines to be stopped within a single cycle when an error is detected and enables a corresponding single-error-correct (SEC) operation to be performed over multiple cycles while the state machines are in a suspended mode.

Owner:INTEL CORP

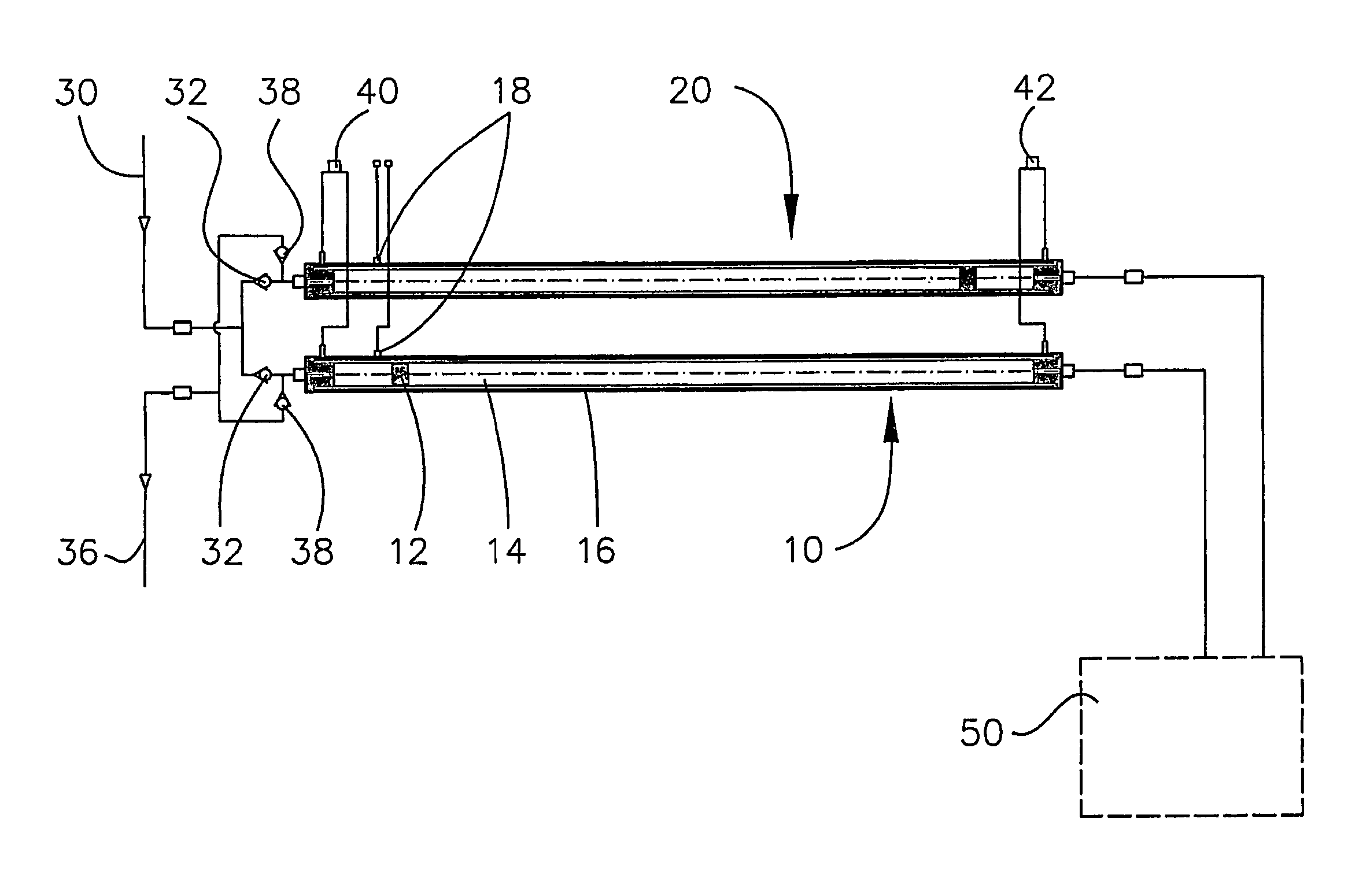

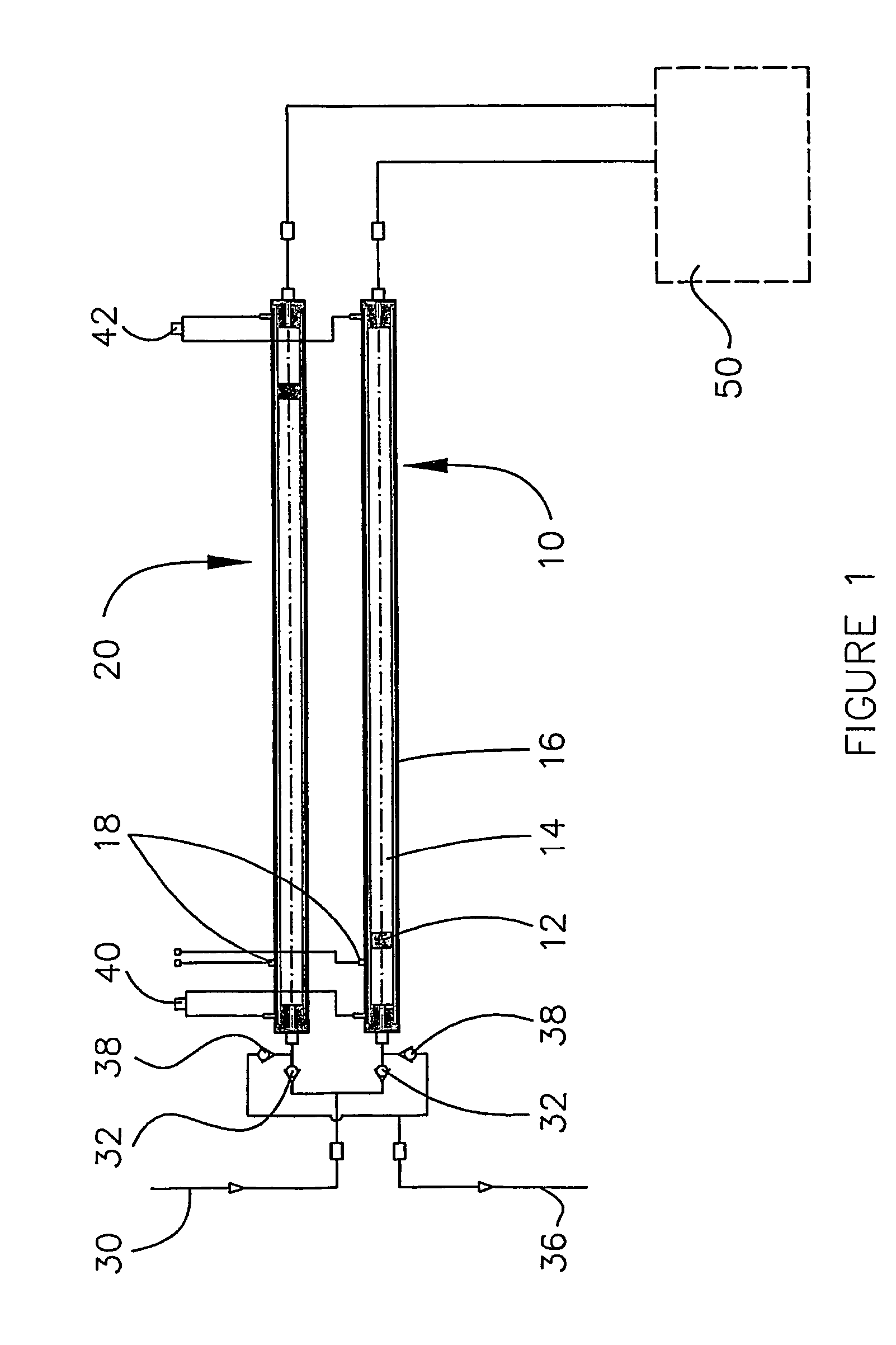

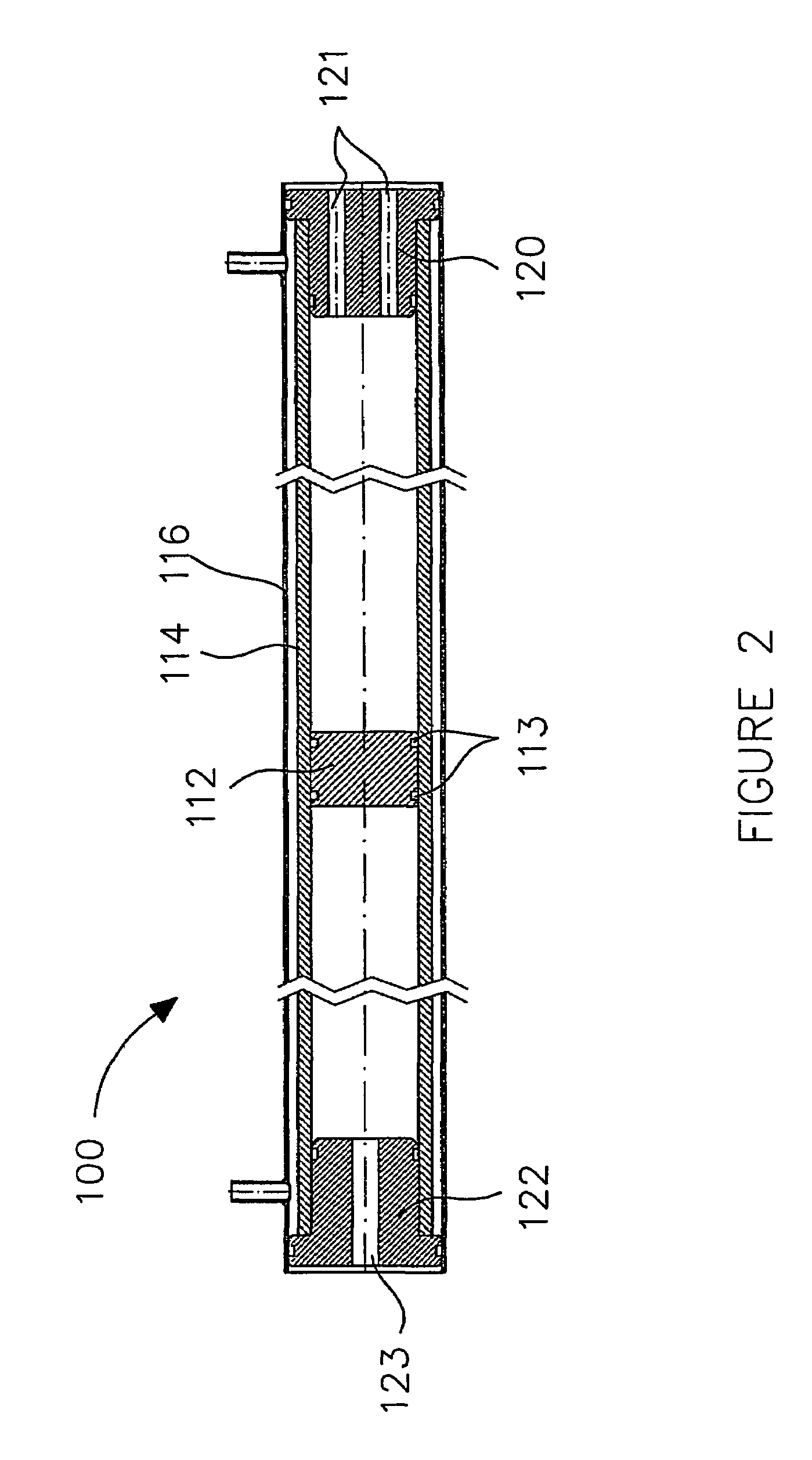

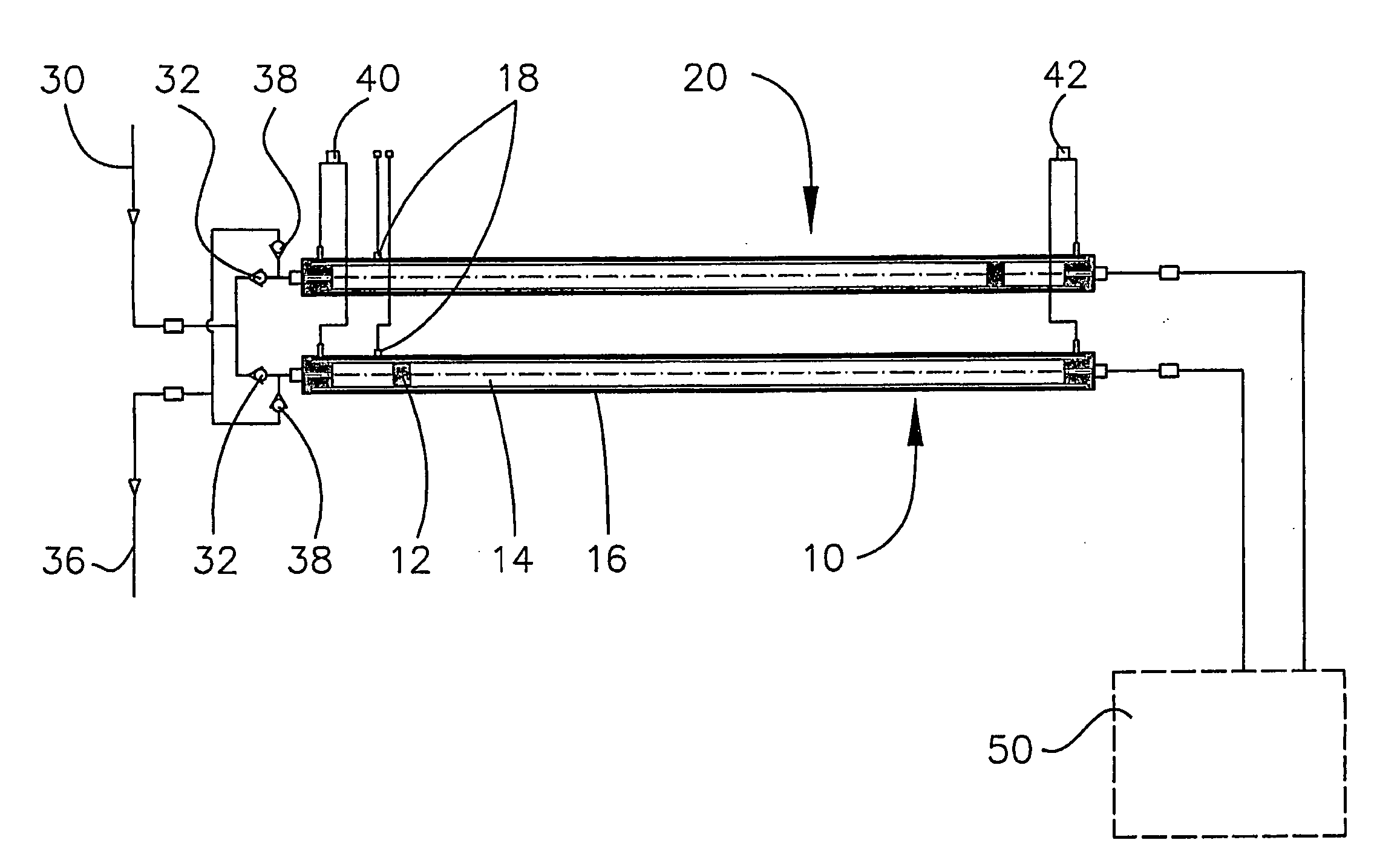

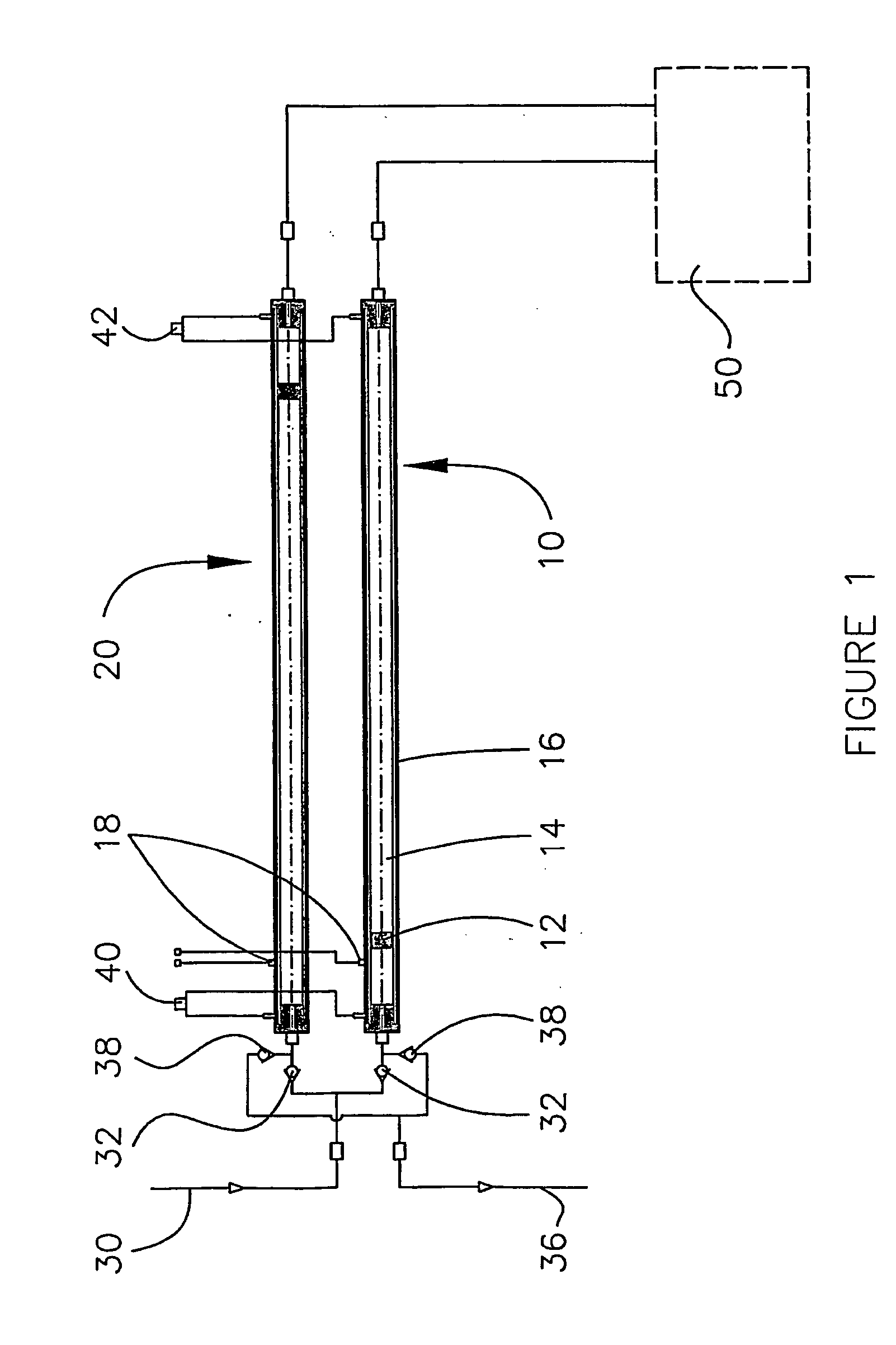

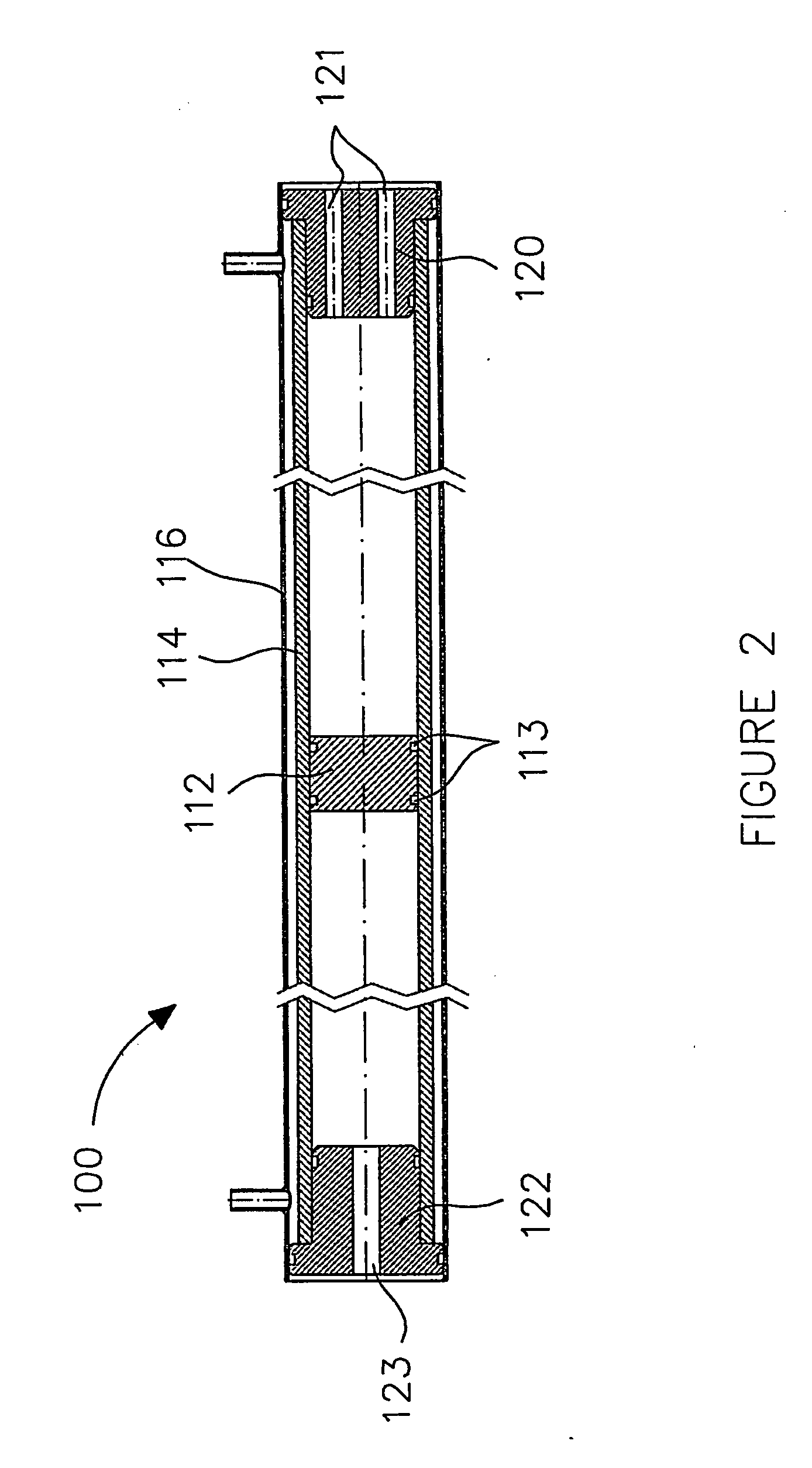

Method and apparatus for compressing a gas to a high pressure

ActiveUS7527482B2Increase volumeReduce volumePositive displacement pump componentsFlexible member pumpsElectronic controllerFoot per second

A method is provided for compressing a gas in a single cycle and in a single cylinder to a pressure of at least 17.2 Mpa with a compression ratio of at least about five to one. The method further comprises dissipating heat from the cylinder during the compression stroke whereby the gas is discharged with a temperature significantly less than isentropic. The apparatus comprises a hollow cylinder and a reciprocable free-floating piston disposed therein. The piston divides the cylinder into: (a) a compression chamber within which a gas can be introduced, compressed, and discharged; and, (b) a drive chamber, into which a hydraulic fluid can be introduced and removed for actuating the piston. The apparatus further comprises a piston stroke length to piston diameter ratio of at least seven to one. For operating the apparatus with a compression ratio of at least five to one, an outlet pressure of at least 17.2 Mpa, and a gas discharge temperature significantly less than isentropic, the apparatus can further comprise a variable displacement hydraulic pump for controlling piston velocity, an electronic controller for maintaining an average piston velocity that is less than 0.5 feet per second, and a heat dissipator for dissipating heat from the cylinder.

Owner:WESTPORT FUEL SYST CANADA INC

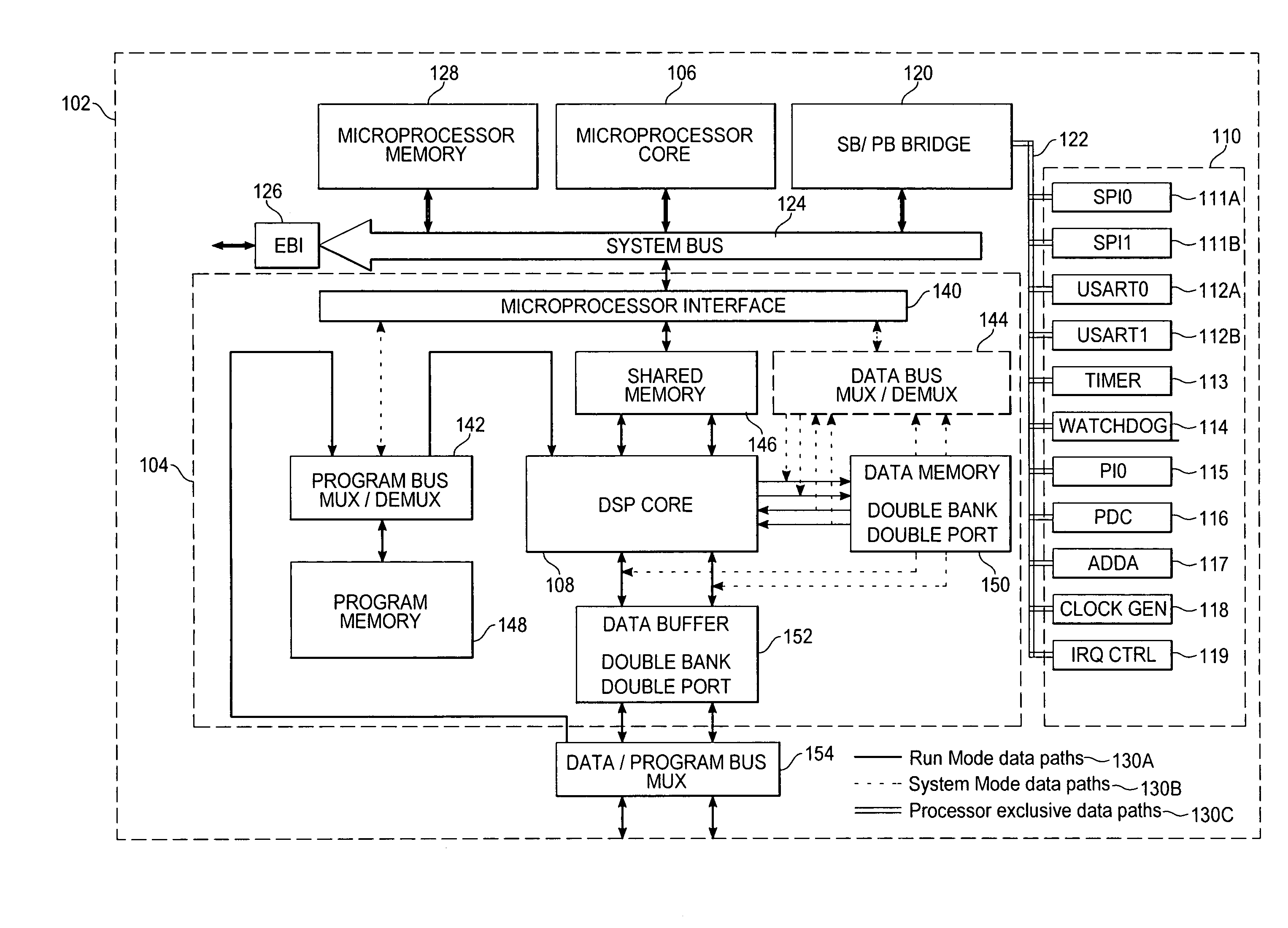

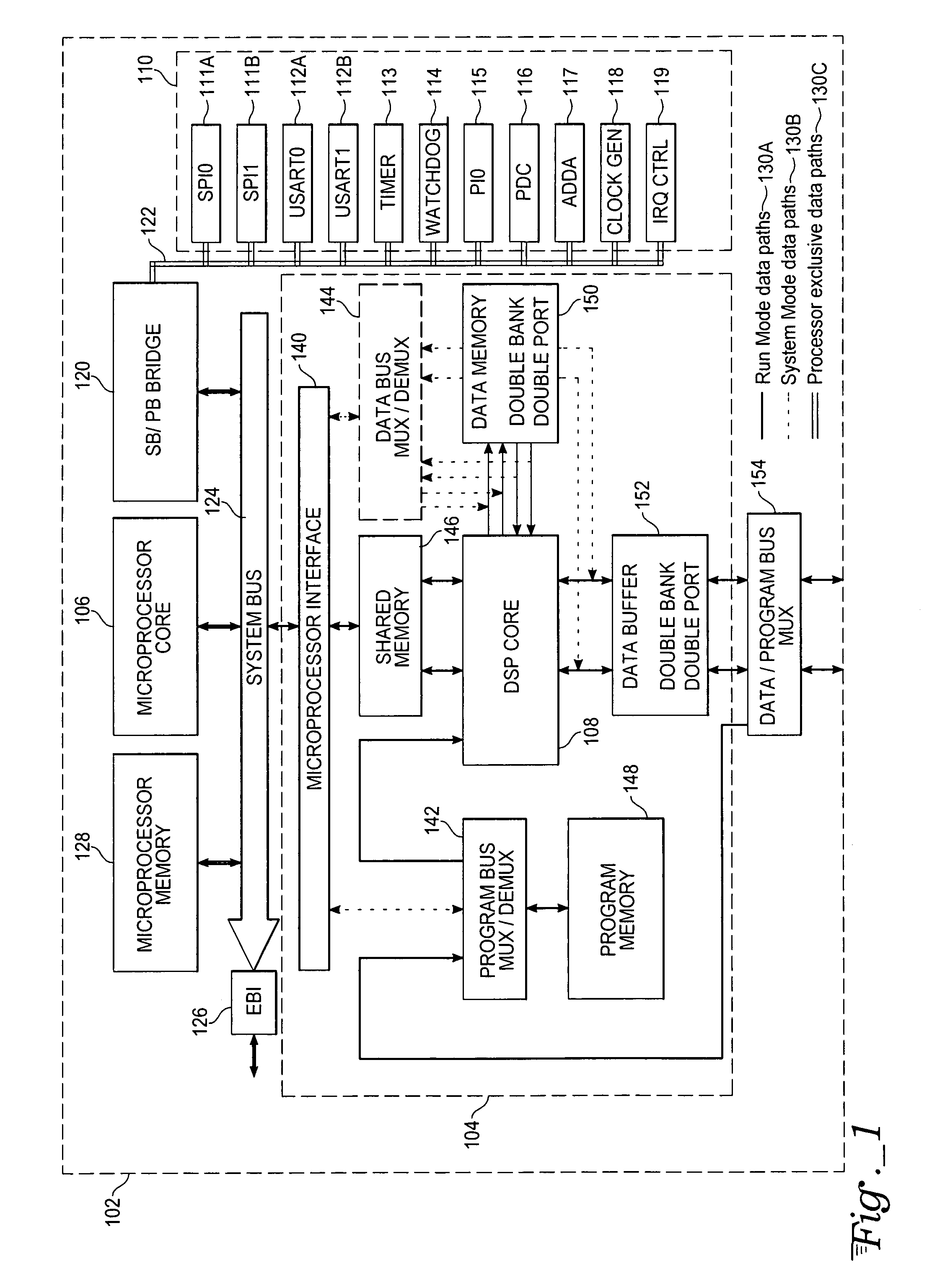

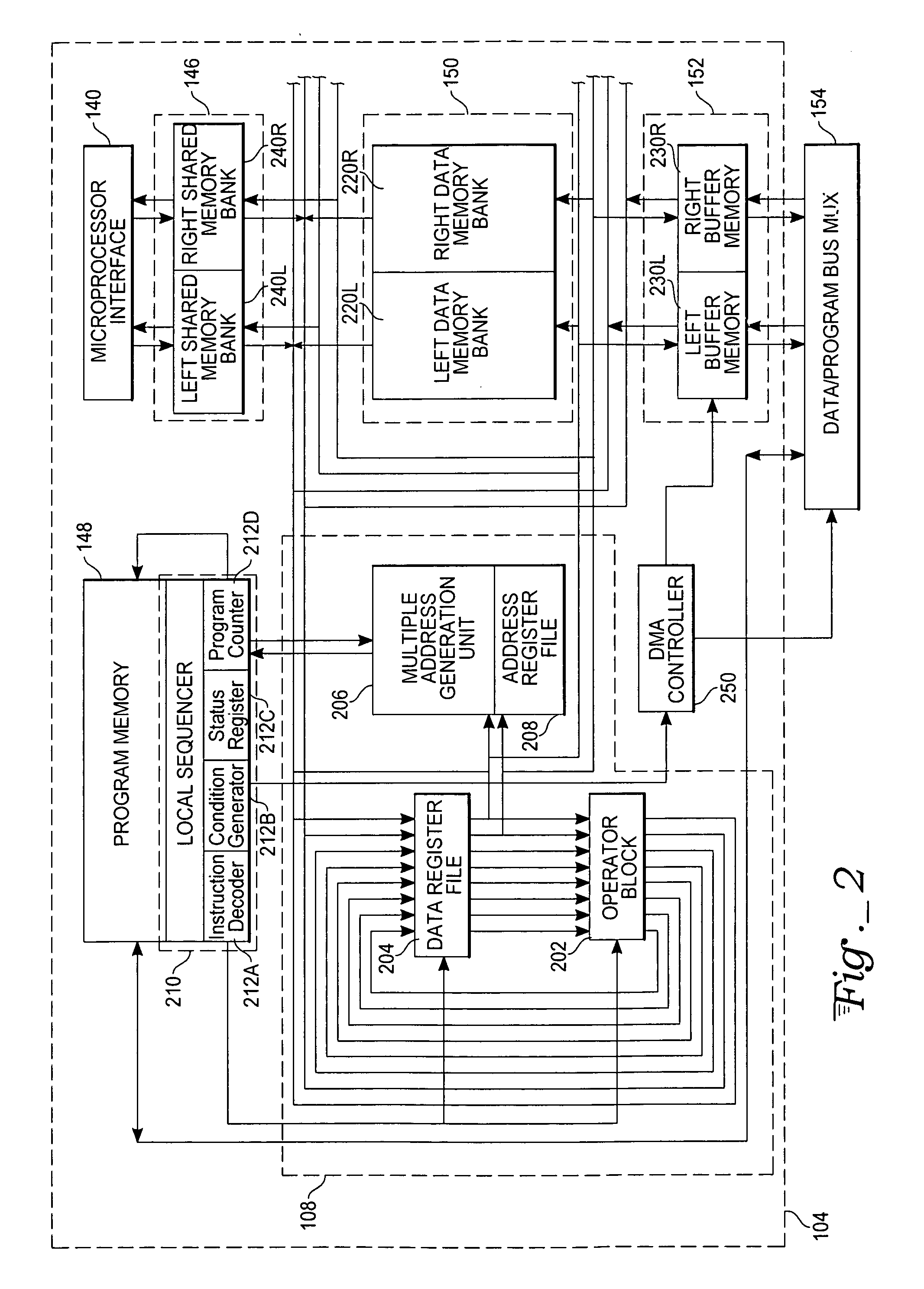

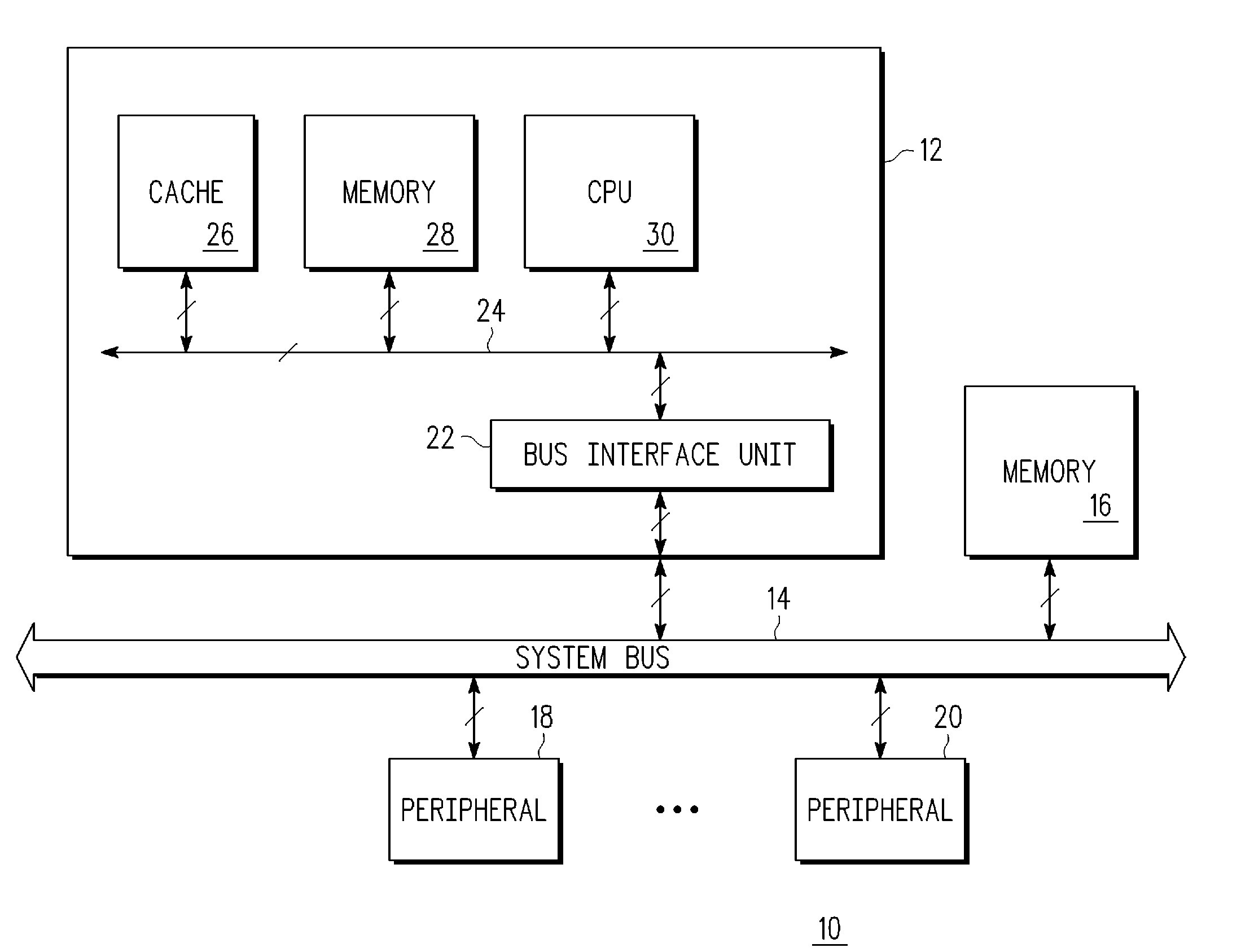

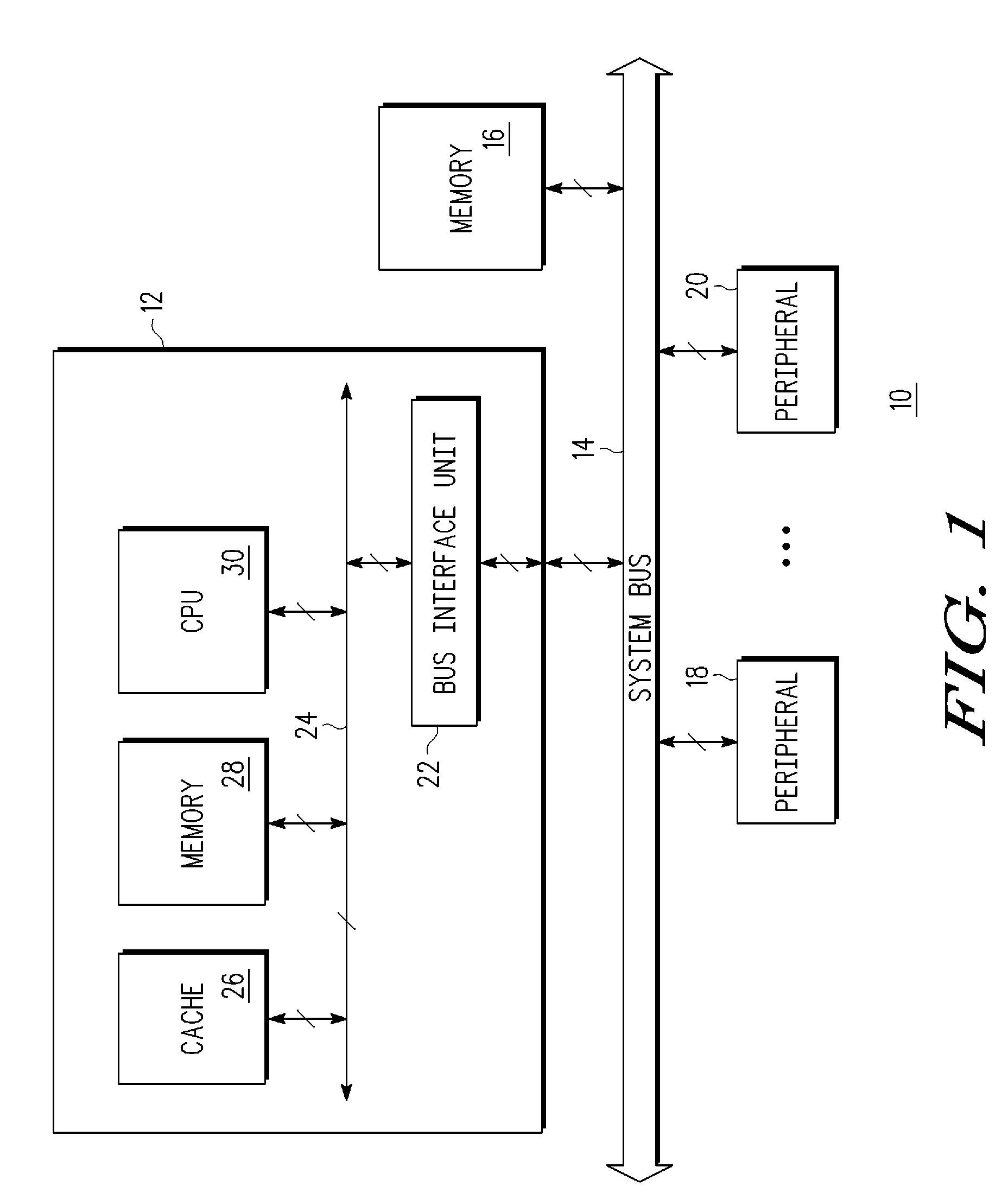

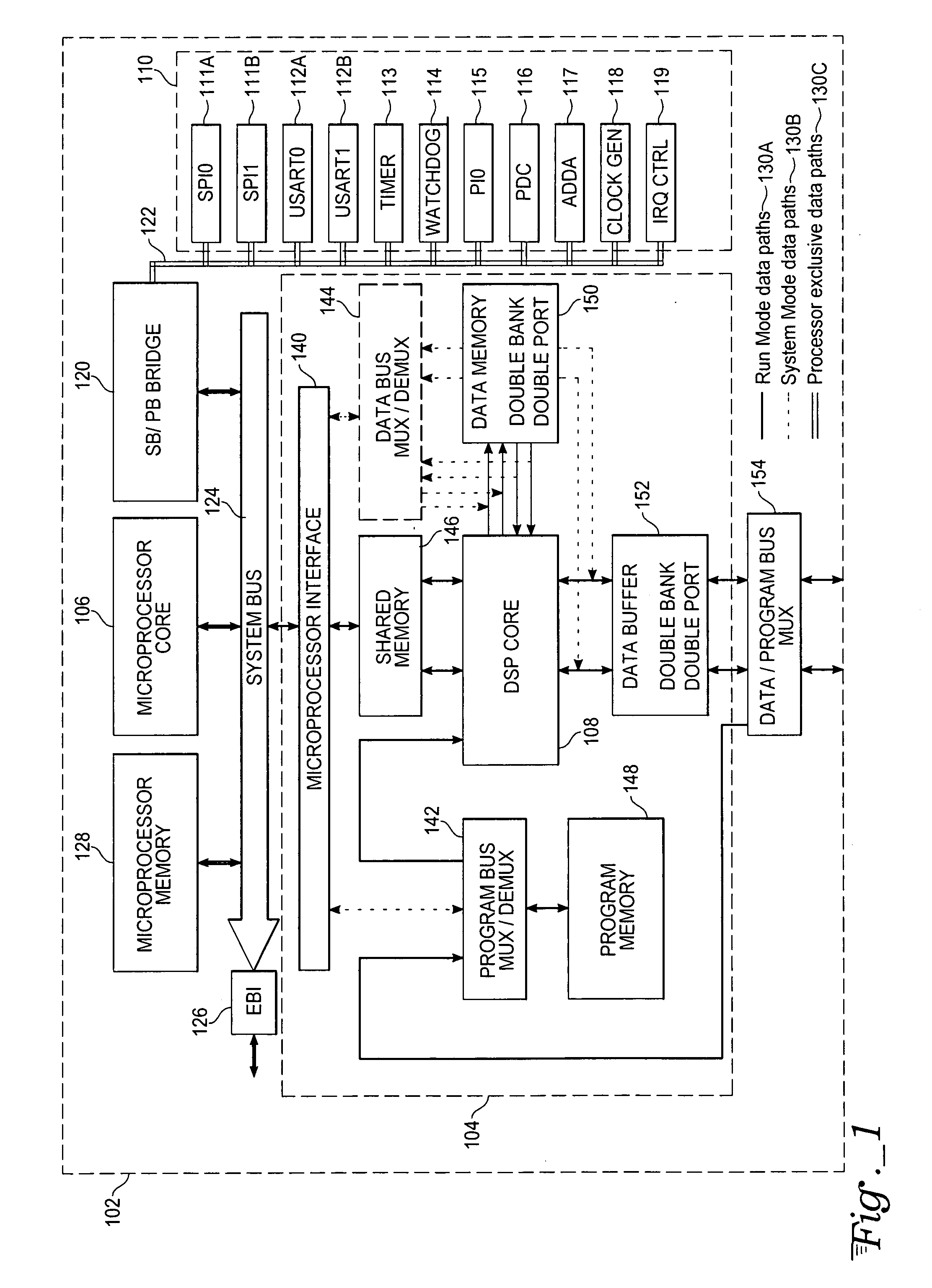

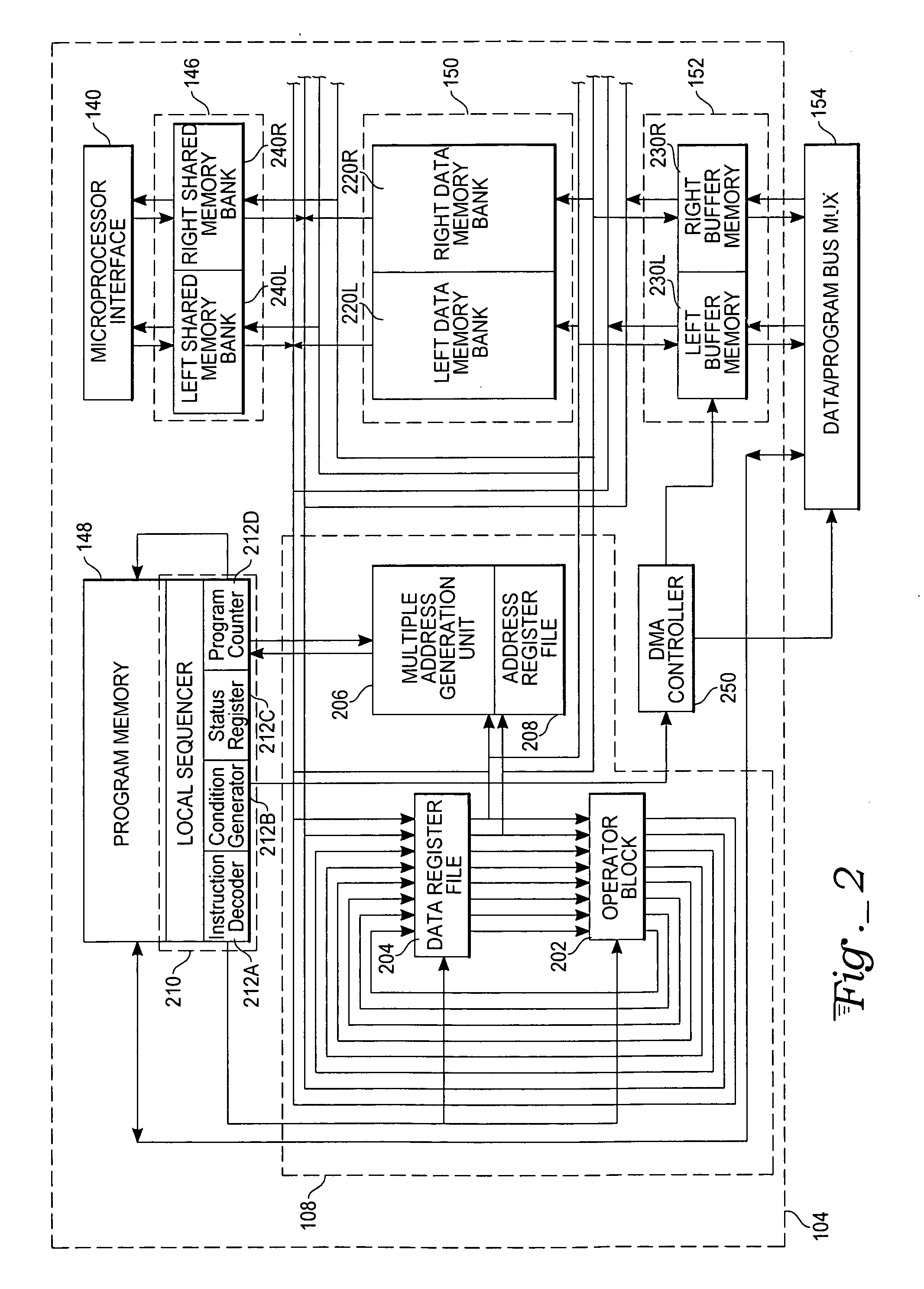

Complex domain floating point VLIW DSP with data/program bus multiplexer and microprocessor interface

ActiveUS7437540B2No performance lossReduce in quantityArchitecture with single central processing unitSpecific program execution arrangementsDigital signal processingProcessing core

A system for digital signal processing, configured as a system on chip (SoC), combines a microprocessor core and digital signal processor (DSP) core with floating-point data processing capability. The DSP core can perform operations on floating-point data in a complex domain and is capable of producing real and imaginary arithmetic results simultaneously. This capability allows a single-cycle execution of, for example, FFT butterflies, complex domain simultaneous addition and subtraction, complex multiply accumulate (MULACC), and real domain dual multiply-accumulators (MACs). The SoC may be programmed entirely from a microprocessor programming interface, using calls from a DSP library to execute DSP functions. The cores may also be programmed separately. Capability for programming and simulating the entire SoC are provided by a separate programming environment. The SoC may have heterogeneous processing cores in which either processing core may act as master or slave, or both cores may operate simultaneously and independently.

Owner:ATMEL CORP

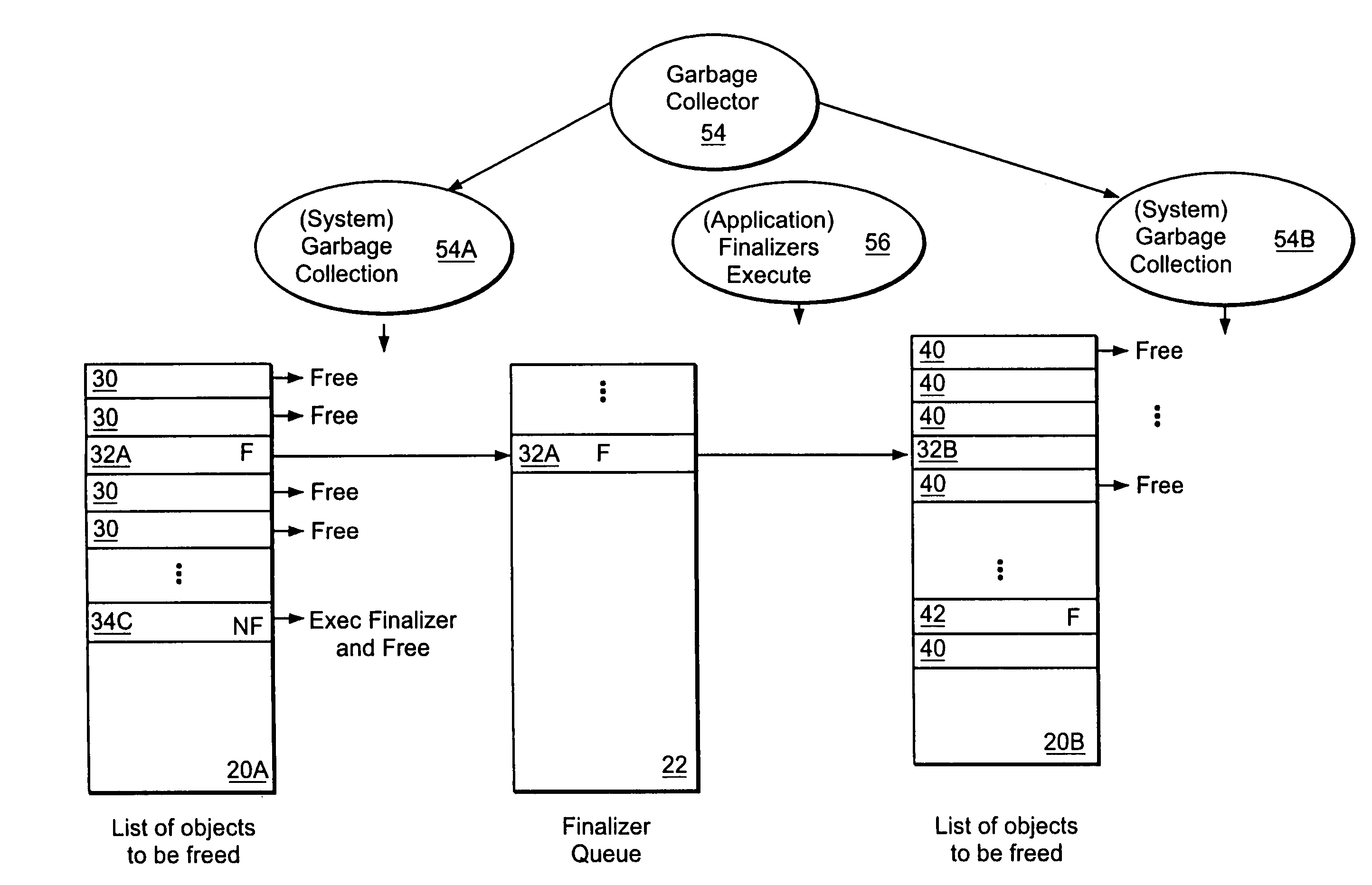

Timely finalization of system resources

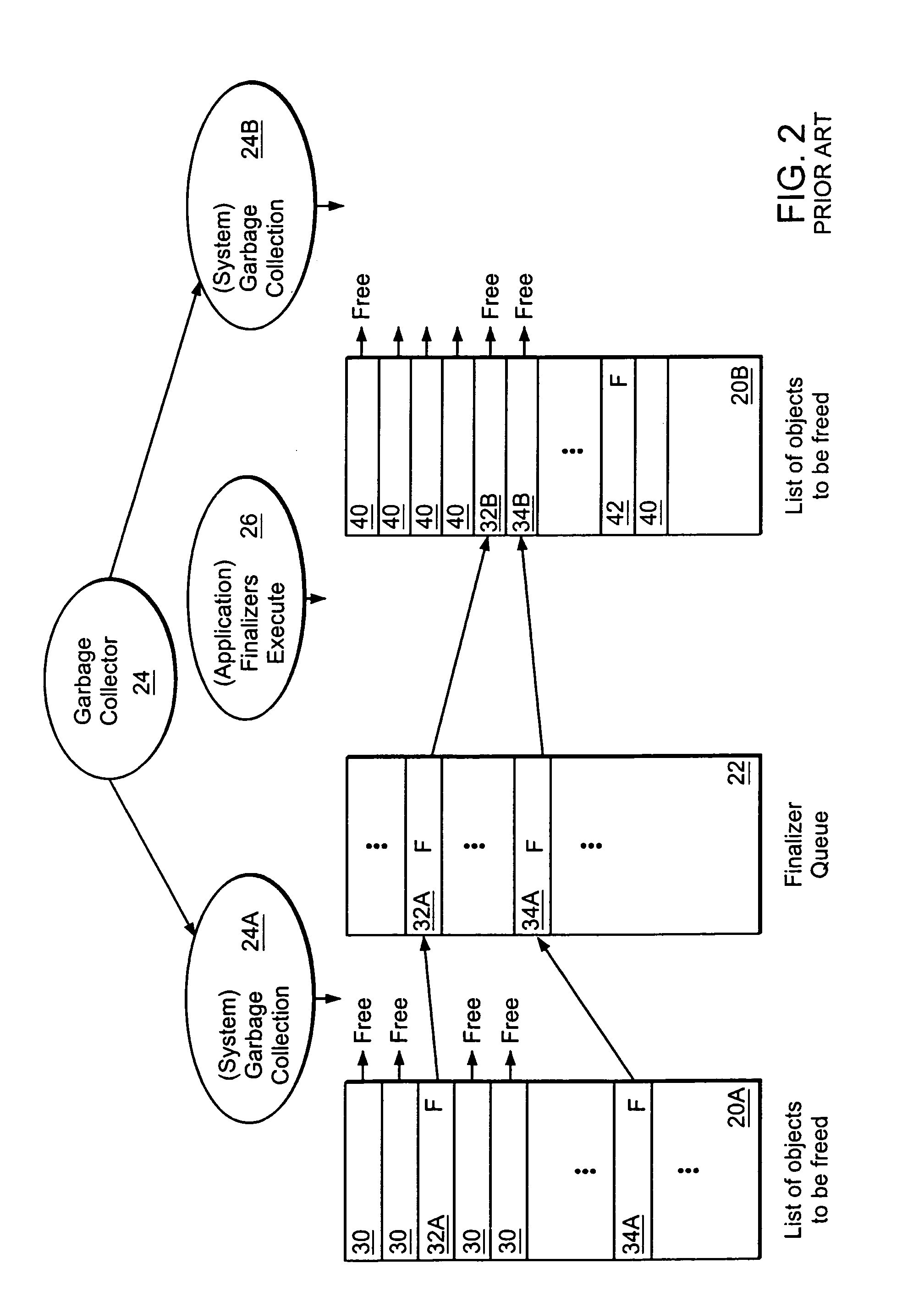

ActiveUS7069279B1Timely and efficient cleanup of system resourceTimely and efficientData processing applicationsProgram controlWaste collectionSingle cycle

A garbage collector, from time to time, and within a single cycle, determines objects that are eligible to have their associated memory freed; executes high-priority finalizers associated with such eligible objects as are determined; and after execution of a high-priority finalizer, deallocates the memory of the associated object. The garbage collector queues references to eligible objects that have non-high-priority finalizers in a list. After garbage collection is completed, a finalizer thread runs the queued non-high-priority finalizers and marks the associated objects as ready for deallocation. The garbage collector, during a subsequent cycle, then deallocates the memory associated with marked objects.

Owner:ORACLE INT CORP

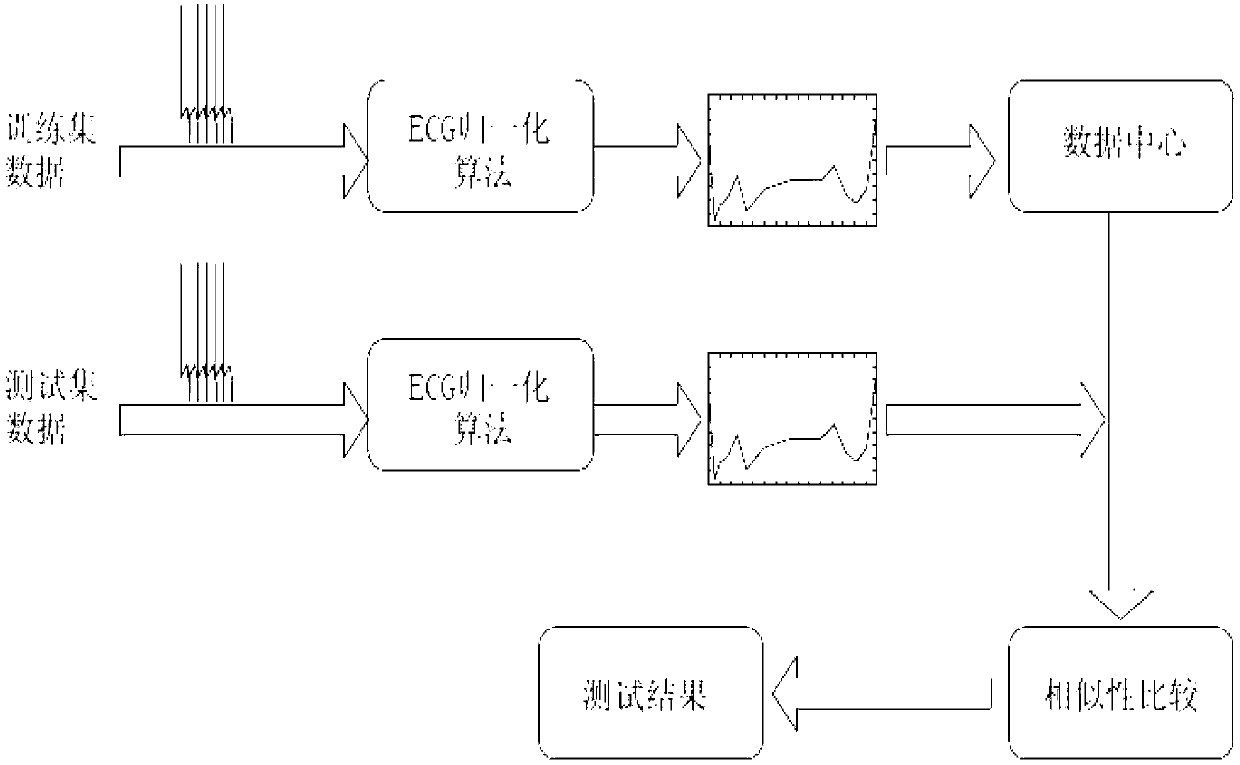

Electrocardiosignal processing method and electrocardiosignal processing system

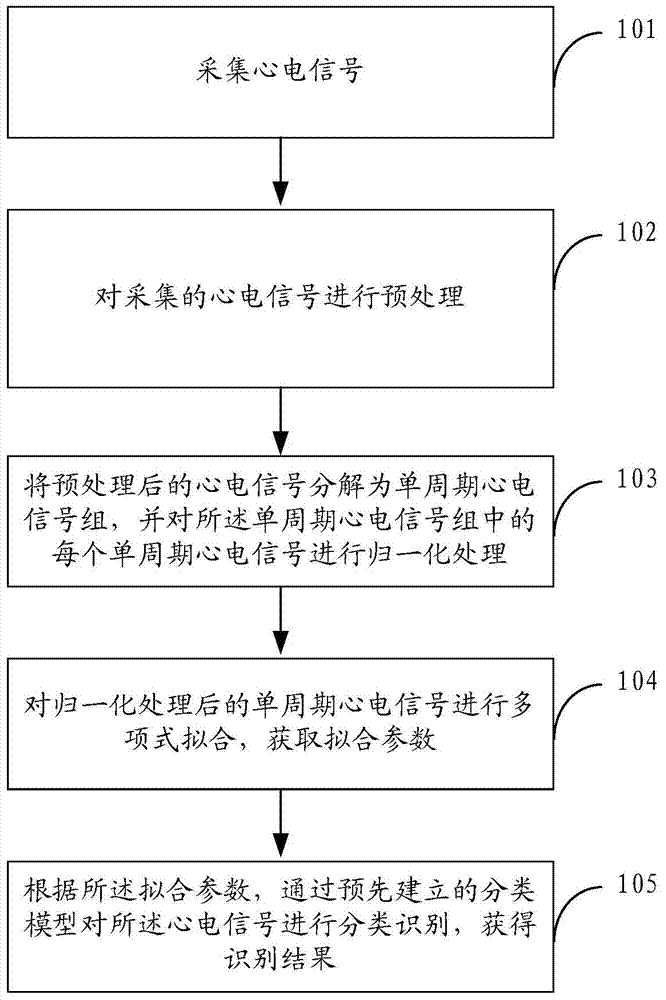

ActiveCN103610457AImprove robustnessAvoid errorsDiagnostic recording/measuringSensorsEcg signalFeature vector

The invention provides an electrocardiosignal processing method and an electrocardiosignal processing system which are applicable to the technical field of data processing. The electrocardiosignal method includes: collecting electrocardiosignals; preprocessing collected electrocardiosignals; disintegrating preprocessed electrocardiosignals into single-cycled electrocardiosignal groups and subjecting each single-cycled electrocardiosignal in the single-cycled electrocardiosignal groups to normalization processing; performing the single-cycled electrocardiosignal subjected to the normalization processing to polynomial fitting to acquire fitting parameters; allowing pre-established disaggregated models to perform classification and identification on the electrocardiosignals according to the fitting parameters to acquire identification results. The polynomial fitting parameters adopted as feature vectors of electrocardiosignal classification are better in robustness, and errors brought by baseline drift of the electrocardiosignals and heart rate variation can be effectively avoided through the normalization processing performed on the single-circled electrocardiosignals.

Owner:SHENZHEN INST OF ADVANCED TECH

Method of estimating the maximum power generation capacity and for controlling a specified power reserve of a single cycle or combined cycle gas turbine power plant, and a power generating system for use with said method

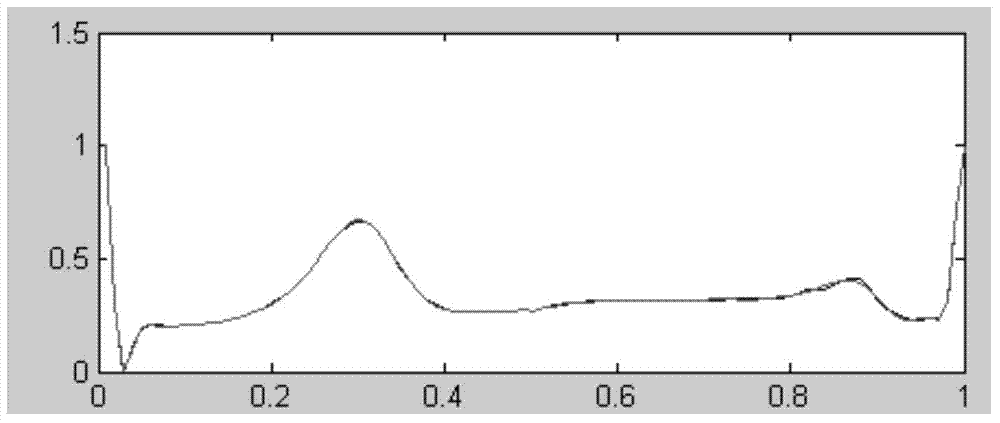

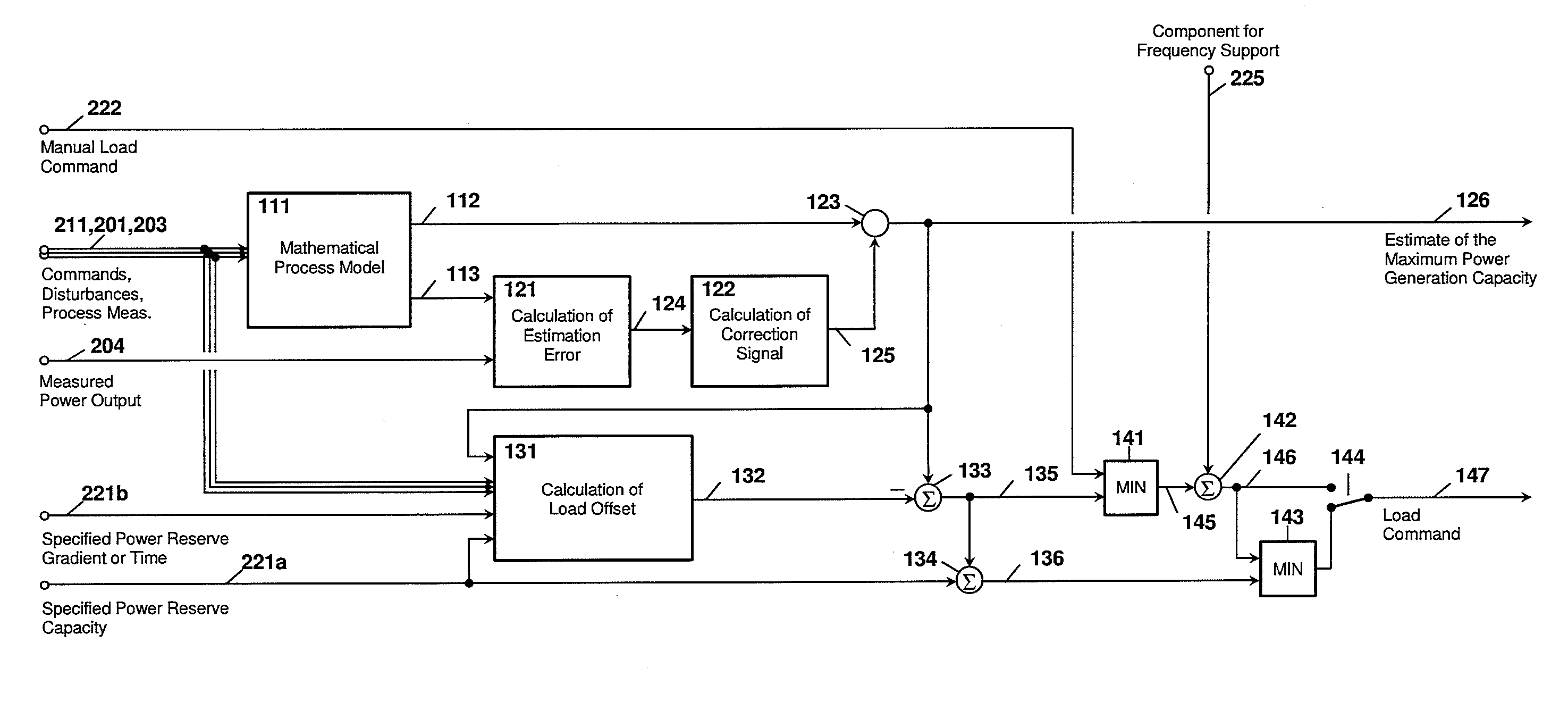

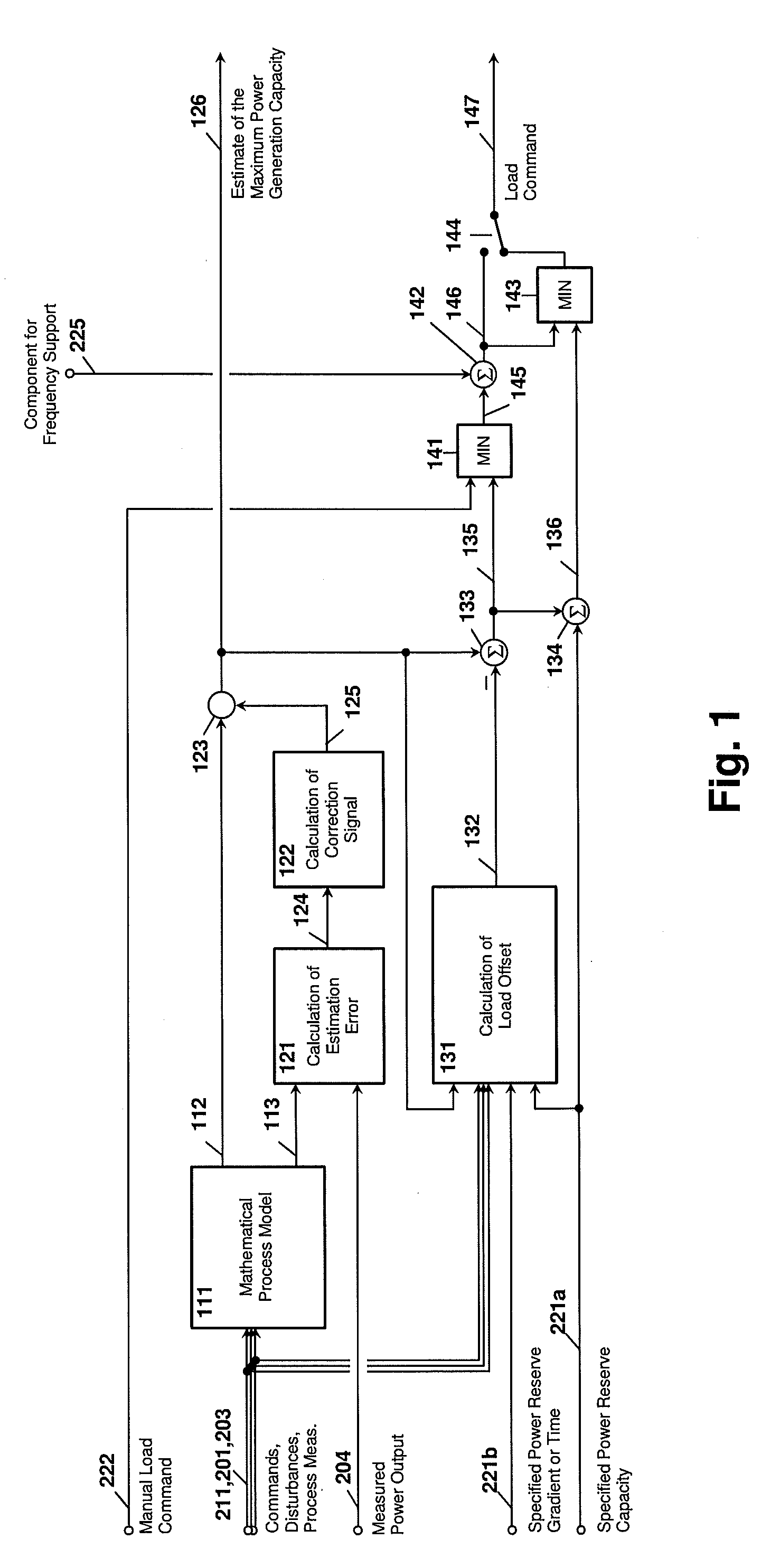

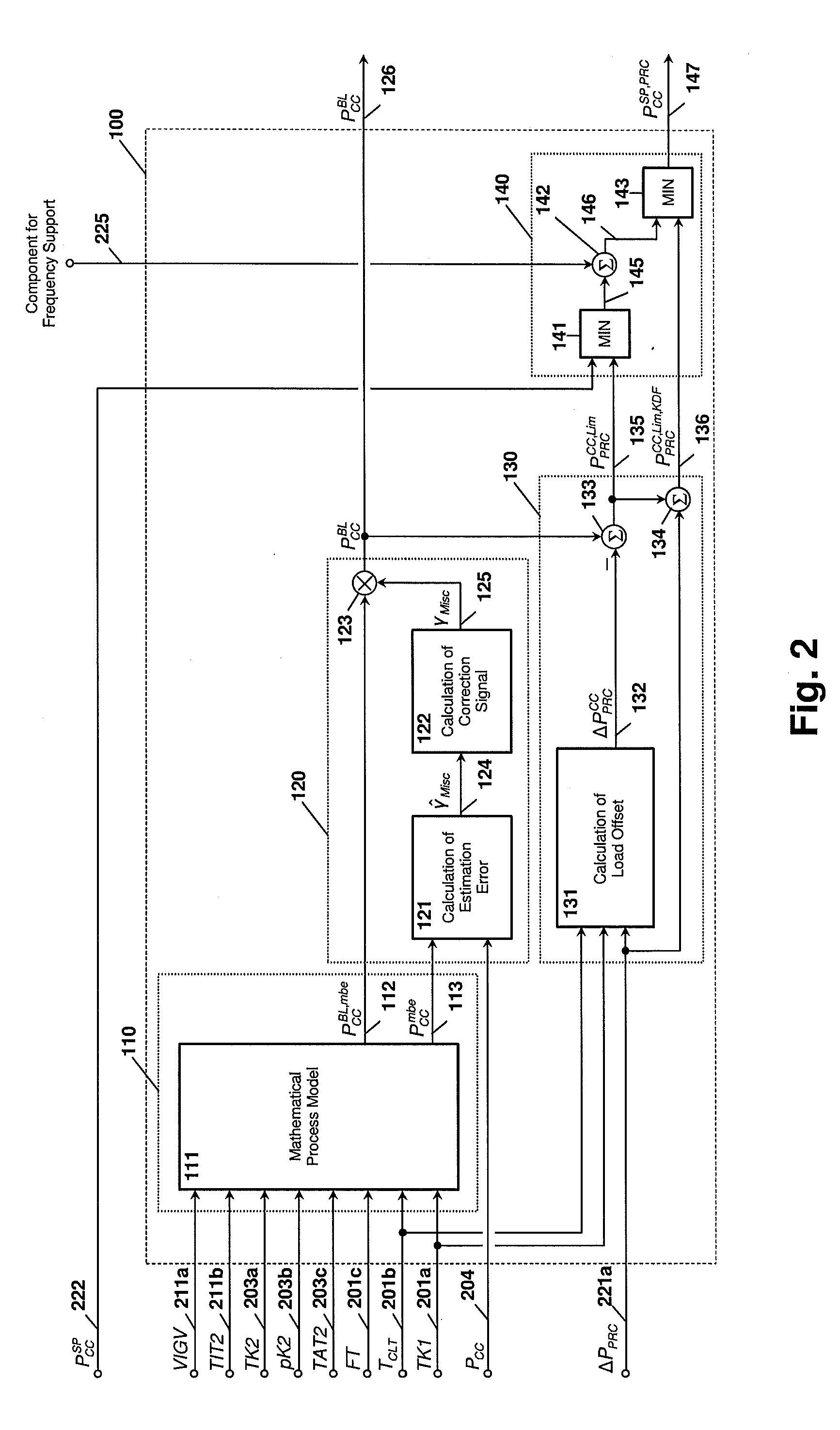

An estimation unit can estimate, on a real-time basis, a maximum power generation capacity of a single cycle or combined cycle gas turbine power plant. For example, the actual power output and the maximum power generation capacity can be calculated relying on a mathematical process model. Subsequently, the calculated actual power output can be compared with the measured power output yielding a model-estimation error. Based on the model-estimation error, a correction signal can be deduced, to correct the calculated maximum power generation capacity. A controller can maintain a specified power reserve. The controller can use an estimate of the maximum power generation capacity as a reference, subtract a load offset, and apply the resulting signal as upper limit of the load set-point.

Owner:ANSALDO ENERGIA IP UK LTD

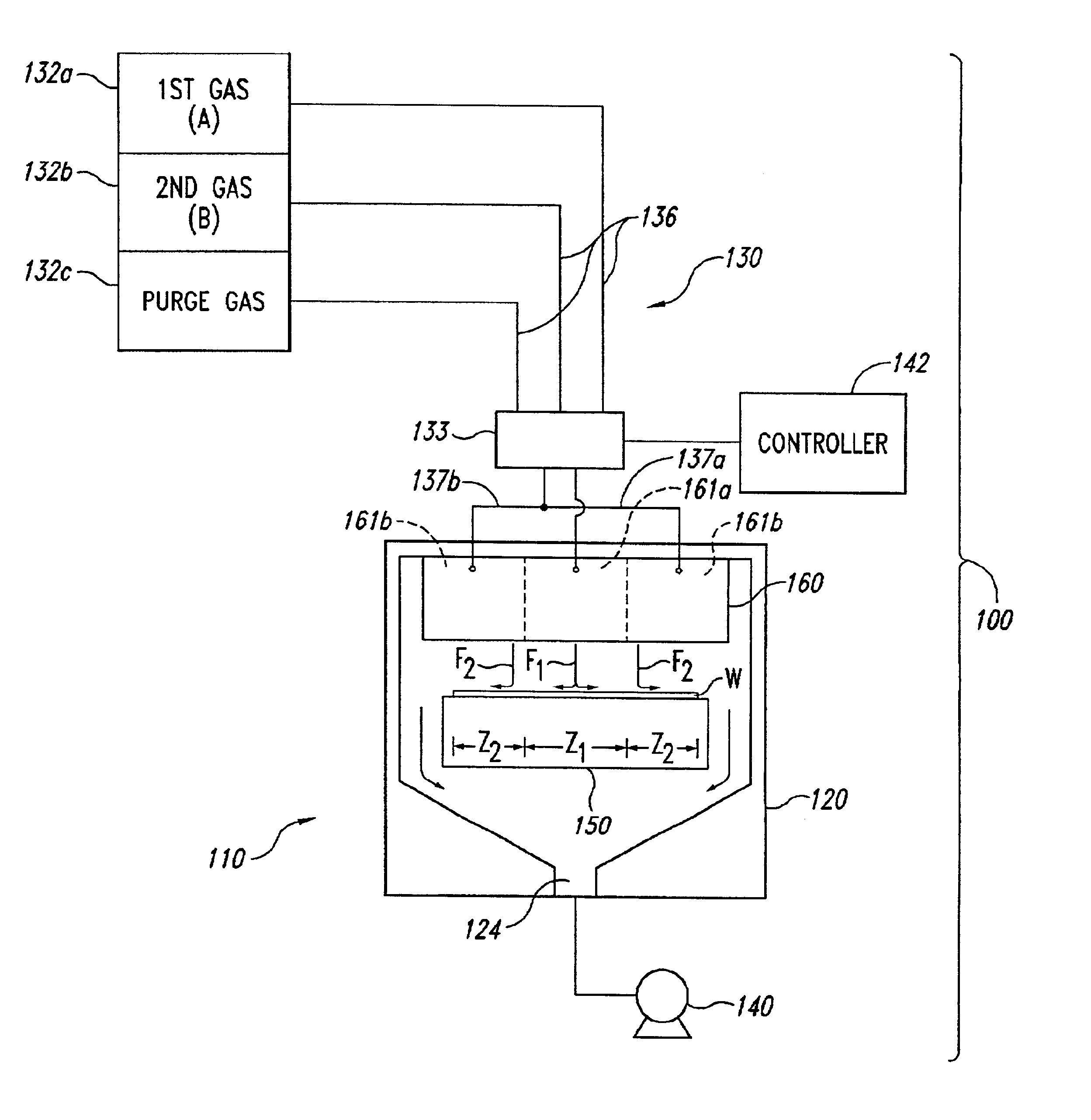

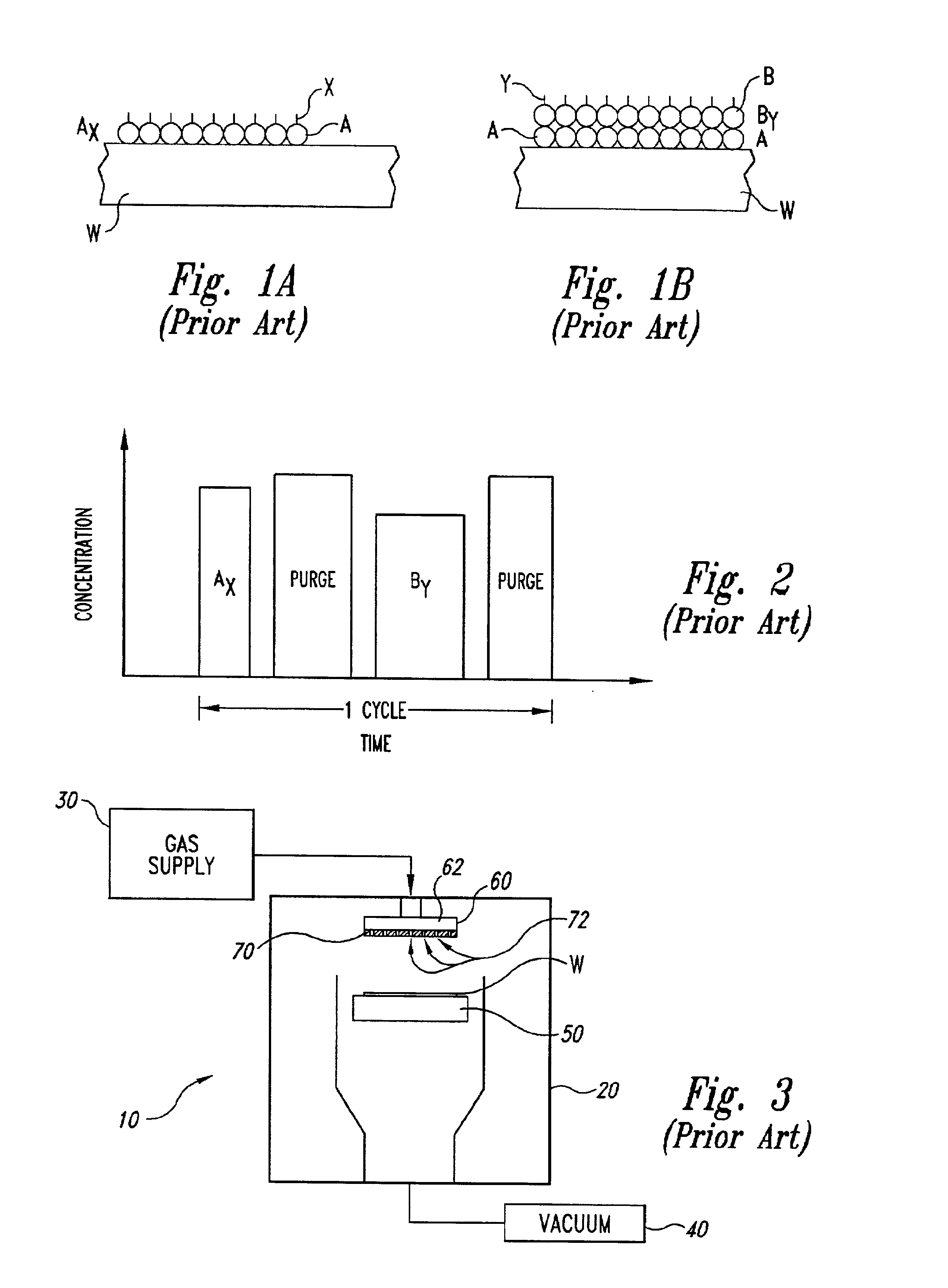

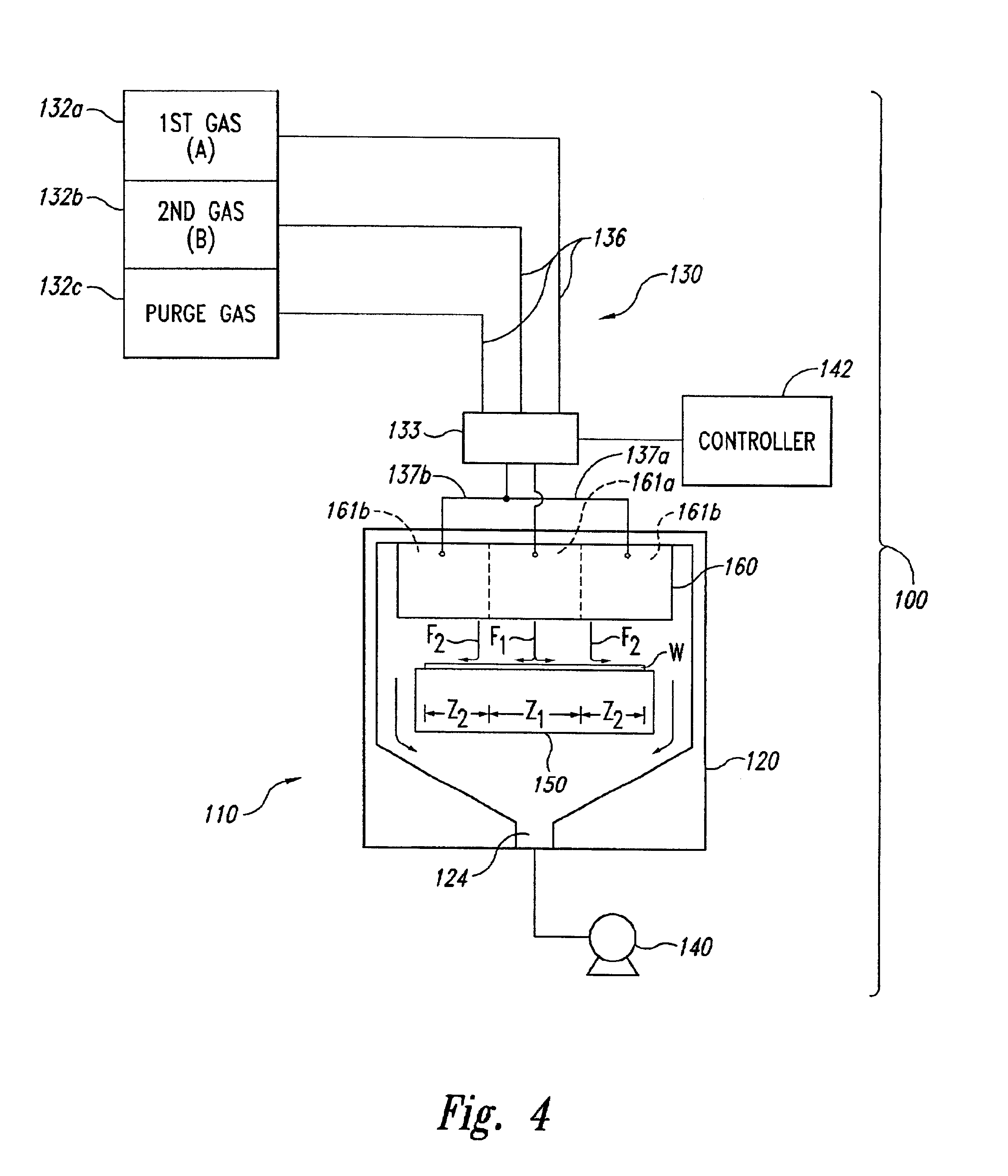

Methods for forming thin layers of materials on micro-device workpieces

InactiveUS6861094B2Reduce processing timeSemiconductor/solid-state device manufacturingChemical vapor deposition coatingThin layerEngineering

A method of forming a layer on a micro-device workpiece includes dispensing a first pulse of a first precursor at a first region of the workpiece to flow toward a second region of the workpiece. The second region of the workpiece is located radially outward relative to the first region of the workpiece. The embodiment of this method further includes dispensing a first pulse of a purge gas at the first region of the workpiece to flow toward the second region of the workpiece after terminating the first pulse of the first precursor. Additionally, this embodiment also includes dispensing a second pulse of a first precursor at the second region of the workpiece to flow radially outward concurrently with dispensing the first pulse of a purge gas in the first region of the workpiece. The first pulse of the purge gas is terminated at the first region of the workpiece, and the second pulse of the first precursor is terminated at the second region. At this stage, the method further includes dispensing a first pulse of a second precursor at the first region of the workpiece to flow radially outward toward the second region, and dispensing a second pulse of the purge gas at the second region of the workpiece to flow radially outward concurrently with the first pulse of the second precursor in the first region. A single cycle of the process can further include dispensing a third pulse of the purge gas onto the first region of the workpiece to flow radially outward after terminating the first pulse of the second precursor, and concurrently dispensing a second pulse of the second precursor in the second region to flow radially outward.

Owner:MICRON TECH INC

Analog-to-digital conversion in pixel arrays

ActiveUS20090256735A1Improve accuracyAvoid the needAnalogue/digital conversionTelevision system detailsExposure periodAnalog signal

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

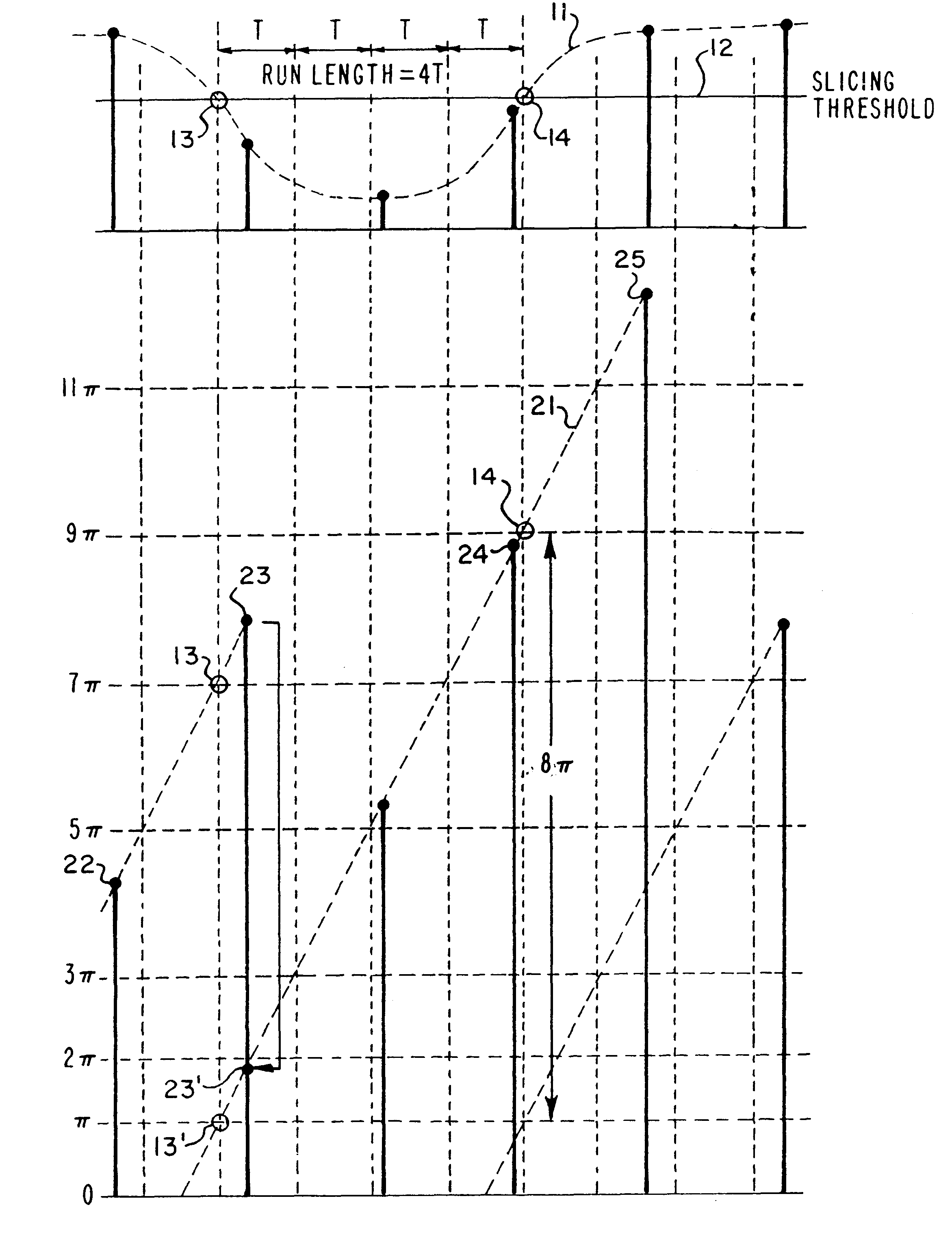

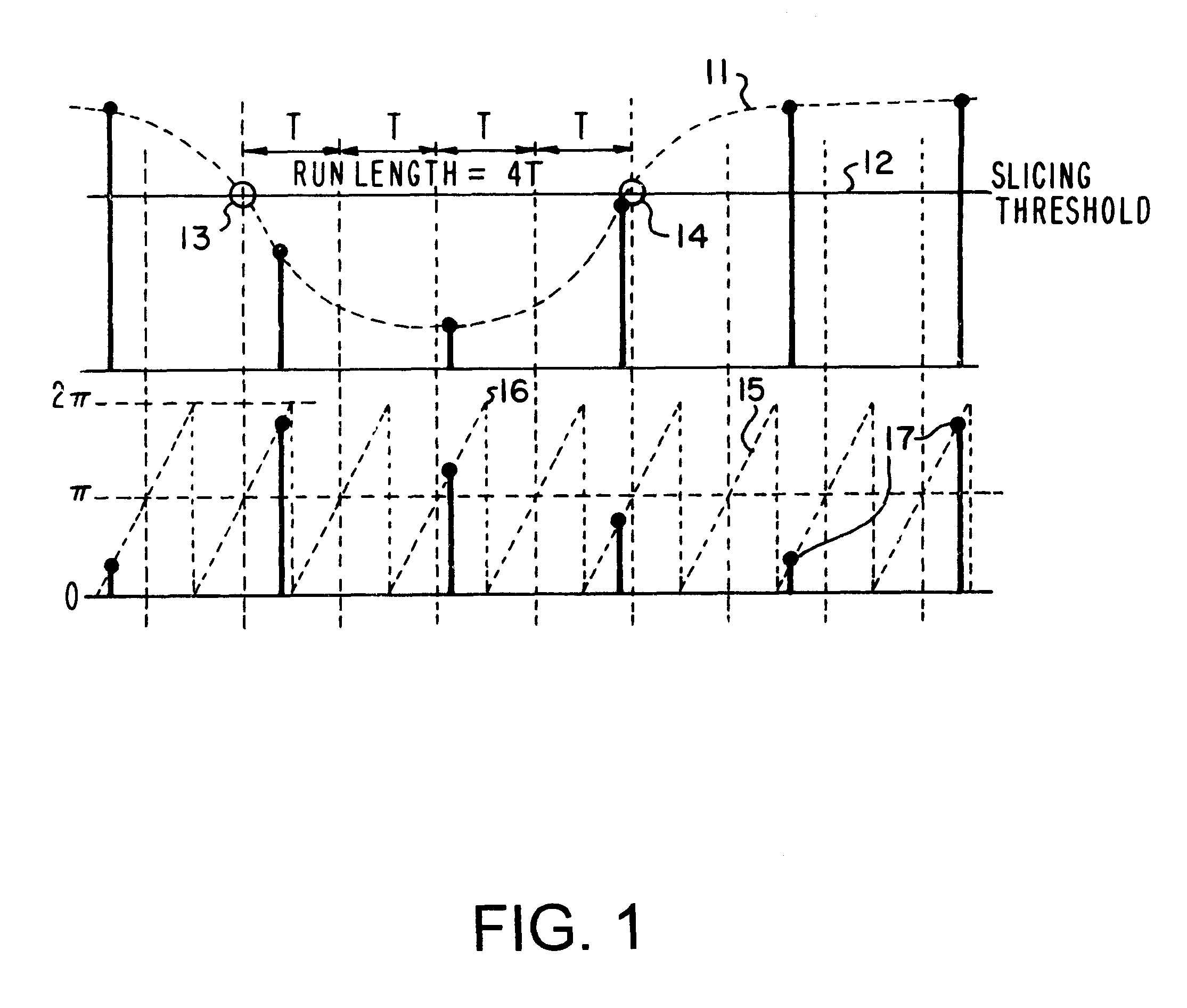

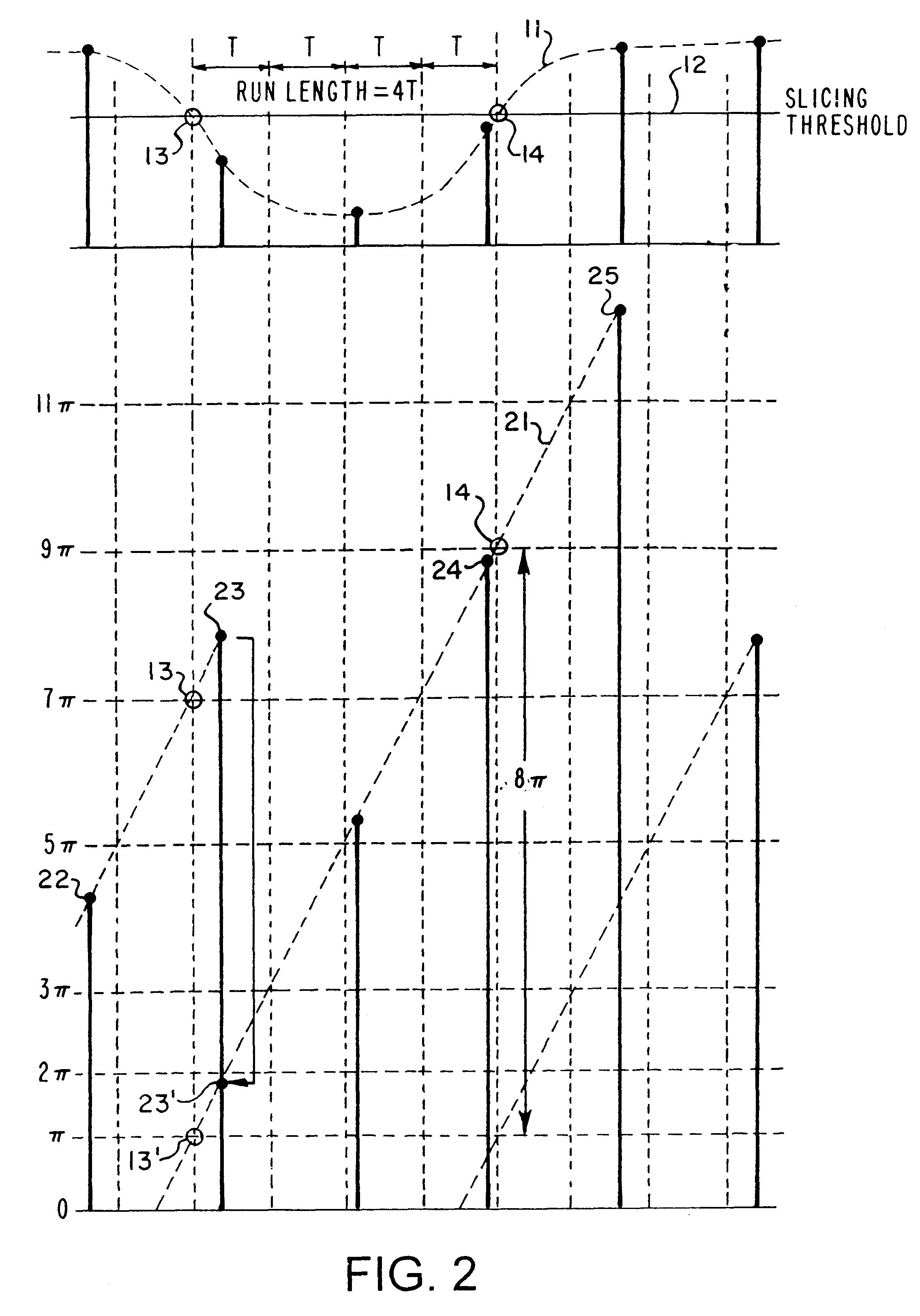

Pulse run-length measurement for HF data signal by dividing accumulated phase difference between first and second zero-crossings by single-cycle range using multiple cycle range sawtooth waveform

InactiveUS6389548B1Modulated-carrier systemsDigital data processing detailsPhase differenceLength measurement

A system and method for accurately measuring a pulse run length in a high frequency (HF) data signal while utilizing a low analog-to-digital conversion (ADC) sampling rate. Four bits are added to the most significant end of an oscillator's accumulator register so that the oscillator generates a sawtooth clock waveform ranging in phase from zero (0) to 32pi radians. An interpolator detects a first zero-crossing transition of the HF data signal at the leading edge of the pulse run length, and a phase detector measures a first phase increment at that time. The MSBs of the accumulator register is then initialized to place the measured first phase increment in a range between zero (0) and 2pi radians. The accumulator register then accumulates phase increments until the interpolator detects a second zero-crossing transition of the HF data signal at the trailing edge of the pulse run length, and the phase detector measures a second phase increment when the second zero-crossing transition is detected. An accumulated phase difference is calculated by subtracting the initialized first phase increment from the measured second phase increment. The pulse run length is then obtained by dividing the accumulated phase difference by 2pi.

Owner:CEVA IRELAND +1

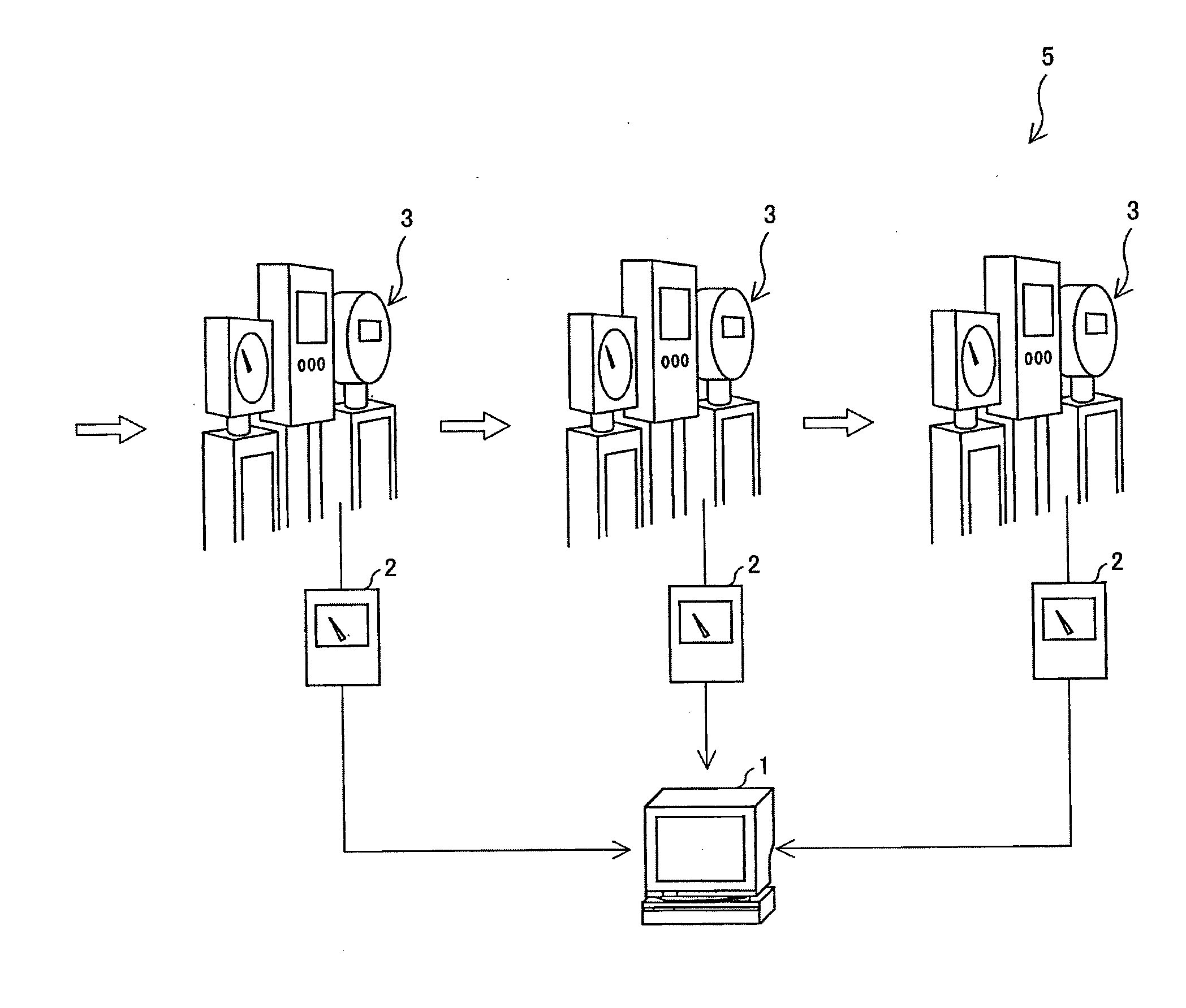

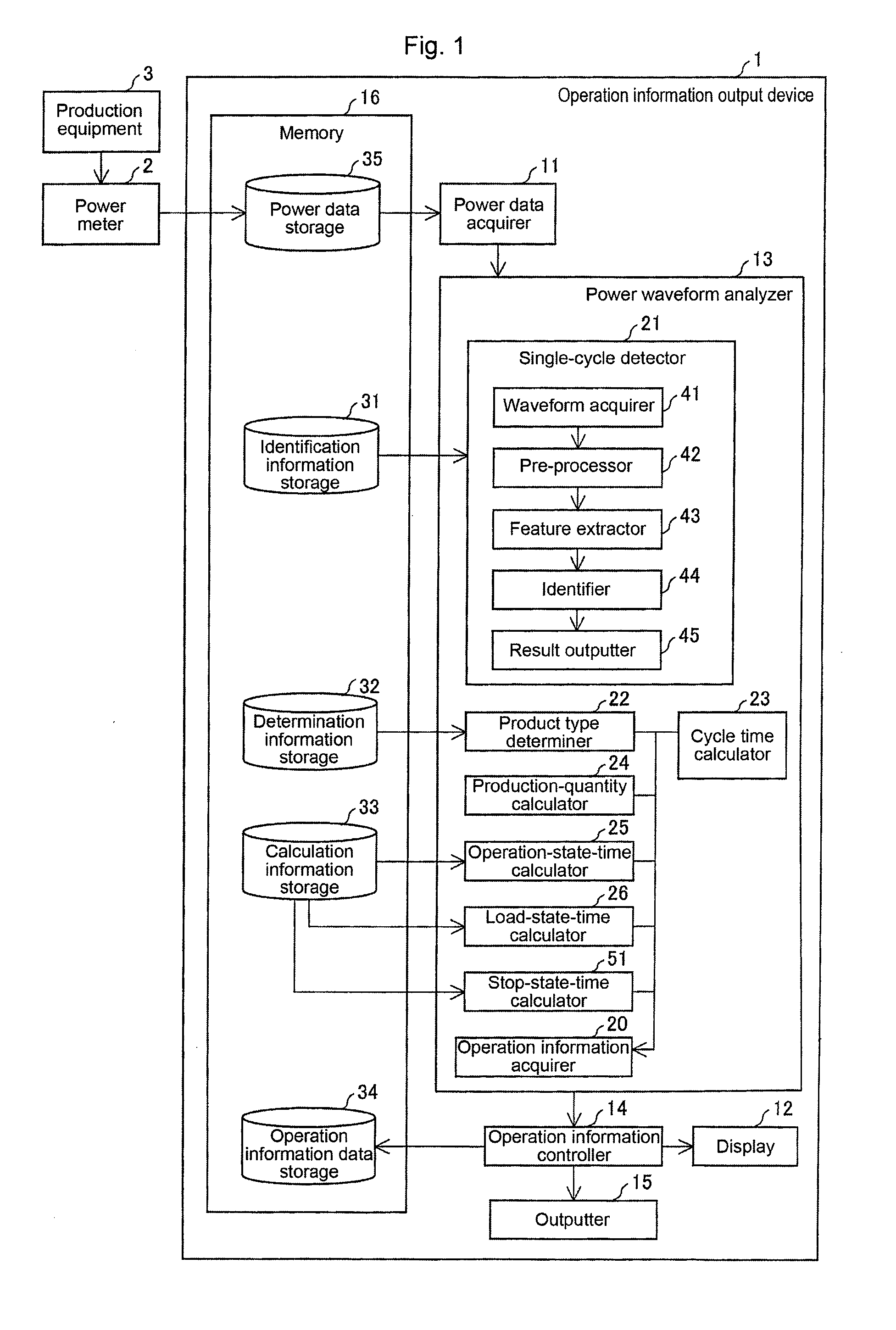

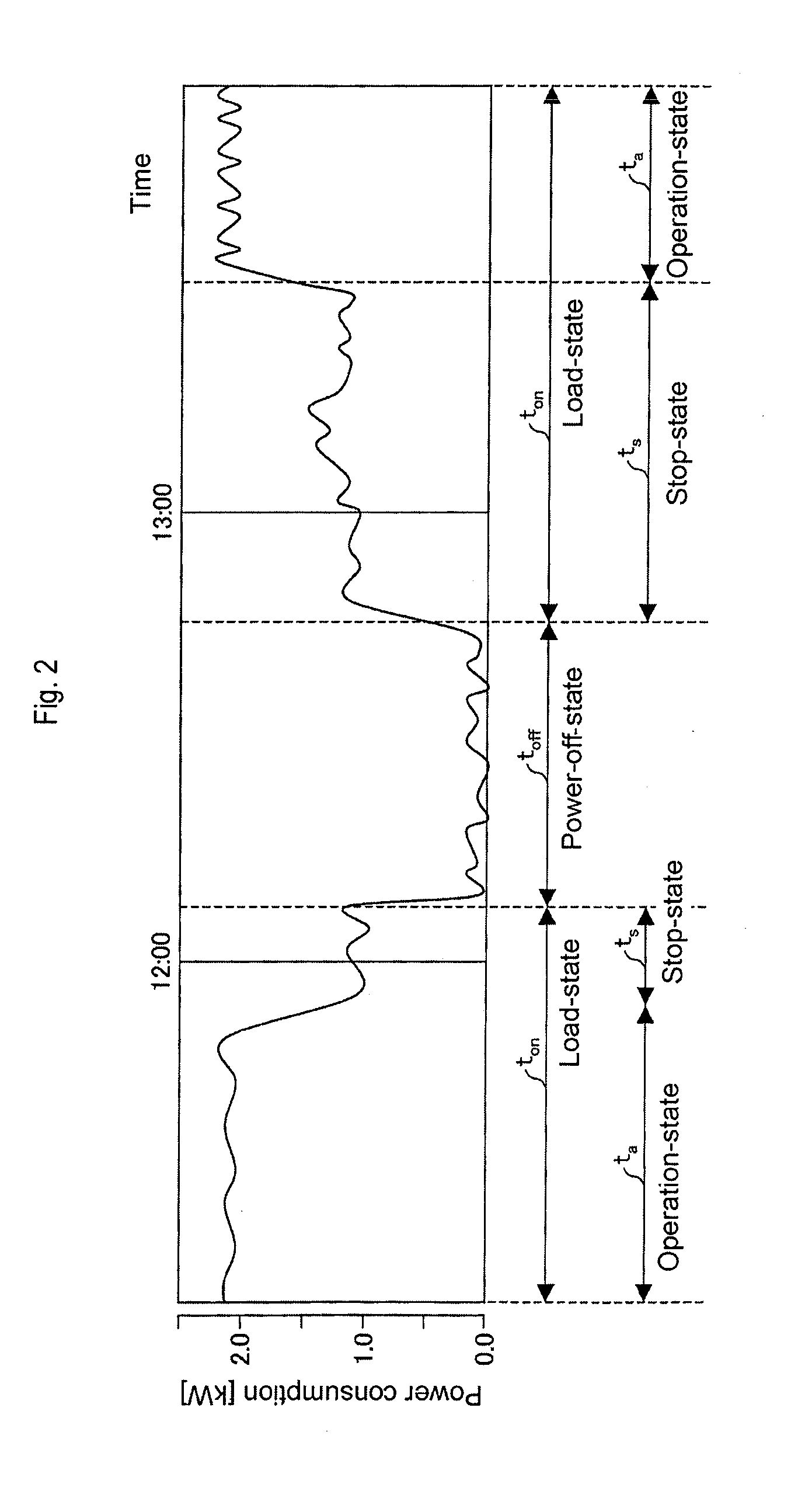

Operation information output device, method for controlling operation information output device, monitoring device, method for controlling monitoring device, and control program

An operation information output device includes: a power data acquirer that acquires time-series data of a physical quantity consumed or generated when production equipment executes a process; a single-cycle detector that detects time-series data of predetermined duration from the time-series data acquired by the power data acquirer, and an operation information acquirer that acquires operation information of the production equipment by use of the time-series data detected by the single-cycle detector, hence it becomes possible to easily calculate and determine detailed operation information.

Owner:ORMON CORP

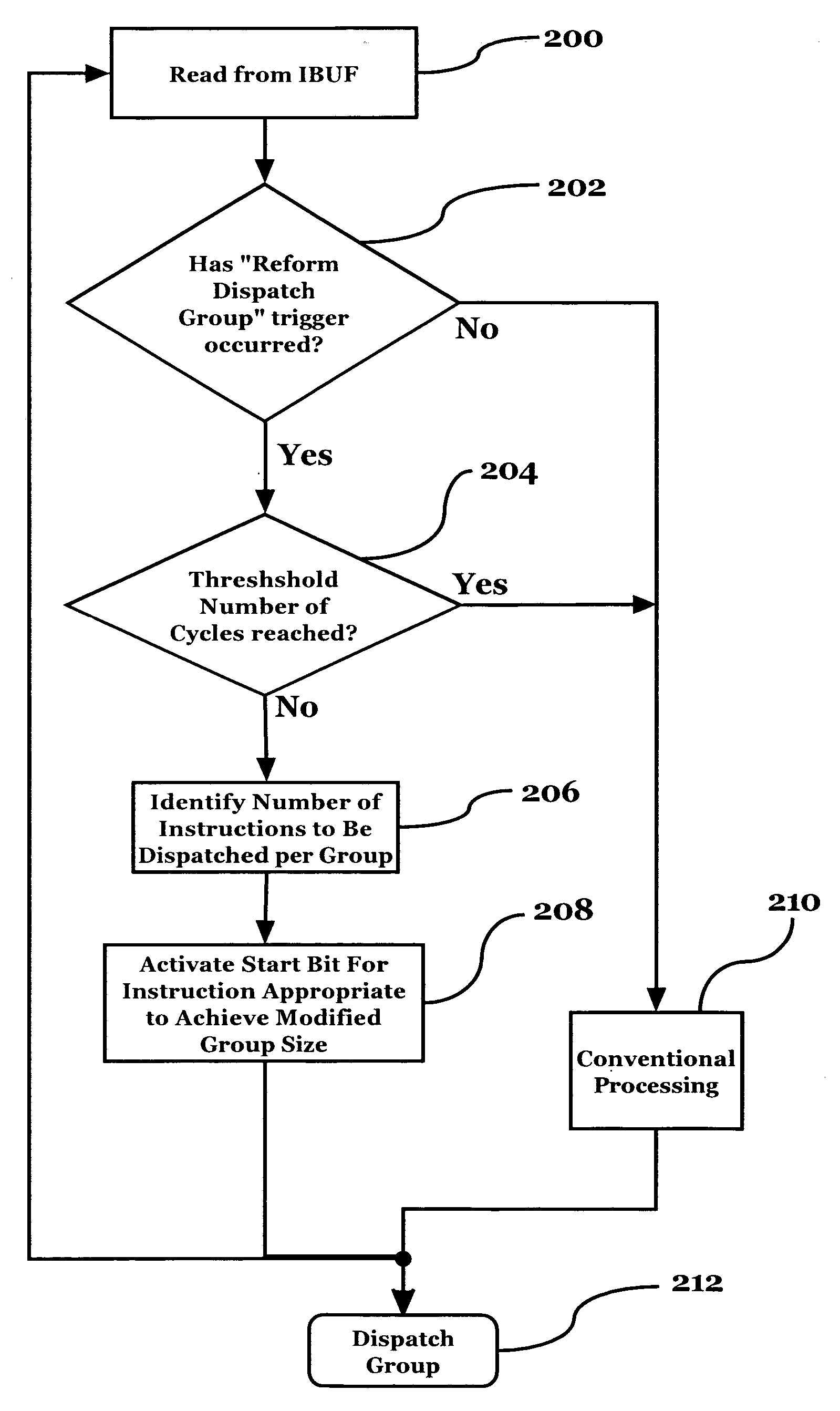

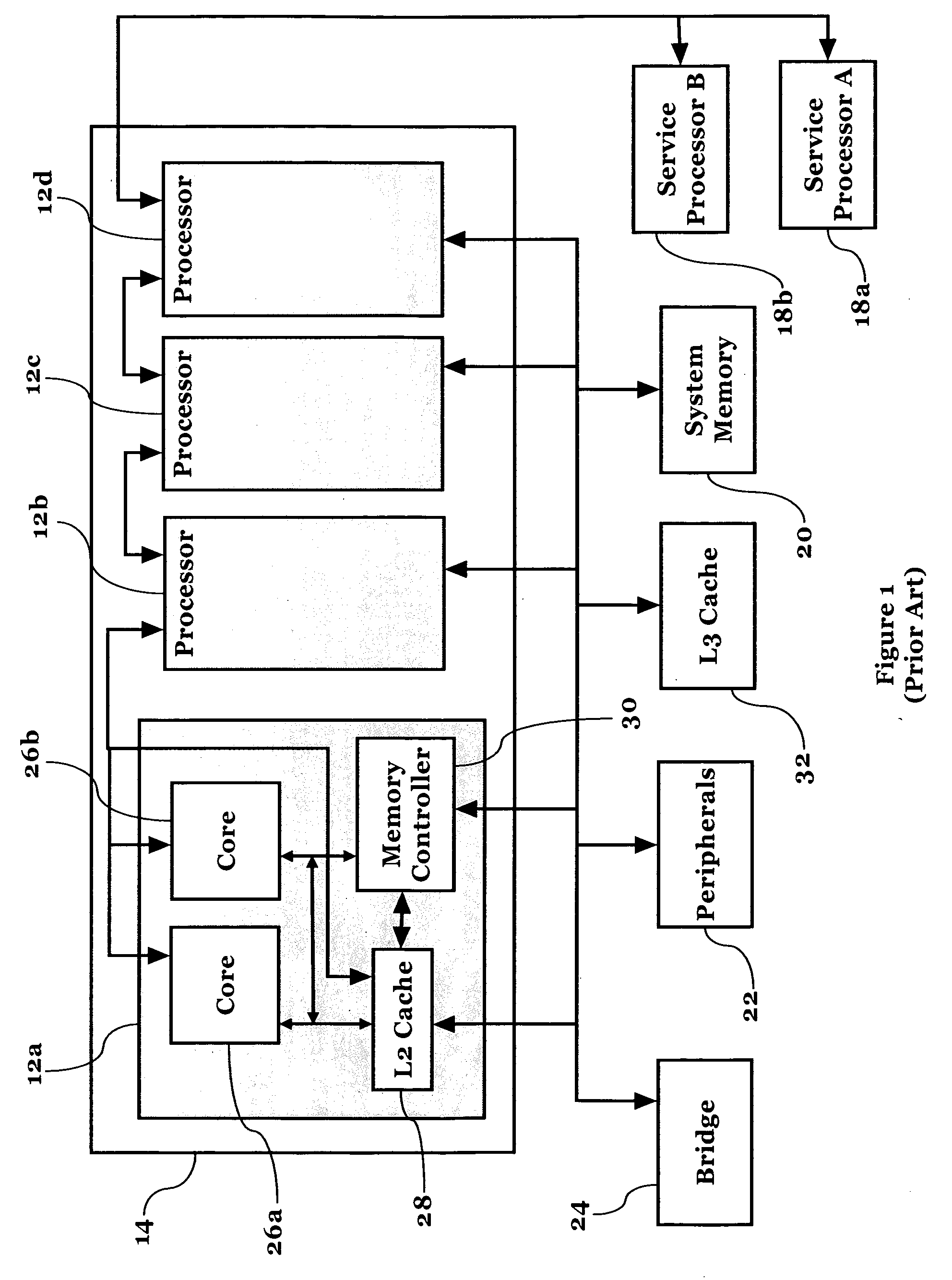

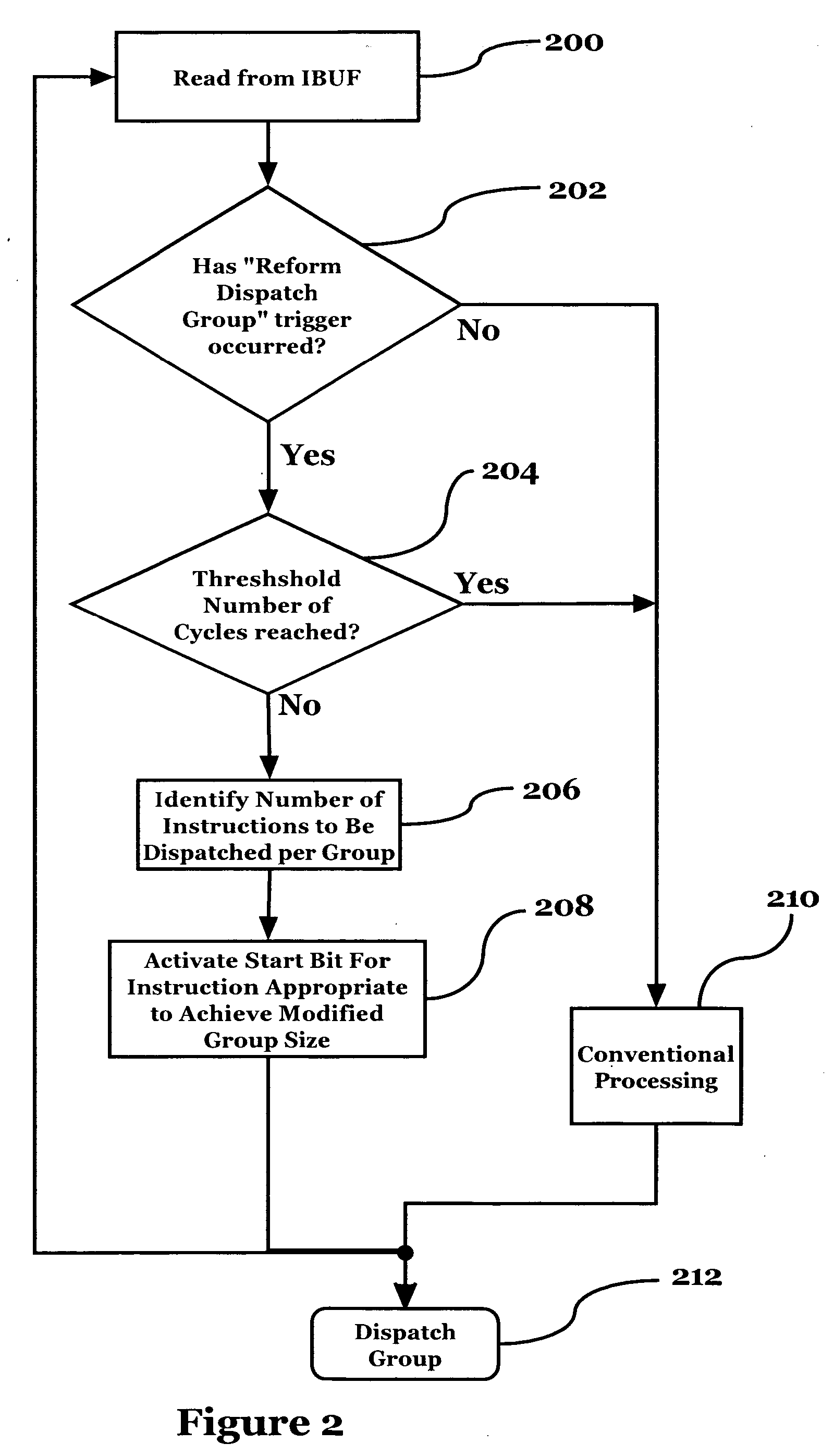

Method and apparatus for dynamic modification of microprocessor instruction group at dispatch

InactiveUS20060184768A1Instruction analysisGeneral purpose stored program computerParallel computingBiological activation

Dynamic reformatting of a dispatch group by selective activation of inactive Start bits of instructions within the dispatch group at the time the instructions are read from the IBUF. The number of instructions in the reformatted dispatch groups can vary from as few as one instruction per group to a maximum number of instructions read from the IBUF per cycle. The reformatted dispatch groupings can be terminated after a single cycle, or they can remain reformatted for as many cycles as desired, depending upon need.

Owner:GOOGLE LLC

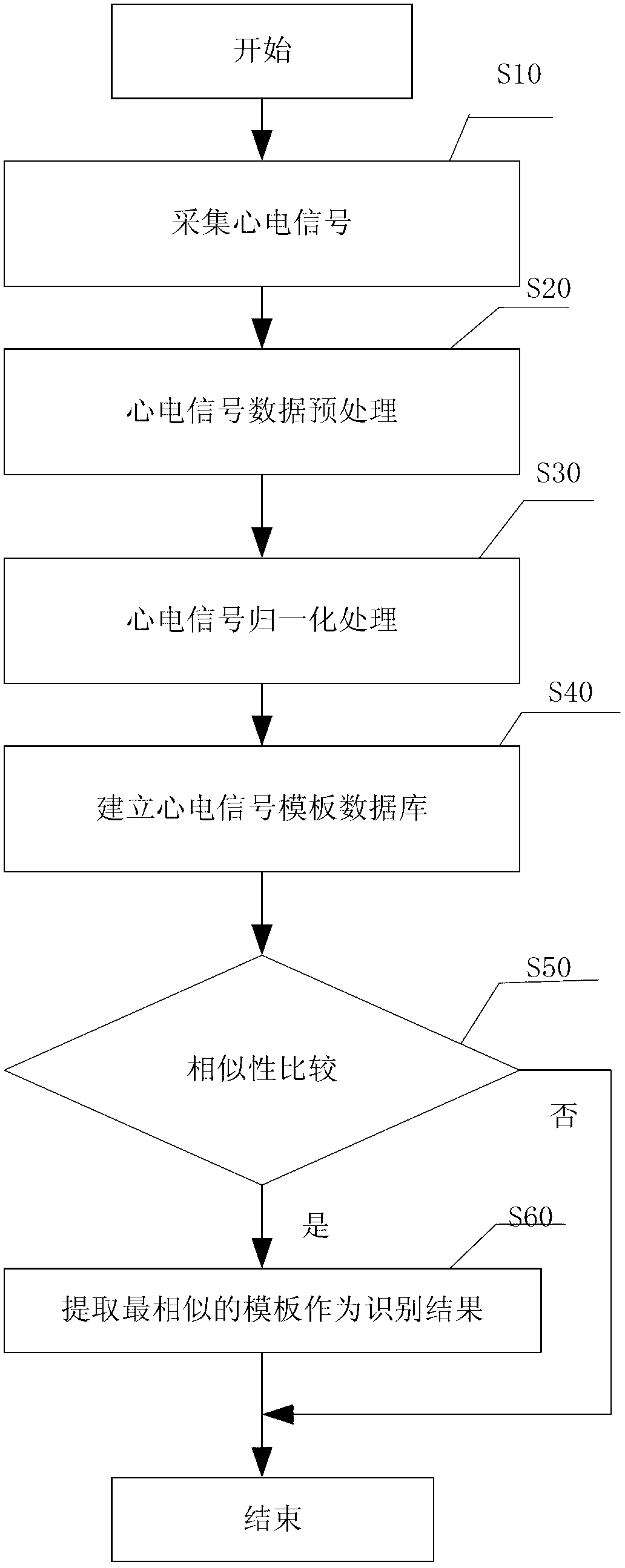

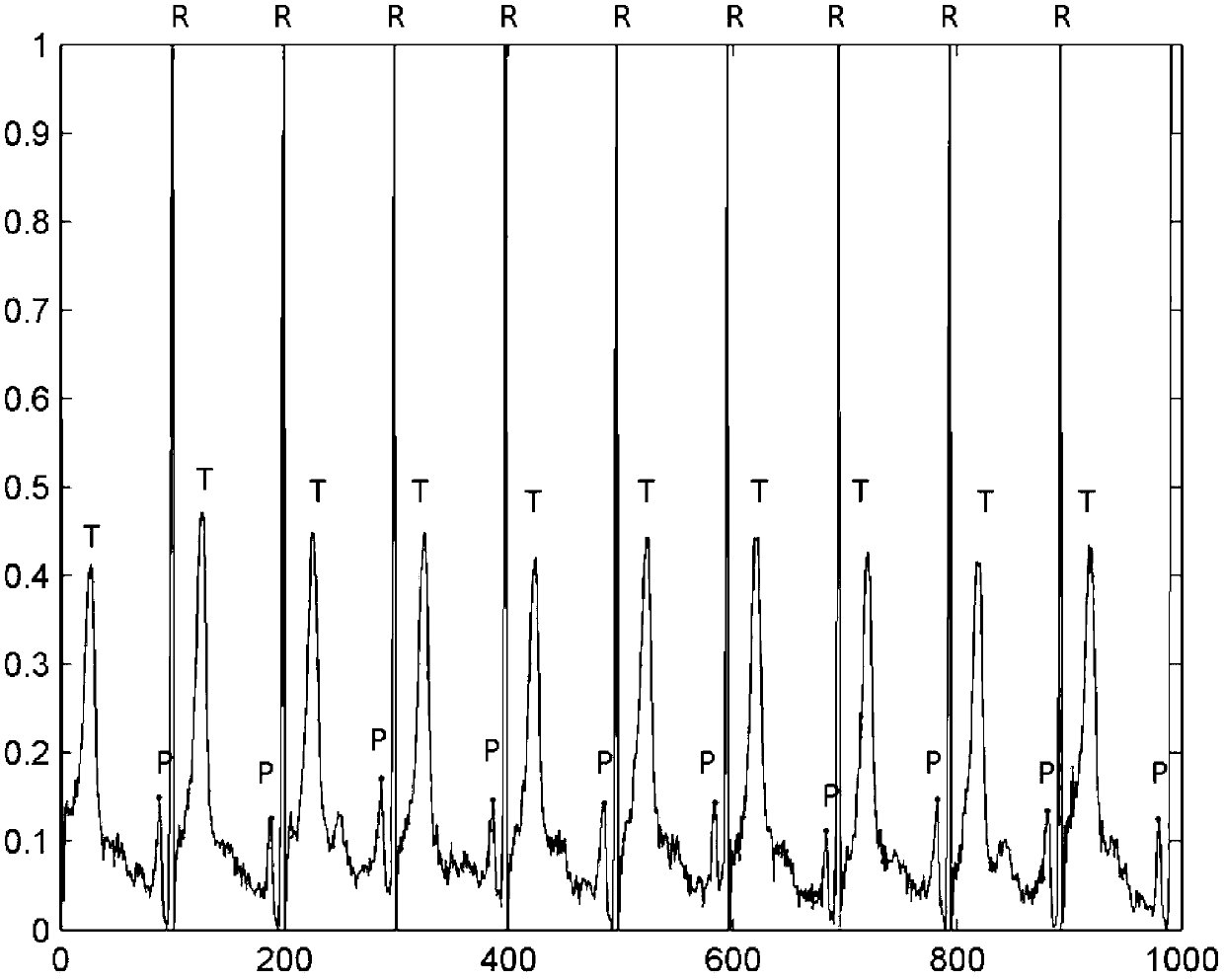

Electrocardiosignal data processing method

ActiveCN103345600AAvoid cumbersomeSimple calculationPerson identificationDigital data authenticationEcg signalSignal classification

The invention discloses an electrocardiosignal data processing method. The electrocardiosignal data processing method comprises the following steps of (1) collecting data of electrocardiosignals; (2) carrying out preprocessing on the collected data of the electrocardiosignals, wherein baseline drift removal processing and de-noising processing are carried out on the collected electrocardiosignals; (3) decomposing the electrocardiosignals into single-cycle electrocardiosignal sets; (4) carrying out characteristic extraction, carrying out signal classification according to single-cycle electrocardiosignals after normalization and the level of similarity of curve signals, and choosing electrocardiosignals in the maximum class as a template; (5) detecting signal input, carrying out similarity comparison between the electrocardiosignals and a central database template to determine the identity. According to the single-leading electrocardiosignal data processing method, the mode of characteristic curve matching is adopted to carry out curve similarity comparative studies on electrocardiosignal sequences, and complex procedures for extracting characteristic points are avoided.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

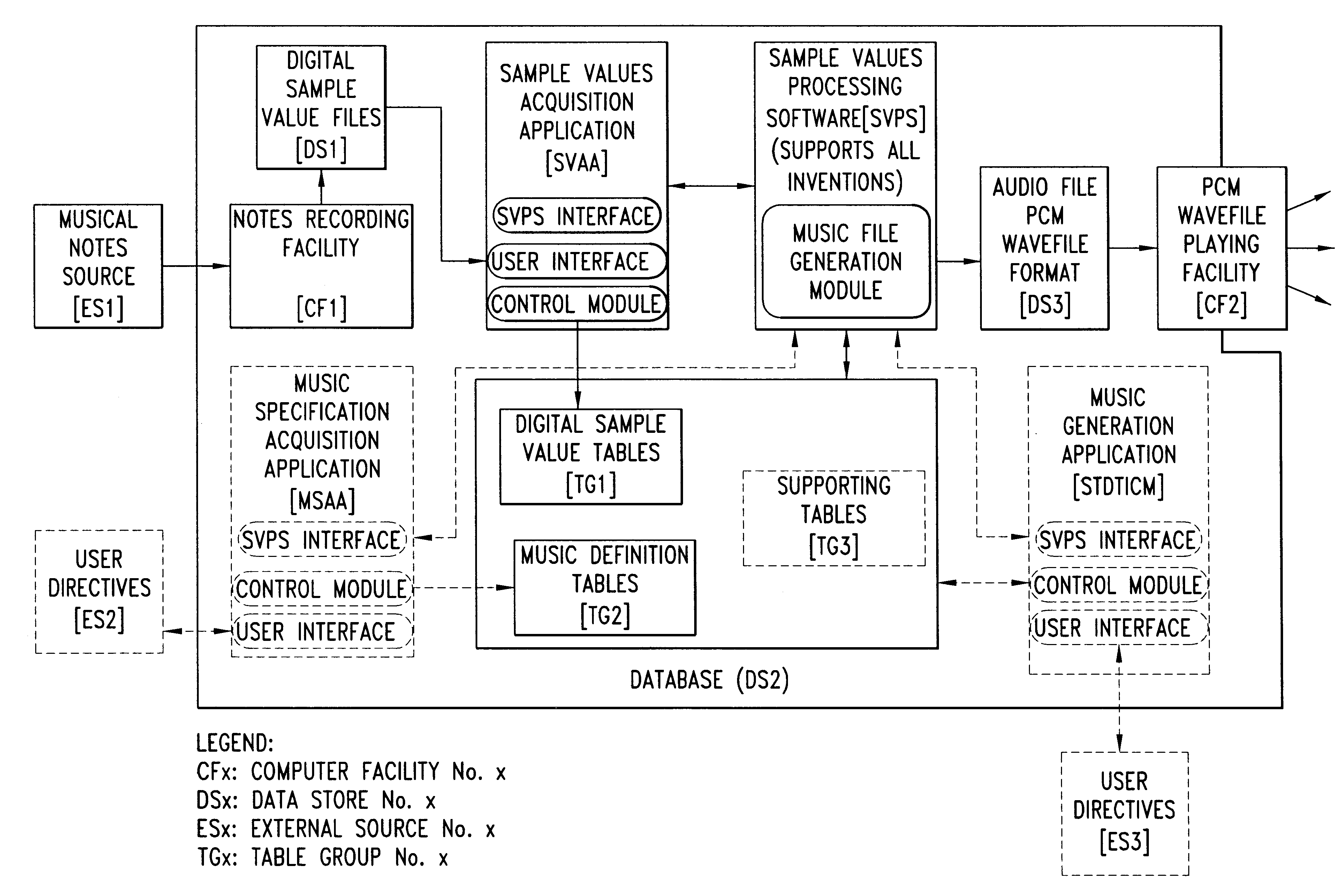

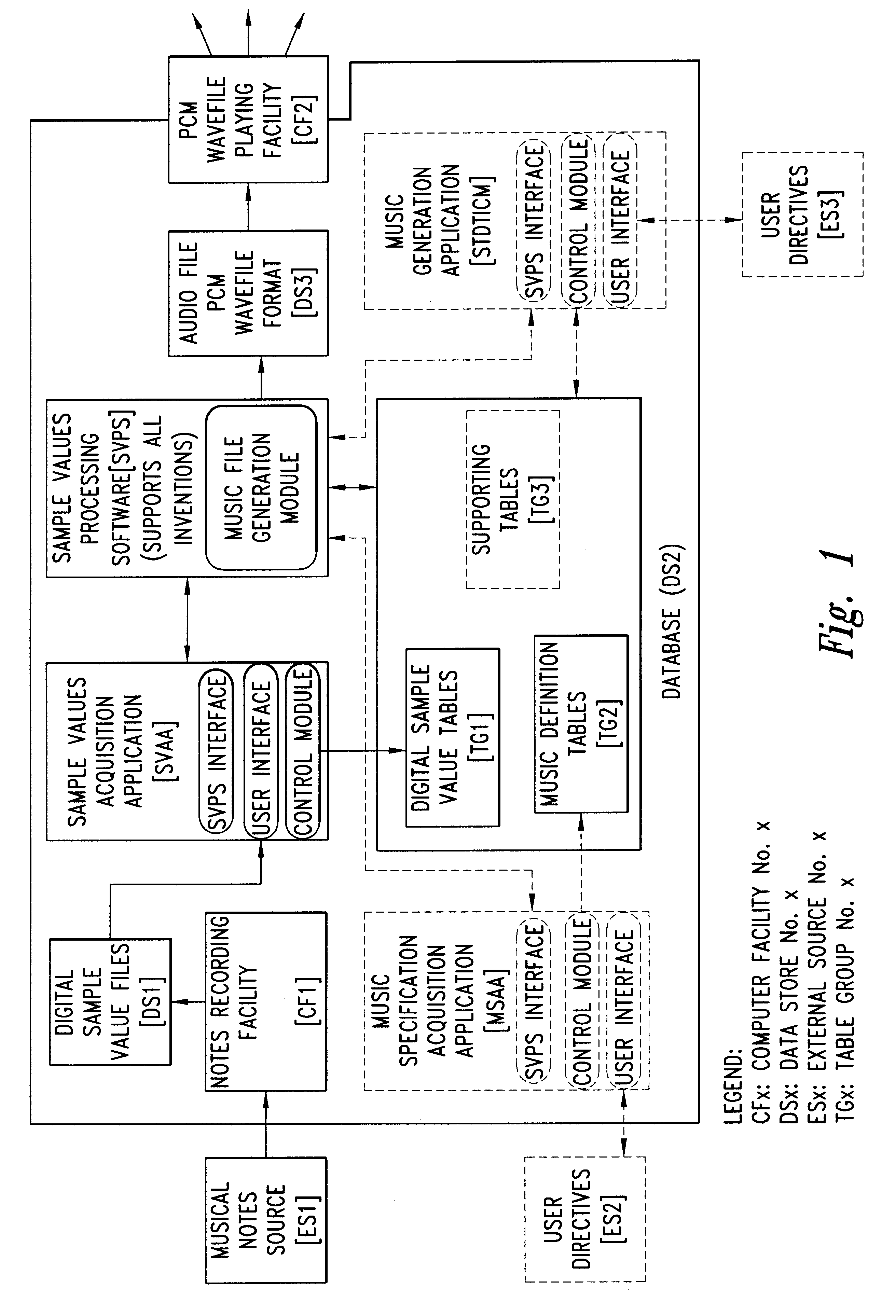

Customizable software-based digital wavetable synthesizer

A software based digital wavetable synthesizer receives musical data from an external source and generates a plurality of digital sample values corresponding to the musical source. The musical source may be a synthesized music source or an actual instrument. In an exemplary embodiment, a sample for each semi-tone for the musical instrument is sampled and stored. A subsequent process analyzes the sampled and selects a single cycle representing that musical instrument at each of the semi-tones. The data is subsequently normalized such that each cycle begins with a zero value and the normalized data is stored in a data structure along with labels indicative of the musical instrument and the musical note. In subsequent use, the user can create synthesized music by selecting the desired instrument and notes. Additional musical rules, such as rules associated with Indian classical music, may be applied to specify the synthesis process. The musical notes, generated in accordance with the associated musical rules are provided to a music output file, which may be converted into a conventional waveform format and played on a conventional sound card. The invention is totally software based and does not rely on synthesized data stored in firmware or hardware on a special musical synthesizer card. Instead, any conventional sound card may be readily used thus allowing portability of the music synthesizer between computing platforms.

Owner:INFORMATION MODELING & MANAGEMENT SERVICES

Single cycle refresh of multi-port dynamic random access memory (DRAM)

A multi-port DRAM having refresh cycles interleaved with normal read and write operations implements a single cycle refresh sequence by deferring the write portion of the sequence until the next refresh cycle. During a single clock cycle, the system writes stored data from a refresh buffer into a row in the memory array and then reads data from one row of the memory array into the buffer.

Owner:GLOBALFOUNDRIES US INC

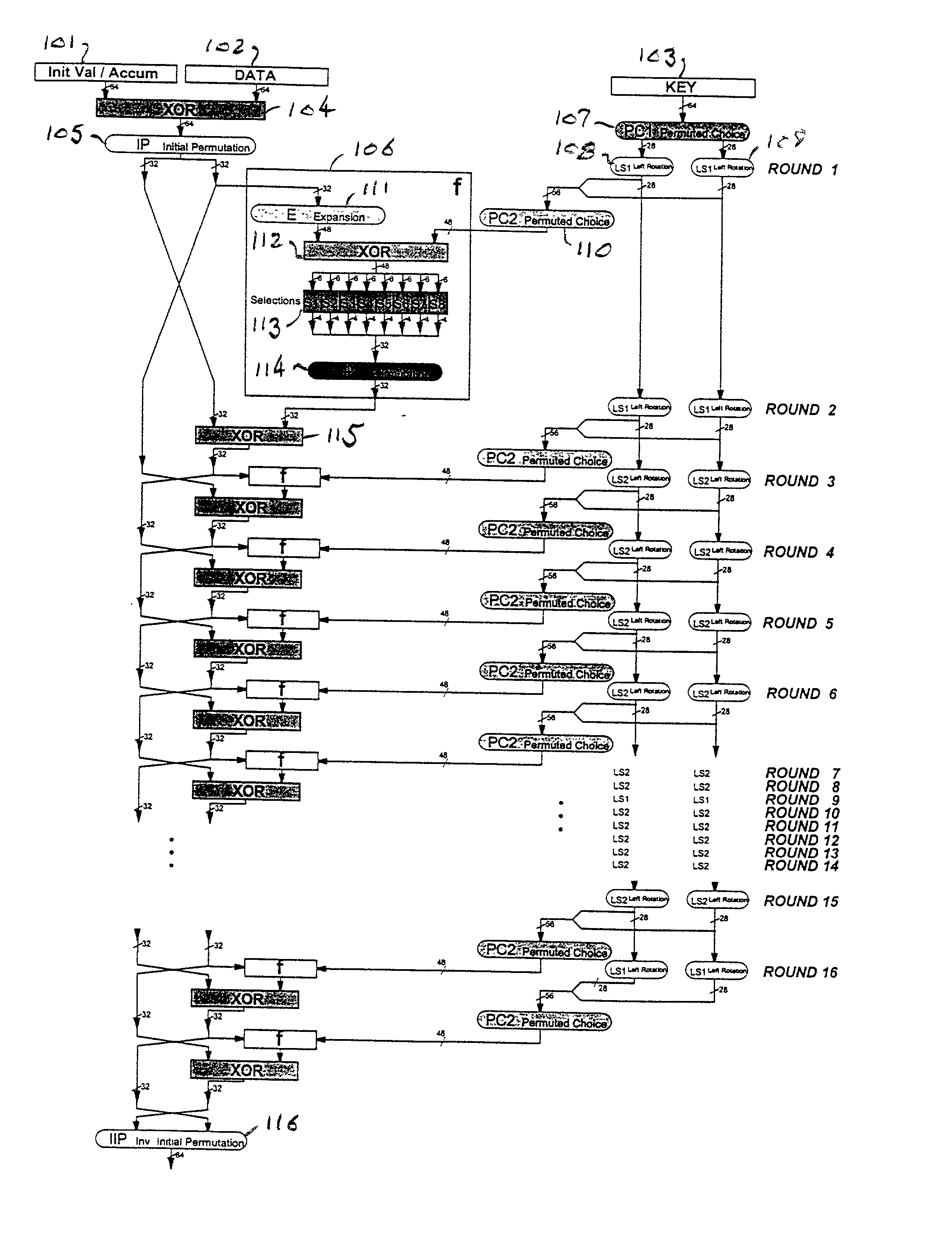

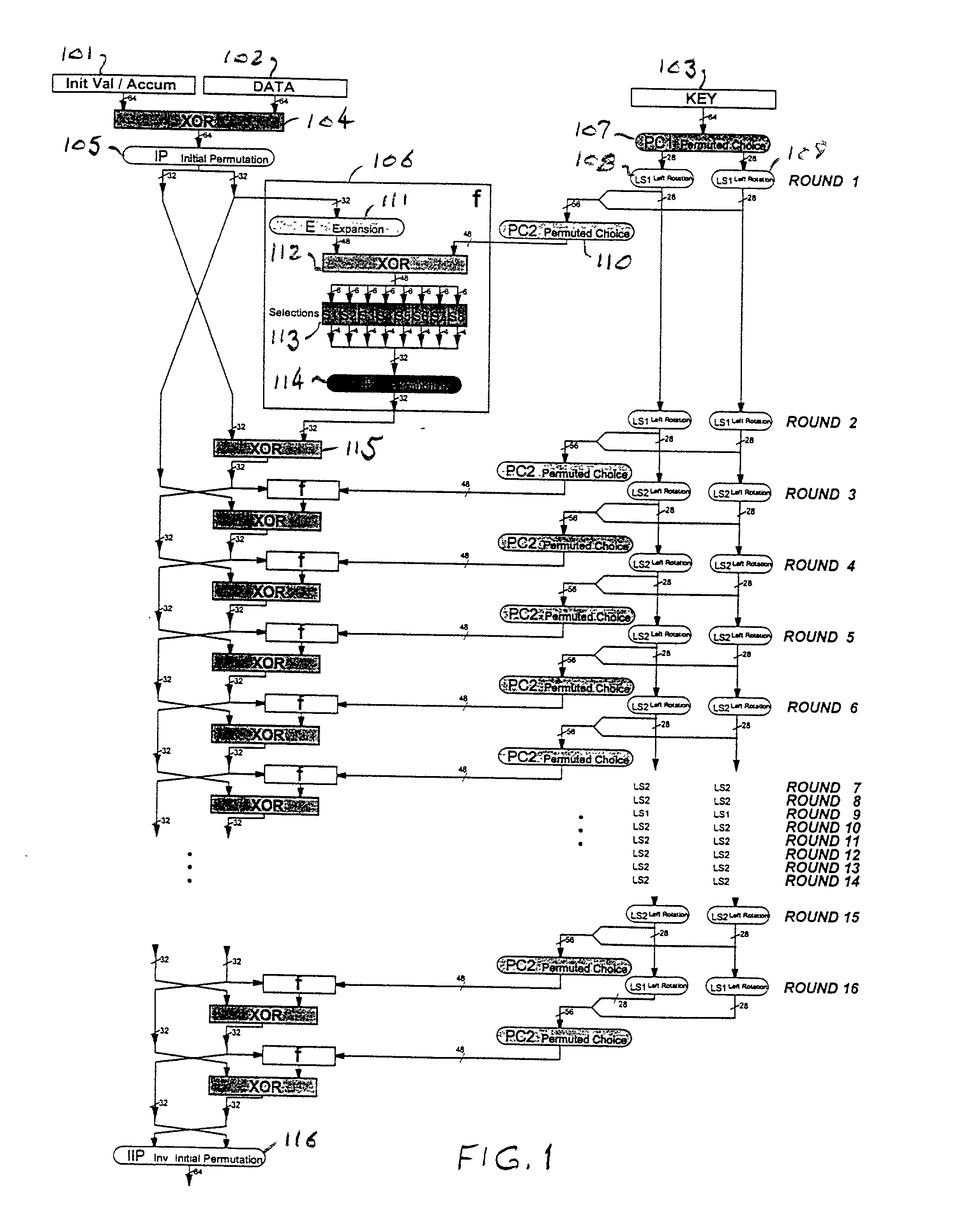

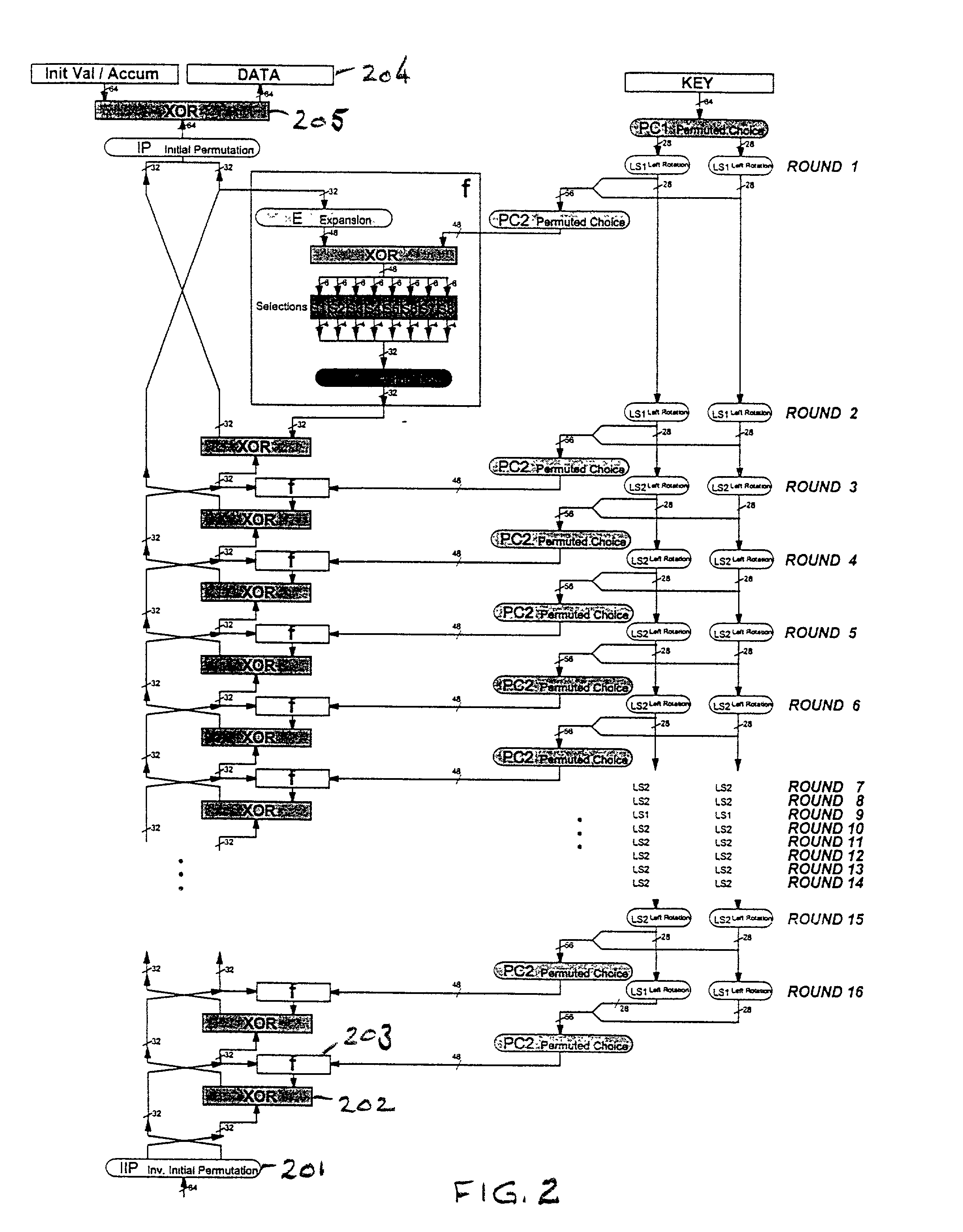

Single-cycle hardware implementation of crypto-function for high throughput crypto-processing

InactiveUS20020101985A1Encryption apparatus with shift registers/memoriesSecret communicationComputer hardwareProcessor register

A hardware implementation of a crypto-function is realized using combinational logic performing computation iterations of the crypto-function on data in a single hardware cycle. Only combinational logic is used to implement the entire cryptographic algorithm, and registers are used only to store input or output from the combinational logic, leading to a very high speed implementation of the crypto-function.

Owner:IBM CORP

Method and apparatus for compressing a gas to a high pressure

ActiveUS20050180864A1Improve compressor efficiencyHigh aspect ratioPositive displacement pump componentsFlexible member pumpsElectronic controllerHydraulic pump

A method is provided for compressing a gas in a single cycle and in a single cylinder to a pressure of at least 17.2 Mpa with a compression ratio of at least about five to one. The method further comprises dissipating heat from the cylinder during the compression stroke whereby the gas is discharged with a temperature significantly less than isentropic. The apparatus comprises a hollow cylinder and a reciprocable free-floating piston disposed therein. The piston divides the cylinder into: (a) a compression chamber within which a gas can be introduced, compressed, and discharged; and, (b) a drive chamber, into which a hydraulic fluid can be introduced and removed for actuating the piston. The apparatus further comprises a piston stroke length to piston diameter ratio of at least seven to one. For operating the apparatus with a compression ratio of at least five to one, an outlet pressure of at least 17.2 Mpa, and a gas discharge temperature significantly less than isentropic, the apparatus can further comprise a variable displacement hydraulic pump for controlling piston velocity, an electronic controller for maintaining an average piston velocity that is less than 0.5 feet per second, and a heat dissipator for dissipating heat from the cylinder.

Owner:WESTPORT FUEL SYST CANADA INC

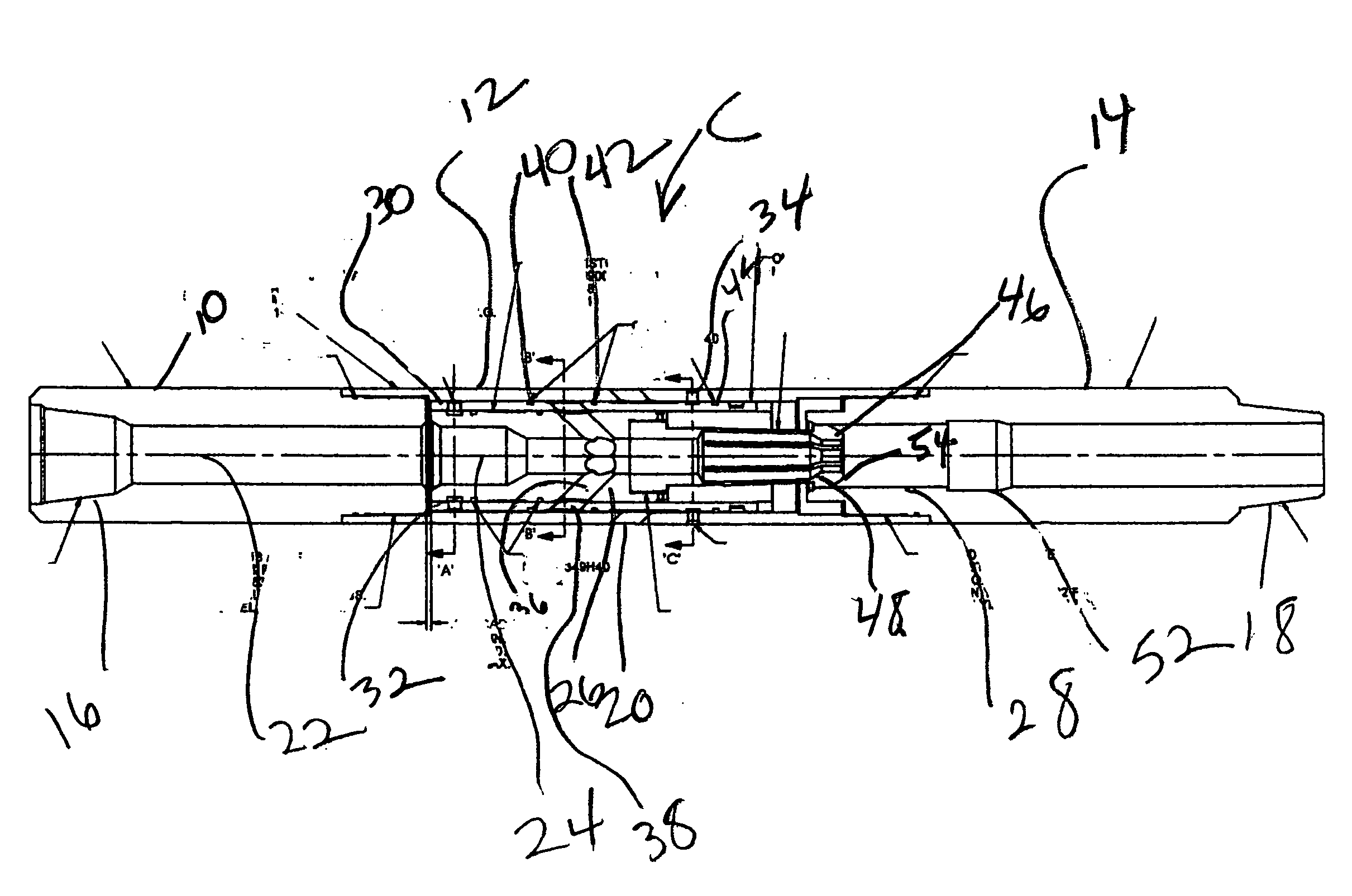

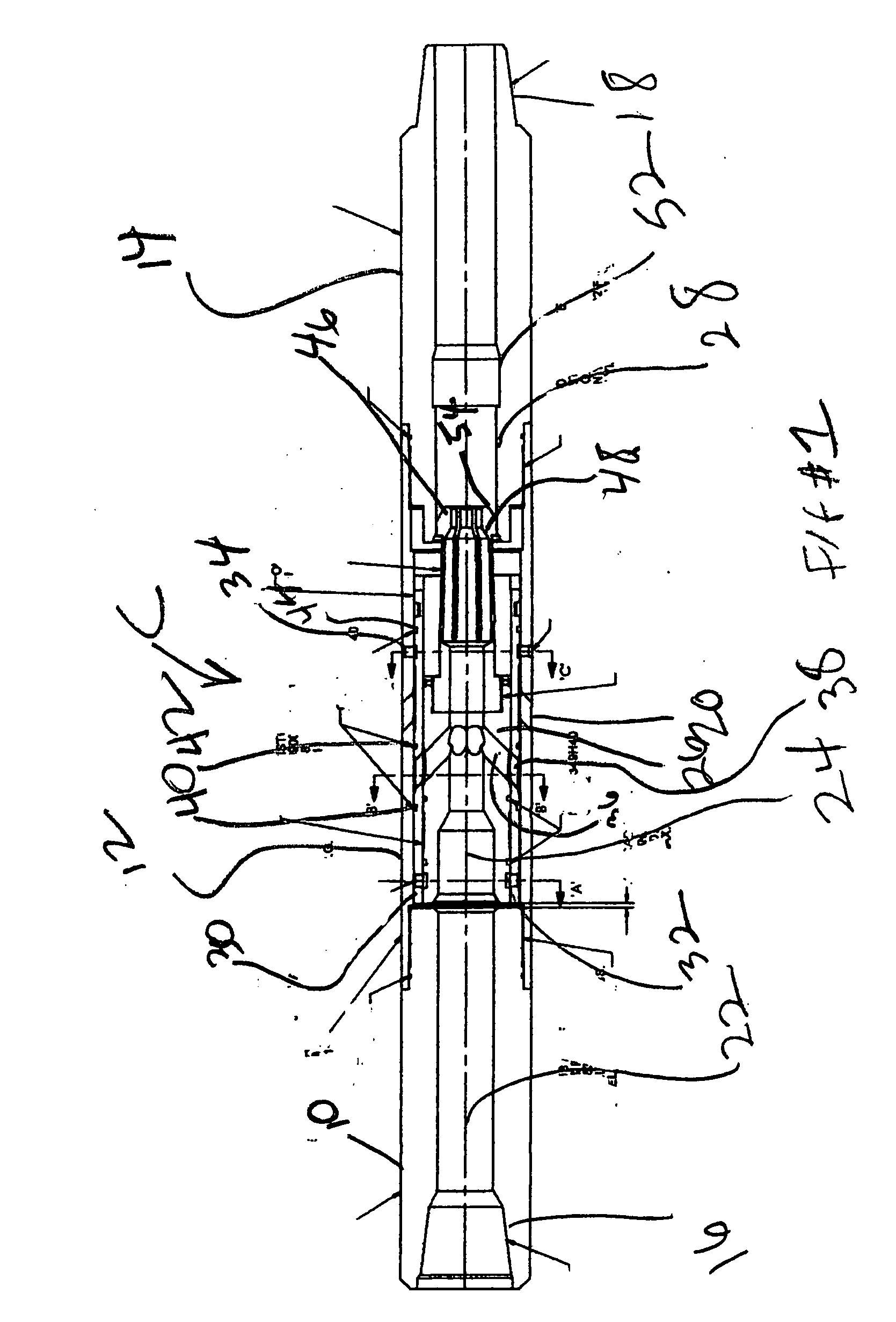

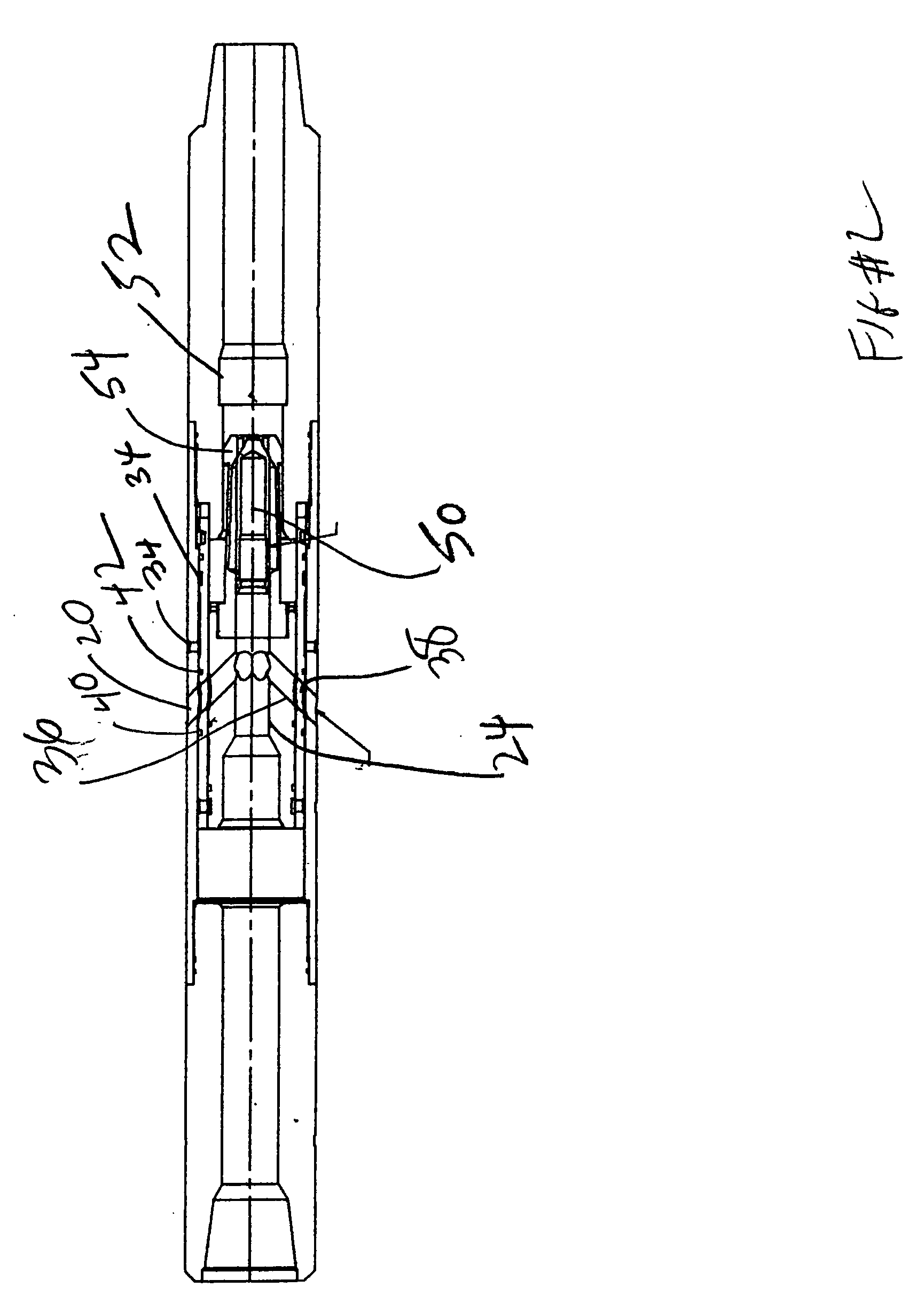

Single cycle dart operated circulation sub

A circulating sub is run in with the circulating port closed. A dart blocks a central passage and moves two concentric pistons in tandem to open the circulation port while retaining the dart. The outer piston shoulders out in the circulation port open position. A second dart lands on the first and with applied pressure moves the inner piston relative to the shouldered outer piston to close the circulation port and only then discharge both darts. Subs can be used in tandem as long as higher located subs accept larger darts than lower subs and preferably the two darts for each sub are the same size. The ejected darts can be used to pressure actuate a downhole tool like a packer.

Owner:BAKER HUGHES INC

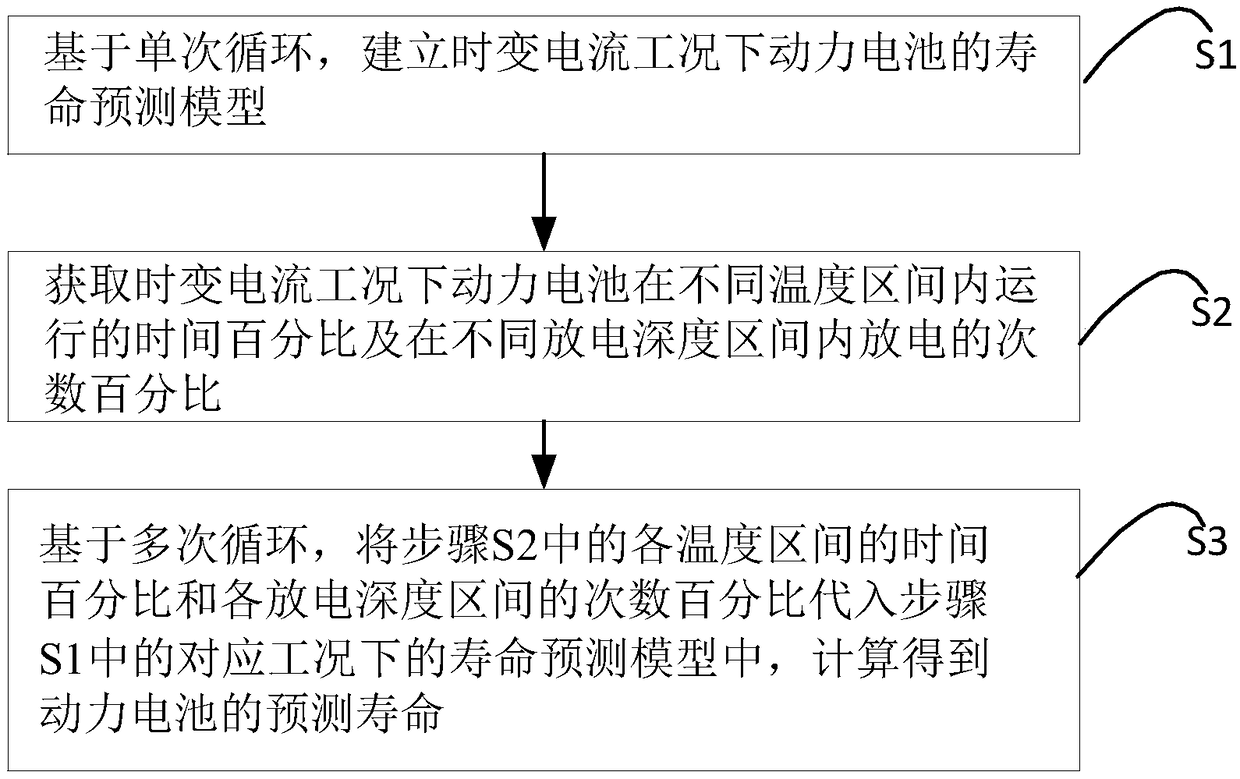

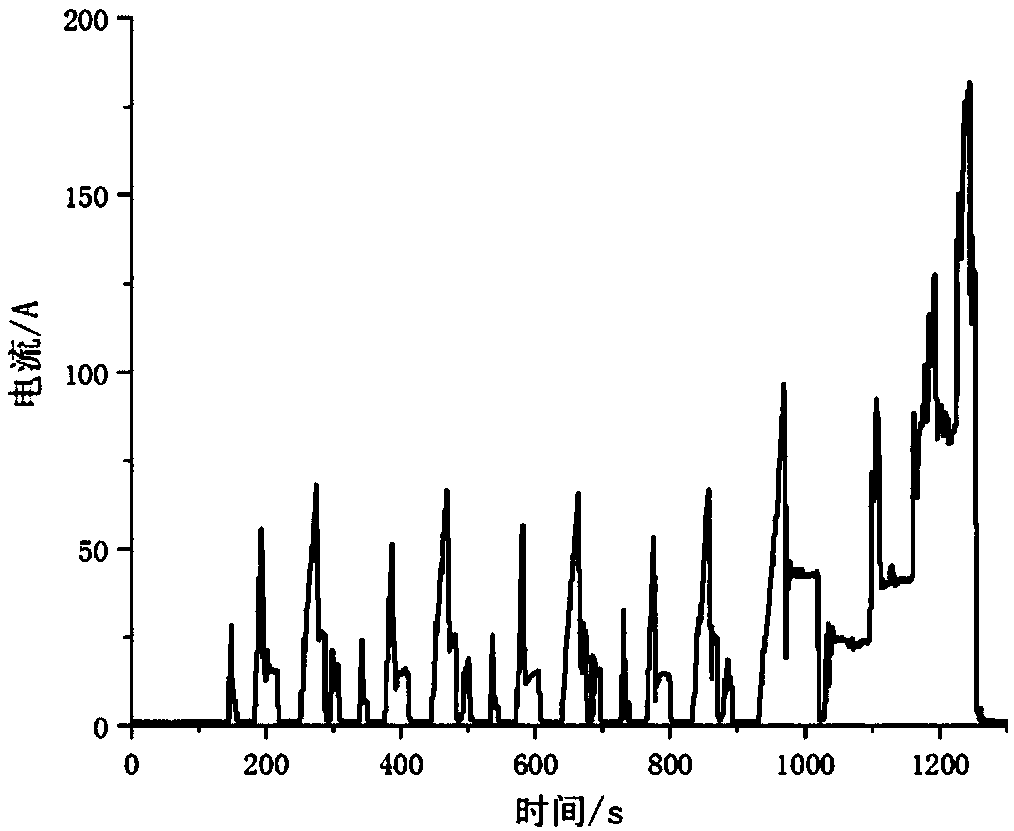

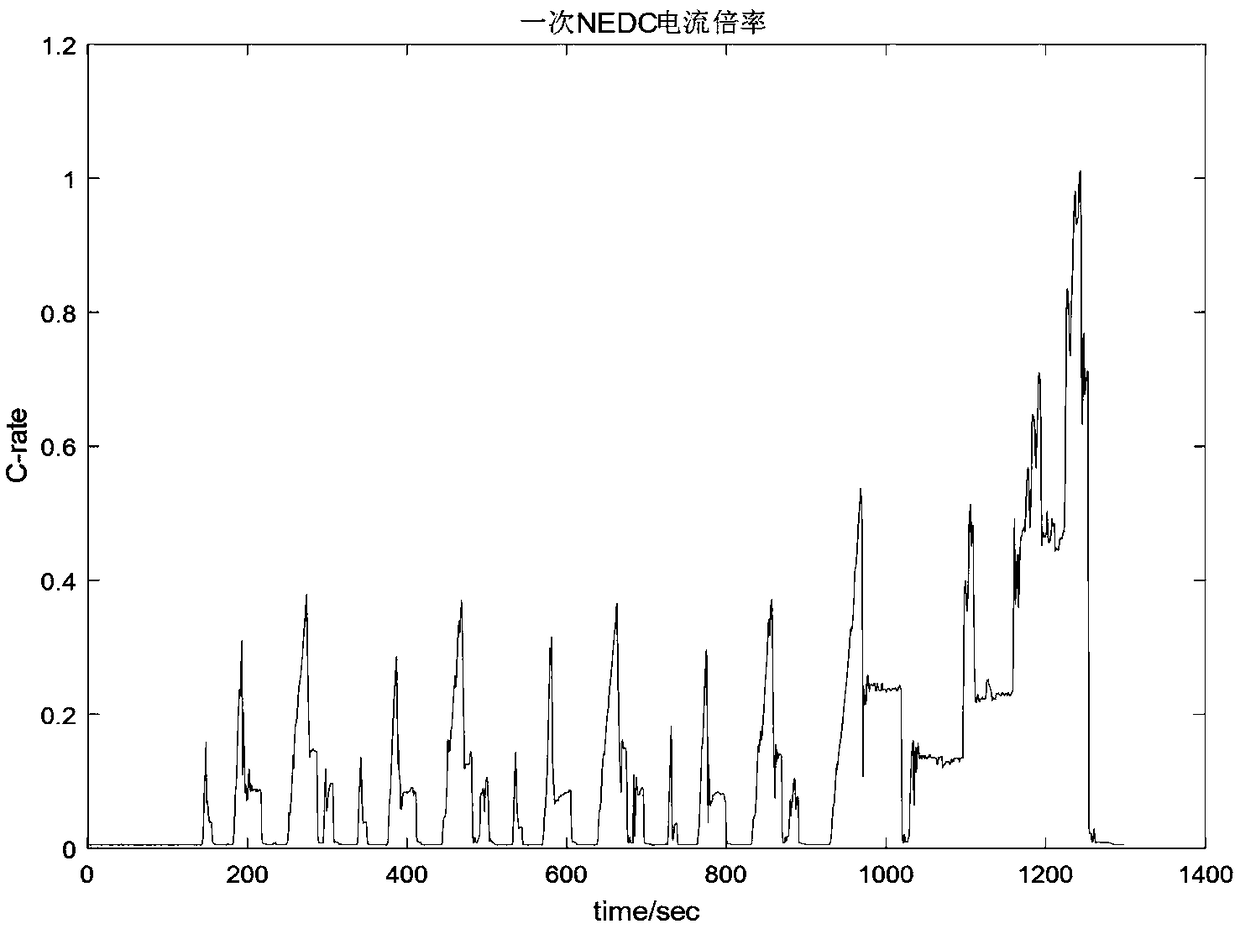

Service life prediction method of power battery in time-varying working condition

The invention provides a service life prediction method of a power battery in a time-varying working condition. The service life prediction method includes the steps that based on an actual working condition of the power battery for a vehicle, three main factors, T, C and DOD, which affect the service life of the power battery are taken as variables, combined with the time-varying characteristicsof affecting factors in a vehicle working condition, firstly, a service life prediction model of the power battery in a time-varying current condition is established in the time scale of a single cycle; in the time scale of multiple cycles, the effects of an operating temperature and a discharge depth DOD on battery service life are considered, and finally, a life model of the power battery in thetime-varying working condition which is closer to the actual working condition is obtained. According to the service life prediction method of the power battery in the time-varying working condition,the accuracy of the service life prediction of the power battery for the vehicle is improved, the battery service life is calculated by the model so that the use, maintenance and replacement of the power battery for the vehicle can be guided, and the safe use of electric vehicles is ensured; and furthermore, the model is simple and easy to calculate, and is beneficial to improving the predictionefficiency.

Owner:CH AUTO TECH CORP CO LTD

Selectively performing a single cycle write operation with ecc in a data processing system

Owner:RAMBUS INC

Dual-processor complex domain floating-point DSP system on chip

ActiveUS20050216702A1No performance lossReduce in quantityArchitecture with single central processing unitSpecific program execution arrangementsProcessing coreReal arithmetic

A system for digital signal processing, configured as a system on chip (SoC), combines a microprocessor core and digital signal processor (DSP) core with floating-point data processing capability. The DSP core can perform operations on floating-point data in a complex domain and is capable of producing real and imaginary arithmetic results simultaneously. This capability allows a single-cycle execution of, for example, FFT butterflies, complex domain simultaneous addition and subtraction, complex multiply accumulate (MULACC), and real domain dual multiply-accumulators (MACs). The SoC may be programmed entirely from a microprocessor programming interface, using calls from a DSP library to execute DSP functions. The cores may also be programmed separately. Capability for programming and simulating the entire SoC are provided by a separate programming environment. The SoC may have heterogeneous processing cores in which either processing core may act as master or slave, or both cores may operate simultaneously and independently.

Owner:ATMEL CORP