Patents

Literature

48results about How to "Reduce noise coupling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

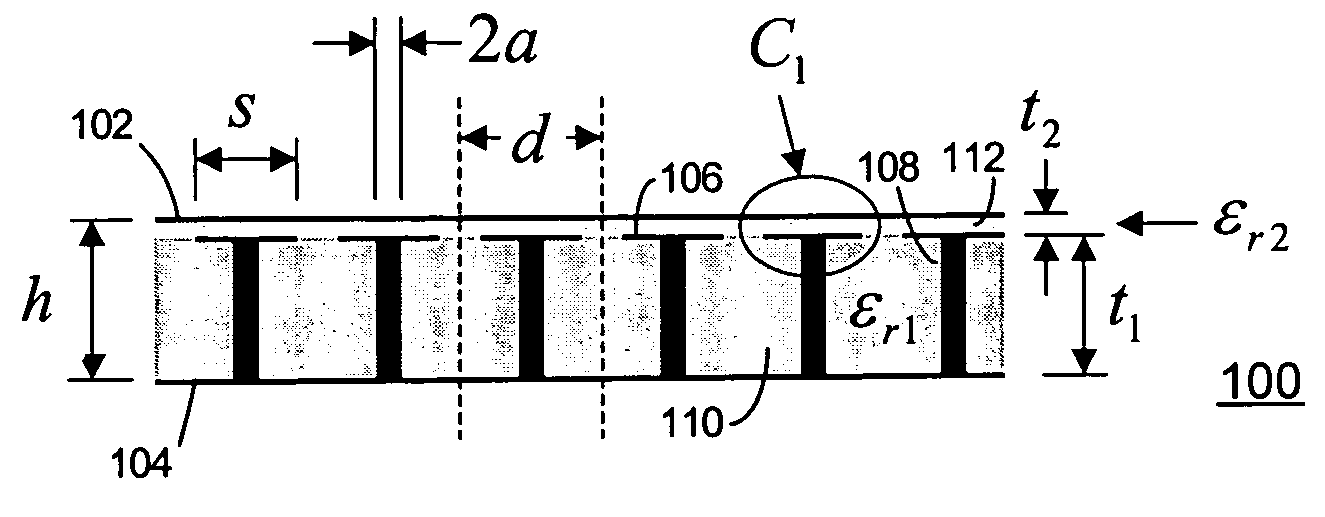

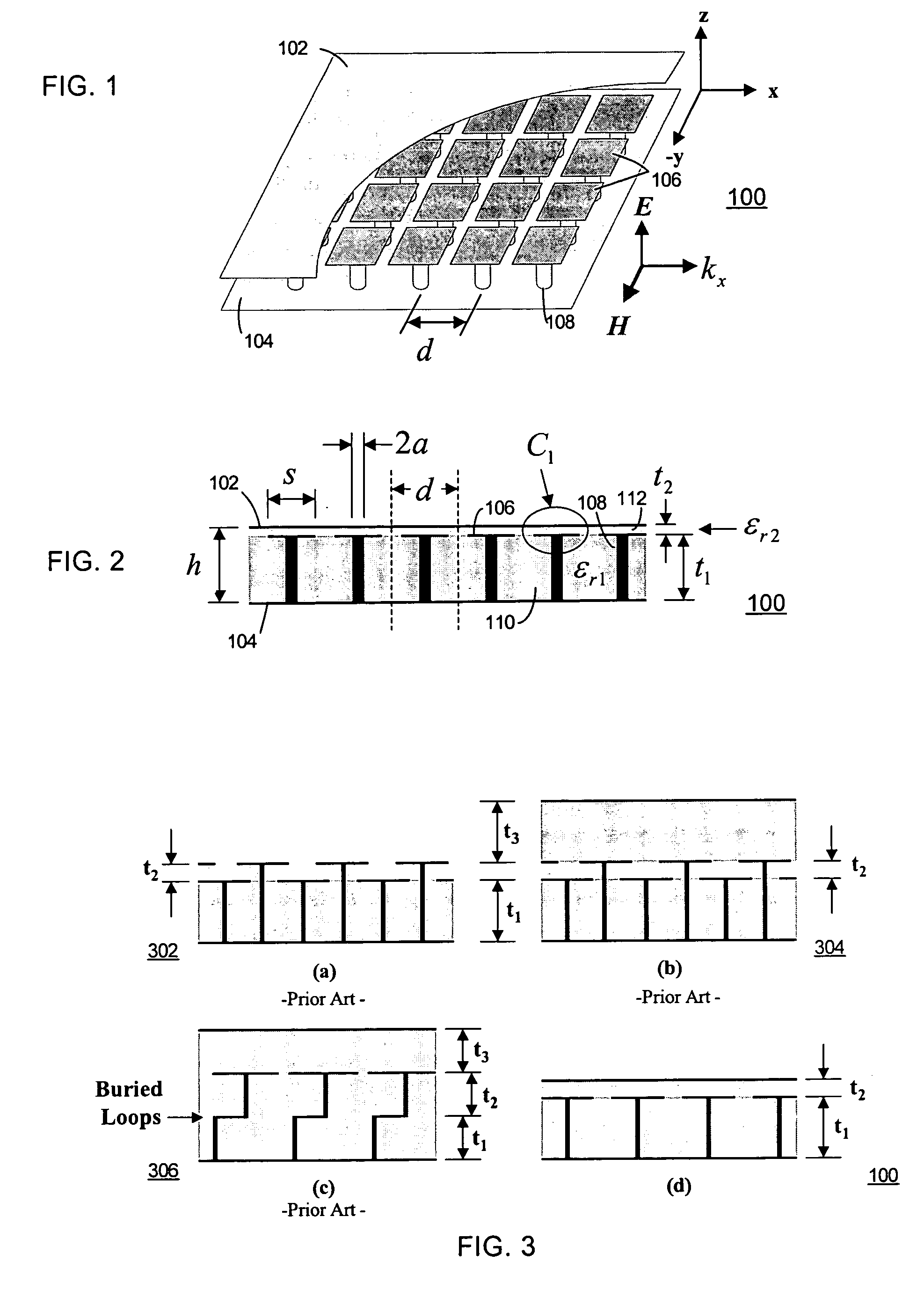

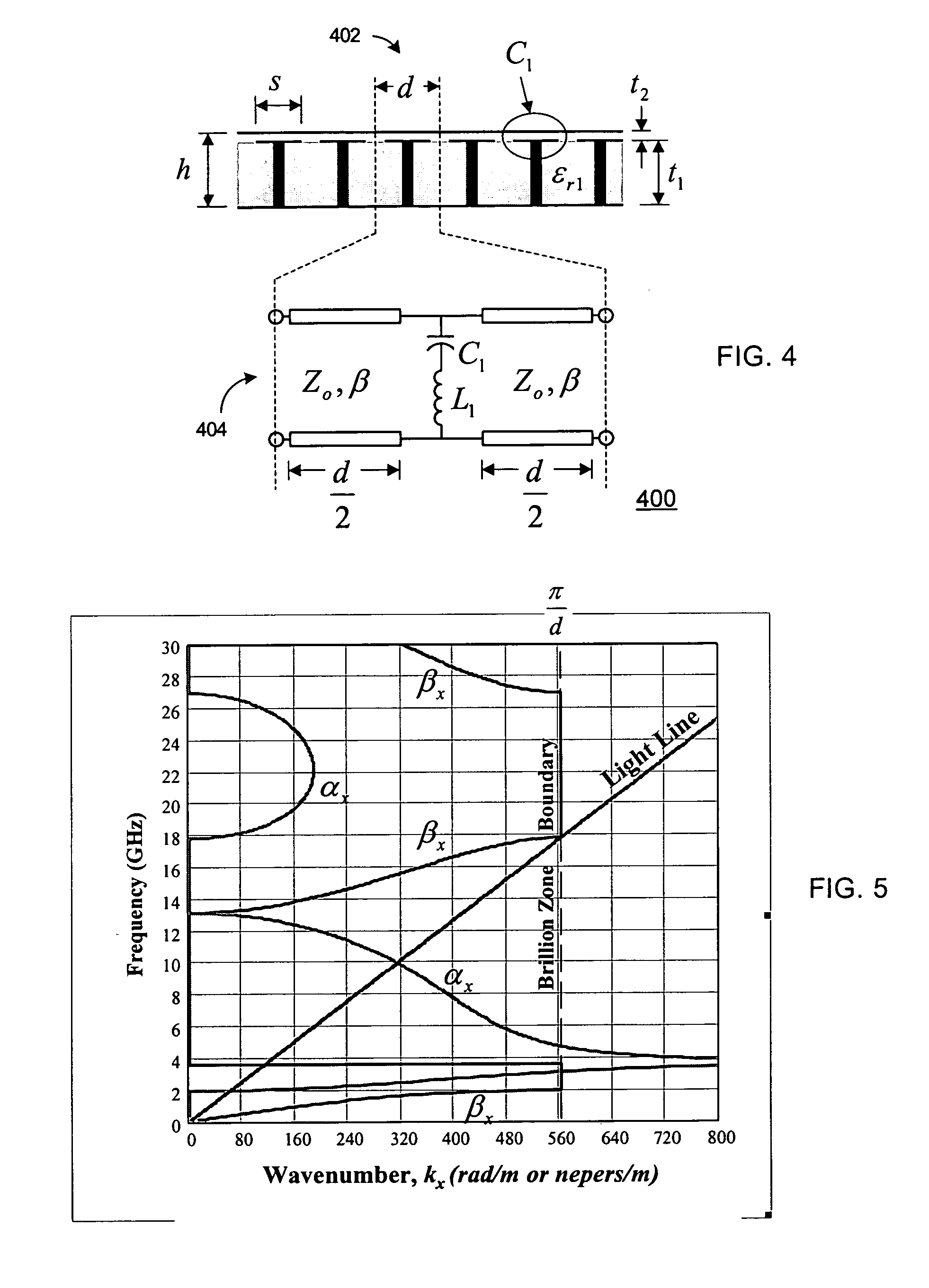

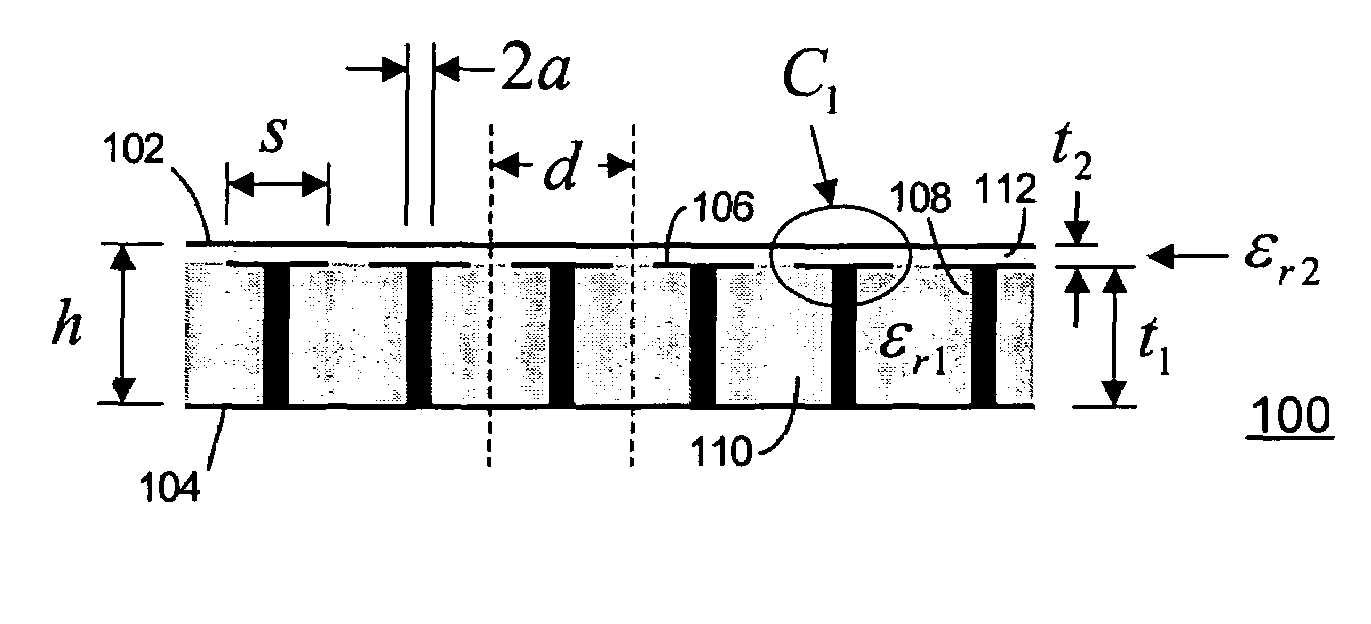

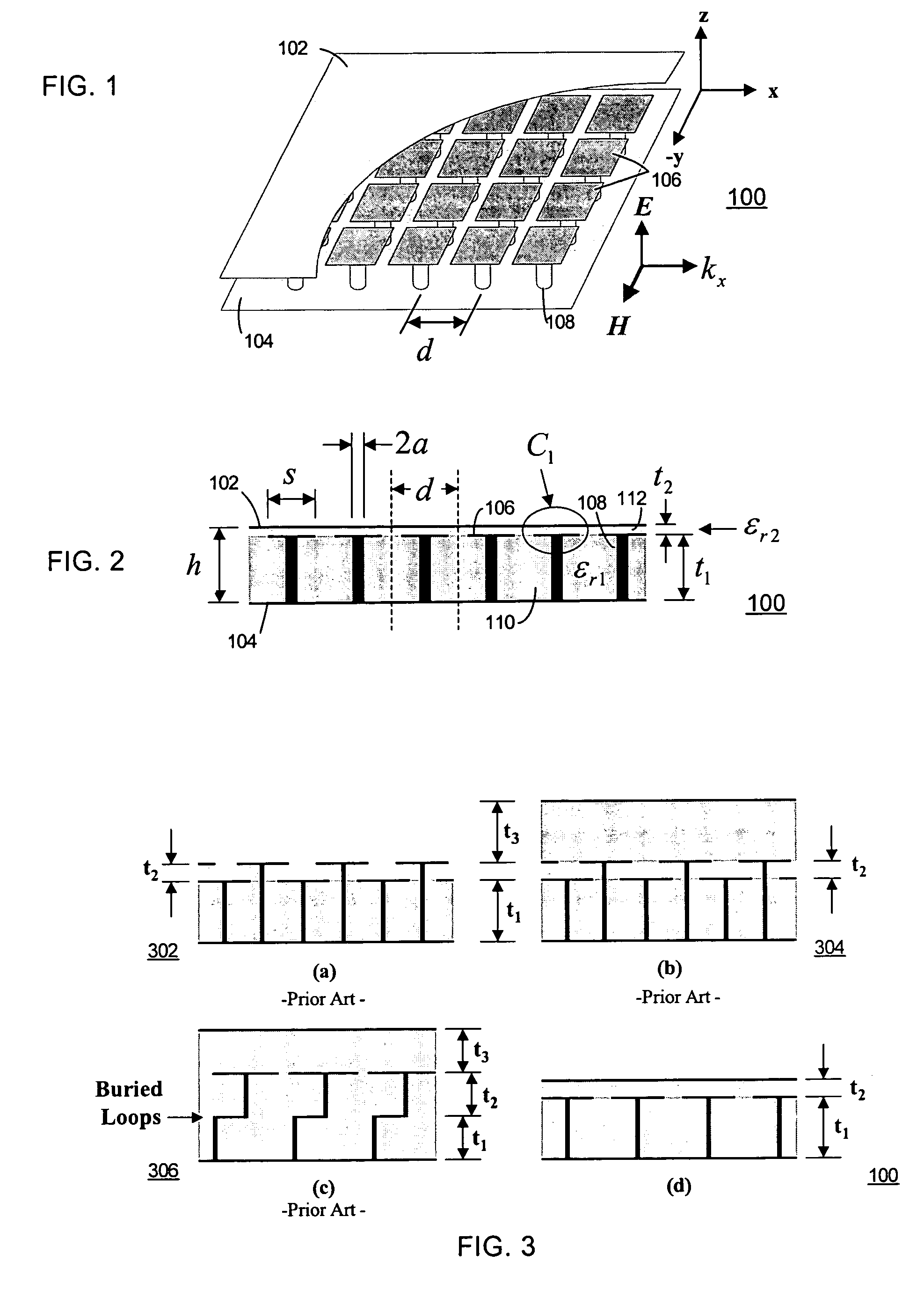

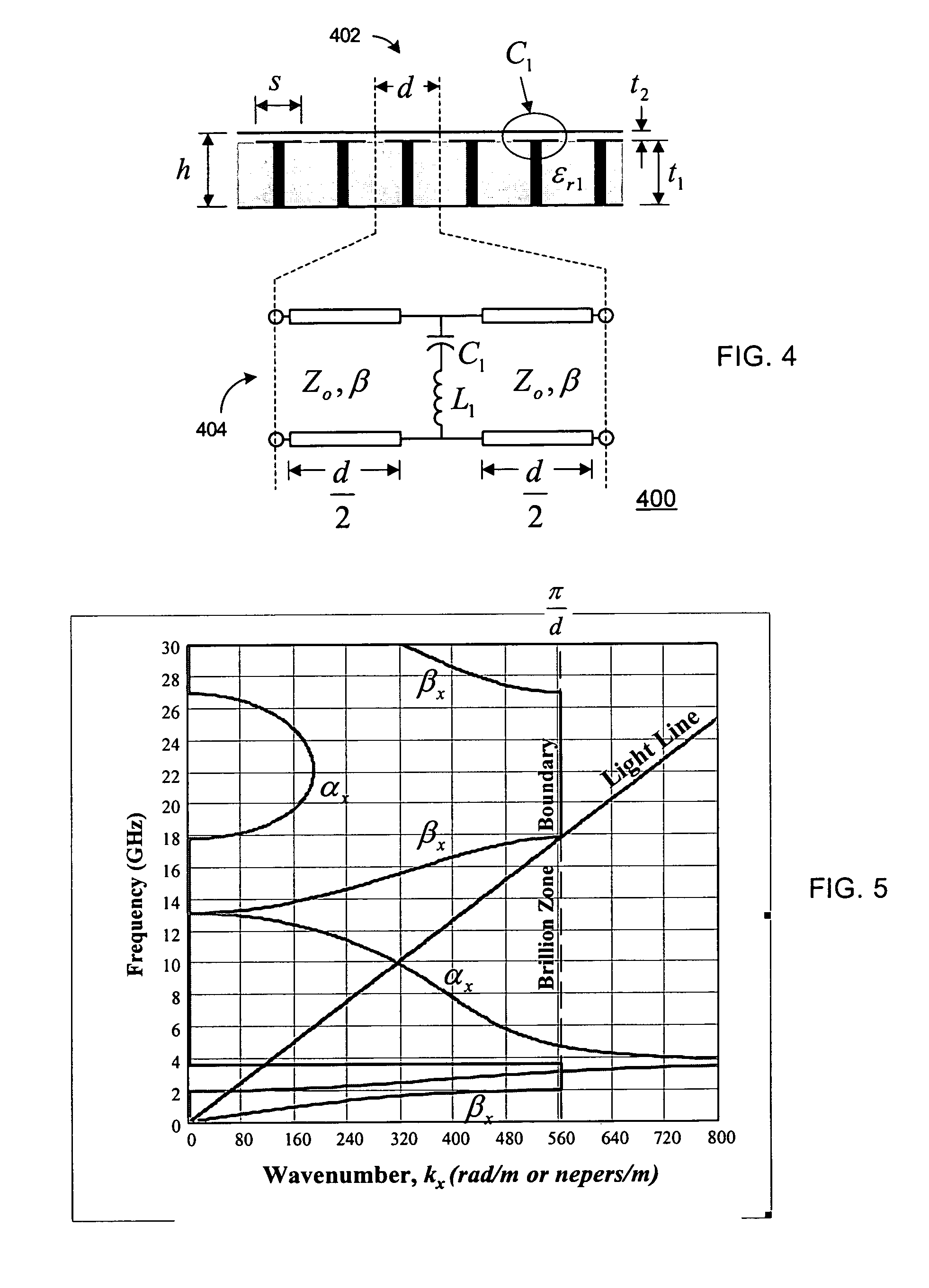

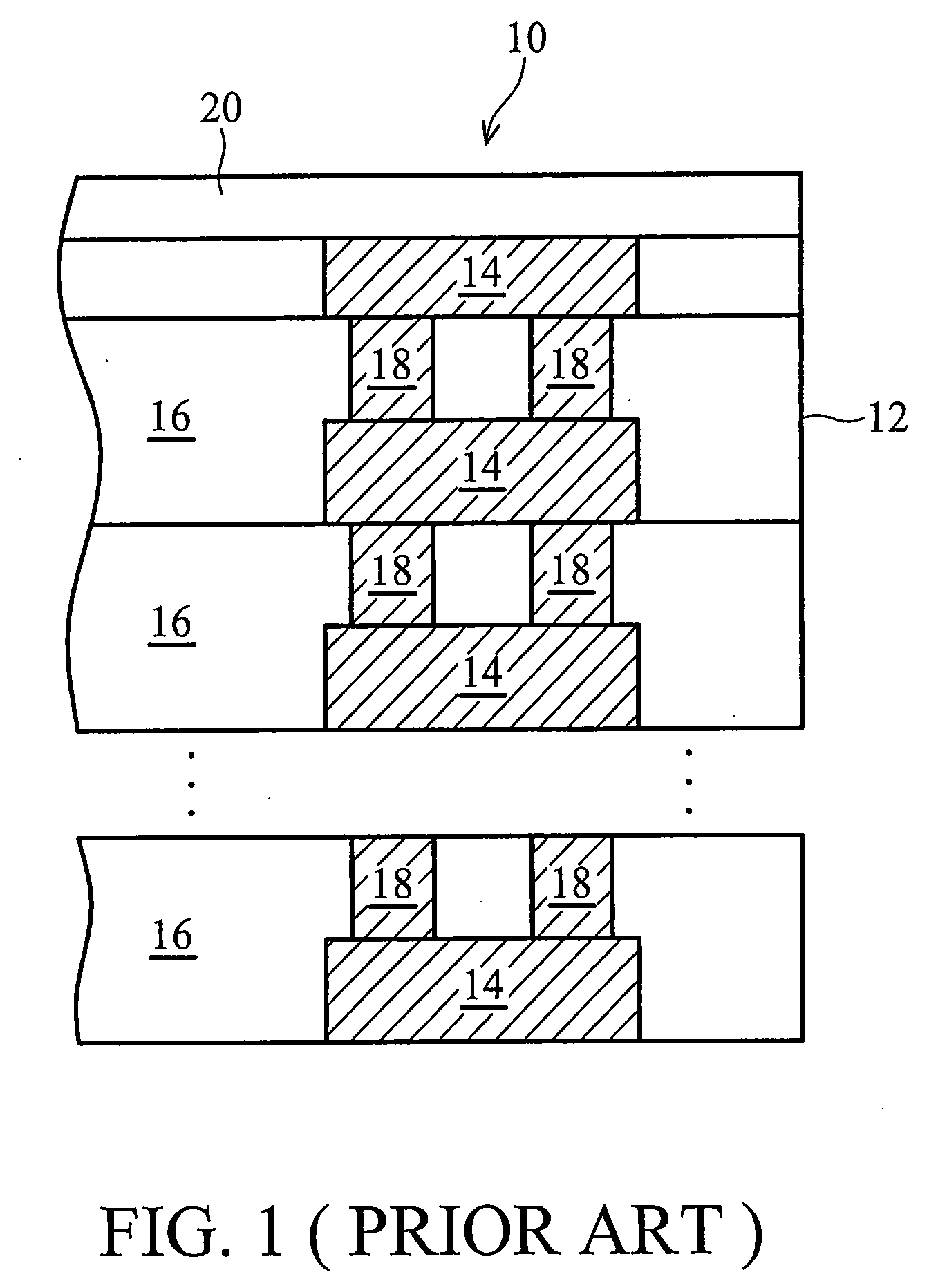

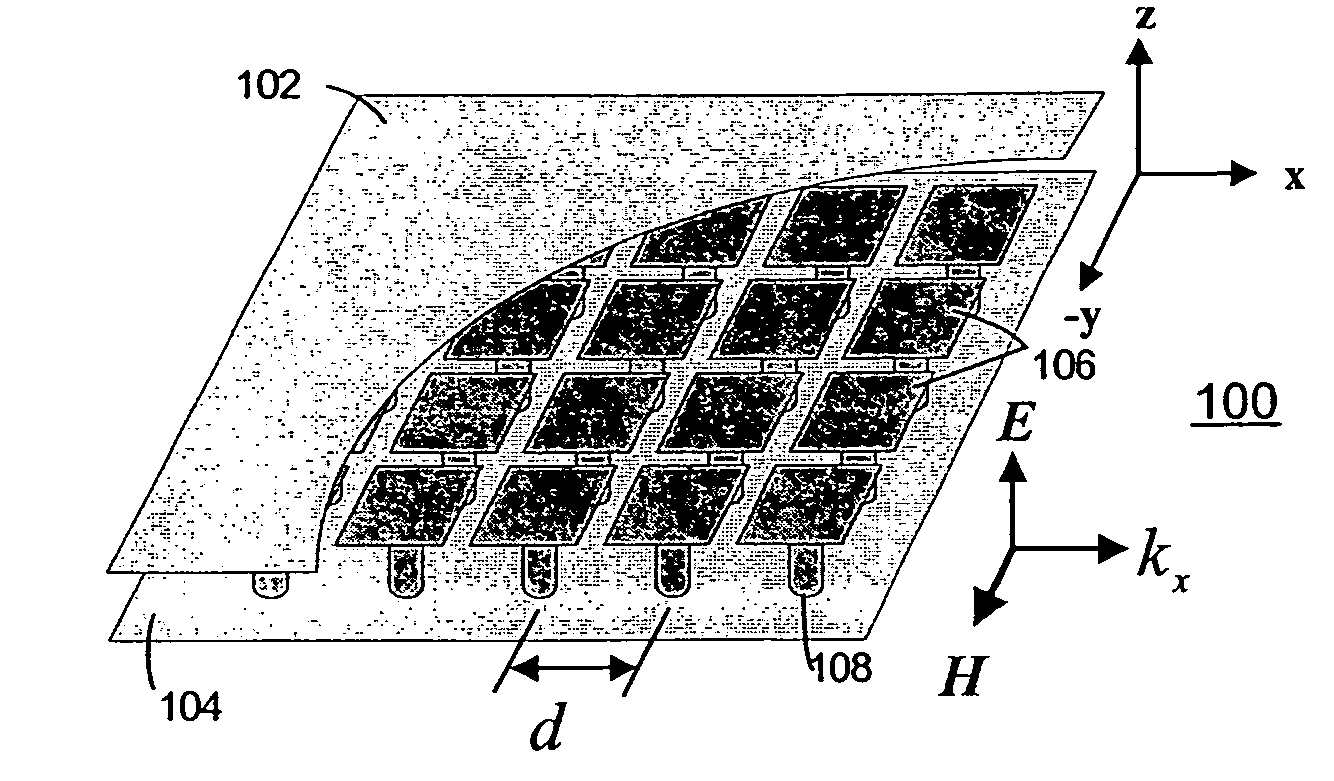

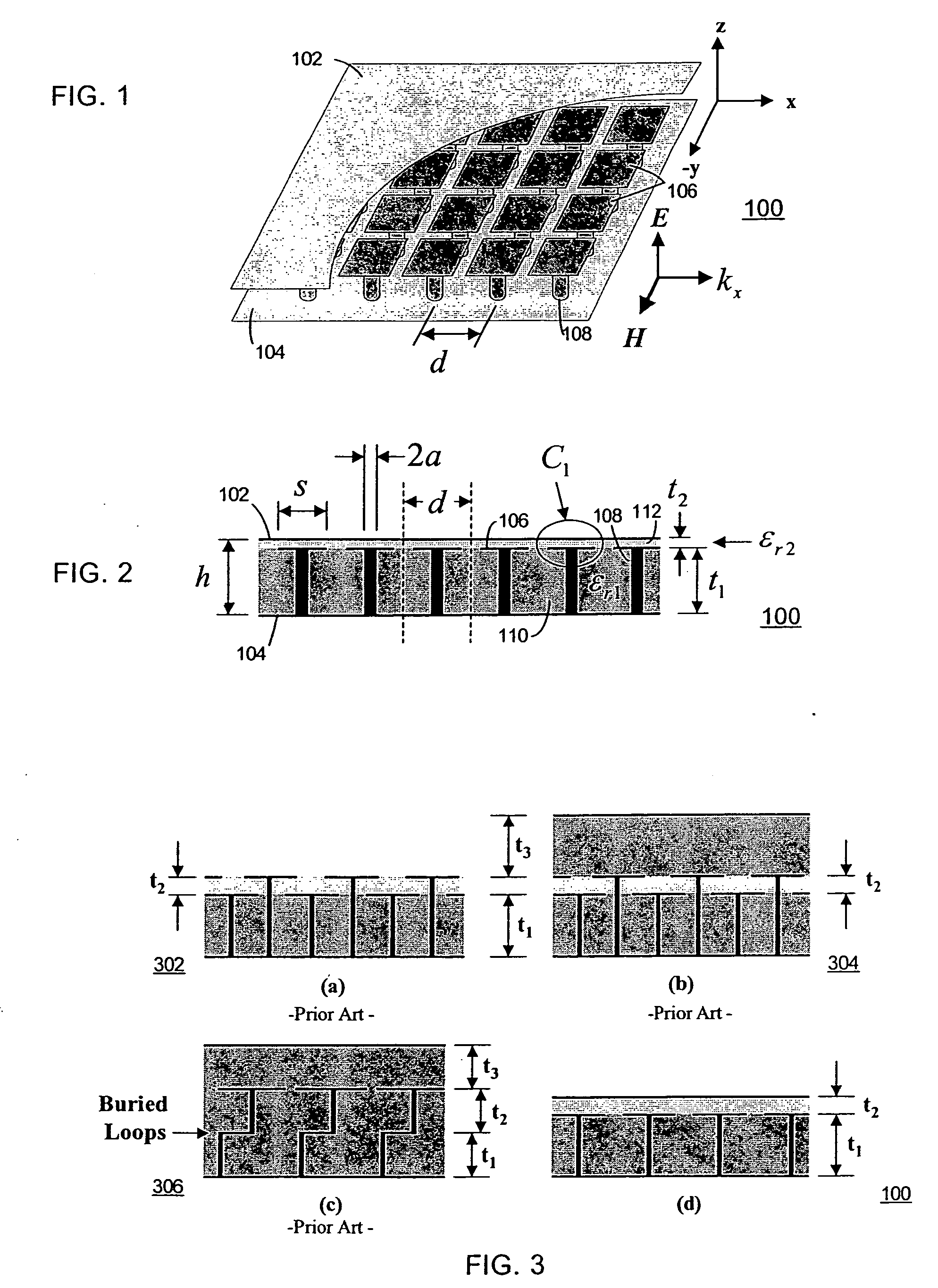

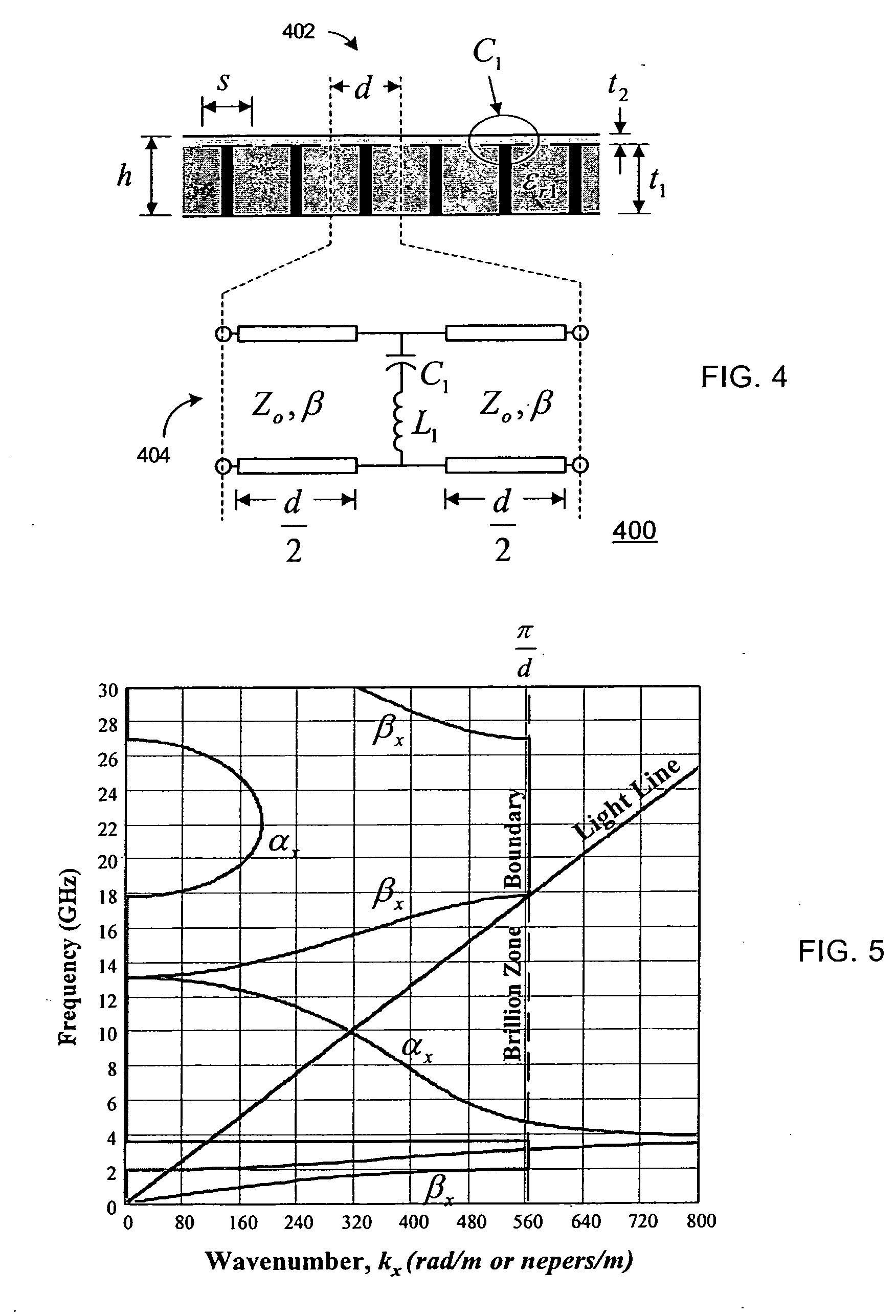

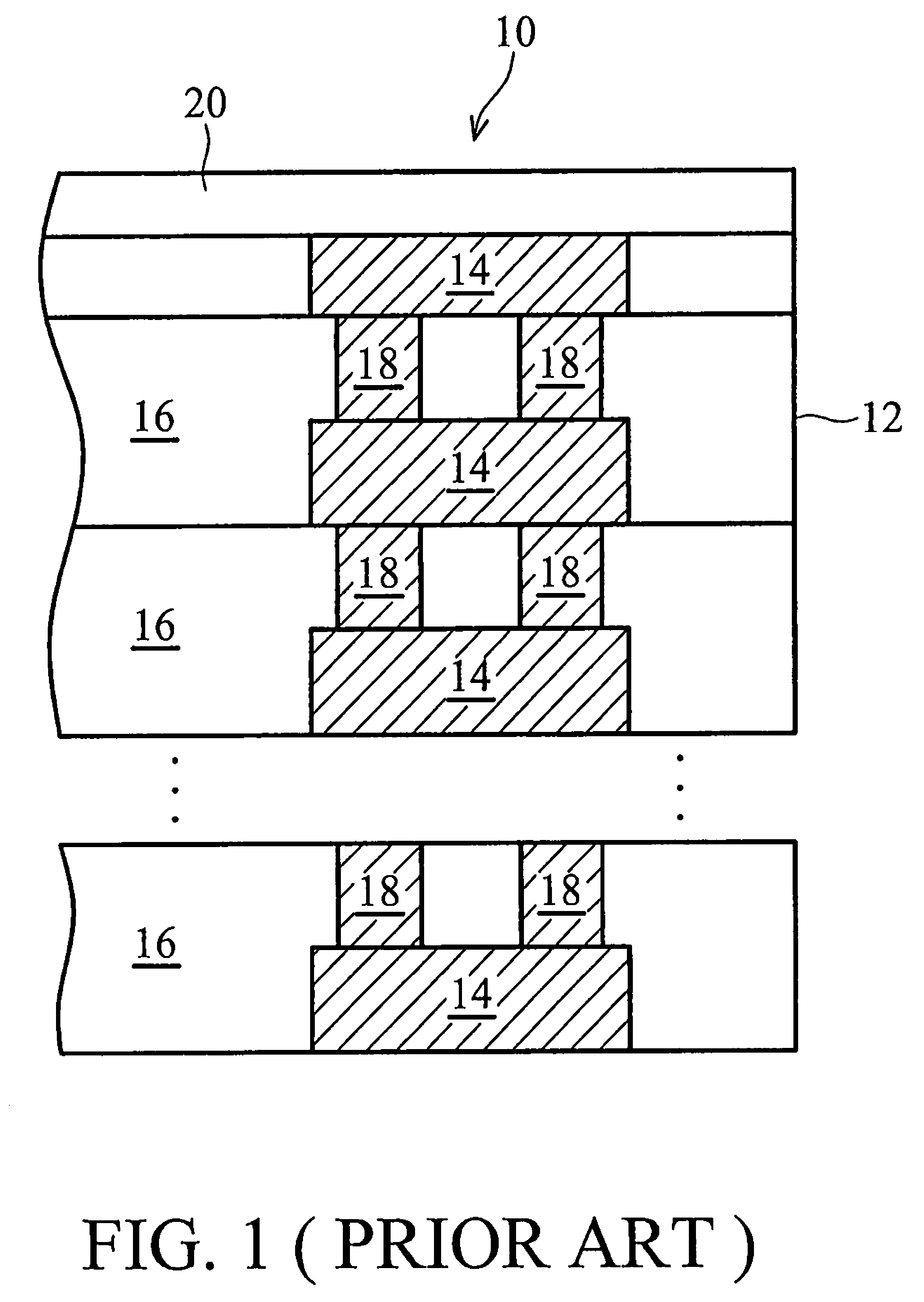

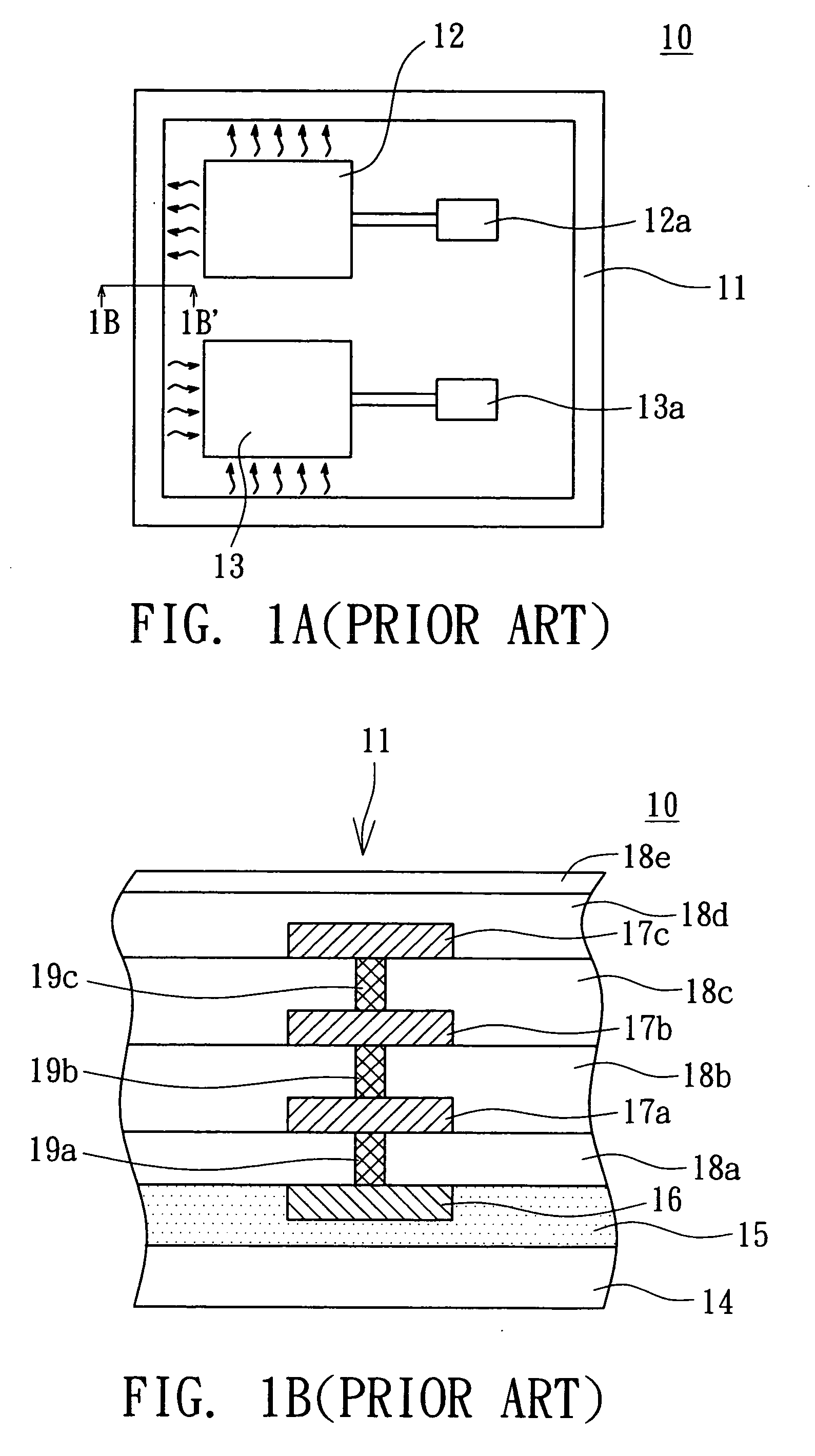

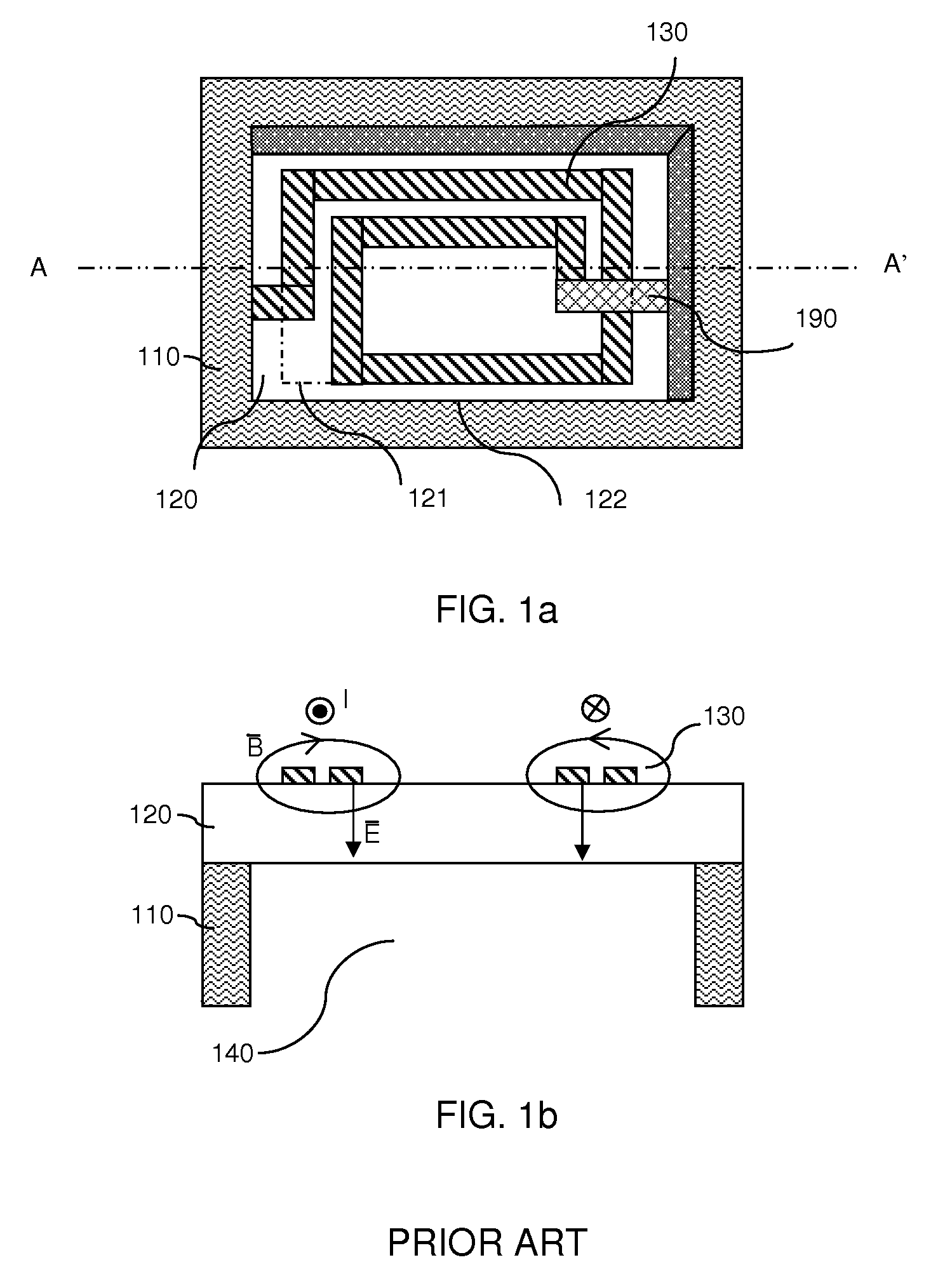

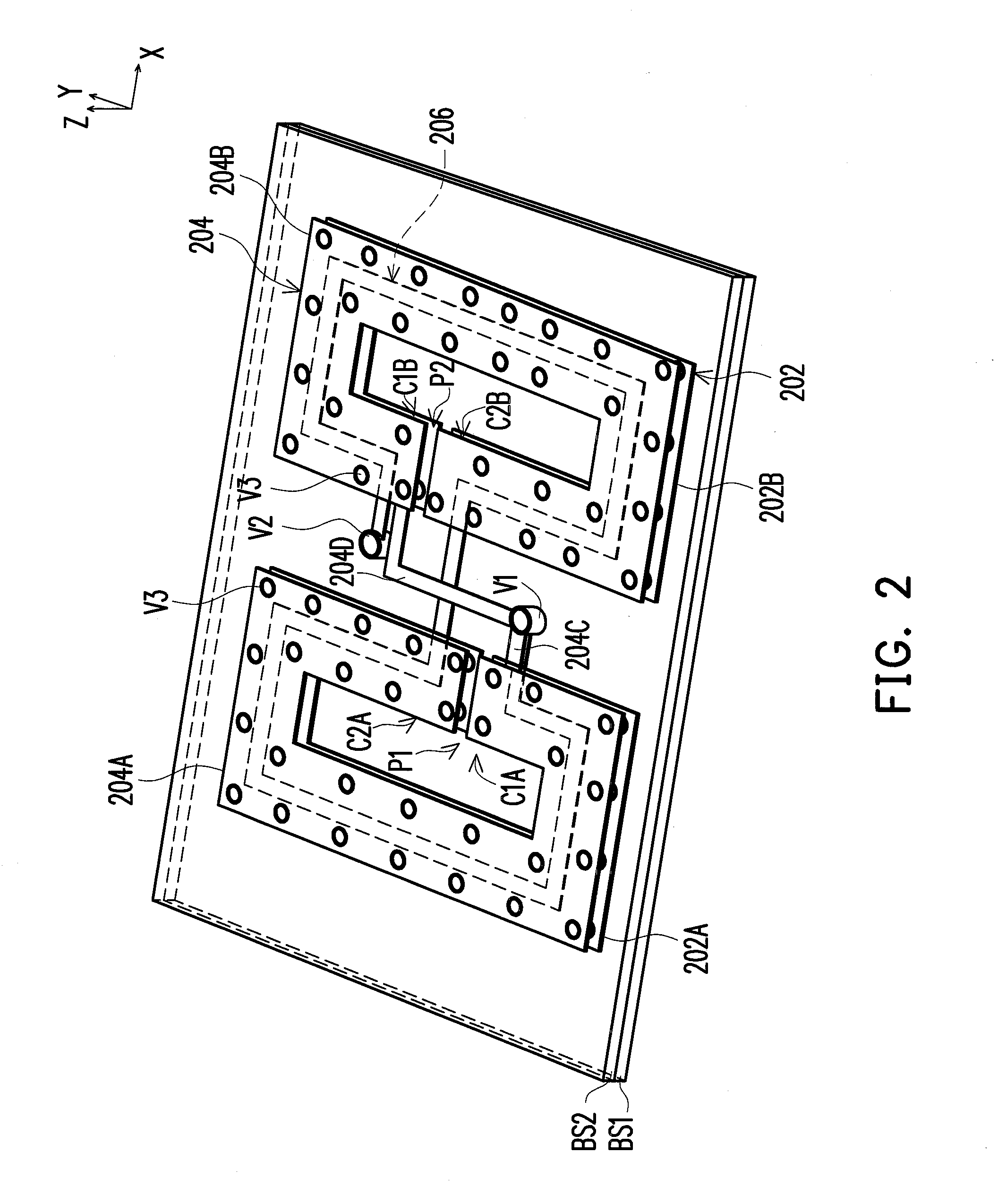

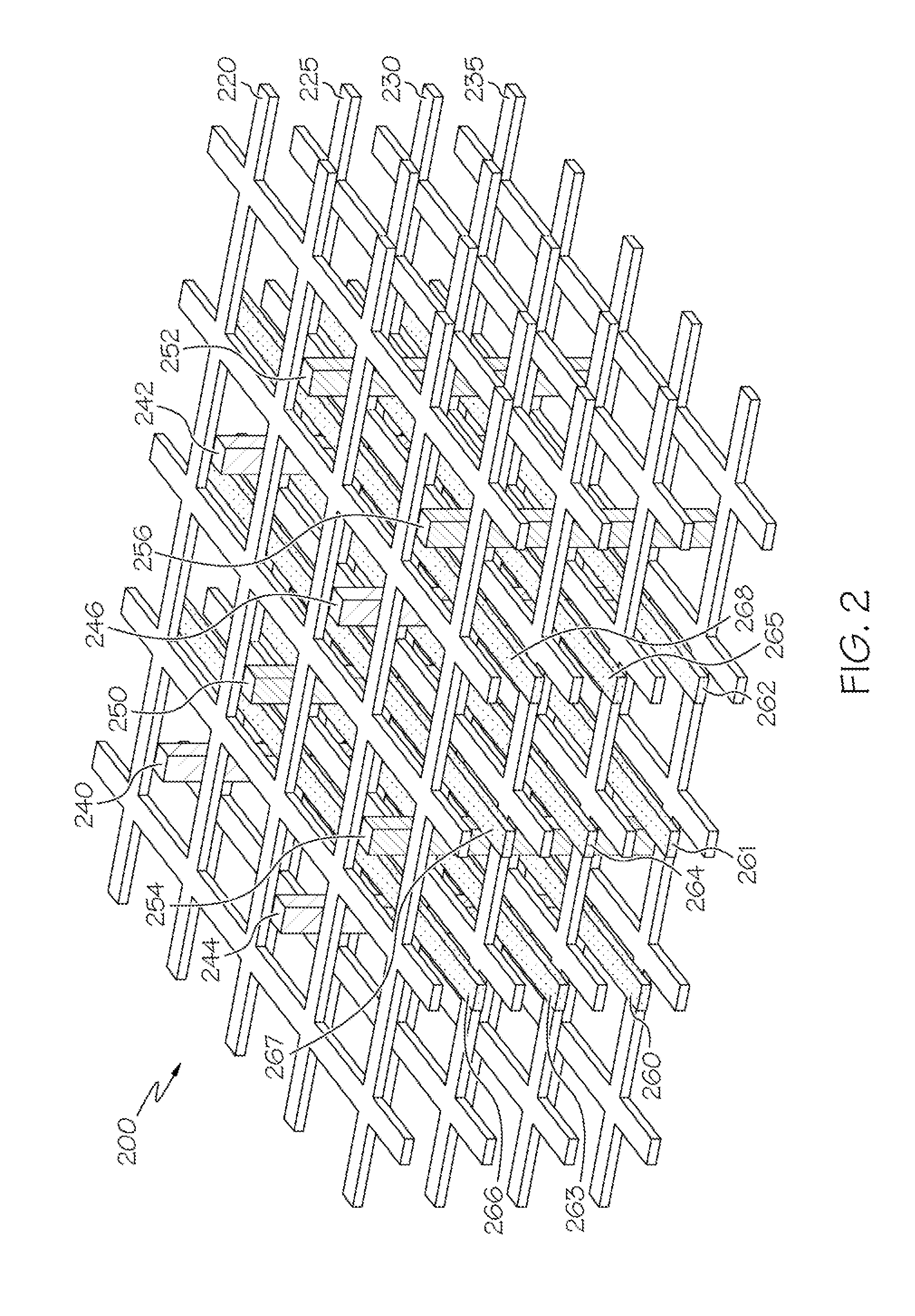

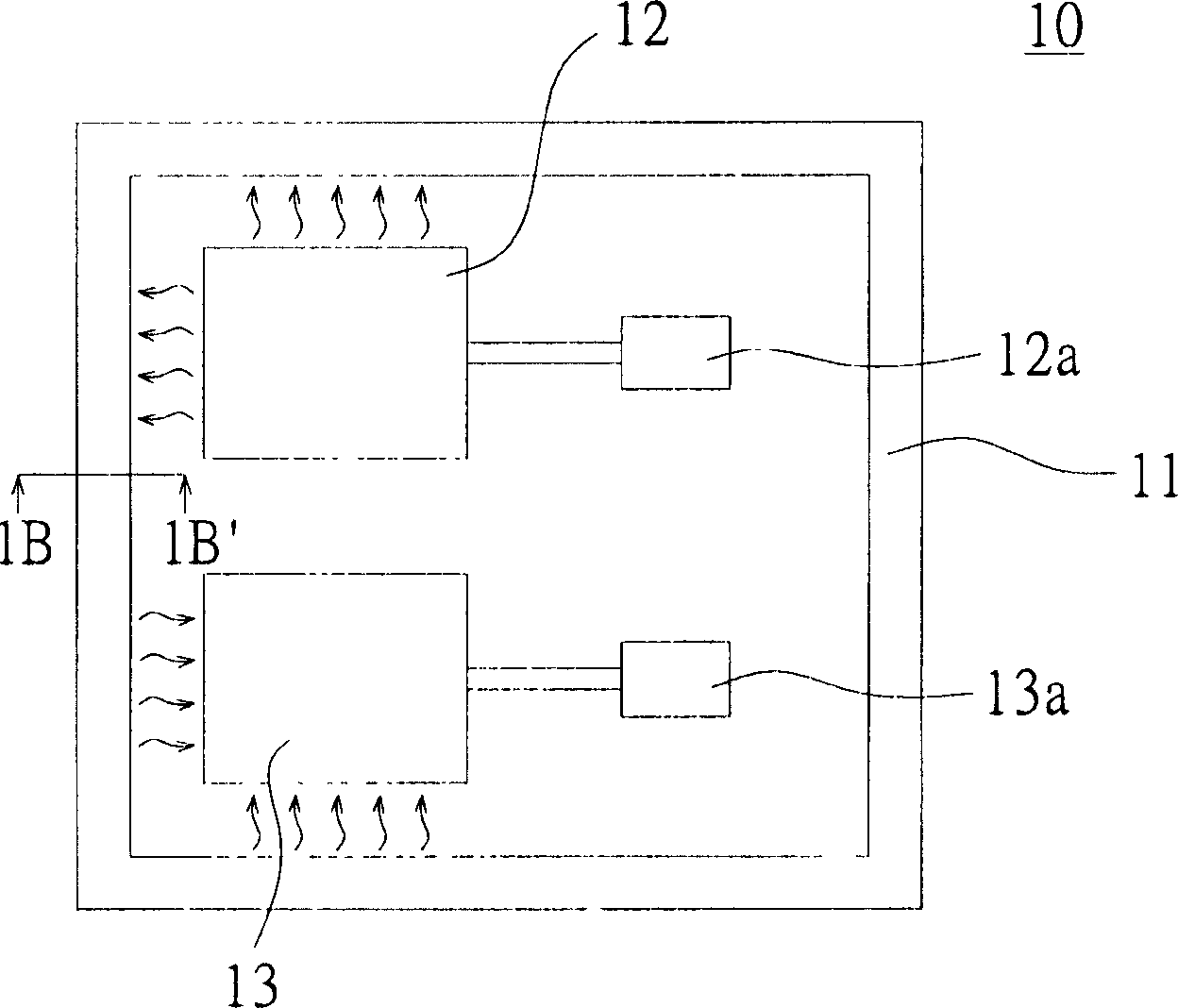

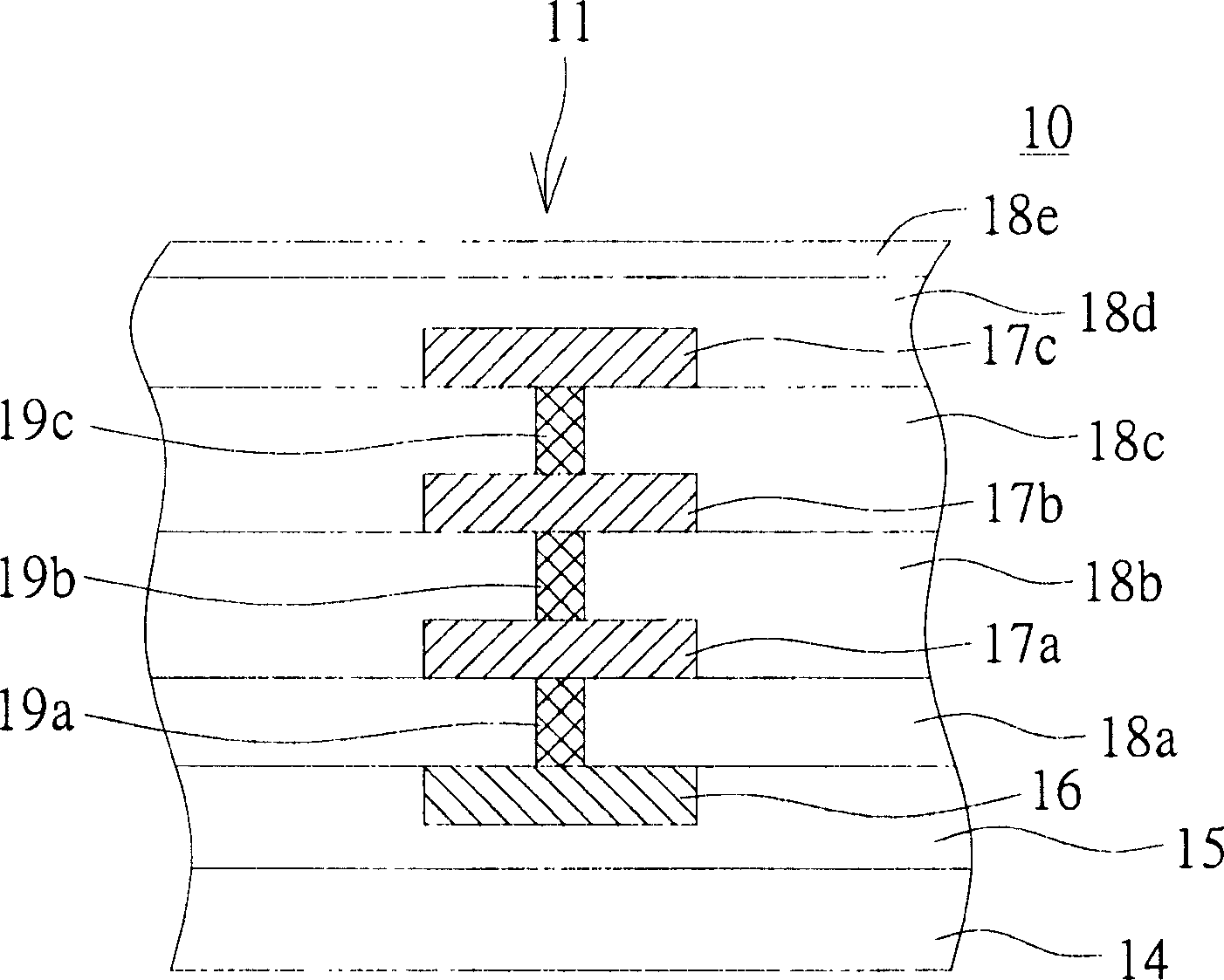

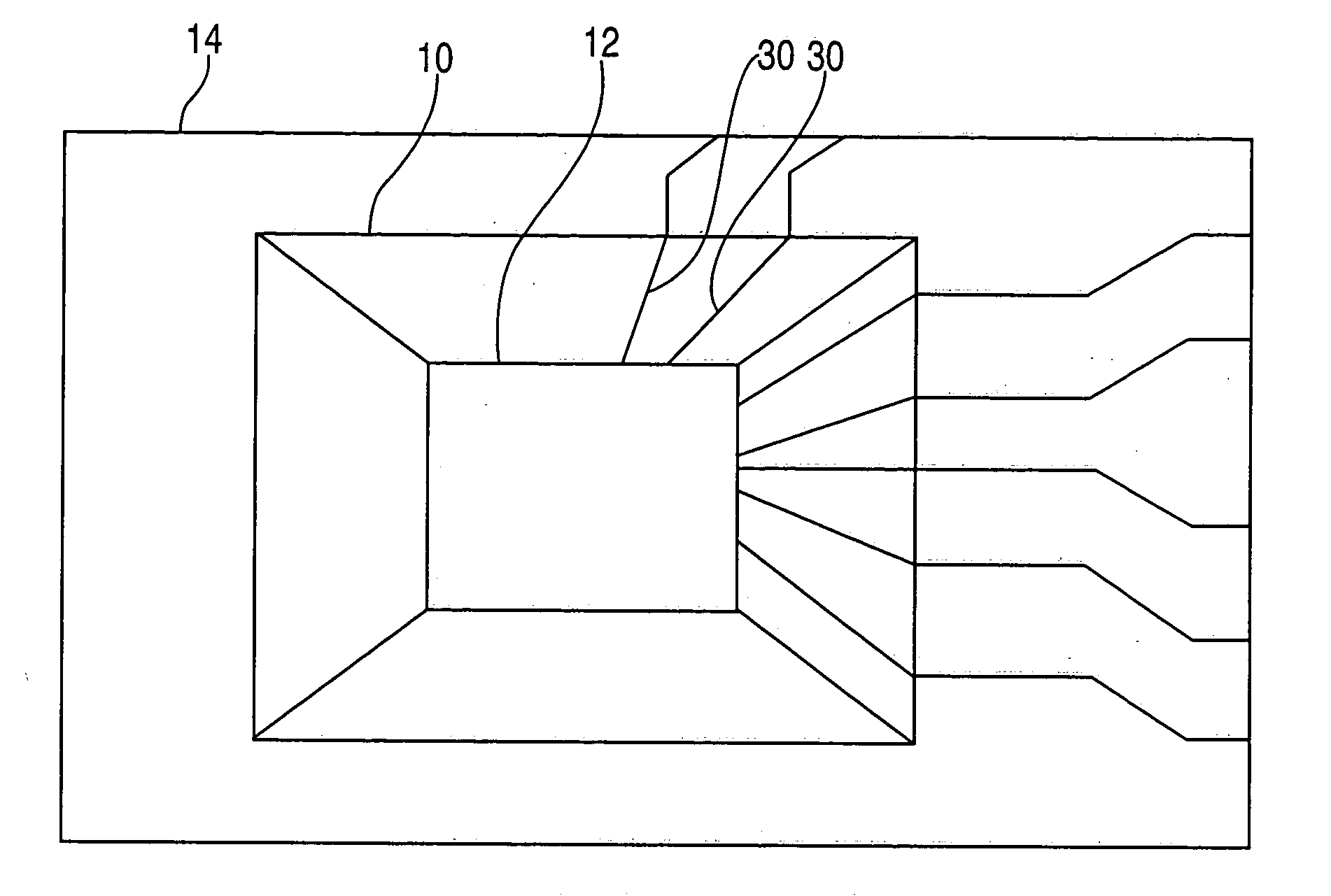

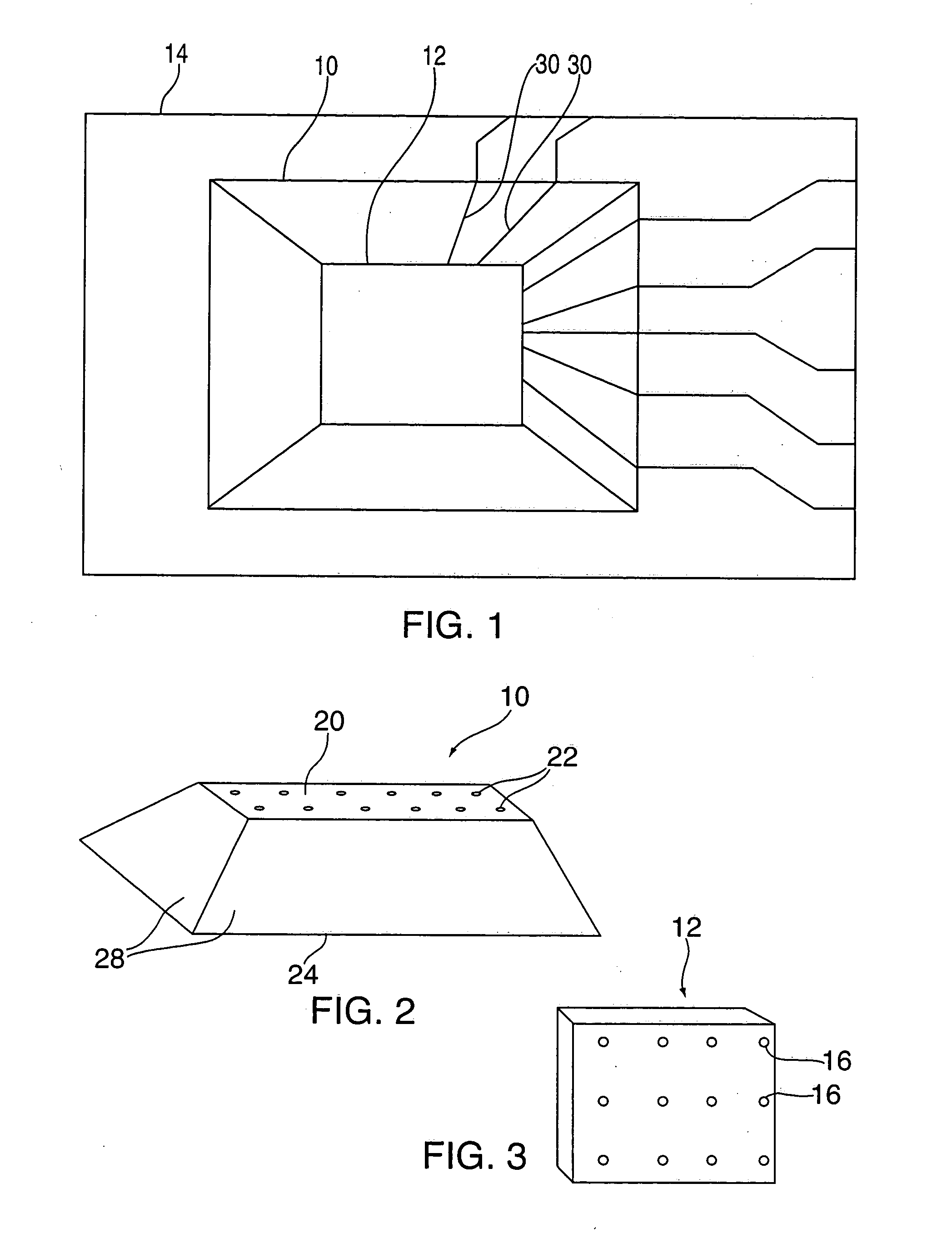

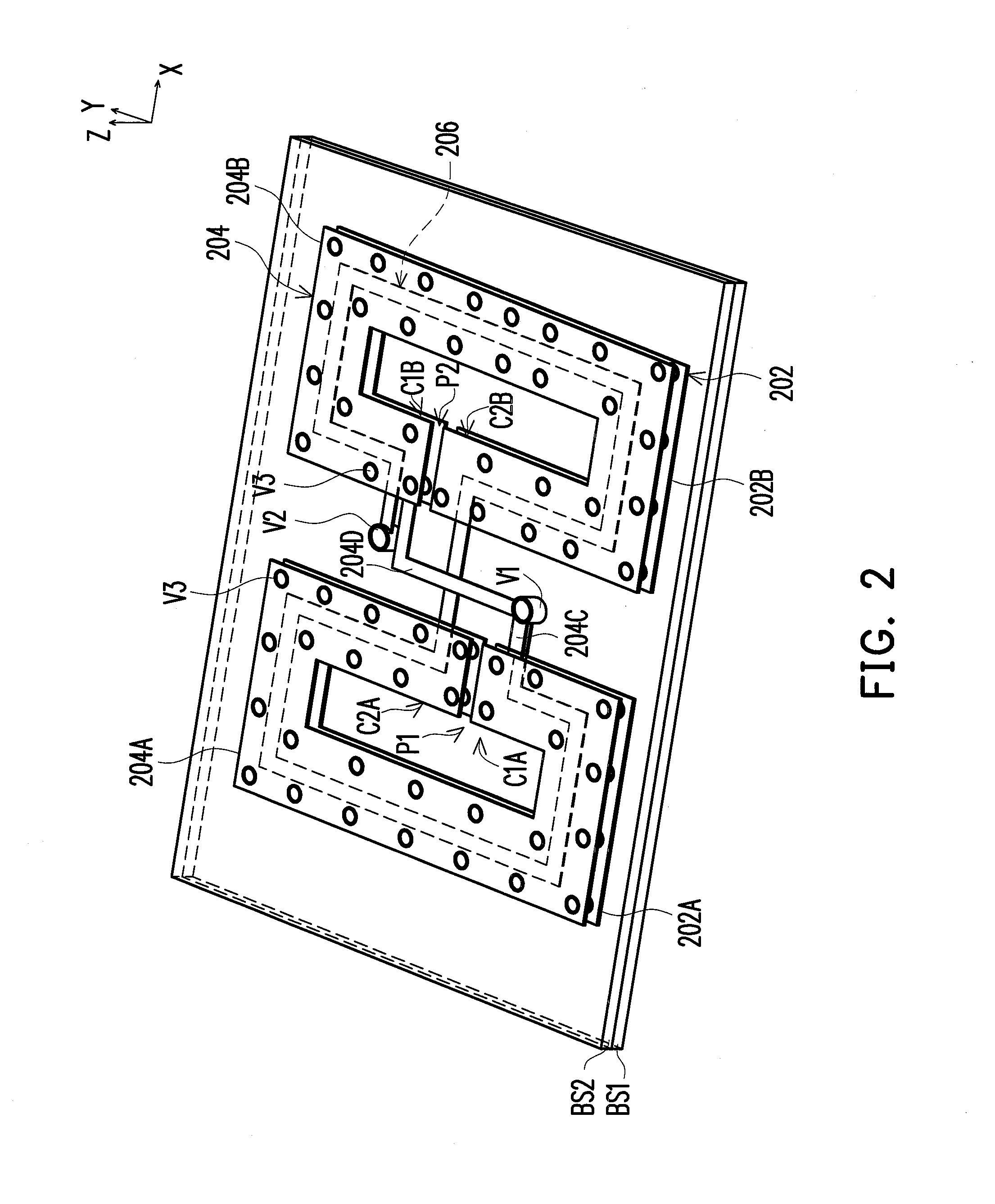

Circuit and method for suppression of electromagnetic coupling and switching noise in multilayer printed circuit boards

InactiveUS20050029632A1Eliminate power plane resonanceSuppress powerTransmission control/equlisationSemiconductor/solid-state device detailsCapacitanceElectromagnetic coupling

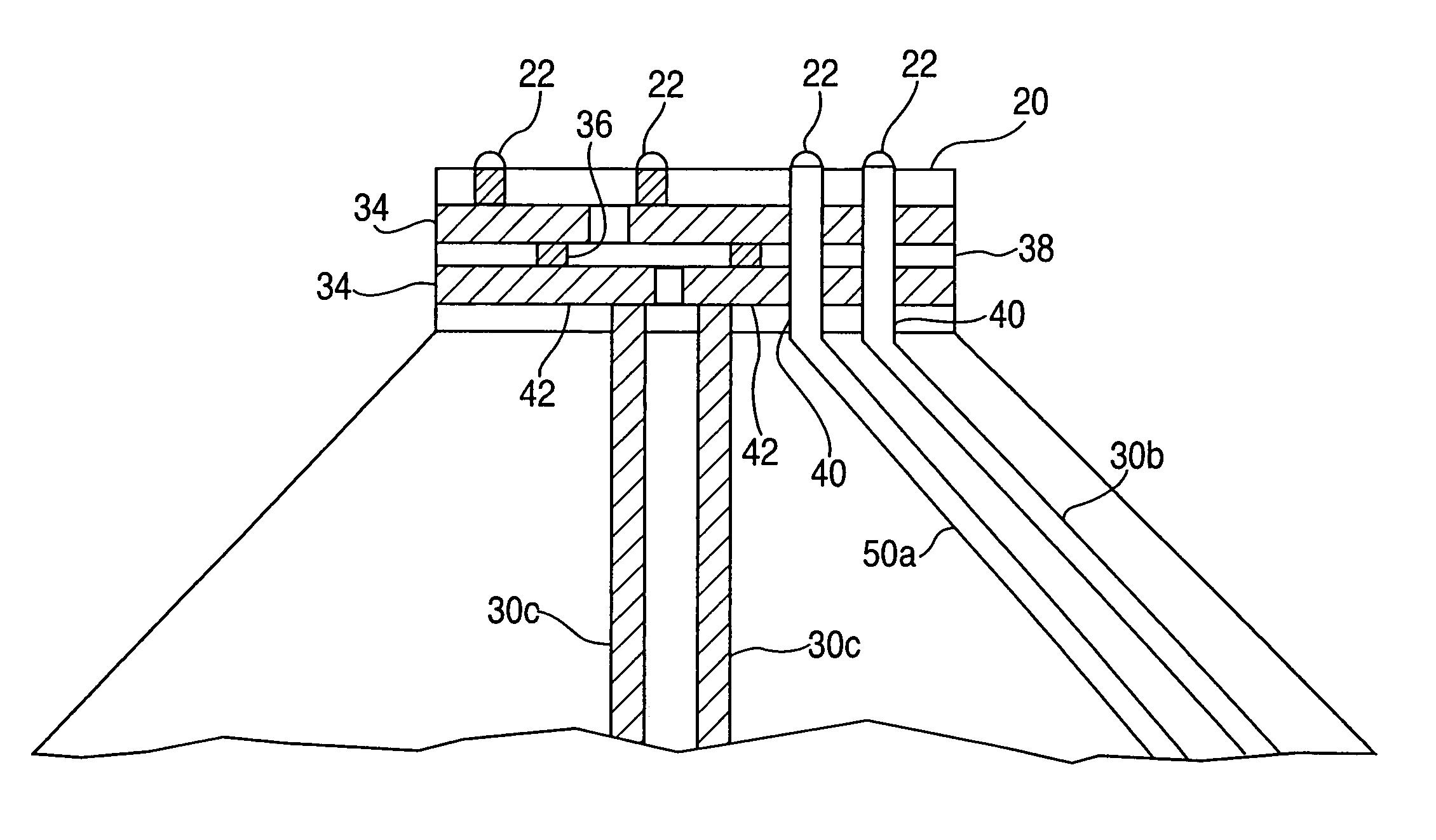

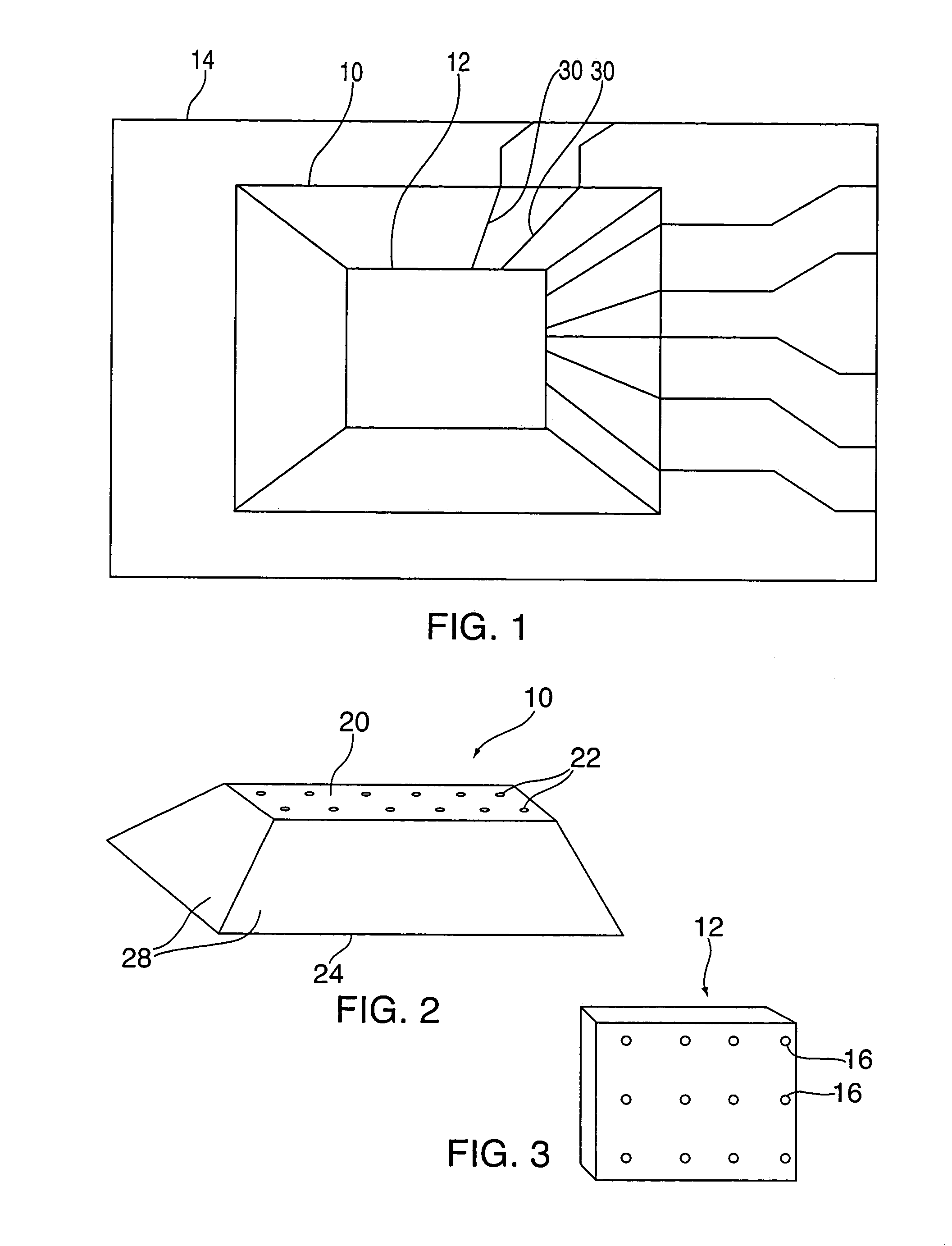

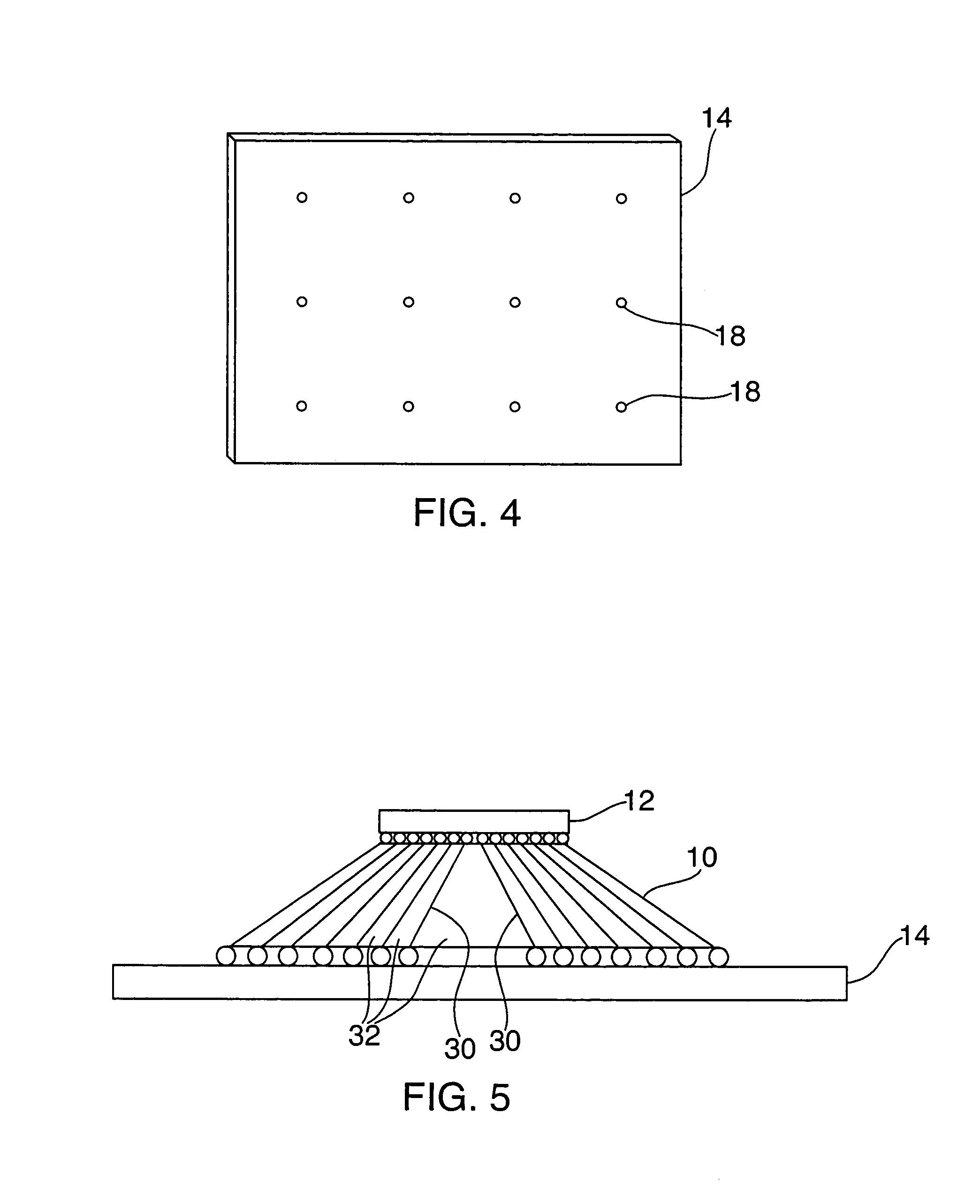

Apparatus for suppressing noise and electromagnetic coupling in the printed circuit board of an electronic device includes an upper conductive plate and an array of conductive coplanar patches positioned a distance t2 from the upper conductive plate. The distance t2 is chosen to optimize capacitance between the conductive coplanar patches and the upper conductive plate for suppression of noise or electromagnetic coupling. The apparatus further includes a lower conductive plate a distance t1 from the array of conductive coplanar patches and conductive rods extending from respective patches to the lower conductive plate.

Owner:WEMTEC

Circuit and method for suppression of electromagnetic coupling and switching noise in multilayer printed circuit boards

InactiveUS7215007B2Suppress powerRemoval of powerTransmission control/equlisationSemiconductor/solid-state device detailsElectromagnetic couplingCapacitance

Apparatus for suppressing noise and electromagnetic coupling in the printed circuit board of an electronic device includes an upper conductive plate and an array of conductive coplanar patches positioned a distance t2 from the upper conductive plate. The distance t2 is chosen to optimize capacitance between the conductive coplanar patches and the upper conductive plate for suppression of noise or electromagnetic coupling. The apparatus further includes a lower conductive plate a distance t1 from the array of conductive coplanar patches and conductive rods extending from respective patches to the lower conductive plate.

Owner:WEMTEC

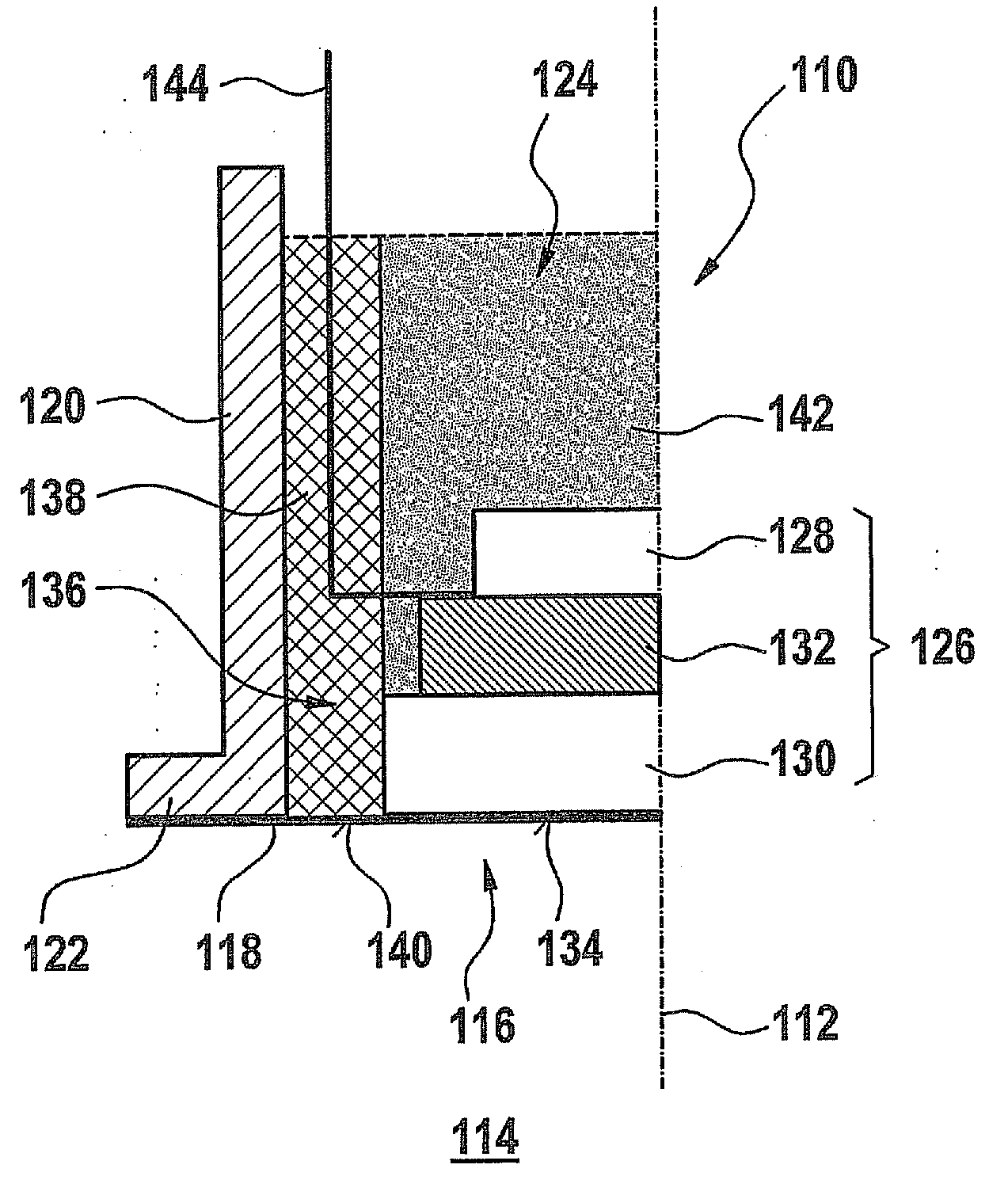

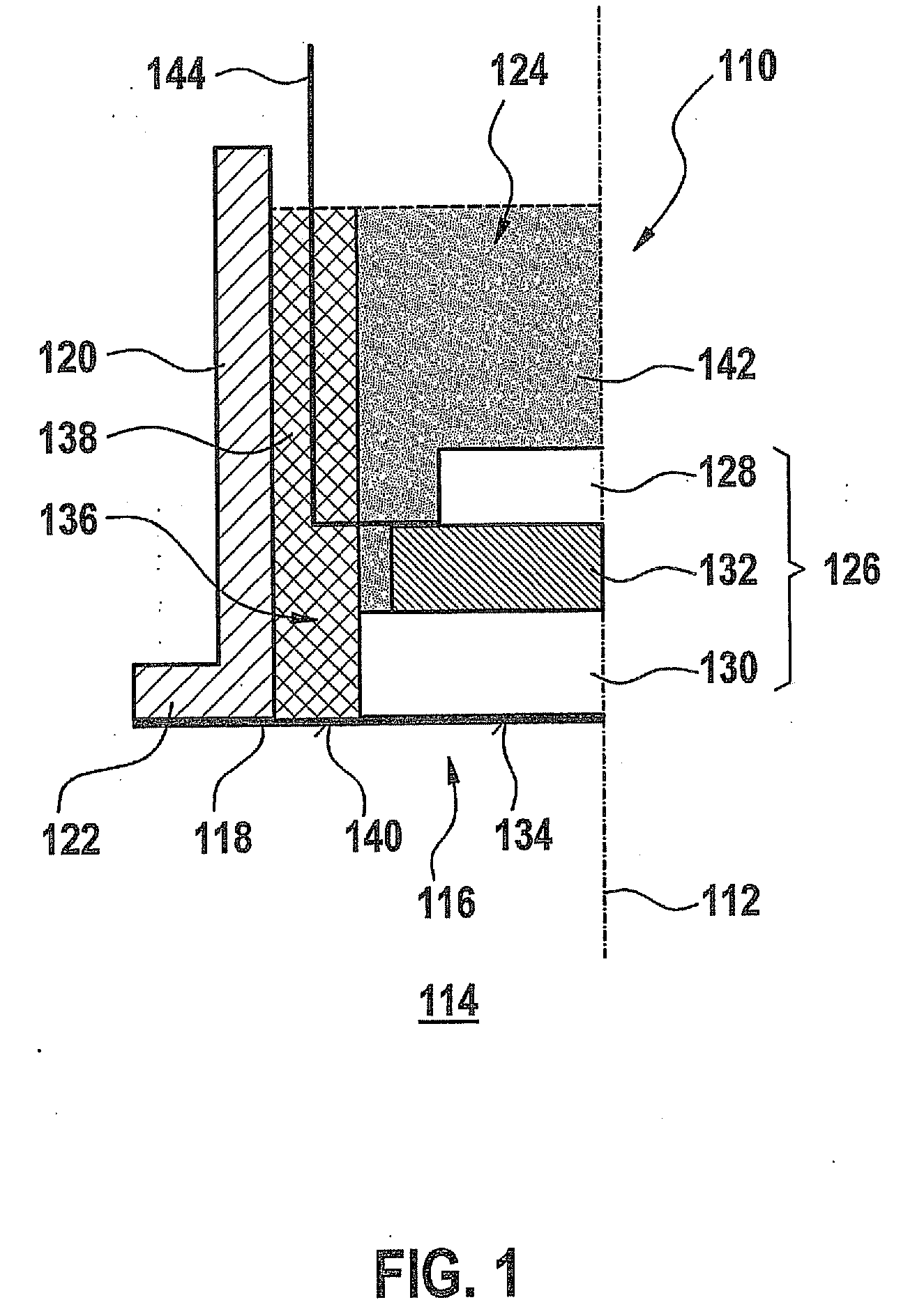

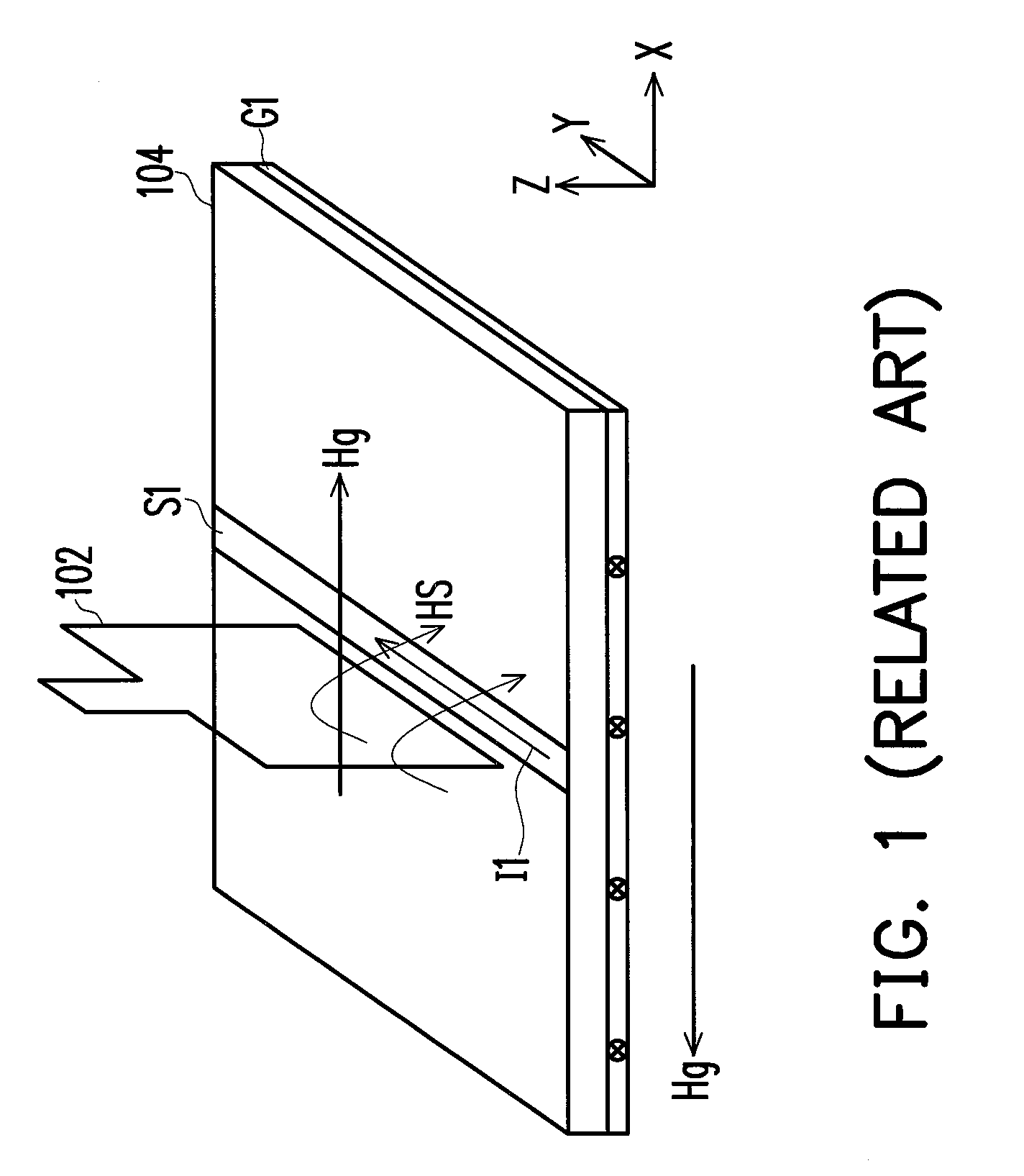

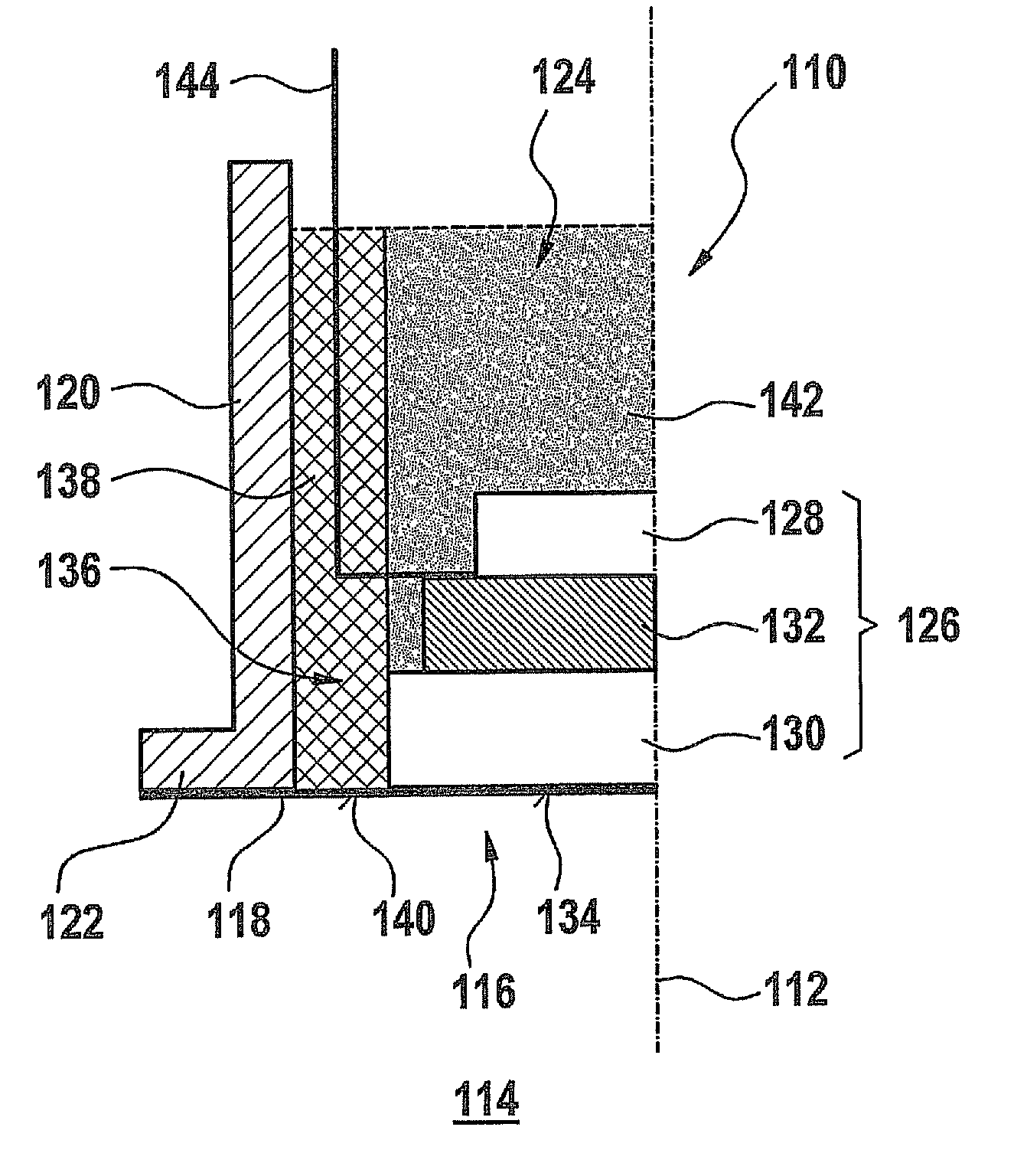

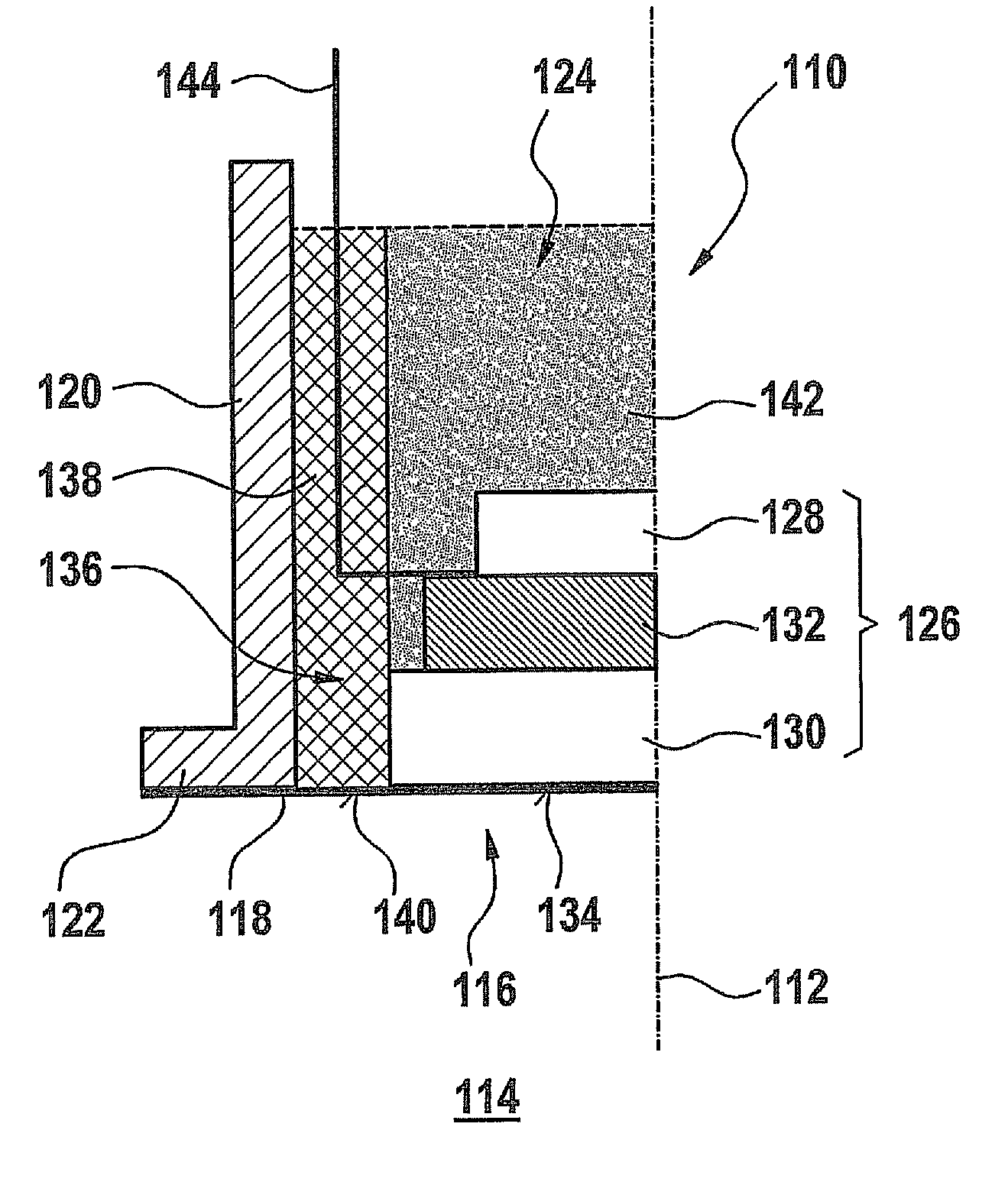

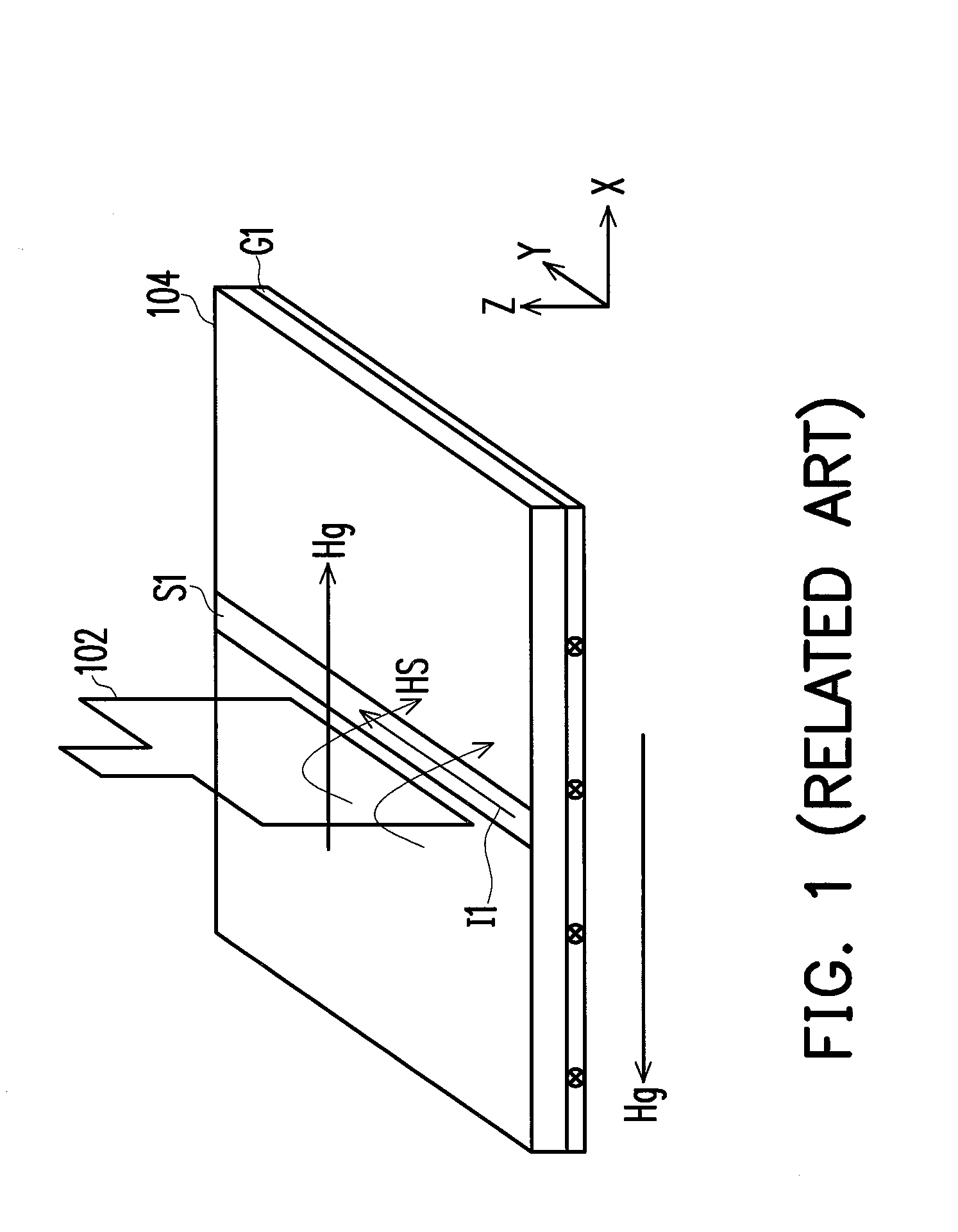

Ultrasonic transducer for use in a fluid medium

InactiveUS20110125024A1Reduce noise couplingHigh materialUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostriction/magnetostriction machinesThermoplasticPlastic materials

An ultrasonic transducer for use in a fluid medium includes at least one transducer core having at least one acoustic / electric transducer element. The ultrasonic transducer furthermore includes at least one decoupling element which is configured to reduce a structure-borne noise coupling between the transducer core and a housing. The decoupling element includes at least one porous plastic material, in particular a foamed plastic material. The porous plastic material includes at least one thermosetting polymer and / or at least one thermoplastic.

Owner:ROBERT BOSCH GMBH

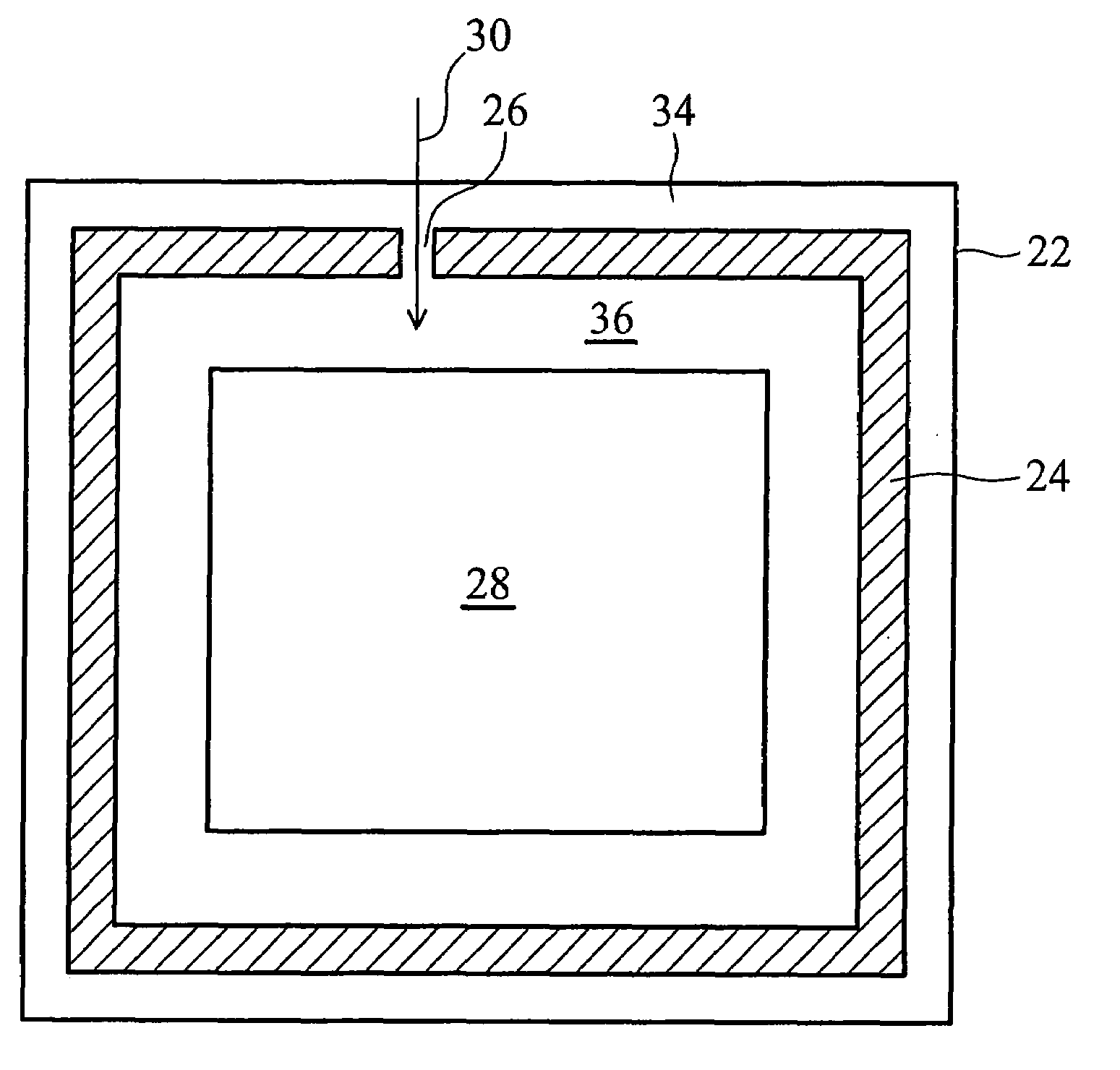

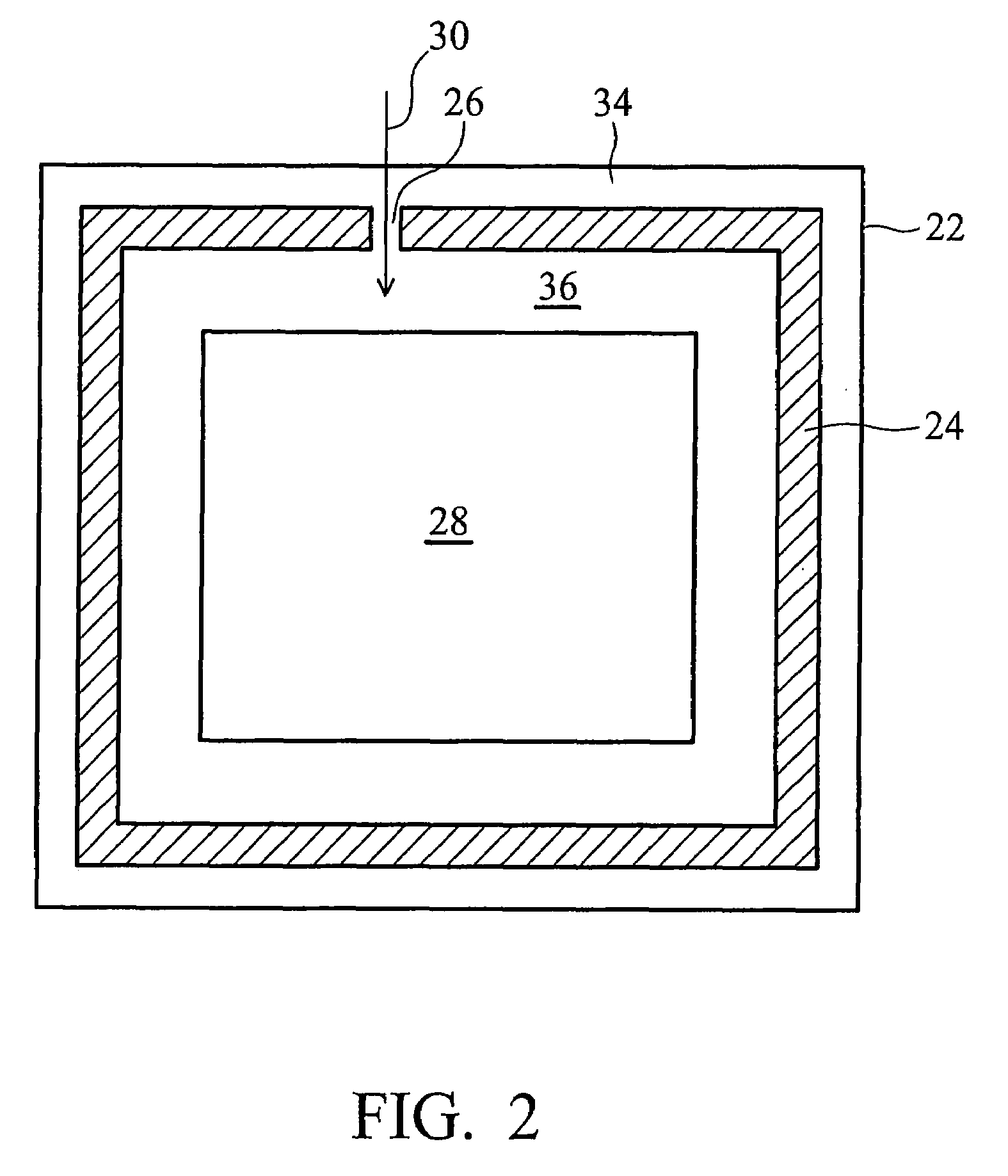

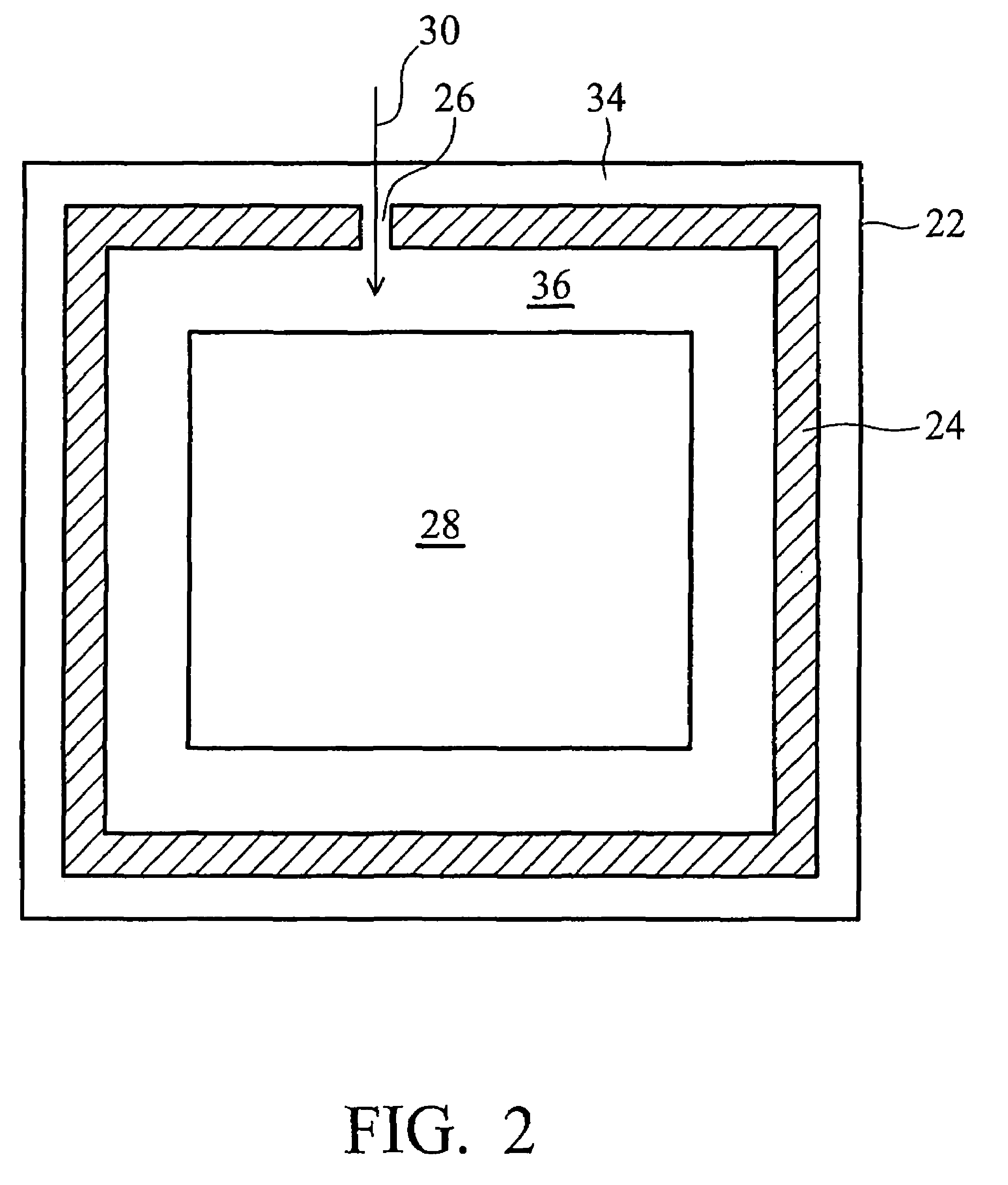

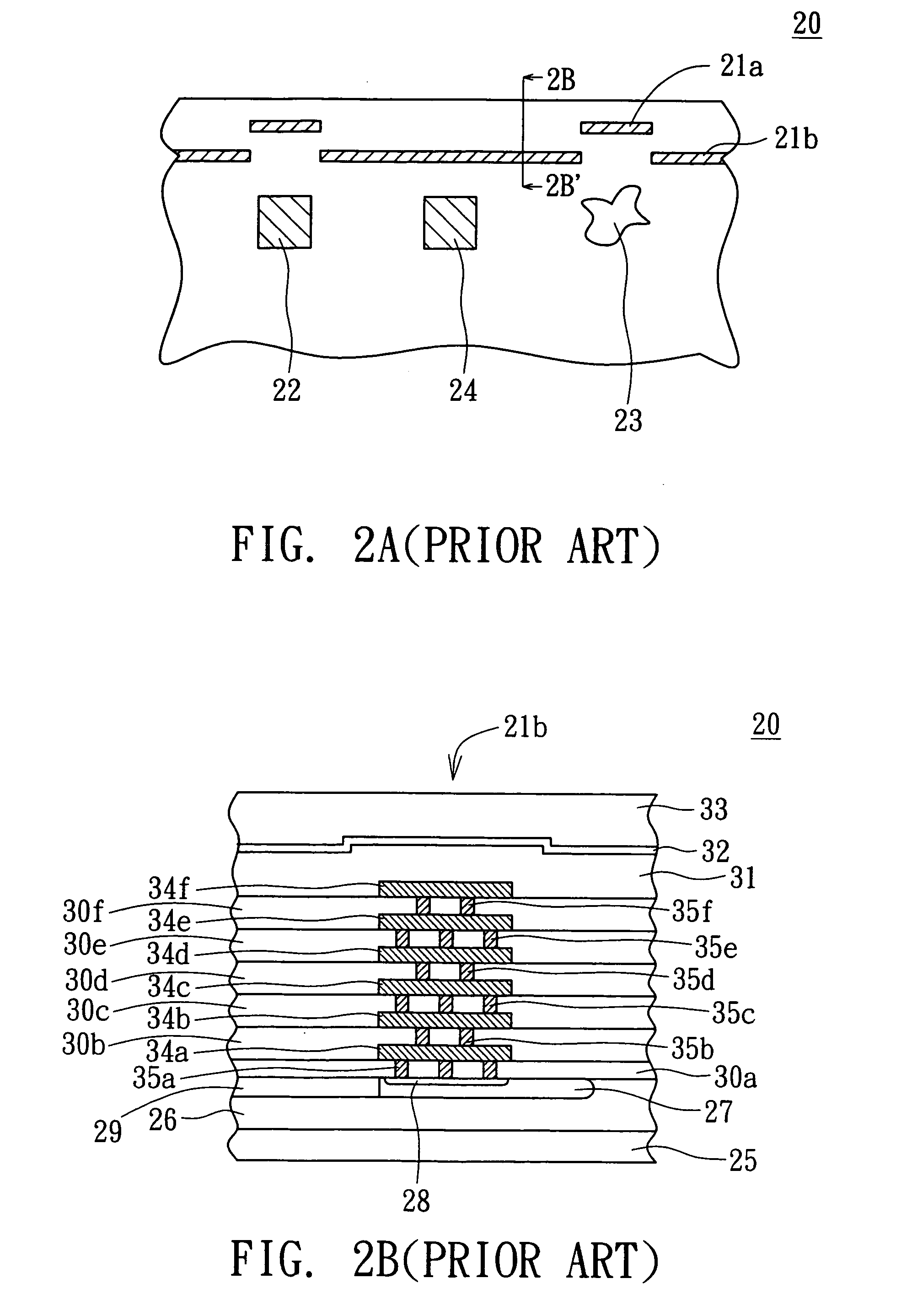

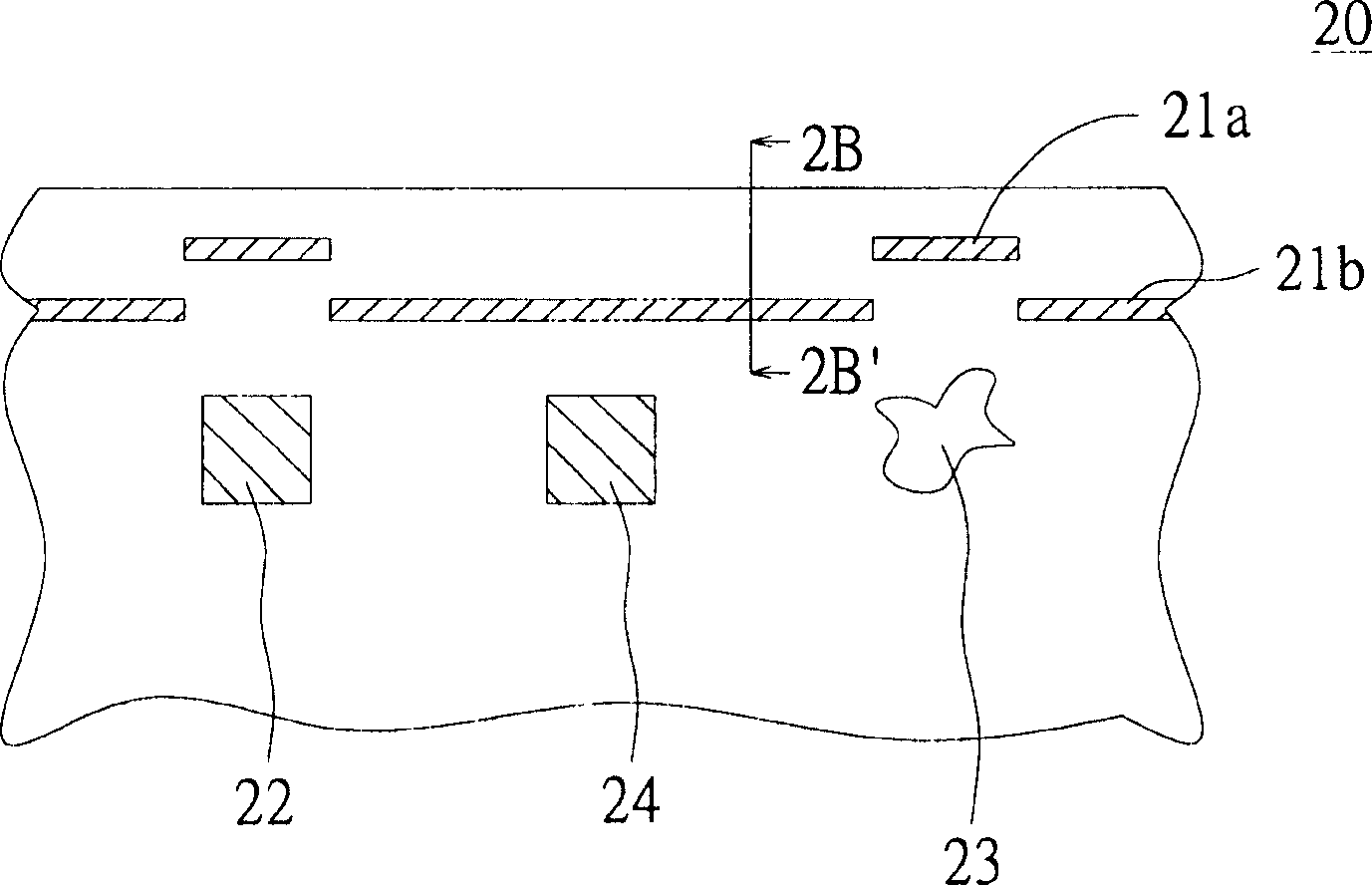

Seal ring structures with reduced moisture-induced reliability degradation

InactiveUS20080251923A1Reduce noise couplingReduce moisture penetrationThyristorSemiconductor/solid-state device detailsSemiconductor chipEngineering

A semiconductor chip includes a seal ring adjacent to edges of the semiconductor chip; an opening extending from a top surface to a bottom surface of the seal ring, wherein the opening has a first end on an outer side of the seal ring and a second end on an inner side of the seal ring; and a moisture barrier having a sidewall parallel to a nearest side of the seal ring, wherein the moisture barrier is adjacent the seal ring and has a portion facing the opening.

Owner:TAIWAN SEMICON MFG CO LTD

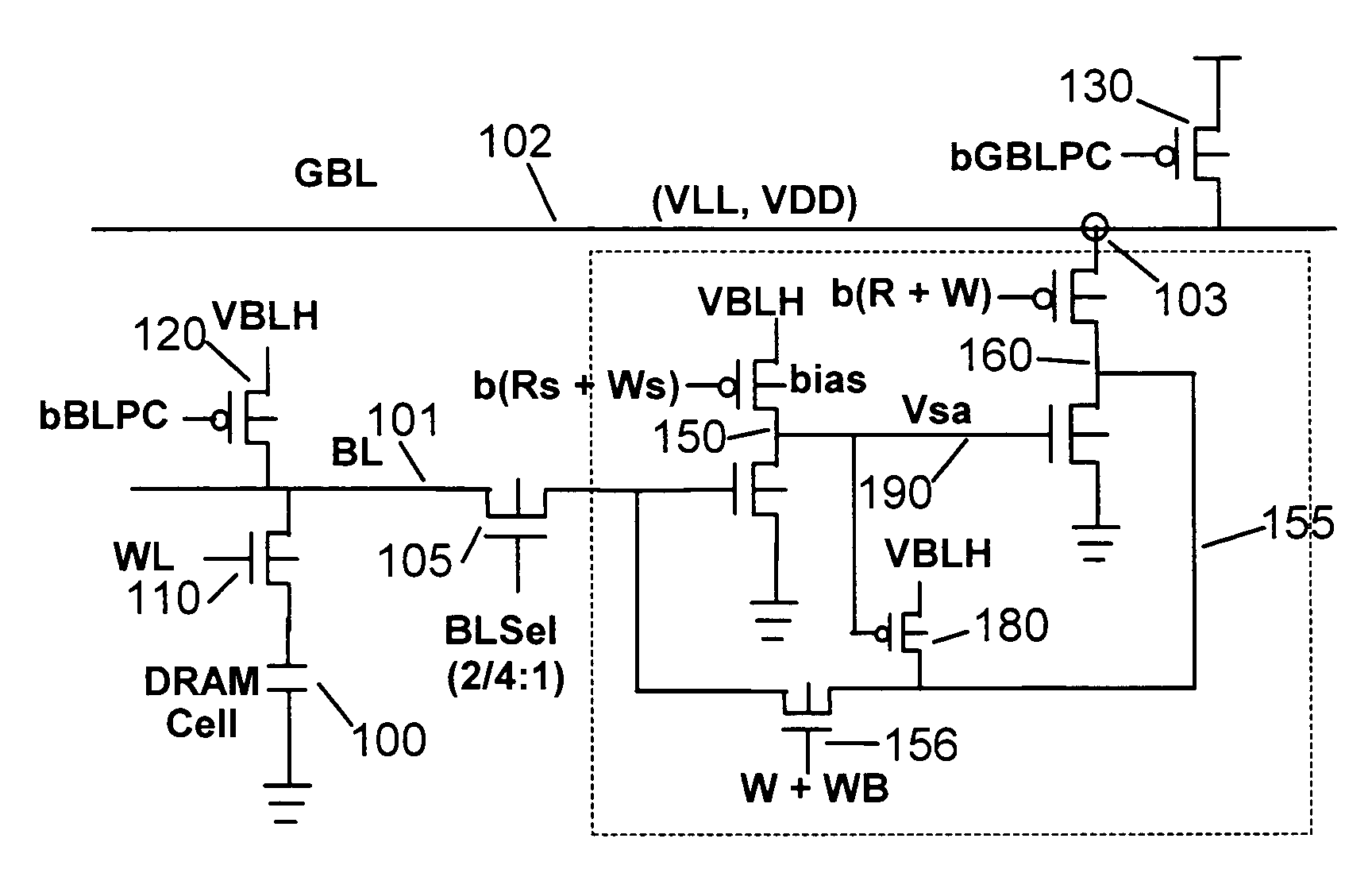

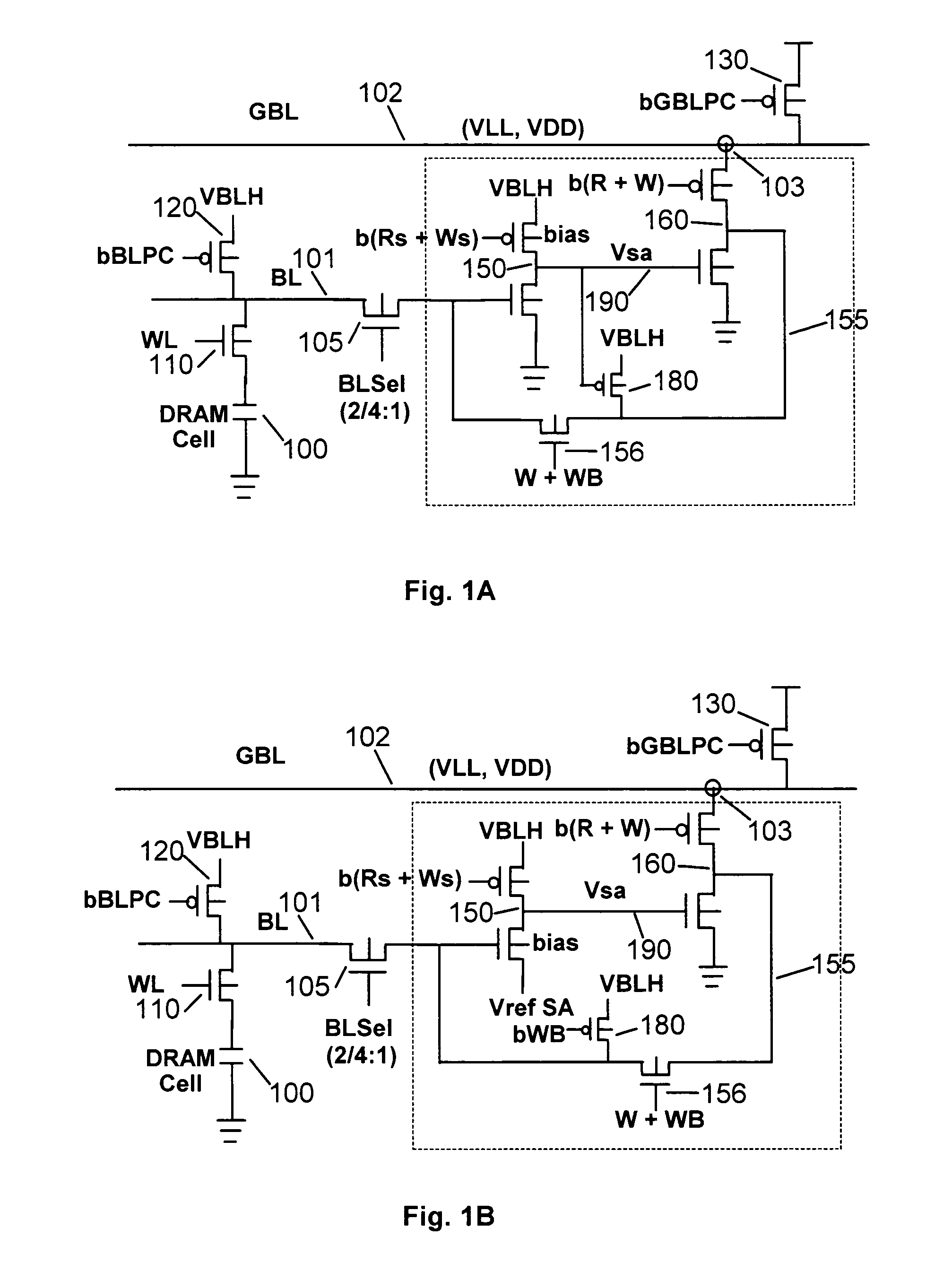

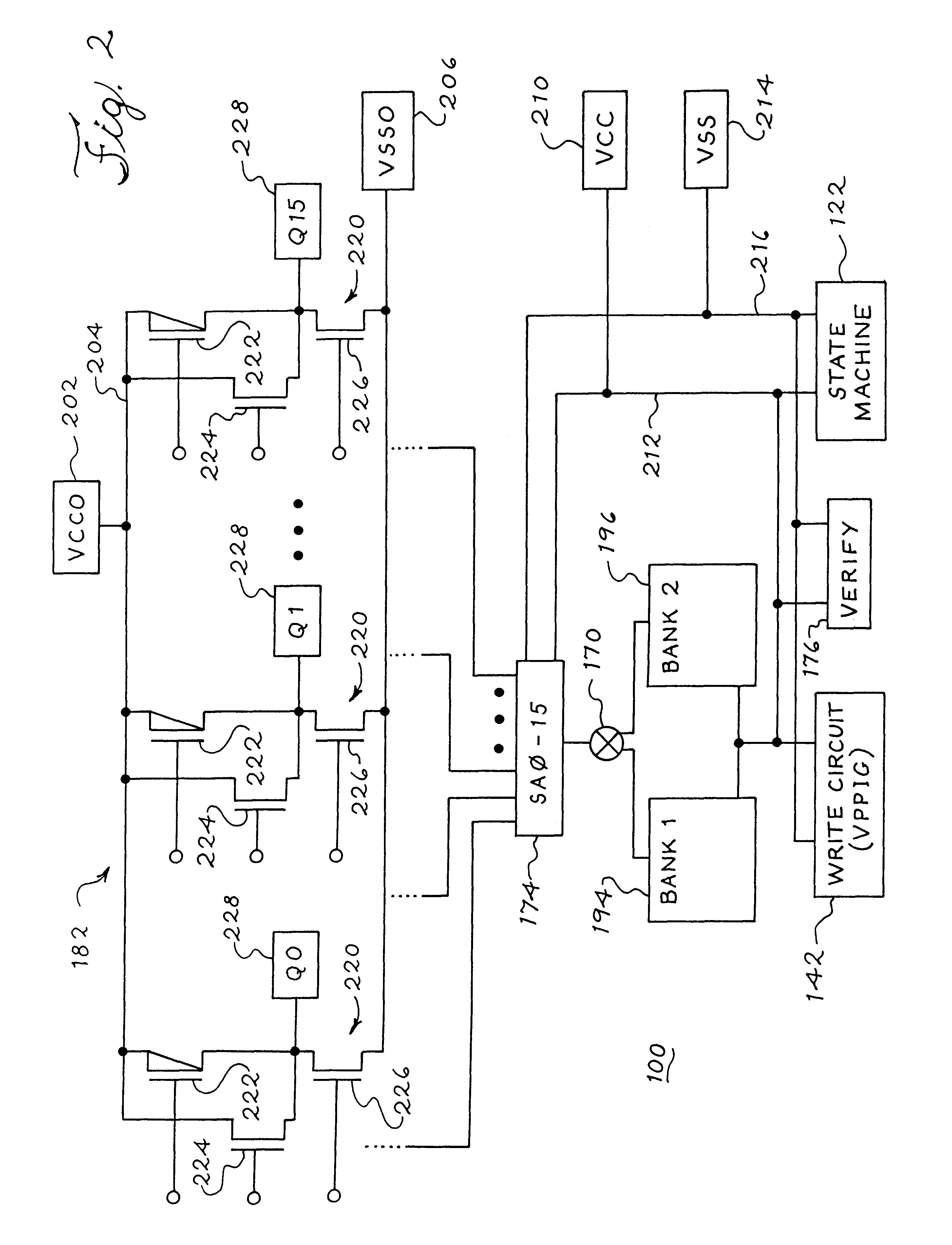

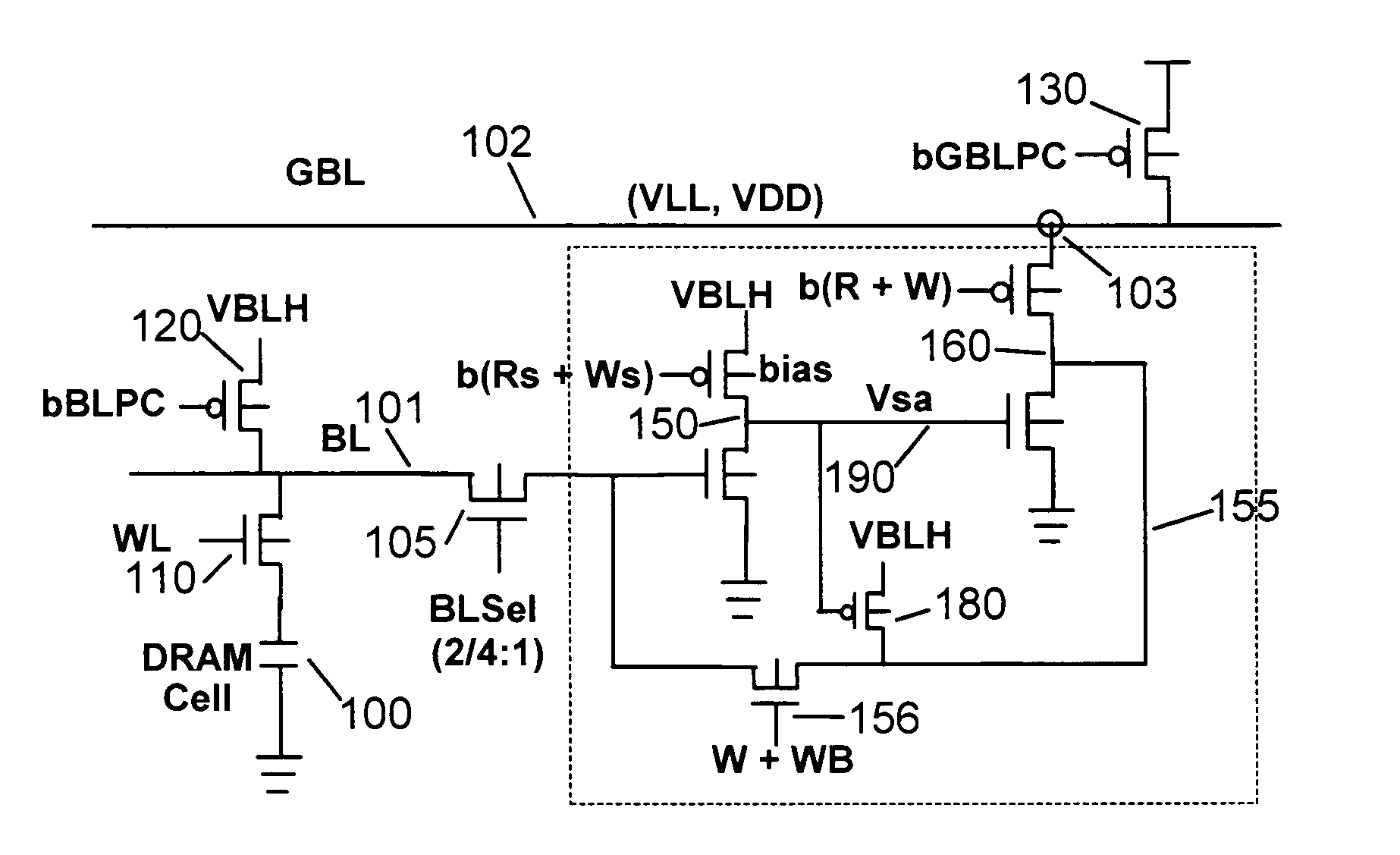

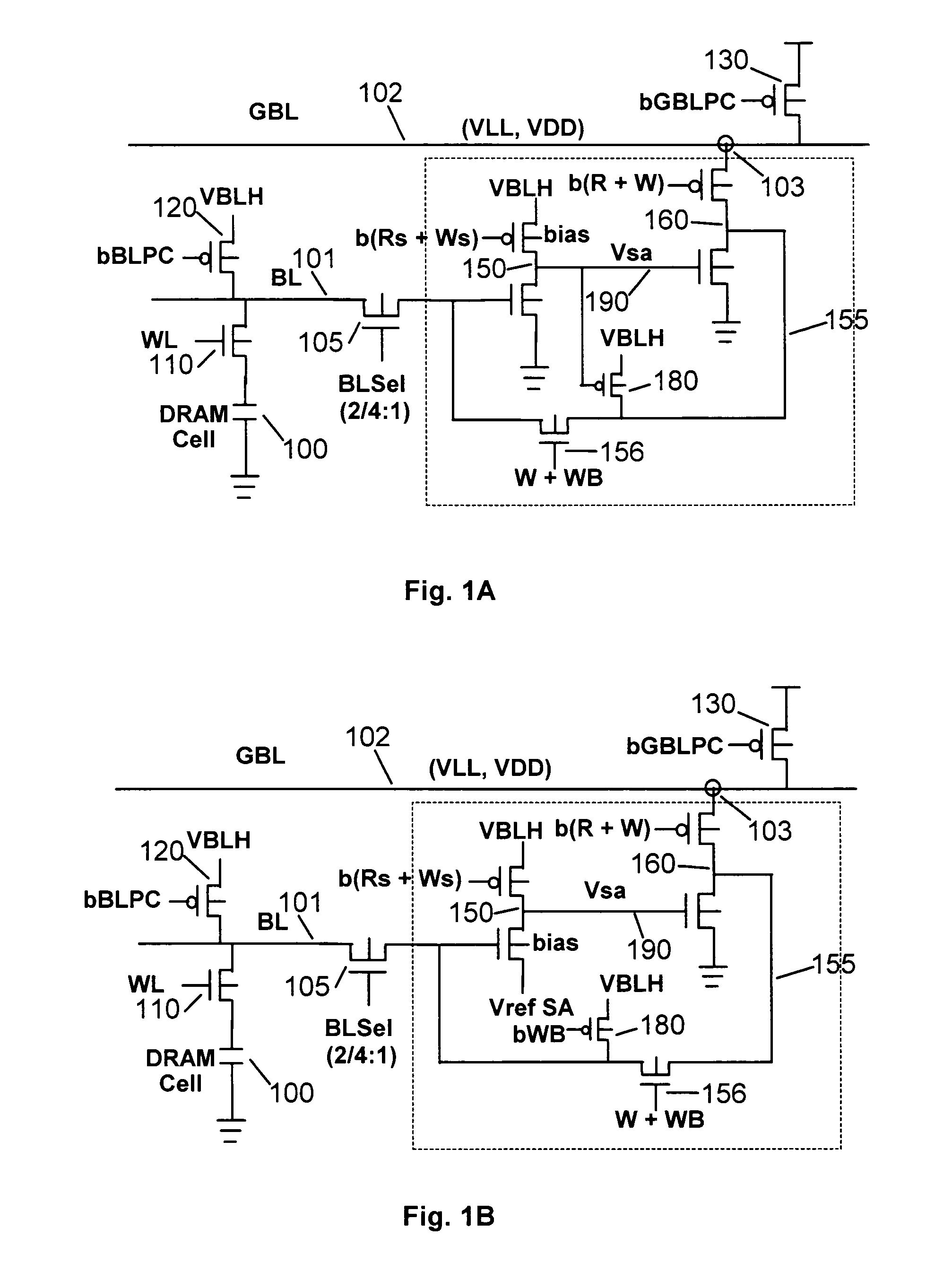

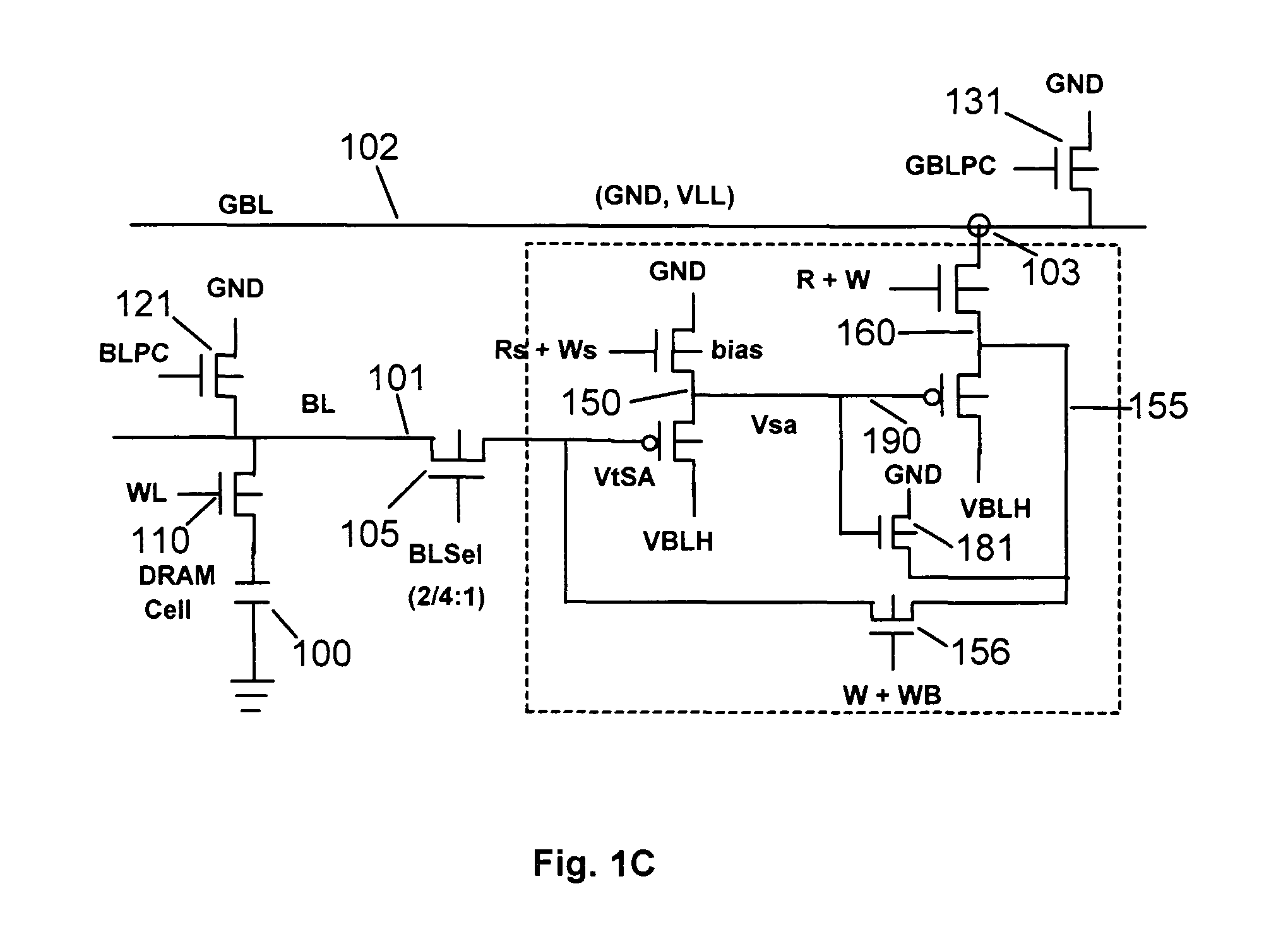

Single cycle read/write/writeback pipeline, full-wordline I/O DRAM architecture with enhanced write and single ended sensing

InactiveUS7099216B2Reduce active powerReduce noise couplingDigital storageComputer architectureAudio power amplifier

A DRAM is disclosed which includes a single ended bitline structure, a single ended global bitline structure, primary sense amplifiers with data storage and data write-back capability and with capability to decouple from the global bitlines, a full-wordline I / O structure where essentially all memory cell that belong to the same wordline are being operated on, and a pipelined architecture. The DRAM further includes a small voltage swing design. The primary sense amplifiers can include more than one amplification stages. Such a DRAM is suitable for applications in conjunction with processors as an embedded DRAM.

Owner:GLOBALFOUNDRIES INC

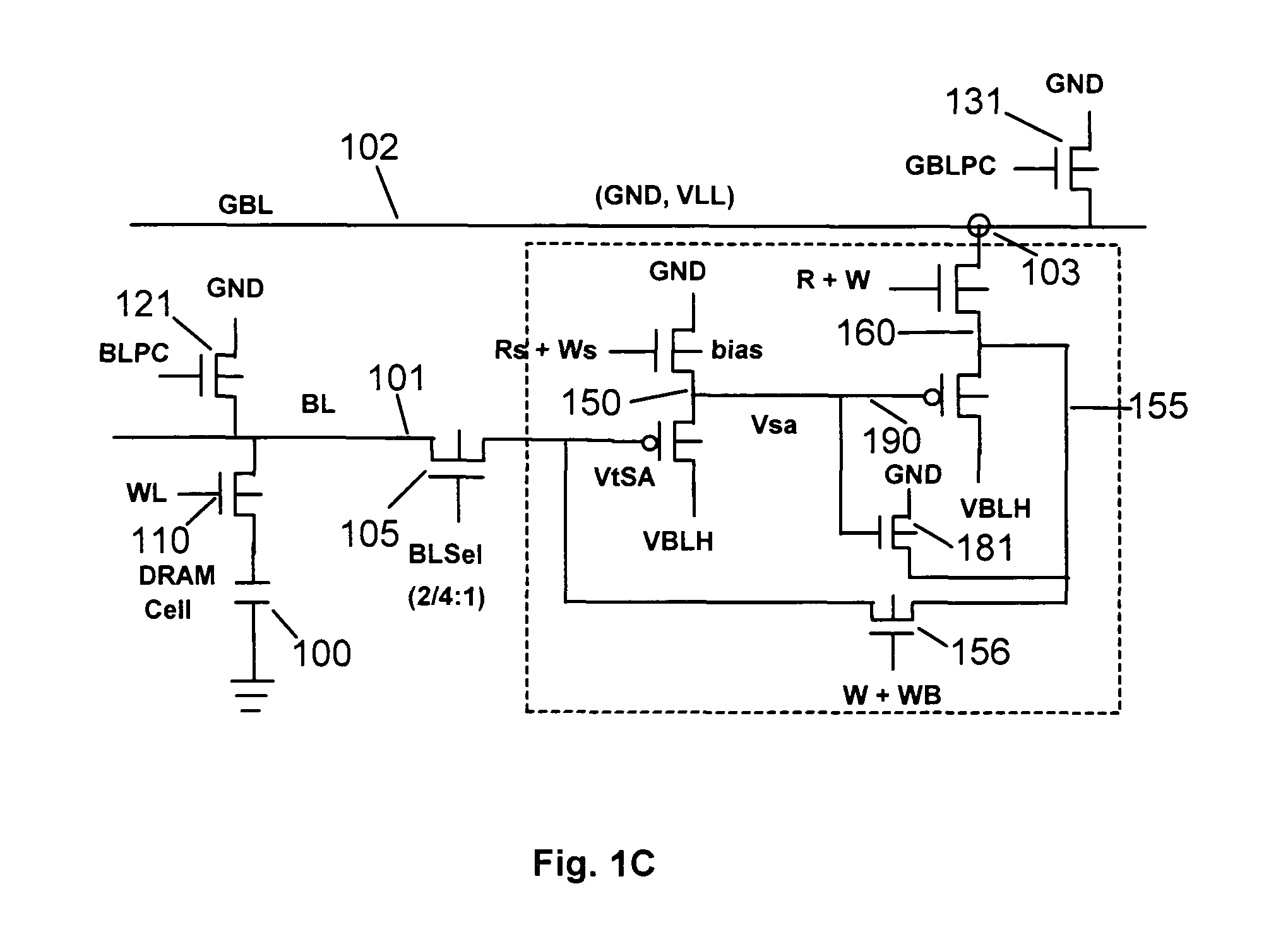

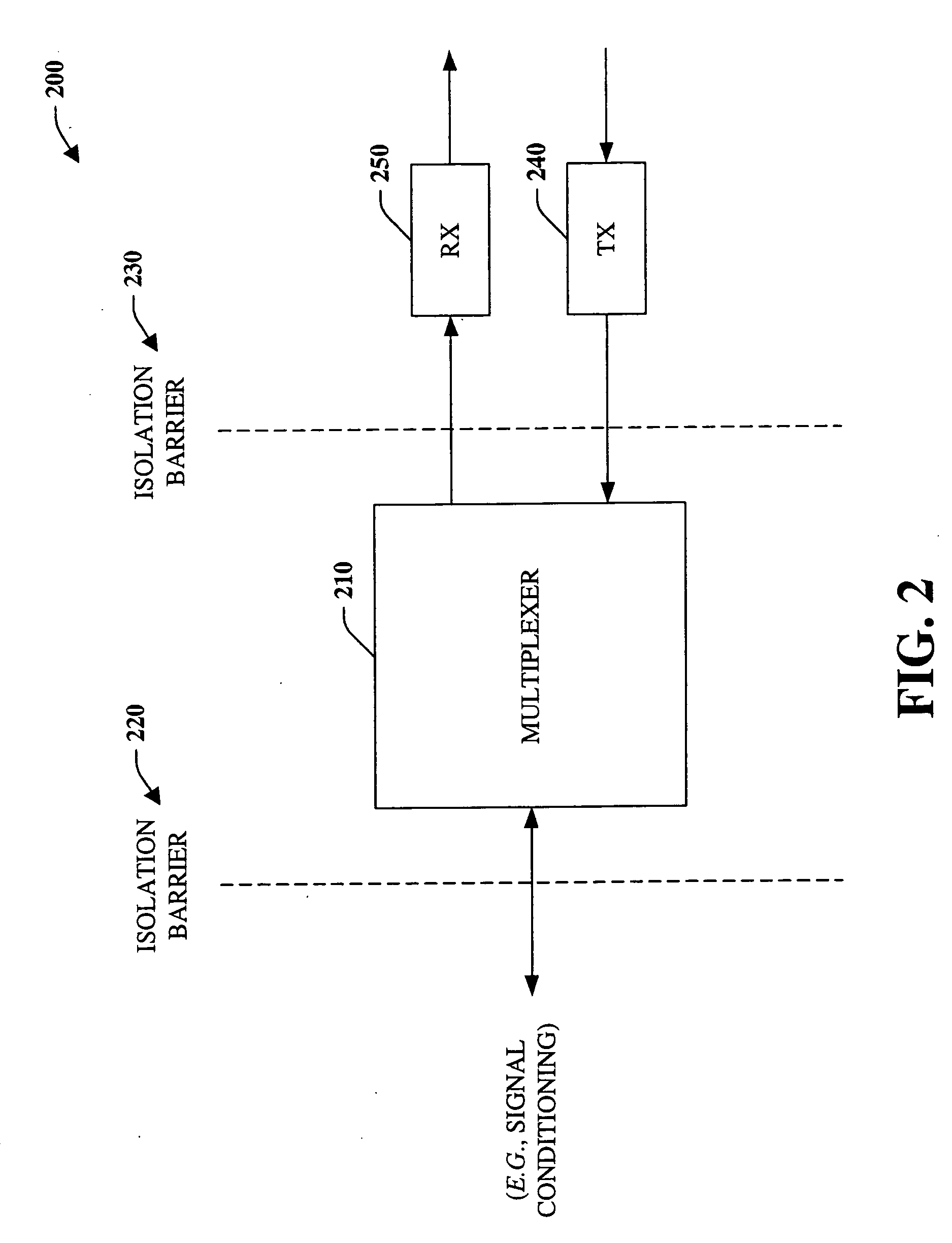

Systems and methods that employ a balanced duplexer

InactiveUS20050070232A1Transmission easilyEasy to receiveResonant long antennasTransmissionEngineeringMobile device

The present invention relates to systems and methods that employ a novel balanced duplexer that can be utilized to facilitate concurrent signal transmission and reception. The systems and methods can be employed within mobile devices such as cell phones and utilize two-filters (e.g., acoustic) with substantially similar input / output impedances interfaced with two couplers (e.g., 3 dB hybrid), which provide isolation and maintain the duplexer's input / output impedance. The couplers interface the filters to front / back ends such as signal processors, transmitters and receivers. The novel aspects of the present invention mitigate the need to employ external directional couplers between the duplexer and front / back ends. In addition, the two-filter topology enables employment of lower powered rated filters. The systems and methods further provide for separation and isolation of transmitters and receivers, which reduces noise coupling and enables the transmitter and receiver to be placed within close proximity.

Owner:NOKIA CORP

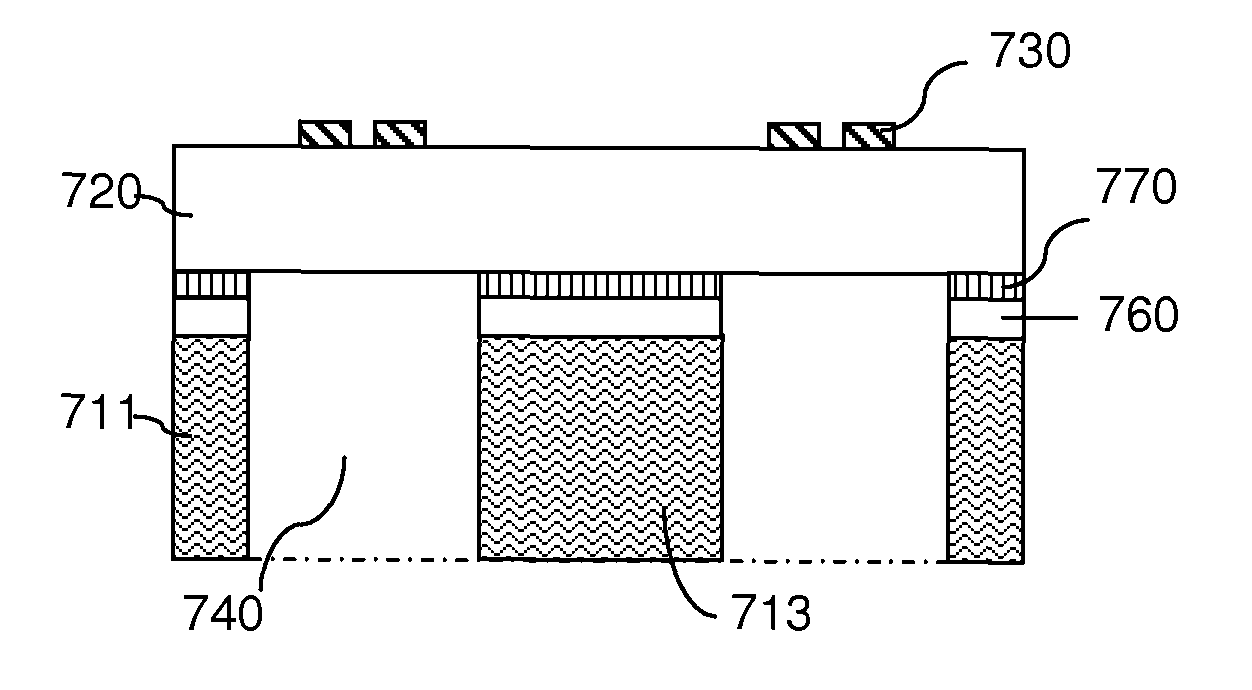

On Chip Antenna And Method Of Manufacturing The Same

InactiveUS20090085133A1Reduce substrate effectReduce impactSemiconductor/solid-state device detailsSolid-state devicesPhysicsIntegrated circuit

An antenna with air-filled trench is integrated with a radio frequency (RF) circuit. The trench locates directly under the metal lines that made up the antenna and is formed by etching from the back side of the semiconductor substrate until all the substrate material in the trench is removed. The air-filled trench greatly reduces the losses due to the semiconductor substrate; therefore the performance of the antenna improves greatly. When the antenna is a large planar spiral inductor, the air-filled trench means the semiconductor substrate inside the spiral inductor is untouched; hence integrated circuit can be built inside the antenna and on that substrate. Therefore the RF integrated circuit has a smaller size. Air-filled trench can also be used to reduce the semiconductor substrate noise coupling between digital circuit block and analog / RF circuit block. This air-filled trench and the air-filled trench under the antenna are formed at the same time.

Owner:DOAN MY THE

Circuit and method for suppression of electromagnetic coupling and switching noise in multilayer printed circuit boards

InactiveUS20070120223A1Suppress powerRemoval of powerTransmission control/equlisationSemiconductor/solid-state device detailsElectromagnetic couplingCapacitance

Apparatus for suppressing noise and electromagnetic coupling in the printed circuit board of an electronic device includes an upper conductive plate and an array of conductive coplanar patches positioned a distance t2 from the upper conductive plate. The distance t2 is chosen to optimize capacitance between the conductive coplanar patches and the upper conductive plate for suppression of noise or electromagnetic coupling. The apparatus further includes a lower conductive plate a distance t1 from the array of conductive coplanar patches and conductive rods extending from respective patches to the lower conductive plate.

Owner:WEMTEC

Seal ring structures with reduced moisture-induced reliability degradation

InactiveUS7893459B2Reduce noise couplingReduce moisture penetrationThyristorSemiconductor/solid-state device detailsSemiconductor chipMoisture barrier

A semiconductor chip includes a seal ring adjacent to edges of the semiconductor chip; an opening extending from a top surface to a bottom surface of the seal ring, wherein the opening has a first end on an outer side of the seal ring and a second end on an inner side of the seal ring; and a moisture barrier having a sidewall parallel to a nearest side of the seal ring, wherein the moisture barrier is adjacent the seal ring and has a portion facing the opening.

Owner:TAIWAN SEMICON MFG CO LTD

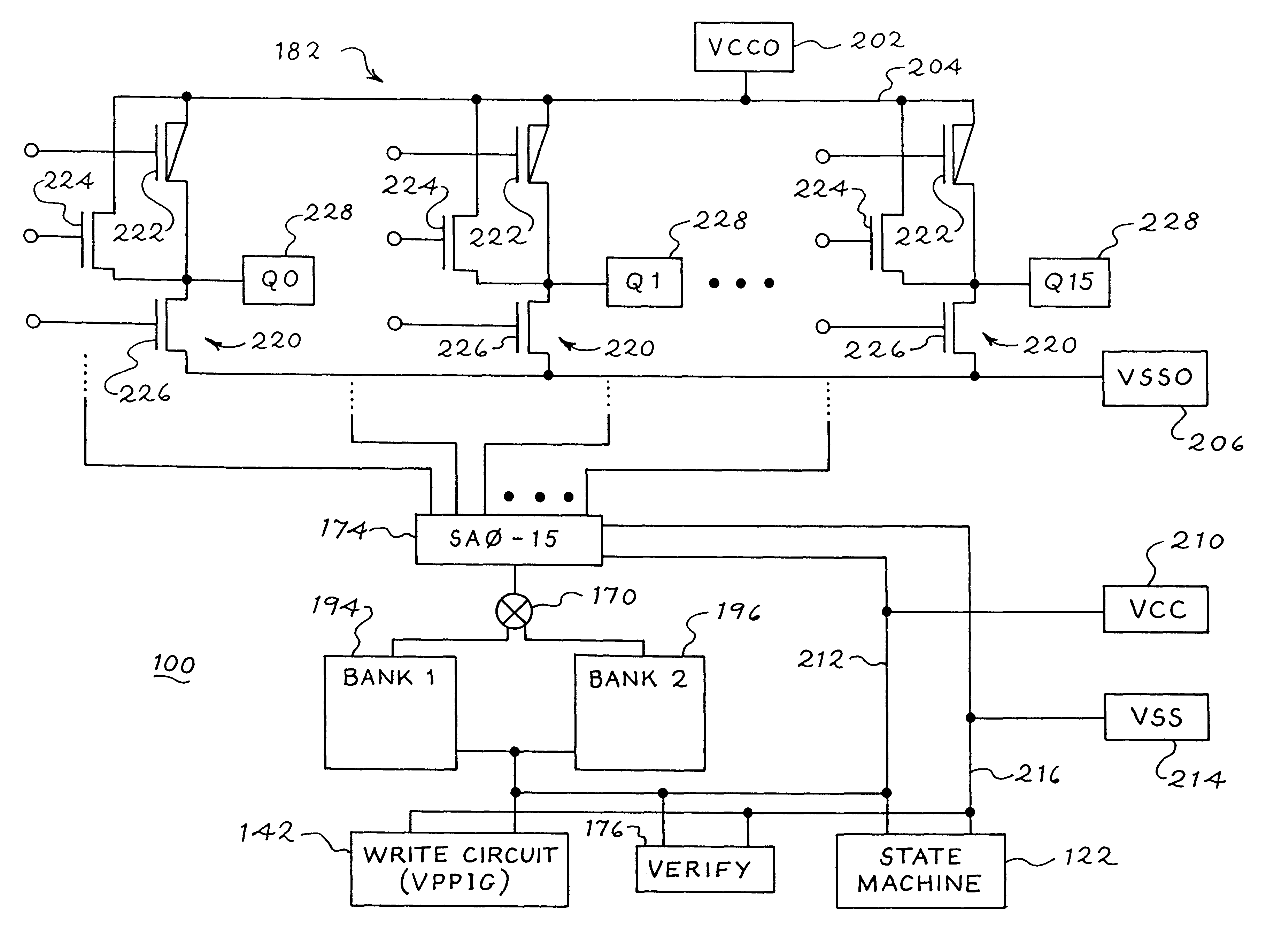

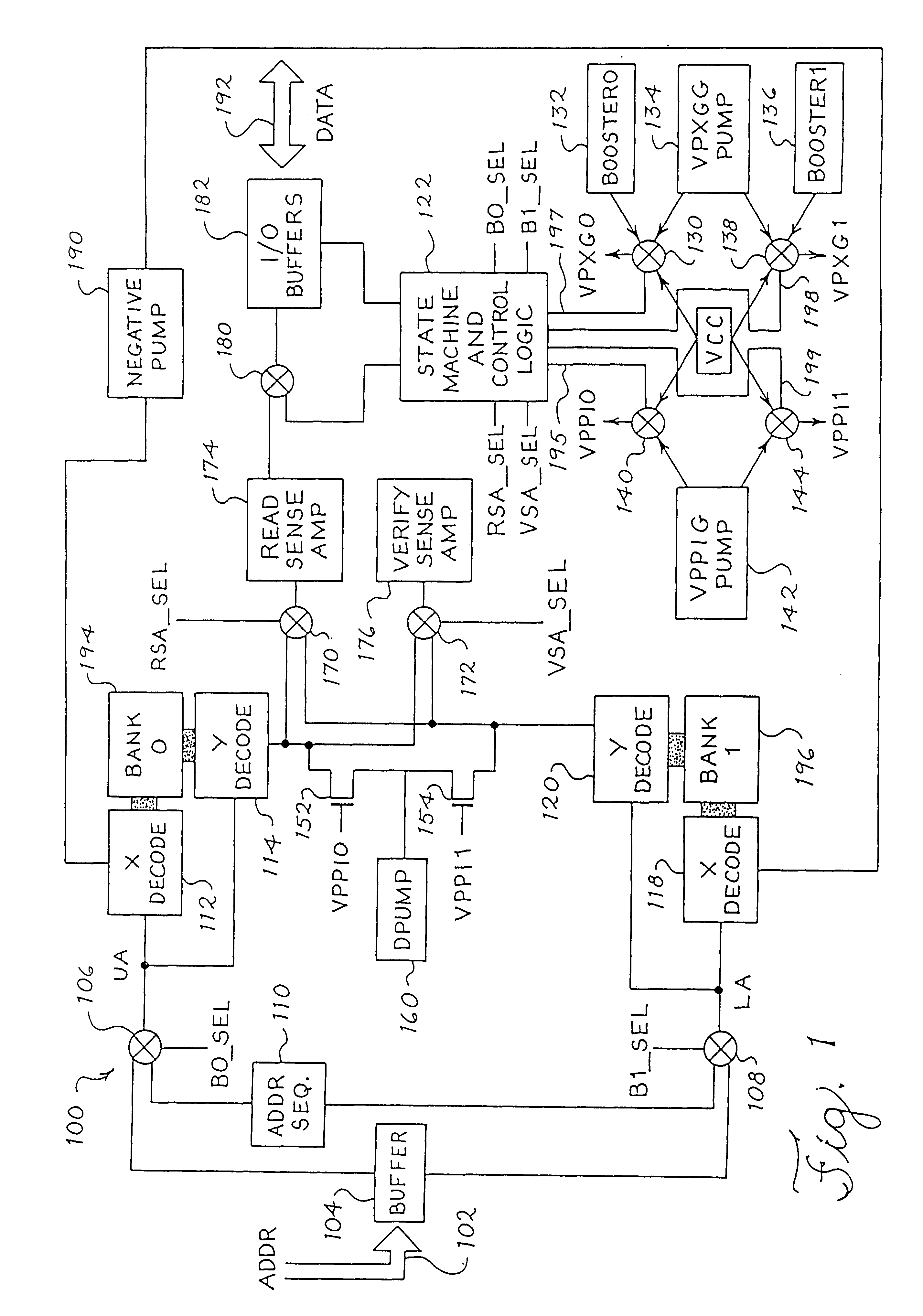

Separate output power supply to reduce output noise for a simultaneous operation

InactiveUS6178129B1Reducing noise couplingReduce noise couplingRead-only memoriesDigital storageElectrical currentFlash memory

A flash memory device (100) provides for simultaneous read and write operations in two banks (194, 196) of flash memory cells. A plurality of output circuits (182) switch large amounts of current during reading of stored data. To reduce noise in read circuitry (174) and write circuitry (142), a separate power supply bus (204) and ground bus (208) is provided for the output circuits. The power supply bus is independent of the power supply bus which serves the internal circuitry, such as the read circuitry and the write circuitry.

Owner:III HLDG 4

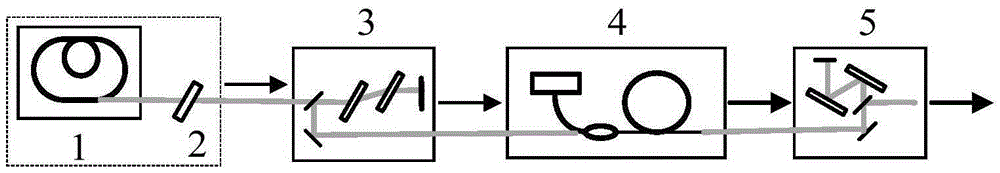

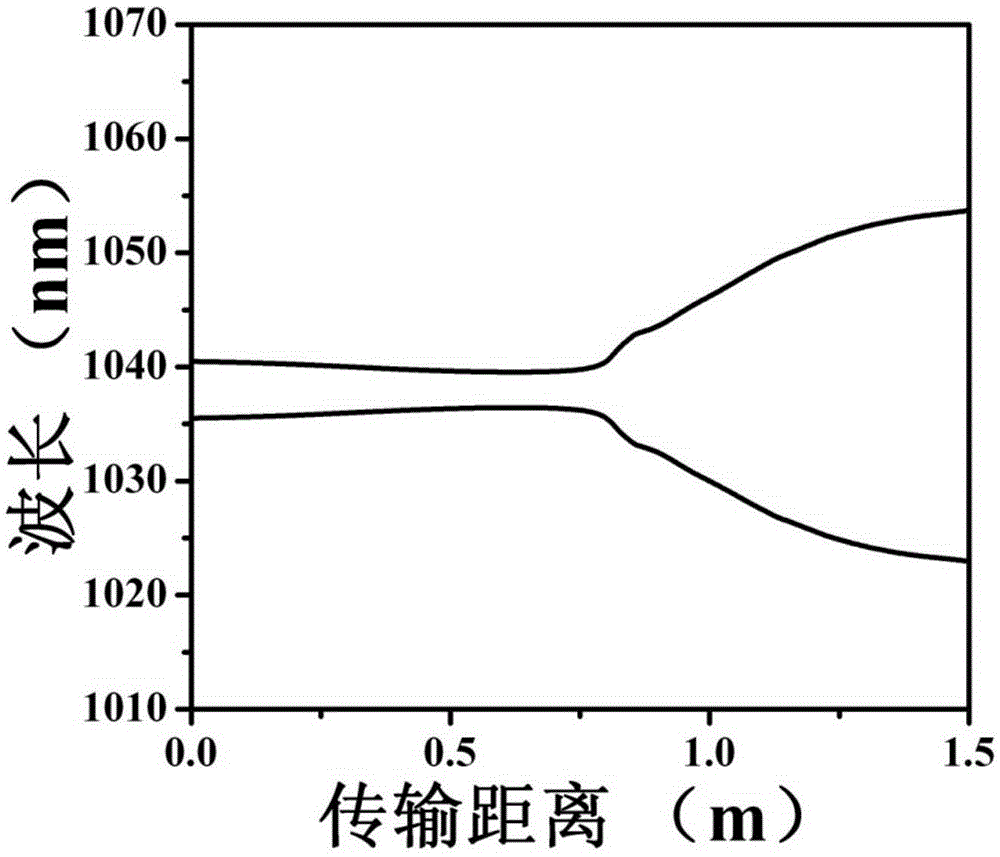

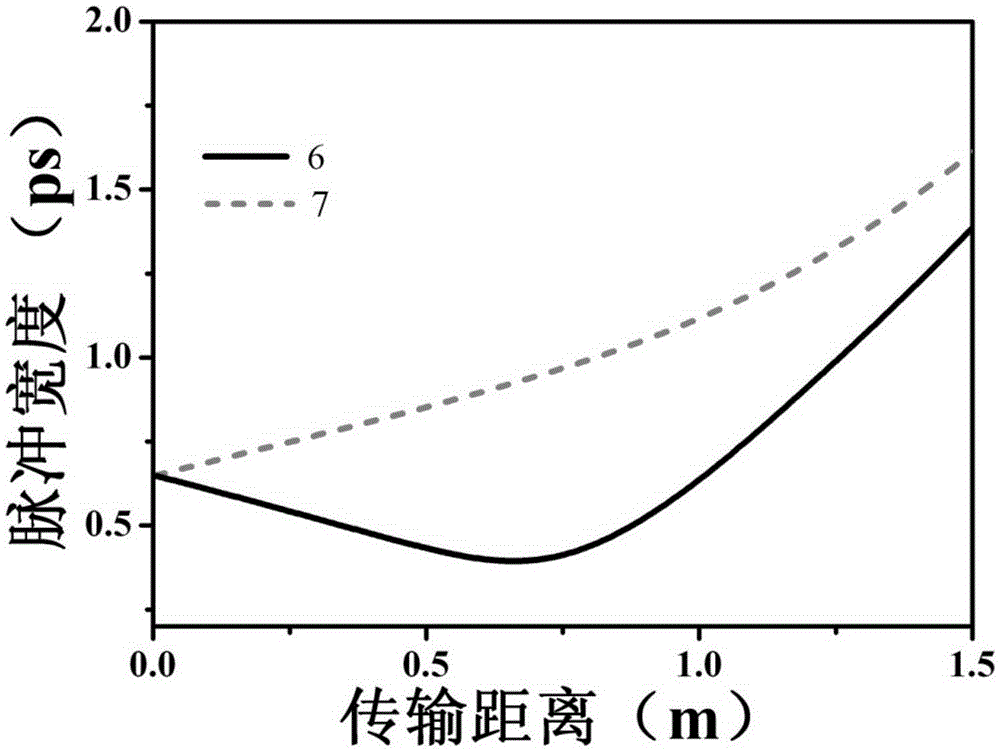

Pre-chirped management based low-noise fiber femtosecond laser amplifier

ActiveCN105390912ASuppression of High Frequency (>1kHz) NoiseLow running costActive medium shape and constructionLow noiseFiber

Provided a pre-chirped management based low-noise fiber femtosecond laser amplifier. The amplifier comprises an ytterbium-doped fiber dispersion management mode-locked laser (1), a spectral interference filter (2), a grating negative dispersive delay line (3), an ytterbium-doped fiber amplifier (4), and a grating pulse compressor (5). The ytterbium-doped fiber dispersion management mode-locked laser (1) generates a breathing soliton pulse sequence; the spectral interference filter (2) adjusts a center wavelength of the breathing soliton pulse sequence and enables it in the gain spectrum center of the ytterbium-doped fiber amplifier (4); the grating negative dispersive delay line (3) introduces a negative chirp into the adjusted breathing soliton pulse sequence, thereby obtaining a seed pulse; the ytterbium-doped fiber amplifier carries out self-similar amplification on the seed pulse, thereby obtaining a parabolic pulse; and the grating pulse compressor (5) compresses the parabolic pulse and generates a femtosecond laser pulse. According to the high-frequency noise of a linear amplifier effectively inhibited by the pre-chirped management based low-noise fiber femtosecond laser amplifier disclosed by the present invention, a Fourier transform-limited femtosecond laser pulse with a narrow pulse width is obtained.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

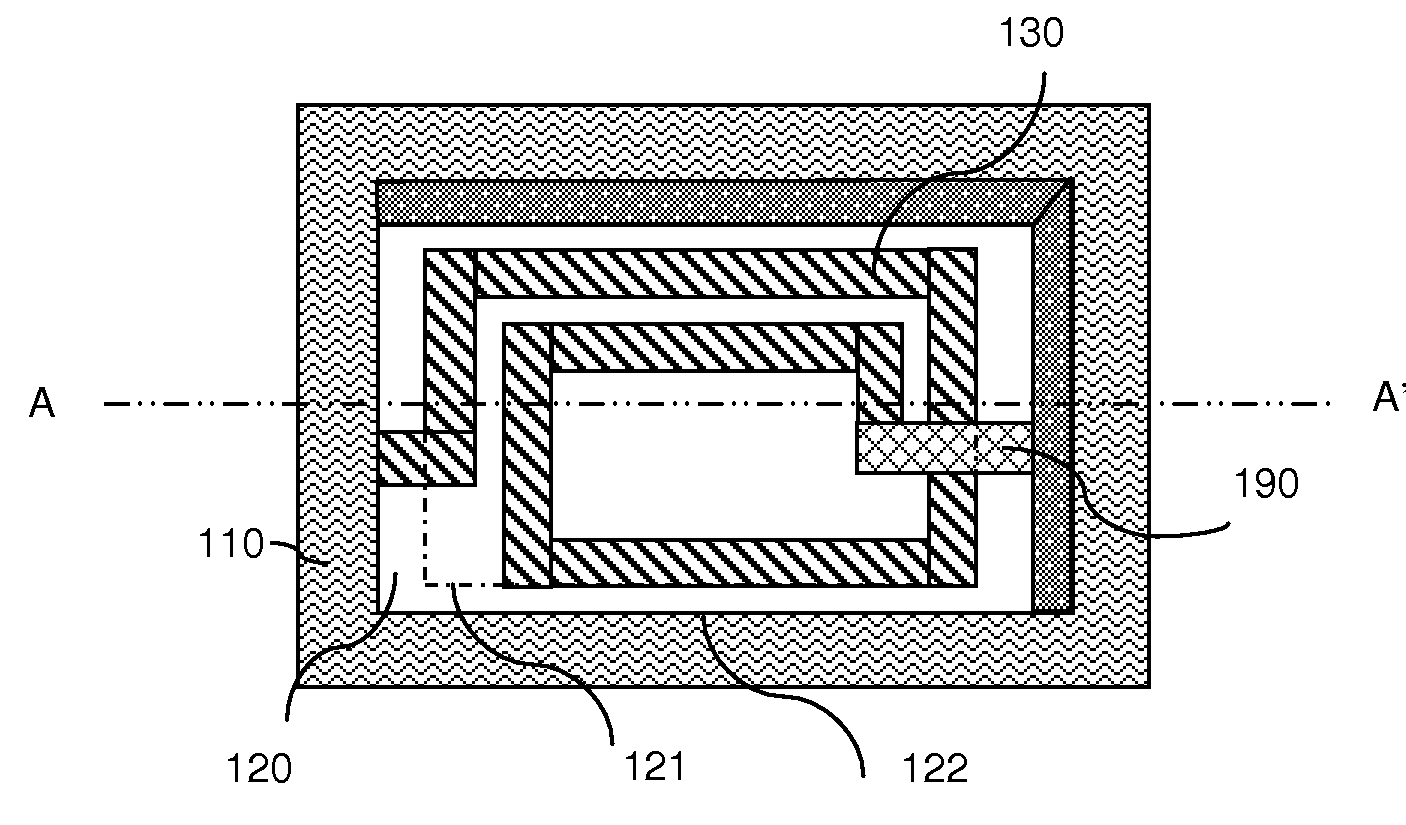

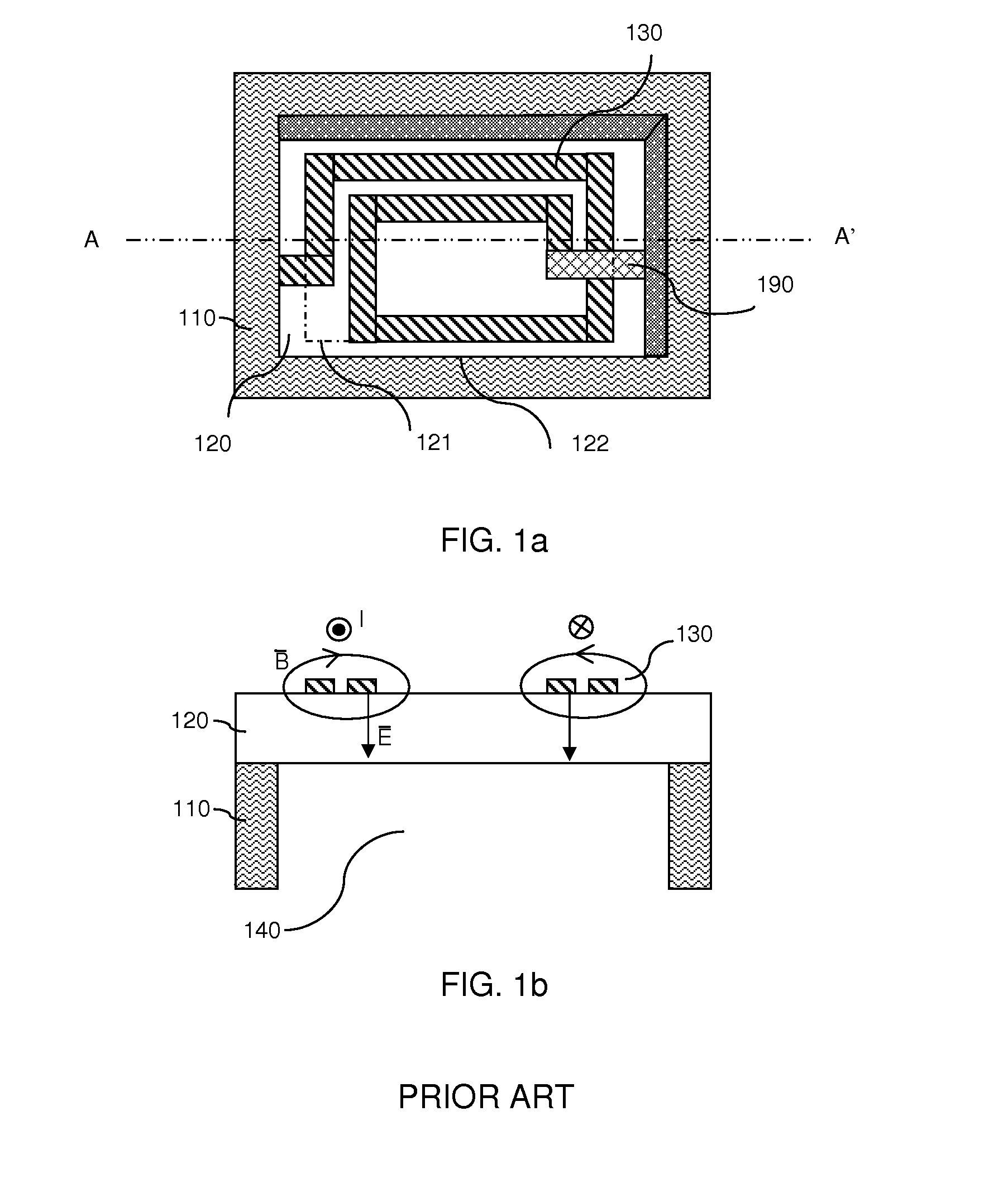

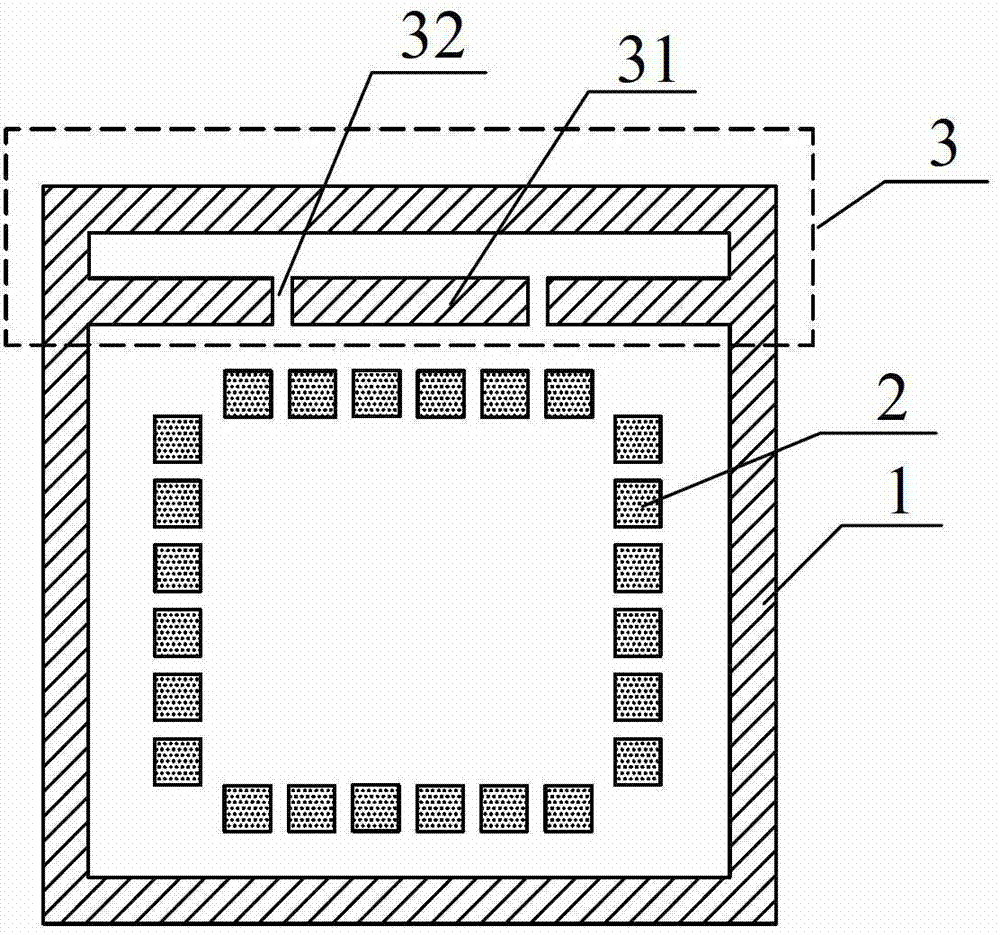

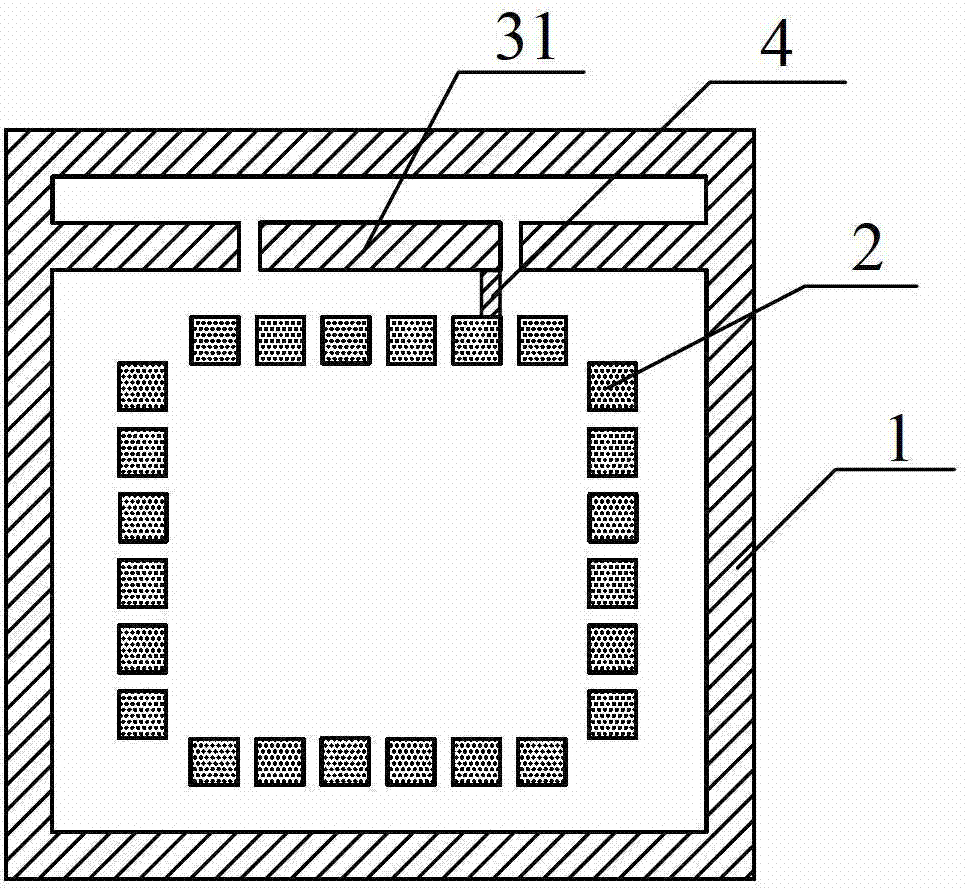

Integrated circuit chip

ActiveUS20060197214A1Reduce noise couplingAvoid accumulationSemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon

An integrated circuit chip is provided. The chip includes a silicon substrate, a circuit, a seal ring, a ground ring and a guard ring. The circuit is formed on the silicon substrate and has an input / output (I / O) pad. The seal ring is formed on the silicon substrate and surrounds the circuit and the I / O pad. The ground ring is formed between the silicon substrate and the I / O pad, and the ground ring is electrically connected with the seal ring. The guard ring is formed above the silicon substrate and surrounds the I / O pad, and the guard ring is electrically connected with the seal ring.

Owner:AIROHA TECHNOLOGY CORPORATION

On chip antenna and method of manufacturing the same

InactiveUS7911014B2Reduce impactReduce noise couplingSemiconductor/solid-state device detailsSolid-state devicesElectricityPlanar spiral inductors

Owner:DOAN MY THE

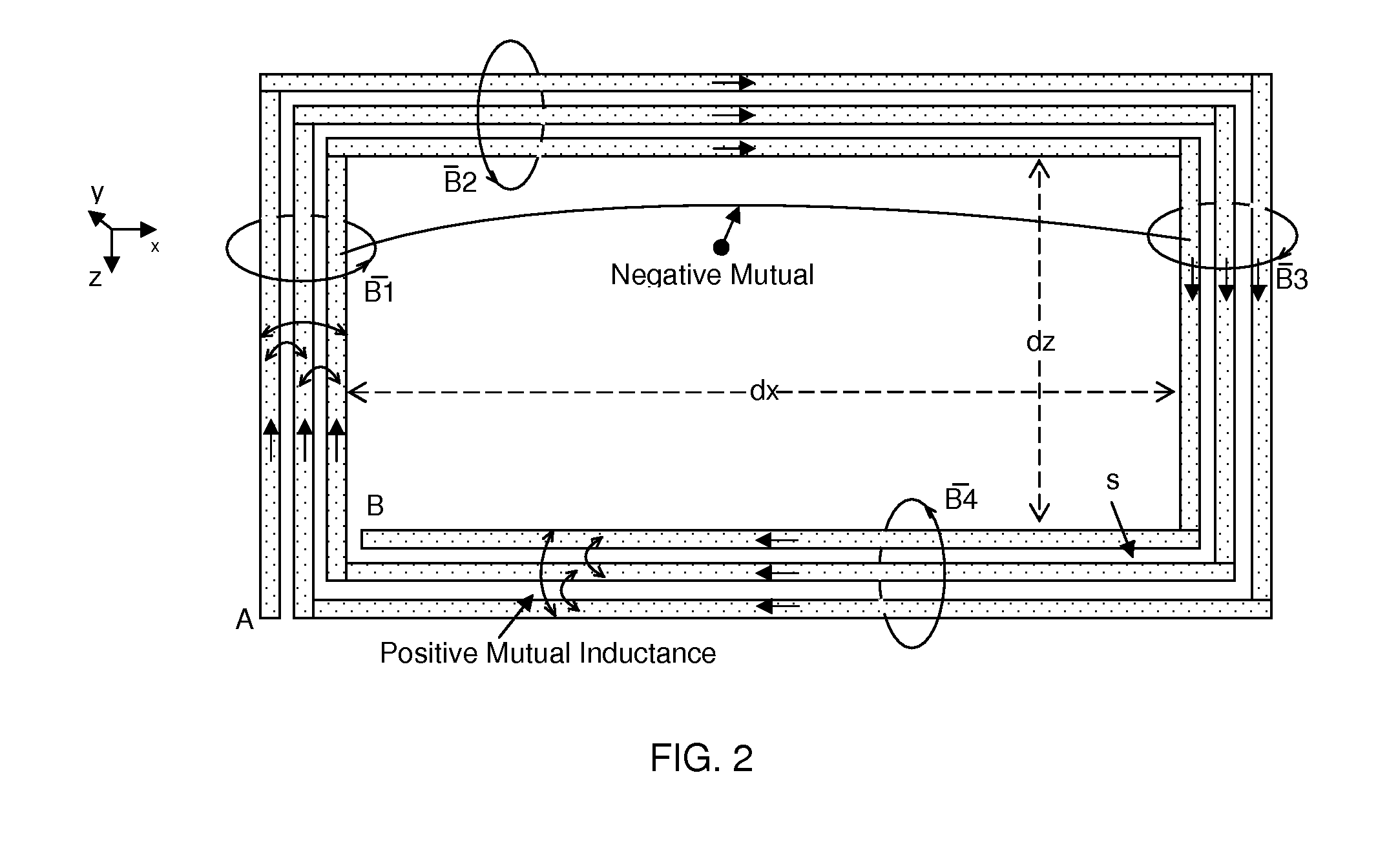

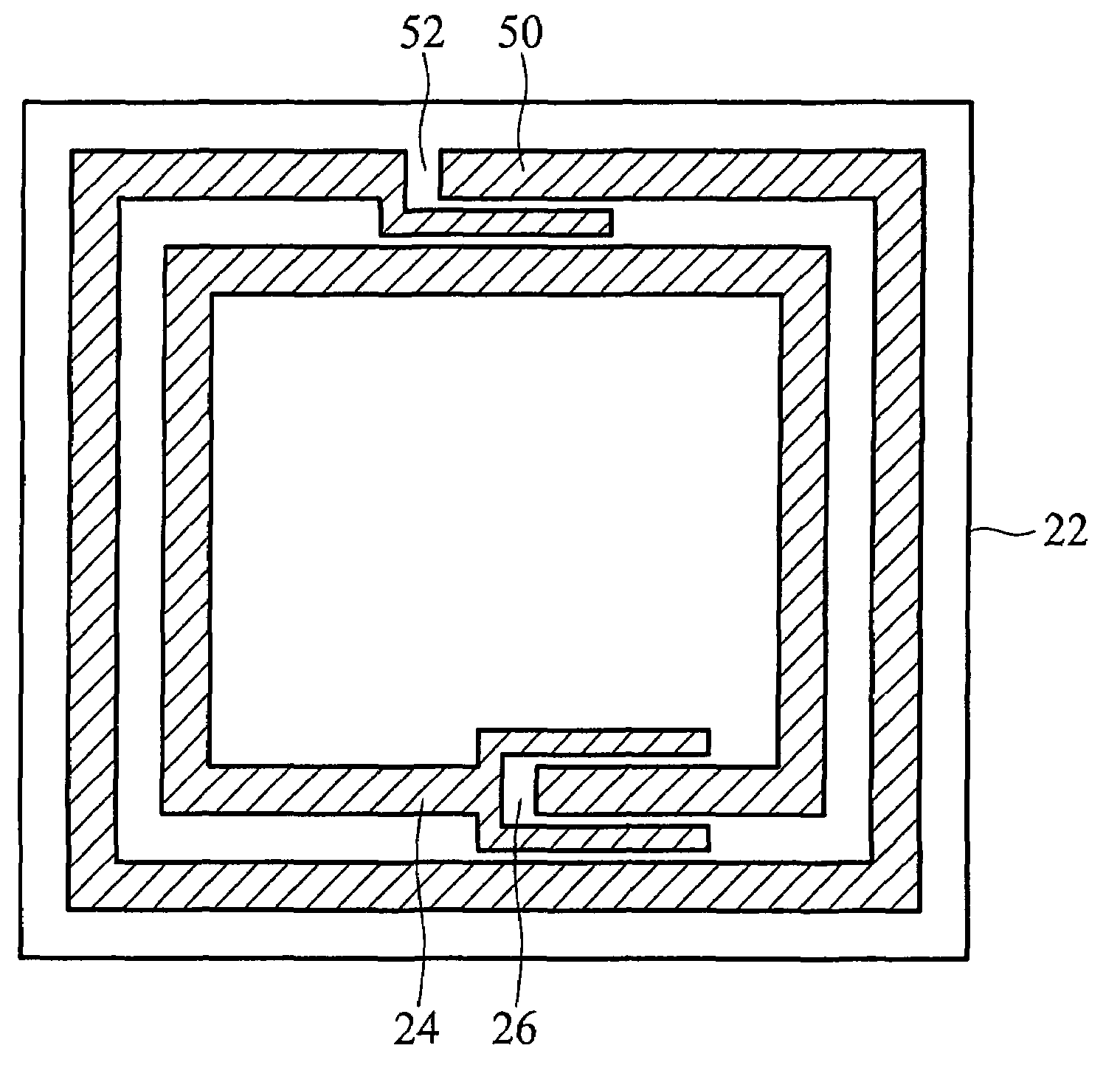

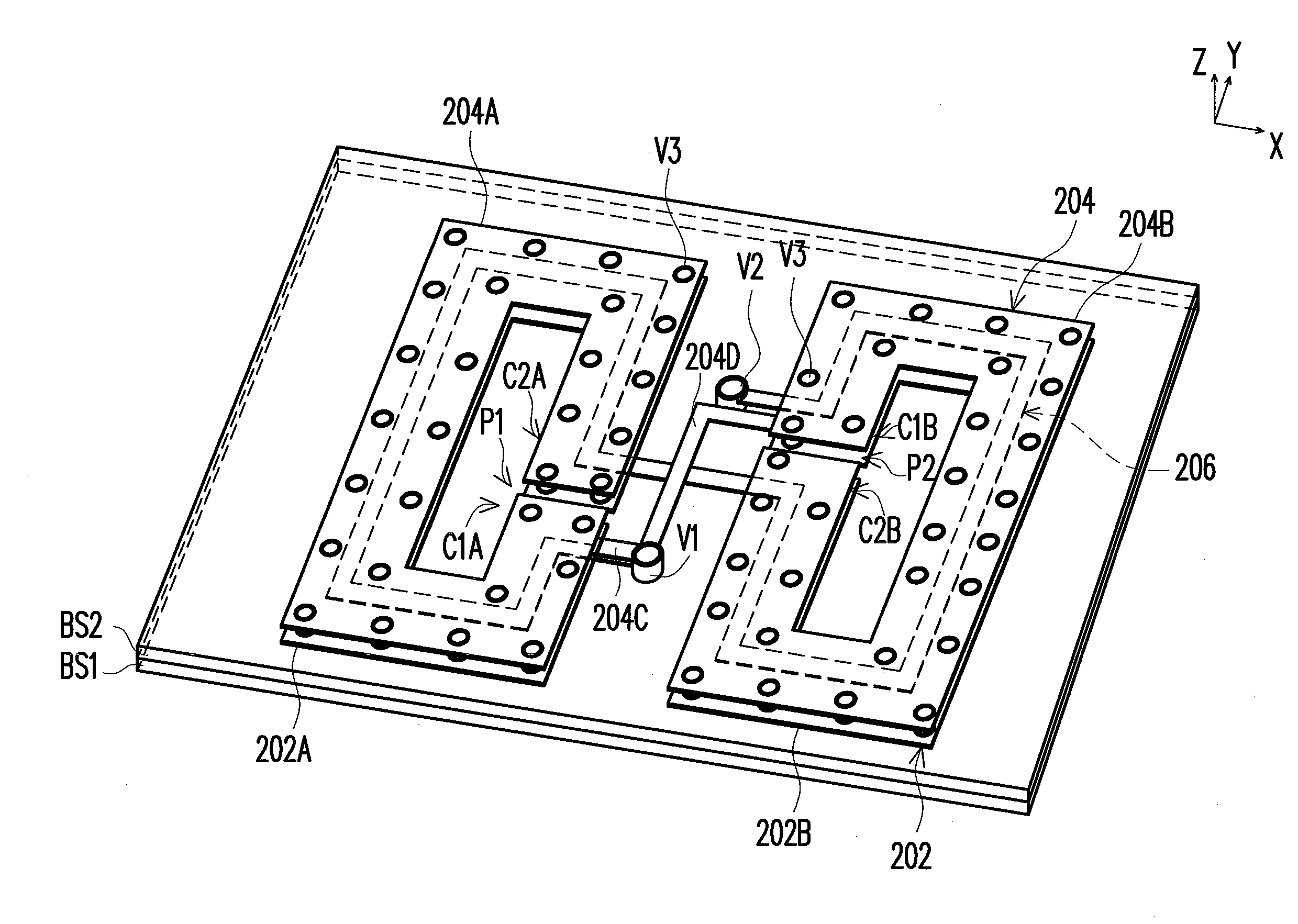

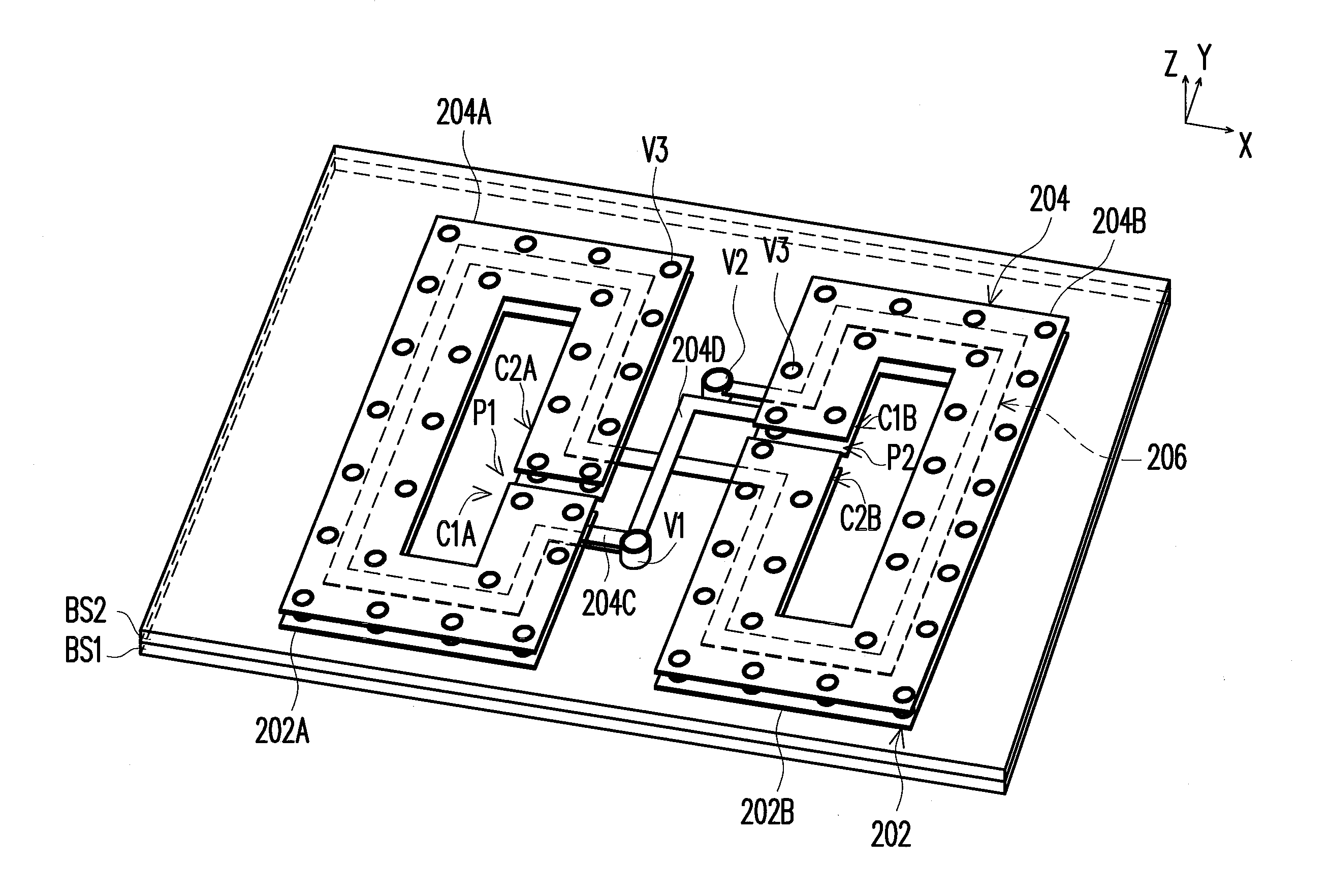

Planar magnetic field probe

InactiveUS8575926B2Accurate measurementReducing the magnetic fieldMagnitude/direction of magnetic fieldsContactless circuit testingUltimate tensile strengthCondensed matter physics

A planar magnetic field probe is provided. The planar magnetic field probe increases the sensitivity of magnetic field intensity detection by using a left multi-sensor loop and a right multi-sensor loop formed by a first patterned metal layer and a second patterned metal layer, and decreases the electric field noise coupling by surrounding the left multi-sensor loop and the right multi-sensor loop with a symmetrical shielding metal structure formed by a first patterned shielding metal layer, a second patterned shielding metal layer and a plurality of through vias.

Owner:TATUNG COMPANY

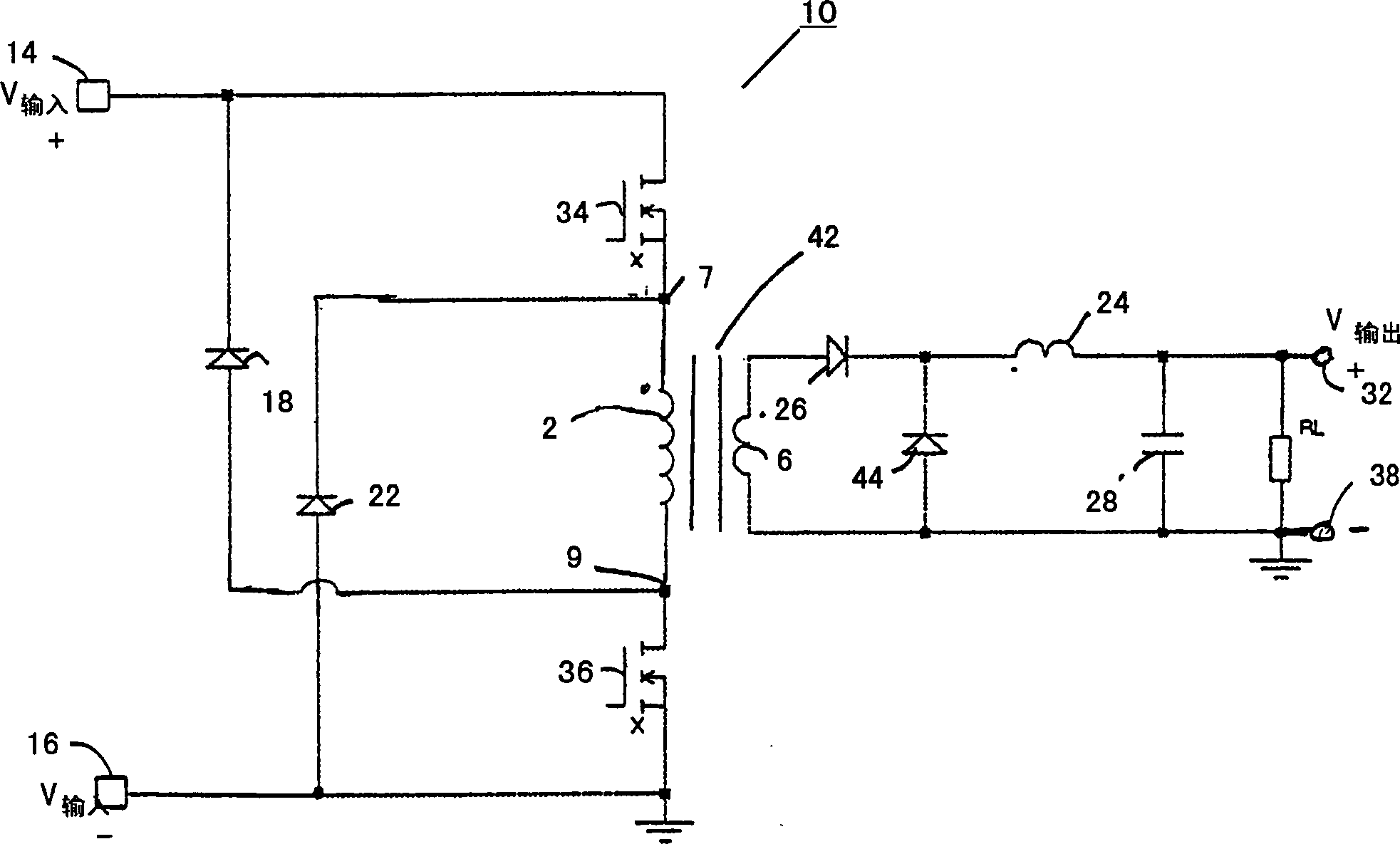

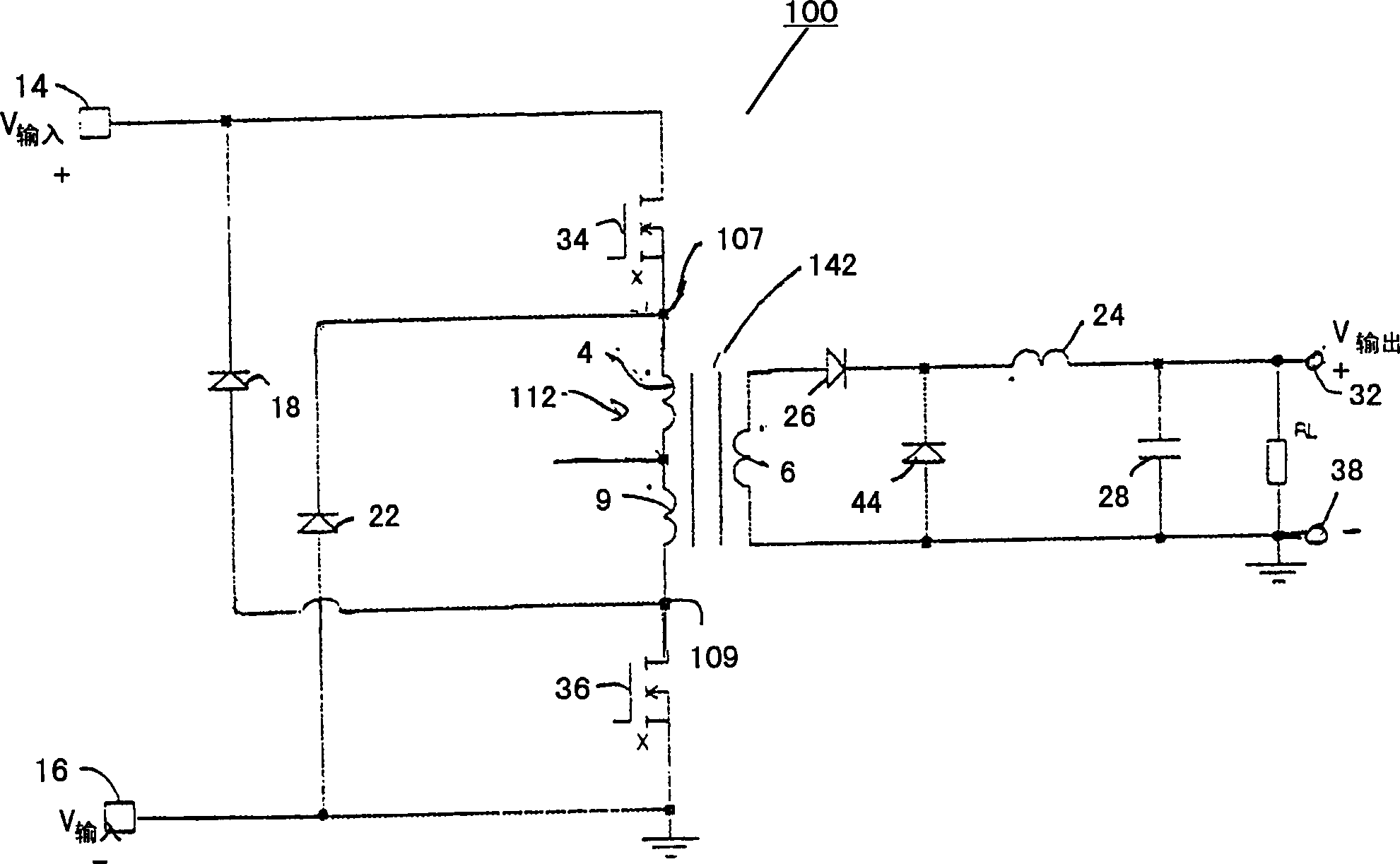

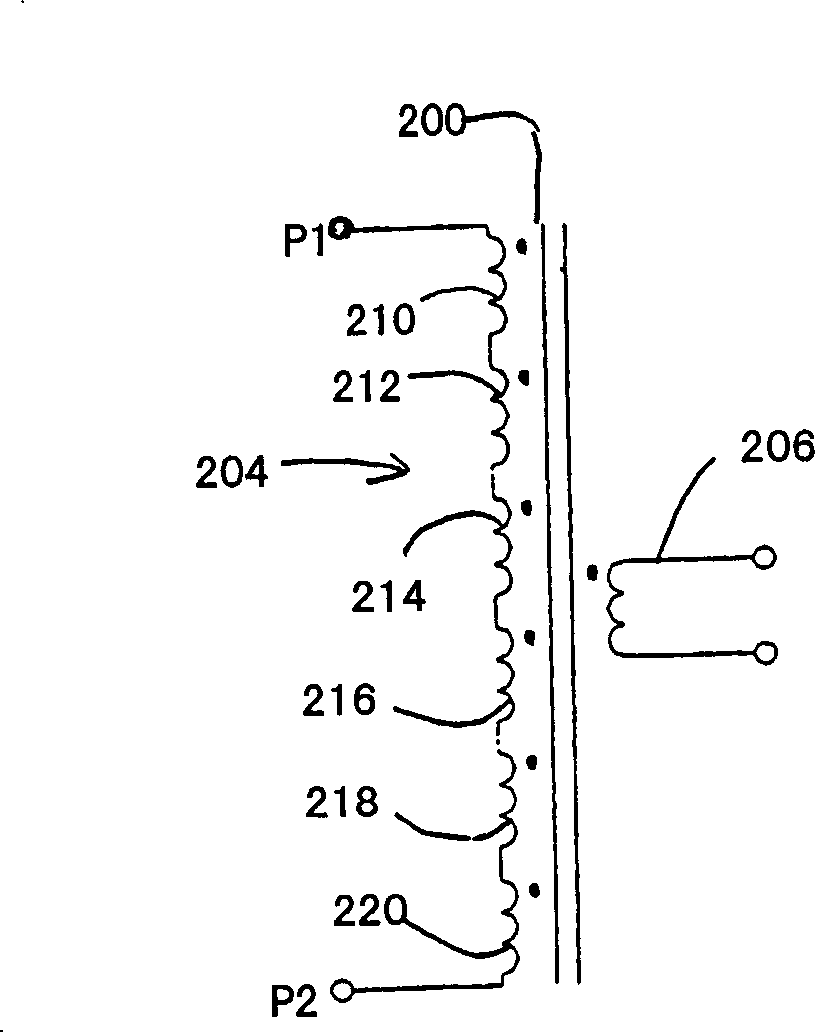

Low noise planar transformer

ActiveCN1770335AImprove EMI performanceReduce common mode noiseTransformers/inductances coils/windings/connectionsUnwanted magnetic/electric effect reduction/preventionLow noiseTransducer

This invention relates to one device and method to reduce co-mode noise from initial coil set to secondary set. For one example, the initial set has two terminals and one PCB layer between two terminals with each PCB layer forms at least one coil. Each PCB layer coil is connection to form initial set with each Terminal connection to the isolated PCB layer overlapped to Form initial set. The second set covers one selected distribution at the middle place between the first and second layers. The nearest coil set to PCB layer is composed of only one coil to reduce co-mode noise. In one alternating sample, the transducer is put in the second to initial distribution with two halves form one PCB set.

Owner:ASTEC INT LTD

Ultrasonic transducer for use in a fluid medium

InactiveUS8288920B2Reduce noise couplingHigh materialUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostriction/magnetostriction machinesThermoplasticUltrasonic sensor

An ultrasonic transducer for use in a fluid medium includes at least one transducer core having at least one acoustic / electric transducer element. The ultrasonic transducer furthermore includes at least one decoupling element which is configured to reduce a structure-borne noise coupling between the transducer core and a housing. The decoupling element includes at least one porous plastic material, in particular a foamed plastic material. The porous plastic material includes at least one thermosetting polymer and / or at least one thermoplastic.

Owner:ROBERT BOSCH GMBH

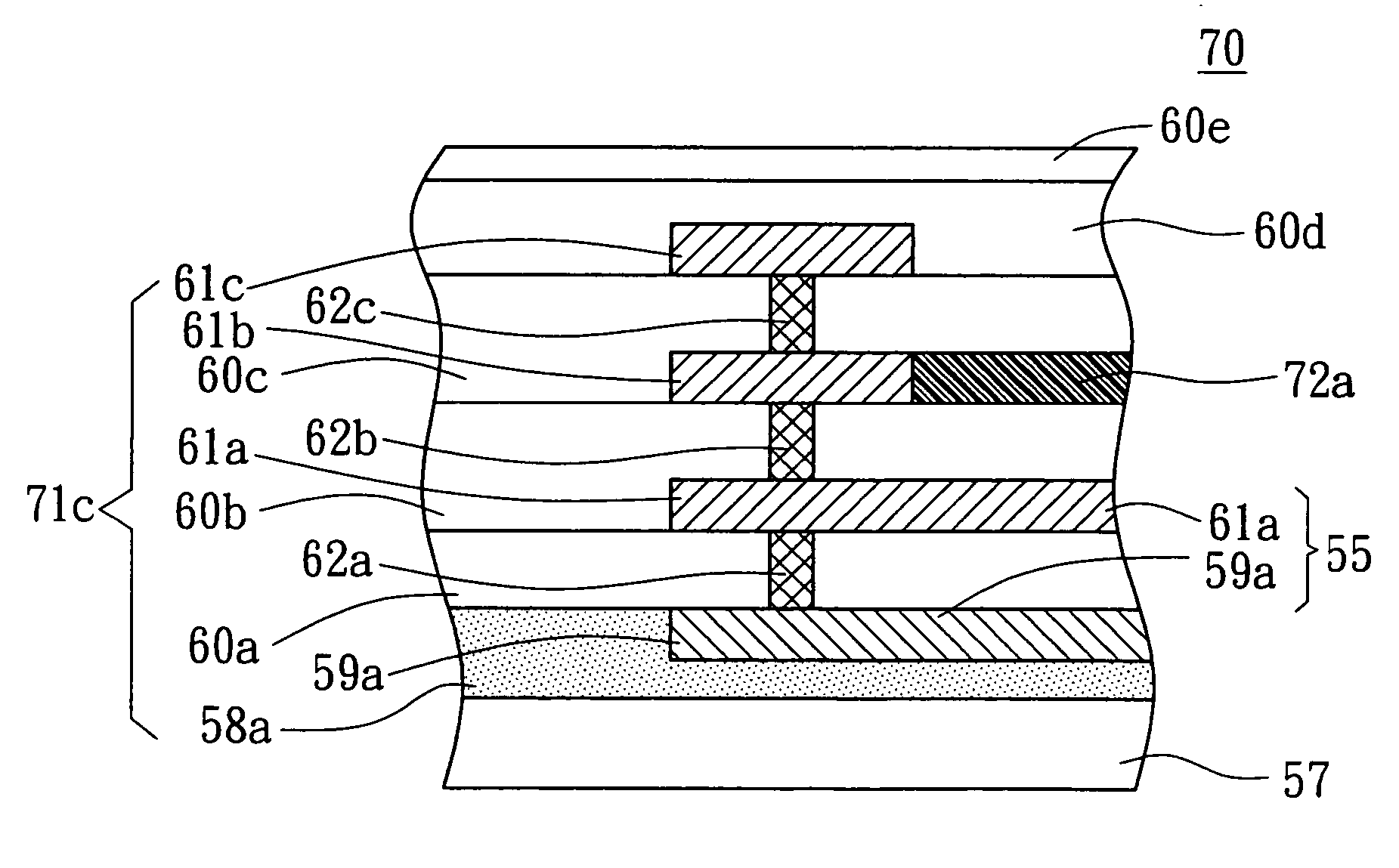

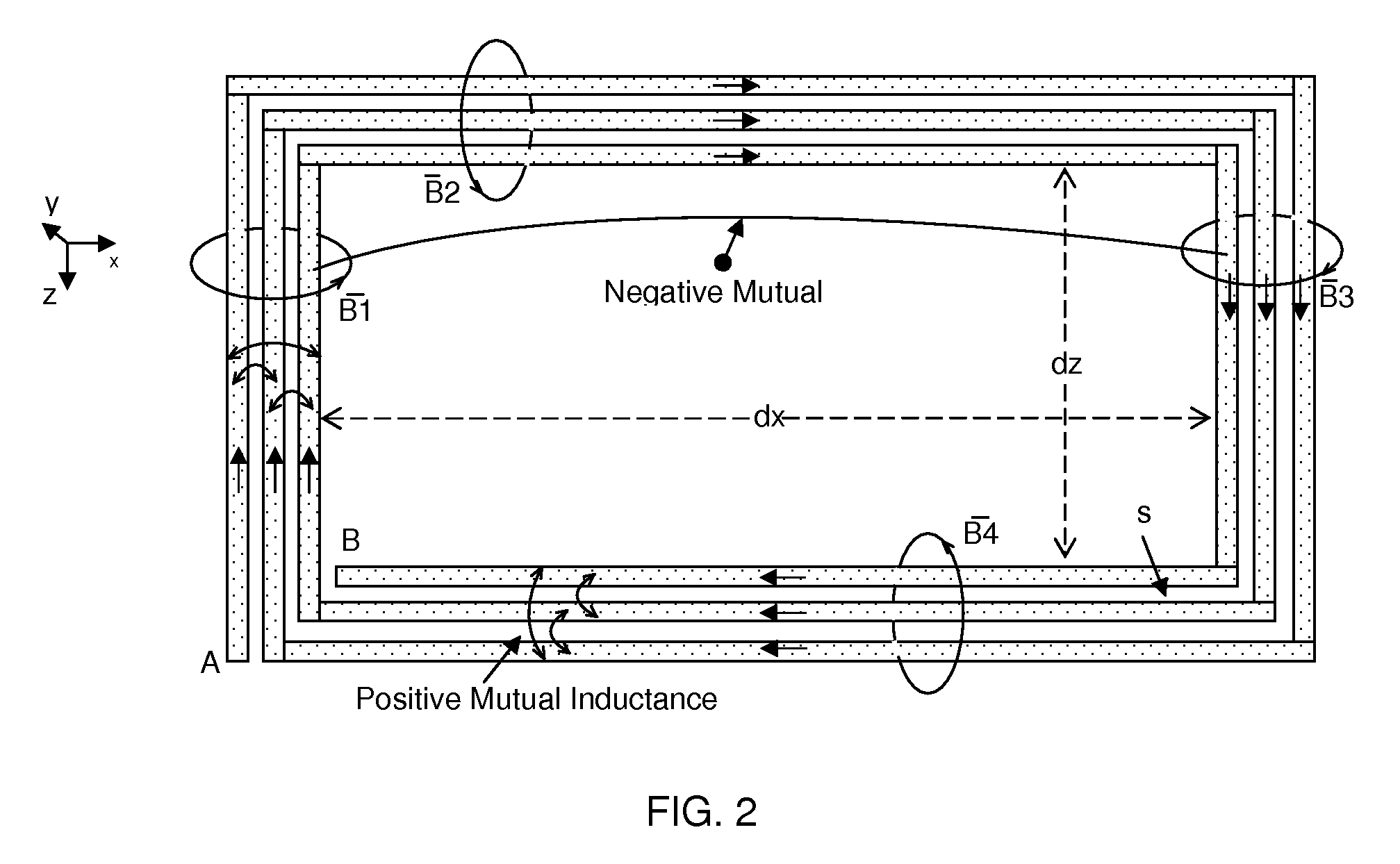

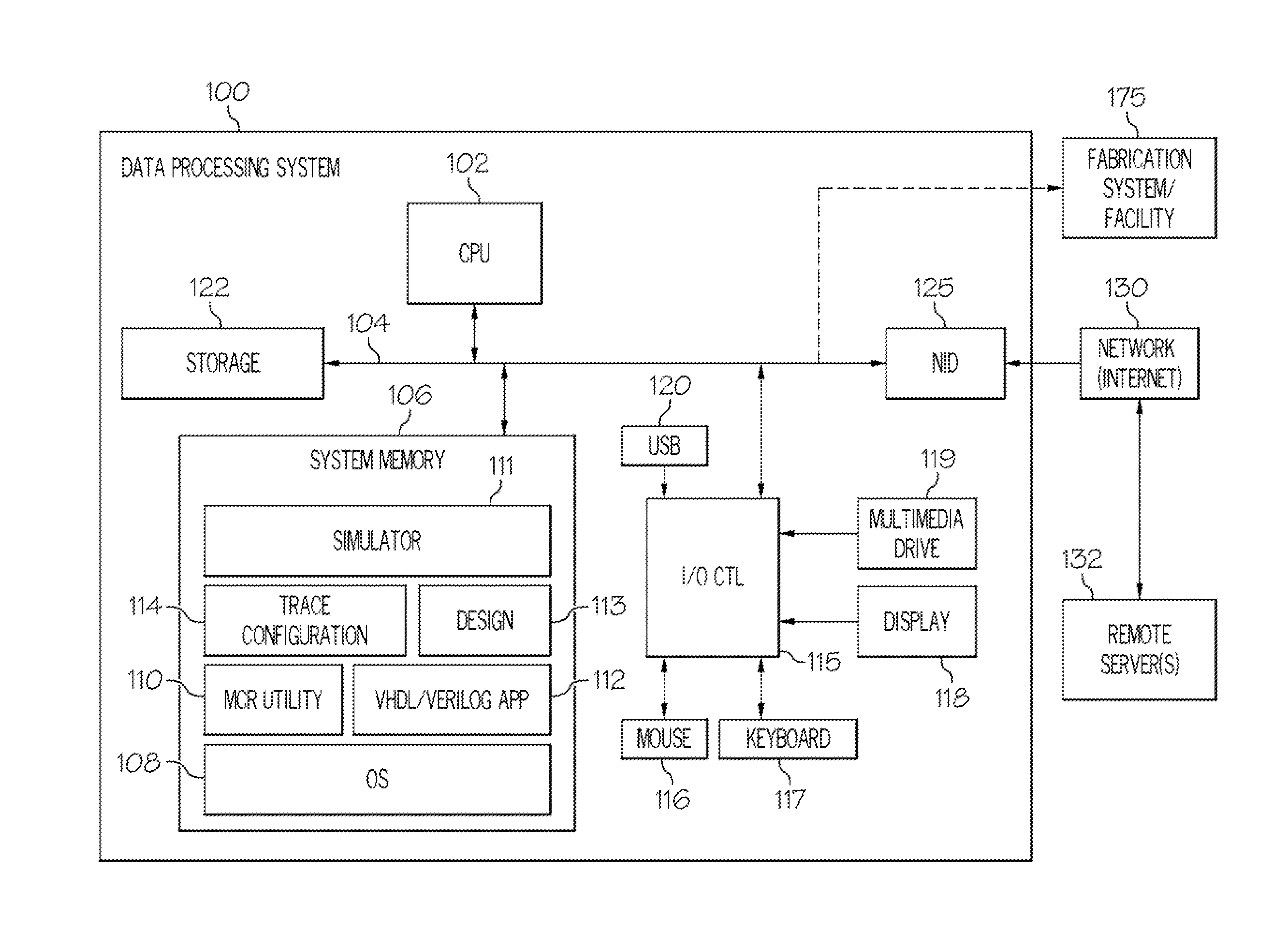

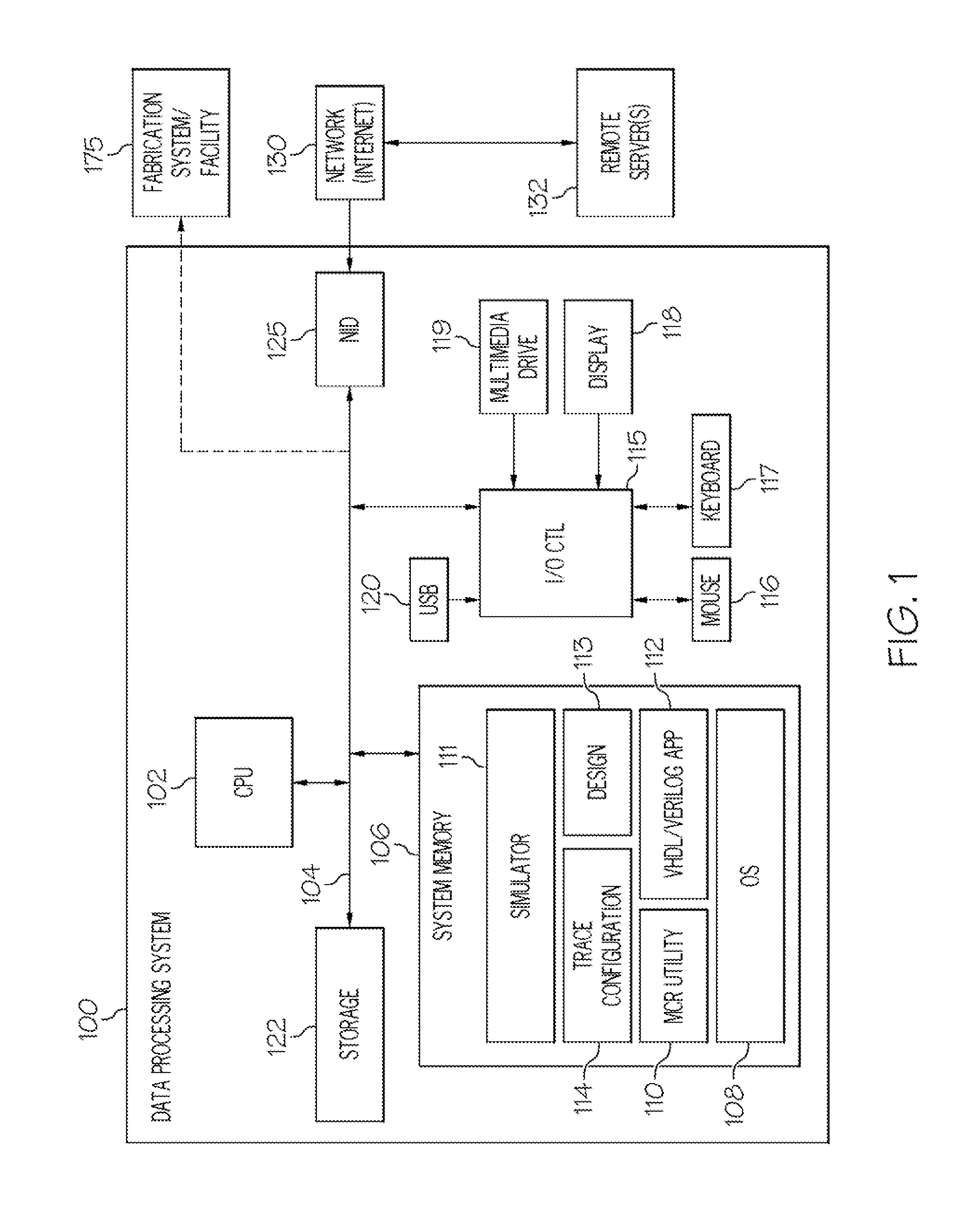

Noise Coupling Reduction and Impedance Discontinuity Control in High-Speed Ceramic Modules

ActiveUS20120204141A1Reduce discontinuityReduce noise couplingSemiconductor/solid-state device detailsCross-talk/noise/interference reductionMechanical engineeringSignal trace

A method reduces coupling noise and controls impedance discontinuity in ceramic packages by: providing at least one reference mesh layer; providing a plurality of signal trace layers, with each signal layer having one or more signal lines and the reference mesh layer being adjacent to one or more of the signal layers; disposing a plurality of vias through the at least one reference mesh layer, with each via providing a voltage (Vdd) power connection or a ground (Gnd) connection; selectively placing via-connected coplanar-type shield (VCS) lines relative to the signal lines, with a first VCS line extended along a first side of a first signal line and a second VCS line extended along a second, opposing side of said first signal line. Each of the VCS lines interconnect with and extend past one or more vias located within a directional path along which the VCS lines extends.

Owner:GLOBALFOUNDRIES U S INC

Single cycle read/write/writeback pipeline, full-wordline I/O DRAM architecture with enhanced write and single ended sensing

InactiveUS20050052897A1Increase widthIncrease in bank numberDigital storageComputer architectureAudio power amplifier

A DRAM is disclosed which includes a single ended bitline structure, a single ended global bitline structure, primary sense amplifiers with data storage and data write-back capability and with capability to decouple from the global bitlines, a full-wordline I / O structure where essentially all memory cell that belong to the same wordline are being operated on, and a pipelined architecture. The DRAM further includes a small voltage swing design. The primary sense amplifiers can include more than one amplification stages. Such a DRAM is suitable for applications in conjunction with processors as an embedded DRAM.

Owner:GLOBALFOUNDRIES INC

Integrated circuit redistribution package

InactiveUS6945791B2Reduce noise couplingReduce the possibilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

The present invention provides a redistribution package having an upper surface that includes contacts with reduced pitch that correspond, for example, to that of a Controlled Collapse Chip Connection (“C4”) structure formed on a chip, and a lower surface having contacts with increased pitch that correspond, for example, to a printed circuit board employing ball grid array (“BGA”) pads. A series of power, signal and ground conductors extend through the body of the redistribution package and interconnect the circuit board contacts to the chip contacts.

Owner:GLOBALFOUNDRIES INC

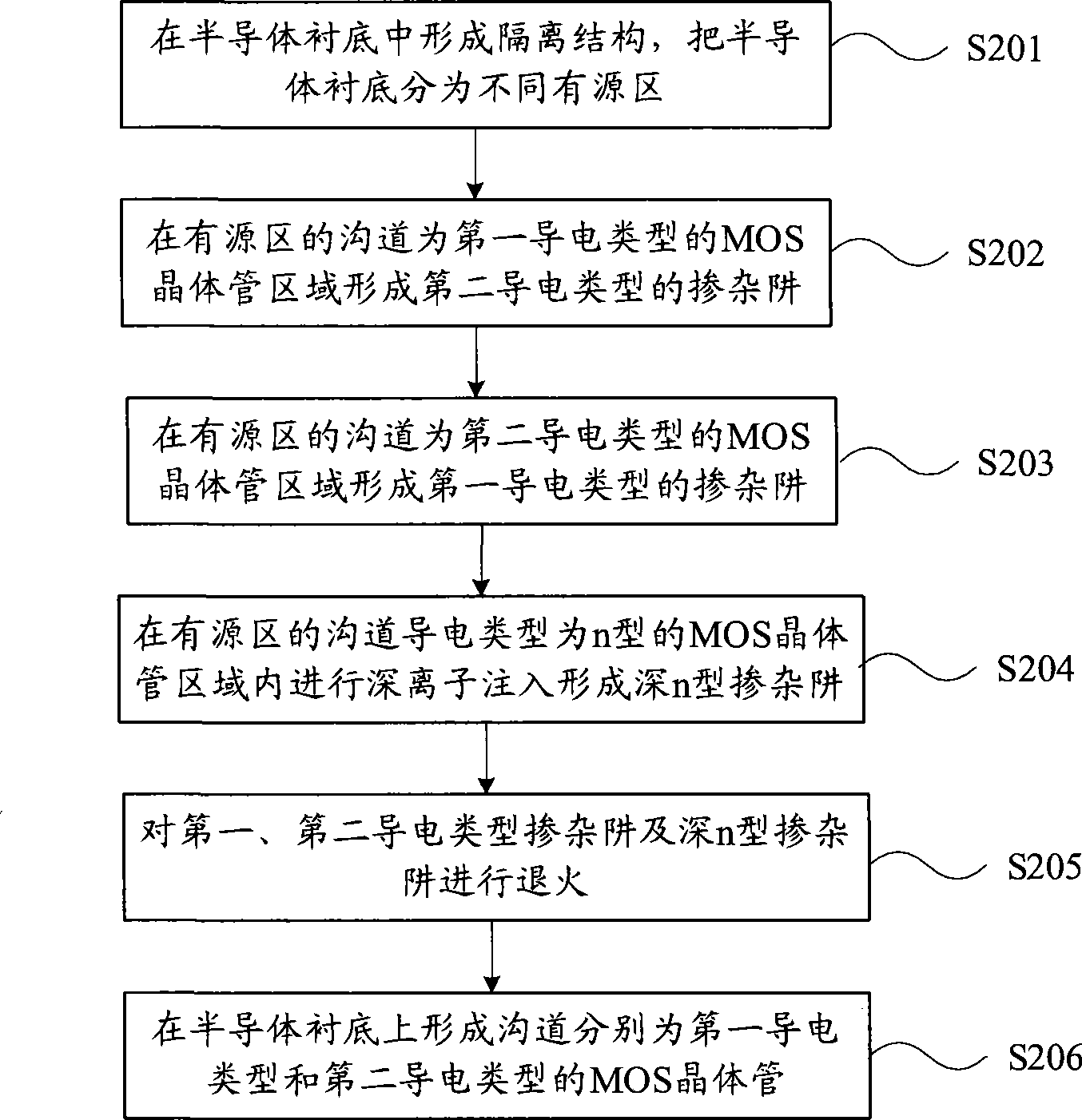

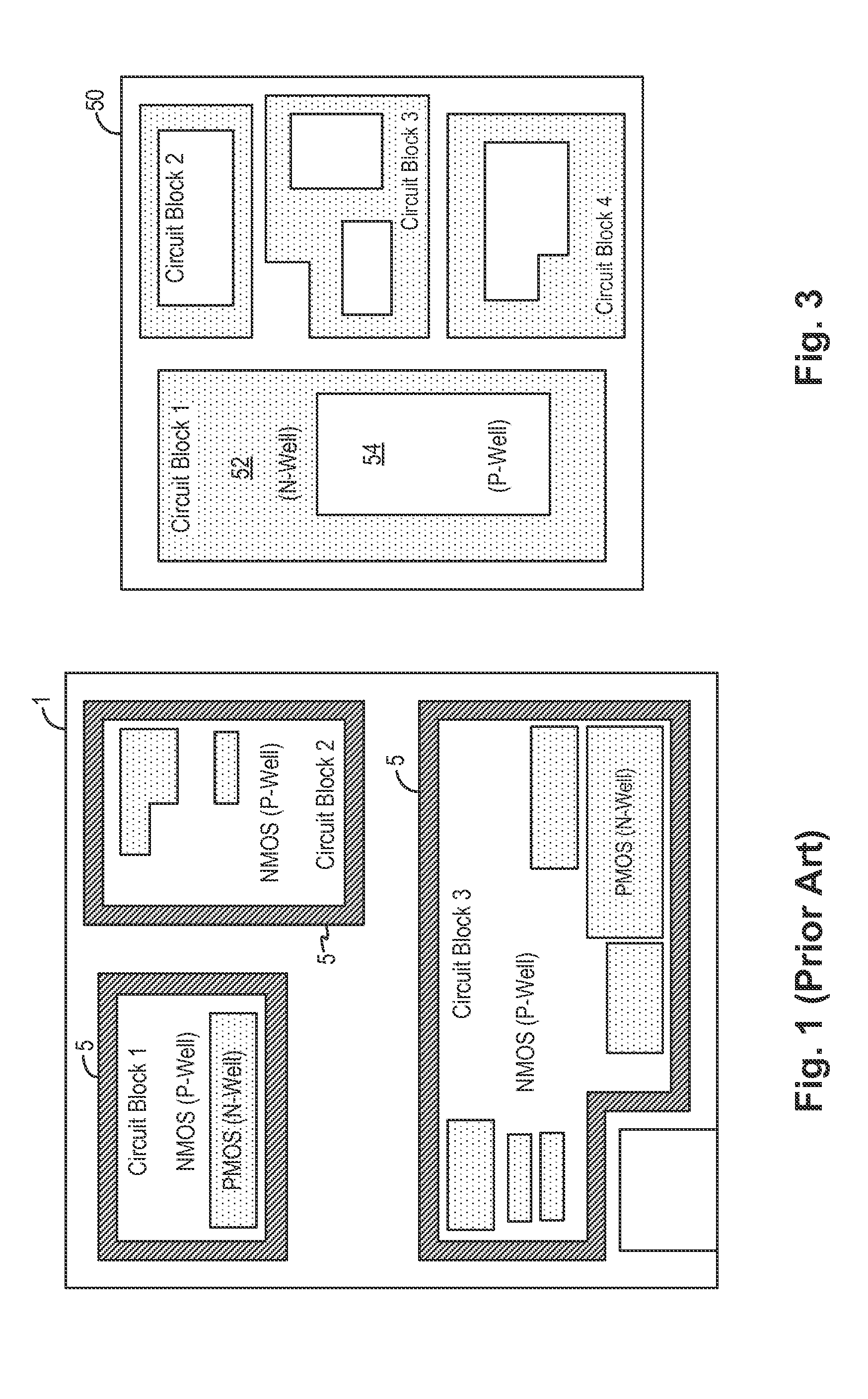

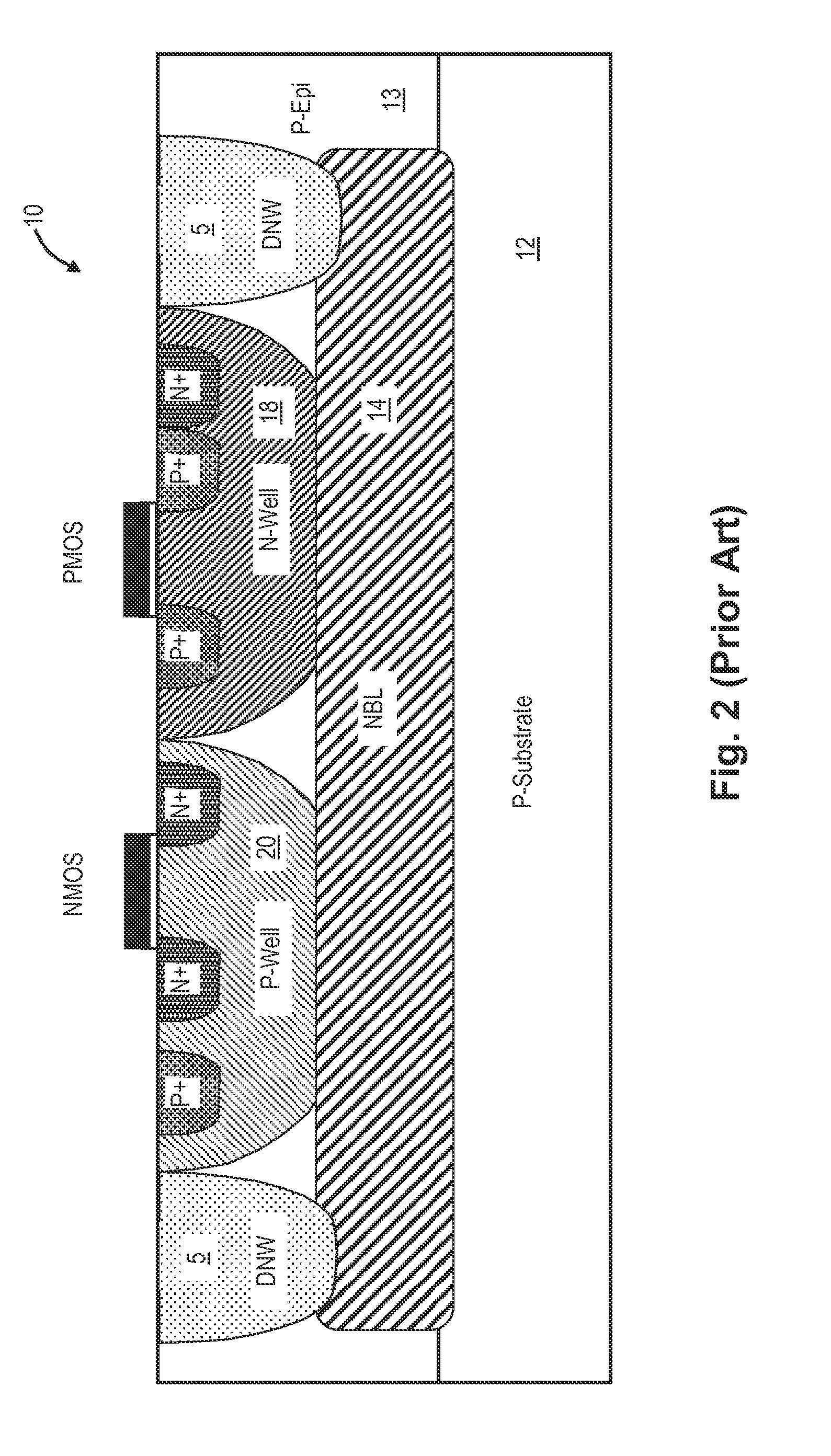

Semiconductor device and method for forming the same

ActiveCN101452886AReduce noise couplingTransistorSemiconductor/solid-state device manufacturingPeak valueP type doping

The invention provides a semiconductor device, which comprises an isolation structure which is positioned in a semiconductor substrate, a deep n-type doping well which is positioned in an MOS transistor region of n channel-conductive type in an active area, as well as an n-type MOS transistor which is formed on the semiconductor substrate, wherein the deep n-type doping well is positioned under a p-type doping well in the region and is electrically connected with n-type doping wells on two sides, and the ion doping concentration peak value of the deep n-type doping well and the doping ion concentration of the n-type doping wells at equal depth are equal in range. The invention also provides a method for forming the semiconductor device. By forming the deep n-type doping well in the region where the n-type MOS transistor is in the semiconductor substrate, the method realizes the longitudinal isolation of the n-type MOS transistor and the semiconductor substrate, as well as the transverse isolation of the semiconductor devices on two sides, and reduces the noise coupling in a hybrid integrated circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP

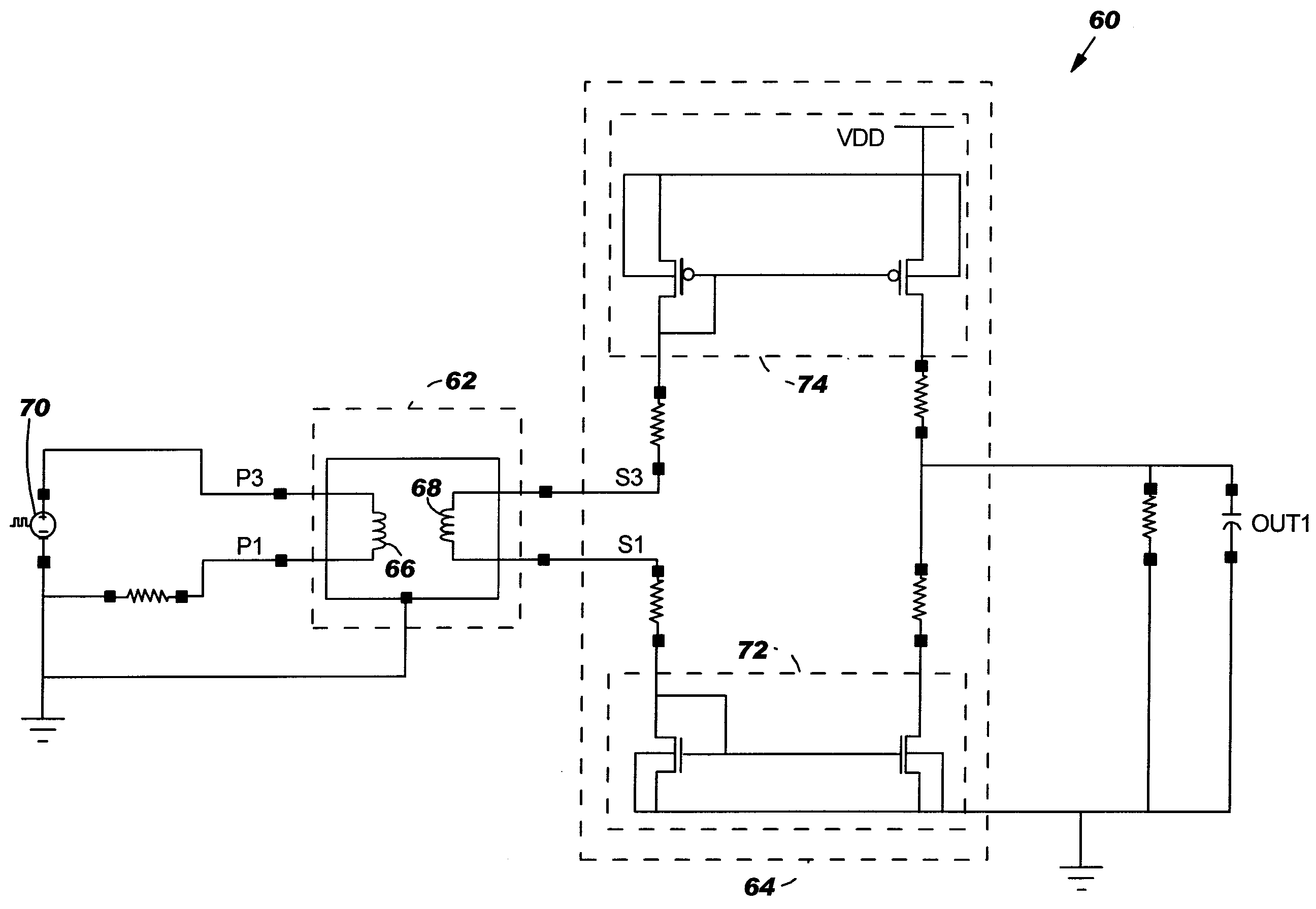

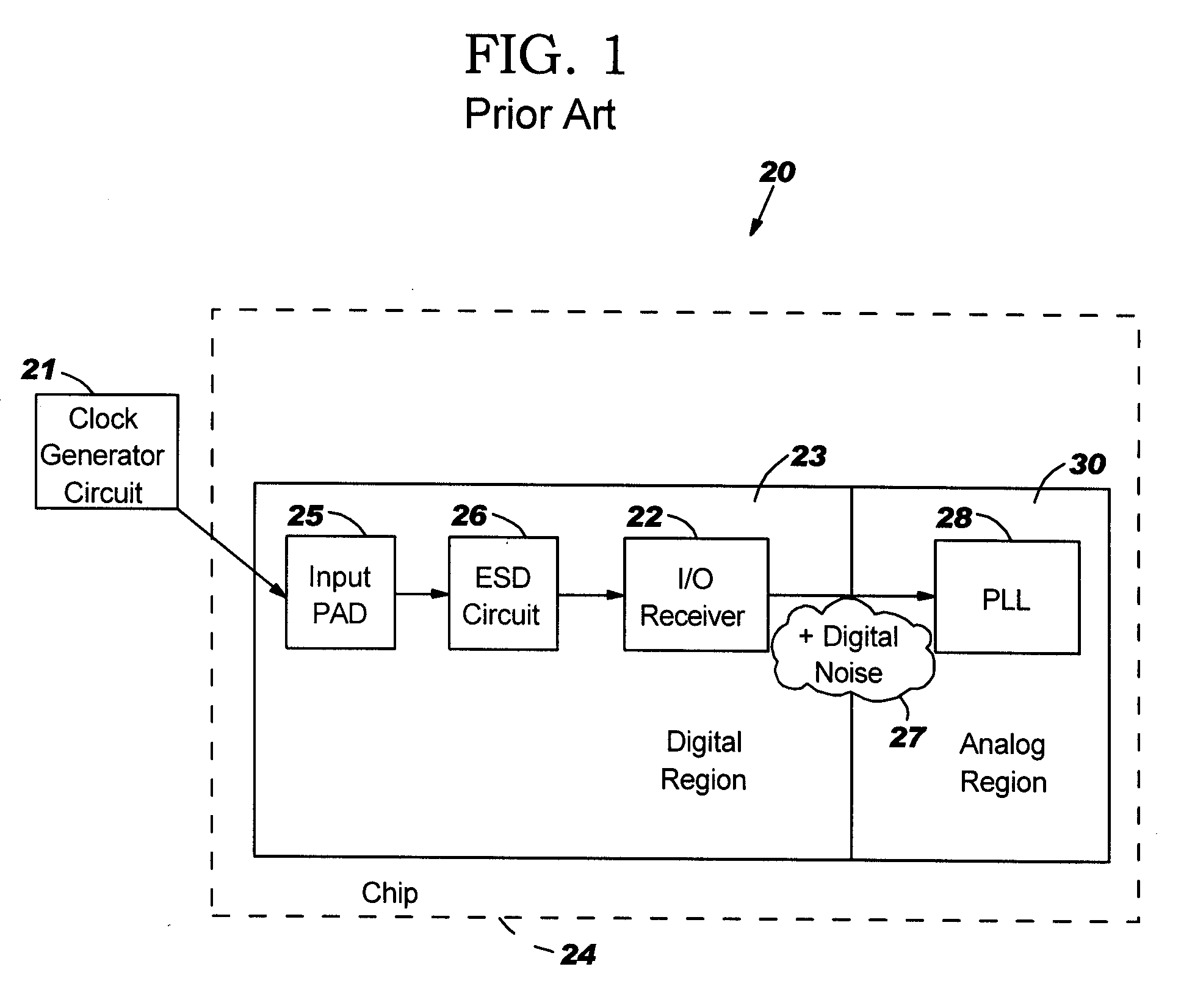

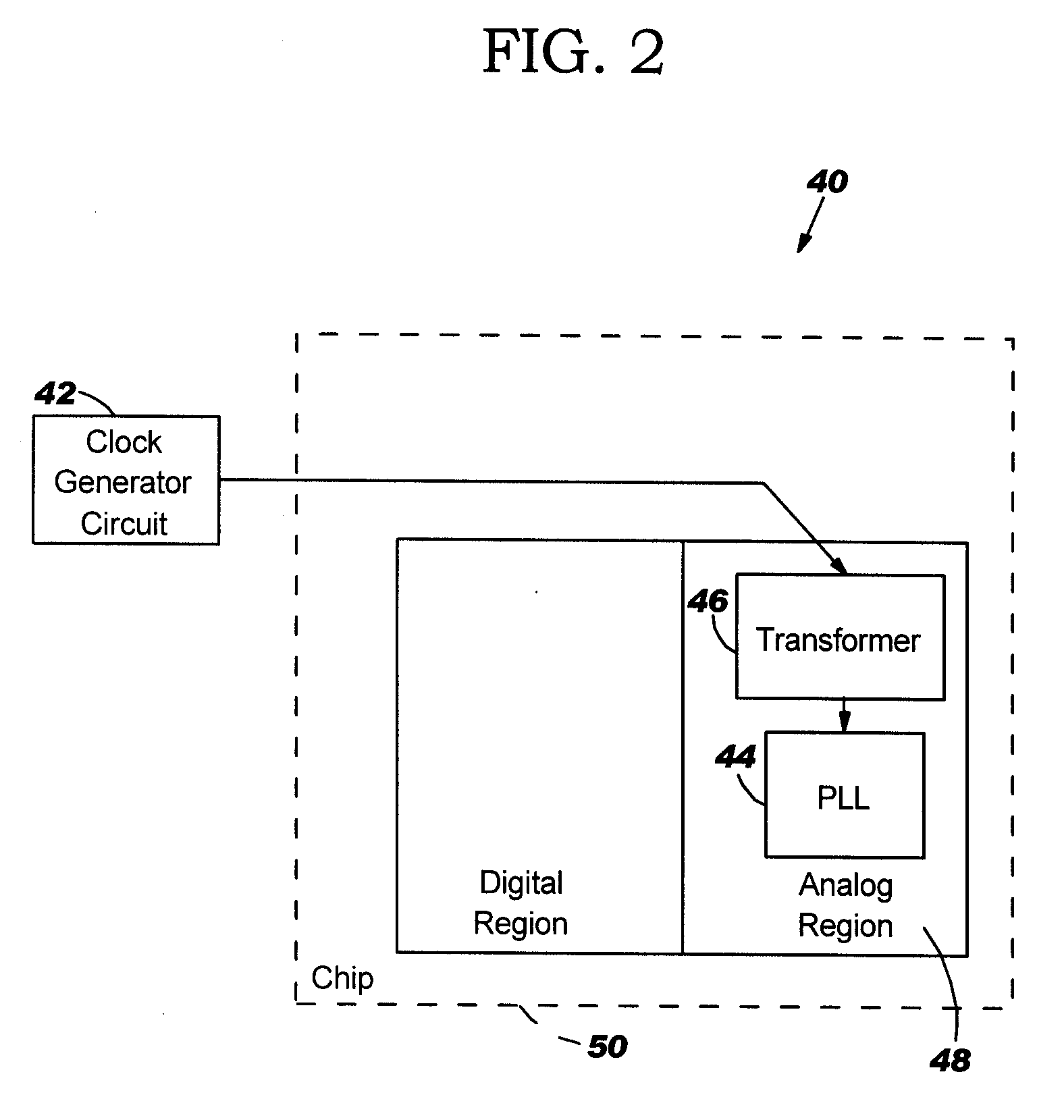

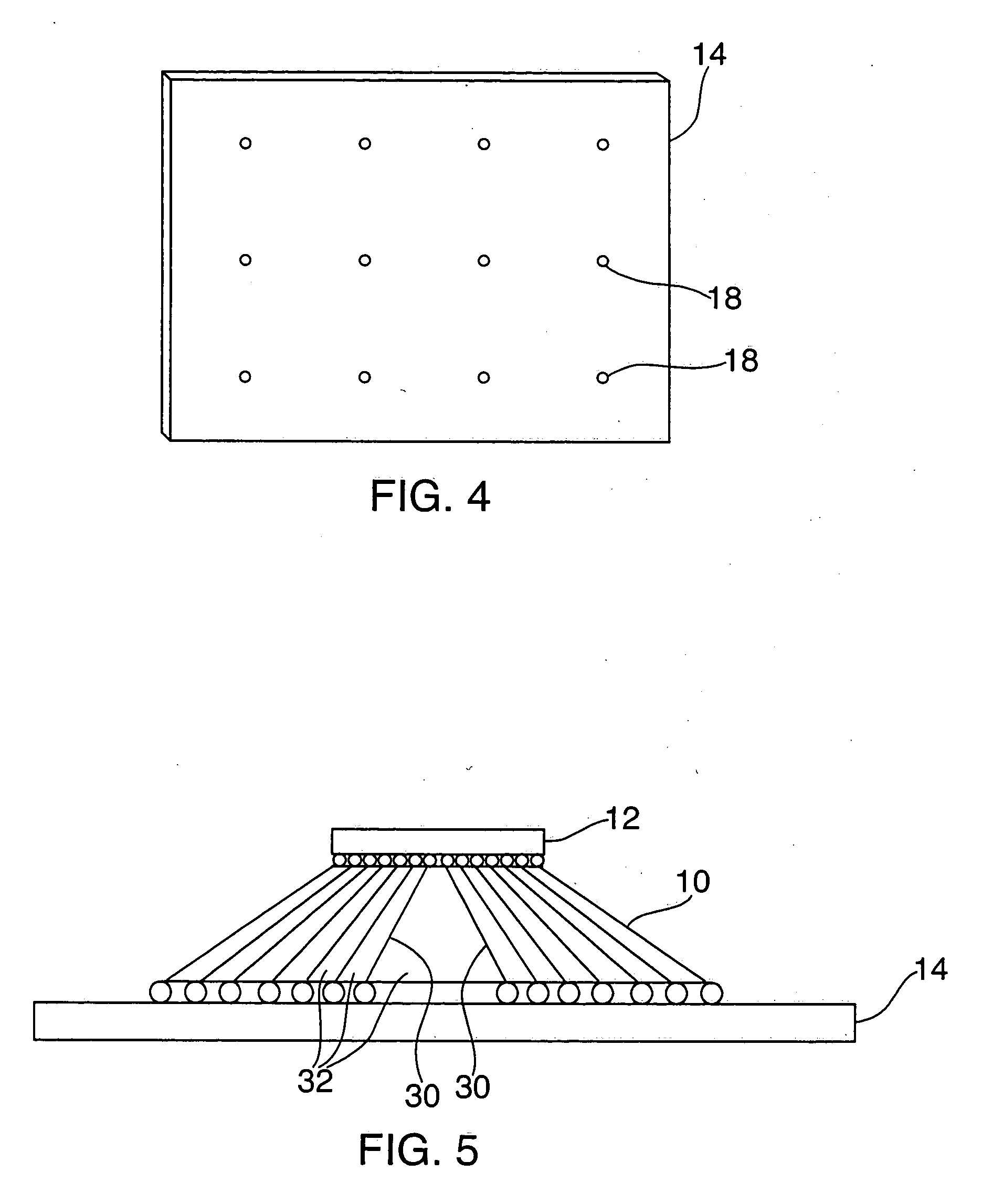

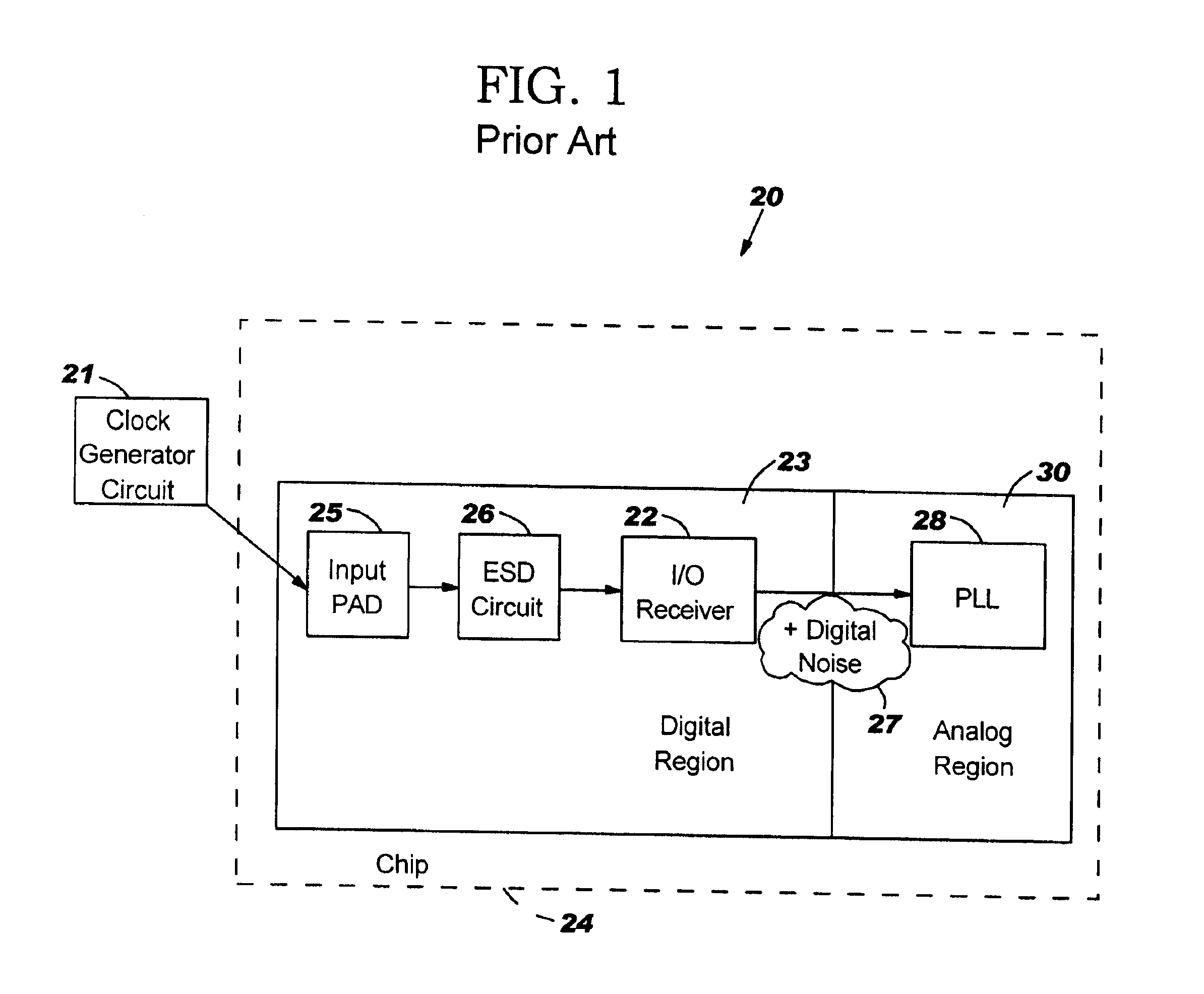

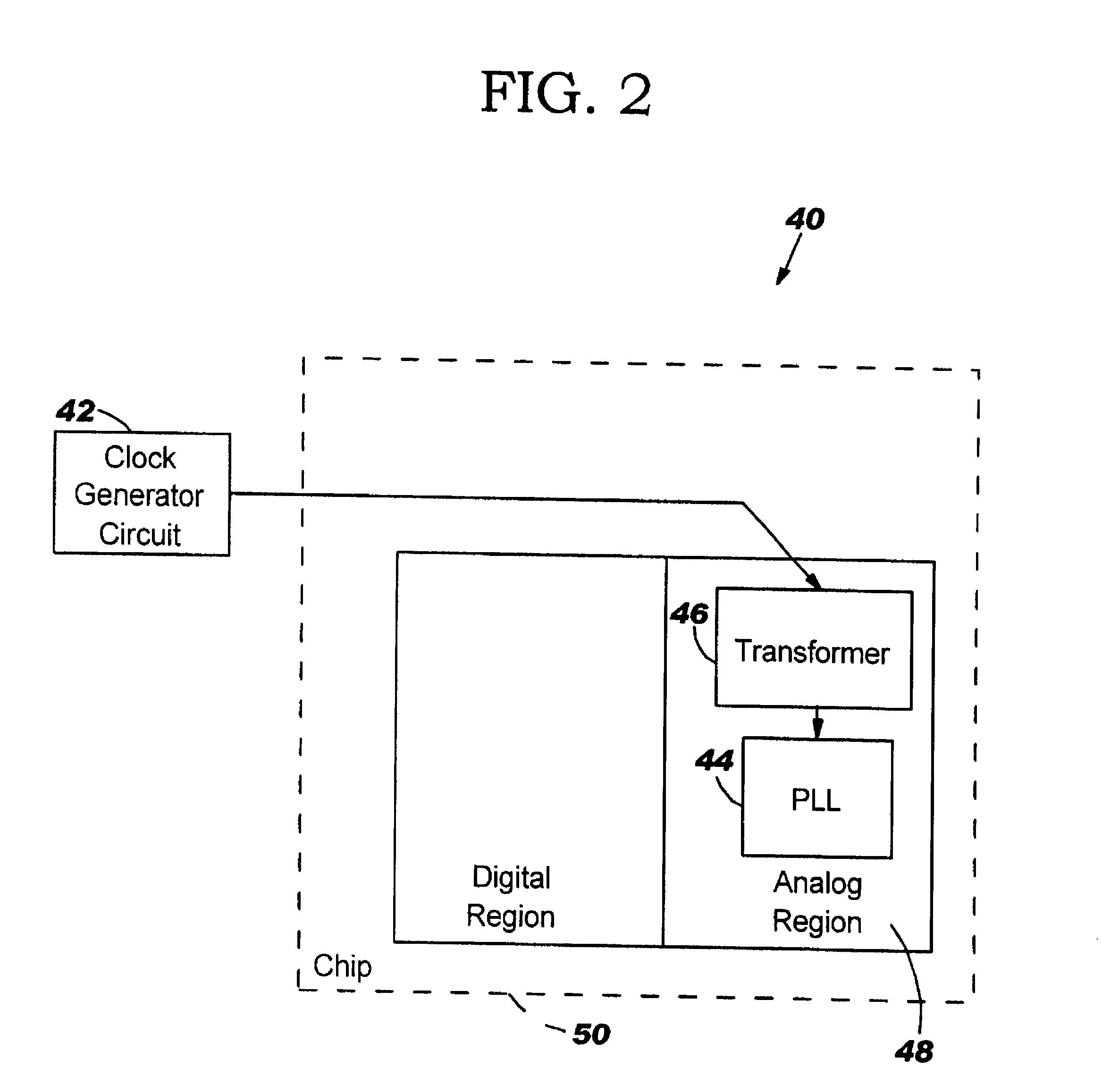

Integrated circuit and method for interfacing two voltage domains using a transformer

InactiveUS20050093620A1Reduce on-chip noise couplingCoupling lossLogic circuit coupling arrangementsPulse automatic controlCoupling lossTransformer

An integrated circuit designed to reduce on-chip noise coupling. In one embodiment, circuit (60) includes the following: a circuit transformer (62) capable of converting a noise sensitive input reference clock signal to an output signal having a voltage compatible with a predetermined sink voltage logic level; and a biased receiver network (64) having a PFET current mirror (74) coupled with a NFET current (72), the biased receiver transistor network designed to multiply the transformer signal to offset a mutual coupling loss of the transformer. In at least one alternative embodiment, the input reference clock signal originates at an off-chip clock generator circuit (42) and the output signal from receiver (64) is input to a PLL (44). In another alternative embodiment, the transformer is a monolithic integrated transformer. Another alternative embodiment of the present invention is a method of reducing on-chip noise coupling.

Owner:IBM CORP

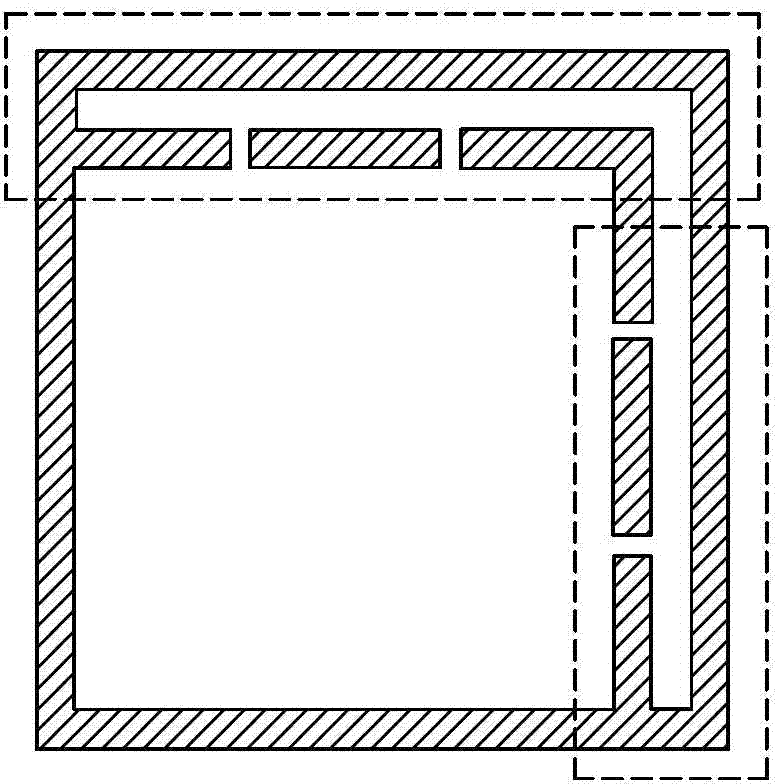

Sealing ring structure used for integrated circuit chip

InactiveCN102832178APrevent penetrationAvoid interferenceSemiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit design

The invention discloses a sealing ring structure used for an integrated circuit chip. The sealing ring structure is characterized in that at least one side edge of the sealing ring is of a double-side structure, and the inner side of at least one double-side structure is provided with at least one opening. The sealing ring structure provided by the invention can prevent hydrosphere from penetrating, can reduce influence on an integrated circuit from the noises transferred by the sealing ring, can reduce noise coupling, and can prevent an electromagnetic signal from interfering the operation of a sensitive circuit and the like; and the structure is simple, the processing is convenient, and the sealing ring structure has strong practicability and can be widely popularized and applied.

Owner:SHANGHAI UNIV OF ENG SCI

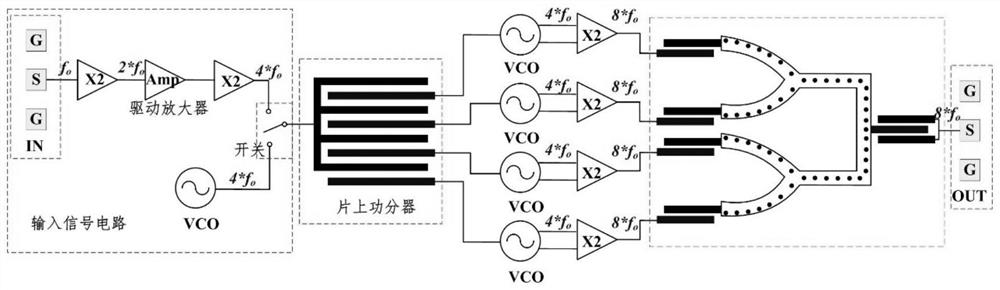

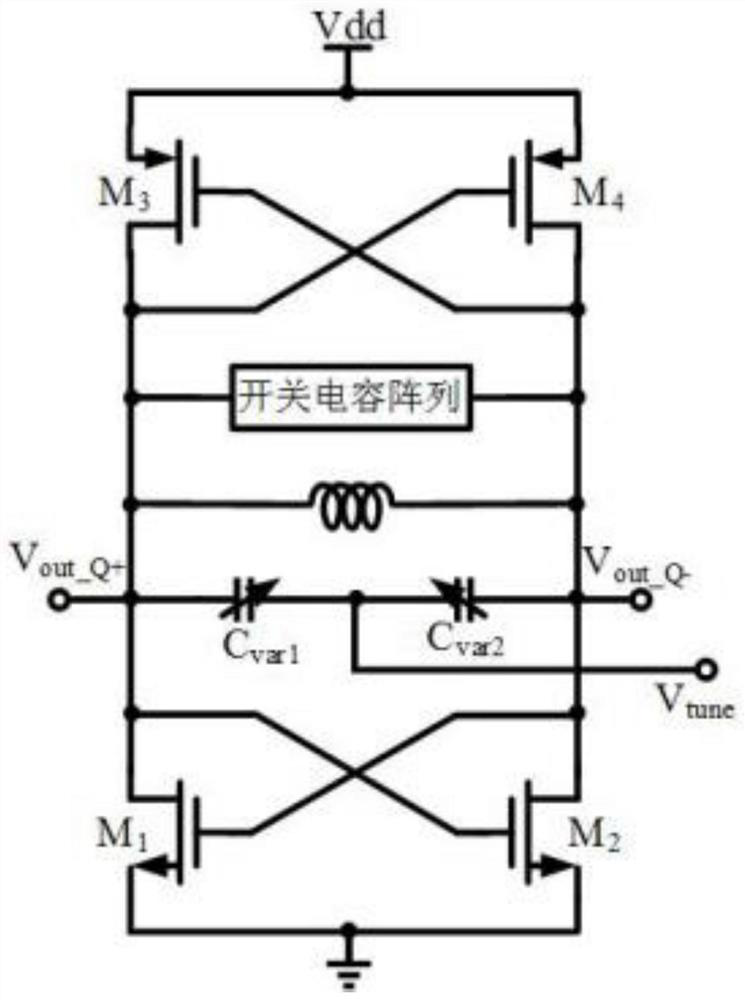

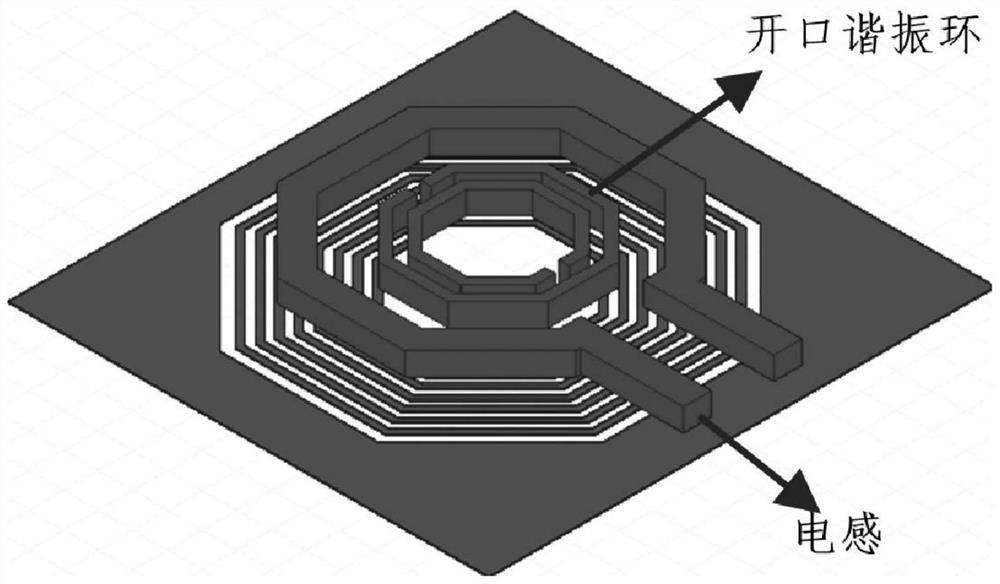

High-power and high-efficiency on-chip silicon-based dual-mode terahertz signal source structure

ActiveCN113839619AIncrease output powerReduce lossPulse automatic controlOscillations generatorsFrequency multiplierHemt circuits

According to the high-power and high-efficiency on-chip silicon-based dual-mode terahertz signal source structure, output signals in a voltage-controlled oscillator array are set to pass through an on-chip combiner, power output by multiple paths of voltage-controlled oscillators is synthesized, meanwhile, the output power of an active circuit including the voltage-controlled oscillator array and a frequency multiplier circuit is improved, the output power of the terahertz source is improved; the efficiency of the terahertz source is improved by improving the quality factor of the inductor in the voltage-controlled oscillator and reducing the loss of the on-chip combiner; the band-stop network is arranged in the frequency multiplier circuit to be grounded, so that frequency signals are prevented from being leaked to the ground, the signals are output from the output end as far as possible, and power and efficiency are improved.

Owner:HANGZHOU DIANZI UNIV

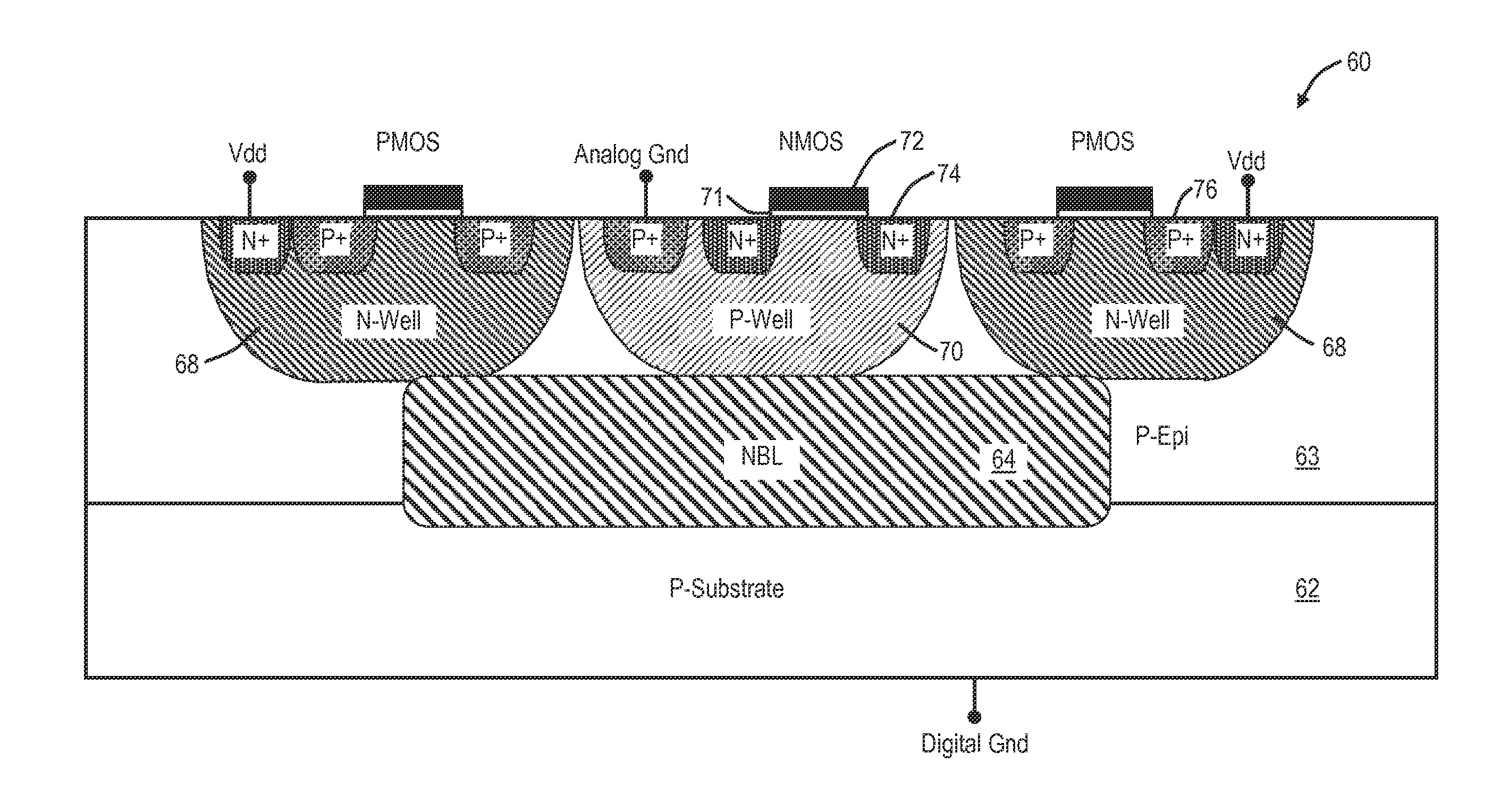

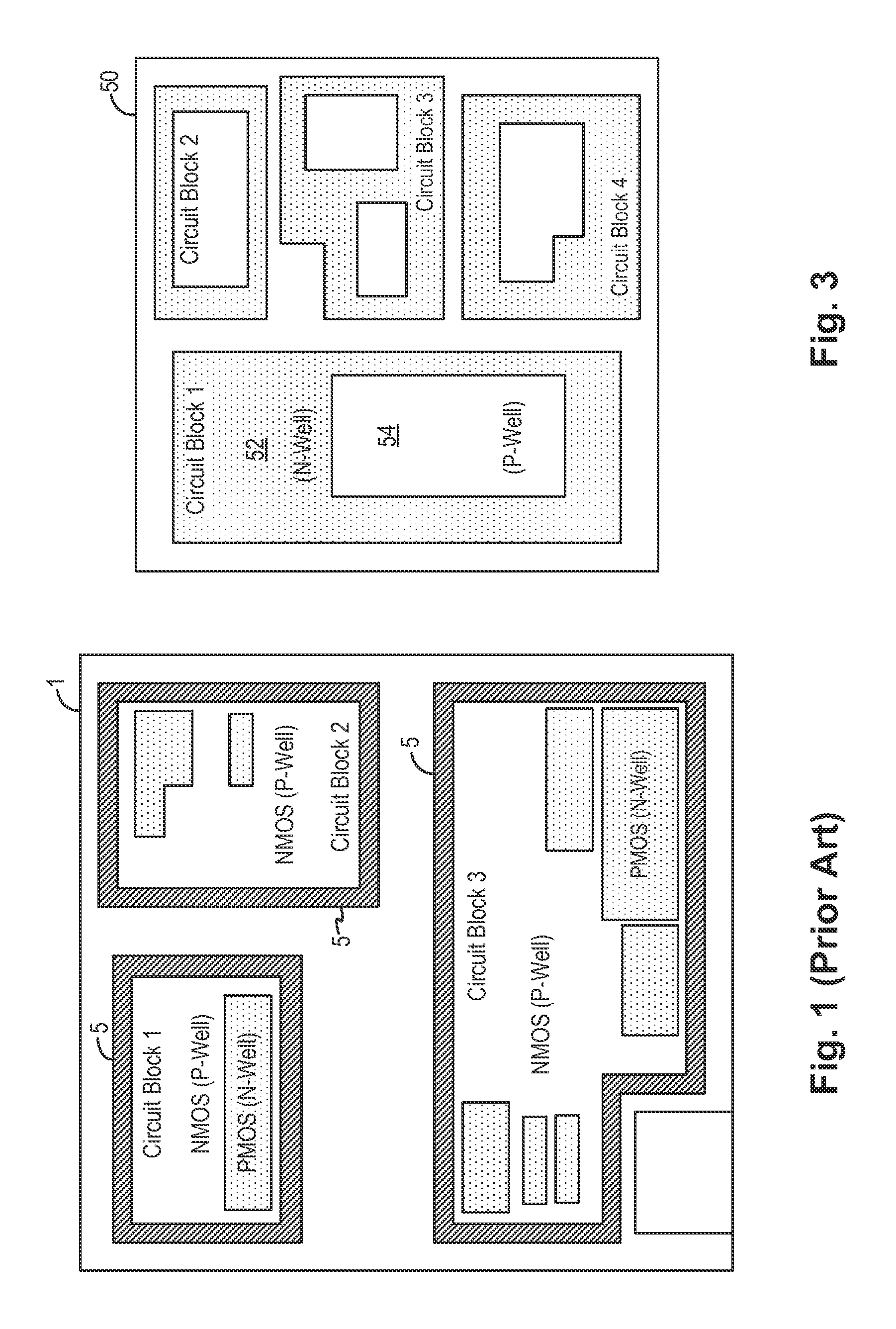

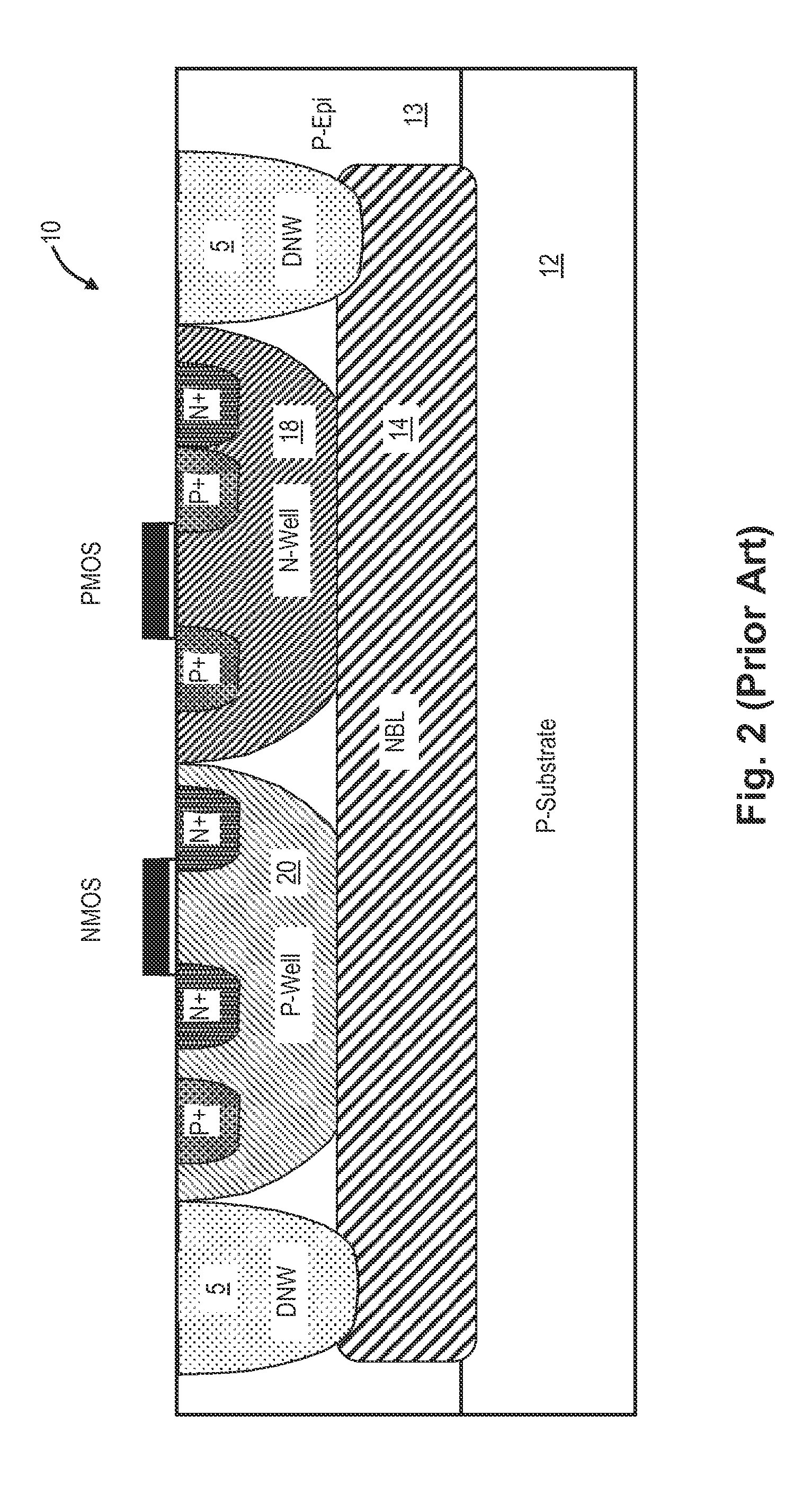

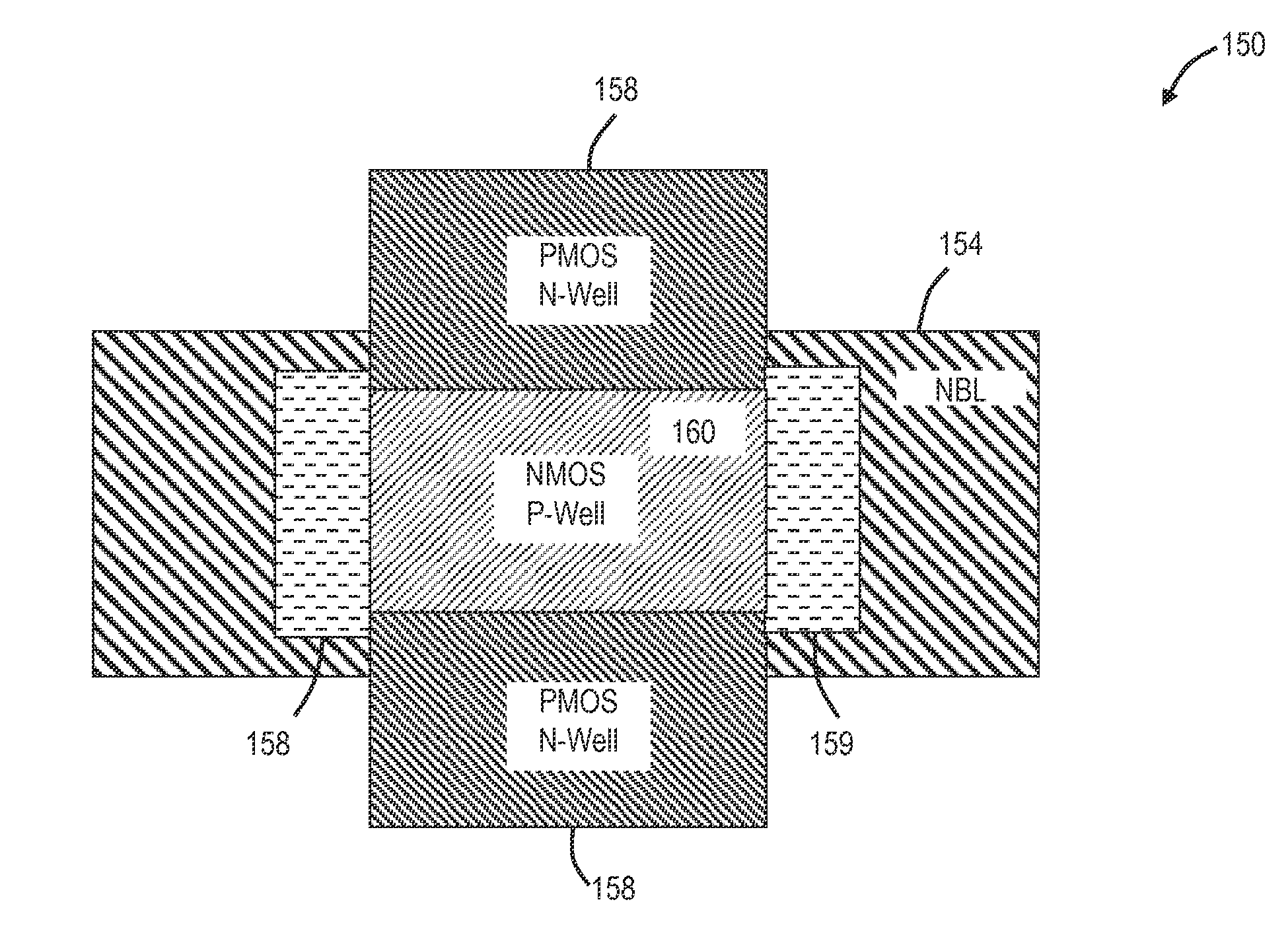

Compact CMOS device isolation

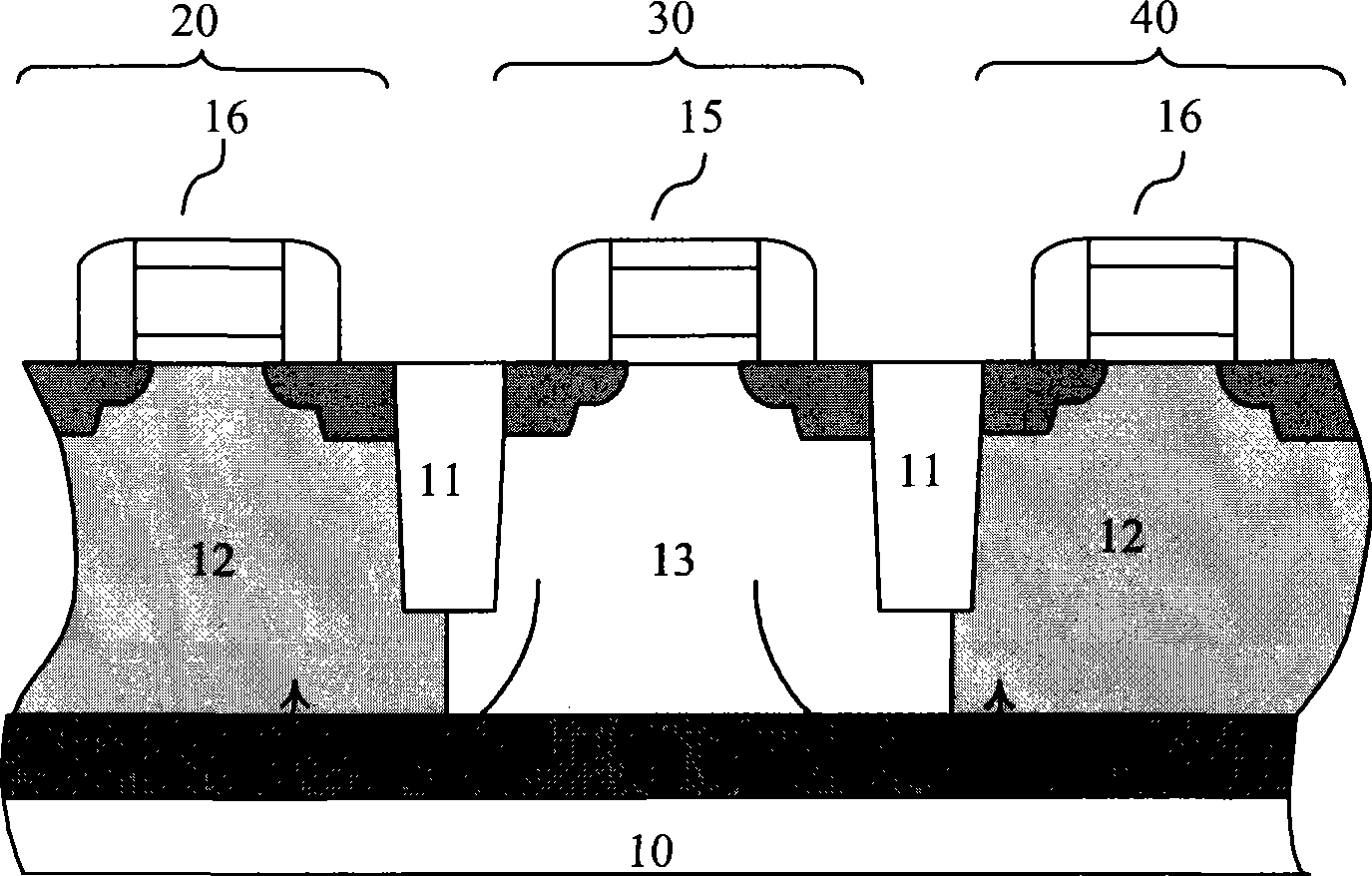

ActiveUS9548307B2Keep the substrate less noisyReduce noise couplingTransistorSolid-state devicesCMOSEngineering

An integrated circuit includes a first well of the first conductivity type formed in a semiconductor layer where the first well housing active devices and being connected to a first well potential, a second well of a second conductivity type formed in the semiconductor layer and encircling the first well where the second well housing active devices and being connected to a second well potential, and a buried layer of the second conductivity type formed under the first well and overlapping at least partially the second well encircling the first well. In an alternate embodiment, instead of the buried layer, the integrated circuit includes a third well of the second conductivity type formed in the semiconductor layer where the third well contains the first well and overlaps at least partially the second well encircling the first well.

Owner:ALPHA & OMEGA SEMICON INC

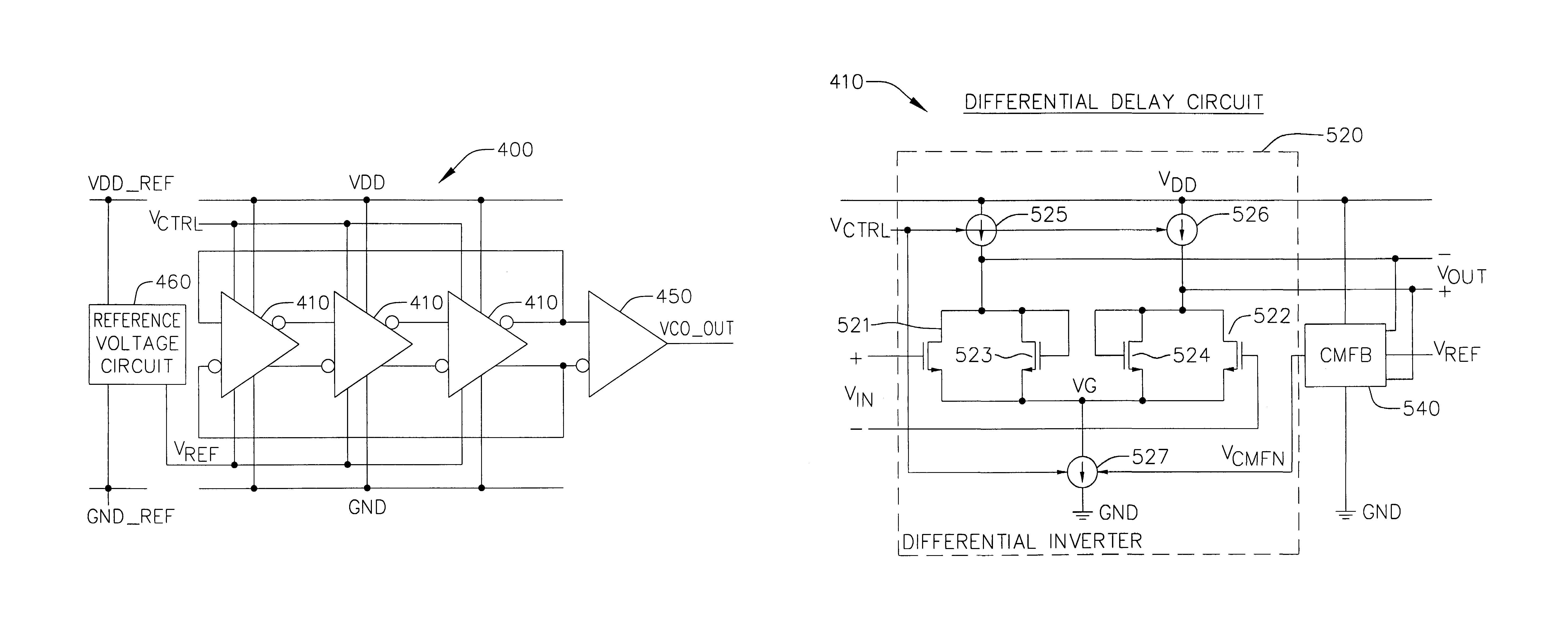

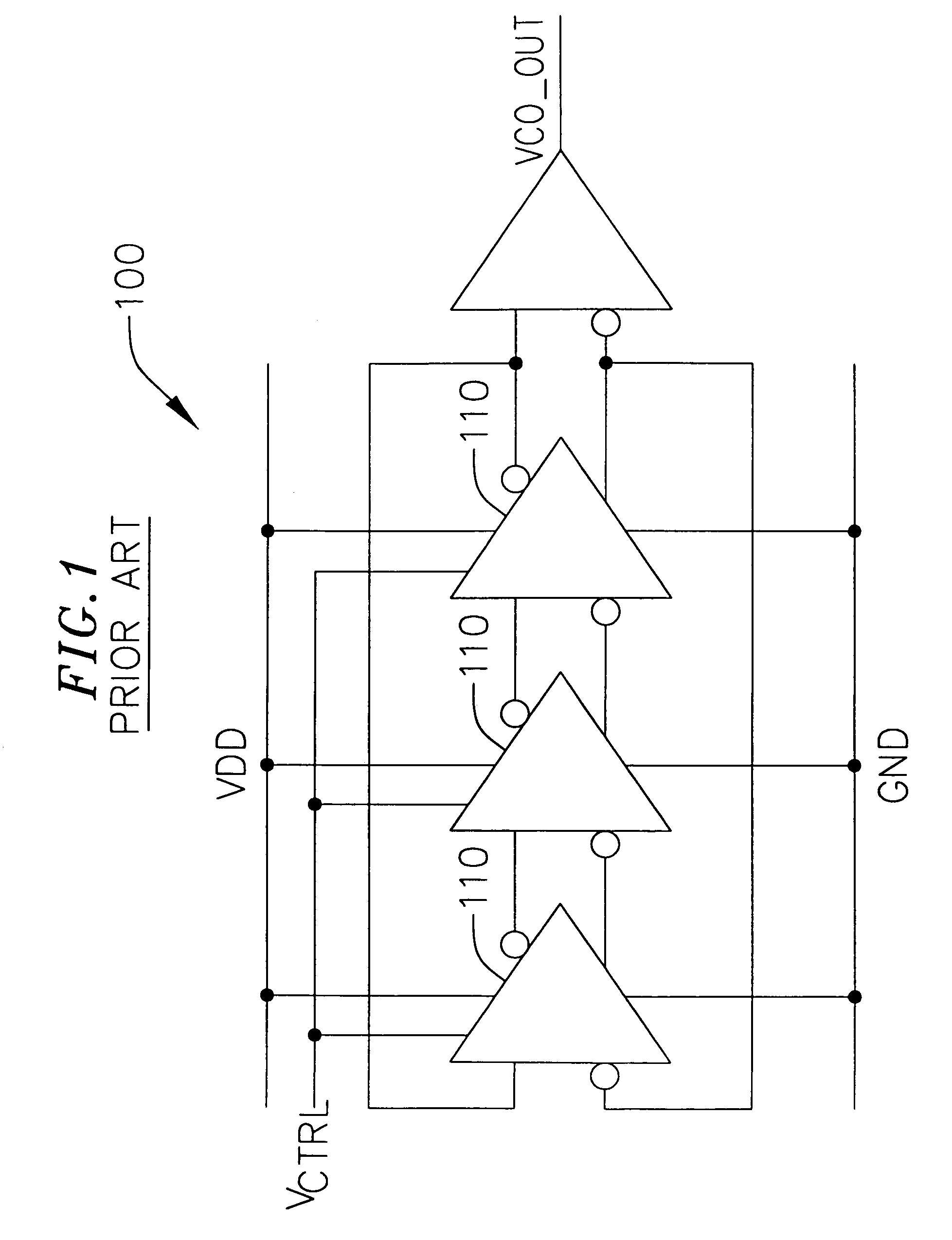

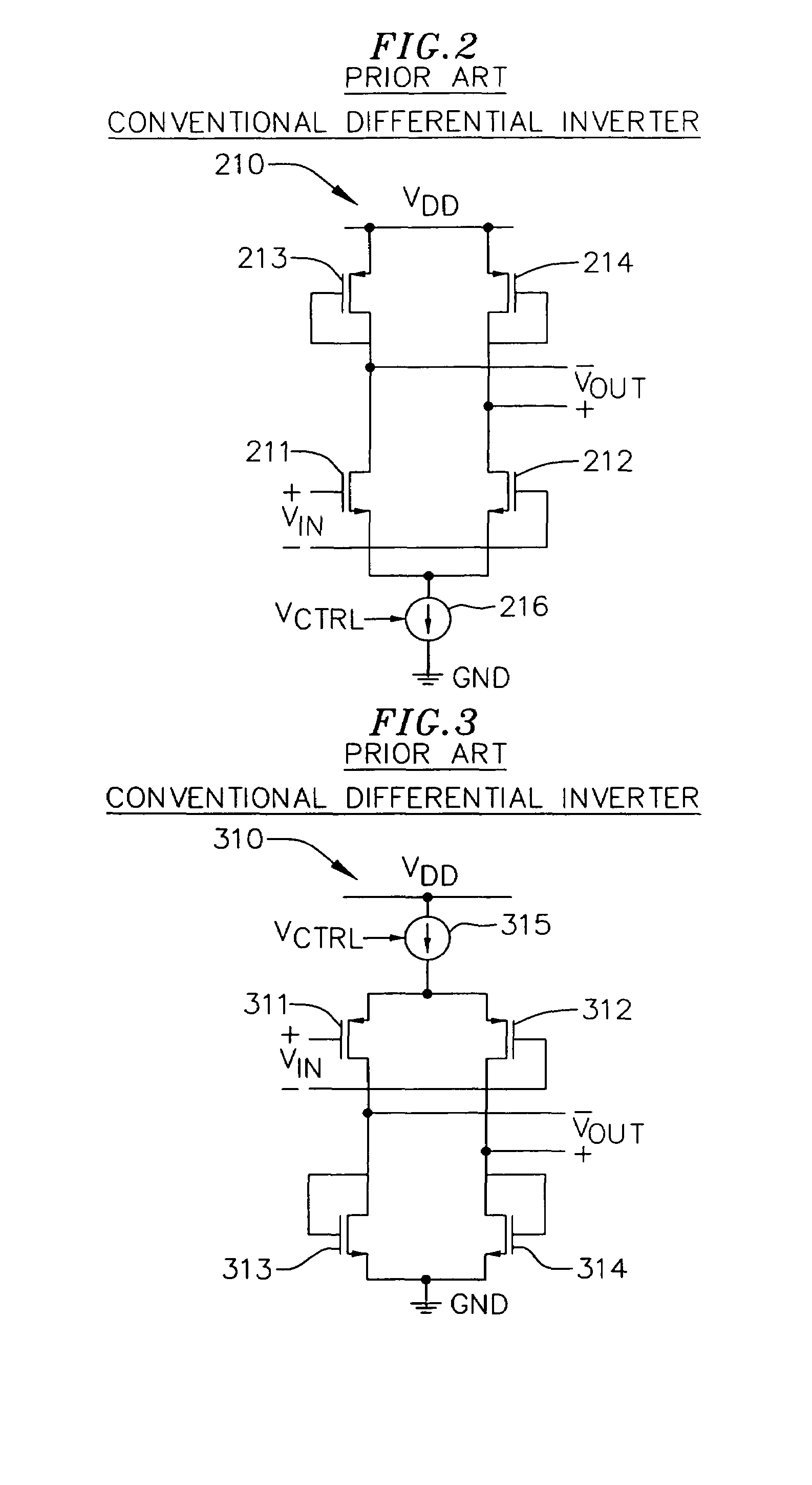

High noise rejection voltage-controlled ring oscillator architecture

InactiveUS6963251B2Improve the level ofReduce noise couplingPulse automatic controlGated amplifiersElectricityCoupling

A ring oscillator circuit, such as a VCO, with a relatively high level of noise rejection for noise originating from both the voltage supply and ground. The ring oscillator circuit is composed of a plurality of differential delay circuits, each differential delay circuit generating a differential output signal that is a delayed (and preferably inverted) version of a differential input signal. ‘Each differential delay circuit includes first and second input transistors for receiving the differential input signal. Each differential delay circuit also includes first and second load transistors coupled in parallel with the respective first and second input transistors. Each differential delay circuit further includes a first current source coupled between the first input transistor and a first power supply terminal (e.g., a voltage supply terminal), a second current source coupled between the second input transistor and the first power supply terminal and a third current source coupled between the first and second input transistors and a second power supply terminal (e.g., a ground terminal). The first and second current sources reduce the coupling of noise from the first power supply terminal to the output. The third current source reduces the coupling of noise from the second power supply terminal to the output.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Integrated circuit chip

ActiveCN1622324AImprove electricity qualityReduce noise couplingSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitSilicon based

The integrated circuit chip includes one silicon base board, at least one circuit, one fixed sealing ring, one earthing ring and at least one protecting ring. The circuit is formed on the silicon base board and has at least one I / O pad. The fixed ring formed on the silicon base board encloses the circuit and the I / O pad. The earthing ring formed between the silicon base board and the I / O pad is connected electrically to the fixed sealing ring. The protecting ring on the silicon base board and around the I / O pad is connected electrically to the fixed sealing ring.

Owner:AIROHA TECHNOLOGY CORPORATION

Integrated circuit redistribution package

InactiveUS20050176273A1Diminish likelihoodReduce pitchSemiconductor/solid-state device detailsSolid-state devicesPhysicsIntegrated circuit

The present invention provides a redistribution package having an upper surface that includes contacts with reduced pitch that correspond, for example, to that of a Controlled Collapse Chip Connection (“C4”) structure formed on a chip, and a lower surface having contacts with increased pitch that correspond, for example, to a printed circuit board employing ball grid array (“BGA”) pads. A series of power, signal and ground conductors extend through the body of the redistribution package and interconnect the circuit board contacts to the chip contacts.

Owner:GLOBALFOUNDRIES INC

Integrated circuit and method for interfacing two voltage domains using a transformer

InactiveUS6927616B2Reduce noise couplingCoupling lossLogic circuit coupling arrangementsPulse automatic controlCoupling lossTransformer

An integrated circuit designed to reduce on-chip noise coupling. In one embodiment, circuit (60) includes the following: a circuit transformer (62) capable of converting a noise sensitive input reference clock signal to an output signal having a voltage compatible with a predetermined sink voltage logic level; and a biased receiver network (64) having a PFET current mirror (74) coupled with a NFET current (72), the biased receiver transistor network designed to multiply the transformer signal to offset a mutual coupling loss of the transformer. In at least one alternative embodiment, the input reference clock signal originates at an off-chip clock generator circuit (42) and the output signal from receiver (64) is input to a PLL (44). In another alternative embodiment, the transformer is a monolithic integrated transformer. Another alternative embodiment of the present invention is a method of reducing on-chip noise coupling.

Owner:INT BUSINESS MASCH CORP

Planar magnetic field probe

InactiveUS20120187944A1Improve sensitivityAccurately measureMagnitude/direction of magnetic fieldsContactless circuit testingMagnetic field magnitudeElectric field

A planar magnetic field probe is provided. The planar magnetic field probe increases the sensitivity of magnetic field intensity detection by using a left multi-sensor loop and a right multi-sensor loop formed by a first patterned metal layer and a second patterned metal layer, and decreases the electric field noise coupling by surrounding the left multi-sensor loop and the right multi-sensor loop with a symmetrical shielding metal structure formed by a first patterned shielding metal layer, a second patterned shielding metal layer and a plurality of through vias.

Owner:TATUNG COMPANY

Compact CMOS device isolation

ActiveUS20150380413A1Keep the substrate less noisyReduce noise couplingTransistorSolid-state devicesCMOSEngineering

An integrated circuit includes a first well of the first conductivity type formed in a semiconductor layer where the first well housing active devices and being connected to a first well potential, a second well of a second conductivity type formed in the semiconductor layer and encircling the first well where the second well housing active devices and being connected to a second well potential, and a buried layer of the second conductivity type formed under the first well and overlapping at least partially the second well encircling the first well. In an alternate embodiment, instead of the buried layer, the integrated circuit includes a third well of the second conductivity type formed in the semiconductor layer where the third well contains the first well and overlaps at least partially the second well encircling the first well.

Owner:ALPHA & OMEGA SEMICON INC