Patents

Literature

377 results about "Spiral inductor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

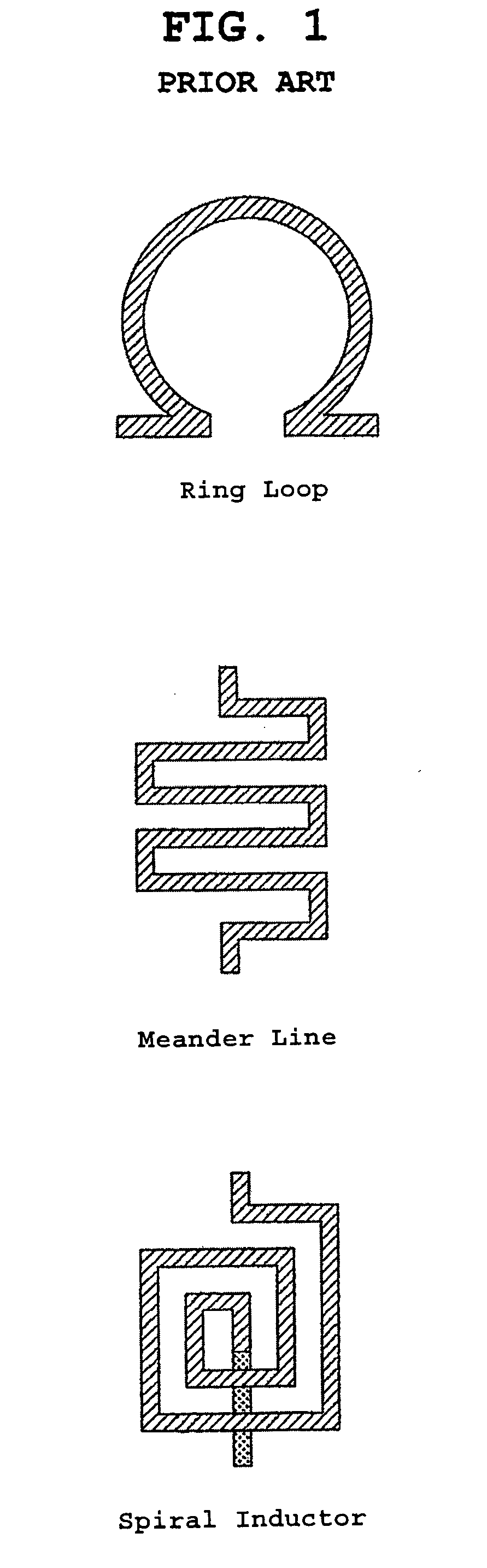

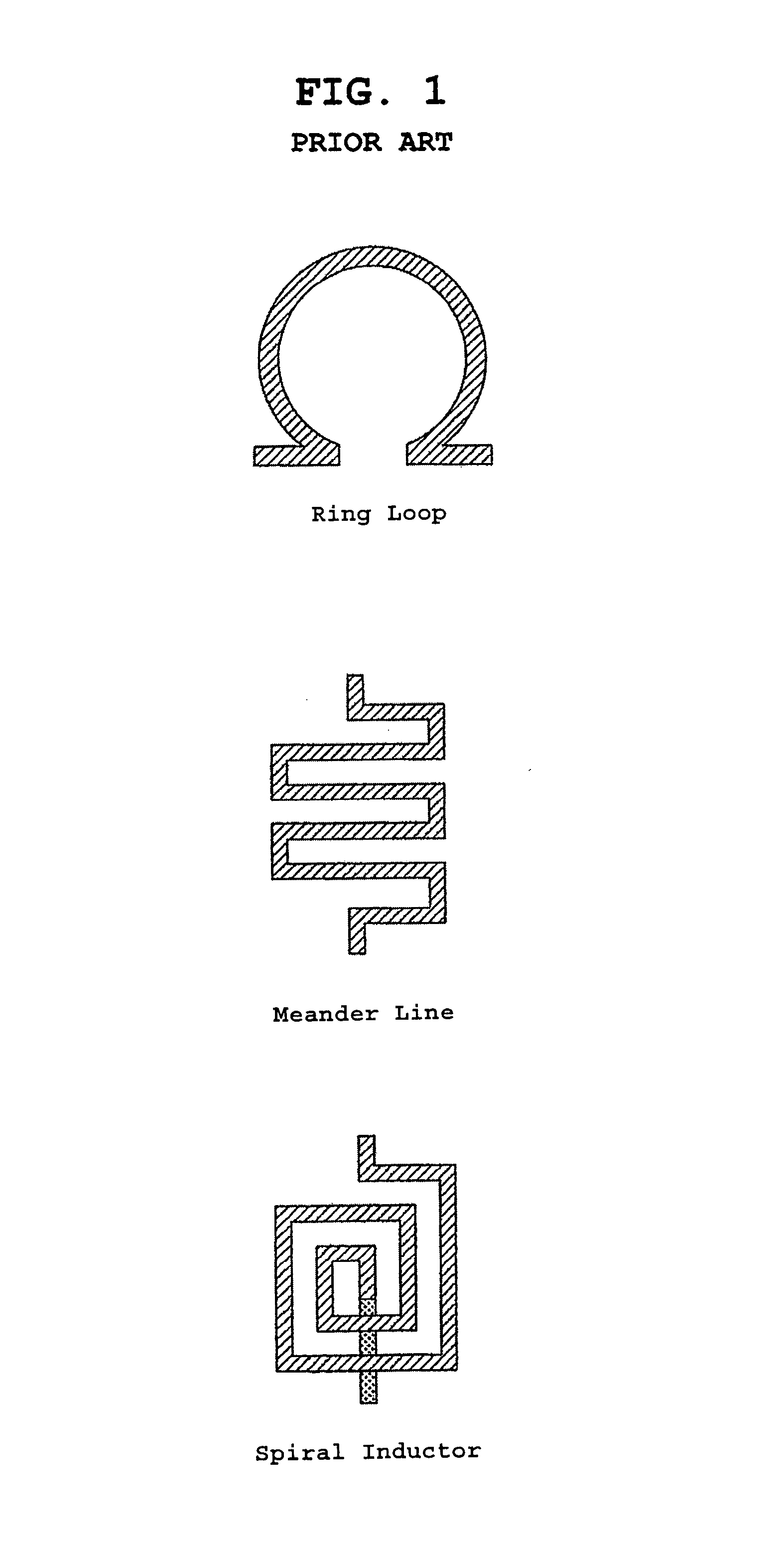

Spiral inductor. Spiral inductors, as well as transformers, are often used in RF circuits. The goal in simulations is to find their inductance (L) and quality factor (Q). Spiral inductors have many parasitic elements, including parallel capacitances.

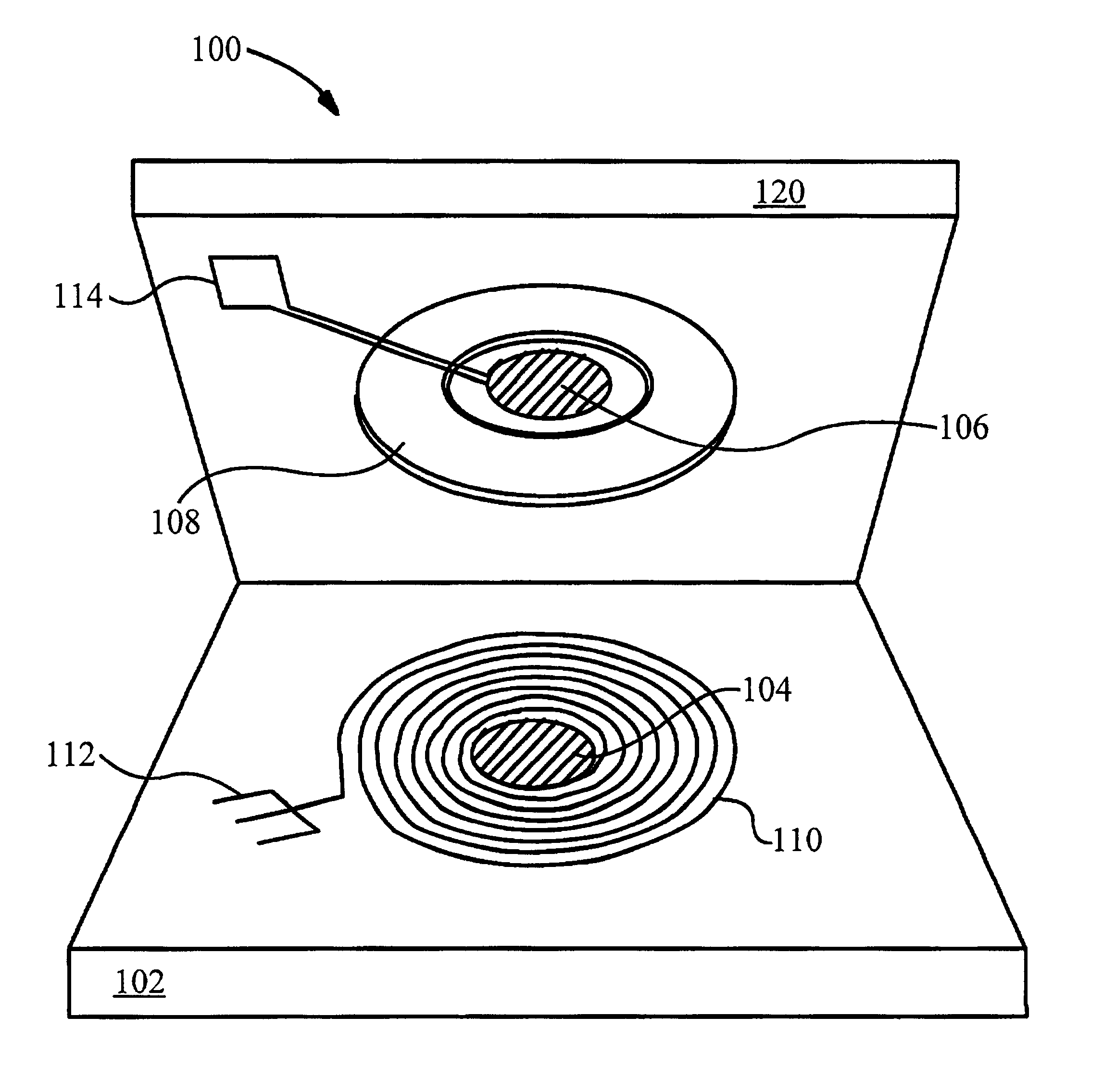

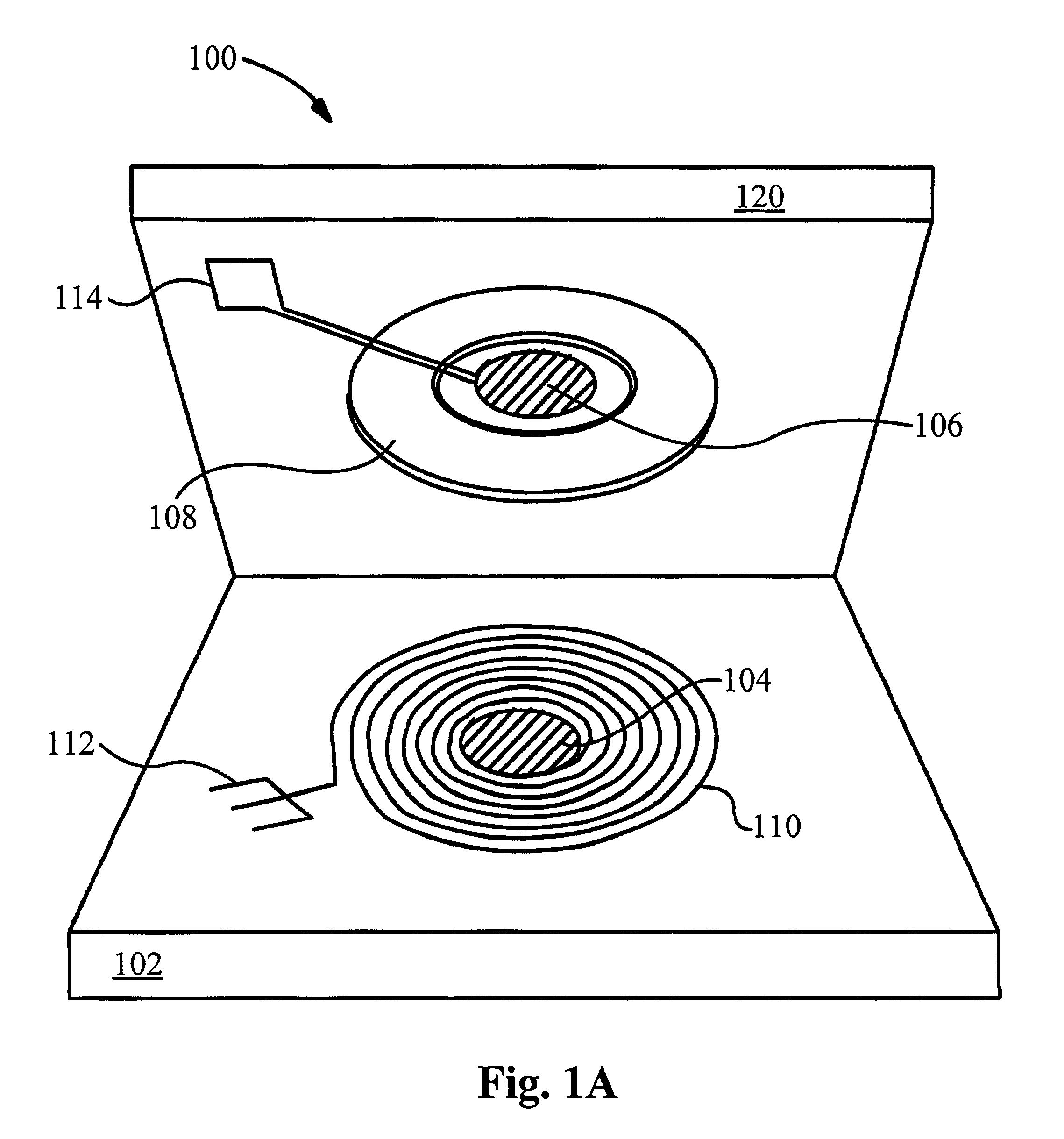

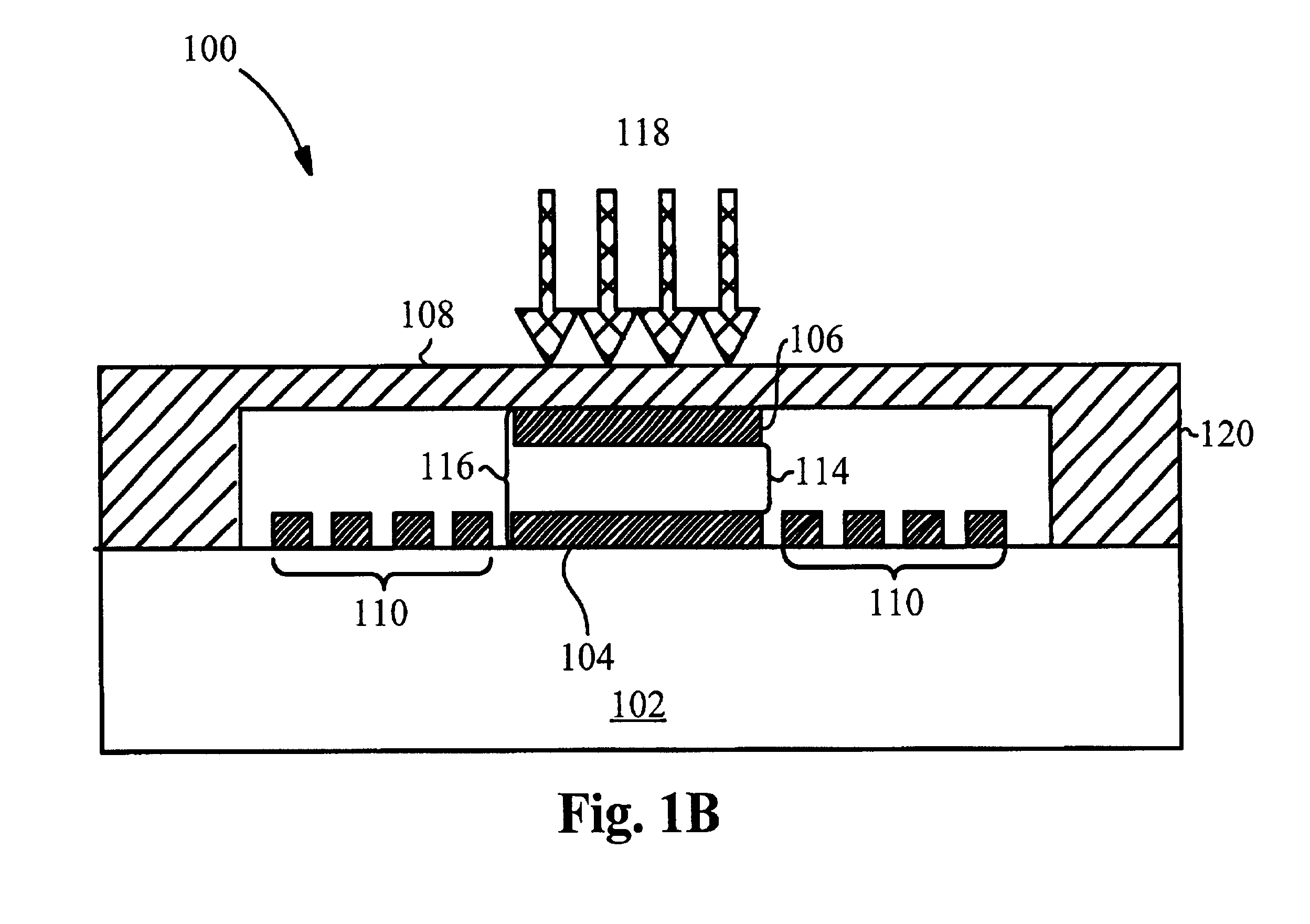

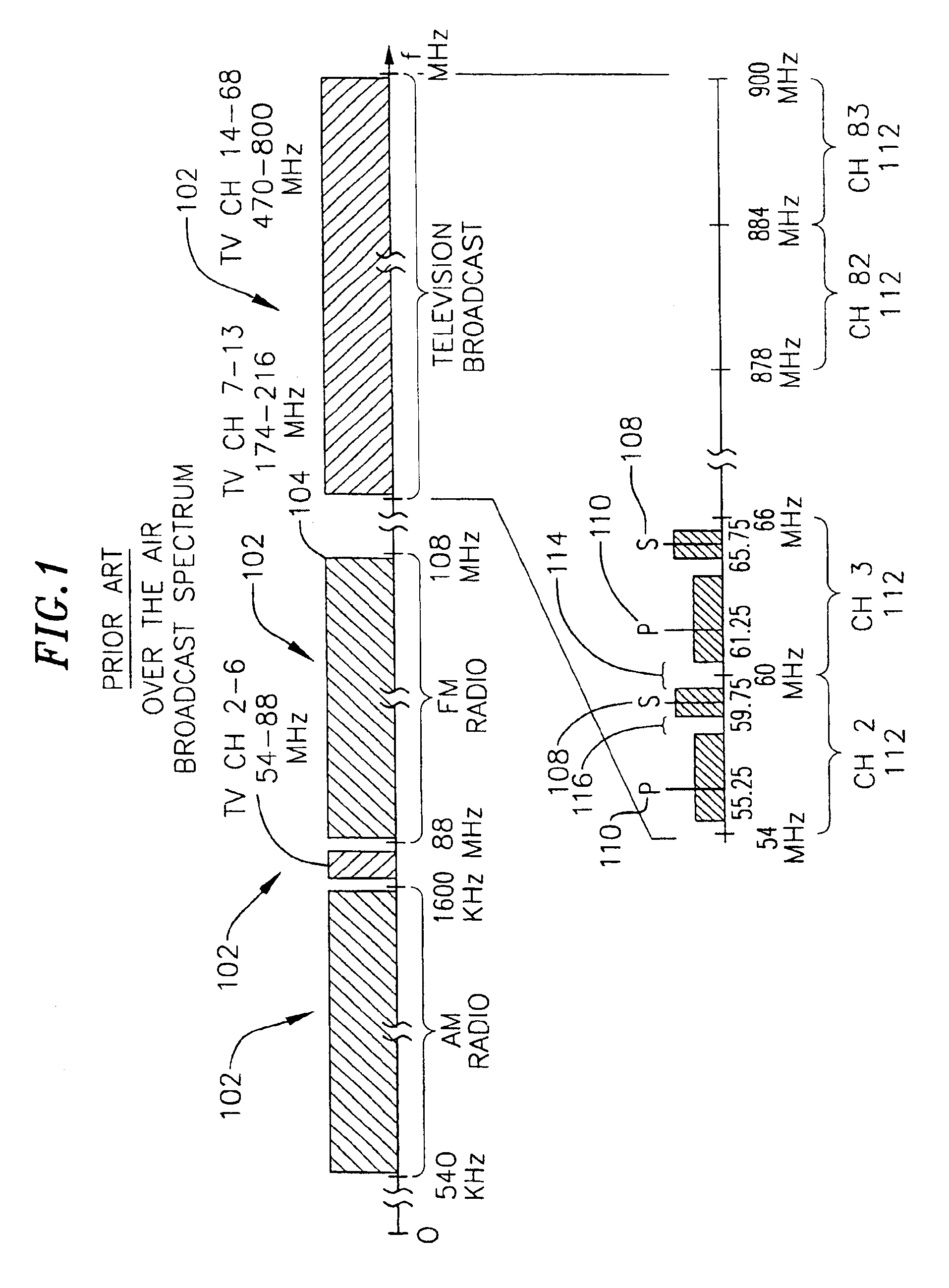

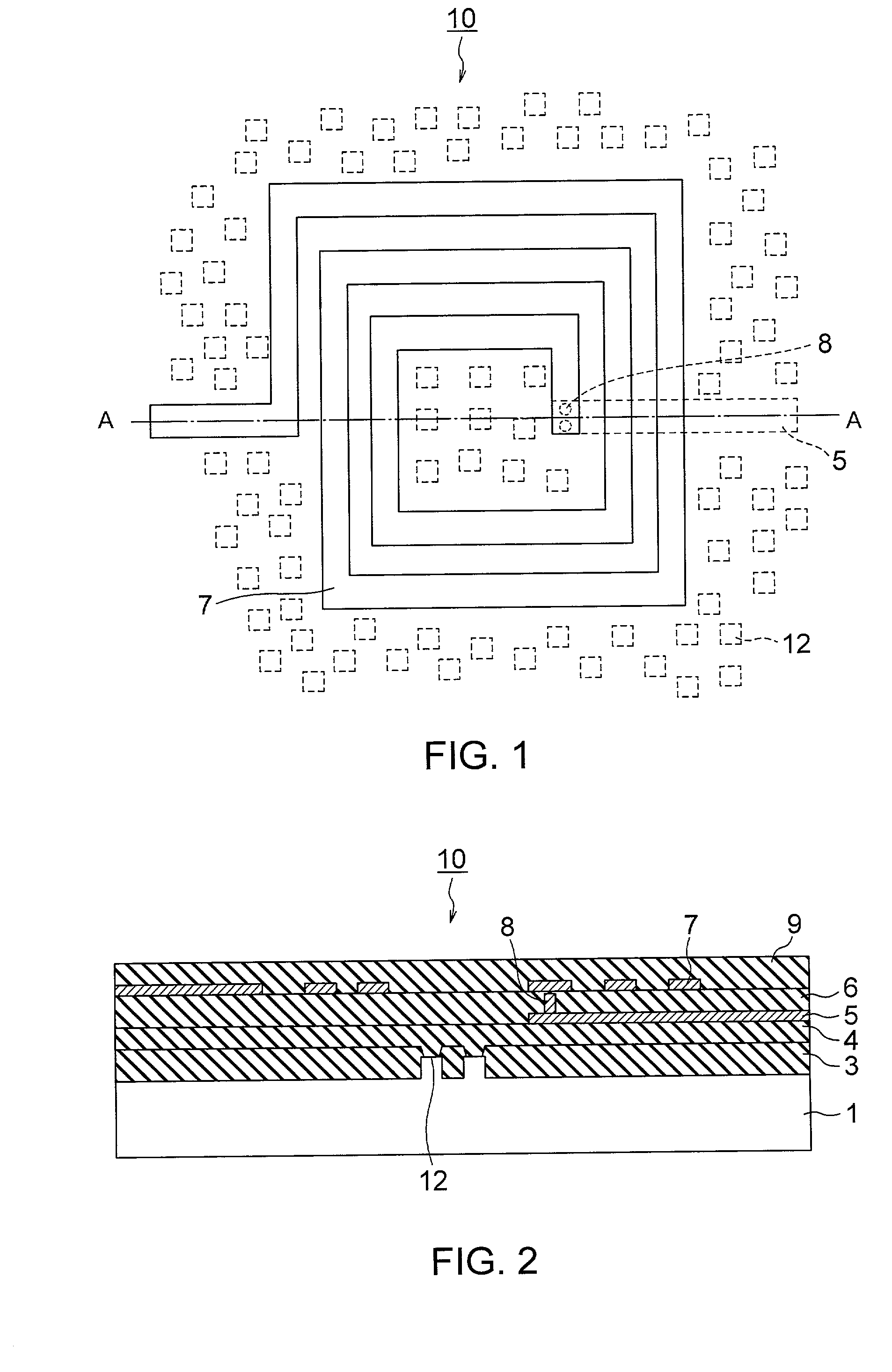

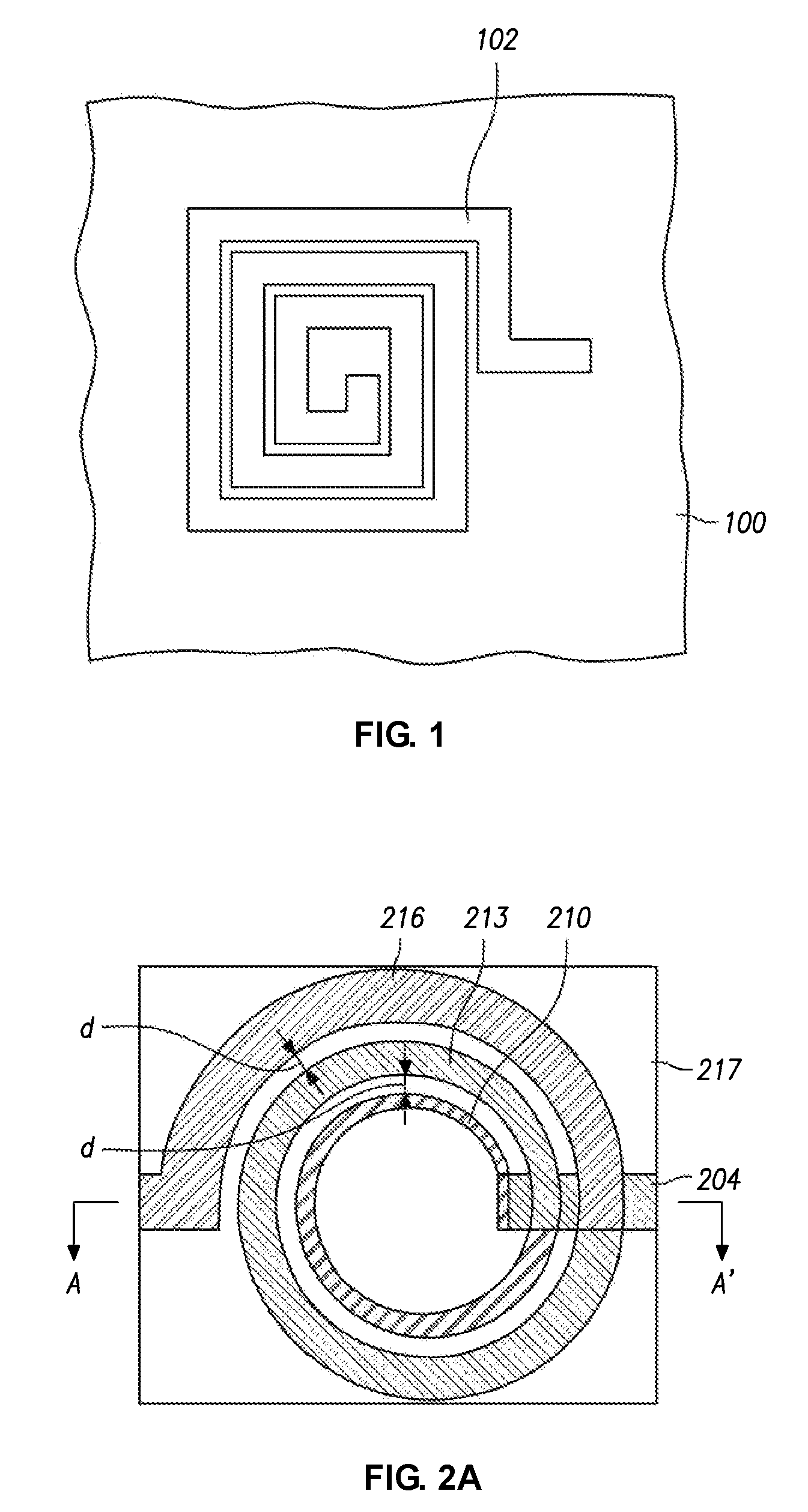

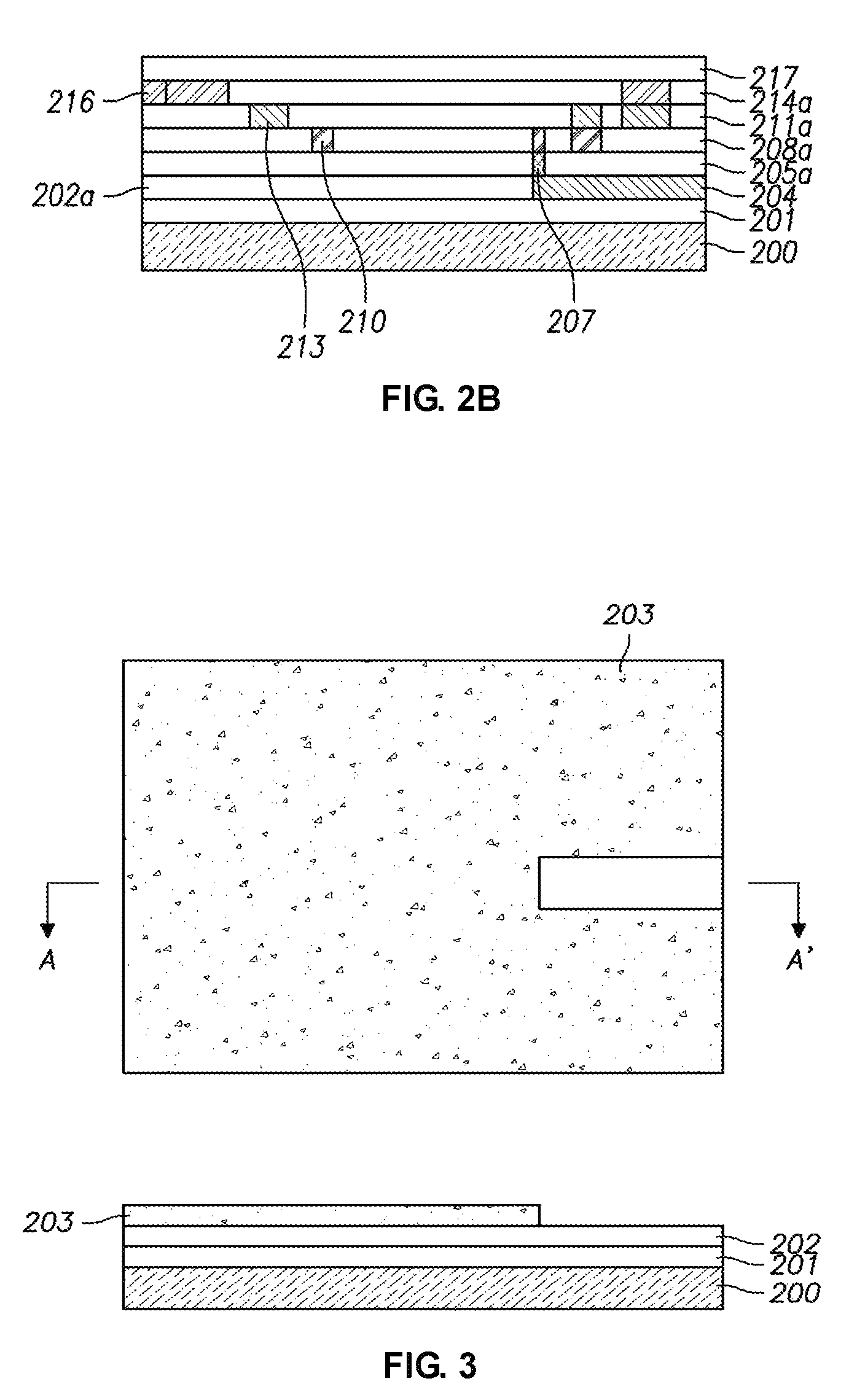

Implantable continuous intraocular pressure sensor

InactiveUS6939299B1Worn safely and comfortably and convenientlyPerson identificationTonometersIntraocular pressureSpiral inductor

An implantable miniaturized pressure sensor integrates a capacitor and an inductor in one small chip, forming a resonant LC circuit having a Q value of 10 or greater. The capacitor has an upper capacitor plate and a lower capacitor plate disposed proximate thereof. The upper and lower capacitor plates are connected to one or more spiral inductor coils. The sensor is micromachined from silicon to form a thin and robust membrane disposed on top of the upper capacitor plate. The sensor is hermetically sealed and the membrane is deflected relative to the upper capacitor plate by an external fluid, gas, or mechanical pressure. The resonant frequency of the sensor can be remotely monitored and continuously measured with an external detector pick up coil disposed proximate the sensor. The sensor can be smaller than 2×2×0.5 mm and is particularly useful for intraocular applications.

Owner:IOSENSOR

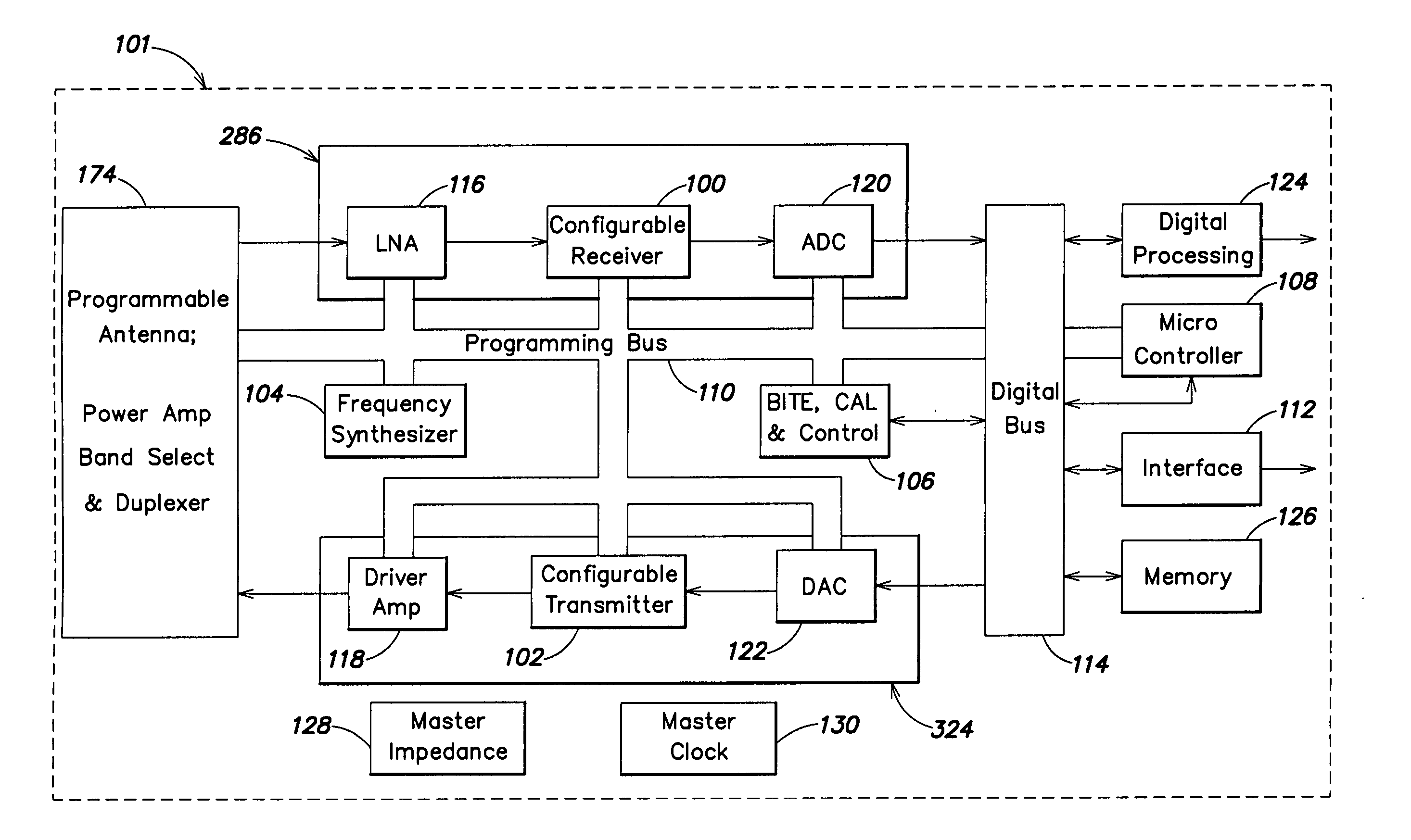

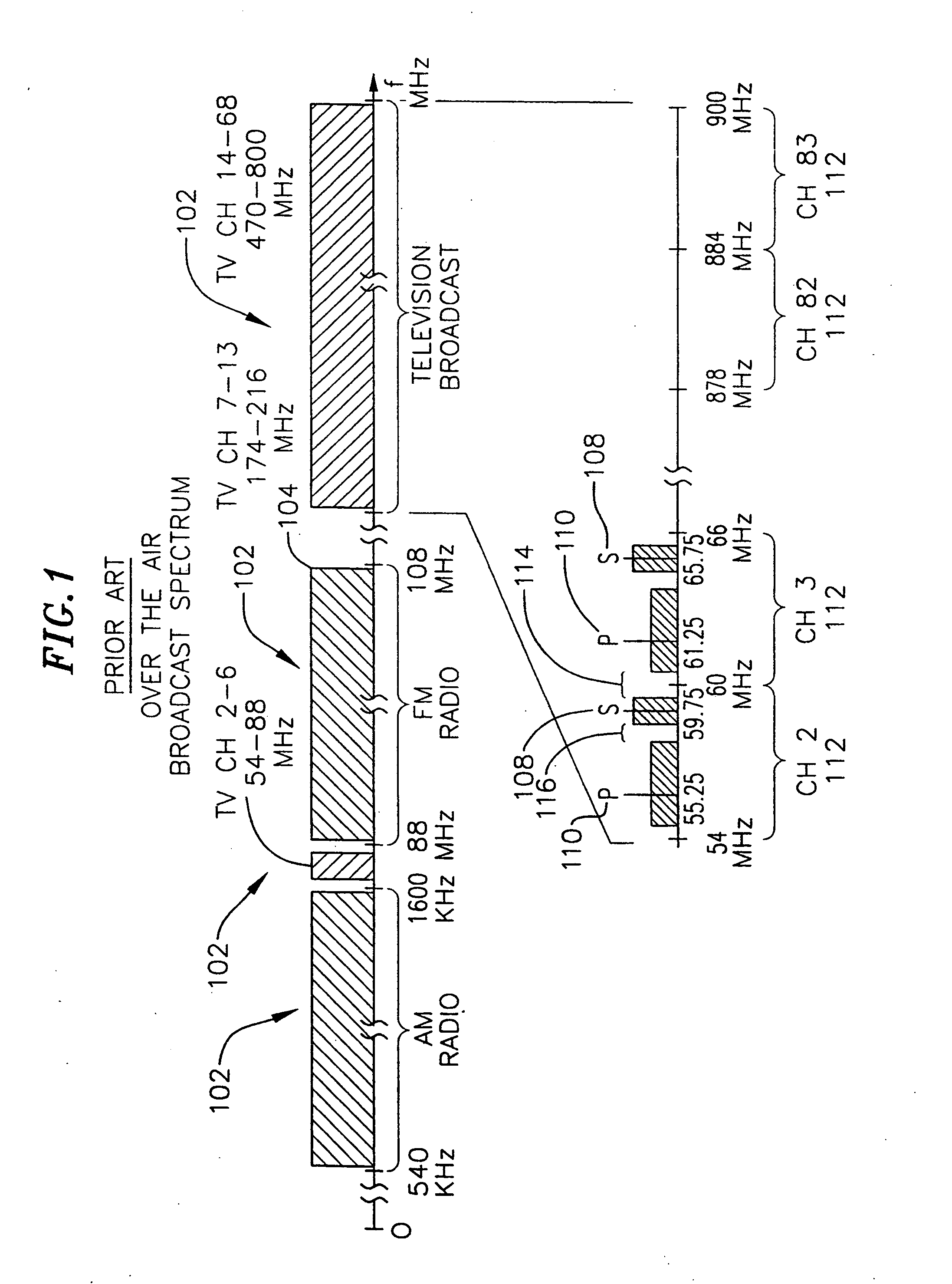

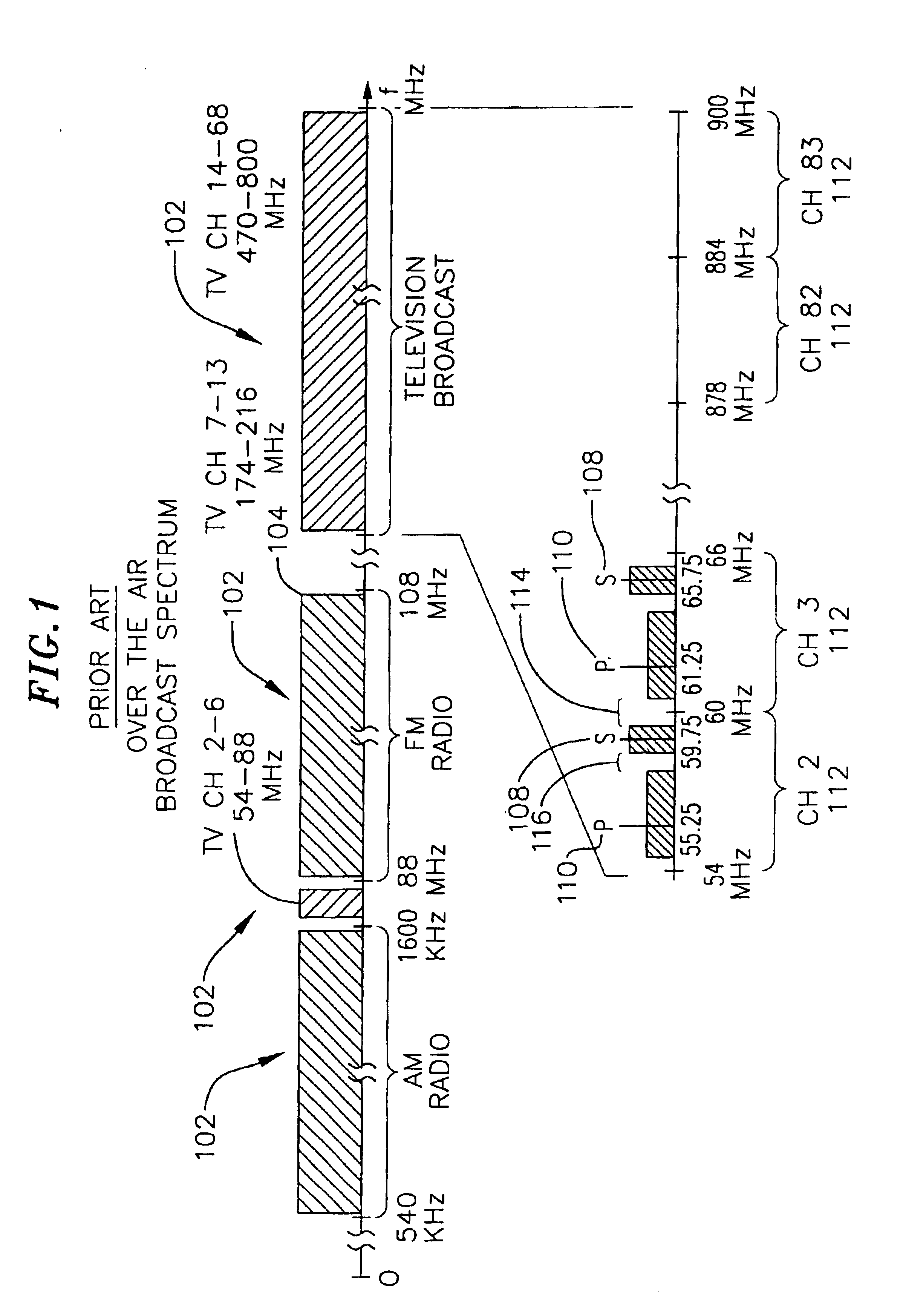

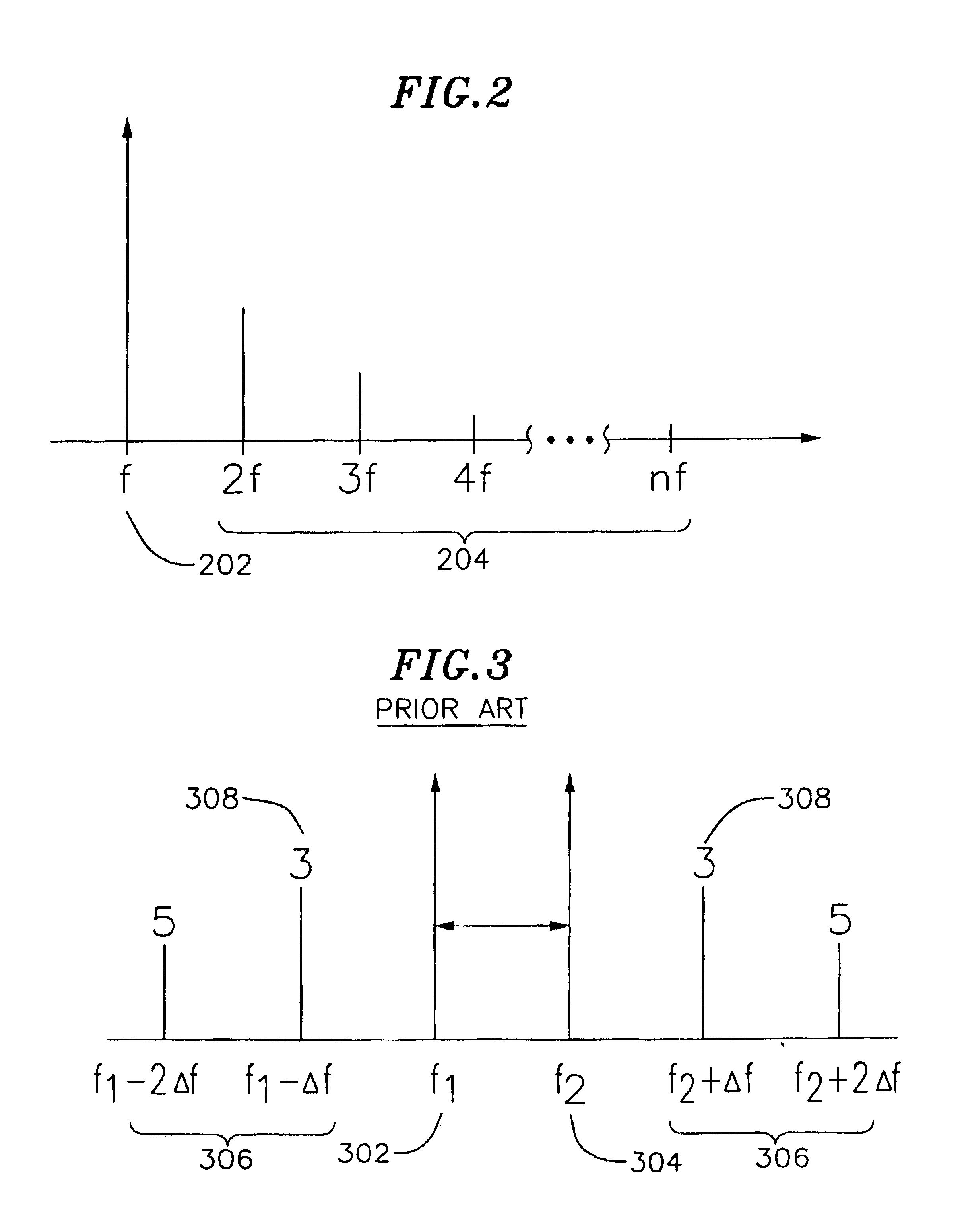

Programmable radio transceiver

ActiveUS20060030277A1Prevent leakageLow noise amplifierSolid-state devicesAmplifier with semiconductor-devices/discharge-tubesExtensibilityTransceiver

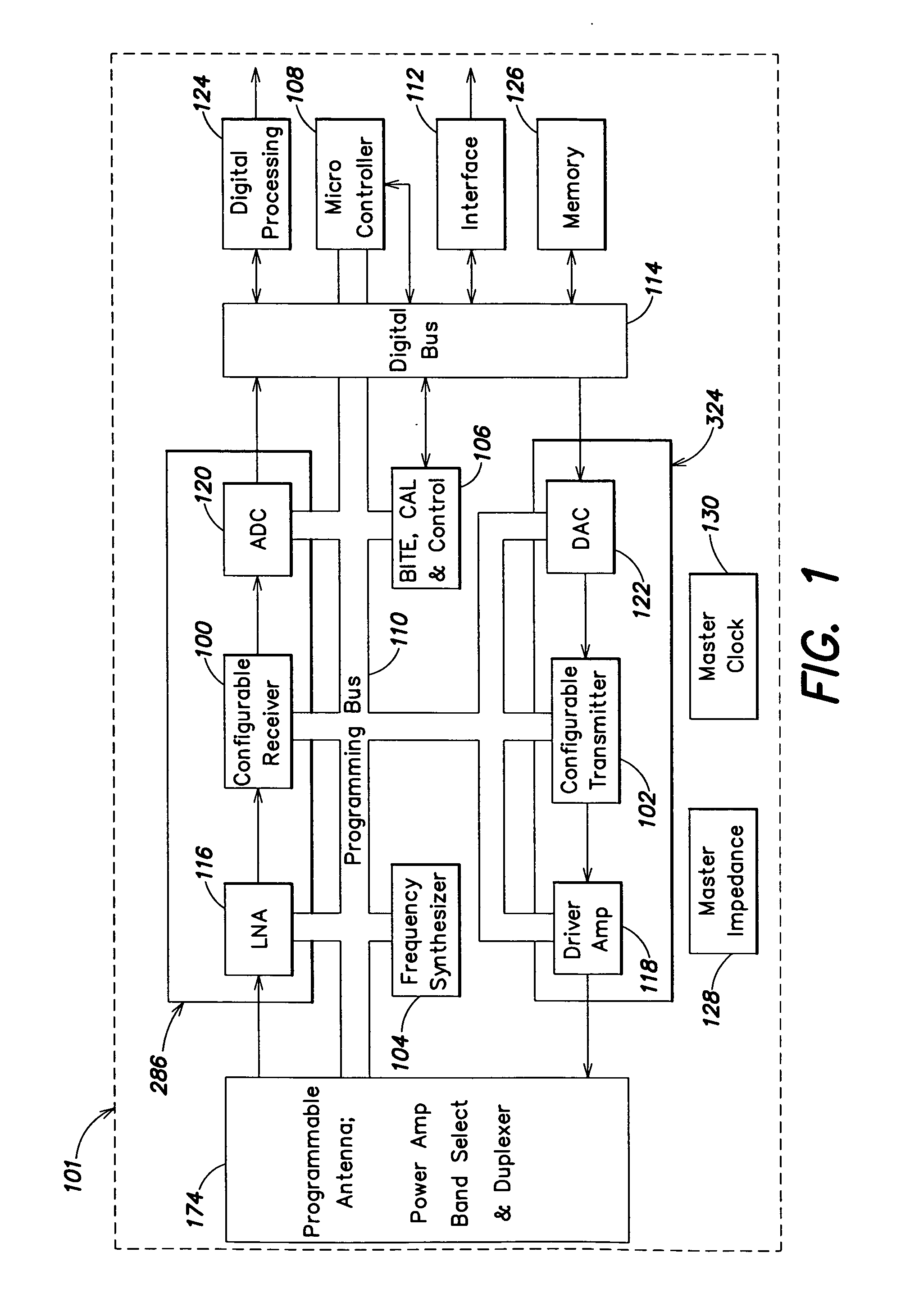

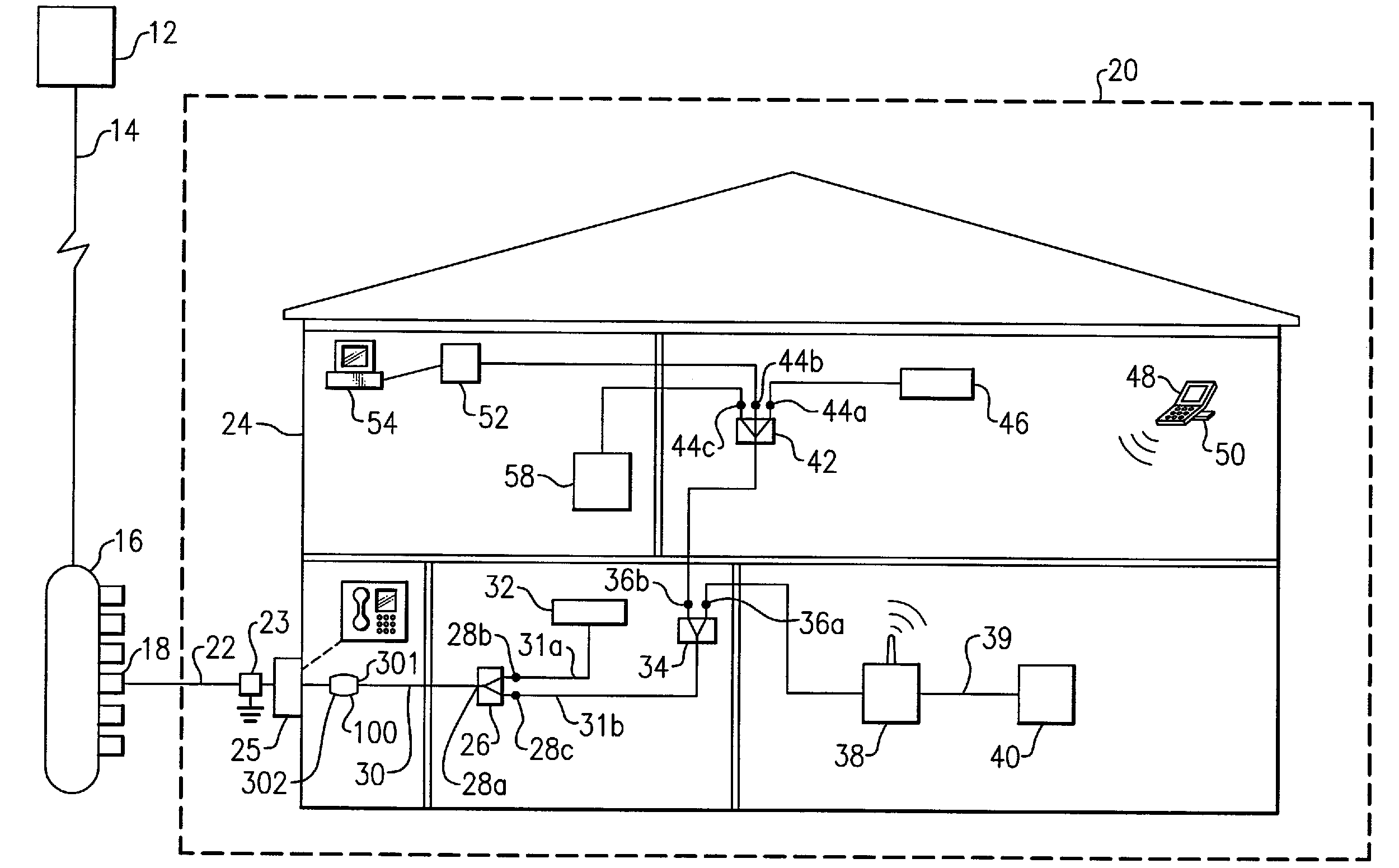

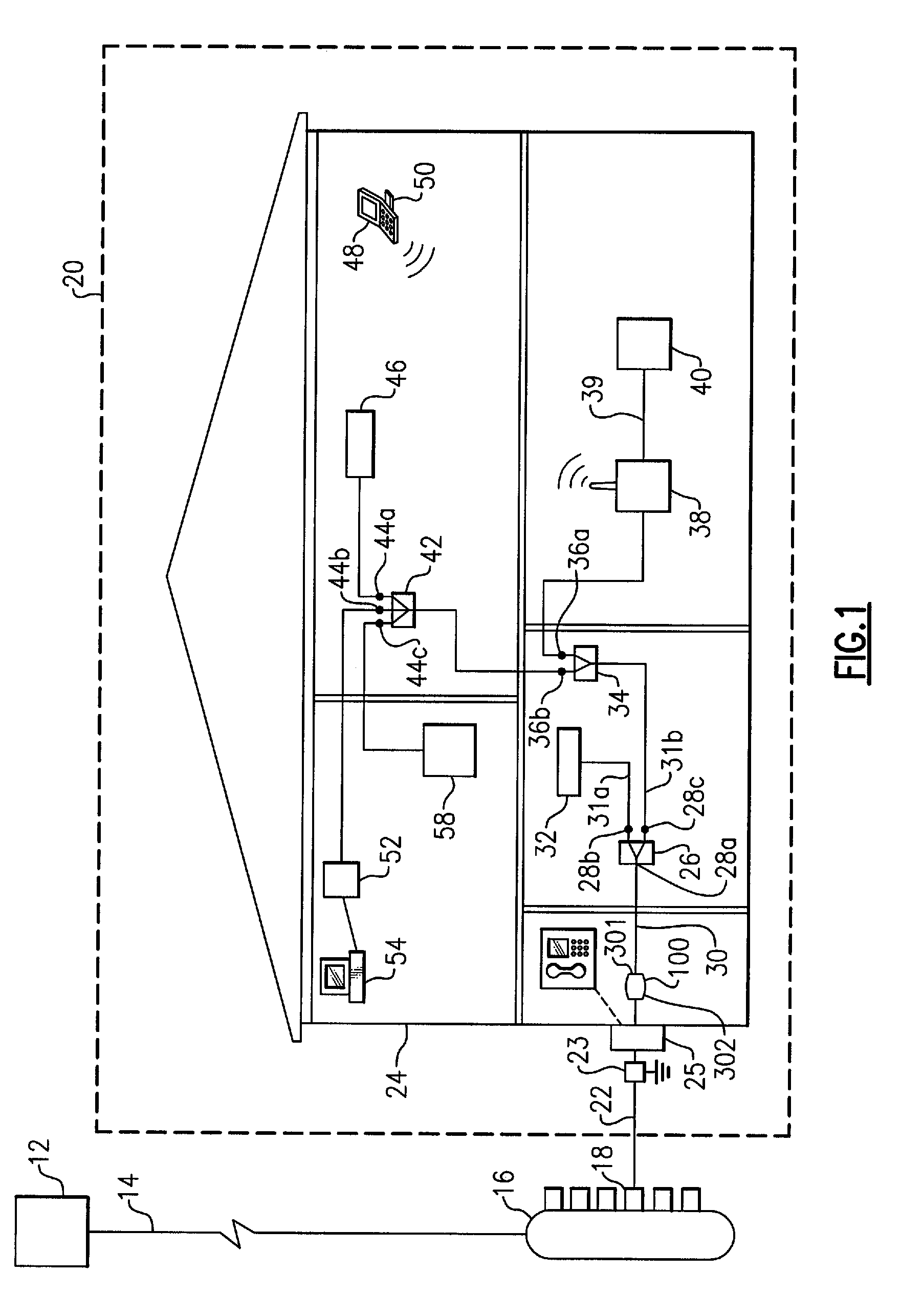

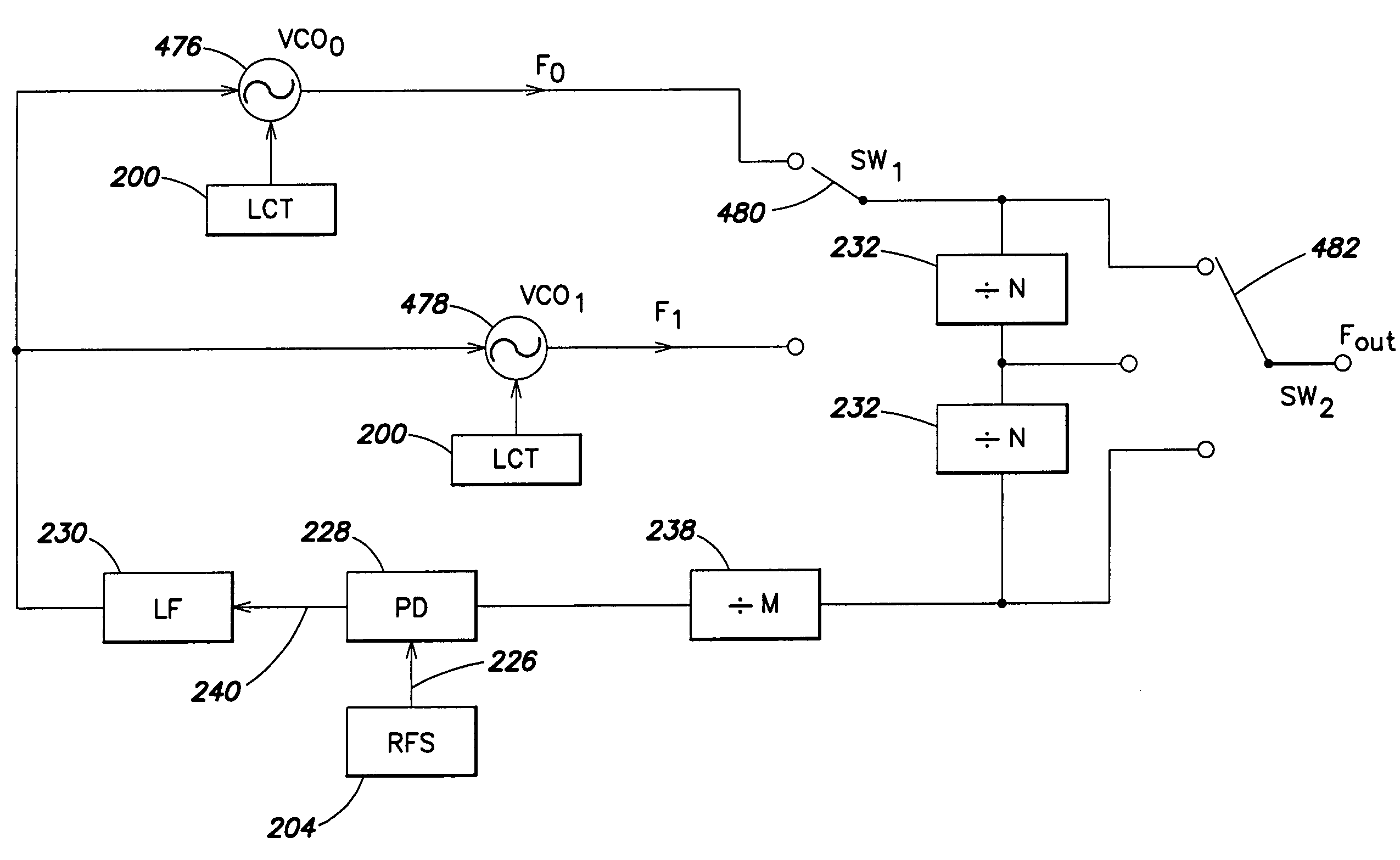

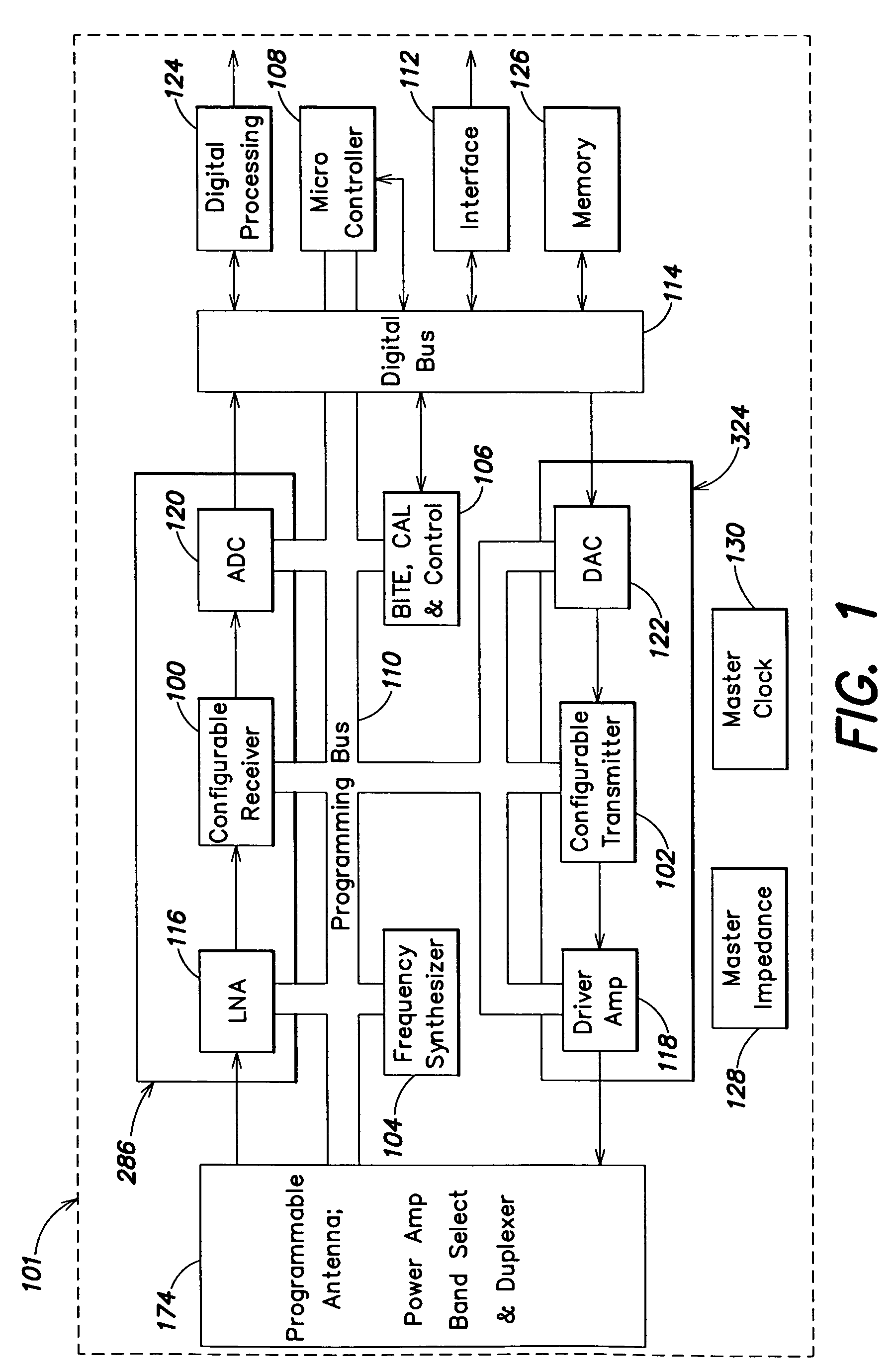

A fully integrated, programmable mixed-signal transceiver comprising a radio frequency integrated circuit (RFIC) which is frequency and protocol agnostic with digital inputs and outputs, the transceiver being programmable and configurable for multiple radio frequency bands and standards and being capable of connecting to many networks and service providers. The RFIC does not use spiral inductors and instead includes transmission line inductors allowing for improved scalability. Components of the transceiver are programmable to allow the transceiver to switch between different frequency bands of operating. Frequency switching can be accomplished though the content of digital registers coupled to the components.

Owner:GULA CONSULTING LLC

Filter circuit

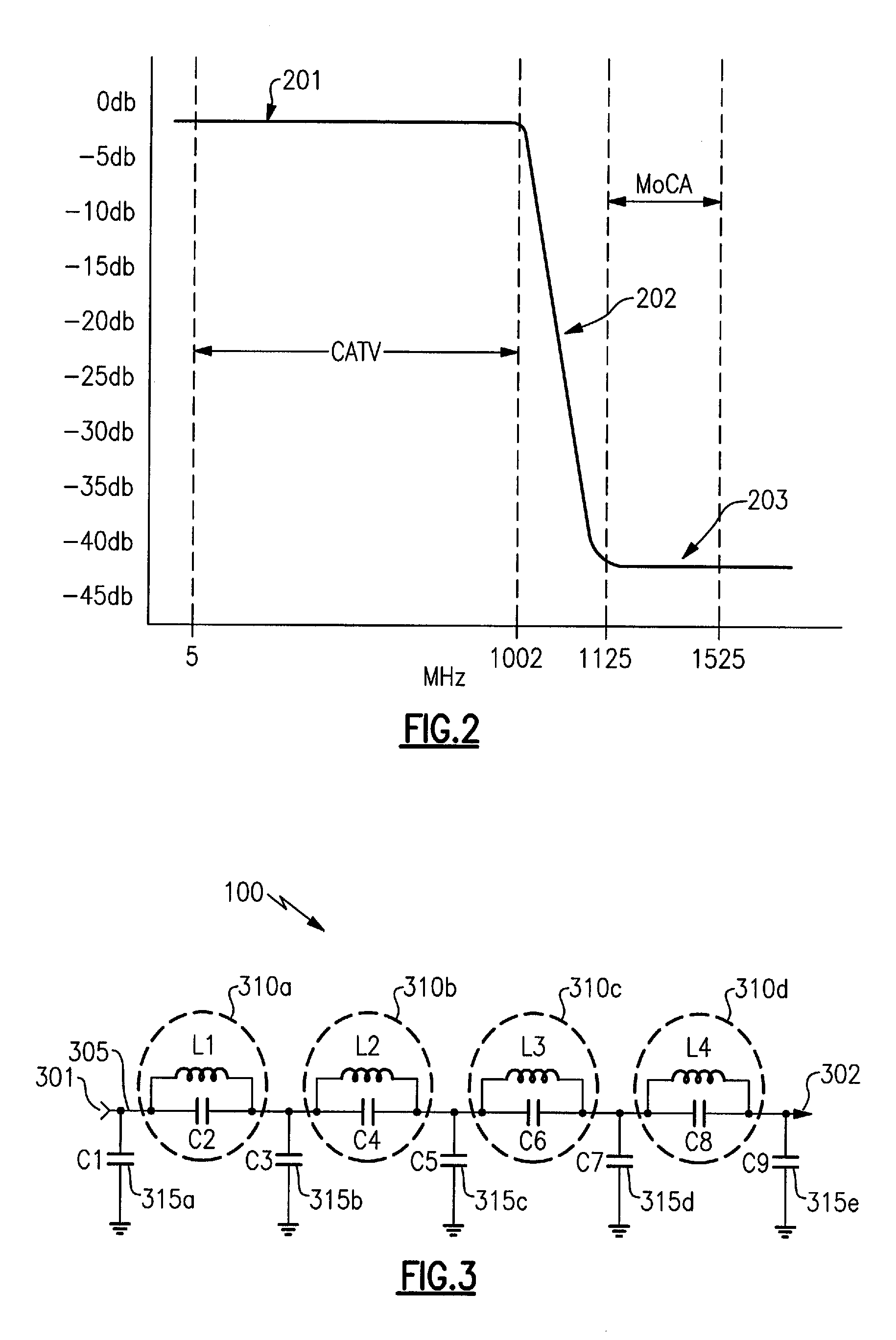

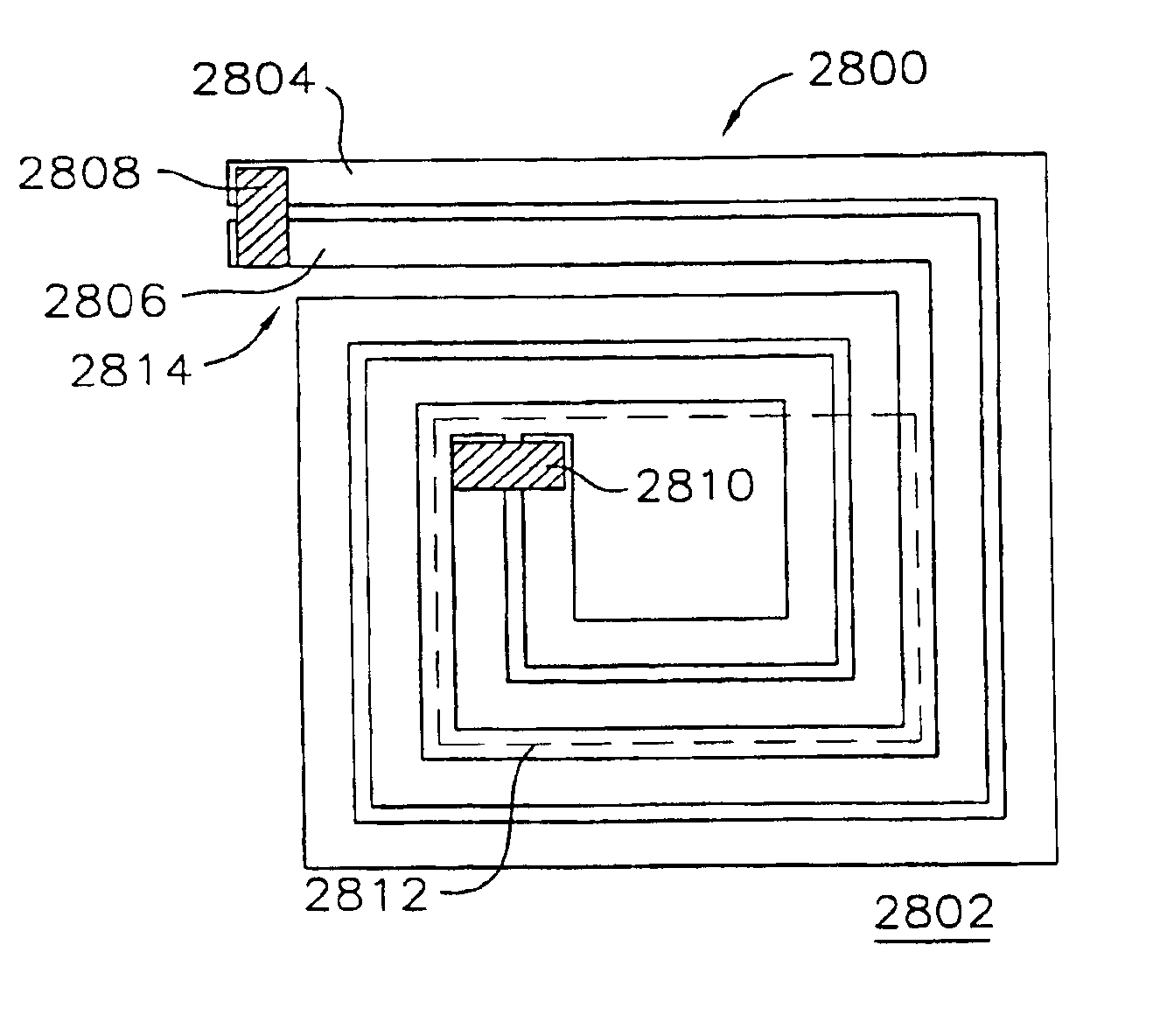

ActiveUS20110010749A1Multiple-port networksCross-talk/noise/interference reductionSquare MillimeterCoaxial cable

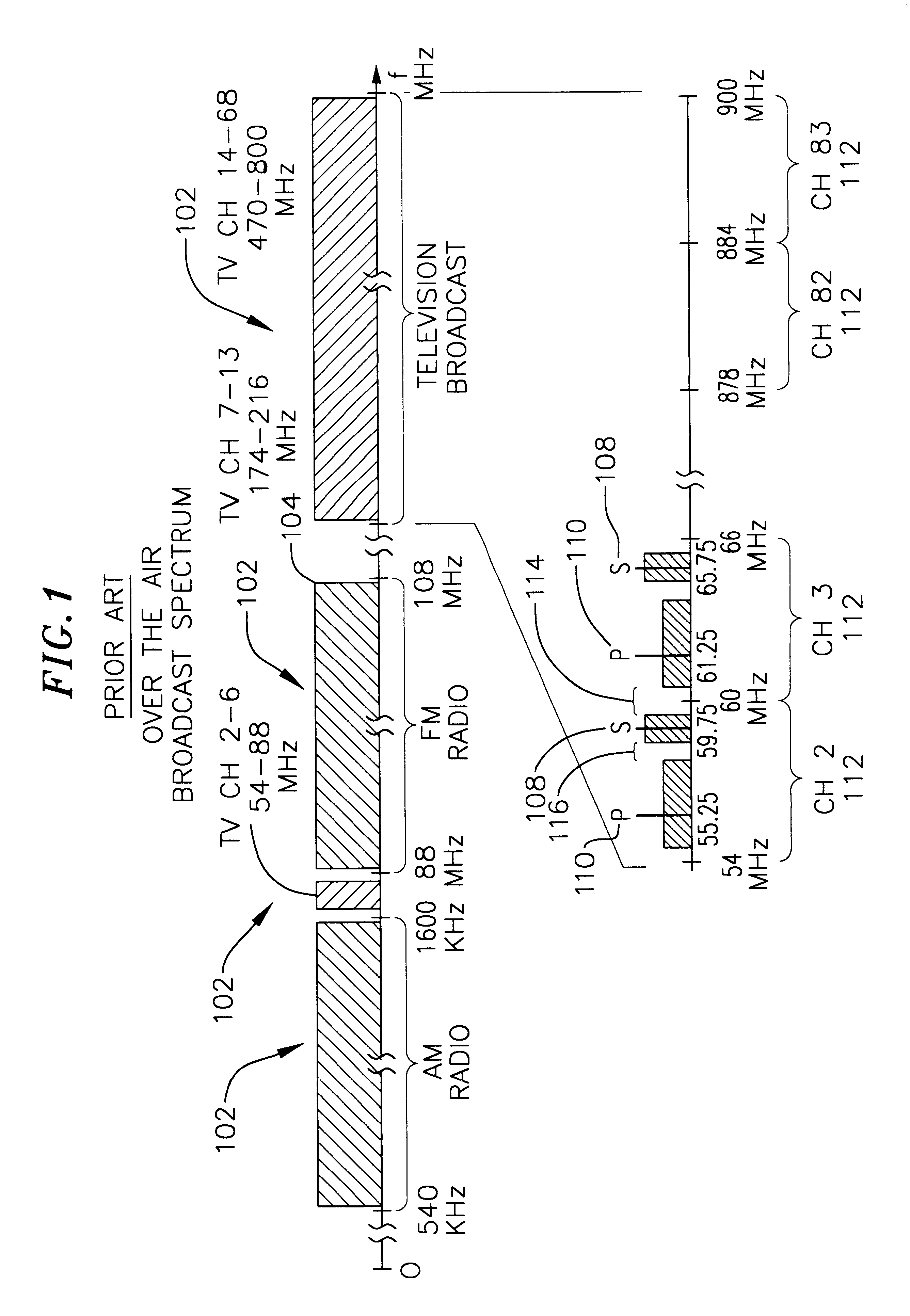

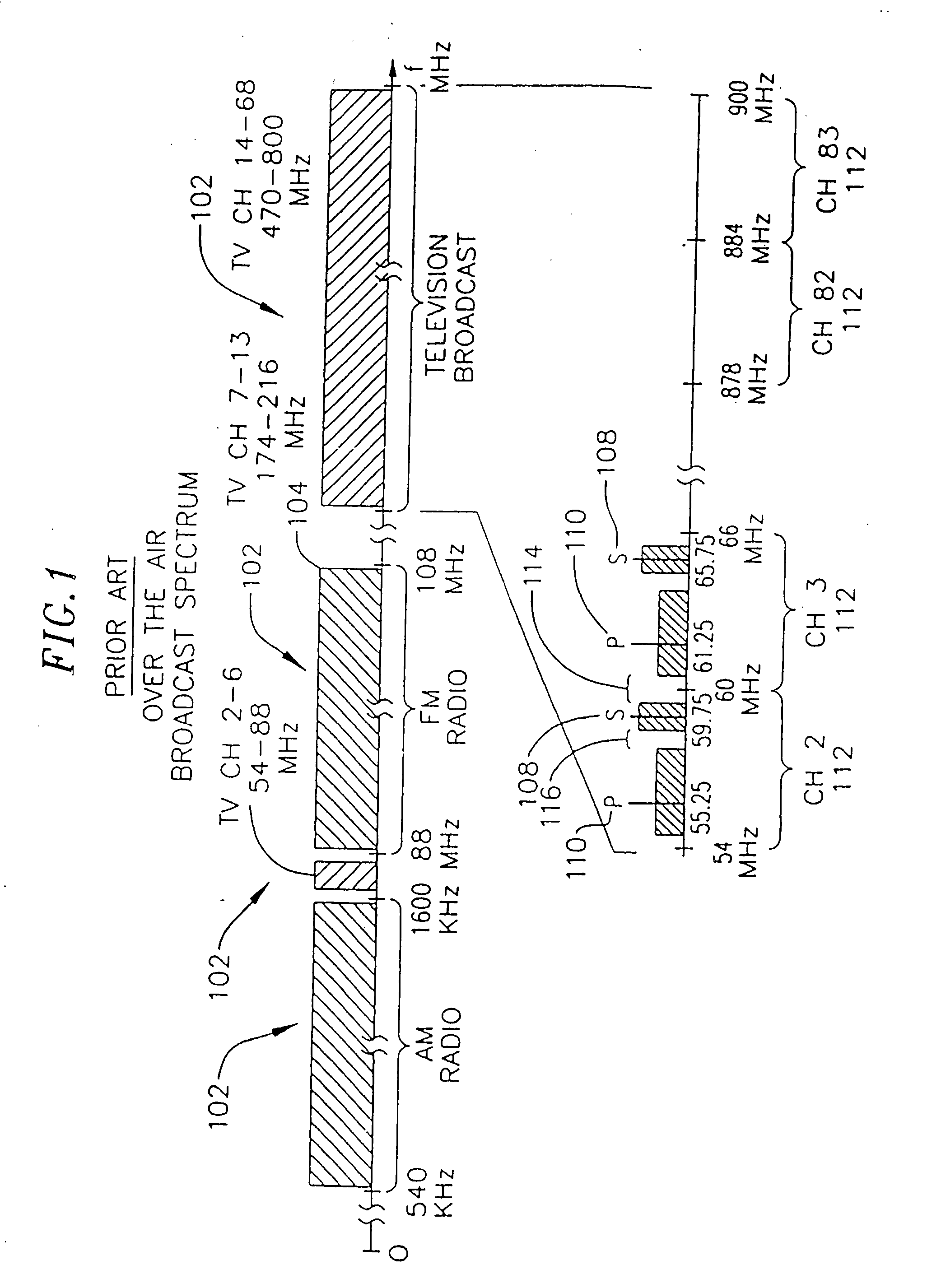

A filter for use in a coaxial cable network includes a printed circuit board having first and second opposed major surfaces, and first and second opposing sides. The opposed major surfaces are substantially parallel to a single plane, and are bisected by a longitudinal axis. The first and second opposing sides are substantially parallel to the longitudinal axis. The filter further includes an input terminal and an output terminal connected to the printed circuit board. The input terminal and the output terminal have an axis extending substantially parallel to the longitudinal axis. A signal path is disposed on the printed circuit board and extends from the input terminal toward the output terminal. The filter further includes a plurality of resonator elements fabricated upon the first opposed major surface. In one embodiment, the inductor elements are arranged in series along the signal path defining a footprint of less than 540 square millimeters. The filter passes a first range of frequencies in a provider bandwidth and attenuates a second range of frequencies in a personal data network bandwidth. In one embodiment, the resonator elements are parallel inductor elements and capacitor elements, the inductor elements being etched spiral inductors.

Owner:PPC BROADBAND INC

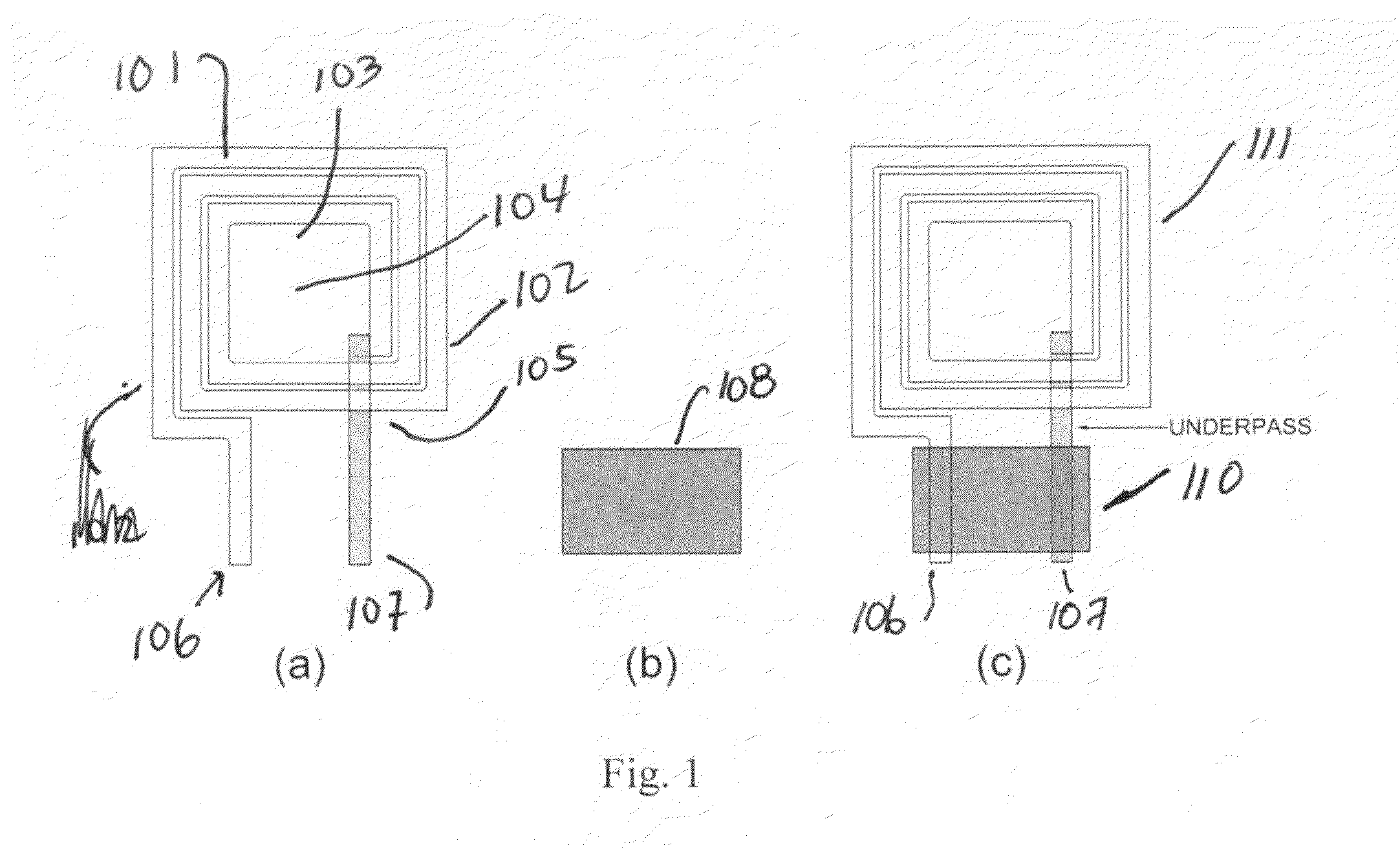

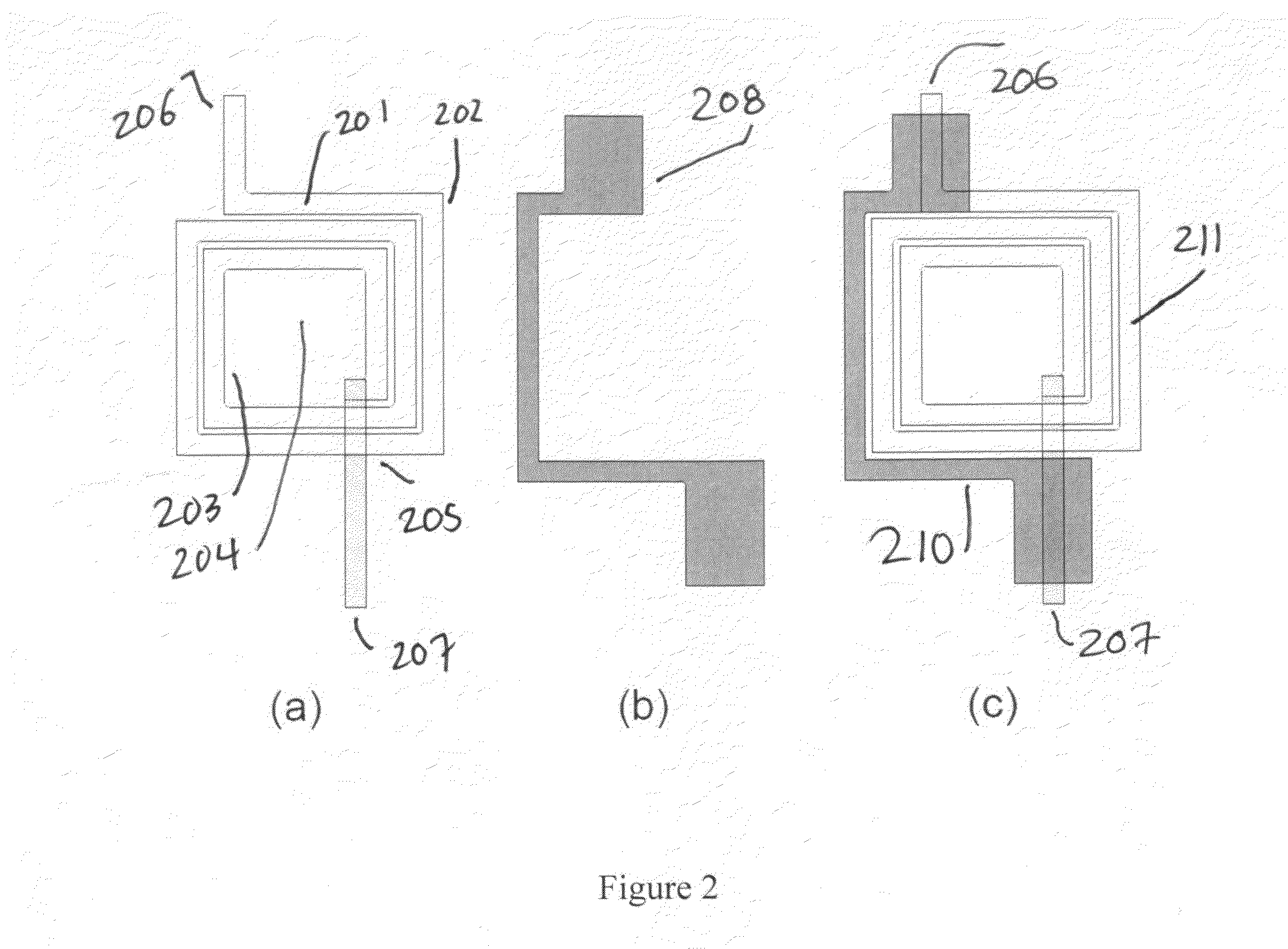

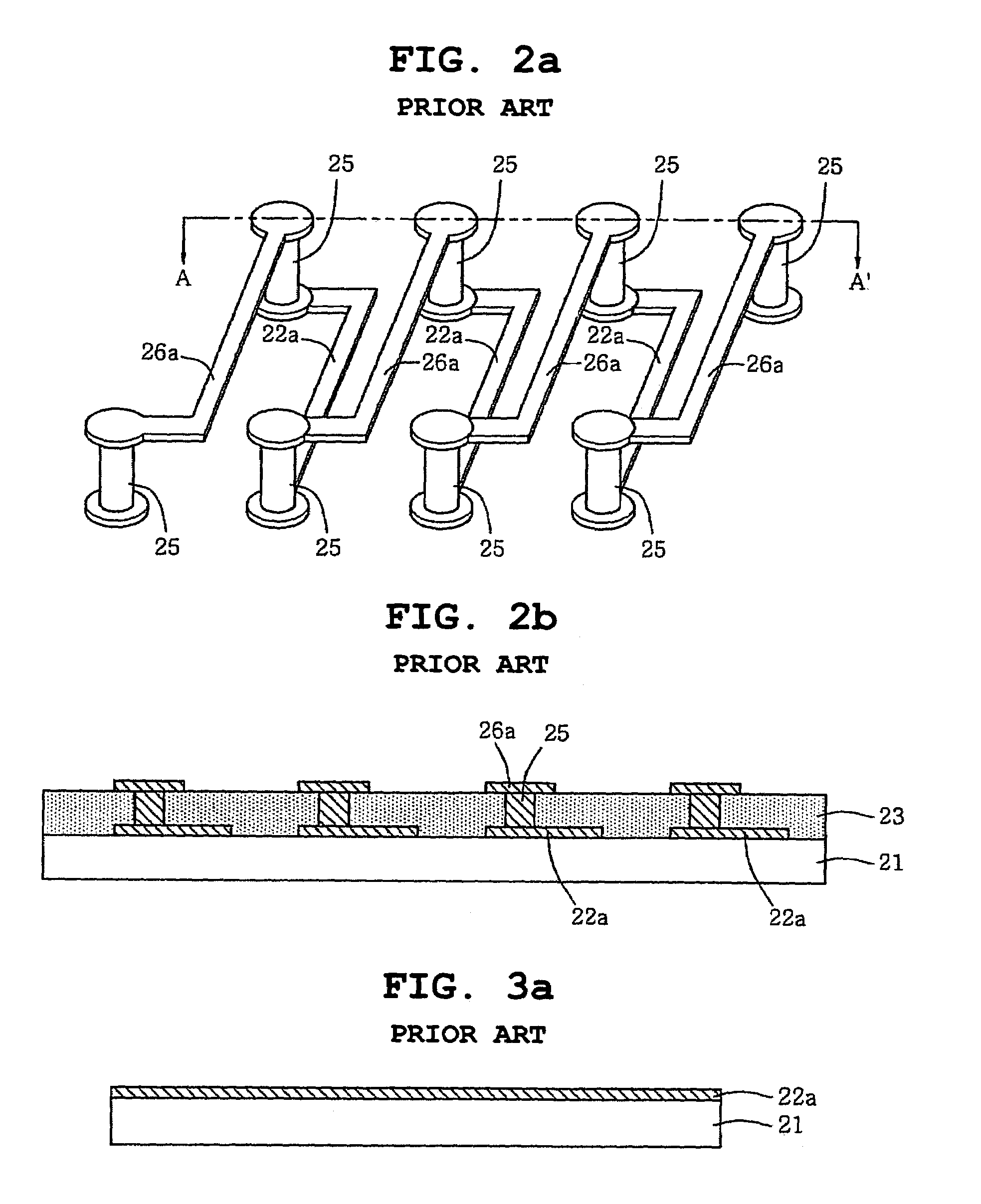

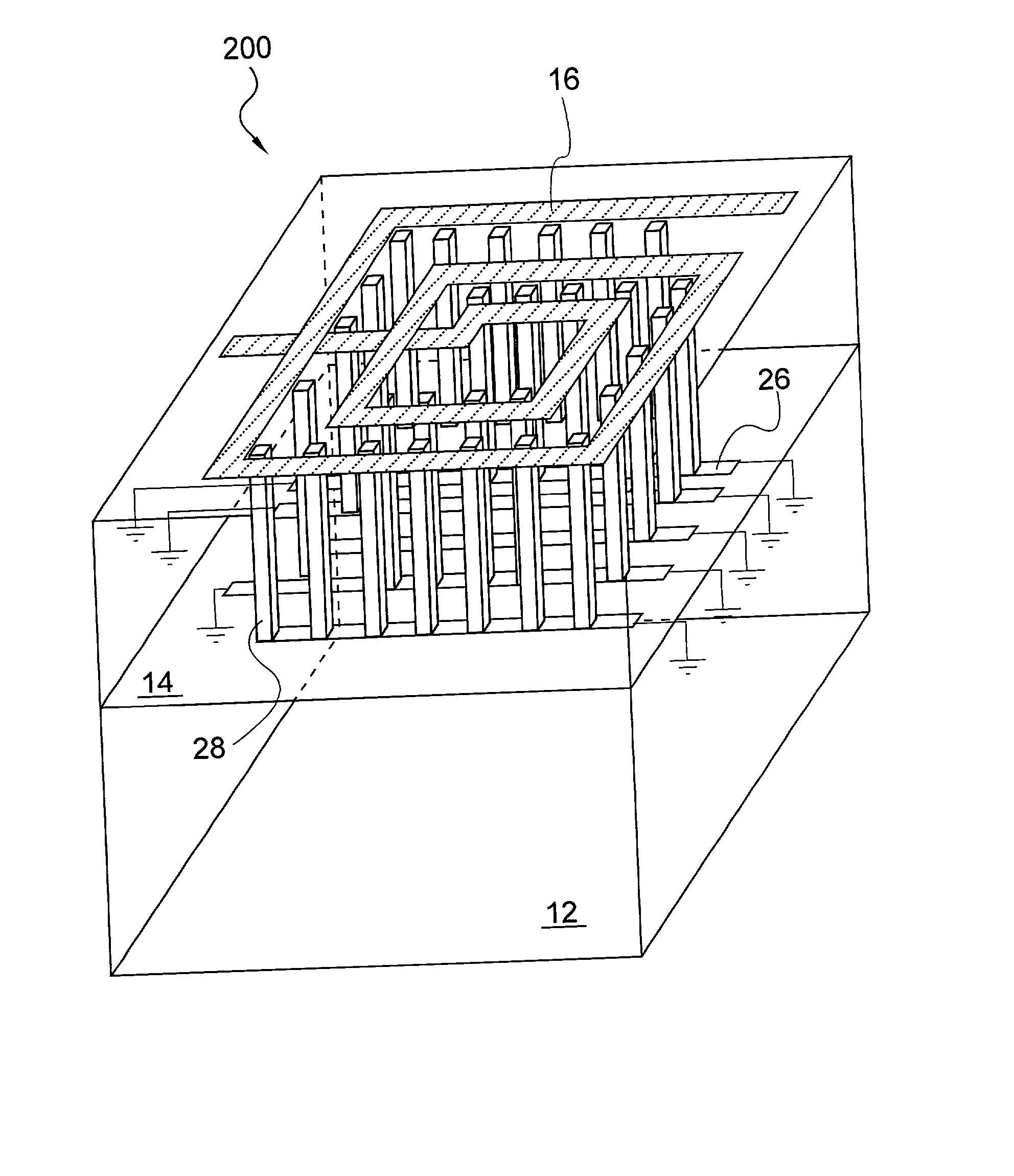

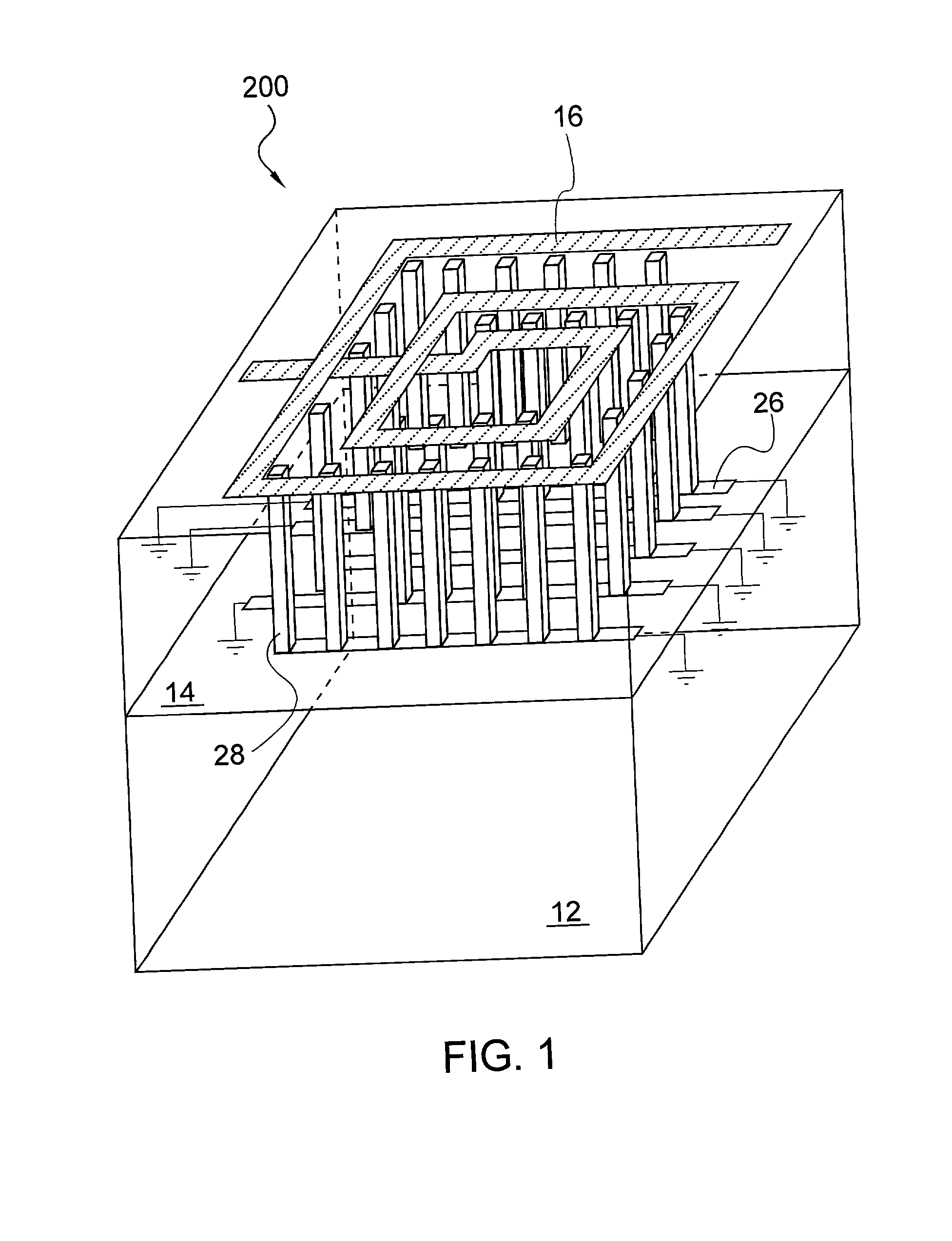

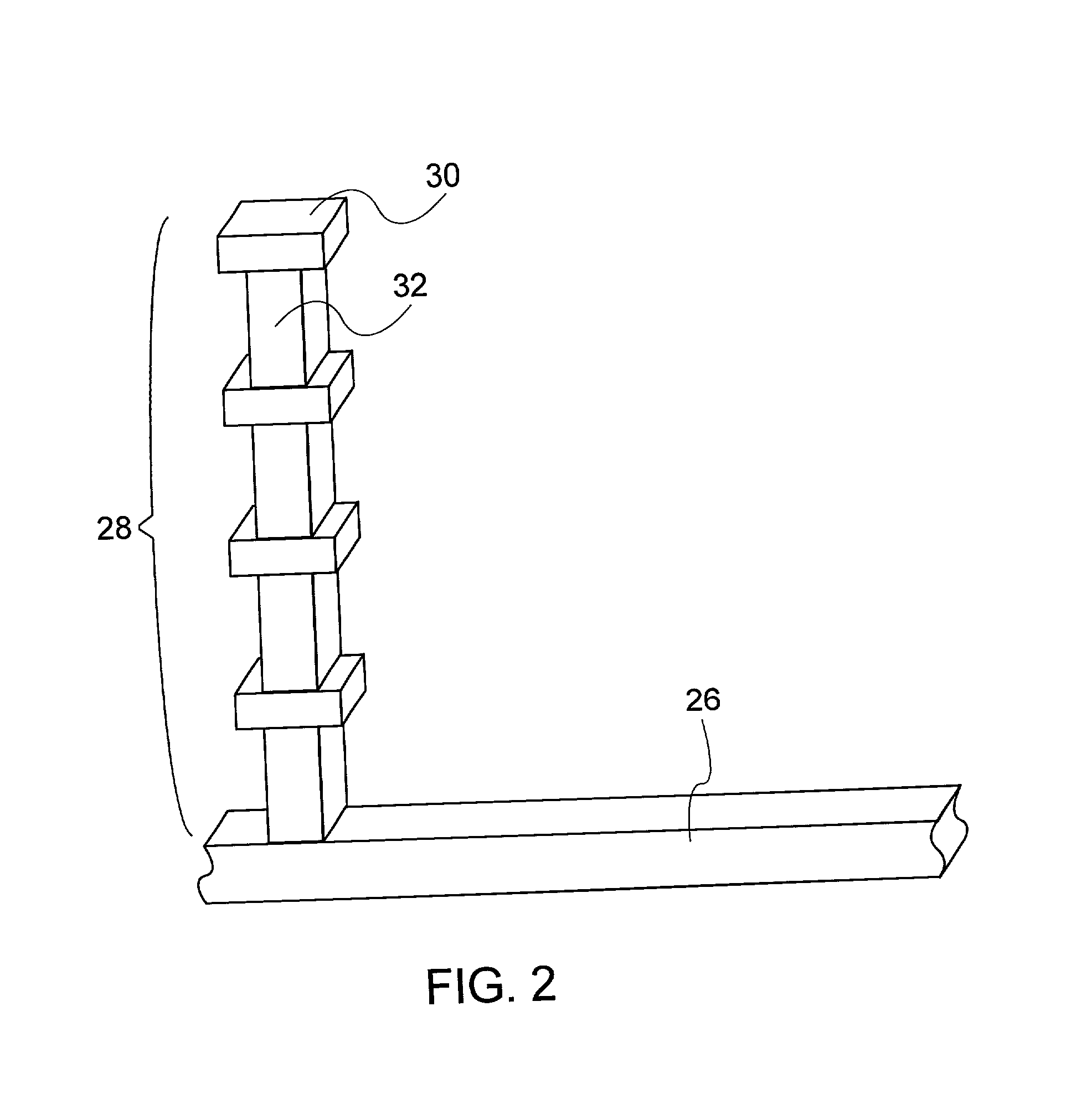

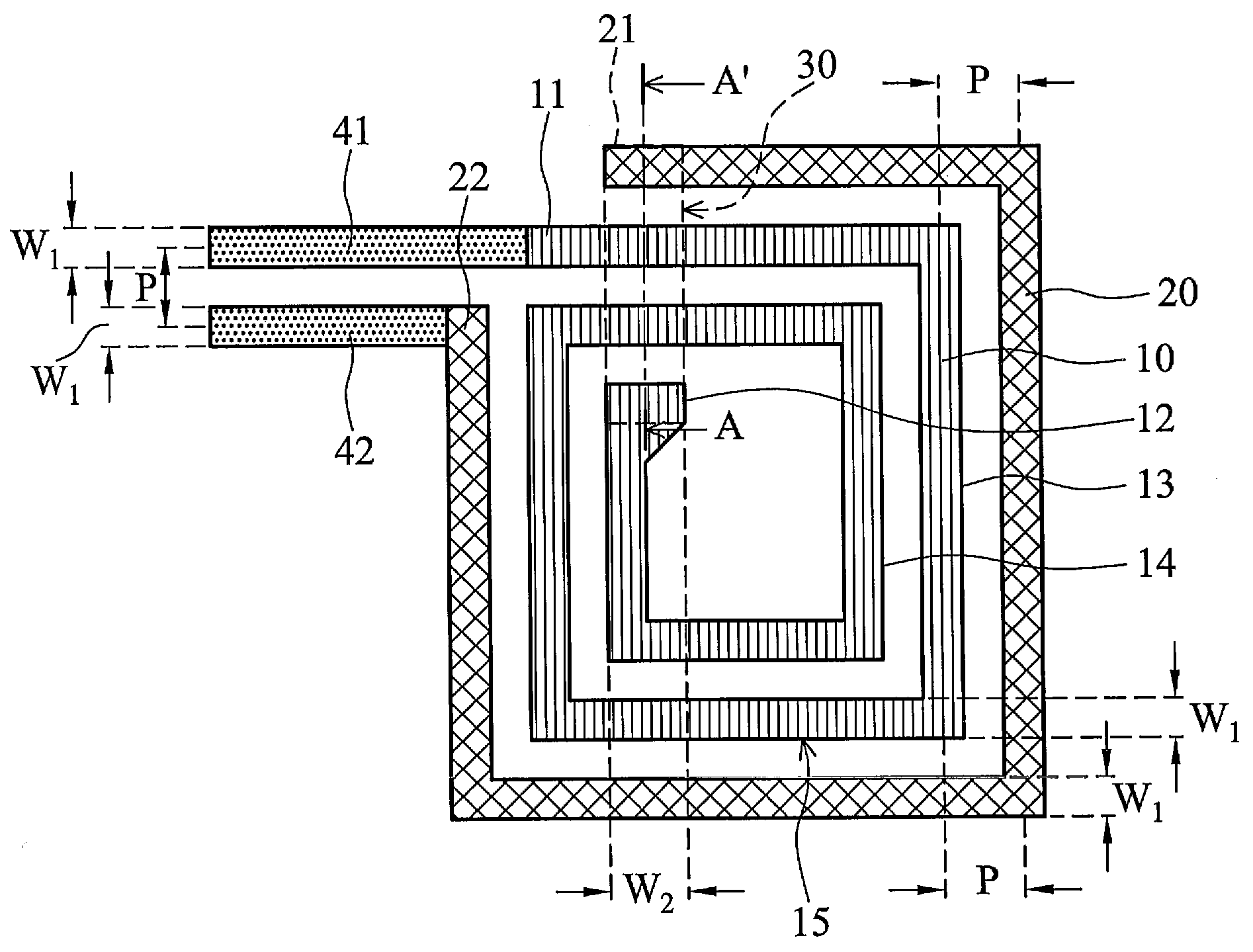

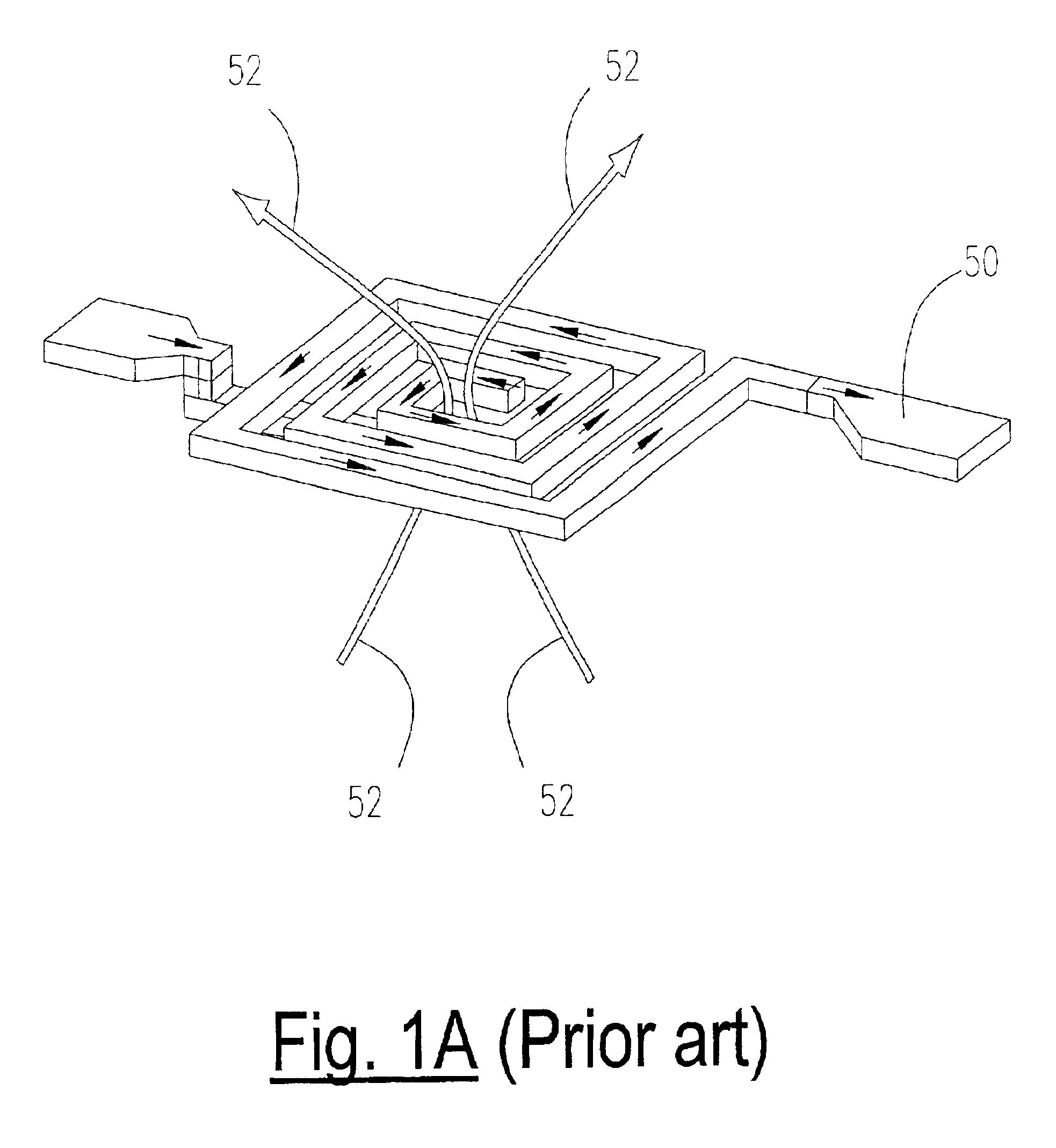

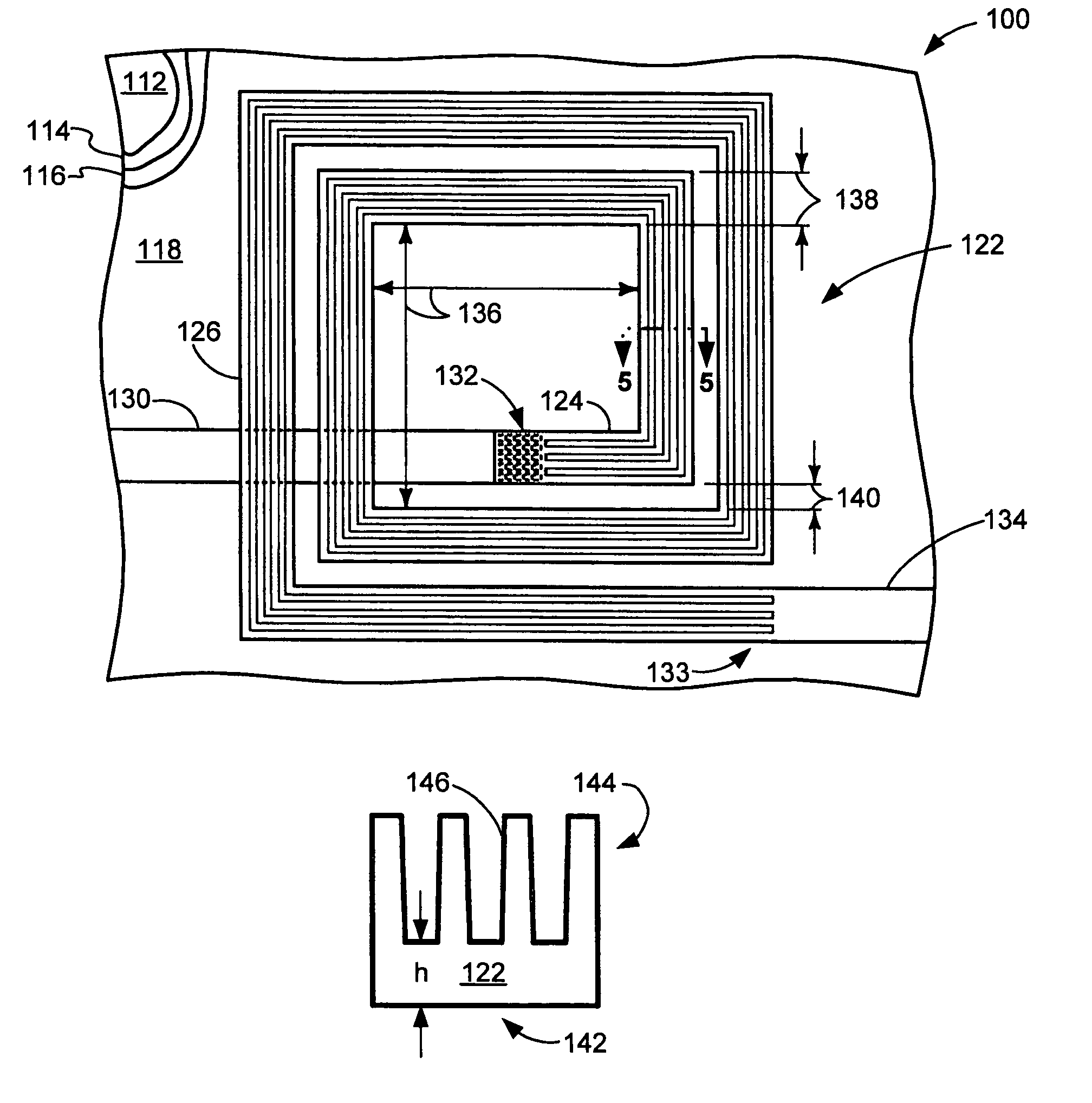

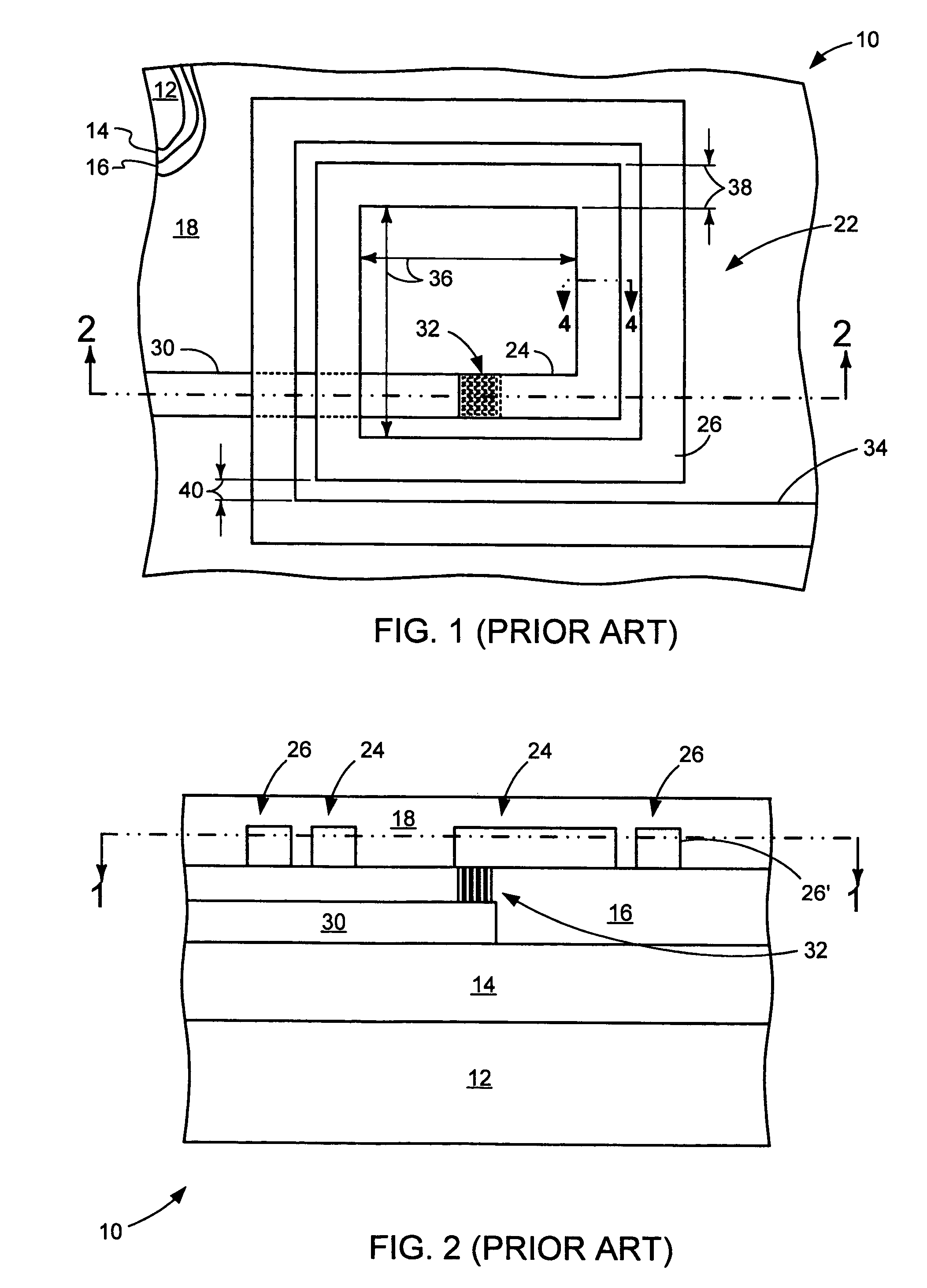

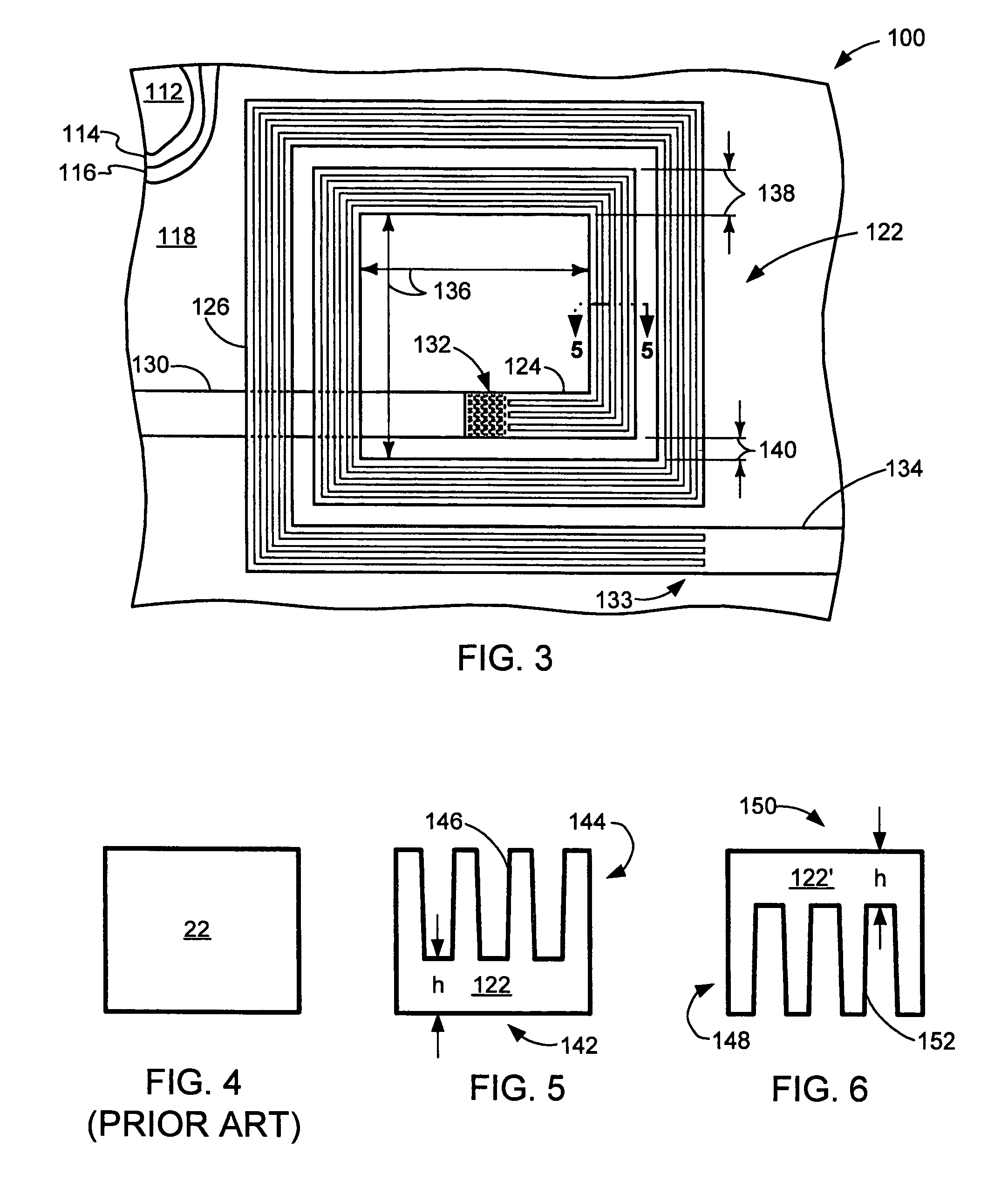

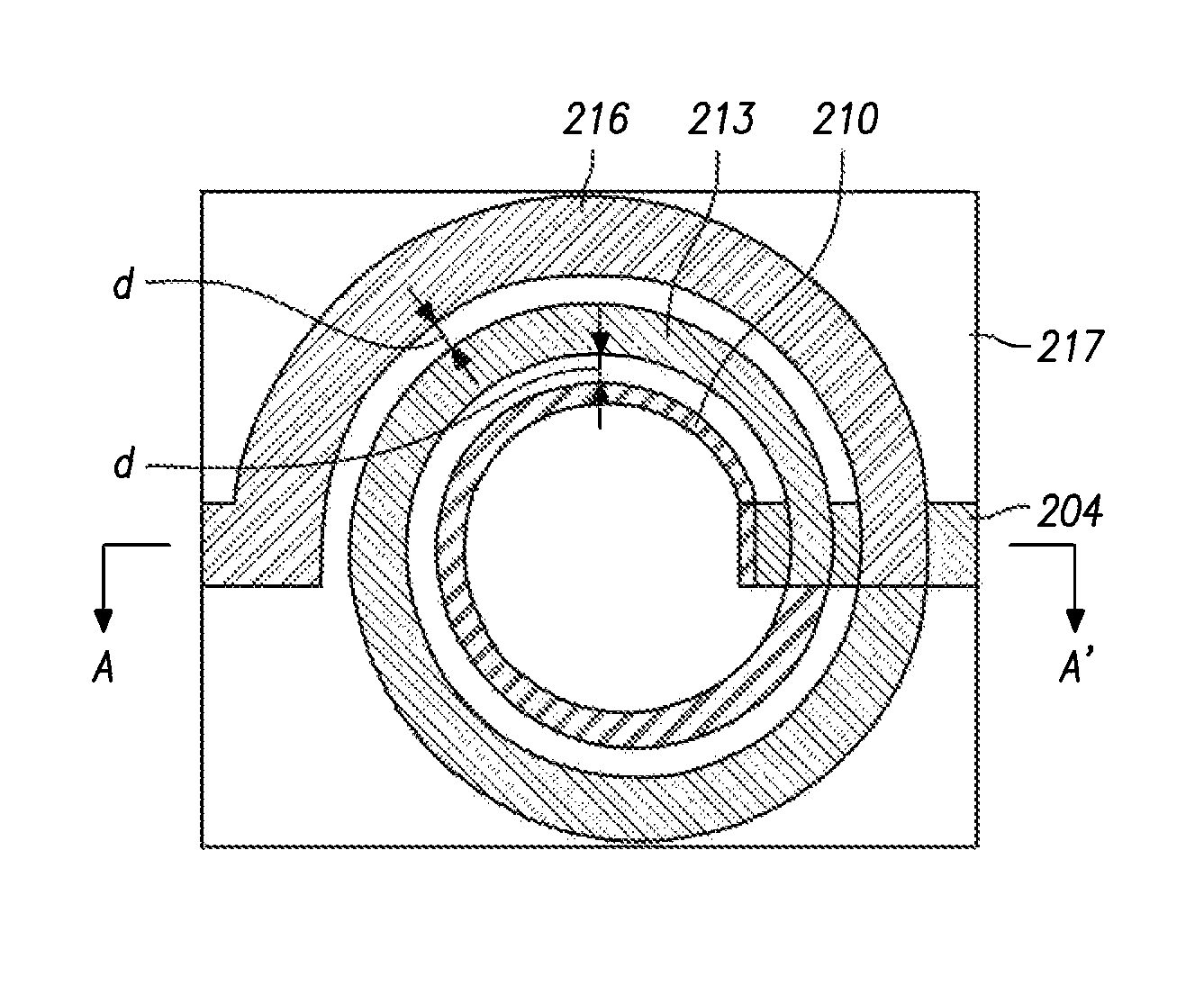

Multi-track integrated spiral inductor

InactiveUS6885275B1Resonant circuit detailsSemiconductor/solid-state device detailsSpiral inductorEngineering

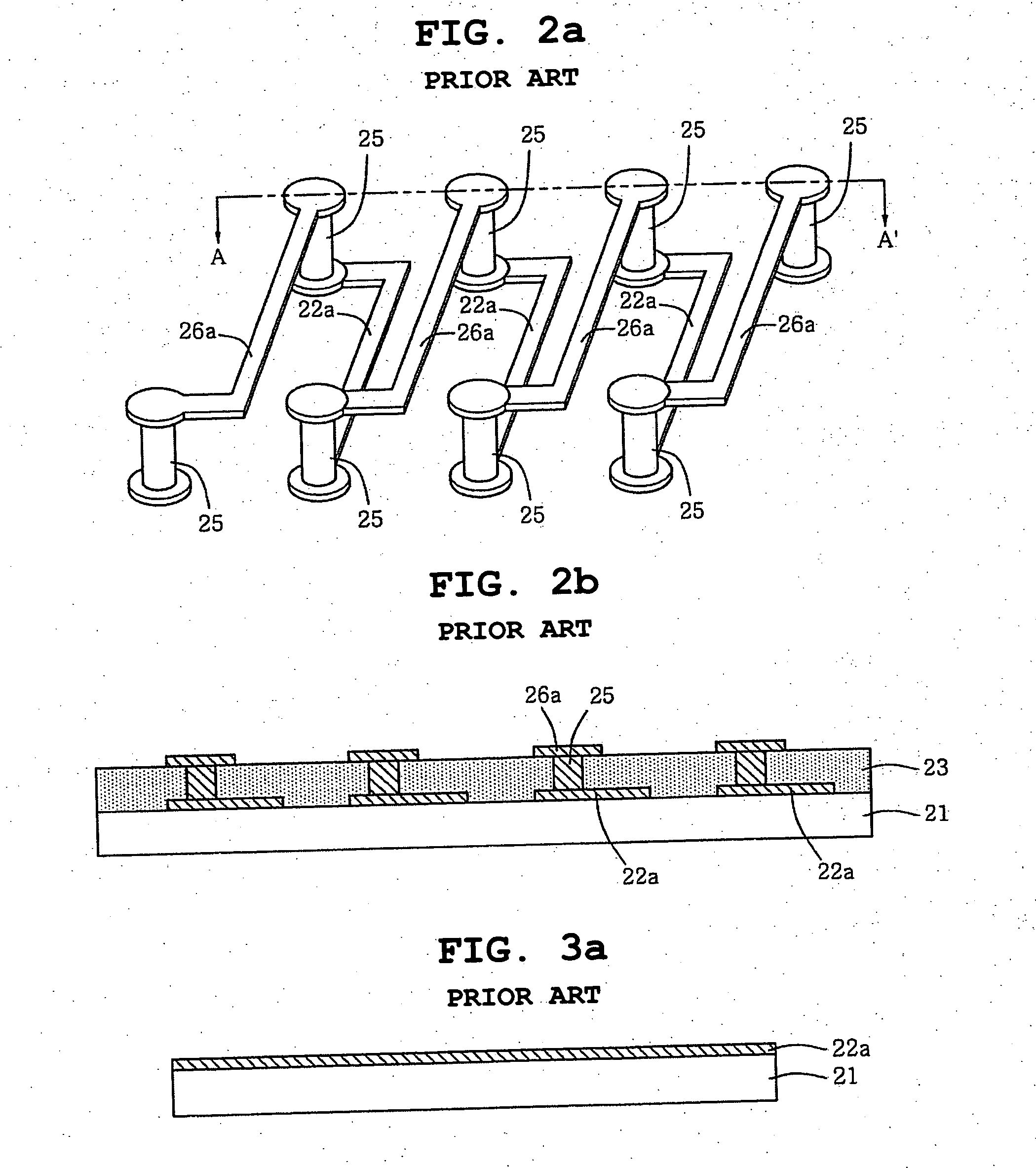

An integrated circuit inductor includes a spiral pattern disposed upon a substrate. The track of the spiral is divided into multiple tracks to form a multi-track inductor. The individual tracks are disposed side by side and in different layers. Tracks that are aligned vertically are coupled by feed throughs, or vias. Multiple vias are used along the length of each of the multiple tracks. Tracks disposed in the same layer are joined together at their beginning, and at their termination. A patterned shield is fabricated from conductive fingers of n+ salicided material that is separated by non conducting polysilicon that fills the gaps between the fingers. The conductive fingers are coupled together in groups, which are in turn tied to a single point ground. In tying the groups together, a gap in the conducting path is provided to prevent ground loop currents. The shield is disposed between the multi-track inductor and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

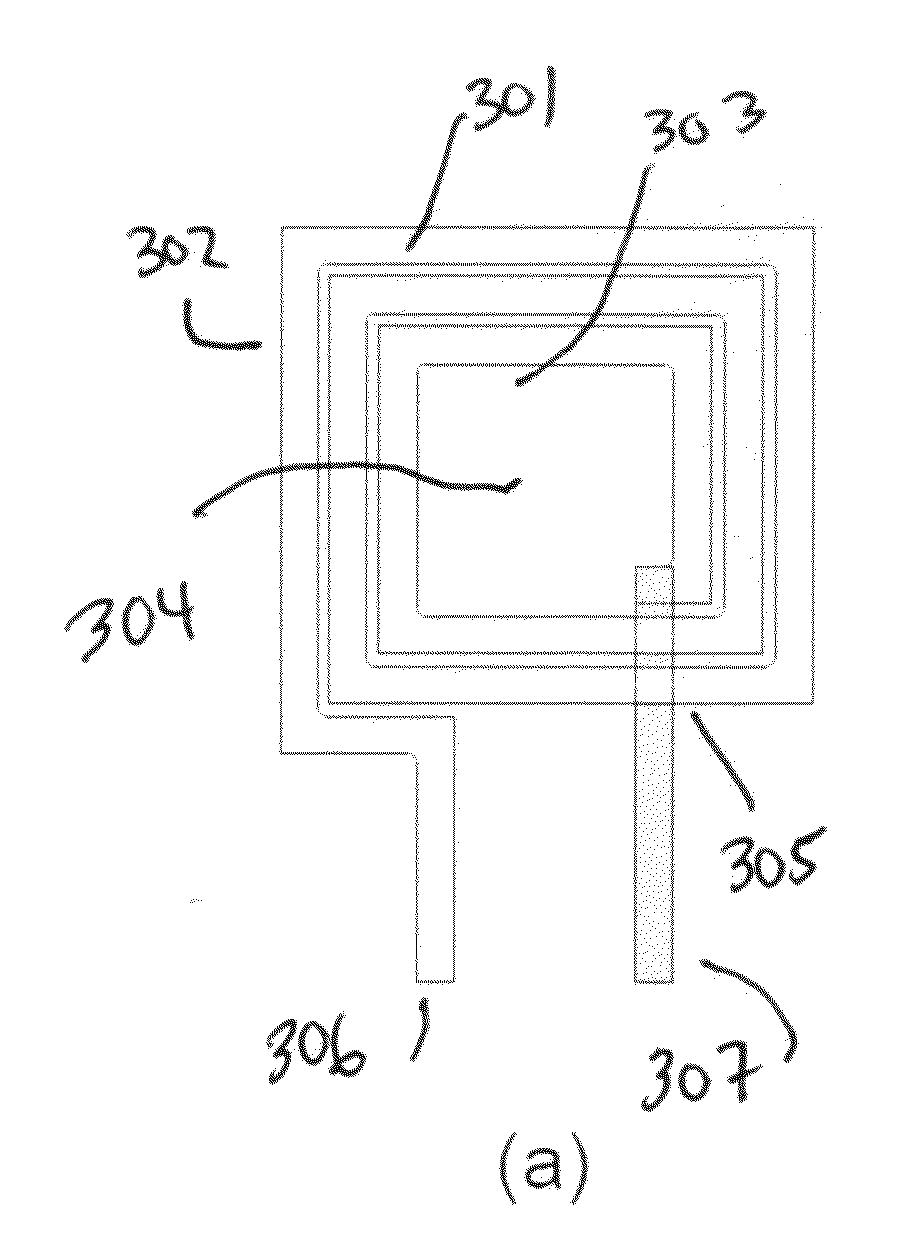

Compact-area capacitive plates for use with spiral inductors having more than one turn

ActiveUS20110279198A1Increase resistanceReduce interactionMultiple-port networksInductances/transformers/magnets manufactureSpiral inductorHelix

A method and an apparatus are described for constructing a compact inductive-capacitive circuit, using a spiral inductor of more than one turn, plus a capacitive plate. This method includes duplicating the layout of the spiral, and then offsetting the duplicate so that the trace pattern of the spiral overlaps its duplicate at an insulating distance away, with the duplicate as an underlying capacitive plate. The plate's trace pattern includes at least one gap, plus an extension of its trace to span the region under the terminals of the spiral inductor. For the case where the spiral inductor has more than one turn—plus an underpass—the capacitive plate may also have more than one turn and may also have an underpass. The resulting pair of underpasses may be either overlapping or nonoverlapping. If overlapping, the full circuit requires at least four metal layers, and at least three if the underpasses are nonoverlapping.

Owner:HANER RONALD LAMBERT

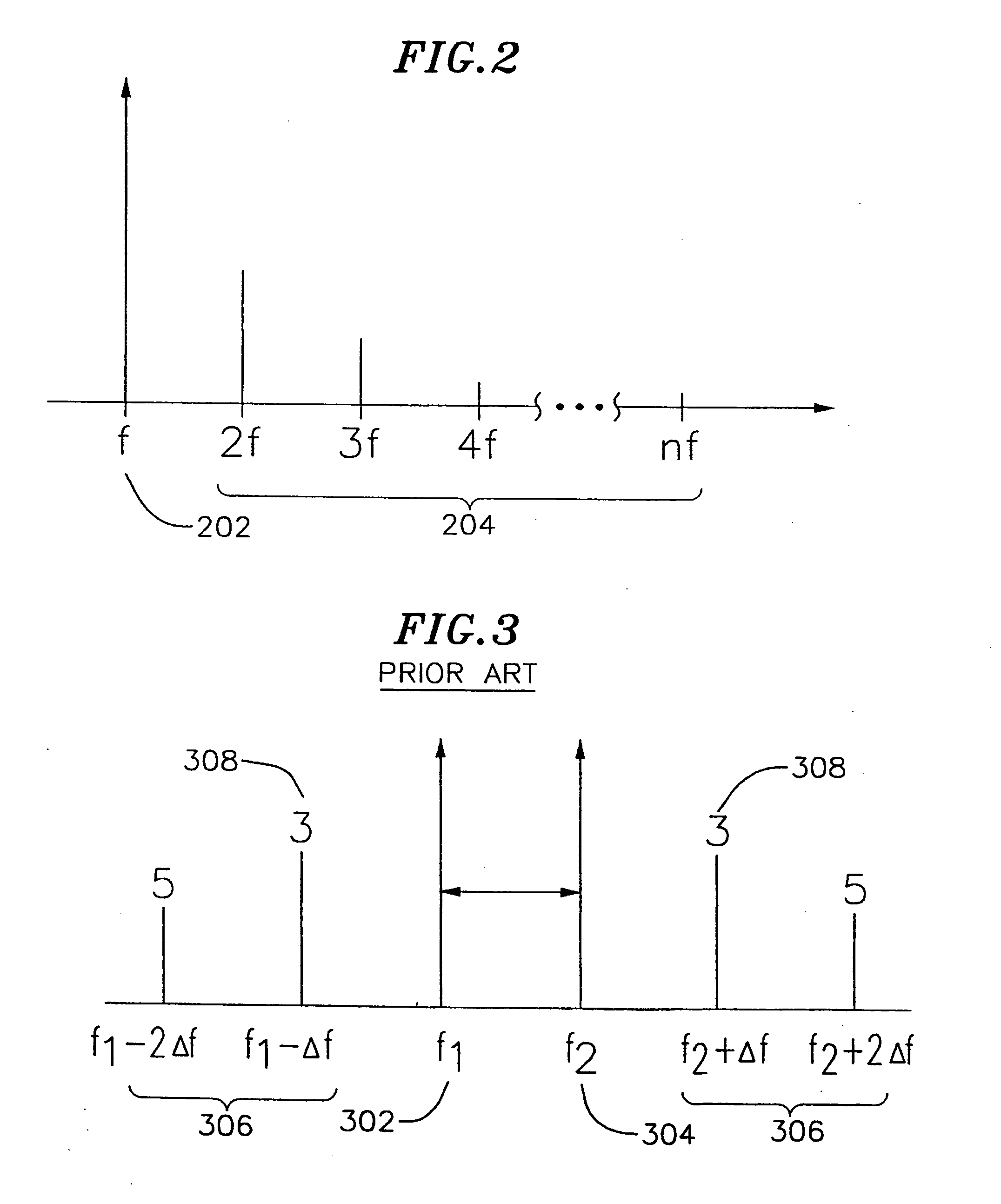

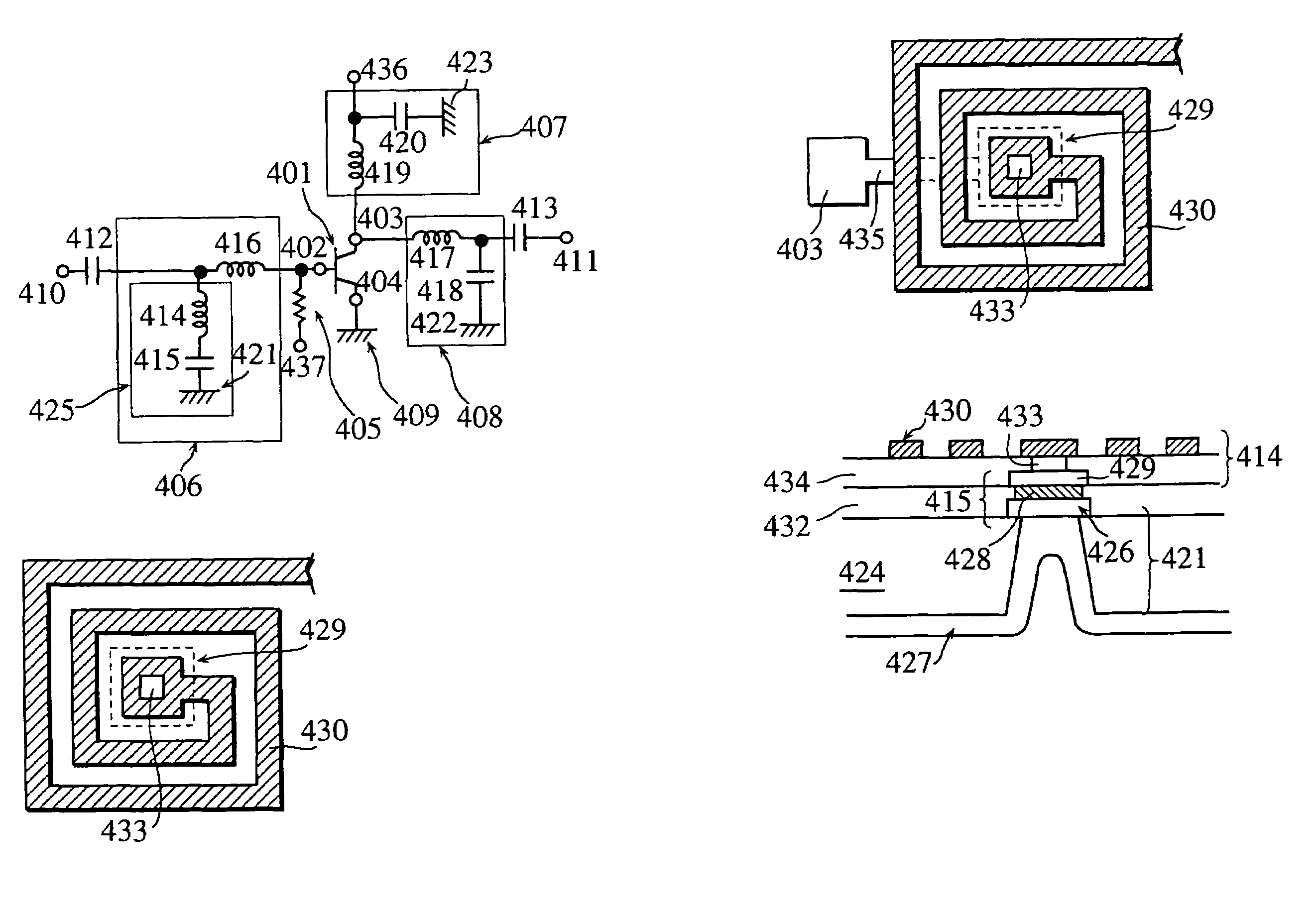

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

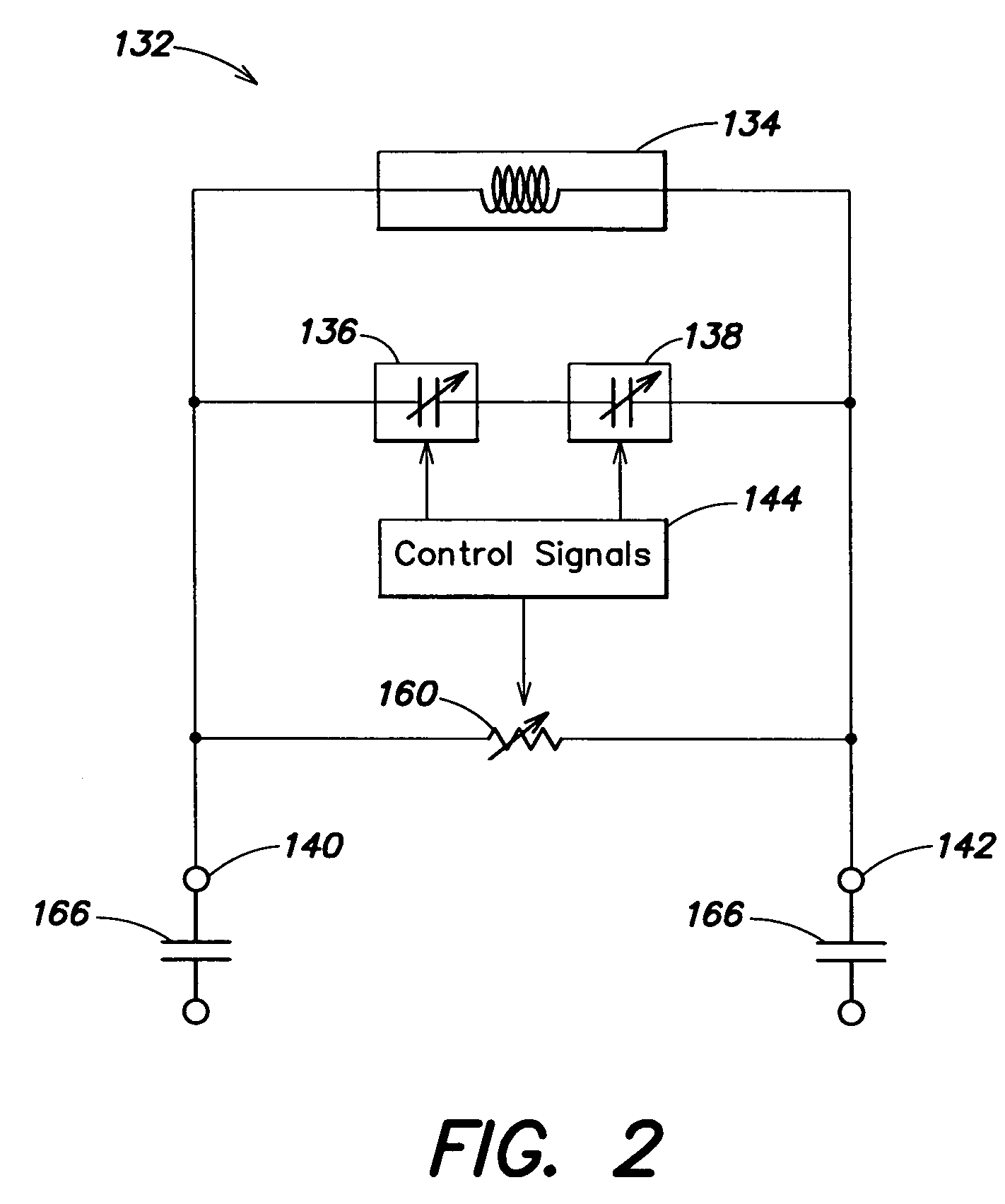

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

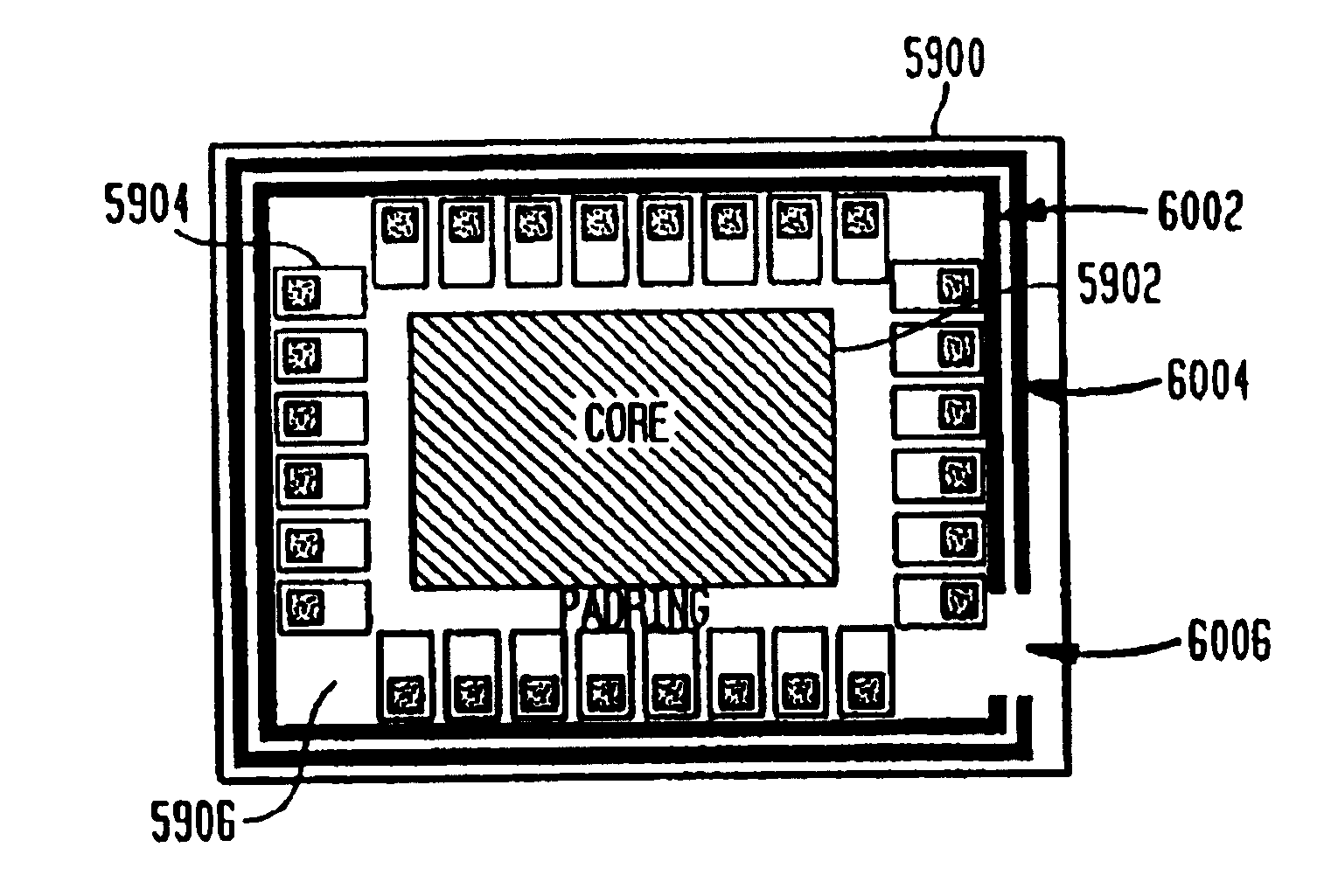

System and method for linearizing a CMOS differential pair

InactiveUS20080036536A1Multiple-port networksSemiconductor/solid-state device detailsShunt DeviceFilter tuning

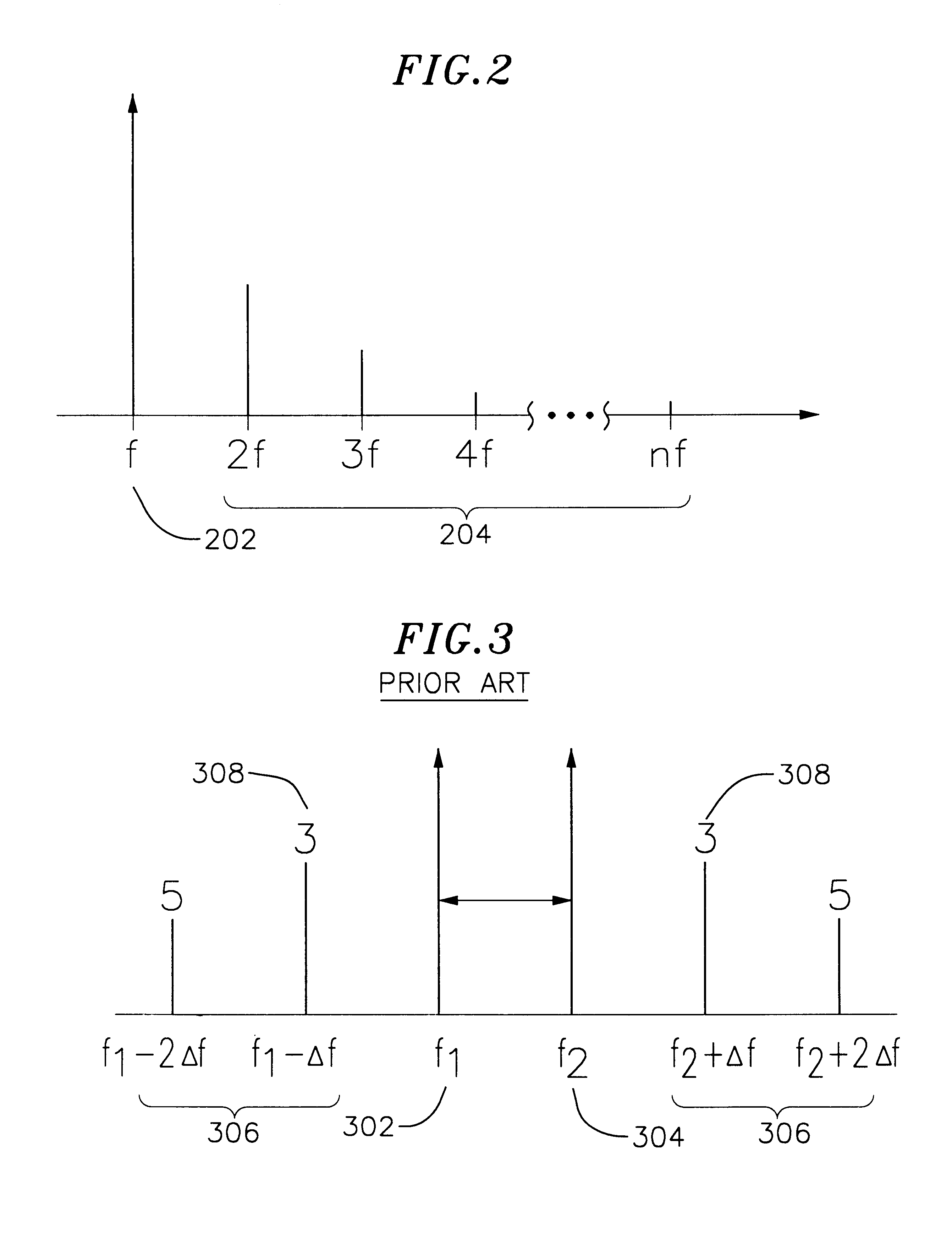

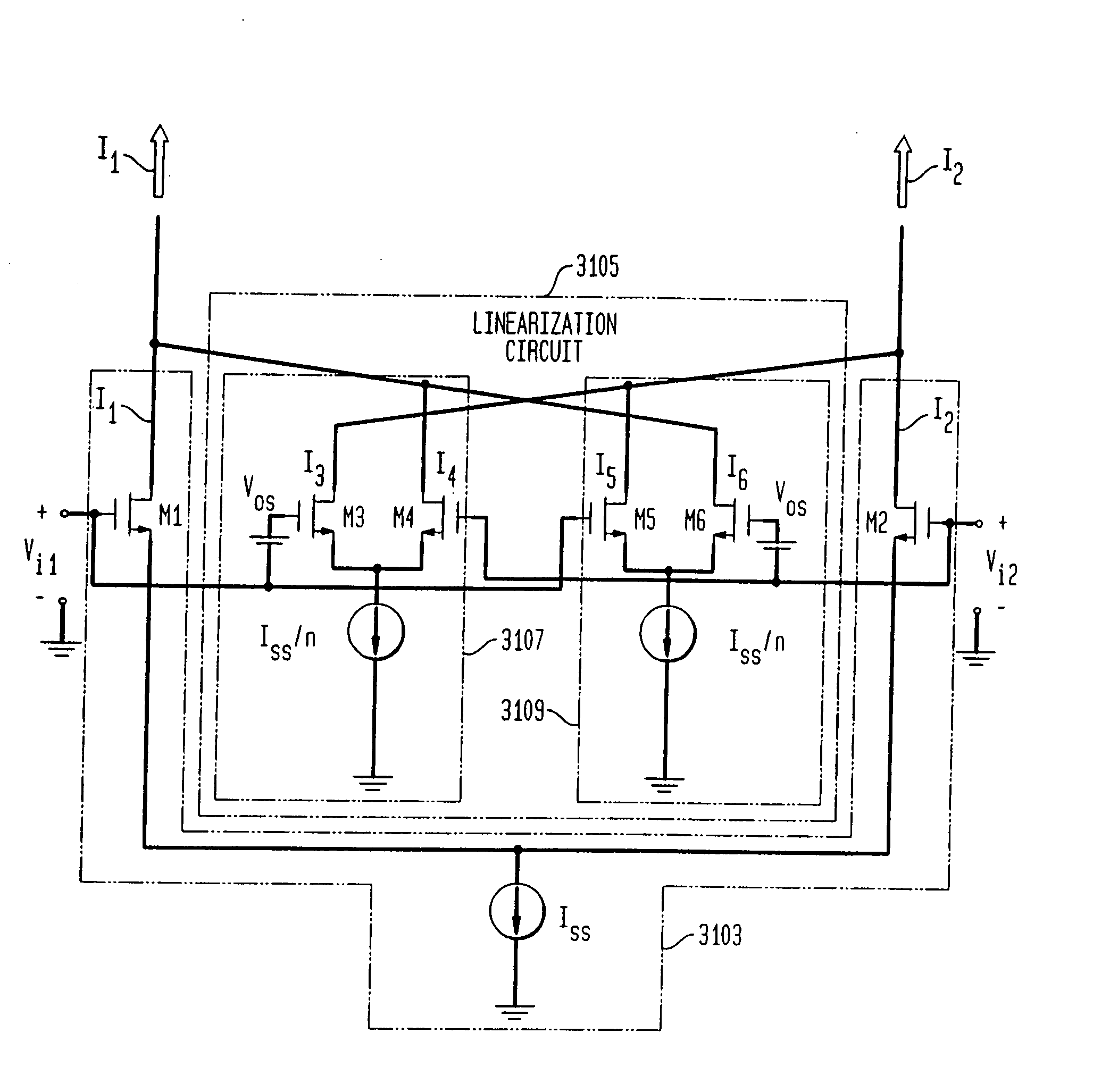

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

Programmable radio transceiver

ActiveUS7508898B2Prevent leakageLow noise amplifierSolid-state devicesAmplifier with semiconductor-devices/discharge-tubesTransceiverRFIC

A fully integrated, programmable mixed-signal transceiver comprising a radio frequency integrated circuit (RFIC) which is frequency and protocol agnostic with digital inputs and outputs, the transceiver being programmable and configurable for multiple radio frequency bands and standards and being capable of connecting to many networks and service providers. The RFIC does not use spiral inductors and instead includes transmission line inductors allowing for improved scalability. Components of the transceiver are programmable to allow the transceiver to switch between different frequency bands of operating. Frequency switching can be accomplished though the content of digital registers coupled to the components.

Owner:GULA CONSULTING LLC

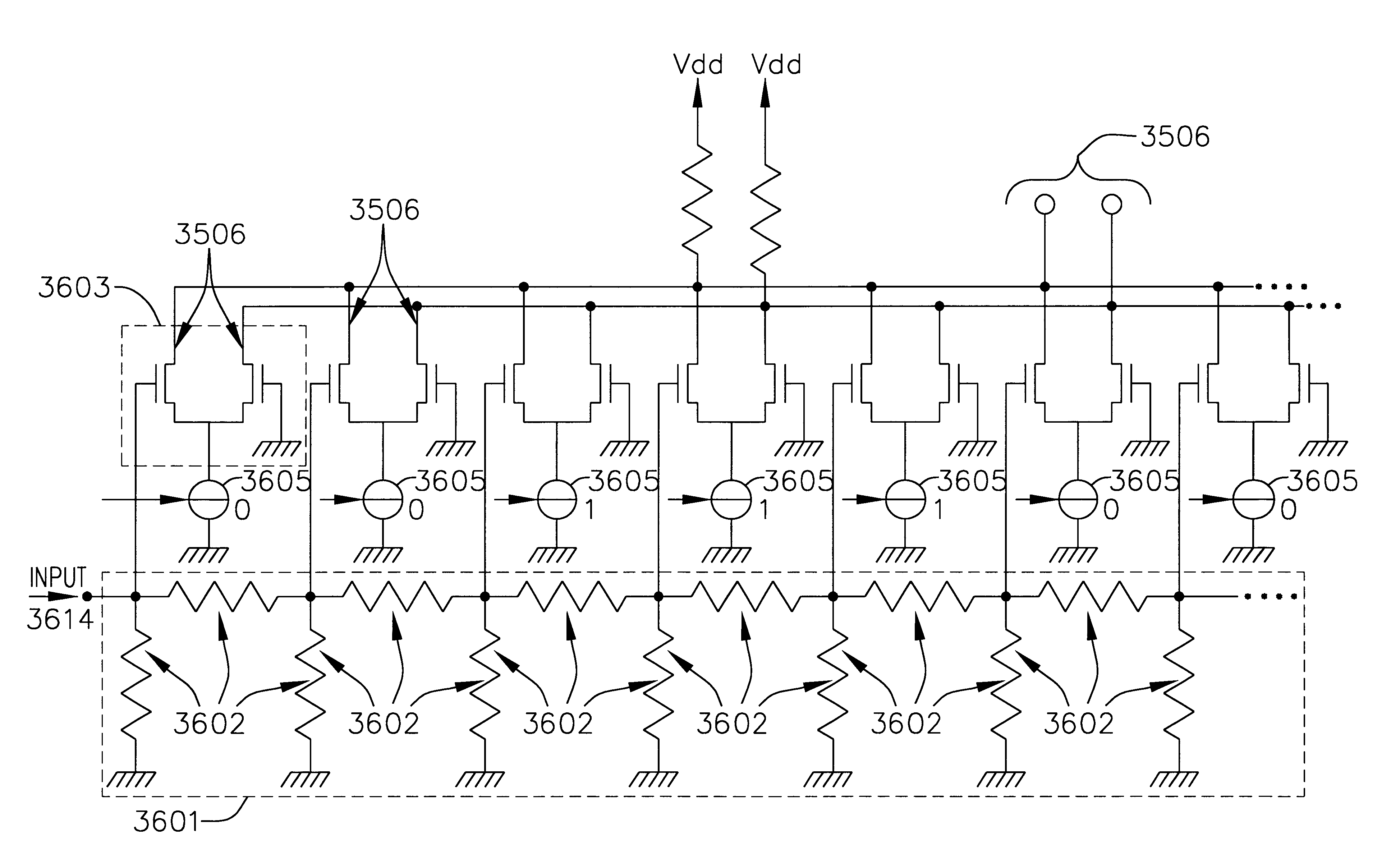

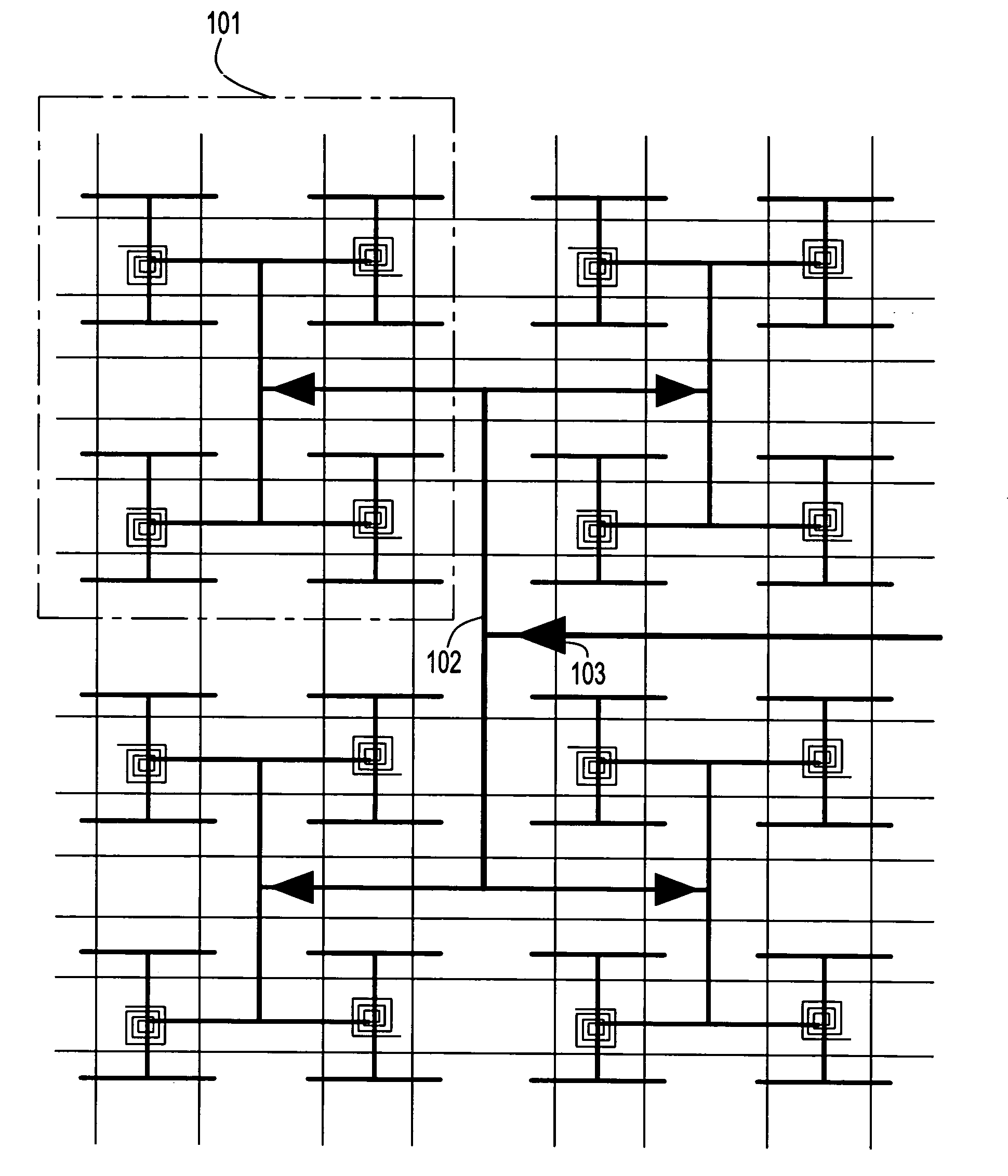

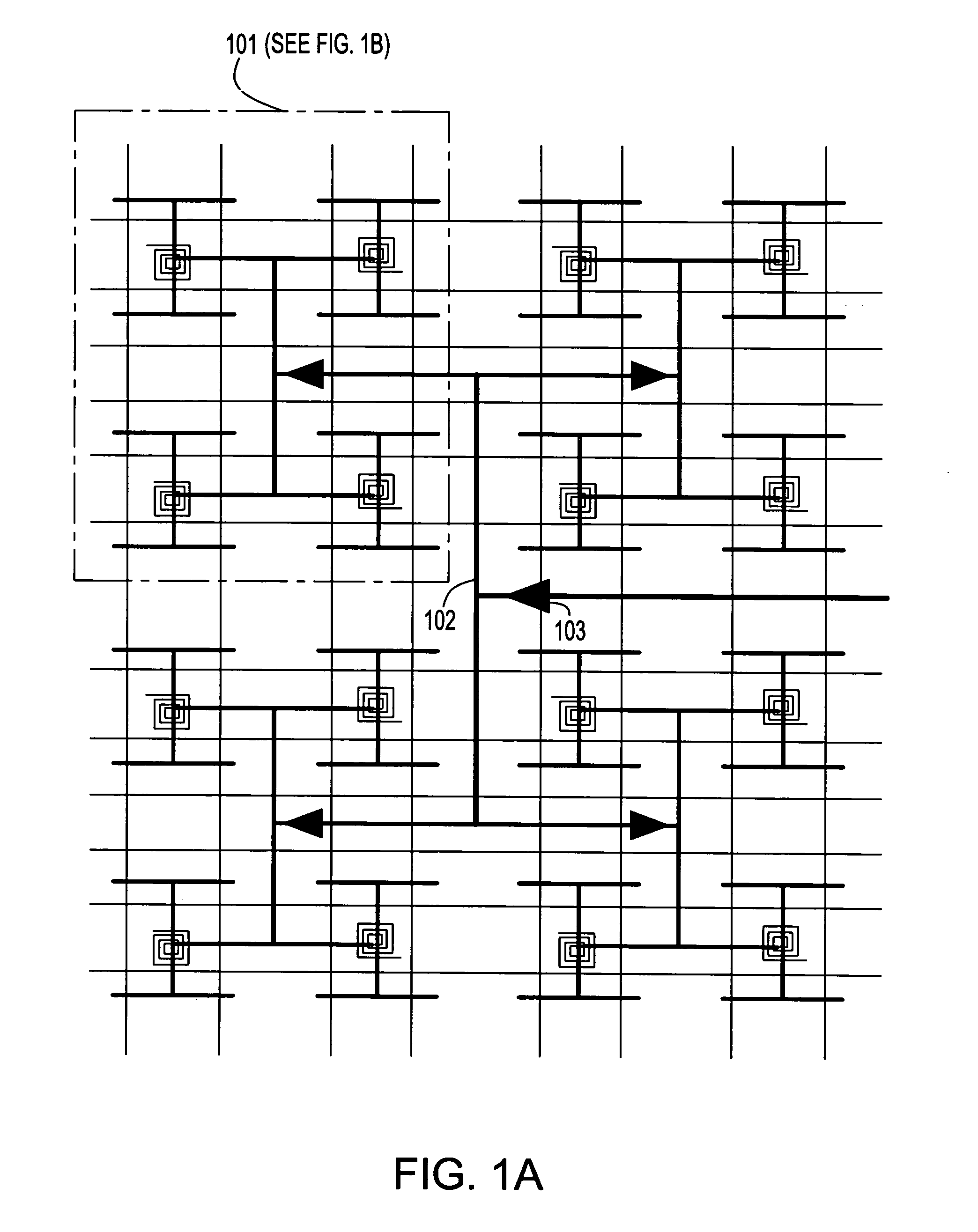

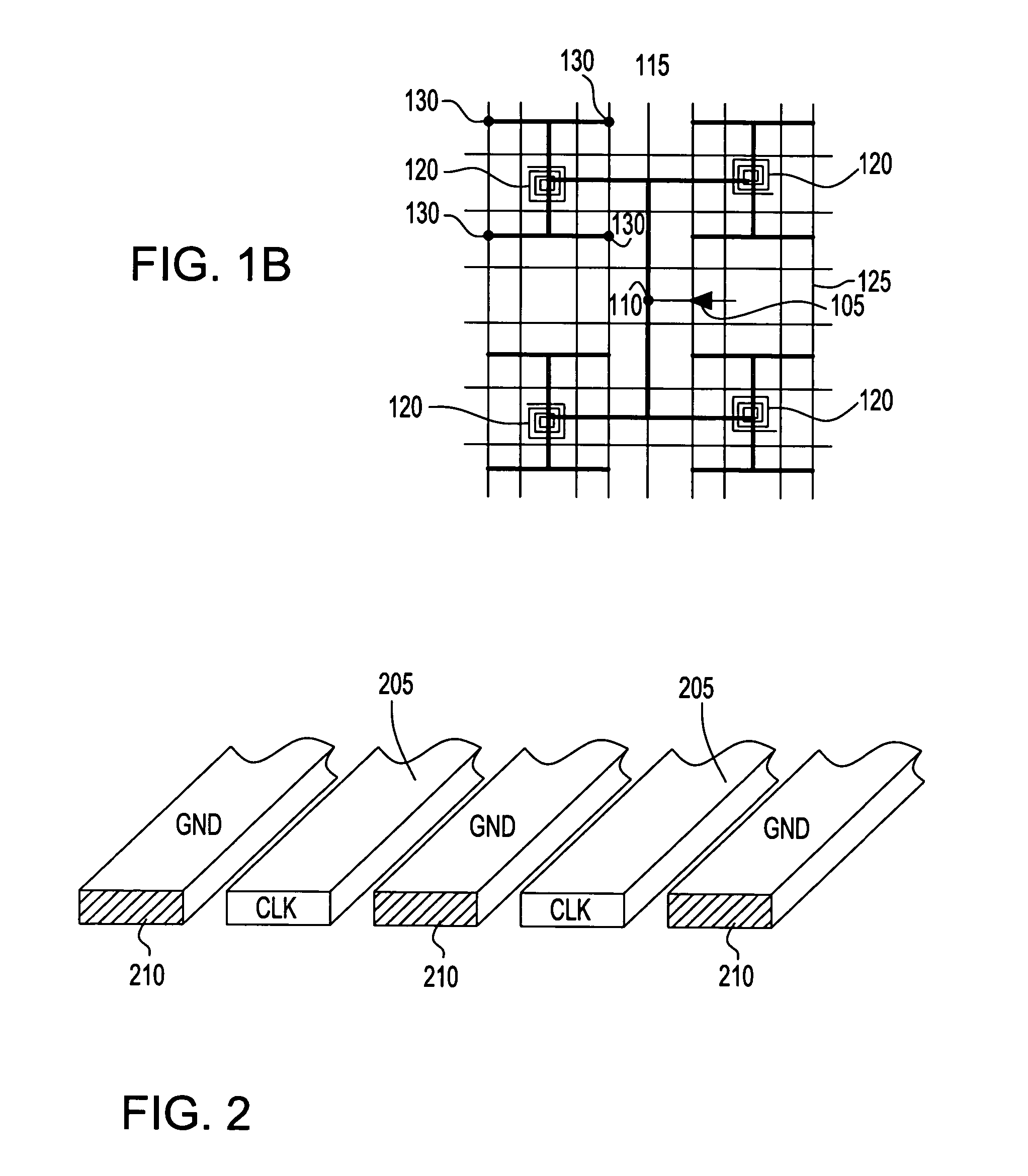

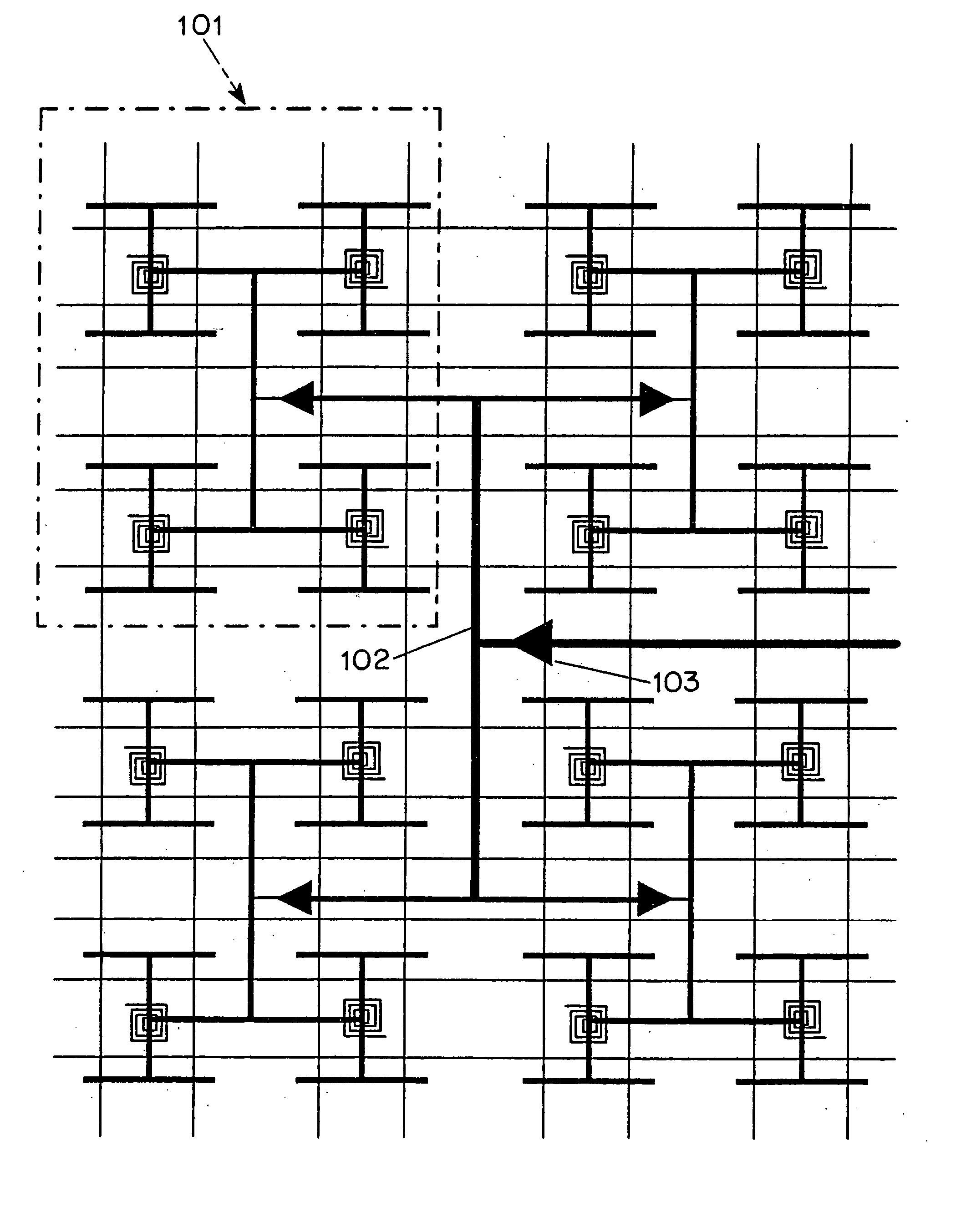

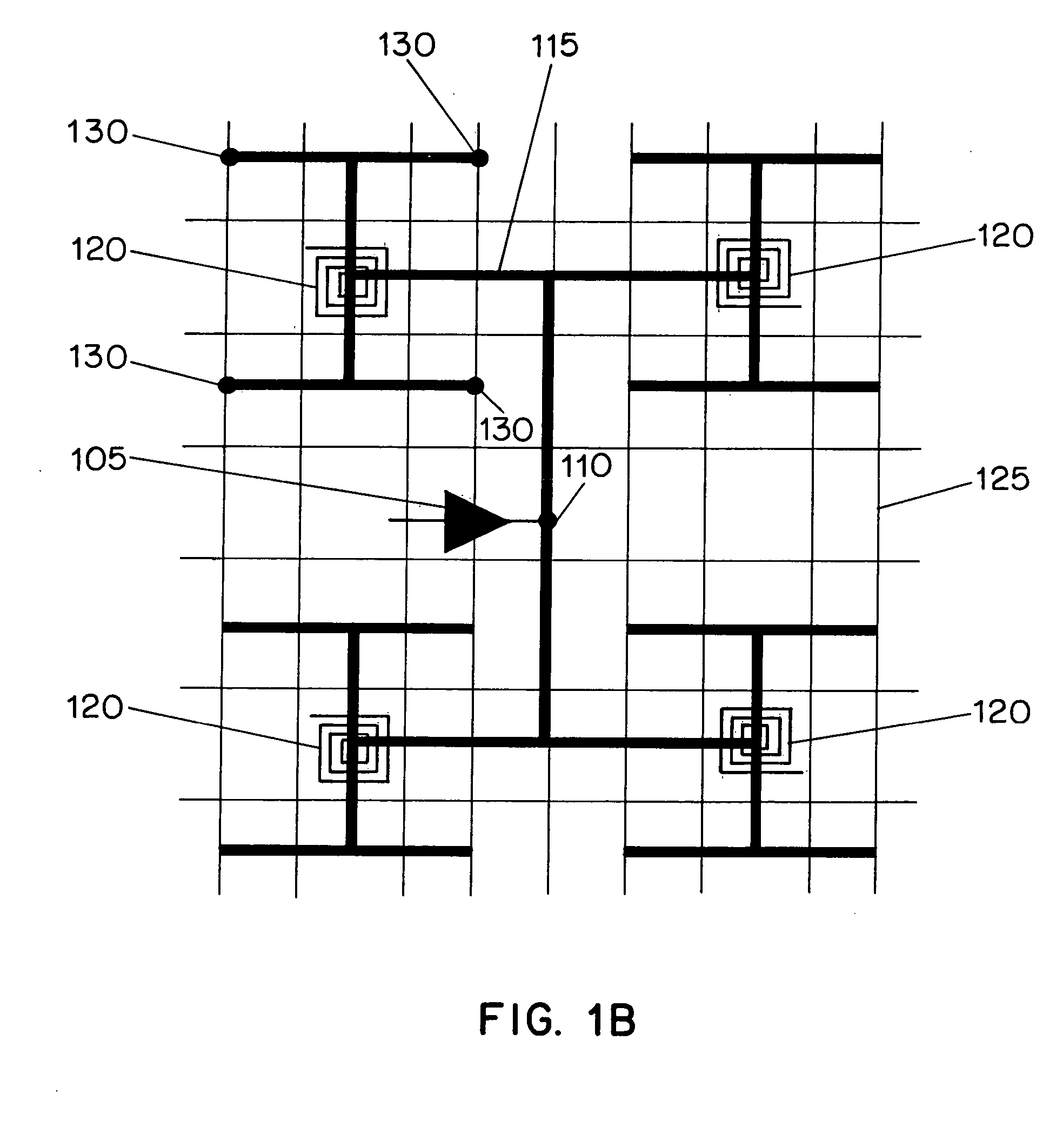

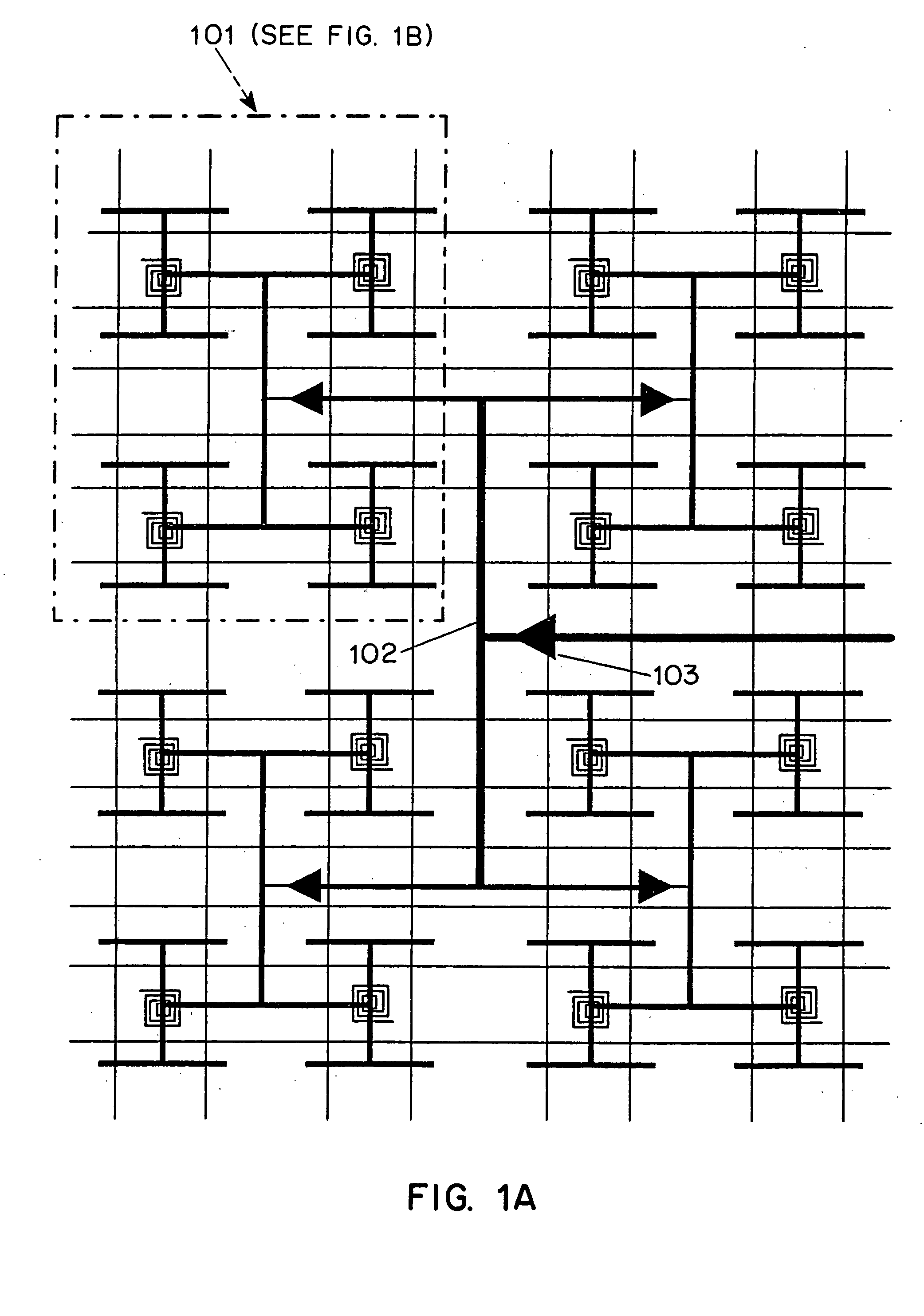

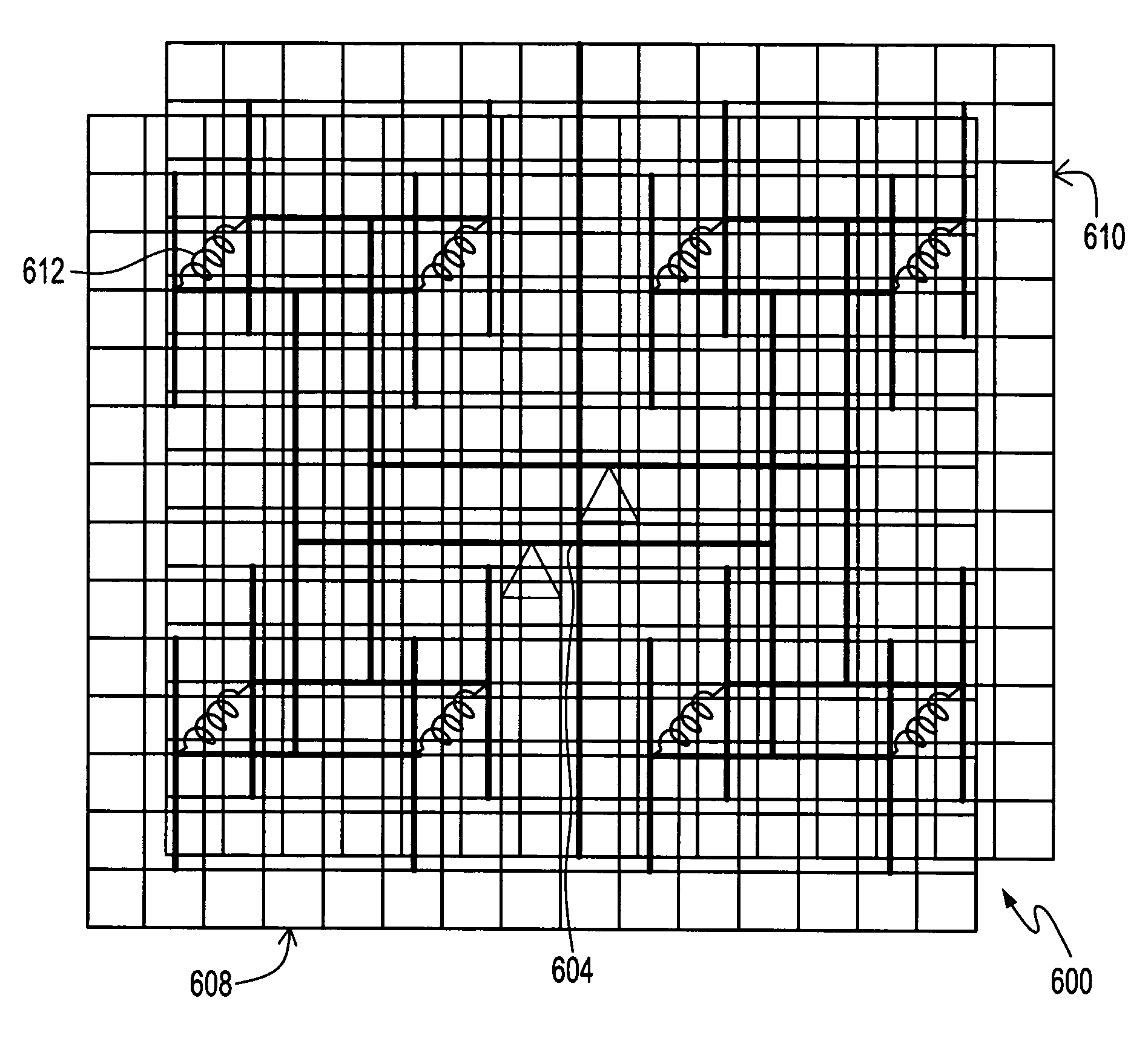

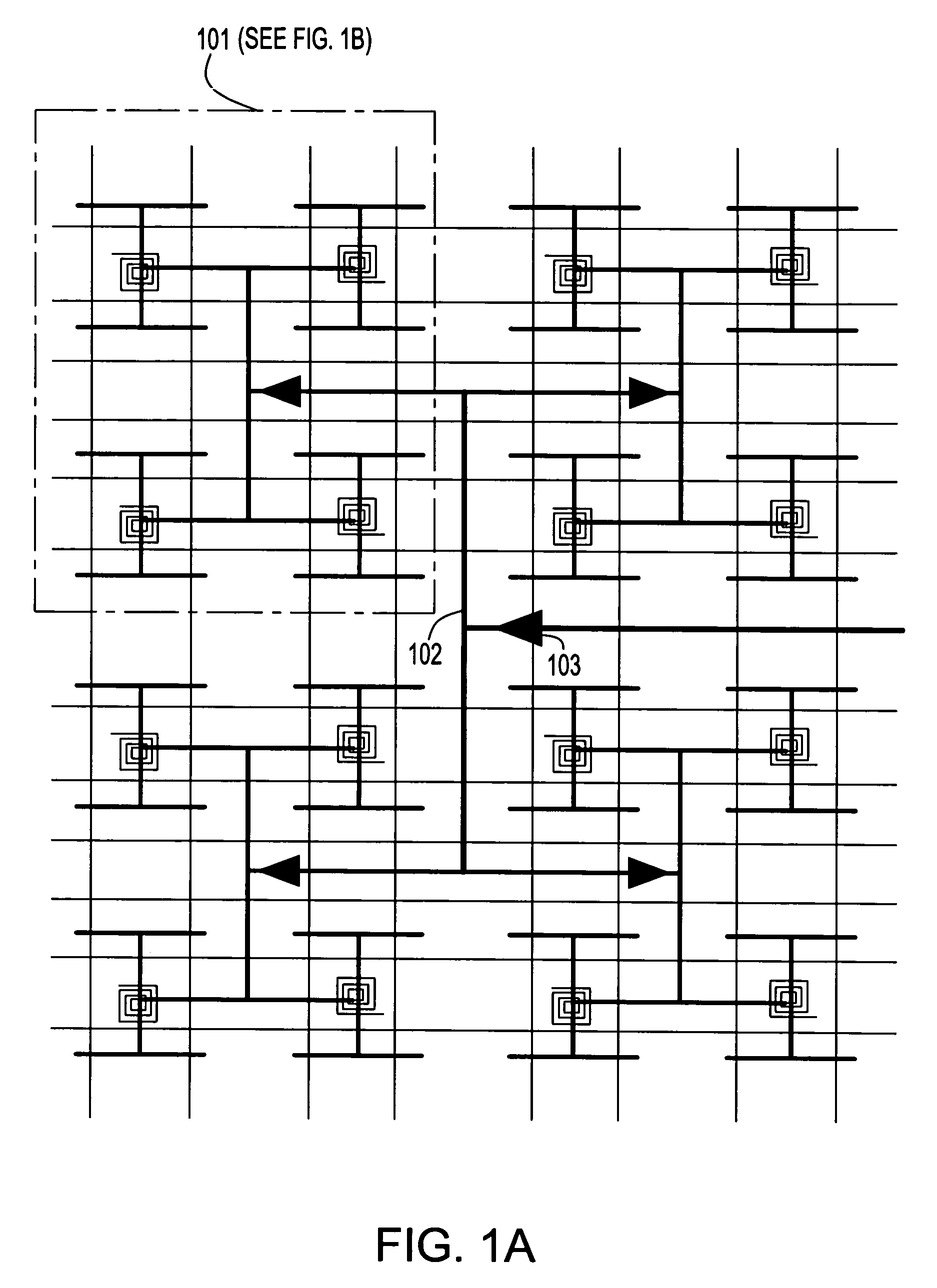

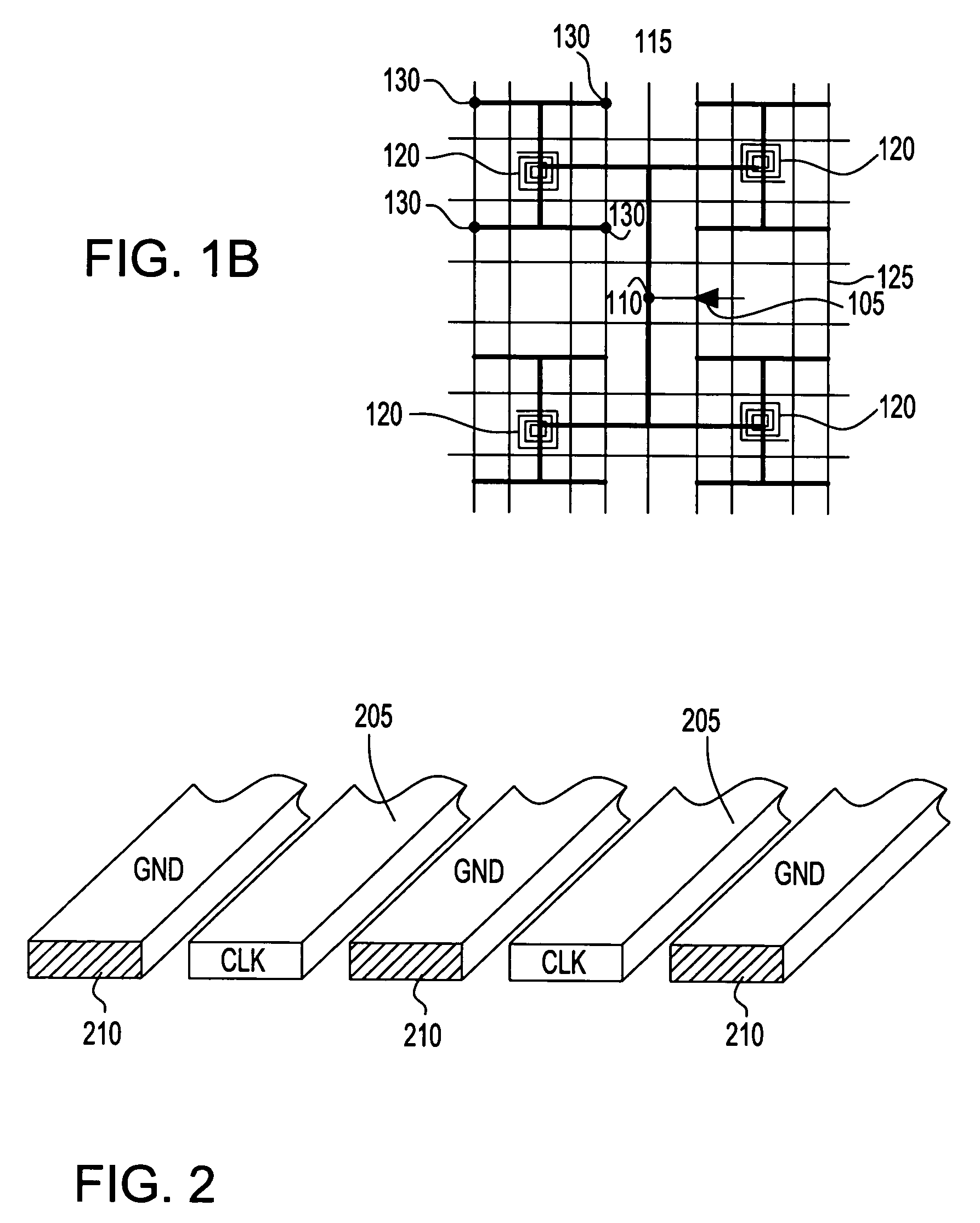

Resonant tree driven clock distribution grid

InactiveUS20050114820A1Effective distributionEfficiently distributedSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceElectrical conductor

An integrated circuit (IC), IC assembly and circuit for distributing a clock signal in an integrated circuit includes a capacitive clock distribution circuit having at least one conductor therein. At least one inductor is formed in a metal layer of the integrated circuit and is coupled to the clock distribution circuit. The inductor, generally in the form of a number of spiral inductors distributed throughout the integrated circuit, provides an inductance value selected to resonate with the capacitive clock distribution circuit at resonance, power dissipation is reduced while skew and jitter performance can be improved.

Owner:IBM CORP

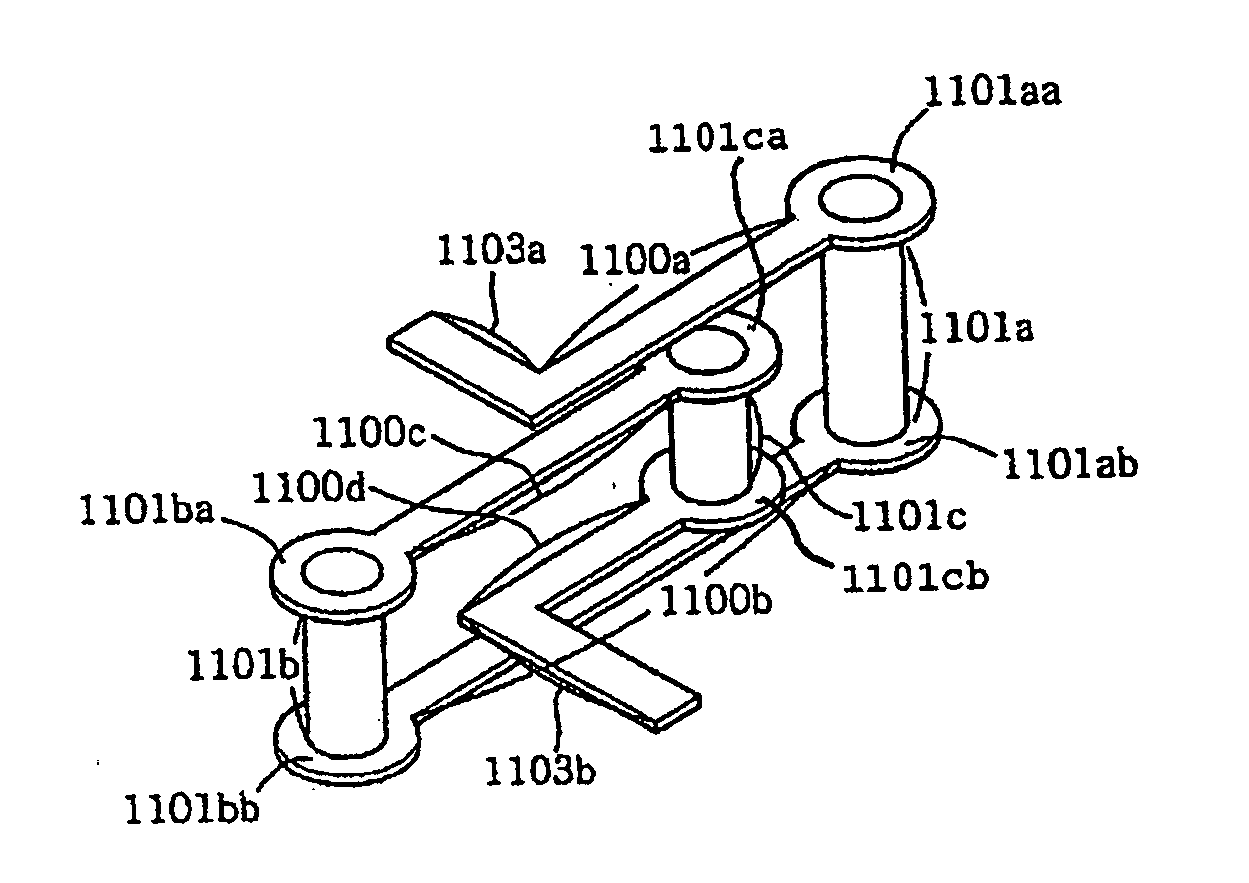

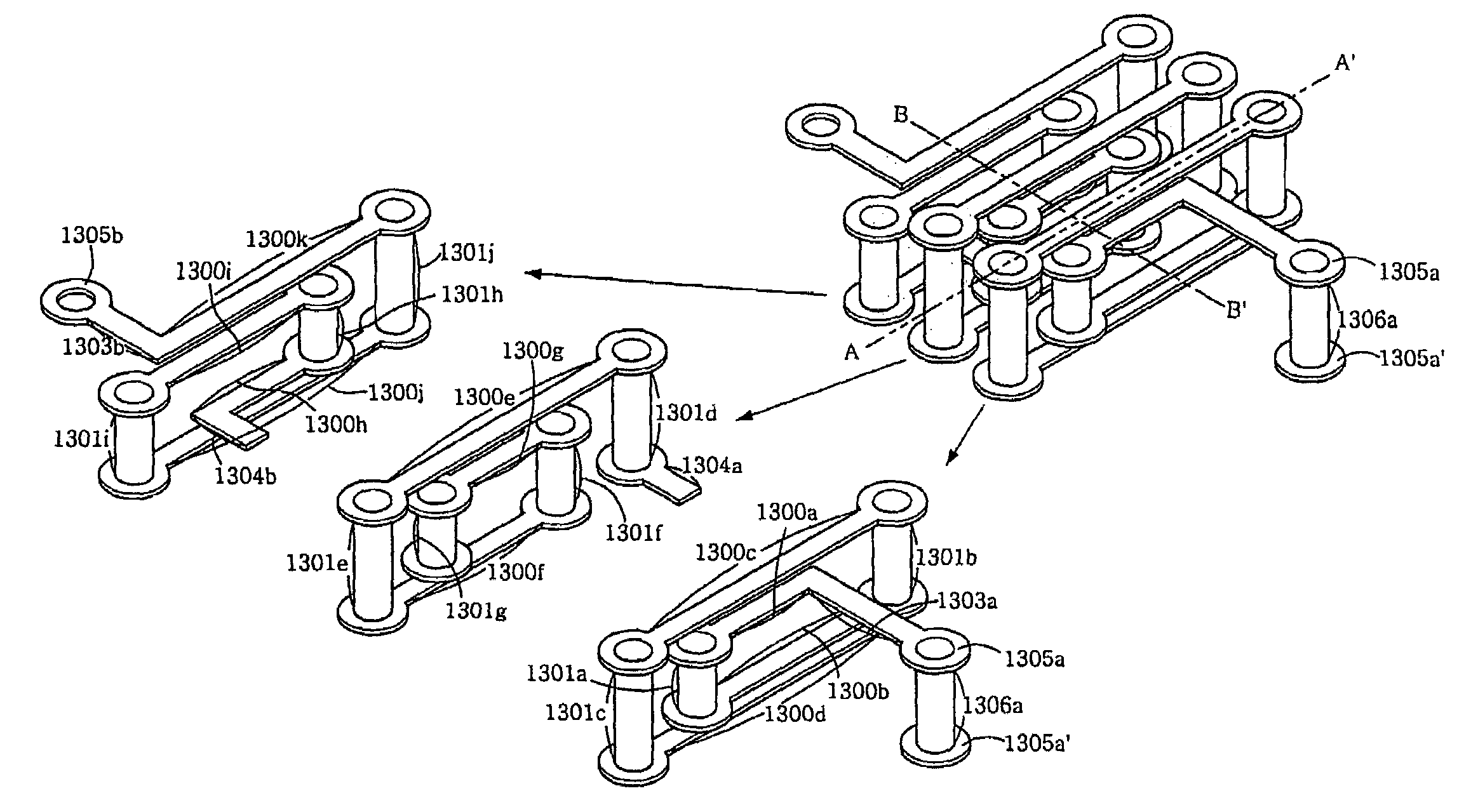

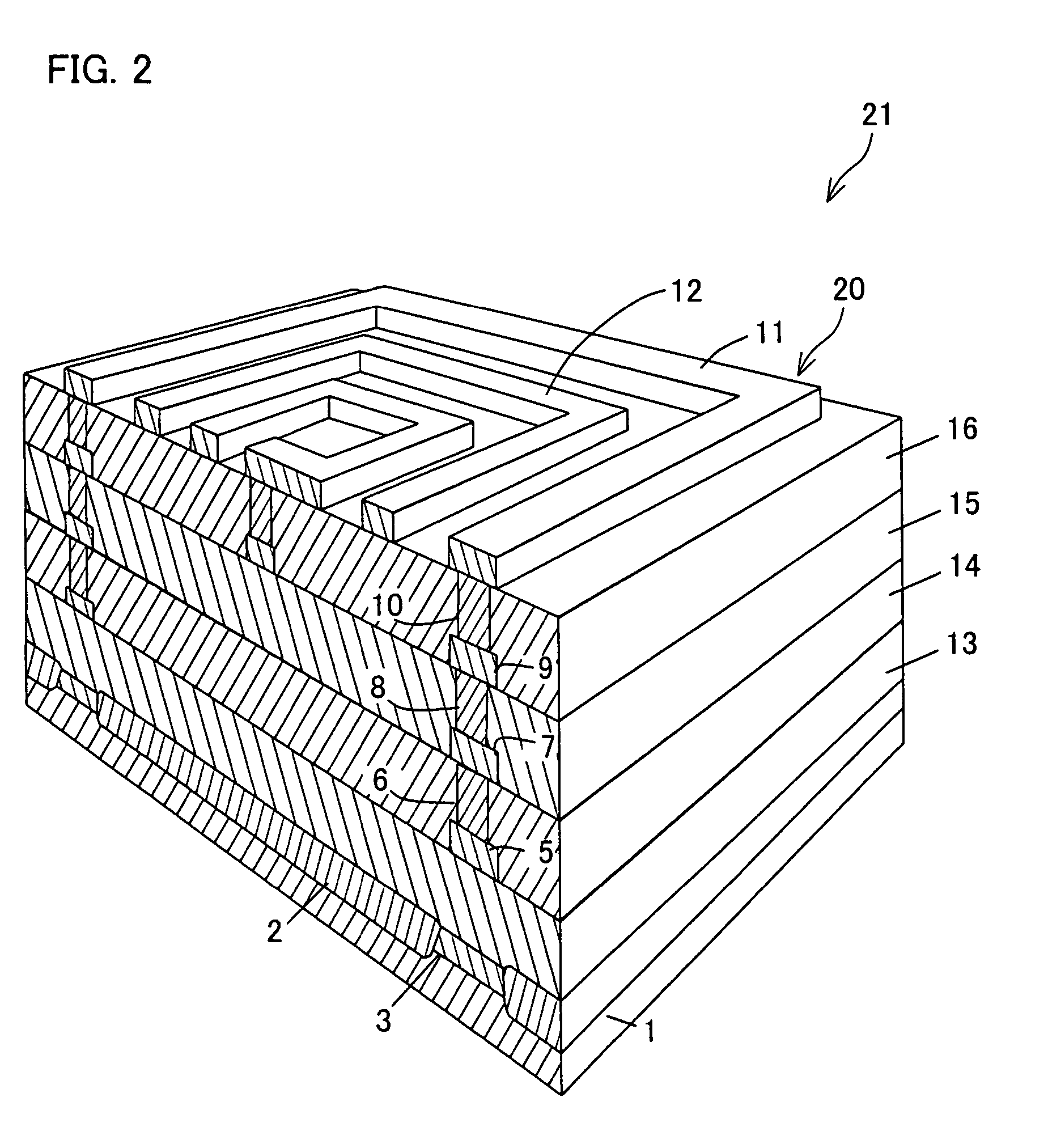

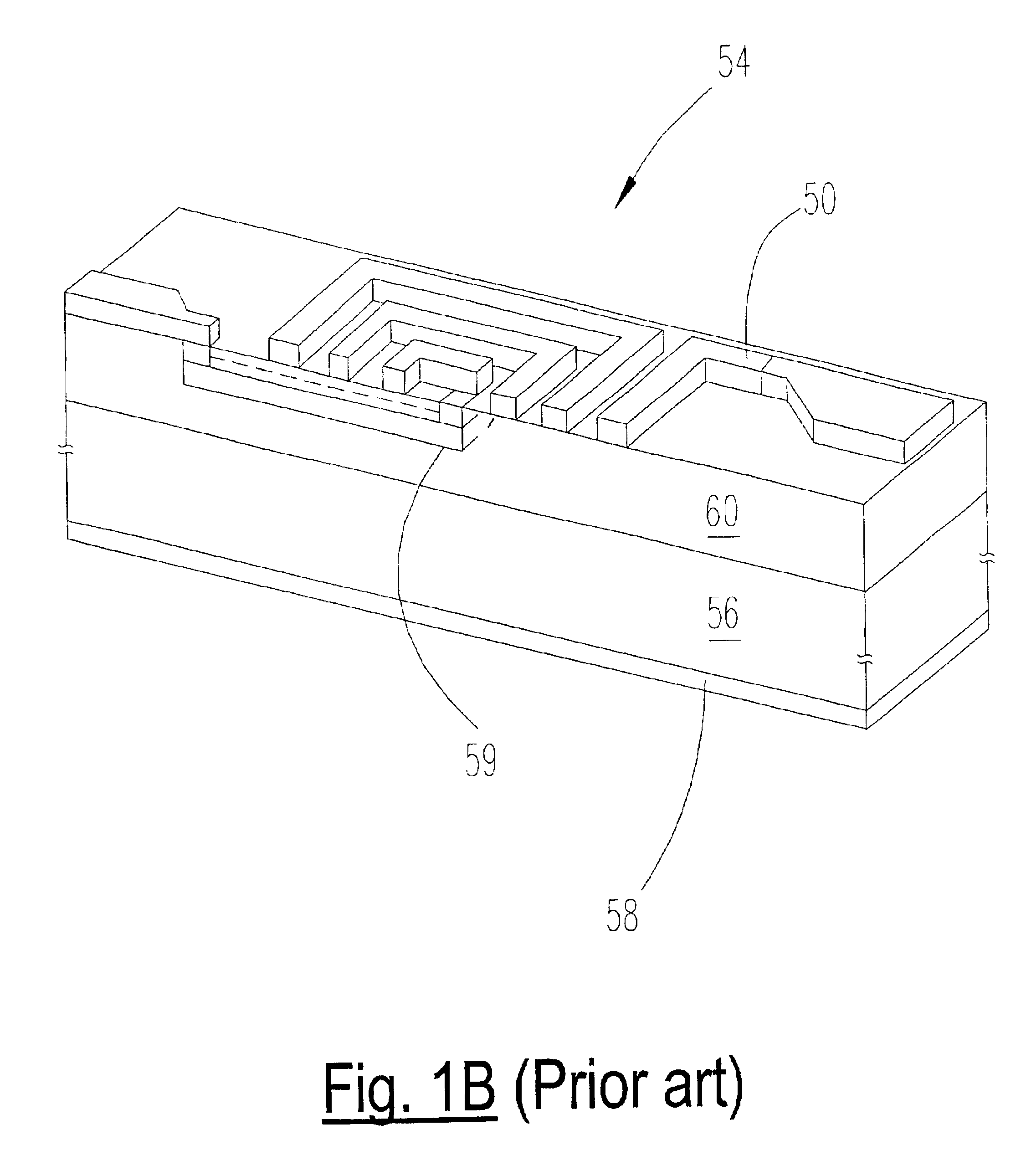

Printed circuit board having three-dimensional spiral inductor and method of fabricating same

ActiveUS20060145805A1Increase inductancePrinted circuit aspectsPrinted circuit manufactureSpiral inductorConductive materials

A printed circuit board (PCB) having a three-dimensional spiral inductor, which includes a plurality of insulating layers and conductor layers. The PCB comprises a plurality of coil conductor patterns made of conductive material and shaped into strips, which is provided on the plurality of conductor layers, respectively, such that the plurality of coil conductor patterns are parallel to each other and positioned on the same plane perpendicular to the conductor layers, and in which each of the plurality of coil conductor patterns is longer than an adjacent inner coil conductor pattern.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

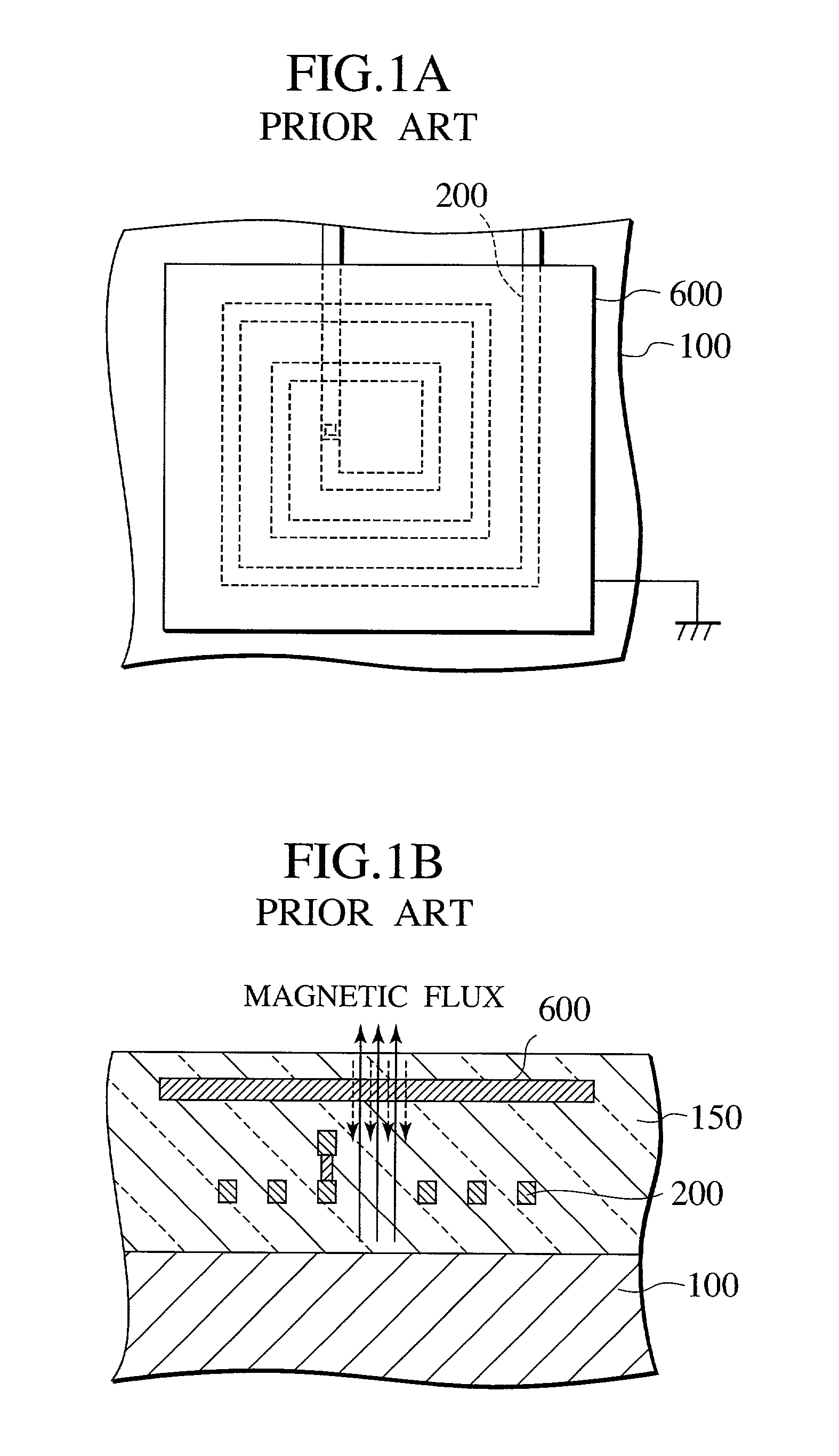

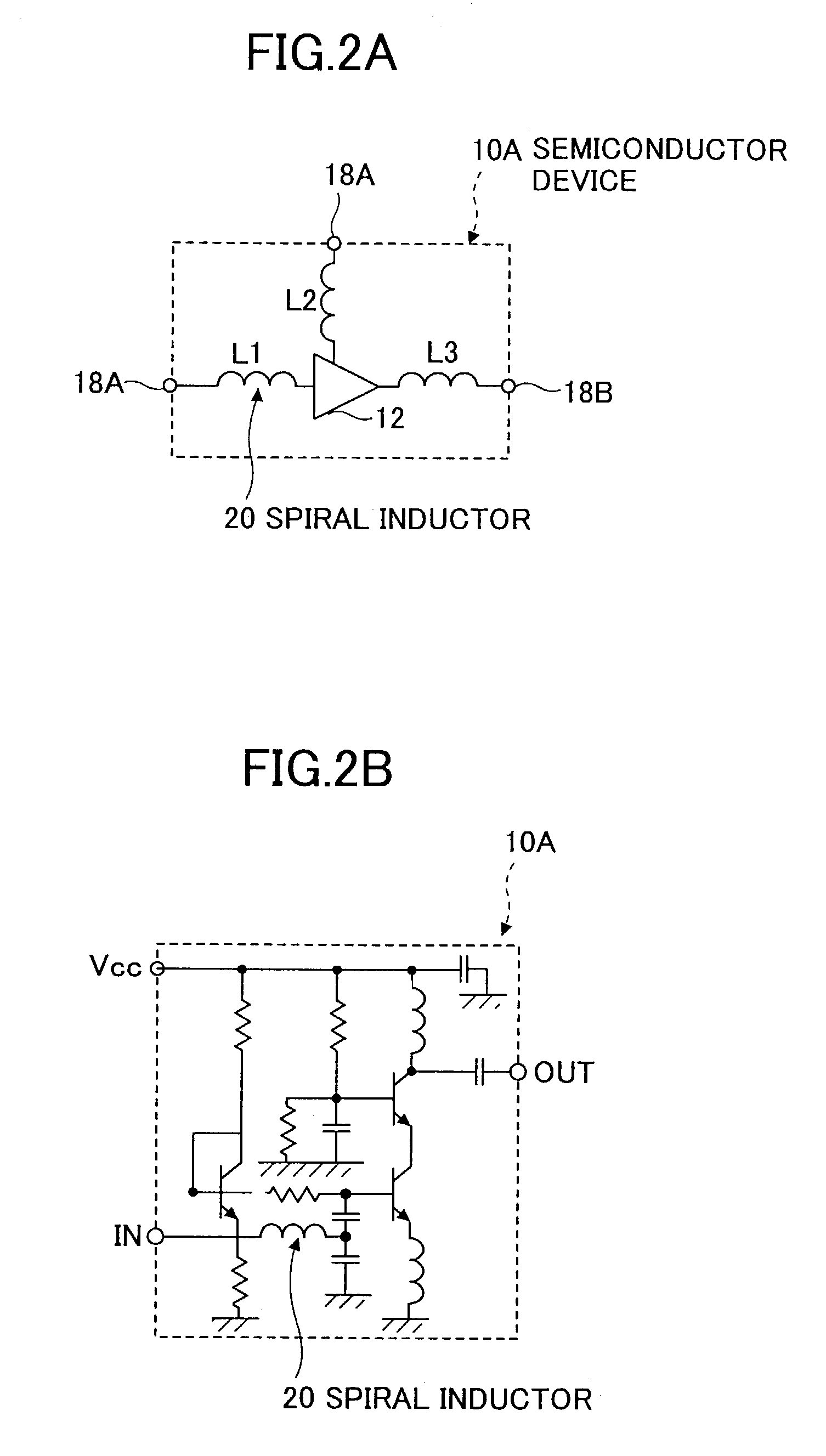

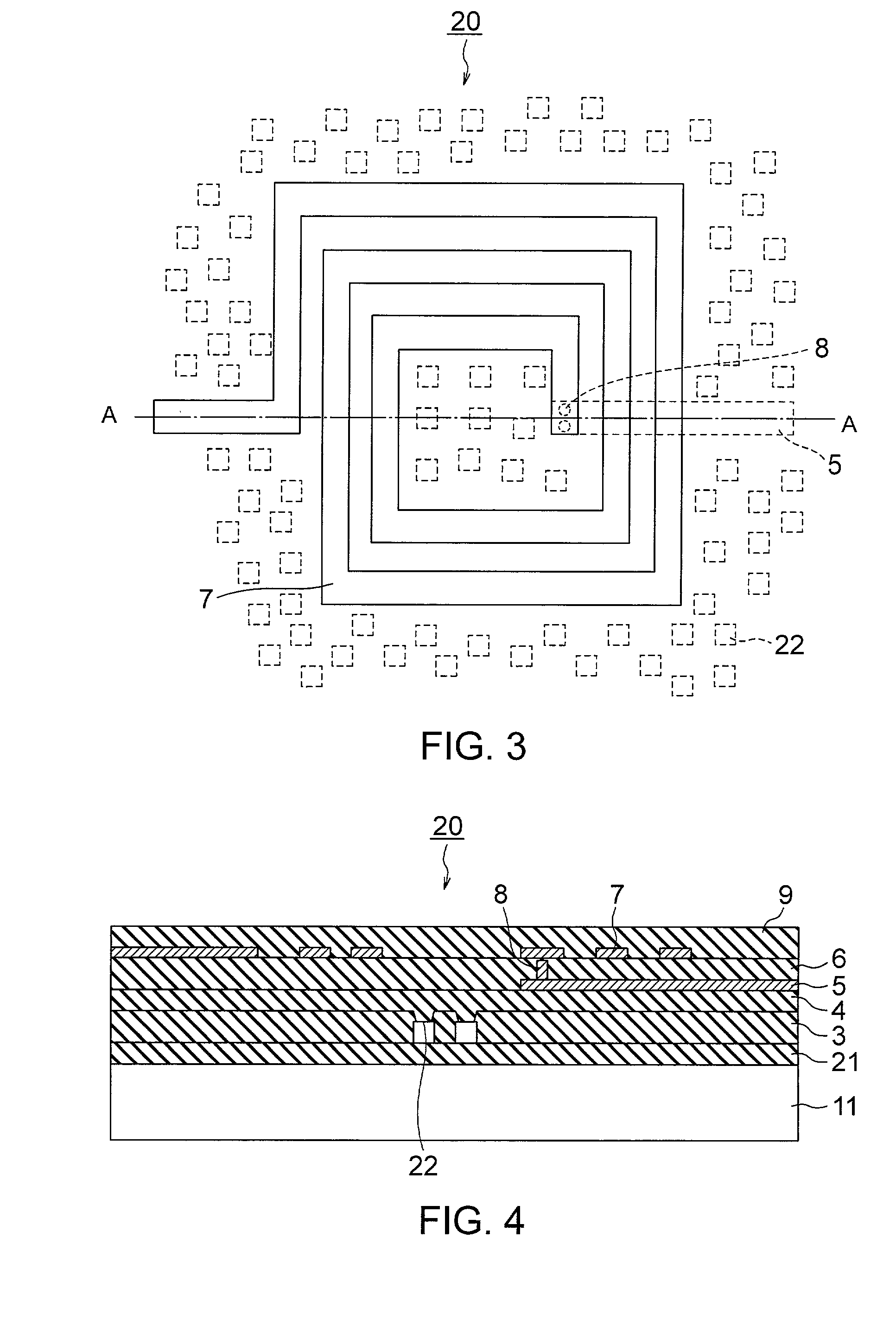

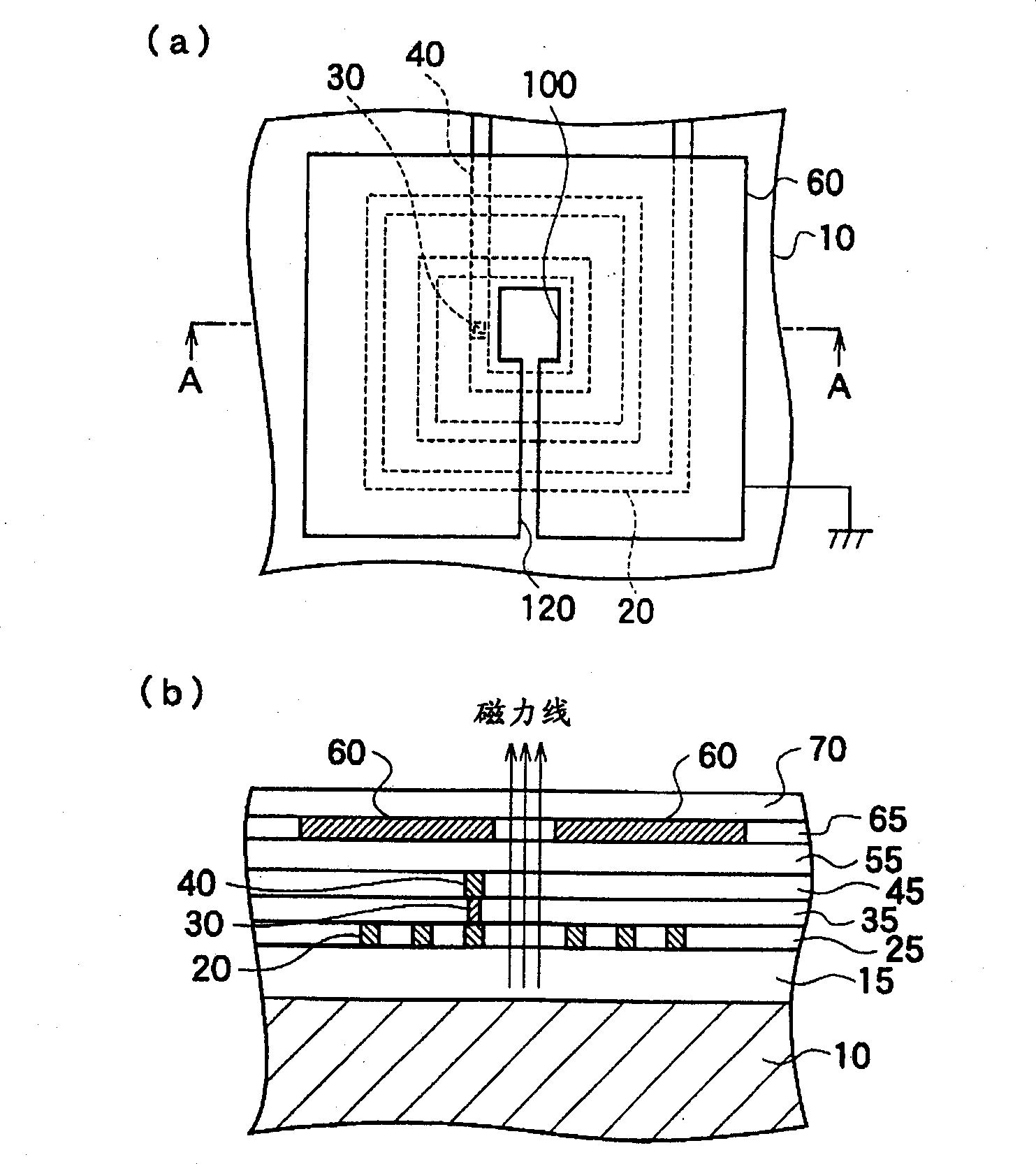

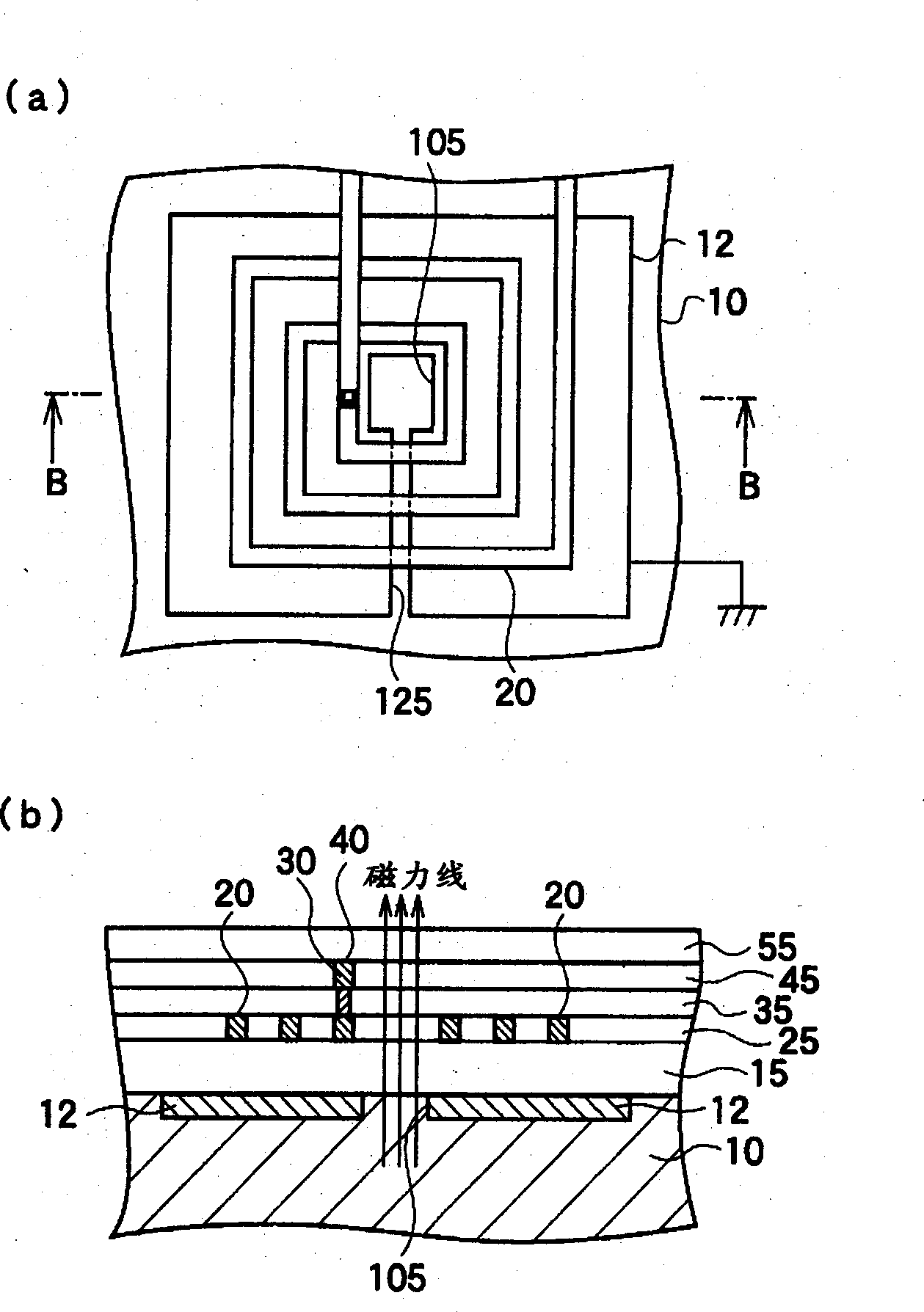

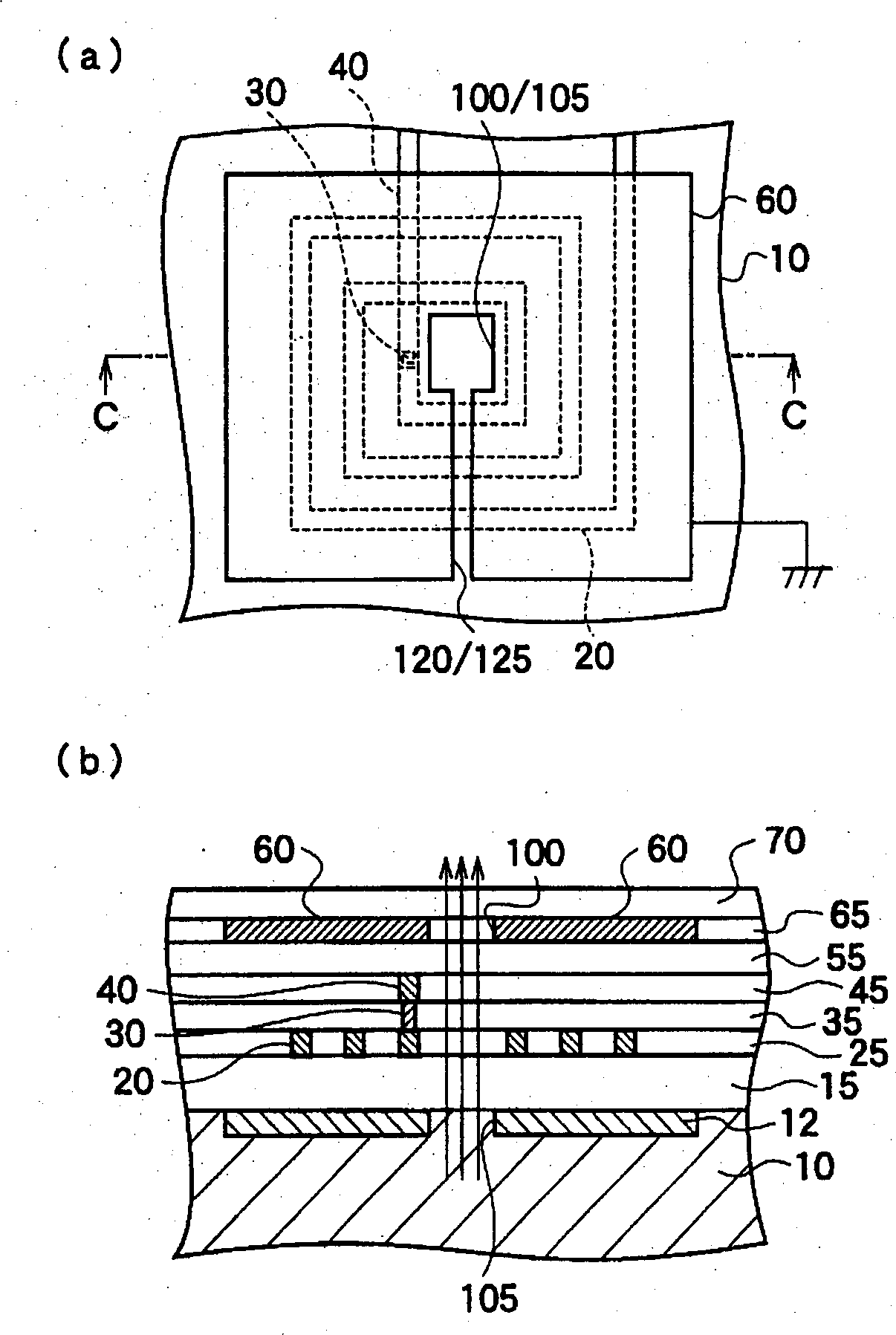

Semiconductor device with a spiral inductor

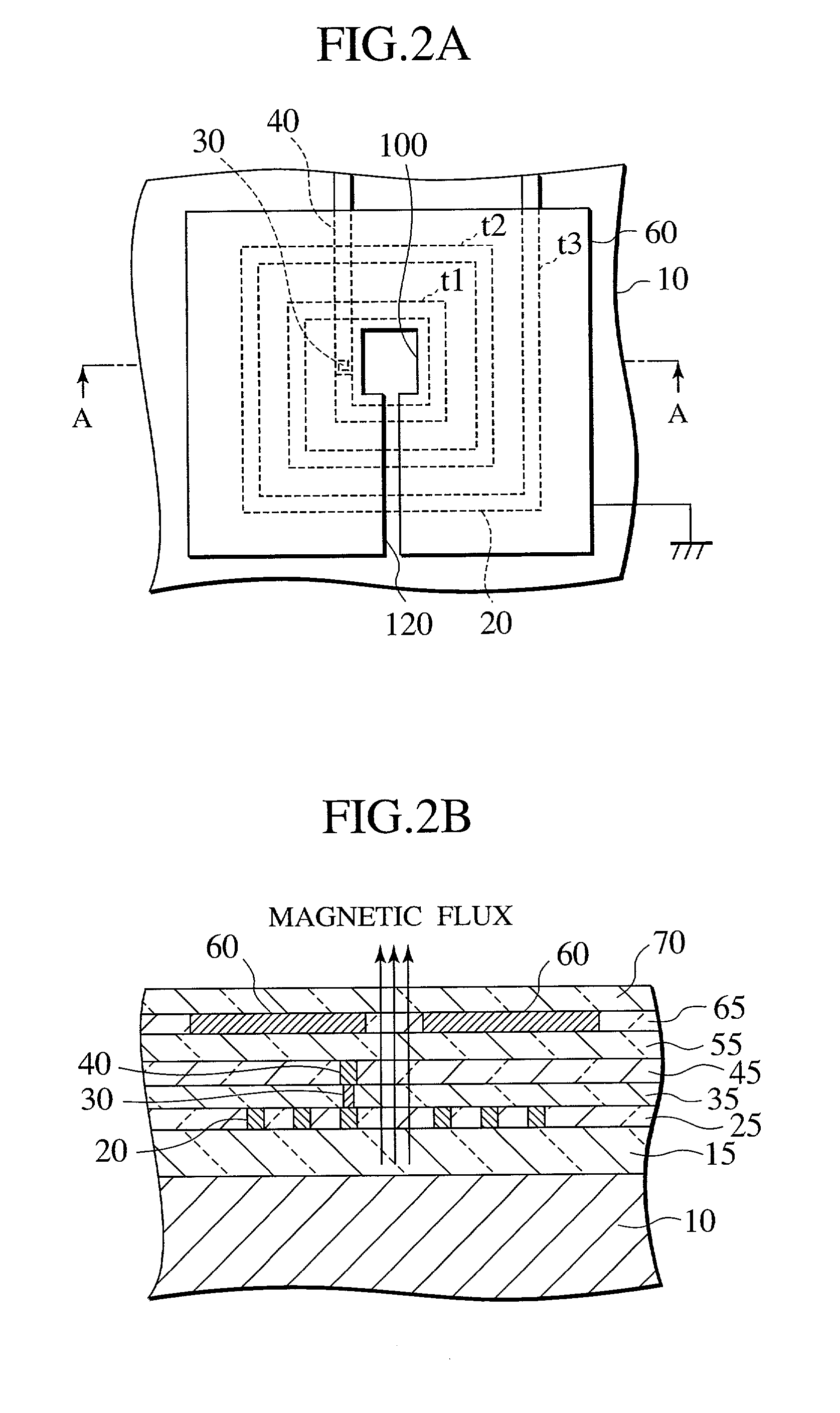

InactiveUS20020158306A1Magnetic/electric field screeningSolid-state devicesSpiral inductorSemiconductor

A first semiconductor device includes a first conductive layer, a second conductive layer located above or below the first conductive layer, and an insulating layer interposed between the first conductive layer and the second conductive layer, a spiral inductor having a spiral pattern that is formed in the first conductive layer, and an electromagnetic wave shield formed in a plane shape in the second conductive layer. The electromagnetic wave shield is grounded or connected to a constant voltage source and is located above or below the spiral inductor. Furthermore the first semiconductor device includes an opening formed in the electromagnetic wave shield. The opening is located in a region corresponding to a region above or below a central region of the spiral pattern of the spiral inductor. A second semiconductor device includes a first conductive layer, a second conductive layer located above or below the first conductive layer, an insulating layer interposed between the first conductive layer and the second conductive layer, a spiral inductor having a spiral pattern that is formed in the first conductive layer, and an electromagnetic wave shield formed in a plane shape in the second conductive layer. The electromagnetic wave shield is grounded or connected to a constant voltage source and is located above or below the spiral inductor. Furthermore the second semiconductor includes a slit formed in the electromagnetic wave shield. The slit extends from a position of the electromagnetic wave shield, the position corresponding to a region above or below a center of the spiral inductor, to a peripheral direction of the electromagnetic wave shield.

Owner:KK TOSHIBA

Resonant clock distribution for very large scale integrated circuits

InactiveUS20050057286A1Effective distributionEfficiently distributedPulse automatic controlGenerating/distributing signalsCapacitanceVery large scale integrated circuits

A circuit for distributing a clock signal in an integrated circuit includes a capacitive clock distribution circuit having at least conductor therein. At least one inductor is formed in a metal layer of the integrated circuit and is coupled to the clock distribution circuit. The inductor, generally in the form of a number of spiral inductors distributed throughout the integrated circuit, provides an inductance value selected to resonate with the capacitive clock distribution circuit. By operating the clock distribution circuit at resonance, power dissipation is reduced while skew and jitter performance can be improved.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

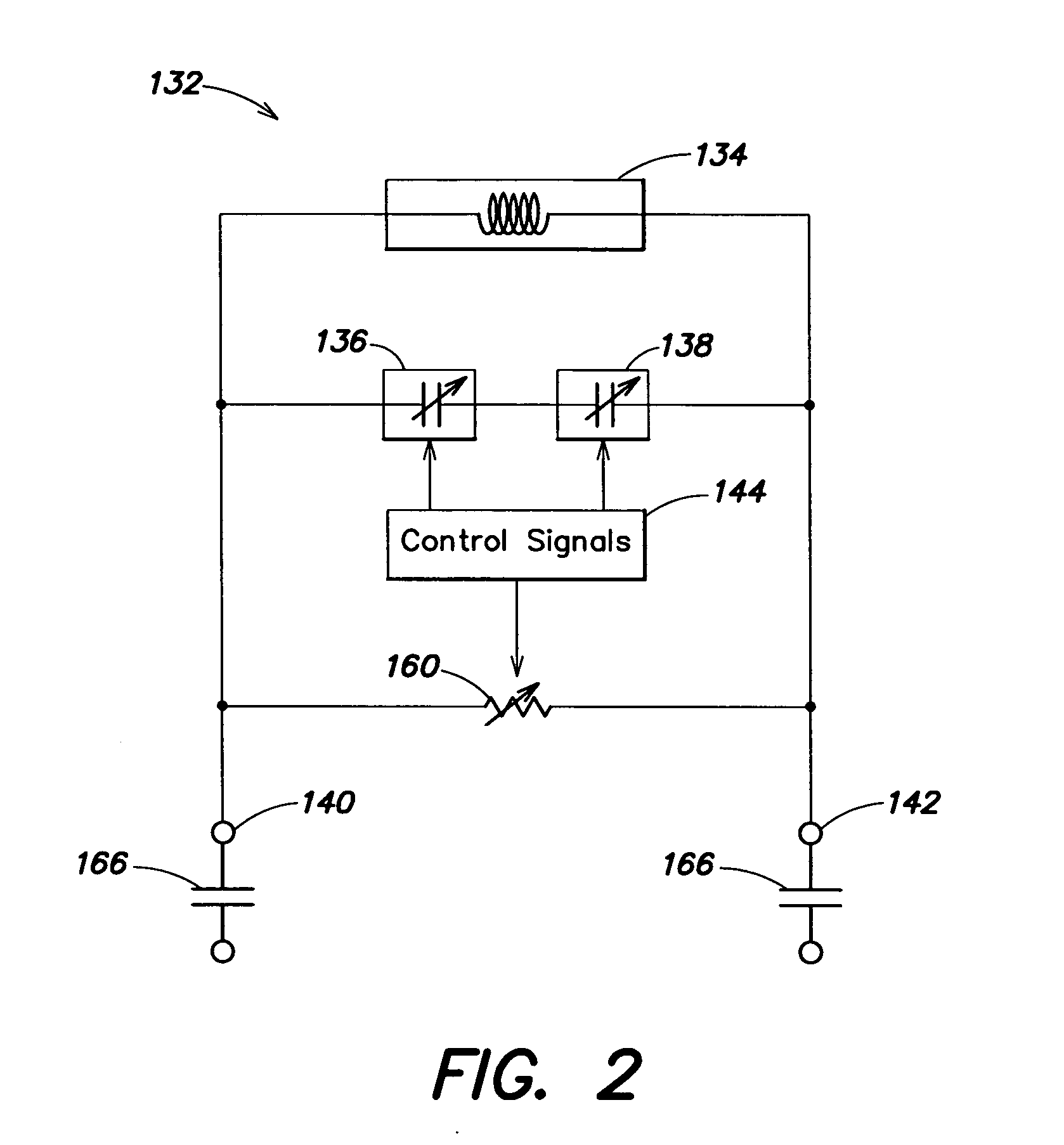

Microwave tunable inductor and associated methods

ActiveUS7148783B2Transformers/inductances coils/windings/connectionsInductance without magnetic coreMicrowaveSpiral inductor

The inductor, preferably a microwave tunable inductor, includes first and second wires twisted together to define a double helix having a first end and second end with a plurality of twists therebetween. First and second terminals are at the first end of the double helix, and a connection at the second end of the double helix electrically connects the first and second wires in series. The inductance is tuned by adjusting a number of twists in the double helix, and the inductance includes a linear tuning range based upon between about 3 to 10 twist for a tuning range of about 7–12 Nanohenries. The inductor can also resonate and filter, and the double helix affords numerous advantages over conventional single helix inductors.

Owner:HARRIS CORP

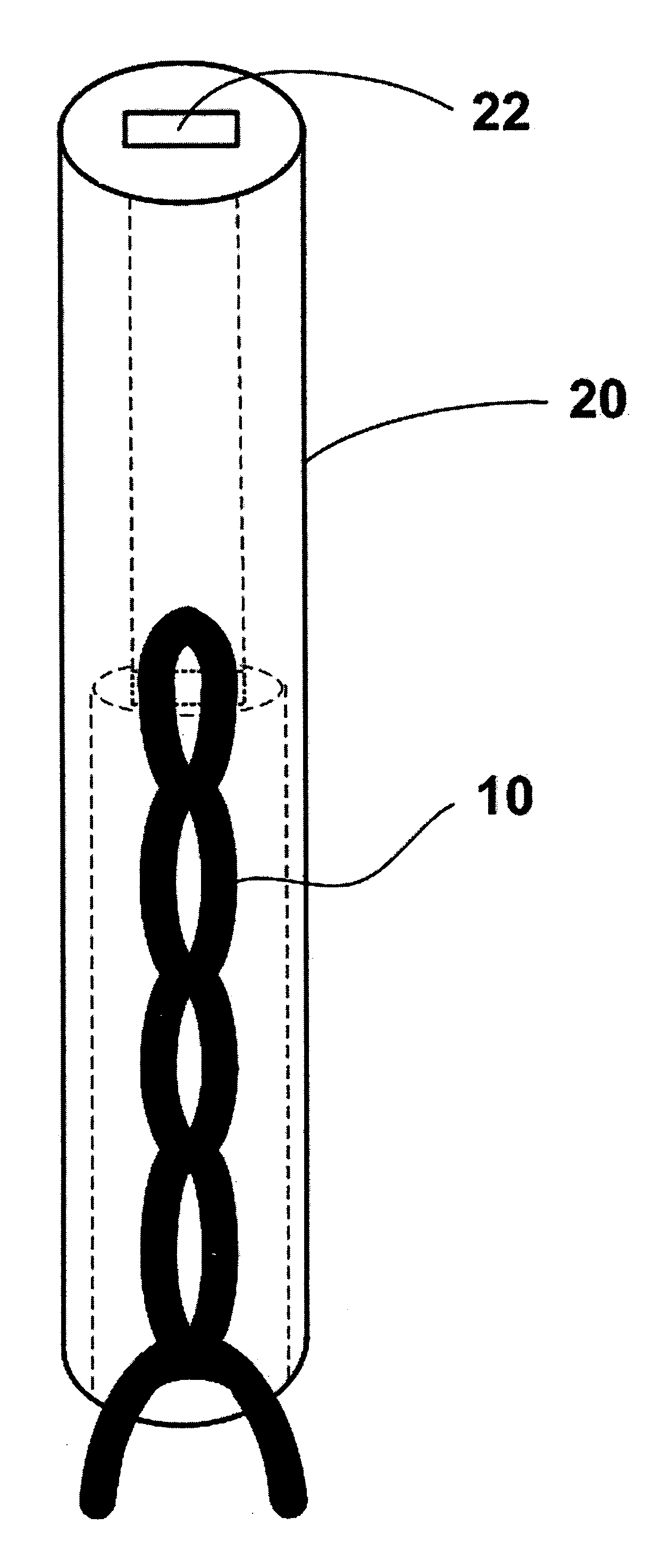

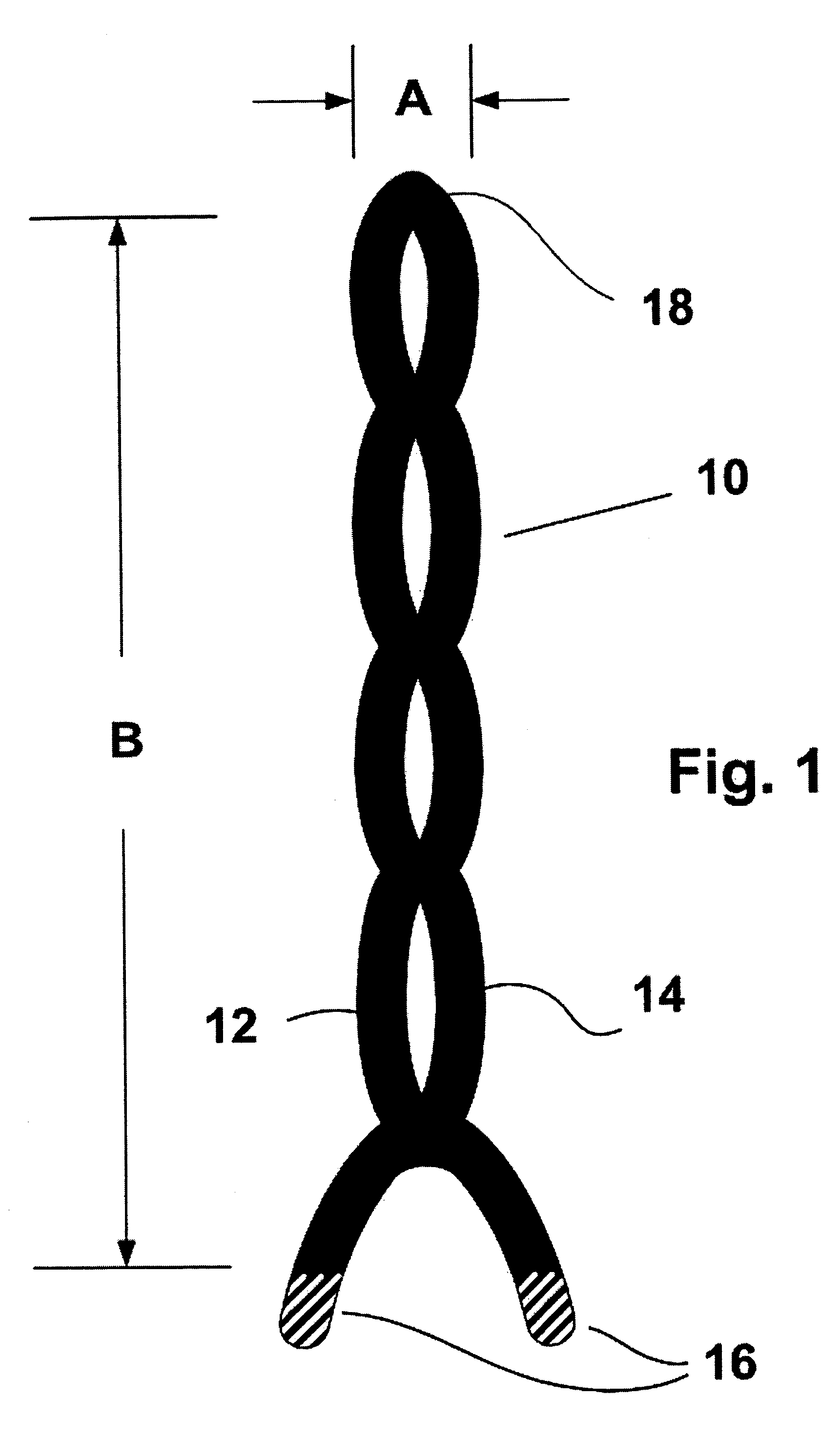

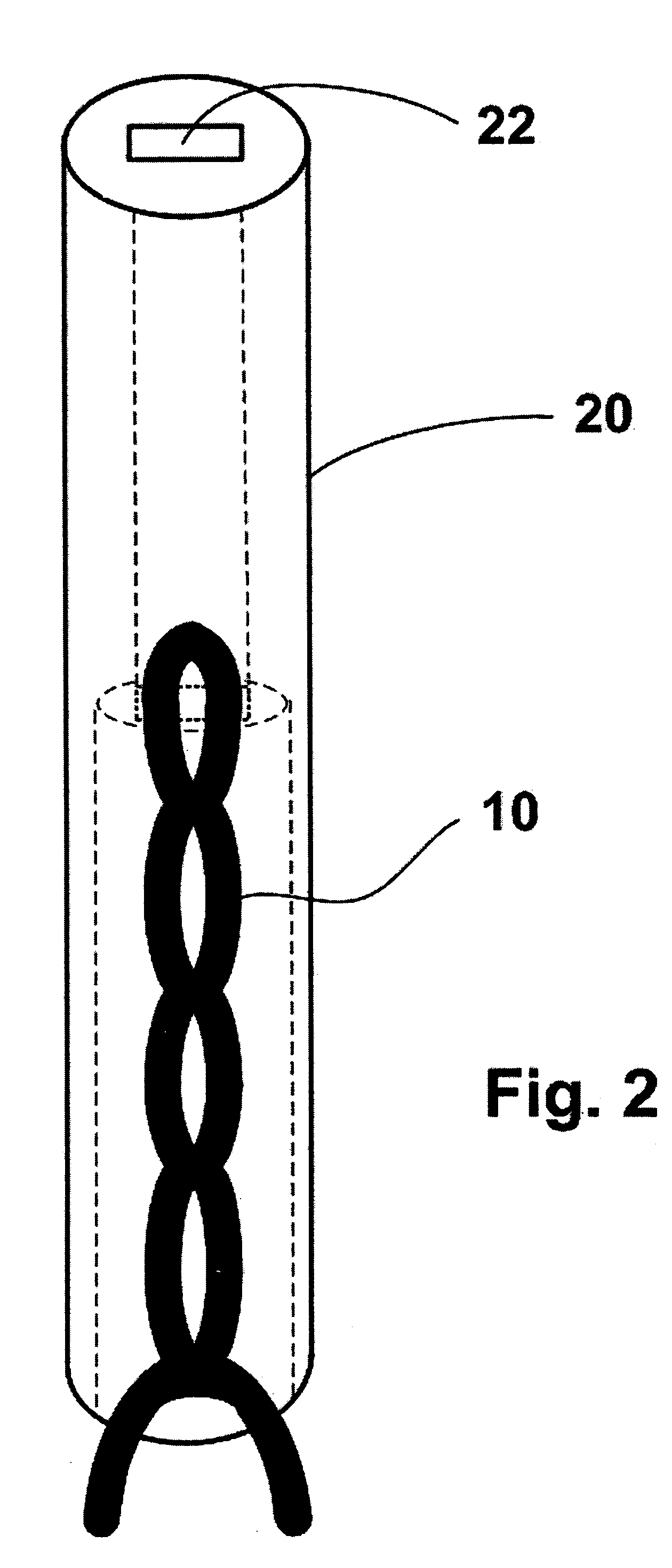

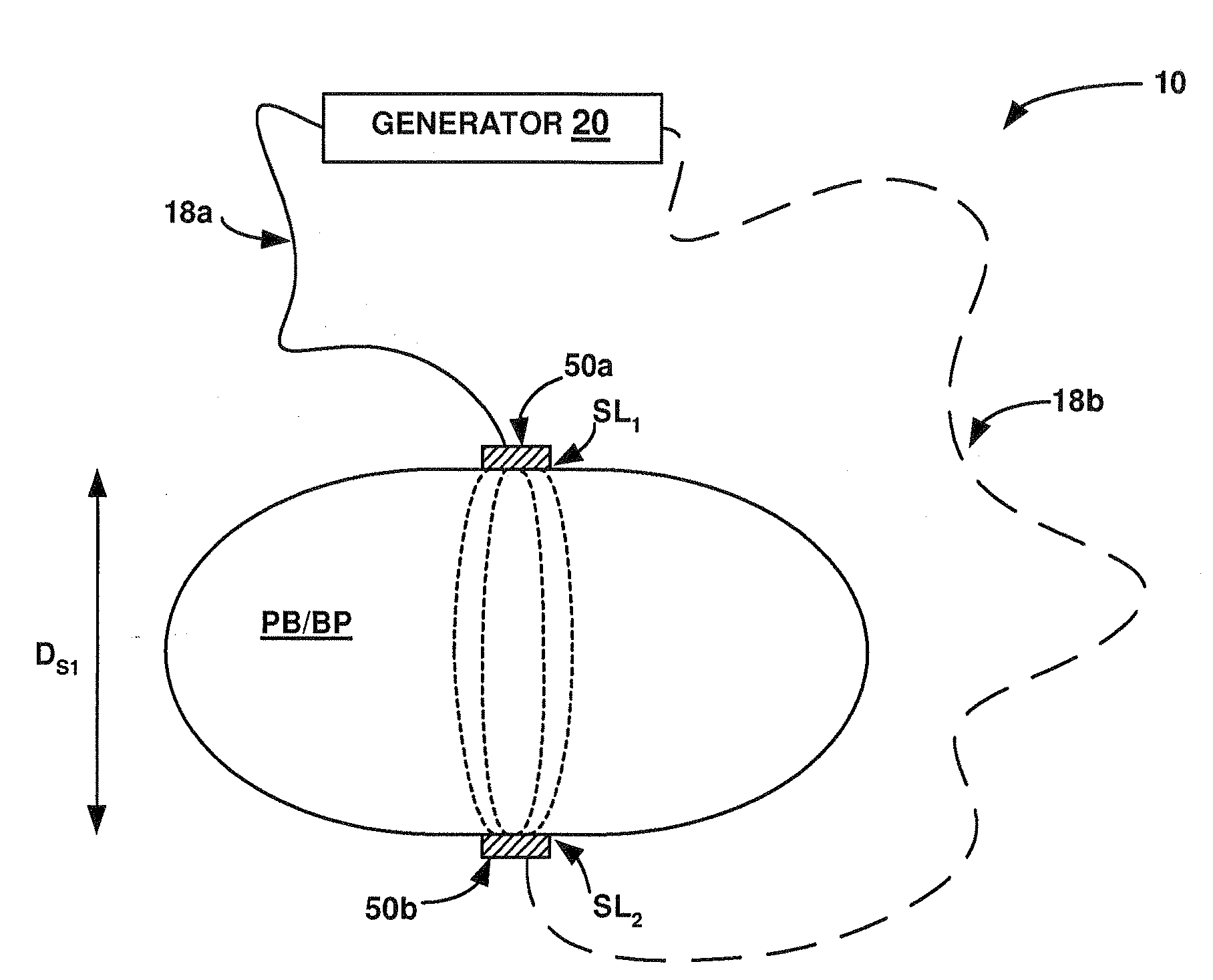

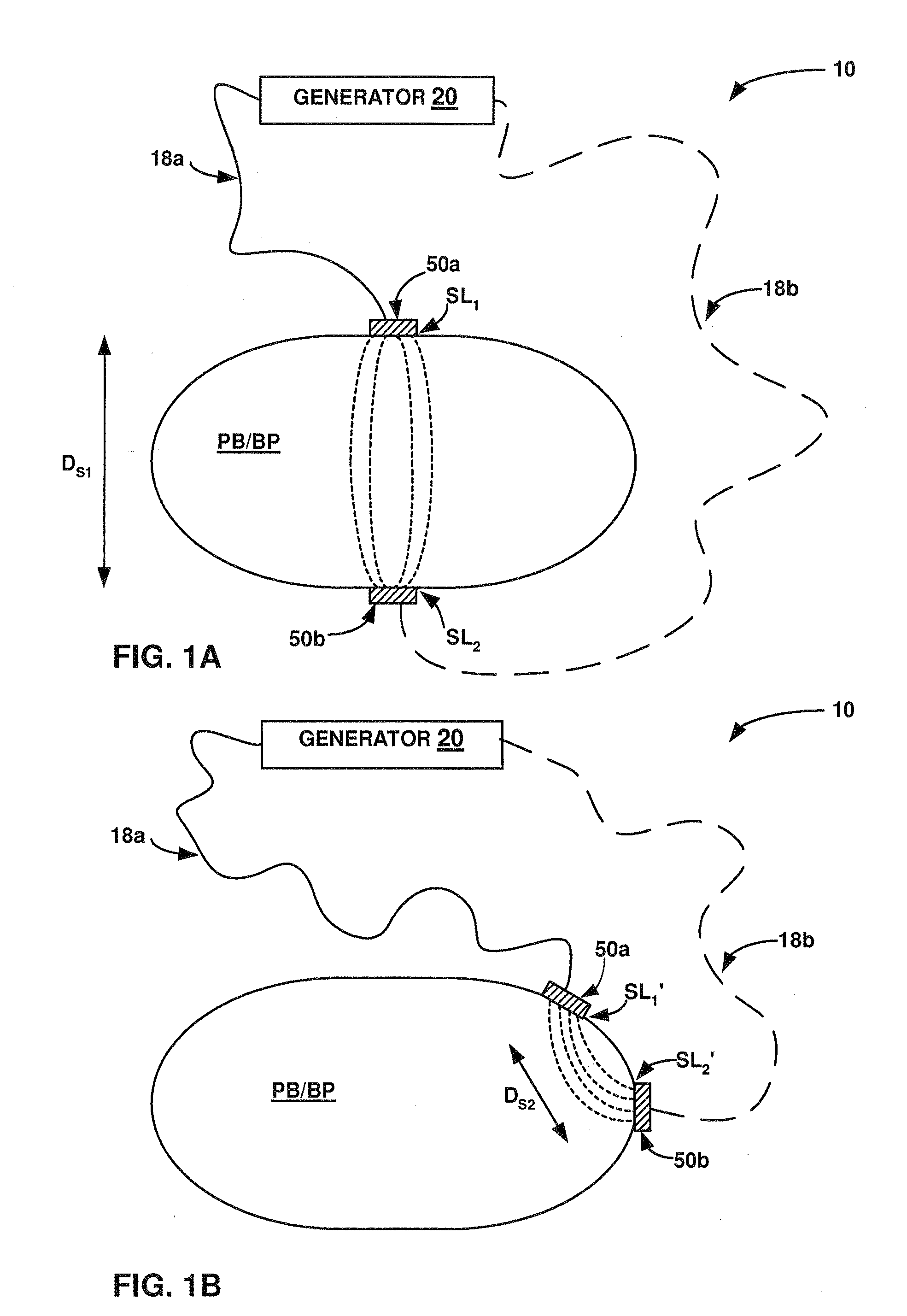

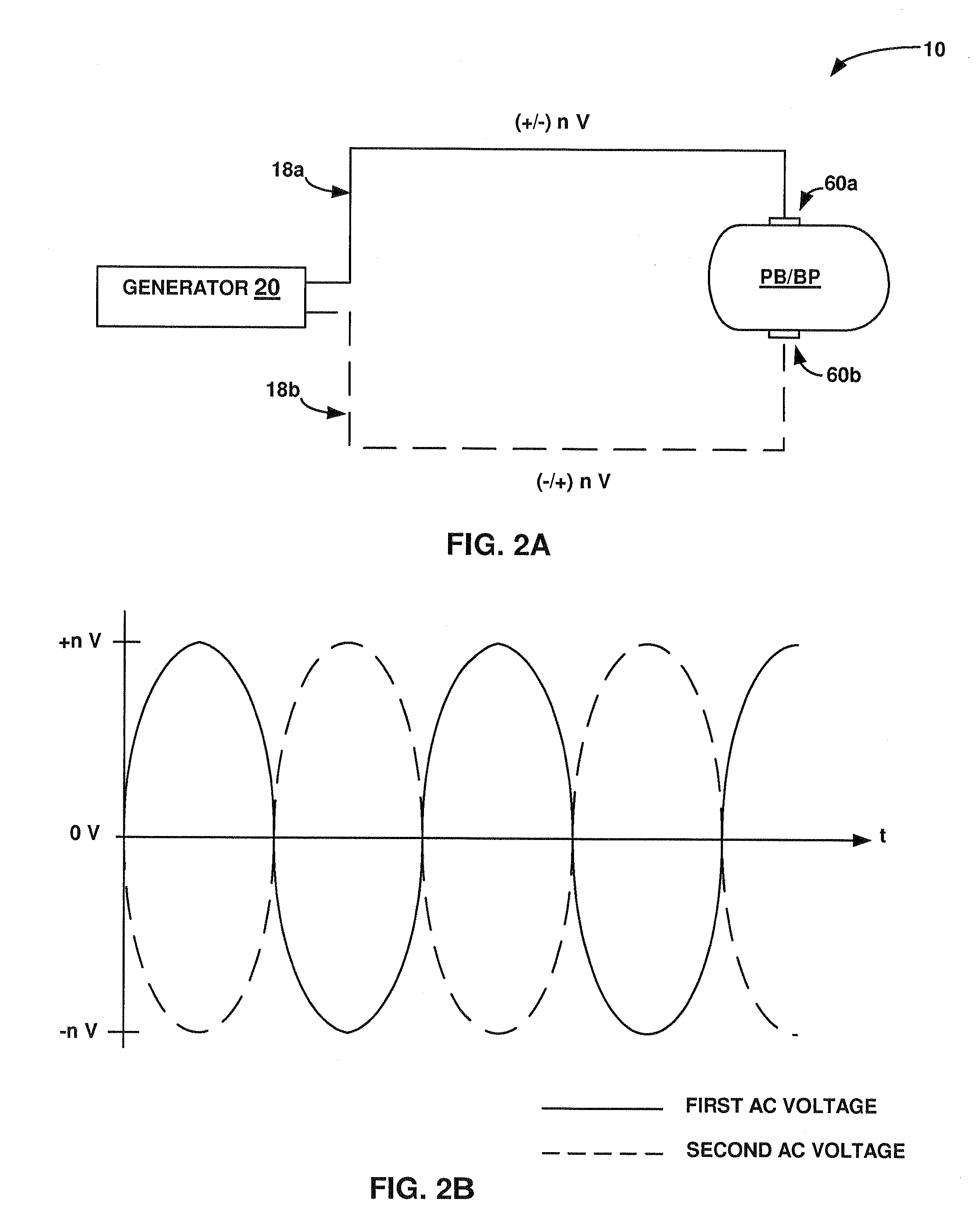

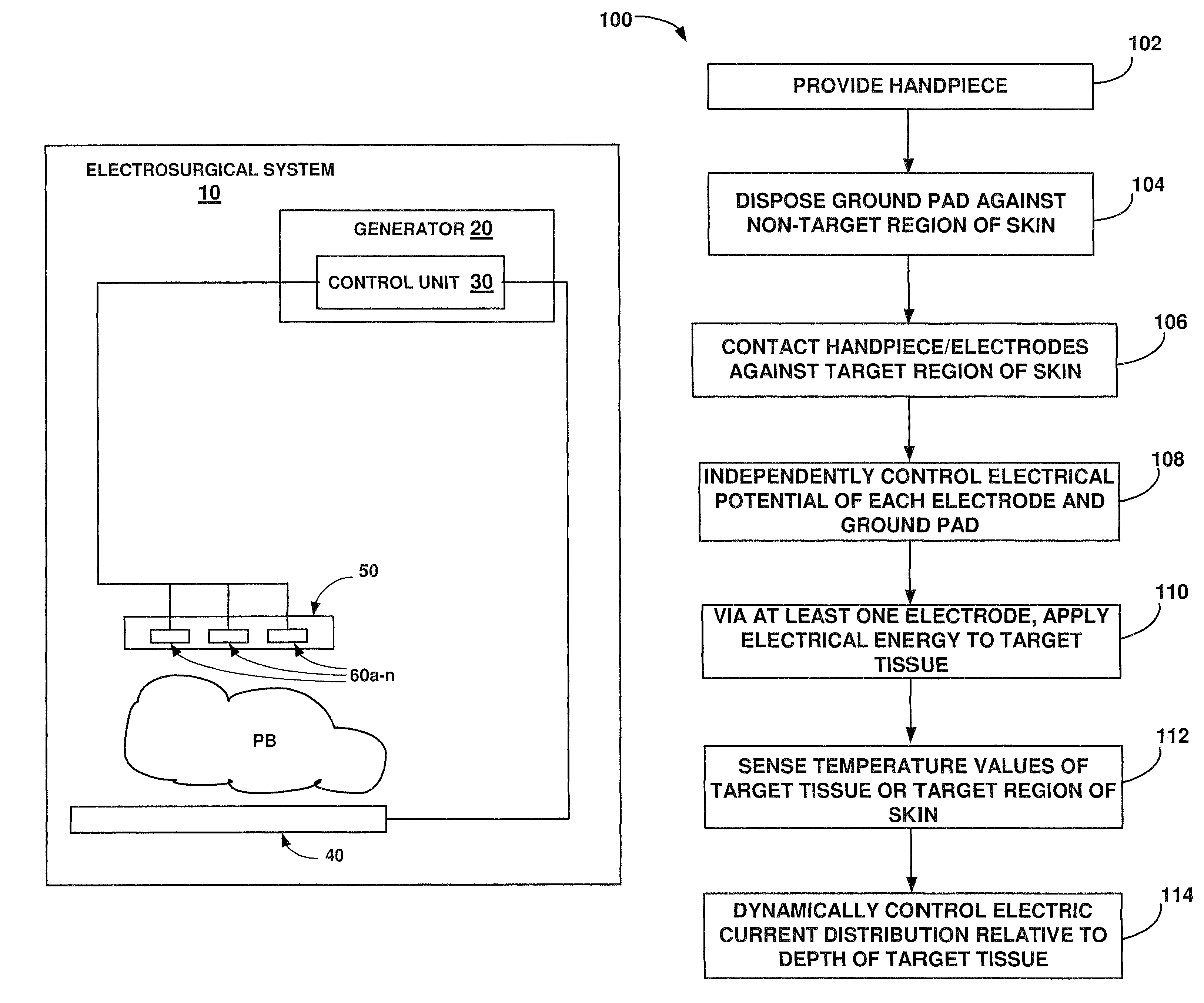

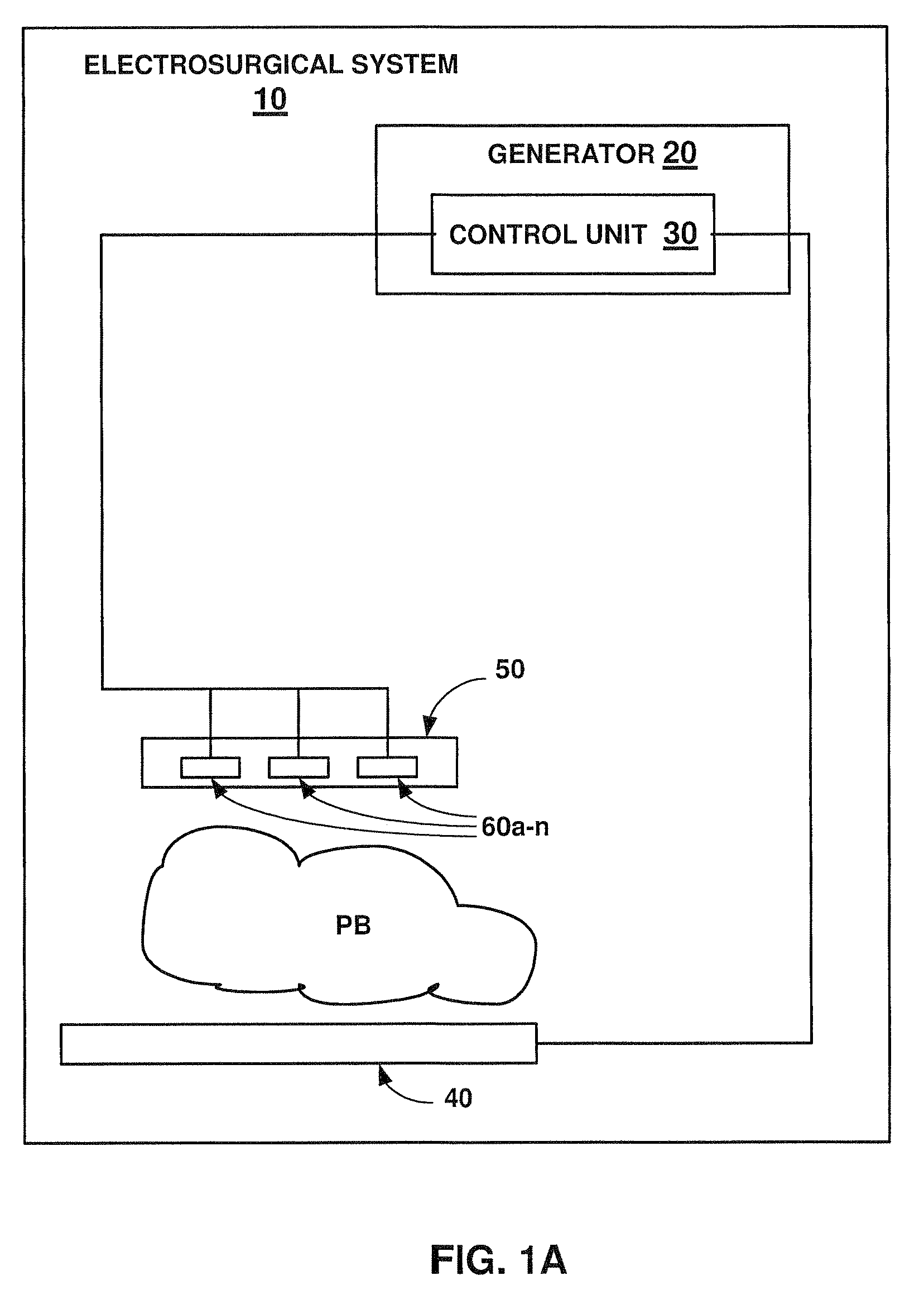

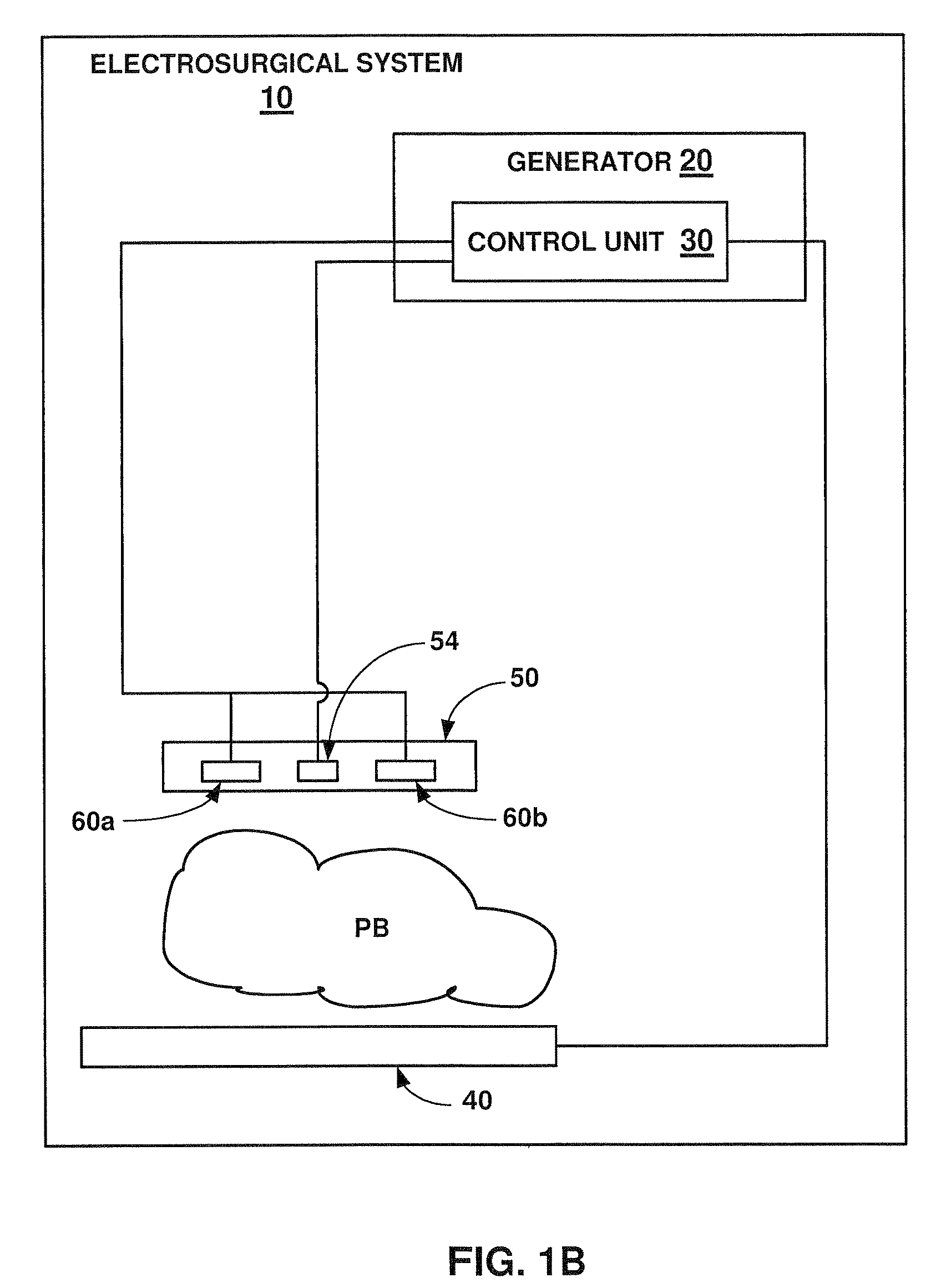

Symmetrical RF electrosurgical system and methods

Systems, apparatus, and methods for treating a patient's tissue via electric energy delivered concurrently from a first electrode of a first handpiece and a second electrode of a second handpiece. Each of the first and second handpieces may have the same or similar structure and may be separately manipulable to different locations on the patient's skin to allow the rapid treatment of target tissue(s) at various regions of the patient's body. The first and second handpieces may each be coupled to an electrosurgical generator configured for providing first and second AC voltages of equal magnitude and opposite polarity to the first and second electrodes, respectively. The first and second electrodes may each comprise a spiral inductor.

Owner:CUTERA

Printed circuit board having three-dimensional spiral inductor and method of fabricating same

ActiveUS7170384B2Increase inductancePrinted circuit aspectsPrinted circuit manufactureSpiral inductorConductive materials

A printed circuit board (PCB) having a three-dimensional spiral inductor, which includes a plurality of insulating layers and conductor layers. The PCB comprises a plurality of coil conductor patterns made of conductive material and shaped into strips, which is provided on the plurality of conductor layers, respectively, such that the plurality of coil conductor patterns are parallel to each other and positioned on the same plane perpendicular to the conductor layers, and in which each of the plurality of coil conductor patterns is longer than an adjacent inner coil conductor pattern.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

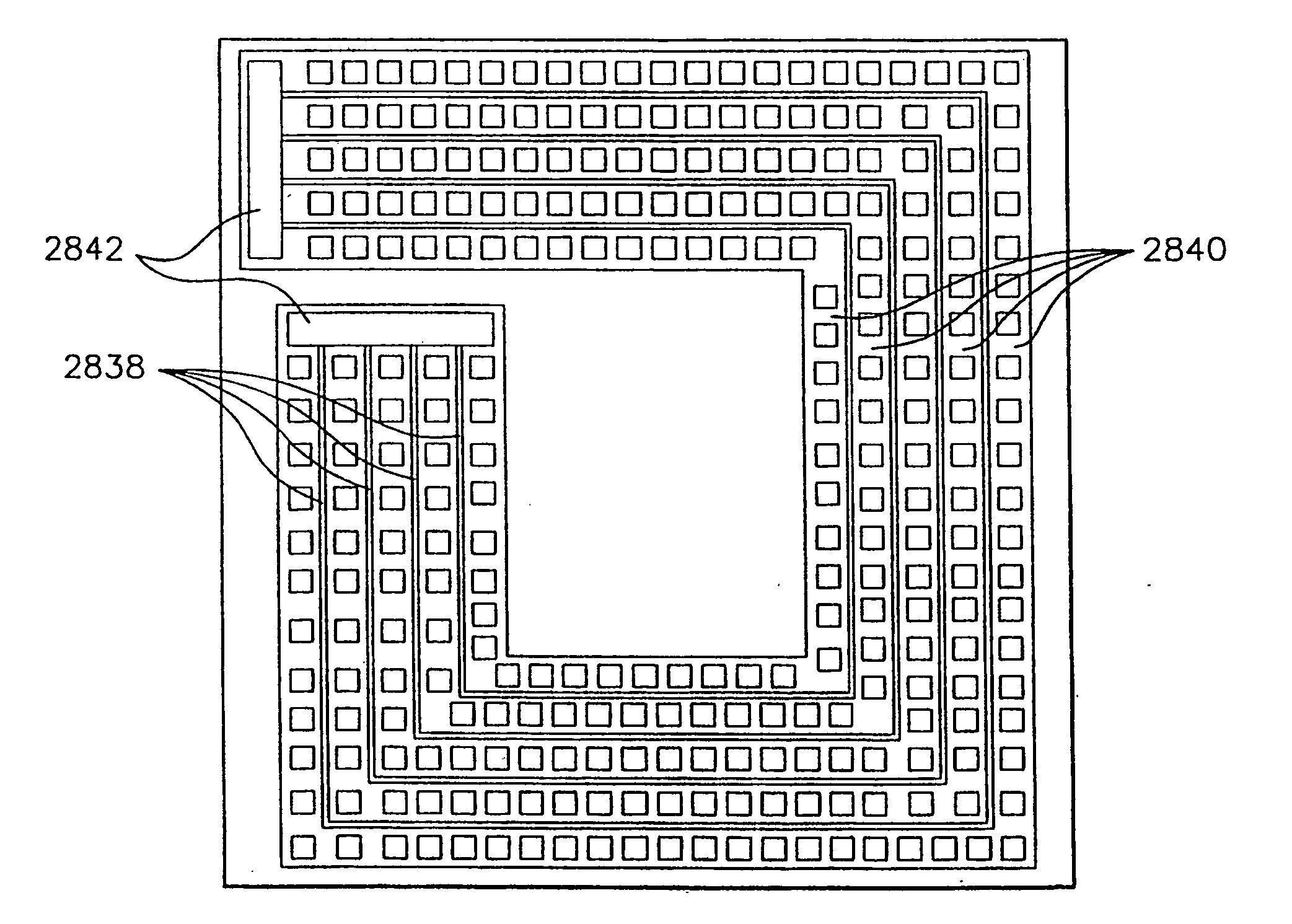

Integrated spiral inductor

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

Spiral inductor semiconducting device with grounding strips and conducting vias

InactiveUS20020084509A1Useful operationGood effectTransformers/reacts mounting/support/suspensionSemiconductor/solid-state device detailsCapacitanceSpiral inductor

An integrated semiconducting device comprises a semiconducting substrate, a plurality of grounding strips disposed above the substrate in a lower metal level of the semiconducting device, an inductor positioned in an upper metal level of the semiconducting device, and a plurality of conducting vias connected to and extending away from the grounding strips towards the inductor. The inductor, conducting via, ground strips structure forms a Faraday cage that acts as a shield against electromagnetic radiation. The number and placement of the conductive vias are adjustable and can be optimized based on the relative importance of maximizing the quality factor Q of the inductor or minimizing the capacitance between the inductor and ground.

Owner:GLOBALFOUNDRIES US INC

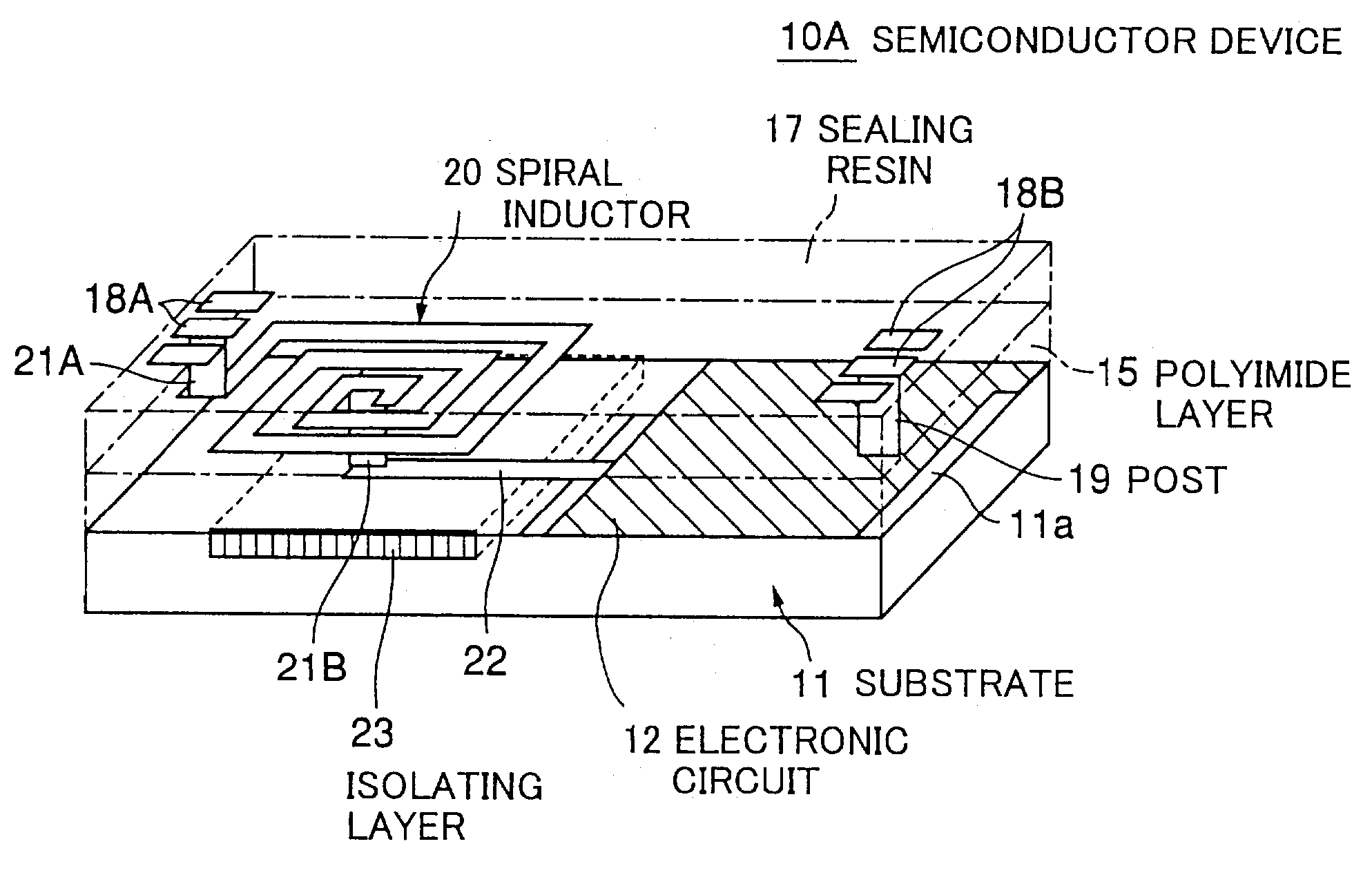

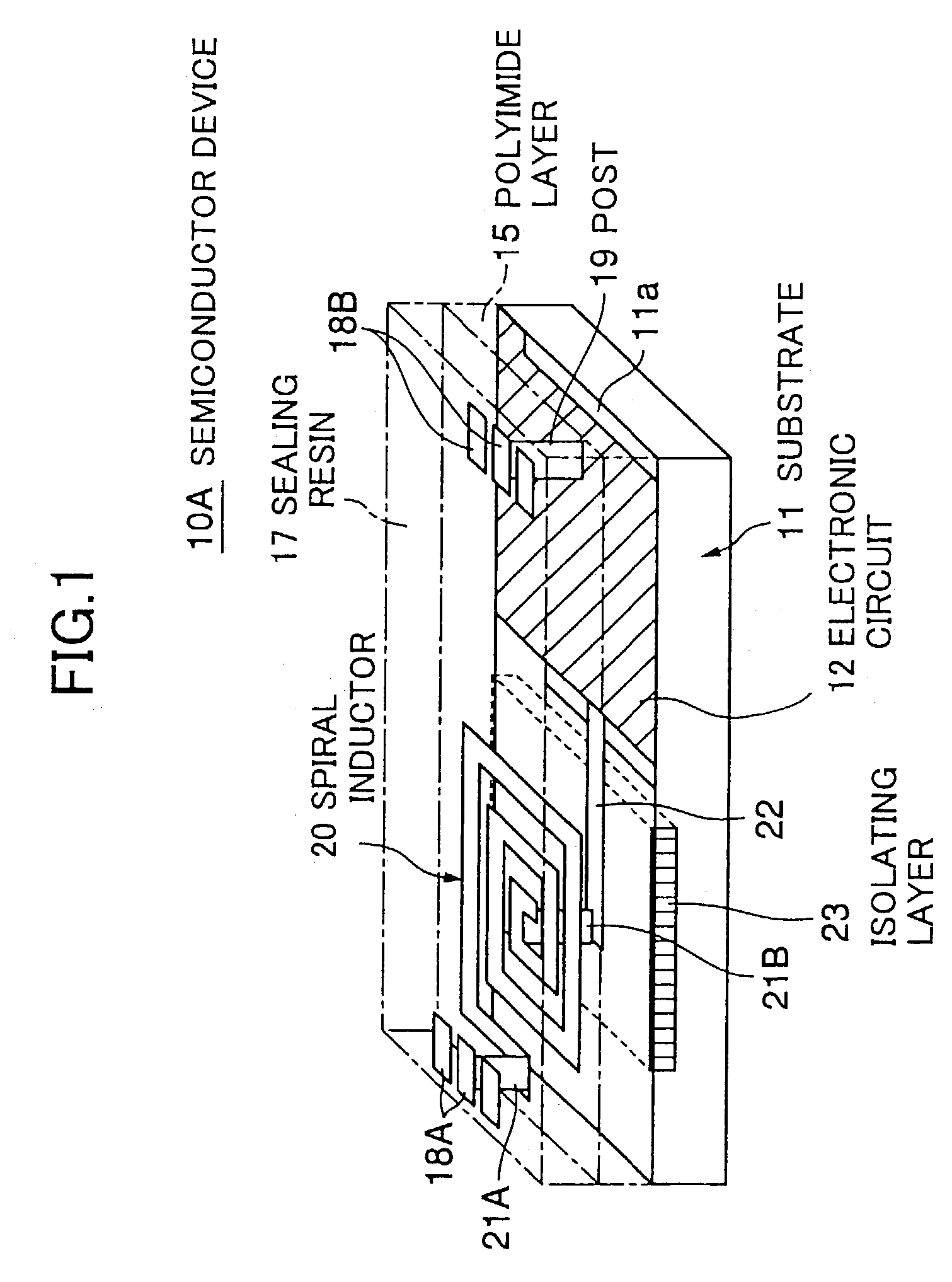

Electronic device

InactiveUS7064645B2Improve reliabilityNot degradedSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsMiniaturizationSpiral inductor

The present invention realizes a miniaturized electronic device that is still capable of maintaining its high reliability even when miniaturized. To this end, the electronic device has an electronic circuit, comprising: a substrate with a circuit formation surface on which one part of the electronic circuit is formed; a polyimide layer that is formed on the circuit formation surface; and a spiral inductor constituting another part of the electronic circuit, which is formed into a pattern on the polyimide layer.

Owner:FUJITSU LTD

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Resonant tree driven clock distribution grid

InactiveUS7237217B2Efficiently distributedConsumes less powerSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceElectrical conductor

An integrated circuit (IC), IC assembly and circuit for distributing a clock signal in an integrated circuit includes a capacitive clock distribution circuit having at least one conductor therein. At least one inductor is formed in a metal layer of the integrated circuit and is coupled to the clock distribution circuit. The inductor, generally in the form of a number of spiral inductors distributed throughout the integrated circuit, provides an inductance value selected to resonate with the capacitive clock distribution circuit at resonance, power dissipation is reduced while skew and jitter performance can be improved.

Owner:IBM CORP

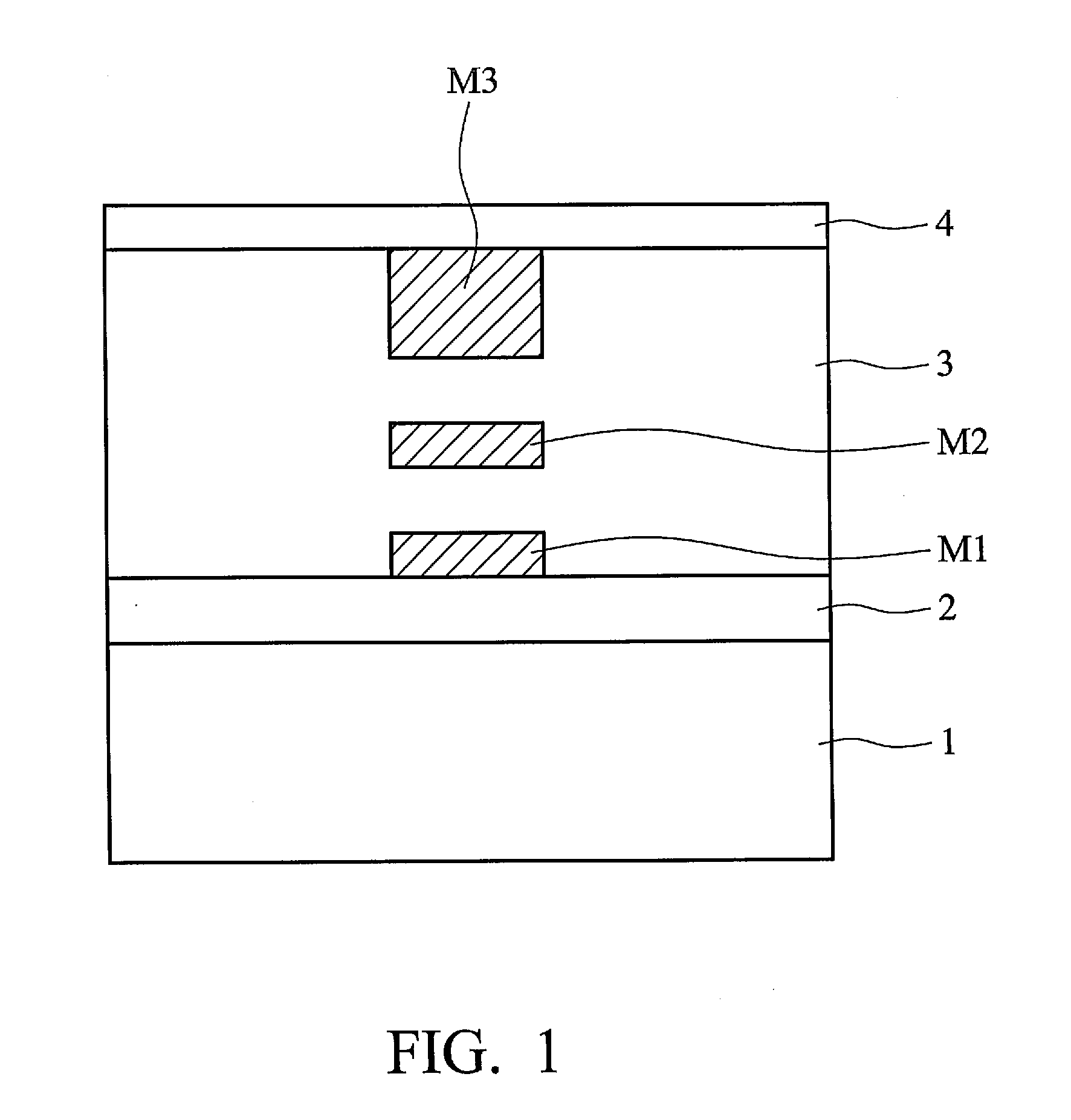

Spiral inductor and method for fabricating semiconductor integrated circuit device having same

InactiveUS20020036335A1Solid-state devicesSemiconductor/solid-state device manufacturingSpiral inductorEngineering

A spiral inductor comprising: a substrate; a protruding portion which is formed on the top face of the substrate and the top of which serves as a dummy element for controlling a chemical mechanical polishing process; and a conductive layer which is formed on the substrate so as to have a spiral shape and which serves as an induction element, wherein the protruding portion is formed in a region other than a region directly below the conductive layer.

Owner:KK TOSHIBA

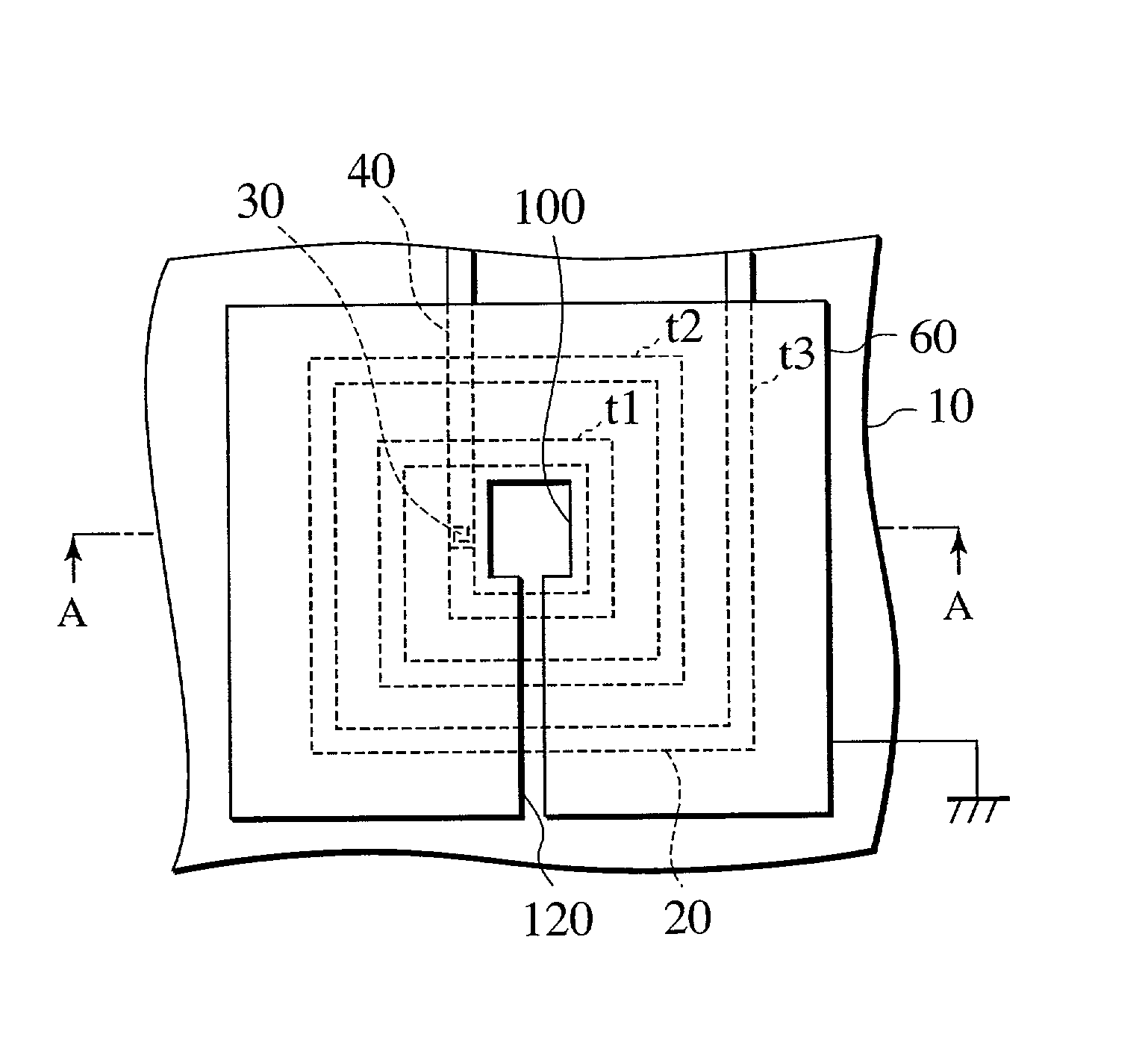

Spiral inductor

ActiveUS20090115562A1Improve performanceHigh quality factorSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsSpiral inductorEngineering

A spiral inductor is provided. The spiral inductor includes a first spiral conductive trace with at least one turn, a second spiral conductive trace, and a connector. The first spiral conductive trace comprises an outer end and an inner end. The second spiral conductive trace surrounds a portion of the outermost turn of the first spiral conductive trace, and comprises a first end and a second end. The connector electrically connects to the inner end and the first end.

Owner:VIA TECH INC

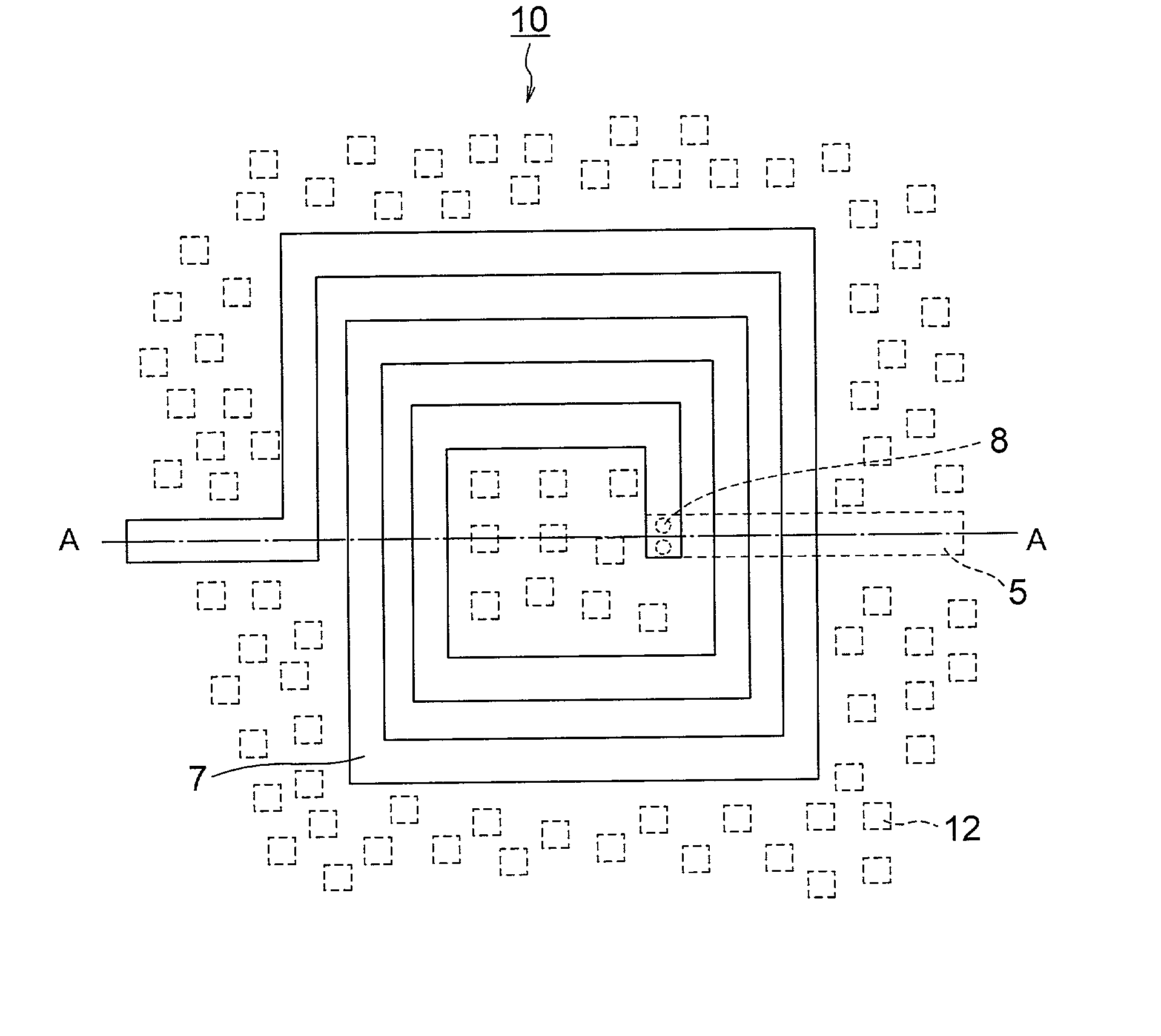

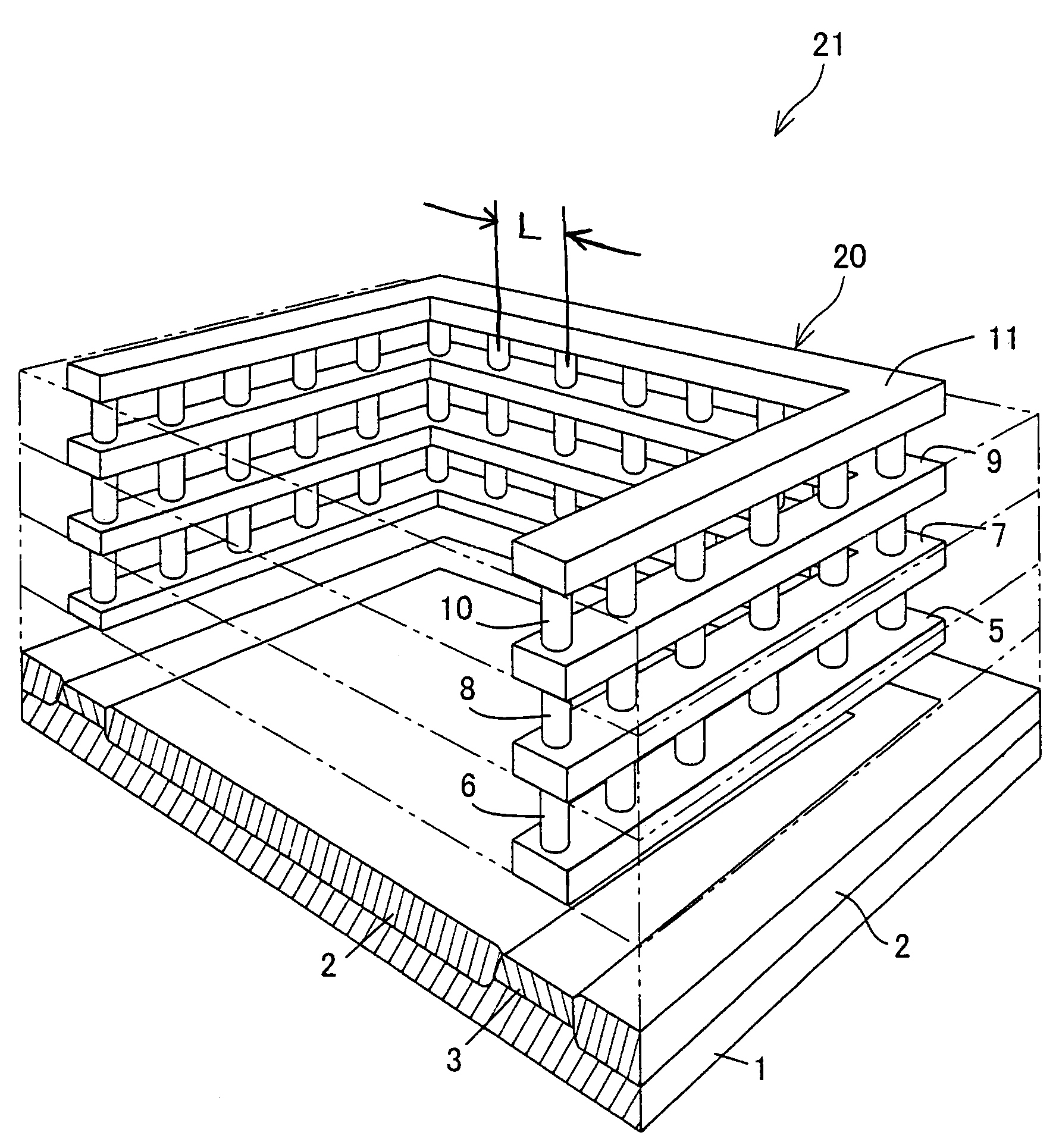

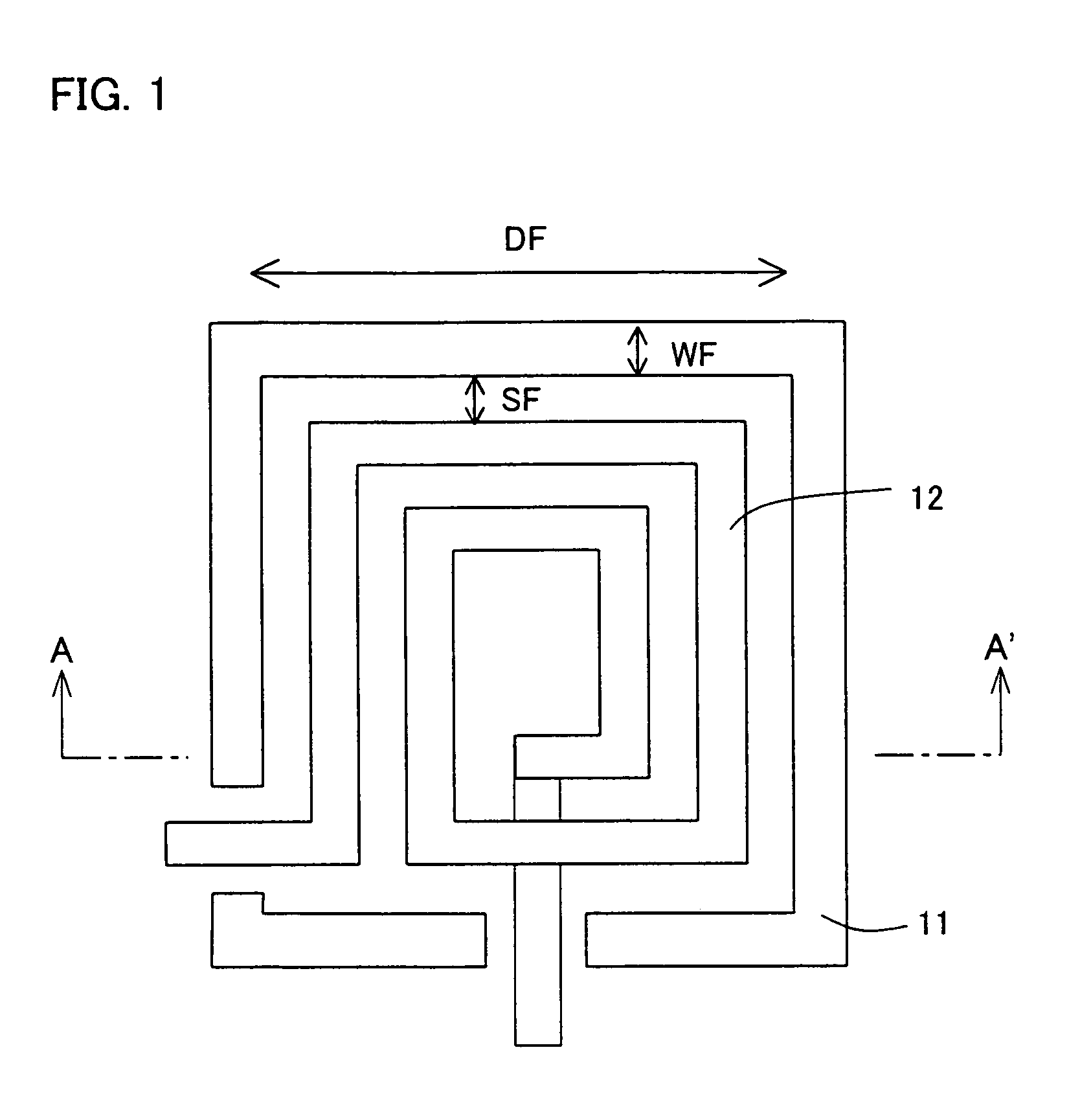

Integrated circuit

InactiveUS6982477B2Decrease electromagnetic coupling noise noiseReduce noiseTransistorSemiconductor/solid-state device detailsElectromagnetic couplingLine width

A lamination of metal wire layers forms an electromagnetic isolation structure. The metal wire layers are connected with each other by vias, so that a metal fence having a laminated structure is formed. The metal fence is provided so as to surround an element (e.g. a spiral inductor) that generates an electromagnetic field in an integrated circuit. The metal wire satisfies d≦λ / 8, WF≧5δ, and L≦λ / 20, where δ is a skin depth of an electromagnetic wave, c is a velocity of light, f is an operating frequency of the integrated circuit, d is a lateral-direction size of a metal-fence region, WF is a surrounding-line width of the metal fence, L is an interval between the vias, and λ=c / f is a wavelength of a signal. With this arrangement, it is possible to decrease electromagnetic coupling noises and coupling noises caused via the substrate.

Owner:SHARP KK

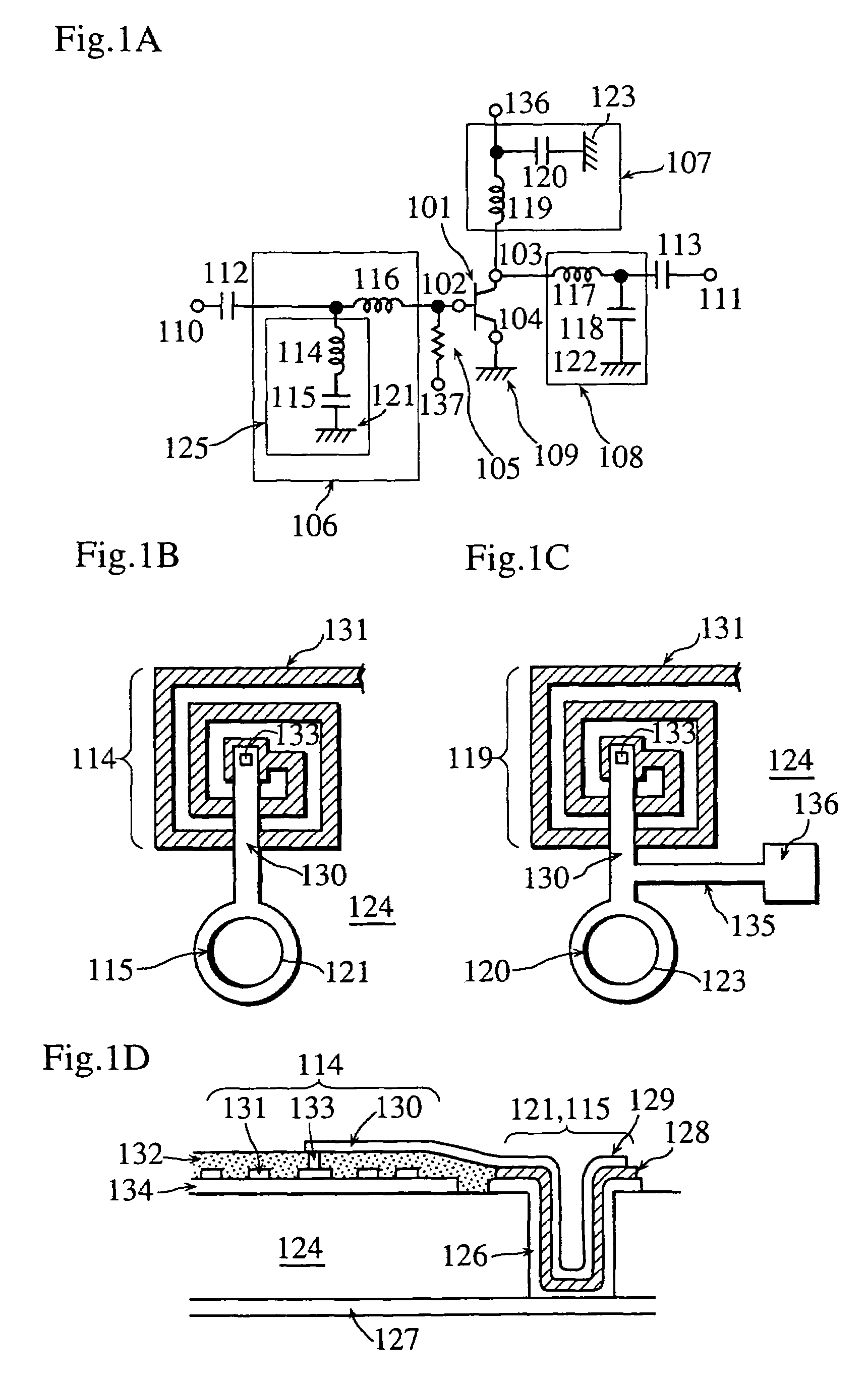

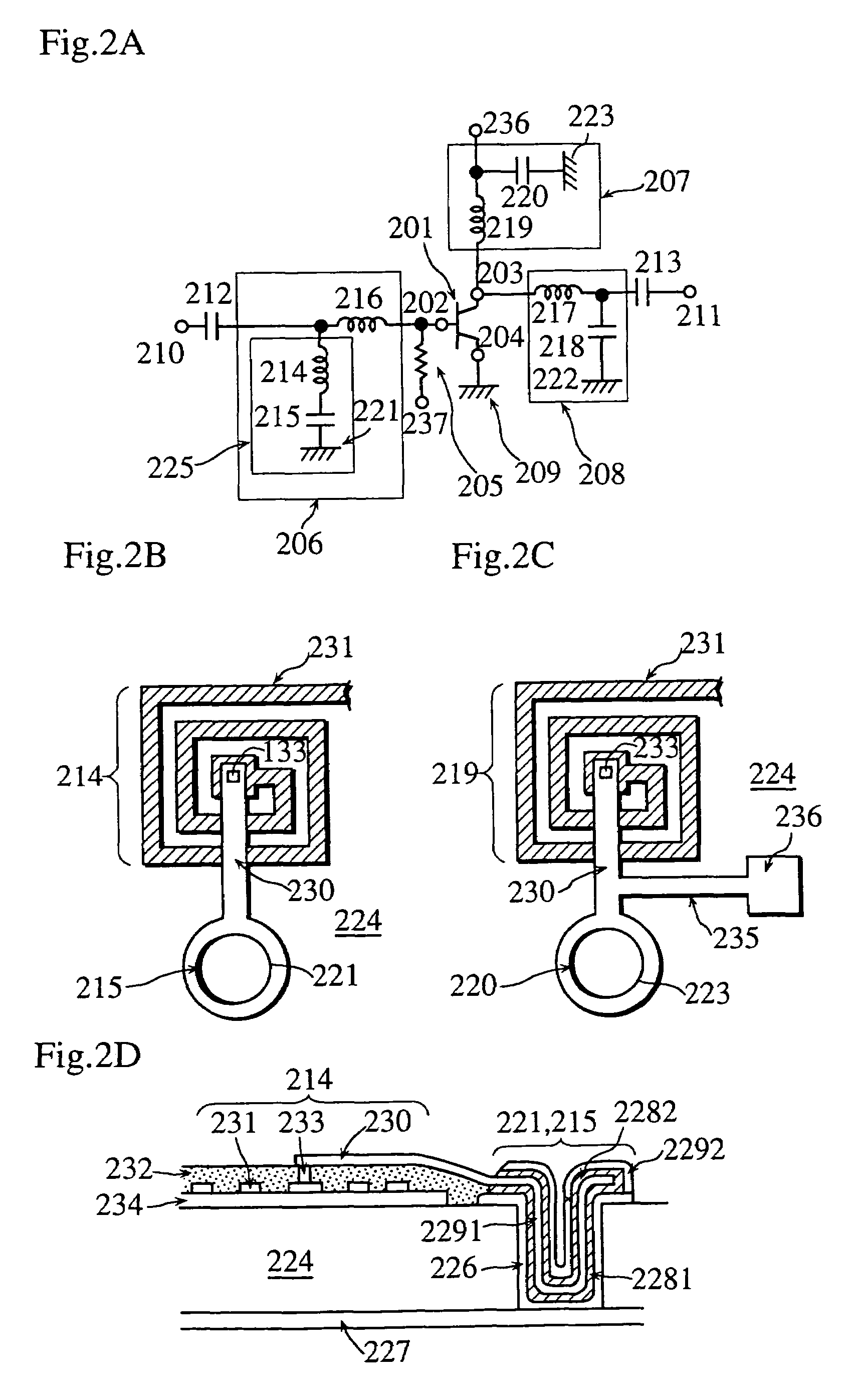

RF passive circuit and RF amplifier with via-holes

InactiveUS7005721B2Reduce occupancyIncrease occupancySemiconductor/solid-state device detailsSolid-state devicesSpiral inductorEngineering

An input matching parallel inductor 114 which utilizes a spiral inductor, and an input matching parallel capacitor 115 which utilizes an MIM capacitor, both being constituting elements of an input matching circuit portion 125, form an input matching parallel capacitor 115 inside an input matching circuit via-hole 121 being formed by applying a method of surface via-hole to the front surface of a GaAs substrate 124. A choke inductor 119 which utilizes a spiral inductor, and a bypass capacitor 120 which utilizes an MIM capacitor, both being constituting elements of a drain voltage feeding circuit 107, form a bypass capacitor 120 inside a drain voltage feeding circuit via-hole 123 formed by applying a method of surface via-hole to the front surface of the GaAs substrate 124. A drain voltage terminal 136 is extended by a drawing wire 135 from between the spiral inductor and the drain voltage feeding circuit via-hole 123.

Owner:PANASONIC CORP

Semi-conductor device

InactiveCN1361550AInhibitionExcellent electromagnetic wave shielding performanceMagnetic/electric field screeningSemiconductor/solid-state device detailsSpiral inductorMagnetic flux

The invention provides a semiconductor device provided with a spiral inductor and an electromagnetic wave shielding layer for demonstrating an excellent electromagnetic wave shielding effect without degrading a Q value. In the electromagnetic wave shielding layer arranged above or below the spiral inductor provided with a spiral pattern, an opening part in a magnetic flux passing area generated at the center of the spiral pattern by the spiral inductor and a slit from the opening part to a peripheral edge are formed.

Owner:KK TOSHIBA

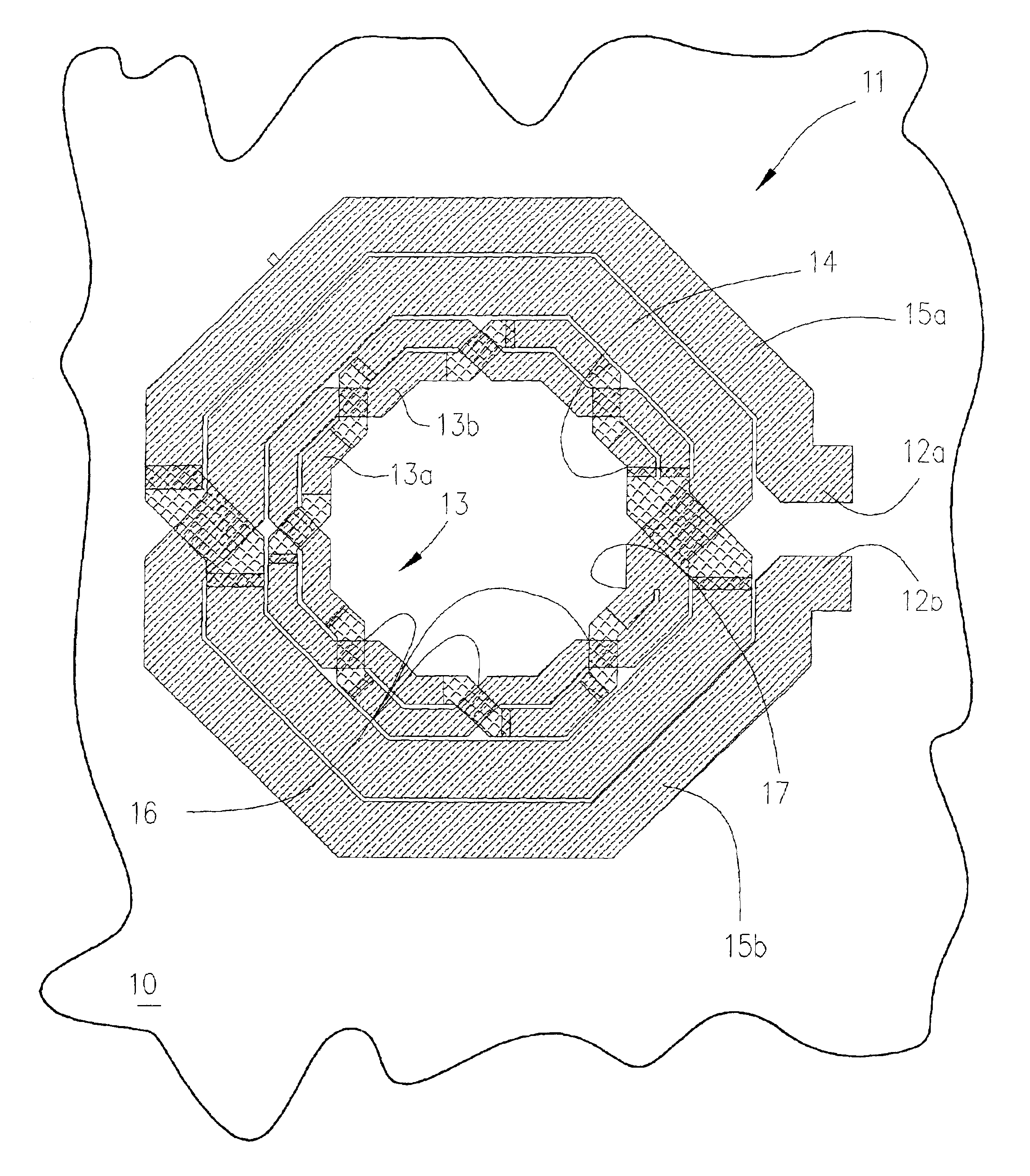

Method for forming a spiral inductor

InactiveUS6922128B2Transformers/reacts mounting/support/suspensionTransformers/inductances casingsTransformerSpiral inductor

A method for forming a spiral inductor (11) or component of a transformer, compatible with very large scale integrated processing, that achieves a higher Q value without occupying more space by splitting at least one turn (13 51) as two or more crisscrossing or interwoven smaller-width turns (13a 13b 52 53 54 55). The at least one turn (51) may, for example, be split into four turns paired up to provide two pairs of two turns, and the turns of each pair may then be interwoven or crisscrossed, and then the two pairs may also be interwoven or crisscrossed. The splitting of a turn into two or more smaller-width turns results in the current being divided among the smaller-width turns.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

Via/line inductor on semiconductor material

InactiveUS7078998B2Increase surface areaHigh quality factorSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsSpiral inductor

A spiral inductor is provided including a substrate and an inductor dielectric layer over the substrate having a spiral opening provided therein. The spiral inductor is in the spiral opening with the spiral inductor including a plurality of parallel spiral vias connected together at center proximate and center distal ends of the spiral inductor.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Spiral inductor

InactiveUS7486168B2Reduce parasitic capacitanceQuality improvementTransformers/inductances coils/windings/connectionsSolid-state devicesSpiral inductorDielectric layer

The present invention relates to a spiral inductor for use in a semiconductor device. The spiral inductor comprises a dielectric layer formed of a plurality of layers stacked on a semiconductor substrate, and a plurality of curved metal lines formed in the dielectric layers which are serially connected in order to form a circular spiral shape.

Owner:DSS TECH MANAGEMENT

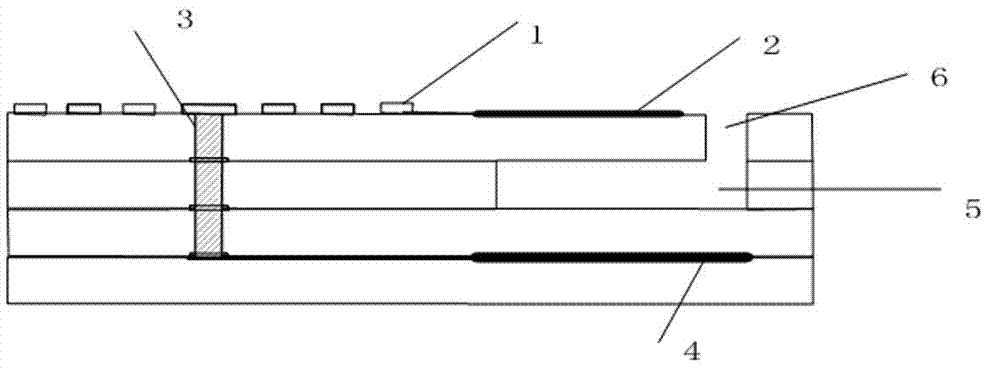

High-temperature pressure sensor and production method thereof

ActiveCN103115704AAvoid it happening againHigh sensitivityPrecision positioning equipmentLamination ancillary operationsCapacitanceSpiral inductor

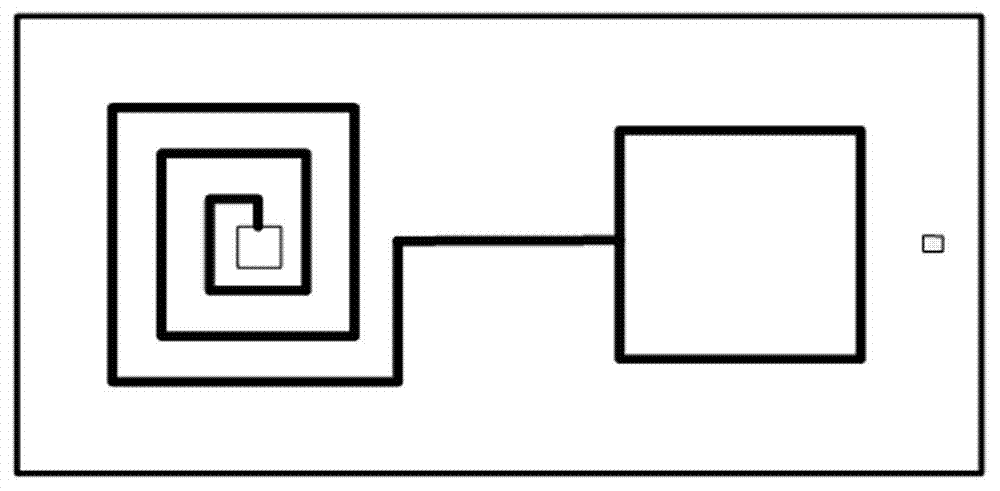

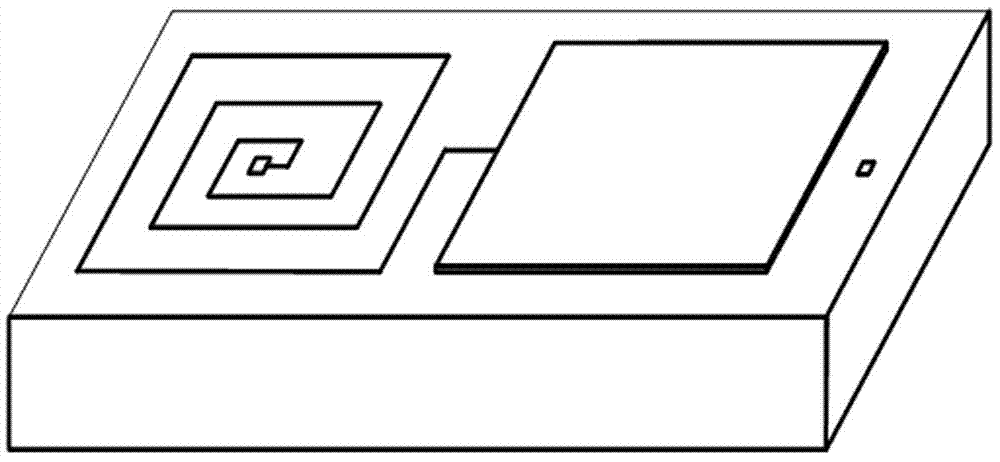

The invention belongs to the technical field of pressure sensors, particularly relates to a high-temperature pressure sensor and a production method thereof and solves the problem that the existing pressure sensor fails to operate normally in environments of high temperature, moistness and the like due to the insufficiently reasonable design. The high-temperature pressure sensor comprises four layers. A planar square spiral inductor and a capacitor upper electrode are made on the first layer by pasting; a sealed pressure cavity is arranged on the second layer; a capacitor electrode is made on the fourth layer by pasting and is connected with an inner circular core of the top planar square spiral inductor. The production method includes filling the pressure cavity with carbon paste; subjecting the laminated structure to high-temperature sintering to volatilize carbon from air holes so as to form a complete cavity; and after sintering, placing glass beads at the air holes to allow for secondary sintering sealing. The high-temperature pressure sensor is capable of operating at normal temperature and high temperature more than 400 DEG C, and is simple in structure, small in size, simple in manufacture process and easy for industrial production.

Owner:ZHONGBEI UNIV