Patents

Literature

537 results about "Very large scale integrated circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

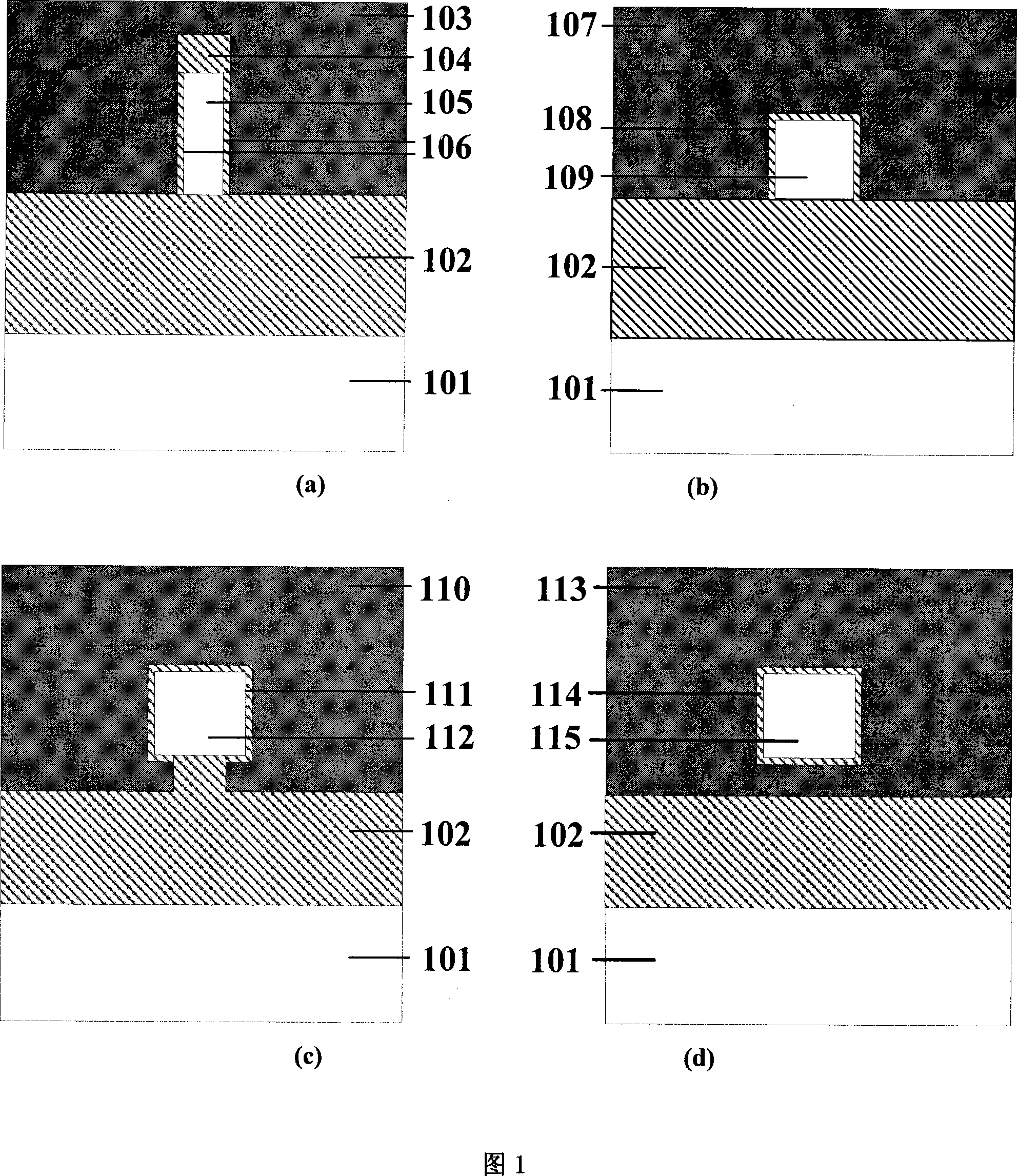

Single-electron floating-gate MOS memory

A Single Electron MOS Memory (SEMM), in which one bit of information is represented by storing only one electron, has been demonstrated at room temperature. The SEMM is a floating gate Metal-Oxide-Semiconductor (MOS) transistor in silicon with a channel width (about 10 nanometers) which is smaller than the Debye screening length of a single electron stored on the floating gate, and a nanoscale polysilicon dot (about 7 nanometers by 7 nanometers by 2 nanometers) as the floating gate which is positioned between the channel and the control gate. An electron stored on the floating gate can screen the entire channel from the potential on the control gate, and lead to: (i) a discrete shift in the threshold voltage; (ii) a staircase relation between the charging voltage and the shift; and (iii) a self-limiting charging process. The structure and fabrication of the SEMM is well adapted to the manufacture of ultra large-scale integrated circuits.

Owner:MINNESOTA RGT UNIV OF A CORP OF MN

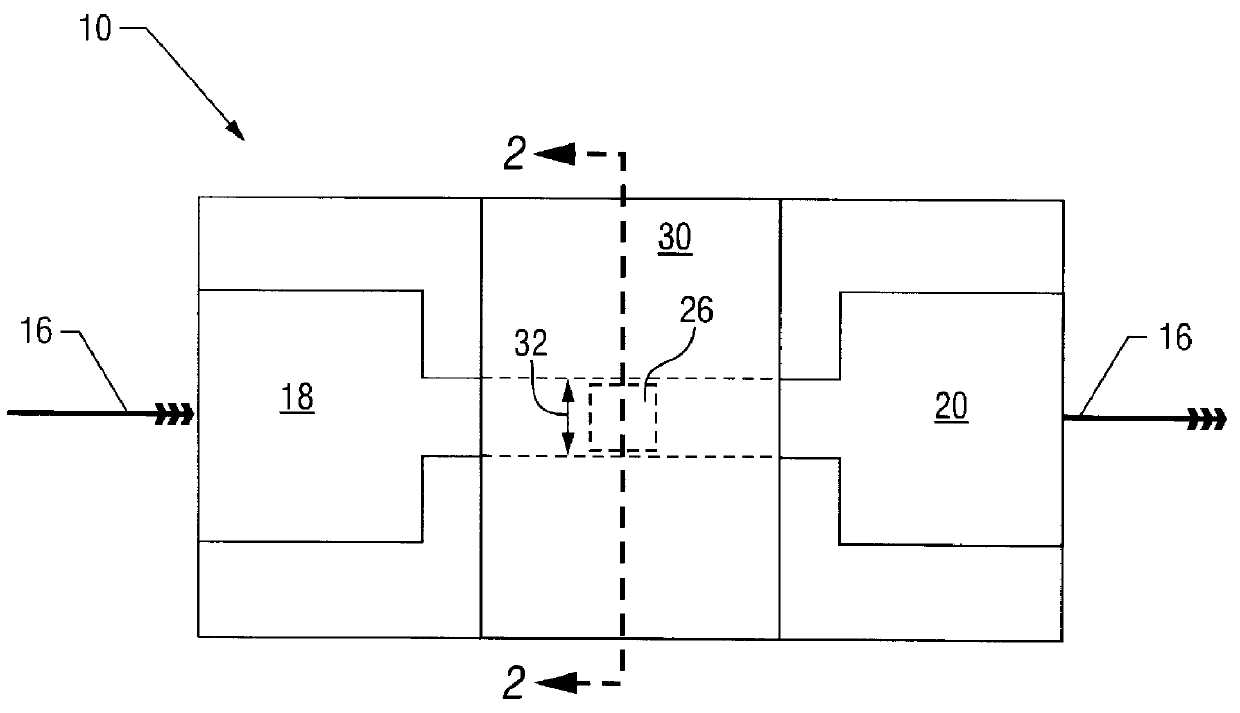

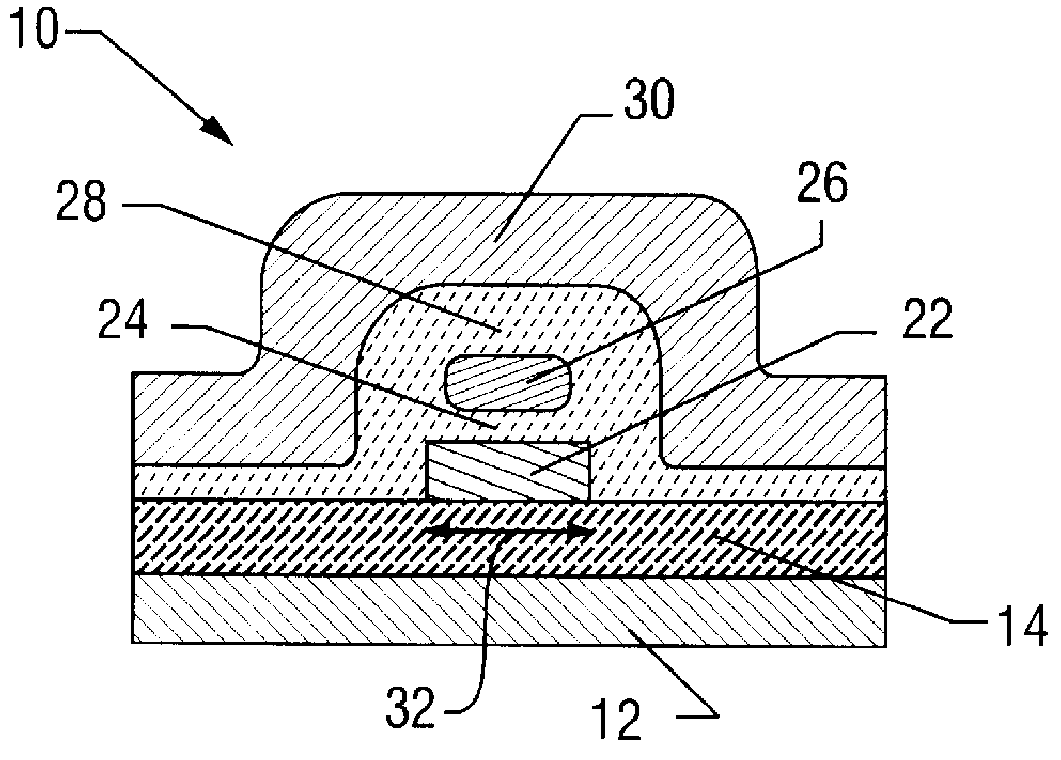

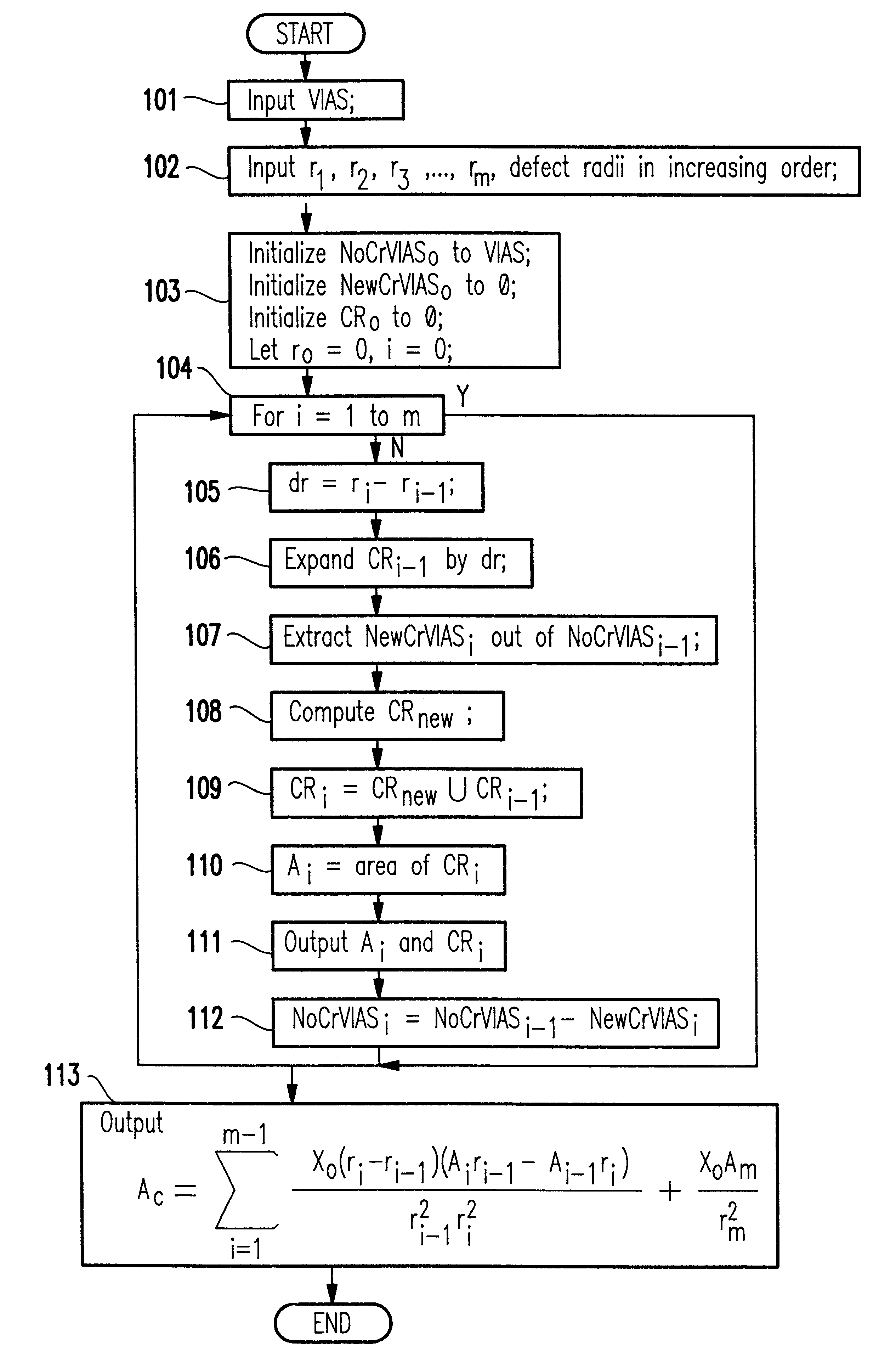

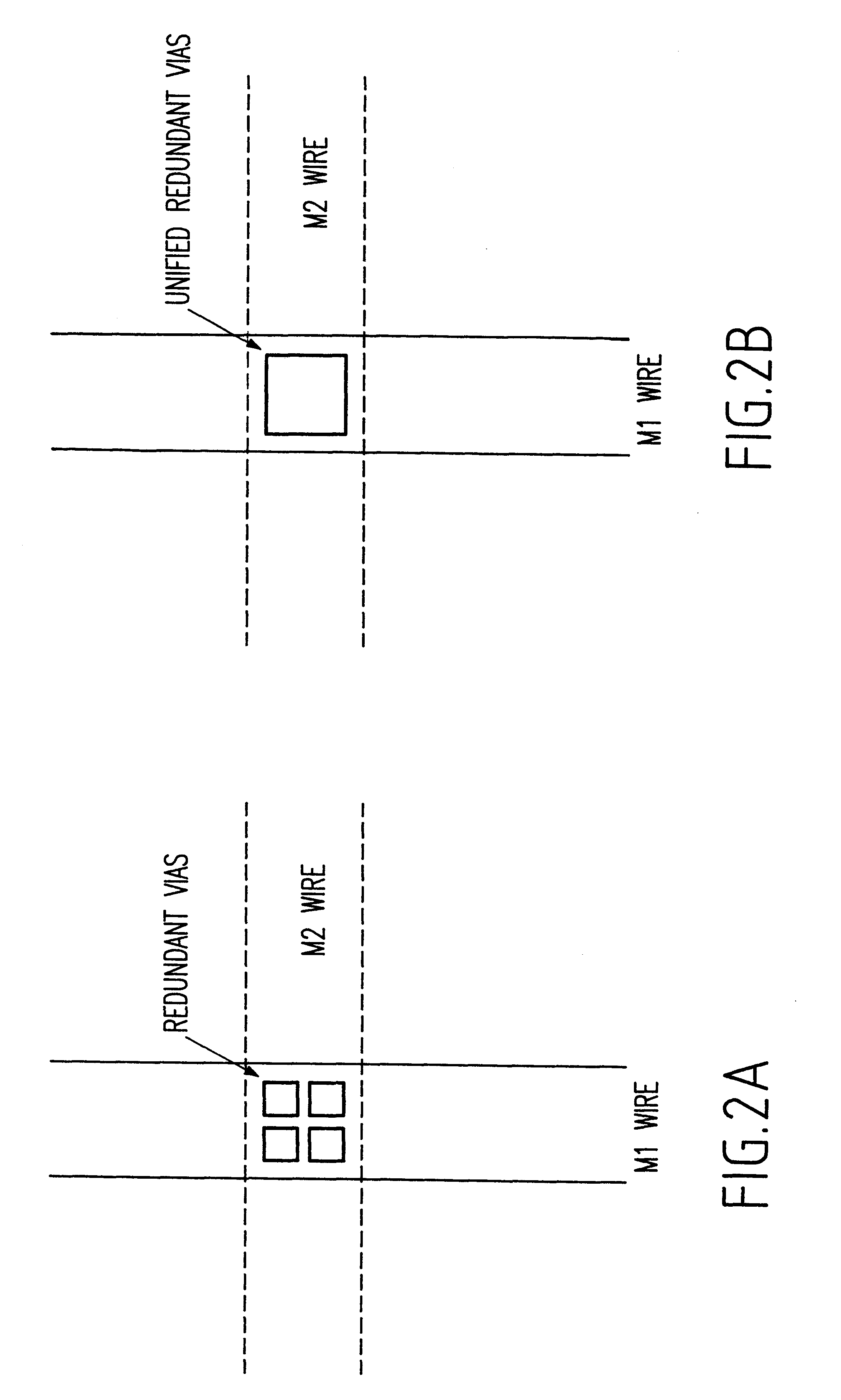

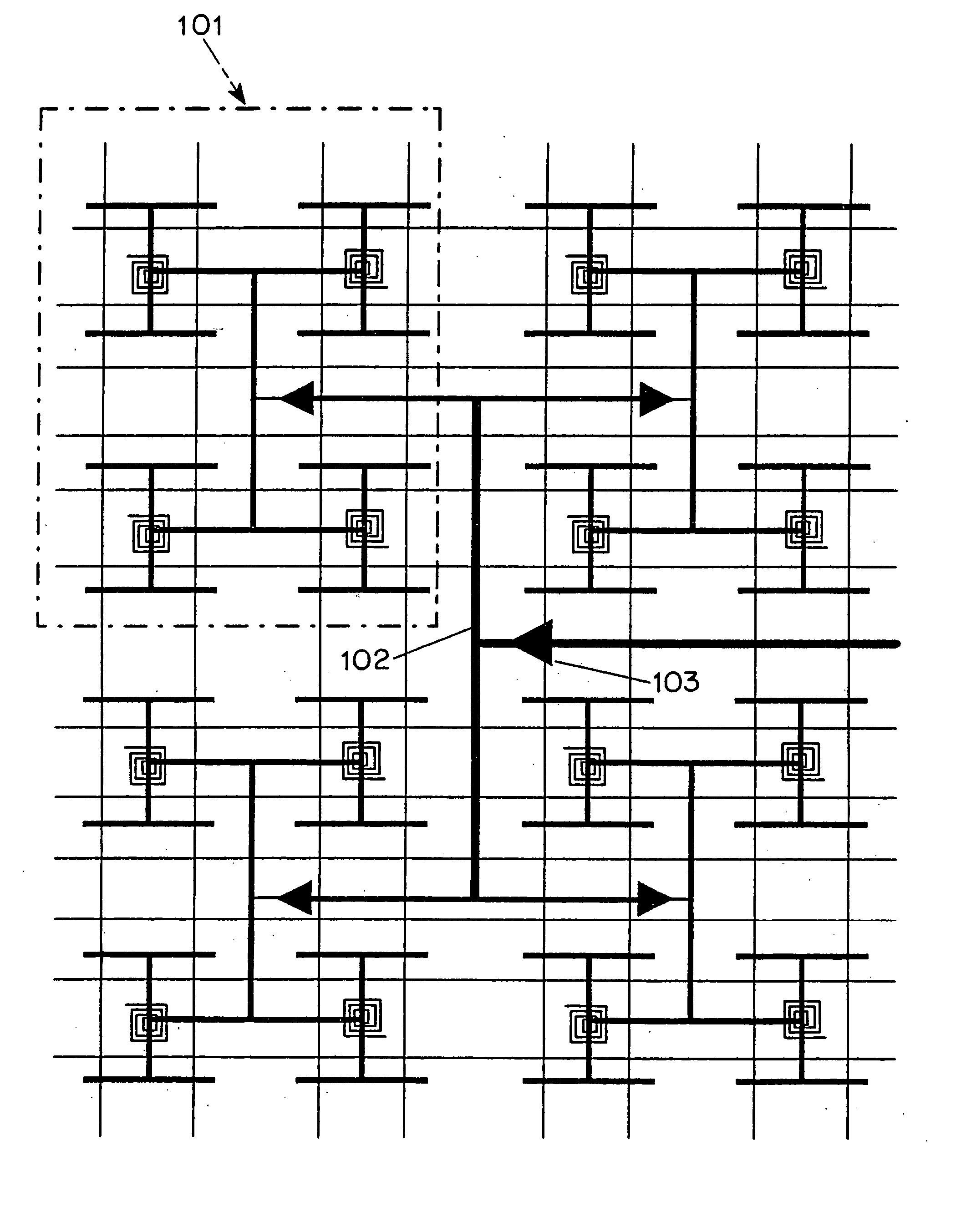

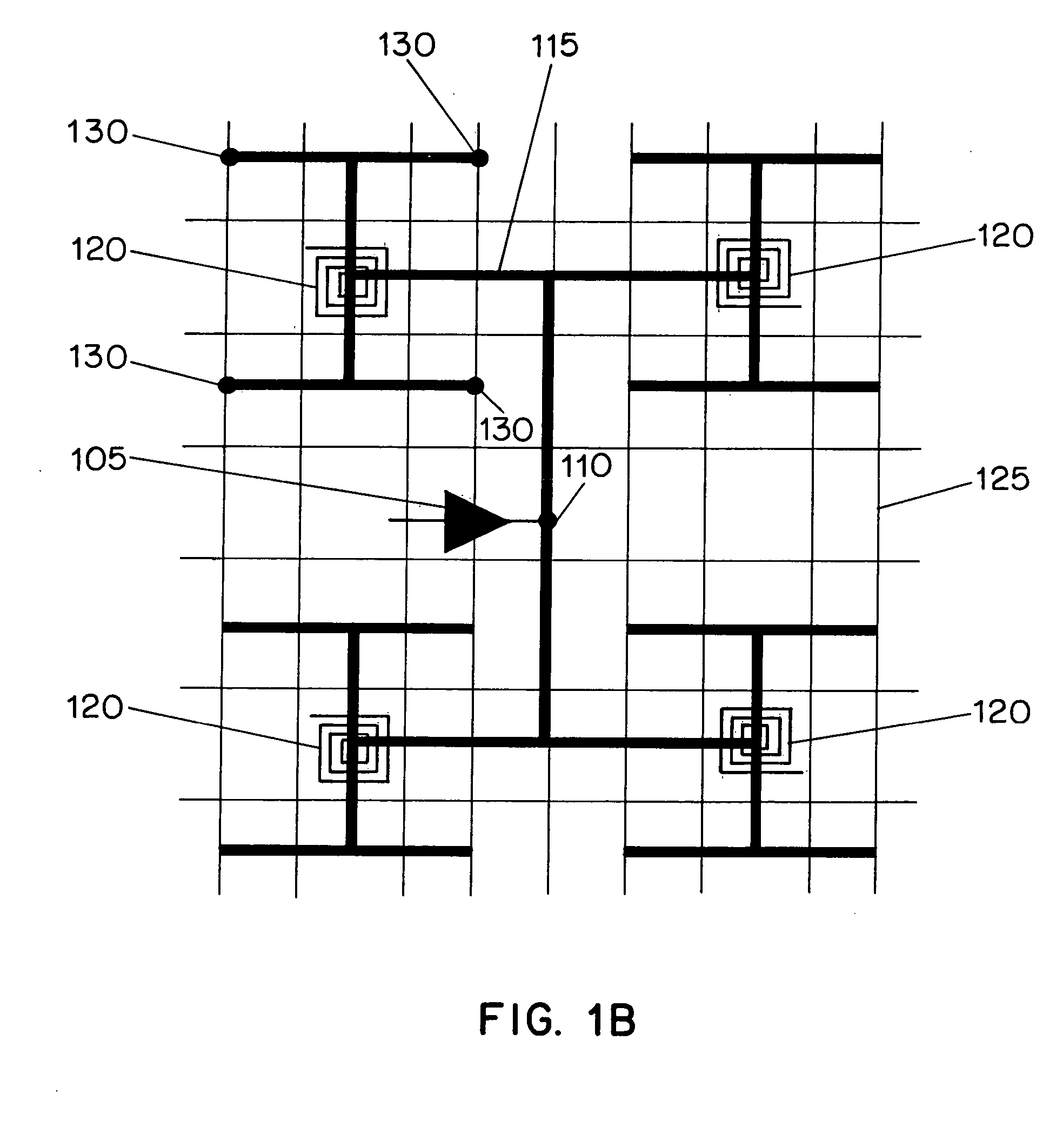

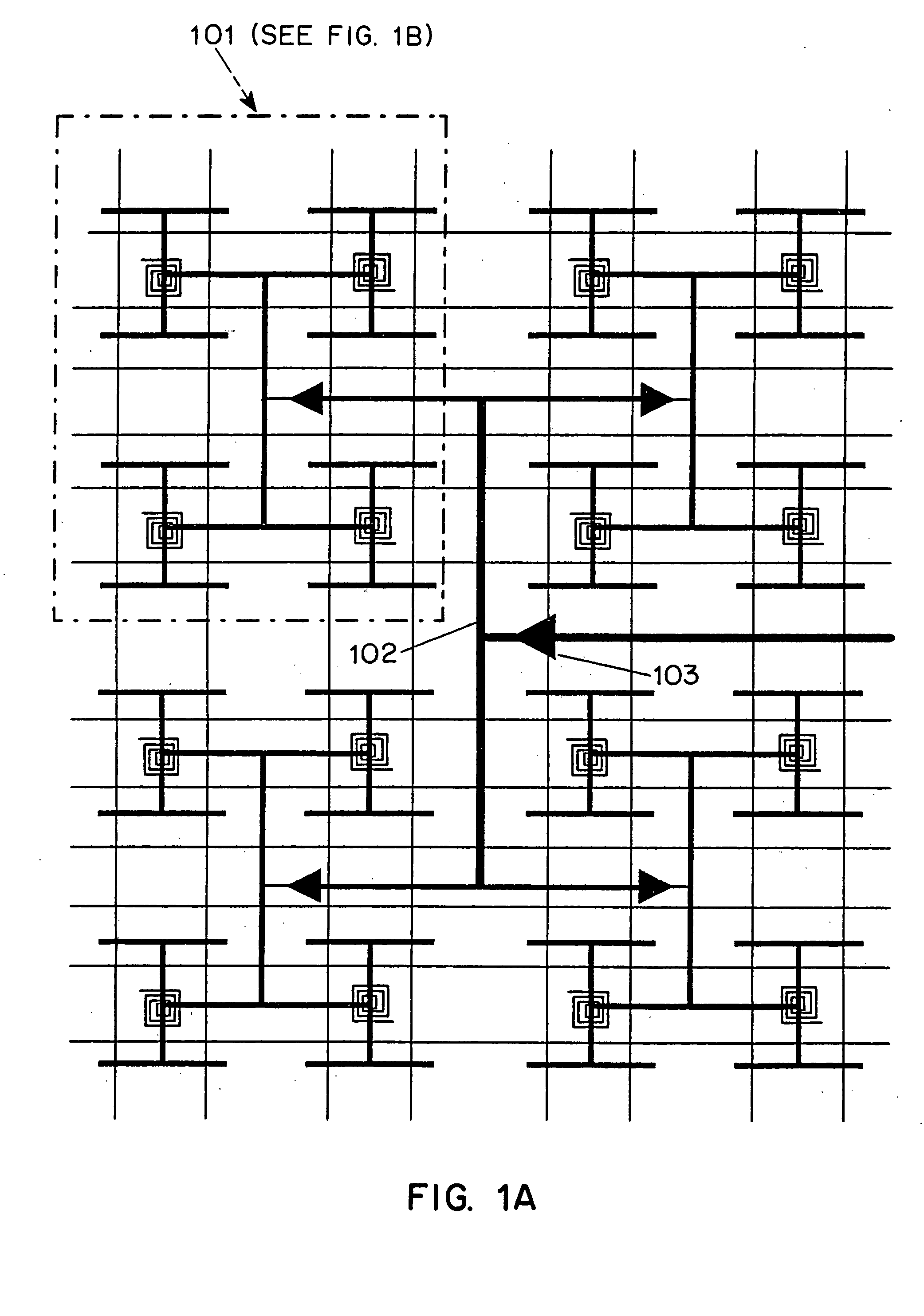

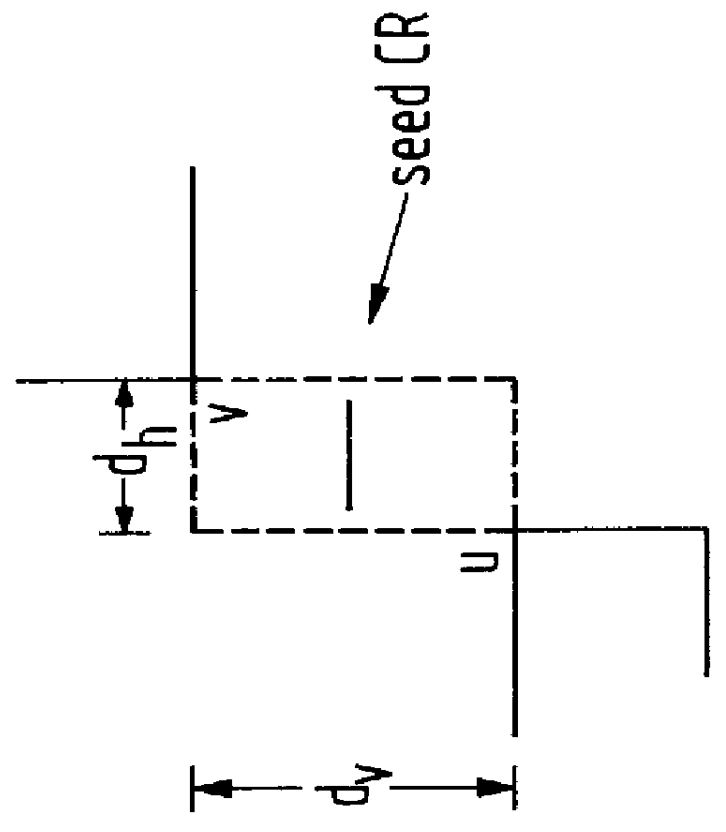

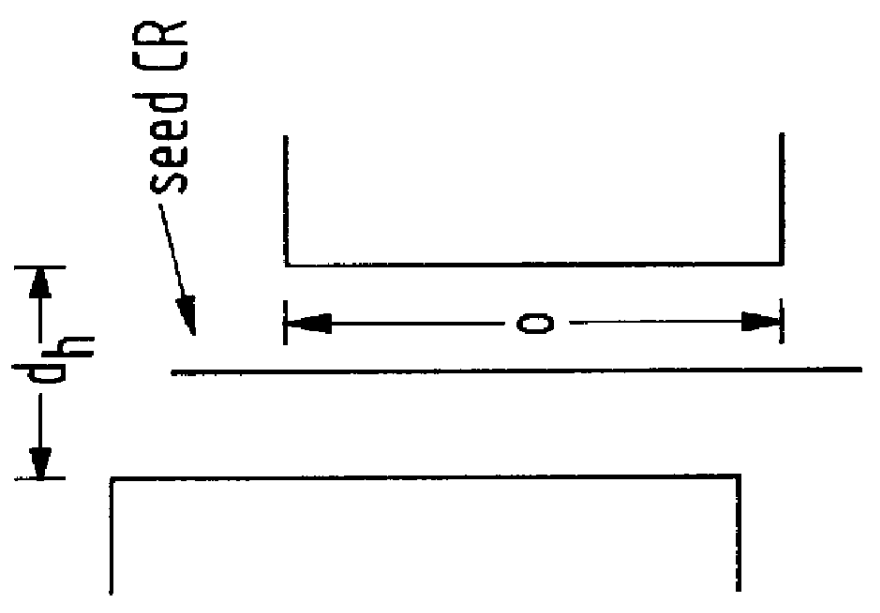

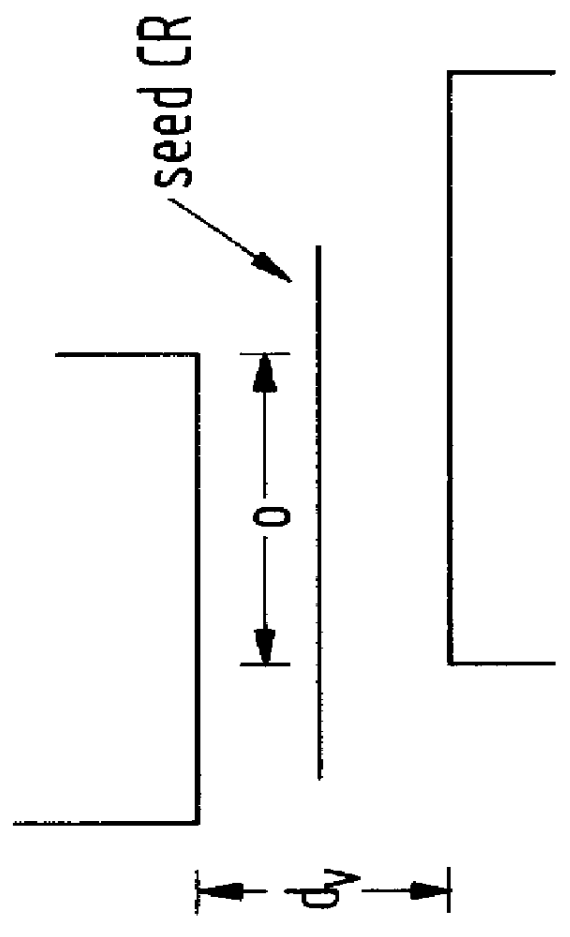

Incremental method for critical area and critical region computation of via blocks

InactiveUS6247853B1Reduce manufacturing costSemiconductor/solid-state device testing/measurementSpecial data processing applicationsData miningIncremental methods

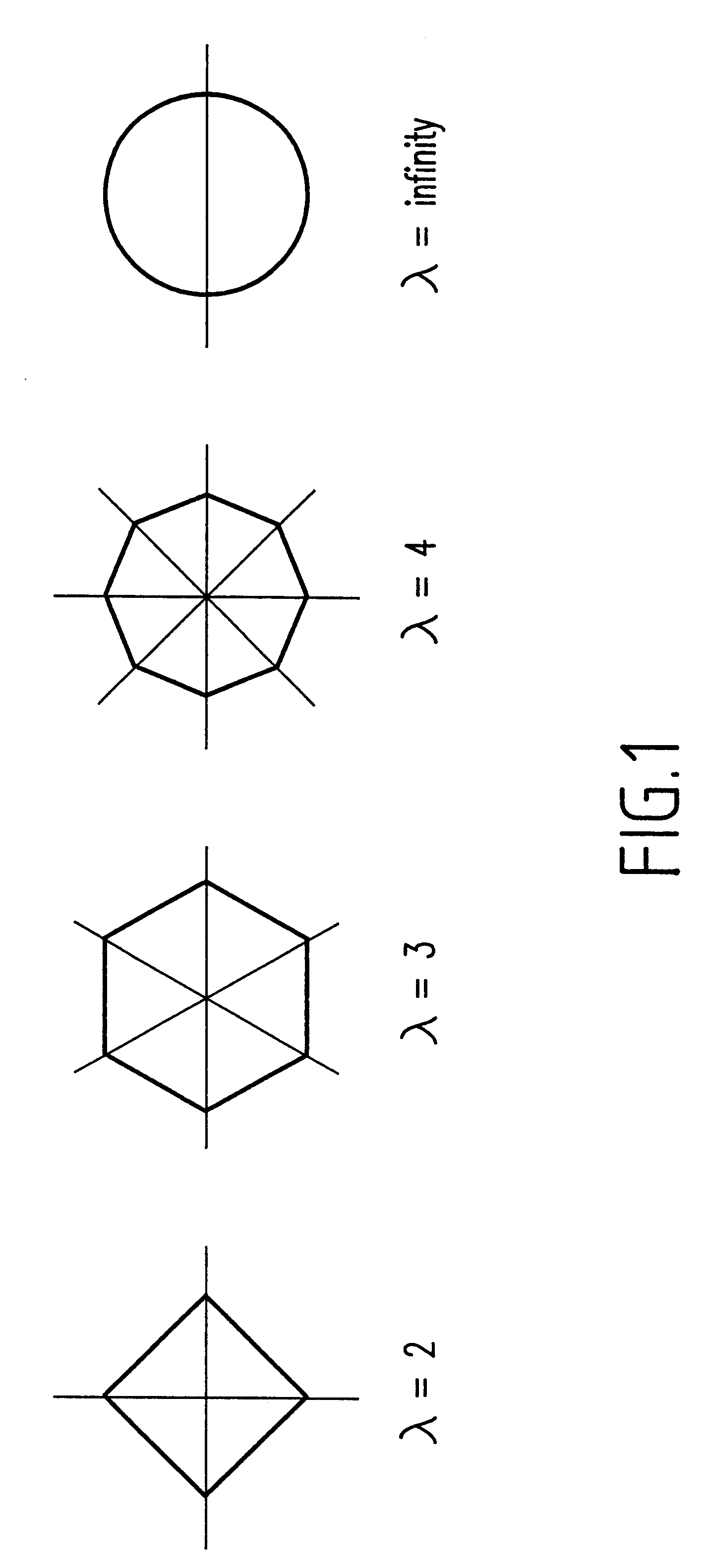

An efficient computer implemented method computes critical area for via blocks in Very Large Scale Integrated (VLSI) circuits. The method is incremental and takes advantage of the hierarchy in the design. In order to increase the efficiency further we use the Linfin or the L1 metric instead of the Euclidean geometry.

Owner:GLOBALFOUNDRIES INC

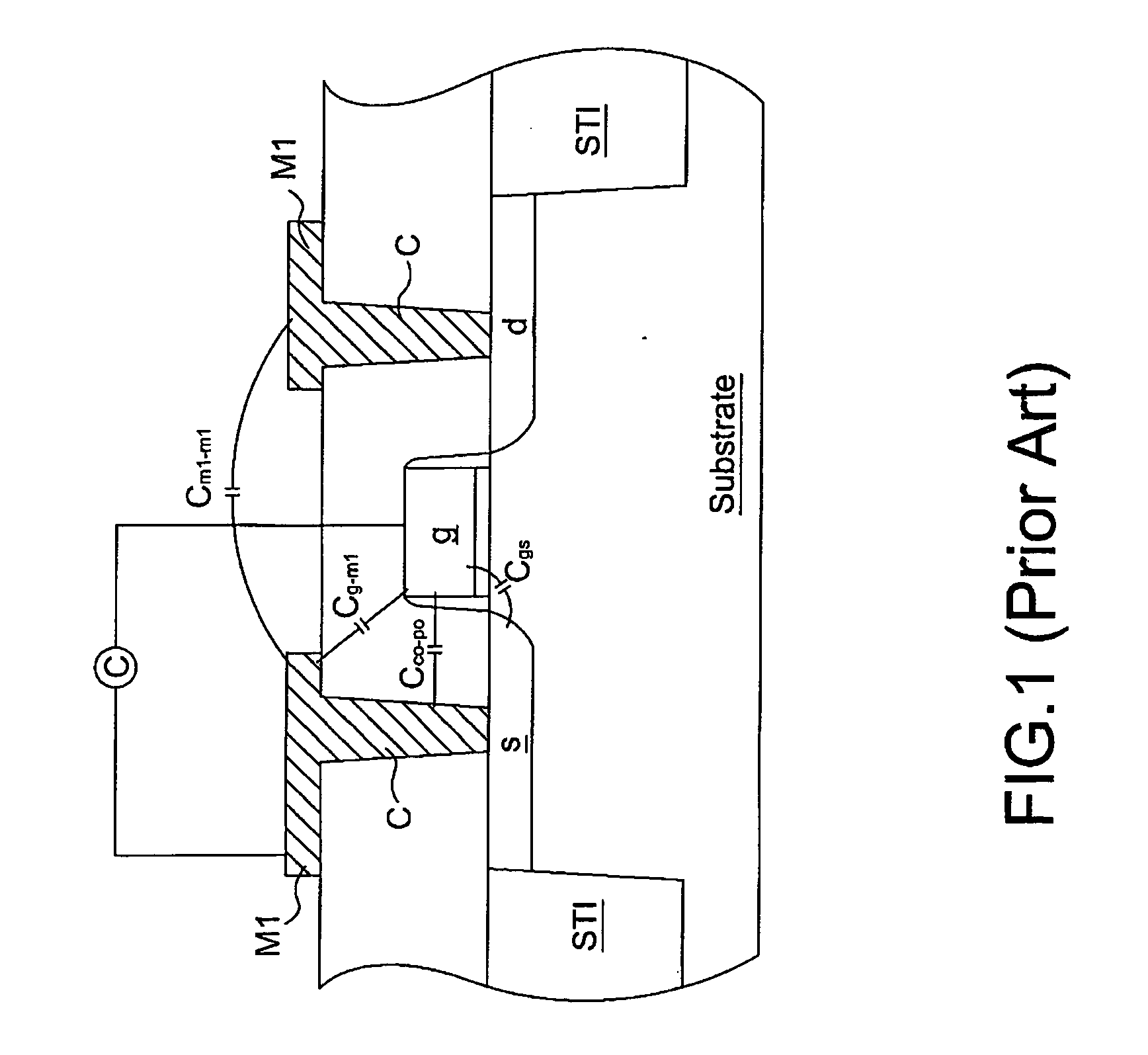

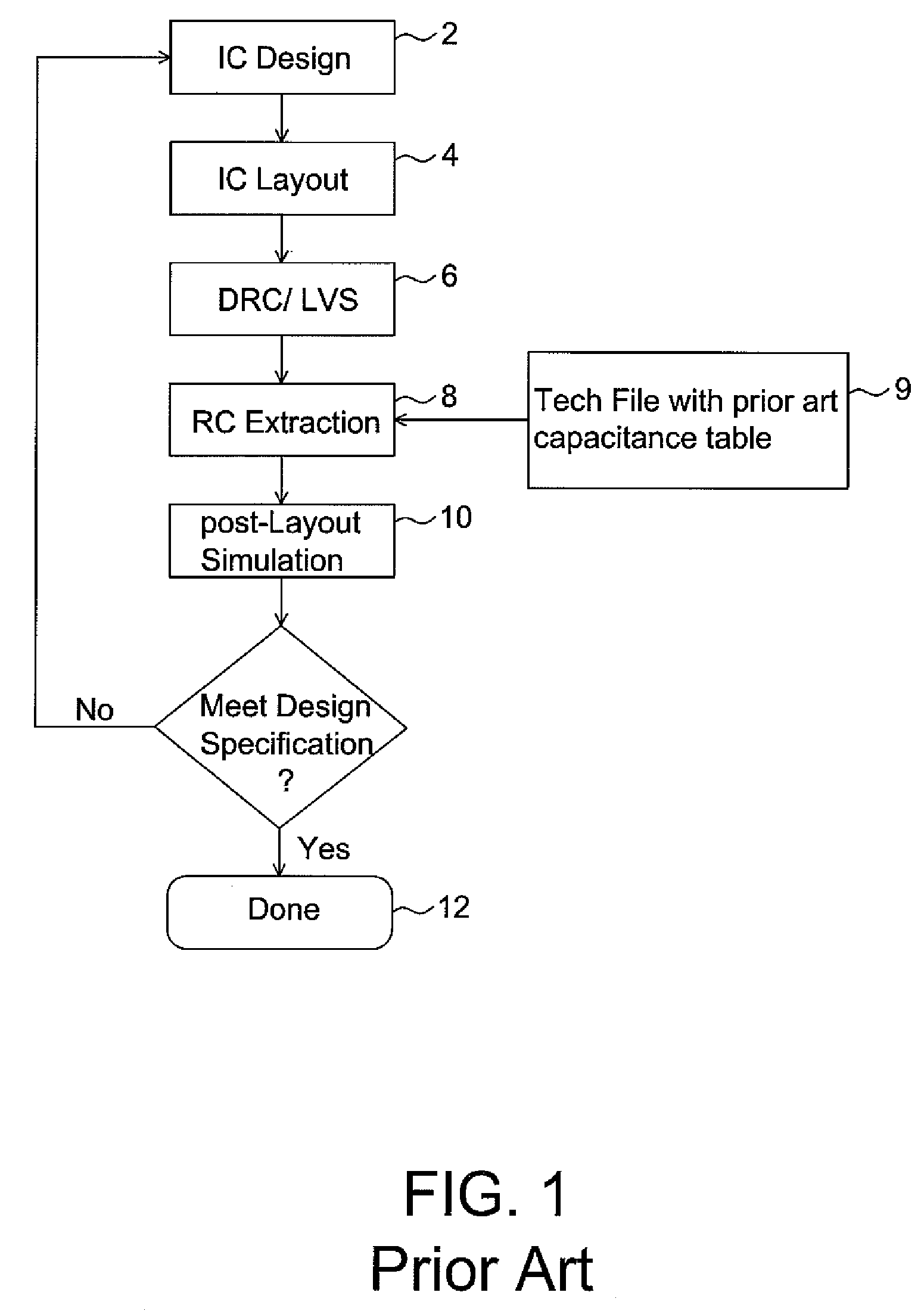

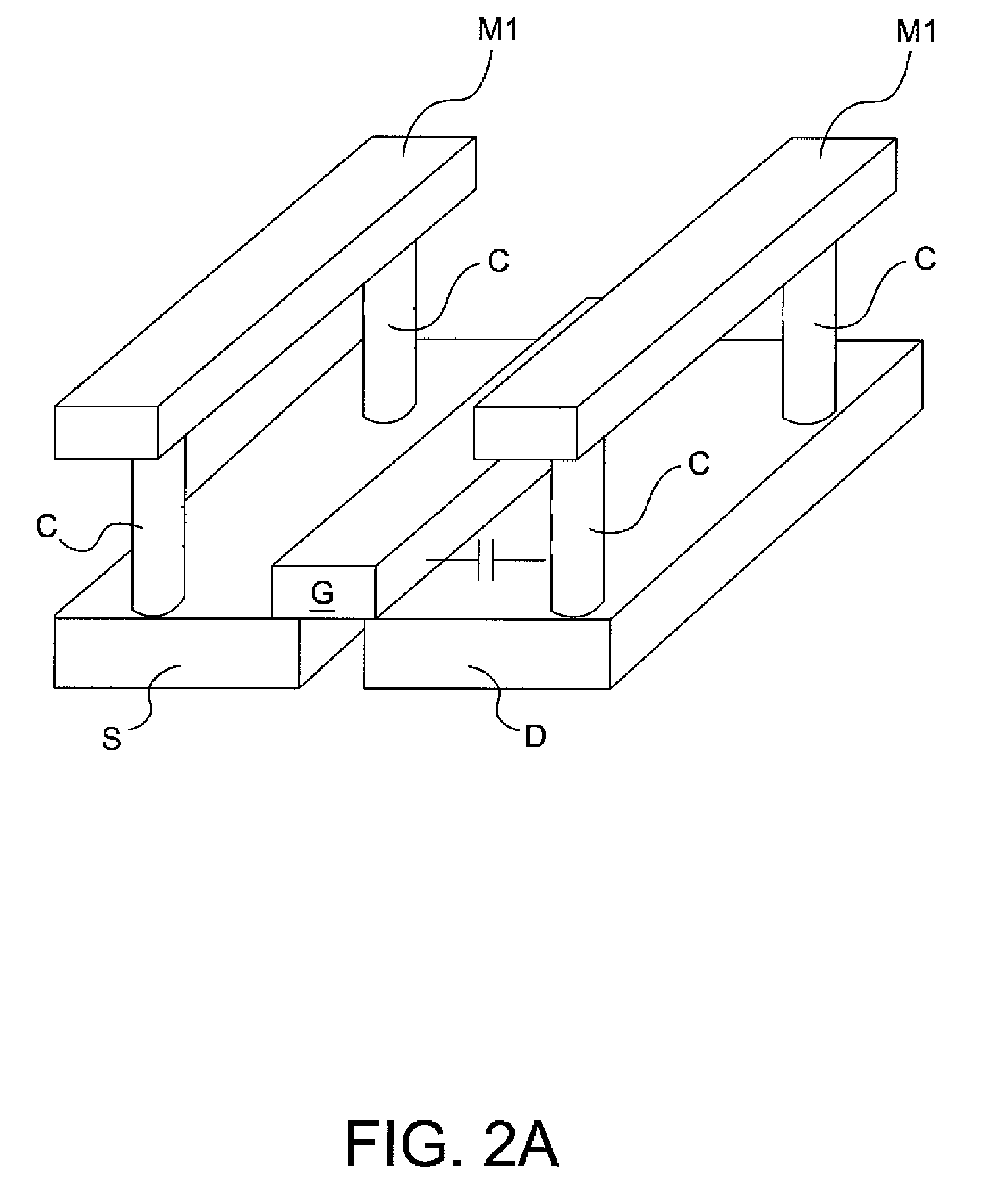

Accurate Capacitance Measurement for Ultra Large Scale Integrated Circuits

ActiveUS20090002012A1Improve accuracyEliminate the effects ofSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVery large scale integrated circuitsReference test

Test structures and methods for measuring contact and via parasitic capacitance in an integrated circuit are provided. The accuracy of contact and via capacitance measurements are improved by eliminating not-to-be-measured capacitance from the measurement results. The capacitance is measured on a target test structure that has to-be-measured contact or via capacitance. Measurements are then repeated on a substantially similar reference test structure that is free of to-be-measured contact or via capacitances. By using the capacitance measurements of the two test structures, the to-be-measured contact and via capacitance can be calculated.

Owner:TAIWAN SEMICON MFG CO LTD

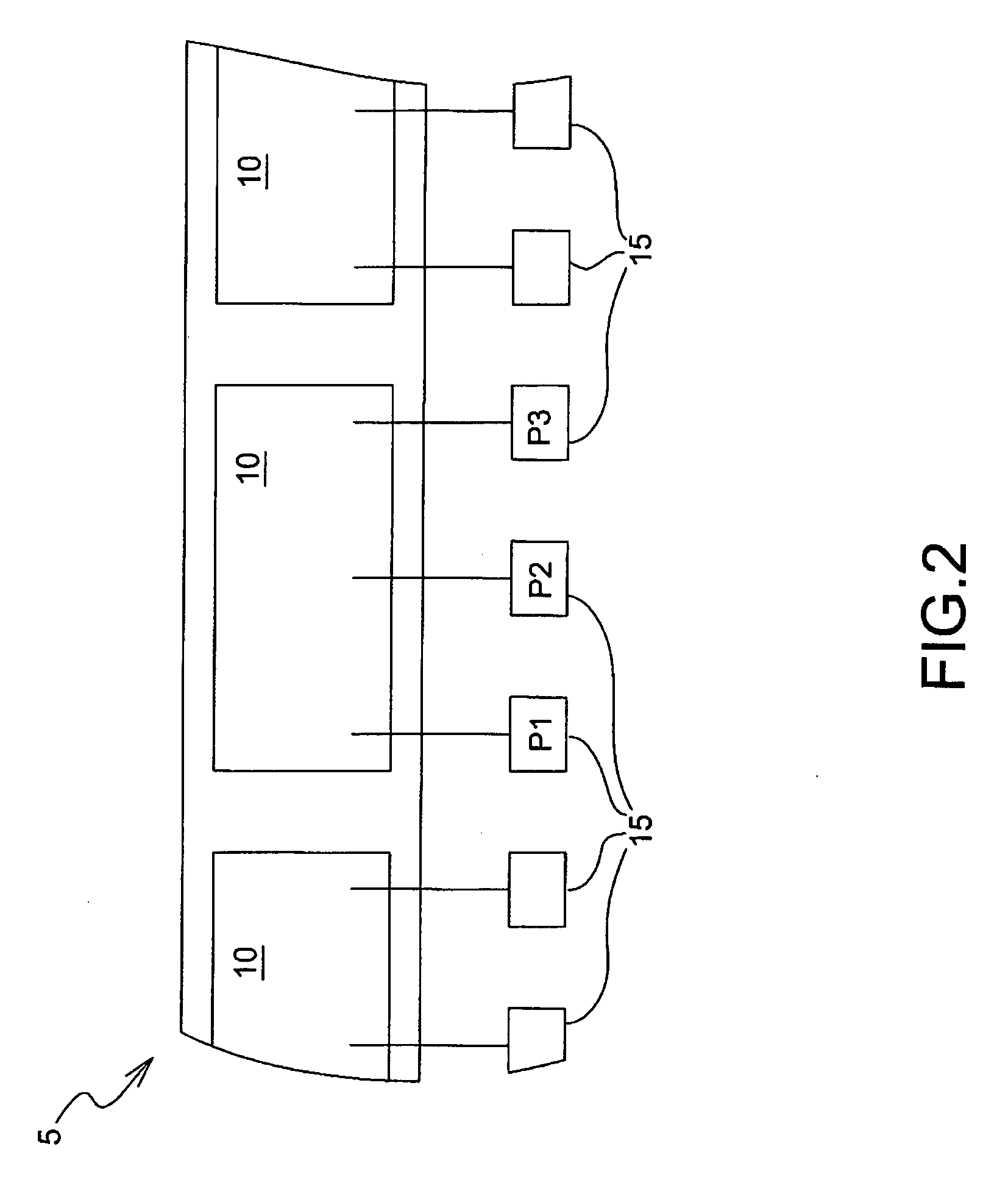

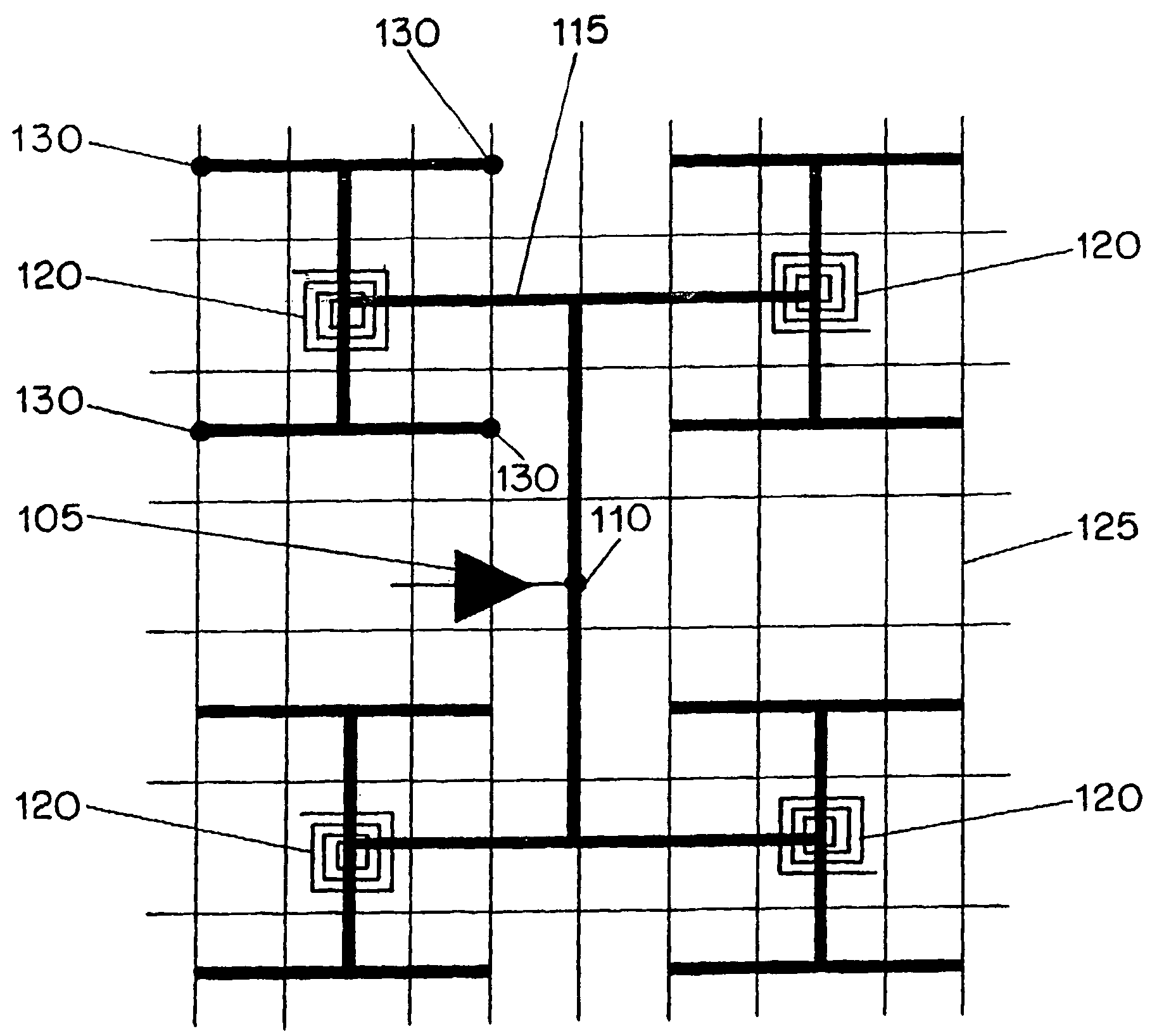

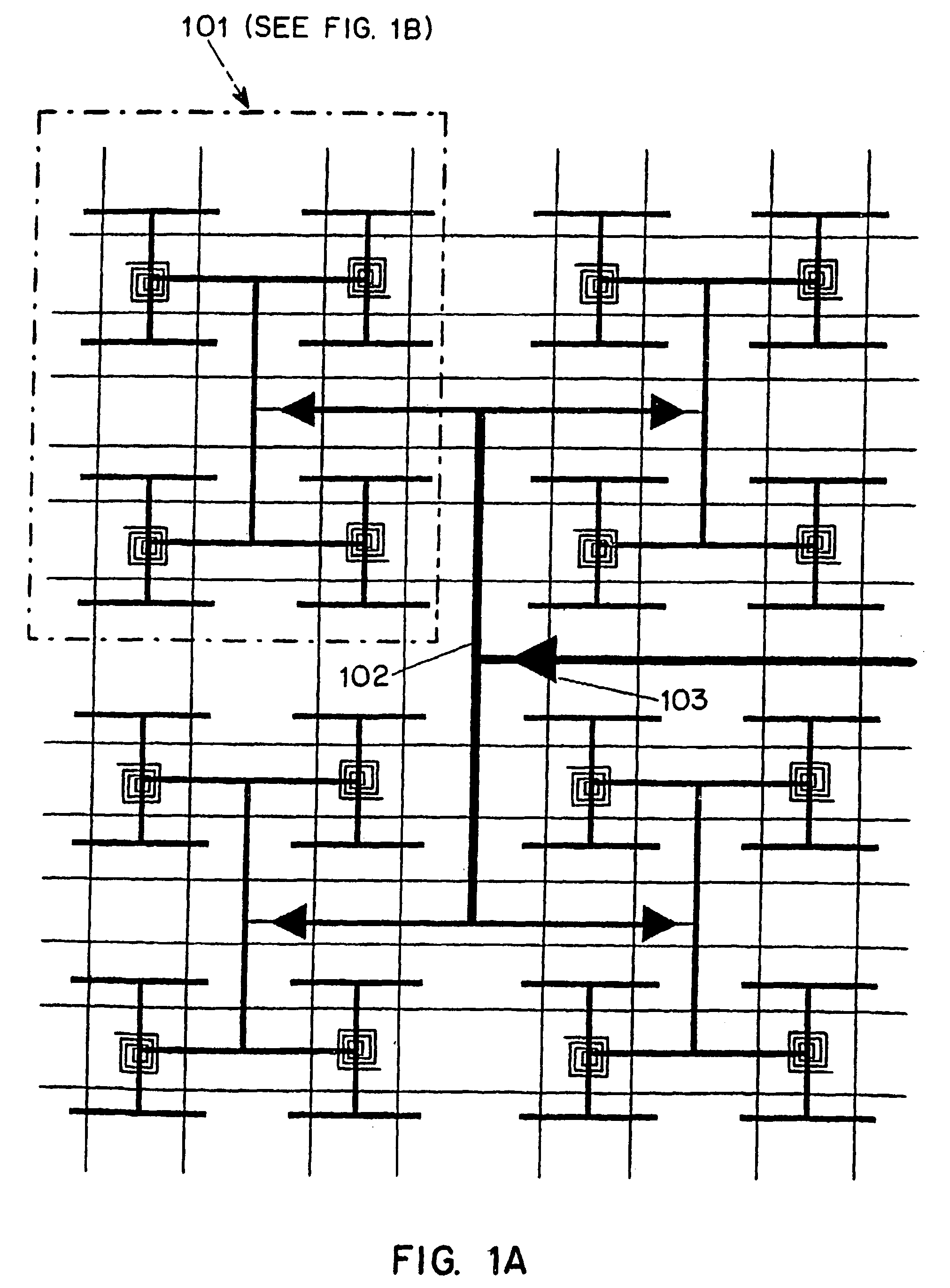

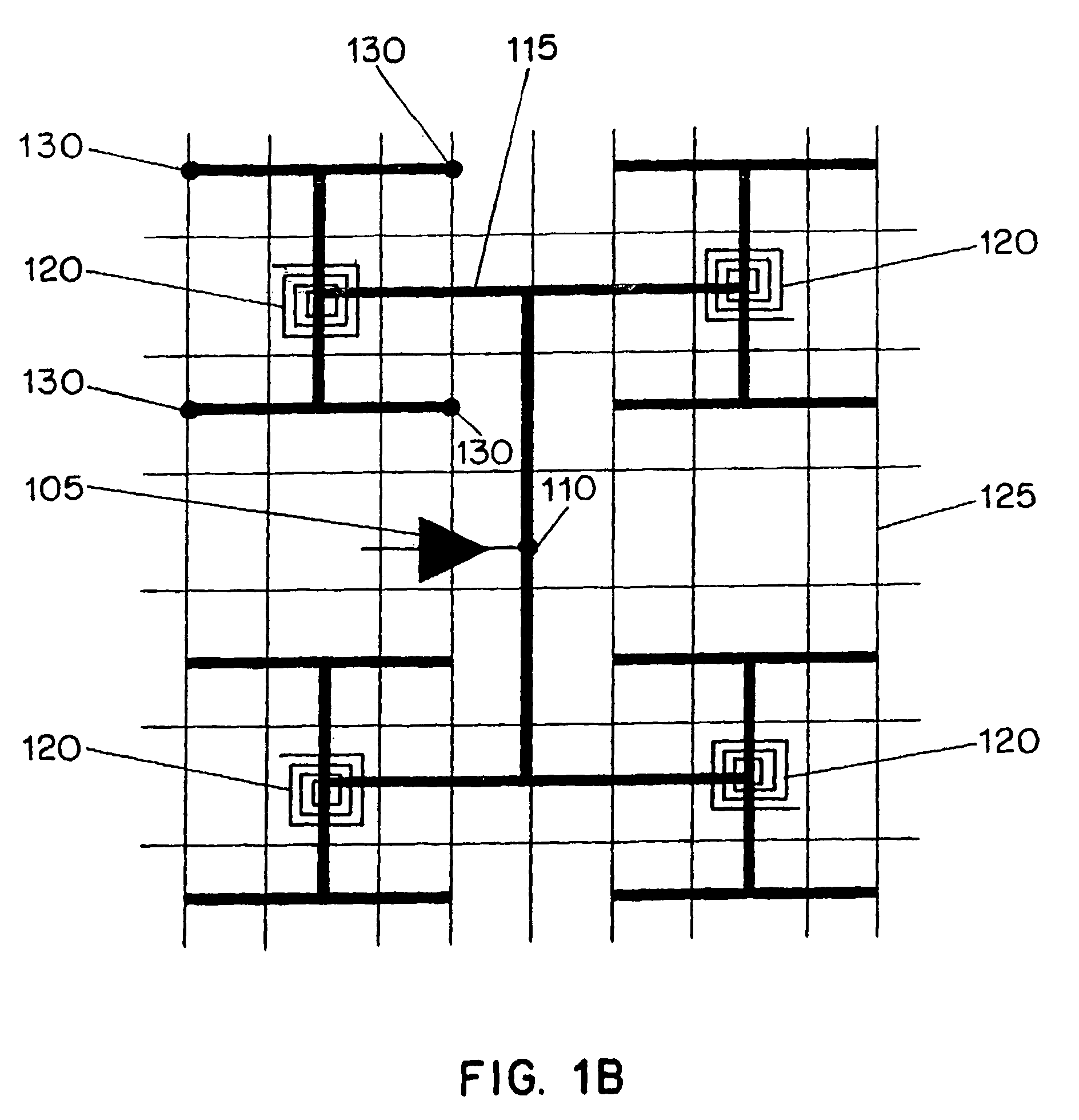

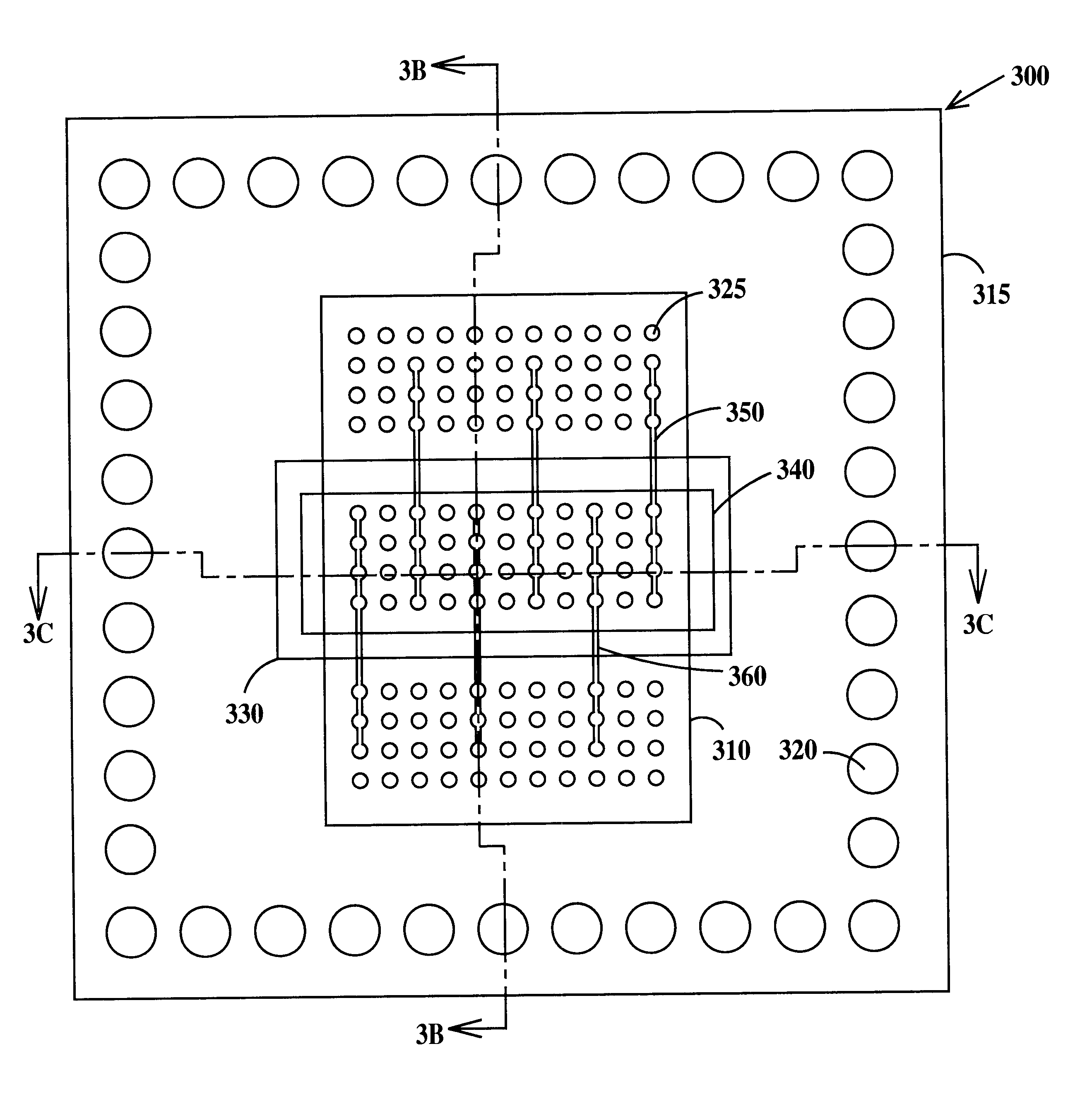

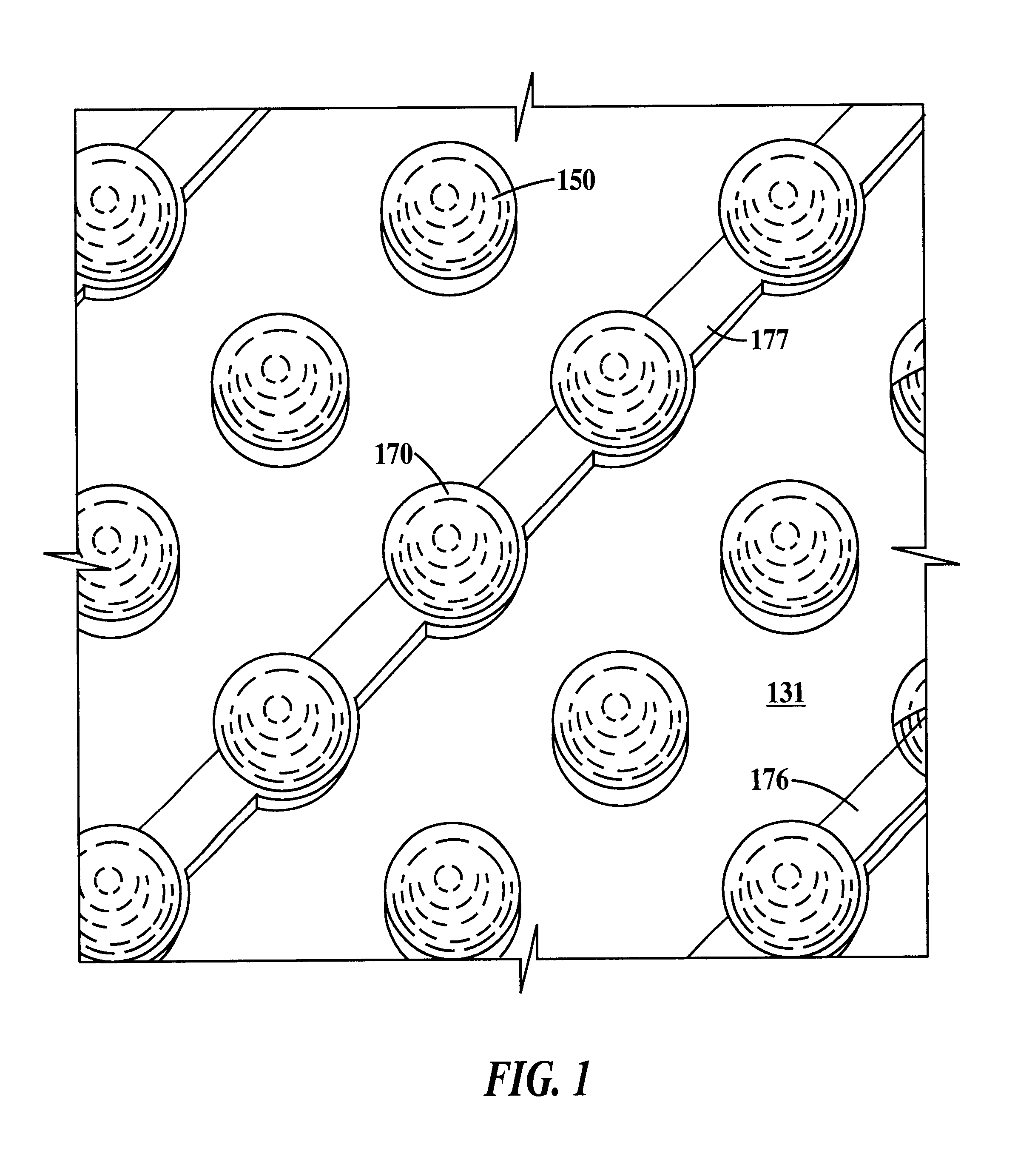

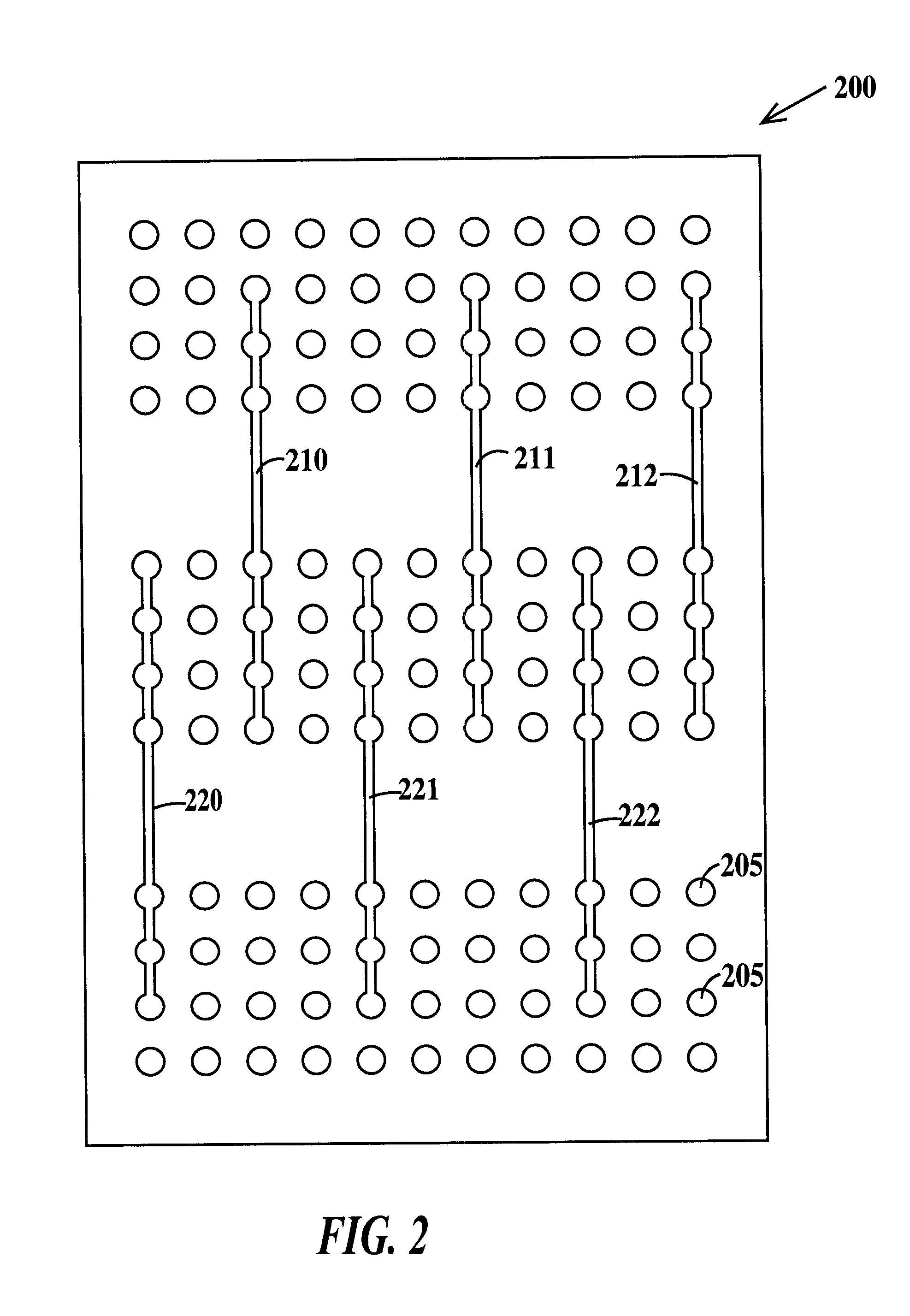

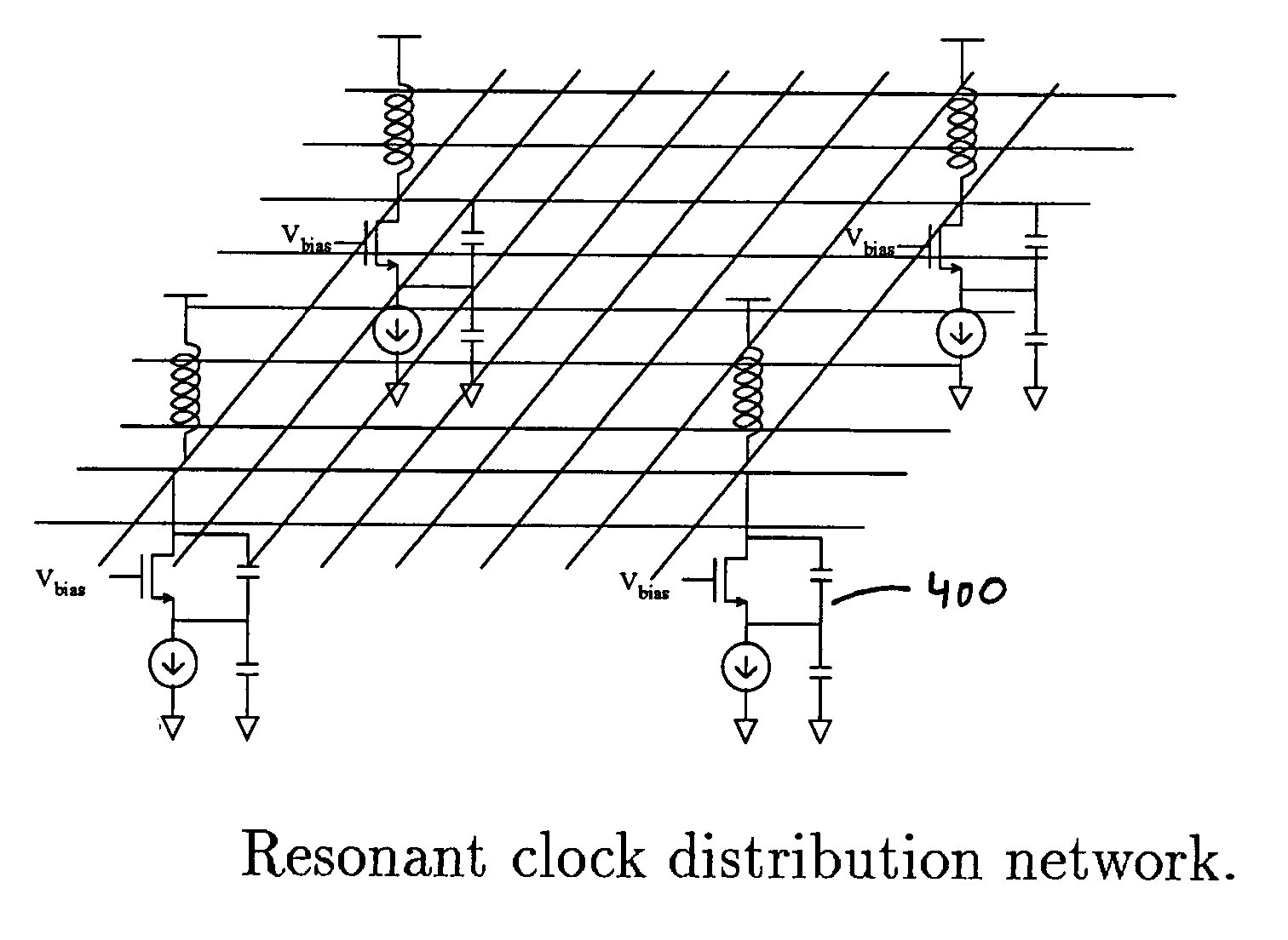

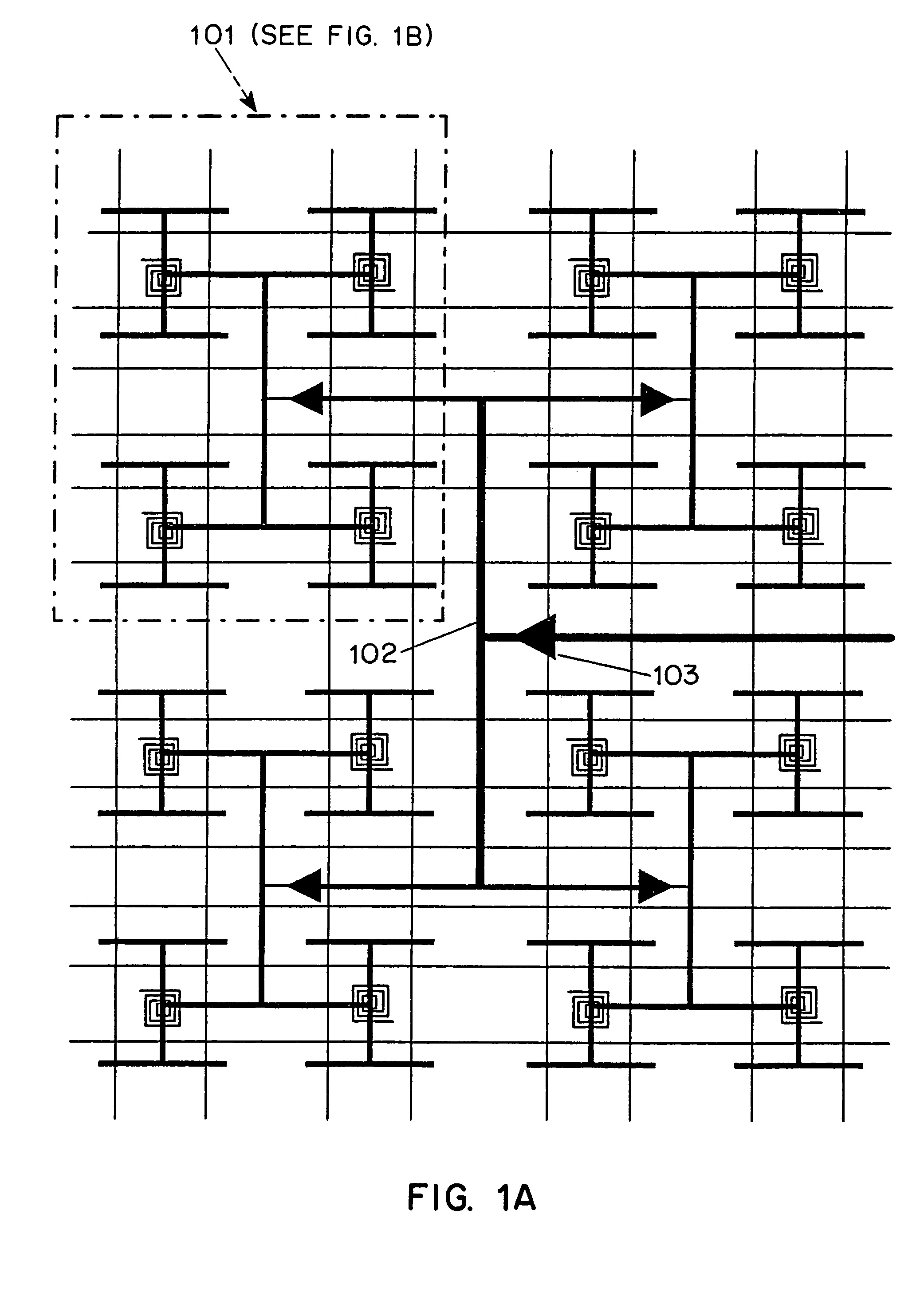

Resonant clock distribution for very large scale integrated circuits

InactiveUS20050057286A1Effective distributionEfficiently distributedPulse automatic controlGenerating/distributing signalsCapacitanceVery large scale integrated circuits

A circuit for distributing a clock signal in an integrated circuit includes a capacitive clock distribution circuit having at least conductor therein. At least one inductor is formed in a metal layer of the integrated circuit and is coupled to the clock distribution circuit. The inductor, generally in the form of a number of spiral inductors distributed throughout the integrated circuit, provides an inductance value selected to resonate with the capacitive clock distribution circuit. By operating the clock distribution circuit at resonance, power dissipation is reduced while skew and jitter performance can be improved.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

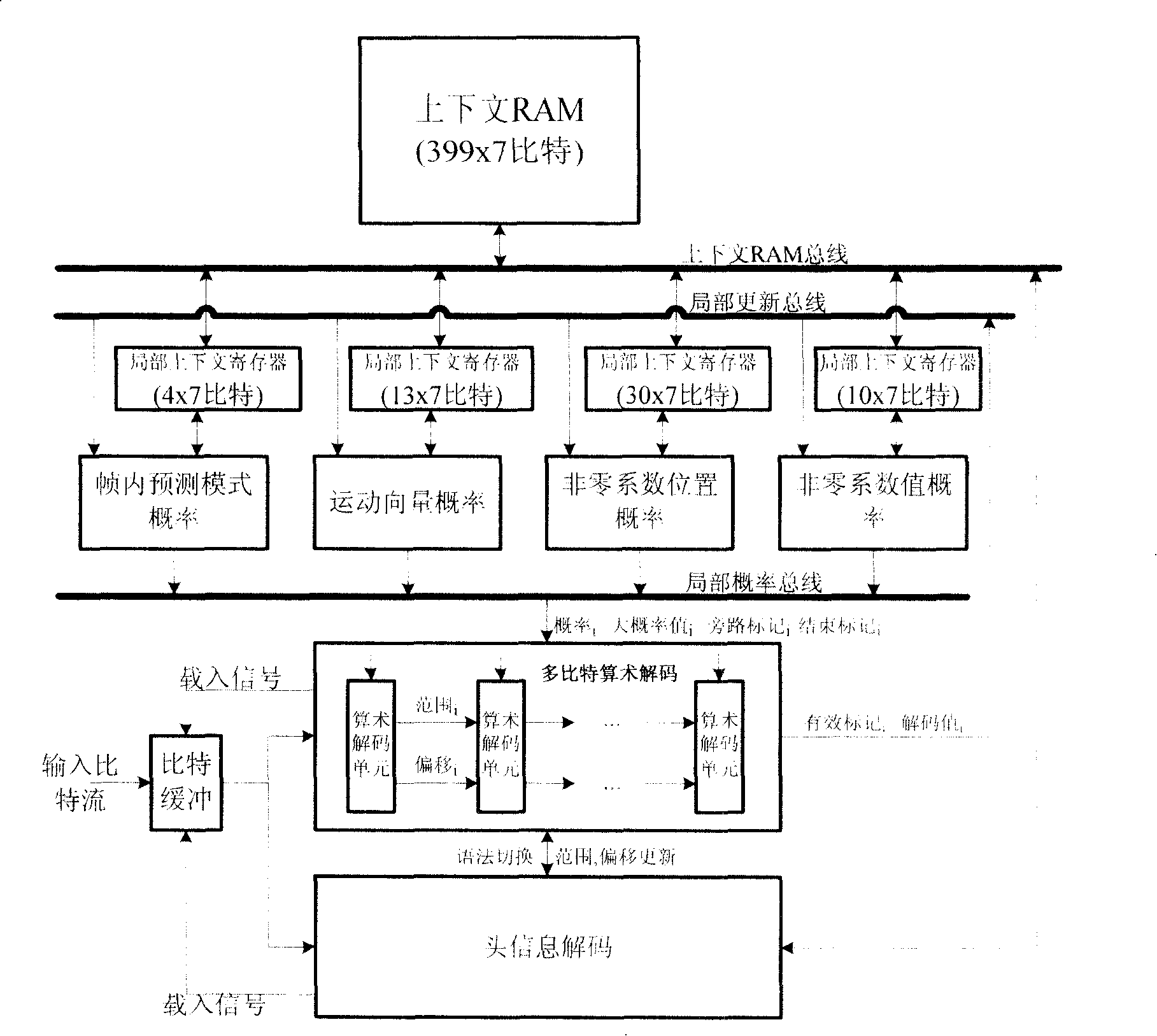

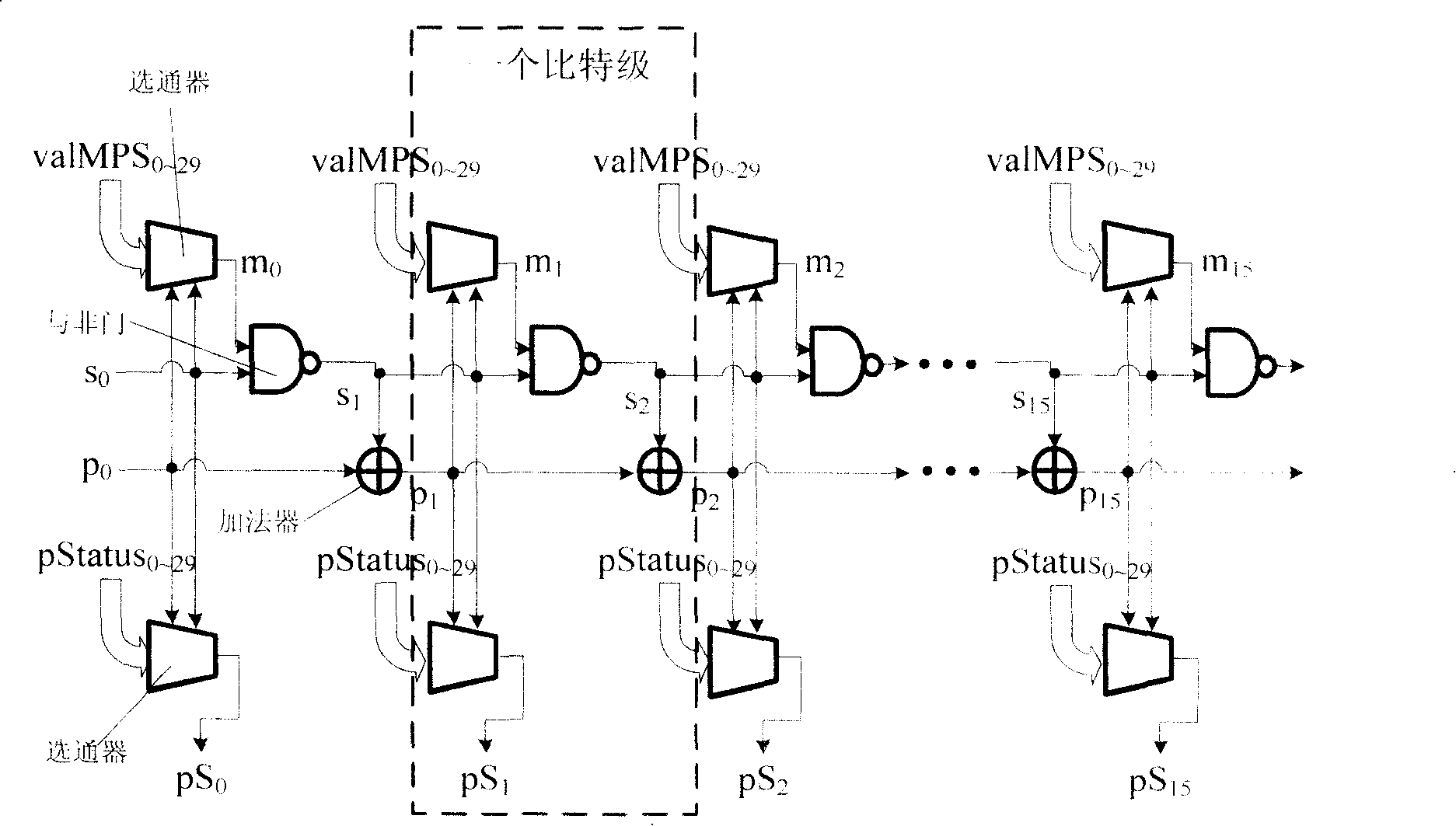

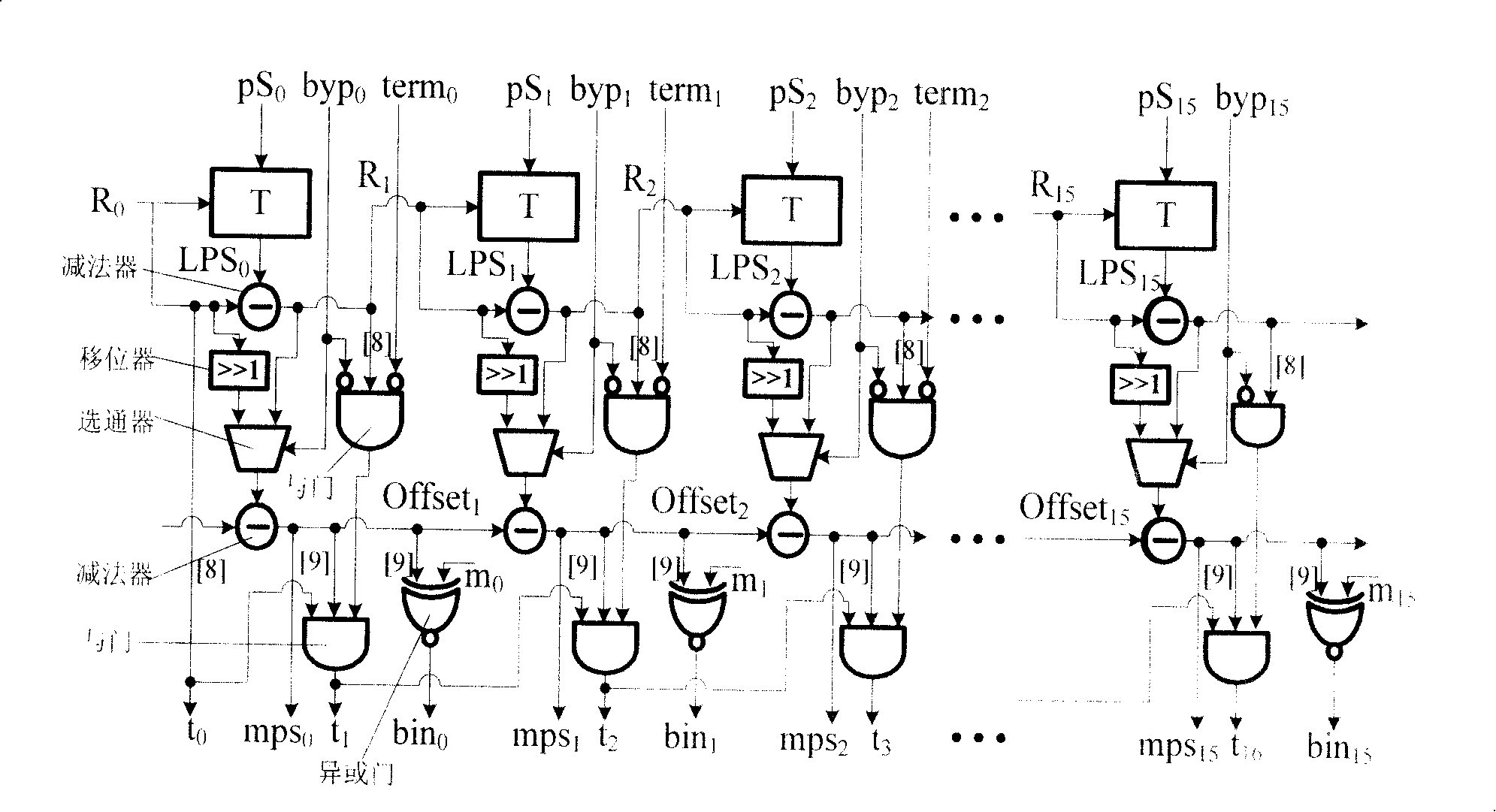

Efficient and parallel CABAC decoding method and device

ActiveCN101212676AGuaranteed real-time decodingTelevision systemsDigital video signal modificationVery large scale integrated circuitsContext based

The invention relates to a method for decoding high efficient and concurrent CABAC (adaptive binary arithmetic coding based on context) and a device thereof. The method and the device is in particular used for realizing novel VLSI (Very Large Scale Integrated circuits) with video decoding standard H.264 as well as aims at the CABAC decoding process regulated in main grade. The invention includes a method for decoding variable arithmetic, a device for decoding the concurrent binary arithmetic as well as a device for generating and updating concurrent probability. The decoding device can guarantees real time decoding of a video image with high definition (1080i system 30Mbps) in the worst situation.

Owner:BEIJING SPREADTRUM HI TECH COMM TECH CO LTD

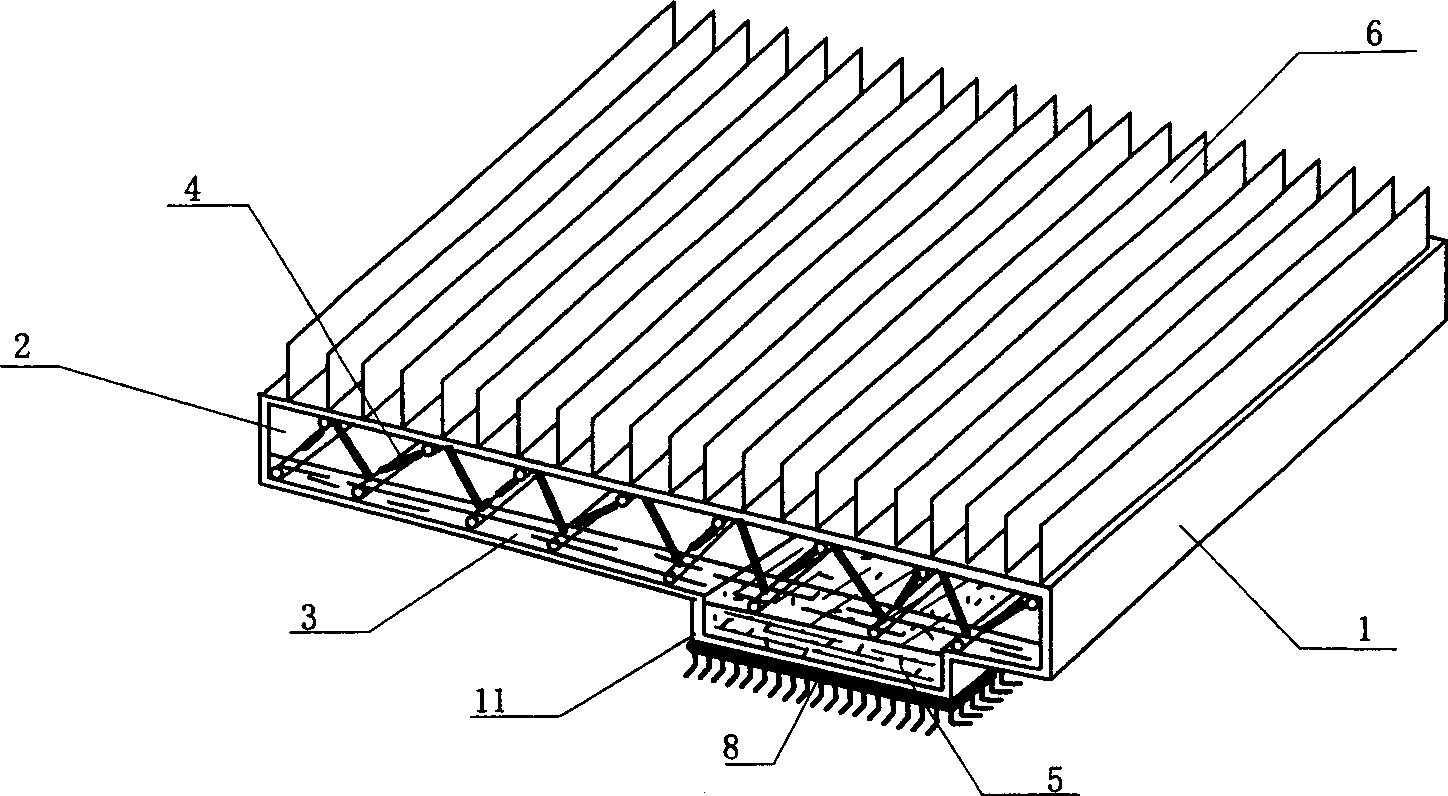

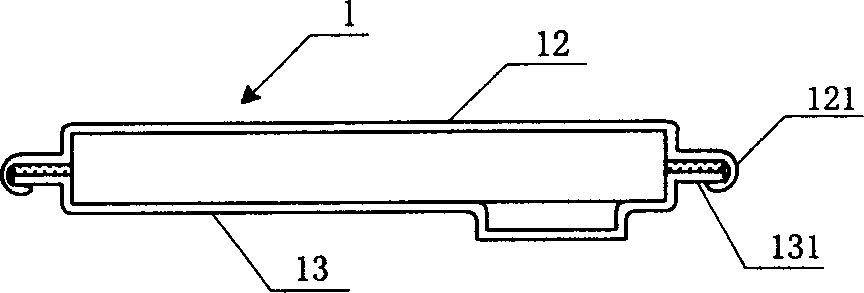

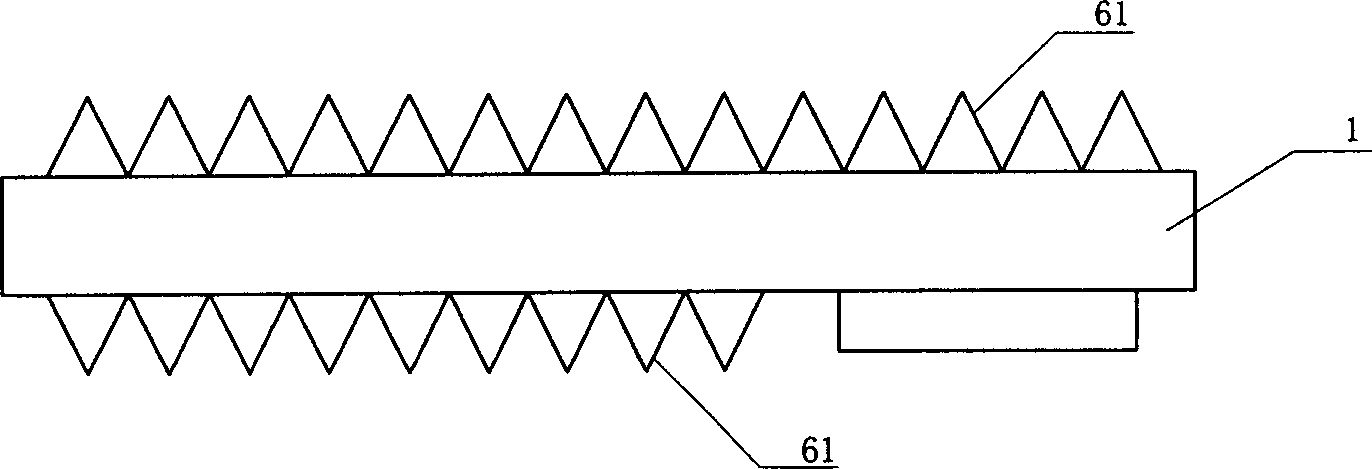

Plate-type heat-pipe radiator

InactiveCN1805133AHigh working reliabilitySimple structureDigital data processing detailsSemiconductor/solid-state device detailsVery large scale integrated circuitsMiniaturization

The invention relates to a plate heat pipe radiator, which comprises a sheet sealed case made from metallic sheet, whose inner chamber is vacuum and filled with liquid working substance which can be gasified when heated; the outer side of the bottom of case has a heat adsorption end face which is close to the surface of heating electric element to adsorb the heat; the chamber of case has a support element which is connected to the inner surface of said case to eliminate the case deformation caused by the pressure generated by the outer atmosphere pressure of the gasified liquid working substance. The invention via the heat pipe and strengthening the structure of sheet case, overcomes the defects of traditional aluminum alloy heat radiator on the miniaturization and high speed development.

Owner:杨洪武

Resonant clock distribution for very large scale integrated circuits

InactiveUS7145408B2Efficiently distributedConsumes less powerGenerator stabilizationElectric pulse generatorCapacitanceVery large scale integrated circuits

A circuit for distributing a clock signal in an integrated circuit includes a capacitive clock distribution circuit. At least one additional inductor is formed in a metal layer of the integrated circuit and is coupled to the clock distribution circuit. The inductor, which may distributed throughout the integrated circuit, has an inductance value selected to resonate with impedance of the capacitive clock distribution circuit. By operating the clock distribution circuit at resonance, power dissipation is reduced while skew and jitter performance can be improved.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Incremental critical area computation for VLSI yield prediction

InactiveUS6044208ASemiconductor/solid-state device testing/measurementSolid-state devicesMaterial defectLinear approximation

An efficient method to compute critical area for shorts and breaks in rectilinear layouts in Very Large Scale Integrated (VLSI) circuits. The method is incremental and works in the L INFINITY geometry and has three major steps: Compute critical area for rectilinear layouts for both extra material and missing material defects (i.e., shorts and opens) by modeling defects as squares (which corresponds to the L INFINITY metric) instead of circles (Euclidean geometry). Treat the critical region for shorts and opens between any two edges or corners of the layout as a rectangle that grows uniformly as the defect radius increases. This is valid for rectilinear layouts and square defects (L INFINITY metric) . Use an incremental critical area algorithm for shorts and opens, which are computed for rectilinear layouts assuming square defects. Non-rectilinear layouts are approximated, first, by a rectilinear layout using a shape processing tool. The critical area for the rectilinear approximation is computed using the preferred incremental method.

Owner:GLOBALFOUNDRIES INC

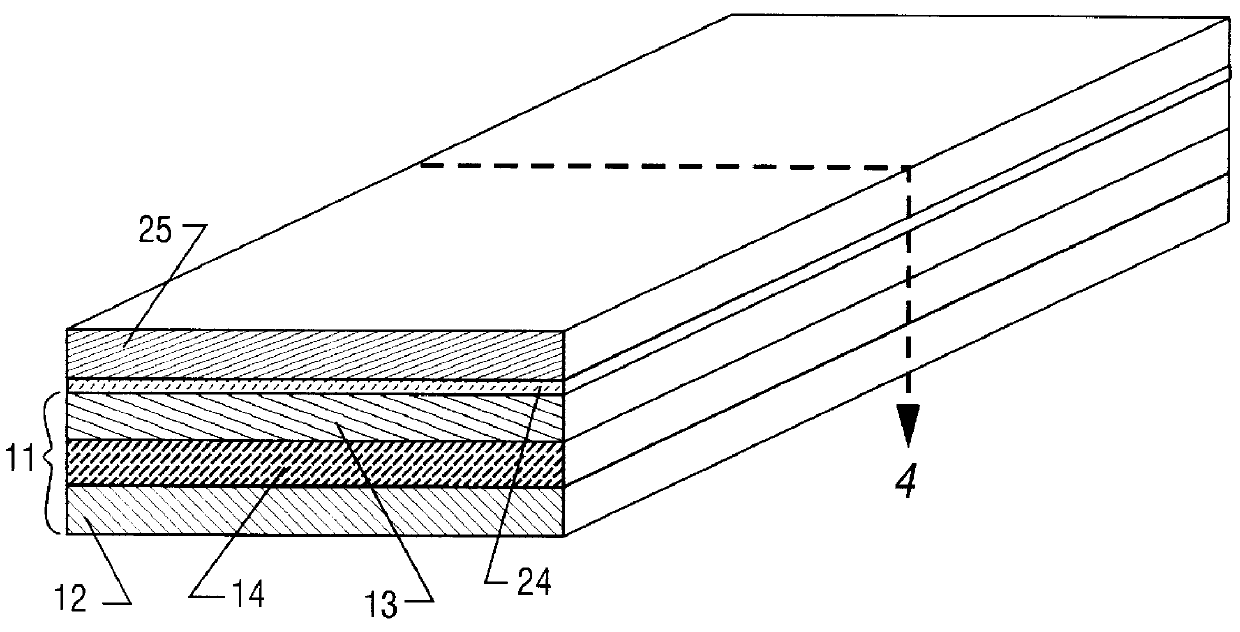

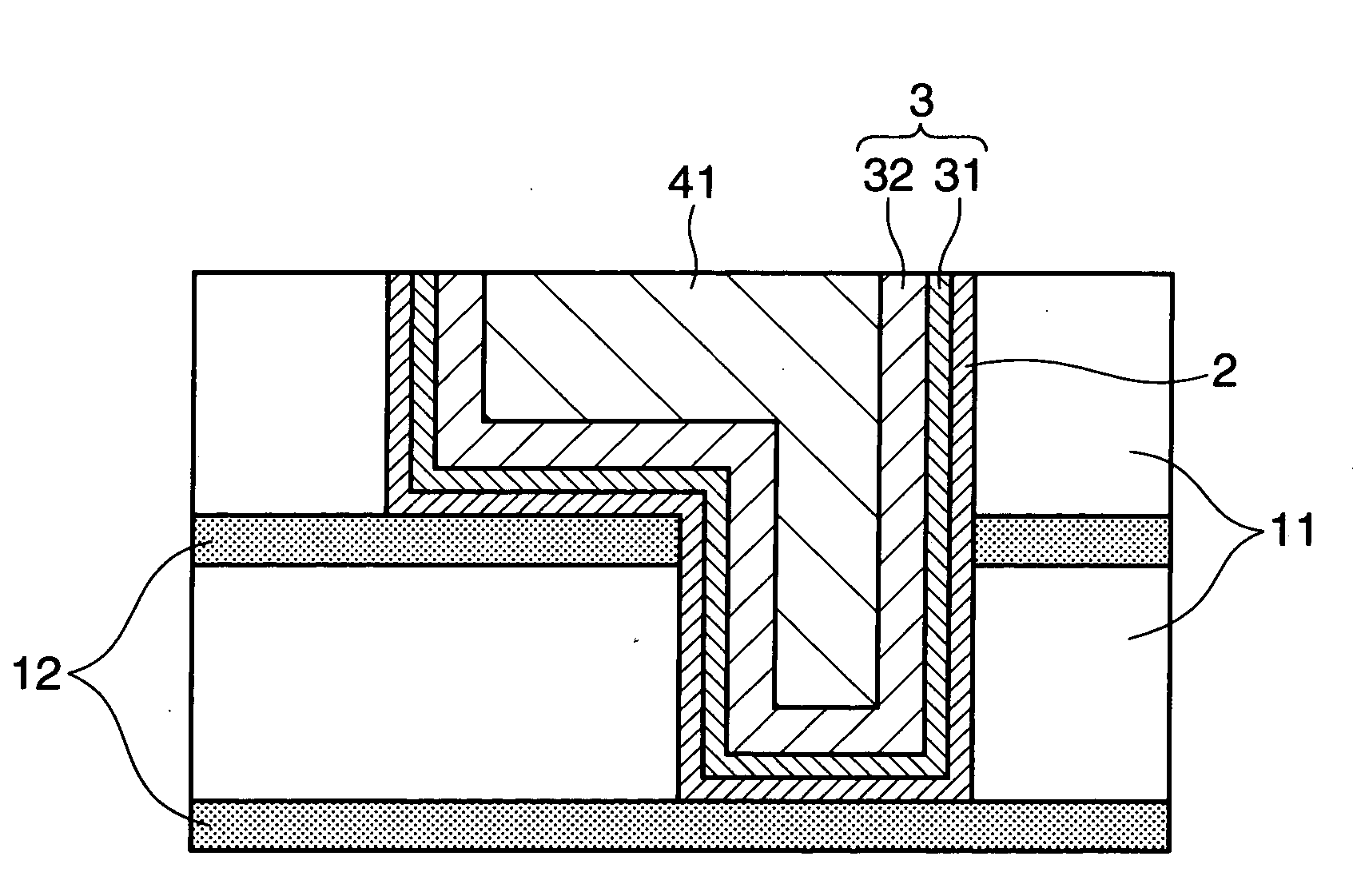

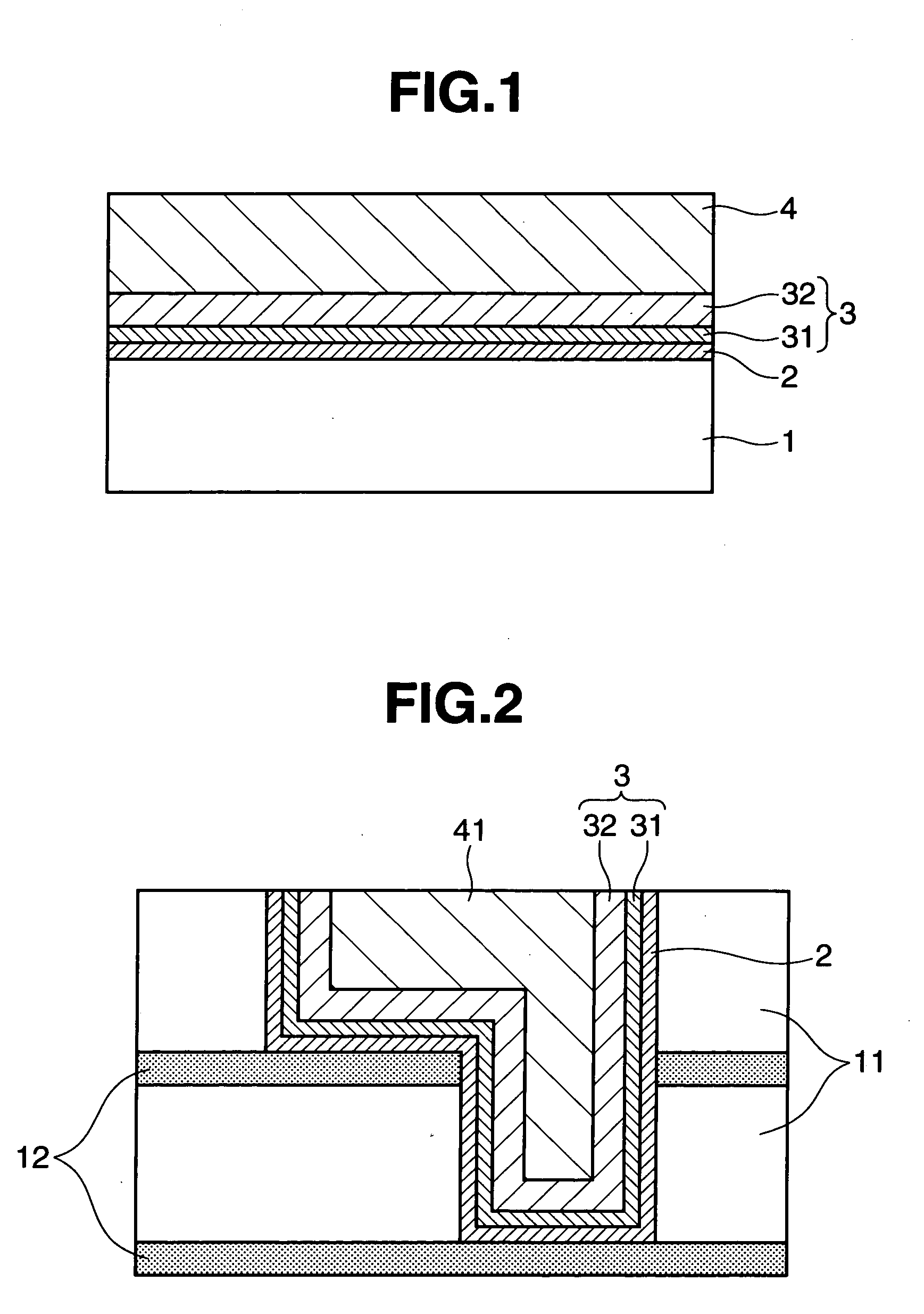

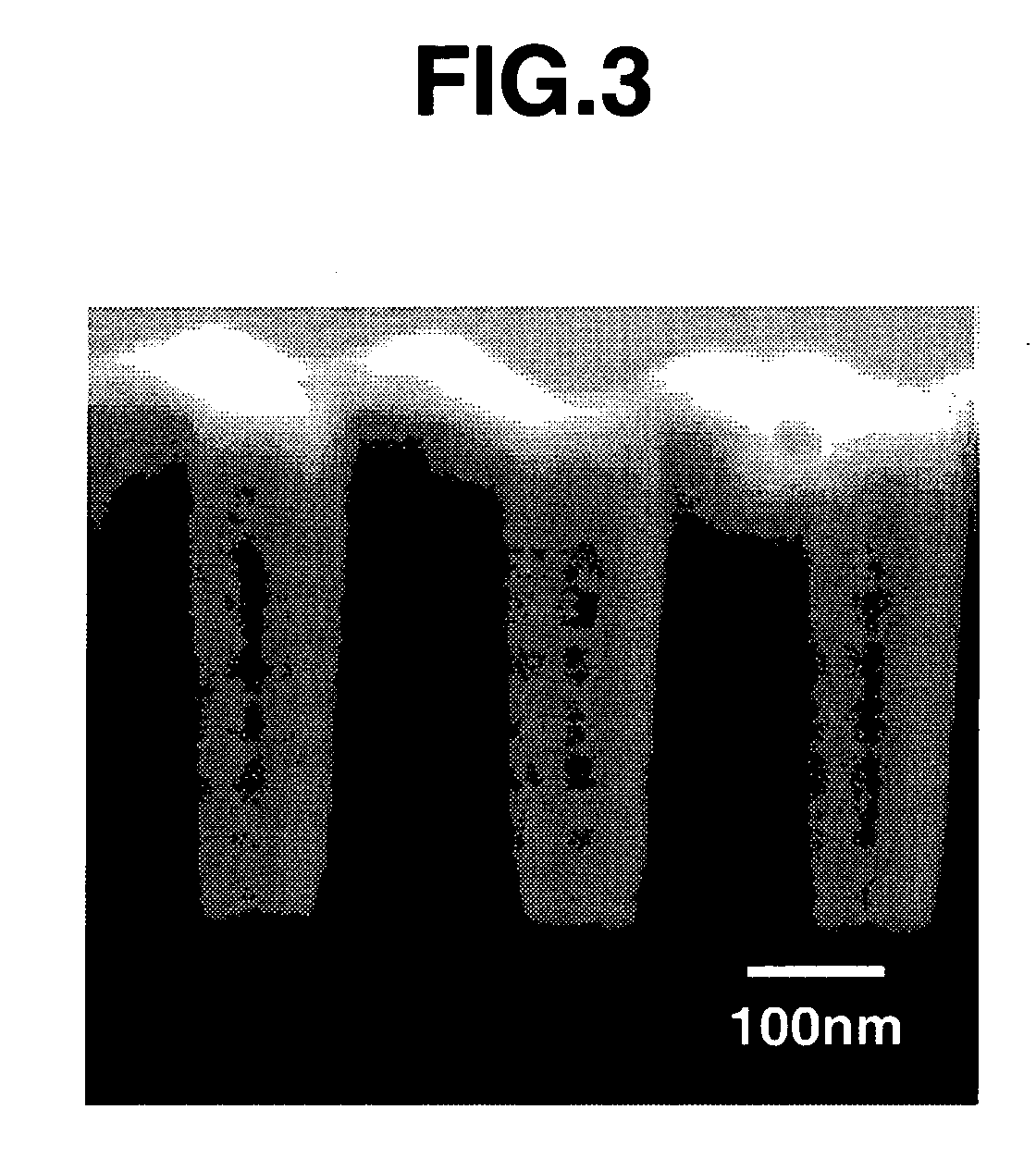

Laminated structure, very-large-scale integrated circuit wiring board, and method of formation thereof

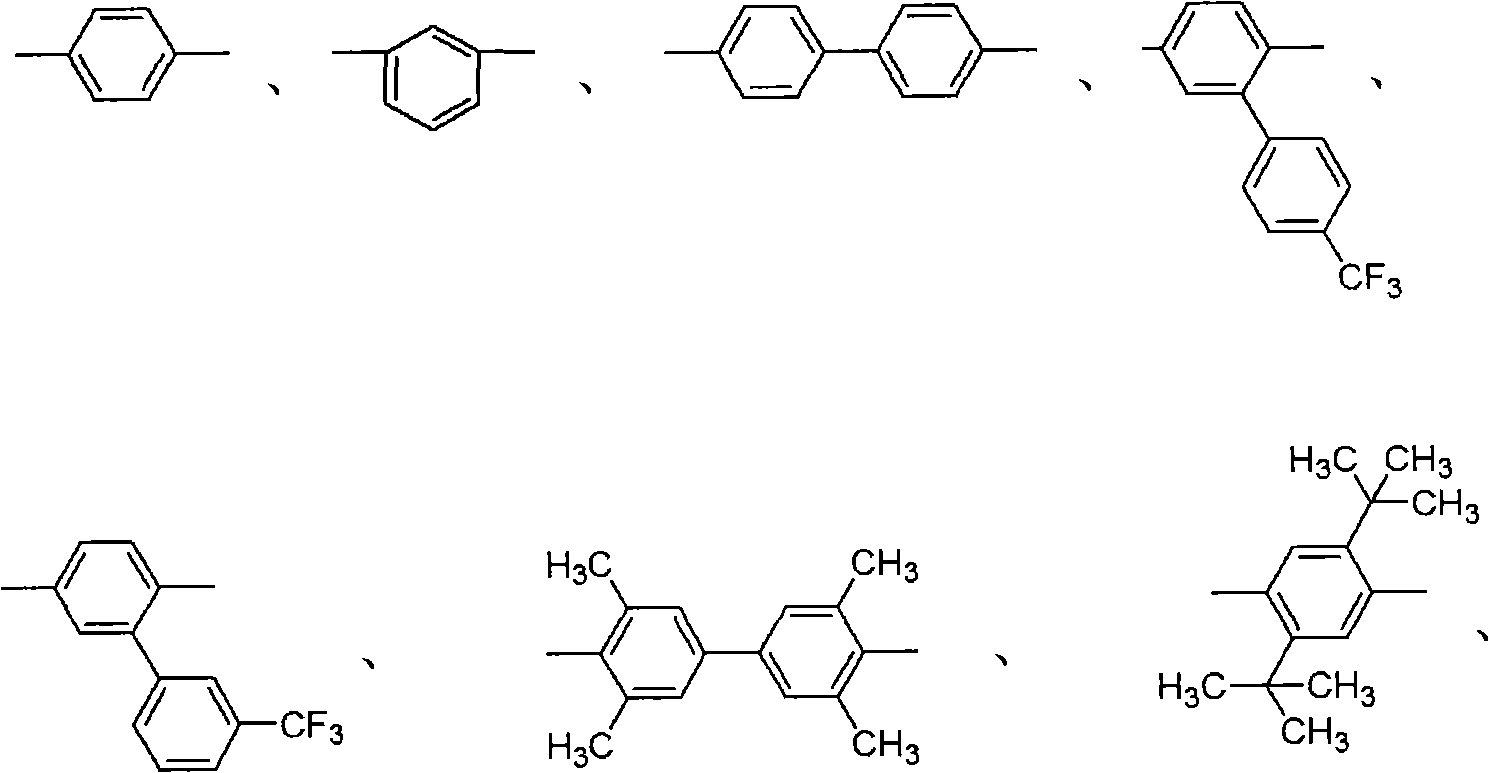

InactiveUS20080079154A1Prevent peelingEfficient manufacturingSemiconductor/solid-state device detailsSolid-state devicesVery large scale integrated circuitsCopper plating

The laminated structure includes a substrate of low dielectric constant material of silicon compound and an electroless copper plating layer laminated thereon with a barrier layer. The barrier layer is interposed between the substrate and the copper layer, and the barrier layer is formed by electroless plating. And the laminated structure is characterized in that the barrier layer is formed on the substrate with a monomolecular layer of organosilane compound and a palladium catalyst which are interposed between the substrate and the barrier layer, the palladium catalyst modifies the terminal, adjacent to the barrier layer, of the monomolecular layer, and the barrier layer includes an electroless NiB plating layer which is disposed on the substrate side, and a electroless CoWP plating layer.The present invention makes it possible to coat the low dielectric constant material of silicon compound in a simple all-wet process with a firmly adhering barrier layer and an electroless copper plating layer as the wiring layer. the advantage of requiring. Thus, the laminated structure formed in this way includes a substrate of low dielectric constant material of silicon compound, a barrier layer, and a copper layer as the wiring layer formed by electroless plating, which firmly adhere to one another. In addition, the laminated structure is suitable for the copper wiring in a ULSI, particularly the one which is to be formed in a narrower trench than conventional one.

Owner:WASEDA UNIV

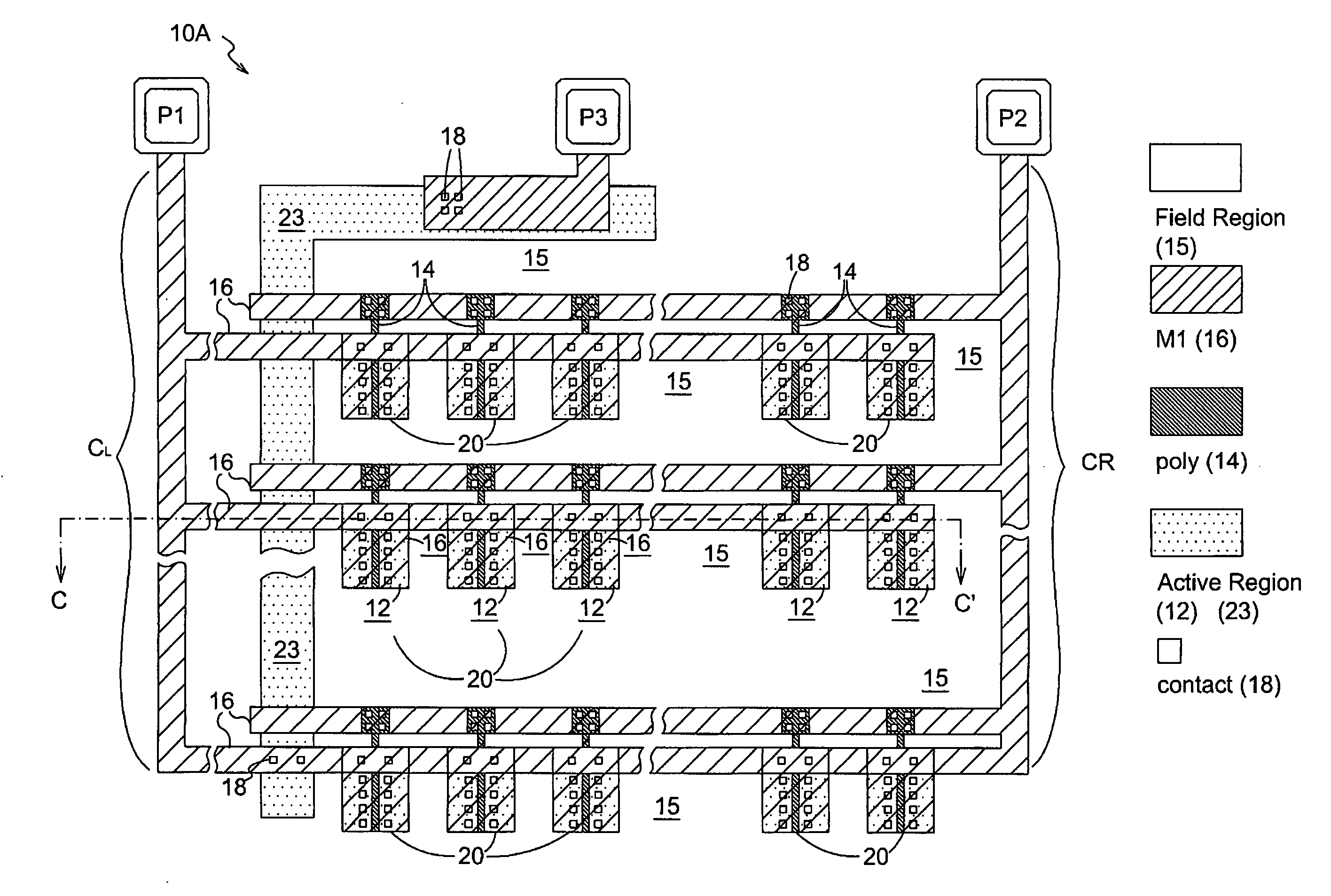

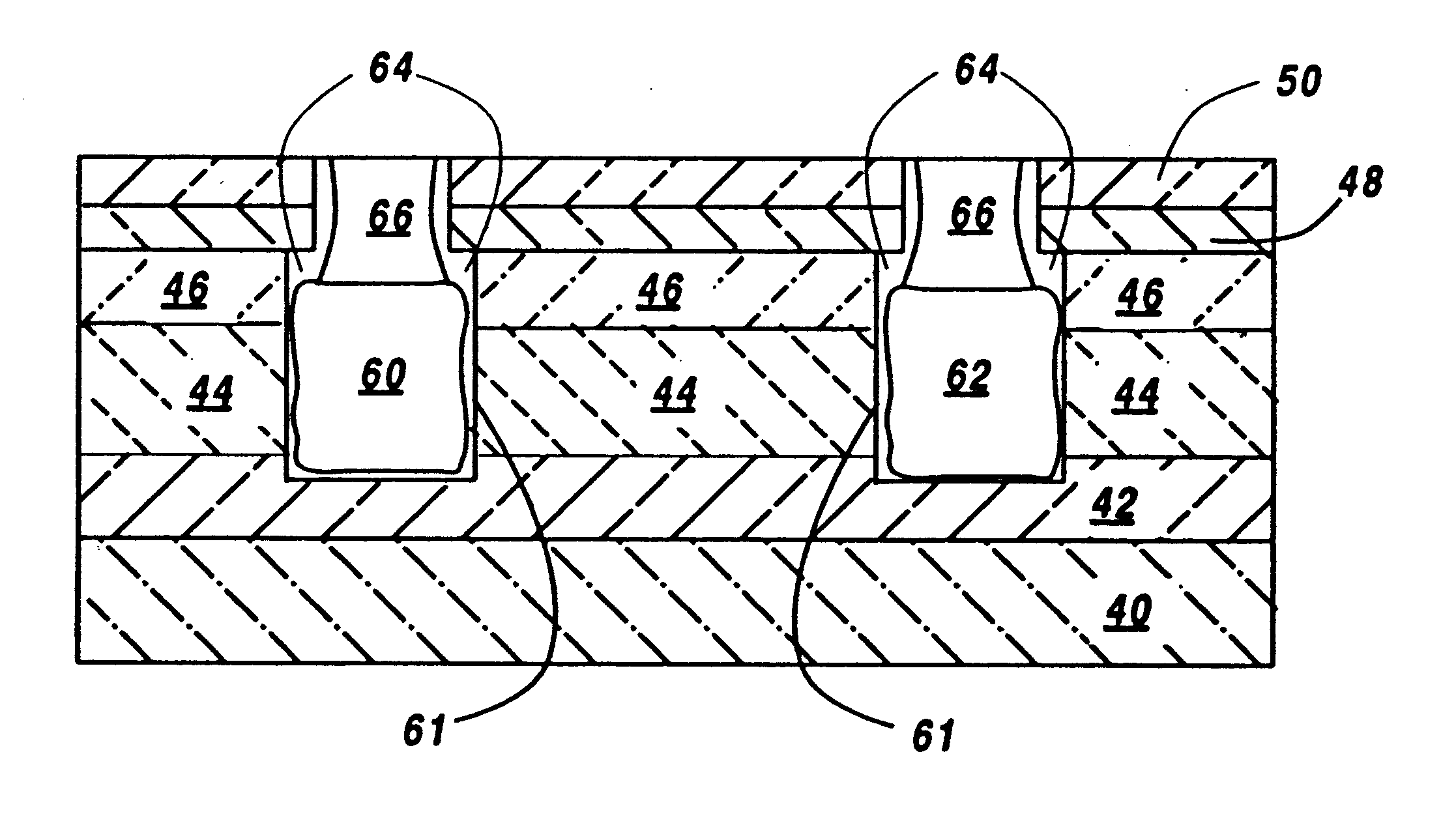

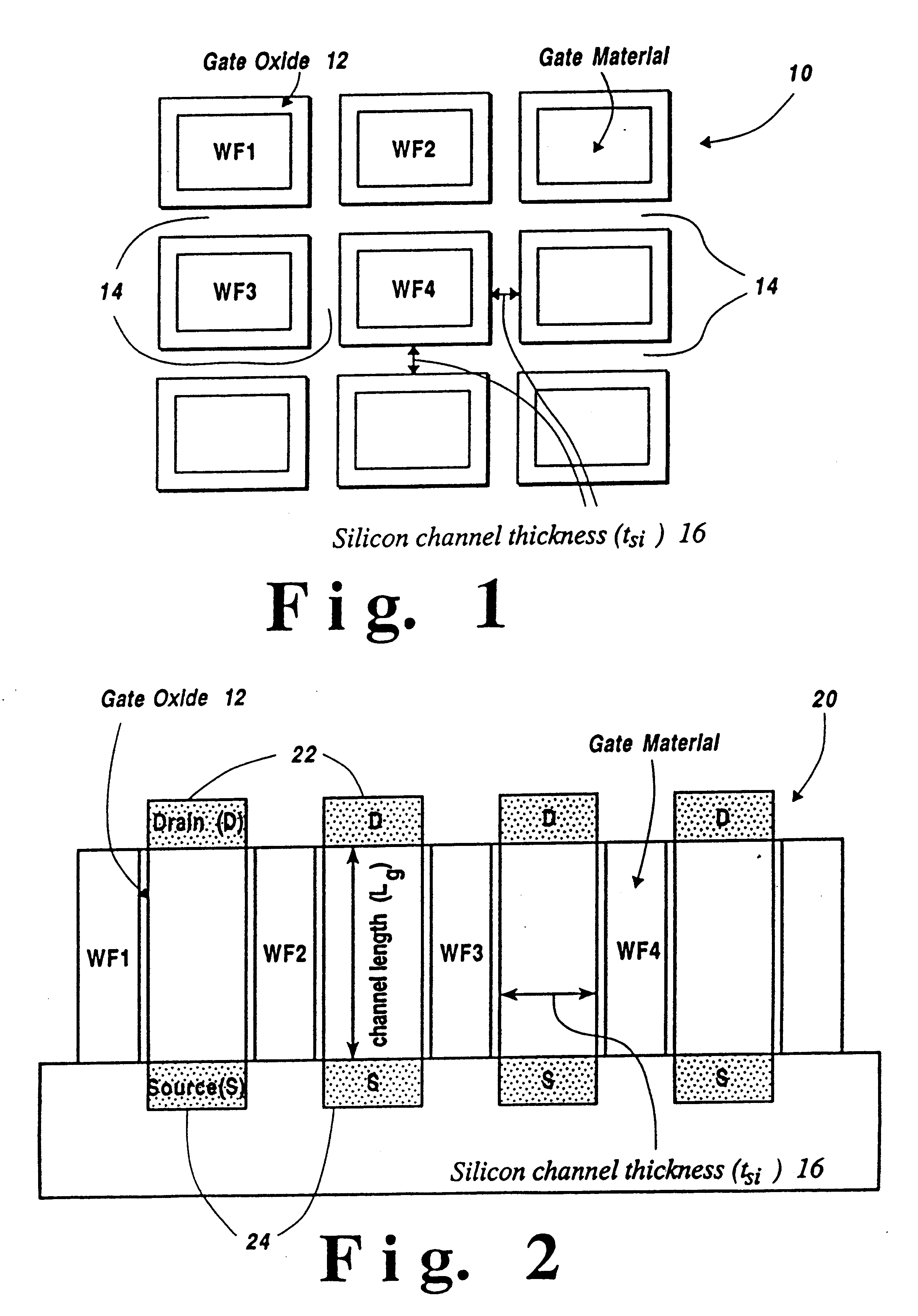

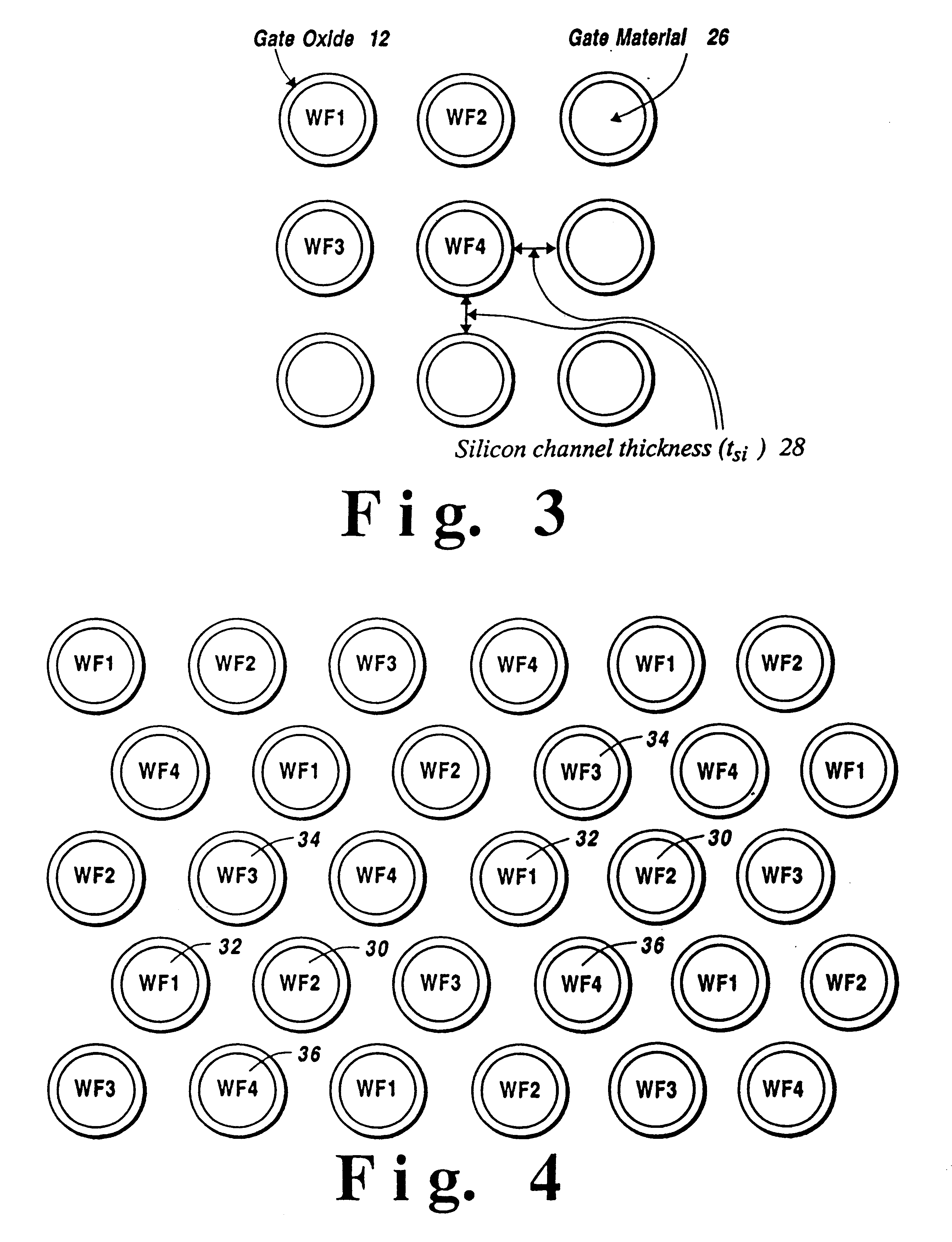

Multiple threshold voltage FET using multiple work-function gate materials

InactiveUS6448590B1Control flowSolid-state devicesSemiconductor/solid-state device manufacturingVery large scale integrated circuitsWork function

A shorter gate length FET for very large scale integrated circuit chips is achieved by providing a wafer with multiple threshold voltages. Multiple threshold voltages are developed by combining multiple work function gate materials. The gate materials are geometrically aligned in a predetermined pattern so that each gate material is adjacent to other gate materials. A patterned linear array embodiment is developed for a multiple threshold voltage design. The method of forming a multiple threshold voltage FET requires disposing different gate materials in aligned trenches within a semiconductor wafer, wherein each gate material represents a separate work function. The gate materials are arranged to be in close proximity to one another to accommodate small gate length designs.

Owner:GLOBALFOUNDRIES INC

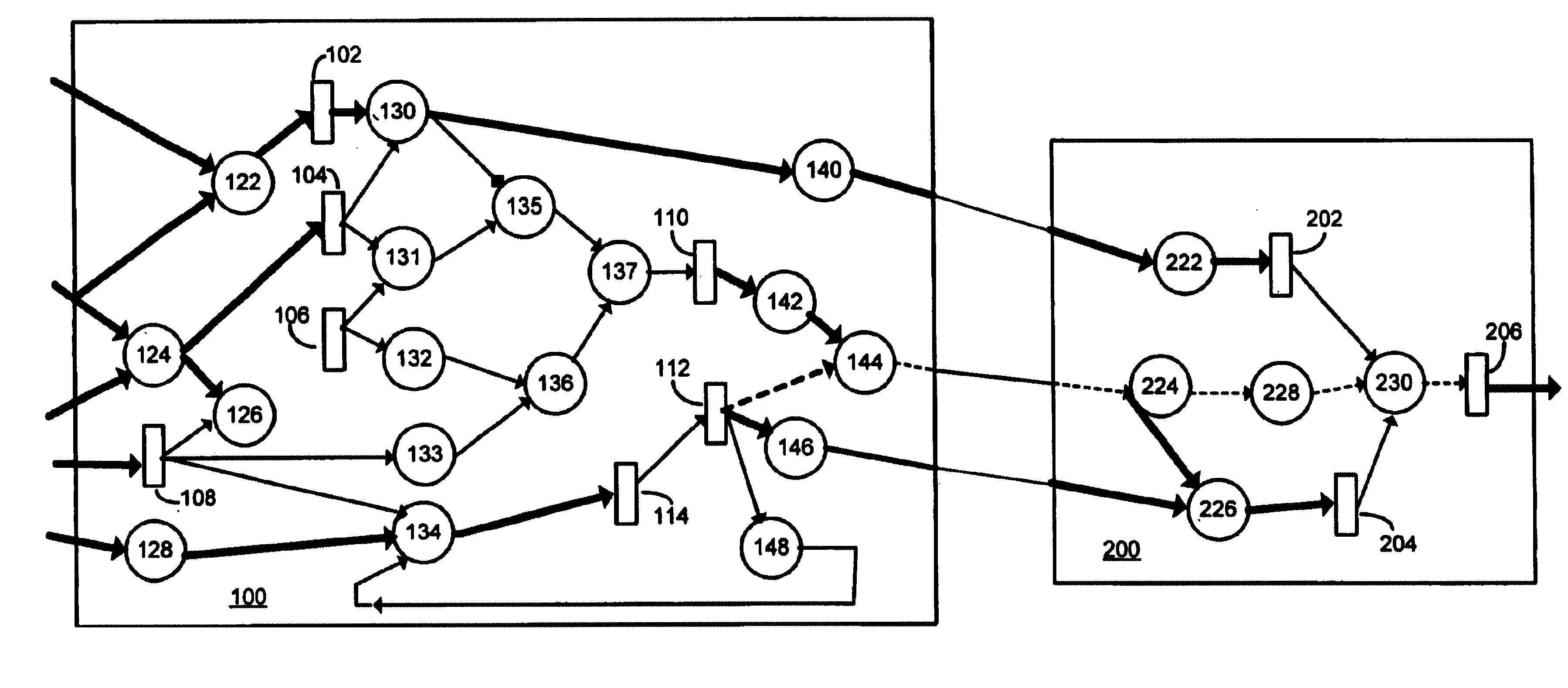

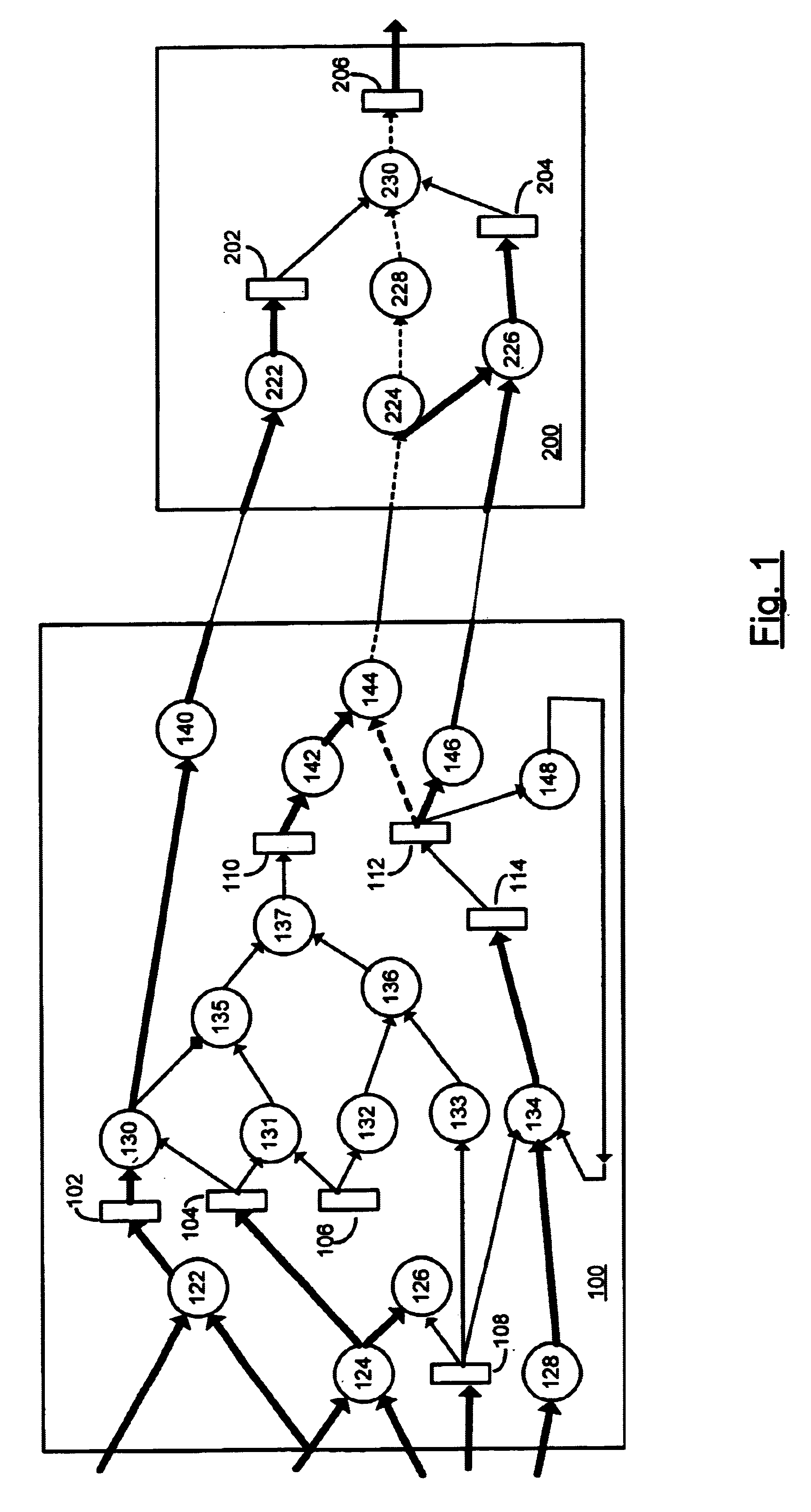

Timing verification method employing dynamic abstraction in core/shell partitioning

InactiveUS6622290B1Electronic circuit testingComputer aided designVery large scale integrated circuitsComputer architecture

A method for timing verification of very large scale integrated circuits reduces required CPU speed and memory usage. The method involves steps including partitioning the circuit into a plurality of blocks and then partitioning the verification between shell path components and core path components. Timing verification is then conducted for only shell path components while core path components are abstracted or ignored. Finally, timing verification for core path components in each block completes the process for the entire design.

Owner:CADENCE DESIGN SYST INC

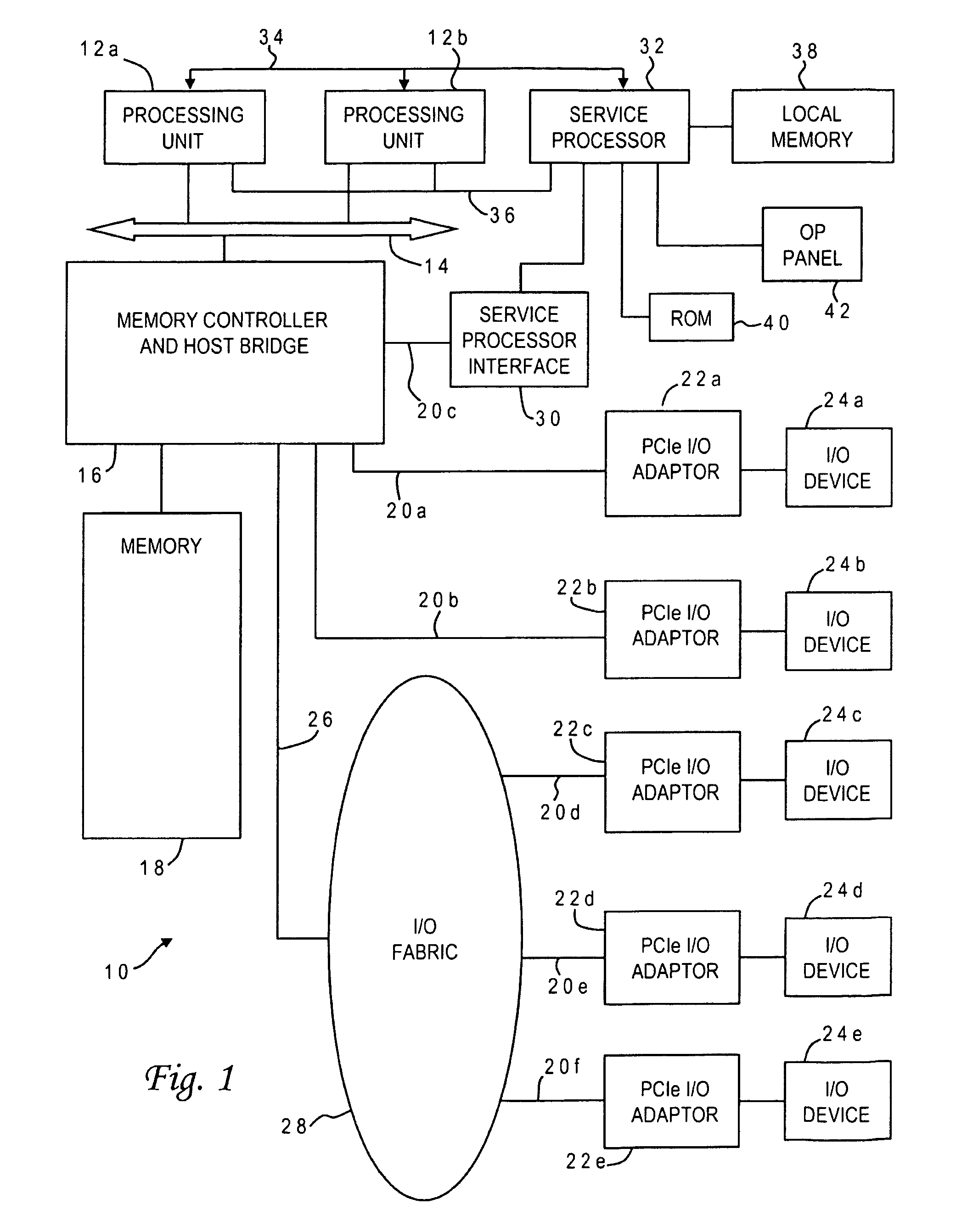

Low impedance power distribution structure for a semiconductor chip package

InactiveUS6661100B1Semiconductor/solid-state device detailsSolid-state devicesVery large scale integrated circuitsElectricity

A low impedance power distribution structure and method for substrate packaging of semiconductor chips containing very large scale integrated circuit (VLSI) circuits, such as microprocessors and associated memory, is presented. The power distribution structure incorporates under bump metallurgy (UBM) solder bump forming technology to produce not only solder bump connections that are vertically oriented, but also low impedance distribution wires that are horizontally oriented, and which provide electrical interconnection between various selected electrical contact points, such as solder bumps. These low impedance distribution wires introduce the benefits of low characteristic impedance to the substrate's power distribution structure.

Owner:GLOBALFOUNDRIES US INC

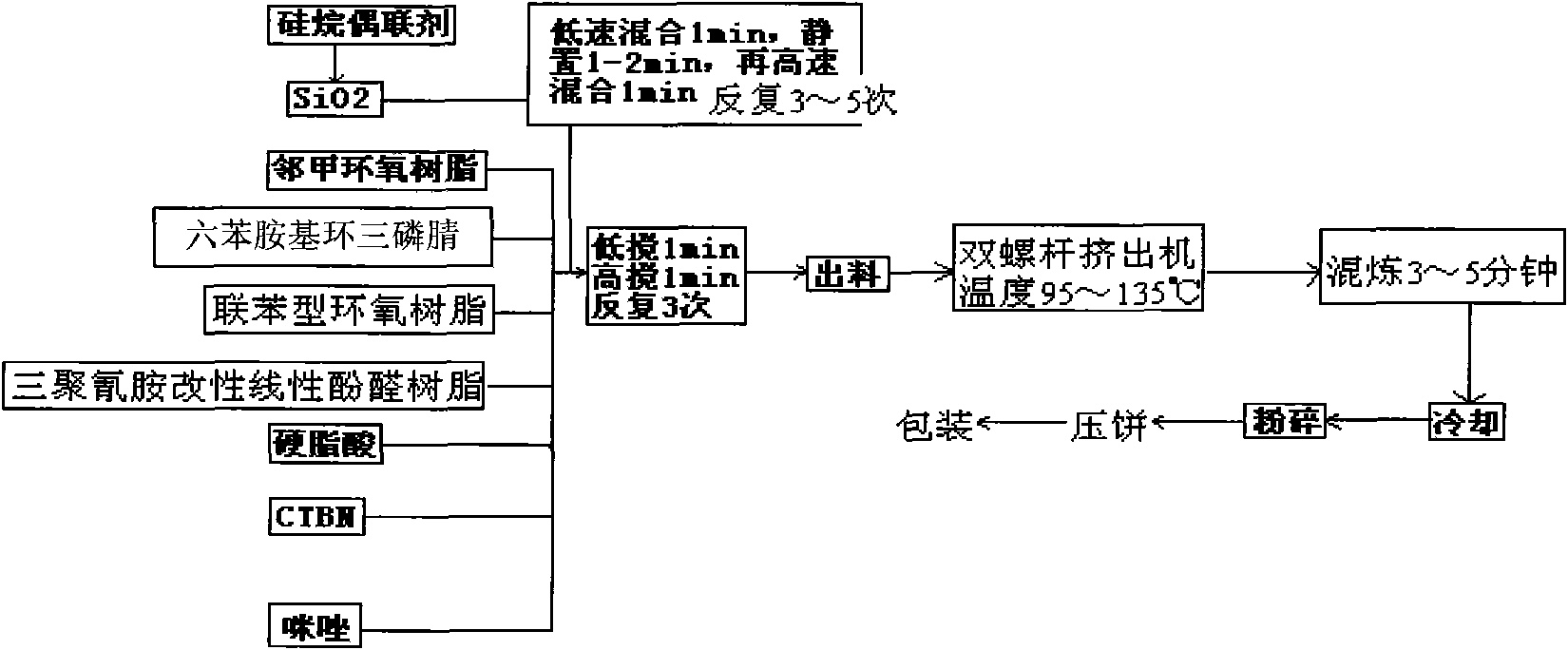

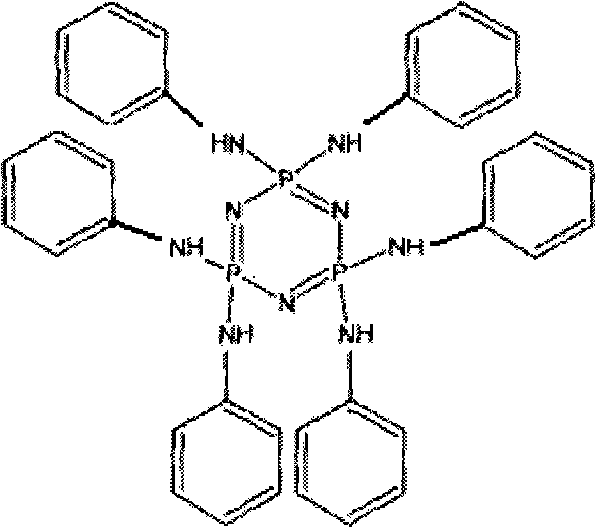

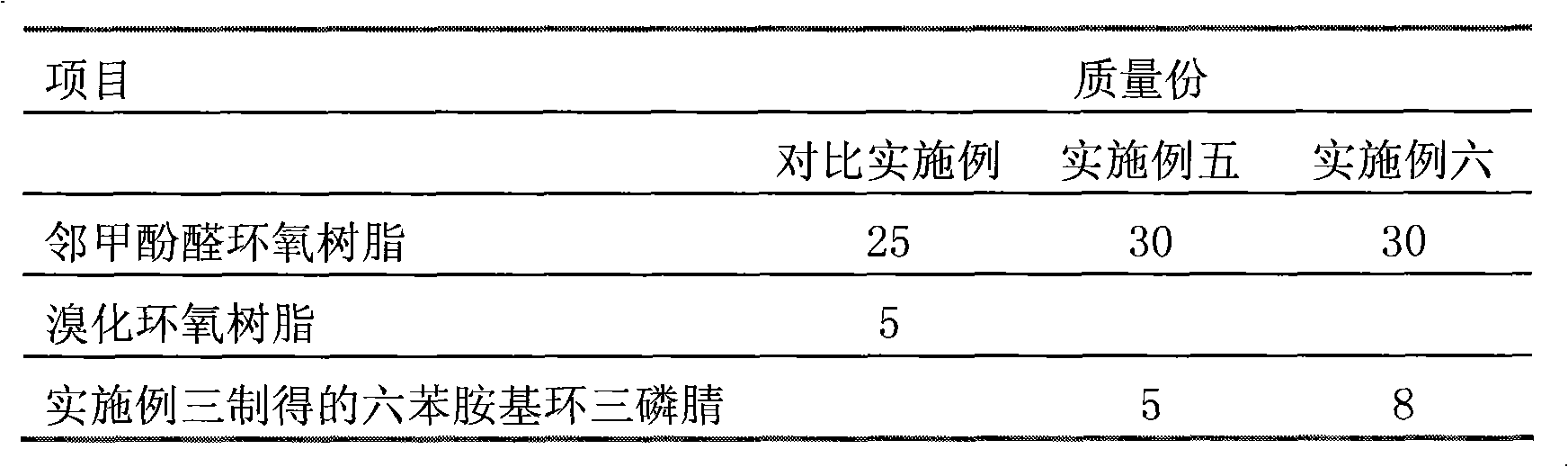

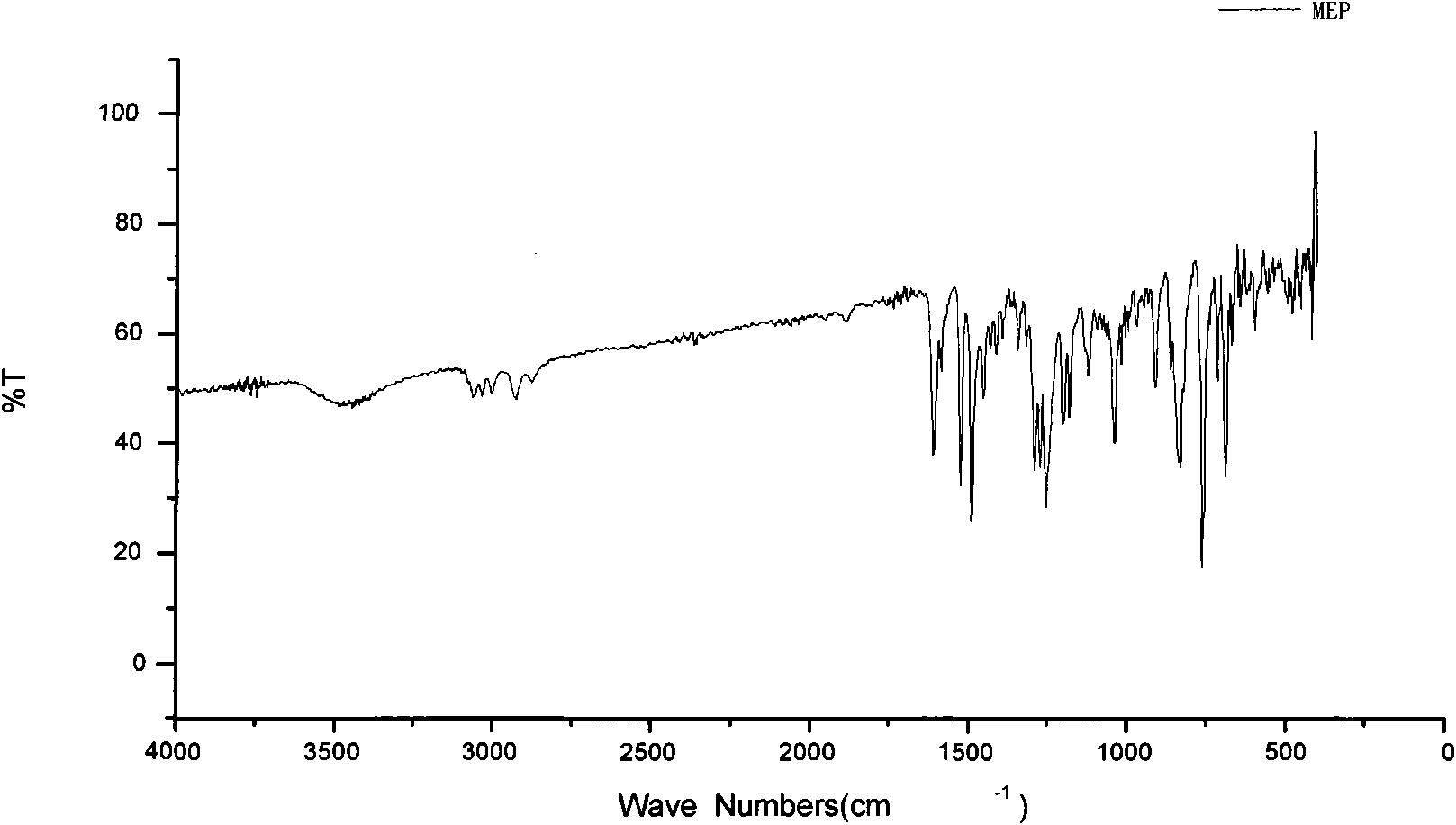

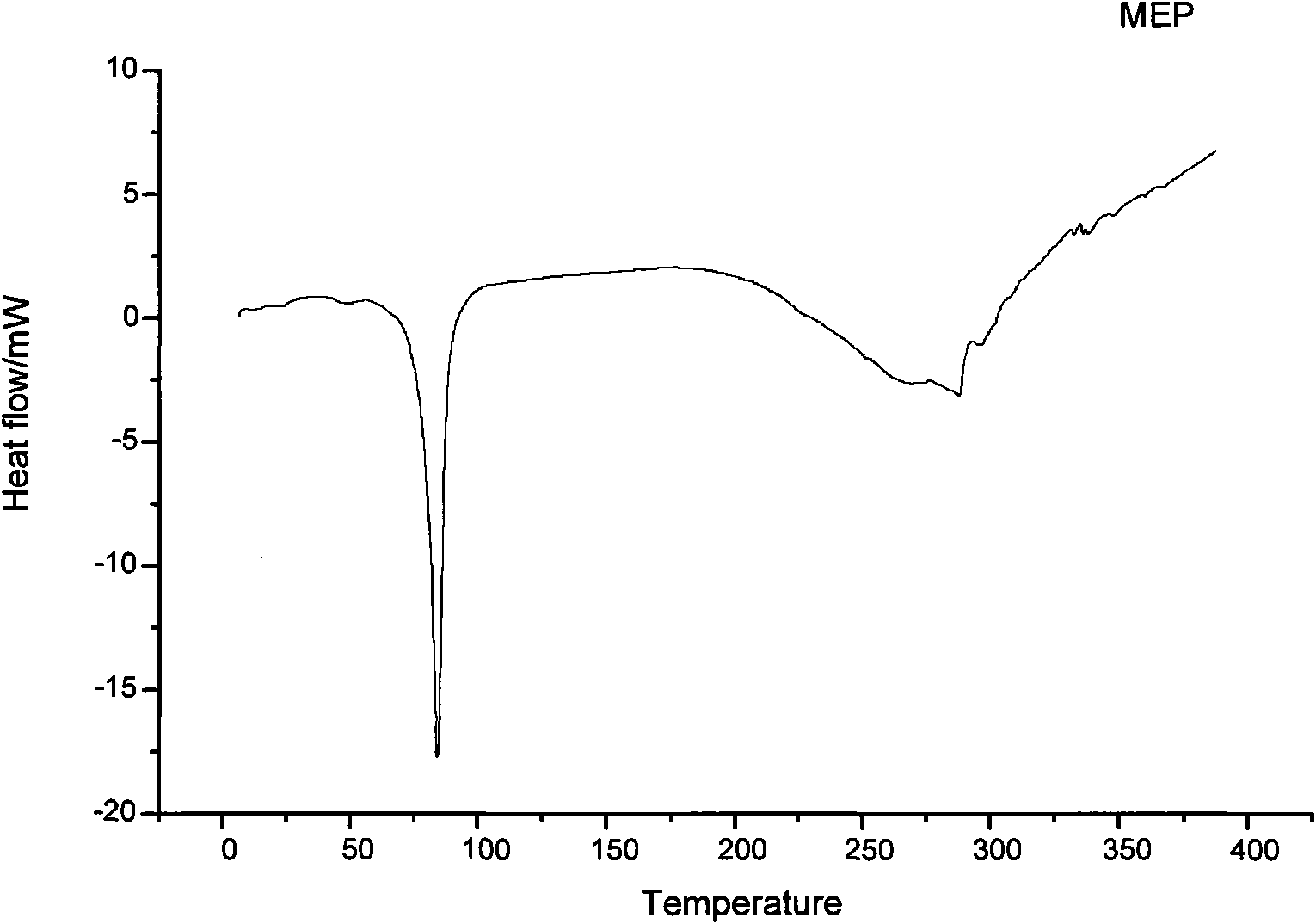

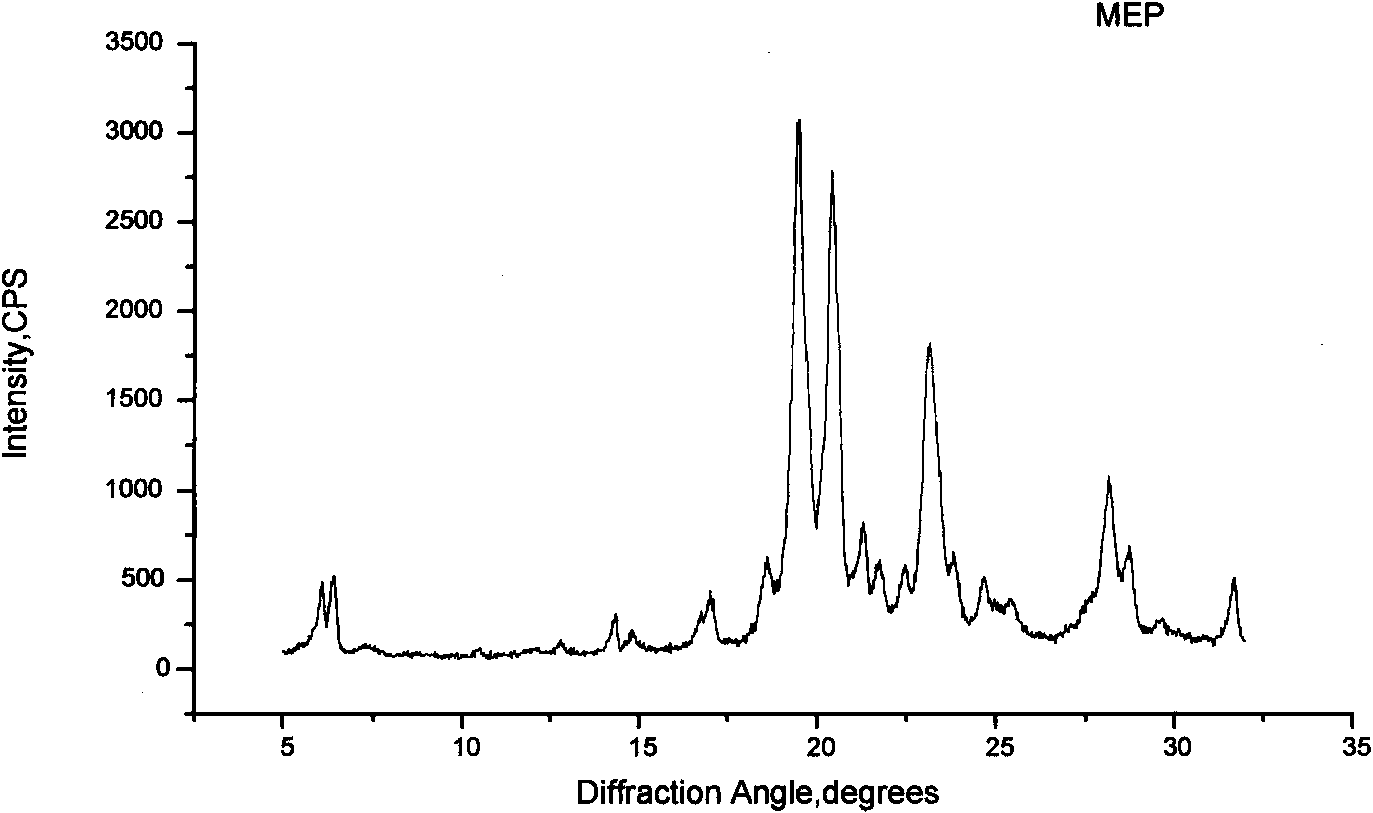

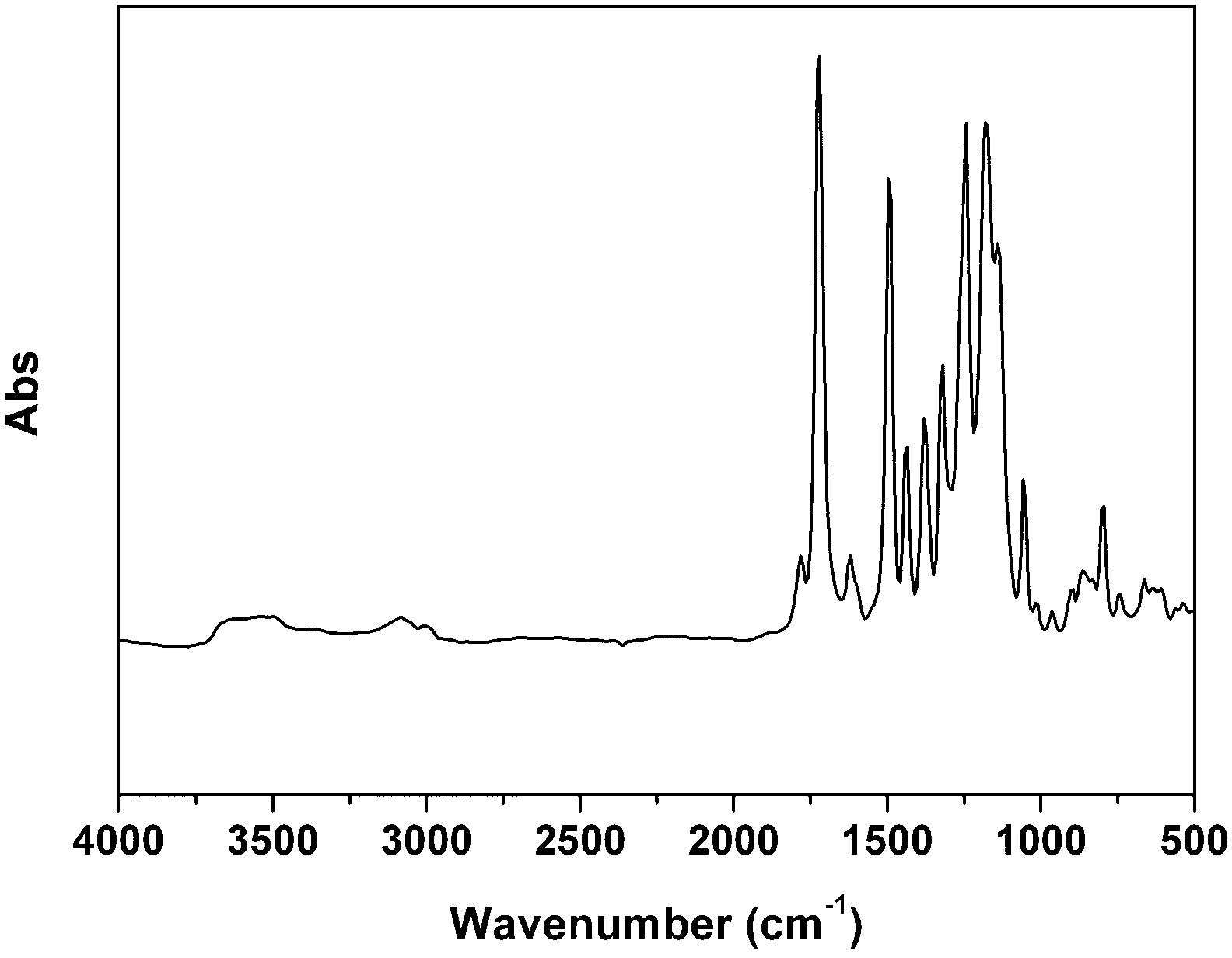

Preparation method of hexaaniline cyclotriphosphazene and non-halogen flame retardant epoxy resin composition

InactiveCN101597308AImprove performanceImprove flame retardant performanceGroup 5/15 element organic compoundsEpoxyPolymer science

The invention discloses a preparation method of hexaaniline cyclotriphosphazene and non-halogen flame retardant epoxy resin composition. The preparation method of hexaaniline cyclotriphosphazene comprises the following steps: adding solvent, hexachlorocyclotriphosphazene, aniline and acid-binding agent into a reaction device, stirring and introducing nitrogen for protection, heating the mixture to 50-120 DEG C, adding catalyst into the reaction device, reacting for 5-16h and cooling to room temperature, filtering, carrying out reduced pressure distillation on the filtrate, carrying out evaporation to remove solvent to obtain brown thick product, placing the product in a drying oven, drying for 8h in vacuum at 40-70 DEG C, crushing to obtain powder product, namely the hexaaniline cyclotriphosphazene. The non-halogen flame retardant epoxy resin composition applied to large-scale and very-large-scale integrated circuits encapsulation is prepared by mixing the prepared hexaaniline cyclotriphosphazene with o-cresol formaldehyde epoxy resin, microsilica, curing catalyst, silane coupling agent, lubricant, flexibilizer and stearic acid, milling, crashing and demagnetizing.

Owner:GUANGDONG RONGTAI IND +1

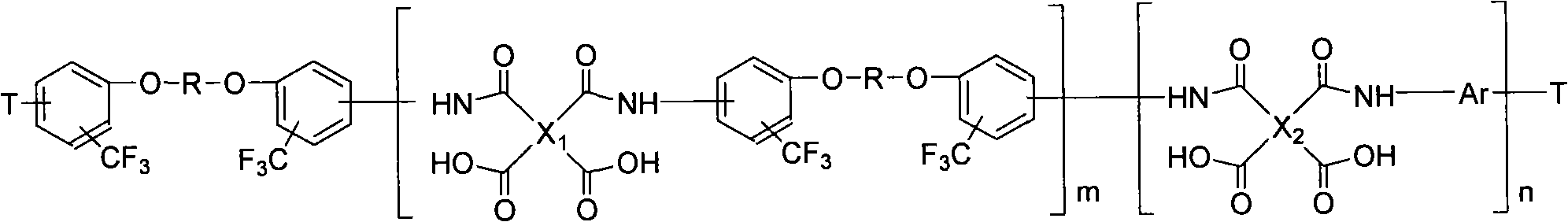

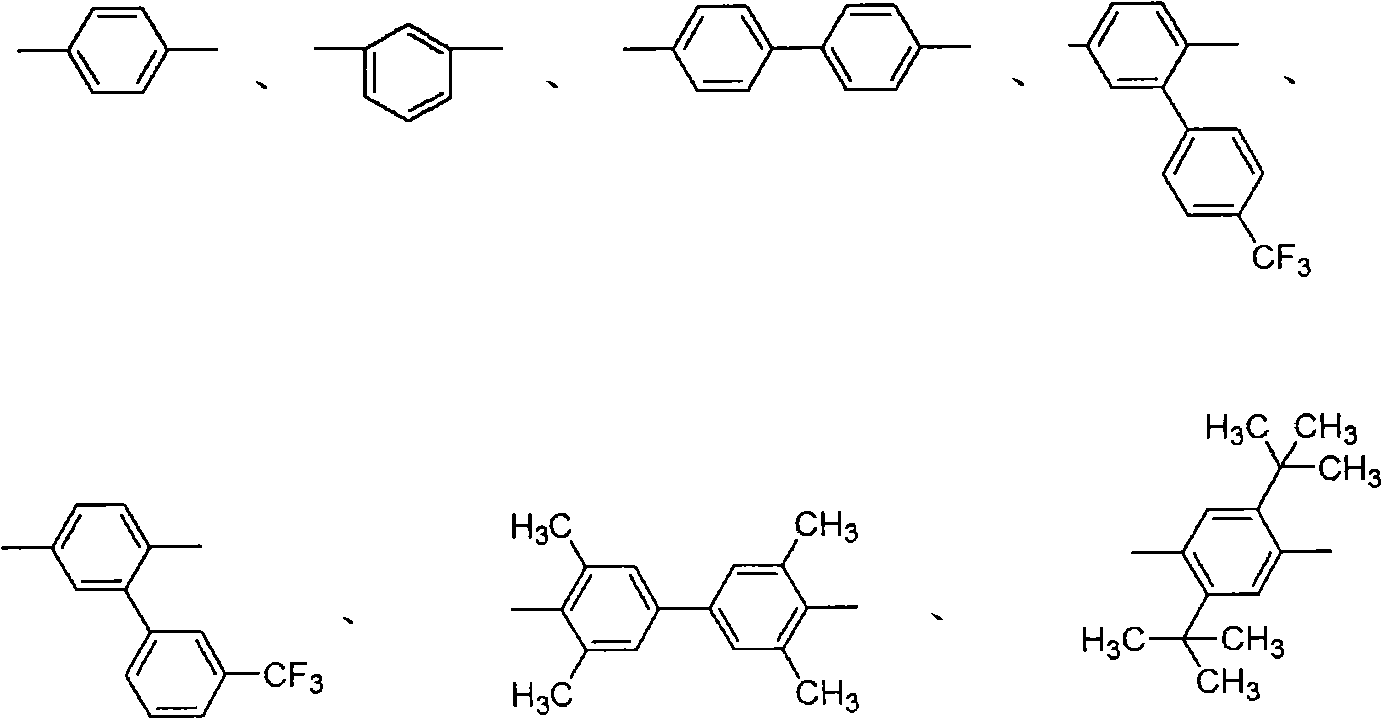

Polyimide resin, its midbody, preparation method and application thereof

ActiveCN101343362AImprove heat resistanceImprove mechanical propertiesLamination ancillary operationsSynthetic resin layered productsChemical structureMetal foil

The invention discloses polyamide resin and intermediate compound thereof as well as the preparation method and the application. The polyamide resin is provided with the chemical structure shown in formula II, wherein, X1 and X2 can be identical or different, representing quadrivalent aryl; Ar represents bivalent aryl, and T represents end capping reagent. The polyamide resin is obtained by polyamic acid shown in formula I structure general formula through chemical imidization or thermal imidization. The polyamide resin is dipped through prosomatic polyamic acid solution or polyamic acid solution being obtained after being dissolved with solvent with a low-boiling point, the basal body is strengthened, and the prepreg is obtained. After the heat-press forming operation is performed, a metal foil layer is covered, and a metal foil layer pressing plate is obtained. The polyamide resin provided by the invention has the advantages of excellent heat resisting property, high mechanical property, low dielectric constant and dissipation, high electrical insulation property and low water absorbing capacity, thereby being especially suitable for manufacturing core plates of packaging subsctrates for packaging super large-scale integrated circuits.

Owner:INST OF CHEM CHINESE ACAD OF SCI

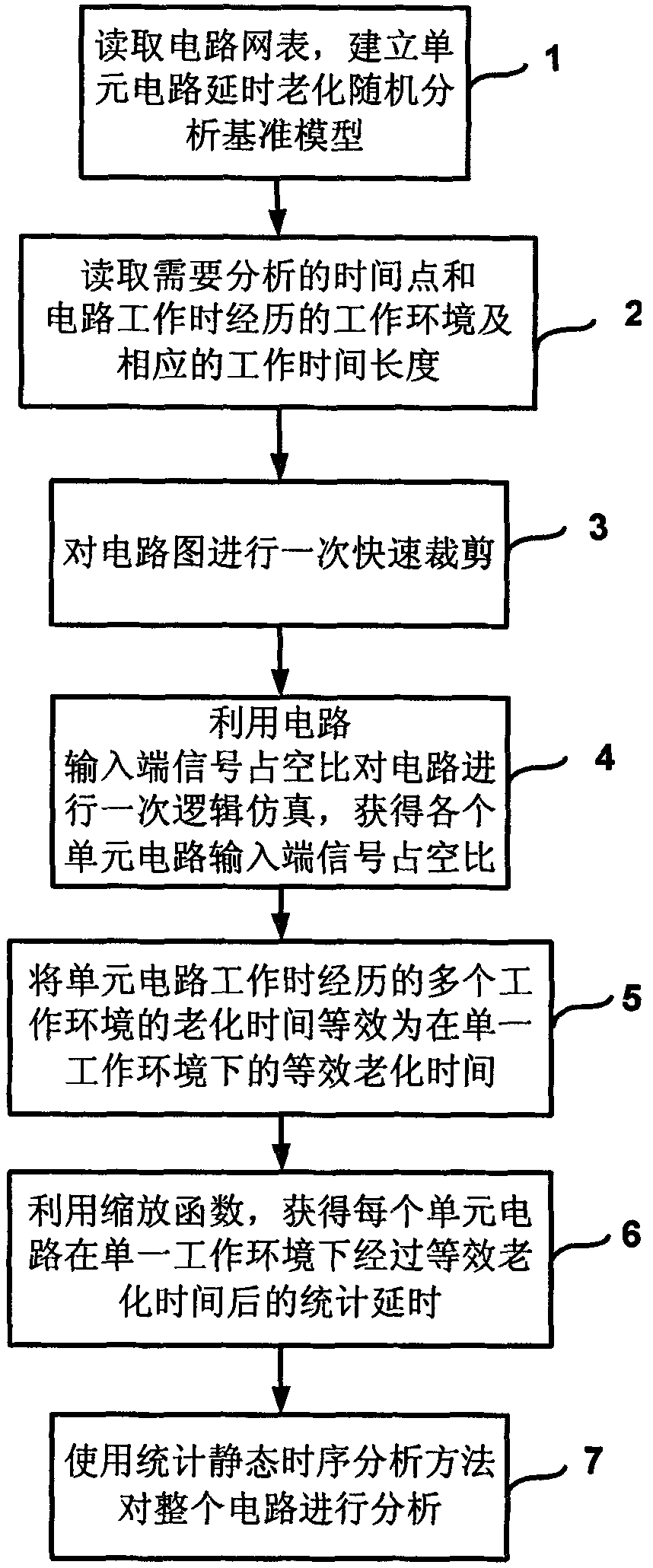

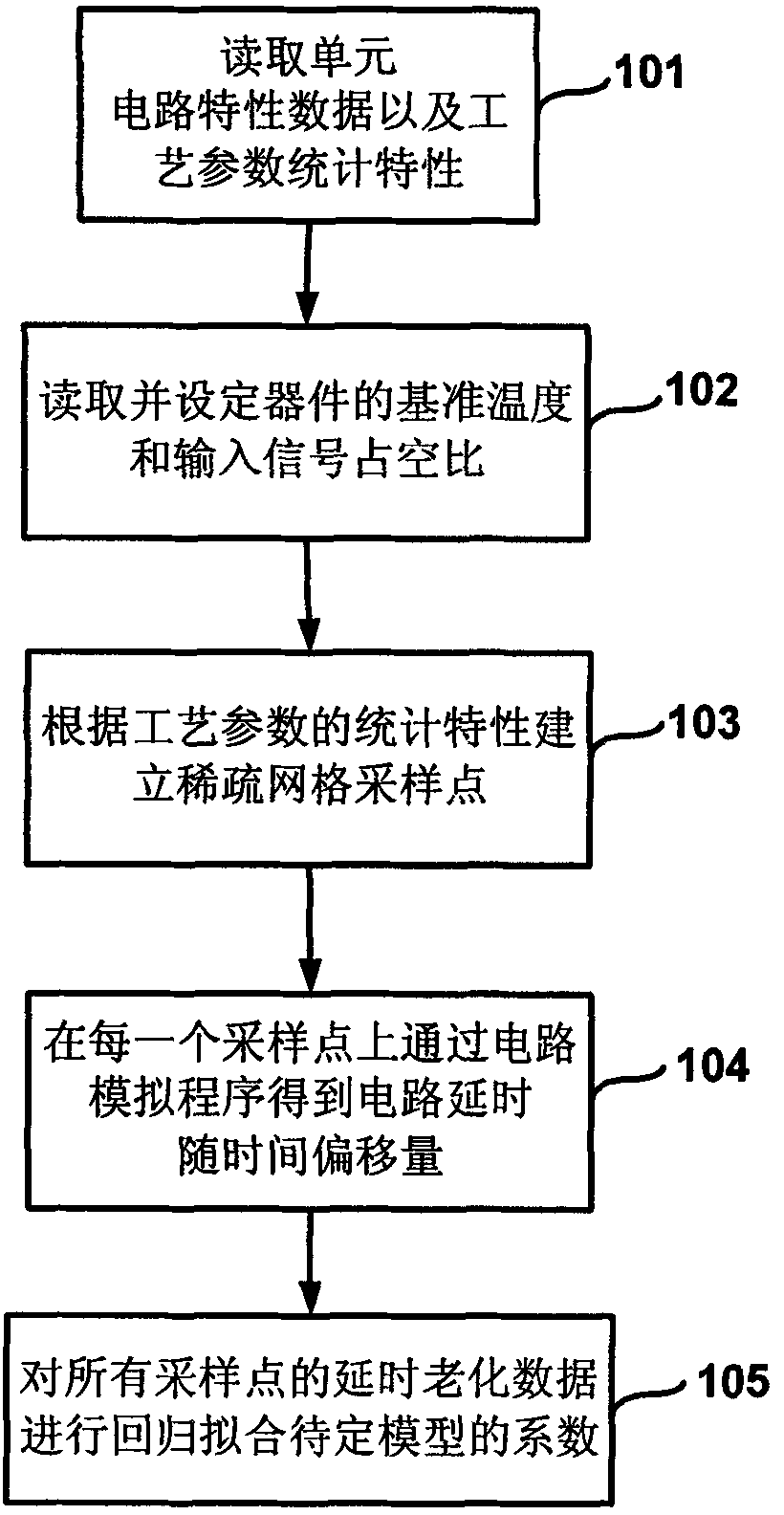

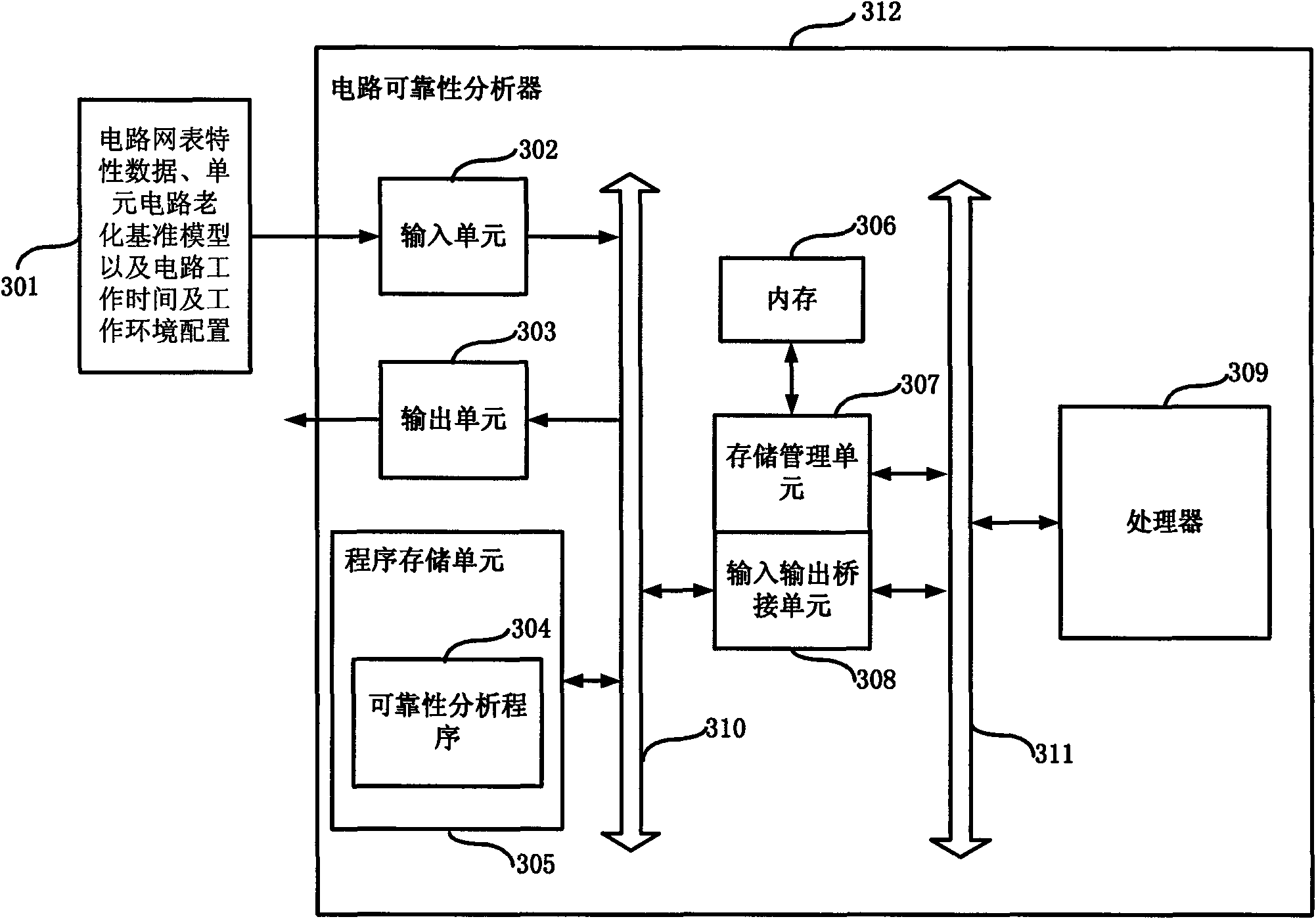

Method and device for analyzing reliability of integrated circuit

ActiveCN101964003AMeet analysis needsExtension of timeSpecial data processing applicationsProcess deviationsCircuit delay

The invention relates to a method and a device for analyzing the reliability of an integrated circuit. In the analytical method, a unit circuit delayed aging stochastic analysis reference model in consideration with both negative bias temperature instability (NBTI) effect and process parameter perturbation is established, a scaling function and an equivalent aging time concept are provided to solve the delayed statistical distribution of a unit circuit under the actual work environment quickly from the reference model, and the pre-clipping process of the circuit is provided to reduce the complexity of reliable analysis. The device of the invention comprises an input unit, an output unit, a program storage unit, an external bus, a memory, a storage administration unit, an input / output bridging unit, a system bus and a processor. In the method and the device, the effect of the process parameter perturbation, the NBTI effect and the work environment of the circuit on reliability are considered simultaneously, and the complexity of the reliable analysis can be reduced effectively by utilizing the scaling function, equivalent aging time and the pre-clipping technology so as to realize the quick analysis on the reliability of super-large-scale integrated circuits in consideration with process deviation.

Owner:FUDAN UNIV

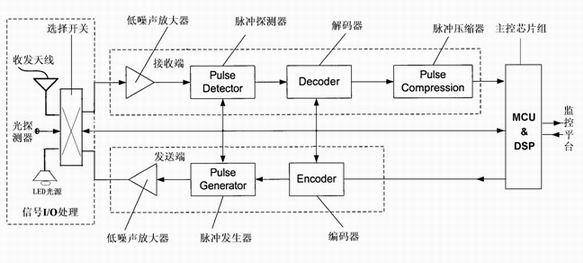

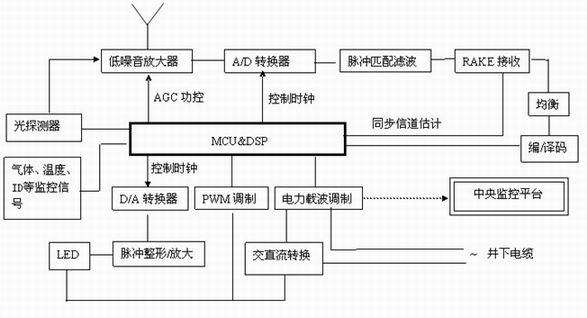

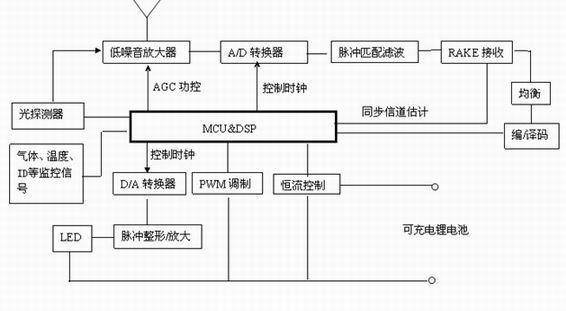

LED visible light wireless communication system for mine

InactiveCN102624455AReduce power consumptionLow powerClose-range type systemsMulti-frequency code systemsVery large scale integrated circuitsIntrinsic safety

The invention discloses an LED visible light wireless communication system for a mine, which comprises a signal I / O processing part, a receiving end part, an emitting end part, a main control chip set and a software control part, wherein hardware equipment comprises an LED mine lamp and an LED head lamp. In the invention, the communication system can avoid that the communication reliability is influenced because an optical detector is easily polluted due to large dust in the mine for the traditional LED visible light communication technology by adopting a communication mode of combining a UWB (Ultra-wide Band) wireless communication technology with an LED visible light communication technology on the basis of the design scheme of a programmable super-large-scale integration circuit chip, and can fully utilize the advantages of green illumination of LED visible light, wide coverage range, large transmission capacity and high modulation rate. The LED visible light wireless communication system is extremely low in power consumption, has the power consumption of hundreds mu W to tens mW which is only 1 / 10-1 / 100 that of the traditional radio station during high-speed communication, and is more easily realized in intrinsic safety design suitable for the mine.

Owner:武汉华炬光电有限公司

Resonant clock distribution for very large scale integrated circuits

InactiveUS7015765B2Efficiently distributedConsumes less powerAngle modulation by variable impedencePulse automatic controlCapacitanceVery large scale integrated circuits

A circuit for distributing a clock signal in an integrated circuit includes a capacitive clock distribution circuit having at least conductor therein. At least one inductor is formed in a metal layer of the integrated circuit and is coupled to the clock distribution circuit. The inductor, generally in the form of a number of spiral inductors distributed throughout the integrated circuit, provides an inductance value selected to resonate with the capacitive clock distribution circuit. By operating the clock distribution circuit at resonance, power dissipation is reduced while skew and jitter performance can be improved.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

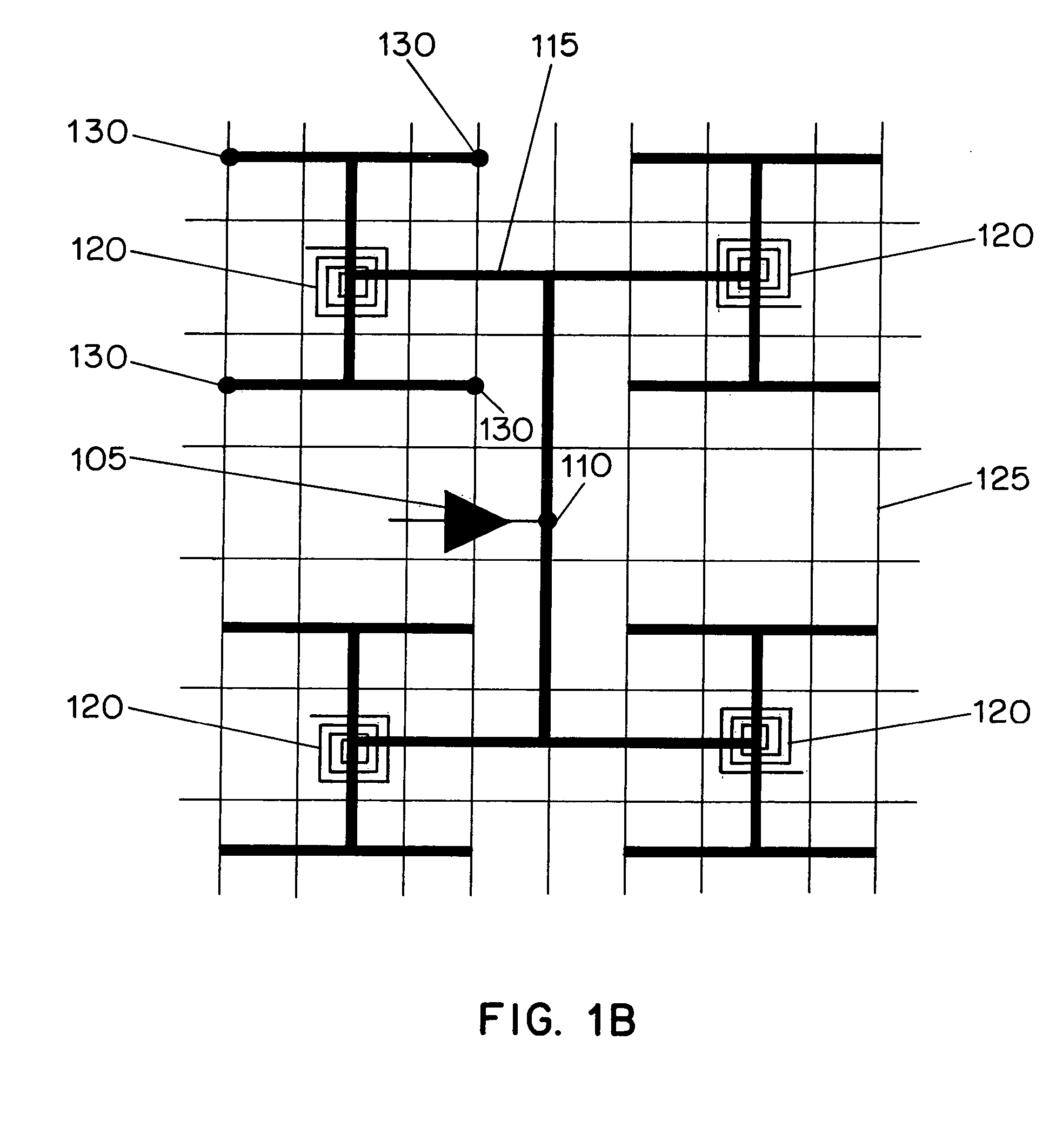

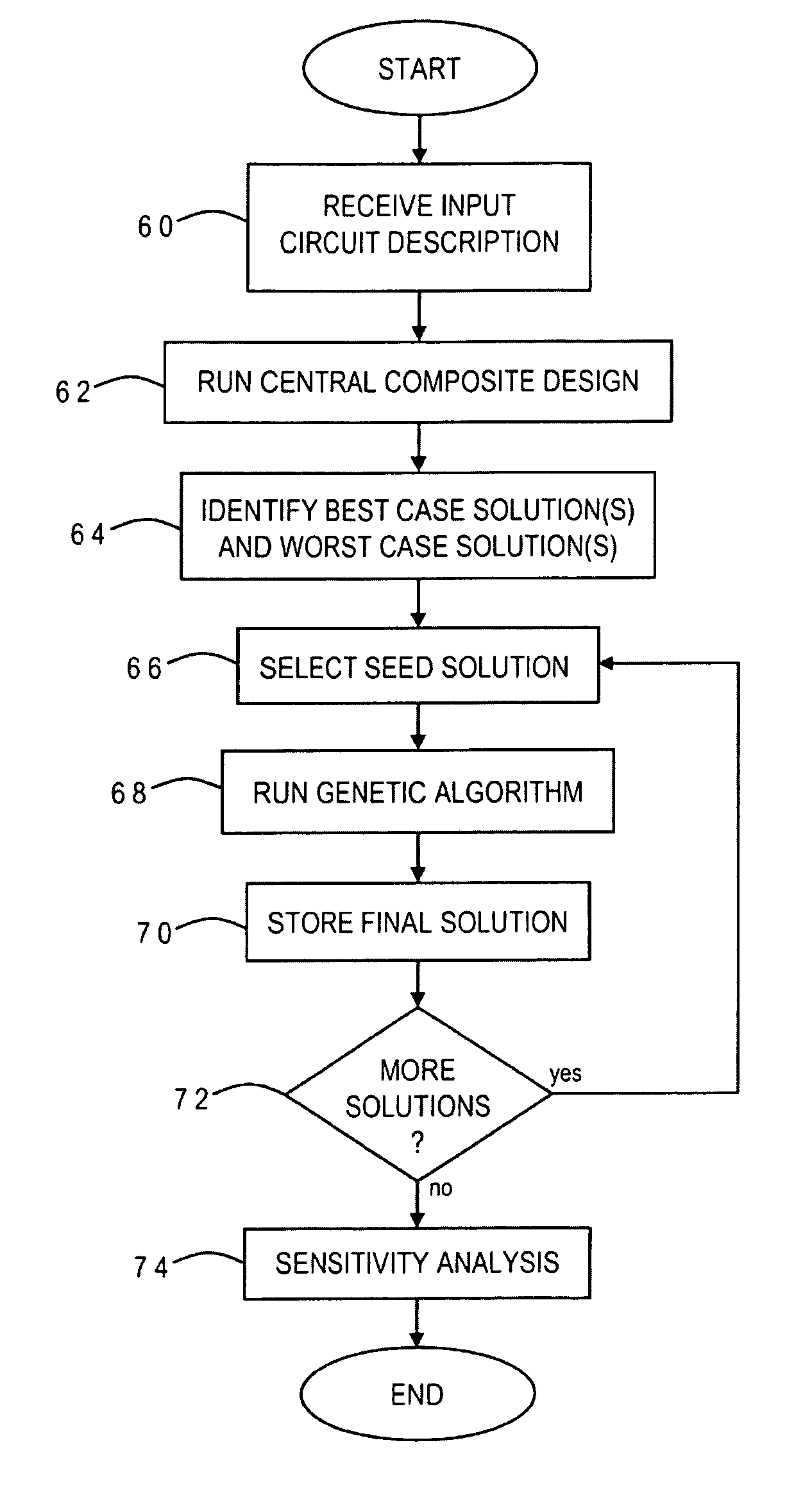

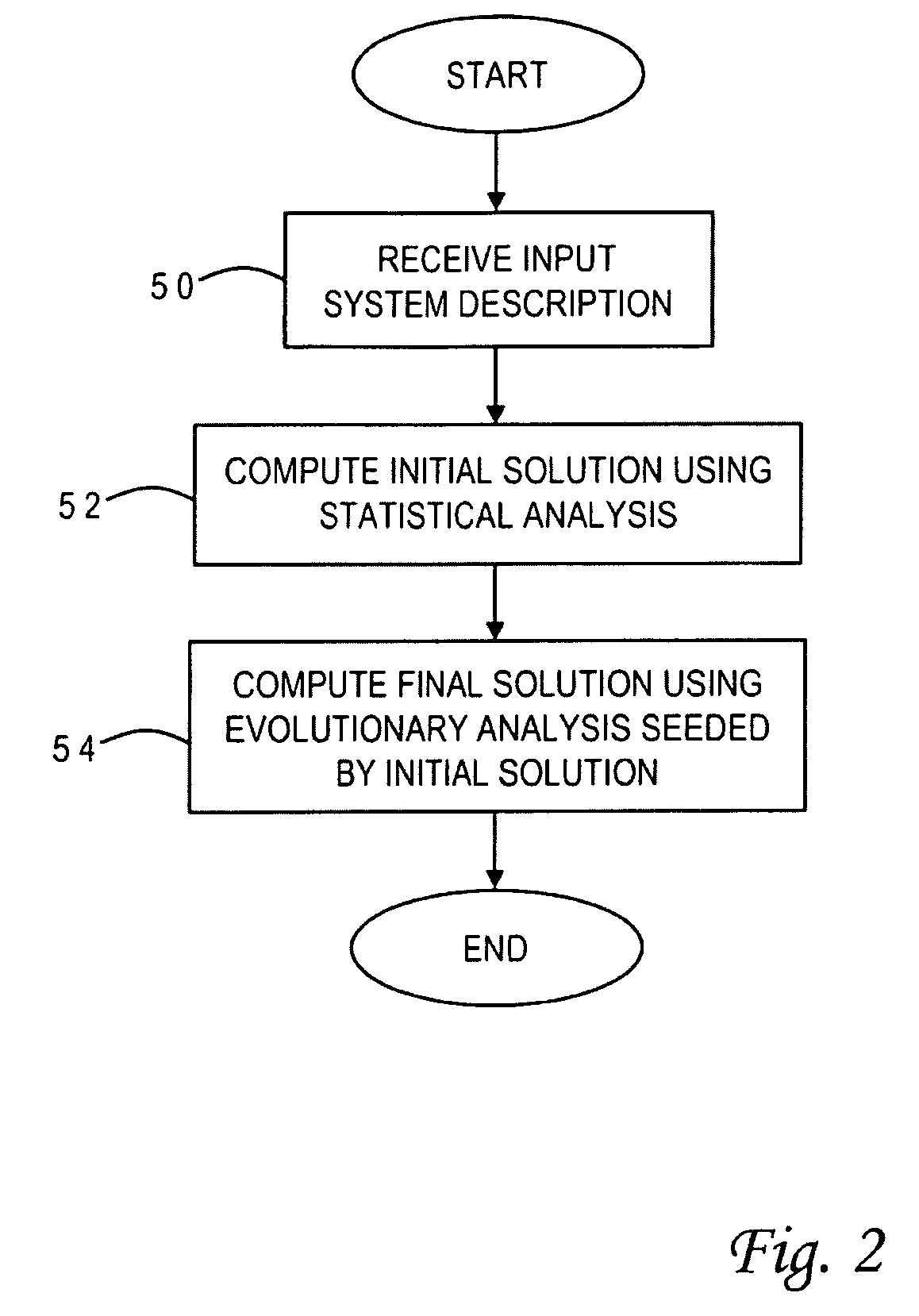

Solution efficiency of genetic algorithm applications

InactiveUS20090307636A1Simple methodAccurate representationDigital computer detailsMulti-objective optimisationVery large scale integrated circuitsStatistical analysis

A method of optimizing a very large scale integrated circuit design takes a circuit description which includes interconnected circuit components and characteristic variables assigned to the circuit components such as environmental, operational or process parameters, computes a first solution for the characteristic variables using a statistical analysis, and then computes a second solution for the characteristic variables using an evolutionary analysis seeded by the first solution. In the exemplary implementation the statistical analysis is a central composite design (CCD) and the evolutionary analysis is a genetic algorithm. Best case and worst case CCD solutions may be used to seed separate genetic algorithm runs and derive global best case and global worst case solutions. These solutions may be compared for sensitivity analysis. The method thereby provides significant reduction in time-to-solution with accurate simulation results.

Owner:GLOBALFOUNDRIES INC

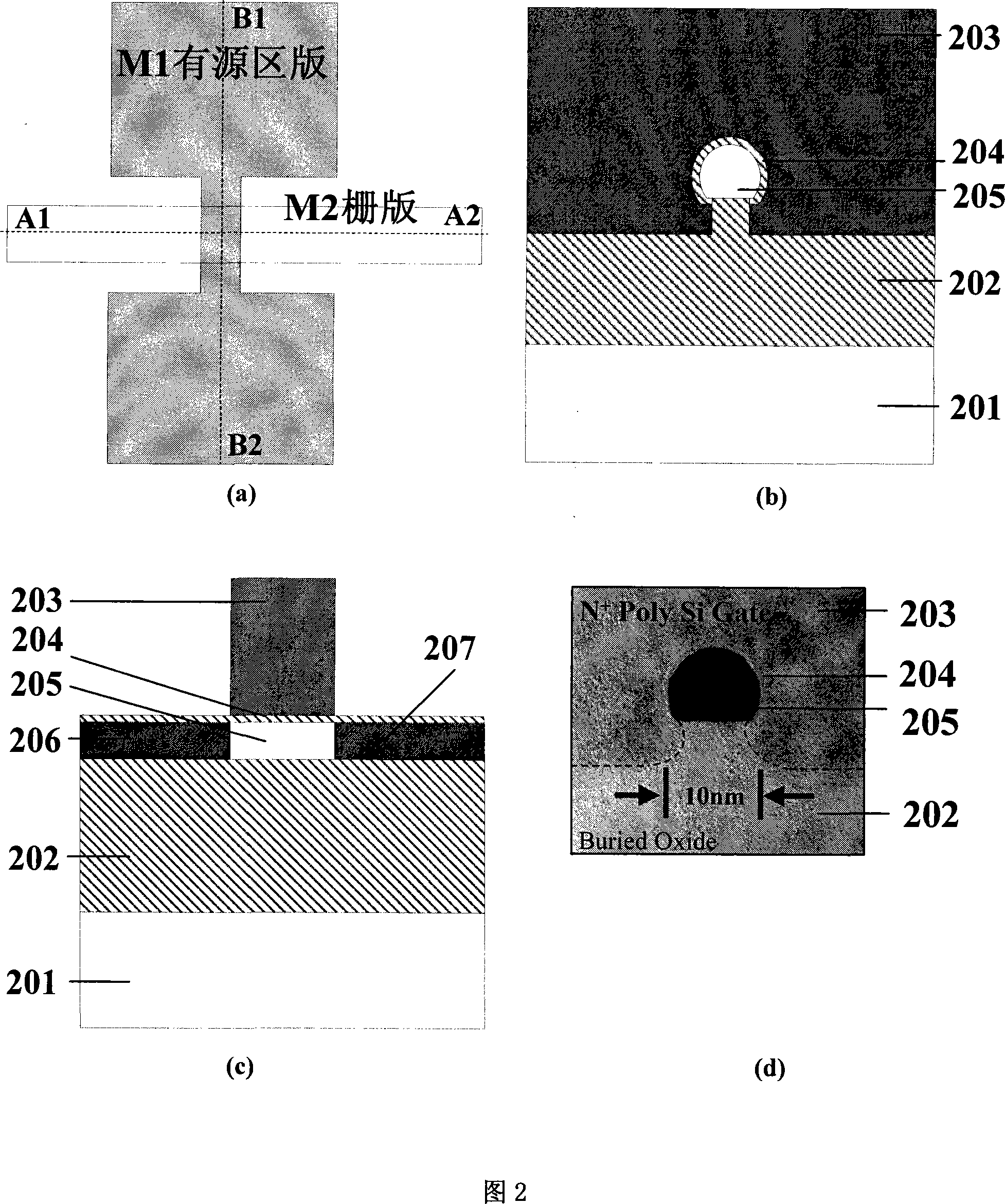

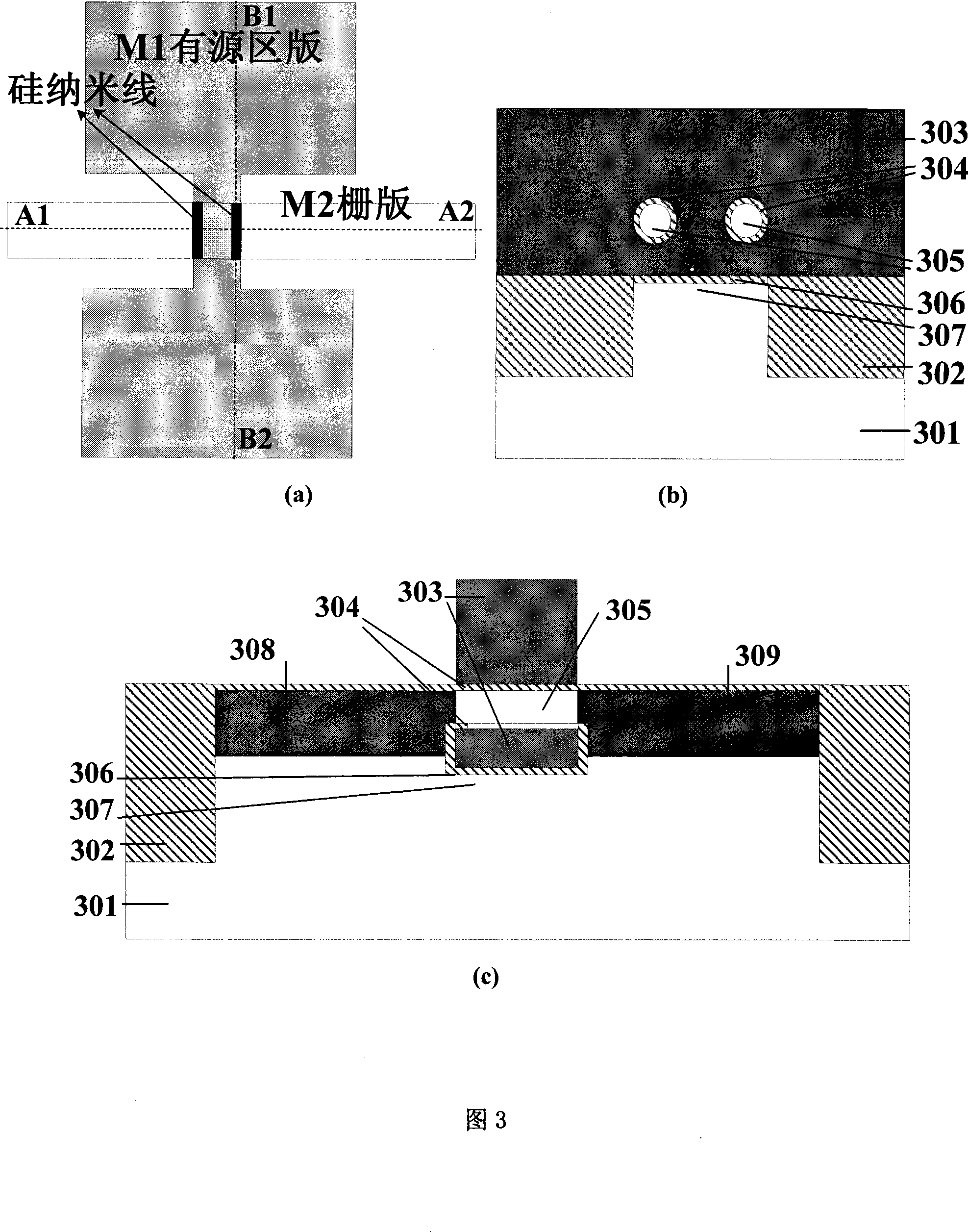

A double silicon nanowire wrap gate field-effect transistor and its manufacture method

InactiveCN101060135AImprove featuresLow costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSoi cmos technology

The provided double-silicon nano line enclose-grid FET belonged to MOSFET technique in ULSI comprises: a silicon substrate, double silicon lines as the channels, a grid anode and multicrystal silicon grid enclosing the nano lines to form the enclose-grid structure, both source and drain connecting with the substrate, and a thick SiO2 layer between the right bottom of channel and substrate. This invention is compatible to common CMOS technique, reduces cost and power consumption, and has wide application.

Owner:PEKING UNIV

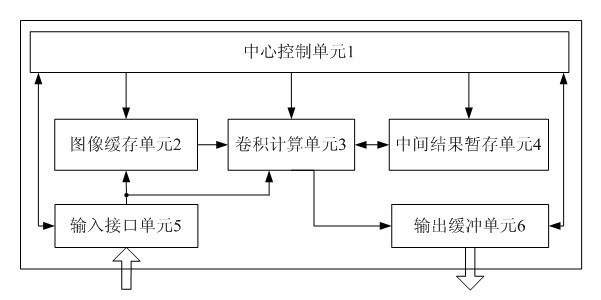

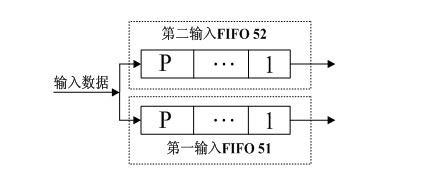

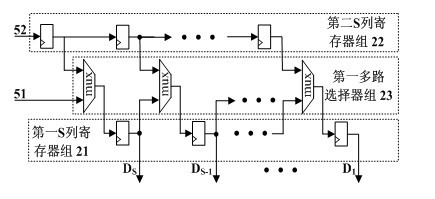

2-dimensional (2-d) convolver

InactiveCN102208005AReduce capacityCapacity adjustmentComputing operations for integral formationVery large scale integrated circuitsComputer architecture

2-dimensional (2-D) convolution calculation is widely applied in the field of image processing. The invention discloses a 2-D convolver. By decomposing the 2-D convolution calculation into parallel calculation of multiple 1-D convolution calculation windows and adopting the strategy that image data are input in a row or column leading Zigzag scanning format, the capacity of an on-chip memory is reduced, and on-chip resource overhead is reduced; because the 2-D convolver can accept two different image data input formats of row or column leading Zigzag scanning formats, the 2-D convolver is suitable for different application systems; and by adjusting the depth W of each double-port system random access memory (SRAM) in an intermediate result temporary storage unit and making good compromise between the capacity of the on-chip memory and the external bandwidth, flexibility of system design is brought. Compared with the conventional 2-D convolver, the 2-D convolver occupies fewer hardware resources, the throughput can meet the real-time requirements of most image processing systems, and the 2-D convolver can be used for realizing the 2-D convolution calculation in a low-cost embedded system. The 2-D convolver belongs to the field of super-large-scale integrated circuit structure design.

Owner:HUAZHONG UNIV OF SCI & TECH

Preparing methods of liquid crystal epoxy resin oligomer and epoxy resin composition

InactiveCN101585821AReduce melt viscositySmall coefficient of linear expansionOrganic chemistryEpoxySide chain

The invention discloses a preparing method of liquid crystal epoxy resin oligomer and epoxy resin composition. The method comprises that: p-phenylphenol, epoxy chloropropane, phase transfer catalyst, sodium hydroxide and distilled water as raw materials are reacted to prepare the liquid crystal epoxy resin oligomer. The epoxy resin composition comprises: mixing the prepared liquid crystal epoxy resin oligomer and other raw materials based on weight proportionality: 10-30 parts of liquid crystal epoxy resin oligomers by weight, 10-30 parts of o-cresol-formaldehyde epoxy resins by weight, 5-25 parts of melamine modified linear phenol aldehyde resins by weight, 60-150 parts of spherical silicon micronized quartz powders by weight, 0.1-2 parts of curing accelerators by weight, 2-10 parts of flexibilizers by weight, 0.6-5 parts of resin acceptors by weight and 0.5-5 parts of lubricants by weight, which are mixed for smelting, crushed and demagnetizing to prepare the epoxy resin composition comprising side chain liquid crystal structure. The epoxy composition has good heat-resistant property and good physical mechanical property, is suitable for the encapsulations of large scale and grand scale integrated circuits.

Owner:GUANGDONG RONGTAI IND +1

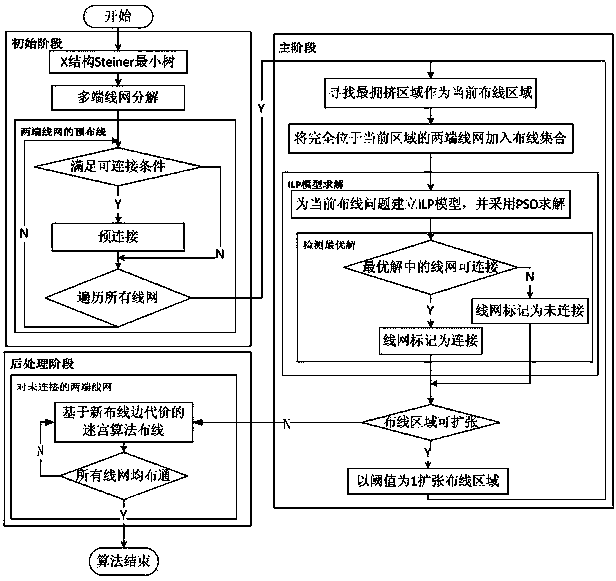

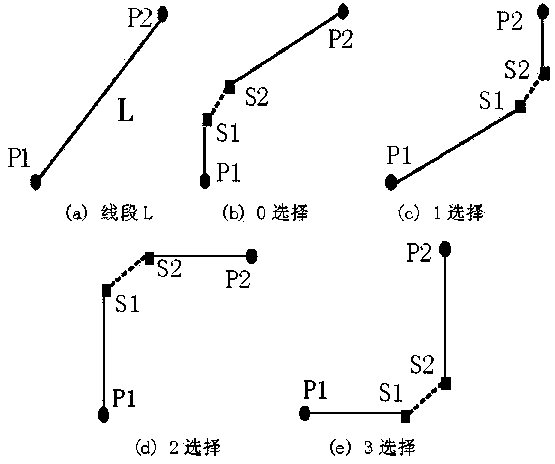

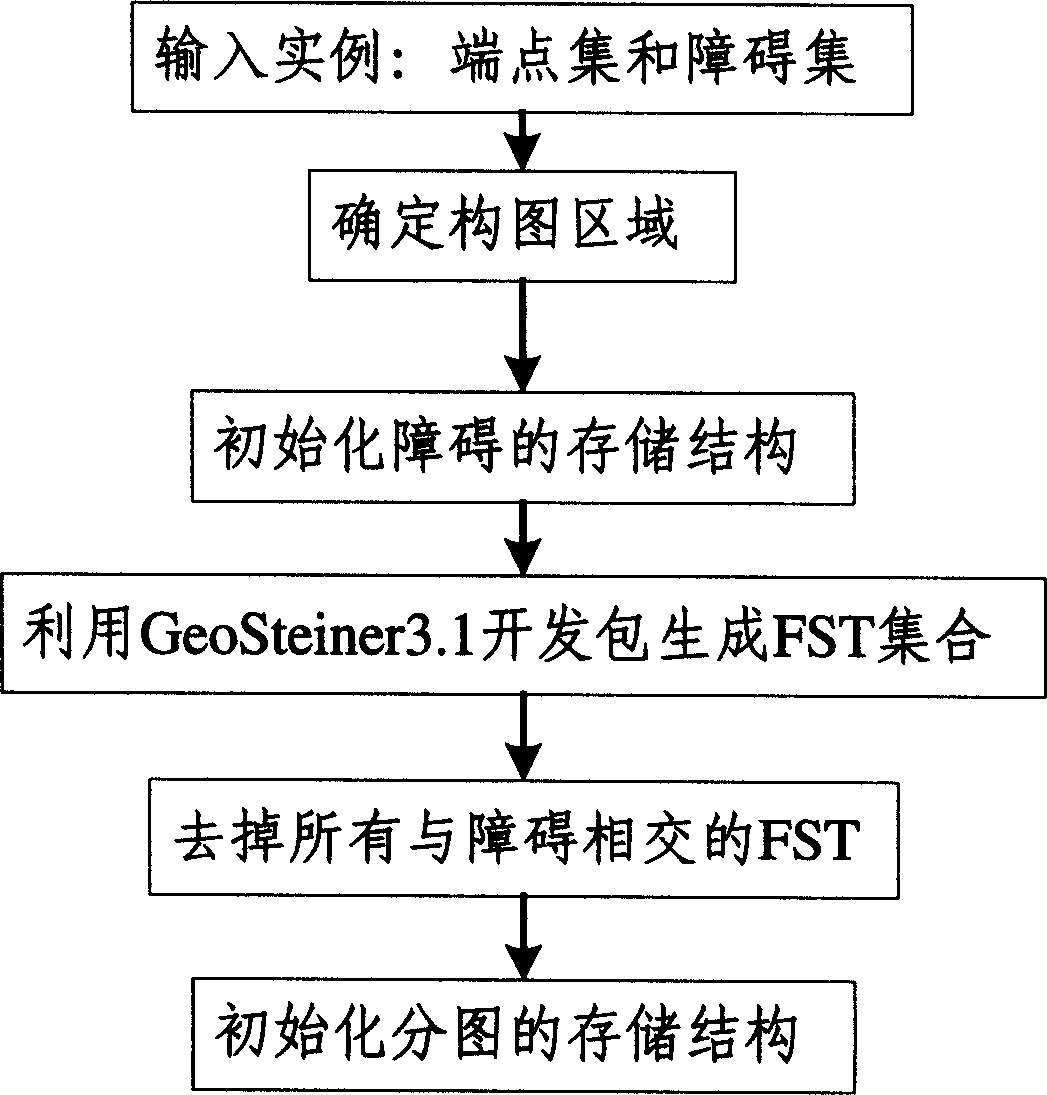

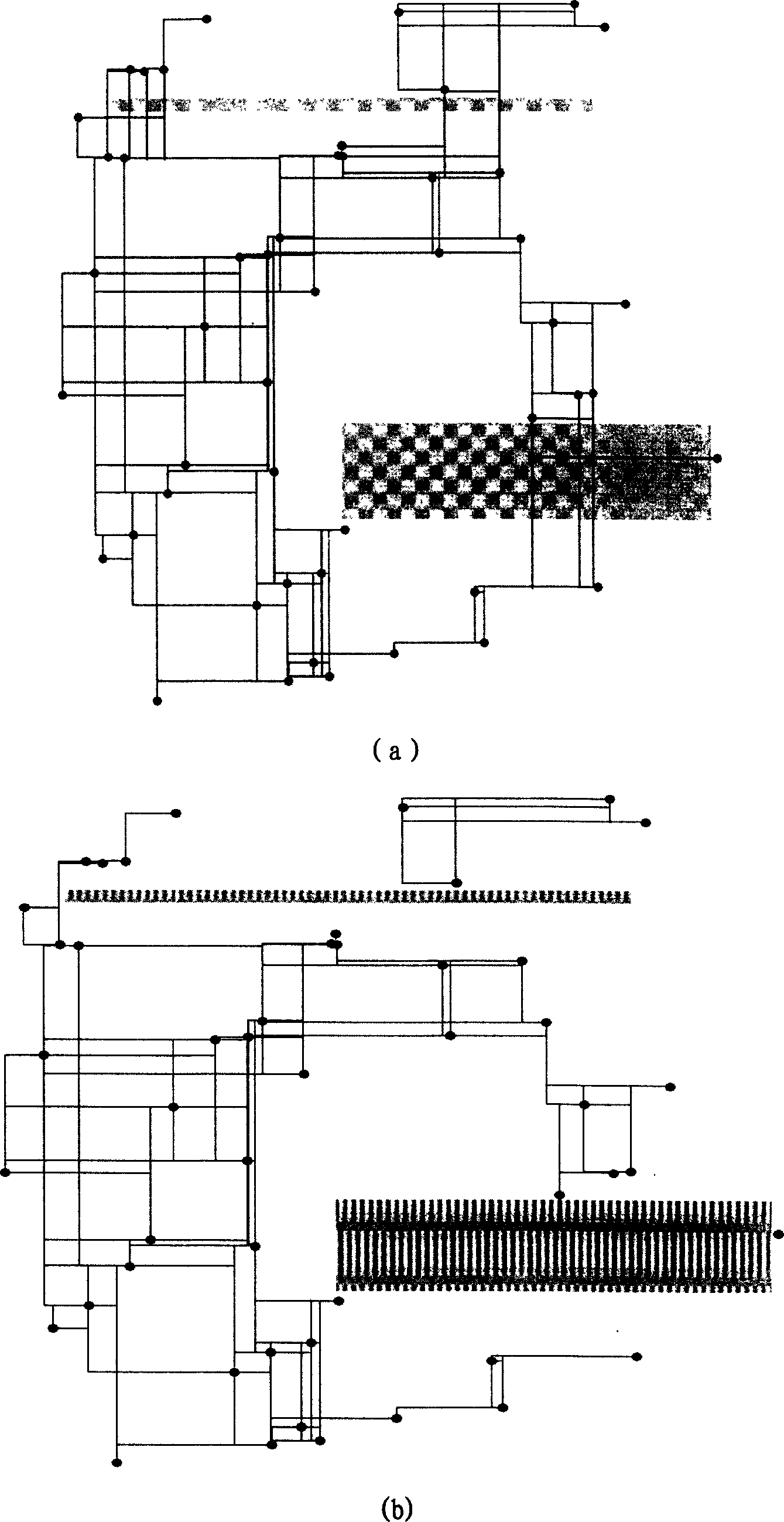

Overall wiring method for super-large-scale integrated circuit under X structure

ActiveCN103902774AAvoid dependencyEliminate biasSpecial data processing applicationsVery large scale integrated circuitsEngineering

The invention relates to an overall wiring method for a super-large-scale integrated circuit under an X structure. The overall wiring method comprises the following steps of an initial stage: discomposing a multi-terminal wire network into a plurality of two-terminal wire networks by using a Steiner minimum tree method, and performing side connection on connectable two-terminal wire networks by using the X structure, namely performing initial wiring to obtain approximate wiring crowded distribution conditions; a main stage: selecting the most crowded area from the approximate initial wiring result as a current wiring area, establishing an integral linear programming model for the current wiring area, solving the integral linear programming model, continuously expanding the wiring area, and sequentially solving the wiring area until the wiring area is expanded to a whole chip; and an aftertreatment stage: redefining wiring side cost, and performing wiring on the two-terminal wire networks which are not communicated to one another by using a labyrinth algorithm based on the wiring side cost so as to obtain the final overall wiring result. By using the overall wiring method, the quality of a wiring scheme can be improved; and the overall wiring method is easy to implement, and is high in using effect.

Owner:FUZHOU UNIV

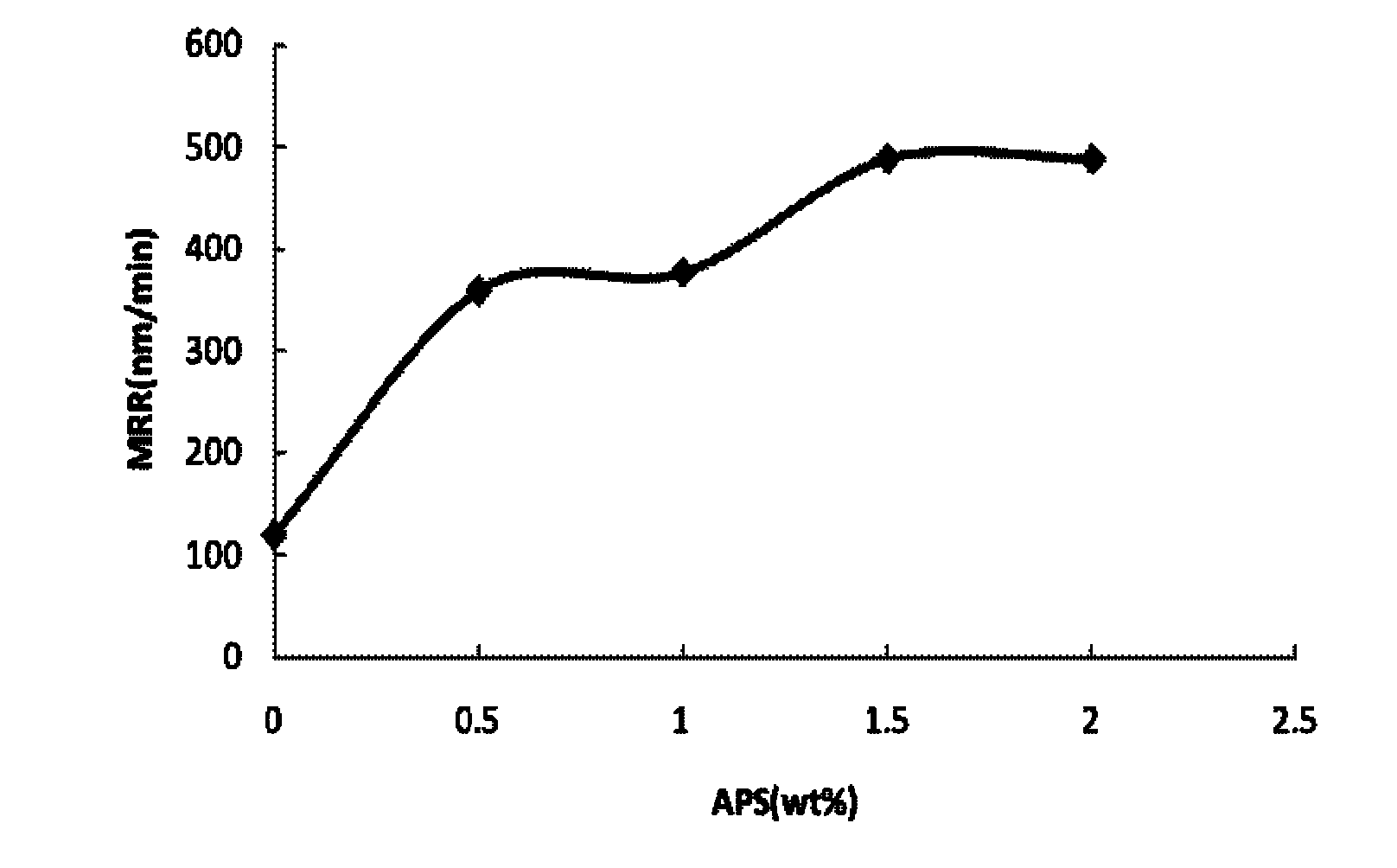

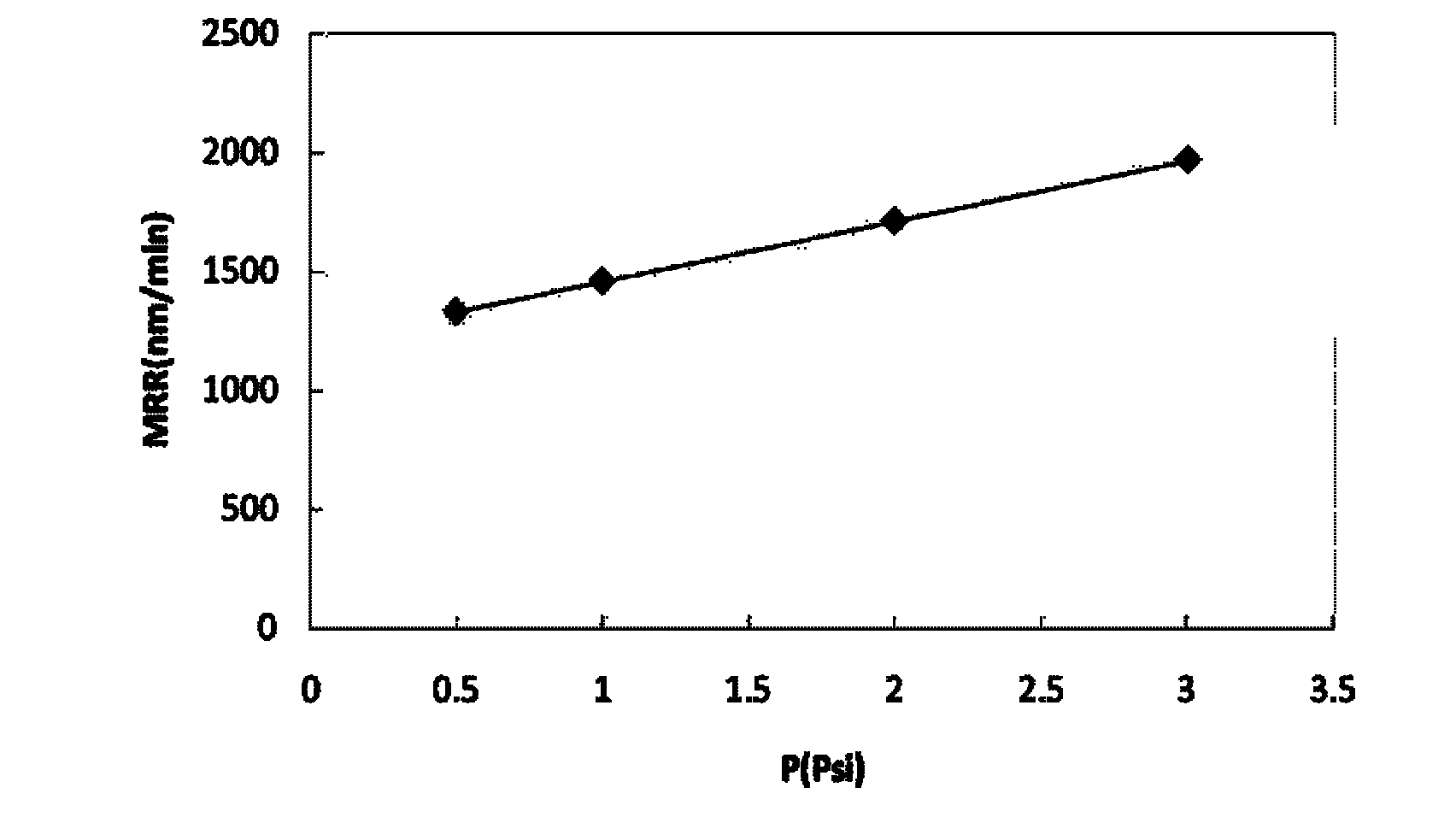

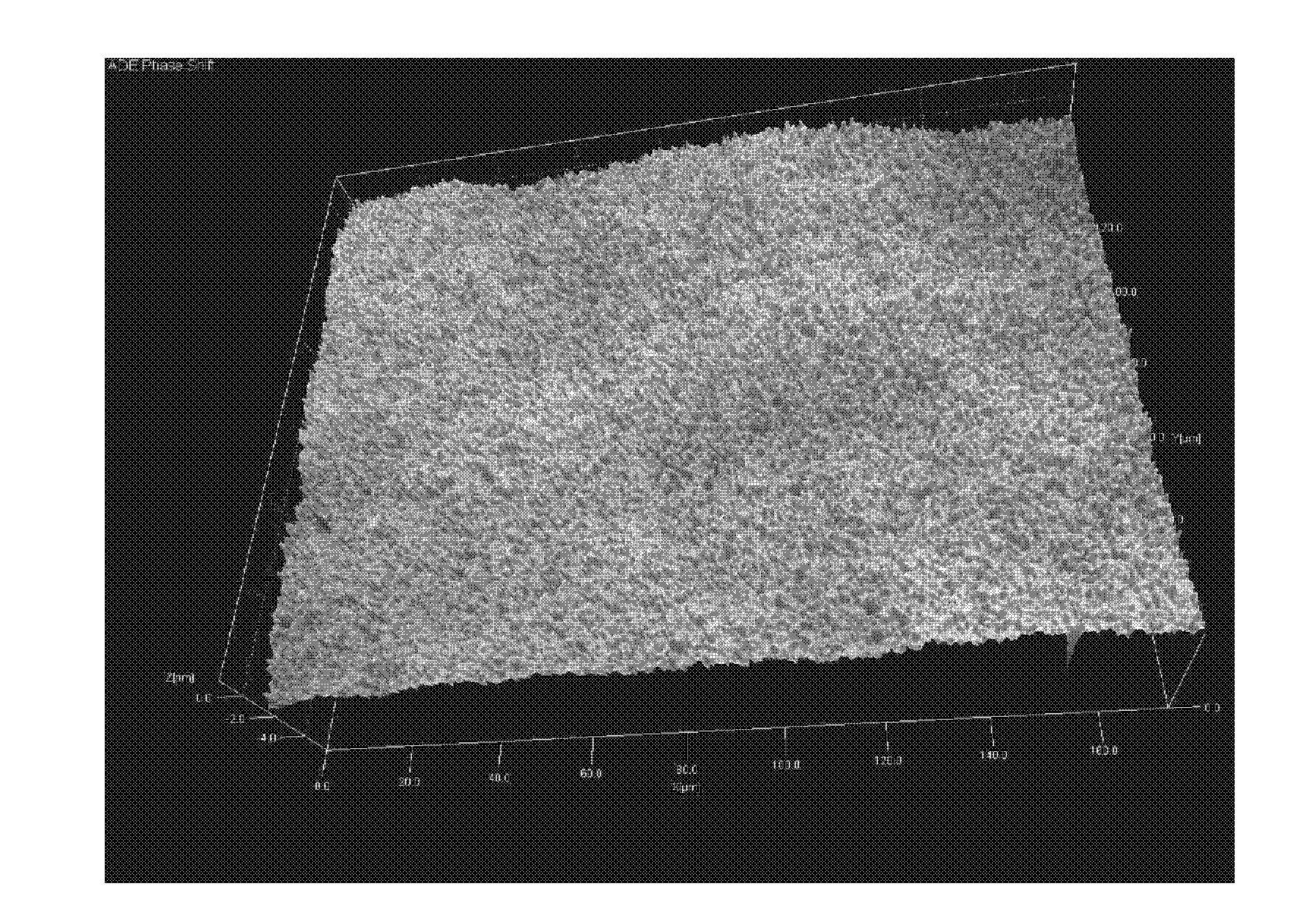

Composition for low downforce chemically mechanical polishing of coppers in ULSI (Ultra Large Scale Integrated Circuit) multi-layered copper wiring

ActiveCN102181232AImprove performanceStay decentralizedSemiconductor/solid-state device manufacturingPolishing compositions with abrasivesVery large scale integrated circuitsSemiconductor chip

The invention provides a composition for low downforce chemically mechanical polishing of coppers in ULSI (Ultra Large Scale Integrated Circuit) multi-layered copper wiring, which belongs to the field of chemically mechanical polishing aqueous composition. The invention provides an aqueous composition suitable for polishing coppers on a semiconductor chip under a downforce of less than 1.0 Psi (6.89 kPa); and the composition contains abrasive, an oxidant, a pH regulator, a buffering agent and water and also mainly contains a sulfur-containing corrosion balancing agent applicable to a situation with low downforce weak mechanical effect. Low downforce polishing is carried out on the coppers in the ultra large scale integrated circuit multi-layered copper wiring by using the polishing composition provided by the invention, high smoothing efficiency and high polishing speed are obtained and polishing defects can be furthest avoided.

Owner:TSINGHUA UNIV

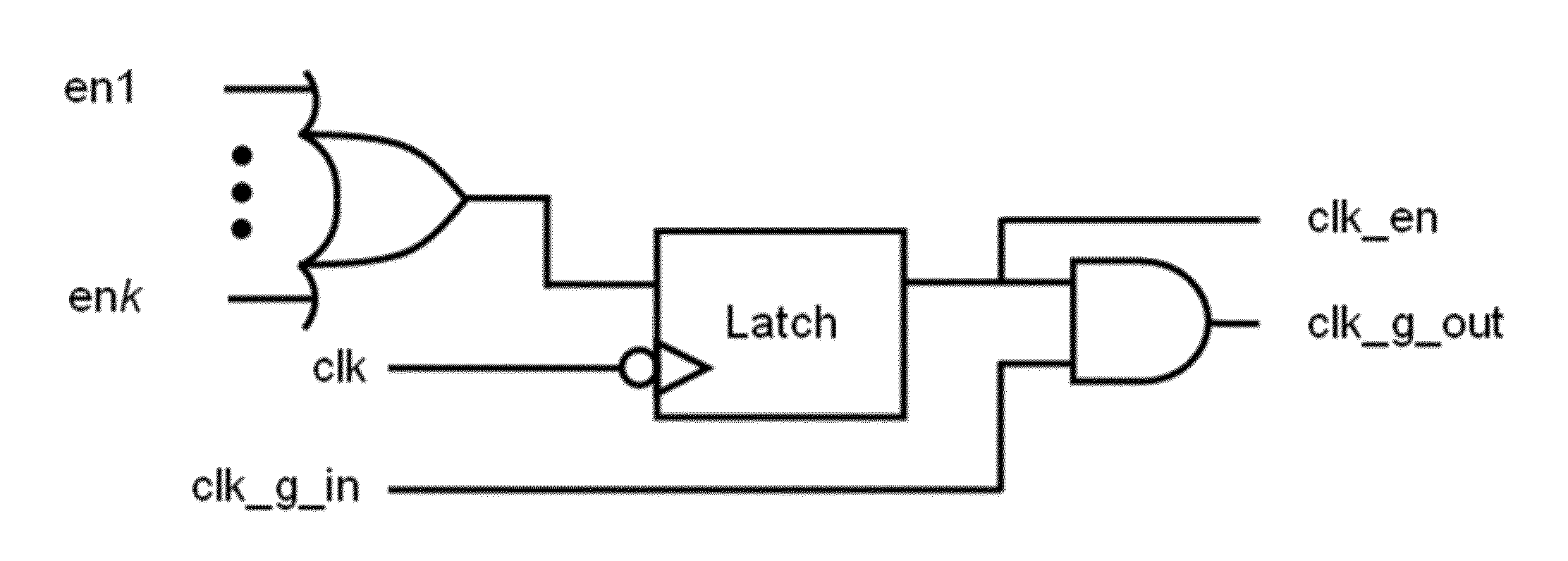

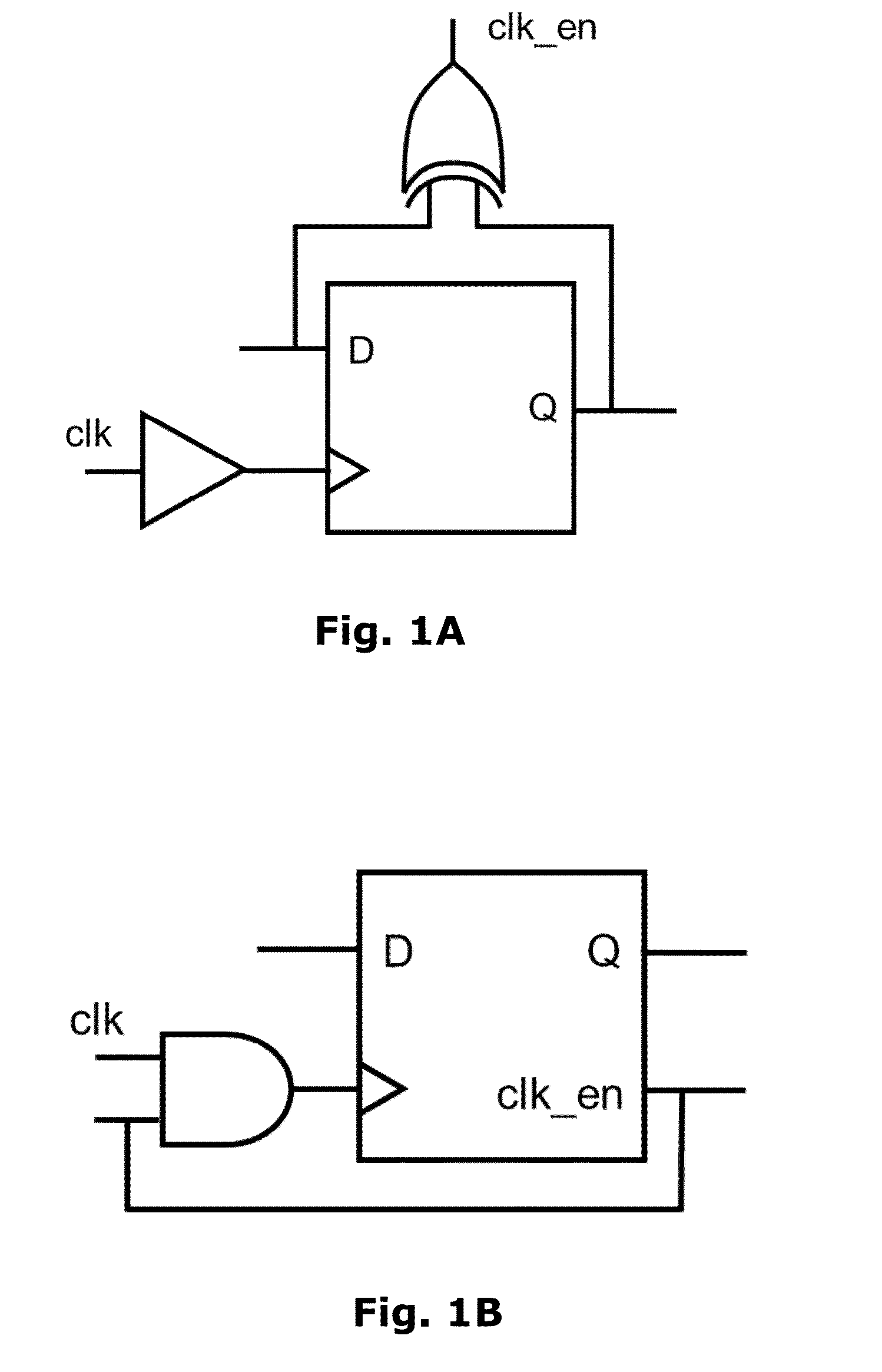

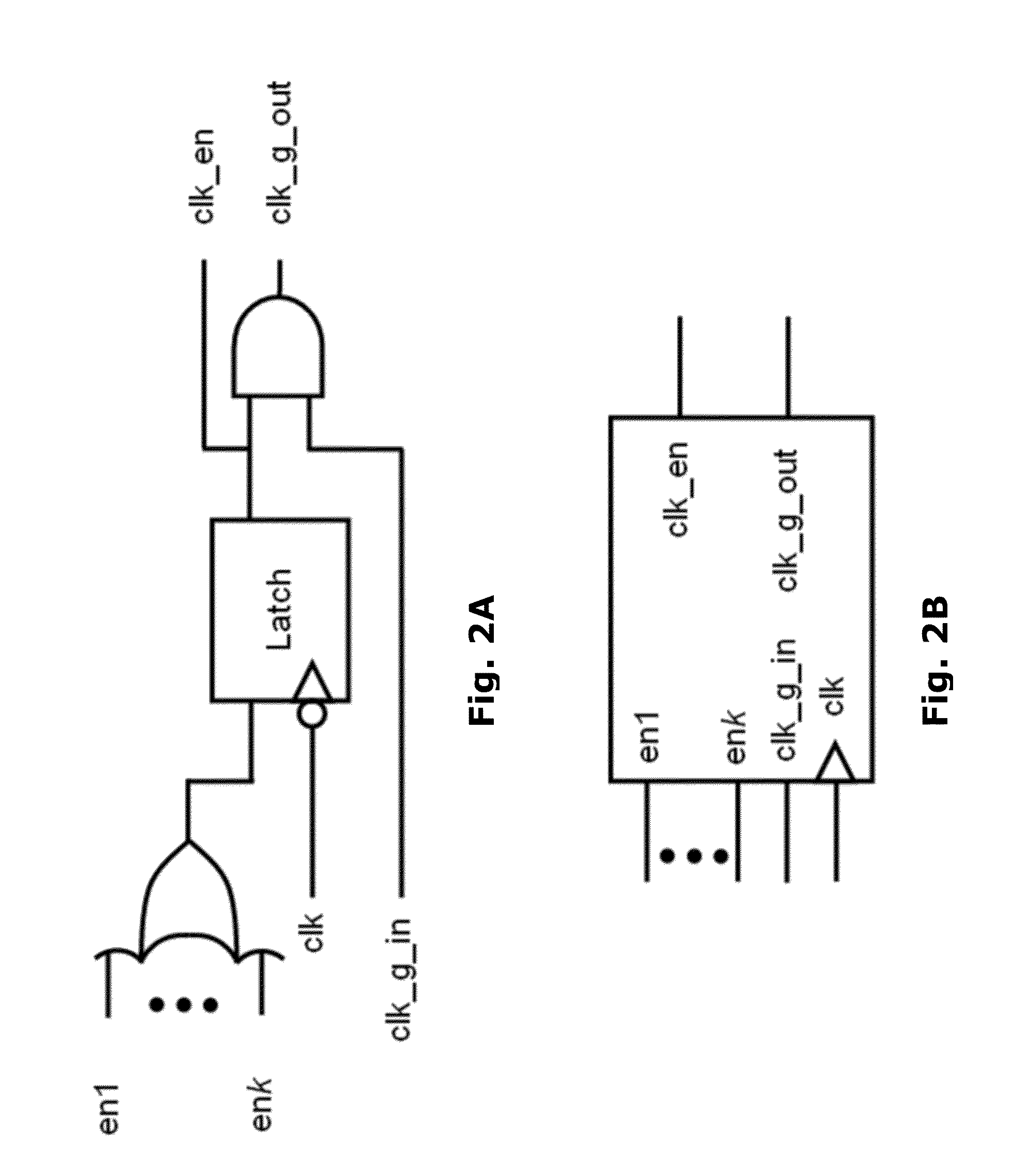

System and method for generating a clock gating network for logic circuits

InactiveUS20130194016A1Reduce Switching Power ConsumptionExpected power savingPower reduction by control/clock signalElectric pulse generatorVery large scale integrated circuitsPower efficient

A system and method for generating a power efficient clock gating network for a Very Large Scale Integration (VLSI) circuit. Statistical analysis is performed upon the activity of component registers of the circuit and registers having correlated toggling behavior are clustered into sets and provided with common clock gaters. The clock gating network may be generated independently from the logical structure of the circuit.

Owner:BAR ILAN UNIV

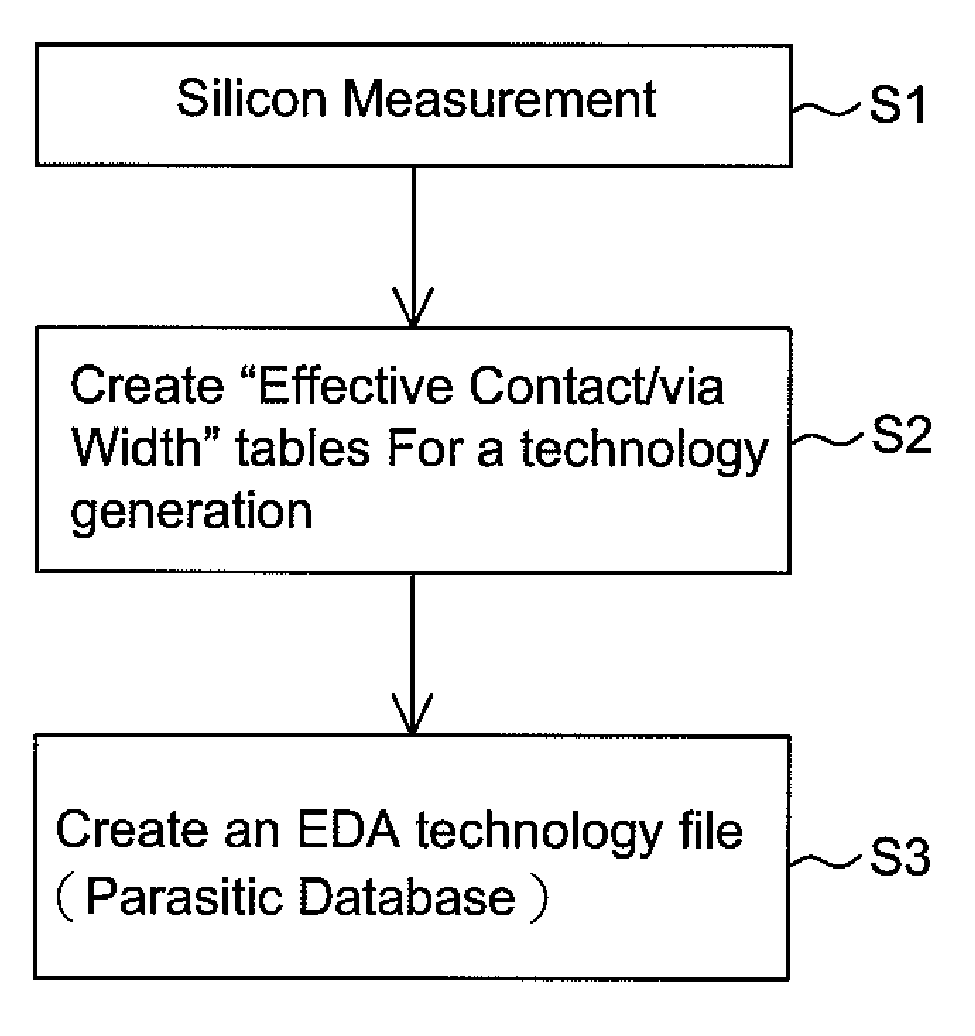

Accurate Parasitic Capacitance Extraction for Ultra Large Scale Integrated Circuits

InactiveUS20090007035A1Improve accuracySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVery large scale integrated circuitsParasitic capacitance

A system and method for extracting the parasitic contact / via capacitance in an integrated circuit are provided. Parasitic extraction using this system can lead to an improved accuracy on contact / via parasitic capacitance extraction by taking into account of the actual contact / via shape and size variation. The common feature of the various embodiments includes the step of generating a technology file, in which the contact / via capacitance in the capacitance table is derived from an effective contact / via width table. Each element of the effective contact / via width table is calibrated to have a parasitic capacitance matching to that of an actual contact / via configuration occurring in an IC.

Owner:TAIWAN SEMICON MFG CO LTD

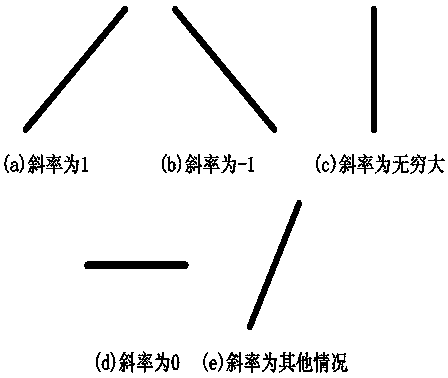

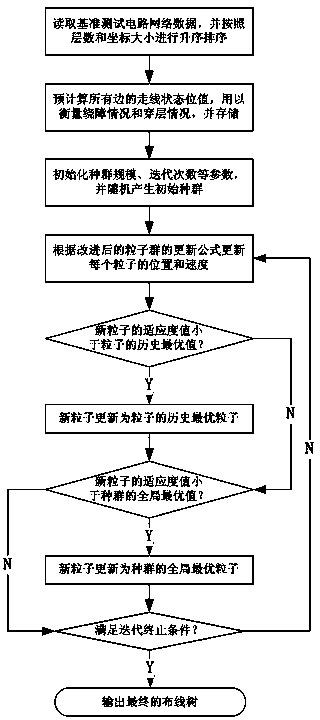

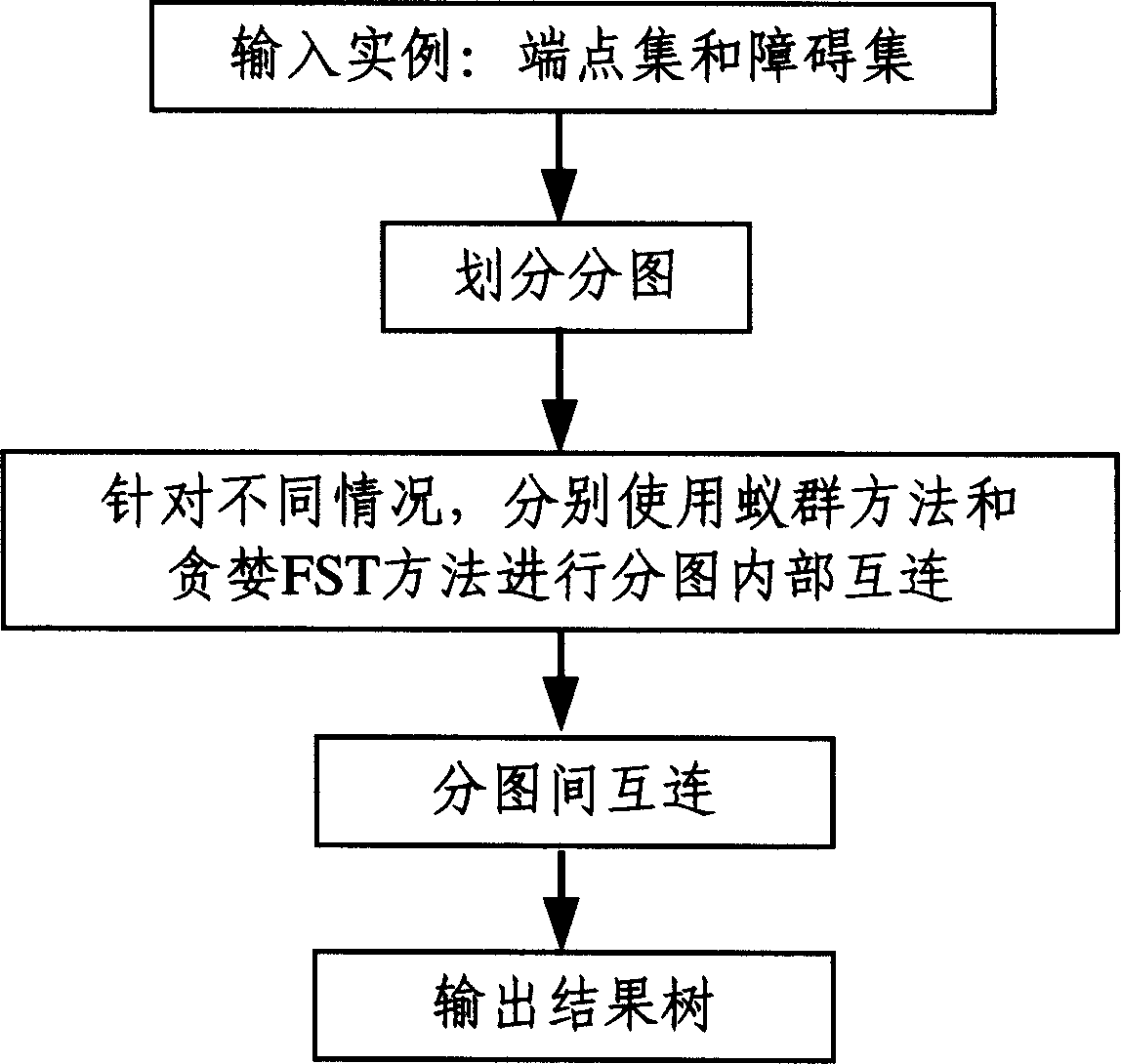

Multilayer obstacle-avoiding Steiner minimal tree construction method for very large scale integration

ActiveCN103902775AQuality improvementExcellent solutionGenetic modelsSpecial data processing applicationsVery large scale integrated circuitsSteiner minimal tree

The invention relates to a multilayer obstacle-avoiding Steiner minimal tree construction method for a very large scale integration. The method includes the following steps: 1, reading benchmark test circuit network data; 2, initializing parameters such as population sizes and iterations, and generating initial populations randomly; 3, updating positions and speeds of particles according to a particle updating formula; 4, calculating fitness values of new particles according to a punishment mechanism based fitness calculation function, judging whether or not the fitness values of the new particles are smaller than historical optimal values of the particles, and if yes, updating the new particles as historical optimal particles of the particles; 5, judging whether or not the fitness values of the new particles are smaller than global optimal values of the populations, and if yes, updating the new particles as global optimal particles of the populations; 6, judging whether iteration end conditions are met or not, if yes, outputting final wiring trees, and if not, returning to the step 3 for next iteration. By the method, total wiring cost is reduced, and quality of the wiring trees is improved.

Owner:上海立芯软件科技有限公司

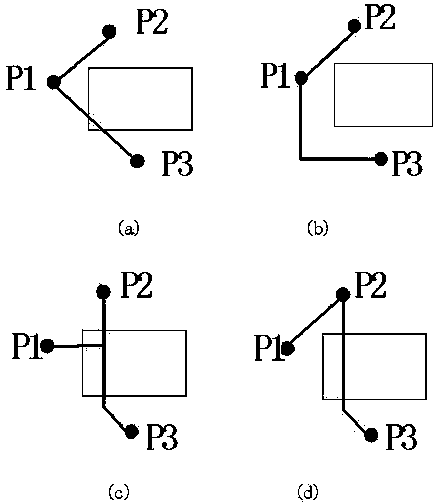

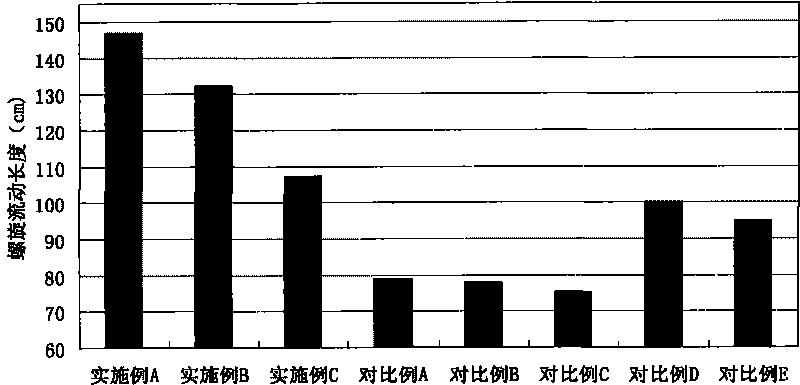

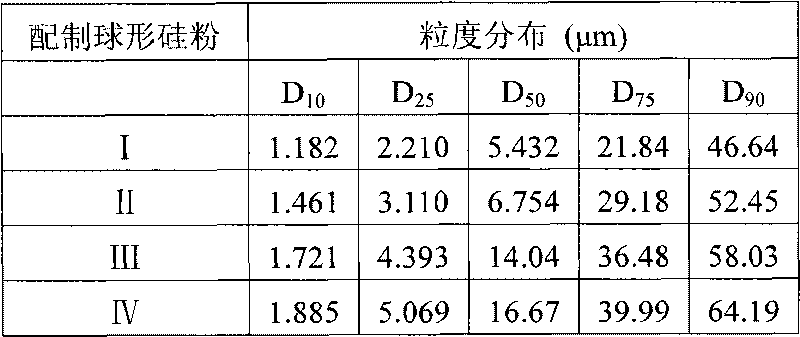

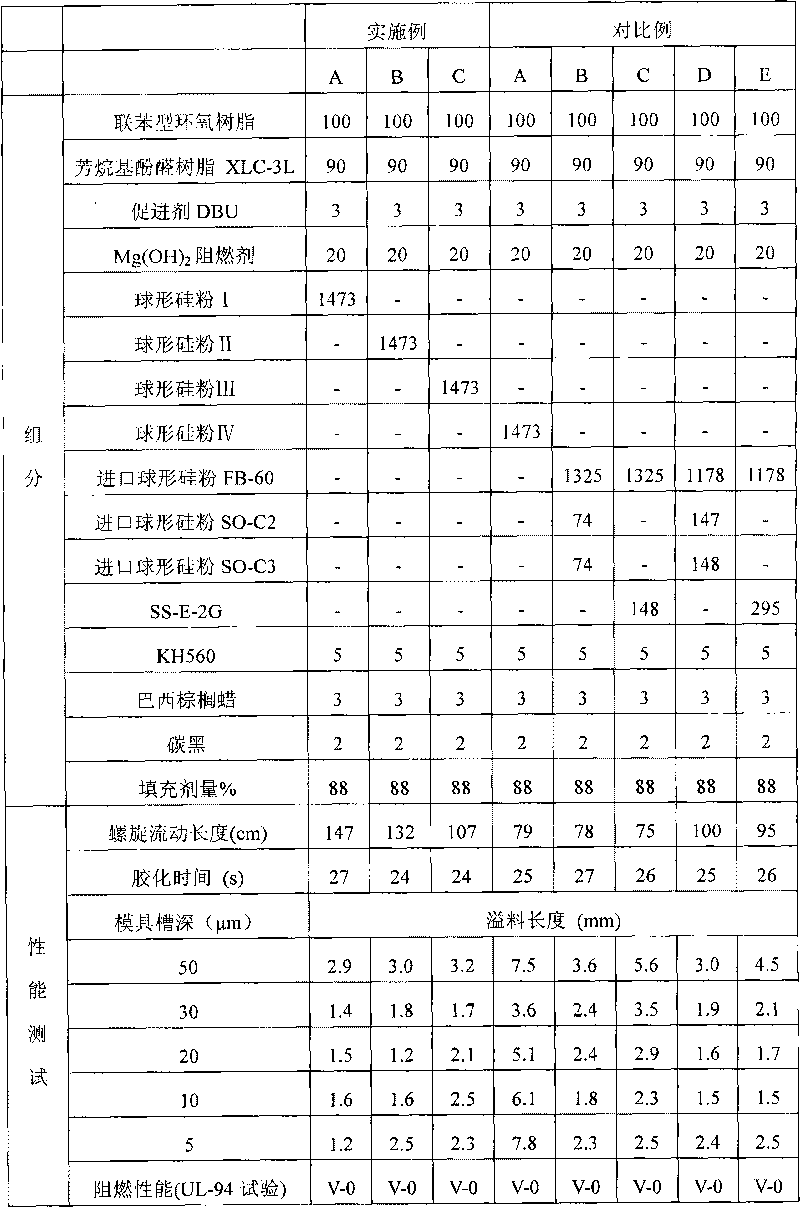

Epoxy resin composite taking spherical silicon powder as filler, preparation method and application thereof

InactiveCN101696317AImprove liquidityReduce spillsSemiconductor/solid-state device detailsSolid-state devicesEpoxyVery large scale integrated circuits

The invention provides an epoxy resin composite taking home-made spherical silicon powder as a filler. The epoxy resin composite consists of an epoxy resin, a phenolic resin, spherical silicon dioxide powder, a flame retardant, an accelerant, a coupling agent, a release agent and a colorant, wherein the spherical silicon dioxide powder is prepared by a melted jet method by taking natural silicon dioxide powder as a raw material; and the silicon powder with median particle diameter of 5-20 microns is prepared from the spherical silicon powder with different grain diameters. The epoxy resin composite comprises 84-90 percent of filler. The invention has the advantages of excellent fluidity, few overflow materials, good moulding processing property and capability of packaging large-scale or super-large scale integrated circuit.

Owner:北京中新泰合电子材料科技有限公司

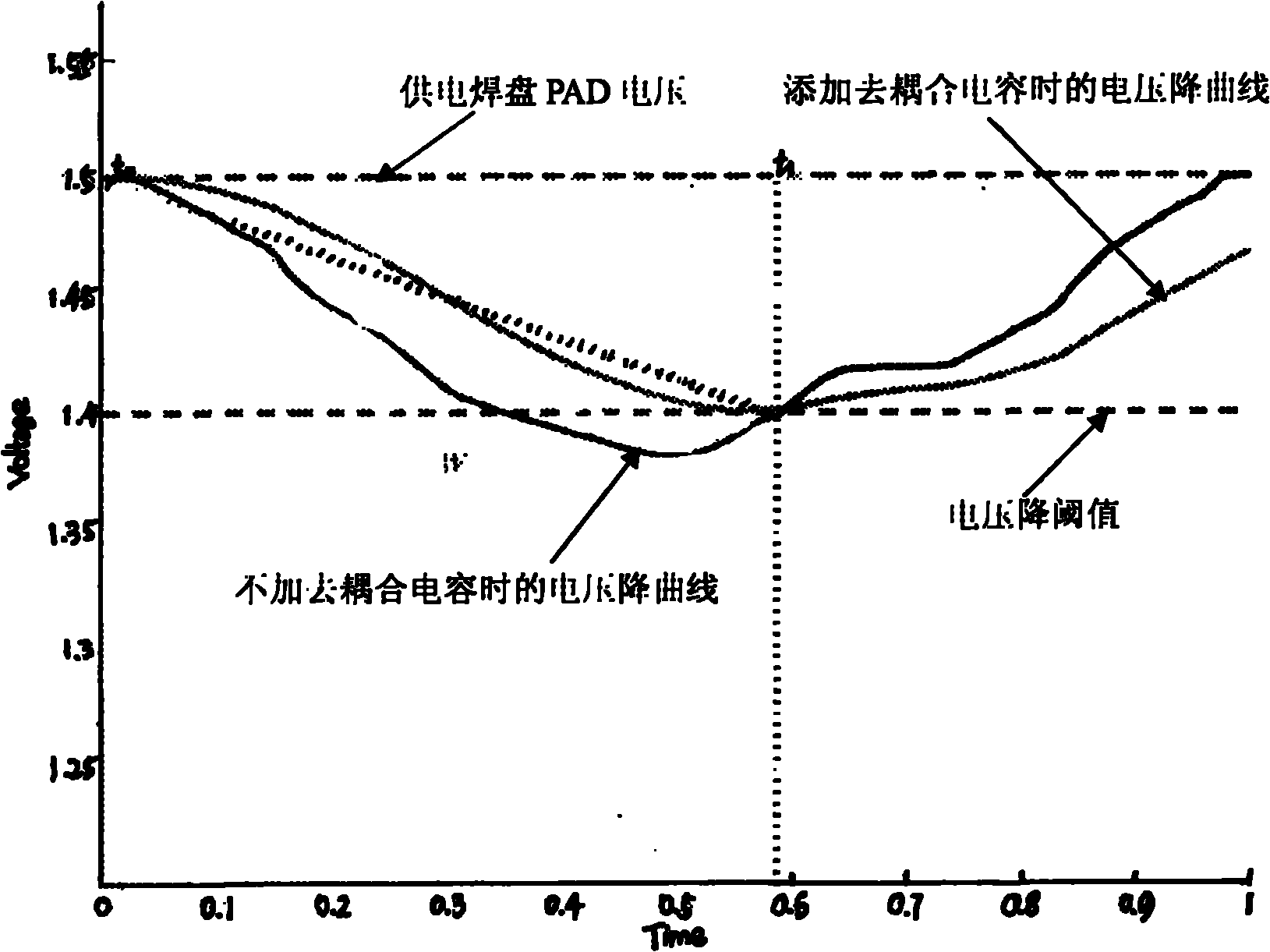

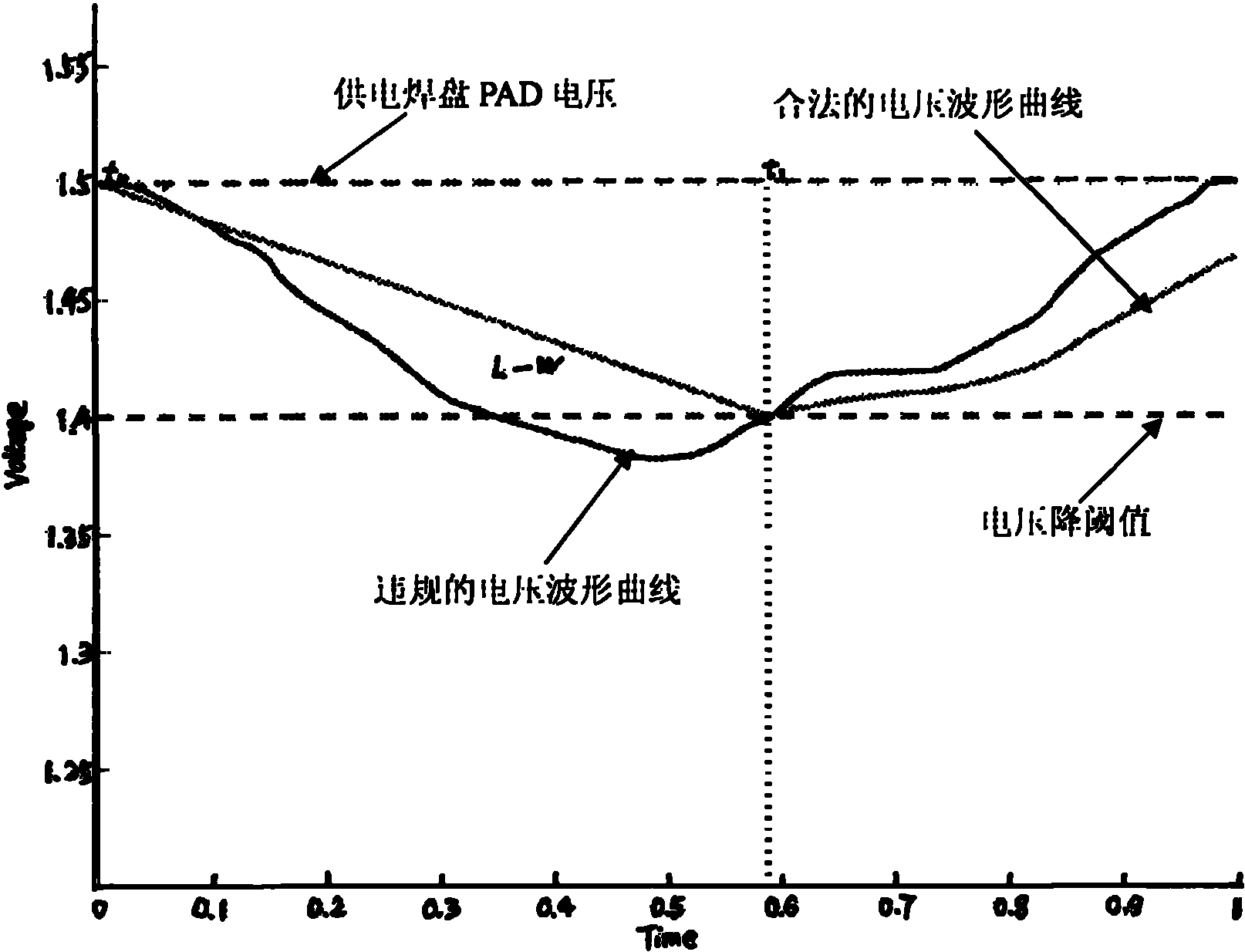

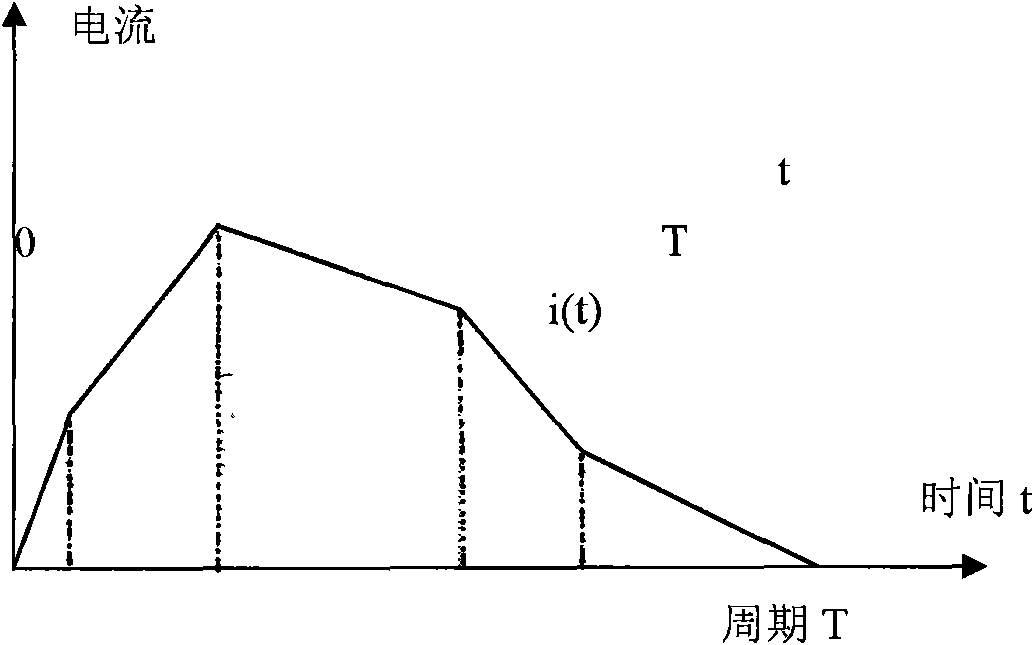

Method for restraining integrated circuit electricity supply network noise by using decoupling capacitance

ActiveCN101872377AReduce usageConvenient power supplySpecial data processing applicationsCapacitanceVery large scale integrated circuits

The invention discloses a method for restraining integrated circuit electricity supply network transient voltage drop noise by using decoupling capacitance, belonging to the physical design field of superlarge-scale integrated circuit, in particular to the technical category of optimizing network noise of transient power wire earth wires, which is characterized in that the creation points lie in that: (1) proposing a rapid method for estimating a decoupling capacitance demand in a layout stage; proposing a two-dimensional function showing the decoupling capacitance demand in a chip; (3) establishing a supply and demand system for the demand of the decoupling capacitance by utilizing the two-dimensional function to guide that the layout process is performed toward the direction being beneficial for reducing the demand of the decoupling capacity; and (4) proposing a layout algorithm for adding the decoupling capacitance through integrating the above model and the method into a force direction layout. Experiments prove that the method of the invention is effective, and can achieve the layout result that the total amount of the decoupling capacity is decreased by about 35% with the cost that the on-line length is increased by about 0.5%.

Owner:TSINGHUA UNIV

Rectangular steiner tree method of super large size integrated circuit avoiding barrier

InactiveCN1588381ASpecial data processing applicationsVery large scale integrated circuitsComputer-aided

The obstacle avoiding rectangular Steiner tree method for very large scale integrated circuit (VLSI) design belongs to the field of computer-aided VLSI design technology, and is especially VLSI wiring design. The present invention features the first application of full Steiner tree (FST) end point separating method, subsequent construction of son Steiner tree by means of ant swarm method and voracious FST method for different son sets, and final connection of all the son Steiner trees in detour method. The said algorithm can process multiple end point wire mesh; can process complex obstacles and can process large scale issue in relatively short time. The present invention realizes obstacle avoiding rectangular Steiner tree constructing method with optimized wire length and time efficiency in VLSI wiring design.

Owner:TSINGHUA UNIV

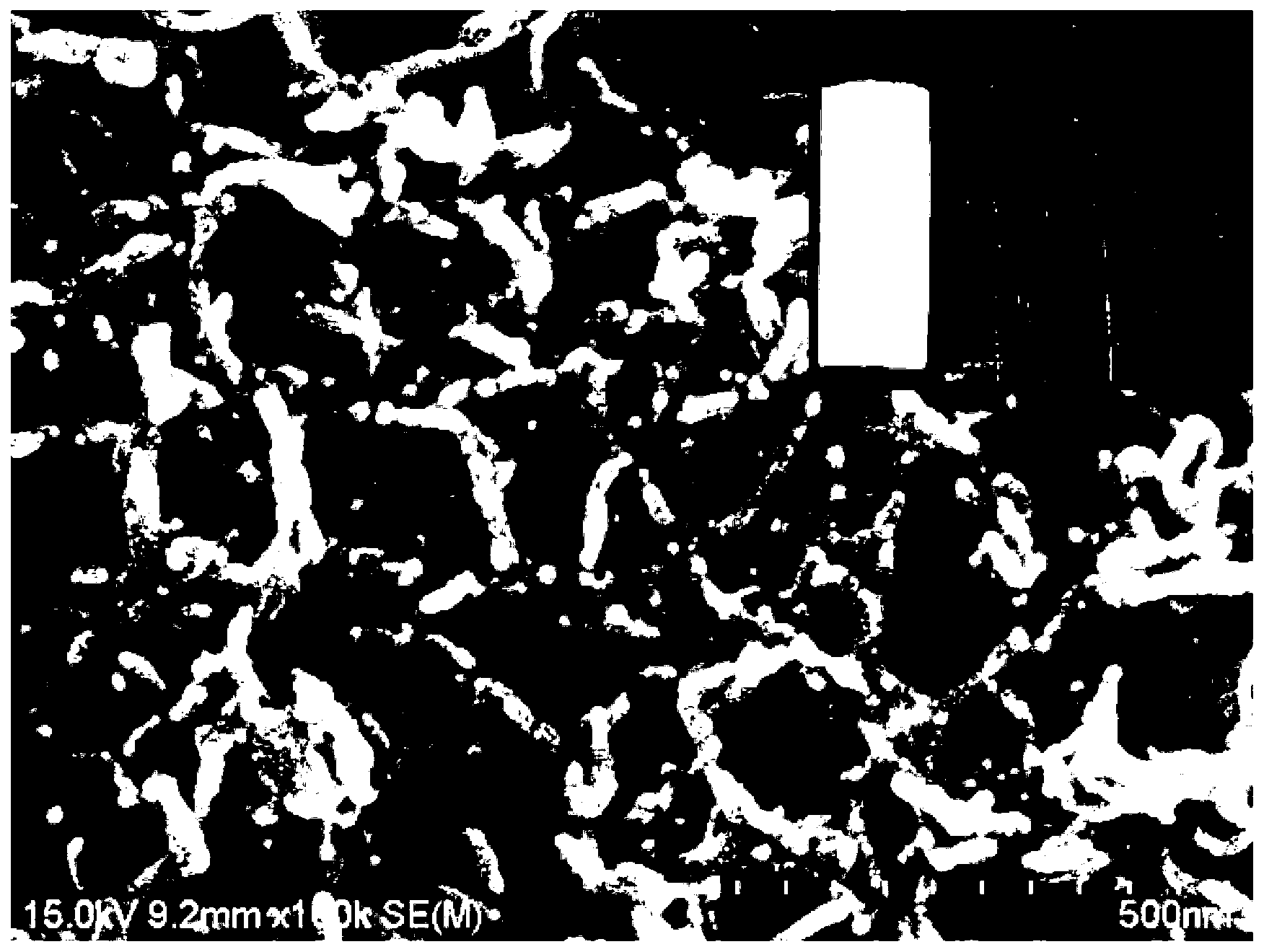

Intrinsic hydrophobic polyimide aerogel and preparation method as well as application thereof

The invention discloses intrinsic hydrophobic polyimide aerogel and a preparation method as well as an application thereof. The structure of the aerogel is shown in a structural formula (I); special groups, such as a hydrophobic fluorin-containing group and an alicyclic group at low polarity are introduced to a polyimide molecular structure to endow a polyimide aerogel material with excellent hydrophobic performance; in addition, the polyimide aerogel has the characteristics of high porosity, low heat conductivity, low density, large specific surface area, low dielectric constant, low dielectric loss and the like, and therefore is of significant application values in the fields of thermal insulating components of spacecrafts, such as airplanes and satellites, interlayer dielectric materials of super-large-scale integrated circuits, thermal insulating layers of buildings, environment protection, deep ocean detection, oil exploration, energy-saving buildings, household appliances, warm-keeping clothes, sports equipment and the like. Formula I is shown in the specification.

Owner:INST OF CHEM CHINESE ACAD OF SCI