Patents

Literature

210 results about "Temperature instability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

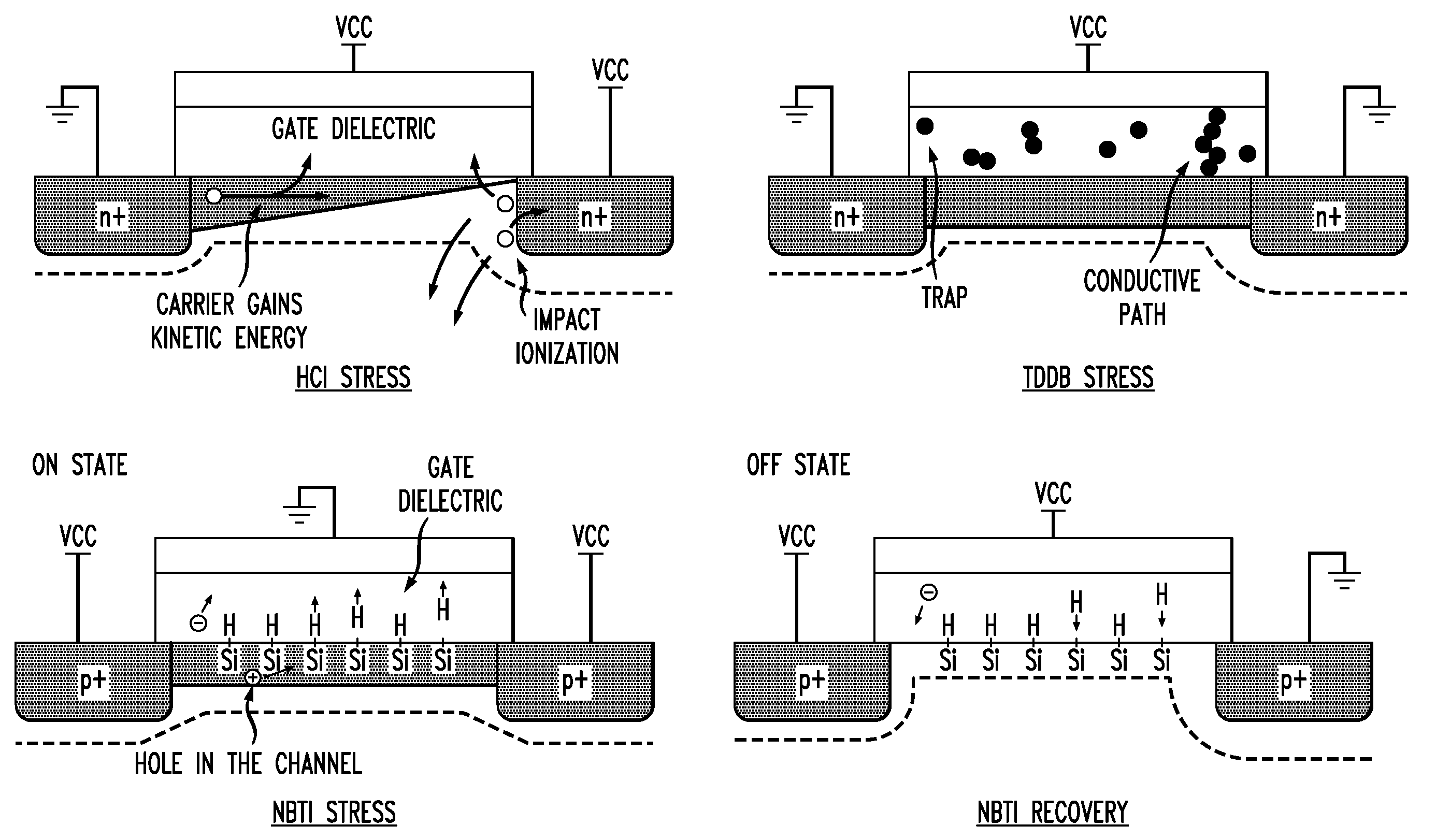

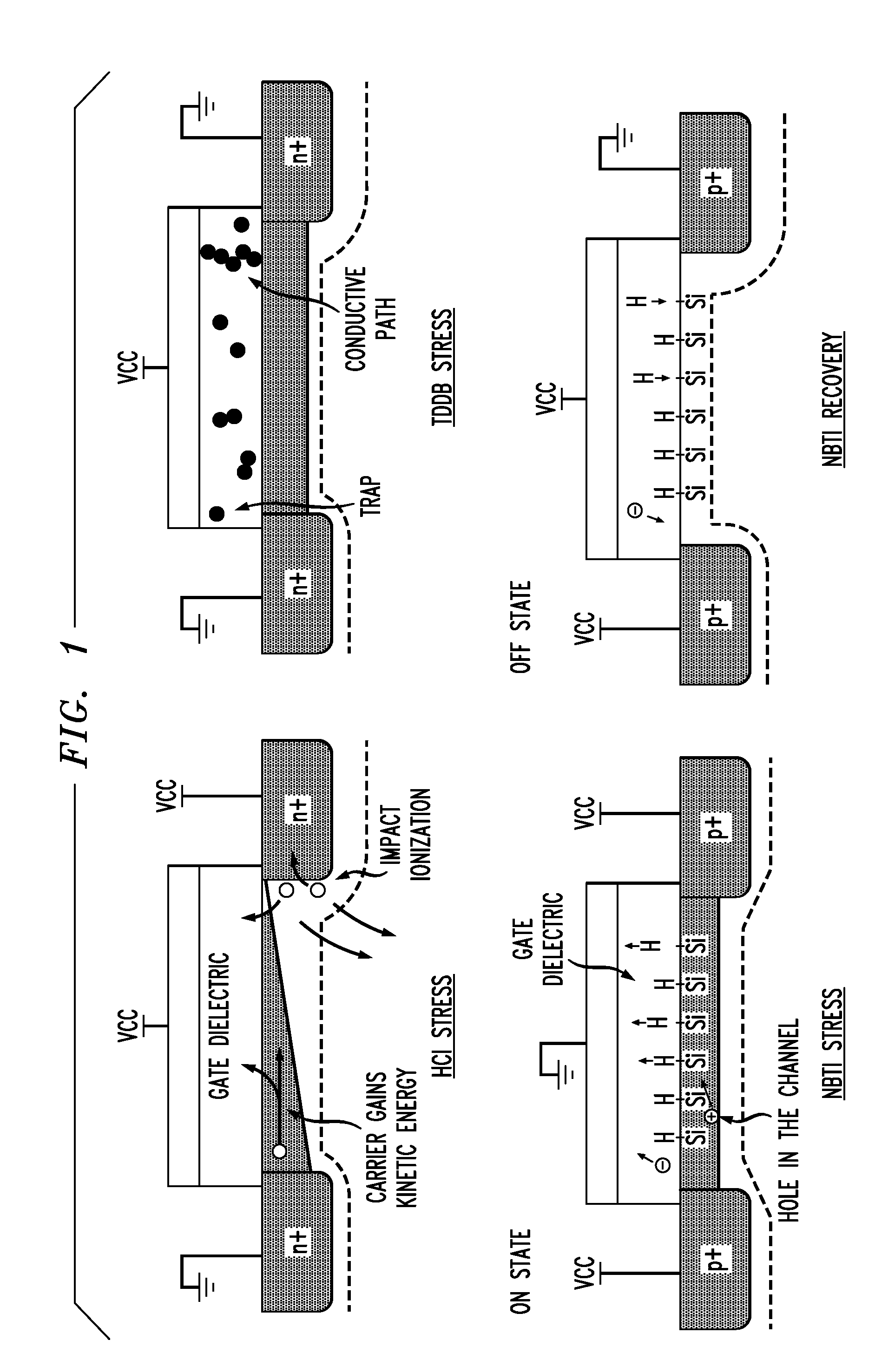

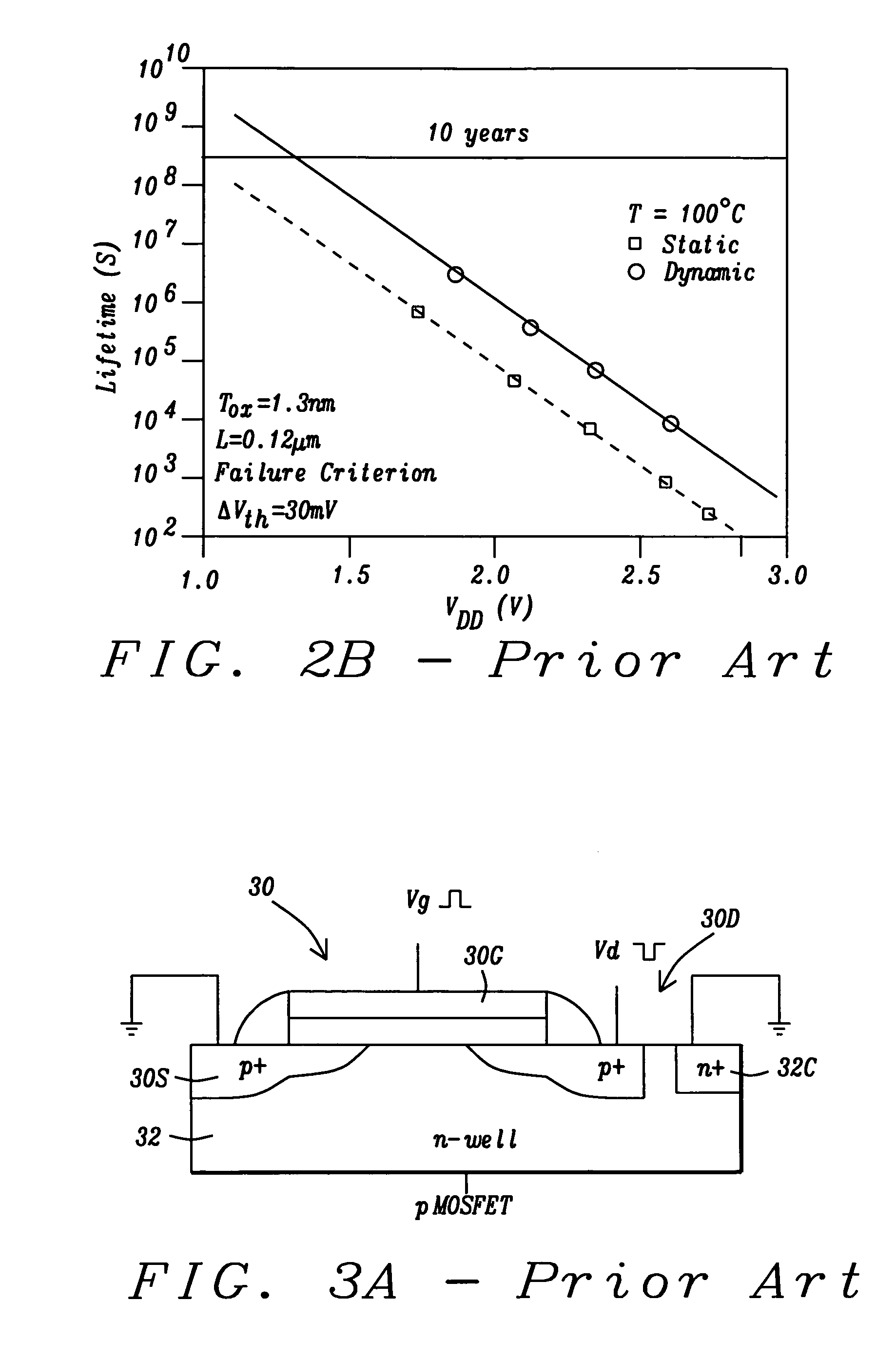

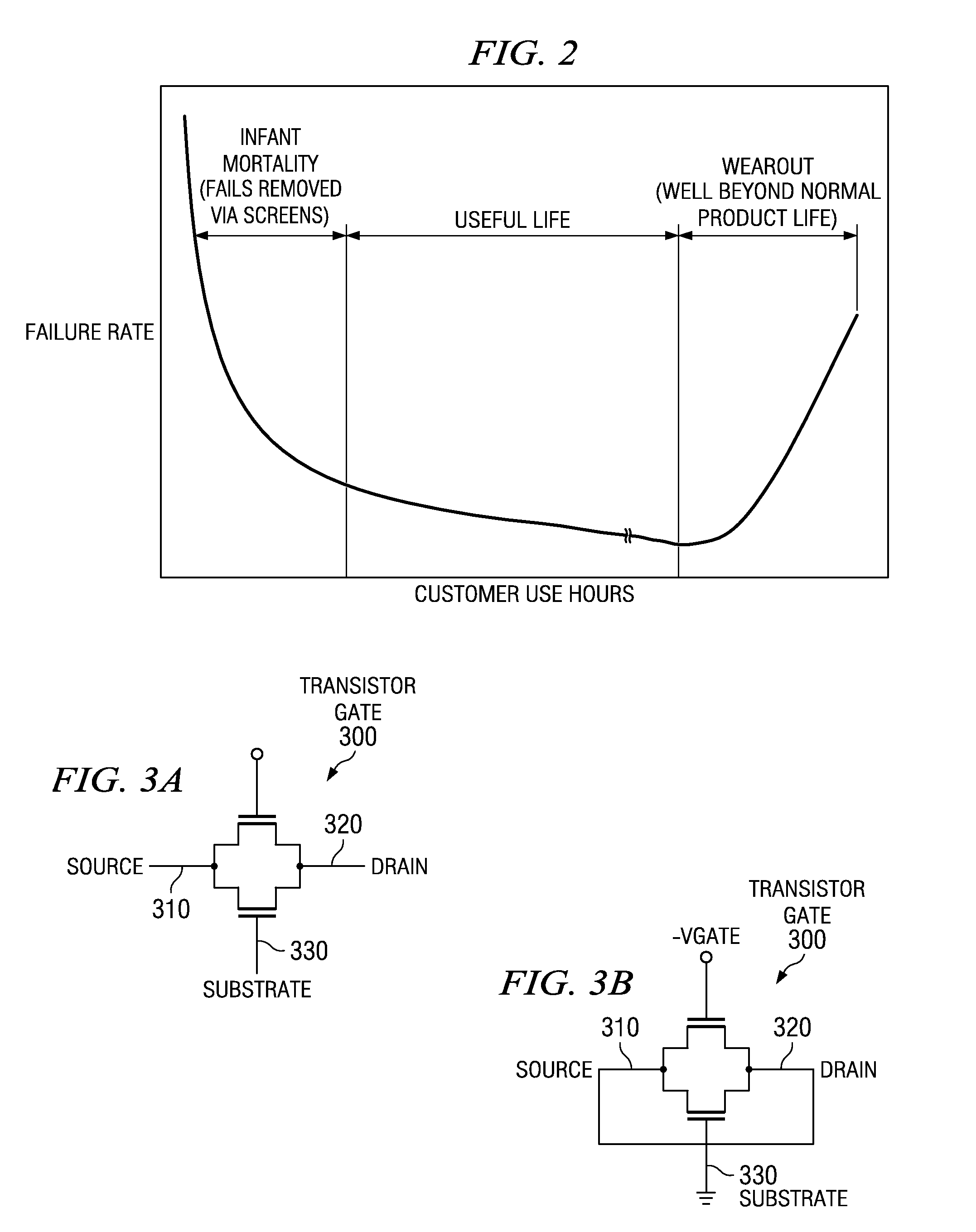

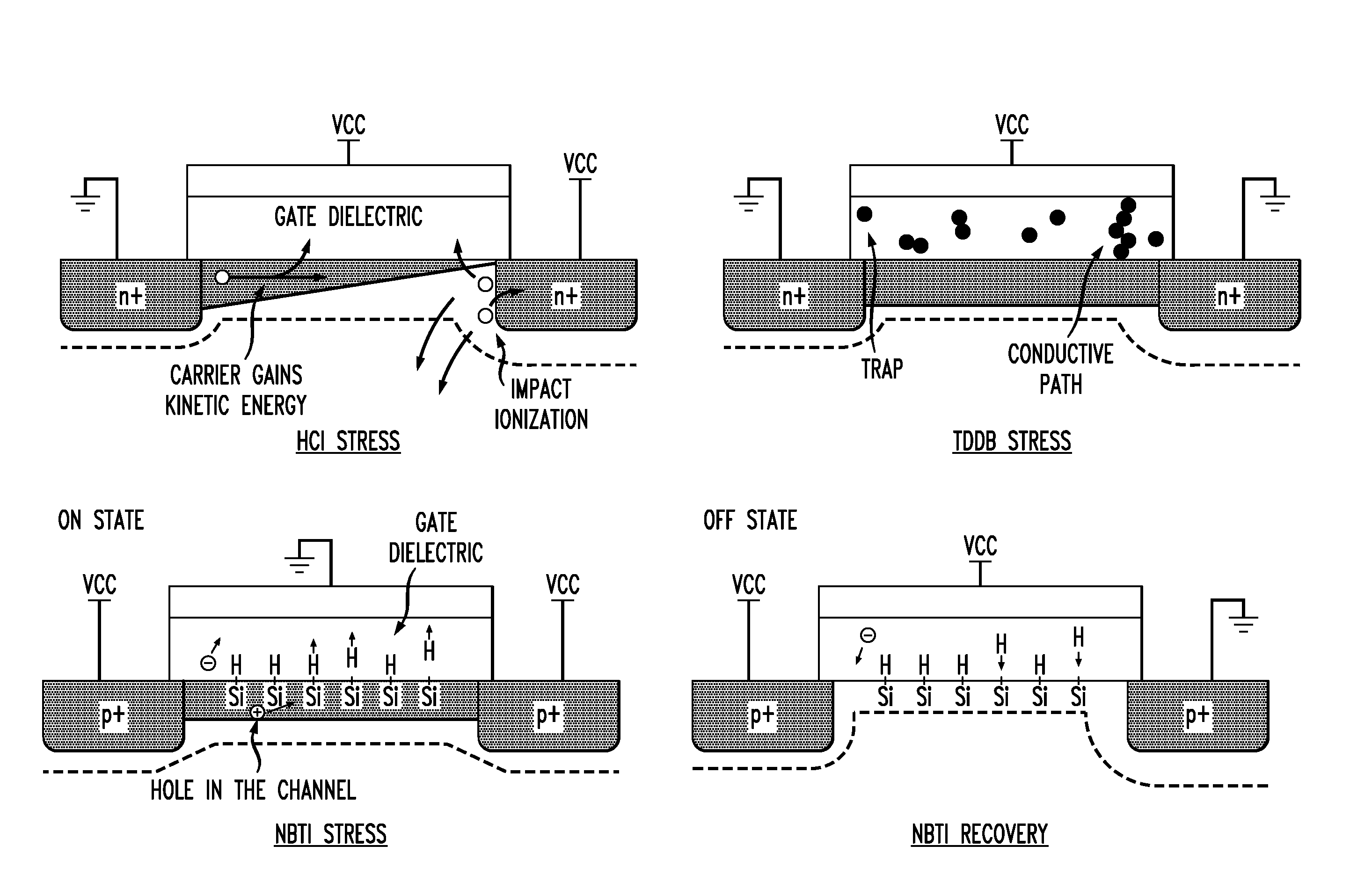

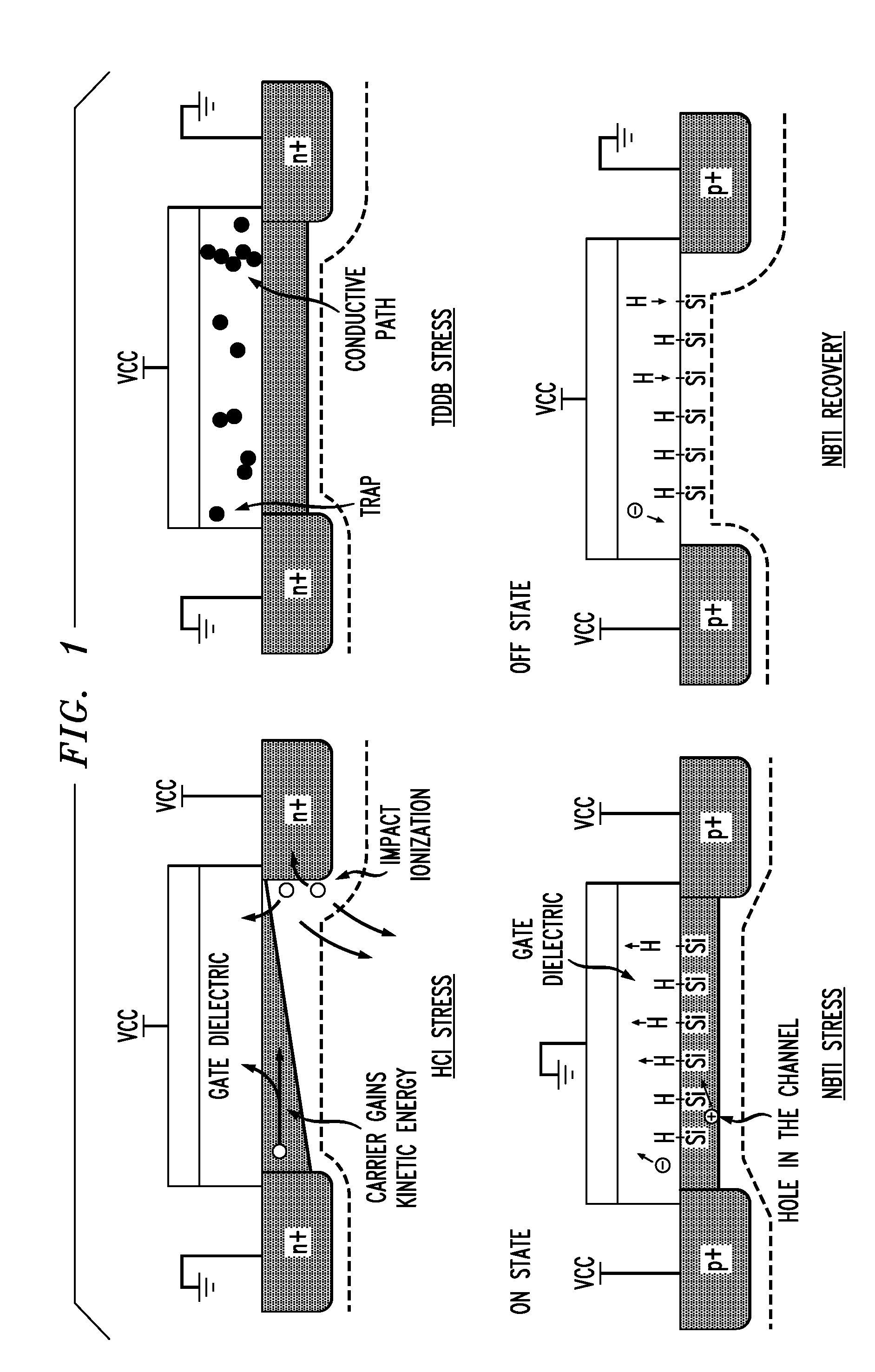

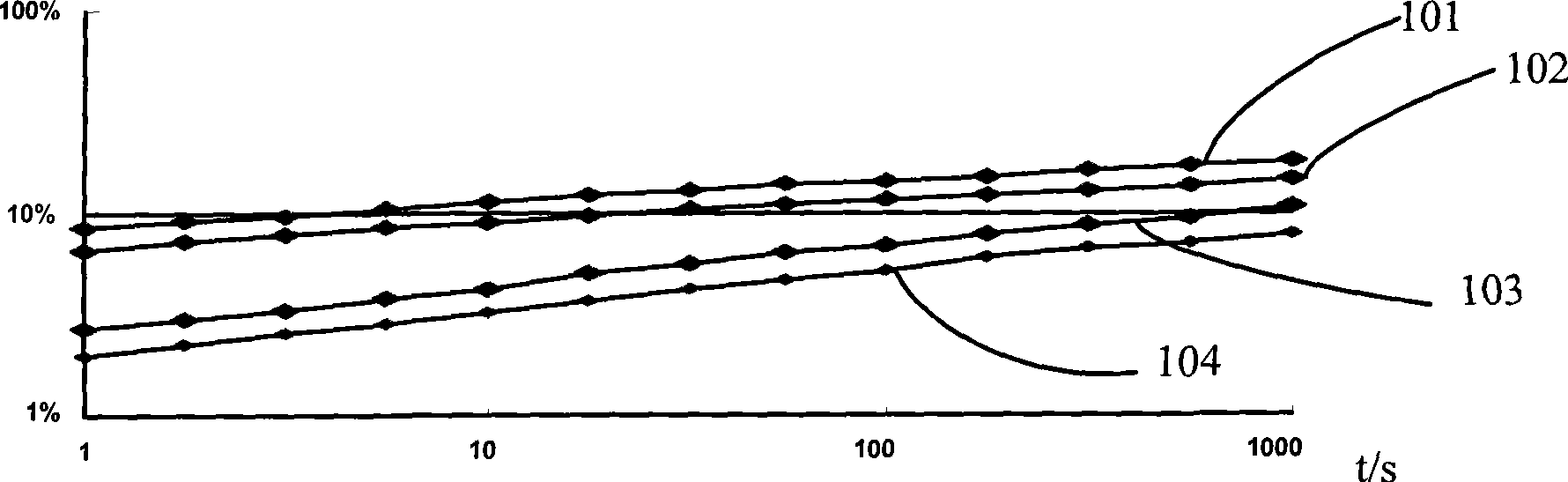

Negative-bias temperature instability (NBTI) is a key reliability issue in MOSFETs. NBTI manifests as an increase in the threshold voltage and consequent decrease in drain current and transconductance of a MOSFET. The degradation is often approximated by a power-law dependence on time.

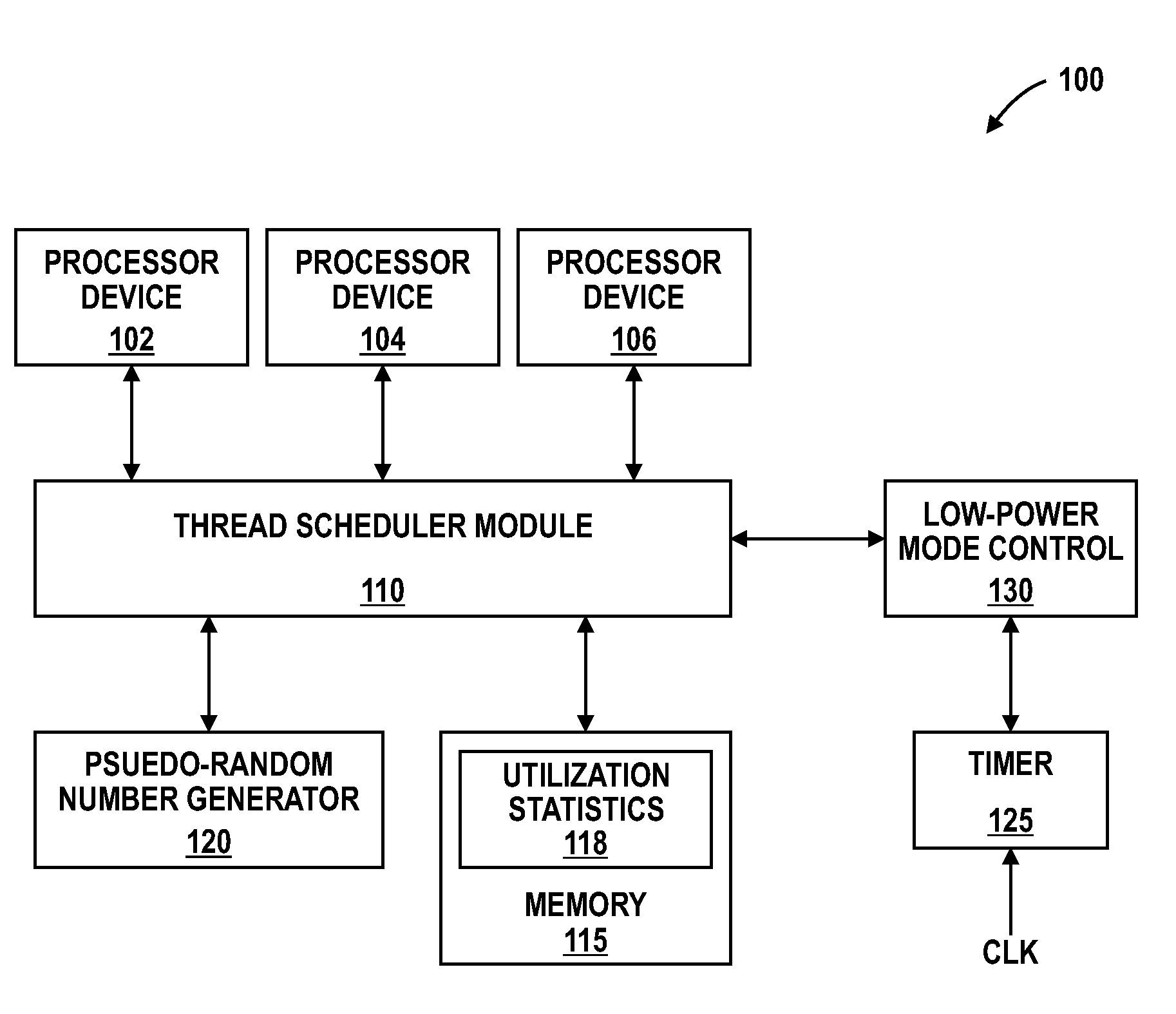

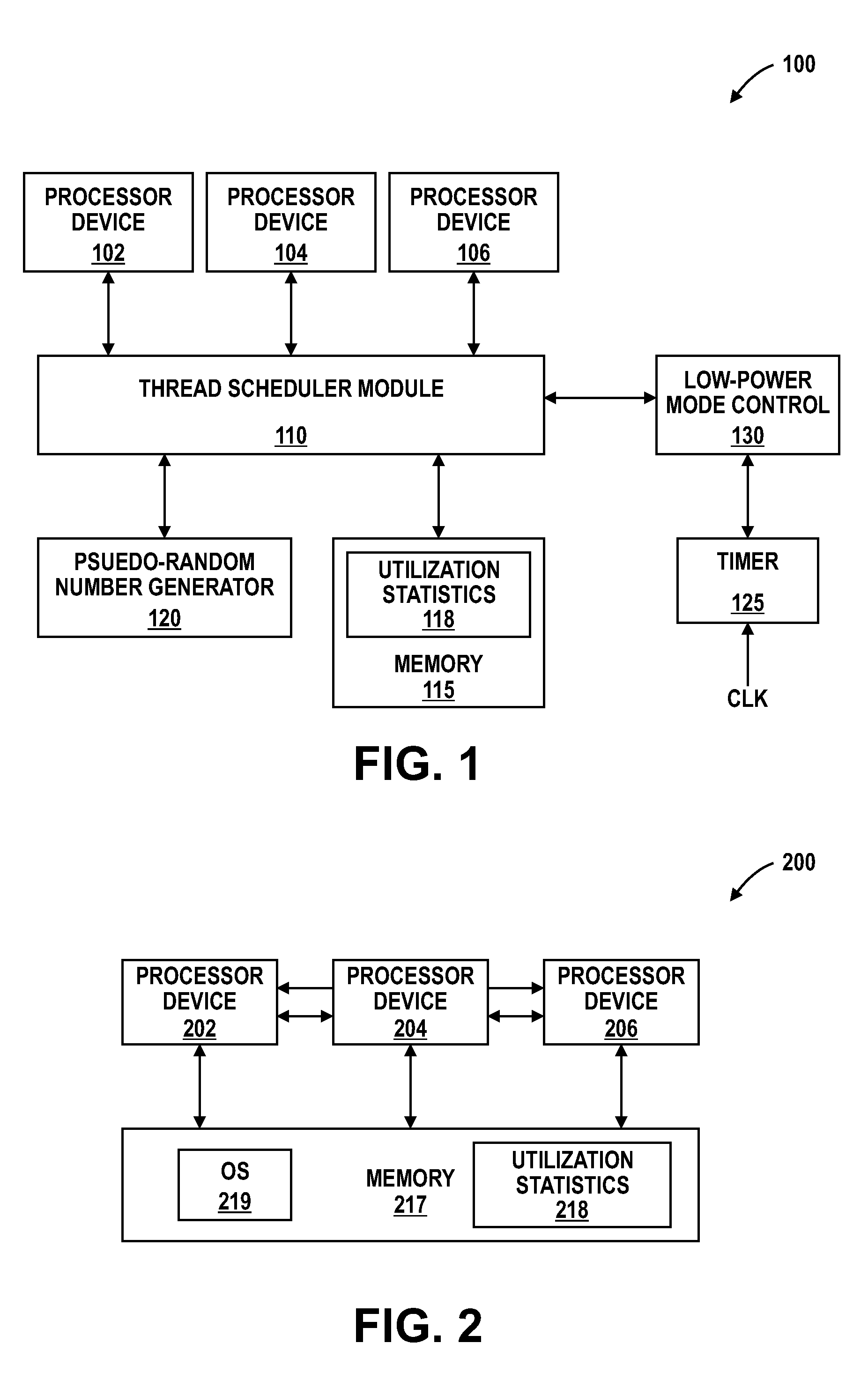

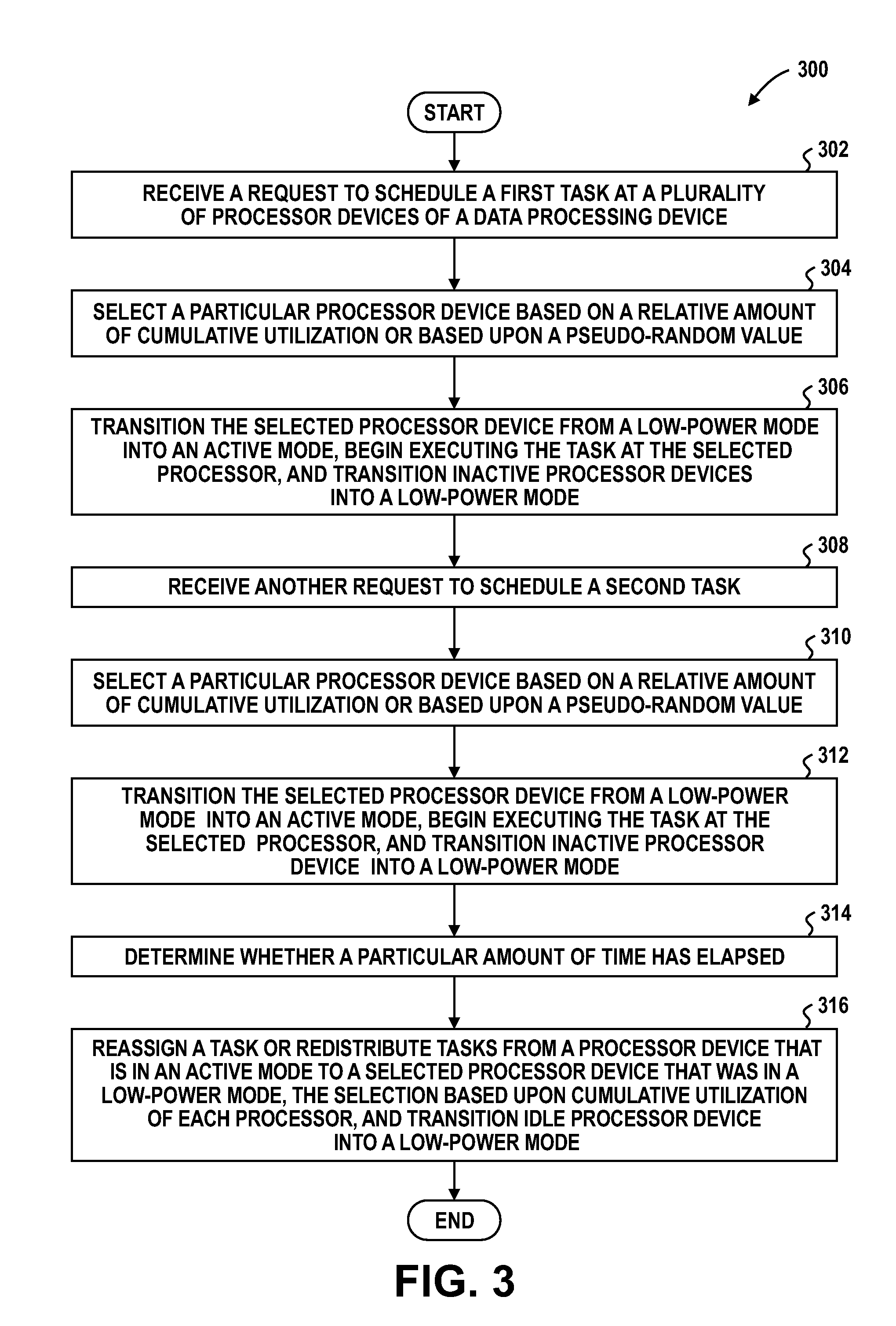

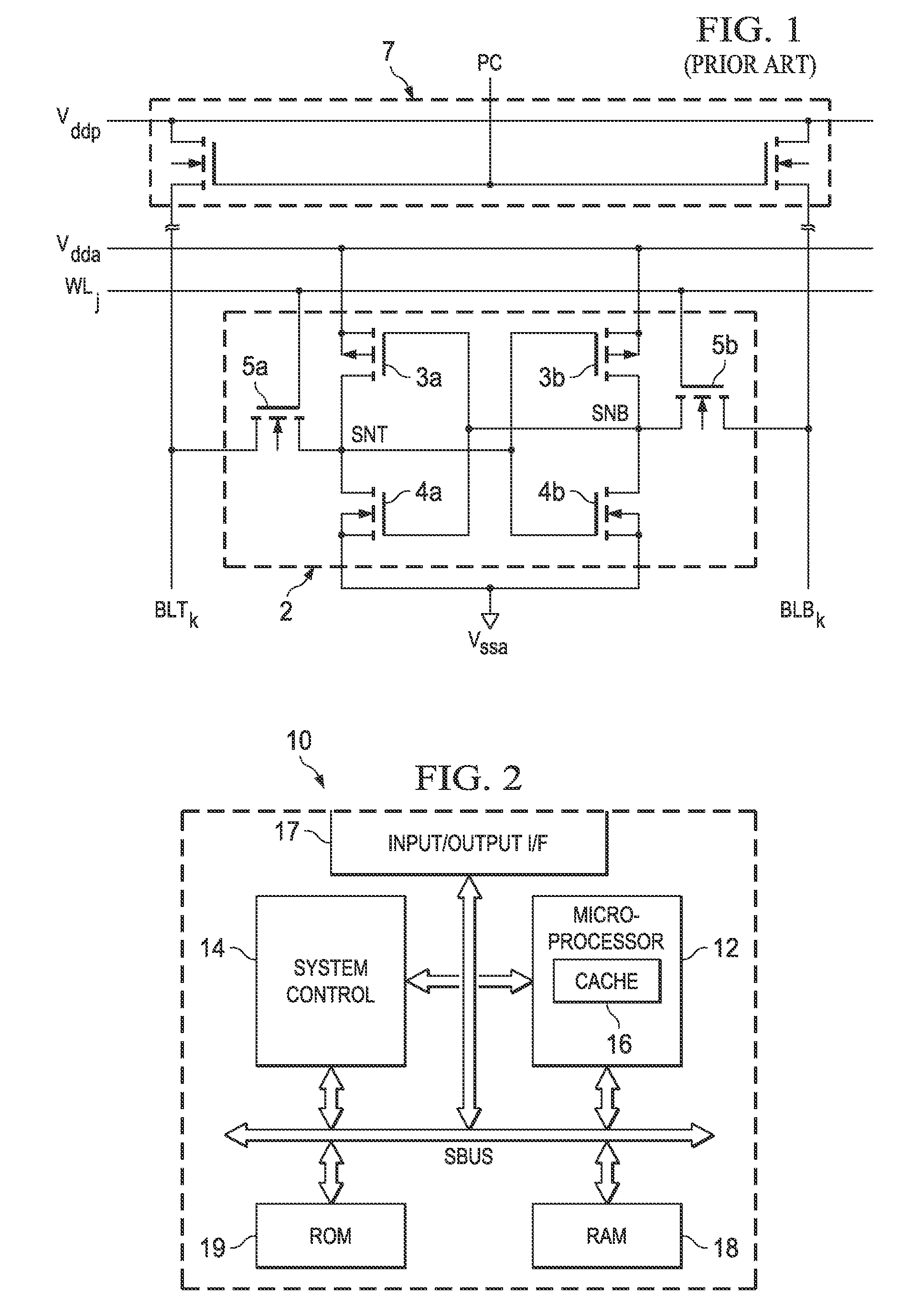

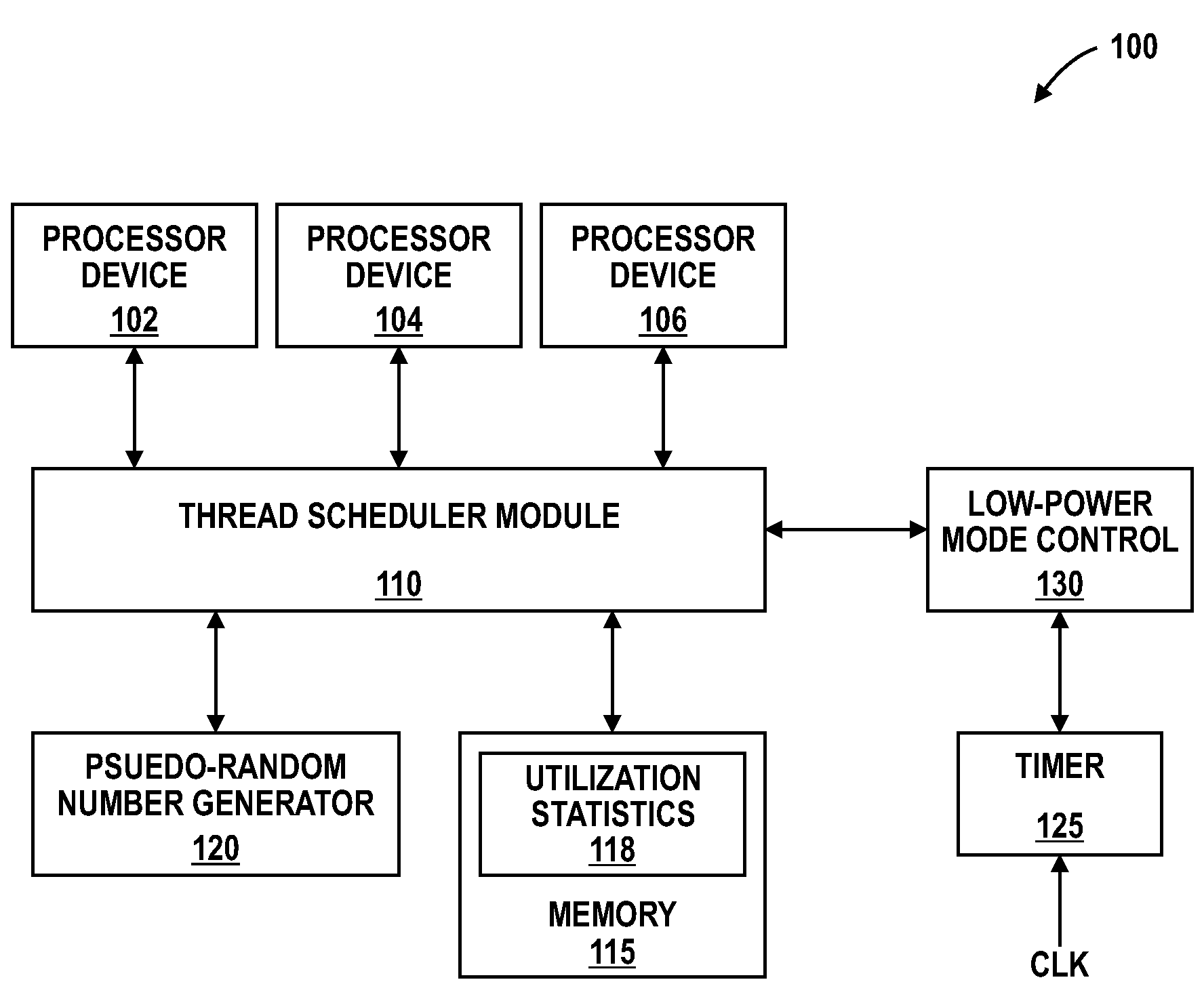

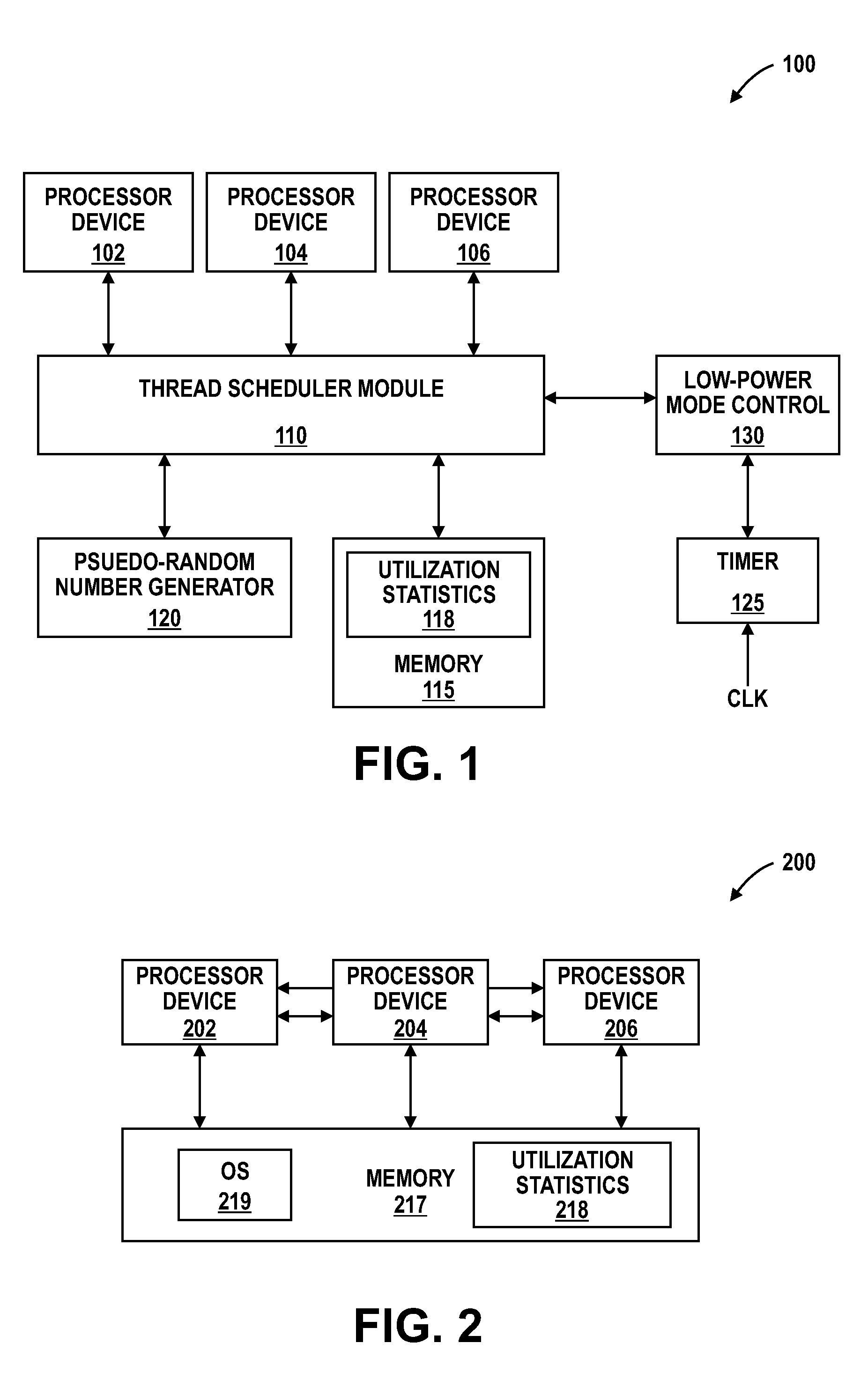

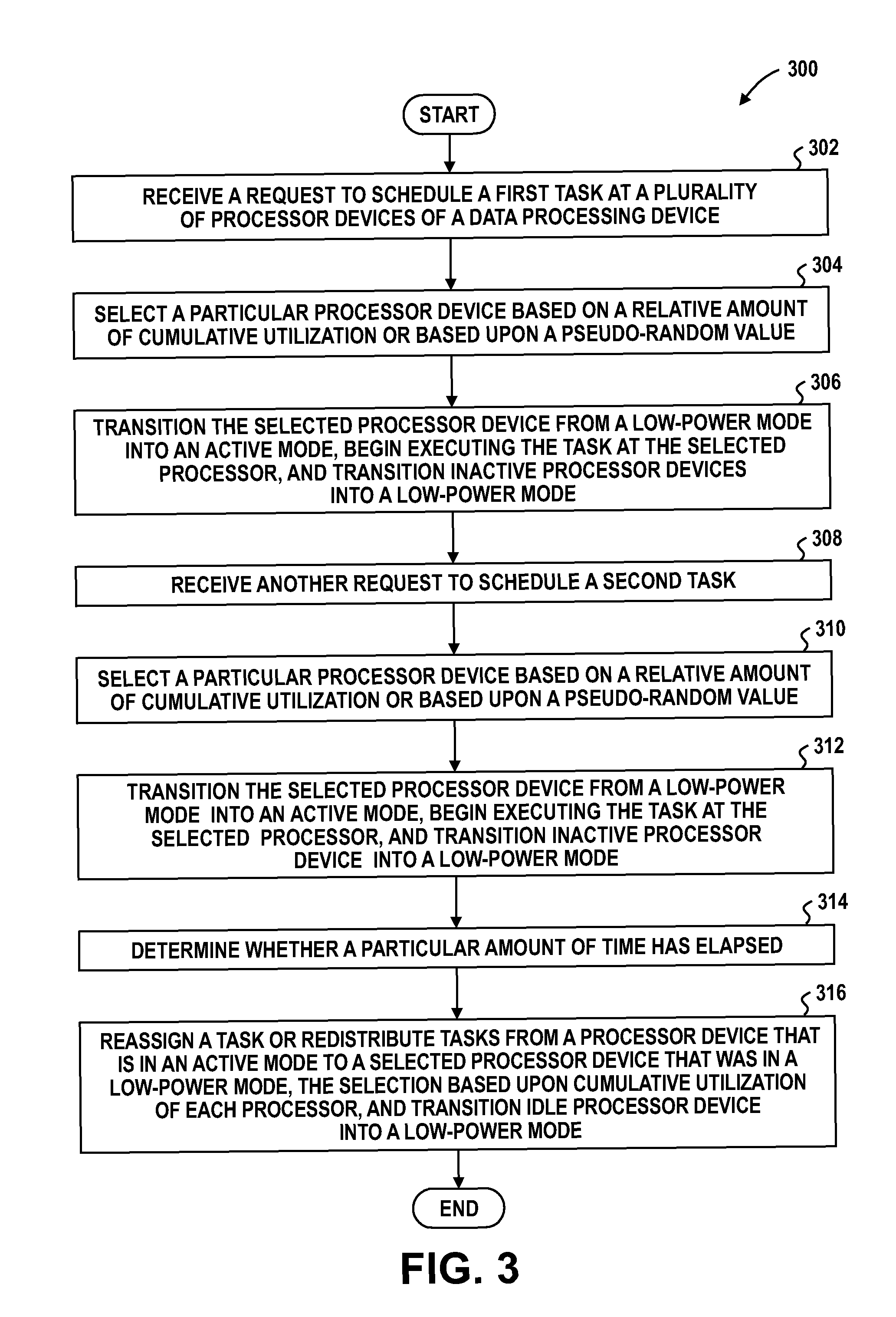

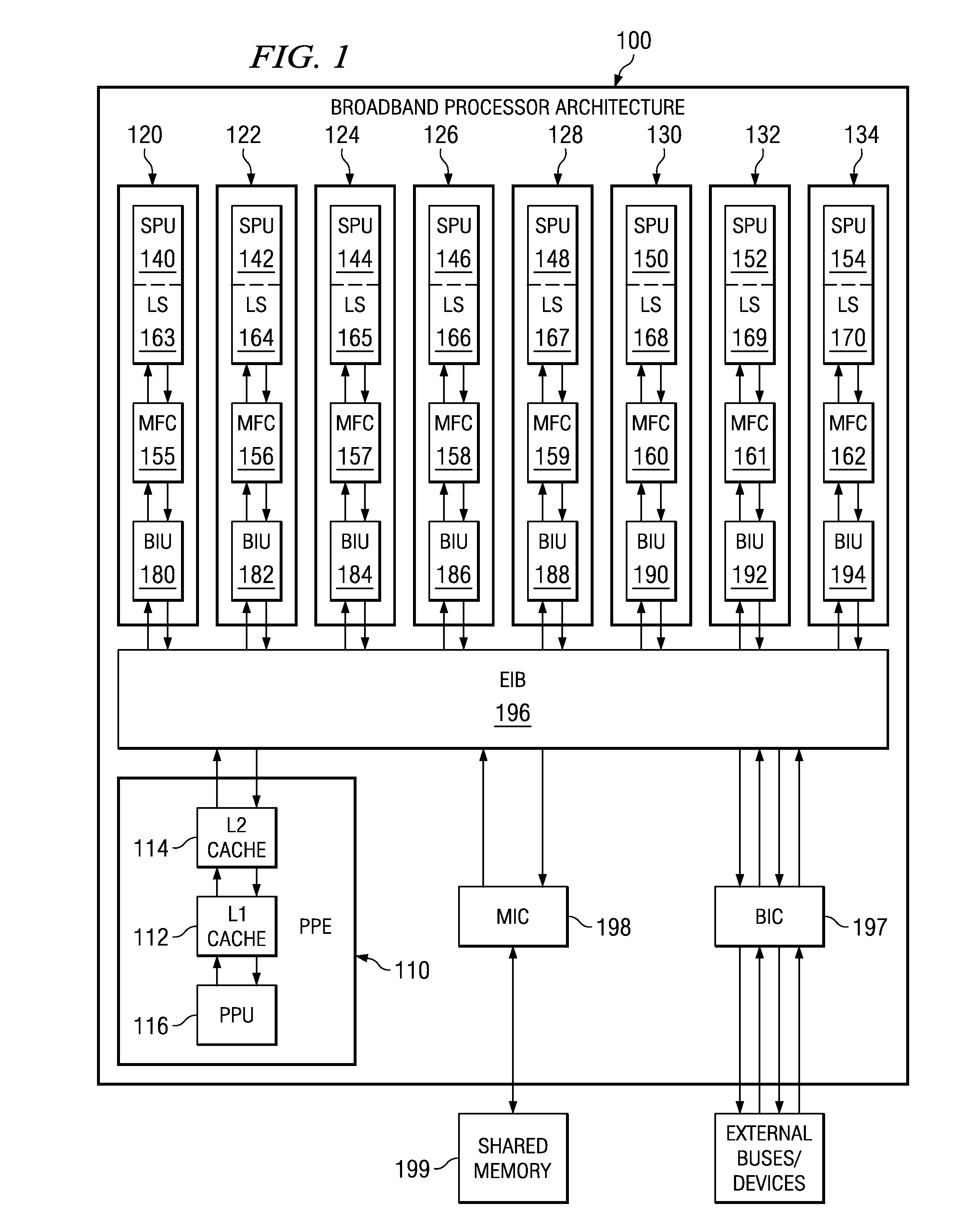

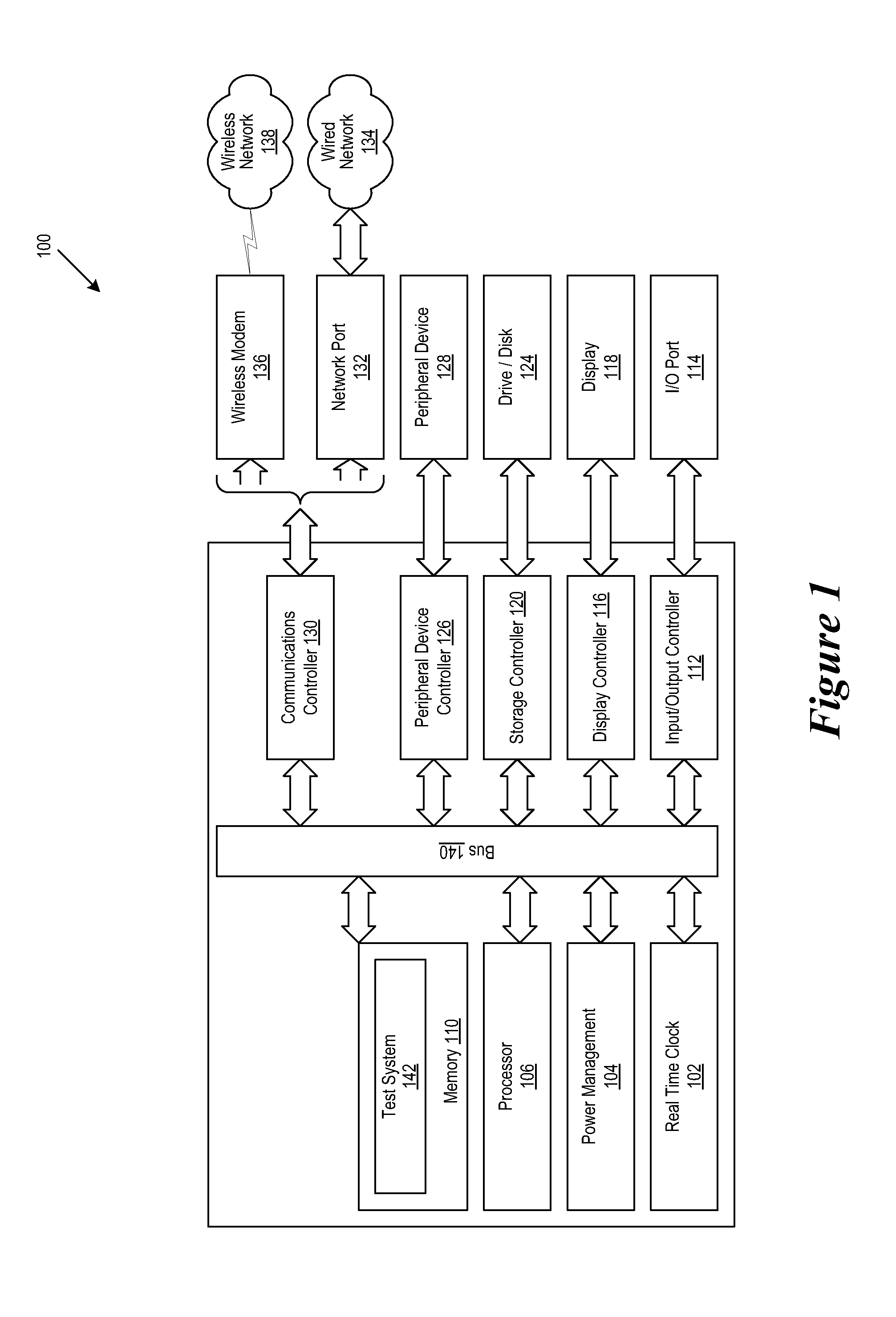

Scheduler for processor cores and methods thereof

ActiveUS20100107166A1Digital computer detailsMultiprogramming arrangementsParallel computingFixed sequence

A data processing device assigns tasks to processor cores in a more distributed fashion. In one embodiment, the data processing device can schedule tasks for execution amongst the processor cores in a pseudo-random fashion. In another embodiment, the processor core can schedule tasks for execution amongst the processor cores based on the relative amount of historical utilization of each processor core. In either case, the effects of bias temperature instability (BTI) resulting from task execution are distributed among the processor cores in a more equal fashion than if tasks are scheduled according to a fixed order. Accordingly, the useful lifetime of the processor unit can be extended.

Owner:MEDIATEK INC

Apparatus and method for measuring degradation of CMOS VLSI elements

ActiveUS20130015876A1Minimization requirementsEliminate the effects ofSemiconductor operation lifetime testingDielectricAND gate

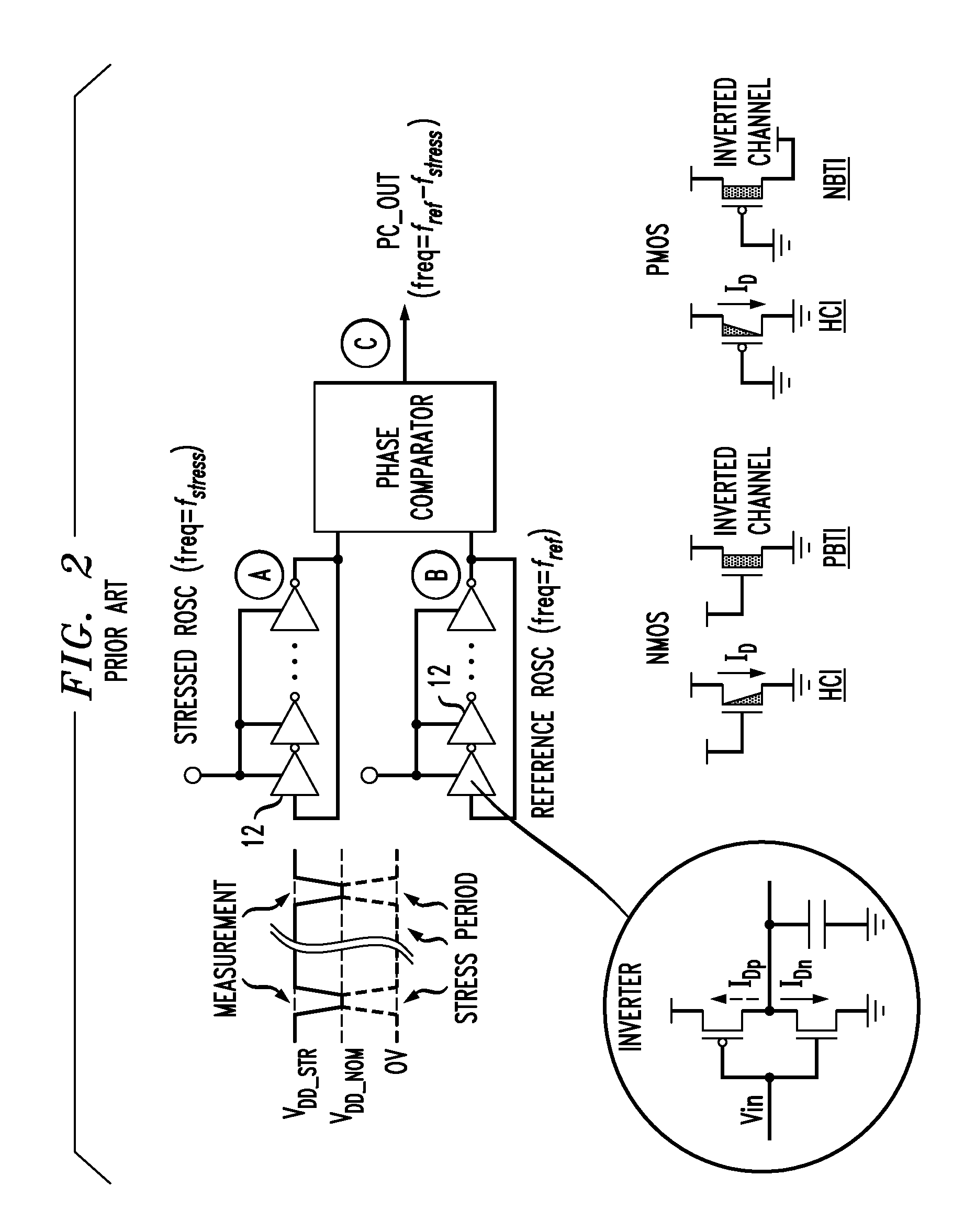

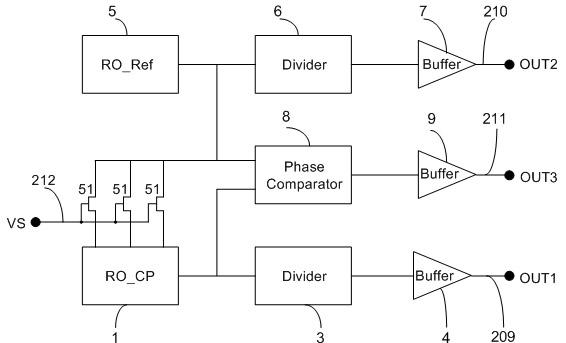

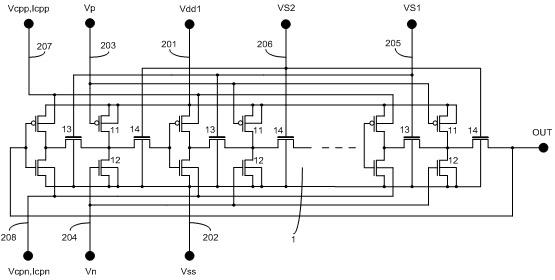

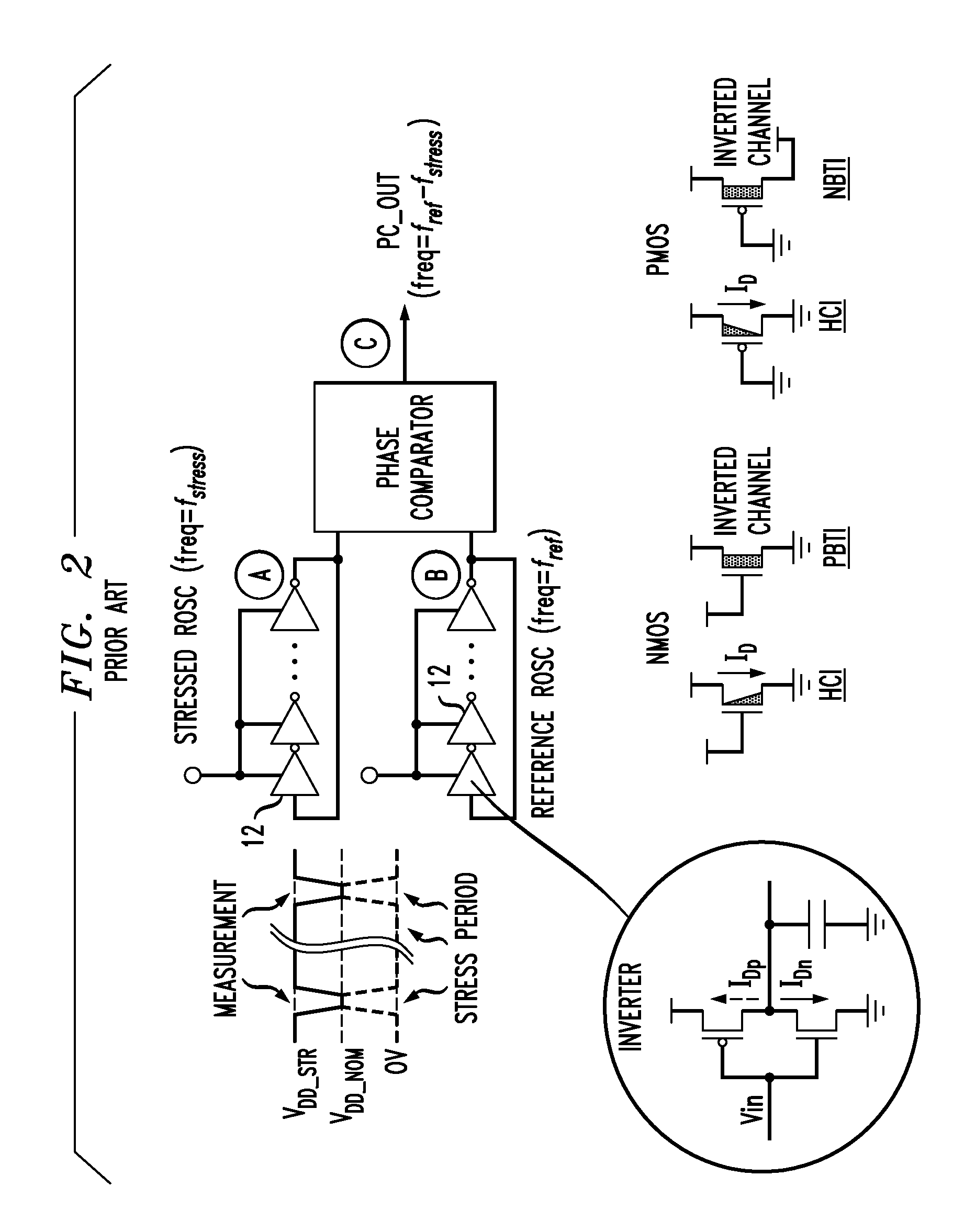

The reliability of an integrated circuit is inferred from the operational characteristics of sample metal oxide semiconductor (MOS) devices switchably coupled to drain / source bias and gate input voltages that are nominal, versus voltage and current conditions that elevate stress and cause temporary or permanent degradation, e.g., hot carrier injection (HCI), bias temperature instability (BTI, NBTI, PBTI), time dependent dielectric breakdown (TDDB). The MOS devices under test (preferably both PMOS and NMOS devices tested concurrently or in turn) are configured as current sources in the supply of power to a ring oscillator having cascaded inverter stages, thereby varying the oscillator frequency as a measure of the effects of stress on the devices under test, but without elevating the stress applied to the inverter stages.

Owner:TAIWAN SEMICON MFG CO LTD

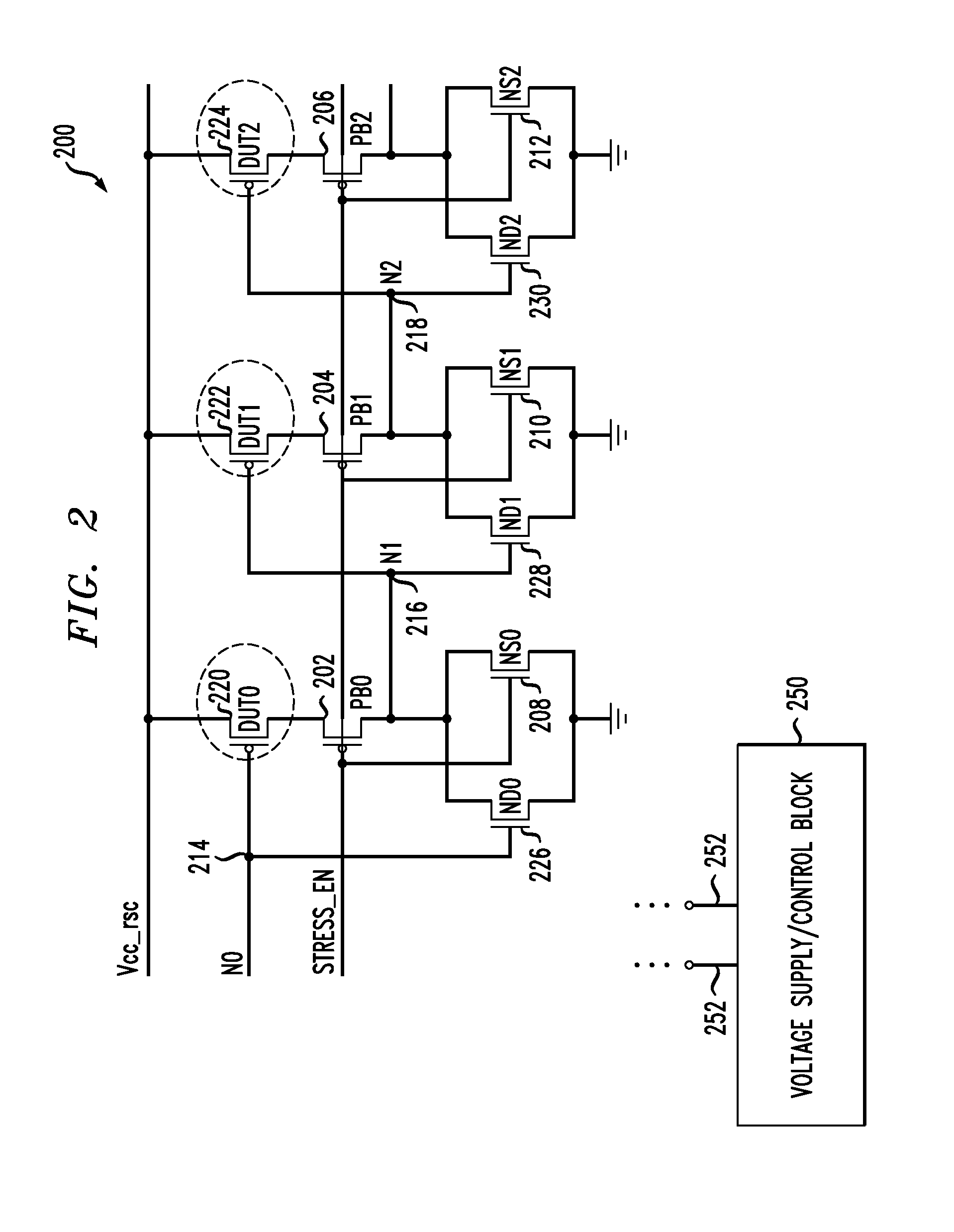

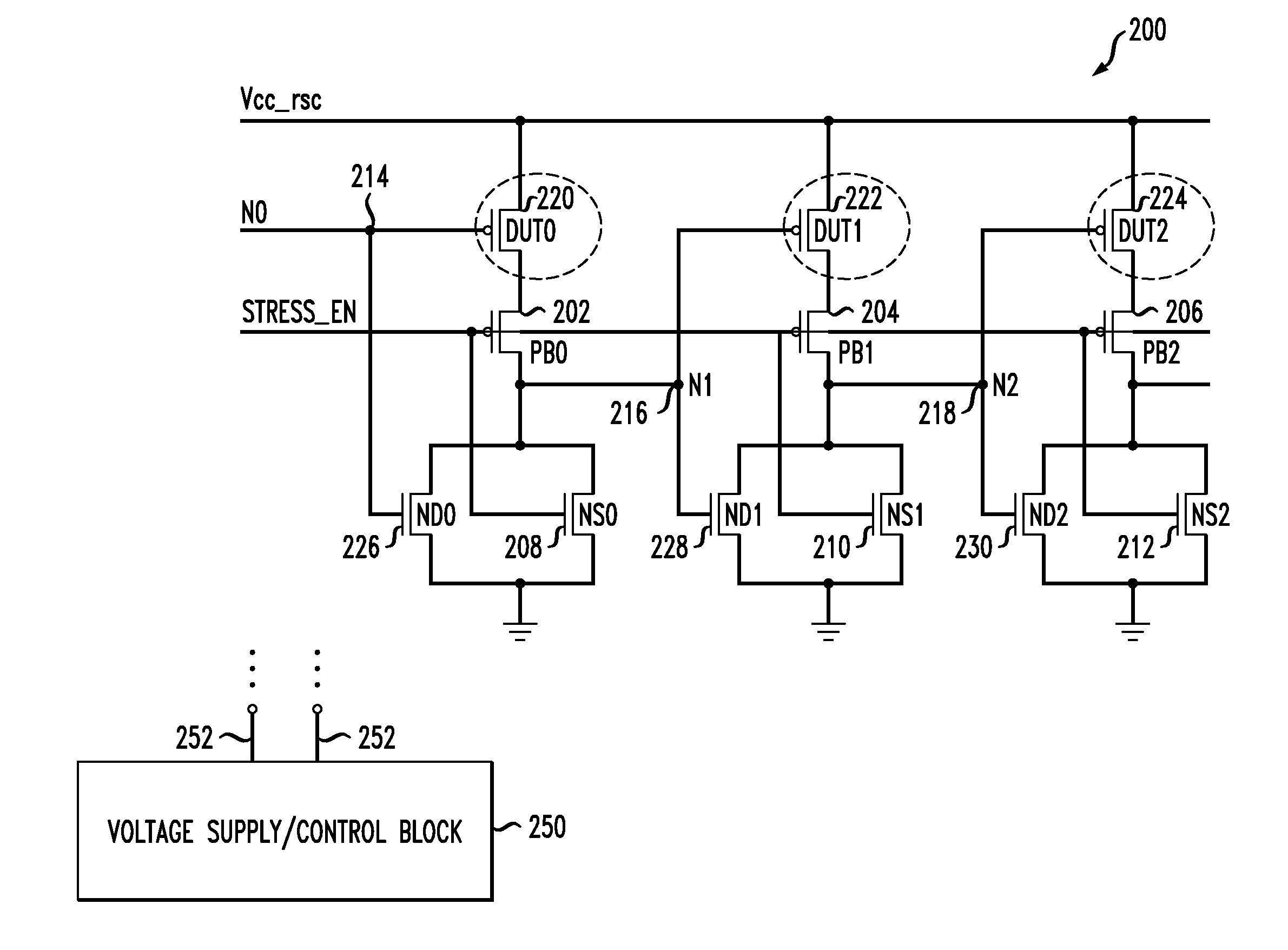

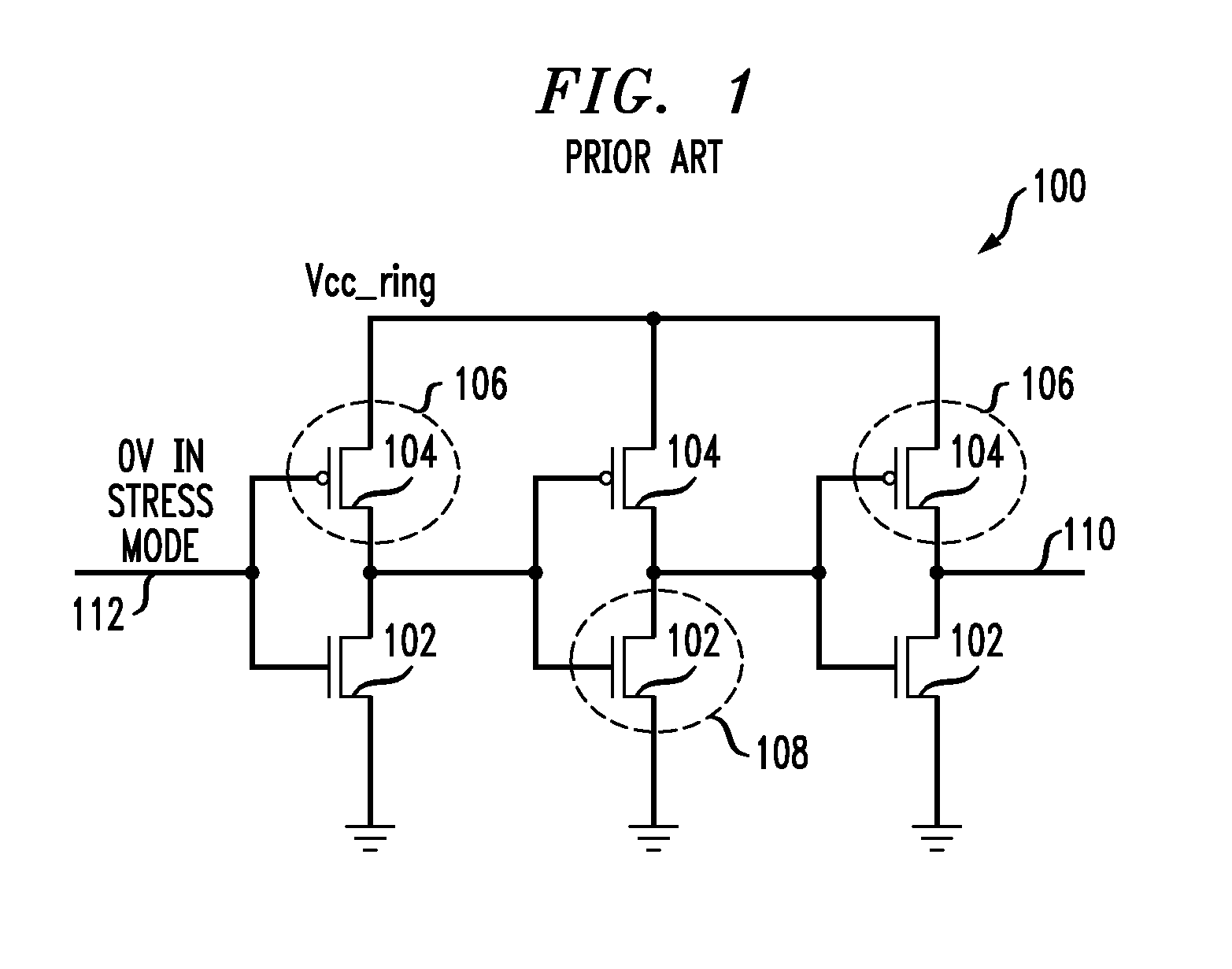

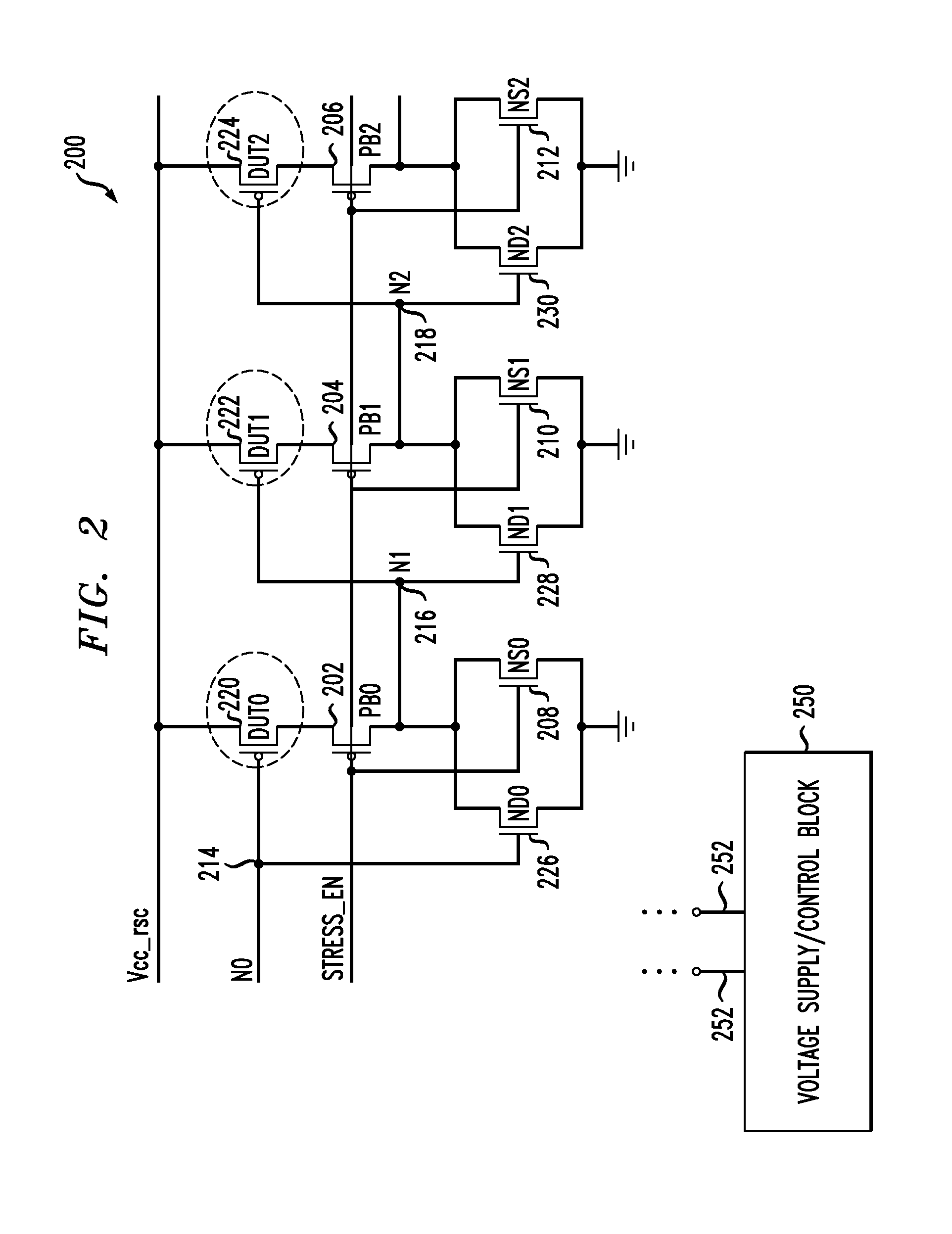

Circuits and design structures for monitoring nbti (negative bias temperature instability) effect and/or pbti (positive bias temperature instability) effect

ActiveUS20090189703A1High power supply voltageResistance/reactance/impedencePulse generation by logic circuitsNOR gateNAND gate

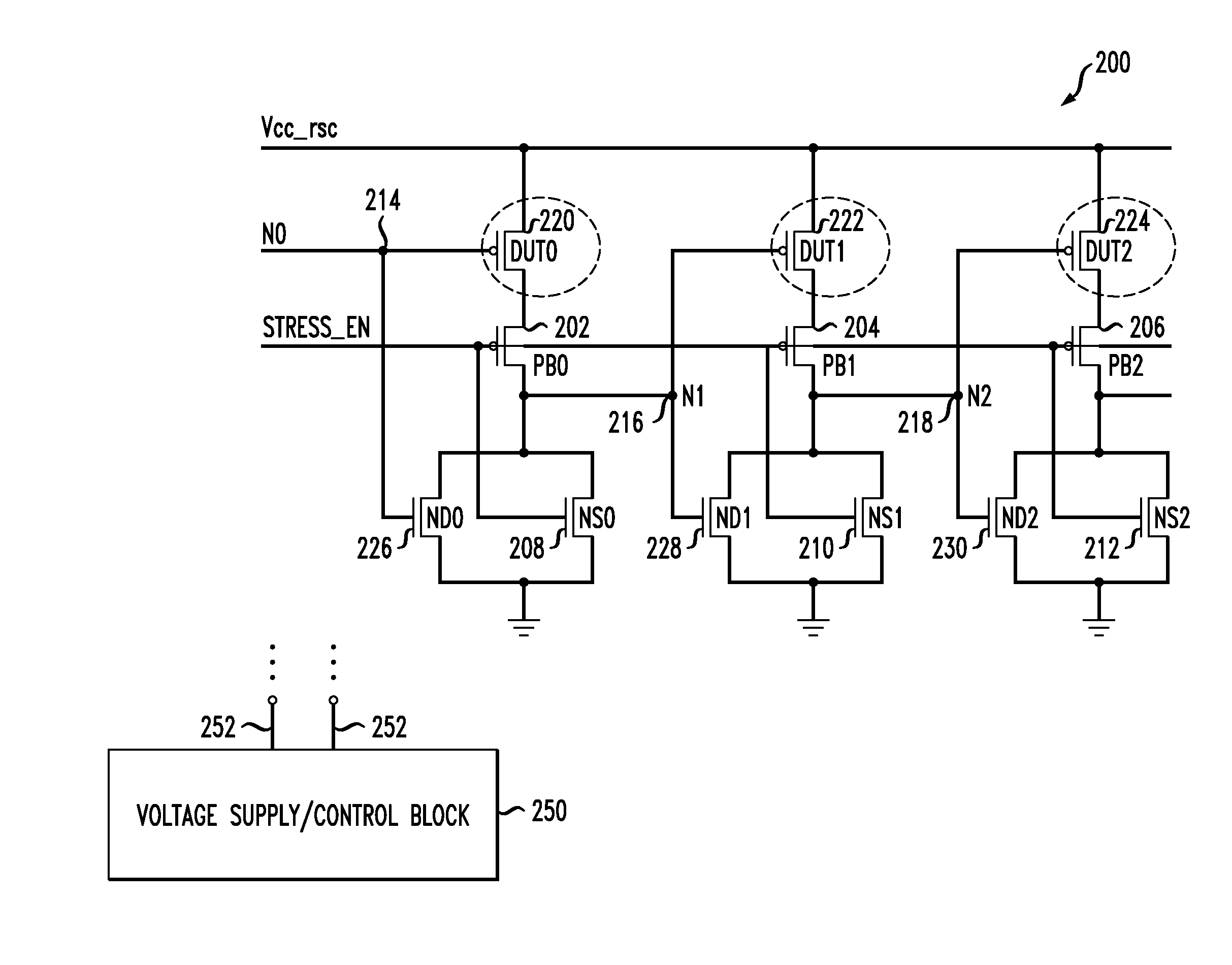

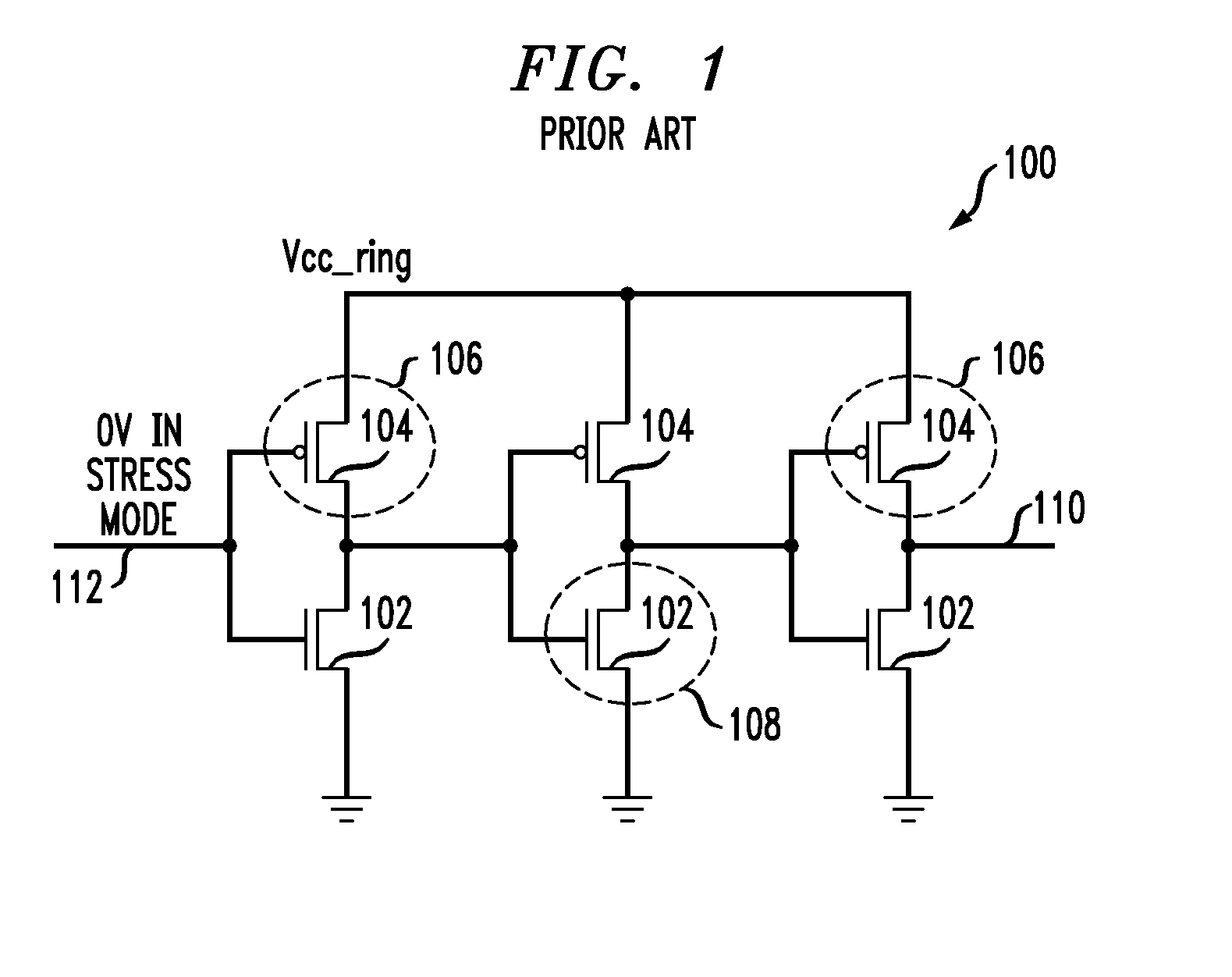

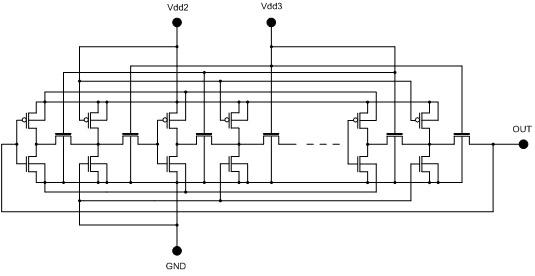

A ring oscillator has an odd number of NOR-gates greater than or equal to three, each with first and second input terminals, a voltage supply terminal, and an output terminal. The first input terminals of all the NOR-gates are interconnected, and each of the NOR-gates has its output terminal connected to the second input terminal of an immediately adjacent one of the NOR-gates. During a stress mode, a voltage supply and control block applies a stress enable signal to the interconnected first input terminals, and an increased supply voltage to the voltage supply terminals. During a measurement mode, this block grounds the interconnected first input terminals, and applies a normal supply voltage to the voltage supply terminals. Also included are an analogous NAND-gate based circuit, a circuit combining the NAND- and NOR-aspects, a circuit with a ring oscillator where the inverters may be coupled directly or through inverting paths, and circuits for measuring the bias temperature instability effect in pass gates.

Owner:GLOBALFOUNDRIES US INC

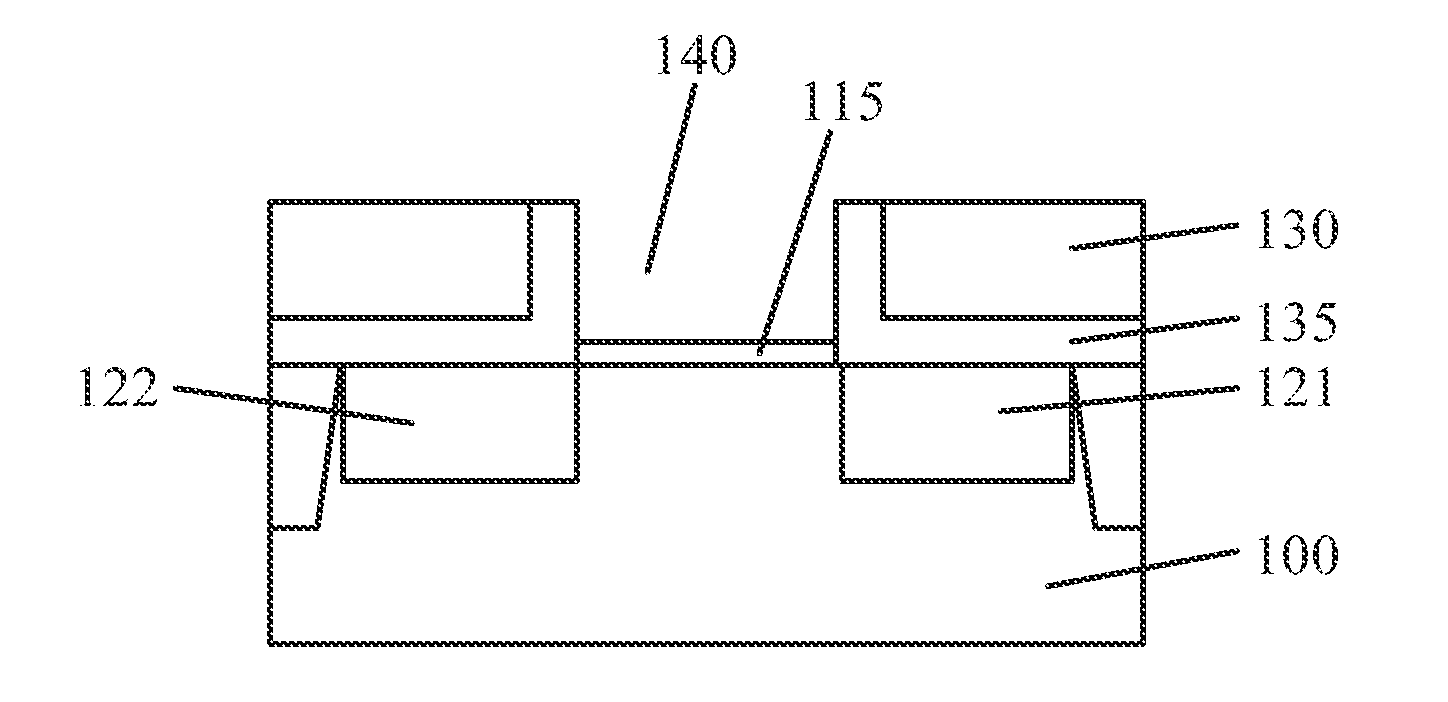

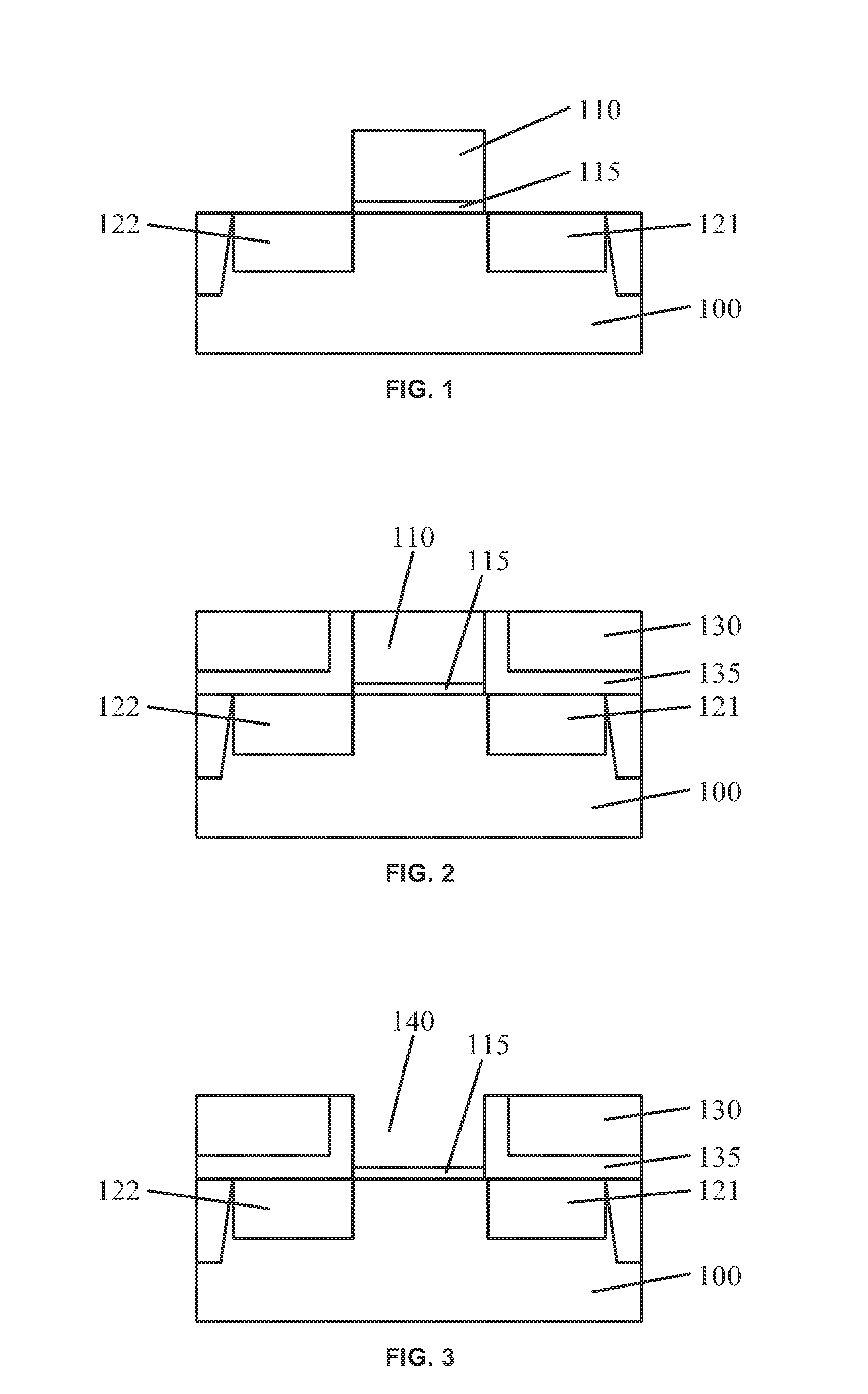

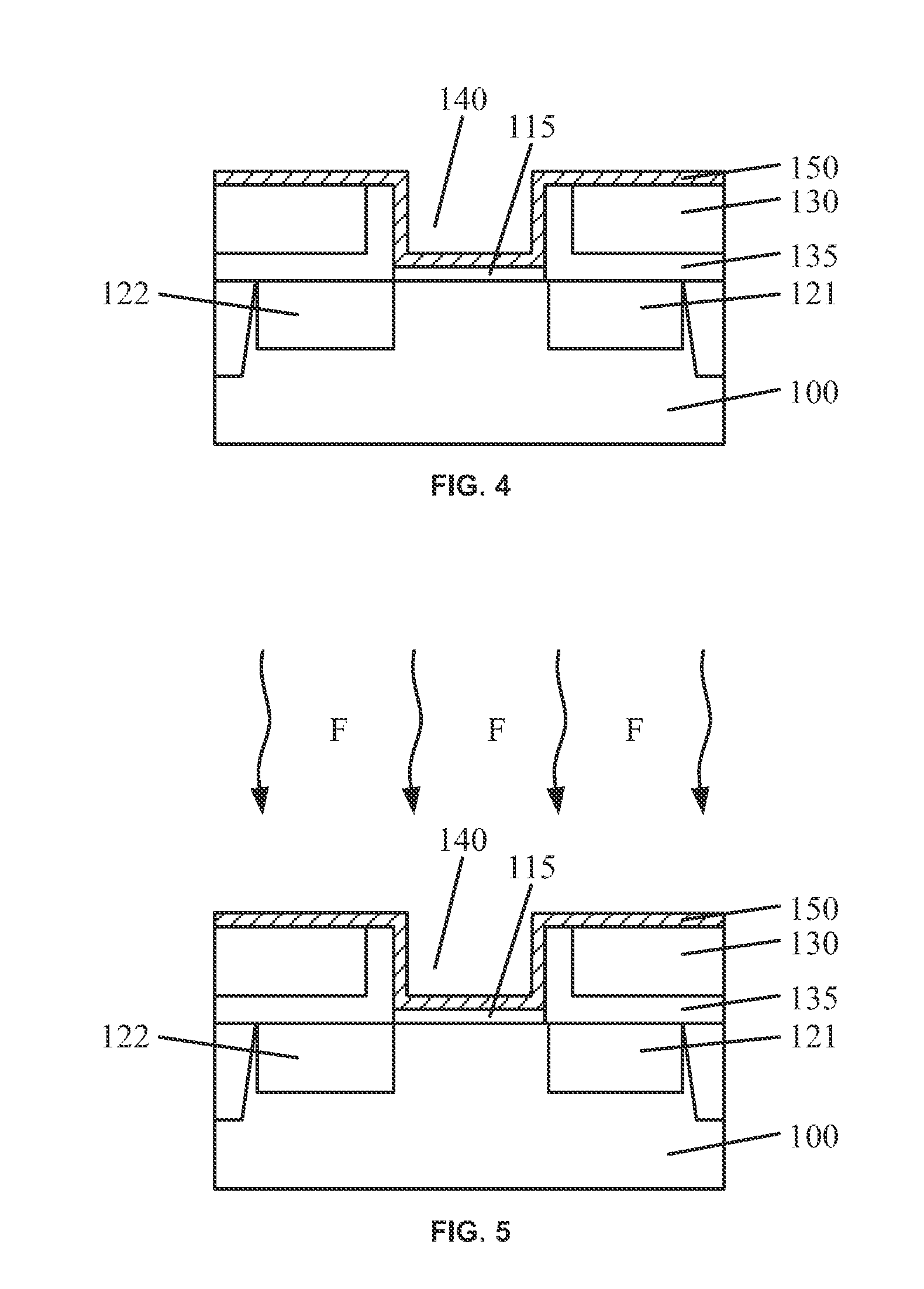

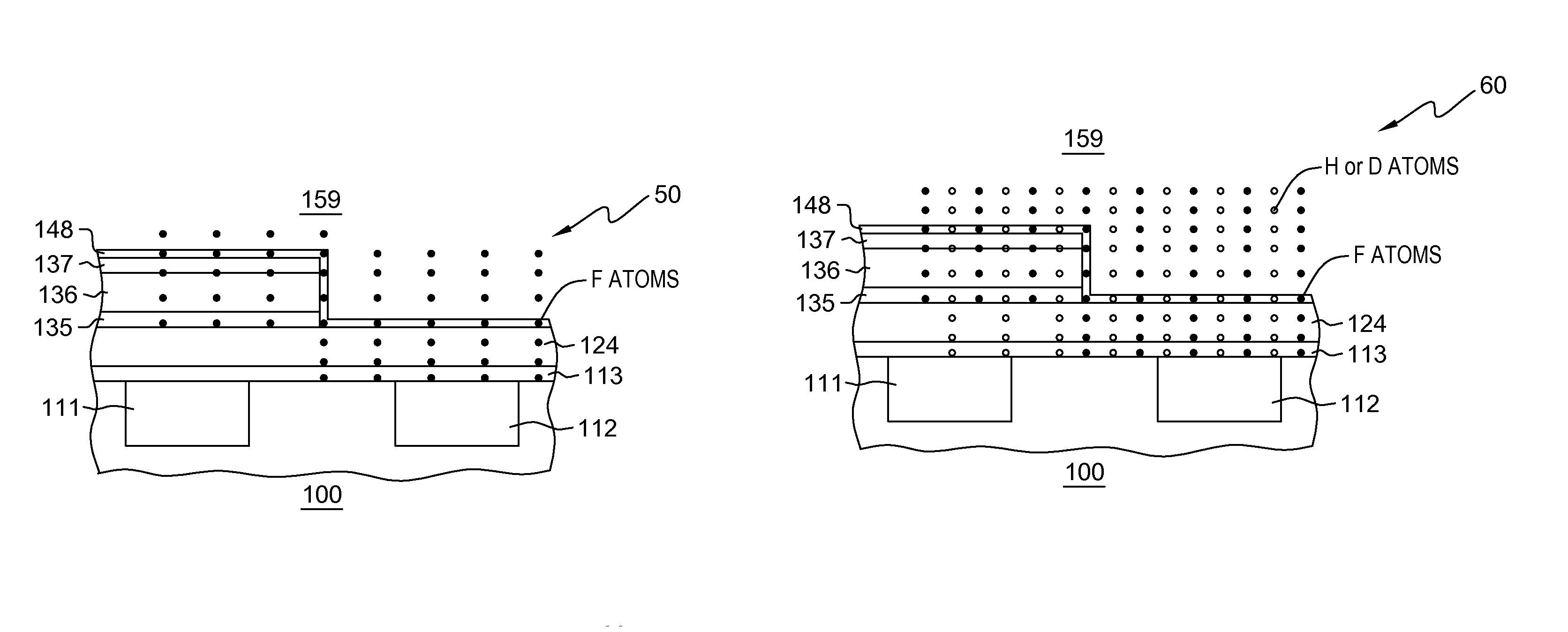

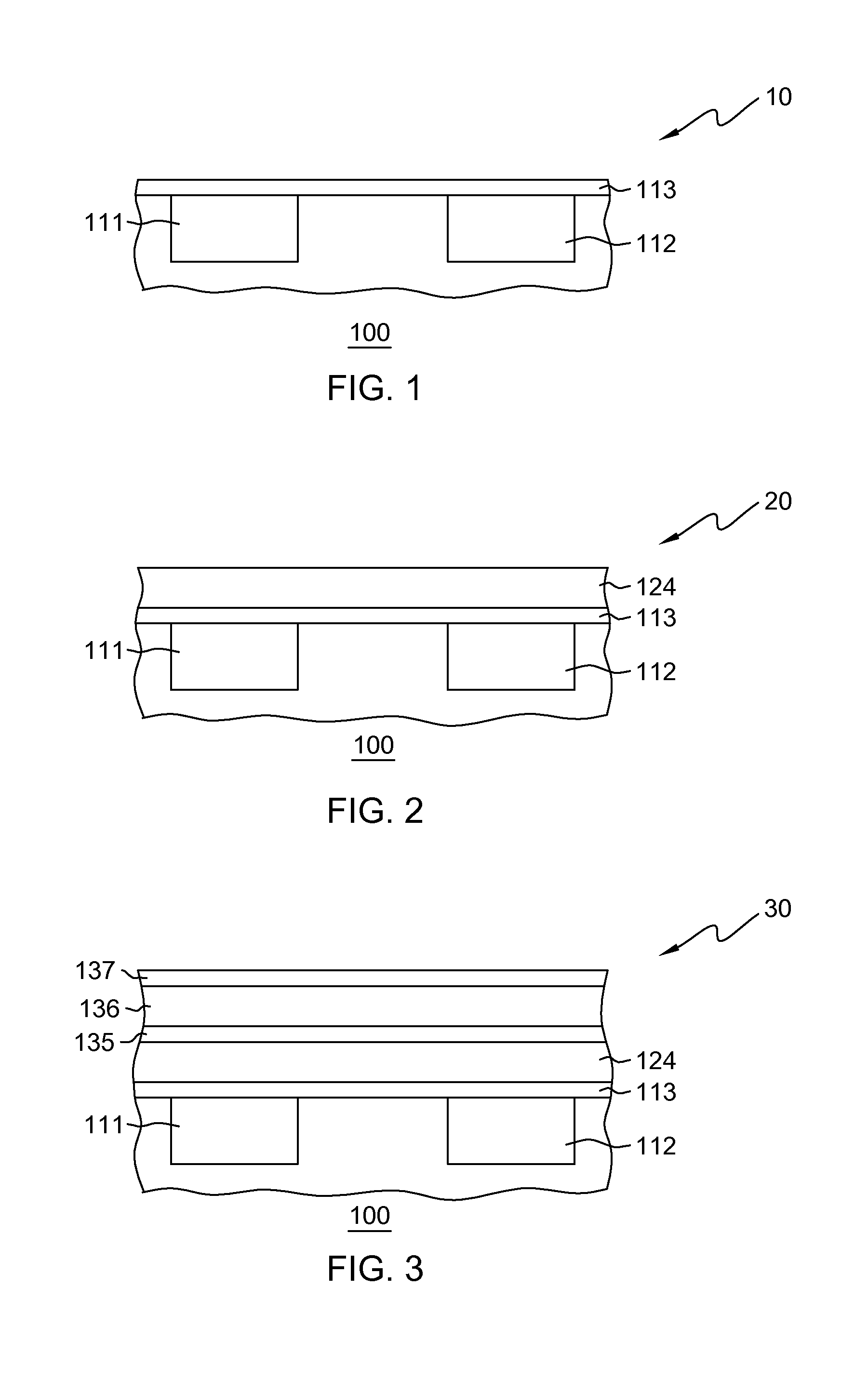

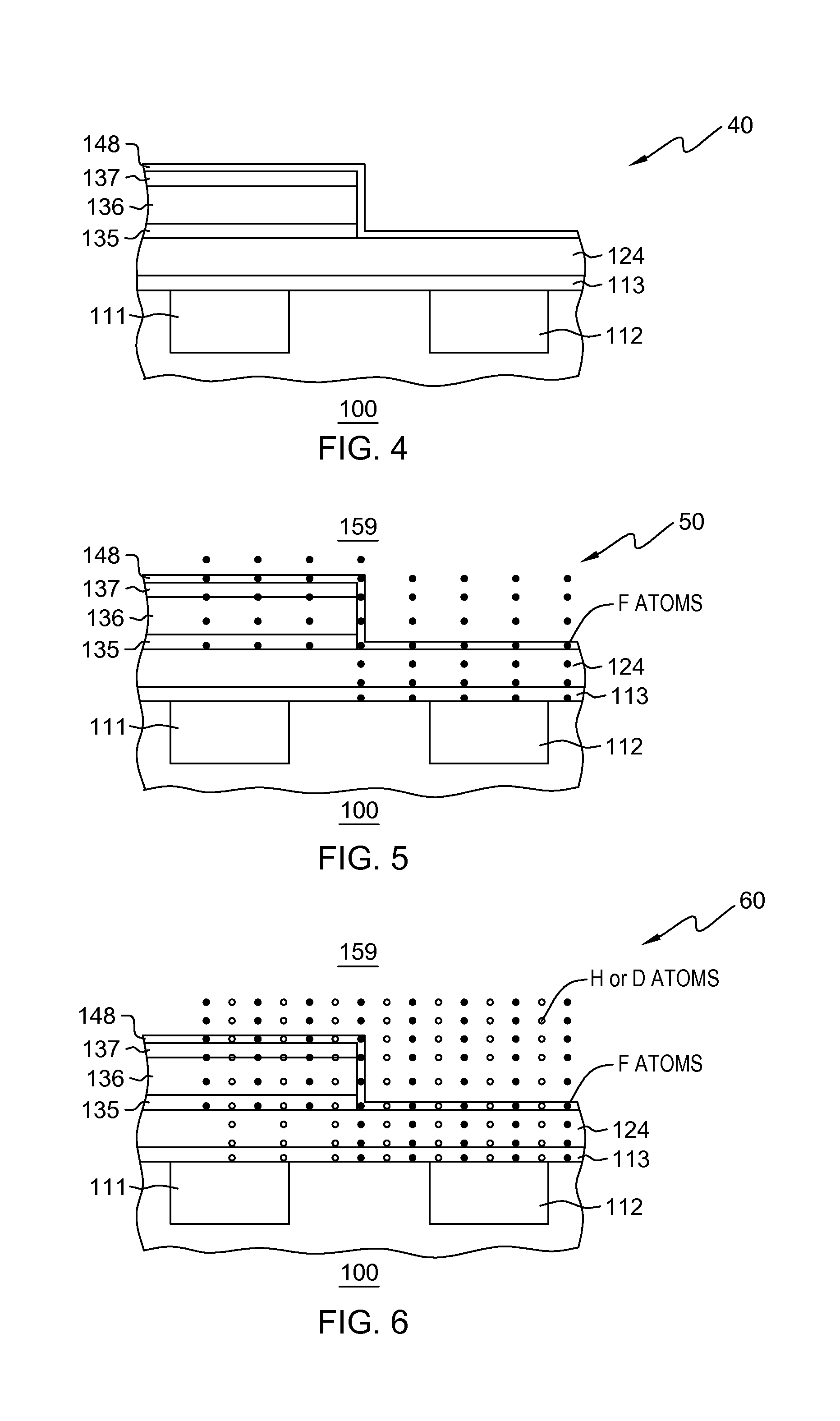

Transistor device and fabrication method

ActiveUS20140077313A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerNegative-bias temperature instability

Various embodiments provide transistors and their fabrication methods. An exemplary method for forming a transistor includes removing a dummy gate to form a trench over a semiconductor substrate. A high-k dielectric layer can be conformally formed on surface of the trench and then be fluorinated to form a fluorinated high-k dielectric layer. A functional layer can be formed on the fluorinated high-k dielectric layer and a metal layer can be formed on the functional layer to fill the trench with the metal layer. Due to fluorination of the high-k dielectric layer, negative bias temperature instability of the formed transistor can be reduced and oxygen vacancies can be passivated to reduce positive bias temperature instability of the transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

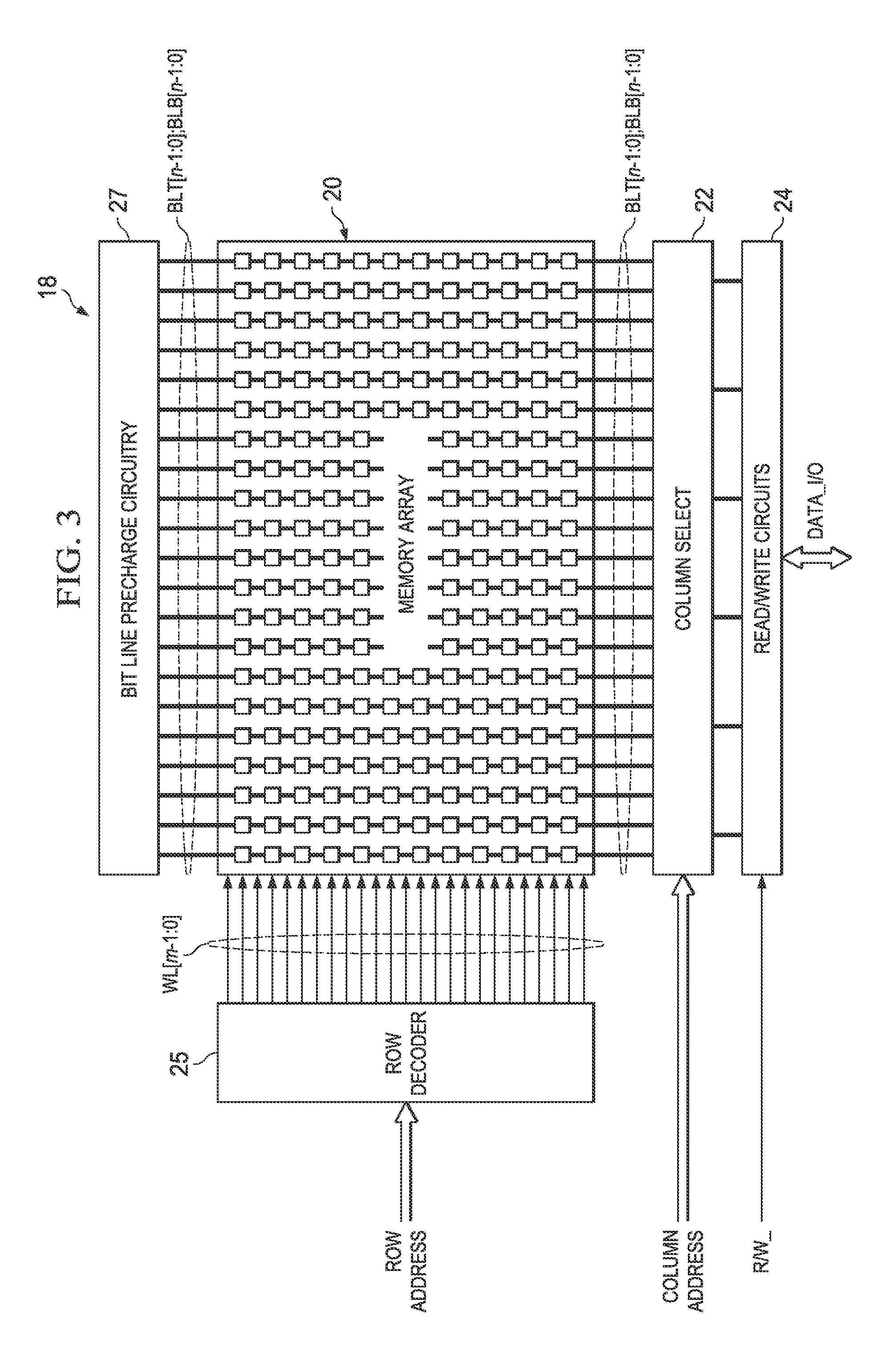

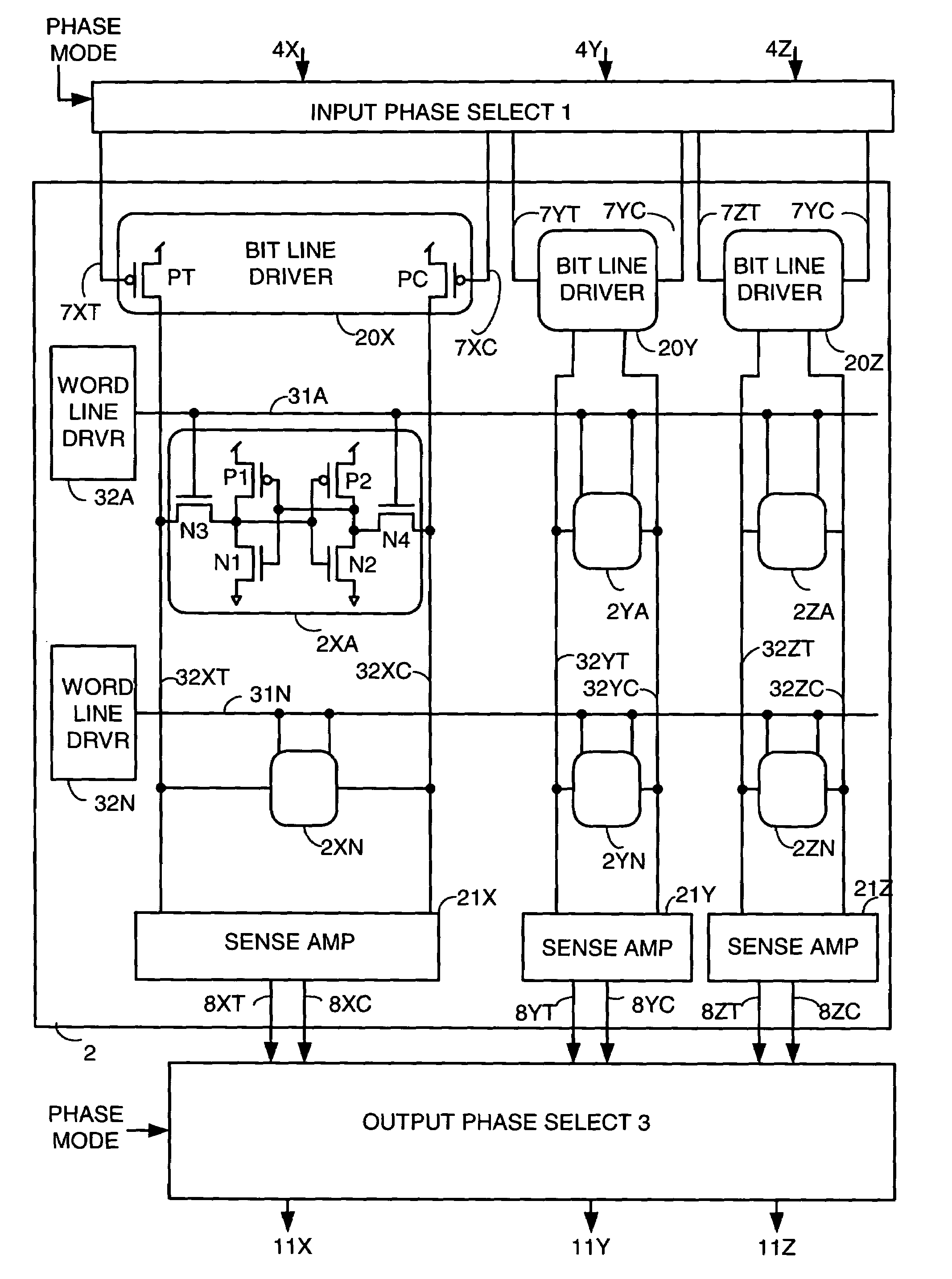

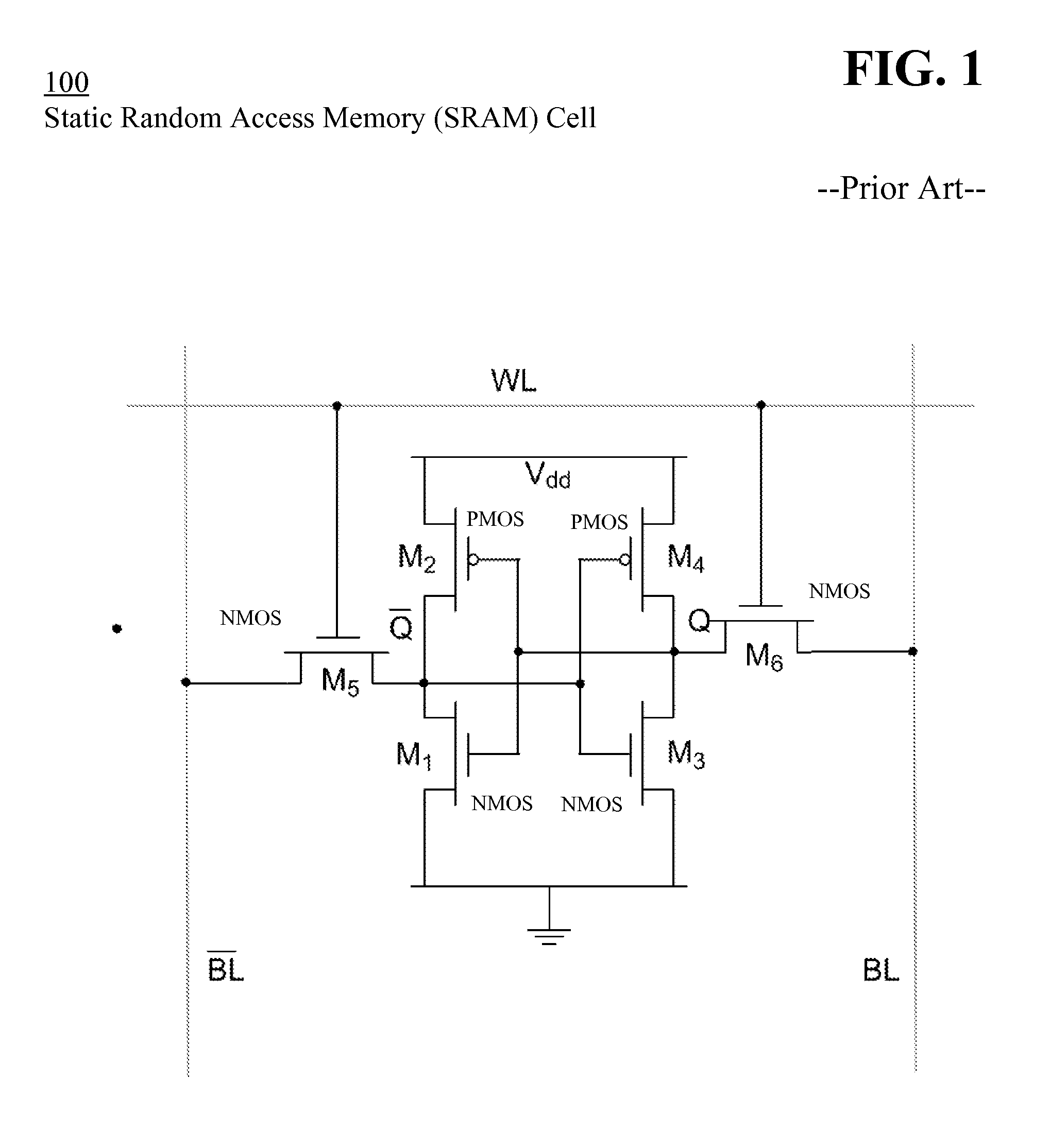

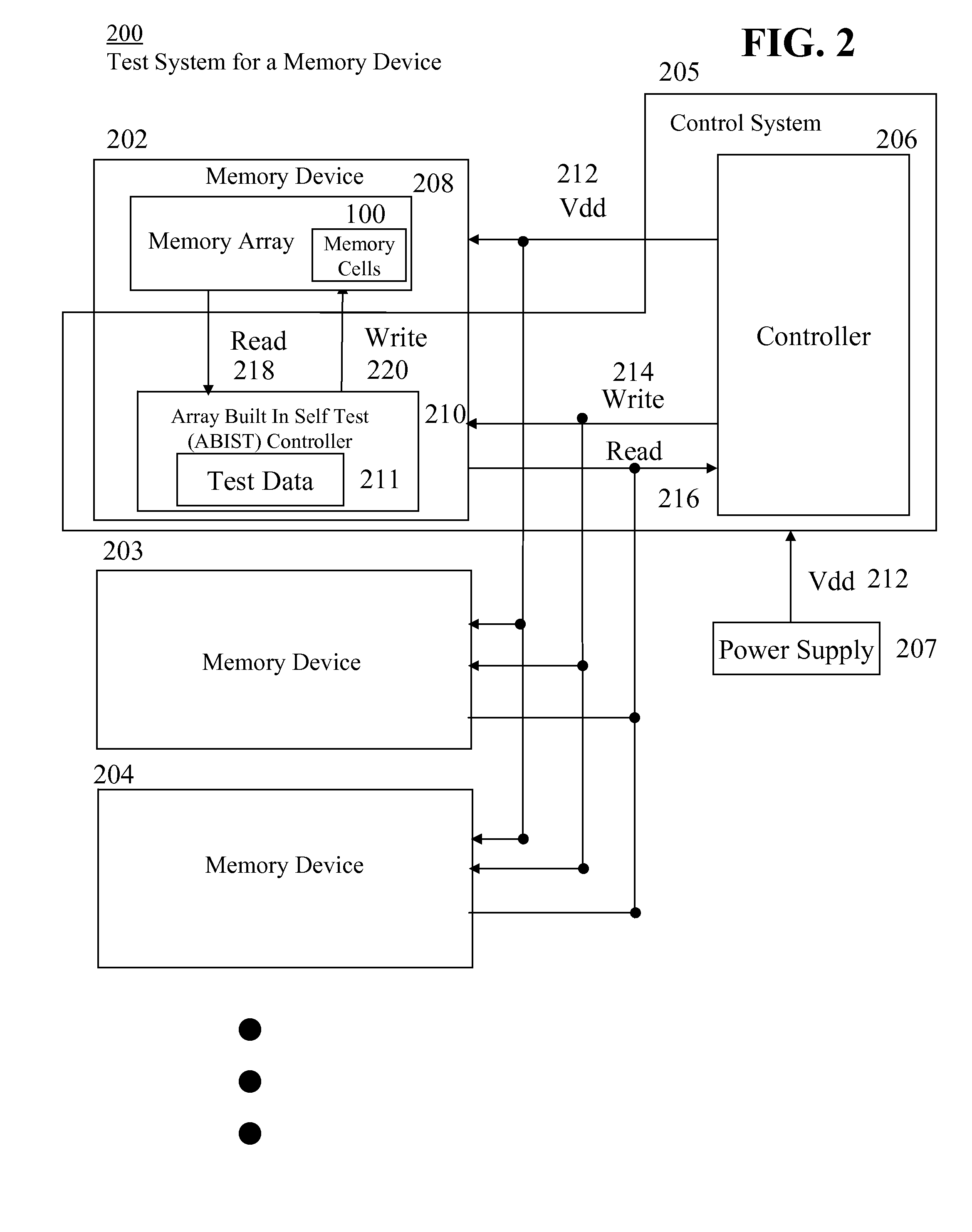

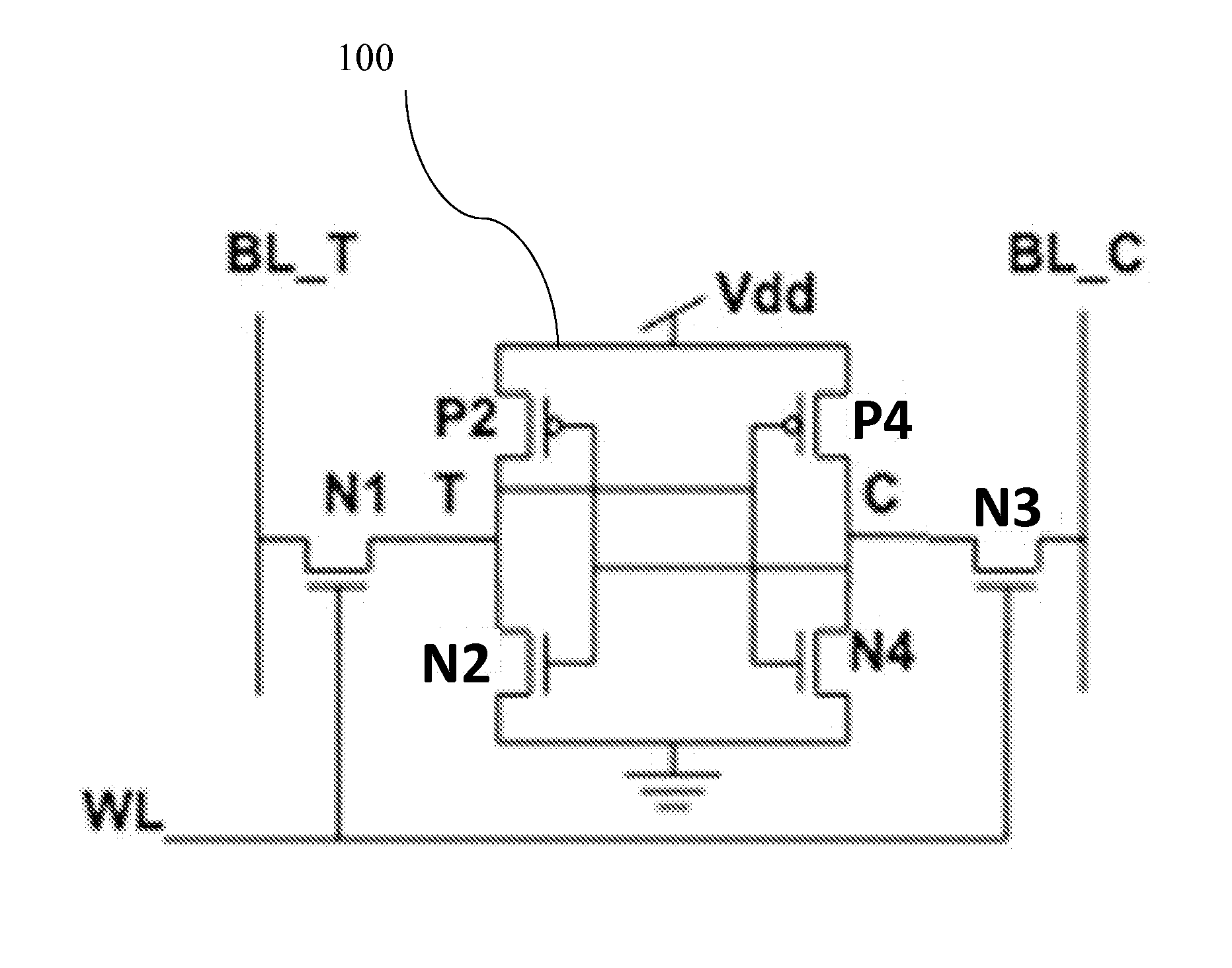

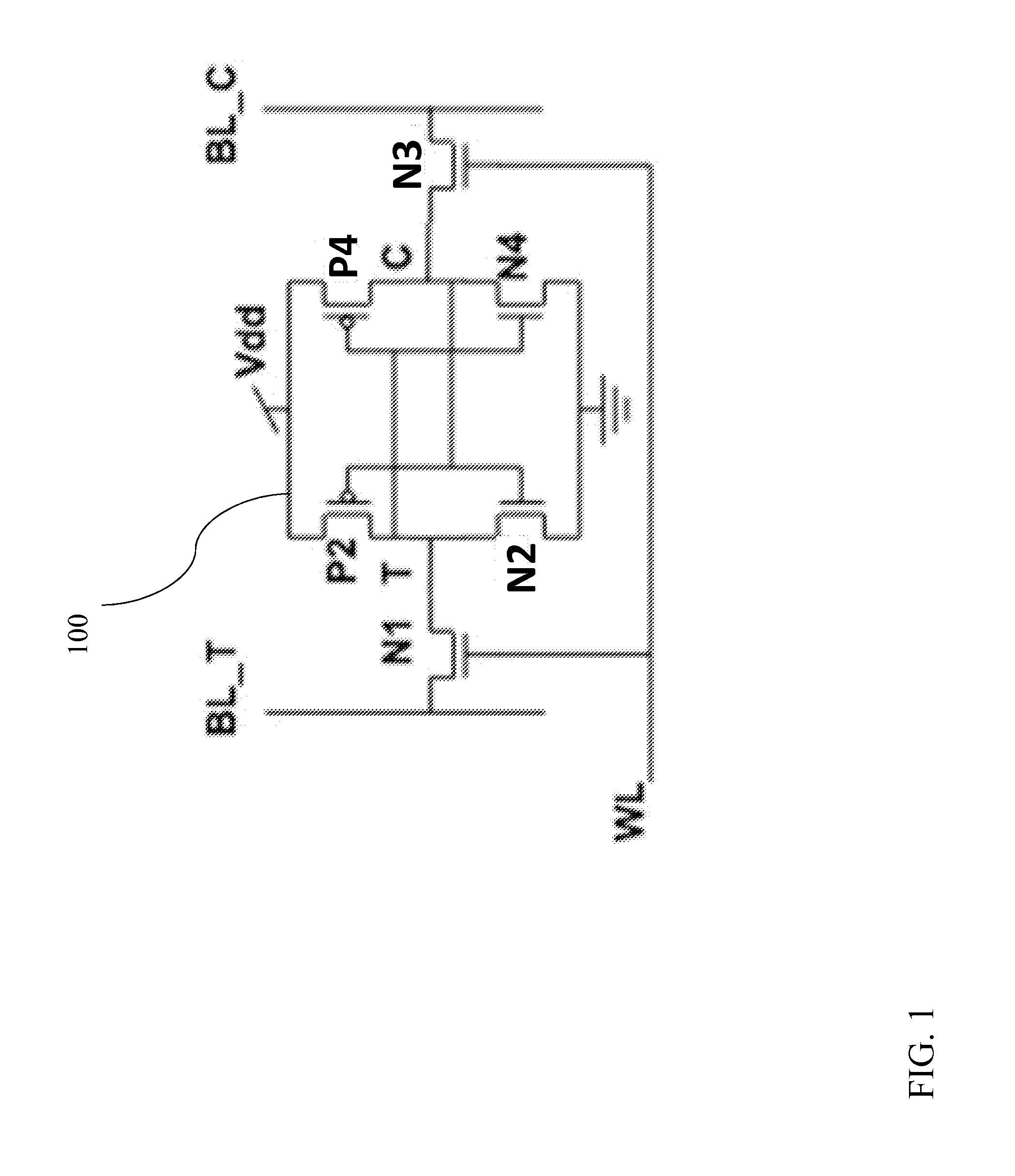

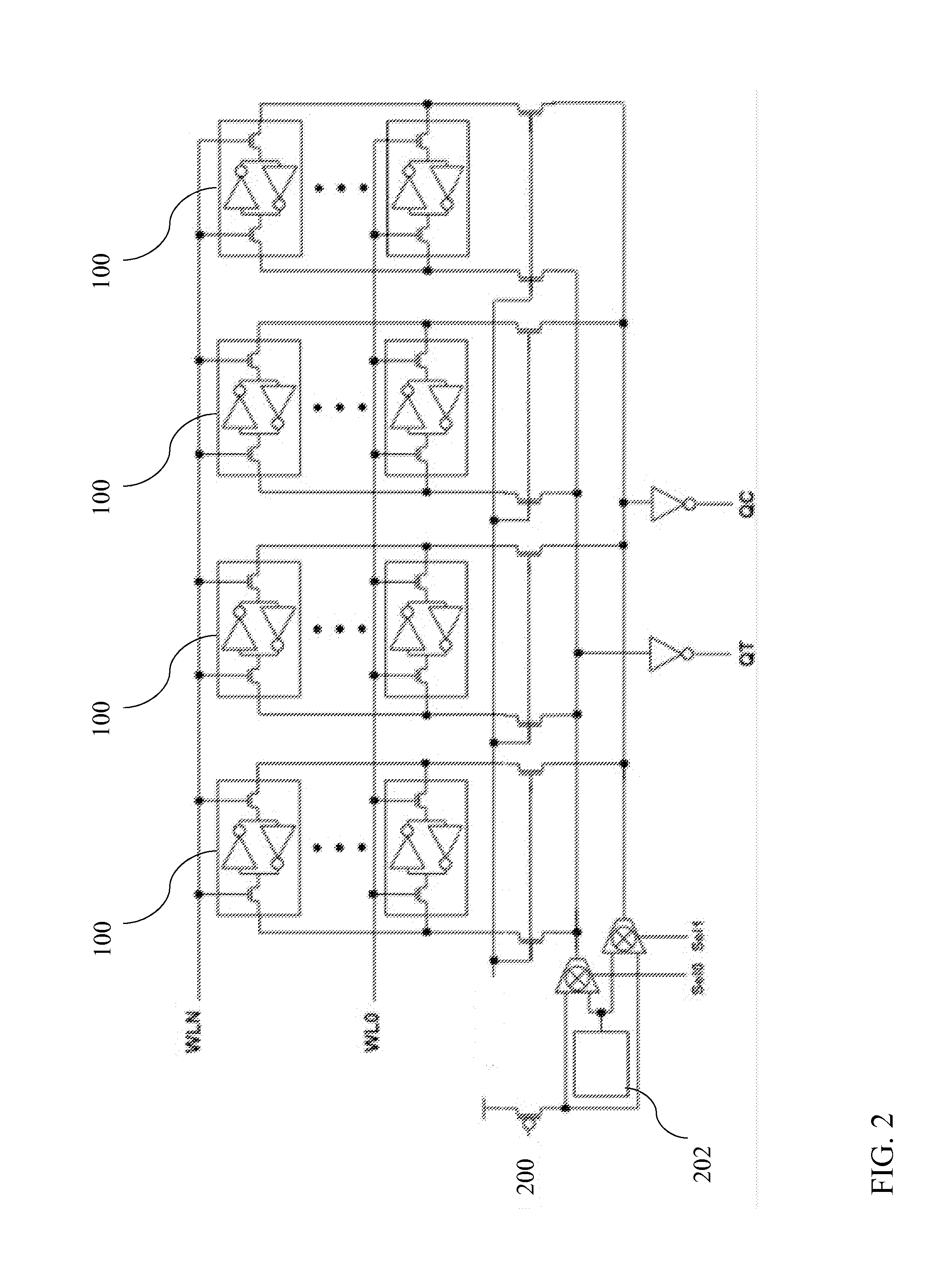

Array Power Supply-Based Screening of Static Random Access Memory Cells for Bias Temperature Instability

ActiveUS20130021864A1Reduce biasIncreased ground voltageDigital storageStatic random-access memoryNon symmetric

A method of screening complementary metal-oxide-semiconductor CMOS integrated circuits, such as integrated circuits including CMOS static random access memory (SRAM) cells, for transistors susceptible to transistor characteristic shifts over operating time. For the example of SRAM cells formed of cross-coupled CMOS inverters, separate ground voltage levels can be applied to the source nodes of the driver transistors, or separate power supply voltage levels can be applied to the source nodes of the load transistors (or both). Asymmetric bias voltages applied to the transistors in this manner will reduce the transistor drive current, and can thus mimic the effects of bias temperature instability (BTI). Cells that are vulnerable to threshold voltage shift over time can thus be identified.

Owner:TEXAS INSTR INC

Circuits and design structures for monitoring NBTI (negative bias temperature instability) effect and/or PBTI (positive bias temperature instability) effect

A ring oscillator has an odd number of NOR-gates greater than or equal to three, each with first and second input terminals, a voltage supply terminal, and an output terminal. The first input terminals of all the NOR-gates are interconnected, and each of the NOR-gates has its output terminal connected to the second input terminal of an immediately adjacent one of the NOR-gates. During a stress mode, a voltage supply and control block applies a stress enable signal to the interconnected first input terminals, and an increased supply voltage to the voltage supply terminals. During a measurement mode, this block grounds the interconnected first input terminals, and applies a normal supply voltage to the voltage supply terminals. Also included are an analogous NAND-gate based circuit, a circuit combining the NAND- and NOR-aspects, a circuit with a ring oscillator where the inverters may be coupled directly or through inverting paths, and circuits for measuring the bias temperature instability effect in pass gates.

Owner:GLOBALFOUNDRIES US INC

Forming method of metal gate, forming method of MOS transistor and forming method of CMOS structure

ActiveCN103681276AStrong oxidation abilityReduced negative bias temperature instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBond energyOxygen vacancy

Owner:SEMICON MFG INT (SHANGHAI) CORP

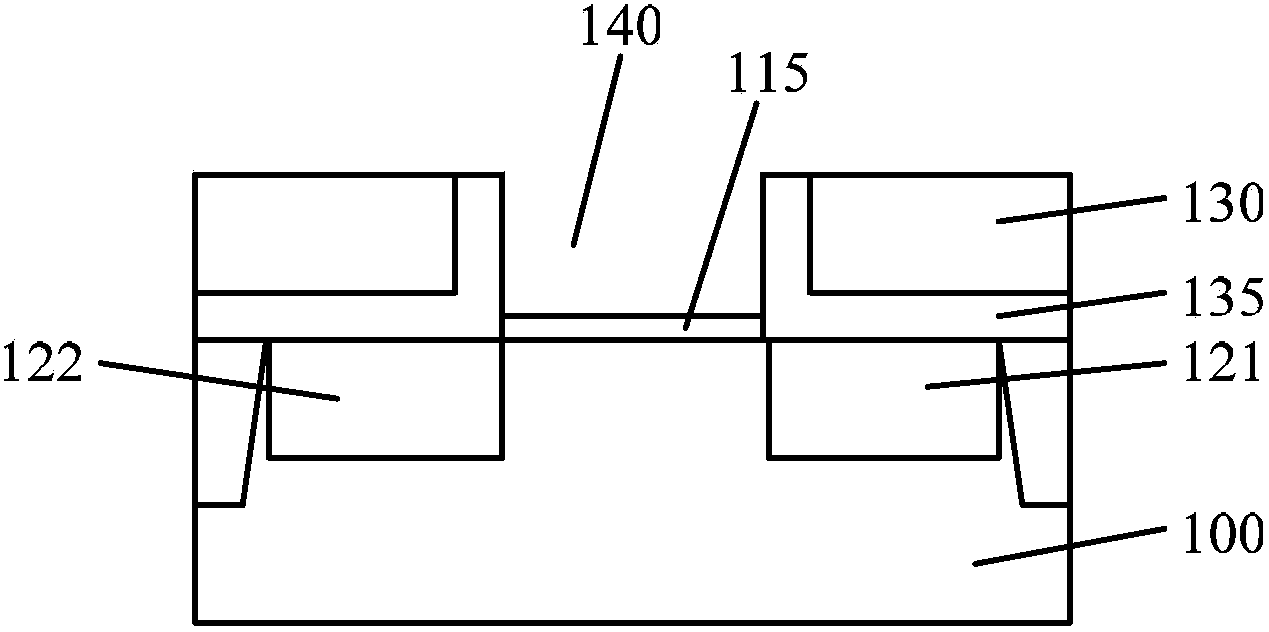

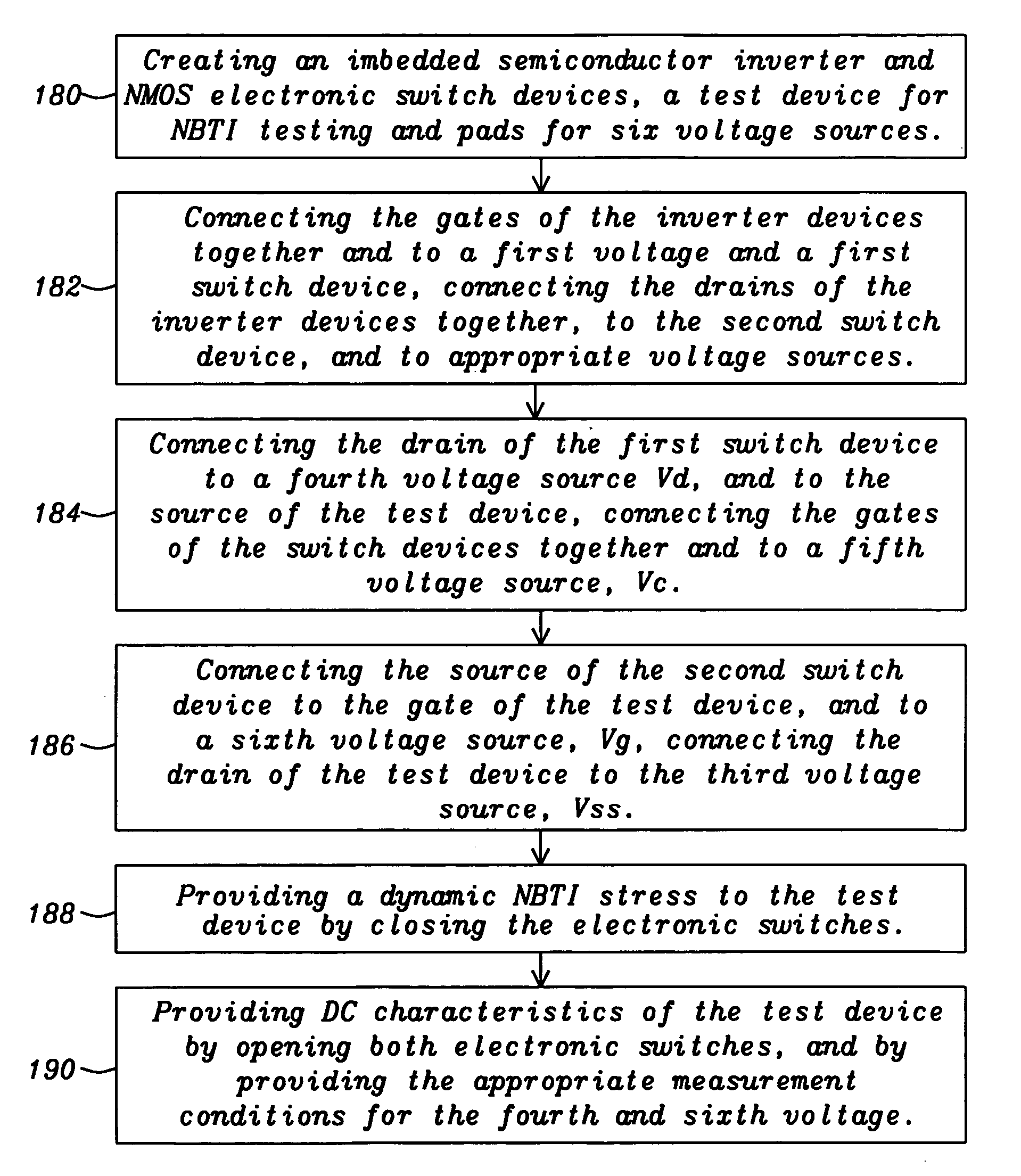

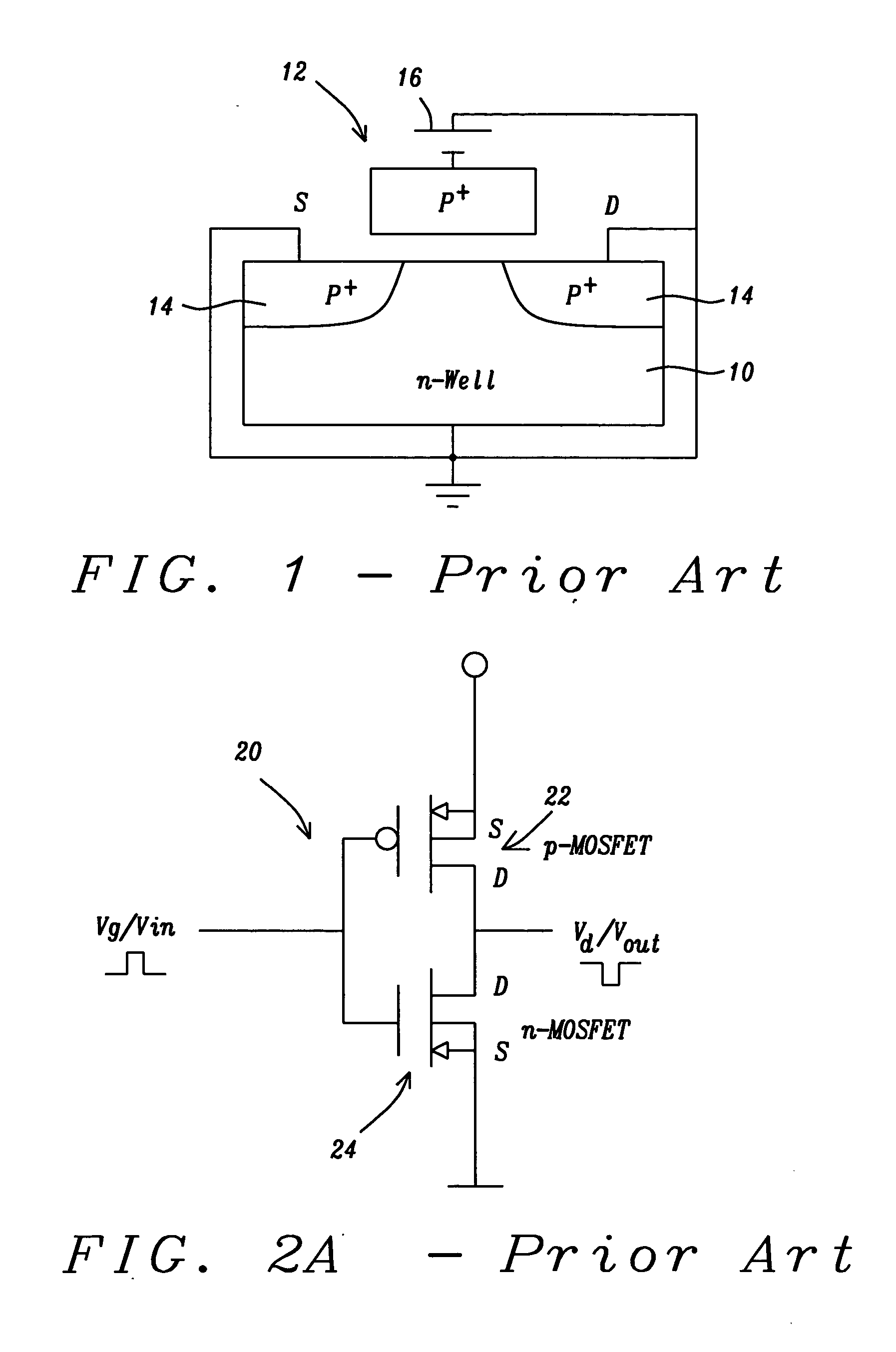

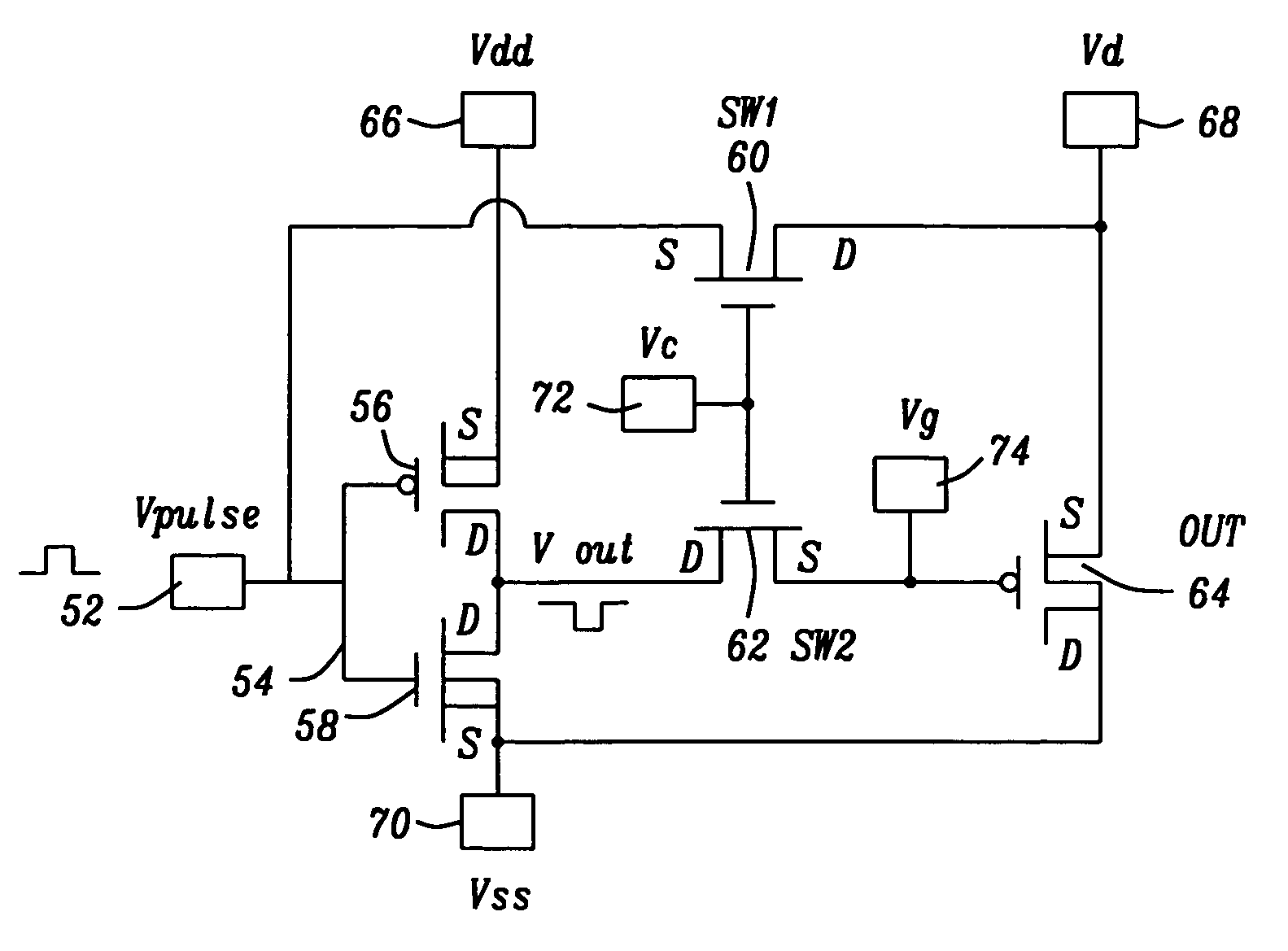

Novel test structure for automatic dynamic negative-bias temperature instability testing

InactiveUS20050278677A1Minimize parasitic capacitanceMinimizes parasitic capacitanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectronic switchEngineering

The invention describes a novel test structure and process to create the structure for performing automatic dynamic stress testing of PMOS devices for Negative Bias Temperature Instability (NBTI). The invention consists of an integrated inverter, two integrated electronic switches for switching from stress mode to device DC characterization measurement mode, and a PMOS FET device under test (DUT). The inverter assures the proper 180 degree phase relationship between the test device source and gate voltage while the imbedded electronic switches provide isolation of the test device during DC characterization testing. Another embodiment of the invention enables the testing of multiple devices under test (DUT's).

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Multifunctional test circuit of integrated circuit stress degradation and test method thereof

The invention belongs to a integrated circuit reliability test technology field and especially relates to a multifunctional test circuit of integrated circuit stress degradation and a test method thereof. A core part of the test circuit takes an annular oscillator as a basis. Several auxiliary transistors, switch transistors and control terminals are added. By using the circuit and the method of the invention, a negative bias temperature instability, a positive bias temperature instability, hot hole injection or hot electron injection stress can be applied to pMOSFETs or nMOSFETs in a ring vibration inverter respectively; a ring oscillator is in a normal oscillation and stress oscillation state; the pMOSFETs or nMOSFETs of the inverter in the ring oscillator is in a measuring state of a charge pump. The degradation of the MOSFETs in the ring vibration inverter can be shown through changes of a ring oscillator oscillation frequency after the stress and can be shown through the changes of a CP current (Icpp or Icpn) of the pMOSFETs or nMOSFETs in the ring oscillator.

Owner:FUDAN UNIV

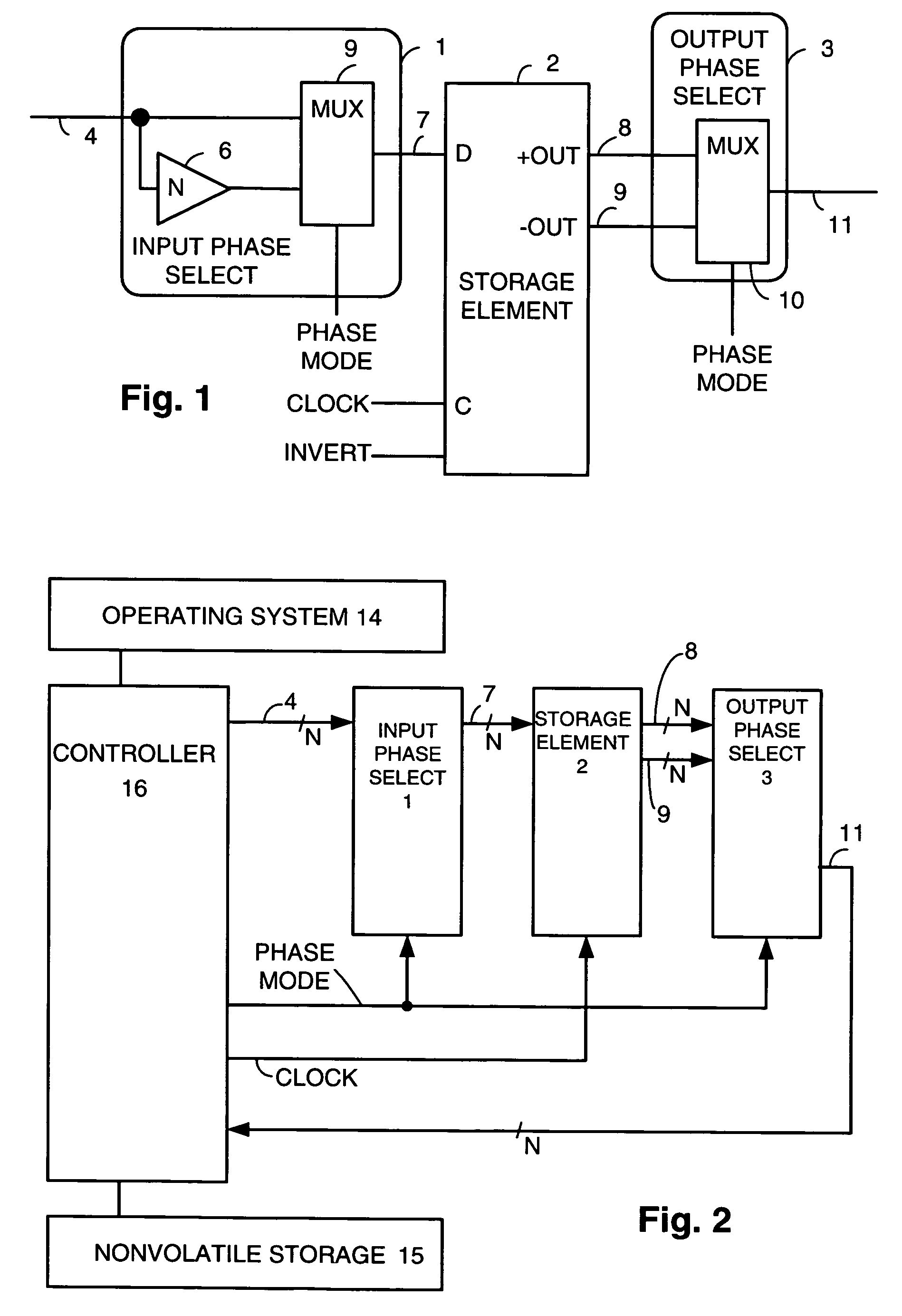

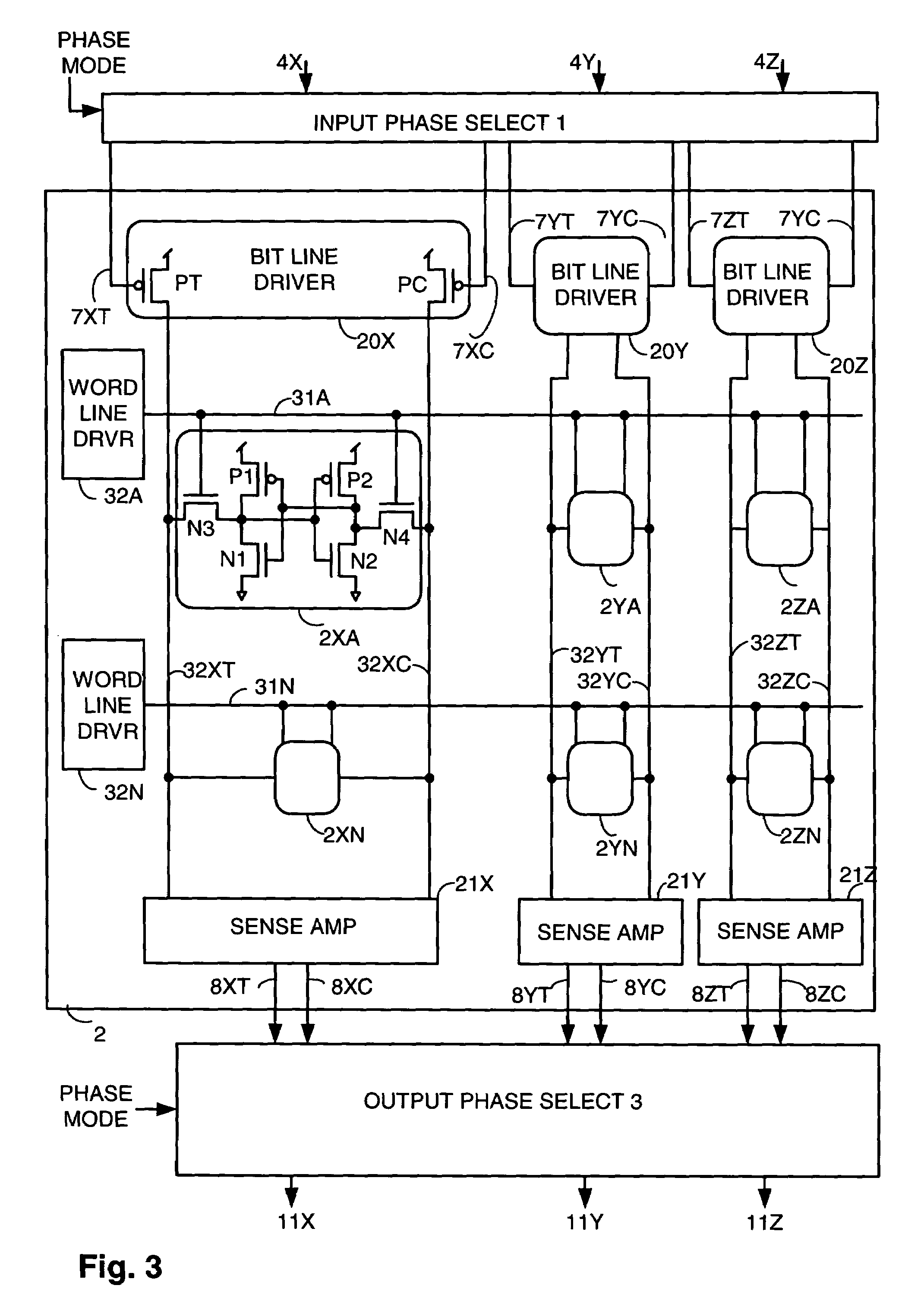

Method and apparatus to reduce bias temperature instability (BTI) effects

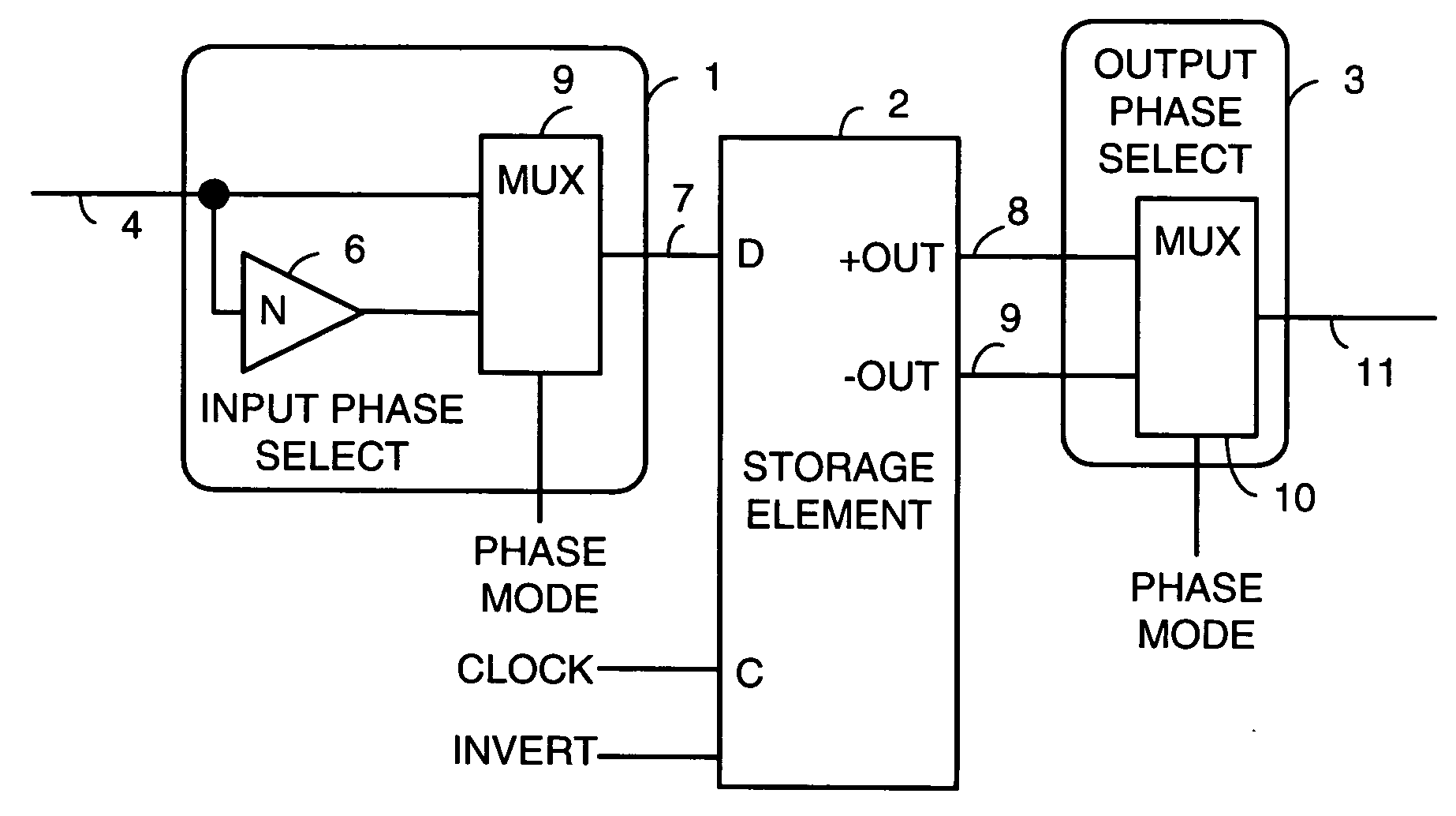

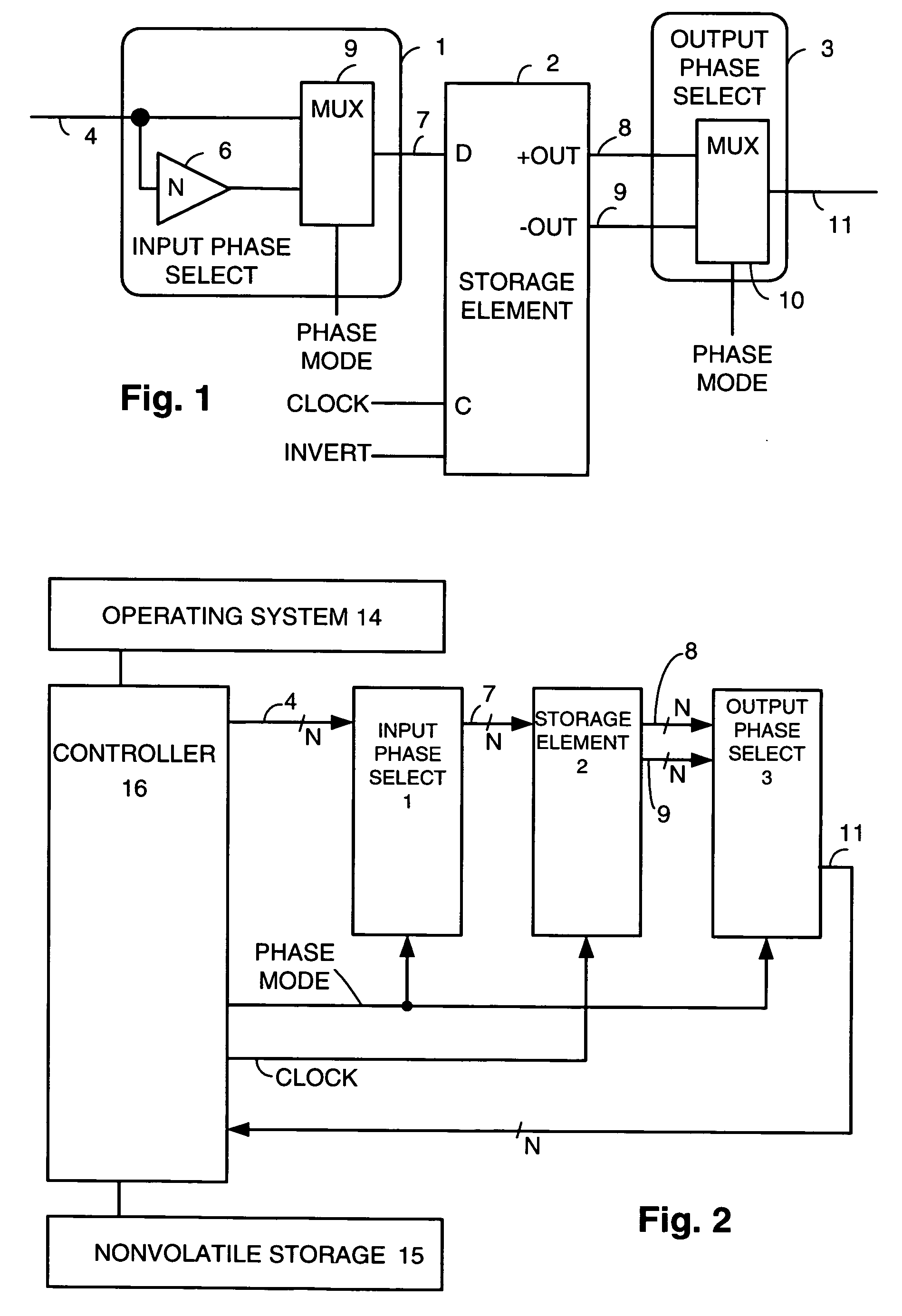

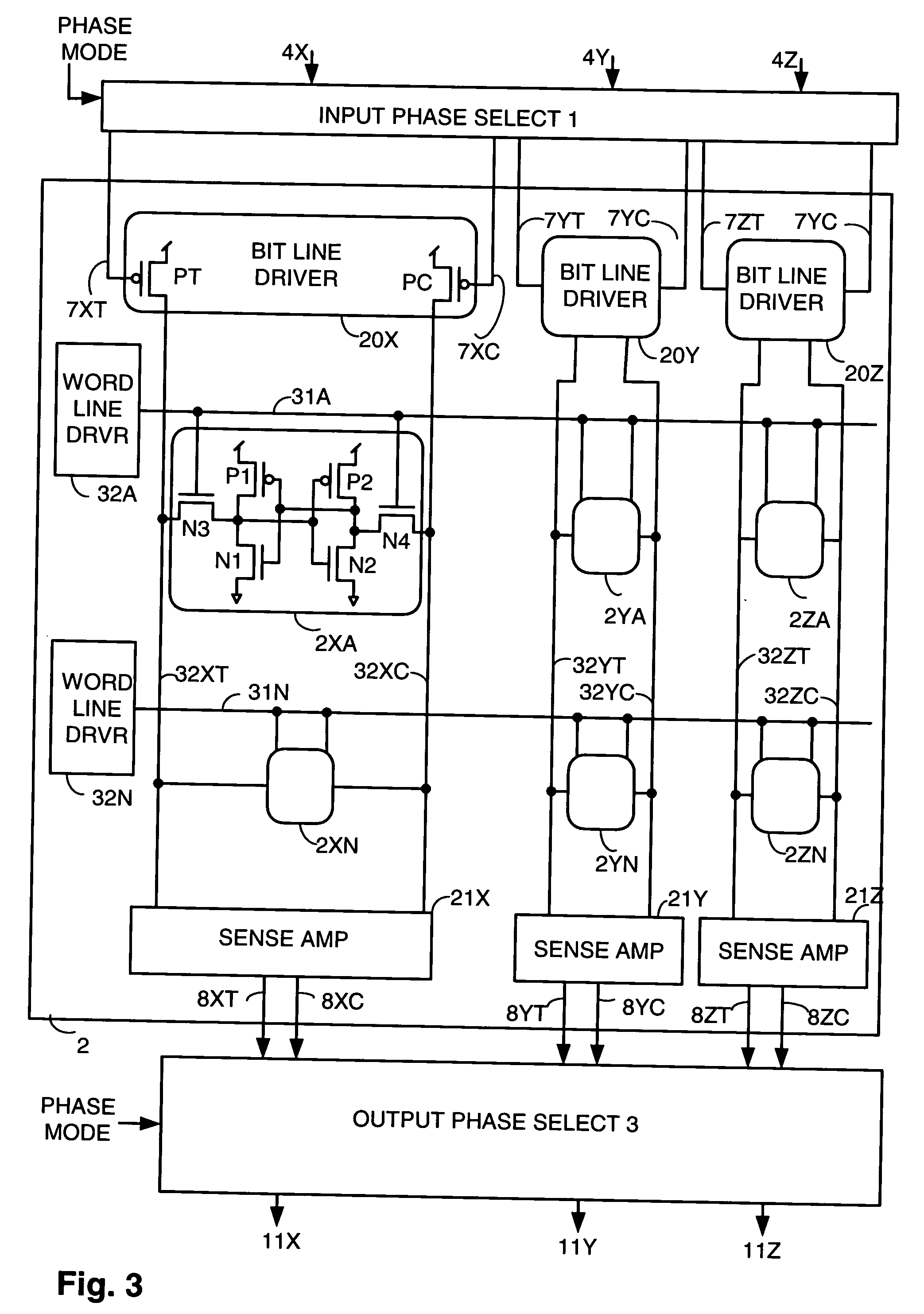

Methods and apparatus are disclosed that allow an electronic system implemented with field effect transistors (FETs) to reduce threshold voltage shifts caused by bias temperature instability (BTI). BTI caused VT shifts accumulate when an FET is in a particular voltage stress condition. Many storage elements in an electronic system store the same data for virtually the life of the system, resulting in significant BTI caused VT shifts in FETs in the storage elements. An embodiment of the invention ensures that a particular storage element is in a first state for a first portion of time the electronic system operates, during which data is stored in a storage element in a first phase, and that the particular storage element is in a second state for a second portion of time the electronic system operates, during which data is stored in the storage element in a second phase.

Owner:INT BUSINESS MASCH CORP

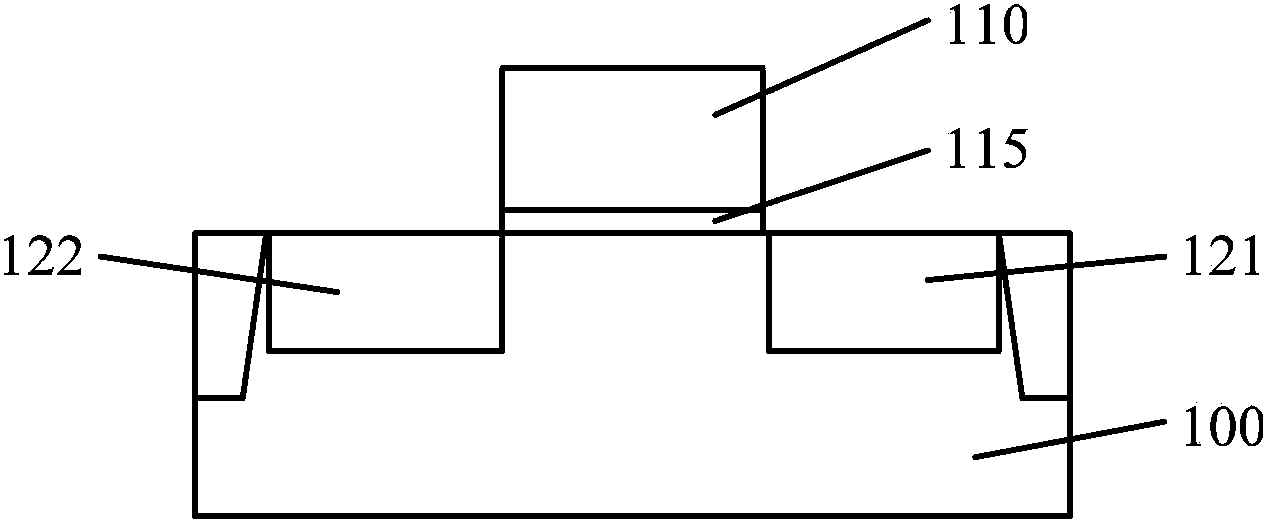

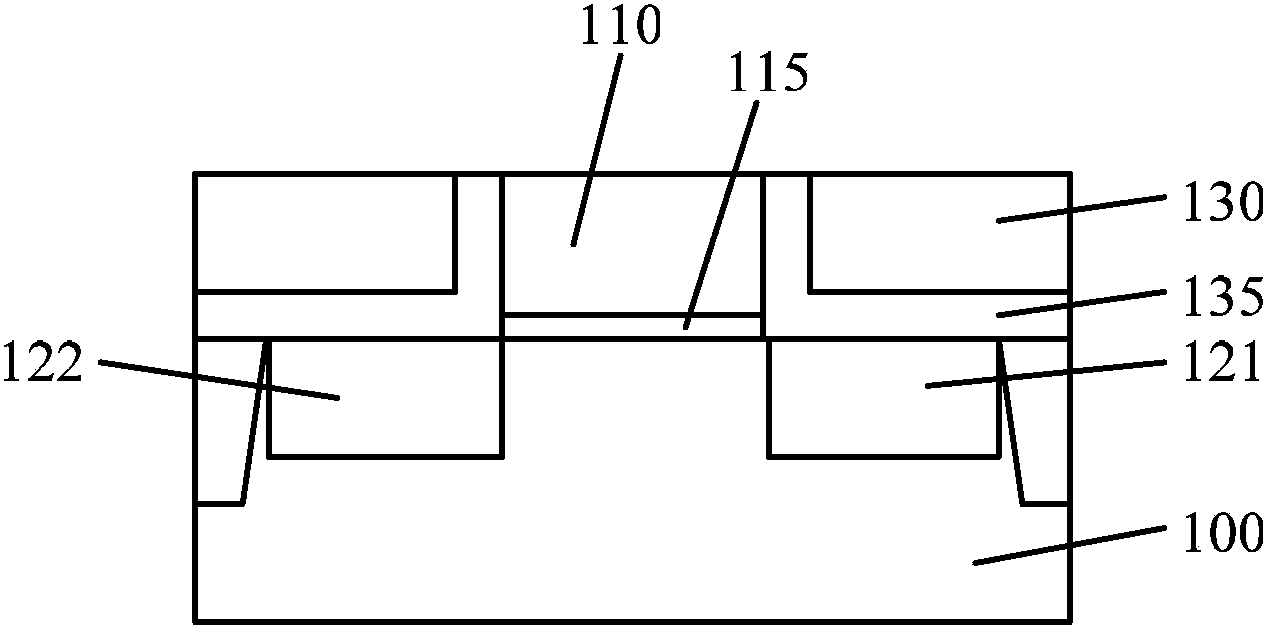

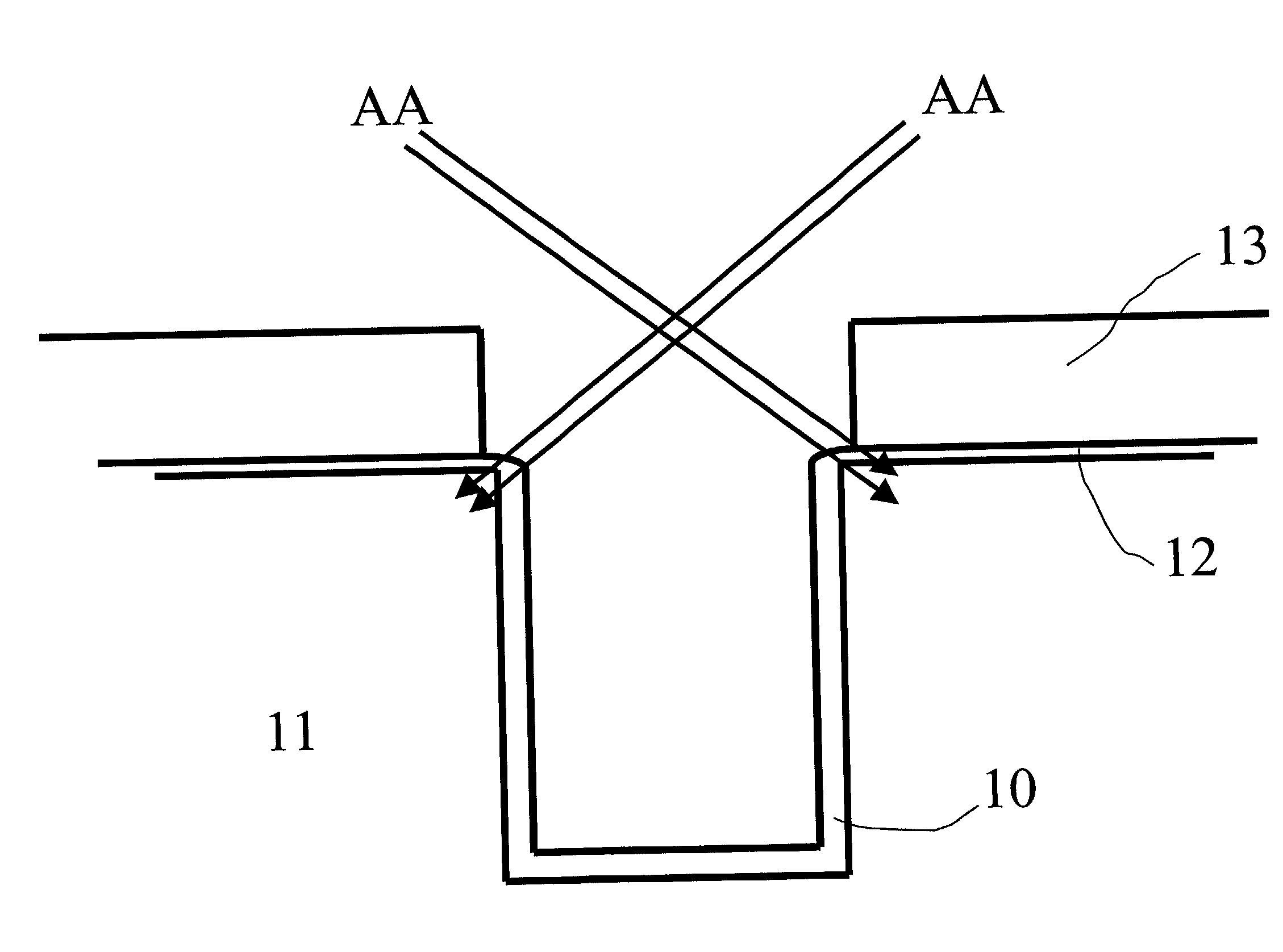

Reduction of negative bias temperature instability in narrow width PMOS using F2 implantation

InactiveUS6780730B2Suppress instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityEngineering

In a process of fabricating a narrow channel width PMOSFET device, the improvement of affecting reduction of negative bias temperature instability by use of F2 side wall implantation, comprising:a) forming a shallow trench isolation (STI) region in a substrate;b) forming a gate on a gate oxide in the substrate;c) forming a liner layer in said shallow trench isolation region and subjecting the liner layer to oxidation to form a STI liner oxidation layer;d) implanting F2 into side walls of the STI liner oxidation layer at a large tilted angle in sufficient amounts to affect reduction of negative bias temperature instability after a high density plasma fill of the STI F2 implanted liner oxidation layer; ande) filling the STI F2 implanted structure from step d) with a high density plasma (HDP) fill to affect reduction of negative bias temperature instability.

Owner:INFINEON TECH AG

Method and apparatus to reduce bias temperature instability (BTI) effects

Methods and apparatus are disclosed that allow an electronic system implemented with field effect transistors (FETs) to reduce threshold voltage shifts caused by bias temperature instability (BTI). BTI caused VT shifts accumulate when an FET is in a particular voltage stress condition. Many storage elements in an electronic system store the same data for virtually the life of the system, resulting in significant BTI caused VT shifts in FETs in the storage elements. An embodiment of the invention ensures that a particular storage element is in a first state for a first portion of time the electronic system operates, during which data is stored in a storage element in a first phase, and that the particular storage element is in a second state for a second portion of time the electronic system operates, during which data is stored in the storage element in a second phase.

Owner:IBM CORP

Work balancing scheduler for processor cores and methods thereof

A data processing device assigns tasks to processor cores in a more distributed fashion. In one embodiment, the data processing device can schedule tasks for execution amongst the processor cores in a pseudo-random fashion. In another embodiment, the processor core can schedule tasks for execution amongst the processor cores based on the relative amount of historical utilization of each processor core. In either case, the effects of bias temperature instability (BTI) resulting from task execution are distributed among the processor cores in a more equal fashion than if tasks are scheduled according to a fixed order. Accordingly, the useful lifetime of the processor unit can be extended.

Owner:MEDIATEK INC

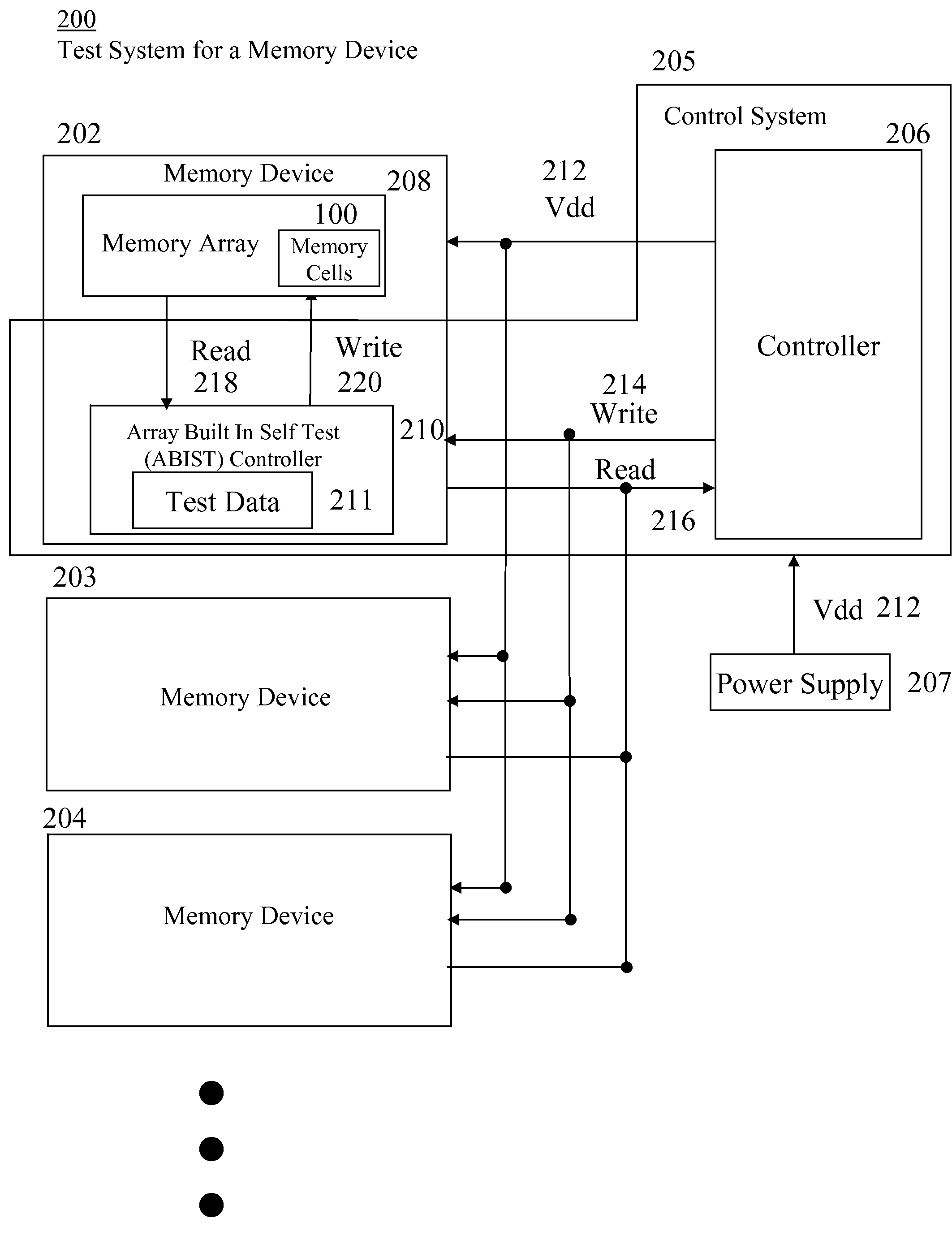

Testing a memory device having field effect transistors subject to threshold voltage shifts caused by bias temperature instability

InactiveUS20090285044A1Reduce power supply voltageHigh power supply voltageLighting heating/cooling arrangementsDigital storageEngineeringField-effect transistor

A supply voltage is set for a memory device at a first supply voltage level. Test data is written to the memory device at the first supply voltage level in response to setting the supply voltage. The supply voltage is decreased for the memory device to a second supply voltage level below the first supply voltage level in response to writing the test data. The test data is read from the memory device at the second supply voltage level in response to decreasing the supply voltage. The supply voltage is increased for the memory device to a third supply voltage level above the second supply voltage level in response to reading the test data. The test data is read from the memory device at the third supply voltage level in response to increasing the supply voltage. The test data written to the memory device at the first supply voltage level is compared to the test data read from the memory device at the third supply voltage level in response to reading the test data from the memory device at the third supply voltage level.

Owner:QUALCOMM INC

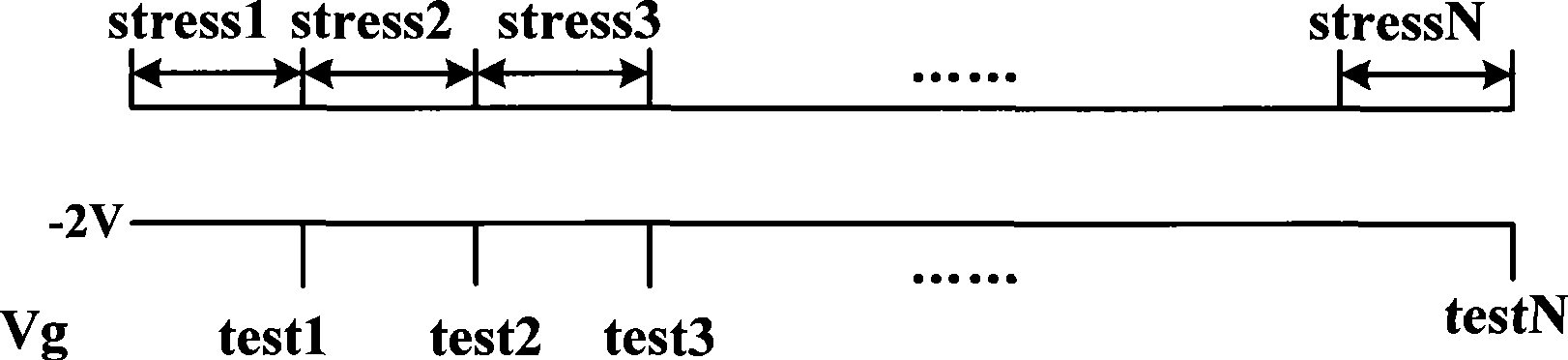

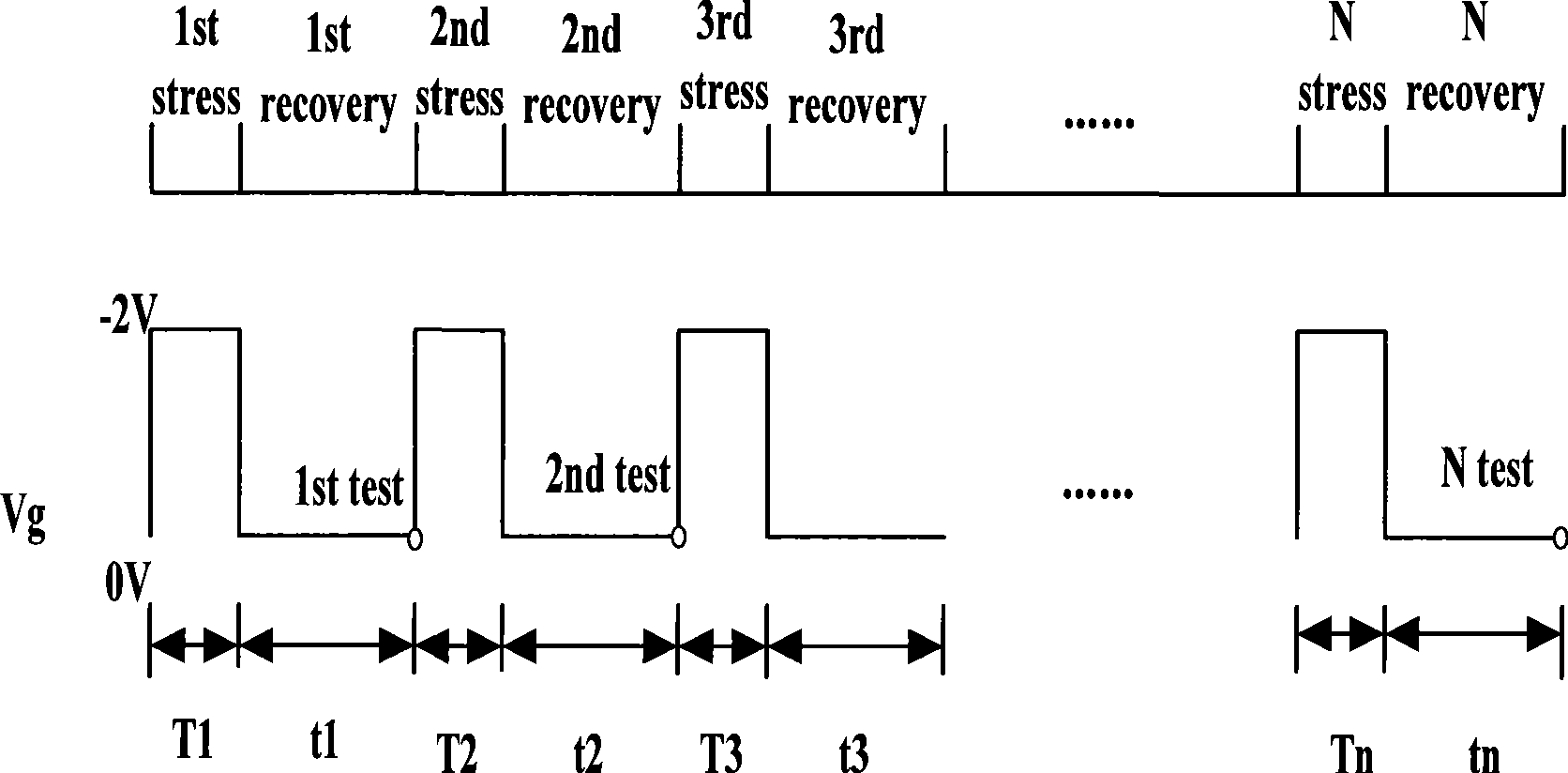

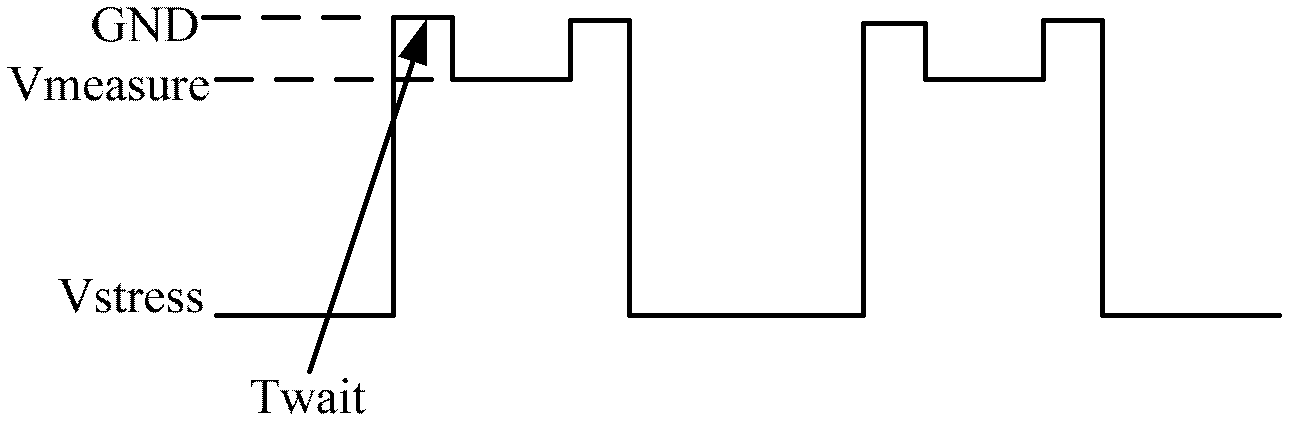

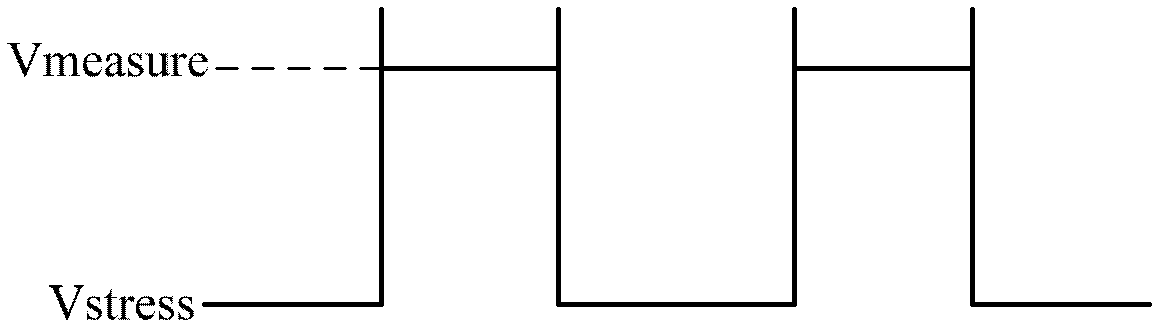

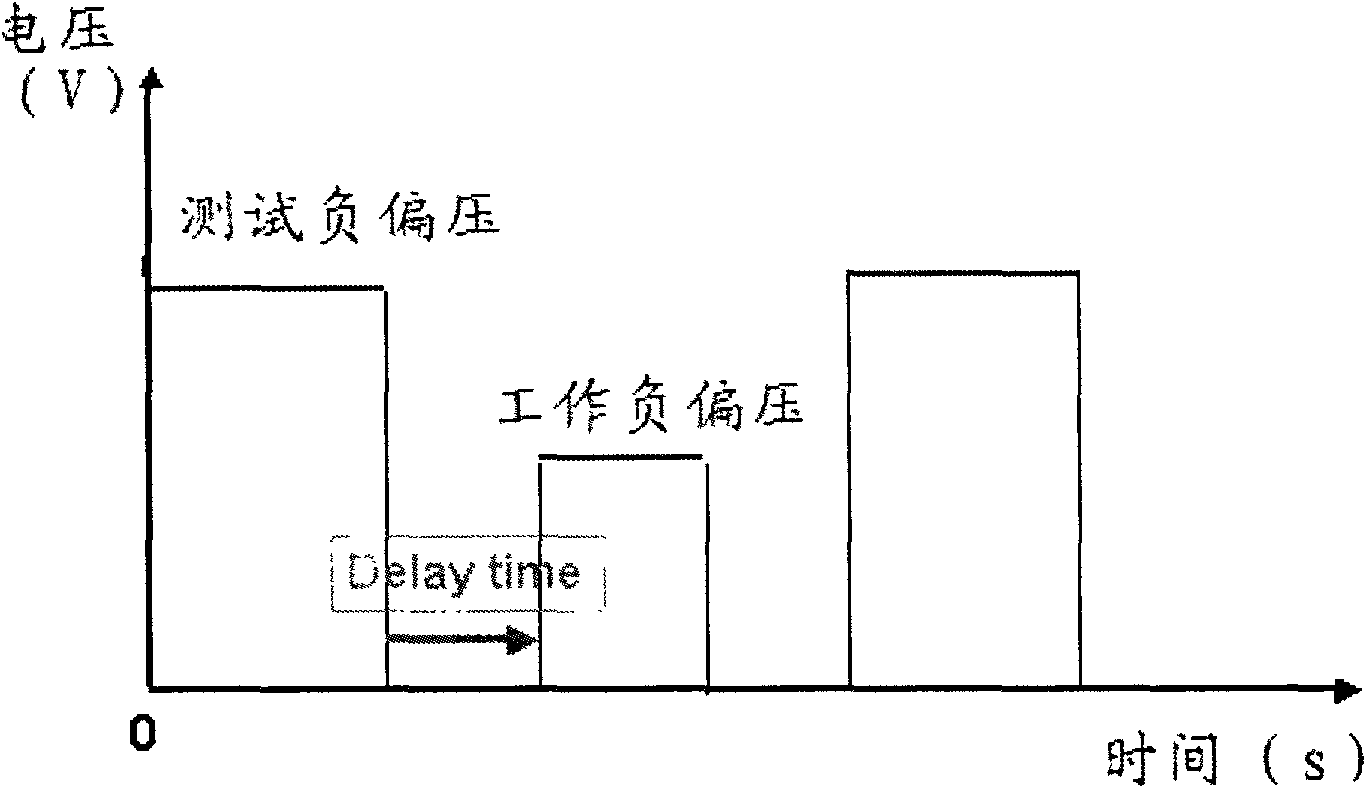

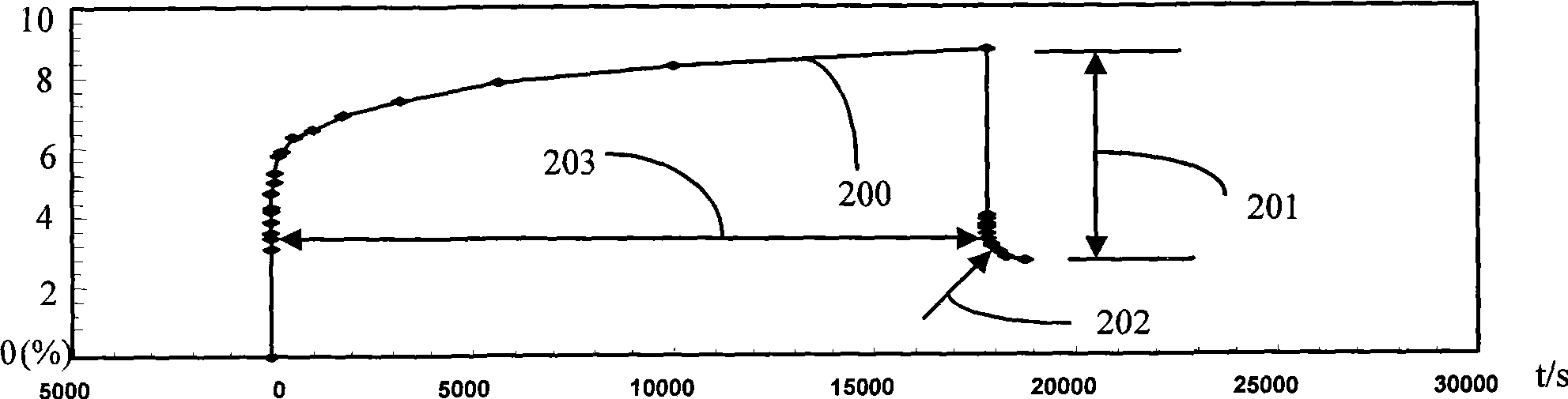

Method for testing temperature instability under minus bias pressure

InactiveCN101441245AThe test result is accurateIncrease productivitySemiconductor/solid-state device testing/measurementIndividual semiconductor device testingEngineeringDependability

A method for testing temperature instability under negative bias relates to the field of semiconductor technology processing procedure. The method comprises the following steps: 1. the method for testing temperature instability under negative bias is characterized in that step 1, stress is applied to gate voltage to lift the gate voltage to gate voltage and then the gate voltage is reduced to an absolute value smaller or equal to working voltage in t; step 2, when the recovery stage finishes and before the next stress stage begins, an MOS transistor is measured; step 3, step 1 and step 2 are circularly executed until the accumulated stress time reaches reliability test standard. The method has the advantages of accurately testing temperature instability effect under negative bias, improving the accuracy of reliability assessment of semiconductor products, being beneficial to improving the technology of temperature instability under negative bias, shortening the cycle of product development and saving production cost.

Owner:SEMICON MFG INT (SHANGHAI) CORP

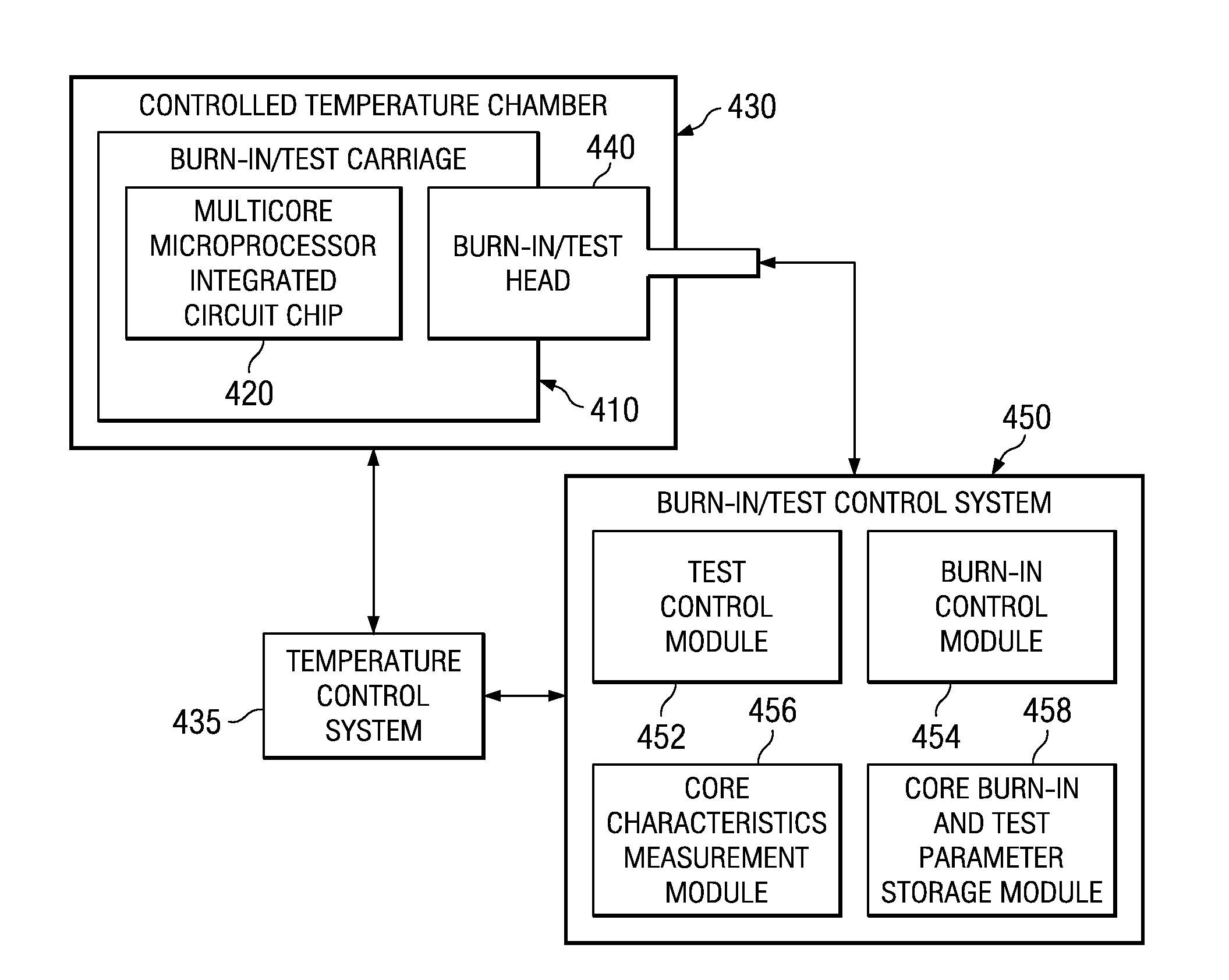

Apparatus and method for customized burn-in of cores on a multicore microprocessor integrated circuit chip

InactiveUS7268570B1Reduce chip costUniform powerFault location by increasing destruction at faultPeak valueEngineering

An apparatus and method for providing a multi-core integrated circuit chip that reduces the cost of the package and board while optimizing performance of the cores for use with a single voltage plane. The apparatus and method of the illustrative embodiments make use of a dynamic burn-in technique that optimizes all of the cores on the chip to run at peak performance at a single voltage. Each core is burned-in with a customized burn-in voltage that provides uniform power and performance across the whole chip. This results in a higher burn-in yield and lower overall power in the integrated circuit chip. The optimization of the cores to run at peak performance at a single voltage is achieved through use of the negative bias temperature instability affects on the cores imparted by the burn-in voltages applied.

Owner:GOOGLE LLC

Reduction of negative bias temperature instability in narrow width PMOS using F2 implanation

InactiveUS20030143812A1Suppress instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityEngineering

In a process of fabricating a narrow channel width PMOSFET device, the improvement of affecting reduction of negative bias temperature instability by use of F2 side wall implantation, comprising: a) forming a shallow trench isolation (STI) region in a substrate; b) forming a gate on a gate oxide in the substrate; c) forming a liner layer in said shallow trench isolation region and subjecting the liner layer to oxidation to form a STI liner oxidation layer; d) implanting F2 into side walls of said STI liner oxidation layer at a large tilted angle in sufficient amounts to affect reduction of negative bias temperature instability after a high density plasma fill of the STI F2 implanted liner oxidation layer; and e) filling the STI F2 implanted structure from step c) with a high density plasma (HDP) fill to affect reduction of negative bias temperature instability.

Owner:INFINEON TECH AG

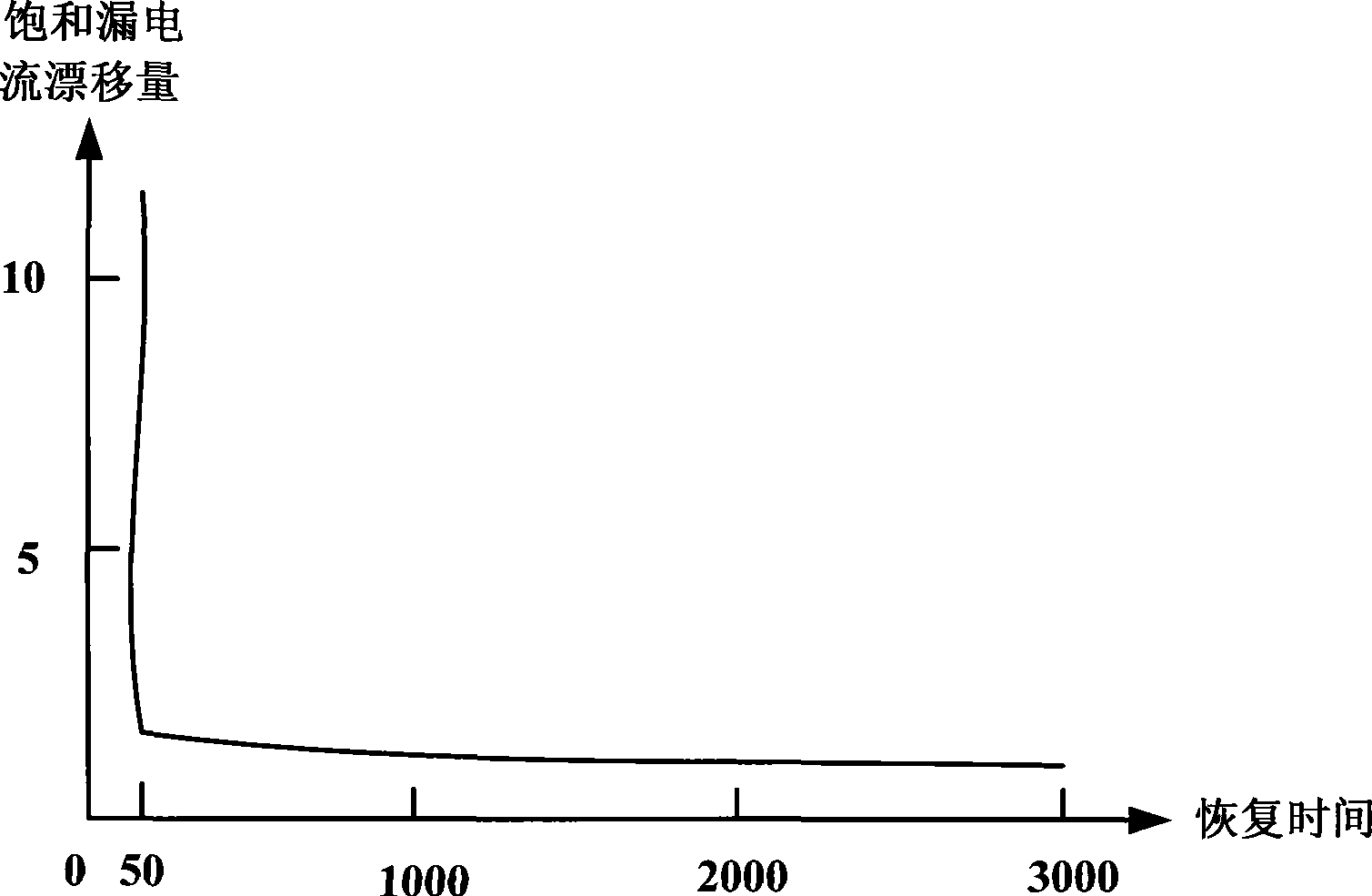

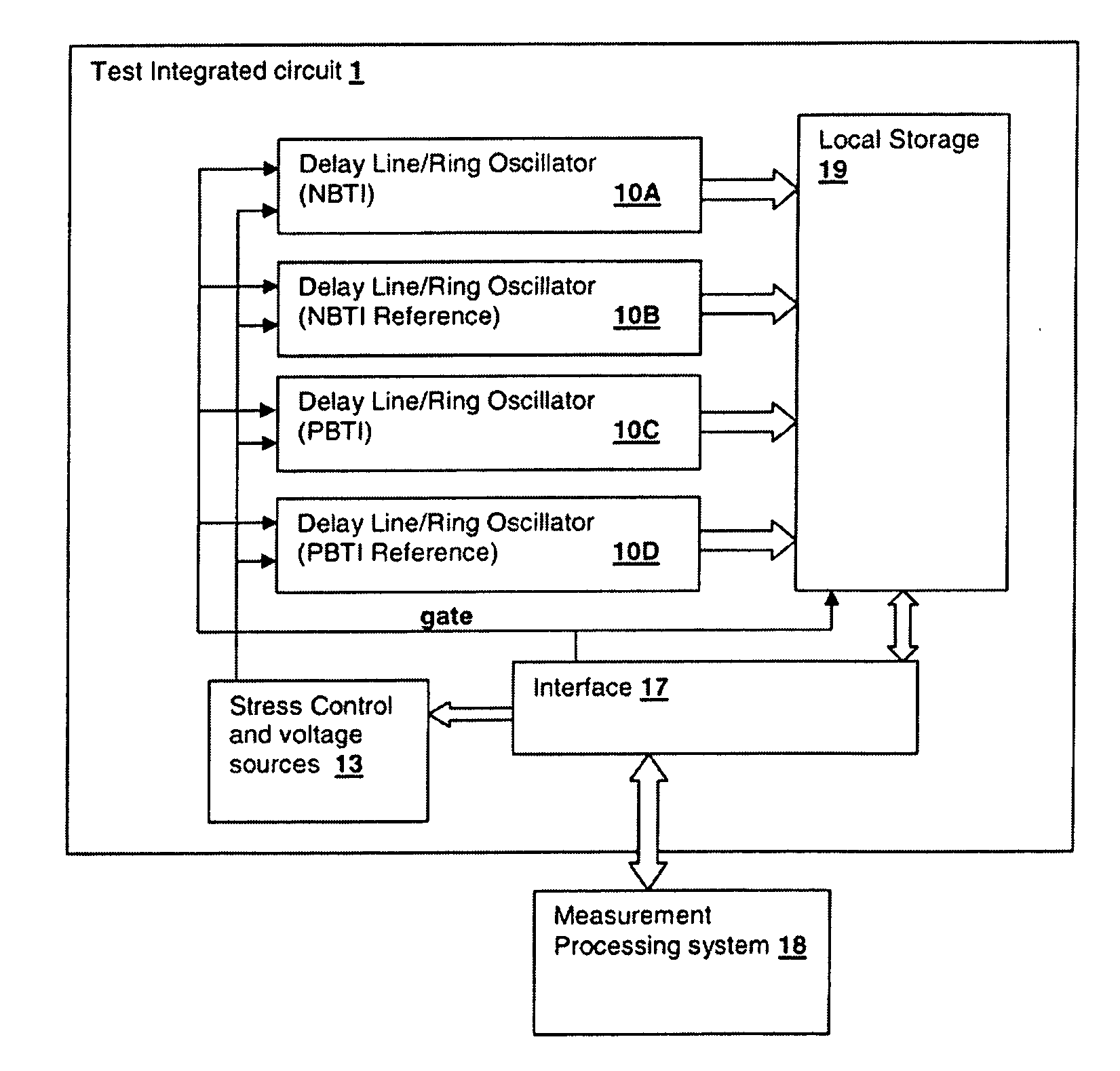

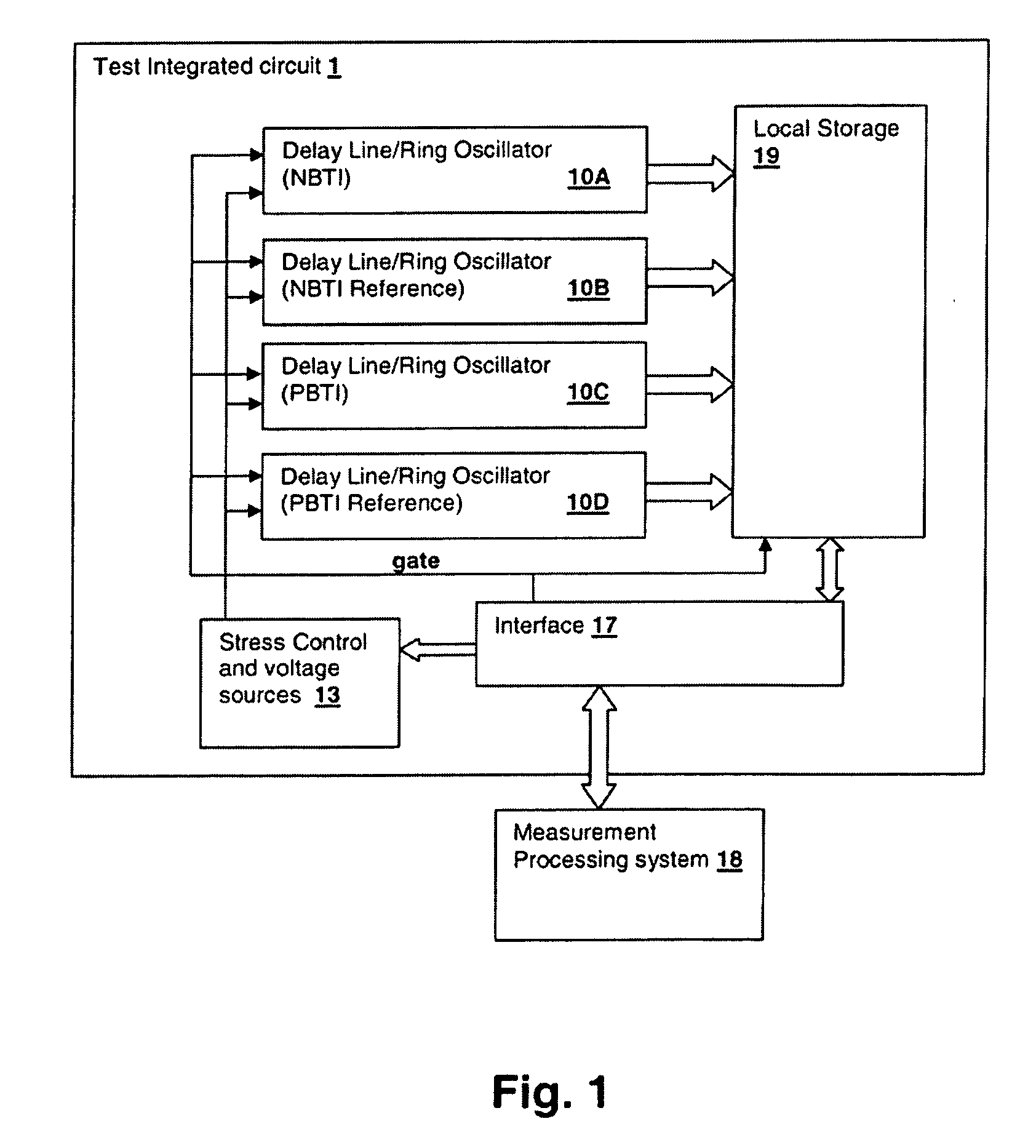

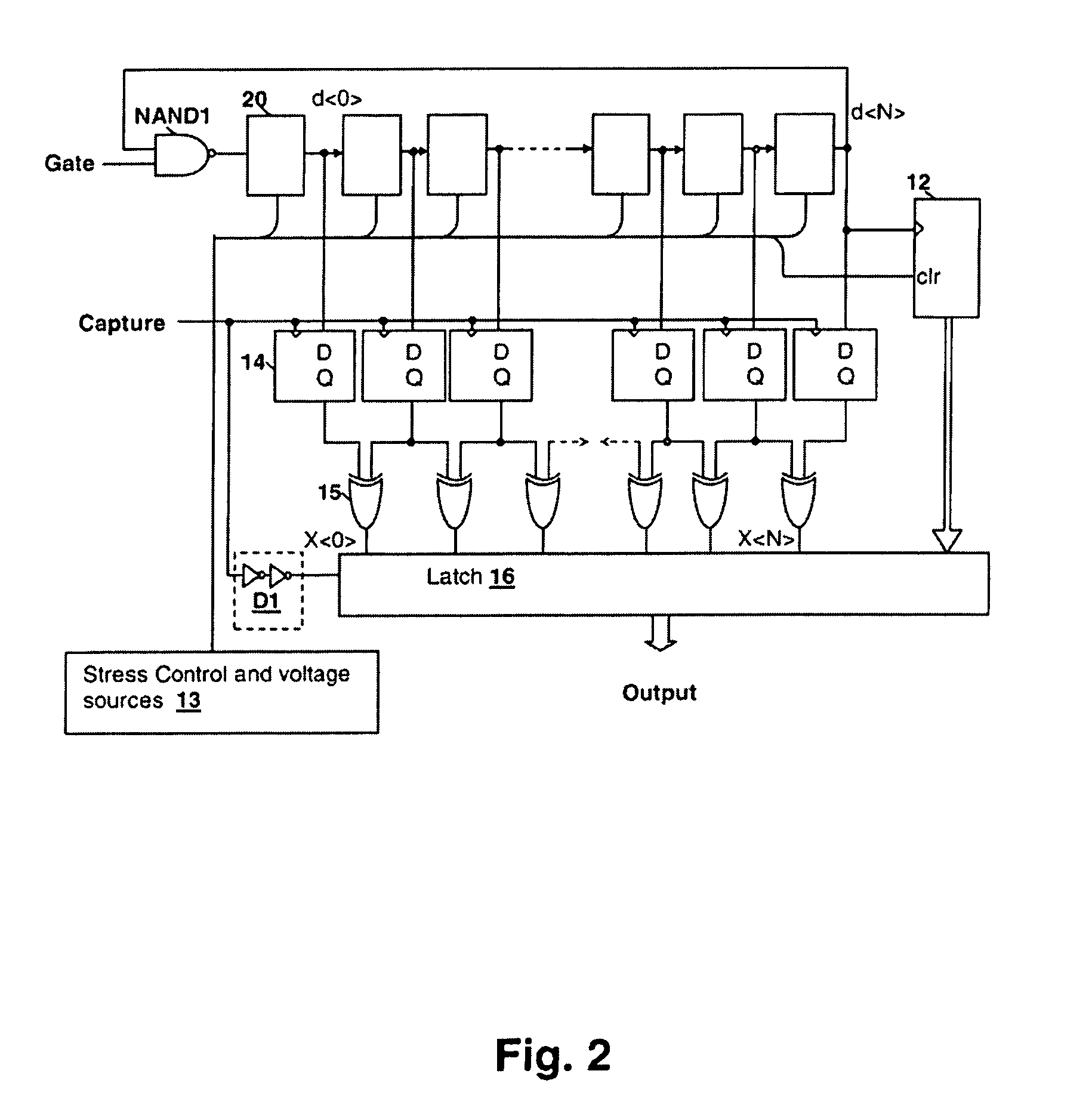

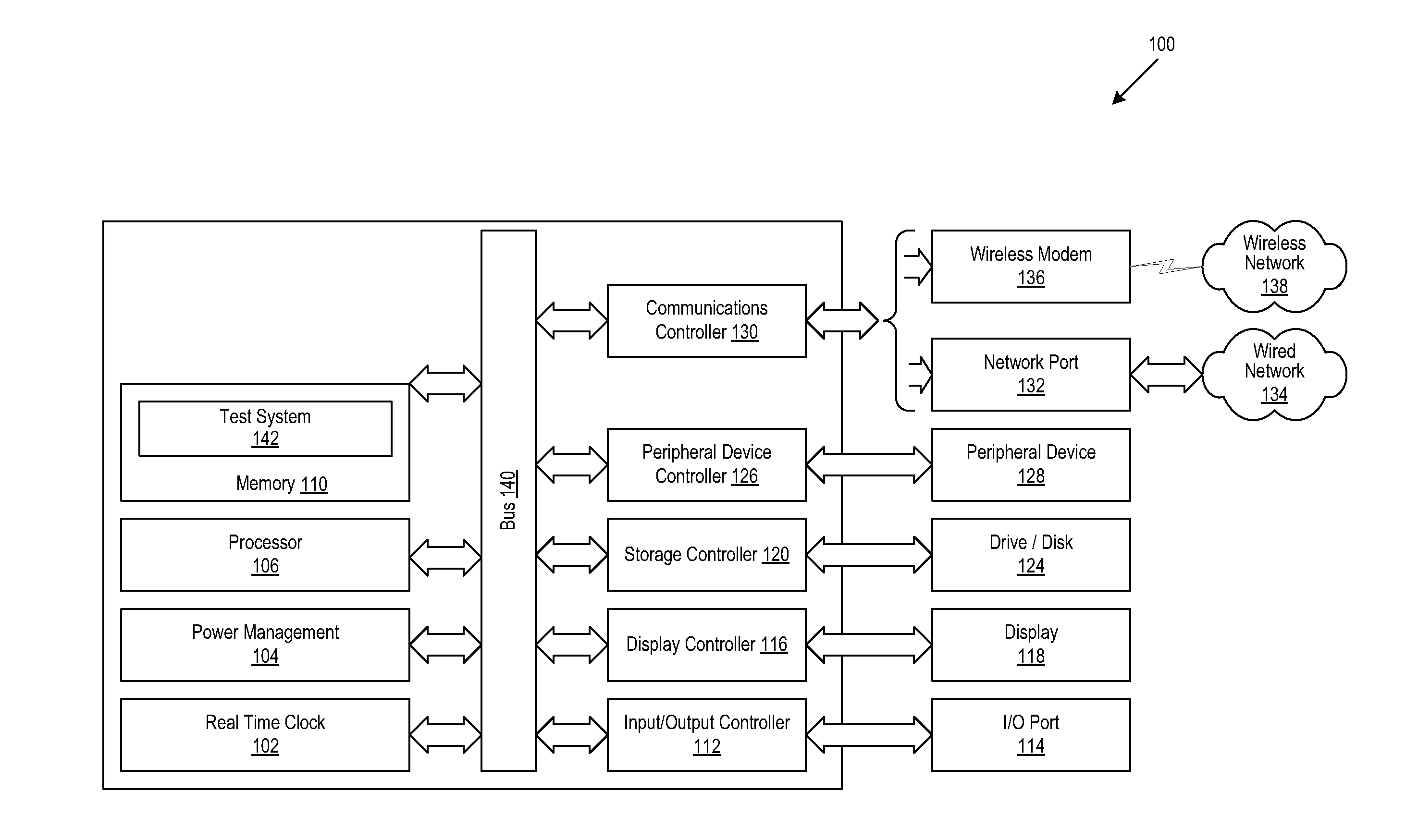

Delay-Based Bias Temperature Instability Recovery Measurements for Characterizing Stress Degradation and Recovery

InactiveUS20090319202A1Improve dynamic rangeHigh resolutionForce measurementWork measurementNanosecondFrequency measurements

A method, test circuit and test system provide measurements to accurately characterize threshold voltage changes due to negative bias temperature instability (NBTI) and positive bias temperature instability (PBTI). Both the bias temperature instability recovery profile and / or the bias temperature shifts due to rapid repetitions of stress application can be studied. In order to provide accurate measurements when stresses are applied at intervals on the order of tens of nanoseconds while avoiding unwanted recovery, and / or to achieve recovery profile sampling resolutions in the nanosecond range, multiple delay or ring oscillator frequency measurements are made using a delay line that is formed from delay elements that have delay variation substantially caused only by NBTI or PBTI effects. Devices in the delay elements are stressed, and then the delay line / ring oscillator is operated to measure a threshold voltage change for one or more measurement periods on the order of nanoseconds.

Owner:IBM CORP

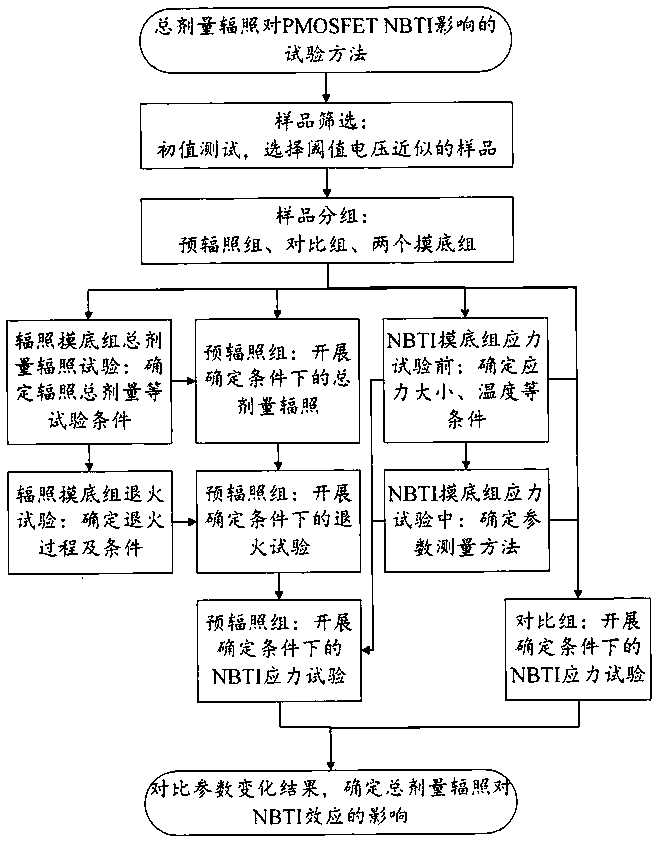

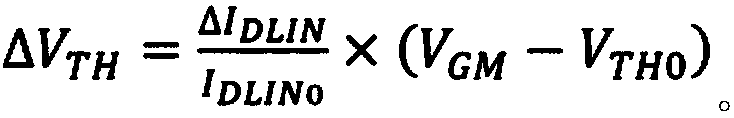

Test method for influence of total dose irradiation on PMOSFET negative bias temperature instability

ActiveCN108037438AEnsure consistencySemiconductor operation lifetime testingPre irradiationTest sample

The invention relates to a method for testing the influence of total dose irradiation on the PMOSFET negative bias temperature instability. The method includes test sample grouping and test parameterselection; the total dose irradiation and annealing tests of the test sample; and the negative bias temperature instability measurement of the test sample. In order to ensure the consistency and accuracy of the test result, the sample is divided into a pre-irradiation group, a comparison group and two pre-test groups, and on the basis of the pre-test, the total dose irradiation and annealing testsare carried out on the pre-irradiation group under the determination condition, the comparison group and the pre-irradiation group are subjected to a negative bias temperature instability test underthe same condition, and the test result is compared, the influence of the total dose irradiation on the negative bias temperature instability of the sample is obtained. The method provided by the invention can represent the influence of the total dose irradiation on the negative bias temperature instability of a P-channel metal oxide semiconductor field effect transistor.

Owner:XINJIANG TECHN INST OF PHYSICS & CHEM CHINESE ACAD OF SCI

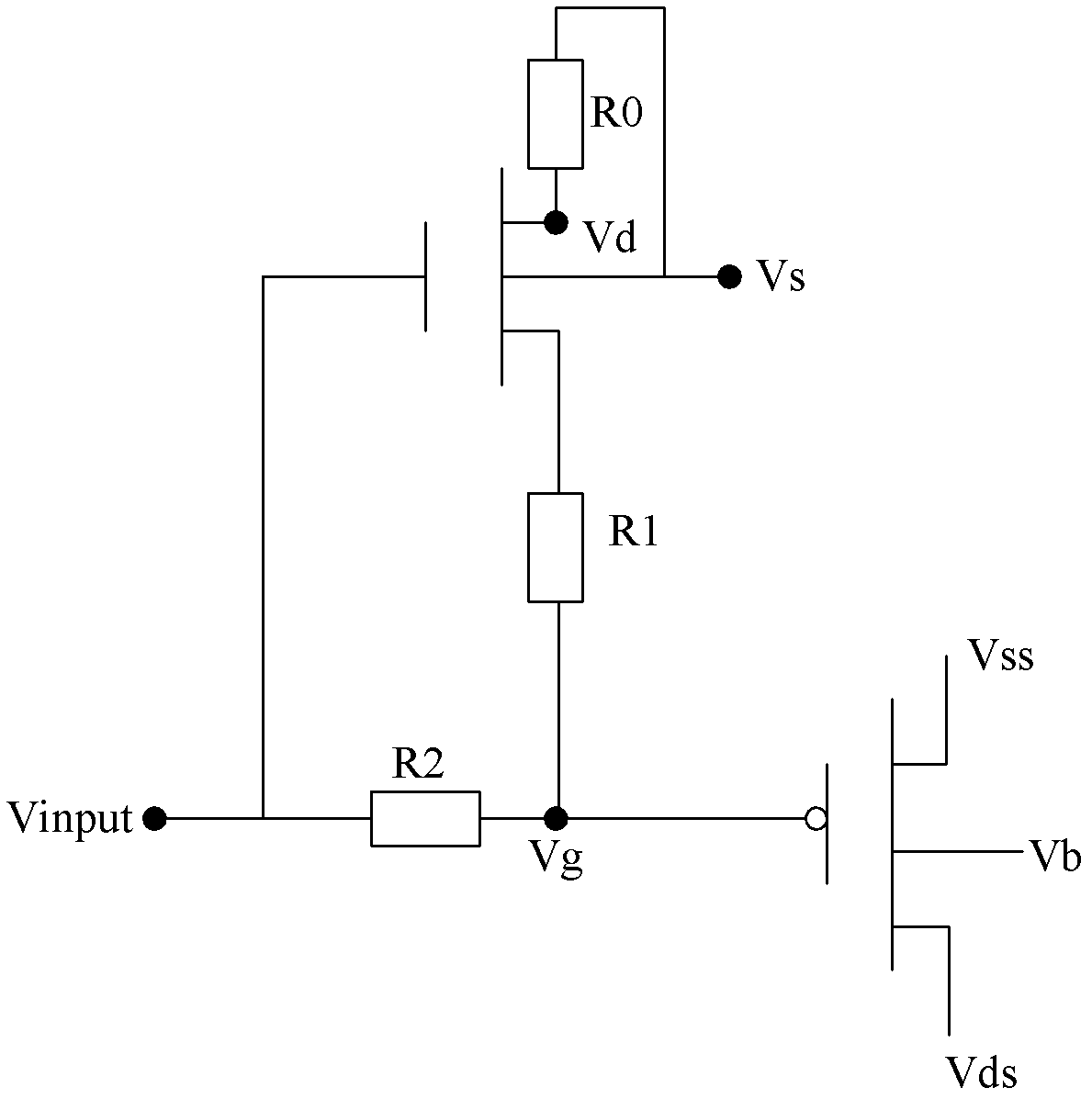

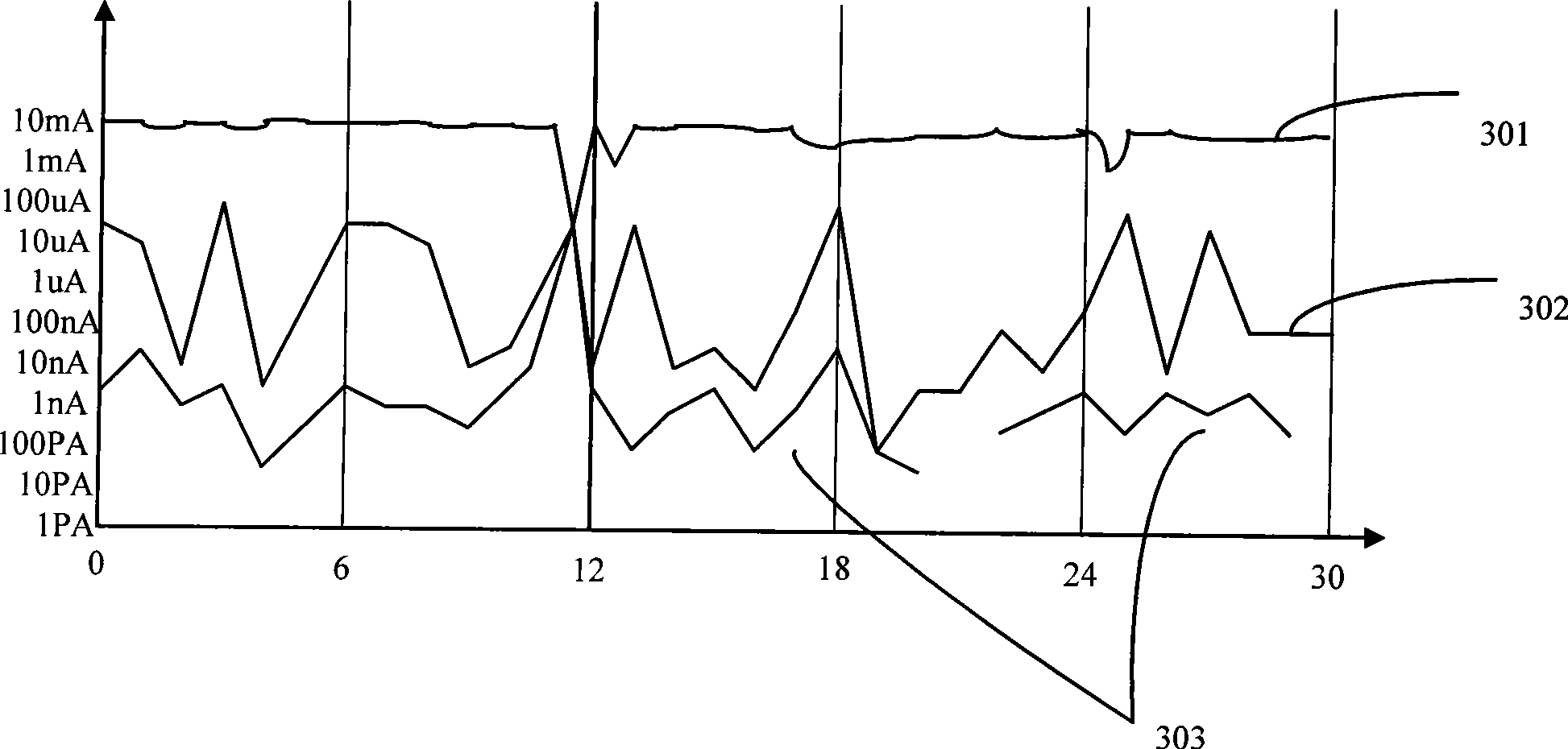

Building-out circuit and testing method for testing negative bias temperature instability

ActiveCN102866340ARestoration Effect InhibitionAccurate measurementIndividual semiconductor device testingEngineeringP channel

The invention provides a building-out circuit and a testing method for testing the negative bias temperature instability (NBTI). The building-out circuit is respectively connected with a source-measurement unit and a PMOS (P-channel Metal Oxide Semiconductor) to be measured; the building-out circuit comprises an NMOS (N-channel metal oxide semiconductor); a base electrode of the NMOS is electrically connected with a source electrode of the NMOS by a resistor R0; a drain electrode fo the NMOS is electrically connected with a grid electrode of the PMOS to be measured by a resistor R1; a grid electrode fo the NMOS is electrically connected with the grid electrode of the PMOS to be measured by a resistor R2; the potential of the base electrode of the NMOS is set into a value of less than 0V; and the voltage input end of the source-measurement unit is connected with the grid electrode of the NMOS. When an input voltage of the source-measurement unit is changed into 0V, due to the voltage division of the resistor R2, the voltage of the grid electrode of the PMOS to be measured is less than 0V, i.e. when the NBTI recovery effect occurs after the stress voltage is switched off, a partial pressure of the R2 is still applied to the grid electrode of the PMOS to be measured to inhibit the NBTI recovery effect in the PMOS, so that the measurement result is more accurate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Forming a semiconductor structure for reduced negative bias temperature instability

InactiveUS9502307B1Improve negative bias temperature instabilityTransistorSolid-state devicesGate dielectricSemiconductor structure

An approach to forming a semiconductor structure with improved negative bias temperature instability includes forming an interfacial layer on a semiconductor substrate with an nFET and a pFET. The approach includes depositing a gate dielectric layer on the interfacial layer. Additionally, the approach includes an nFET work function metal layer deposited on the interfacial layer. Additionally, the approach includes removing the nFET work function metal from an area above the pFET and depositing a pFET work function metal layer on a portion of the exposed gate dielectric layer where the portion of the exposed gate dielectric layer is over the pFET. Furthermore, the approach includes depositing a gate metal on the pFET work function metal layer where the gate metal is deposited in an environment with a fluorine containing gas followed by an anneal in a reducing environment.

Owner:IBM CORP

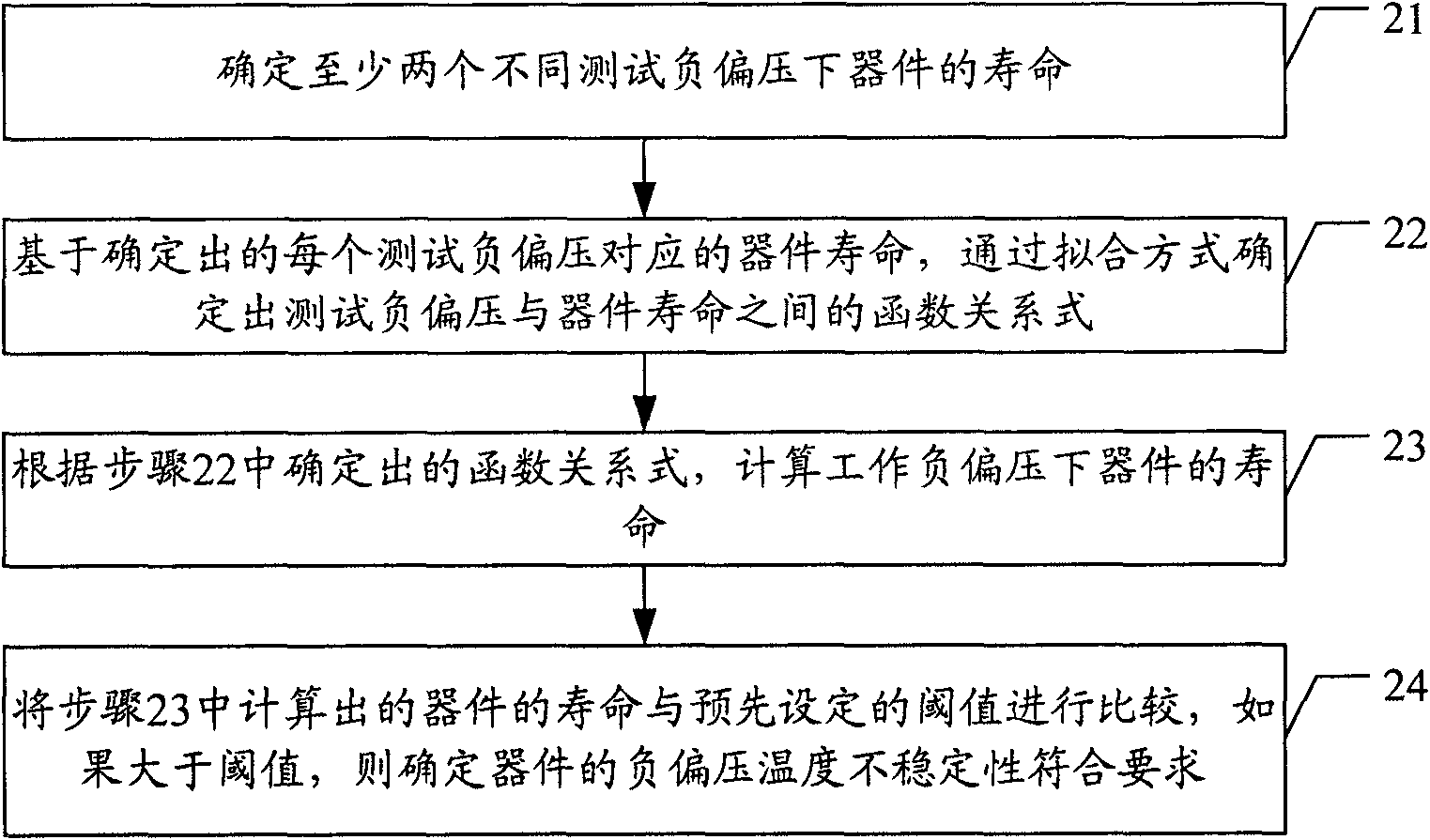

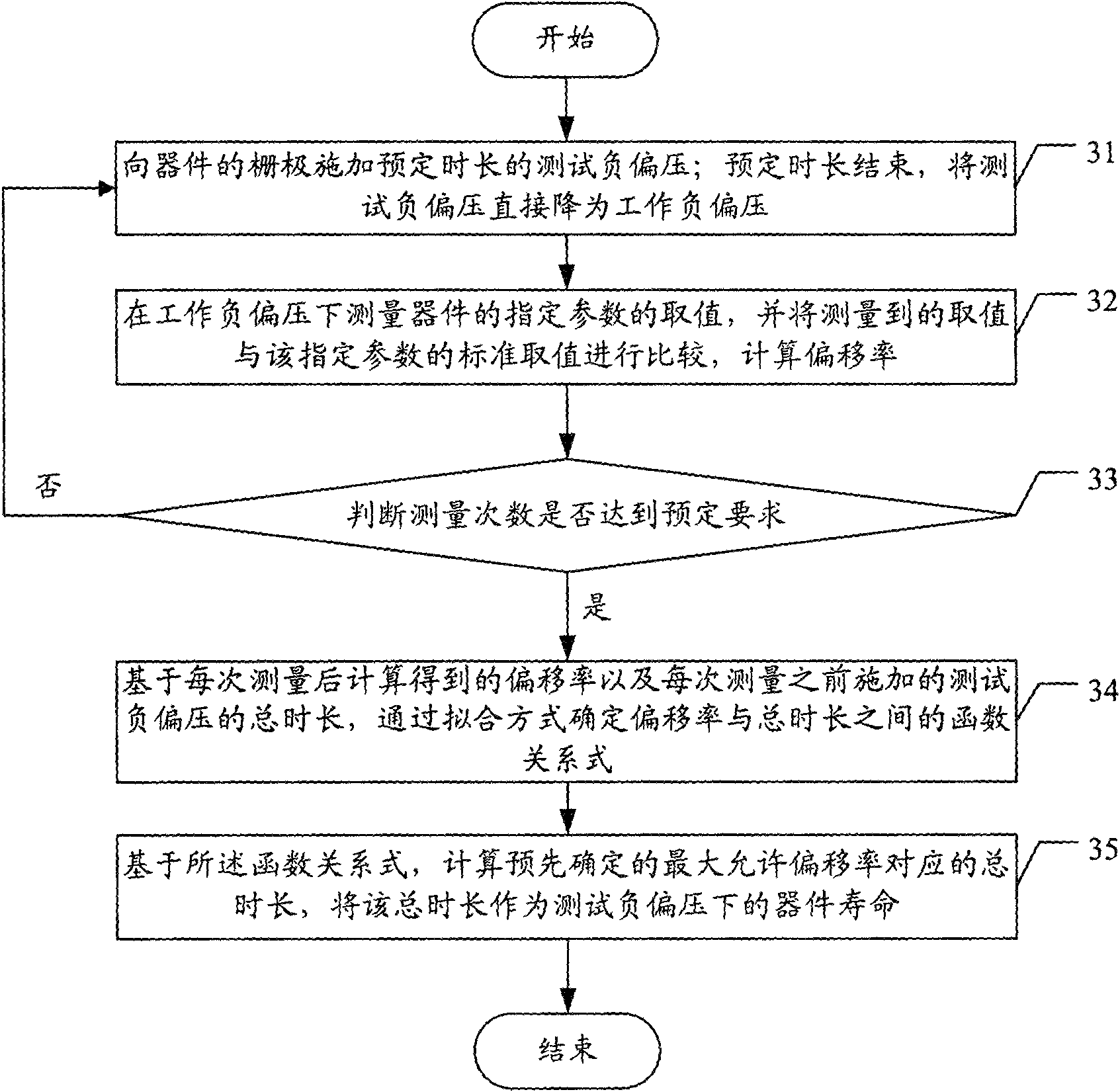

Method for testing instability of a negative bias temperature

InactiveCN102004216ARestore performanceGuaranteed accuracySemiconductor/solid-state device testing/measurementIndividual semiconductor device testingInstabilityEngineering

The invention discloses a method for testing instability of a negative bias temperature. The method comprises the following steps: determining the service life of a device under at least two different test negative biases, and determining a functional relationship between the test negative bias and the service life of the device in a fitting manner; calculating the service life of the device in a normal working state under a working negative bias according to the determined functional relationship; and comparing the calculated service life of the device with a pre-set threshold, wherein if the calculated service life is longer than the threshold, the test is passed. In the process of testing the service life of the device under different test negative biases, the test negative bias is reduced to the working negative bias before measuring a designated parameter of the device each time so as to avoid recovery of the device performance, ensure the accuracy of the measurement result and the accuracy of the entire test process and increase the processing speed of the entire test process; and moreover, compared with the prior art, only one important parameter of the device is tested in the scheme of the invention, and thus the test speed is further increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

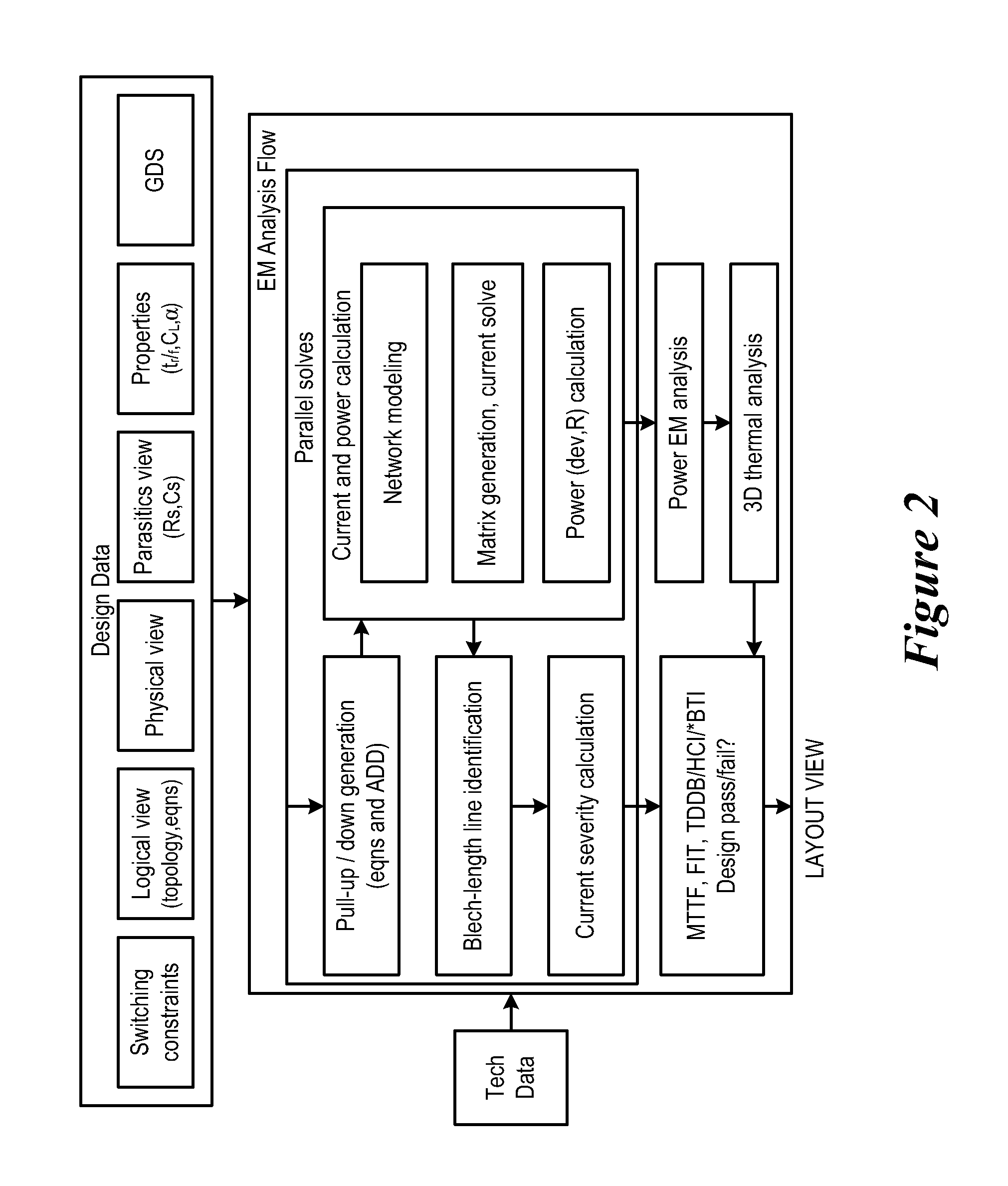

Interconnect and Transistor Reliability Analysis for Deep Sub-Micron Designs

ActiveUS20120096424A1Accurate modelingAccurate captureDetecting faulty computer hardwareComputer aided designDielectricInstability

A system and method for providing a statistical budgeting approach to modeling reliability effects such as interconnect electromigration (EM), transistor time-dependant dielectric breakdown (TDDB), hot-carrier injection effects (HCI) and bias temperature instability (BTI) is disclosed. A static analysis flow captures the effects of design topology, switching constraints, interactions between signal nets and supply rails as well as thermal gradients due to interconnect and transistor self as well as mutual heating, and was used to verify successive iterations of deep sub-micron integrated circuit designs.

Owner:ADVANCED MICRO DEVICES INC

Methods and circuits for generating physically unclonable function

Various embodiments include solutions for generating a physically unclonable function. In some cases, a method includes an electronic circuit including: a static random access memory (SRAM) device having at least one memory cell with at least one transistor device therein, SRAM bias temperature instability aging circuitry coupled with the SRAM device and configured to apply aging conditions to the at least one memory cell to degrade the at least one transistor device within the at least one memory cell, and at least one computing device coupled with the SRAM device and configured to: skew a storage cell value in the at least one transistor device, measure a skewed value of the storage cell after the skewing, and create a physically unclonable function from the skewed value of the storage cell.

Owner:IBM CORP

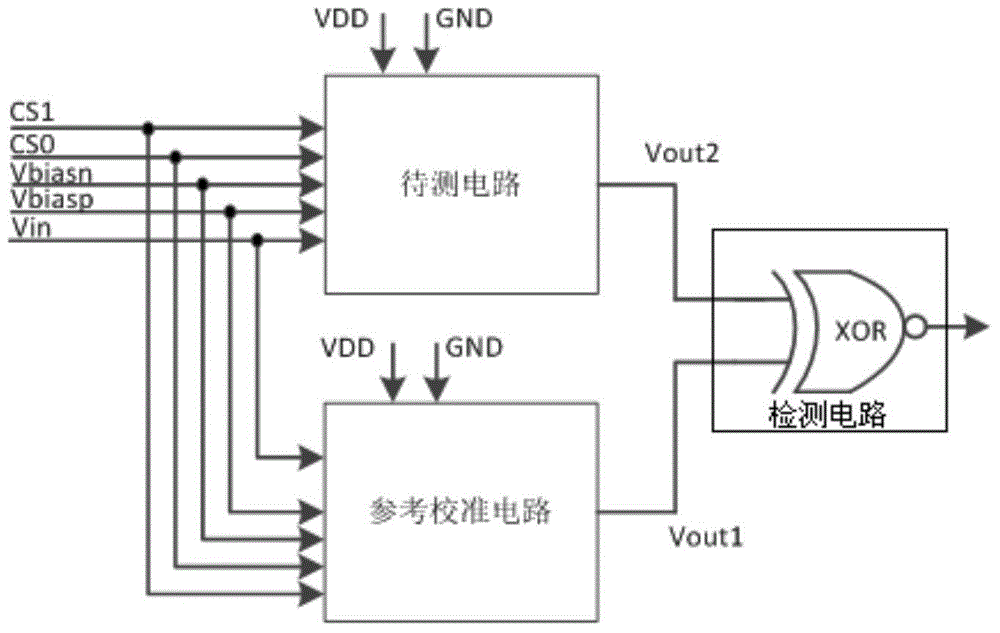

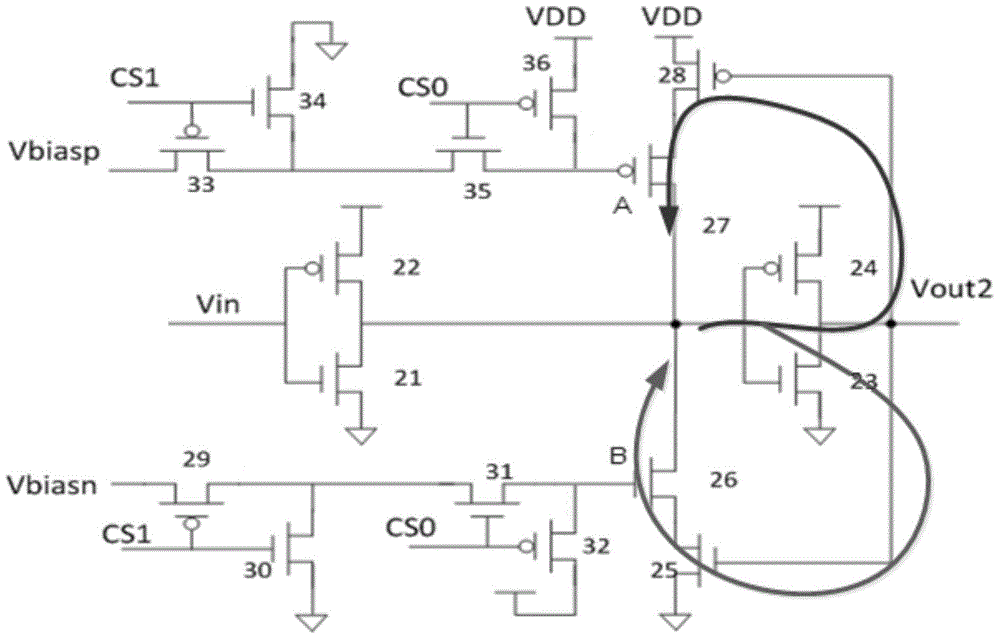

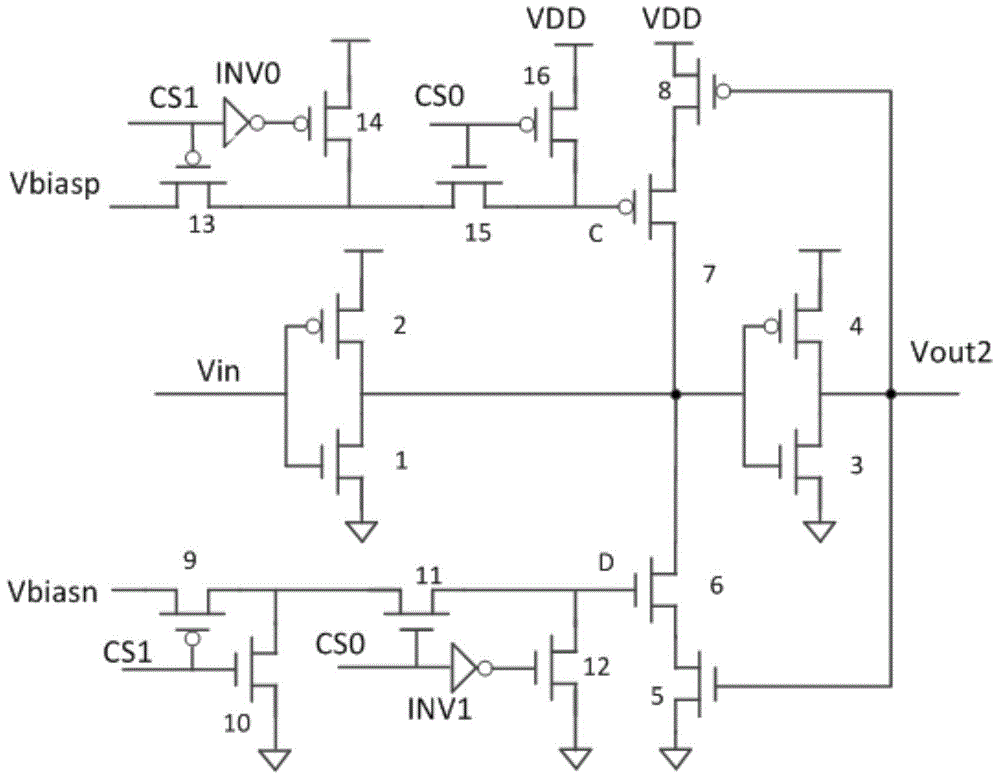

Device and method thereof for testing bias temperature instability degrading of MOS (metal oxide semiconductor) device

ActiveCN104483611ASimple structureImprove test accuracyIndividual semiconductor device testingHysteresisSchmitt trigger

The invention discloses a device for testing bias temperature instability degrading of a MOS (metal oxide semiconductor) device. The device comprises a to-be-tested circuit, a reference calibration circuit and a detection circuit, wherein the output ends of the to-be-tested circuit and the reference calibration circuit are simultaneously connected with the detection circuit, a first feedback control assembly and a first Schmitt trigger are arranged in the to-be-tested circuit, the first feedback control assembly is used for applying stress on to-be-tested feedback loop components in the first Schmitt trigger so as to generate degrading, the to-be-tested circuit is used for outputting degraded actual hysteresis voltage signals, the reference calibration circuit is used for outputting standard hysteresis voltage signals, and the detection circuit is used for comparing and measuring the difference between the actual hysteresis voltage signals and the reference standard hysteresis voltage signals, so as to test the degrading degree of the feedback loop components. The device has the characteristics that the NBTI (negative bias temperature instability) and PBTI (positive bias temperature instability) properties can be tested, the circuit structure is simple, and the testing accuracy is high. The invention discloses a method for testing the bias temperature instability degrading of the MOS device.

Owner:EAST CHINA NORMAL UNIVERSITY +1

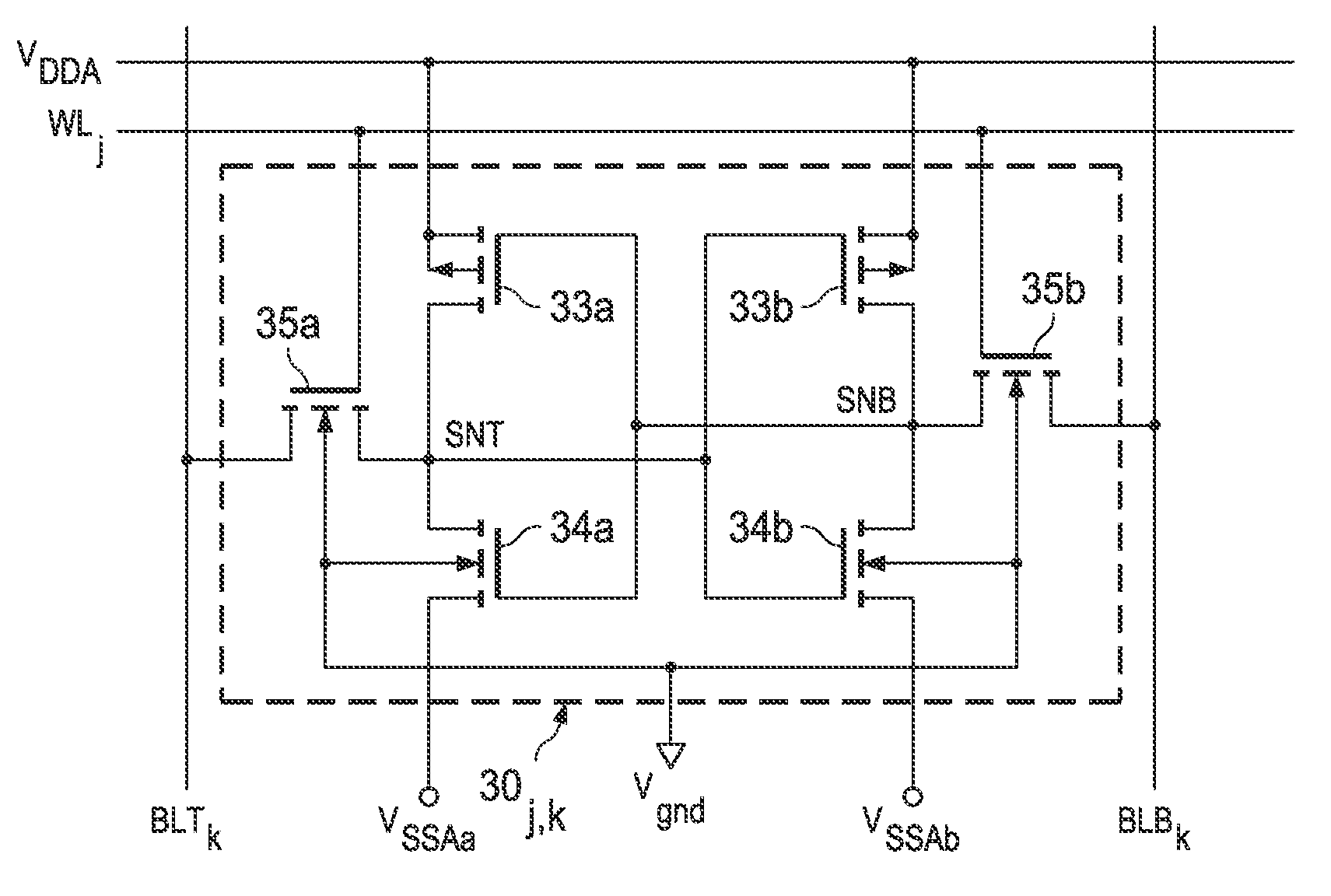

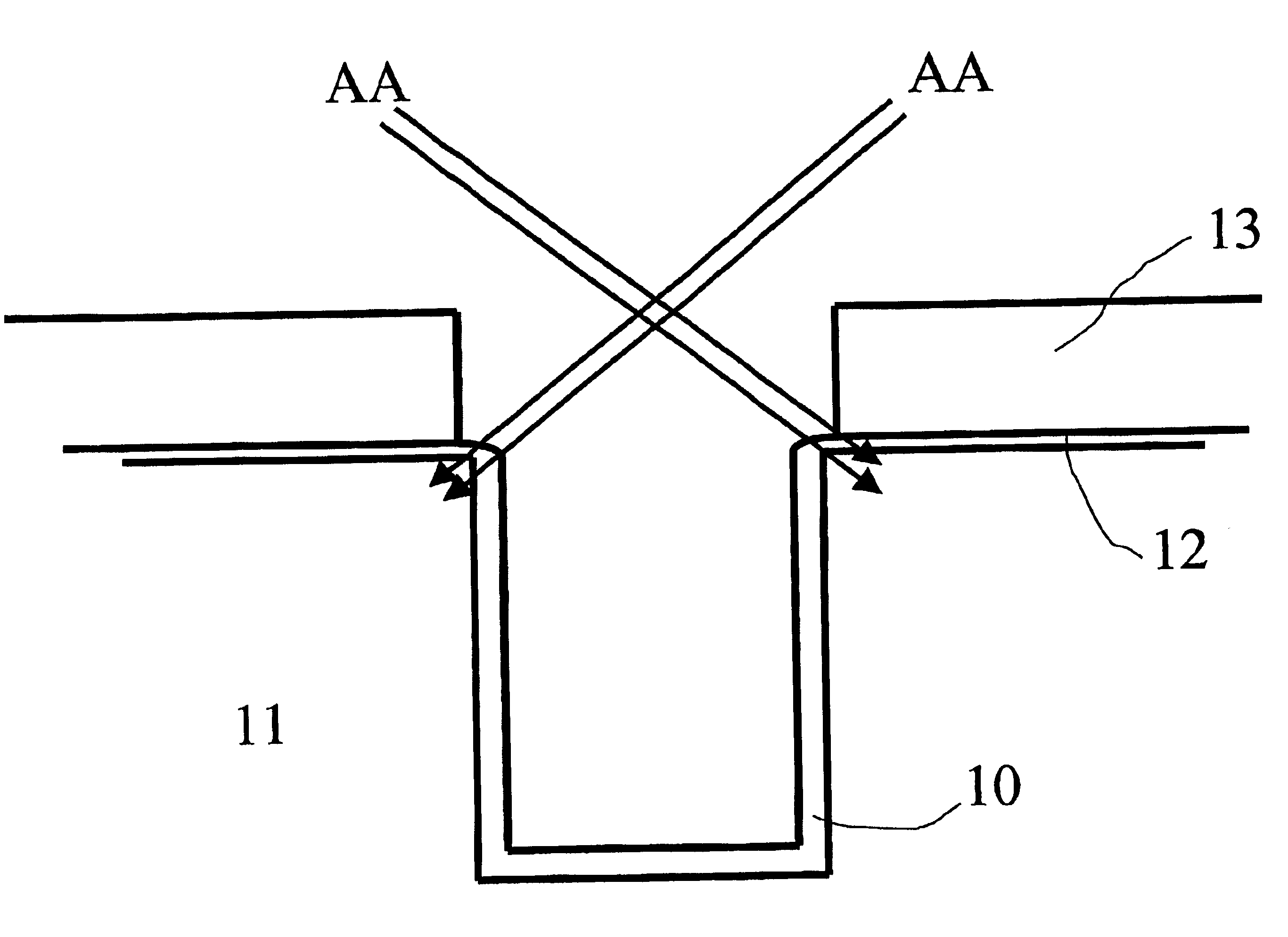

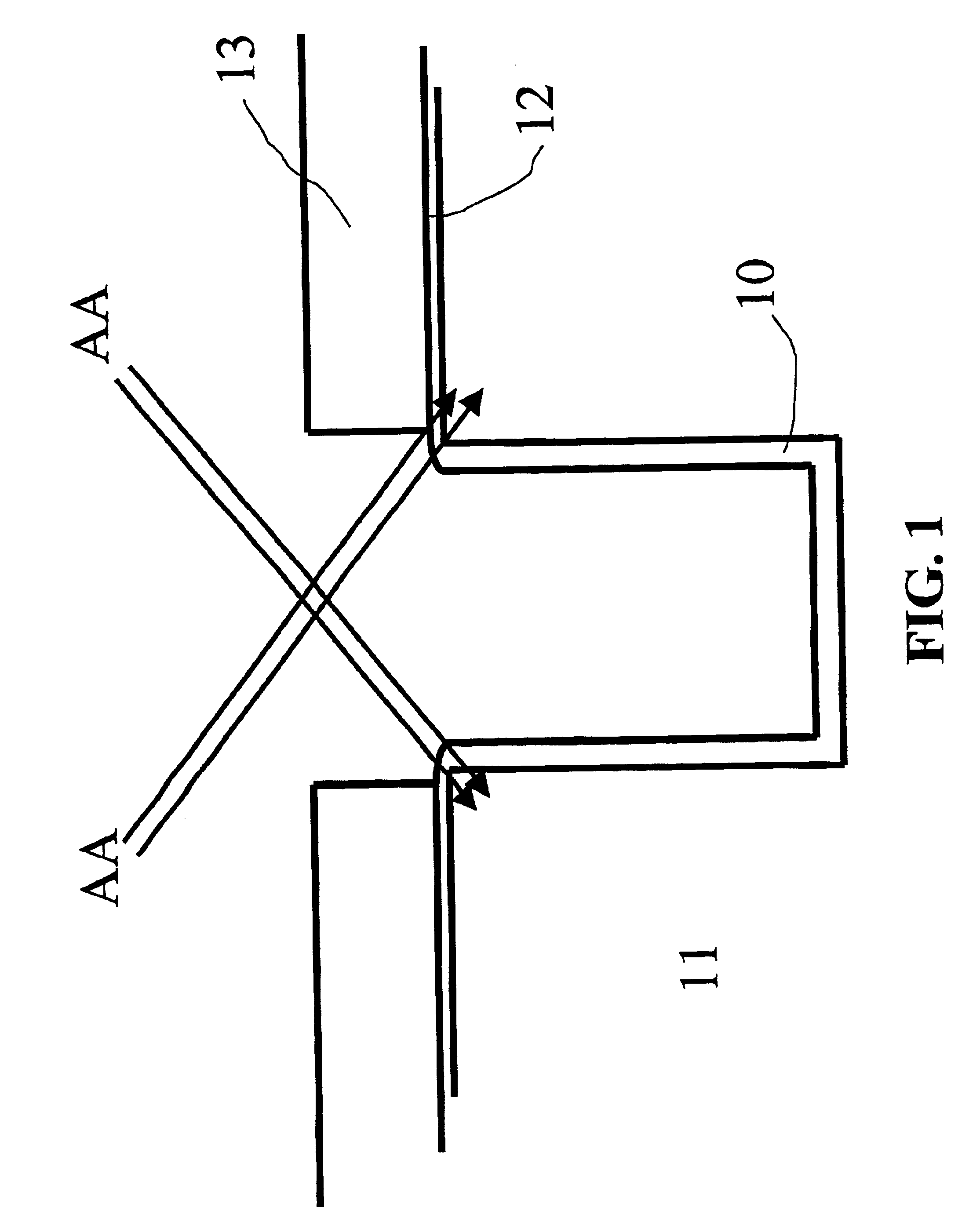

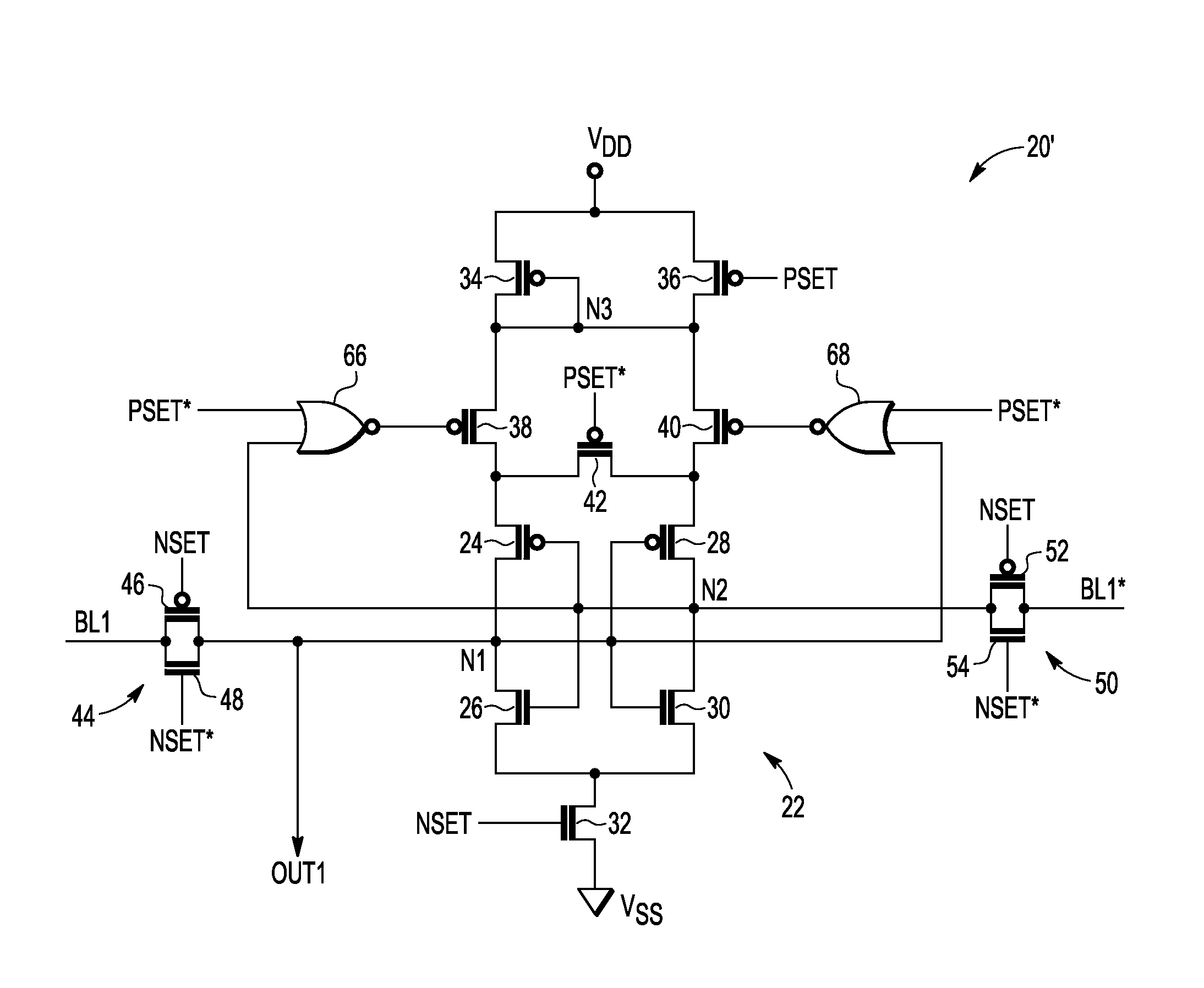

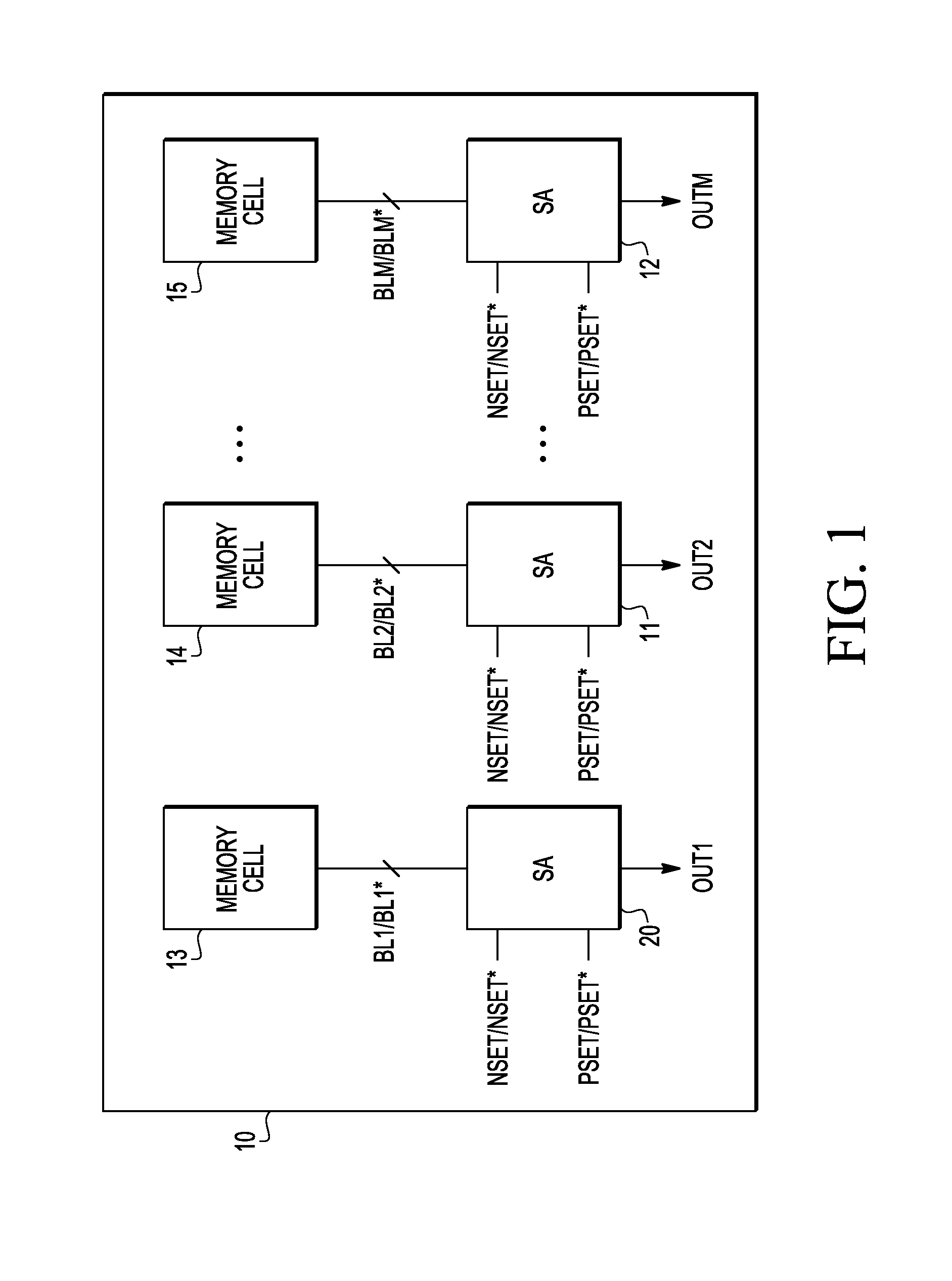

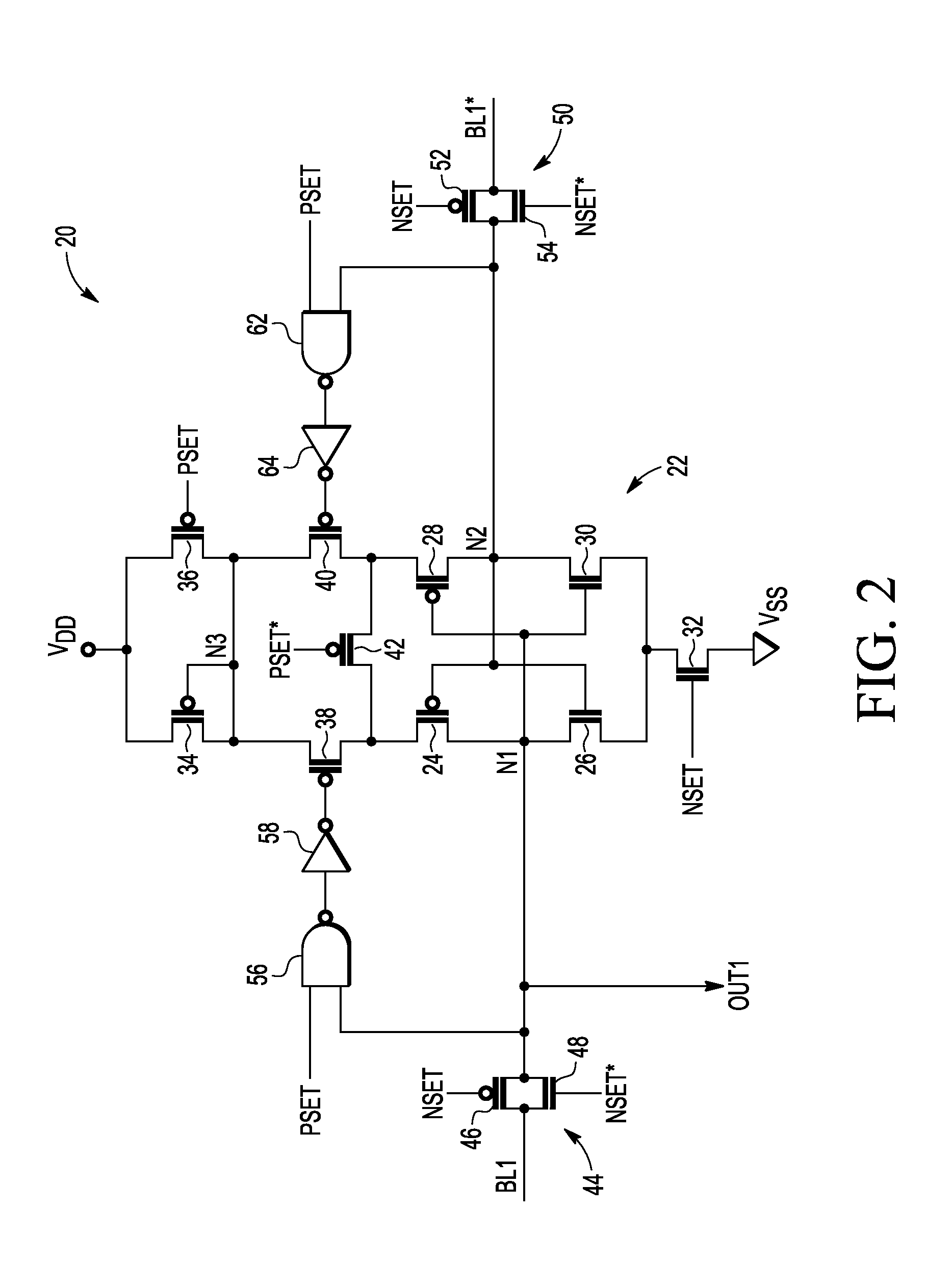

Memory having a latching sense amplifier resistant to negative bias temperature instability and method therefor

An integrated circuit includes a memory cell and a sense amplifier coupled to the memory cell via a first bit line and a second bit line. The sense amplifier includes first and second inverters cross-coupled to provide a latch. The first inverter is responsive to a first data signal provided by the memory cell over the first bit line. The second inverter is responsive to a second data signal as provided by the memory cell over the second bit line. A first negative bias temperature instability (NBTI) compensation transistor includes a source electrode coupled to receive a reference voltage, a drain electrode coupled to a source electrode of the first inverter, and a gate electrode coupled to first logic responsive to the first data signal. A second NBTI compensation transistor includes a source electrode coupled to receive the reference voltage, a drain electrode coupled to a source electrode of the second inverter, and a gate electrode coupled to second logic responsive to the second data signal, wherein the second data signal is a logical complement of the first data signal.

Owner:VLSI TECH LLC

Test structure for automatic dynamic negative-bias temperature instability testing

InactiveUS7103861B2Minimizes parasitic capacitanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectronic switchElectron

The invention describes a novel test structure and process to create the structure for performing automatic dynamic stress testing of PMOS devices for Negative Bias Temperature Instability (NBTI). The invention consists of an integrated inverter, two integrated electronic switches for switching from stress mode to device DC characterization measurement mode, and a PMOS FET device under test (DUT). The inverter assures the proper 180 degree phase relationship between the test device source and gate voltage while the imbedded electronic switches provide isolation of the test device during DC characterization testing. Another embodiment of the invention enables the testing of multiple devices under test (DUT's).

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Apparatus and method for measuring degradation of CMOS VLSI elements

ActiveUS8692571B2Eliminate the effects ofDigital circuit testingSemiconductor operation lifetime testingDielectricIntegrated circuit

The reliability of an integrated circuit is inferred from the operational characteristics of sample metal oxide semiconductor (MOS) devices switchably coupled to drain / source bias and gate input voltages that are nominal, versus voltage and current conditions that elevate stress and cause temporary or permanent degradation, e.g., hot carrier injection (HCI), bias temperature instability (BTI, NBTI, PBTI), time dependent dielectric breakdown (TDDB). The MOS devices under test (preferably both PMOS and NMOS devices tested concurrently or in turn) are configured as current sources in the supply of power to a ring oscillator having cascaded inverter stages, thereby varying the oscillator frequency as a measure of the effects of stress on the devices under test, but without elevating the stress applied to the inverter stages.

Owner:TAIWAN SEMICON MFG CO LTD

Circuitry and method for measuring negative bias temperature instability (NBTI) and hot carrier injection (HCI) aging effects using edge sensitive sampling

InactiveUS9564884B1Electrical testingSingle output arrangementsTransition densityCritical path method

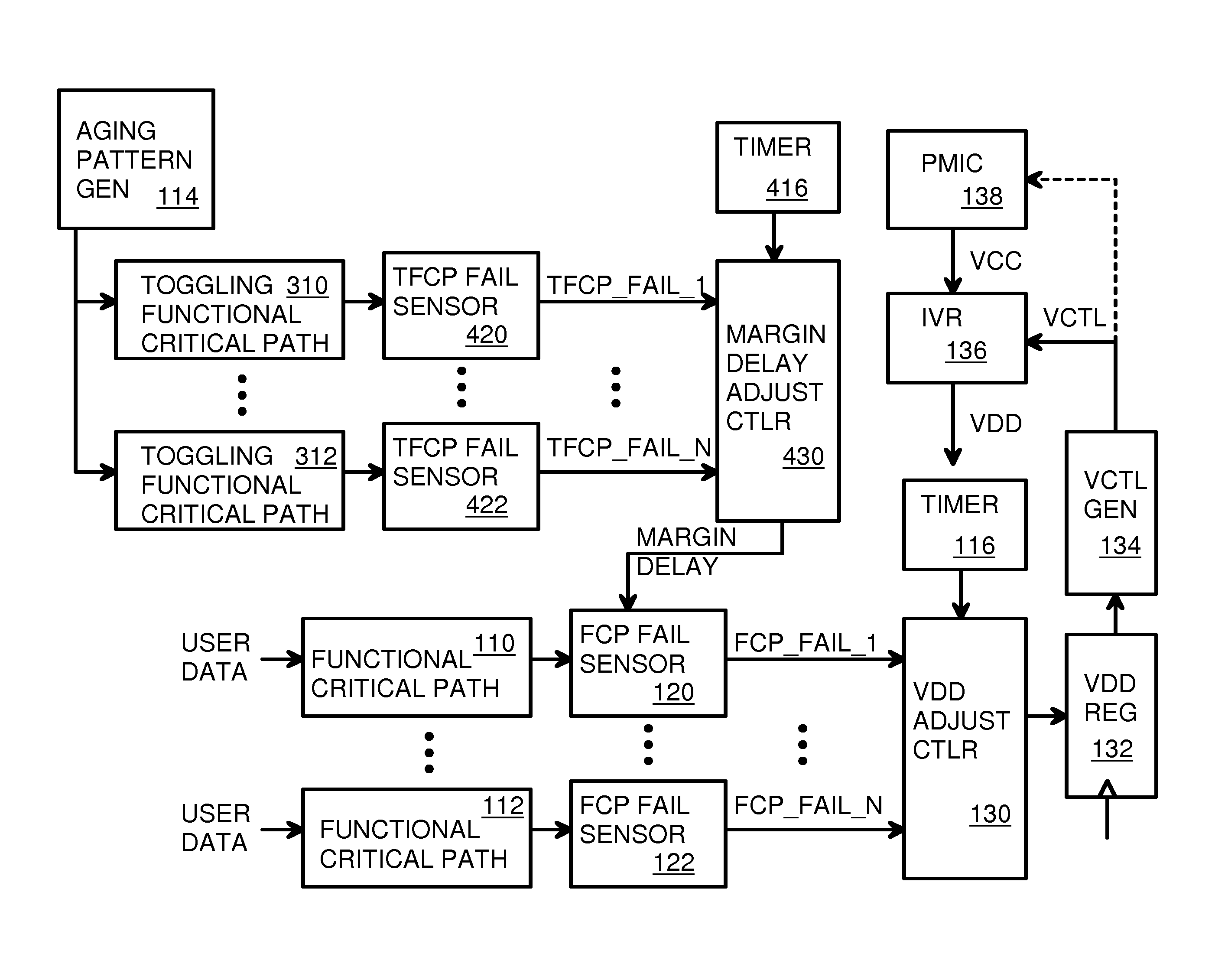

Toggling functional critical path timing sensors measure delays in toggling functional critical paths that continuously receive patterns from an aging pattern generator. Wear is accelerated. A margin delay adjustment controller sweeps margin delays until failures occur to measure delays. The margin delay is then adjusted in functional critical path timing sensors that add the margin delay to functional critical paths that carry user data or chip controls during normal operation. When the path delays fail to meet requirements, the functional critical path timing sensors signal a controller to increase VDD. When no failures occur over a period of time, the controller decreases VDD. Wear on the toggling functional critical paths is accelerated using both toggle and low-transition-density patterns. Circuit aging is compensated for by increasing margin delays to timing sensors.

Owner:QUALCOMM INC

Wafer grade reliability parallel test method for field effect tube negative temperature instability

InactiveCN101452042AReduce the impactQuick measurementIndividual semiconductor device testingProbe cardNegative temperature

A WRL testing method of field effect tube negative temperature instability is disclosed, each port of the field effect tube is connected with a measuring unit through a probe card, for testing saturation current of the field effect tube; a grid and a drain electrode of the field effect tube are respectively connected with the measuring unit through the probe card; all the grounding ports of the field effect tube are connected in series arranged on the same measuring unit through the probe card; source electrodes of two adjacent field effect tubes are connected in series to arranged on the same measuring unit through the probe card. The testing method can effectively reduce testing time and reduce electrostatic effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP