Patents

Literature

128results about How to "Minimizes parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

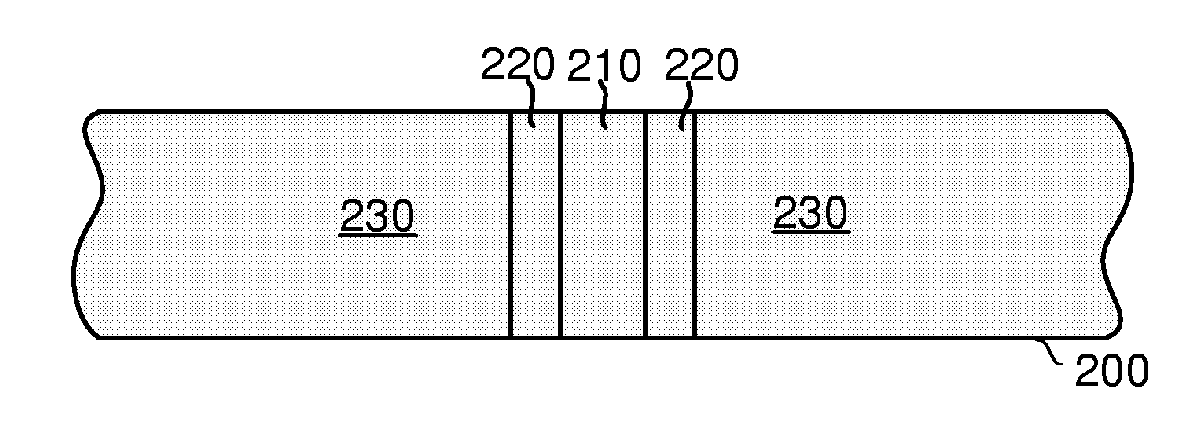

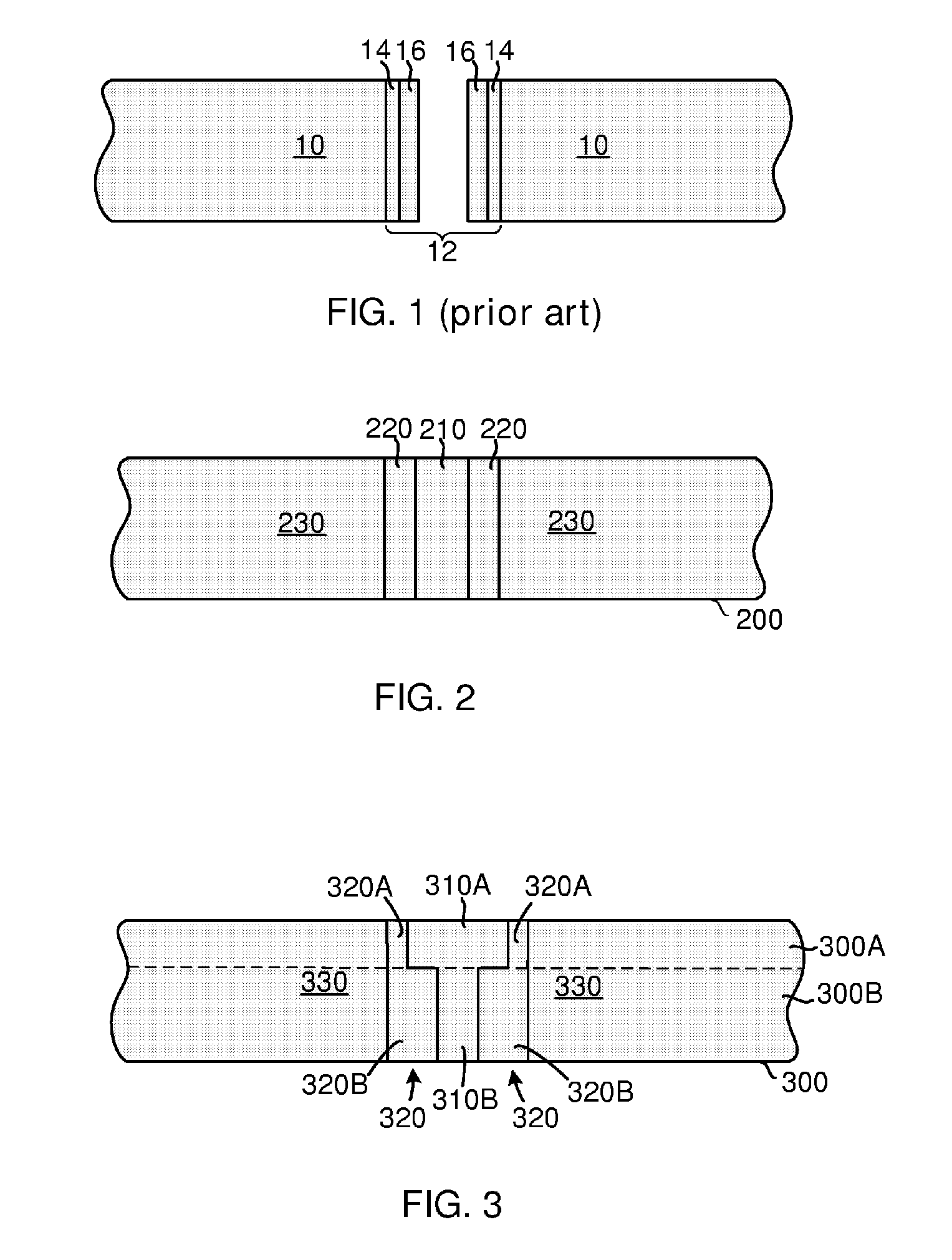

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

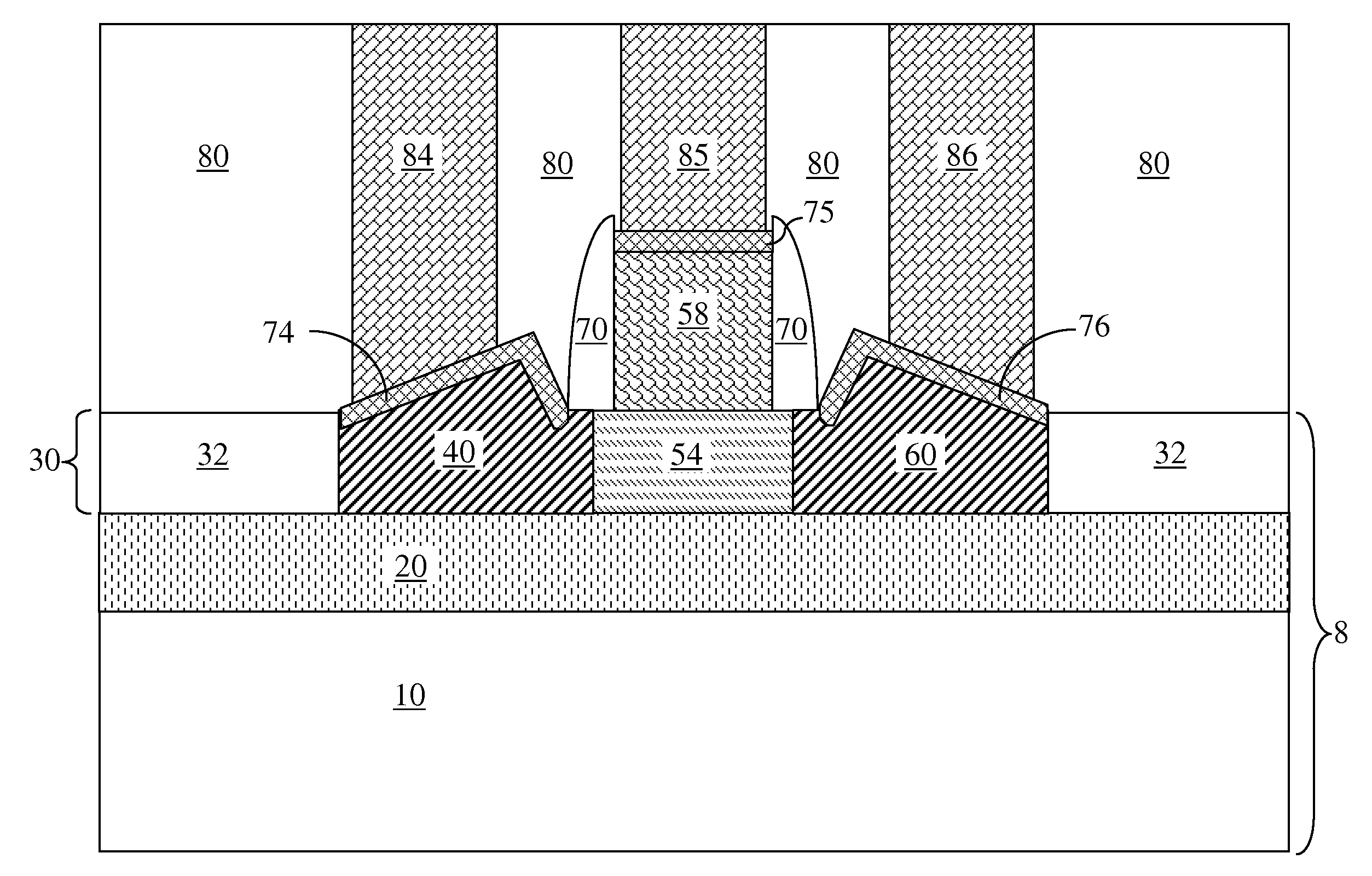

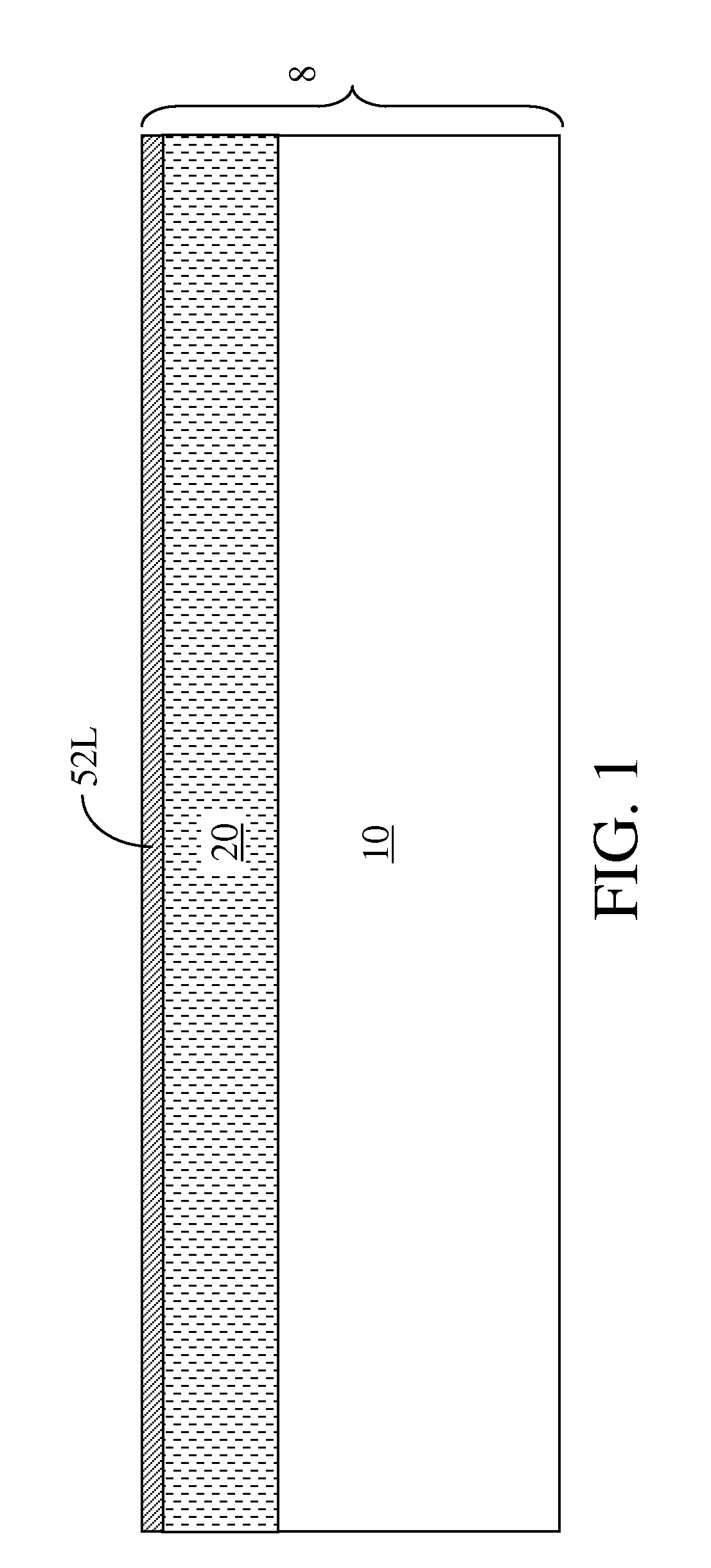

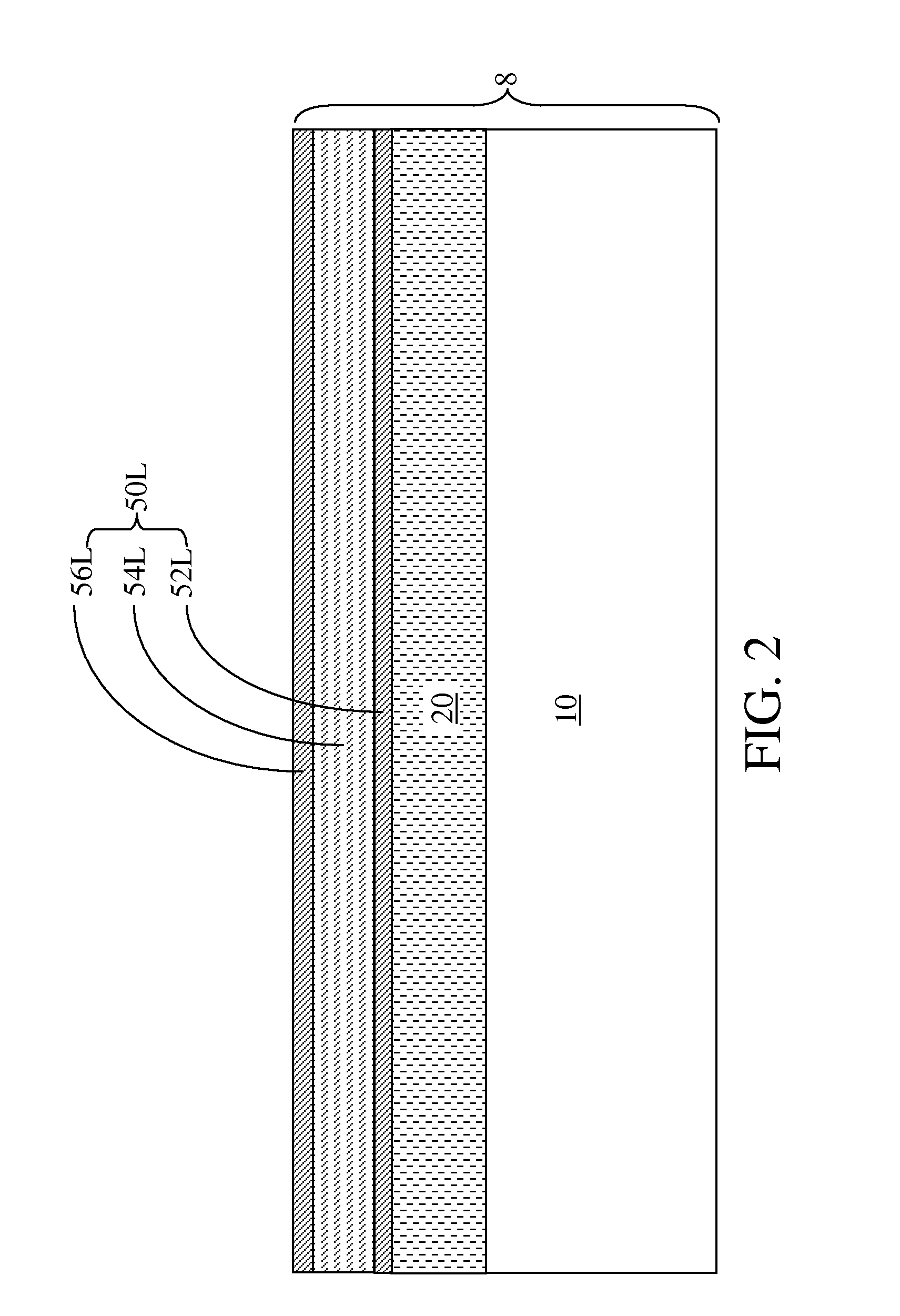

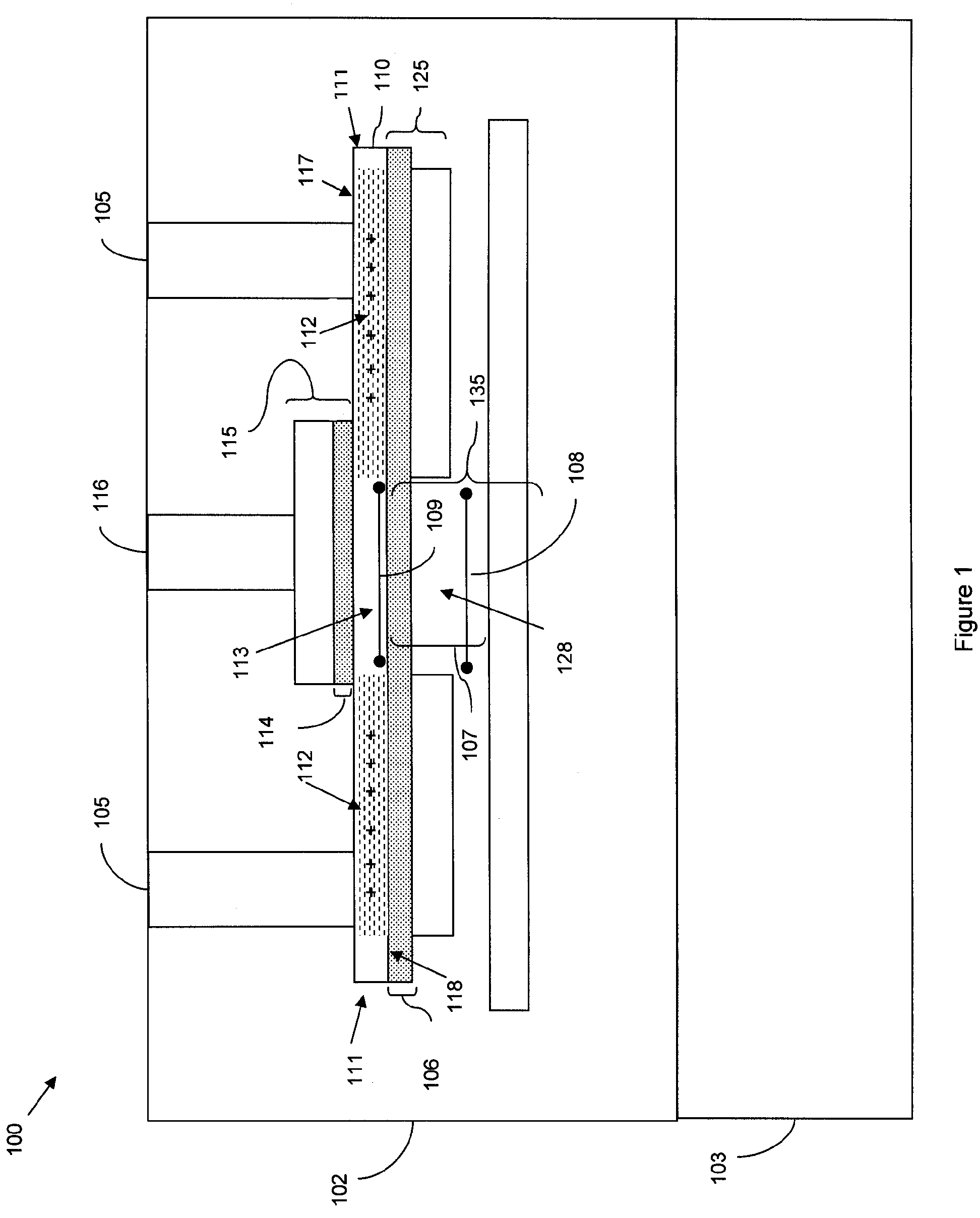

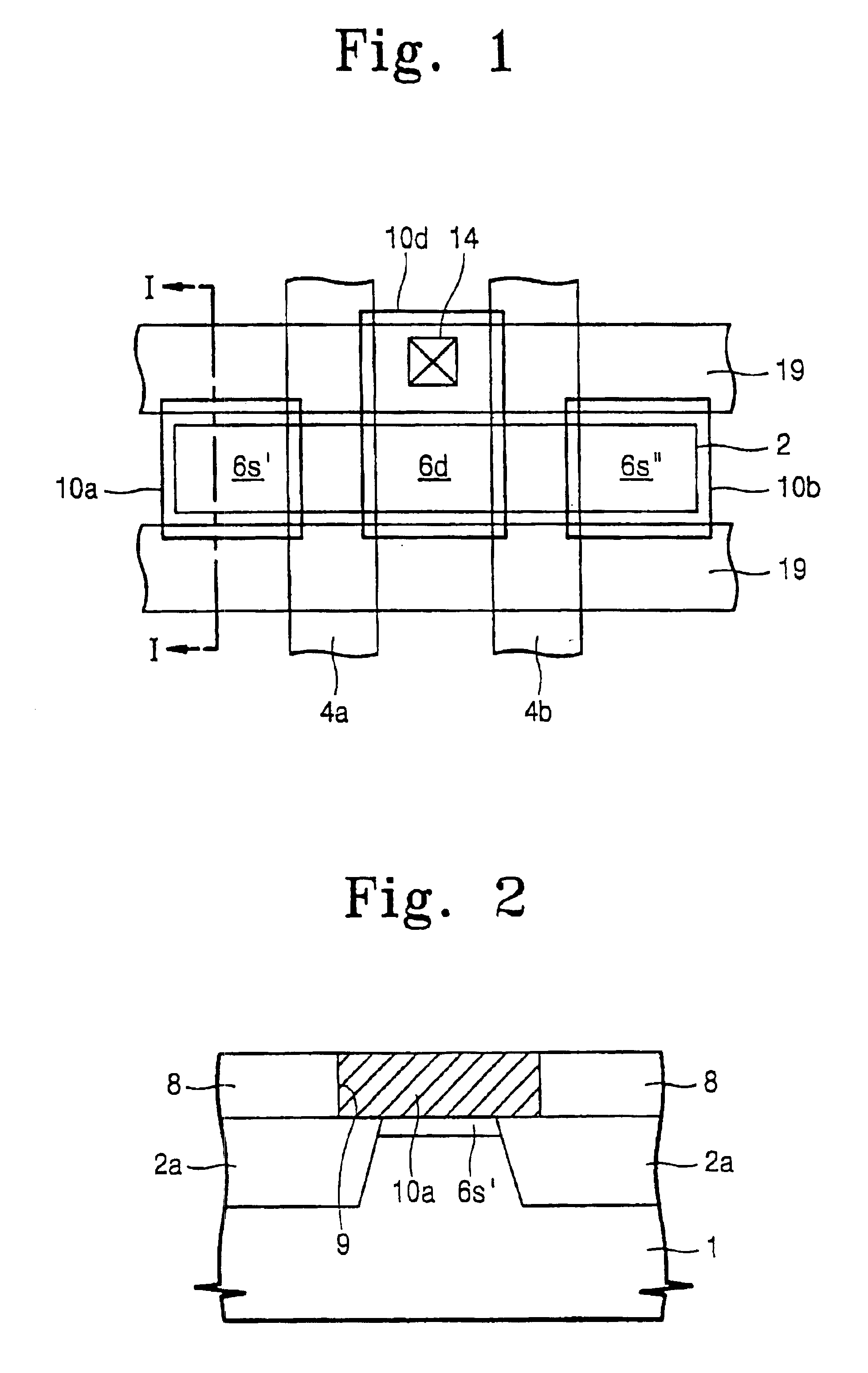

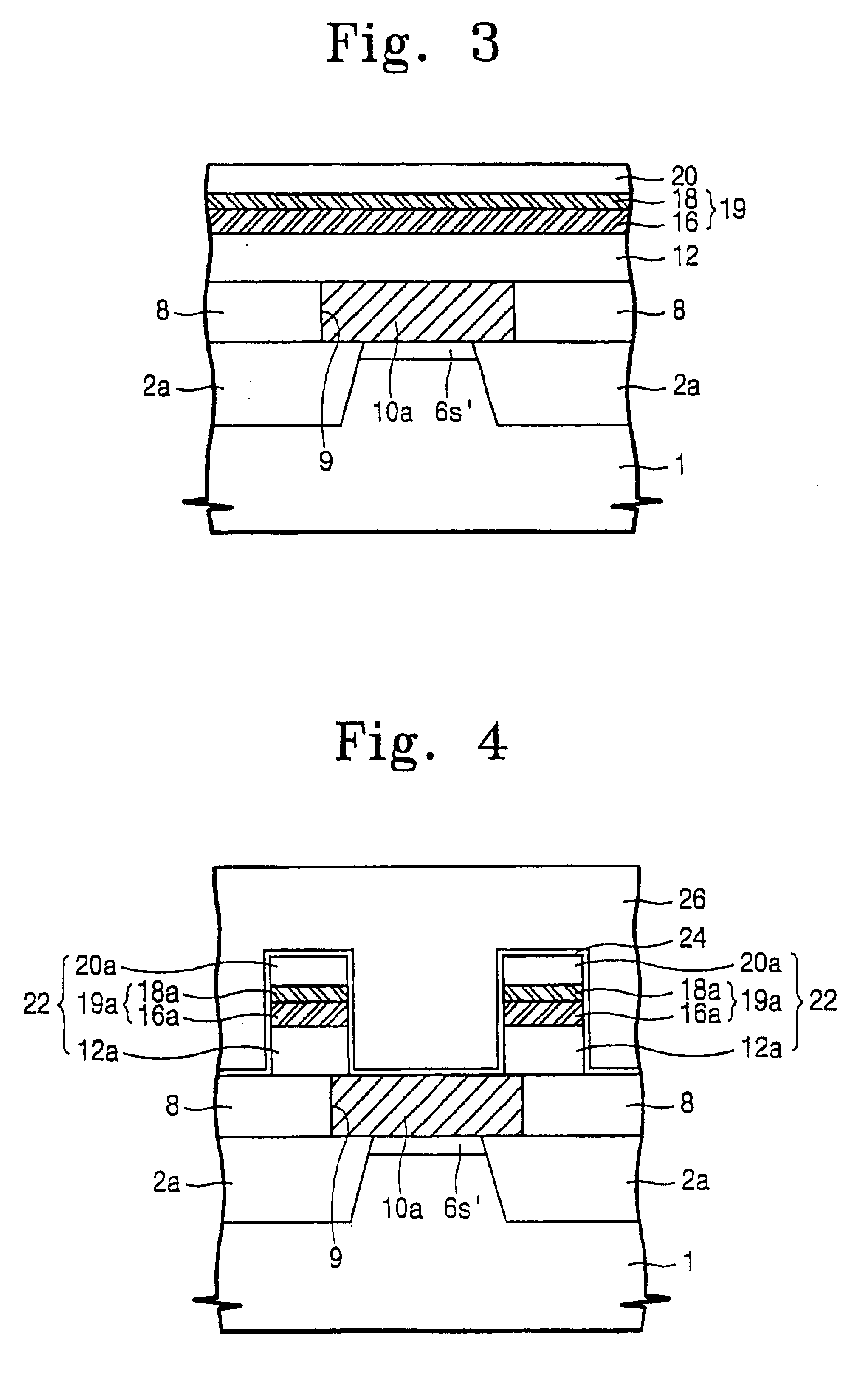

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

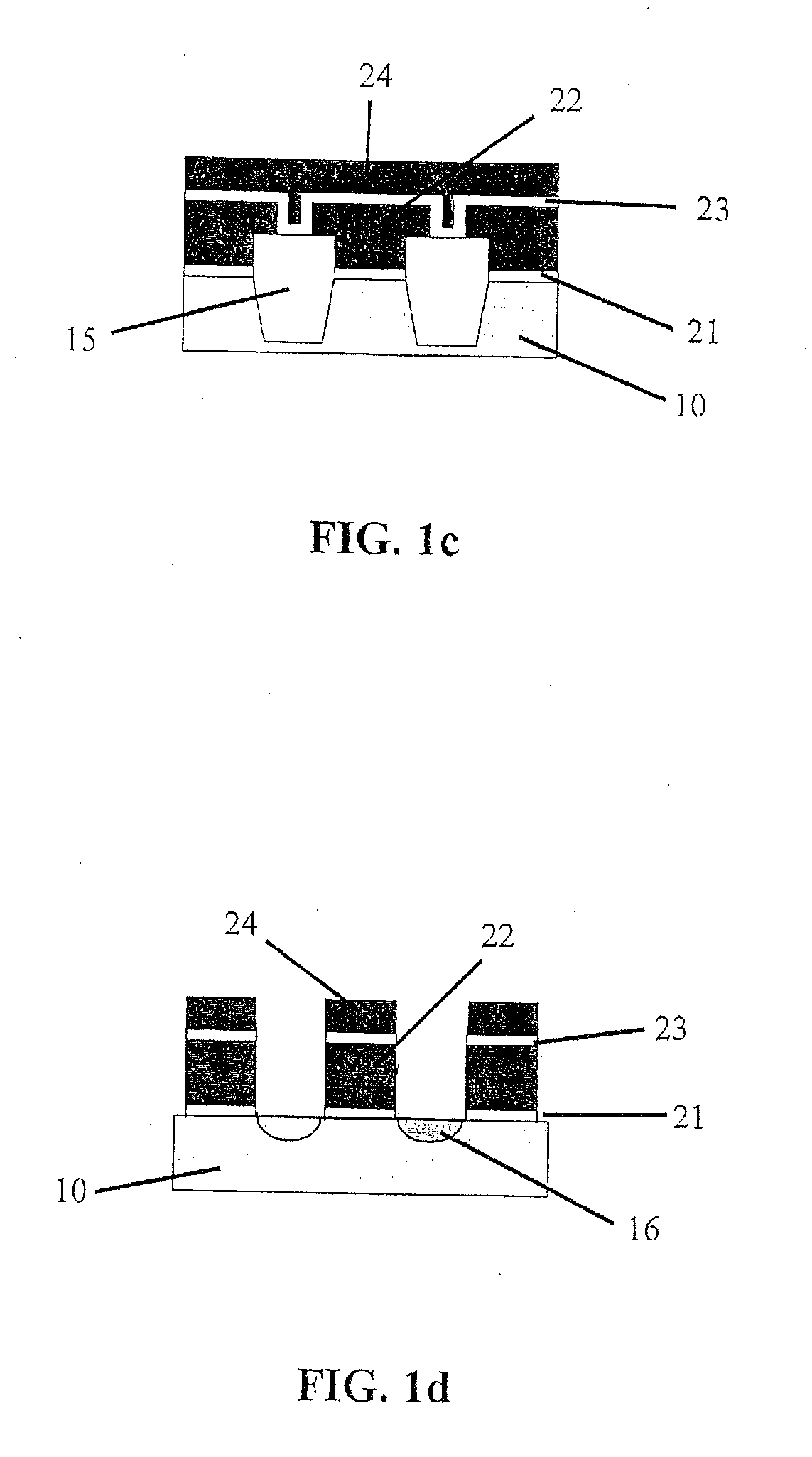

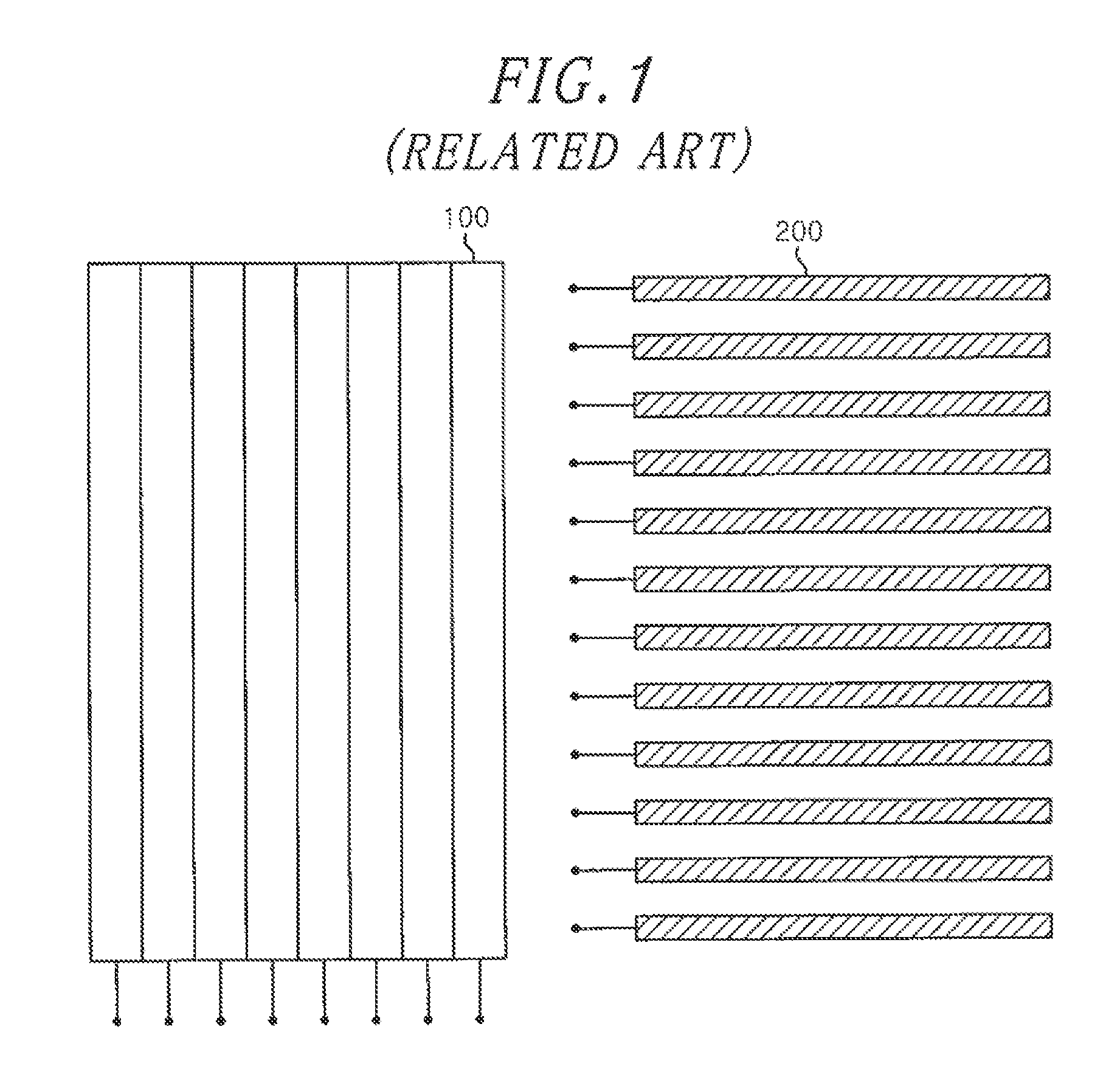

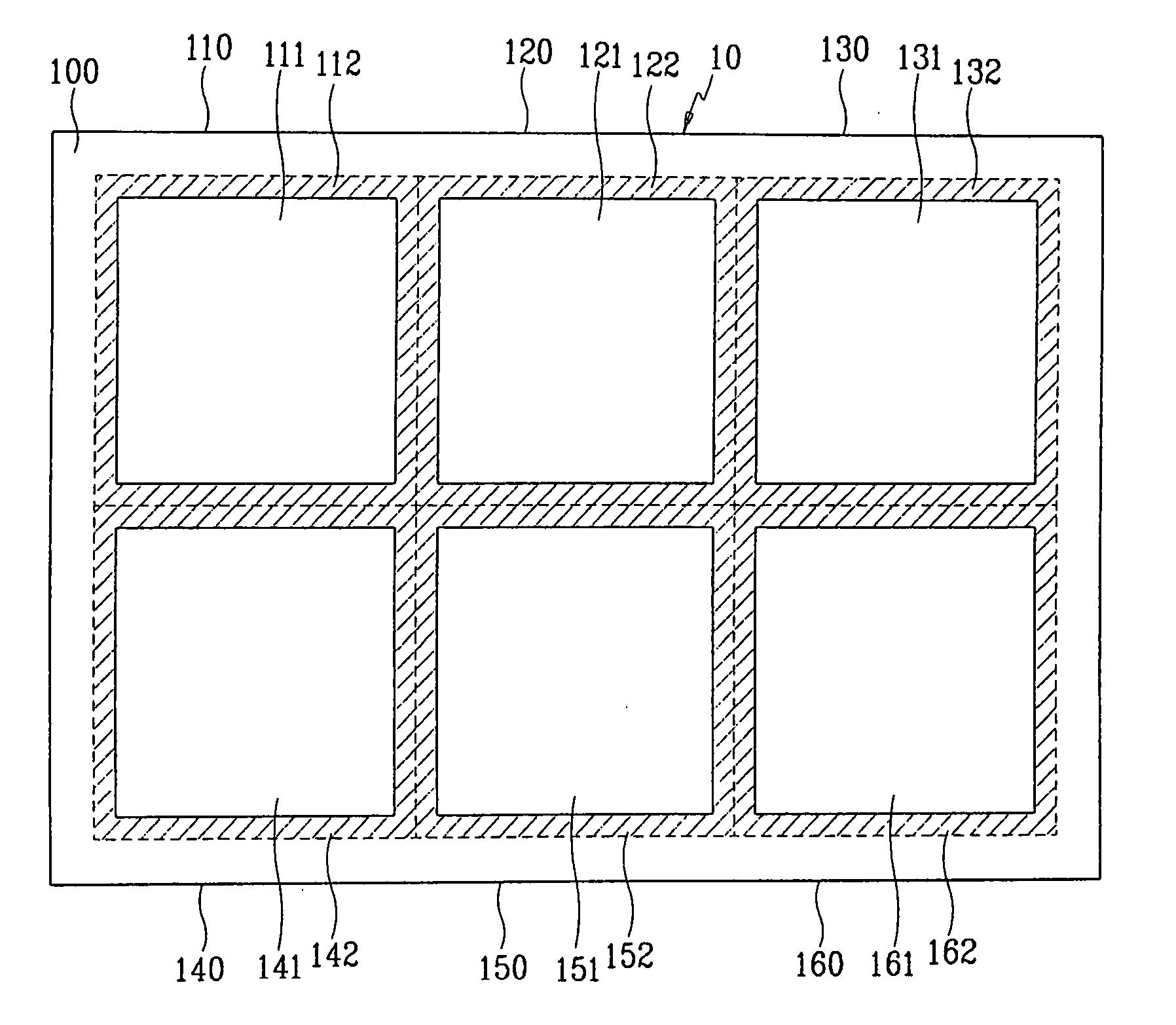

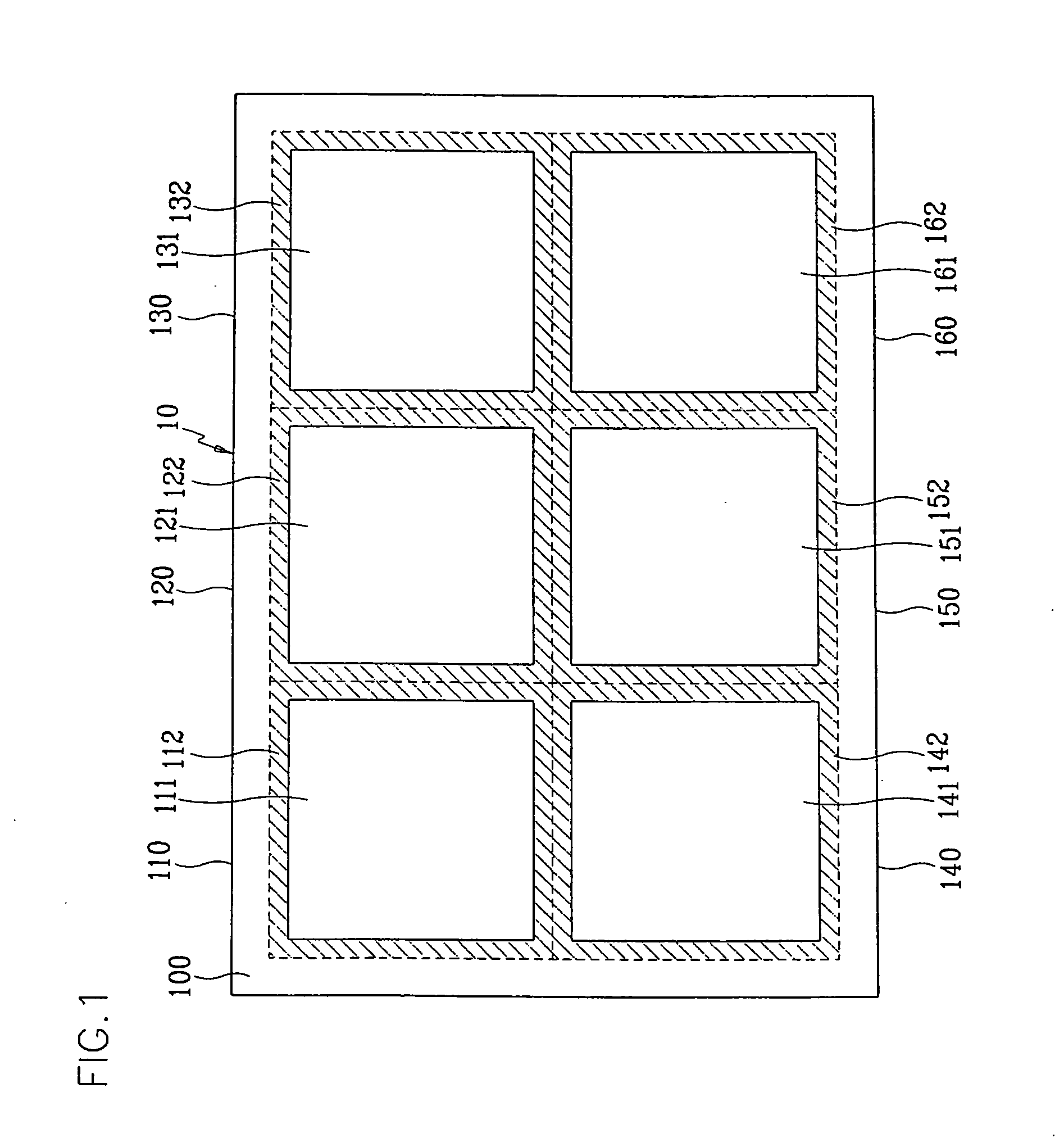

Pixel current driver for organic light emitting diode displays

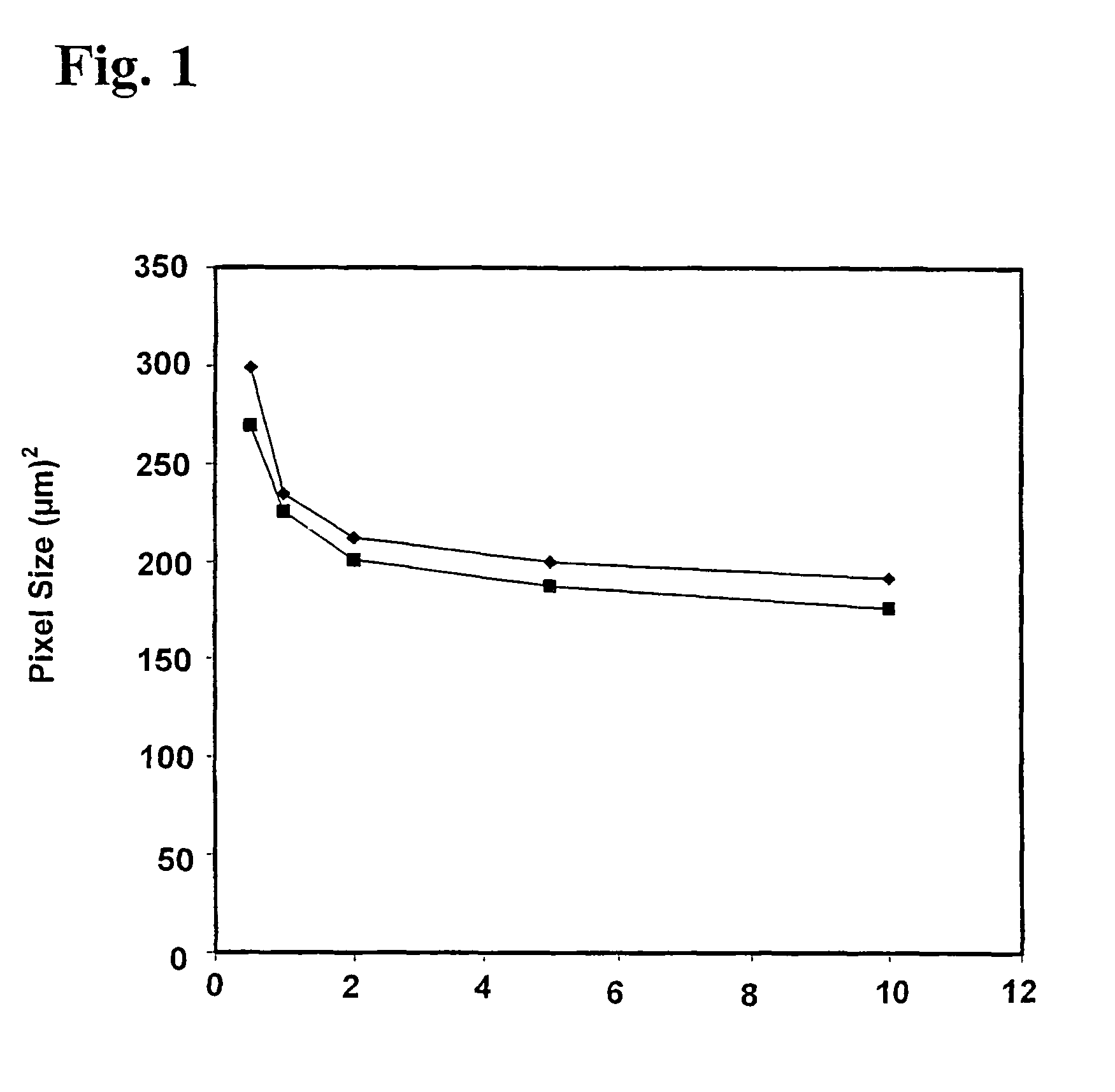

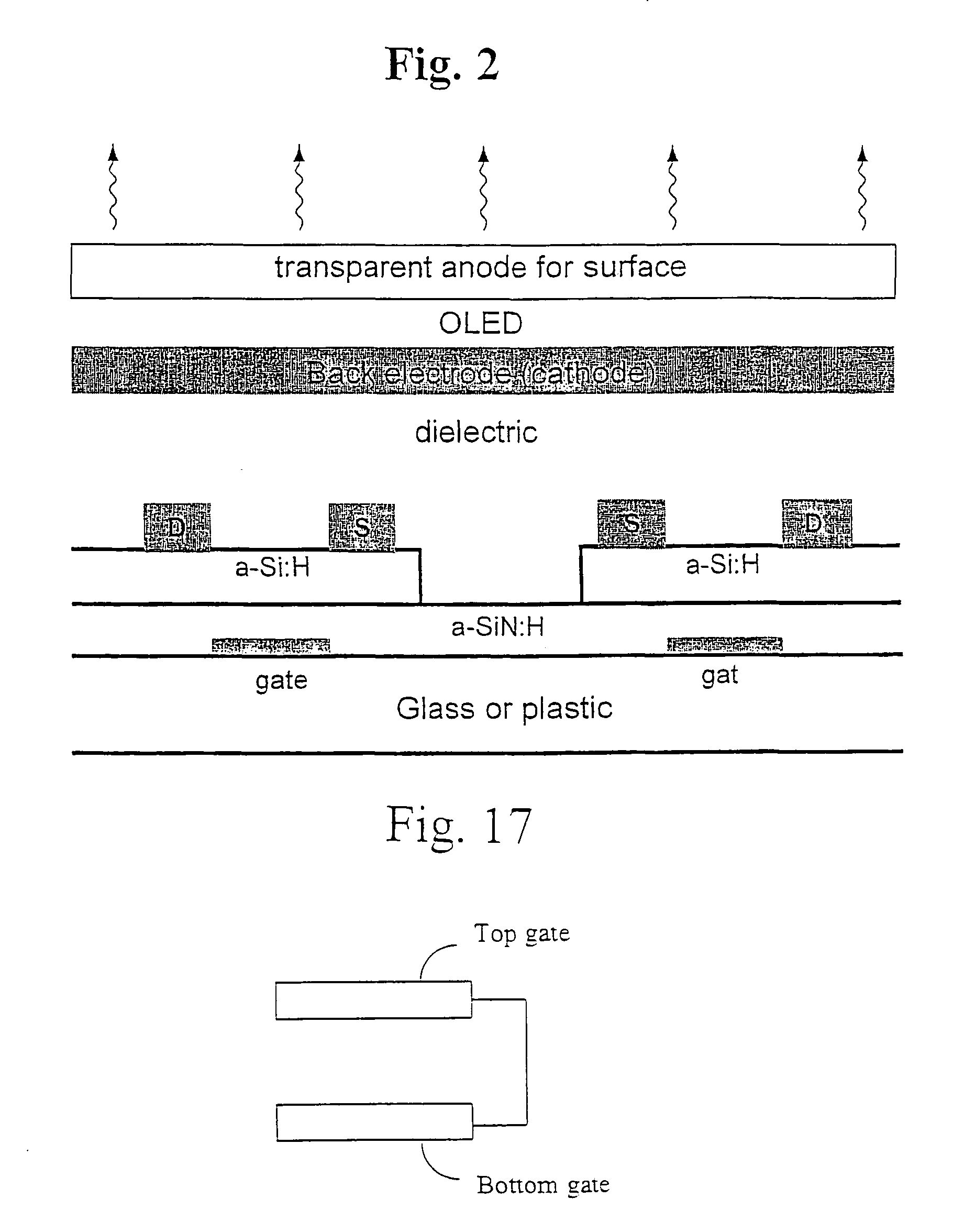

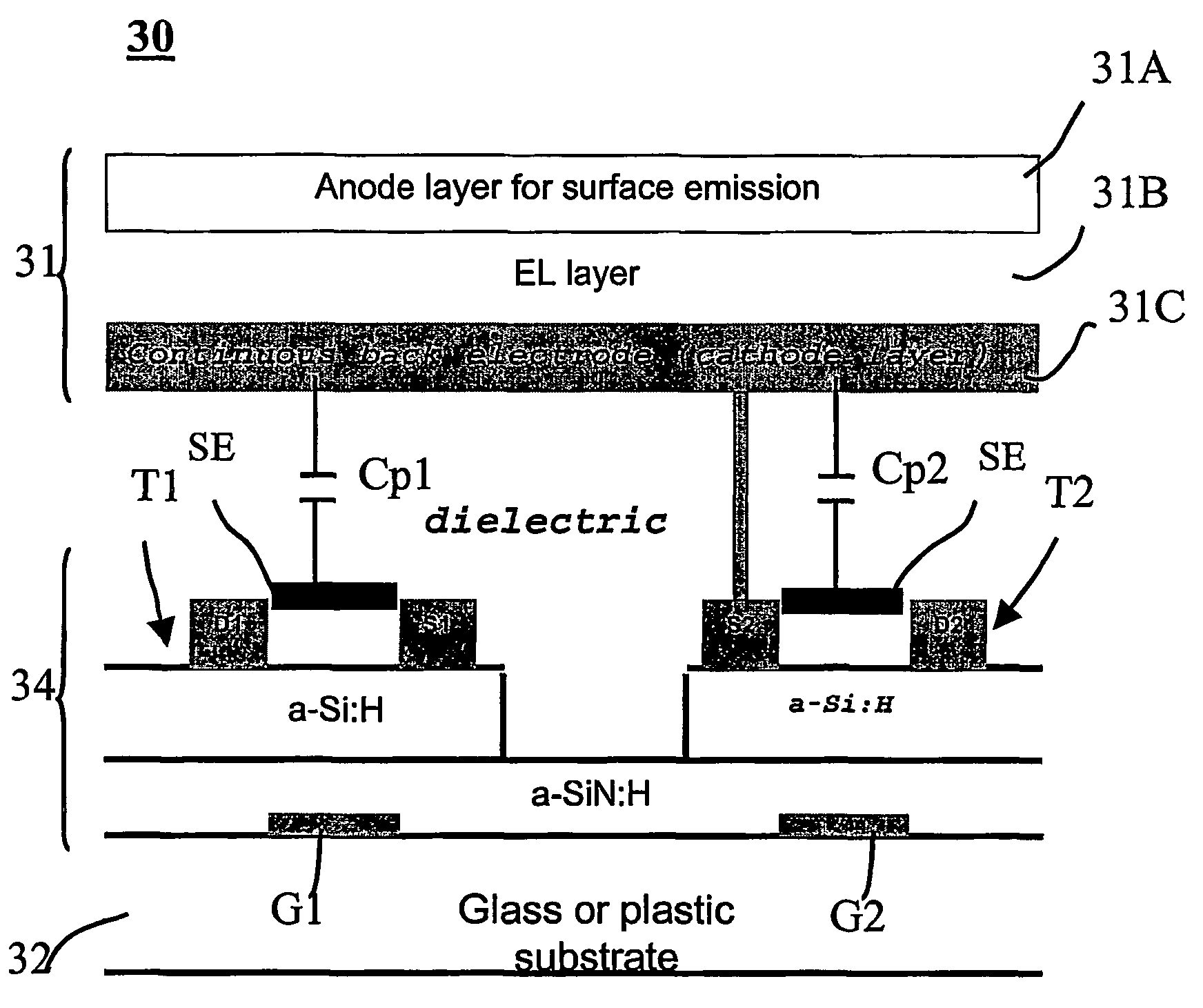

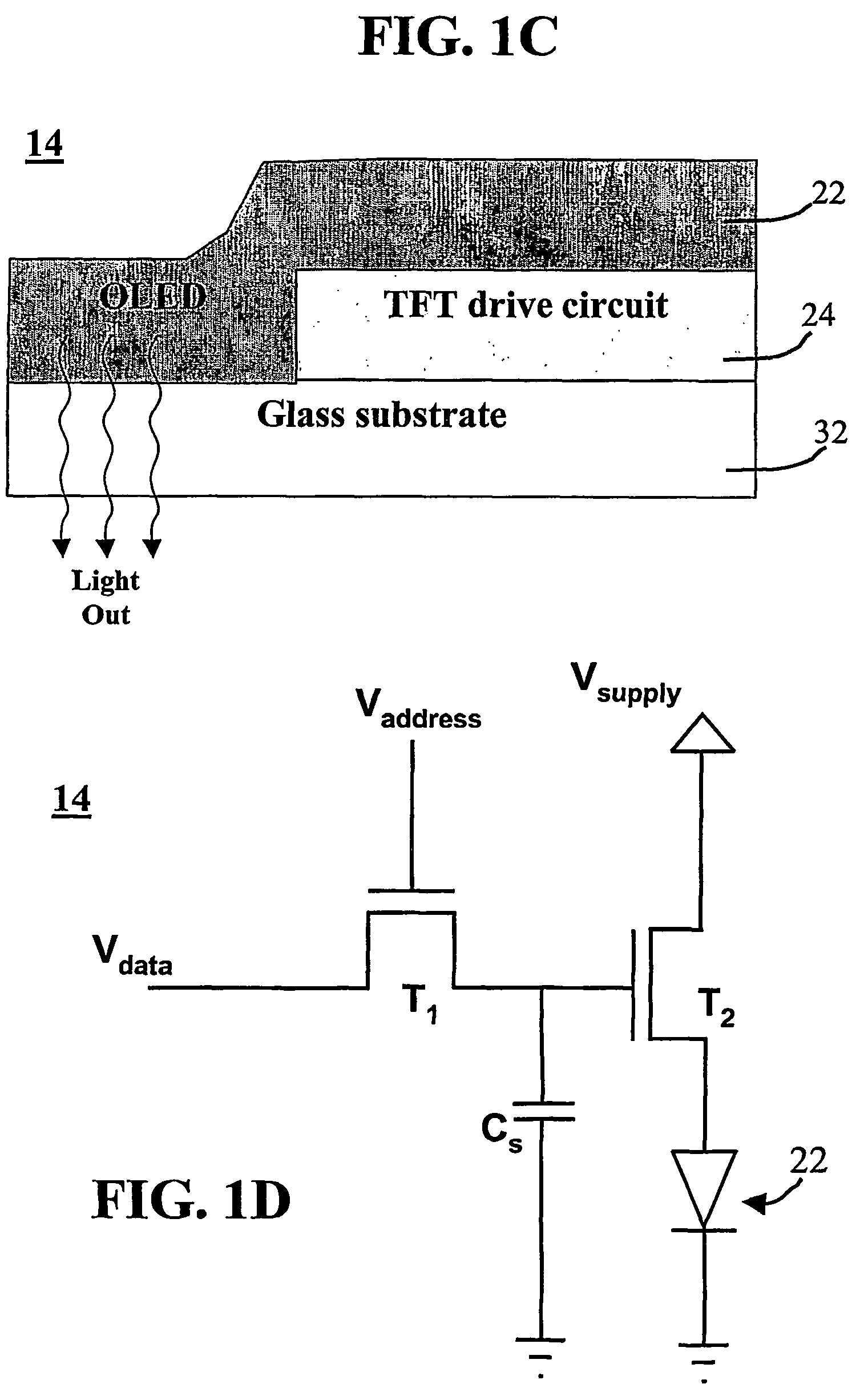

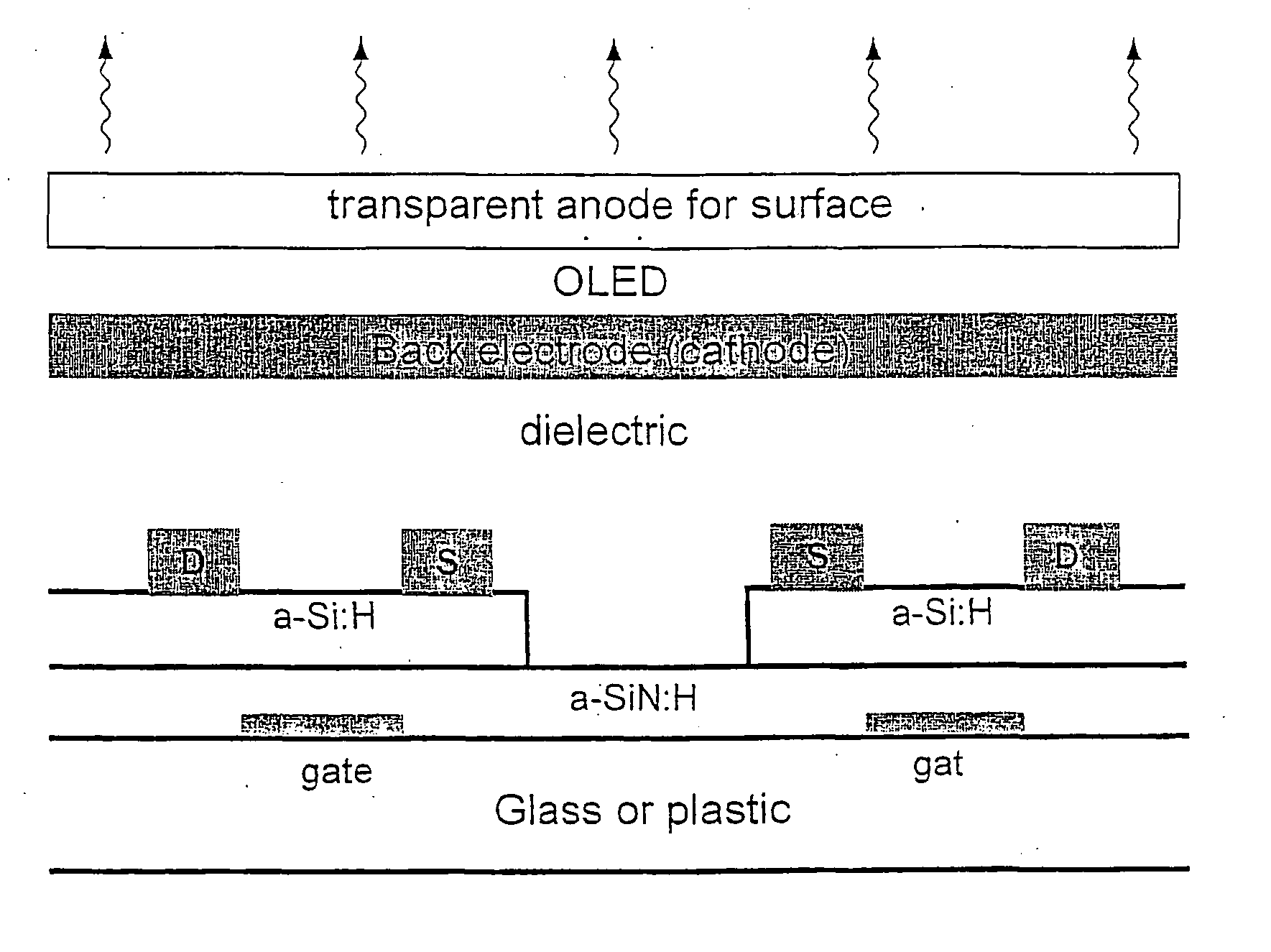

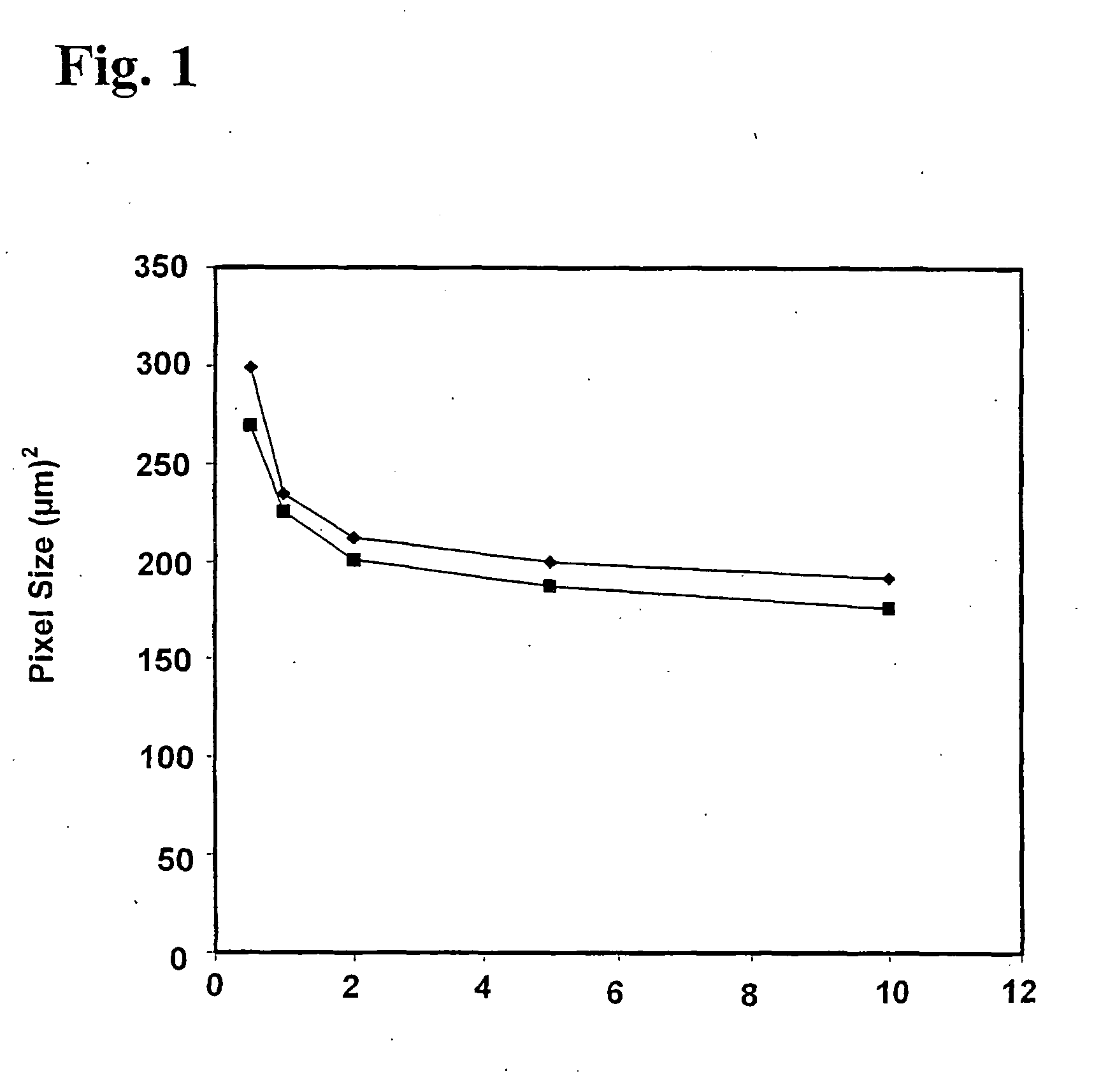

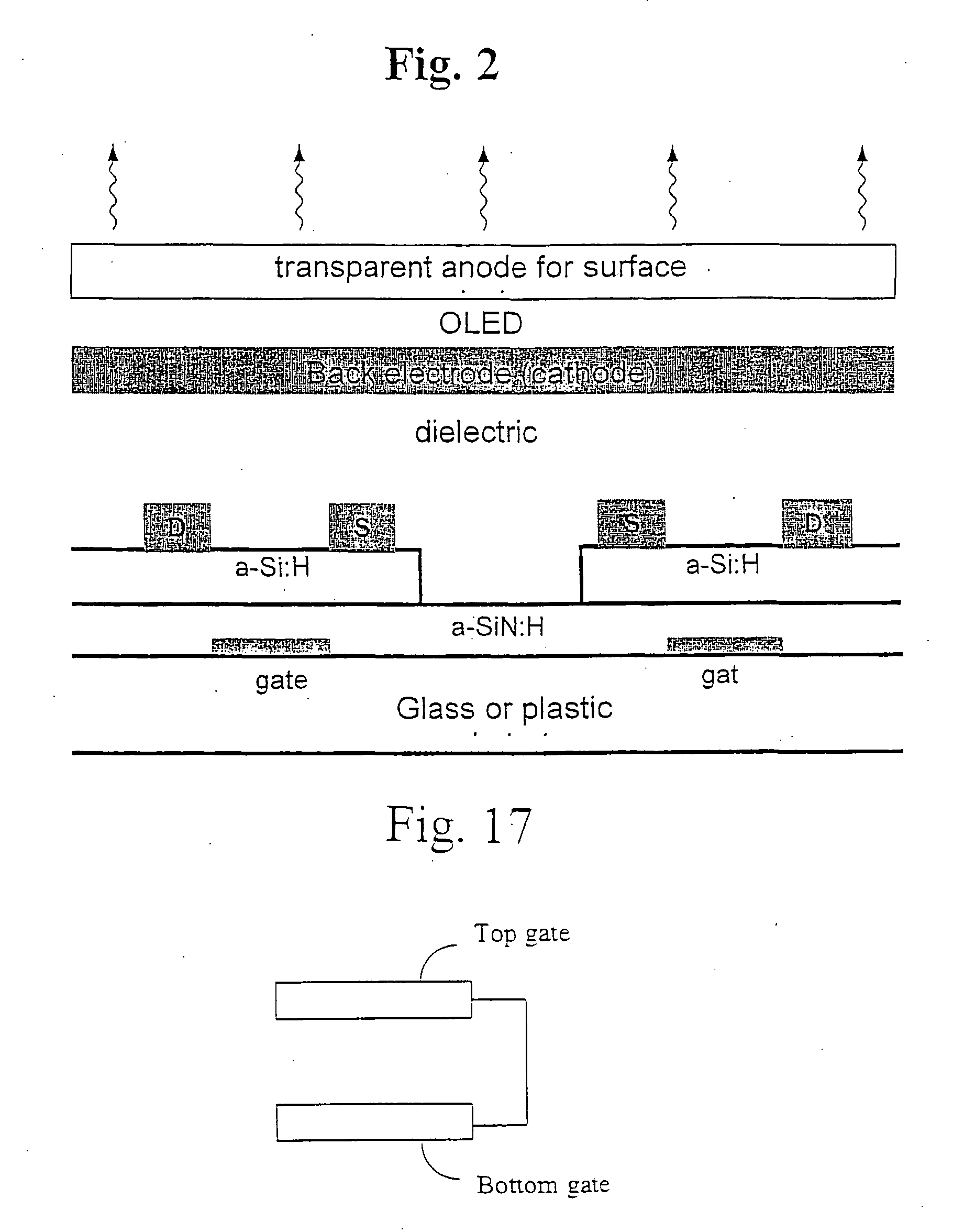

InactiveUS7414600B2Minimizing parasitic couplingMinimizes parasitic capacitanceTransistorStatic indicating devicesBottom gateDisplay device

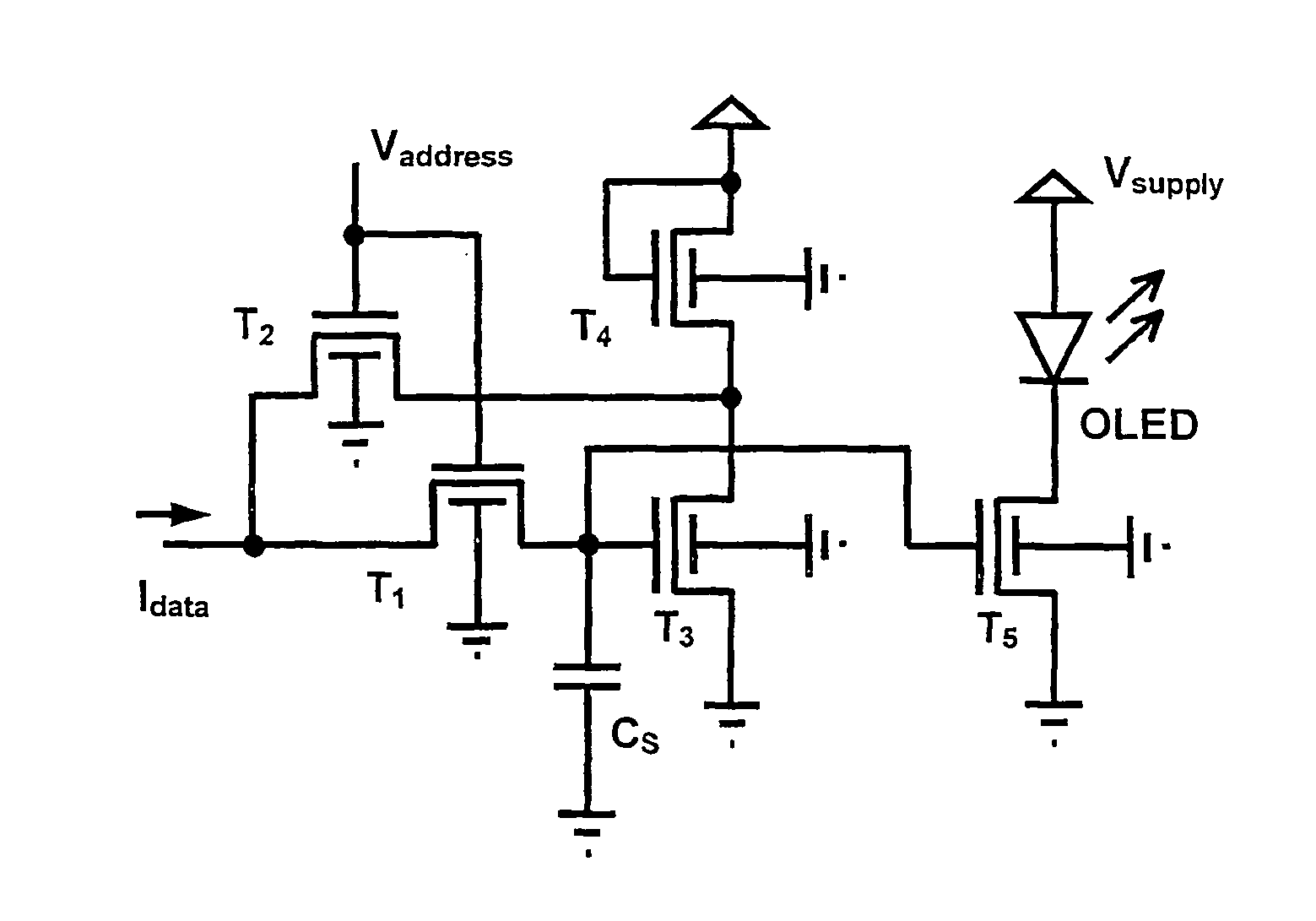

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

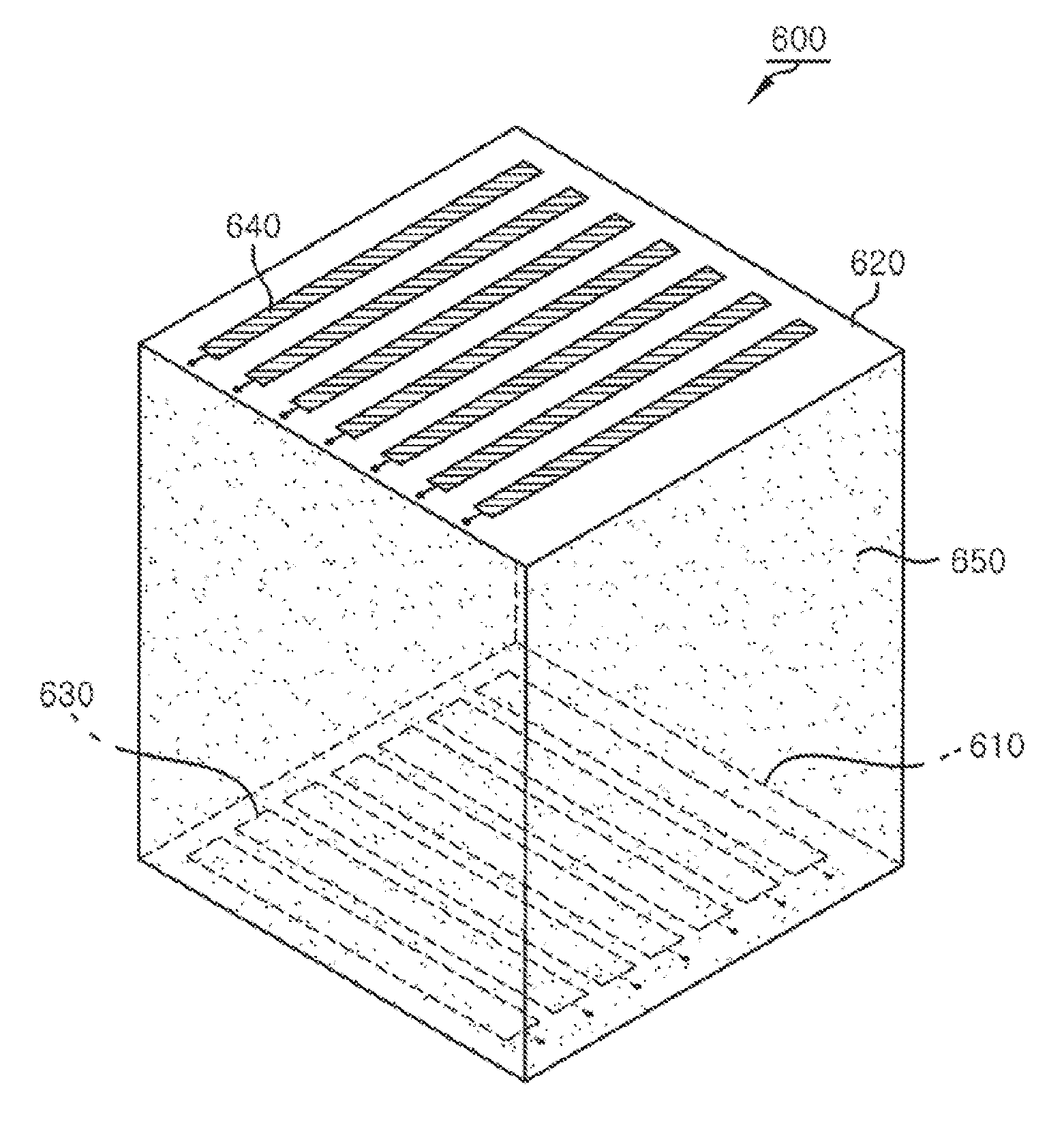

Organic light emitting diode display having shield electrodes

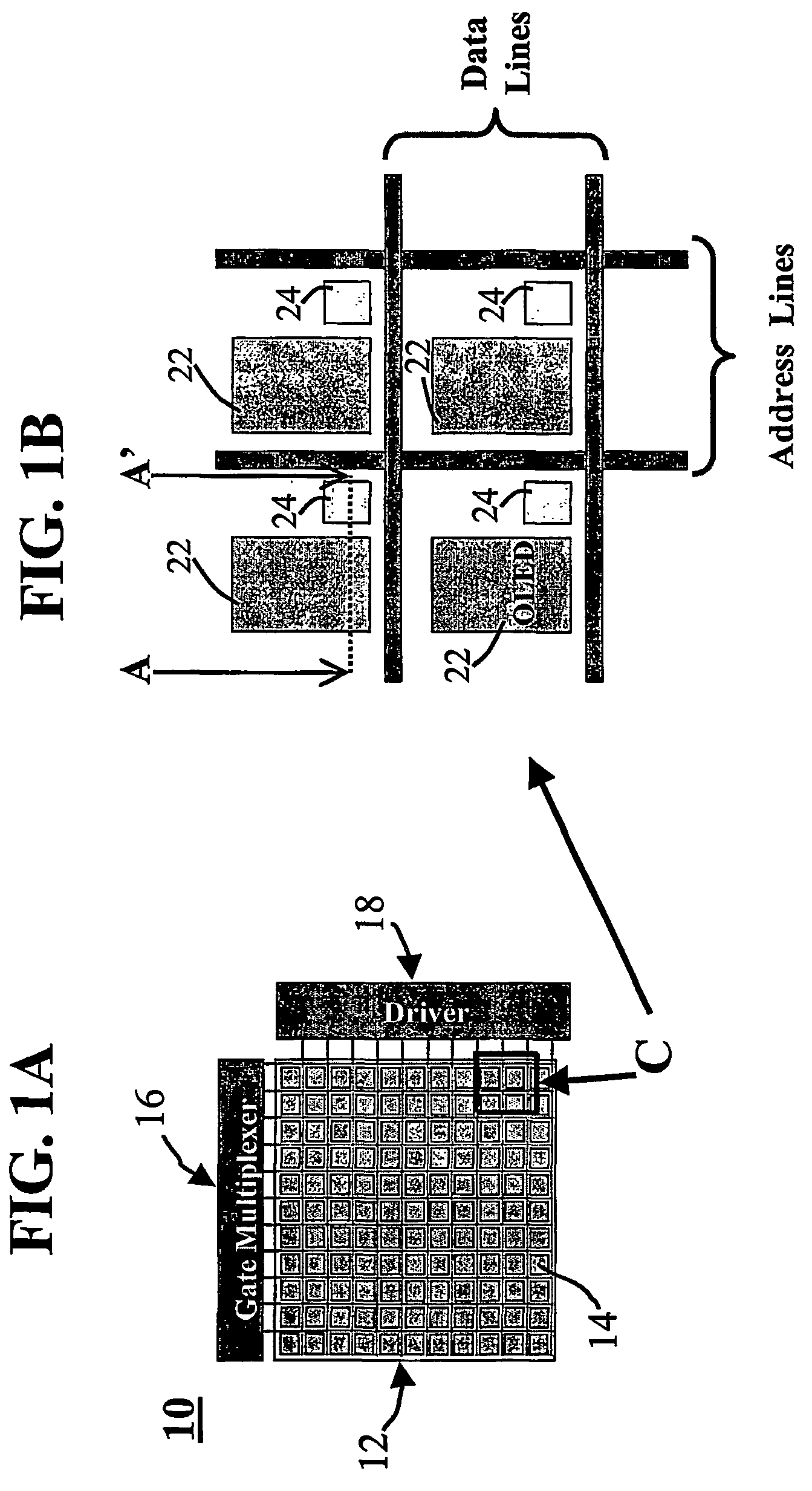

InactiveUS7248236B2Minimize parasitic capacitanceImprove performanceTransistorStatic indicating devicesDisplay deviceEngineering

An organic light emitting diode (OLED) display includes at least one shield electrode between a cathode layer and an OLED drive circuit. The OLED drive circuit has at least one thin-film transistor (TFT), and the shield electrode is disposed to correspond to the thin-film transistor and closer to the cathode layer, covering an entire region between the source and drain of the thin-film transistor. The shield electrode is either grounded or tied to the gate of the thin-film transistor, to thereby minimize parasitic capacitances in the pixels of the display to enhance the display performance. The presented architecture enables high density drive circuit integration in amorphous silicon or other technologies, yet preserving a high display aperture ratio.

Owner:IGNIS INNOVATION

Pixel current driver for organic light emitting diode displays

InactiveUS20060027807A1Improve circuit performanceMinimize chargeTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

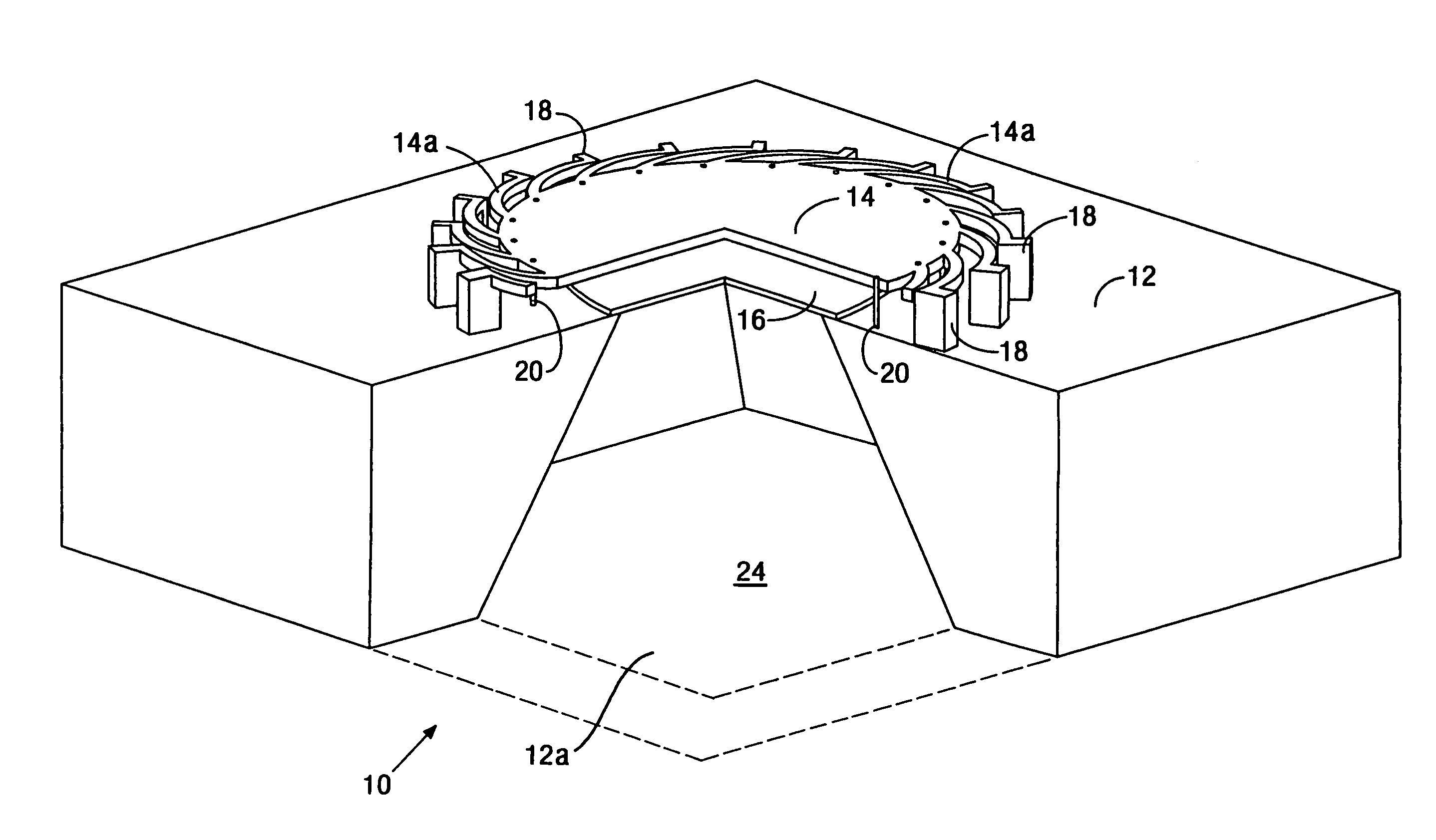

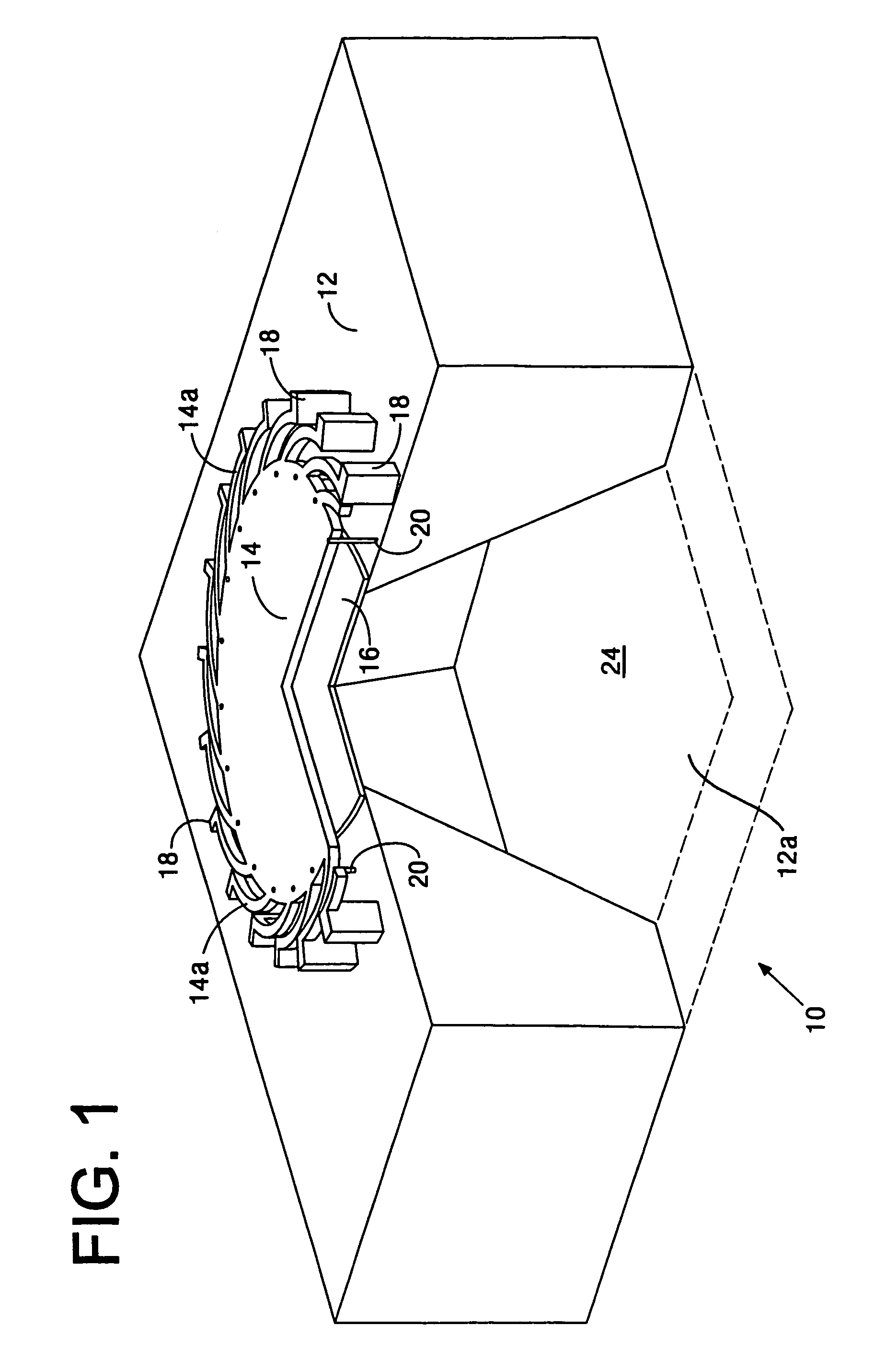

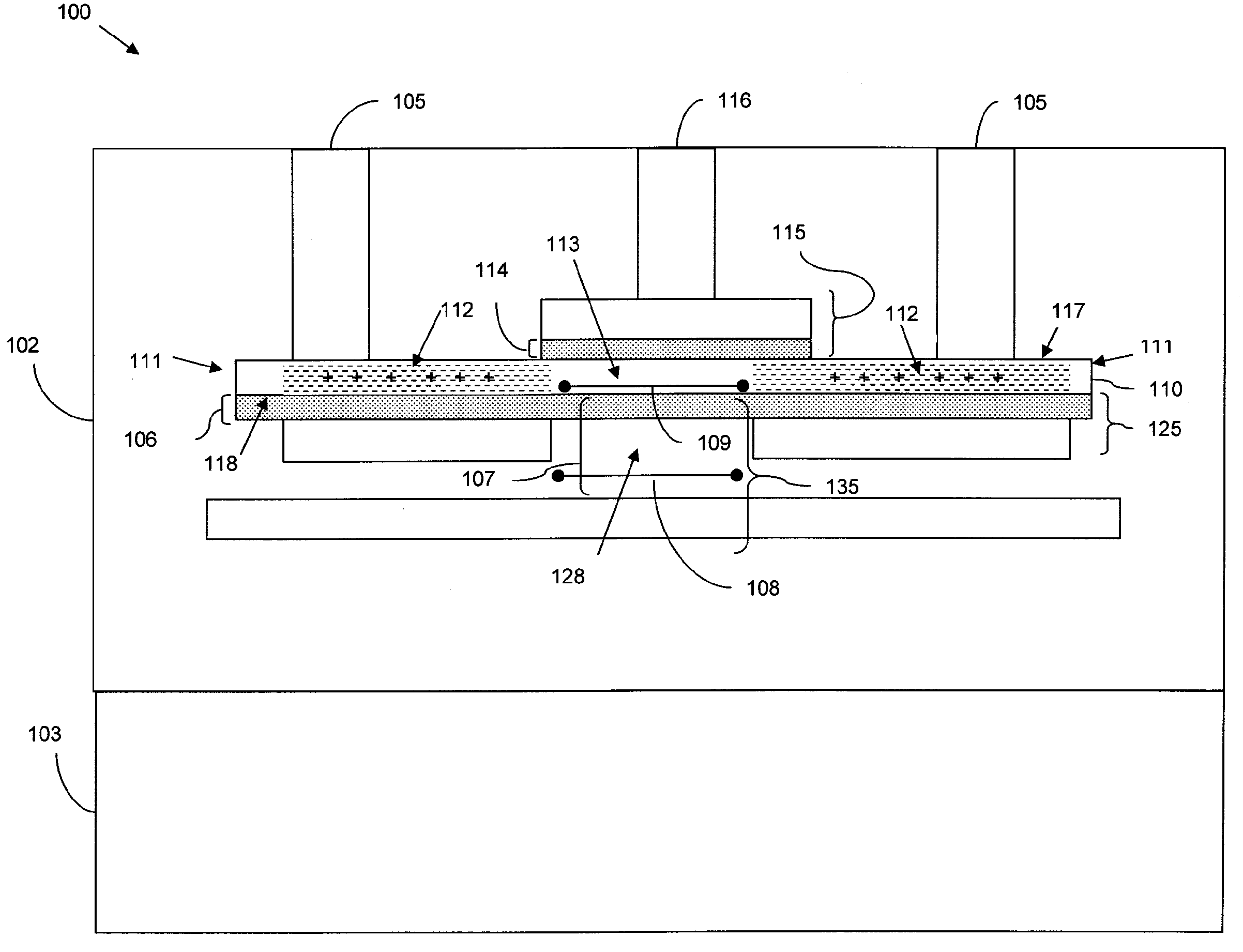

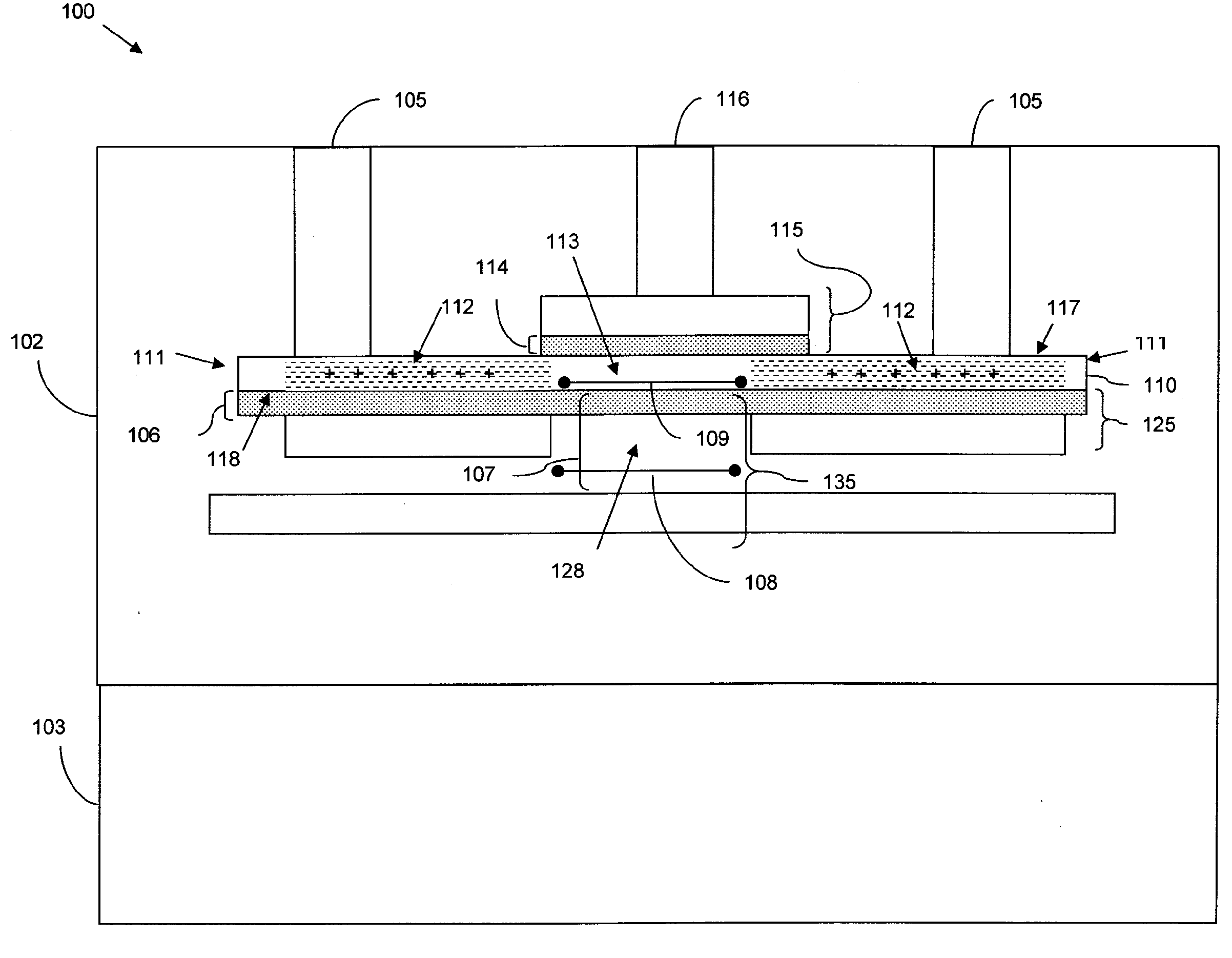

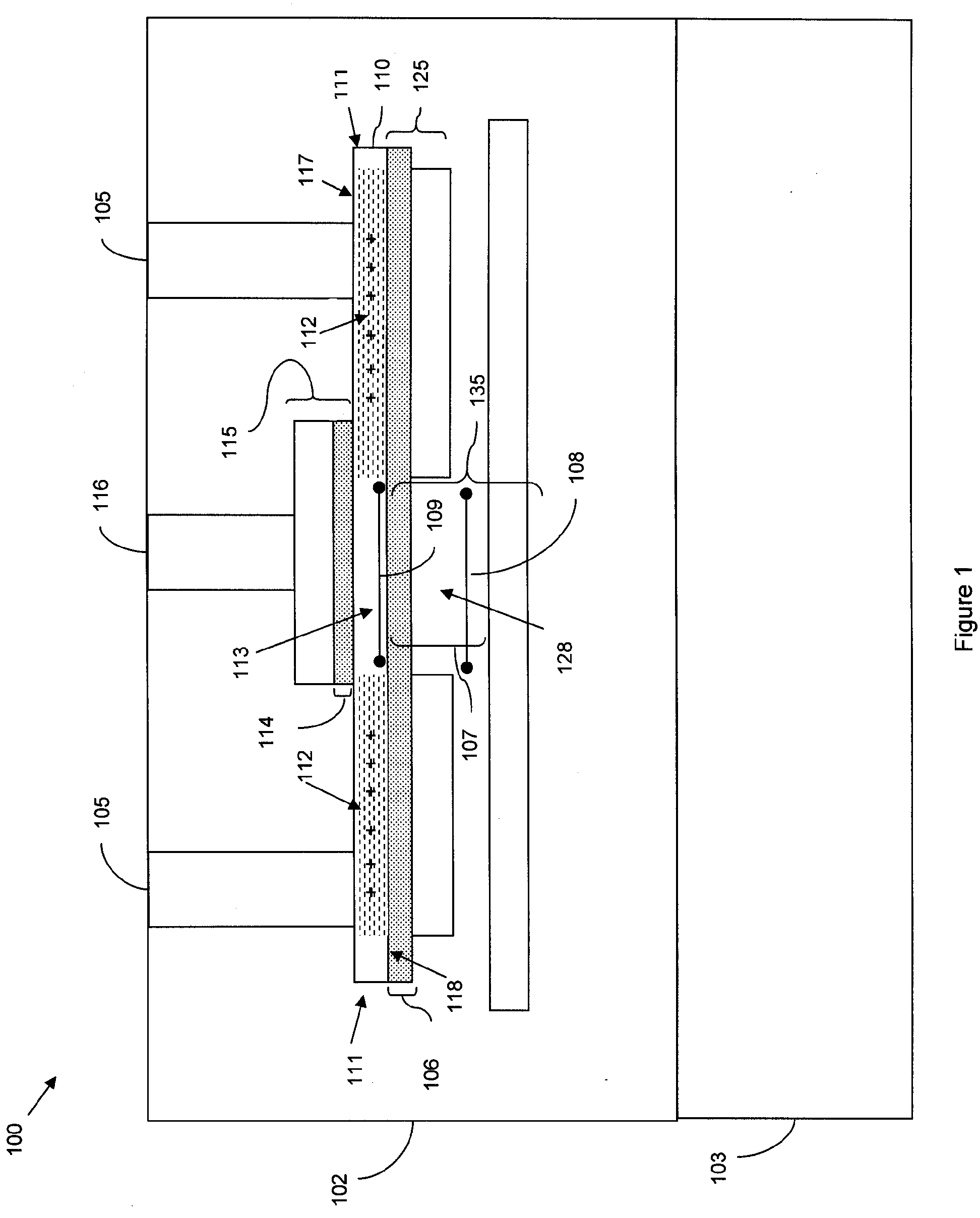

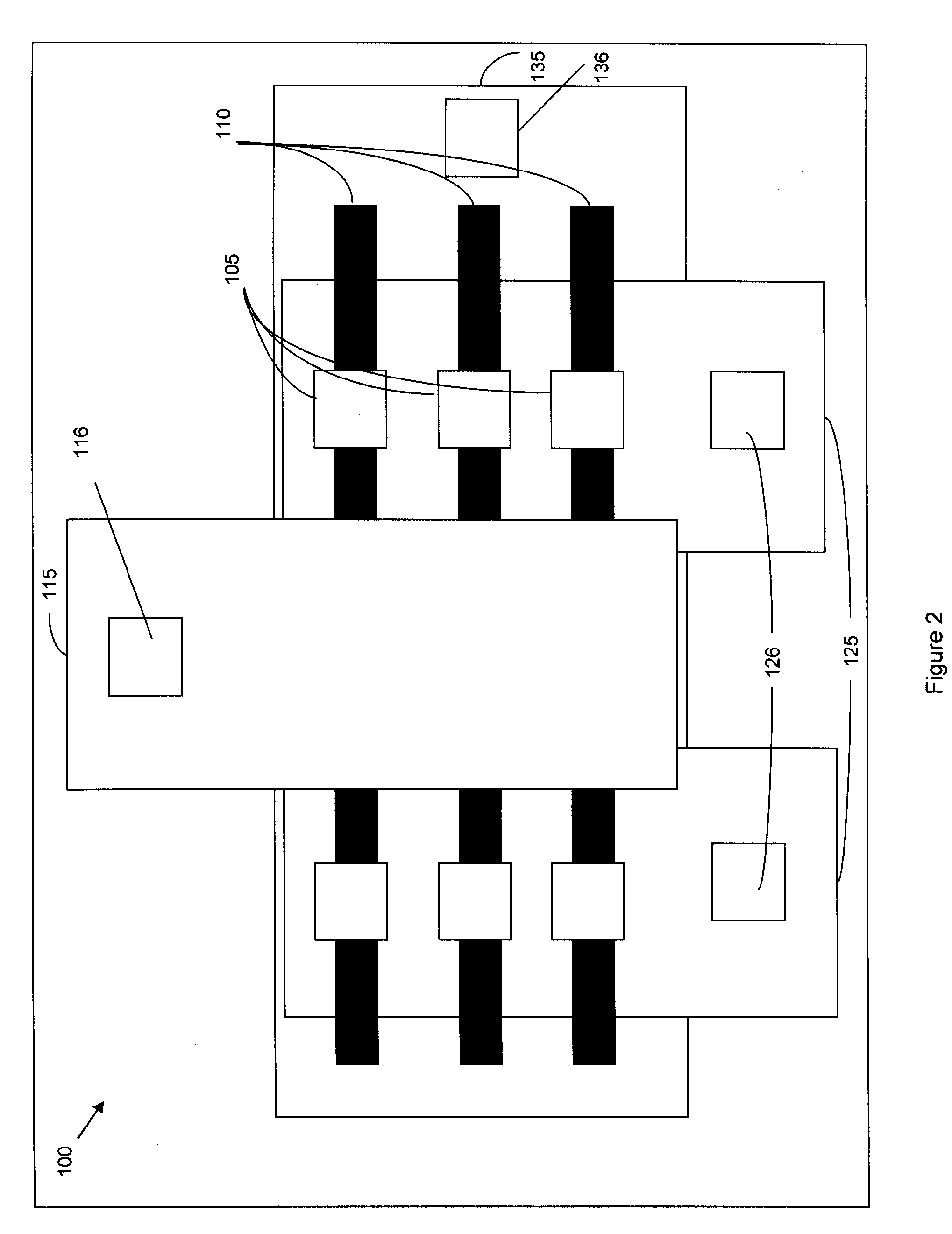

Through-Wafer Interconnection

ActiveUS20080203556A1Great freedomMinimizes parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorInterconnection

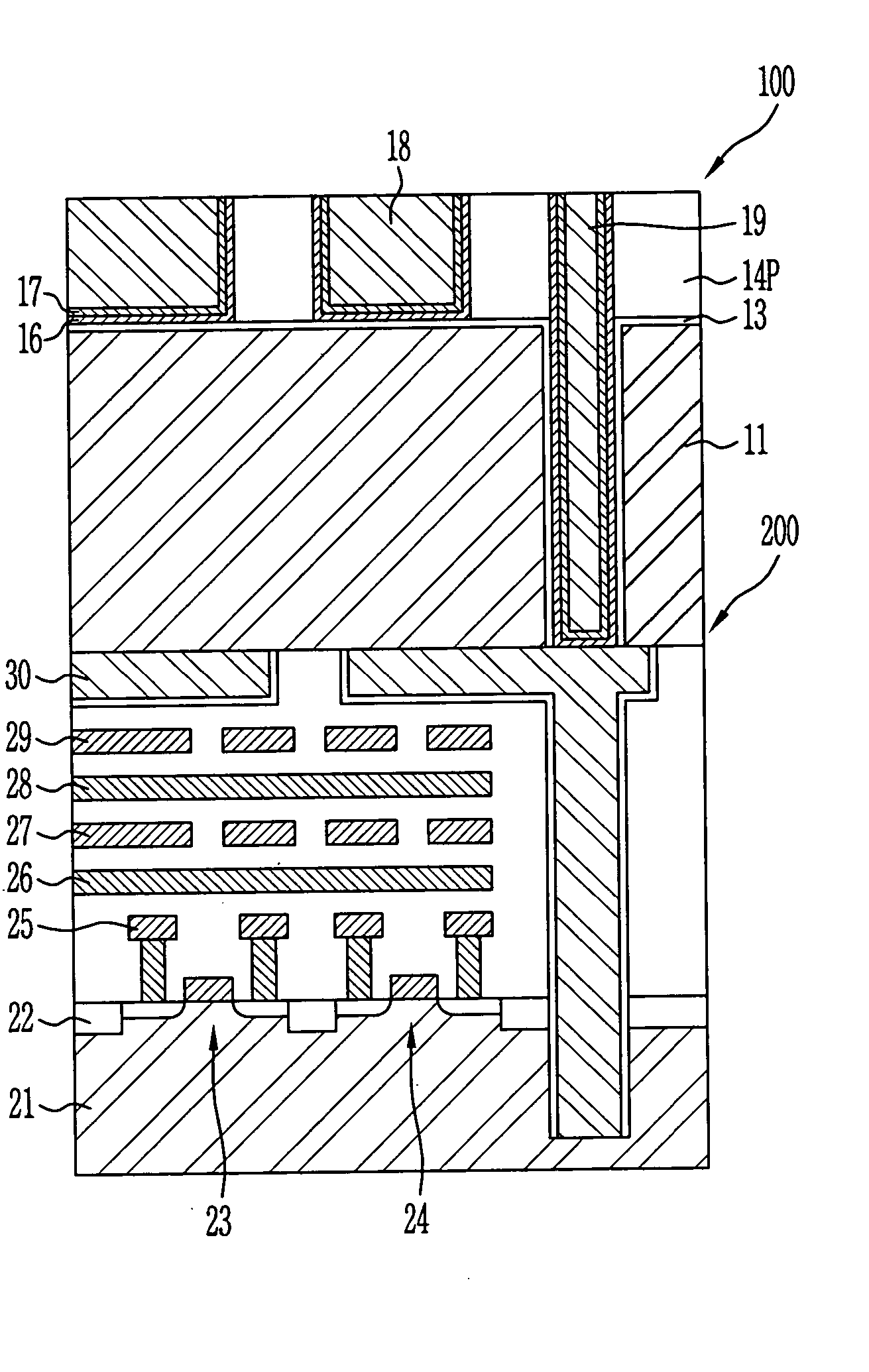

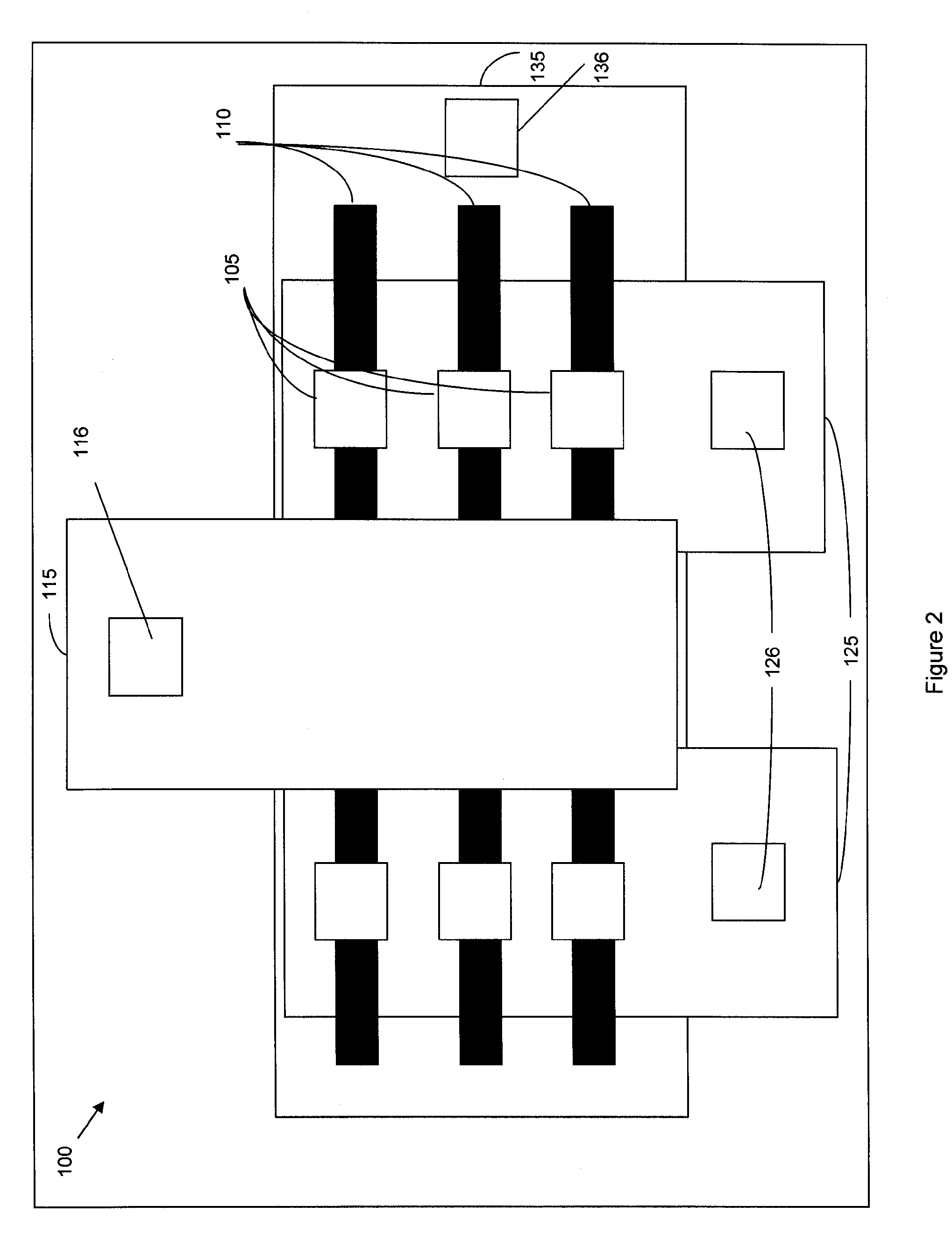

A through-wafer interconnect and a method for fabricating the same are disclosed. The method starts with a conductive wafer to form a patterned trench by removing material of the conductive wafer. The patterned trench extends in depth from the front side to the backside of the wafer, and has an annular opening generally dividing the conductive wafer into an inner portion and an outer portion whereby the inner portion of the conductive wafer is insulated from the outer portion and serves as a through-wafer conductor. A dielectric material is formed or added into the patterned trench mechanical to support and electrically insulate the through-wafer conductor. Multiple conductors can be formed in an array.

Owner:KOLO MEDICAL (SUZHOU) CO LTD

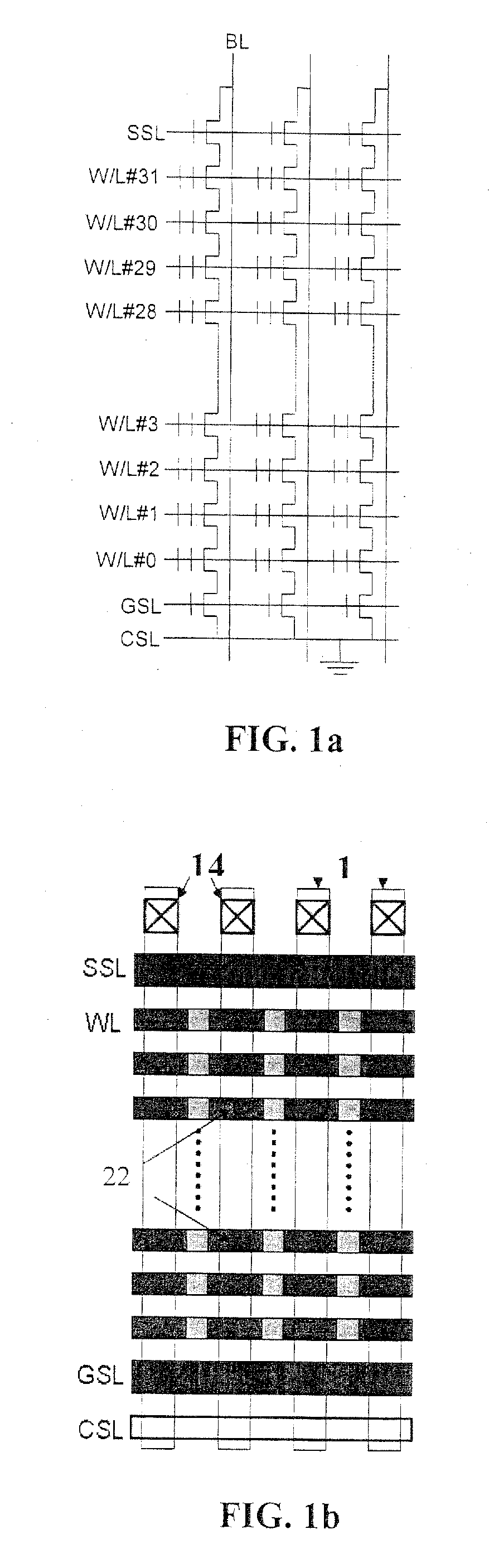

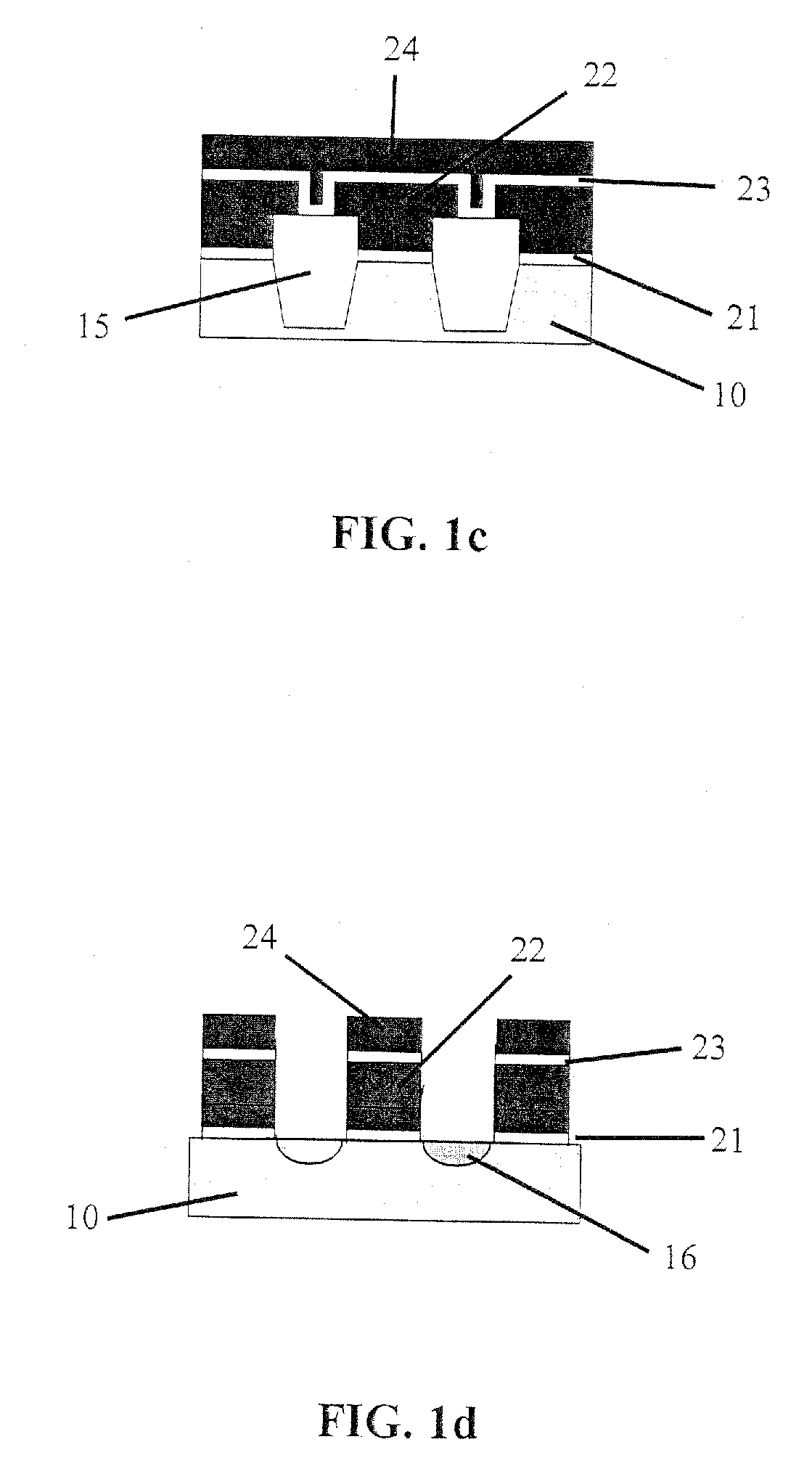

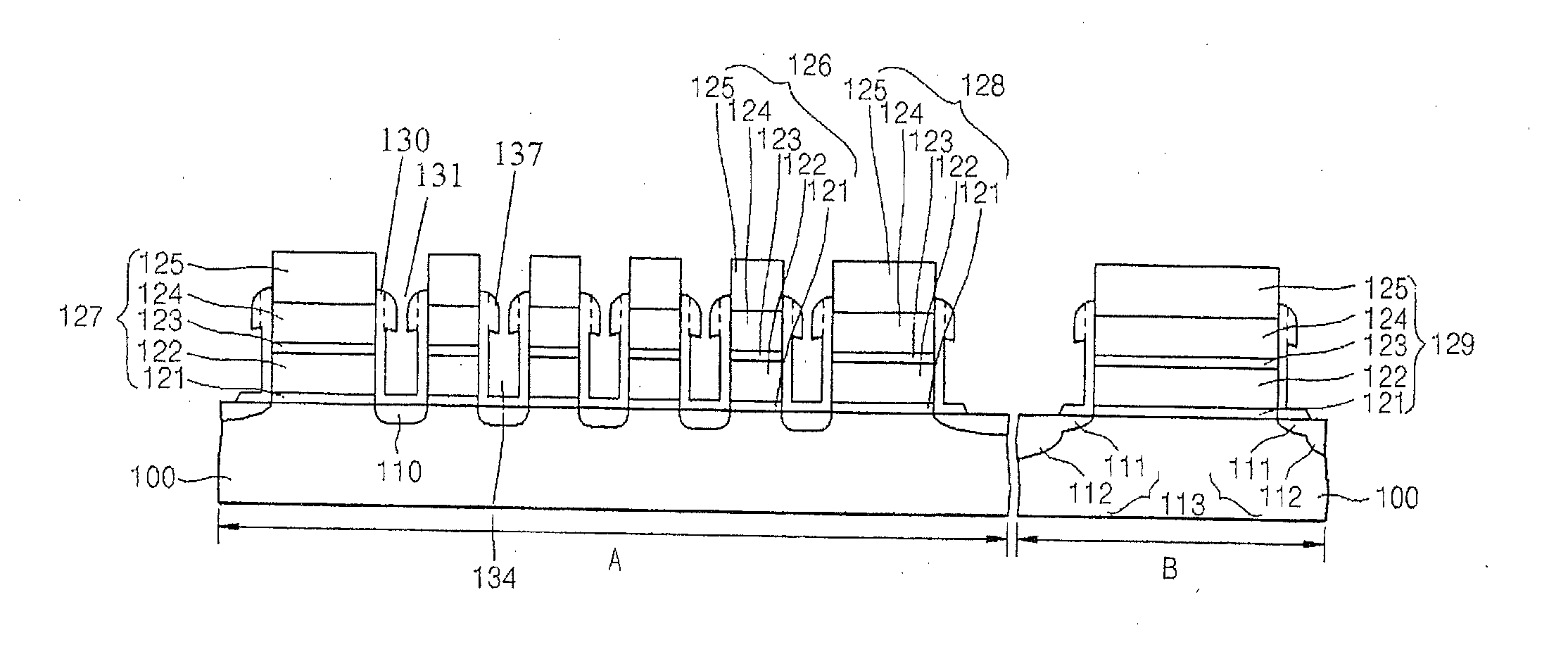

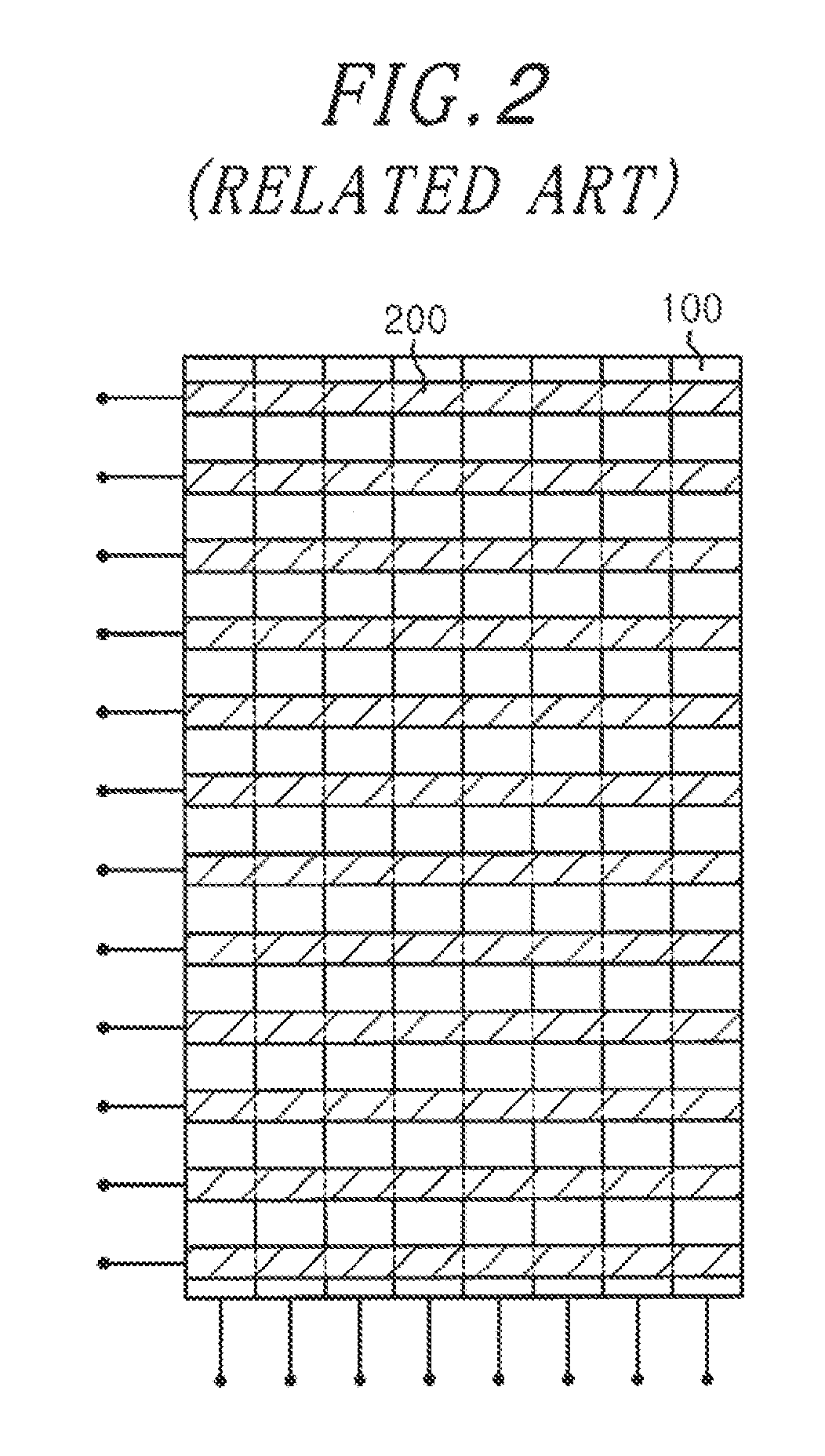

Semiconductor device and method for fabricating the same

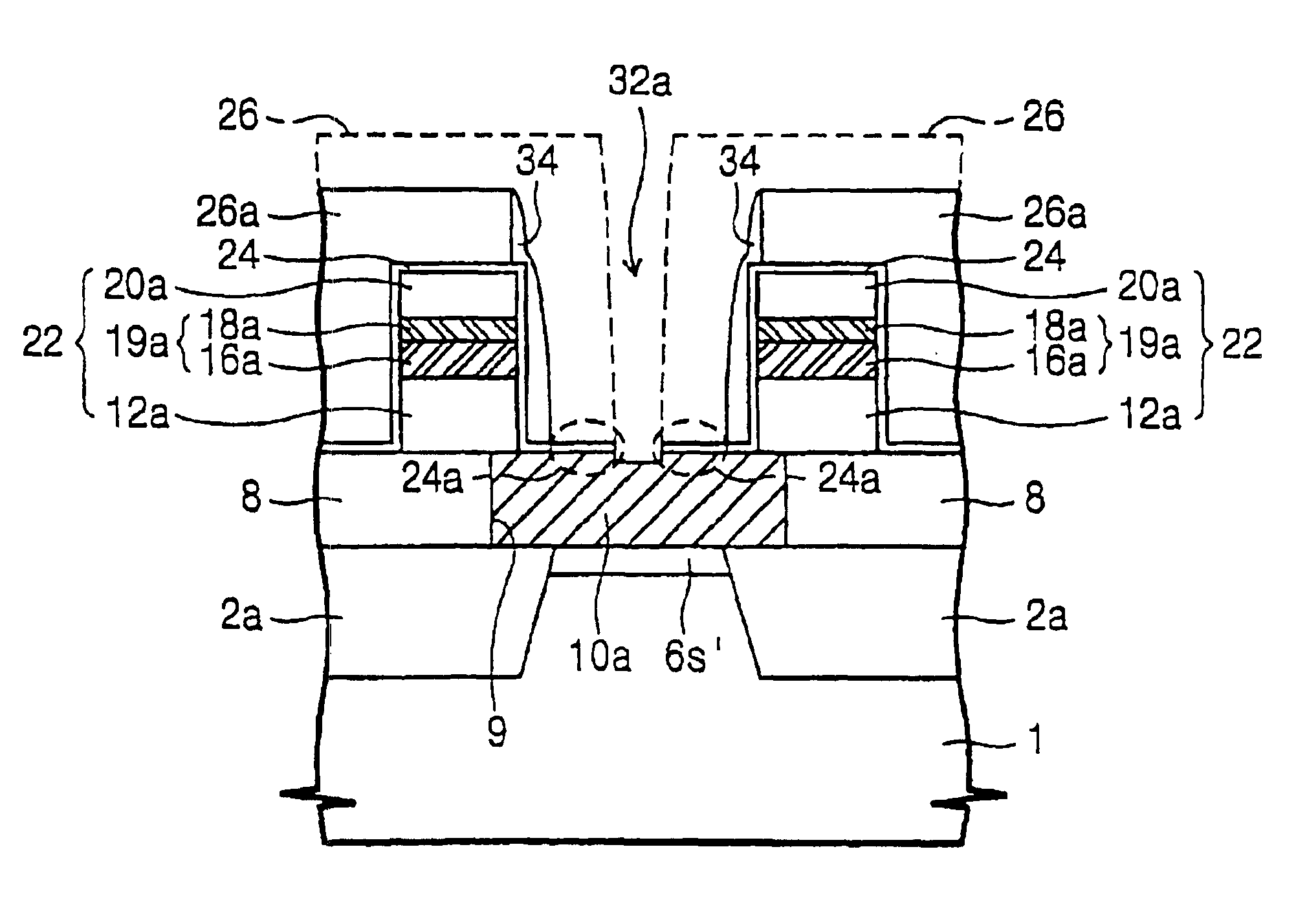

InactiveUS20070096202A1Minimize parasitic capacitanceMaximize volume of airSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitorInsulation layer

Methods for forming semiconductor memory structures including air gaps between adjacent gate structures are provided. The volume of the air gaps is maximized and the width thereof made uniform in order to minimize the parasitic capacitance and any variance therein between the gate structures. The methods include forming an insulation layer between adjacent gate structures and subsequently etching the insulation layer to leave an air gap. Devices fabricated in accordance with the methods are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

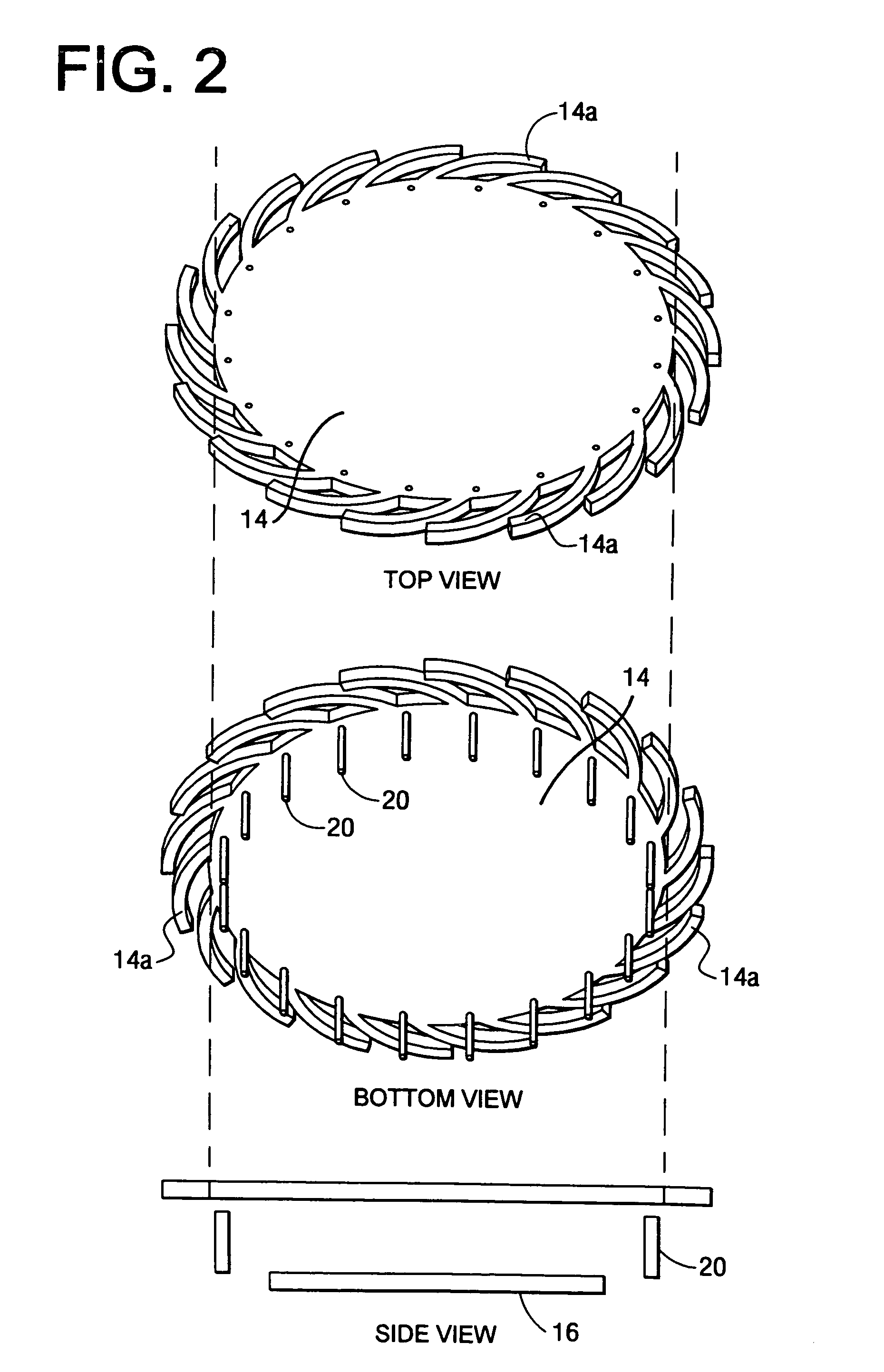

Silicon microphone

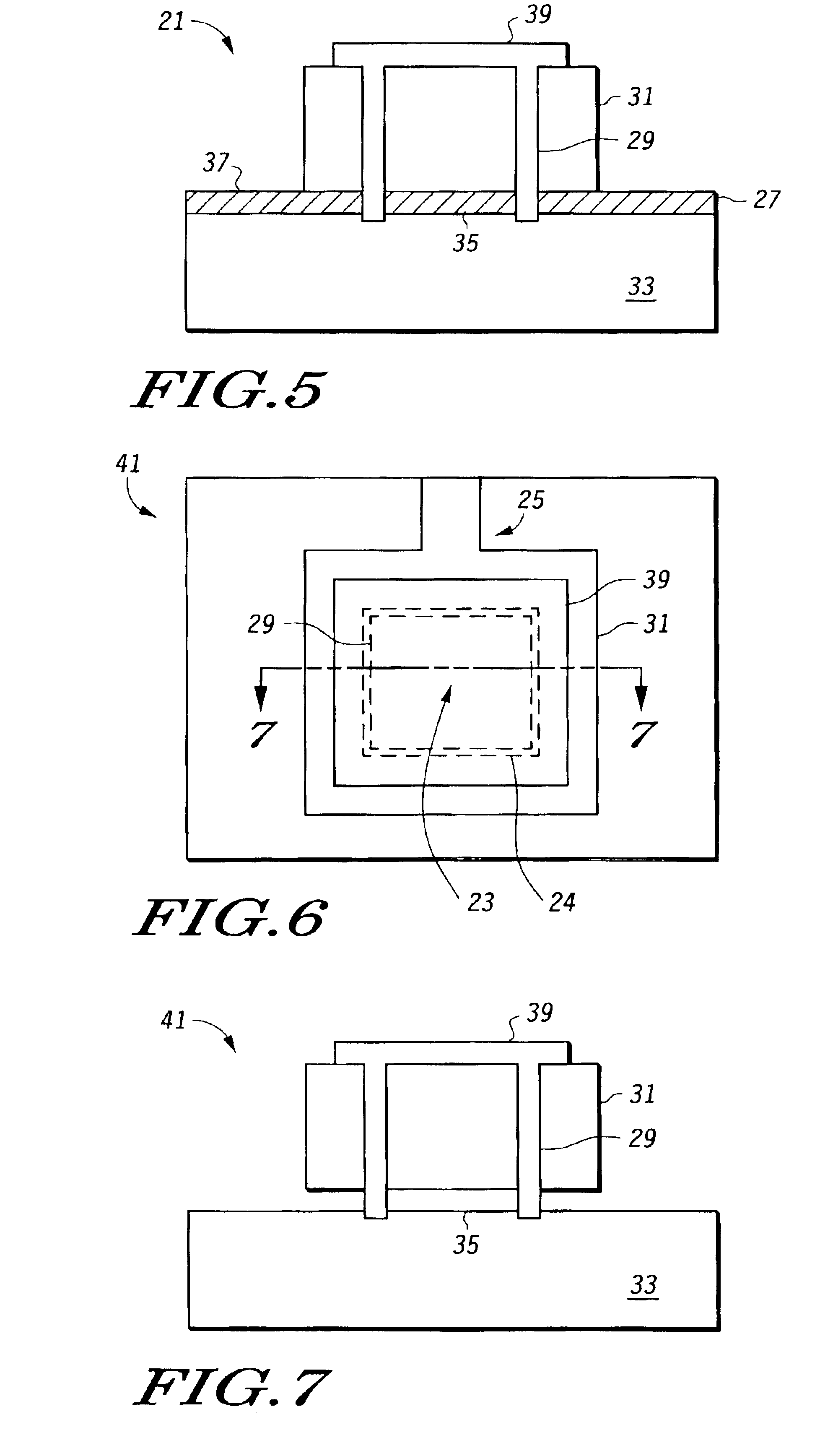

InactiveUS7023066B2Simplify the manufacturing processMinimizes parasitic capacitanceSemiconductor electrostatic transducersSemiconductor/solid-state device manufacturingEngineeringSound pressure

A solid-state transducer is disclosed. The transducer comprises a semi-conductor substrate forming a support structure and having an opening. A thin-film structure forming a diaphragm responsive to fluid-transmitted acoustic pressure is disposed over the opening. The transducer further includes a plurality of semi-conductor supports and tangential arms extending from the diaphragm edge for connecting the periphery of the diaphragm to the supports. The tangential arms permit the diaphragm to rotate relative to the supports to relieve film stress in the diaphragm. The transducer still further includes a plurality of stop bumps disposed between the substrate and the diaphragm. The stop bumps determine the separation of the diaphragm from the substrate when the transducer is biased.

Owner:KNOWLES ELECTRONICS INC

Through-wafer interconnection

ActiveUS8105941B2Great freedomMinimizes parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorInterconnection

A through-wafer interconnect and a method for fabricating the same are disclosed. The method starts with a conductive wafer to form a patterned trench by removing material of the conductive wafer. The patterned trench extends in depth from the front side to the backside of the wafer, and has an annular opening generally dividing the conductive wafer into an inner portion and an outer portion whereby the inner portion of the conductive wafer is insulated from the outer portion and serves as a through-wafer conductor. A dielectric material is formed or added into the patterned trench mechanical to support and electrically insulate the through-wafer conductor. Multiple conductors can be formed in an array.

Owner:KOLO MEDICAL (SUZHOU) CO LTD

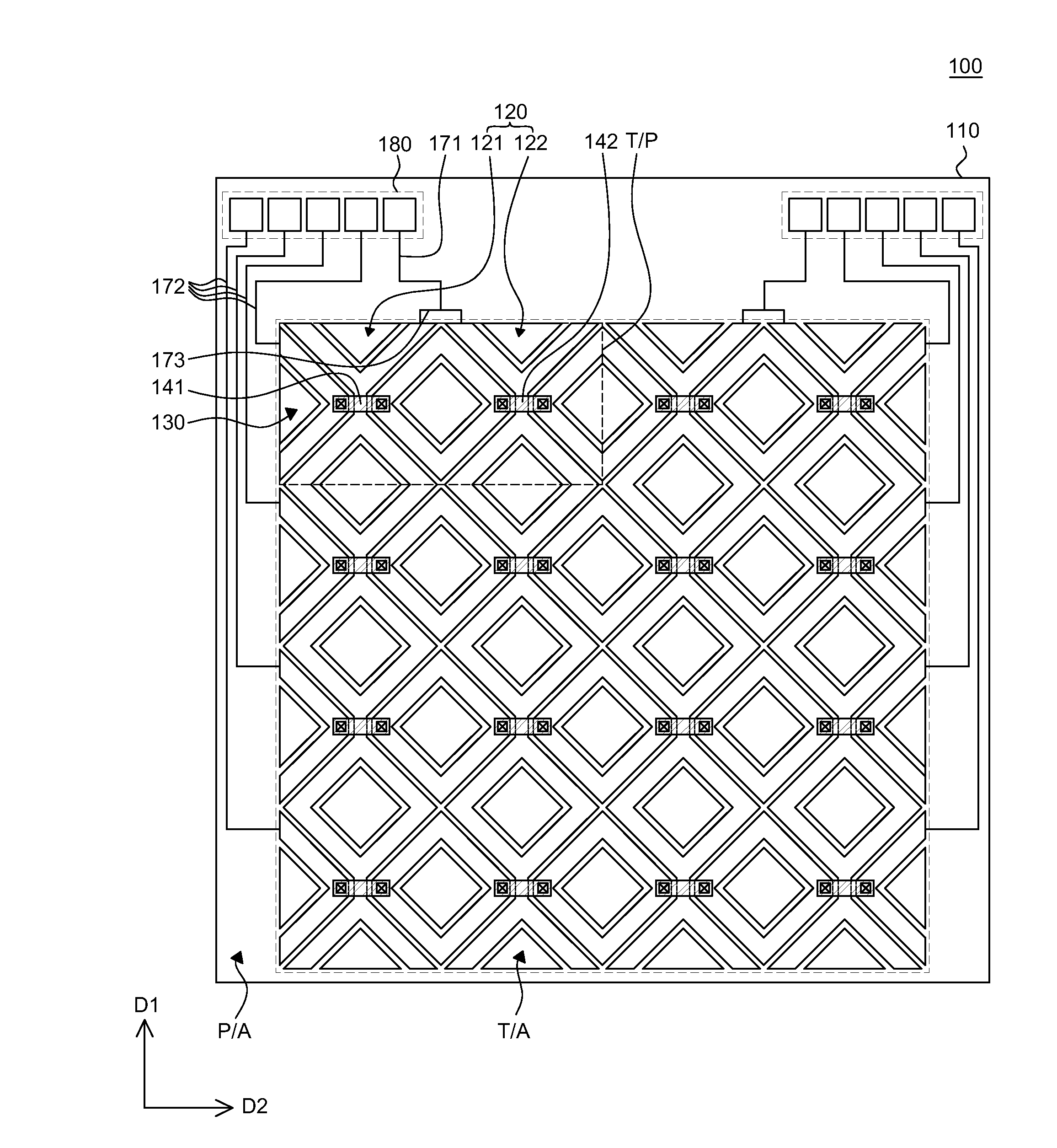

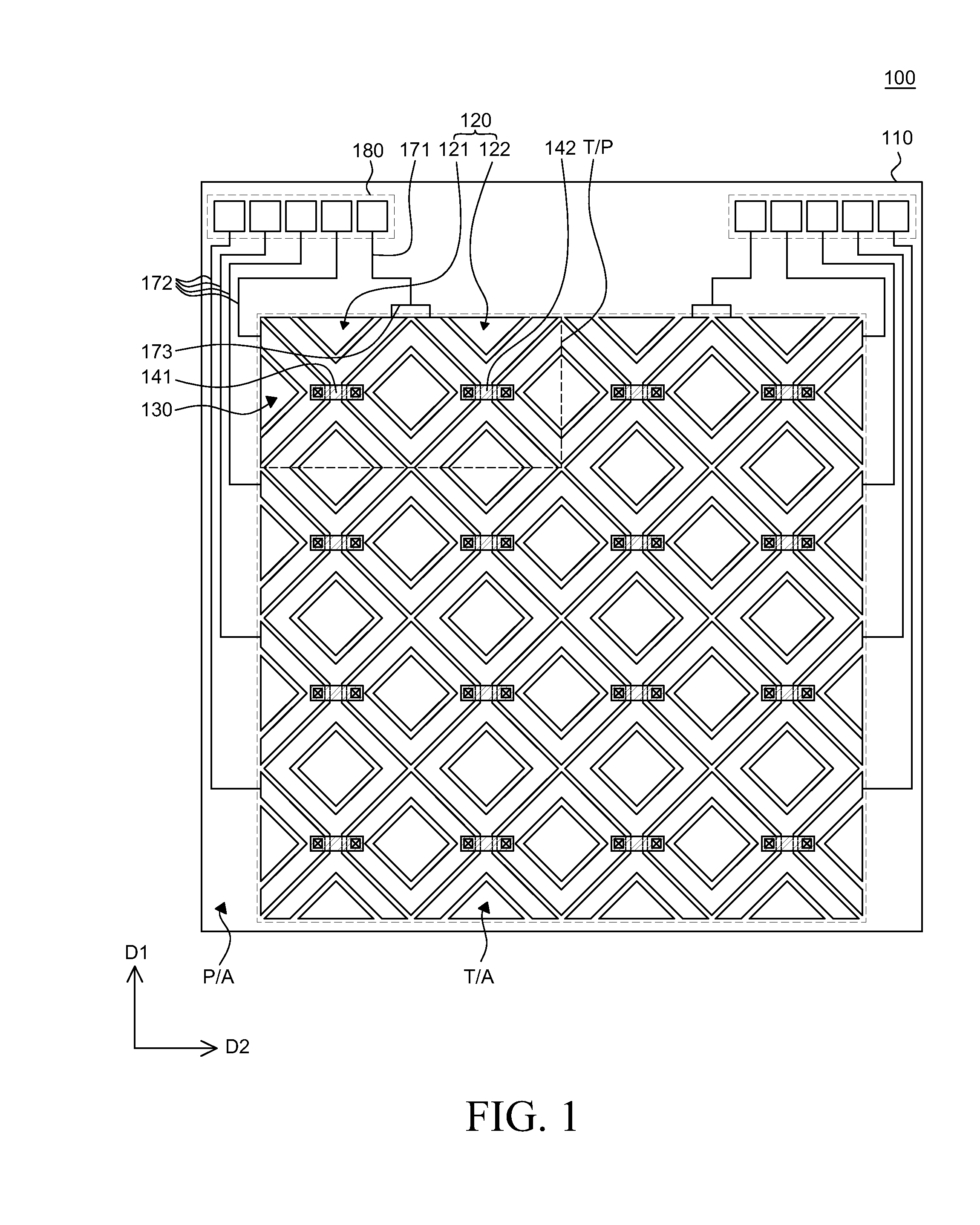

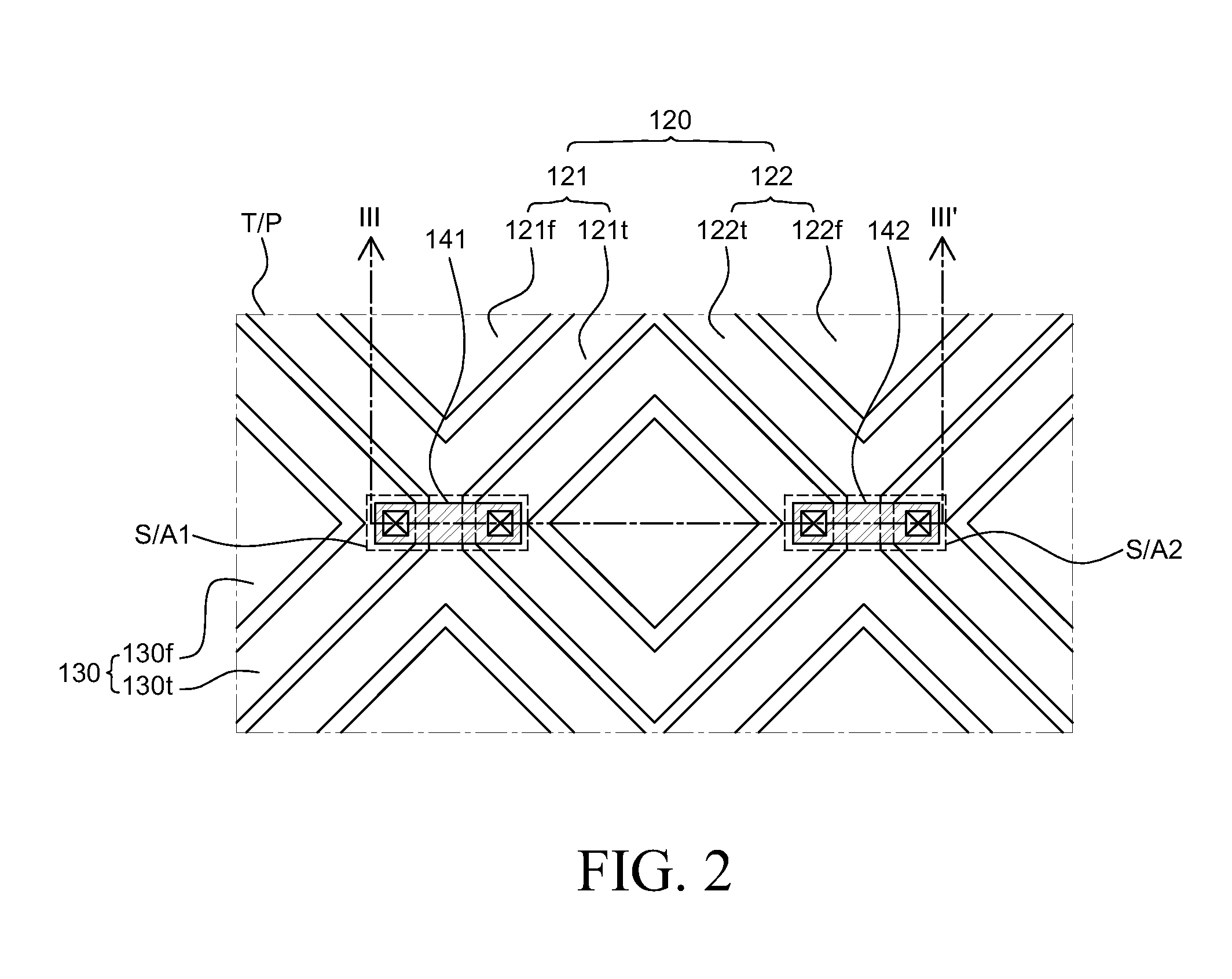

Touch panel and touch panel-integrated organic light emitting display device

ActiveUS20160117031A1Minimizes parasitic capacitanceReduce capacitanceInput/output processes for data processingDisplay deviceTouch panel

Provided is a touch panel-integrated organic light emitting display device. The touch panel-integrated organic light emitting display device includes an upper substrate, a lower substrate and a touch panel positioned between the upper substrate and the lower substrate. The touch panel includes an array of first touch electrodes connected in a first direction under the upper substrate, an array of second touch electrodes, in a same plane as the first touch electrodes, connected in a second direction perpendicular to the first direction under the upper substrate, a plurality of connection electrodes connecting the second touch electrodes in the second direction, and at least one of the first and second touch electrodes includes a touch detection part and a floating part electrically isolated from the touch detection part.

Owner:LG DISPLAY CO LTD

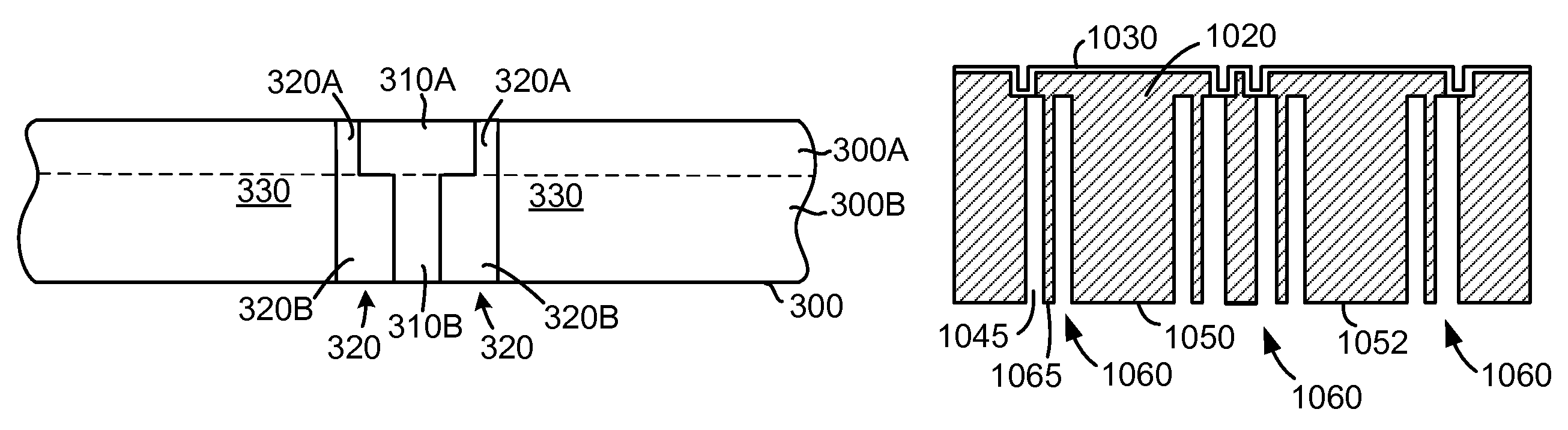

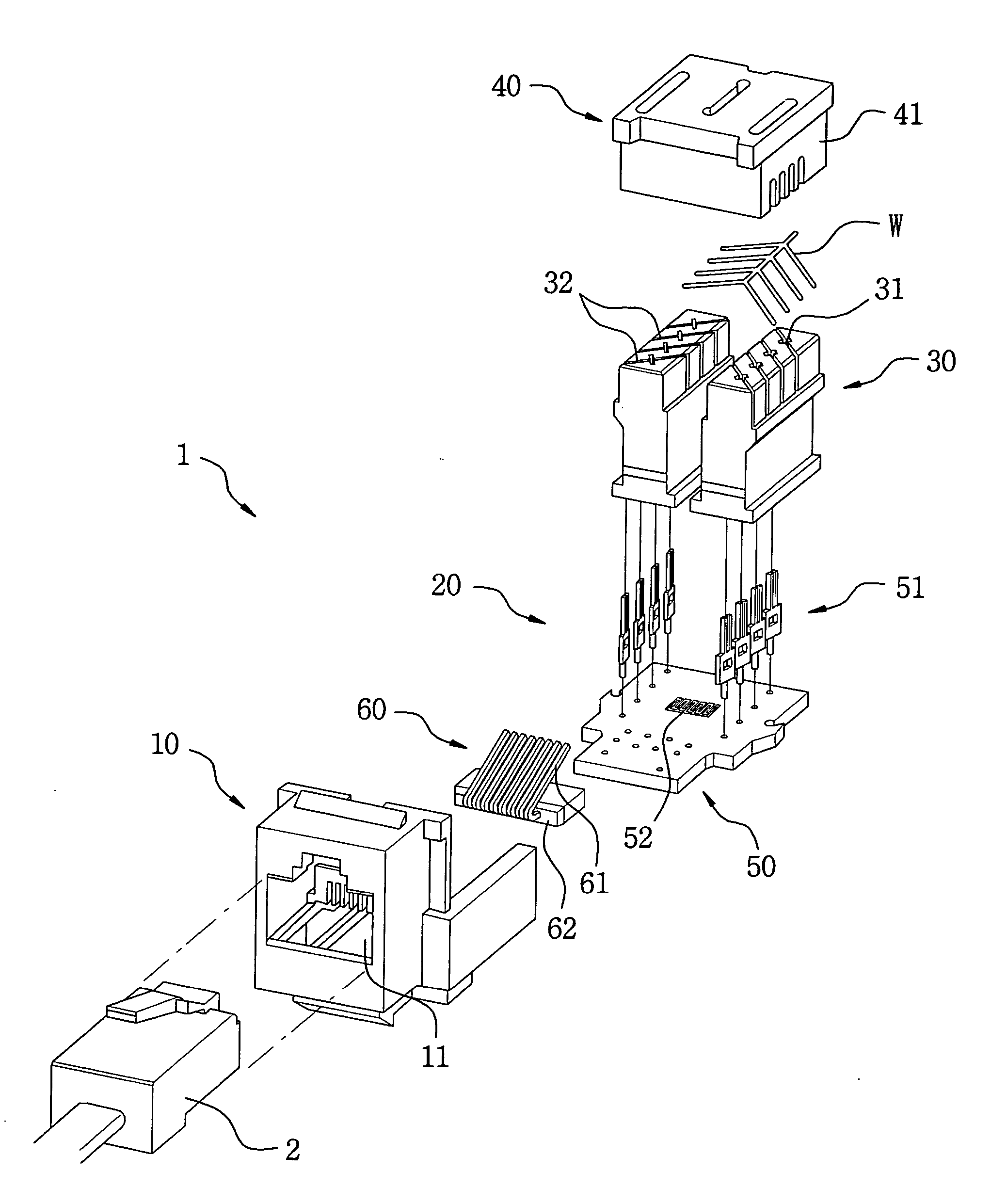

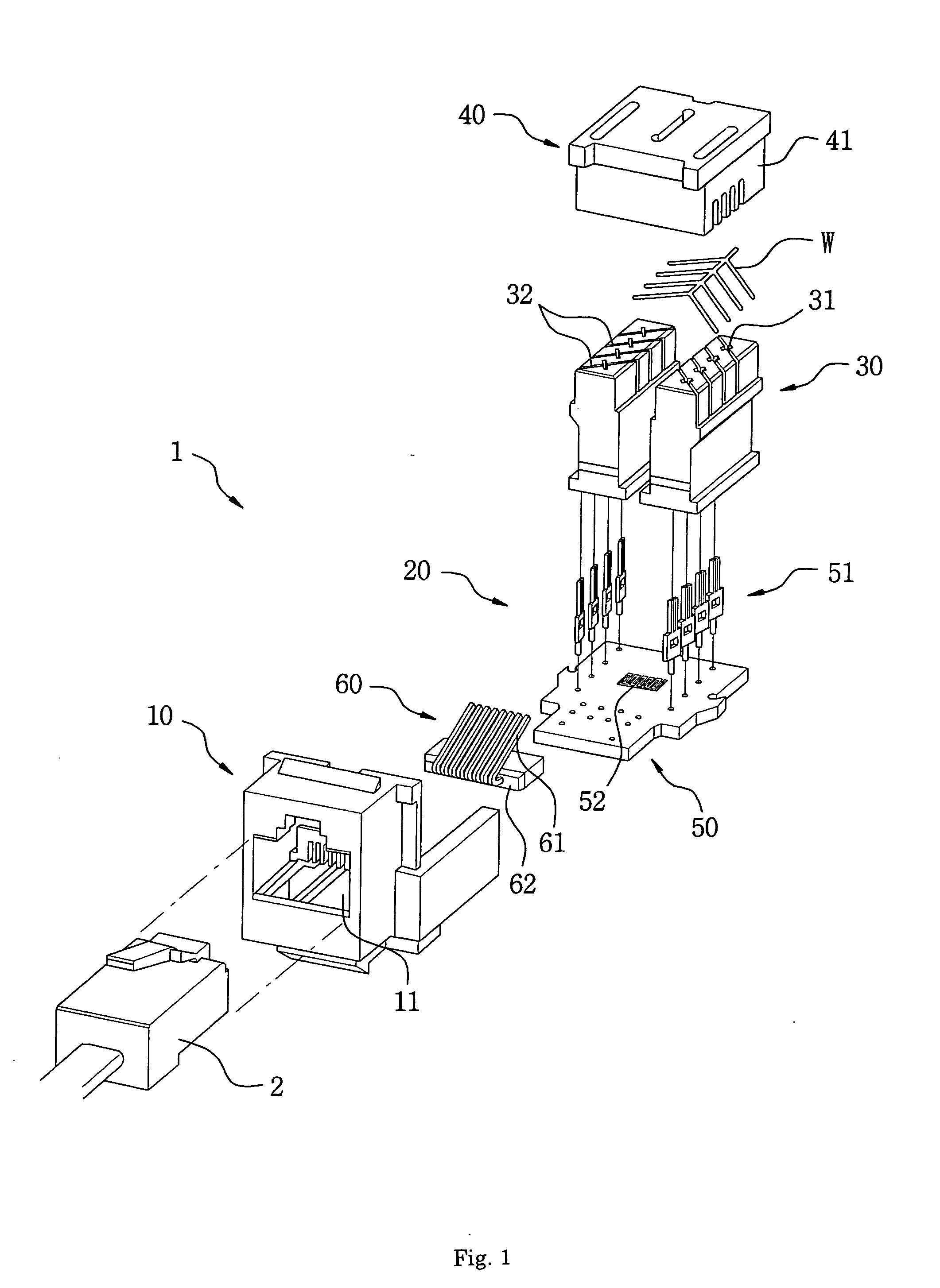

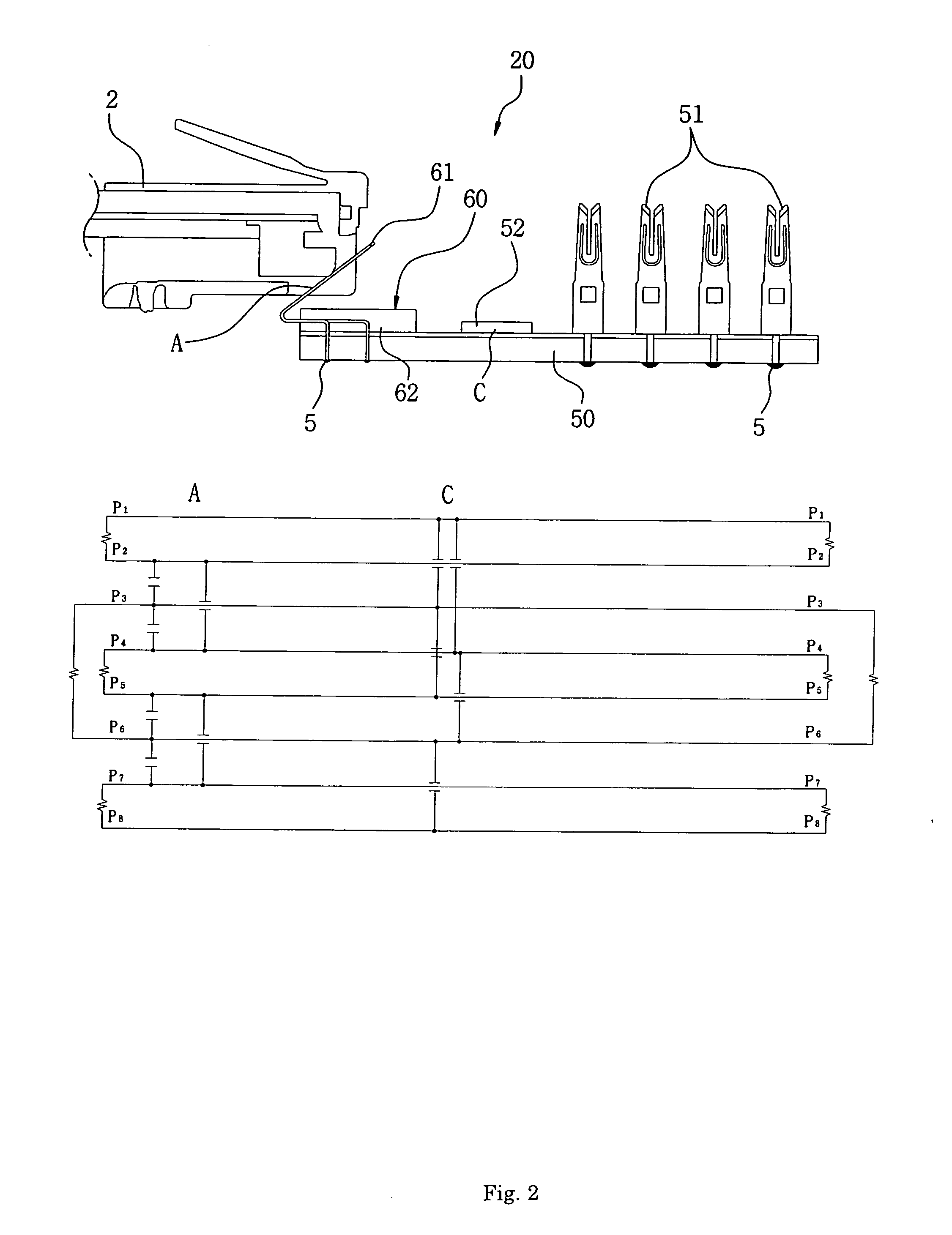

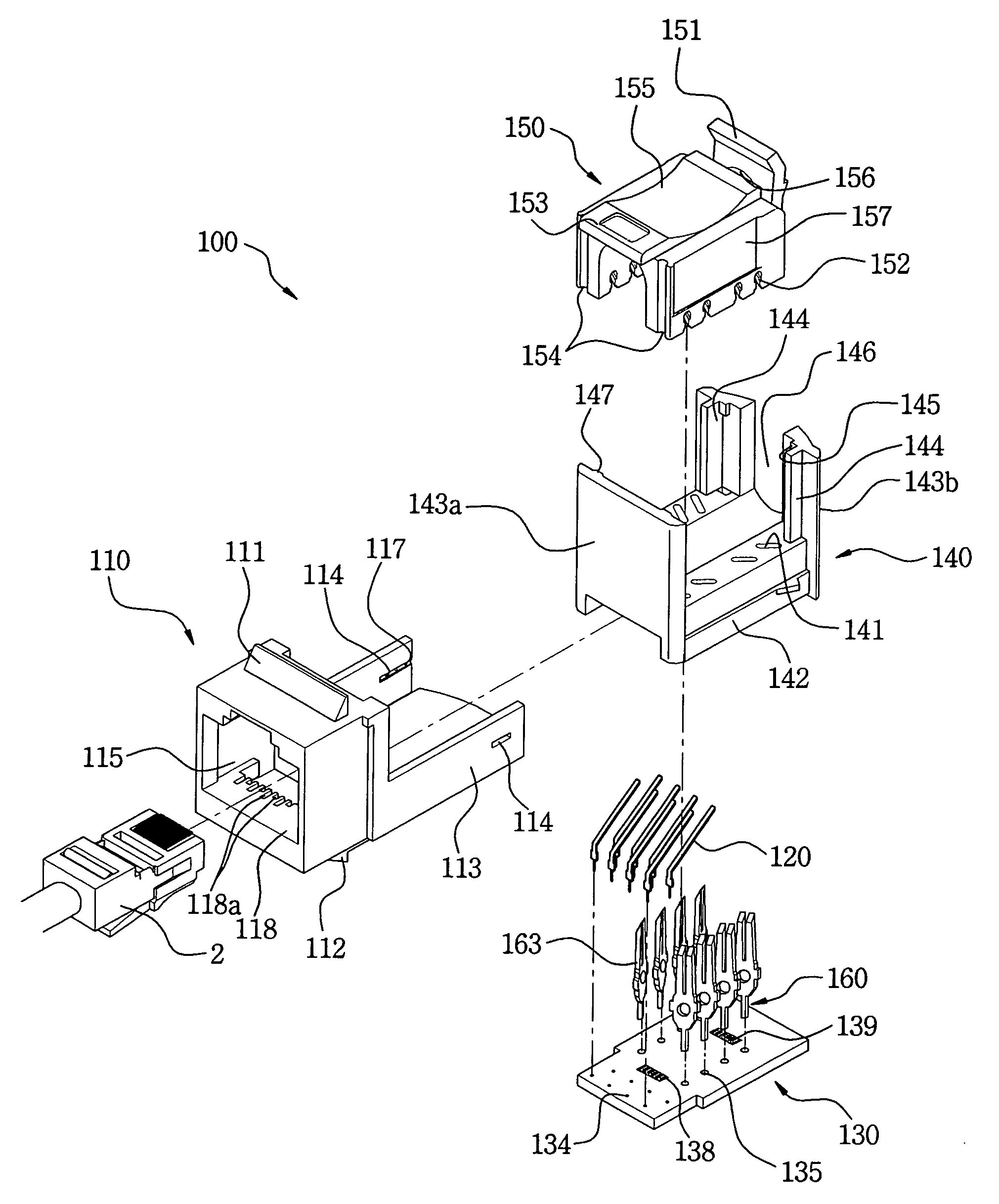

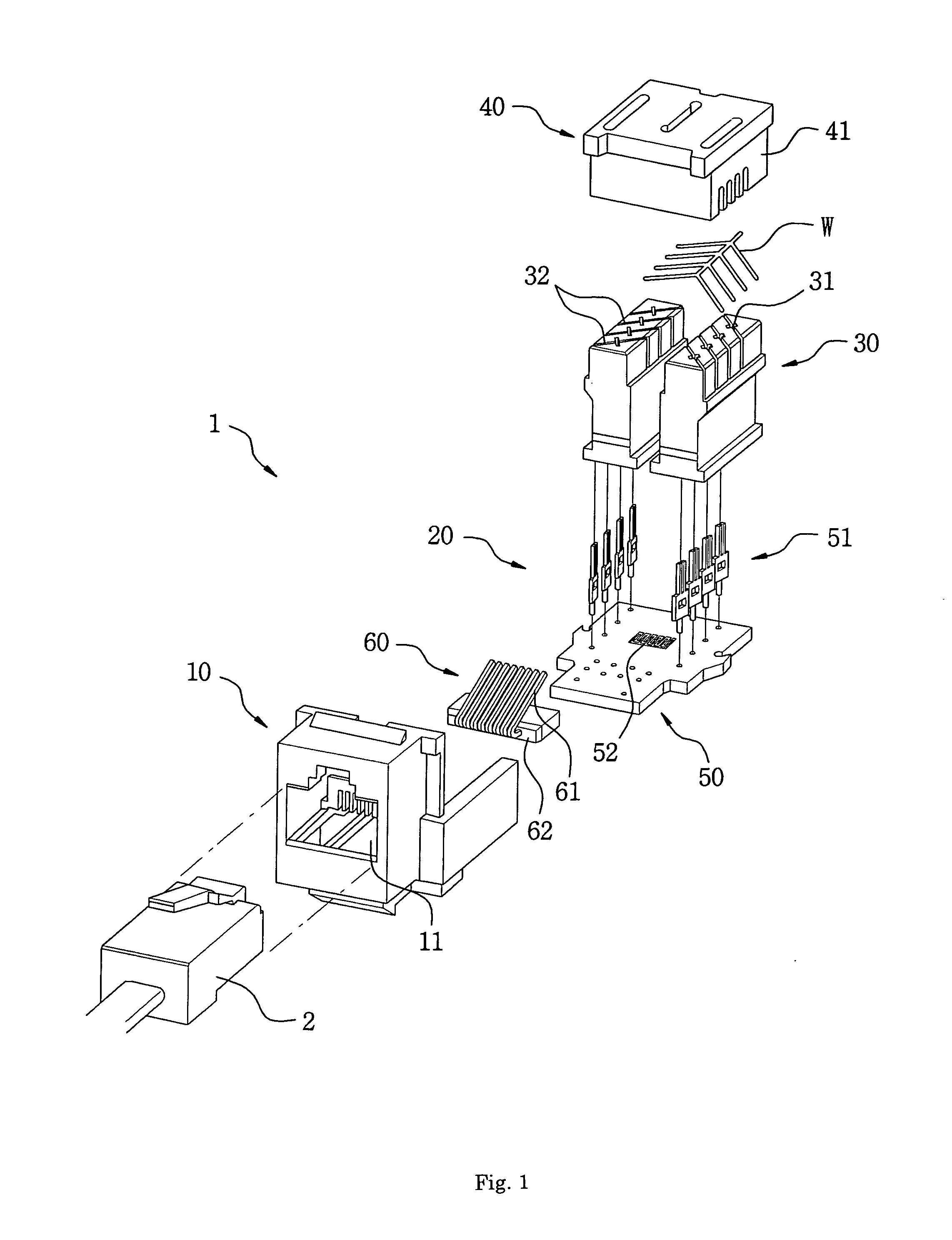

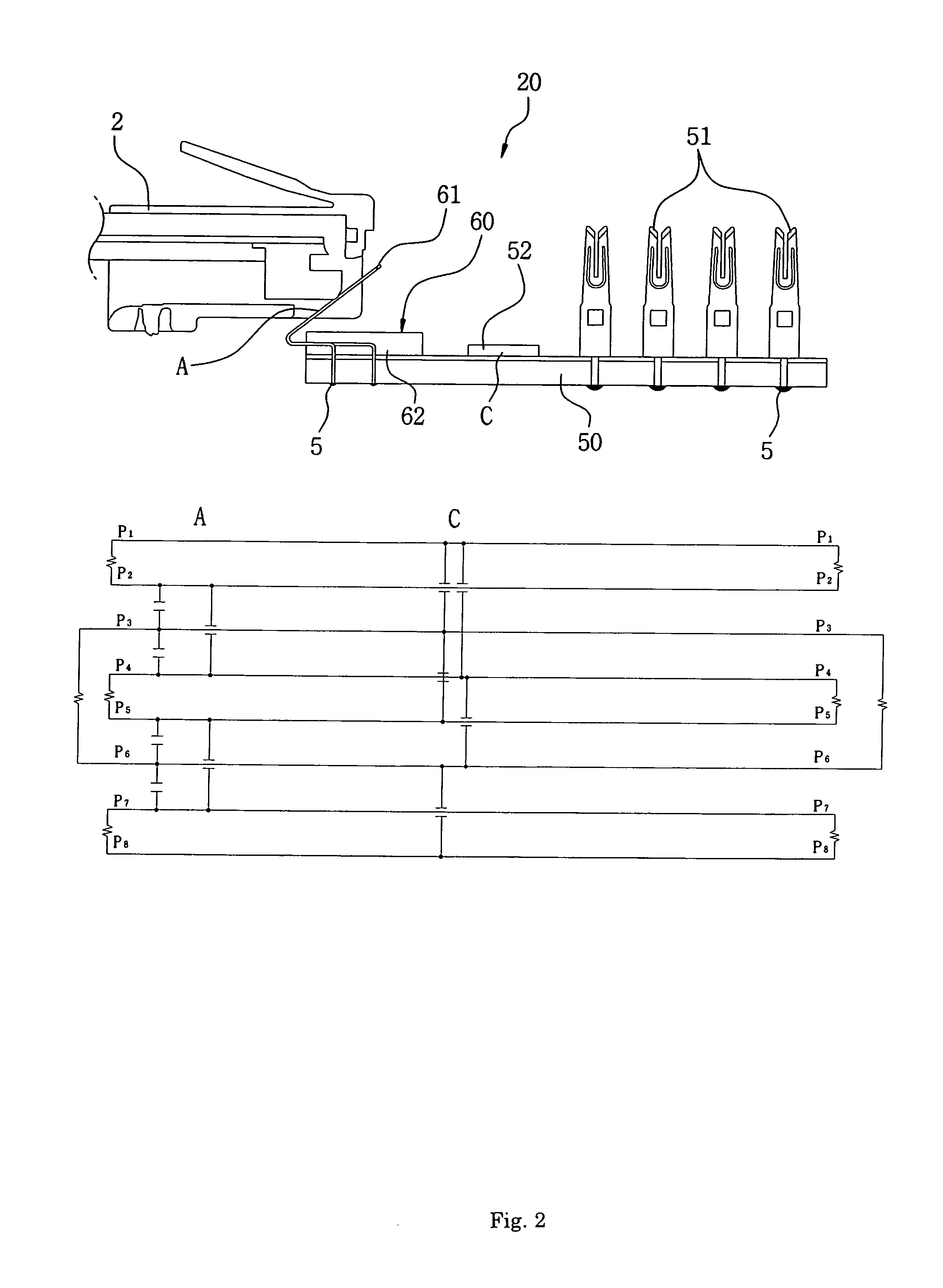

Crosstalk canceling pattern for high-speed communications and modular jack having the same

InactiveUS20060154531A1Minimizing initial near-end crosstalkEasy to optimizeCoupling device detailsPrinted circuit aspectsPrinted circuit boardLayered structure

Disclosed herein are a crosstalk canceling pattern for high-speed communications and a modular jack having the same, which includes a compensating capacitor on a transmission line to cancel crosstalk due to parasitic capacitance generated between neighboring insert pins, and includes a second compensating capacitor to correct phase mismatch due to parasitic inductance generated in insert pins and transmission lines, when a high-frequency signal is applied. The modular jack having the crosstalk canceling pattern for high-speed communications includes a housing, a printed circuit board, a lower contact block, and an upper contact block. The hosing includes a plug insert hole, an insert pin locking plate, and a coupling guide part. The printed circuit board is a multi-layered structure having a plurality of compensating capacitors. The lower contact block is mounted to the lower surface of the printed circuit board. The upper contact block is mounted to the upper portion of the lower contact block, and divides UTP cable wires to be connected to IDC terminals.

Owner:DAE EUN ELECTRONICS

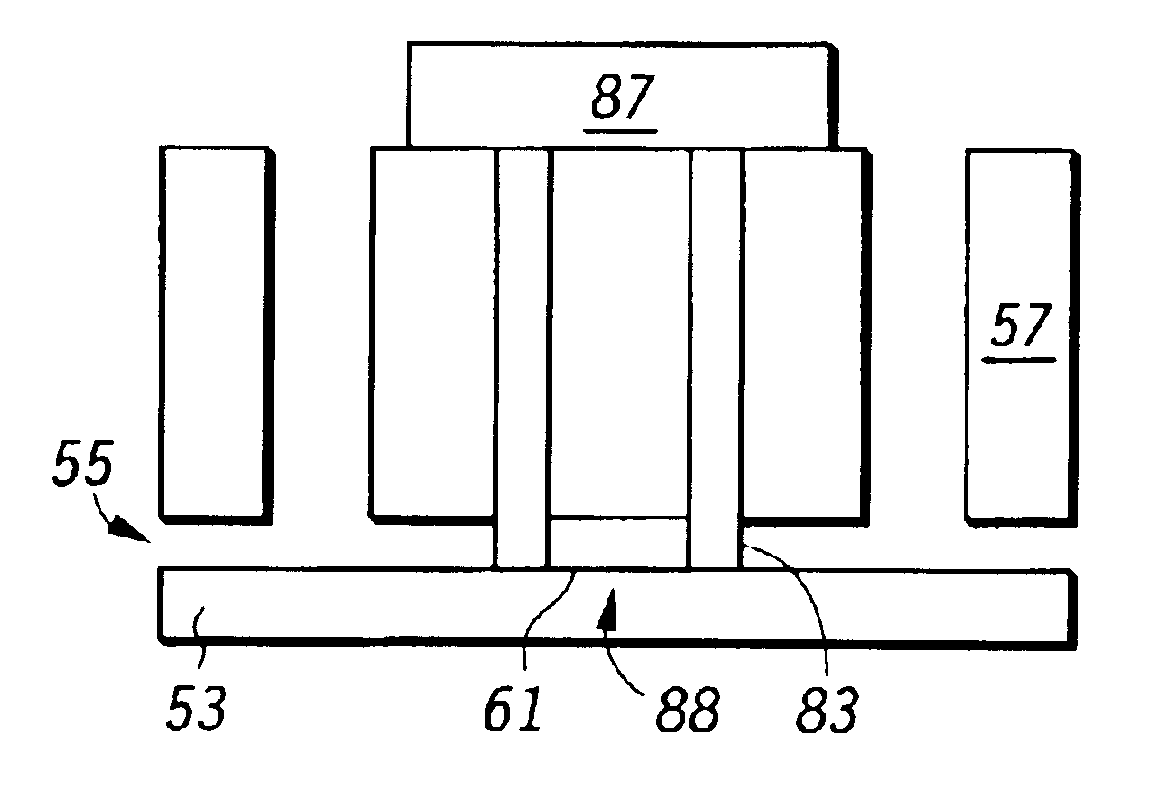

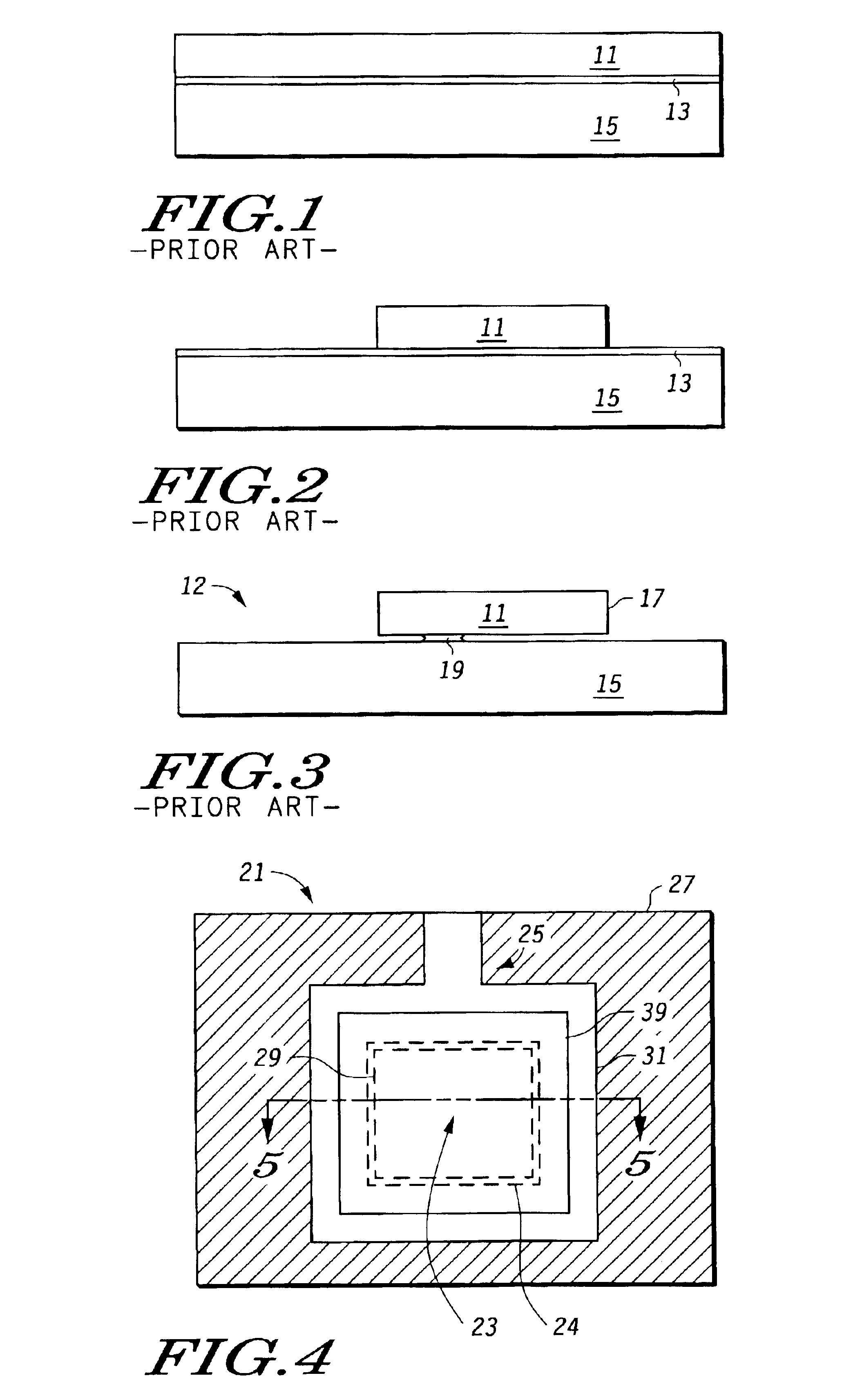

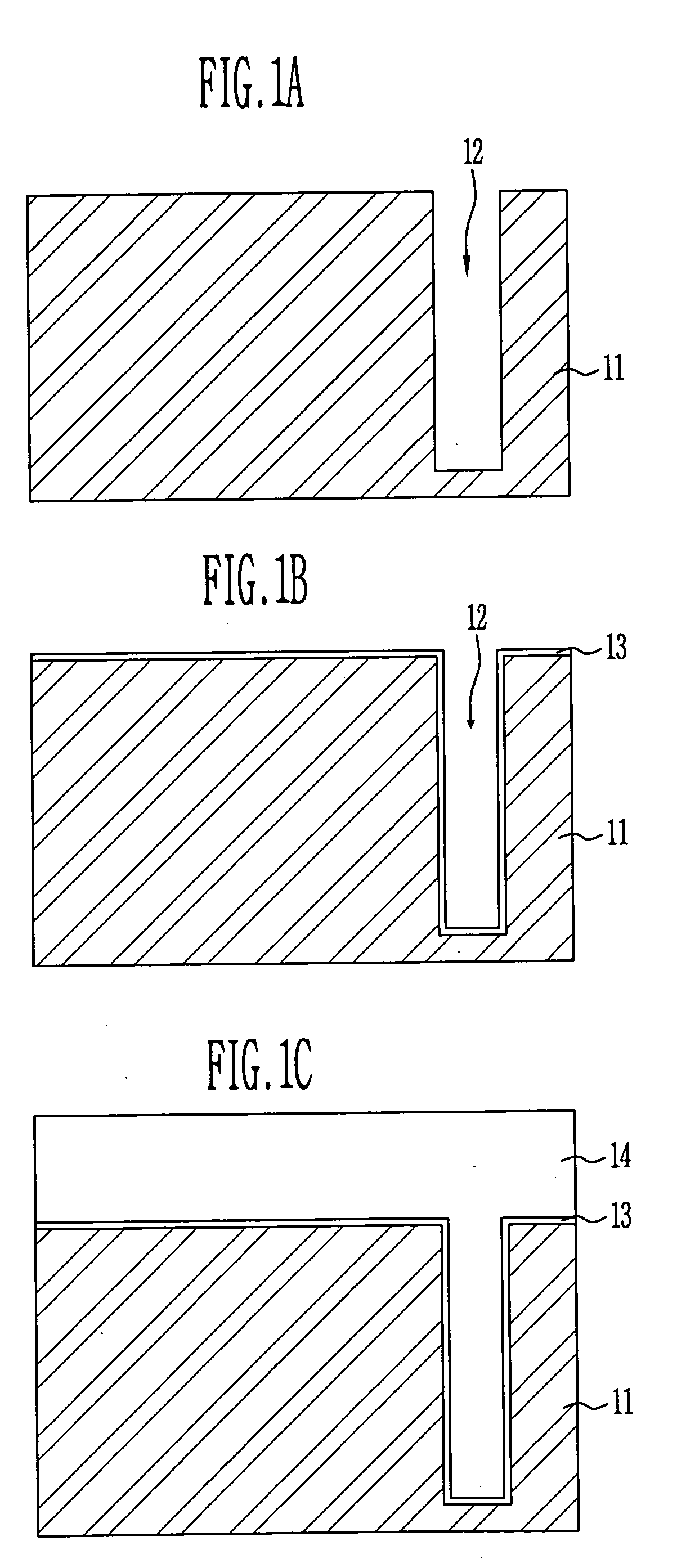

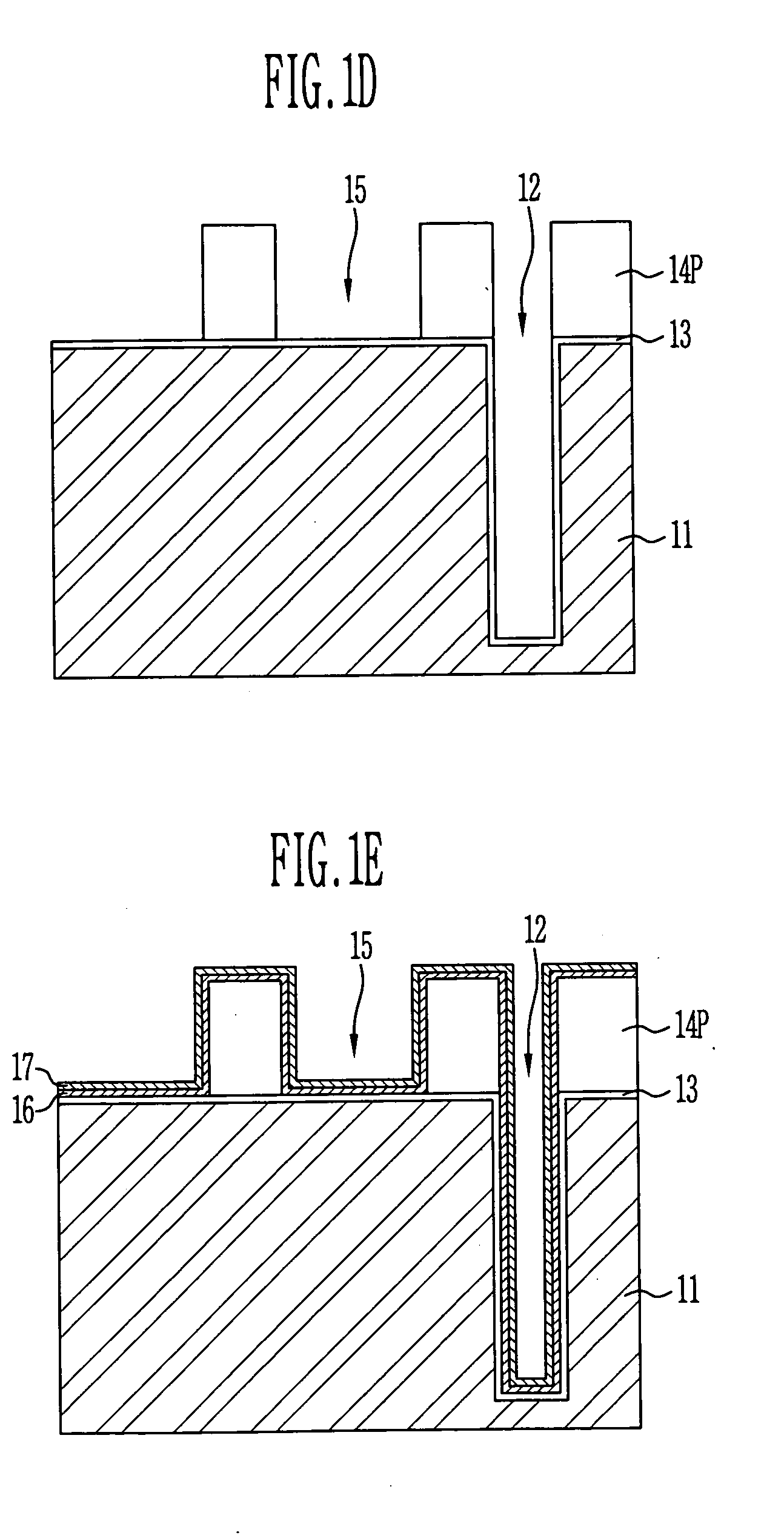

SOI polysilicon trench refill perimeter oxide anchor scheme

InactiveUS6913941B2Minimize parasitic capacitanceReduce mold sizeDecorative surface effectsSemiconductor/solid-state device manufacturingSilicon dioxideSilicon

A method for creating a MEMS structure is provided. In accordance with the method, a substrate (53) is provided having a sacrificial layer (55) disposed thereon and having a layer of silicon (57) disposed over the sacrificial layer. A first trench (59) is created which extends through the silica layer and the sacrificial layer and which separates the sacrificial layer into a first region (61) enclosed by the first trench and a second region (63) exterior to the first trench. A first material (65) is deposited into the first trench such that the first material fills the first trench to a depth at least equal to the thickness of the sacrificial layer. A second trench (71) is created exterior to the first trench which extends through at least the silicon layer and exposes at least a portion of the second region of the sacrificial layer. The second region of the sacrificial layer is contacted, by way of the second trench, with a chemical etching solution adapted to etch the sacrificial layer, said etching solution being selective to the first material.

Owner:NORTH STAR INNOVATIONS

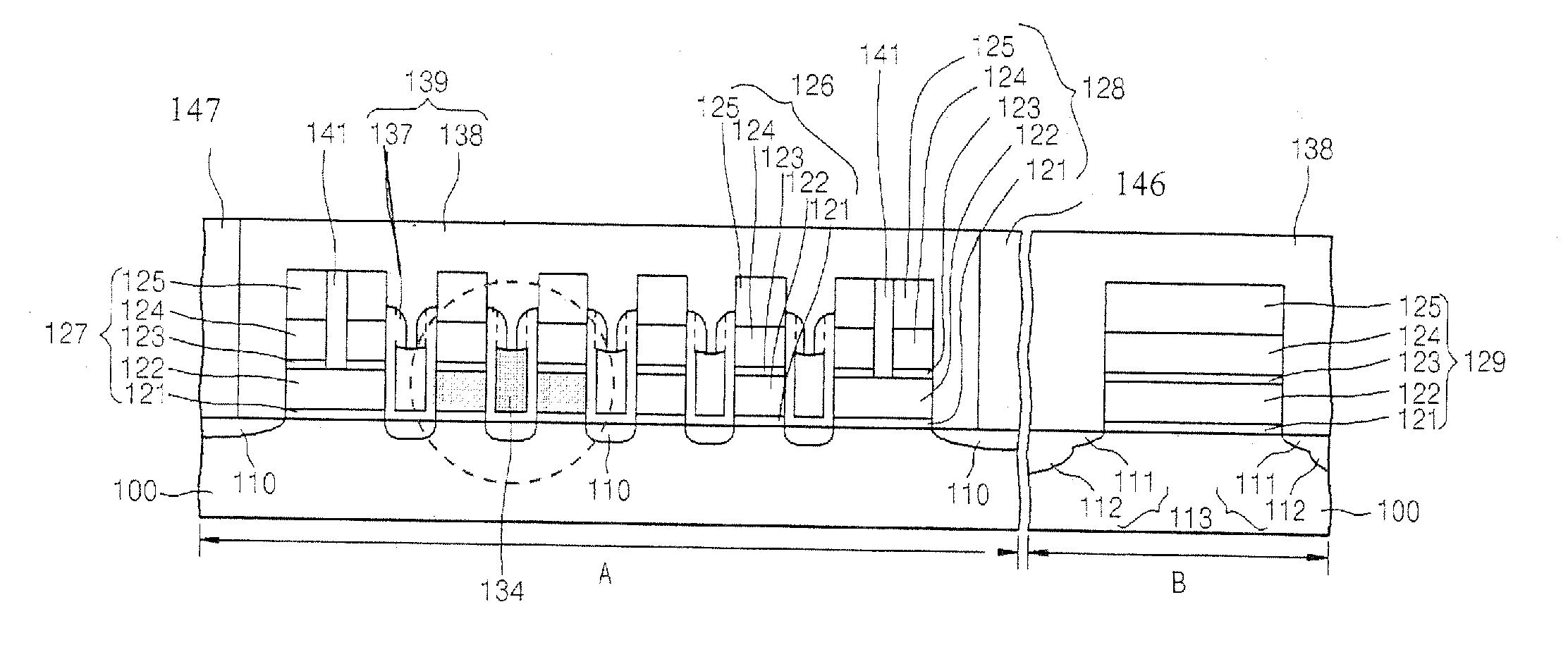

Radio frequency semiconductor device and method of manufacturing the same

ActiveUS20050139954A1Minimize parasitic capacitanceOvercome decouplingSemiconductor/solid-state device detailsSolid-state devicesRadio frequencyInductor

The present invention discloses a high frequency device including a first wafer providing an inductor having via contact plugs passing through the first wafer and a second wafer bonded to the first wafer, wherein the second wafer provides logic devices and inductor connection lines on an upper side thereof.

Owner:KEY FOUNDRY CO LTD

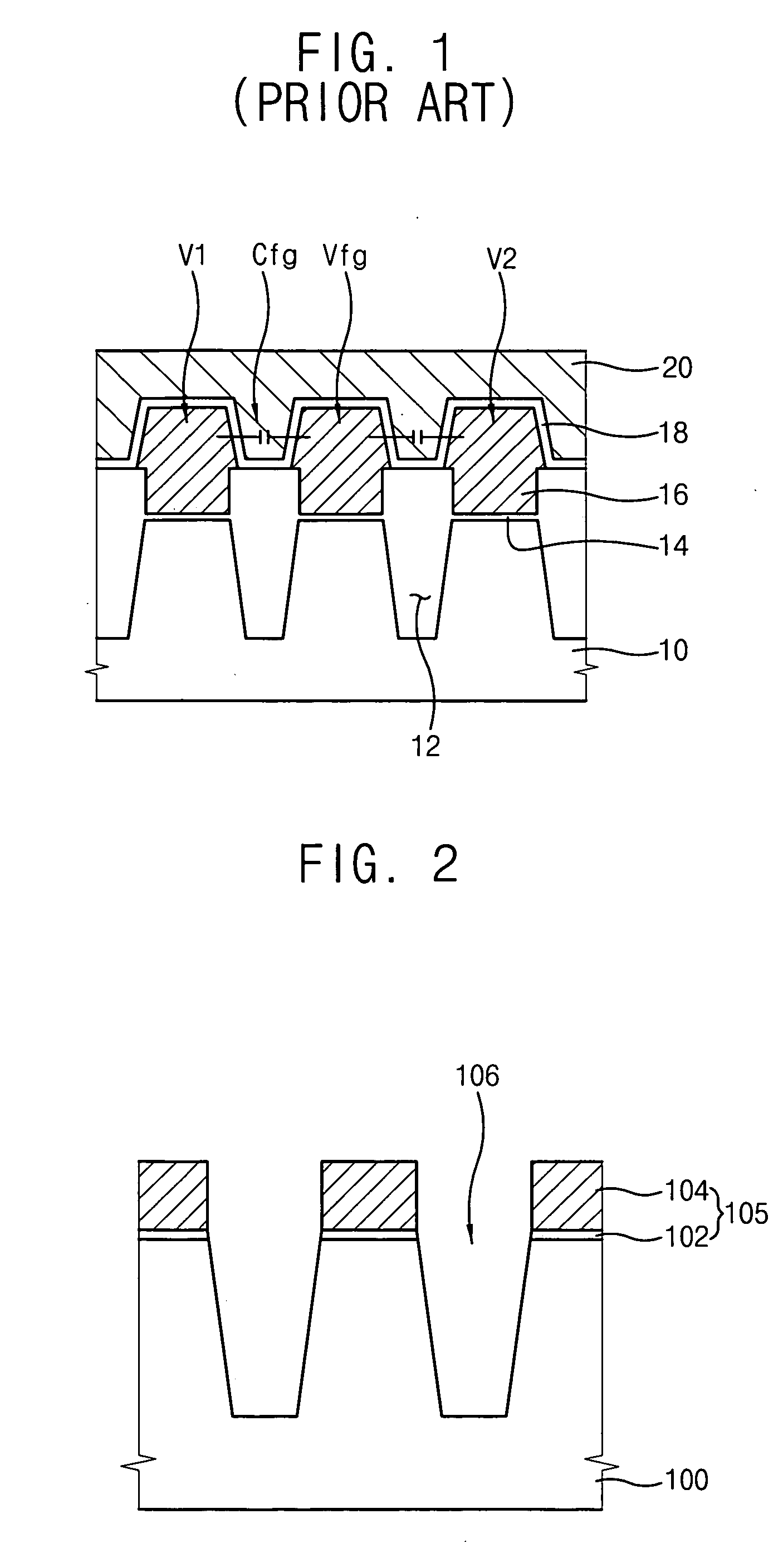

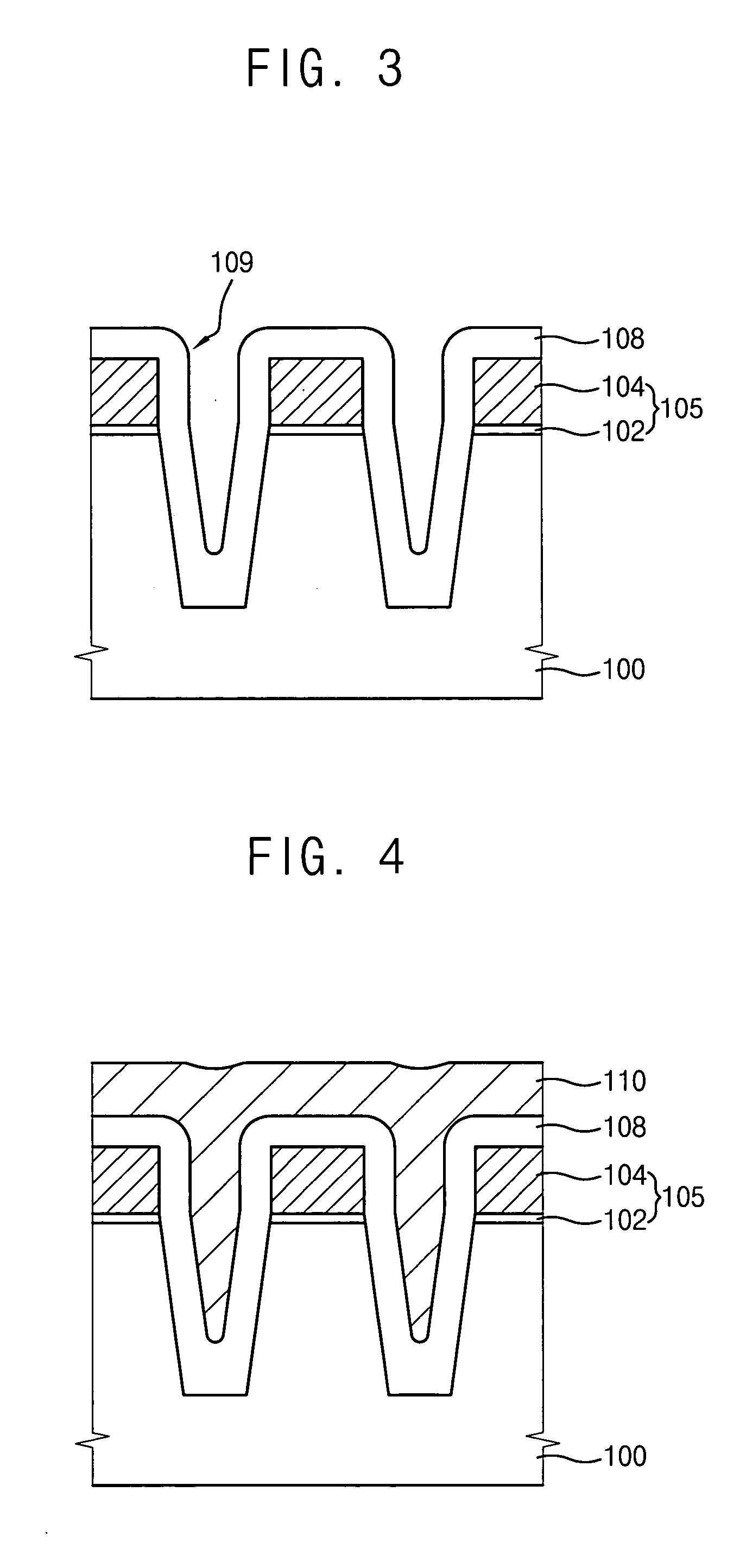

Semiconductor devices comprising a plurality of gate structures

ActiveUS20100295113A1Volume maximizationMade uniformTransistorSolid-state devicesGate dielectricDevice material

Semiconductor devices including a plurality of gate structures disposed on a semiconductor substrate are provided. Each of the gate structures includes a tunnel dielectric layer, a floating gate, an inter-gate dielectric layer, a control gate, and a mask layer. Liners cover opposing sidewalls of adjacent floating gates. Spacers are disposed on the liners, the spacers protruding from opposing sidewalls of adjacent ones of the gate structures, and a top of each of the spacers is disposed below a top of a corresponding one of the gate structures. The liners define sidewalls of respective air gaps and the spacers define tops of the respective air gaps.

Owner:SAMSUNG ELECTRONICS CO LTD

Complementary carbon nanotube triple gate technology

InactiveUS7492015B2Facilitate conductionMinimizes parasitic capacitanceTransistorNanoinformaticsElectrical resistance and conductanceParasitic capacitance

Disclosed is a CNT technology that overcomes the intrinsic ambipolar properties of CNTFETs. One embodiment of the invention provides either a stable p-type CNTFET or a stable n-type CNTFET. Another embodiment of the invention provides a complementary CNT device. In order to overcome the ambipolar properties of a CNTFET, source / drain gates are introduced below the CNT opposite the source / drain electrodes. These source / drain gates are used to apply either a positive or negative voltage to the ends of the CNT so as to configure the corresponding FET as either an n-type or p-type CNTFET, respectively. Two adjacent CNTFETs, configured such that one is an n-type CNTFET and the other is a p-type CNTFET, can be incorporated into a complementary CNT device. In order to independently adjust threshold voltage of an individual CNTFET, a back gate can also be introduced below the CNT and, particularly, below the channel region of the CNT opposite the front gate. In this manner parasitic capacitances and resistances are minimized.

Owner:GLOBALFOUNDRIES INC

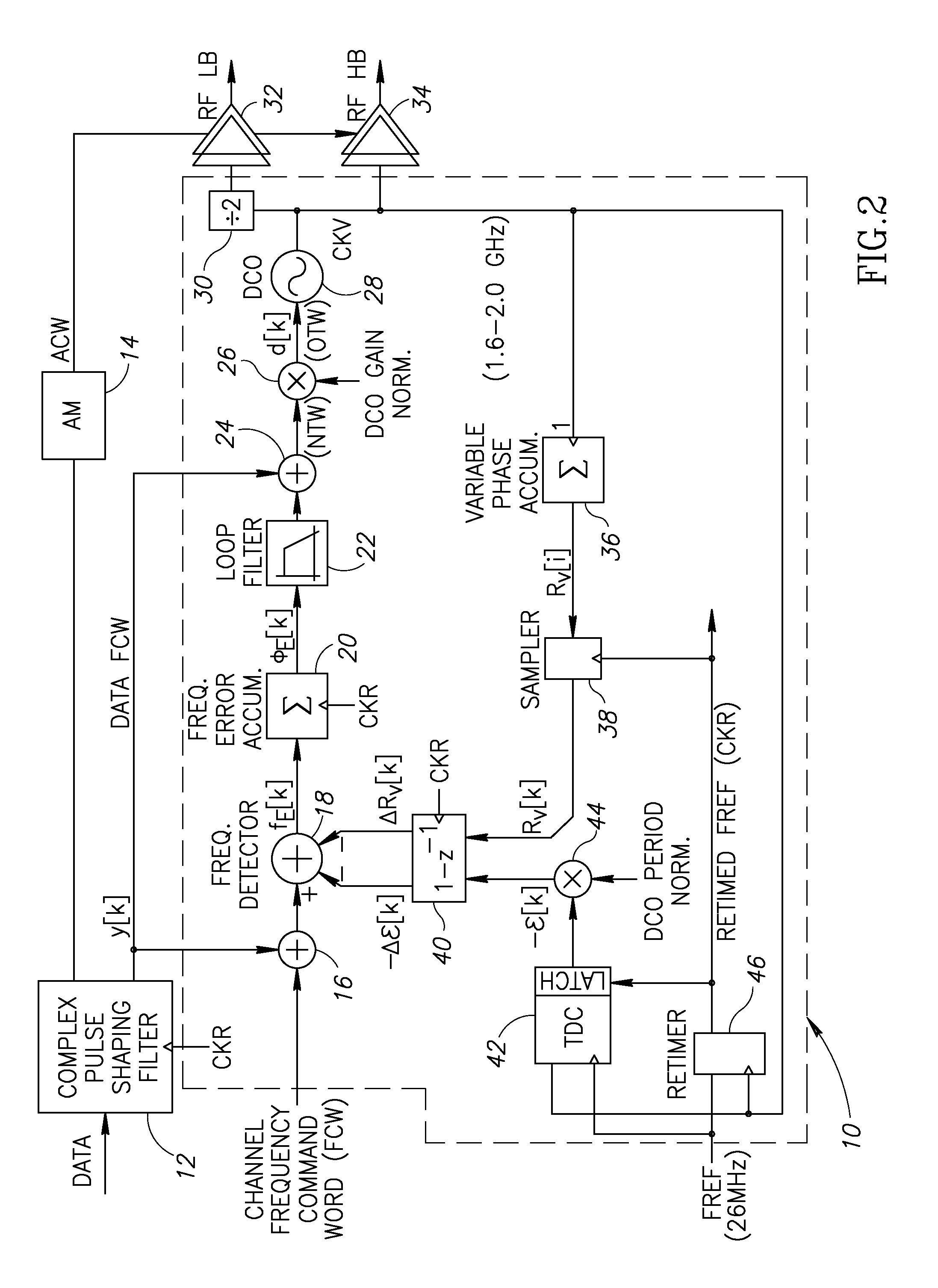

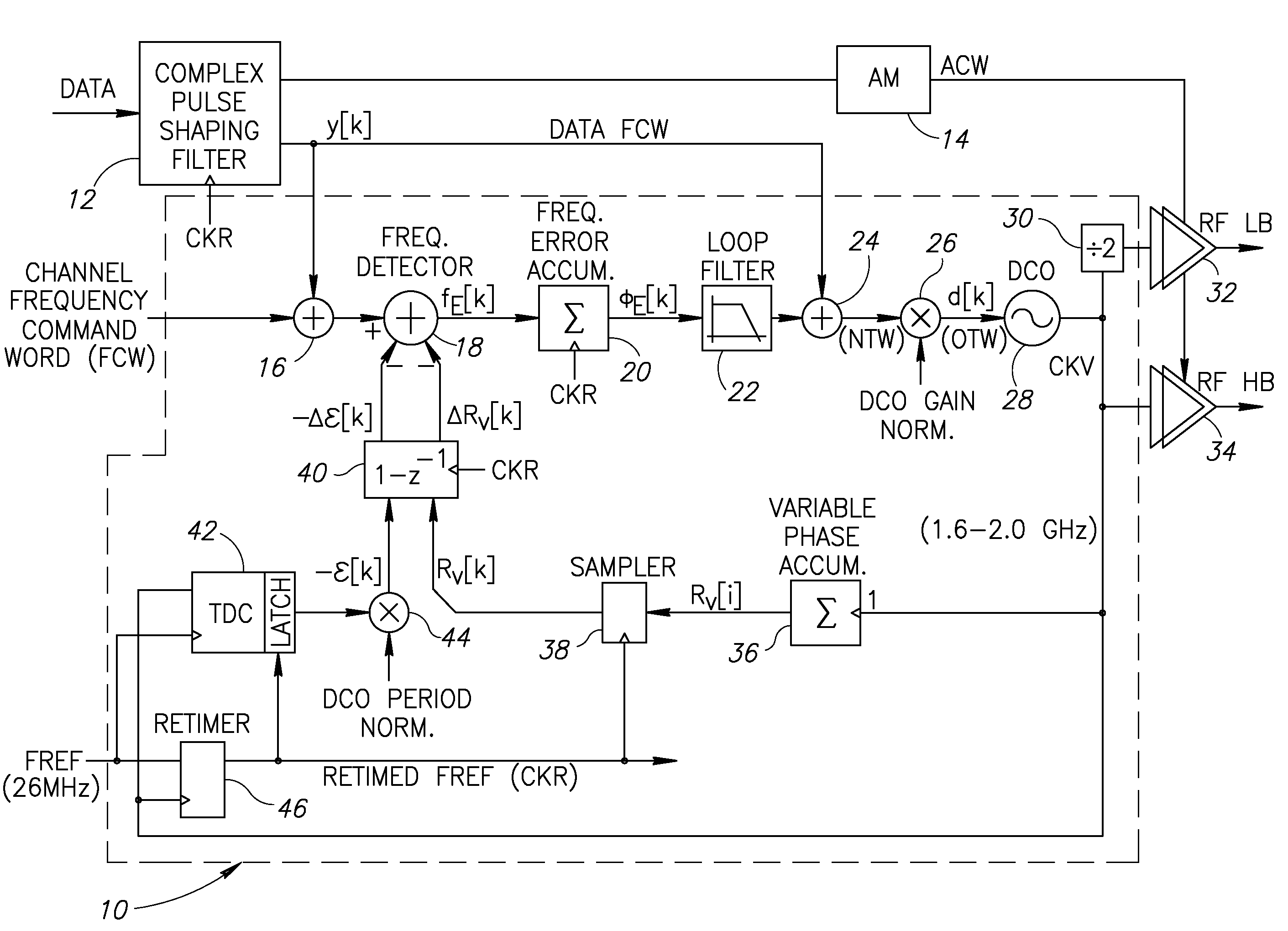

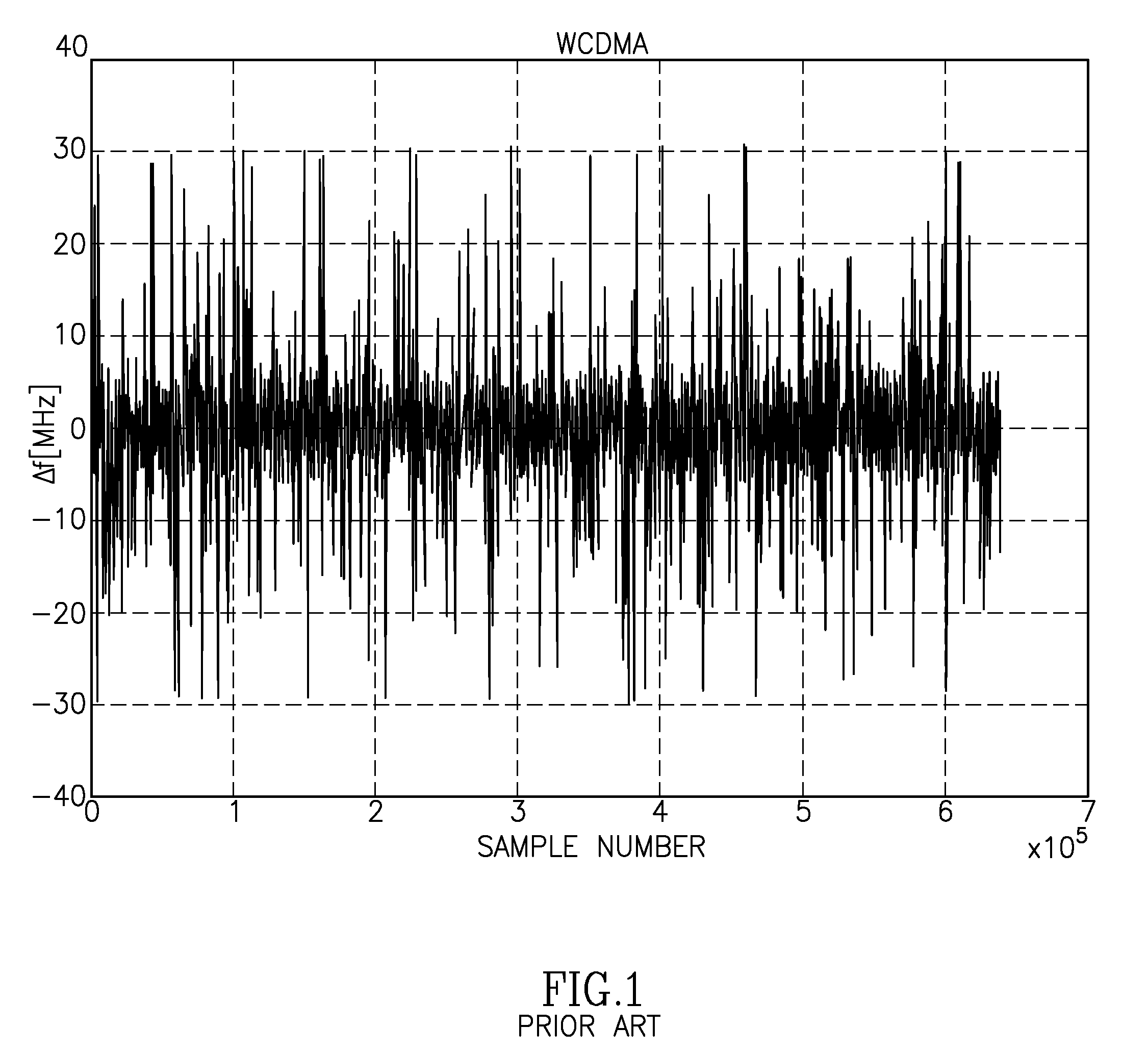

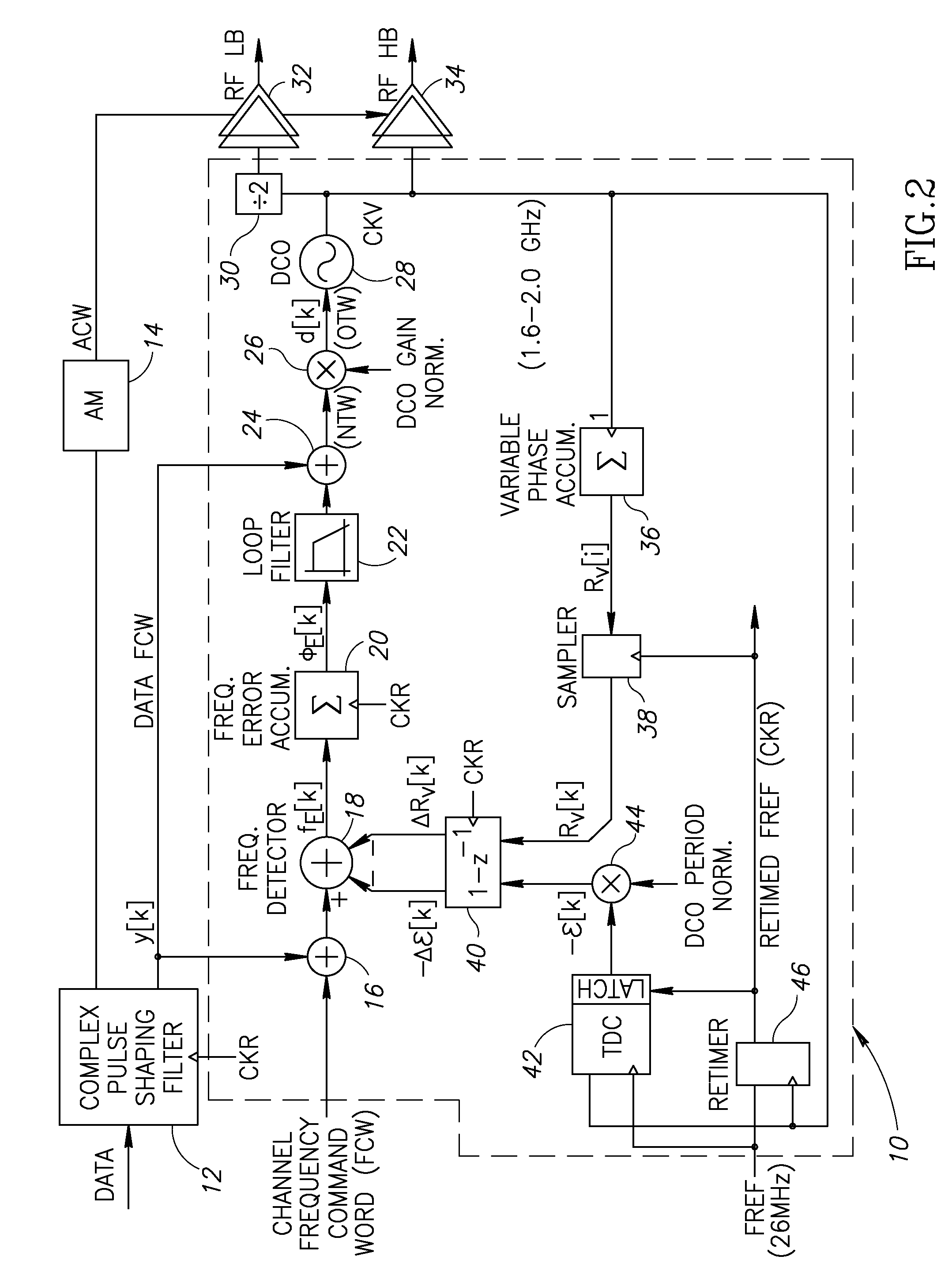

Harmonic Characterization and Correction of Device Mismatch

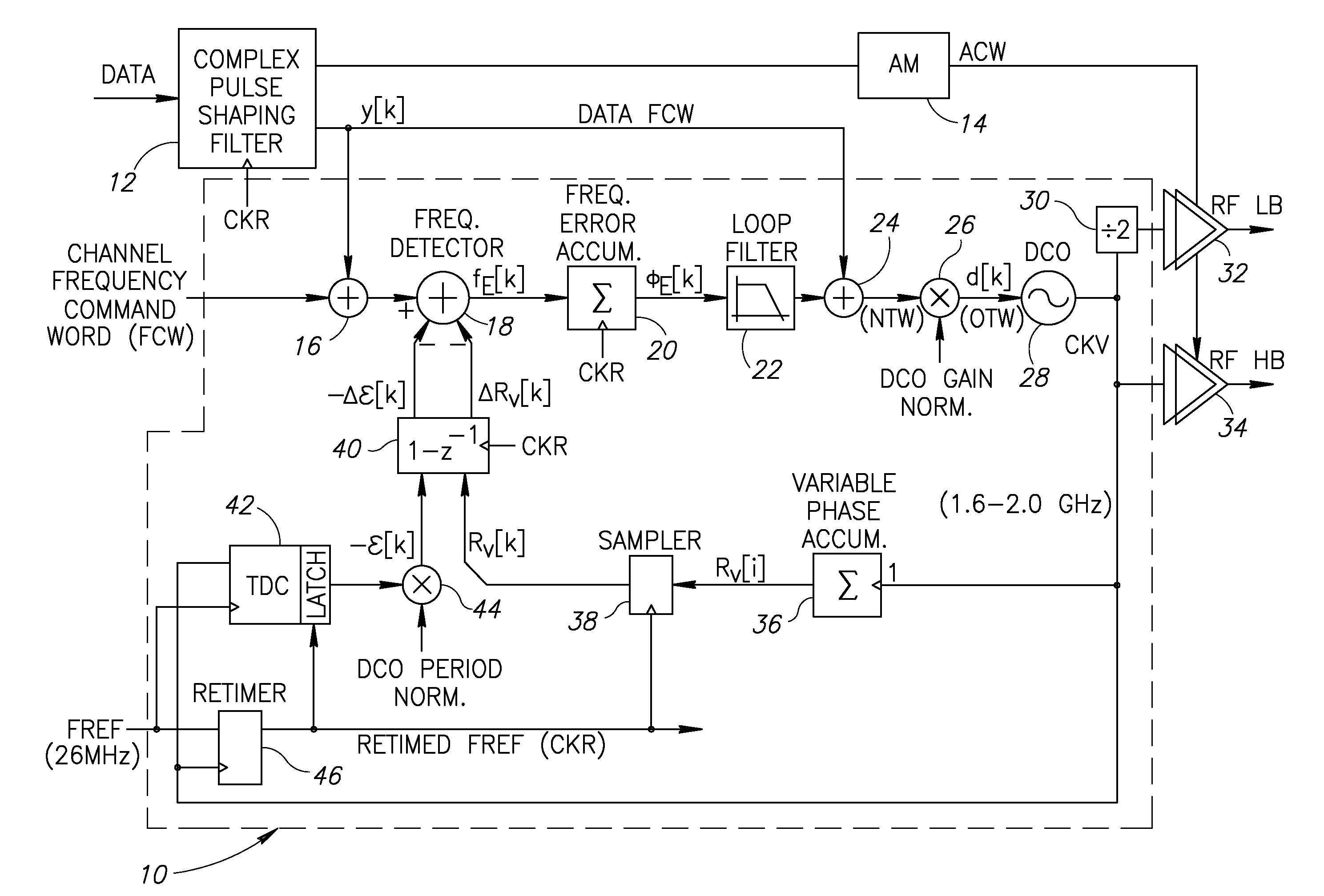

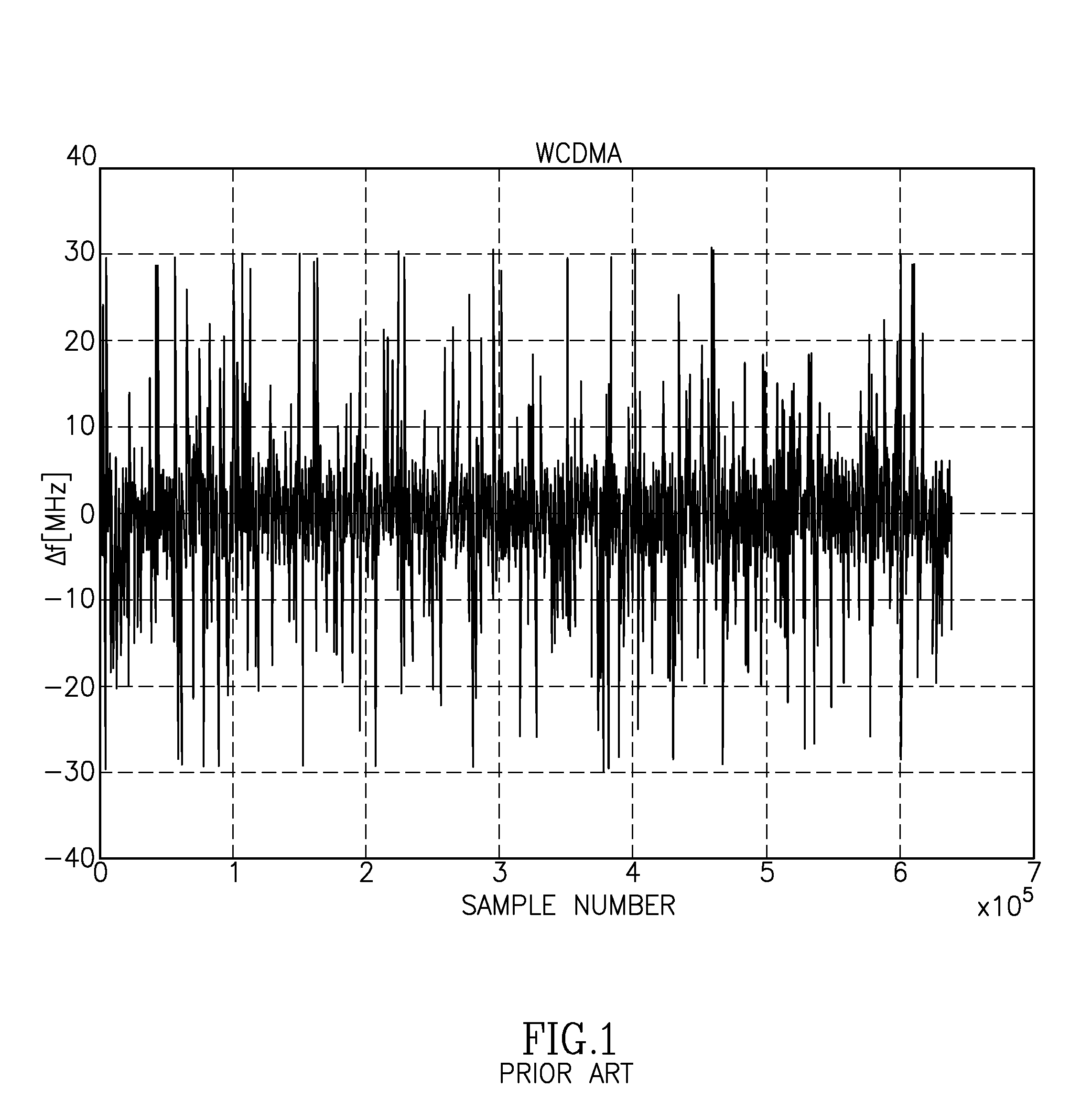

A novel apparatus for and method of harmonic characterization and ratio correction of device mismatch between coarse and fine varactor tuning devices within a segmented unified varactor bank of a radio frequency (RF) digitally controlled oscillator (DCO). The DCO uses a single unified bank of varactors that is divided into an MSB bank, LSB bank and sigma-delta (SD-LSB) bank. Any ratio mismatches between MSBs and LSBs are digitally calibrated out using a DCO step-size pre-distortion scheme wherein the LSB steps are adjusted to account for the ratio mismatch between the MSB / LSB step sizes. A harmonic characterization technique is used to estimate the mismatches in the minimal size CMOS tuning varactors of a digitally controlled RF oscillator (DCO), wherein the nominal ratio mismatch between the MSB and LSB devices is estimated using hybrid stochastic gradient DCO gain estimation algorithms. The nominal ratio mismatch and the mismatches in the MSB and LSB banks are used to determine the average MSB / LSB mismatch. The average mismatch value is then used to correct the LSB steps.

Owner:TEXAS INSTR INC

Complementary carbon nanotube triple gate technology

InactiveUS20070102747A1Facilitate conductionMinimizes parasitic capacitanceNanoinformaticsSolid-state devicesCarbon nanotubeEngineering

Disclosed is a CNT technology that overcomes the intrinsic ambipolar properties of CNTFETs. One embodiment of the invention provides either a stable p-type CNTFET or a stable n-type CNTFET. Another embodiment of the invention provides a complementary CNT device. In order to overcome the ambipolar properties of a CNTFET, source / drain gates are introduced below the CNT opposite the source / drain electrodes. These source / drain gates are used to apply either a positive or negative voltage to the ends of the CNT so as to configure the corresponding FET as either an n-type or p-type CNTFET, respectively. Two adjacent CNTFETs, configured such that one is an n-type CNTFET and the other is a p-type CNTFET, can be incorporated into a complementary CNT device. In order to independently adjust threshold voltage of an individual CNTFET, a back gate can also be introduced below the CNT and, particularly, below the channel region of the CNT opposite the front gate. In this manner parasitic capacitances and resistances are minimized.

Owner:GLOBALFOUNDRIES INC

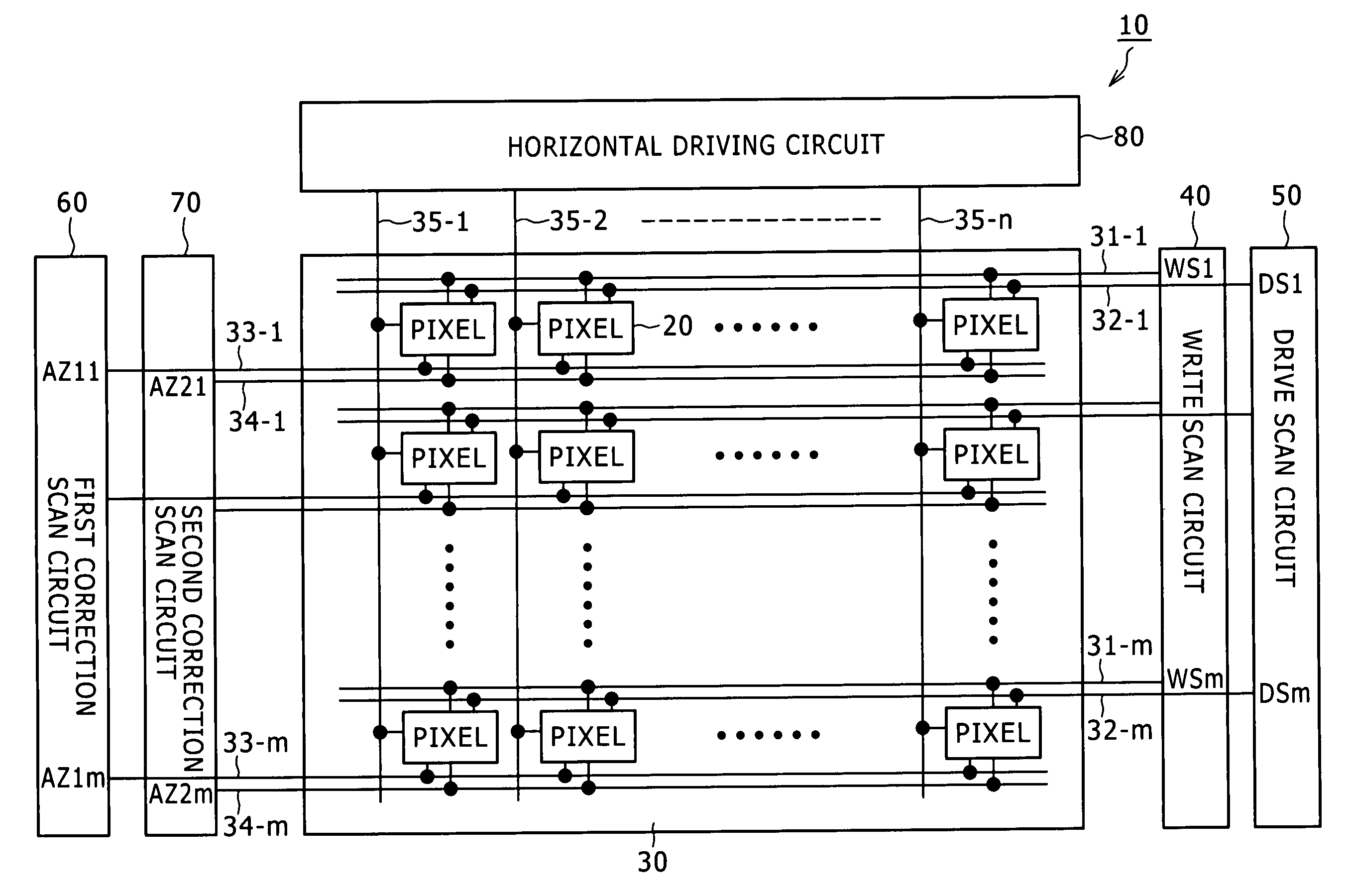

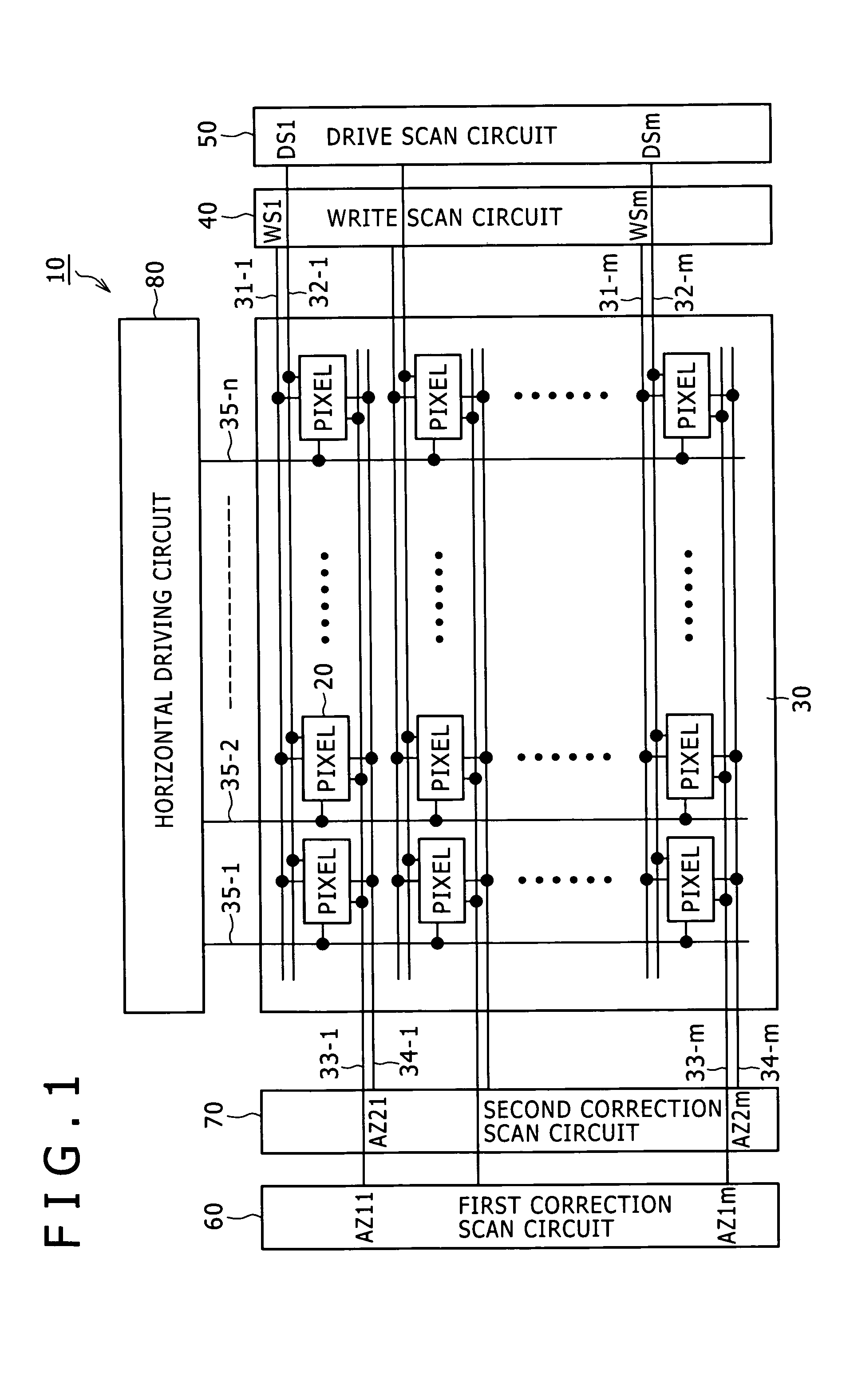

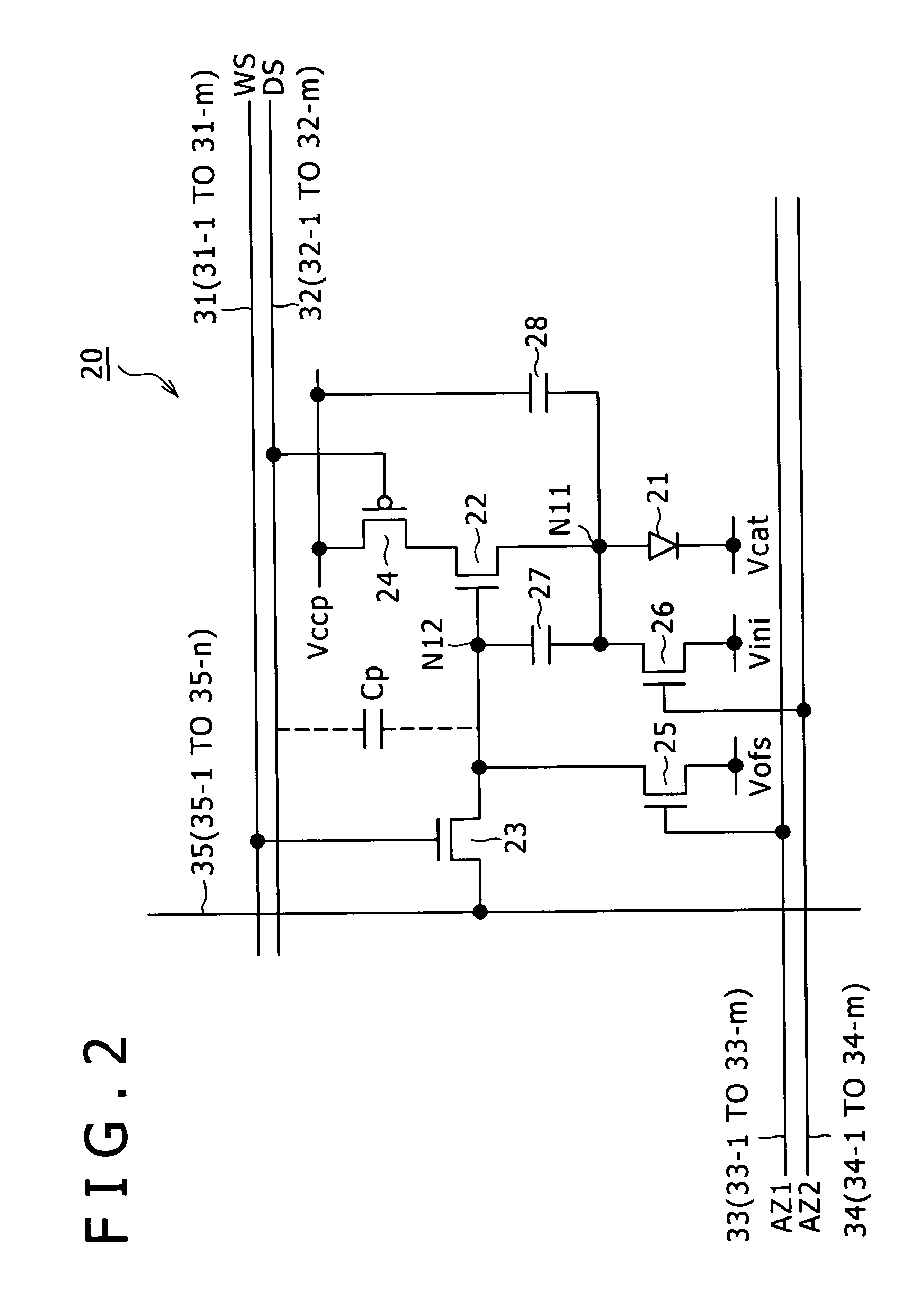

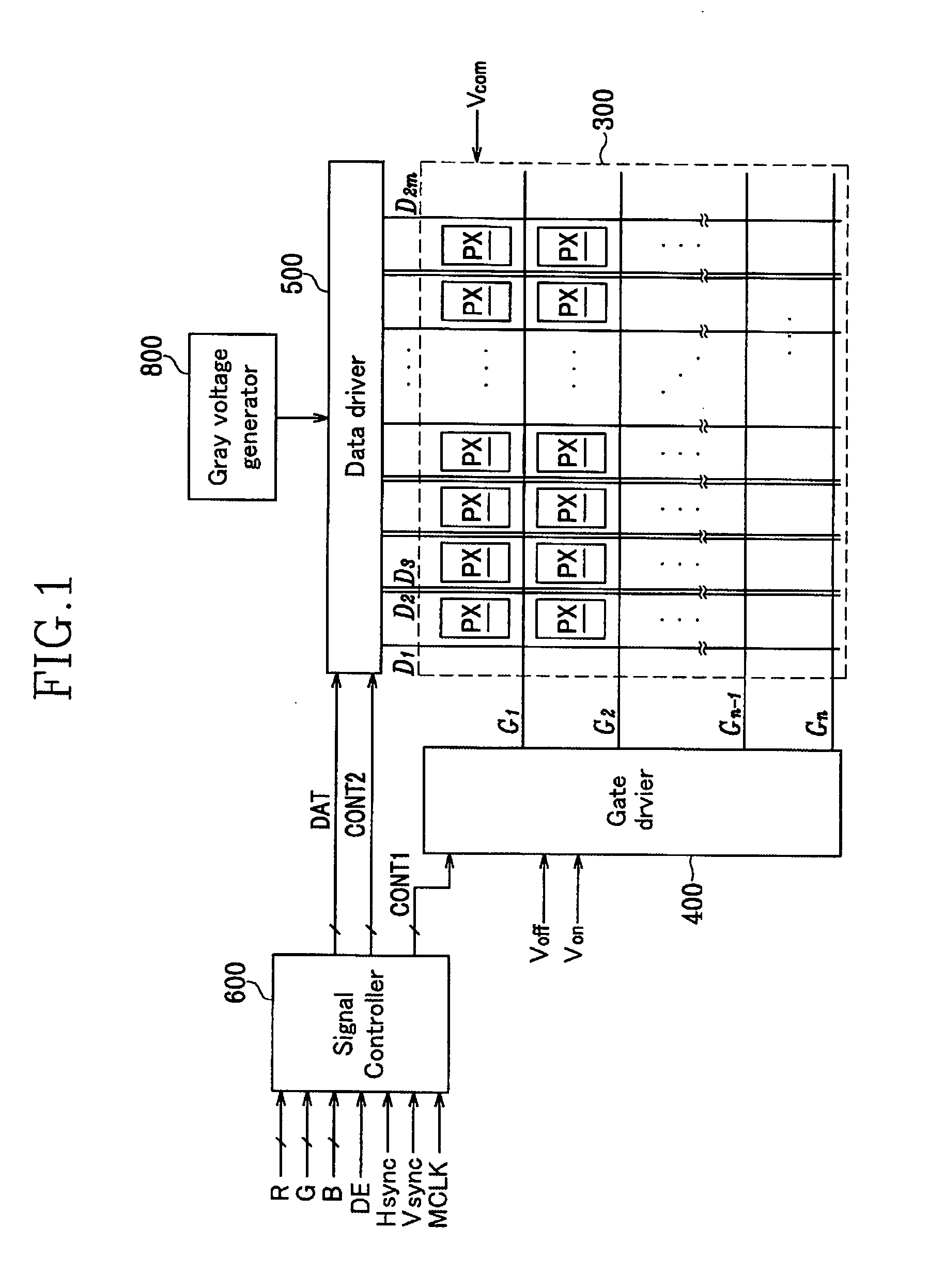

Display device and electronic equipment

ActiveUS20090046041A1Avoid couplingMinimize parasitic capacitanceStatic indicating devicesSolid-state devicesCapacitanceScan line

The present invention provides a display device including a pixel array section, the pixel array section having pixels arranged in a matrix form, each of the pixels including: an electro-optical element; a write transistor; a holding capacitance; a drive transistor; and a switching transistor; a write scan line disposed for each of pixel rows of the pixel array section and adapted to convey a write signal to be applied to the gate electrode of the write transistor; and a correction scan line, wherein the wiring structure of the write scan line does not intersect with the wiring pattern connected to the gate electrode of the drive transistor.

Owner:SONY CORP

Crosstalk canceling pattern for high-speed communications and modular jack having the same

InactiveUS7175476B2Minimizes parasitic capacitanceMinimizes parasitic inductance generatedCoupling device detailsPrinted circuit aspectsCouplingParasitic capacitance

Owner:DAE EUN ELECTRONICS

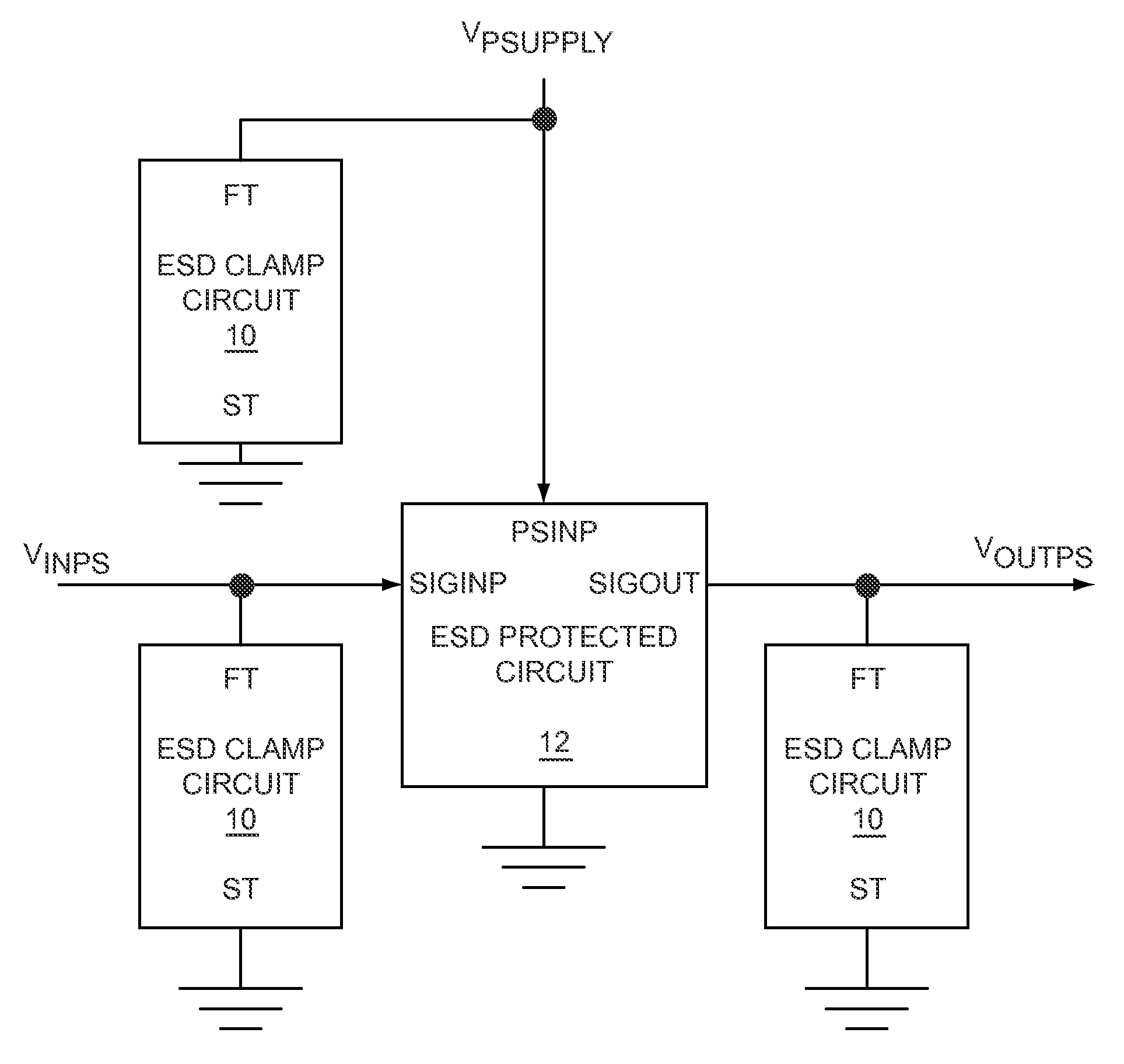

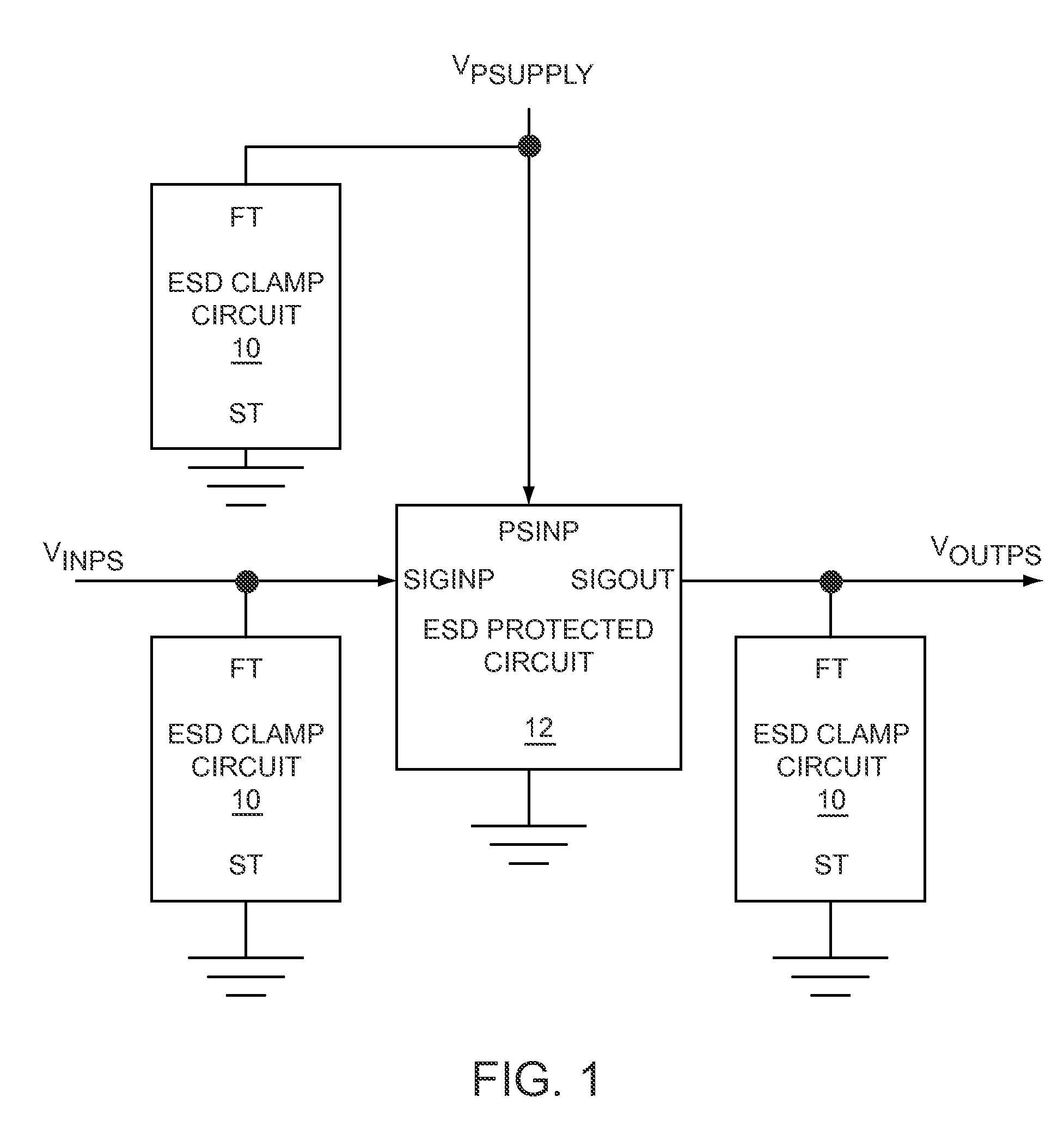

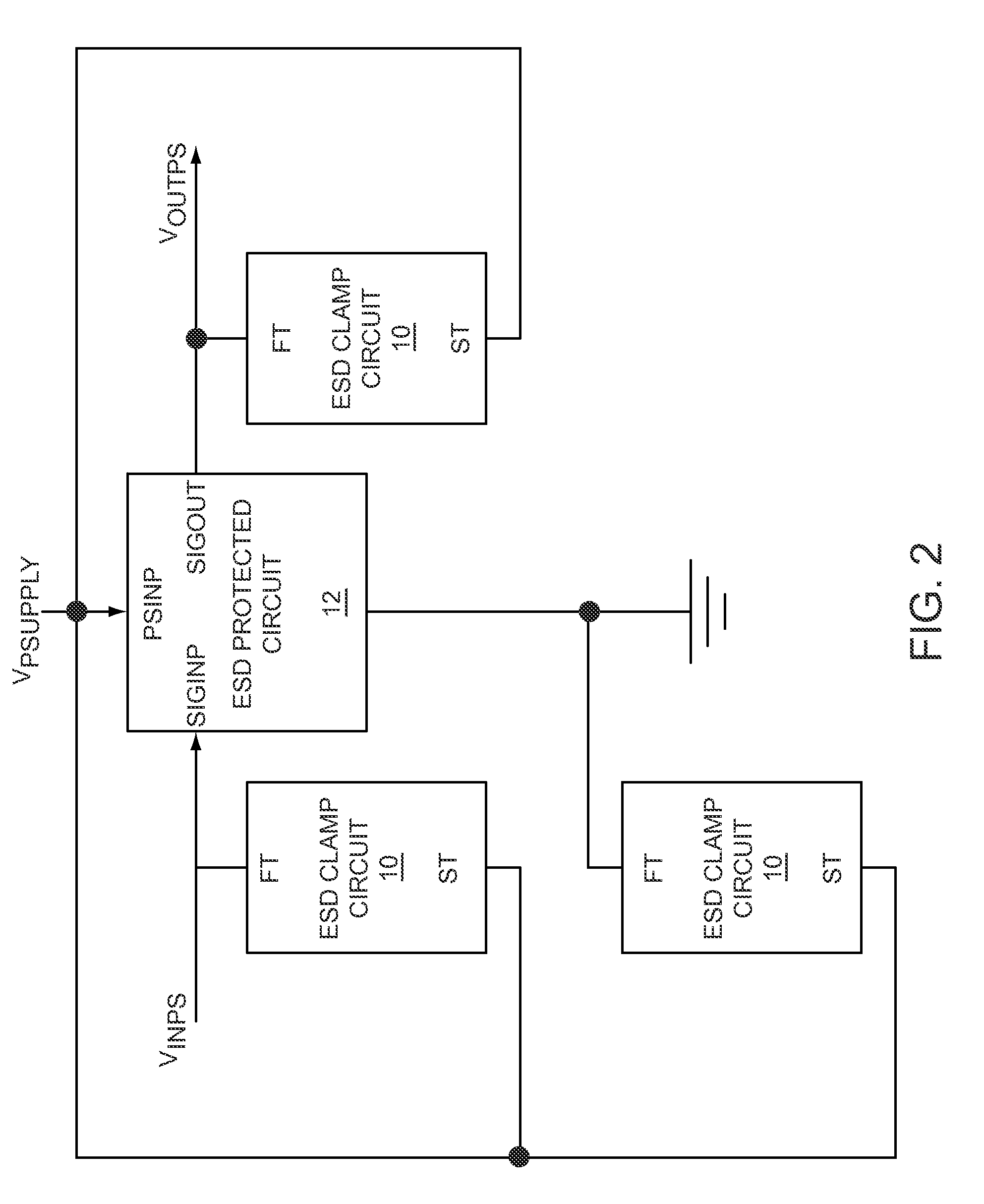

Depletion-mode field effect transistor based electrostatic discharge protection circuit

InactiveUS7881029B1Minimize parasitic capacitanceMaximize linearityAntennas earthing switches associationAmplifier protection circuit arrangementsLevel shiftingEngineering

The present invention relates to an electrostatic discharge (ESD) clamp circuit that is used to protect other circuitry from high voltage ESD events. The ESD clamp circuit may include a field effect transistor (FET) element as a clamping element, which is triggered by using a drain-to-gate capacitance and a drain-to-gate resistance of the FET element and a resistive element as a voltage divider to divide down an ESD voltage to provide a triggering gate voltage of the FET element. In its simplest embodiment, the ESD clamp circuit includes only an FET element, a resistive element, a source-coupled level shifting diode, and a reverse protection diode. Therefore, the ESD clamp circuit may be small compared to other ESD protection circuits. The simplicity of the ESD clamp circuit may minimize parasitic capacitances, thereby maximizing linearity of the ESD clamp circuit over a wide frequency range.

Owner:QORVO US INC

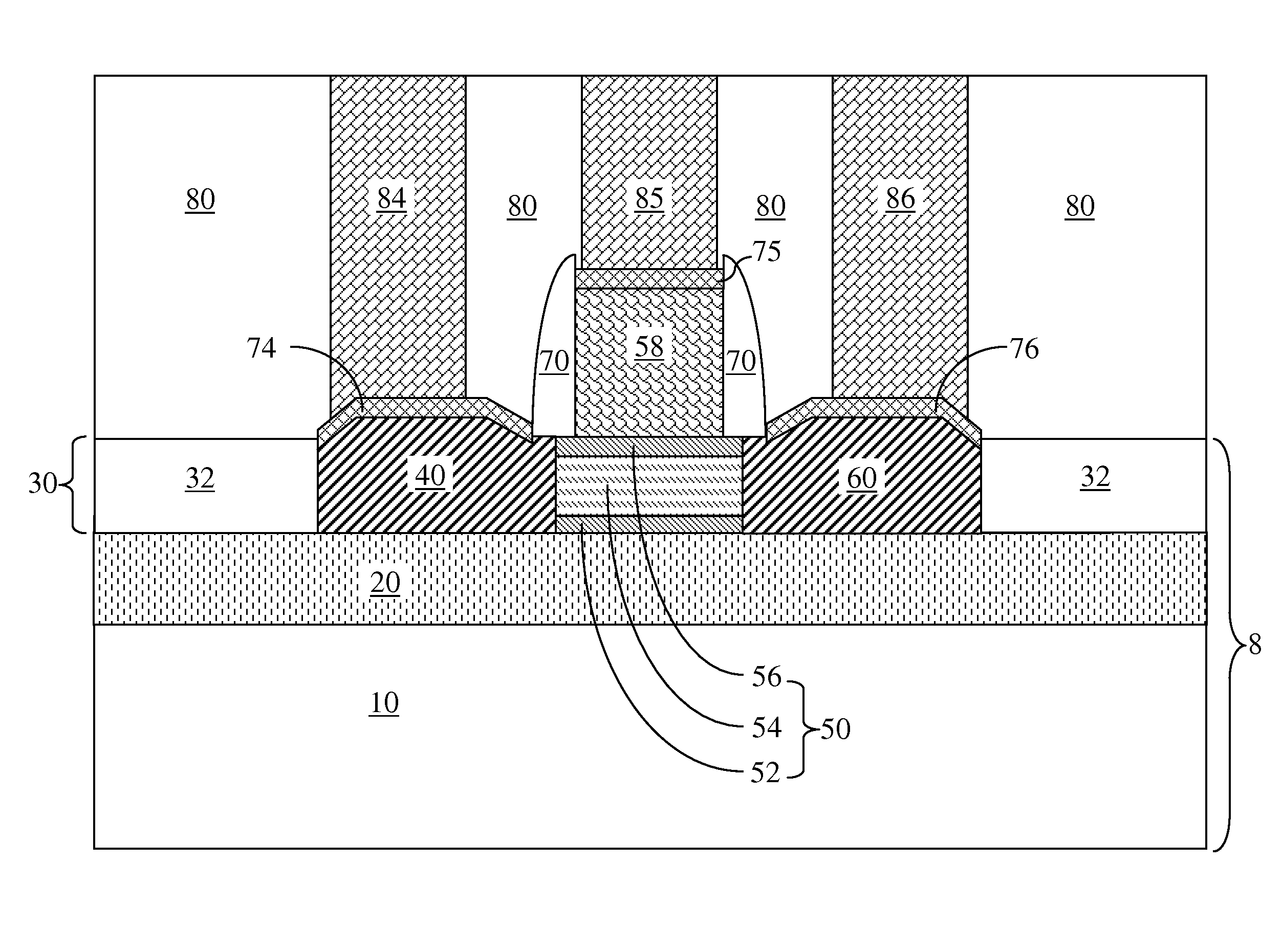

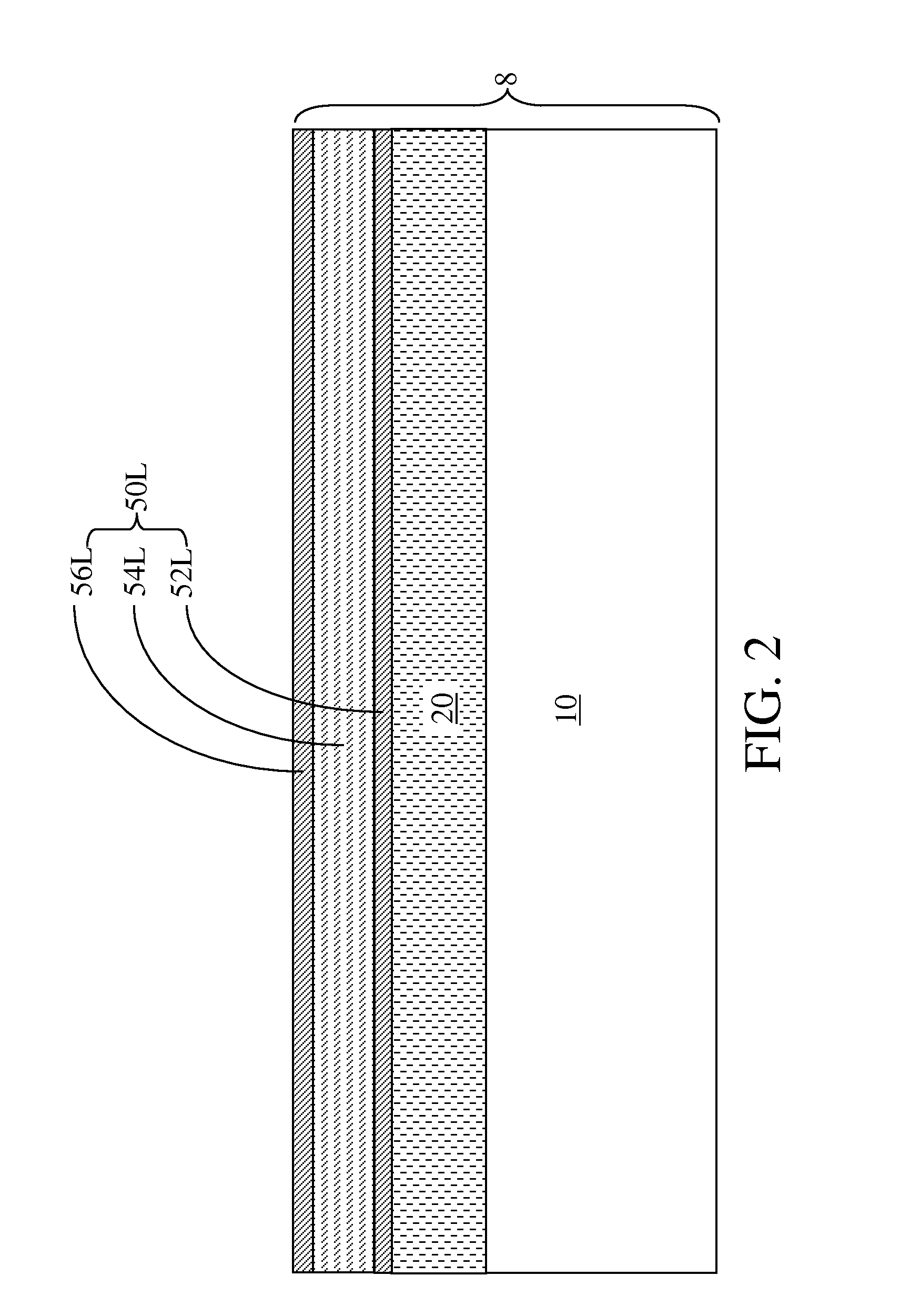

SOI SiGe-base lateral bipolar junction transistor

ActiveUS8288758B2Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

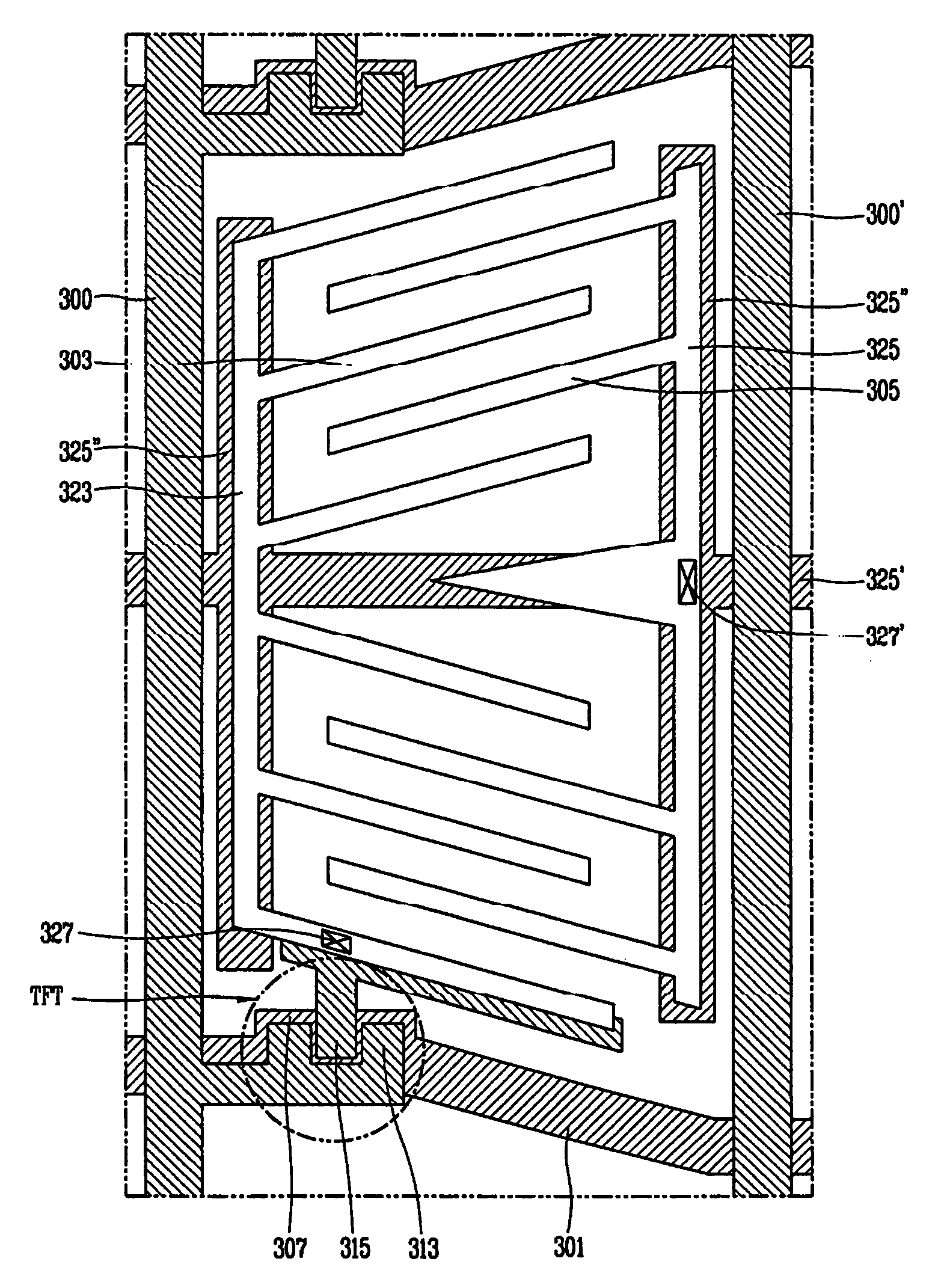

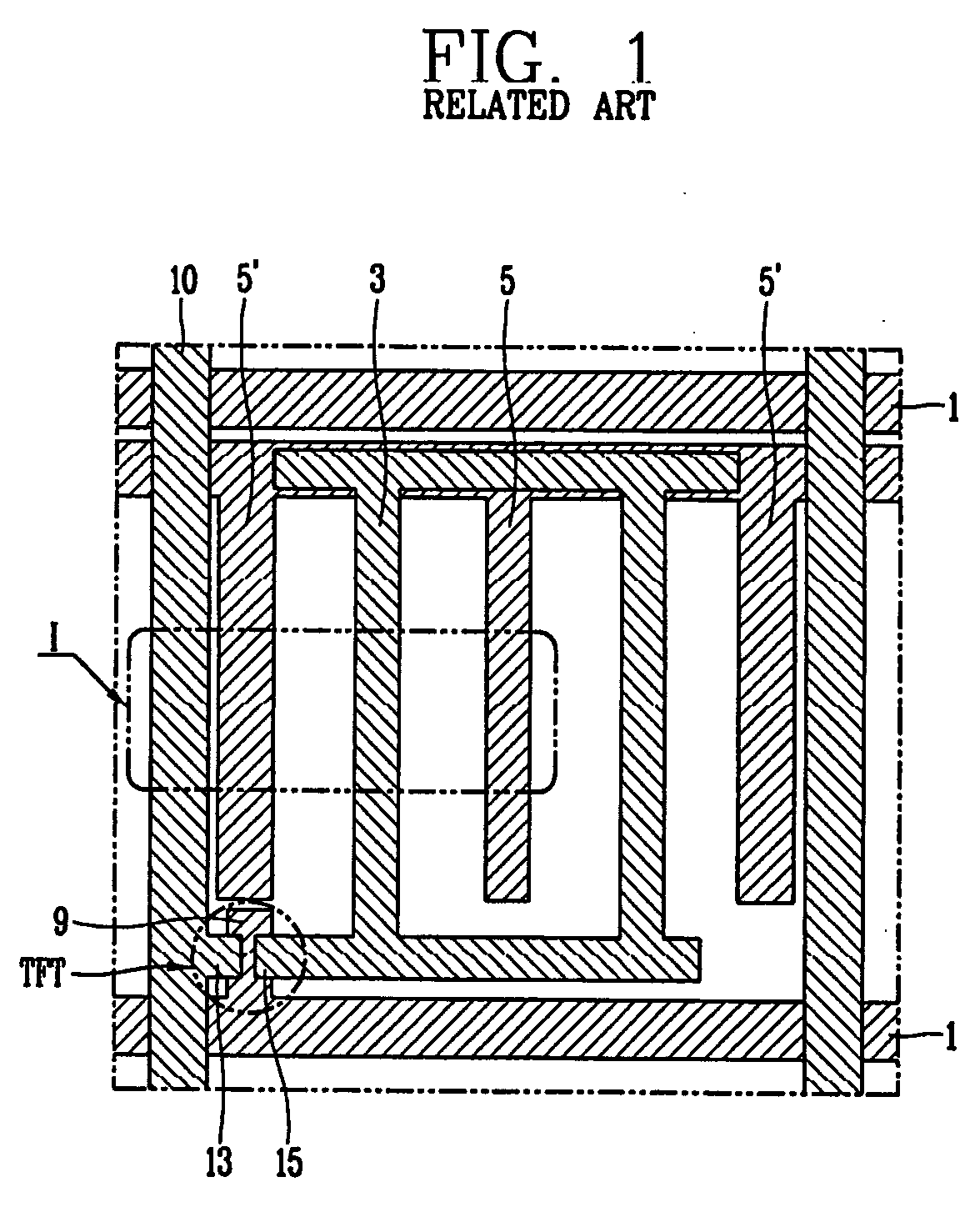

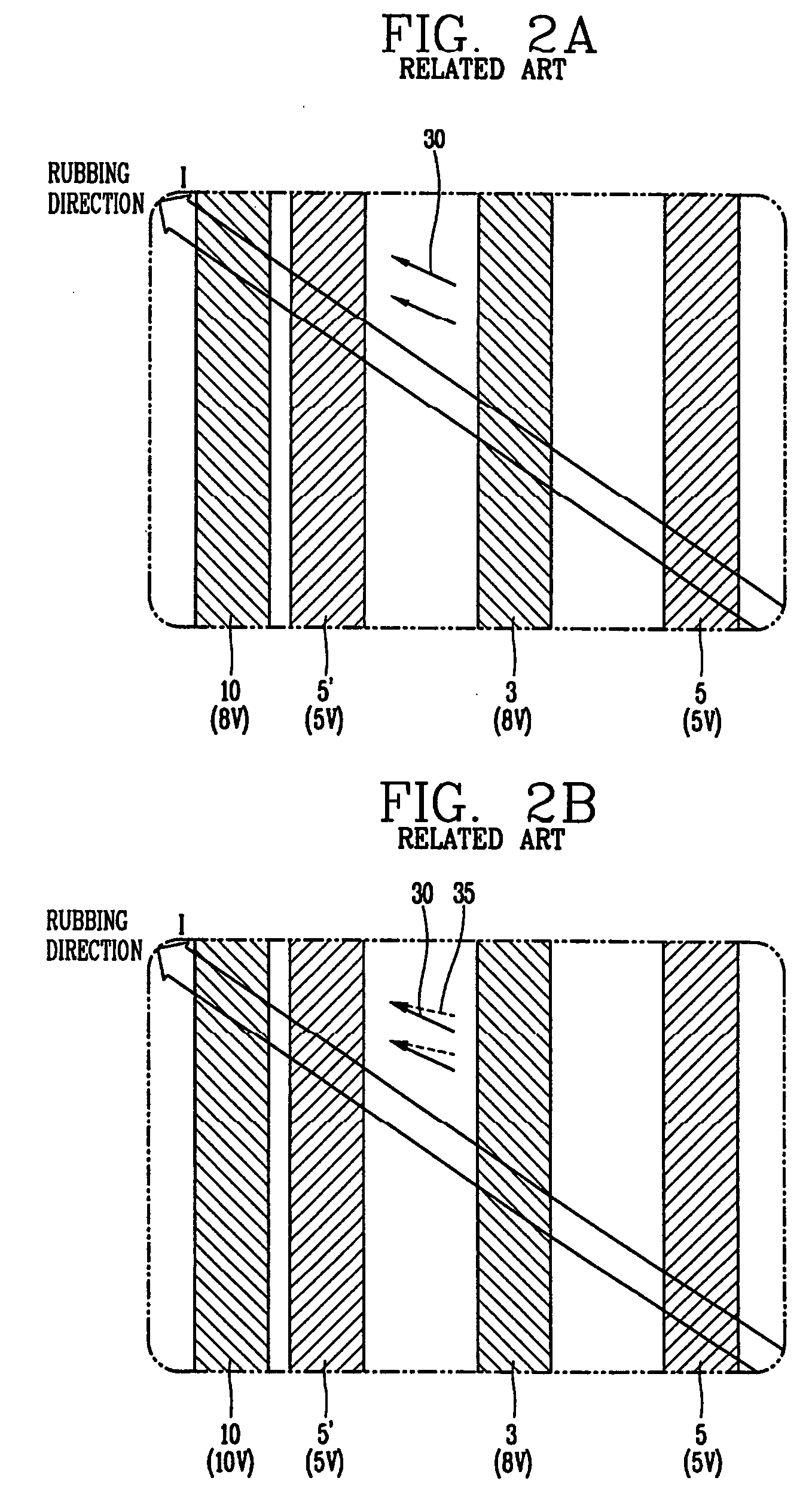

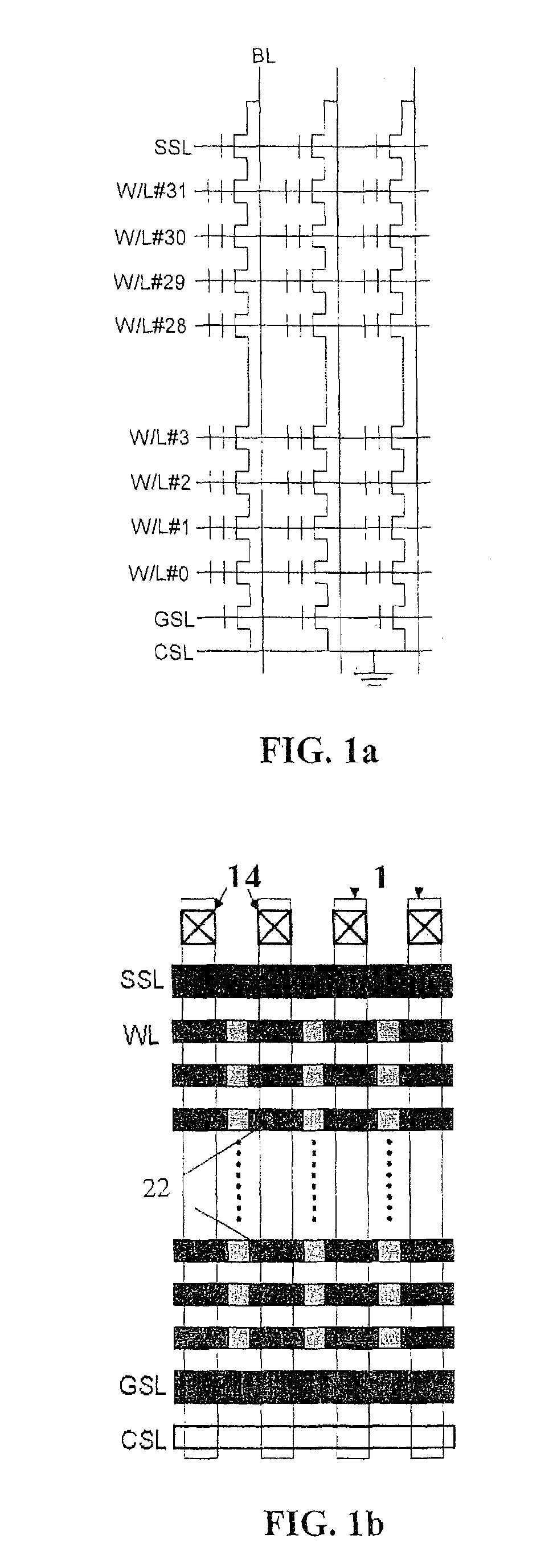

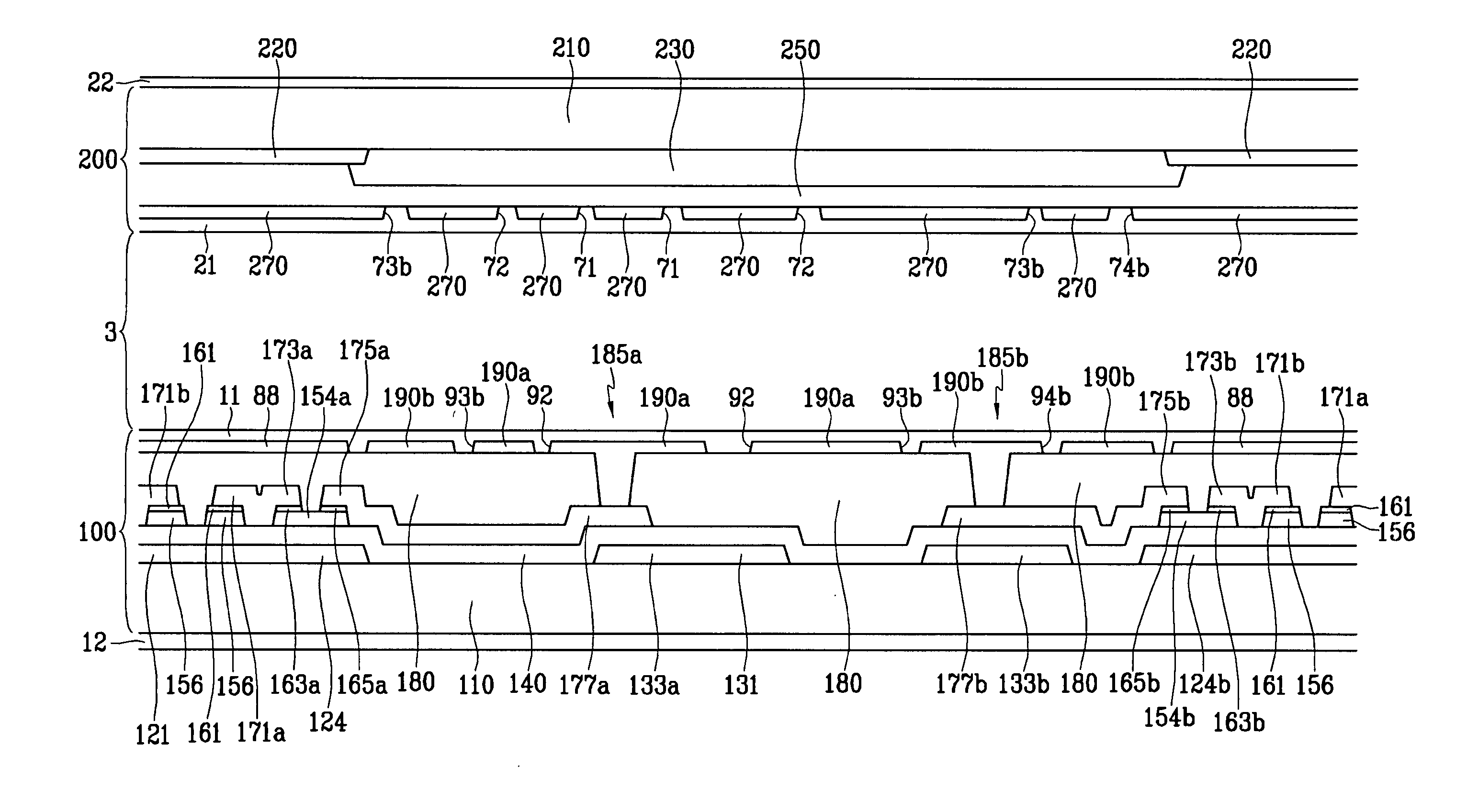

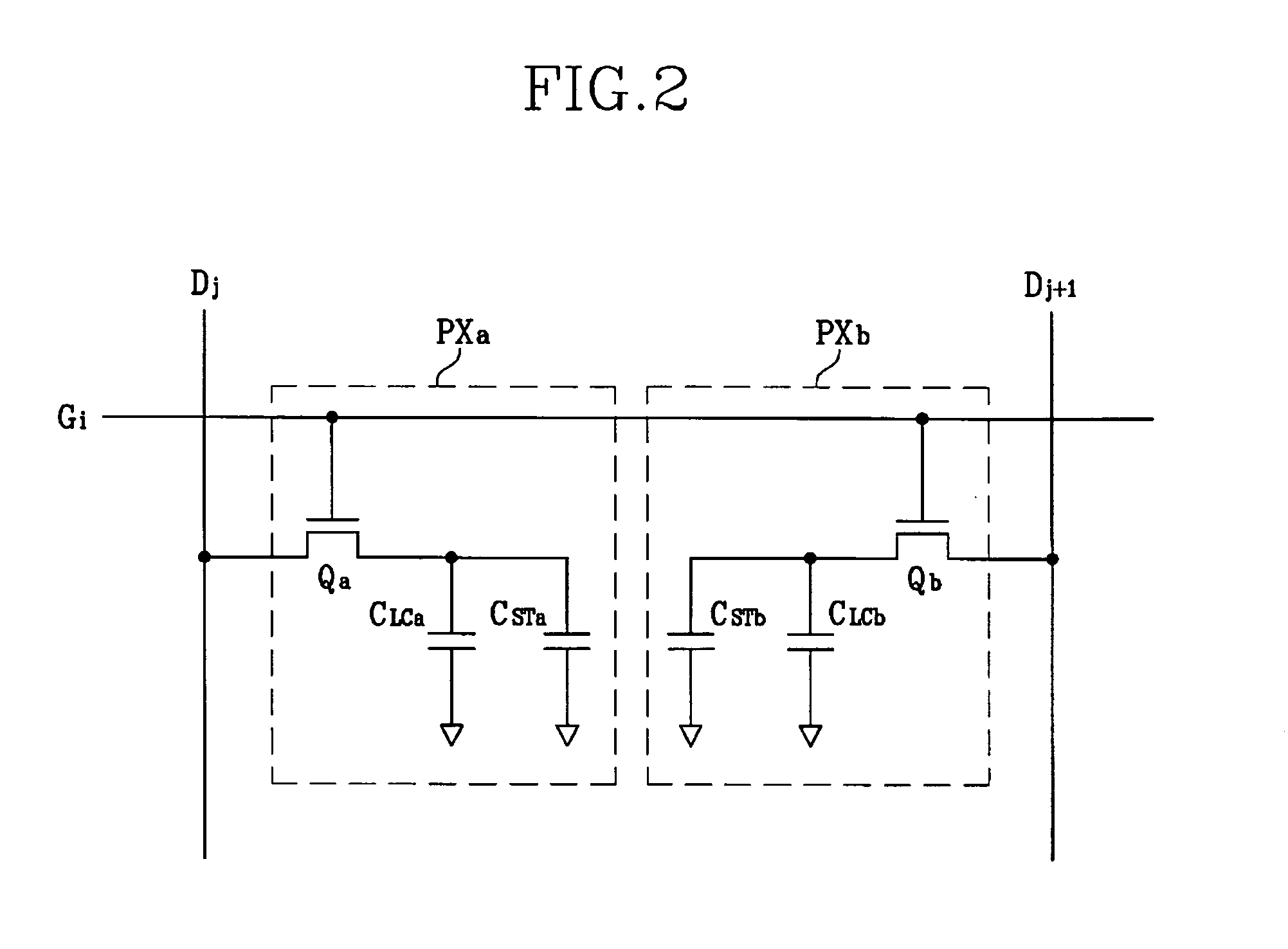

In-plane switching mode liquid crystal display device

ActiveUS20060145990A1Improve picture qualityMinimize parasitic capacitanceStatic indicating devicesNon-linear opticsIn planeLiquid-crystal display

An in-plane switching mode liquid crystal display device includes first and second substrates, a gate line on the first substrate, a data line crossing the gate line defining a unit pixel region, a thin film transistor at the crossing of the gate line and the data line, a pixel electrode line in parallel with the data line, a plurality of pixel electrodes formed to be protruded in an extended direction of the gate line from the pixel electrode line, a common electrode line adjacent to a data line of a neighboring pixel in the extended direction of the gate line and in parallel therewith, a plurality of common electrodes protruded from the common electrode line and alternately arranged in parallel with the plurality of pixel electrodes to generate an in-plane electric field, and a liquid crystal layer between the first and second substrates.

Owner:LG DISPLAY CO LTD

Touch Sensor Panel

InactiveUS20130050108A1Maximizing contour lineReduce areaInput/output processes for data processingEngineeringElectrode

Owner:DONGBU HITEK CO LTD

Semiconductor devices comprising a plurality of gate structures

ActiveUS8362542B2Volume maximizationMade uniformTransistorSolid-state devicesGate dielectricDevice material

Semiconductor devices including a plurality of gate structures disposed on a semiconductor substrate are provided. Each of the gate structures includes a tunnel dielectric layer, a floating gate, an inter-gate dielectric layer, a control gate, and a mask layer. Liners cover opposing sidewalls of adjacent floating gates. Spacers are disposed on the liners, the spacers protruding from opposing sidewalls of adjacent ones of the gate structures, and a top of each of the spacers is disposed below a top of a corresponding one of the gate structures. The liners define sidewalls of respective air gaps and the spacers define tops of the respective air gaps.

Owner:SAMSUNG ELECTRONICS CO LTD

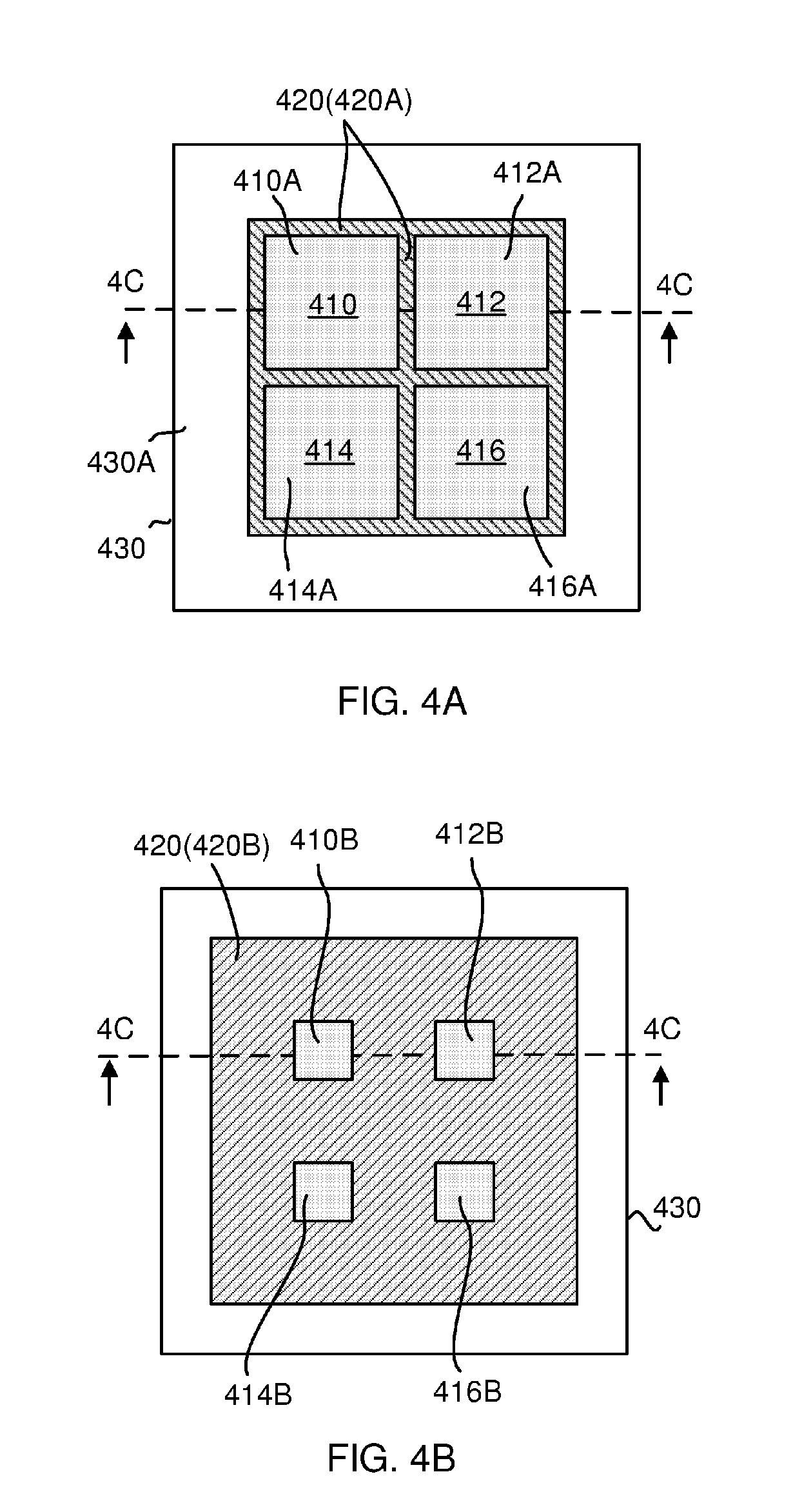

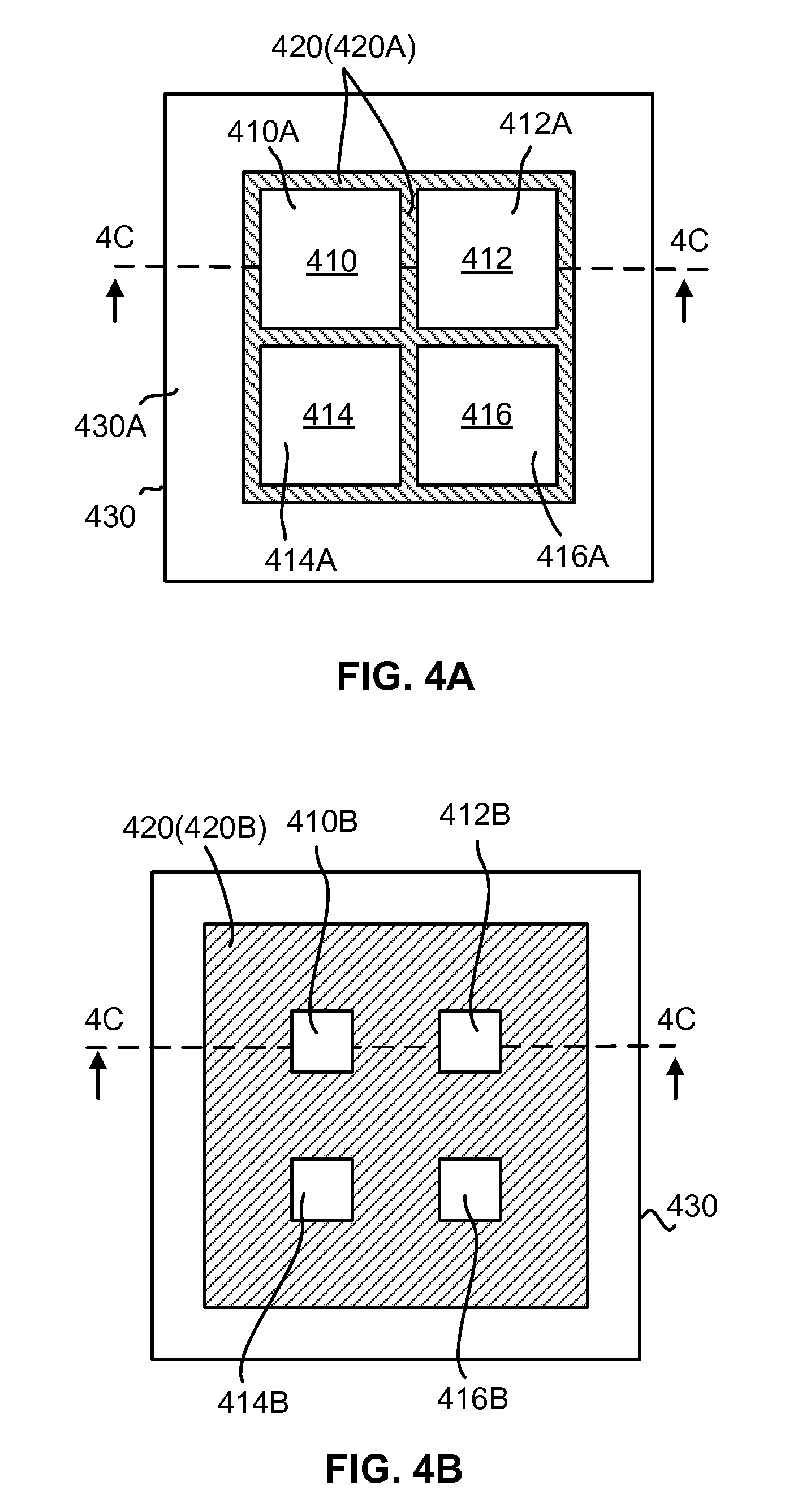

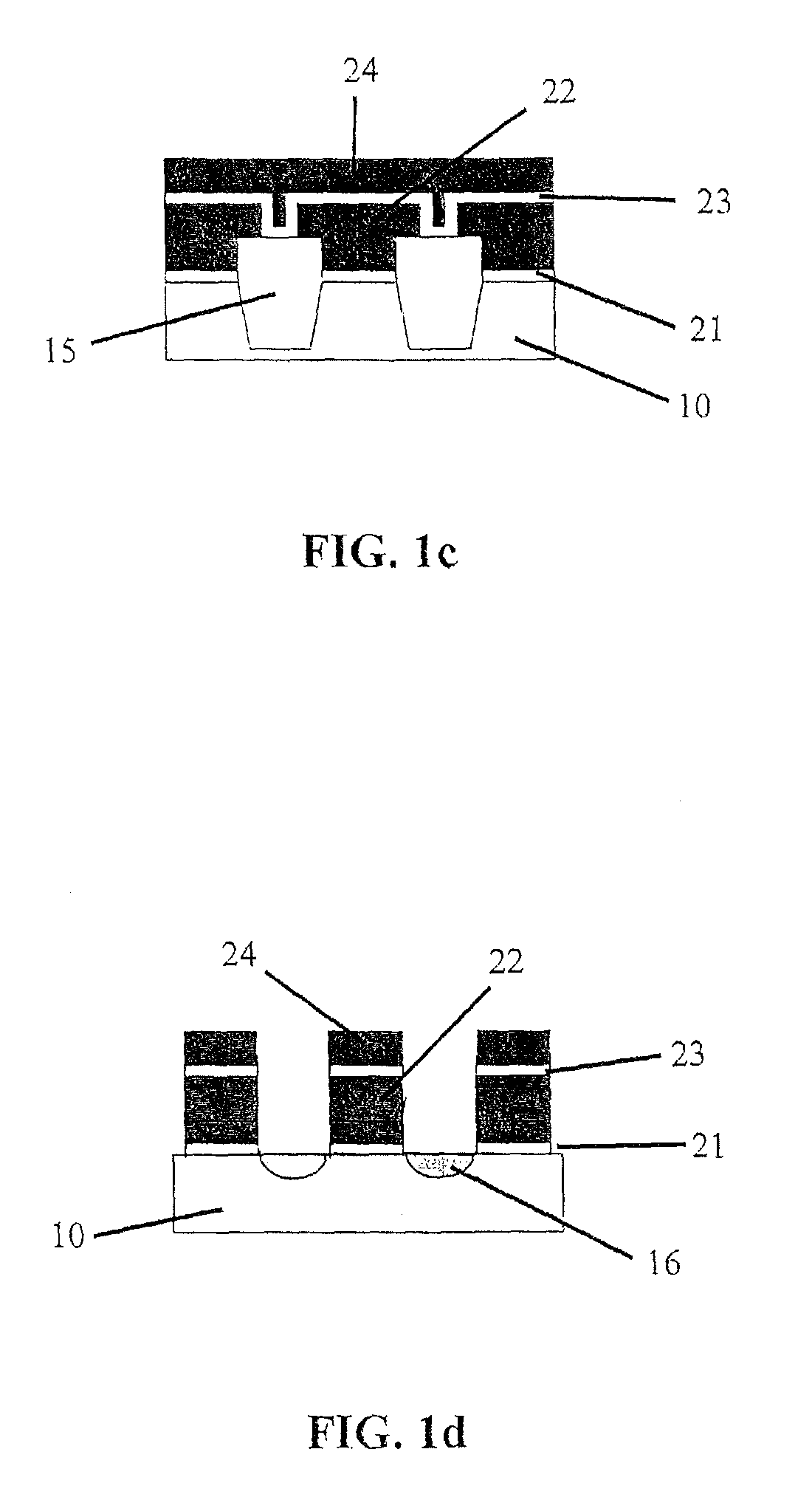

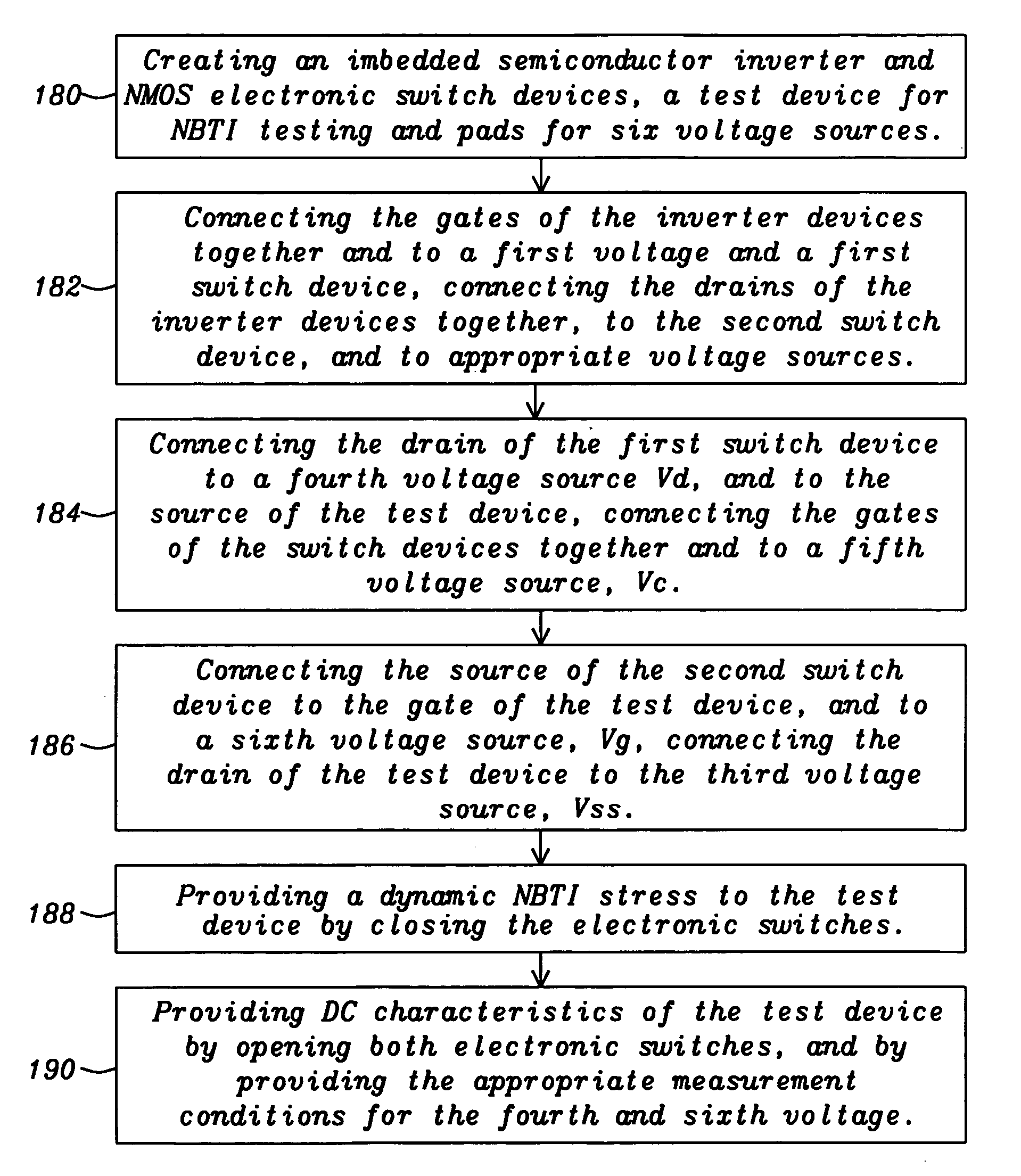

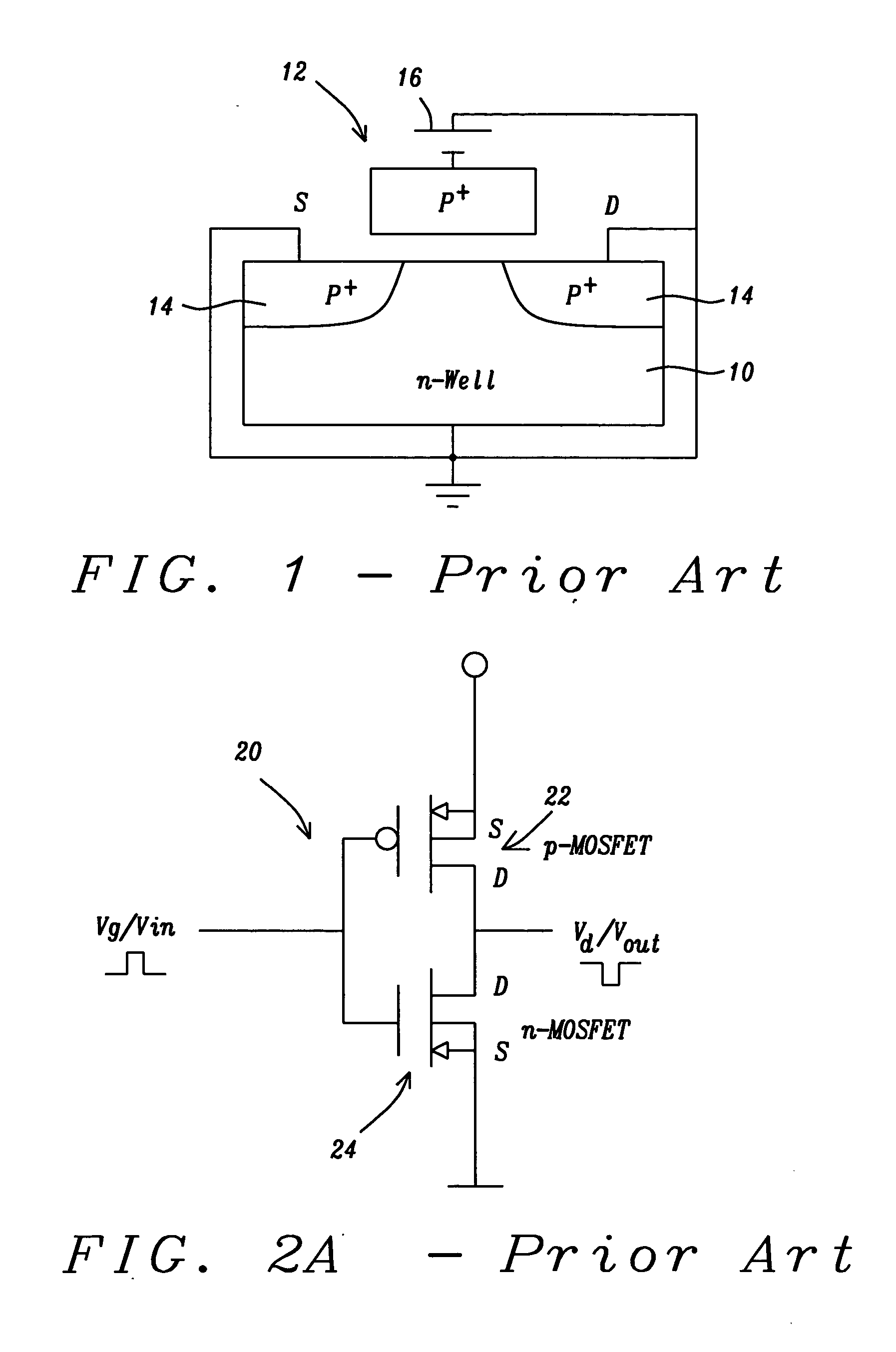

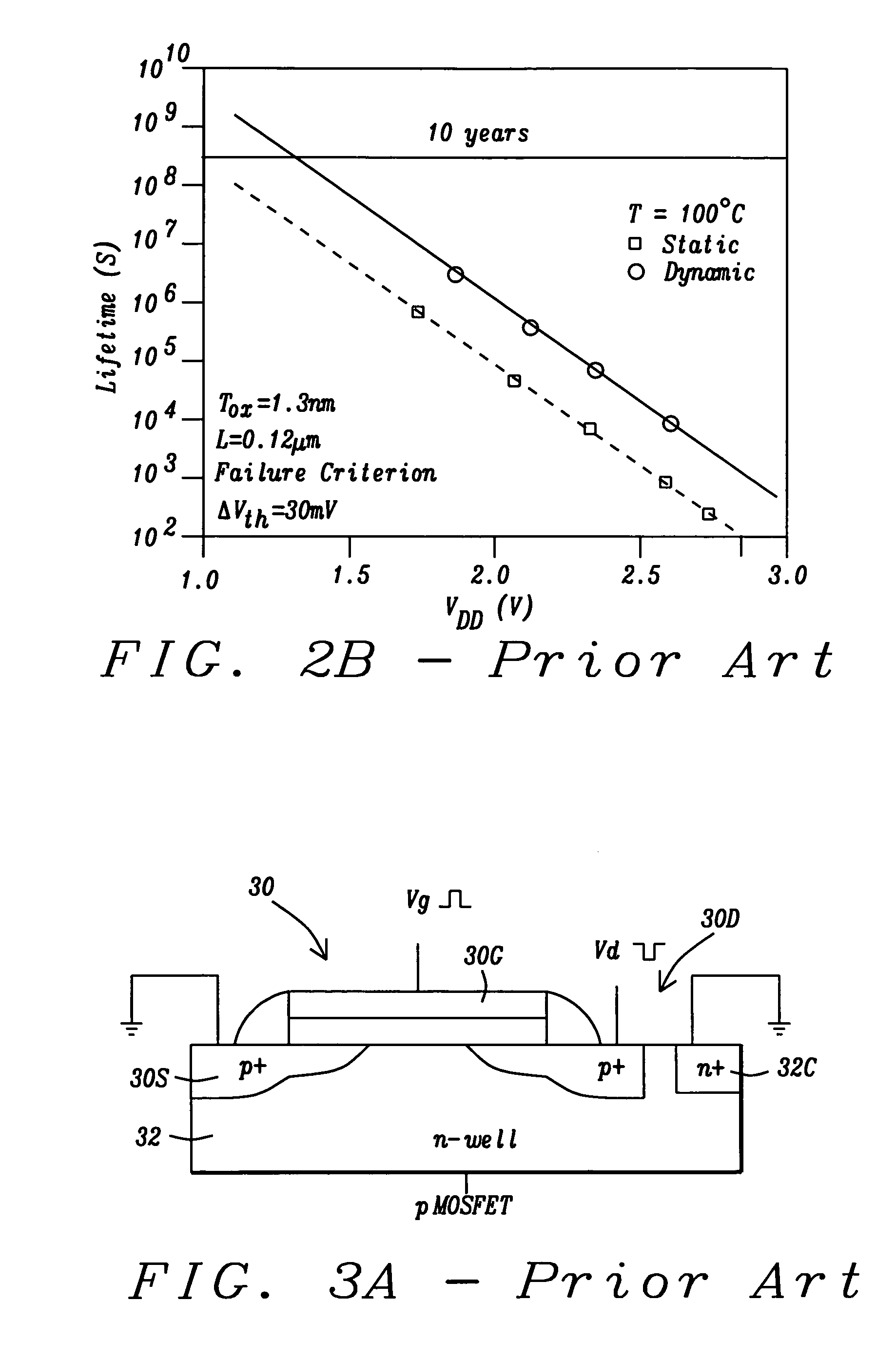

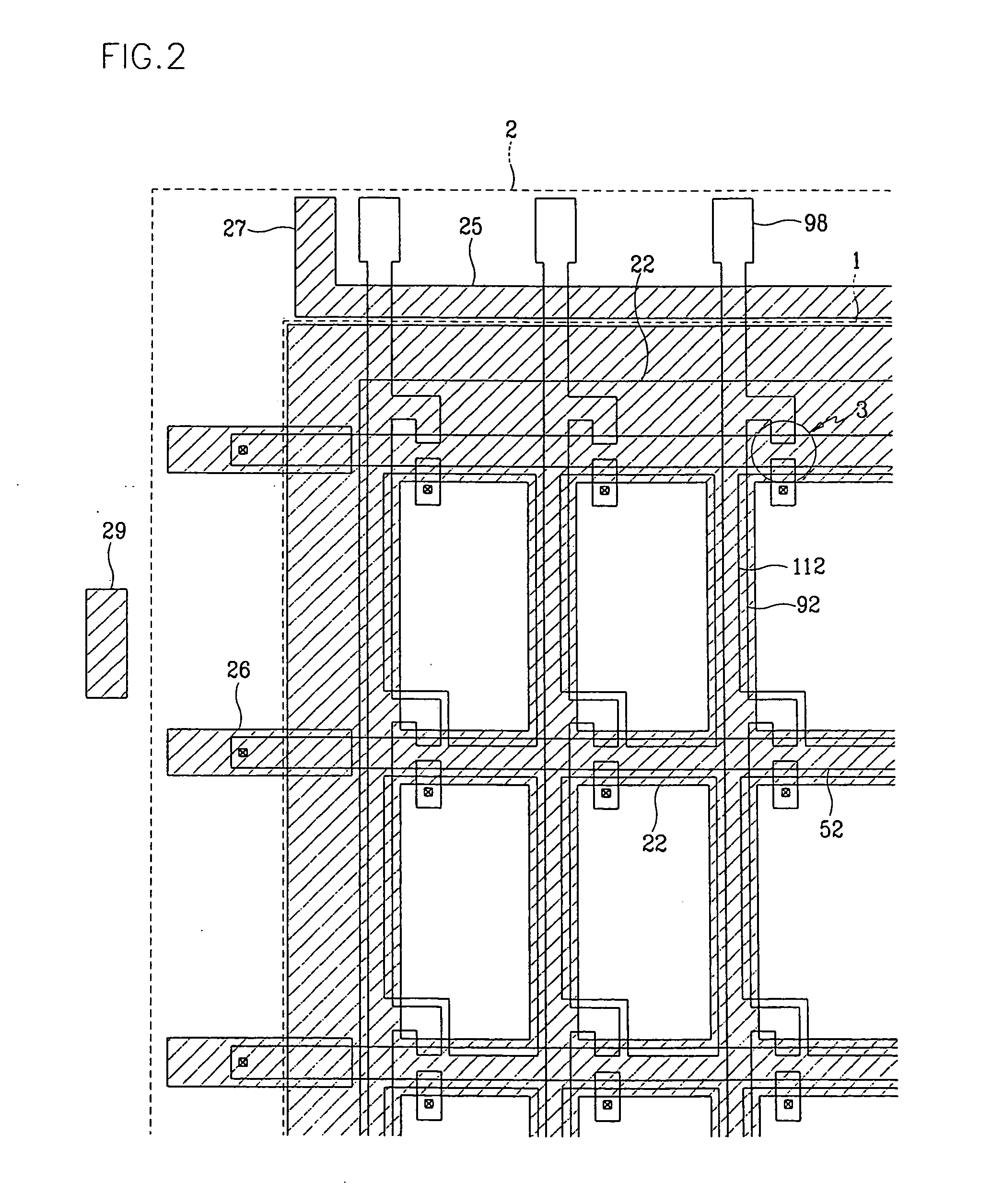

Novel test structure for automatic dynamic negative-bias temperature instability testing

InactiveUS20050278677A1Minimize parasitic capacitanceMinimizes parasitic capacitanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectronic switchEngineering

The invention describes a novel test structure and process to create the structure for performing automatic dynamic stress testing of PMOS devices for Negative Bias Temperature Instability (NBTI). The invention consists of an integrated inverter, two integrated electronic switches for switching from stress mode to device DC characterization measurement mode, and a PMOS FET device under test (DUT). The inverter assures the proper 180 degree phase relationship between the test device source and gate voltage while the imbedded electronic switches provide isolation of the test device during DC characterization testing. Another embodiment of the invention enables the testing of multiple devices under test (DUT's).

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Thin film transistor array panel for liquid crystal display

InactiveUS20060231846A1Minimizing misalignment problemIncrease the apertureOptical filtersSolid-state devicesOhmic contactEngineering

A black matrix having an opening at pixels of a matrix array in a display area, a common wire including common pads and common signal lines, and gate pads in a peripheral area, and an alignment key in outer area to align interlayer thin films are formed on an insulating substrate. Red, blue and green color filters the edge of which overlap the black matrix are formed at the pixels on the insulating substrate, and an organic insulating layer covering the black matrix and the color filters and having a contact hole exposing the gate pad is formed thereon. A gate wire including a gate line connected to the gate pad through the contact hole and a gate electrode connected to the gate line is formed on the organic insulating layer, and a gate insulating layer covering the gate wire is formed on the organic insulating layer. A semiconductor pattern and ohmic contact layers are sequentially formed on the gate insulating layer of the gate electrode. A data wire including a source electrode and a drain electrode that are made of a same layer on the ohmic contact layers and separated from each other, and a data line connected to the source electrode and defining the pixels of a matrix array by crossing the gate line is formed on the gate insulating layer. A passivation layer covering the data wire and having contact holes exposing the gate pad and the data pad is formed, and a pixel wire including a pixel electrode, a redundant gate pad, a redundant data pad that are respectively connected to the drain electrode, the gate pad and the data pad through the contact holes.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Frequency tuning range extension and modulation resolution enhancement of a digitally controlled oscillator

ActiveUS20070188243A1Easy to adjustIncrease rangeSimultaneous amplitude and angle modulationPulse automatic controlCMOSImage resolution

A novel apparatus and method of extending the frequency tuning range and improving the modulation resolution of an RF digitally controlled oscillator (DCO). In addition to the coarse PVT MIM varactor bank, the DCO uses a single unified bank of varactors that is further subdivided divided into an MSB bank, LSB bank and sigma-delta (SD-LSB) bank. Any ratio mismatches between MSBs and LSBs are digitally calibrated out using a DCO step-size pre-distortion scheme wherein the LSB steps are adjusted to account for the ratio mismatch between the MSB / LSB step sizes. A harmonic characterization technique is used to estimate the mismatches in the minimal size CMOS tuning varactors of a digitally controlled RF oscillator (DCO), wherein the nominal ratio mismatch between the MSB and LSB devices is estimated using hybrid stochastic gradient DCO gain estimation algorithms. The nominal ratio mismatch and the mismatches in the MSB and LSB banks are used to determine the average MSB / LSB mismatch. The average mismatch value is then used to correct the LSB steps.

Owner:TEXAS INSTR INC

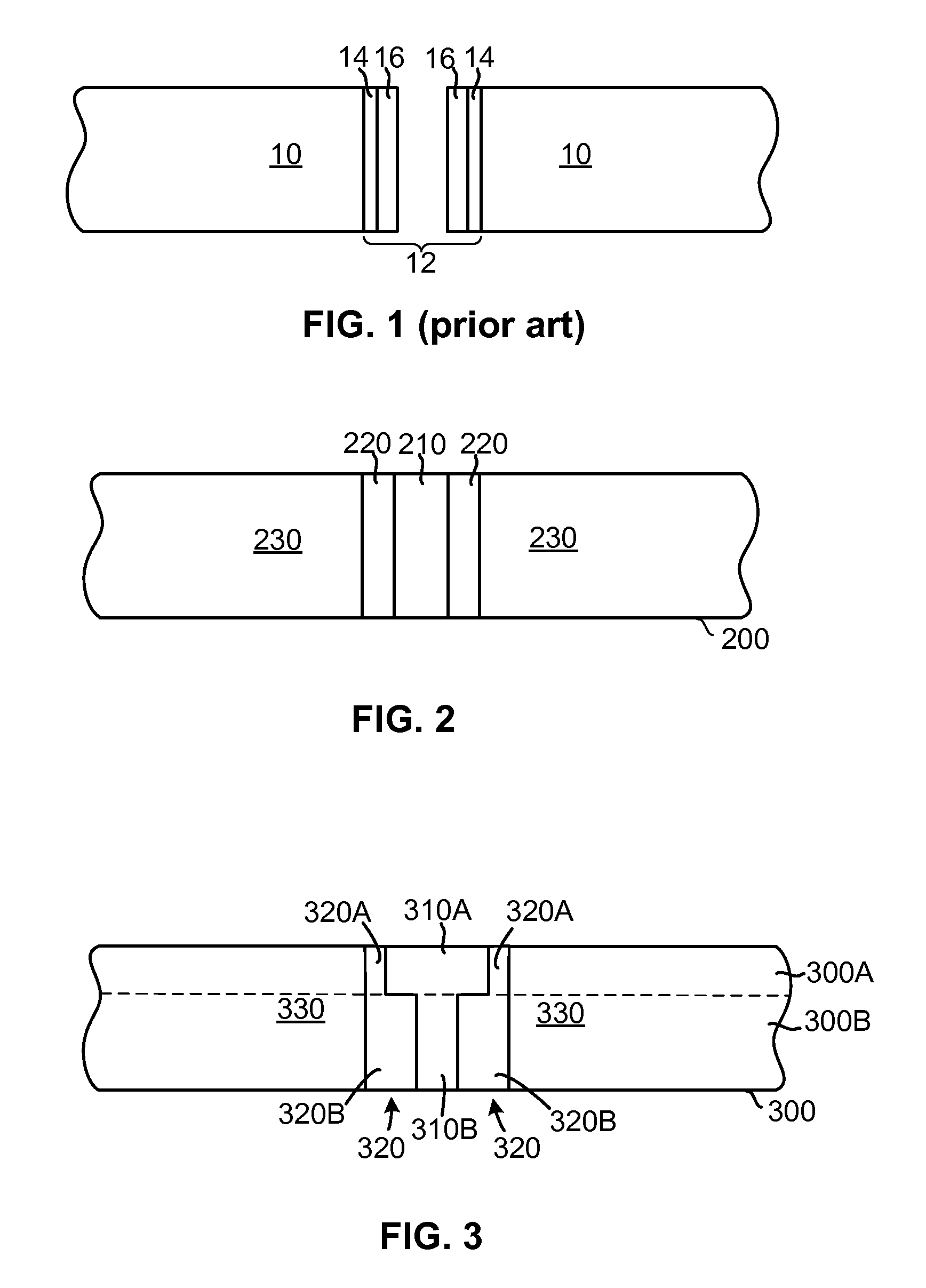

Liquid crystal display and method

InactiveUS20060215071A1Minimize parasitic capacitanceMinimizes parasitic capacitanceNon-linear opticsLiquid-crystal displayImaging quality

A liquid crystal display includes a plurality of gate lines extending in a first direction to transmit gate signals and a plurality of data lines extending in a second direction to transmit data voltages. The data lines cross the gate lines. A plurality of thin film transistors are connected to the gate and the data lines, and a plurality of pixel electrodes are connected to the thin film transistors. A passivation layer is formed on the gate and the data lines. A shielding electrode extends along the gate and the data lines such that the shielding electrode overlaps the gate and the data lines, and the shielding electrode overlapping the gate line has a width larger than the width of the gate line. As the shielding electrode completely covers the data and the gate lines, the parasitic capacitance between the data and gate lines and the pixel electrode is reduced, thereby preventing deterioration of the display image quality.

Owner:SAMSUNG ELECTRONICS CO LTD

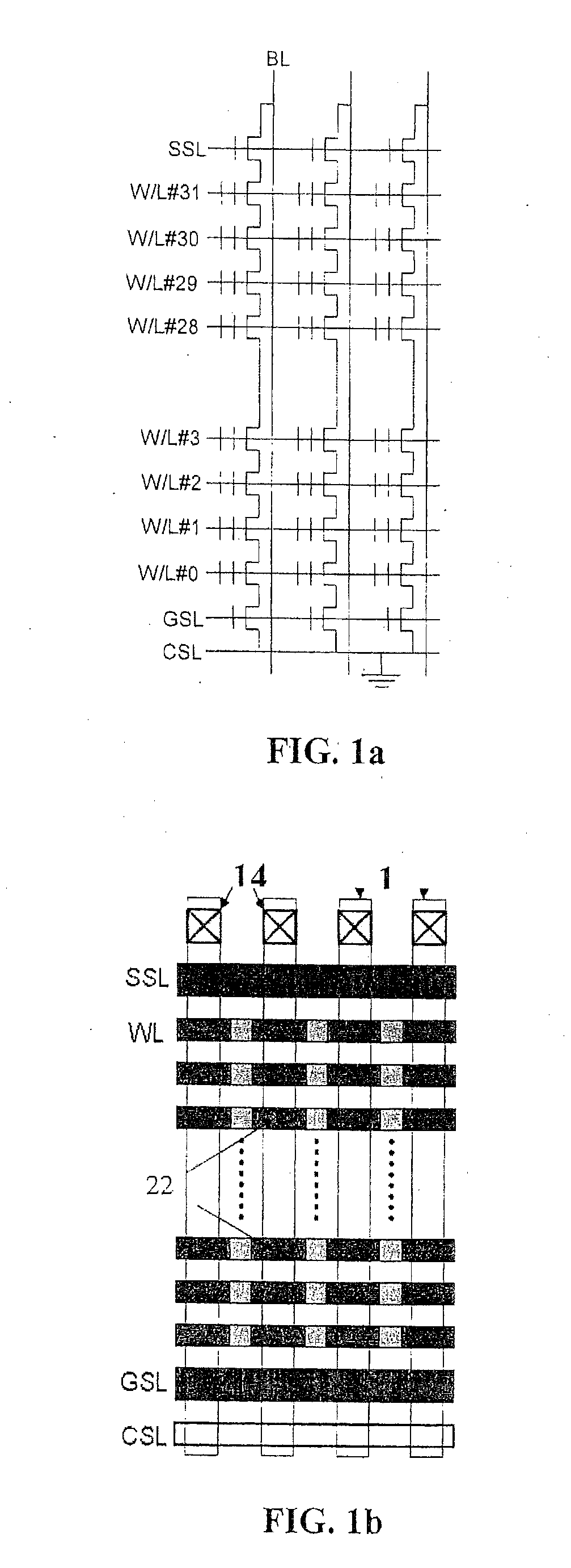

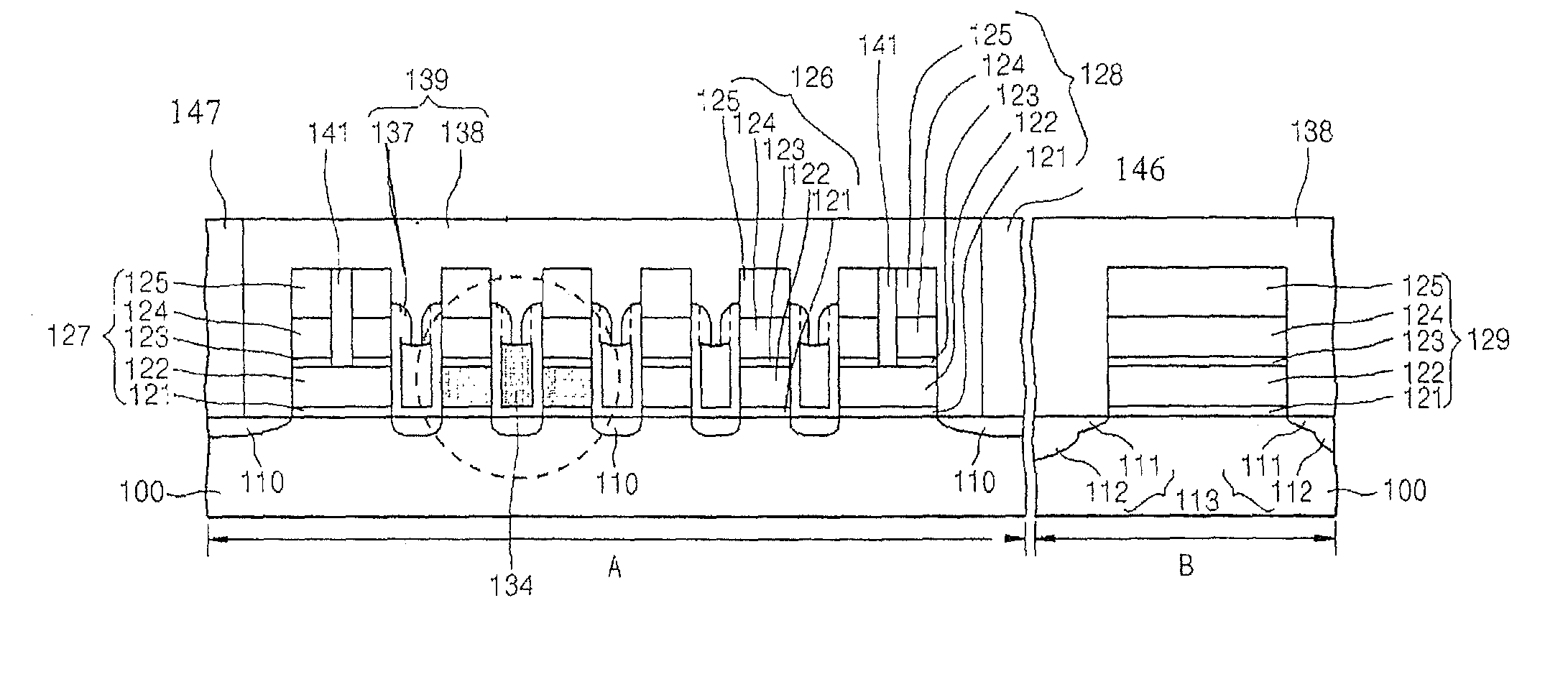

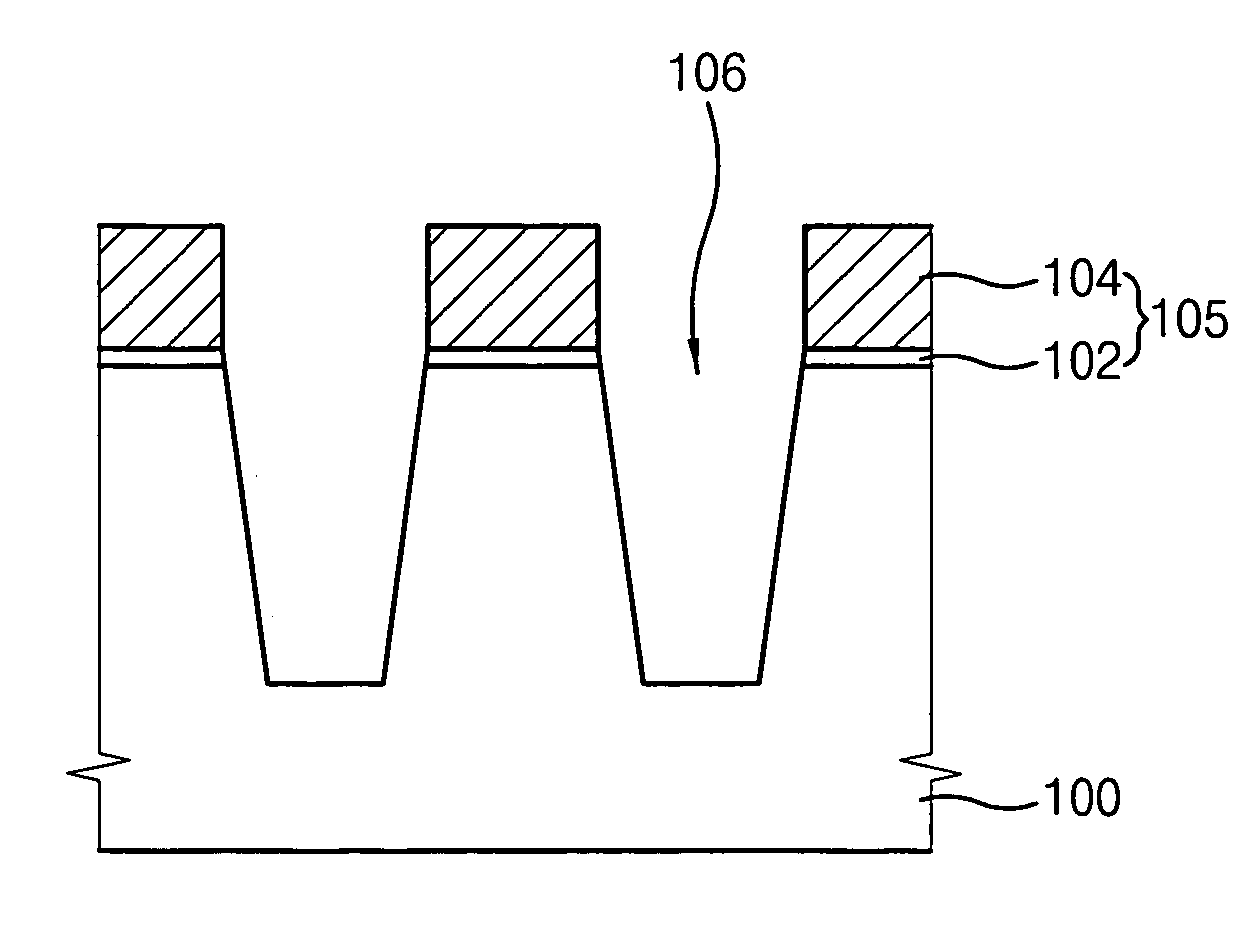

Method of forming a trench isolation layer and method of manufacturing a non-volatile memory device using the same

InactiveUS20060094203A1Reduce parasitic capacitanceMinimizes parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerParasitic capacitance

In a method of forming a device isolation layer for minimizing a parasitic capacitor and a non-volatile memory device using the same, a trench is formed on a substrate. A first insulation layer is formed on a top surface of the substrate and on inner surfaces of the trench, so that the trench is partially filled with the first insulation layer. A second insulation layer is formed on the first insulation layer to a thickness to fill up the trench, thereby forming a preliminary isolation layer. An etching rate of the second insulation layer is different from that of the first insulation layer. A recess is formed at a central portion of the preliminary isolation layer by partially removing the first and second insulation layers, thereby forming the device isolation layer including the recess. The recess in the device isolation layer reduces a parasitic capacitance in a non-volatile memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of forming self-aligned contact structures in semiconductor integrated circuit devices

InactiveUS6881659B2Minimize parasitic capacitanceImprove reliabilityTransistorSolid-state devicesEtchingInterconnection

Methods of forming integrated circuit devices (e.g., memory devices) include the use of preferred self-aligned contact hole fabrication steps. These steps improve process reliability by reducing the likelihood that contact holes will become misaligned to underlying integrated circuit device structures and thereby potentially expose the structures in an adverse manner. Typical methods include the steps of forming a plurality of interconnection patterns on a substrate and then covering a surface of the interconnection patterns and a portion of the substrate with a capping insulating layer such as silicon nitride layer. The capping insulating layer is then covered with an upper interlayer insulating layer different from the capping insulating layer. The upper interlayer insulating layer and the capping insulating layer are then dry-etched in sequence to form a first narrow contact hole that exposes the substrate, but preferably does not expose the interconnection patterns. The first contact hole is then widened in a self-aligned manner using the capping insulating layer as an etch-stop layer. This widening step is performed by wet etching sidewalls of the first contact hole using an etchant that etches the upper interlayer insulating layer faster than the capping insulating layer. In this manner, the first contact hole may be formed to initially compensate for potential misalignment errors and then a self-aligned wet etching step may be performed to widen the first contact hole into a second contact hole so that low resistance contacts (e.g., contact plugs) can be provided therein.

Owner:SAMSUNG ELECTRONICS CO LTD

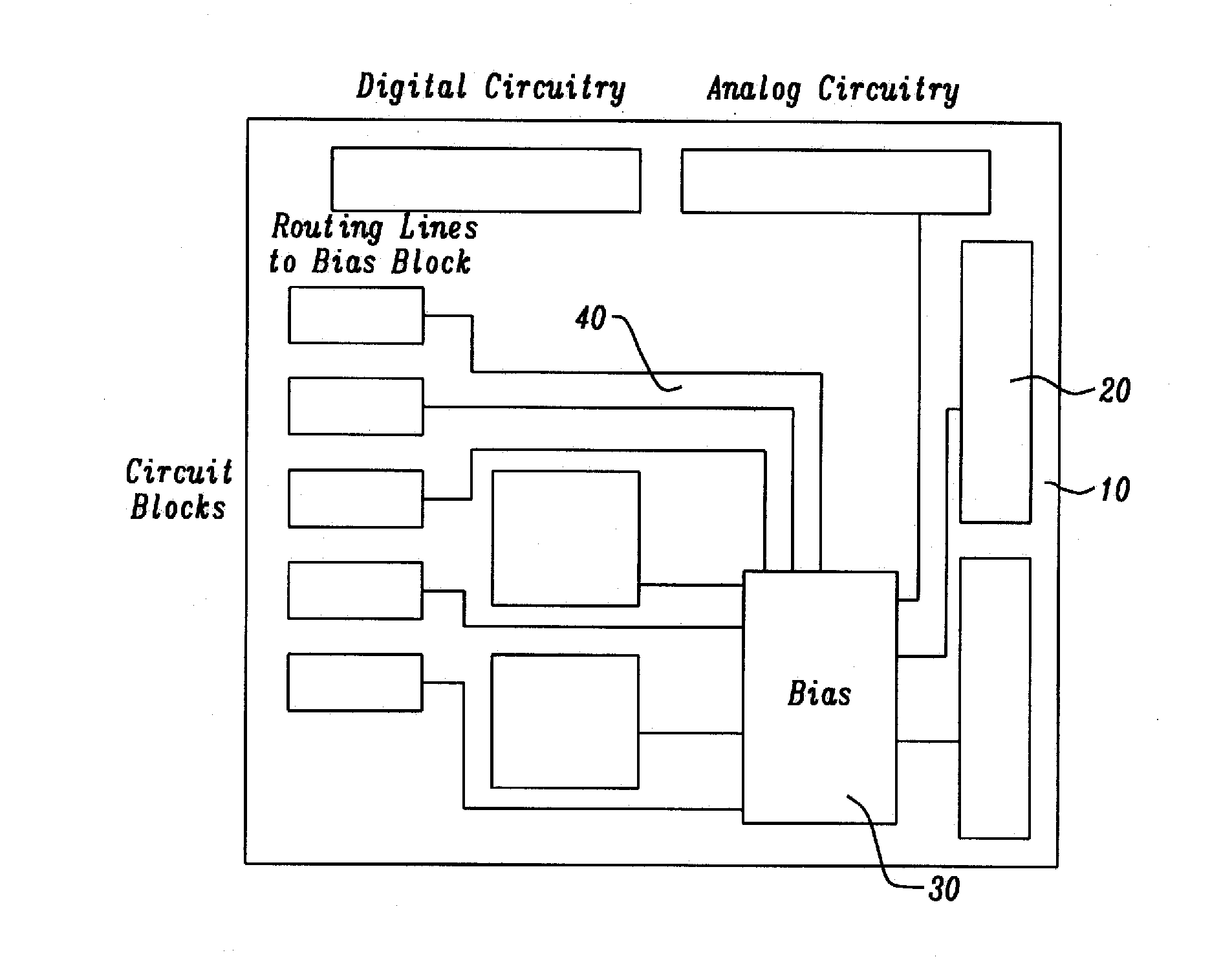

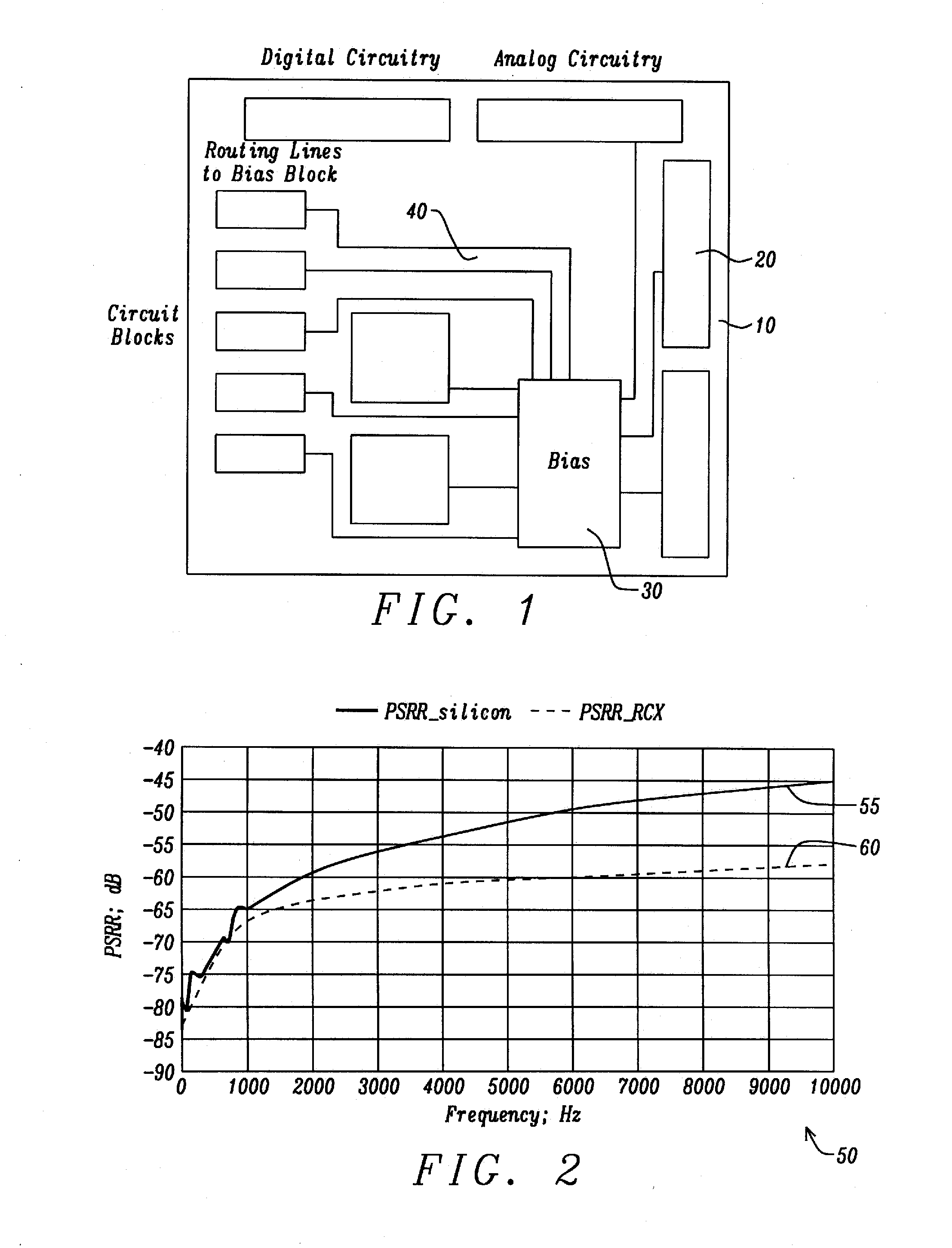

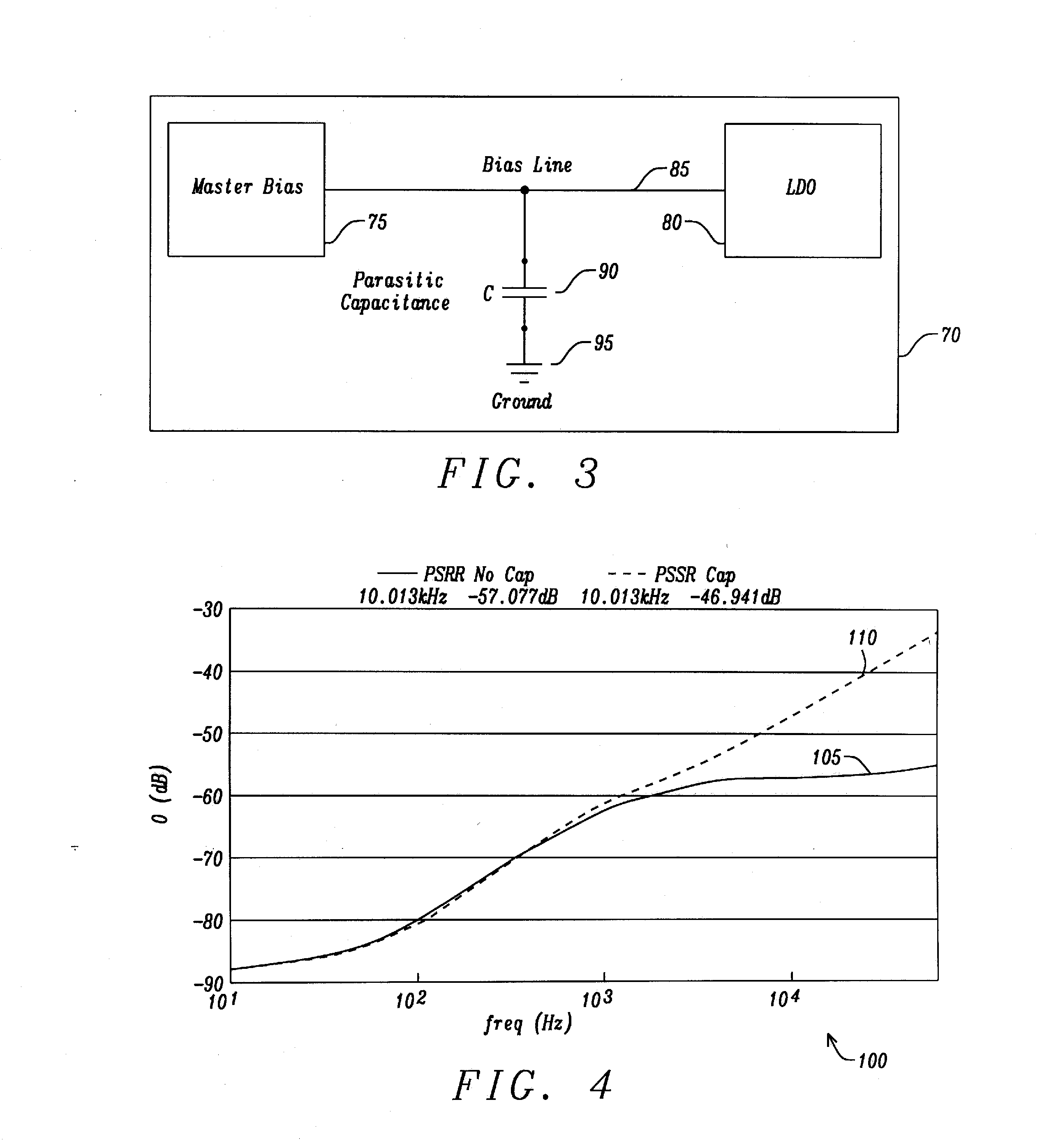

Apparatus and Method for a Voltage Regulator with Improved Power Supply Reduction Ratio (PSRR) with Reduced Parasitic Capacitance on Bias Signal Lines

ActiveUS20150123628A1Reduce the impactReduce impactElectric variable regulationMOSFETReduction ratio

An apparatus and method for a system with improved power supply rejection ratio (PSRR) over a wide frequency range. The improved PSRR is achieved by negating the influence of the parasitic capacitance associated with the bias lines and the introduction of a regulated power supply with embodiments associated with providing a ripple free and regulated supply. With reduction of parasitic capacitance, and providing an ENABLE switch by a pre-regulated supply, the degradation of the PSRR is achieved. The embodiments include both n-channel and p-channel MOSFETs implementations, and a positive and negative regulated power supply voltage. With the combined influence of the utilization of the VREG supply, and the lowering of battery-to-bias line capacitance using design layout and improved floor planning an improved PSRR over a wide frequency distribution is achieved.

Owner:DIALOG SEMICONDUCTOR GMBH