Patents

Literature

35 results about "Carrier scattering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Defect types include atom vacancies, adatoms, steps, and kinks that occur most frequently at surfaces due to the finite material size causing crystal discontinuity. What all types of defects have in common, whether surface or bulk defects, is that they produce dangling bonds that have specific electron energy levels different from those of the bulk. This difference occurs because these states cannot be described with periodic Bloch waves due to the change in electron potential energy caused by the missing ion cores just outside the surface. Hence, these are localized states that require separate solutions to the Schrödinger equation so that electron energies can be properly described. The break in periodicity results in a decrease in conductivity due to defect scattering.

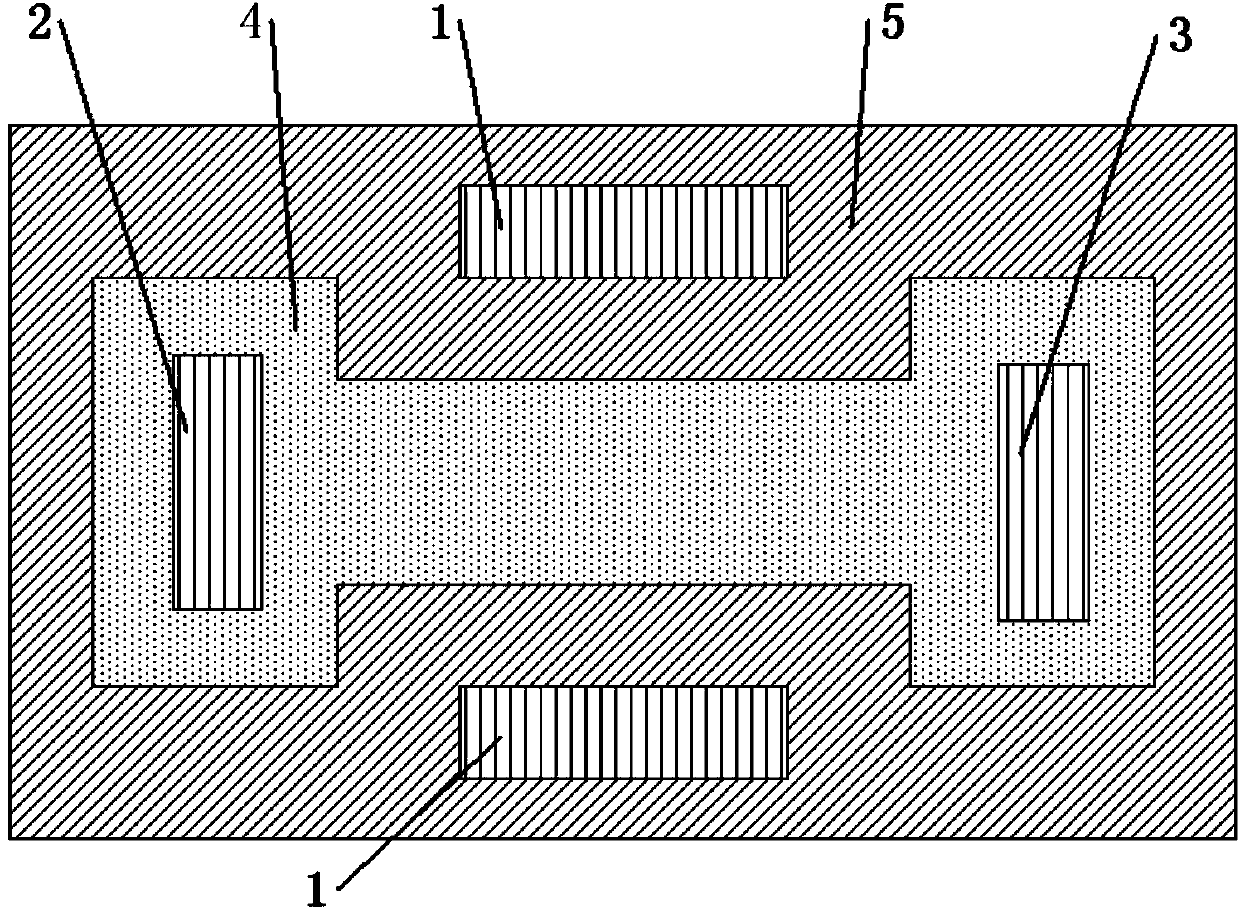

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

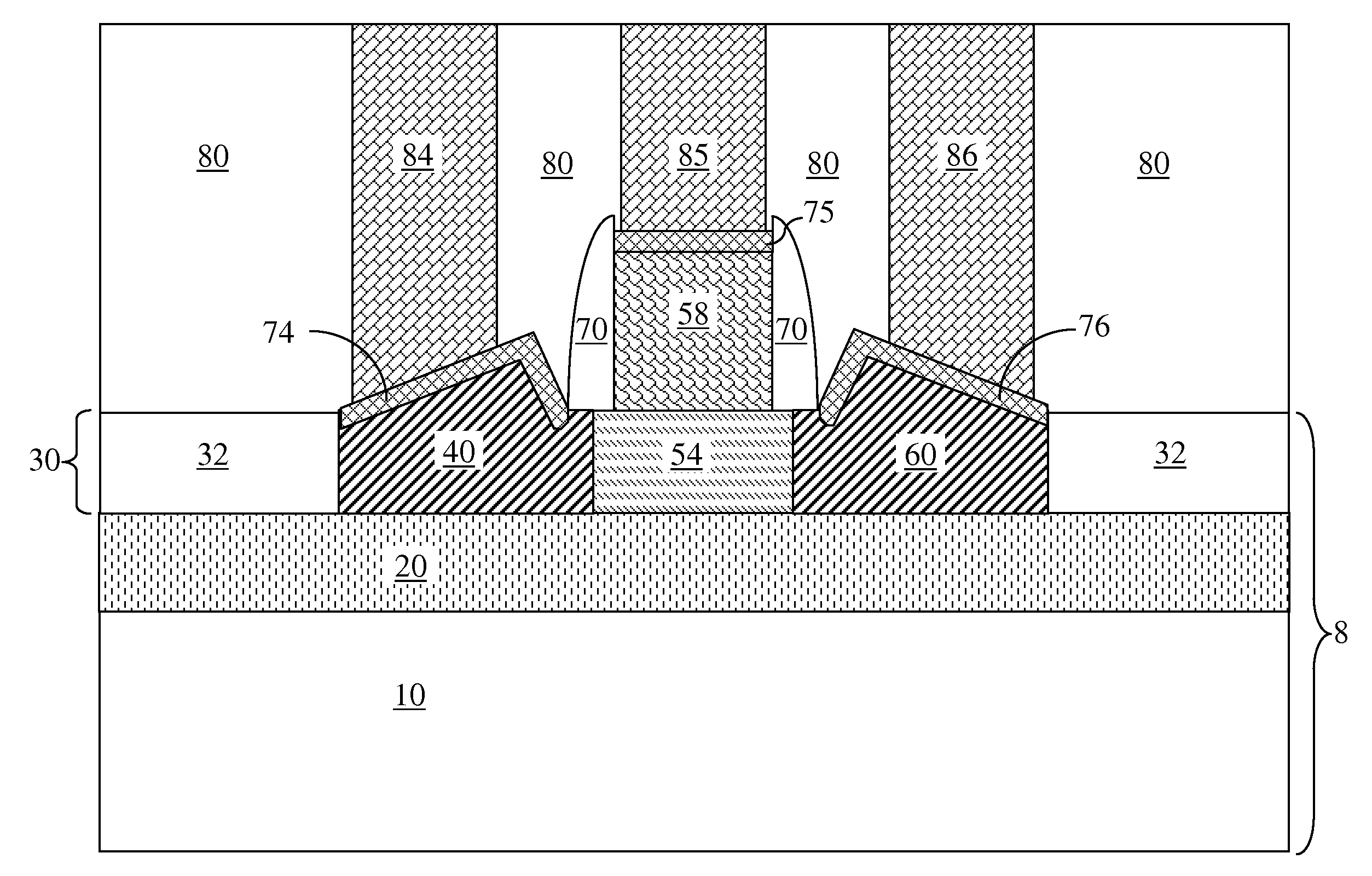

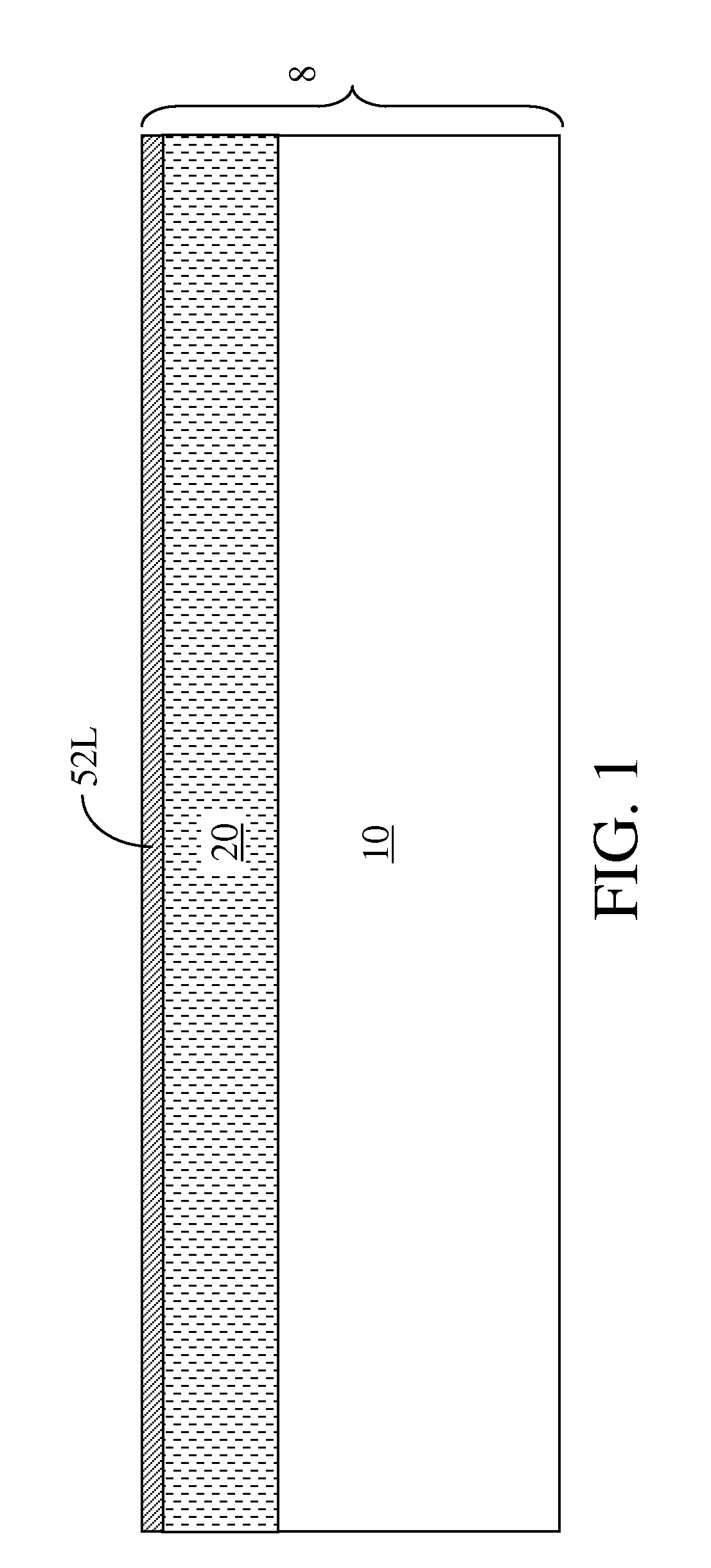

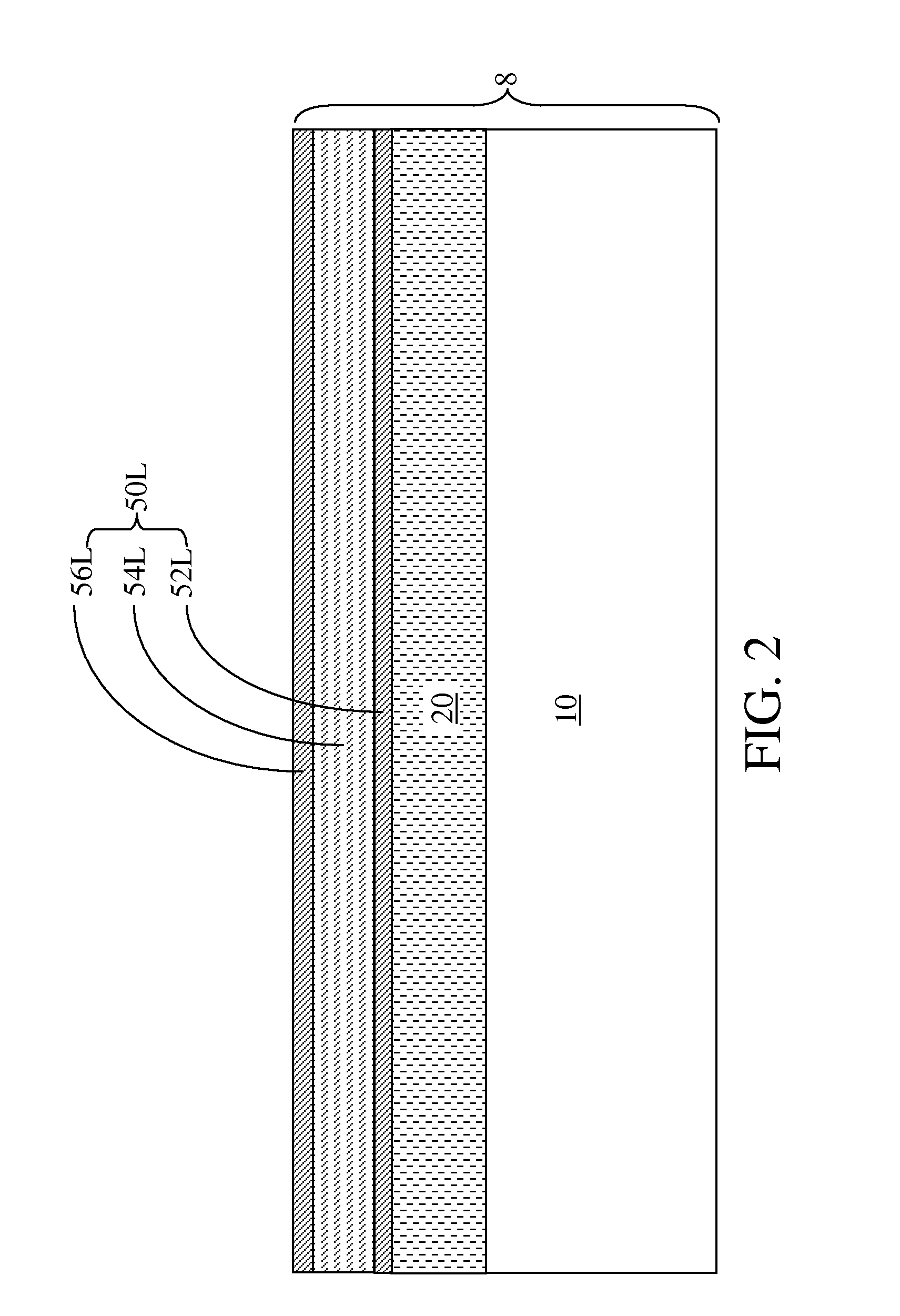

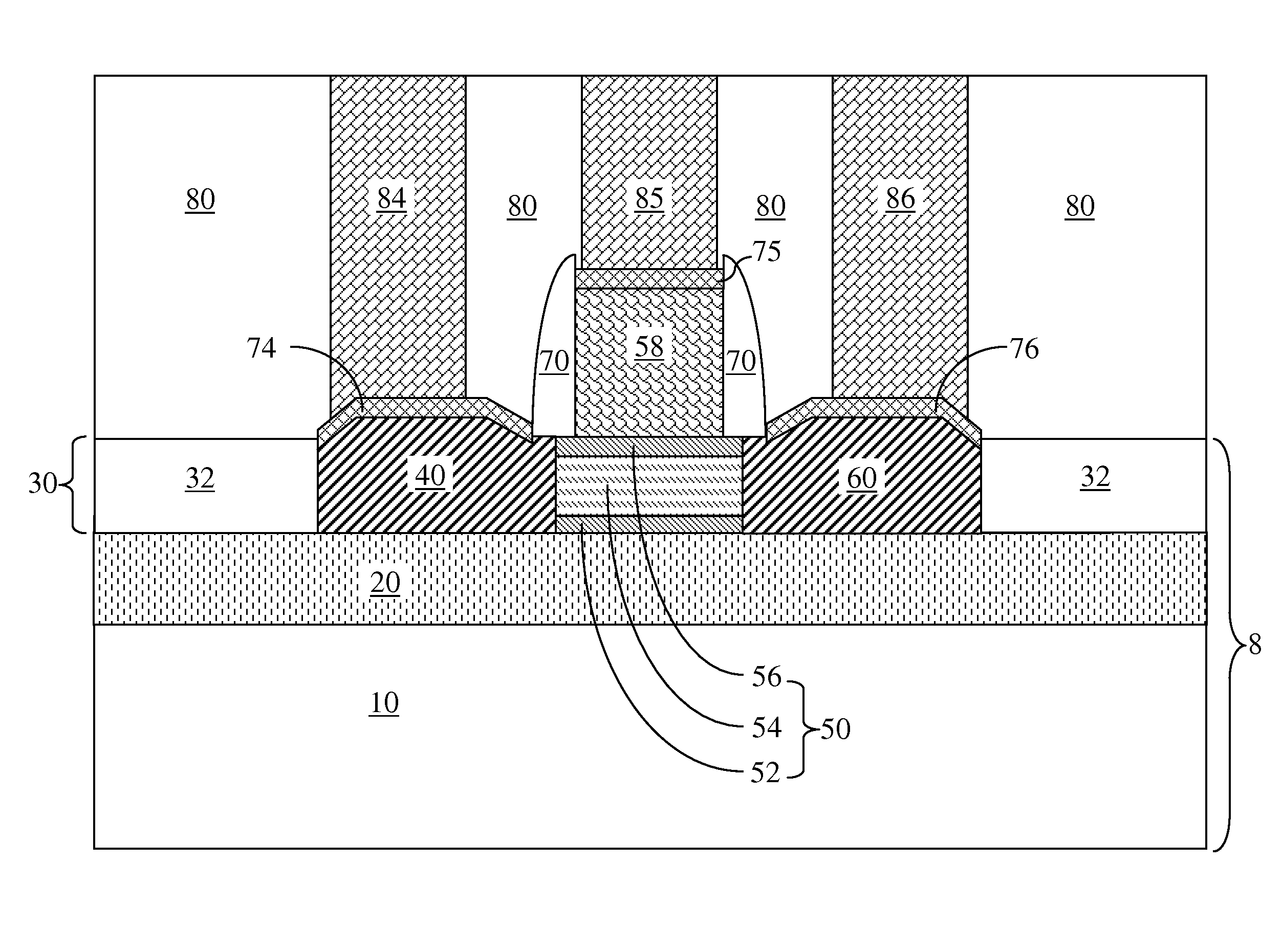

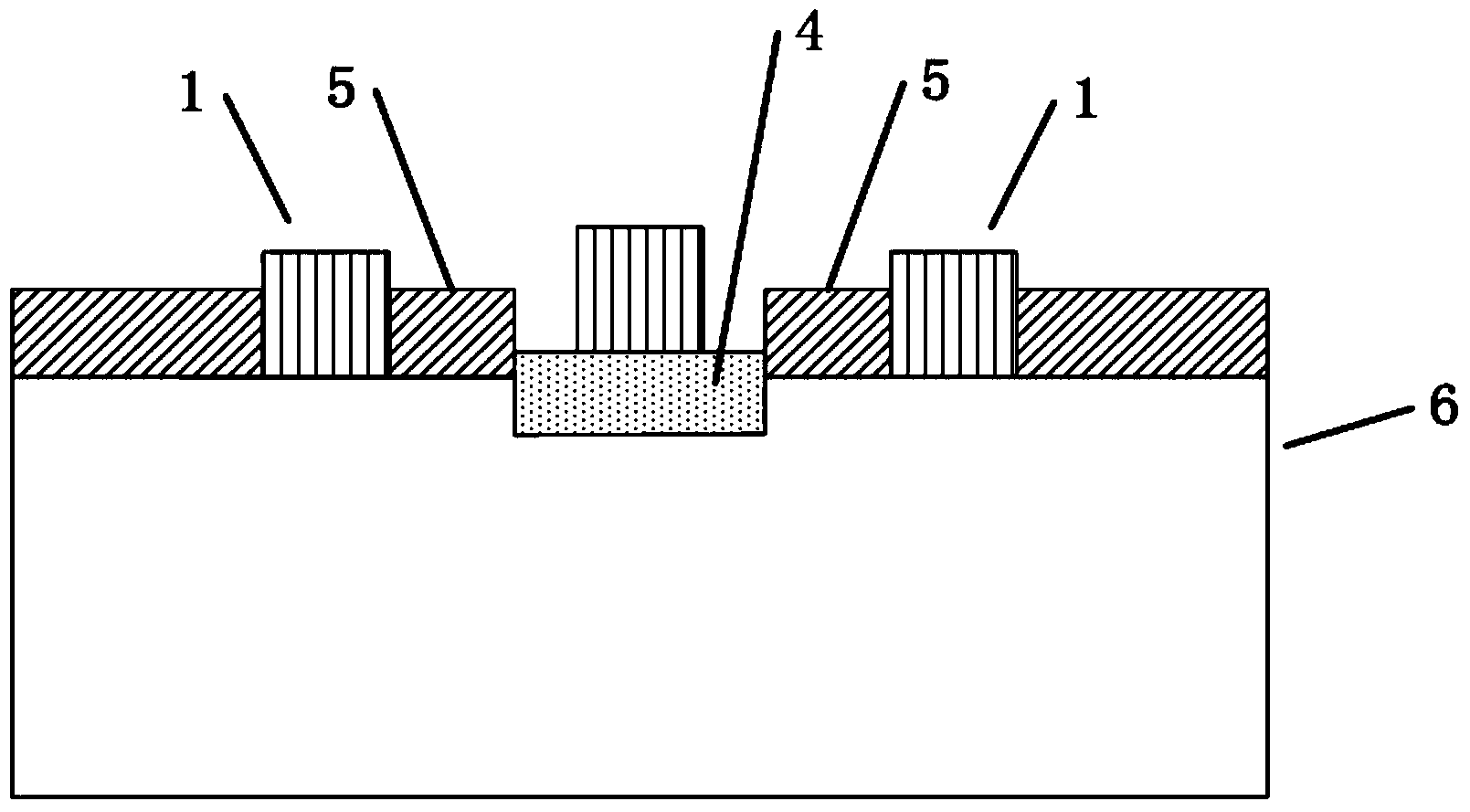

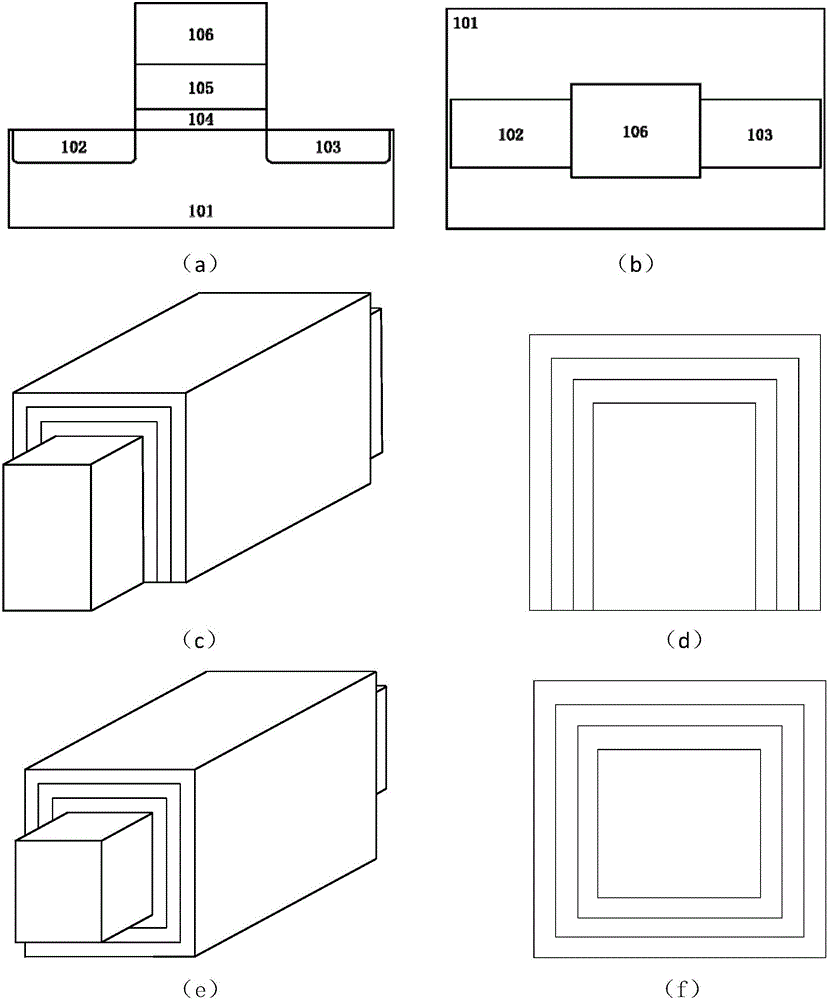

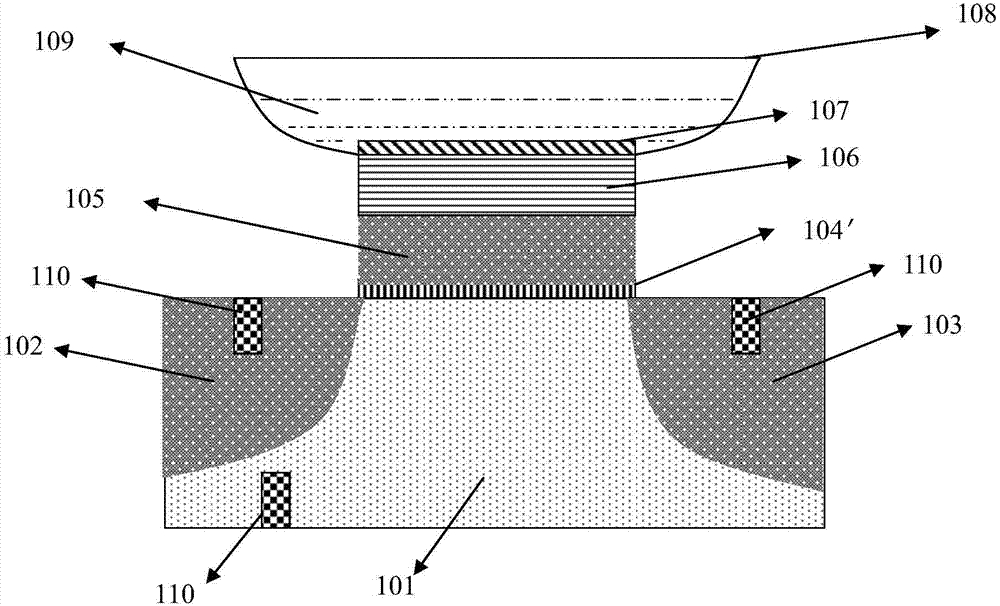

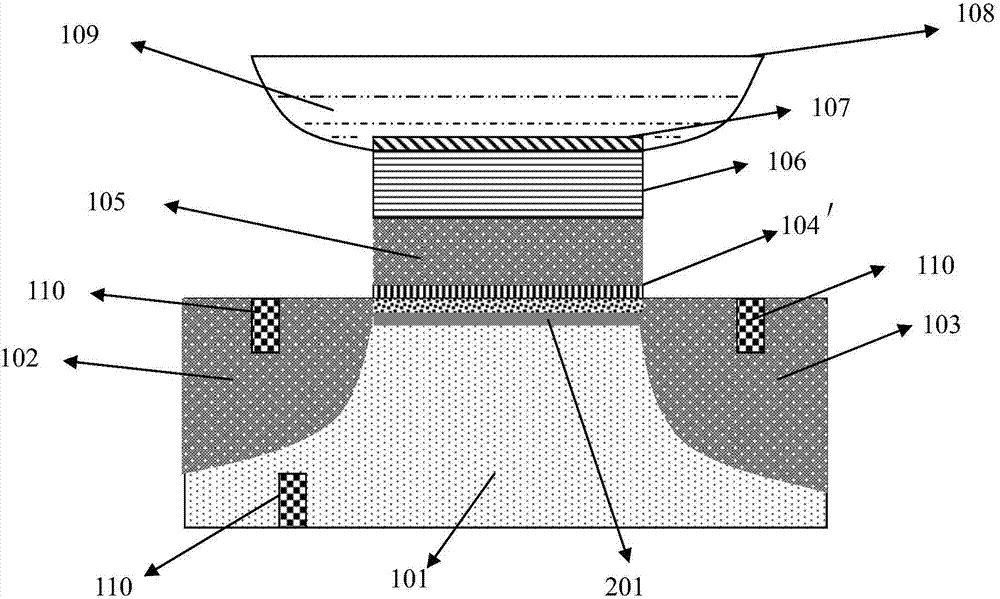

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

SOI SiGe-base lateral bipolar junction transistor

ActiveUS8288758B2Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

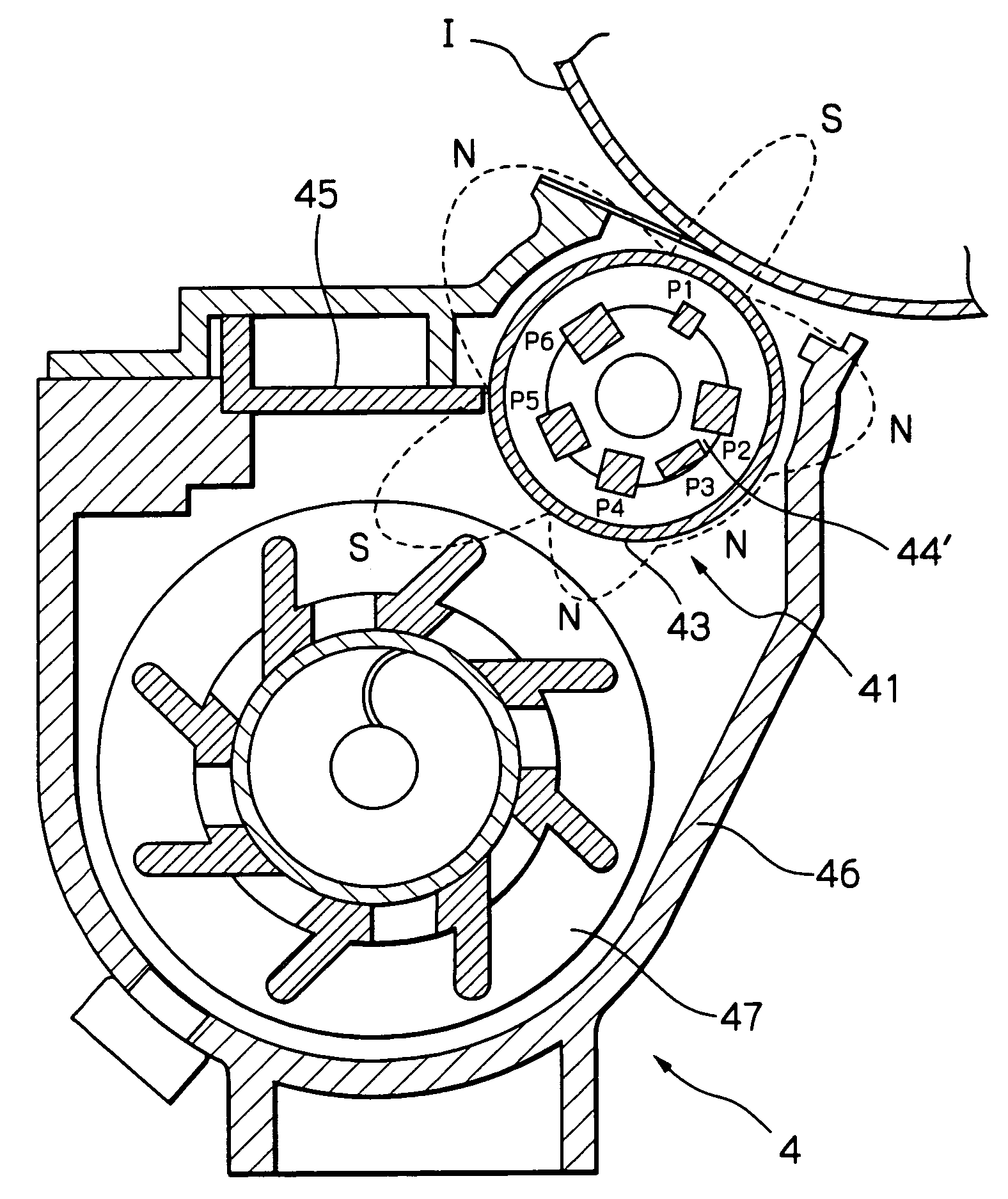

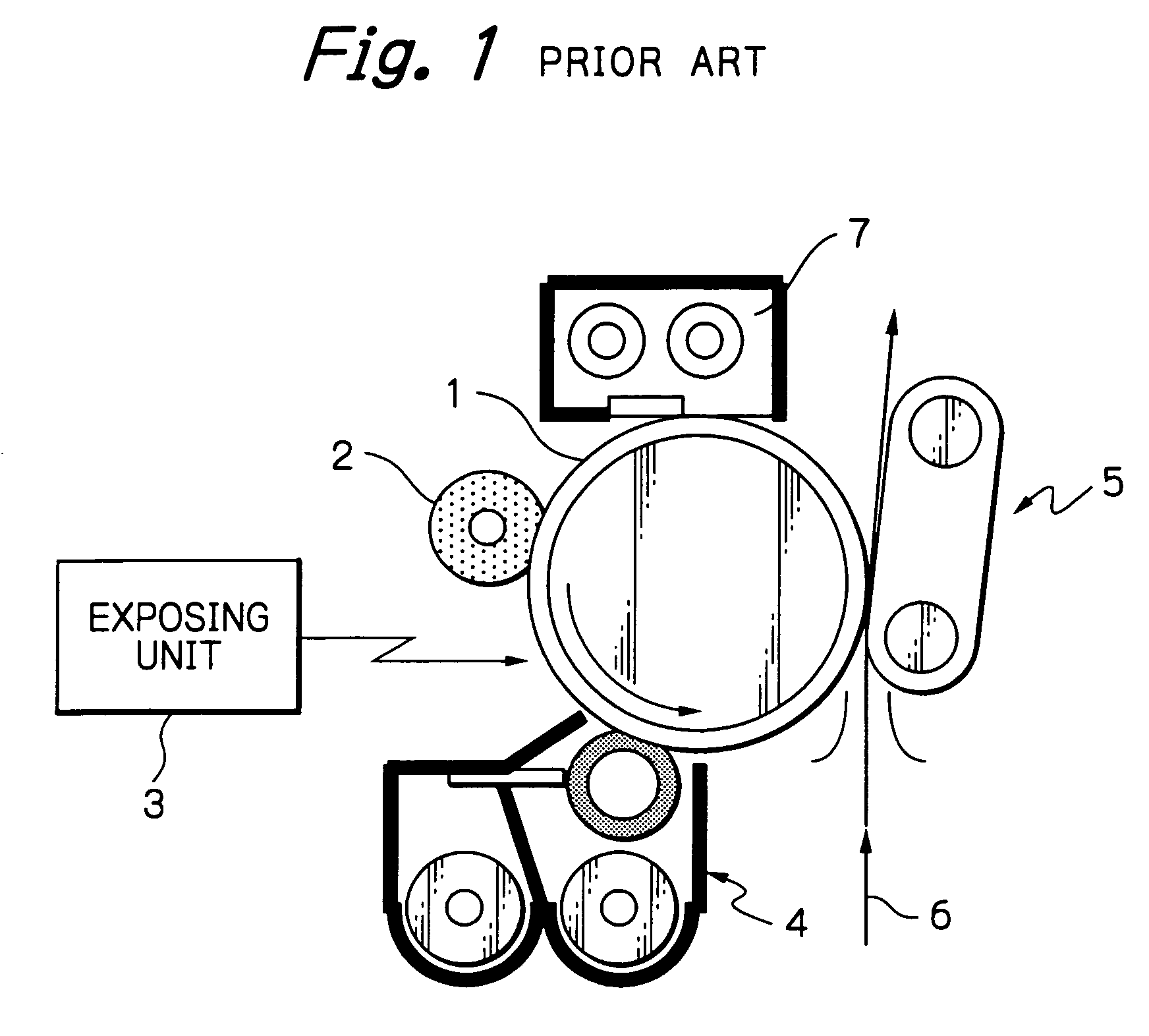

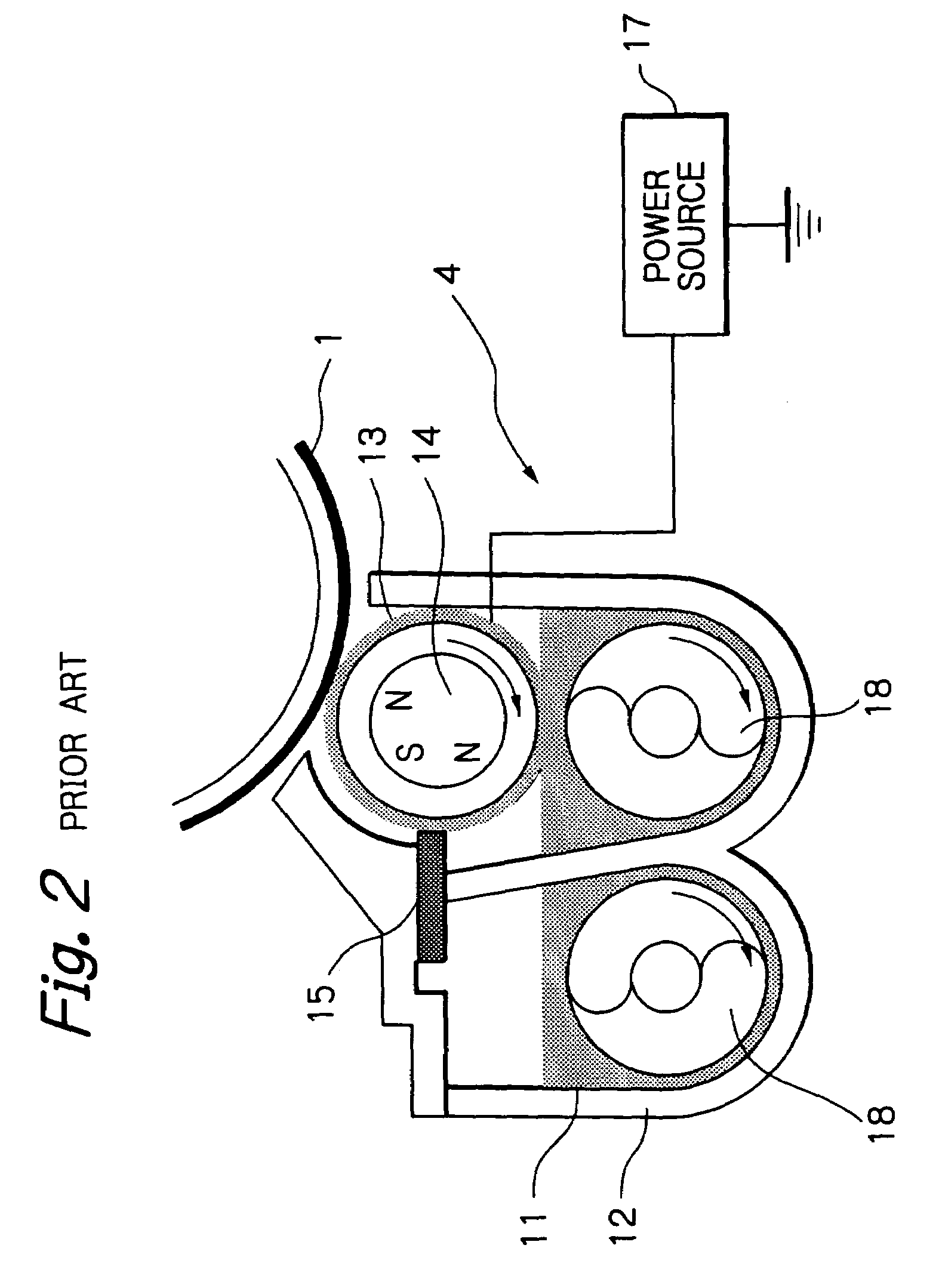

Image forming apparatus

InactiveUS6978109B2Improve the development effectElectrographic process apparatusDevelopersCarrier scatteringGranularity

An electrophotographic image forming apparatus of the present invention frees images from various defects including the thinning of horizontal lines, the omission of the trailing edge of an image, background contamination, granularity particular to a halftone image, carrier scattering, and image noise. Further, the apparatus of the present invention solves problems ascribable to patches used to sense image density. Moreover, the apparatus of the present invention faithfully reproduces tonality and has a high developing ability.

Owner:RICOH KK

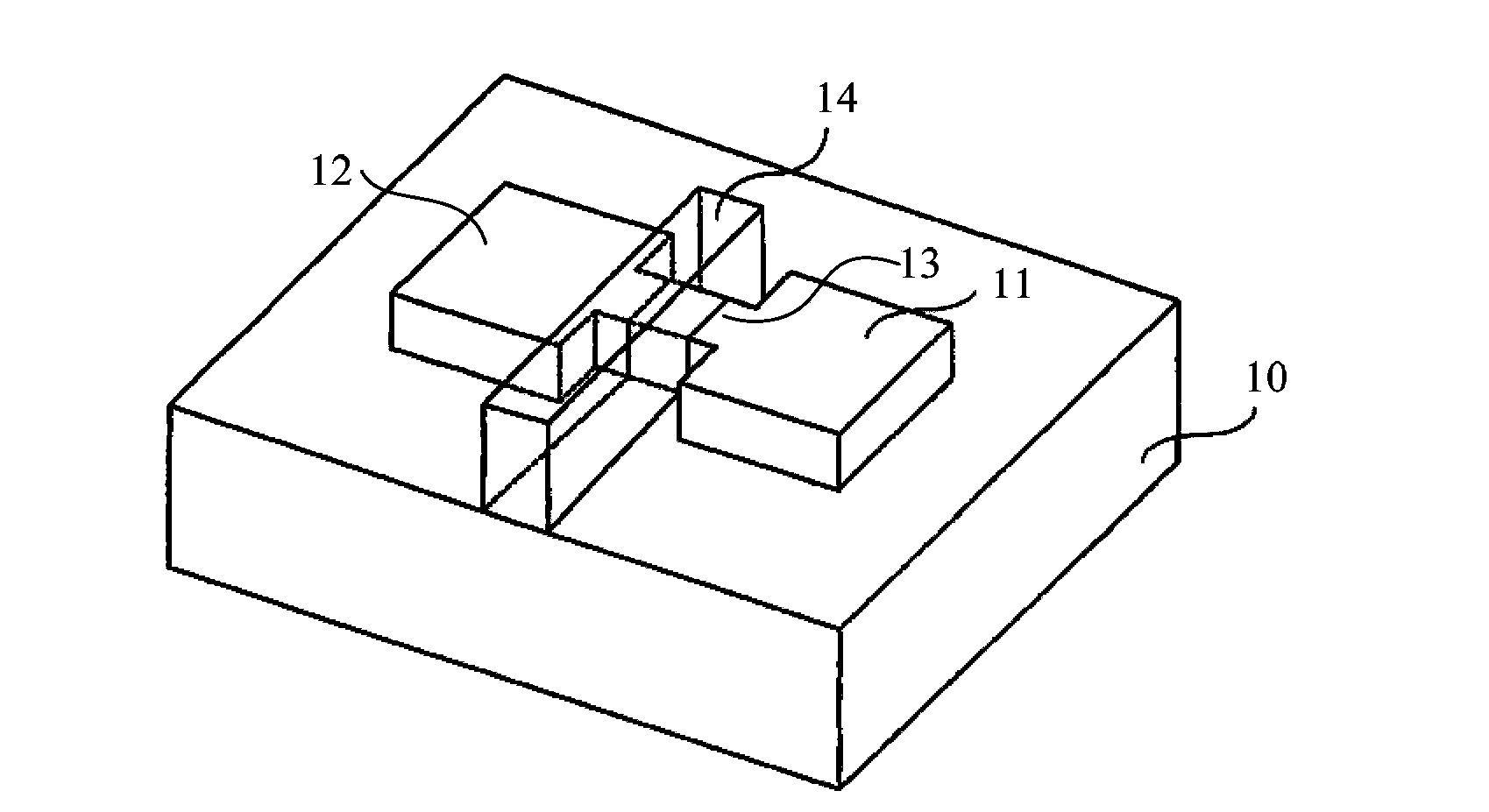

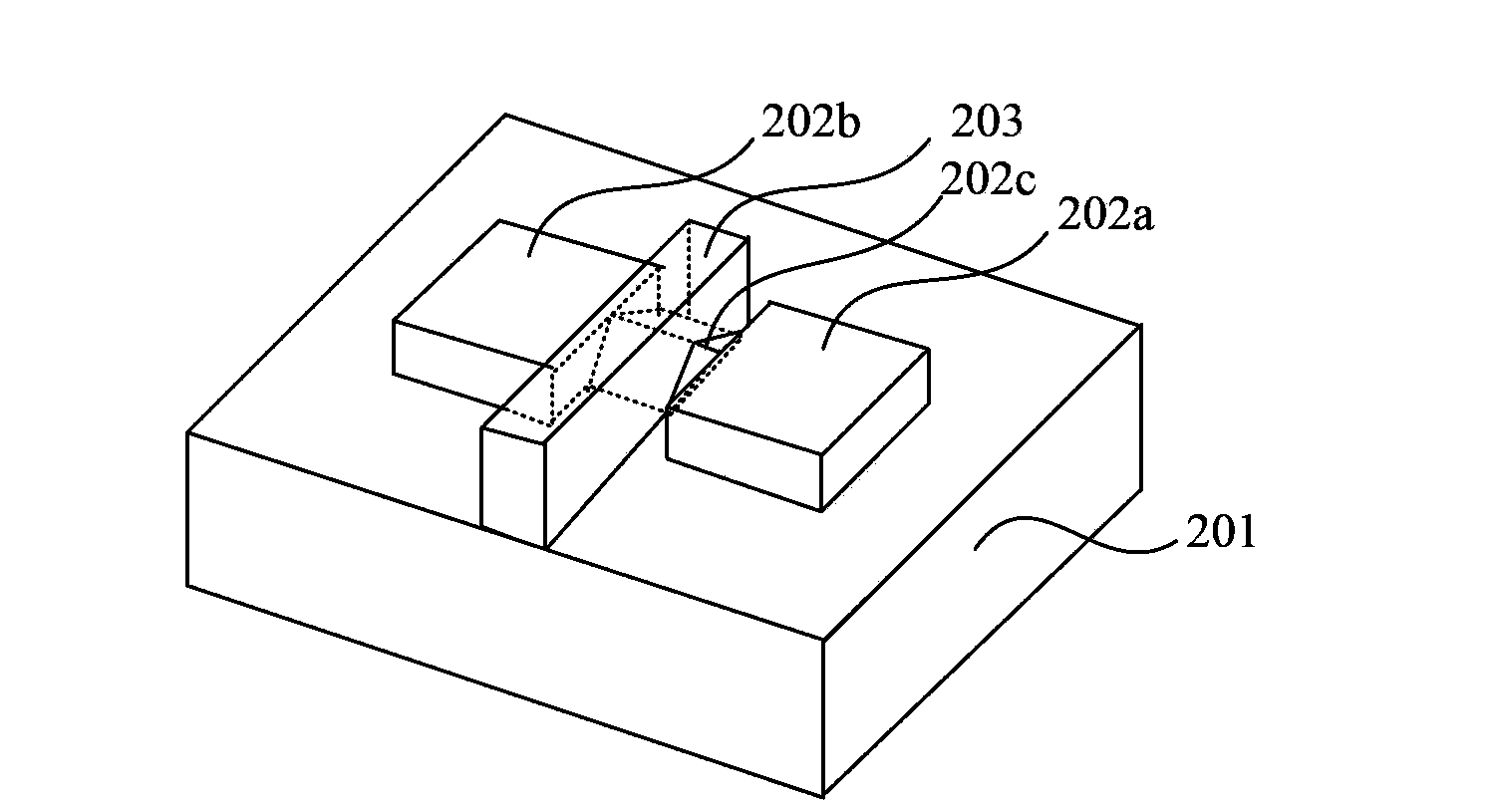

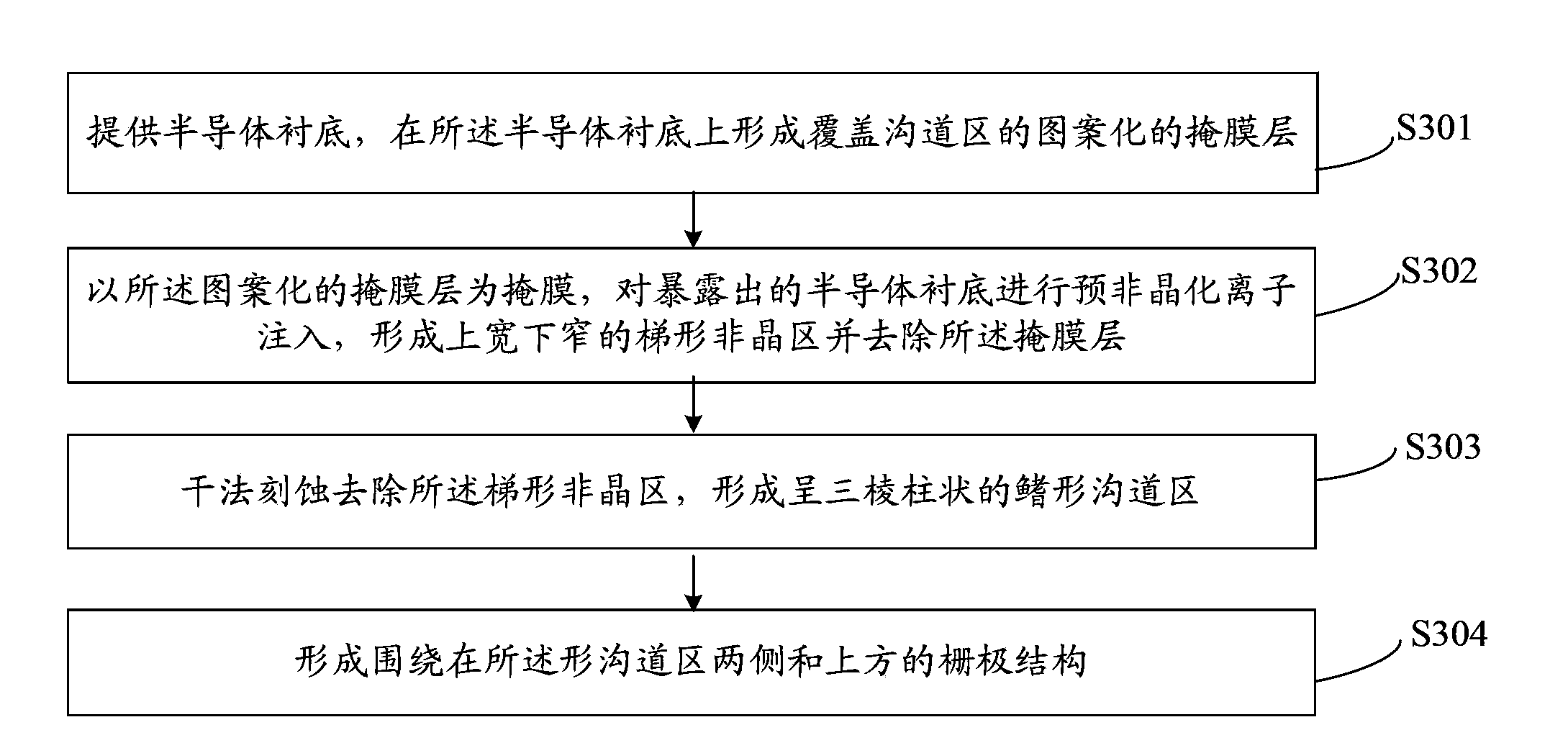

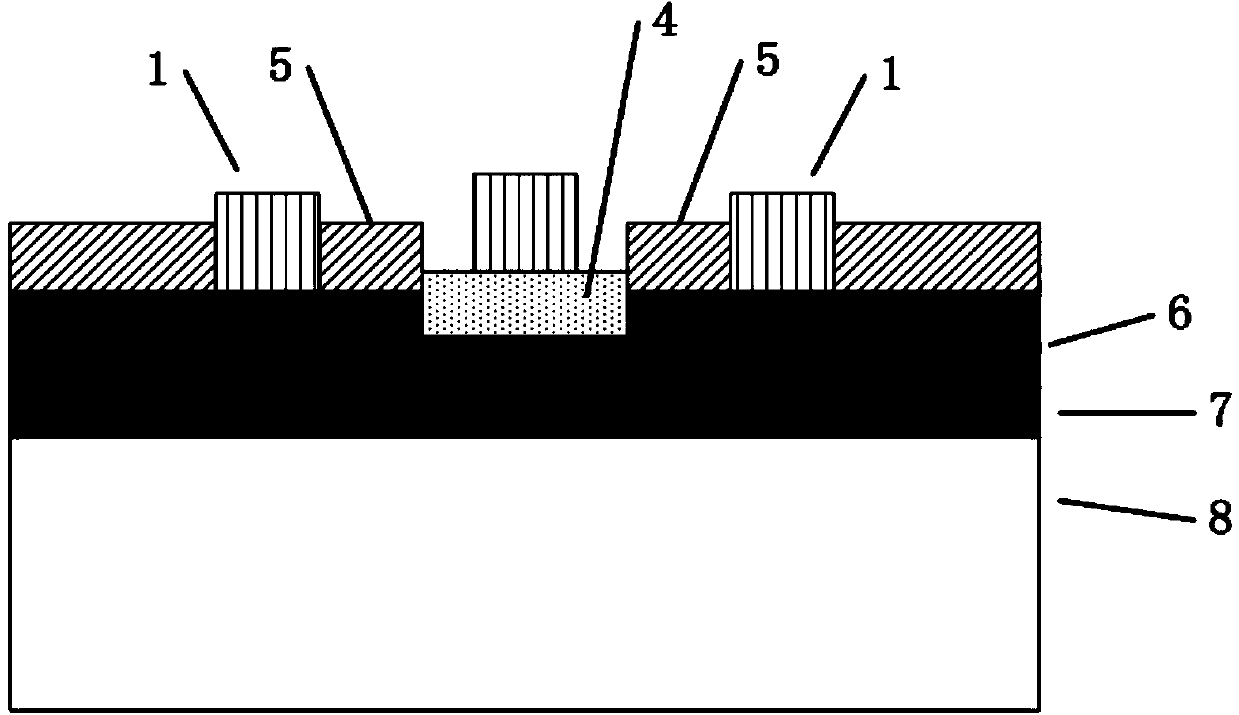

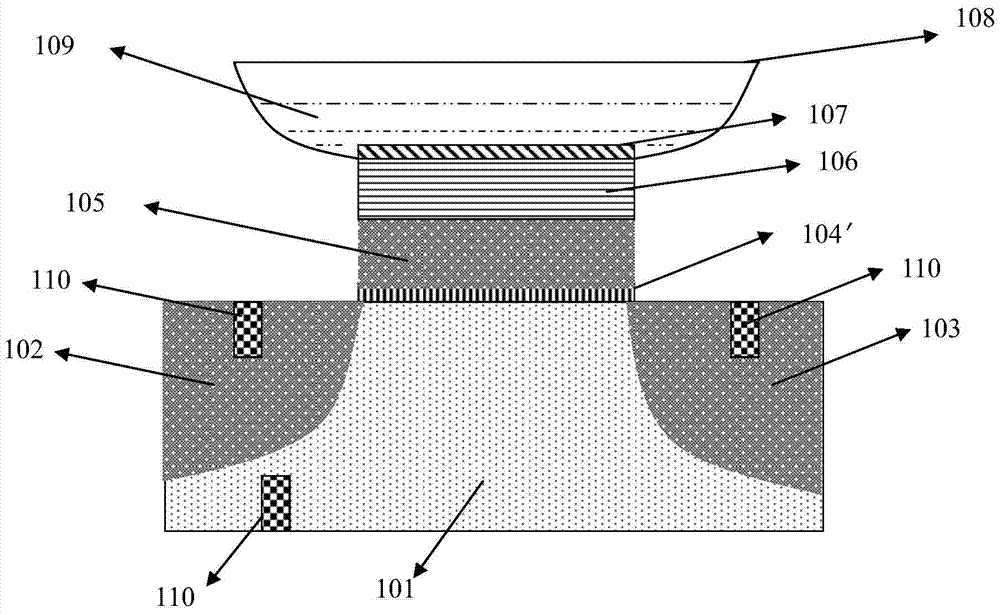

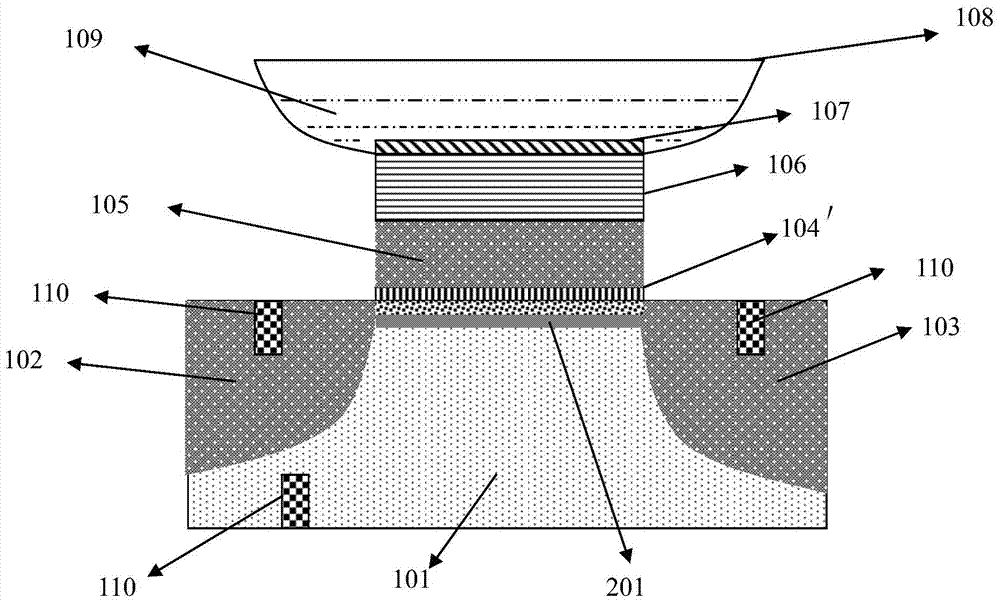

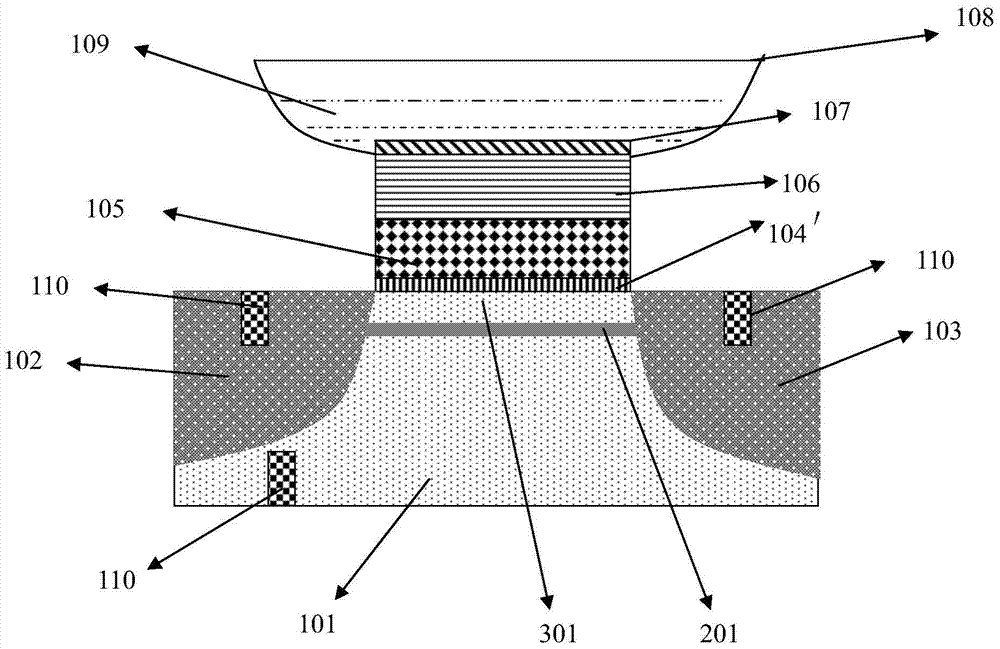

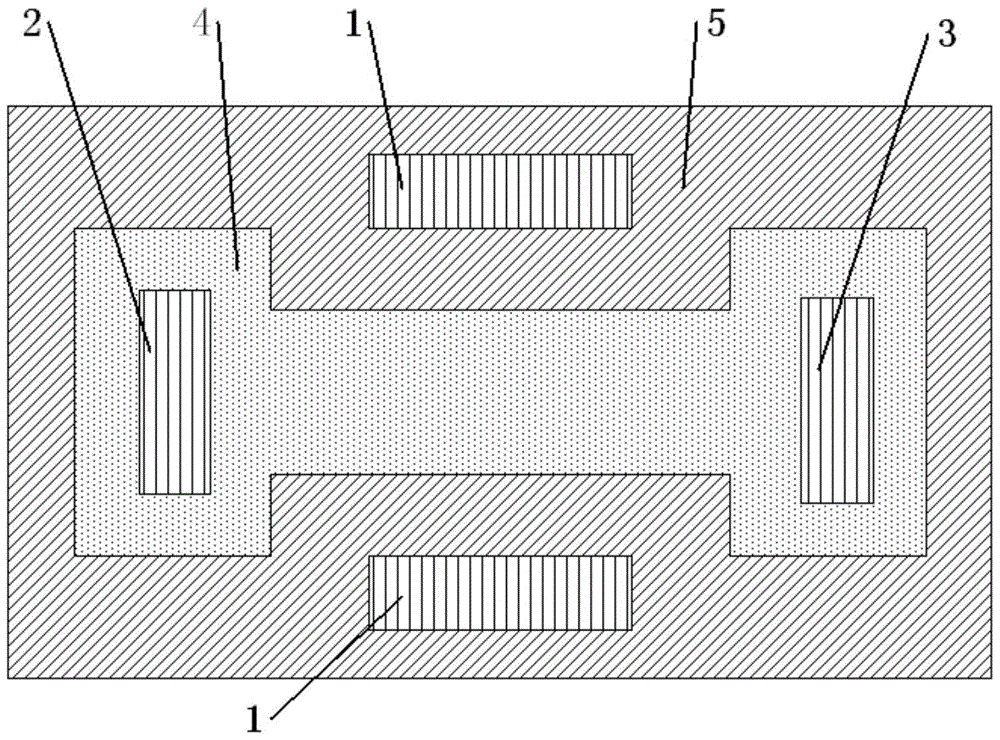

FinFET structure and manufacturing method thereof

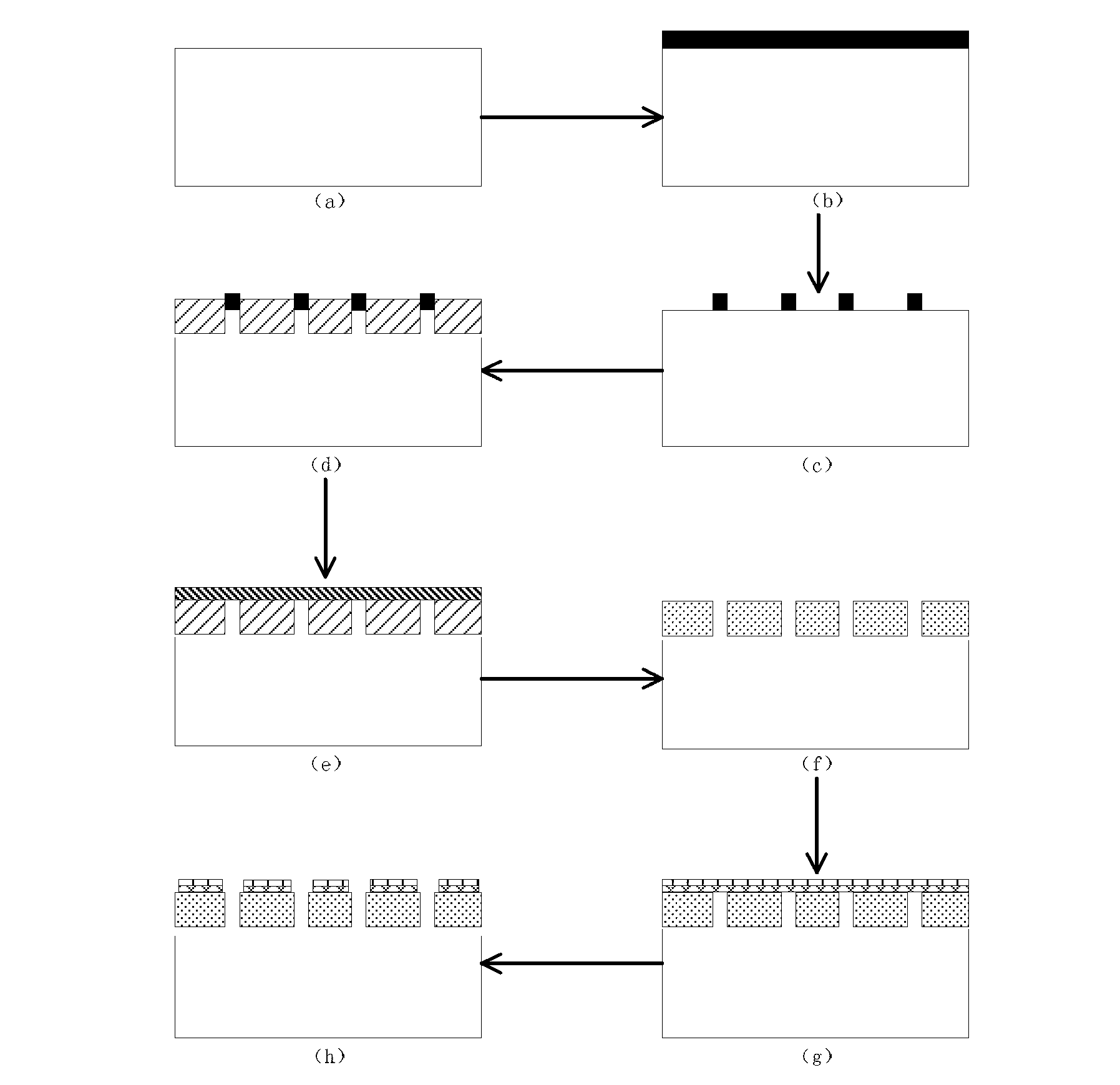

InactiveCN103383961AReduced scattering effectIncrease storage capacitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentPower flow

The invention provides a FinFET structure and a manufacturing method of the FinFET structure. According to the manufacturing method of the FinFET structure, a fin-shaped channel region shaped like a triangular prism is adopted to replace a fin-shaped channel region shaped like a cuboid, two protruding faces of the FinFET structure form opposite crystal face crystal orientation structures, the scattering effect of carriers is reduced, the charge storage capacity is improved, the structure that the fin-shaped channel region is used up is formed more easily when the FinFET structure is controlled by a grid electrode, the conductive path of channels is thoroughly cut off, and therefore the driving current of an FinFET element is improved. The FinFET structure and the manufacturing method of the FinFET structure are suitable for manufacturing the FinFET element of smaller size and with higher drive current.

Owner:SEMICON MFG INT (SHANGHAI) CORP

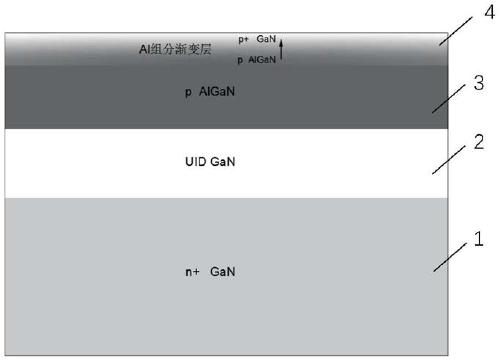

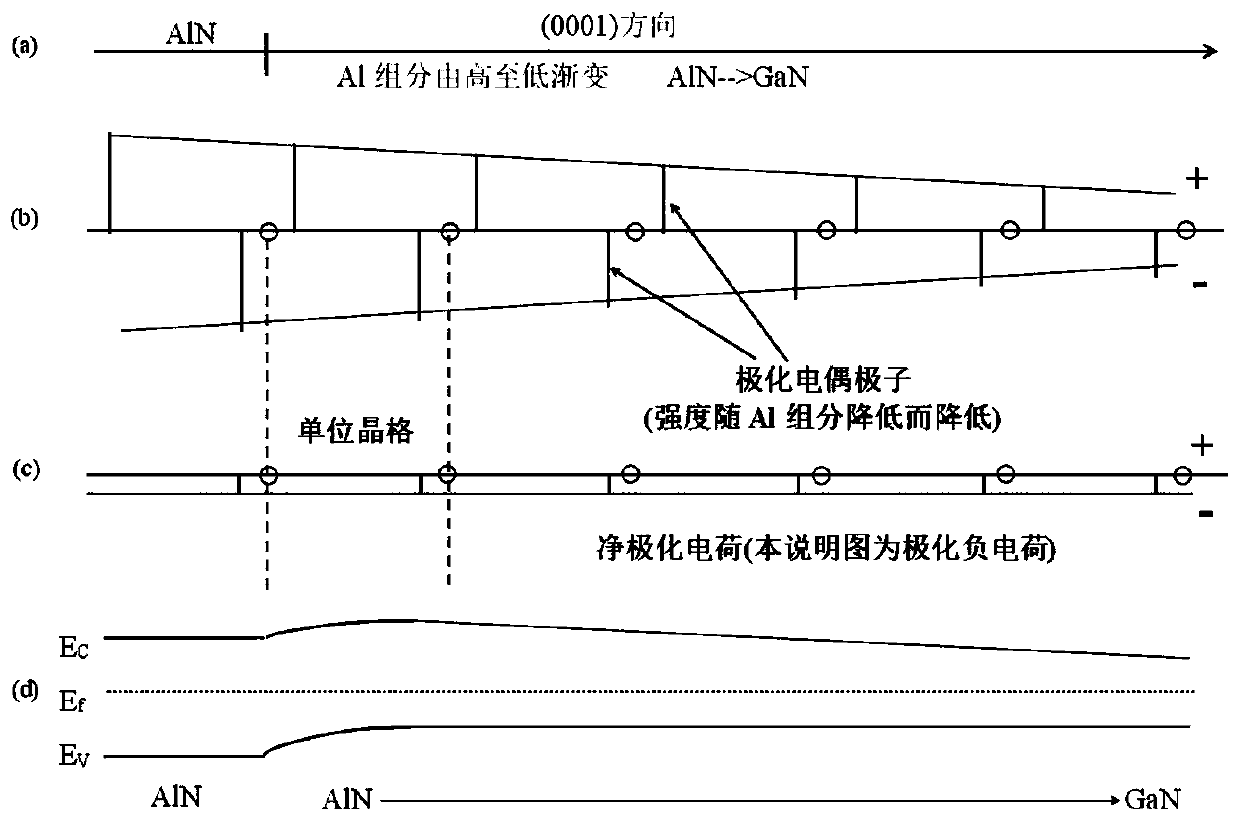

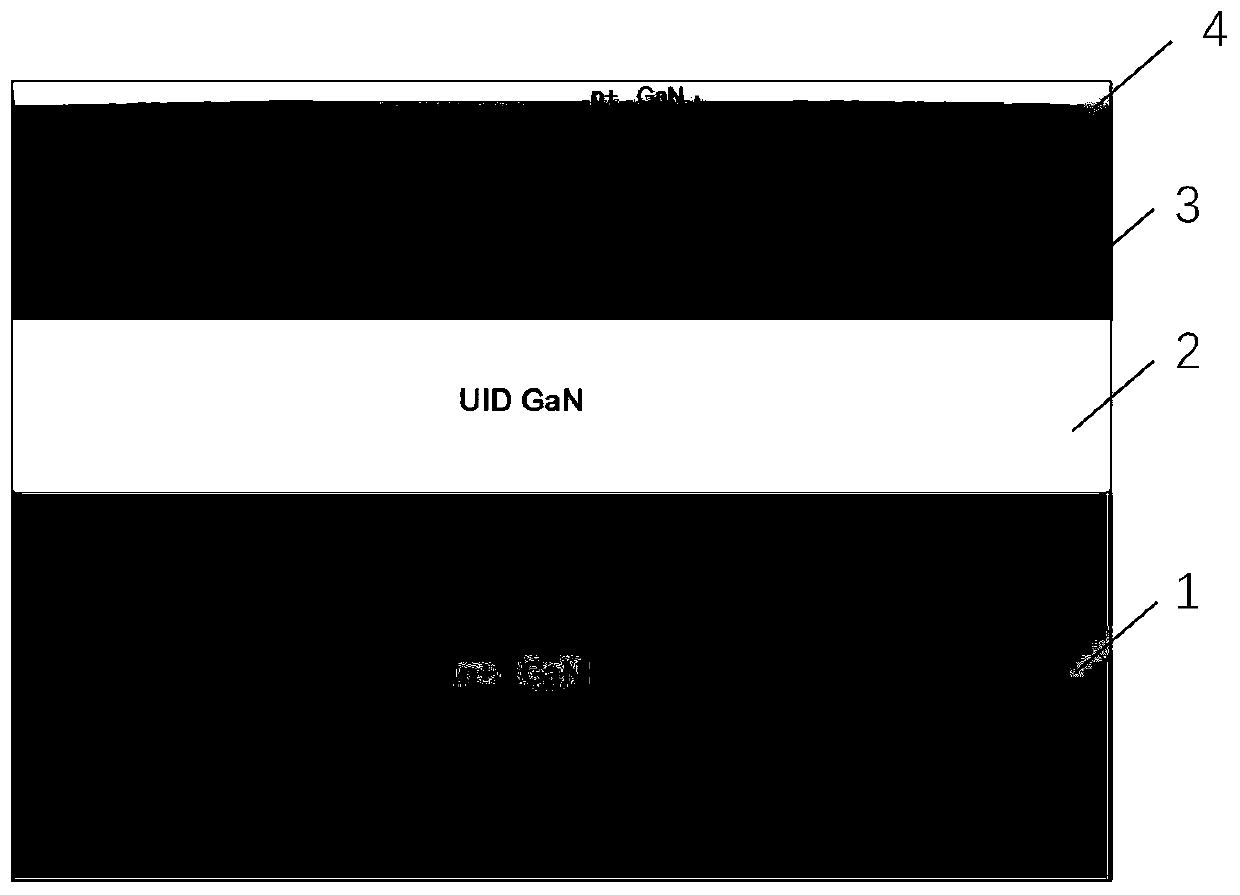

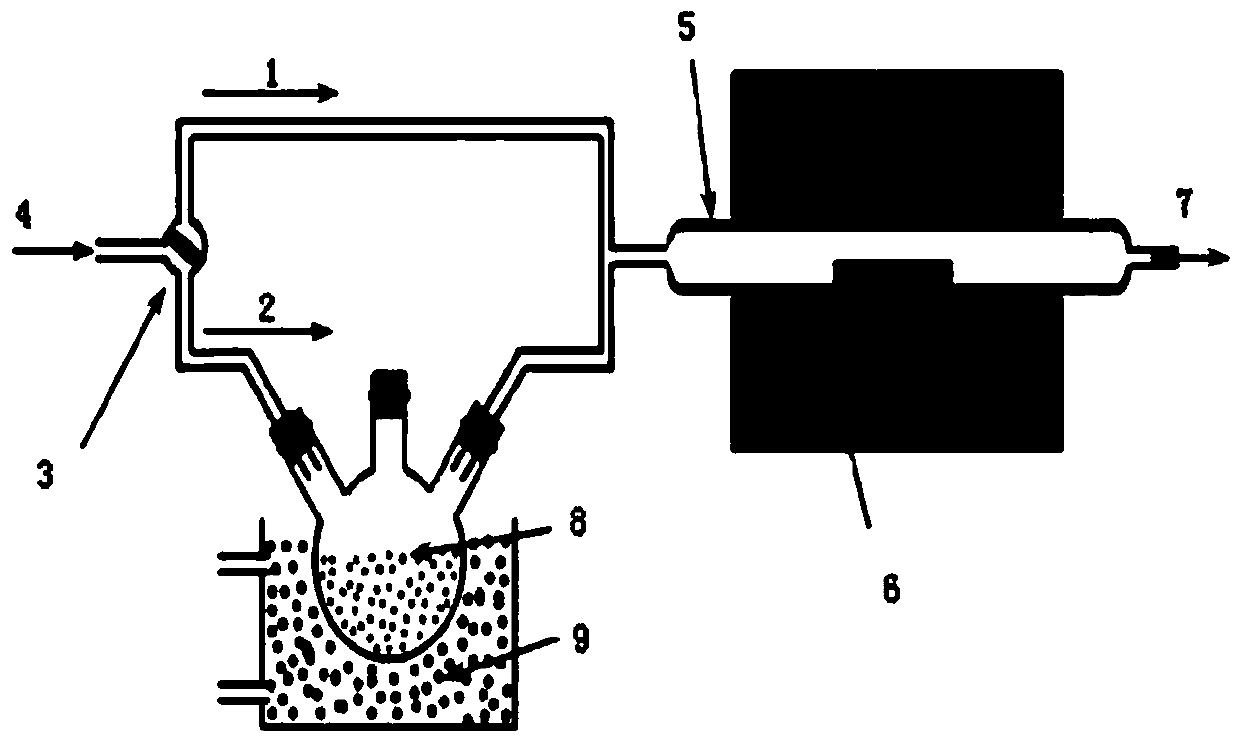

GaN-based PN diode and preparation method thereof

PendingCN111180527AEasy to getReduce scatterSemiconductor/solid-state device manufacturingDiodeElectron holeOhmic contact

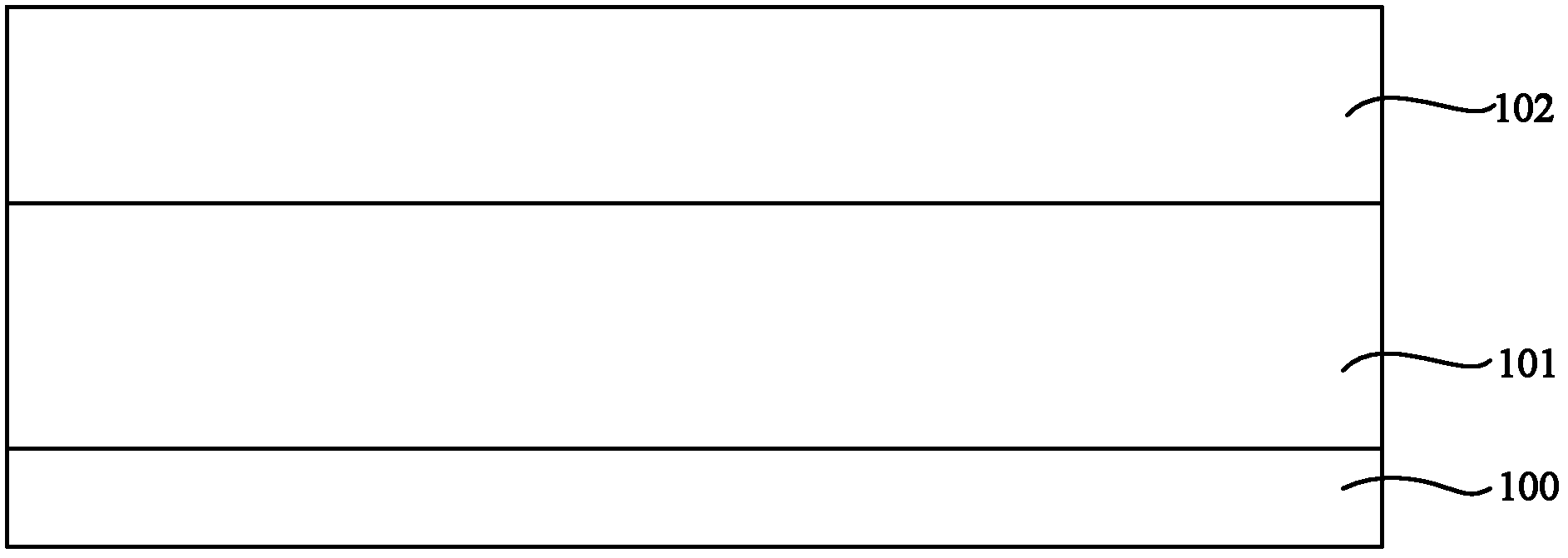

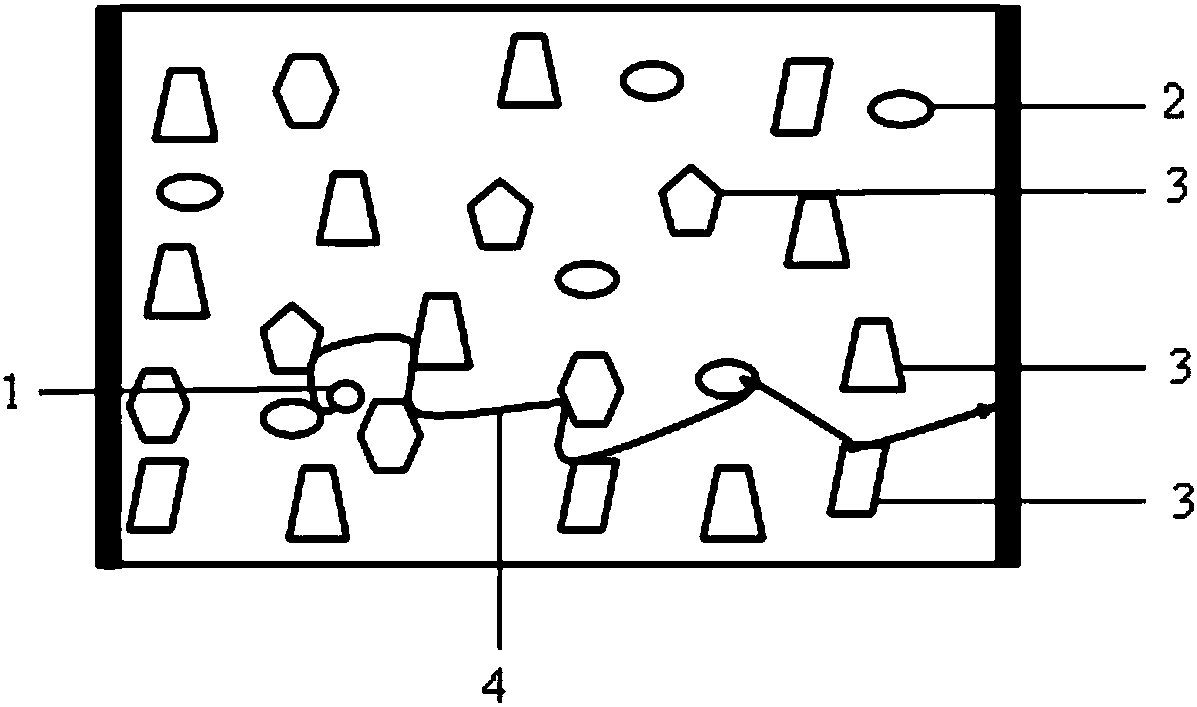

The invention provides a GaN-based PN diode and a preparation method thereof. The GaN-based PN diode sequentially comprises a highly-doped n+ type GaN substrate 1, a non-doped GaN layer 2, a p type AlGaN layer 3 and a p type AlGaN gradient structure 4 from bottom to top, wherein the molar content of an Al component in the p type AlGaN layer 3 is 0.2-0.4 of the sum of the Al component and a Ga component; and in the p-type AlGaN gradual change structure 4, the Al component is gradually reduced from bottom to top, and the reduction gradient is gradually increased until the top of the p-type AlGaNgradual change structure is a GaN layer. Because of the polarization effect of the gradient structure, fixed negative polarization charges are introduced to induce generation of free holes, the doping efficiency is improved, the carrier scattering probability can be reduced and the carrier mobility is improved while high hole concentration is realized at relatively low doping concentration, so that the PN diode can obtain high-quality P-type ohmic contact and higher output current more easily.

Owner:SHENZHEN INST OF WIDE BANDGAP SEMICON

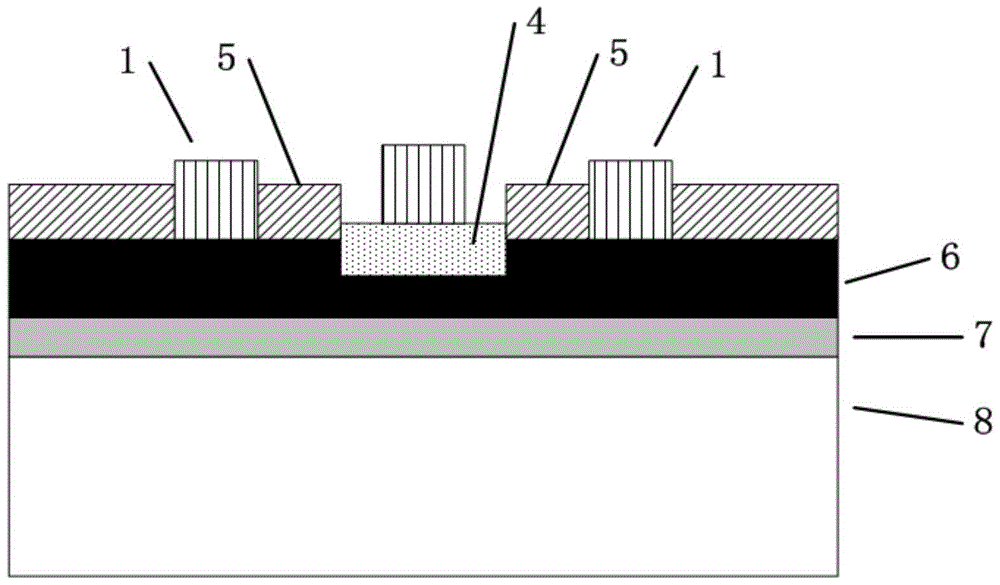

Double-gate graphene transistor with aluminum oxide as gate dielectric and manufacturing method thereof

ActiveCN103840003AHigh dielectric constantLarge physical thicknessTransistorSemiconductor/solid-state device manufacturingCarbon filmDielectric

Owner:XIDIAN UNIV

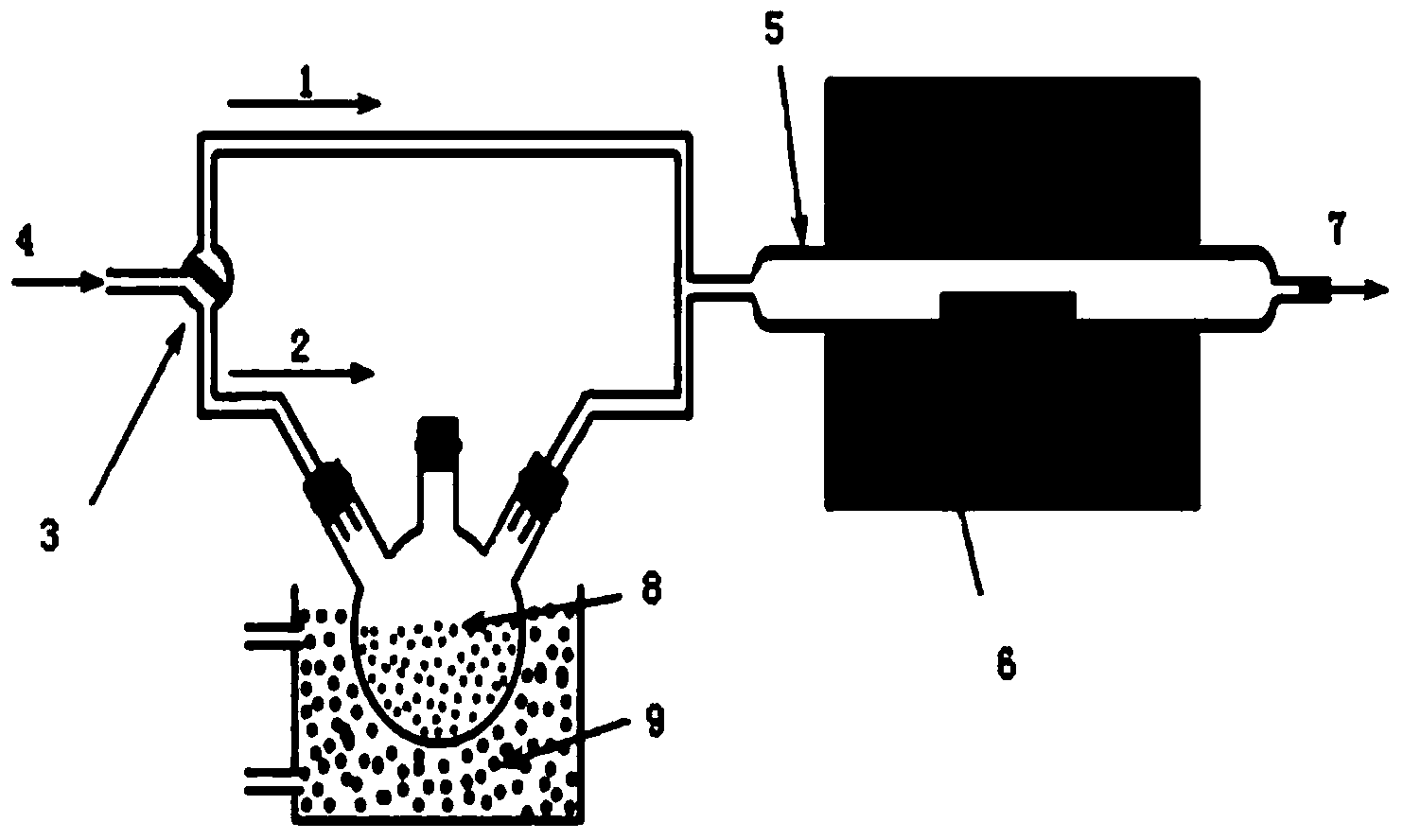

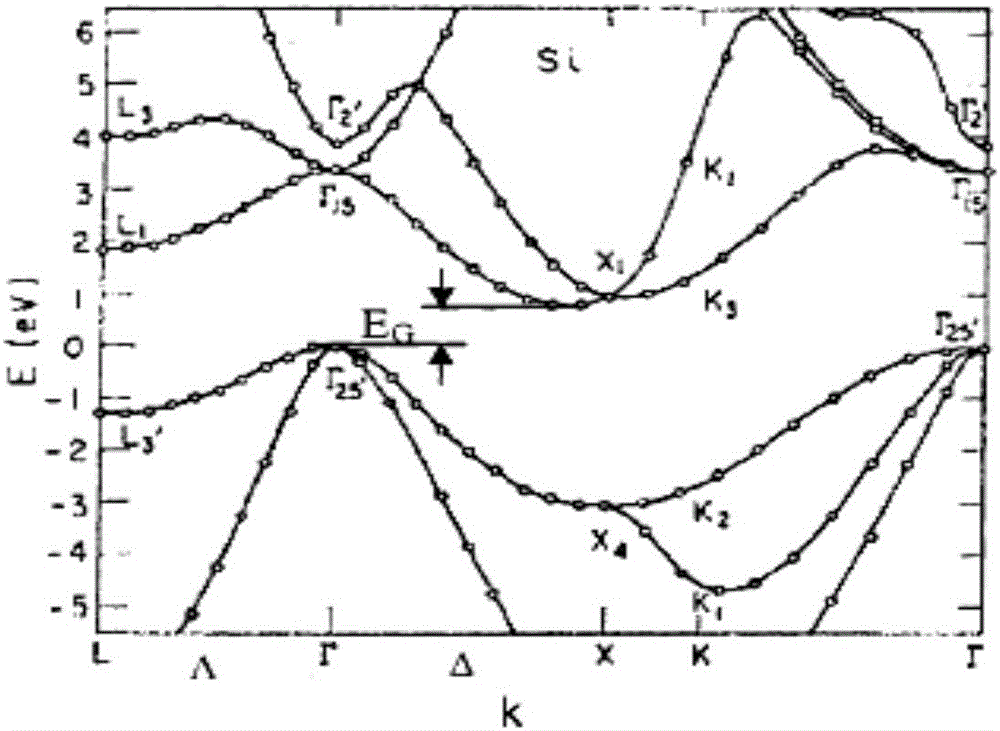

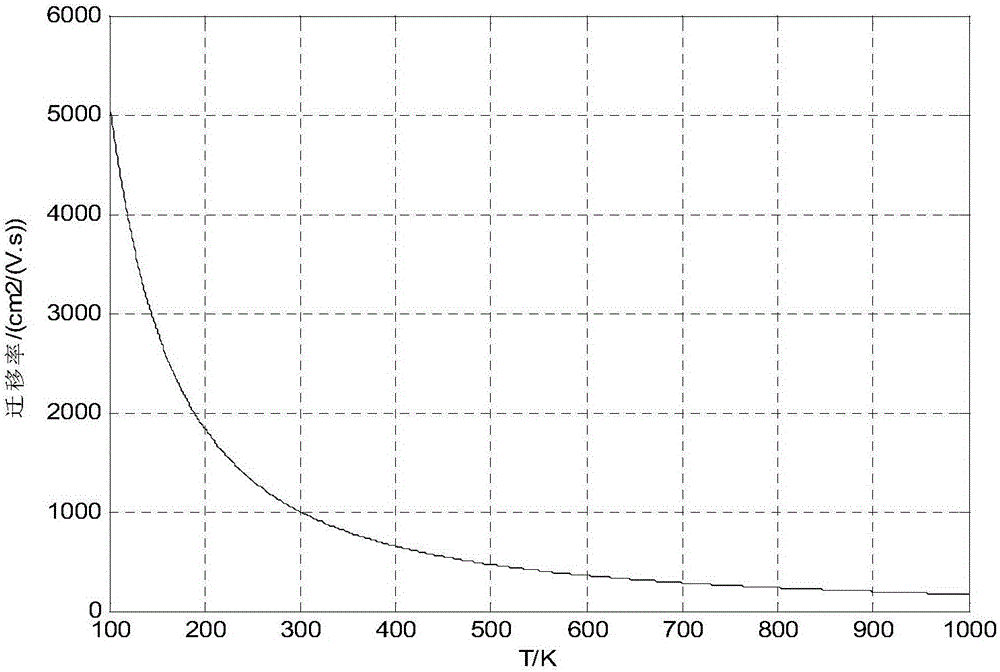

Monte Carlo simulation method for electronic transportation problem of n-type Si material

InactiveCN104992020AAvoid errorsSpecial data processing applicationsExperimental testingSemiconductor materials

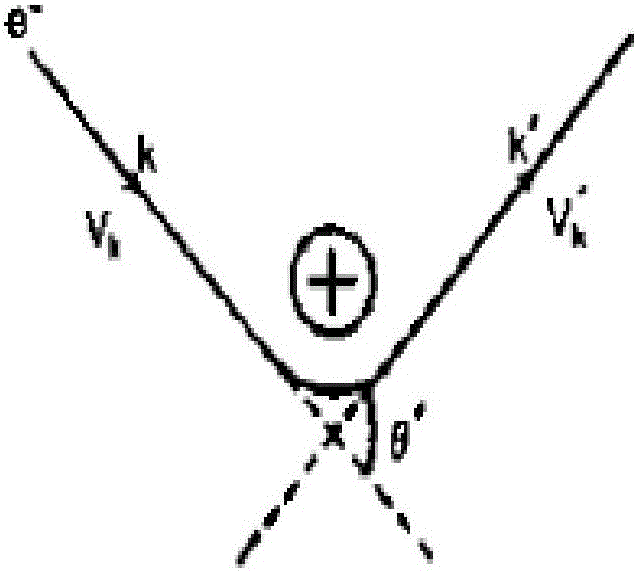

The present invention discloses a Monte Carlo simulation method for the electronic transportation problem of an n-type Si material. The Monte Carlo simulation method comprises the following steps of: 1, determination of a carrier scattering mechanism and calculation of various scattering ratios under corresponding input conditions; 2, establishment of a carrier drift model and calculation of energy and a wave vector after carrier drift; 3, establishment of a carrier scattering model and selection of a scattering type; and 4, implementation of simulating an electronic transportation problem calculating program of the n-type semiconductor Si material by the Monte Carlo method. According to the present invention, an average rate and a drift mobility of the n-type Si material are simple, rapid and convenient to calculate; a series of problems of difficulty in testing, a large error and the like, which are caused by influence of the size of a semiconductor device and experiment conditions when an experimental testing method is used before, are avoided; moreover, the method has high popularization performance; and the carrier transportation or microscopic particle collision problem of other semiconductor materials also can be calculated by changing corresponding input parameters.

Owner:HARBIN INST OF TECH

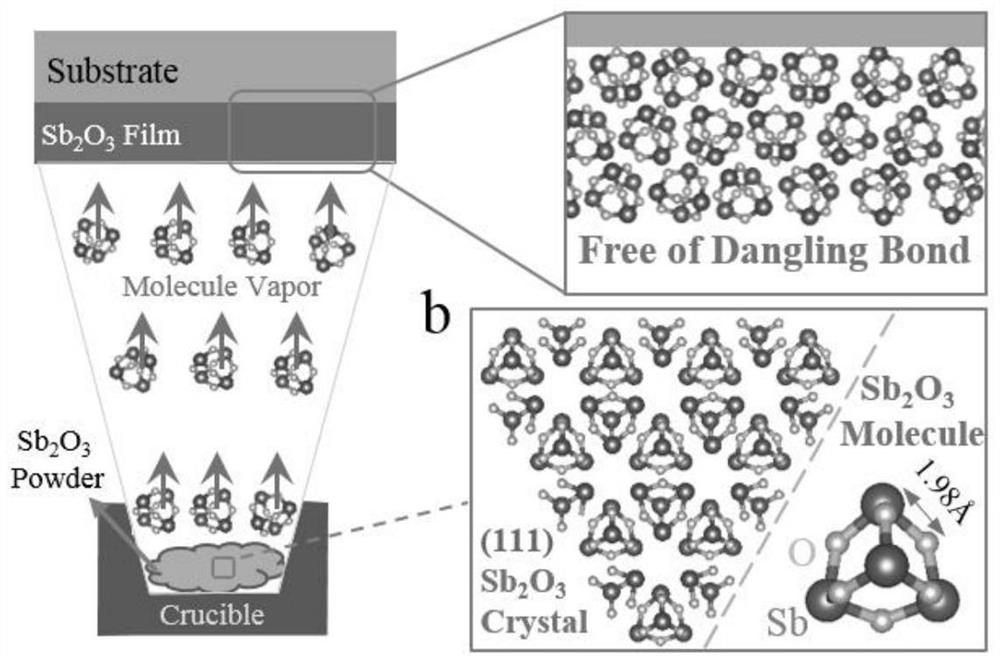

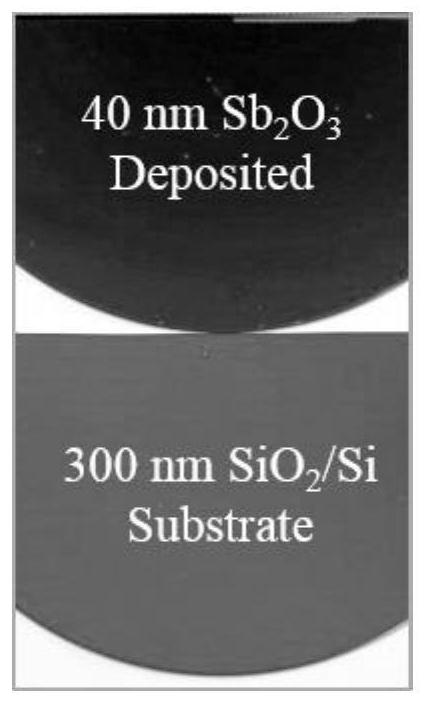

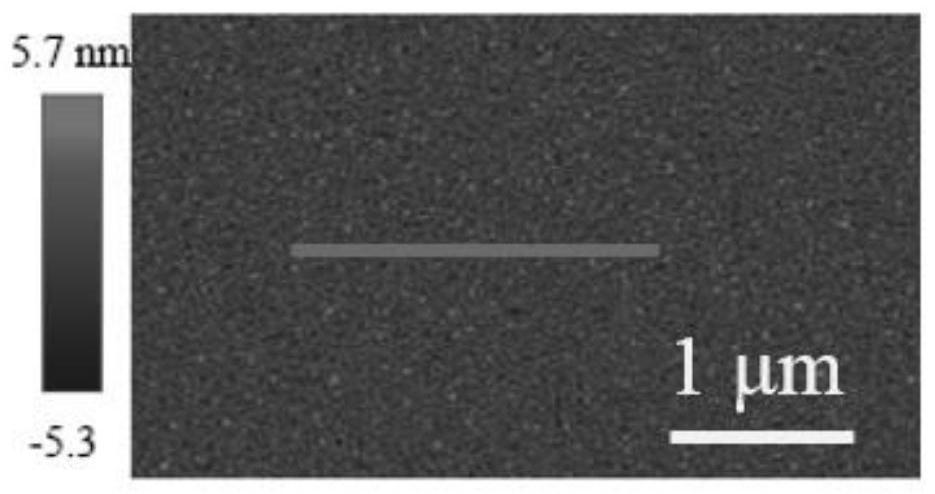

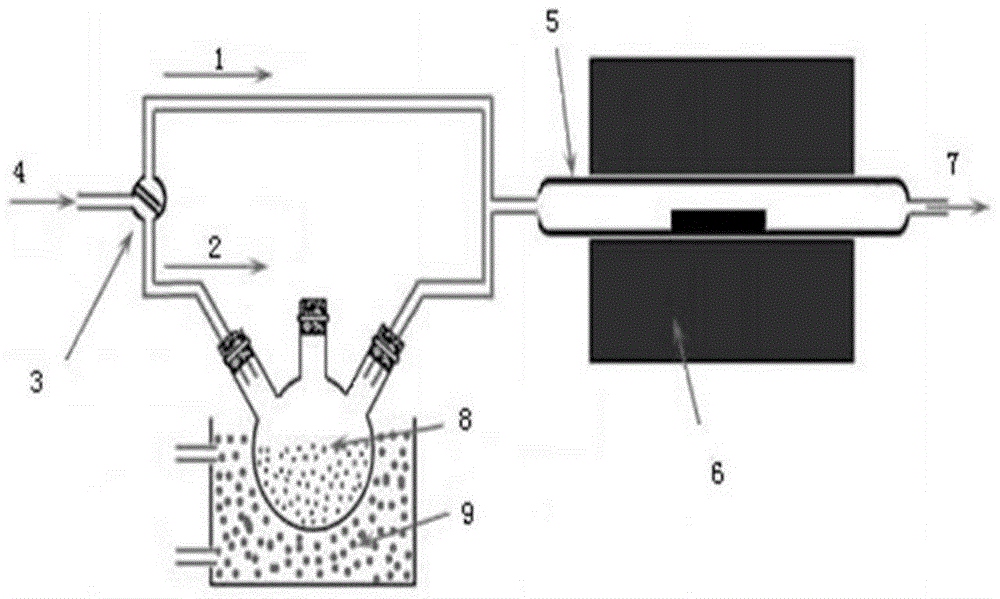

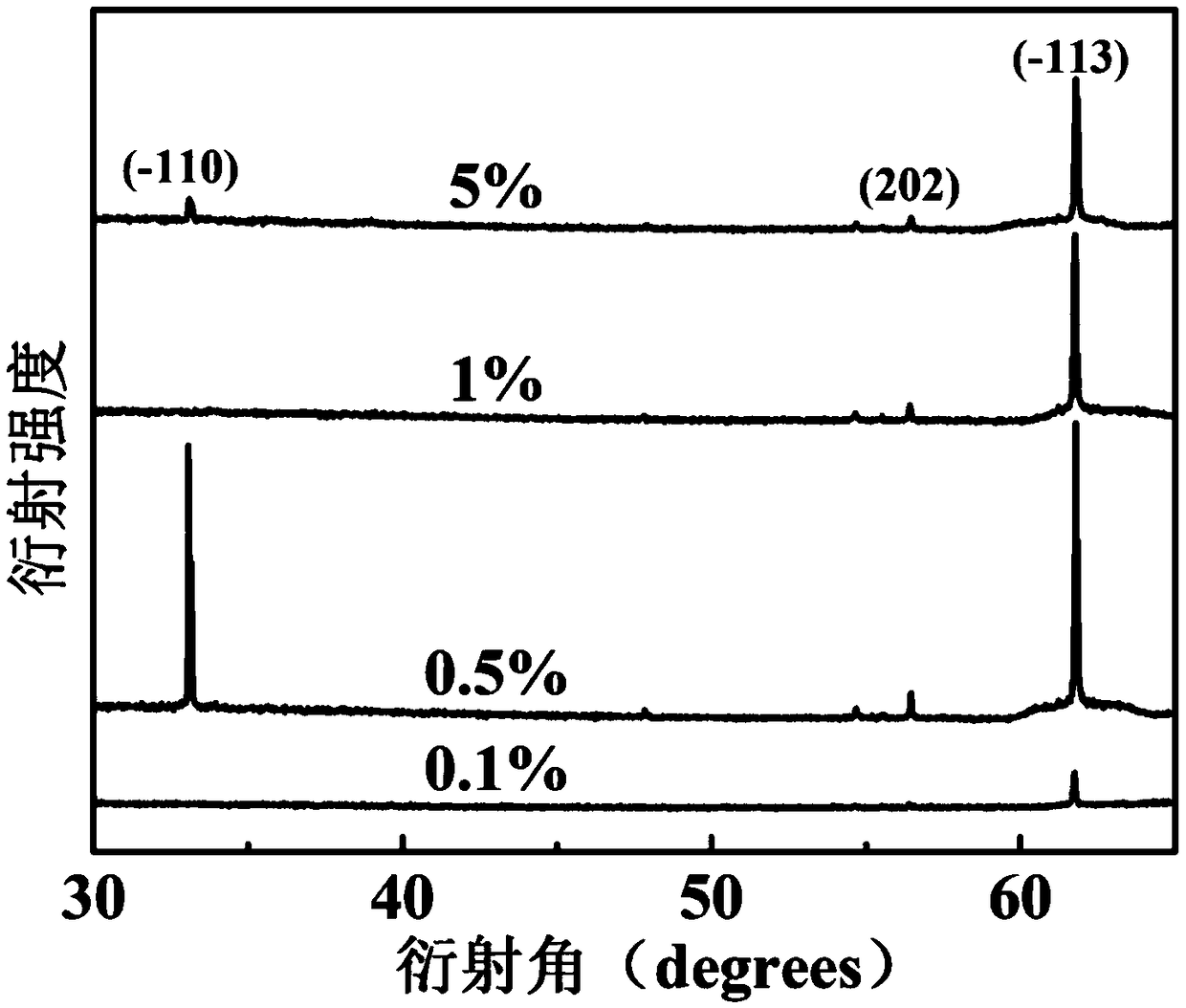

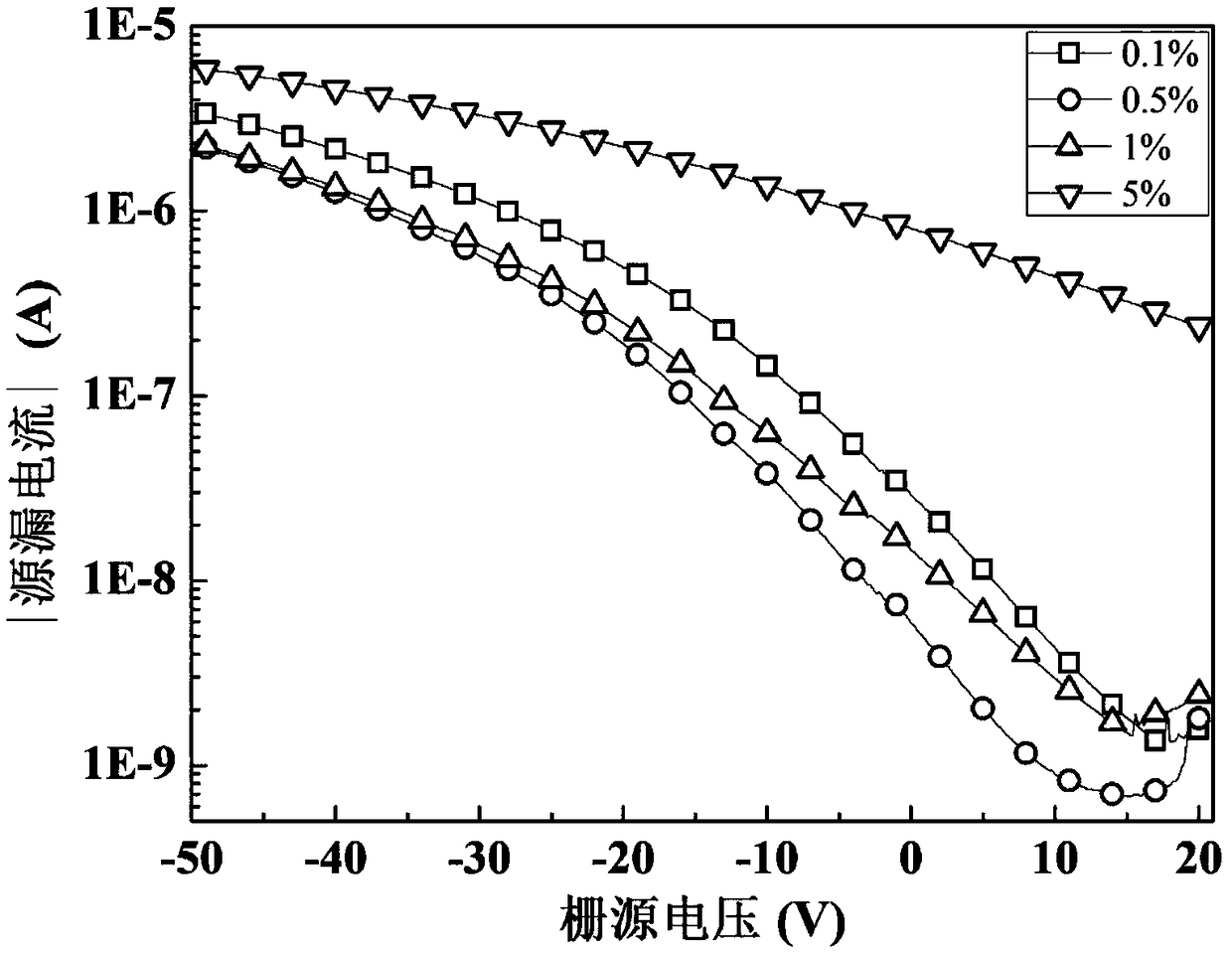

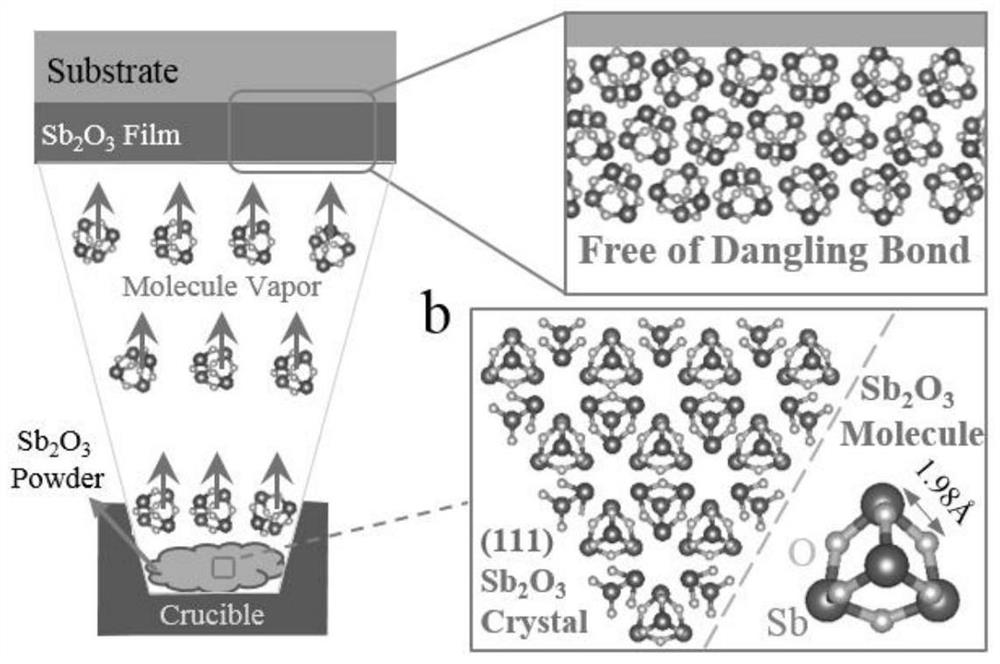

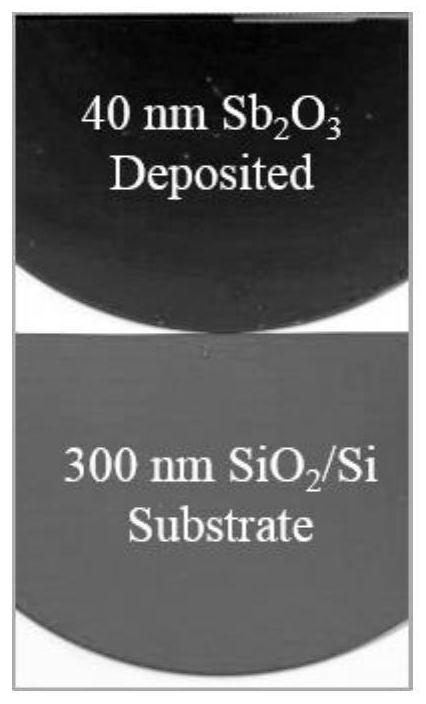

VDW dielectric material and preparing method and application thereof

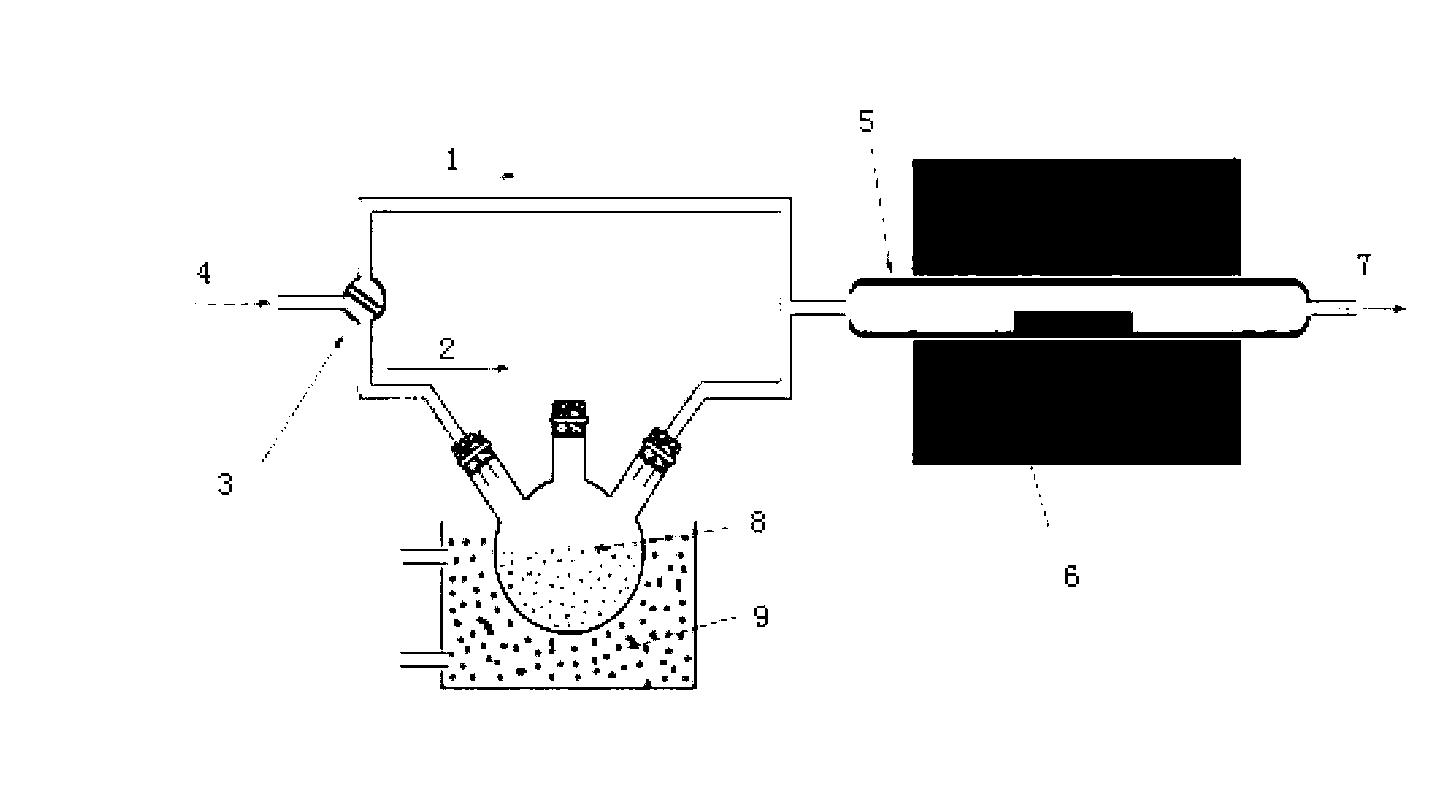

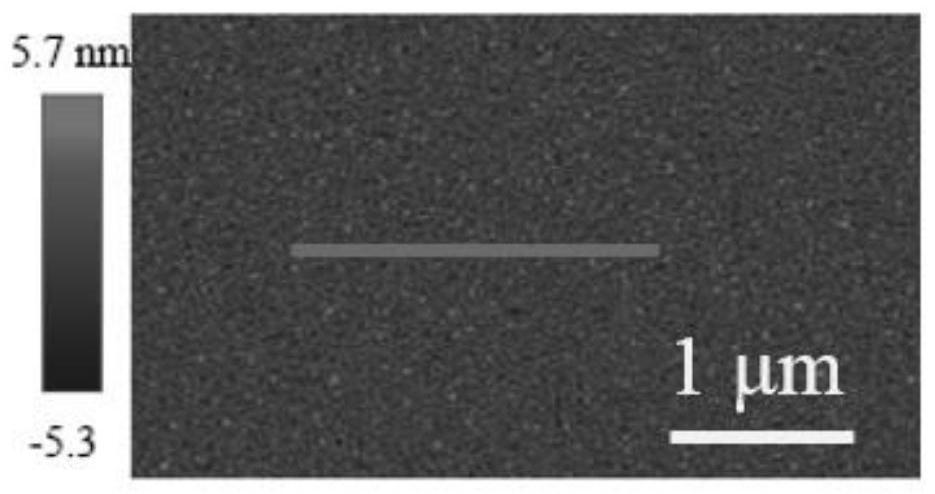

ActiveCN111621746AEasy to integrateImprove insulation performanceVacuum evaporation coatingSputtering coatingDielectricMolecular solid

The invention belongs to the field of two-dimensional material preparing, and particularly discloses a VDW dielectric material and a preparing method and application thereof. The method comprise the following steps that an inorganic molecular crystal serves as an evaporation source, a heat evaporation method is adopted, the inorganic molecular crystal is subjected to sublimation under the high vacuum, meanwhile, a perfect molecular structure of the crystal can be kept, evaporation is carried out, and a VDW film is obtained. Due to the fact that unsaturated chemical bonds do not exist in inorganic molecules, the VDW film surface has no suspension bonds, and preparing of the VDW dielectric material can be finished. The prepared VDW film can serve as a dielectric material of a two-dimensionalmaterial electronic device, the scattering source of carriers in a two-dimensional groove material can be obviously reduced, it is ensured that a two-dimensional material has the high migration rate,meanwhile, a preparing technology and a semiconductor preparing technology are compatible, and scale preparing and integrating are easy.

Owner:HUAZHONG UNIV OF SCI & TECH

Double-gate graphene transistor with silicon substrate and aluminium oxide gate dielectric, and preparation method

ActiveCN103811556ALarge physical thicknessSolve leakage currentTransistorSemiconductor/solid-state device manufacturingCarbon filmGate dielectric

The invention discloses a double-gate graphene transistor with a silicon substrate and an aluminium oxide gate dielectric, and a preparation method, which are mainly used for solving the problems of low channel carrier mobility and carrier scattering of a graphene transistor prepared by the prior art. The preparation method comprises the following realization steps of: depositing a layer of Al2O3 on an epitaxial 3C-SiC surface on a Si substrate, and photoetching a double-gate graph; placing the etched sample in a quartz tube, generating a carbon film by reacting Cl2 with SiC, then placing the carbon film sample in Ar gas and annealing to generate graphene; etching off Al2O3 at the both sides of the graphene sample and 60-400 nm away from a conductive channel to form a double-gate groove; finally depositing a metal layer on the graphene sample and etching to form transistor metal contact. The double-gate graphene transistor provided by the preparation method disclosed by the invention has the advantages of being high in carrier mobility, good in scattering effect suppression performance, and capable of regulating a channel carrier concentration, as well as can be used for producing a large-scale integrated circuit.

Owner:XIDIAN UNIV

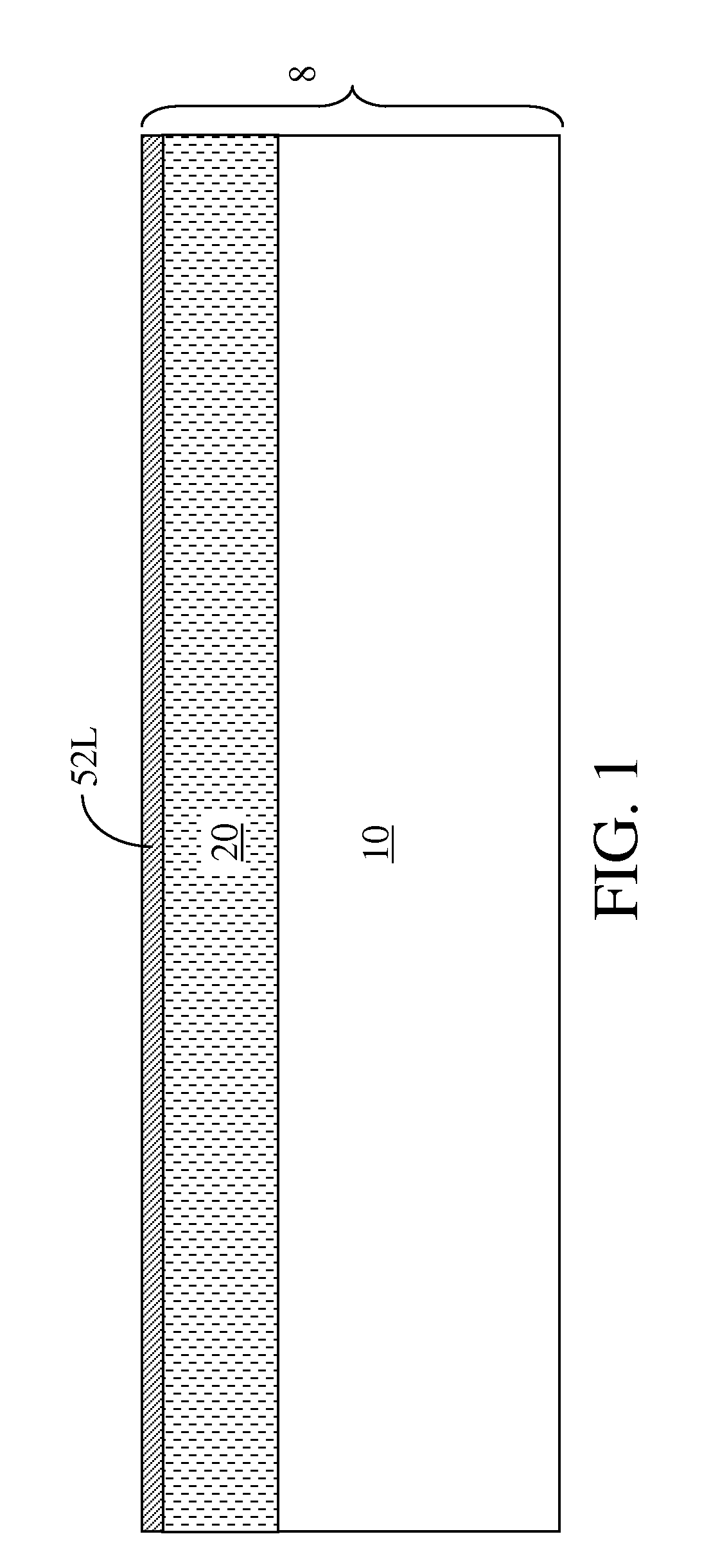

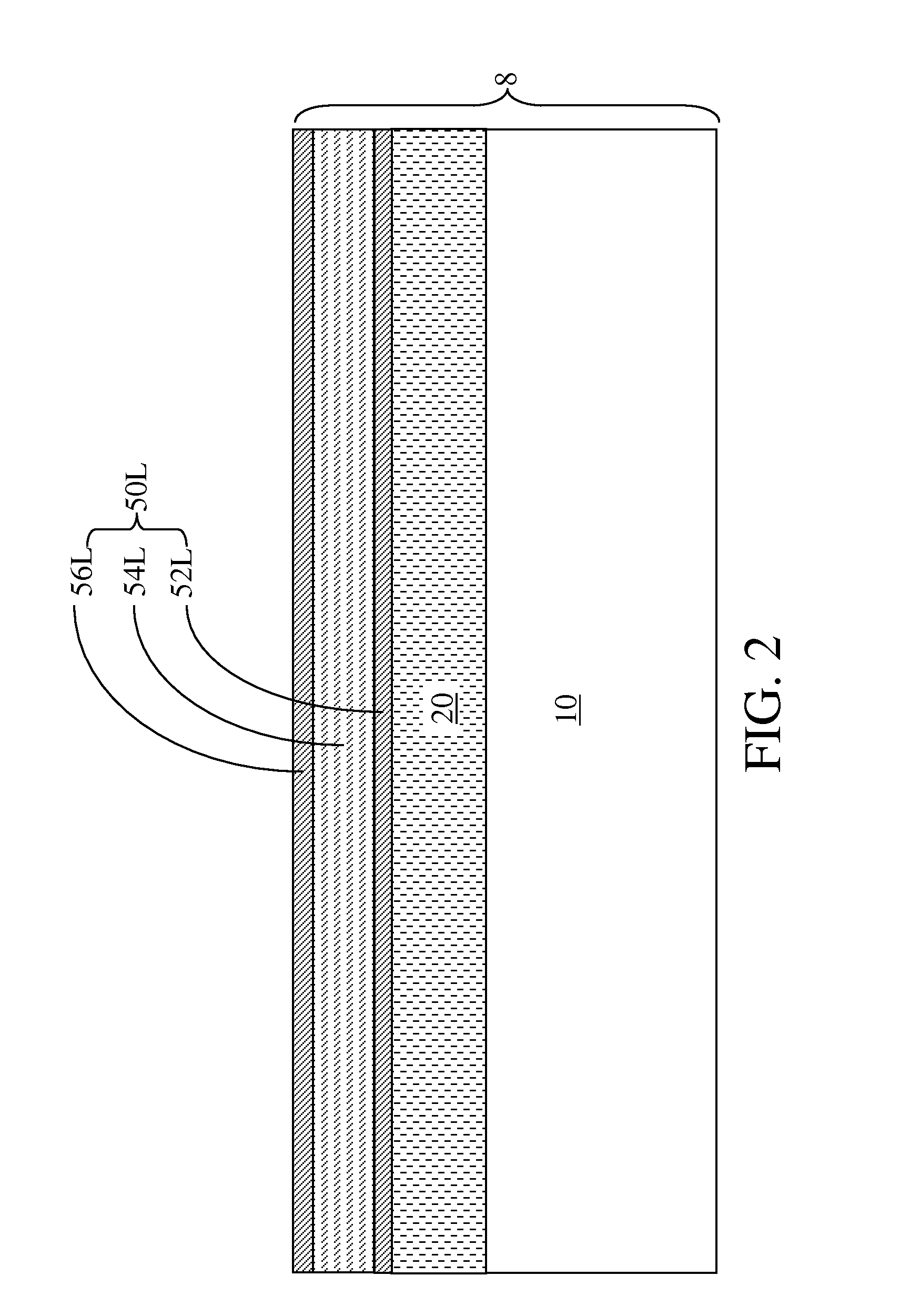

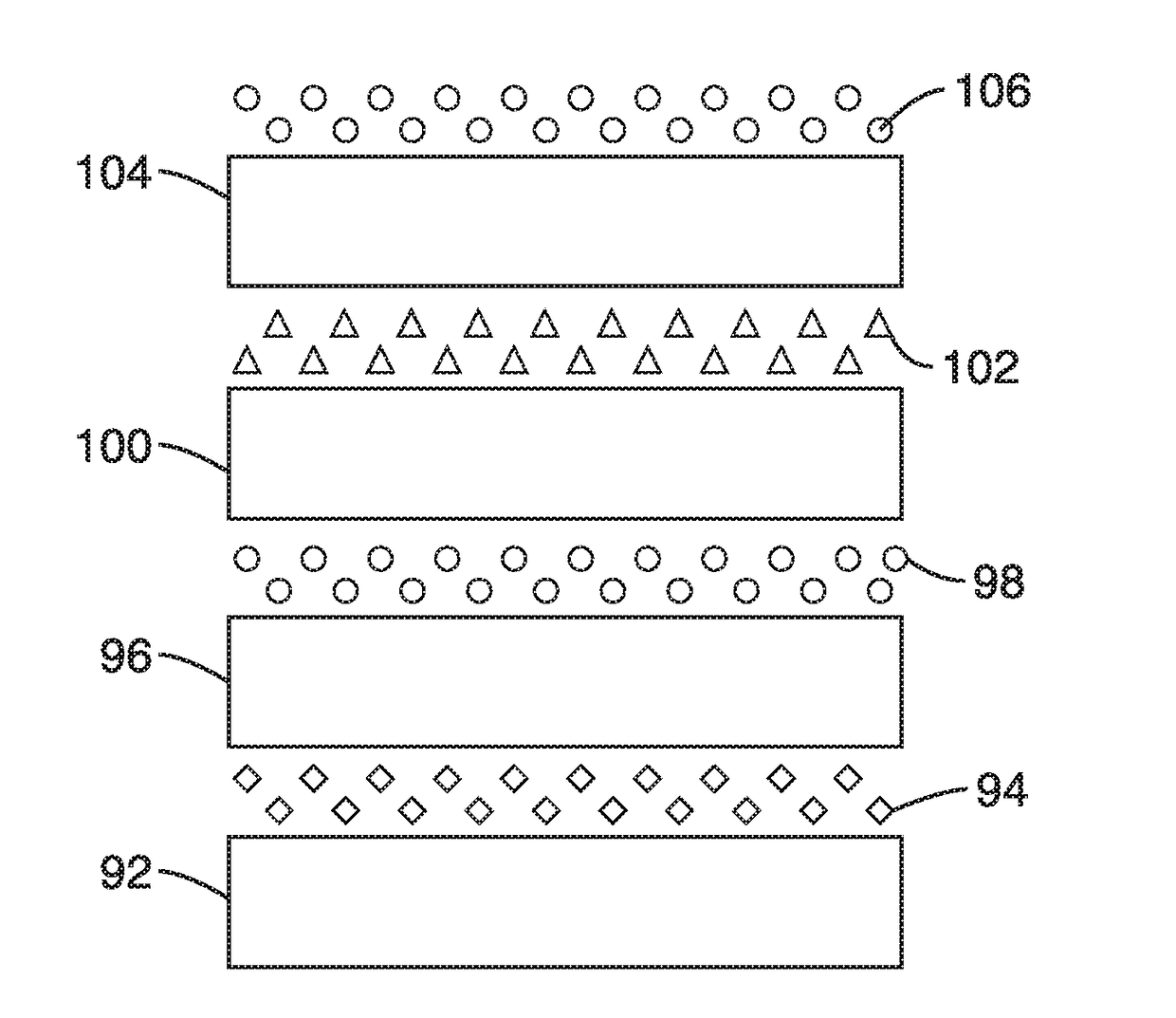

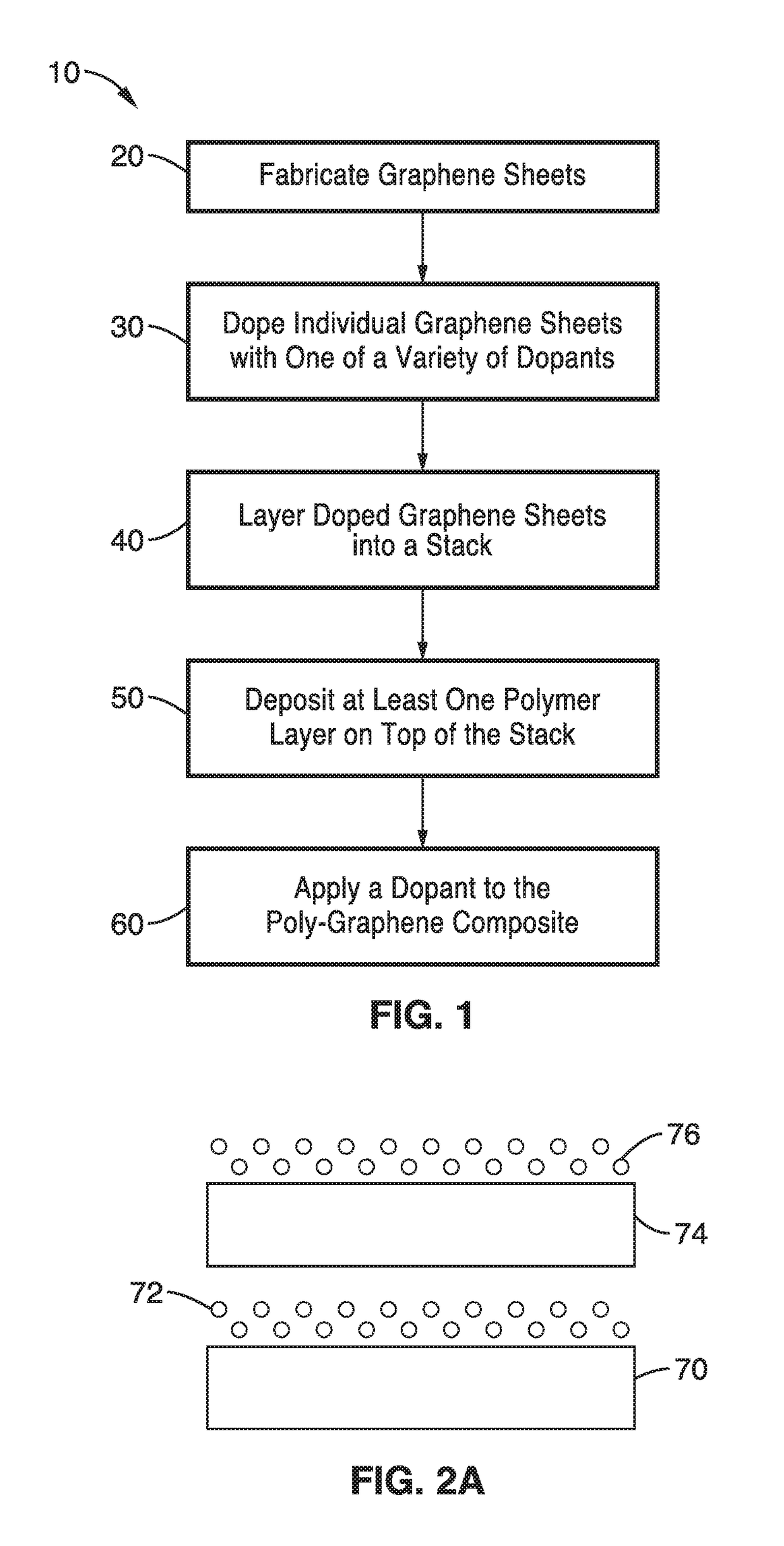

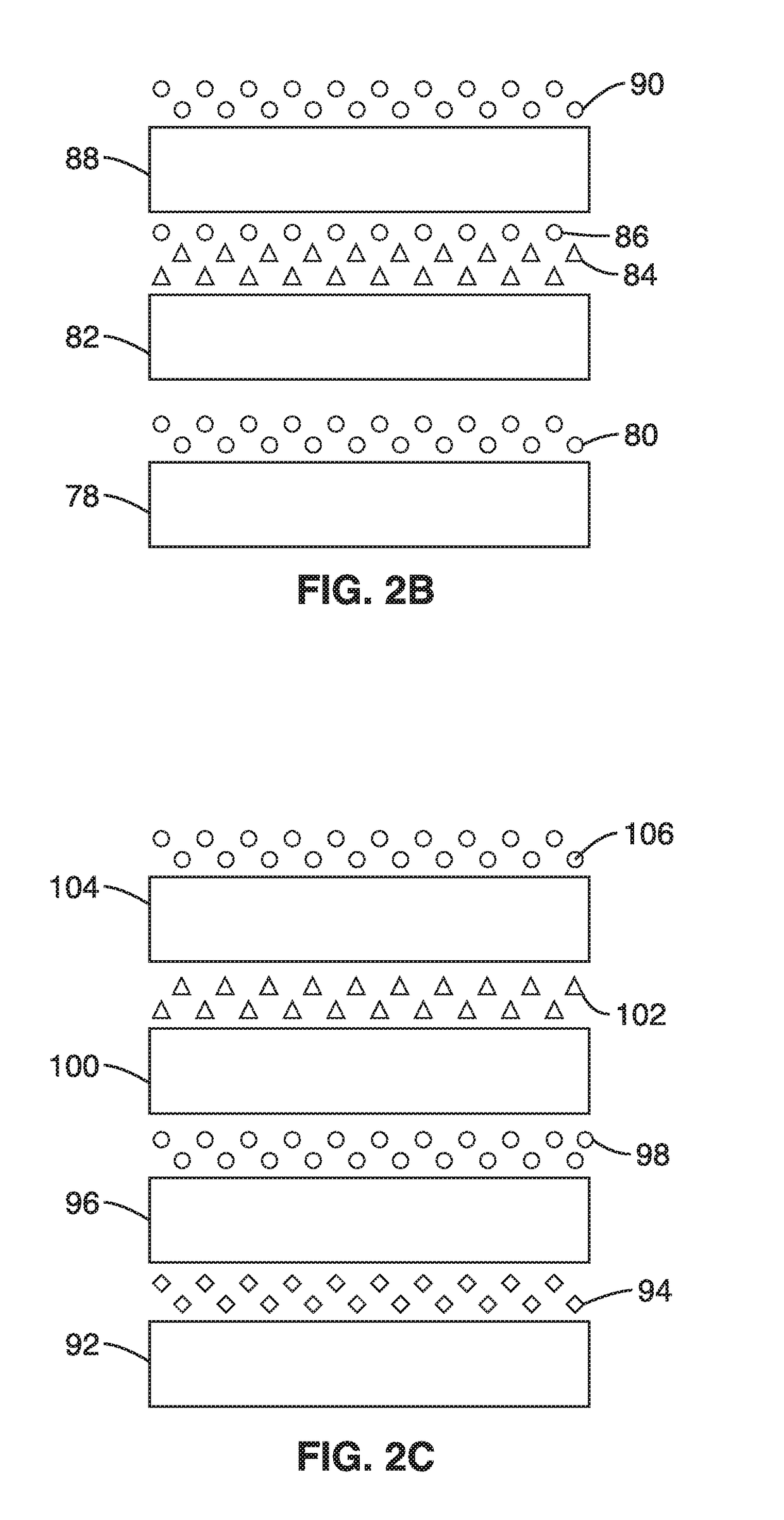

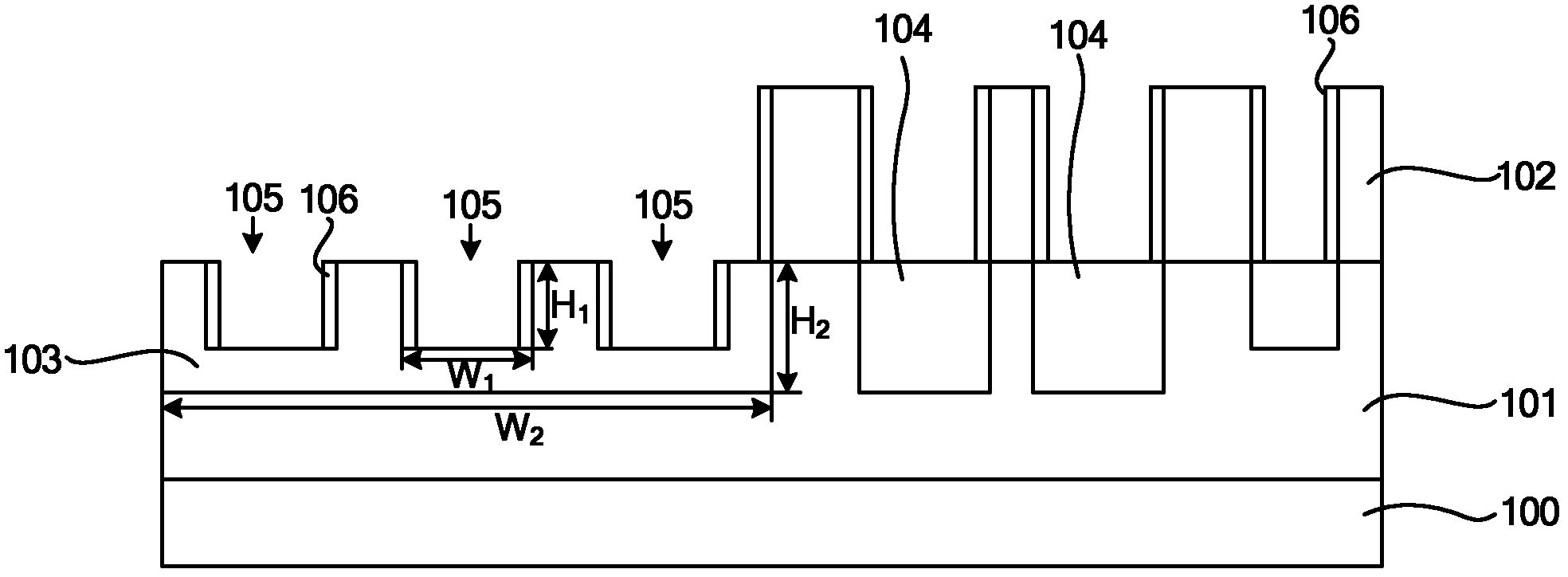

Graphene-polymer nanocomposites incorporating chemically doped graphene-polymer heterostructure for flexible and transparent conducting films

InactiveUS20180130569A1Low costReduce grain boundaries, carbon vacancies, lattice defectsConductive materialGrapheneDoped grapheneCarrier scattering

Flexible, conductive, graphene-polymer nanocomposites incorporating doped graphene and conductive polymer materials in a layered structure and tunable methods of fabrication are provided. The layered graphene-polymer nanocomposites exhibit resistance quenching by suppressing defect induced carrier scattering in graphene while keeping the optical transmittance greater than 90%, which is essential for many optoelectronic applications. Nanocomposites also demonstrate high mobility and carrier density compared to known TCF materials as well as very low sheet resistance with flexibility of more than ±90 degrees of bending angle. The methods employ layer-by-layer mixed chemical doping strategies that incorporate different doping species to enhance electrical and optical properties individually. The synthesis of the graphene-polymer nanocomposite may be conducted by chemical processes to provide mass production capabilities.

Owner:KING ABDULAZIZ CITY FOR SCIENCE AND TECHNOLOGY +1

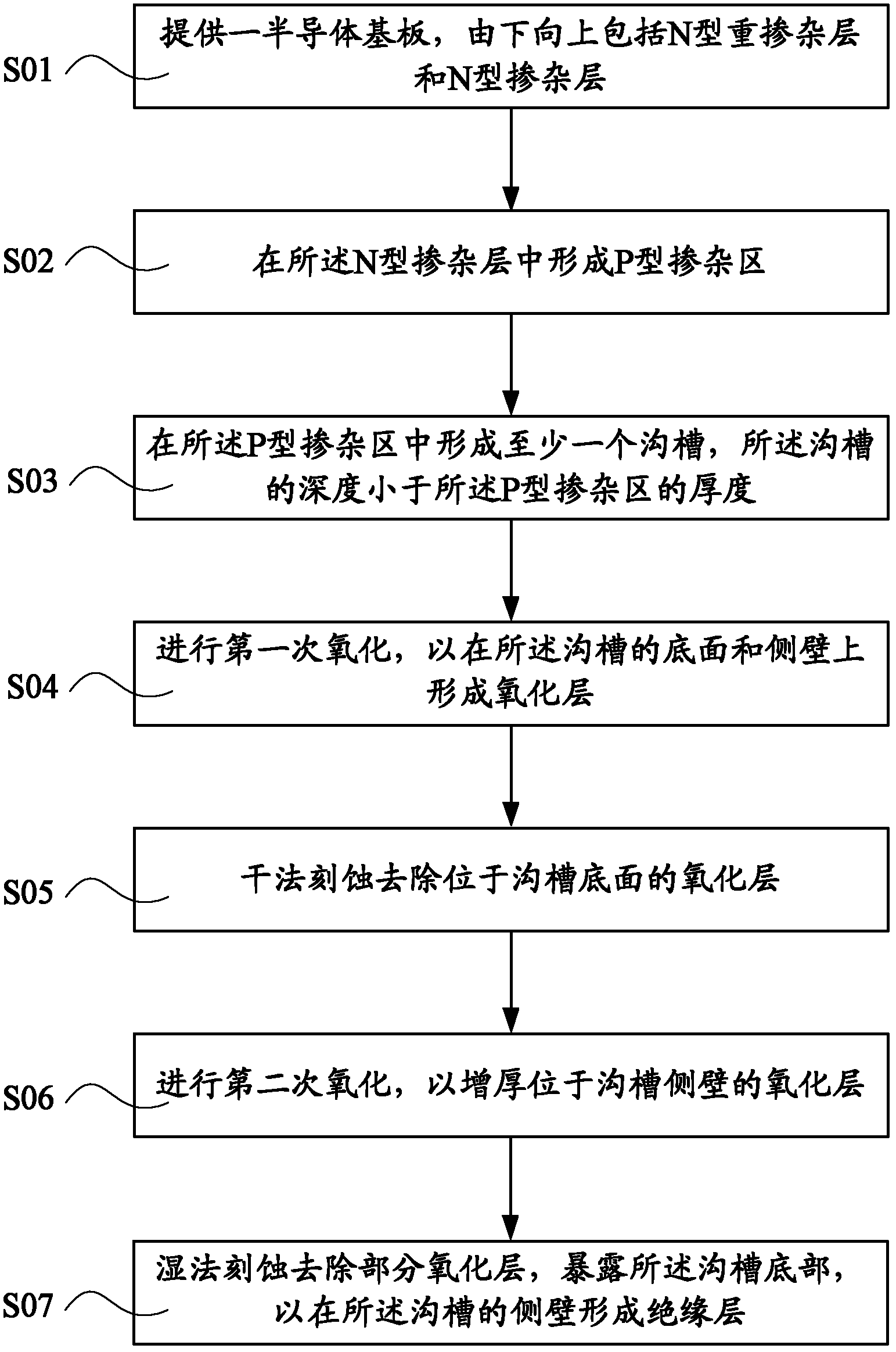

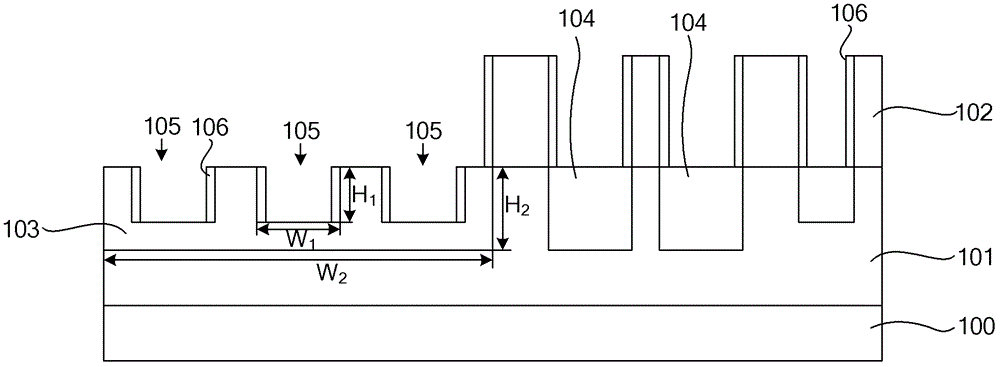

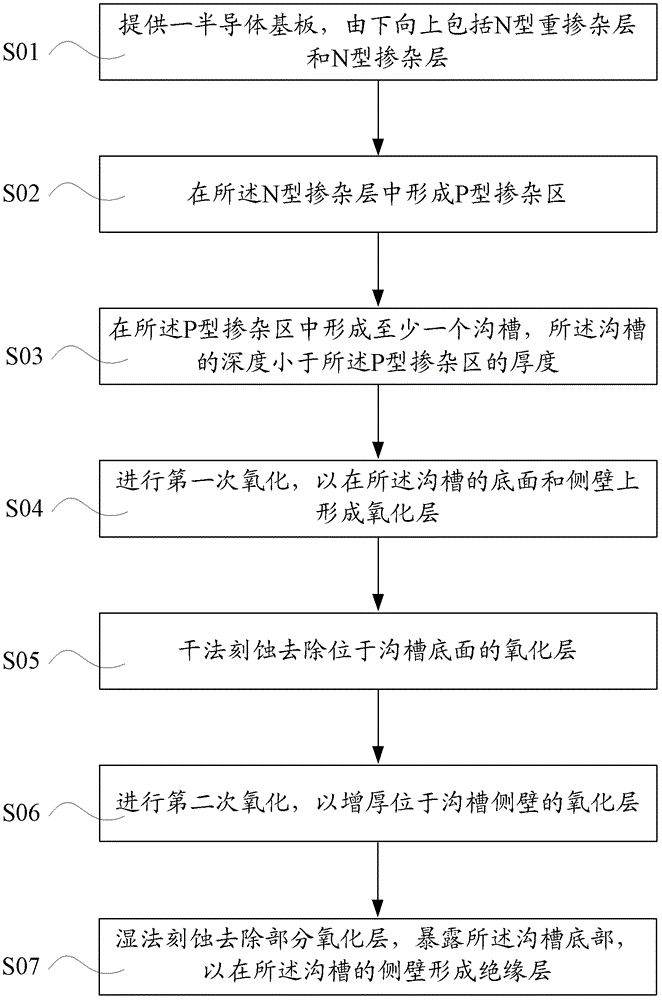

Fast recovery diode (FRD) device structure and manufacturing method thereof

ActiveCN102437200AImproved reverse recovery characteristicsImprove on-state pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerCharge carrier

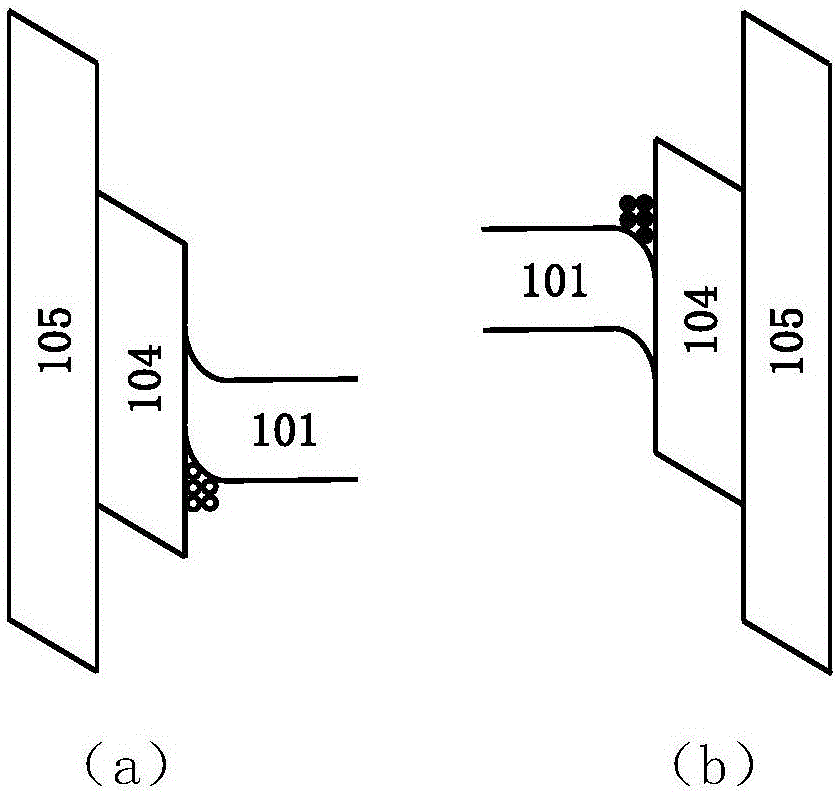

The invention provides a fast recovery diode (FRD) device structure and a manufacturing method thereof. An insulation layer is formed on the side wall of a trench of the FRD device structure, and the insulation layer is combined with the surface of a P-type doped region to form a combining center, so that a combining route from the P-type doped region to the insulation layer is formed, and the reverse recovery characteristic of the device is improved effectively; furthermore, due to the presence of the insulation layer on the side wall of the trench, partial combined current carriers which reach the upper surface of the P-type doped region from the P-type doped region through the combining route are shielded by the insulation layer and combined on the surface of the insulation layer, so that the emission efficiency is improved and the state voltage drop is reduced; moreover, the doping concentration at the bottom of the trench in the P-type doped region is controlled, so that the diffusion length of the current carriers is prevented from being dramatically reduced, the scattering of the current carriers and an auger combining effect are avoided, the emission efficiency of the bottom region of the trench in the P-type doped region is improved, the rising of the state voltage drop of the trench caused by doping reduction is compensated, and the forward voltage drop is improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

Germanium channel quantum well field effect transistor with low power consumption and high performance

InactiveCN106549039AIncrease working currentLimited shipping spaceSemiconductor devicesInsulation layerCarrier scattering

Owner:ZHEJIANG UNIV

Preparation method based on Ni membrane annealing for SiC substrate side grid graphene transistor

InactiveCN103077893AAvoid reduced mobilityAvoid performance degradationSemiconductor/solid-state device manufacturingDielectricGrid pattern

The invention discloses a preparation method based on Ni membrane annealing for a SiC substrate side grid graphene transistor and mainly solves the problems of low graphene channel carrier mobility and carrier scattering caused by top grid dielectric of a graphene transistor prepared by the prior technology. The preparation method is implemented by the following steps that a SiC sample substrate is cleaned; a SiO2 layer is deposited on the surface of the SiC sample substrate, and a side grid pattern is formed on the SiO2 layer in a photo-etching manner; the photo-etched sample substrate is placed in a quartz tube, and a carbon membrane is generated through the reaction of gaseous CCl4 and SiC; then the sample substrate with the carbon membrane is placed in a buffer hydrofluoric acid solution to remove the SiO2; a Ni membrane is deposited on the carbon membrane of the sample substrate, and the sample substrate is placed in Ar gas for annealing, so graphene of a side grid is generated; and finally, a metal Pd / Au layer is deposited on the graphene sample substrate and is etched to form metal contacts of a side grid transistor. The side grid graphene transistor prepared by the preparation method has high carrier mobility and can effectively restrain the scattering effect, so that the modulation effect of the grid of the graphene transistor on the channel carrier concentration is improved.

Owner:XIDIAN UNIV

Ion sensitive field effect transistor and preparation process thereof

InactiveCN103940885AMaterial analysis by electric/magnetic meansCarrier scatteringOrganic field-effect transistor

Relating to transistors, the invention discloses an ion sensitive field effect transistor and a preparation process thereof. The ion sensitive field effect transistor comprises a semiconductor substrate, a gate insulating layer, a source electrode and a drain electrode formed by doping, and a buried channel with the same doping type to the source electrode and the drain electrode. The buried channel is in the semiconductor substrate and near the upper surface, and the buried channel and the upper surface of the semiconductor substrate do not contact. The source electrode and the drain electrode are respectively located on two sides of the buried channel. The gate insulating layer is positioned on the semiconductor substrate above the buried channel. Compared with the prior art, when current is generated between the source electrode and the drain electrode in the transistor provided by the invention, the current flows through the buried channel in priority rather than pass through a contact interface between the gate insulating layer and the semiconductor substrate, thereby avoiding current measurement noise generated by surface defects of the contact interface, and preventing surface carrier scattering from reducing the signal-to-noise ratio and ion measurement sensitivity of the device.

Owner:FUDAN UNIV

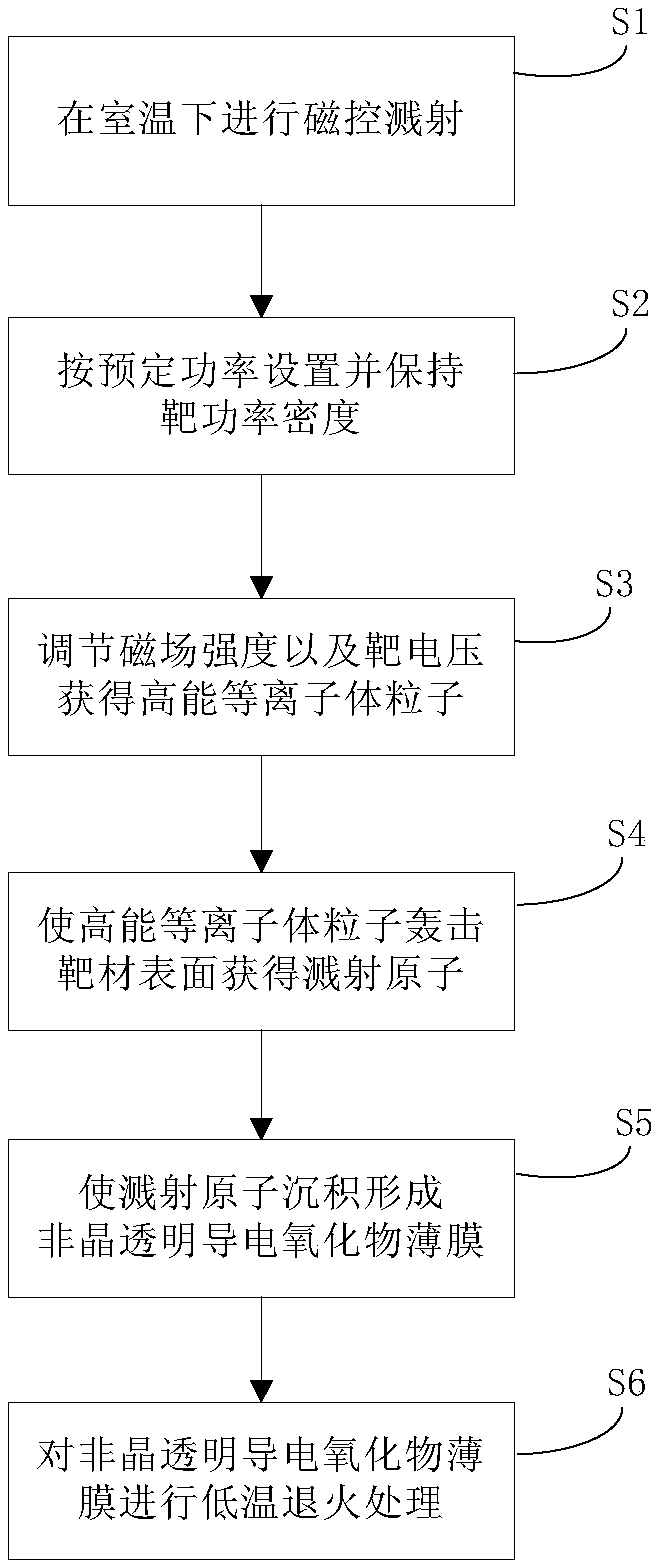

Preparation method of amorphous transparent conductive oxide thin film

InactiveCN107557745AReduce scatterReduce ionized impurity scatteringVacuum evaporation coatingSputtering coatingPlasma particleHigh energy

The invention discloses a preparation method of amorphous transparent conductive oxide thin film. The preparation method comprises the step of carrying out magnetron sputtering under the room temperature, and further comprises the steps of setting the target power density according to the preset power in the preparation process, and keeping the target power density unchanged; adjusting the magnetic field intensity and the target voltage to obtain the high-energy plasma particles with the energy higher than or equal to 100 eV; making the high-energy plasma particles bombard the surface of a target material to obtain sputtering atoms; making the sputtering atoms deposit on a base to obtain amorphous transparent conductive oxide thin film according to the preset deposition speed; and carryingout low-temperature annealing treatment on the amorphous transparent conductive oxide thin film. According to the preparation method of amorphous transparent conductive oxide thin film, grain boundary scattering, ionized impurity scattering and carrier scattering are greatly reduced, the influence caused by grain boundary scattering, ionized impurity scattering and carrier scattering to carrier mobility in amorphous transparent conductive oxide thin film obtained in the prior art is eliminated, and then, the purpose that the carrier mobility of TCO thin film is effectively improved on the premise that energy consumption is low is achieved.

Owner:BEIJING JUNTAIINNOVATION TECH CO LTD

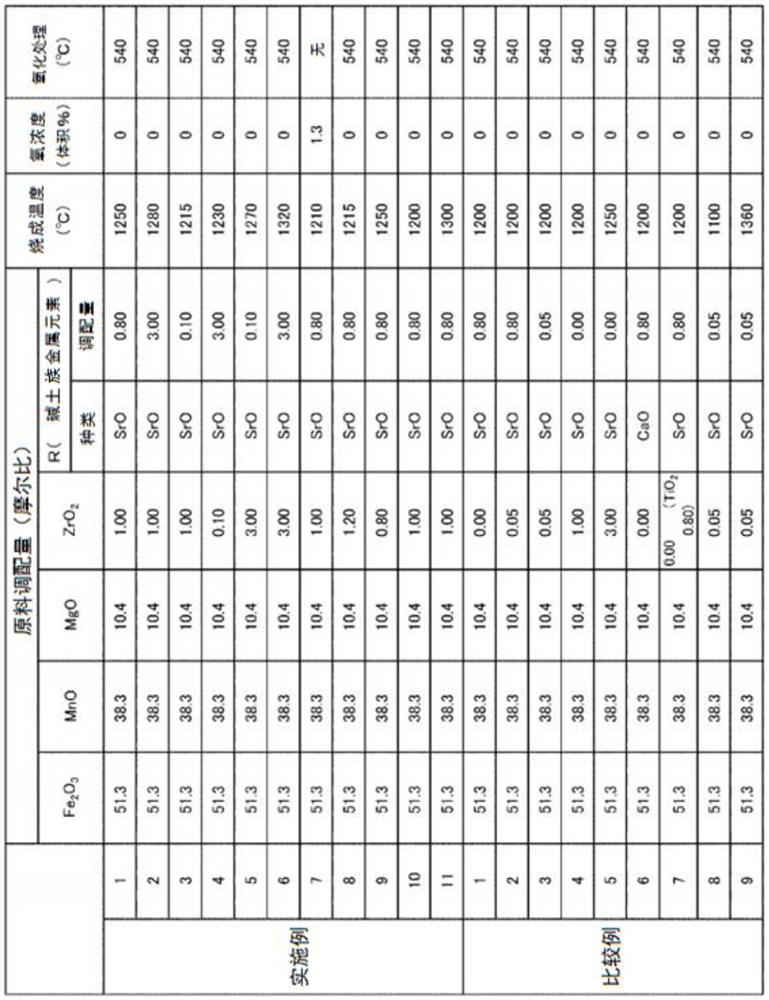

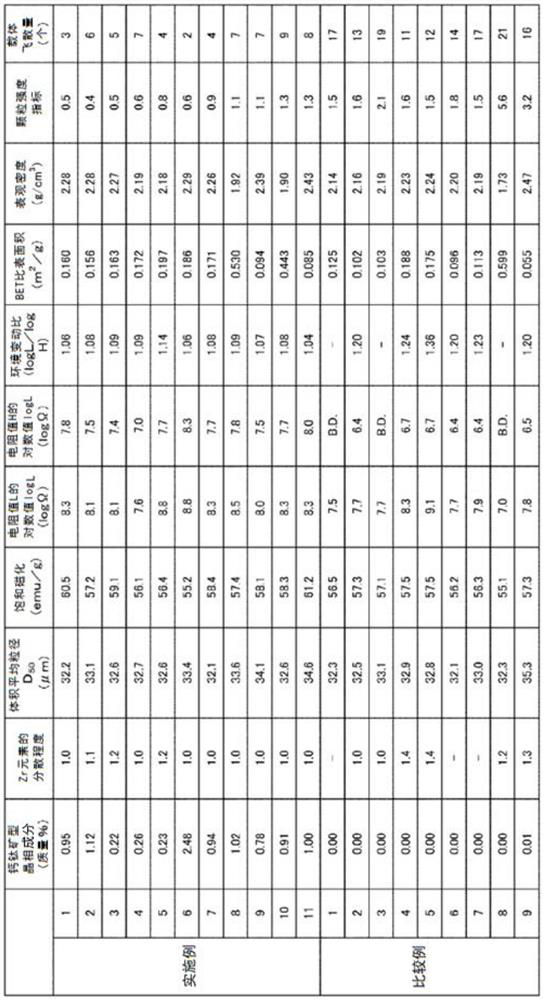

Ferrite carrier core material and ferrite carrier for electrophotographic developer, methods for manufacturing these, and electrographic developer using the ferrite carrier

ActiveUS9081318B2Improve charging effectProlong lifeDevelopersCarrier scatteringConditional expression

It is an object of the present invention to provide a ferrite carrier core material and a ferrite carrier for an electrophotographic developer, which have an excellent charging property, hardly cause carrier scattering due to cracking and chipping of the core material, and have a prolonged life, and methods for manufacturing these, and an electrophotographic developer using the ferrite carrier. For this object, the ferrite carrier core material and a ferrite carrier for an electrophotographic developer, wherein (1) the ferrite composition contains 0.5 to 2.5% by weight of Sr, and the presence amount of Sr—Fe oxides satisfies a specific conditional expression, (2) the distribution in the number of the shape factor SF-2 is in a specific range, (3) the BET specific surface area is 0.15 to 0.30 m2 / g, (4) the average particle diameter D50 is 20 to 35 μm, and (5) the magnetization is 50 to 65 Am2 / kg.

Owner:POWDERTECH

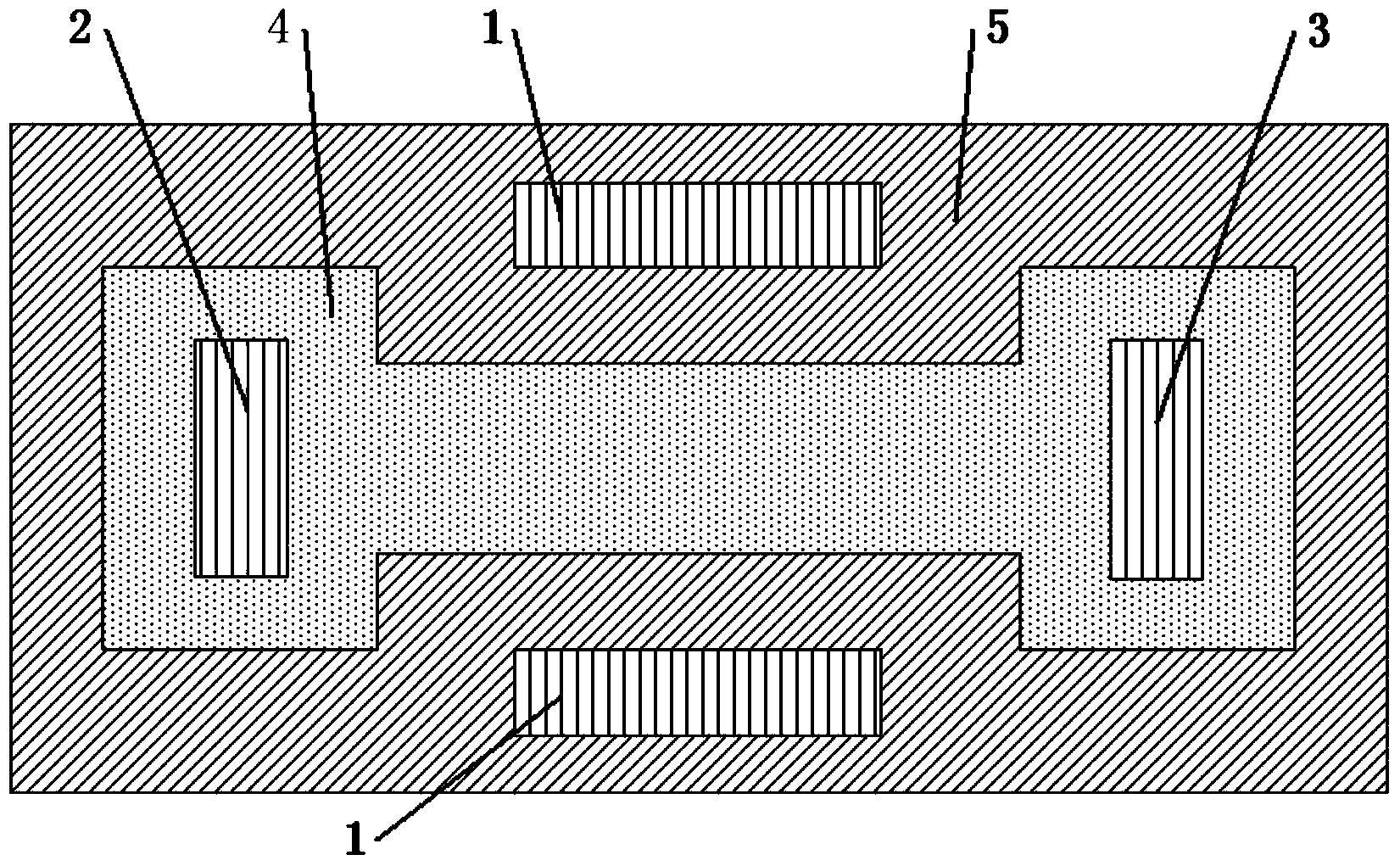

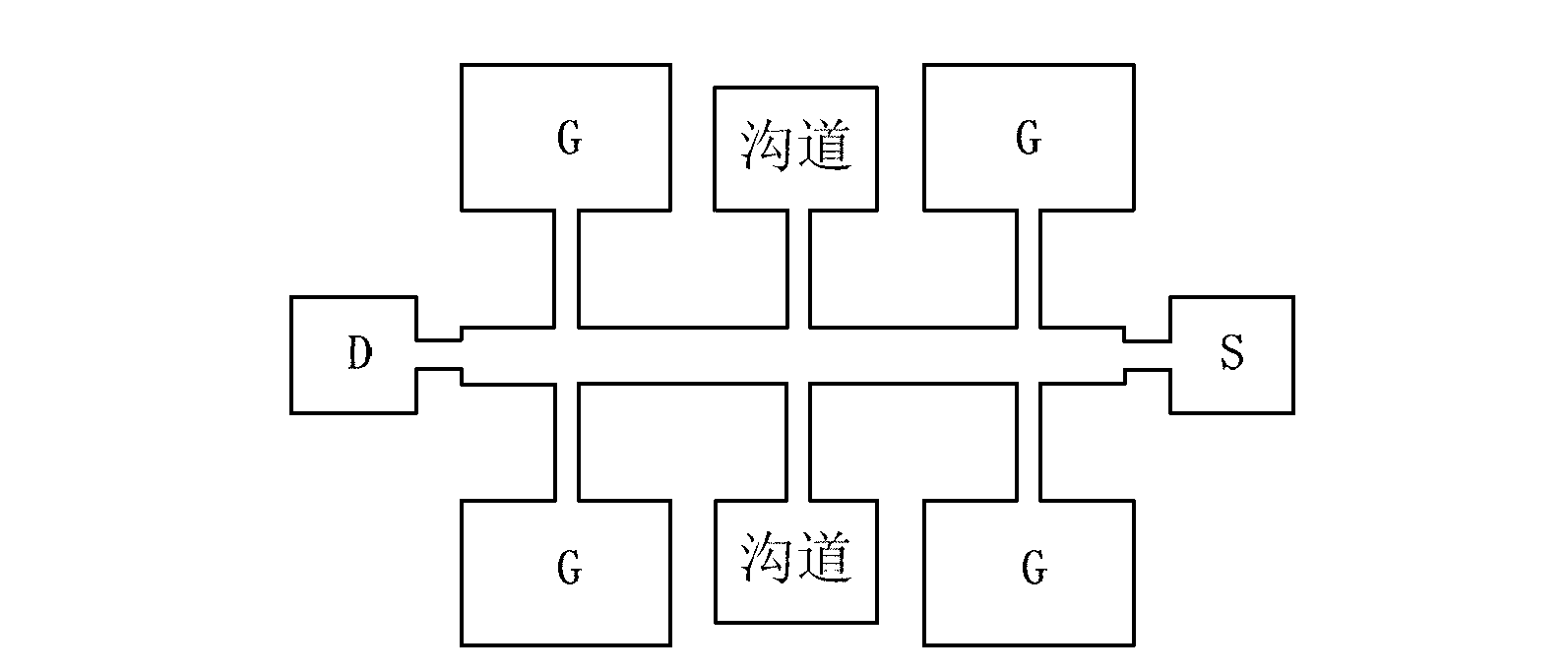

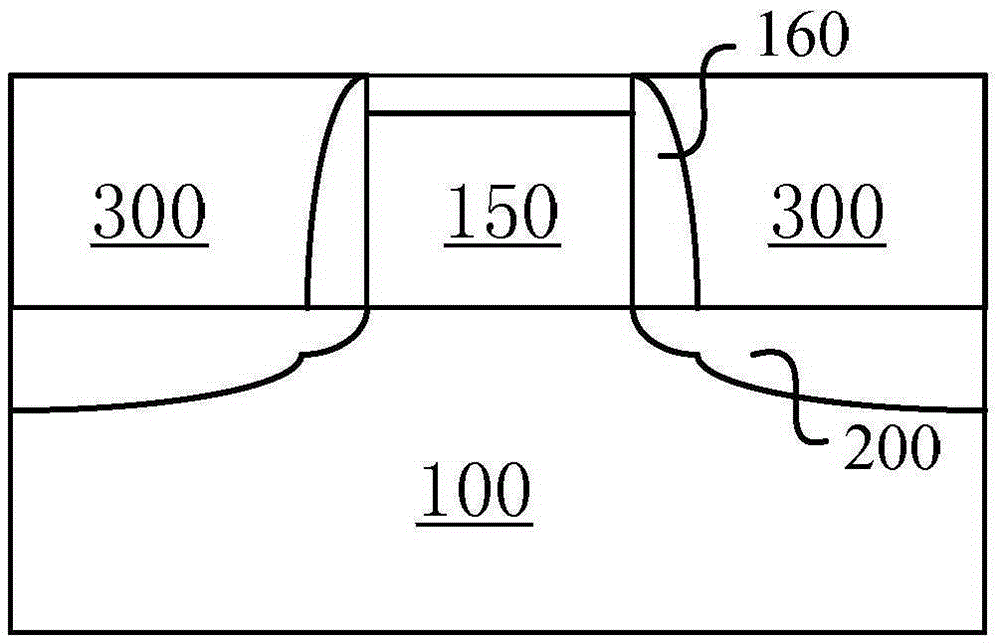

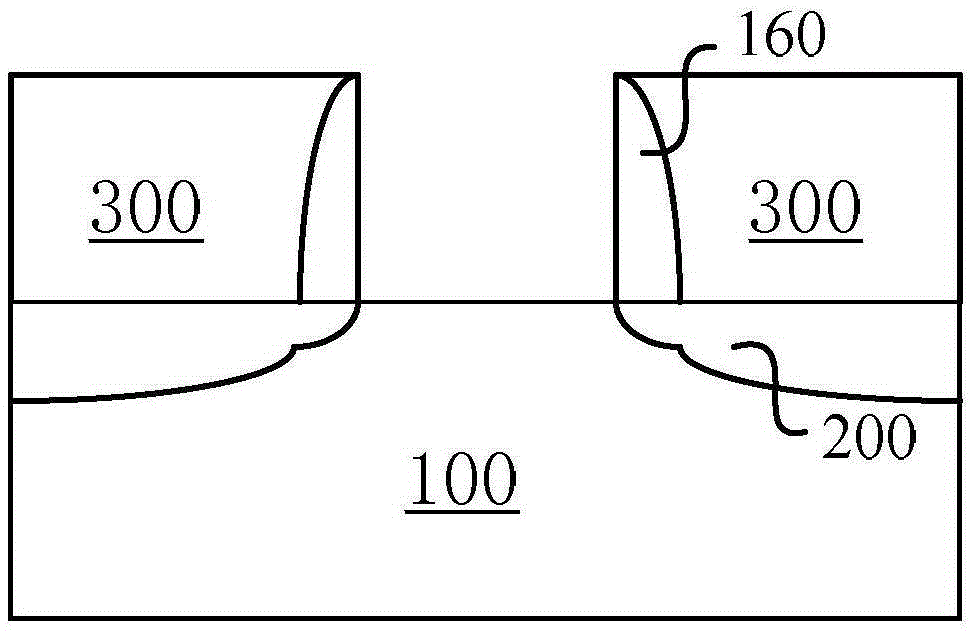

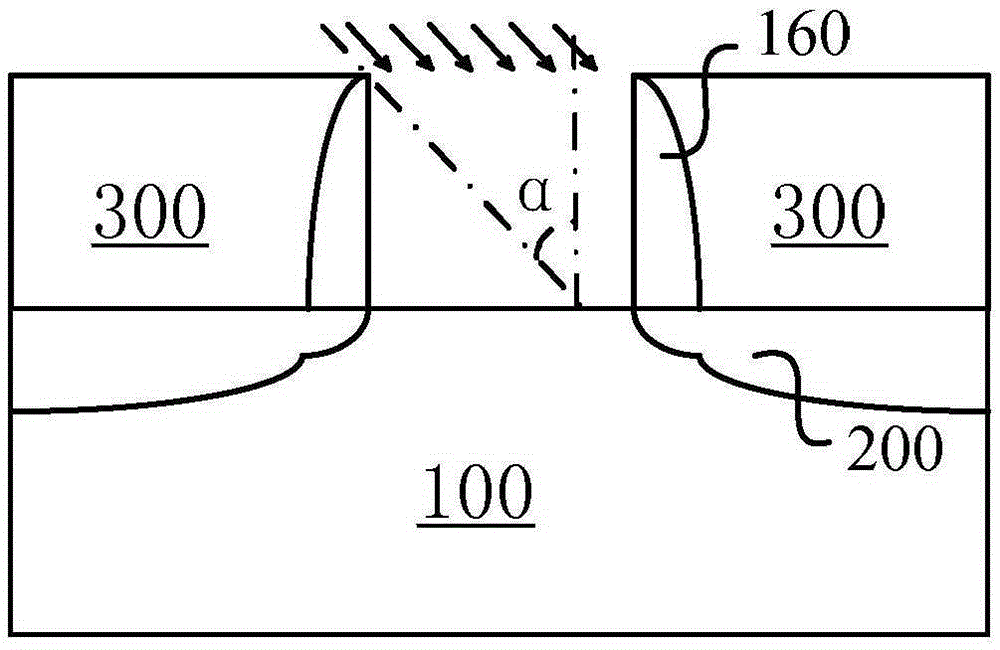

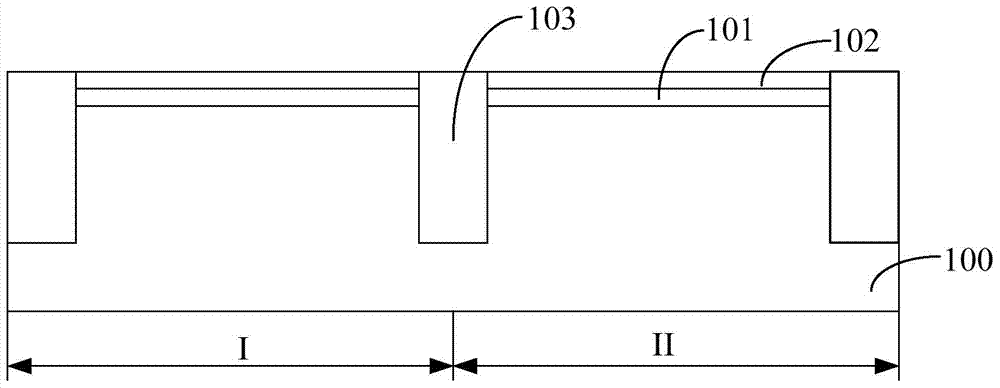

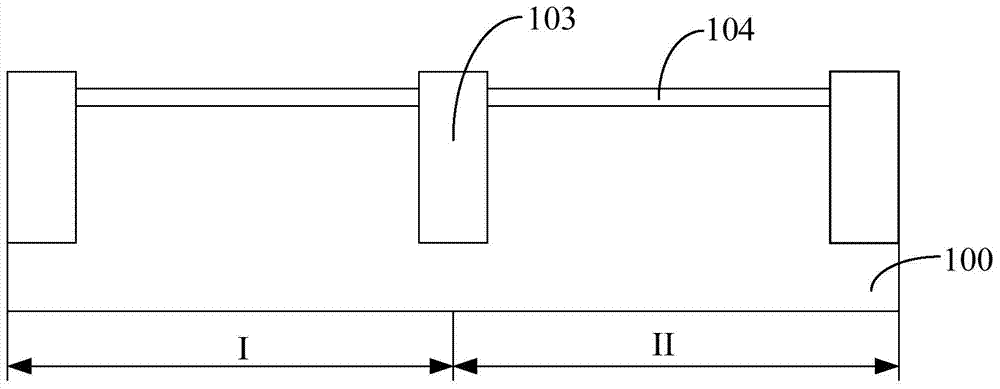

A mosfet structure and its manufacturing method

ActiveCN103606524BReduce jump chanceReduce the numberSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

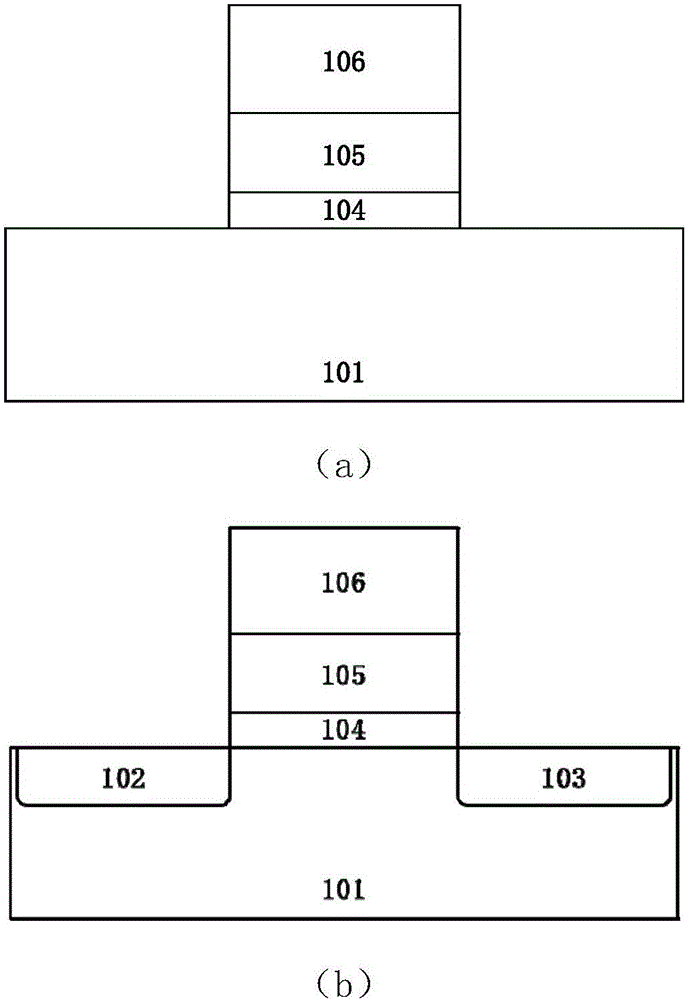

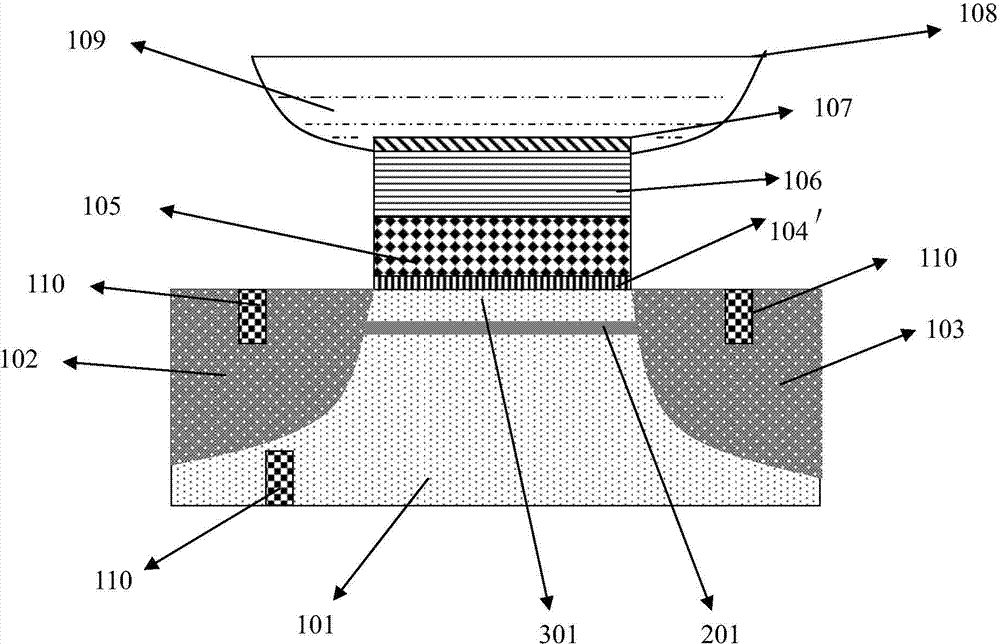

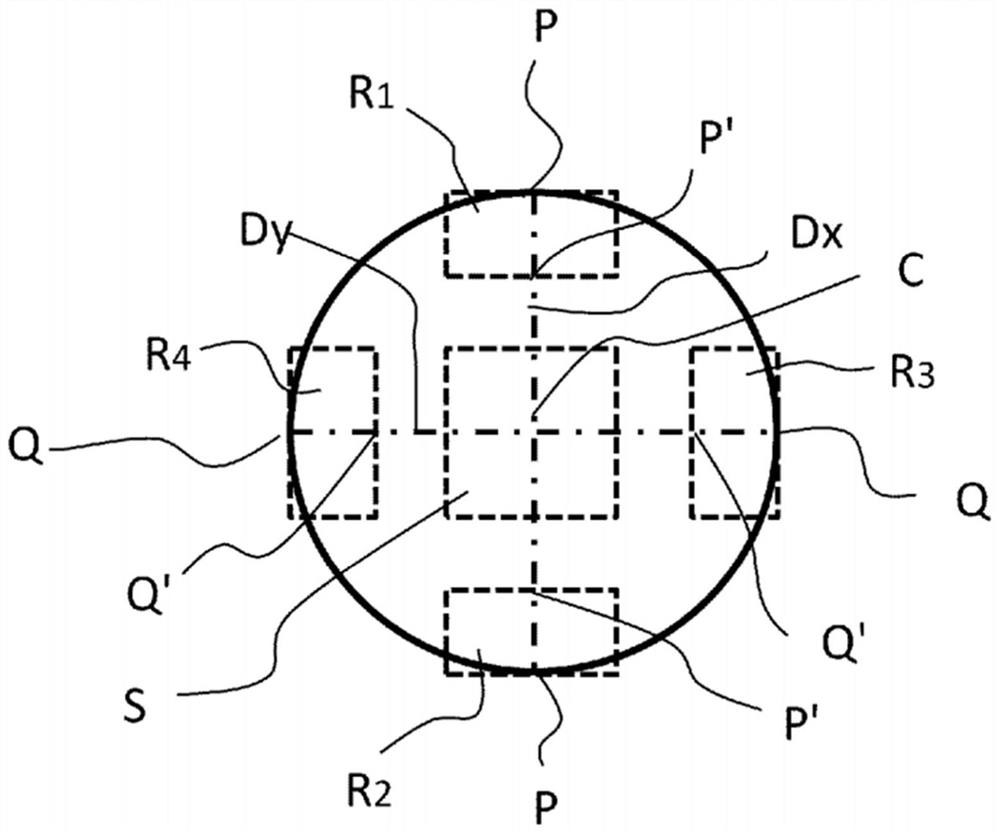

The present invention provides a method of manufacturing a MOSFET, comprising: a. providing a substrate (100), a source / drain region (200), a pseudo-gate stack (150), an interlayer dielectric layer (300), and a sidewall (160); b. removing the pseudo-gate stack (150) to form a pseudo-gate vacancy; c. performing inclined ion injection on the semiconductor structure, and forming a carrier scattering region (400), the carrier scattering region (400) being located below a surface of the semiconductor structure on a side of a drain; and d. depositing a gate stack layer (500) in the pseudo-gate vacancy. According to the method for reducing a probability of hot carrier transition provided by the present invention, scattering impurities, that is, non-ionized impurities are injected in a channel material near a side of a drain, so that a probability that a hot carrier is scattered in a pinch-off region is increased, a carrier is subject to increased resistance in the movement in the pinch-off region, the energy of a hot carrier is reduced, and accordingly the quantity and probability of hot carriers that enter a gate dielectric layer are reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

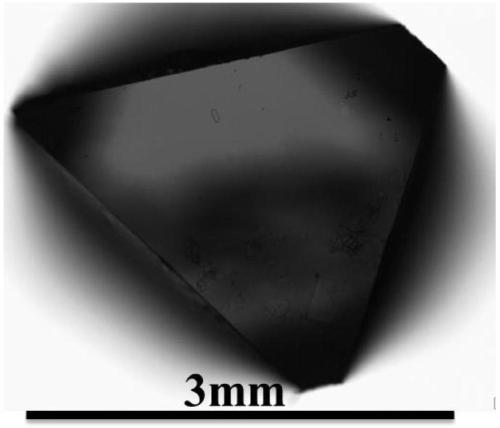

Lead-free perovskite Cs2AgBiBr6, preparation method and method for obtaining diffusion coefficient of lead-free perovskite Cs2AgBiBr6

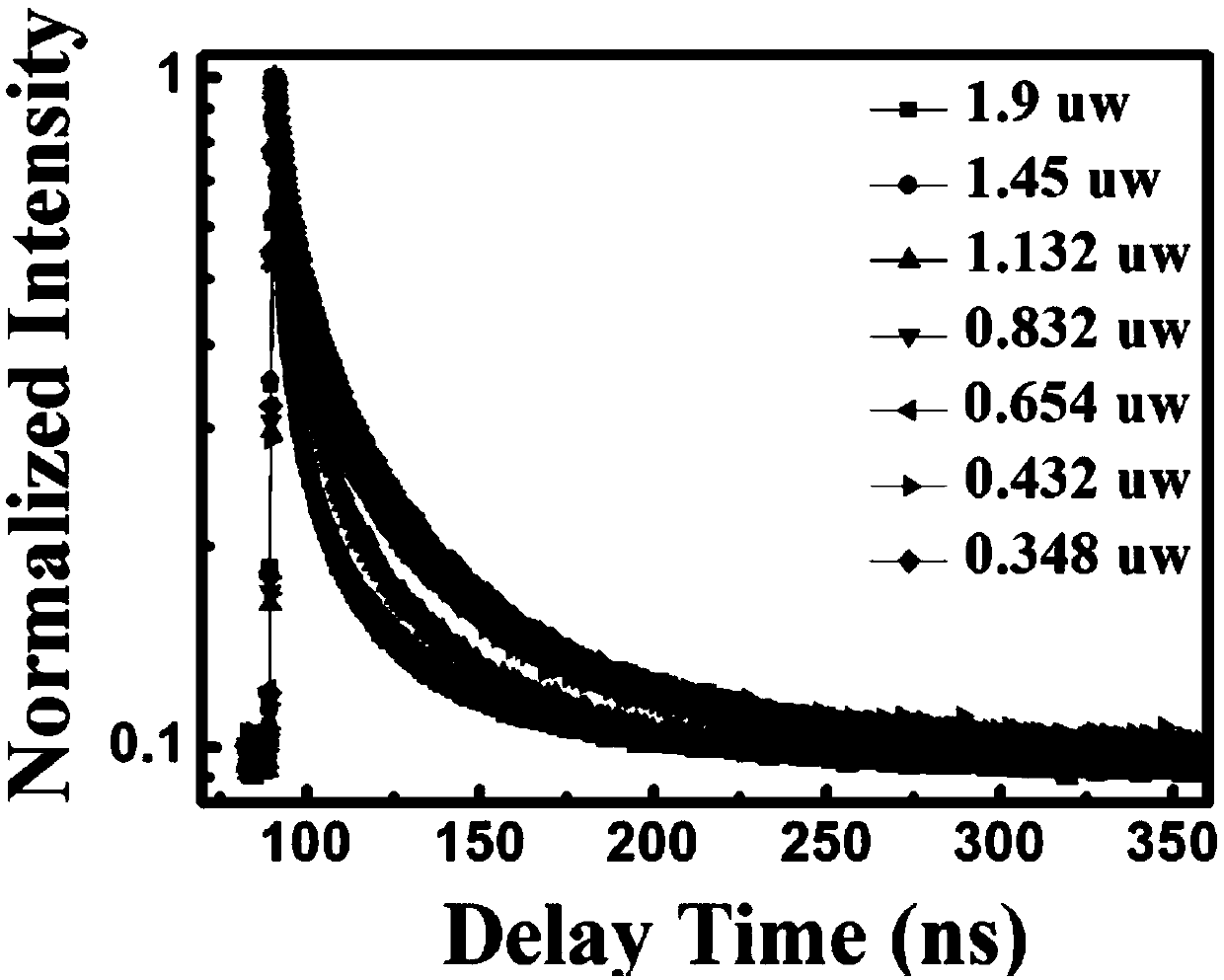

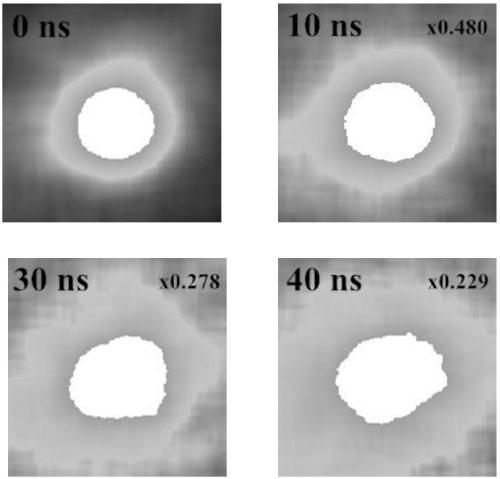

InactiveCN111233035APreparation of single crystal with few surface defectsMorphological rulesFluorescence/phosphorescenceLuminescent compositionsChemical physicsLight spot

The invention discloses lead-free perovskite Cs2AgBiBr6, a preparation method of the lead-free perovskite Cs2AgBiBr6 and a method for obtaining a diffusion coefficient of the lead-free perovskite Cs2AgBiBr6, and belongs to the field of material luminescence. And the lead-free perovskite Cs2AgBiBr6 is synthesized by adopting a crystallization method. Fluorescence imaging light spots of the lead-free perovskite Cs2AgBiBr6 are collected under low energy, the light spots at different moments are extracted, then normalization is carried out with the light spot intensity at the zero moment as the benchmark, and it can be clearly seen that the diameter of the light spots is increased, so that the light spots are more uniform. According to direct evidence, the diffusion process of the lead-free perovskite Cs2AgBiBr6 is observed. The diffusion coefficient D of the Cs2AgBiBr6 is obtained through Gaussian fitting of the fluorescence intensity, and the mobility of the Cs2AgBiBr6 is obtained through conversion. Through fitting of diffusion coefficients D at different temperatures, it is obtained that carrier scattering of the Cs2AgBiBr6 is in an optical wave scattering mode, and guiding significance is provided for research and development of lead-free perovskite.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

Ferrite particles, electrophotographic developer carrier core material, electrophotographic developer carrier, and electrophotographic developer

PendingCN113474295AHigh strengthSuppression of scatteringInorganic material magnetismFerric oxidesAlkaline earth metalHigh humidity

The present invention addresses the problem of providing: high-strength ferrite particles that can suppress the occurrence of carrier scattering even in high temperature, high humidity environments; an electrophotographic developer carrier core material; an electrophotographic developer carrier; and an electrophotographic developer. In order to resolve the aforementioned problem, provided are the ferrite particles comprising a crystal phase component comprising perovskite crystals represented by the compositional formula RZrO3 (wherein R is an alkaline earth metal element), the ferrite particles having an apparent density within a prescribed range. The ferrite particles are used as an electrophotographic developer carrier core material. Using the same, an electrophotographic developer carrier and an electrophotographic developer are obtained.

Owner:POWDERTECH

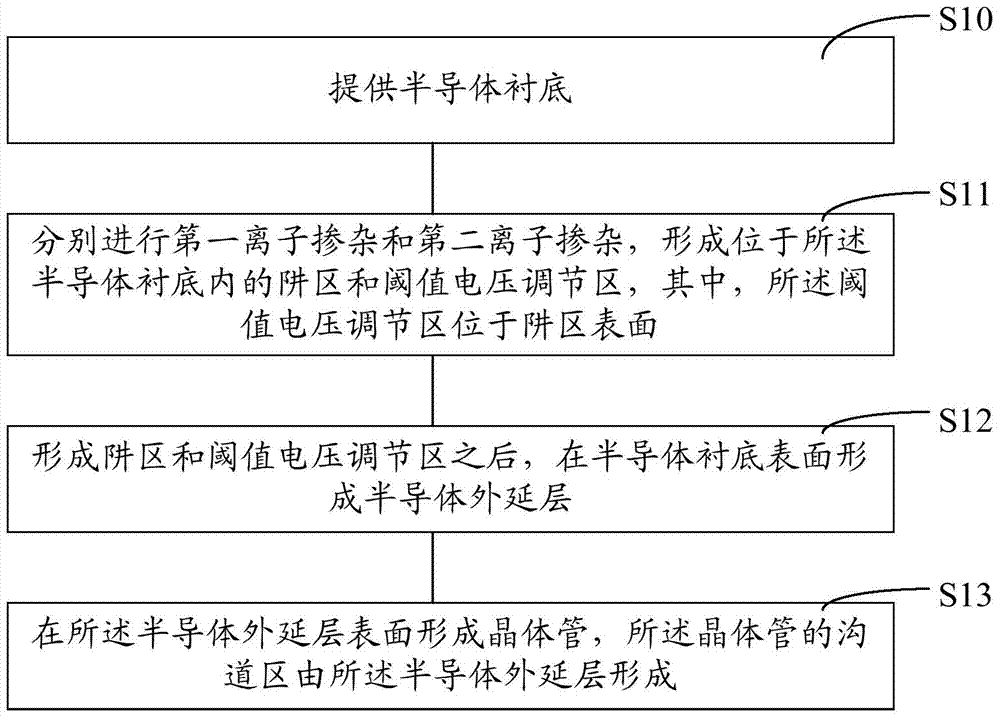

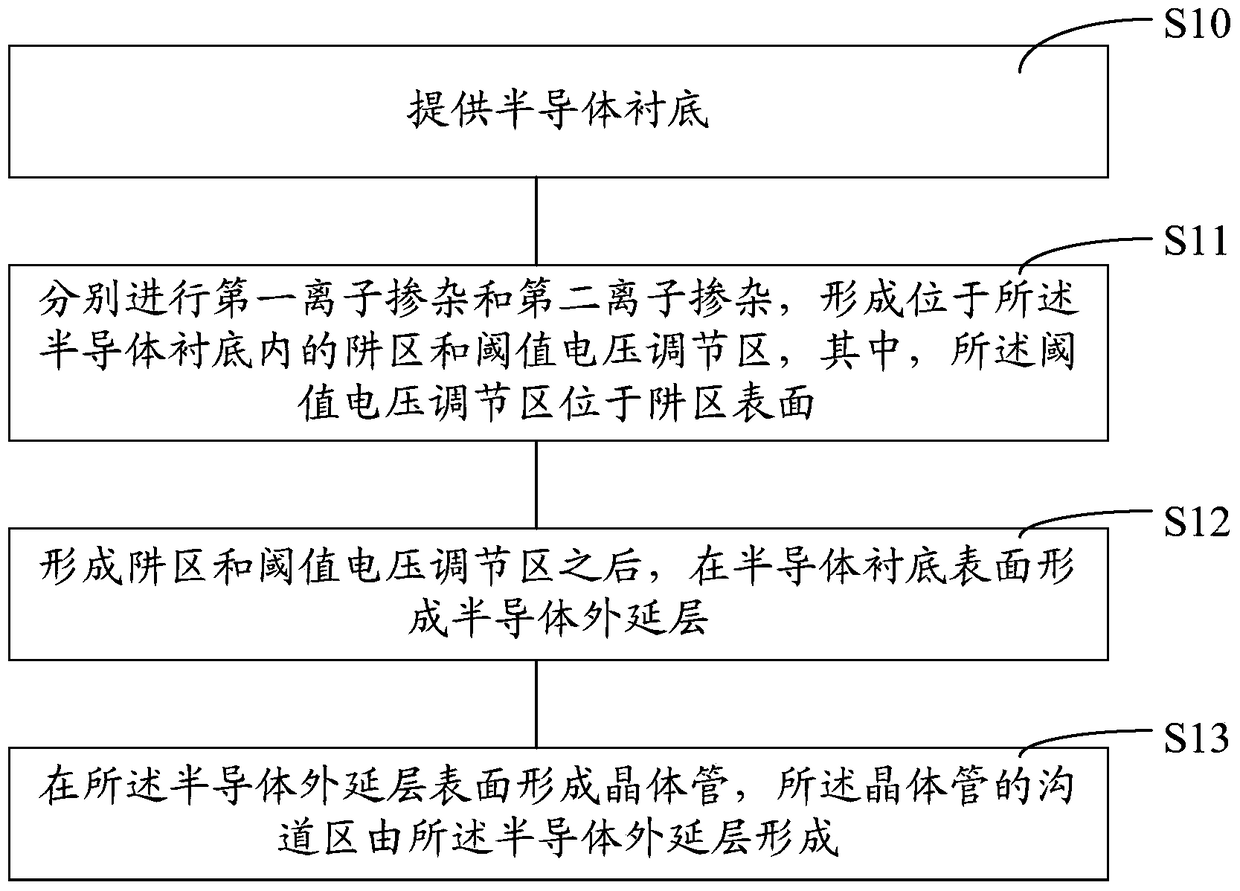

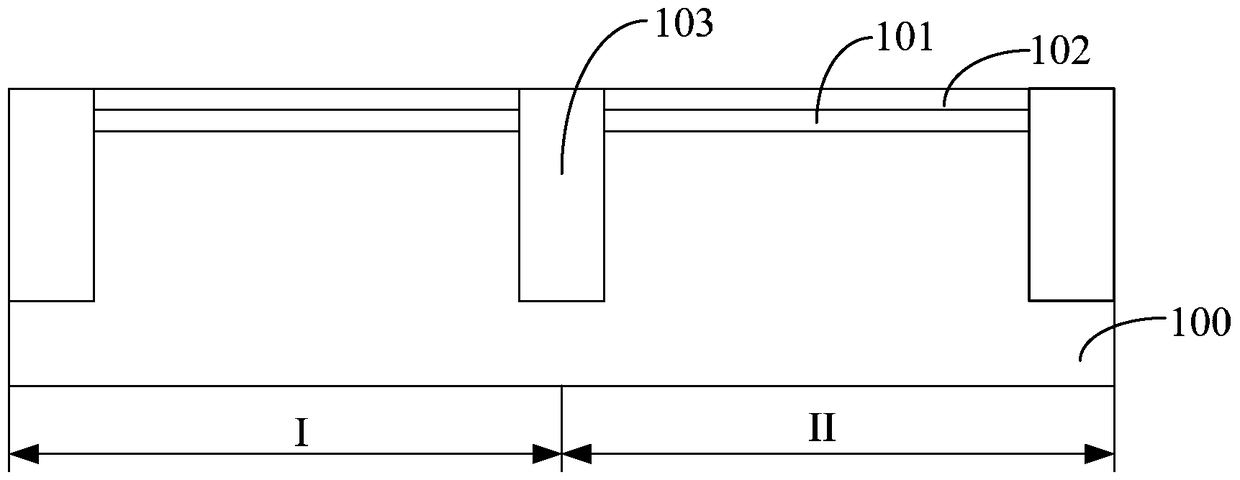

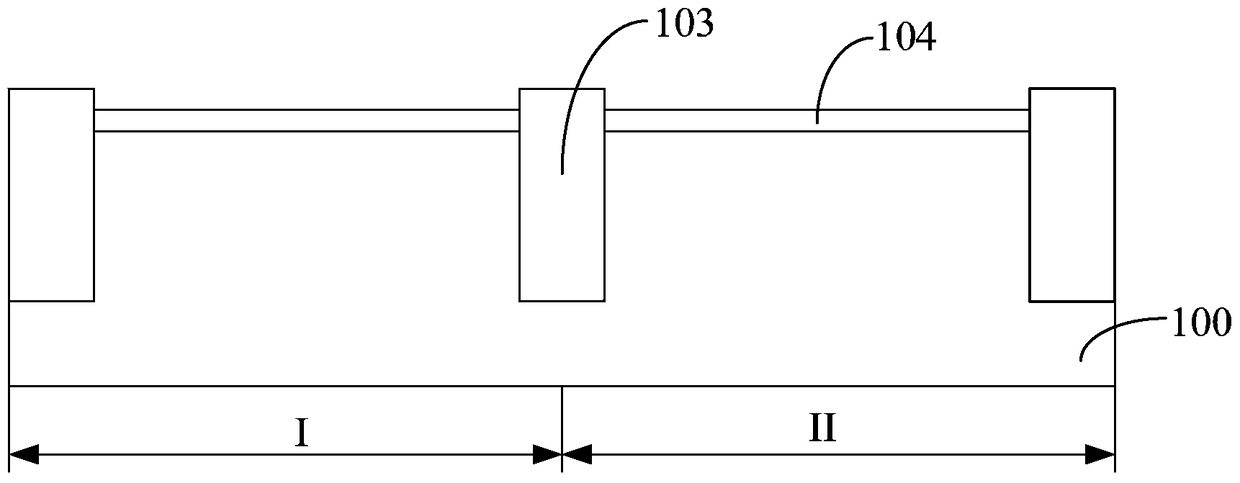

Method for forming semiconductor device

ActiveCN104733308AHigh carrier mobilityQuality improvementSemiconductor/solid-state device manufacturingPower semiconductor deviceCarrier scattering

The invention relates to a method for forming a semiconductor device, comprising the following steps: providing a semiconductor substrate; carrying out first ion doping and second ion doping to form a well region and a threshold voltage regulation region disposed in the semiconductor substrate, wherein the threshold voltage regulation region is disposed on the surface of the well region; forming a semiconductor epitaxial layer on the surface of the semiconductor substrate after the formation of the well region and the threshold voltage regulation region; and forming a transistor on the surface of the semiconductor epitaxial layer, wherein the channel region of the transistor is formed by the semiconductor epitaxial layer. According to the method for forming a semiconductor device, the semiconductor epitaxial layer, as the channel region of the transistor, avoids lattice damage caused by ion doping. Moreover, the semiconductor epitaxial layer used for forming the channel region is not doped or is lightly doped with boron. Thus, carrier scattering is reduced, the carrier migration rate of the transistor is high, and the device performance is superior.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A kind of frd device structure and manufacturing method thereof

ActiveCN102437200BImproved reverse recovery characteristicsImprove on-state pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerCarrier scattering

The invention provides a fast recovery diode (FRD) device structure and a manufacturing method thereof. An insulation layer is formed on the side wall of a trench of the FRD device structure, and the insulation layer is combined with the surface of a P-type doped region to form a combining center, so that a combining route from the P-type doped region to the insulation layer is formed, and the reverse recovery characteristic of the device is improved effectively; furthermore, due to the presence of the insulation layer on the side wall of the trench, partial combined current carriers which reach the upper surface of the P-type doped region from the P-type doped region through the combining route are shielded by the insulation layer and combined on the surface of the insulation layer, so that the emission efficiency is improved and the state voltage drop is reduced; moreover, the doping concentration at the bottom of the trench in the P-type doped region is controlled, so that the diffusion length of the current carriers is prevented from being dramatically reduced, the scattering of the current carriers and an auger combining effect are avoided, the emission efficiency of the bottom region of the trench in the P-type doped region is improved, the rising of the state voltage drop of the trench caused by doping reduction is compensated, and the forward voltage drop is improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

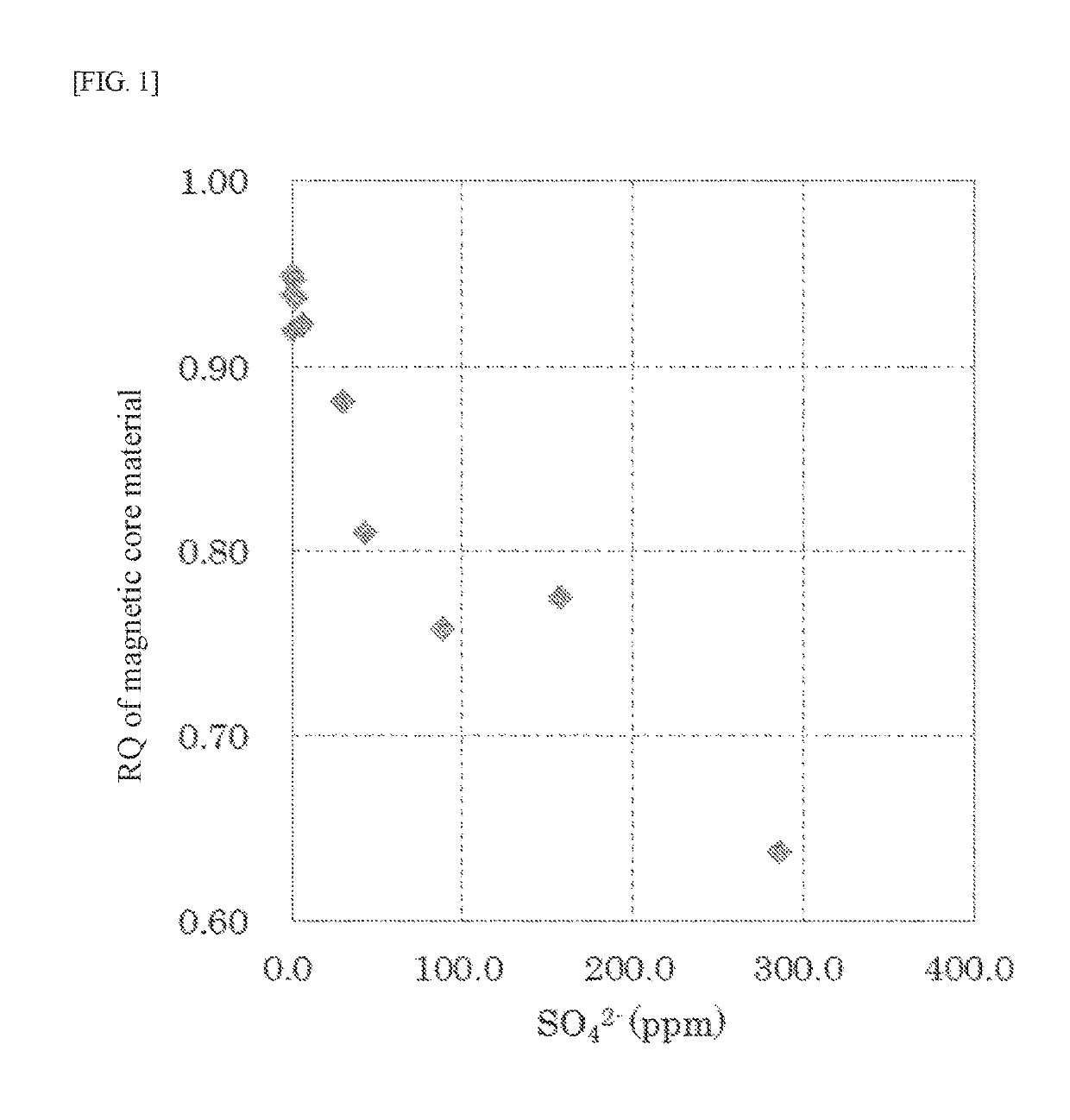

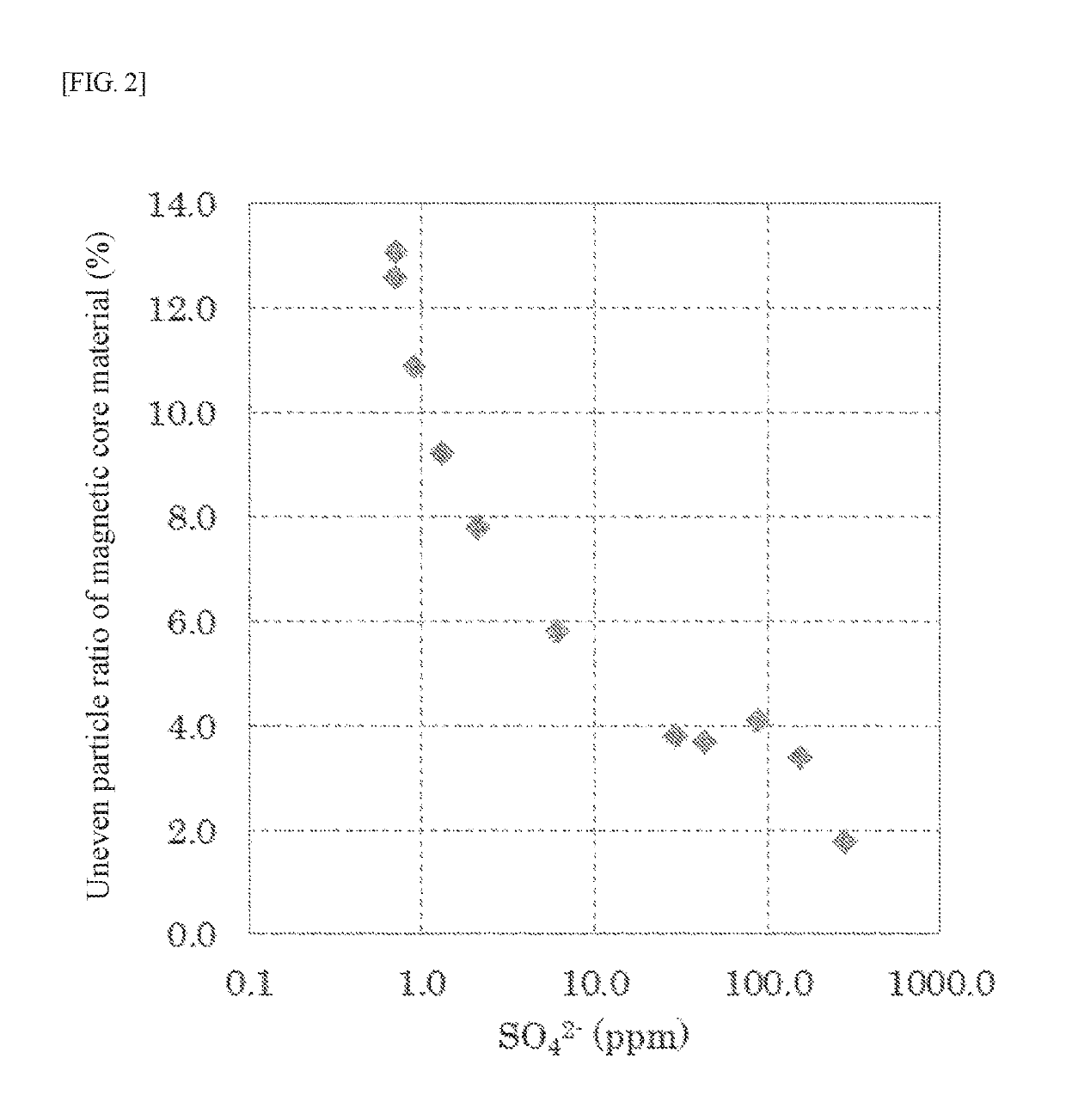

Magnetic core material for electrophotographic developer, carrier for electrophotographic developer, developer, method for producing magnetic core material for electrophotographic developer, method for producing carrier for electrophotographic developer, and method for producing developer

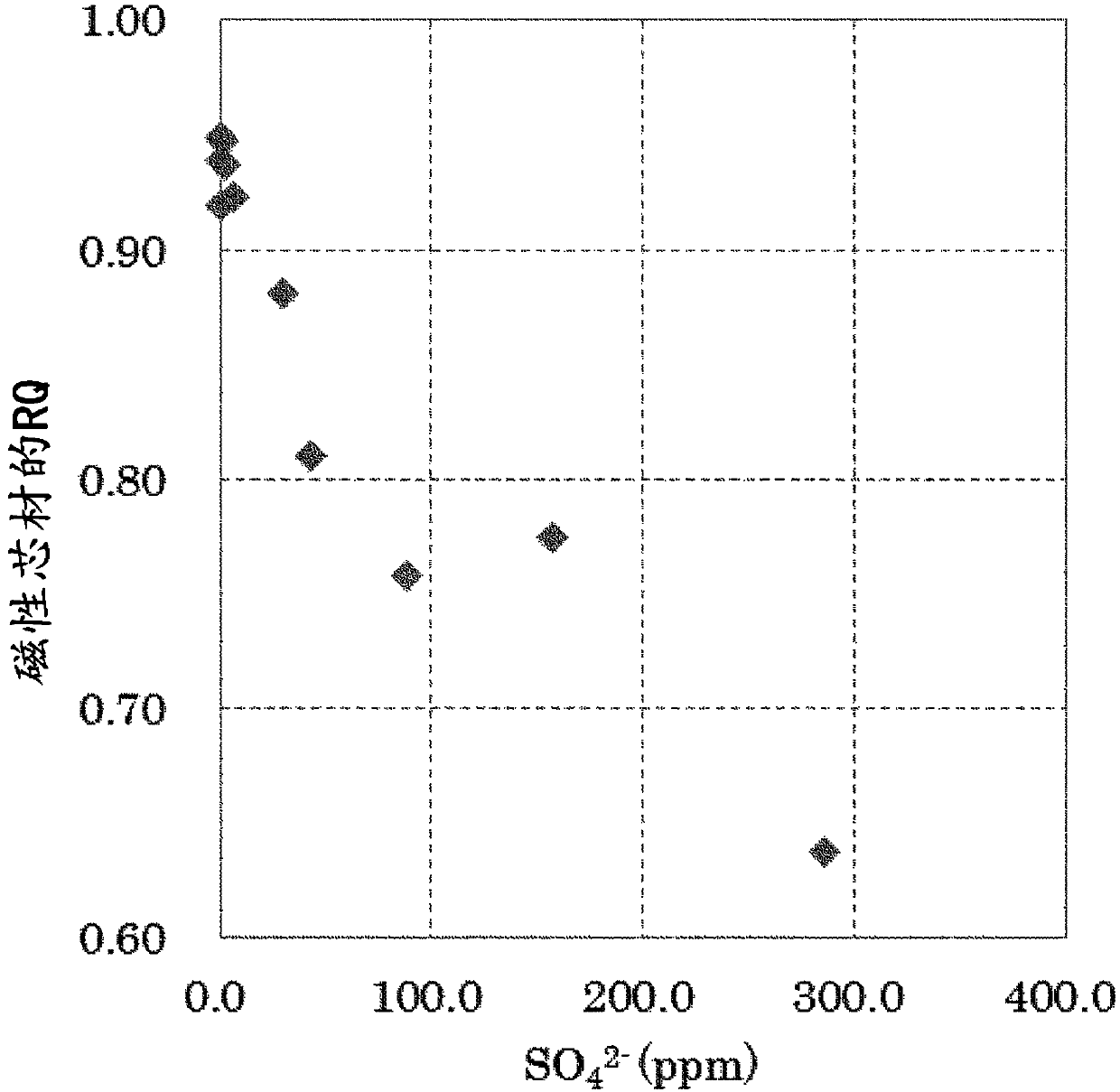

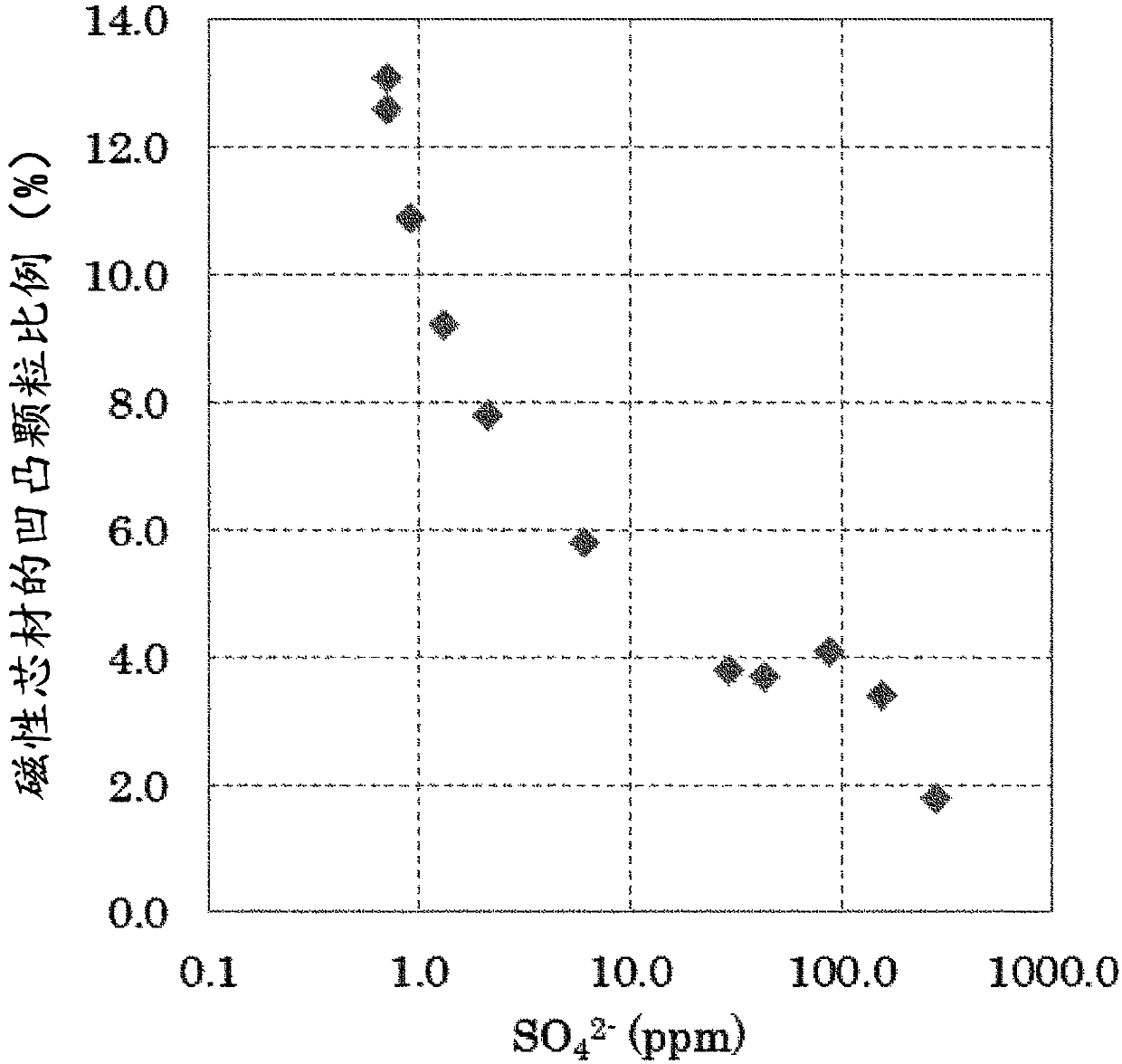

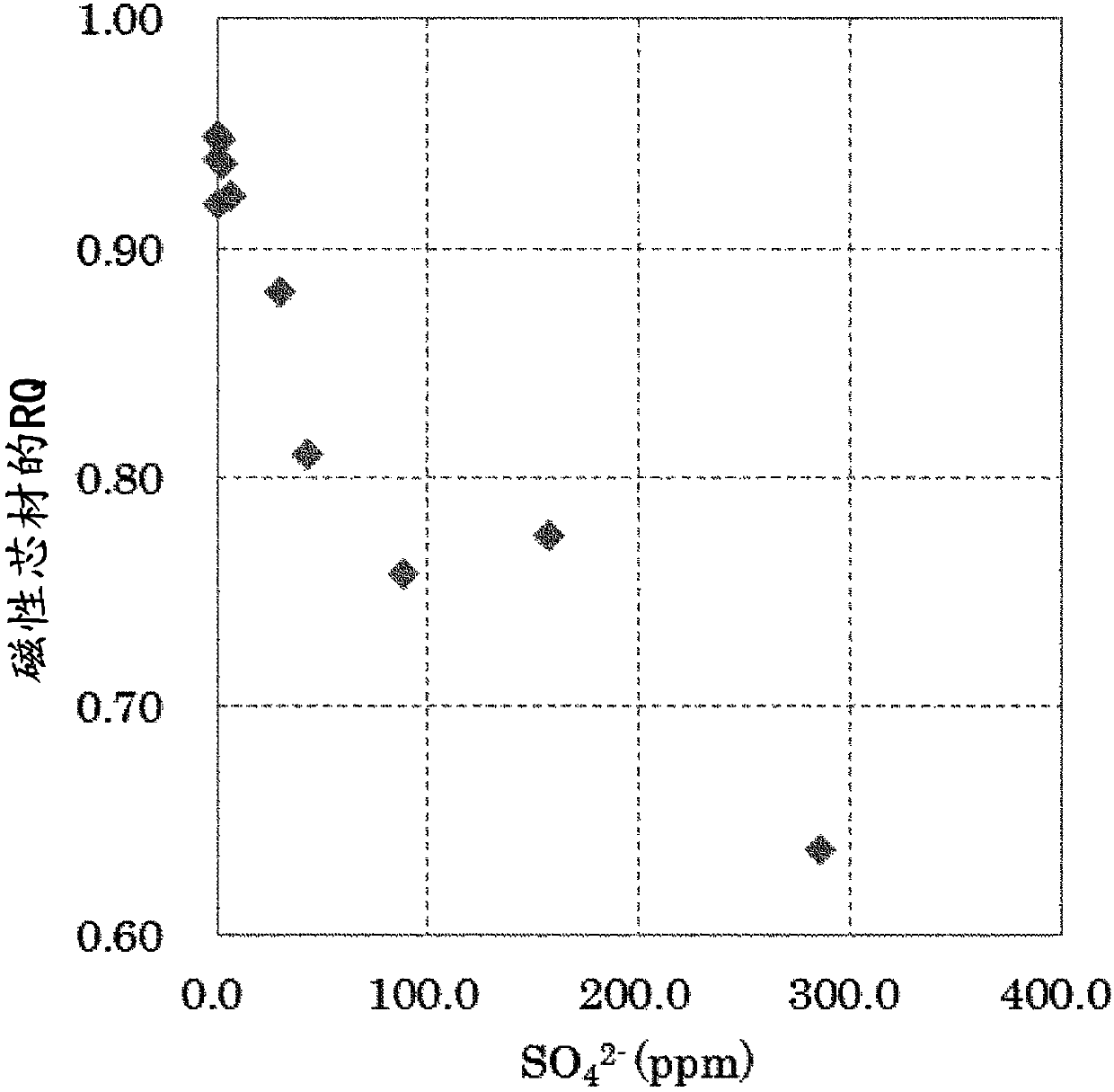

InactiveUS20190204761A1Improve charging characteristicsReduction in carrier scatteringDevelopersSulfurCarrier scattering

To provide a magnetic core material for electrophotographic developer and carrier for electrophotographic developer which are excellent in a rising-up of charge amount, can suppress a carrier scattering, and can stably provide good images; a developer containing the carrier; a method for producing the magnetic core material for electrophotographic developer; a method for producing the carrier for electrophotographic developer; and a method for producing the developer.The magnetic core material for electrophotographic developer, containing a sulfur component in a content of from 1 to 45 ppm in terms of a sulfate ion.

Owner:POWDERTECH

Aluminum oxide gate dielectric double gate graphene transistor on silicon substrate and preparation method thereof

ActiveCN103811556BLarge physical thicknessSolve leakage currentTransistorSemiconductor/solid-state device manufacturingCarbon filmGate dielectric

The invention discloses a double-gate graphene transistor with a silicon substrate and an aluminium oxide gate dielectric, and a preparation method, which are mainly used for solving the problems of low channel carrier mobility and carrier scattering of a graphene transistor prepared by the prior art. The preparation method comprises the following realization steps of: depositing a layer of Al2O3 on an epitaxial 3C-SiC surface on a Si substrate, and photoetching a double-gate graph; placing the etched sample in a quartz tube, generating a carbon film by reacting Cl2 with SiC, then placing the carbon film sample in Ar gas and annealing to generate graphene; etching off Al2O3 at the both sides of the graphene sample and 60-400 nm away from a conductive channel to form a double-gate groove; finally depositing a metal layer on the graphene sample and etching to form transistor metal contact. The double-gate graphene transistor provided by the preparation method disclosed by the invention has the advantages of being high in carrier mobility, good in scattering effect suppression performance, and capable of regulating a channel carrier concentration, as well as can be used for producing a large-scale integrated circuit.

Owner:XIDIAN UNIV

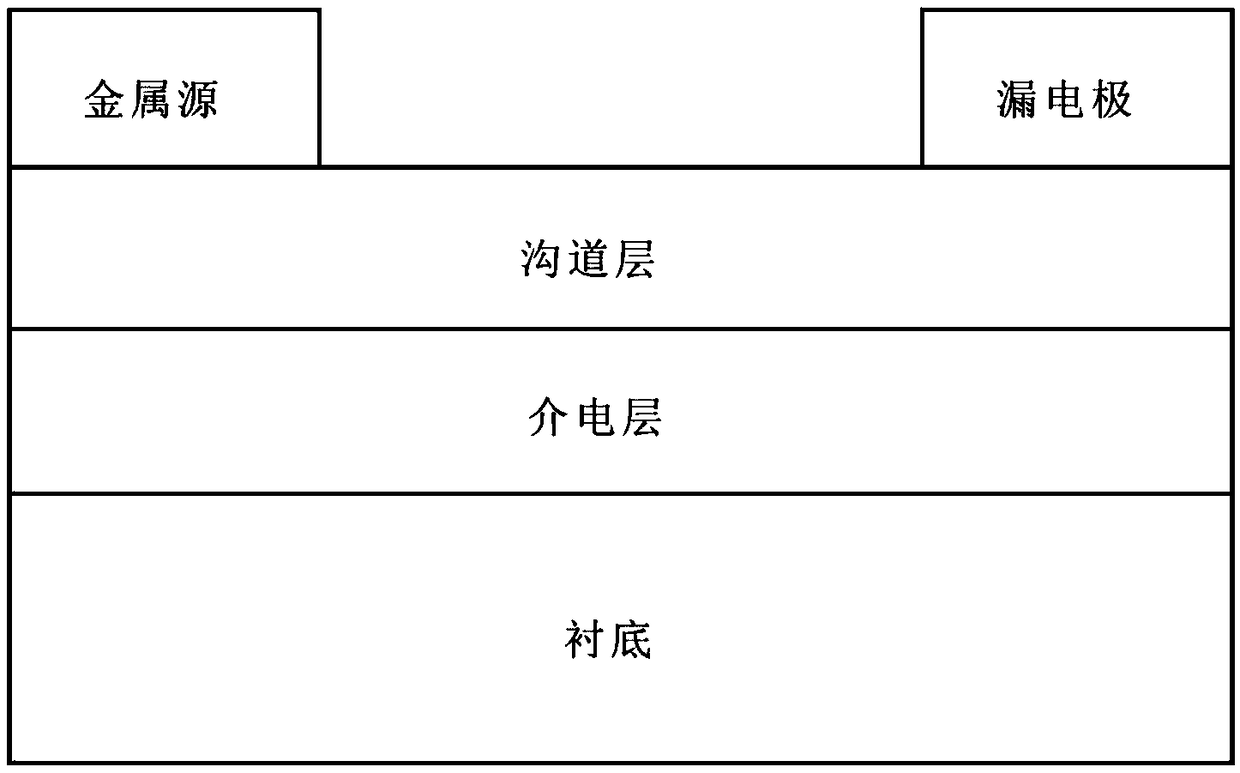

A nickel-doped copper oxide thin film transistor and a preparation method thereof

ActiveCN109037031AImprove performanceImprove film qualityTransistorSemiconductor/solid-state device manufacturingCarrier scatteringSpins

A nickel-doped copper oxide thin film transistor and a preparation method thereof are disclosed. A precursor solution is prepared, the precursor solution is spin-coated on a heavily doped silicon wafer to form a nickel-doped copper oxide film, a metal source and a drain electrode are prepared on the nickel-doped copper oxide film by using a mask plate, and the preparation of a back gate structuretransistor, i. e., a p-type thin film transistor, is completed. The performance of the back gate structure transistor is obviously improved compared with that of the copper oxide thin film transistor.The nickel-doped copper oxide thin film prepared by the invention has the beneficial effects of high quality of the thin film, reduced carrier scattering, high hole transmission capability and low hole scattering, so that the quality of the contact interface between the thin film and the dielectric layer and the electrode is improved, and the purpose of improving the mobility of the thin film transistor is achieved.

Owner:EAST CHINA NORMAL UNIV

Ferrite carrier core material and ferrite carrier for electrophotographic developer, methods for manufacturing these, and electrographic developer using the ferrite carrier

ActiveUS20130171558A1Large BET specific surface areaImprove charging effectDevelopersCarrier scatteringMagnetization

It is an object of the present invention to provide a ferrite carrier core material and a ferrite carrier for an electrophotographic developer, which have an excellent charging property, hardly cause carrier scattering due to cracking and chipping of the core material, and have a prolonged life, and methods for manufacturing these, and an electrophotographic developer using the ferrite carrier. For this object, the ferrite carrier core material and a ferrite carrier for an electrophotographic developer, wherein (1) the ferrite composition contains 0.5 to 2.5% by weight of Sr, and the presence amount of Sr—Fe oxides satisfies a specific conditional expression, (2) the distribution in the number of the shape factor SF-2 is in a specific range, (3) the BET specific surface area is 0.15 to 0.30 m2 / g, (4) the average particle diameter D50 is 20 to 35 μm, and (5) the magnetization is 50 to 65 Am2 / kg.

Owner:POWDERTECH

A kind of van der Waals dielectric material and its preparation method and application

ActiveCN111621746BEasy to integrateImprove insulation performanceVacuum evaporation coatingSputtering coatingDielectricEvaporation (deposition)

The invention belongs to the field of two-dimensional material preparation, and specifically discloses a van der Waals dielectric material and its preparation method and application. Sublimation occurs under high vacuum while maintaining its complete molecular structure, so that the van der Waals film is obtained by evaporation. Since there is no unsaturated chemical bond in the inorganic molecule, there is no dangling bond on the surface of the van der Waals thin film, thereby completing the preparation of the van der Waals dielectric material. The van der Waals thin film prepared by the present invention can be used as a dielectric material for two-dimensional material electronic devices, and can significantly reduce the carrier scattering source in the two-dimensional channel material, thereby ensuring that the two-dimensional material has high mobility; at the same time, the preparation process and The semiconductor preparation process is compatible, and it is easy to realize large-scale preparation and integration.

Owner:HUAZHONG UNIV OF SCI & TECH

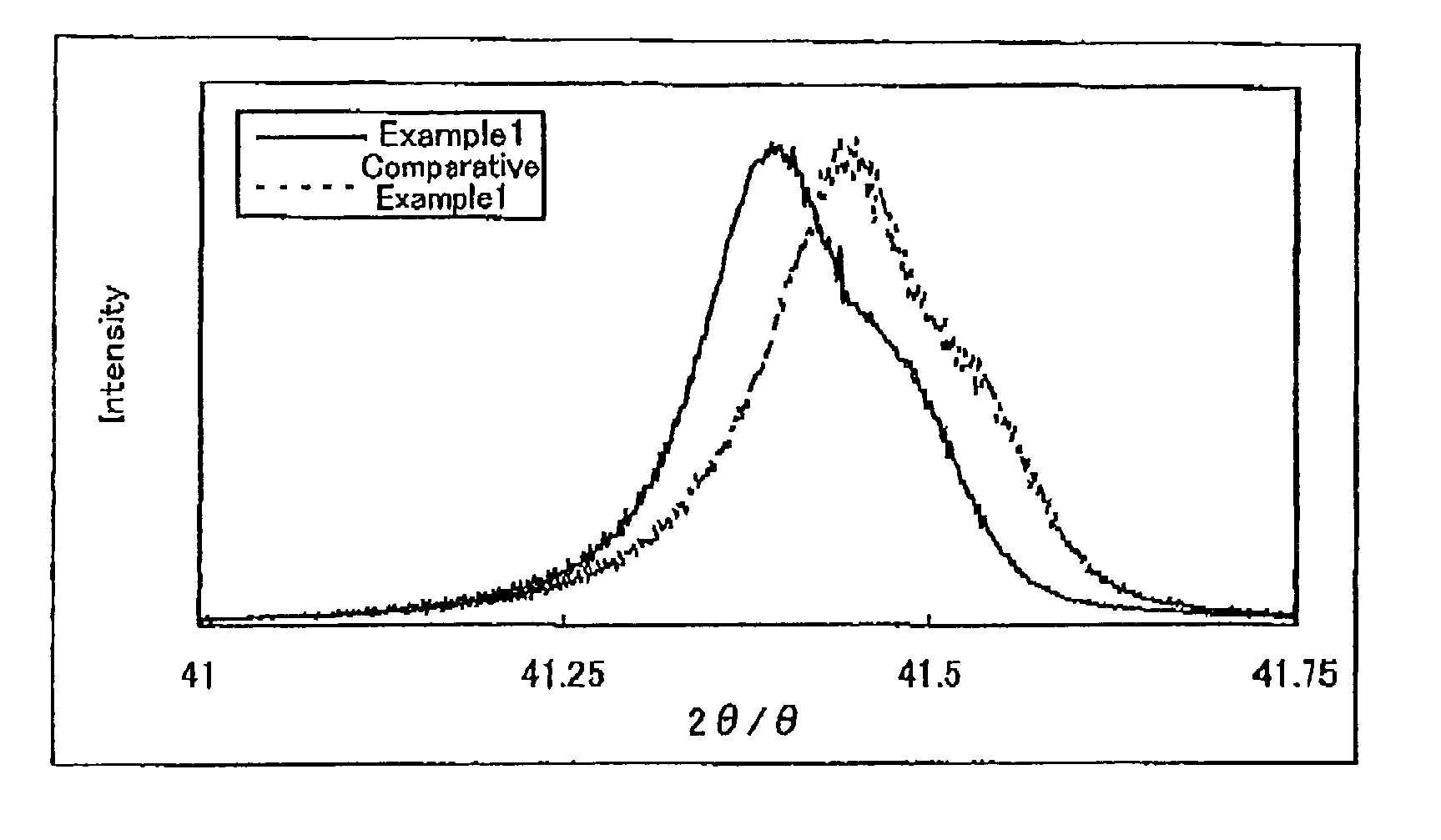

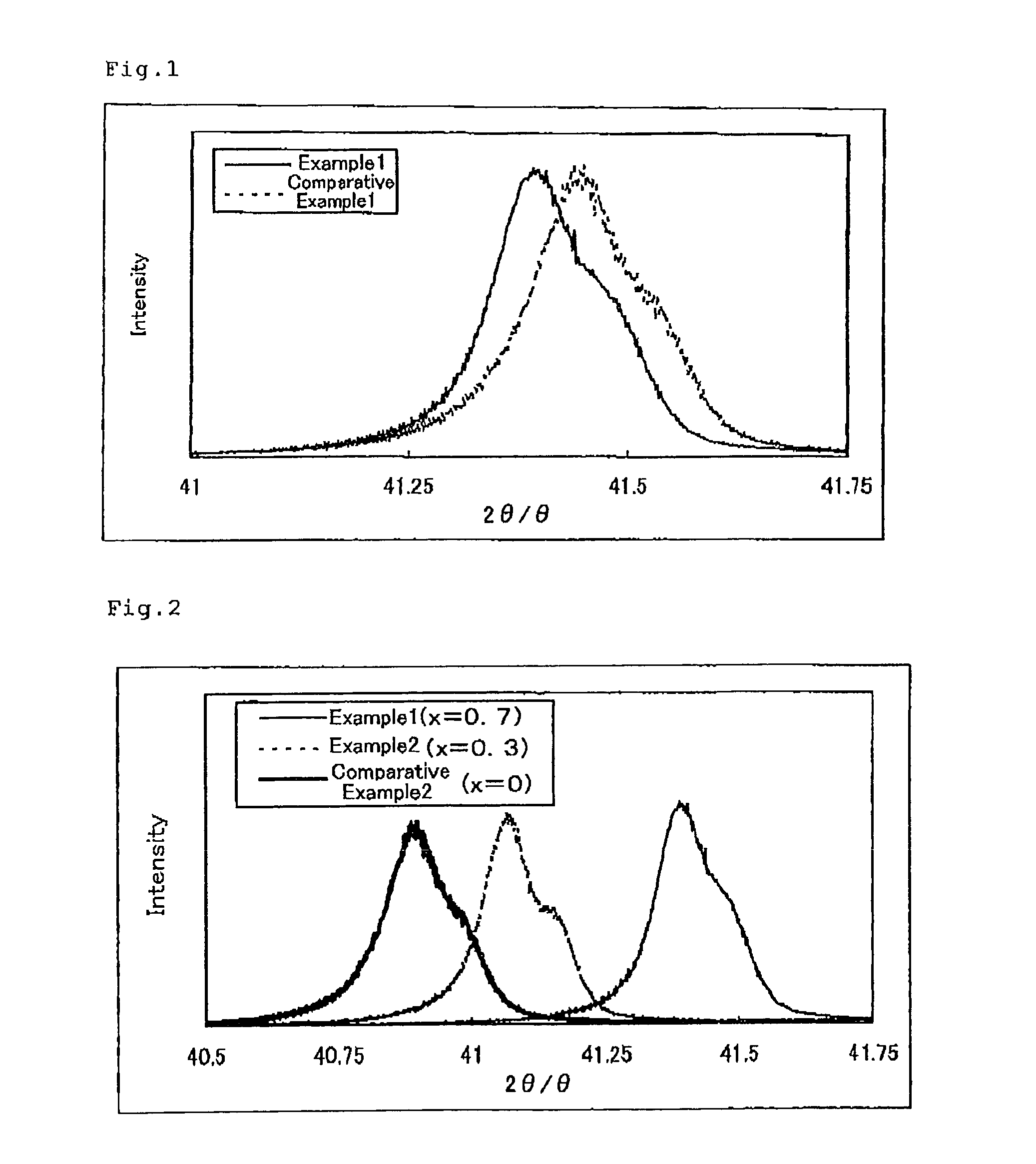

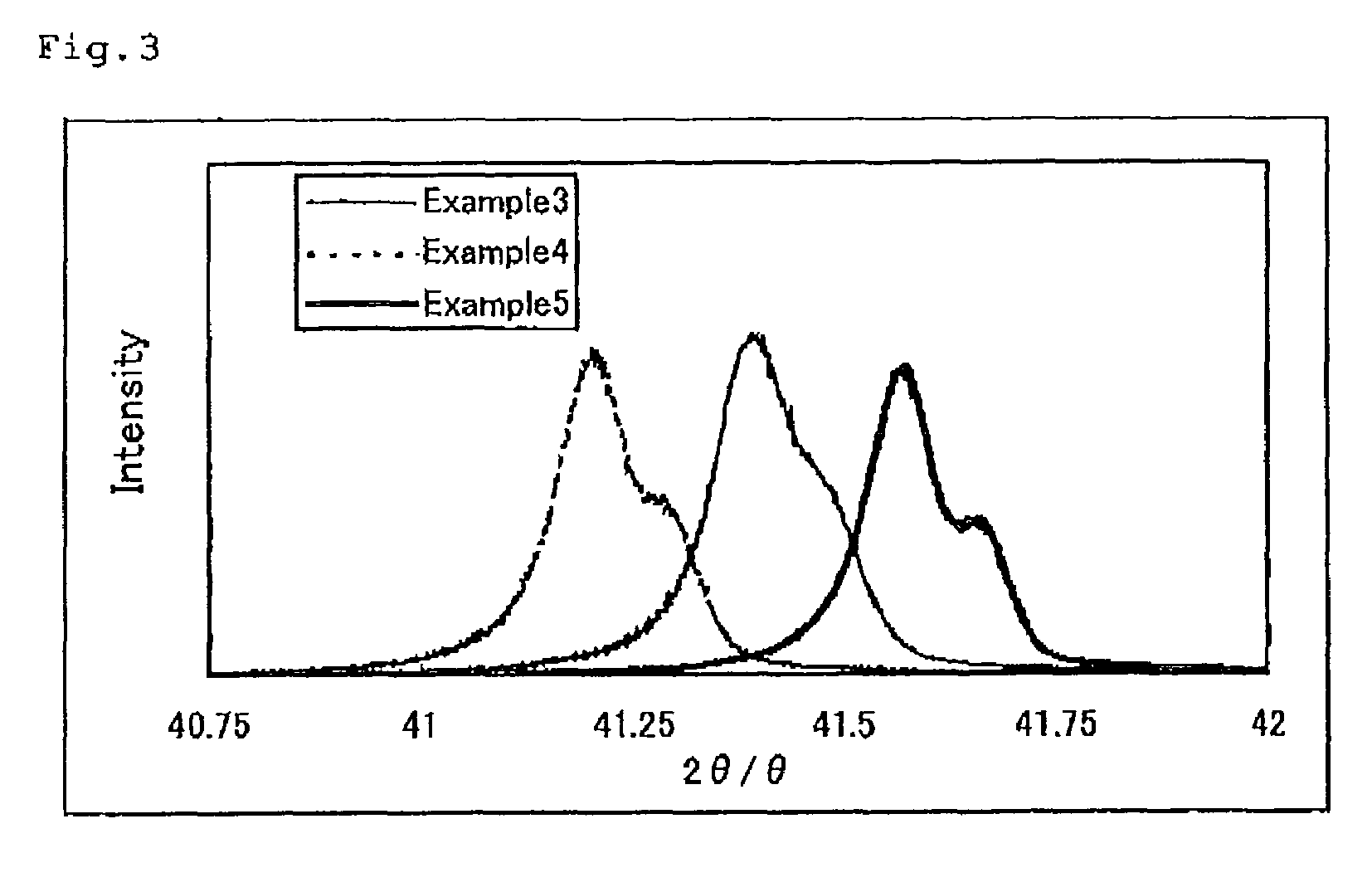

Carrier core material for electrophotographic developer, and manufacturing method of the same, carrier for electrophotographic developer, and electrophotographic developer

To provide a carrier for electrophotographic developer, capable of realizing a high image quality and full colorization and reducing carrier scattering, and a manufacturing method of the same, and an electrophotographic developer containing the carrier. A carrier core material for electrophotographic developer, with a general formula expressed by MgxMn(1-x)FeyO4 (where 0<x<1, and 1.6≦y≦2.4), wherein a half-value width B of a peak having a maximum intensity in a powder XRD pattern satisfies B≦0.180 (degree), is manufactured and from this carrier core material for electrophotographic developer, the carrier for electrophotographic developer and the electrophotographic developer are manufactured.

Owner:DOWA ELECTRONICS MATERIALS CO LTD +1

Method for forming semiconductor device

ActiveCN104733308BHigh carrier mobilityQuality improvementSemiconductor/solid-state device manufacturingPower semiconductor deviceCarrier scattering

The invention relates to a method for forming a semiconductor device, comprising the following steps: providing a semiconductor substrate; carrying out first ion doping and second ion doping to form a well region and a threshold voltage regulation region disposed in the semiconductor substrate, wherein the threshold voltage regulation region is disposed on the surface of the well region; forming a semiconductor epitaxial layer on the surface of the semiconductor substrate after the formation of the well region and the threshold voltage regulation region; and forming a transistor on the surface of the semiconductor epitaxial layer, wherein the channel region of the transistor is formed by the semiconductor epitaxial layer. According to the method for forming a semiconductor device, the semiconductor epitaxial layer, as the channel region of the transistor, avoids lattice damage caused by ion doping. Moreover, the semiconductor epitaxial layer used for forming the channel region is not doped or is lightly doped with boron. Thus, carrier scattering is reduced, the carrier migration rate of the transistor is high, and the device performance is superior.

Owner:SEMICON MFG INT (SHANGHAI) CORP