Preparation method based on Ni membrane annealing for SiC substrate side grid graphene transistor

A graphene and transistor technology, applied in the field of microelectronics, can solve the problems of decreased mobility of top-gate TG-GFETs, easily damaged graphene films, and high energy consumption, so as to avoid device performance degradation and avoid carrier migration. The effect of reducing the rate and improving the safety

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

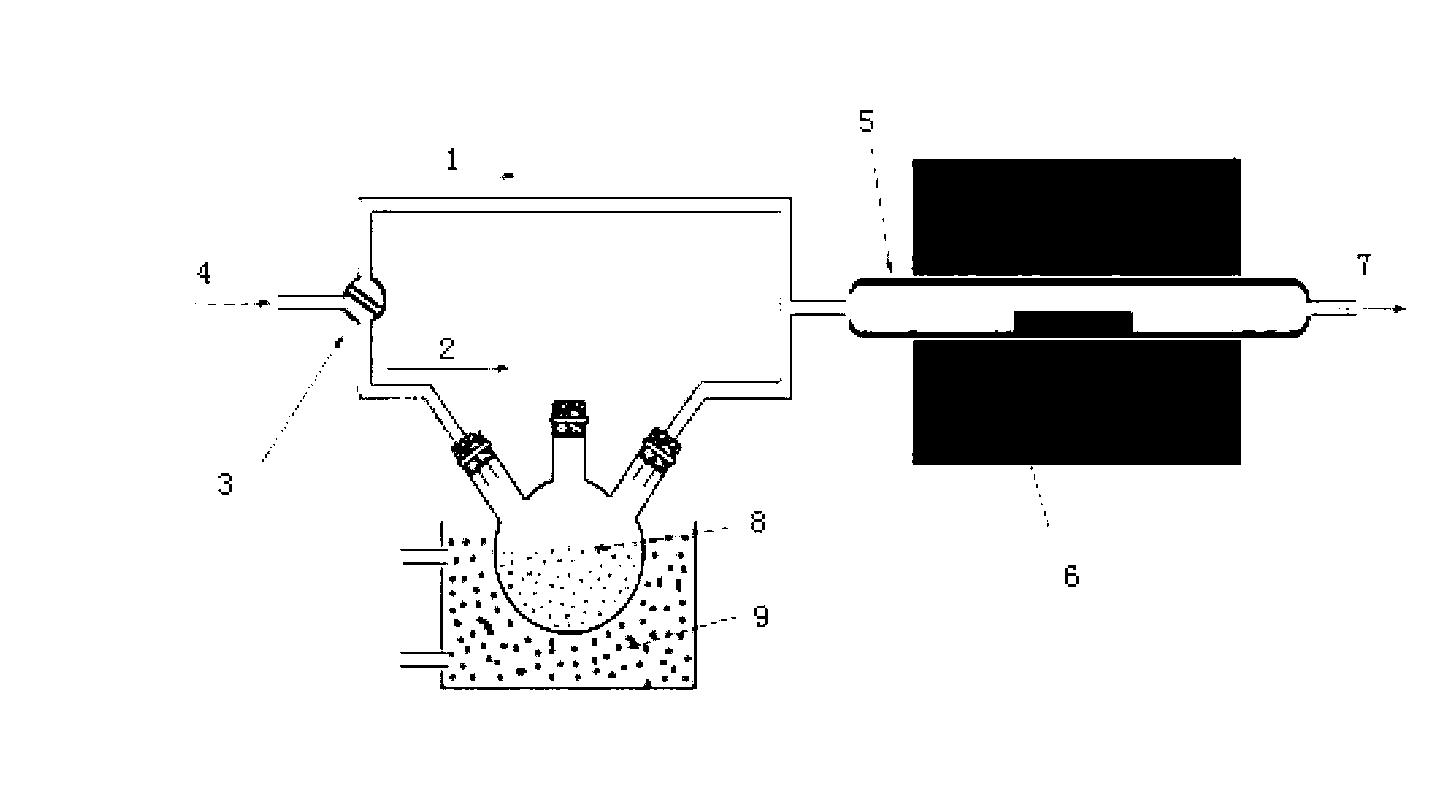

Method used

Image

Examples

Embodiment 1

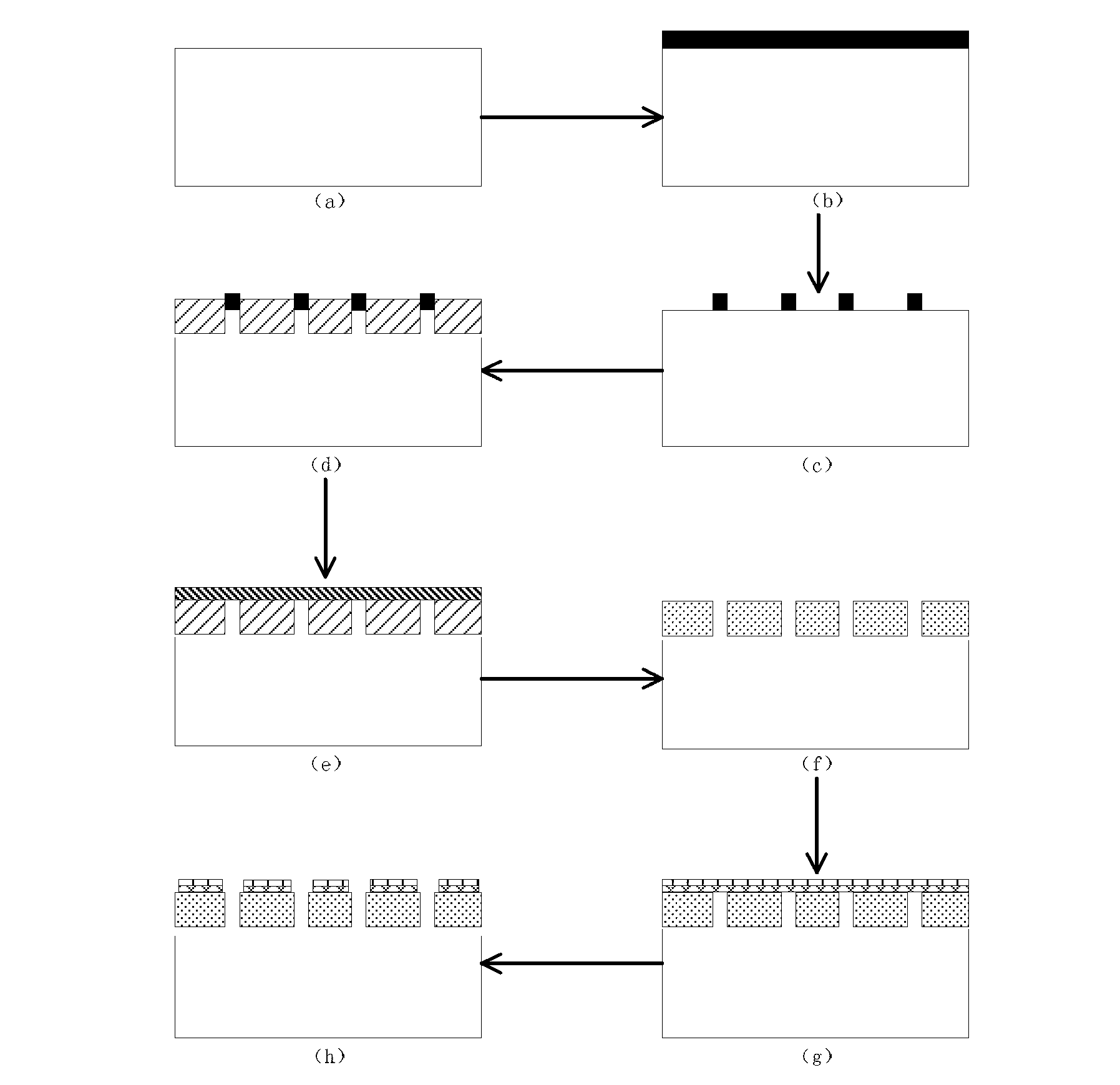

[0034] refer to figure 2 , the present invention makes the step of connection type side-gate graphene transistor as follows:

[0035] Step 1: Wash the 6H-SiC sample to remove surface contaminants such as figure 2 (a).

[0036] (1.1) Use NH for 6H-SiC samples 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample;

[0037] (1.2) Use HCl+H on the 6H-SiC sample after removing the surface organic residues 2 o 2 The reagent soaked the sample for 10 minutes, took it out and dried it to remove ionic contamination.

[0038]Step 2: Deposit a layer of SiO on the surface of the 6H-SiC sample 2 ,Such as figure 2 (b).

[0039] (2.1) Put the cleaned 6H-SiC sample into the plasma-enhanced chemical vapor deposition PECVD equipment system, adjust the internal pressure of the system to 3.0Pa, adjust the radio frequency power to 100W, and adjust the temperature to 150°C;

[0040] (2.2) Introduce ...

Embodiment 2

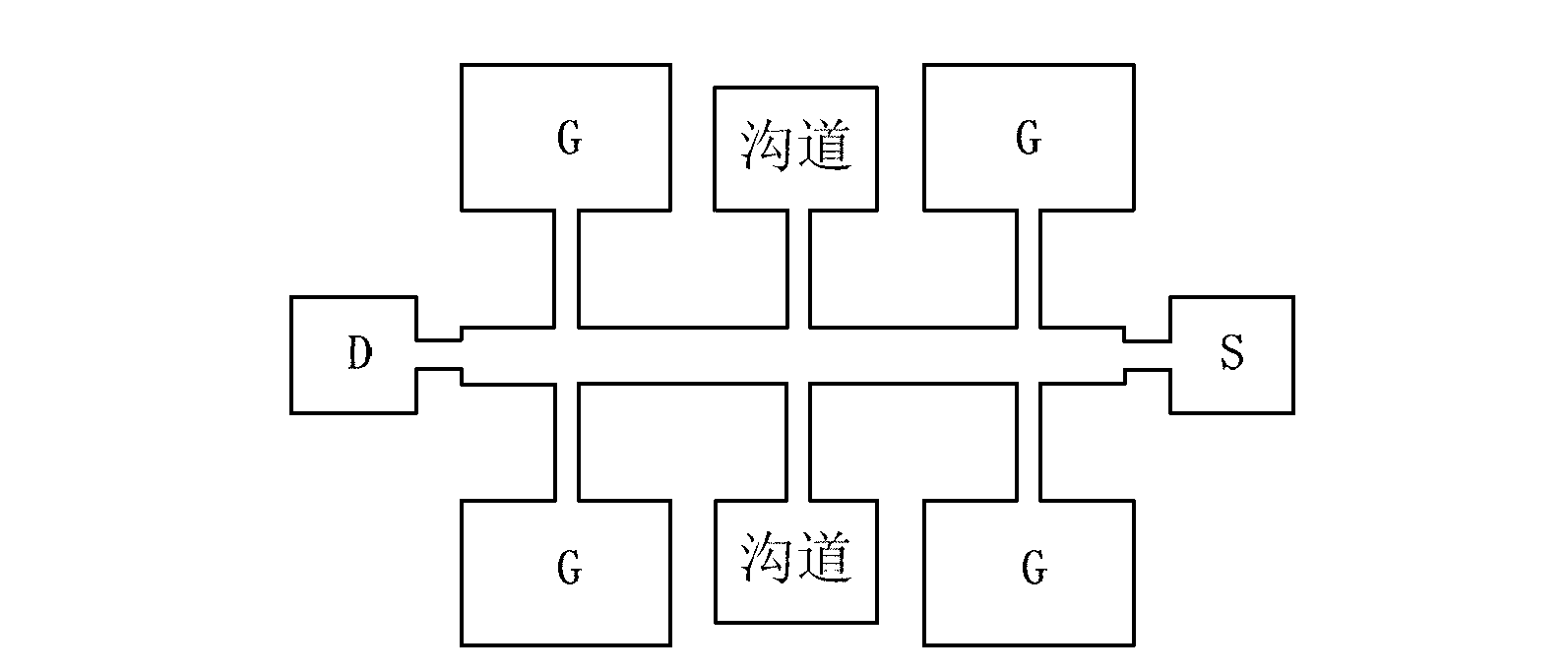

[0069] refer to Figure 4 , the present invention makes the steps of the non-connected side-gate graphene transistor as follows:

[0070] Step 1: Clean the 4H-SiC sample to remove surface contaminants such as Figure 4 (a).

[0071] Use NH for 4H-SiC samples 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample; use HCl+H 2 o 2 The reagent soaked the sample for 10 minutes, took it out and dried it to remove ionic contamination.

[0072] Step 2: Deposit a layer of SiO on the surface of the 4H-SiC sample 2 ,Such as Figure 4 (b).

[0073] Put the cleaned 4H-SiC sample into the plasma-enhanced chemical vapor deposition PECVD equipment system, adjust the internal pressure of the system to 3.0Pa, adjust the radio frequency power to 100W, and adjust the temperature to 150°C; SiH at a flow rate of 30 sccm 4 , with a flow rate of 60 sccm of N 2 O and N at a flow rate of 200 sccm 2 ,, s...

Embodiment 3

[0096] refer to figure 2 , the present invention makes the step of connection type side-gate graphene transistor as follows:

[0097] Step A: Use NH on the 4H-SiC substrate substrate 4 OH+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove the organic residue on the surface of the sample; use HCl+H 2 o 2 Soak the sample in the reagent for 10 minutes, take it out and dry it to remove ionic contaminants such as figure 2 (a).

[0098] Step B: Put the cleaned 4H-SiC sample into the plasma-enhanced chemical vapor deposition PECVD equipment system, adjust the internal pressure of the system to 3.0Pa, adjust the radio frequency power to 100W, and adjust the temperature to 150°C; SiH 4 , N 2 O and N 2 Three gases, of which SiH 4 The flow rate is 30 sccm, N 2 O flow rate is 60 sccm, N 2 The flow rate is 200sccm, making SiH 4 with N 2 O was reacted for 60 minutes to deposit a layer of SiO with a thickness of 0.8 μm on the surface of th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More