Patents

Literature

325results about How to "Increase working current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

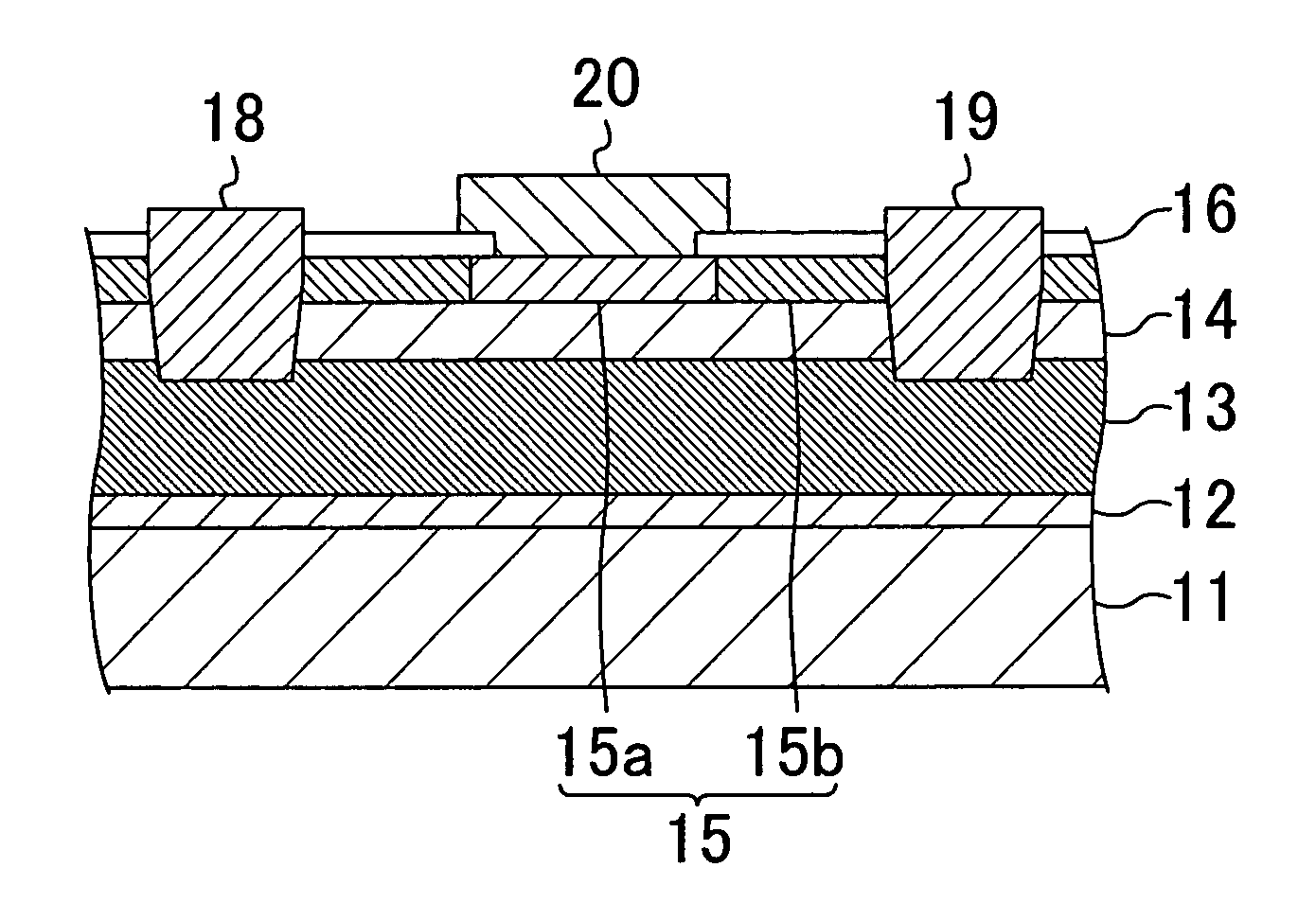

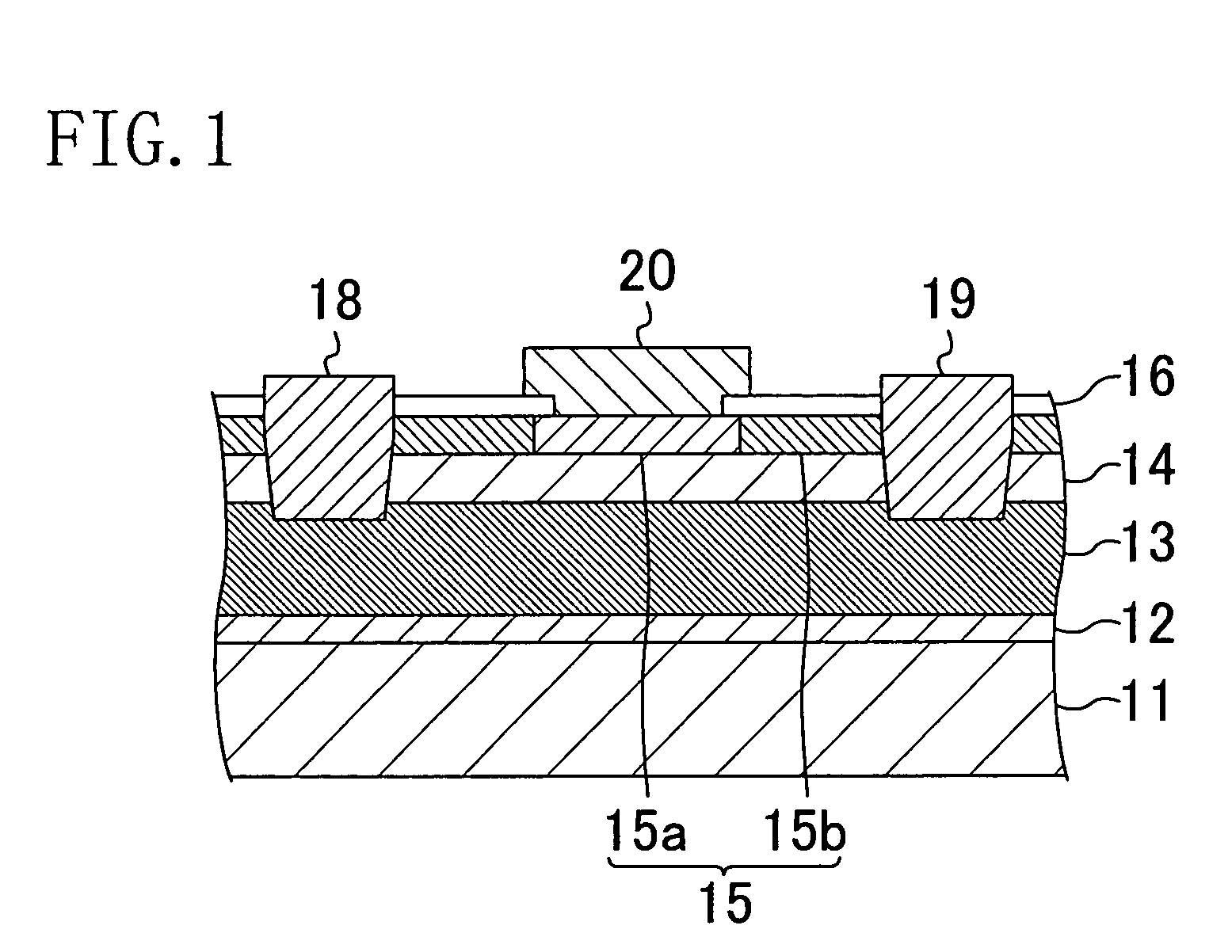

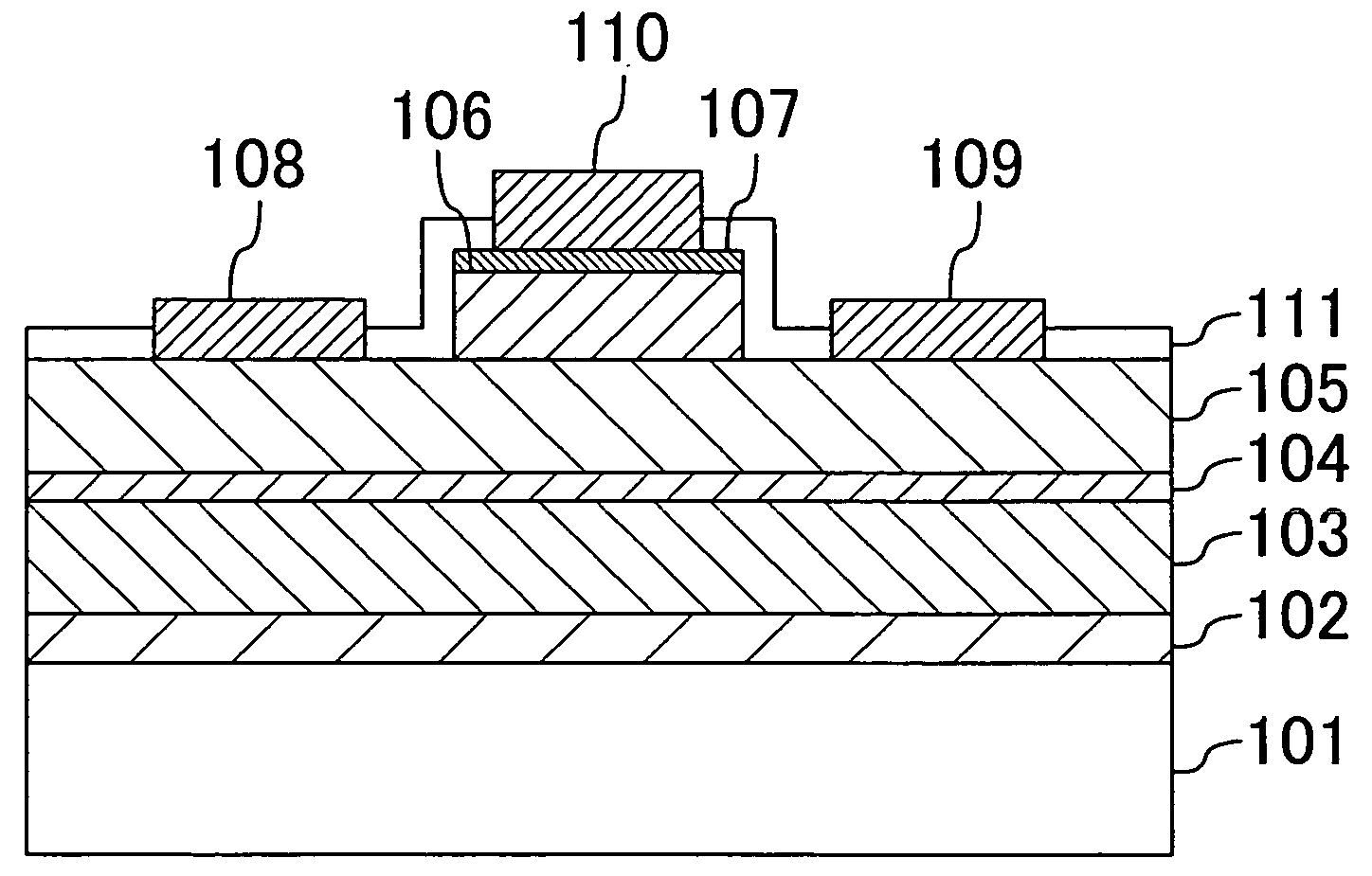

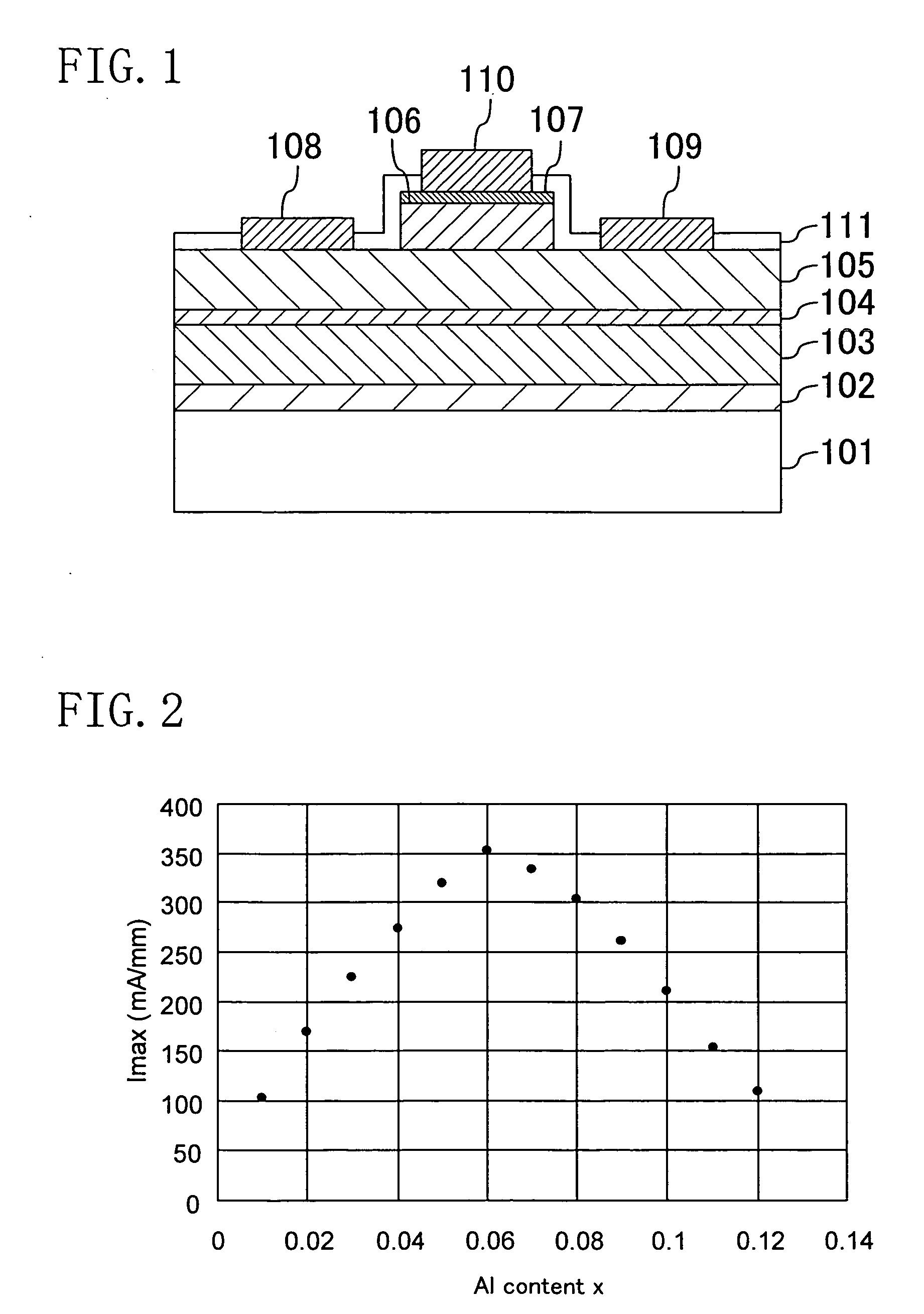

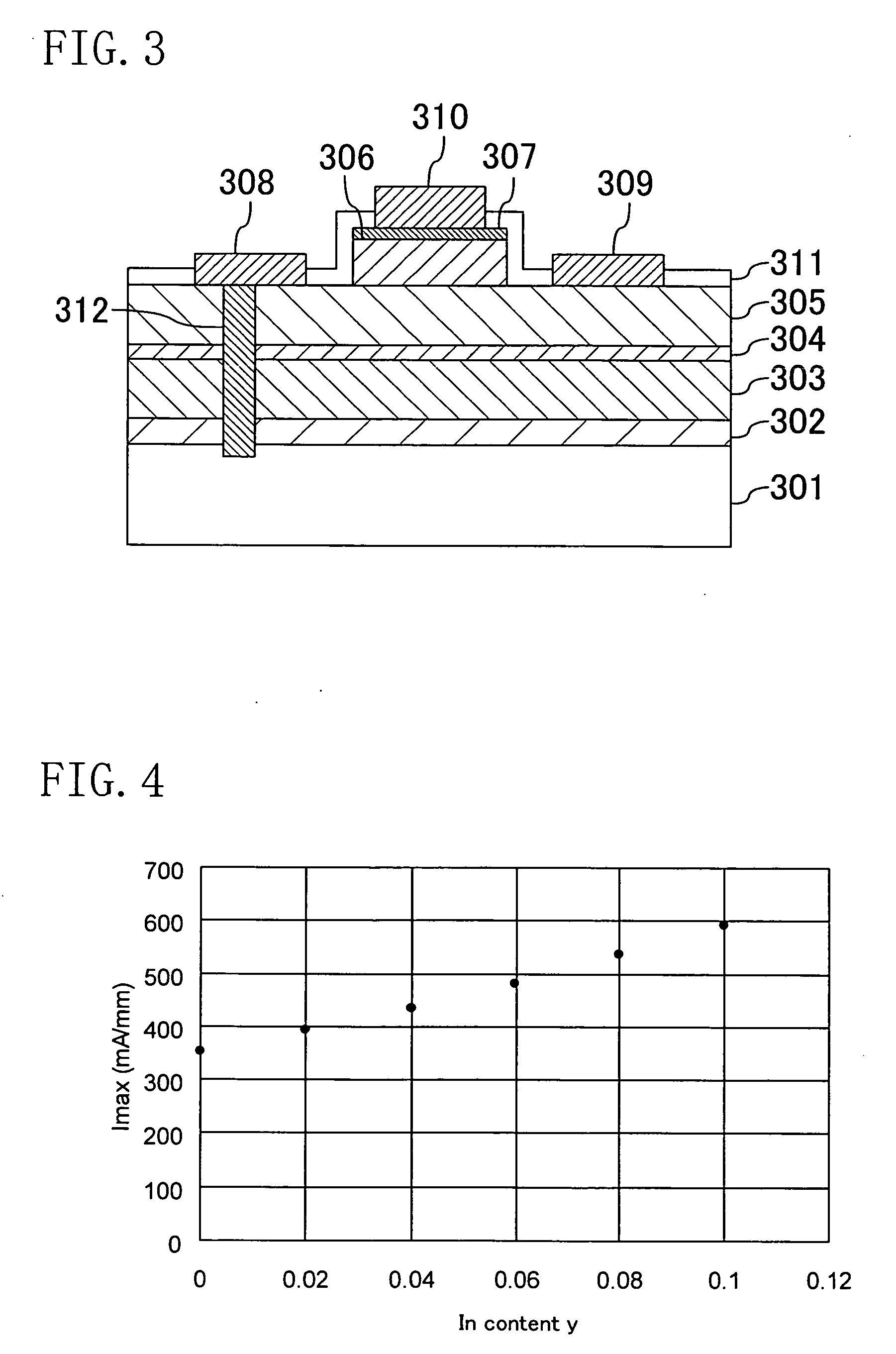

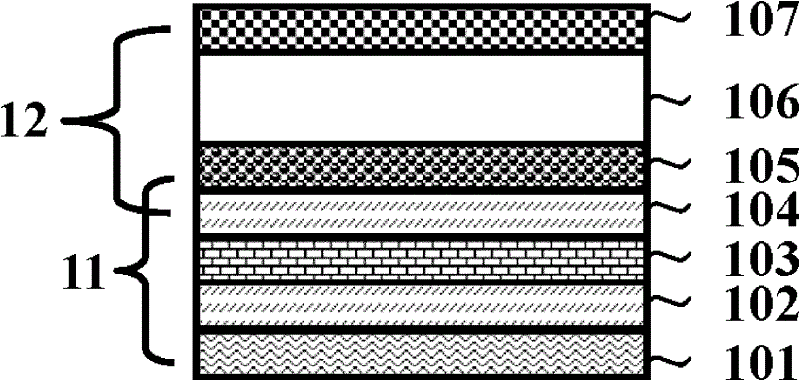

Nitride semiconductor device and method for fabricating the same

ActiveUS20080087915A1Large operating currentImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceWide band

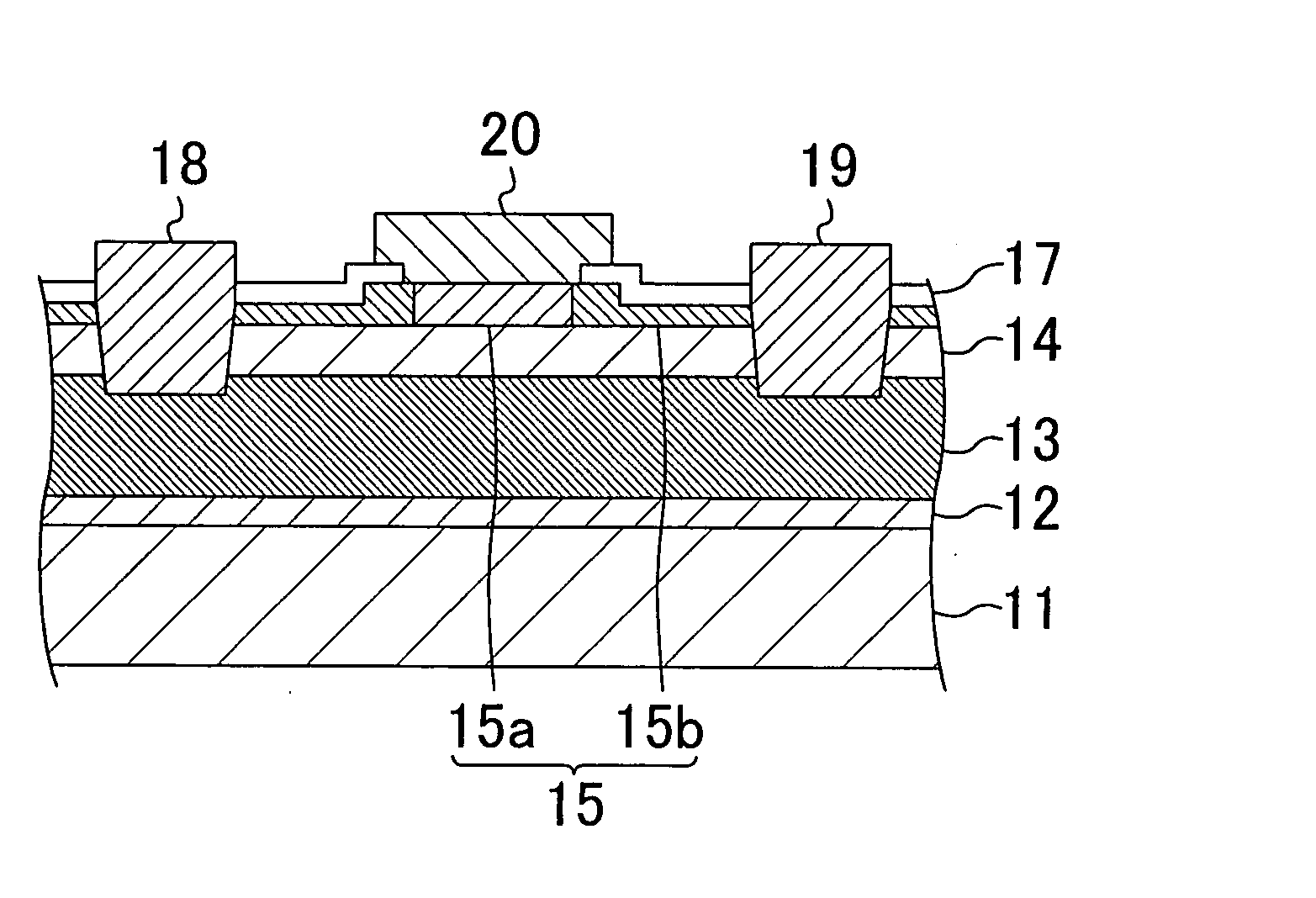

A nitride semiconductor device includes: a first nitride semiconductor layer; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider band gap than the first nitride semiconductor layer; and a third nitride semiconductor layer formed on the second nitride semiconductor layer. A region of the third nitride semiconductor layer located below the gate electrode is formed with a control region having a p-type conductivity, and a region of the third nitride semiconductor layer located between the gate electrode and each of the source electrode and the drain electrode is formed with a high resistive region having a higher resistance than the that of the control region.

Owner:PANASONIC CORP

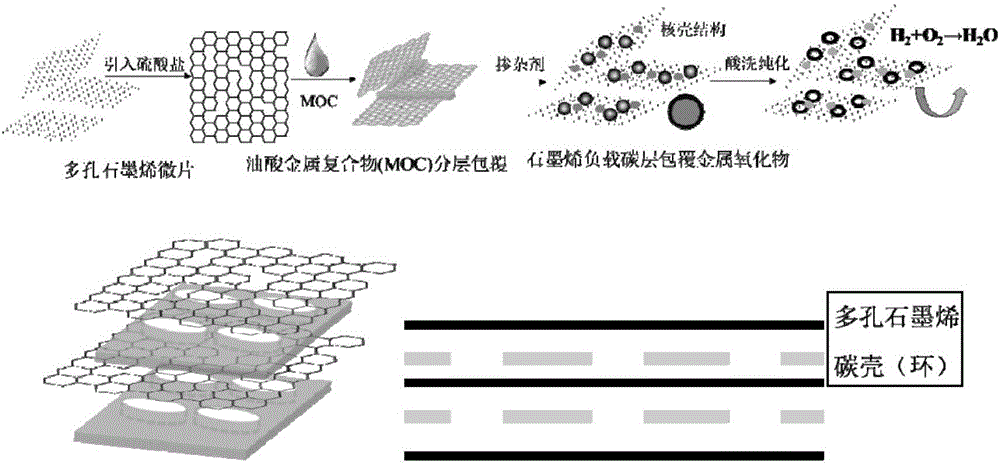

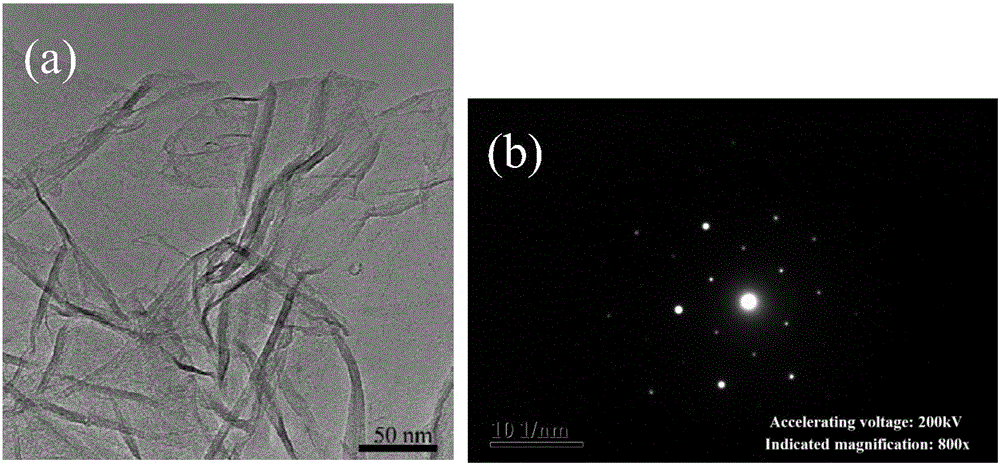

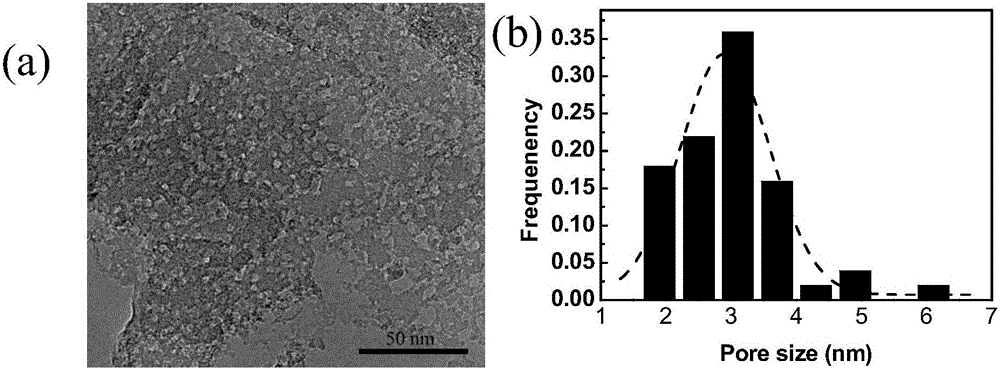

Preparation method of heteroatom doped graphene hierarchical pore carbon material

A preparation method of a heteroatom doped graphene hierarchical pore carbon material comprises the following steps: preparing graphene micro-sheet dispersing liquid by using graphene, then carrying out pore-forming etching on graphene micro-sheets in the graphene micro-sheet dispersing liquid, and preparing porous graphene micro-sheets; mixing the porous graphene micro-sheets with a fatty acid metal compound coating agent and a dopant to obtain oil-phase viscous graphene-based precursor; carrying out programmed heat treatment; carrying out acid pickling, water washing and solid-liquid separation on a product after heat treatment, and drying solid to obtain the final product. The preparation method has the advantages of low cost, simple process, low energy consumption, wide raw material source, and capability of large-scale production.

Owner:SHANXI INST OF COAL CHEM CHINESE ACAD OF SCI

Nitride semiconductor device and method for fabricating the same

ActiveUS8129748B2Large operating currentImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceHigh resistance

A nitride semiconductor device includes: a first nitride semiconductor layer; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider band gap than the first nitride semiconductor layer; and a third nitride semiconductor layer formed on the second nitride semiconductor layer. A region of the third nitride semiconductor layer located below the gate electrode is formed with a control region having a p-type conductivity, and a region of the third nitride semiconductor layer located between the gate electrode and each of the source electrode and the drain electrode is formed with a high resistive region having a higher resistance than the that of the control region.

Owner:PANASONIC CORP

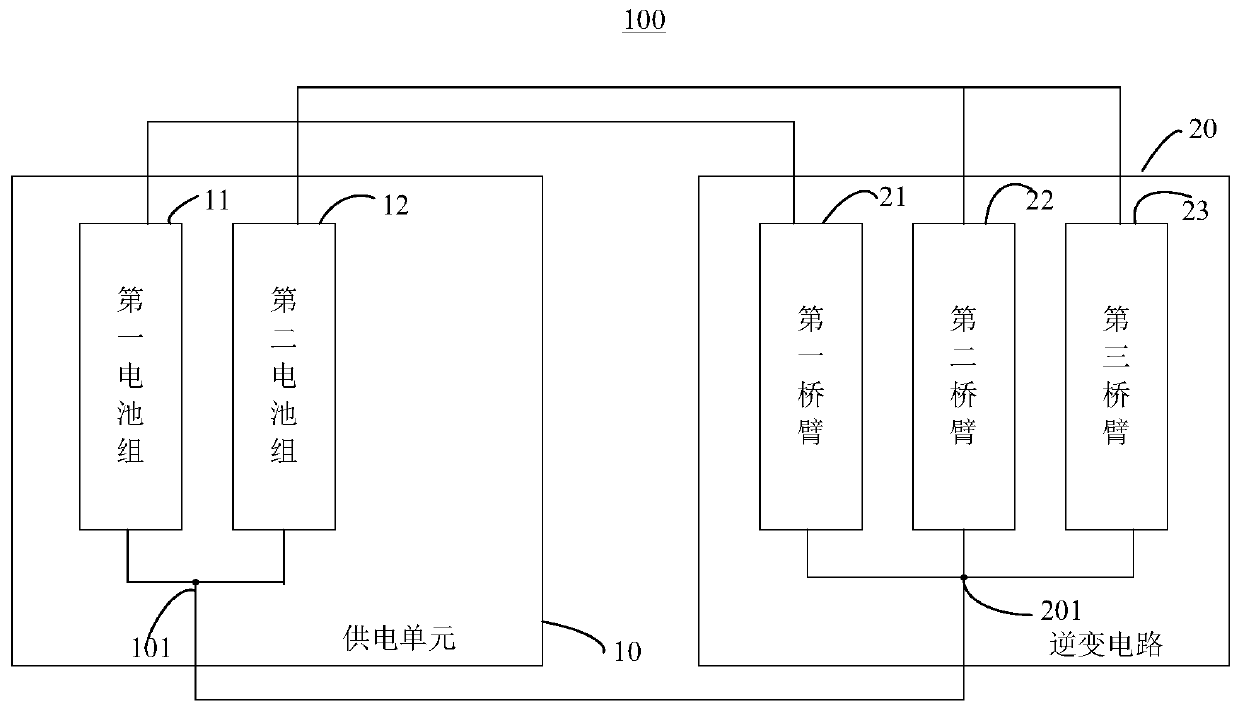

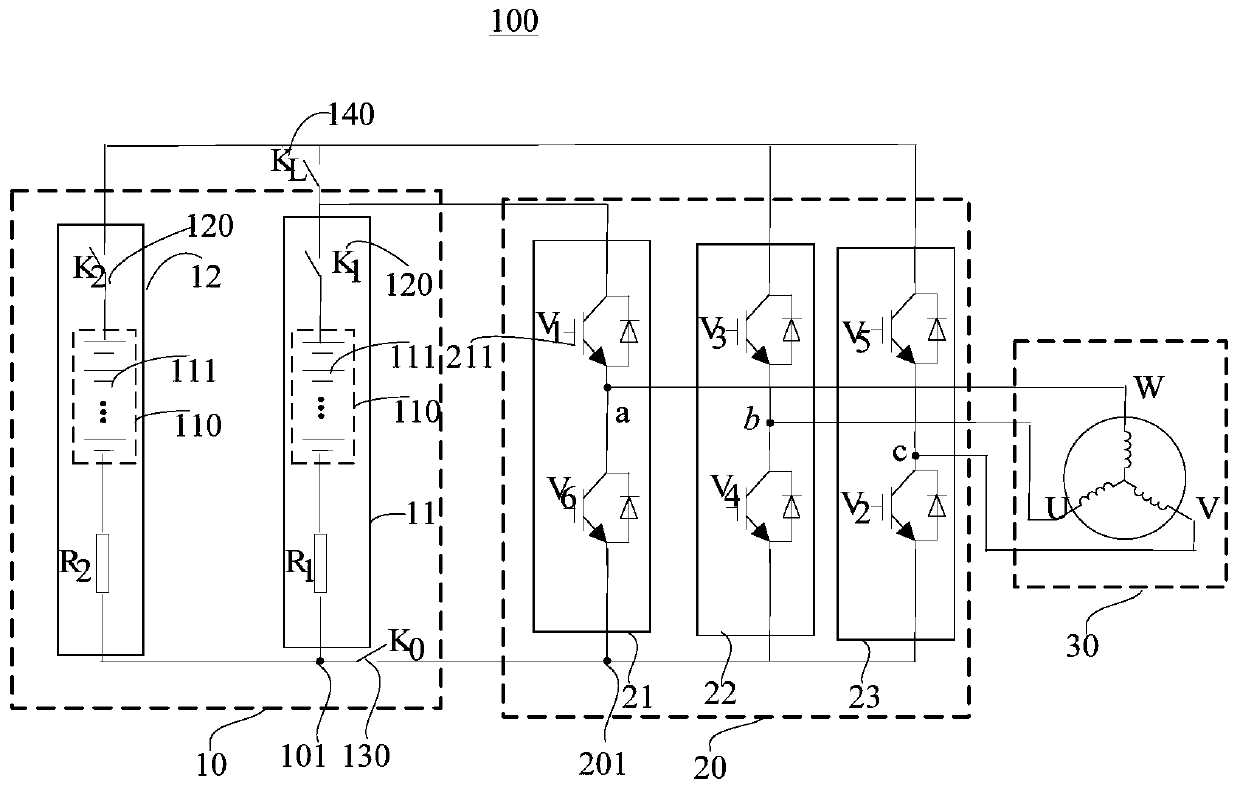

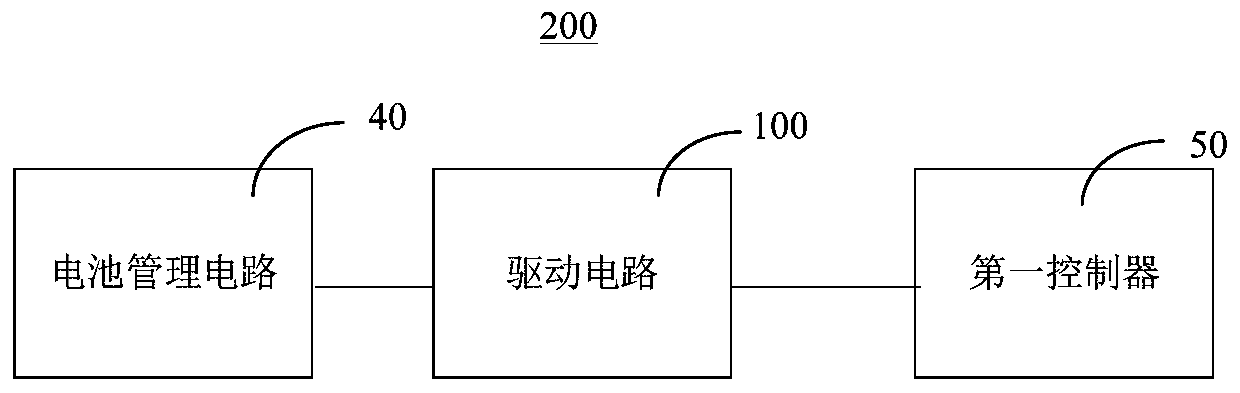

Electric vehicle driving system, driving circuit and electric vehicle battery heating method

PendingCN110116653AIncrease working currentAchieve controllable temperature riseVehicular energy storageElectric energy managementElectrical batteryAutomotive battery

The invention provides an electric vehicle driving system, a driving circuit and an electric vehicle battery heating method. The electric vehicle driving system comprises a first controller, a power supply unit and an inverter circuit. The power supply unit includes two battery packs. When electric vehicle batteries are heated, one ends of the two battery packs are independent of each other, and the other ends of the two battery packs are collinear. The electric vehicle battery heating method comprises the steps that opening and closing of three bridge arms of the inverter circuit are controlled through the first controller, the two battery packs are charged and discharged mutually with the assistance of a motor coil, and the power supply unit is further enabled to be polarized, so that the controllable temperature rise of the batteries of the power supply unit is realized. The maximum working current of a power switching device in the inverter circuit is higher, and the electric vehicle battery heating method can realize high-power heating without additionally arranging other devices by using the electric vehicle driving system, so that the heating efficiency is effectively improved.

Owner:TSINGHUA UNIV

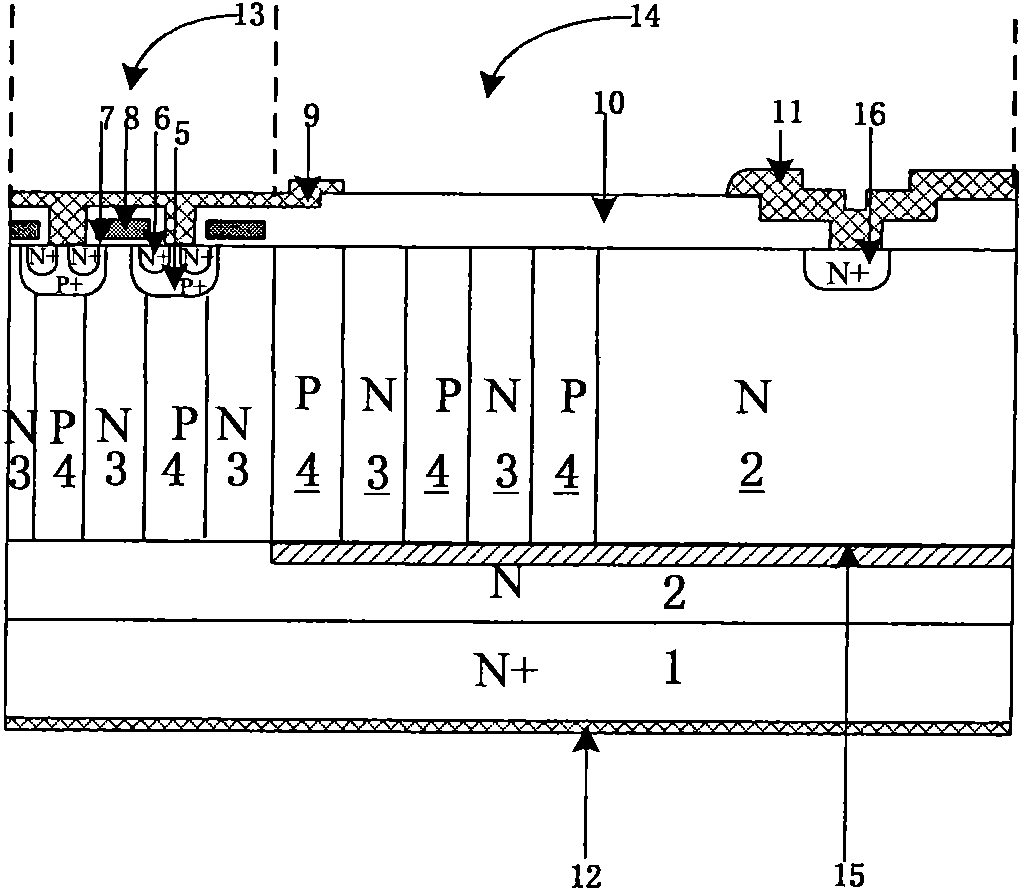

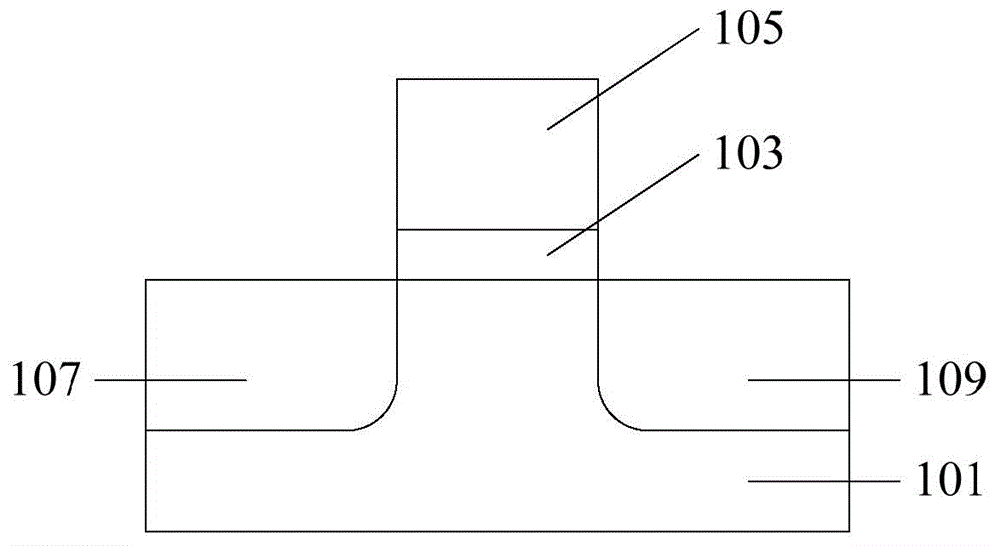

Semiconductor tube of hyperconjugation longitudinal double diffusion metal oxide with N channels

InactiveCN101552291AIncrease working currentGuaranteed withstand voltage levelSemiconductor devicesDouble diffusionHyperconjugation

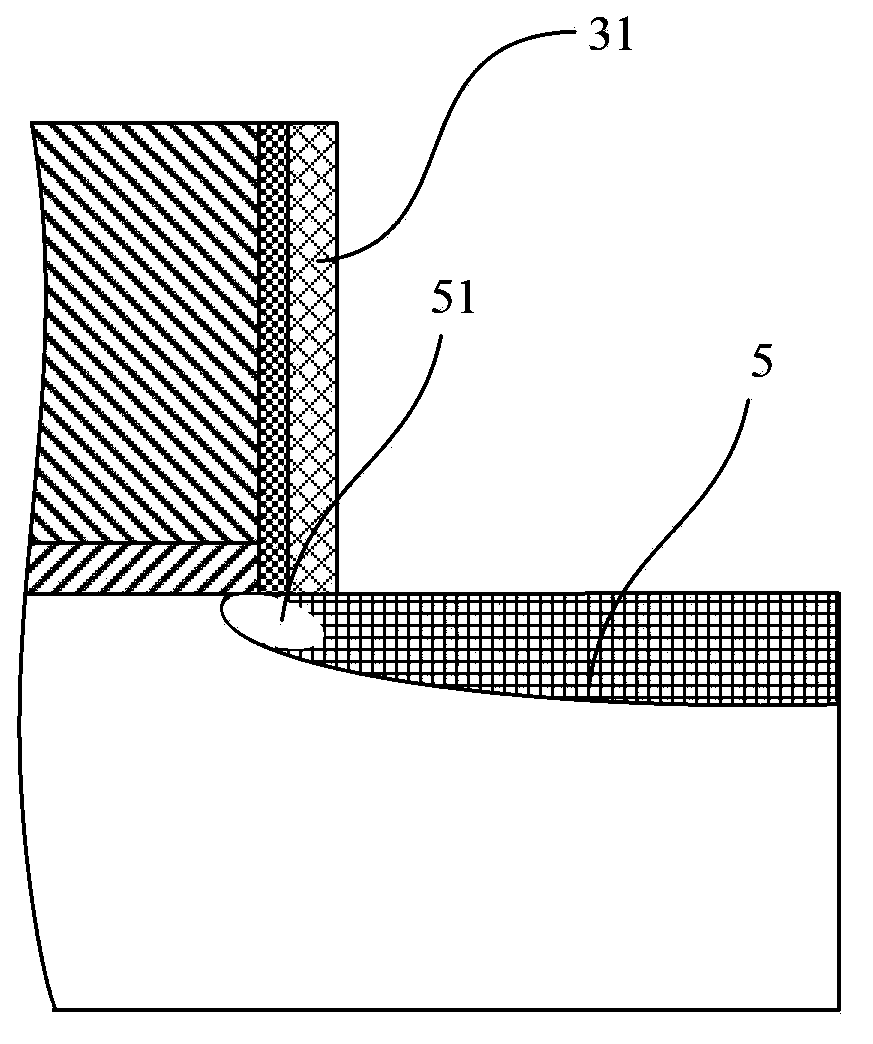

The invention relates to a semiconductor tube of hyperconjugation longitudinal double diffusion metal oxide with N channels, comprising an N-type doped silicon substrate which is also used as a drain region, an N-type doped silicon epitaxial layer, a primitive cell region and a terminal region arranged at the periphery of the primitive cell region; the N-type doped silicon epitaxial layer is arranged on the N-type doped silicon substrate; the primitive cell region and the terminal region are arranged on the N-type doped silicon epitaxial layer; the terminal region comprises a first hyperconjugation structure and an N-type silicon doped semiconductor region, wherein the first hyperconjugation structure comprises a P-type column and a N-type column; an N-type heavily doped semiconductor region is arranged in the N-type silicon doped semiconductor region; the first hyperconjugation structure and the N-type silicon doped semiconductor region are respectively provided with a field oxidation layer; and the N-type heavily doped semiconductor region is connected with a metal layer. The semiconductor tube is characterized in that the first hyperconjugation structure and the N-type silicon doped semiconductor region are respectively provided with the field oxidation layer.

Owner:SOUTHEAST UNIV

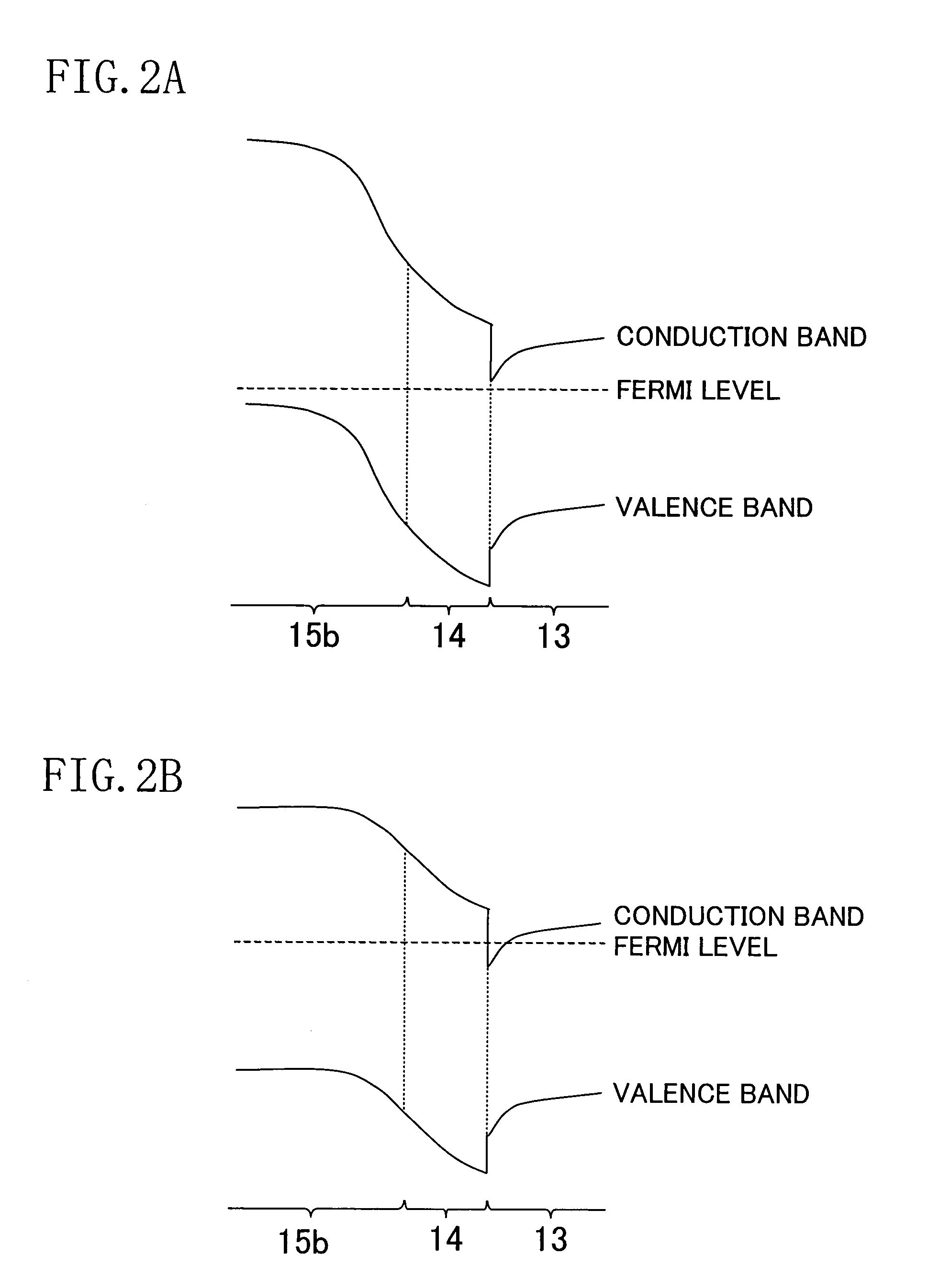

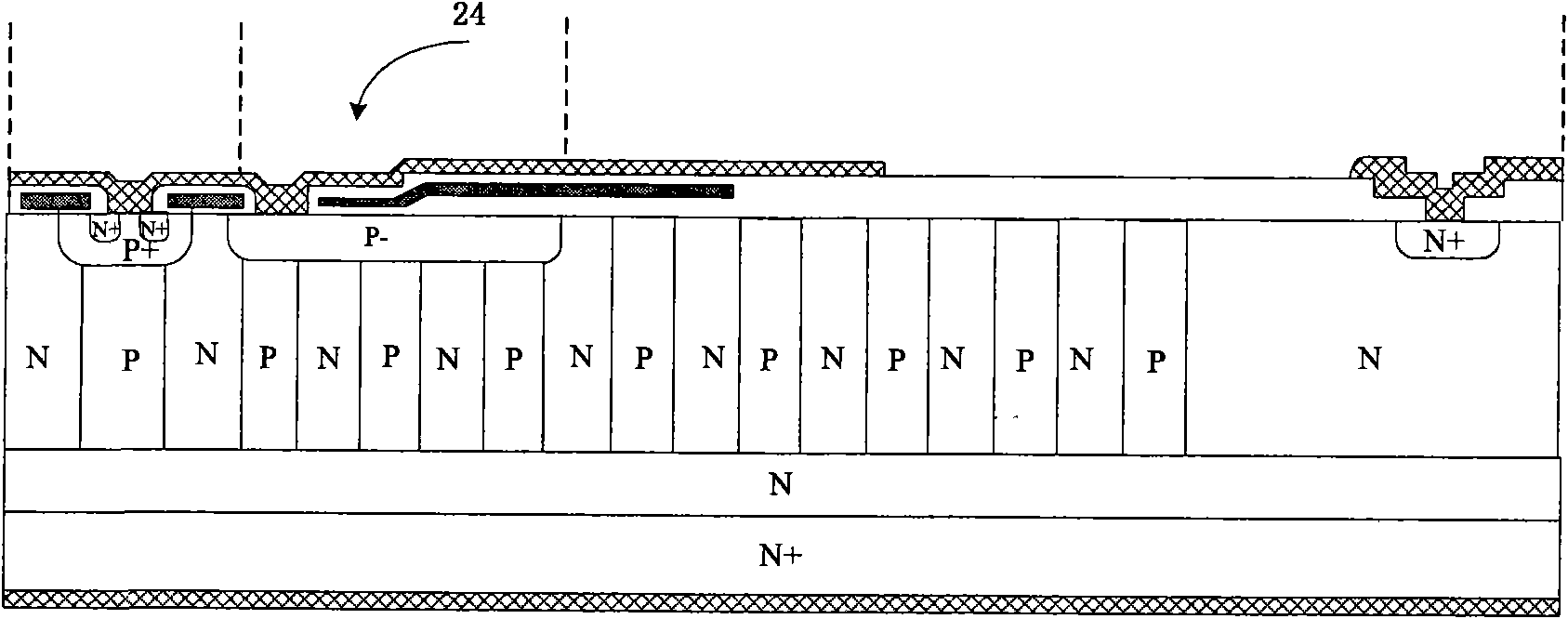

Nitride semiconductor device

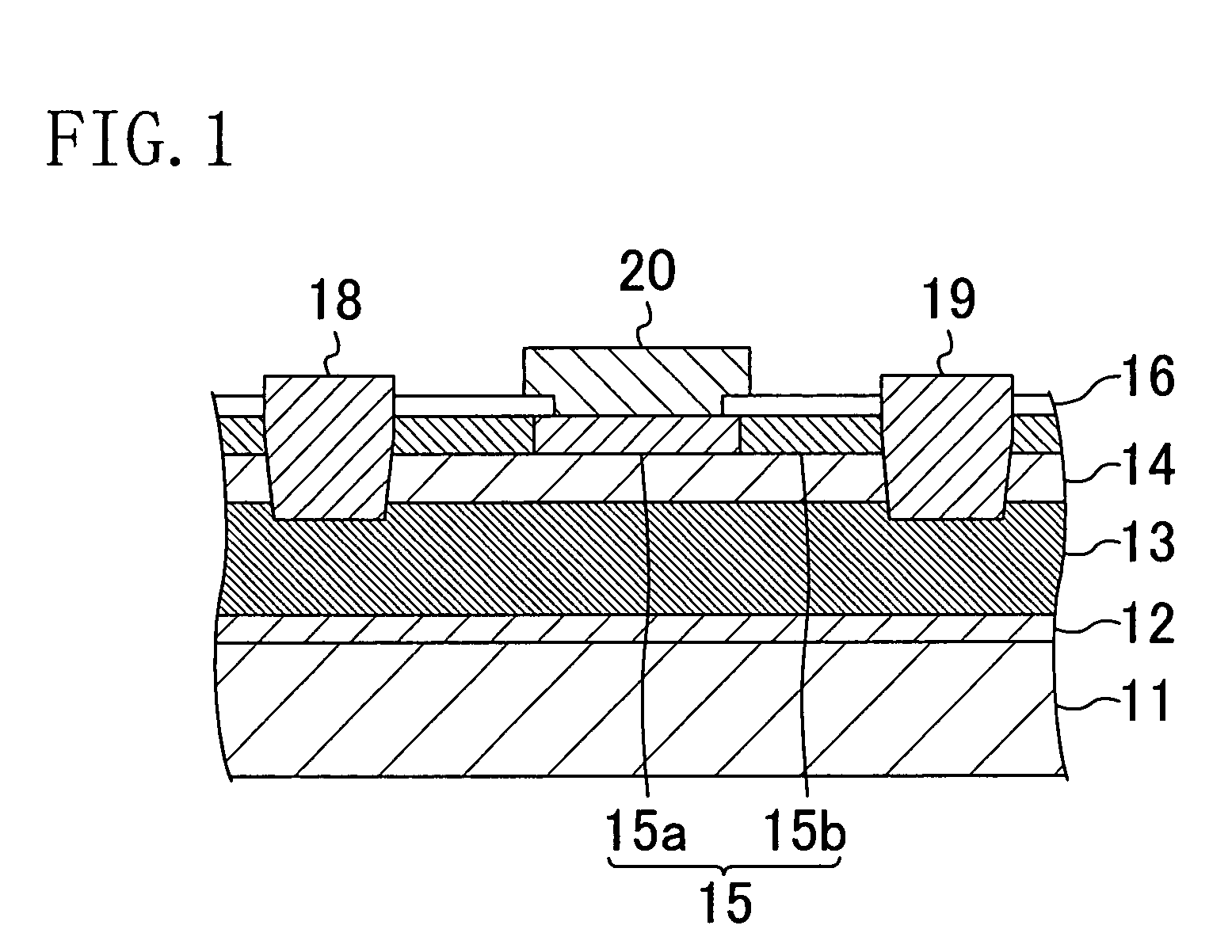

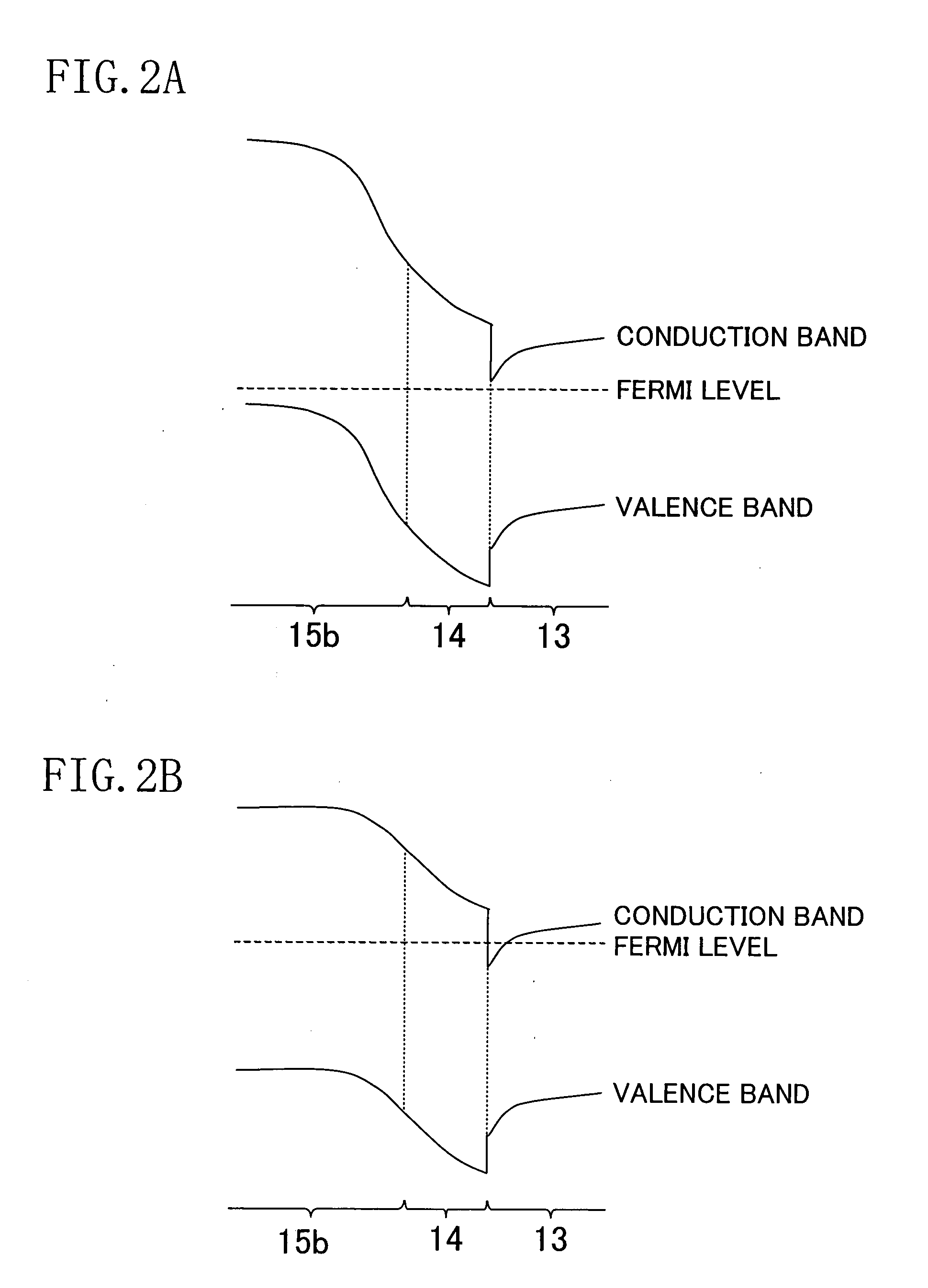

ActiveUS20070170463A1Allowed to operateOperating currentSemiconductor/solid-state device manufacturingSemiconductor devicesValence bandElectrical conductor

A nitride semiconductor device includes: a first semiconductor layer made of first nitride semiconductor; a second semiconductor layer formed on a principal surface of the first semiconductor layer and made of second nitride semiconductor having a bandgap wider than that of the first nitride semiconductor; a control layer selectively formed on, or above, an upper portion of the second semiconductor layer and made of third nitride semiconductor having a p-type conductivity; source and drain electrodes formed on the second semiconductor layer at respective sides of the control layer; a gate electrode formed on the control layer; and a fourth semiconductor layer formed on a surface of the first semiconductor layer opposite to the principal surface, having a potential barrier in a valence band with respect to the first nitride semiconductor and made of fourth nitride semiconductor containing aluminum.

Owner:PANASONIC CORP

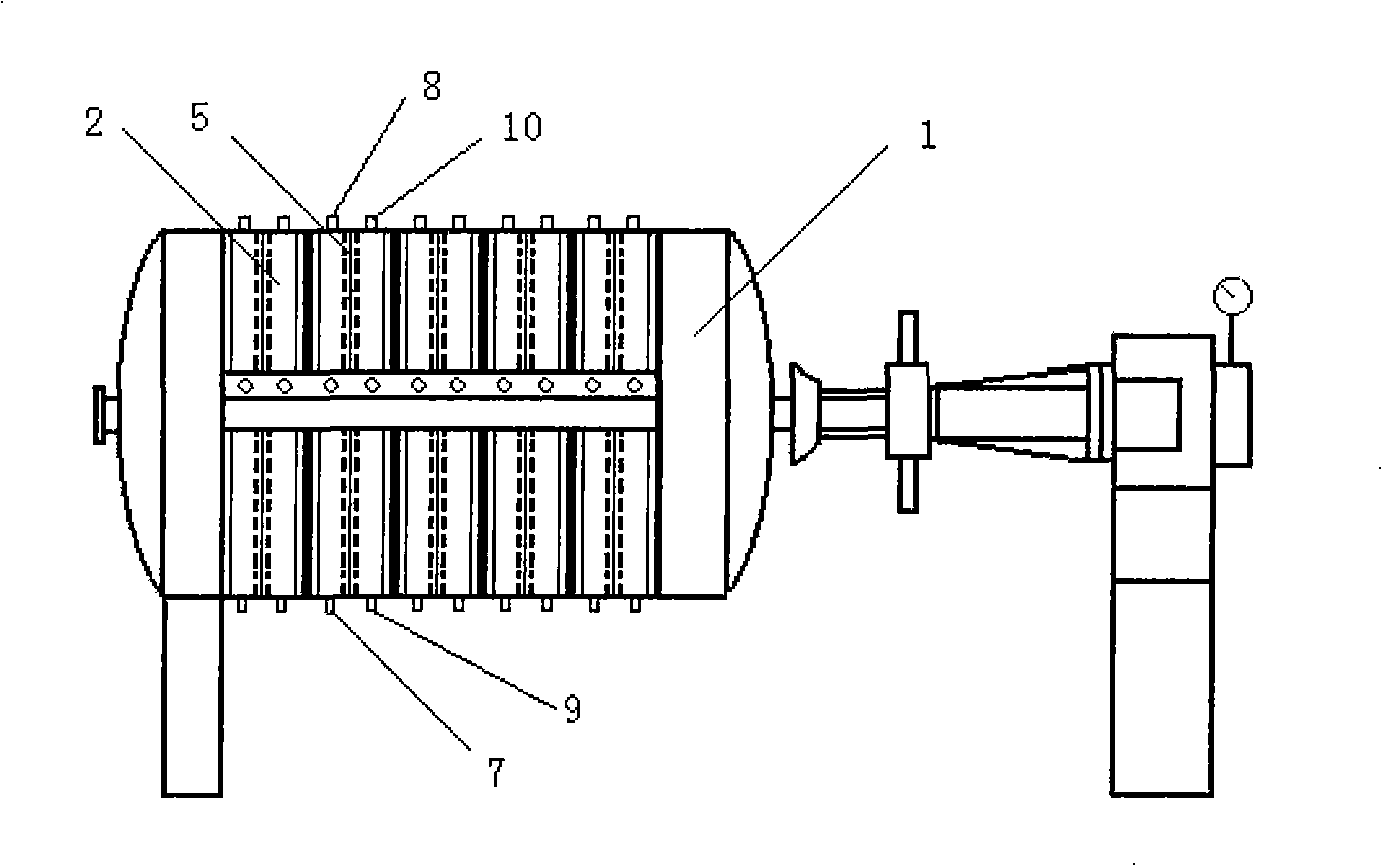

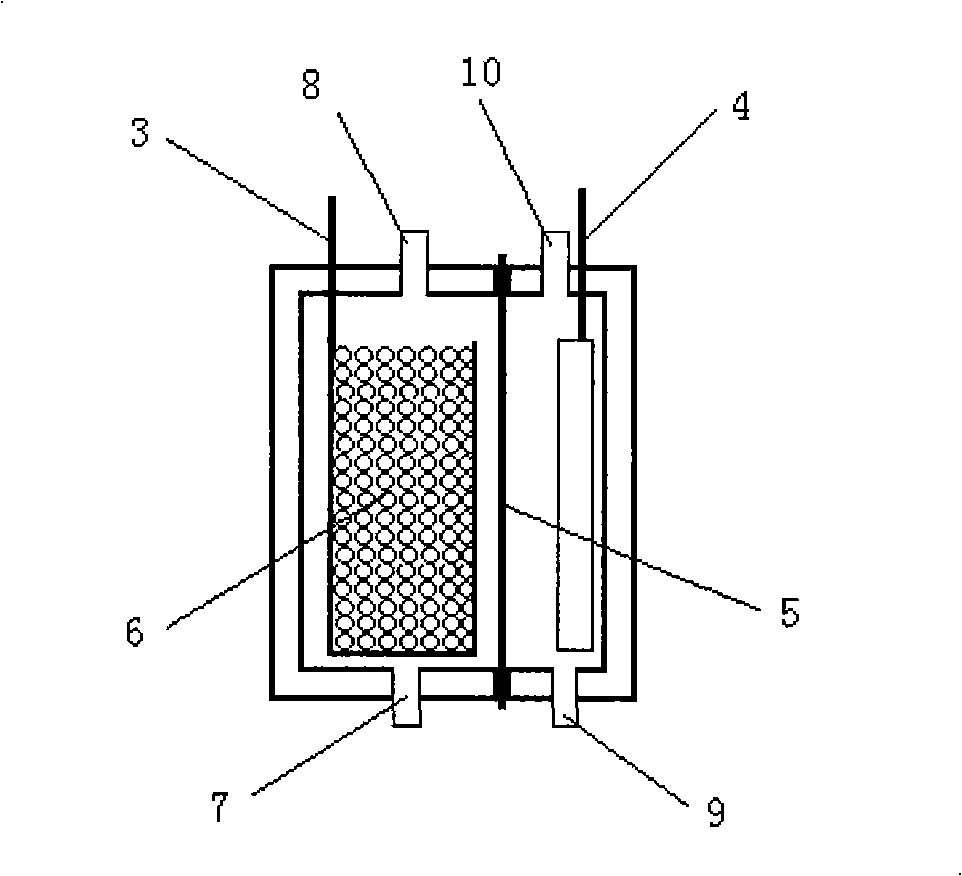

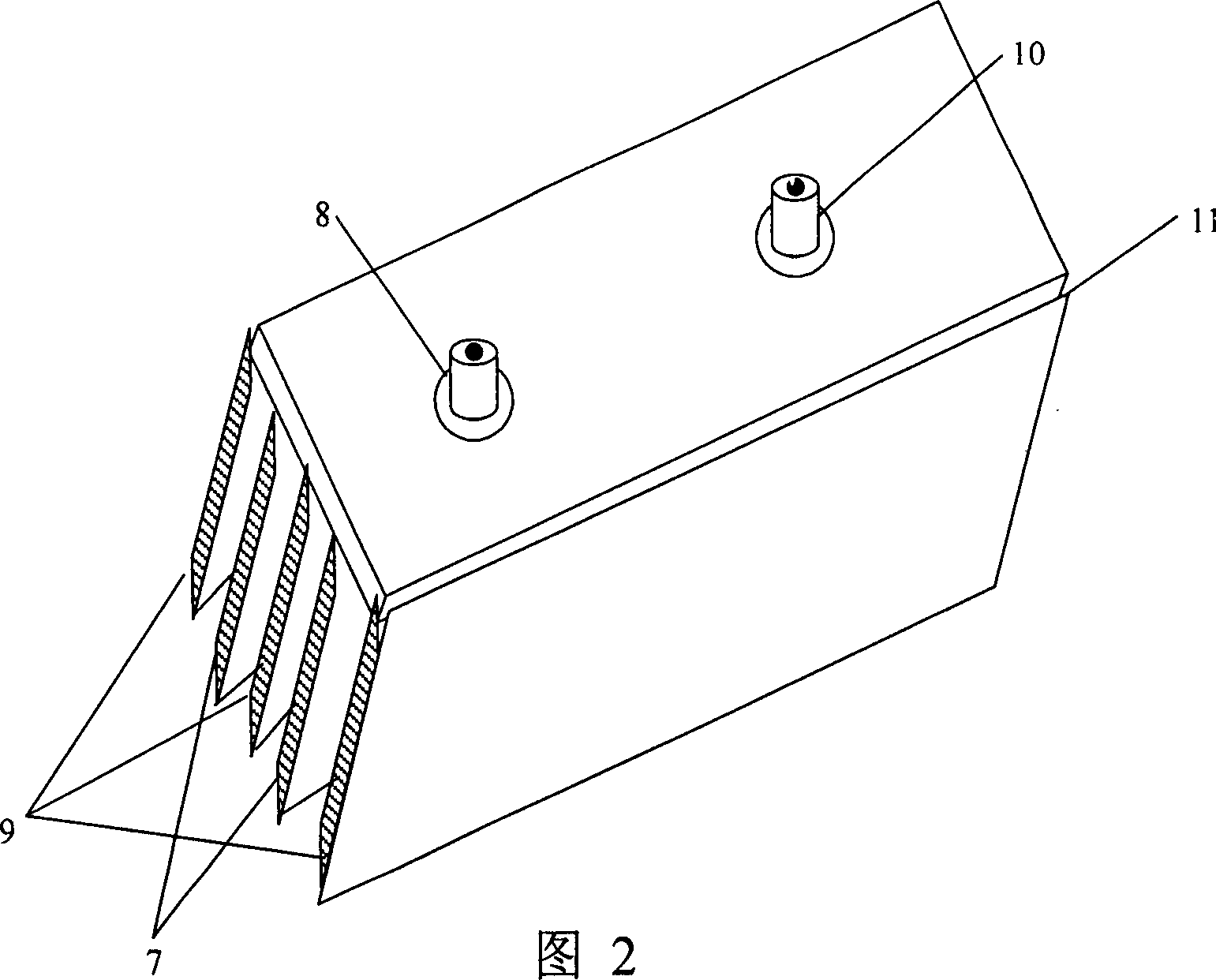

Device and technique for indirectly electric oxidation synthesis of organic substance electrolytic regeneration medium

InactiveCN101260530AIncrease working currentCompact structureElectrolysis componentsElectrolytic organic productionEngineeringStorage tank

The invention discloses an electrolysis unit and a technology used for indirect electric oxo synthesis of organic matters and electrolytic regeneration of media. The electrolysis unit is formed by compression of a plurality of elementary electrolytic cells which are connected in series through a plate-and-frame filter press, wherein, the elementary electrolytic celles comprise anode chambers and cathode chambers which are separated off by cation diaphragms; the anode chambers and the cathode chambers are respectively provided with electrolyte inlets and electrolyte outlets which are communicated with electrolyte storage tanks; and anodes which are arranged inside the anode chambers adopt granular packed bed electrodes which take titanium baskets or titanium baskets provided with coatings as frame bodies. By adoption of the electrolysis unit, low valence state media which are generated during the process of indirect electric oxo synthesis of the organic matters are reoxidized and regenerated into high valence state media through electrolysis. The electrolysis unit has the advantages of large working current, convenient opening of a pressure filter for replacement of the diaphragms and filling of granules, compact structure and high space-time efficiency and is particularly suitable for indirect electric oxidation regeneration reaction by adoption of Mn<3+> / Mn<2+>, Ce<4+> / Ce<3+> and Cr2O7 <2-> / Cr 3+> as media.

Owner:ZHEJIANG UNIV OF TECH

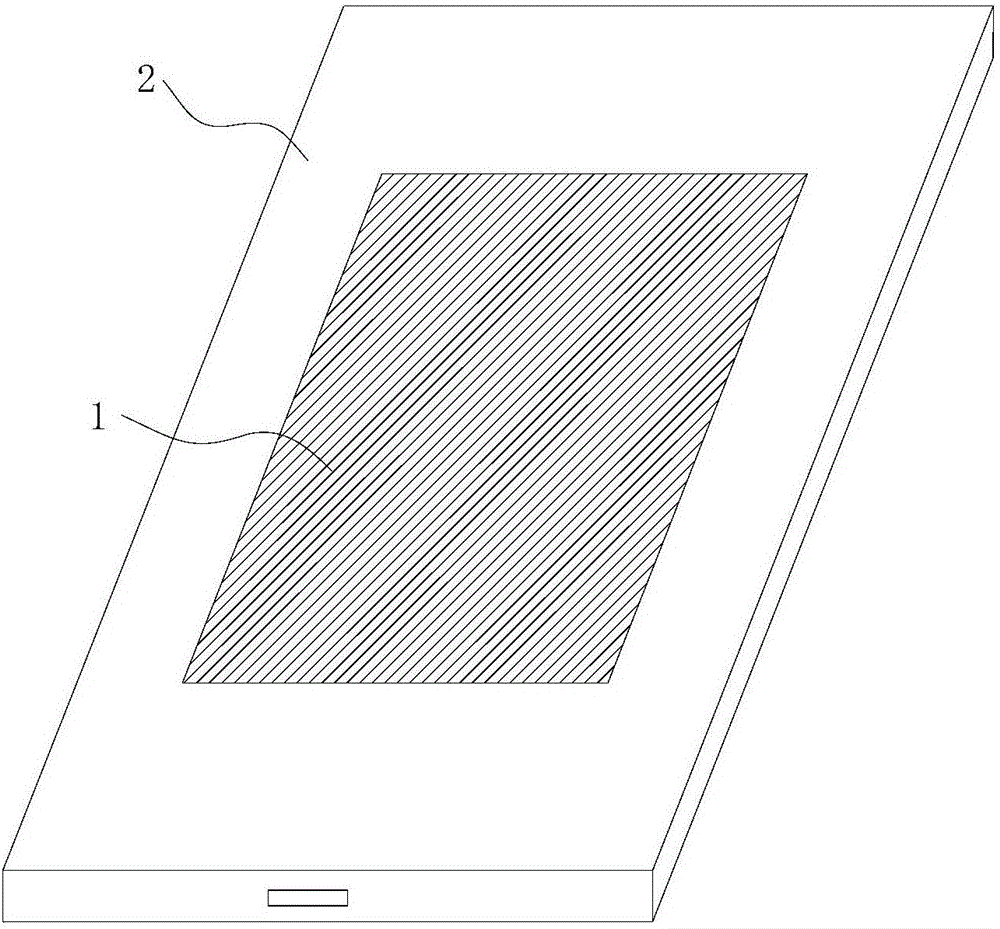

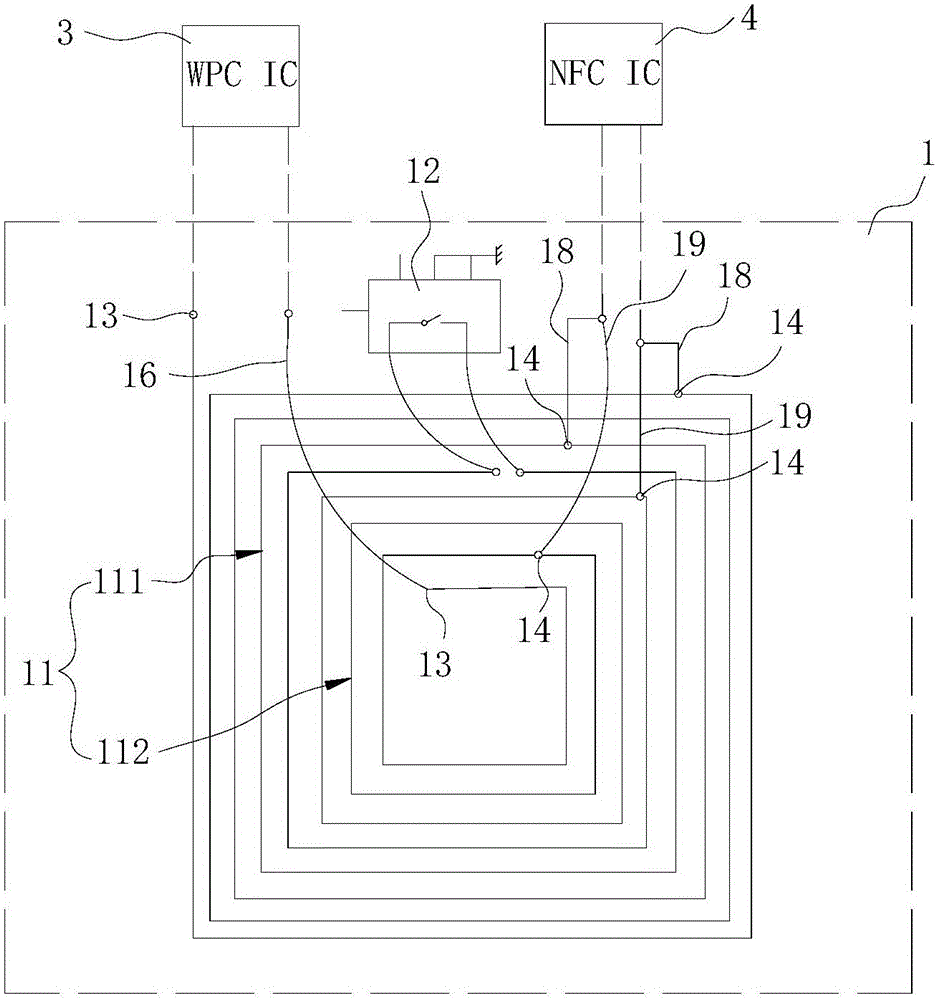

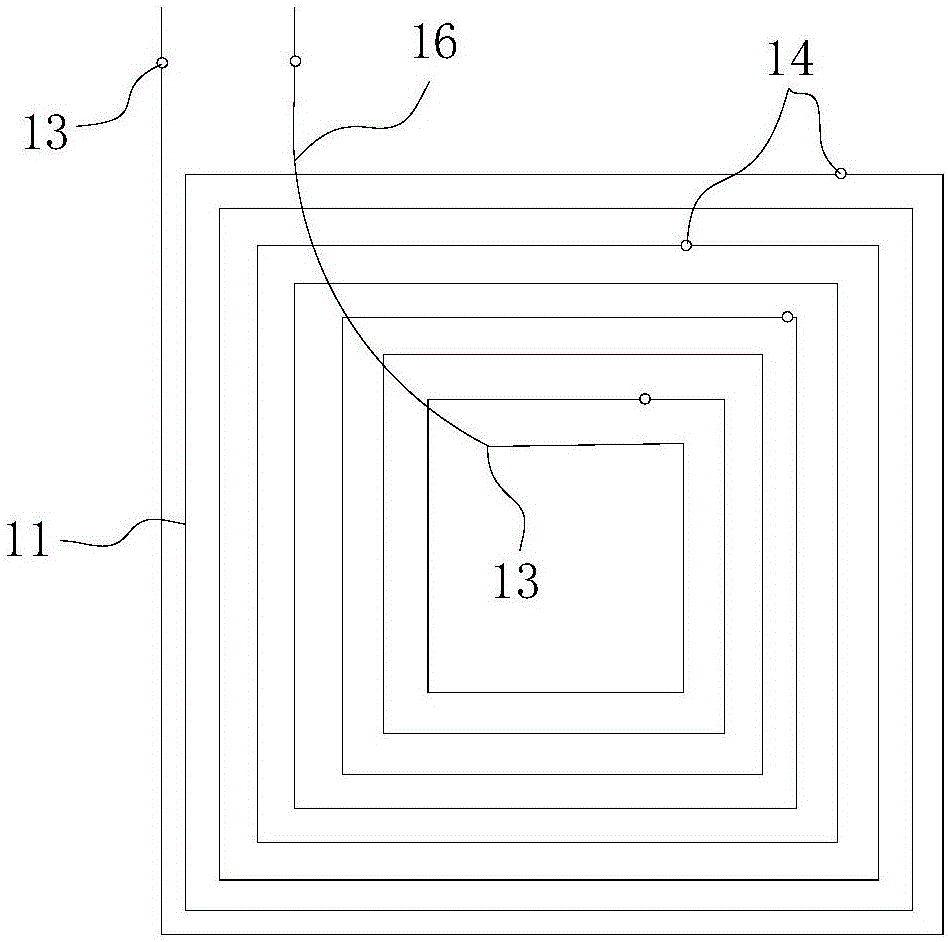

Antenna device and mobile terminal with same

ActiveCN106329114AReduced design area requirementsEnables miniaturization compatible designAntenna supports/mountingsLoop antennasMultiplexingComputer terminal

The invention provides an antenna device and a mobile terminal with the same. The antenna device comprises at least two layers of stacked coils; a second feed point electrically connected to an NFC (Near Field Communication) chip or an RFID (Radio Frequency Identification) chip is respectively arranged on the coils, and a first feed point electrically connected to a WPC (Wireless Power Consortium) chip or an FM (Frequency Modulation) chip is respectively arranged on the two coils of the surface; and the two adjacent layers of coils are isolated by an isolating unit, and the isolating unit is configured to isolate working signals of the NFC chip or the RFID chip. The antenna device realizes superposition of effective area of antennas via multilayer superposed coils, the coils can be connected or isolated to support two different functions, and multiplexing of the antenna device is realized; meanwhile, in the NFC or RFID working mode, the intensity of the radiation electromagnetic field can be improved, and the NFC or RFID communication performance is optimized.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

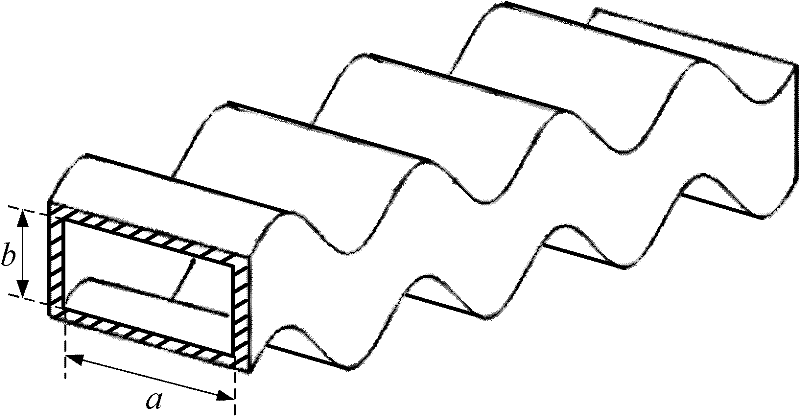

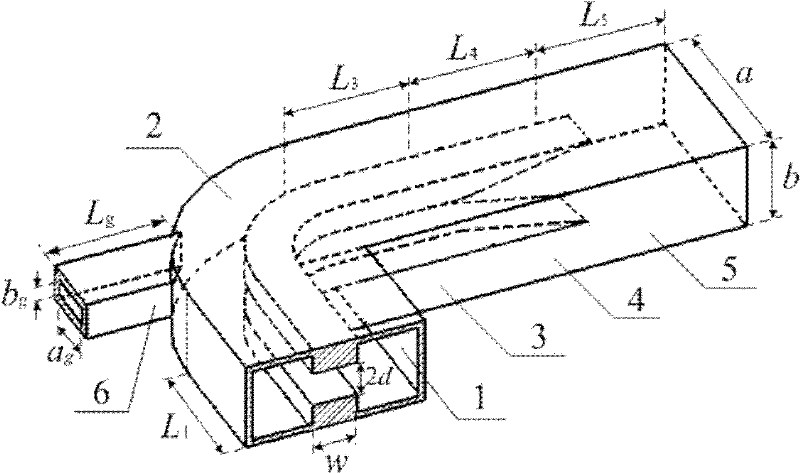

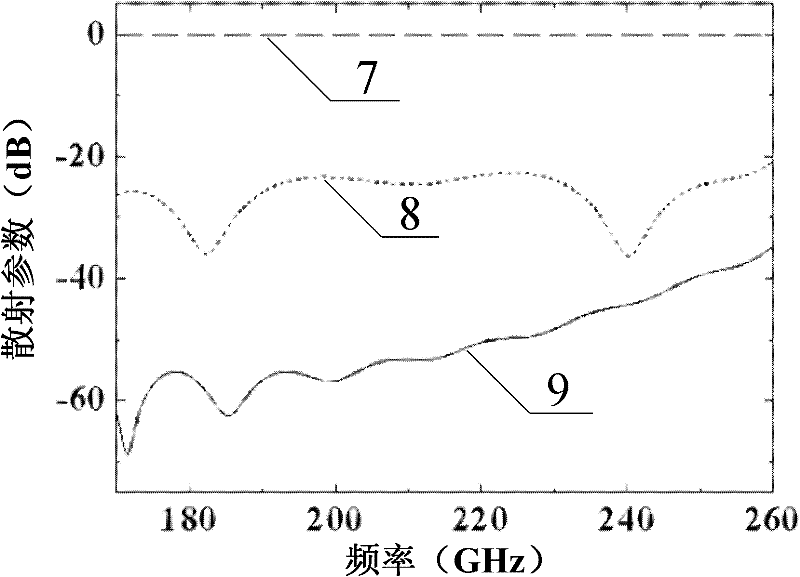

Input/output structure of broadband phase shift travelling wave tube

InactiveCN102315063ASimple structureEasy to processTransit-tube coupling devicesPhase shiftedBand shape

The invention, which belongs to the vacuum electronic technology field, relates to an input / output structure of a broadband phase shift travelling wave tube. The structure comprises six parts of waveguide type elements: a first double-ridge loading rectangular wave guide; a double-ridge loading rectangular wave guide, which is in a bending state of 90 degrees; a second double-ridge loading rectangular wave guide; a double-ridge gradient double-ridge loading rectangular wave guide; a first rectangular wave guide and a second rectangular wave guide. The first double-ridge loading rectangular wave guide and the second double-ridge loading rectangular wave guide are respectively connected with two ends of the double-ridge loading rectangular wave guide that is in a 90 degree bending; the double-ridge gradient double-ridge loading rectangular wave guide is connected between the second double-ridge loading rectangular wave guide and the first rectangular wave guide; and the second rectangular wave guide is connected with an outboard curved surface window of the double-ridge loading rectangular wave guide that is in a 90 degree bending, wherein a central axis of the double-ridge loading rectangular wave guide that is in a 90 degree bending is superposed with a central axis of the first rectangular wave guide. According to the invention, broadband microwave signal energy and a band shape electronic beam can be well introduced and a sine wave guide structure can be lead out; besides, the input / output structure is simple and is easy to process and realize.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

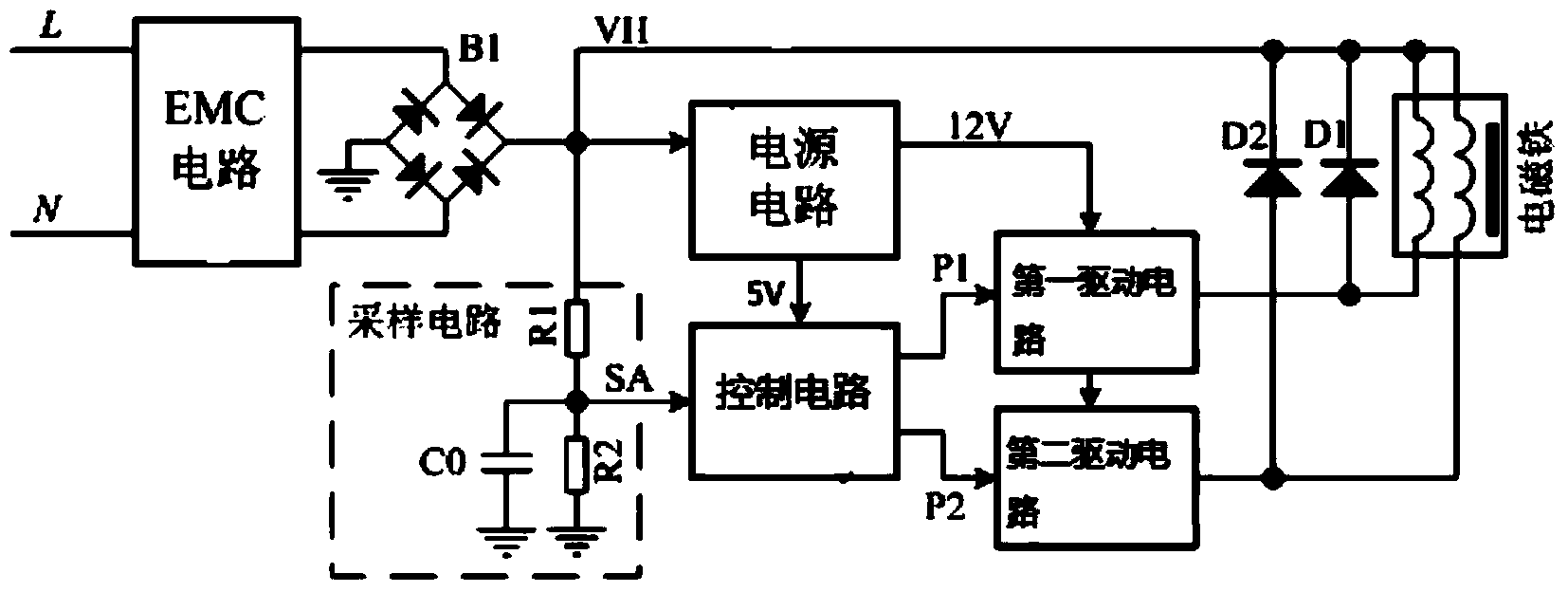

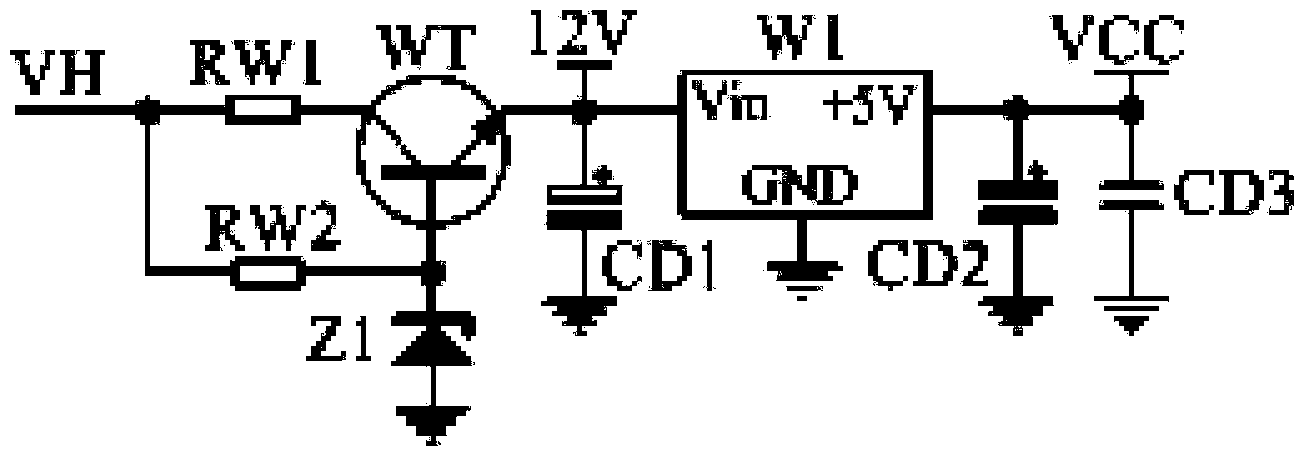

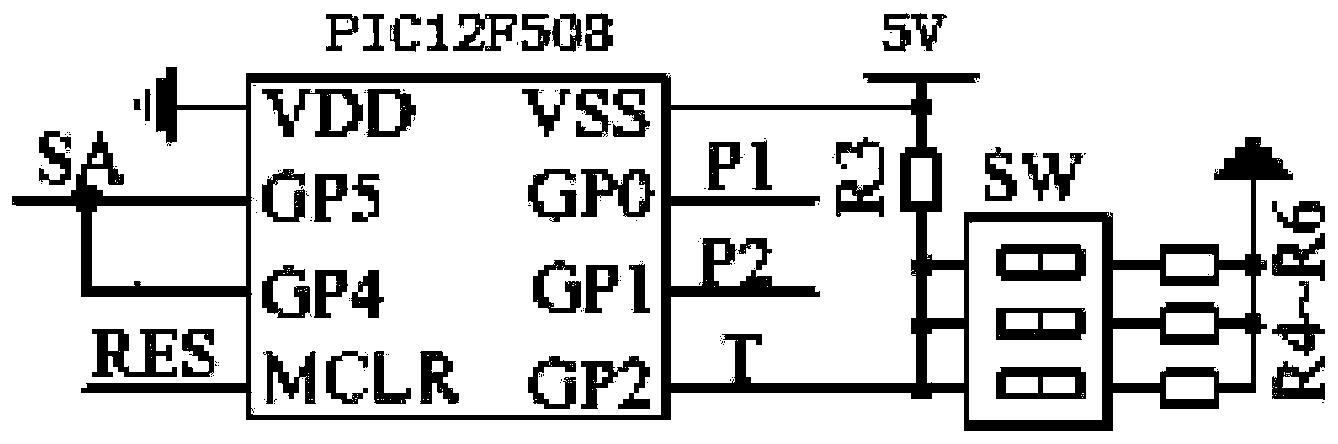

Electromagnetic under-voltage release and controlling method thereof

ActiveCN103647250ASimple and ingenious structureIncrease working currentArrangements responsive to undervoltageMicrocomputerDual coil

The invention provides an electromagnetic under-voltage release comprising a filtering rectifying circuit, a sampling circuit, a power supply circuit, a control module, a driver module and an electromagnet. A direct-current resistance of a starting winding is less than a direct-current resistance of a working winding. According to the electromagnetic under-voltage release and the controlling method thereof, a microcomputer is used for controlling the control circuit, and the controlling thinking is clear and the circuit structure is simplified and ingenious. The starting winding-working winding dual-coil electromagnet is arranged at the circuit, and the direct-current resistance of the starting winding is less than the direct-current resistance of the working winding and the working current of the starting winding is high and the starting torque is large, so that the pull-in performance of the electromagnet can be ensured. And the working current of the working winding is low and thus the basic power for pull-in maintaining of the electromagnet is provided, so that the heating value is extremely low.

Owner:JIANGSU GUOXING ELECTRIC EQUIP

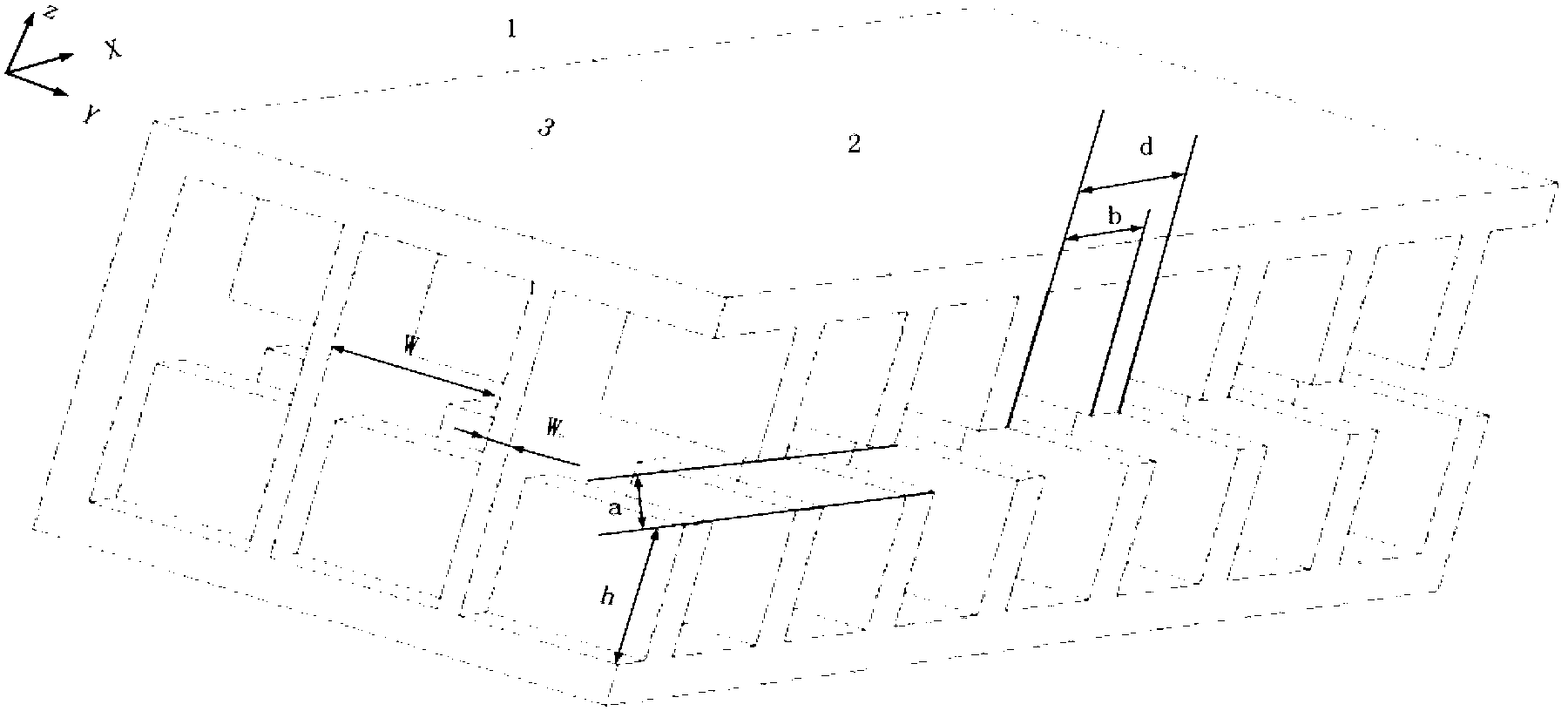

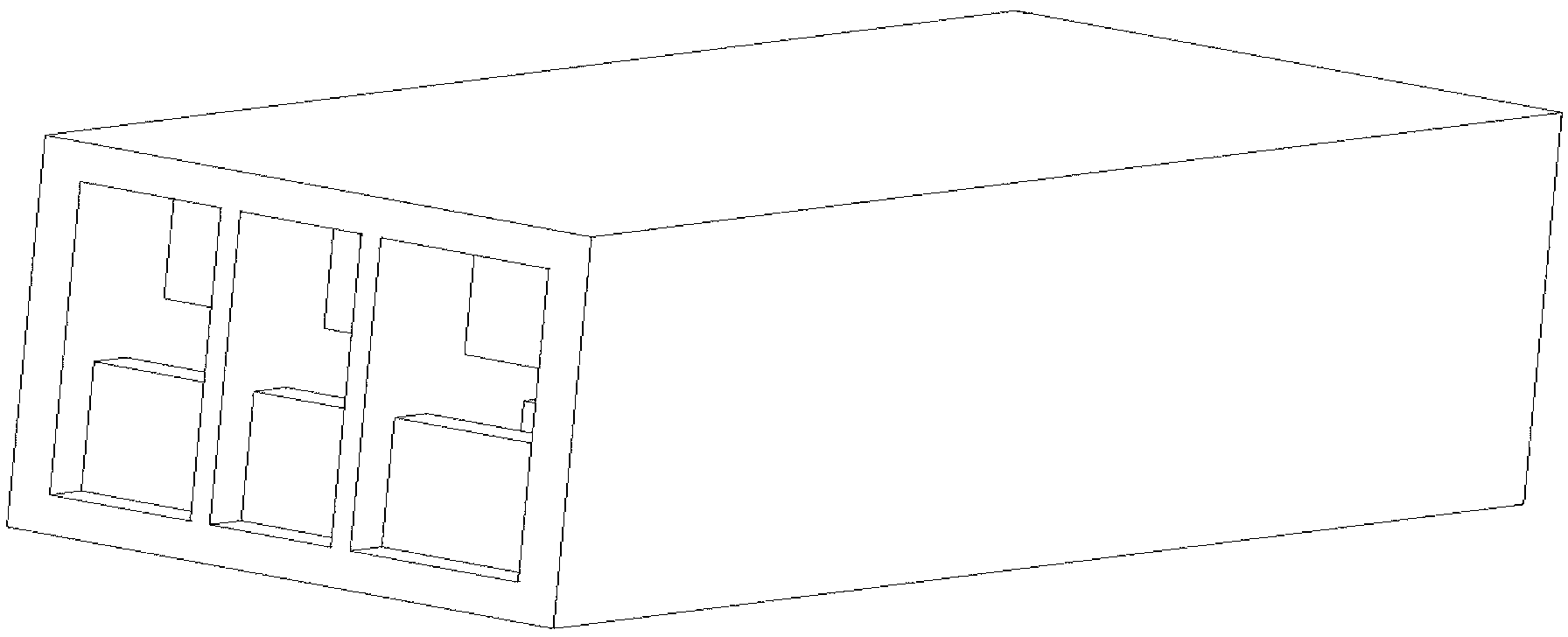

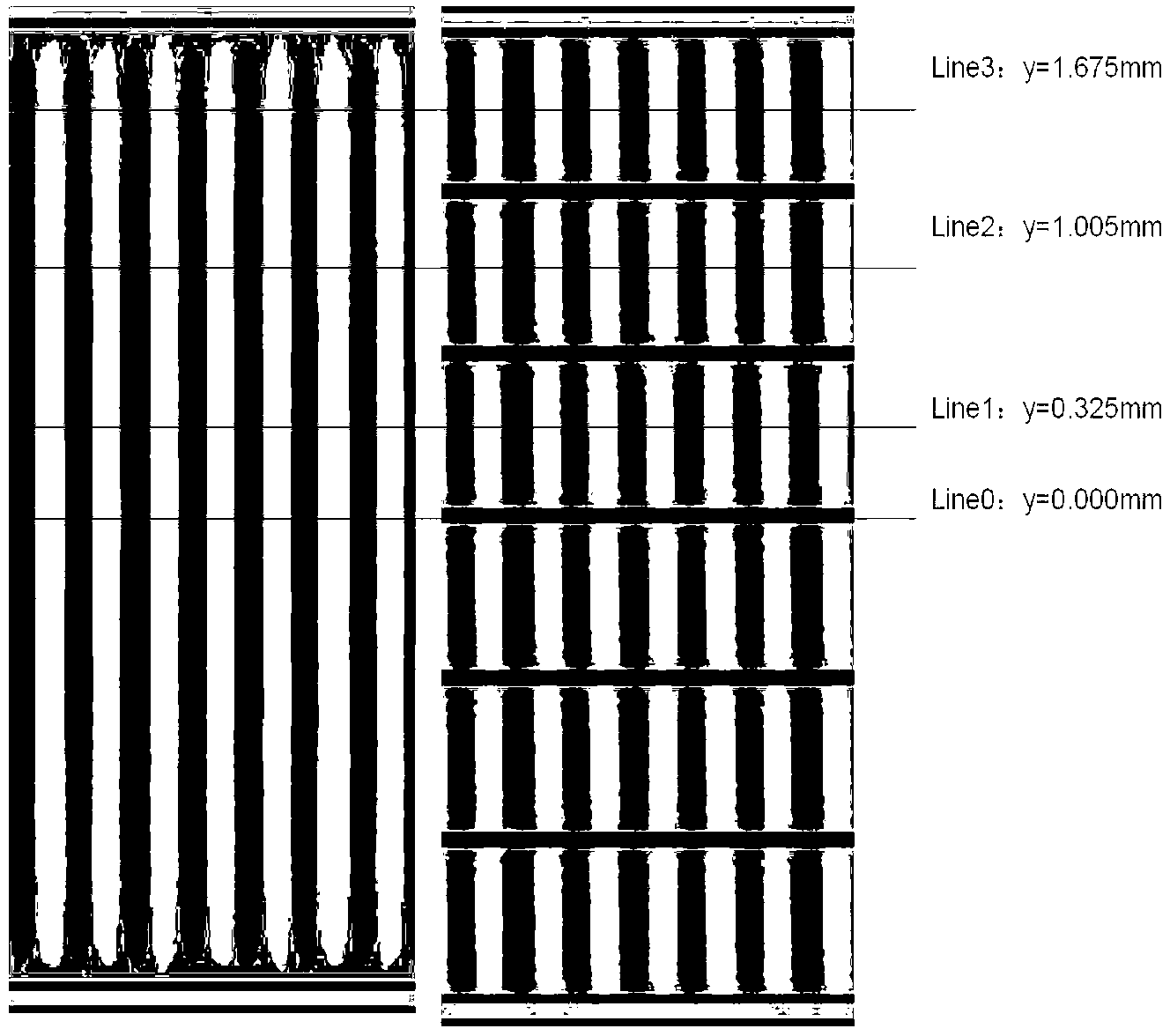

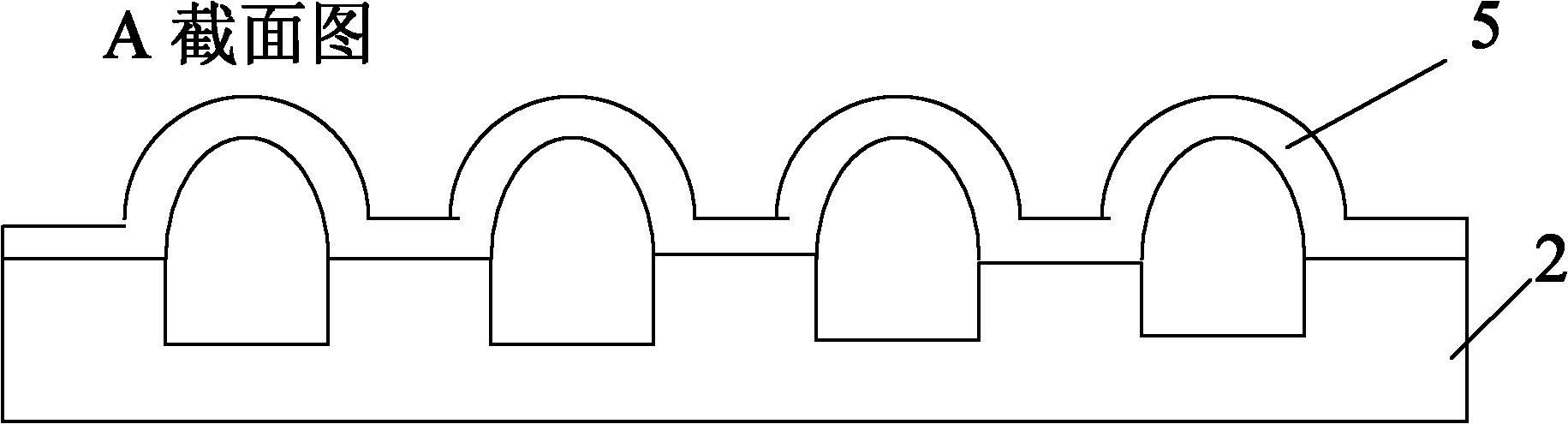

Comb-shaped slow-wave structure for multi-band electron beam channel

ActiveCN103077872ARealize pre-modulationThe main structure is simpleTransit-tube circuit elementsMulti bandWave structure

The invention discloses a comb-shaped slow-wave structure for a multi-band electron beam channel. The comb-shaped slow-wave structure for the multi-band electron beam channel comprises a rectangular wave guide wall of which the two ends are open; double rows of comb-shaped teeth are arranged on the inner walls of the upper end surface and the lower end surface of the rectangular wave guide wall in a staggered way; a plurality of insertion pieces are inserted into the rectangular wave guide wall at equal intervals; XYZ three-dimensional coordinates are established by taking the lower-left corner of the front end surface of the rectangular wave guide wall of which the two ends are open as an original point; the direction which is upwards vertical to the original point is the Z-axis; the direction which is leftwards horizontally is the Y-axis; the direction which is backwards horizontally is the X-axis; the teeth are at equal intervals and are parallel to the YZ plane; and the insertion pieces are parallel to the XZ plane. The comb-shaped slow-wave structure for the multi-band electron beam channel has a simple main structure, is easy to machine and is compatible with the modern micro electronic mechanical system (MEMS) technology; a transverse edge effect of the comb teeth can be ignored; the working frequency band is widened obviously; the beam-wave interaction efficiency is high; the working current is improved; the output power is increased; and the comb-shaped slow-wave structure is a novel slow-wave structure which extremely has application potential.

Owner:HEFEI UNIV OF TECH

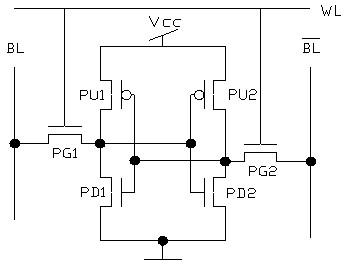

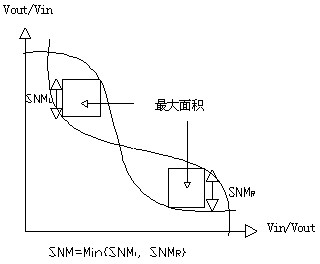

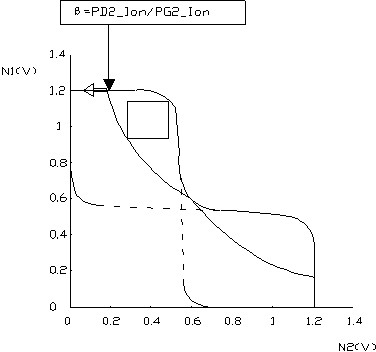

SRAM (Static Random Access Memory) unit structure based on fake contact etch stop layer technology and preparation method of SRAM unit structure

InactiveCN102420231AIncreased static noise redundancyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorUnit structure

The invention discloses a static random access memory (SRAM) unit structure based on a fake contact etch stop layer (CESL) technology and a preparation method of the SRAM unit. In the production process of the SRAM, a tensile liner covers a pull-down transistor of the SRAM and a compressive liner covers a pull-up transistor and a channel transistor of the SRAM. According to the SRAM structure based on the fake CESL technology and the preparation method of the SRAM structure, provided by the invention, a beta value is increased by covering the tensile liner on the pull-down transistor (NMOS (N-channel Metal Oxide Semiconductor) device) and covering the compressive liner on the channel transistor (NMOS device), so that a static noise margin (SNM) is effectively increased and the aim of realizing the stability of the SRAM unit is realized.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

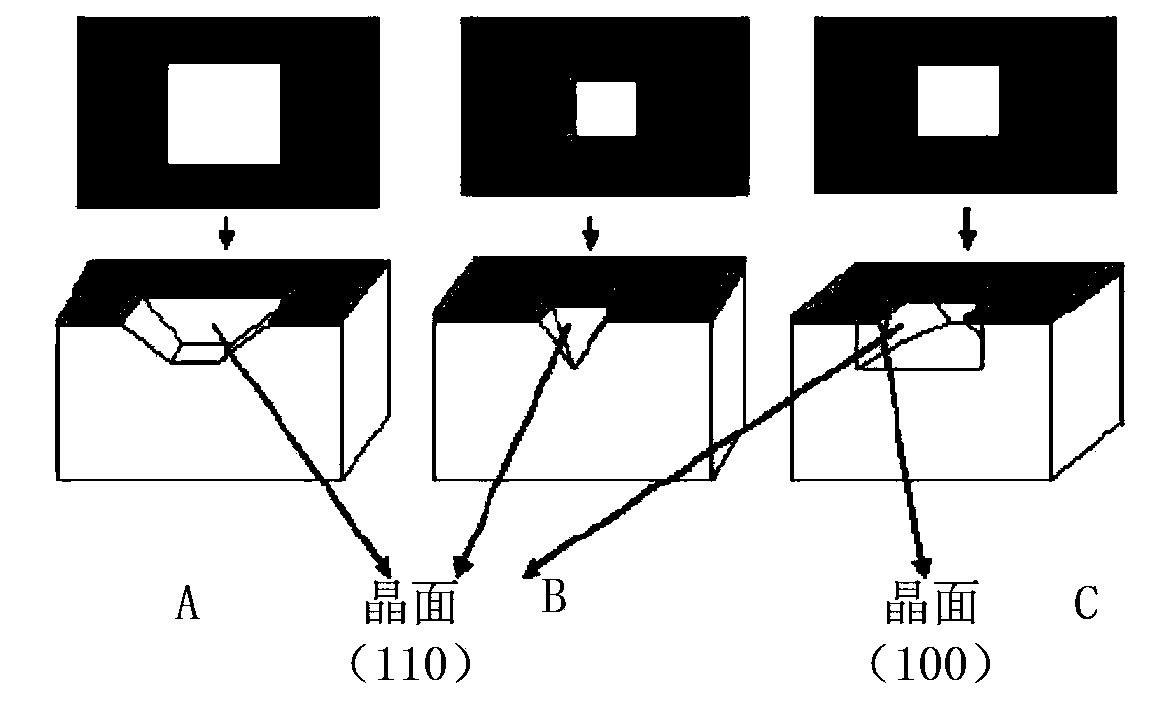

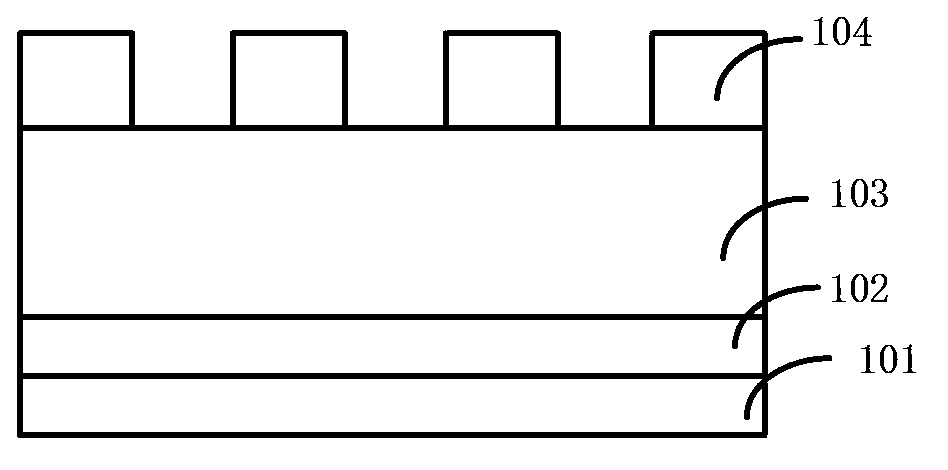

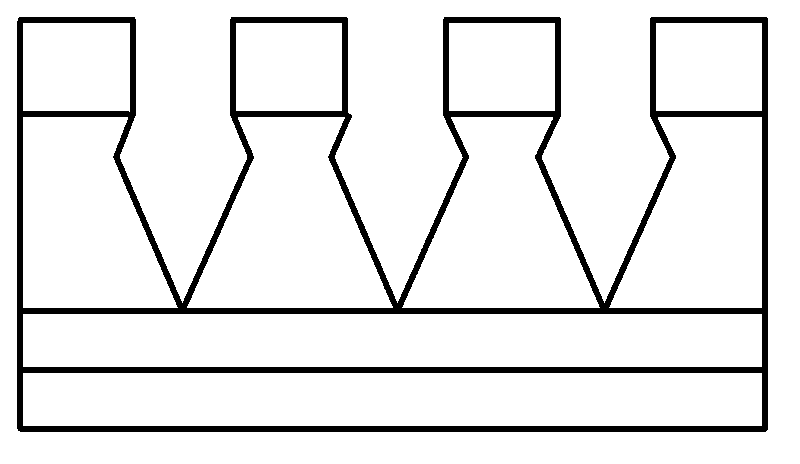

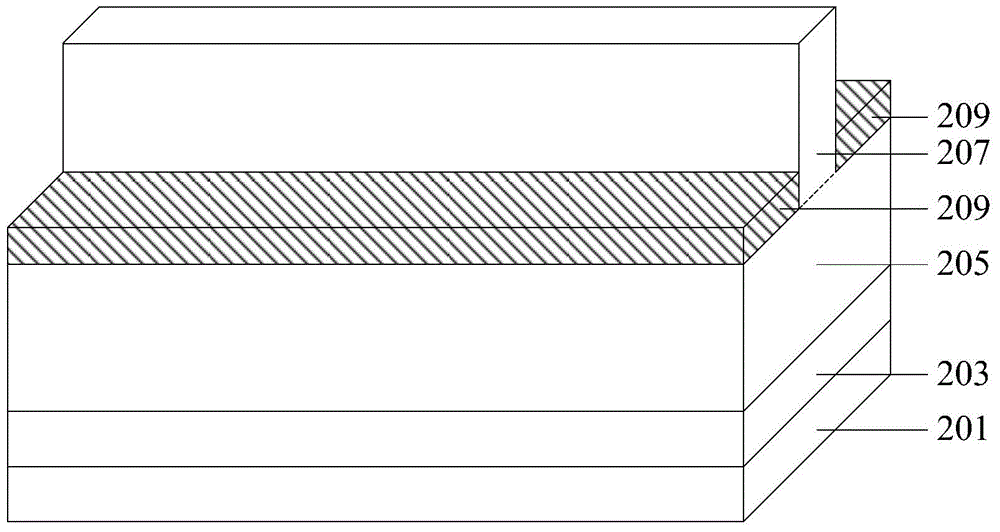

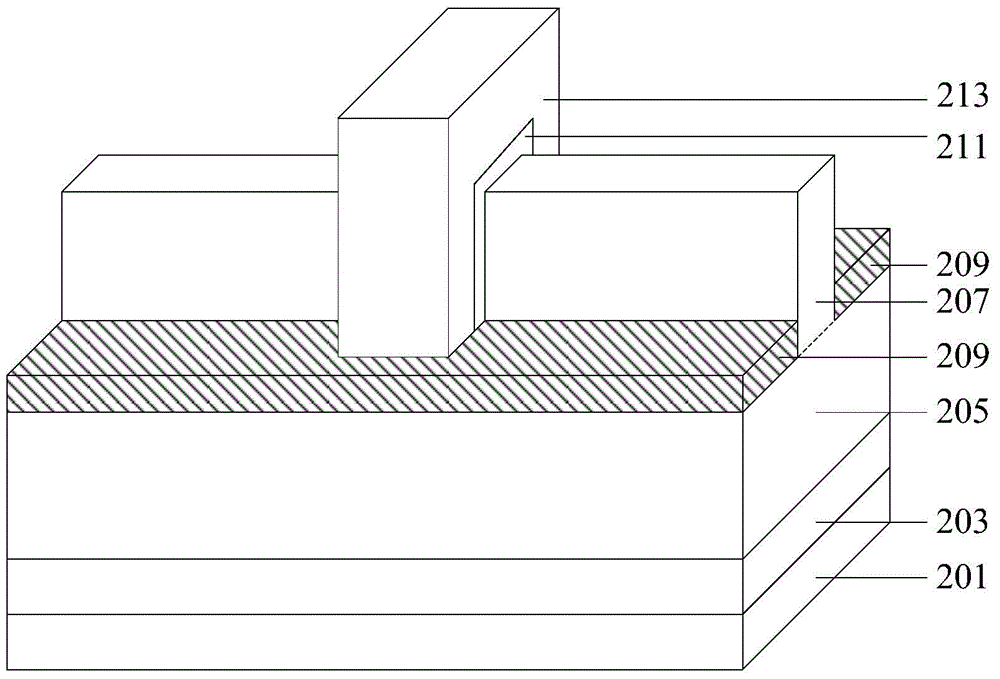

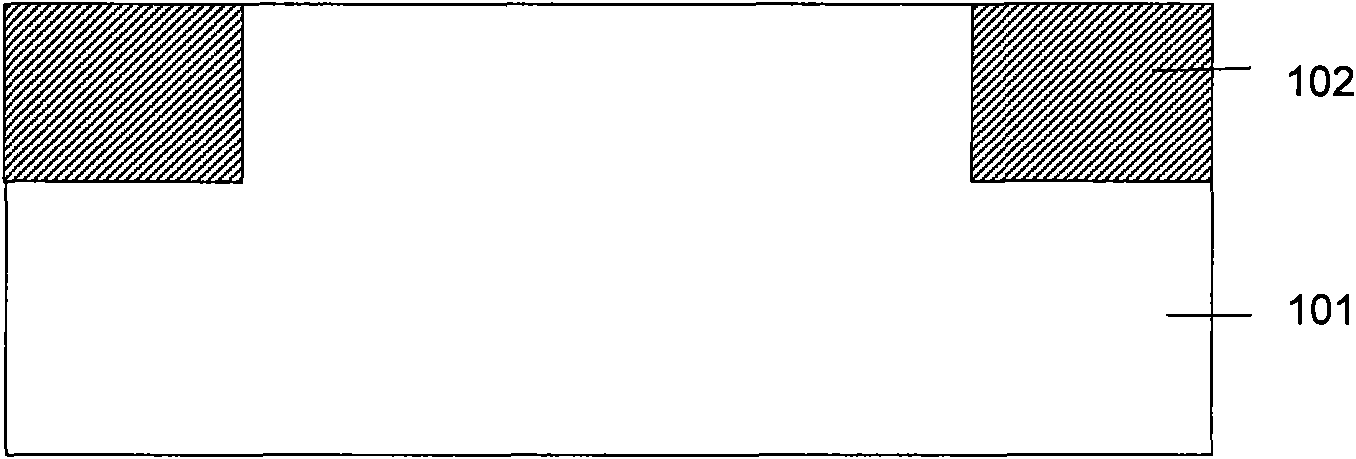

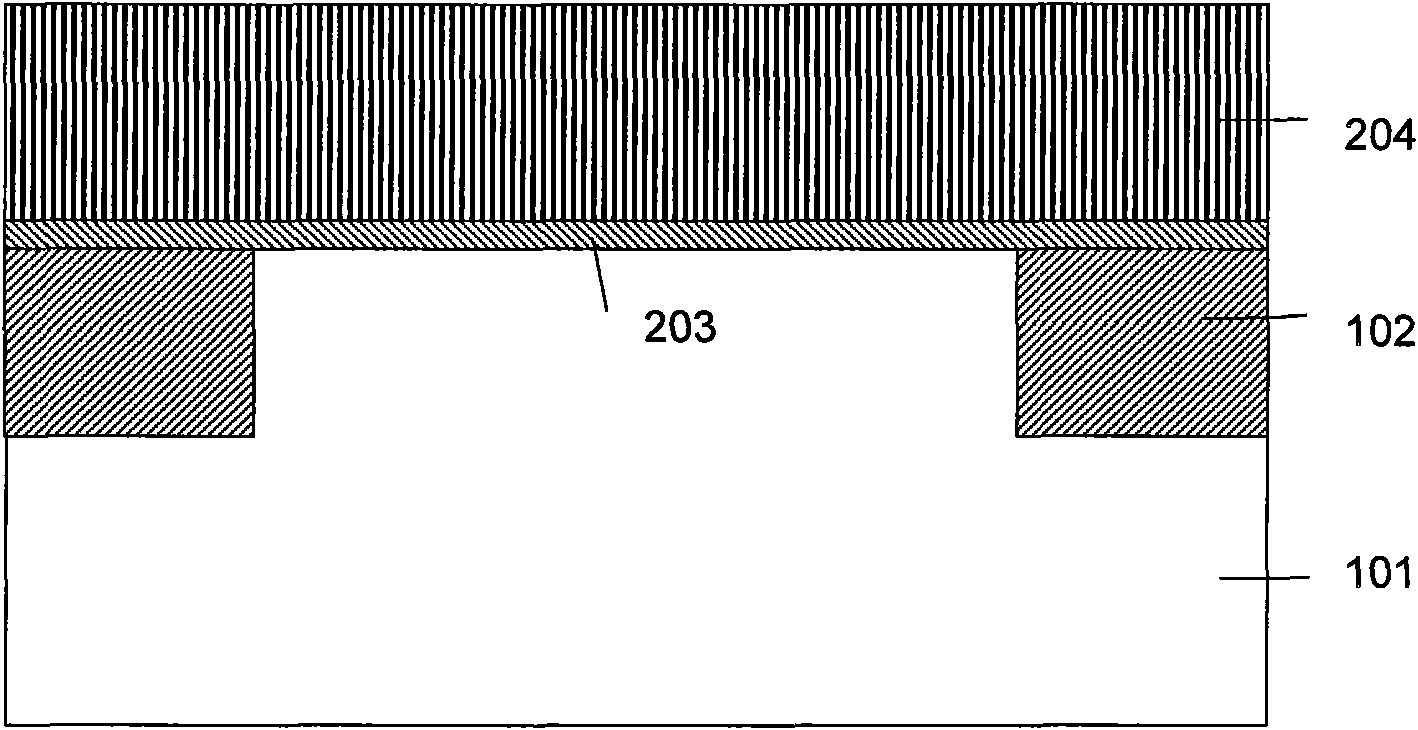

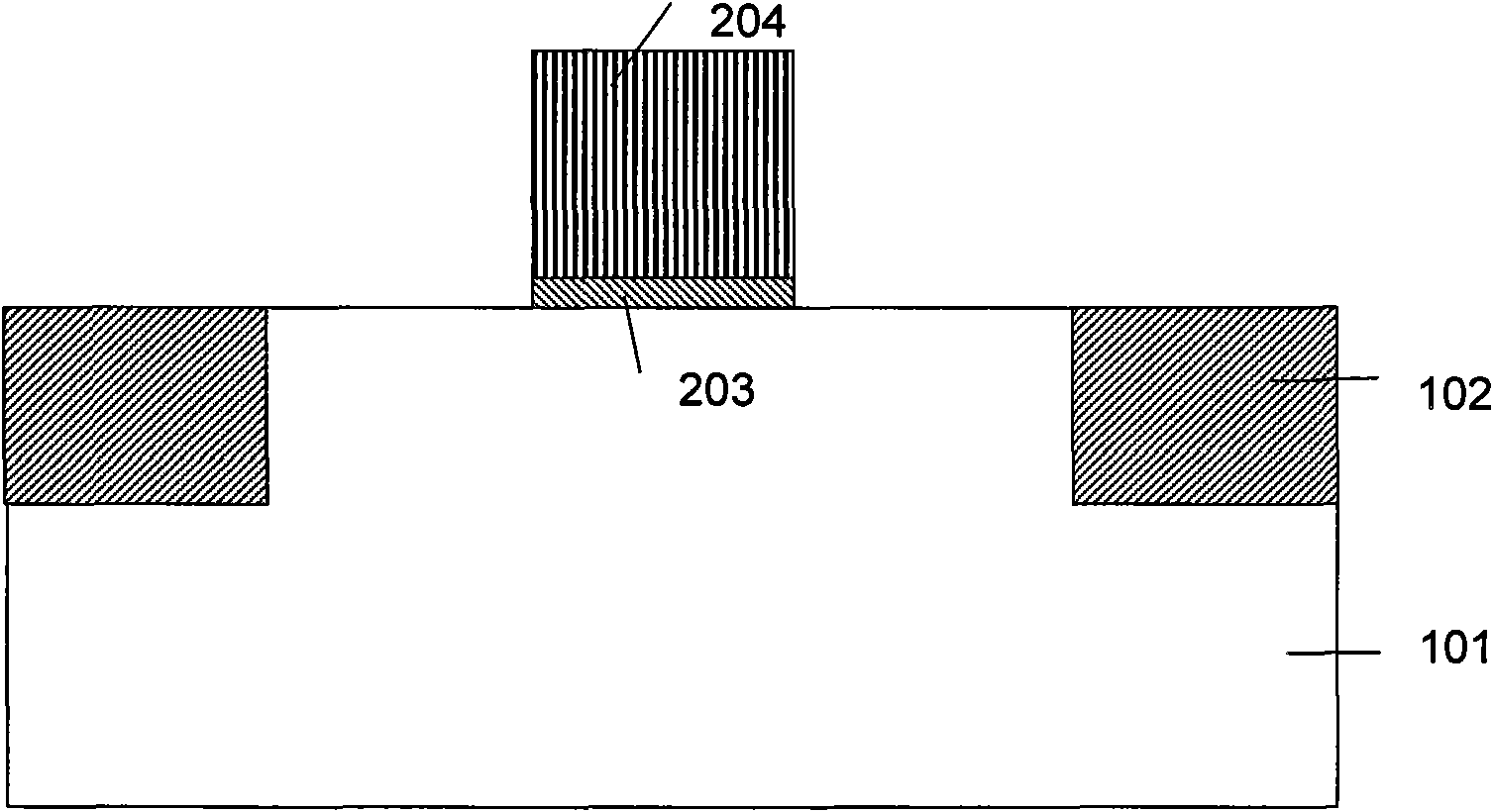

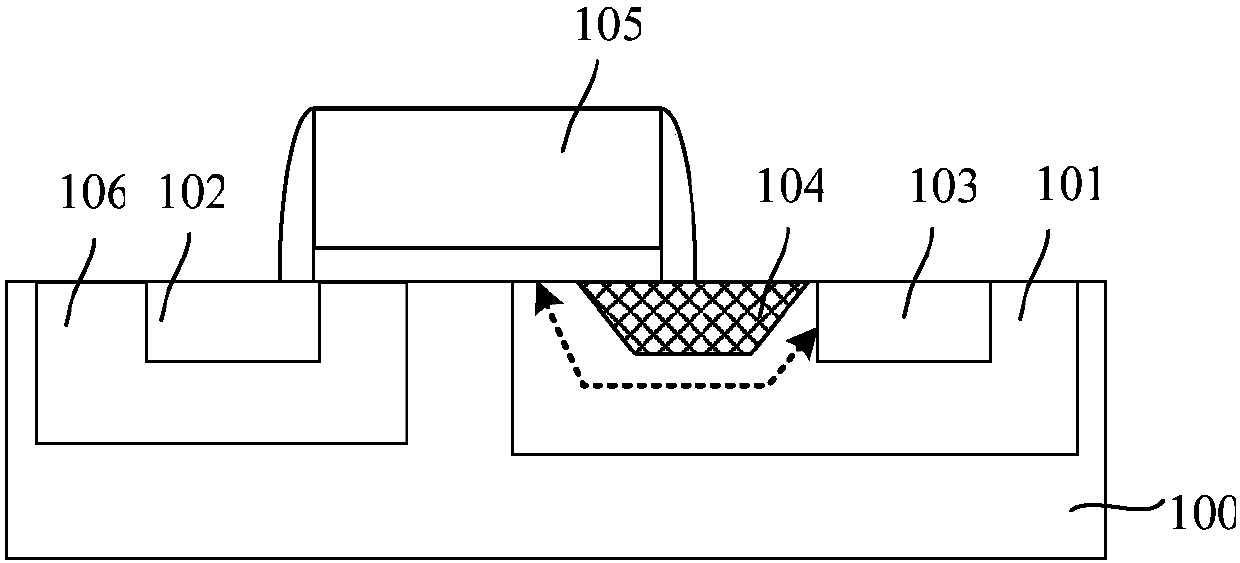

Semiconductor device and method for preparing same

ActiveCN103794498AHighly integratedImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceBasement

The present invention relates to a semiconductor device and a method for preparing the same. The method comprises the steps of providing a semiconductor substrate, wherein the substrate comprises a basement, an oxide layer and a semiconductor material layer; forming a patterned hard mask layer on the substrate, wherein the hard mask layer comprises a plurality of openings; etching the semiconductor material layer by taking the hard mask layer as a mask to form a sigma-shaped groove; epitaxially growing a SiGe layer in the groove to form a fin; removing the hard mask layer to expose the semiconductor material layer; etching the semiconductor material layer to expose the fin. According to the method of the present invention, the hard mask layer is formed on a SOI substrate, and then the sigma-shaped groove is formed by controlling the etching conditions, then the SiGe layer is grown epitaxially to obtain the rhombic fin, and finally a gate all around (GAA) is formed, so that the lower surface of the fin is totally used as a groove area, a working current can be increased further, and the integration level and performance of the device are improved further.

Owner:SEMICON MFG INT (SHANGHAI) CORP

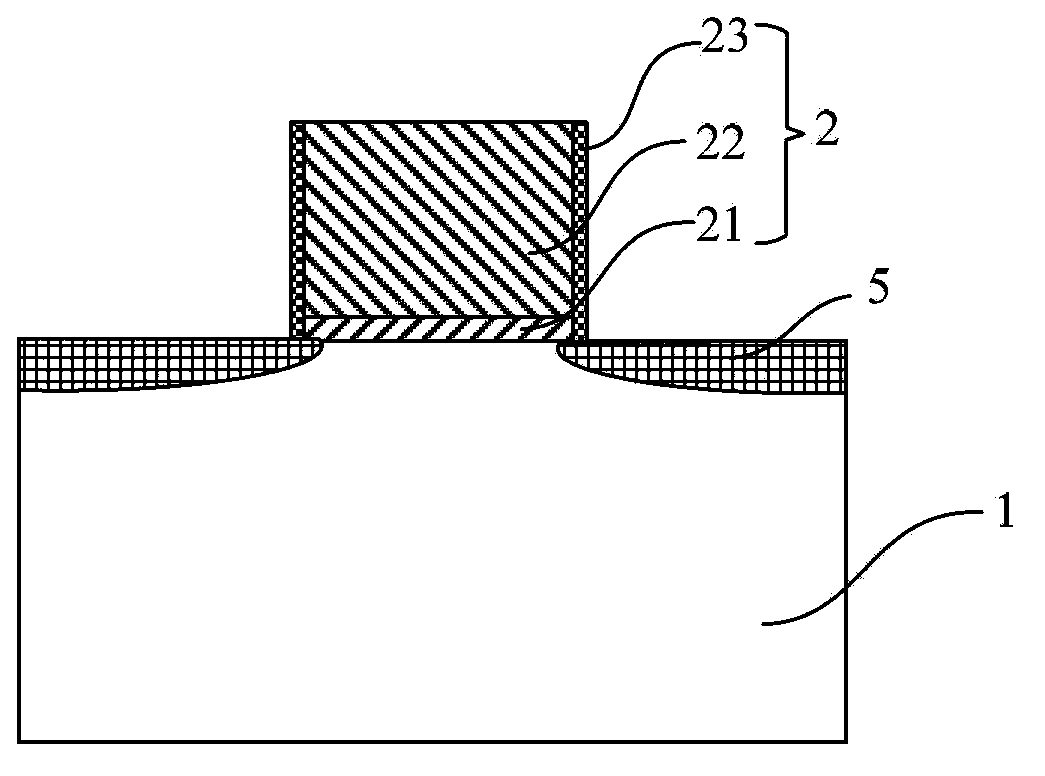

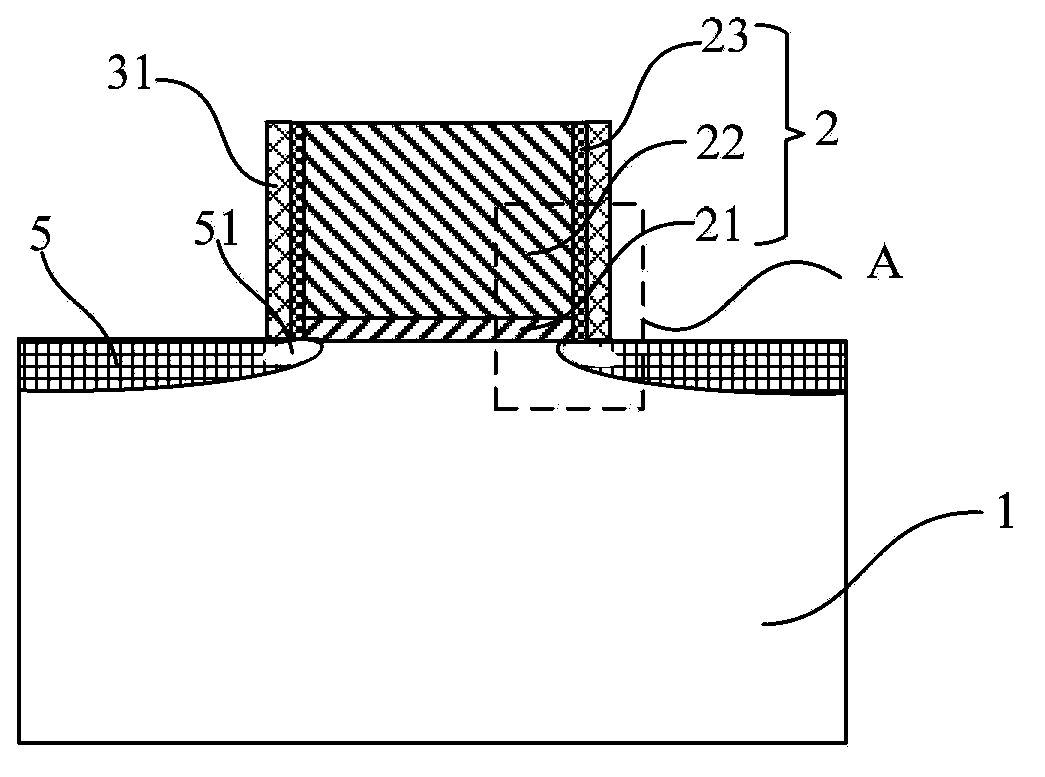

Method for manufacturing PMOS transistor

ActiveCN103985634AIncrease working currentImprove work performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowCharge carrier mobility

The invention provides a method for manufacturing a PMOS transistor. First of all, a second groove is formed through etching in a stress filling layer which is about to be predoped to prepare a source region and a drain region, the side wall of the second groove below a gate area being adjacent to a reserved part of a lightly doped source leakage extension area before the stress filling layer is formed, and afterwards, the second groove is filled so as to form an adjustment layer whose doping concentration is higher than that of the stress filling layer so that at the time when a source-drain area is prevented from generating break-through currents, the Ge and B doping concentrations on the surfaces of the source region and the drain region are improved; on one hand, the lost B doping impurities in the reserved part of the lightly doped source leakage extension area are supplemented, the B doping concentration of the lightly doped source leakage extension area is increased, the resistance of a channel region, the source region and the drain region is reduced, the electric field of the channel region is reduced, and the working currents are improved; and on the other hand, the stress applied to the channel region by the source region and the drain region is enhanced, the carrier mobility of the device channel region is improved, and the working currents of the PMOS transistor are increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP

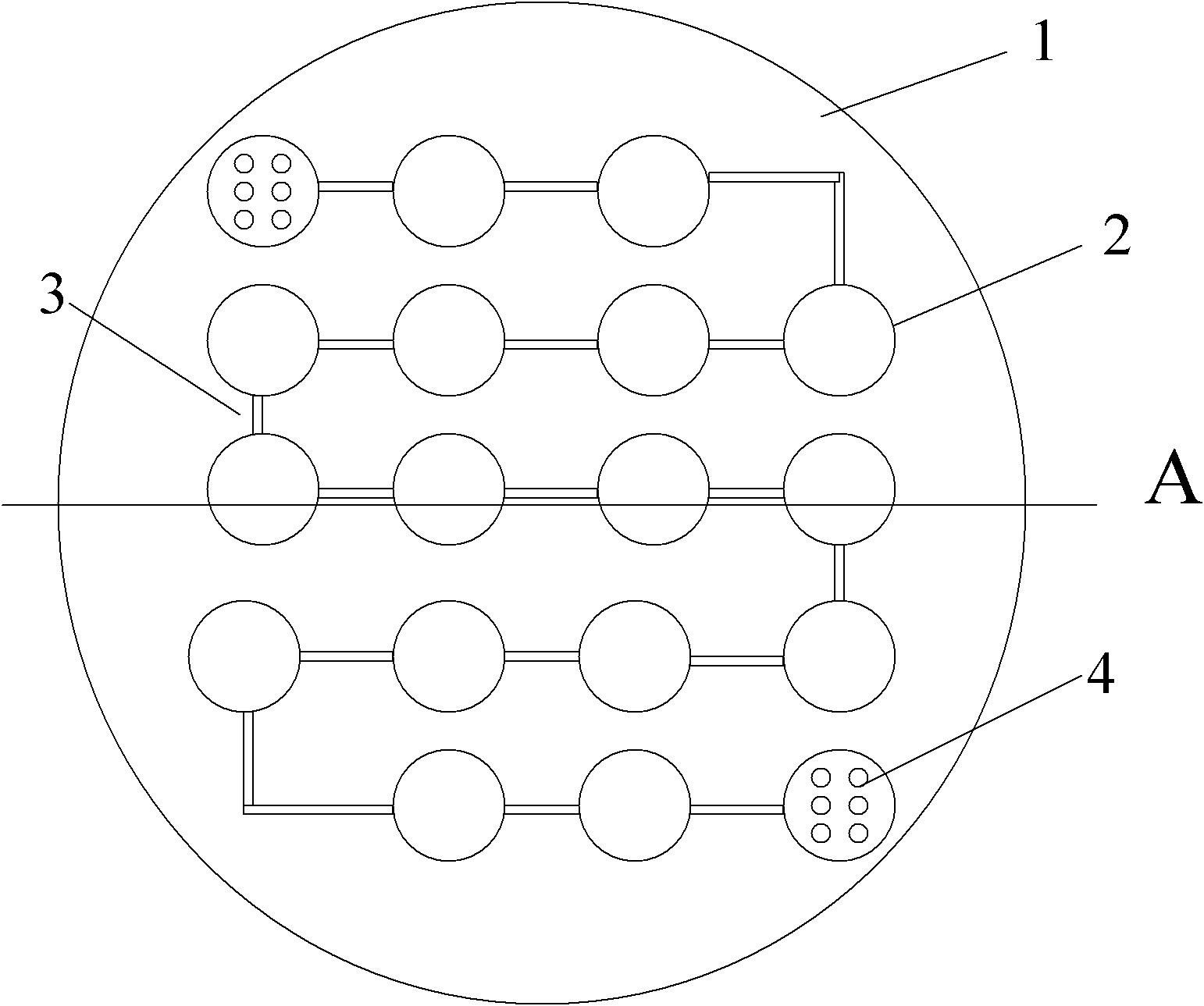

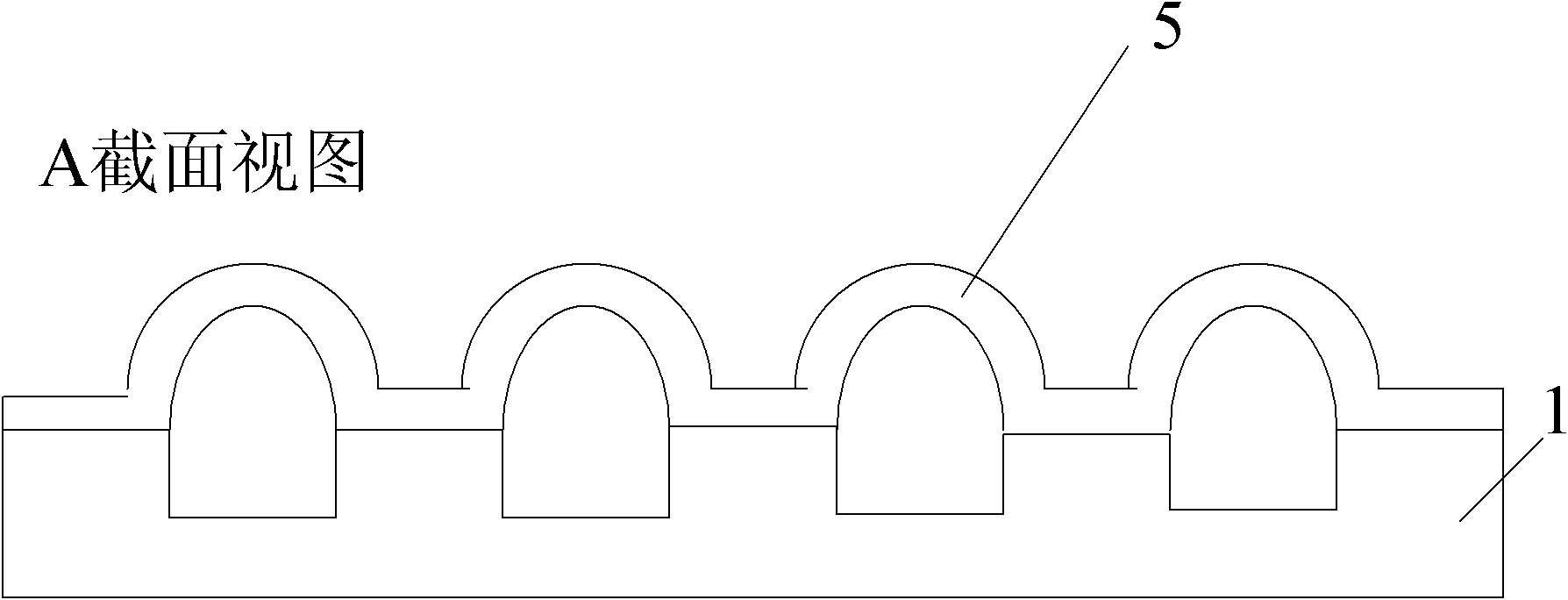

Method for packaging glass-silicon wafer-grade chiponboard (COB) of light emitting diode (LED)

ActiveCN102097545AReduce luminous attenuationImprove performanceSolid-state devicesSemiconductor devicesHeat resistanceSilica gel

The invention discloses a method for packaging a glass-silicon wafer-grade chiponboard (COB) of a light emitting diode (LED). The method comprises the following steps: 1, etching a silicon micro slot array with the micro slots communicated with each other through micro channels, and placing a proper amount of heat outgas agent in the micro slots; 2, performing anodic bonding on the Si wafer with patterns and the heat outgas agent and borosilicate glass wafer in air or in vacuum to form a sealed cavity; 3, heating and preserving heat to form a spherical glass micro cavity, cooling the cavity to normal temperature, annealing and removing silicon to obtain a wafer-grade glass micro cavity; 4, preparing a lead substrate; 5, mounting a chip and leading a wire; 6, carrying out wafer-grade bonding; and 7, filling silica gel to realize the wafer-grade packaging of the LED. By achieving the integration with the wafer-grade LED reflecting cup, the method reduces heat resistance and cost.

Owner:SOUTHEAST UNIV

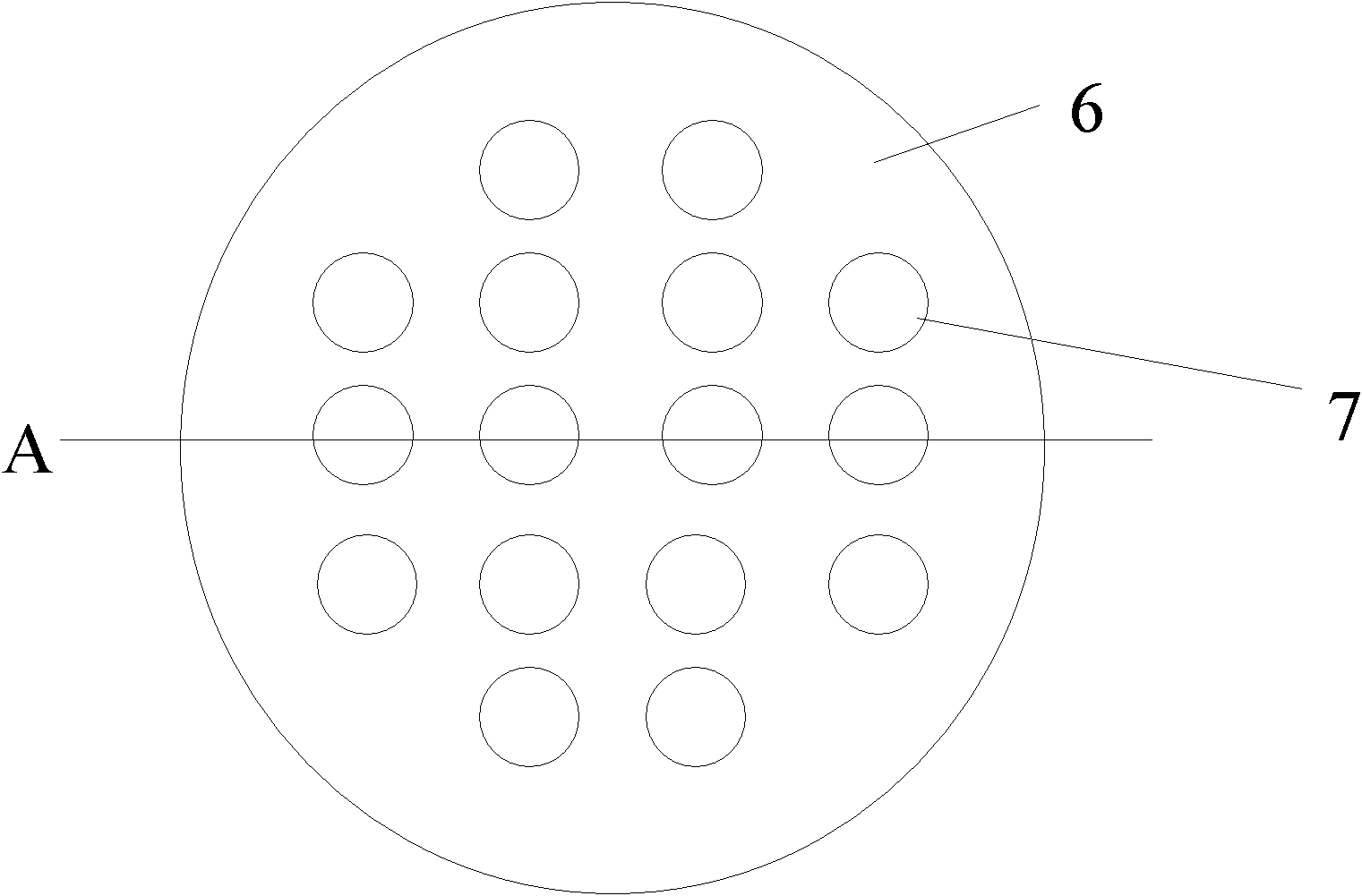

Method for packaging wafer level glass micro-cavity of light-emitting diode (LED)

ActiveCN102110750AReduce optical interfaceGood optical performanceSolid-state devicesSemiconductor devicesLed arrayLight beam

The invention discloses a method for packaging a wafer level glass micro-cavity of a light-emitting diode (LED), and the method comprises the following steps: (1) etching a micro-slot array corresponding to the pattern of a packaged LED array on a silicon wafer, wherein the micro-slots are communicated through a micro-channel, and a proper amount of heat gas releasing agent is arranged inside the micro-slots; (2) forming a closed cavity; (3) heating the bonded wafer in the air to form a spherical glass micro-cavity and a cylindrical glass micro-channel connected with the spherical glass micro-cavity, cooling to room temperature, annealing, and removing silicon to obtain a wafer level glass micro-cavity; (4) sputtering a metal layer on the silicon wafer, and preparing a metal lead through photolithography, so as to obtain a lead substrate, wherein the position of the metal lead corresponds to the position of the micro-channel of the glass micro-cavity; (5) mounting an LED chip on the lead substrate, and leading; (6) bonding the wafer level glass micro-cavity with the substrate to form a bonded wafer; and (7) filling the gap between the LED chip and the wafer level glass micro-cavity with silicone through the glass micro-channel. According to the invention, the light emitting efficiency is high, and a packaged glass lens realizes beam collimation.

Owner:SOUTHEAST UNIV

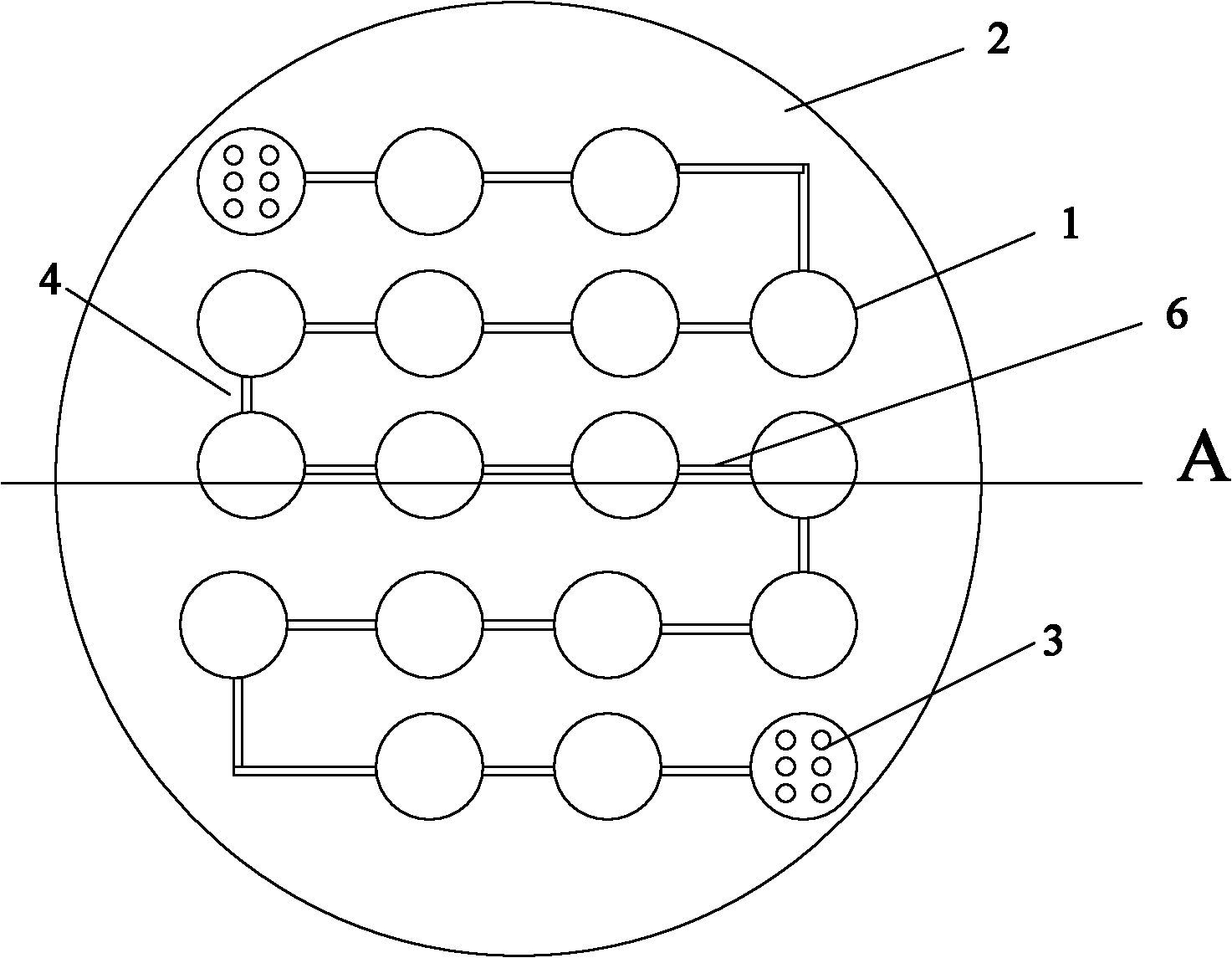

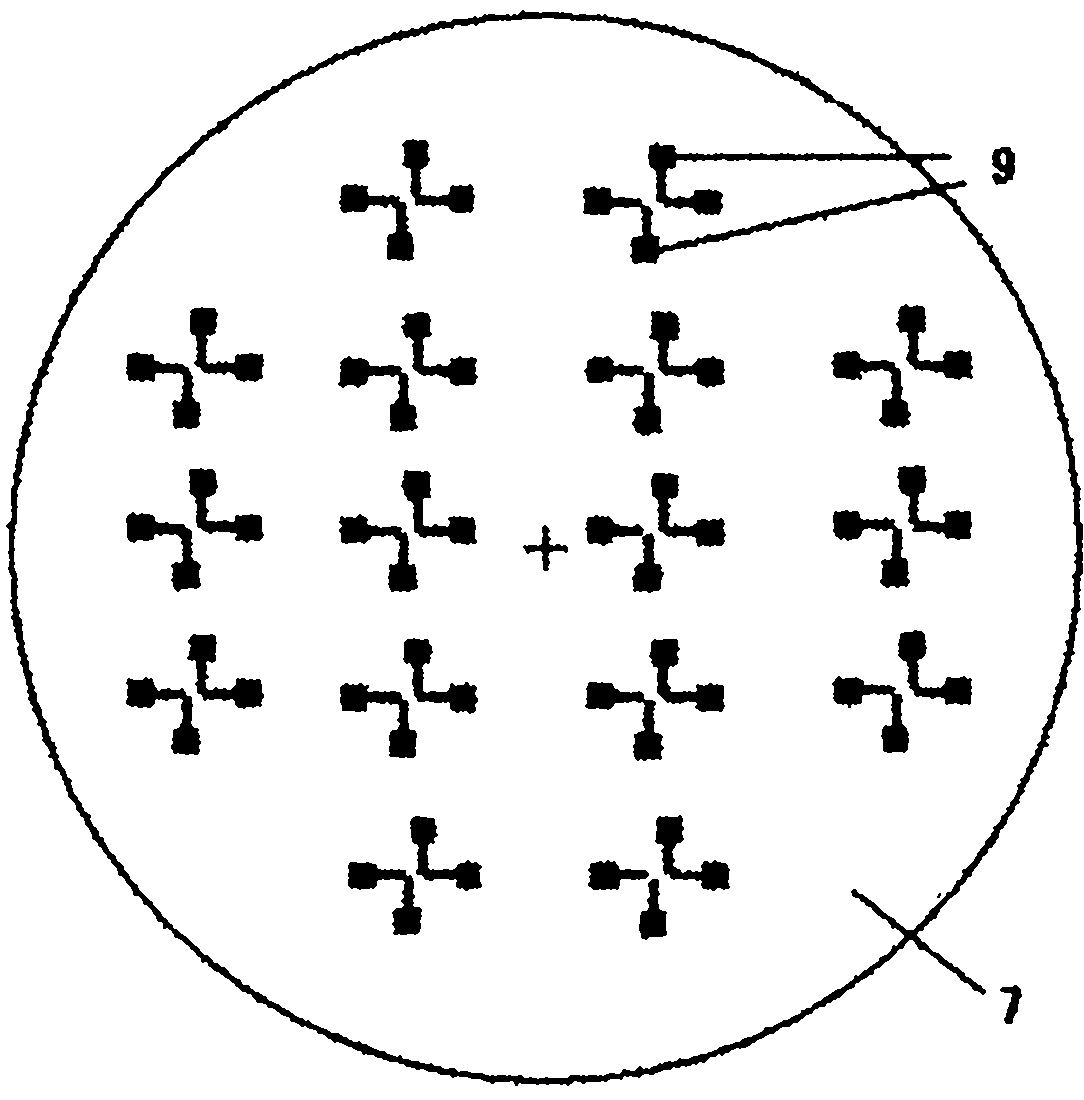

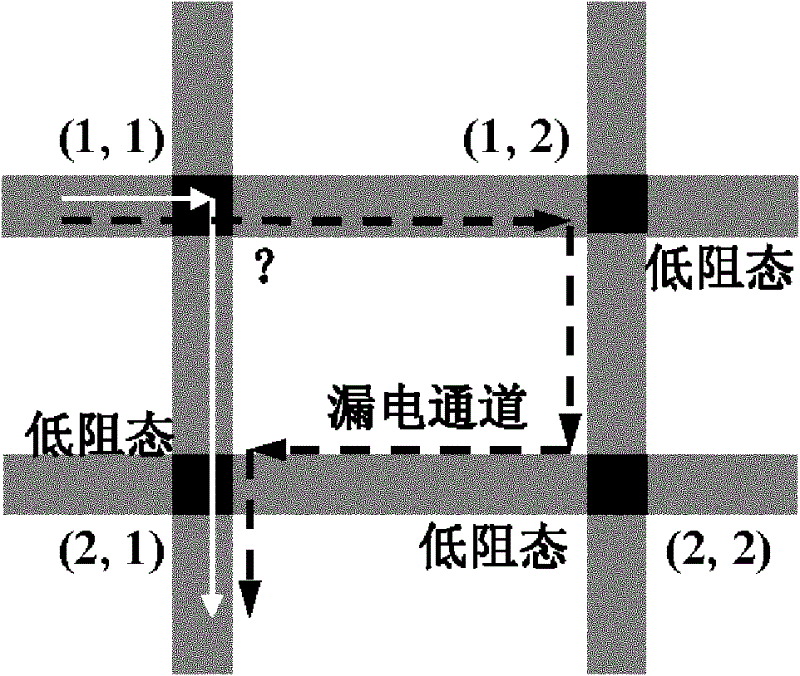

Resistive random access memory unit and resistive random access memory

ActiveCN102623045AReduce leakage pathIncrease working currentSolid-state devicesDigital storageStatic random-access memoryRandom access memory

The invention discloses a resistive random access memory unit and a resistive random access memory. The resistive random access memory unit comprises a resistive random access memory and a double-state resistor, wherein the resistive random access memory and the double-state resistor are connected in series. A positive electrode and a negative electrode of the double-state resistor all can provide large working currents and thus a leakage passage in an intersection array is reduced so that read crosstalk is eliminated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method and device for preparing metal powder in electro-deposition manner

The invention discloses a method and device for preparing metal powder in an electro-deposition manner, and belongs to the field of an electrochemical technology and equipment. According to the method and device, electrolyte is electrolyzed by adopting graphite felt or carbon felt as anode materials; and the form and the size of the metal powder deposited at cathodes can be adjusted by adjusting working currents. According to the method and device for preparing metal powder in an electro-deposition manner, the graphite felt or the carbon felt, which has an extremely large specific surface area, is adopted as an anode, so that the anode can obtain great working currents under the condition that the electric current density is extremely small, and phenomena of"air curtain" and electrolytic corrosion of conventional dense anode materials can be avoided; and besides, the graphite felt or the carbon felt is easy to cut and can be spliced, so that the anode is extremely convenient to make; additionally, the electric current density of the cathode is increased, so that a cathode product is changed from compact into loose, the shape of the cathode product is changed from blocks or tablets into particles or powder, and in terms of form, the cathode product is changed from big to small, and a metal powder collecting mechanism is facilitated to continuously and automatically collect cathode metal powder.

Owner:黄芃 +2

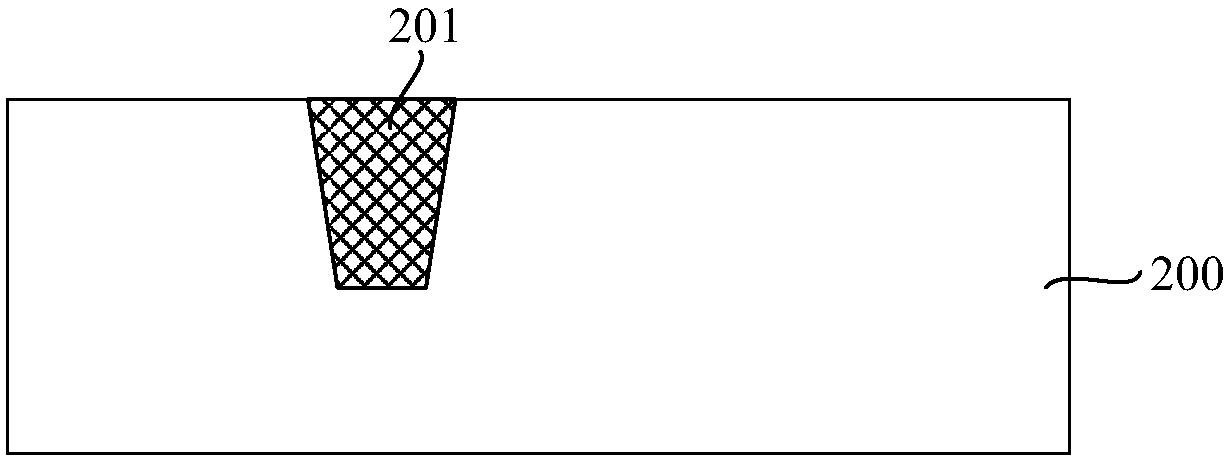

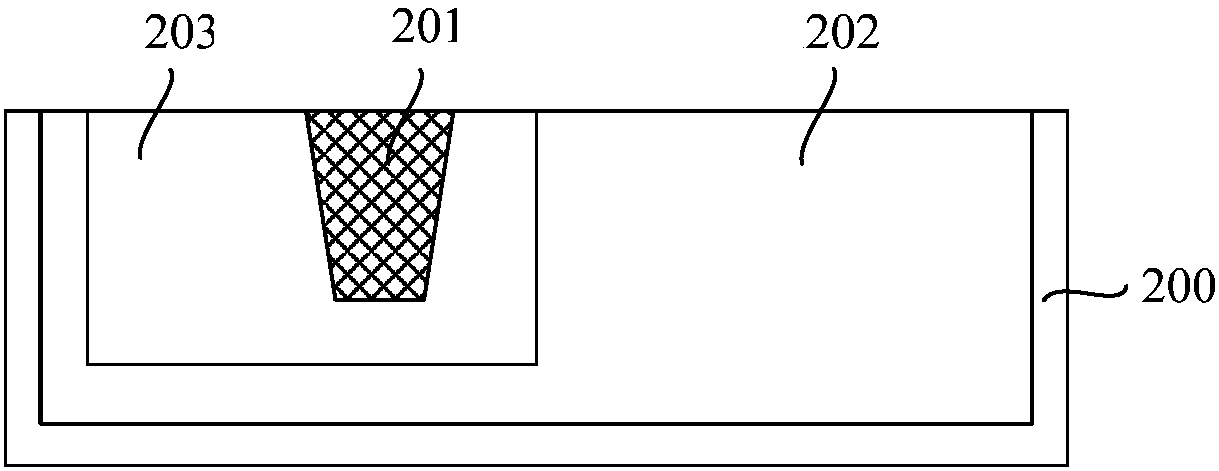

Tunneling field effect transistor and forming method thereof

ActiveCN104425593AIncrease working currentImprove driving abilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSemiconductor

A tunneling field effect transistor and a forming method thereof are provided. The tunneling field effect transistor comprises a semiconductor substrate including a fin, a gate structure across the middle of the fin, a source across one end of the fin, and a drain disposed at the other end of the fin, wherein the conductivity type of the drain is a first conductivity type, and the conductivity type of the source is a second conductivity type different from the first conductivity type. The PN junction tunneling area of the tunneling field effect transistor provided by the invention is large, the working current of the tunneling field effect transistor is high, and the response speed of a device including the tunneling field effect transistor is increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP

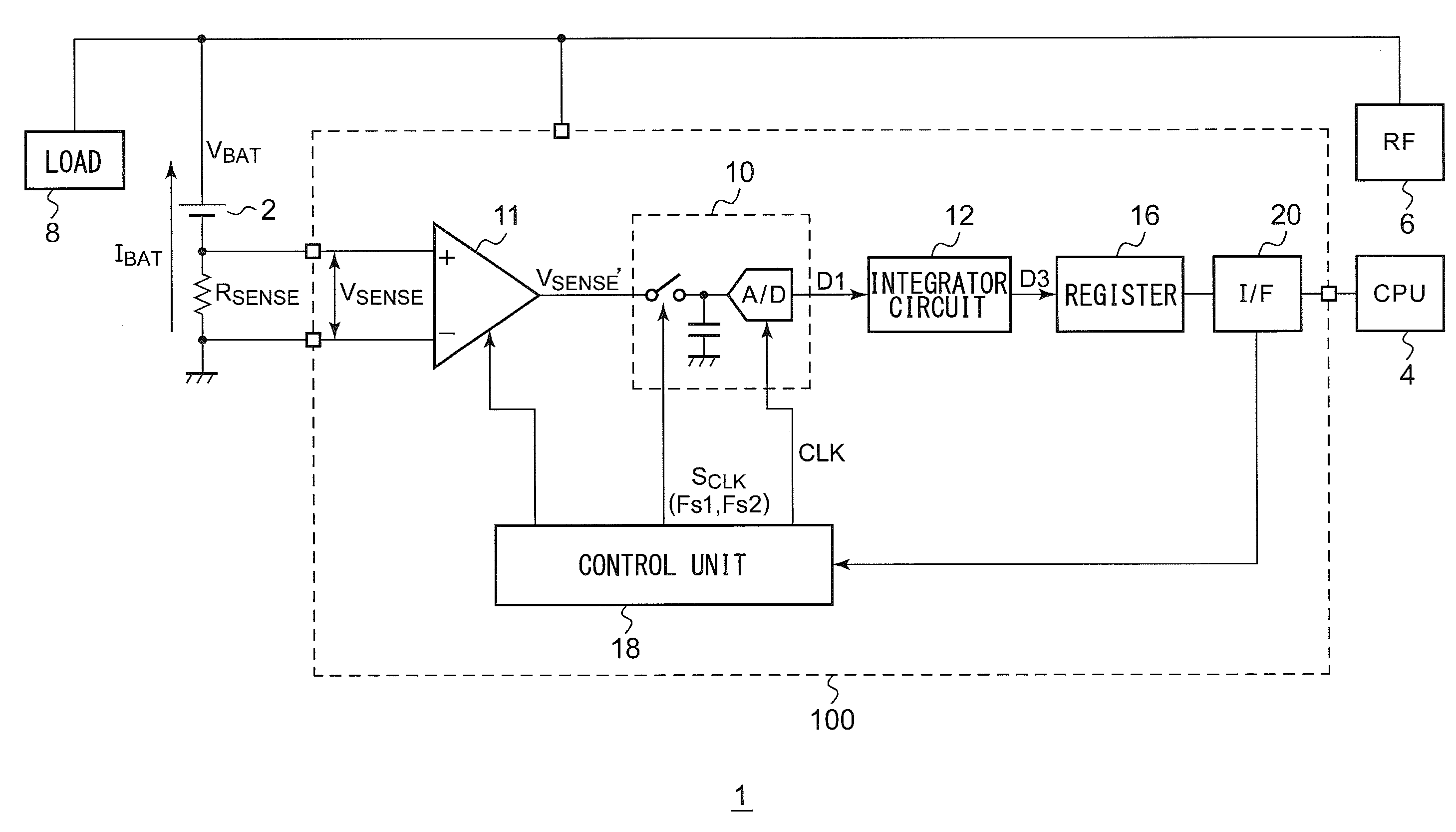

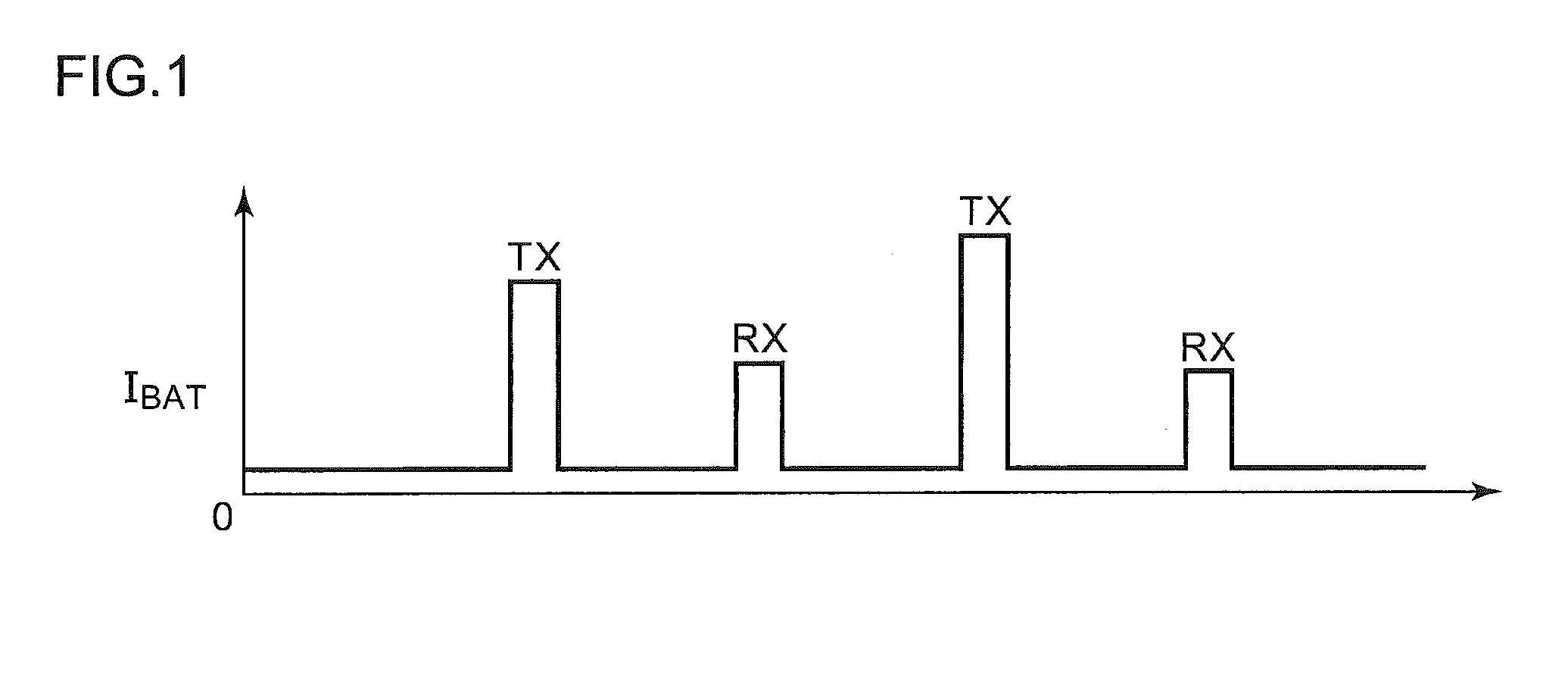

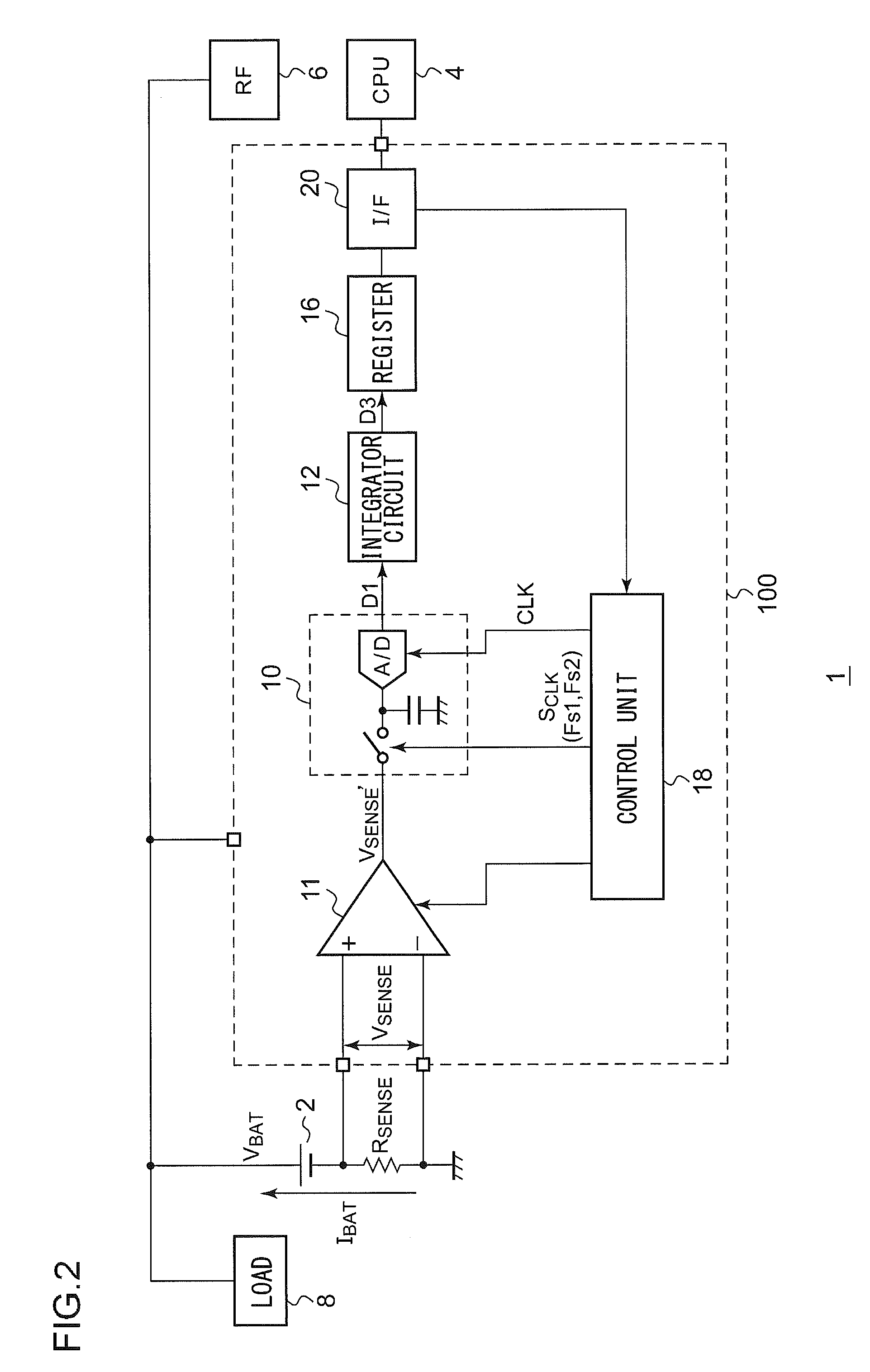

Battery fuel gauge circuit

ActiveUS20120203484A1Reduce the amount of calculationReduction in numberPower managementSecondary cellsElectrical batteryInterface circuits

A detection circuit is mounted on an electronic device having a communication function, including at least a battery, a CPU, and a communication unit, and is configured to detect the remaining battery charge. An A / D converter performs sampling of a magnitude of a current IBAT discharged from the battery, and converts the current IBAT thus sampled into a digital current value. An interface circuit receives, from the CPU, control data which indicates a period in which there is an increase in the current discharged from the battery. Based upon the control data, a control unit raises the sampling frequency of the A / D converter in the period in which there is an increase in the current IBAT.

Owner:ROHM CO LTD

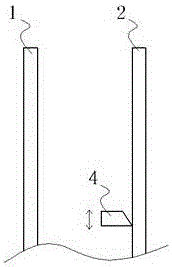

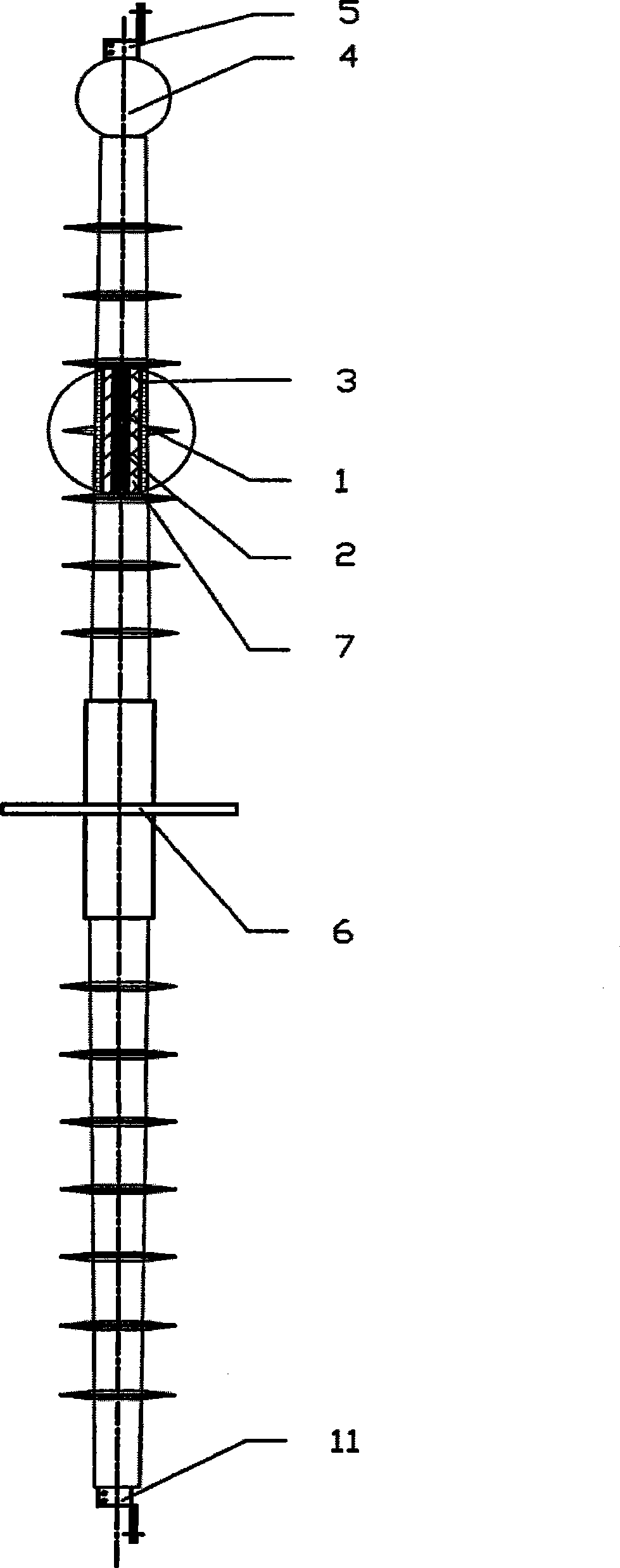

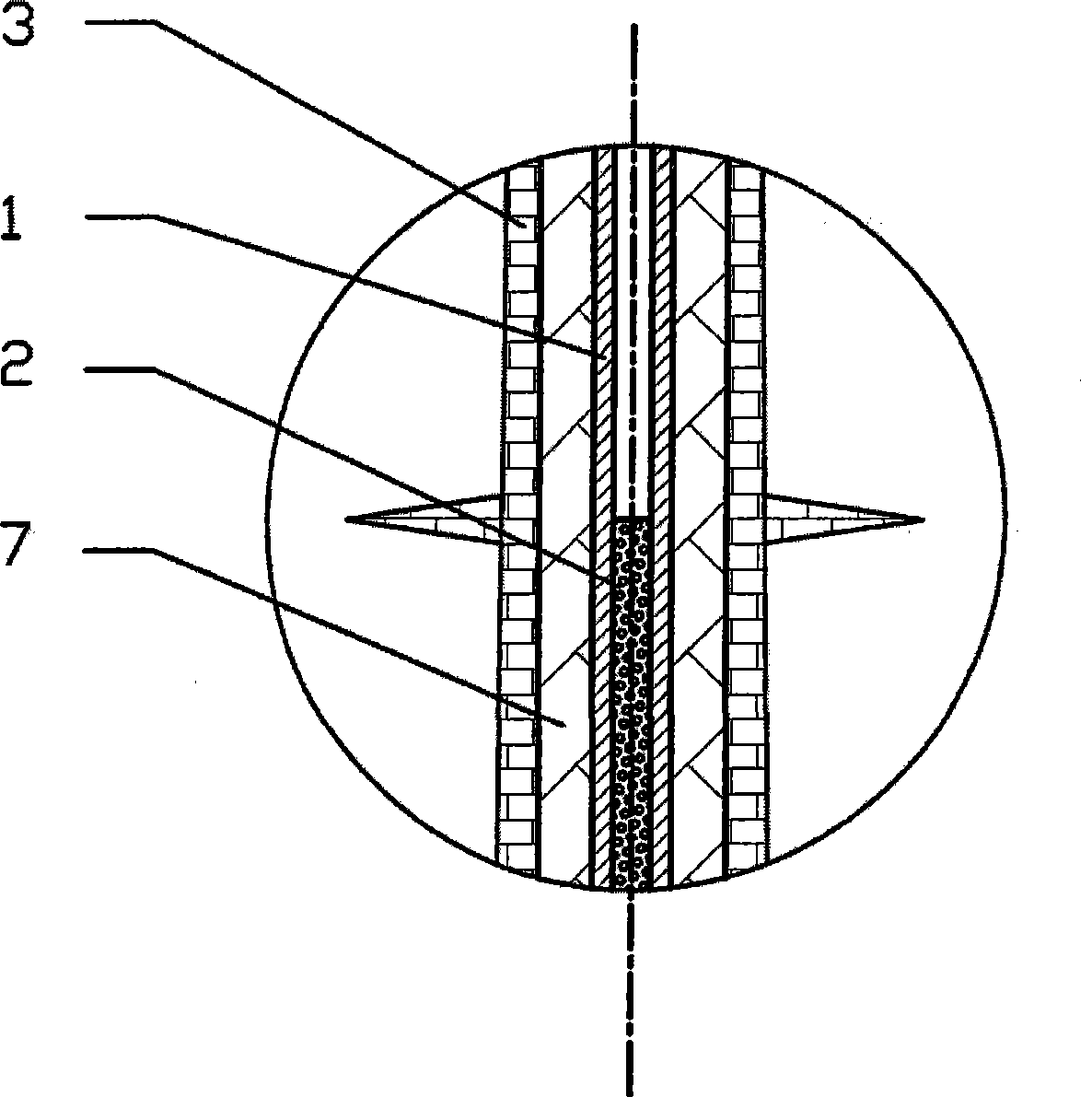

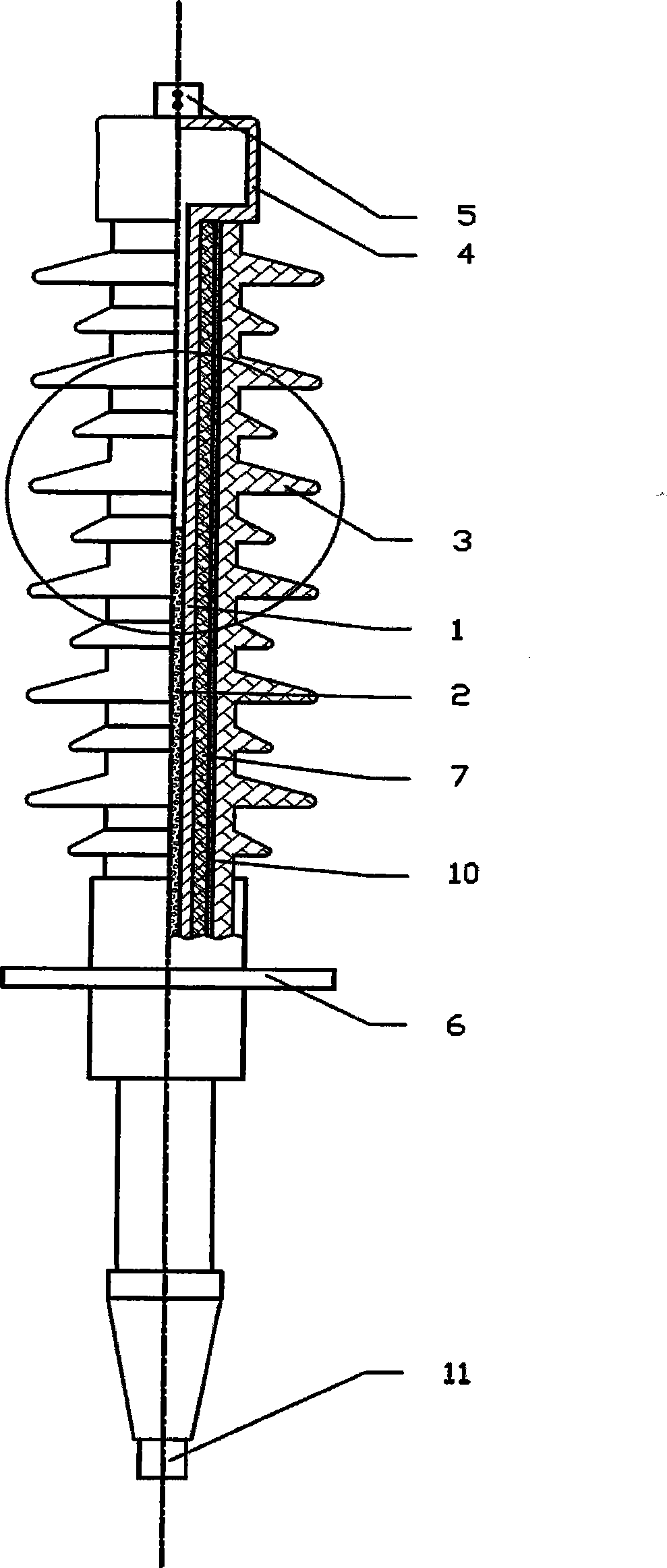

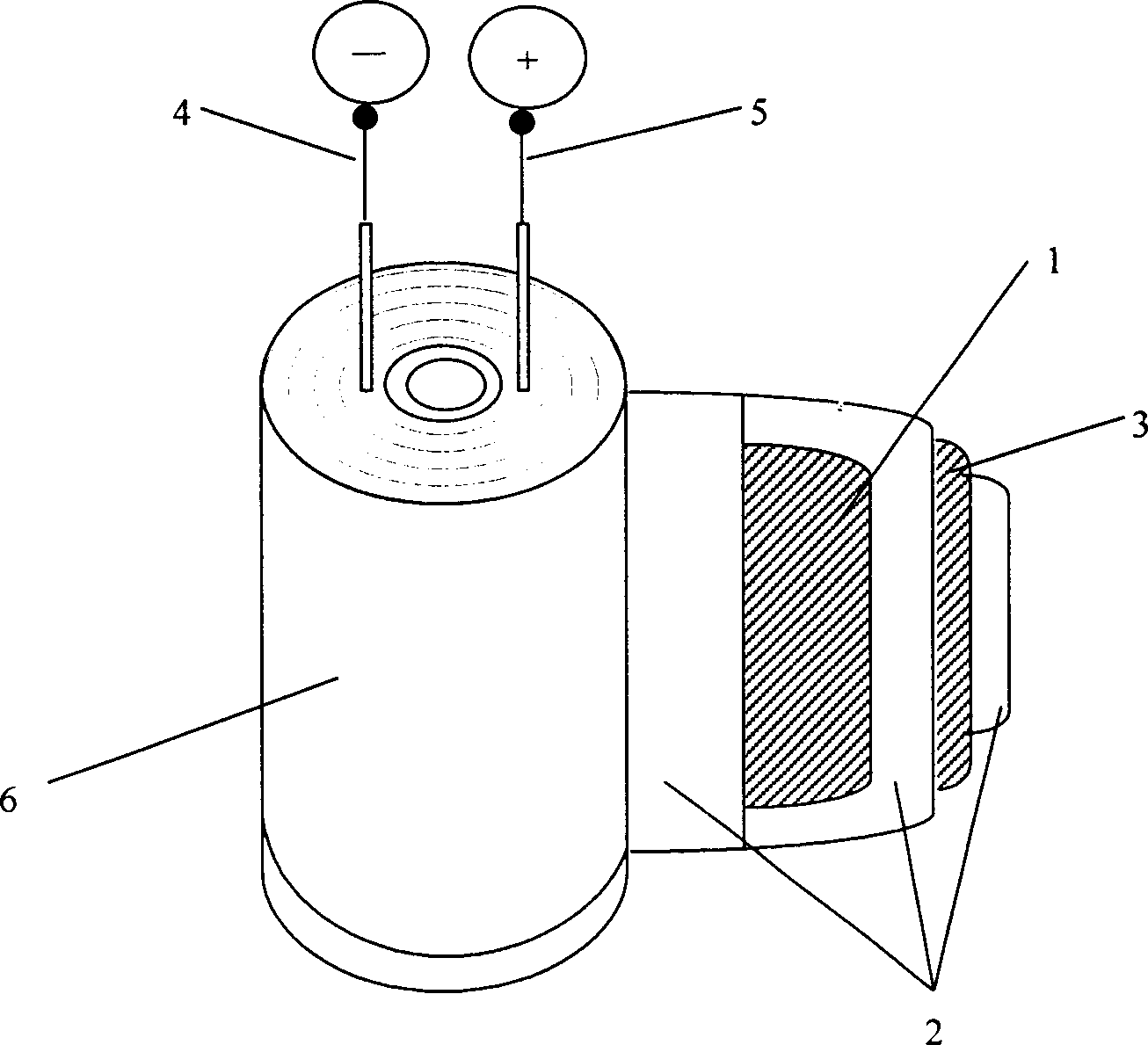

Heat pipe type transformer tube

InactiveCN101369483AImprove cooling effectIncrease working currentTransformers/inductances coils/windings/connectionsTransformerEngineering

A heat-tube type transformer bushing comprises a conduction tube 1, a radiator 4, a main insulating layer 7, an insulating external bushing 3 and a connection flange 6. The conduction tube 1 is a hollow metal tube, one end of which is connected with the radiator 4, the other end of which is connected with a connecting terminal 11. Non-combustible environment protection type cooling fluid 2 is filled in the conduction tube 1. The radiator 4 is a hollow metal cavity, the cavity internal is connected with the internal cavity of the conduction tube to form an enclosed cavity. The main insulating layer 7 winds the external of the conduction tube 1, the insulating external bushing 3 and the connection flange 6 are bushed in the outside of the main insulating layer 7. The invention has advantages of no combustion and explosion hidden troubles, low temperature rise, small volume and light weight.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

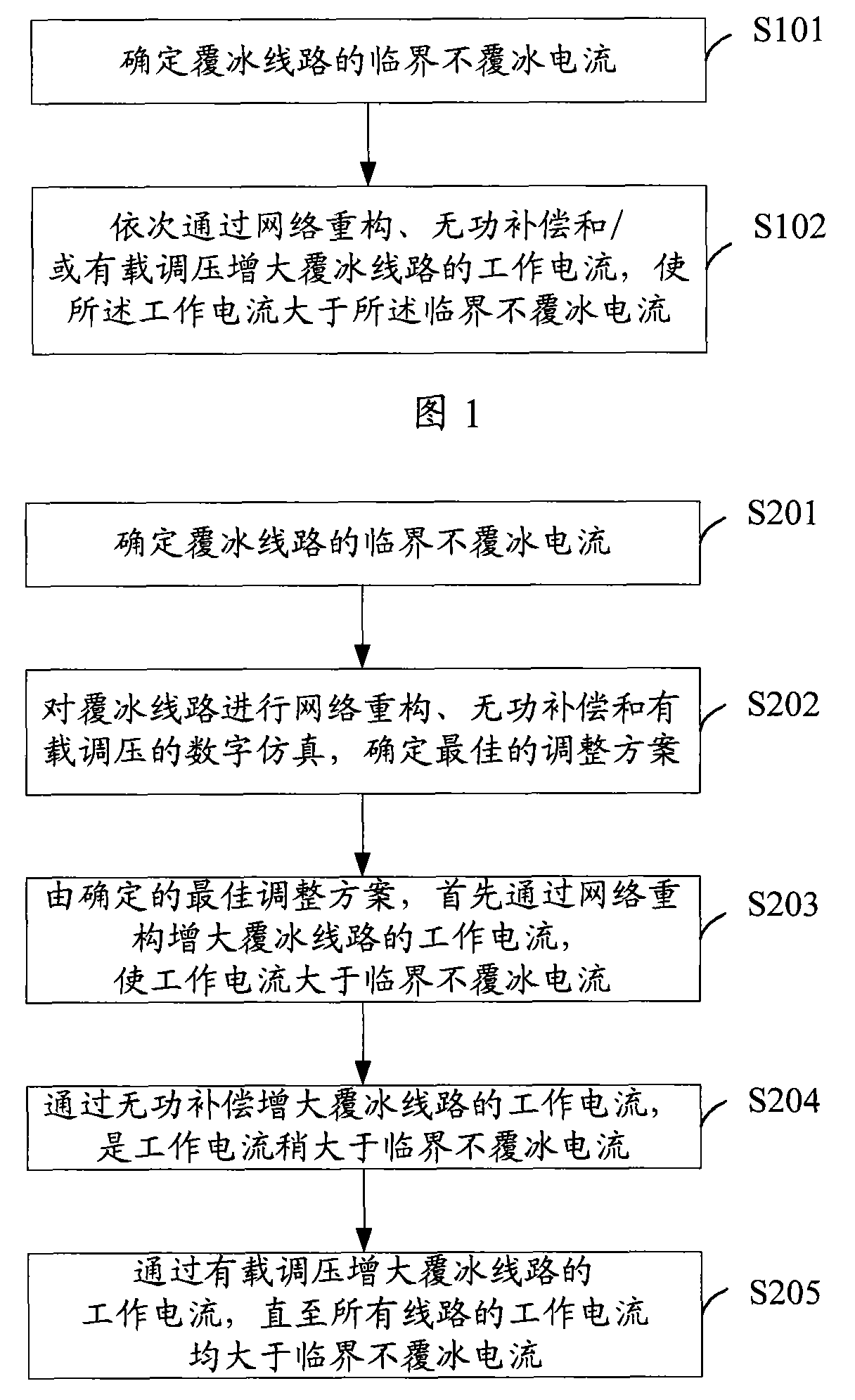

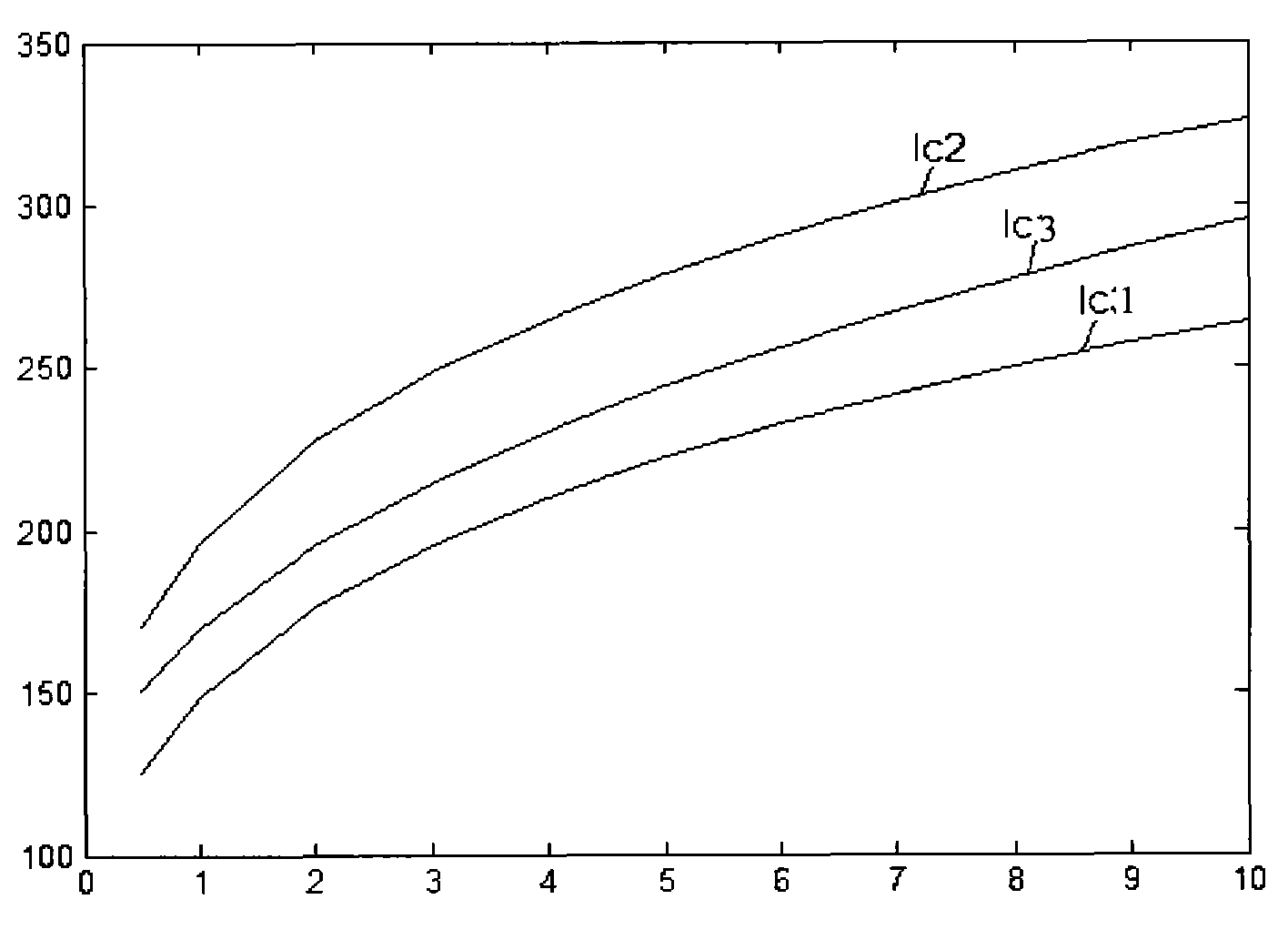

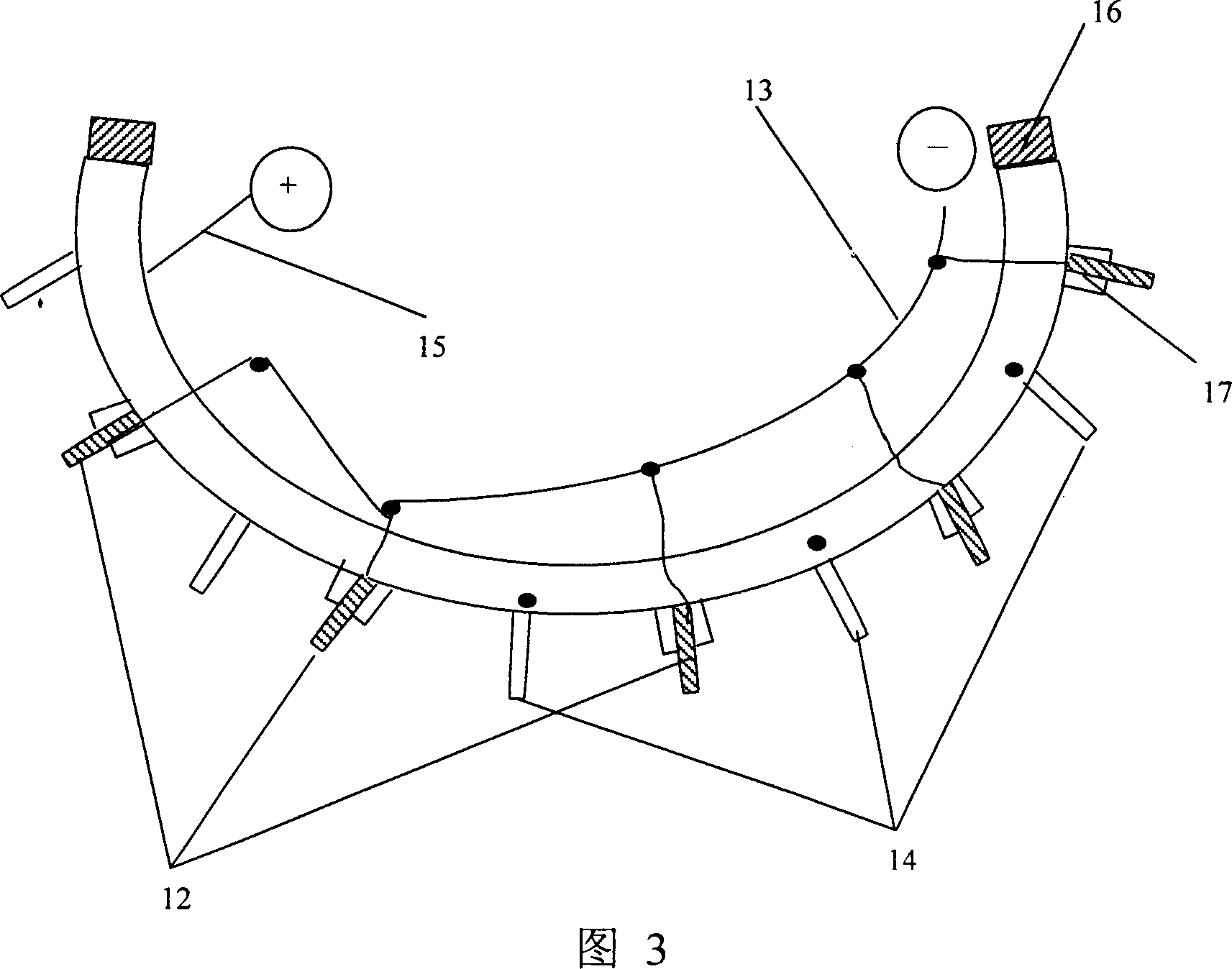

Method and device for preventing ice coating in electric transmission line

ActiveCN101656407AIncrease working currentAvoid formingOverhead installationApparatus for overhead lines/cablesTransmission lineMaterial resources

The invention provides a method and a device for preventing ice coating in an electric transmission line. The method comprises the following steps: determining the critical non-ice-coating current ofan ice coating line; increasing the working current of the ice coating line by network reconstruction, reactive compensation and / or active pressure regulation sequentially and enabling the working current to be greater than the critical non-ice-coating current. The invention balances heat required by the ice coating of the line by enhancing the working current of the line through the heat of linepower loss generated by the working current, thereby destroying a formation condition of the ice coating and preventing the formation of the ice coating of the line. The invention also provides the device for preventing the ice coating in the electric transmission line. Before ice coating, the invention carries out defence and avoids the formation of the ice coating, thereby the large input of manpower and material resources after ice coating can be avoided, the cost is low, and the economic benefit is good; moreover, the invention can prevent ice coating without interrupting the operation ofthe electric transmission line, thereby the normal operation of the industrial and agricultural production can be ensured.

Owner:STATE GRID CORP OF CHINA +1

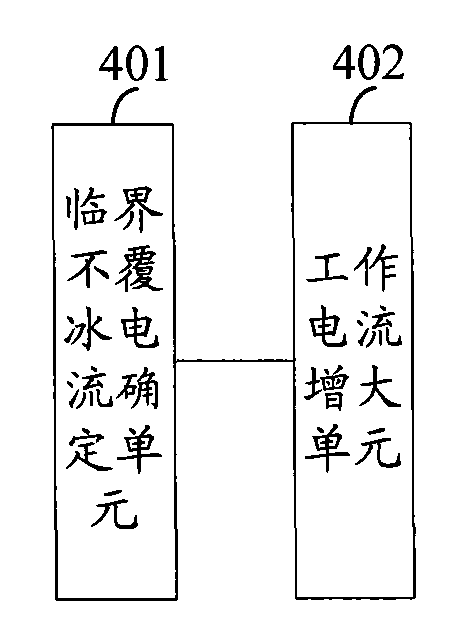

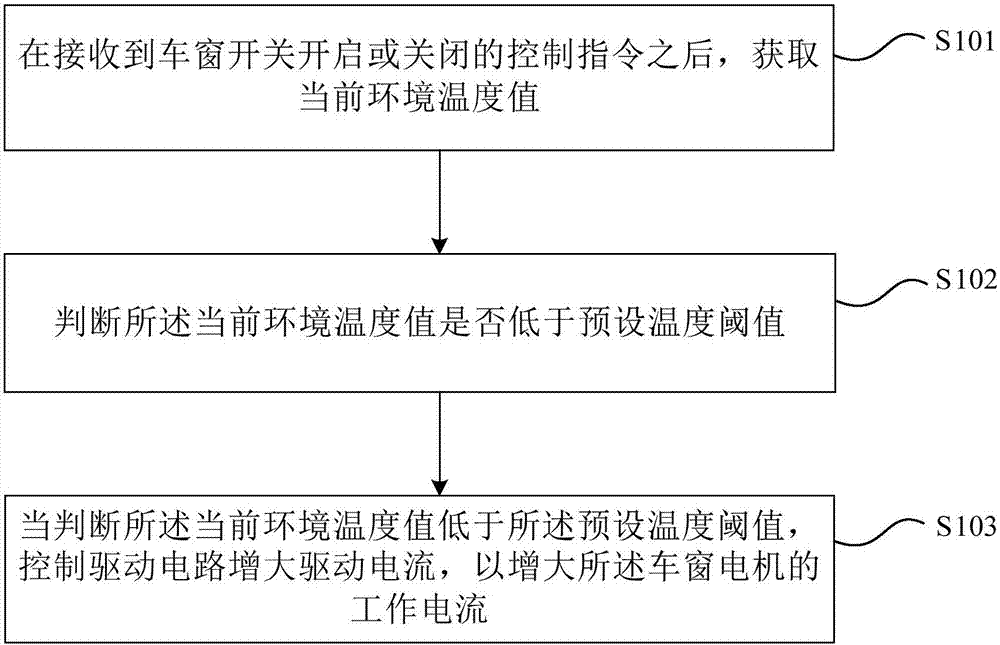

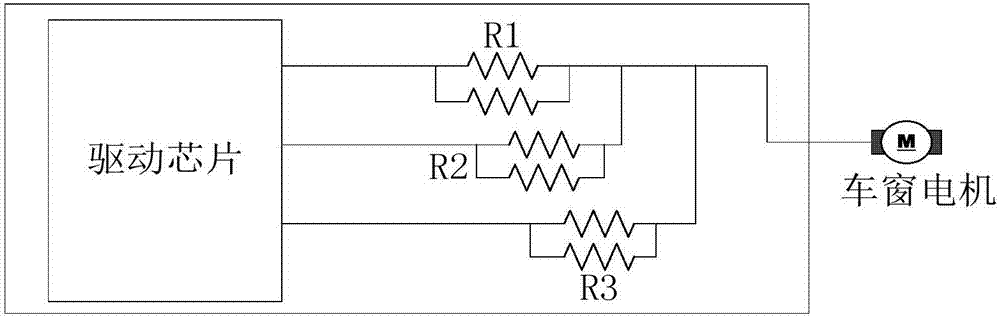

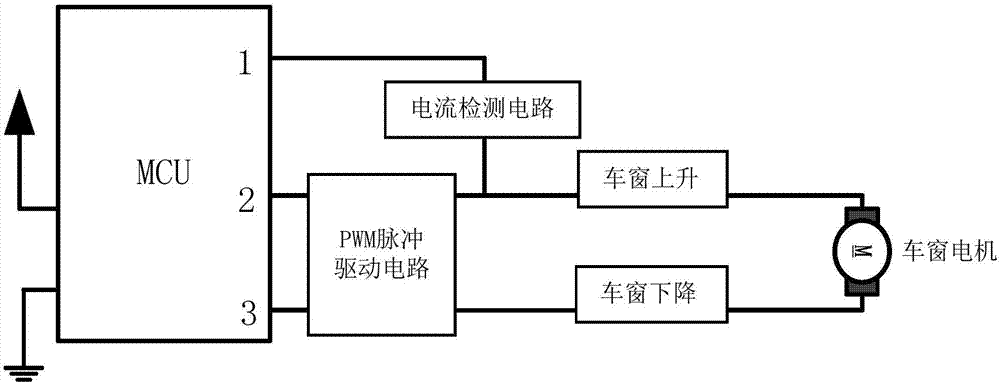

Automobile window motor control method and system and automobile

ActiveCN107060566AIncrease output powerAvoid stuckPower-operated mechanismAutomotive engineeringPower flow

The invention provides an automobile window motor control method and system and an automobile. The current environment temperature value is obtained, and whether the current environment temperature value is lower than a preset temperature threshold value or not is judged; and when it is judged that the current environment temperature value is lower than the preset temperature threshold value, a driving circuit is controlled to increase a driving current so as to increase a working current of an automobile window motor. By increasing the driving current, the output power of the automobile window motor is increased correspondingly to enough drive an automobile window to overcome operation resistance, so that clamping is avoided, the situation that clamping of the automobile window causes rotating blocking of the automobile window motor, so that the current in the circuit is increased rapidly to reach the rotating blocking threshold value of the automobile window motor is further avoided, and namely, smooth opening or closing of the automobile window in a cold environment can be achieved.

Owner:BAIC MOTOR CORP LTD

Seawater battery

InactiveCN1391300ASmall environmental effectImprove environmental performancePrimary cell electrodesImmersion cellsEngineeringSeawater

A seawater battery has cathode and anode isolated from each other. Said anode is made of Mg-alloy. Said cathode is a nno-soluble electric conducting substrate modified by AgCl, CuCl2, AgO, Ag2O, or electrically conductive high-molecular film. Its advantages are simple structure, high weight, small size, high working current, and high environment protection effect.

Owner:SOUTH CHINA UNIV OF TECH

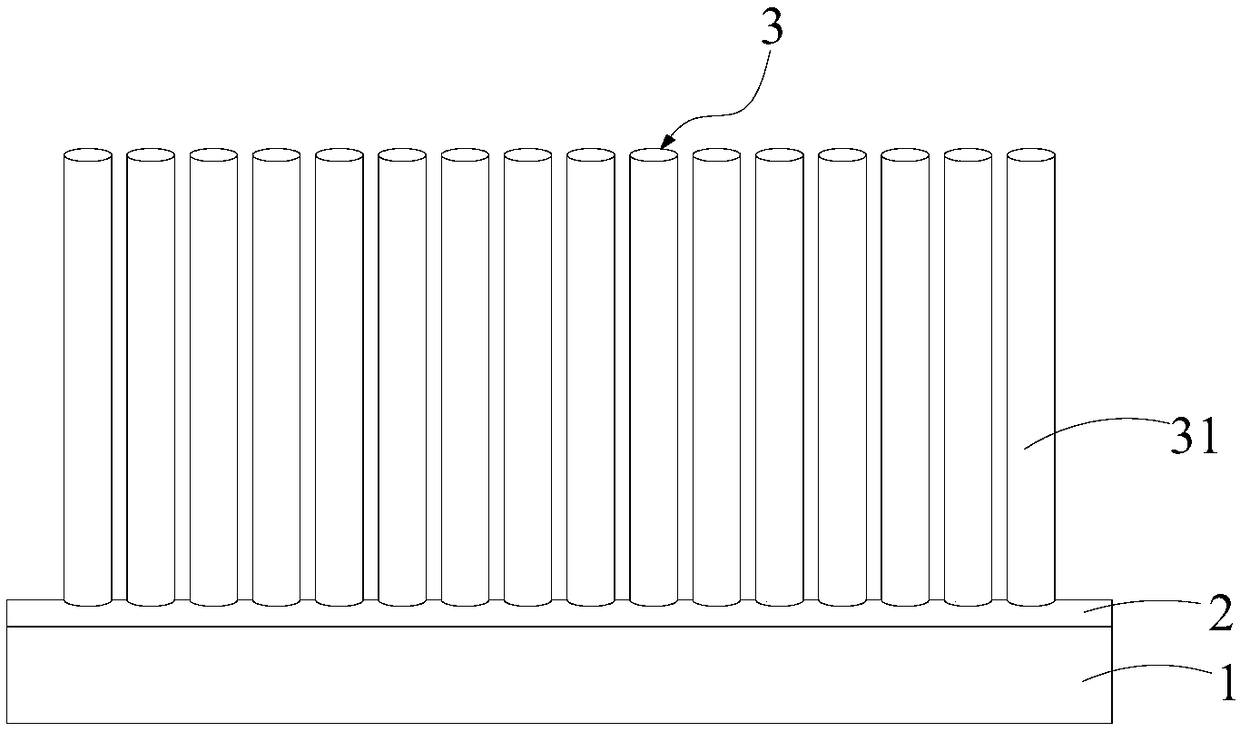

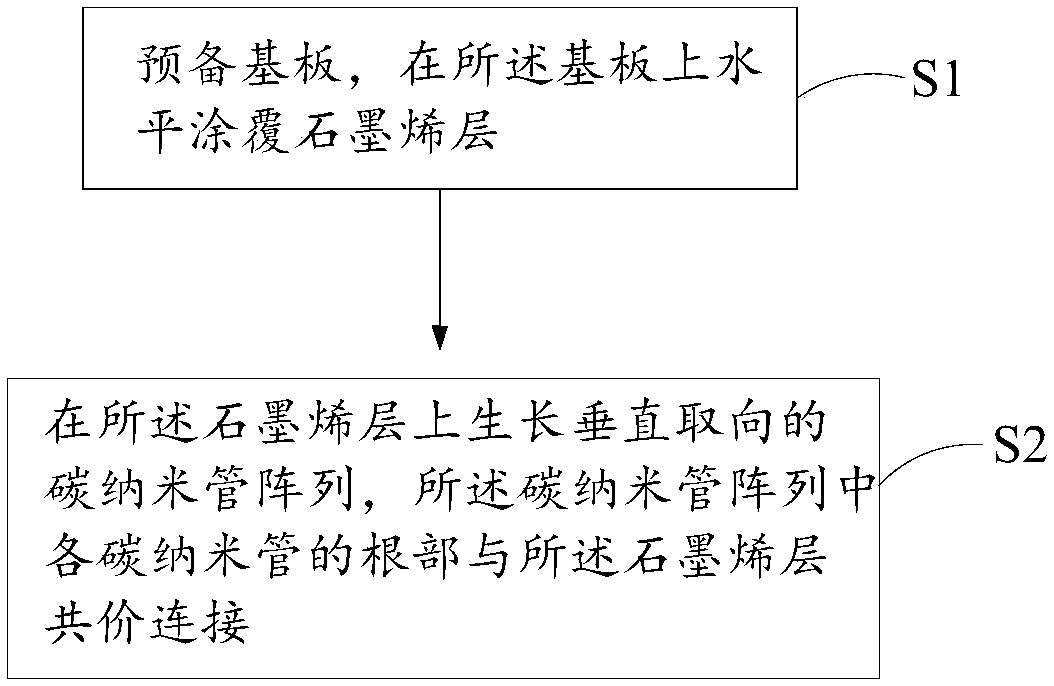

Carbon-nano-field emission cathode and manufacturing method and application

ActiveCN108172488ALaunch stableReduce the turn-on electric fieldCathode ray tubes/electron beam tubesX-ray tube electrodesElectrical resistance and conductancePower flow

The invention, which relates to the technical field of field emission, provides a carbon-nano-field emission cathode and a manufacturing method and application. The carbon-nano-field emission cathodecomprises a substrate, a graphene layer horizontally coated on the substrate, and a carbon nanotube array arranged on the graphene layer. Roots of all carbon nanotubes in the carbon nanotube array arein covalent linkage with the graphene layer. According to the invention, because the roots of all carbon nanotubes are in covalent linkage with the graphene layer, the interface resistance is extremely low and thus the carbon nanostructure has excellent conductivity, so that the opening electric field of the cathode is reduced obviously; the heat generated during the field emission process is lowand thus the cathode can be emitted stably at the high current, so that the operating current of the cathode is improved substantially. Moreover, because the three-dimensional covalent structure hasexcellent thermal conductivity, the emission stability of the cathode is improved.

Owner:SHENZHEN INST OF ADVANCED TECH

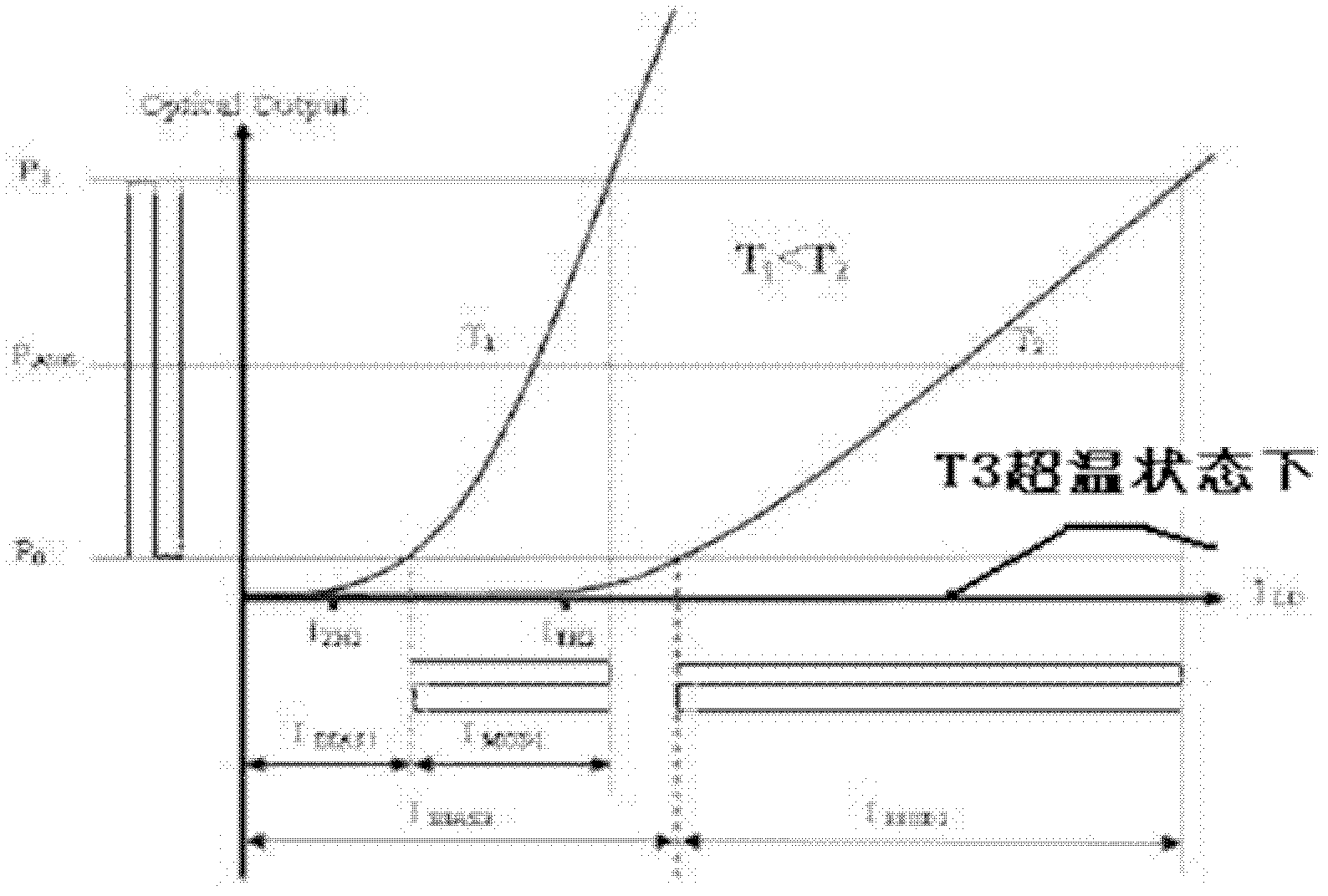

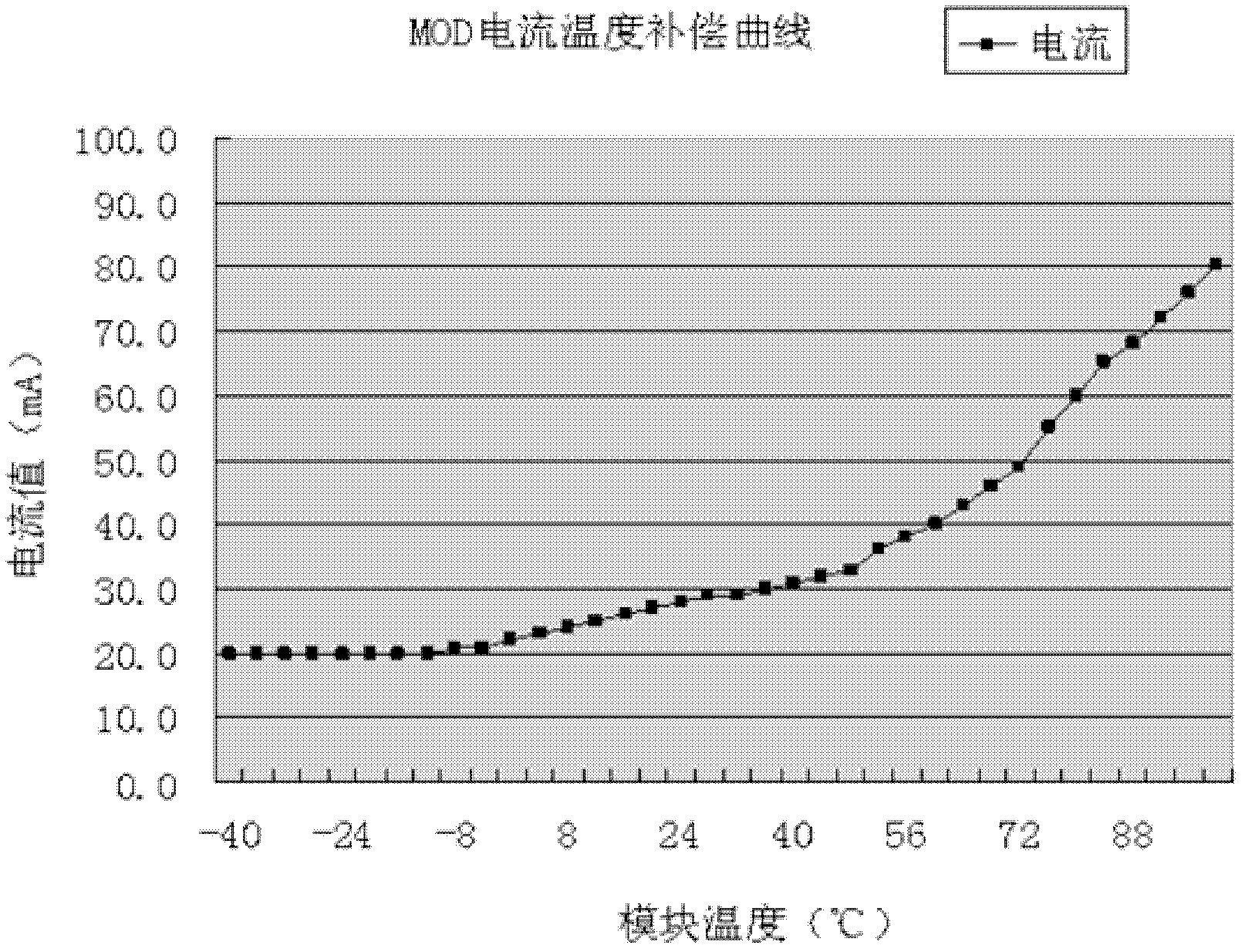

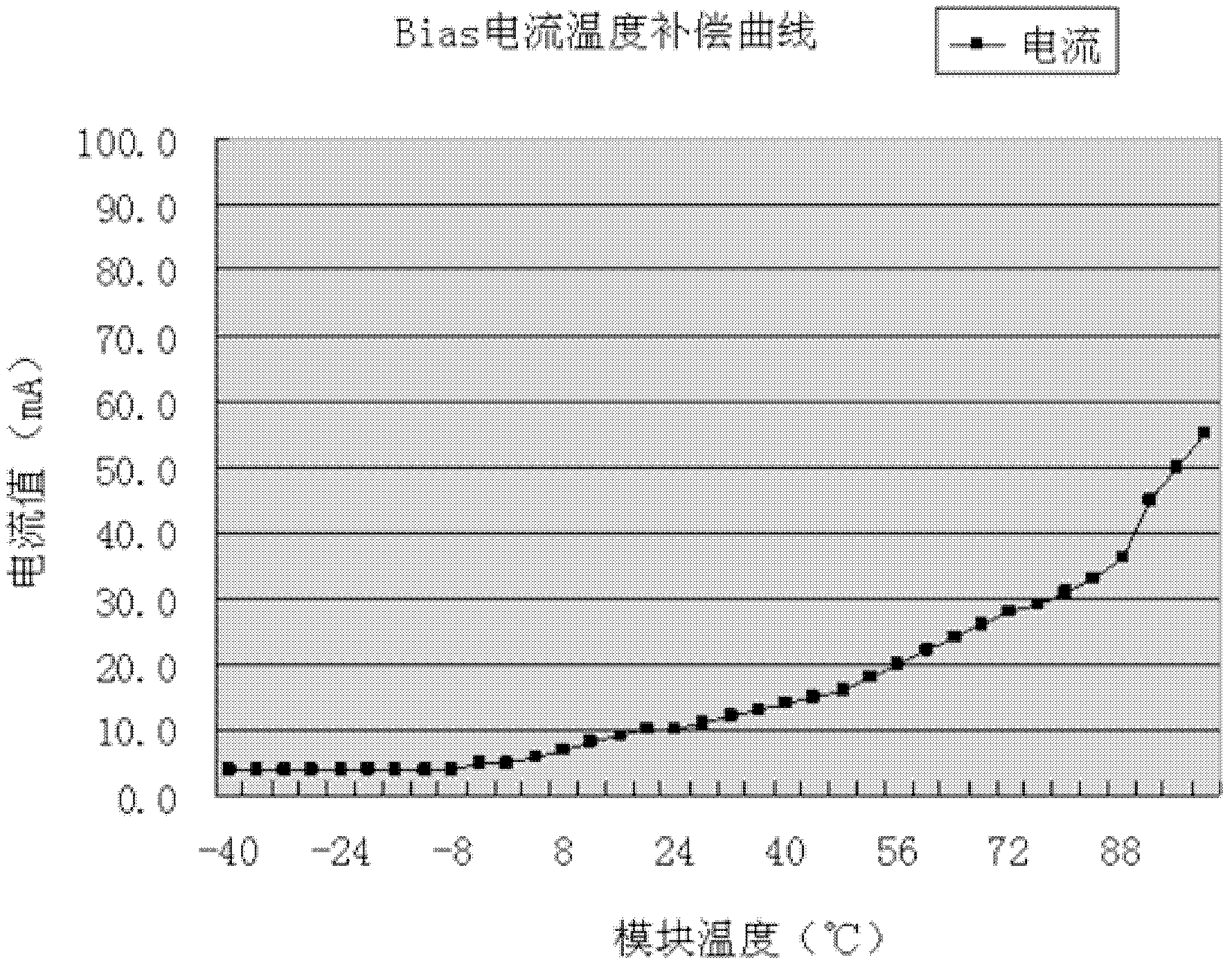

Intelligent guarantee method for optical module in high temperature environment

InactiveCN102361217AIncrease working currentProgramme controlLaser detailsOptical ModuleComputer module

The invention discloses an intelligent guarantee method for an optical module in a high temperature environment. The method comprises the following steps of: setting the highest set temperature for the optical module; when the optical module works in the high temperature environment, tracking and sampling the working temperature and the working current of the optical module; when the working temperature of the optical module exceeds the highest set temperature, stopping increasing the working current of a laser, so that the working temperature of the optical module does not increase any longer; setting the maximum current value for the working current of the laser; and when the working current of the laser exceeds the maximum current value, revising the working current of the laser into the maximum current value, so as to protect the optical module at high temperature.

Owner:JIANGSU ALLRAY

Field-effect transistor and preparation method thereof

InactiveCN101887917AIncrease working currentFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesP–n junctionField-effect transistor

The invention belongs to the technical field of micro electronic appliances and in particular discloses an asymmetrical source and drain field-effect transistor and a preparation method thereof. The field-effect transistor structure comprises a semiconductor substrate, a grid structure, a source region and a drain region, wherein the source region has a mixed junction and the drain region has a PN junction respectively; the source region and the drain region are structurally asymmetrical; one of the source region and the drain region consists of the PN junction, and the other one consist of the mixed structure; and the mixed junction consists of a Schottky junction and the PN junction. The position of a doping region formed by ion injection is controlled by changing the inclination angle of the ion injection and the unique structure of the asymmetrical source and drain field-effect transistor is formed.

Owner:FUDAN UNIV

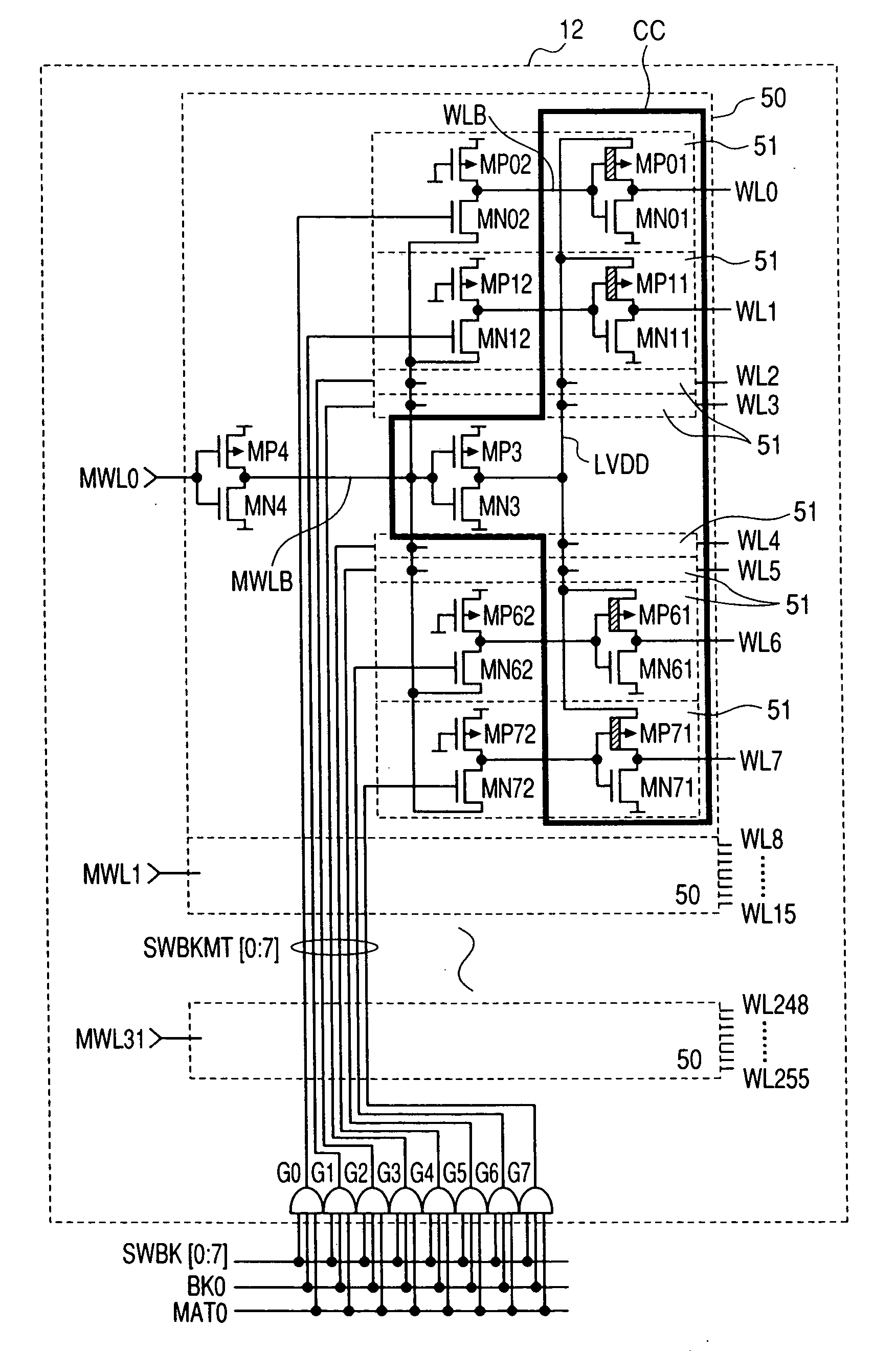

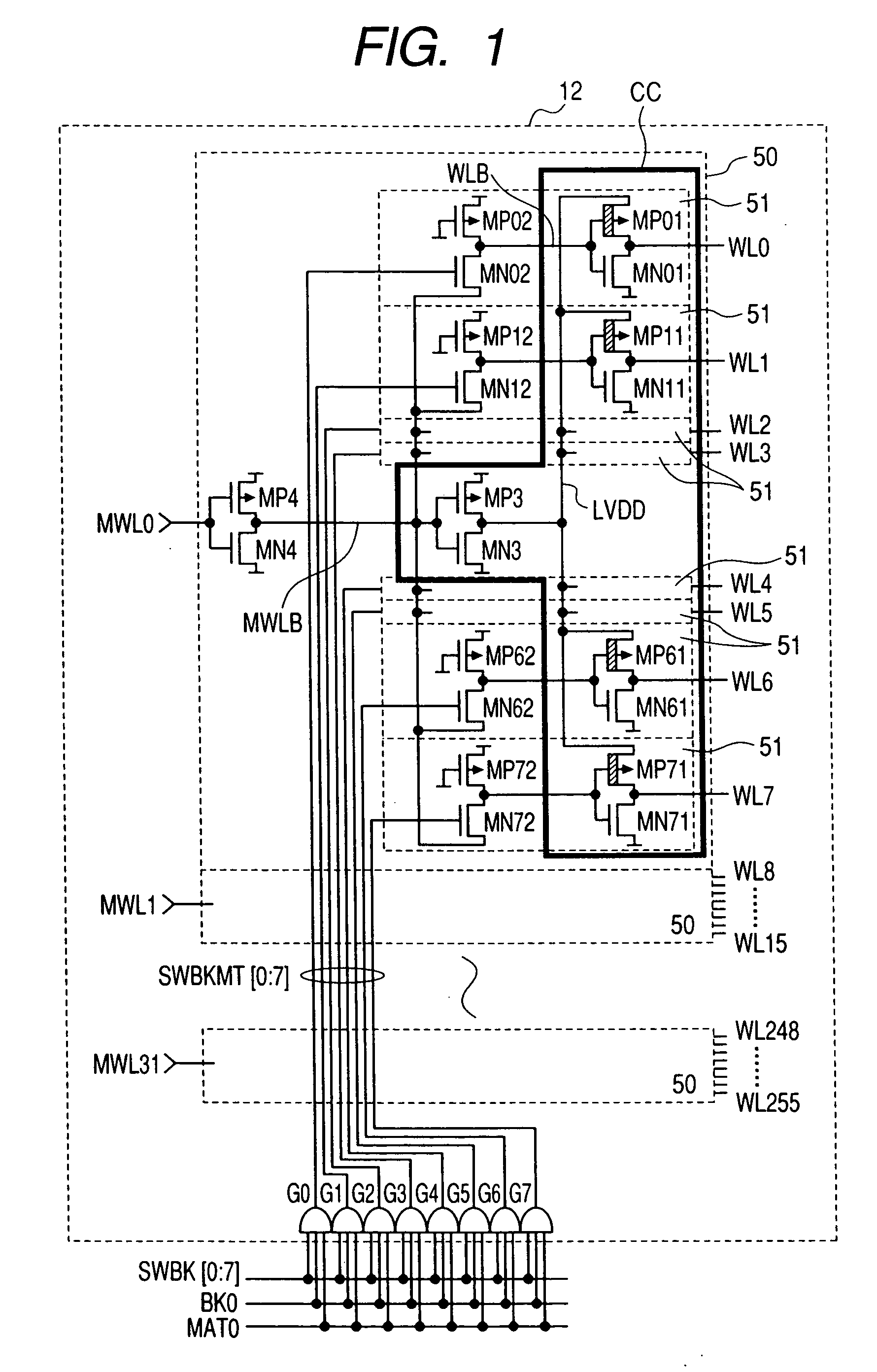

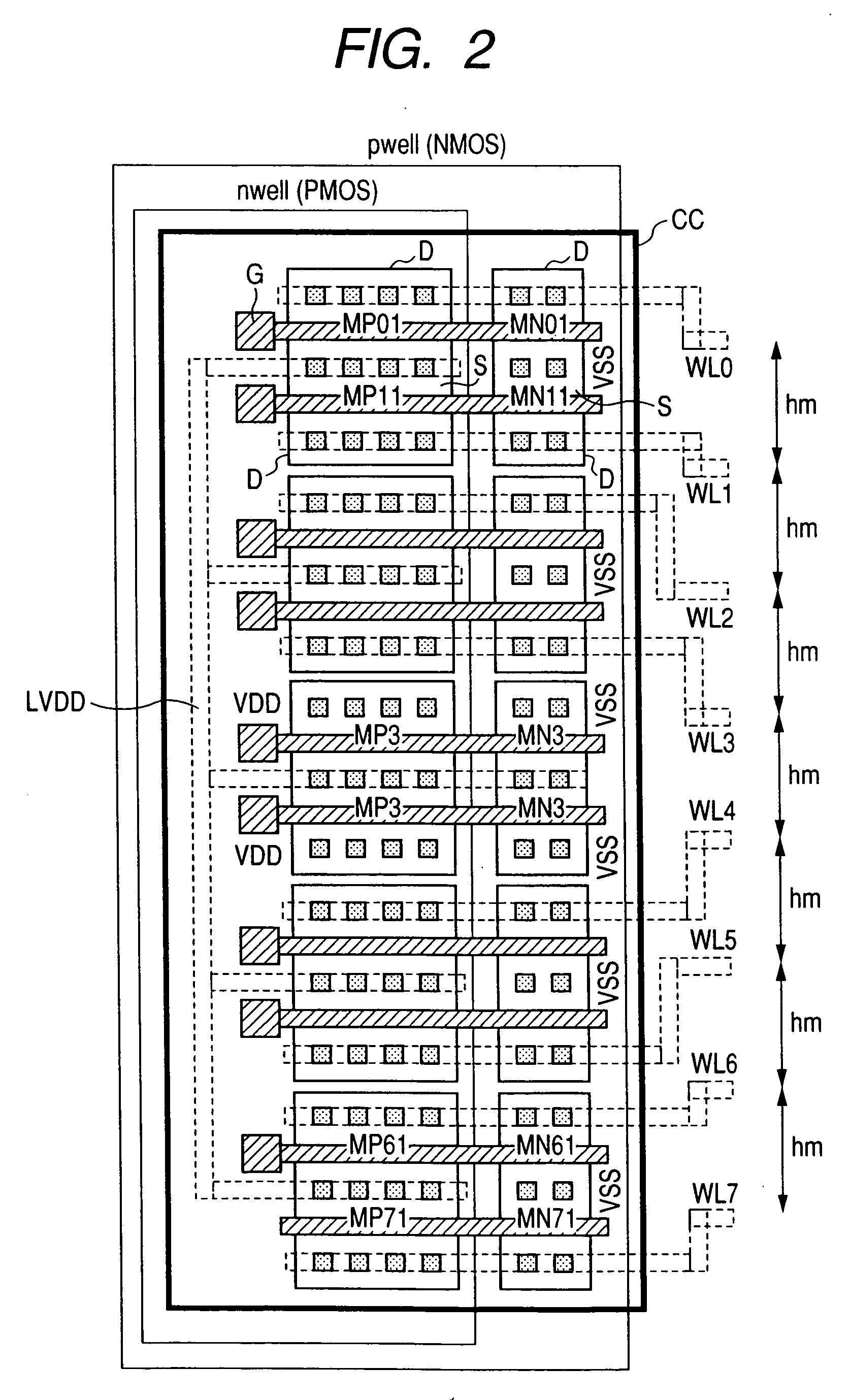

Semiconductor integrated circuit device

ActiveUS20060181955A1Reduce leakage currentIncrease working currentSolid-state devicesDigital storageCMOSBit line

A semiconductor integrated circuit device provided with a memory circuit having a word line selection circuit with reduced leakage current is provided. The memory circuit includes: second word lines with which memory cells are connected; multiple bit lines that are extended in a direction orthogonal thereto and electrically connected with memory cells corresponding to selected second word lines of a plurality of the second word lines; and word drivers, constructed of CMOS inverter circuits, that select or deselect the second word lines. The sources of p-channel MOSFETs that constitute a plurality of word drivers including second word lines corresponding to selected bit lines are supplied with a voltage at a level at which second word lines are selected. The sources of the p-channel MOSFETs of the other word drivers are supplied with a voltage corresponding to a level at which second word lines are deselected.

Owner:RENESAS ELECTRONICS CORP

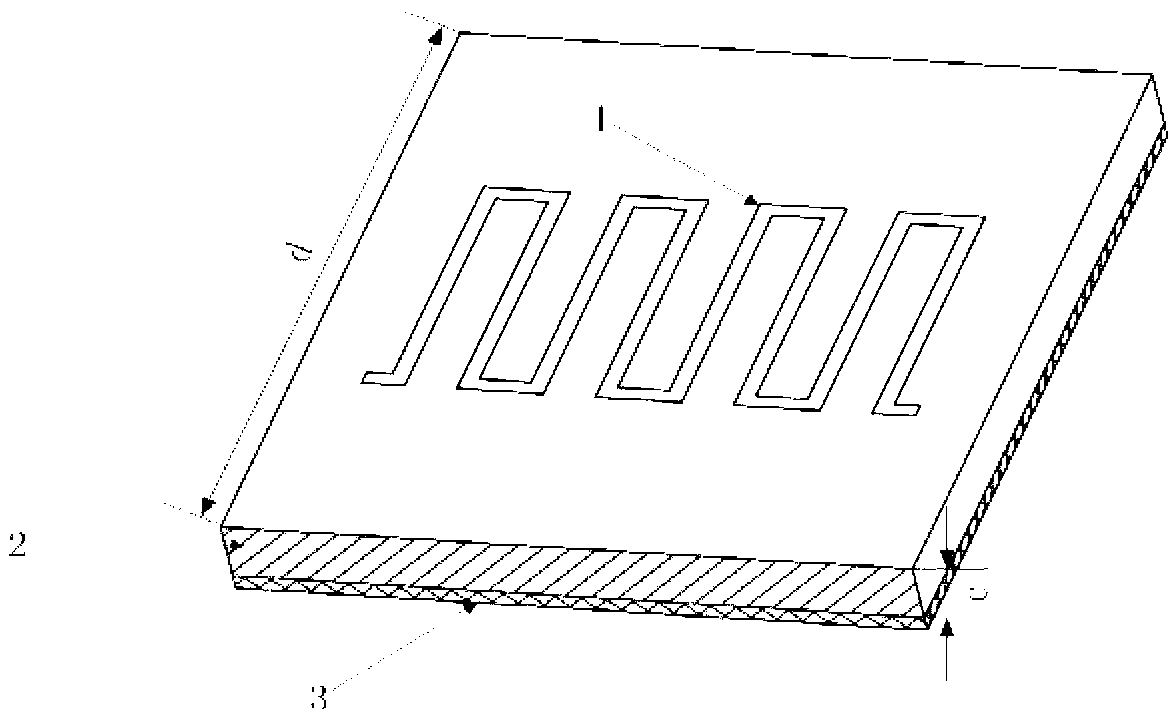

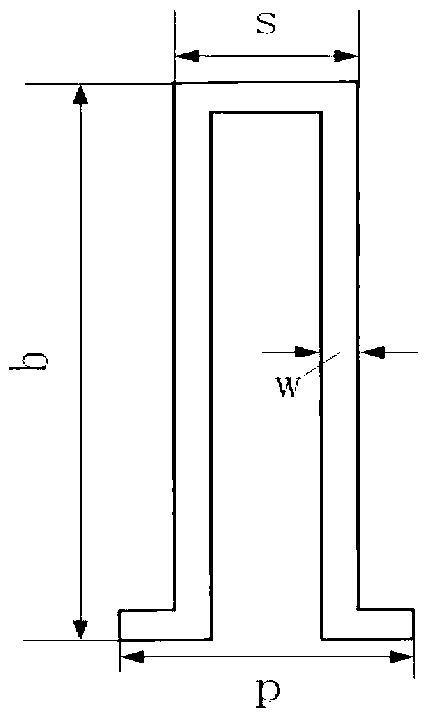

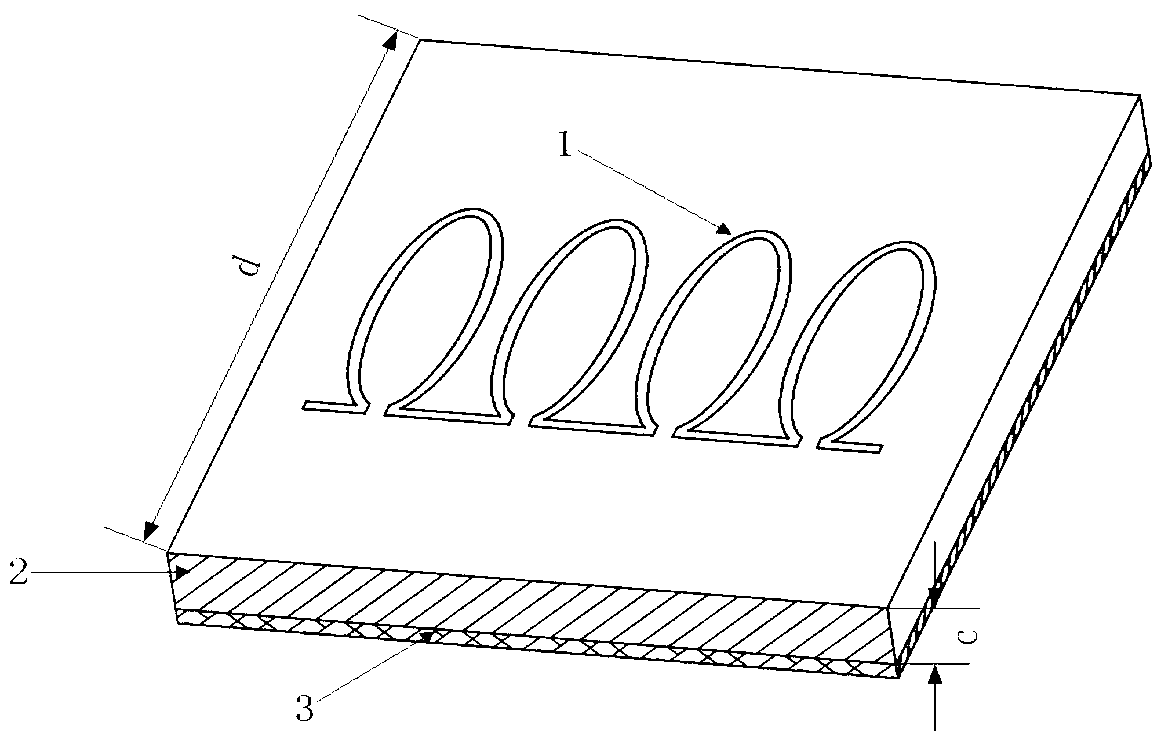

Microstrip line slow-wave structure

InactiveCN103258703AReduce volumeReduce weightTransit-tube circuit elementsWave structureElectricity

The invention discloses a microstrip line slow-wave structure and belongs to the technical field of microwave vacuum electrons and relates to an O-shaped electron vacuum device. The microstrip line slow-wave structure comprises a microsrip transmission line structure which is formed by a metal microstrip line (1), a medium substrate (2) and a metal base plate (3), wherein the metal microstrip line (1) is of a periodic structure which is formed by a plurality of O-shaped metal microstrip line units, the O-shaped metal microstrip line units are in end-to-end connection, each O-shaped metal microstrip line unit is composed of an ellipse opening ring microstrip line and two microstrip lines, and the two microstrip lines are respectively connected with two ends of an opening of the ellipse opening ring microstrip line respectively. Compared with a traditional N-shaped microstrip line slow-wave structure, the microstrip line slow-wave structure has higher coupling impedance and lower working voltages under the size of the same devices, and comprehensive requirements for the aspects such as output power, the working voltages and weight of a traveling-wave tube can be further met.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

LDMOS transistor and formation method thereof

ActiveCN107564816AIncrease working currentImprove bulk distributionTransistorSemiconductor/solid-state device manufacturingLDMOSBody region

A LDMOS transistor and a formation method thereof are provided; the method comprises the following steps: providing a semiconductor substrate, and forming a shallow trench isolation structure in the semiconductor substrate; forming a drift region in the semiconductor substrate, wherein the drift region encloses the shallow trench isolation structure; forming a body region in the semiconductor substrate on the drift region side; forming a gate structure crossing and covering partial the body region, the drift region and the shallow trench isolation structure; forming a drain region in the driftregion on the gate structure side; forming a source region in the body region on the other side of the gate structure; forming a first shallow doping region in the drain region on the gate structureside and in the drift region on the gate structure bottom, wherein the first shallow doping region doping type is same with the drain region doping type, and the first shallow doping region depth is smaller than the drain region depth and drift region depth. The method can improve the LDMOS transistor working current.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1