Patents

Literature

1785 results about "LDMOS" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

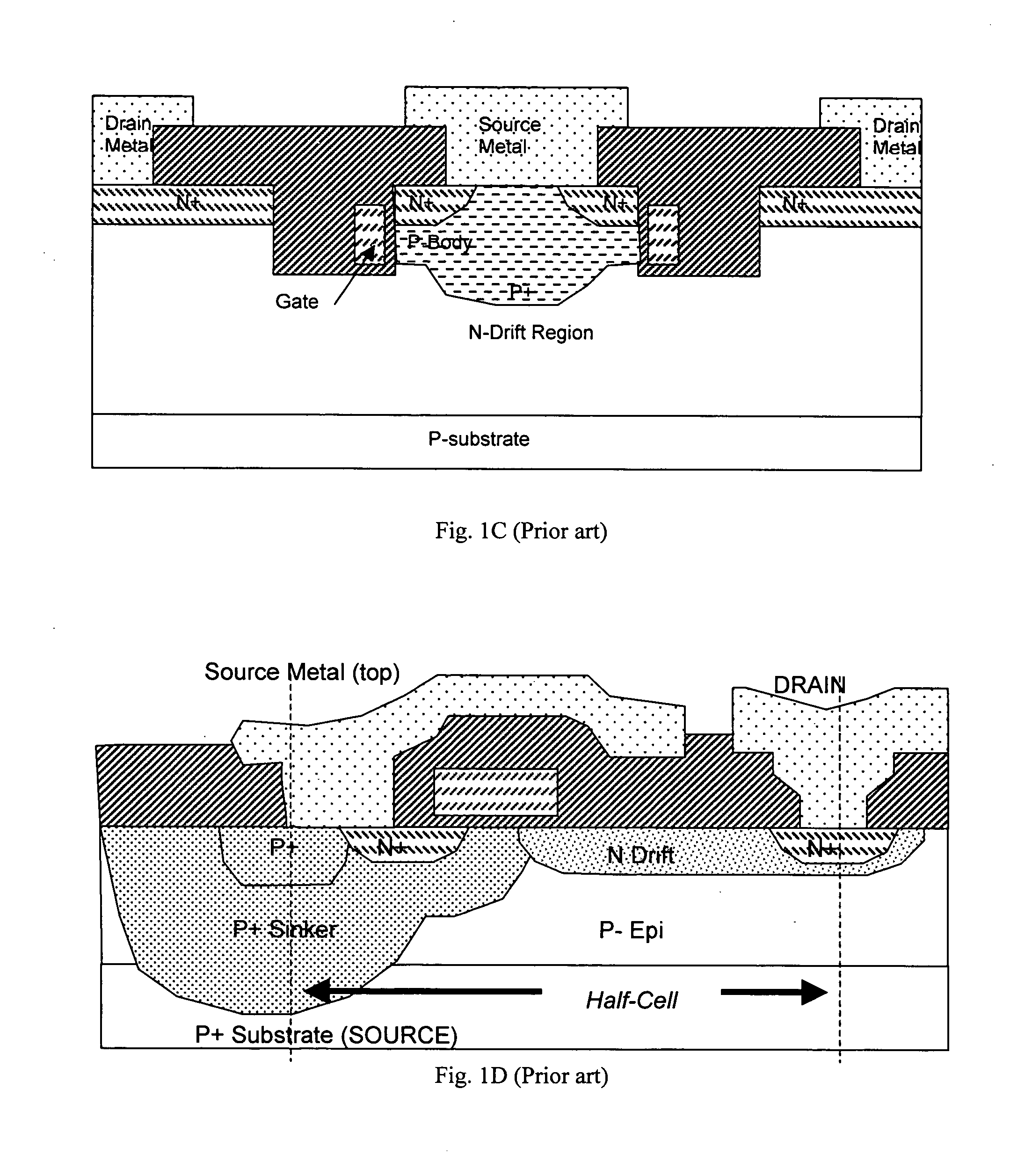

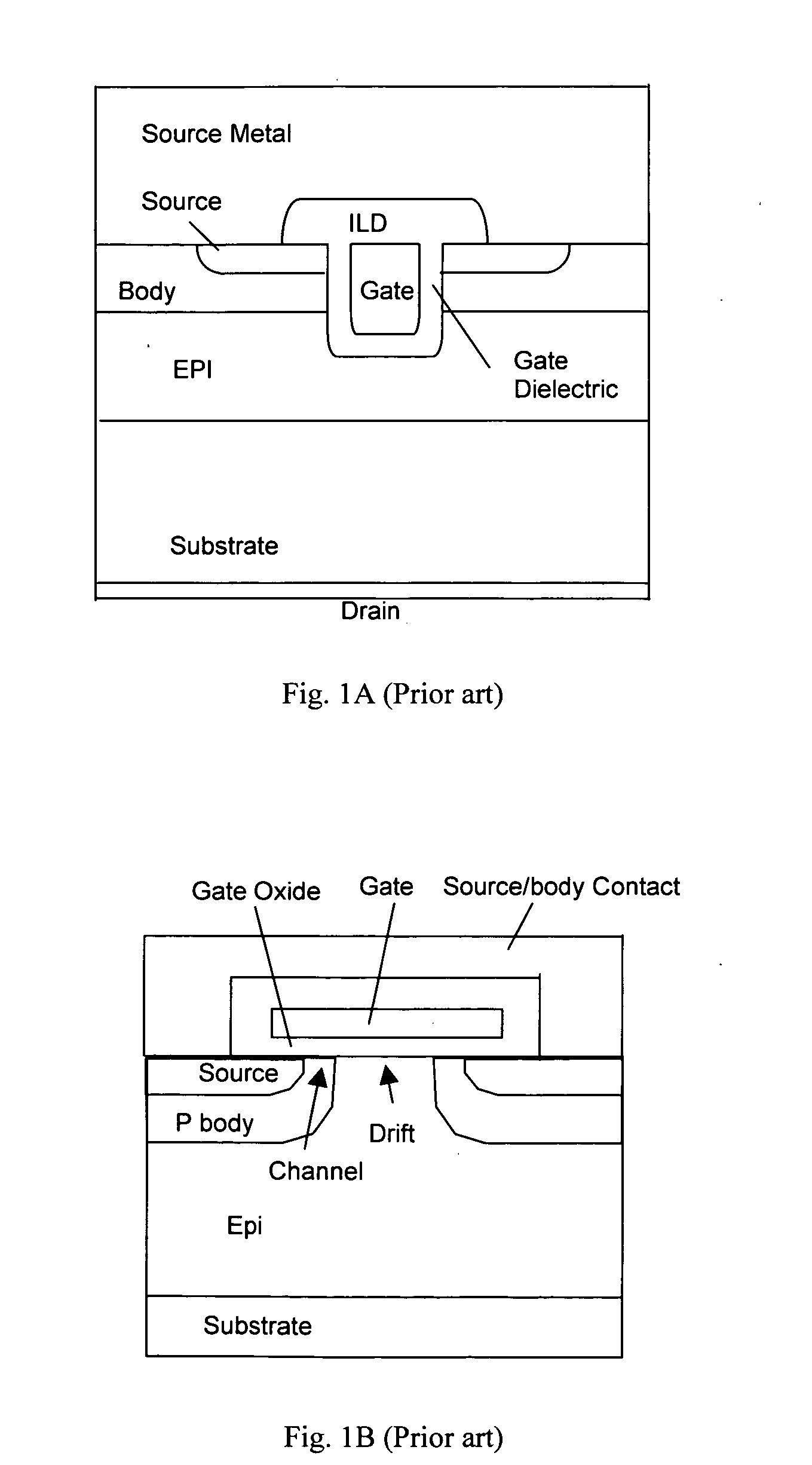

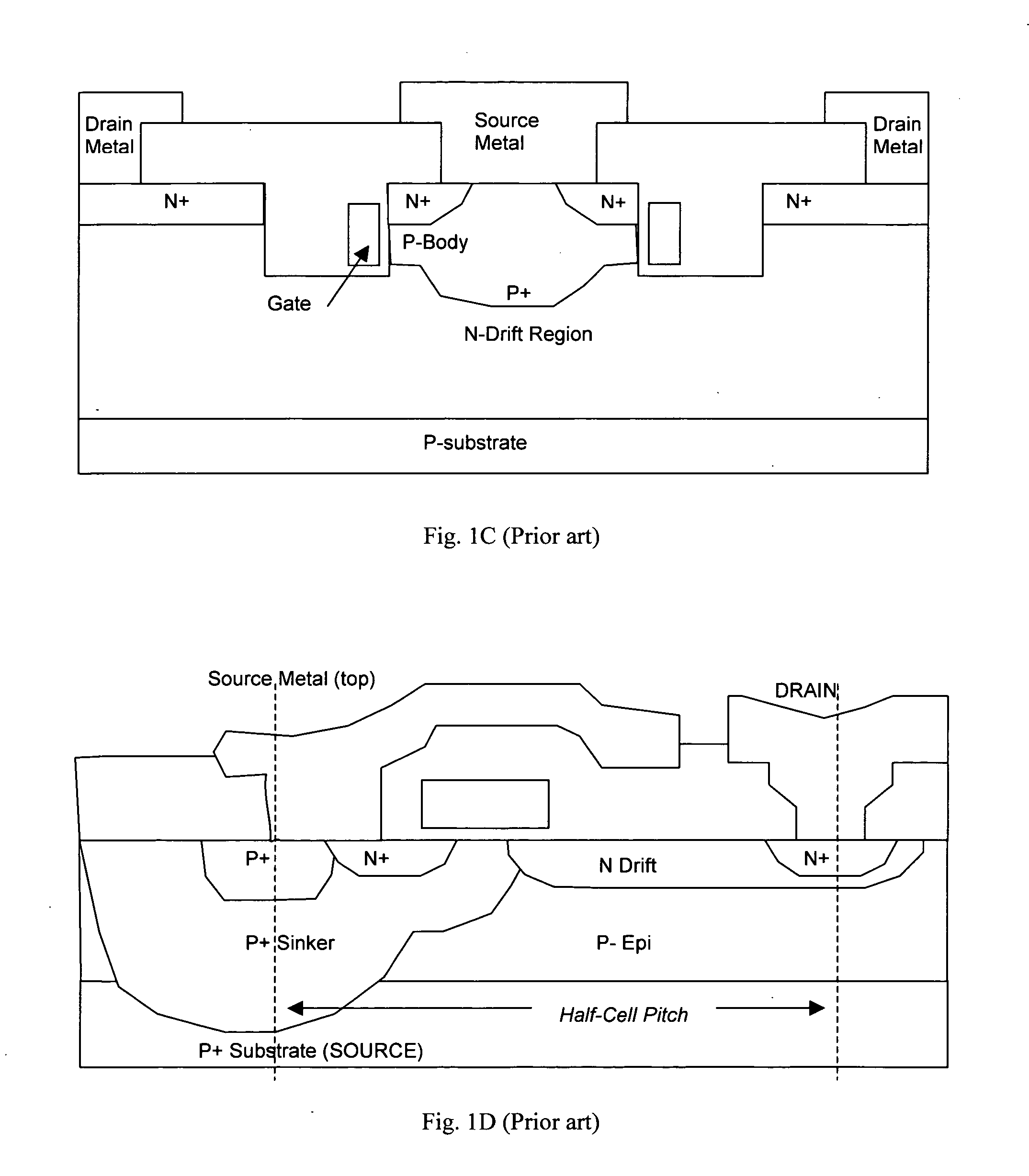

LDMOS (laterally-diffused metal-oxide semiconductor) is a planar double-diffused MOSFET (metal-oxide-semiconductor field-effect transistor) used in microwave/RF power amplifiers as well as audio power amplifiers. These transistors are often fabricated on p/p⁺ silicon epitaxial layers. The fabrication of LDMOS devices mostly involves various ion-implantation and subsequent annealing cycles. As an example, The drift region of this power MOSFET is fabricated using up to three ion implantation sequences in order to achieve the appropriate doping profile needed to withstand high electric fields.

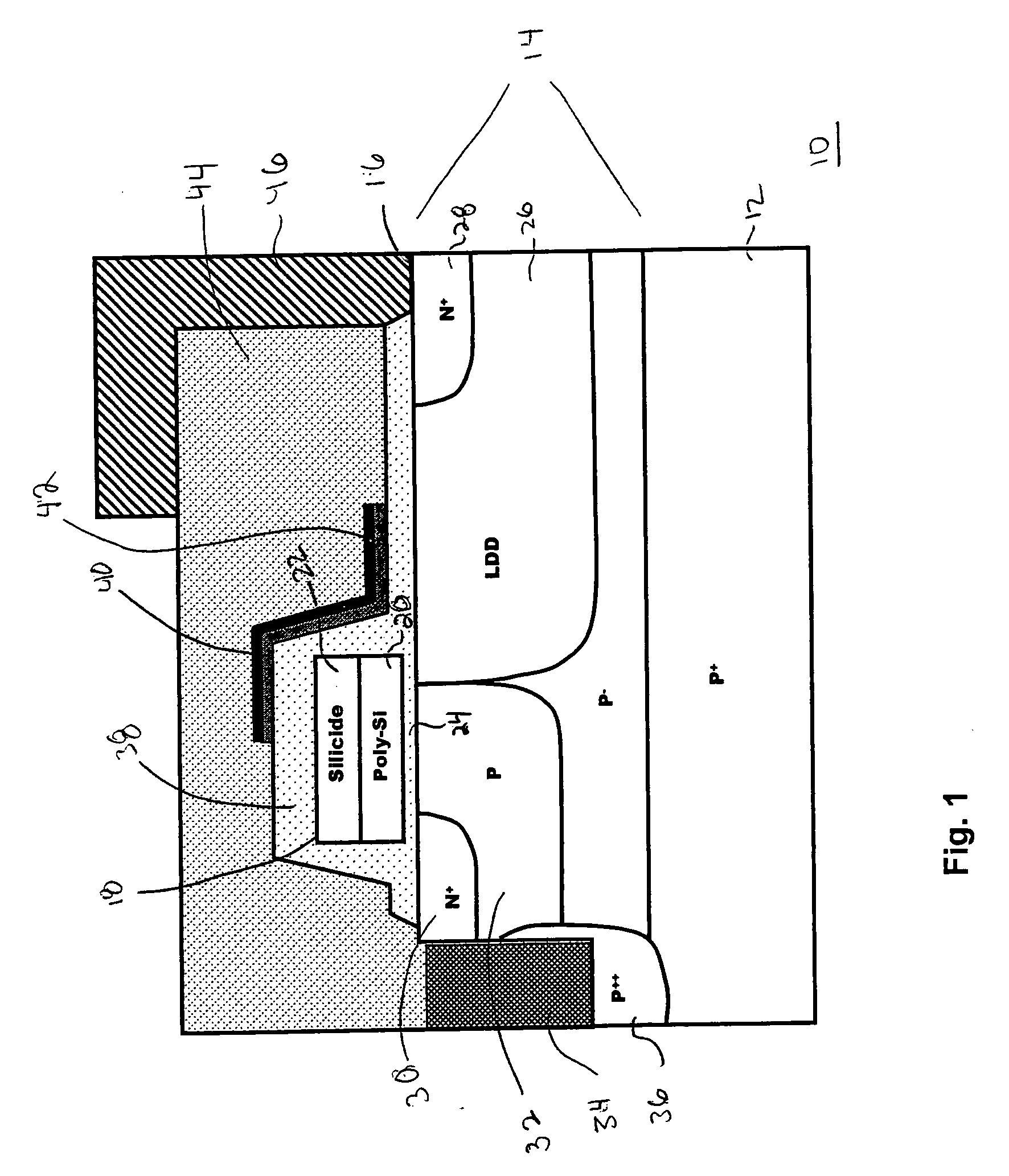

Laterally diffused metal oxide semiconductor device and method of forming the same

InactiveUS7230302B2TransistorSemiconductor/solid-state device manufacturingLDMOSCondensed matter physics

Owner:TAHOE RES LTD

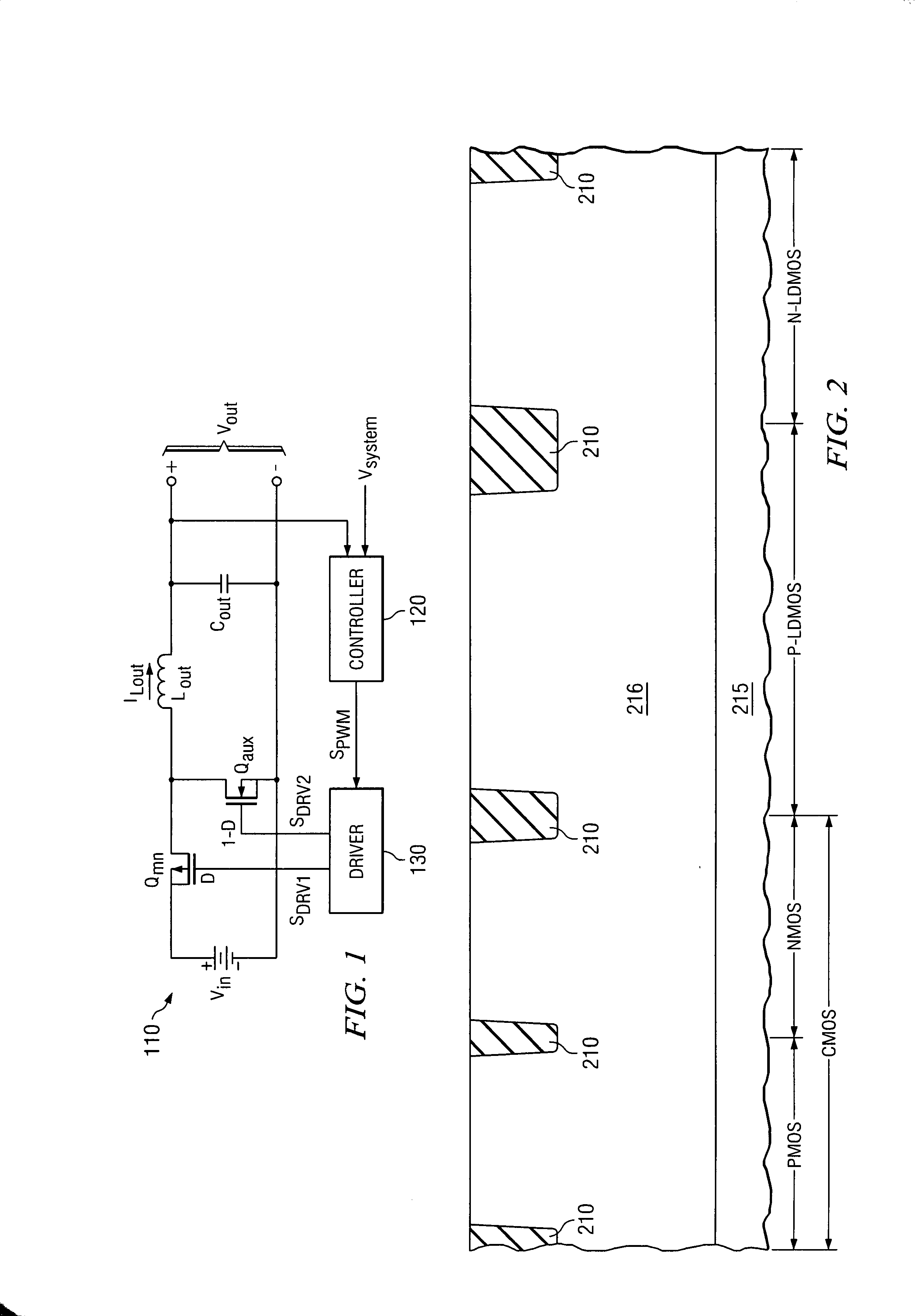

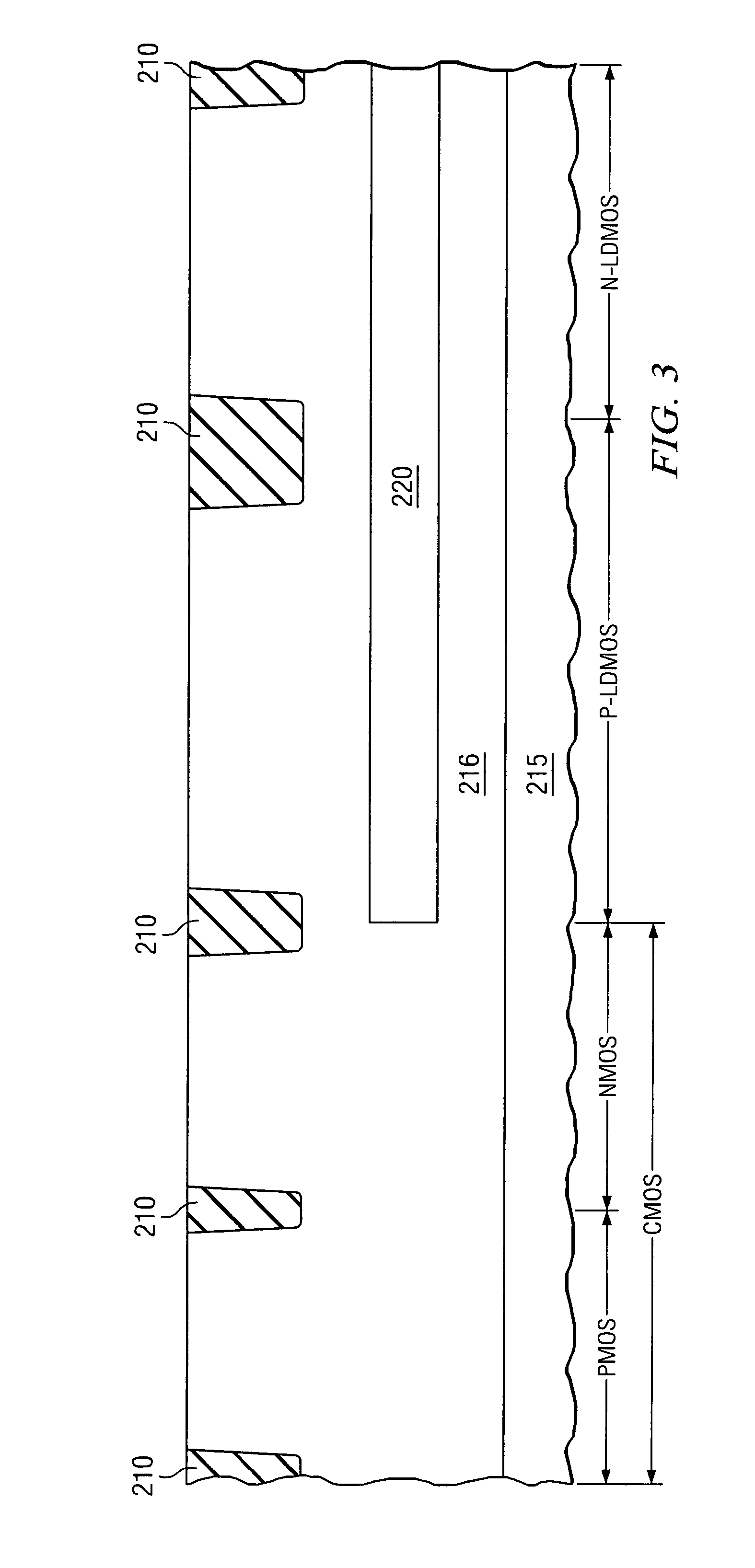

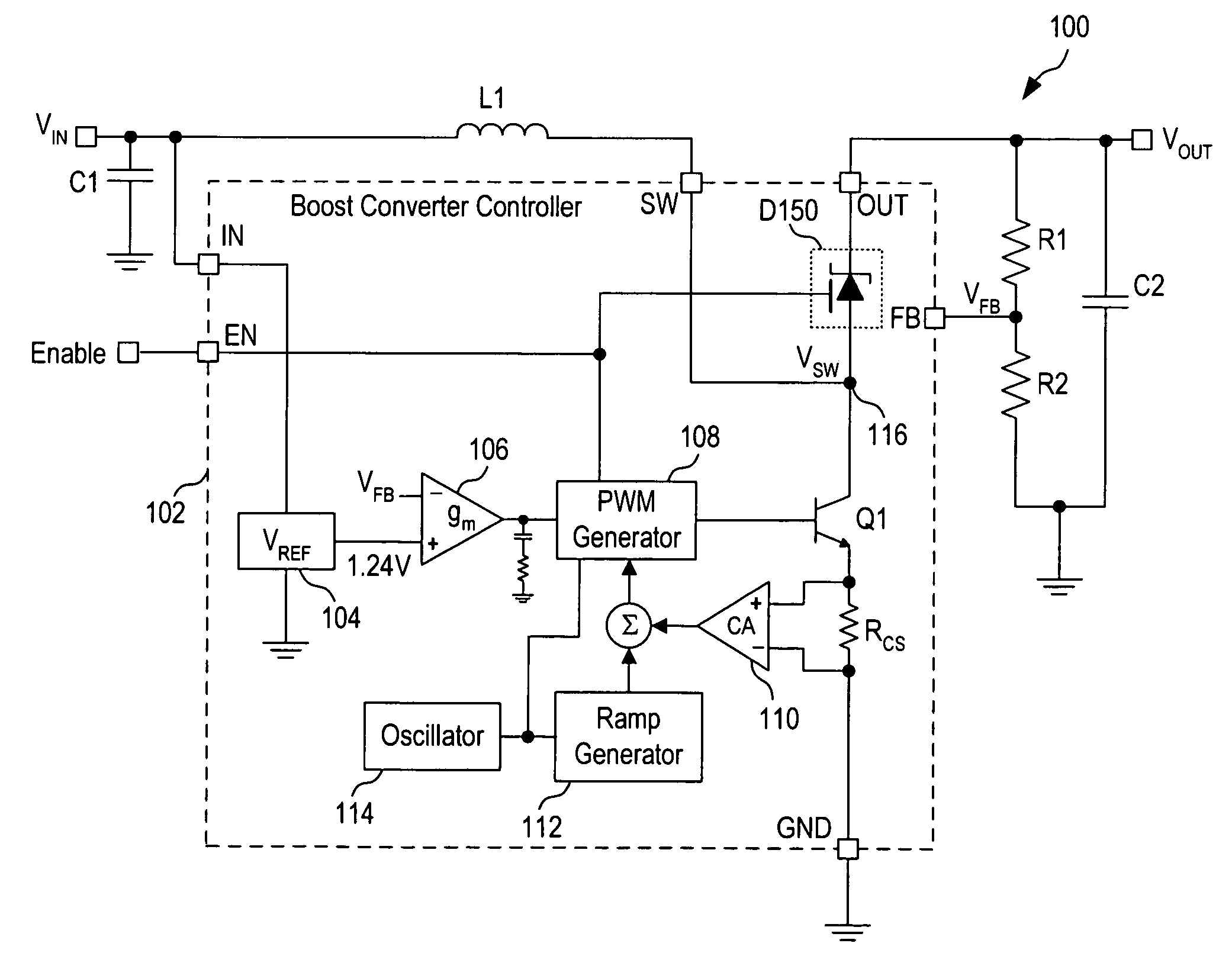

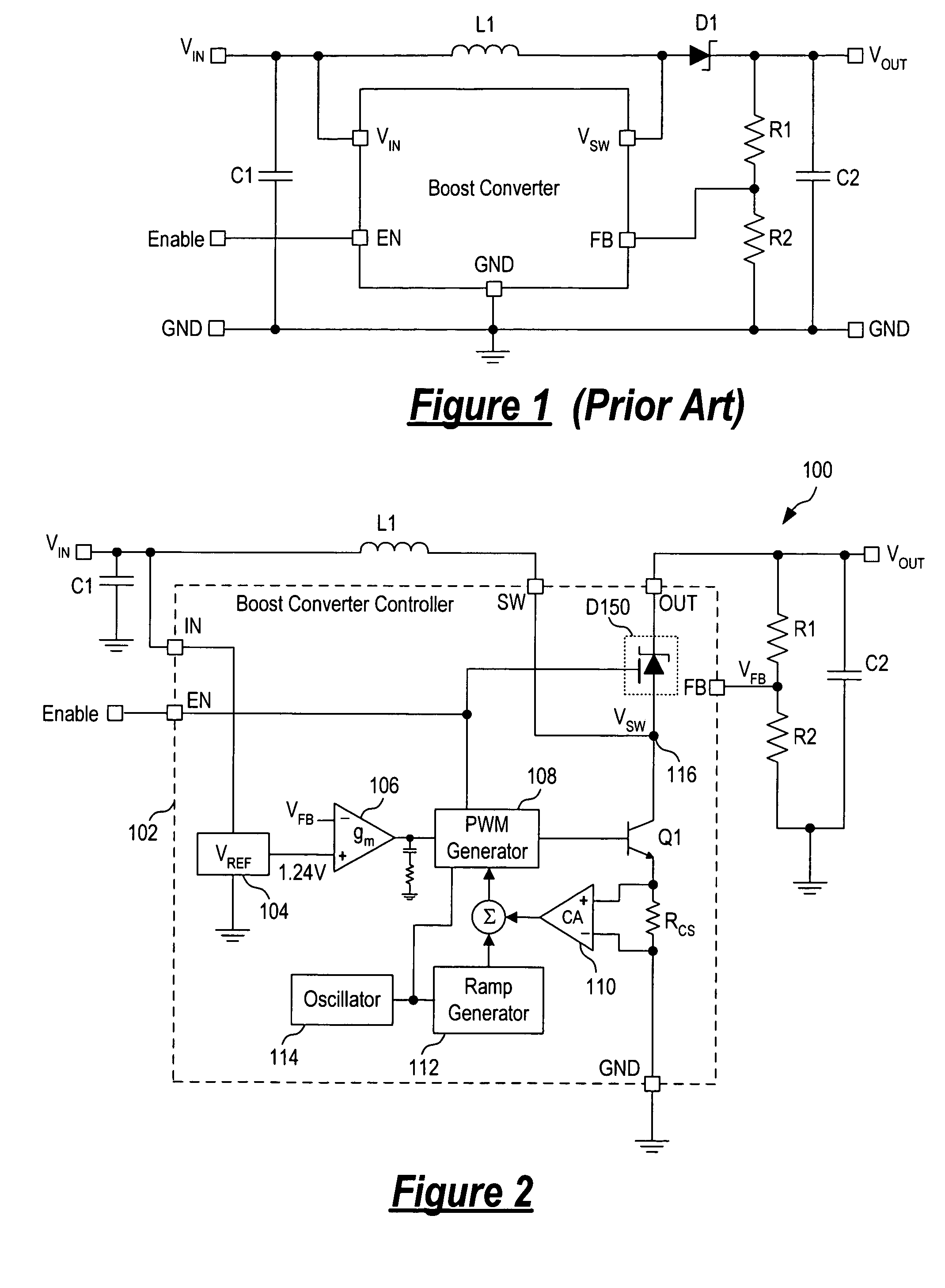

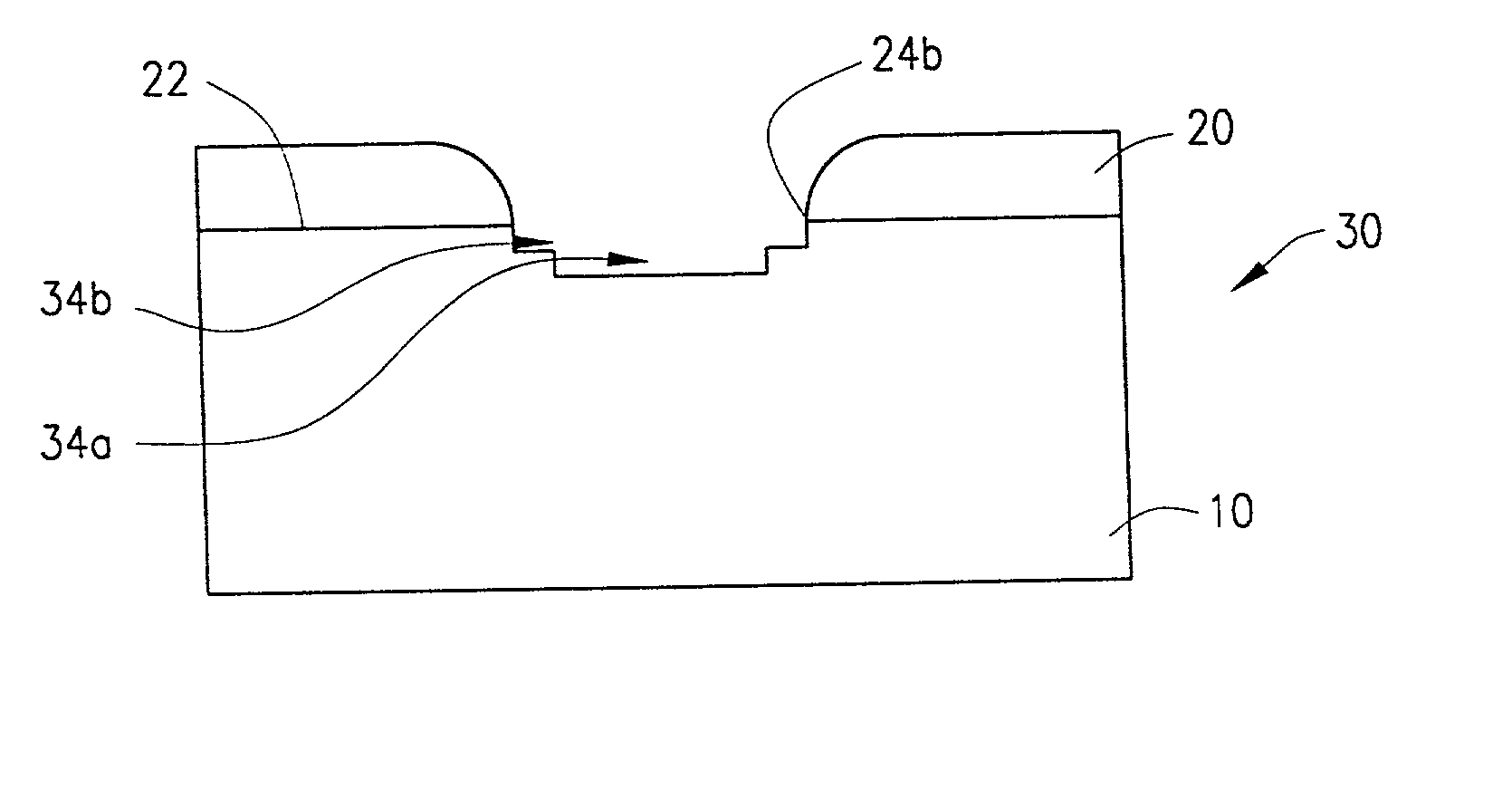

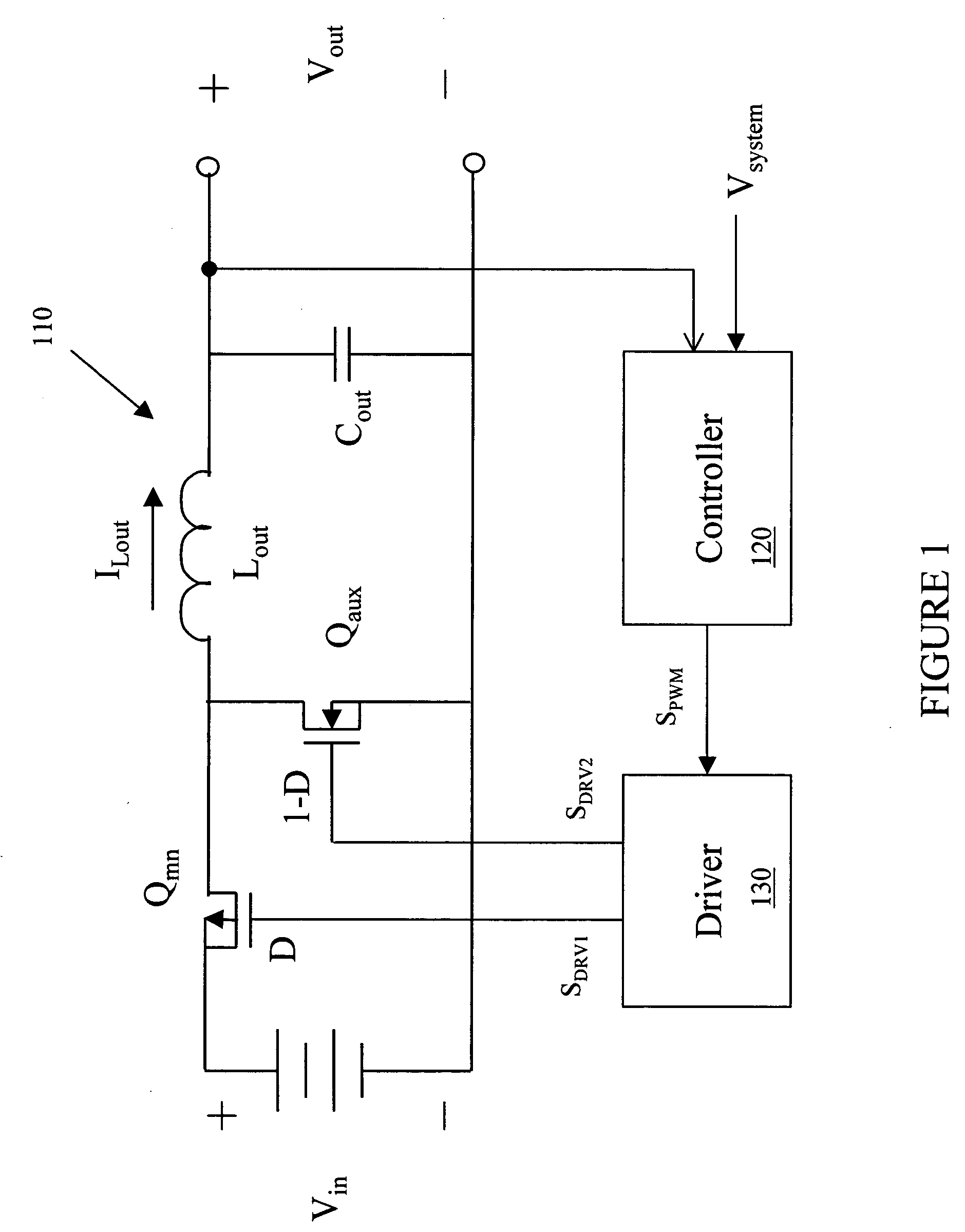

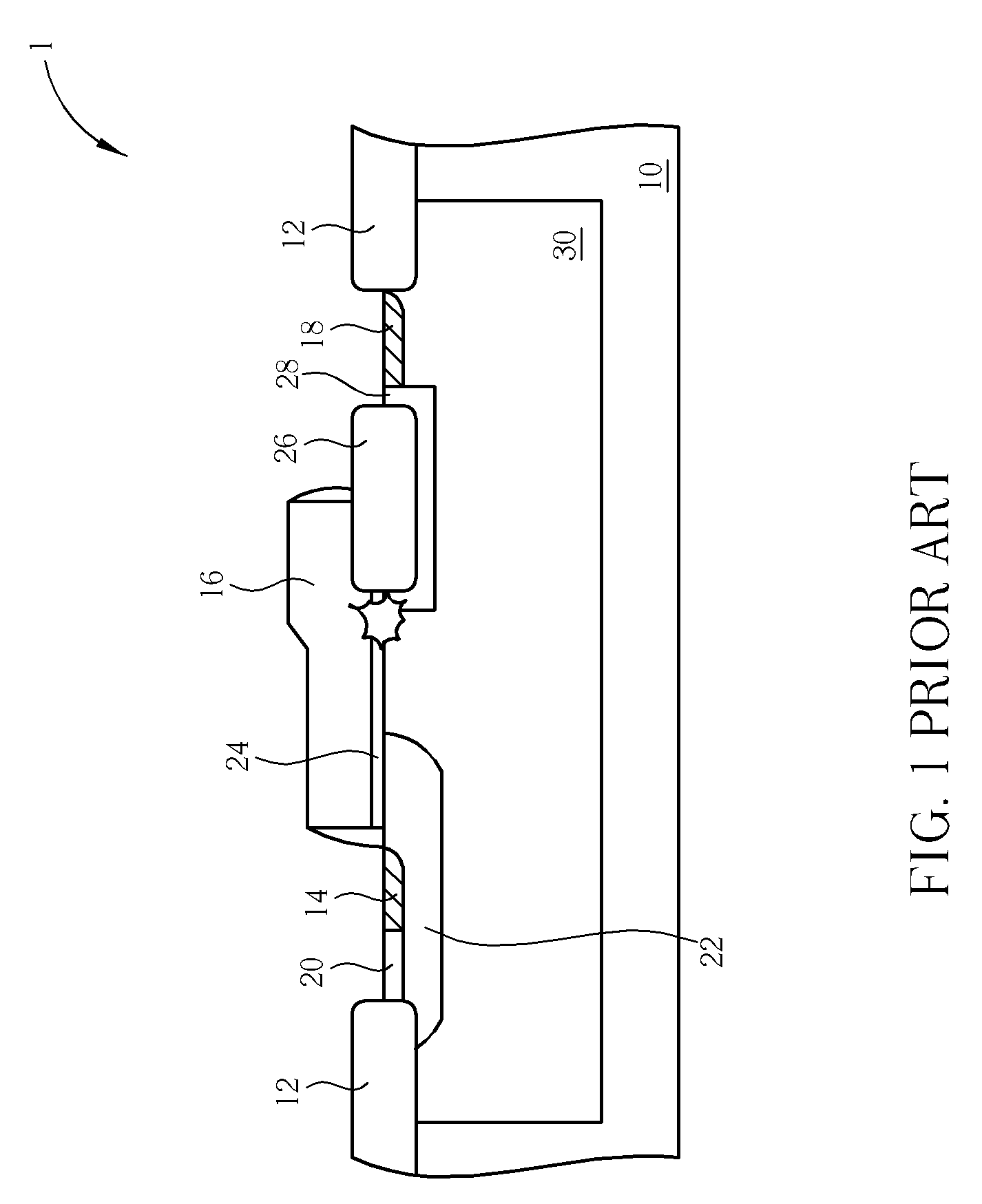

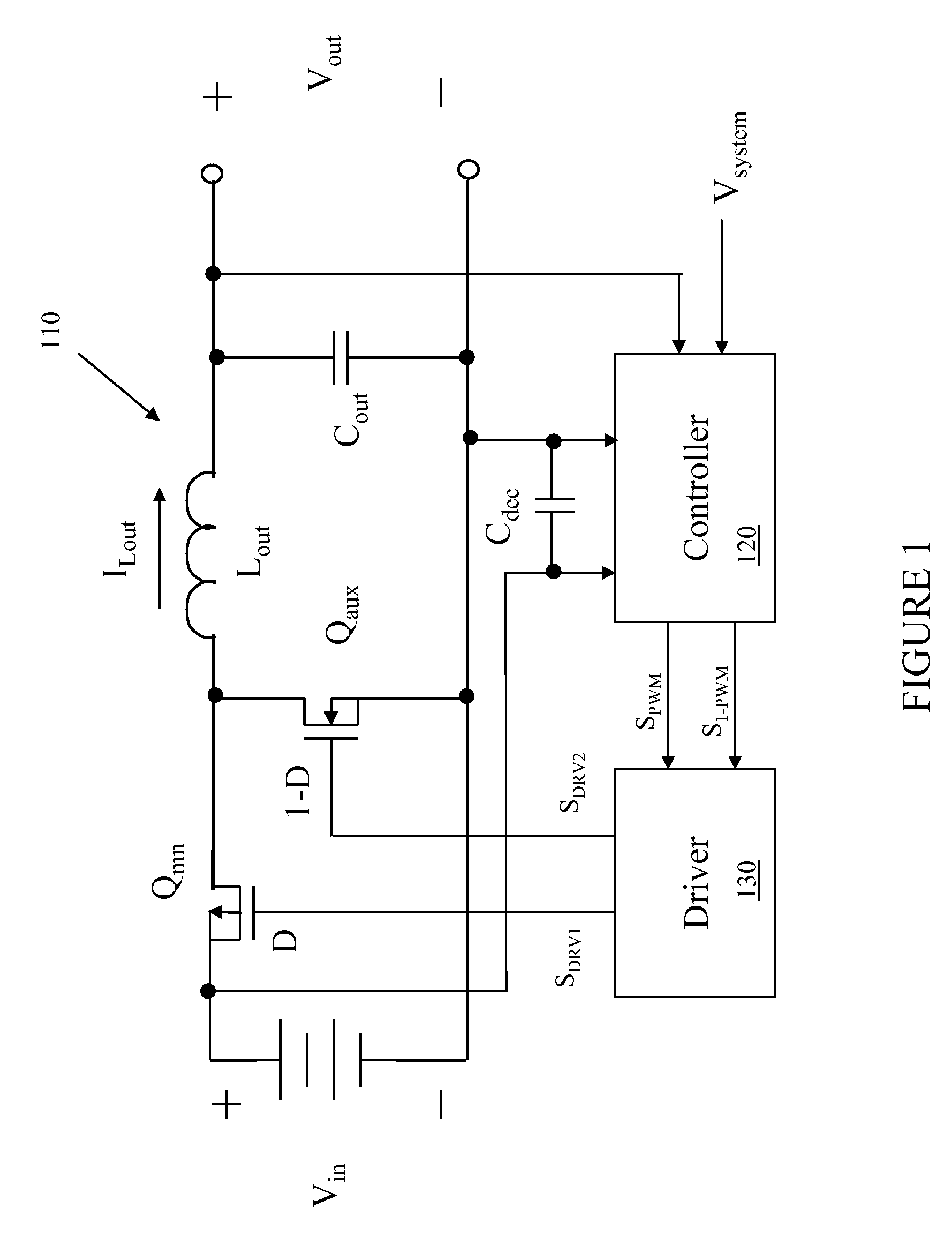

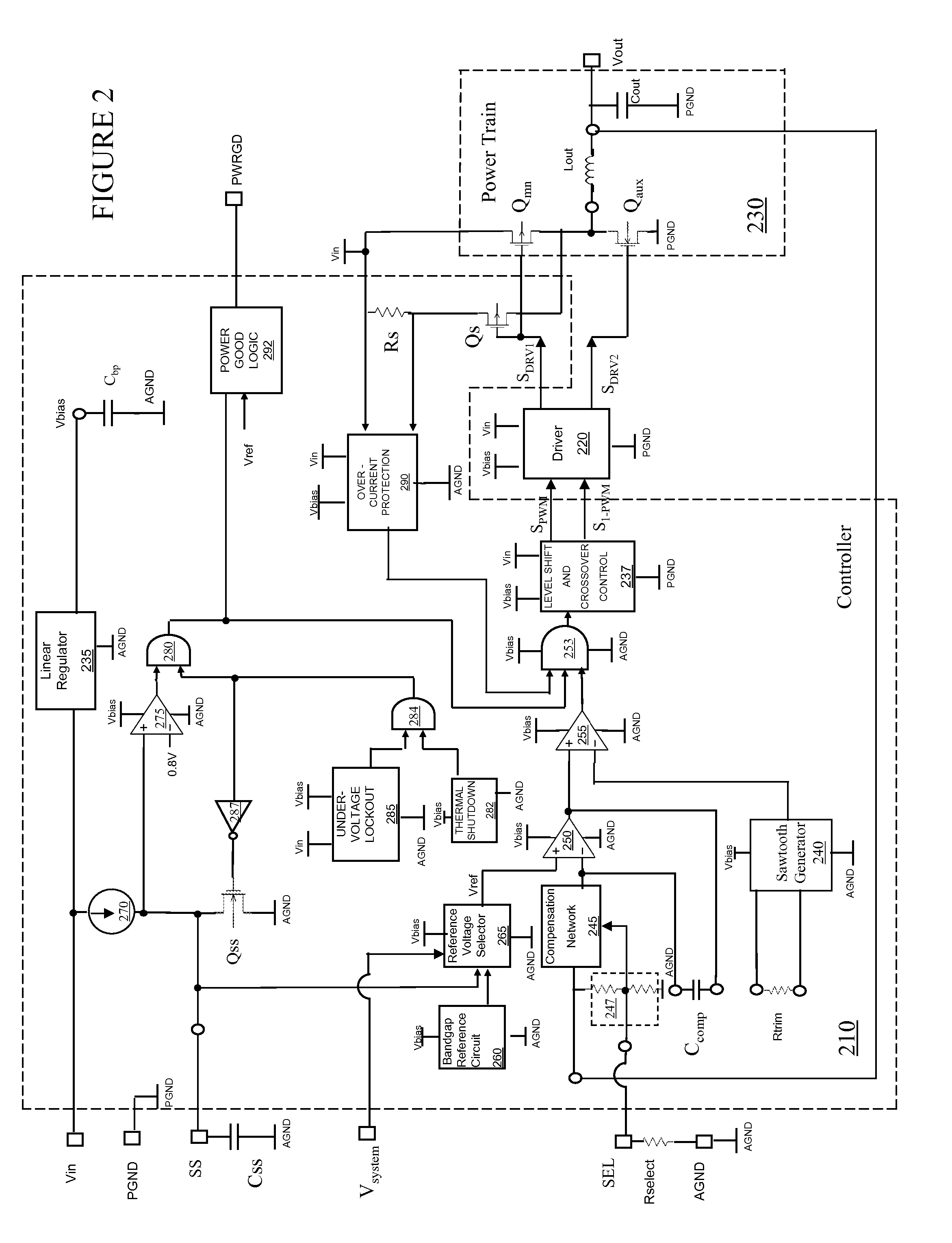

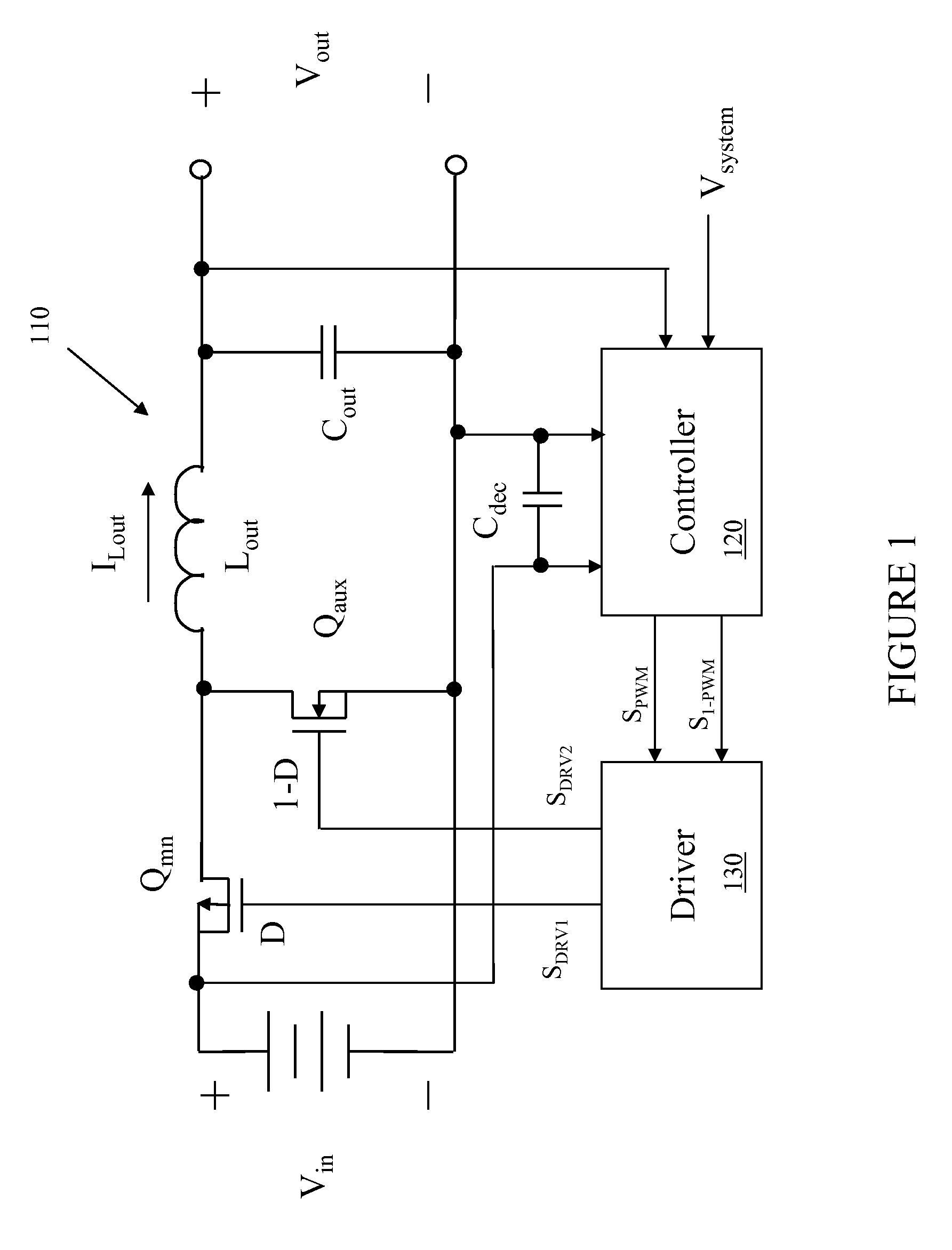

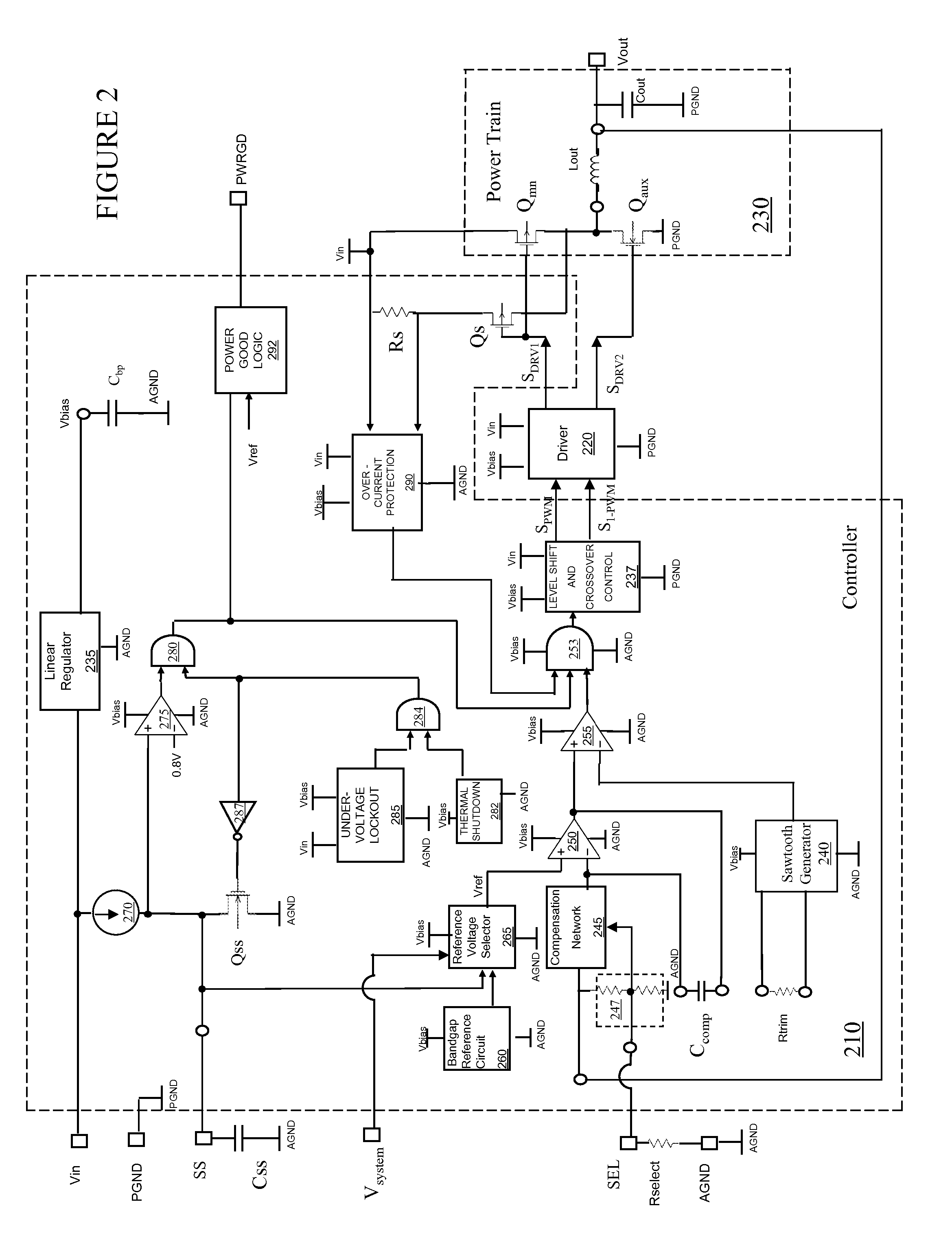

Non-synchronous boost converter including switched schottky diode for true disconnect

ActiveUS20060176029A1Avoid conductionTransistorEfficient power electronics conversionLDMOSControl signal

A non-synchronous boost converter includes a switched Schottky diode to rectify the switched output voltage of the boost converter where the switched Schottky diode has forward conduction blocking capability. The switched Schottky diode has an anode terminal coupled to receive the switched output voltage, a cathode terminal providing the output DC voltage, and a gate terminal coupled to receive a control signal. The control signal has a first state for turning the switched Schottky diode on where the switched Schottky diode conducts current when forward biased and a second state for turning the switched Schottky diode off where forward conduction of the switched Schottky diode is blocked even when the diode is forward biased. The switched Schottky diode can be a JFET controlled or an LDMOS gate controlled Schottky diode. Furthermore, the switched Schottky diode can be formed on-chip or off-chip of the controller circuit of the boost converter.

Owner:MICREL

Sloped trench etching process

InactiveUS20020166838A1Easy to controlEasy to makeAcceleration measurement using interia forcesDecorative surface effectsLDMOSEtching

Method and apparatus for etching a tapered trench in a layer of material with a highly controllable wall profile. The layer of material has a mask adjacent a surface thereof having an opening which defines a location on the layer of material at which the trench is to be formed. Vertical etch process steps and opening enlarging process steps are then performed in an alternating manner until the trench has been etched to a desired depth. The method permits very deep tapered trenches of up to 80-100 um or more to be formed in a silicon substrate or other layer of material in a highly controllable manner. The method can be incorporated into processes for manufacturing numerous devices including MEMS devices and high power RF devices such as LDMOS and VDMOS devices.

Owner:INST OF MICROELECTRONICS A SINGAPORE COMPANY LIMITED BY GUARANTEE

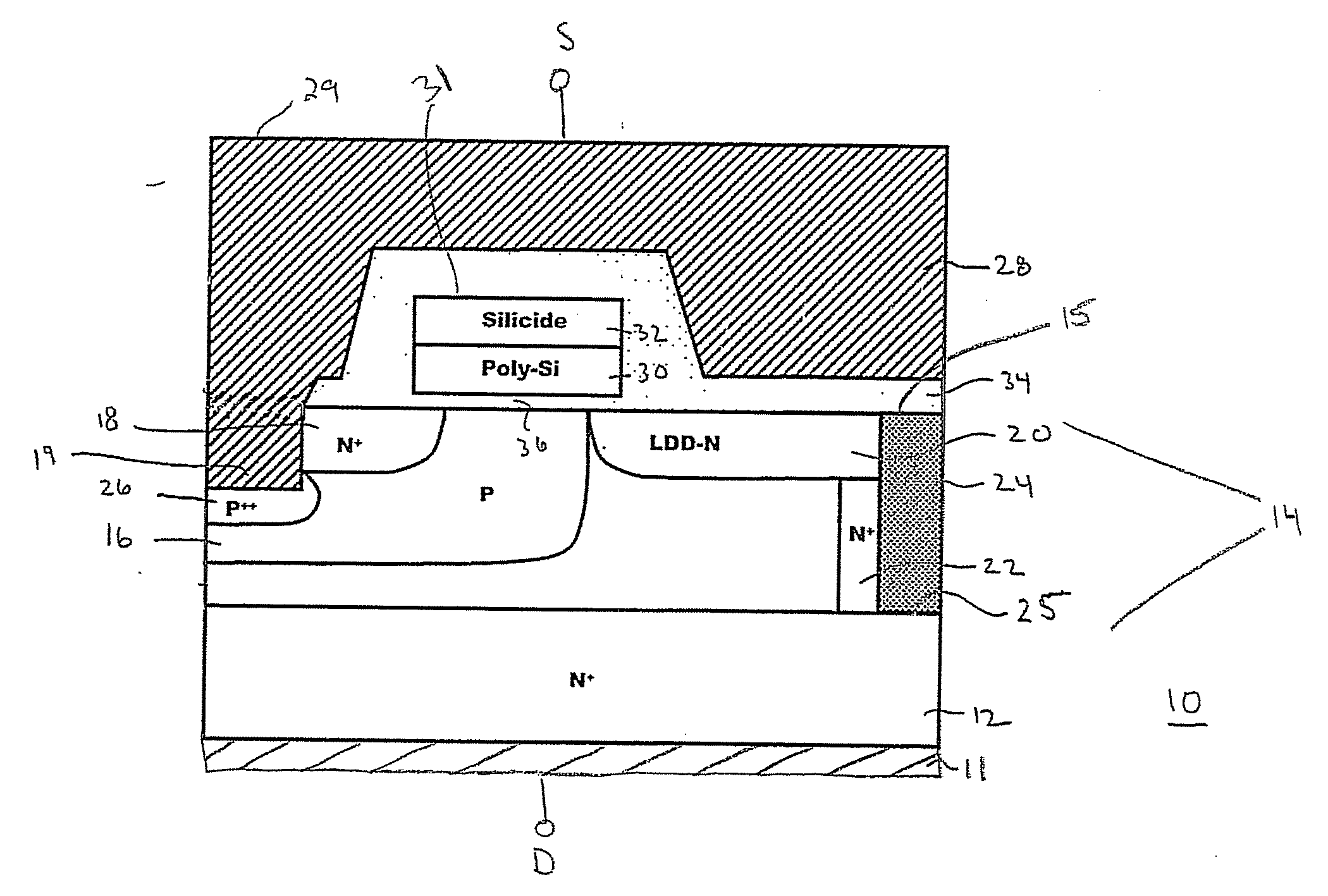

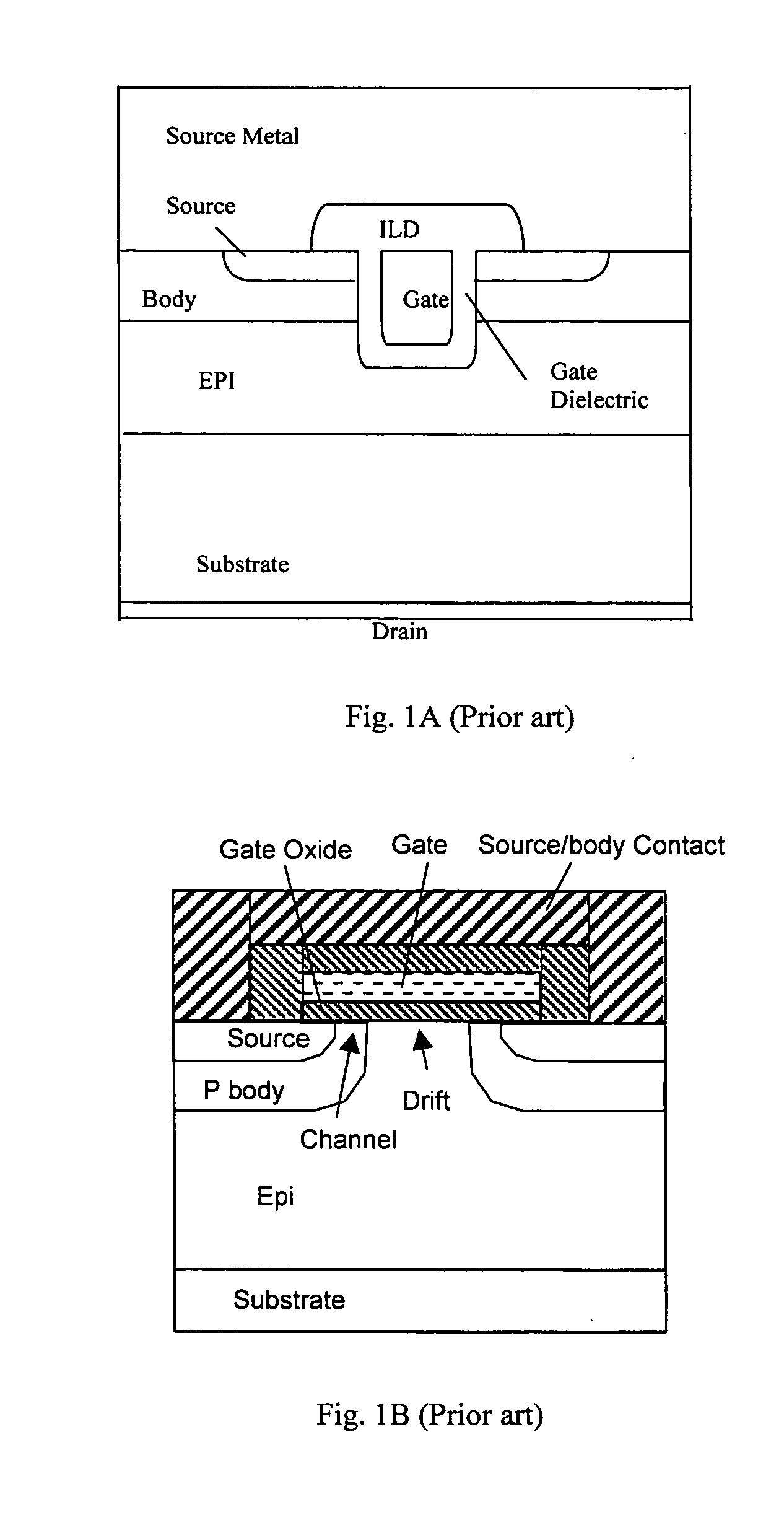

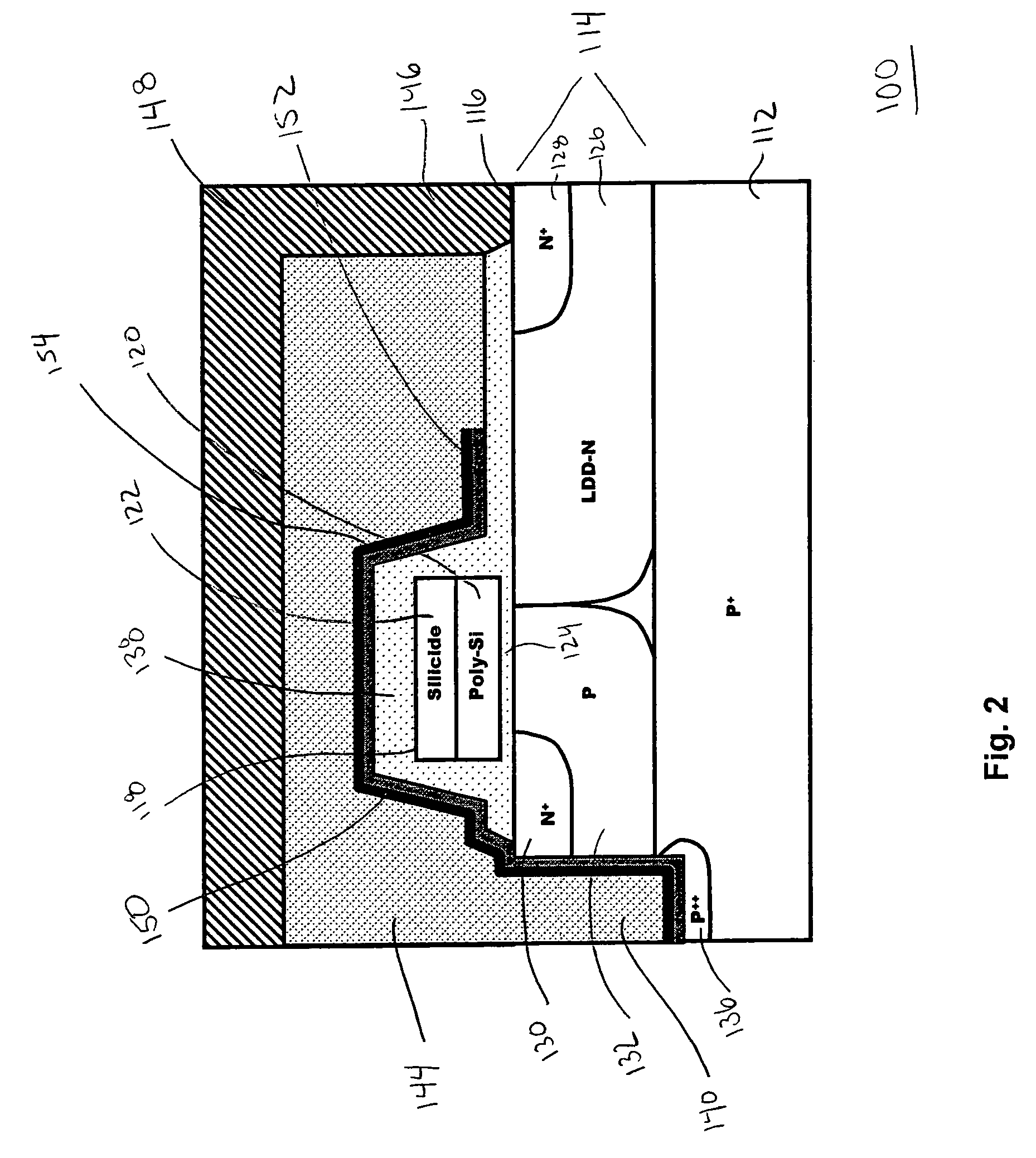

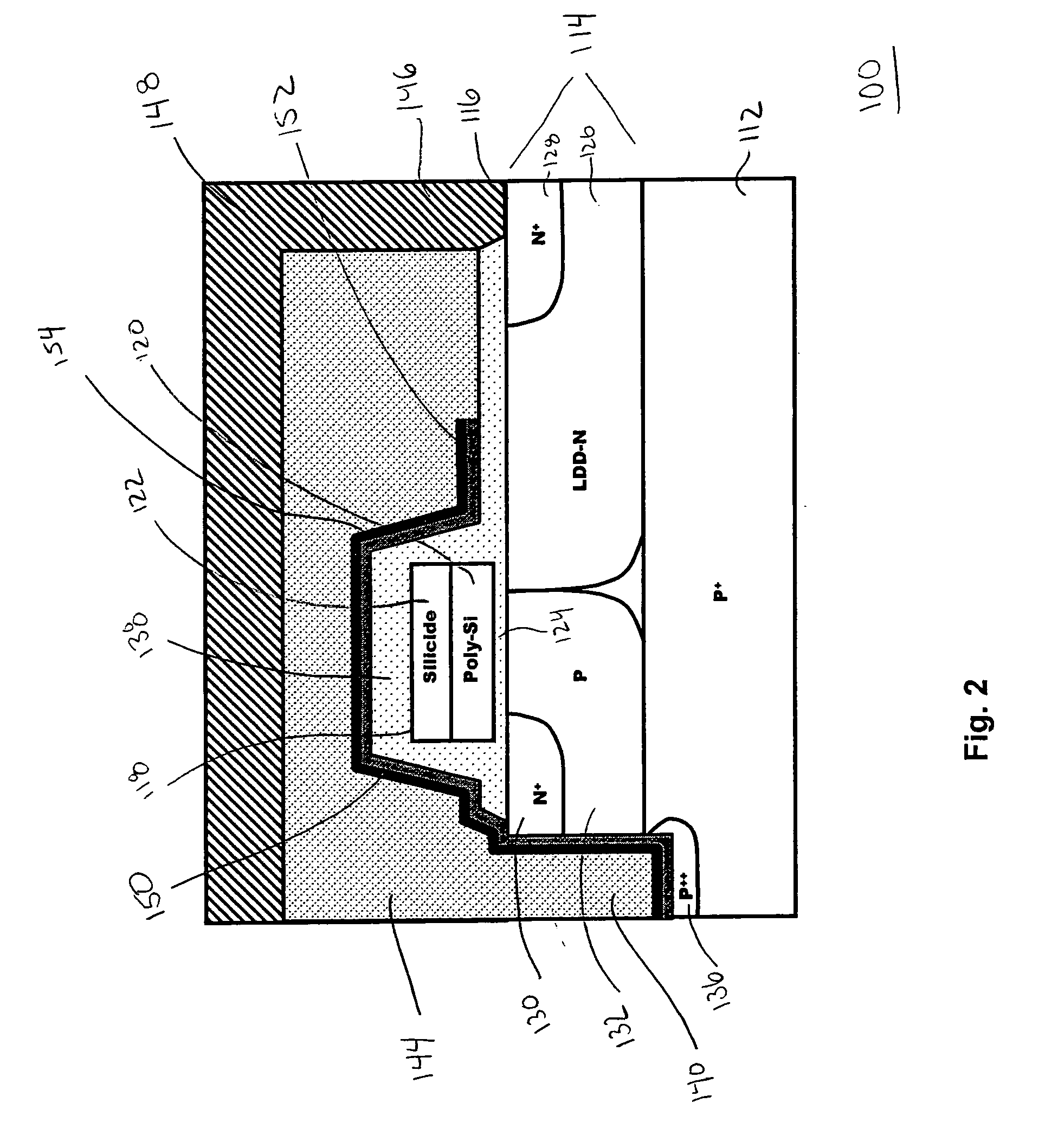

Power ldmos transistor

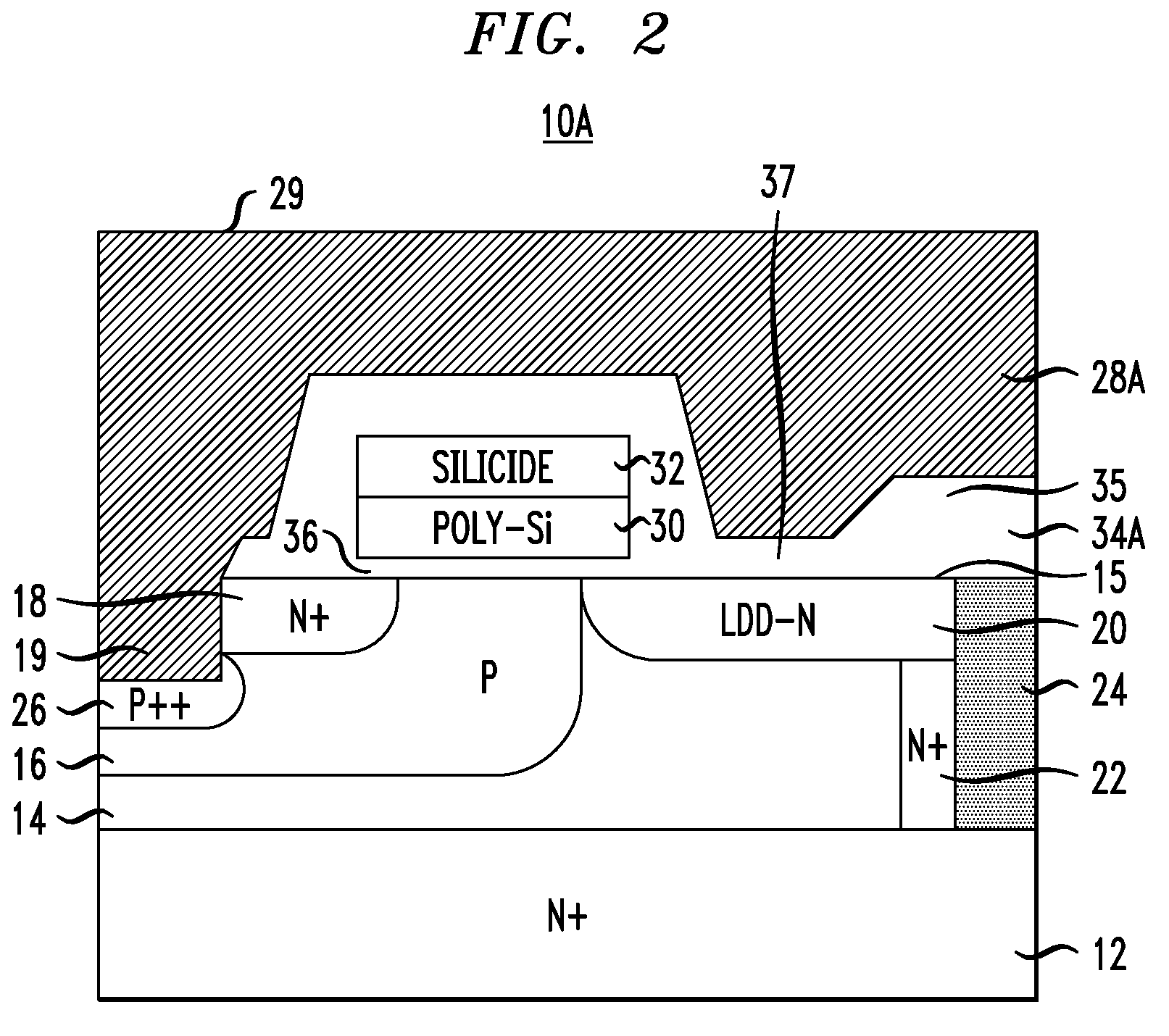

ActiveUS20070138548A1Semiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate dielectric

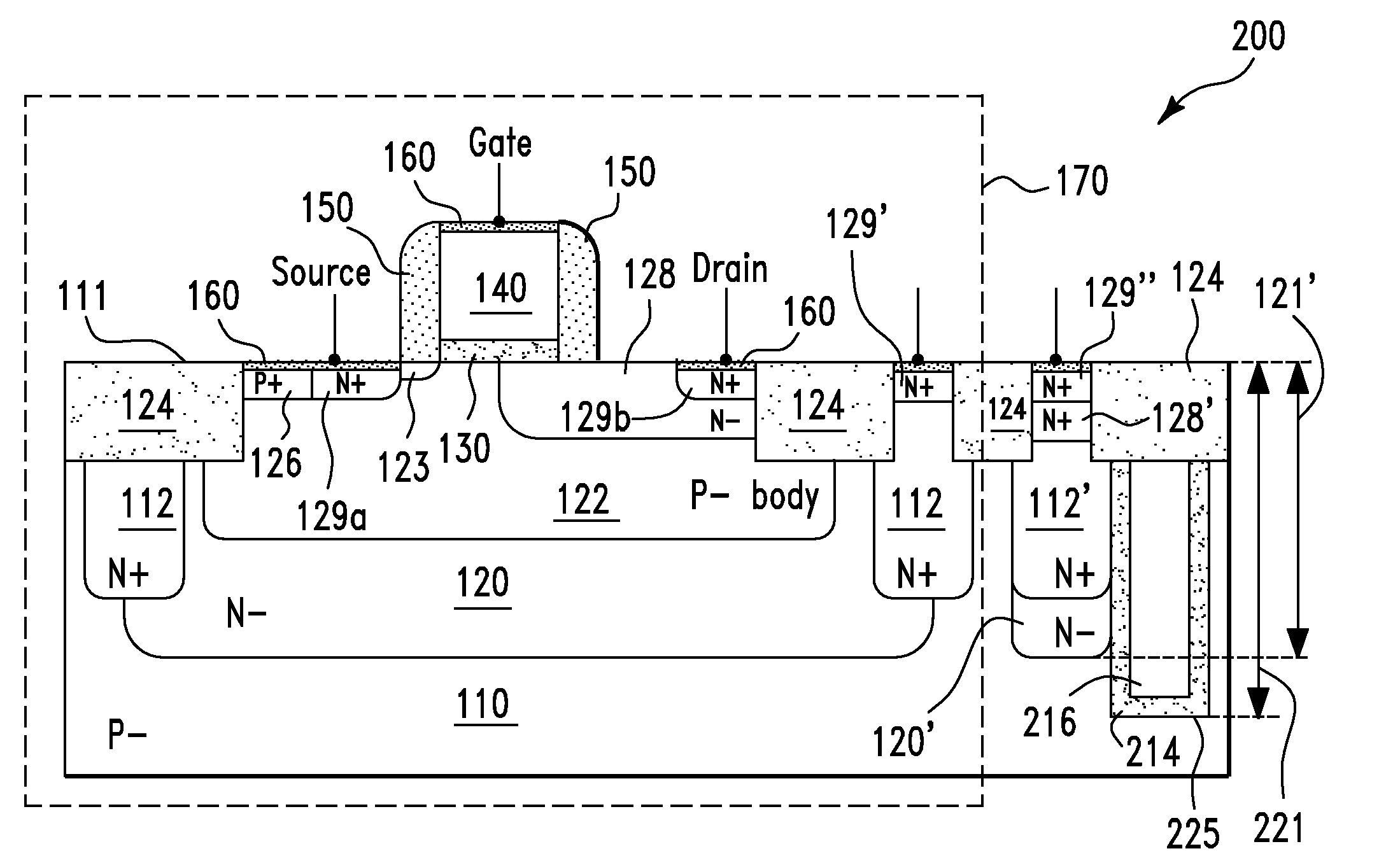

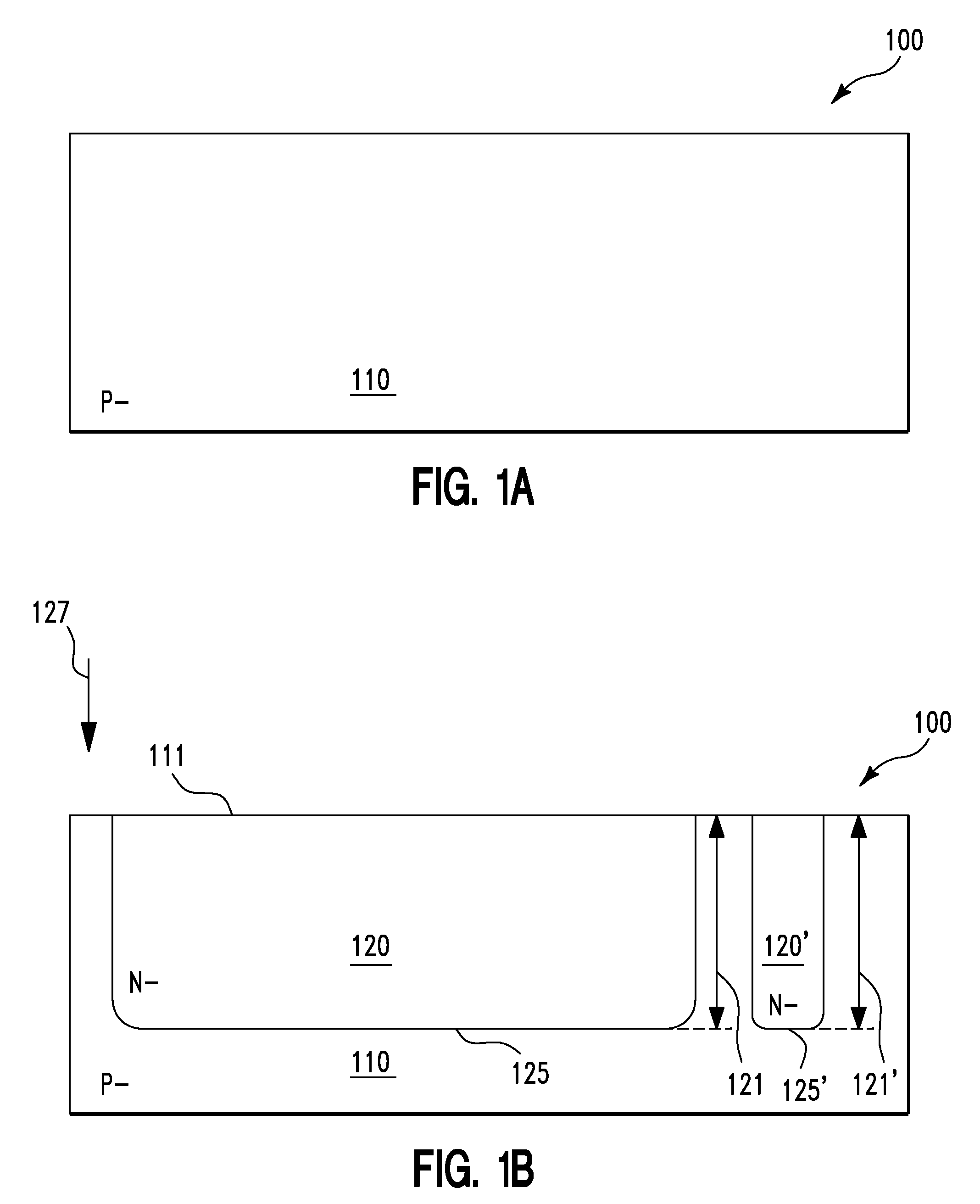

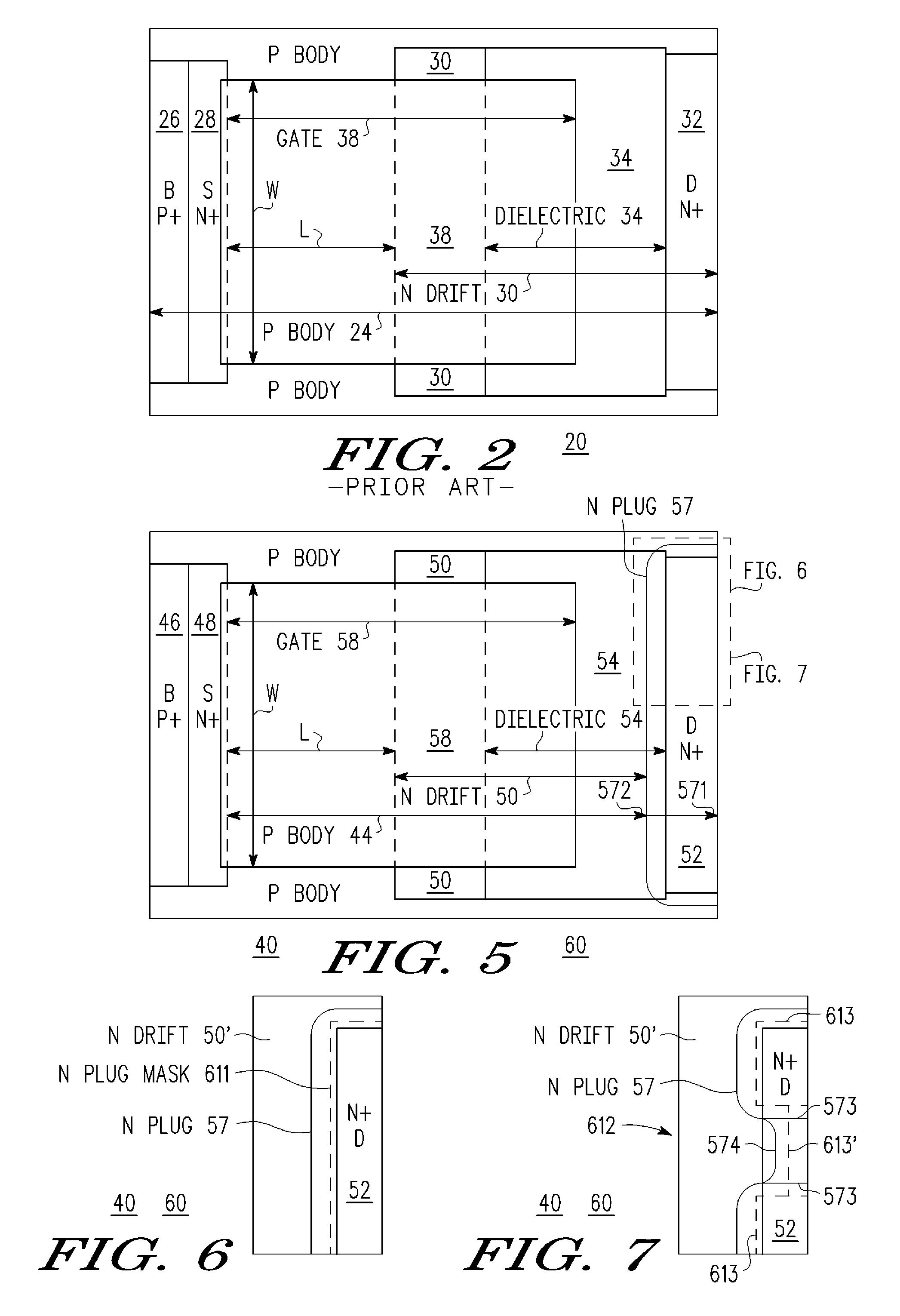

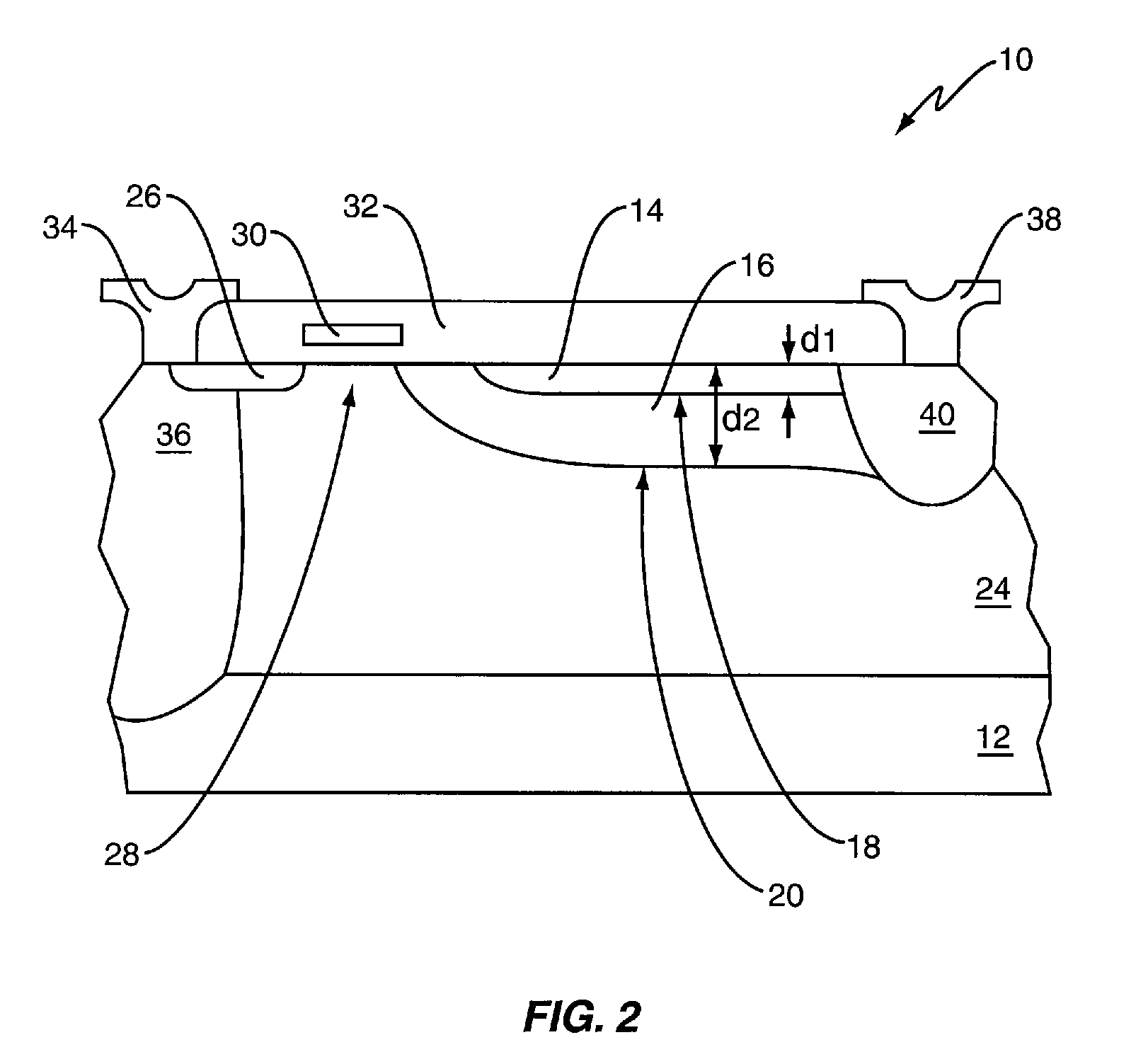

A laterally diffused metal-oxide-semiconductor transistor device includes a substrate having a first conductivity type with a semiconductor layer formed over the substrate. A source region and a drain extension region of the first conductivity type are formed in the semiconductor layer. A body region of a second conductivity type is formed in the semiconductor layer. A conductive gate is formed over a gate dielectric layer that is formed over a channel region. A drain contact electrically connects the drain extension region to the substrate and is laterally spaced from the channel region. The drain contact includes a highly-doped drain contact region formed between the substrate and the drain extension region in the semiconductor layer, wherein a topmost portion of the highly-doped drain contact region is spaced from the upper surface of the semiconductor layer. A source contact electrically connects the source region to the body region.

Owner:TEXAS INSTR LEHIGH VALLEY

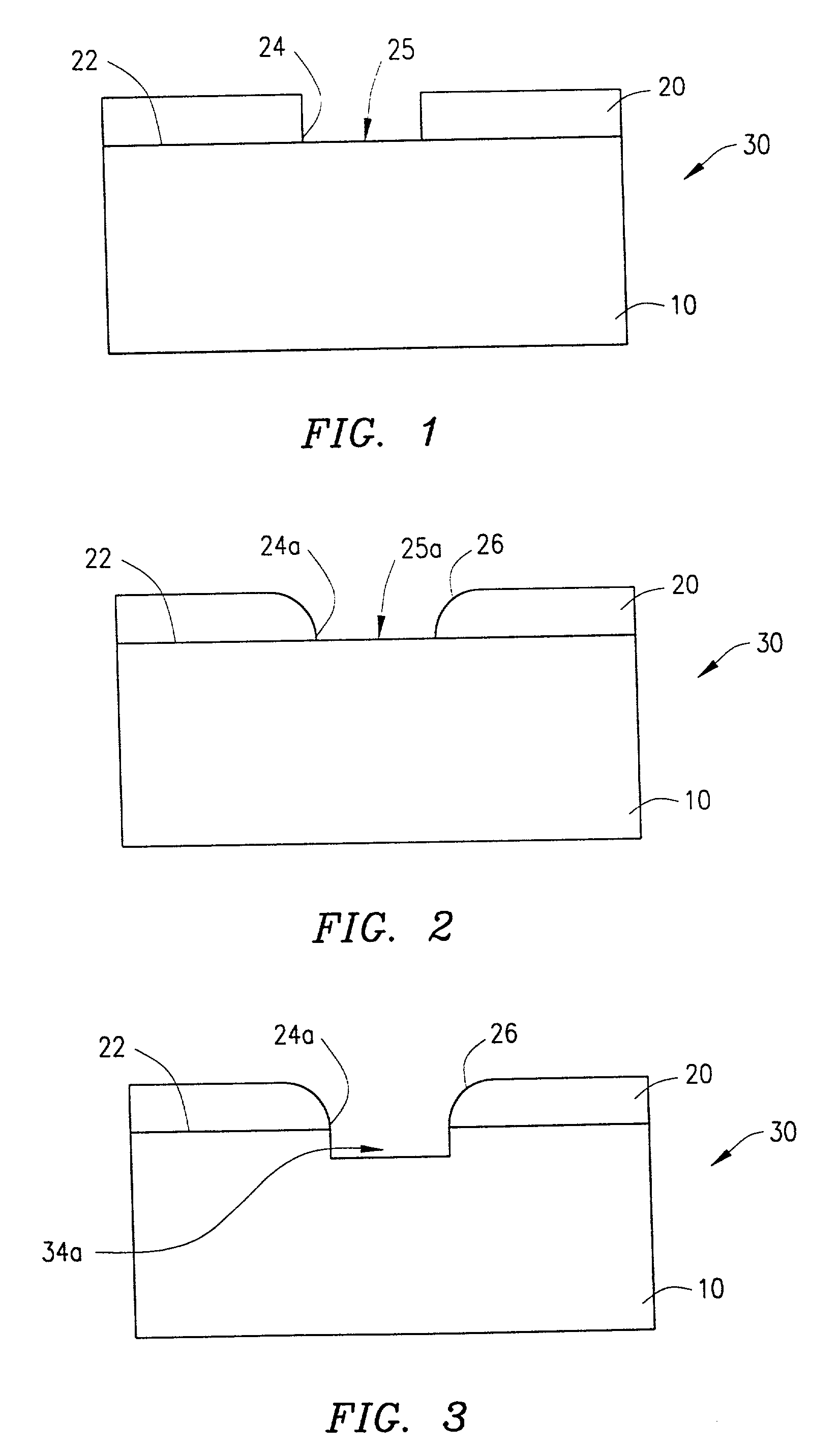

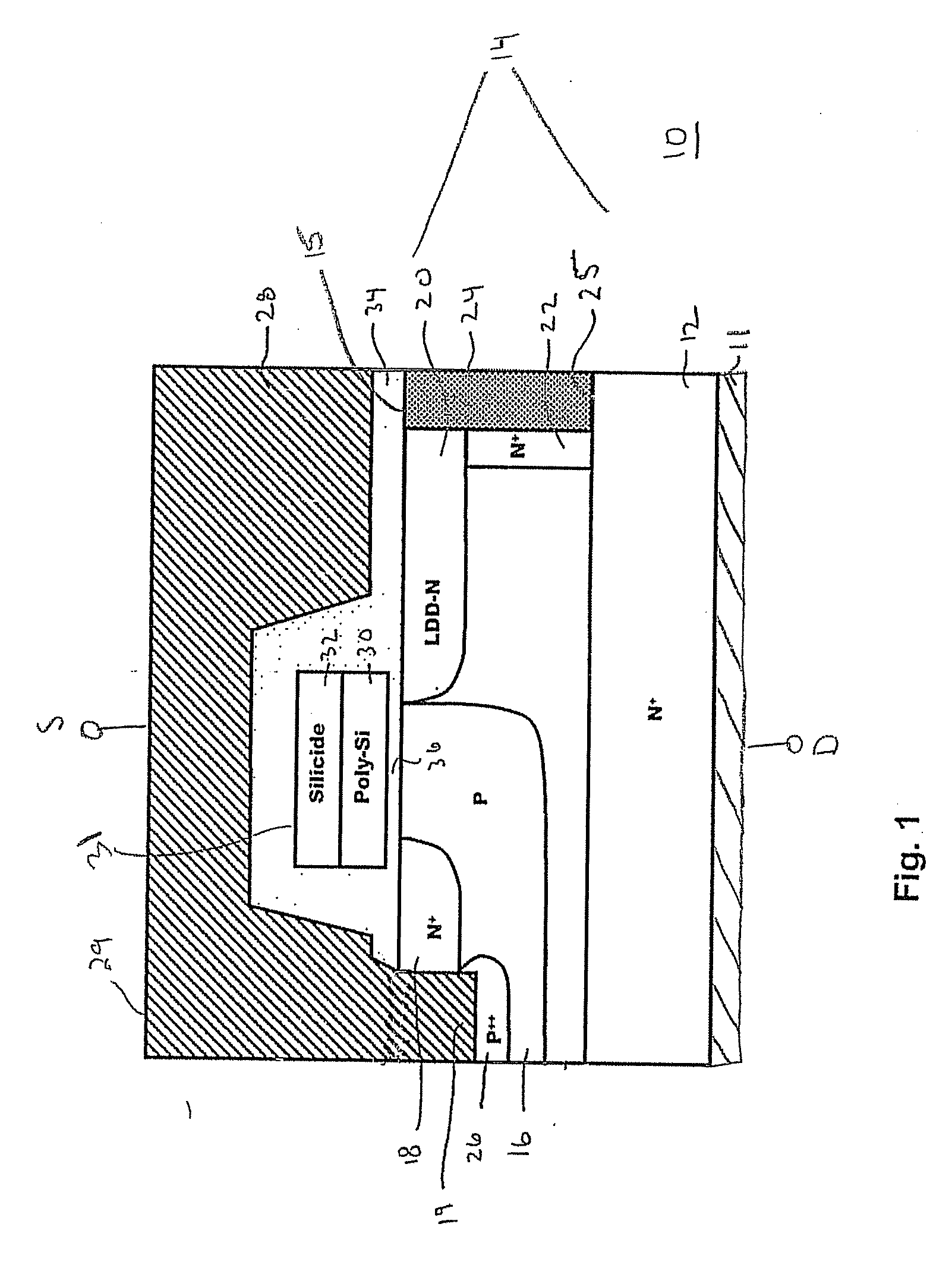

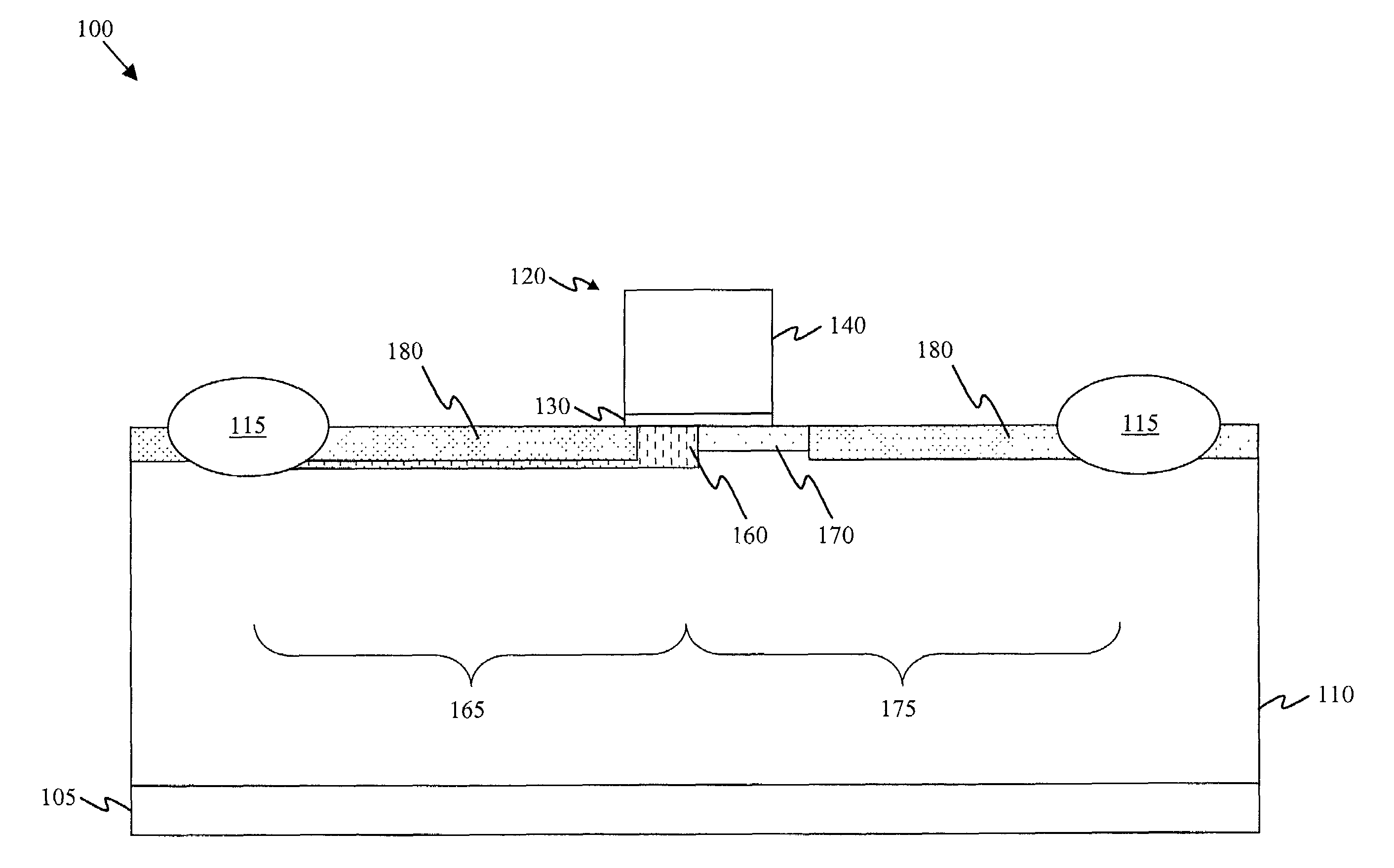

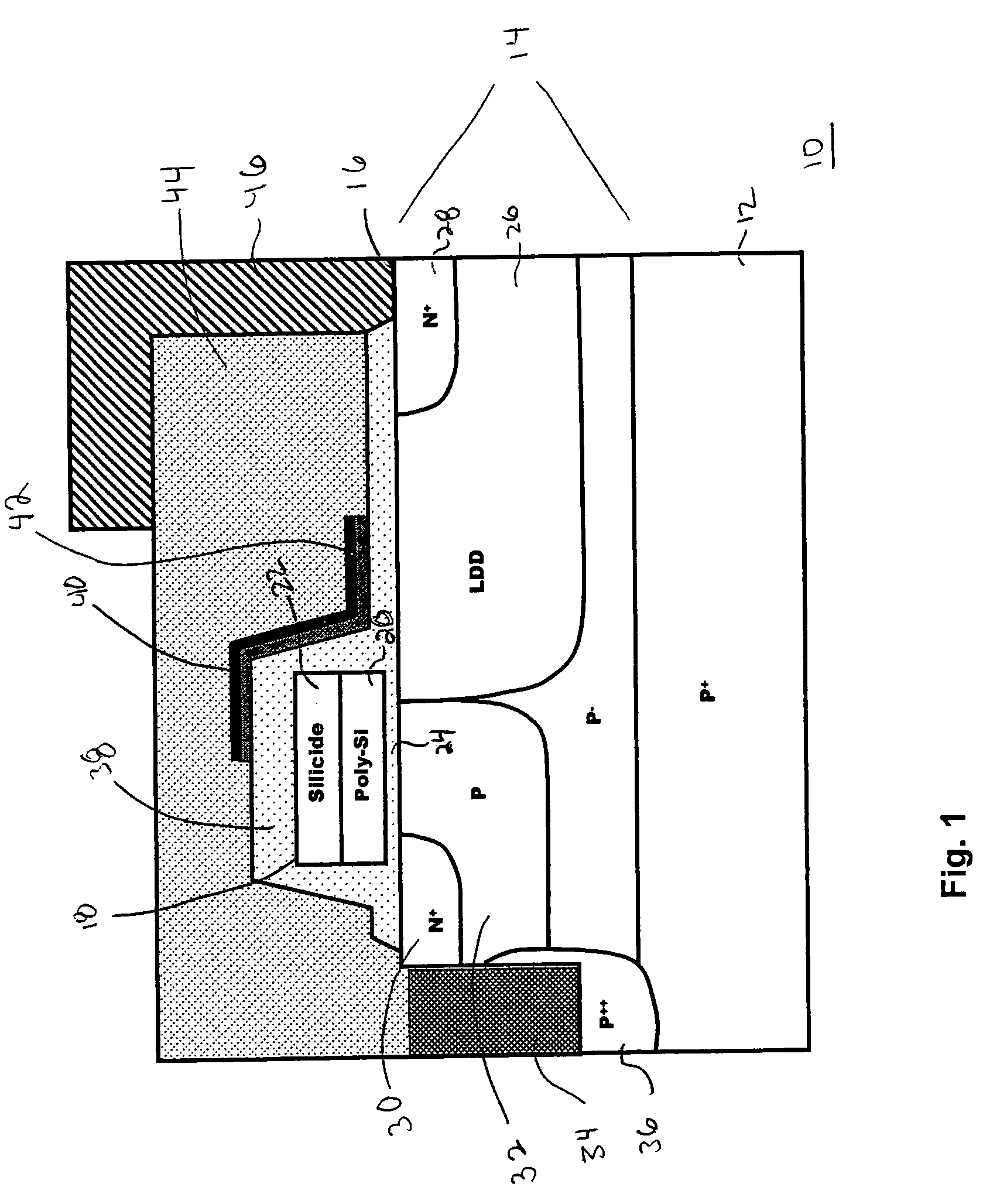

Laterally diffused metal oxide semiconductor device and method of forming the same

InactiveUS20050167756A1TransistorSemiconductor/solid-state device manufacturingLDMOSCondensed matter physics

A transistor advantageously embodied in a laterally diffused metal oxide semiconductor device having a gate located over a channel region recessed into a semiconductor substrate and a method of forming the same. In one embodiment, the laterally diffused metal oxide semiconductor device includes a source / drain having a lightly doped region located adjacent the channel region and a heavily doped region located adjacent the lightly doped region. The laterally diffused metal oxide semiconductor device further includes an oppositely doped well located under and within the channel region, and a doped region, located between the heavily doped region and the oppositely doped well, having a doping concentration profile less than a doping concentration profile of the heavily doped region.

Owner:TAHOE RES LTD

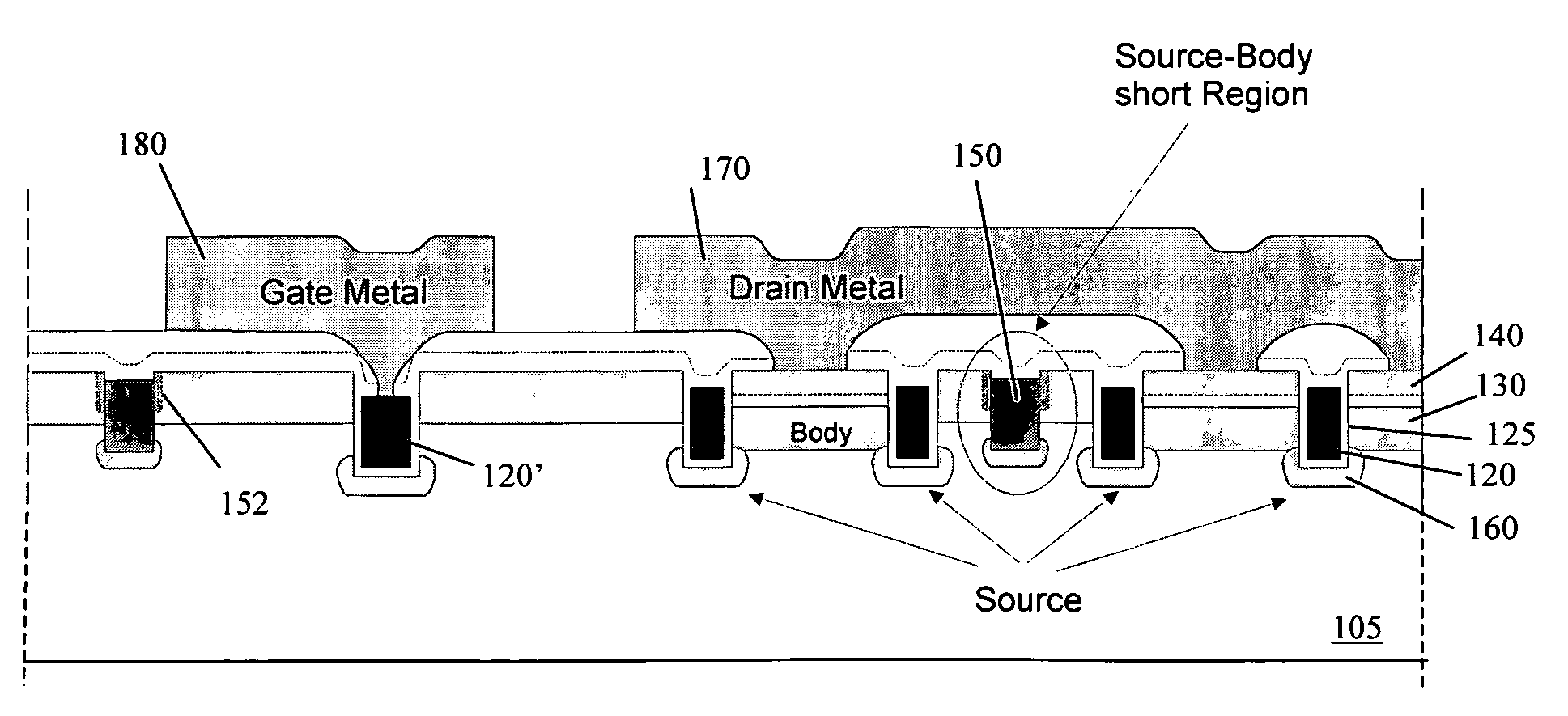

Power LDMOS transistor

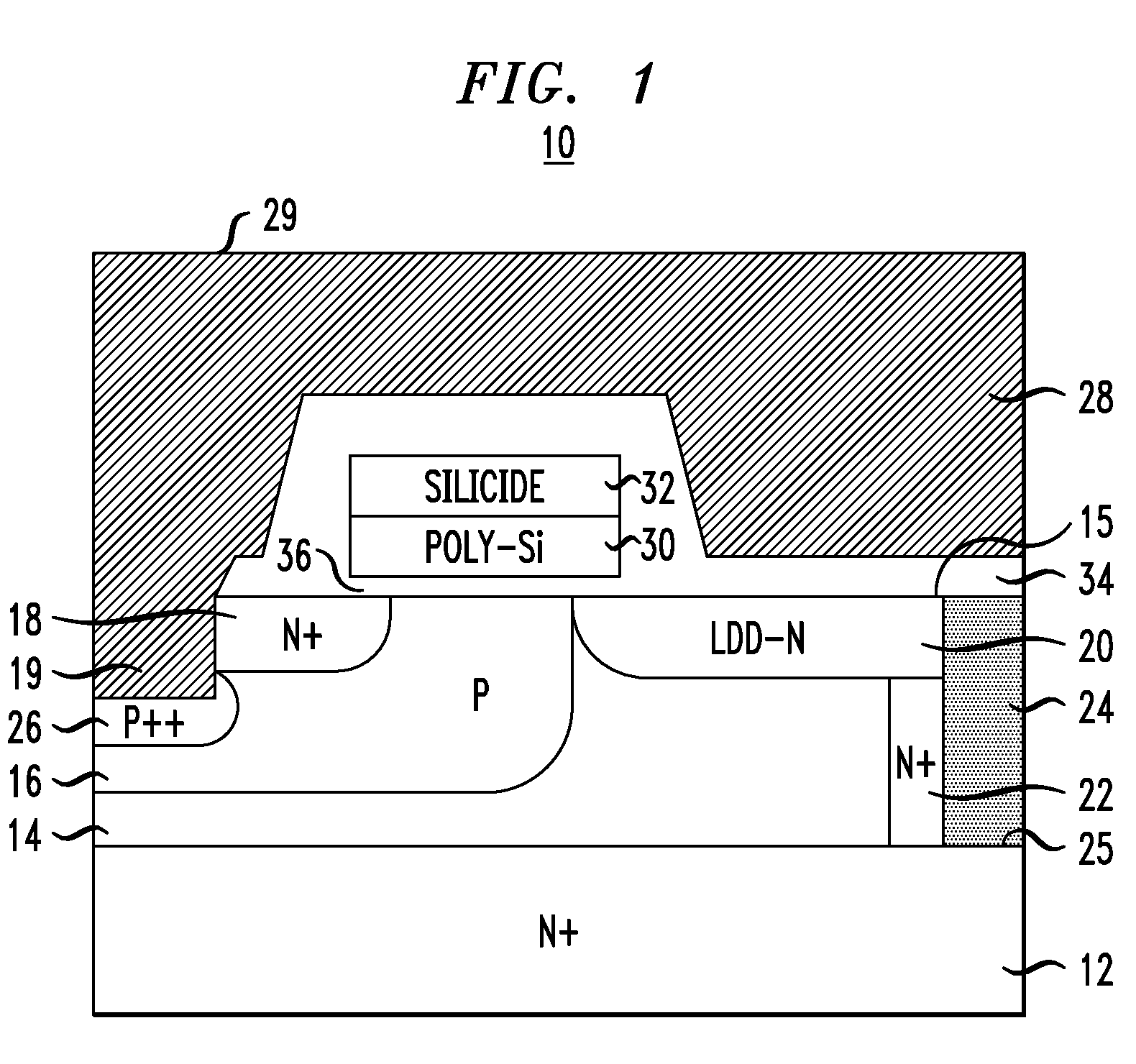

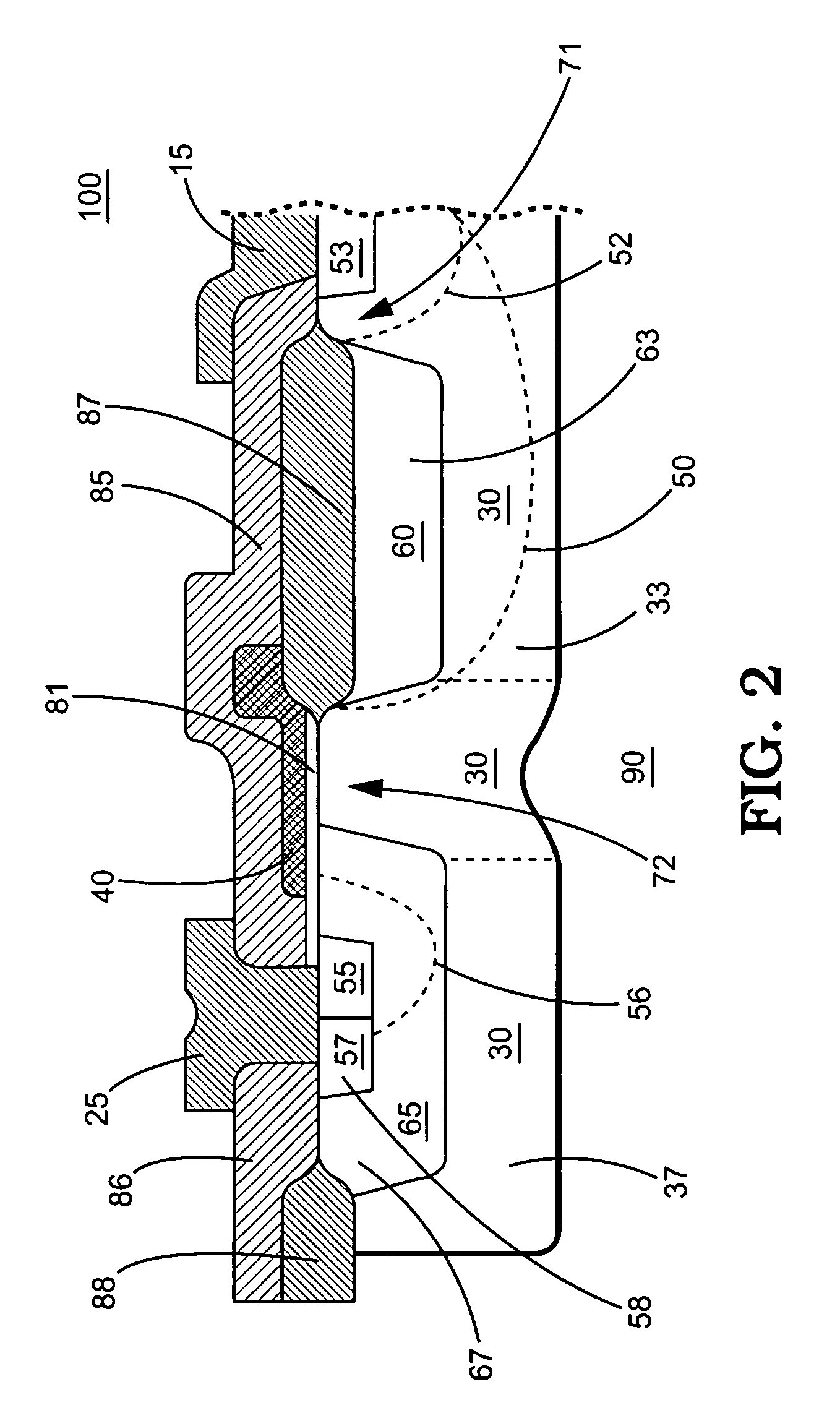

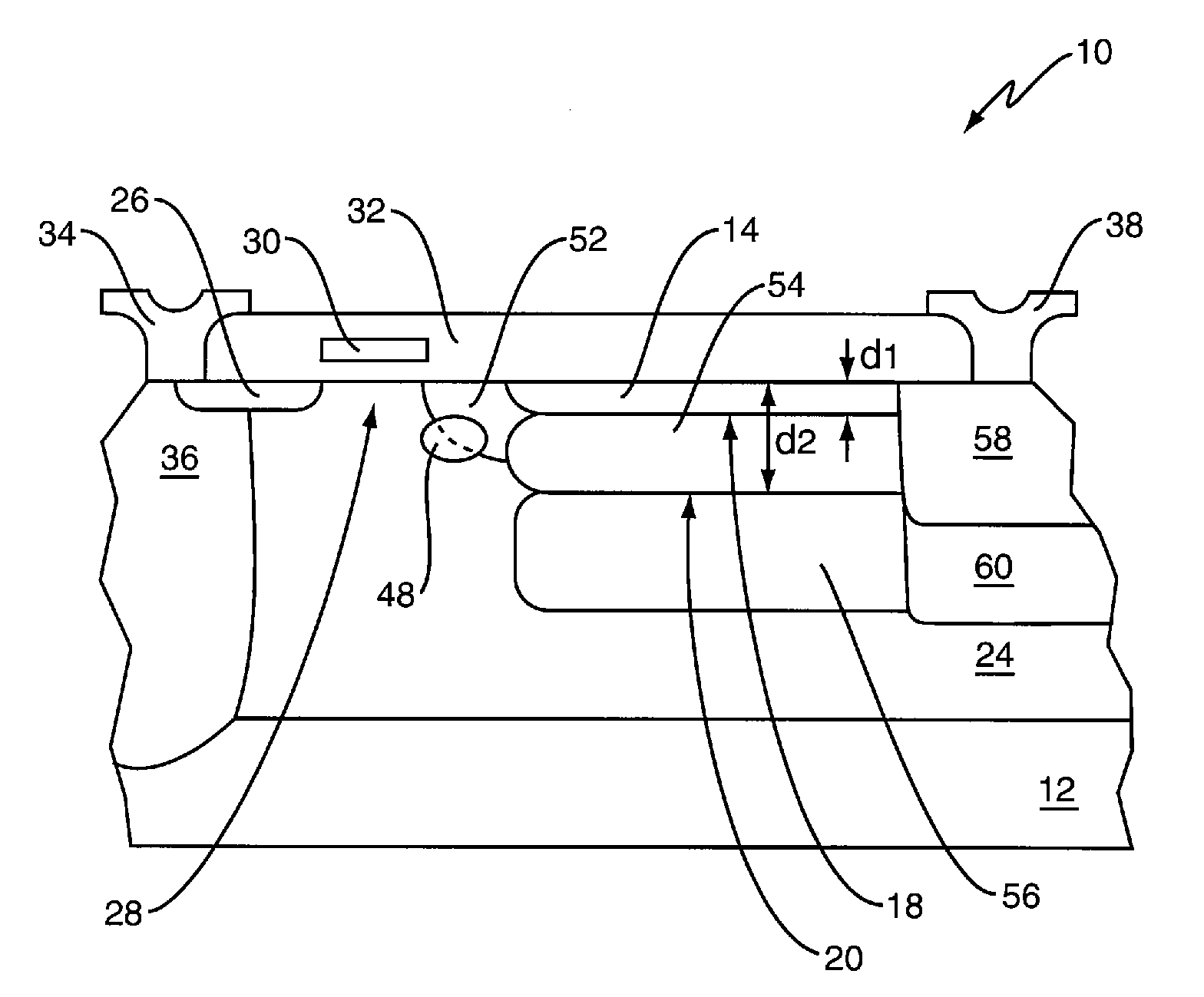

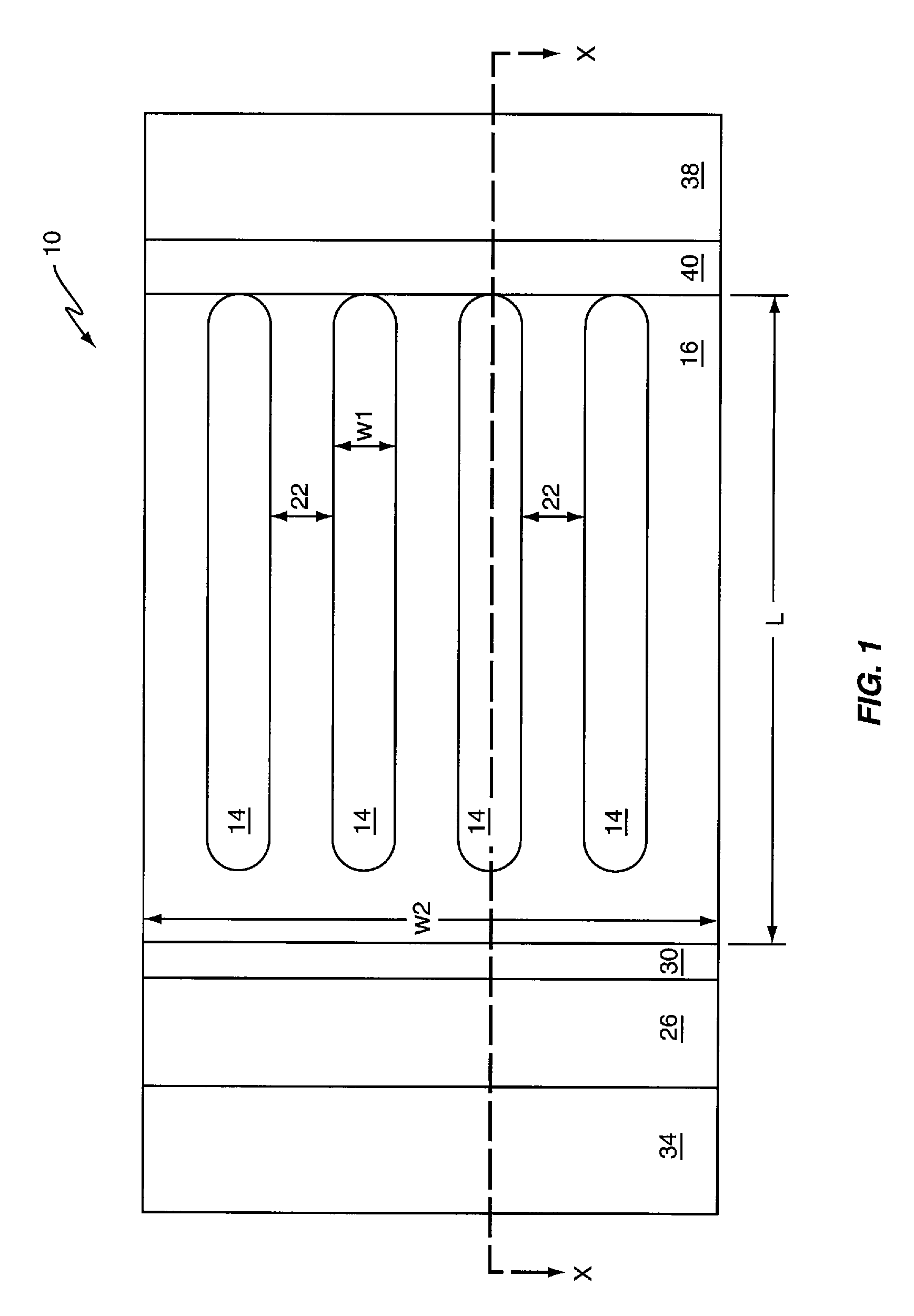

ActiveUS7282765B2Semiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate dielectric

An LDMOS device comprises a substrate having a first conductivity type and a lightly doped epitaxial layer thereon having an upper surface. Source and drain regions of the first conductivity type are formed in the epitaxial layer along with a channel region of a second conductivity type formed therebetween. A conductive gate is formed over a gate dielectric layer. A drain contact electrically connects the drain region to the substrate, comprising a first trench formed from the upper surface of the epitaxial layer to the substrate and having a side wall along the epitaxial layer, a highly doped region of the first conductivity type formed along the side wall of the first trench, and a drain plug in the first trench adjacent the highly doped region. A source contact is provided and an insulating layer is formed between the conductive gate and the source contact.

Owner:CICLON SEMICON DEVICE

LDMOS transistors and methods for making the same

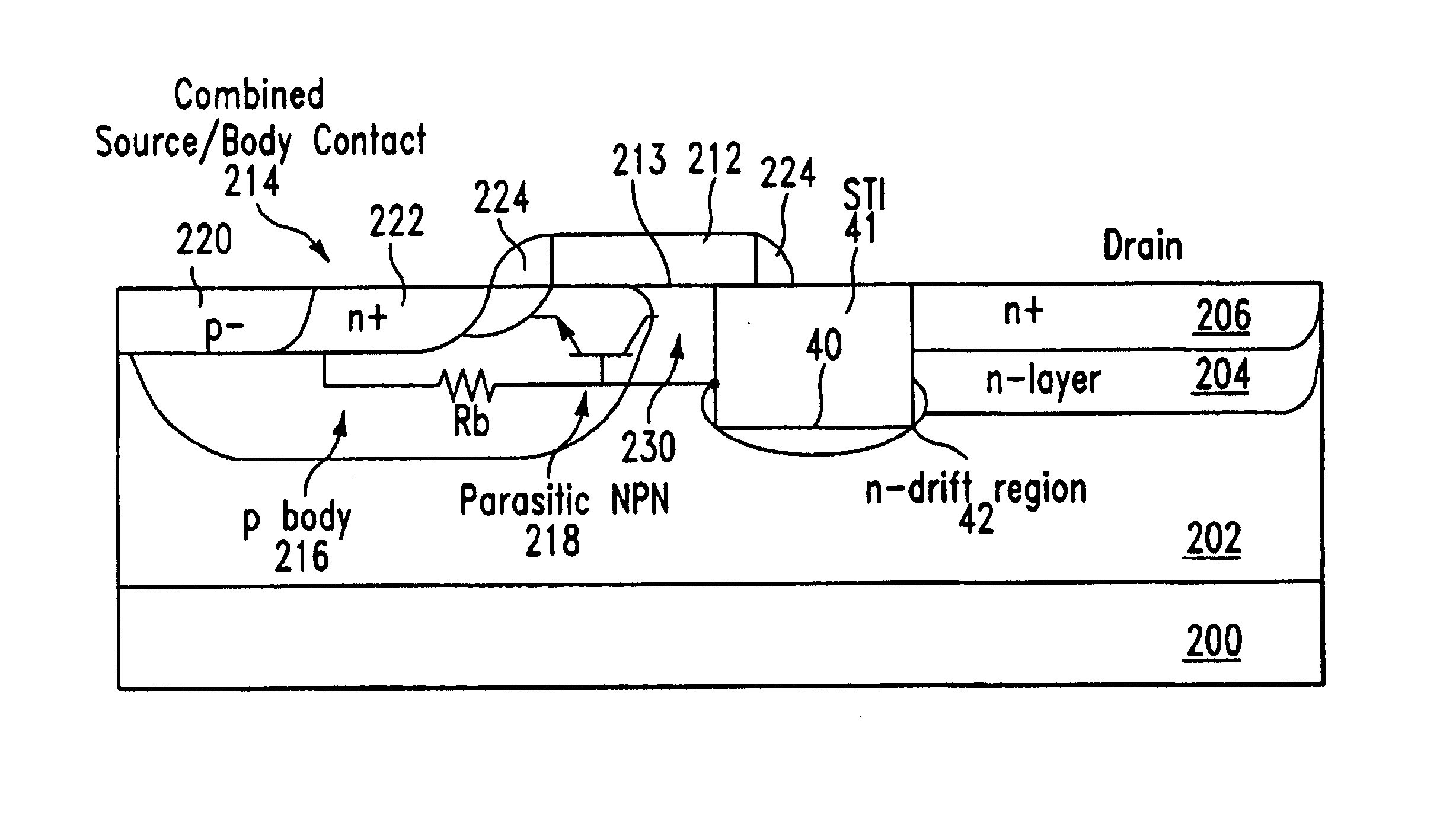

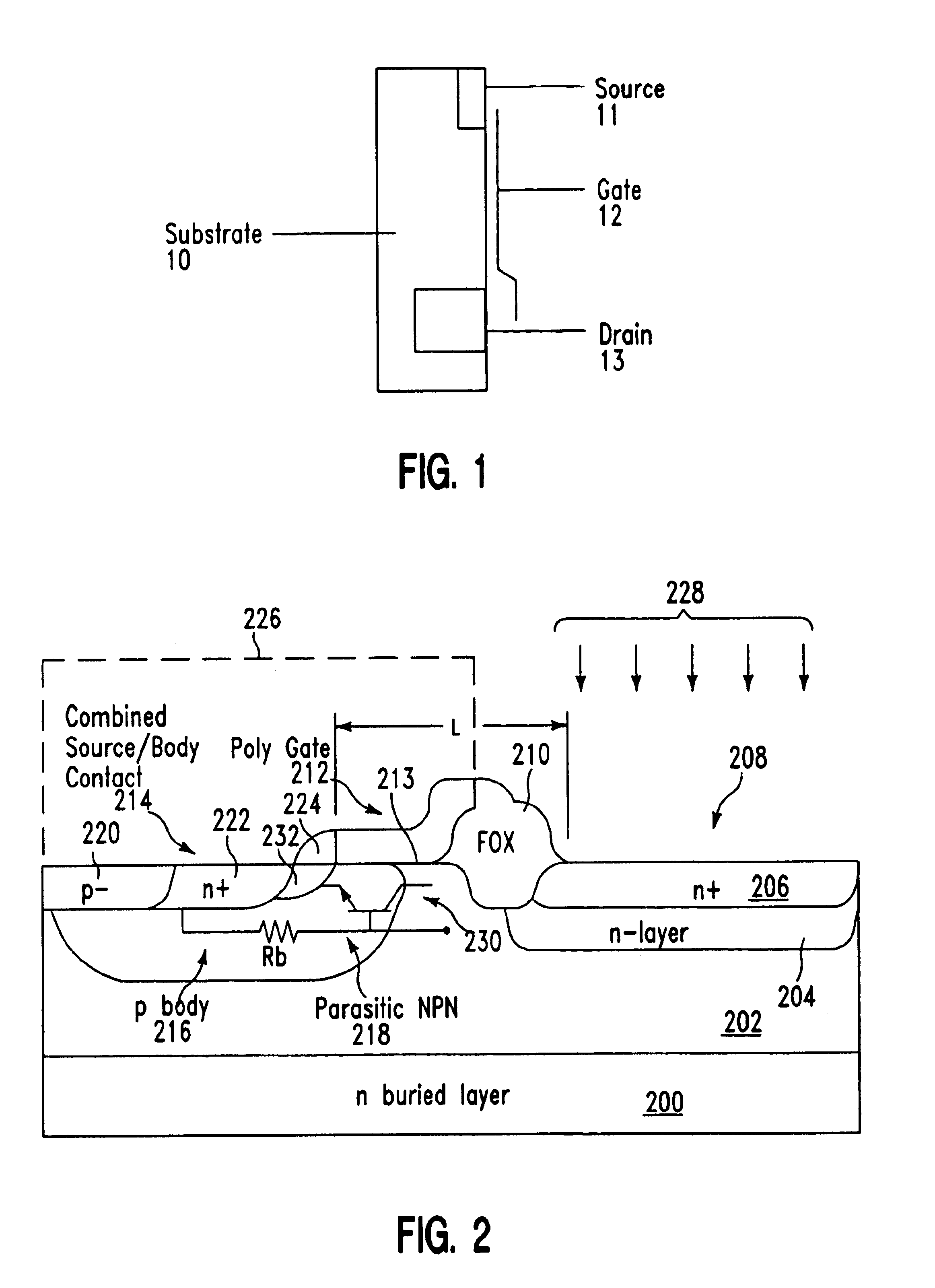

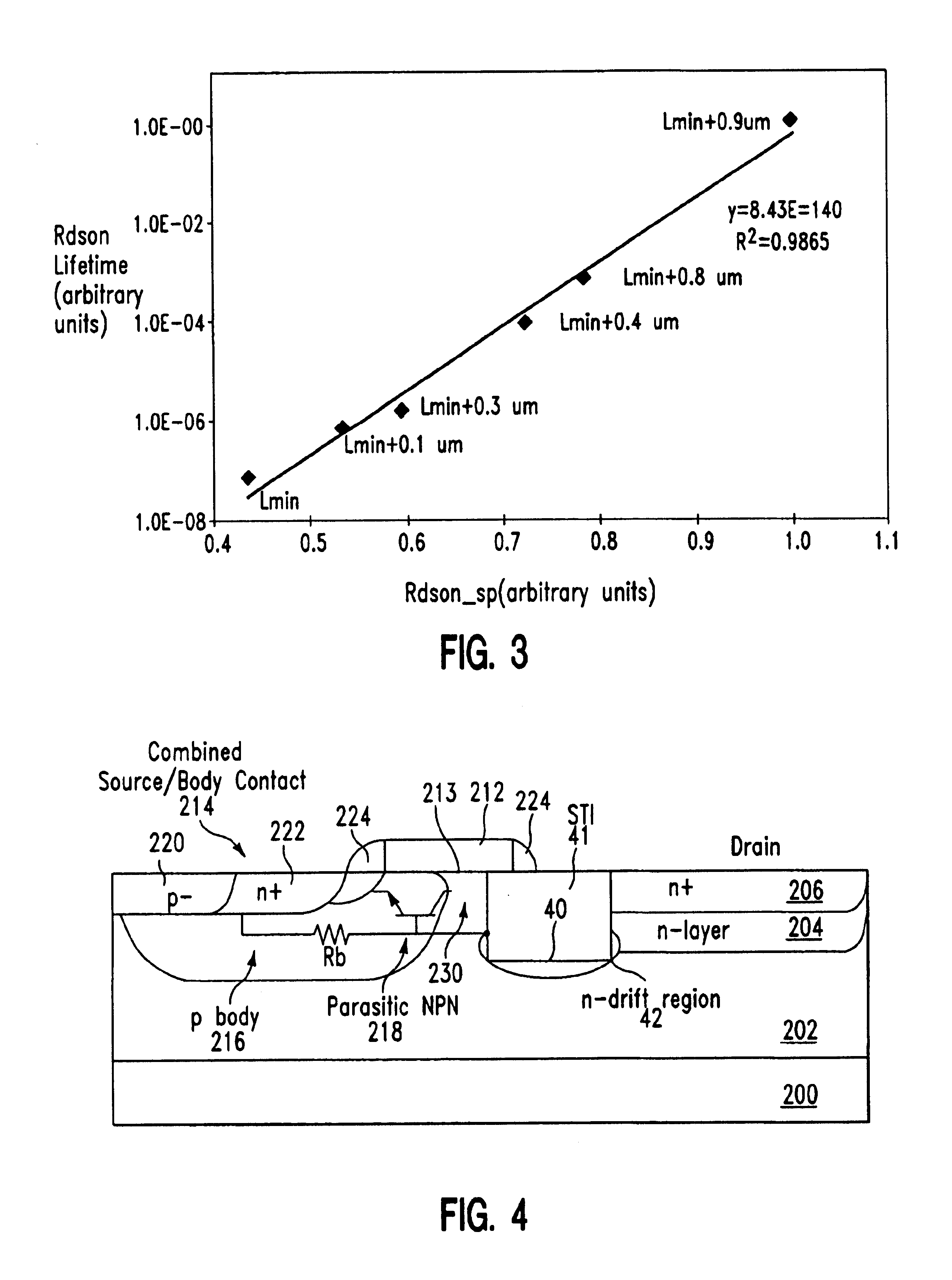

InactiveUS6900101B2Reduce or inhibit current flow constrictionLower on-state resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantDielectric

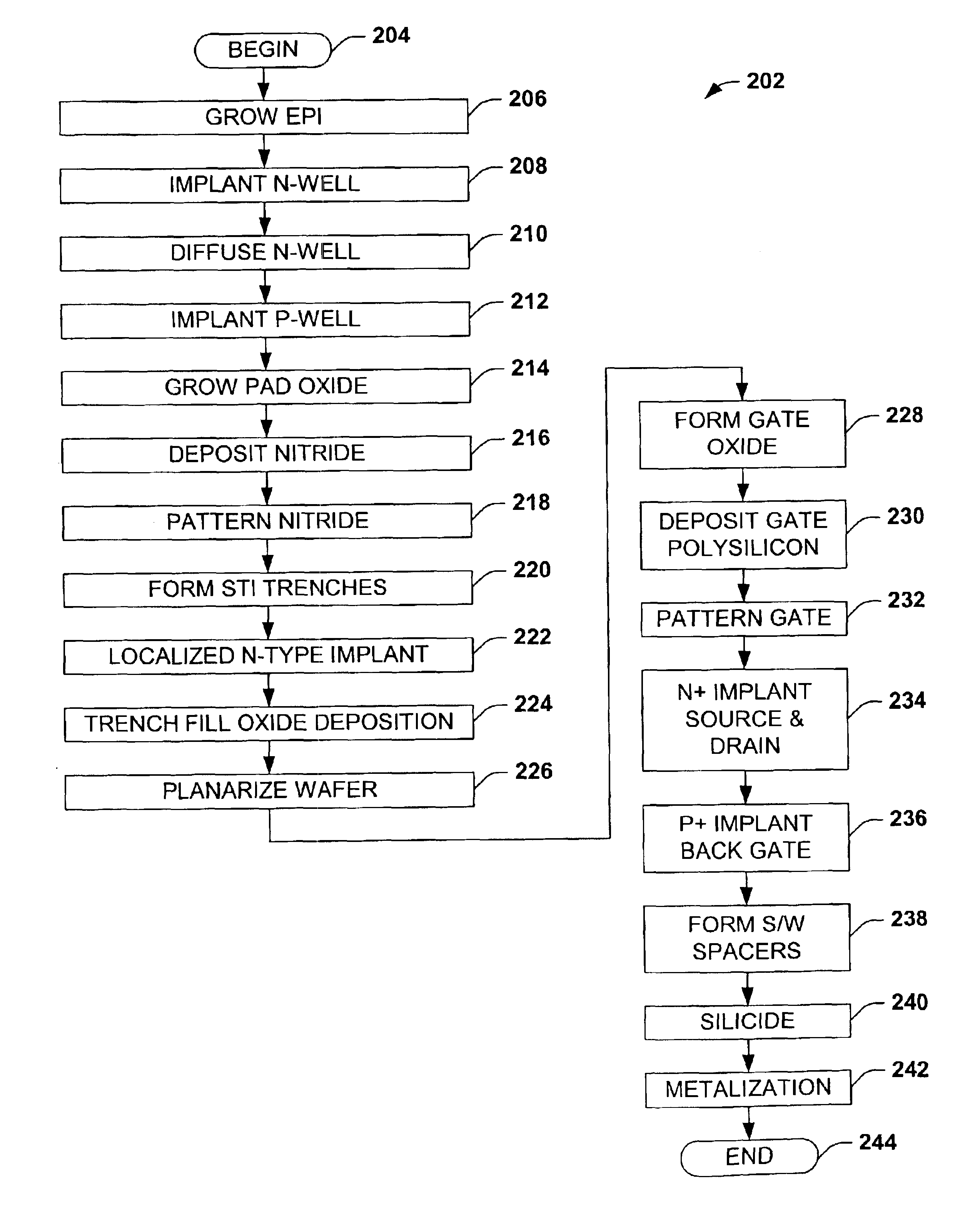

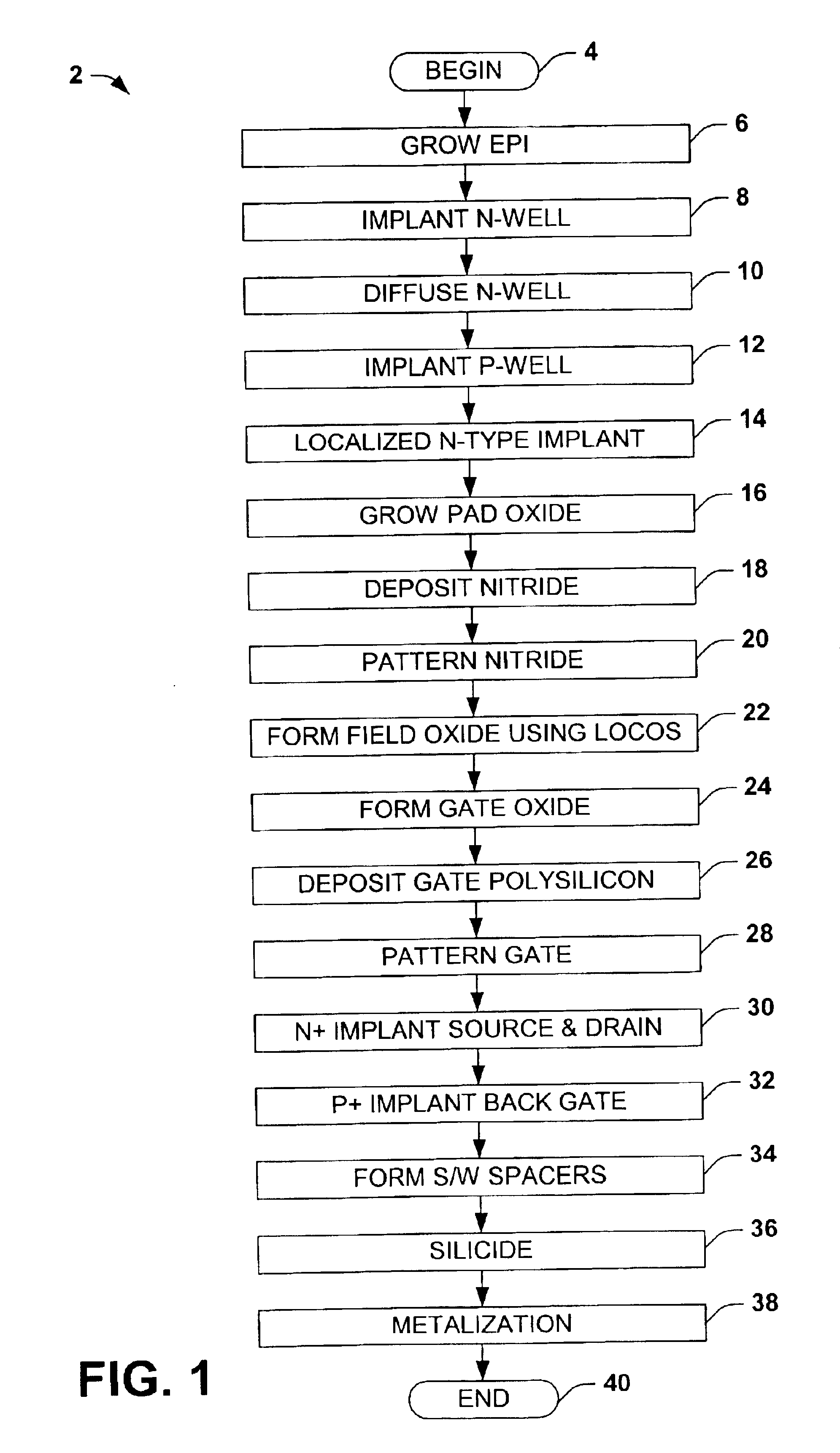

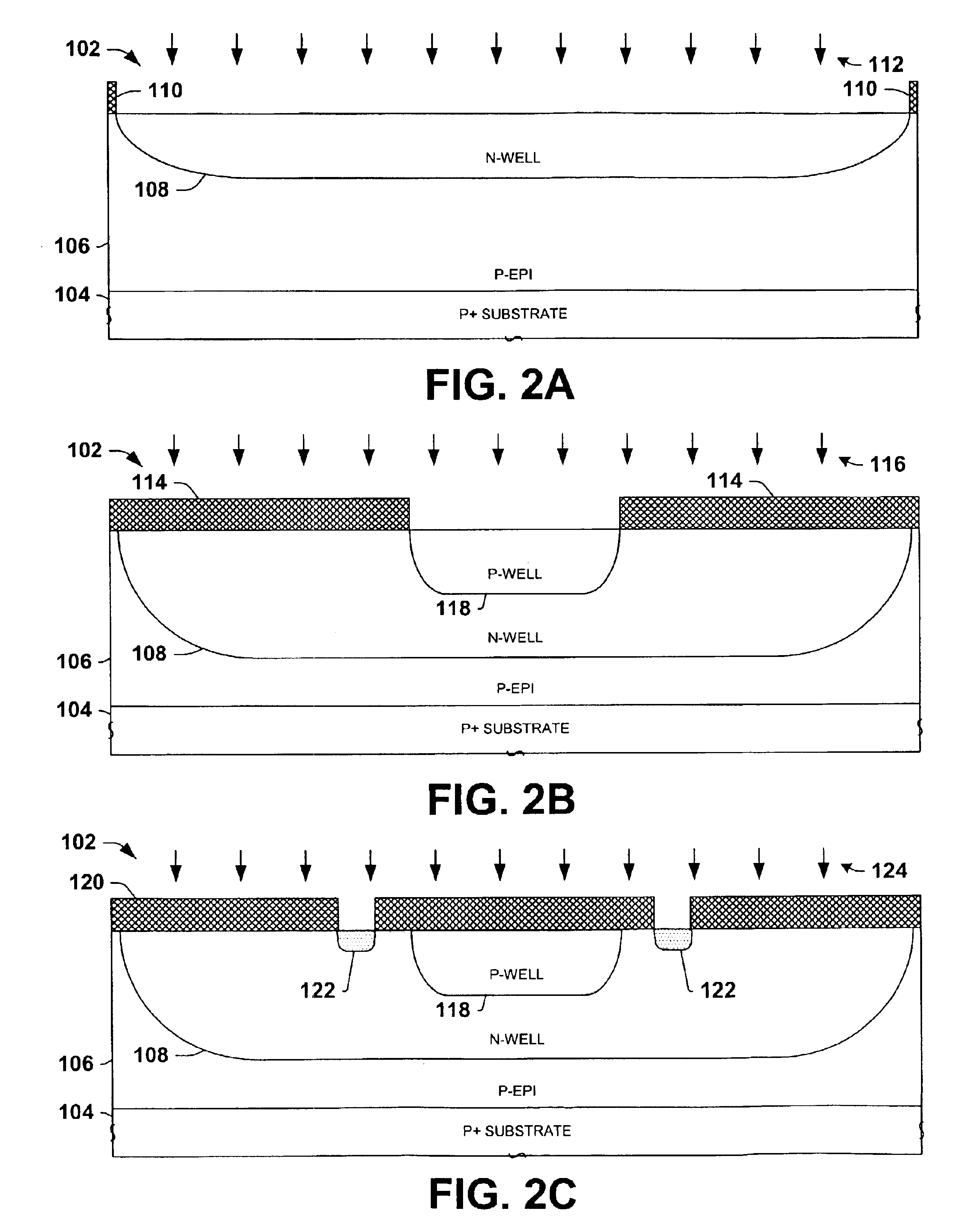

LDMOS transistor devices and fabrication methods are provided, in which additional dopants are provided to region of a substrate near a thick dielectric between the channel and the drain to reduce device resistance without significantly impacting breakdown voltage. The extra dopants are added by implantation prior to formation of the thick dielectric, such as before oxidizing silicon in a LOCOS process or following trench formation and before filling the trench in an STI process.

Owner:TEXAS INSTR INC

Semiconductor device and method for fabricating such device

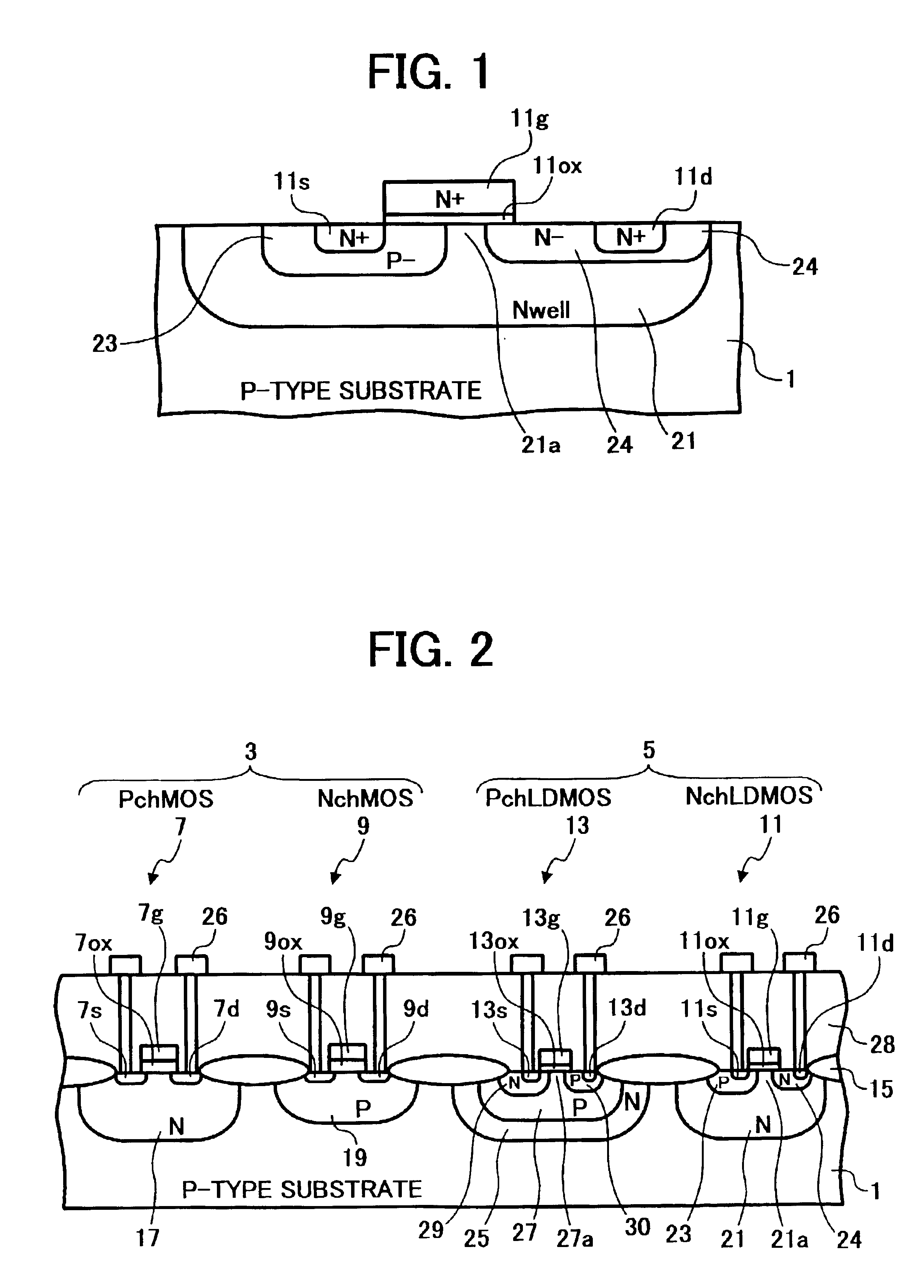

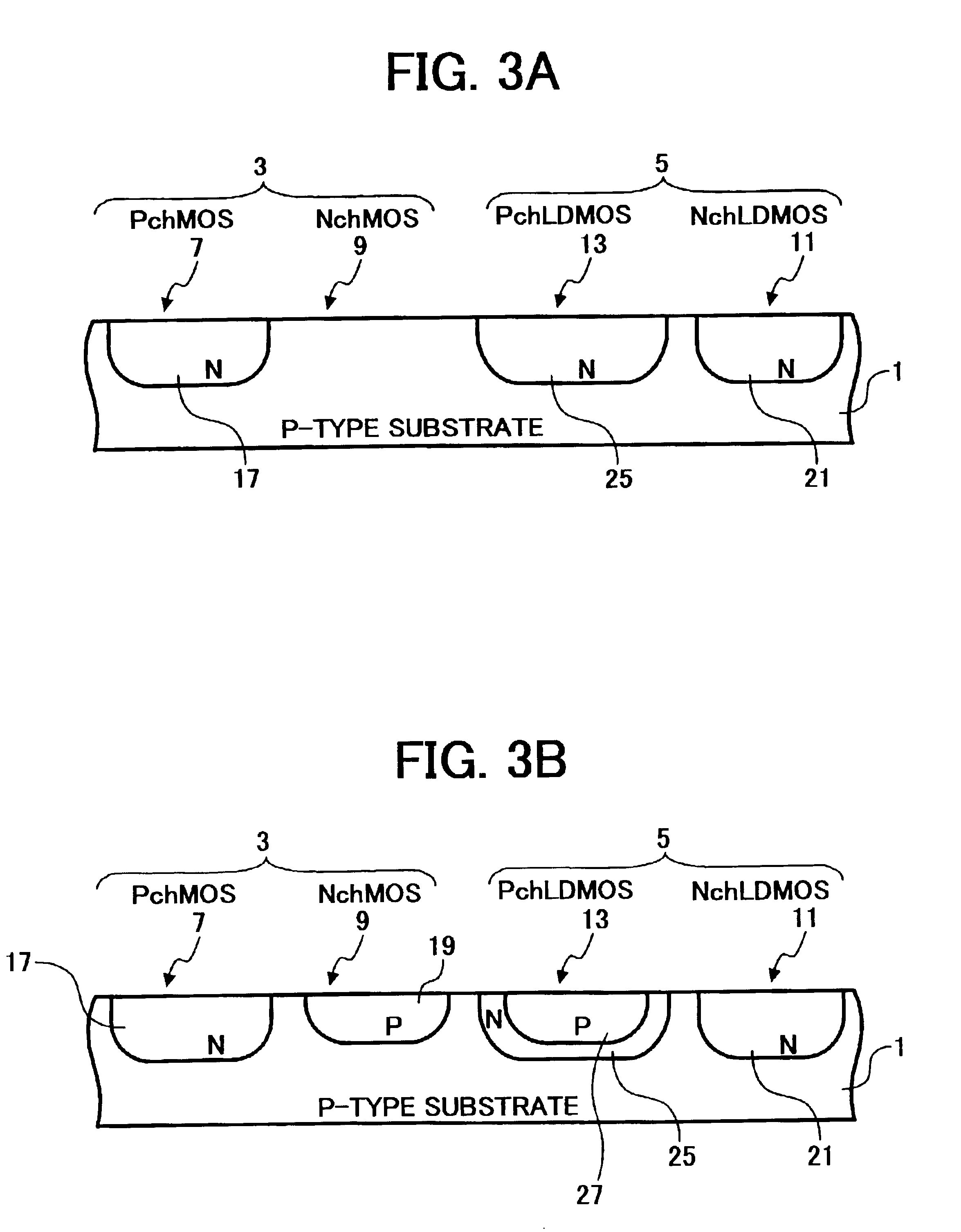

InactiveUS6911694B2Stable operational characteristicAvoid layeringTransistorSolid-state devicesLDMOSGate dielectric

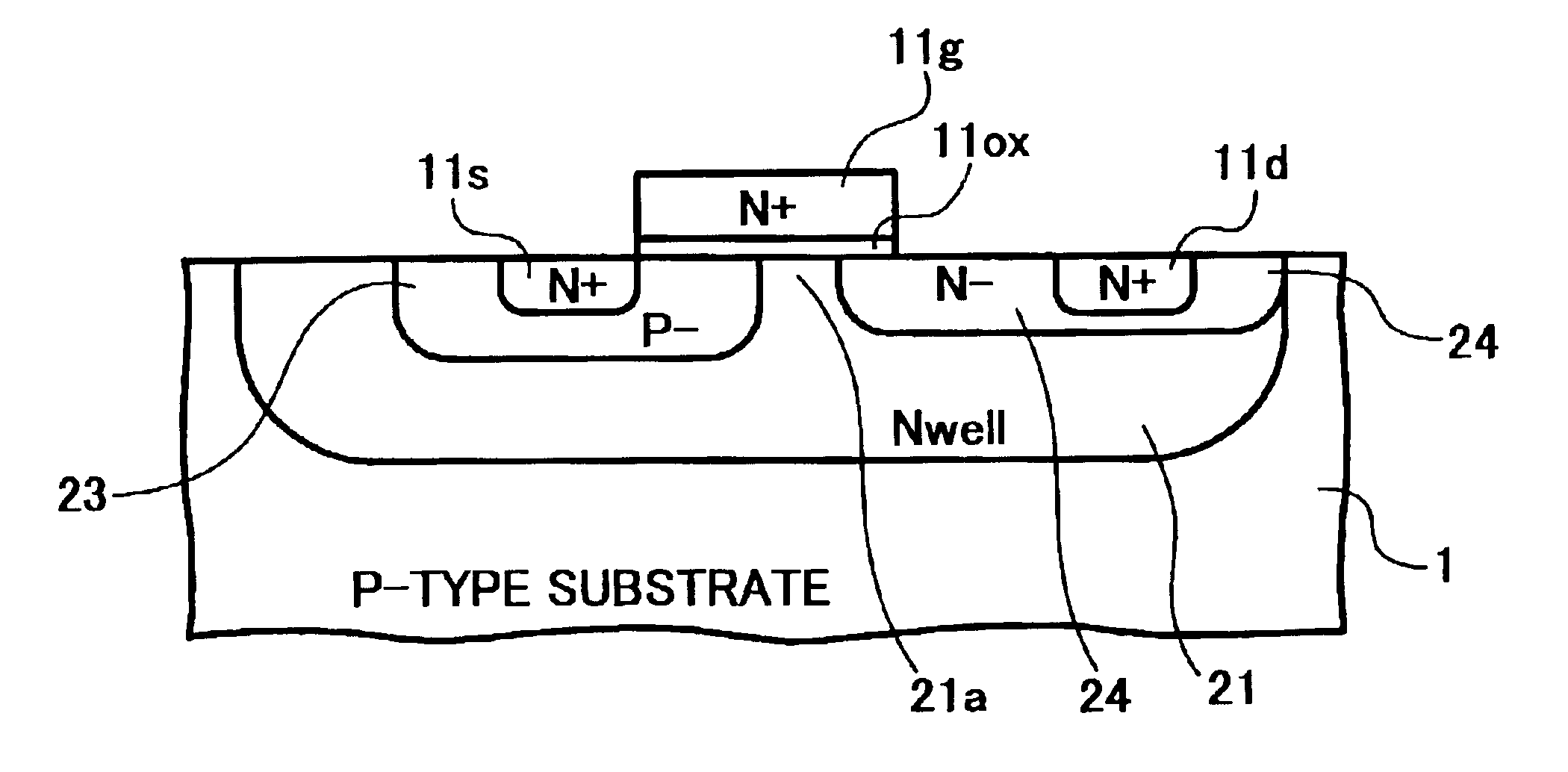

An LDMOS transistor and a bipolar transistor with LDMOS structures are disclosed for suitable use in high withstand voltage device applications, among others. The LDMOS transistor includes a drain well region 21 formed in P-type substrate 1, and also formed therein spatially separated one another are a channel well region 23 and a medium concentration drain region 24 having an impurity concentration larger than that of drain well region 21, which are simultaneously formed having a large diffusion depth through thermal processing. A source 11s is formed in channel well region 23, while a drain 11d is formed in drain region 24 having an impurity concentration larger than that of drain region 24. In addition, a gate electrode 11g is formed over the well region, overlying the partially overlapped portions with well region 23 and drain region 24 and being separated from drain 11d. Since the source 11s, well region 23, and drain region 24 are respectively self-aligned to the gate electrode 11g, resultant transistor characteristics are stabilized, and the decrease in the on resistance and improved drain threshold voltages can be achieved. Also disclosed herein are bipolar transistors with LDMOS structures, which are capable of obviating the breakdown of gate dielectric layers even at high applied voltage and achieving improved stability in transistor characteristics.

Owner:RICOH KK

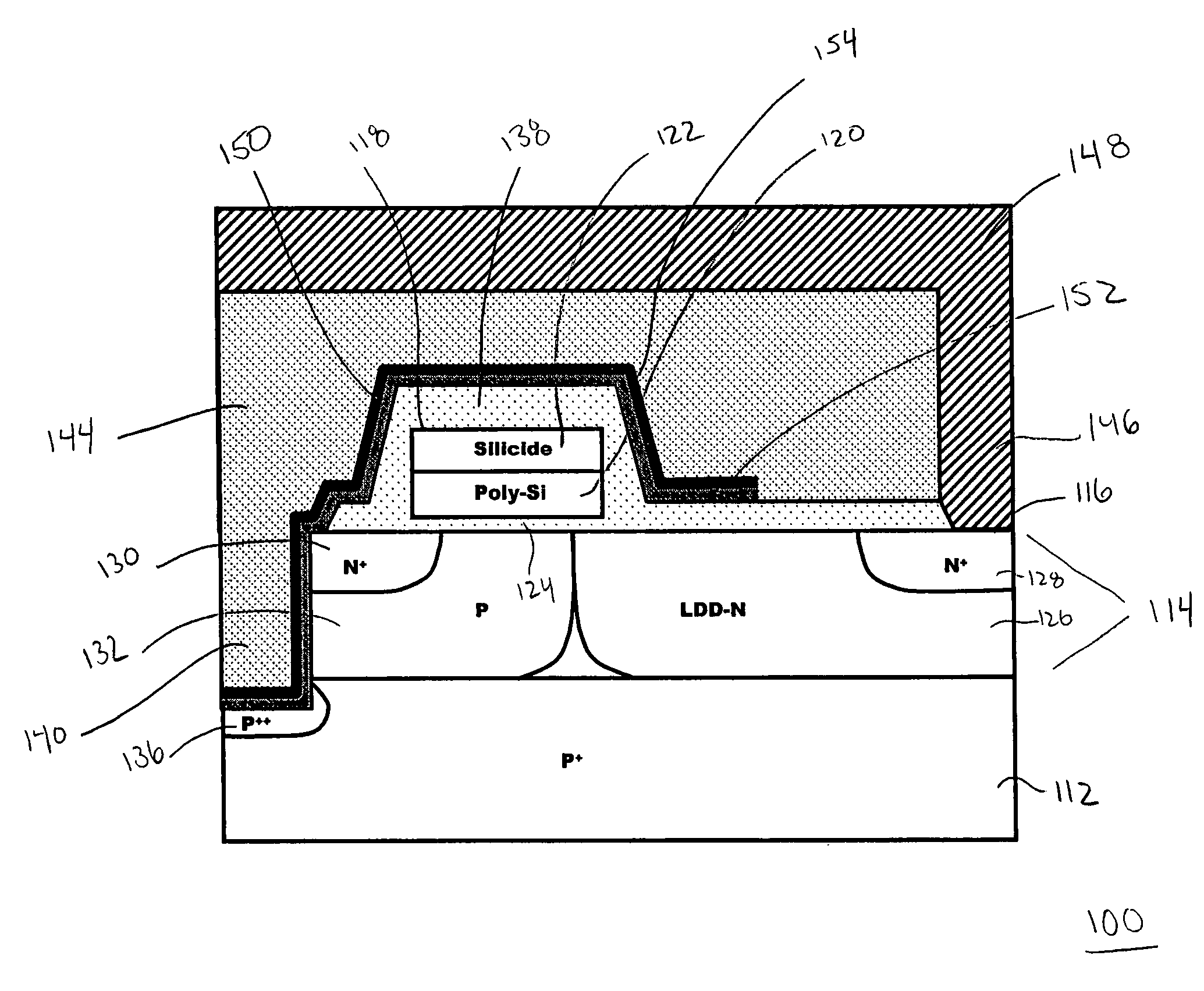

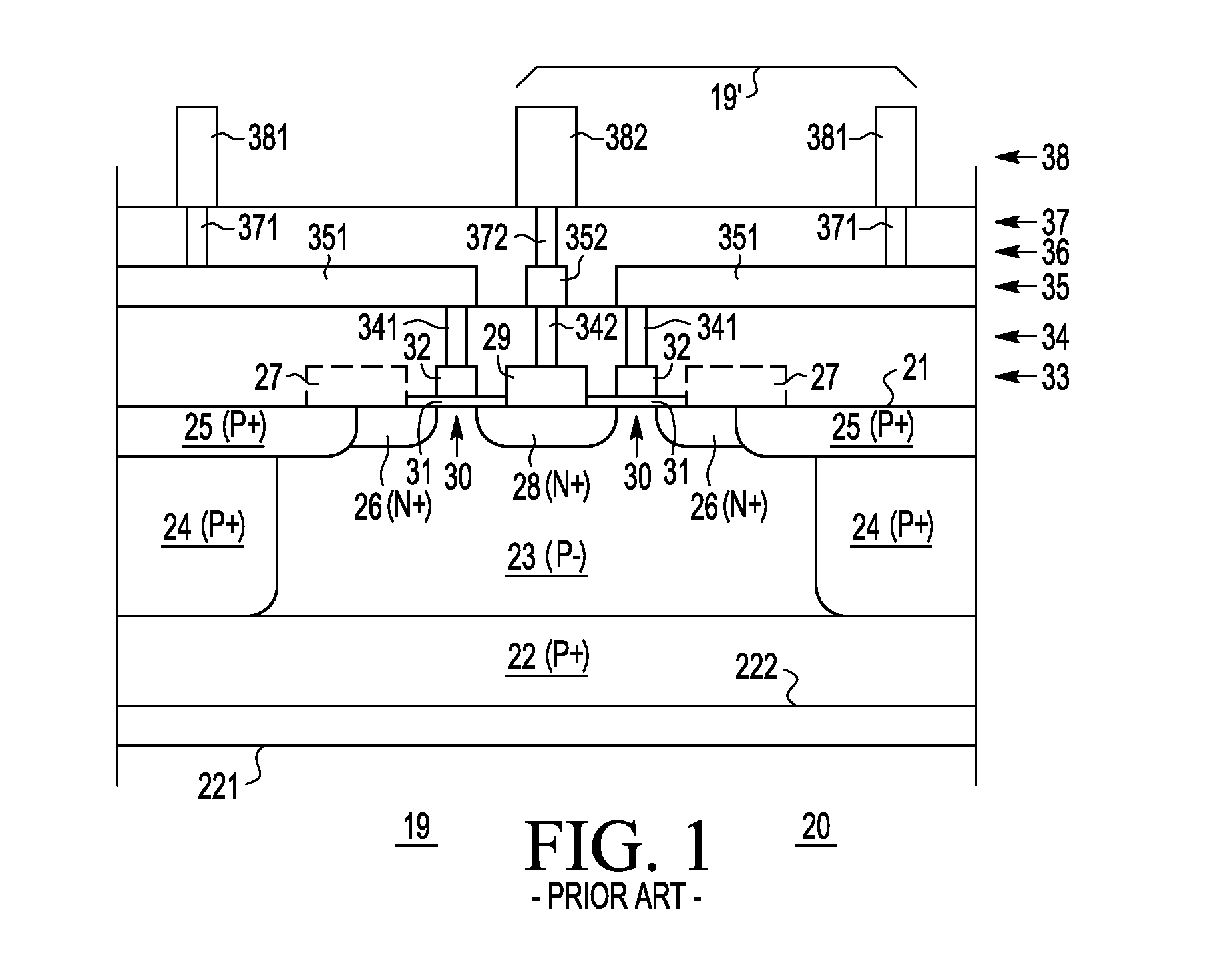

Ldmos device with isolation guard rings

InactiveUS20050073007A1Avoid leakage currentLatch-up, early breakdown and reliability issues are preventedSemiconductor/solid-state device detailsSolid-state devicesLDMOSDevice material

A method of forming a LDMOS semiconductor device and structure for same. A preferred embodiment comprises forming a first guard ring around and proximate the drain of a LDMOS device, and forming a second guard ring around the first guard ring. The first guard ring comprises a P+ base guard ring, and the second guard ring comprises an N+ collector guard ring formed in a deep N-well, in one embodiment. The first guard ring and second guard ring prevent leakage current from flowing from the drain of the LDMOS device to the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

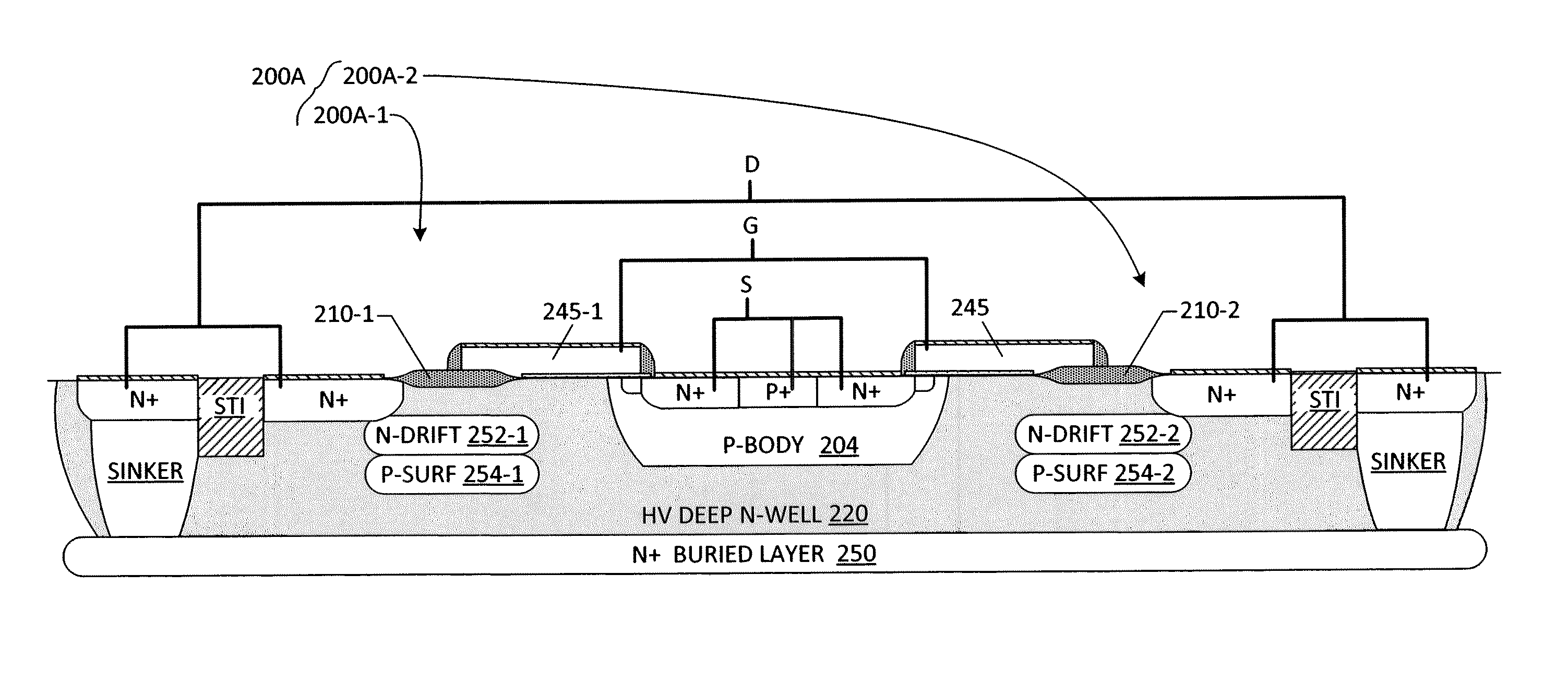

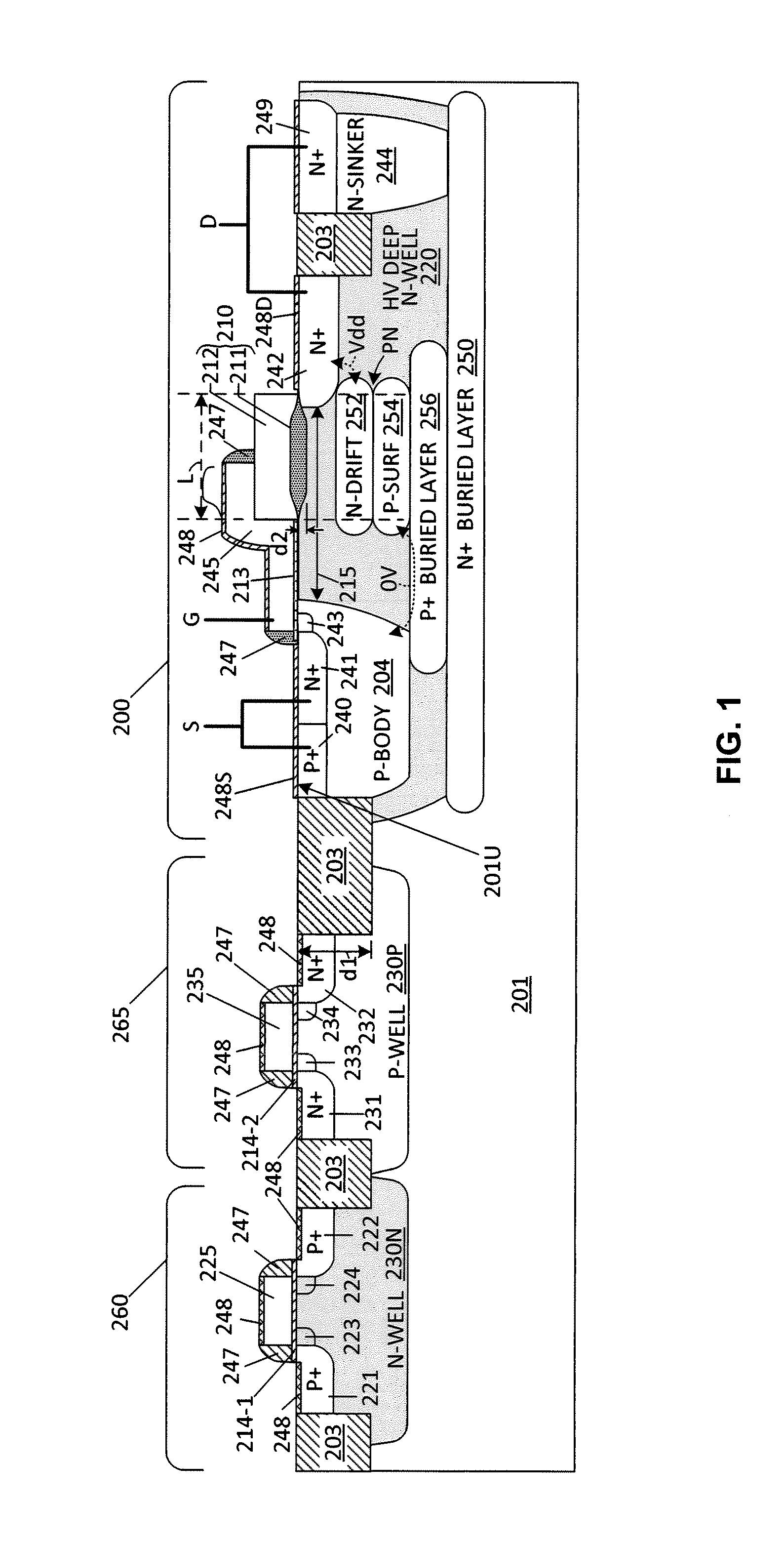

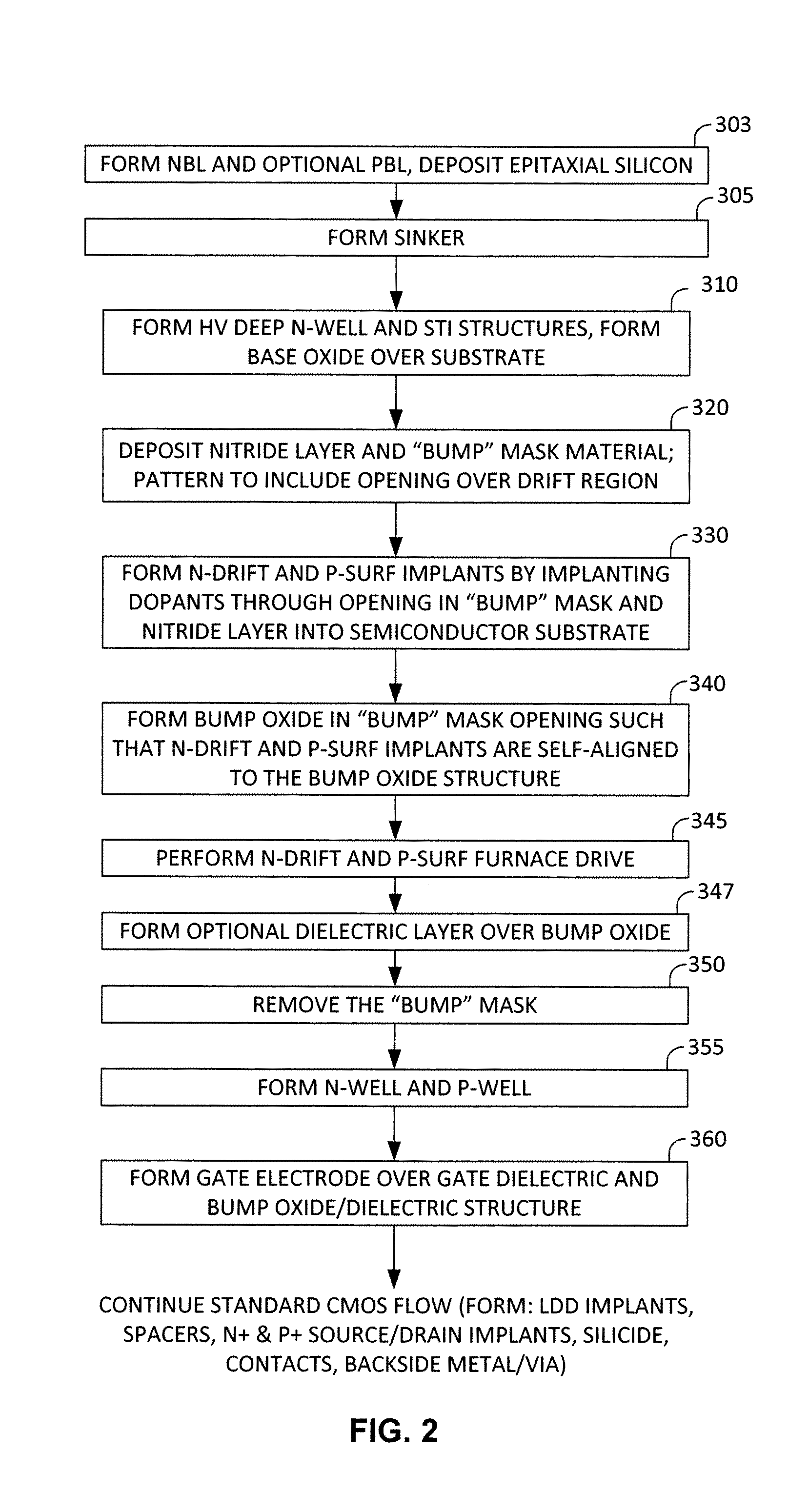

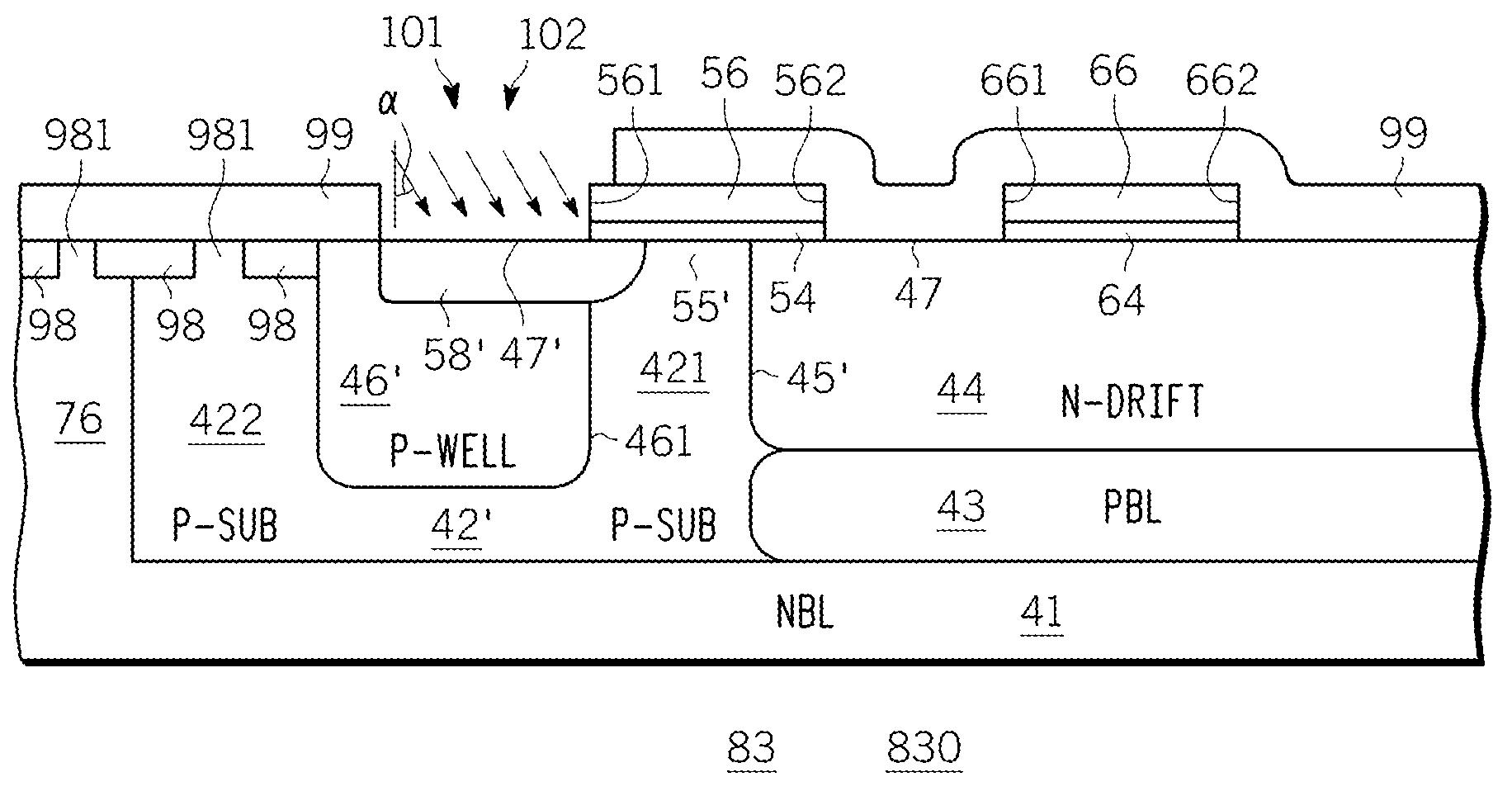

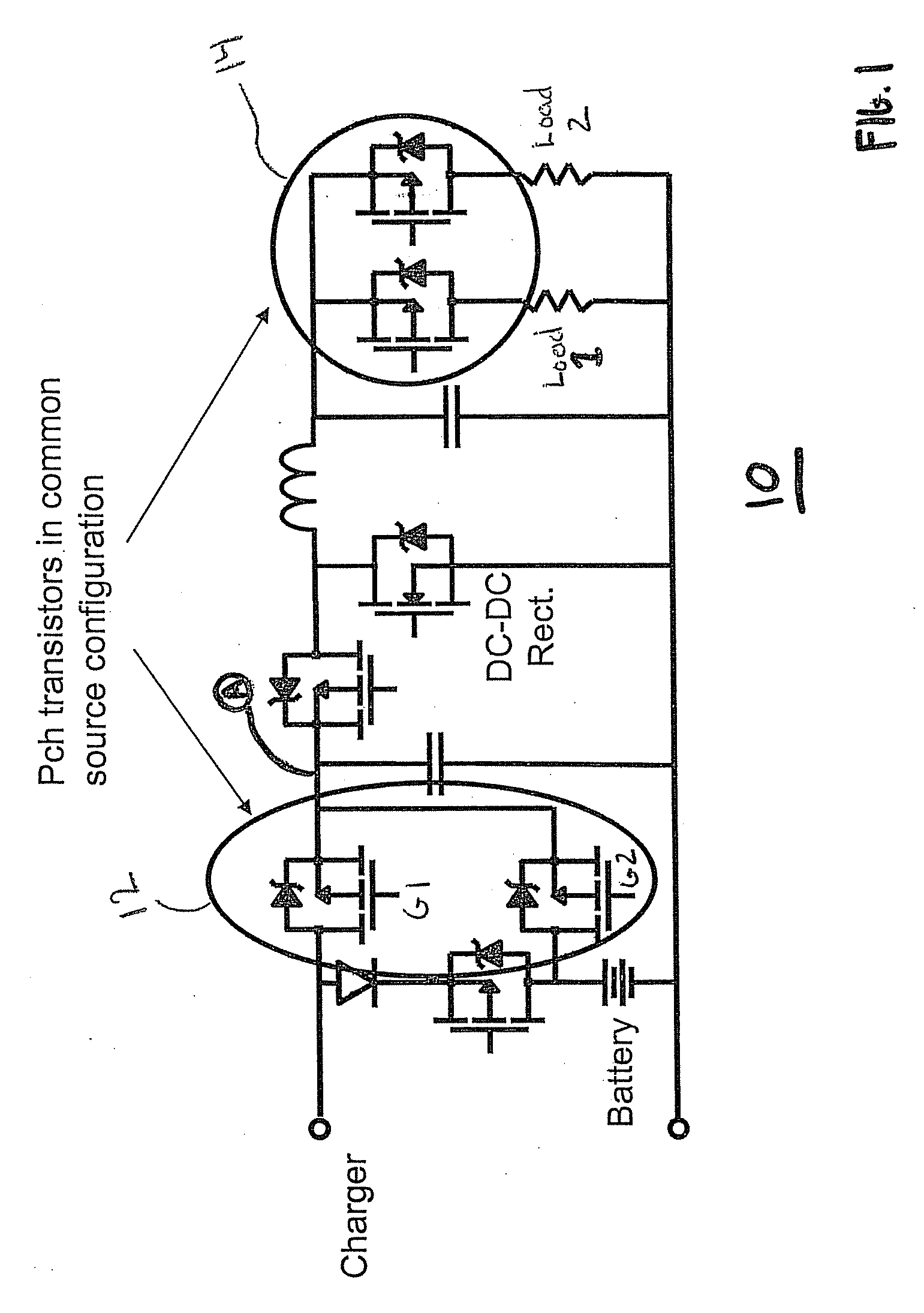

Double-Resurf LDMOS With Drift And PSURF Implants Self-Aligned To A Stacked Gate "BUMP" Structure

ActiveUS20140070315A1Ideal overall performanceHighest possible BVTransistorSolid-state devicesLDMOSGate dielectric

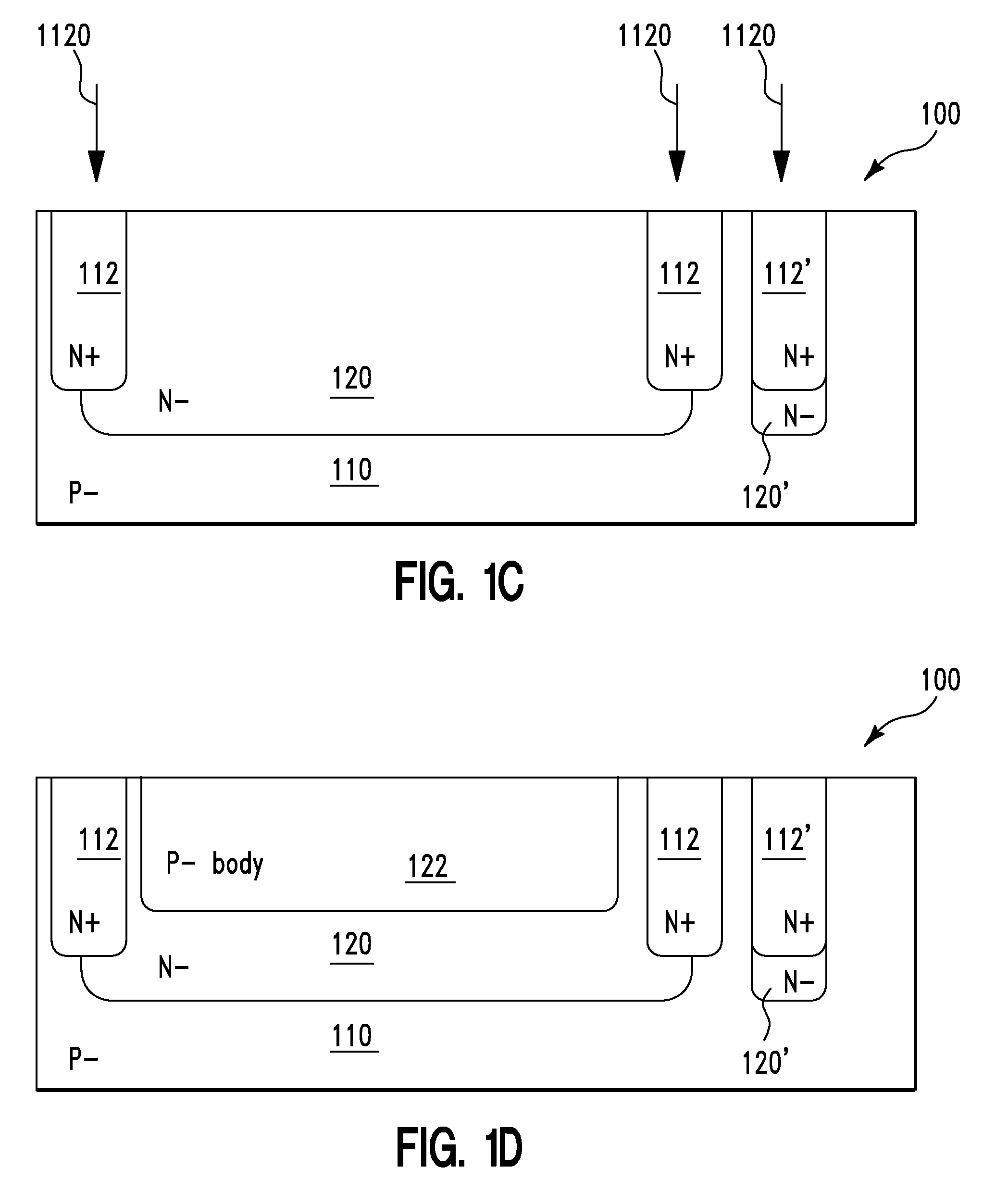

A double-RESURF LDMOS transistor has a gate dielectric structure including a shallow field “bump” oxide region and an optional raised dielectric structure that provides a raised support for the LDMOS transistor's polysilicon gate electrode. Fabrication of the shallow field oxide region is performed through a hard “bump” mask and controlled such that the bump oxide extends a minimal depth into the LDMOS transistor's drift (channel) region. The hard “bump” mask is also utilized to produce an N-type drift (N-drift) implant region and a P-type surface effect (P-surf) implant region, whereby these implants are “self-aligned” to the gate dielectric structure. The N-drift implant is maintained at Vdd by connection to the LDMOS transistor's drain diffusion. An additional Boron implant is utilized to form a P-type buried layer that connects the P-surf implant to the P-body region of the LDMOS transistor, whereby the P-surf implant is maintained at 0V.

Owner:TOWER SEMICONDUCTOR

Method for manufacturing a laterally diffused metal oxide semiconductor device

ActiveUS7638380B2Reduce in quantityLow costSemiconductor/solid-state device manufacturingSemiconductor devicesDopantLDMOS

A laterally diffused metal oxide semiconductor (LDMOS) device and a method of manufacture therefor. The method of manufacturing the LDMOS device includes forming an amorphous region in a semiconductor substrate between isolation structures and adjacent a gate structure, by implanting an amorphizing element, such as silicon or germanium, in the semiconductor substrate. The method further includes diffusing a channel dopant laterally in the amorphous region, to form a first portion of a channel.

Owner:BELL SEMICON LLC +1

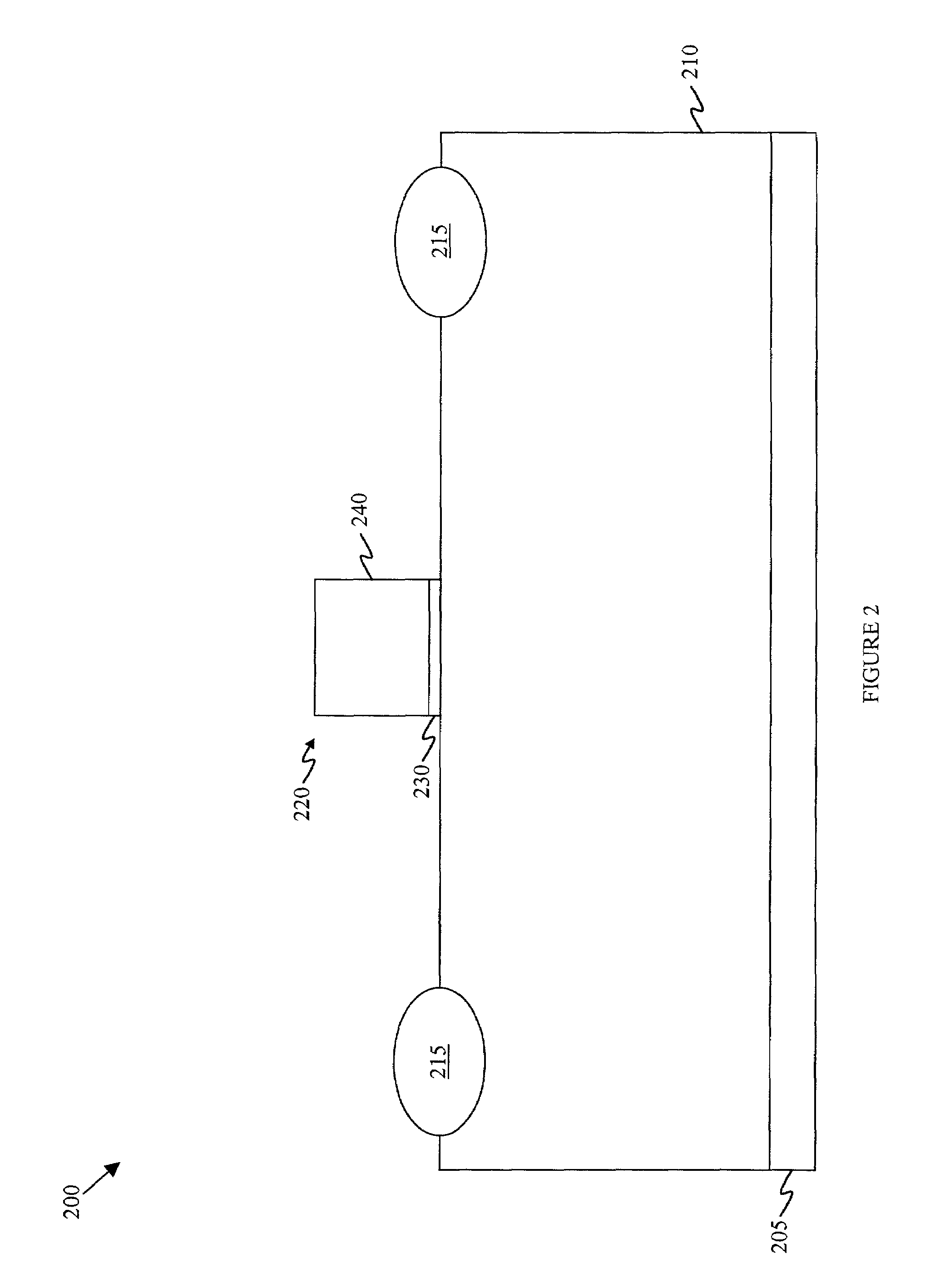

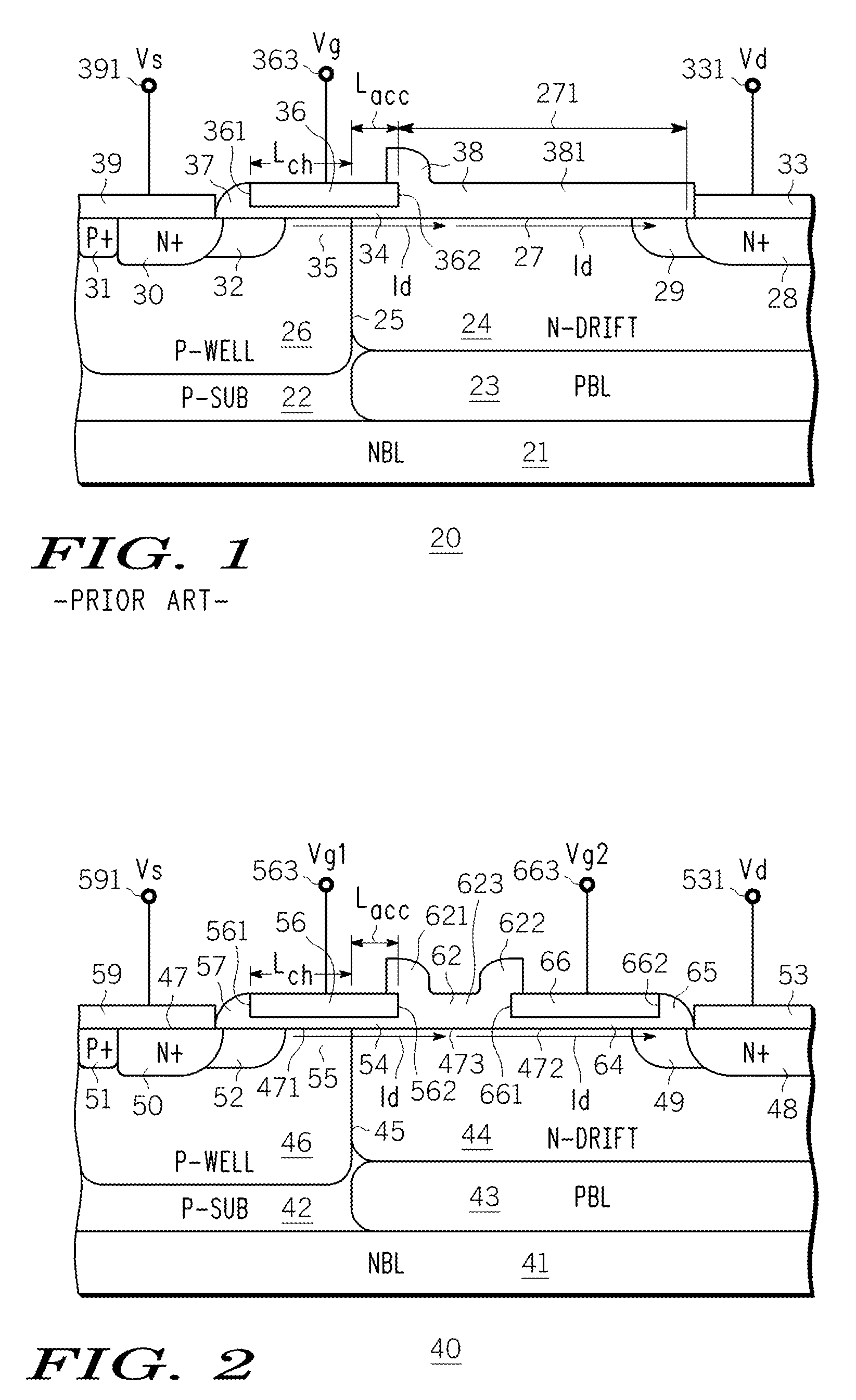

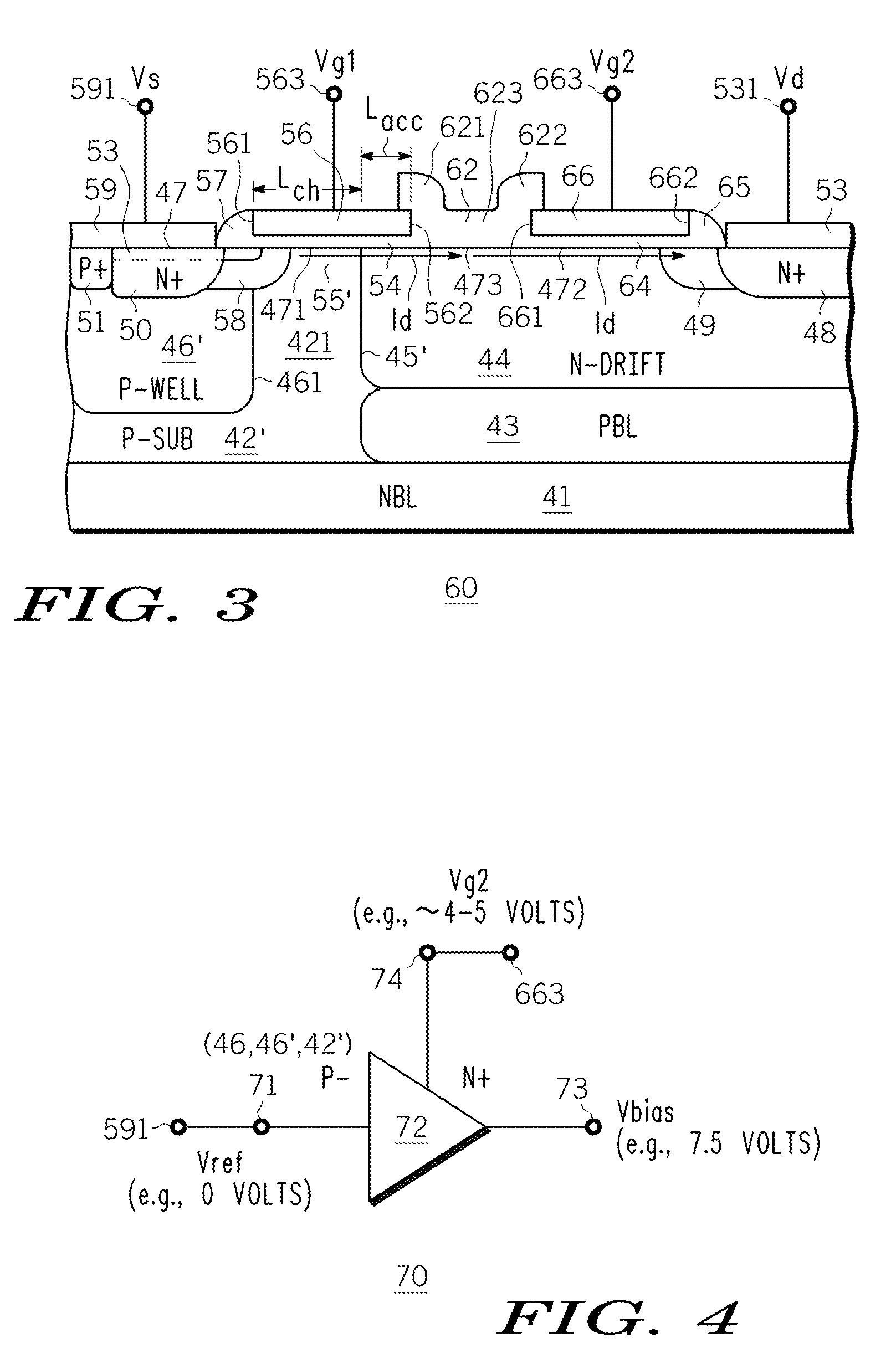

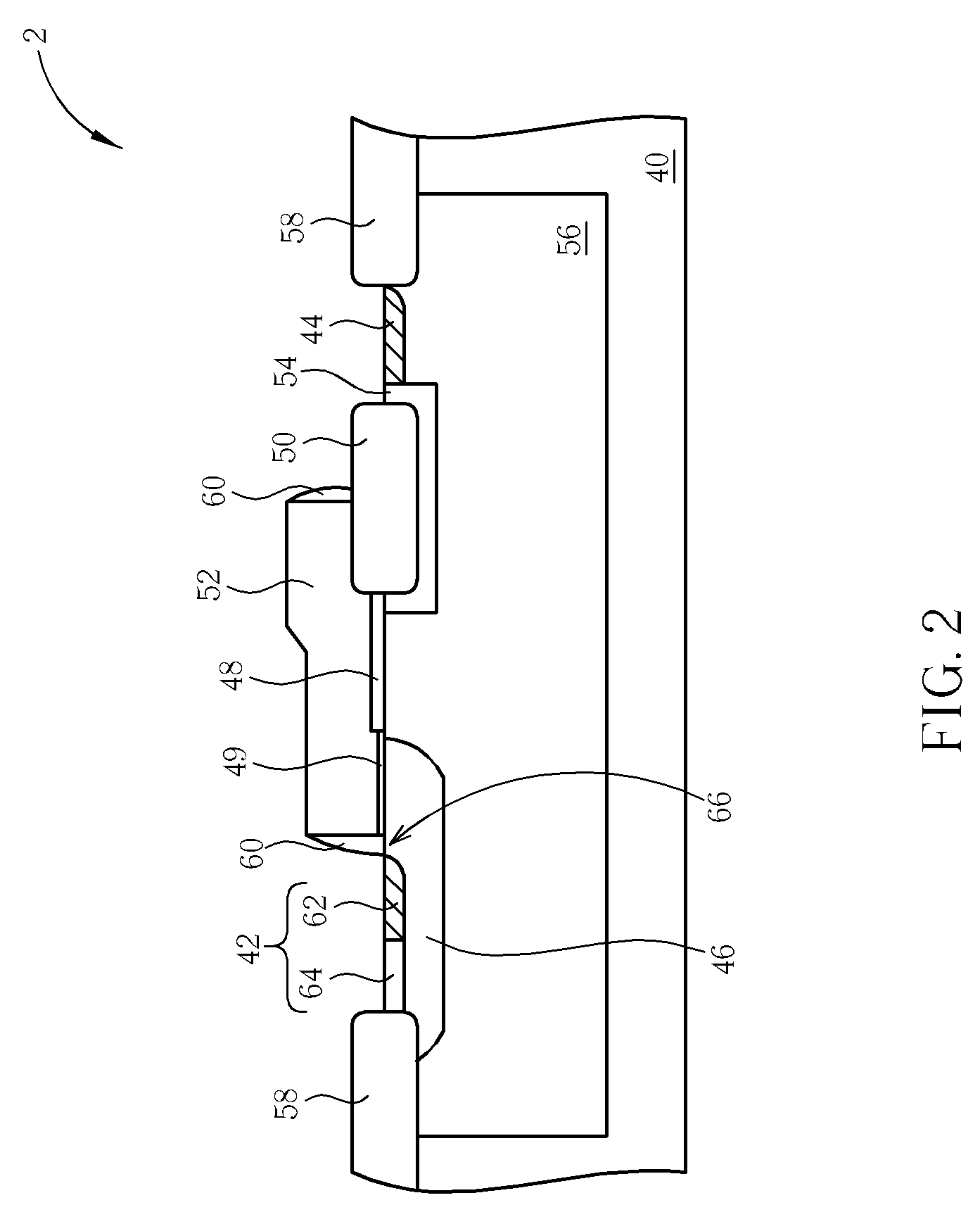

Dual gate ldmos device and method

InactiveUS20080182394A1Semiconductor/solid-state device manufacturingSemiconductor devicesLDMOSBody contact

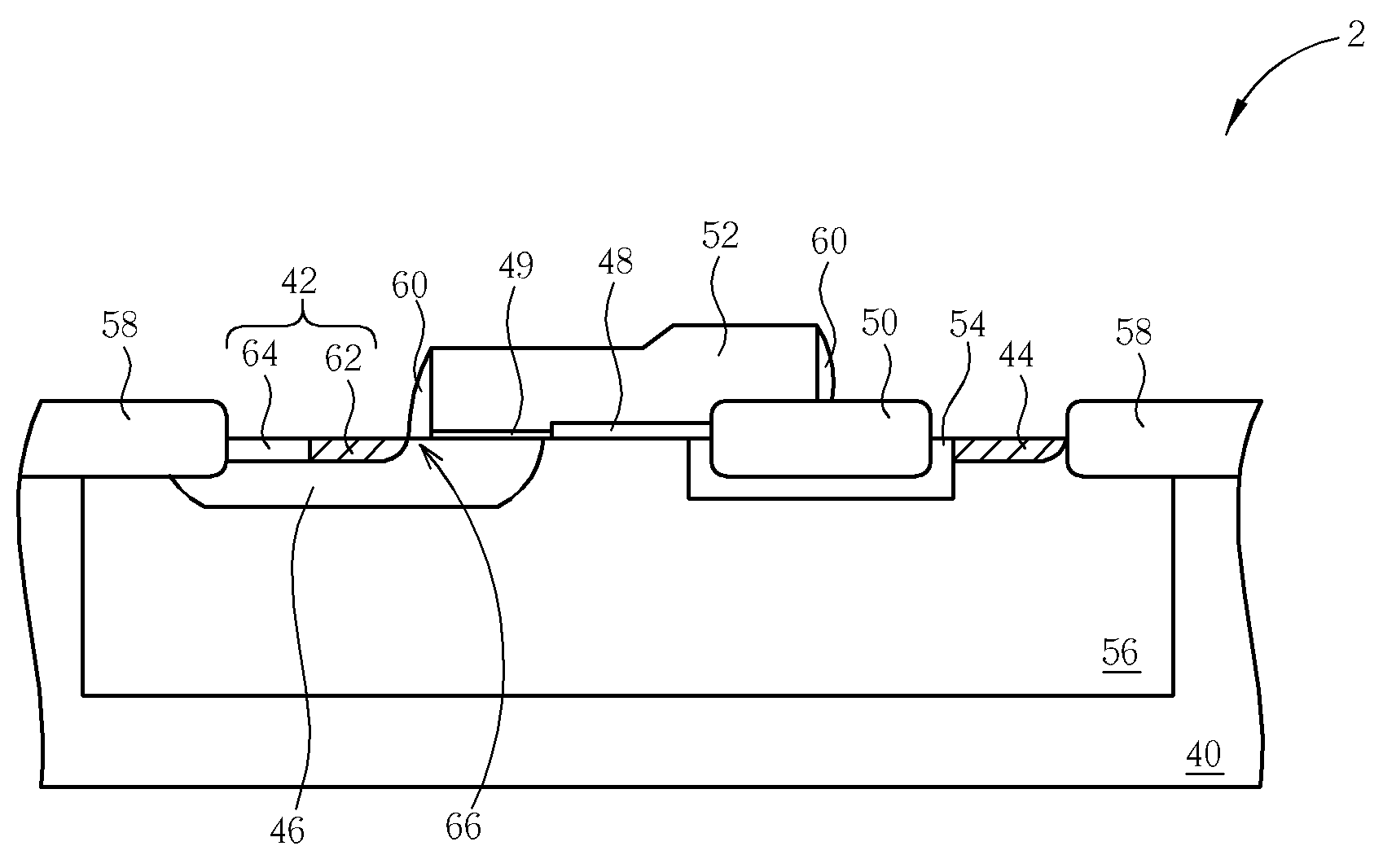

An N-channel device (40, 60) is described having a lightly doped substrate (42, 42′) in which adjacent or spaced-apart P (46, 46′) and N (44) wells are provided. A lateral isolation wall (76) surrounds at least a portion of the substrate (42, 42′) and is spaced apart from the wells (46, 46′, 44). A first gate (G1) (56) overlies the P (46) well or the substrate (42′) between the wells (46′, 44) or partly both. A second gate (G2) (66), spaced apart from G1 (56), overlies the N-well (44). A body contact (74) to the substrate (42, 42′) is spaced apart from the isolation wall (76) by a first distance (745) within the space charge region of the substrate (42, 42′) to isolation wall (76) PN junction. When the body contact (74) is connected to G2 (66), a predetermined static bias Vg2 is provided to G2 (66) depending upon the isolation wall bias (Vbias) and the first distance (745). The resulting device (40, 60) operates at higher voltage with lower Rdson and less HCI.

Owner:NORTH STAR INNOVATIONS

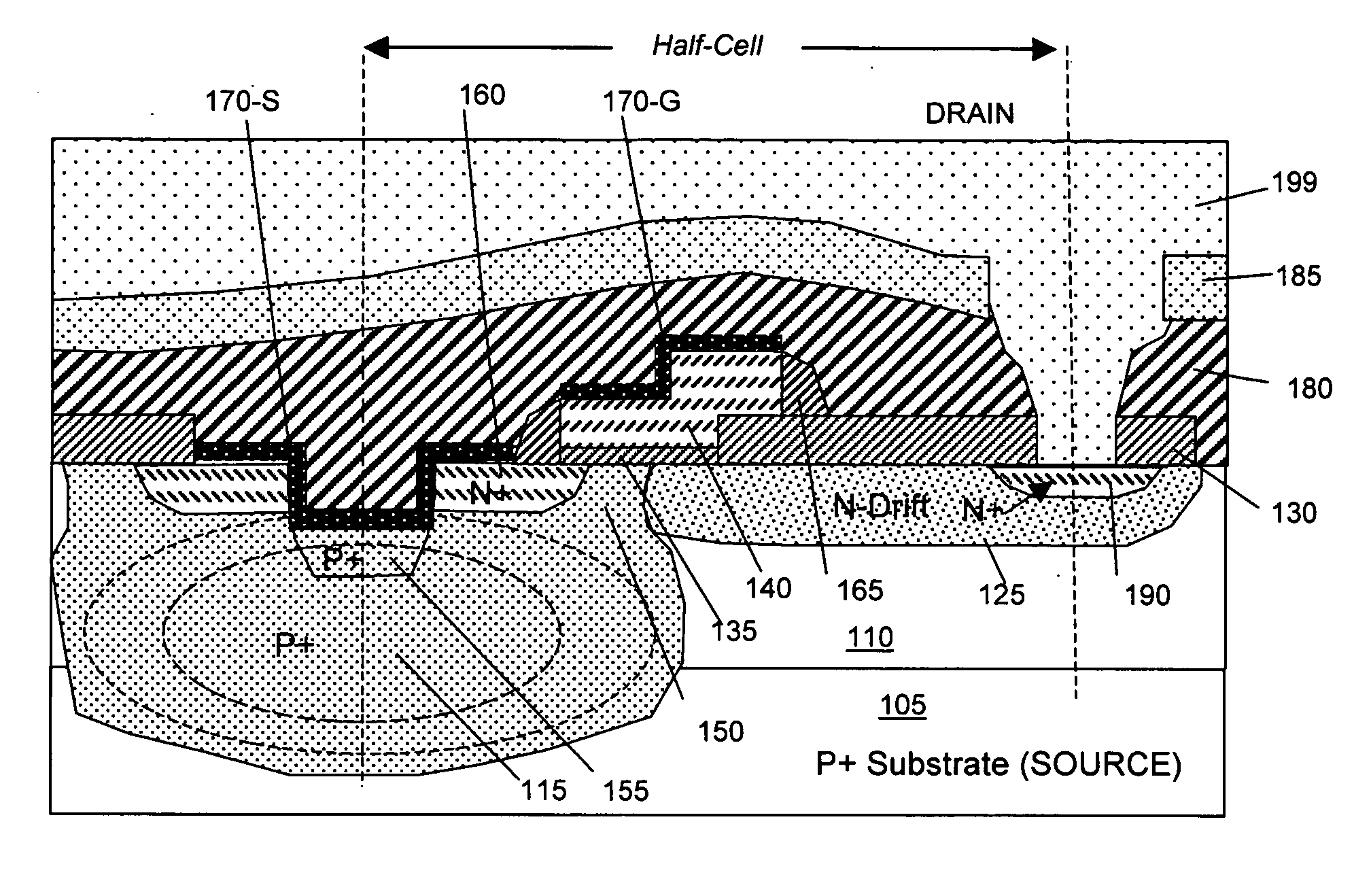

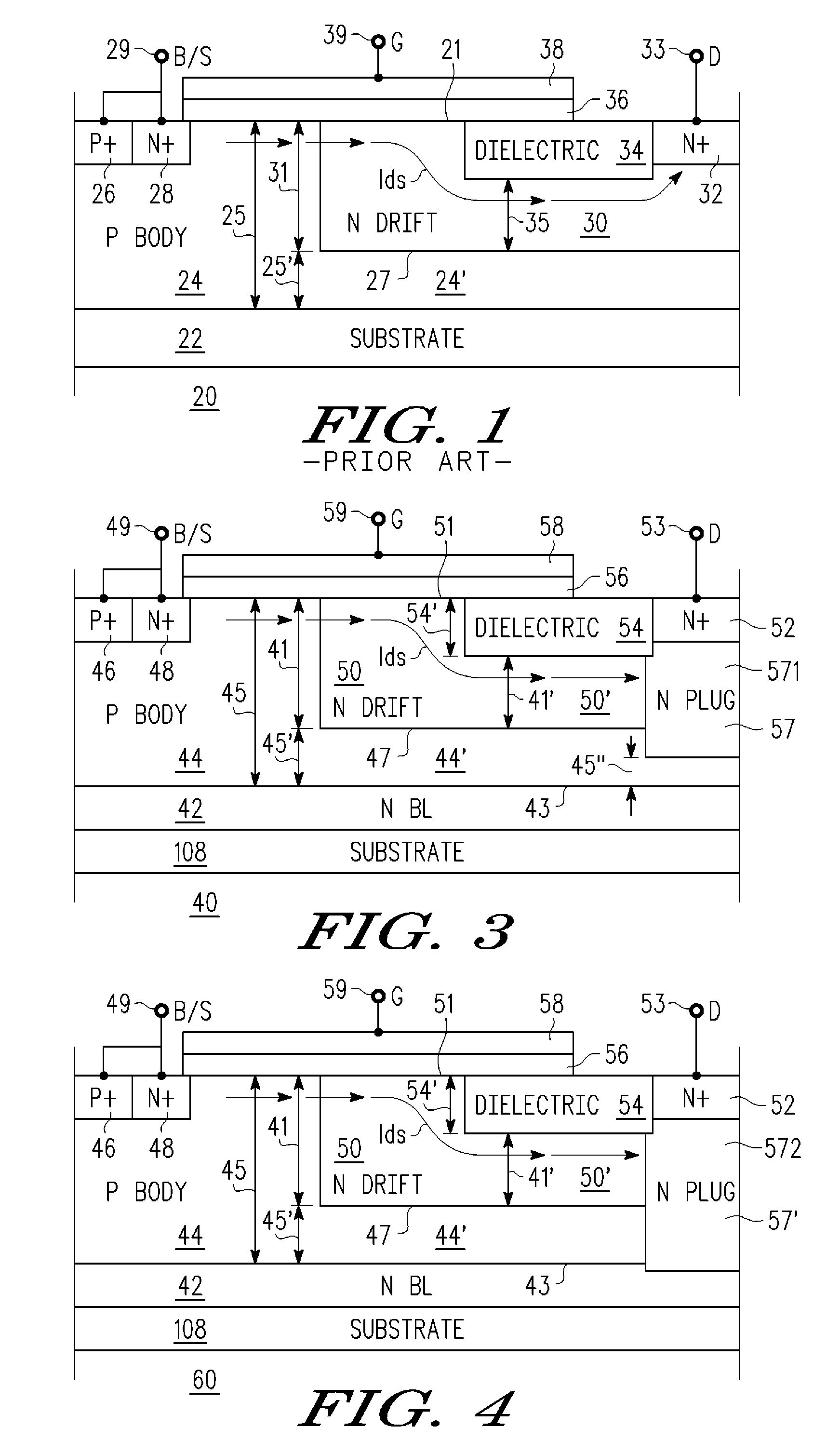

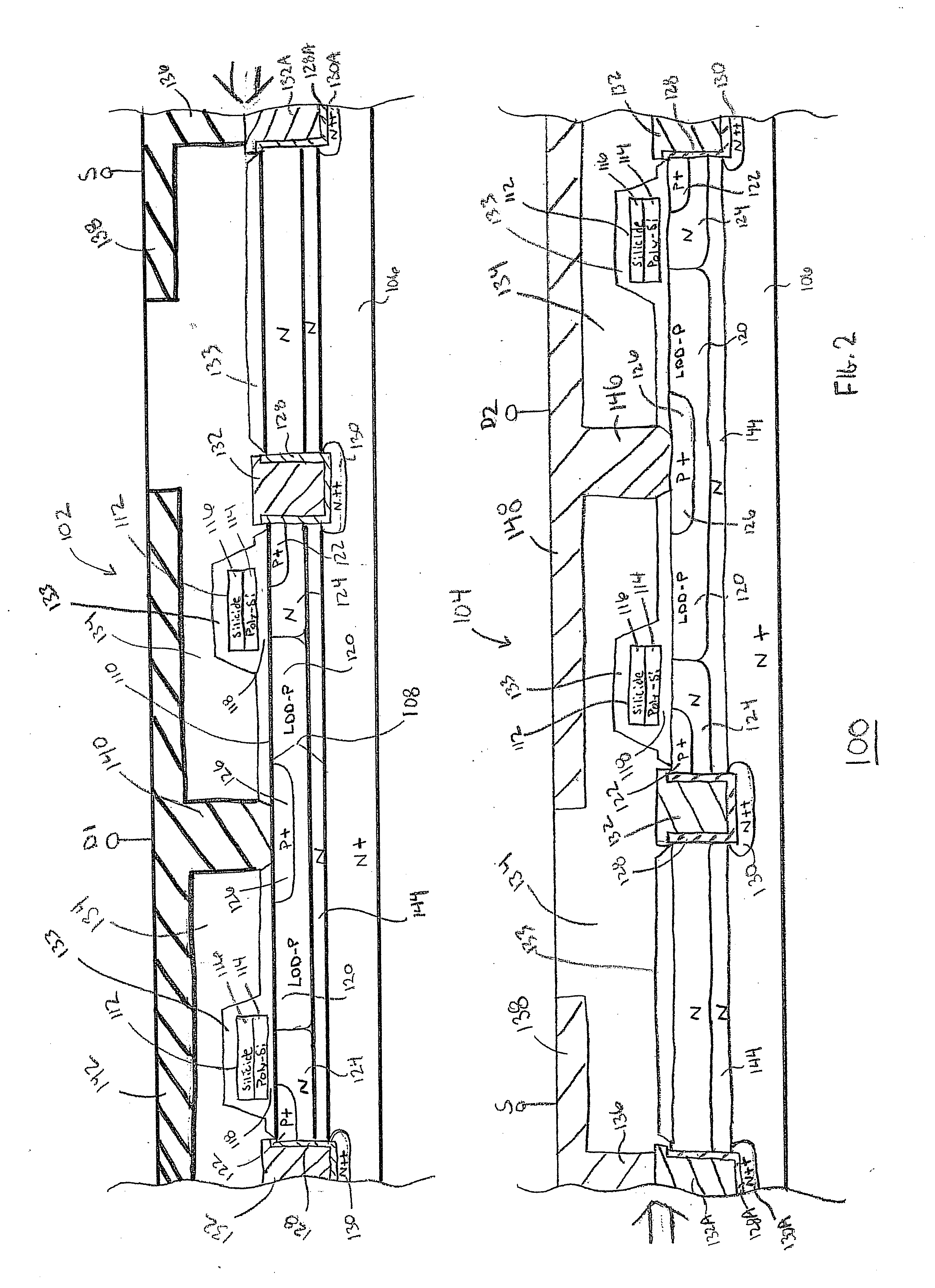

Bottom source LDMOSFET structure and method

ActiveUS20080023785A1Reduce manufacturing costReduce cell pitchTransistorSemiconductor/solid-state device detailsCapacitanceLDMOS

This invention discloses bottom-source lateral diffusion MOS (BS-LDMOS) device. The device has a source region disposed laterally opposite a drain region near a top surface of a semiconductor substrate supporting a gate thereon between the source region and a drain region. The BS-LDMOS device further has a combined sinker-channel region disposed at a depth in the semiconductor substrate entirely below a body region disposed adjacent to the source region near the top surface wherein the combined sinker-channel region functioning as a buried source-body contact for electrically connecting the body region and the source region to a bottom of the substrate functioning as a source electrode. A drift region is disposed near the top surface under the gate and at a distance away from the source region and extending to and encompassing the drain region. The combined sinker-channel region extending below the drift region and the combined sinker-channel region that has a dopant-conductivity opposite to and compensating the drift region for reducing the source-drain capacitance.

Owner:ALPHA & OMEGA SEMICON LTD

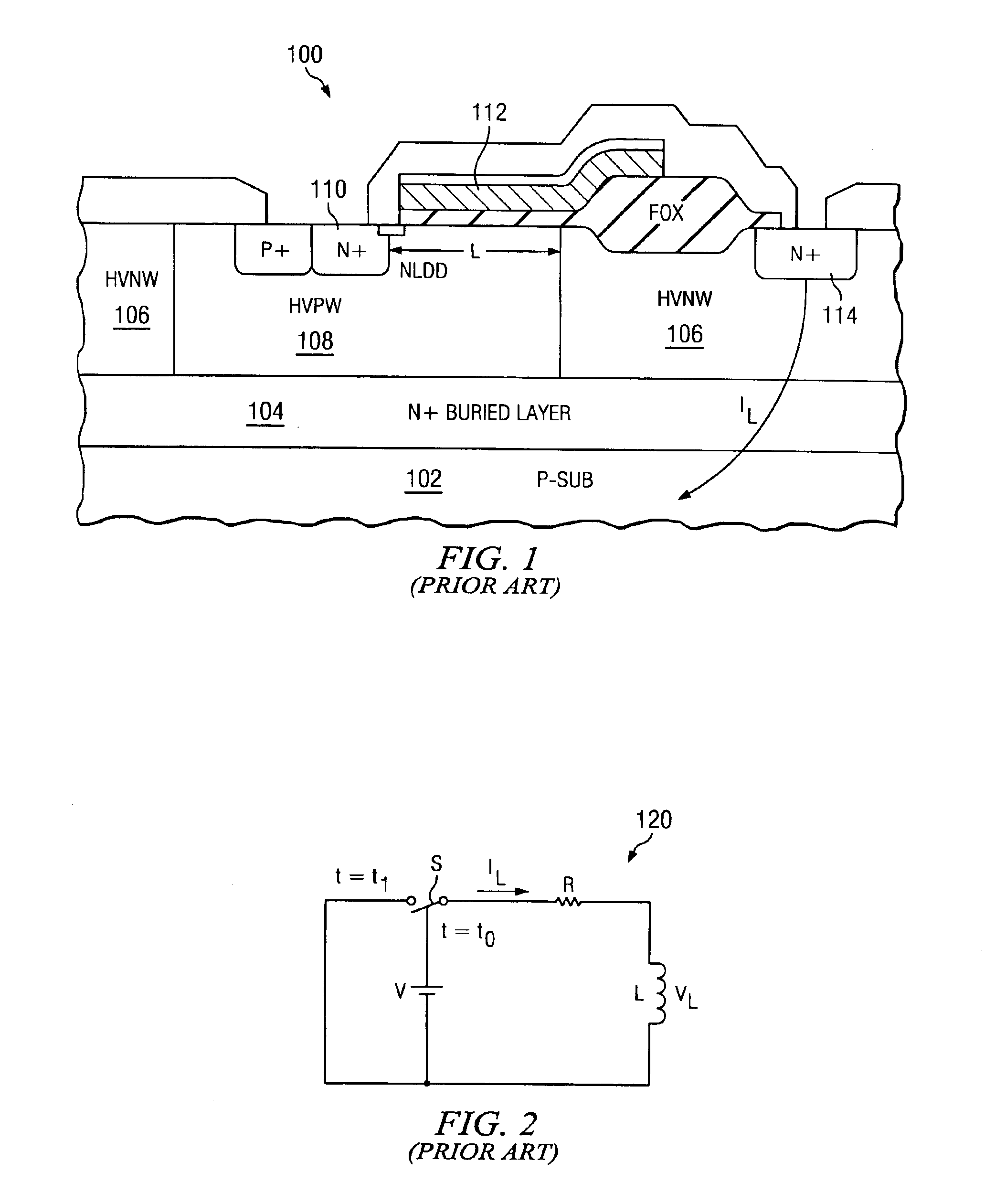

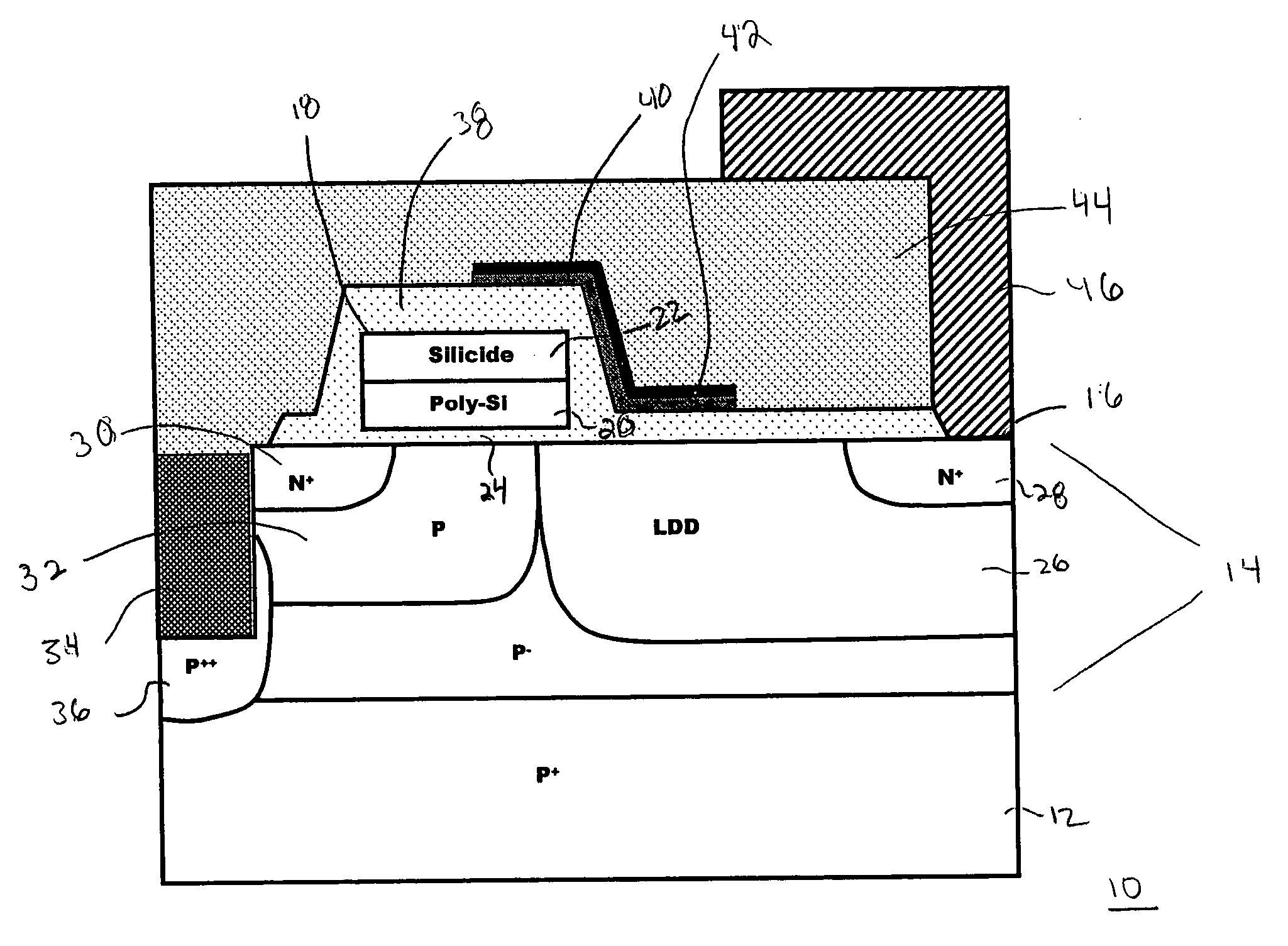

High voltage N-LDMOS transistors having shallow trench isolation region

InactiveUS6876035B2Improved channel length controlReduce clutterTransistorSemiconductor/solid-state device detailsLDMOSEngineering

A method and structure is disclosed for a transistor having a gate, a channel region below the gate, a source region on one side of the channel region, a drain region on an opposite side of the channel region from the source region, a shallow trench isolation (STI) region in the substrate between the drain region and the channel region, and a drain extension below the STI region. The drain extension is positioned along a bottom of the STI region and along a portion of sides of the STI. Portions of the drain extension along the bottom of the STI may comprise different dopant implants than the portions of the drain extensions along the sides of the STI. Portions of the drain extensions along sides of the STI extend from the bottom of the STI to a position partially up the sides of the STI. The STI region is below a portion of the gate. The drain extension provides a conductive path between the drain region and the channel region around a lower perimeter of the STI. The drain region is positioned further from the gate than the source region.

Owner:IBM CORP

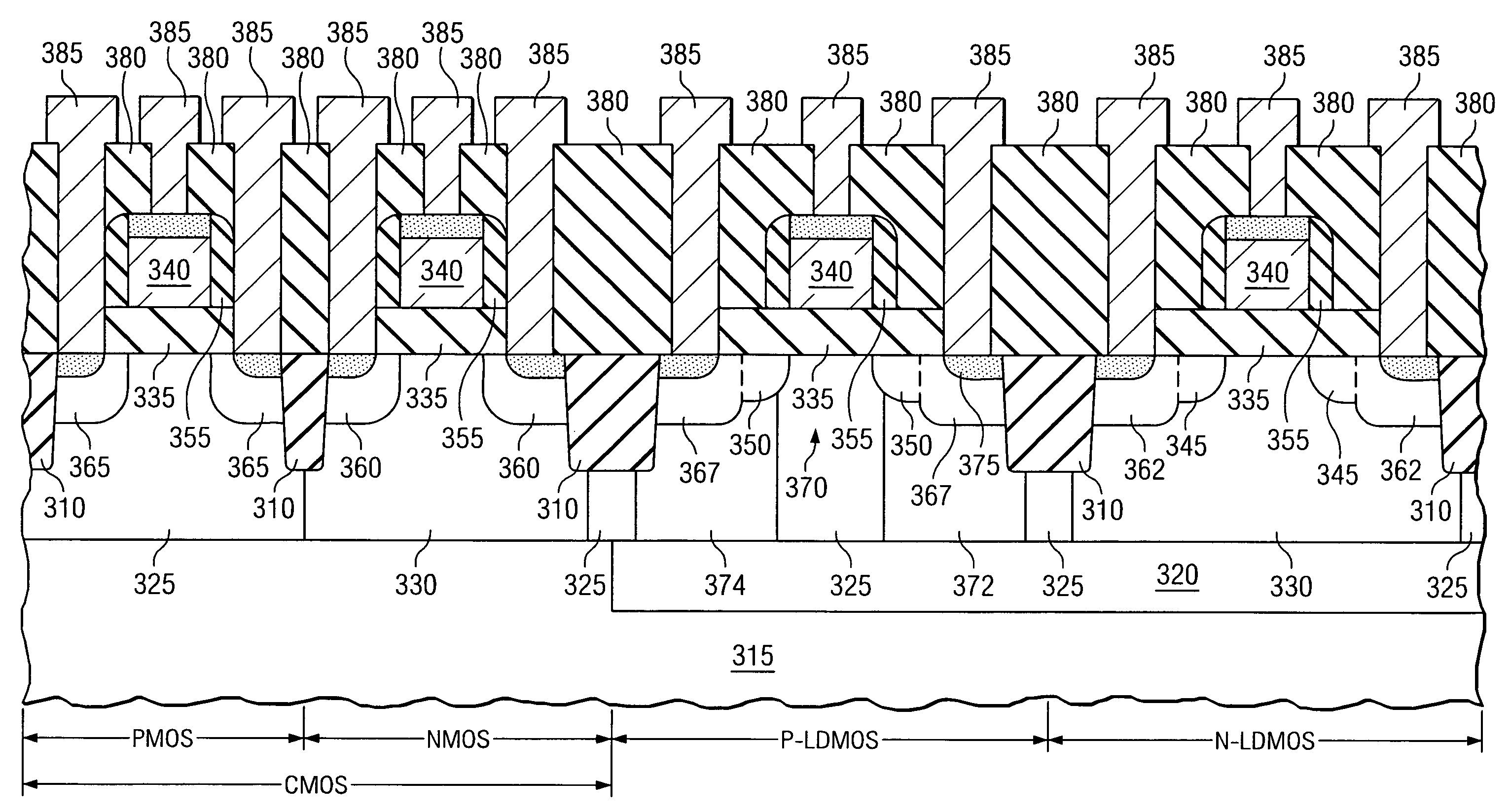

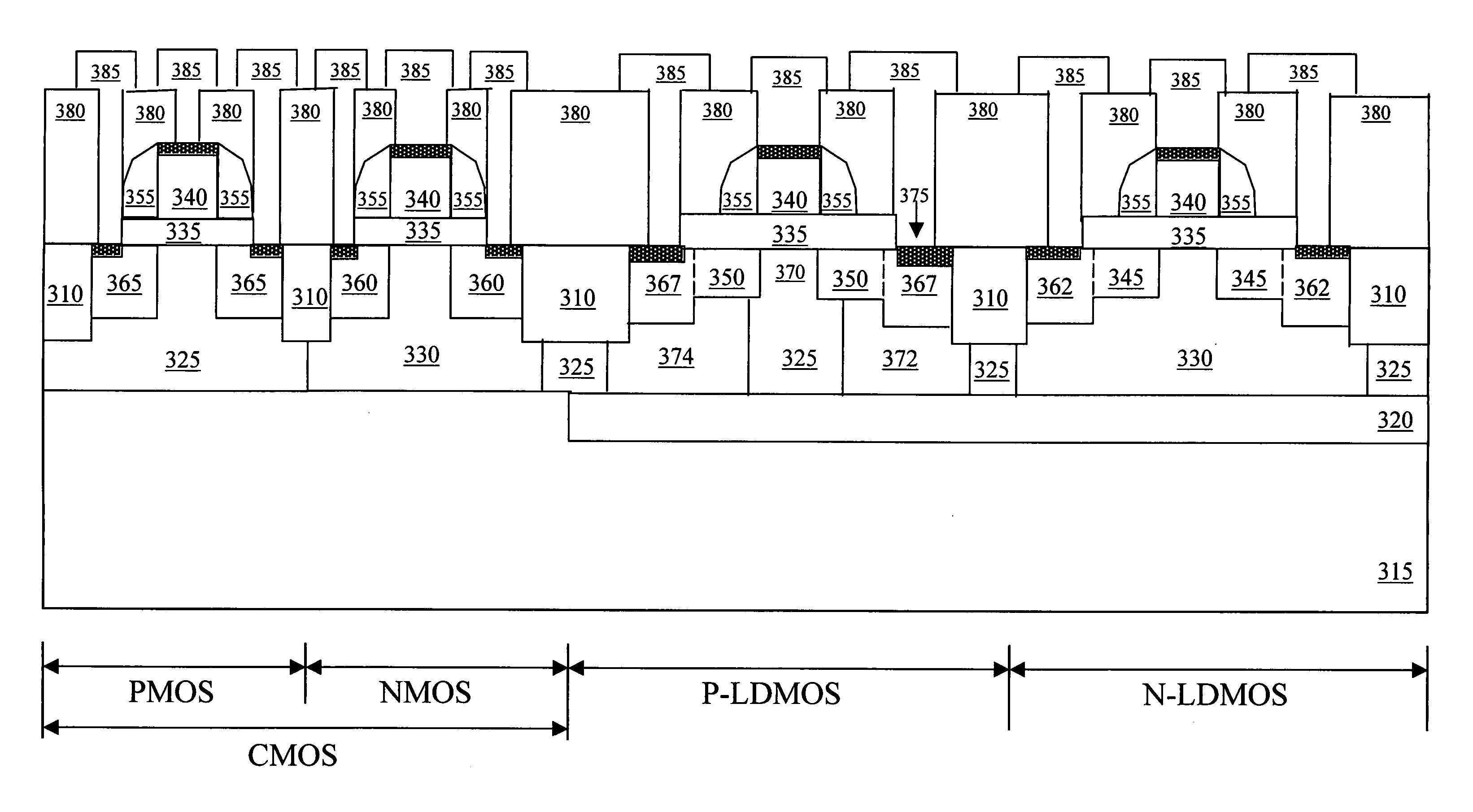

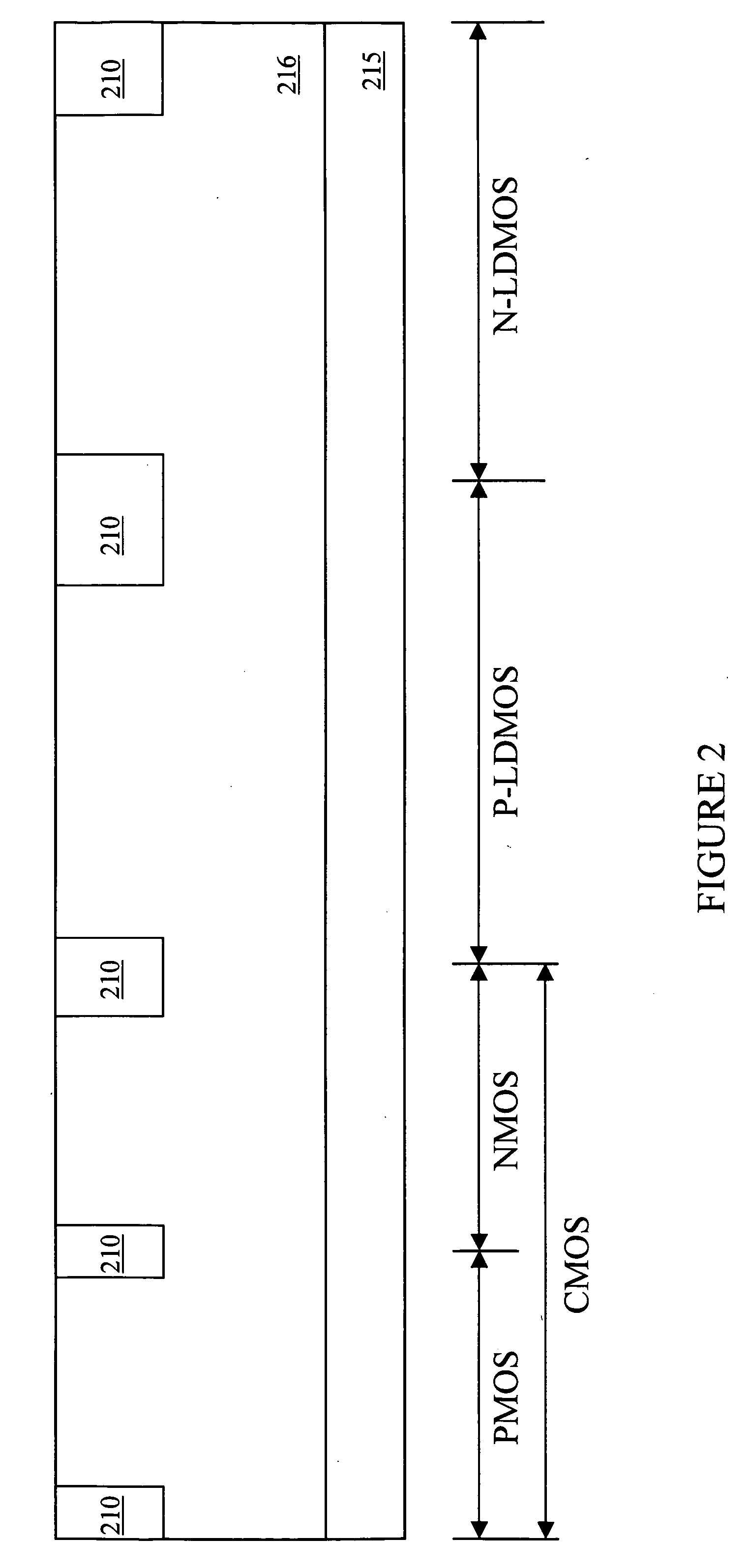

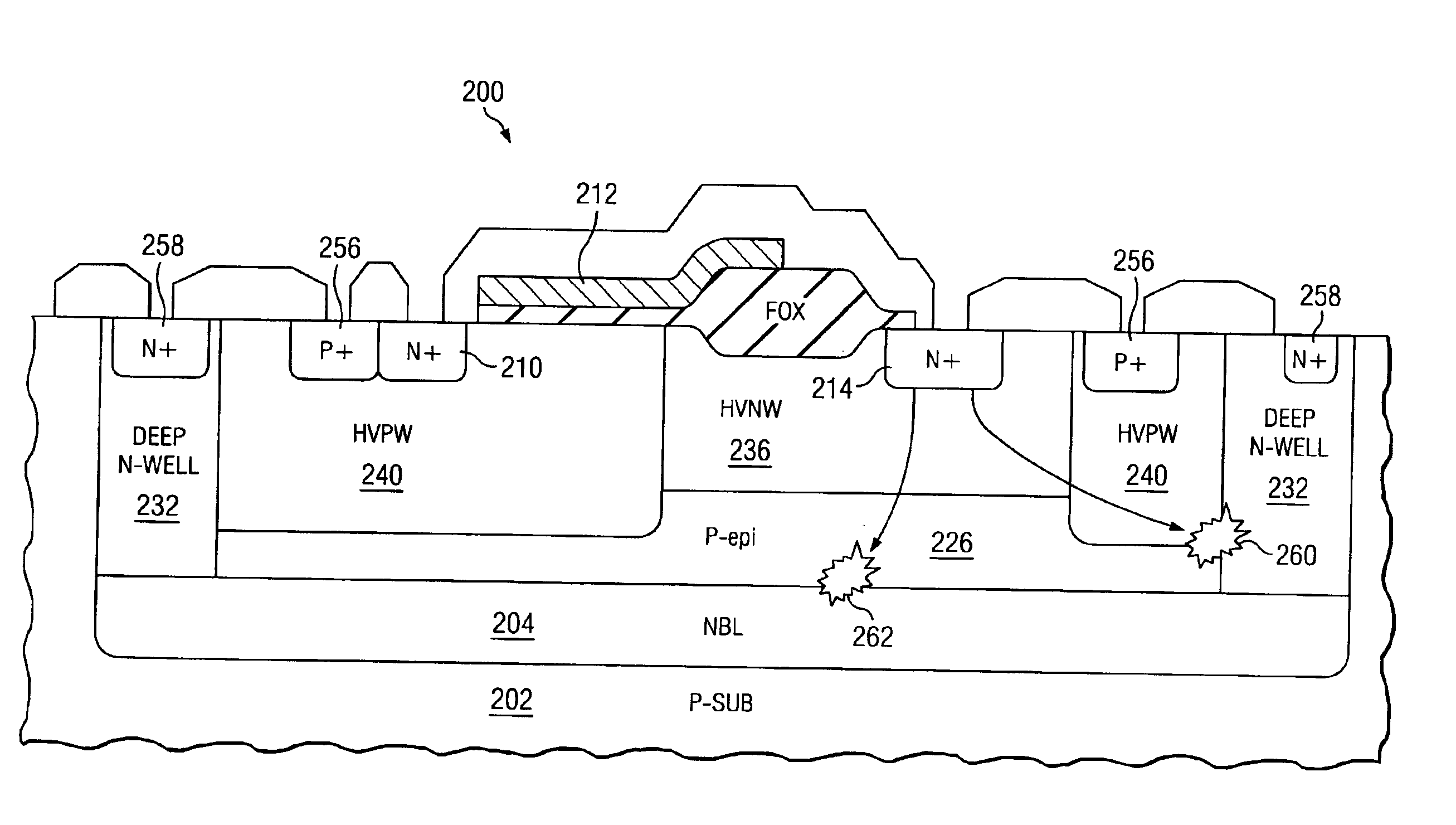

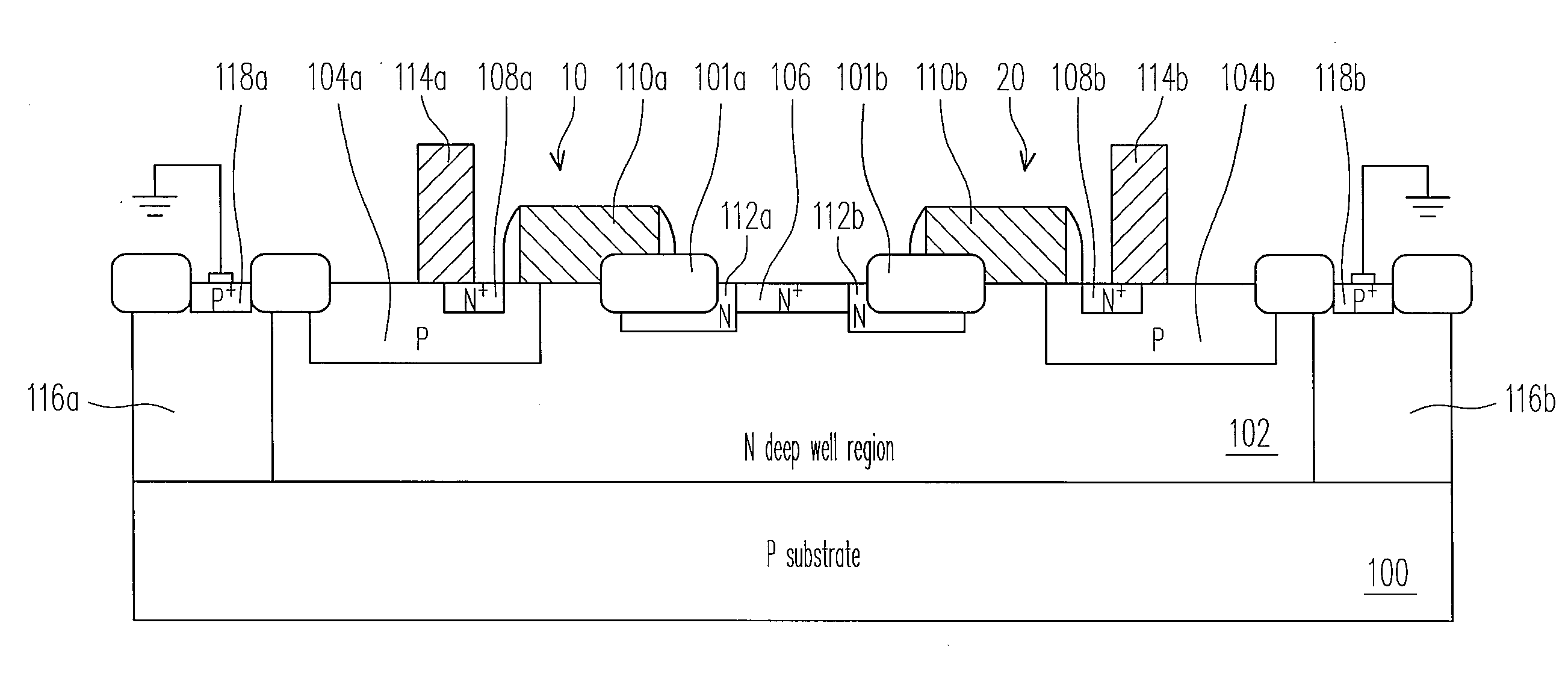

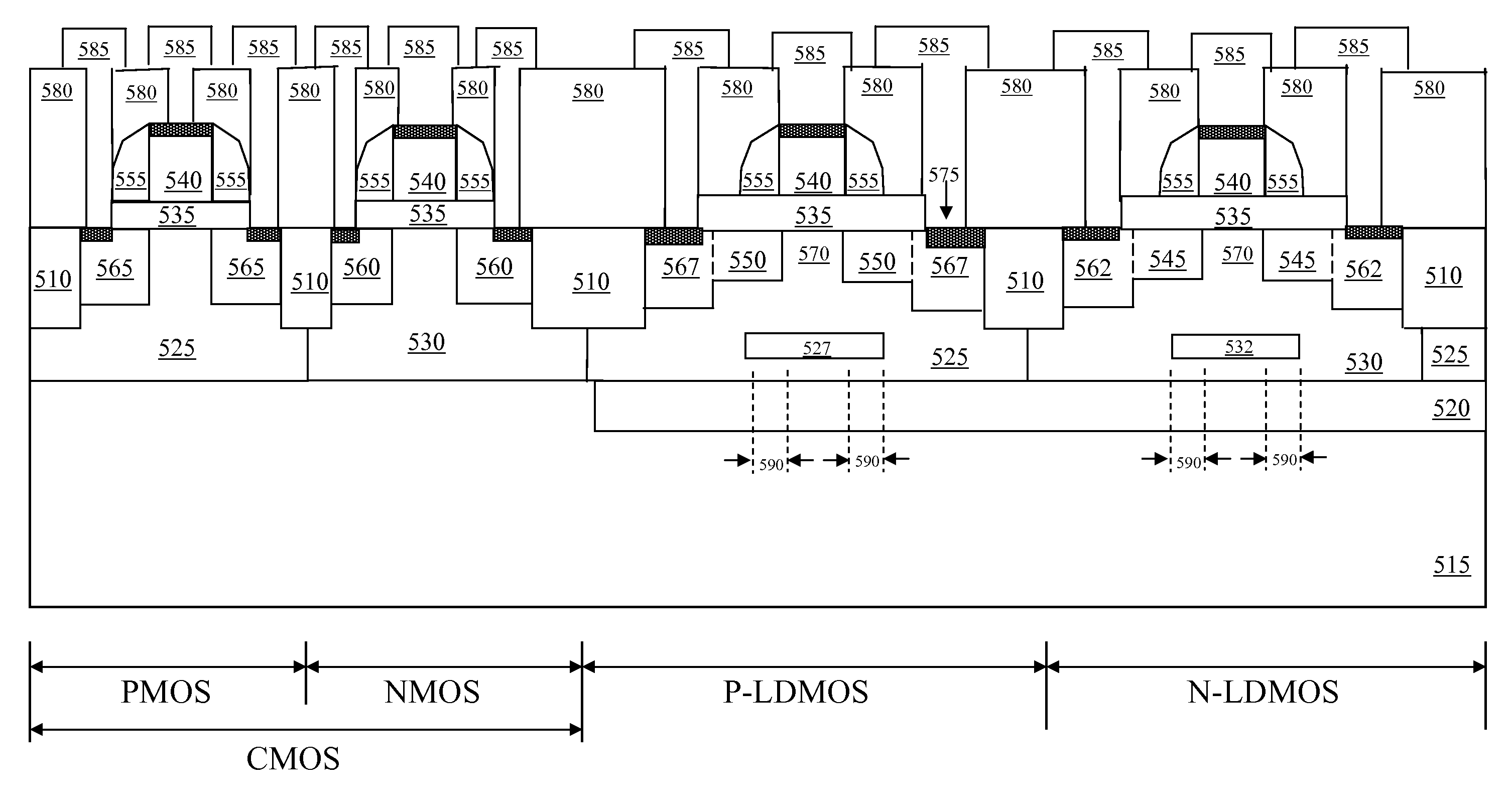

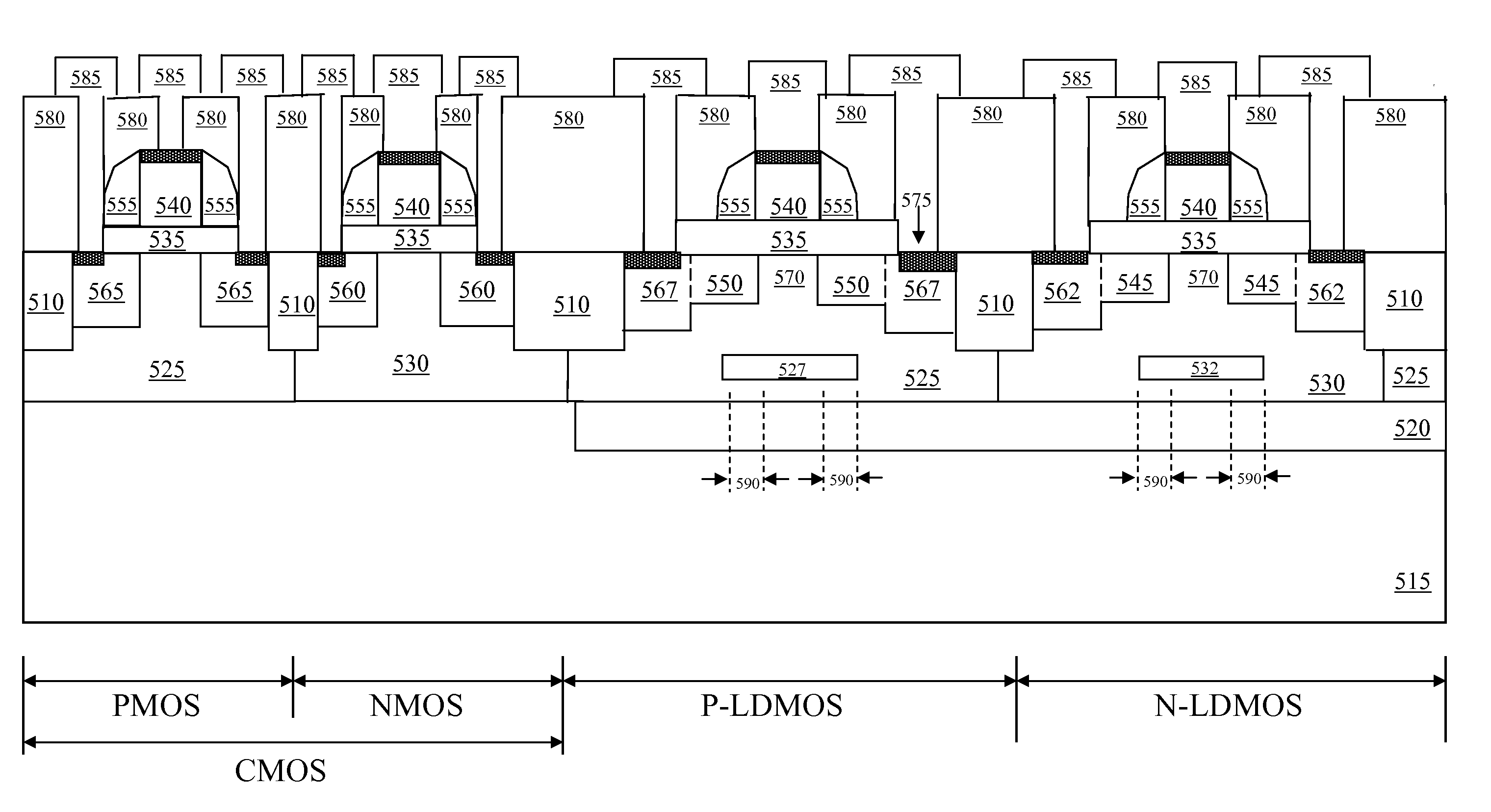

Guard ring structures for high voltage CMOS/low voltage CMOS technology using ldmos (lateral double-diffused metal oxide semiconductor) device fabrication

A semiconductor structure and a method for forming the same. The method includes providing a semiconductor structure. The semiconductor structure includes a semiconductor substrate. The method further includes simultaneously forming a first doped transistor region of a first transistor and a first doped guard-ring region of a guard ring on the semiconductor substrate. The first doped transistor region and the first doped guard-ring region comprise dopants of a first doping polarity. The method further includes simultaneously forming a second doped transistor region of the first transistor and a second doped guard-ring region of the guard ring on the semiconductor substrate. The second doped transistor region and the second doped guard-ring region comprise dopants of the first doping polarity. The second doped guard-ring region is in direct physical contact with the first doped guard-ring region. The guard ring forms a closed loop around the first and second doped transistor regions.

Owner:GLOBALFOUNDRIES INC

Laterally diffused metal-oxide-semiconductor device and method of making the same

ActiveUS20090072308A1Minimize impactSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate dielectric

A laterally diffused metal-oxide-semiconductor (LDMOS) device as well as a method of making the same is disclosed. A gate is formed on a semiconductor substrate between a source region and a drain region with one side laterally extending onto a part of a field oxide layer and the opposite side beside the source region. A gate dielectric layer is formed between the gate and the semiconductor substrate, wherein the gate dielectric layer comprises two or more portions having different thicknesses arranged laterally in a way that the thicknesses of the portions gradually increase from one side beside the source doping region to the opposite side bordering the field oxide layer. With such structure, the hot carrier impact is minimized and the gate length can be scaled down to gain Idlin.

Owner:UNITED MICROELECTRONICS CORP

LDMOS device with isolation guard rings

InactiveUS6924531B2Avoid leakage currentLatch-up, early breakdown and reliability issues are preventedSemiconductor/solid-state device detailsSolid-state devicesLDMOSEngineering

A method of forming a LDMOS semiconductor device and structure for same. A preferred embodiment comprises forming a first guard ring around and proximate the drain of a LDMOS device, and forming a second guard ring around the first guard ring. The first guard ring comprises a P+ base guard ring, and the second guard ring comprises an N+ collector guard ring formed in a deep N-well, in one embodiment. The first guard ring and second guard ring prevent leakage current from flowing from the drain of the LDMOS device to the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

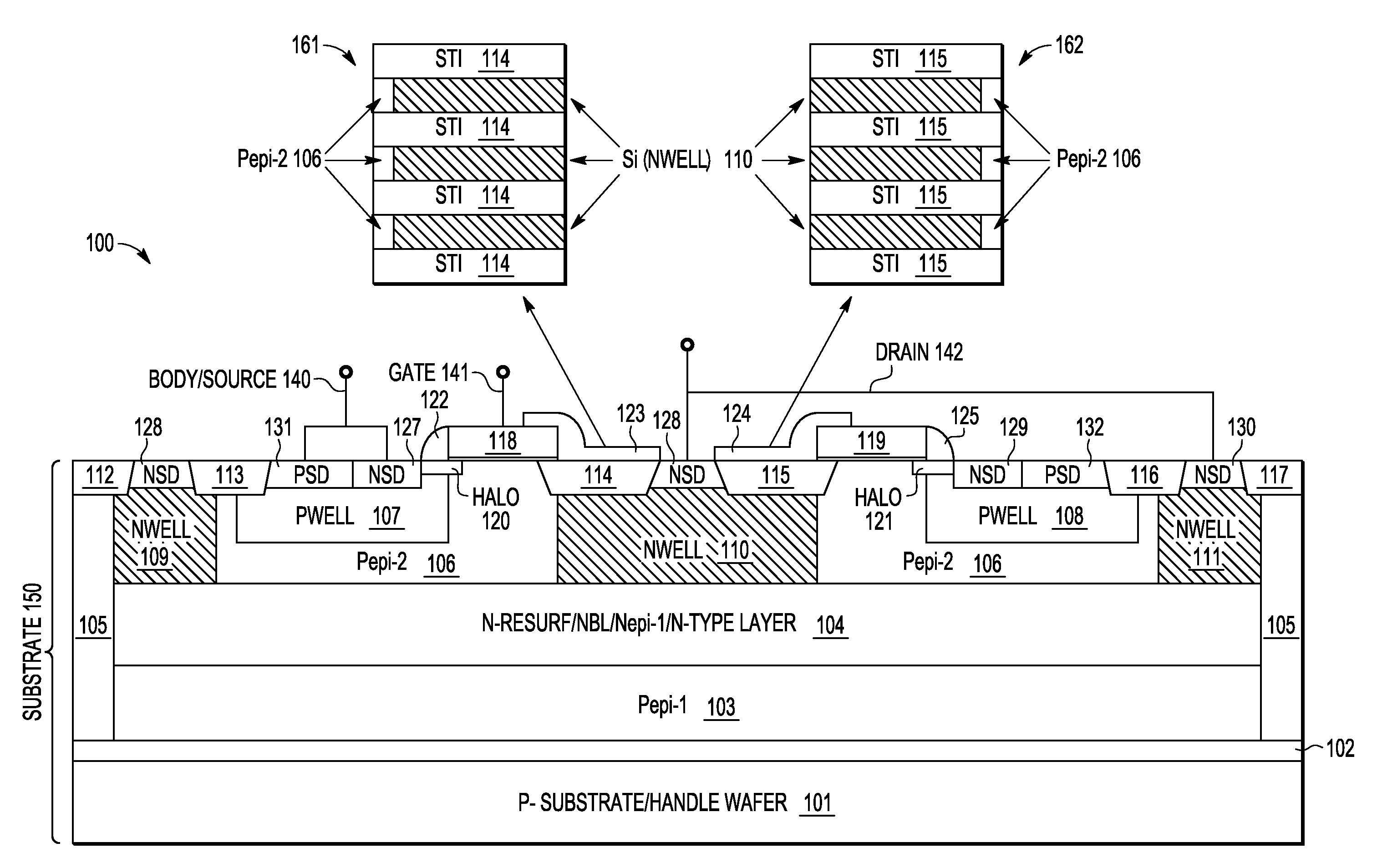

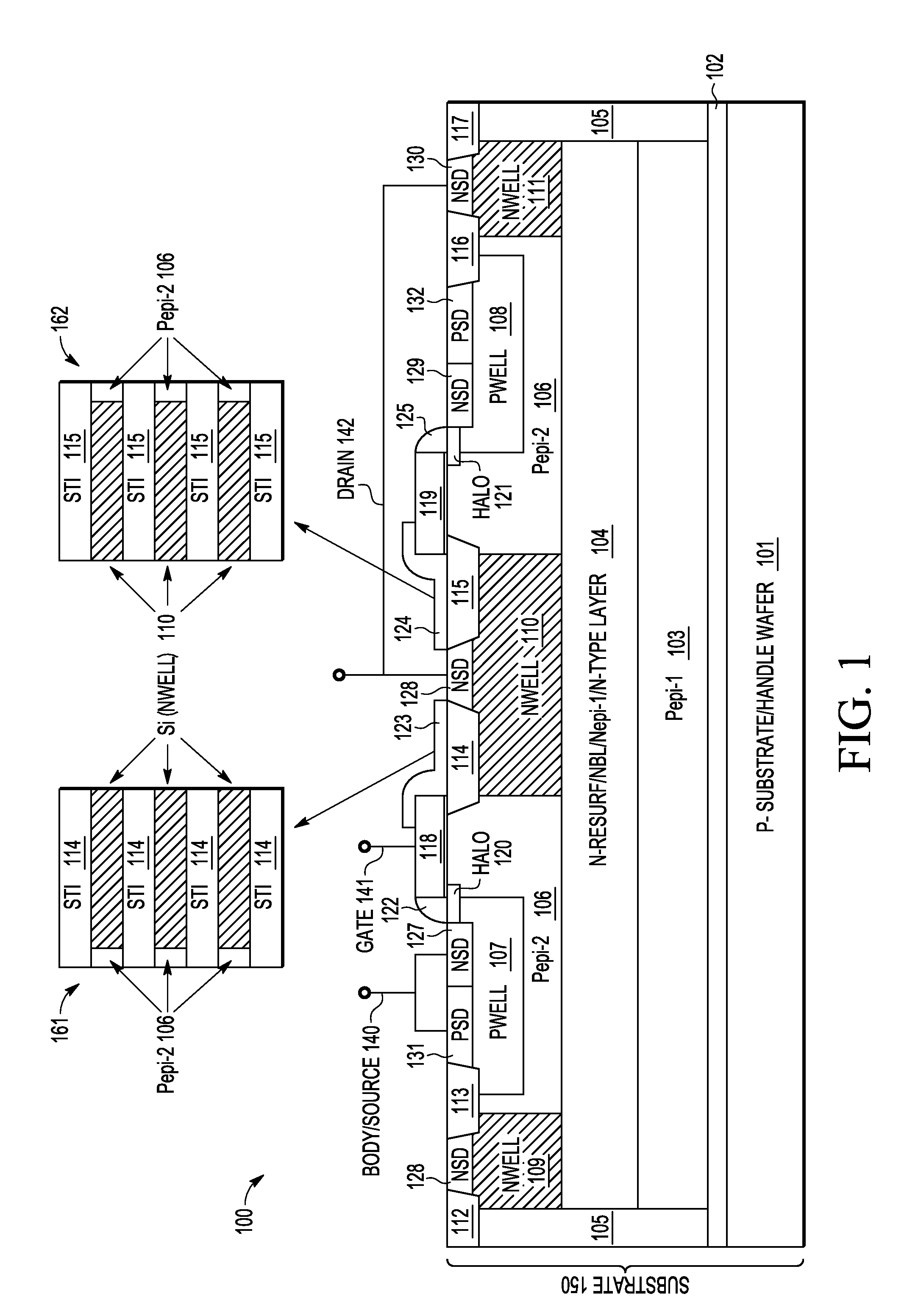

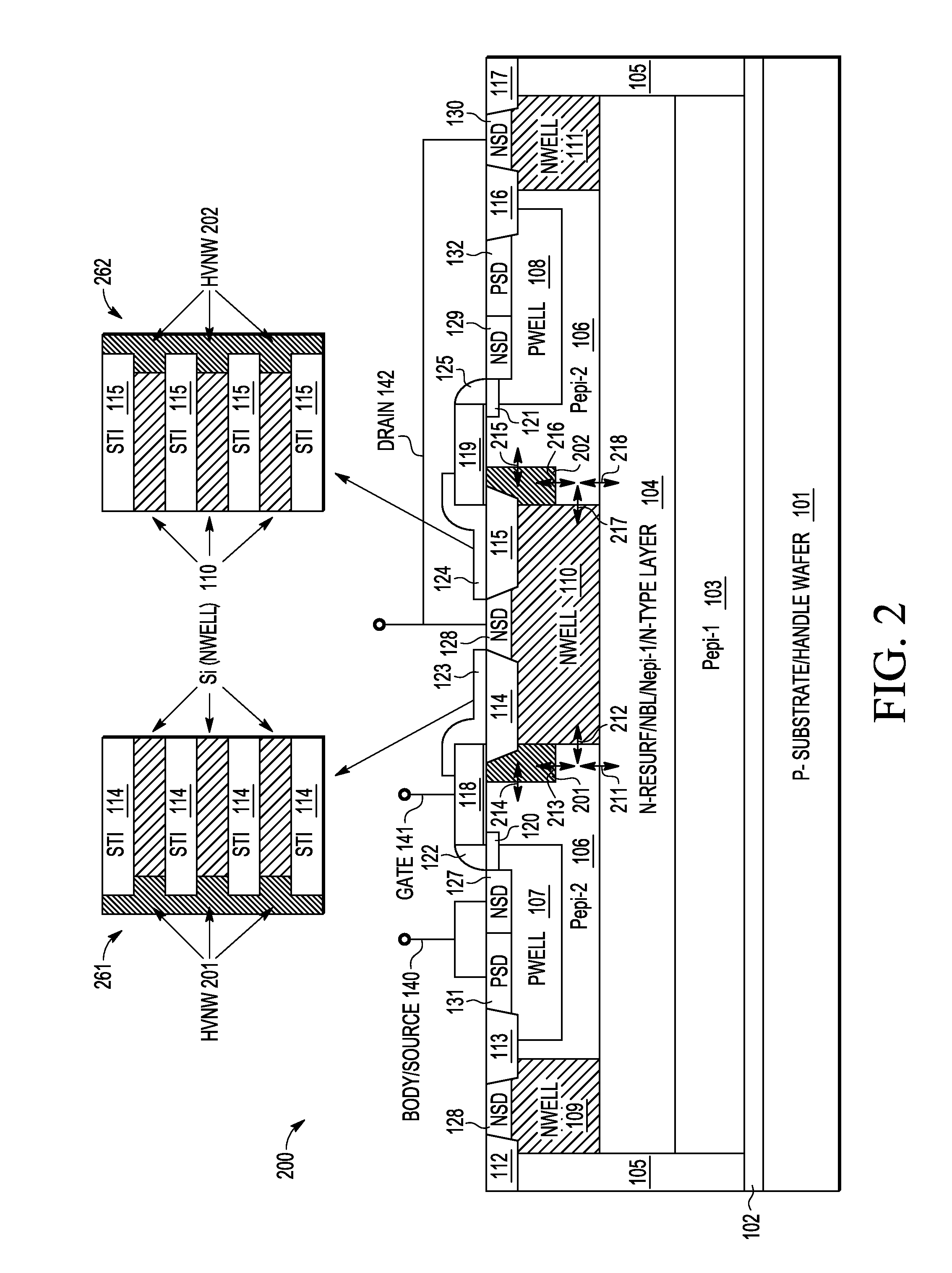

Partially Depleted Dielectric Resurf LDMOS

ActiveUS20120043608A1Solid-state devicesSemiconductor/solid-state device manufacturingLDMOSCondensed matter physics

An partially depleted Dieler LDMOSFET transistor (100) is provided which includes a substrate (150), a drift region (110) surrounding a drain region (128), a first well region (107) surrounding source region (127), a well buffer region (106) separating the drift region and first well region to at least partly define a first channel region, a gate electrode (118) formed over the first channel region having a source-side gate edge aligned with the first well region (107), an LDD extension region (120) extending from the source region to the channel region, and a dielectric RESURF drain extension structure (161) formed at the drain of the gate electrode (118) using the plurality of STI stripes (114).

Owner:NXP USA INC

Power LDMOS transistor

ActiveUS7235845B2Breakdown behavior is improvedImprove reliabilitySemiconductor devicesLDMOSSemiconductor

Owner:CICLON SEMICON DEVICE

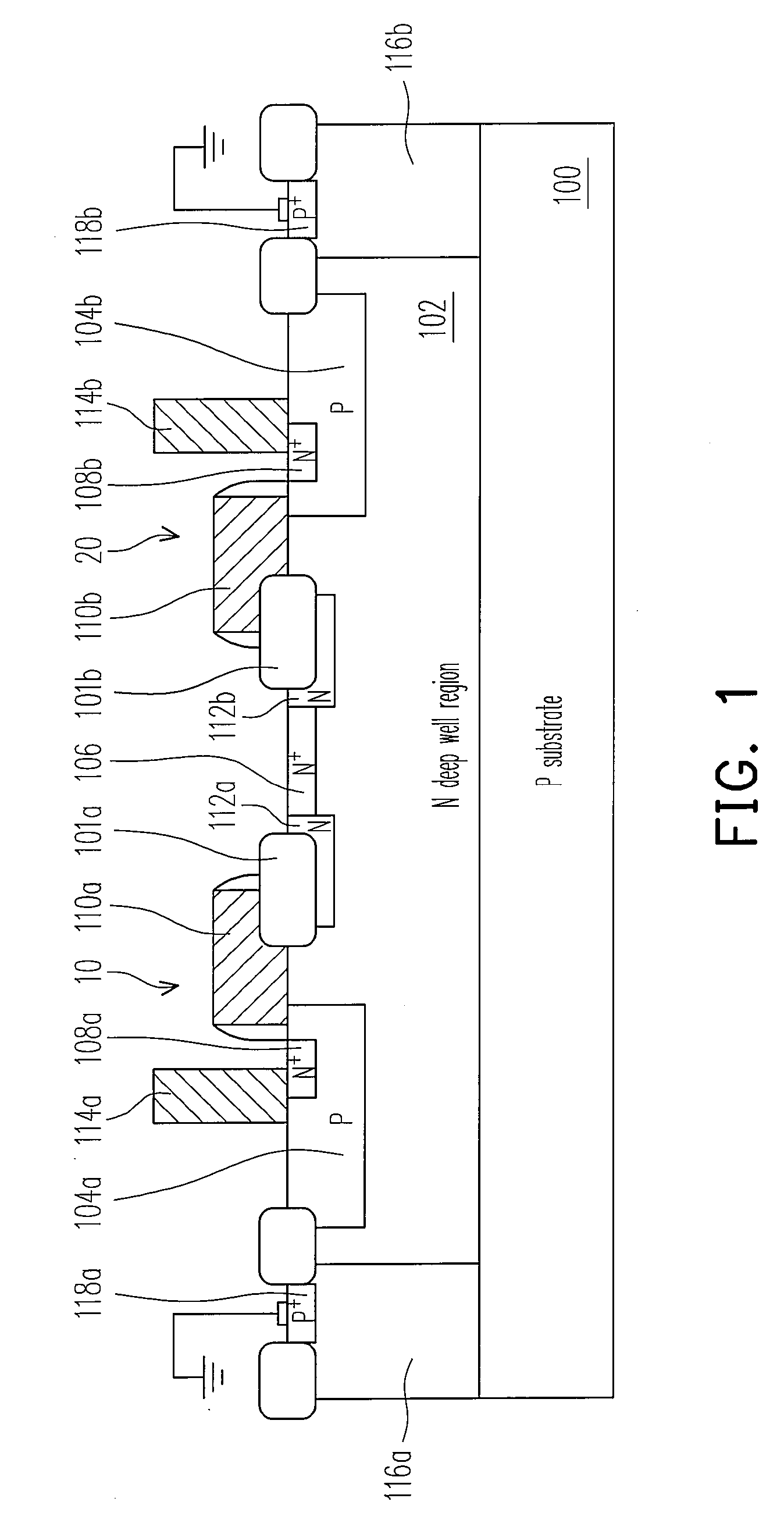

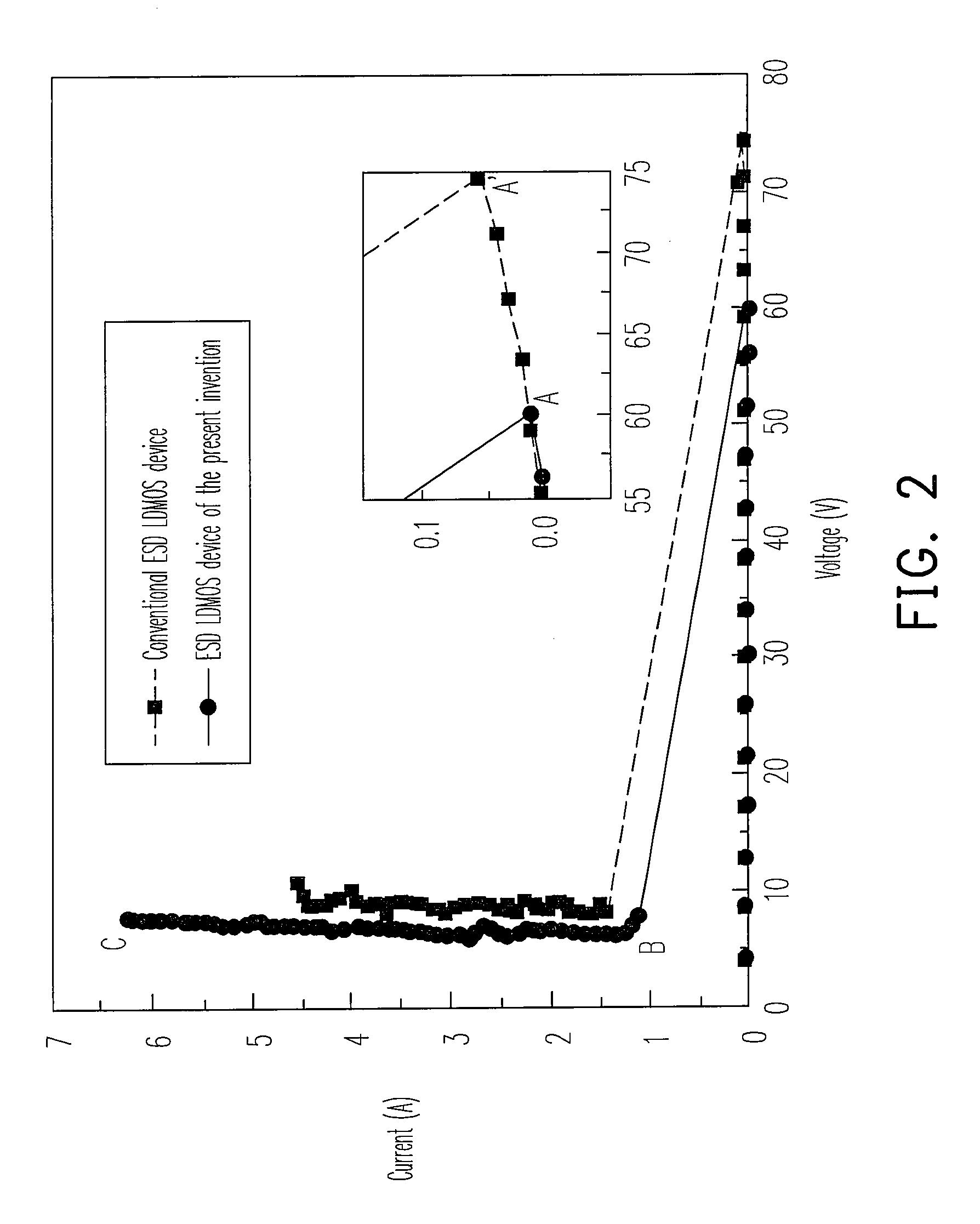

Ldmos device for ESD protection circuit

ActiveUS20100032758A1Turned on more quicklyIncrease resistanceTransistorSolid-state devicesLDMOSBody region

A LDMOS device for an ESD protection circuit is provided. The LDMOS device includes a substrate of a first conductivity type, a deep well region of a second conductivity type, a body region of the first conductivity type, first and second doped regions of the second conductivity type, and a gate electrode. The deep well region is disposed in the substrate. The body region and the first doped region are respectively disposed in the deep well region. The second doped region is disposed in the body region. The gate electrode is disposed on the deep well region between the first and second doped regions. It is noted that the body region does not include a doped region of the first conductivity type having a different doped concentration from the body region.

Owner:UNITED MICROELECTRONICS CORP

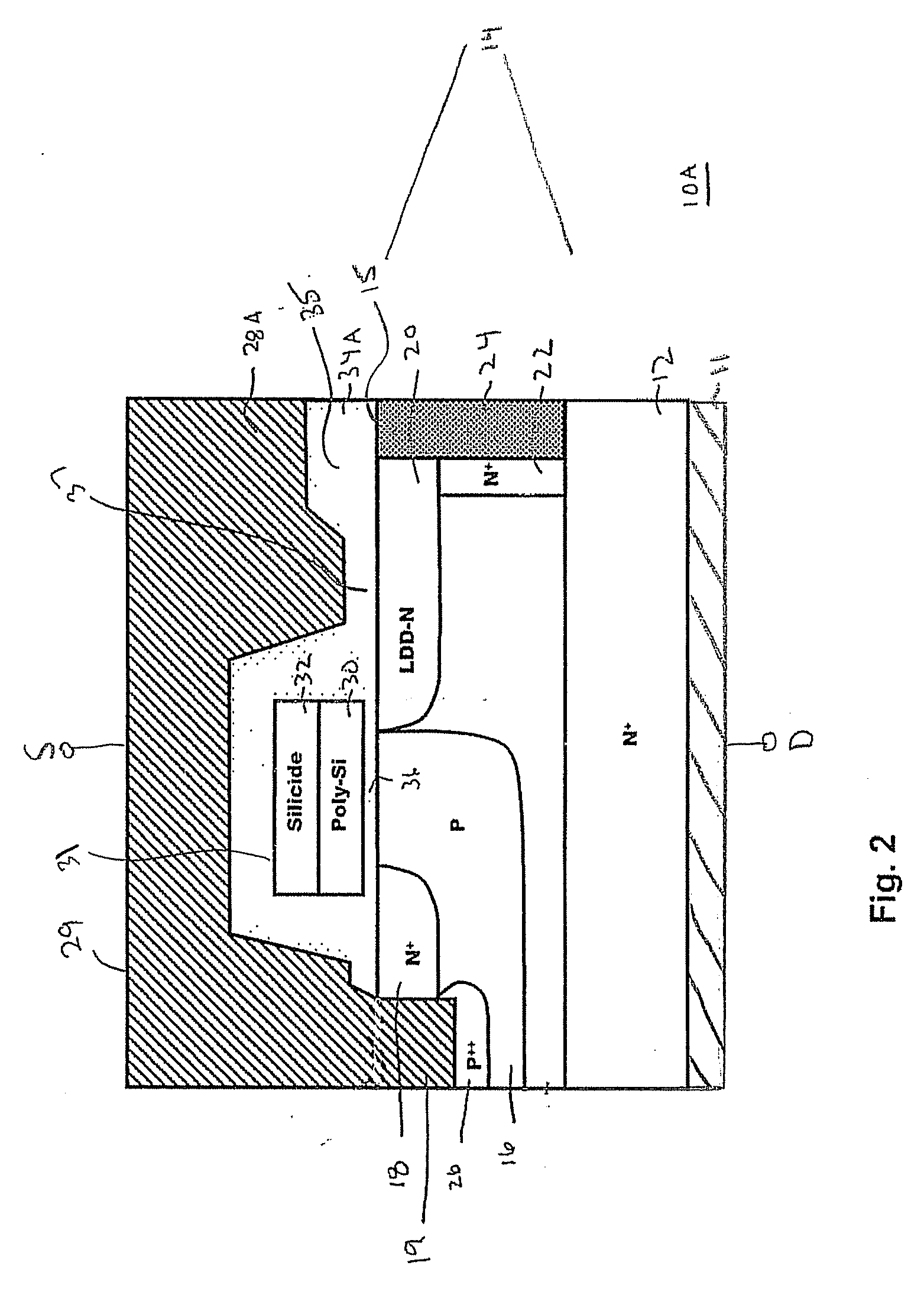

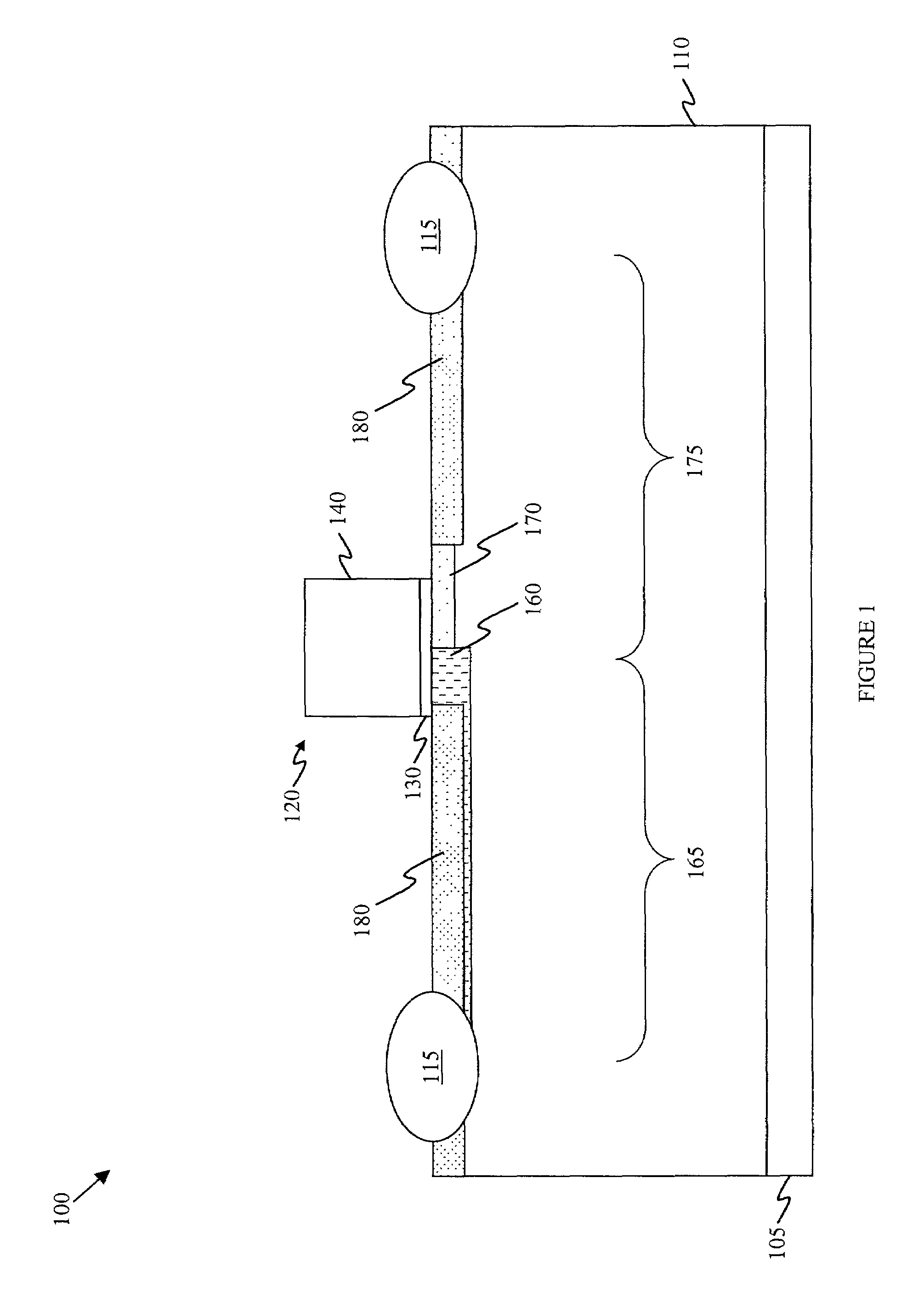

Integrated Circuit with a Laterally Diffused Metal Oxide Semiconductor Device and Method of Forming the Same

ActiveUS20110049621A1Reduce voltageMagnetic-field-controlled resistorsSolid-state devicesLDMOSEngineering

An integrated circuit with a transistor advantageously embodied in a laterally diffused metal oxide semiconductor device having a gate located over a channel region recessed into a semiconductor substrate and a method of forming the same. In one embodiment, the transistor includes a source / drain including a lightly or heavily doped region adjacent the channel region, and an oppositely doped well extending under the channel region and a portion of the lightly or heavily doped region of the source / drain. The transistor also includes a channel extension, within the oppositely doped well, under the channel region and extending under a portion of the lightly or heavily doped region of the source / drain.

Owner:TAHOE RES LTD

Integrated Circuit with a Laterally Diffused Metal Oxide Semiconductor Device and Method of Forming the Same

ActiveUS20100052052A1Reduce voltageSolid-state devicesSemiconductor/solid-state device manufacturingLDMOSEngineering

An integrated circuit with a transistor advantageously embodied in a laterally diffused metal oxide semiconductor device having a gate located over a channel region recessed into a semiconductor substrate and a method of forming the same. In one embodiment, the transistor includes a source / drain including a lightly or heavily doped region adjacent the channel region, and an oppositely doped well extending under the channel region and a portion of the lightly or heavily doped region of the source / drain. The transistor also includes a channel extension, within the oppositely doped well, under the channel region and extending under a portion of the lightly or heavily doped region of the source / drain.

Owner:TAHOE RES LTD

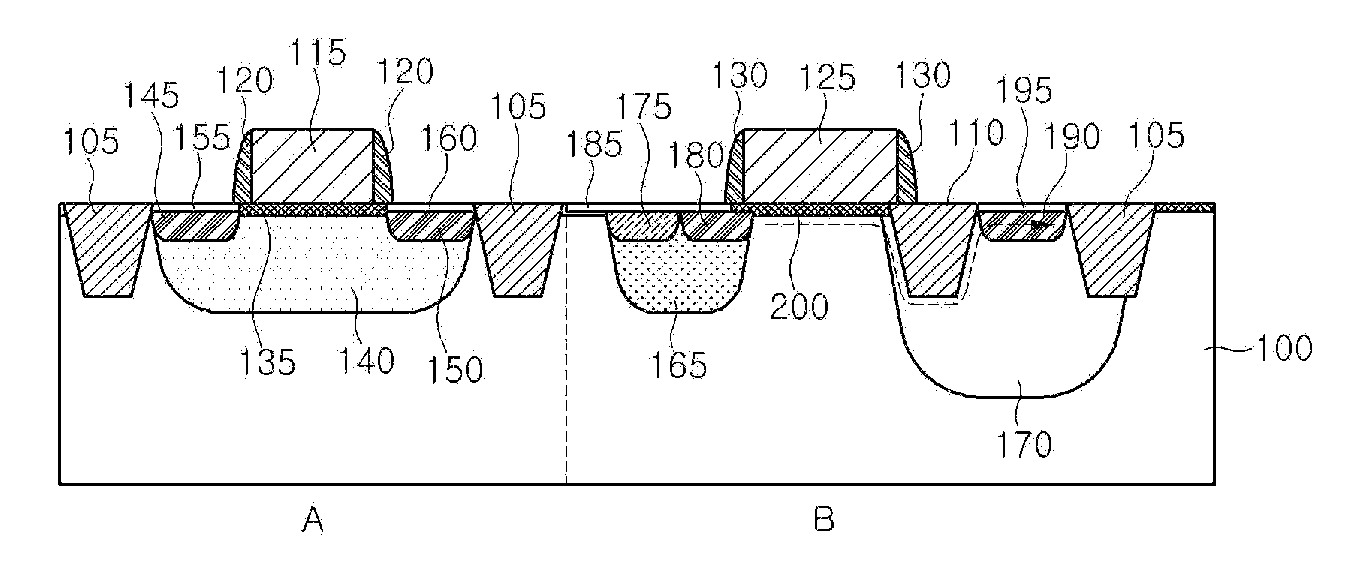

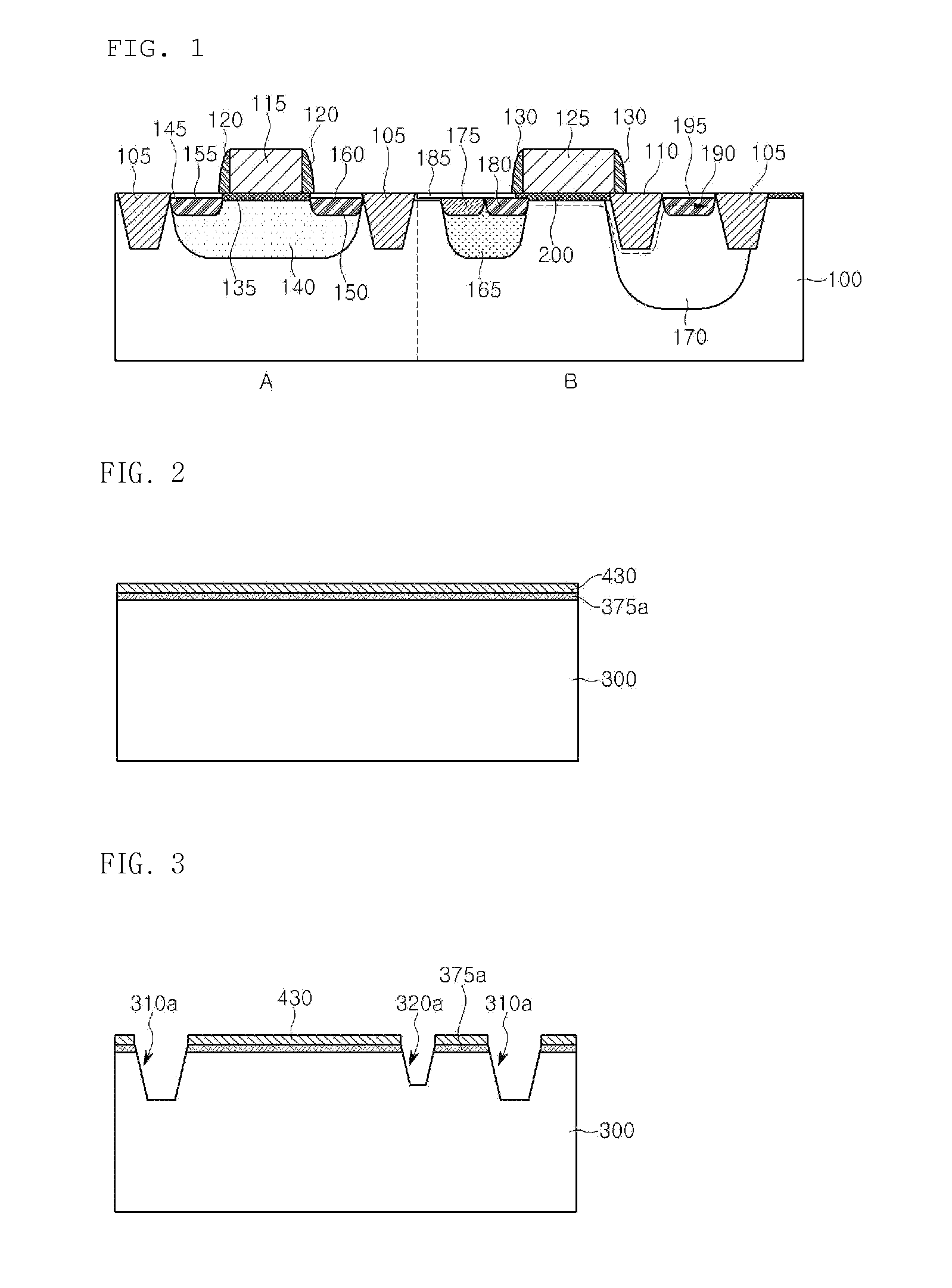

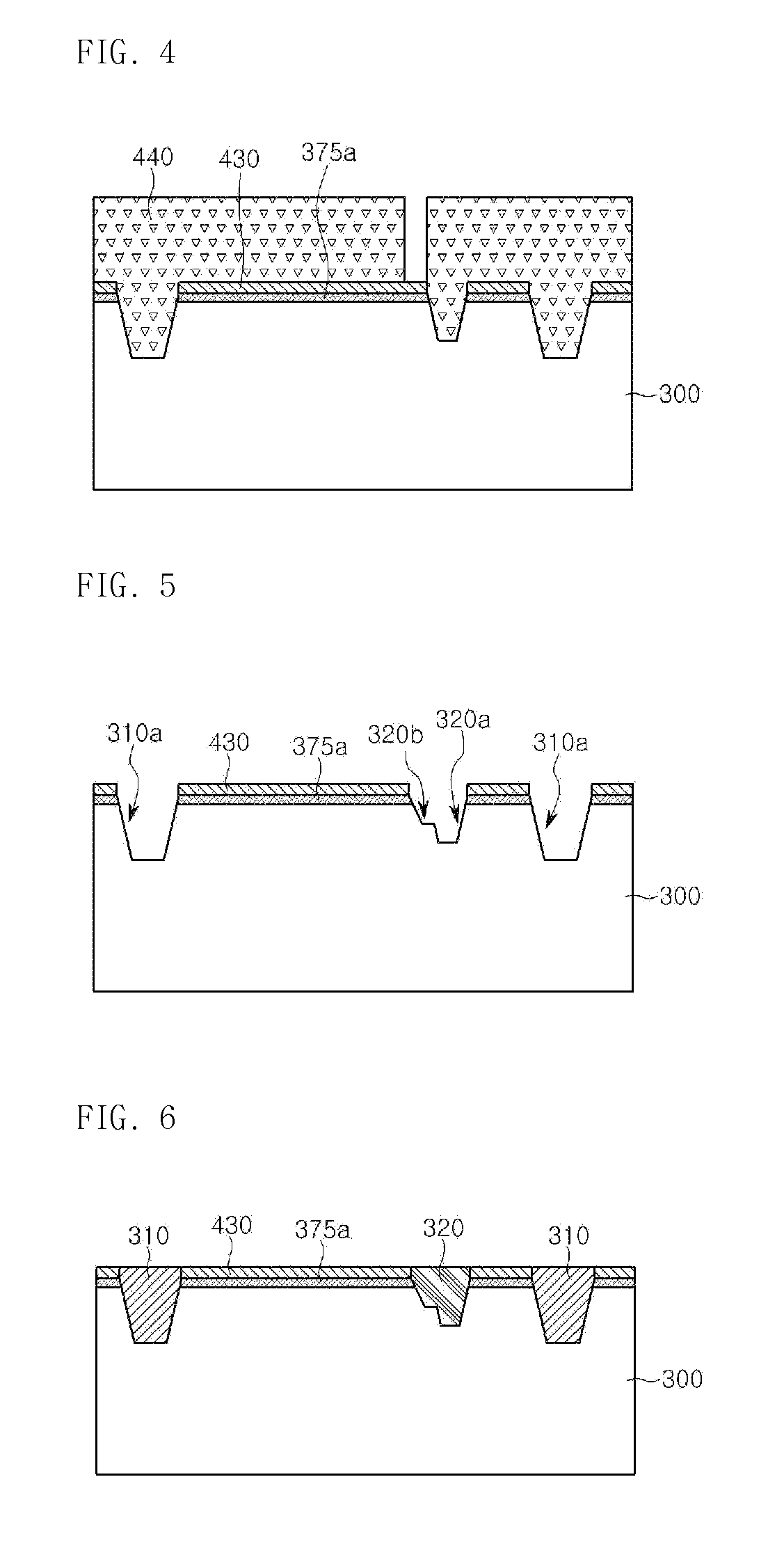

Lateral Double Diffused Metal Oxide Semiconductor (LDMOS) Device and Method of Manufacturing LDMOS Device

InactiveUS20100006937A1Improve breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSIsolation layer

A method for manufacturing a lateral double diffused metal oxide semiconductor (LDMOS) device includes forming an oxide layer on a semiconductor substrate, forming first and second trenches by partially etching the oxide layer and the semiconductor substrate, forming a small trench overlapping with the second trench so that the second trench has a stepped structure, and depositing one or more dielectric layers so that the first trench forms a device isolation layer defining a semiconductor device region and the second trench having a stepped structure forms a drain extension device isolation layer. The breakdown voltage of the LDMOS device may be improved while reducing the on-resistance, thereby improving the operational reliability of the device.

Owner:COLUMBA TECH INC

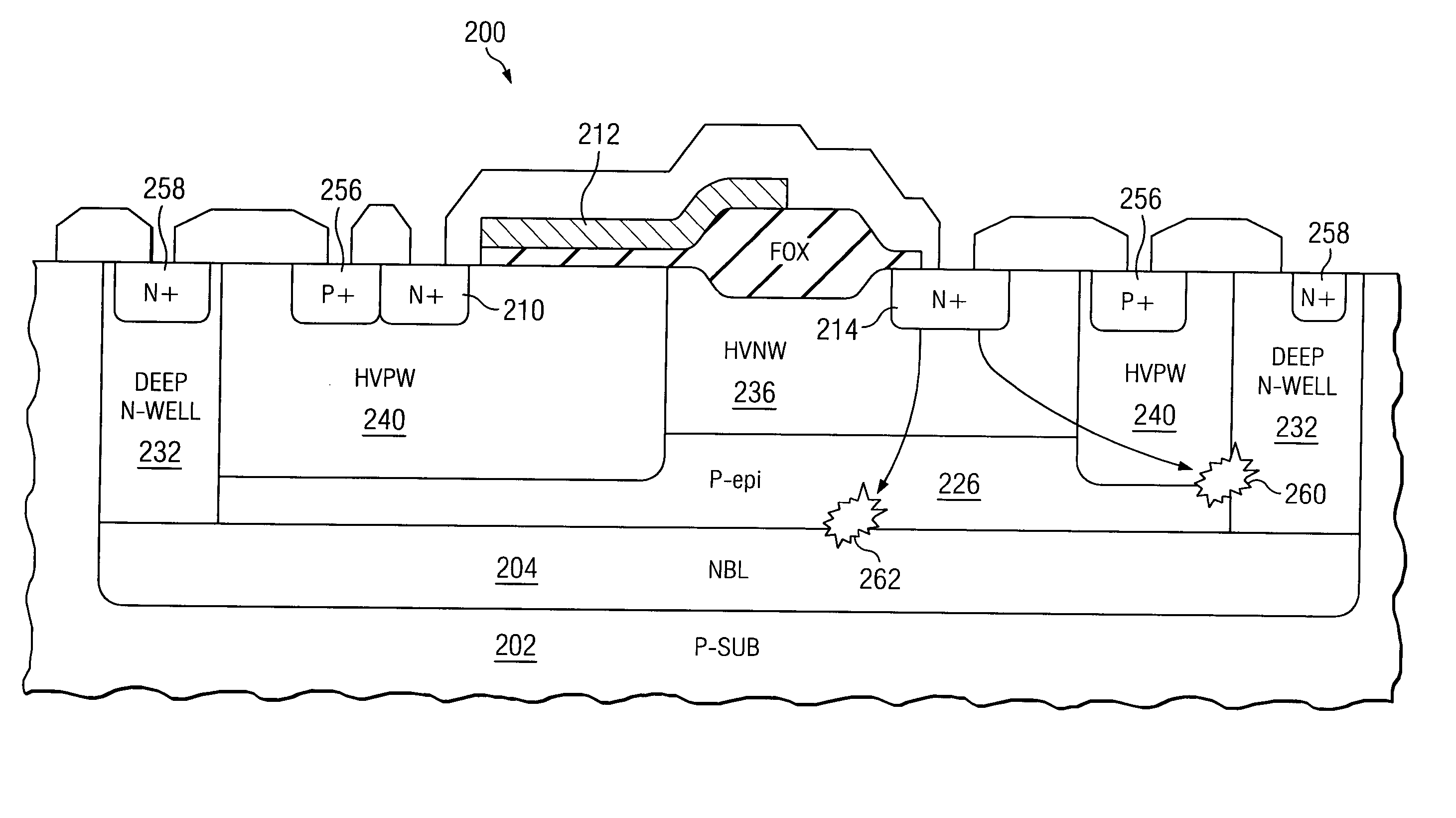

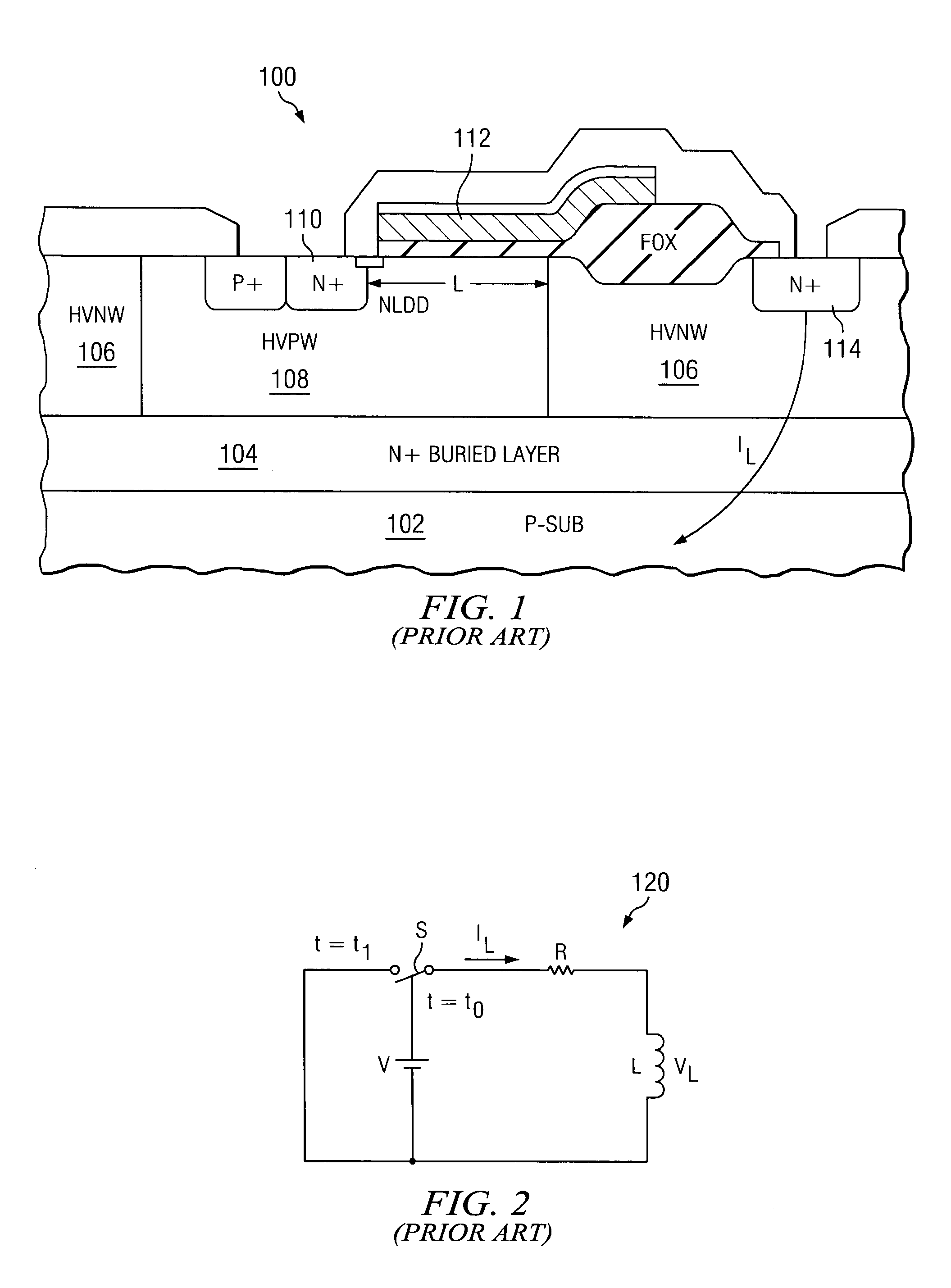

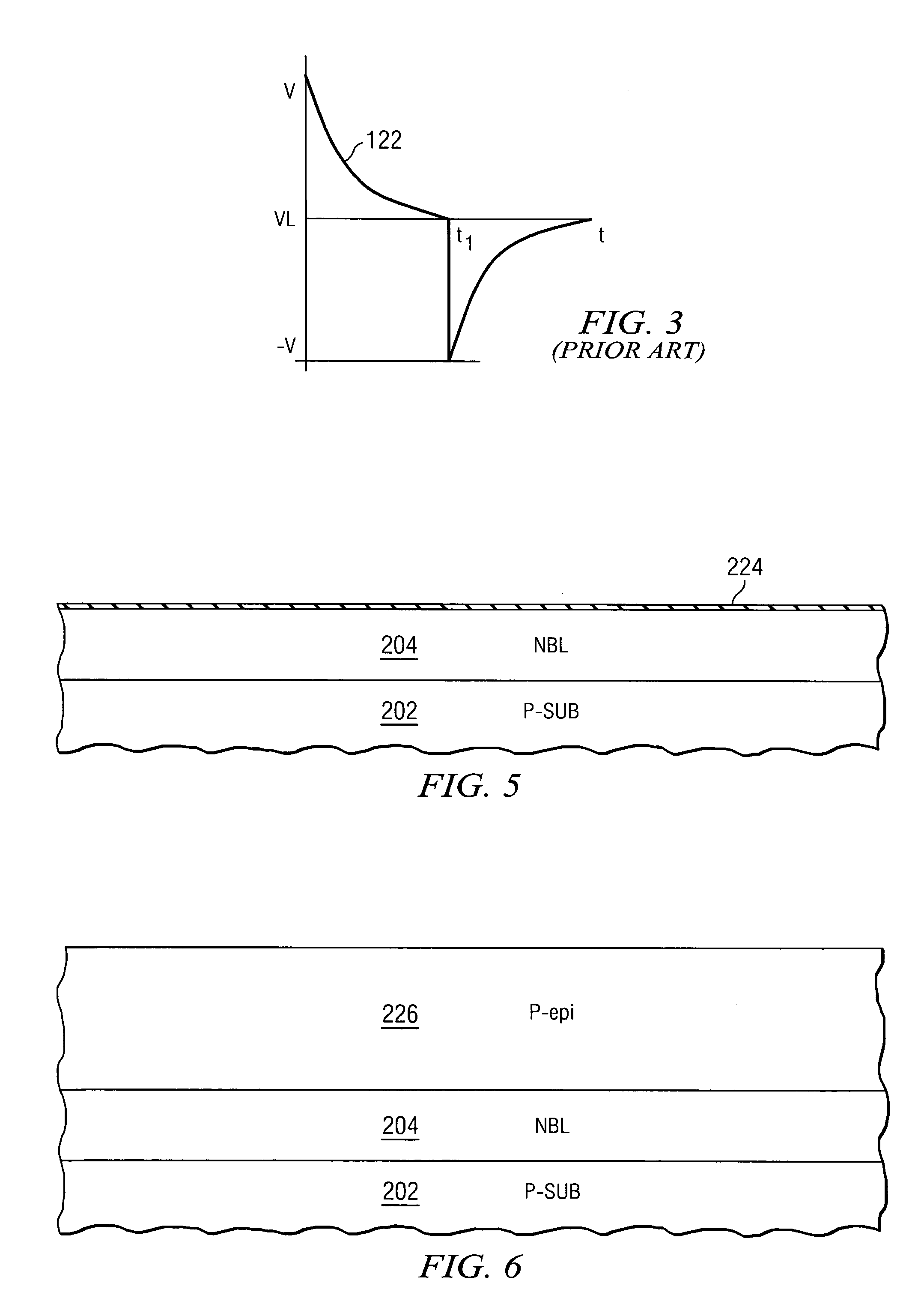

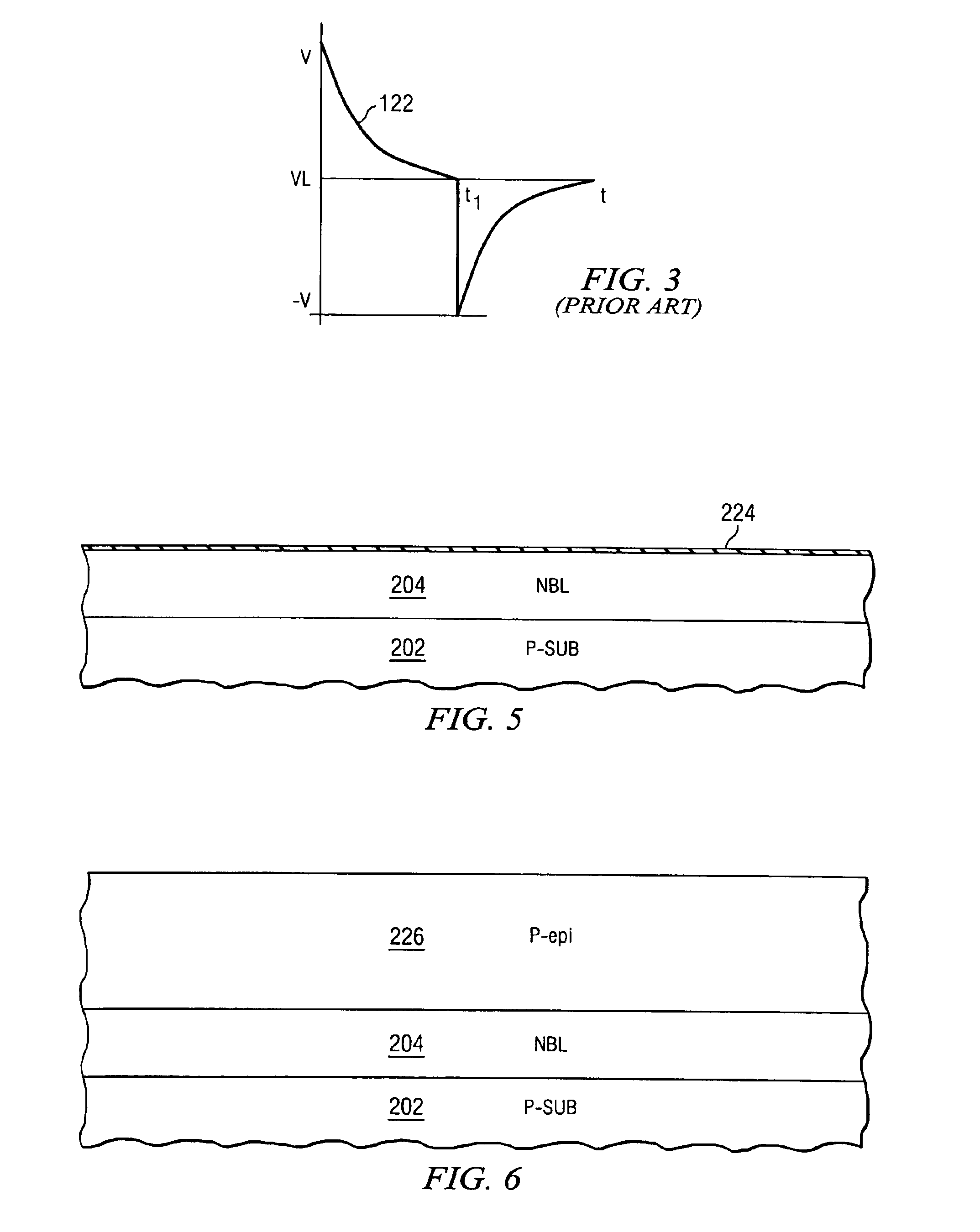

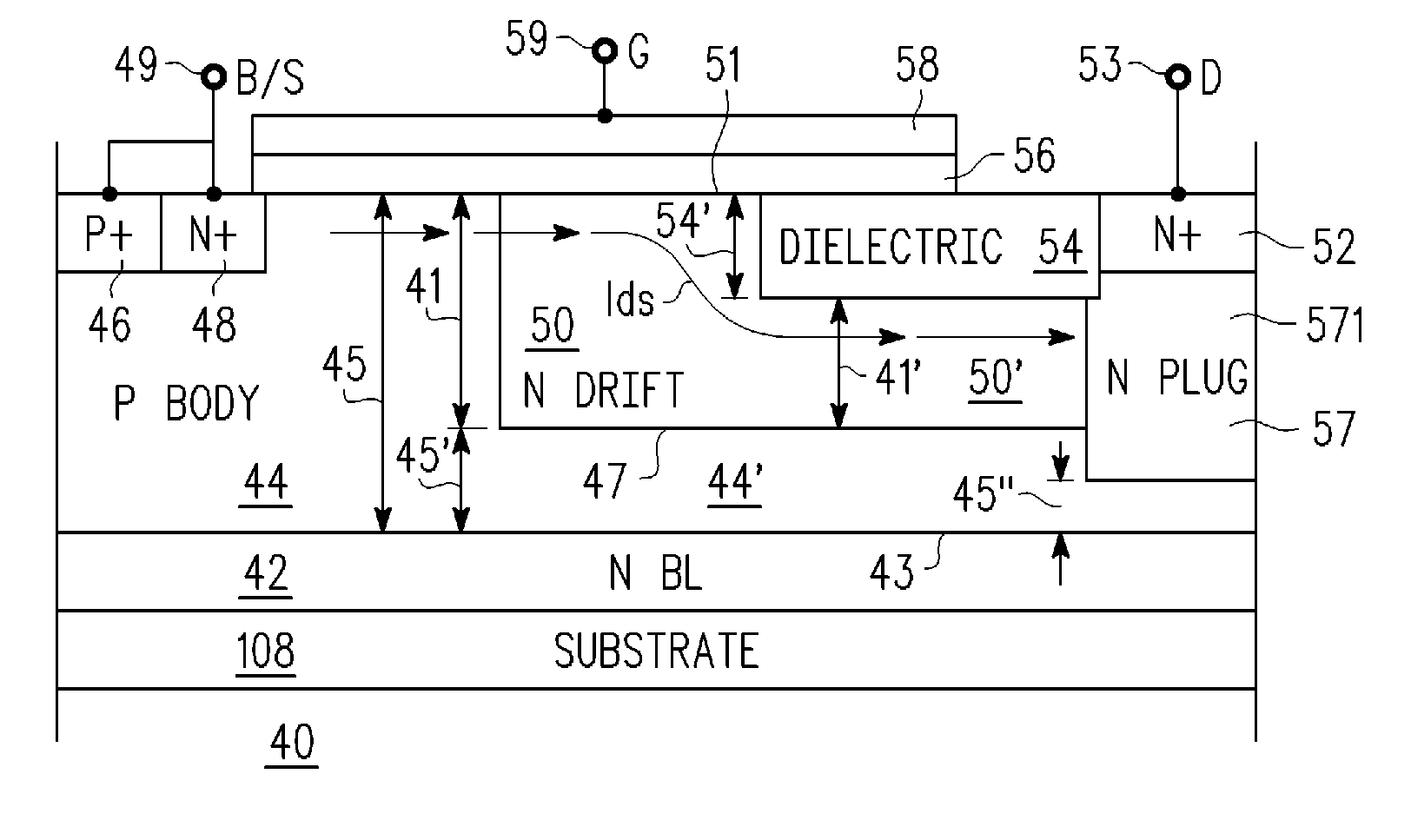

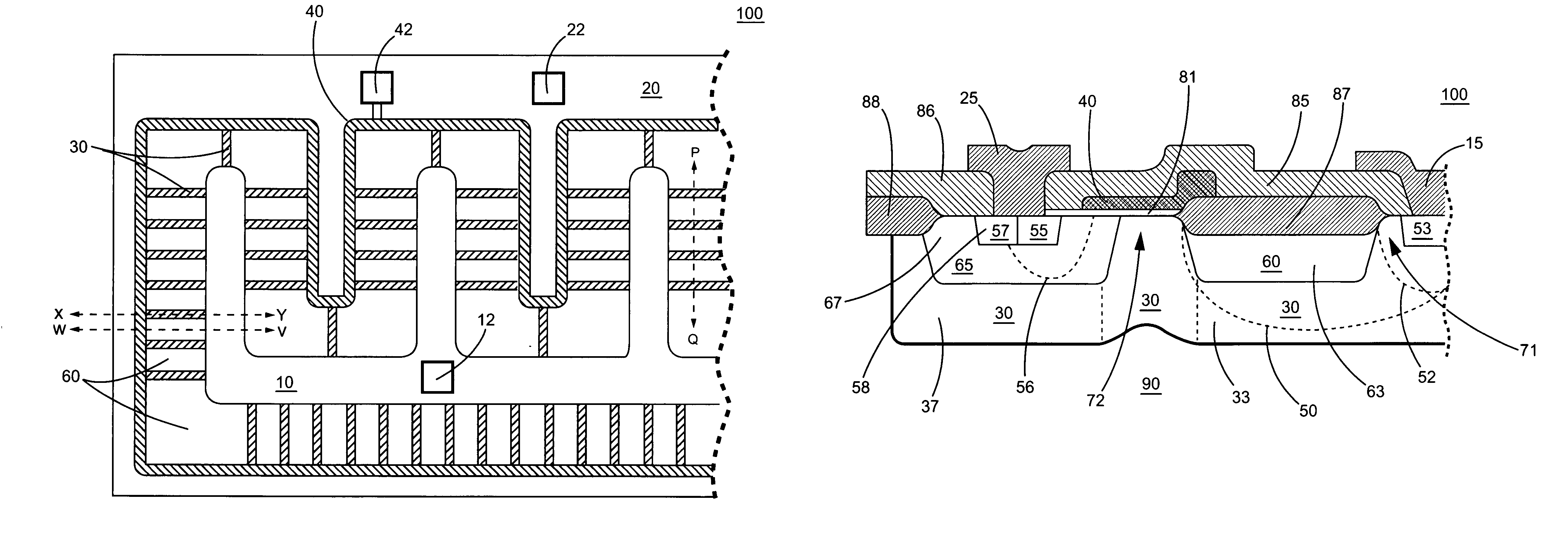

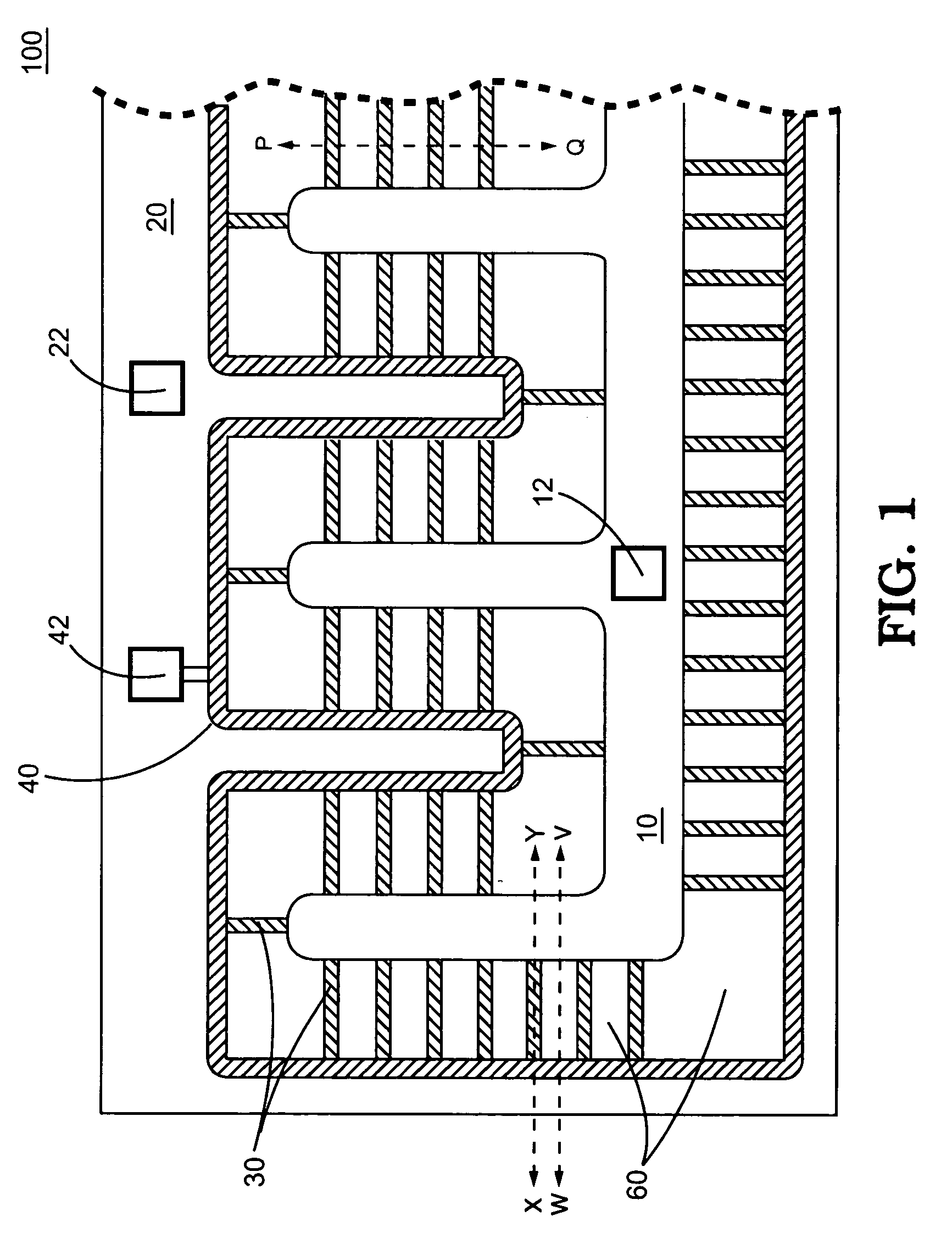

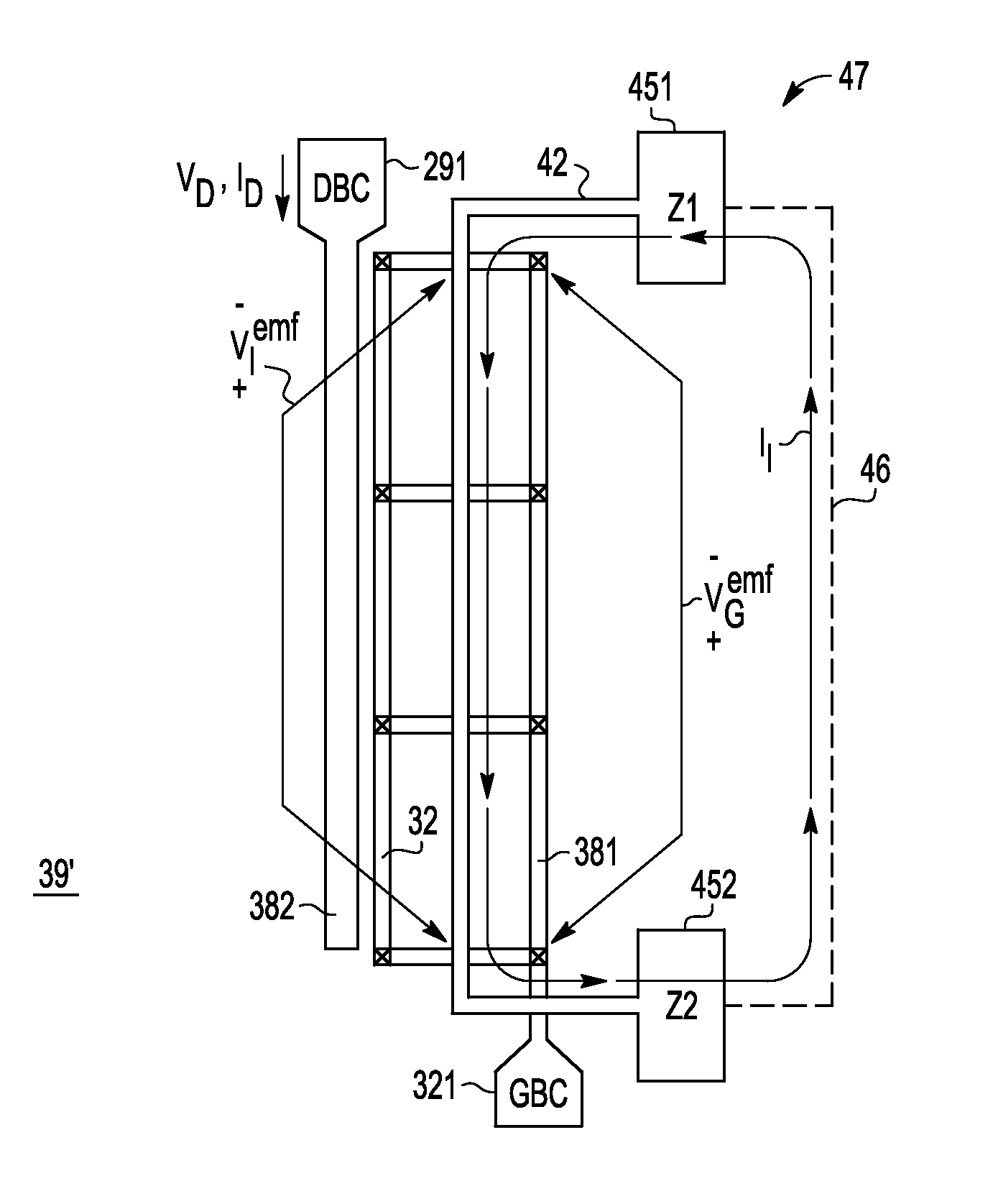

Resurf semiconductor device charge balancing

Breakdown voltage BVdss is enhanced and ON-resistance reduced in RESURF devices (40, 60, 80, 80′, 80″), e.g., LDMOS transistors, by careful charge balancing, even when body (44, 44′, 84, 84′) and drift (50, 50′, 90, 90′) region charge balance is not ideal, by: (i) providing a plug or sinker (57) near the drain (52, 92) and of the same conductivity type extending through the drift region (50, 50′, 90, 90′) at least into the underlying body region (44, 44′ 84, 84′), and / or (ii) applying bias Viso to a surrounding lateral doped isolation wall (102) coupled to the device buried layer (42, 82), and / or (iii) providing a variable resistance bridge (104) between the isolation wall (102) and the drift region (50, 50′, 90, 90′). The bridge (104) may be a FET (110) whose source-drain (113, 114) couple the isolation wall (102) and drift region (50, 50′, 90, 90′) and whose gate (116) receives control voltage Vc, or a resistor (120) whose cross-section (X, Y, Z) affects its resistance and pinch-off, to set the percentage of drain voltage coupled to the buried layer (42, 82) via the isolation wall (102).

Owner:NXP USA INC

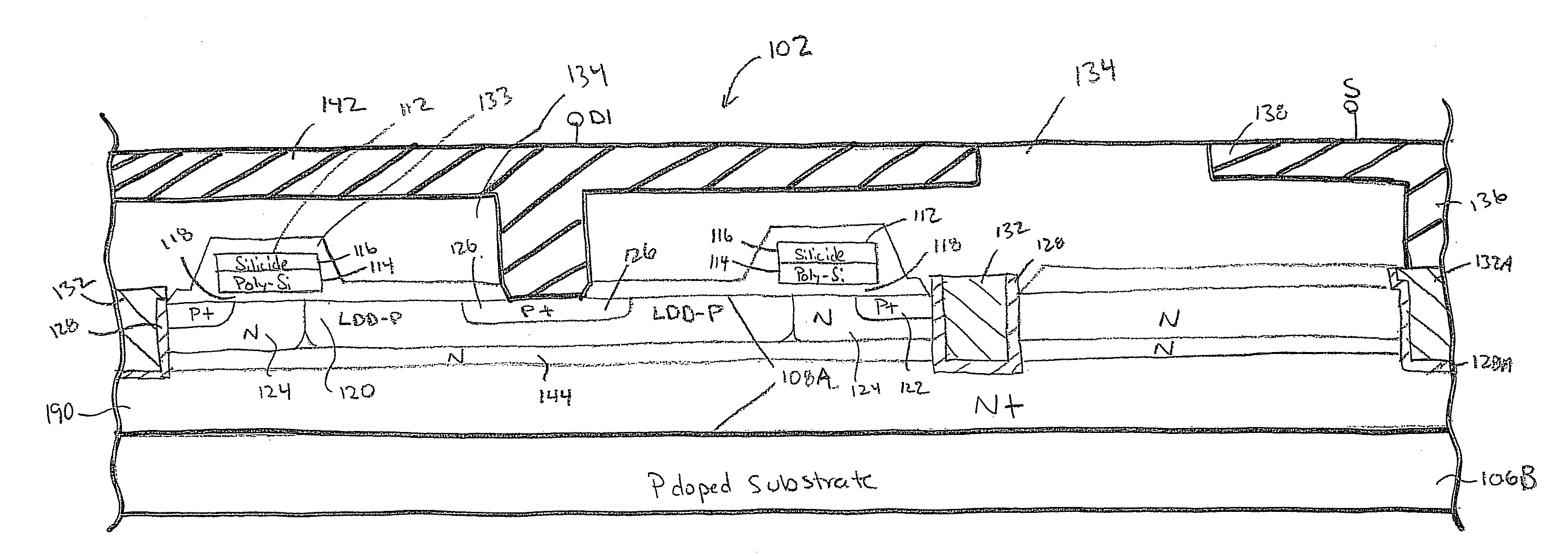

Mos transistor device in common source configuration

A semiconductor device includes a semiconductor substrate, a first p-channel laterally diffused metal oxide semiconductor (LDMOS) transistor formed over the semiconductor substrate and additional p-channel LDMOS transistors formed over the semiconductor substrate. First drain and gate electrodes are formed over the substrate and are coupled to the first LDMOS transistor. Additional drain and gate electrodes are formed over the substrate and are coupled to the second LDMOS transistor. A common source electrode for the first and second LDMOS transistors is also formed over the substrate.

Owner:TEXAS INSTR LEHIGH VALLEY

Inverted-trench grounded-source FET structure with trenched source body short electrode

ActiveUS20080067584A1Reduce manufacturing costReduced cell pitchTransistorSolid-state devicesCapacitanceLDMOS

This invention discloses bottom-source lateral diffusion MOS (BS-LDMOS) device. The device has a source region disposed laterally opposite a drain region near a top surface of a semiconductor substrate supporting a gate thereon between the source region and a drain region. The BS-LDMOS device further has a combined sinker-channel region disposed at a depth in the semiconductor substrate entirely below a body region disposed adjacent to the source region near the top surface wherein the combined sinker-channel region functioning as a buried source-body contact for electrically connecting the body region and the source region to a bottom of the substrate functioning as a source electrode. A drift region is disposed near the top surface under the gate and at a distance away from the source region and extending to and encompassing the drain region. The combined sinker-channel region extending below the drift region and the combined sinker-channel region that has a dopant-conductivity opposite to and compensating the drift region for reducing the source-drain capacitance.

Owner:ALPHA & OMEGA SEMICON LTD

Isolated high-voltage LDMOS transistor having a split well structure

The isolated high-voltage LDMOS transistor according to the present invention includes a split N-well and P-well in the extended drain region. The P-well is split in the extended drain region of the N-well to form a split junction-field in the N-well. The split N-well and P-well deplete the drift region, which shifts the electric field maximum into the bulk of the N-well. This achieves a higher breakdown voltage and allows the N-well to have a higher doping density. Furthermore, the LDMOS transistor according to the present invention includes a N-well embedded beneath the source diffusion region. This creates a low-impedance path for the source region, which restricts the transistor current flow between the drain region and the source region.

Owner:FAIRCHILD TAIWAN

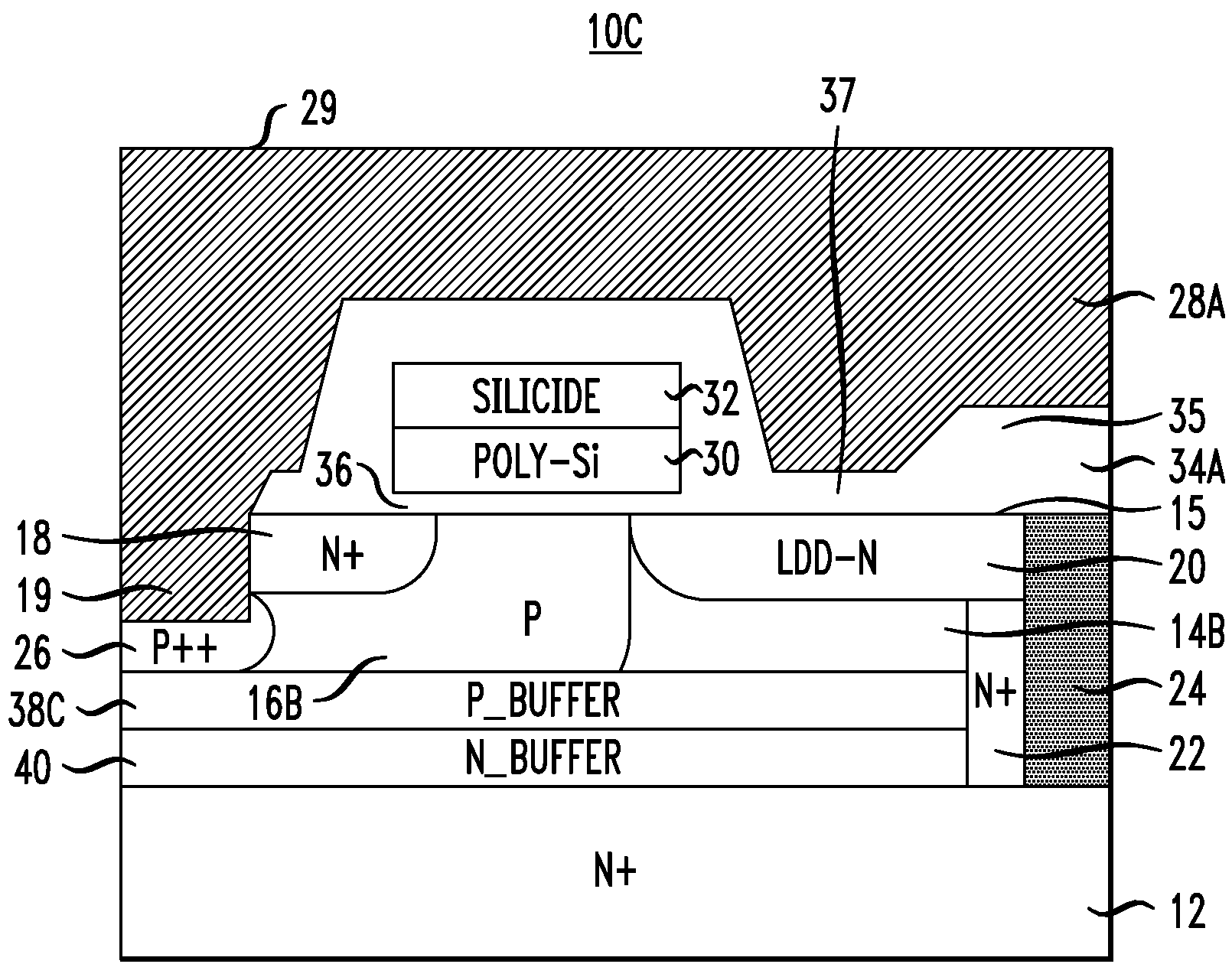

Power LDMOS transistor

A laterally diffused metal-oxide-semiconductor (LDMOS) transistor device includes a doped substrate having an epitaxial layer thereover having source and drain implant regions and body and lightly doped drain regions formed therein. The channel region and lightly doped drain regions are doped to a depth to abut the top surface of the substrate. In alternative embodiments, a buffer region of the second conductivity type and having dopant concentration greater than or equal to about the channel region is formed over the top surface of the substrate between the top surface of the substrate and the channel region and lightly doped drain region, wherein the channel region and lightly doped drain regions are doped to a depth to abut the buffer region.

Owner:CICLON SEMICON DEVICE

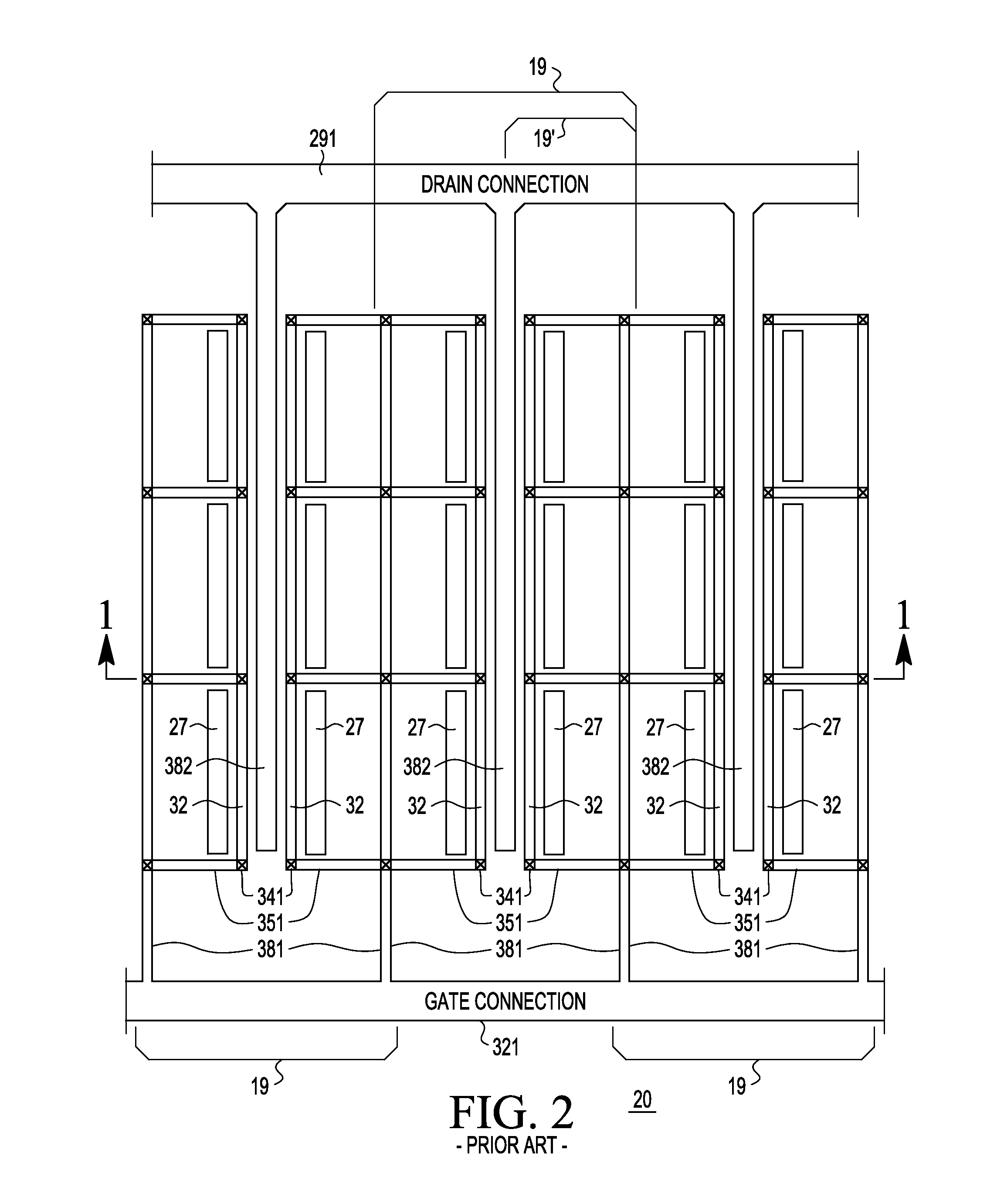

Semiconductor device with feedback control

An electronic element (39′, 39, 40) having feedback control is provided by placing an inductive interposer (42) between the output connection or bus (382) and the input connection or bus (381), wherein the inductive interposer (42) forms part of a closed circuit (47) with the inductive interposer (42) substantially parallel with the output connection or bus (382) and input connection or bus (381) for a distance permitting significant inductive coupling therebetween. In a preferred embodiment, the closed circuit (47) containing the inductive interposer (42) comprises impedance ZT. By including various circuit elements (e.g., resistance, capacitance, and / or inductance) in ZT, the output-to-input feedback can be modified to advantage. This greatly increases the available design freedom, especially for power devices, such as for example, field effect, MOSFET, LDMOS. bipolar and other power devices that use substantially parallel input and output bus structures.

Owner:NXP USA INC

LDMOS device

InactiveUS7626233B2Semiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

An LDMOS transistor comprises source, channel and extended drain regions. The extended drain region comprises a plurality of islands that have a conductivity type that is opposite to the extended drain region. The islands have a depth less than a depth of the extended drain region.

Owner:INFINEON TECH AG