Patents

Literature

141results about How to "Lower on-state resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

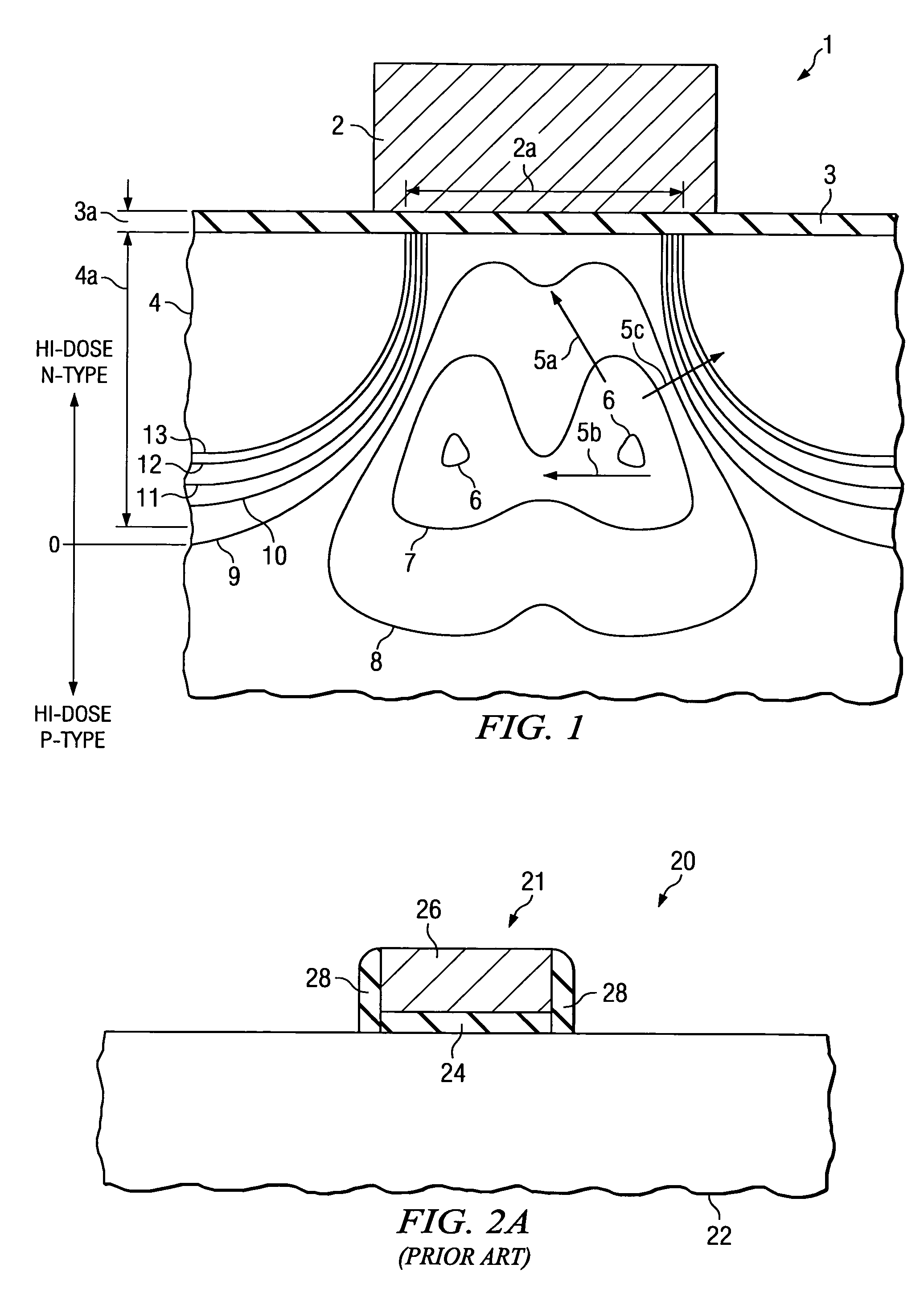

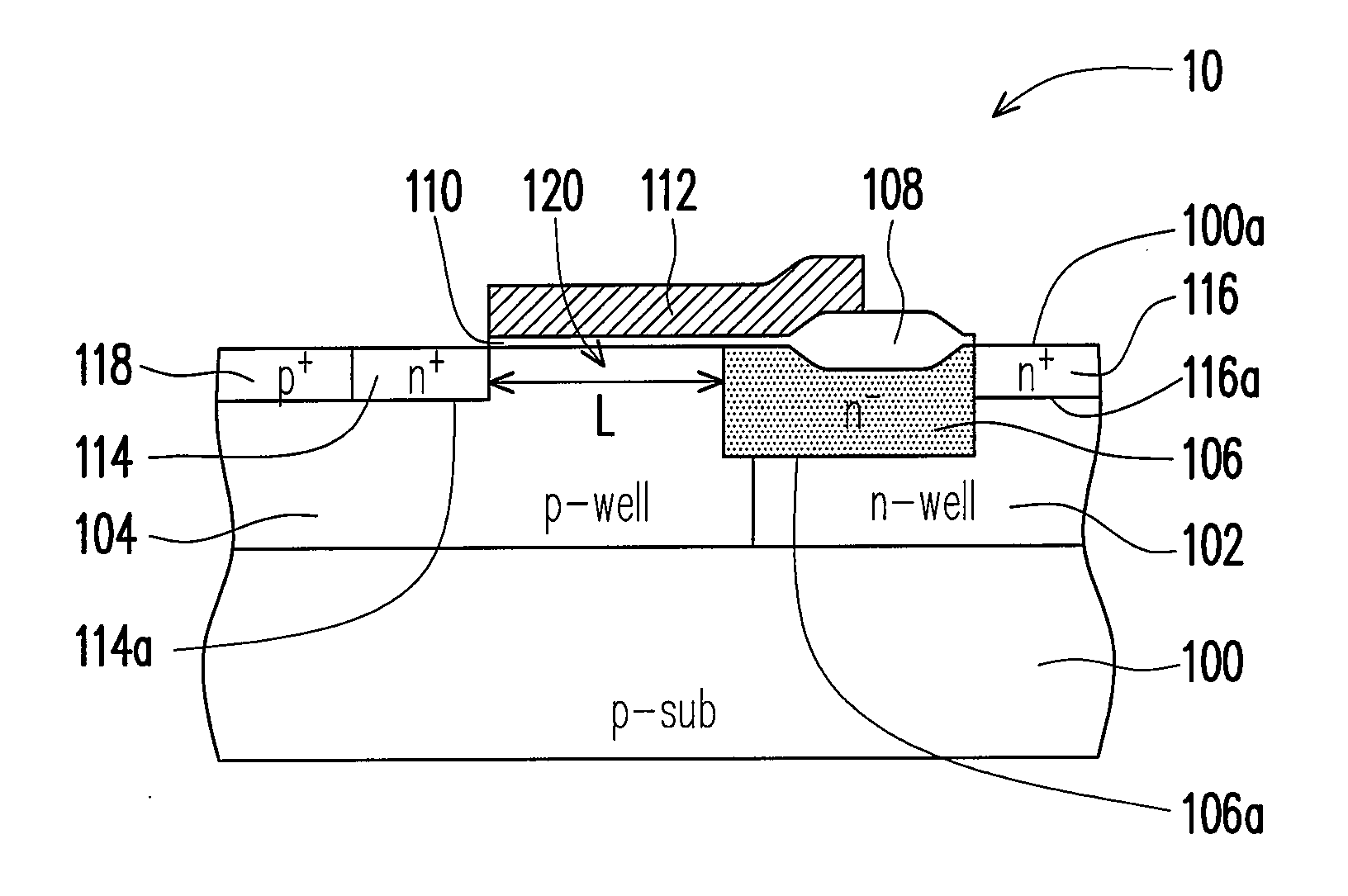

Method to produce localized halo for MOS transistor

InactiveUS7064039B2Accurate and repeatable formationLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSilicon

Methods are discussed for forming a localized halo structure and a retrograde profile in a substrate of a semiconductor device. The method comprises providing a gate structure over the semiconductor substrate, wherein a dopant material is implanted at an angle around the gate structure to form a halo structure in a source / drain region of the substrate and underlying a portion of the gate structure. A trench is formed in the source / drain region of the semiconductor substrate thereby removing at least a portion of the halo structure in the source / drain region. A silicon material layer is then formed in the trench using an epitaxial deposition.

Owner:TEXAS INSTR INC

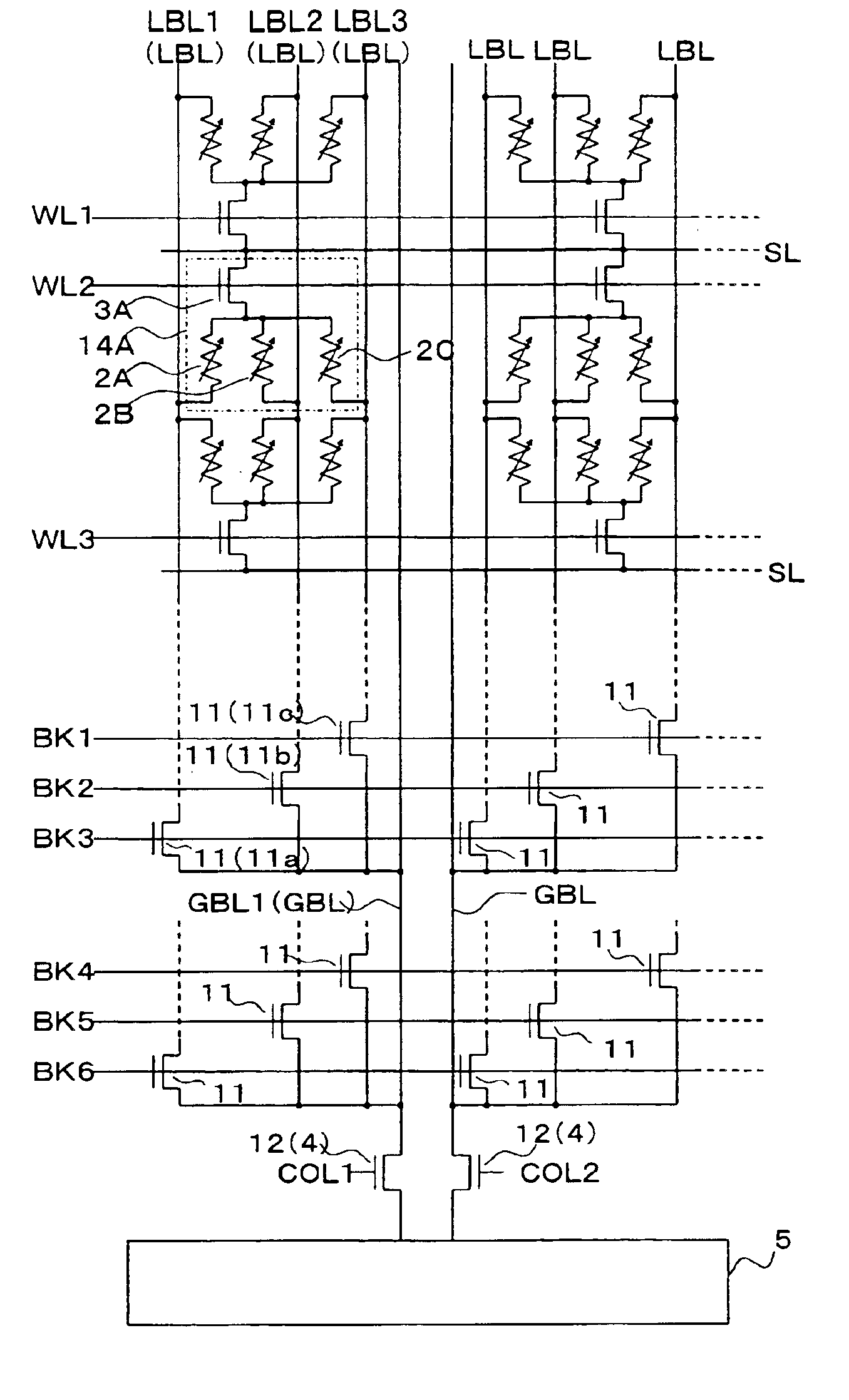

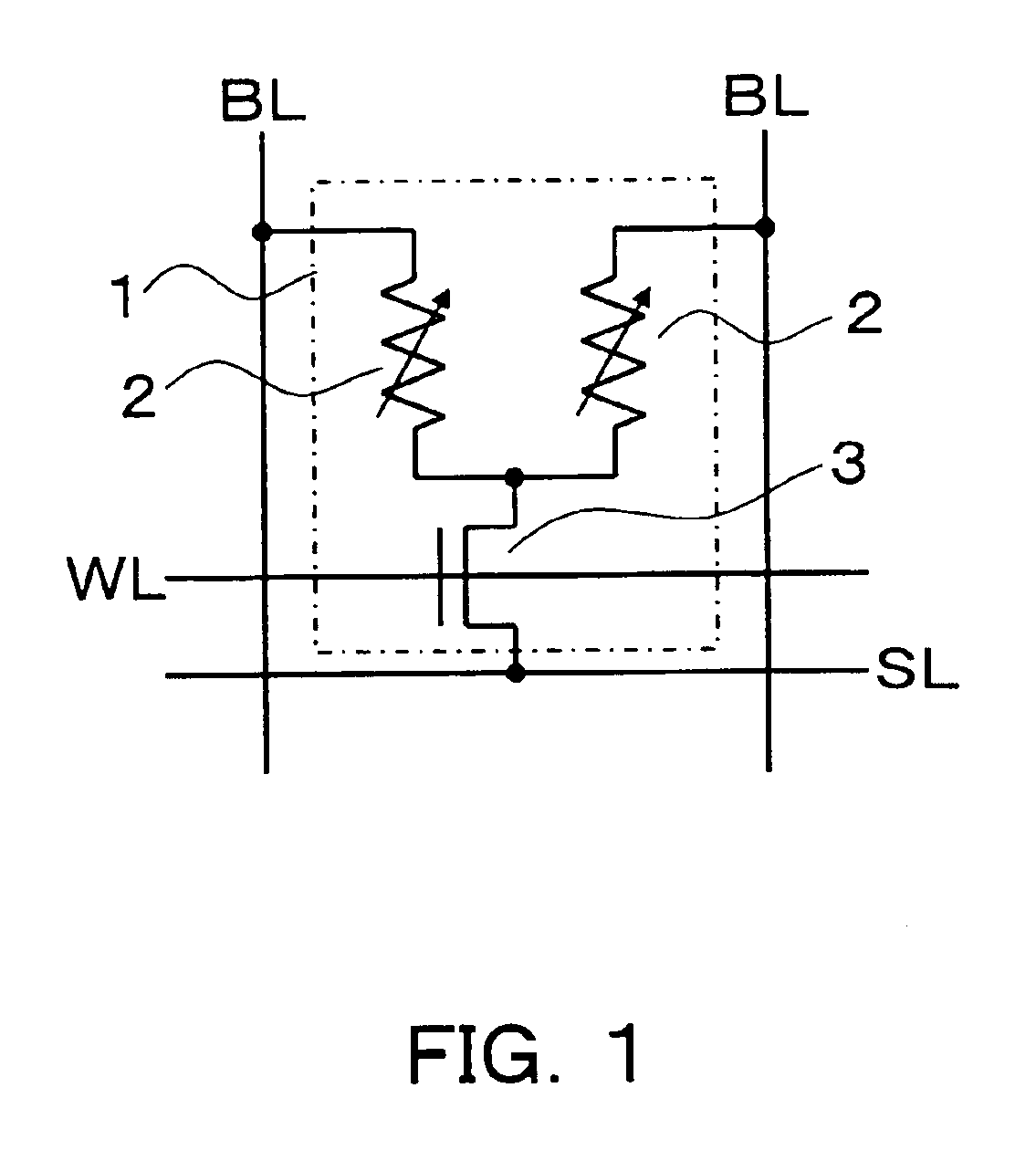

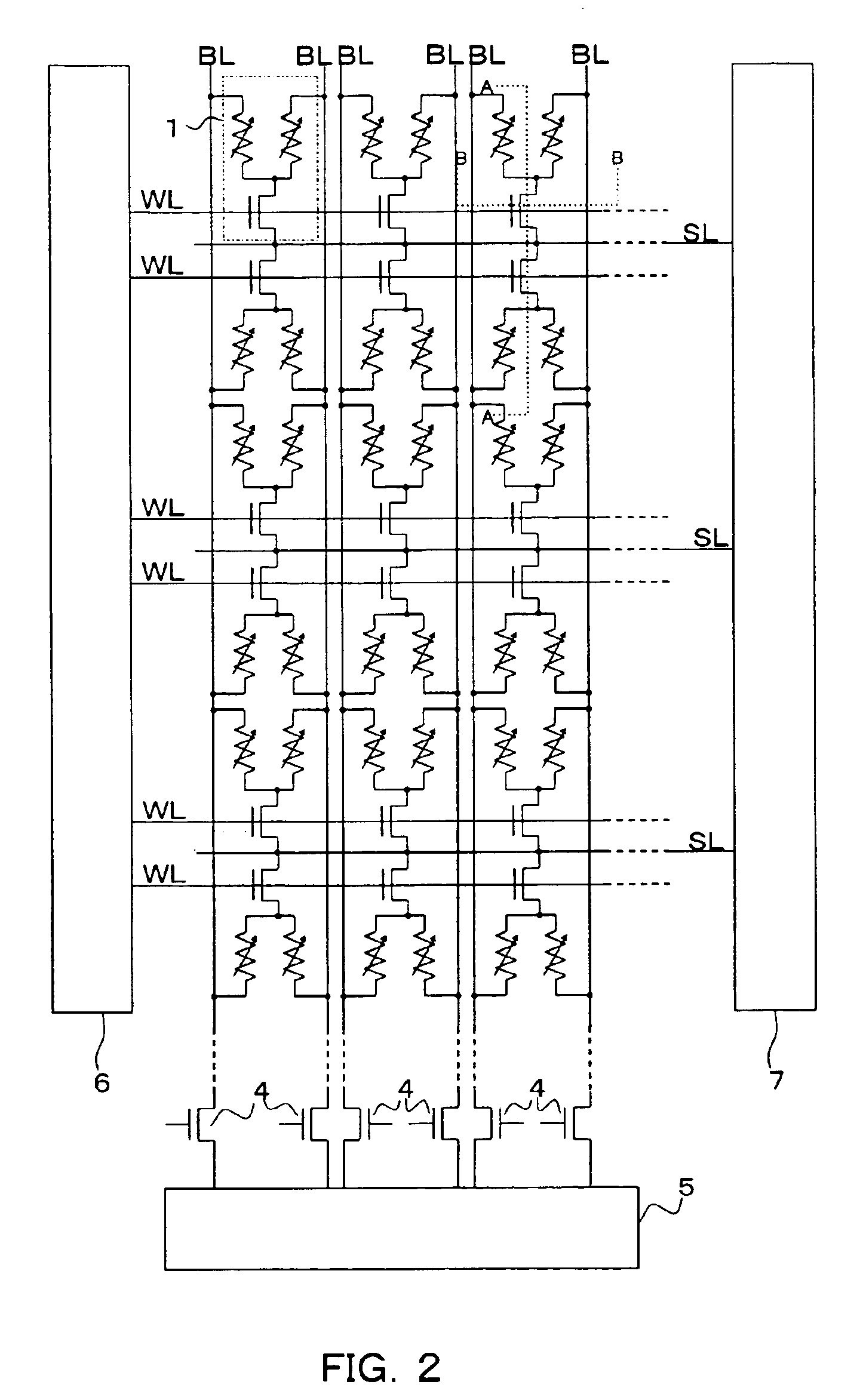

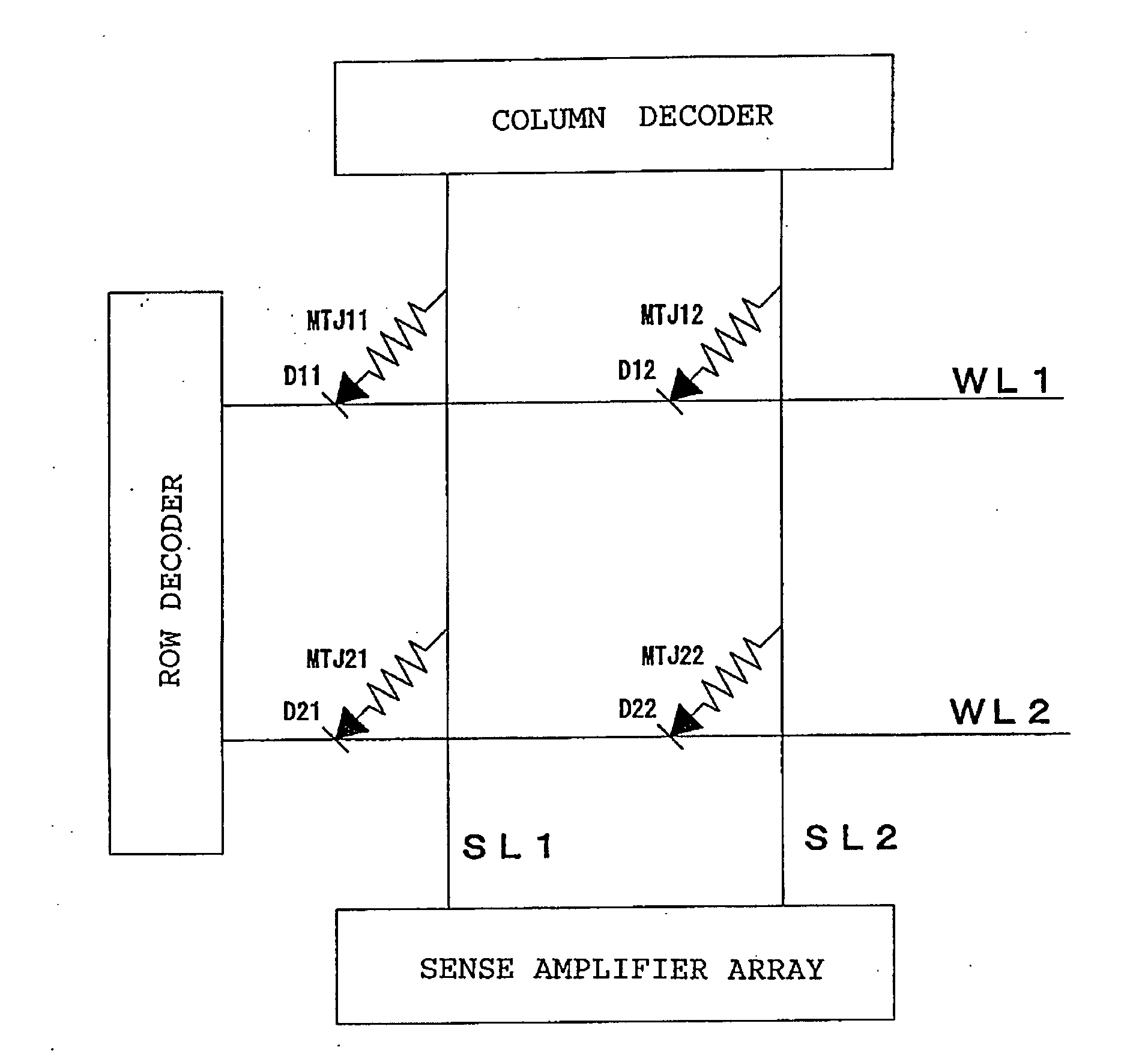

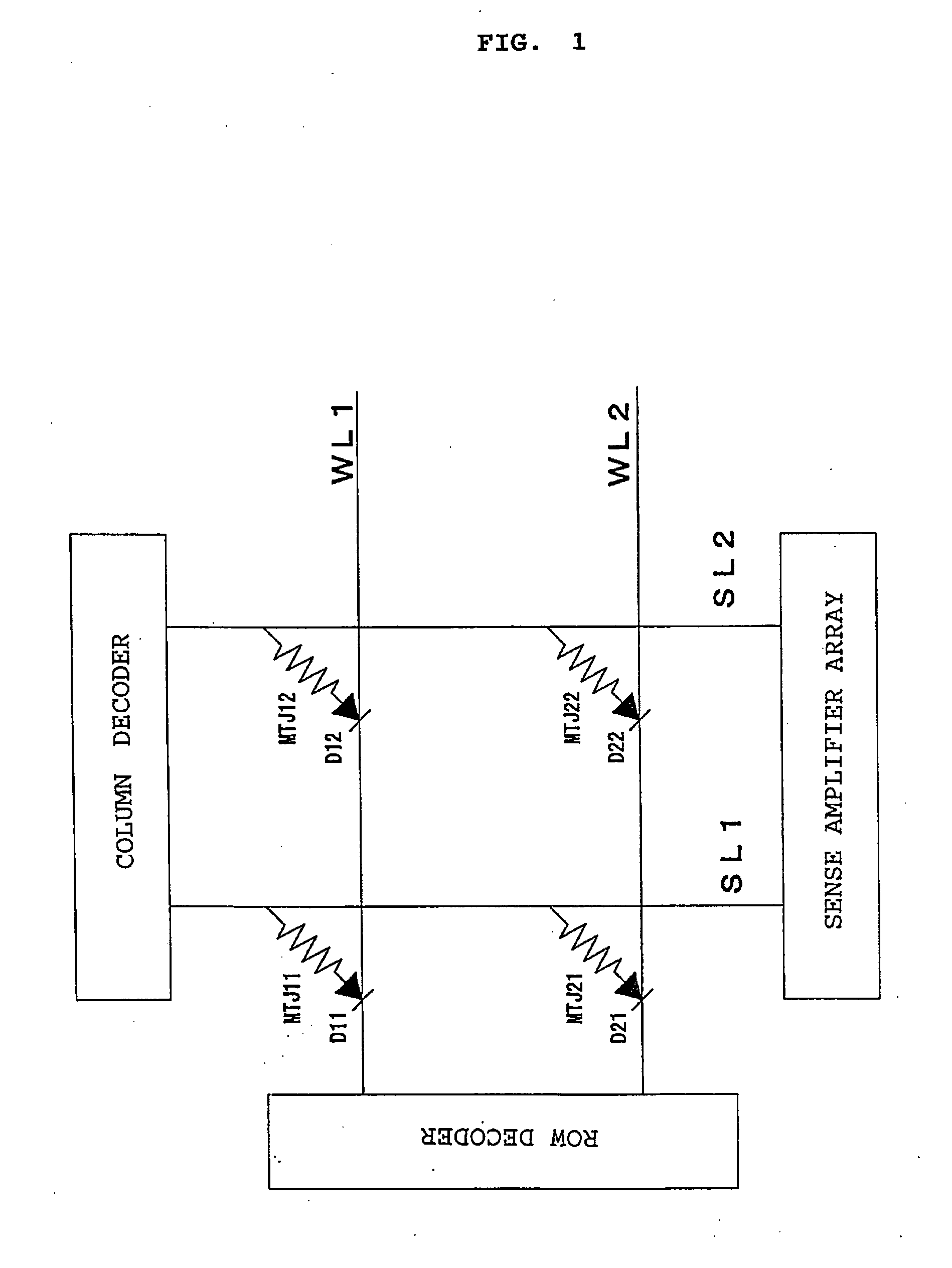

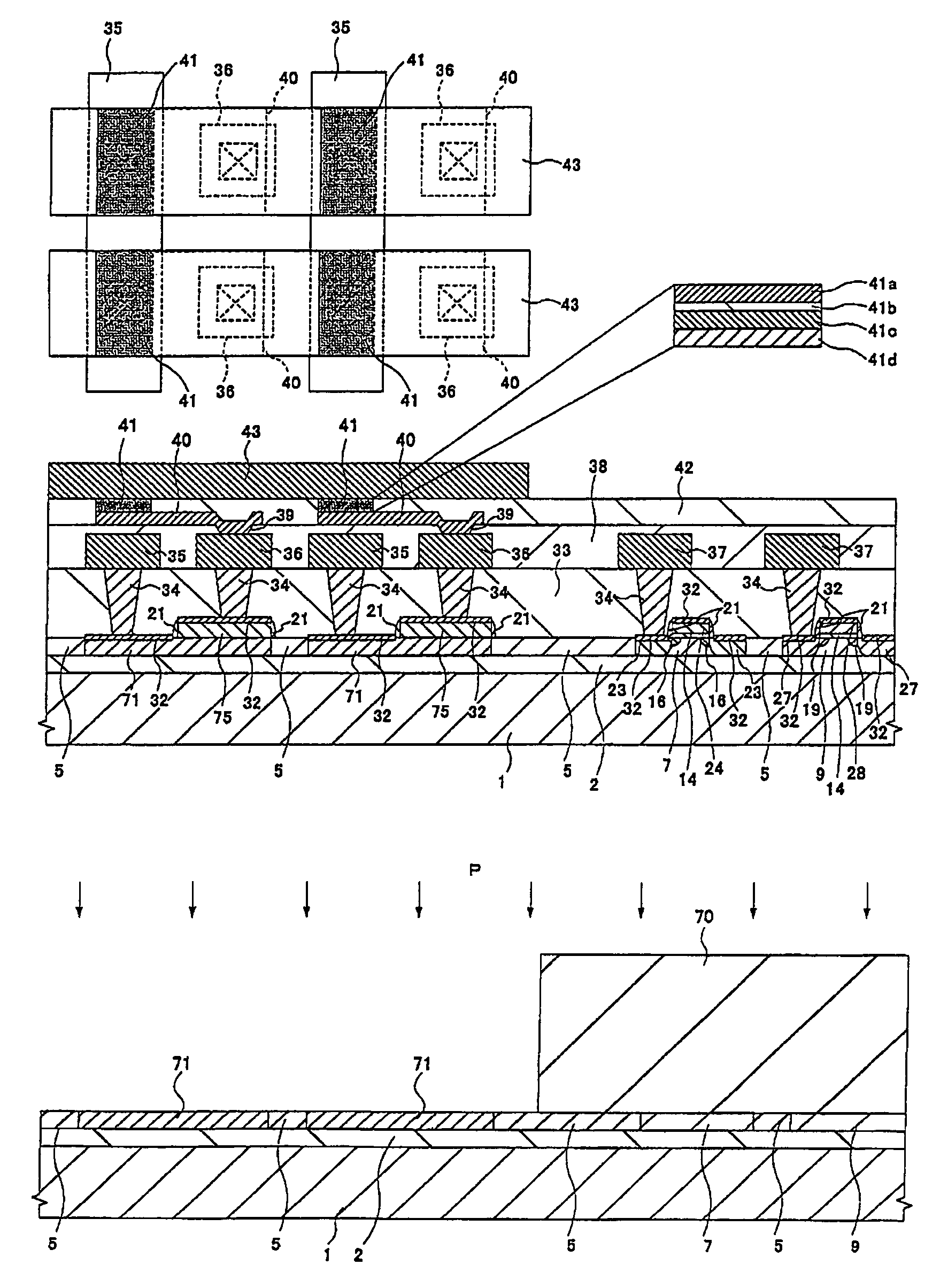

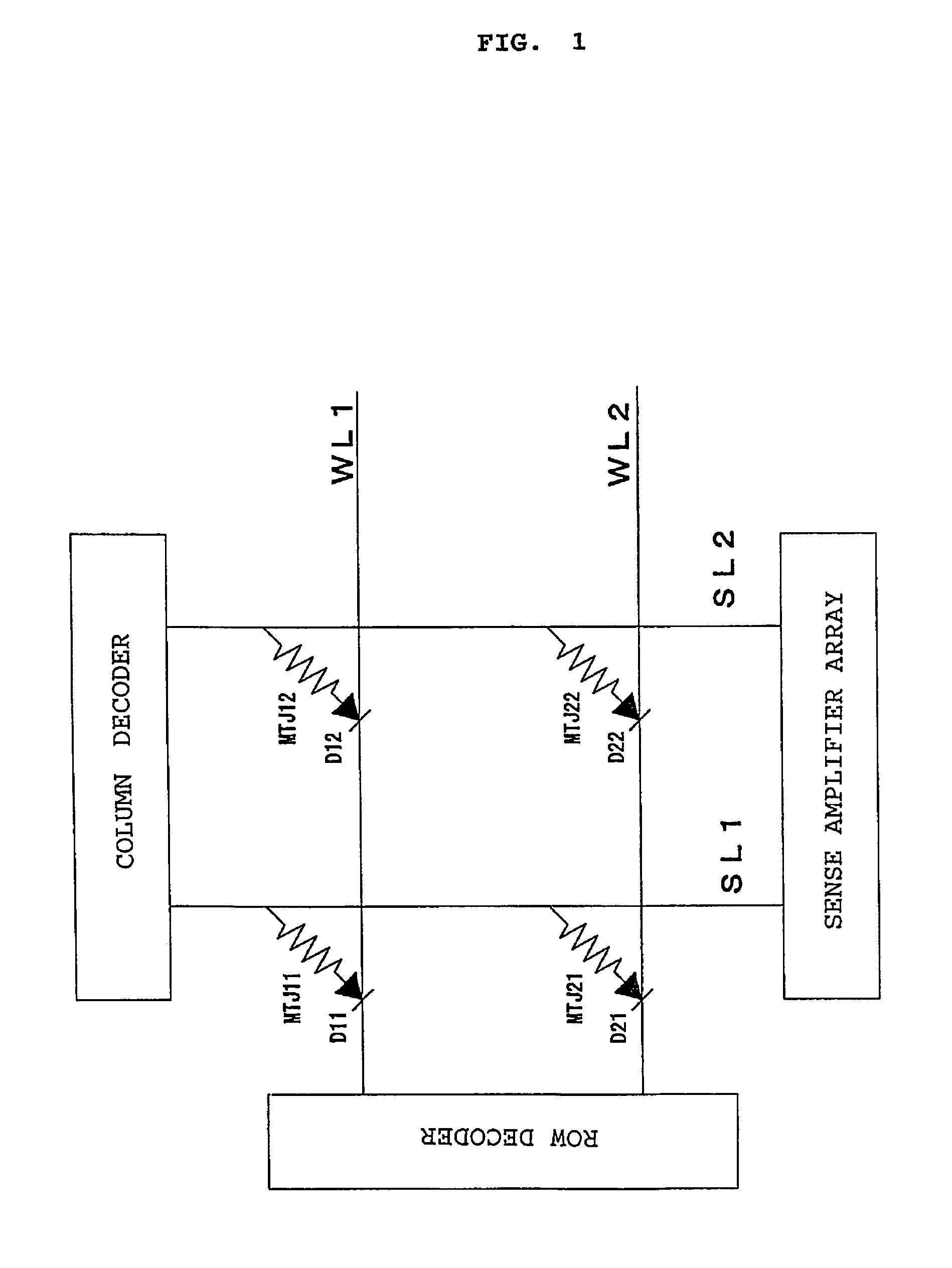

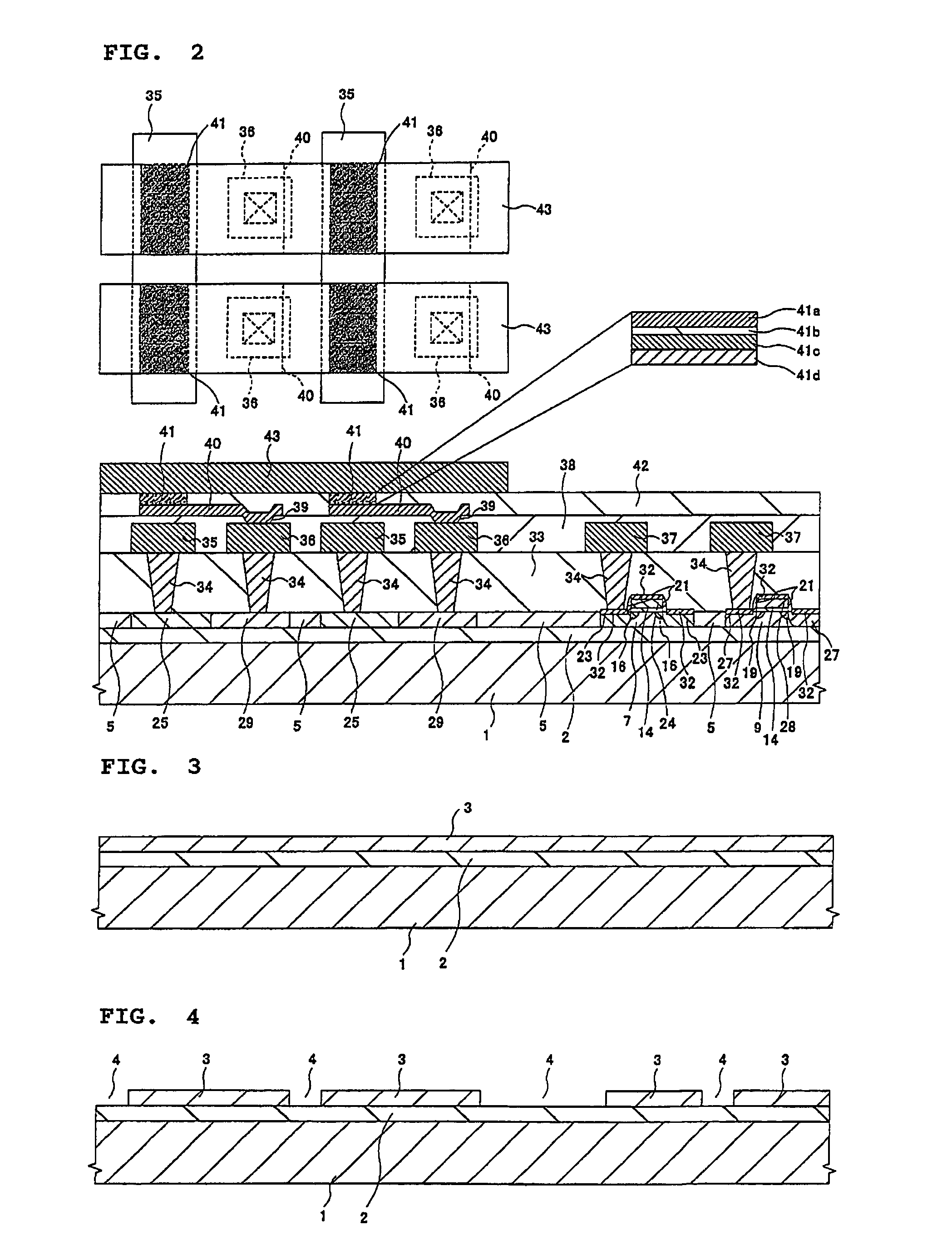

Nonvolatile memory cell and nonvolatile semiconductor memory device

ActiveUS6937505B2Decrease influenceLower on-state resistanceMagnetic-field-controlled resistorsSolid-state devicesResistive elementMOSFET

It is an object of the present invention to make it possible to decrease the on-state resistance of a selection transistor of a memory cell without increasing the whole area of a memory cell array and accelerate and stabilize the reading operation of data stored in the memory cell. Therefore, a plurality of variable resistive elements capable of storing information in accordance with a change of electrical resistances is included, one ends of the variable resistive elements are connected each other, and an electrode of a selection element constituted by a MOSFET or diode element for selecting the variable resistive elements in common is connected with one end of each of the variable resistive elements to constitute a memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

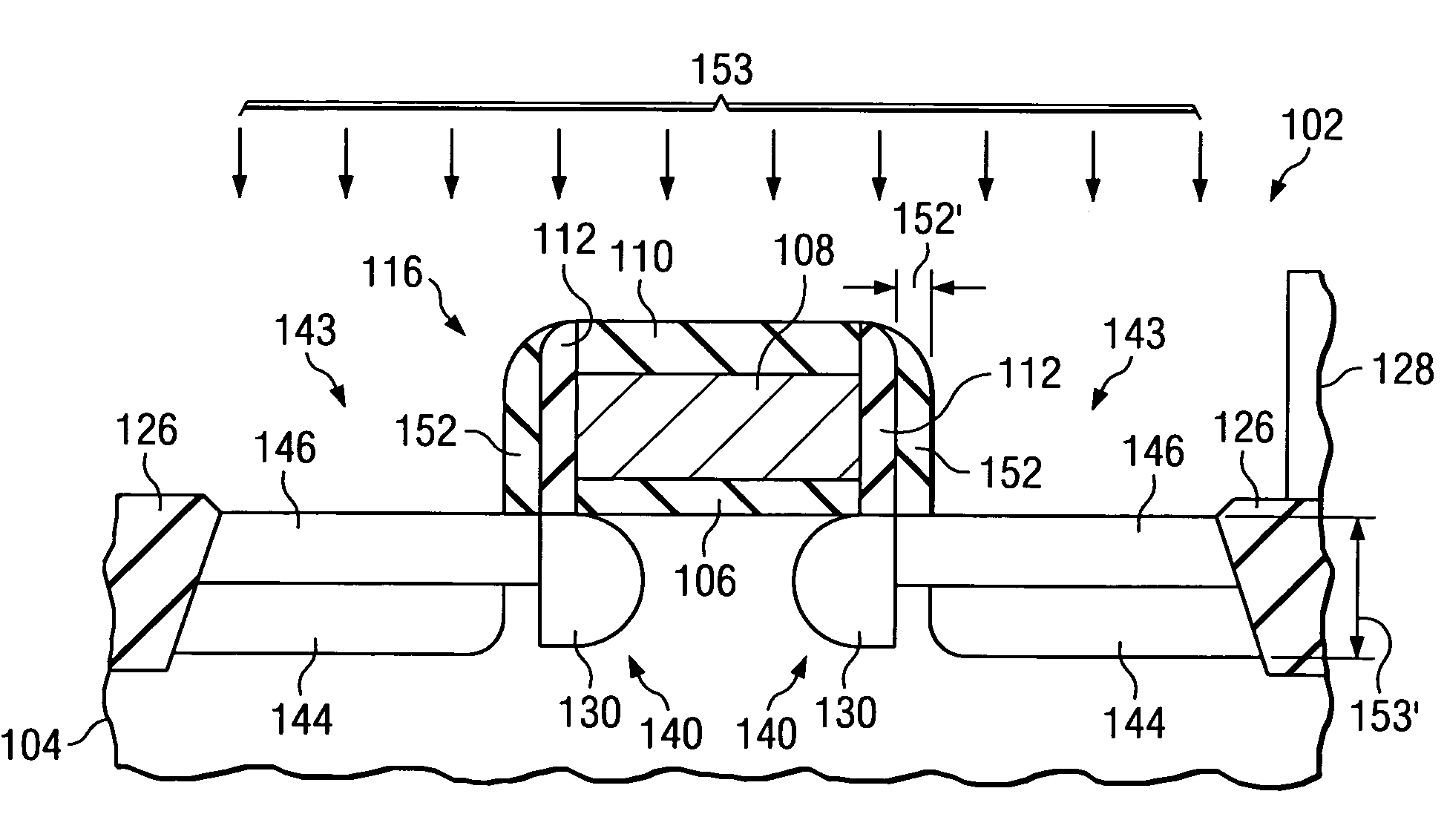

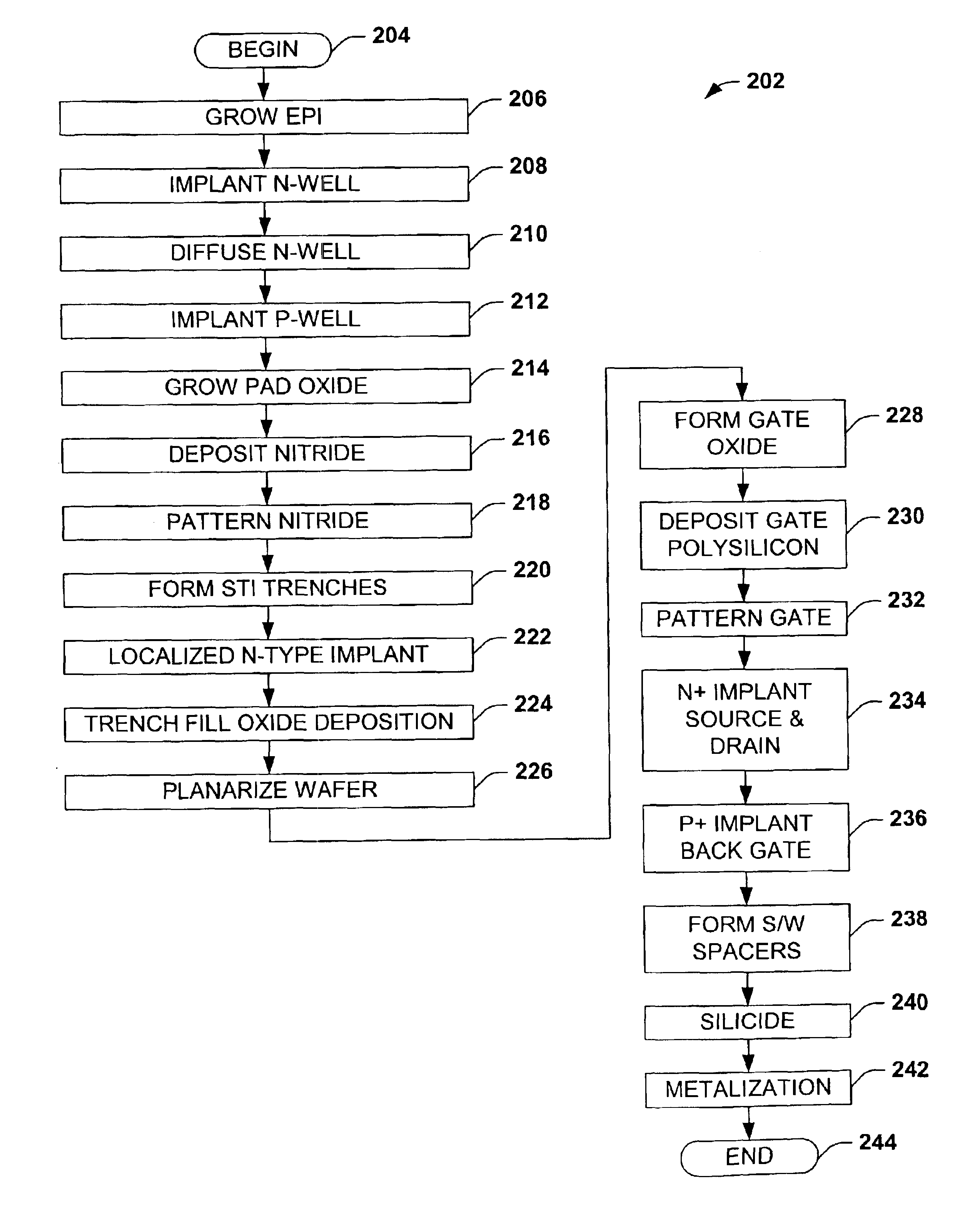

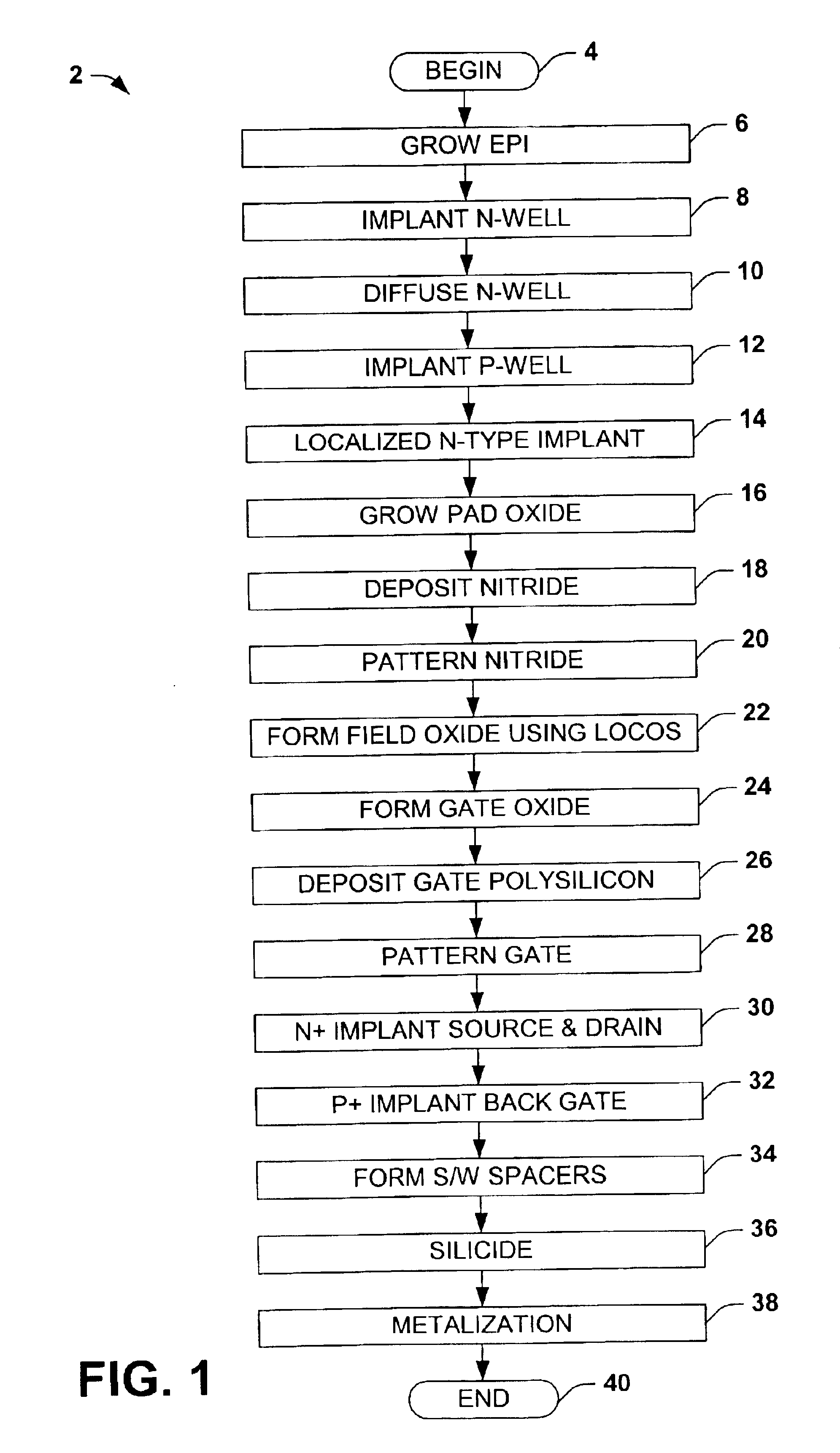

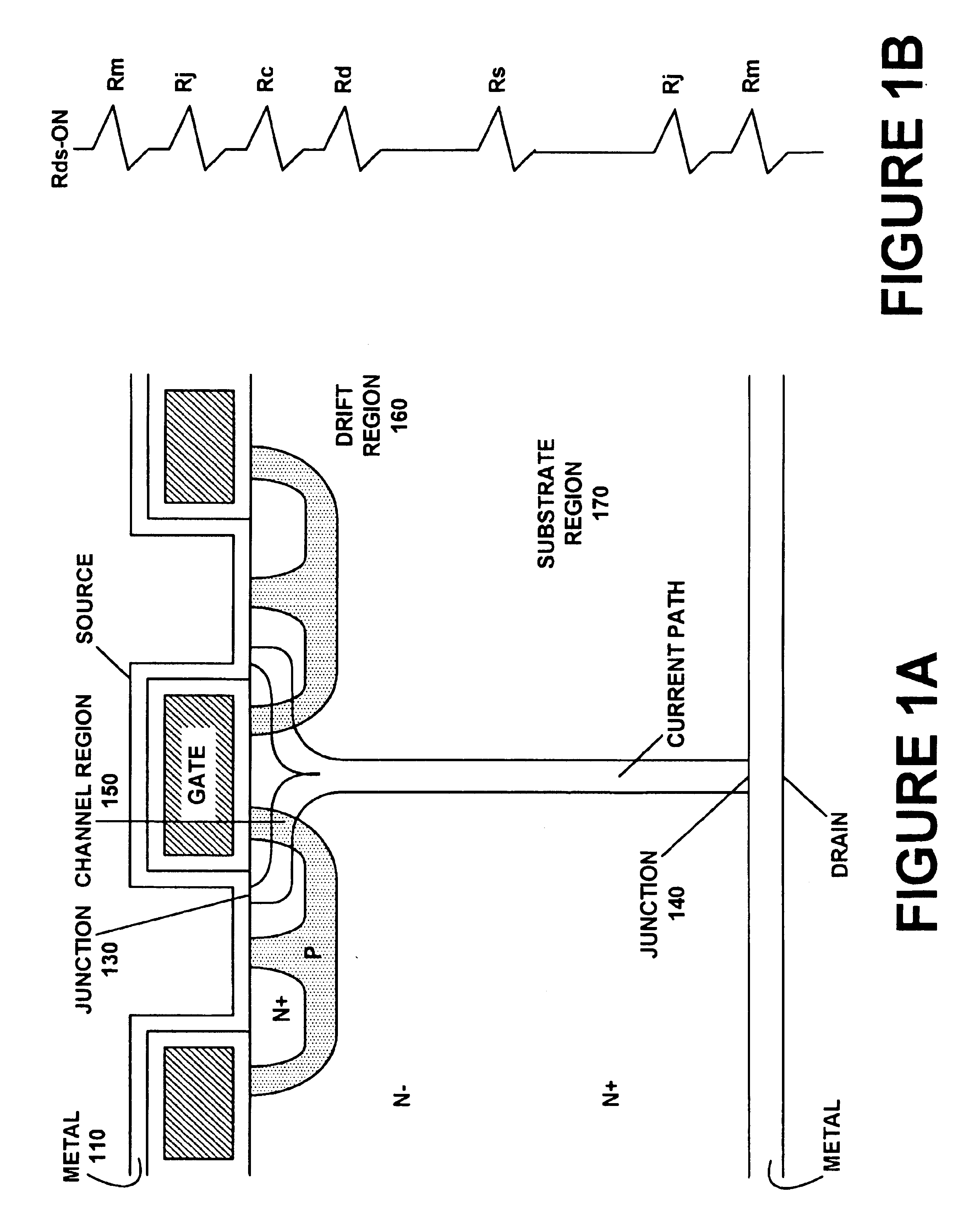

LDMOS transistors and methods for making the same

InactiveUS6900101B2Reduce or inhibit current flow constrictionLower on-state resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantDielectric

LDMOS transistor devices and fabrication methods are provided, in which additional dopants are provided to region of a substrate near a thick dielectric between the channel and the drain to reduce device resistance without significantly impacting breakdown voltage. The extra dopants are added by implantation prior to formation of the thick dielectric, such as before oxidizing silicon in a LOCOS process or following trench formation and before filling the trench in an STI process.

Owner:TEXAS INSTR INC

Group III nitride semiconductor device, production method therefor, power converter

ActiveUS20110068371A1Lower on-state resistanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceHeterojunction

Provided is an HEMT exhibiting a normally-off characteristic and low on-state resistance, which includes a first carrier transport layer; two separate second carrier transport layers formed of undoped GaN and provided on two separate regions of the first carrier transport layer; and carrier supply layers formed of AlGaN and respectively provided on the two separate second carrier transport layers. The second carrier transport layers and the carrier supply layers are respectively formed through crystal growth on the first carrier transport layer. The heterojunction interface between the second carrier transport layer and the carrier supply layer exhibits high flatness, and virtually no growth-associated impurities are incorporated in the vicinity of the heterojunction interface. Therefore, reduction in mobility of 2DEG is prevented, and on-state resistance is reduced.

Owner:TOYODA GOSEI CO LTD

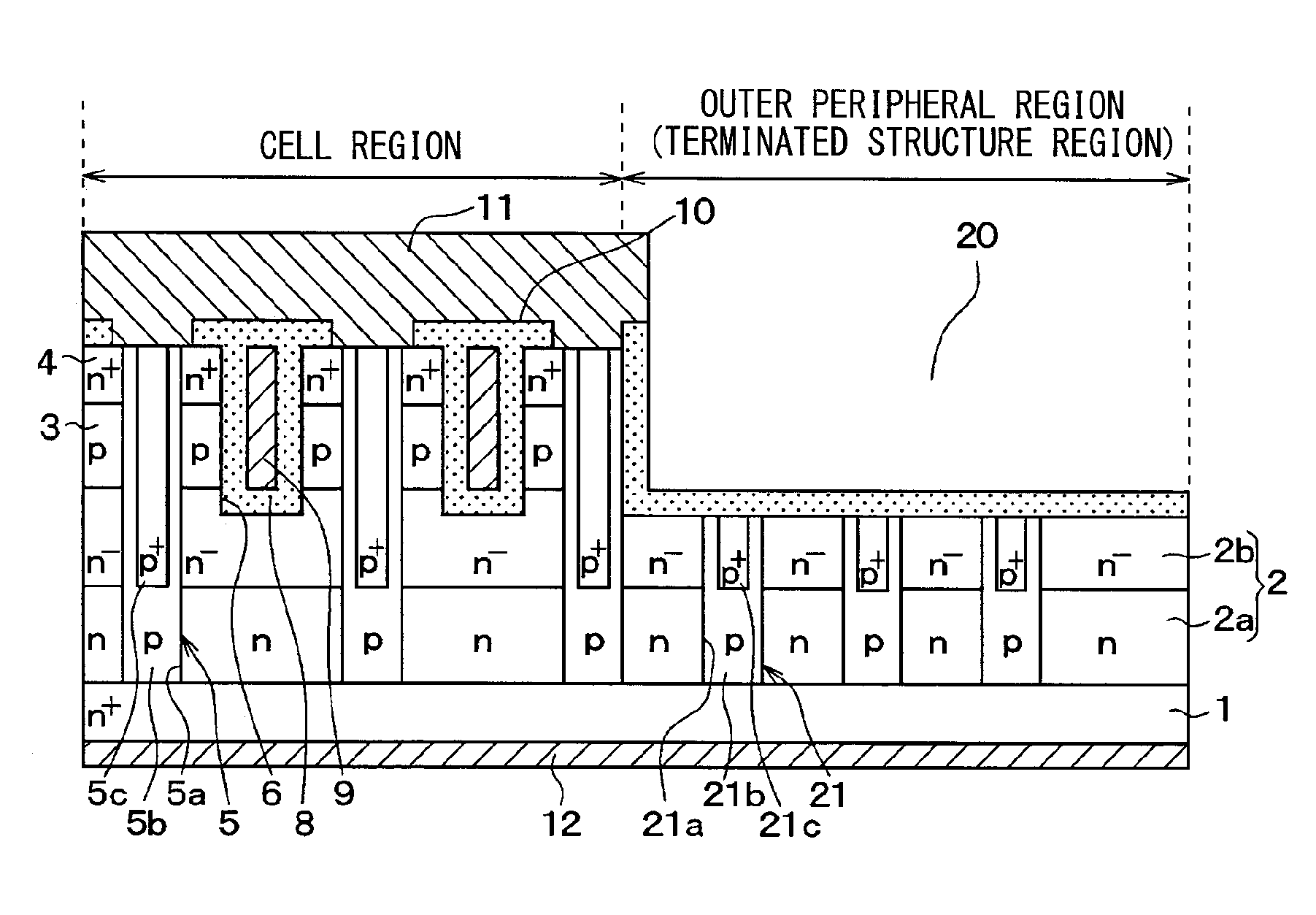

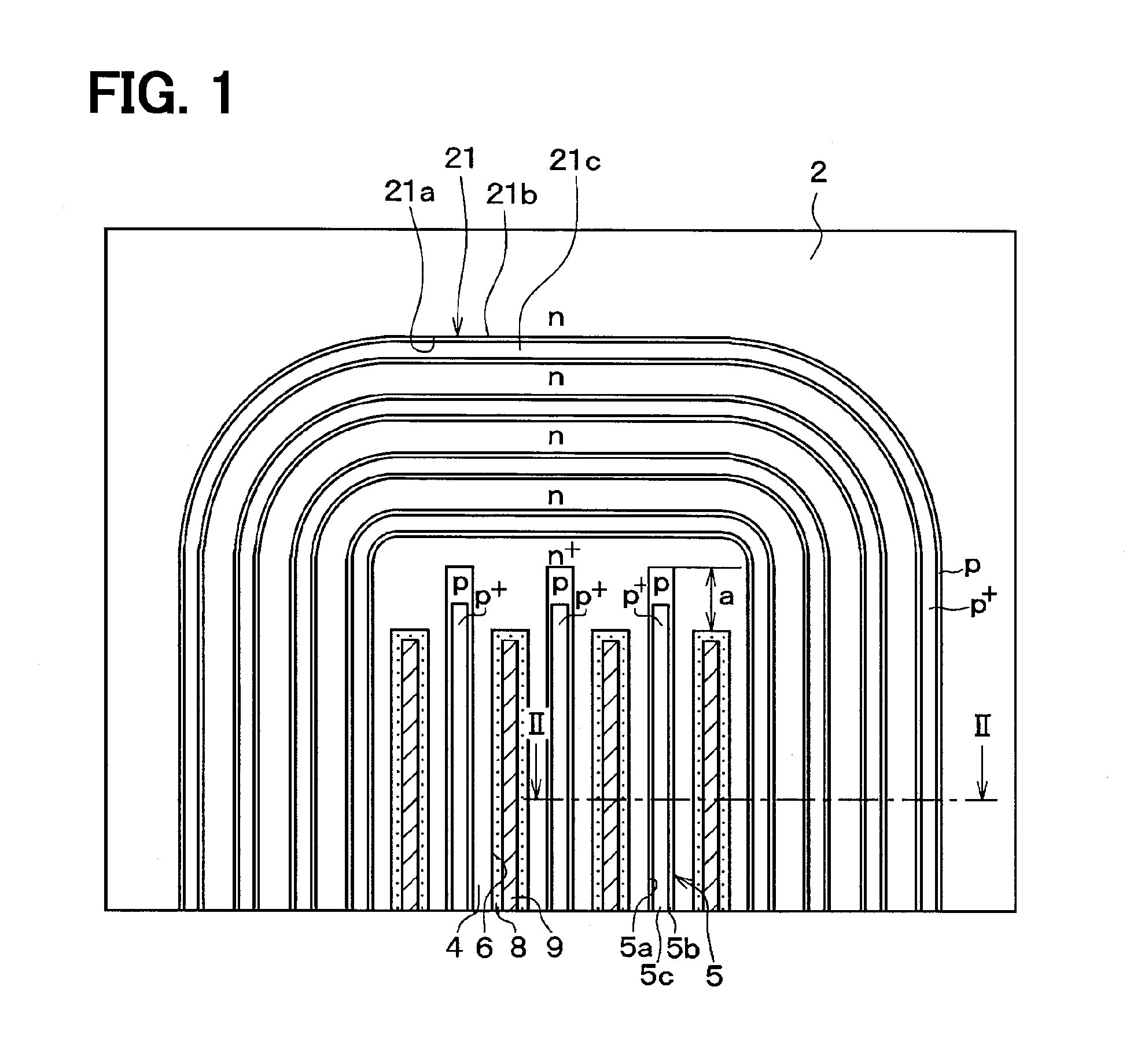

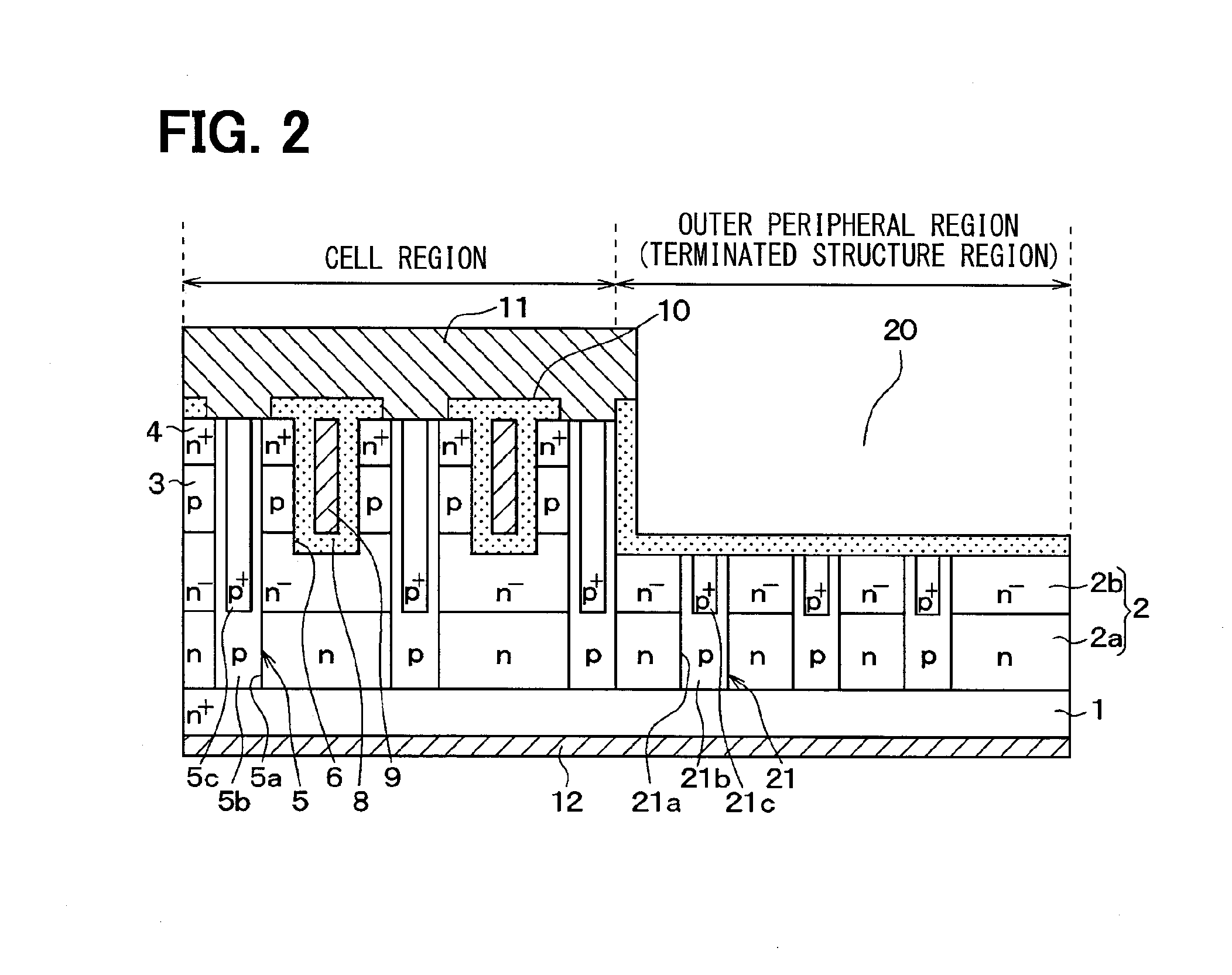

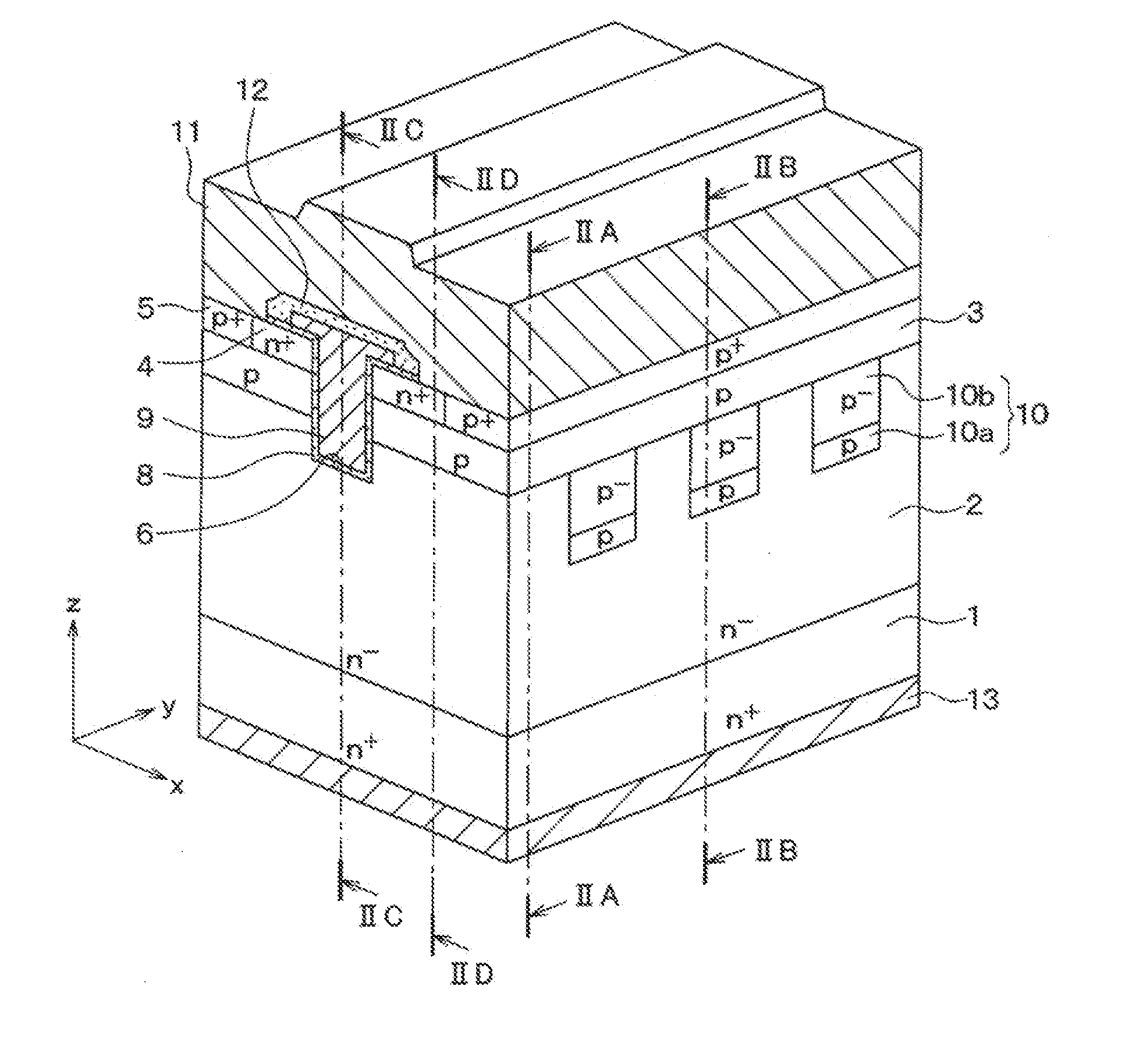

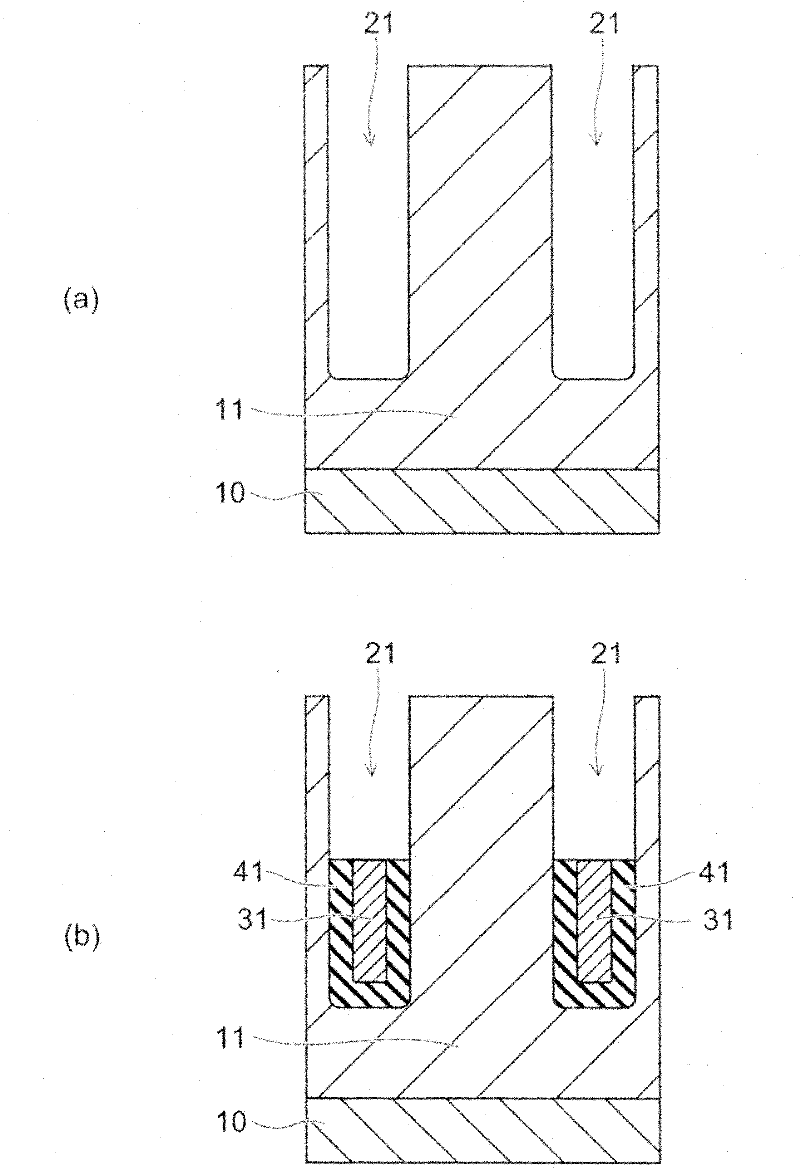

Silicon carbide semiconductor device and method for producing the same

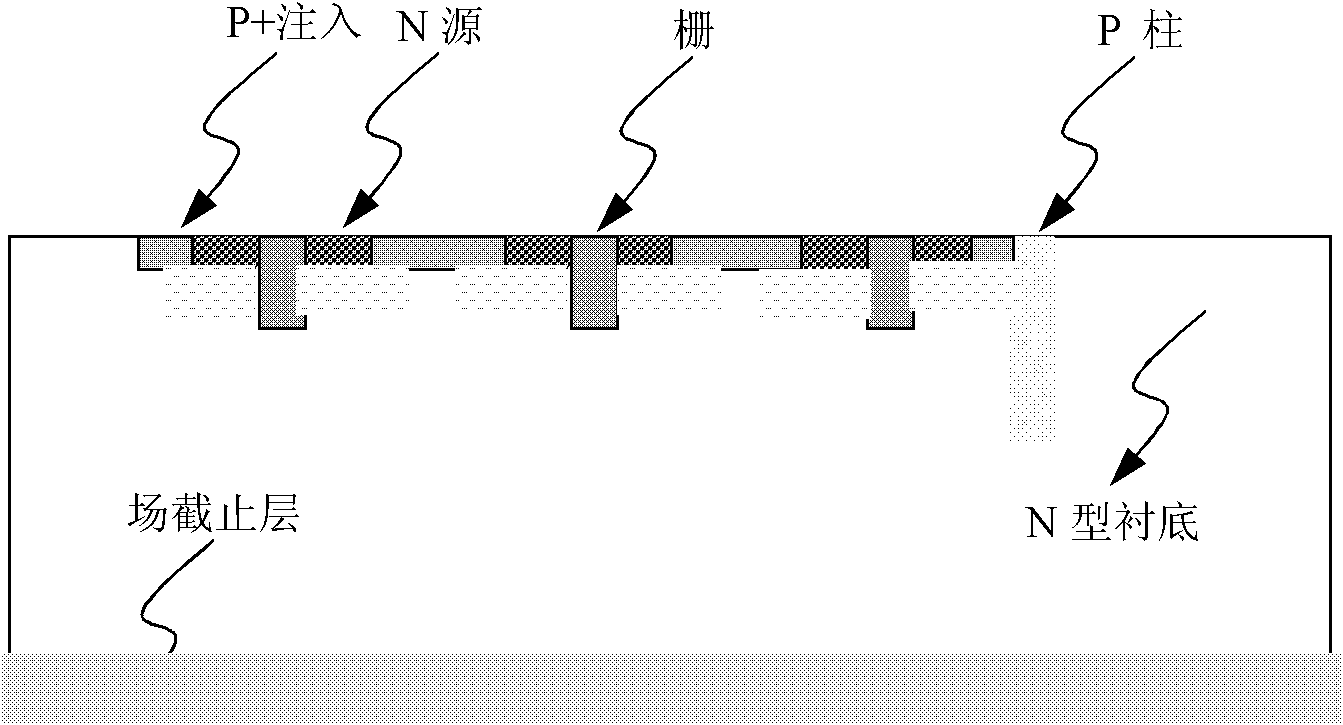

ActiveUS20150115286A1Simple processLower on-state resistanceSemiconductor/solid-state device manufacturingDiodeHigh concentrationCell region

An SiC semiconductor device has a p type region including a low concentration region and a high concentration region filled in a trench formed in a cell region. A p type column is provided by the low concentration region, and a p+ type deep layer is provided by the high concentration region. Thus, since a SJ structure can be made by the p type column and the n type column provided by the n type drift layer, an on-state resistance can be reduced. As a drain potential can be blocked by the p+ type deep layer, at turnoff, an electric field applied to the gate insulation film can be alleviated and thus breakage of the gate insulation film can be restricted. Therefore, the SiC semiconductor device can realize the reduction of the on-state resistance and the restriction of breakage of the gate insulation film.

Owner:DENSO CORP +1

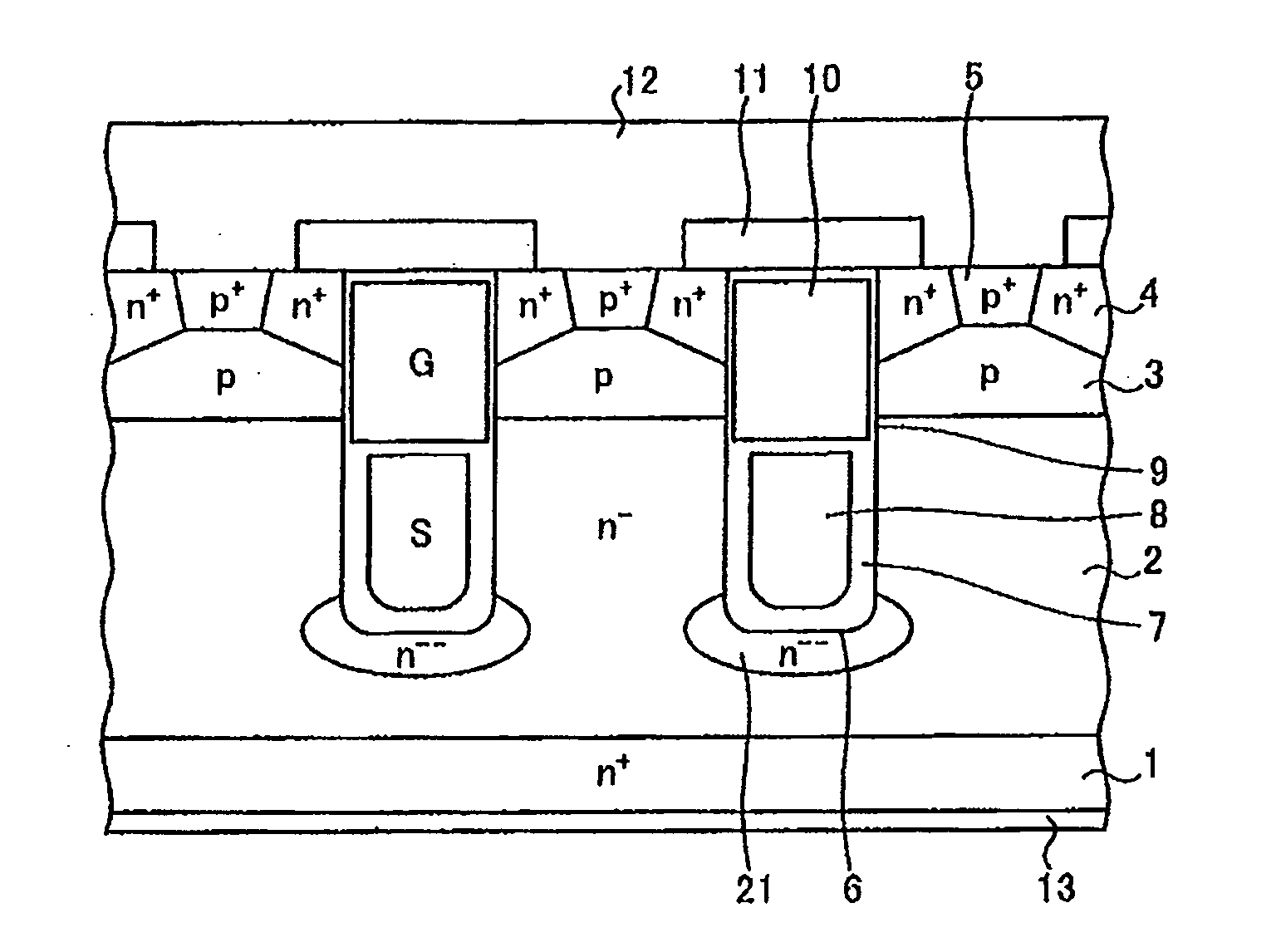

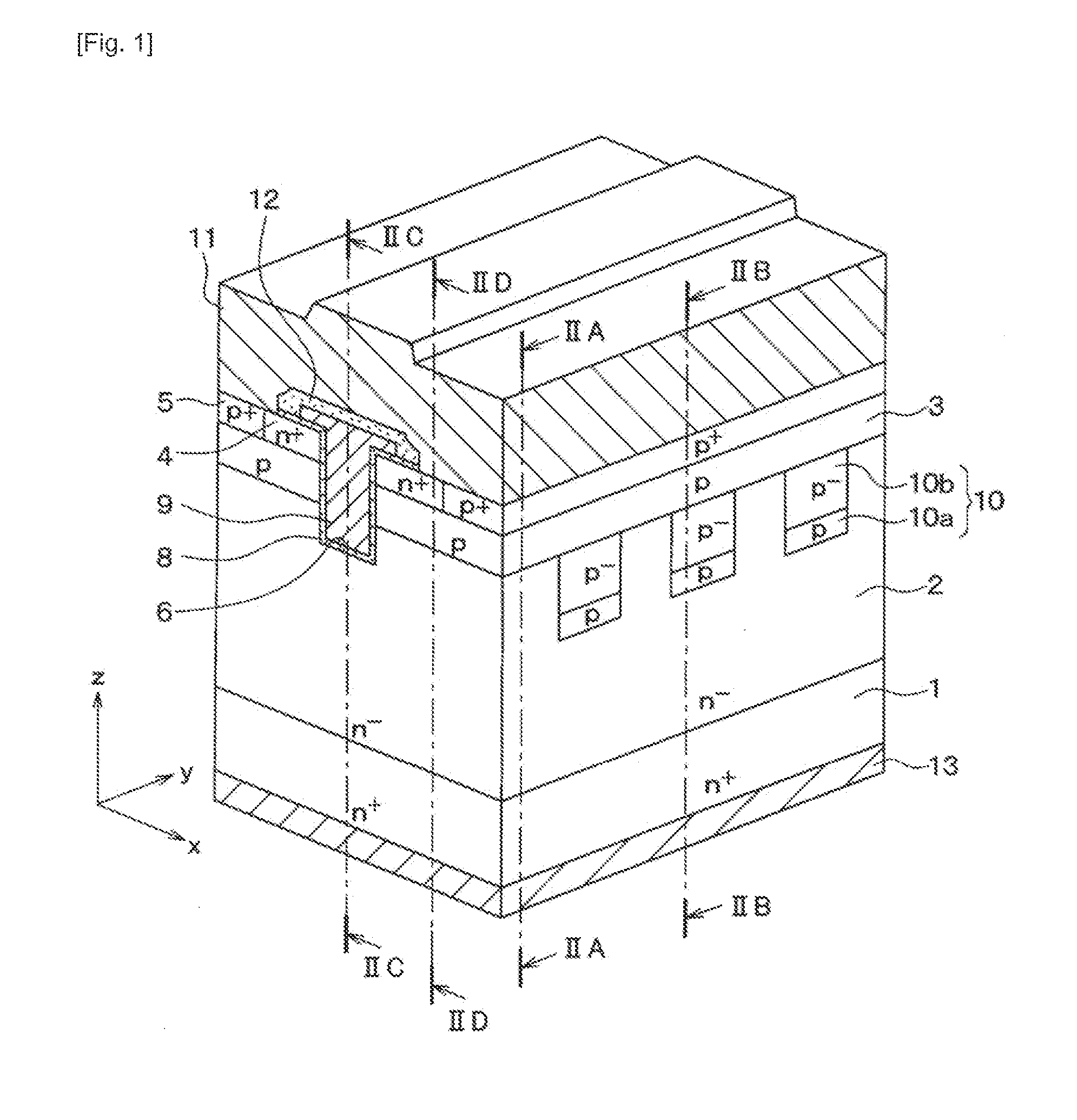

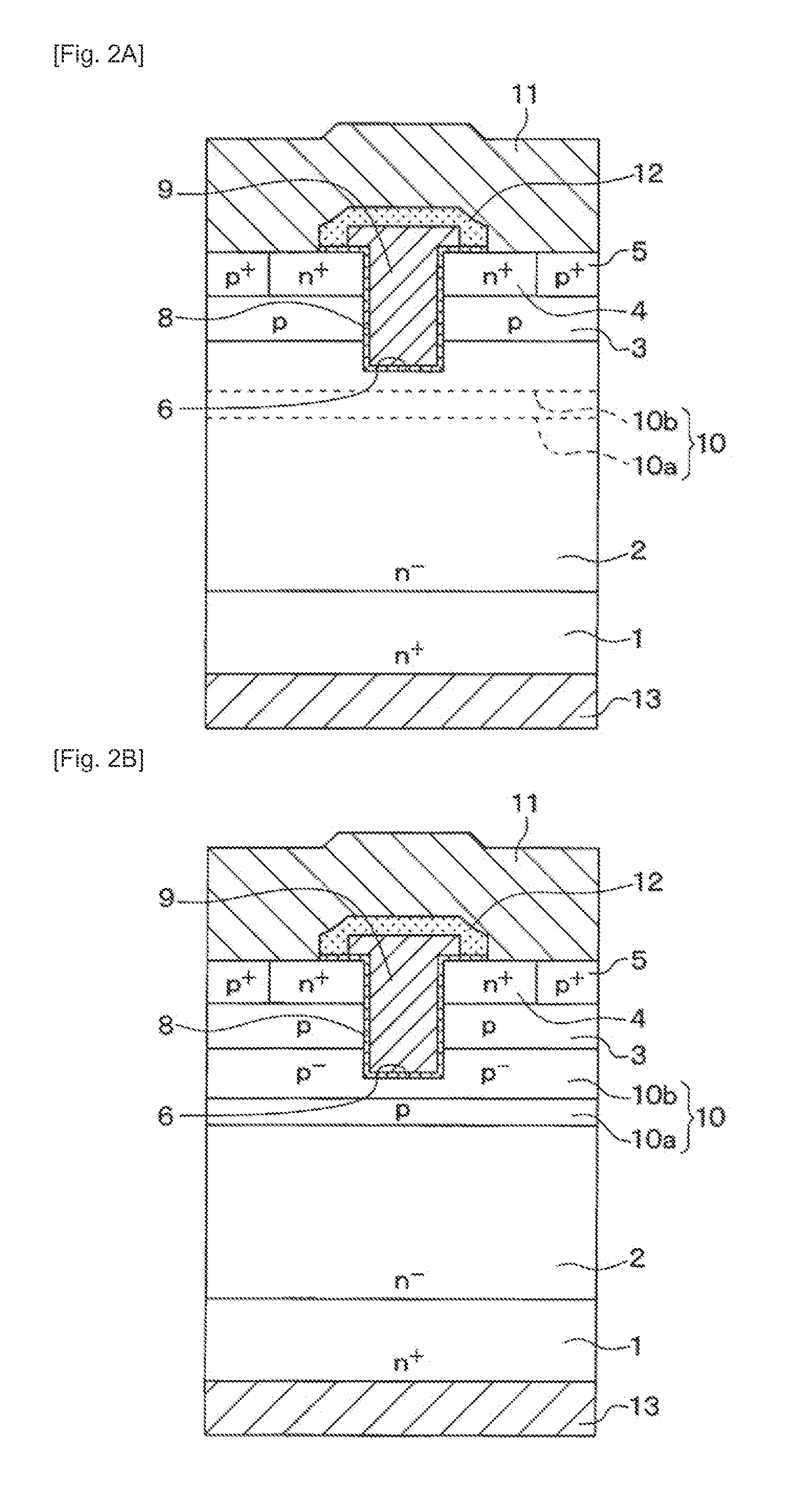

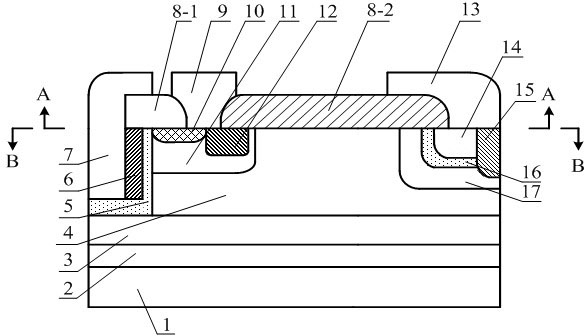

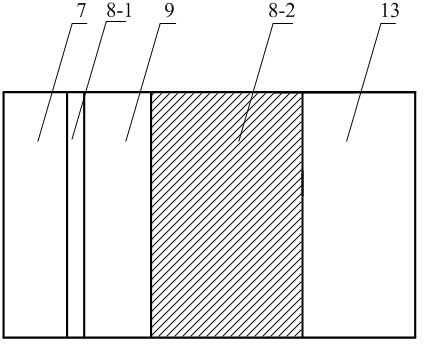

Semiconductor device and the method of manufacturing the same

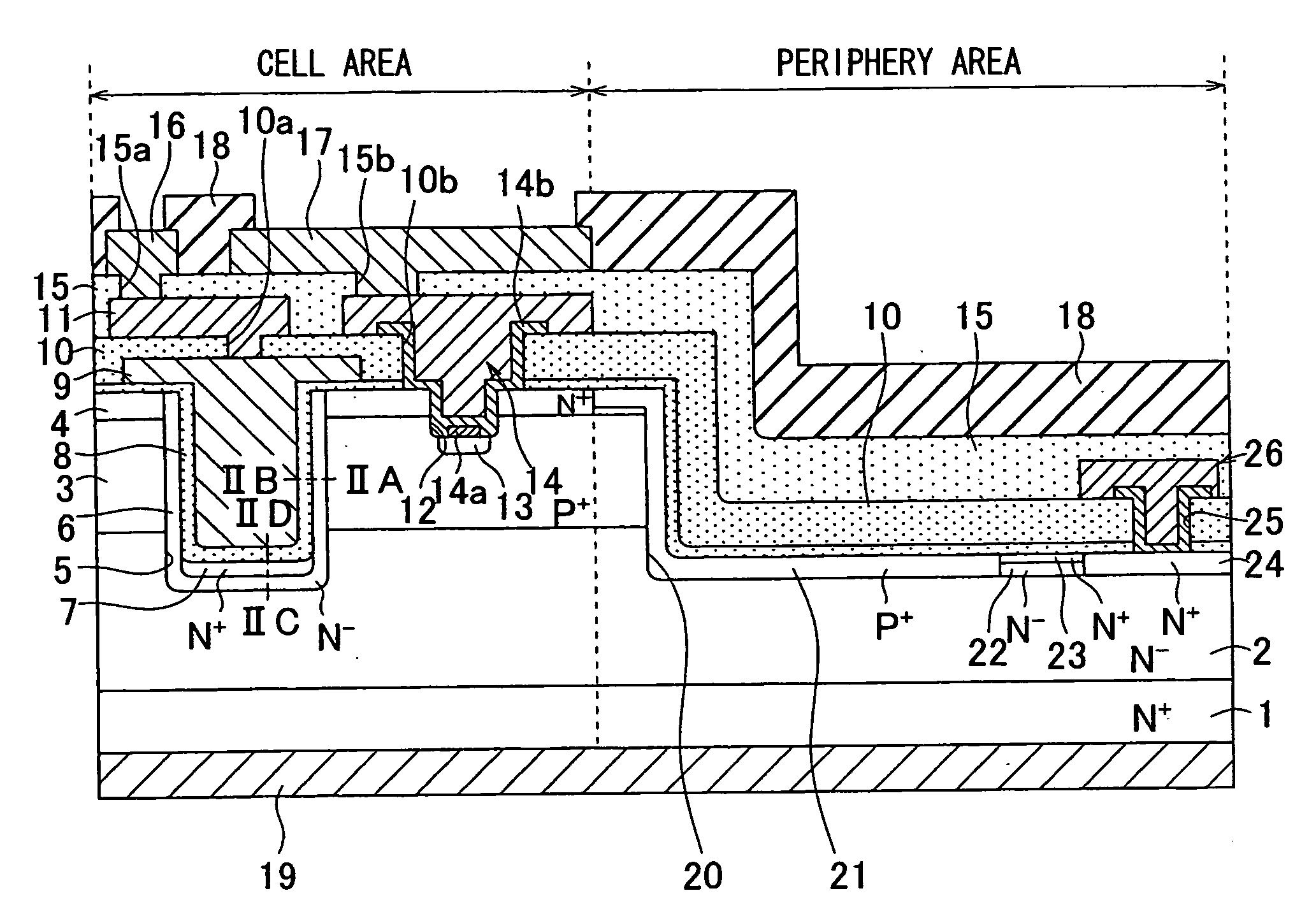

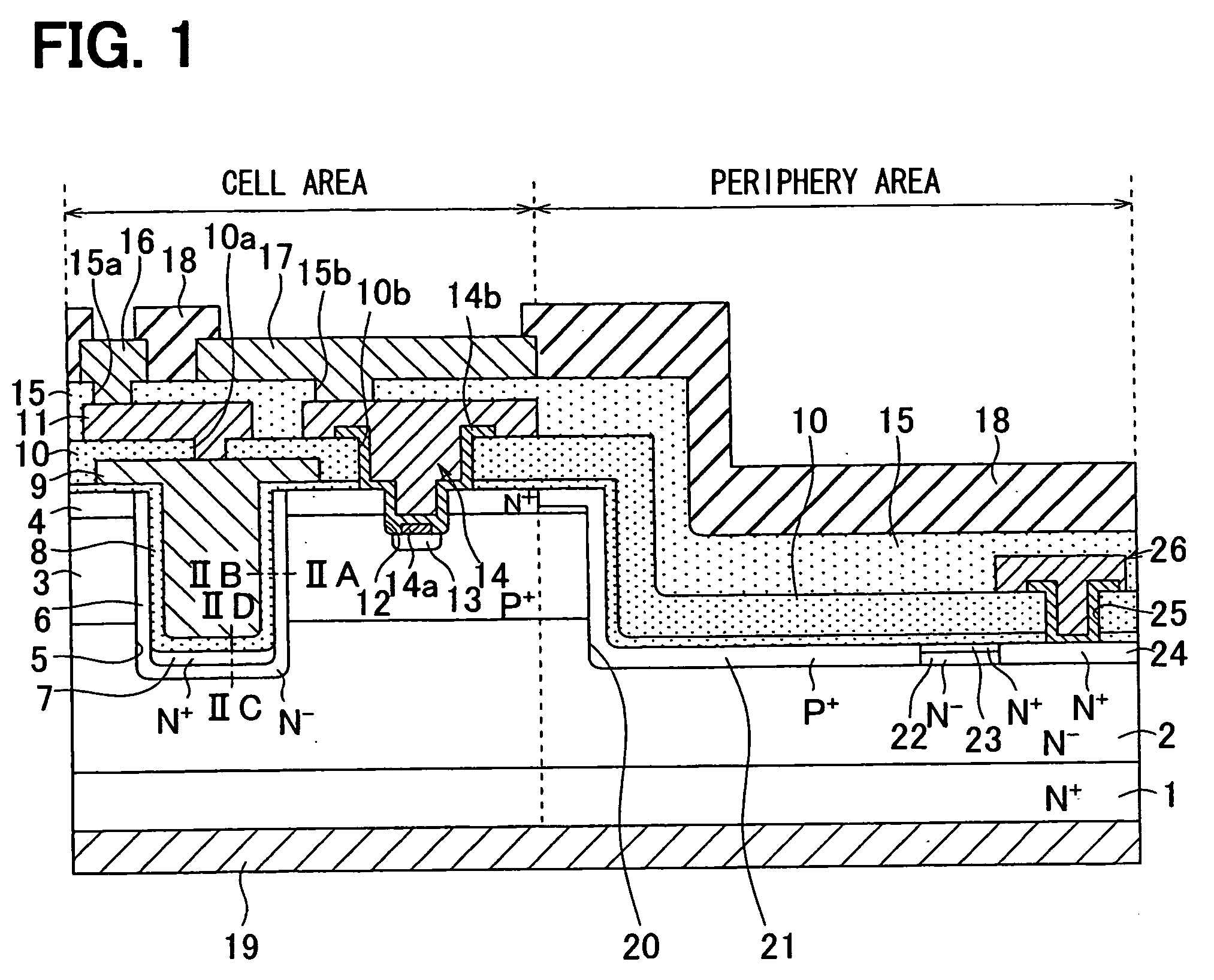

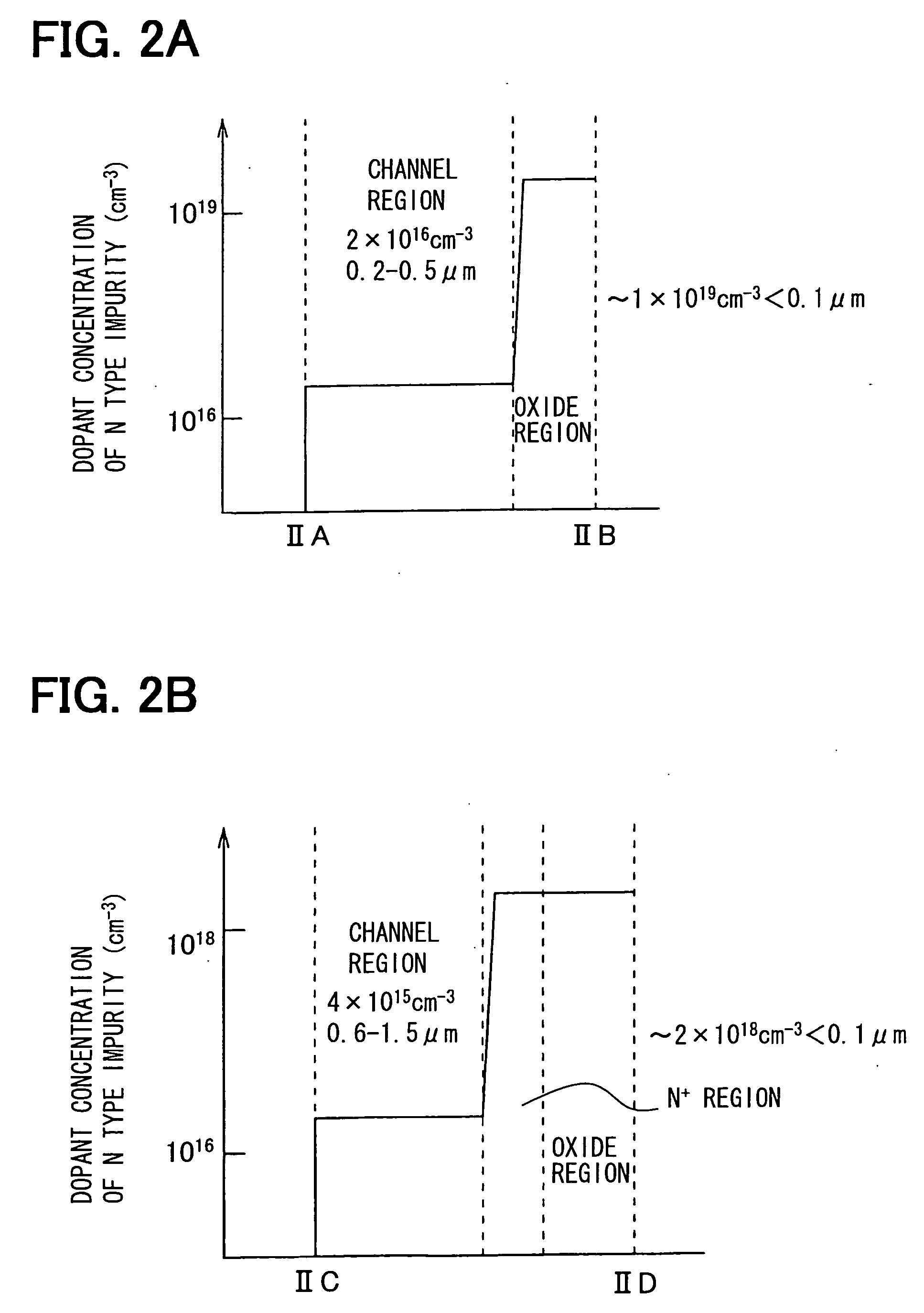

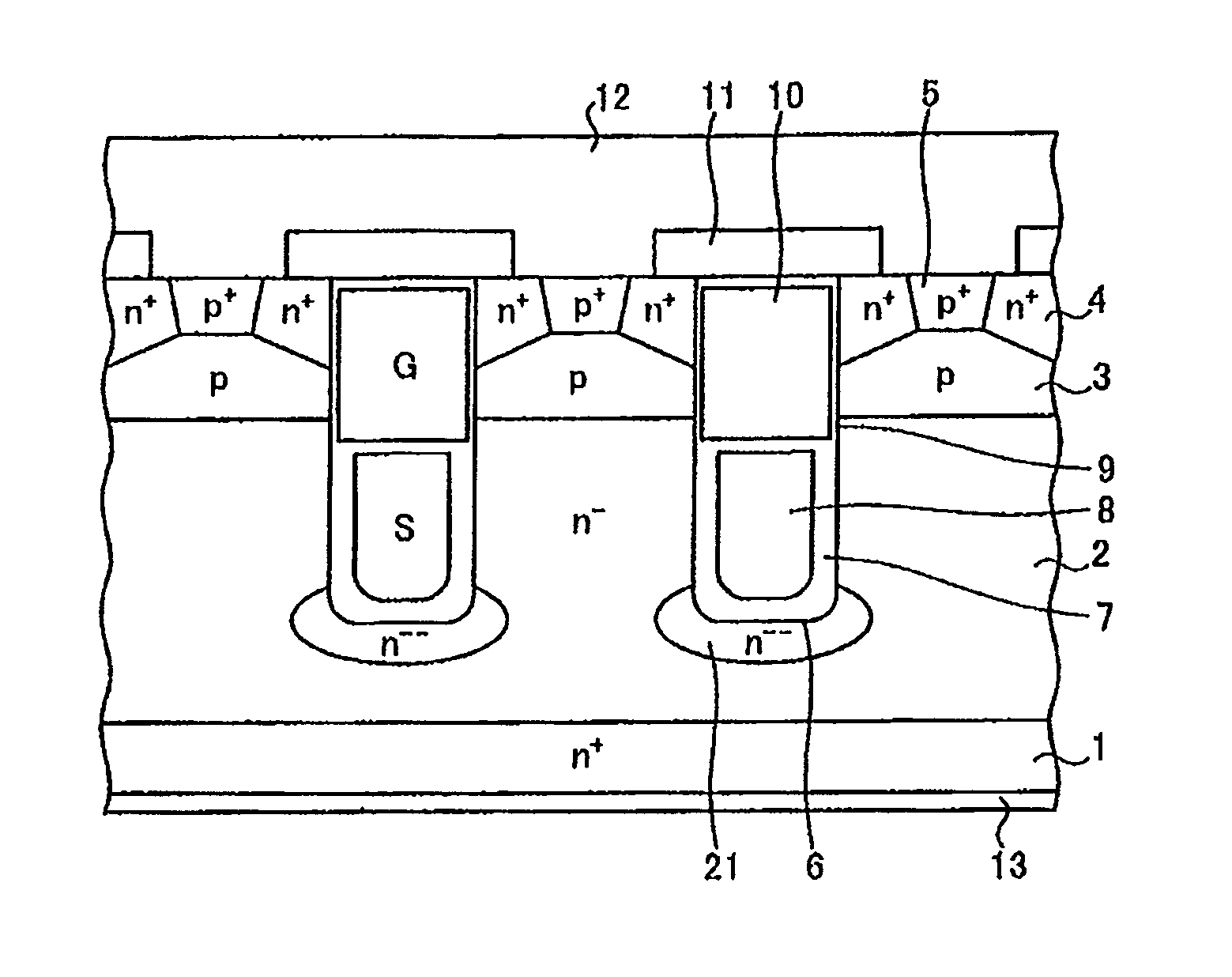

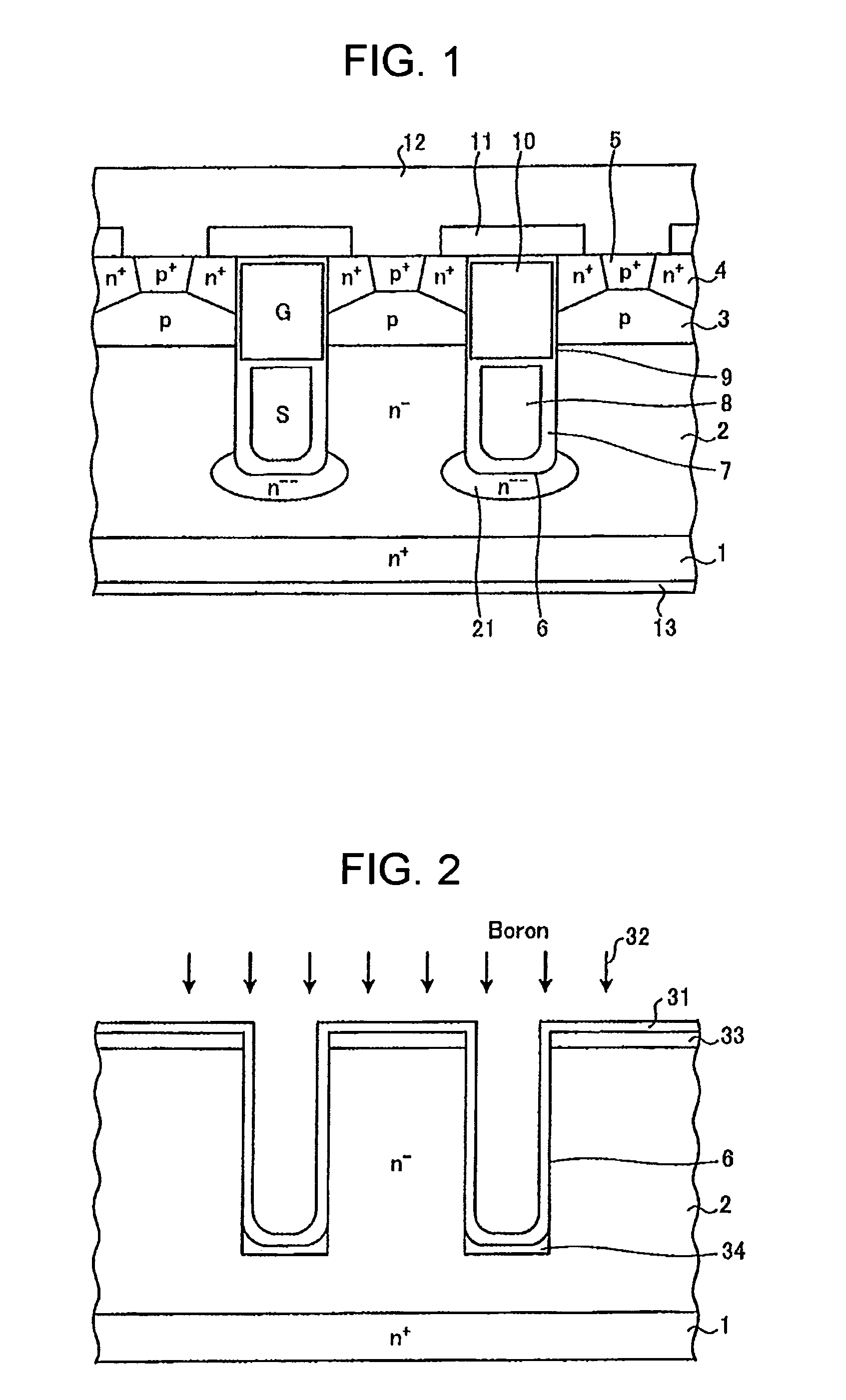

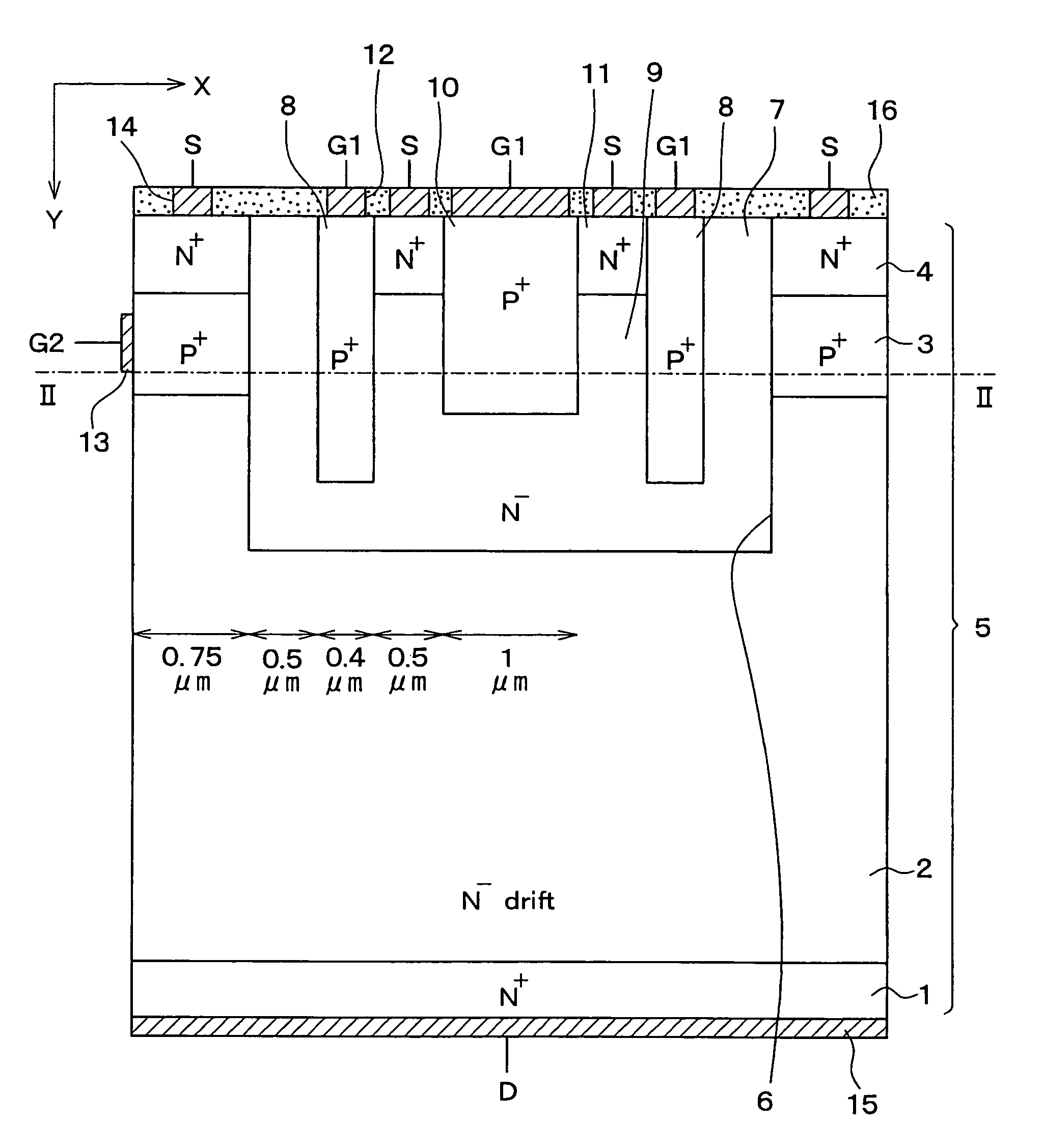

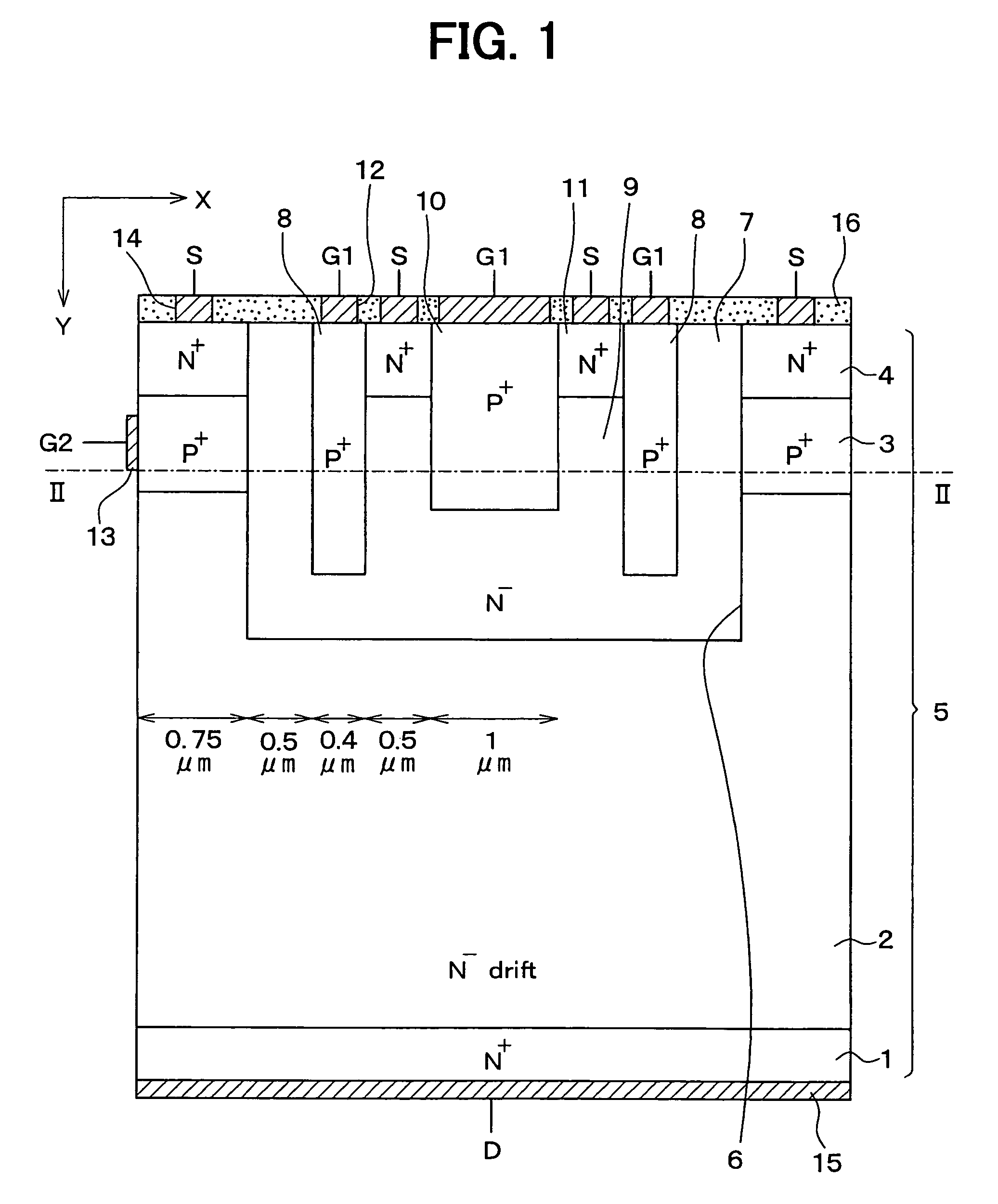

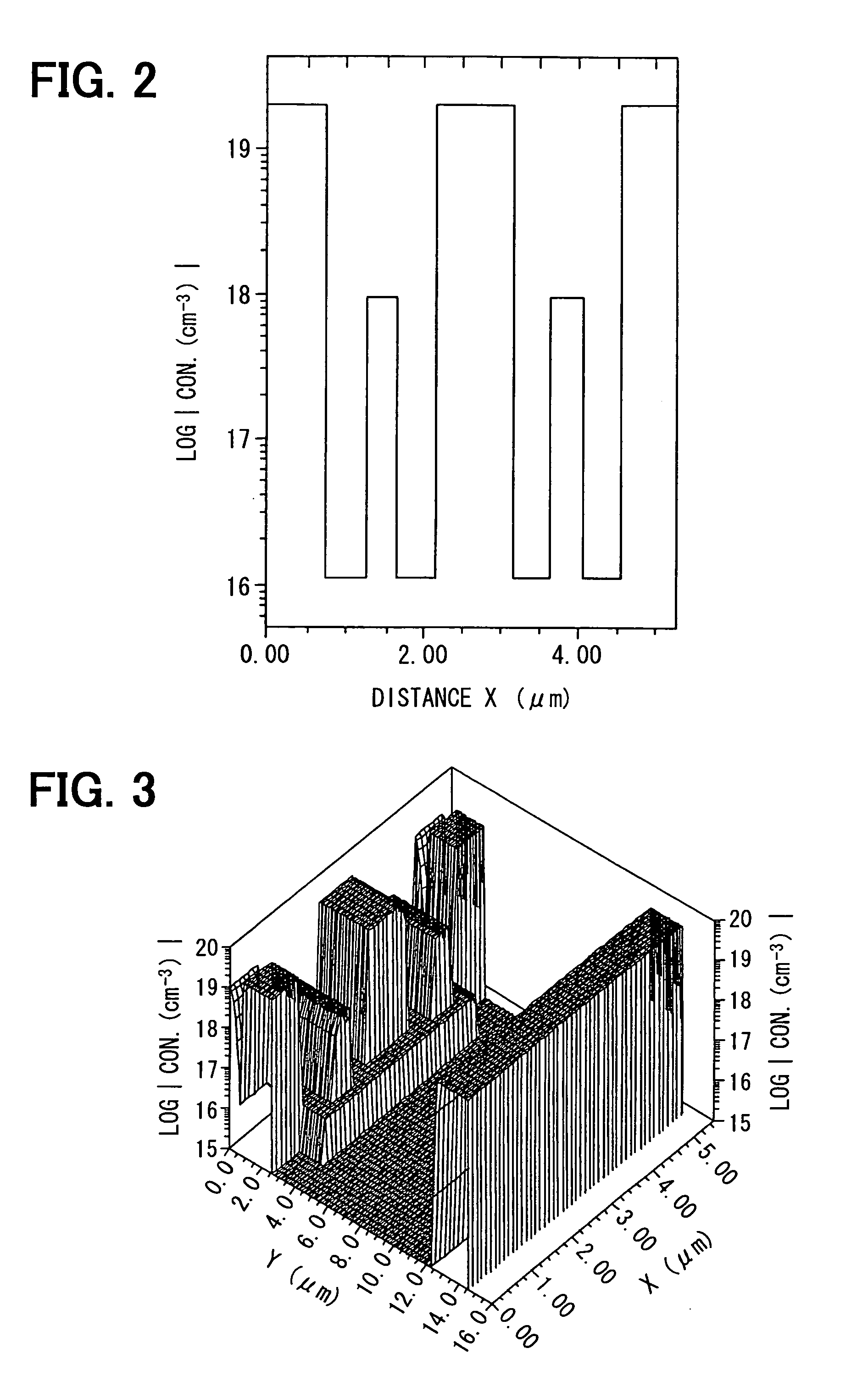

ActiveUS20110303925A1Lower on-state resistanceLow impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionPower semiconductor device

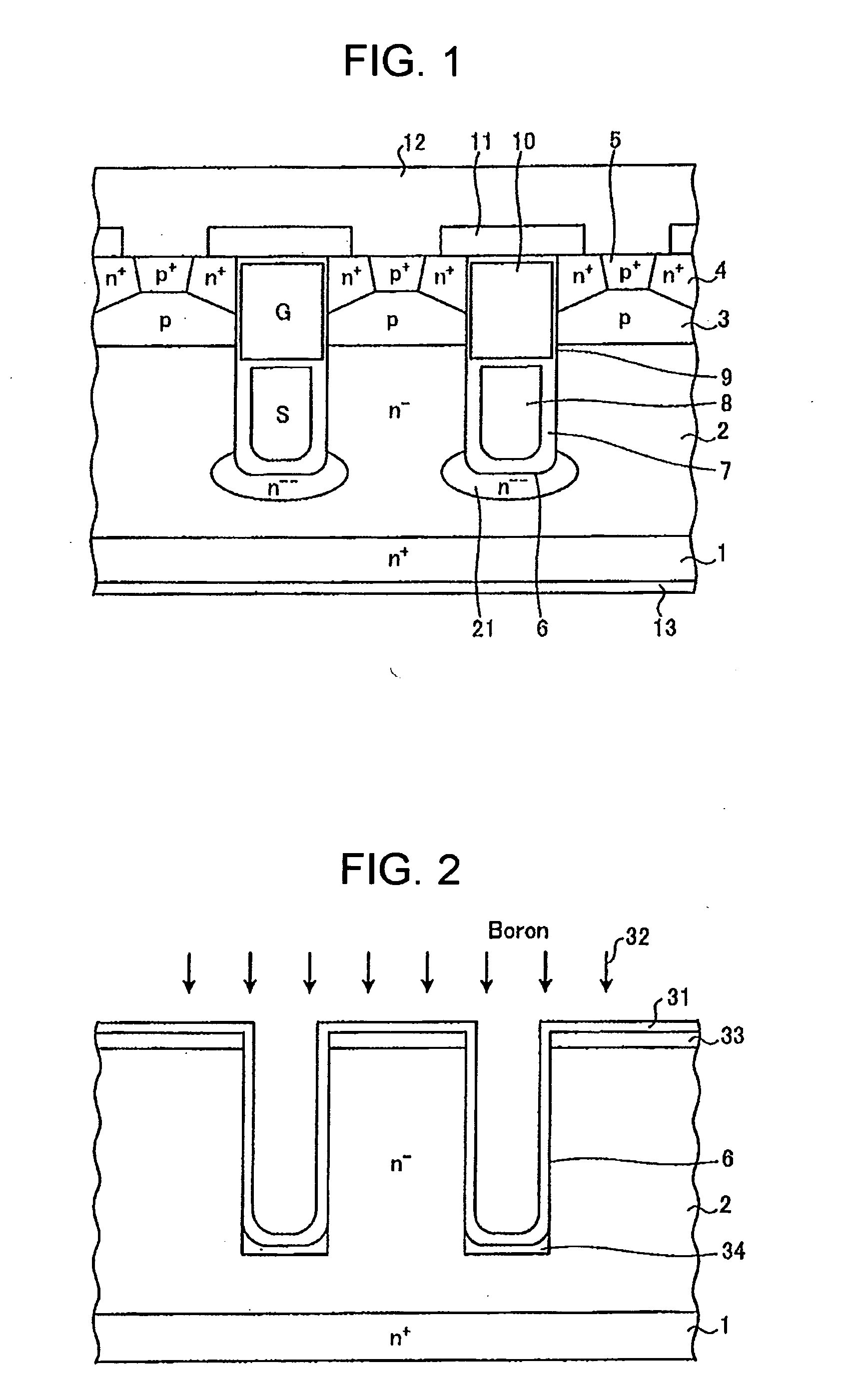

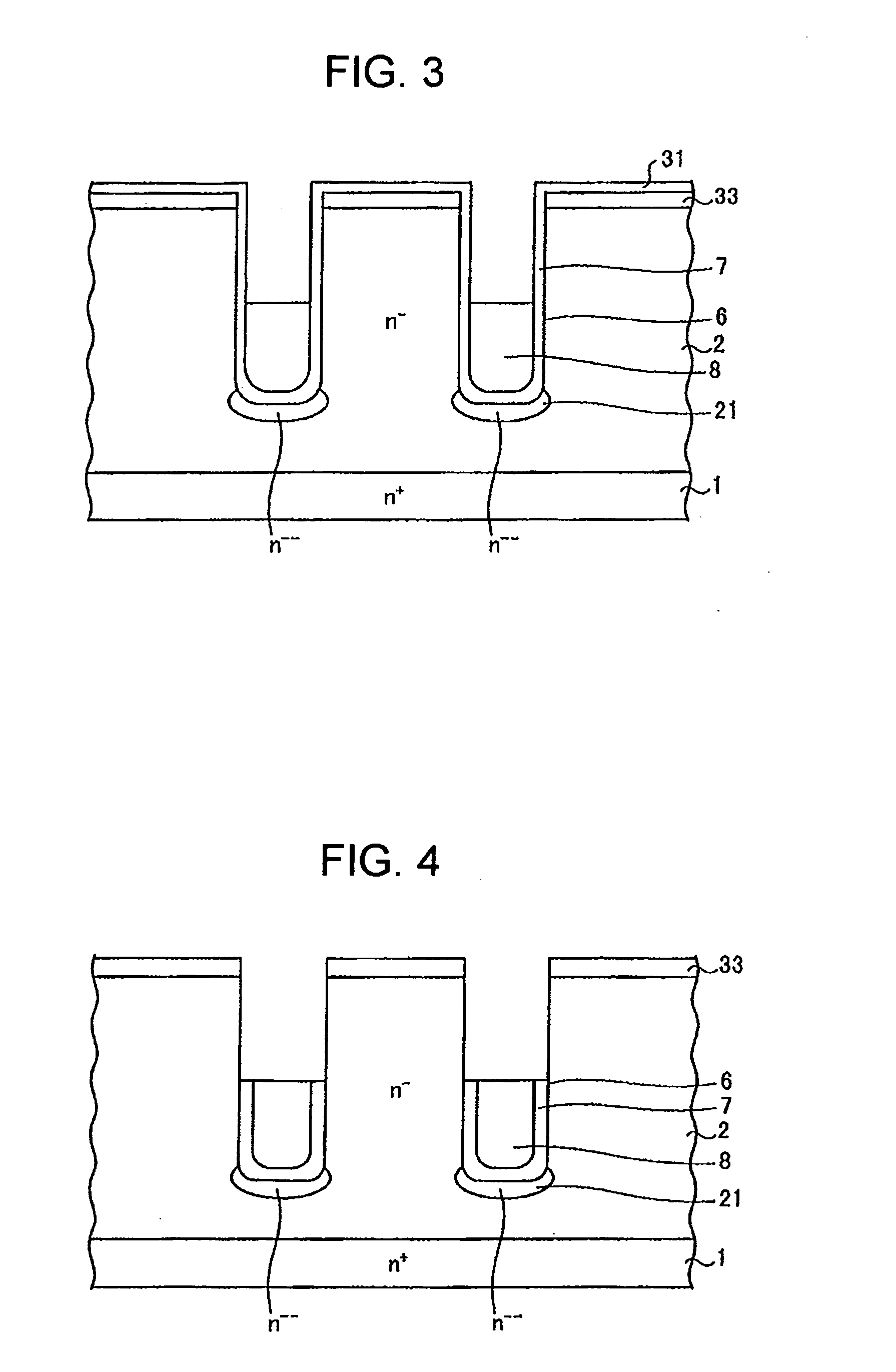

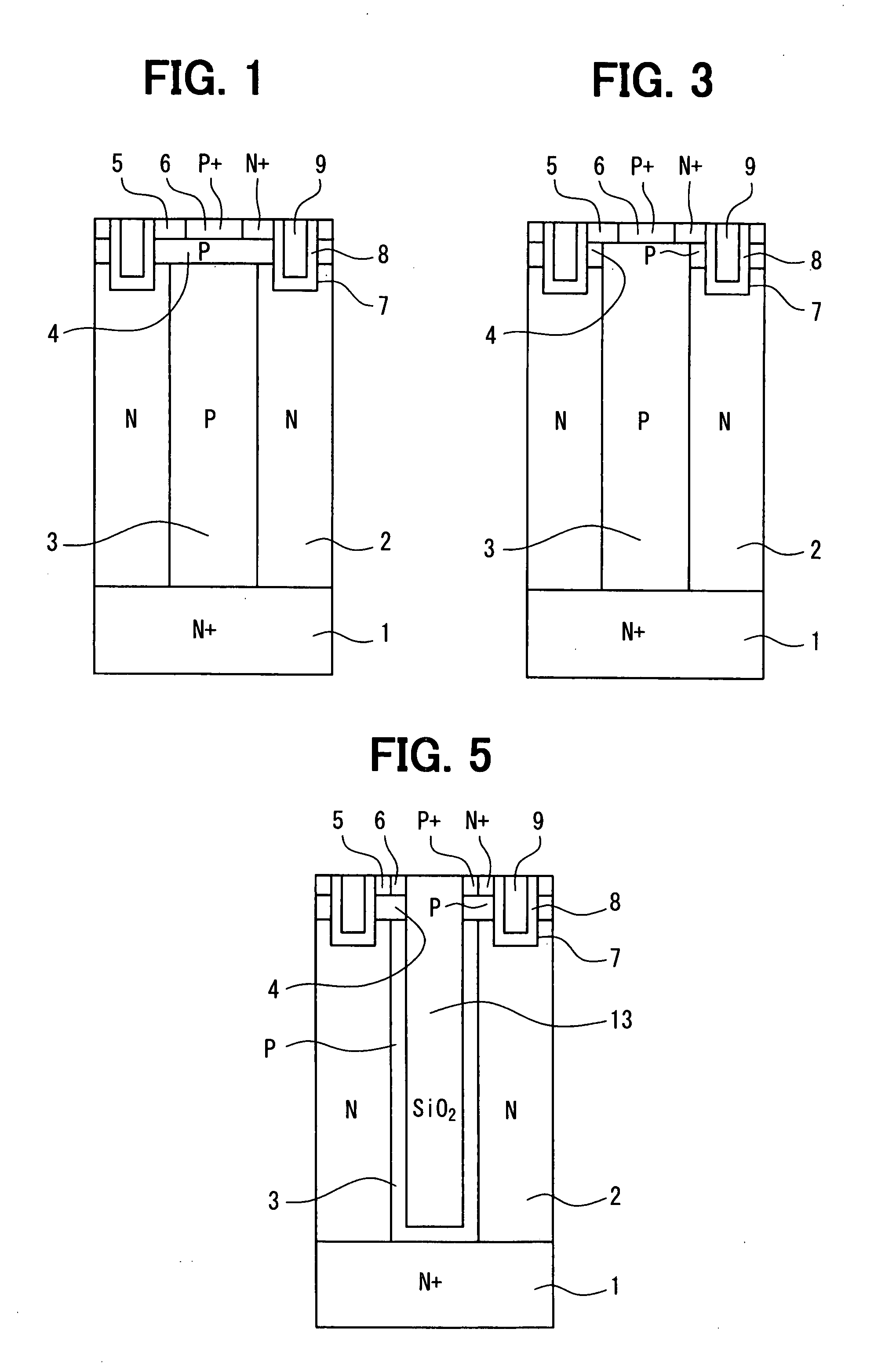

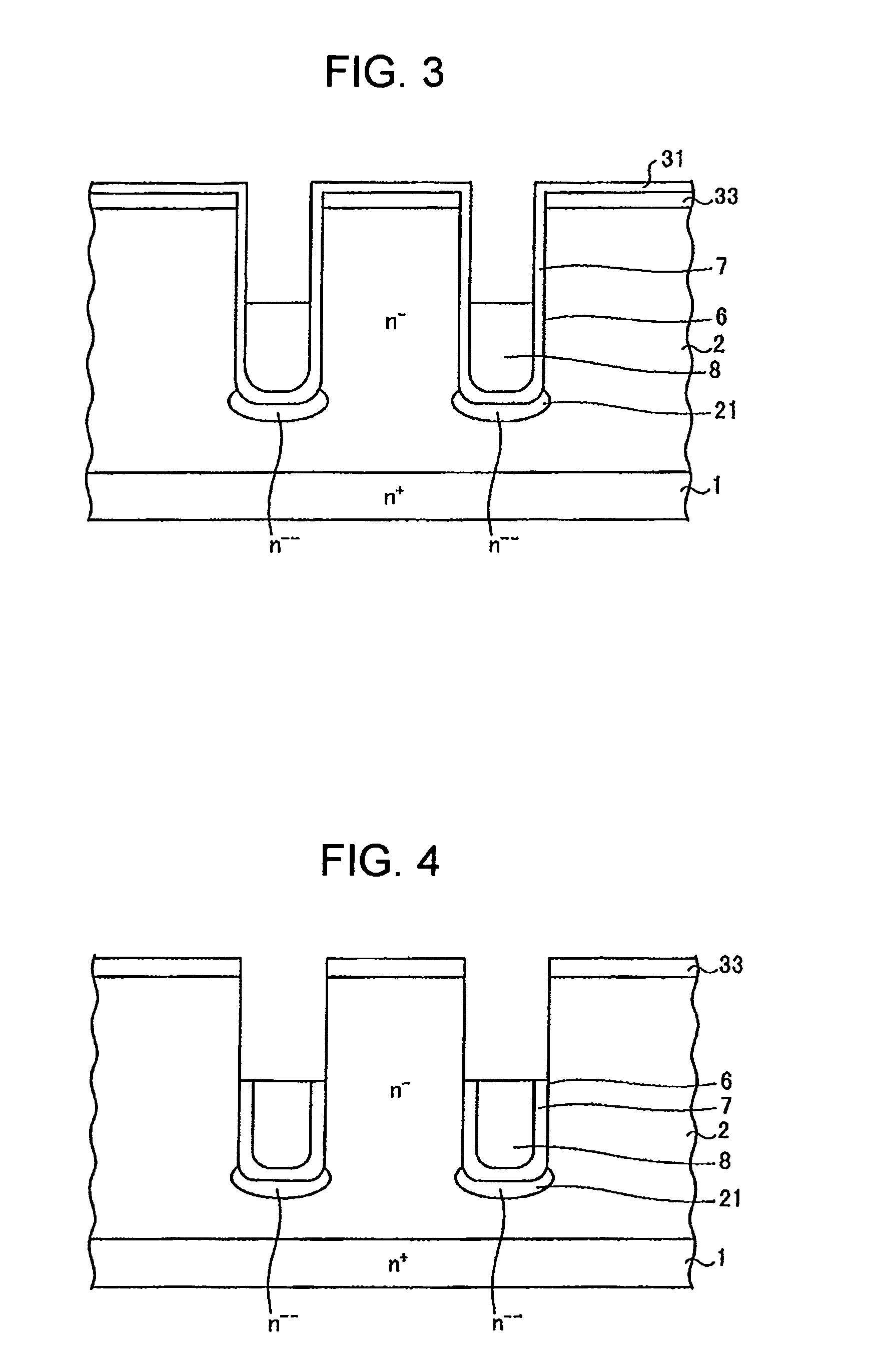

A semiconductor device according to the invention includes p-type well region 3 and n+ source region 4, both formed selectively in the surface portion of n− drift region 2; trench 6 in contact with n+ source region 4 and extending through p-type well region 3 into n− drift region 2; field plate 8 formed in trench 6 with first insulator film 7 interposed between the trench 6 inner surface and field plate 8; gate electrode 10 formed in trench 6 with second insulator film 9 interposed between the trench 6 side wall and gate electrode 10, gate electrode 10 being formed above field plate 8; first insulator film 7 being thicker than second insulator film 9; and n−− lightly doped region 21 in n− drift region 2, n−− lightly doped region 21 crossing under the bottom surface of trench 6 from the corner portion thereof, n−− lightly doped region 21 covering the bottom surface of trench 6.The semiconductor device according to the invention and the method of manufacturing the semiconductor device according to the invention facilitate lowering the ON-state voltage, preventing the breakdown voltage from lowering, lowering the gate capacitance, and reducing the manufacturing costs.

Owner:FUJI ELECTRIC CO LTD

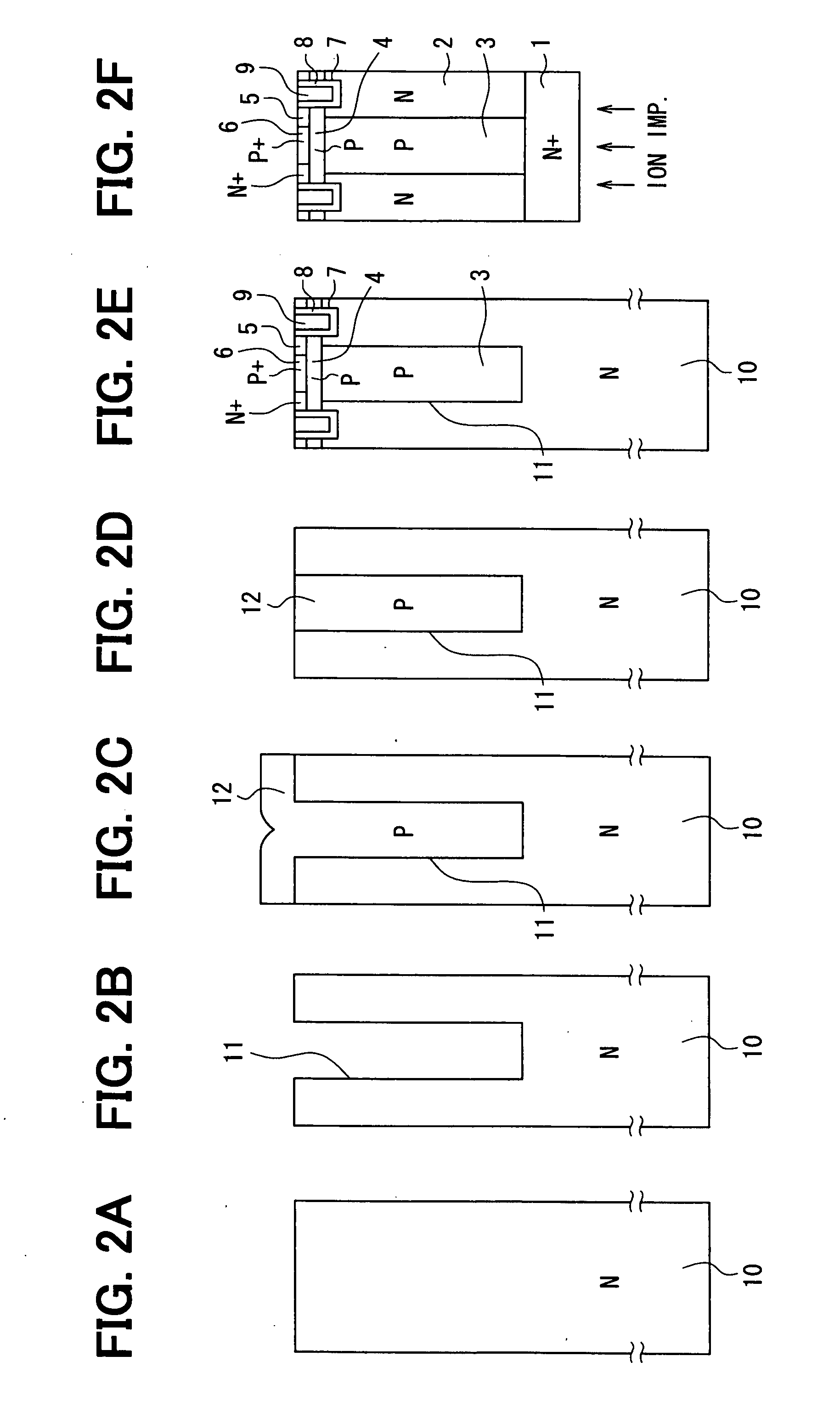

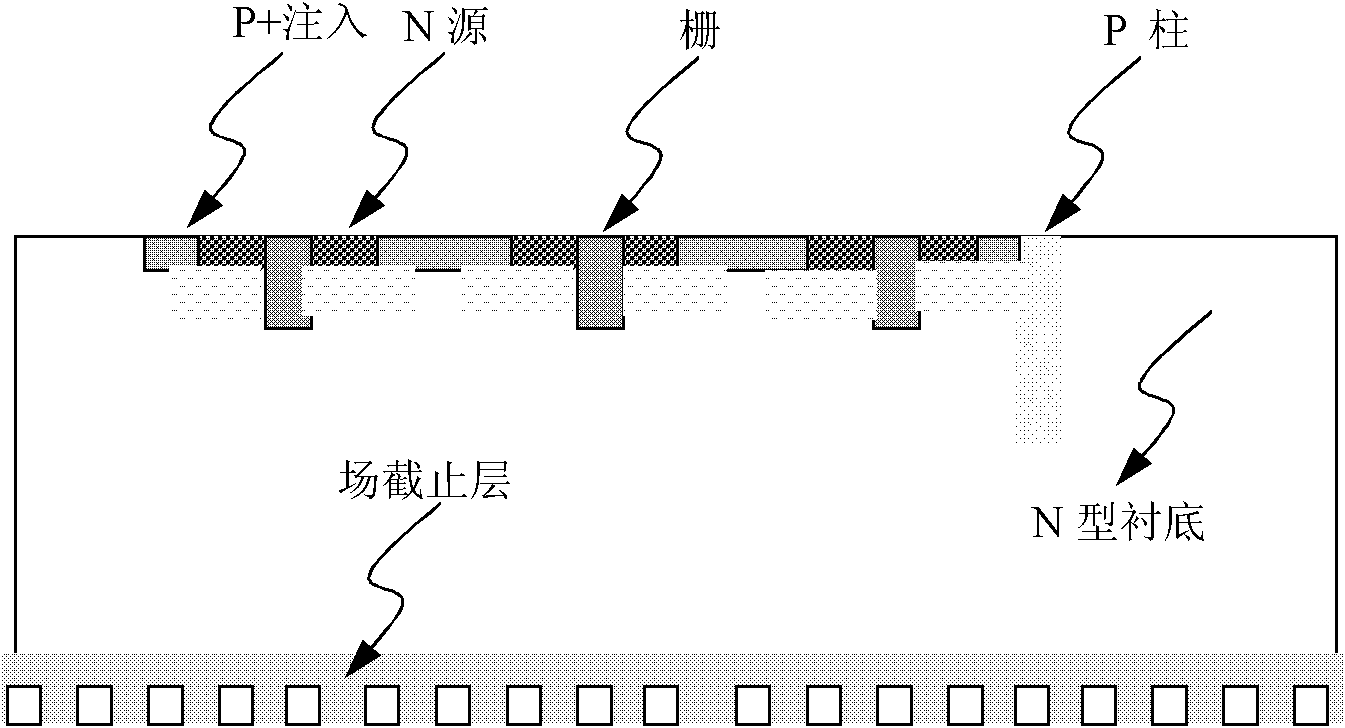

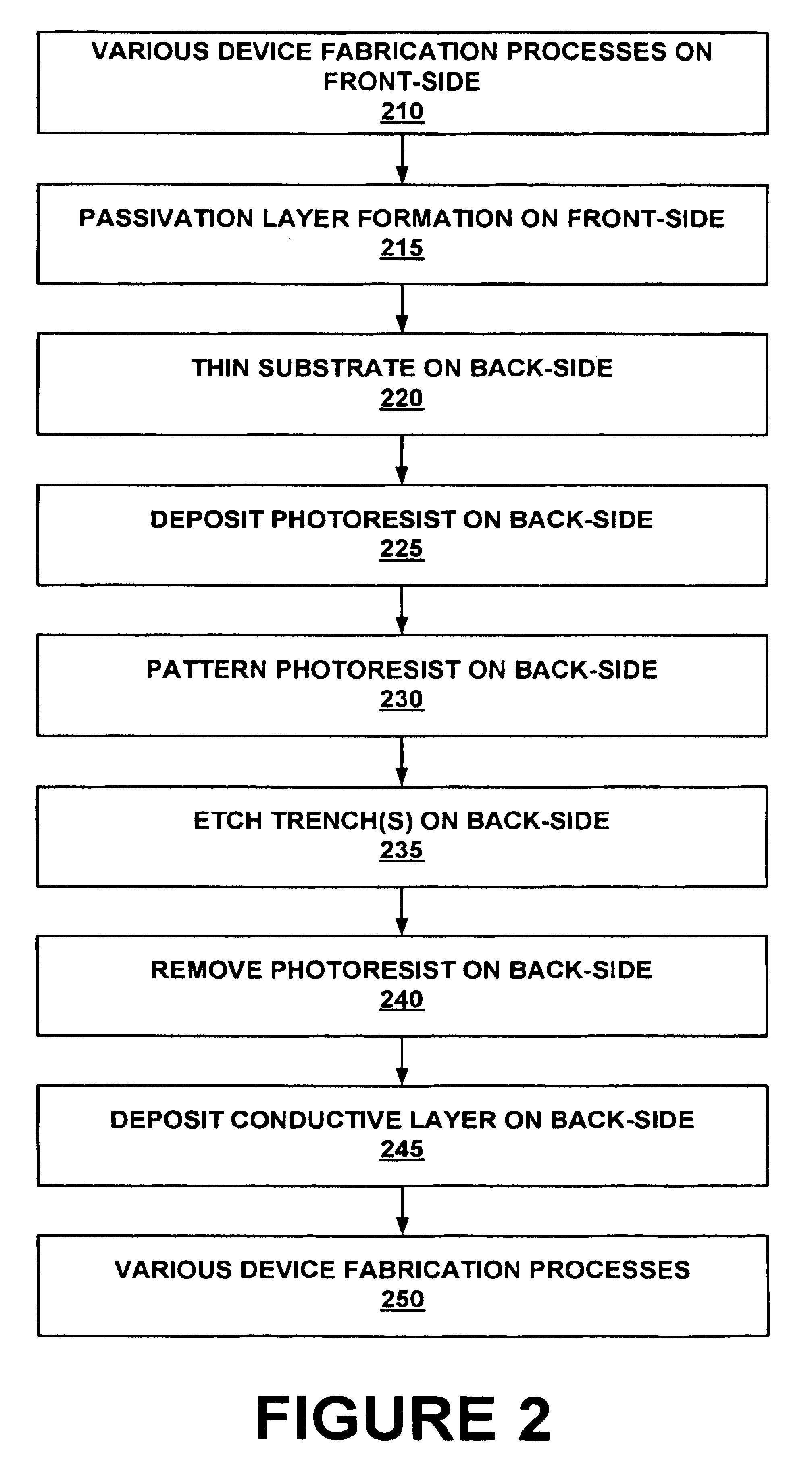

Method for manufacturing semiconductor device

ActiveUS20080038850A1Reduce manufacturing costReduce time costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSemiconductor

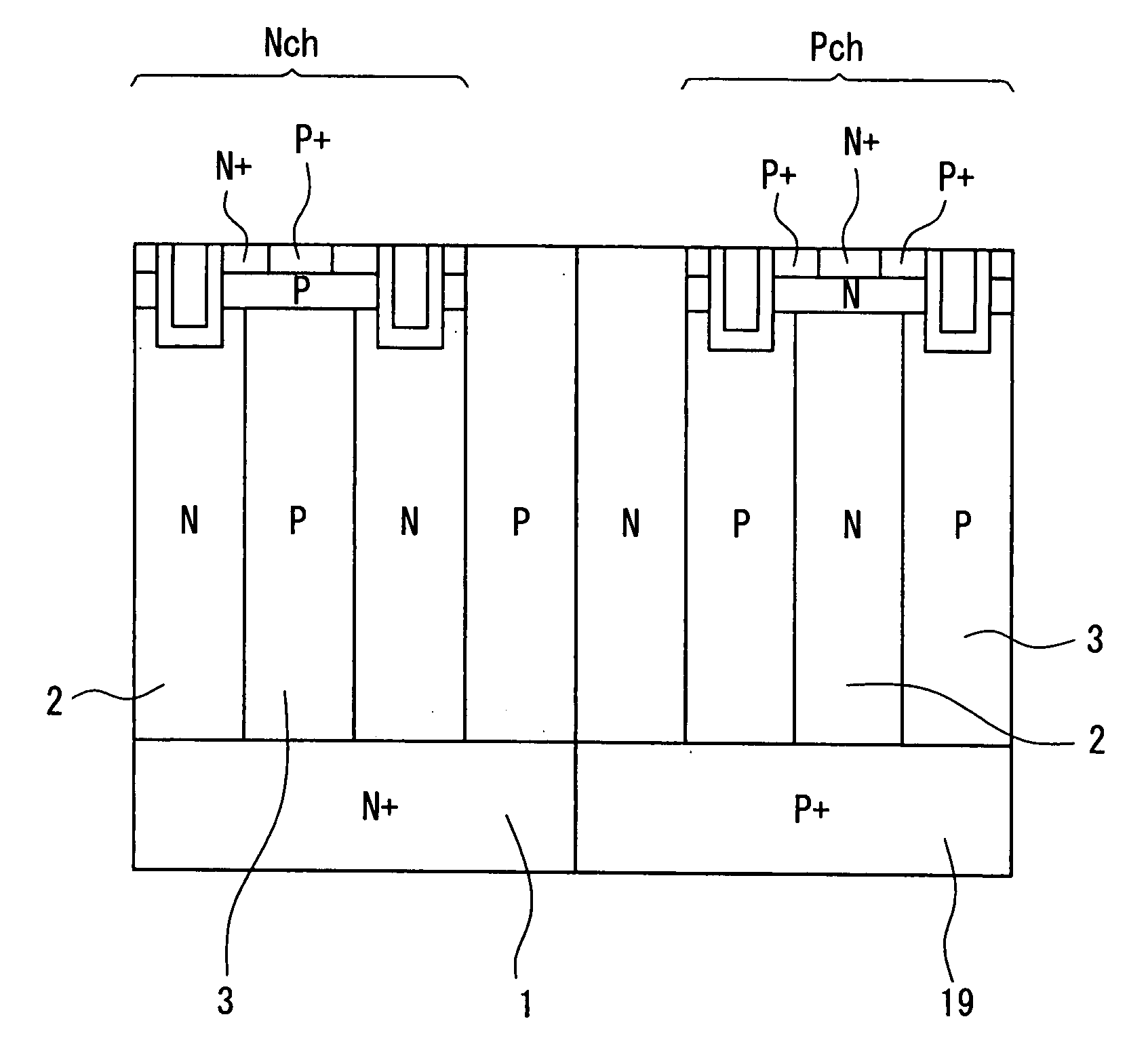

A manufacturing method of a semiconductor device includes: forming multiple trenches on a semiconductor substrate; forming a second conductive type semiconductor film in each trench to provide a first column with the substrate between two trenches and a second column with the second conductive type semiconductor film in the trench, the first and second columns alternately repeated along with a predetermined direction; thinning a second side of the substrate; and increasing an impurity concentration in a thinned second side so that a first conductive type layer is provided. The impurity concentration of the first conductive type layer is higher than the first column. The first column provides a drift layer so that a vertical type first-conductive-type channel transistor is formed.

Owner:DENSO CORP

Silicon carbide semiconductor device and method for manufacturing the same

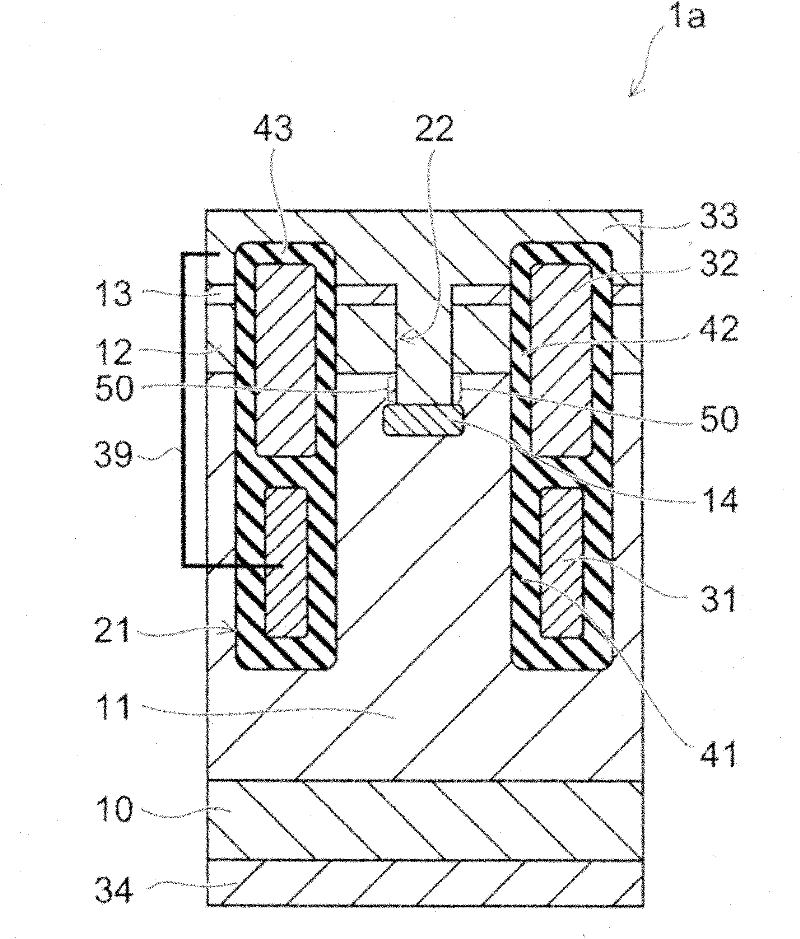

ActiveUS20060097267A1Reliability and high performance be improveON-state resistance be reduceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor

A method for manufacturing a silicon carbide semiconductor device includes the steps of: preparing a semiconductor substrate including a silicon carbide substrate and first to third semiconductor layers; forming a trench in a cell region of the semiconductor substrate; forming a fourth semiconductor layer in the trench; forming an oxide film in the trench such that a part of the fourth semiconductor layer on a sidewall of the trench is thermally oxidized; forming a gate electrode on the oxide film in the trench; forming a first electrode electrically connecting to the third semiconductor layer; and forming a first electrode electrically connecting to the silicon carbide substrate.

Owner:DENSO CORP

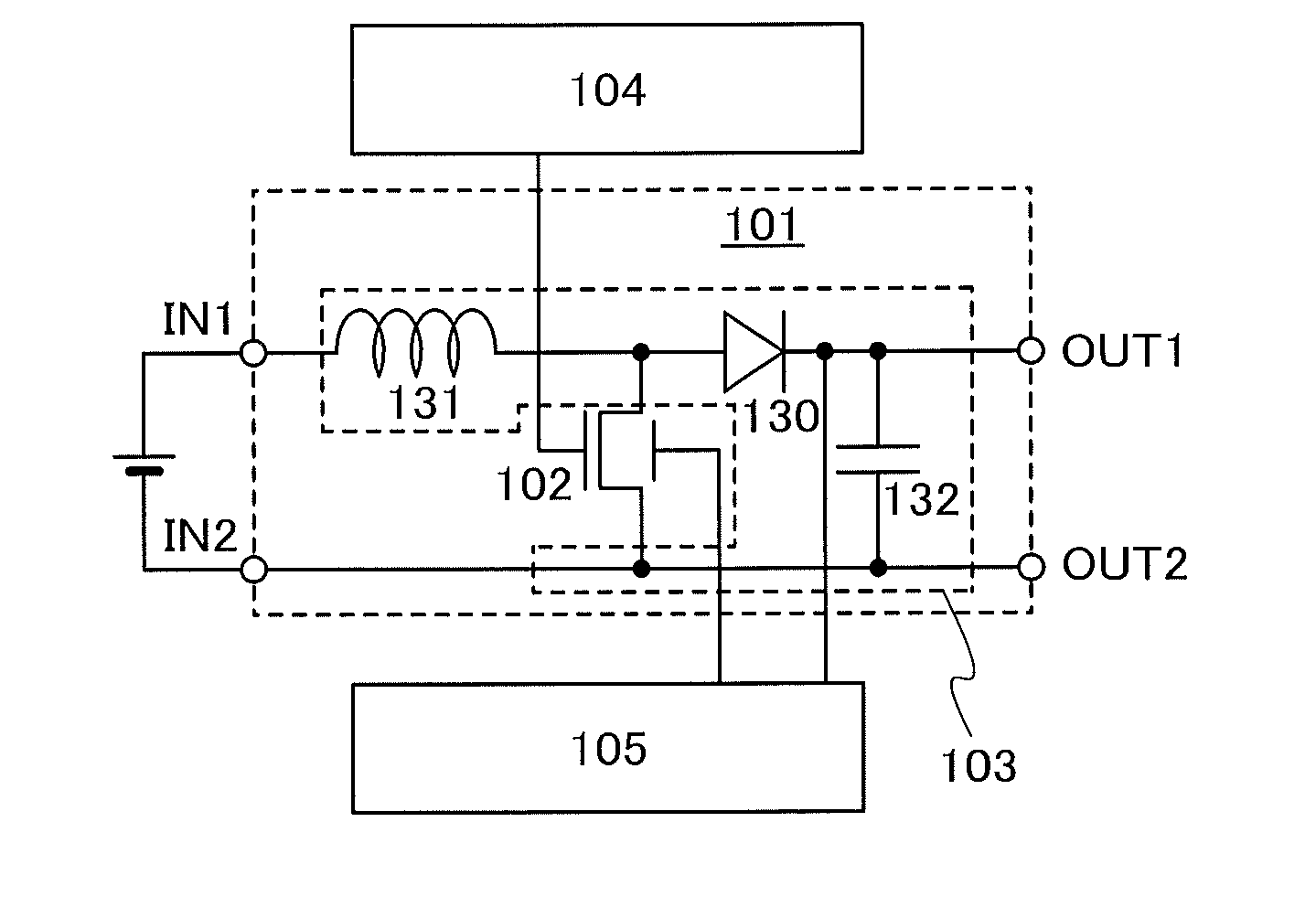

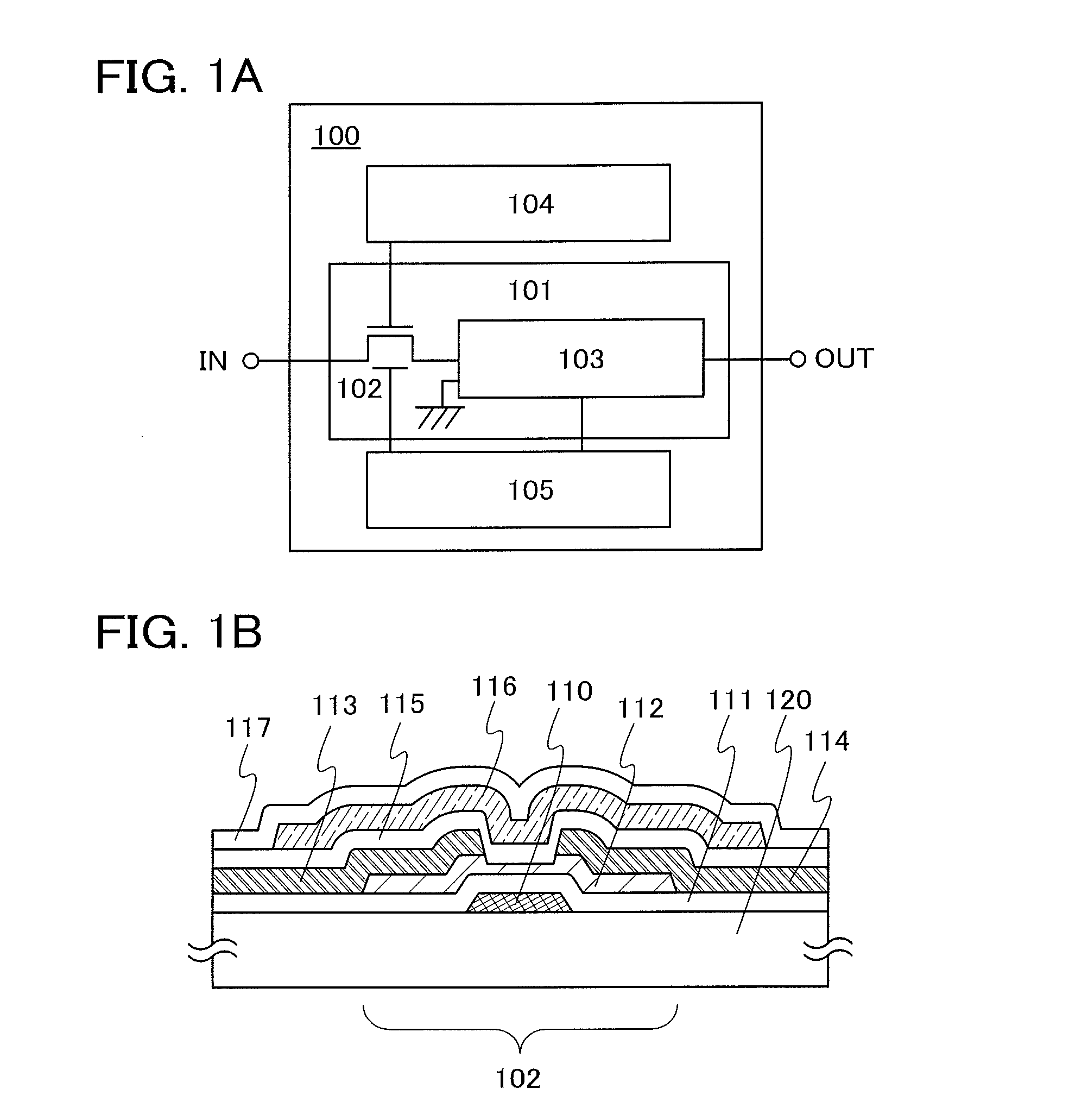

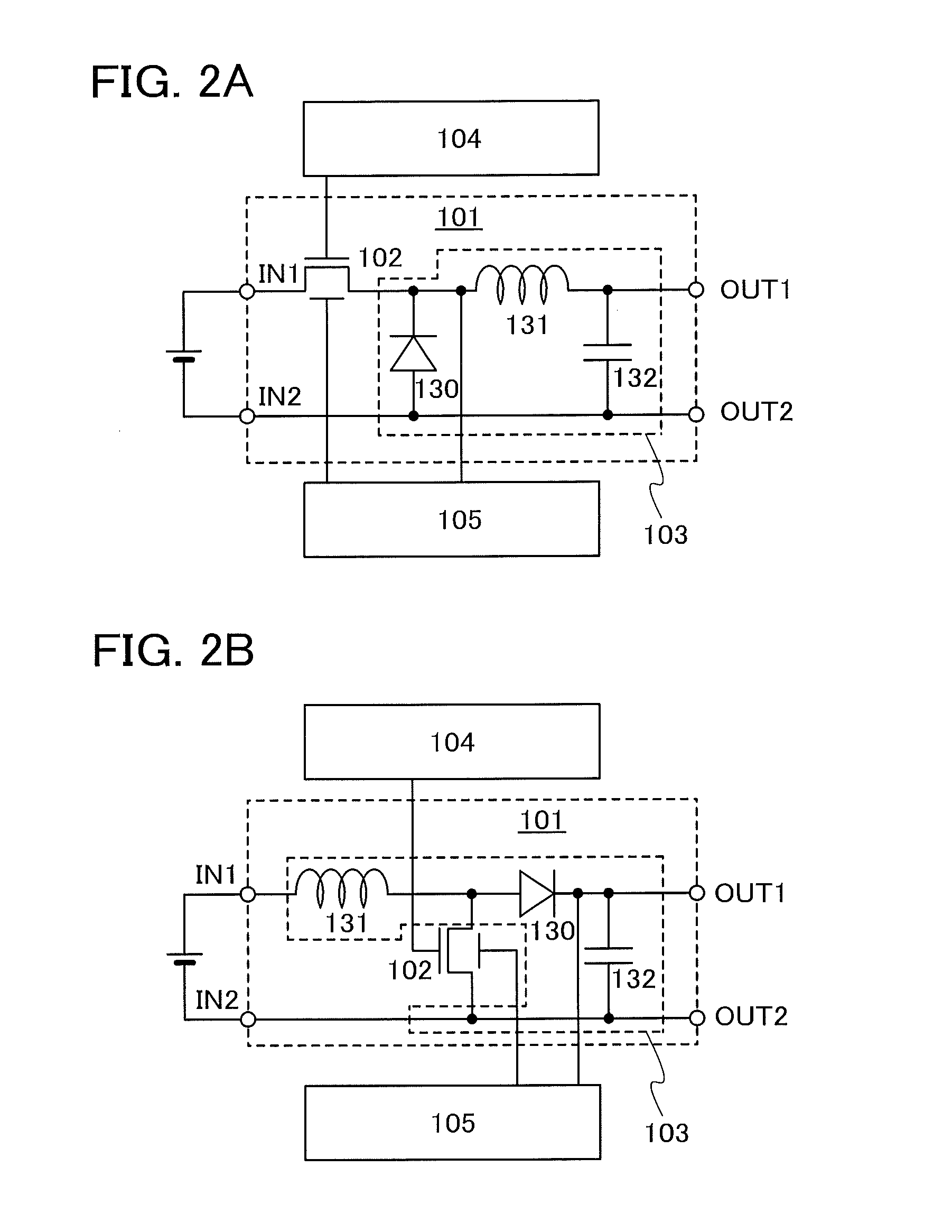

Dc/dc converter, power supply circuit, and semiconductor device

ActiveUS20110304311A1Improve power conversion efficiencyLower on-state resistanceEfficient power electronics conversionDc-dc conversionSemiconductor materialsPower control

Provided is a DC-DC converter with improved power conversion efficiency. A transistor which is incorporated in the DC-DC converter and functions as a switching element for controlling output power includes, in its channel formation region, a semiconductor material having a wide band gap and significantly small off current compared with silicon. The transistor further comprises a back gate electrode, in addition to a general gate electrode, and a back gate control circuit for controlling a potential applied to the back gate electrode in accordance with the output power from the DC-DC converter. The control of the potential applied to the back gate electrode by the back gate control circuit enables the threshold voltage to decrease the on-state resistance when the output power is high and to increase the off-state current when the output power is low.

Owner:SEMICON ENERGY LAB CO LTD

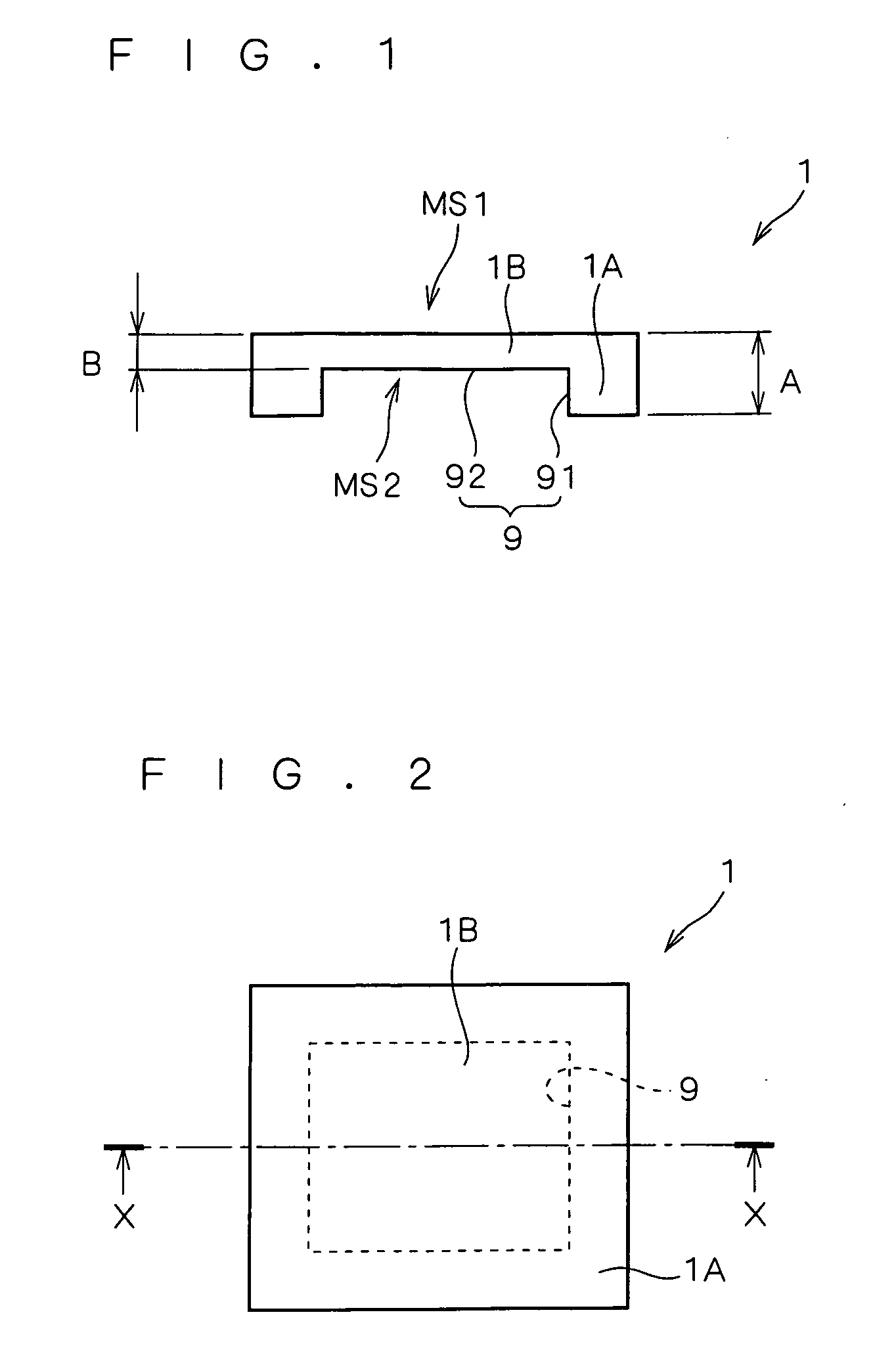

Semiconductor device

InactiveUS20050156283A1Satisfactory breakdown voltageSatisfactory performanceSolid-state devicesSemiconductor/solid-state device manufacturingLithography processDevice material

A semiconductor device in which a main current flows in a direction of thickness of a semiconductor substrate and which offers satisfactory performance and breakdown voltage and also satisfactory mechanical strength of the semiconductor substrate, and which needs no inconvenient control of the exposure system etc. during a photolithography process. The semiconductor device has a semiconductor substrate having a first main surface, a second main surface opposite to the first main surface, and a recess defined in the second main surface by side surfaces and a bottom surface. A semiconductor region is provided in the bottom surface of the recess of the semiconductor substrate, semiconductor regions are provided in the surface of a peripheral region on the second main surface side, and insulating films are provided on the side surfaces of the recess to electrically insulate the semiconductor regions.

Owner:MITSUBISHI ELECTRIC CORP

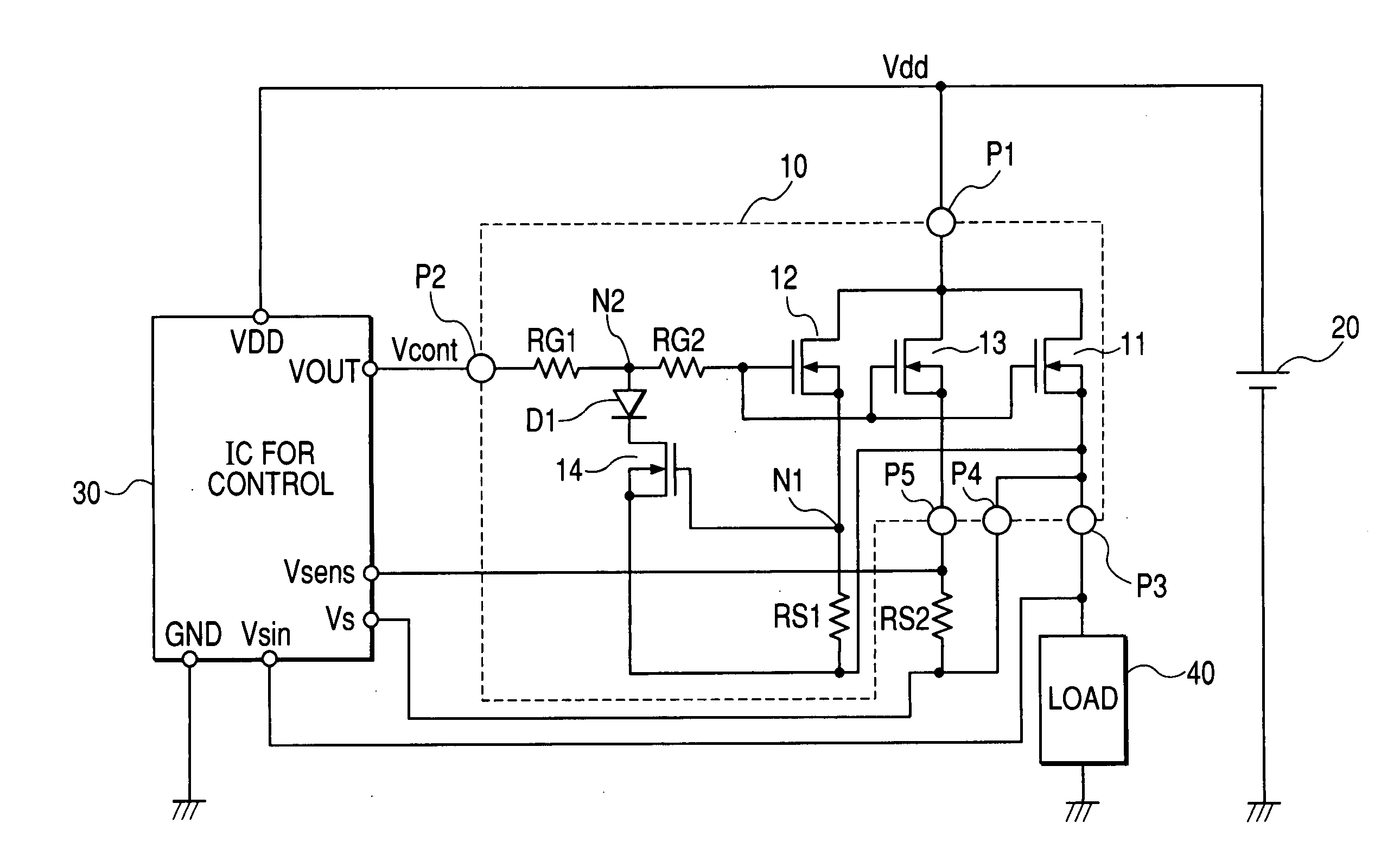

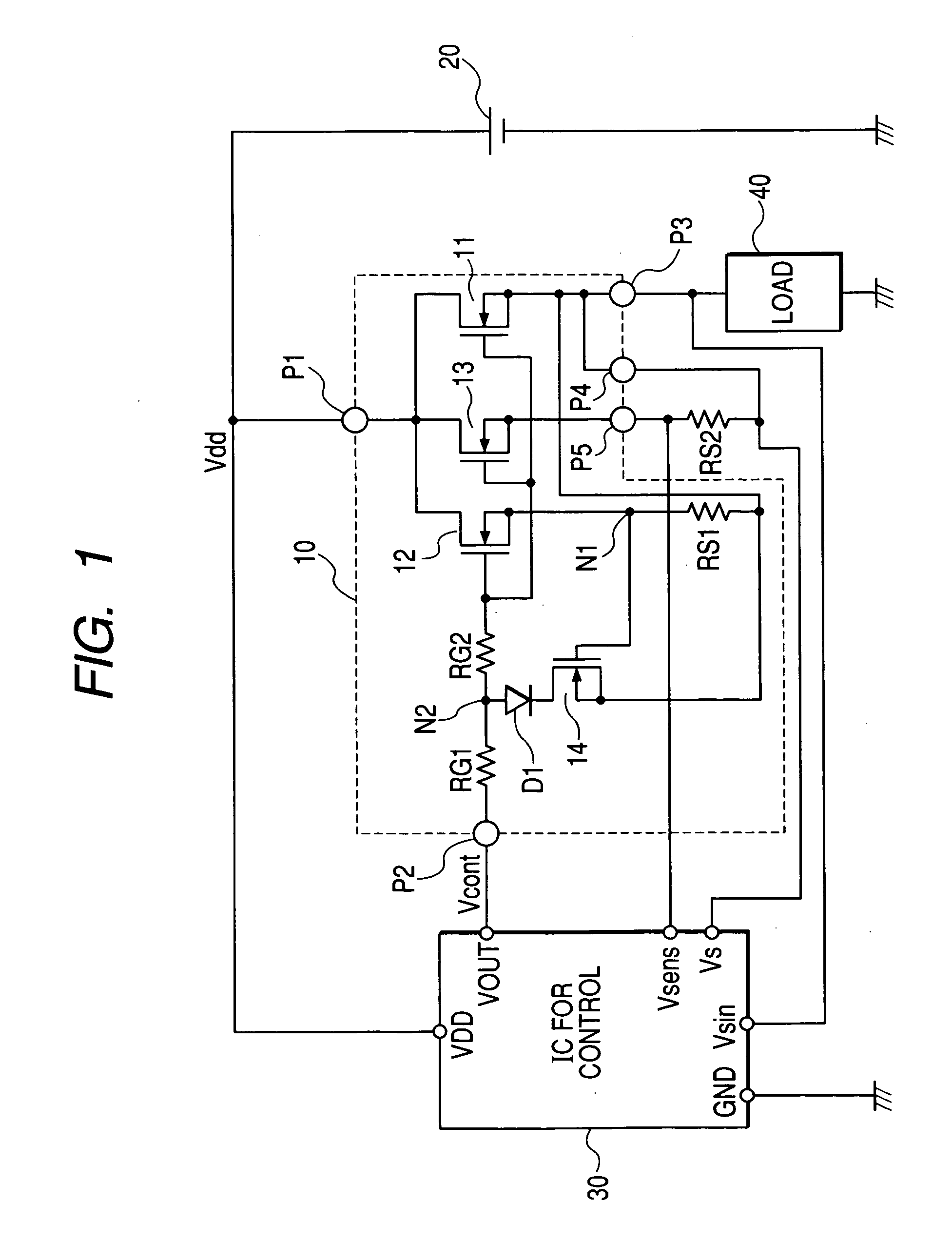

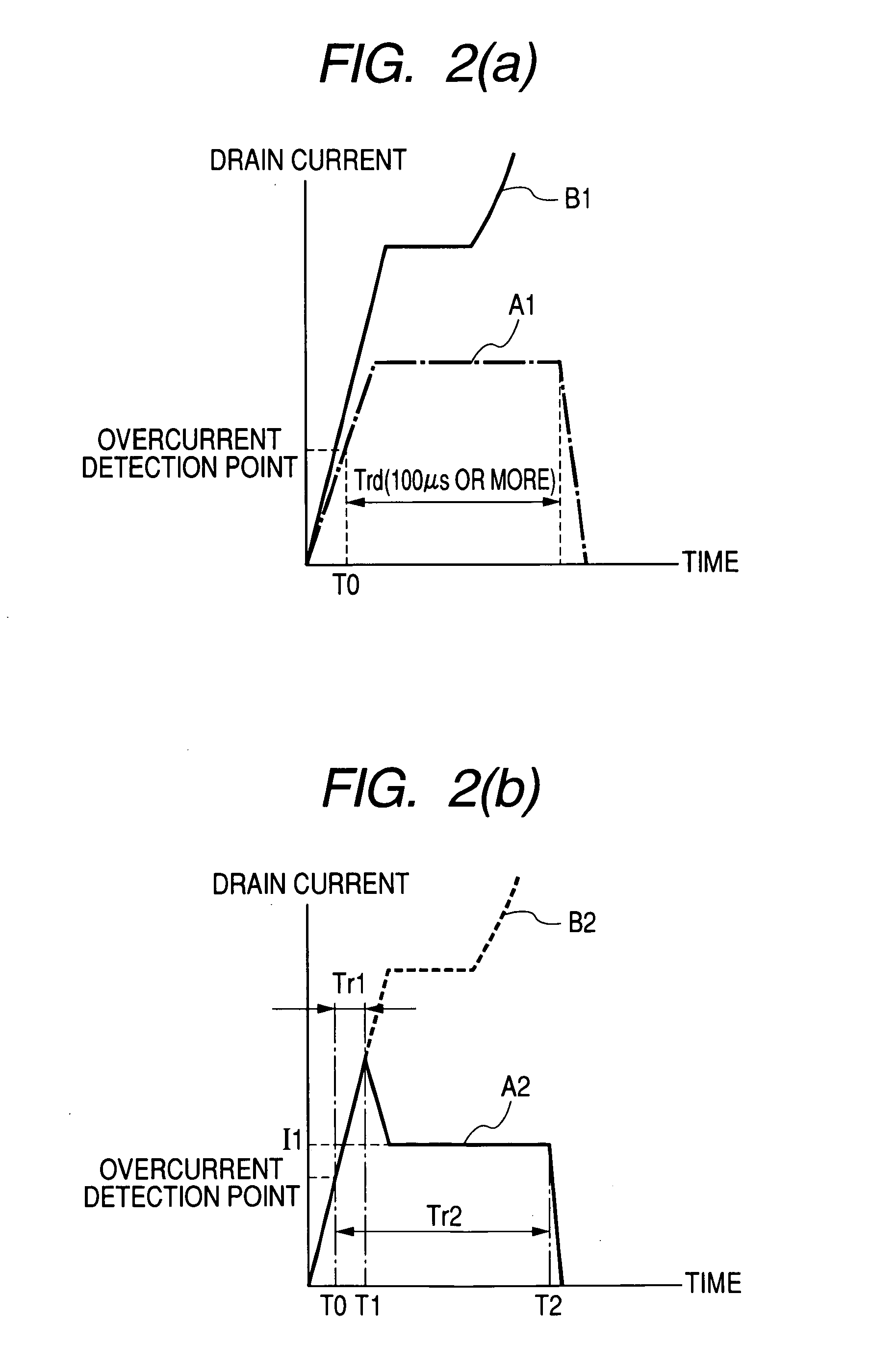

Power transistor device and a power control system for using it

InactiveUS20050286194A1Reduce loss in the transistorLower on-state resistanceTransistorSolid-state devicesElectrical conductorPower control system

The object of the invention is to protect a power MOS transistor using a transistor having trench structure from overcurrent and to enhance the reliability. To achieve the object, a power MOS transistor, a transistor for detecting current for detecting the current of the power MOS transistor and generating a detection signal supplied to an external control circuit and devices configuring a protection circuit for detecting the current of the power MOS transistor and inhibiting current by forcedly dropping the gate voltage of the power MOS transistor when current equal to or exceeding a predetermined value flows are provided in the same semiconductor chip.

Owner:FUJIKI ATSUSHI +1

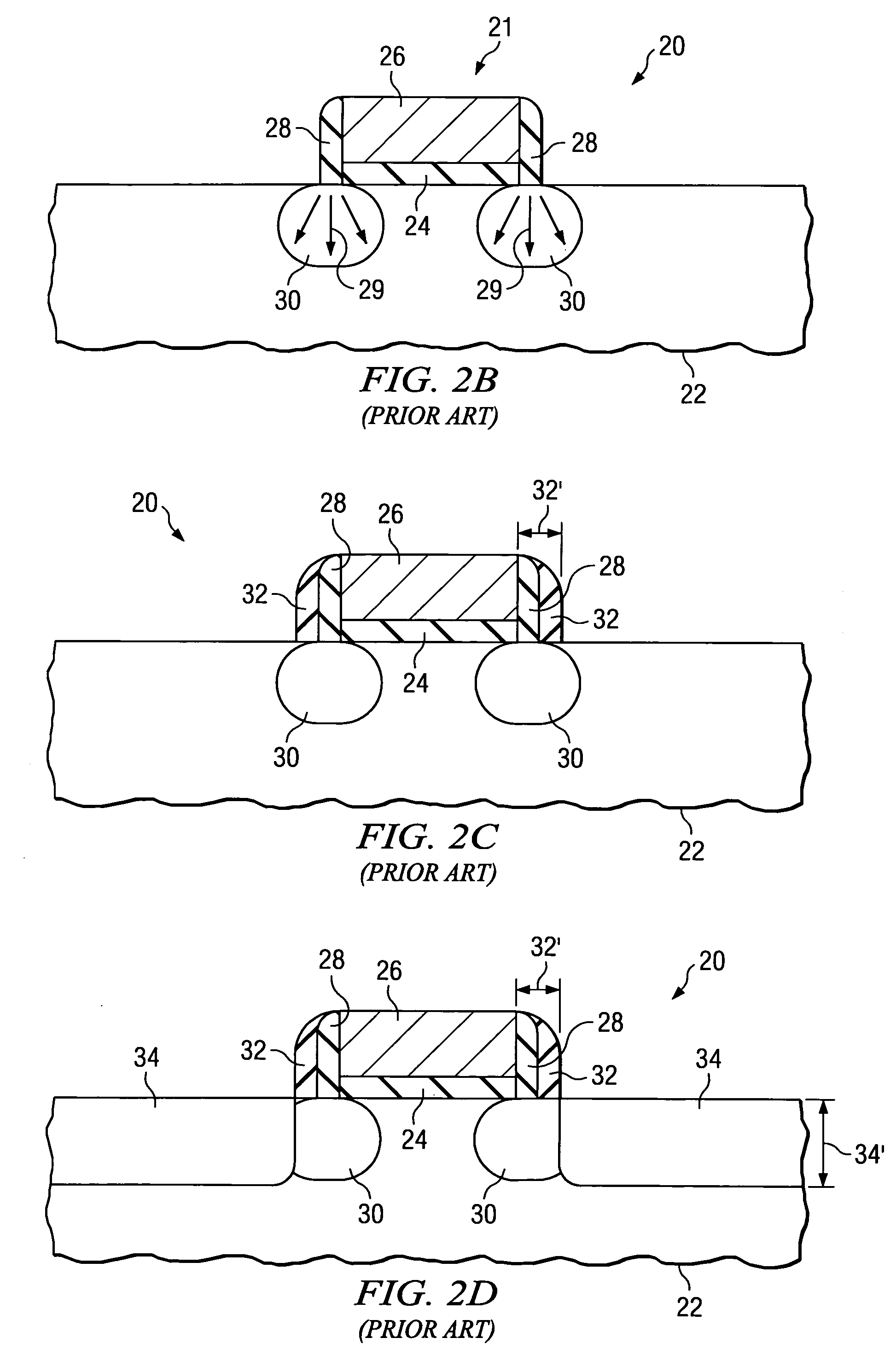

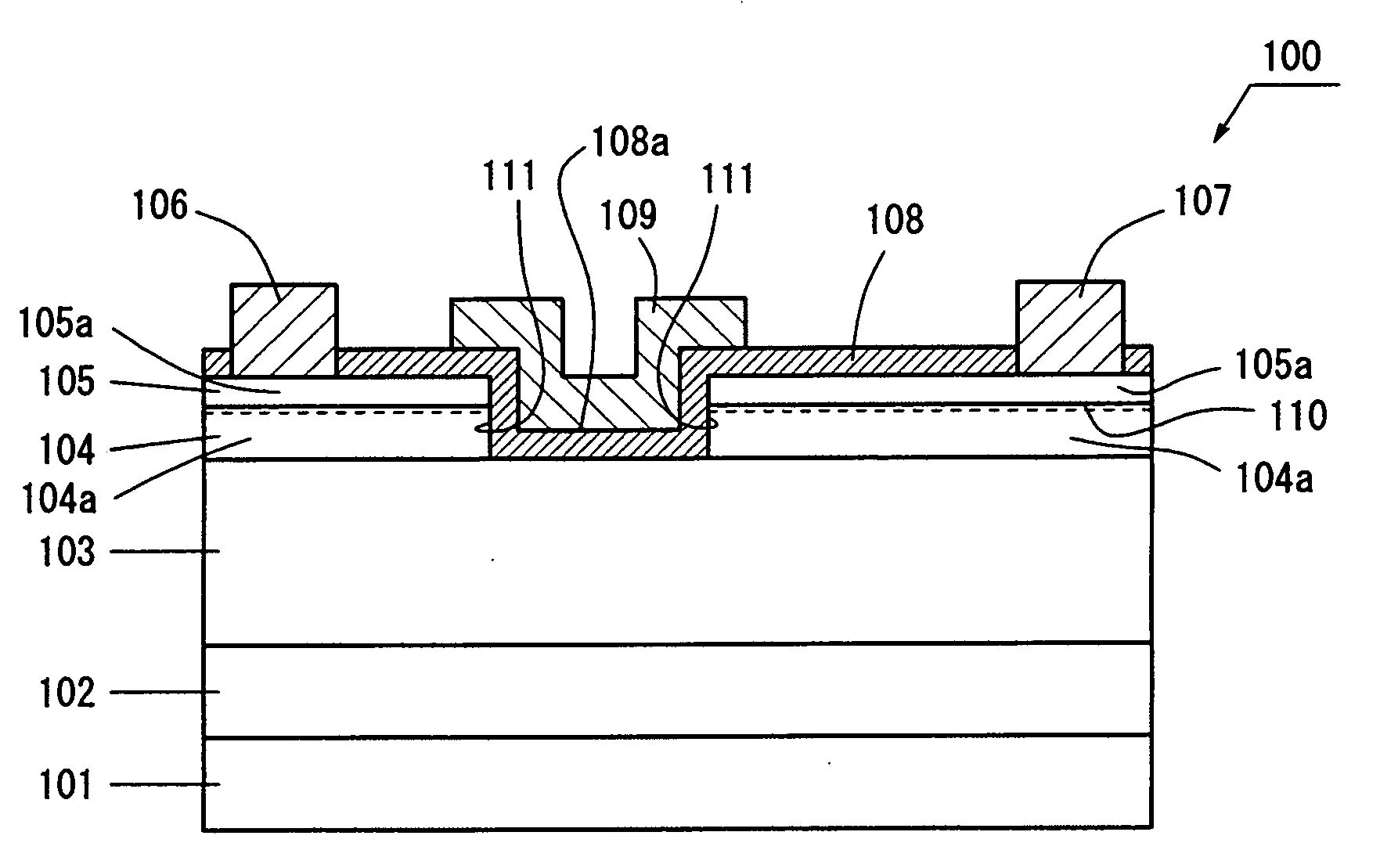

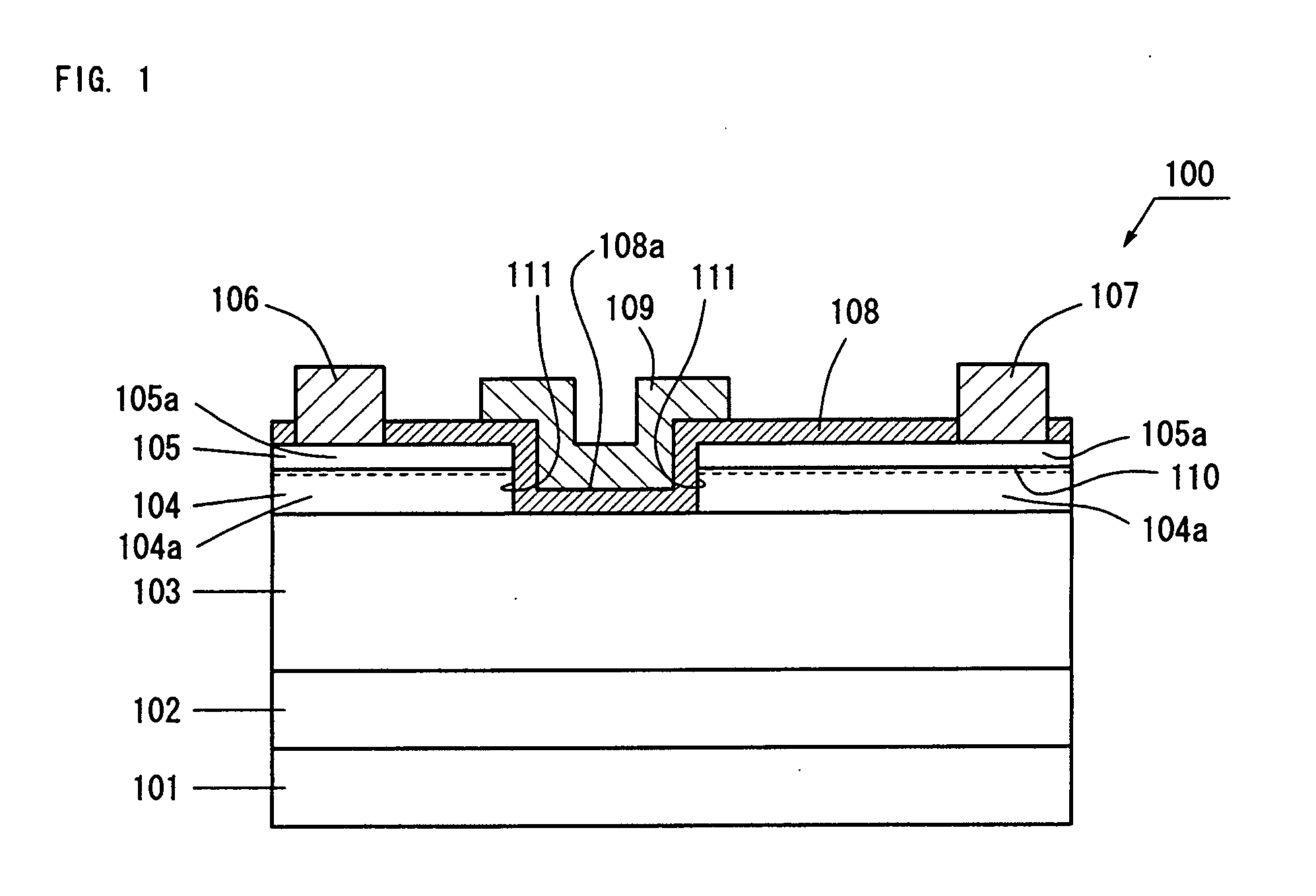

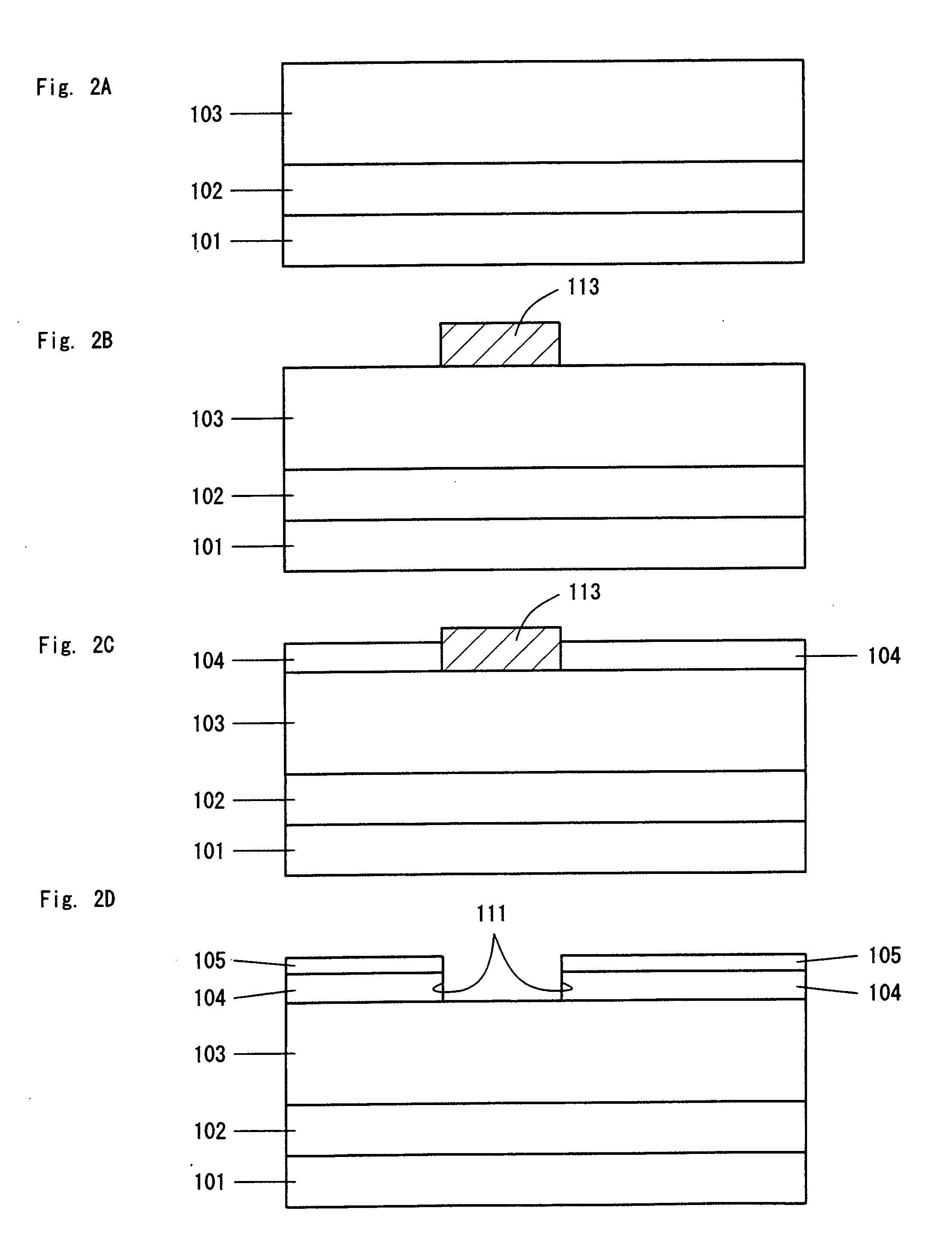

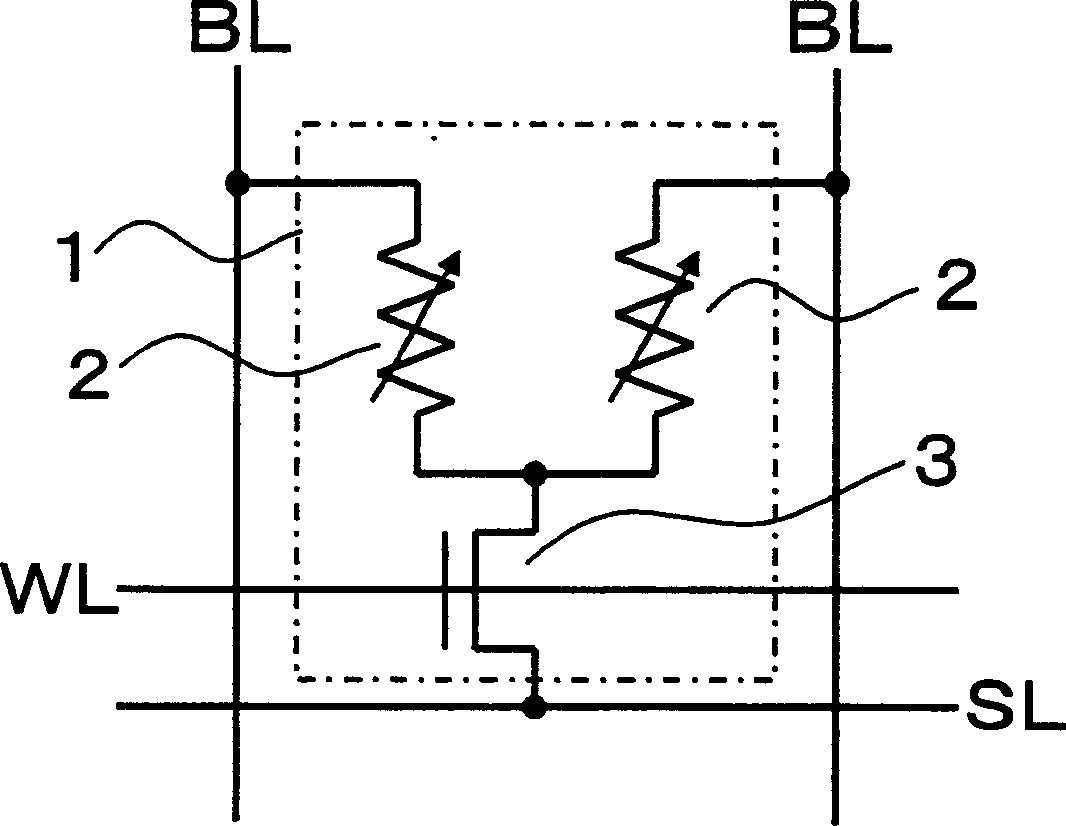

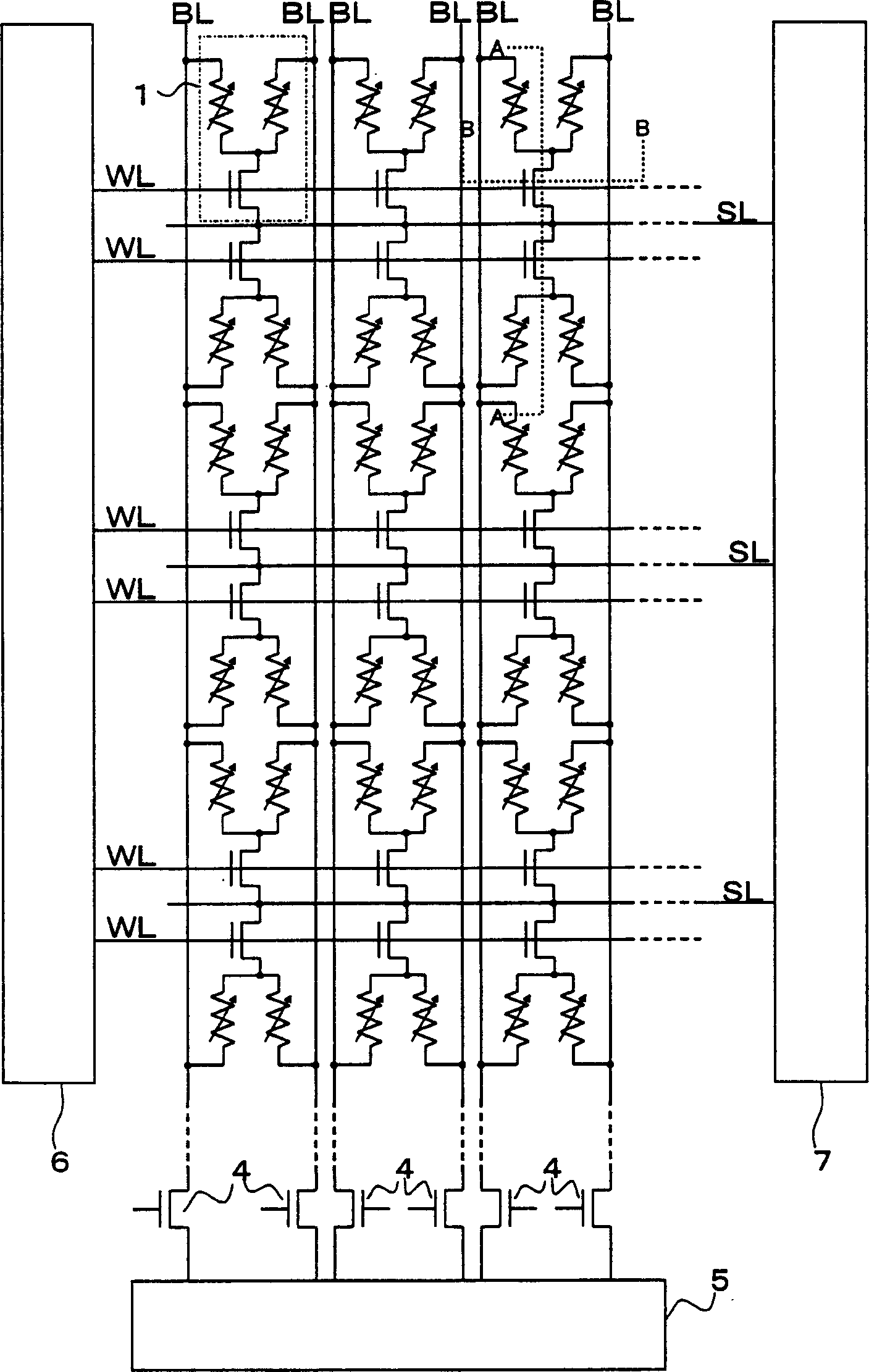

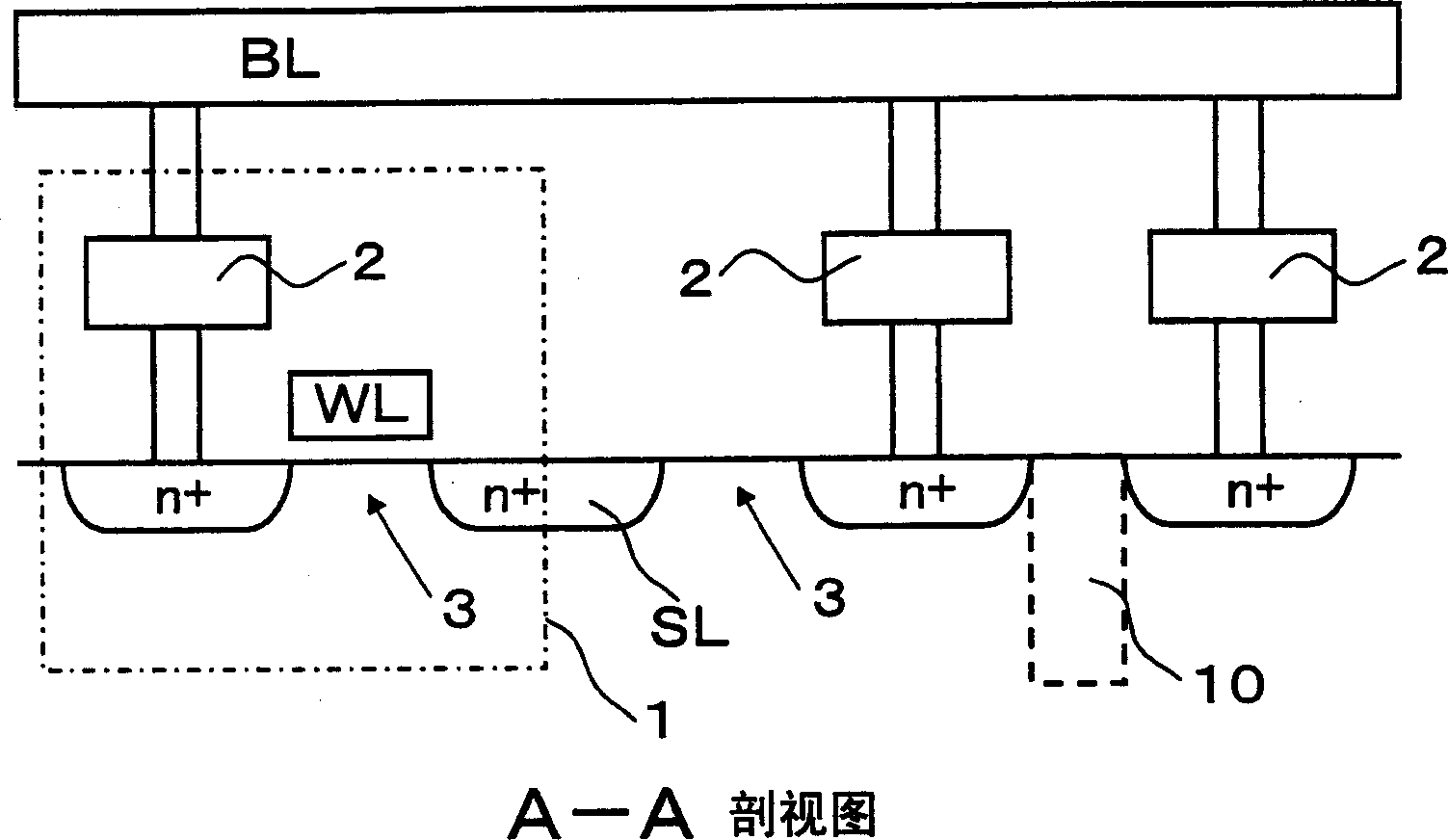

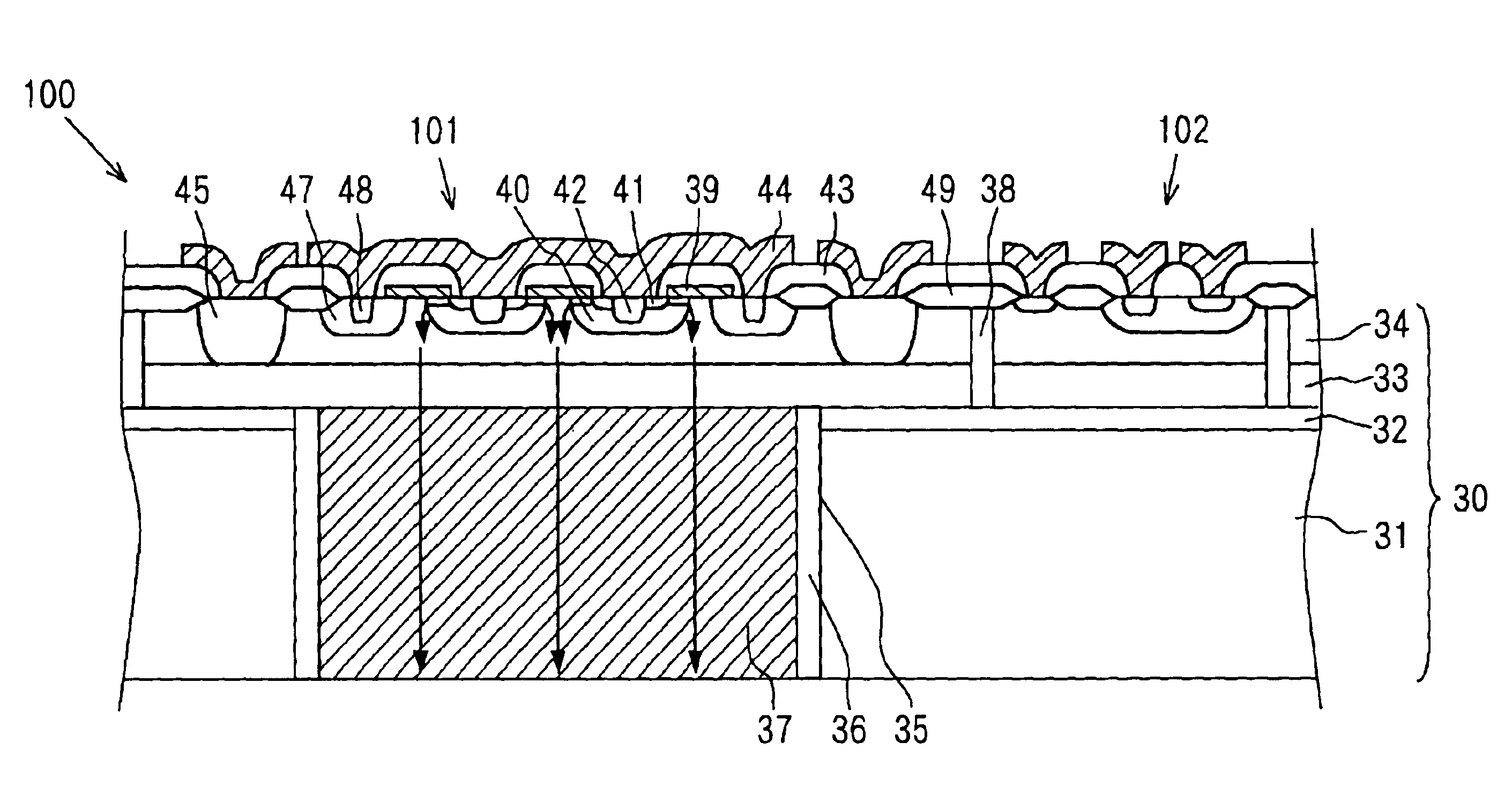

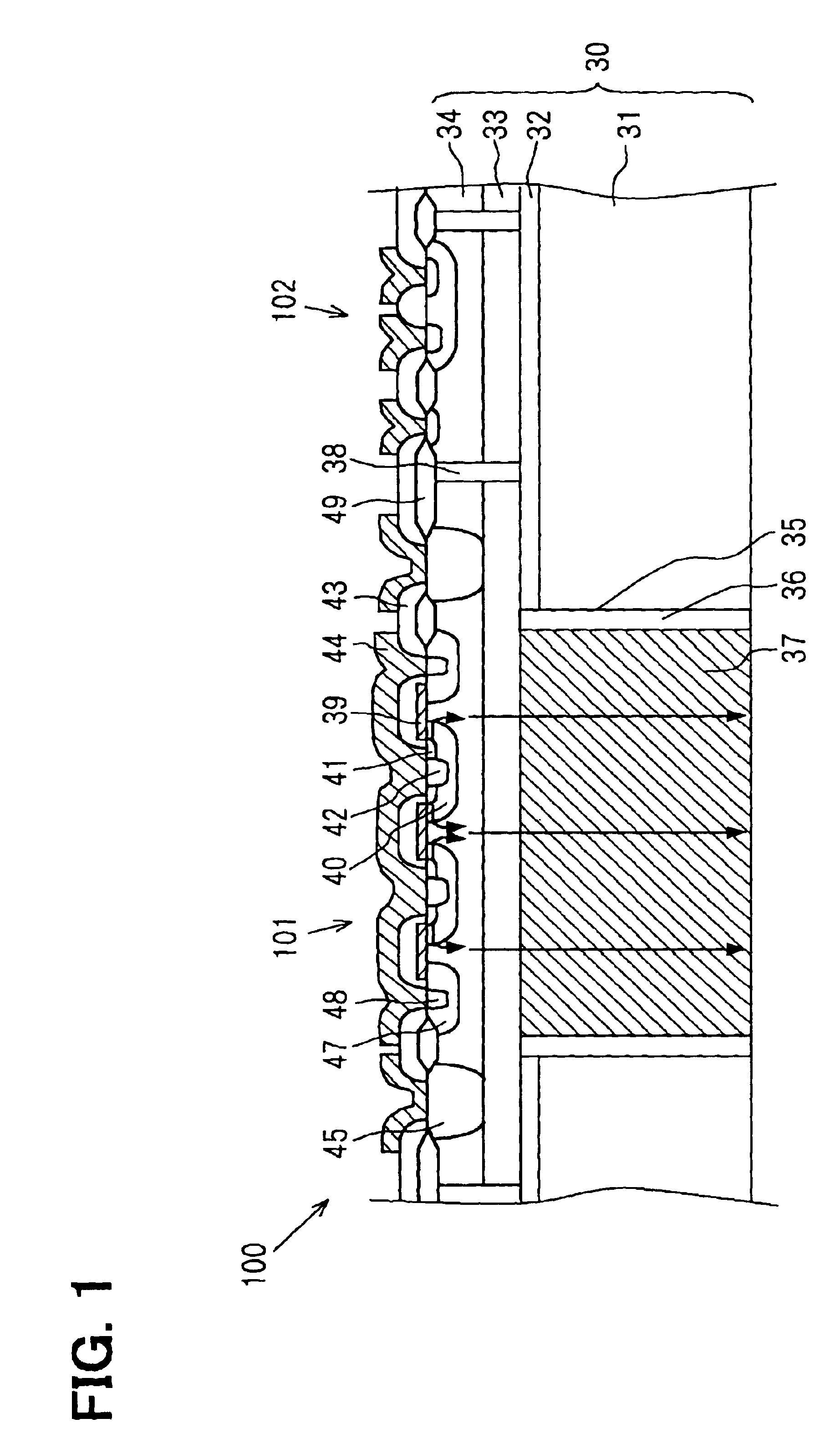

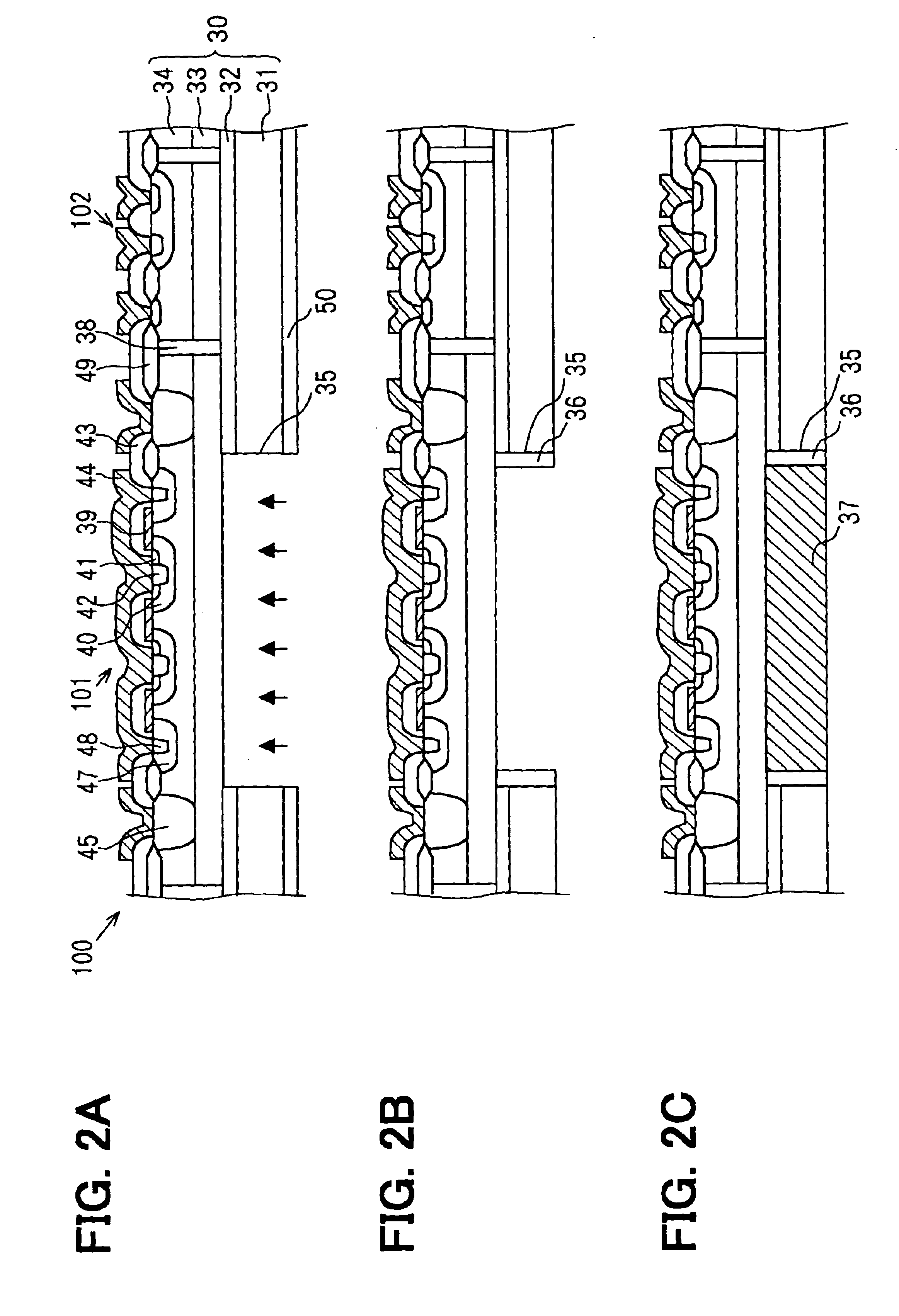

Nonvolatile memory cell and non-volatile semiconductor memory device

ActiveCN1505043ALower on-state resistanceRead operation speed upMagnetic-field-controlled resistorsSolid-state devicesMOSFETElectrical resistance and conductance

It is an object of the present invention to make it possible to decrease the on-state resistance of a selection transistor of a memory cell without increasing the whole area of a memory cell array and accelerate and stabilize the reading operation of data stored in the memory cell. Therefore, a plurality of variable resistive elements capable of storing information in accordance with a change of electrical resistances is included, one ends of the variable resistive elements are connected each other, and an electrode of a selection element constituted by a MOSFET or diode element for selecting the variable resistive elements in common is connected with one end of each of the variable resistive elements to constitute a memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Silicon carbide semiconductor device and method for manufacturing the same

InactiveUS20120319136A1Low jfet resistanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate voltage

A SiC device includes an inversion type MOSFET having: a substrate, a drift layer, and a base region stacked in this order; source and contact regions in upper portions of the base region; a trench penetrating the source and base regions; a gate electrode on a gate insulating film in the trench; a source electrode coupled with the source and base region; a drain electrode on a back of the substrate; and multiple deep layers in an upper portion of the drift layer deeper than the trench. Each deep layer has an impurity concentration distribution in a depth direction, and an inversion layer is provided in a portion of the deep layer on the side of the trench under application of the gate voltage.

Owner:DENSO CORP +1

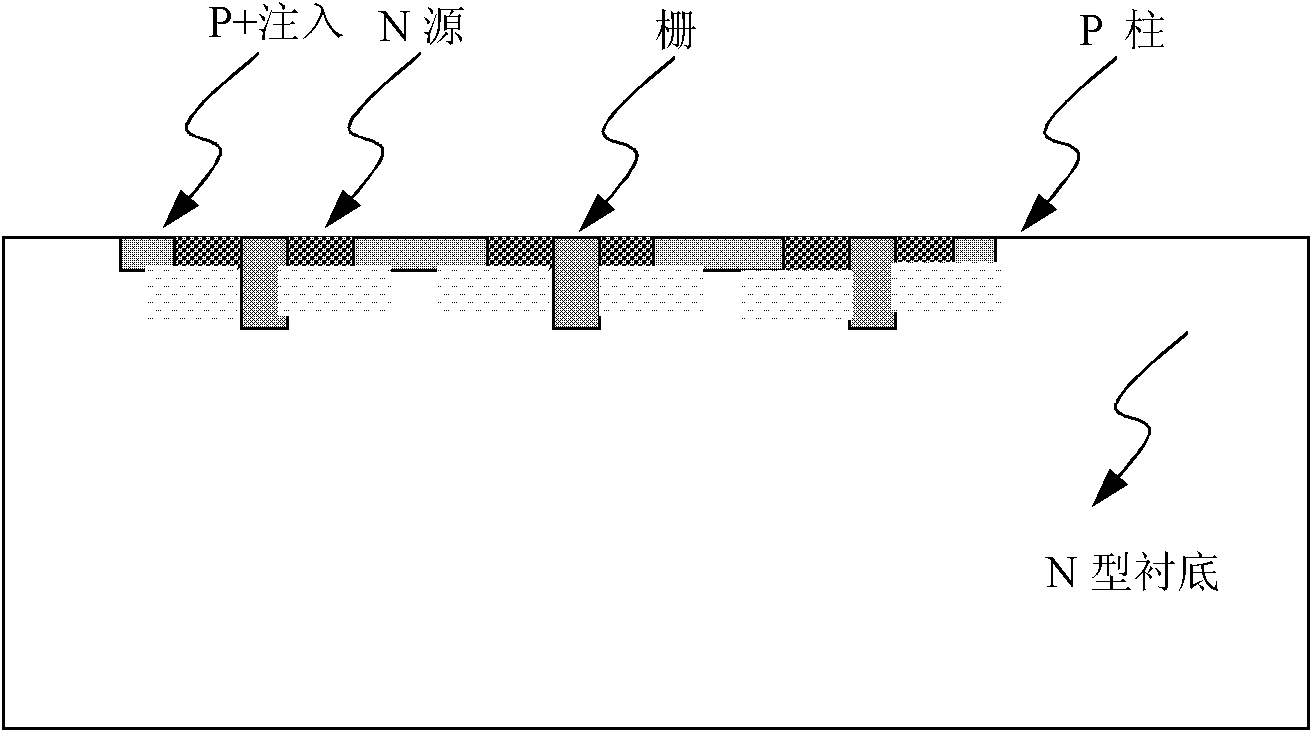

Method for manufacturing insulated gate bipolar transistor (IGBT) component combined with fast recovery diode (FRD)

ActiveCN103137472ALow costLower on-state resistanceSemiconductor/solid-state device manufacturingPhysicsSubstrate concentration

The invention discloses a method for manufacturing an insulated gate bipolar transistor (IGBT) component combined with a fast recovery diode (FRD). The method comprises the steps of defining exposure of a trench gate, growing and doping N-type polycrystalline silicon, etching the polycrystalline gate, conducting injection and drive-in to a source and a P trap in the front, reducing silicon slices at the back, conducting the phosphonium ion injection at the back, conducting the phosphonium ion drive-in at the back under a high temperature and for a long time at the back, digging a groove at the back, growing and highly doping N-type polycrystalline silicon in the groove at the back, conducting the collector electrode B injection at the back, and conducting the collector electrode B drive-in and the collector electrode gold evaporation. The IGBT component manufacturing method has a larger substrate concentration of the IGBT component and a lower cost than the prior art. The PNP base width of the IGBT combined with the fast recovery diode is smaller than that of a common IGBT, on-state resistance is smaller, generated joule heat is smaller, dropping detention time is shorter and bearable short-circuit current is larger under the same voltage during off-state.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

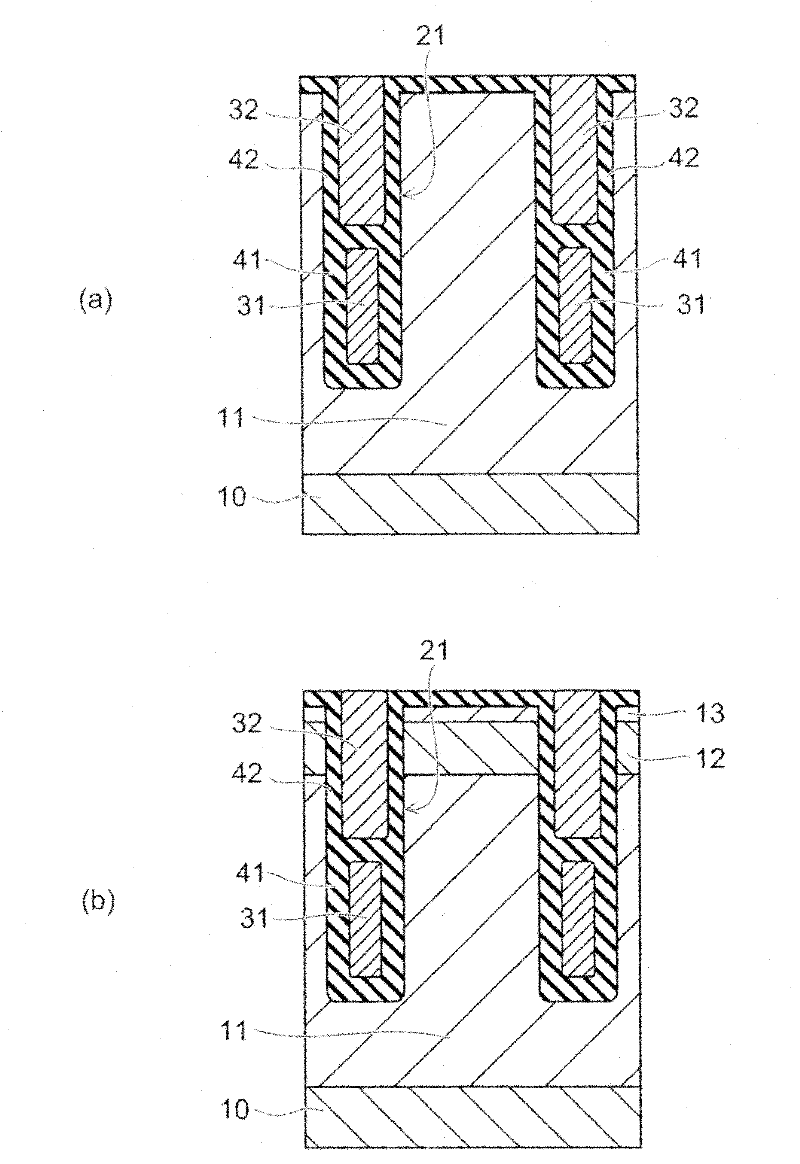

Semiconductor device and the method of manufacturing the same

ActiveUS8482061B2Lower on-state resistanceElectric field in the vicinity of the trench bottom surface is relaxed more effectivelySemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionSemiconductor

A semiconductor device according to the invention includes p-type well region 3 and n+ source region 4, both formed selectively in the surface portion of n− drift region 2; trench 6 in contact with n+ source region 4 and extending through p-type well region 3 into n− drift region 2; field plate 8 formed in trench 6 with first insulator film 7 interposed between the trench 6 inner surface and field plate 8; gate electrode 10 formed in trench 6 with second insulator film 9 interposed between the trench 6 side wall and gate electrode 10, gate electrode 10 being formed above field plate 8; first insulator film 7 being thicker than second insulator film 9; and n−− lightly doped region 21 in n− drift region 2, n−− lightly doped region 21 crossing under the bottom surface of trench 6 from the corner portion thereof, n−− lightly doped region 21 covering the bottom surface of trench 6. The semiconductor device according to the invention and the method of manufacturing the semiconductor device according to the invention facilitate lowering the ON-state voltage, preventing the breakdown voltage from lowering, lowering the gate capacitance, and reducing the manufacturing costs.

Owner:FUJI ELECTRIC CO LTD

Semiconductor element and method for manufacturing same

ActiveUS20090101918A1Performance deteriorationGuaranteed equipment performanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor deviceSilicon carbide

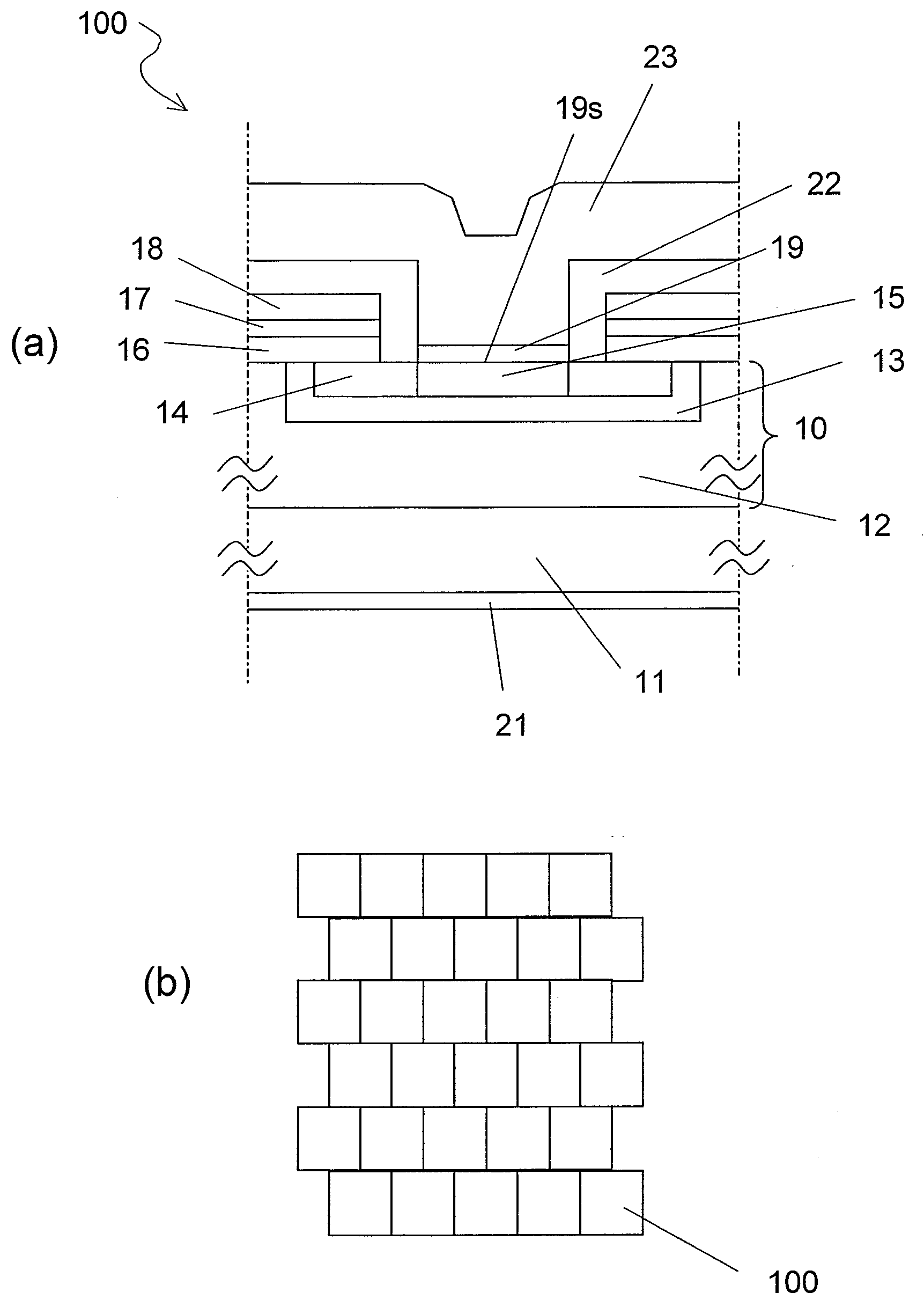

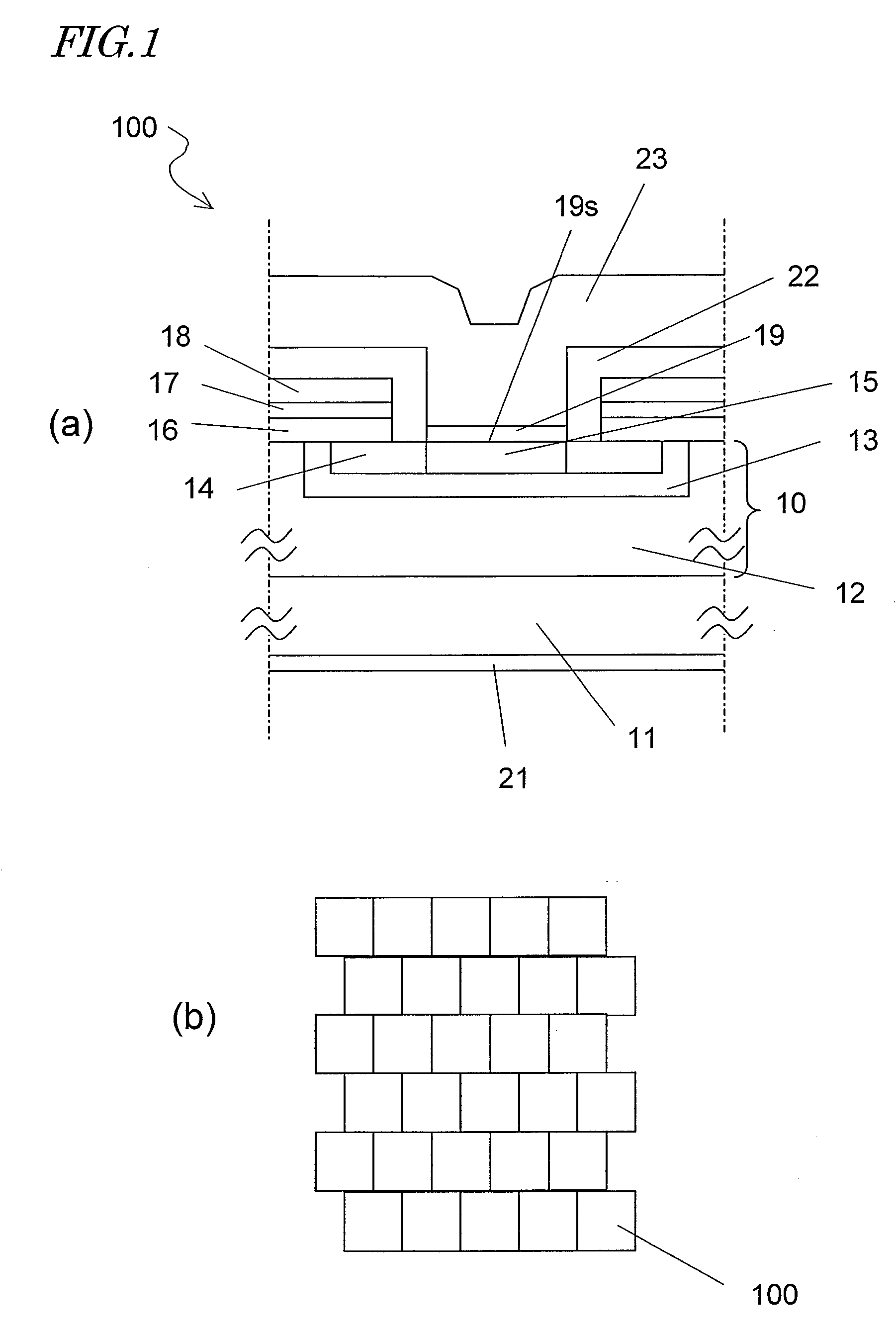

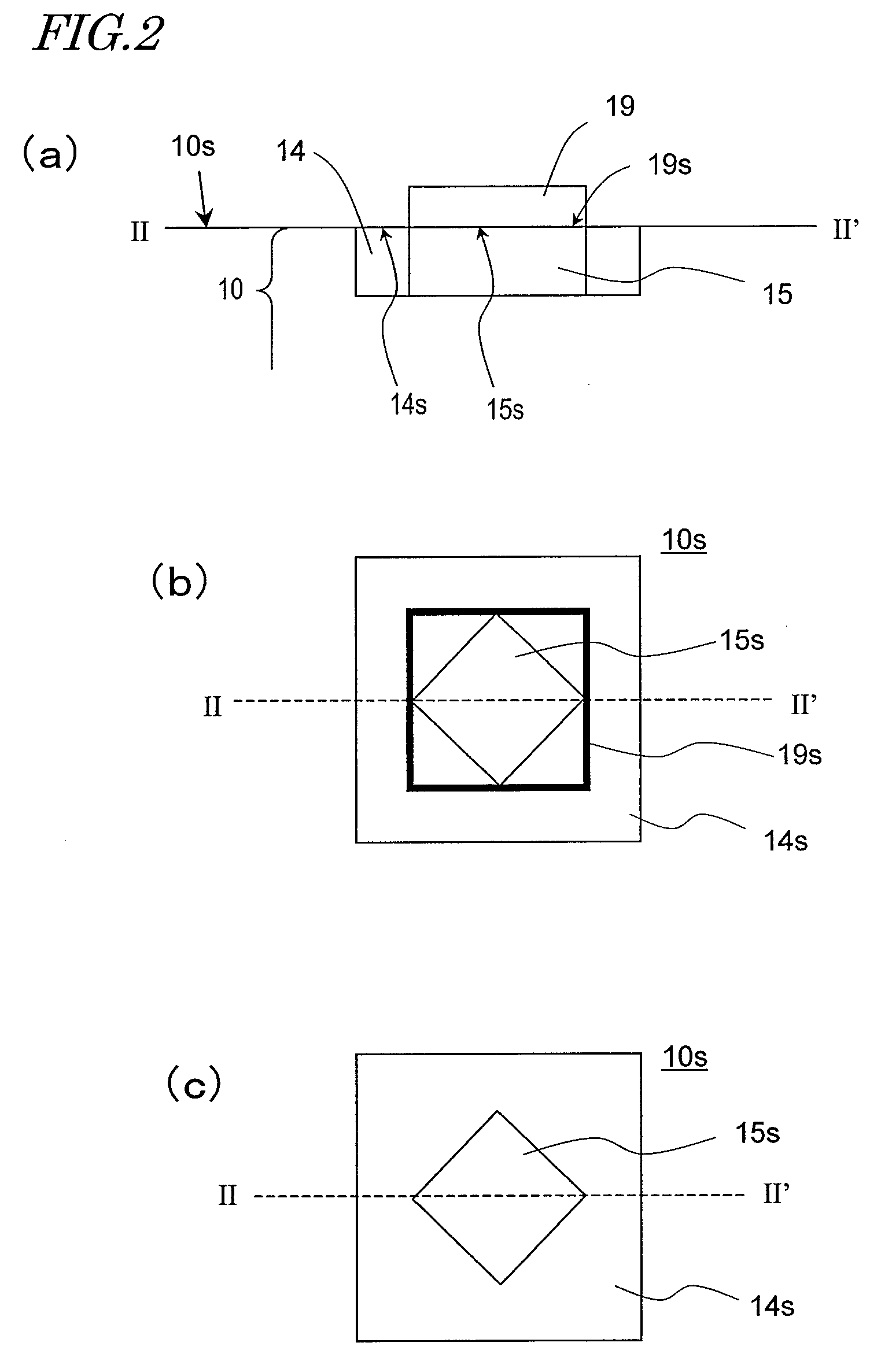

A semiconductor device includes: a semiconductor layer 10; a semiconductor region 15s of a first conductivity type defined on the surface 10s of the semiconductor layer; a semiconductor region 14s of a second conductivity type defined on the surface 10s of the semiconductor layer to surround the semiconductor region 15s; and a conductor 19 with a conductive surface 19s to contact with the semiconductor regions 15s and 14s. The semiconductor layer 10 includes silicon carbide. At least one of the semiconductor region 15s and the conductive surface 19s is not circular. The semiconductor region 15s and the conductive surface 19s are shaped such that as the degree of misalignment between the conductive surface 19s and the semiconductor region 15s increases from zero through one-third of the width of the conductive surface 19s, a portion of the profile of the conductive surface 19s that crosses the semiconductor region 15s has smoothly changing lengths.

Owner:PANASONIC CORP

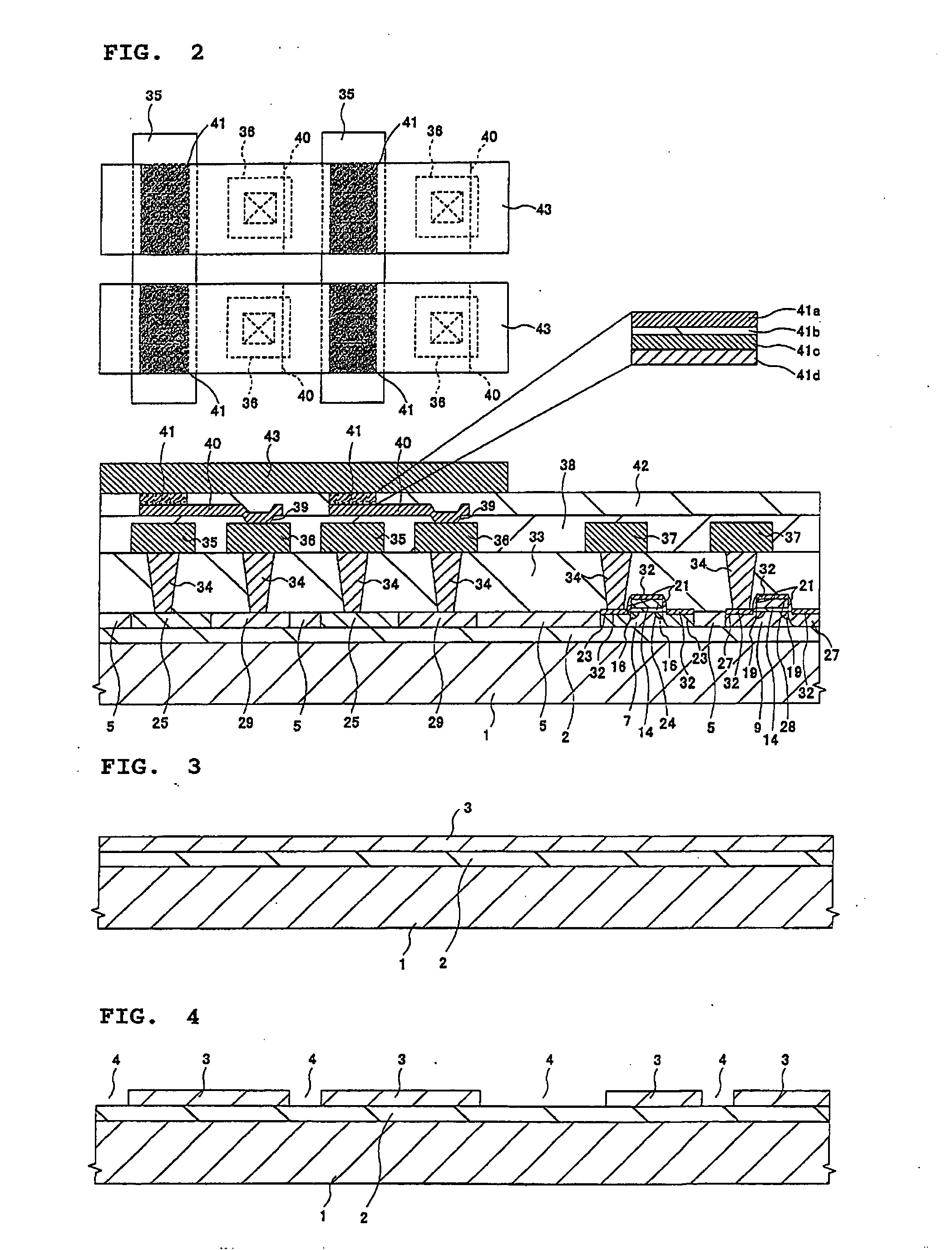

Image displaying method and image displaying device

InactiveUS20050042825A1Stable cell operationReduce cell areaSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateSemiconductor

Provided is an MRAM memory cell structure capable of preventing generation of parasitic transistors. Diodes are adopted as switching elements of an MRAM memory cell. An n-type semiconductor layer and a p-type semiconductor layer, which collectively constitute a diode, are formed on a surface semiconductor layer of an SOI substrate. The n-type semiconductor layer and the p-type semiconductor layer are disposed in a lateral direction and isolated by an isolation region, whereby the diode is isolated electrically from other elements and from the substrate.

Owner:IBM CORP

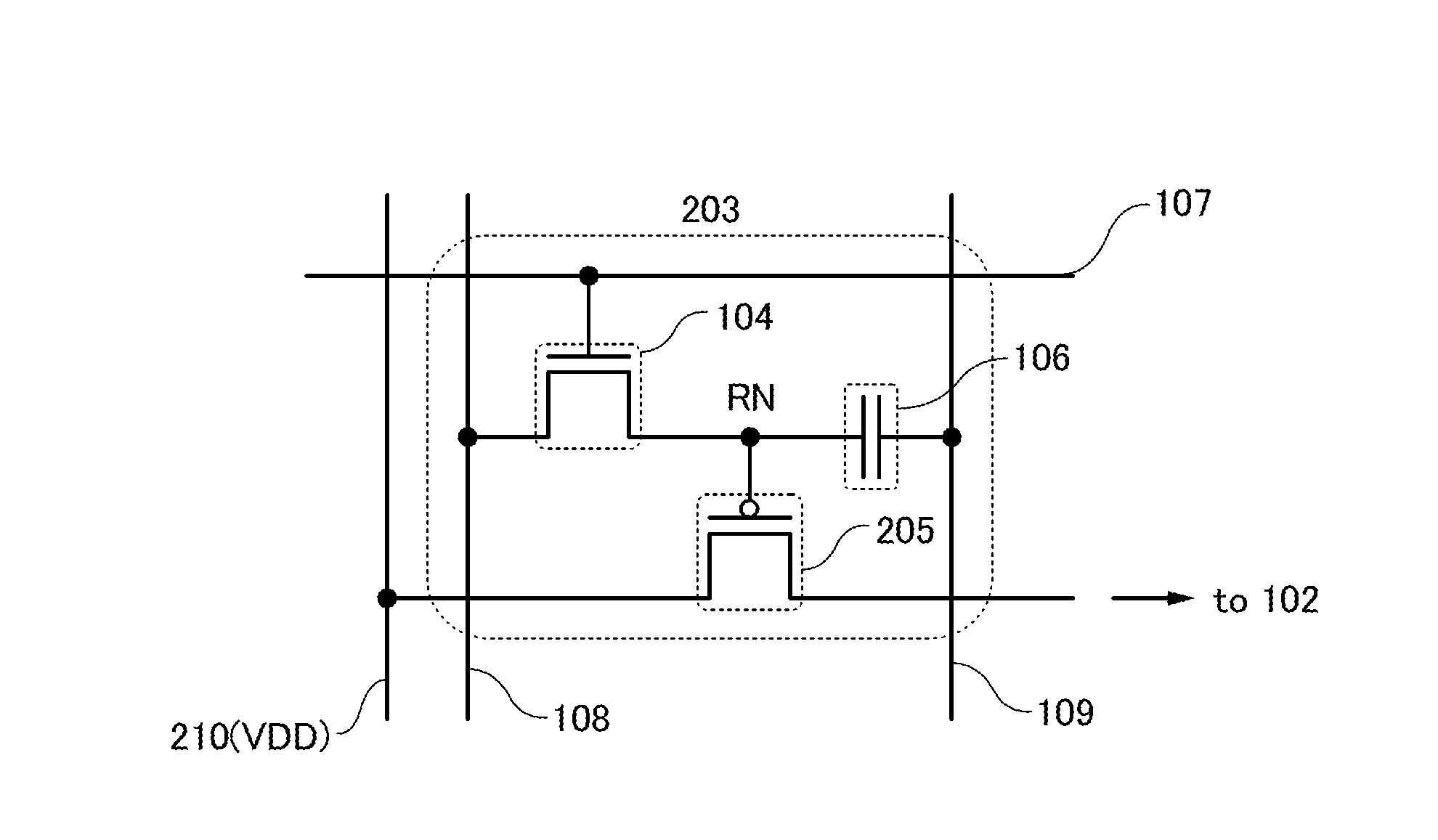

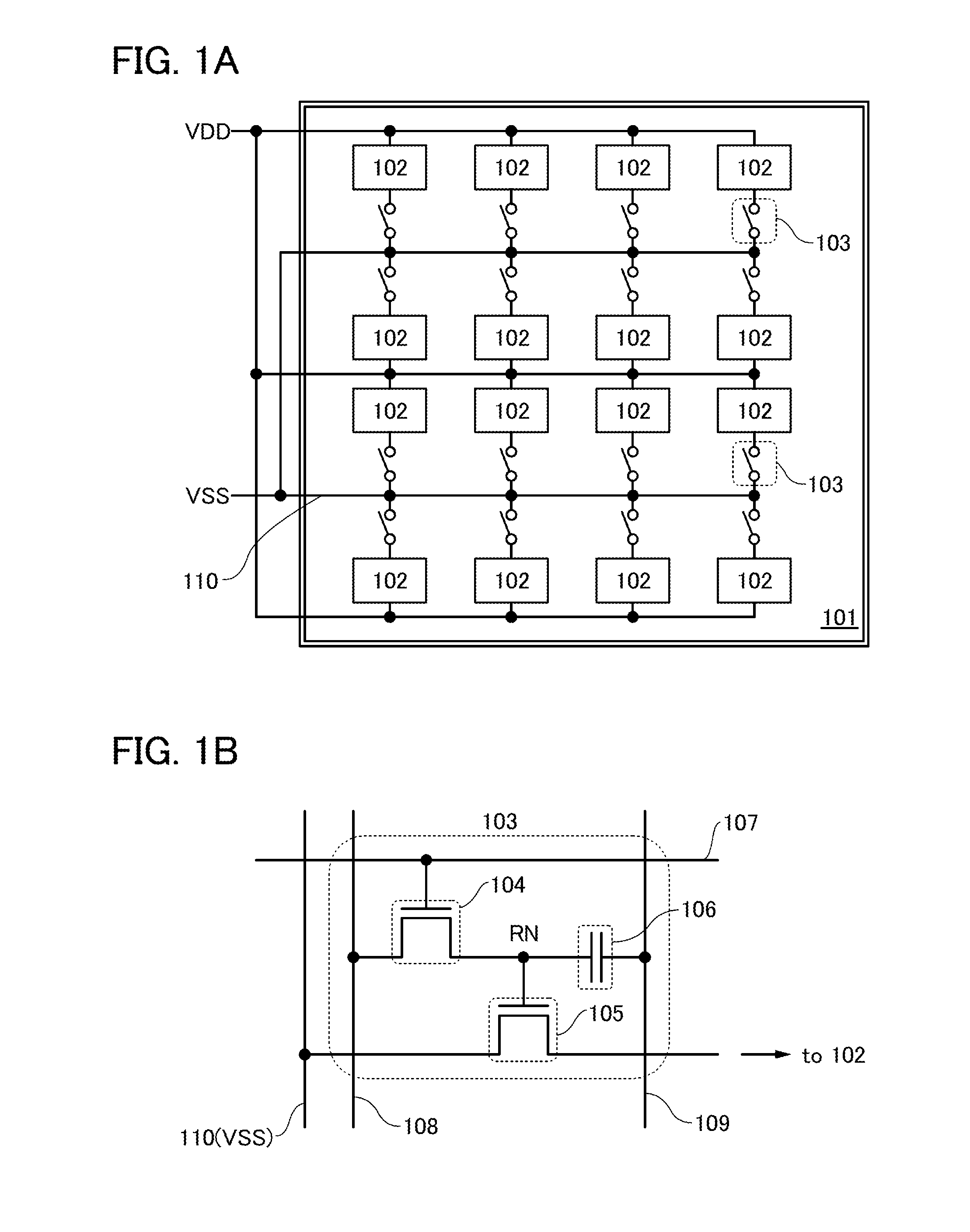

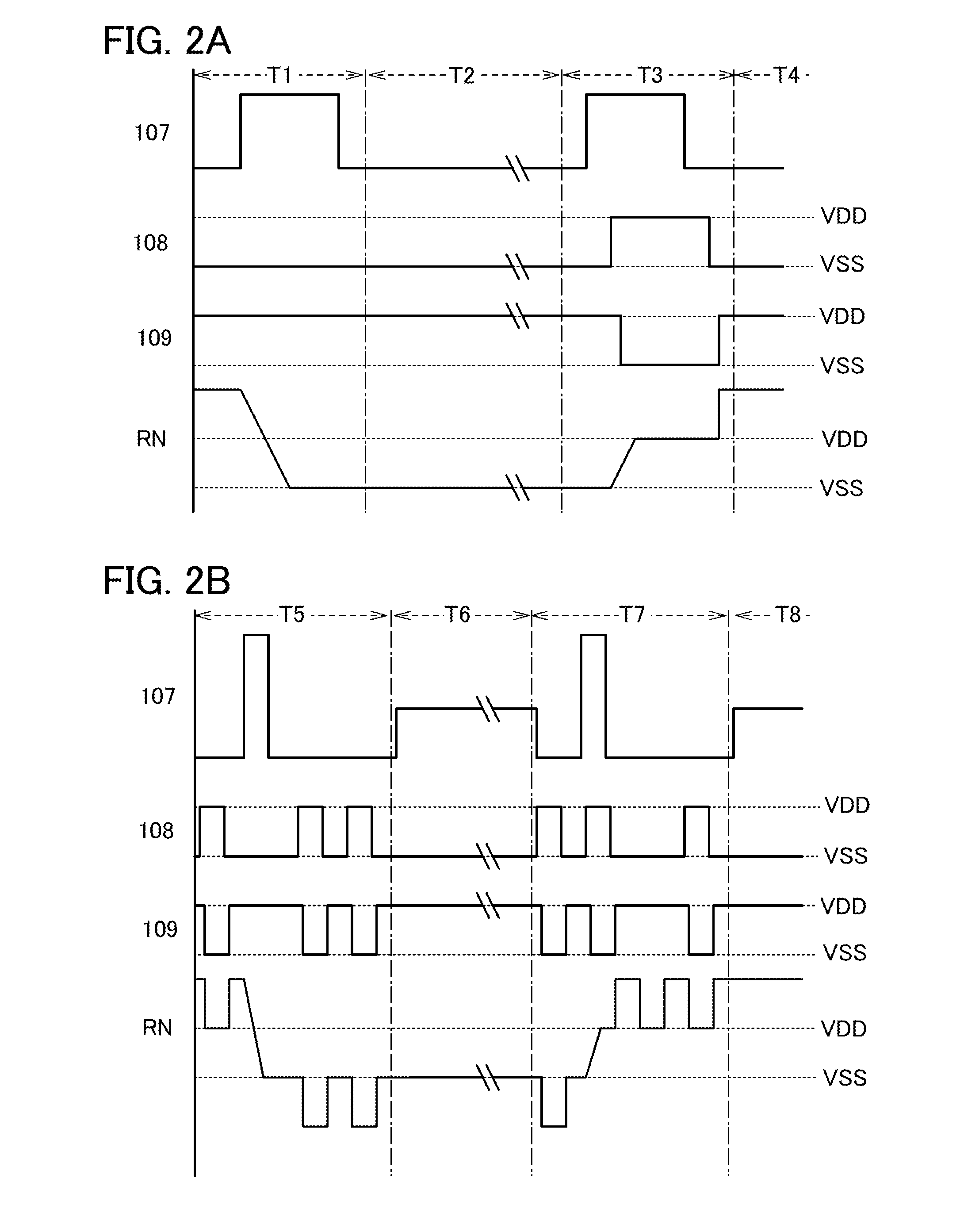

Method of driving semiconductor device

ActiveUS20130293266A1Reduce power consumptionLower on-state resistanceReliability increasing modificationsPower reduction by control/clock signalPower semiconductor deviceCapacitor

A programming element including a first transistor, a second transistor, and a capacitor between a logic circuit using a semiconductor element and a power supply is provided. In the programming element, a node where a drain electrode of the first transistor, a gate electrode of the second transistor, and one of electrodes of the capacitor are electrically connected to each other is formed. A potential can be supplied to each of a source electrode of the first transistor and the other of the electrodes of the capacitor. The power supply and the logic circuit are electrically connected to each other through a source electrode and a drain electrode of the second transistor. A connection state between the power supply and the logic circuit is controlled in accordance with the state of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

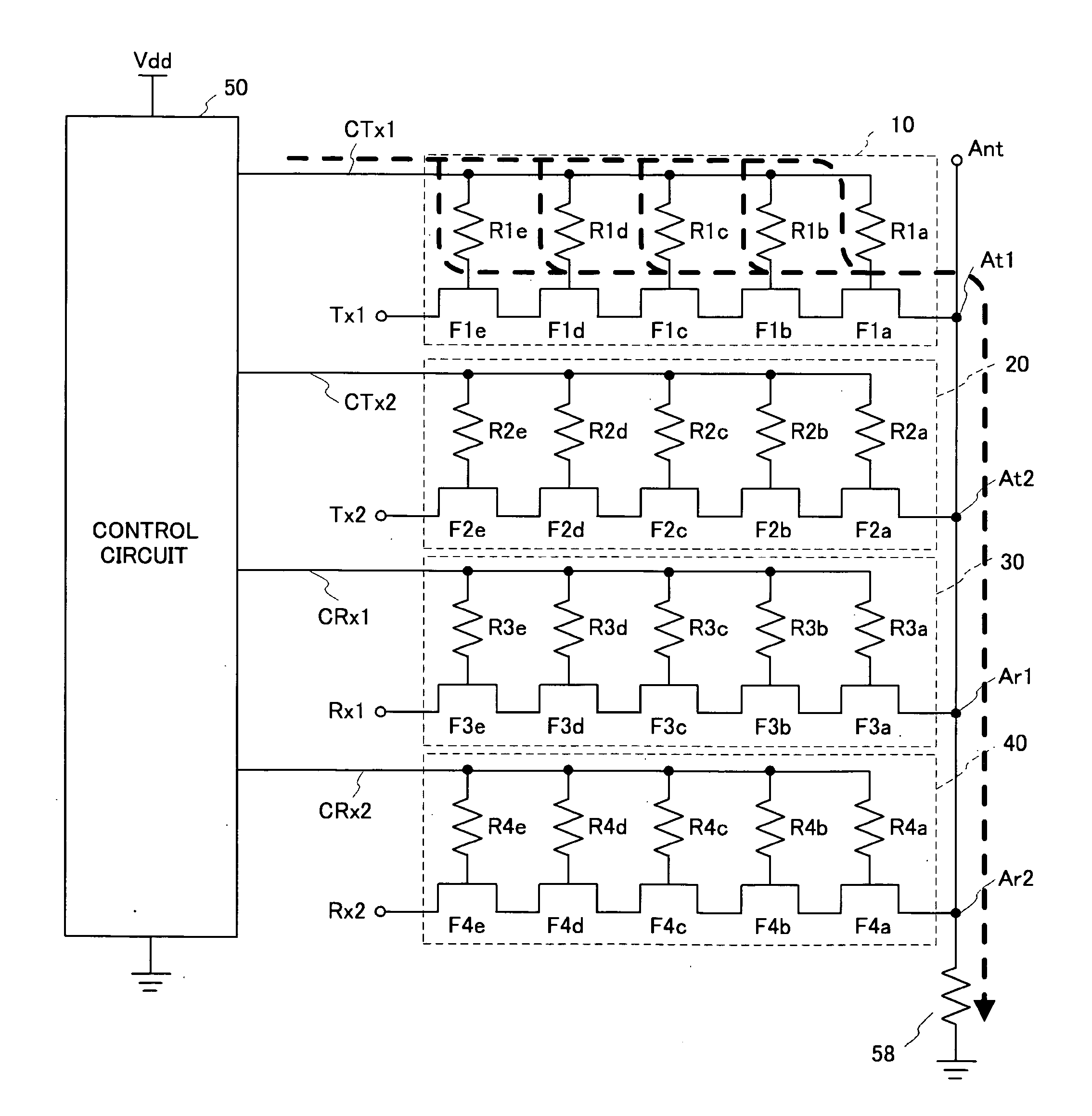

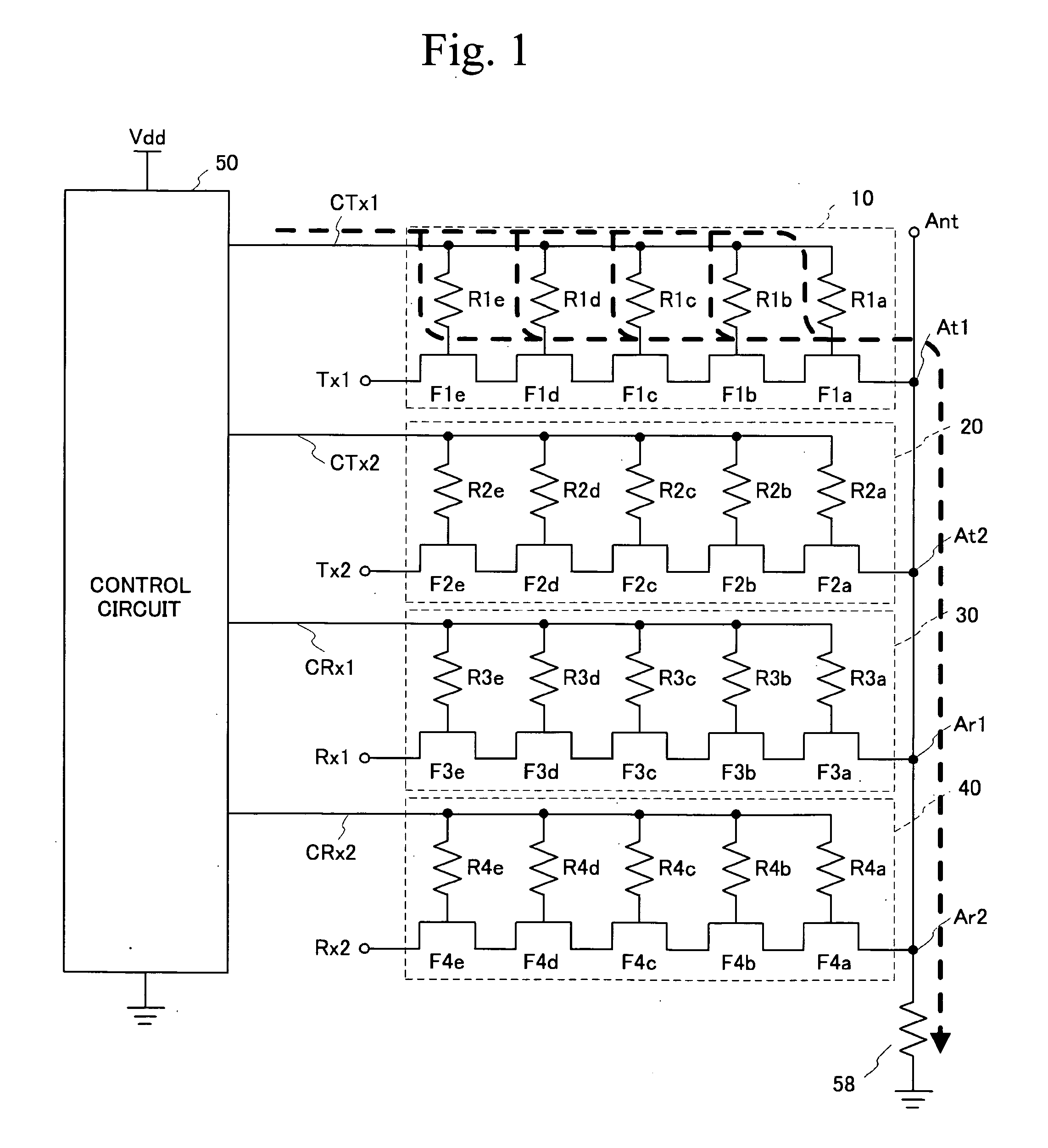

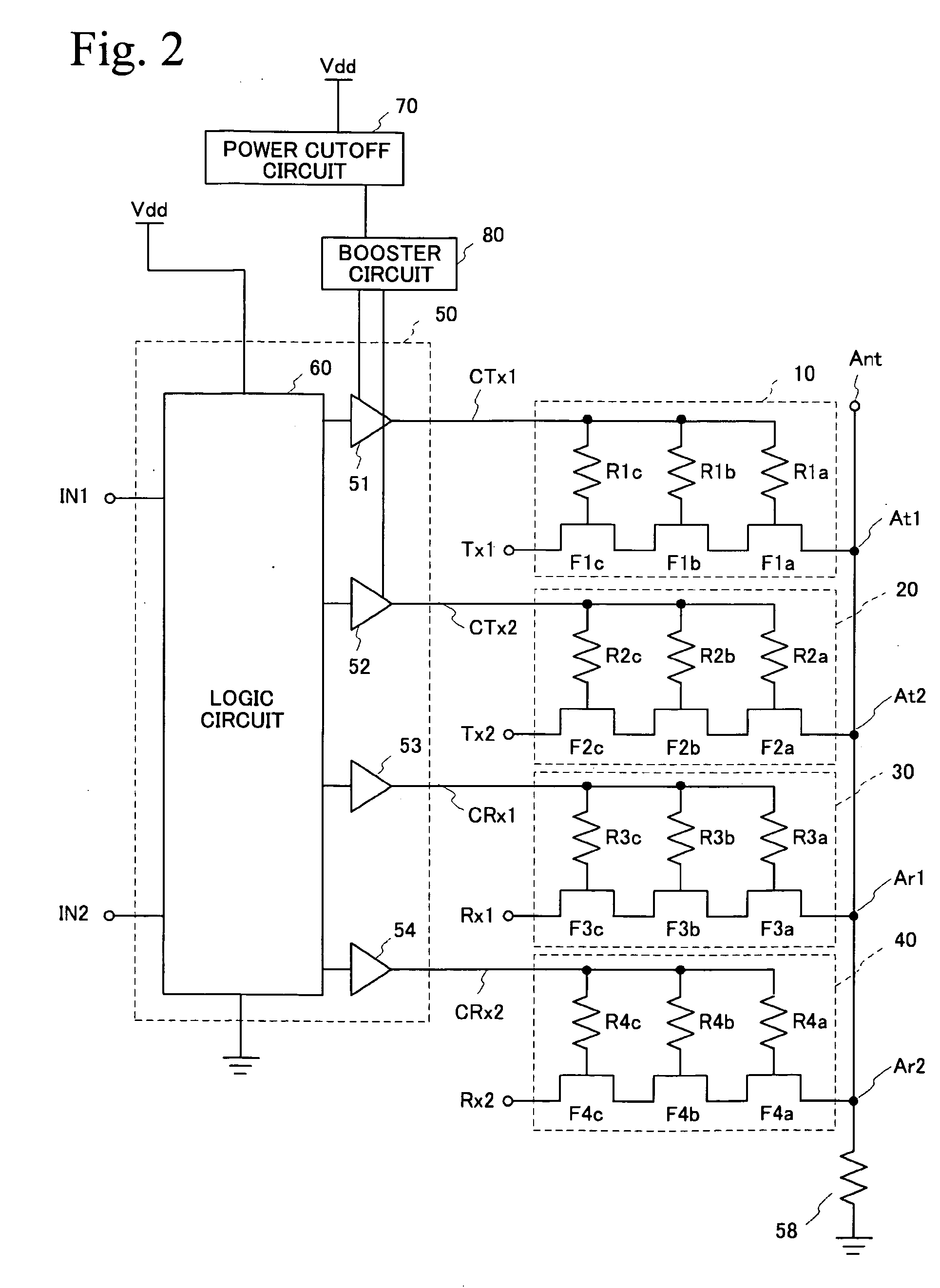

Semiconductor device and method of controlling the same

InactiveUS20070013432A1Reduce power leakageLower on-state resistanceTransistorElectronic switchingField-effect transistorSemiconductor

A semiconductor device includes: a transmission switch having multiple first FETs connected in series between a first terminal connected to a transmission part and a second terminal connected to a common connection portion, gates of the multiple first FETs being connected to transmission drive circuits; a reception switch having multiple second FETs connected in series between a third terminal connected to a reception part and a fourth terminal connected to the common connection portion, gates of the multiple second FETs being connected to reception drive circuits; and a booster circuit generates a boosted voltage having a positive or negative polarity on the basis of a given power supply voltage. When the transmission switch is in a conducting state, the boosted voltage is applied to gates of the multiple first FETs in order to switch the transmission switch to a non-conducting state.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

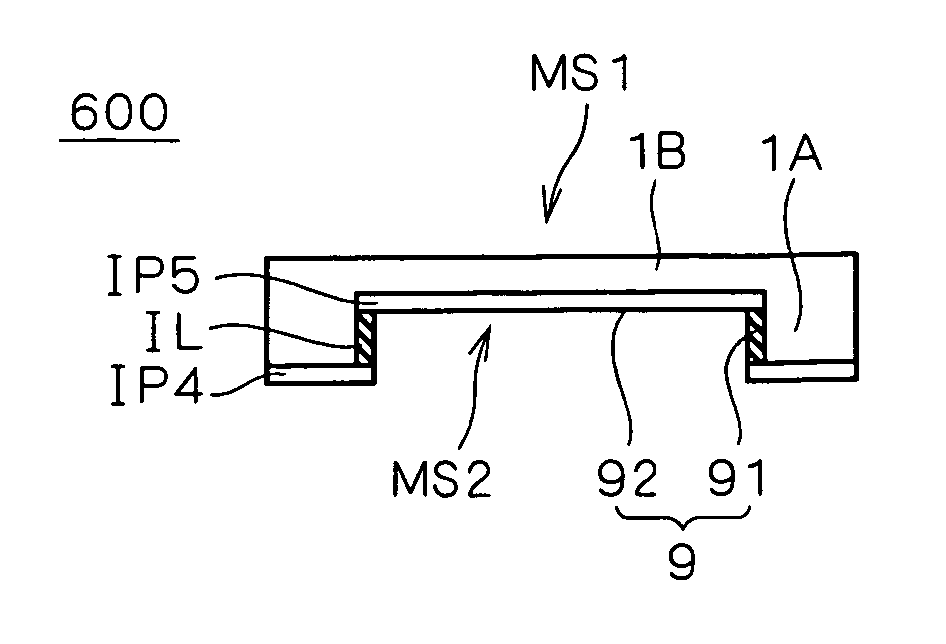

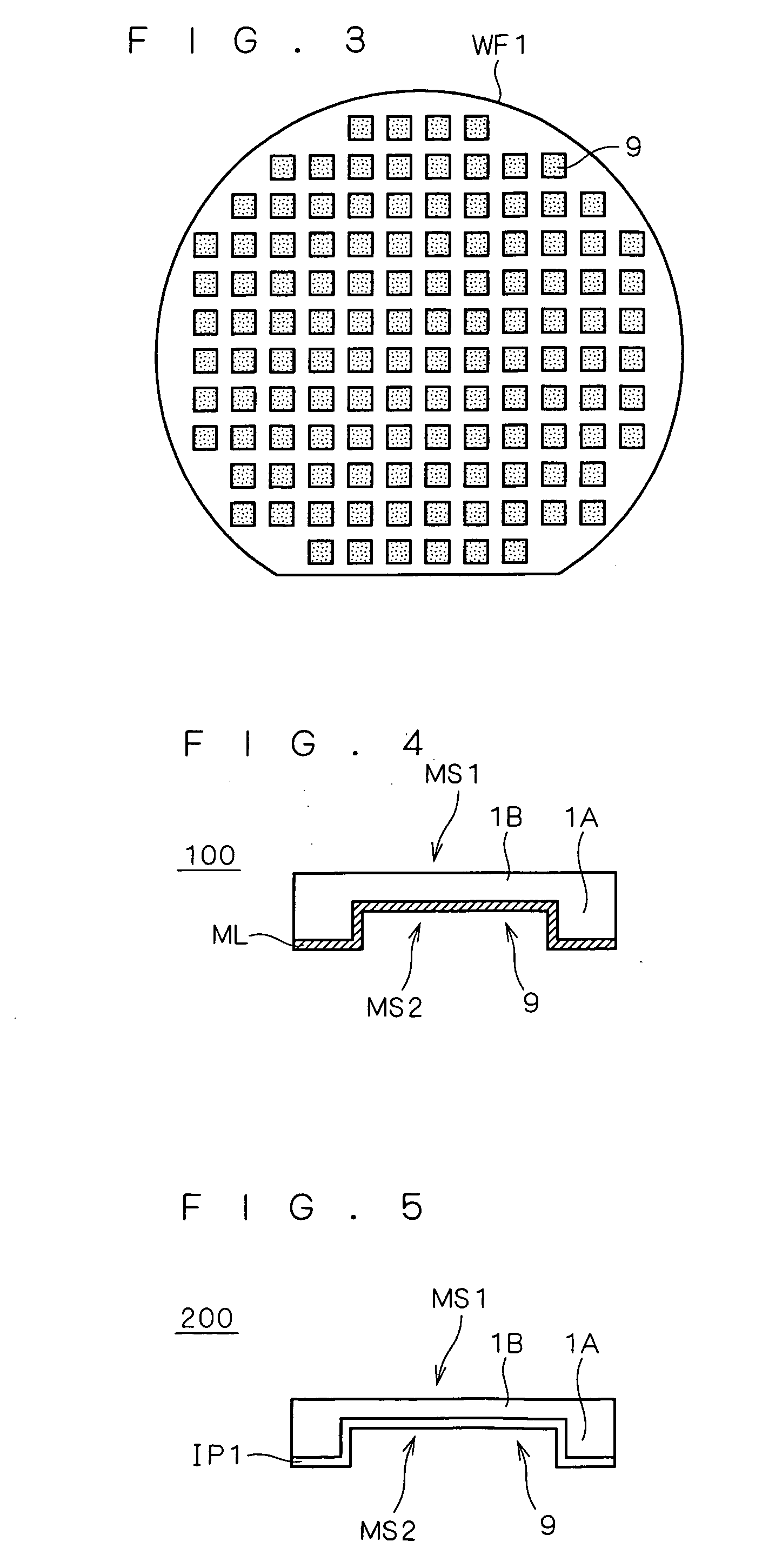

Semiconductor equipment

InactiveUS6940144B2Increase heat radiationCompact mountingTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

Semiconductor equipment includes a semiconductor substrate with a semiconductor layer embedded therein and a vertical type transistor. The substrate has a principal side, a rear side opposite to the principal side, and a trench disposed in the rear side of the substrate. The vertical type transistor has a first electrode disposed in the principal side of the substrate, a second electrode disposed in the rear side, and a diffusion region disposed in the principal side. The first electrode connects to the diffusion region through an interlayer insulation film. The second electrode is disposed in the trench and connects to the semiconductor layer exposed in the trench. This vertical transistor has a low ON-state resistance.

Owner:MX ENTERTAINMENT +1

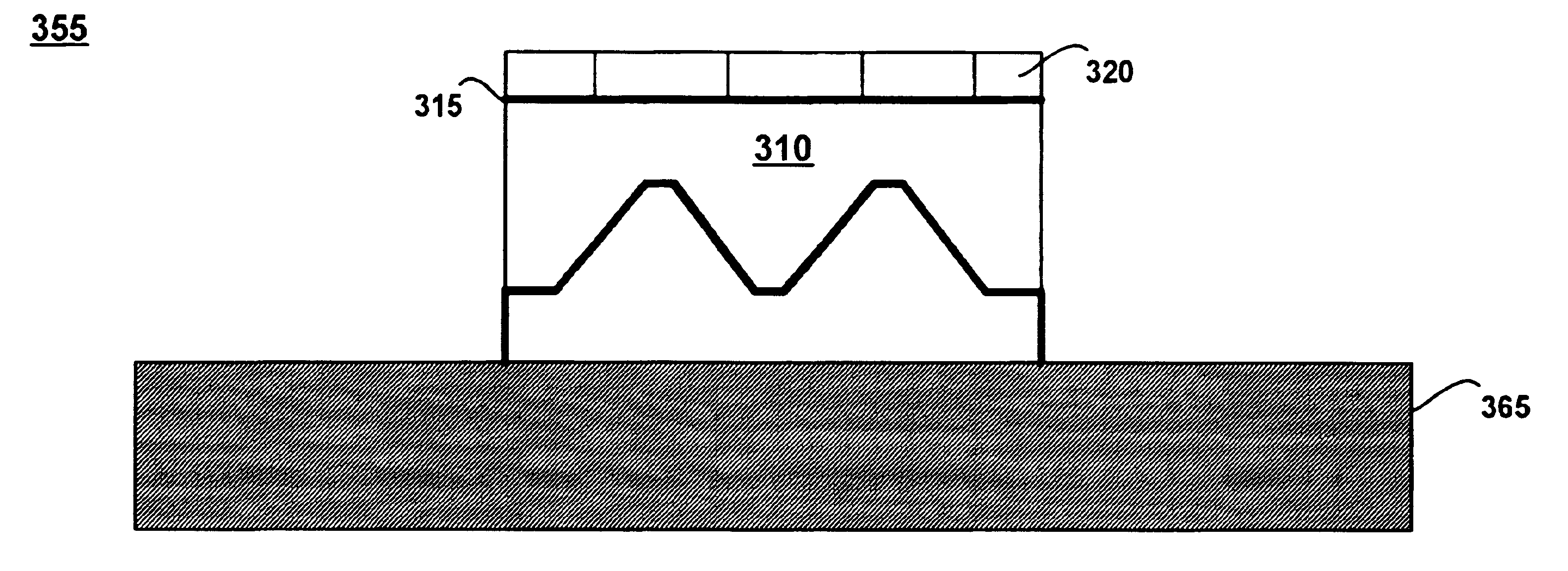

Metal-oxide-semiconductor device having trenched diffusion region and method of forming same

ActiveUS20080093667A1Lower on-state resistanceIncrease the output capacitanceTransistorSolid-state devicesSemiconductorMetal

An MOS device includes a semiconductor layer of a first conductivity type and first and second source / drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The first and second source / drain regions are spaced apart relative to one another. A gate is formed above and electrically isolated from the semiconductor layer, at least partially between the first and second source / drain regions. At least a given one of the first and second source / drain regions is configured having an effective width that is substantially greater than a width of a junction between the semiconductor layer and the given source / drain region.

Owner:BELL SEMICON LLC

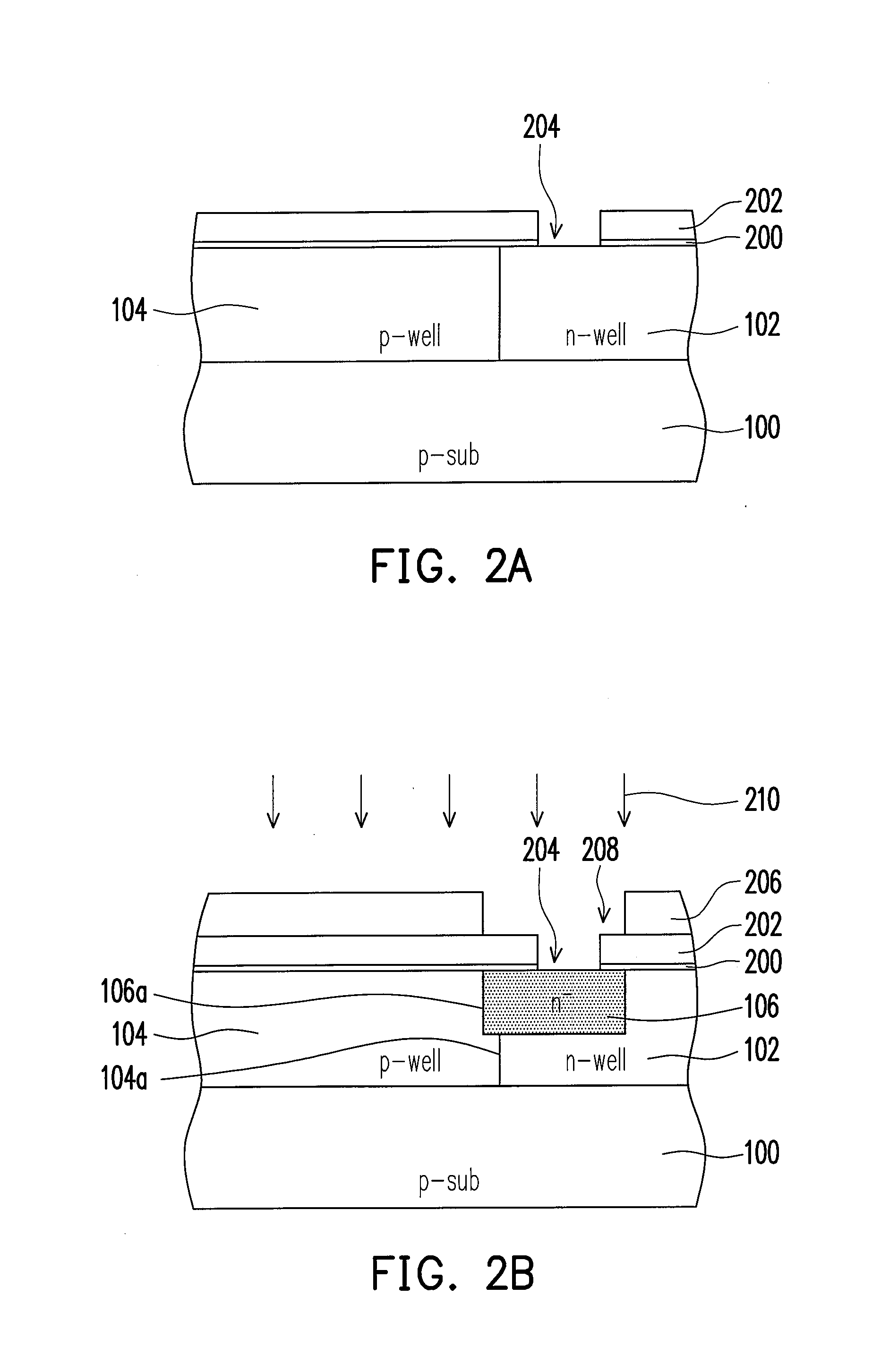

Low on-resistance lateral double-diffused mos device and method of fabricating the same

ActiveUS20080315308A1Lower on-state resistanceIncrease saturation currentSemiconductor/solid-state device detailsSolid-state devicesEngineeringField oxide

A lateral-double diffused MOS device is provided. The device includes: a first well having a first conductive type and a second well having a second conductive type disposed in a substrate and adjacent to each other; a drain and a source regions having the first conductive type disposed in the first and the second wells, respectively; a field oxide layer (FOX) disposed on the first well between the source and the drain regions; a gate conductive layer disposed over the second well between the source and the drain regions extending to the FOX; a gate dielectric layer between the substrate and the gate conductive layer; a doped region having the first conductive type in the first well below a portion of the gate conductive layer and the FOX connecting to the drain region. A channel region is defined in the second well between the doped region and the source region.

Owner:MACRONIX INT CO LTD

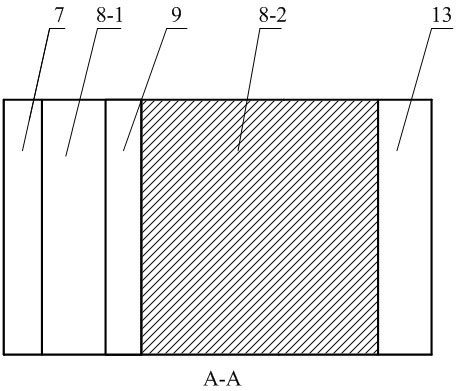

SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157550AReduce adverse effectsImprove vertical pressure resistanceSemiconductor devicesMetal electrodesConductivity modulation

The invention relates to an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The existing products restrict the improvement of the device structures and the electrical properties. The device unit comprises a p-type semiconductor substrate, a buried oxide layer and a p buried layer region in sequence, wherein a metal gate, an n-type heavily doped polysilicon gate, a gate oxide layer and an n-type lightly doped drift region are arranged at the top of the p buried layer region side by side in sequence; a first p-type well region and an n-type buffer region are respectively embedded at the two sides at the top of the n-type lightly doped drift region; an n-type cathode region and a first p well ohmic contact region are embedded at the top of the first p-type well region; a second p-type well region and an anode short-circuit point region are embedded at the top of the n-type buffer region; a second p well ohmic contact region is embedded at the top of the second p-type well region; and a first field oxide layer, a second field oxide layer, an anode metal electrode and a cathode metal electrode are arranged at the top of the device unit. The device unit has the beneficial effects of reducing the spreading resistance, improving the conductivity modulation effect of the drift region, reducing the on-state power consumption and obviously improving the thermal property of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

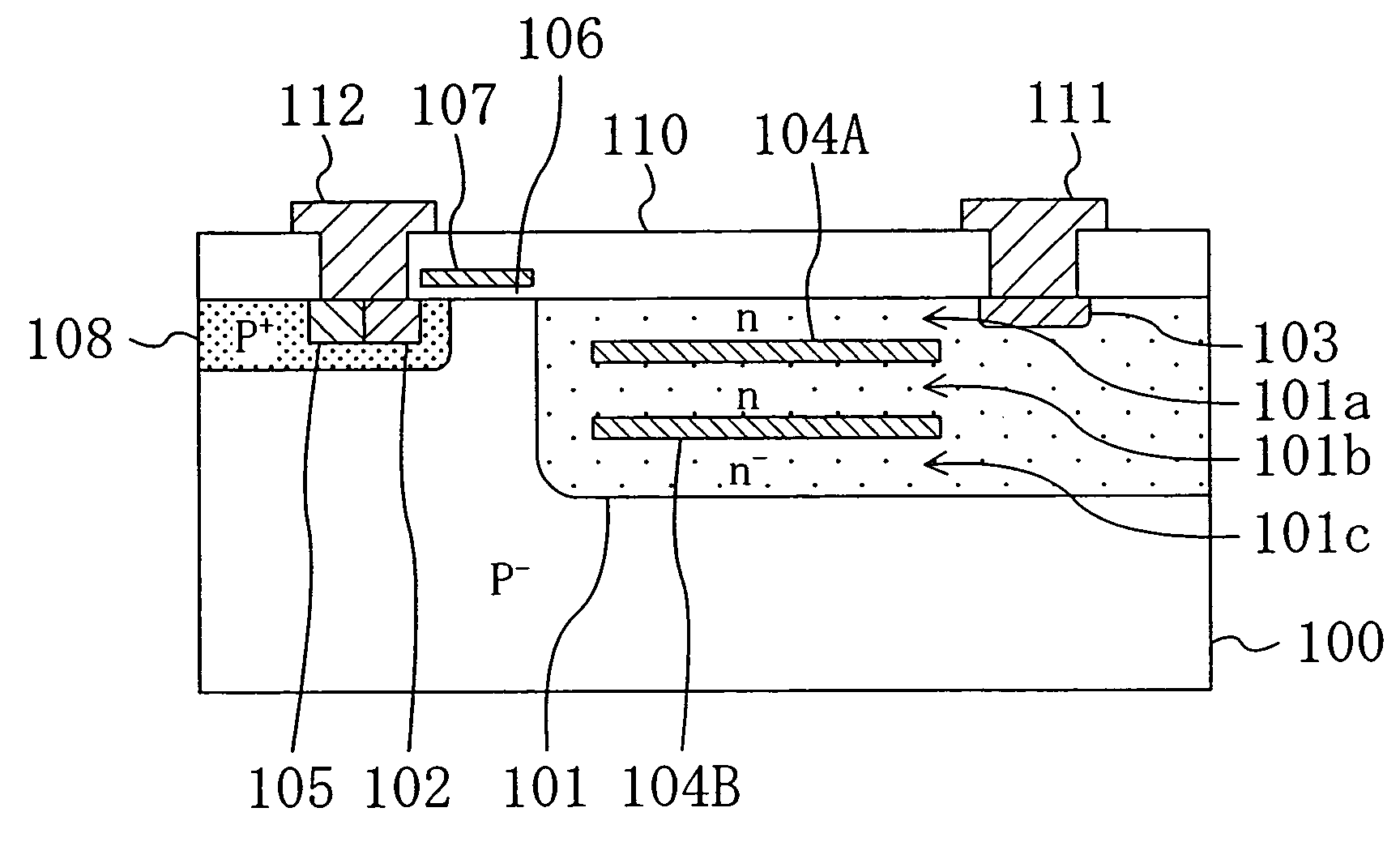

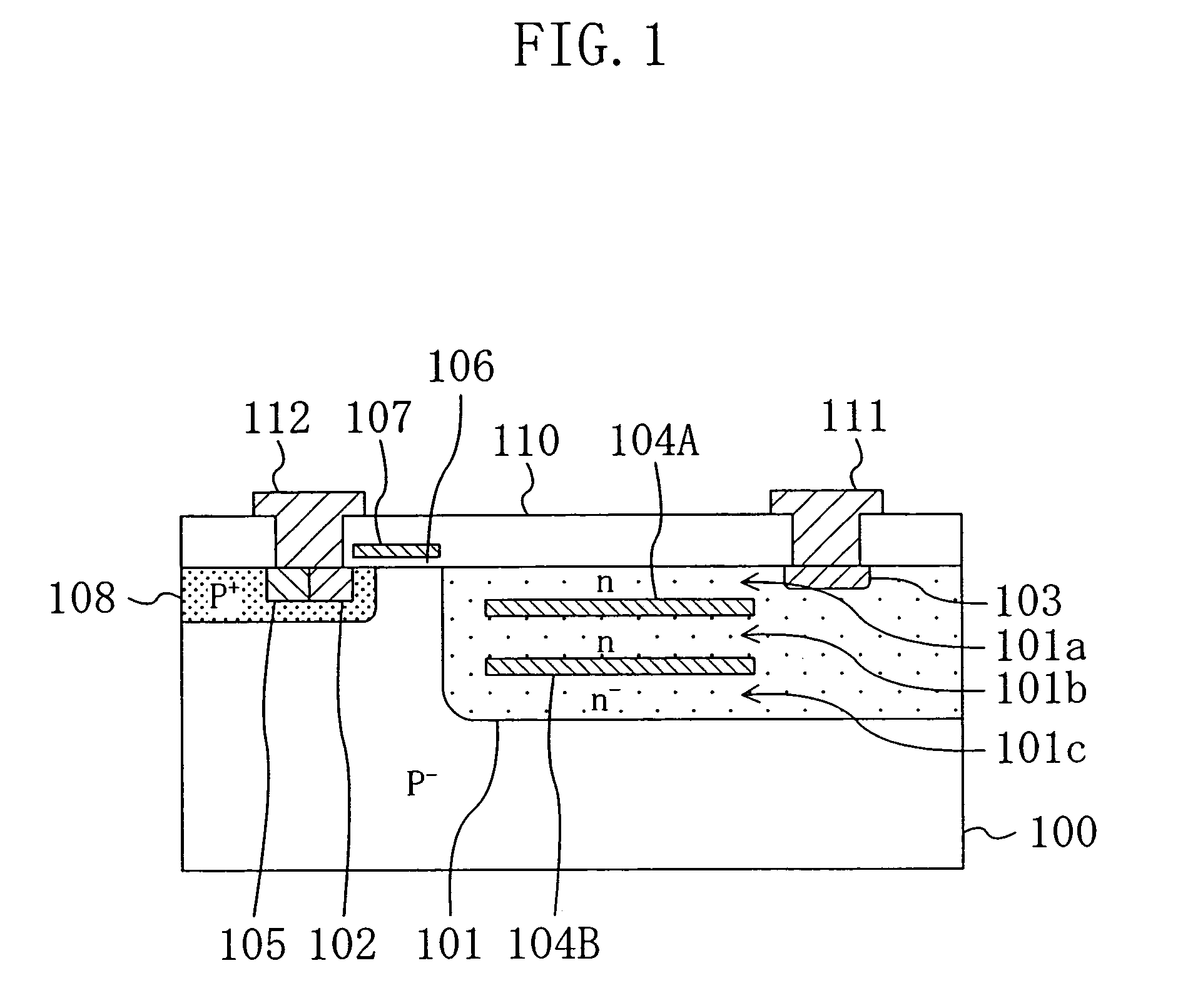

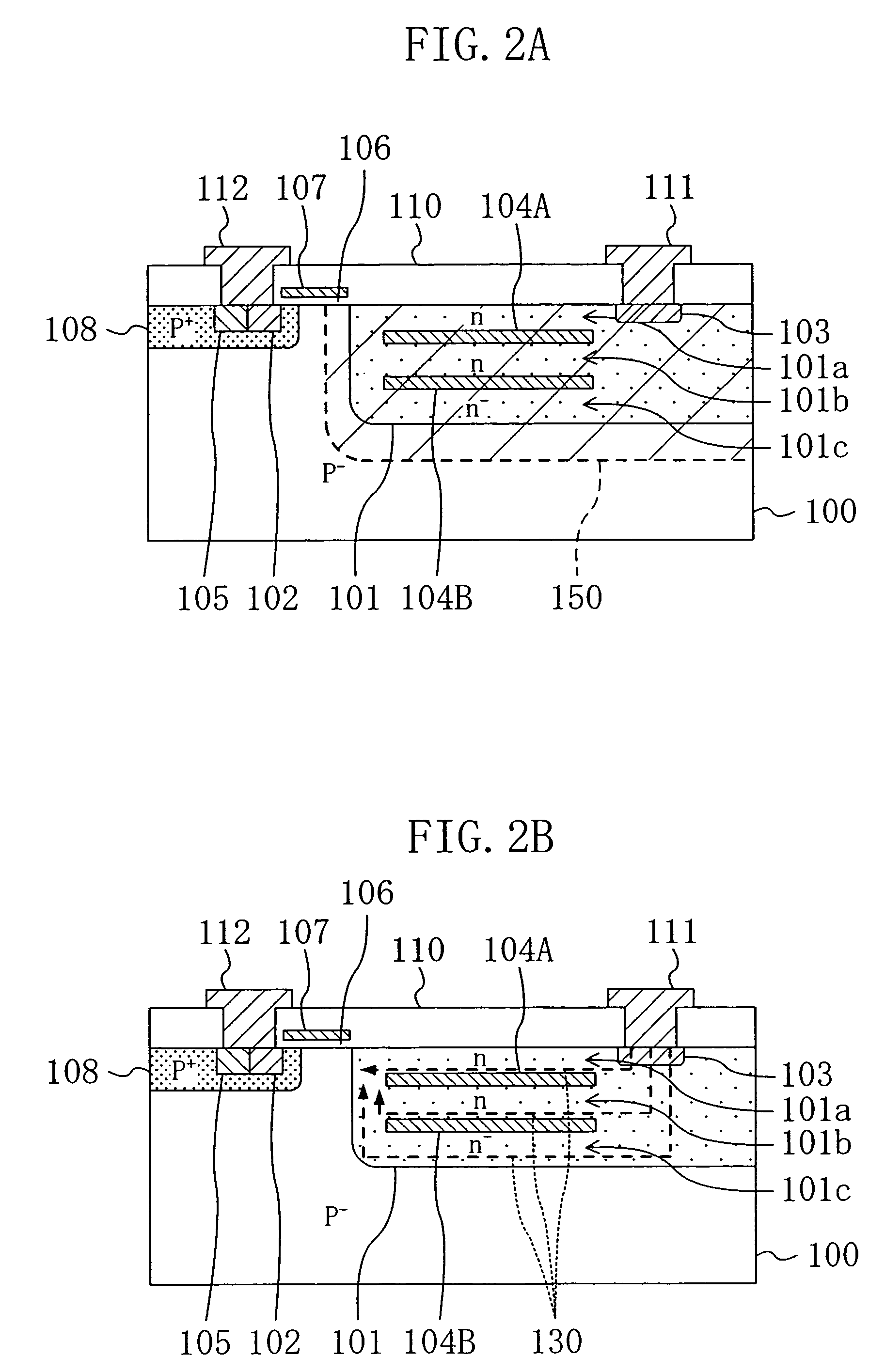

Method of manufacturing a semiconductor device having a high breakdown voltage and low on-resistance

InactiveUS7008865B2Reliably formLower on-state resistanceSemiconductor/solid-state device detailsSolid-state devicesSubstrate surfaceSemiconductor

A semiconductor device includes a semiconductor substrate of a first conductivity type, in which an extended drain region of a second conductivity type and a source region of the second conductivity type are formed with an interval therebetween, wherein the extended drain region includes a plurality of buried layers, each formed by burying an impurity layer of the first conductivity type, the plurality of buried layers extending substantially parallel to a substrate surface and with an interval therebetween in a depth direction. A concentration of an impurity of the second conductivity type in the extended drain region at a depth of about 6 μm from the substrate surface is about 1×1015 / cm3 or more and is about 30% or more of that at a depth of about 2 μm from the substrate surface.

Owner:PANASONIC CORP

Silicon carbide semiconductor device having junction field effect transistor and method for manufacturing the same

ActiveUS7230275B2Reduce resistanceLower on-state resistanceTransistorSemiconductor/solid-state device manufacturingField-effect transistorSemiconductor

Owner:DENSO CORP

Semiconductor device

InactiveCN102403315ALower on-state resistanceSuppress leakage currentSolid-state devicesDiodeMOSFETPower semiconductor device

The present invention provides a semiconductor device capable of reducing on-resistance of an MOSFET and suppressing leakage current of a Schottky barrier diode. The semiconductor device includes: a first semiconductor layer of a first conductivity type; a second semiconductor layer of a second conductivity type, provided on the first semiconductor layer; a third semiconductor layer of the first conductivity type, provided on the second semiconductor layer; an embedded electrode provided in a first trench via a first insulating film; a control electrode provided above the embedded electrode via a second insulating film in the first trench; a fourth semiconductor layer of the second conductivity type, selectively provided in the first semiconductor layer and connected to a lower end of a second trench; a first main electrode electrically connected to the first semiconductor layer; and a second main electrode provided in the second trench and connected to the second semiconductor layer, the third semiconductor layer and the fourth semiconductor layer. The embedded electrode is electrically connected to one of the second main electrode and the control electrode. A Schottky junction formed of the second main electrode and the first semiconductor layer is formed at a sidewall of the second trench.

Owner:KK TOSHIBA

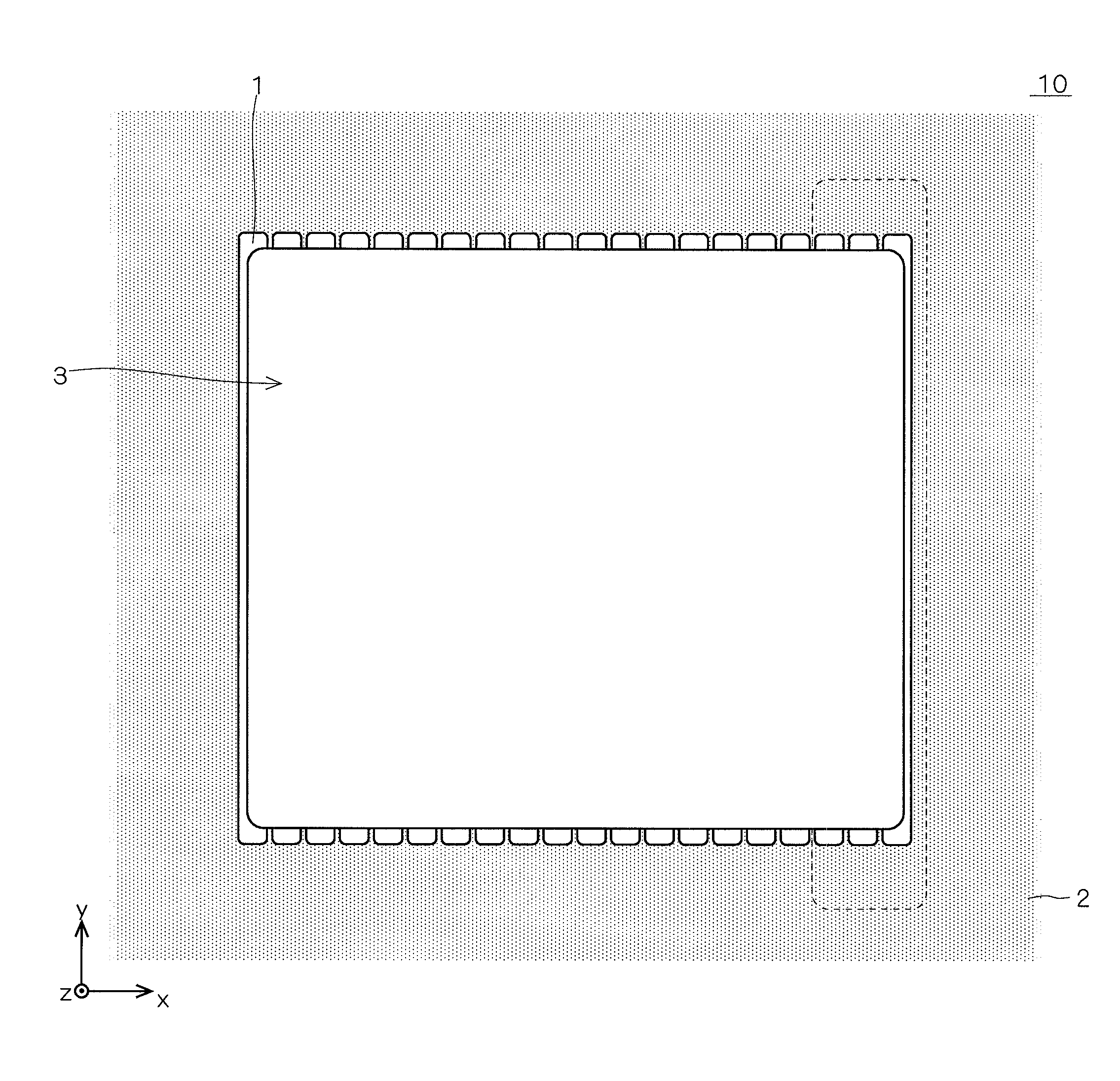

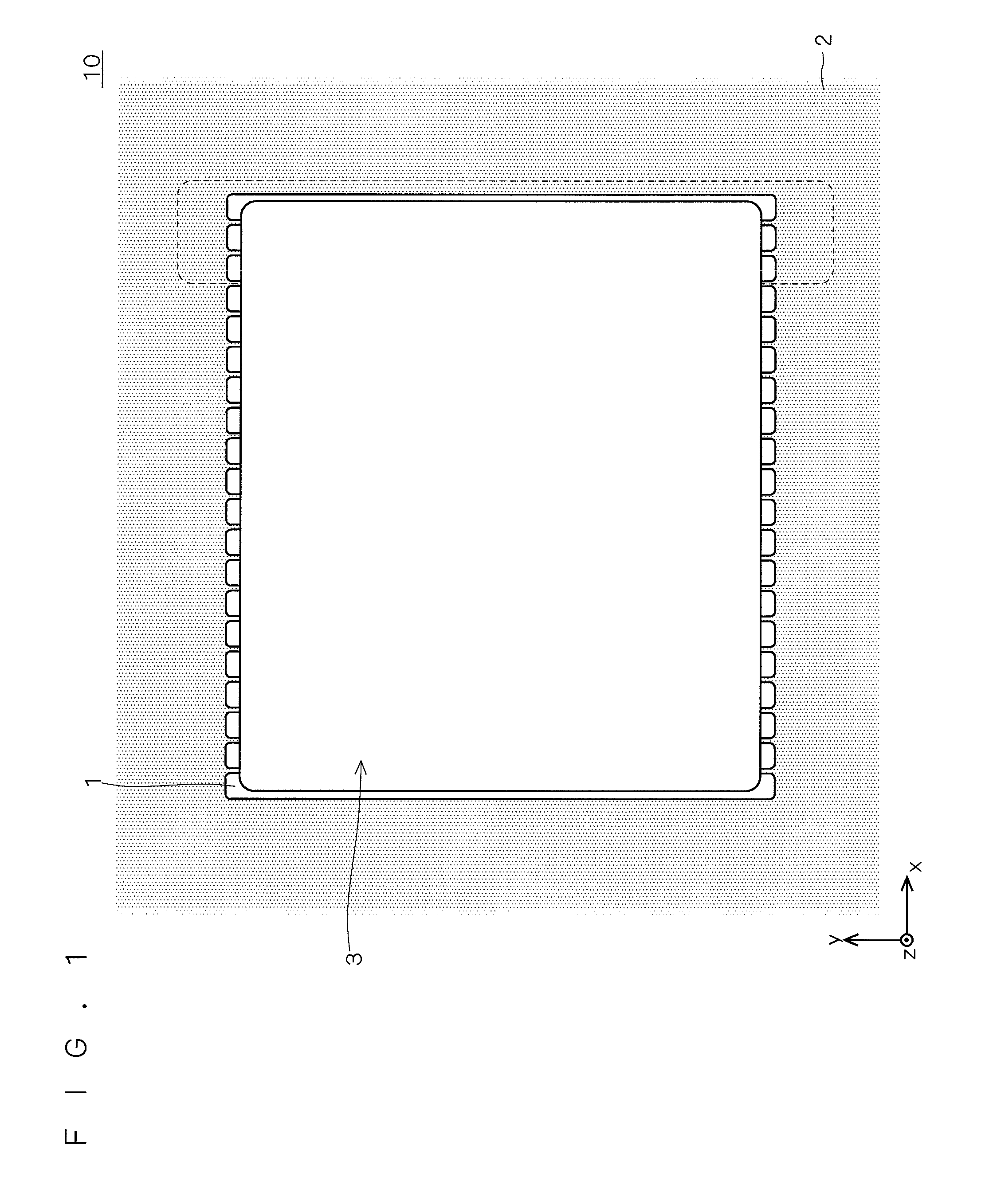

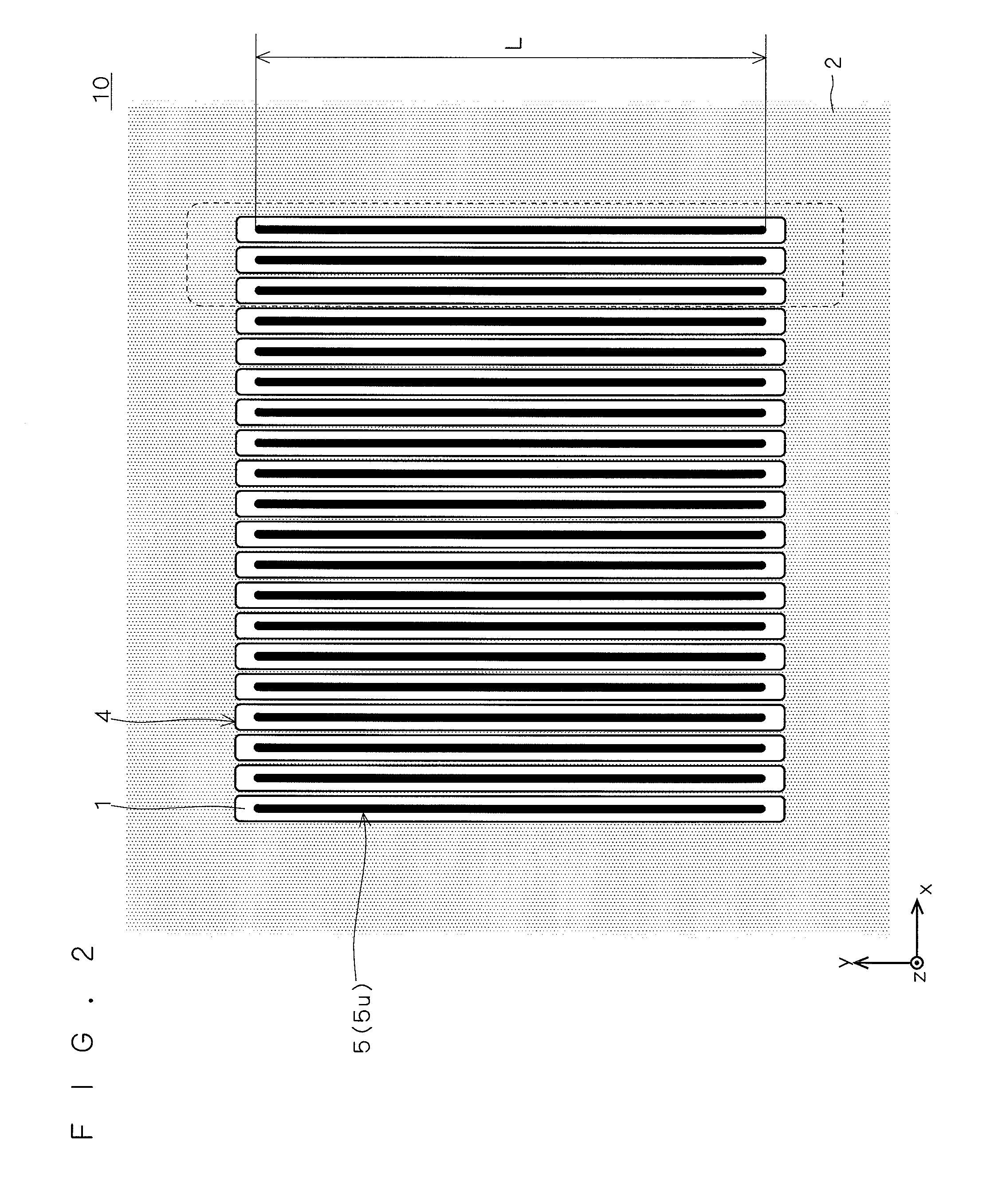

Semiconductor substrate with trenches for reducing substrate resistance

InactiveUS6858471B1Lowering substrate resistanceAssure mechanical stiffnessRelieving strain on wire connectionSolid-state devicesElectrical resistance and conductanceConductive materials

In one embodiment of the present invention, a method for fabricating semiconductor devices comprises forming an active region about a front-side of a substrate. A plurality of trenches are then formed about a back-side of the substrate. A grid of banks separates the trenches. A conductive material is then applied to the back-side of the substrate. The trenches and the conductive material act to reduce the on-state resistance of the substrate and enhance thermal conductivity, while the grid of banks maintains the structural strength of the wafer.

Owner:VISHAY SILICONIX LLC

Semiconductor device

InactiveUS20070228519A1Excellent propertyMaintain good propertiesTransistorSemiconductor/solid-state device manufacturingElectric fieldCathode electrode

A semiconductor device made of a group-III nitride semiconductor having excellent properties is provided. The semiconductor device has a horizontal diode structure of Schottky type or P—N junction type, or combined type thereof having a main conduction pathway in the horizontal direction in a conductive layer with unit anode portions and unit cathode electrodes being integrated adjacently to each other in the horizontal direction. The conductive layer is preferably formed by depositing a group-III nitride layer and generating a two-dimensional electron gas layer on the interface. Forming the conductive layer of the group-III nitride having high breakdown field allows the breakdown voltage to be kept high while the gap between electrodes is narrow, which achieves a semiconductor device having high output current per chip area. Further, an electrode pad layer provided on an insulation protecting layer relieves electric field concentration at a junction of each unit anode portion and each unit cathode electrode, which achieves higher breakdown voltage.

Owner:NGK INSULATORS LTD

Semiconductor device

InactiveUS7084437B2Avoid it happening againExcellent in size advantageSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateUnit structure

Provided is an MRAM memory cell structure capable of preventing generation of parasitic transistors. Diodes are adopted as switching elements of an MRAM memory cell. An n-type semiconductor layer and a p-type semiconductor layer, which collectively constitute a diode, are formed on a surface semiconductor layer of an SOI substrate. The n-type semiconductor layer and the p-type semiconductor layer are disposed in a lateral direction and isolated by an isolation region, whereby the diode is isolated electrically from other elements and from the substrate.

Owner:INT BUSINESS MASCH CORP

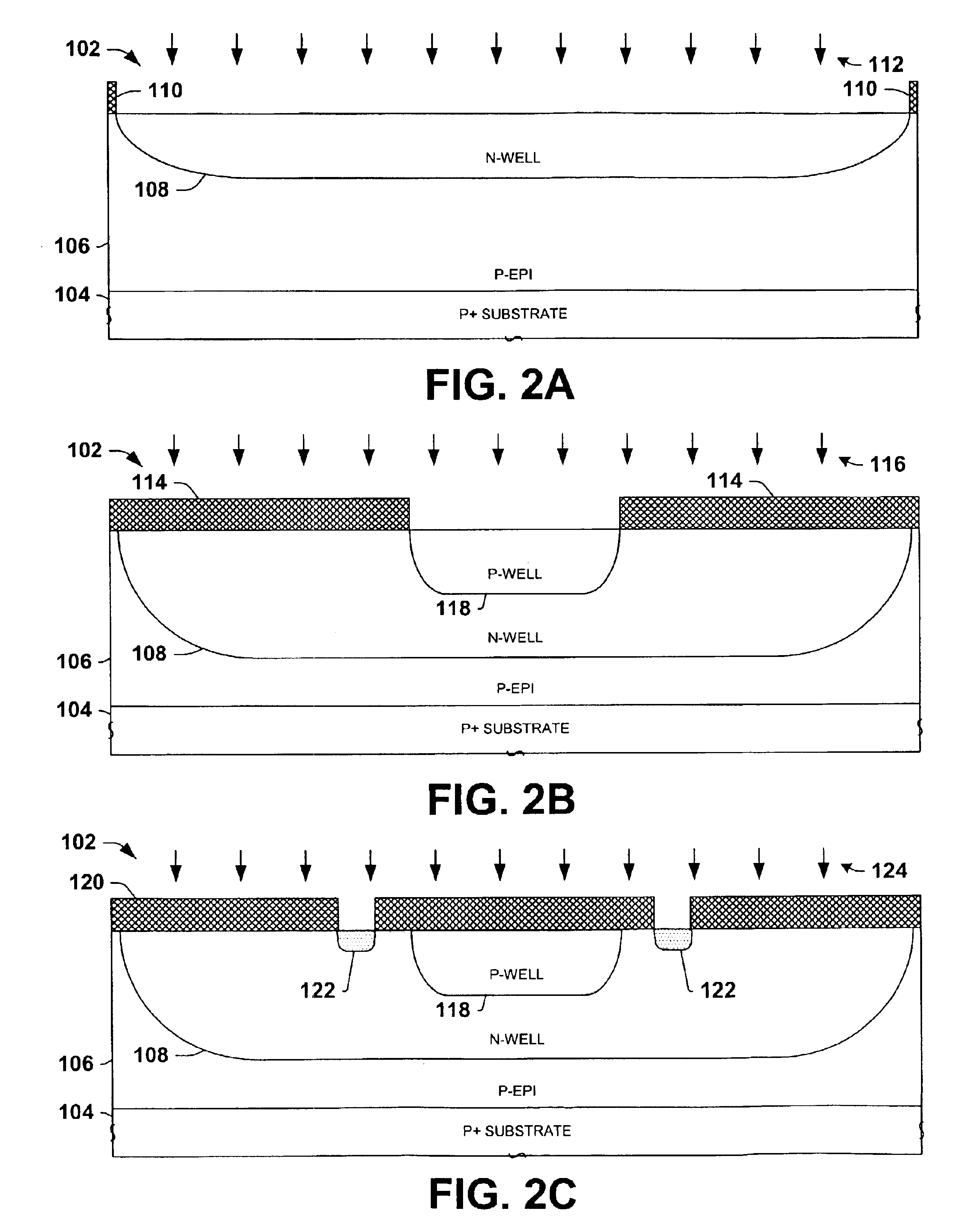

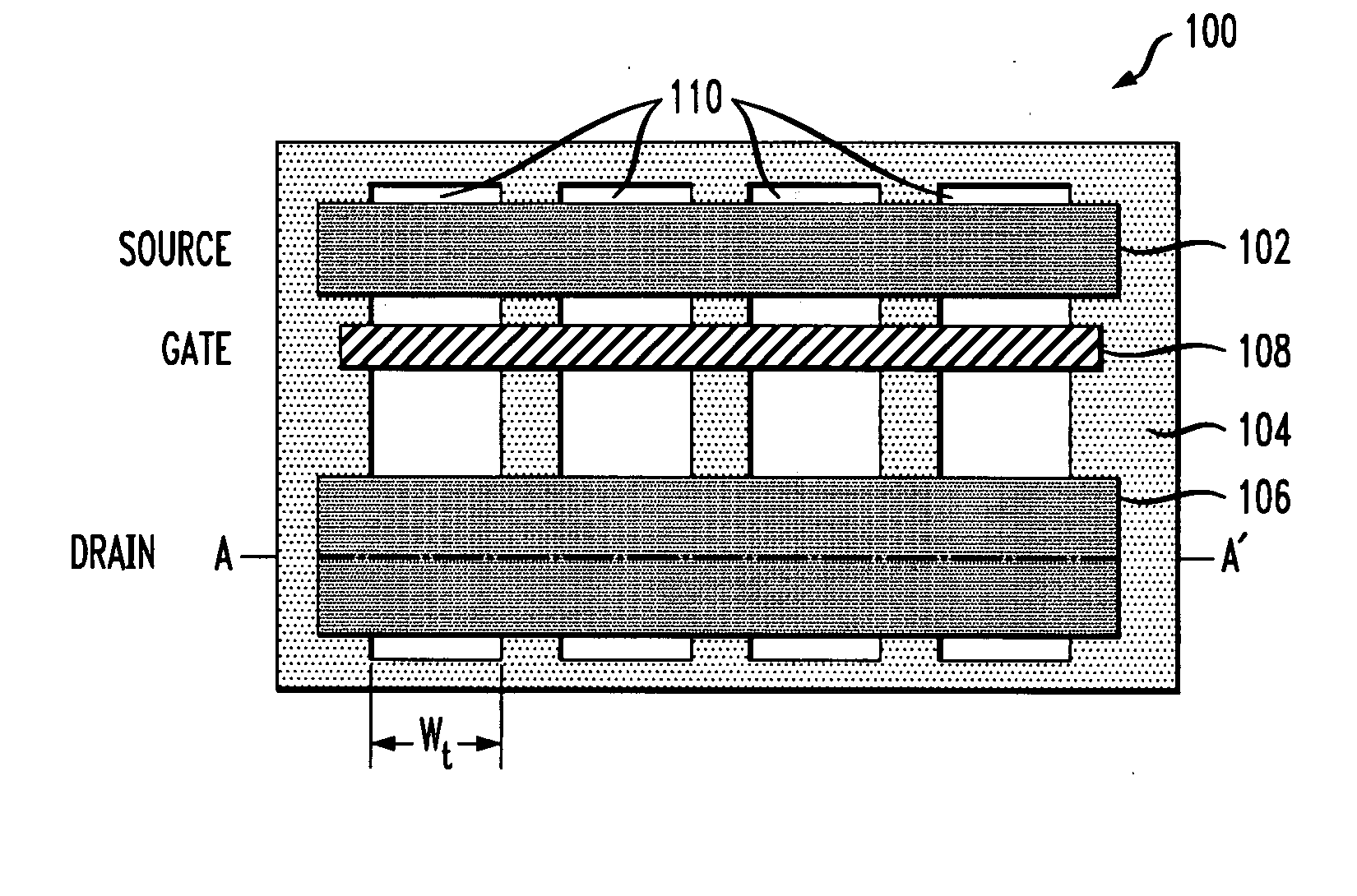

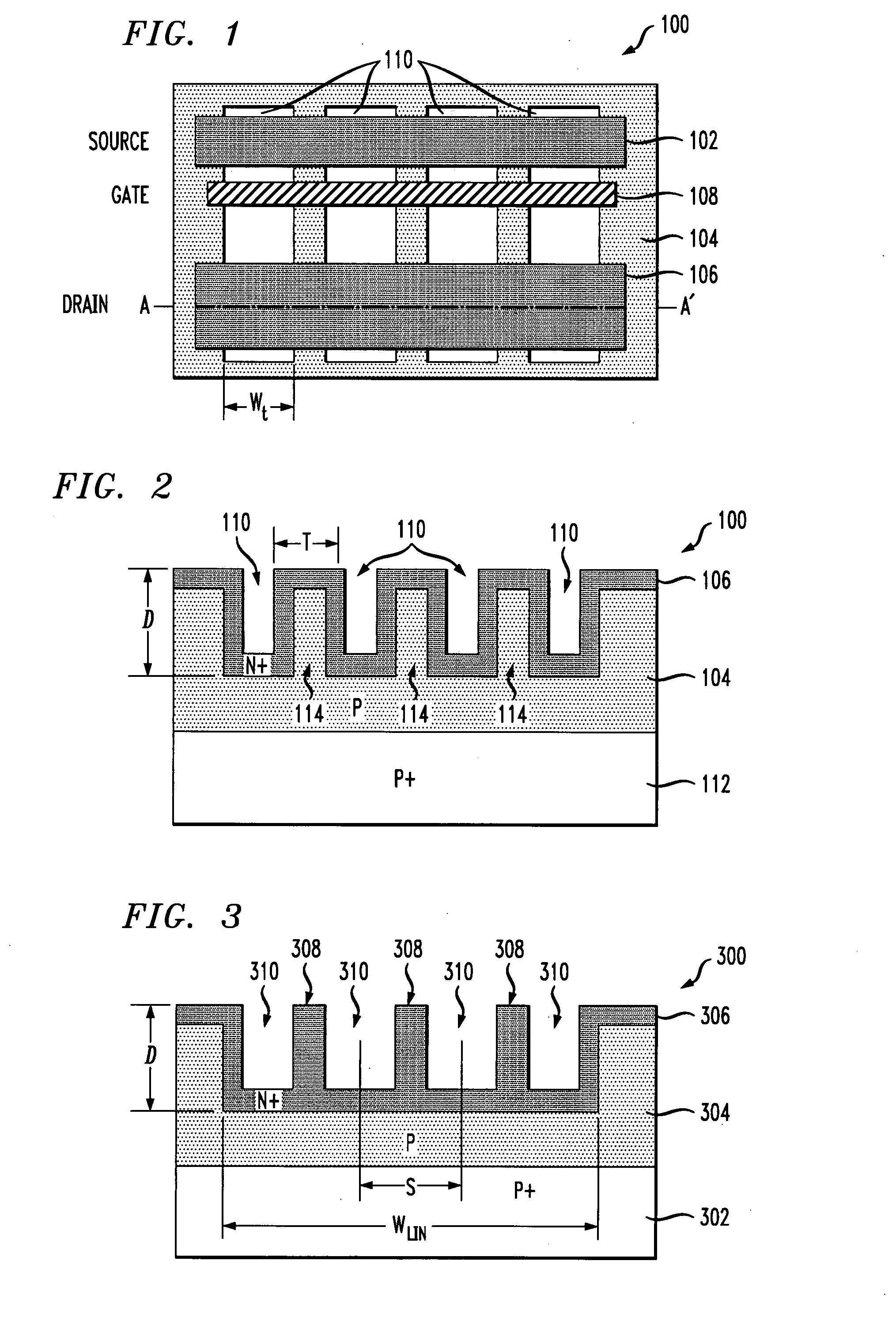

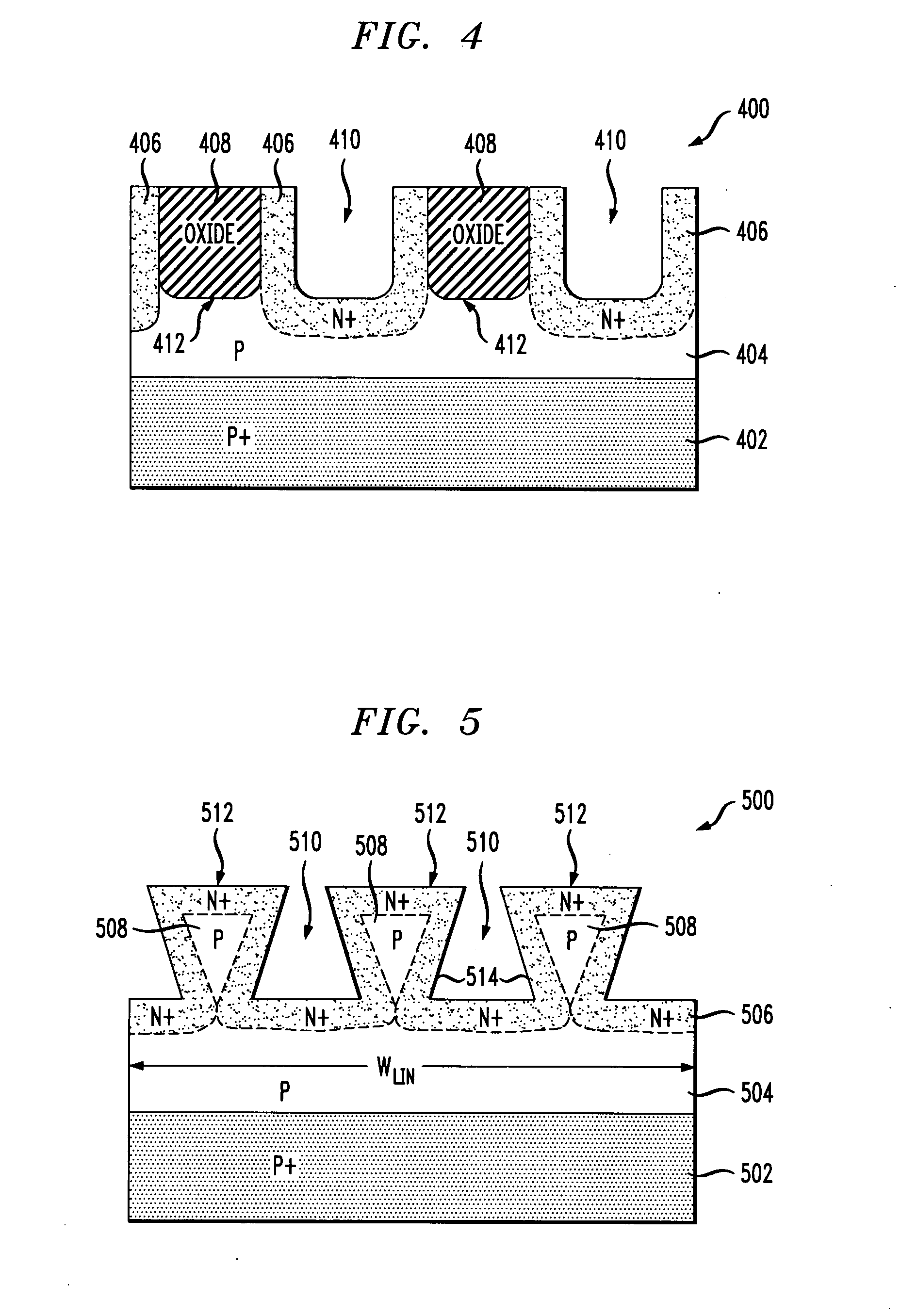

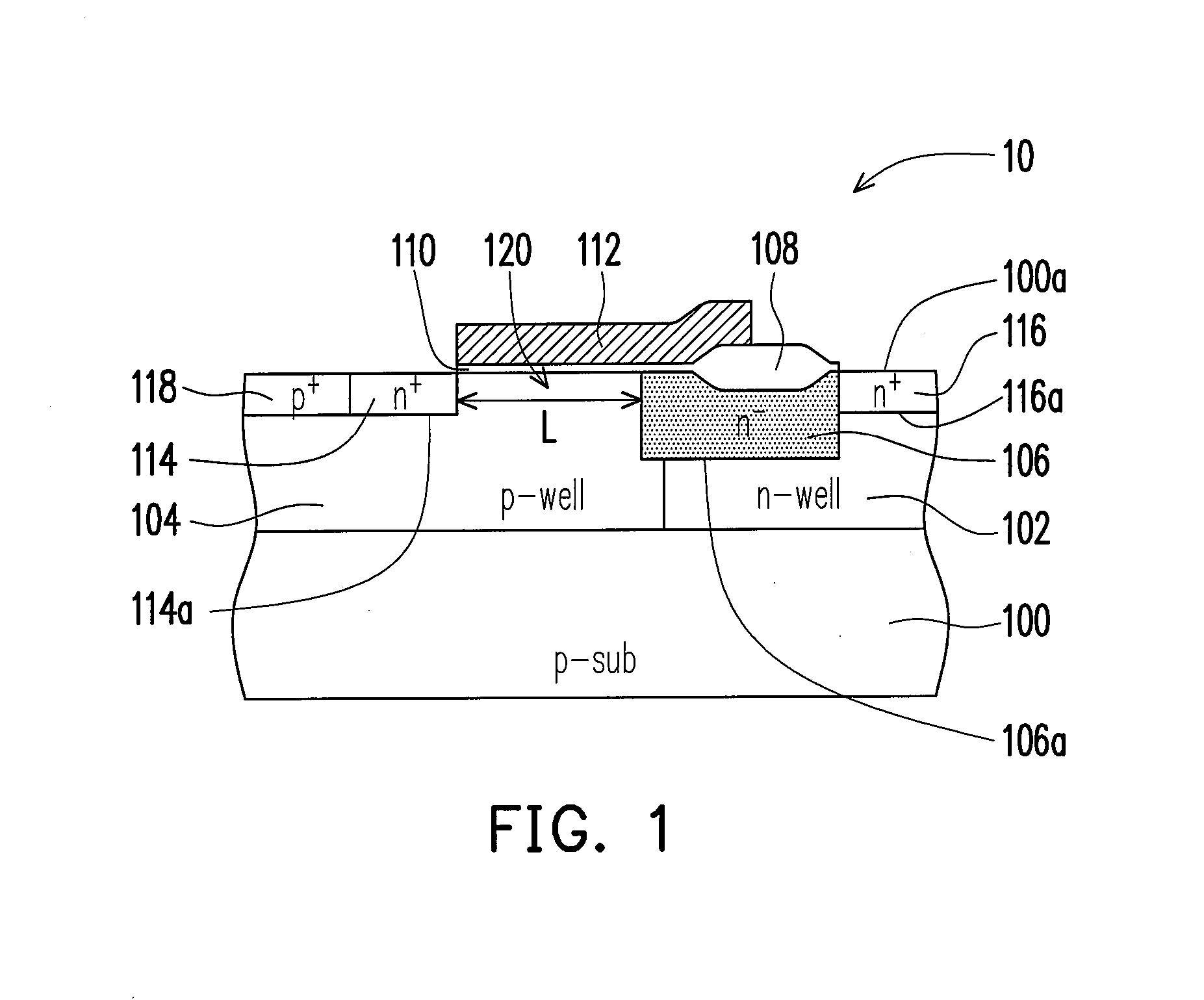

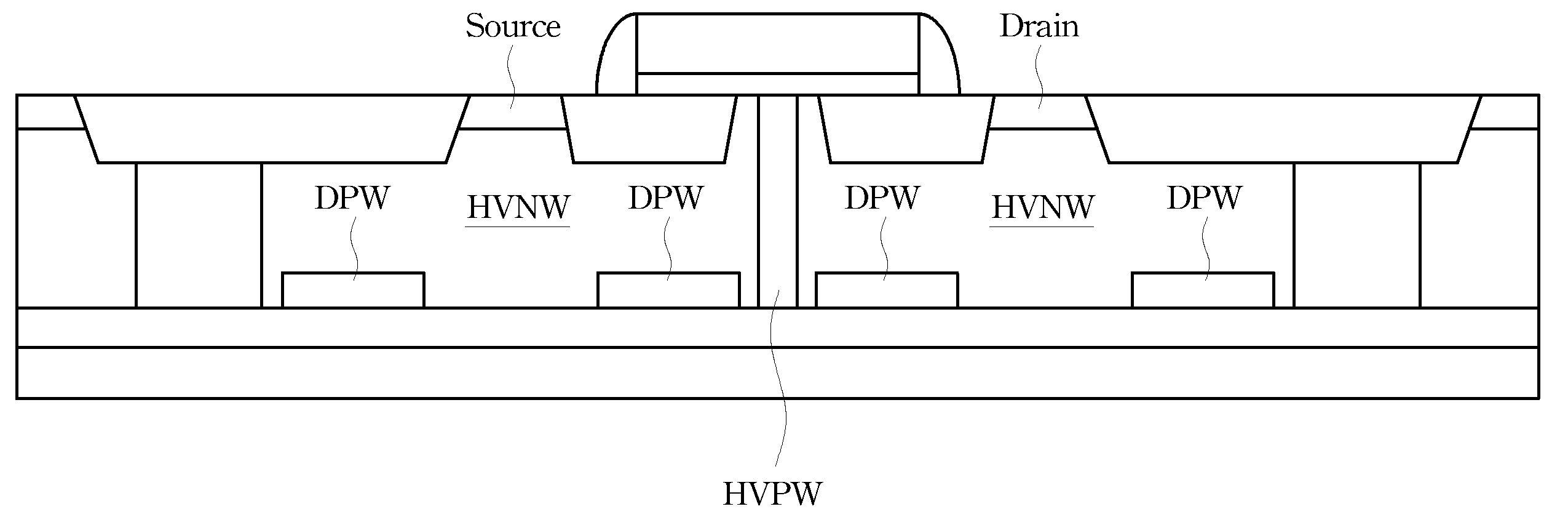

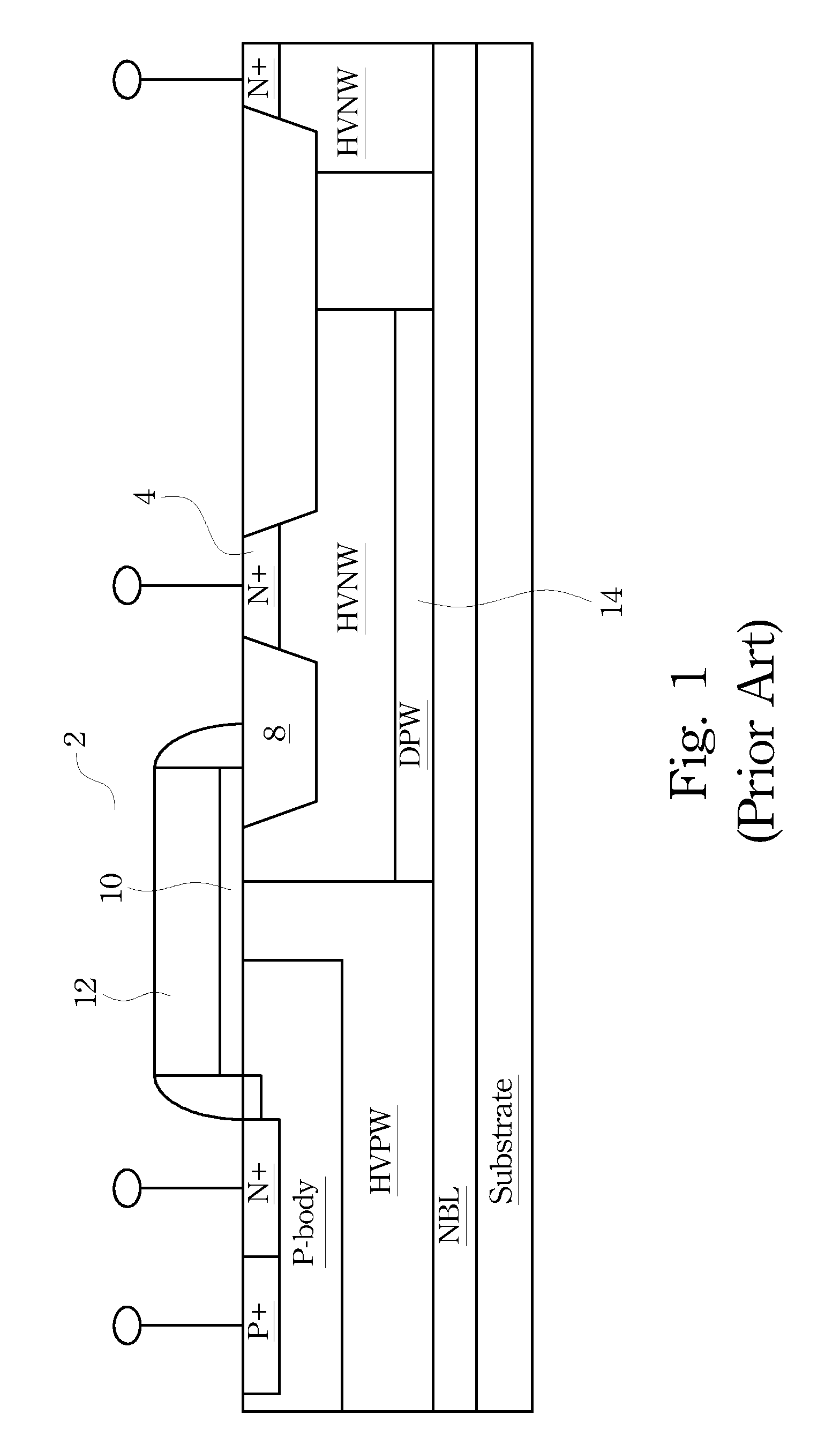

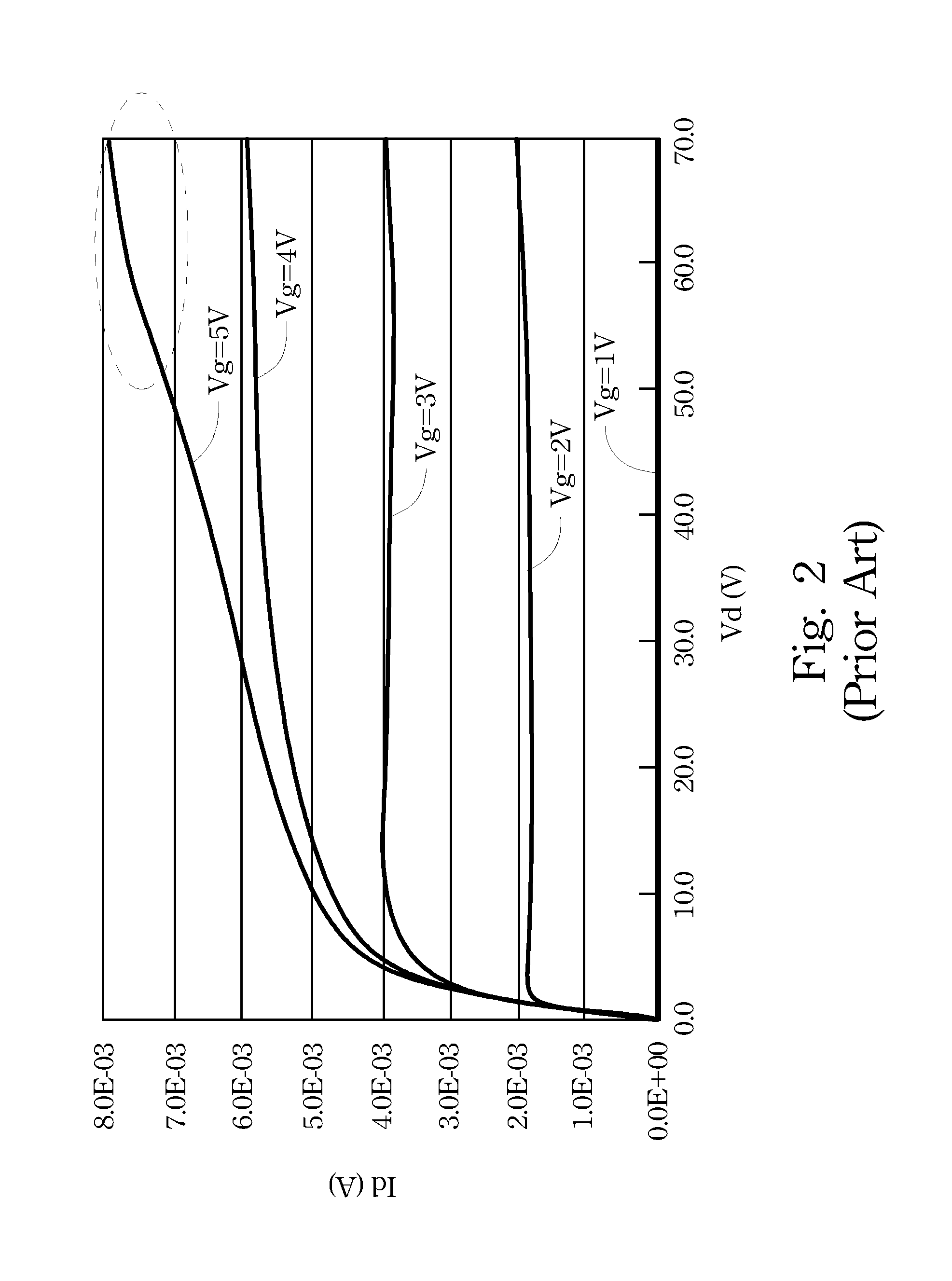

Disconnected DPW Structures for Improving On-State Performance of MOS Devices

ActiveUS20090256200A1Improve performanceON-state resistance be reduceSemiconductor devicesEngineeringSemiconductor structure

A semiconductor structure includes a semiconductor substrate; a first high-voltage well (HVW) region of a first conductivity type overlying the semiconductor substrate; a second HVW region of a second conductivity type opposite the first conductivity type overlying the substrate and laterally adjoining the first HVW region; a gate dielectric extending from over the first HVW region to over the second HVW region; a gate electrode on the gate dielectric; a drain region in the second HVW region; a source region at an opposite side of the gate dielectric than the drain region; and a deep well region of the first conductivity type underlying the second HVW region. Substantially no deep well region is formed directly underlying the drain region.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com