Patents

Literature

45results about How to "Improve vertical pressure resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

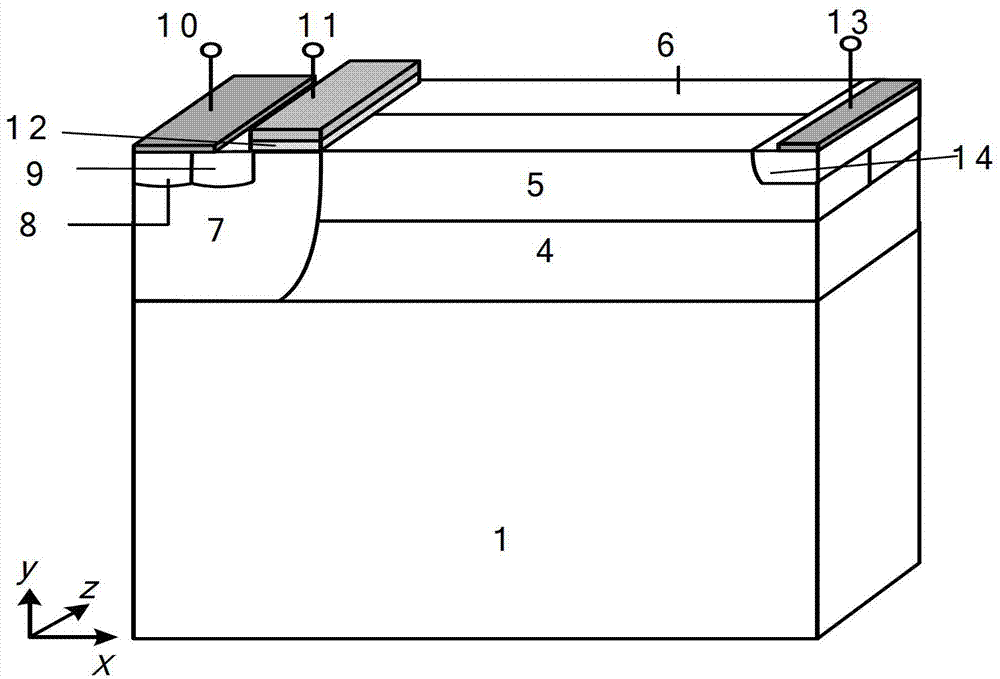

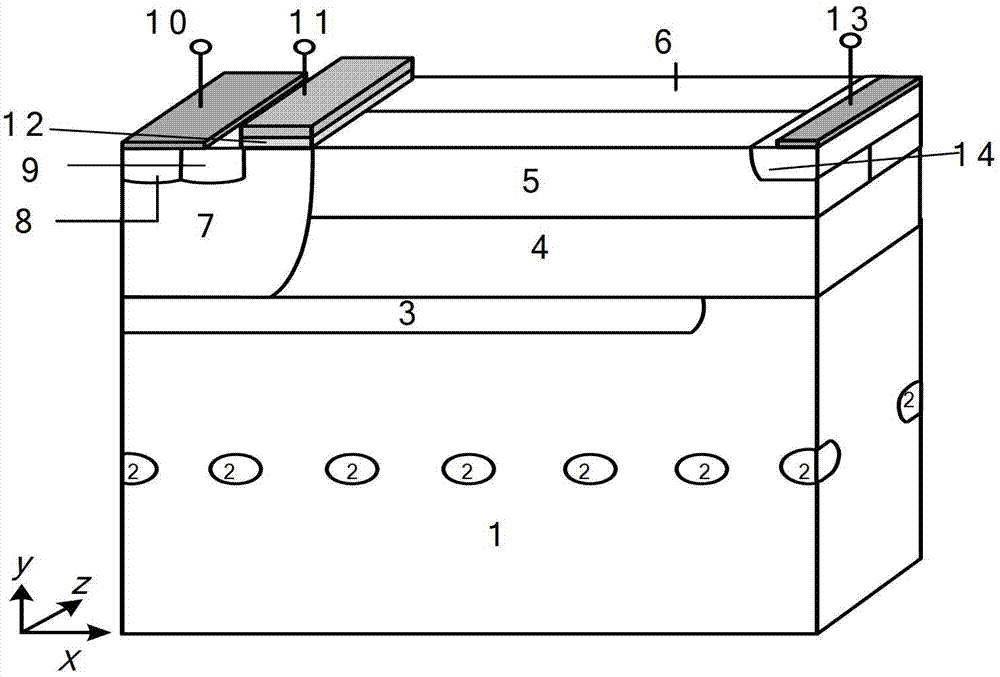

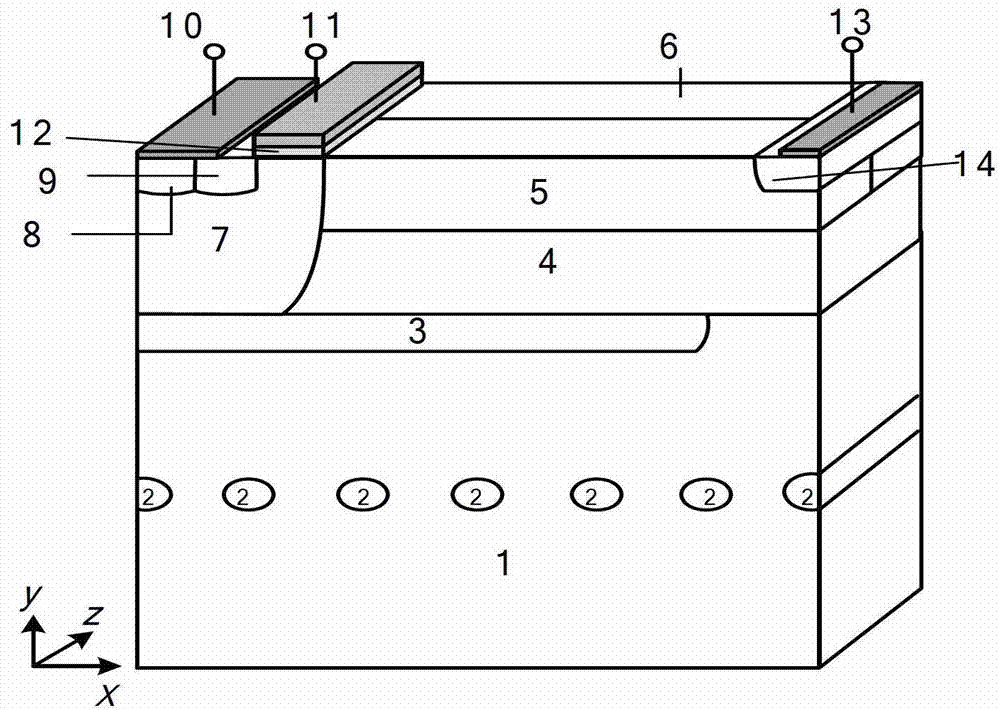

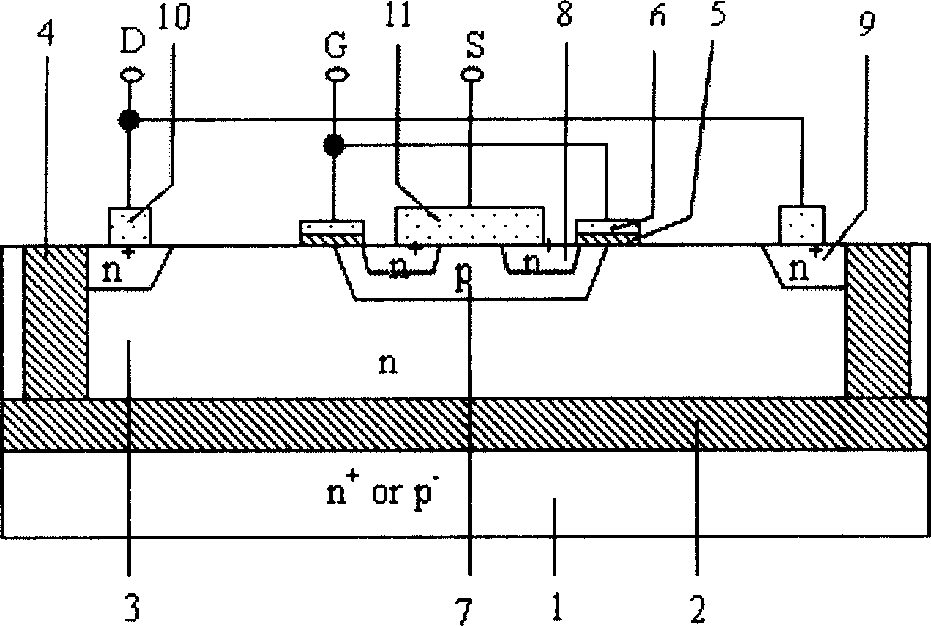

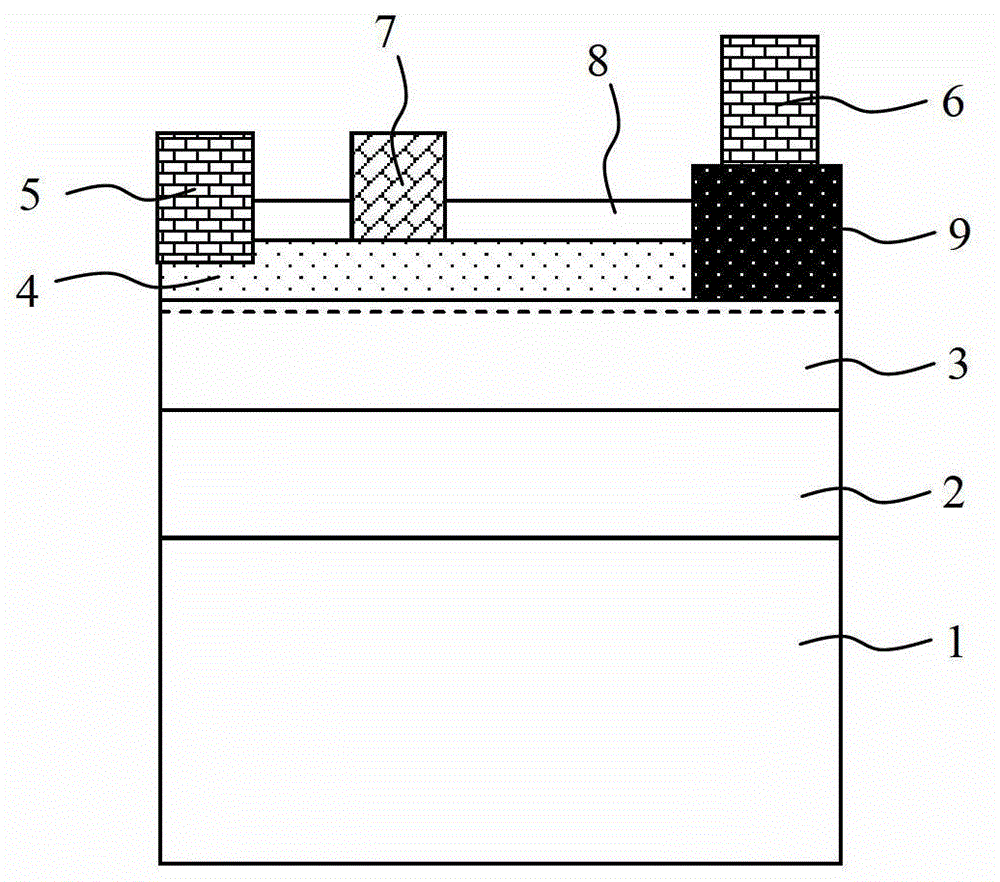

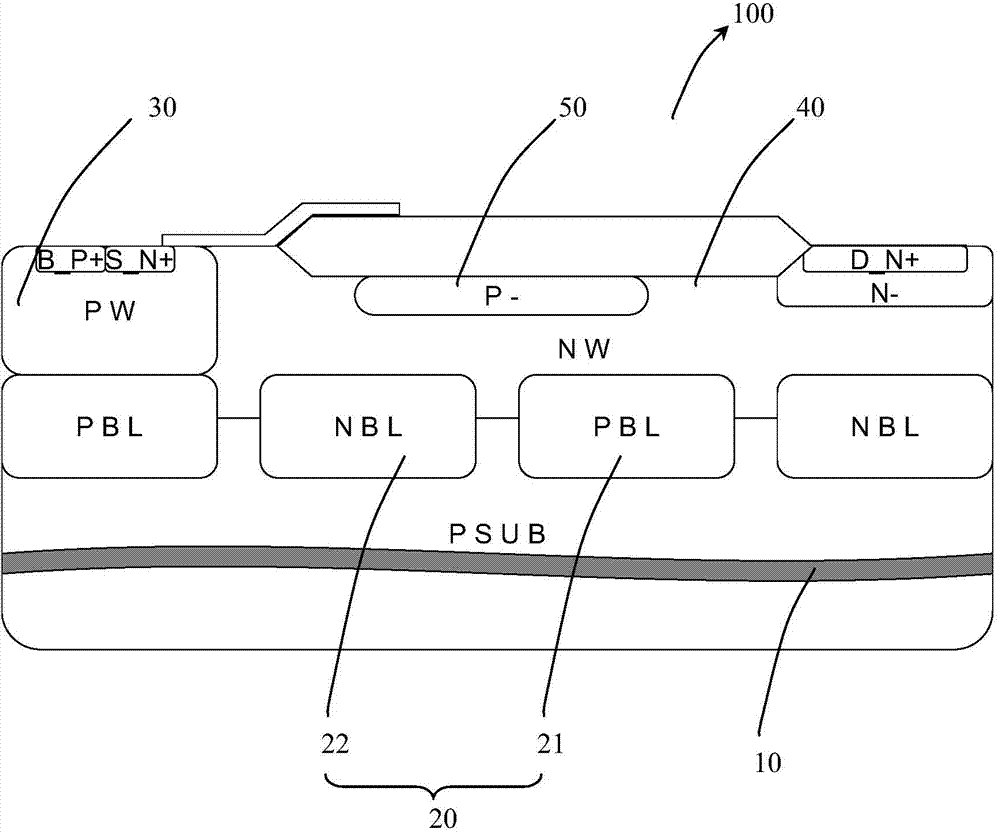

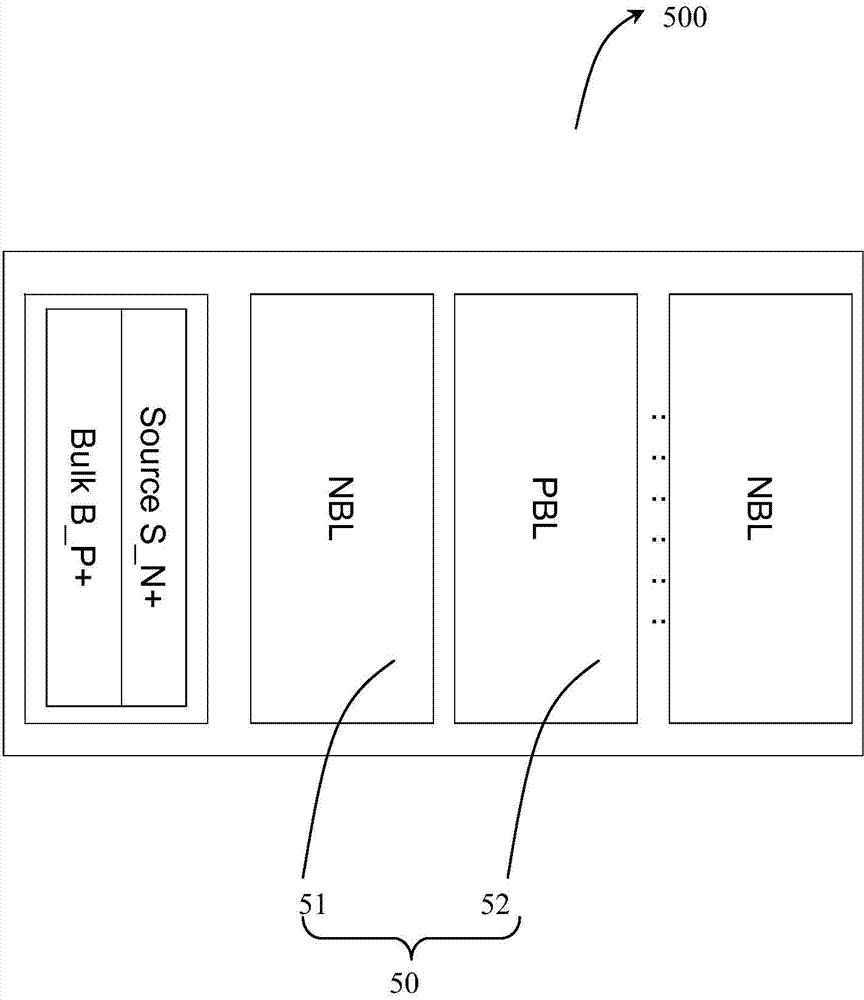

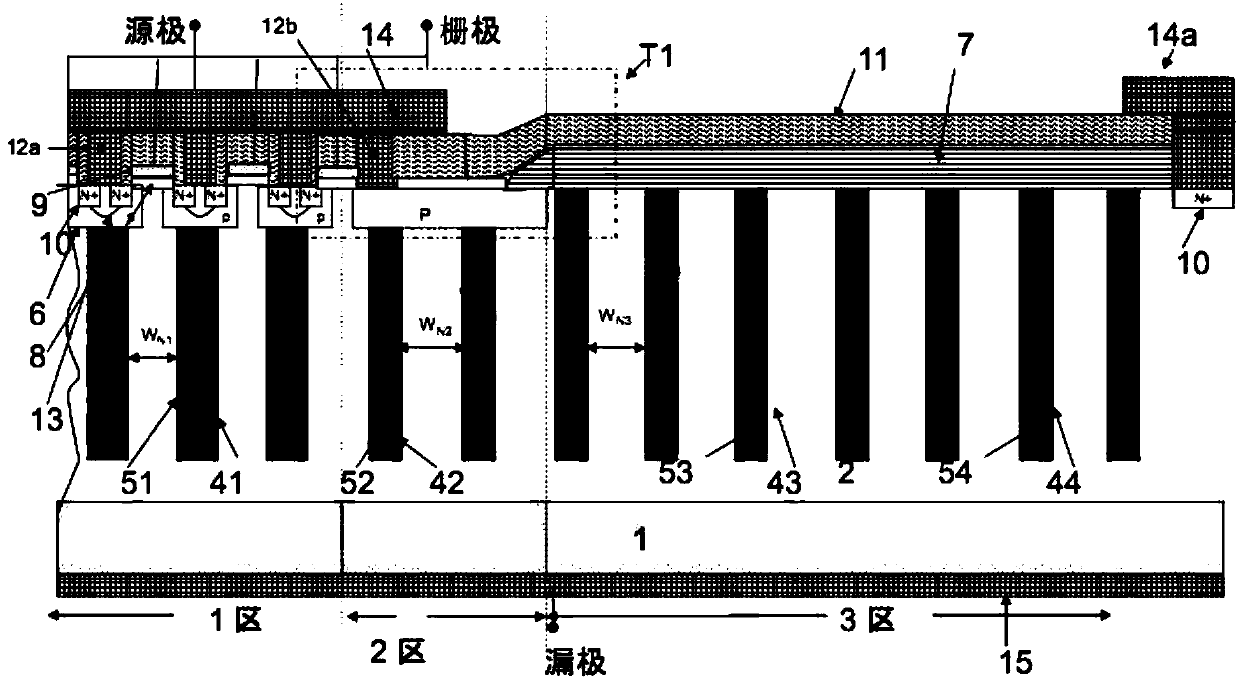

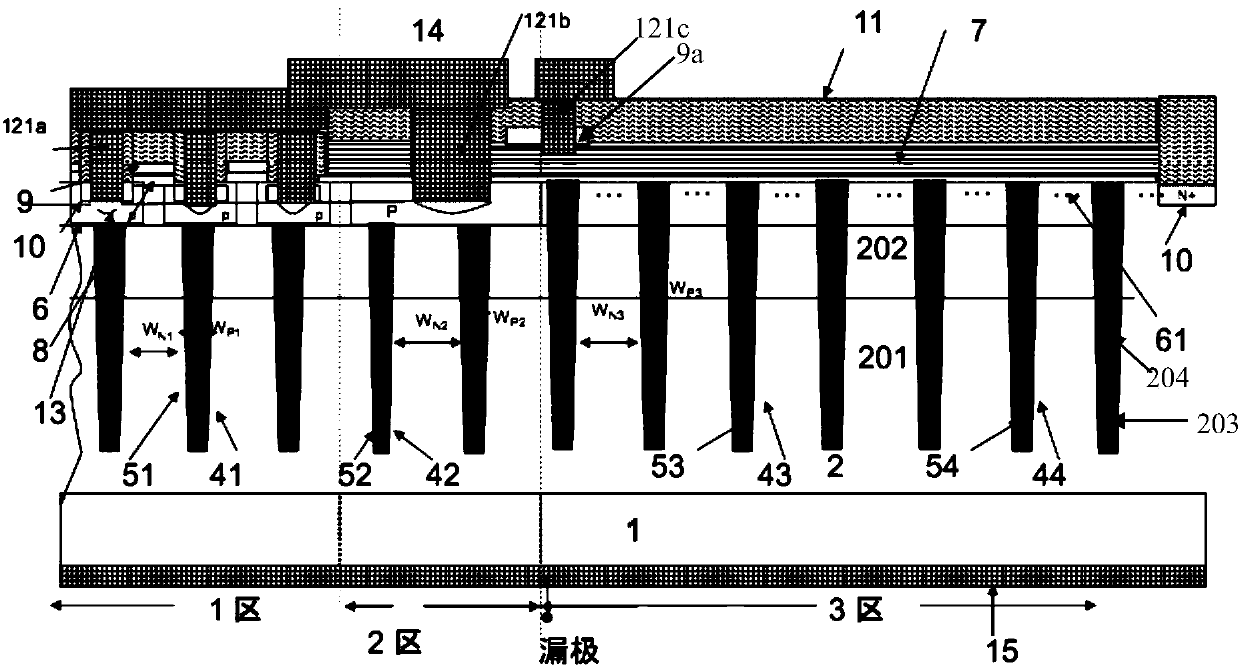

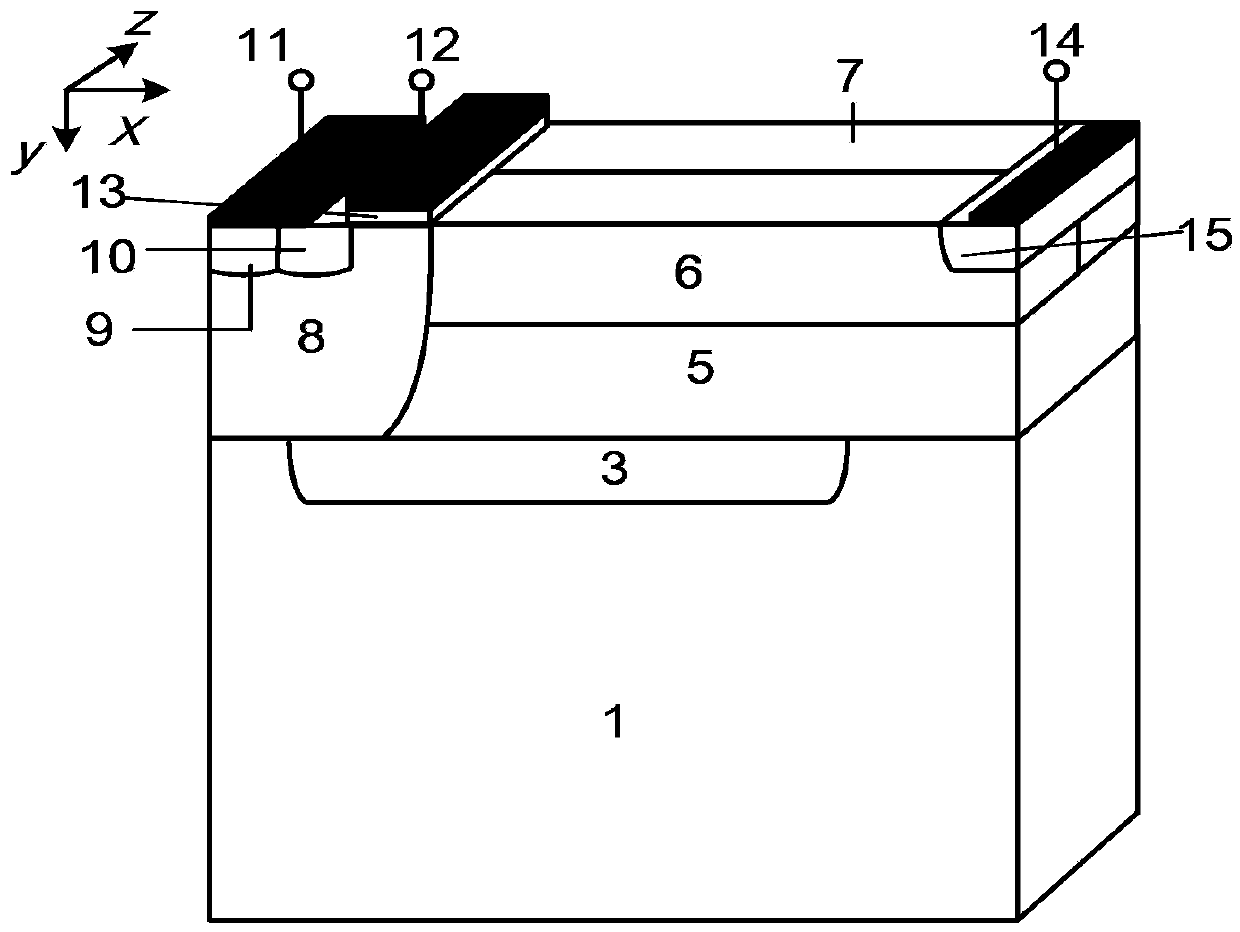

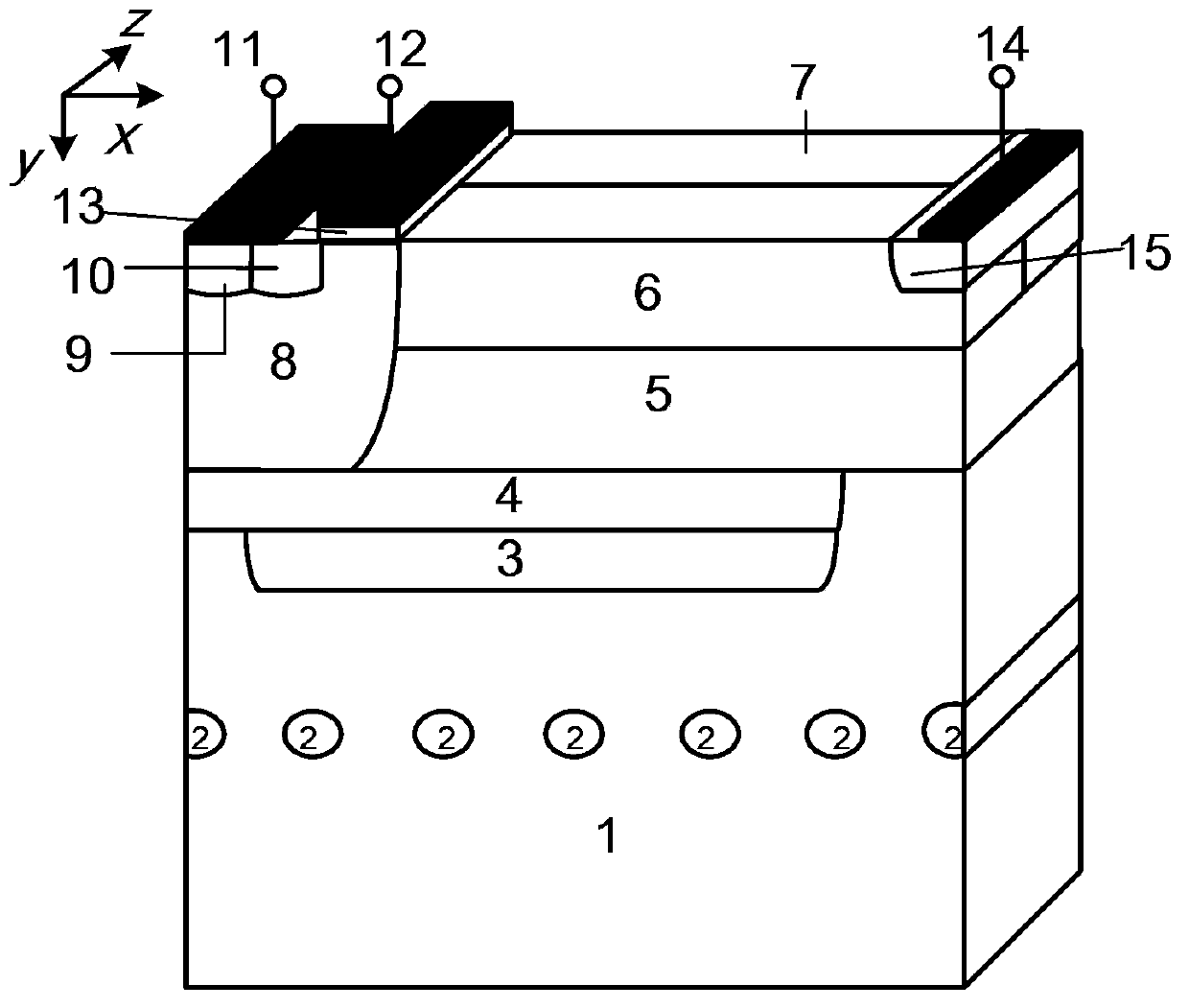

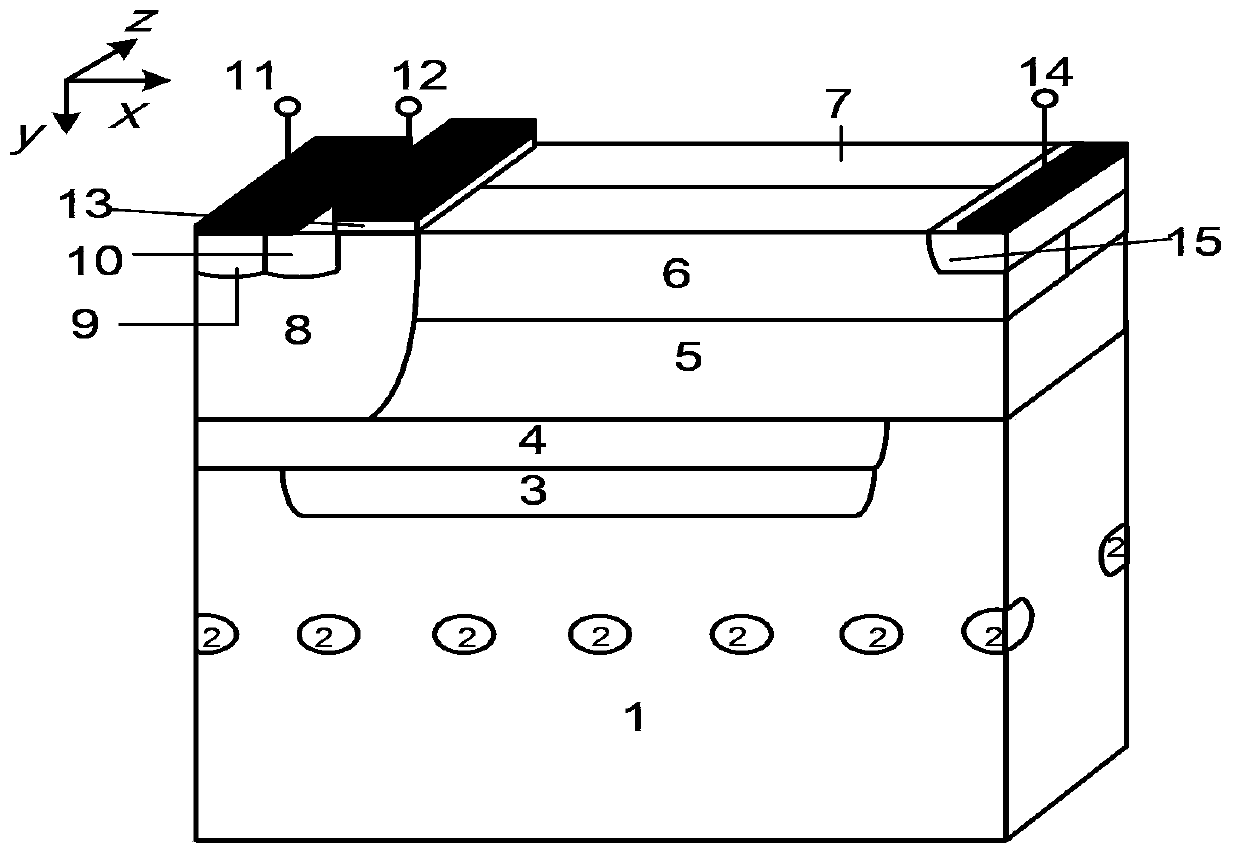

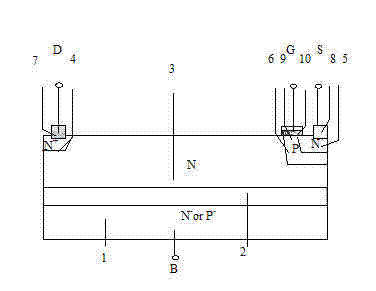

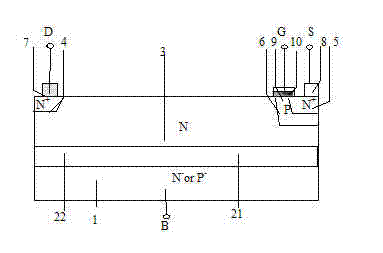

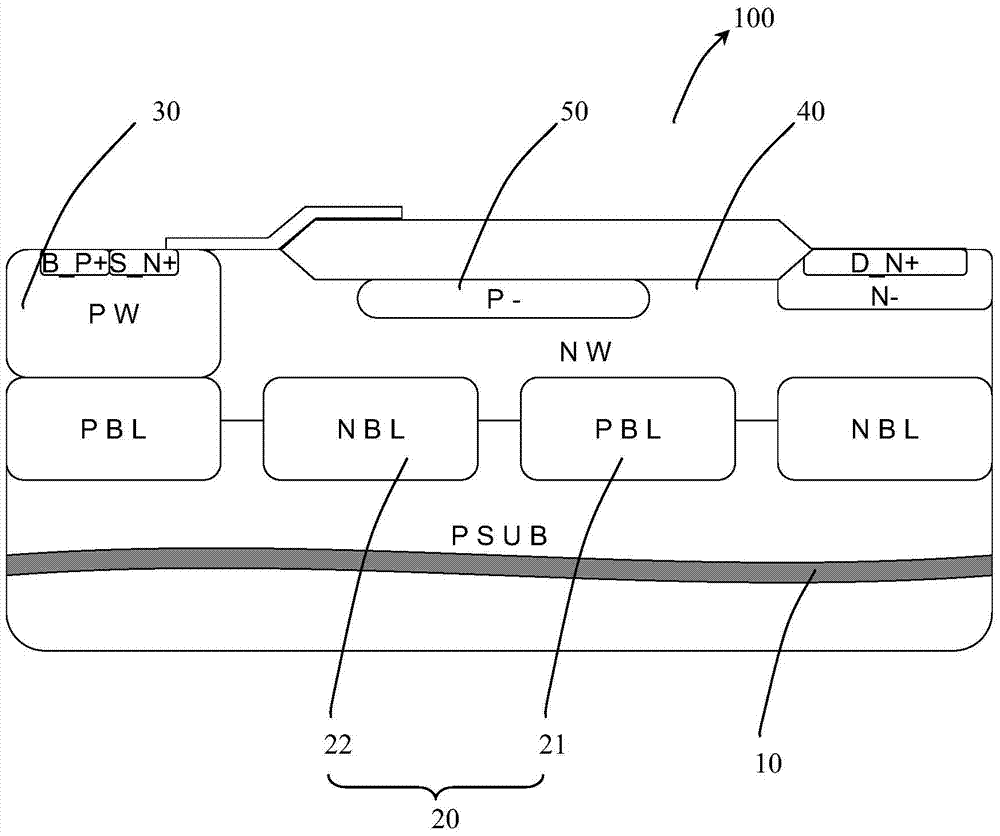

Super junction lateral double-diffused metal-oxide semiconductor (LDMOS) device

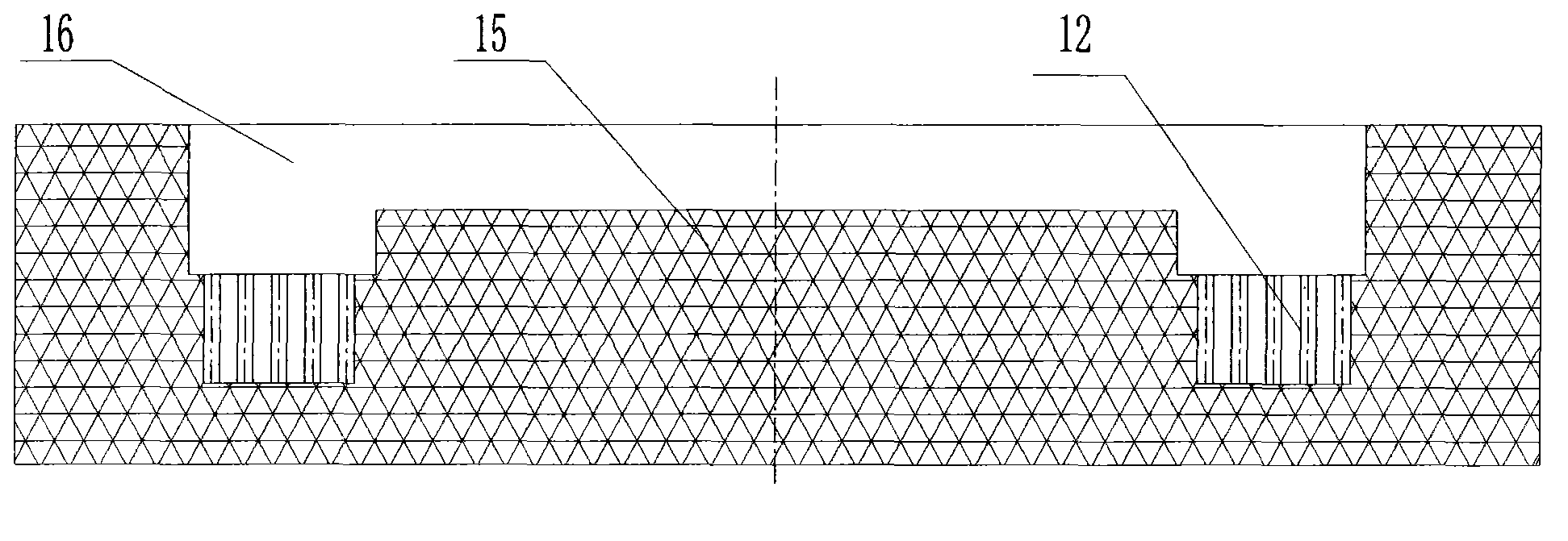

InactiveCN103165678AImprove vertical pressure resistanceImprove breakdown voltageSemiconductor devicesLDMOSPeak value

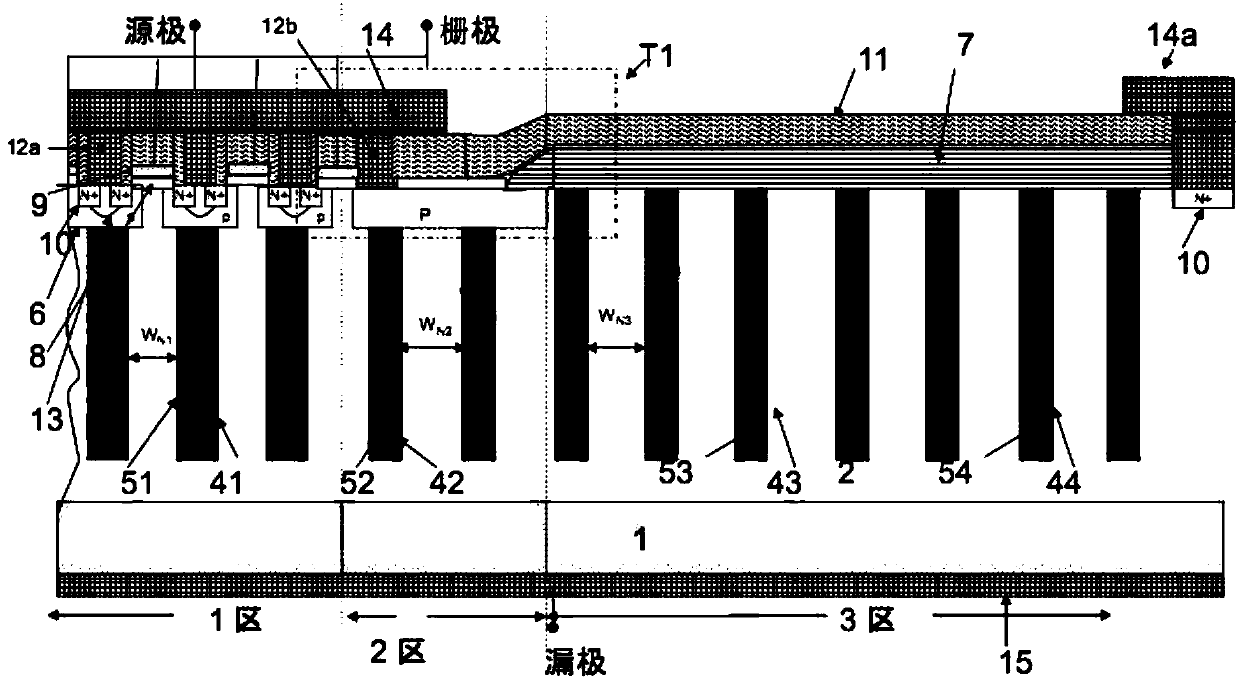

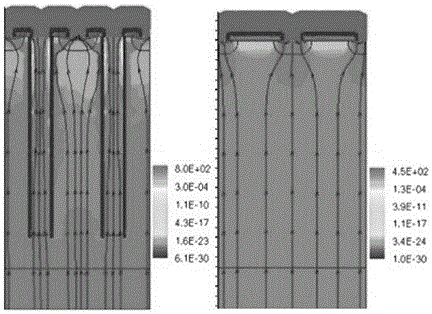

The invention relates to a super junction lateral double-diffused metal-oxide semiconductor (LDMOS) device and belongs to the field of semiconductor power devices. By means of the super junction LDMOS device, evenly distributed N+ islands are embedded in a P type substrate of a traditional super junction LDMOS device, and a P type electric field screening buried layer is added between an active area and the substrate. An N+ island (2) can improve longitudinal withstand voltage of the device by enhancing internal electric field, simultaneously generates extra electric charge to eliminate substrate auxiliary depletion effect, and further improves breakdown voltage of the device. The P type electric field screening buried layer (3) can screen high electric fields generated by an N+ island near an active end, lower electric field peak value near the active area, and form super junction with an N type cushion layer; and a super junction drift area is provided, the device is enabled to have multiple super junction structures, accordingly electric field distribution inside the device can be effectively improved, breakdown voltage of the device is improved, conduction ratio resistance of the device is simultaneously lowered by improving dosage concentration of the drift area, and finally the aim of effectively reducing device area and lower device cost can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

SOI structure with low k dielectric buried layer and its power device

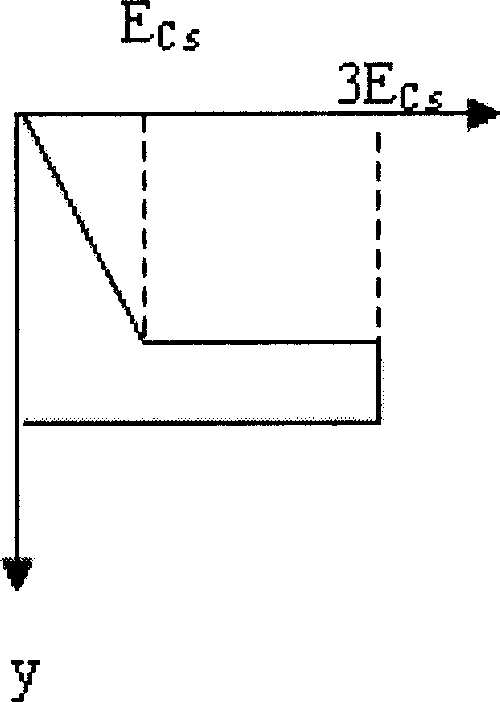

InactiveCN1845332AImprove vertical pressure resistanceImprove lateral pressure resistanceTransistorThyristorCapacitanceLayer interface

The disclosed SOI power device with VLk SOI, Lk SOI, VLk PSOI and Lk PSOI four structures apples the low-k (dielectric coefficient) material to increase longitudinal electric field strength of the buried layer and modulate Si active electric field by the additional field on variable-k layer interface, while decrease the capacitor between drift region and substrate to improve on-off speed. This invention can be used to lots of new high pressure-resistant devices, such as lateral dual-diffusion FET, PN diode, etc.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

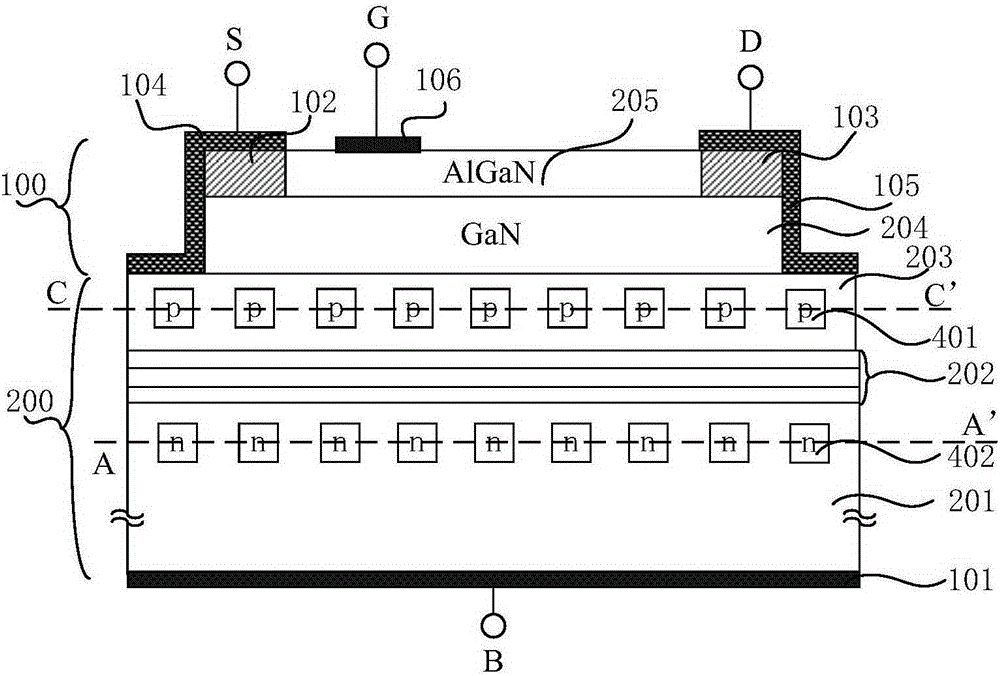

Nitride high-voltage device on silicon substrate and manufacturing method thereof

ActiveCN102916046AImprove vertical pressure resistanceImprove growth efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureNitride

The invention provides a nitride high-voltage device on silicon substrate and a manufacturing method thereof. According to the nitride high-voltage device on the silicon substrate, a high-voltage tolerance layer is led into a drain electrode region, and the thickness of a partial epitaxial layer is thickened to bear higher voltage reduction, so that high punch through voltage resistant device is achieved. Via the method of partial generation, the high punch through voltage resistant device is achieved, the problems of warping and chap of nitride epitaxial layer, which are caused by a whole material with over thickness, are avoided, therefore, material generation quality is ensured, material generation efficiency is improved, and the cost is lowered.

Owner:ENKRIS SEMICON

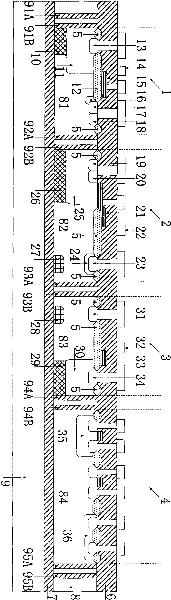

SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157550AReduce adverse effectsImprove vertical pressure resistanceSemiconductor devicesMetal electrodesConductivity modulation

The invention relates to an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The existing products restrict the improvement of the device structures and the electrical properties. The device unit comprises a p-type semiconductor substrate, a buried oxide layer and a p buried layer region in sequence, wherein a metal gate, an n-type heavily doped polysilicon gate, a gate oxide layer and an n-type lightly doped drift region are arranged at the top of the p buried layer region side by side in sequence; a first p-type well region and an n-type buffer region are respectively embedded at the two sides at the top of the n-type lightly doped drift region; an n-type cathode region and a first p well ohmic contact region are embedded at the top of the first p-type well region; a second p-type well region and an anode short-circuit point region are embedded at the top of the n-type buffer region; a second p well ohmic contact region is embedded at the top of the second p-type well region; and a first field oxide layer, a second field oxide layer, an anode metal electrode and a cathode metal electrode are arranged at the top of the device unit. The device unit has the beneficial effects of reducing the spreading resistance, improving the conductivity modulation effect of the drift region, reducing the on-state power consumption and obviously improving the thermal property of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

High-voltage LDMOS (laterally-diffused metal oxide semiconductor) device

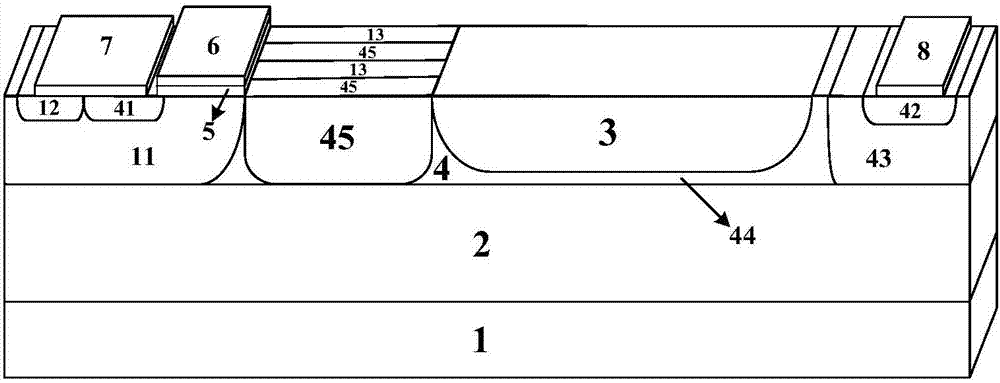

ActiveCN104518023AIncrease the cross-sectional areaReduce push timeSemiconductor devicesOxide semiconductorOxide

A high-voltage lateral double-diffused metal oxide semiconductor (LDMOS) device comprises a P-type channel region, an N-type drift region, a voltage-resistance layer, and a P-type substrate located at the bottom, the voltage-resistance layer being provided between the P-type substrate and the N-type drift region. For the high-voltage LDMOS device, the trapping time in the process is shortened by adding a voltage-resistance layer, thereby increasing a sectional area of a current channel, improving the on resistance, and further enhancing lateral voltage resistance by enhancing longitudinal voltage resistance.

Owner:CSMC TECH FAB2 CO LTD

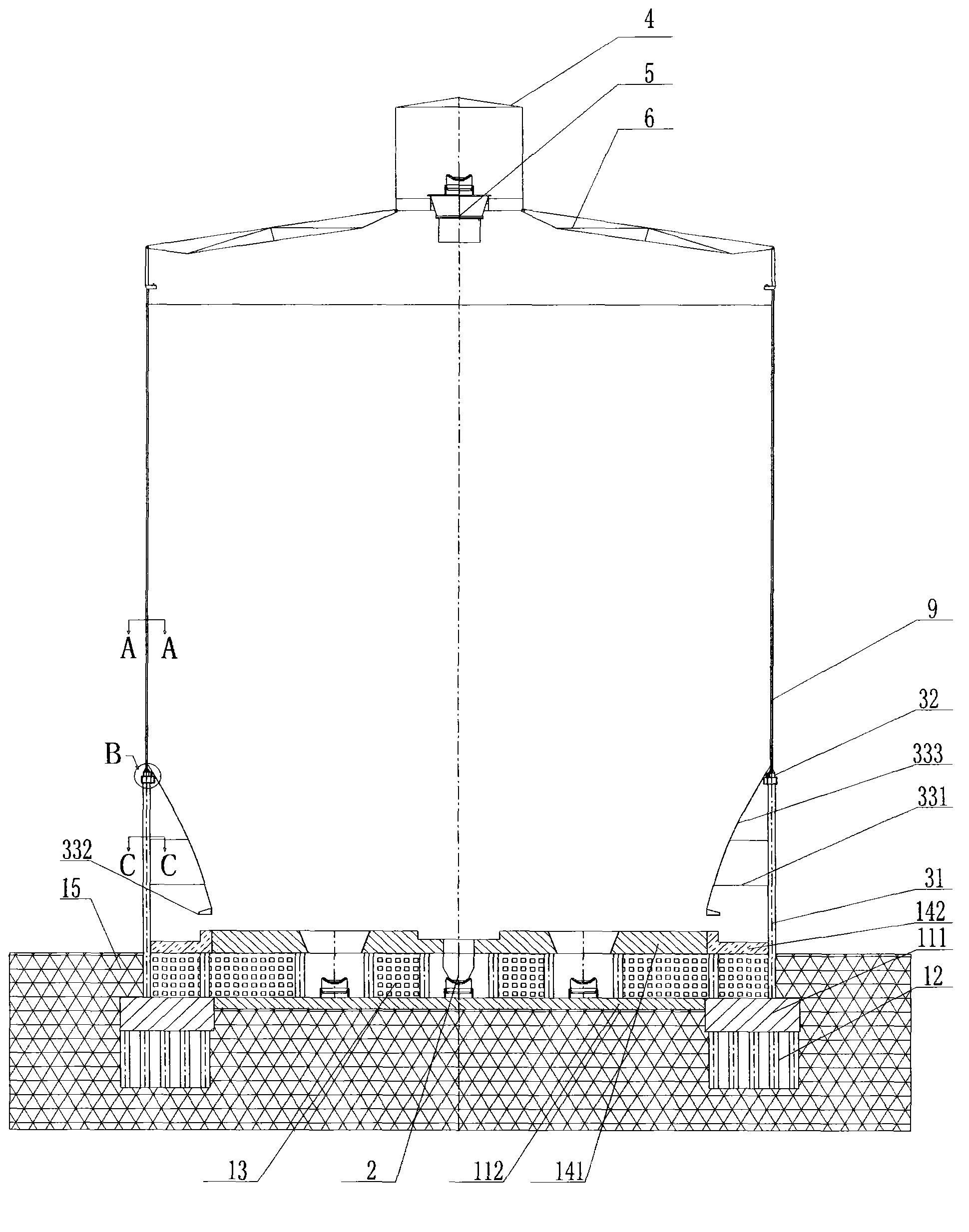

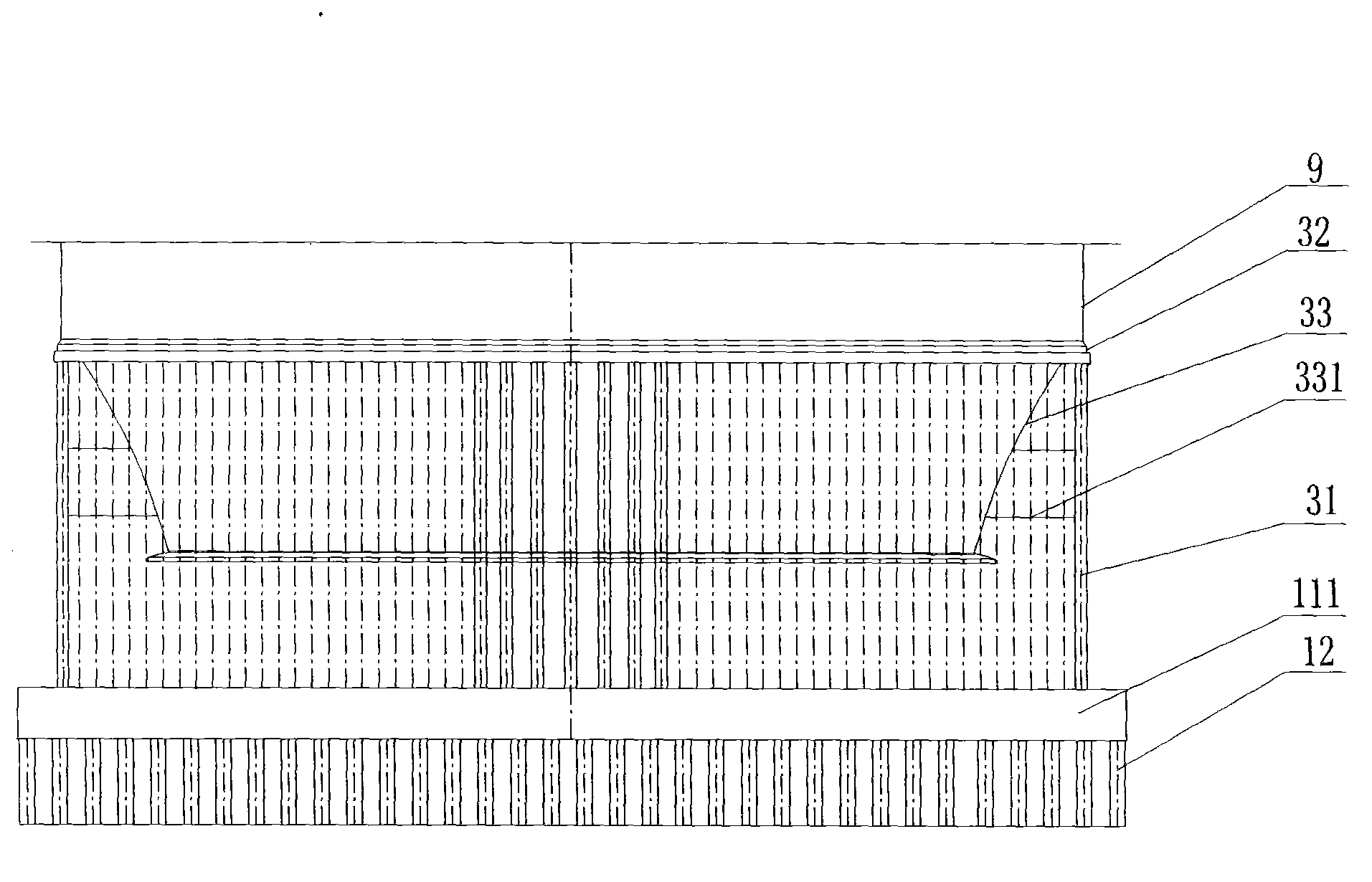

Ultra-large dual-layer steel plate concrete silo prestressed technology and structure of ultra-large dual-layer steel plate concrete silo

InactiveCN103573002AIncrease the difficulty of constructionLong construction periodBulk storage containerSoil preservationSheet steelReinforced concrete

The invention discloses an ultra-large dual-layer steel plate concrete silo prestressed technology and a structure of an ultra-large dual-layer steel plate concrete silo. The technology comprises the steps of firstly digging a foundation pit, hitting a pile foundation, making a foundation plate, mounting a silo assembly, and sealing the bottom of a silo; after the silo assembly and foundation water in the silo are prestressed for a certain time, pouring concrete into the silo assembly to form a dual-layer steel plate concrete silo wall and removing the water pressure after consolidation; prestressing the foundation in the silo for a certain time by the rest prestressed water filling body, removing the prestressed water, and finally performing secondary pouring on the foundation plate in the silo. The structure of the ultra-large dual-layer steel plate concrete silo comprises the foundation, a belt corridor, the silo assembly, a belt trestle, a central blanking drum, a rainshed and a bottom sealing film. The characteristics of strong pulling resistant performance of the steel plate and the strong crushing resistance of the concrete are utilized, so the soil is prestressed by the actual load of loaded materials; in the structure, a steel pipe support pouring concrete is adopted to replace a steel plate or concrete support, and a steel structure cone is used for replacing a reinforced concrete cone, so the problems that after the silo is put into use, the use of the foundation is influenced caused by unevenness and deformation due to unbalanced loading of the materials and the like are avoided.

Owner:朱耀平

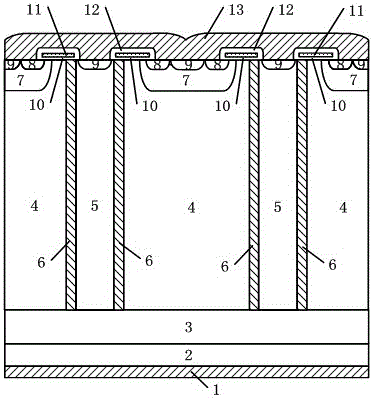

Super junction device and manufacturing method thereof

ActiveCN109755291AImprove vertical pressure resistanceImprove the ability to withstand voltage verticallySemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyEngineering

The invention discloses a super junction device, grooves of a super junction structure are of a lateral inclined structure, the doping concentration of N-type epitaxial layers are distributed in a stepped mode, and P-type columns are formed of a plurality of layers of P-type epitaxial layers which are filled in the grooves in an overlapped mode; and the doping concentration of the P-type epitaxiallayers of the P-type columns is decreased successively from bottoms to tops of the grooves. A protective epoxy film wraps around the circumferential side of a current flow region; and the N-type epitaxial layer at the interface of the protective epoxy film and the oxide film epitaxial layer of the N-type epitaxial layer of a terminal region internally comprises a top region with the reduced N-type doping concentration, and the top region can enhance the lateral depletion capacity of the N-type column at the interface of the oxide film epitaxial layer. The invention further discloses a manufacturing method of the super junction device. According to the super junction device, the charge balance between the P-type columns and N-type columns of the super junction structure with the inclined grooves can be improved, the longitudinal voltage endurance capability of the device is improved, and the source leakage breakdown voltage of the device is increased; and the lateral voltage bearing capacity of a device terminal can further be improved, and reliability of the device is improved.

Owner:SHENZHEN SANRISE TECH CO LTD

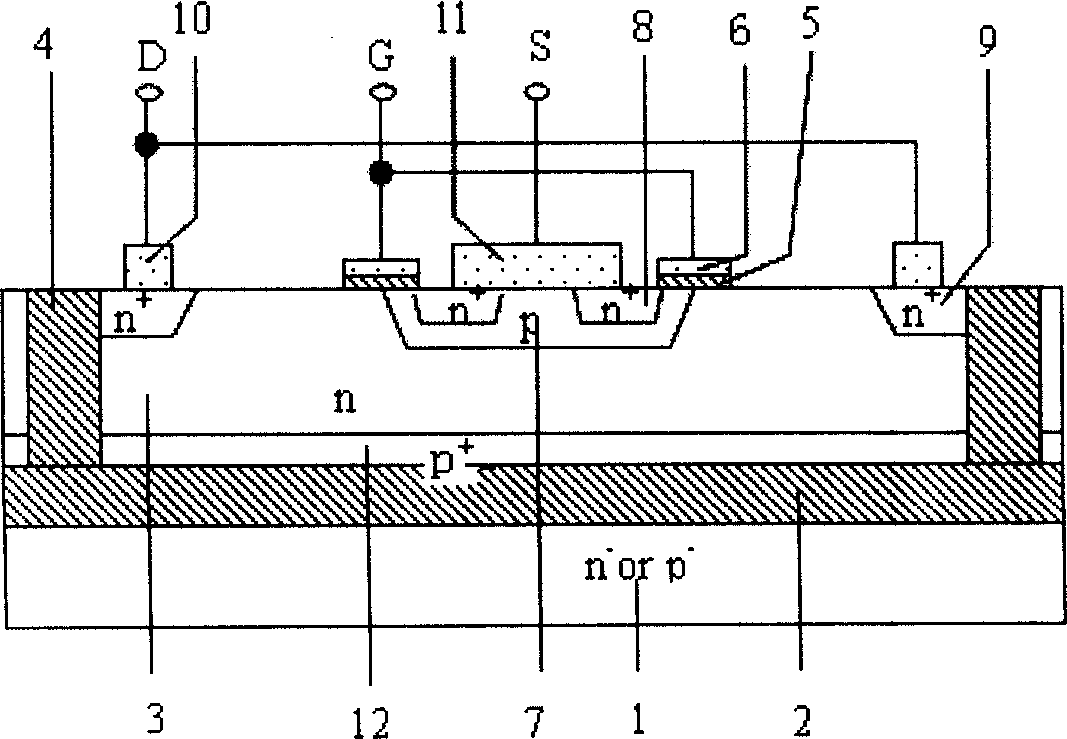

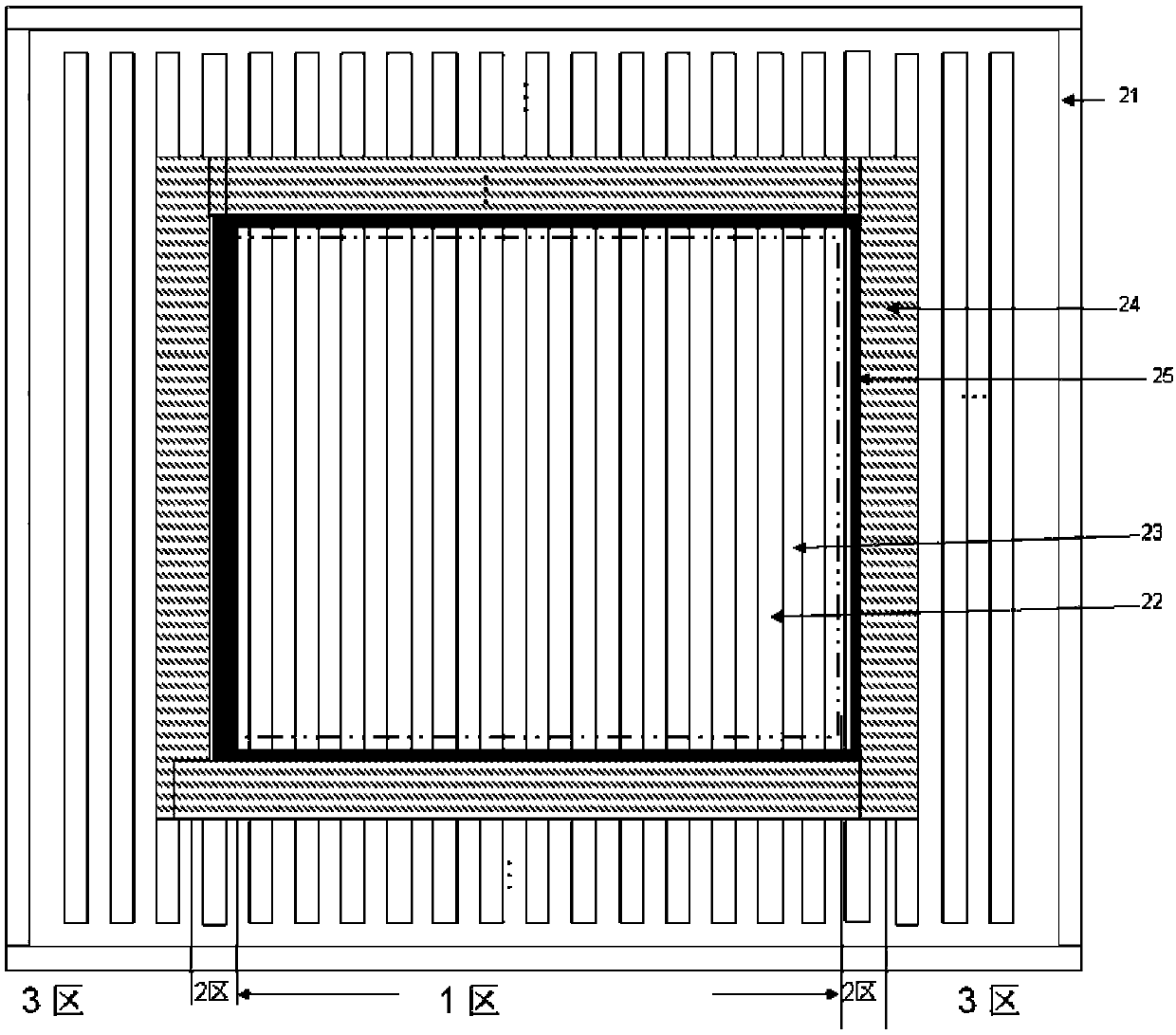

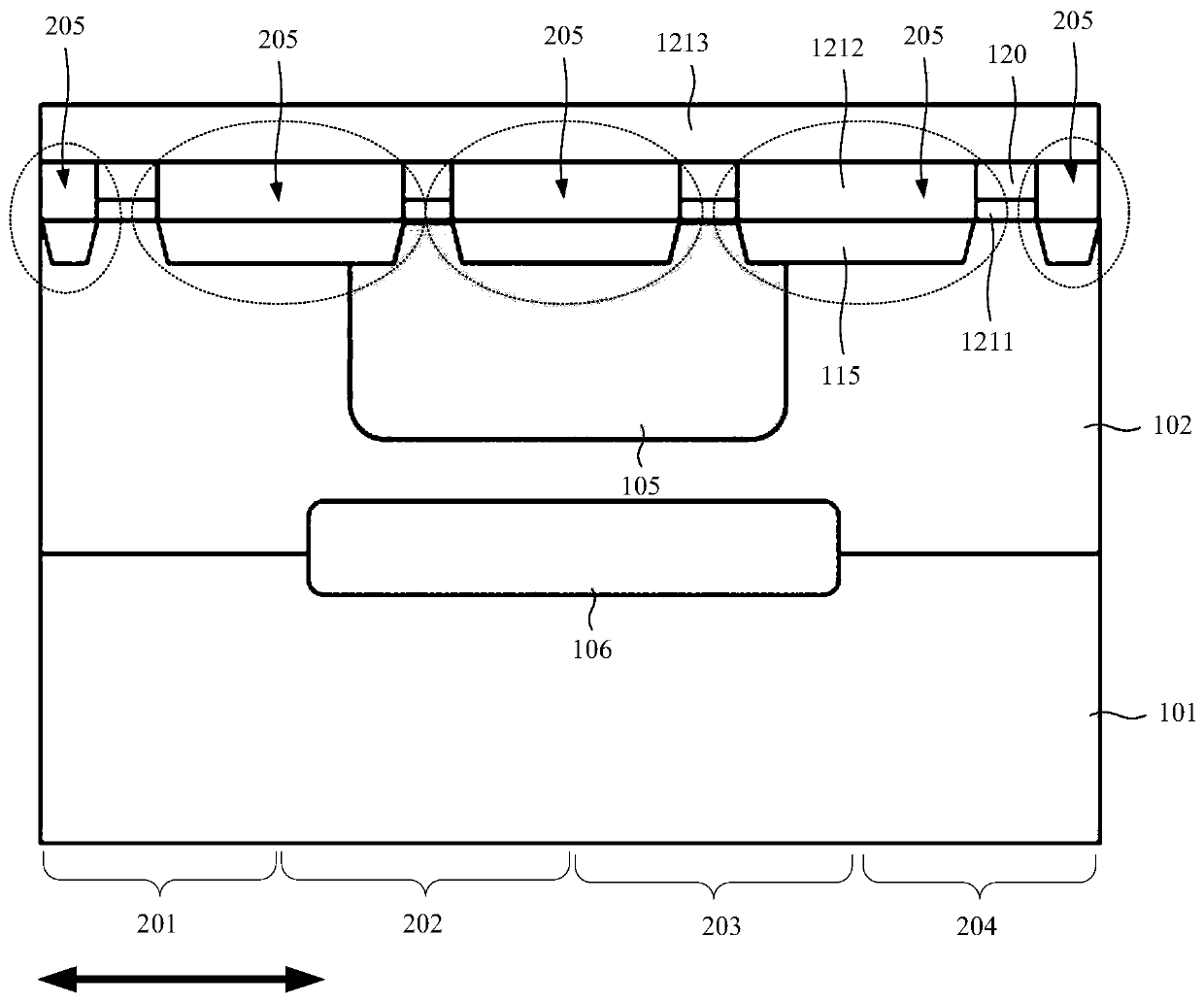

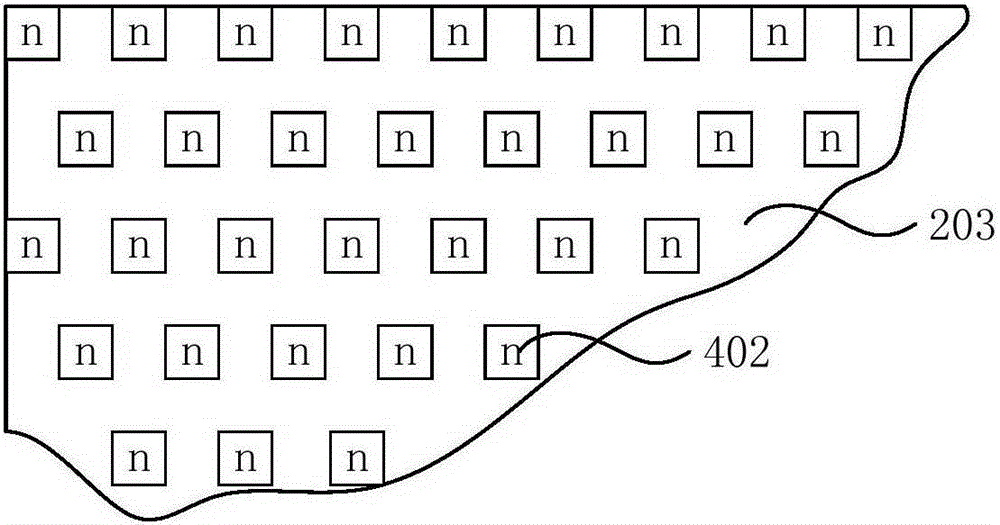

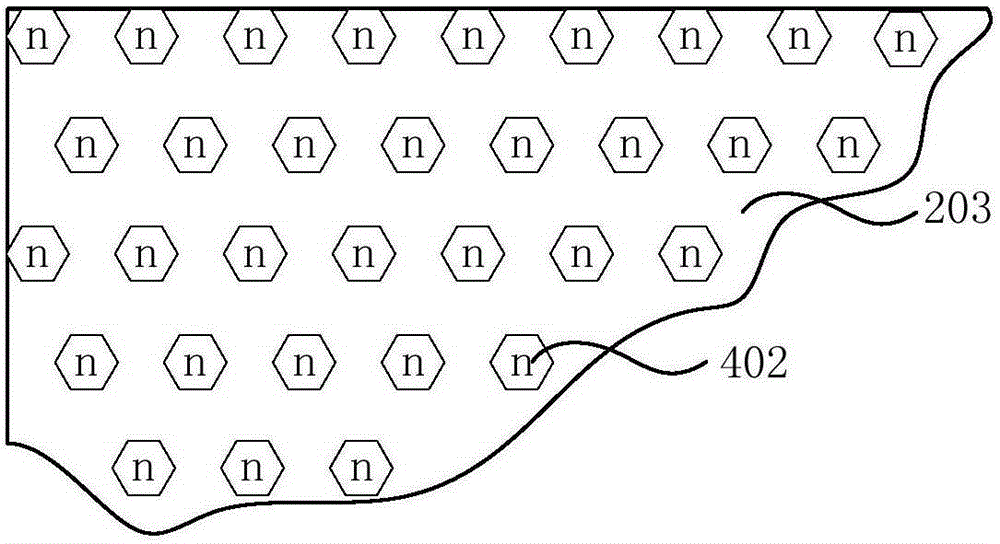

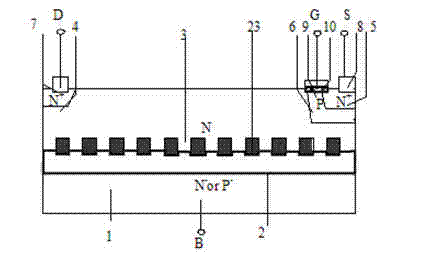

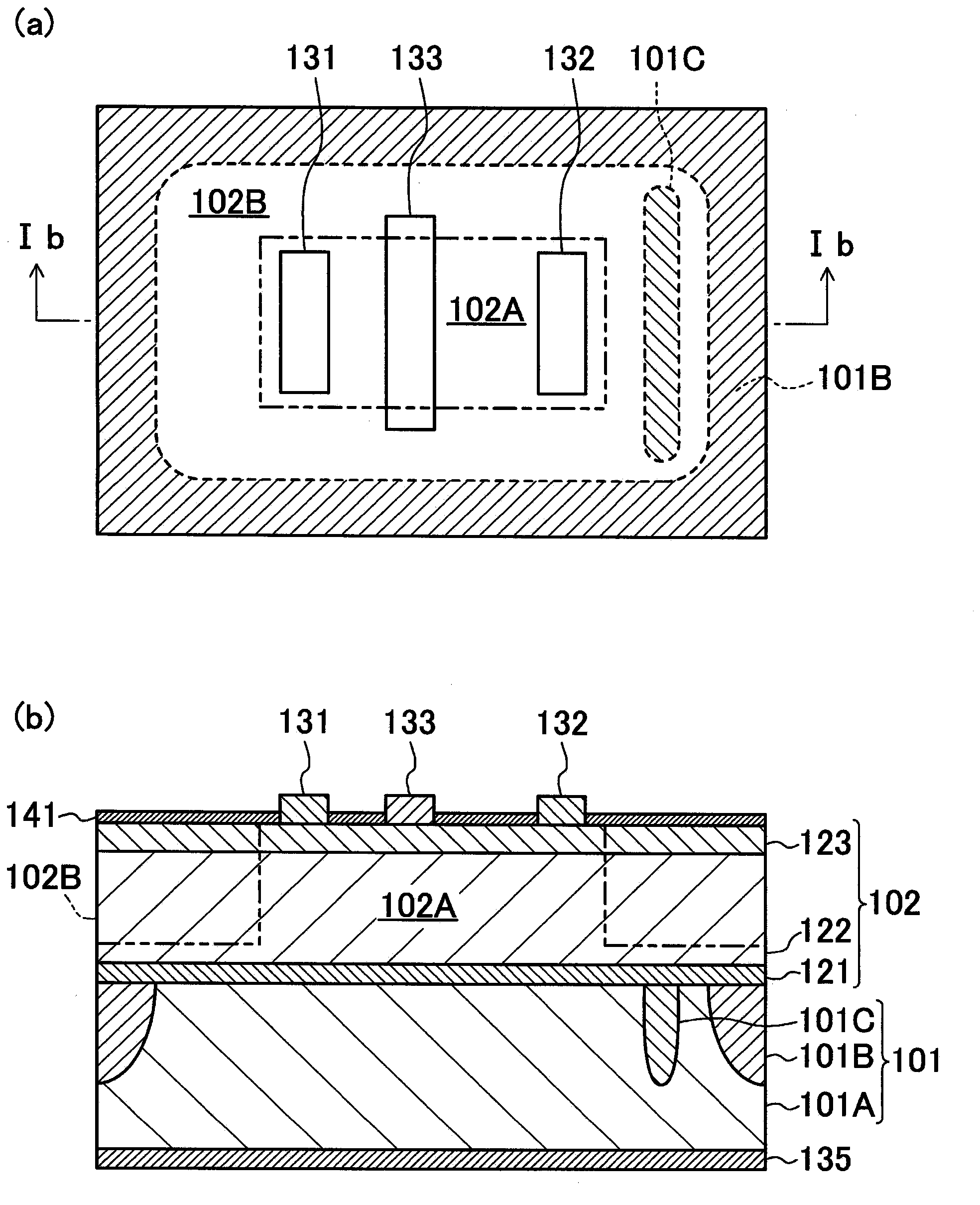

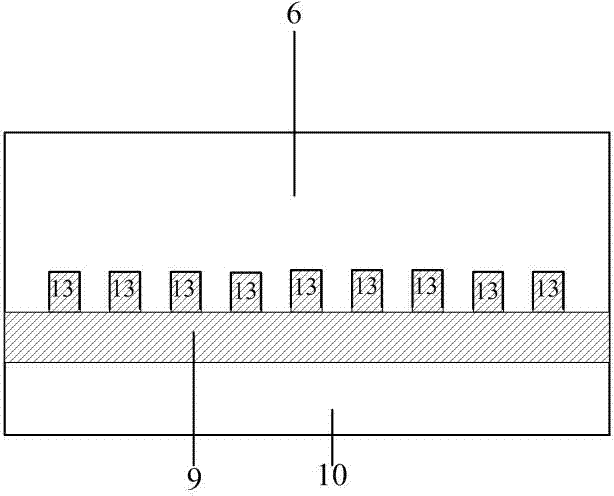

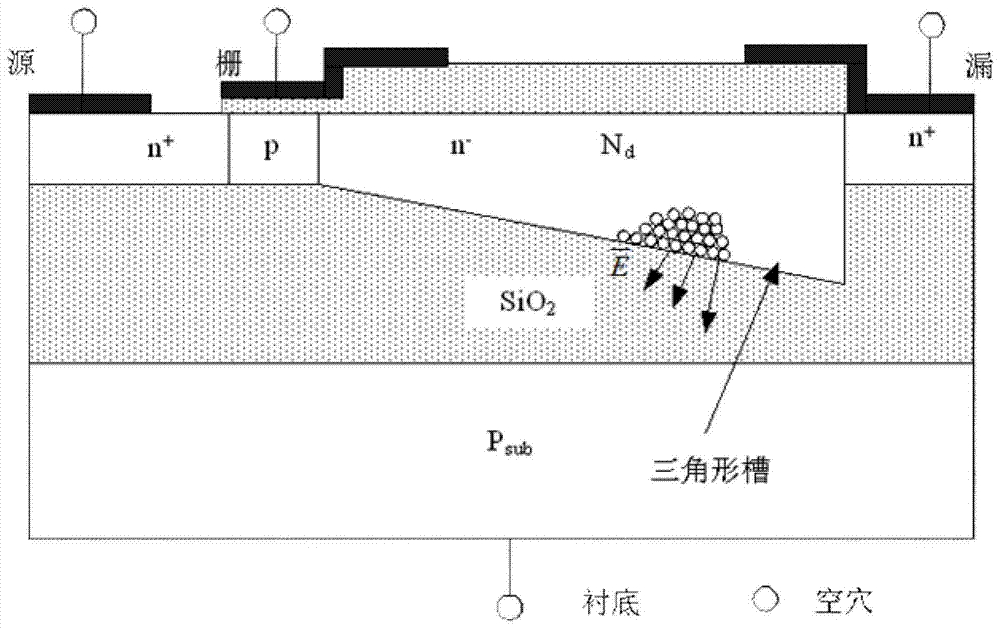

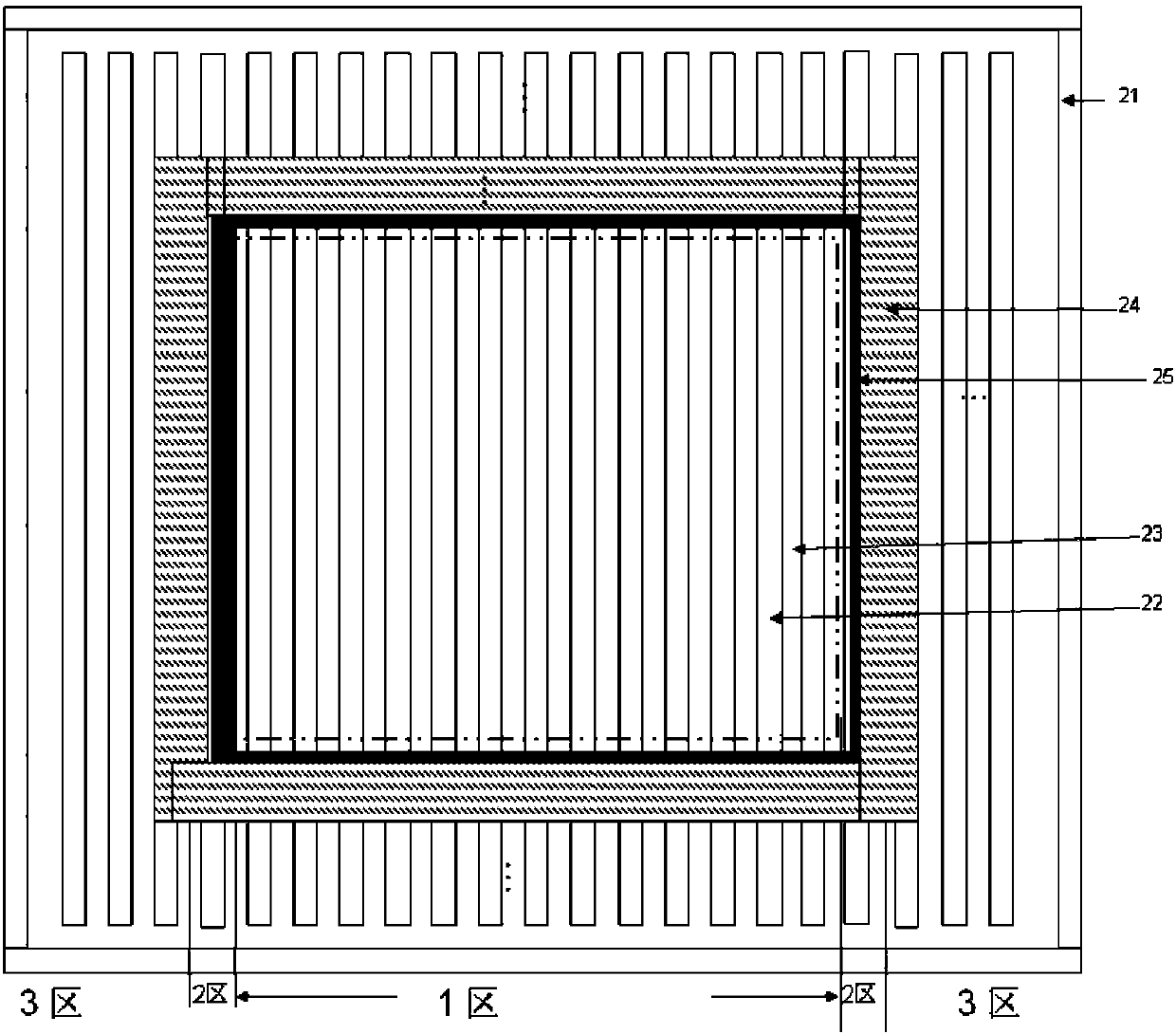

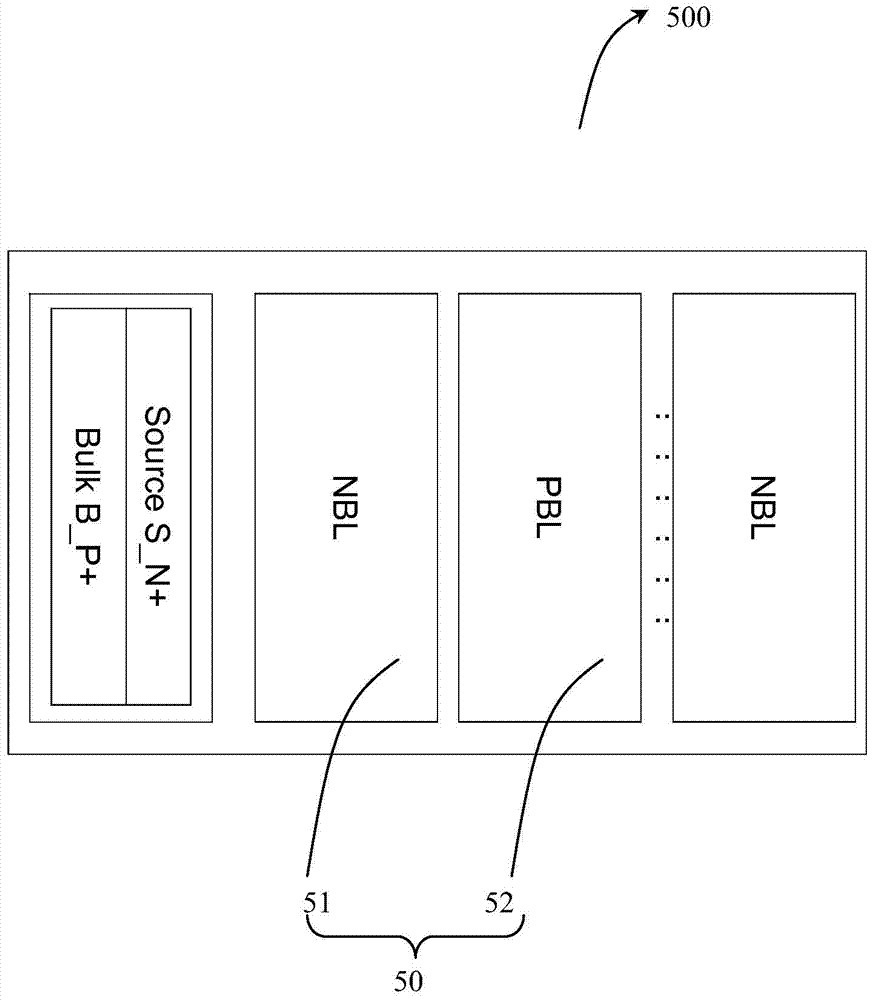

Partial SOI (silicon on insulator) super junction high-voltage power semiconductor device

InactiveCN103426913AUniform electric field distributionImprove electric field distributionSemiconductor devicesPower semiconductor deviceHigh pressure

The invention relates to semiconductor technology, in particular to a partial SOI (silicon on insulator) super junction high-voltage power semiconductor device. The partial SOI super junction high-voltage power semiconductor device is characterized by comprising a plurality of N+ pads and a P-type electric field shielding layer, the N+ pads are uniformly embedded into a P-type substrate, the P-type electric field shielding layer is arranged in the P-type substrate, the upper surface of the P-type electric field shielding layer is connected with a P-type body area and the lower surface of an N-type buffer area close to a source end, and the lower surface of the P-type electric field shielding layer is connected with the upper surface of a buried oxide layer. The partial SOI super junction high-voltage power semiconductor device has the advantages that the doping concentration of a drift region is increased by changing electric field distribution, the voltage resistance of the device is improved, on resistance is reduced, the area of the device is decreased, and cost is reduced. The invention is particularly applicable to the partial SOI super junction high-voltage power semiconductor device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Fiber-enhanced cellulose triacetate reverse osmosis membrane and preparation method thereof

InactiveCN108479399AImprove vertical pressure resistanceStable permeate fluxMembranesReverse osmosisChemistryPlasticizer

The invention discloses a fiber-enhanced cellulose triacetate reverse osmosis membrane and a preparation method thereof. The reverse osmosis membrane comprises a cellulose triacetate separating layeron an outer layer and an S-twist yarn or Z-twist yarn enhancing layer on an inner layer. The thickness of the cellulose triacetate separating layer is 20-200 microns, and the thickness of the S-twistyarn or Z-twist yarn enhancing layer is 100-500 microns. A permeation flux of the reverse osmosis membrane is 10-100 Lm<-2>h<-1>MPa, and a salt removing rate is 90-99%. The method comprises the following steps: A, preparing twisting fibers: twisting a fiber filament to be an S-twist yarn or a Z-twist yarn; B, preparing a membrane forming system: blending cellulose triacetate, a plasticizer and anadditive to obtain the membrane forming system; and C, preparing the reverse osmosis membrane: extruding the membrane forming system through a screw extruder and uniformly coating the outer surface ofthe S-twist yarn or the Z-twist yarn by melt through an annular spinning nozzle, and drafting to a coagulating bath for cooling and forming, to obtain the fiber-enhanced cellulose triacetate reverseosmosis membrane.

Owner:TIANJIN POLYTECHNIC UNIV

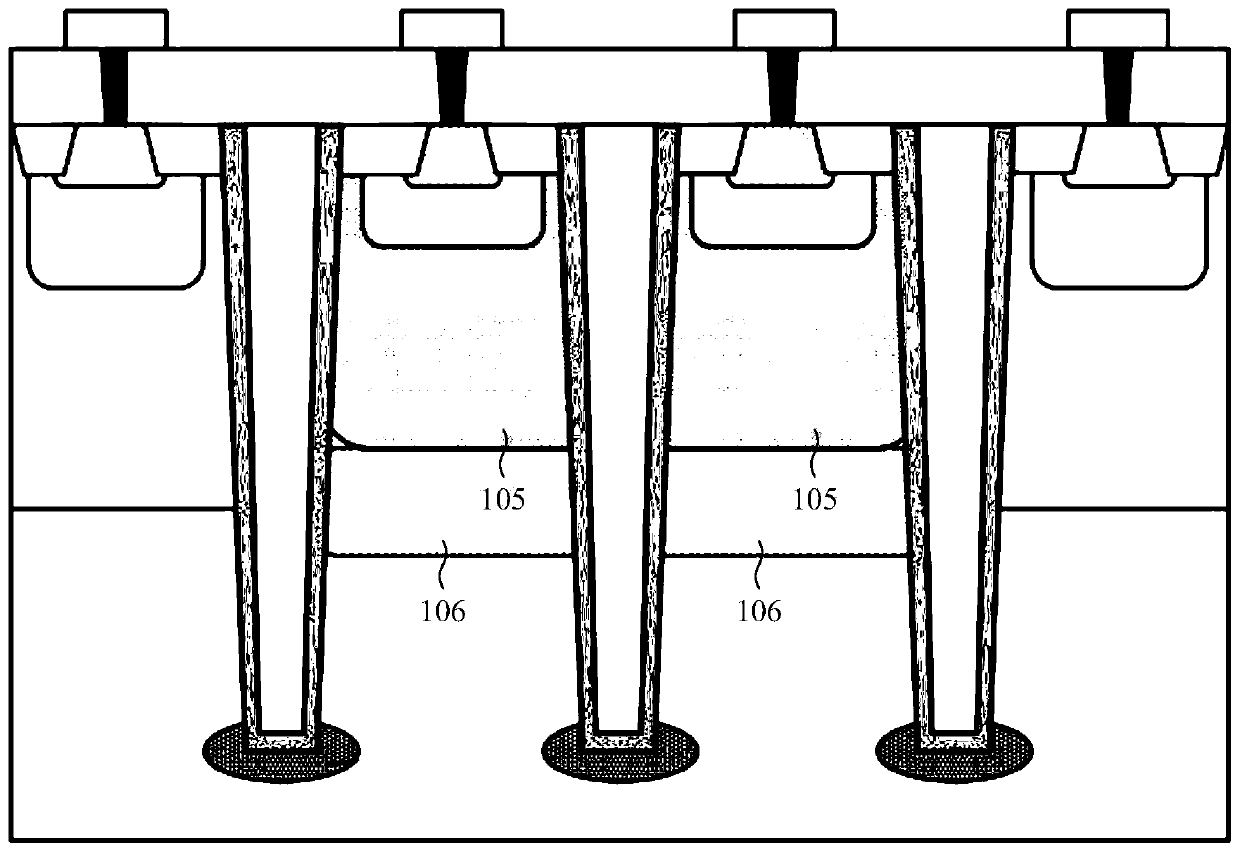

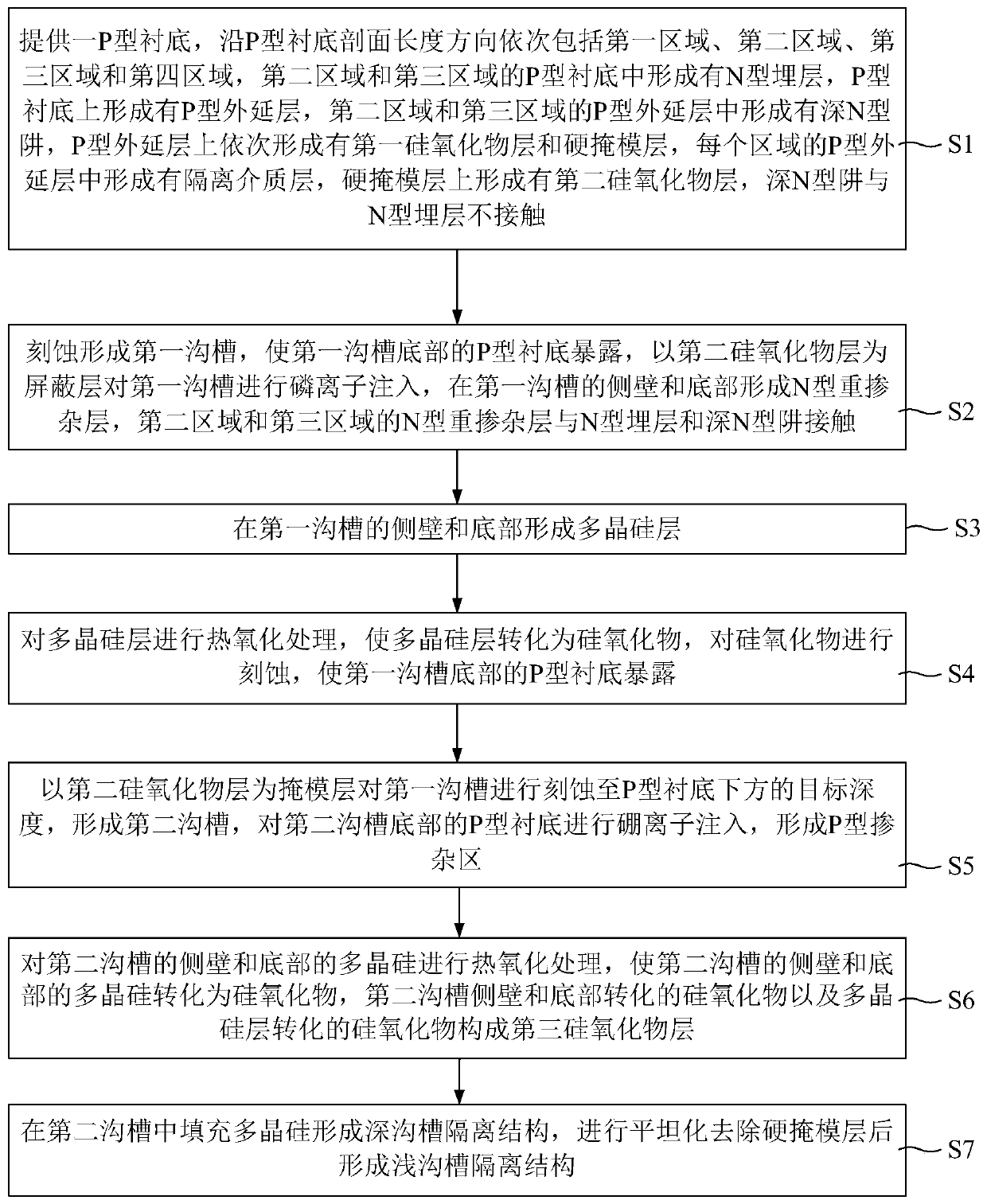

Preparation method of deep trench isolation structure and semiconductor device

PendingCN111354677AImprove breakdown voltageReduce processing timeSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSDevice material

The invention discloses a preparation method of a deep trench isolation structure and a semiconductor device. The device comprises the deep trench isolation structure. According to the invention, in the preparation process of the LDMOS device, after a first trench corresponding to the deep trench isolation structure is formed by etching, phosphorus ion implantation is carried out on the first groove; an N-type heavily doped layer is forme on on the side wall and the bottom of the first trench, the N-type heavily-doped layer can lead out the N-type buried region in contact with the N-type heavily-doped layer, so that the deep N-type well does not need to be diffused to be in contact with the N-type buried layer to facilitate lead-out by consuming long time to carry out high-temperature thermal propulsion when the deep N-type well is formed, the processing time of high-temperature thermal propulsion is shortened, and the manufacturing cost is reduced; meanwhile, due to the fact that thehigh-temperature thermal propulsion time is shortened, upward further diffusion of the N-type buried layer is prevented, the withstand voltage length in the longitudinal structure of the device is increased, and the longitudinal withstand voltage is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

High-voltage heterojunction transistor

InactiveCN105336771AHigh pressureImprove vertical pressure resistanceSemiconductor devicesPhysicsP type doping

The invention relates to the technology of semiconductors, and particularly relates to a high-voltage heterojunction transistor. An N-type structure is doped in partial intervals of a device epitaxial layer and a P-type exhaust structure is doped in partial intervals of a silicon-based substrate layer based on a conventional transverse heterojunction transistor device structure. The substrate and a buffer layer are enabled to be completely exhausted by introduction of a P-type doping region and an N-type doping region so that the substrate is enabled to bear longitudinal withstanding voltage, and thus voltage withstanding capacity of the device can be improved. Meanwhile, height of a barrier layer is increased and a leakage current channel is blocked by introduction of P-type impurities in the epitaxial layer, and finally leakage current is reduced.

Owner:SOUTHWEST JIAOTONG UNIV

SOI LDMOS device with interface N<+> layer

ActiveCN102760753AAvoid premature breakdownImprove vertical pressure resistanceSemiconductor devicesHigh concentrationP type silicon

The invention discloses an SOI (Semiconductor ON Insulator) LDMOS (Laterally Diffused Metal Oxide Semiconductor) device with an interface N<+> layer, and relates to a semiconductor power device. The SOI LDMOS device comprises a substrate silicon layer, a medium buried layer and active top layer silicon, wherein the medium buried layer is arranged between the substrate silicon layer and the active top layer silicon; and the active top layer silicon is divided into an N-type silicon layer, a P-type silicon layer and an N<+> silicon layer from the surface of a semiconductor to the medium buried layer. According to the invention, as the N<+> silicon layer is arranged between the medium buried layer and the active top layer silicon, when the device is in a reverse blocking state, exhausted high-concentration ionized donor at the interface part enhances the electric field of the medium buried layer, the distribution of the electric field in the active top layer silicon is effectively modulated, and accordingly, the longitudinal voltage resistance and the transverse voltage resistance of the device are effectively improved. Meanwhile, the P-type silicon layer in the active top layer silicon can adjust the RESURF (Reduced SURface Field) condition of the device and relieve the contradiction between the breakdown voltage and the on resistance of the device.

Owner:NO 24 RES INST OF CETC

Method for manufacturing SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157434AImprove vertical pressure resistanceLittle impact on performanceSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention relates to a method for manufacturing an SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with a p buried layer and a longitudinal channel. The SOI LIGBT device manufactured by the existing method abruptly degrades and even becomes invalid under a high temperature and large current. In the method, SOI materials with p-type buried layers are adopted to manufacture the SOI LIGBT device with the longitudinal channel; the longitudinal withstand voltage is mainly borne by a reversely biased pn junction depletion layer formed by a p-type buried layer with backward impurity concentration distribution and an n-type top layer semiconductor with forward impurity concentration distribution; and the SOI LIGBT device unit is manufactured through ten-time etching and seven-time oxidizing. The method has the beneficial effects of effectively reducing the on-state resistance, on-state voltage drop and on-state power consumption of the device, improving the on-state current and working efficiency of the device, obviously improving the performance of the SOI LIGBT device and improving the reliability of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

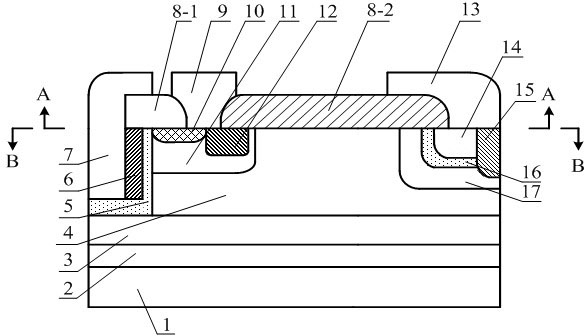

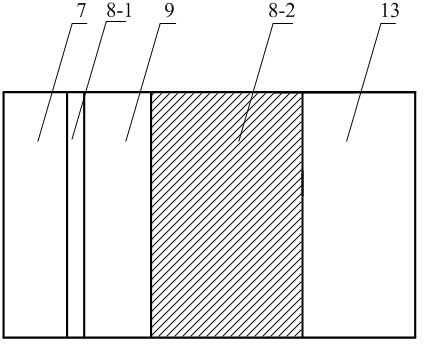

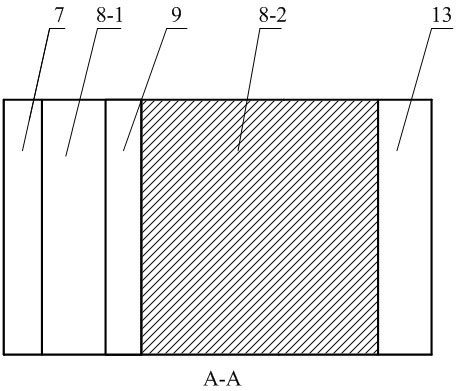

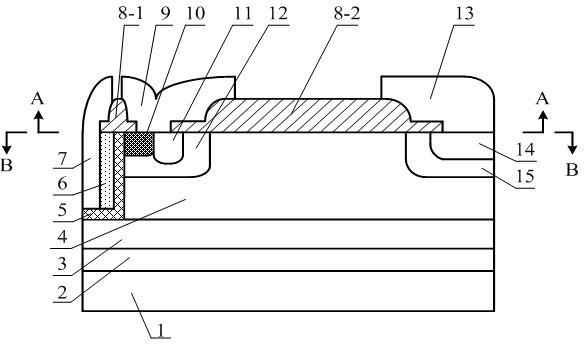

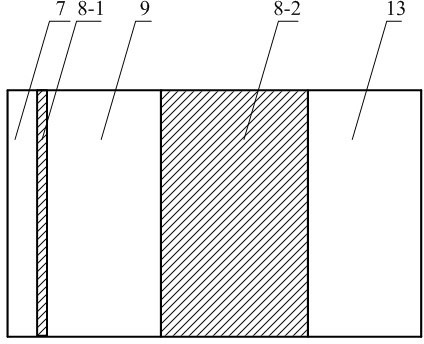

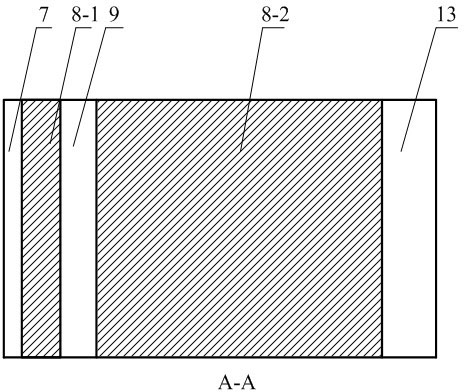

Longitudinal channel SOI (silicon on insulator) nLDMOS (n-type laterally diffused metal oxide semiconductor) device unit with p buried layer

ActiveCN102157561AImprove vertical pressure resistanceReduce self-heating effectSemiconductor devicesEngineeringHigh pressure

The invention relates to a longitudinal channel SOI nLDMOS device unit with a p buried layer. The prior products limit the improvements of device structures and electric properties. The longitudinal channel SOI nLDMOS device unit with the p buried layer related by the invention comprises a p-type semiconductor substrate, a buried oxide layer, a p-type buried layer region, a n-type light doping drift region, a p-type well region, a p-type ohm contact region, a n-type source region, a longitudinal oxide layer, a n-type buffering region, a n-type drain region, a field oxygen region, a longitudinal n-type polysilicon gate and a metal electrode lead. The upper part of the device is provided with a deep groove longitudinal gate oxide, two field oxygen layers, a longitudinal n-type polysilicon gate and a metal layer. In the invention, the p-type buried layer region is led-in between the n-type light doping drift region and the buried oxide layer; when the device is in a forward blocking state and a high voltage exists between drain sources, a reverse biased pn (positive negative) node is formed, and the pn node can bear most of the longitudinal withstand voltage of the device, so that the longitudinal voltage-withstand performance of the device is increased, and the thermal stability and thermostability of the device electric property and the heat radiation property of the device are improved.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

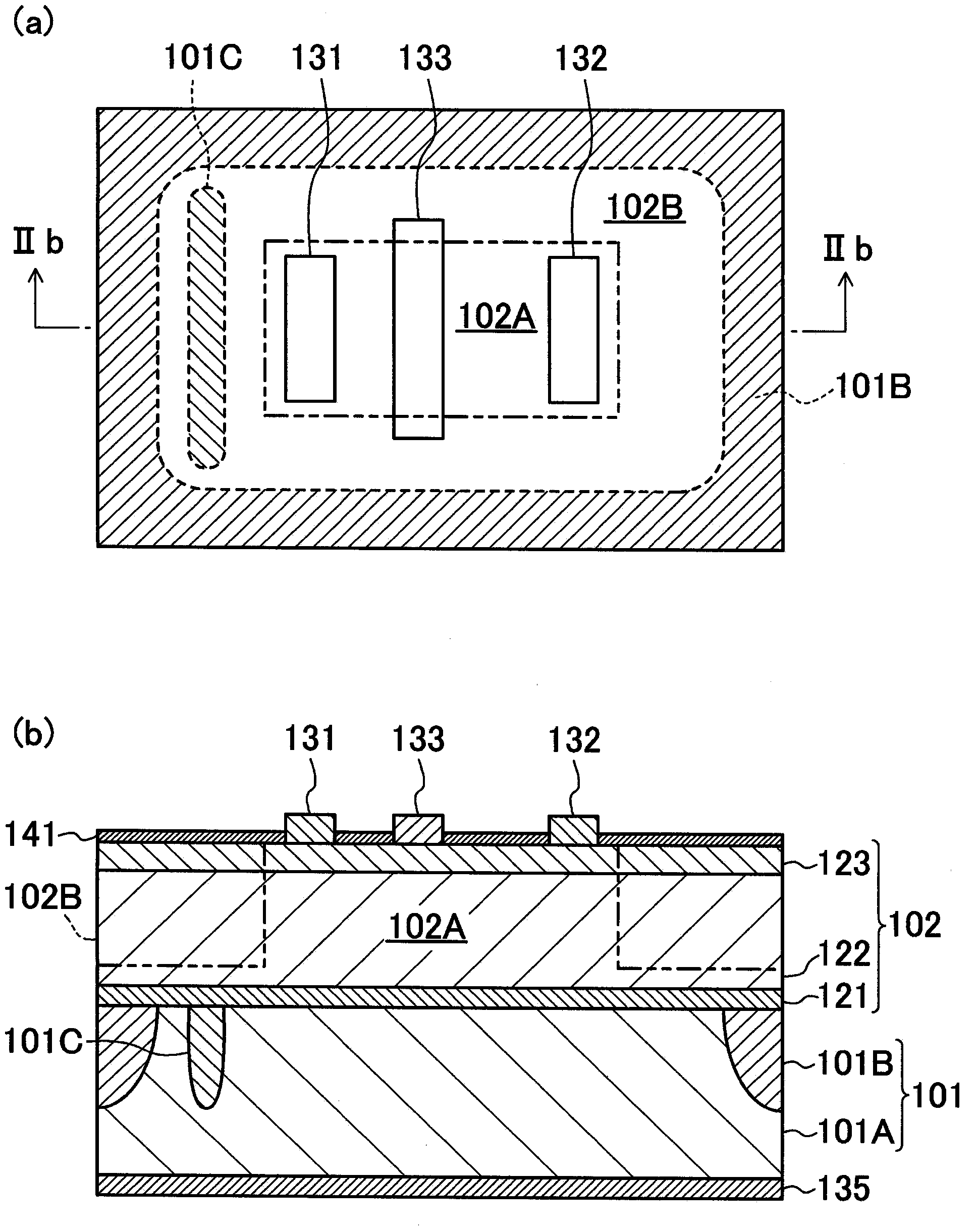

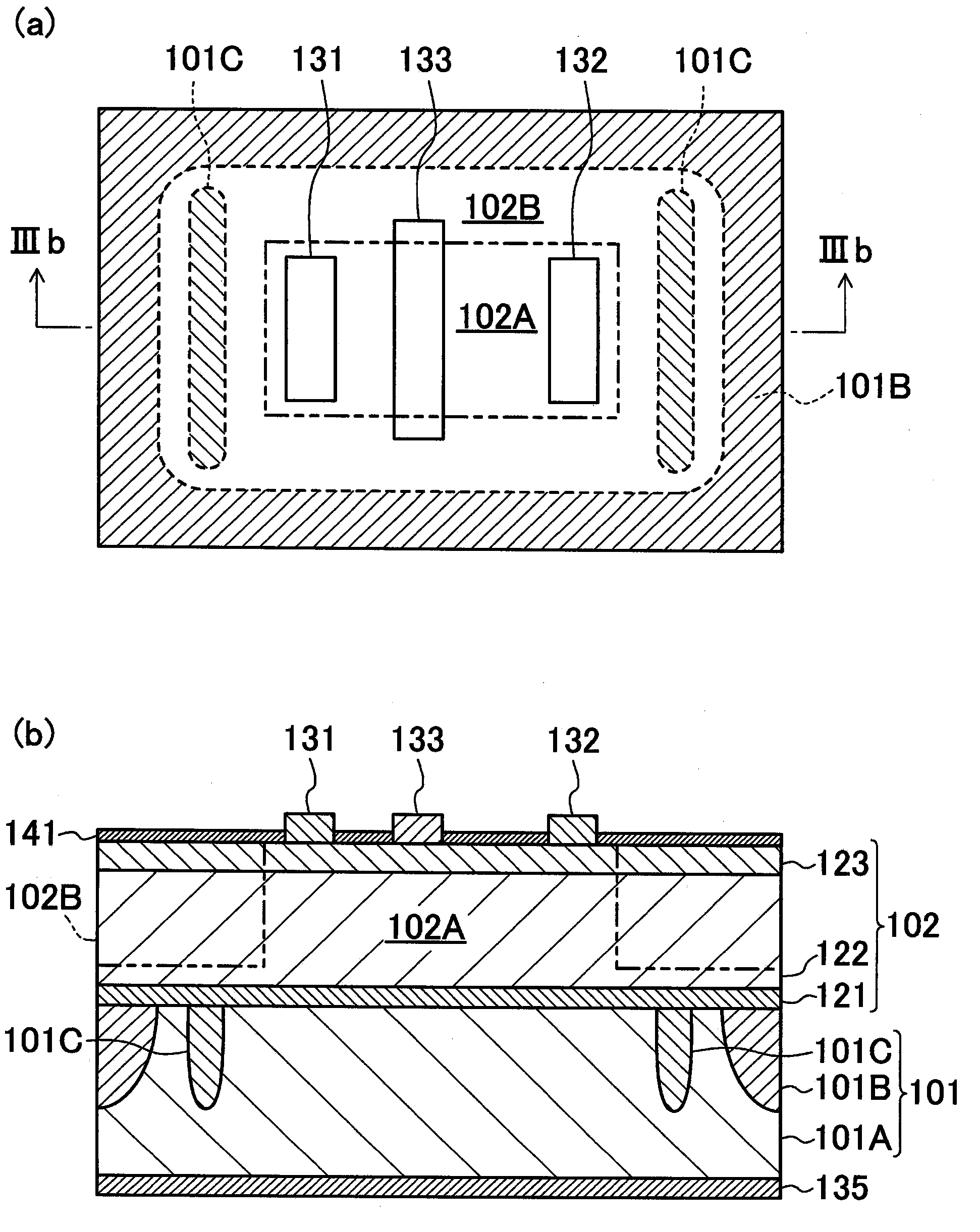

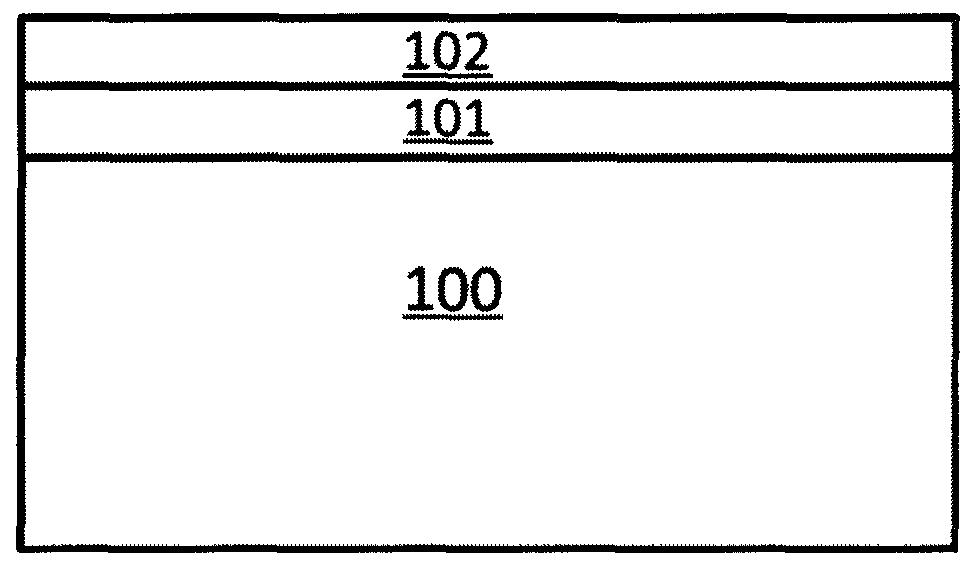

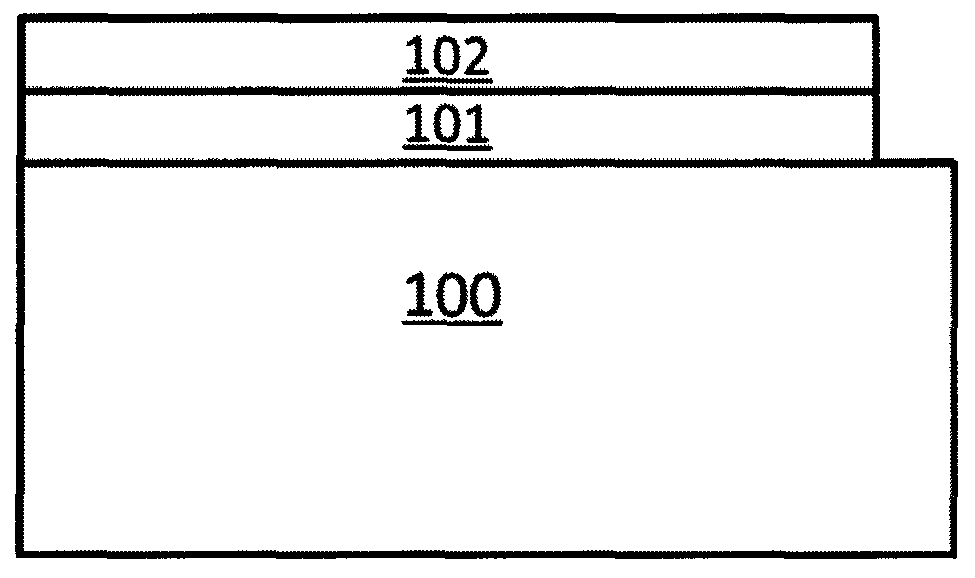

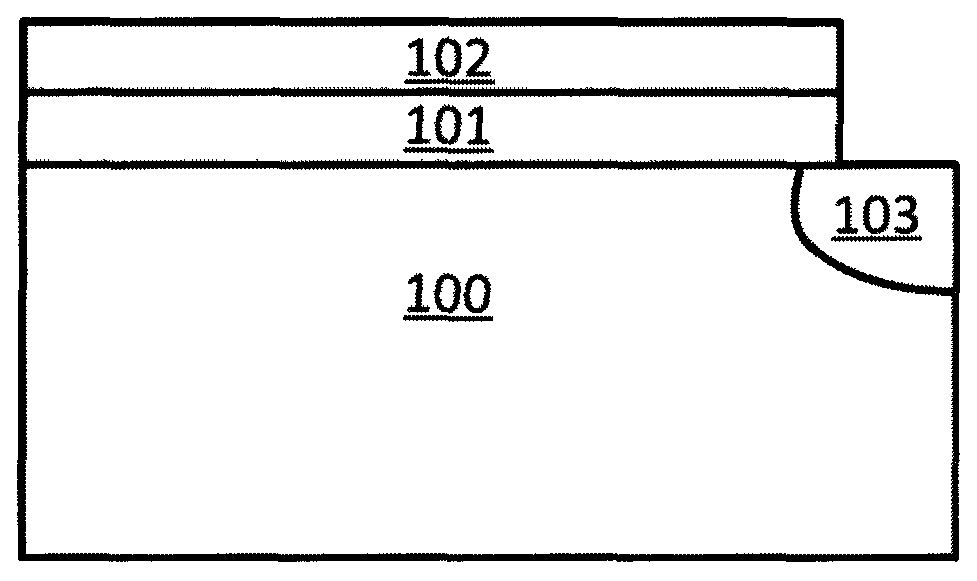

Nitride semiconductor device

ActiveCN103392225AImprove vertical pressure resistanceImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor devicePower flow

This nitride semiconductor device is provided with a semiconductor substrate (101) and a nitride semiconductor layer (102) formed on the semiconductor substrate. The semiconductor substrate (101) comprises a normal region (101A), carrier supply region(s) (101C), and an interface current blocking region (101B). The interface current blocking region surrounds the normal region and carrier supply region(s), and the interface current blocking region and carrier supply region(s) each contain impurities. The carrier supply region(s) forms a source for supplying carriers to a carrier layer formed at the interface between the nitride semiconductor layer and the semiconductor substrate and has a conductivity type that forms an elimination destination for the carriers. The interface current blocking region is of a conductivity type that forms a potential barrier for the carriers.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

SOI power device with medium layer fixed charges

InactiveCN104505403ASolving Self-Heating ProblemsImprove lateral breakdown voltageSemiconductor devicesCMOSHigh concentration

The invention discloses an SOI power device with medium layer fixed charges. The SOI power device comprises a substrate layer, an active layer and an insulating medium buried layer located between the substrate layer and the active layer. A high-concentration fixed charge area is disposed in the edge area of the contact surface of the insulating medium buried layer and the active layer. The area of the high-concentration fixed charge area accounts for 50-75% of the area of the contact surface of the insulating medium buried layer and the active layer. The concentration of the high-concentration fixed charge area is 1*10<17>-1*10<18> / cm<2>. The SOI power device is simple in process, large in fixed charge doping concentration process allowance, small in influence by high-temperature processes, and completely compatible with a conventional CMOS / SOI process. In addition, the voltage resistance of the power device is increased greatly by an enhanced medium buried layer electric field.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Semiconductor device for enhancing voltage resistance of device and preparation method thereof

InactiveCN103887325AImprove vertical pressure resistanceImprove lateral pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention discloses a semiconductor device for enhancing voltage resistance of a device. The semiconductor device is a high-electron-mobility transistor adopting III-V semiconductor material. III-family nitride layer close to a drain electrode part of the semiconductor device is etched via one etching method, and a substrate is doped in an opposite conductive type at the etching part. When the device withstands high voltage, range of an exhaustion region is increased, and thus voltage resistance of the device is enhanced. Modulation is performed from a body electric field to a surface electric field so that vertical voltage resistance of the device is enhanced and transverse voltage resistance is enhanced simultaneously, and thus the whole voltage resistance of the device is enhanced.

Owner:HANGZHOU ENNENG TECH

Manufacturing method of silicon-on-insulator lateral insulated-gate bipolar transistor (SOI LIGBT) device unit of lateral channel with positive (p) buried layer

ActiveCN102169831AImprove vertical pressure resistanceLittle impact on performanceSemiconductor/solid-state device manufacturingReverse biasImpurity

The invention relates to a manufacturing method of a silicon-on-insulator lateral insulated-gate bipolar transistor (SOI LIGBT) device unit of a lateral channel with a positive (p) buried layer. An SOI LIGBT device which is manufactured by the conventional method is abruptly degraded or even invalid in a high-temperature and large-current environment. In the method provided by the invention, the SOI LIGBT device is manufactured by using an SOI material with a p-buried layer; a reverse bias pn junction which is formed by the p-buried layer with reverse impurity concentration distribution and anegative (n) top-layer semiconductor with forward impurity concentration distribution is used for longitudinal voltage resistance; and the SOI LIGBT device unit of the lateral channel with the p buried layer is manufactured by etching for nine times and oxidation twice. The device unit which is manufactured by the method improves the longitudinal voltage resistance of the device under the condition of reducing the thickness of a buried oxidation layer, reduces a self-heating effect, improves the thermal property of the device and improves the reliability of the device.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

Manufacturing method of SOI (Silicon On Insulator) nLDMOS (n Laterally Diffused Metal Oxide Semiconductor) device unit with P buried layer

ActiveCN102157383BExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingRadio frequencyFilm material

The invention relates to a manufacturing method of an SOI (Silicon On Insulator) nLDMOS (n Laterally Diffused Metal Oxide Semiconductor) device unit with a P buried layer. An SOI nLDMOS device manufactured by the traditional method seriously influences the voltage withstanding property of the SOI nLDMOS device and influences the heat radiation of the SOI nLDMOS device. The SOI nLDMOS device with the P buried layer is manufactured by carrying out photoetching on an SOI thick film material with the P buried layer for nine times. The manufactured SOI nLDMOS device bears the vast majority of withstand voltages through a depletion layer formed by a reverse biased PN junction positioned between an N type top silicon film and a P type buried layer when the voltages of a blocking-state drain electrode are increased, thereby enhancing the longitudinal voltage withstanding property of the SOI nLDMOS device and breaking the bottleneck of limiting the improvement of horizontal withstand voltages due to over-low longitudinal withstand voltages; and in addition, the thin buried oxide layer is beneficial to the heat radiation of the SOI nLDMOS device, thereby effectively reducing the self-heating effect. The manufacturing method ensures that electrical and thermal properties of the SOI nLDMOS device integrating power and radio frequency are remarkably improved, and is beneficial to saving ofthe resources and the energy and protecting of the environment.

Owner:江苏拓联智能科技有限公司

Manufacturing method of SOI (Silicon On Insulator) nLDMOS (n Laterally Diffused Metal Oxide Semiconductor) device unit with P buried layer

ActiveCN102157383AExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingRadio frequencyFilm material

The invention relates to a manufacturing method of an SOI (Silicon On Insulator) nLDMOS (n Laterally Diffused Metal Oxide Semiconductor) device unit with a P buried layer. An SOI nLDMOS device manufactured by the traditional method seriously influences the voltage withstanding property of the SOI nLDMOS device and influences the heat radiation of the SOI nLDMOS device. The SOI nLDMOS device with the P buried layer is manufactured by carrying out photoetching on an SOI thick film material with the P buried layer for nine times. The manufactured SOI nLDMOS device bears the vast majority of withstand voltages through a depletion layer formed by a reverse biased PN junction positioned between an N type top silicon film and a P type buried layer when the voltages of a blocking-state drain electrode are increased, thereby enhancing the longitudinal voltage withstanding property of the SOI nLDMOS device and breaking the bottleneck of limiting the improvement of horizontal withstand voltages due to over-low longitudinal withstand voltages; and in addition, the thin buried oxide layer is beneficial to the heat radiation of the SOI nLDMOS device, thereby effectively reducing the self-heating effect. The manufacturing method ensures that electrical and thermal properties of the SOI nLDMOS device integrating power and radio frequency are remarkably improved, and is beneficial to saving of the resources and the energy and protecting of the environment.

Owner:江苏拓联智能科技有限公司

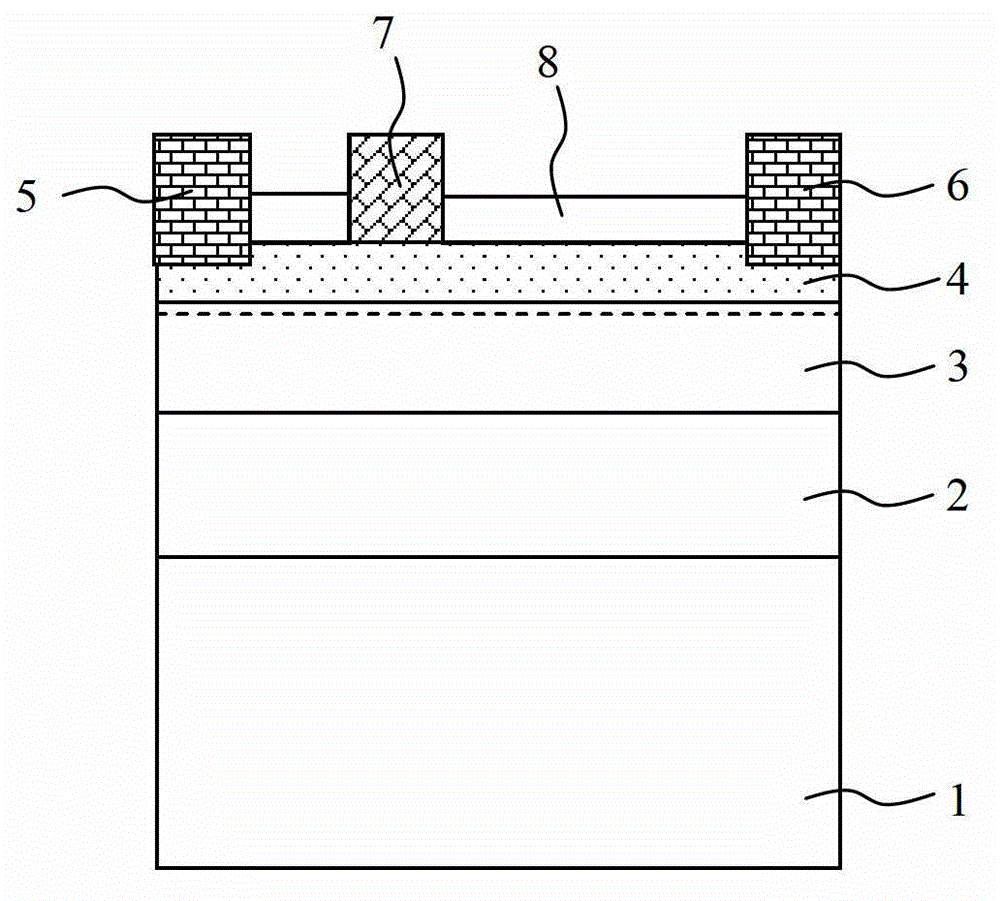

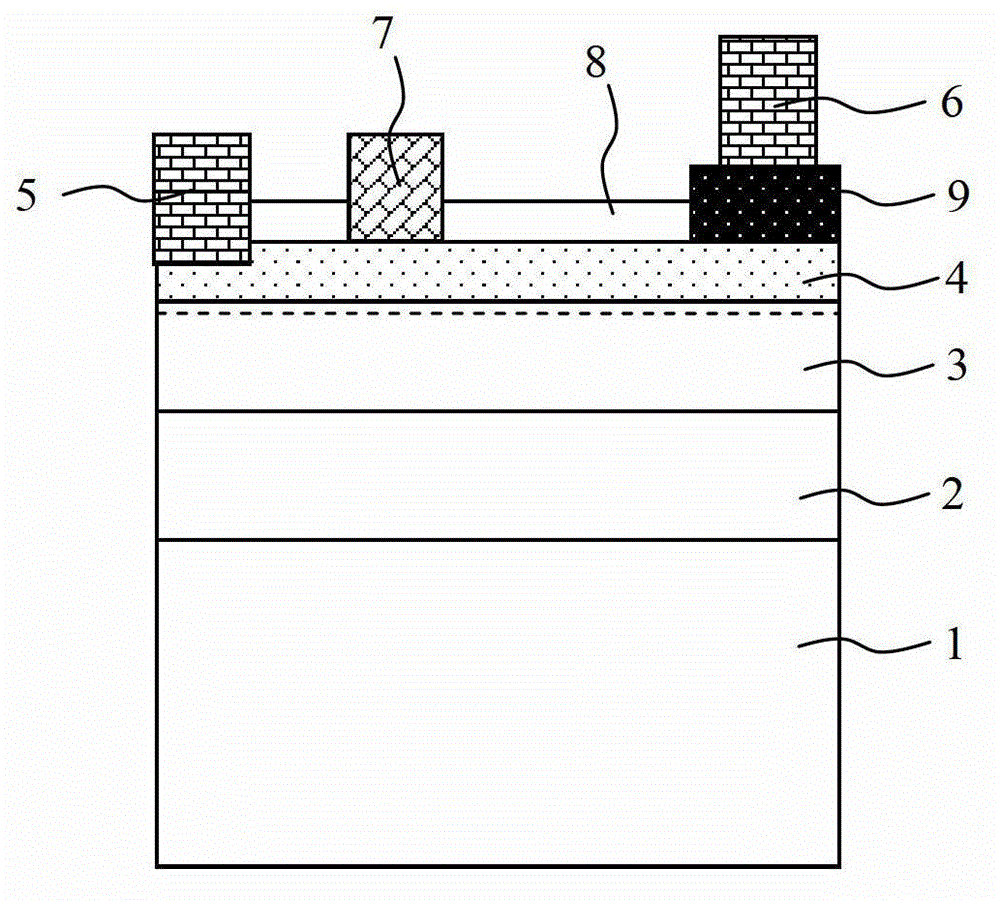

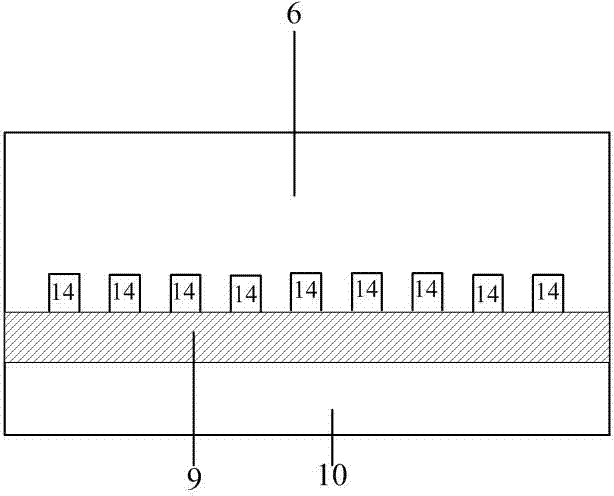

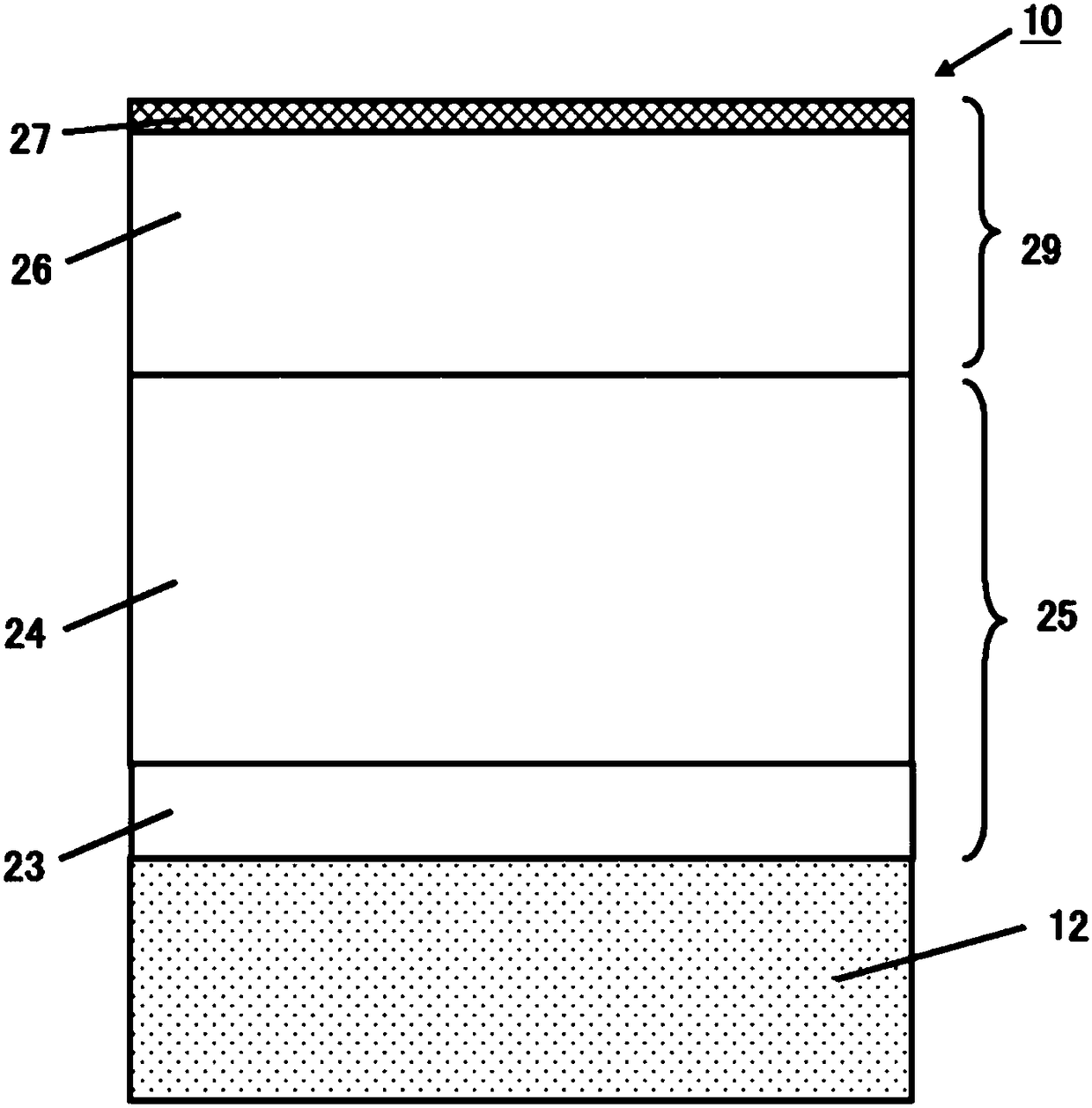

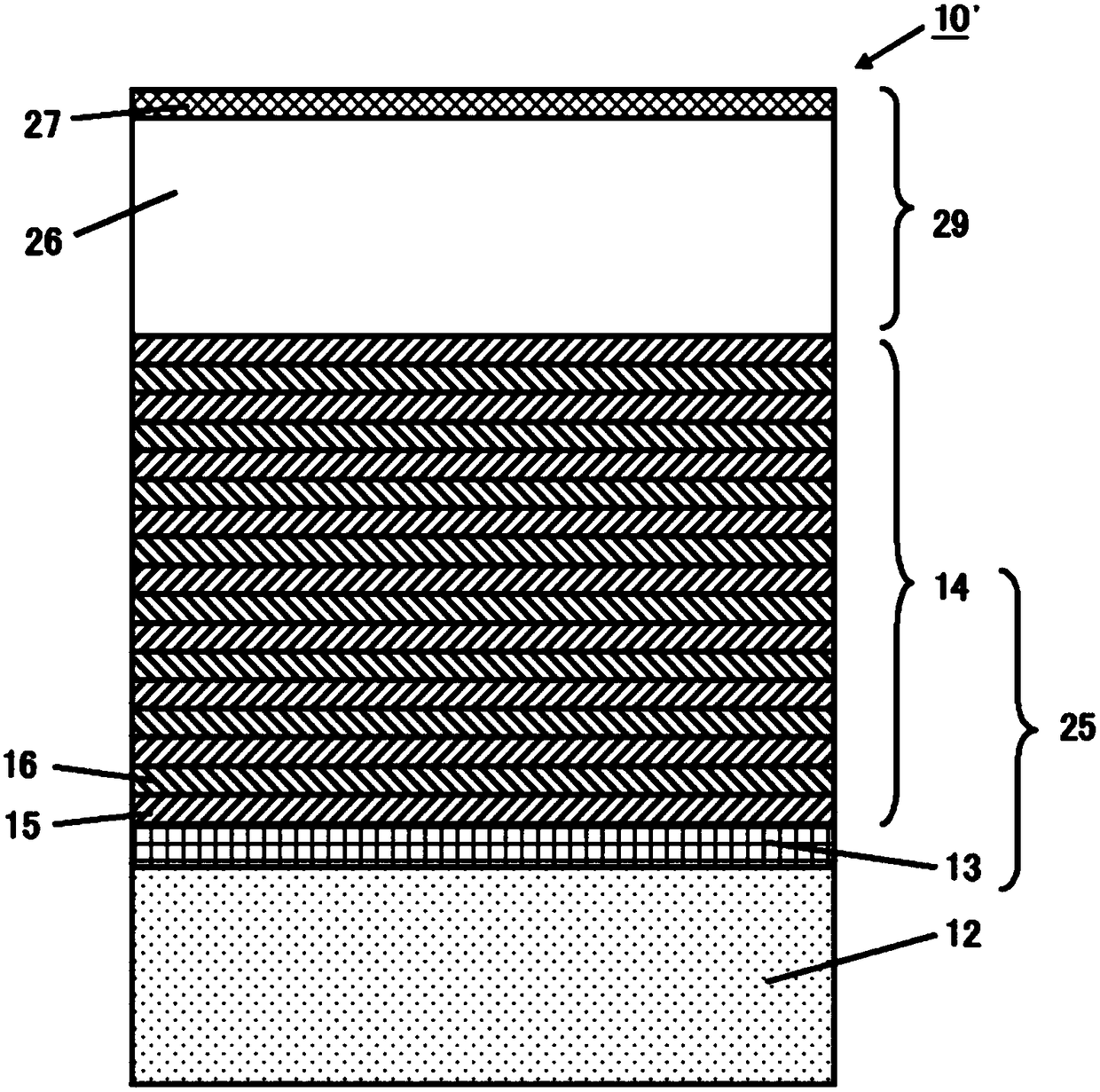

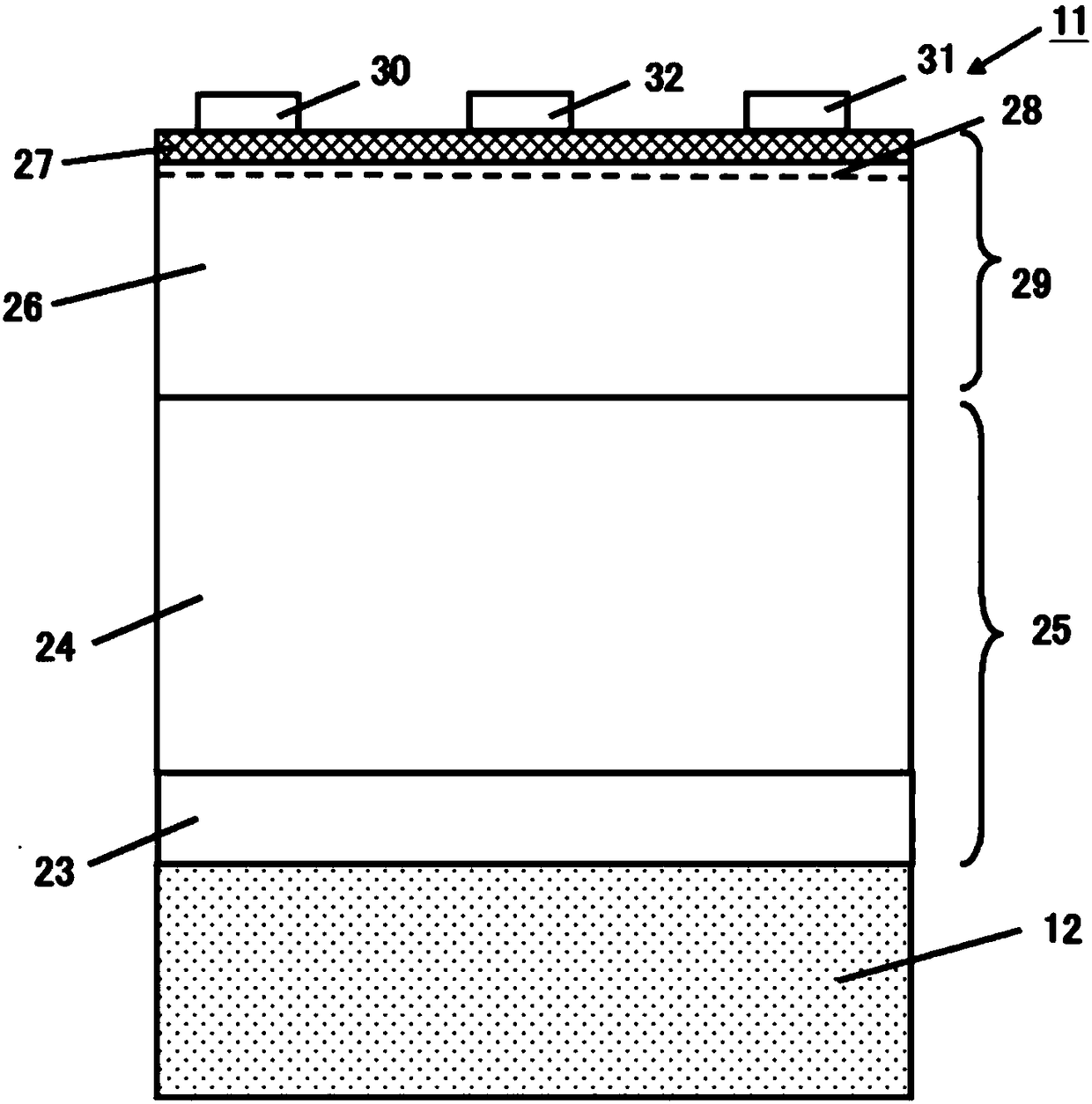

Semiconductor base, semiconductor device, method for manufacturing semiconductor base, and method for manufacturing semiconductor device

ActiveCN108140582AImprove vertical pressure resistanceEnhanced inhibitory effectSolid-state devicesSemiconductor/solid-state device manufacturingAcceptorDevice material

The present invention is a semiconductor base characterized in being provided with: a substrate; a buffer layer comprising a nitride semiconductor, the buffer layer being provided on the substrate; and a channel layer comprising a nitride semiconductor, the channel layer being provided on the buffer layer; the buffer layer including a first region provided on the substrate side so that the concentration of boron is higher than the concentration of an acceptor element, and a second region provided on the first region so that the concentration of boron is lower than the first region and the concentration of the acceptor element is higher than the first region. Consequently, the semiconductor base is provided so that a high pit suppressing effect can be obtained while maintaining high longitudinal pressure resistance.

Owner:SANKEN ELECTRIC CO LTD +1

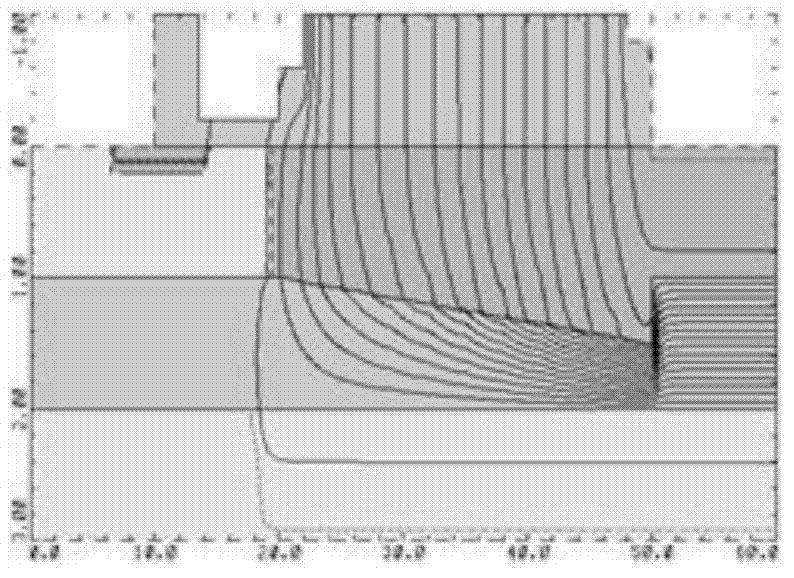

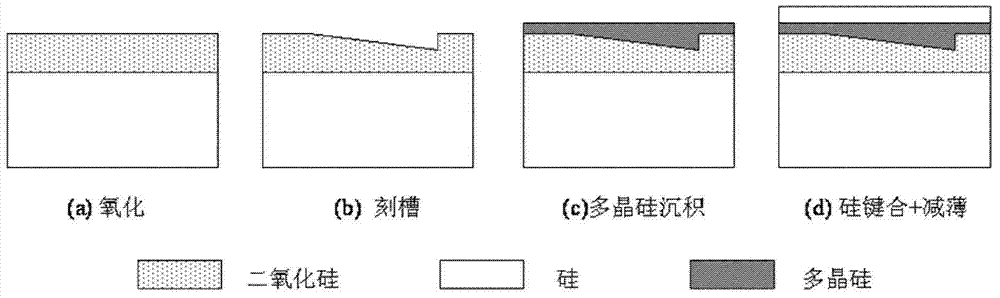

SOI-LDMOS (silicon-on-insulator laterally diffused metal oxide semiconductor) high-tension power device with triangular trench

InactiveCN104241388AImprove vertical pressure resistanceRealize the process is simpleSemiconductor devicesHigh densityEngineering

The invention discloses an SOI-LDMOS (silicon-on-insulator laterally diffused metal oxide semiconductor) high-tension power device with a triangular trench and aims to solve the problems that voltage of a drain of the prior SOI-LDMOS device is induced out of an electronic inversion layer from beneath a buried oxide layer, an equipotential line is prevented from penetrating the buried oxide layer, and early breakdown occurs to a silicon layer, and breakdown voltage withstanding is difficult to increase. The SOI-LDMOS high-tension power device is mainly characterized in that the triangular trench is etched in a buried oxide layer under a drift area; a buried oxide slope exists under the drift area and is capable of constraining positively charged holes, high-density positive charge is produced, and breakdown voltage withstanding of the device is greatly increased through the high-density positive charge; thickness of the drift area linearly increases from a source to a drain, according to the principle of RESURF (reduced surface field), a transverse electric field is uniformized owing to modulation, lateral voltage withstanding can be improved, and rejection ratio on resistance can be increased fast.

Owner:XIHUA UNIV

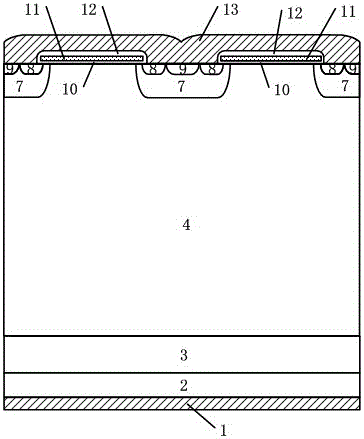

Super-junction device and manufacturing method thereof

ActiveCN109755316AImprove vertical pressure resistanceImprove the ability to withstand voltage verticallySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowLayer interface

The invention discloses a super-junction device. A groove of the super-junction structure is of a side face inclined structure; the doping concentration of an N-type epitaxial layer is of a step distribution structure; a P-type column is composed of a P-type ion implantation region formed at the bottom of the groove, and a P-type epitaxial layer which are arranged in a stacked mode; a protective ring oxide film surrounds the peripheral side of a current flow region; and the N-type epitaxial layer at the oxide film epitaxial layer interface of the N-type epitaxial layer in the protective ring oxide film and a terminal region comprises a top region with lowered N type doping concentration, so that the transverse depletion capability of the N-type column at the interface of the epitaxial layer of the oxidation film can be enhanced. The invention further discloses a manufacturing method of the super-junction device. According to the invention, the charge balance between the P-type column and the N-type column of the super-junction structure with the inclined groove can be improved, the longitudinal voltage withstand capability of the device is improved, and the source and drain breakdown voltage of the device is improved; and the capacity of bearing transverse voltage of the device terminal can be improved, and the reliability of the device can be improved.

Owner:SHENZHEN SANRISE TECH CO LTD

Manufacturing method of silicon-on-insulator lateral insulated-gate bipolar transistor (SOI LIGBT) device unit of lateral channel with positive (p) buried layer

ActiveCN102169831BImprove vertical pressure resistanceLittle impact on performanceSemiconductor/solid-state device manufacturingReverse biasImpurity

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

Silicon-on-insulator (SOI) low-resistance lateral high-voltage device and manufacturing method thereof

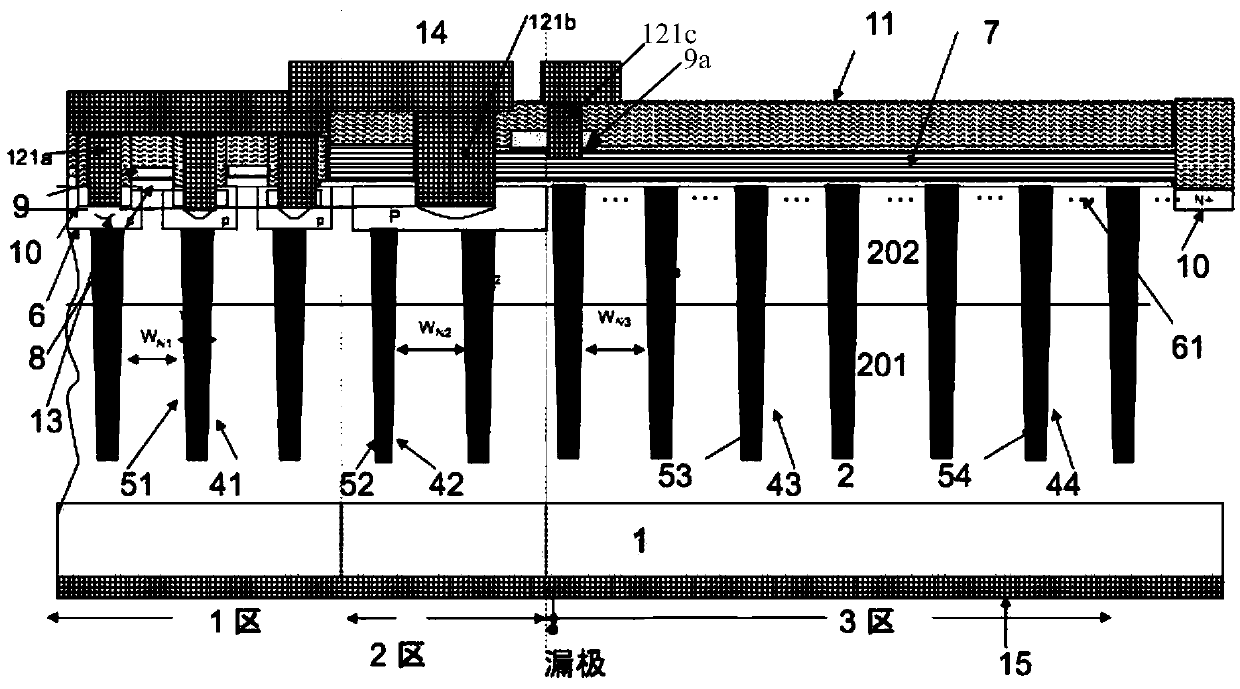

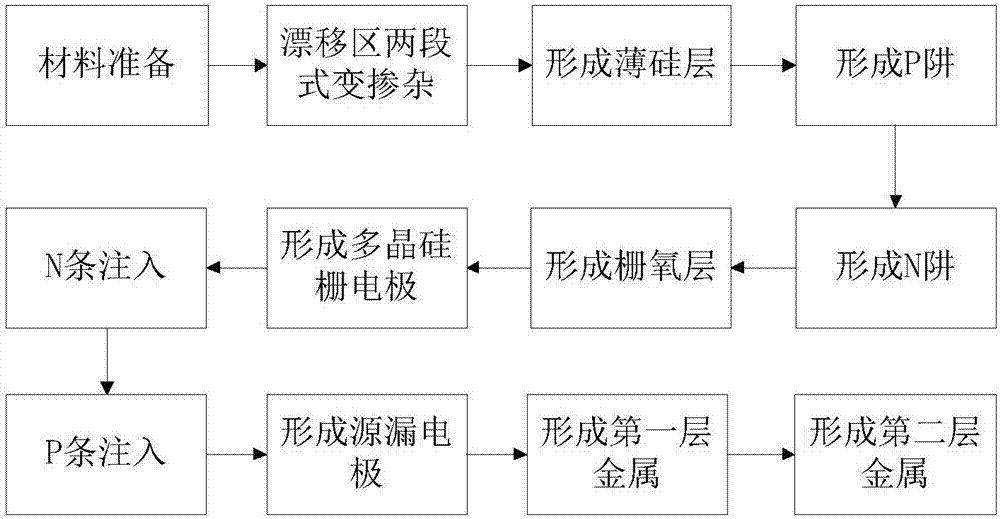

InactiveCN106952809AImprove vertical pressure resistanceLower specific on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactHigh pressure

The invention provides a silicon-on-insulator (SOI) low-resistance lateral high-voltage device and a manufacturing method thereof. The manufacturing method comprises the following steps of taking an SOI as a substrate, forming an N-type linear variable doping thick SOI layer and a thin silicon layer drift region, forming a thin silicon layer region, namely a thick dielectric layer, and forming a Pwell region; and forming an Nwell region, forming a gate oxide layer, forming a poly-silicon gate electrode, forming an N strips, forming a P strip, performing injection of a first P-type heavy-doping region, a first N-type heavy-doping region and a second N-type heavy-doping region to form ohmic contact, etching a first-layer contact hole of a leading-out electrode, depositing aluminum metal, and forming a source contact electrode and a drain contact electrode. The manufacturing method is highly compatible with a traditional process and has universality; with the manufactured device, the device area can be effectively reduced, and the device cost is reduced; and in the SOI low-resistance lateral high-voltage device fabricated by the method, the formulas of BV=950V and R<on, sp>=153 ohms.cm<2> can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Silicon-on-insulator flat panel display driver chip and preparation method thereof

ActiveCN101587901BSolve leakage currentReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageHigh pressure

Display driver chip composed of high-voltage P-type lateral metallic oxide transistors, high-voltage N-type lateral metallic oxide transistors, high-pressure diodes and low-voltage devices, among the high-voltage devices and between the high-voltage and low-voltage devices are separated by double-groove filled with silicon dioxide that extending from a buried oxide layer through a N-type epitaxial layer to a field oxide layer on device surface, partial N-type or P-type heavily dosed buried layer are disposed above the buried oxide layer that positioning under the N-type lateral metallic oxide transistors and the high-pressure diodes. The prepartion method is: preparing a buried oxide layer on a P-type substrate, preparing partial N-type or P-type heavily dosed buried layer above the buried oxide layer, depositing a N-type epitaxial layer, preparing high-voltage P-wells for high-voltage N-type lateral metallic oxide transistors and high-pressure diodes, preparing P-type drift region for high-voltage N-type lateral metallic oxide transistors, then preparing buffer layer of high-voltage tubes, lower-voltage wells of lower-voltage devices, contact holes of source drain region, evaporating aluminum, carving aluminum reversely and forming electrodes and metallic field panel, passivation.

Owner:SOUTHEAST UNIV

Manufacturing method of VC SOI nLDMOS (Vertical Channel Silicon-on-insulator n Lateral Double-diffused Metal Oxide Semiconductor) device unit with p-type buried layer

InactiveCN102157433AExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingEngineeringTemperature resistance

The invention relates to a manufacturing method of a VC SOI nLDMOS (Vertical Channel Silicon-on-insulator n Lateral Double-diffused Metal Oxide Semiconductor) device unit with a p-type buried layer. The SOI nLDMOS device manufactured by the prior art seriously limits vertical voltage resistance and lateral voltage resistance, and has serious self-heating effect and poor high temperature resistance and thermal stability. Through the manufacturing method disclosed by the invention, ten times of photoetching are carried out on an SOI thick film material with the p-type buried layer to manufacture the VC SOI nLDMOS device with the p-type buried layer, and a formed depletion layer bears the vast majority of vertical withstand voltage when the VC SOI nLDMOS device applies a high voltage between a drain electrode and a source electrode in the blocking state, thus the vertical voltage resistance of the VC SOI nLDMOS device is improved, the self-heating effect of the device is remarkably reduced, and the high temperature resistance and the thermal stability are improved; furthermore, the volume and the weight of a system are reduced, the resource is saved, the energy consumption is reduced and the environment is protected.

Owner:HANGZHOU DIANZI UNIV

High voltage ldmos device

ActiveCN104518023BIncrease the cross-sectional areaReduce push timeSemiconductor devicesLDMOSEngineering

A high-voltage LDMOS (lateral double-diffused metal oxide semiconductor) device, including a P-type channel region, an N-type drift region, a voltage-resistant layer, and a P-type substrate at the bottom, and the voltage-resistant layer is located between the P-type substrate and the P-type substrate. Between the N-type drift region. The high-voltage LDMOS device of the present invention reduces the well-pushing time in the process by introducing the voltage-resistant layer, increases the cross-sectional area of the current channel, improves the on-resistance, and improves the lateral voltage resistance by increasing the vertical voltage resistance.

Owner:CSMC TECH FAB2 CO LTD

A p-type insulated gate bipolar transistor structure

ActiveCN103618002BIncrease the current magnification βLower on-resistanceSemiconductor devicesPolysilicon gateDielectric layer

A p-type insulated gate bipolar transistor includes an N-type doped silicon substrate which is also used as a collector region; a collector metal is arranged beneath the N-type doped silicon substrate; a P-type doped silicon buffer layer and a P-type light doped silicon epitaxial layer are sequentially arranged above the N-type doped silicon substrate; the P-type light doped silicon epitaxial layer is internally provided with a N-type column; a P-type and an N-type heavily-doped semiconductor region are arranged in a N-type doped semiconductor region; the N-type column is internally provided with the N-type heavily-doped semiconductor region; a dielectric layer is arranged between the N-type column and the P-type light doped silicon epitaxial layer; a gate oxide layer and a polysilicon gate are sequentially arranged on the P-type light doped silicon epitaxial layer; the polysilicon gate begins above the dielectric layer and ends above the P-type heavily-doped semiconductor region which is adjacent to the dielectric layer; an oxide layer and an emitter metal are orderly arranged above the polysilicon gate; and the P-type and the N-type heavily-doped semiconductor region are electrically connected with the emitter metal.

Owner:SOUTHEAST UNIV

Method for manufacturing SOI (silicon on insulator) LIGBT (lateral insulated gate bipolar transistor) device unit with p buried layer and longitudinal channel

ActiveCN102157434BImprove vertical pressure resistanceLittle impact on performanceSemiconductor/solid-state device manufacturingVoltage dropEngineering

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com