Silicon-on-insulator flat panel display driver chip and preparation method thereof

A display driver and chip technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems affecting chip performance and reliability, affecting device reliability, occupying chip area, etc., to achieve good reliability performance , low chip power consumption, and the effect of improving the vertical withstand voltage level

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

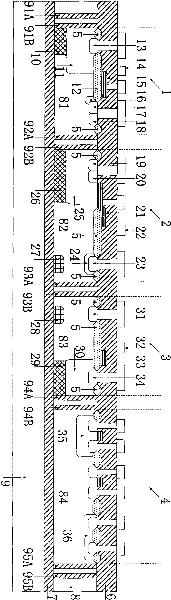

[0023] Below in conjunction with accompanying drawing, structure of the present invention is described in detail, as figure 1As shown, a flat panel display driver chip includes a P-type substrate 9, a buried oxide layer 7 is provided on the P-type substrate 9, and a high-voltage P-type lateral metal oxide semiconductor transistor 1 is provided on the buried oxide layer 7. The high-voltage N-type lateral metal oxide semiconductor transistor 2, the high-voltage diode 3, and the low-voltage device 4 are characterized in that the high-voltage P-type lateral metal oxide semiconductor transistor 1 is adjacent to the high-voltage N-type lateral metal oxide semiconductor transistor 2 and the high-voltage P-type lateral The drain terminal of the metal oxide semiconductor transistor 1 is adjacent to the source terminal of the high-voltage N-type lateral metal-oxide semiconductor transistor 2, and the high-voltage diode 3 is located between the high-voltage N-type lateral metal-oxide semi...

Embodiment 2

[0031] The preparation method of display driver chip of the present invention is as follows:

[0032] The first step: take the impurity concentration as 1.0e15cm -3 The P-type substrate 9 shown in Figure 2 (a) is pre-cleaned; the buried oxide layer 7 is prepared on the P-type substrate 9 as shown in Figure 2 (b); then the N-type impurity concentration is 1.5 e15cm -3 The epitaxial layer 8, while passing a dose of 3e13cm -2 boron ion implantation, on the N-type epitaxial layer 8 to make the first P-type heavily doped buried layer 10, the second P-type heavily doped buried layer 26 and the third P-type heavily doped buried layer 29, the passing dose is 3e12cm -2 The arsenic ion implantation forms the N-type buried layer 27 of the high-voltage N-type lateral metal oxide semiconductor transistor 2 and the N-type buried layer 28 of the high-voltage diode 3 as shown in Figure 2 (c); on the N-type epitaxial layer 8, a high-voltage N The P-type body region 25 of the N-type lateral ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More