Patents

Literature

1557 results about "Buried oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

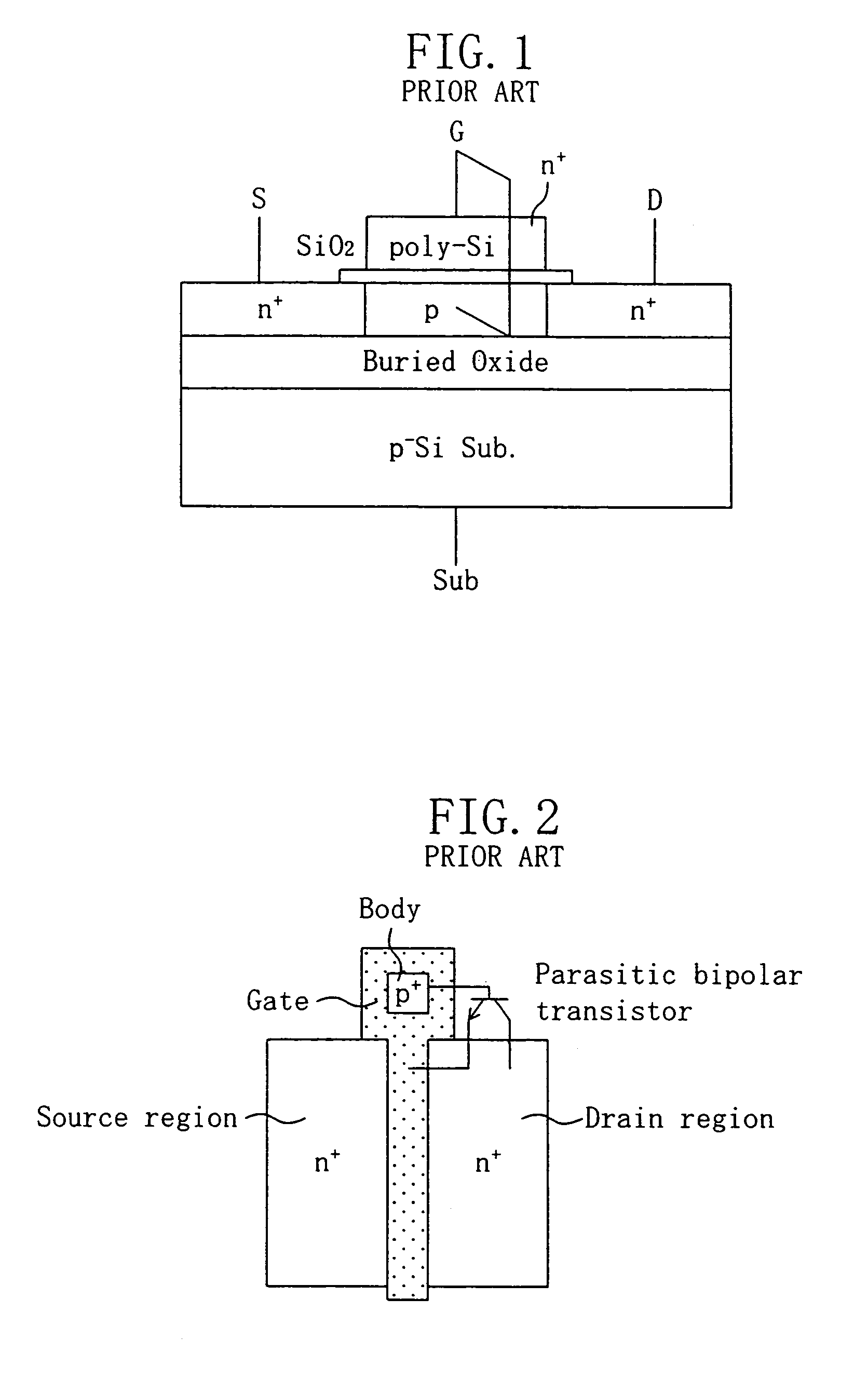

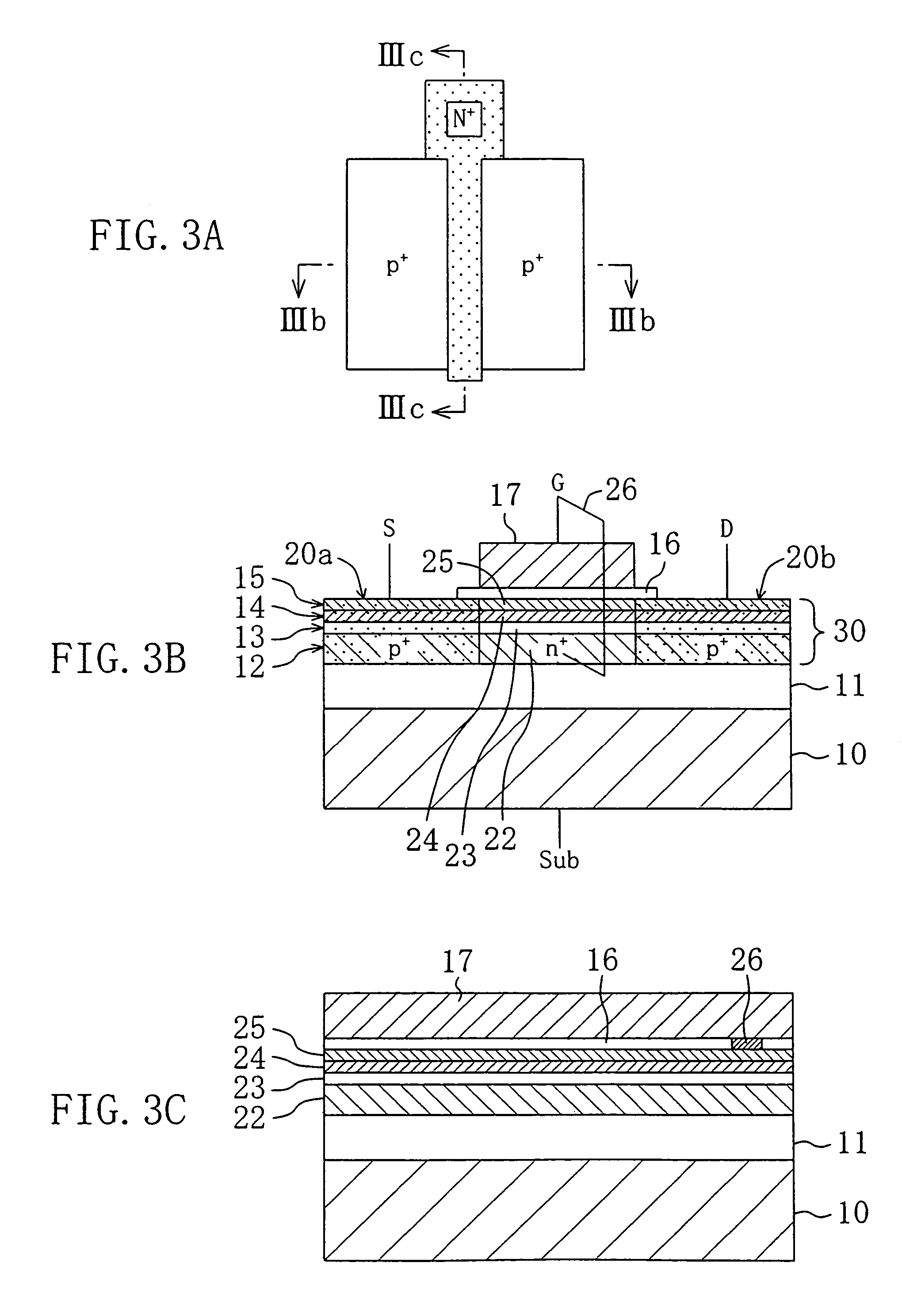

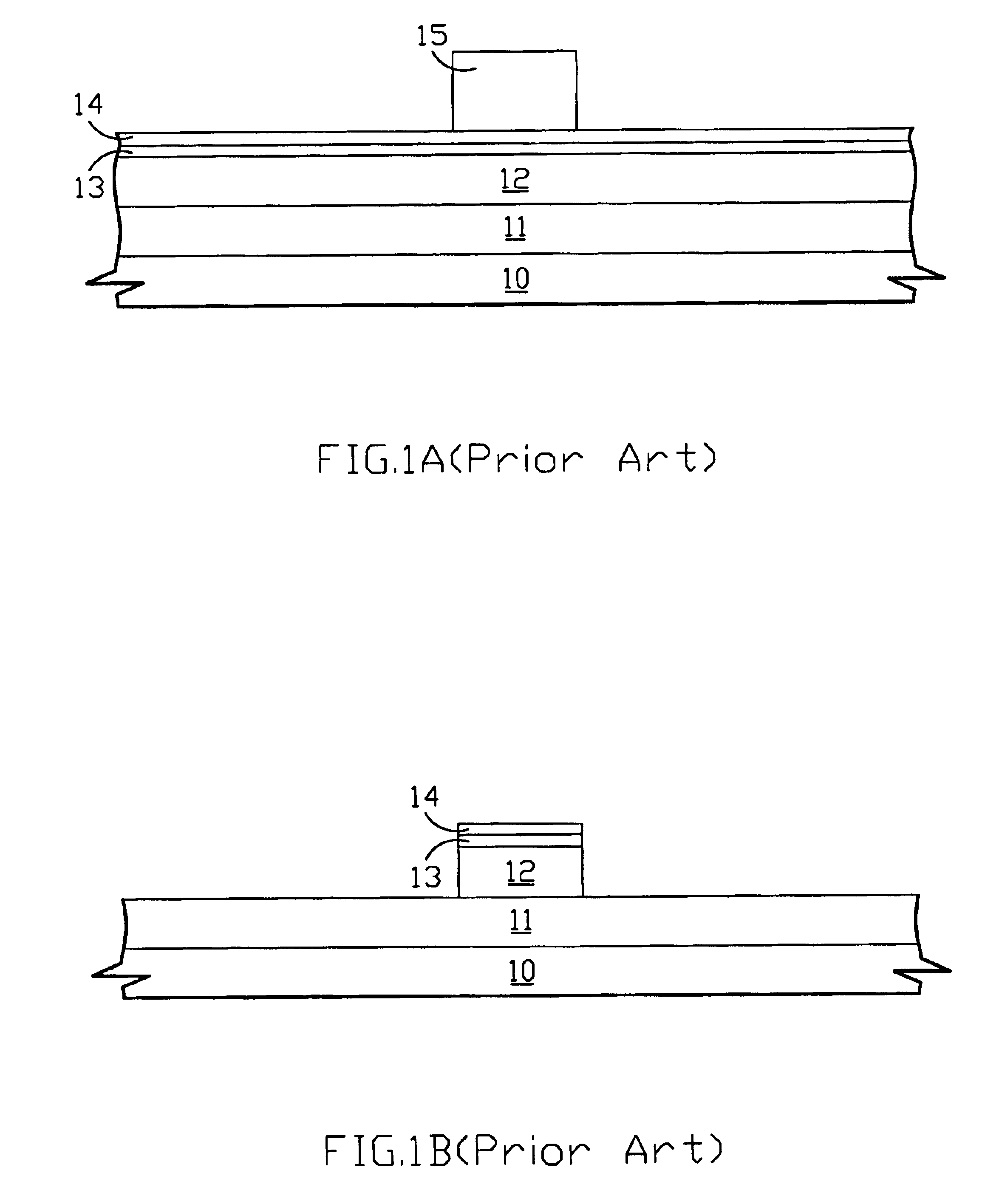

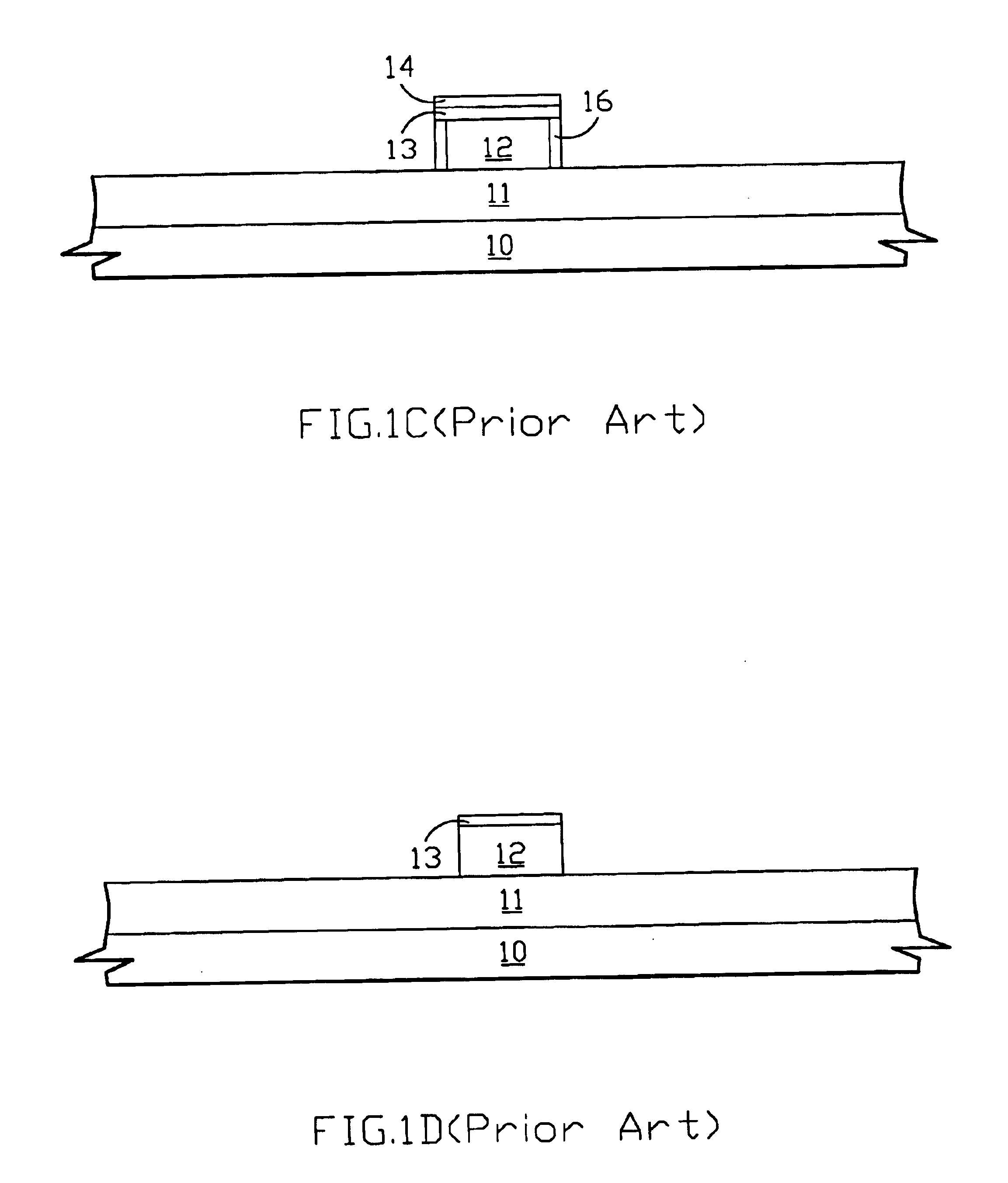

An SOI MOSFET is a semiconductor device in which a semiconductor layer such as silicon or germanium is formed on an insulator layer which may be a buried oxide (BOX) layer formed in a semiconductor substrate. SOI MOSFET devices are adapted for use by the computer industry.

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

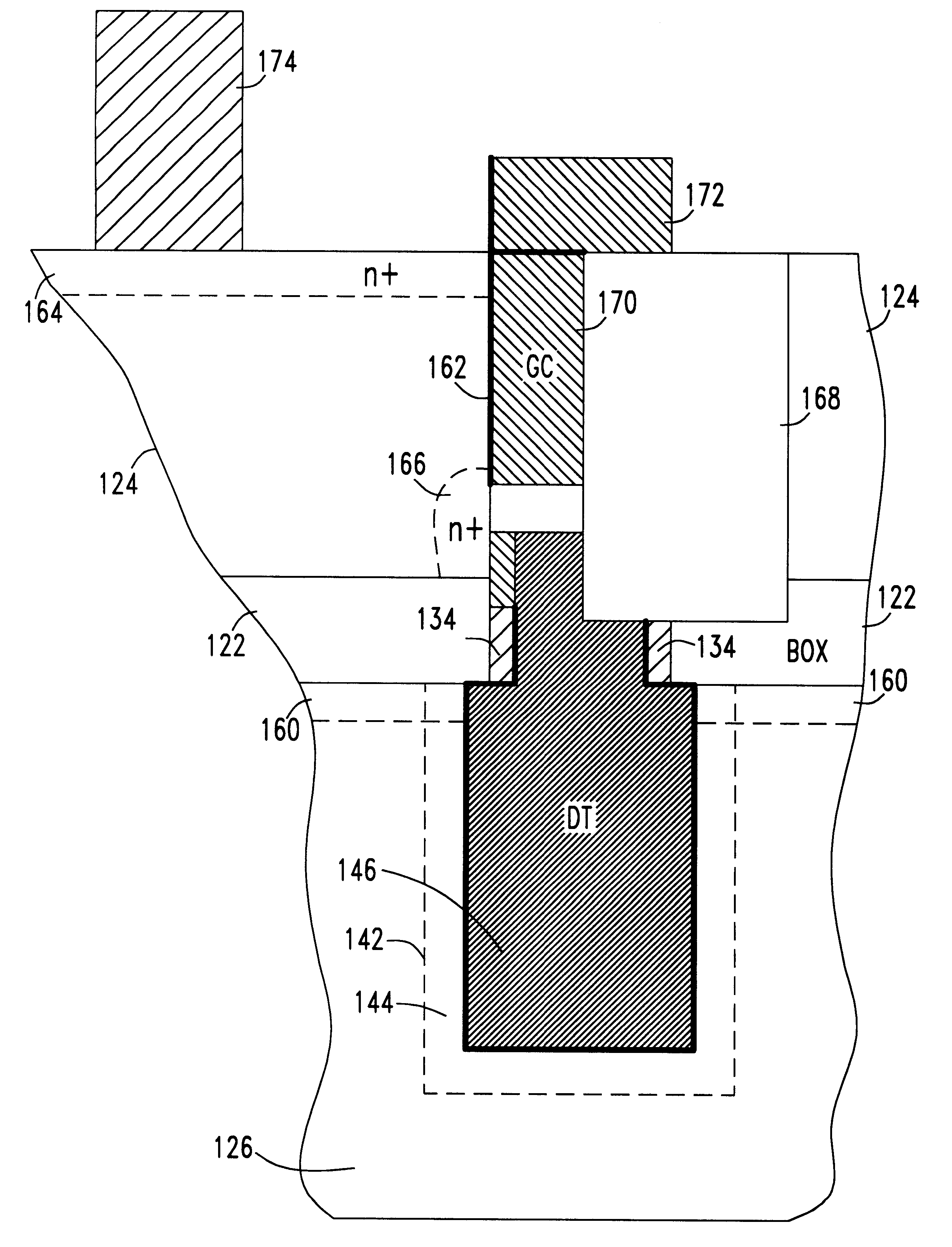

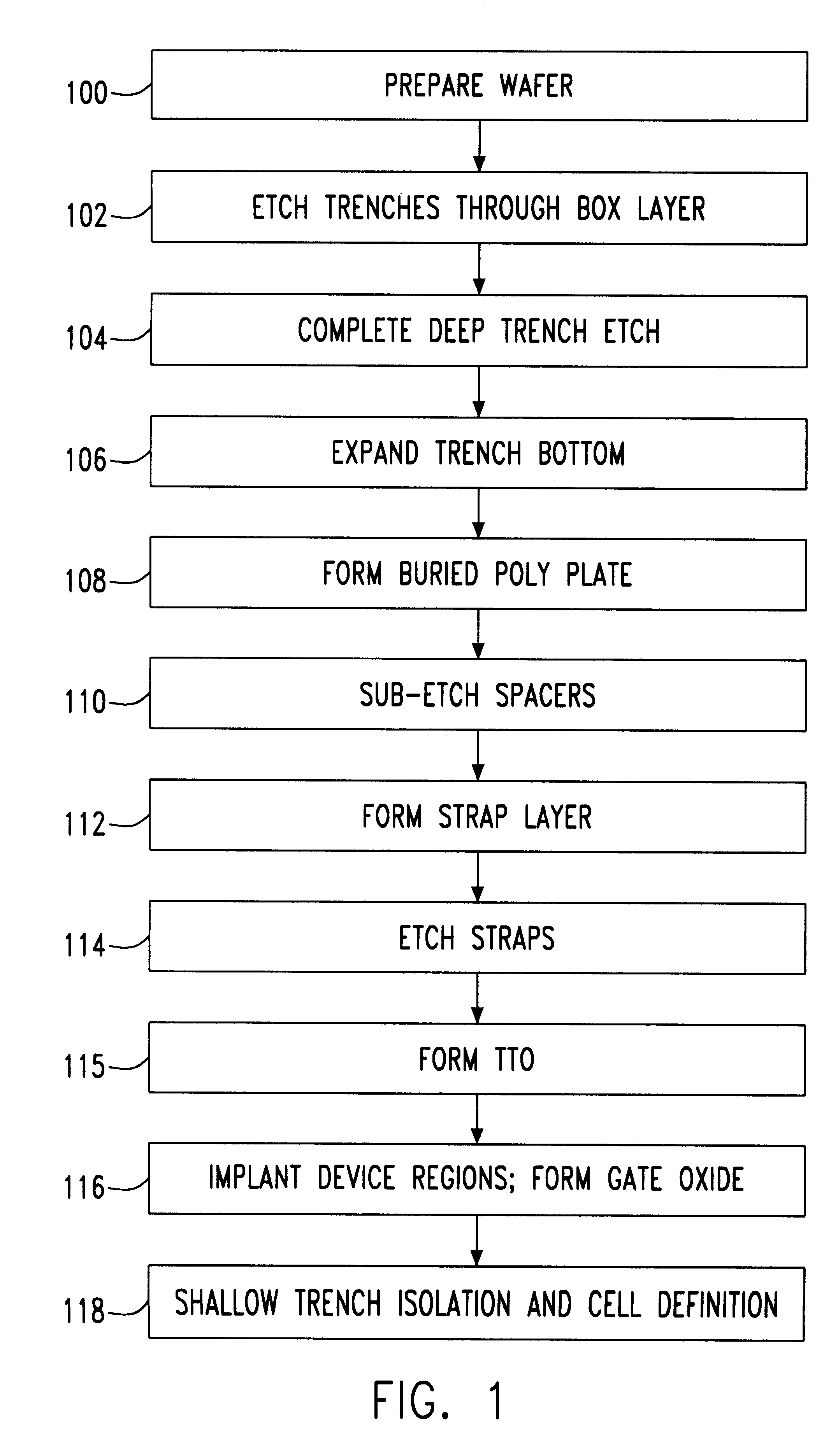

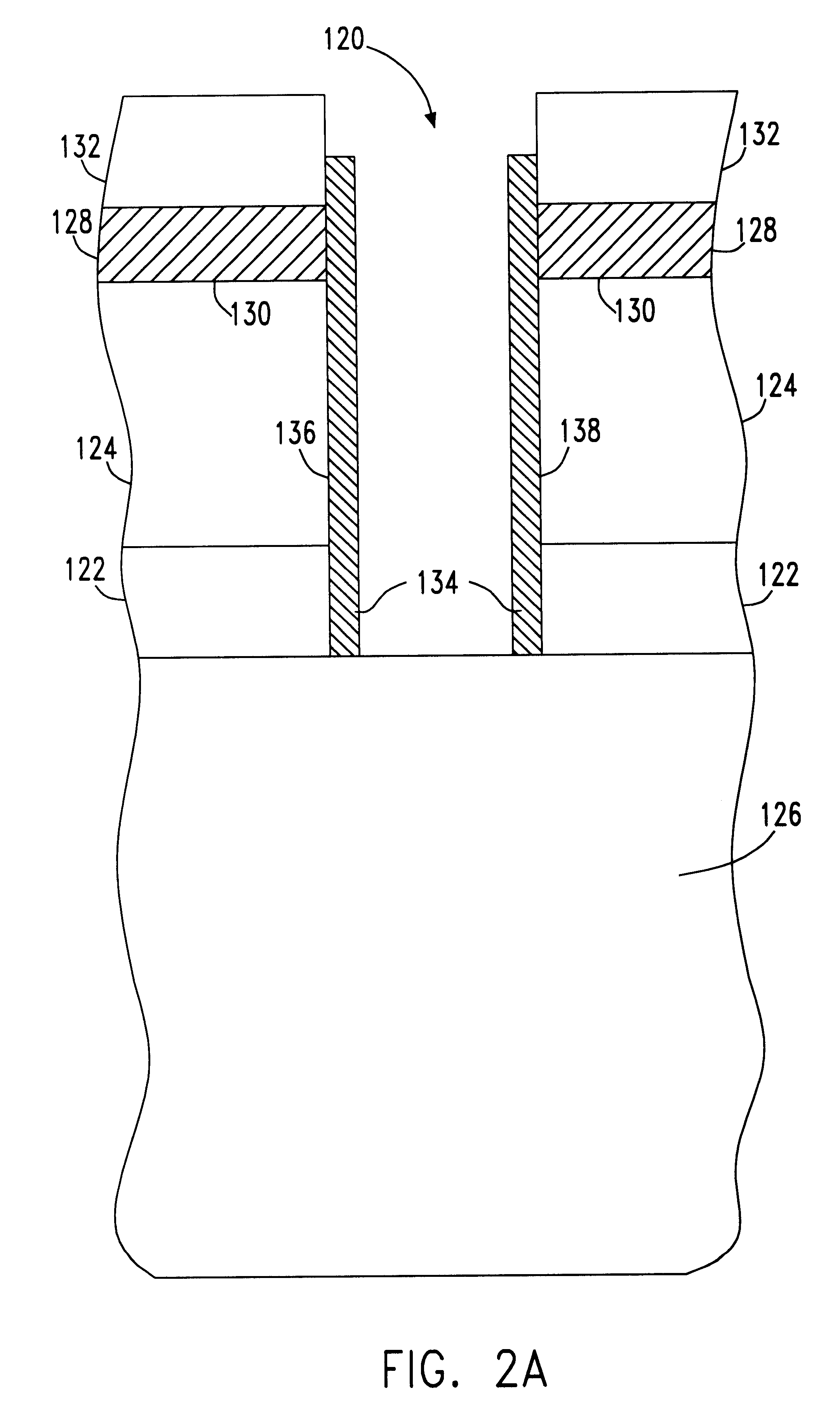

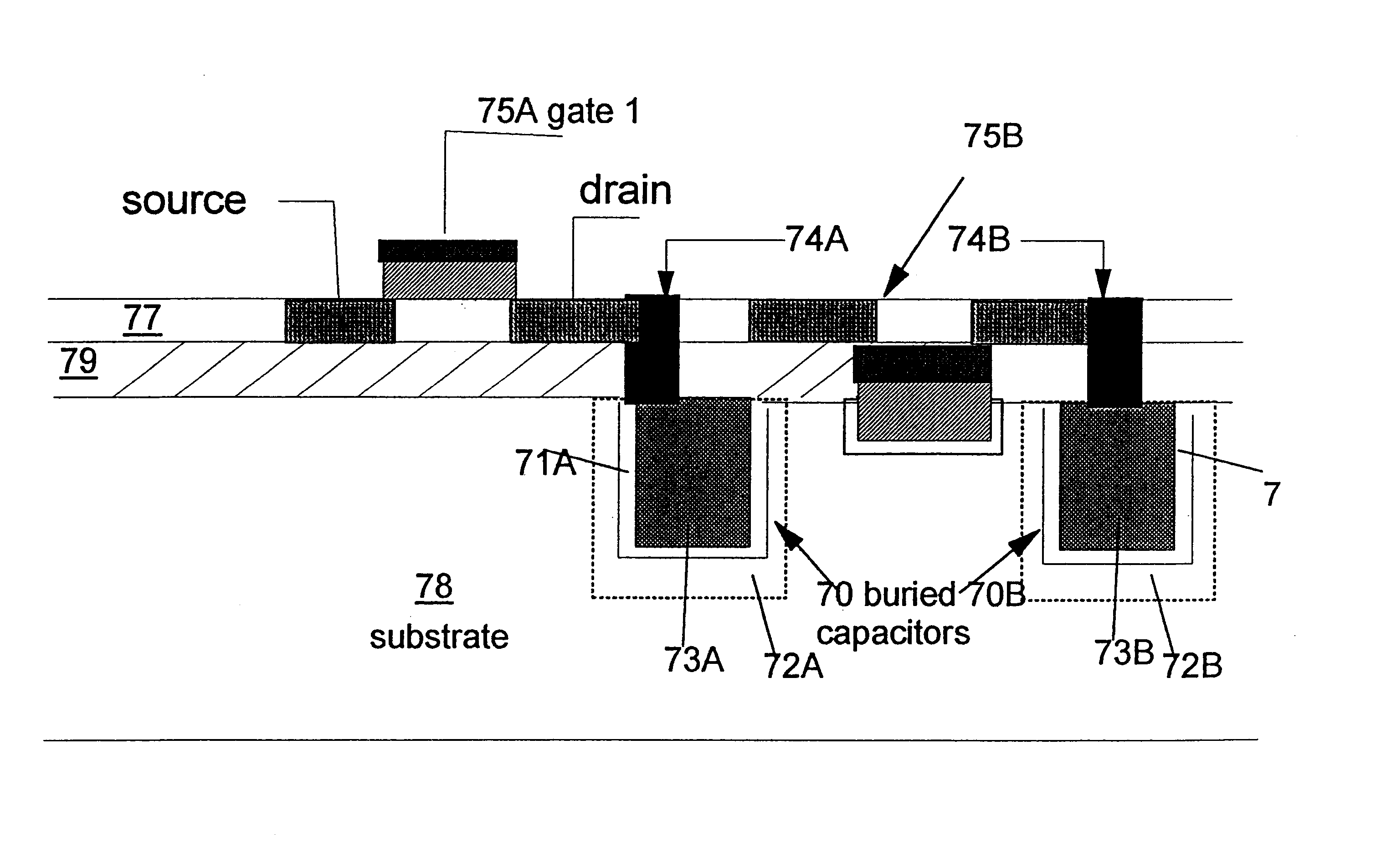

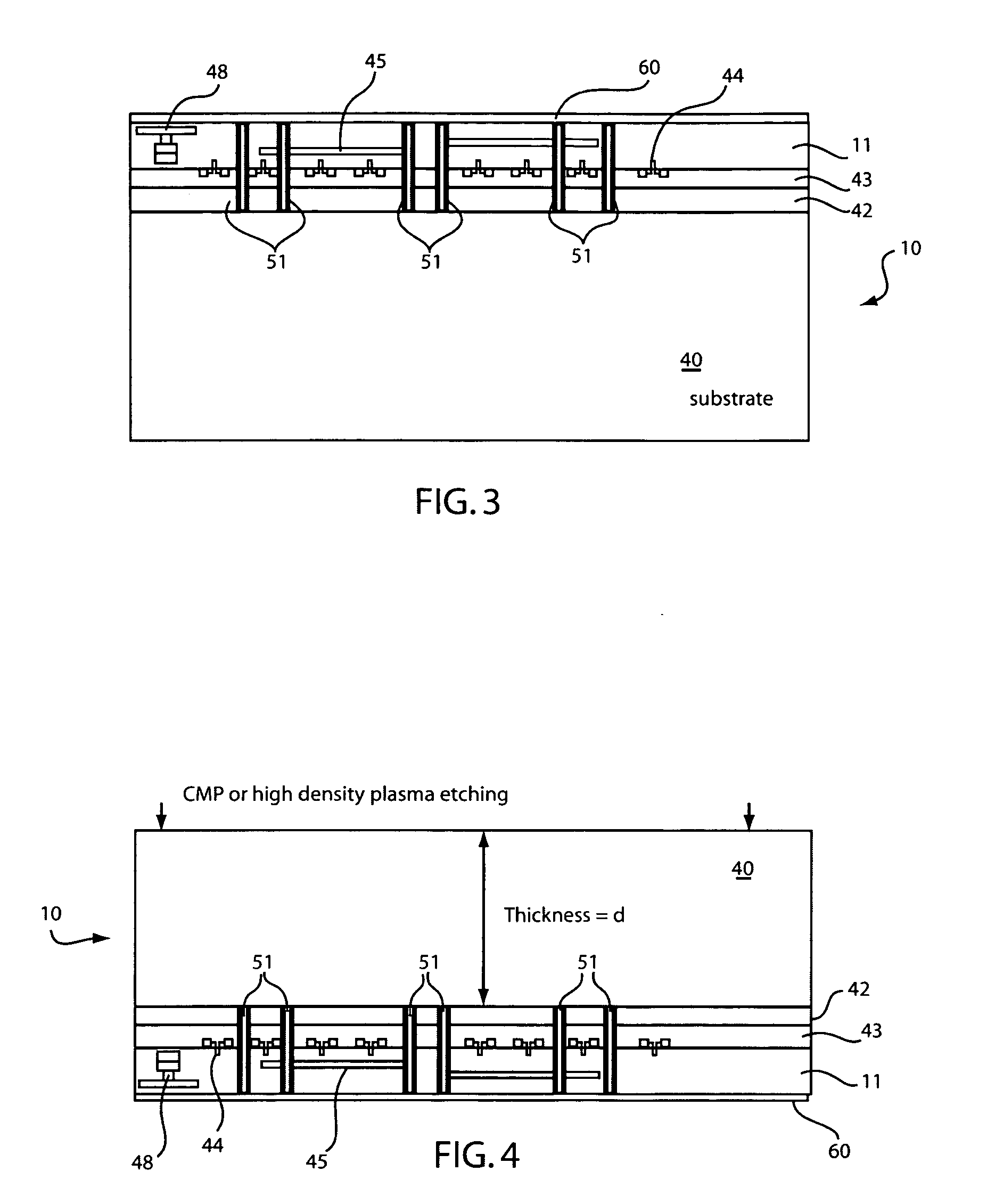

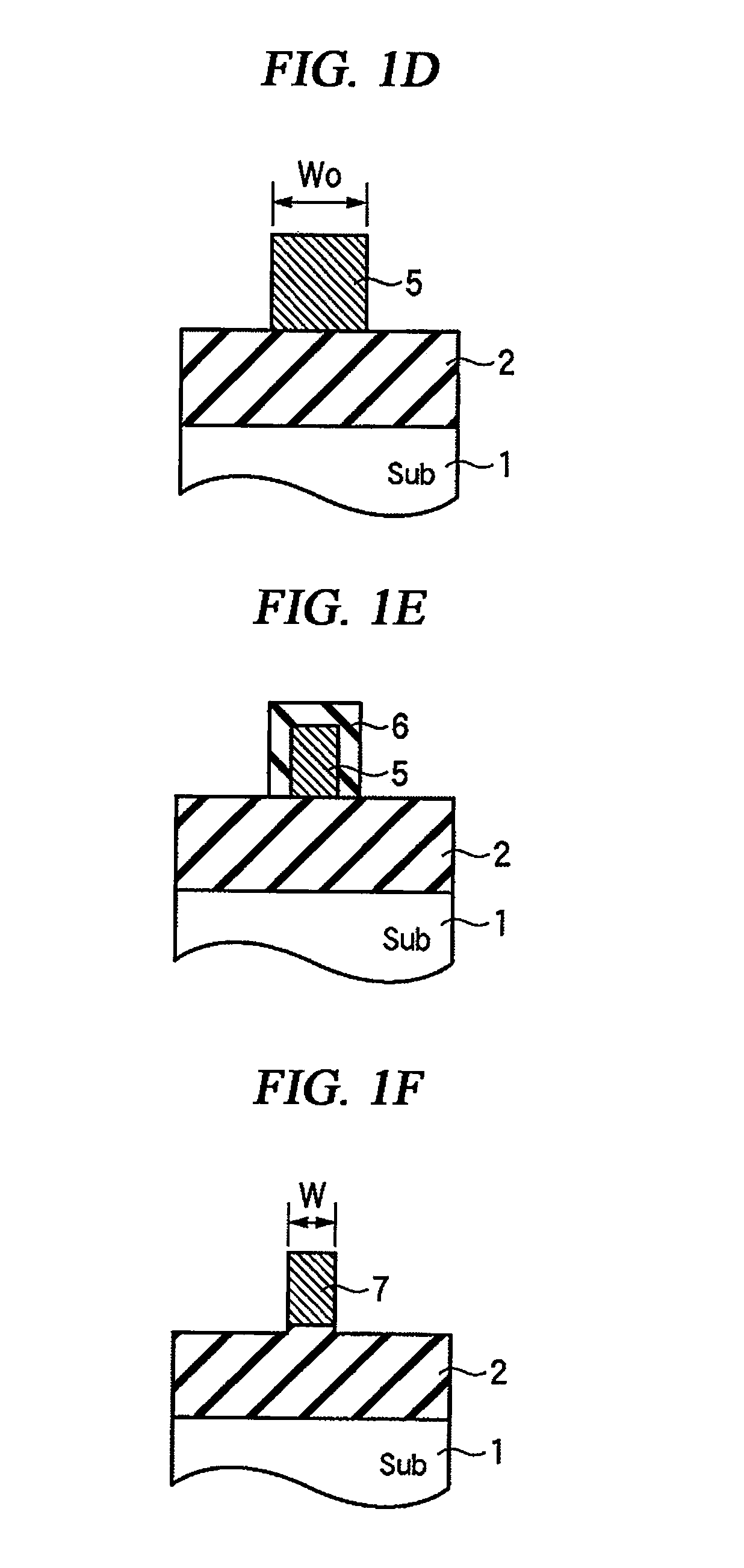

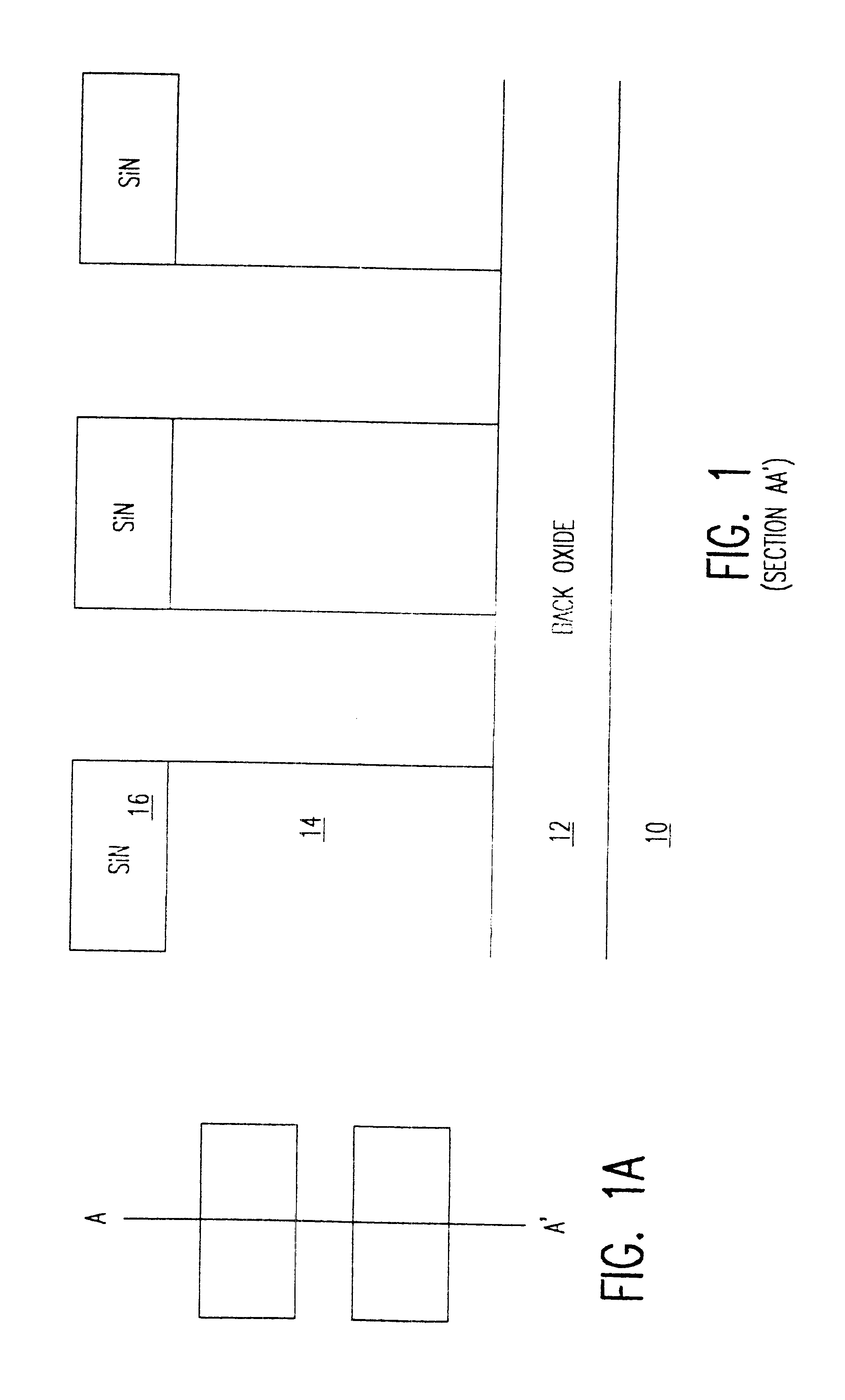

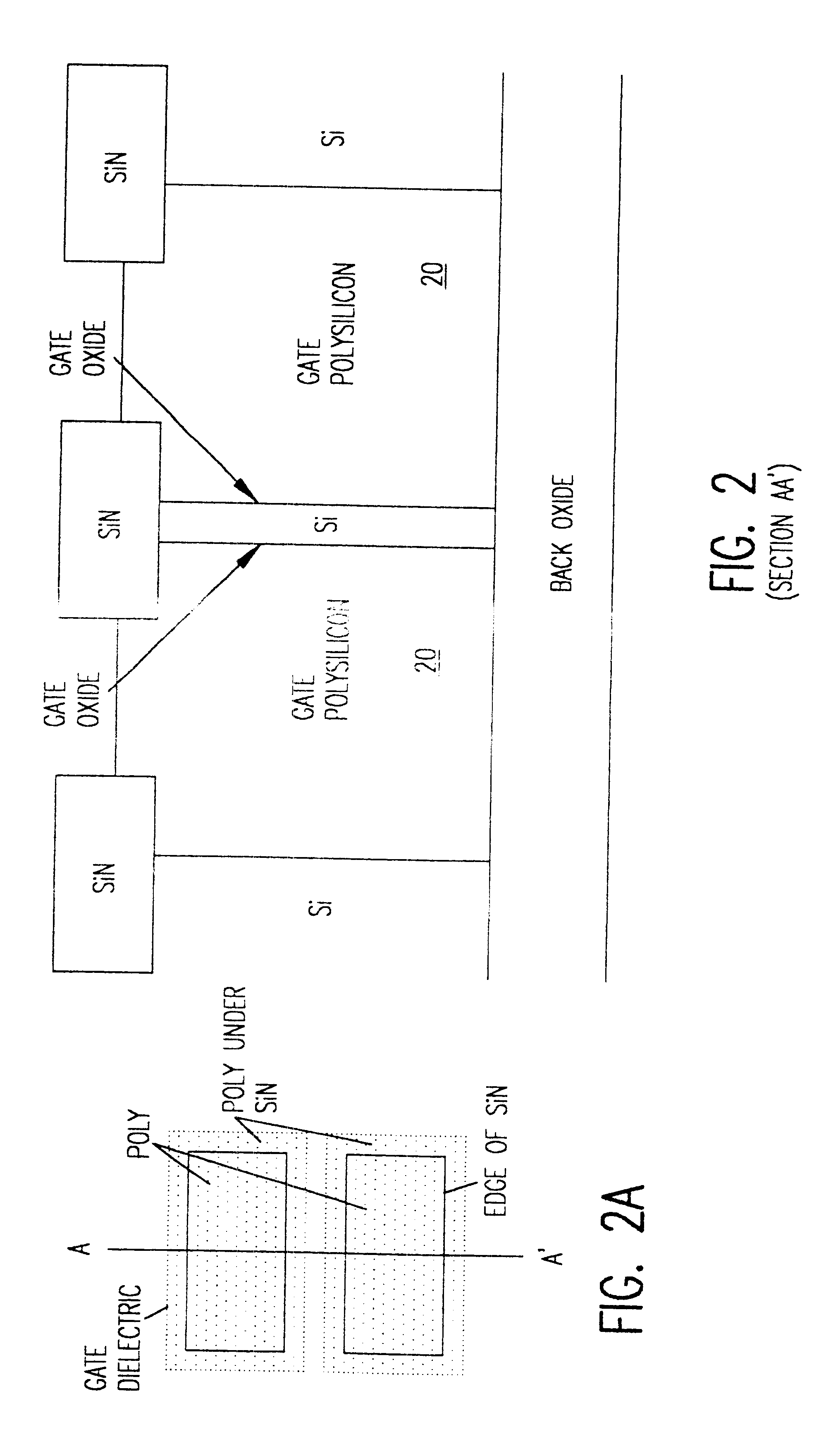

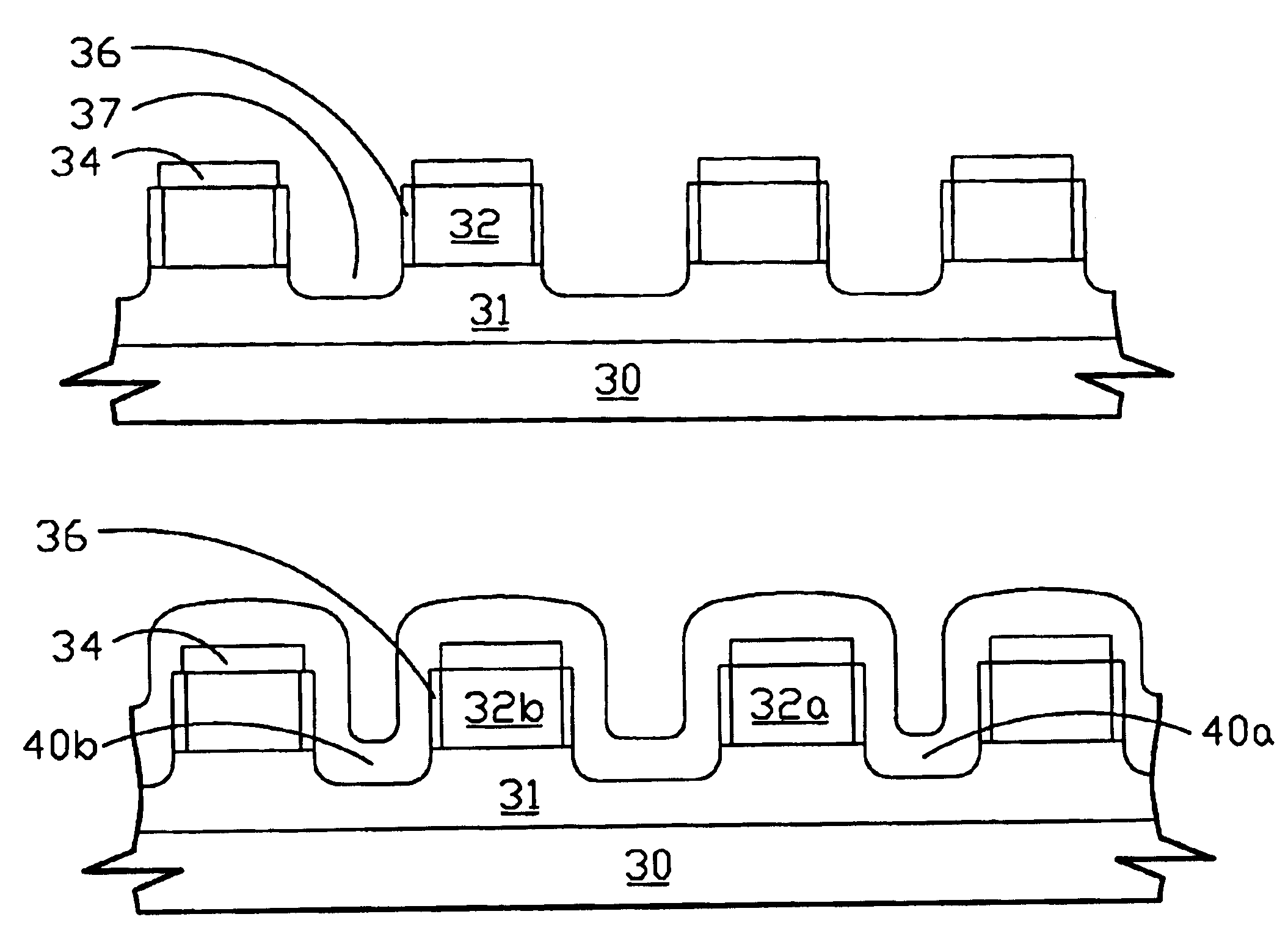

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

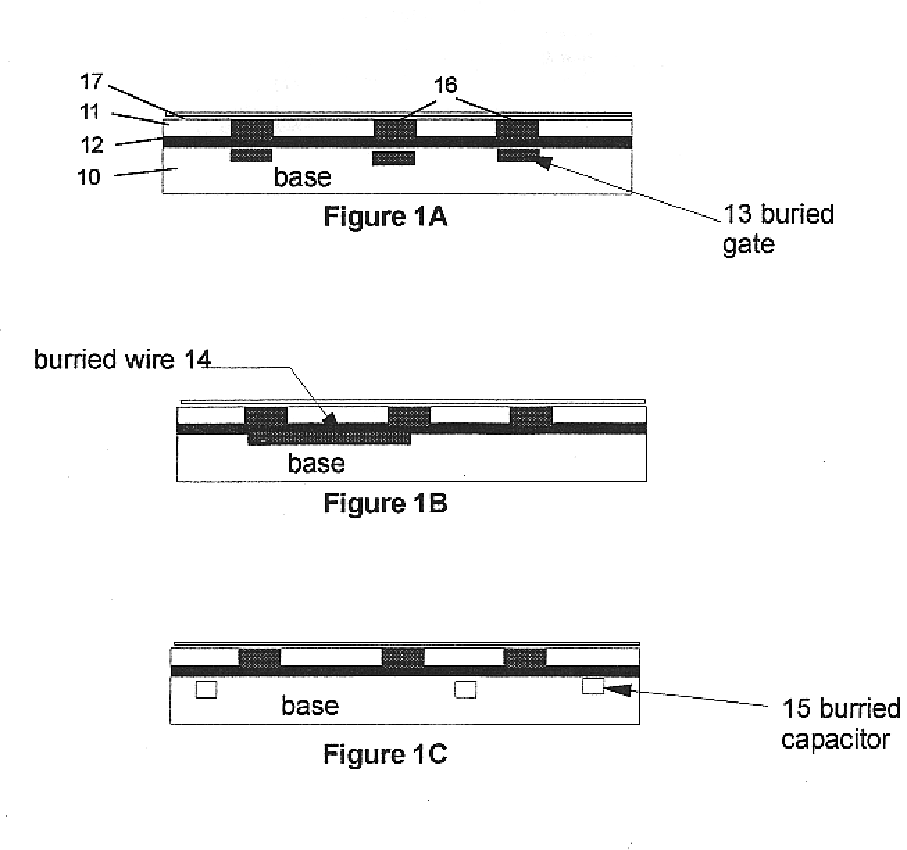

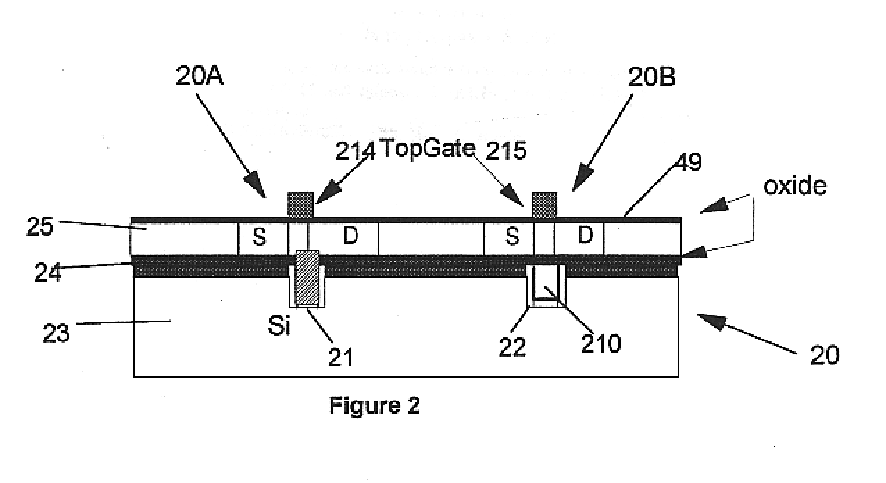

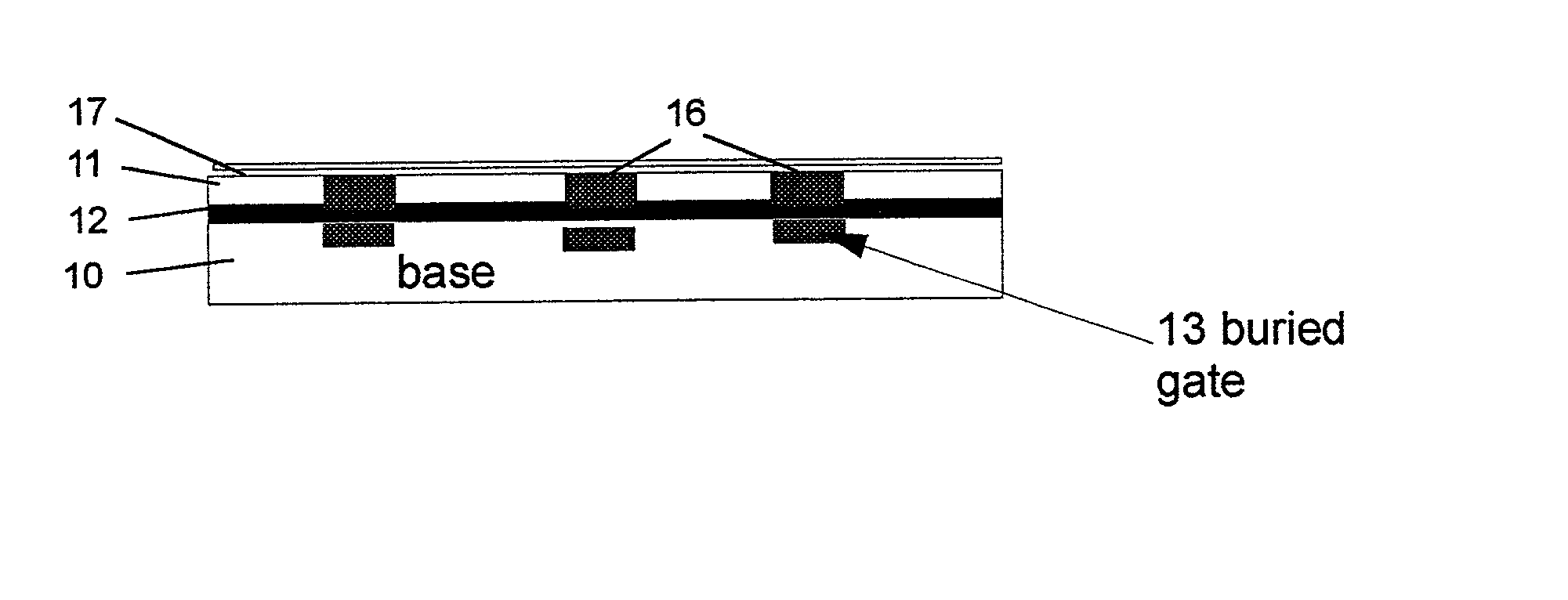

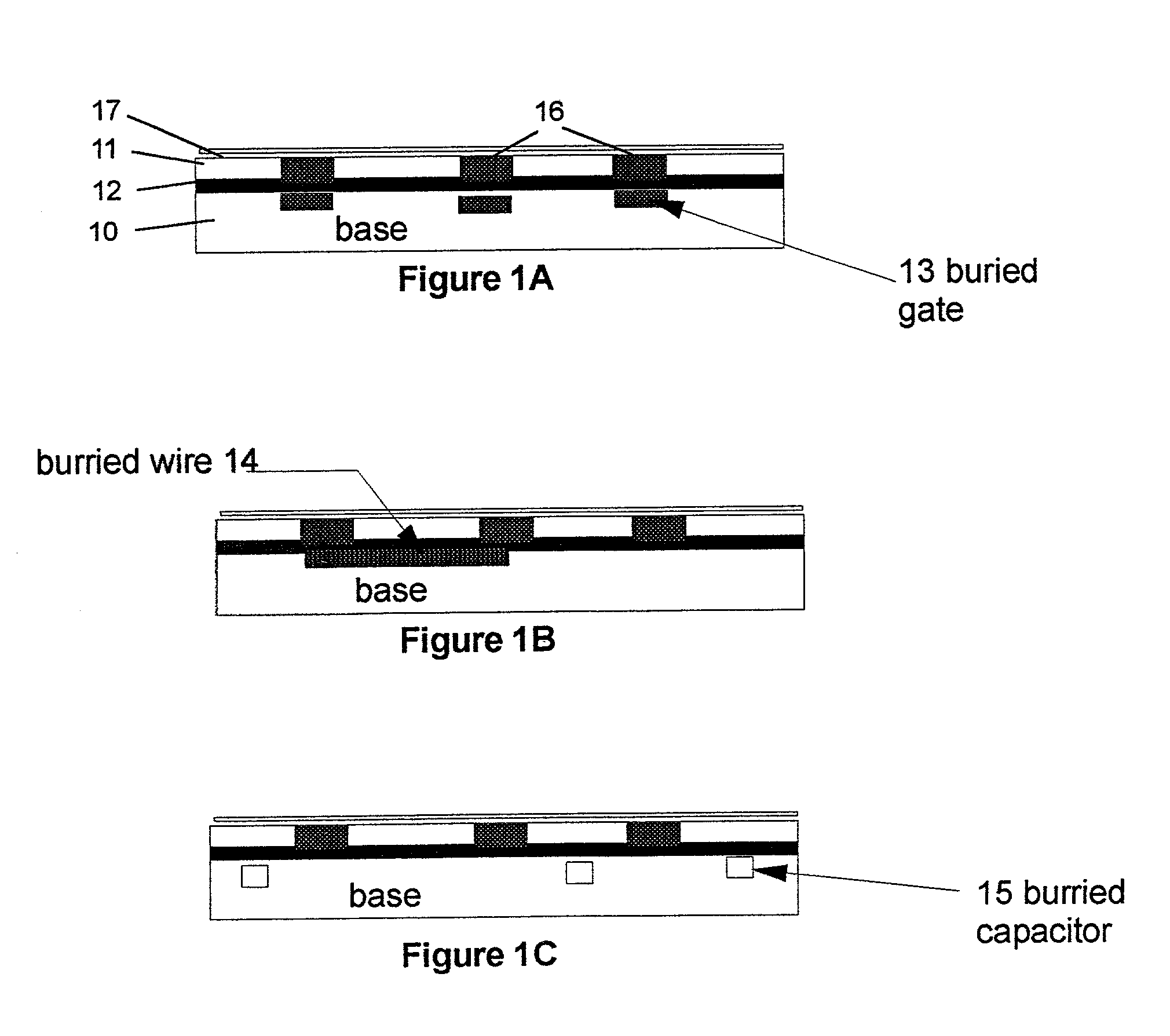

Method and structure for buried circuits and devices

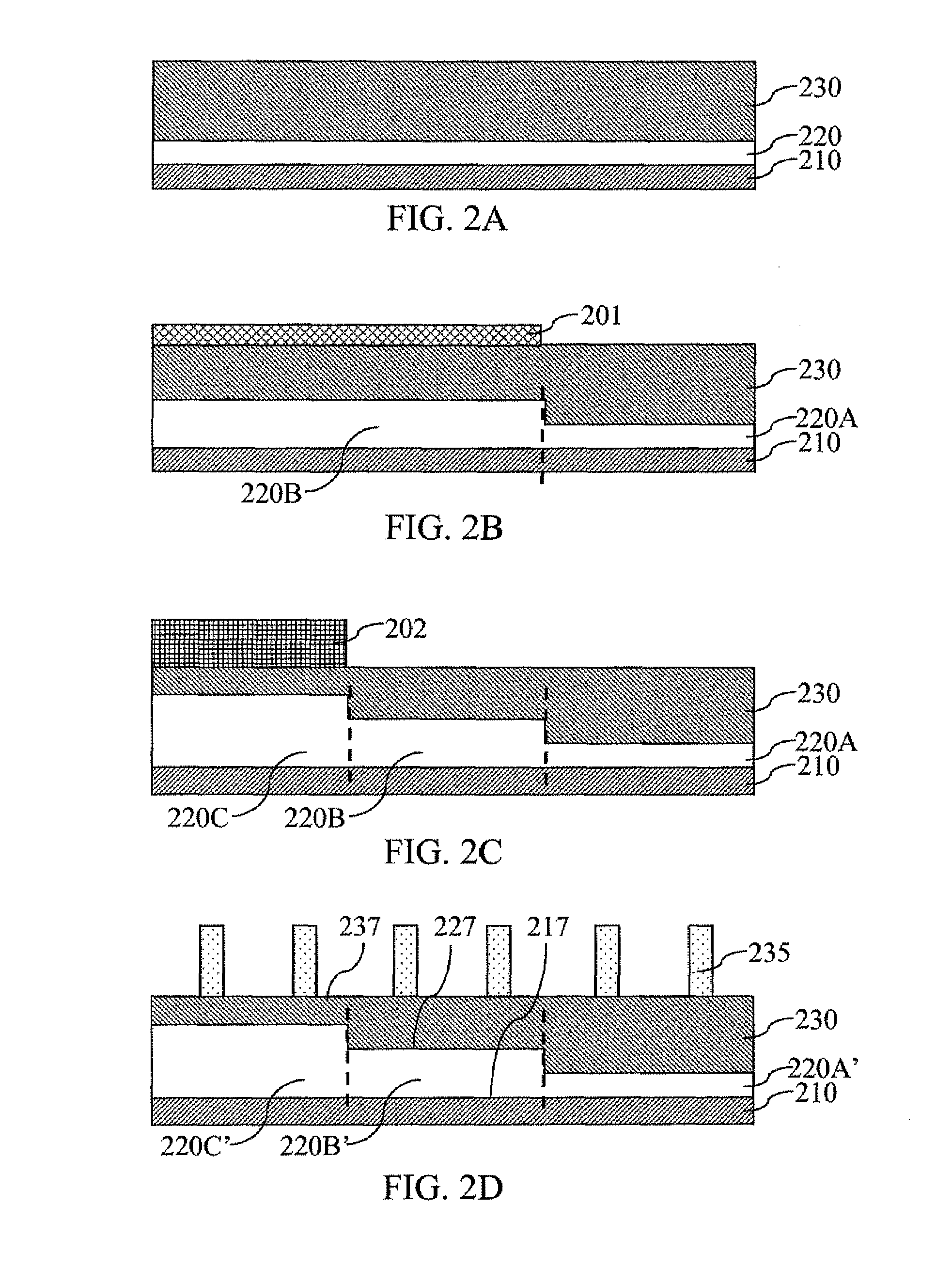

A method and structure for fabricating an electronic device using an SOI technique that results in formation of a buried oxide layer. The method includes fabricating at least one first component of the electronic device and fabricating at least one second component of the electronic device, wherein the first component and the second component are on opposite sides of the buried oxide layer, thereby causing the buried oxide layer to perform a function within the electronic device. Entire circuits can be designed around this technique.

Owner:GLOBALFOUNDRIES U S INC

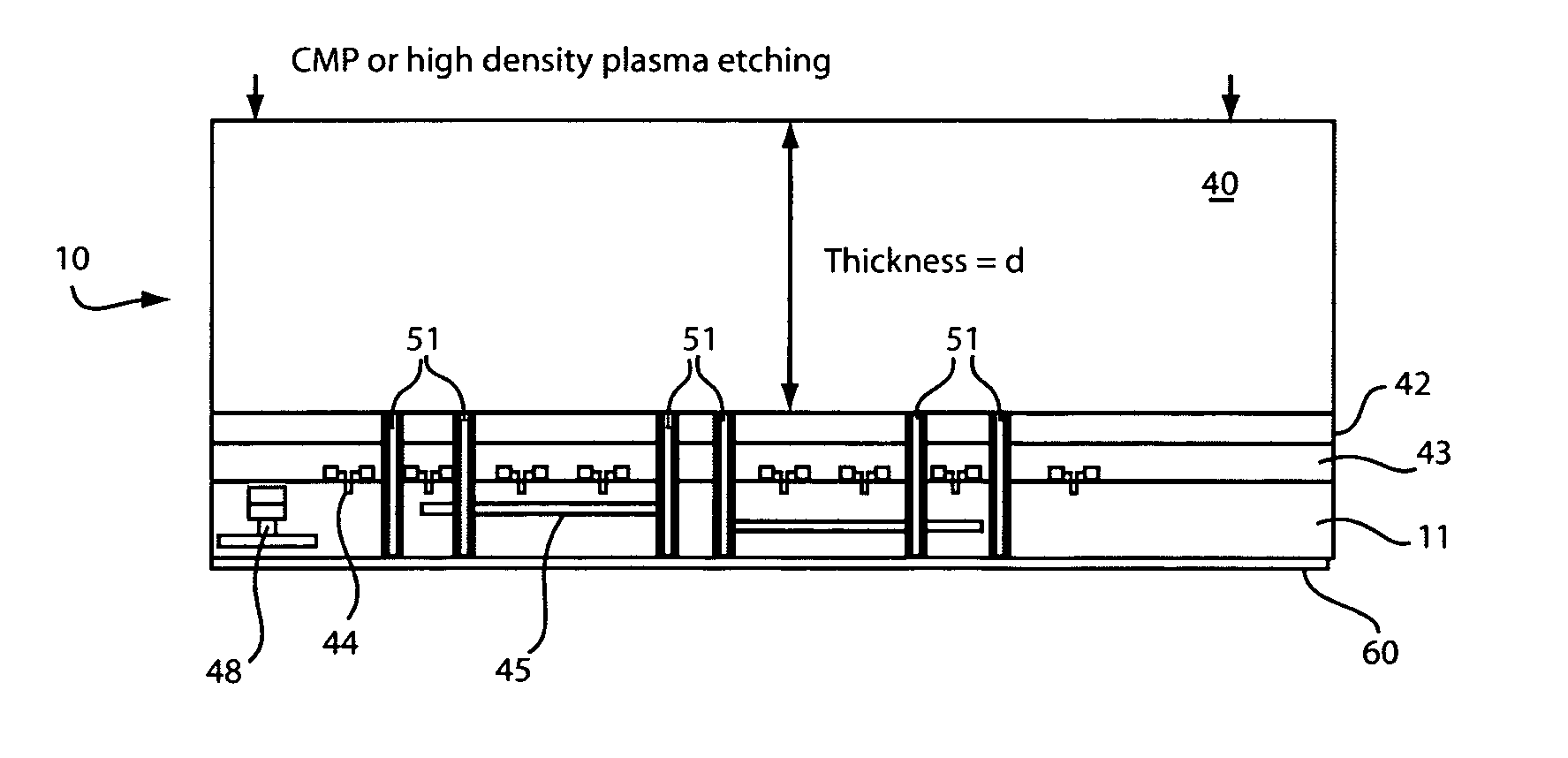

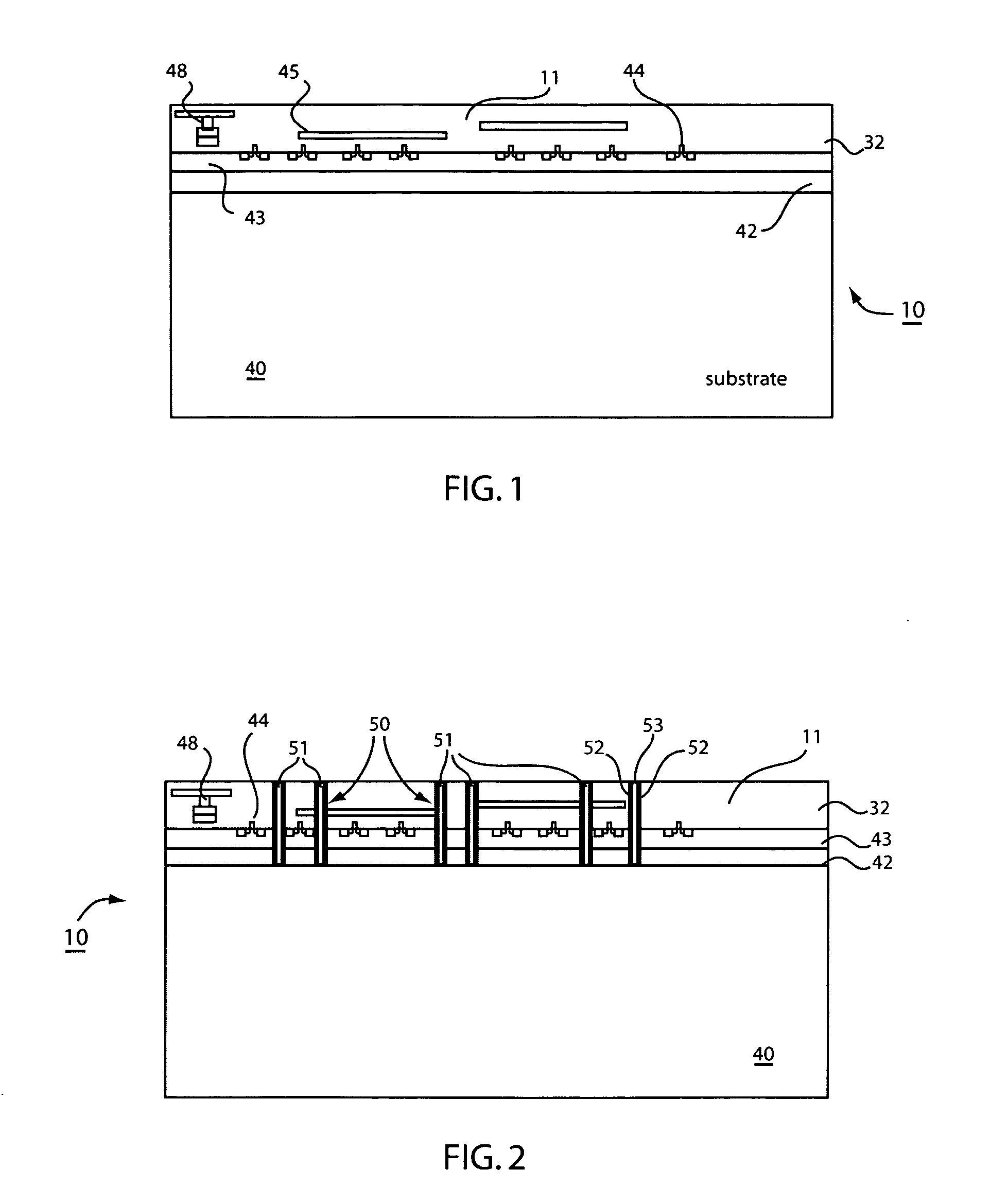

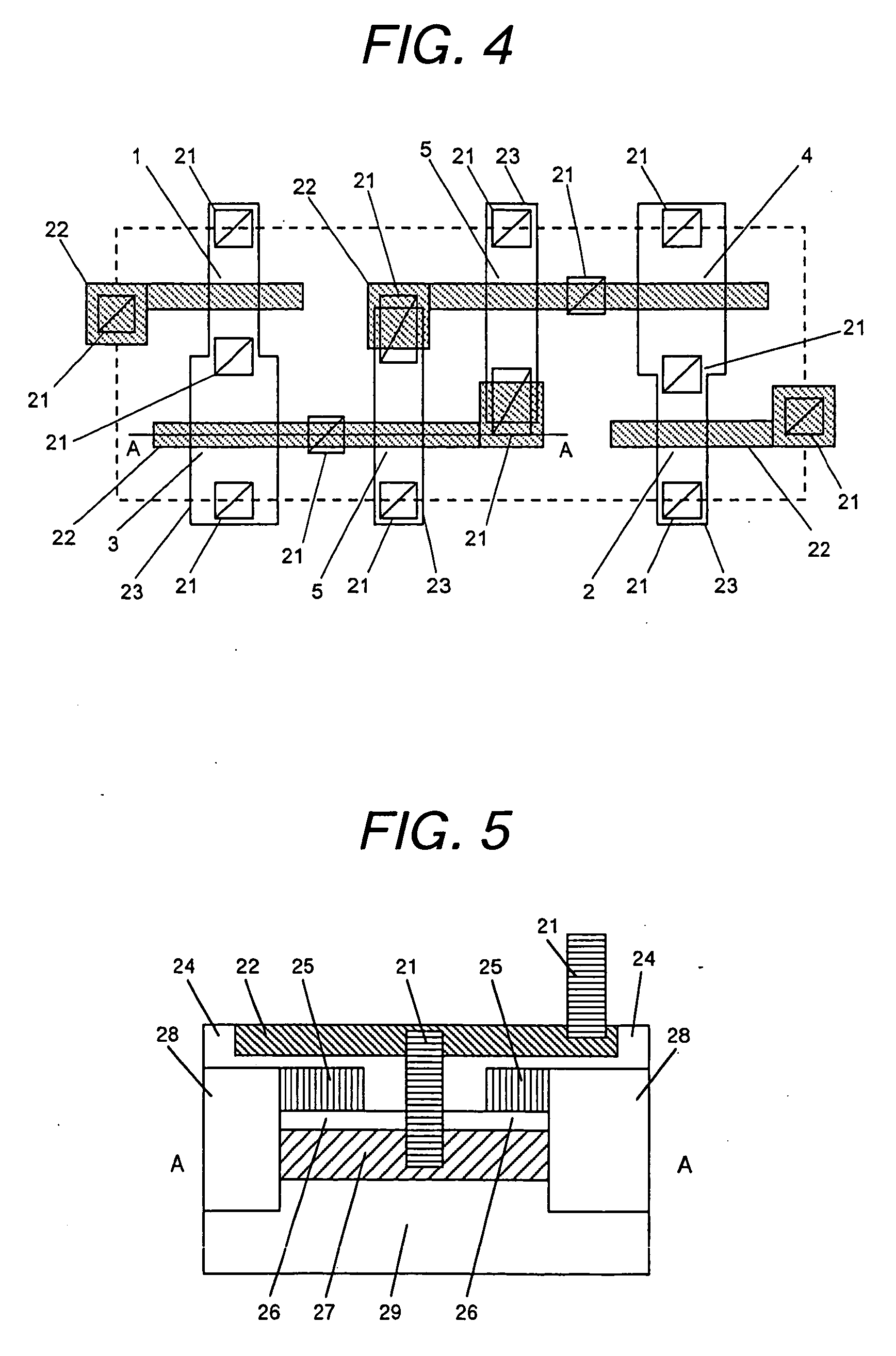

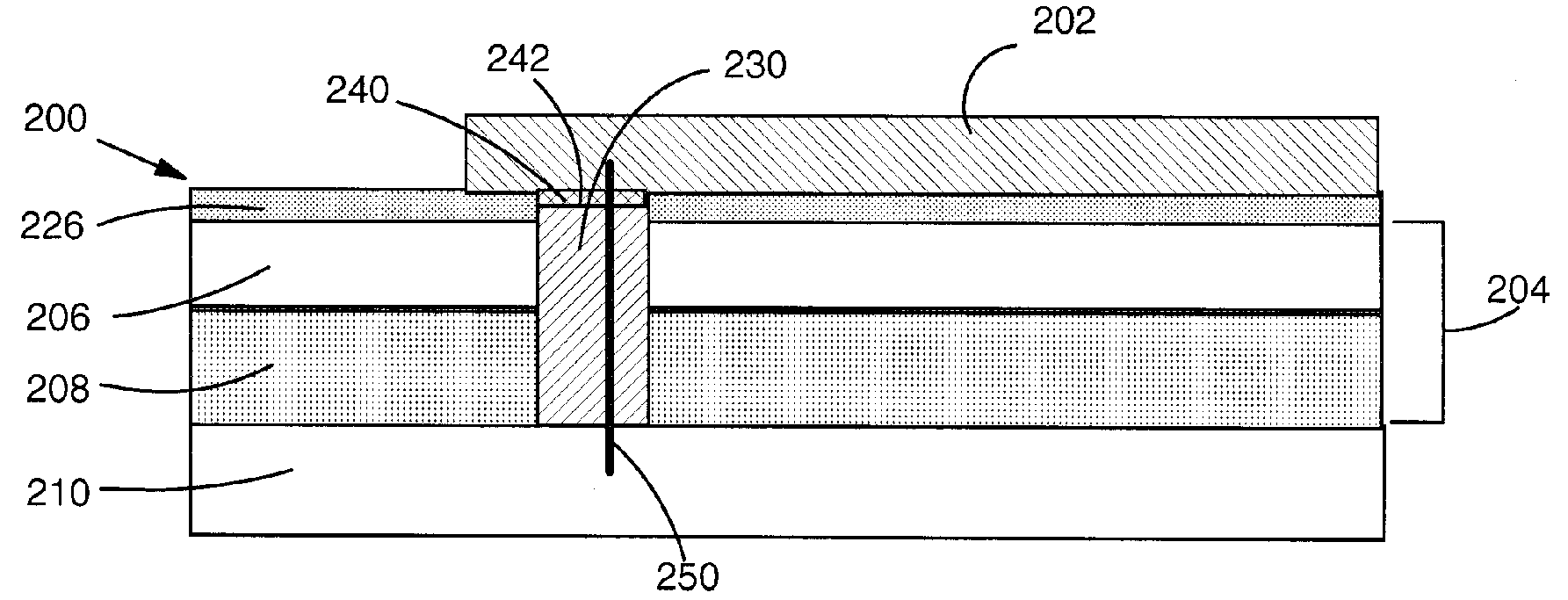

Device and method for fabricating double-sided SOI wafer scale package with through via connections

ActiveUS20060105496A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package includes an SOI wafer having a first side including an integrated circuit system, and a second side, opposite the first side, forming at least one cavity. At least one chip or component is placed in the cavity. A through buried oxide via connects the chip(s) to the integrated circuit system.

Owner:GLOBALFOUNDRIES US INC

Method of forming silicon-on-insulator (SOI) semiconductor substrate and SOI semiconductor substrate formed thereby

InactiveUS7183172B2Inhibited DiffusionImpurity diffusion coefficientSolid-state devicesSemiconductor/solid-state device manufacturingImpurity diffusionDiffusion barrier

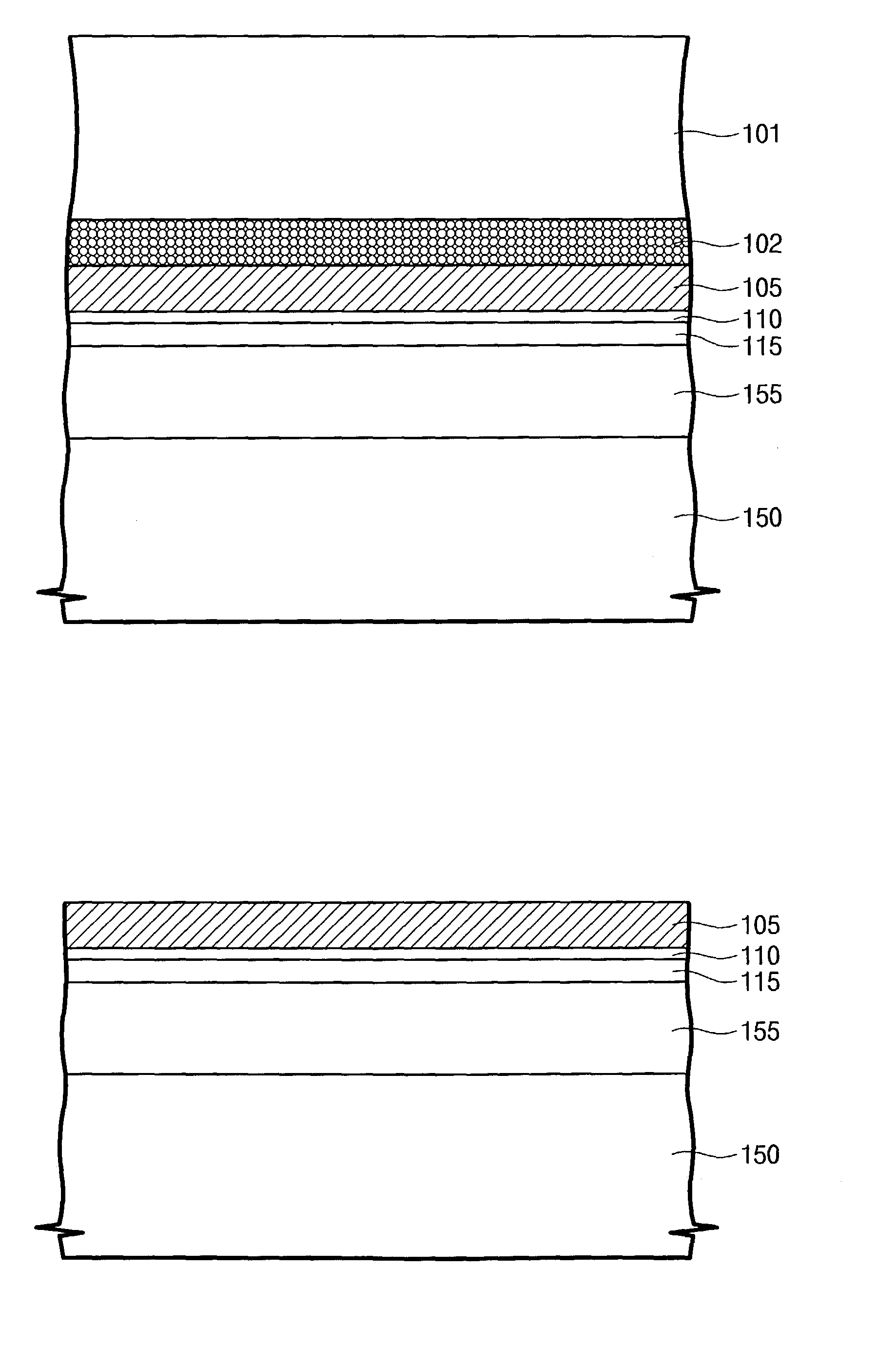

A method of forming an SOI semiconductor substrate and the SOI semiconductor substrate formed thereby, is provided. The method includes forming sequentially buried oxide, diffusion barrier and SOI layers on a semiconductor substrate. The diffusion barrier layer is formed by an insulating layer having a lower impurity diffusion coefficient as compared with the buried oxide layer. The diffusion barrier layer serves to prevent impurities implanted into the SOI layer from being diffused into the buried oxide layer or the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

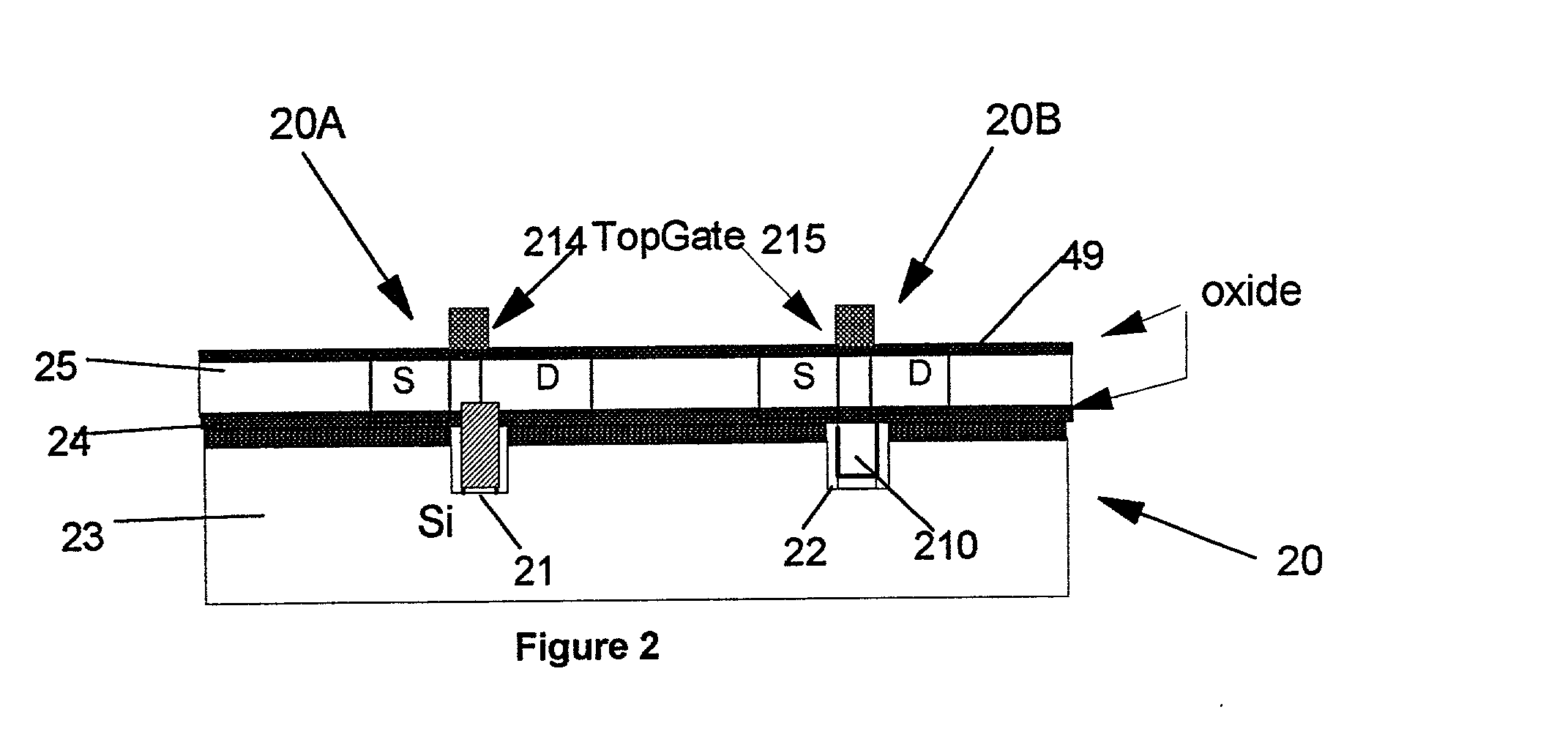

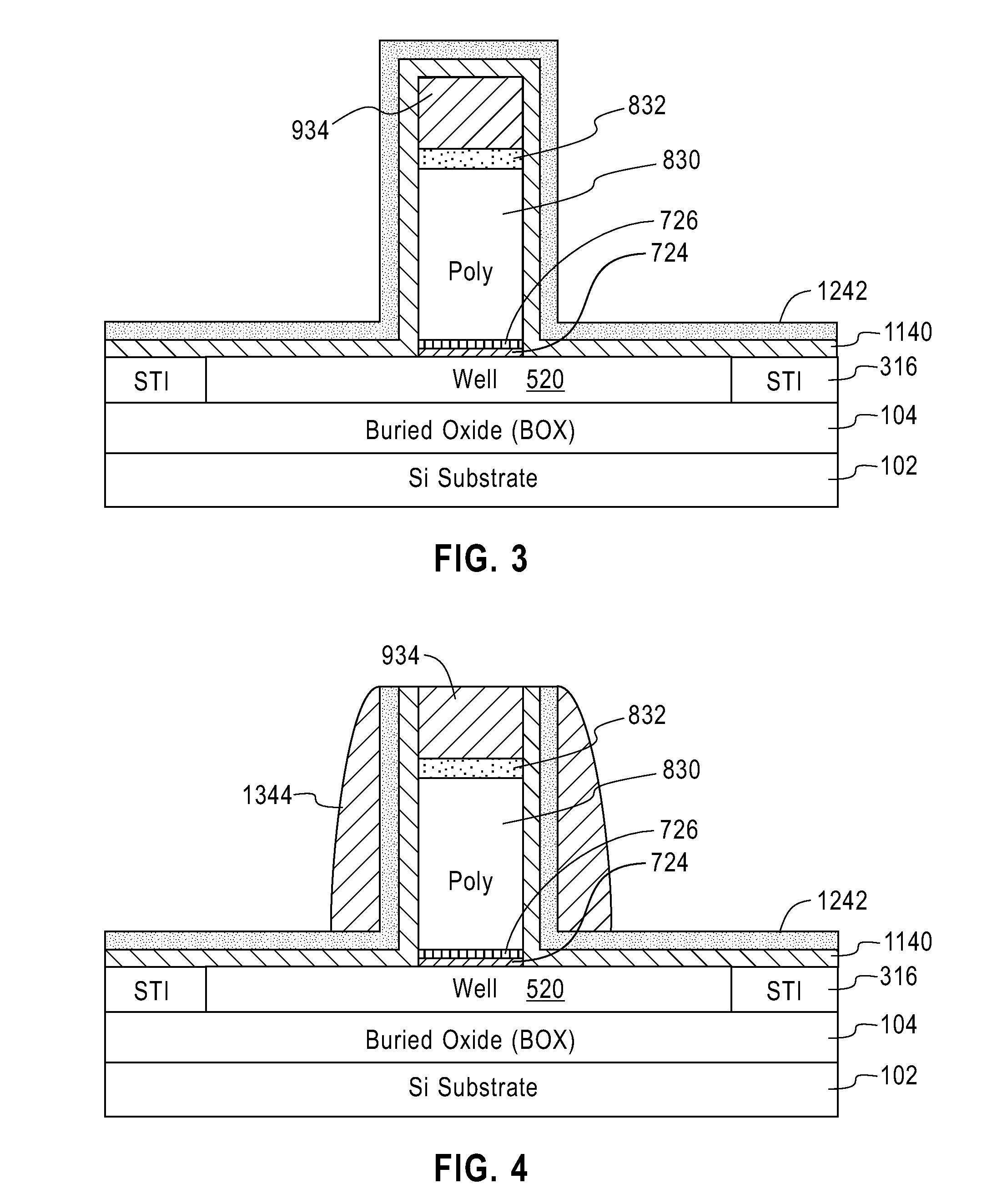

Ultra-thin body super-steep retrograde well (SSRW) FET devices

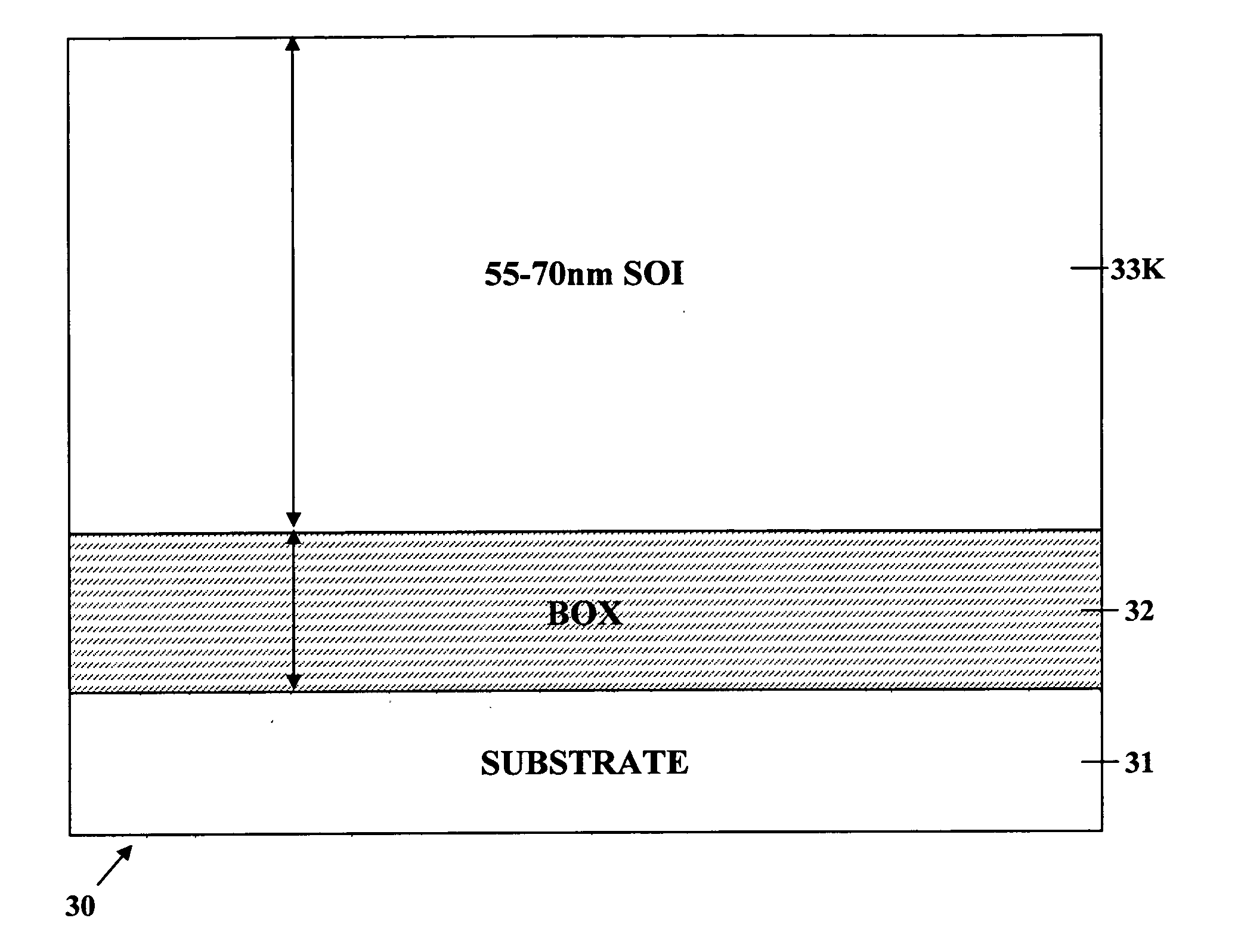

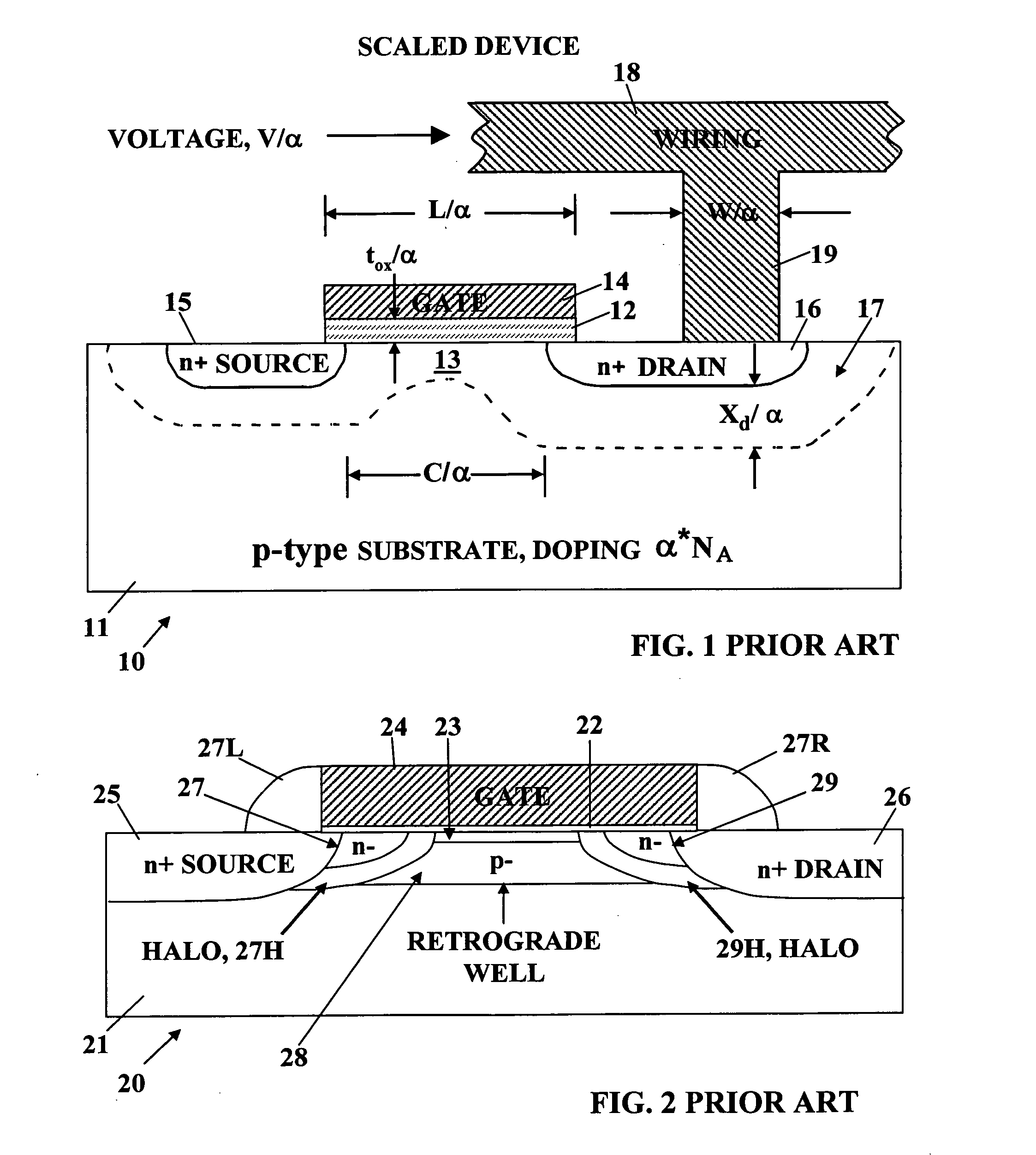

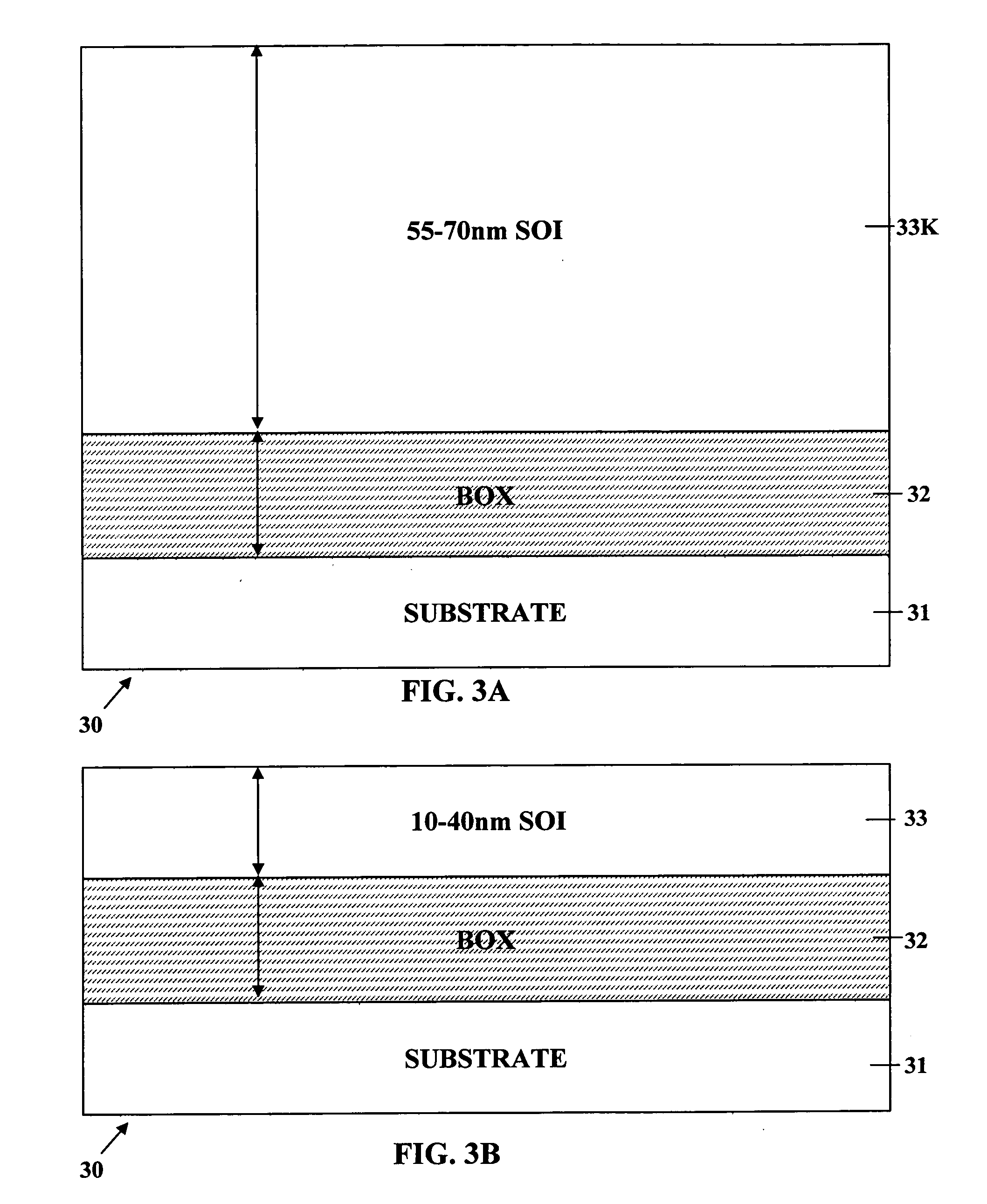

ActiveUS20060022270A1Minimize space-charge related fluctuationReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

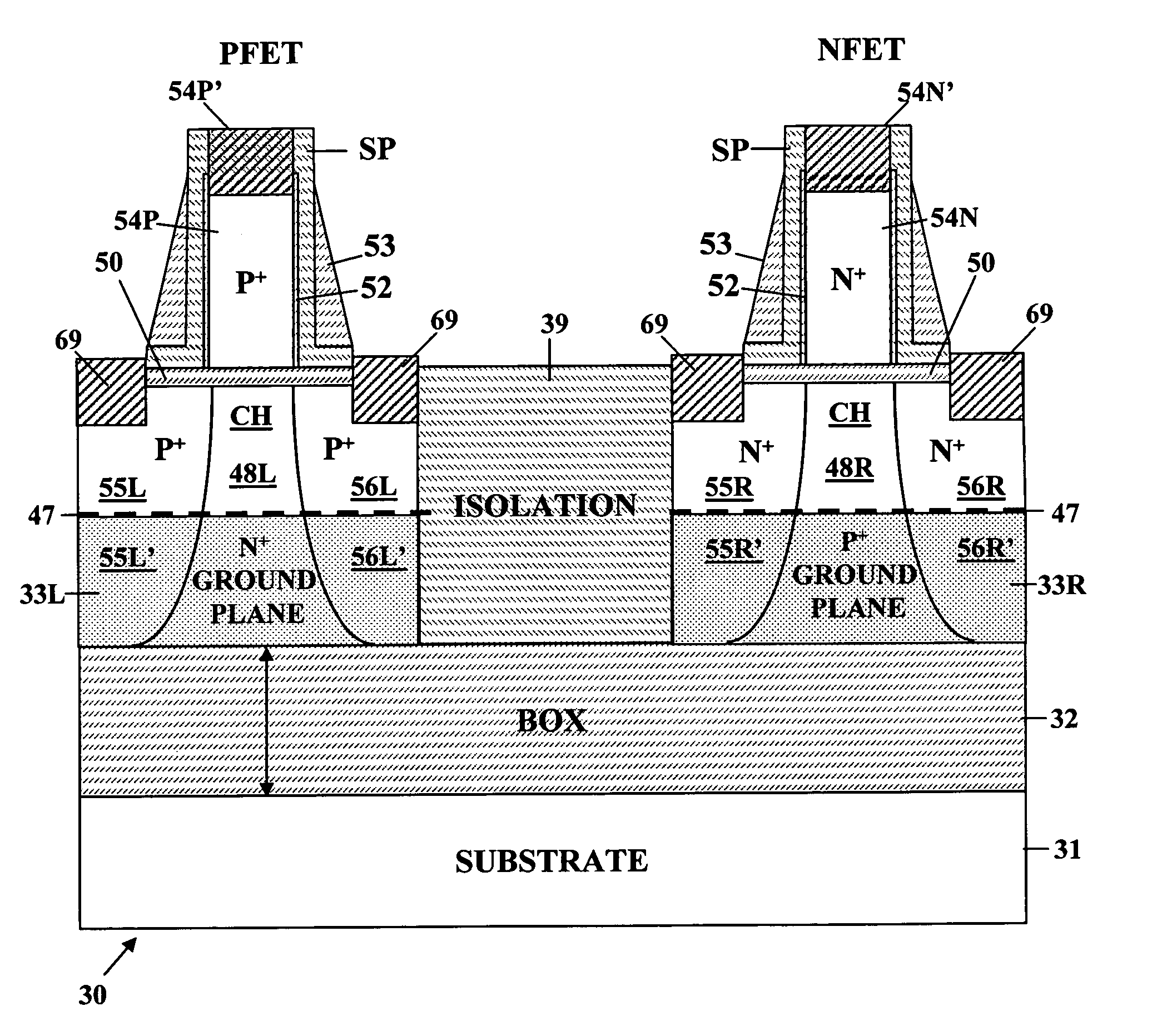

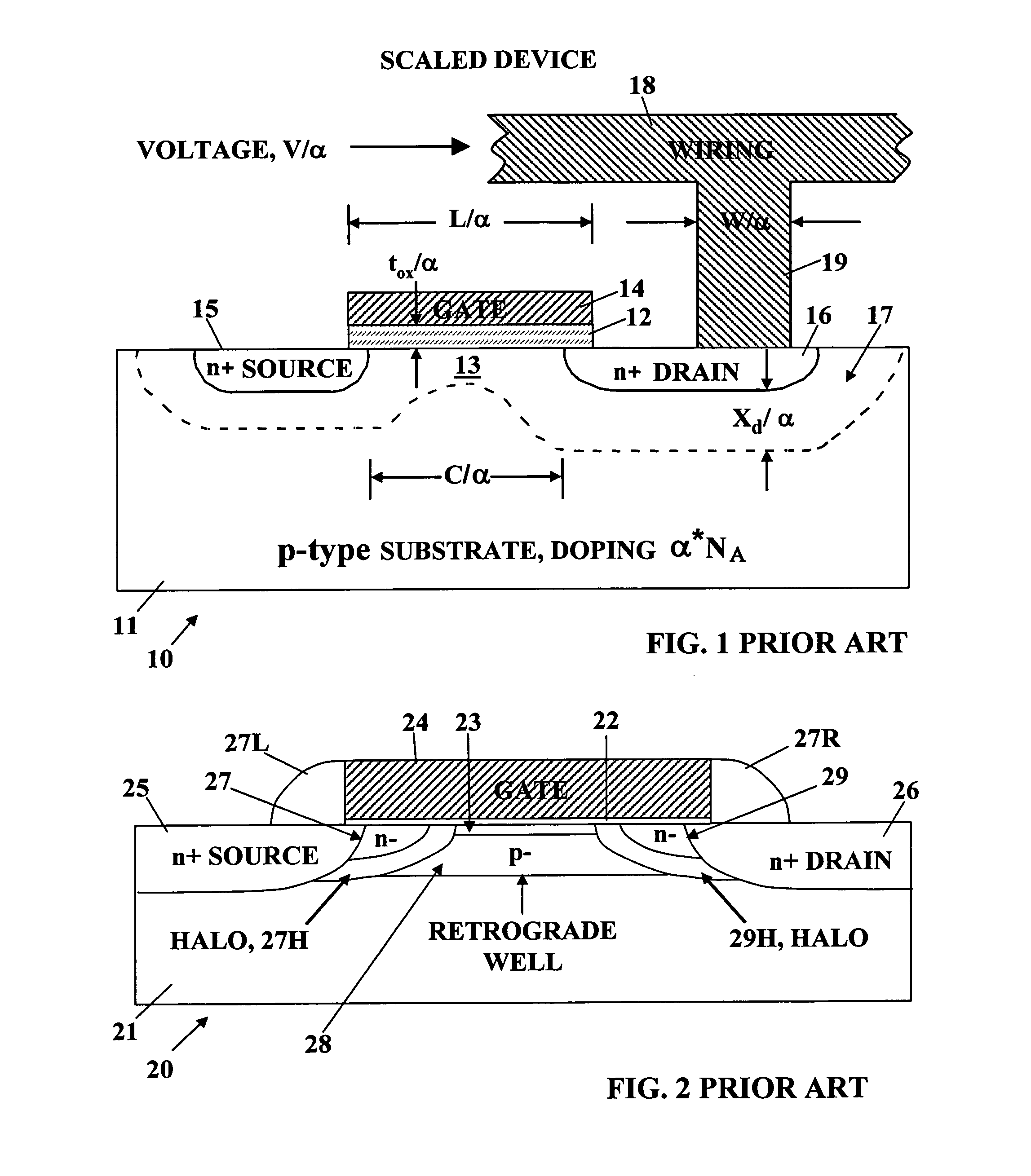

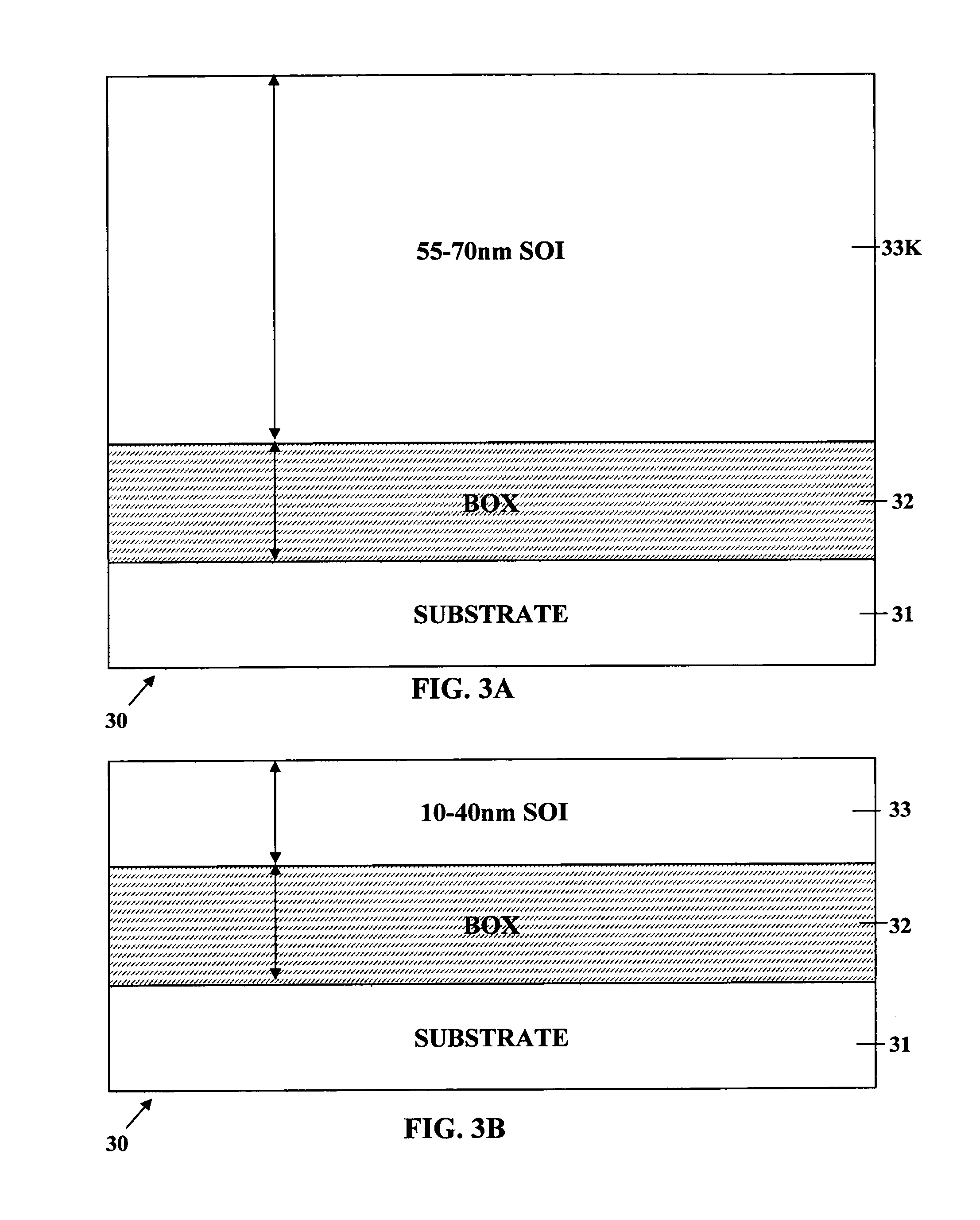

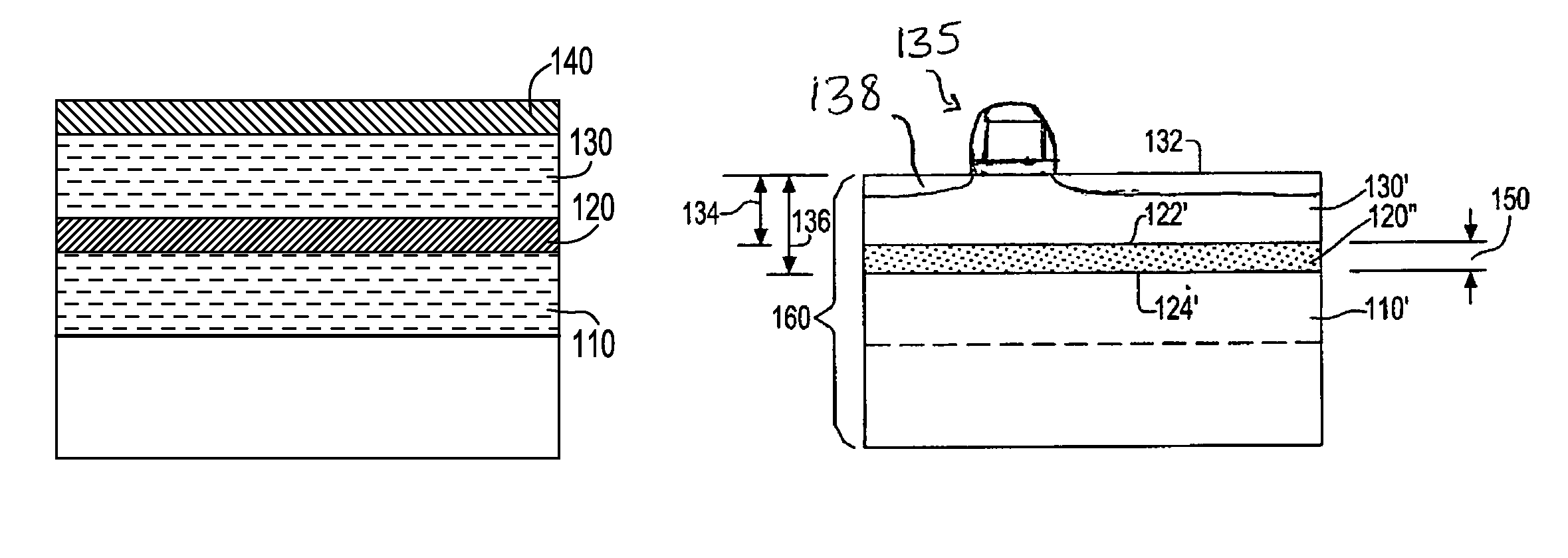

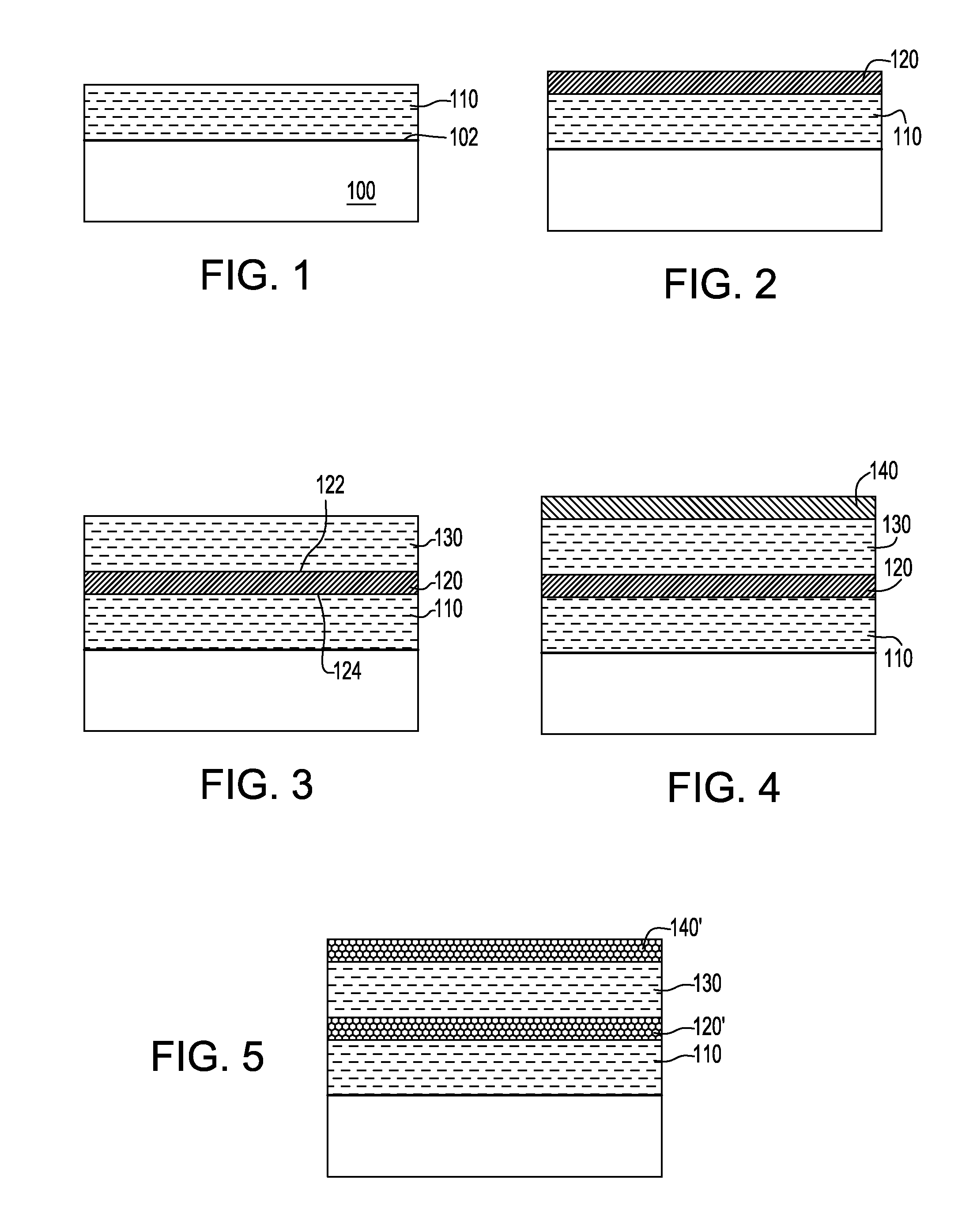

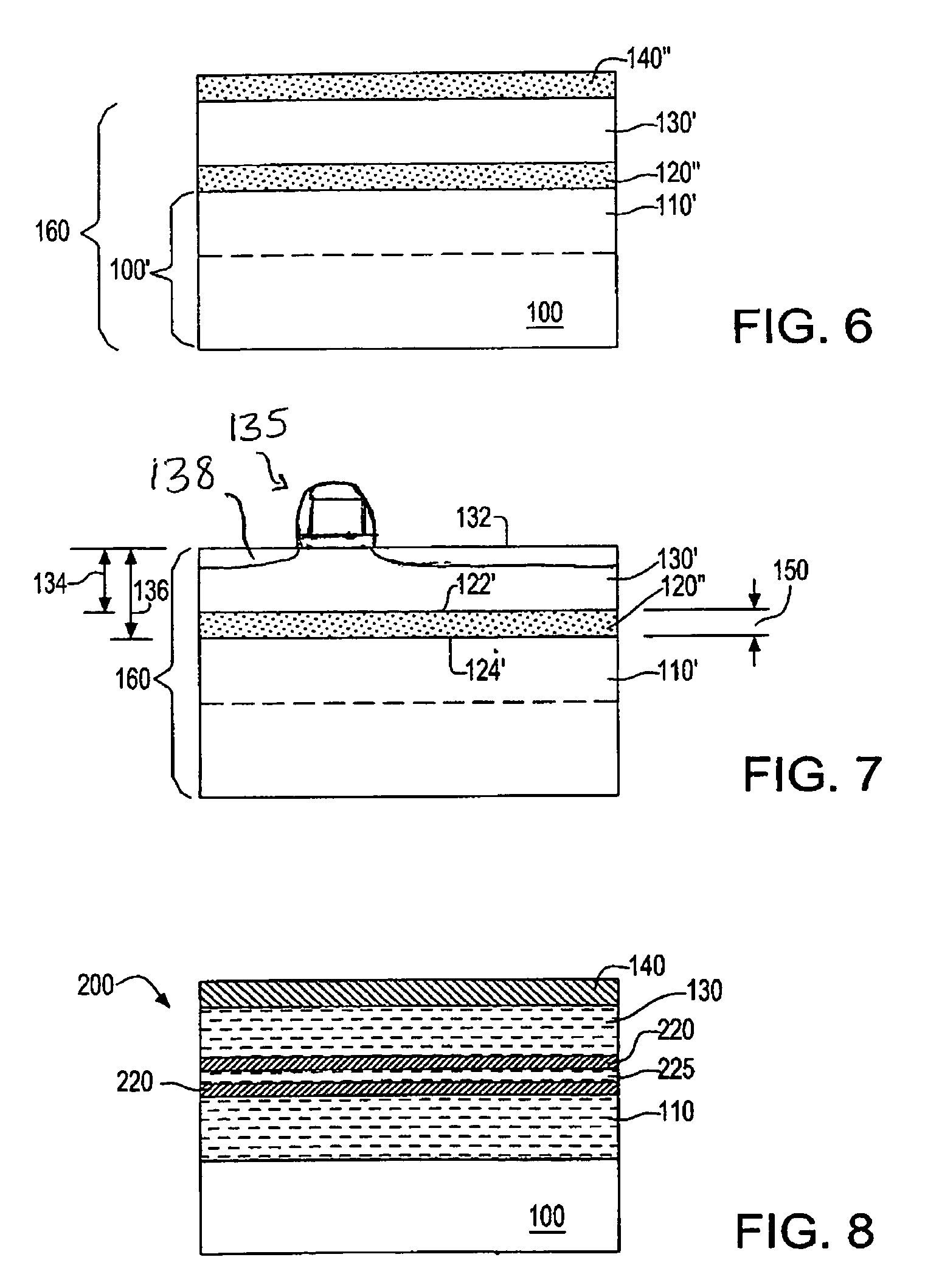

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

Manufacturing method of fin-type field effect transistor

InactiveUS20080171407A1Inhibition formationIncrease etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

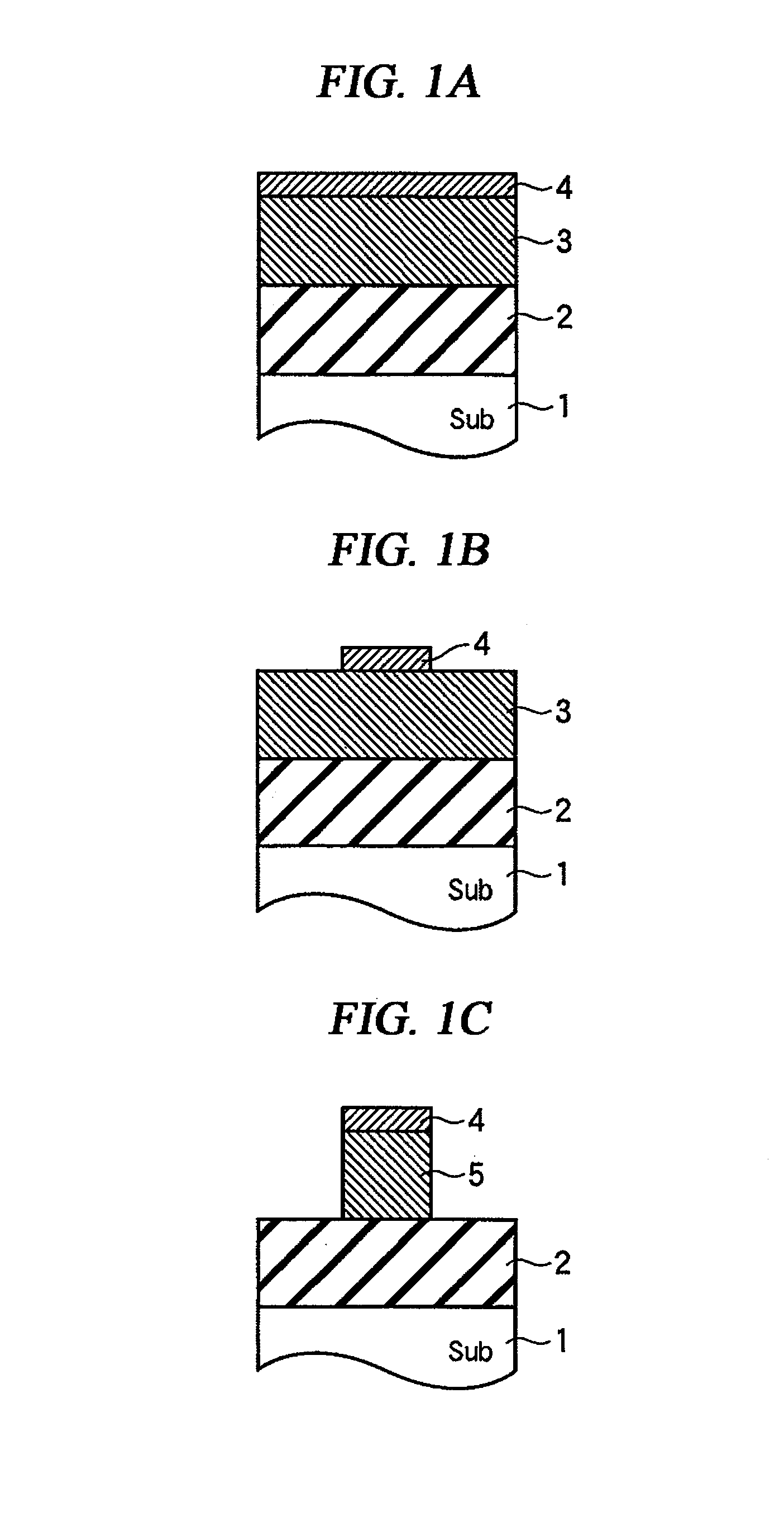

A method for manufacturing a fin-type field effect transistor simply and securely by using a SOI (Silicon On Insulator) wafer, capable of suppressing an undercut formation, is disclosed. The method includes forming a fin-shaped protrusion by selectively dry-etching a single crystalline silicon layer until an underlying buried oxide layer is exposed; forming a sacrificial oxide film by oxidizing a surface of the protrusion including a damage inflicted thereon; and forming a fin having a clean surface by removing the sacrificial oxide film by etching, wherein an etching rate r1 of the sacrificial oxide film is higher than an etching rate r2 of the buried oxide layer during the etching.

Owner:TOKYO ELECTRON LTD

Structure and method for multiple height finfet devices

InactiveUS20080128797A1Improve scalabilityProcessing complexity to minimumSemiconductor devicesEngineeringOxygen

Multiple finFETs containing semiconductor fins with the same height for the top but with different heights for the bottom are formed. Patterned oxygen implant masks are used to form a buried oxide layer with at least two different levels of oxide top surface. After the formation of the buried oxide layer, the top semiconductor layer has a substantially level top surface. Fins are formed by lithographically patterning and etching the top semiconductor layer. The resulting fins may be semiconductor fins with different heights or fins comprising an upper portion of semiconductor fins and a lower portion of oxide fins. In both cases, semiconductor fins of different heights are used to form finFETs with fractional on-current of a full height finFET.

Owner:IBM CORP

Transverse ultra-thin insulated gate bipolar transistor having high current density

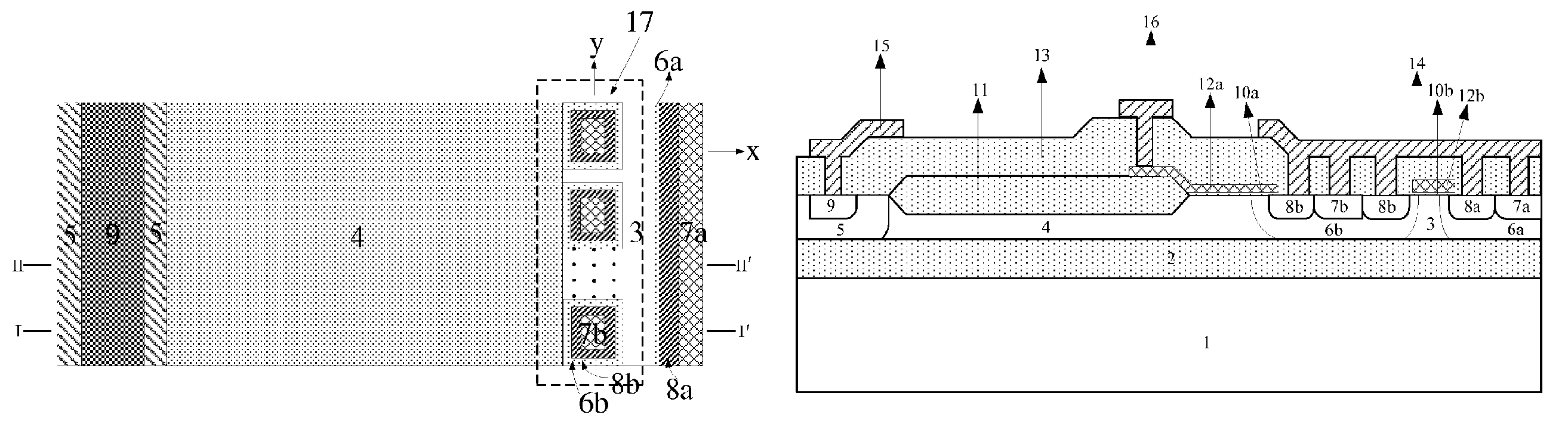

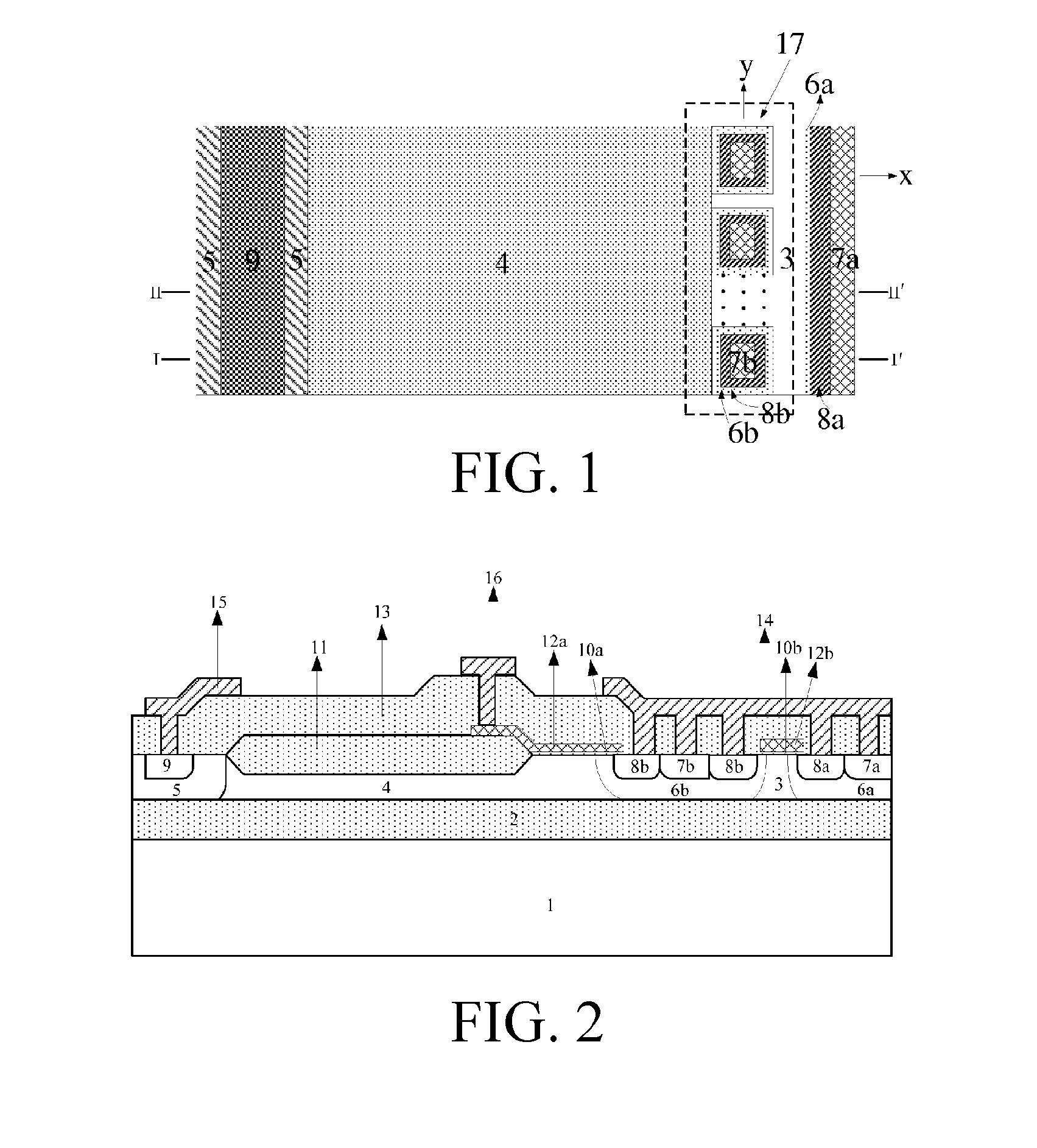

ActiveUS9240469B2High densityIncrease the number ofSemiconductor/solid-state device detailsSolid-state devicesHigh current densityField oxide

A transverse ultra-thin insulated gate bipolar transistor having current density includes: a P substrate, where the P substrate is provided with a buried oxide layer thereon, the buried oxide layer is provided with an N epitaxial layer thereon, the N epitaxial layer is provided with an N well region and P base region therein, the P base region is provided with a first P contact region and an N source region therein, the N well region is provided with an N buffer region therein, the N well region is provided with a field oxide layer thereon, the N buffer region is provided with a P drain region therein, the N epitaxial layer is provided therein with a P base region array including a P annular base region, the P base region array is located between the N well region and the P base region, the P annular base region is provided with a second P contact region and an N annular source region therein, and the second P contact region is located in the N annular source region. The present invention greatly increases current density of a transverse ultra-thin insulated gate bipolar transistor, thus significantly improving the performance of an intelligent power module.

Owner:SOUTHEAST UNIV

Ultra-thin body super-steep retrograde well (SSRW) FET devices

ActiveUS7002214B1Reduce capacitanceReduce junctionSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

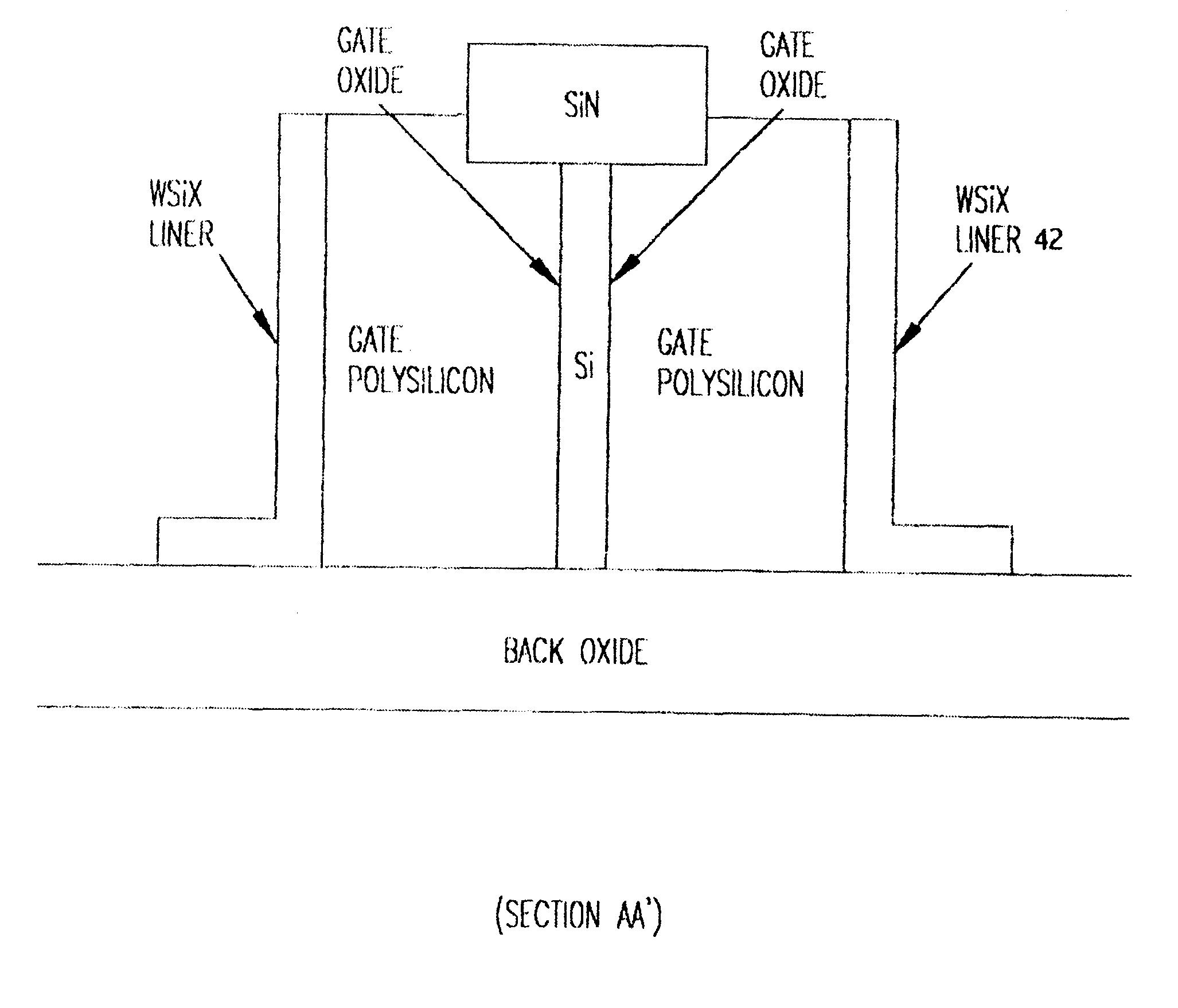

Double gate trench transistor

A field effect transistor is formed with a sub-lithographic conduction channel and a dual gate which is formed by a simple process by starting with a silicon-on-insulator wafer, allowing most etching processes to use the buried oxide as an etch stop. Low resistivity of the gate, source and drain is achieved by silicide sidewalls or liners while low gate to junction capacitance is achieved by recessing the silicide and polysilicon dual gate structure from the source and drain region edges.

Owner:IBM CORP

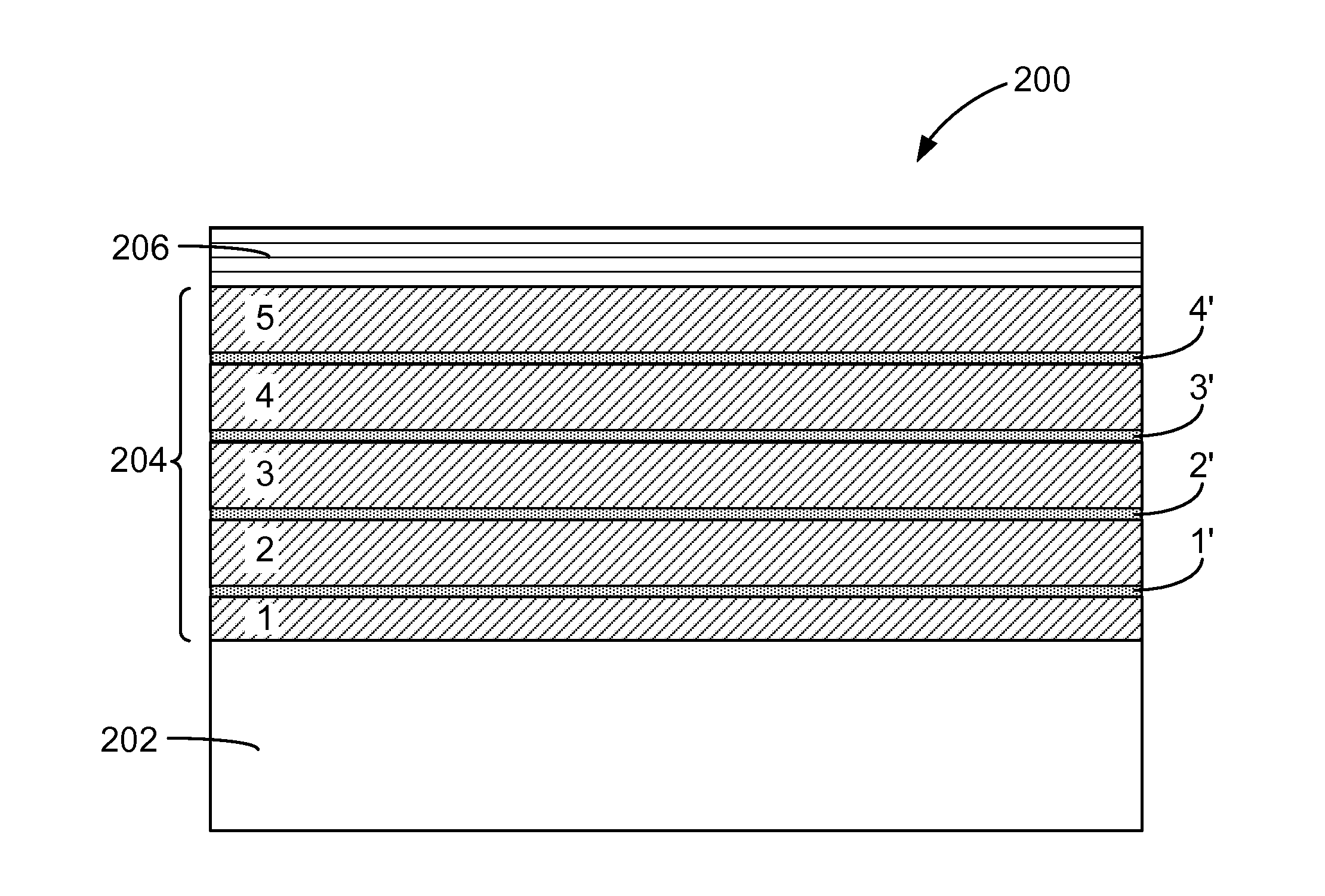

Method of manufacturing high resistivity soi wafers with charge trapping layers based on terminated si deposition

ActiveUS20150115480A1Semiconductor/solid-state device detailsSolid-state devicesWaferingSemiconductor structure

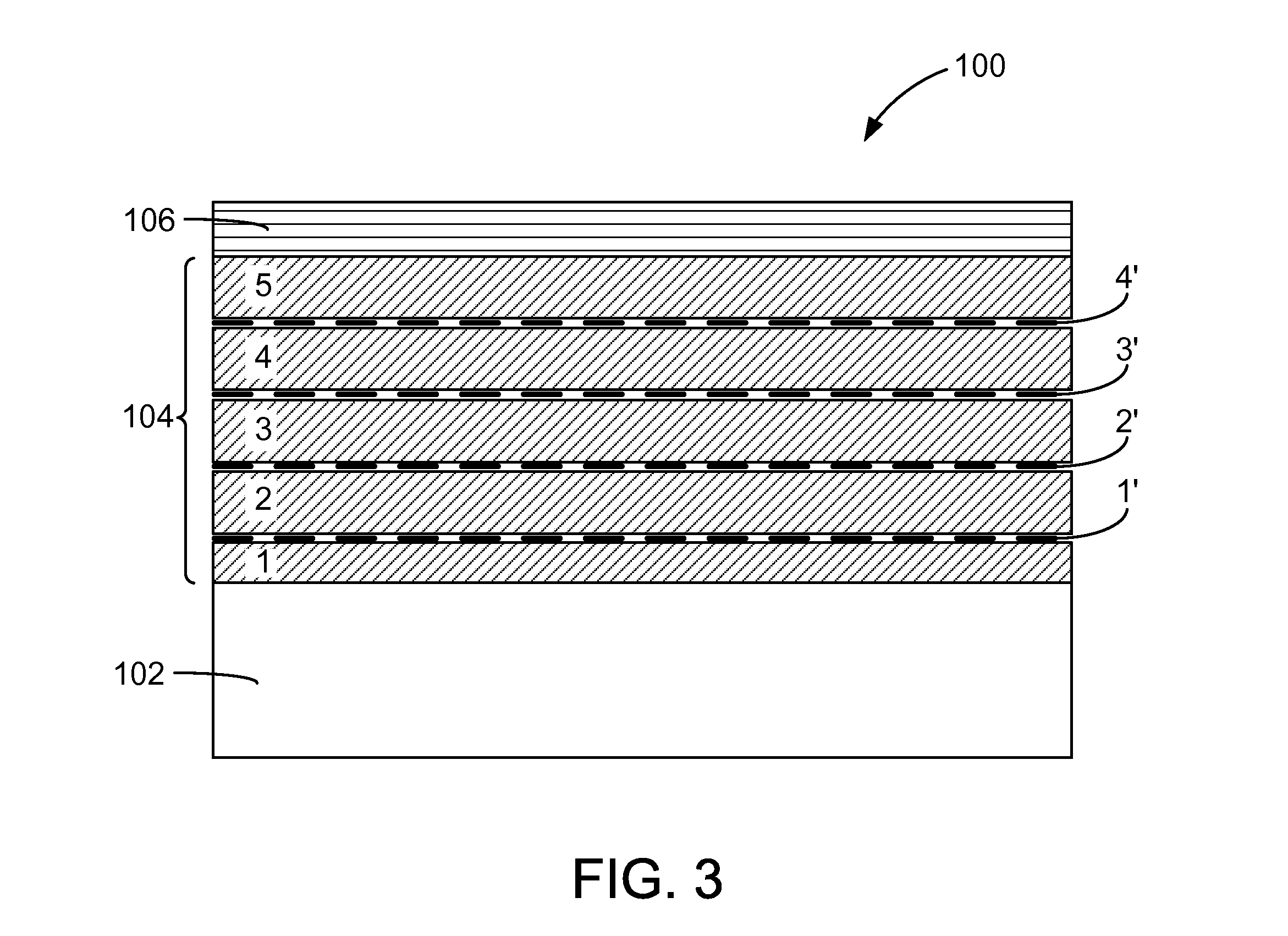

A method of preparing a single crystal semiconductor handle wafer in the manufacture of a silicon-on-insulator device is provided. The method comprises forming a multilayer of passivated semiconductors layers on a dielectric layer of a high resistivity single crystal semiconductor handle wafer. The method additionally comprises forming a semiconductor oxide layer on the multilayer of passivated semiconductor layers. The multilayer of passivated semiconductor layers comprise materials suitable for use as charge trapping layers between a high resistivity substrate and a buried oxide layer in a semiconductor on insulator structure.

Owner:GLOBALWAFERS CO LTD

Formation of SOI by oxidation of silicon with engineered porosity gradient

InactiveUS7772096B2Semiconductor/solid-state device detailsSolid-state devicesPorositySingle crystal

A method is provided for making a silicon-on-insulator substrate. Such method can include epitaxially growing a highly p-type doped silicon-containing layer onto a major surface of an underlying semiconductor region of a substrate. Subsequently, a non-highly p-type doped silicon-containing layer may be epitaxially grown onto a major surface of the p-type highly-doped epitaxial layer to cover the highly p-type doped epitaxial layer. The overlying non-highly p-type doped epitaxial layer can have a dopant concentration substantially lower than the dopant concentration of the highly p-type doped epitaxial layer. The substrate can then be processed to form a buried oxide layer selectively by oxidizing at least portions of the highly p-type doped epitaxial layer covered by the non-highly p-type doped epitaxial layer, the buried oxide layer separating the overlying monocrystalline semiconductor layer from the underlying semiconductor region. Such processing can be performed while simultaneously annealing the non-highly p-type doped epitaxial layer.

Owner:GLOBALFOUNDRIES INC

Method and structure for buried circuits and devices

A method and structure for fabricating an electronic device using an SOI technique that results in formation of a buried oxide layer. The method includes fabricating at least one first component of the electronic device and fabricating at least one second component of the electronic device, wherein the first component and the second component are on opposite sides of the buried oxide layer, thereby causing the buried oxide layer to perform a function within the electronic device. Entire circuits can be designed around this technique.

Owner:GLOBALFOUNDRIES US INC

Maskless Process for Suspending and Thinning Nanowires

ActiveUS20100193770A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireManufacturing technology

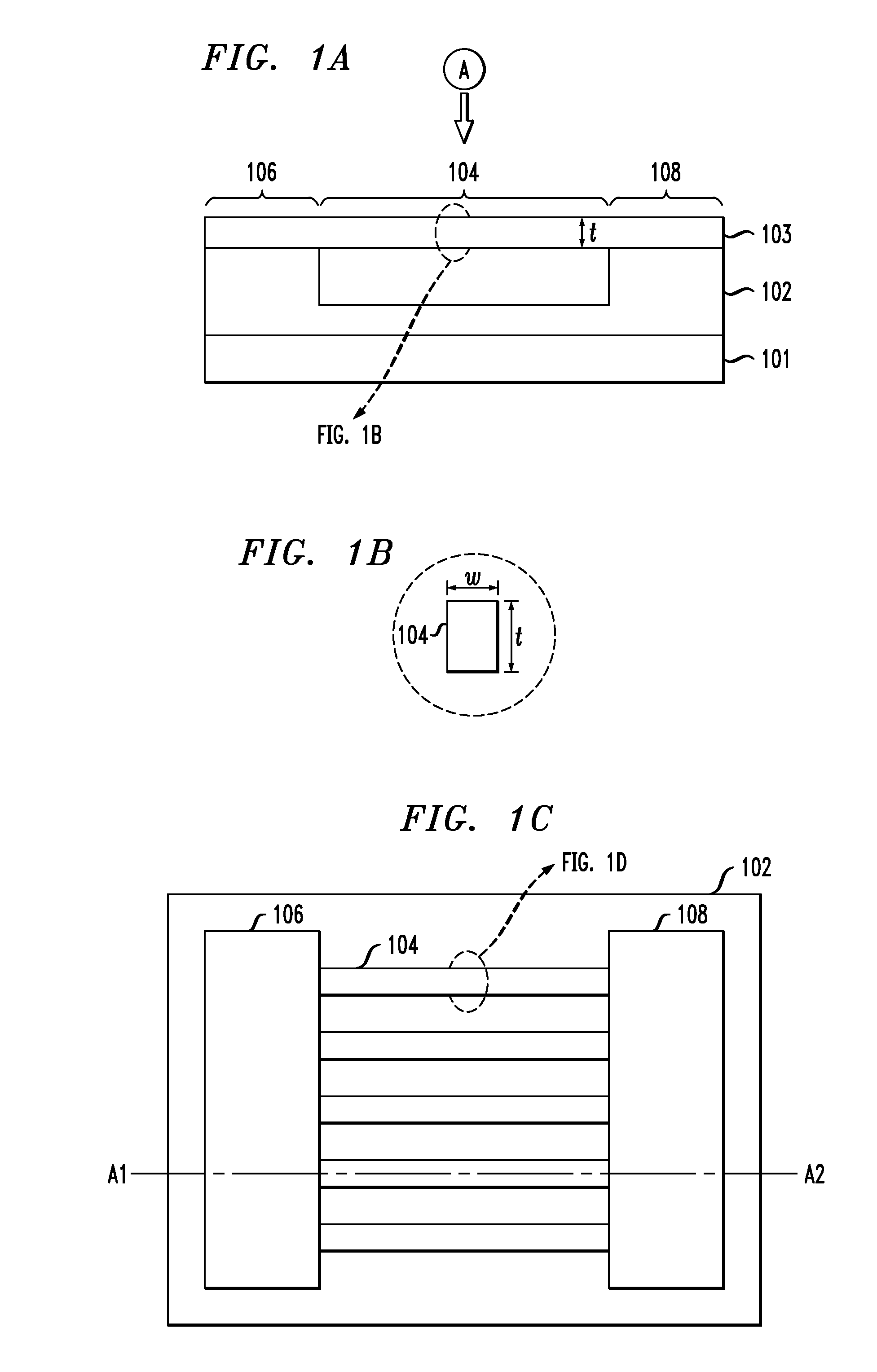

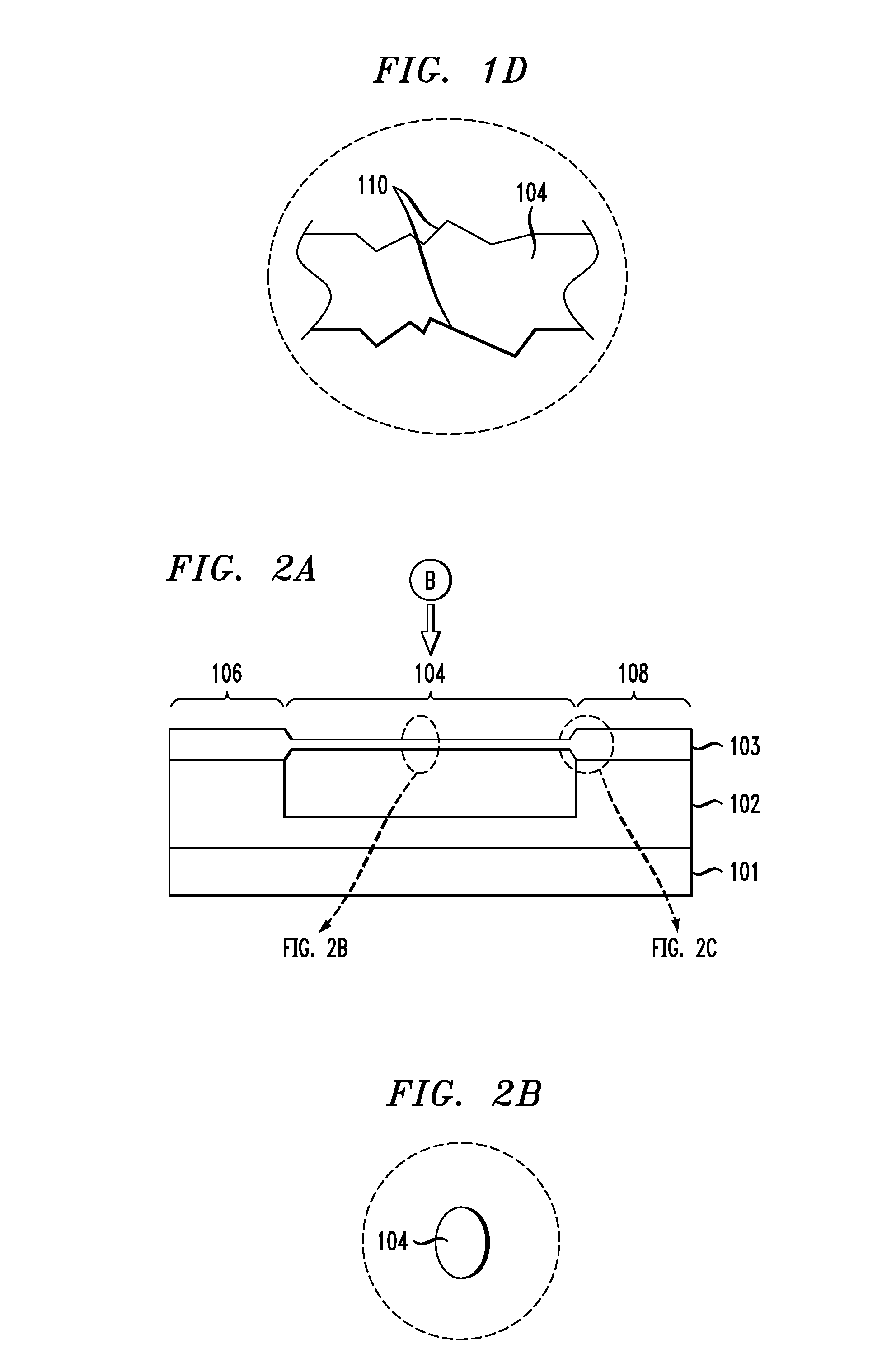

Semiconductor-based electronic devices and techniques for fabrication thereof are provided. In one aspect, a device is provided comprising a first pad; a second pad and a plurality of nanowires connecting the first pad and the second pad in a ladder-like configuration formed in a silicon-on-insulator (SOI) layer over a buried oxide (BOX) layer, the nanowires having one or more dimensions defined by a re-distribution of silicon from the nanowires to the pads. The device can comprise a field-effect transistor (FET) having a gate surrounding the nanowires wherein portions of the nanowires surrounded by the gate form channels of the FET, the first pad and portions of the nanowires extending out from the gate adjacent to the first pad form a source region of the FET and the second pad and portions of the nanowires extending out from the gate adjacent to the second pad form a drain region of the FET.

Owner:IBM CORP

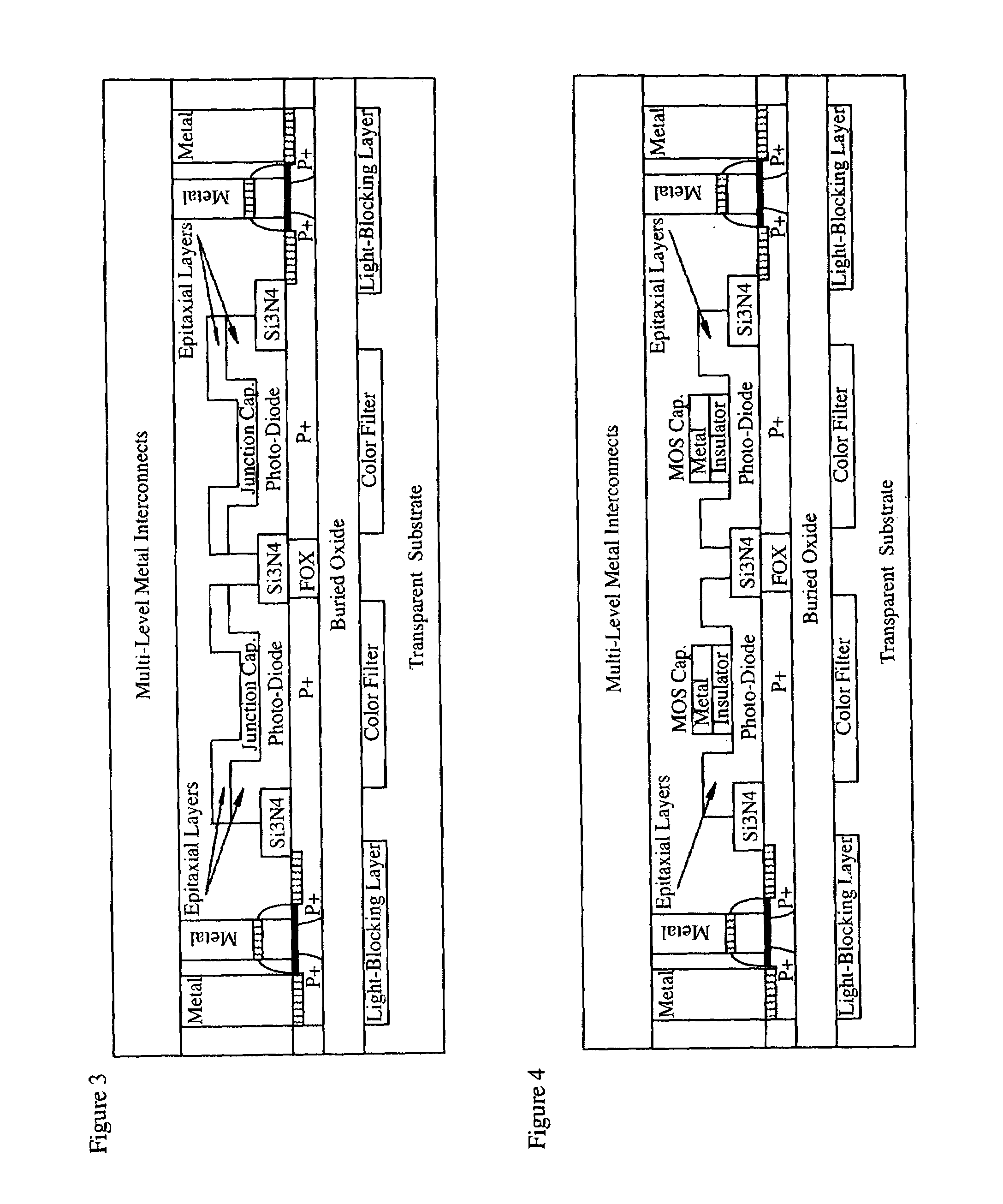

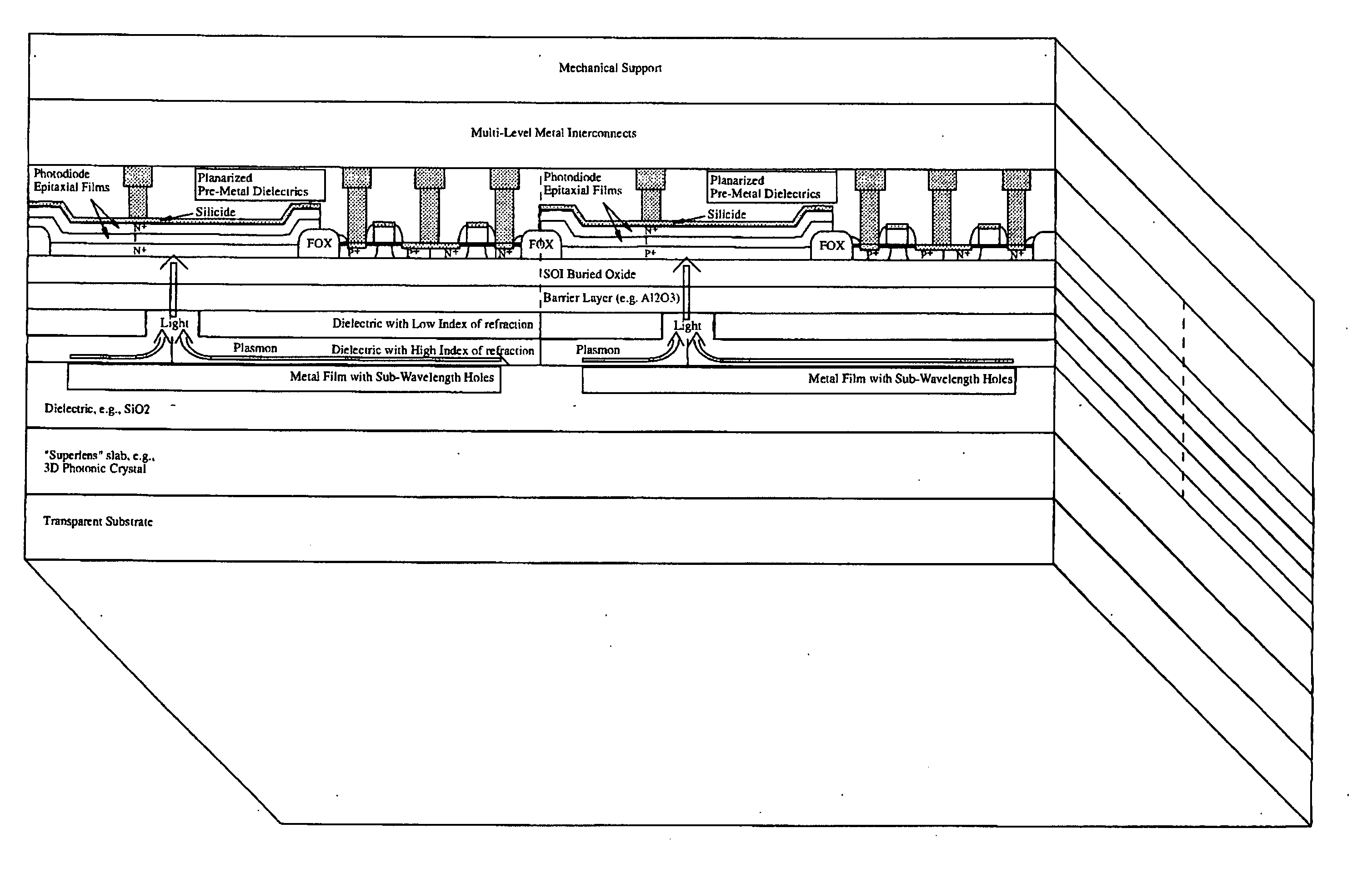

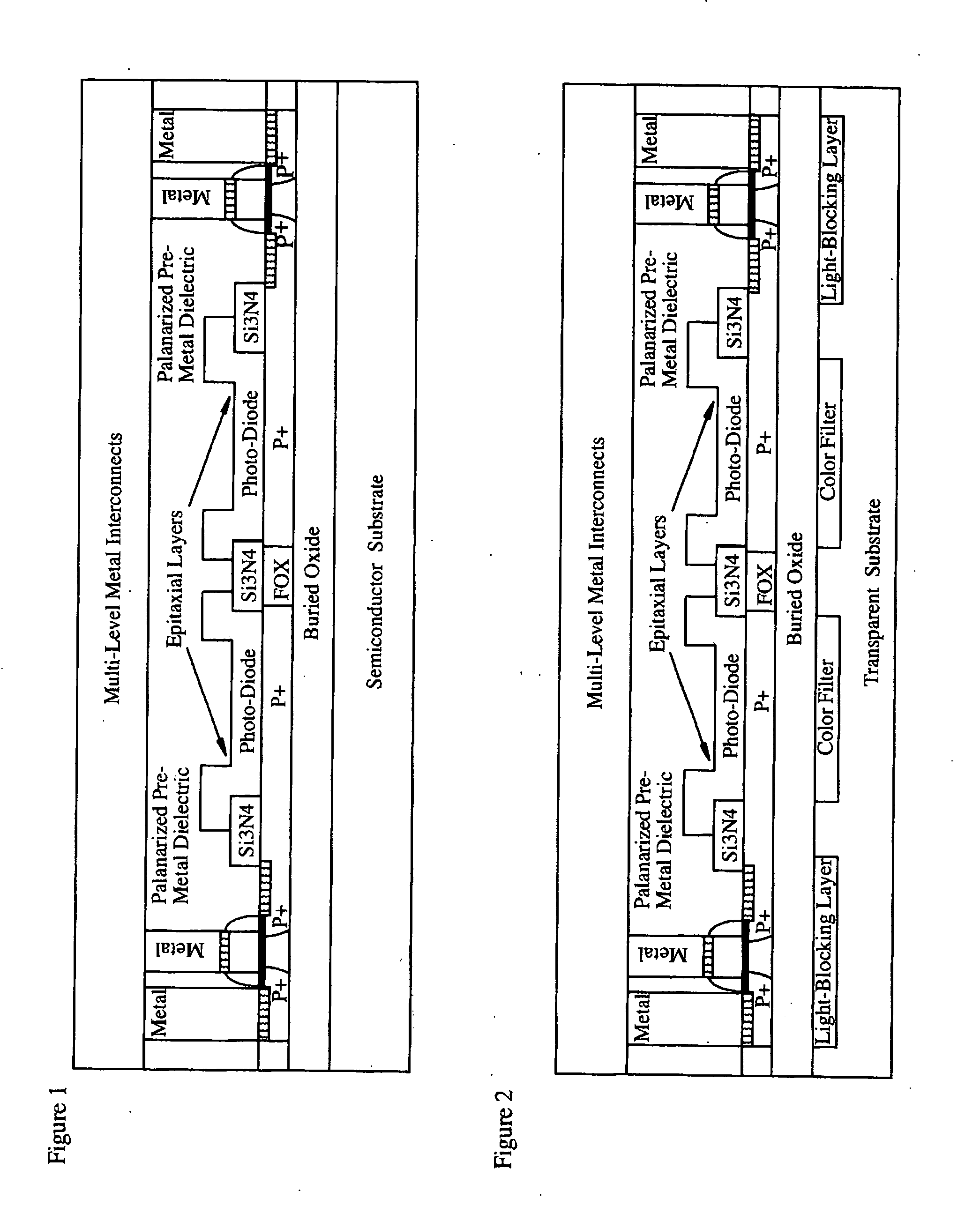

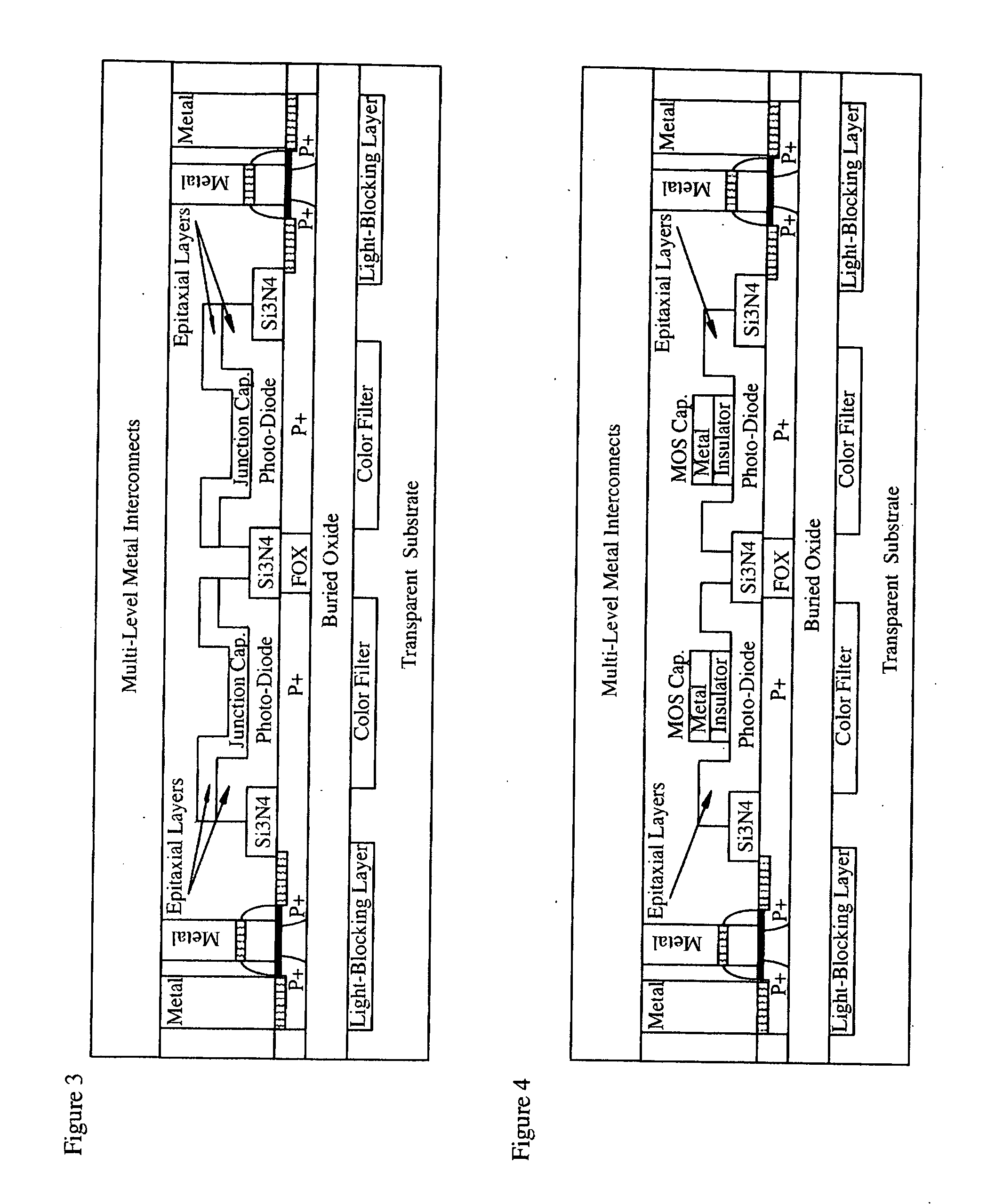

CMOS image sensor

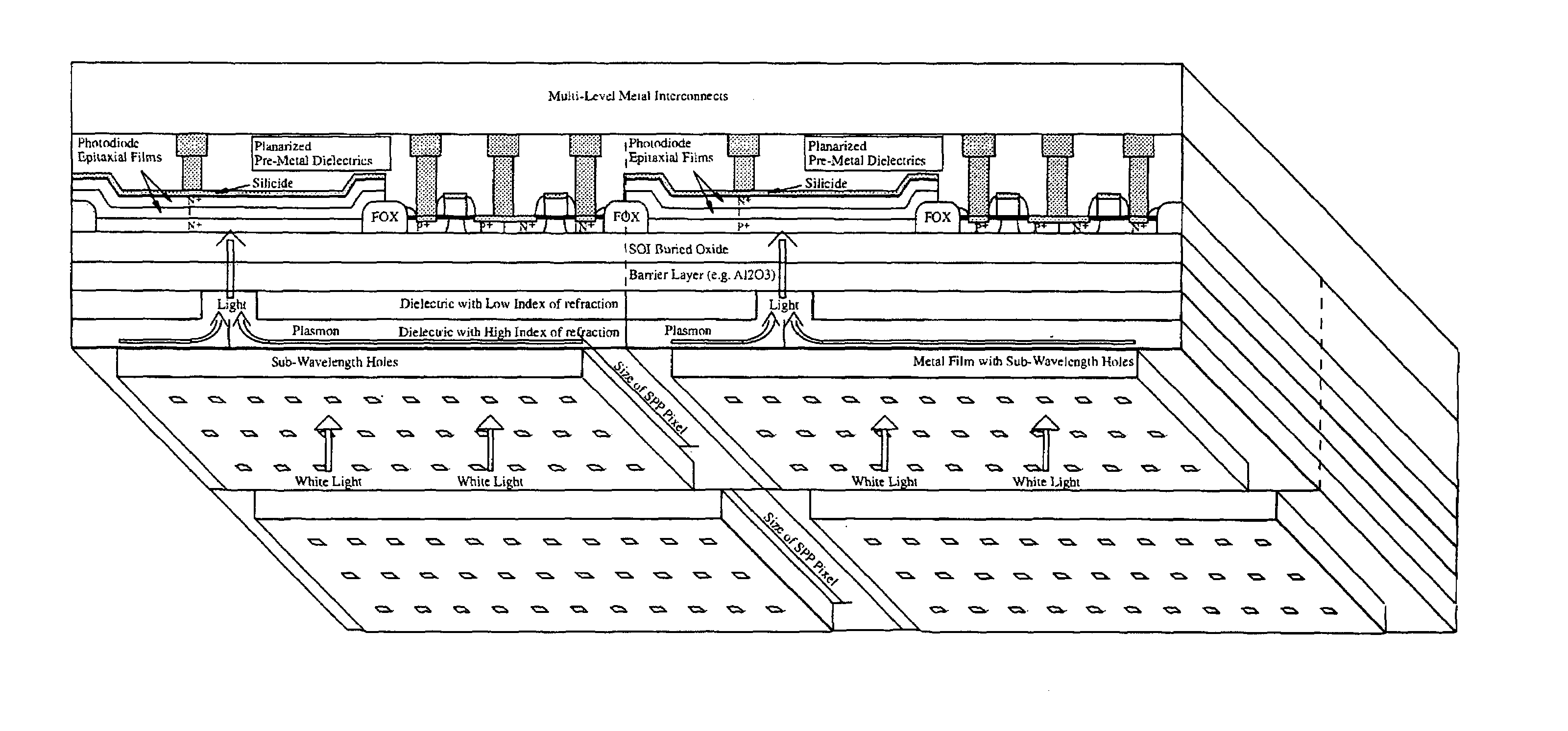

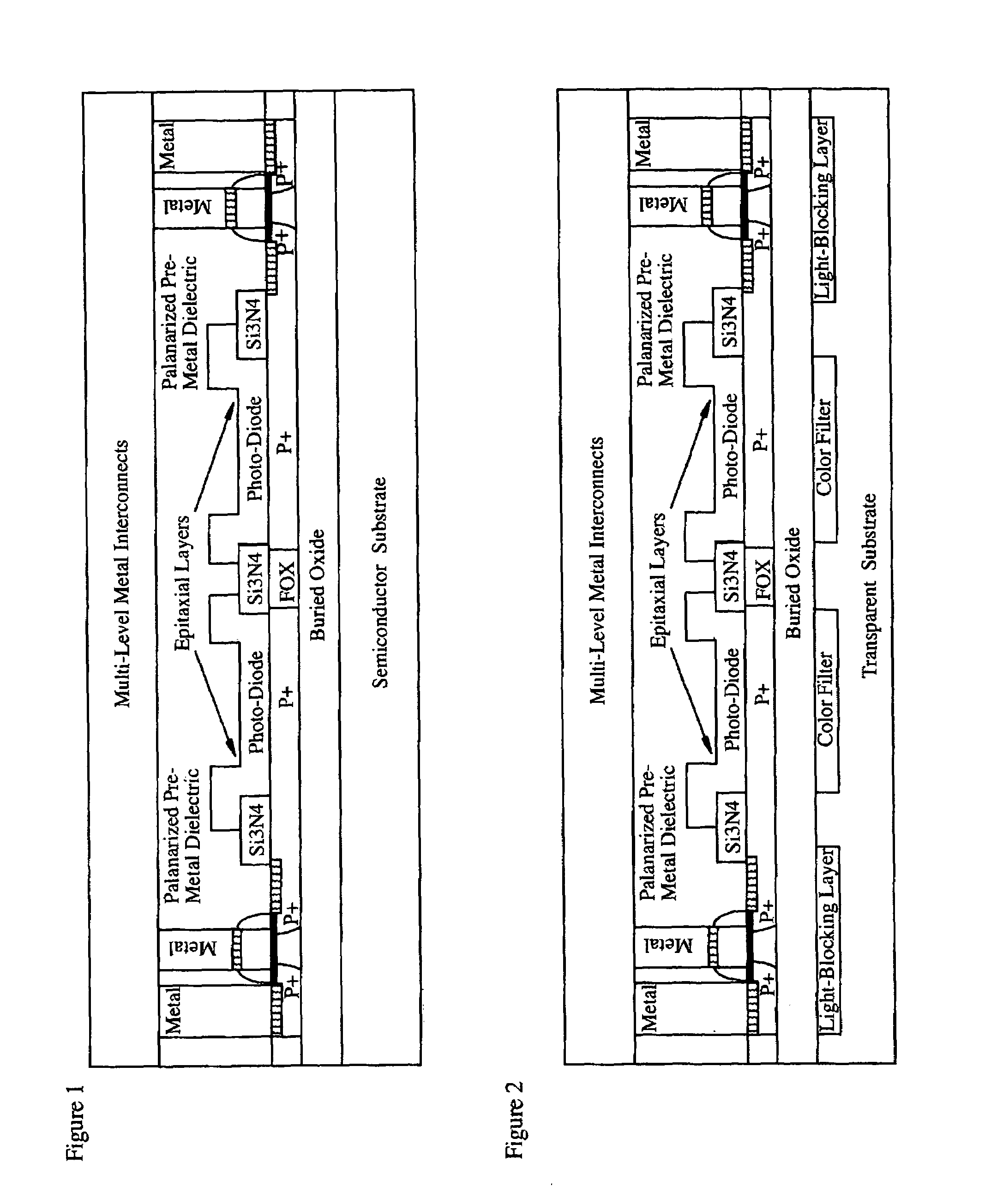

Light sensing devices are monolithically integrates with CMOS devices on Thin-Film Silicon-On-insulator (TF-SOI) or Thin-Film Germanium-On-Insulator (TF-GeOI) substrates. Photo-diode active layers are epitaxially grown on the front-side of the substrate and after full processing of the front-side of the substrate, the substrate material is removed under the buried insulator (buried oxide). Monolithically integrated structures are then fabricated on the back of the buried oxide. The back-side is then bonded to a new substrate that is transparent to the wavelengths of interest. For example, quartz, sapphire, glass, or plastic, are suitable for the visible range. Back-side illumination of the sensor matrix is thereby allowed, with light traveling through the structures fabricated on the back of the substrate, opposite to the side on which CMOS is made.

Owner:QUANTUM SEMICON

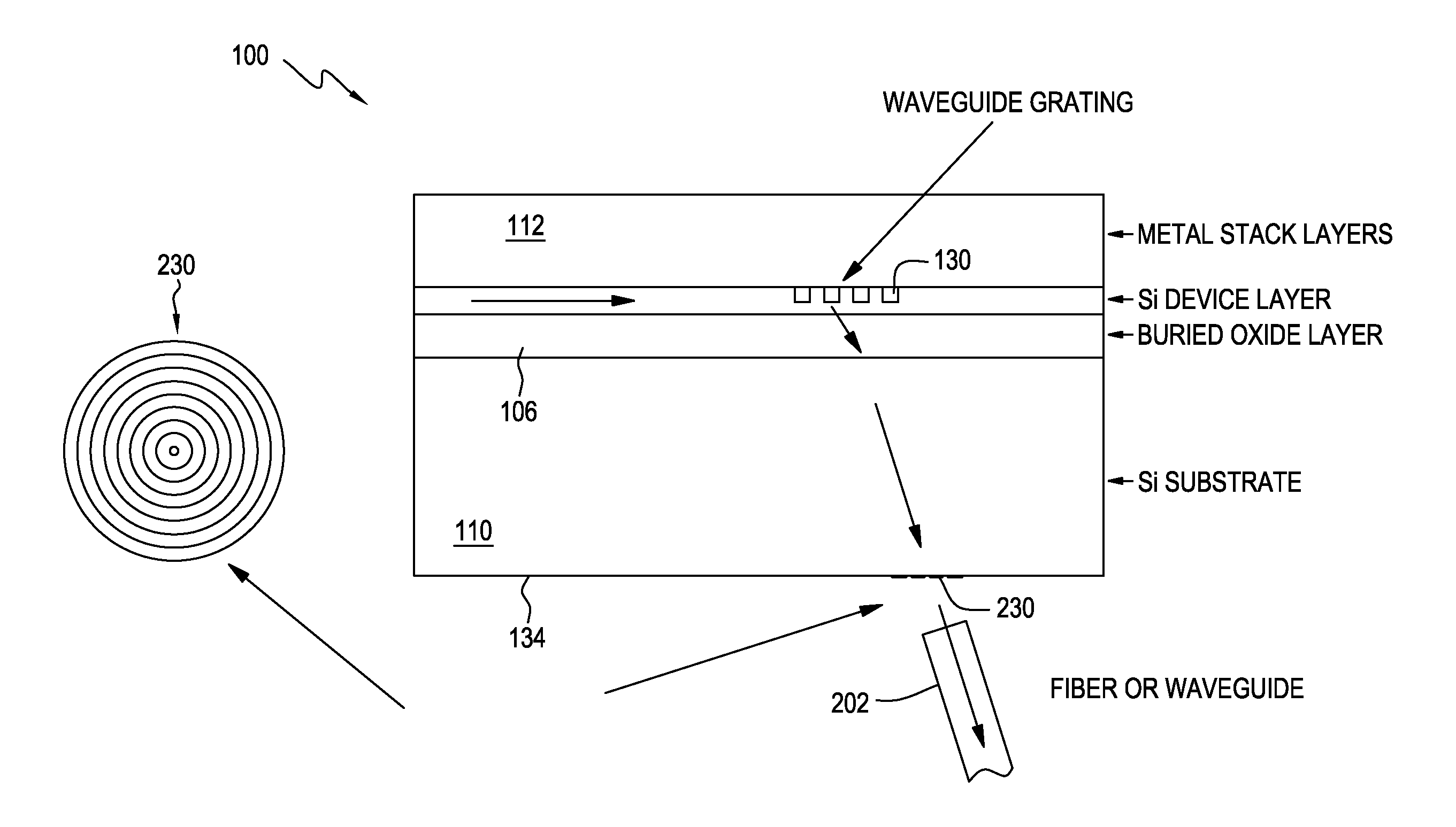

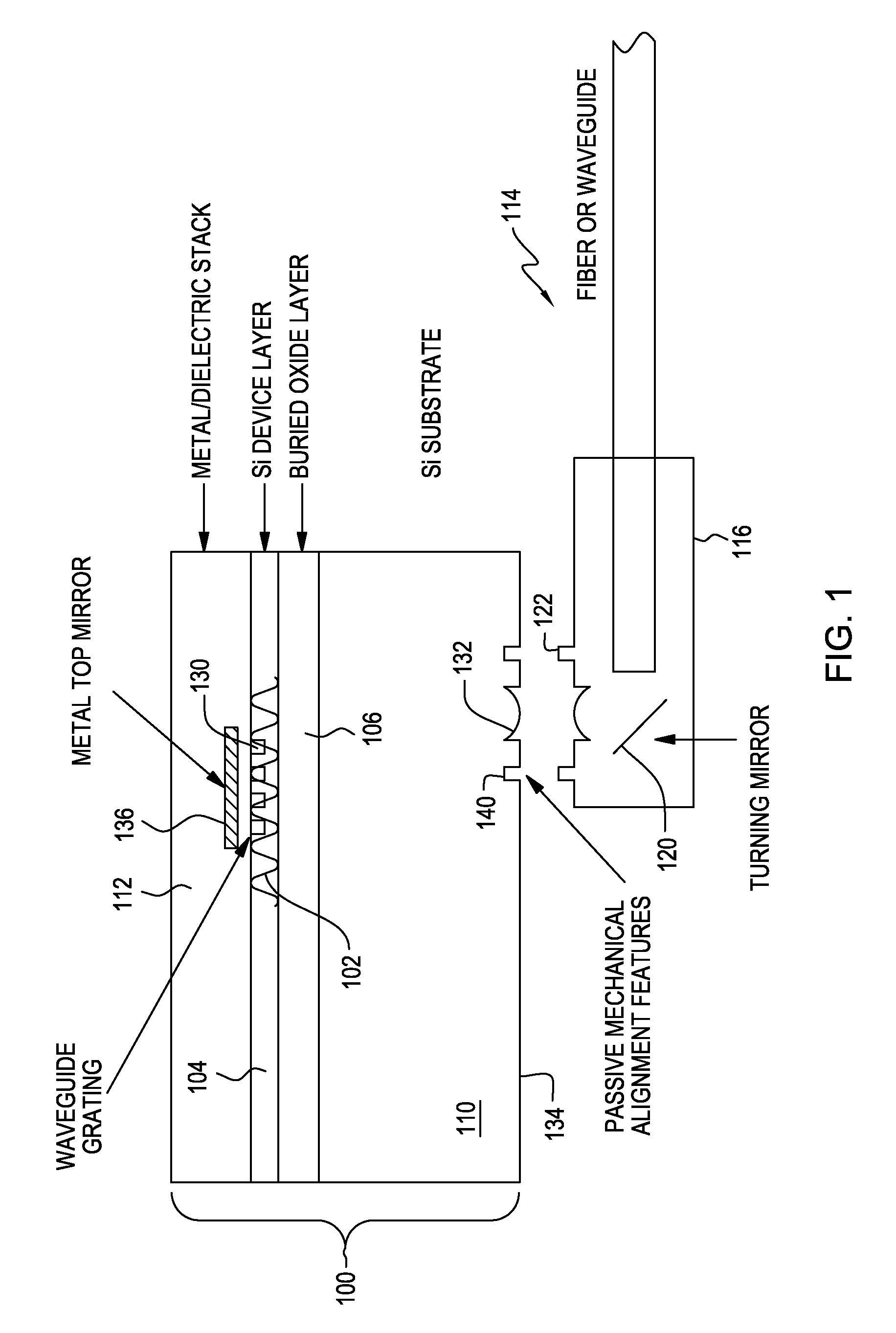

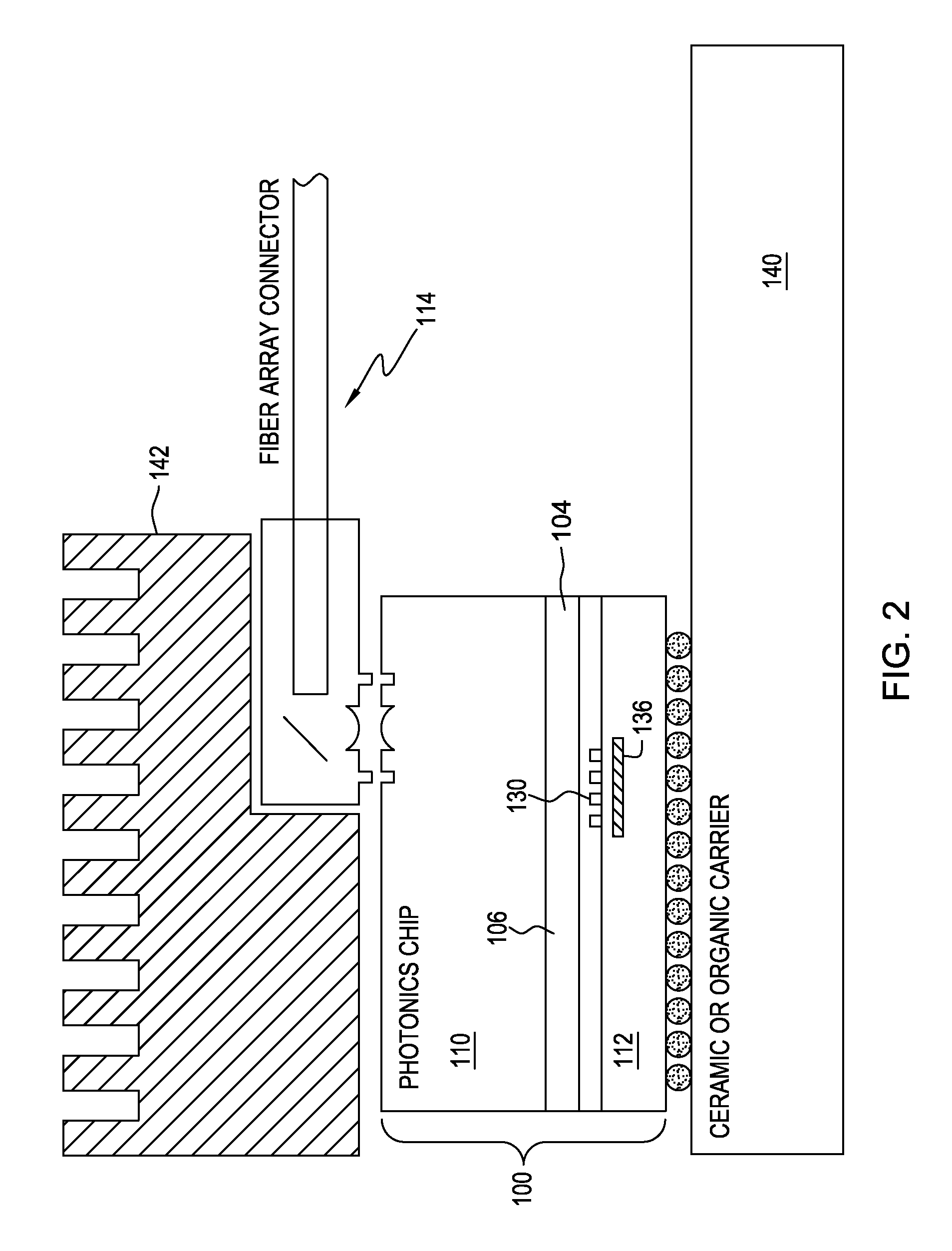

Through-substrate optical coupling to photonics chips

ActiveUS20130209026A1Enhanced couplingHelp positioningSolid-state devicesSemiconductor/solid-state device manufacturingDielectricPhotonic Chip

An optoelectronic integrated circuit for coupling light to or from an optical waveguide formed in an optical device layer in a near-normal angle to that layer. In an embodiment, the integrated circuit comprises a semiconductor body including a metal-dielectric stack, an optical device layer, a buried oxide layer and a semiconductor substrate arranged in series between first and second opposite sides of the semiconductor body. At least one optical waveguide is formed in the optical device layer for guiding light in a defined plane in that device layer. Diffractive coupling elements are disposed in the optical device layer to couple light from the waveguide toward the second surface of the semiconductor body at a near-normal angle to the defined plane in the optical device layer. In an embodiment, an optical fiber is positioned against the semiconductor body for receiving the light from the coupling elements.

Owner:IBM CORP

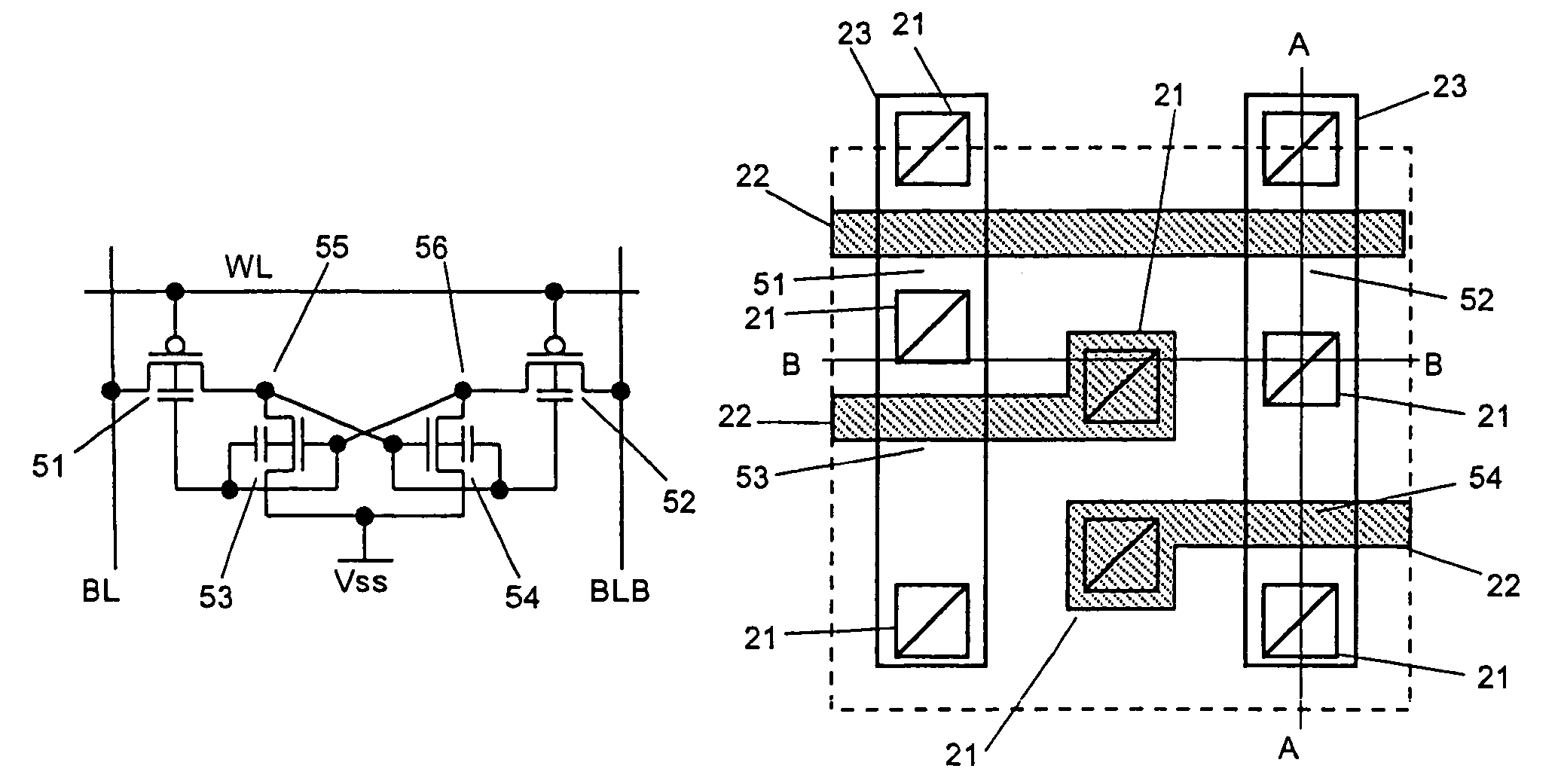

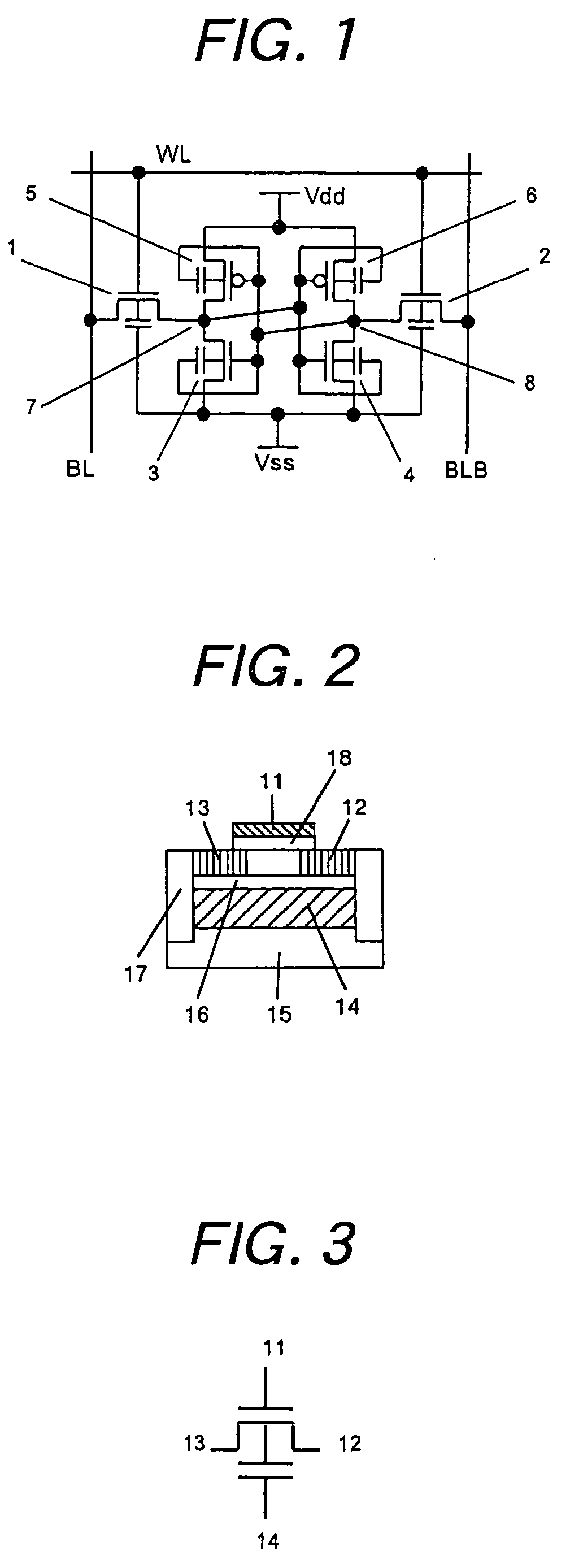

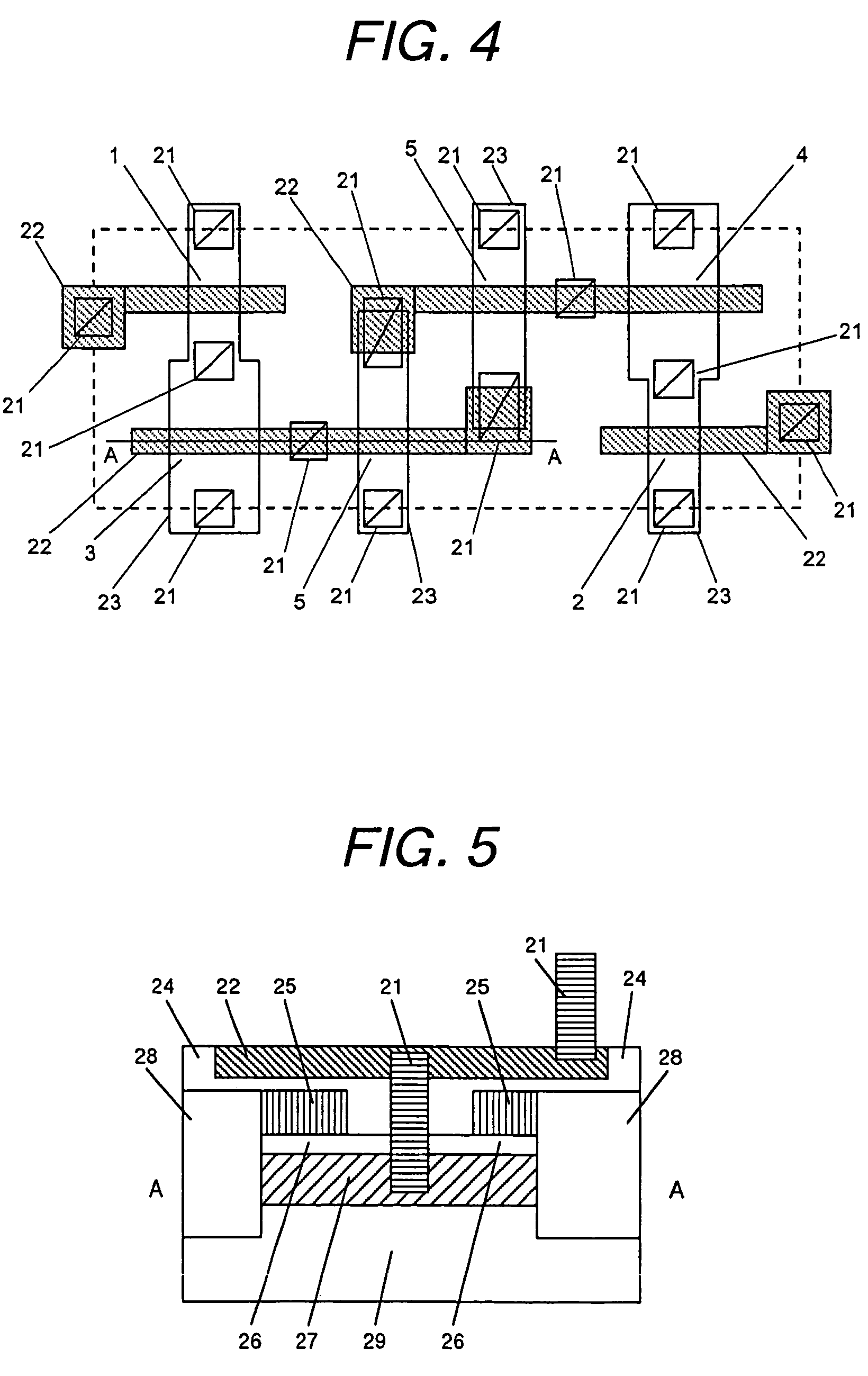

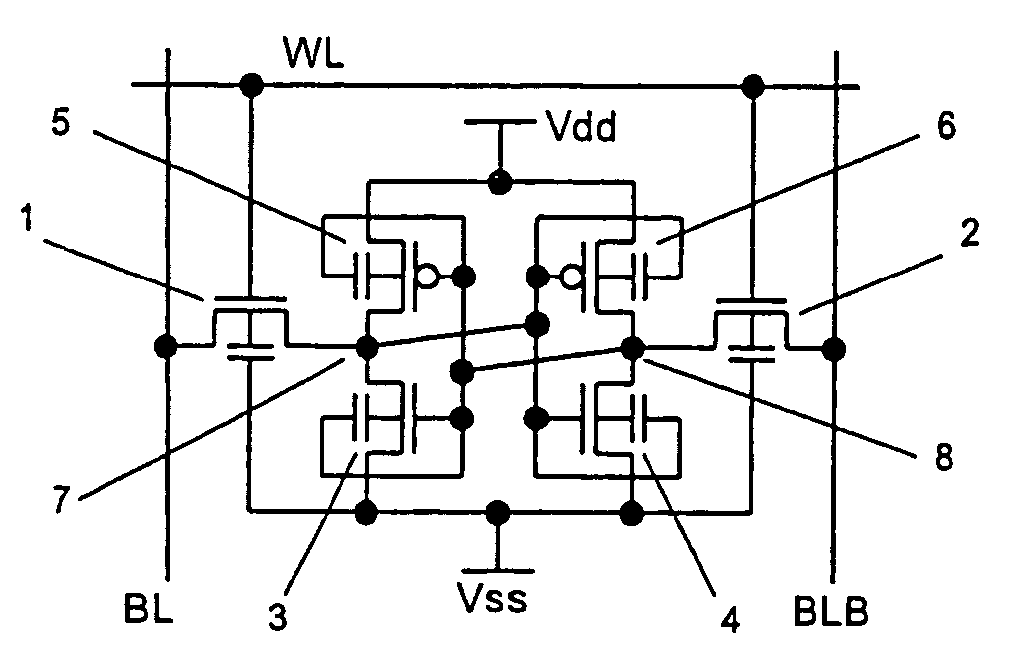

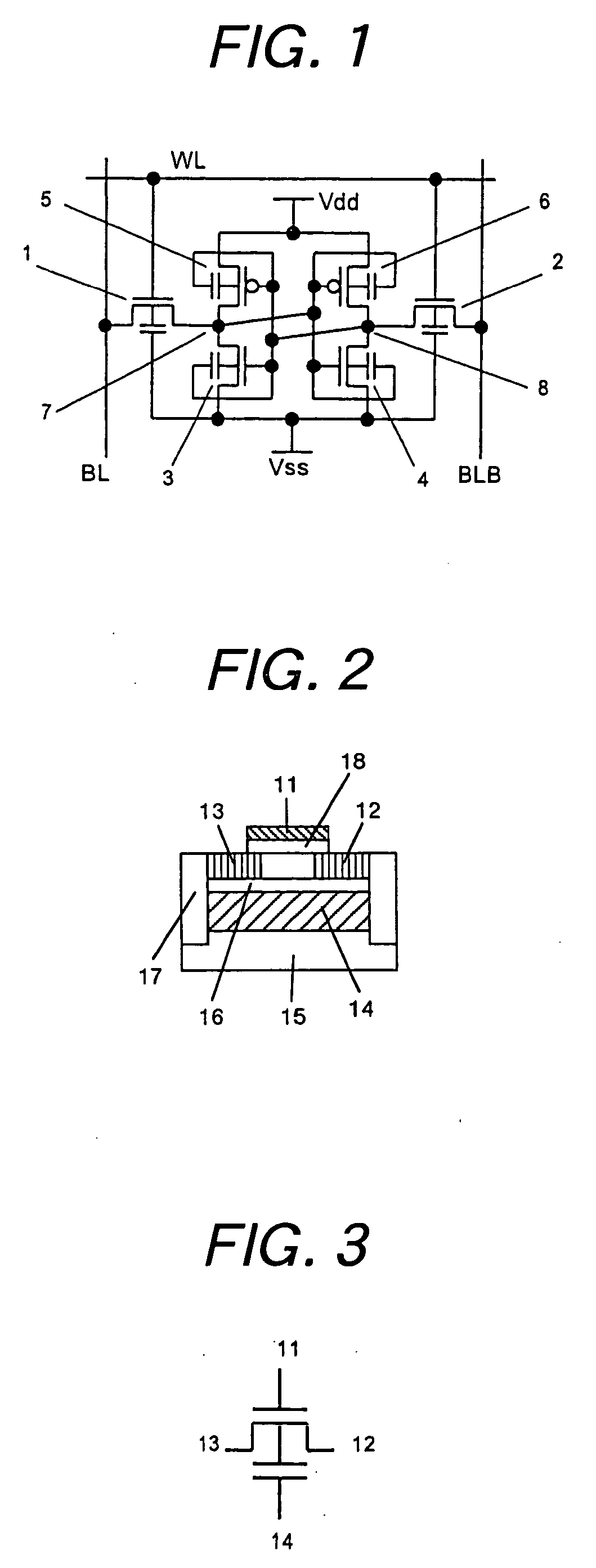

Semiconductor memory

InactiveUS7498637B2Guaranteed uptimeAverage power consumptionTransistorSolid-state devicesSemiconductorThreshold voltage

A SRAM memory is composed of FD-SOI transistors, and performance of the memory cell is improved by controlling an electric potential of a layer under a buried oxide film of a SOI transistor constituting a driver transistor. Performance of the SRAM circuit in the low power voltage state is improved. In the SRAM memory cell composed of the FD-SOI transistor, an electric potential of a well under a BOX layer is controlled to control a threshold voltage Vth, thereby increasing a current. Thus, the operations of the memory cell can be stabilized.

Owner:RENESAS ELECTRONICS CORP

CMOS image sensor

Light sensing devices are monolithically integrates with CMOS devices on Thin-Film Silicon-On-insulator (TF-SOI) or Thin-Film Germanium-On-Insulator (TF-GeOI) substrates. Photodiode active layers are epitaxially grown on the front-side of the substrate and after full processing of the front-side of the substrate, the substrate material is removed under the buried insulator (buried oxide). Monolithically integrated structures are then fabricated on the back of the buried oxide. The back-side is then bonded to a new substrate that is transparent to the wavelengths of interest. For example, quartz, sapphire, glass, or plastic, are suitable for the visible range. Back-side illumination of the sensor matrix is thereby allowed, with light traveling through the structures fabricated on the back of the substrate, opposite to the side on which CMOS is made.

Owner:QUANTUM SEMICON

Semiconductor memory

InactiveUS20050276094A1Improve performanceIncrease in surplus leak currentTransistorSolid-state devicesEngineeringSemiconductor

A SRAM memory is composed of FD-SOI transistors, and performance of the memory cell is improved by controlling an electric potential of a layer under a buried oxide film of a SOI transistor constituting a driver transistor. Performance of the SRAM circuit in the low power voltage state is improved. In the SRAM memory cell composed of the FD-SOI transistor, an electric potential of a well under a BOX layer is controlled to control a threshold voltage Vth, thereby increasing a current. Thus, the operations of the memory cell can be stabilized.

Owner:RENESAS ELECTRONICS CORP

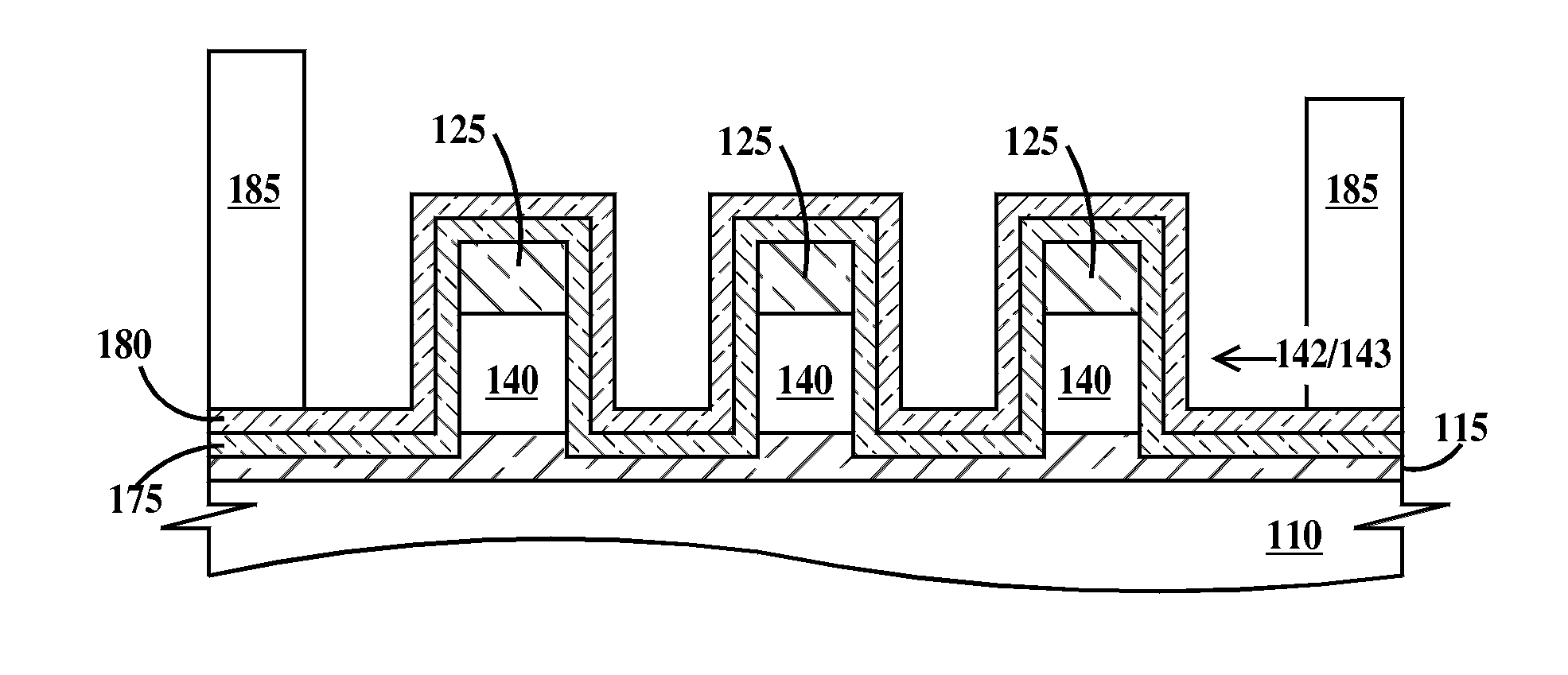

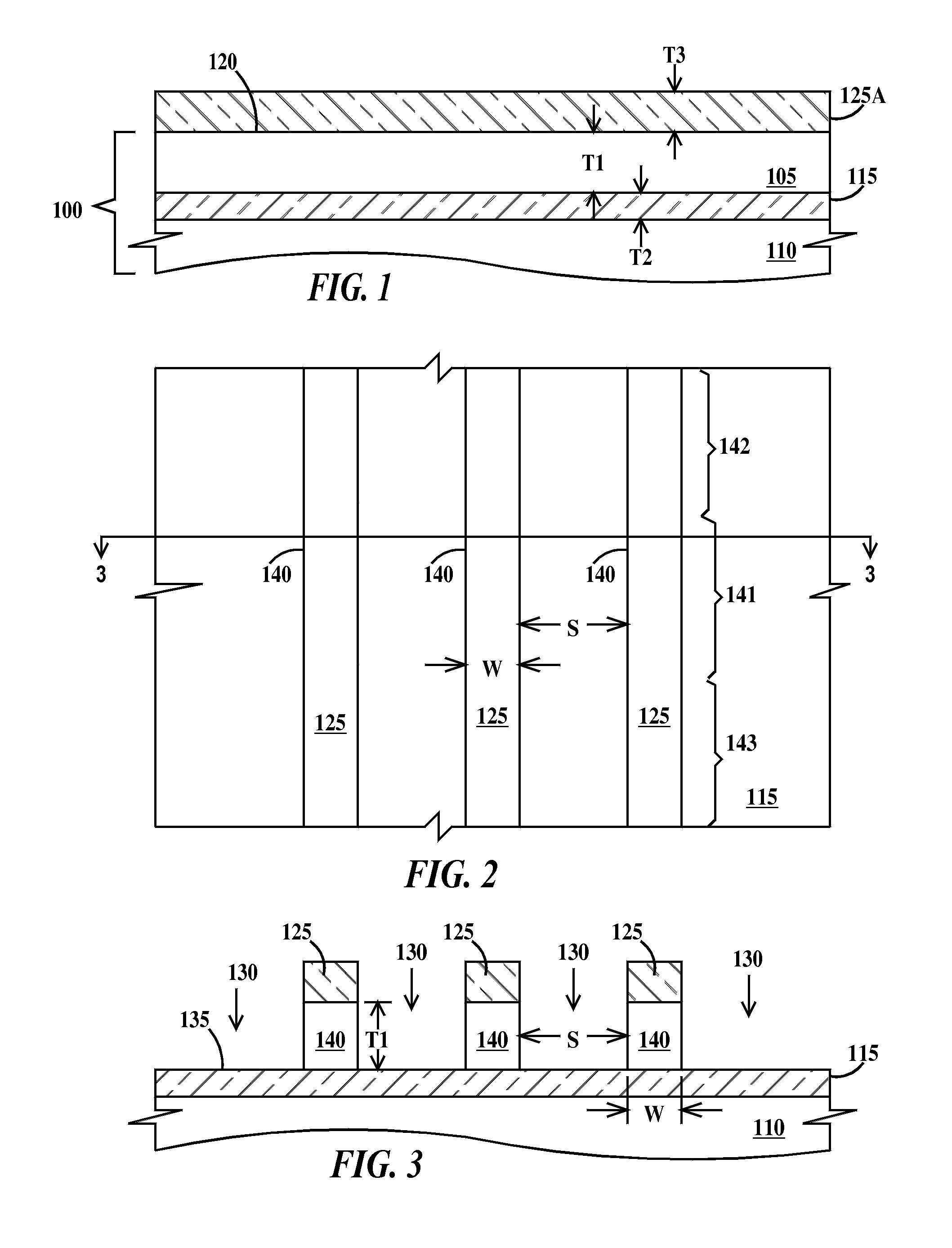

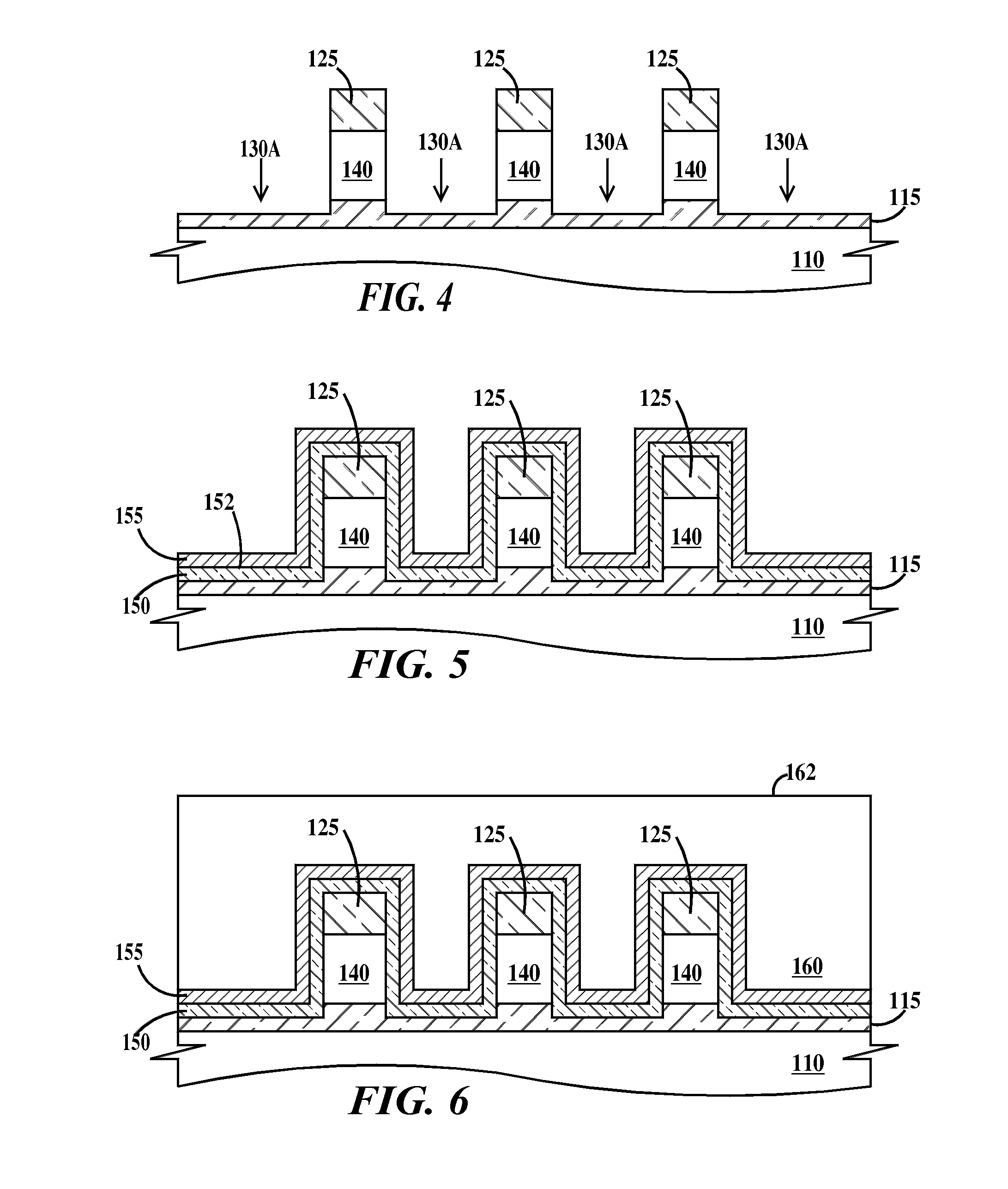

Method and structure to create multiple device widths in finfet technology in both bulk and soi

ActiveUS20050161739A1Remove/reduce unwanted spacersSmall activity areaTransistorSolid-state devicesEngineeringField-effect transistor

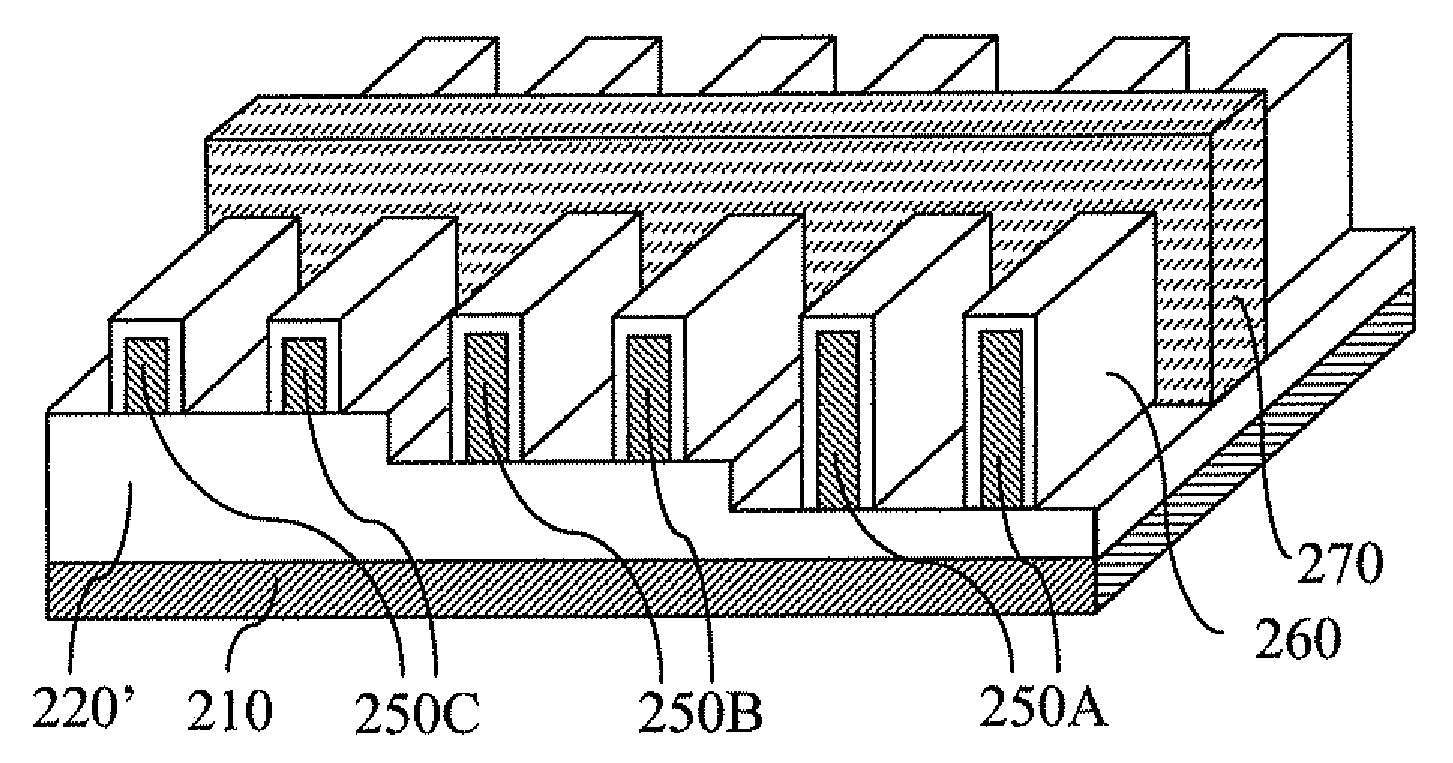

Disclosed is a structure and method for producing a fin-type field effect transistor (FinFET) that has a buried oxide layer over a substrate, at least one first fin structure and at least one second fin structure positioned on the buried oxide layer. First spacers are adjacent the first fin structure and second spacers are adjacent the second fin structure. The first spacers cover a larger portion of the first fin structure when compared to the portion of the second fin structure covered by the second spacers. Those fins that have larger spacers will receive a smaller area of semiconductor doping and those fins that have smaller spacers will receive a larger area of semiconductor doping. Therefore, there is a difference in doping between the first fins and the second fins that is caused by the differently sized spacers. The difference in doping between the first fins and the second fins changes an effective width of the second fins when compared to the first fins.

Owner:GLOBALFOUNDRIES US INC

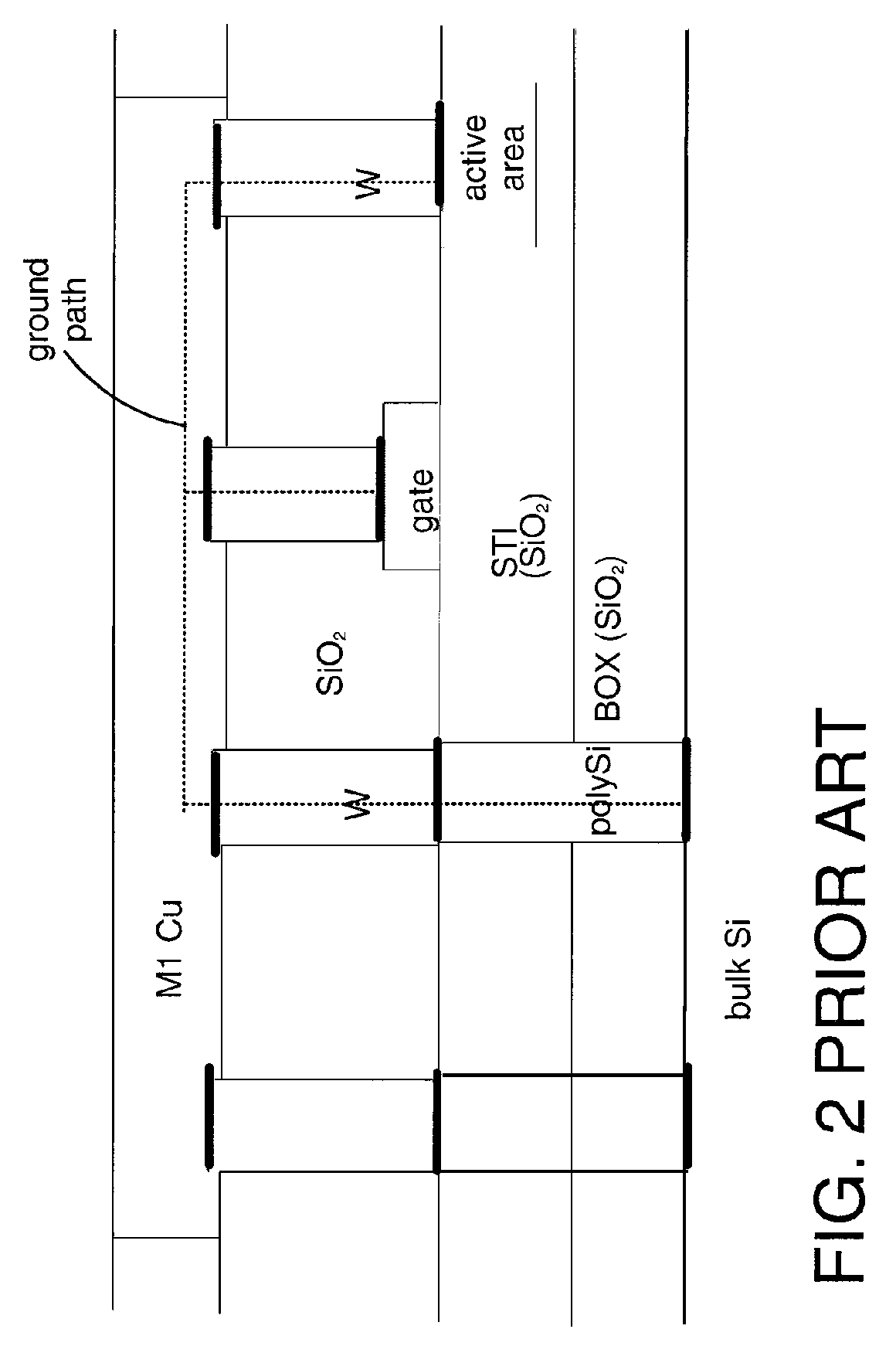

Grounding front-end-of-line structures on a SOI substrate

ActiveUS7518190B2Semiconductor/solid-state device detailsSolid-state devicesGround contactGate stack

Owner:TAIWAN SEMICON MFG CO LTD

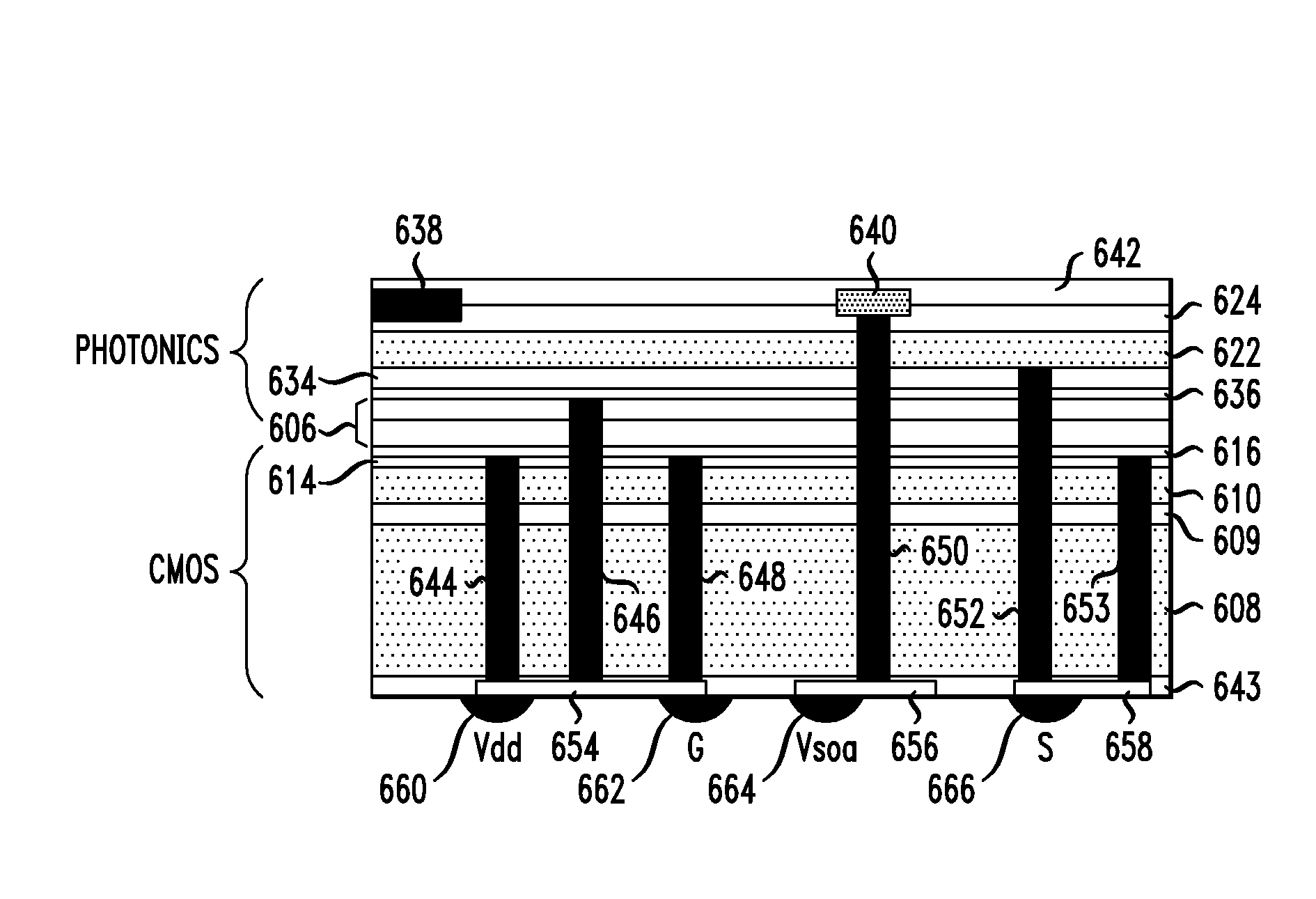

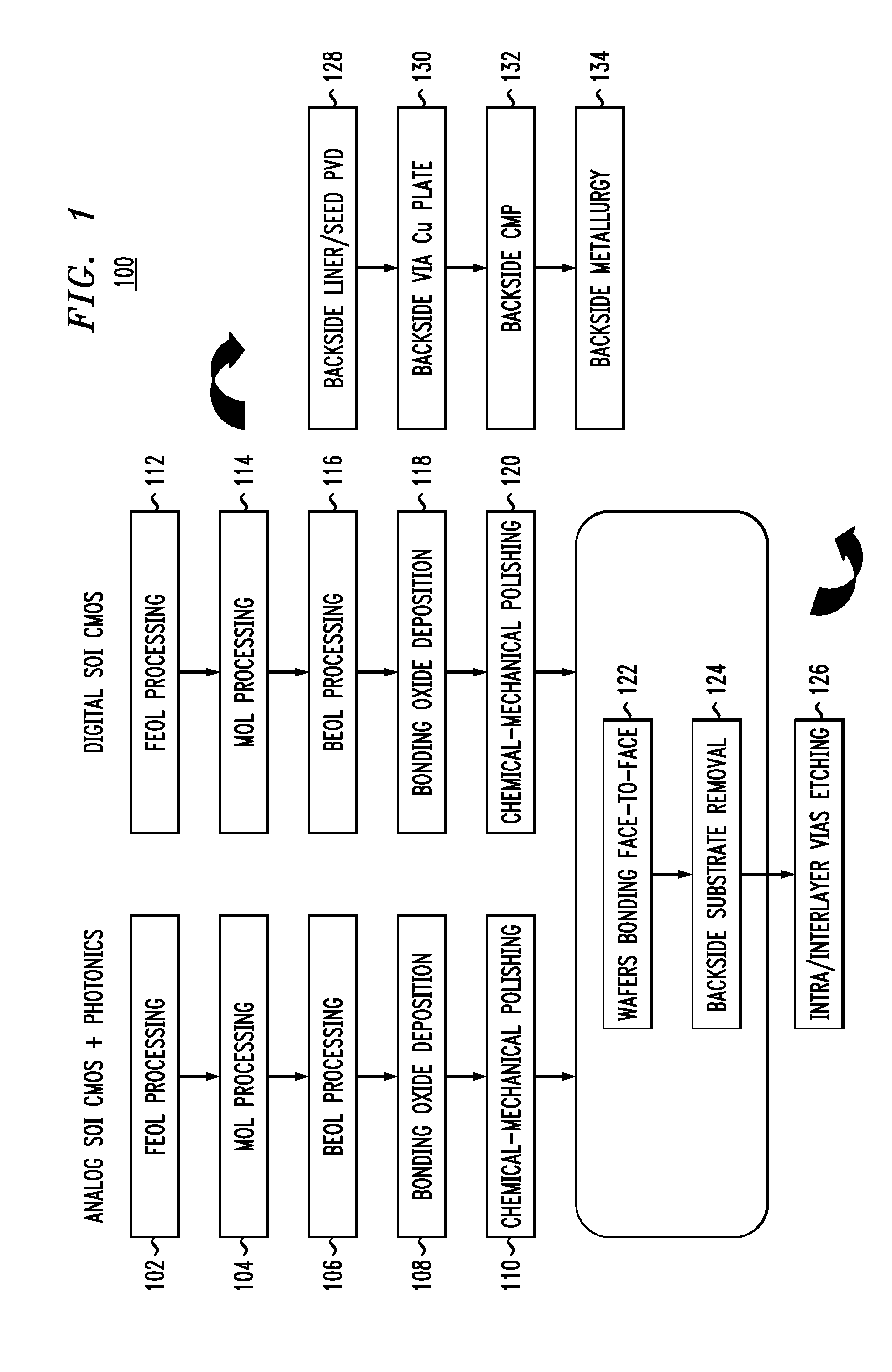

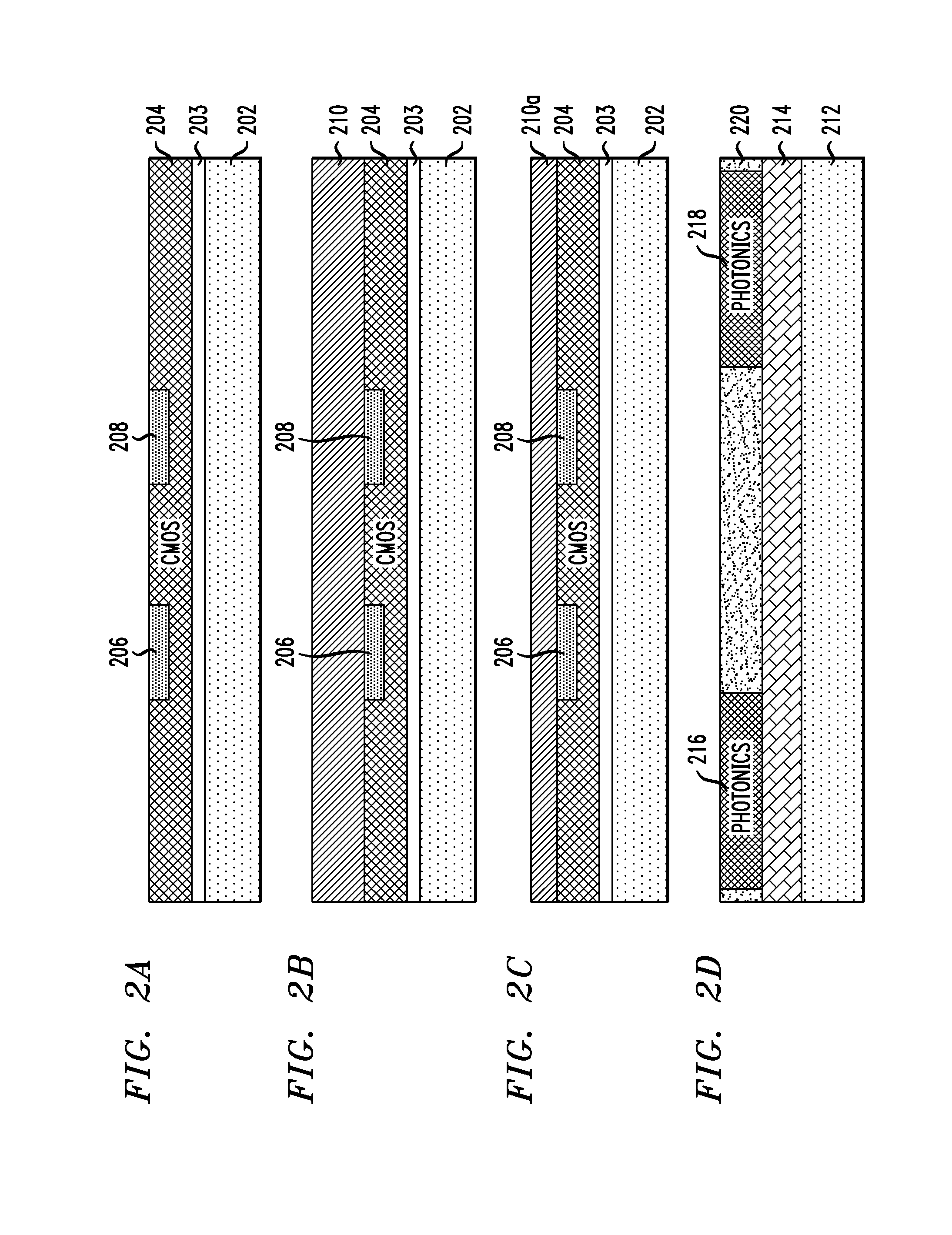

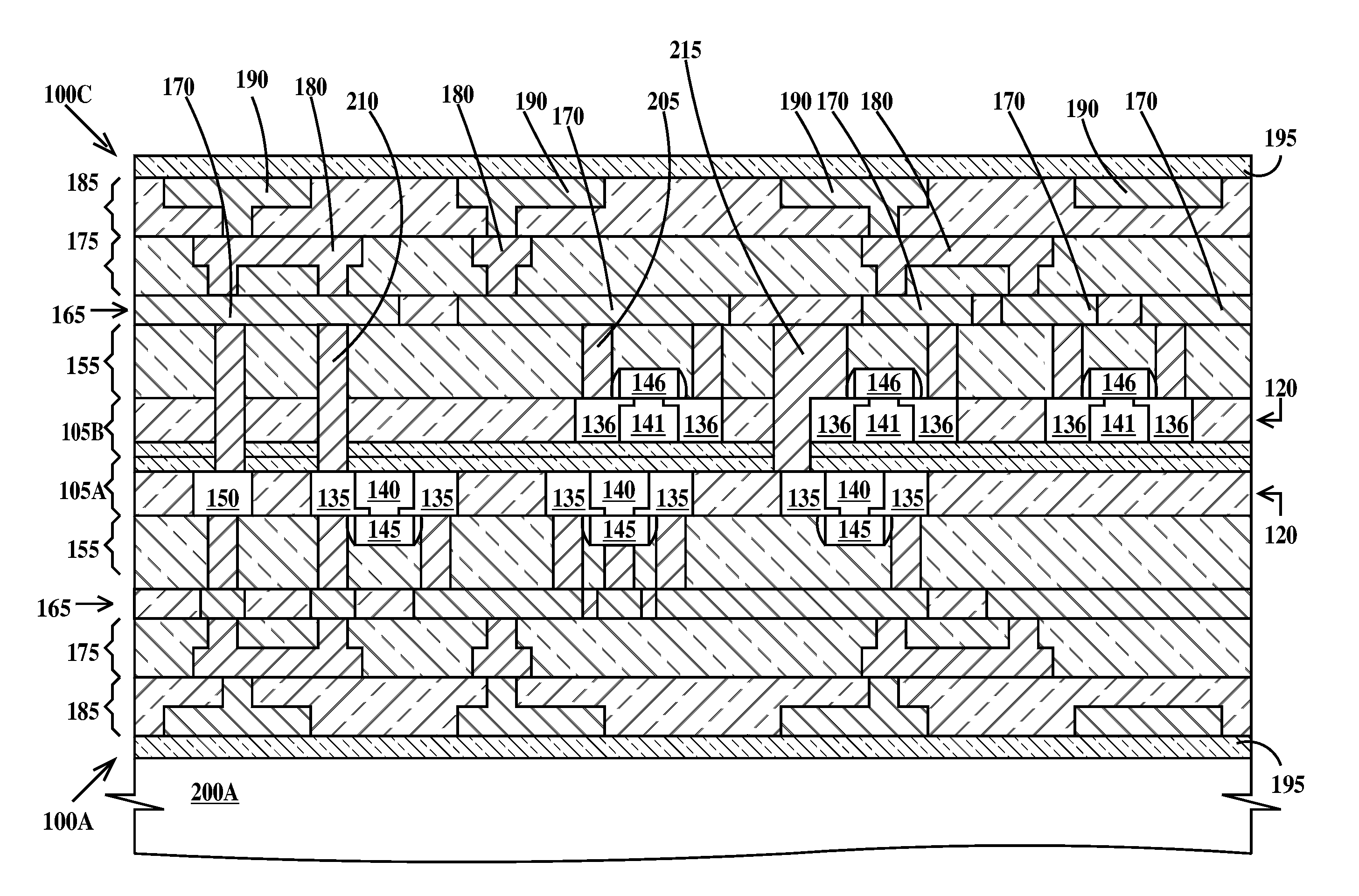

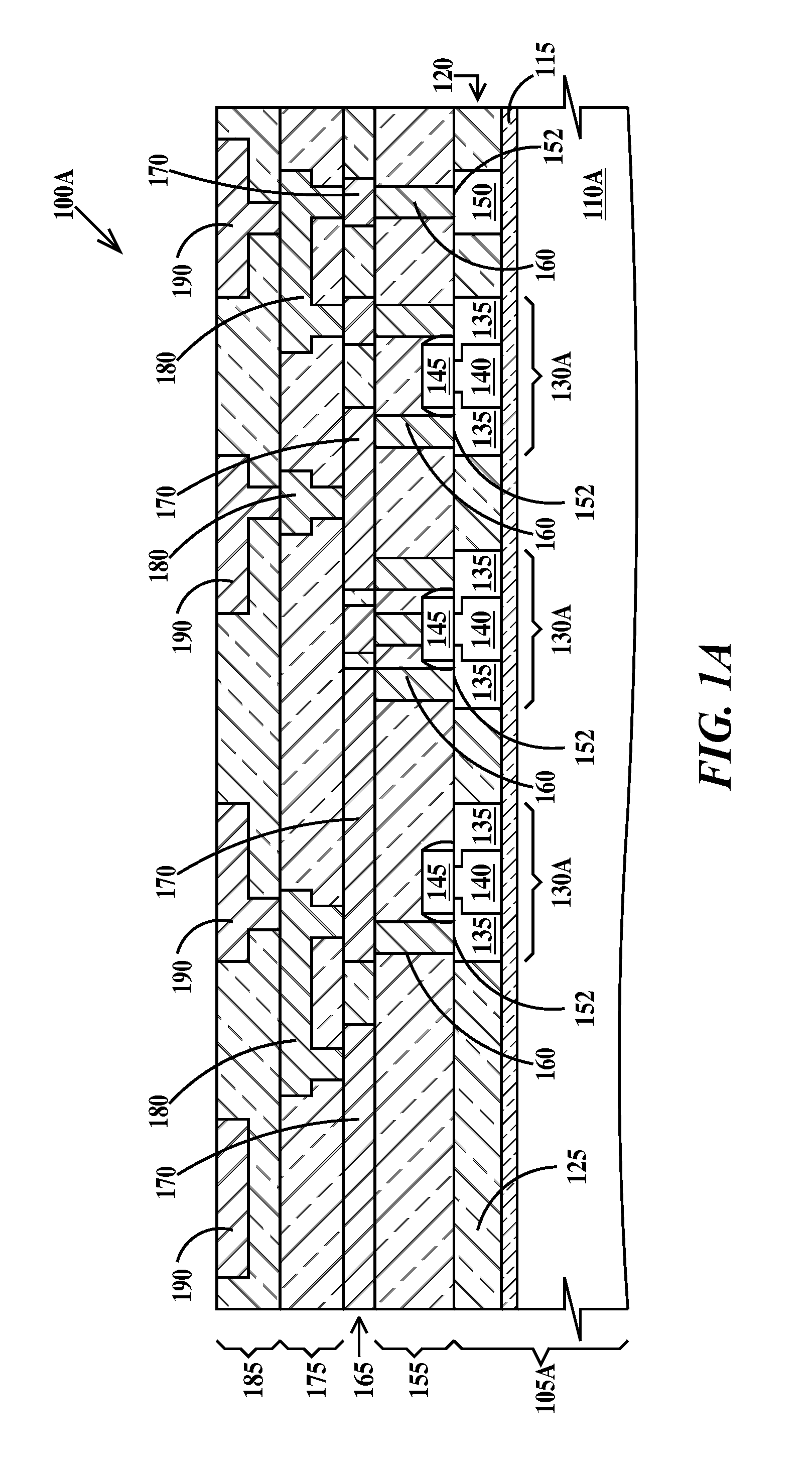

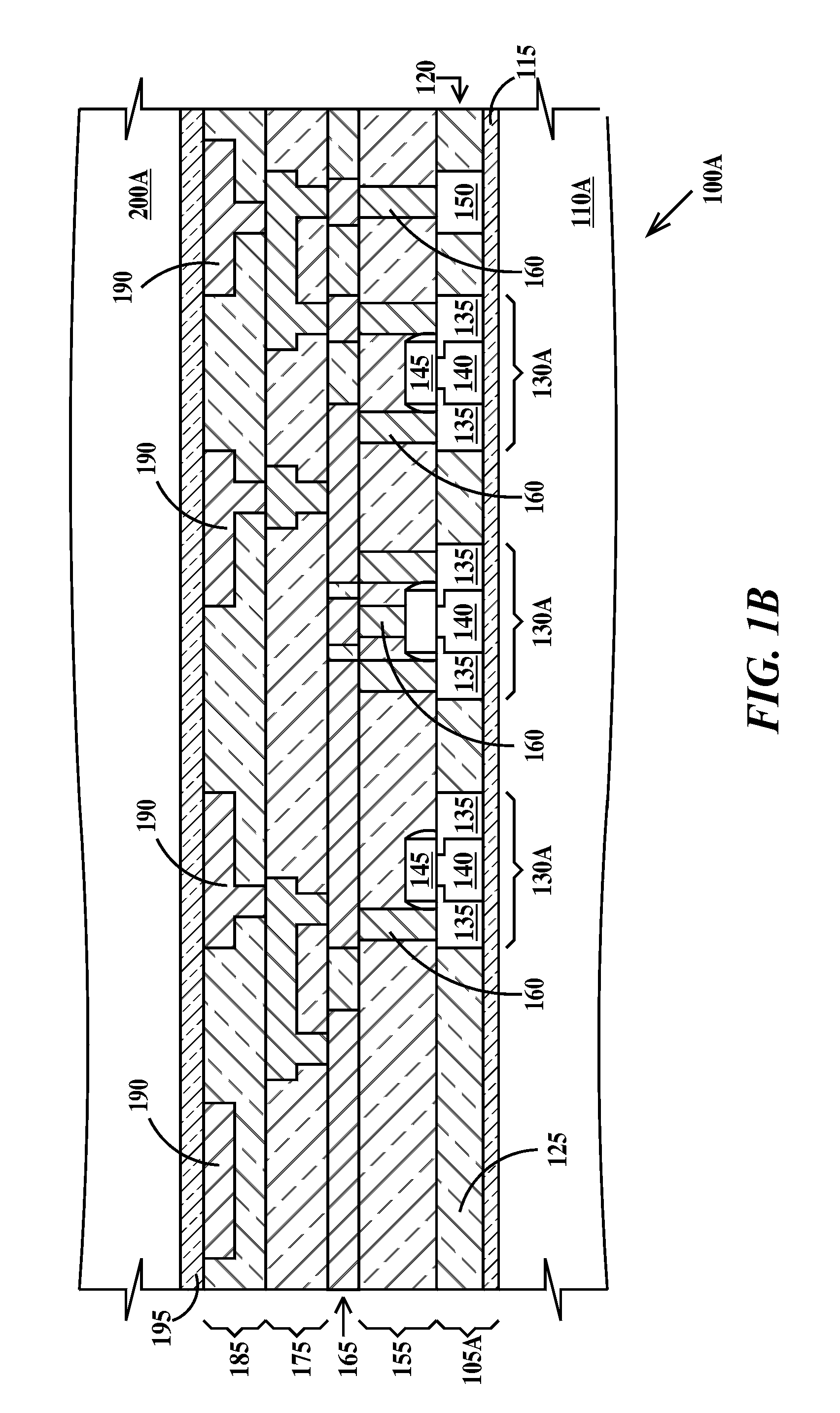

Three-Dimensional Integrated Circuits and Techniques for Fabrication Thereof

ActiveUS20090294814A1Solid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyPhotonics

Integrated circuits having complementary metal-oxide semiconductor (CMOS) and photonics circuitry and techniques for three-dimensional integration thereof are provided. In one aspect, a three-dimensional integrated circuit comprises a bottom device layer and a top device layer. The bottom device layer comprises a substrate; a digital CMOS circuitry layer adjacent to the substrate; and a first bonding oxide layer adjacent to a side of the digital CMOS circuitry layer opposite the substrate. The top device layer comprises an analog CMOS and photonics circuitry layer formed in a silicon-on-insulator (SOI) layer having a buried oxide (BOX) with a thickness of greater than or equal to about 0.5 micrometers; and a second bonding oxide layer adjacent to the analog CMOS and photonics circuitry layer. The bottom device layer is bonded to the top device layer by an oxide-to-oxide bond between the first bonding oxide layer and the second bonding oxide layer.

Owner:GLOBALFOUNDRIES US INC

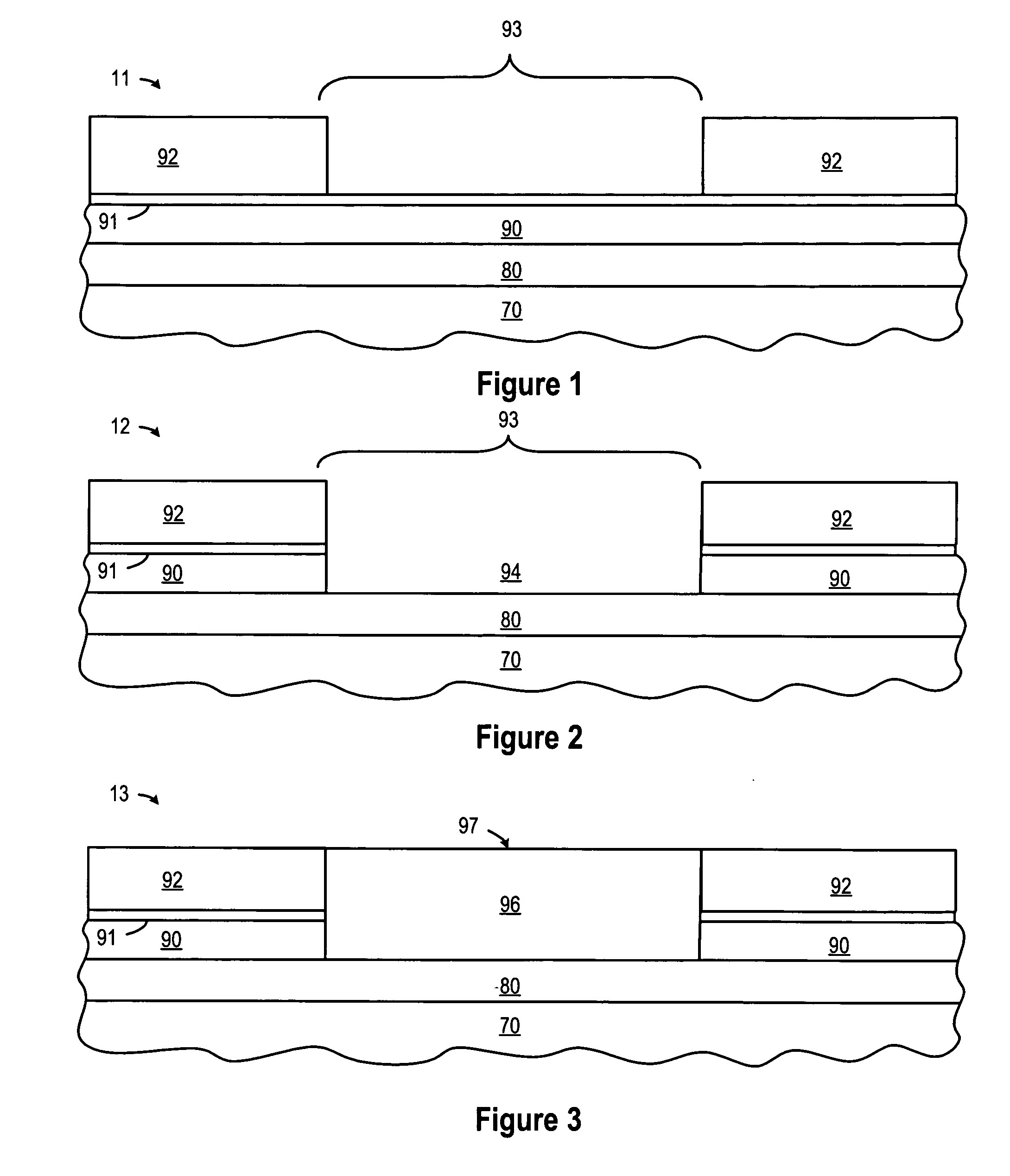

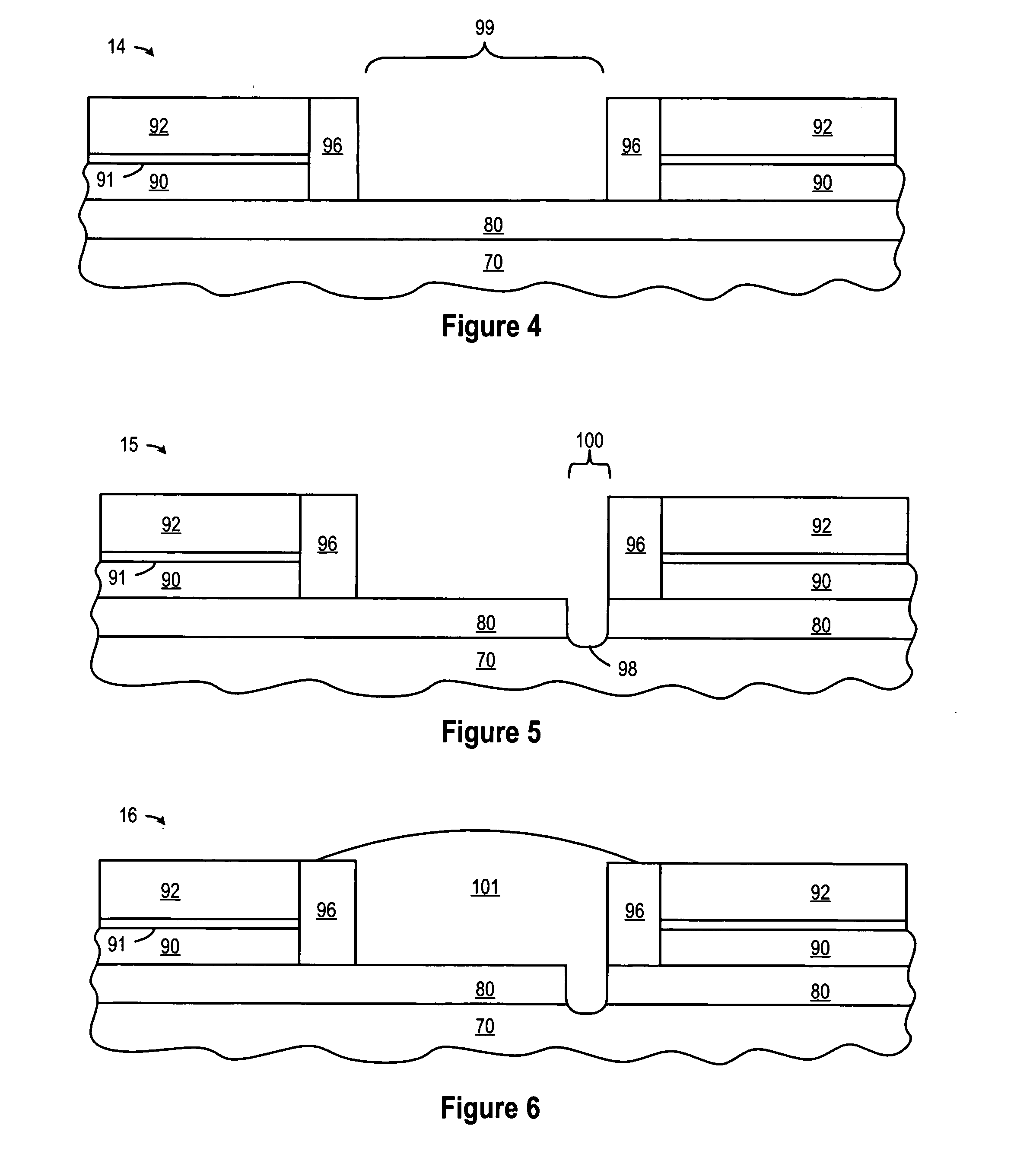

Dual surface SOI by lateral epitaxial overgrowth

InactiveUS20070281446A1Solid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor materials

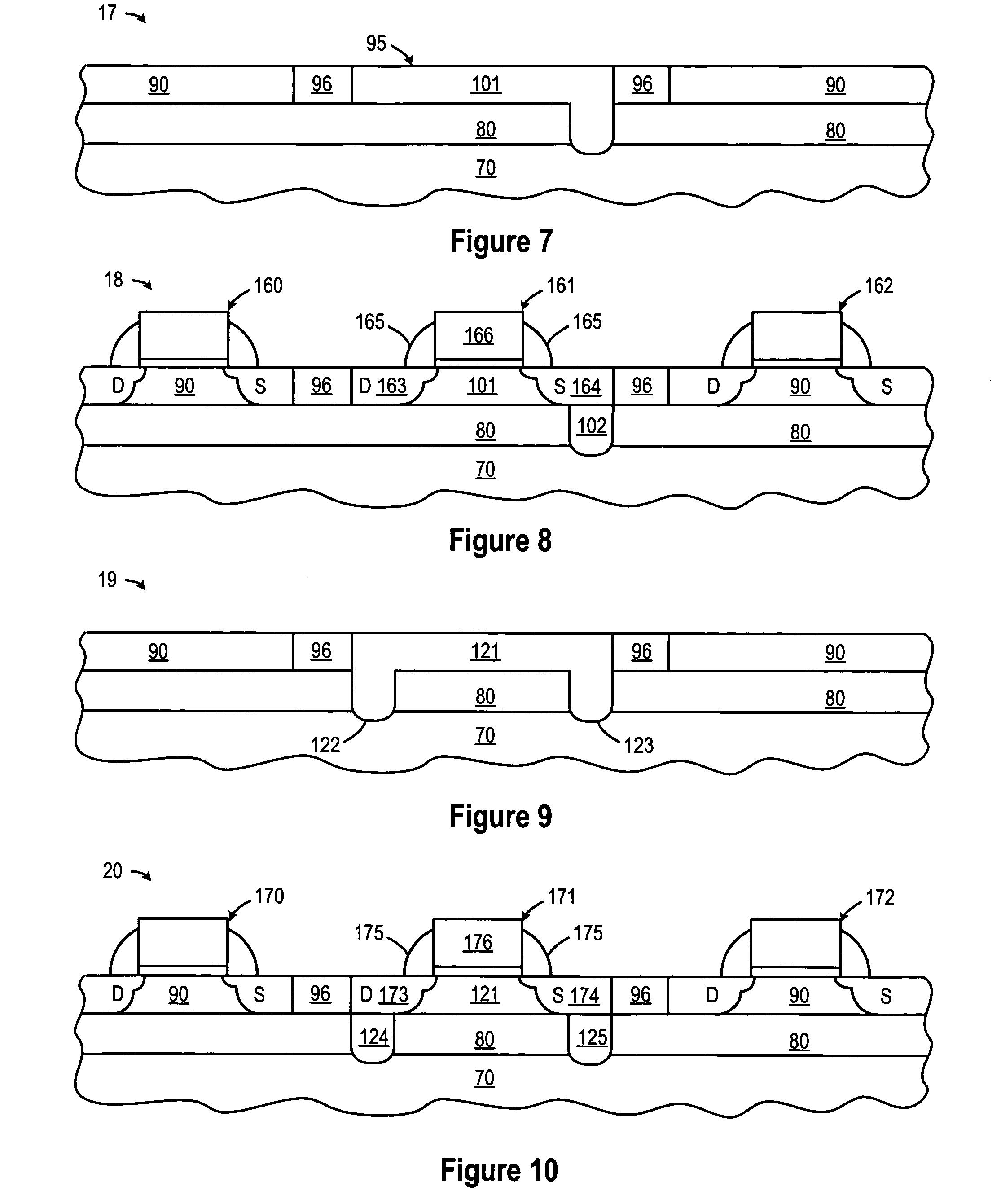

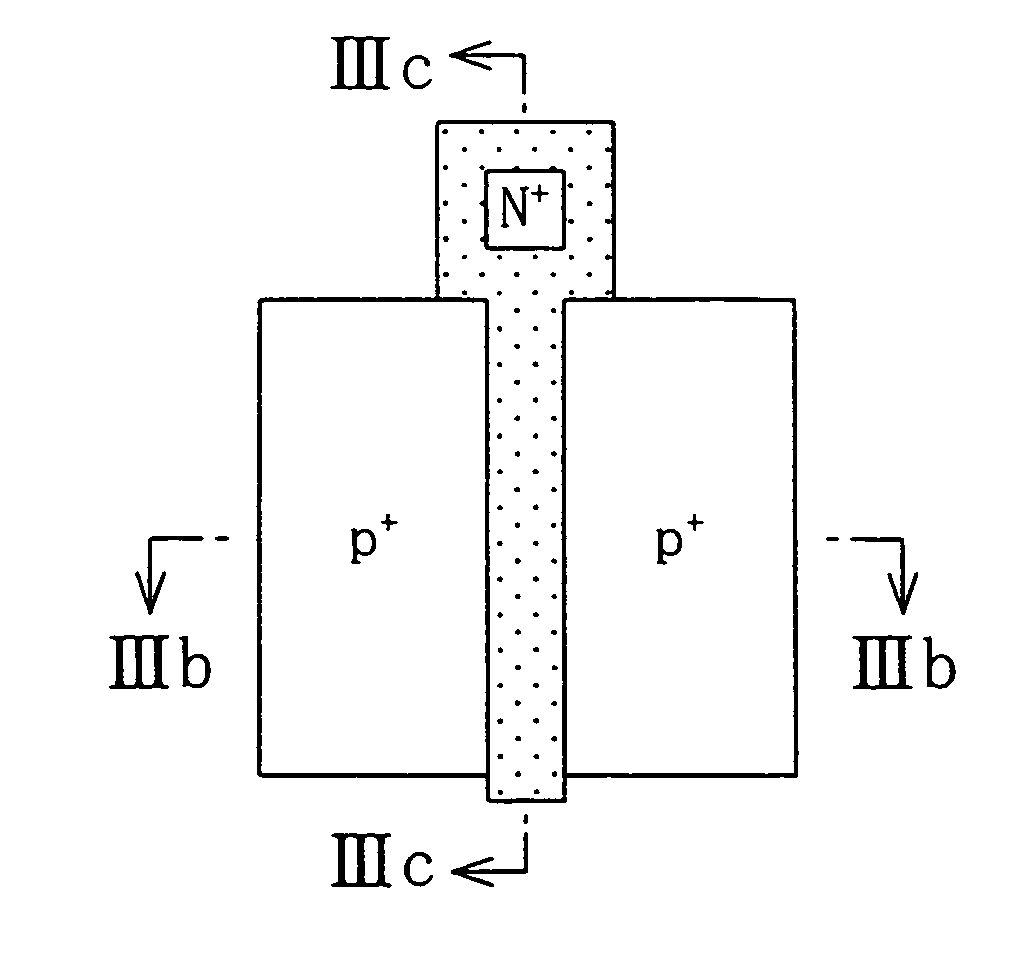

A semiconductor process and apparatus provide a planarized hybrid substrate (18) by exposing a buried oxide layer (80) in a first area (99), selectively etching the buried oxide layer (80) to expose a first semiconductor layer (70) in a second smaller seed area (98), and then epitaxially growing a first epitaxial semiconductor material from the seed area (98) of the first semiconductor layer (70) that fills the second trench opening (100) and grows laterally over the exposed insulator layer (80) to fill at least part of the first trench opening (99), thereby forming a first epitaxial semiconductor layer (101) that is electrically isolated from the second semiconductor layer (90). By forming a first SOI transistor device (160) over a first SOI layer (90) using deposited (100) silicon and forming first SOI transistor (161) over an epitaxially grown (110) silicon layer (101), a high performance CMOS device is obtained.

Owner:NORTH STAR INNOVATIONS

Semiconductor device having SiGe channel region

InactiveUS7205586B2Lower threshold voltageIncrease speedTransistorSolid-state devicesHigh concentrationElectrical conductor

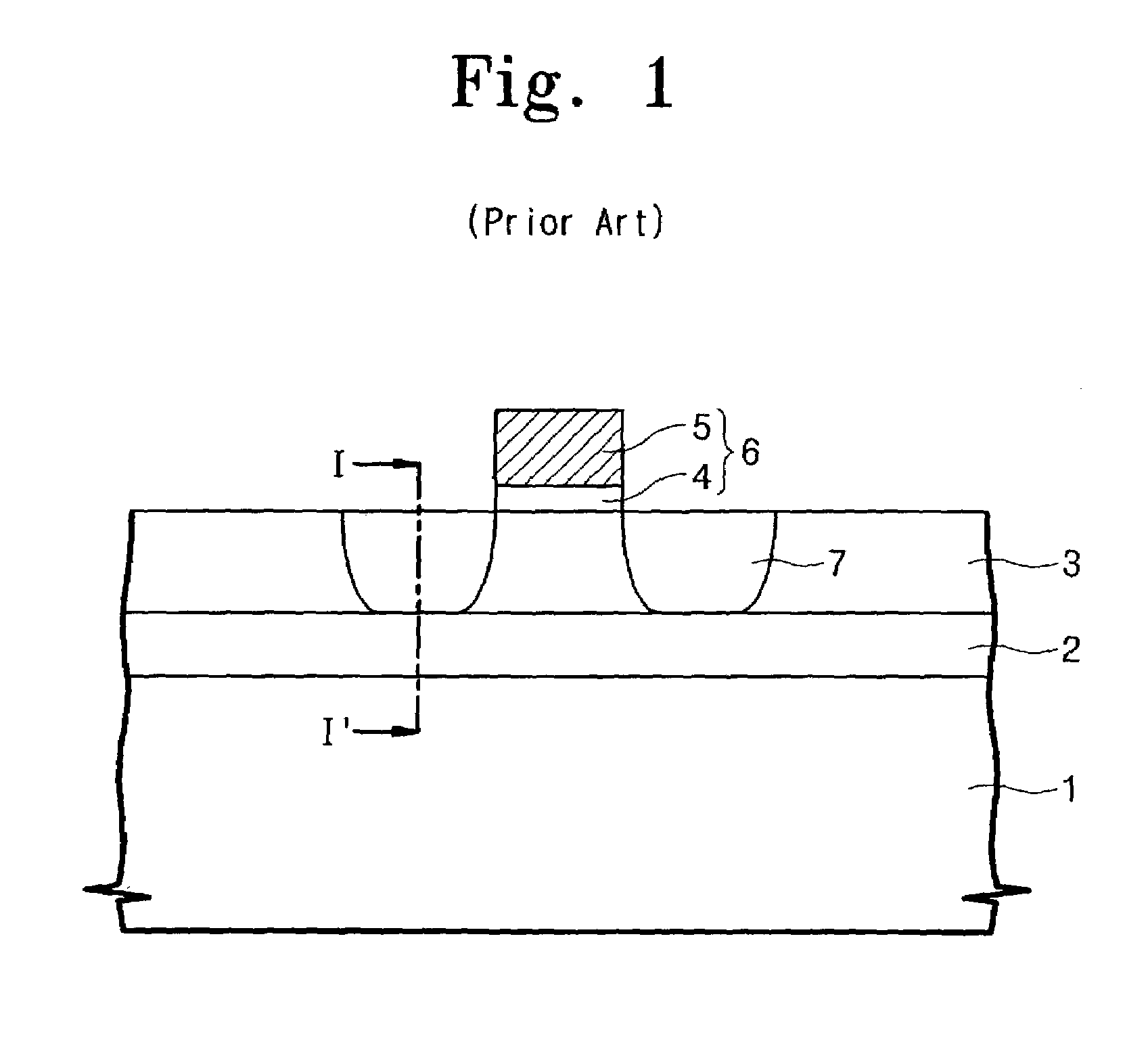

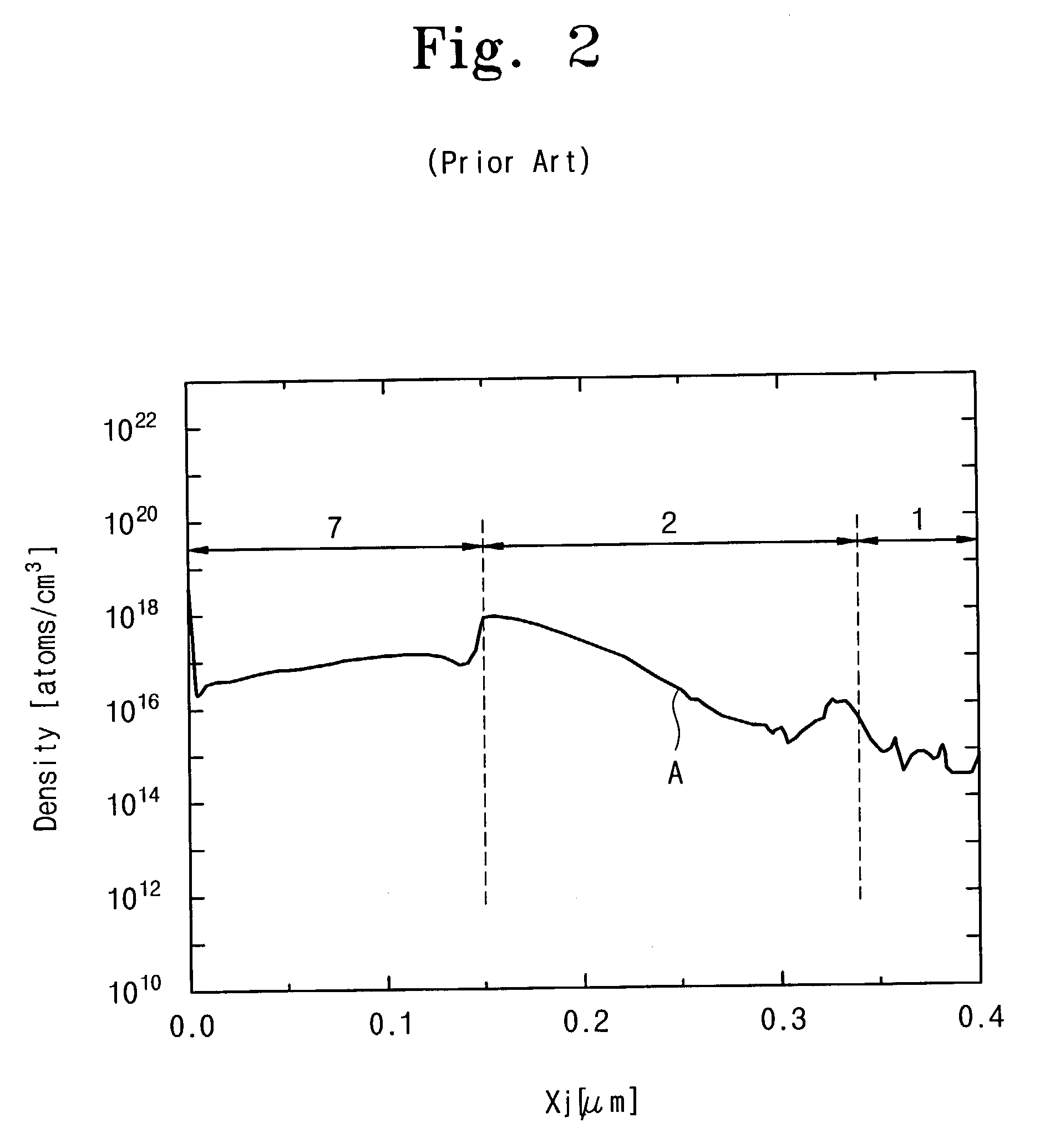

A HDTMOS includes a Si substrate, a buried oxide film and a semiconductor layer. The semiconductor layer includes an upper Si film, an epitaxially grown Si buffer layer, an epitaxially grown SiGe film, and an epitaxially grown Si film. Furthermore, the HDTMOS includes an n-type high concentration Si body region, an n− Si region, a SiGe channel region containing n-type low concentration impurities, an n-type low concentration Si cap layer, and a contact which is a conductor member for electrically connecting the gate electrode and the Si body region. The present invention extends the operation range while keeping the threshold voltage small by using, for the channel layer, a material having a smaller potential at the band edge where carriers travel than that of a material constituting the body region.

Owner:PANNOVA SEMIC

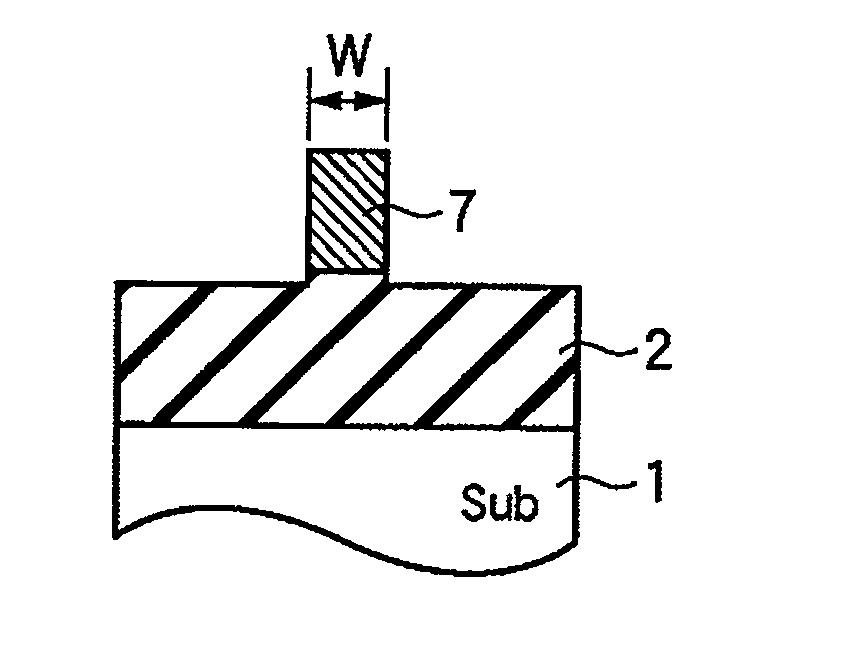

finFETS and methods of making same

A method of fabricating and a structure of a merged multi-fin finFET. The method includes forming single-crystal silicon fins from the silicon layer of an SOI substrate having a very thin buried oxide layer and merging the end regions of the fins by growing vertical epitaxial silicon from the substrate and horizontal epitaxial silicon from ends of the fins such that vertical epitaxial silicon growth predominates.

Owner:AURIGA INNOVATIONS INC

Method of fabricating a double gate MOSFET device

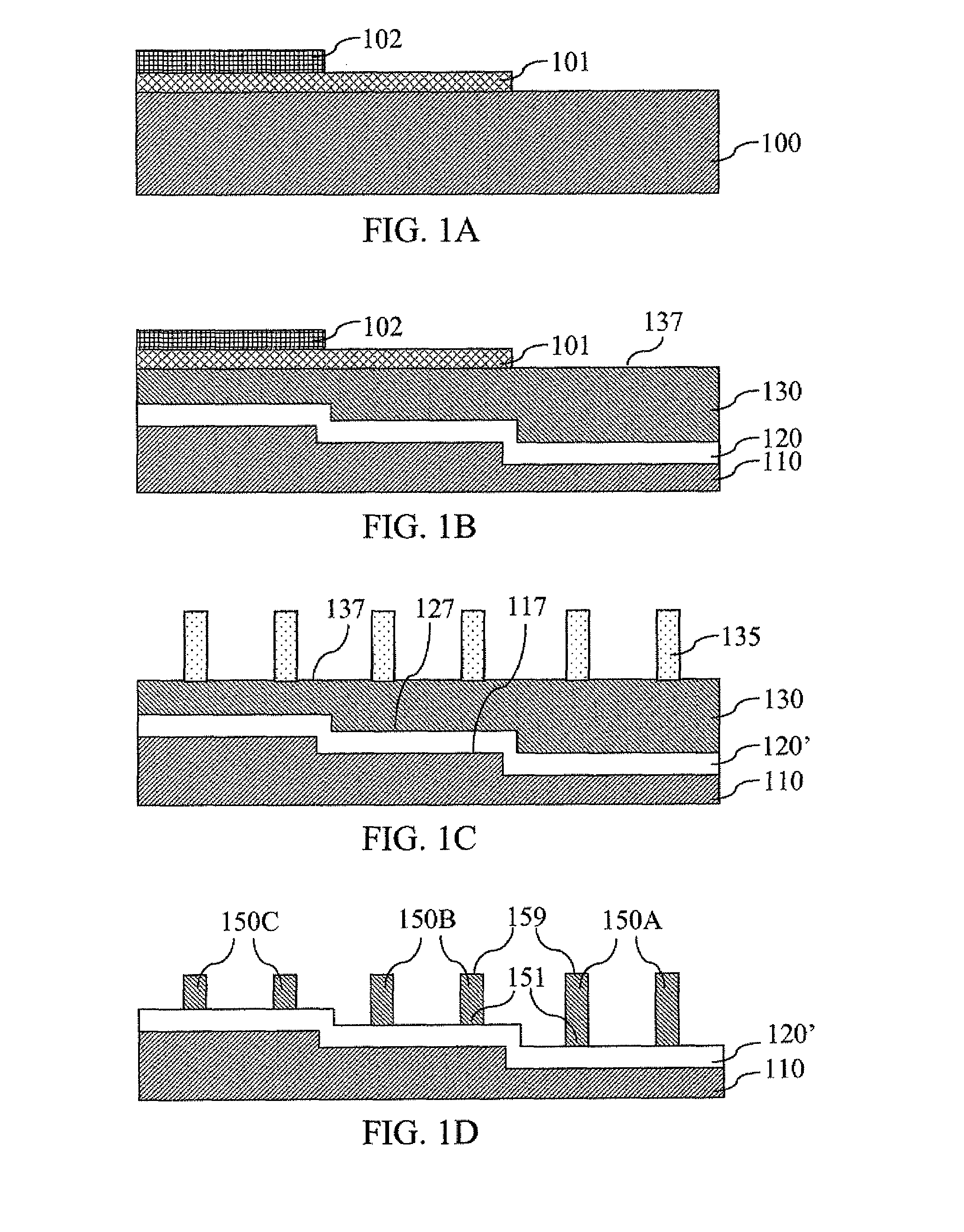

ActiveUS6855588B1Excellent short channel behaviorBetter gate controlTransistorSemiconductor/solid-state device manufacturingDriving currentDouble gate

A method of fabricating a double gate MOSFET device is provided. The present invention overetches a silicon layer overlying a buried oxide layer using a hard mask of cap oxide on the silicon layer as an etching mask. As a result, source, drain and channel regions are formed extending from the buried oxide layer, and a pair of recesses are formed under the channel regions in the buried oxide layer. The channel is a fin structure with a top surface and two opposing parallelly sidewalls. The bottom recess is formed under each opposing sidewall of the fin structure. A conductive gate layer is formed straddling the fin structures. The topography of the conductive gate layer significantly deviates from the conventional plainer profile due to the bottom recess structures under the channel regions, and a more uniformly distributed doped conductive gate layer can be obtained. Hence, the depletion effect of the conductive polysilicon gate while operating the device can be suppressed and the device drive-on currents can be further enhanced.

Owner:UNITED MICROELECTRONICS CORP

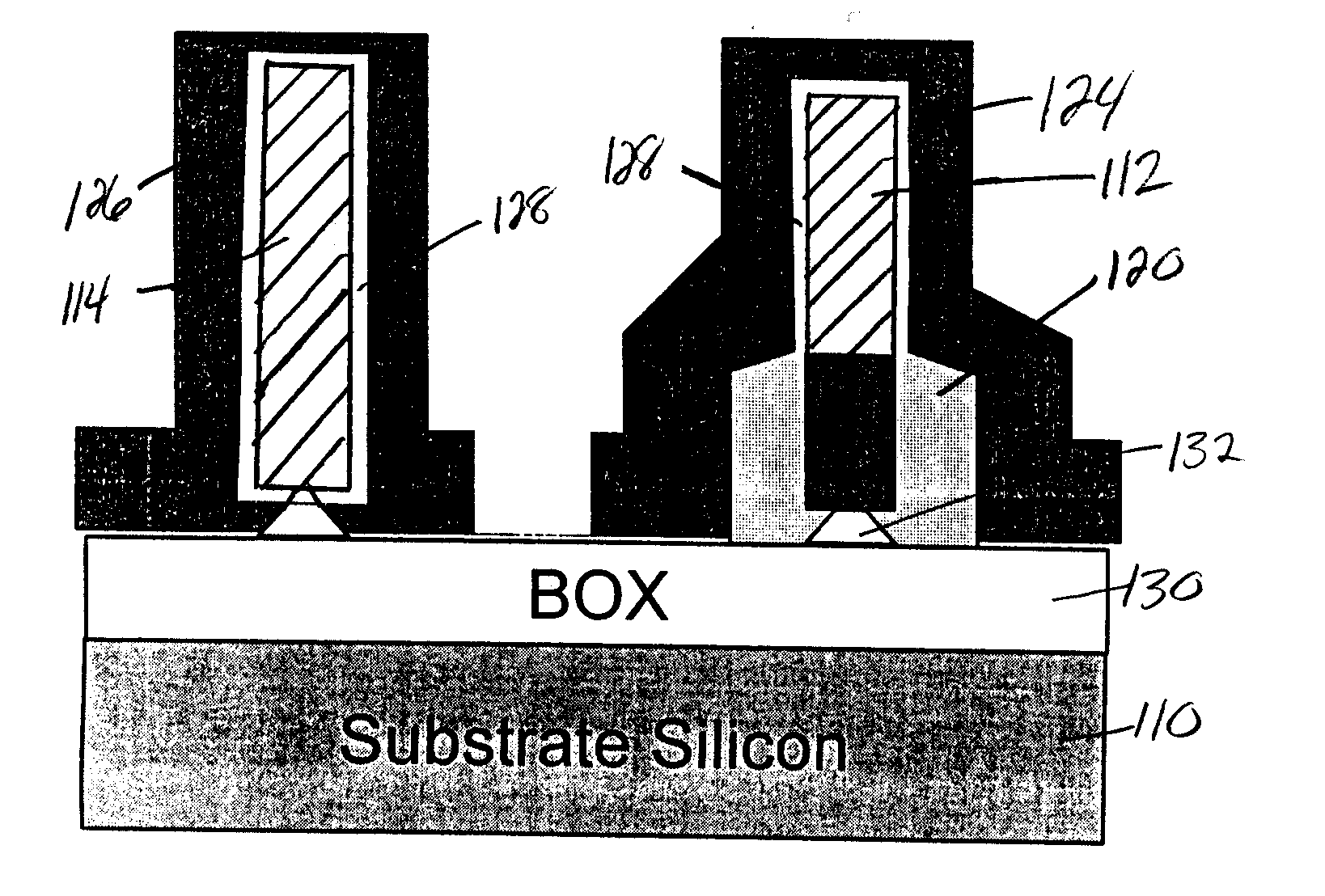

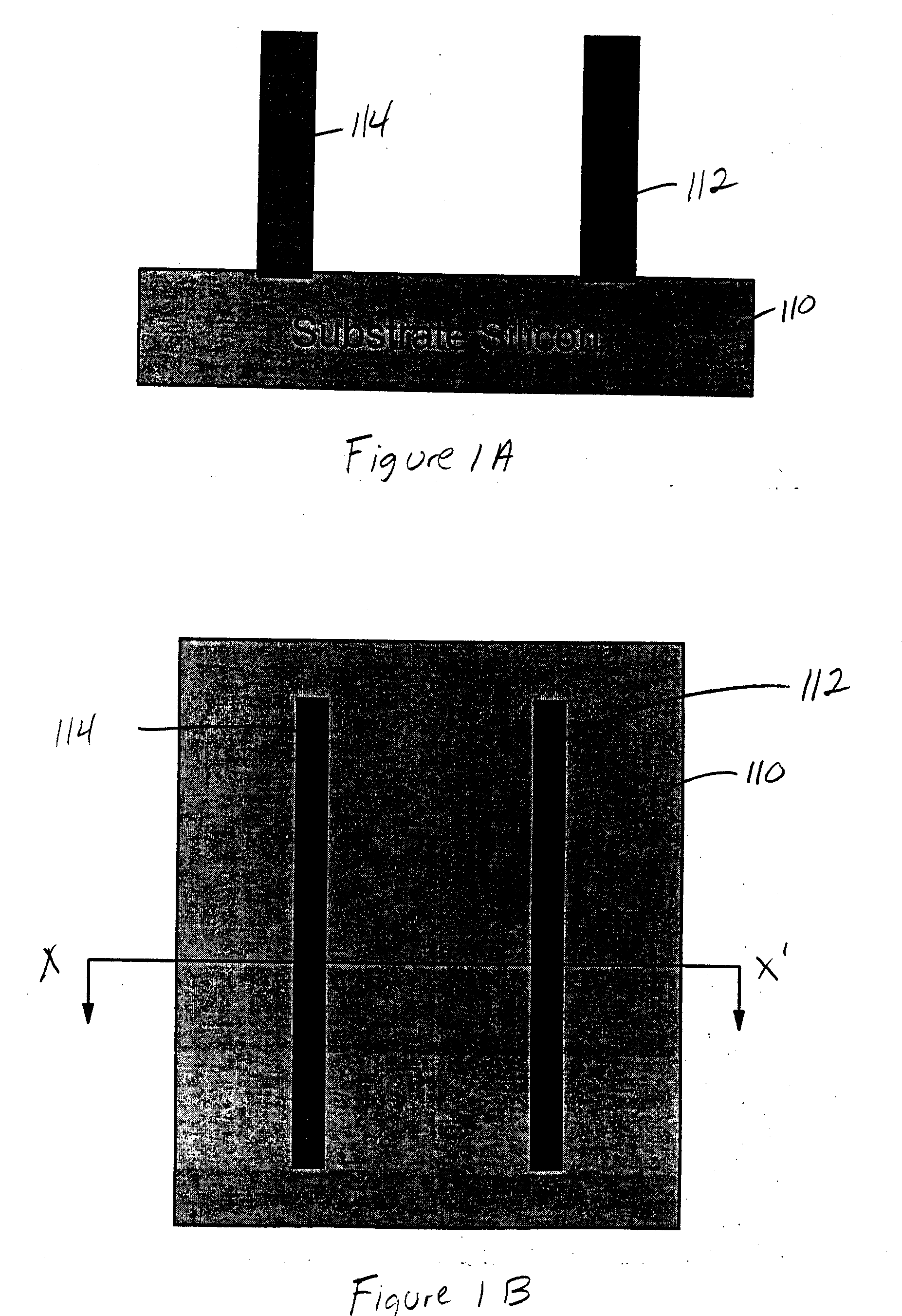

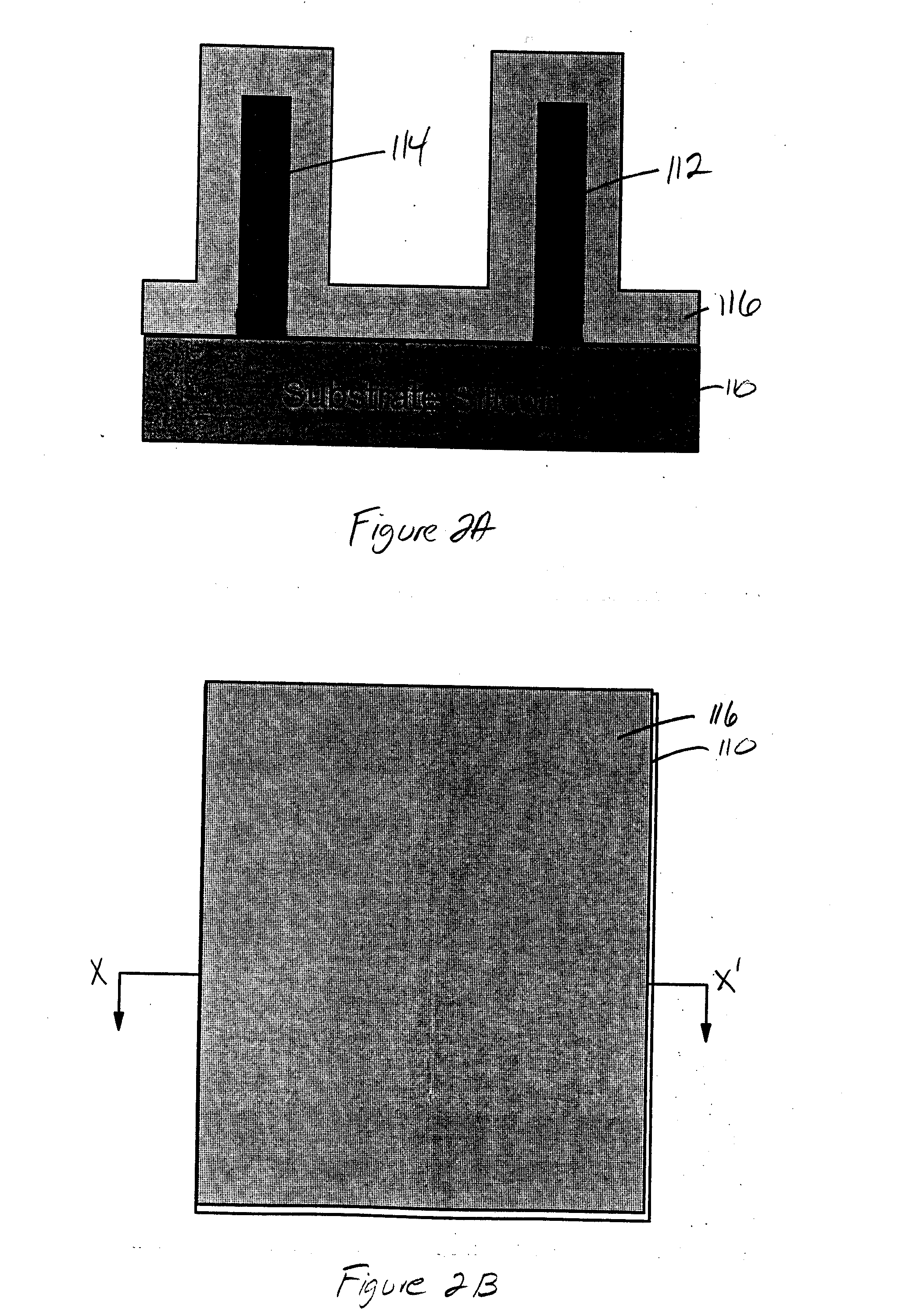

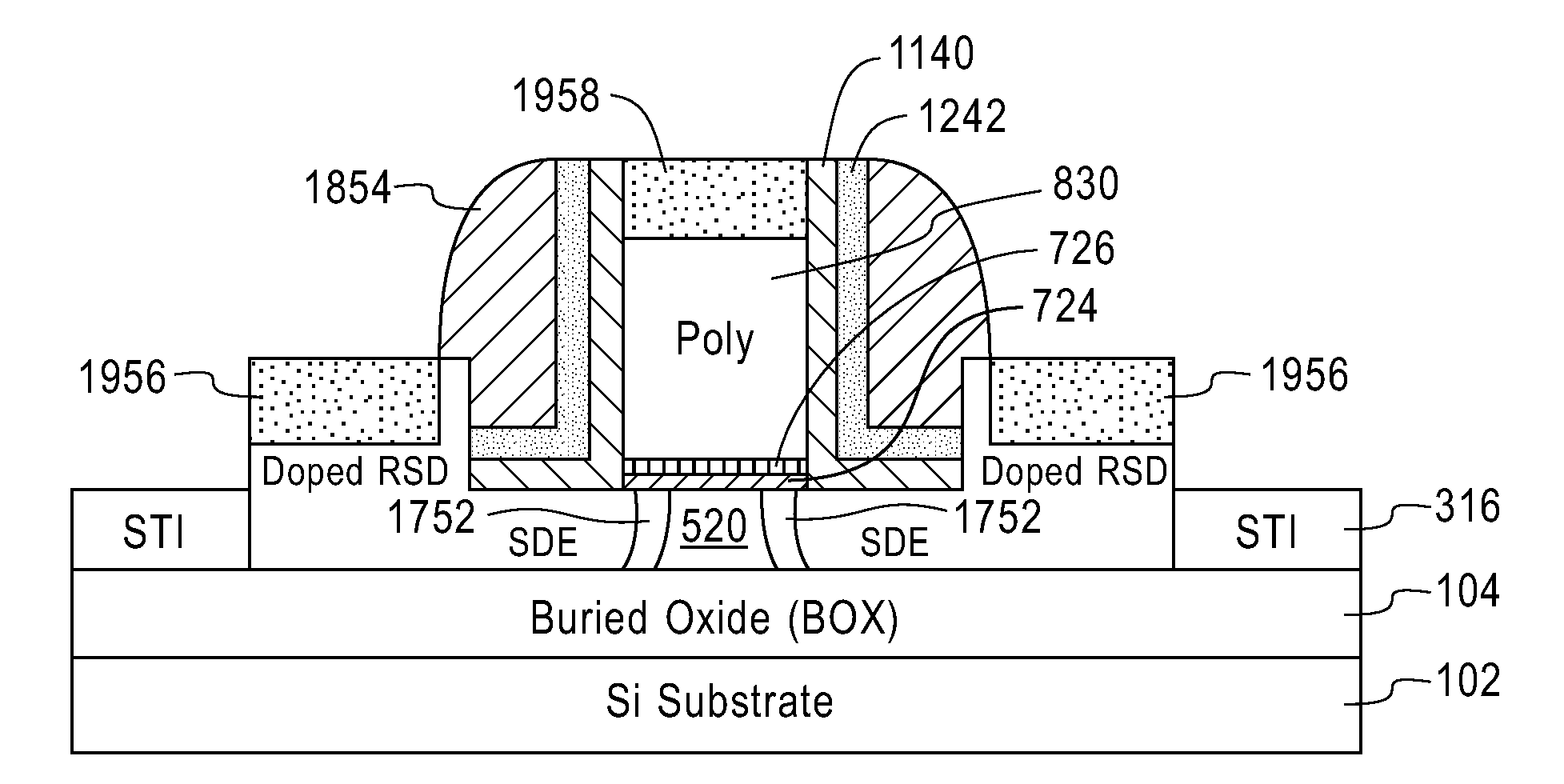

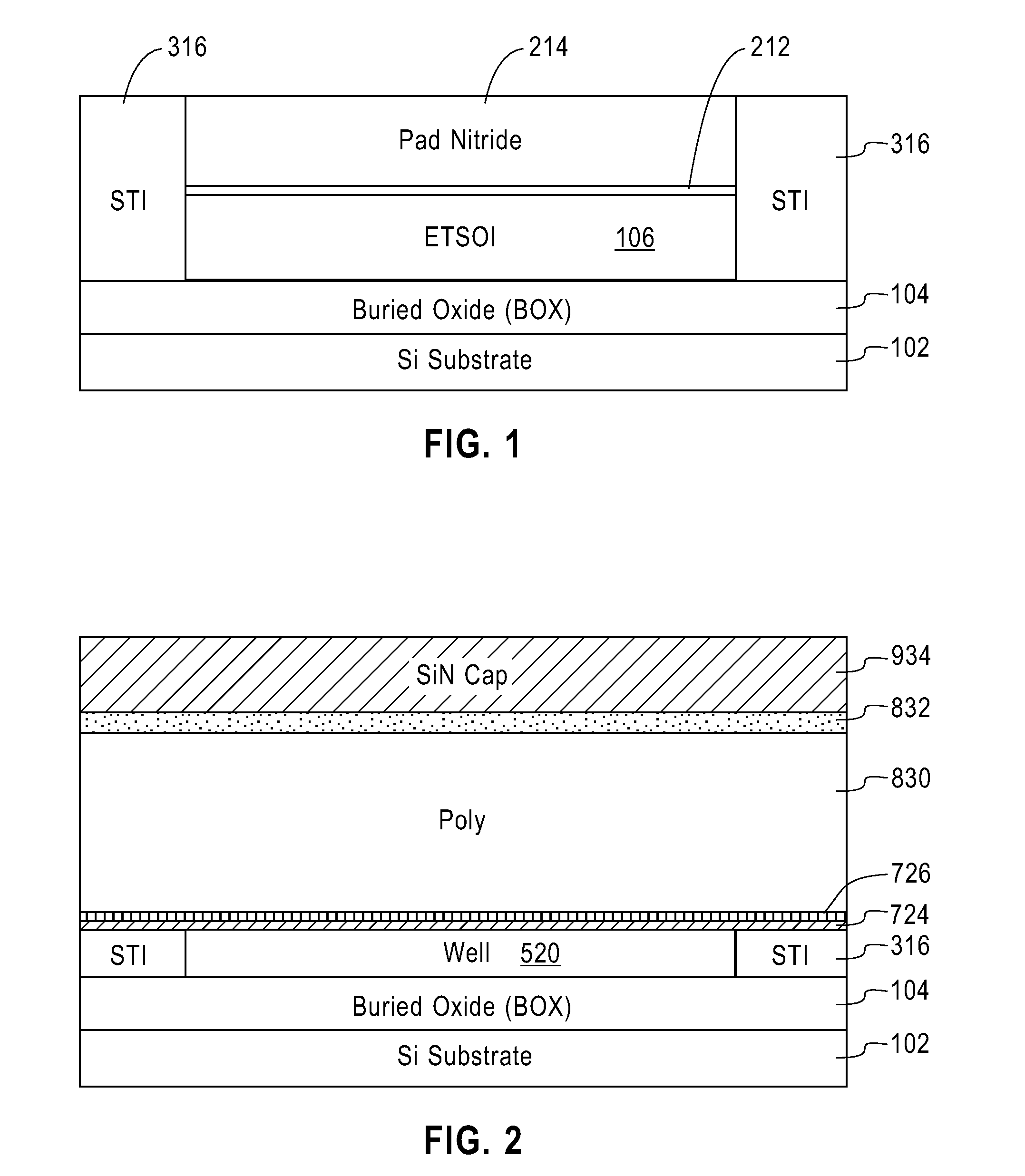

Extremely-thin silicon-on-insulator transistor with raised source/drain

An extremely-thin silicon-on-insulator transistor is provided that includes a buried oxide layer above a substrate, a silicon layer above the buried oxide layer, a gate stack on the silicon layer, a nitride liner on the silicon layer and adjacent to the gate stack, an oxide liner on and adjacent to the nitride liner, and raised source / drain regions. The gate stack includes a high-k oxide layer on the silicon layer and a metal gate on the high-k oxide layer. Each of the raised source / drain regions has a first part comprising a portion of the silicon layer, a second part adjacent to parts of the oxide liner and the nitride liner, and a third part above the second part. Also provided is a method for fabricating an extremely-thin silicon-on-insulator transistor.

Owner:GLOBALFOUNDRIES US INC +1

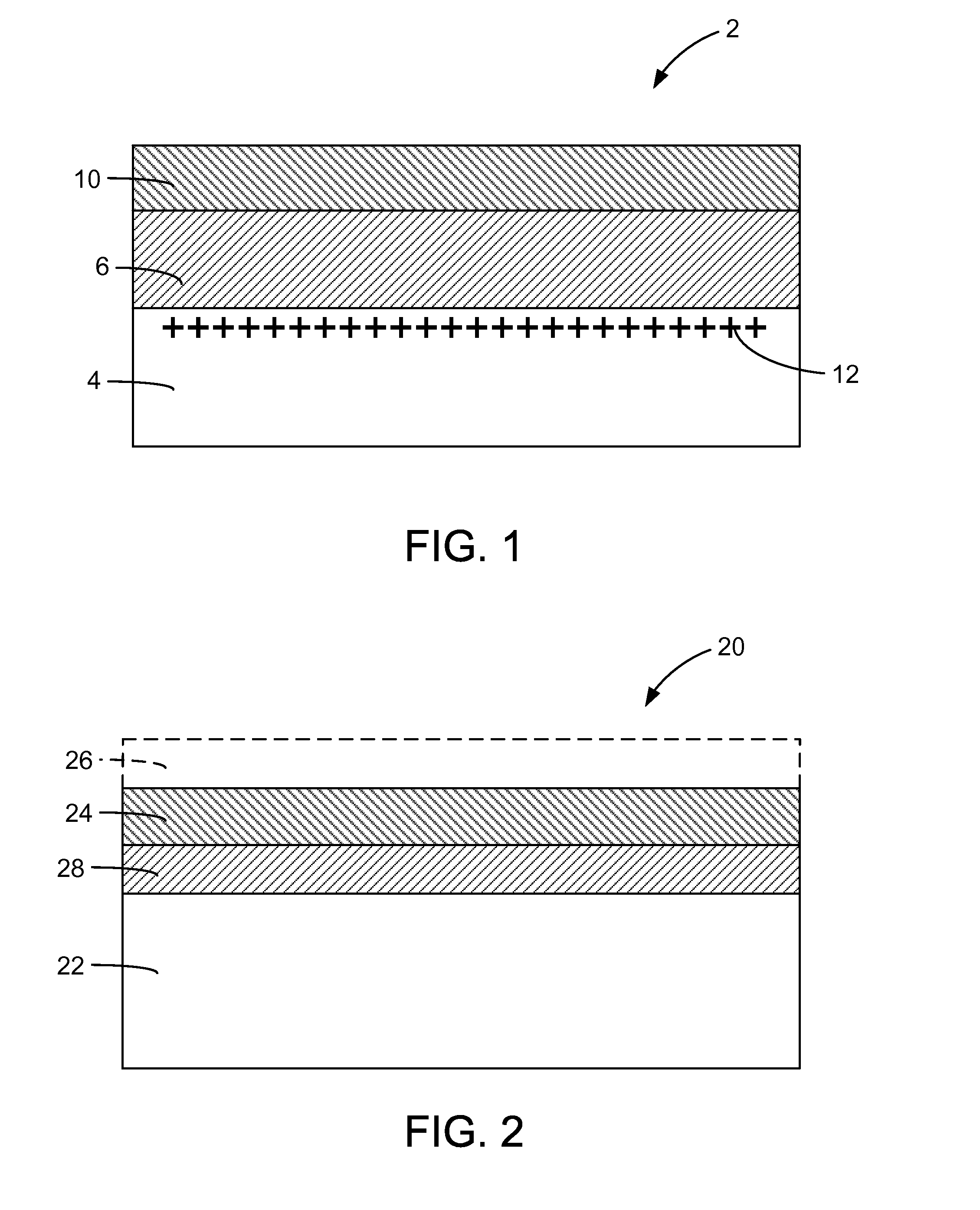

Double-sided integrated circuit chips

ActiveUS20070267723A1Raise the threshold voltageSemiconductor/solid-state device detailsSolid-state devicesBuried oxideIntegrated circuit

A semiconductor structure and method of fabricating the structure. The method includes removing the backside silicon from two silicon-on-insulator wafers having devices fabricated therein and bonding them back to back utilizing the buried oxide layers. Contacts are then formed in the upper wafer to devices in the lower wafer and wiring levels are formed on the upper wafer. The lower wafer may include wiring levels. The lower wafer may include landing pads for the contacts. Contacts to the silicon layer of the lower wafer may be silicided.

Owner:GLOBALFOUNDRIES US INC

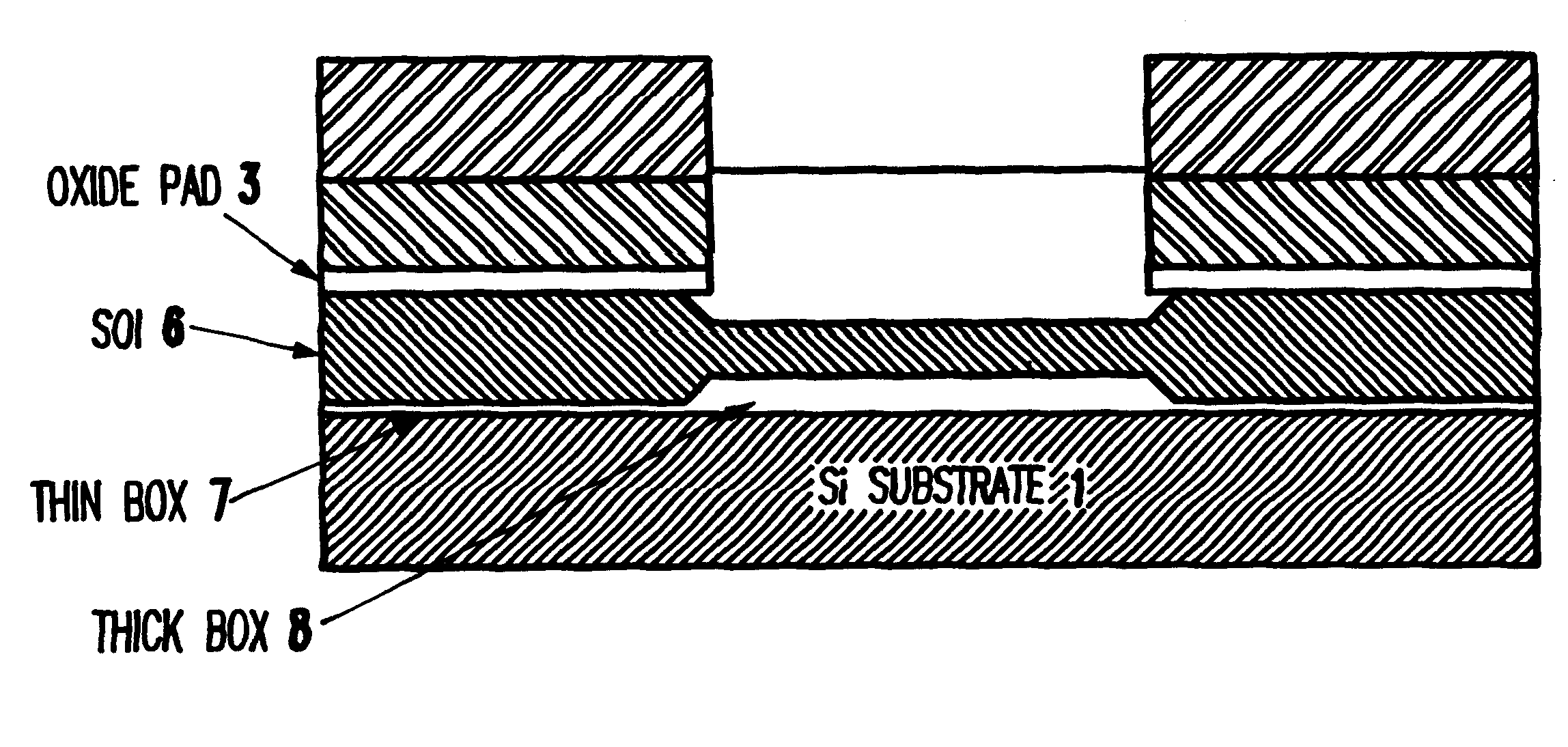

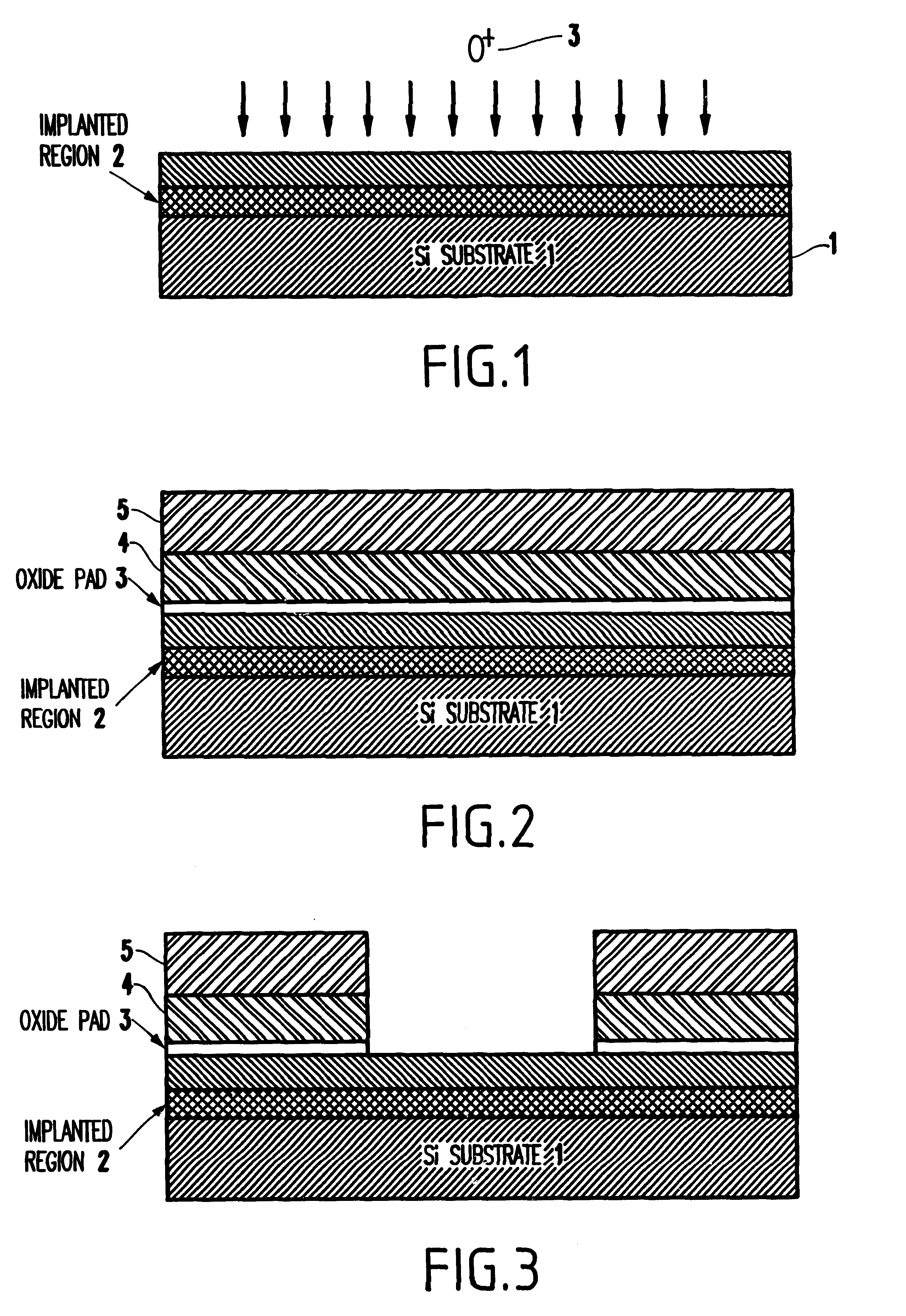

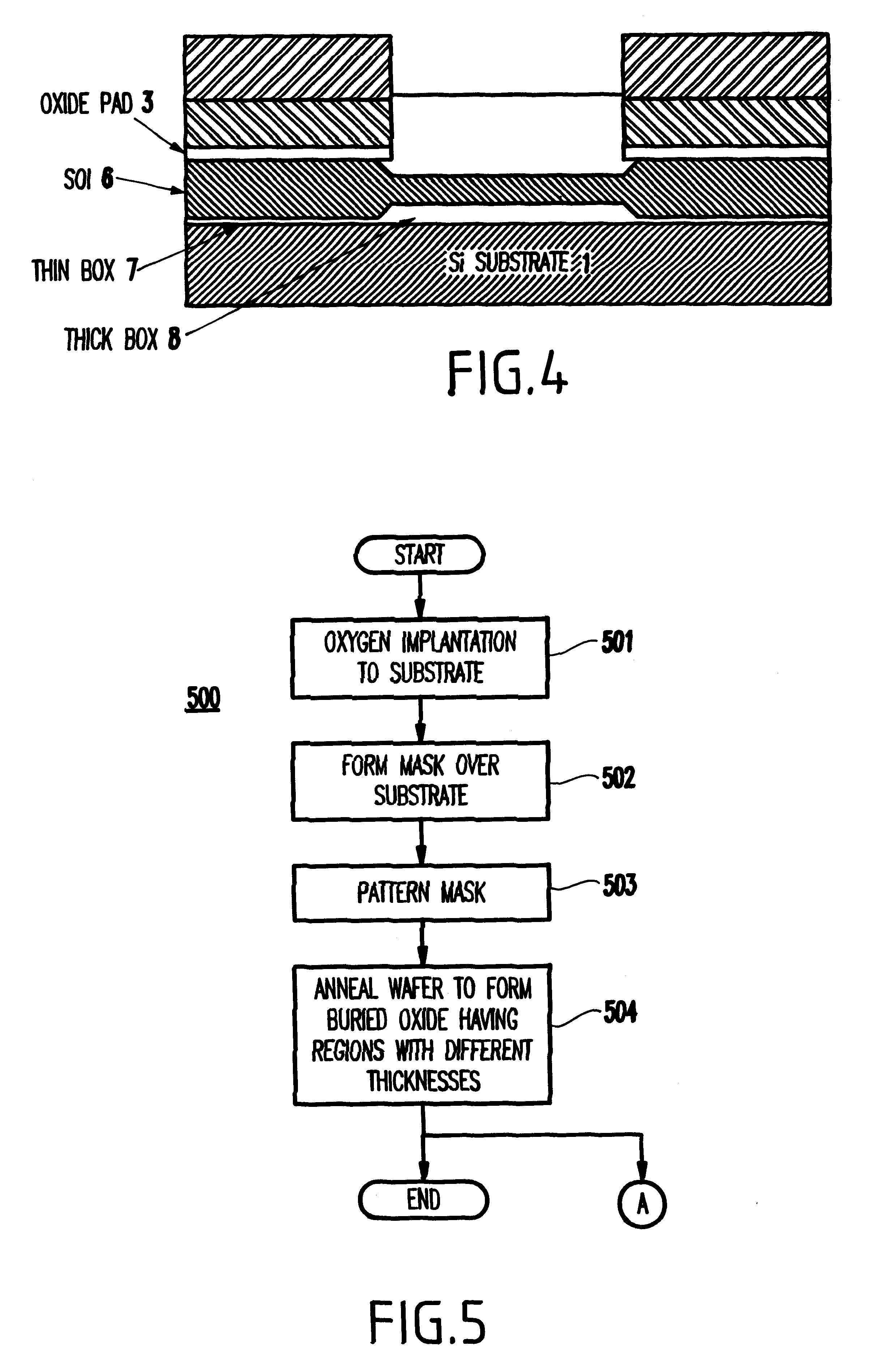

Method for patterning a buried oxide thickness for a separation by implanted oxygen (simox) process

InactiveUS6300218B1Solid-state devicesSemiconductor/solid-state device manufacturingOxygenMaterials science

A method of forming a patterned buried oxide film, includes performing an implantation into a substrate, forming a mask on at least portions of the substrate for controlling the implantation diffusion, and annealing the substrate to form a buried oxide. The mask may be selectively patterned. A region that is covered by the mask has a thinner buried oxide than an area which is exposed directly to the annealing ambient.

Owner:IBM CORP

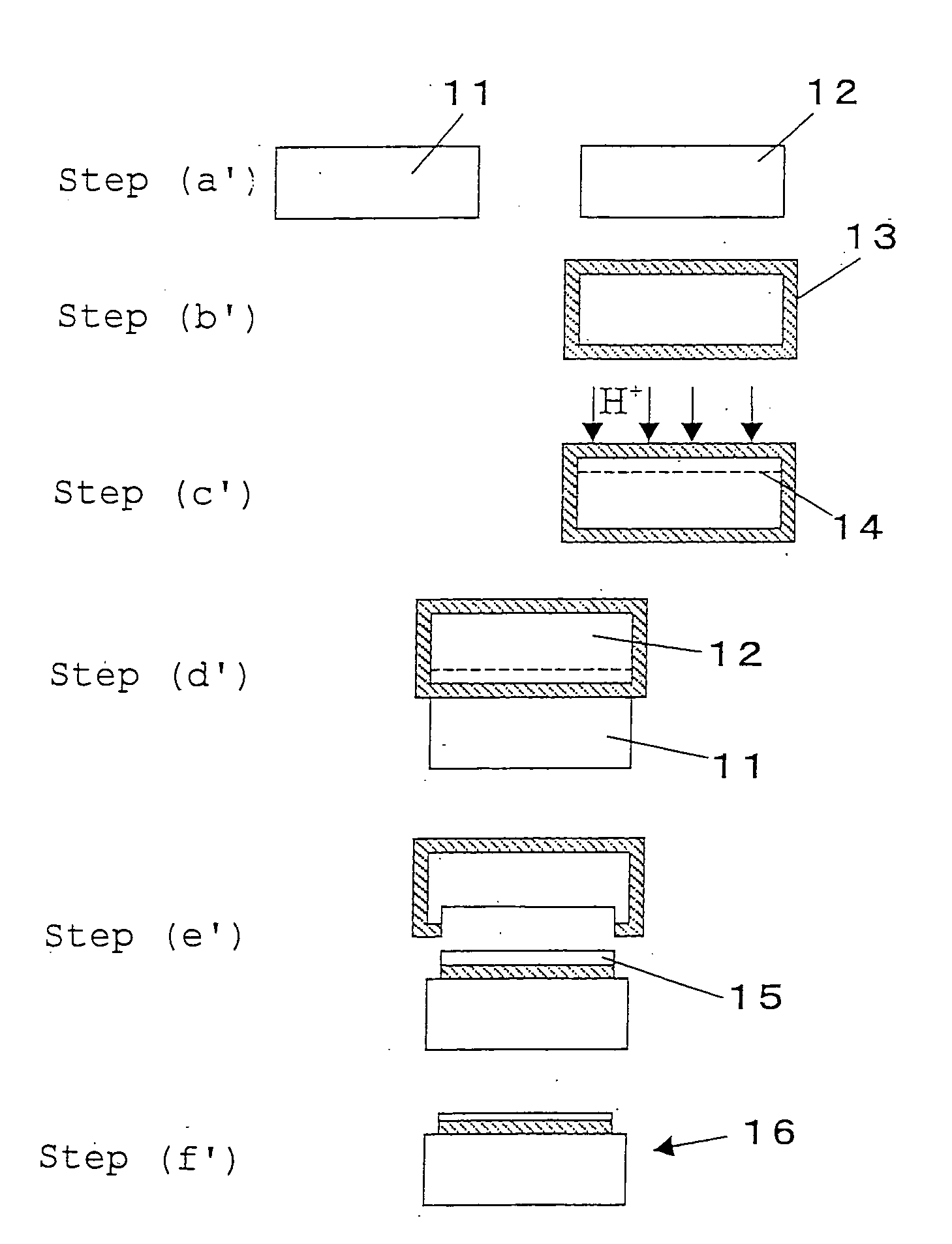

Method of producing soi wafer and soi wafer

InactiveUS20050118789A1High crystallinityHigh yieldSolid-state devicesSemiconductor/solid-state device manufacturingWaferingExtremely good

The present invention relates to a method of producing an SOI wafer in which an SOI layer is formed on a buried oxide film by forming an oxide film on a surface of at least one of a bond wafer and a base wafer, bonding the bond wafer to the base wafer through the formed oxide film, and making the bond wafer into a thin film, wherein after the oxide film is formed so that a total thickness of the oxide film formed on the surface of at least one of the bond wafer and the base wafer is thicker than a thickness of the buried oxide film that the SOI wafer to be produced has, the bond wafer is bonded to the base wafer through the formed oxide film, the bond wafer is made into a thin film to form an SOI layer, and thereafter, an obtained bonded wafer is subjected to heat treatment to reduce a thickness of the buried oxide film. Thereby, there can be provided a method of producing an SOI wafer in which blisters and voids are not generated even if the thickness of the buried oxide film is thinned, and its SOI layer has extremely good crystallinity.

Owner:SHIN-ETSU HANDOTAI CO LTD