Patents

Literature

440 results about "Conduction channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

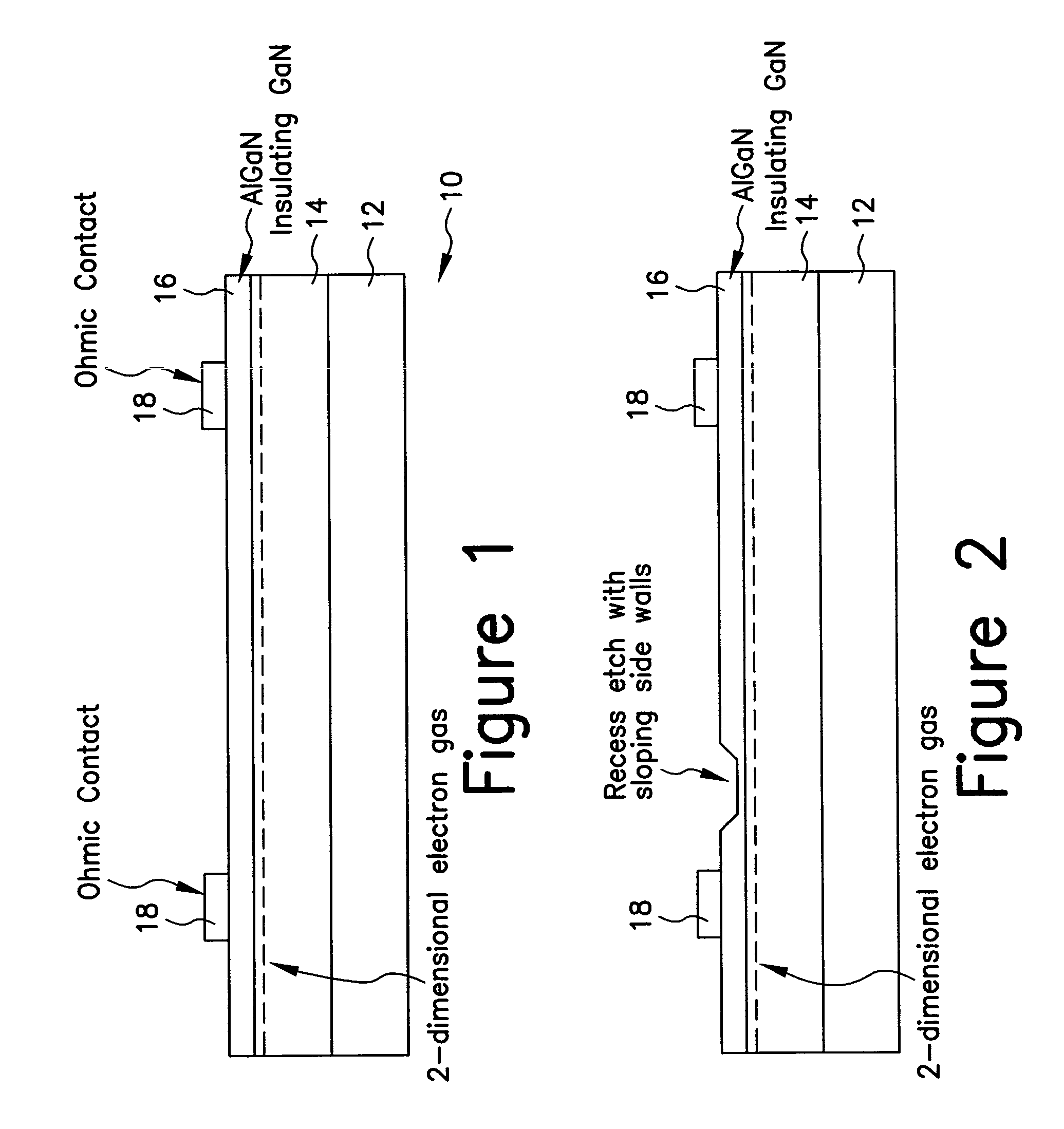

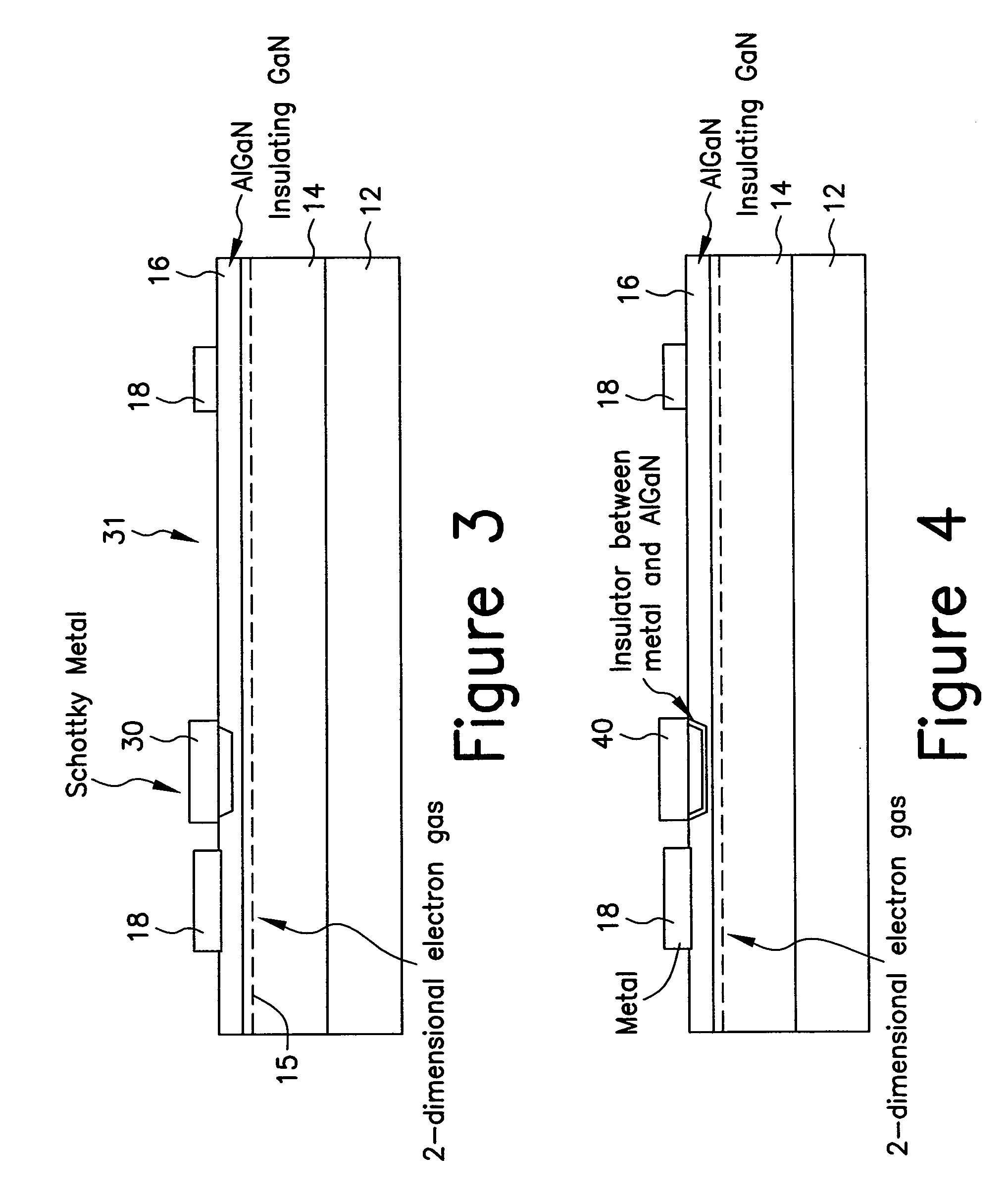

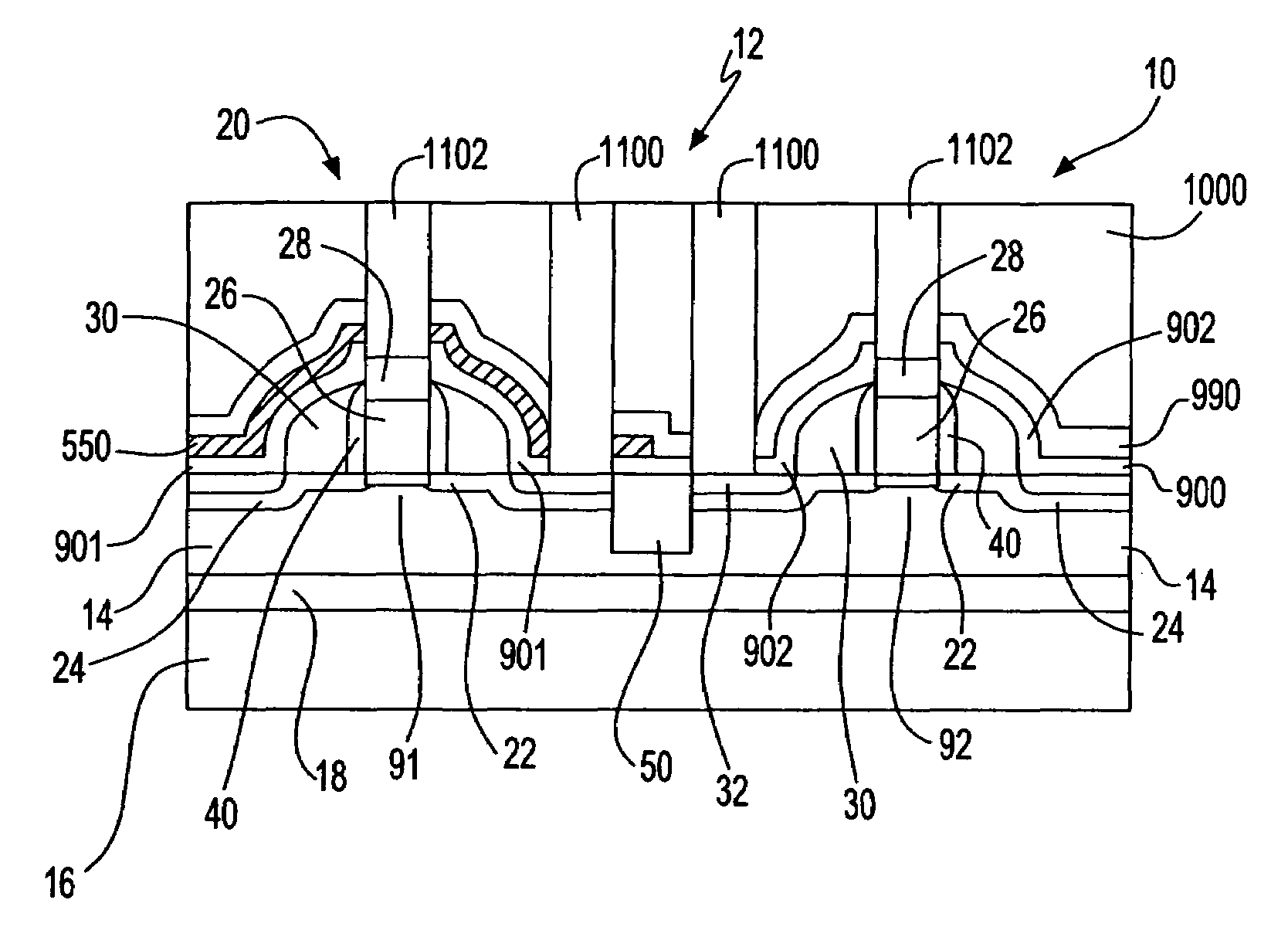

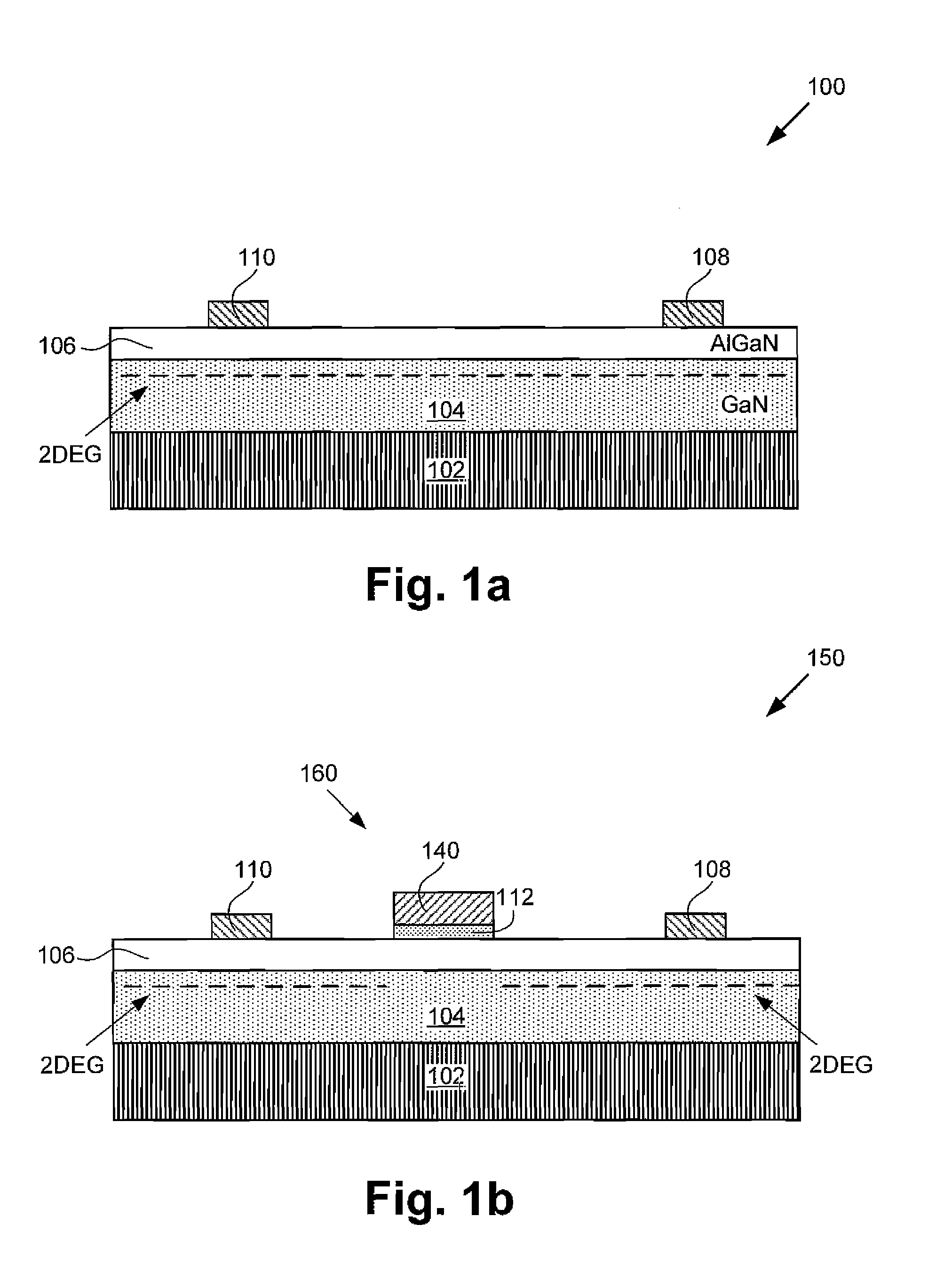

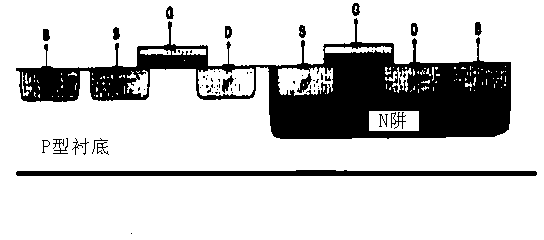

Enhancement mode III-nitride FET

ActiveUS20060060871A1Lower resistanceReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesNitrideConduction channel

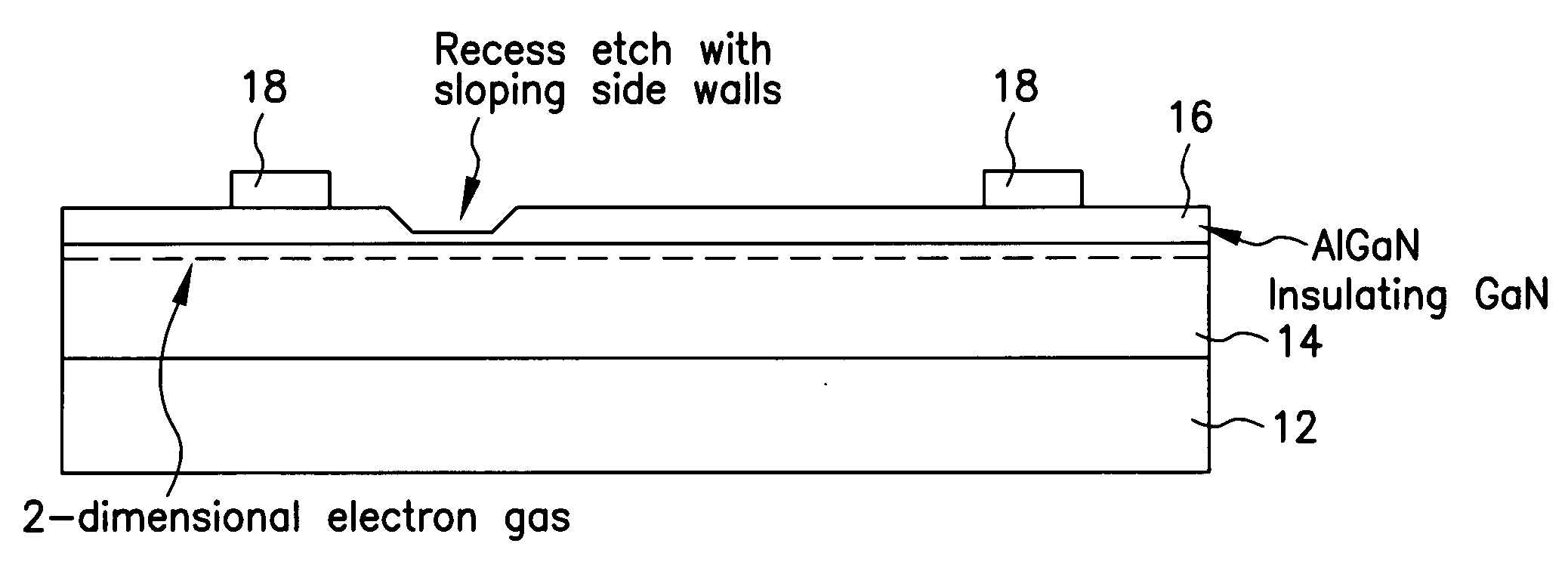

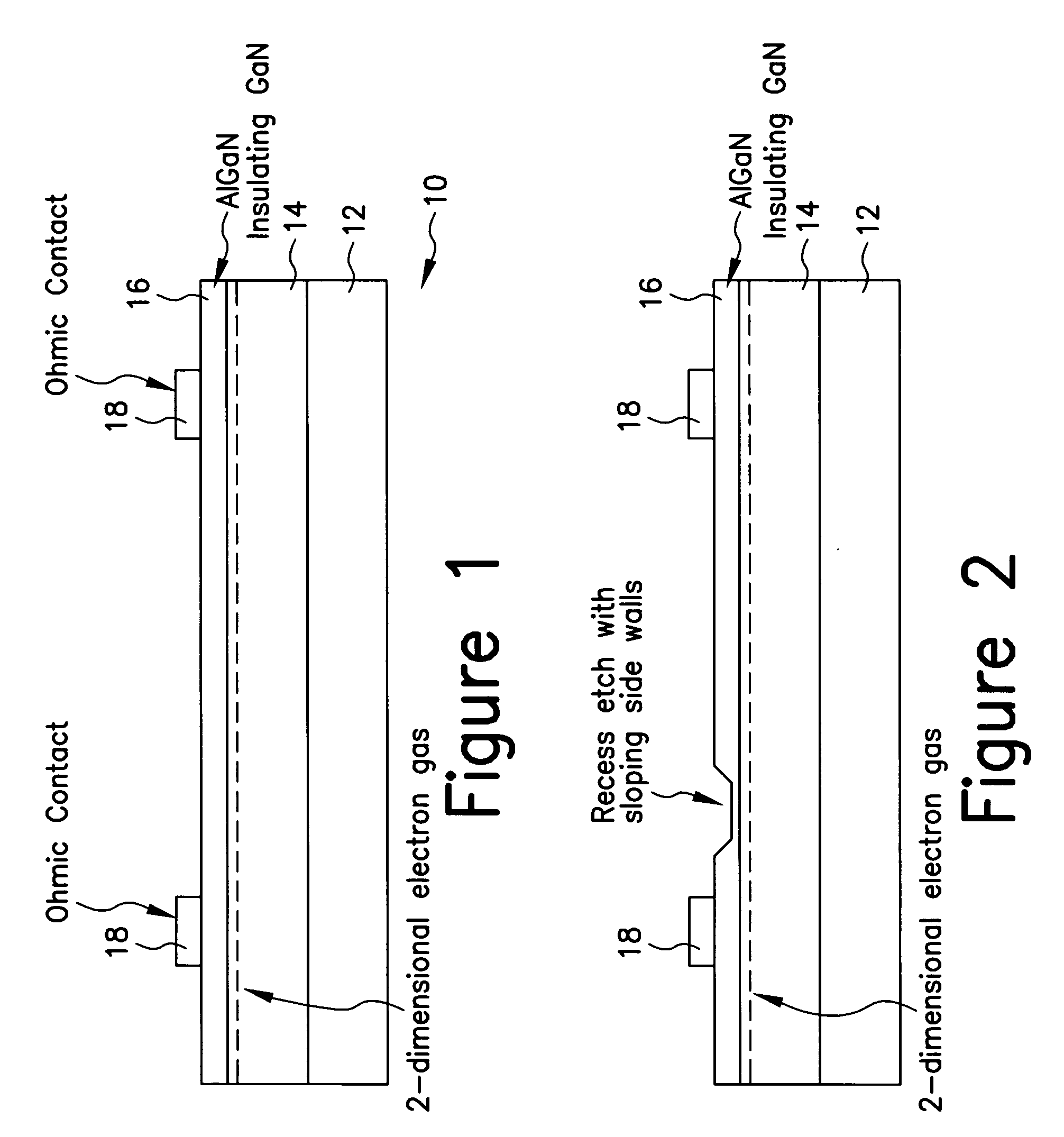

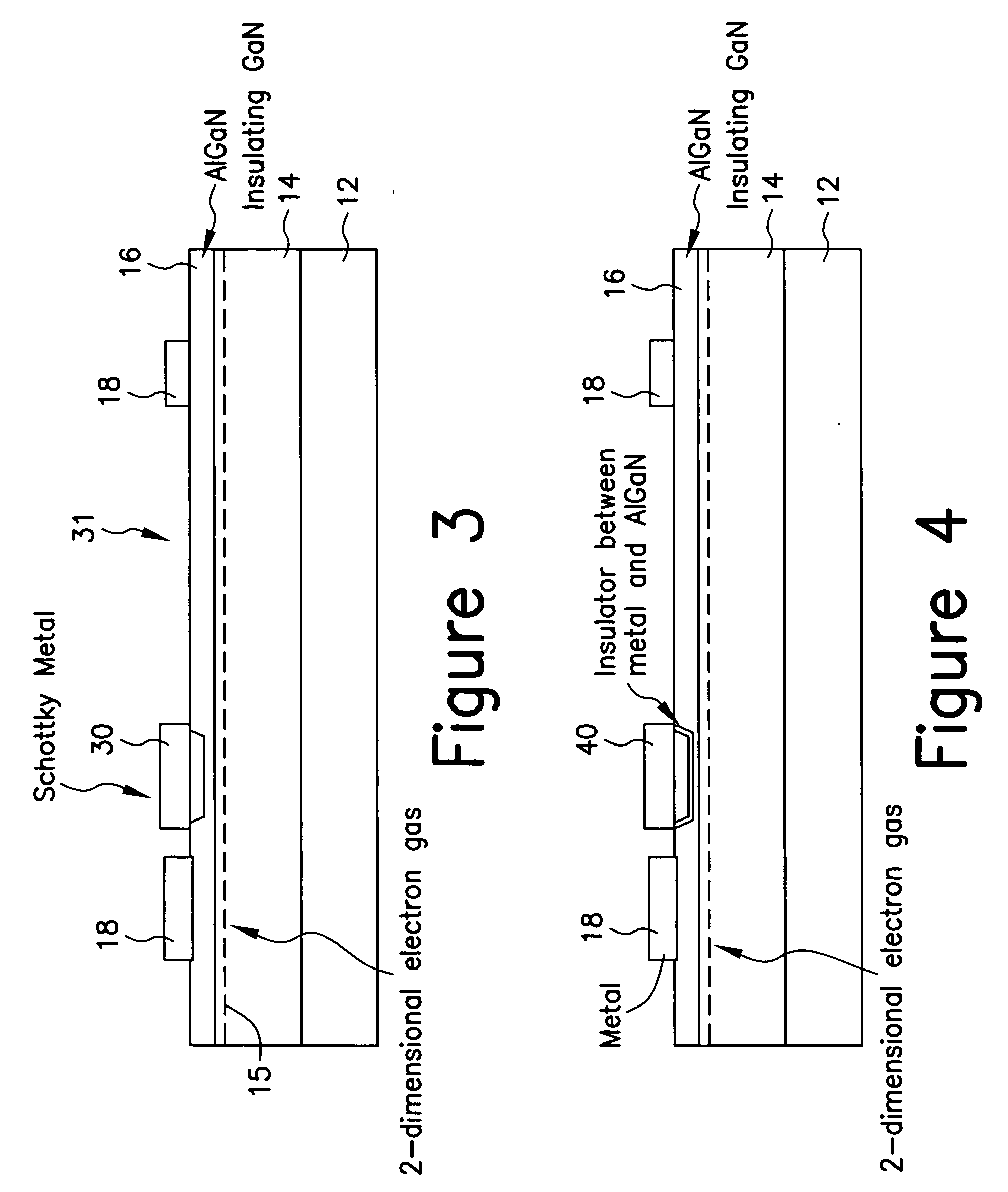

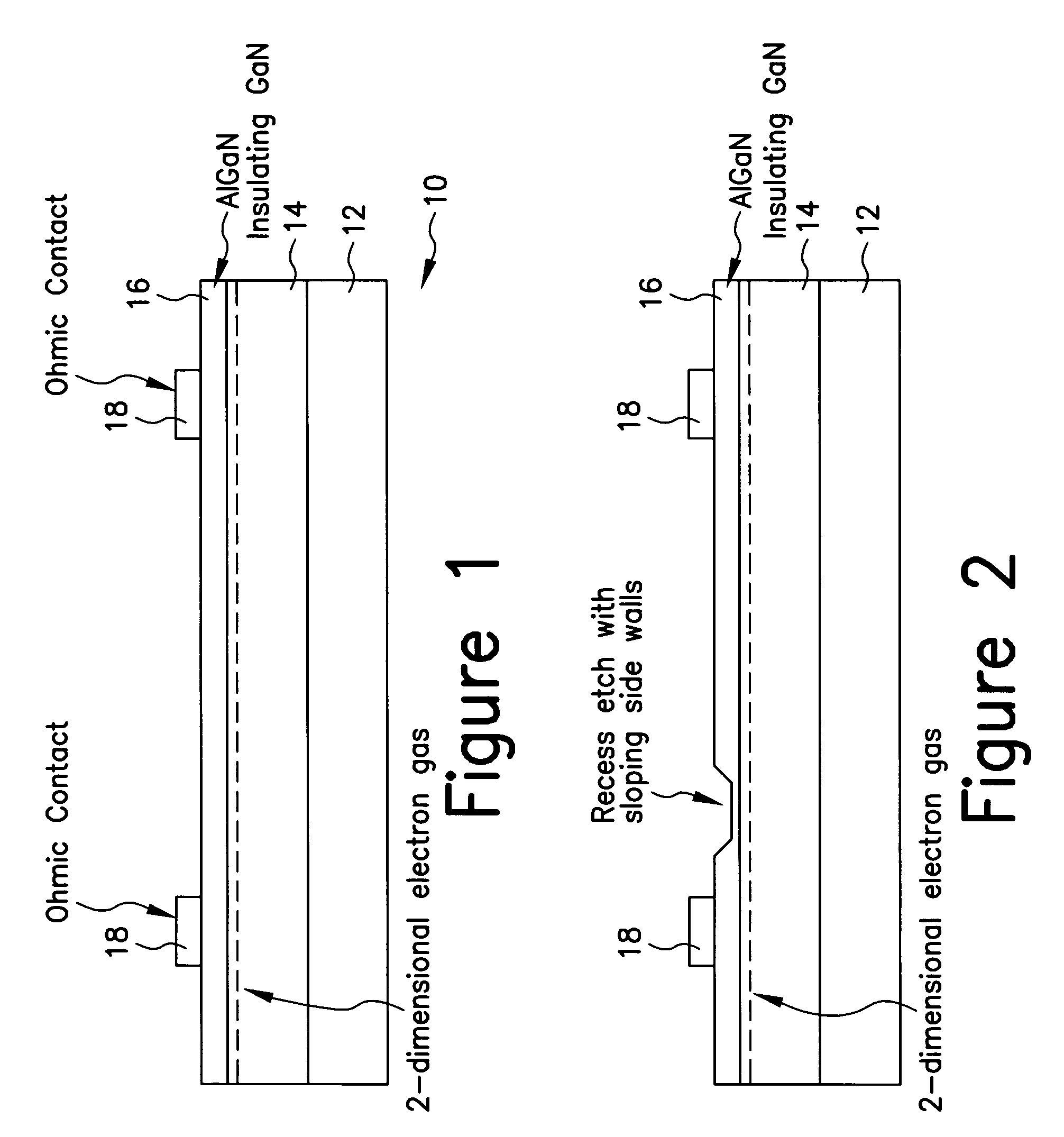

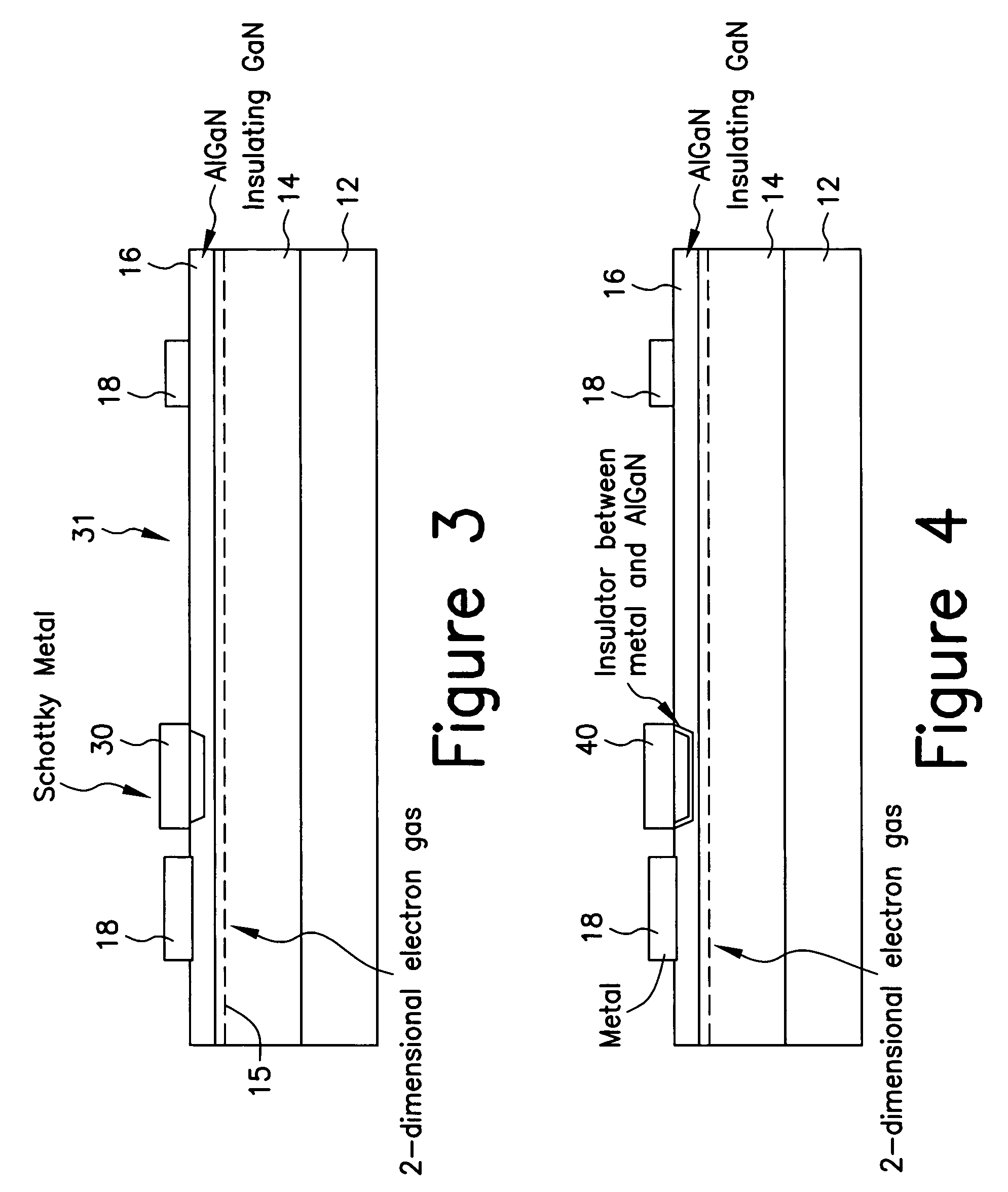

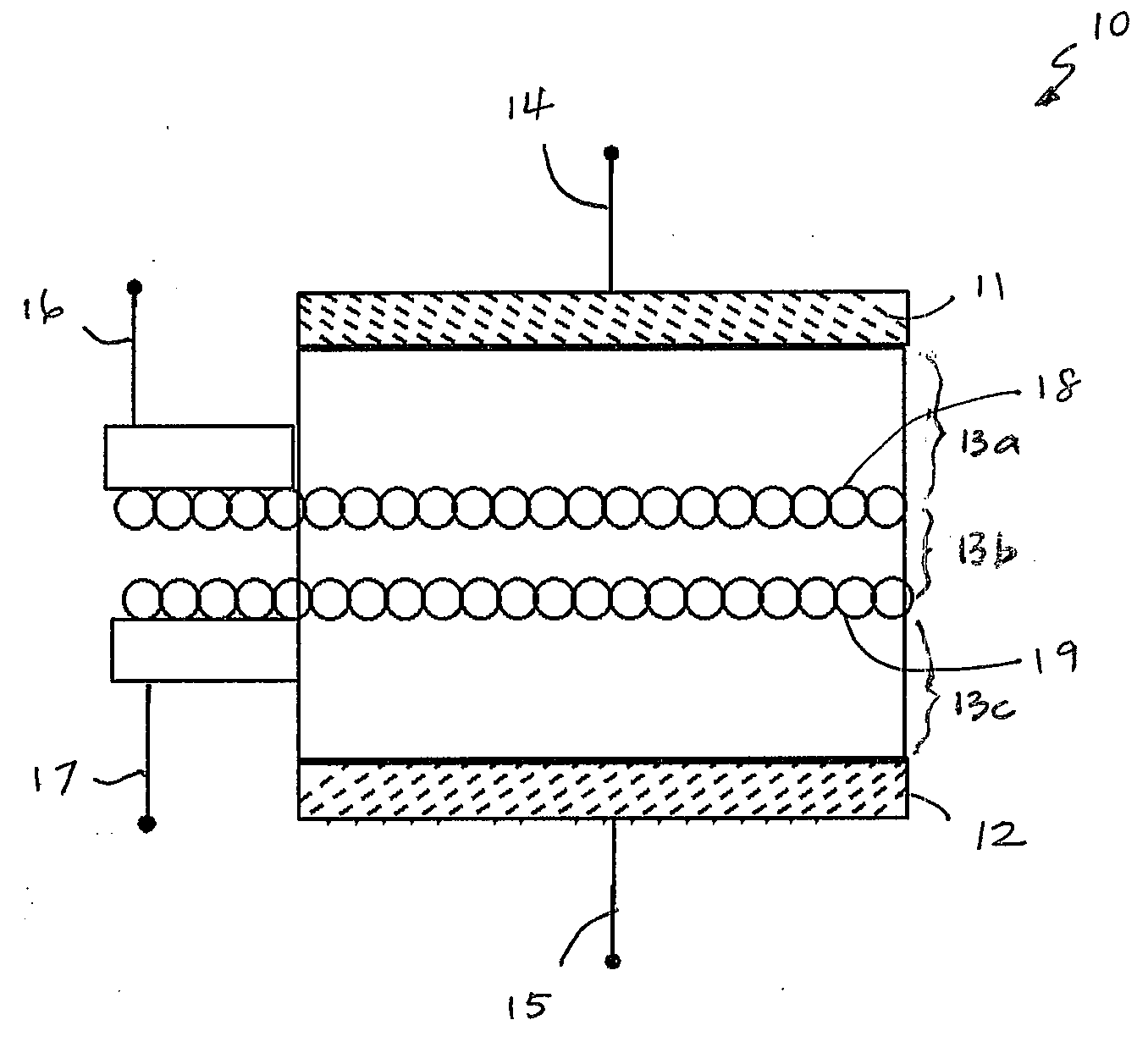

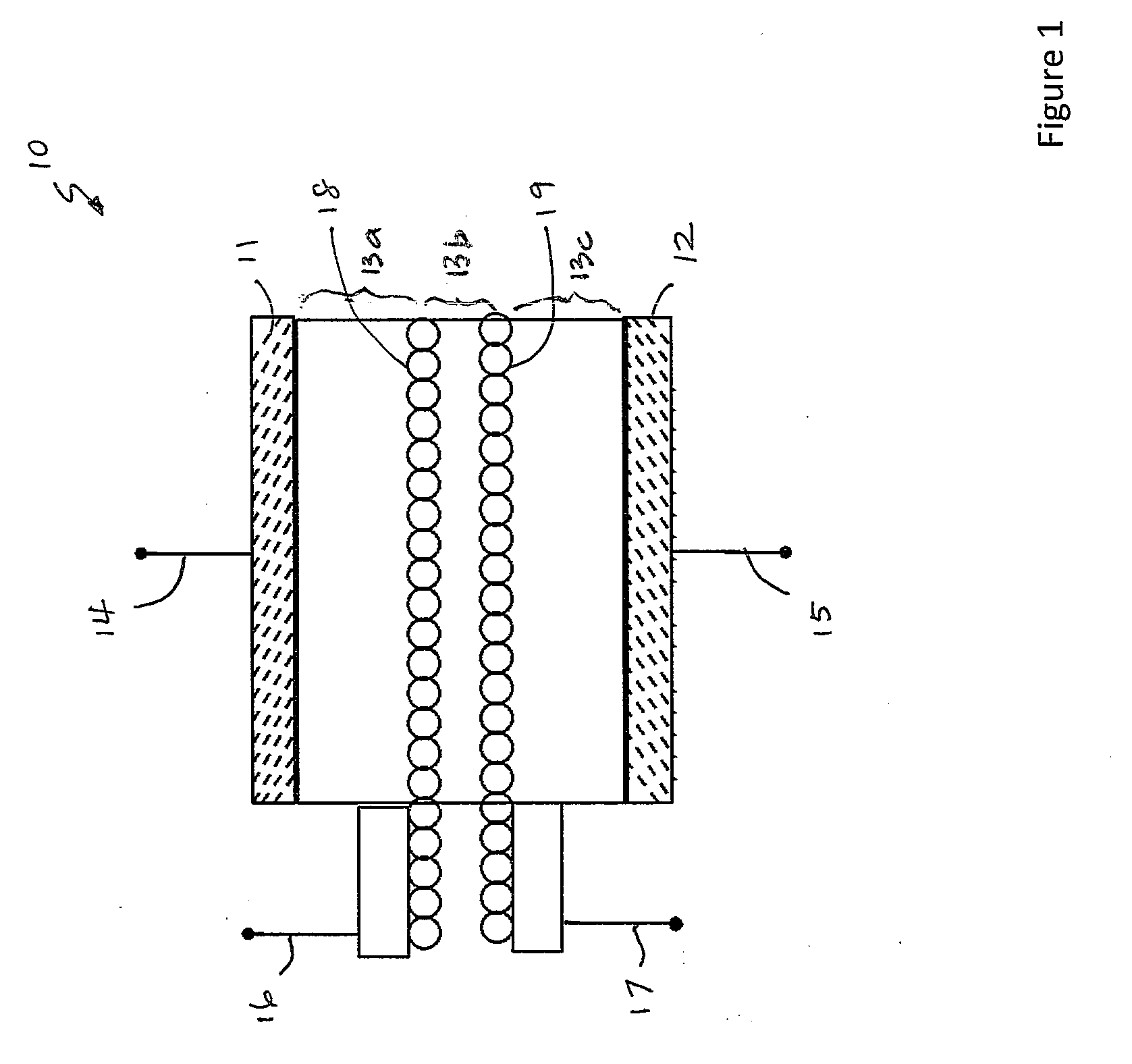

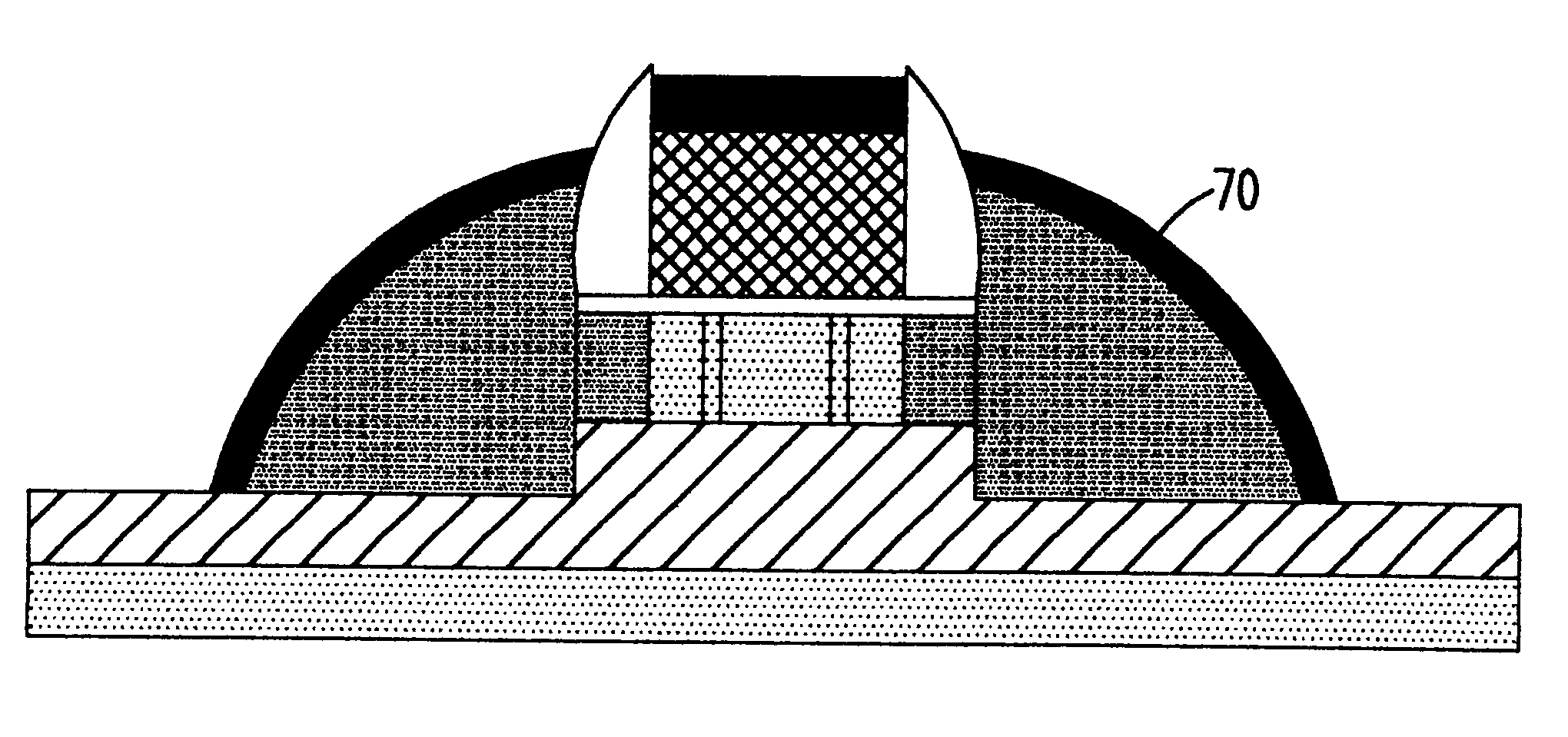

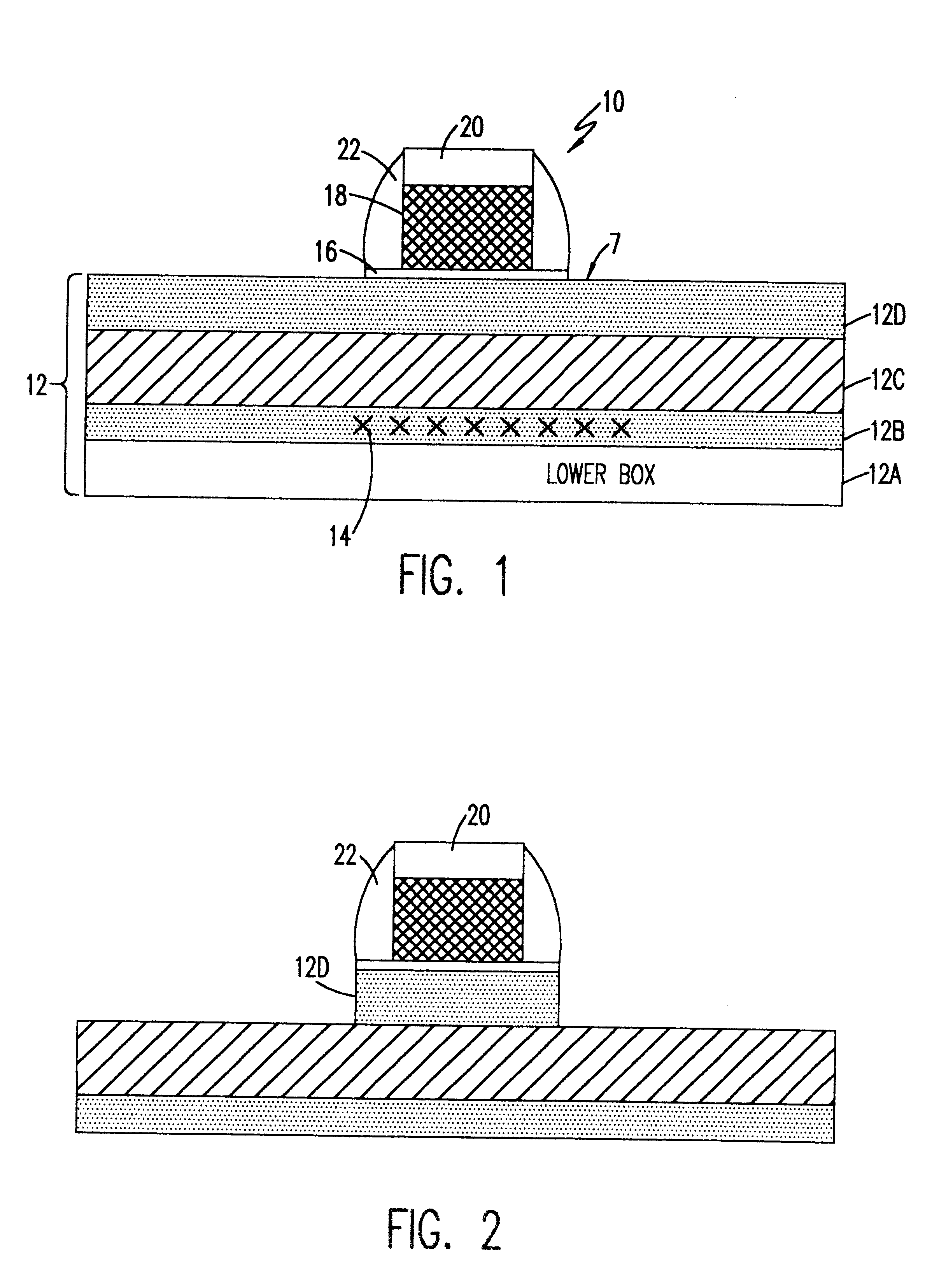

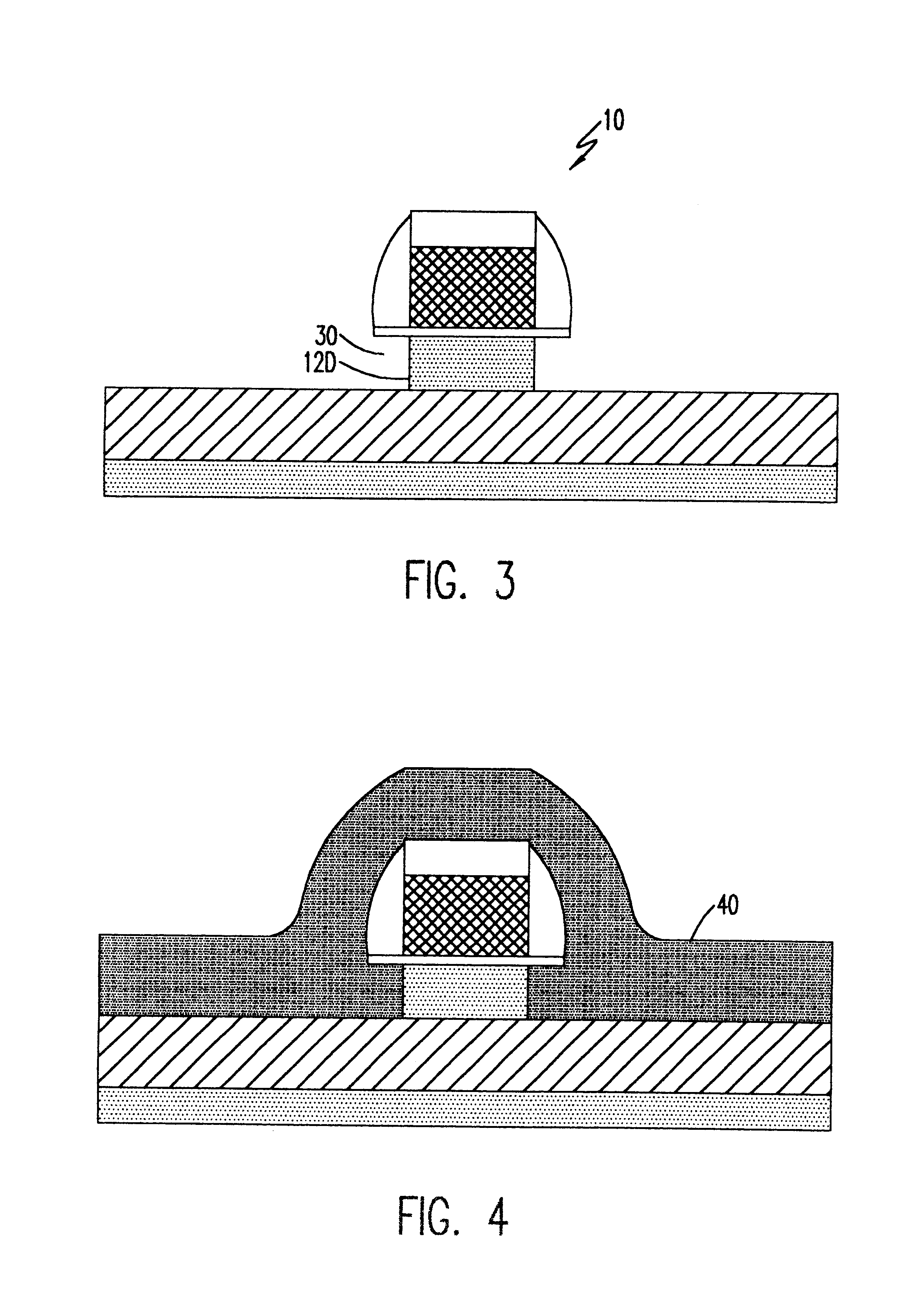

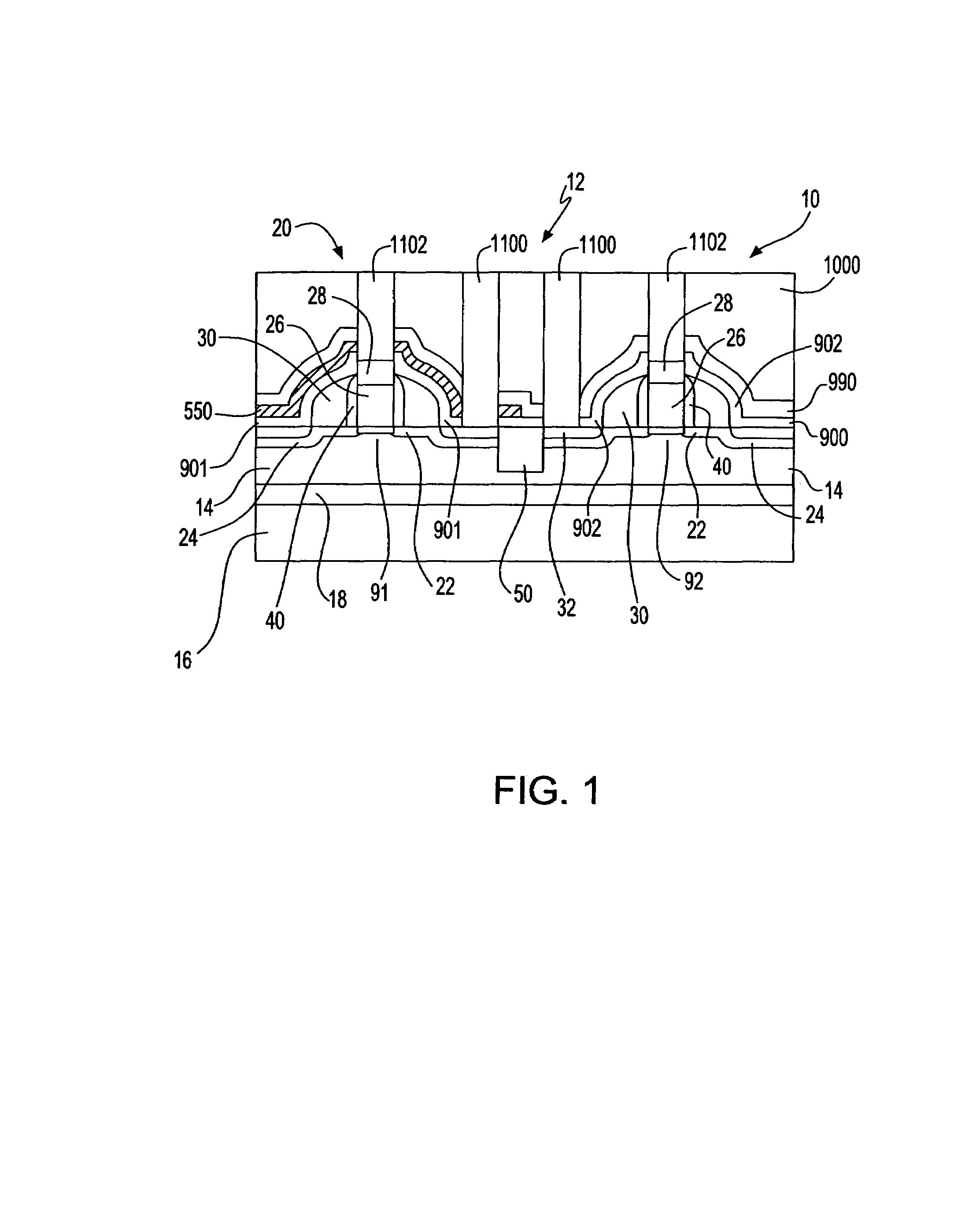

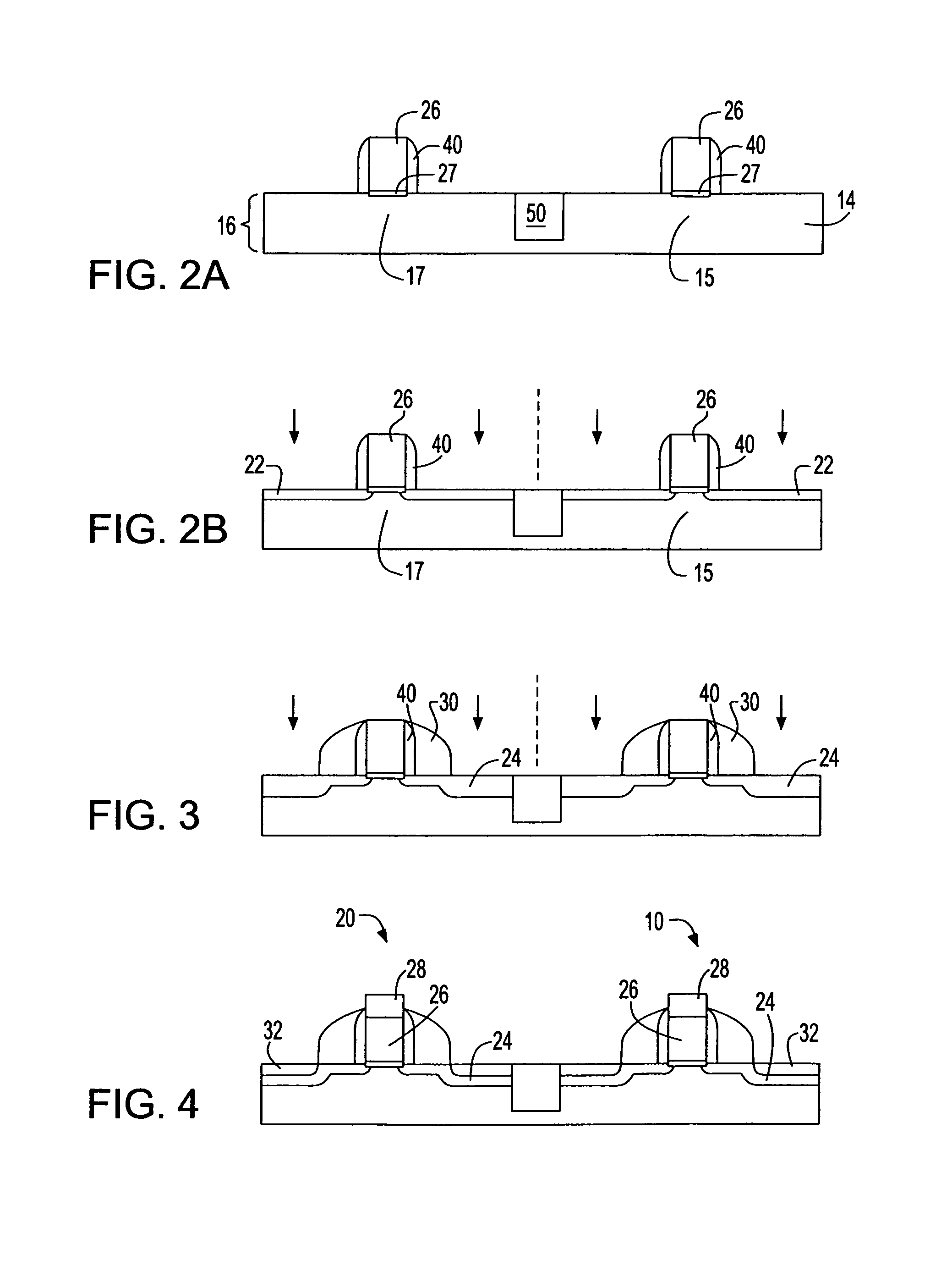

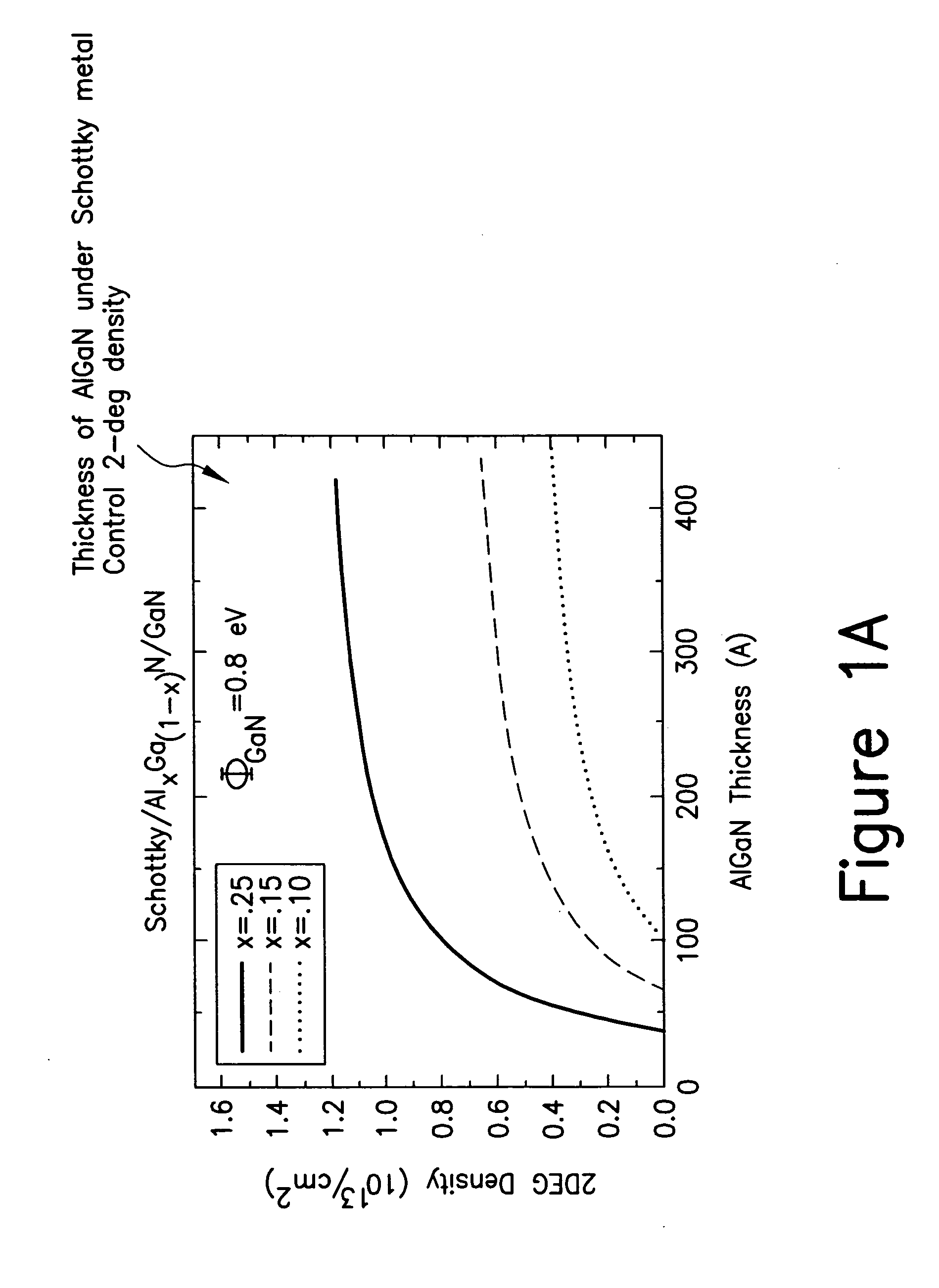

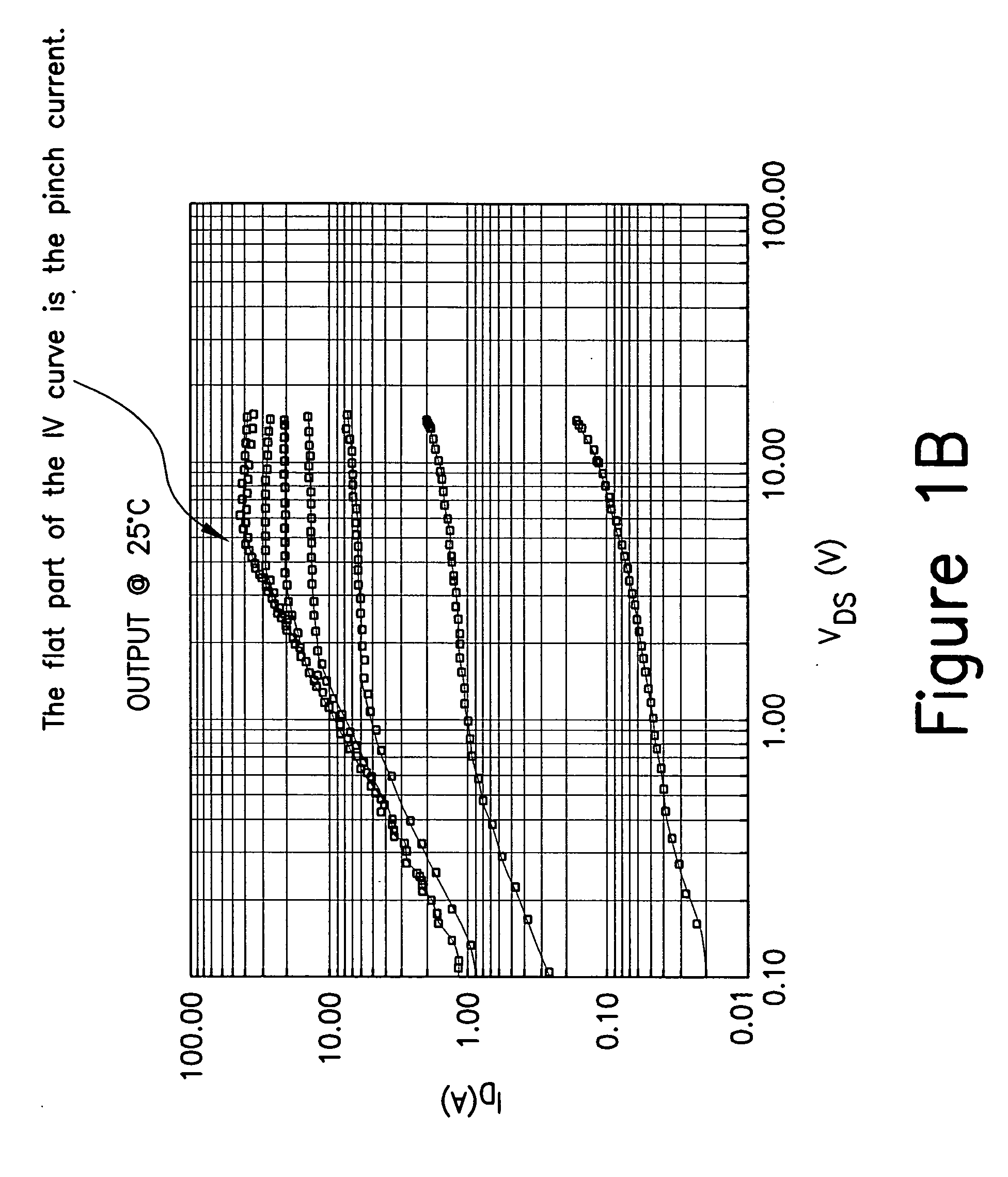

A III-nitride switch includes a recessed gate contact to produce a nominally off, or an enhancement mode, device. By providing a recessed gate contact, a conduction channel formed at the interface of two III-nitride materials is interrupted when the gate electrode is inactive to prevent current flow in the device. The gate electrode can be a schottky contact or an insulated metal contact. Two gate electrodes can be provided to form a bi-directional switch with nominally off characteristics. The recesses formed with the gate electrode can have sloped sides. The gate electrodes can be formed in a number of geometries in conjunction with current carrying electrodes of the device.

Owner:INFINEON TECH AMERICAS CORP

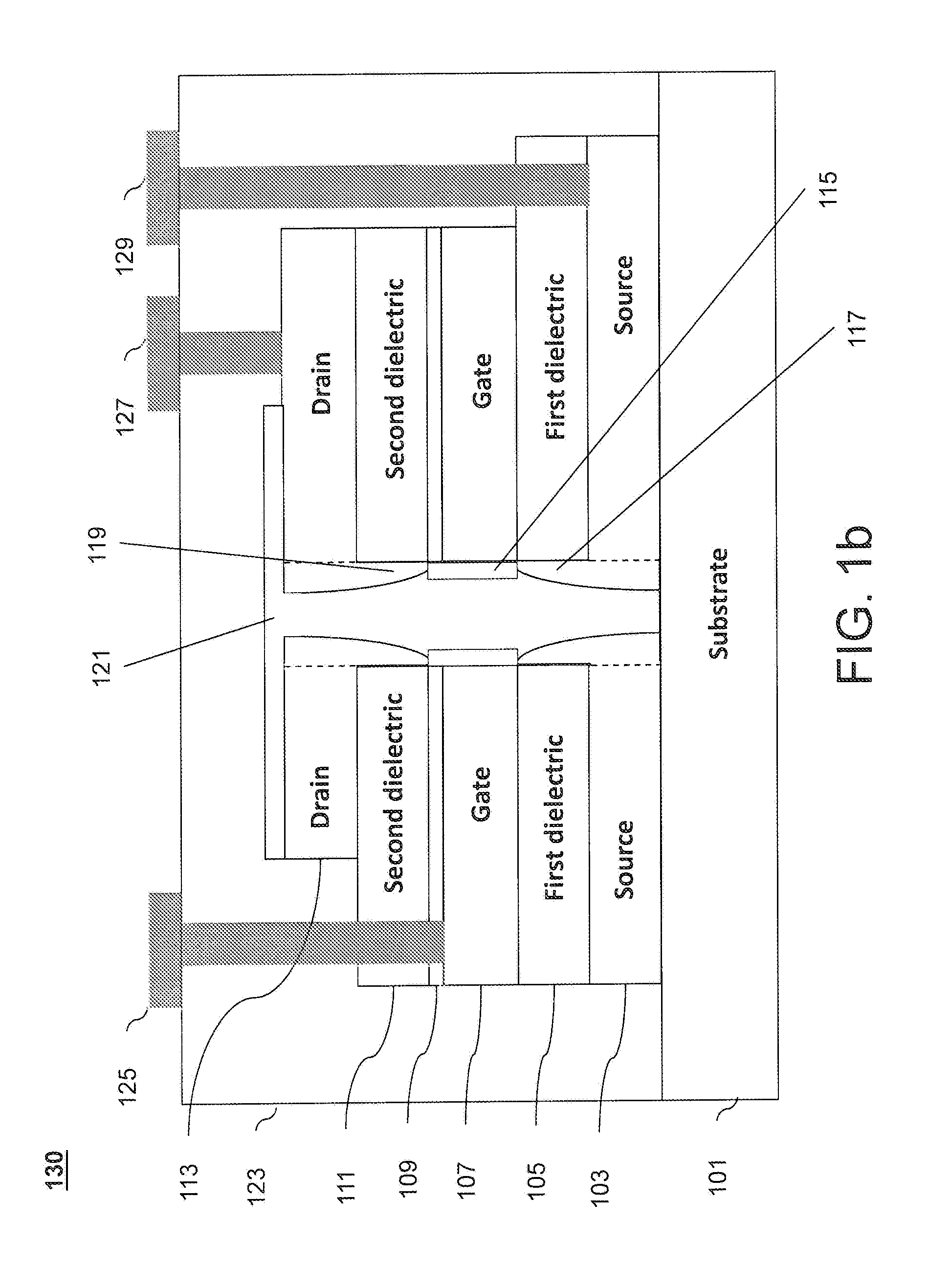

Double gate trench transistor

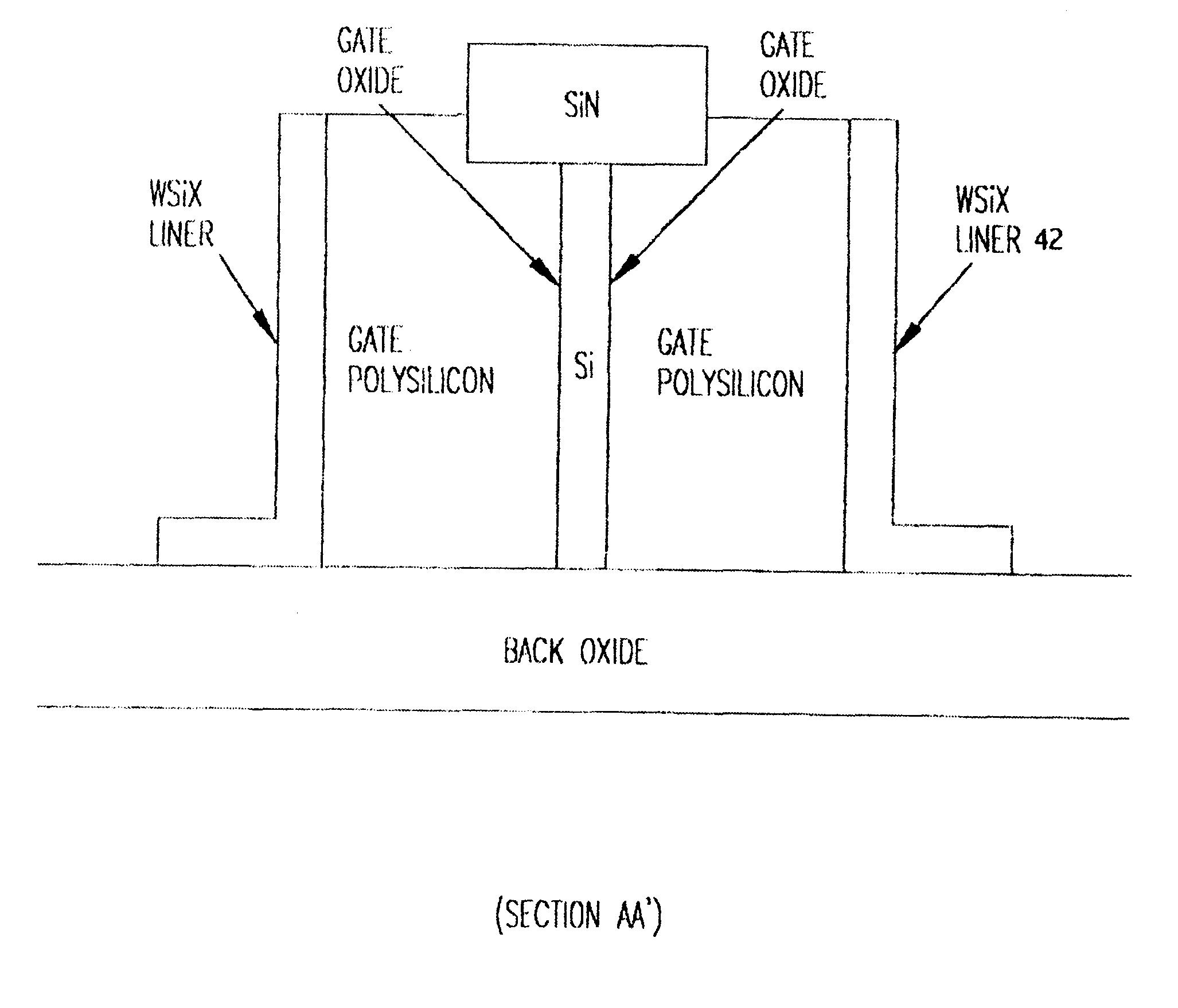

A field effect transistor is formed with a sub-lithographic conduction channel and a dual gate which is formed by a simple process by starting with a silicon-on-insulator wafer, allowing most etching processes to use the buried oxide as an etch stop. Low resistivity of the gate, source and drain is achieved by silicide sidewalls or liners while low gate to junction capacitance is achieved by recessing the silicide and polysilicon dual gate structure from the source and drain region edges.

Owner:IBM CORP

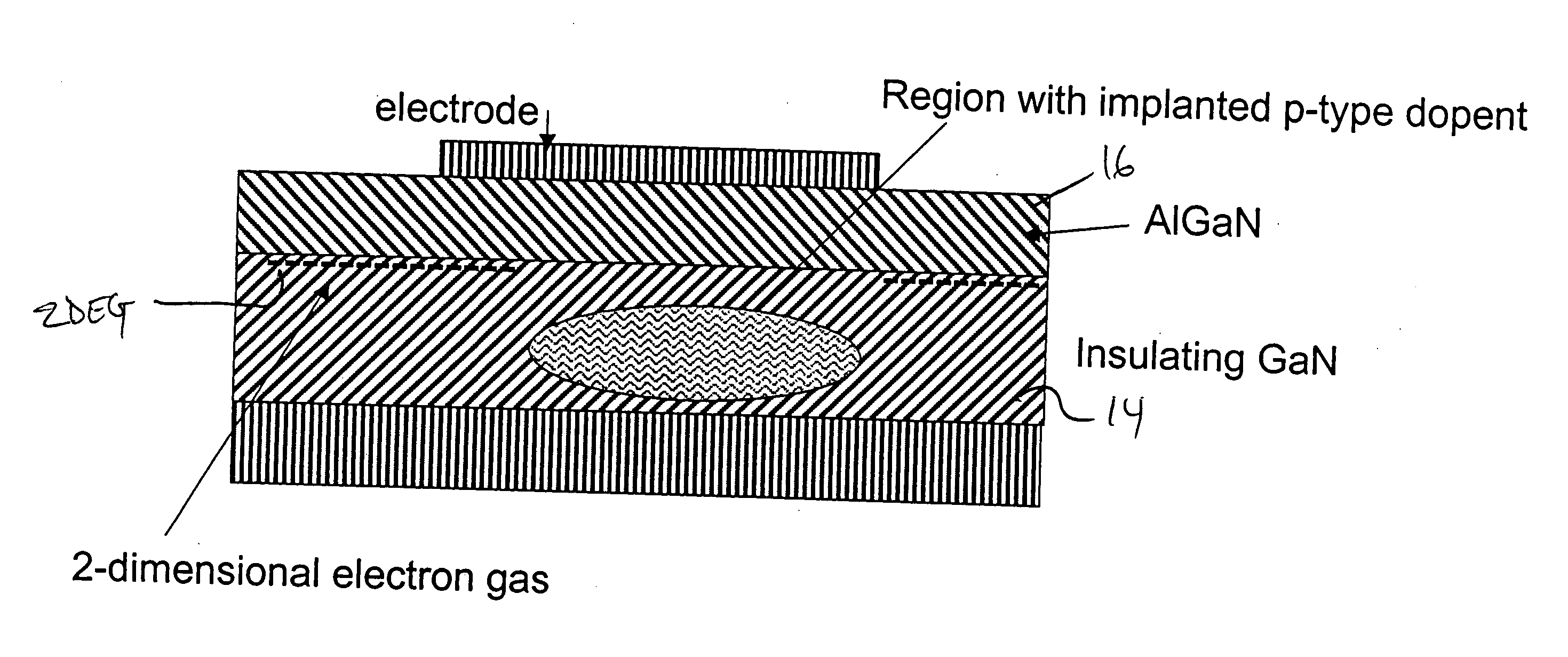

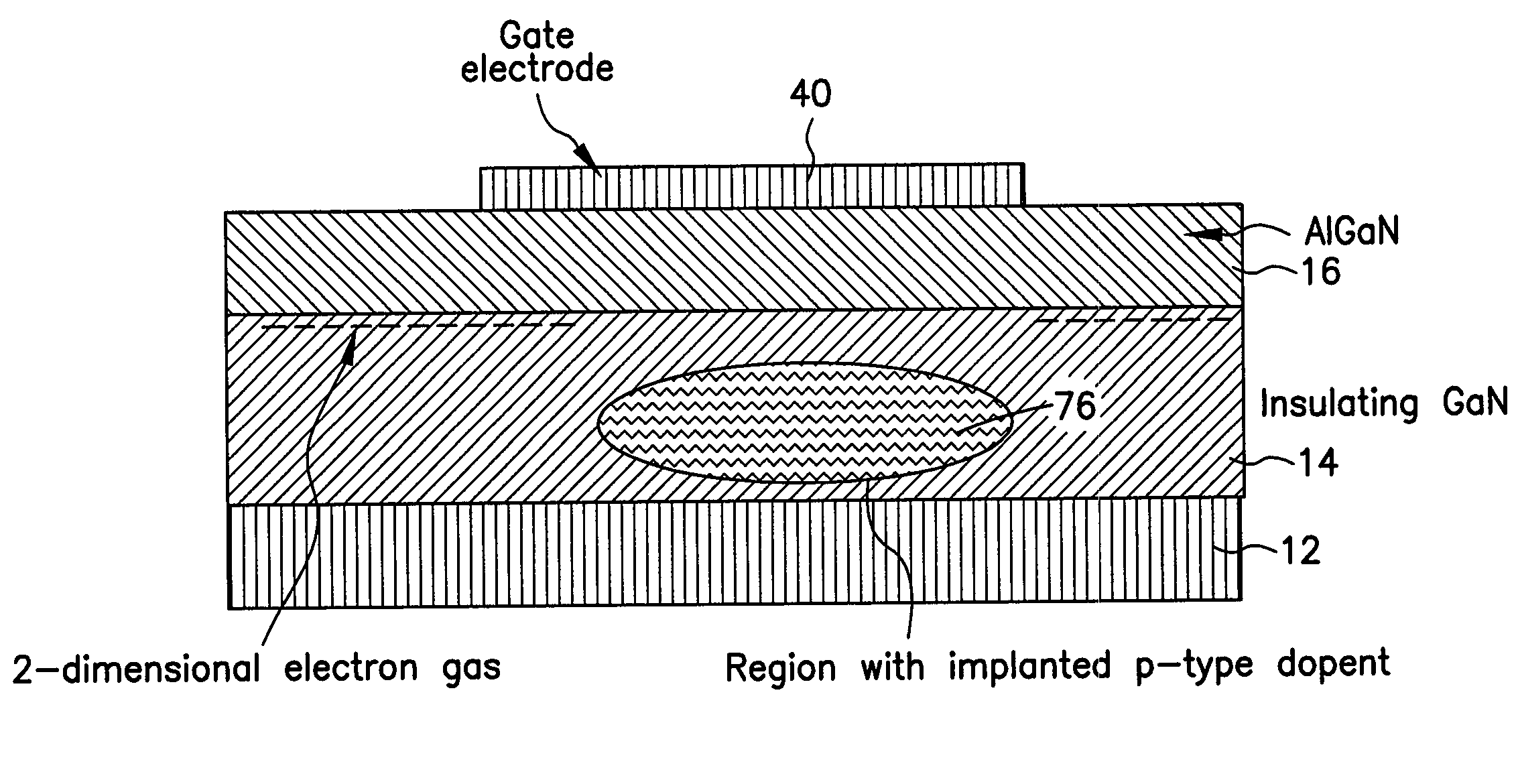

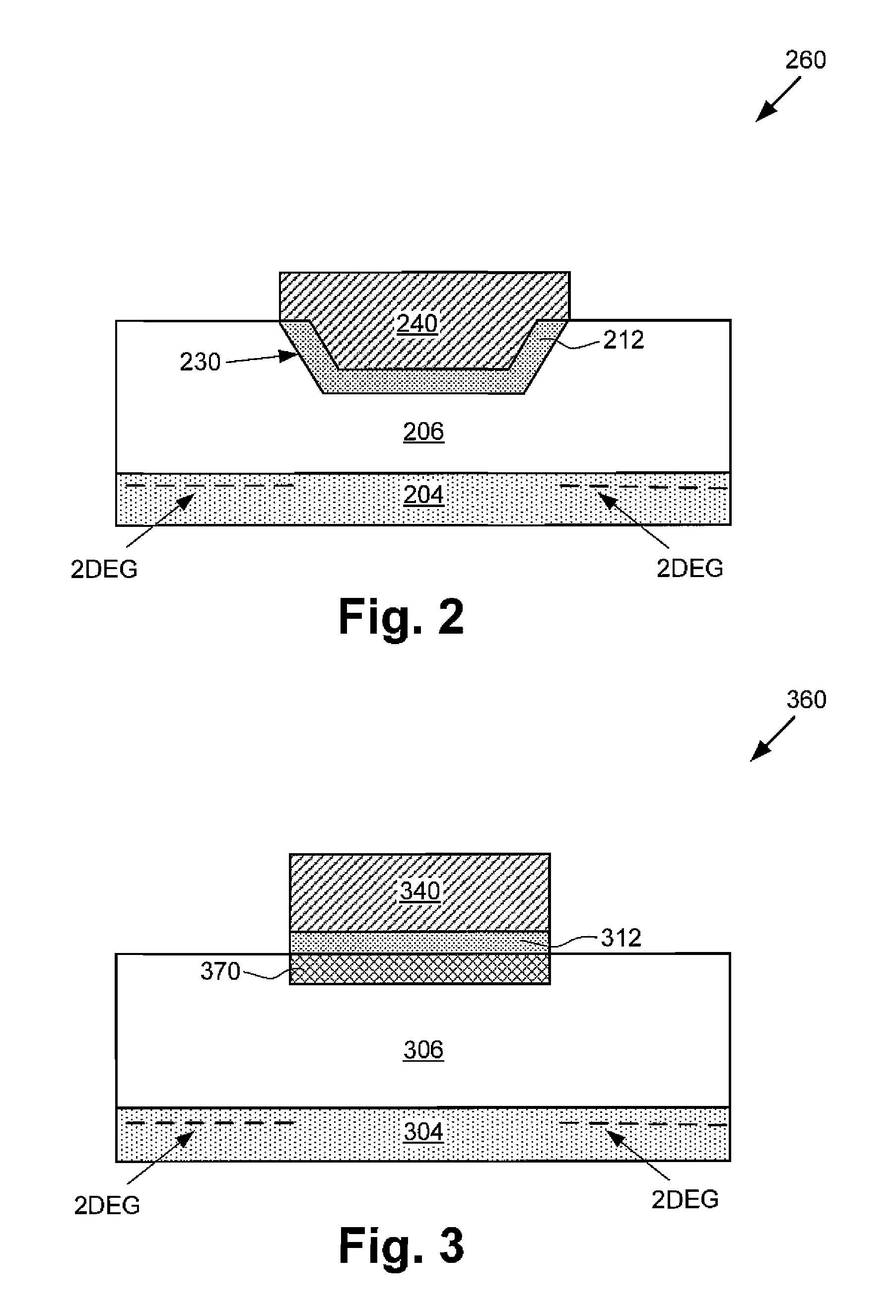

III-Nitride current control device and method of manufacture

ActiveUS20050194612A1Without sacrificing wafer areaReduce leakageSemiconductor/solid-state device detailsSolid-state devicesOhmic contactEngineering

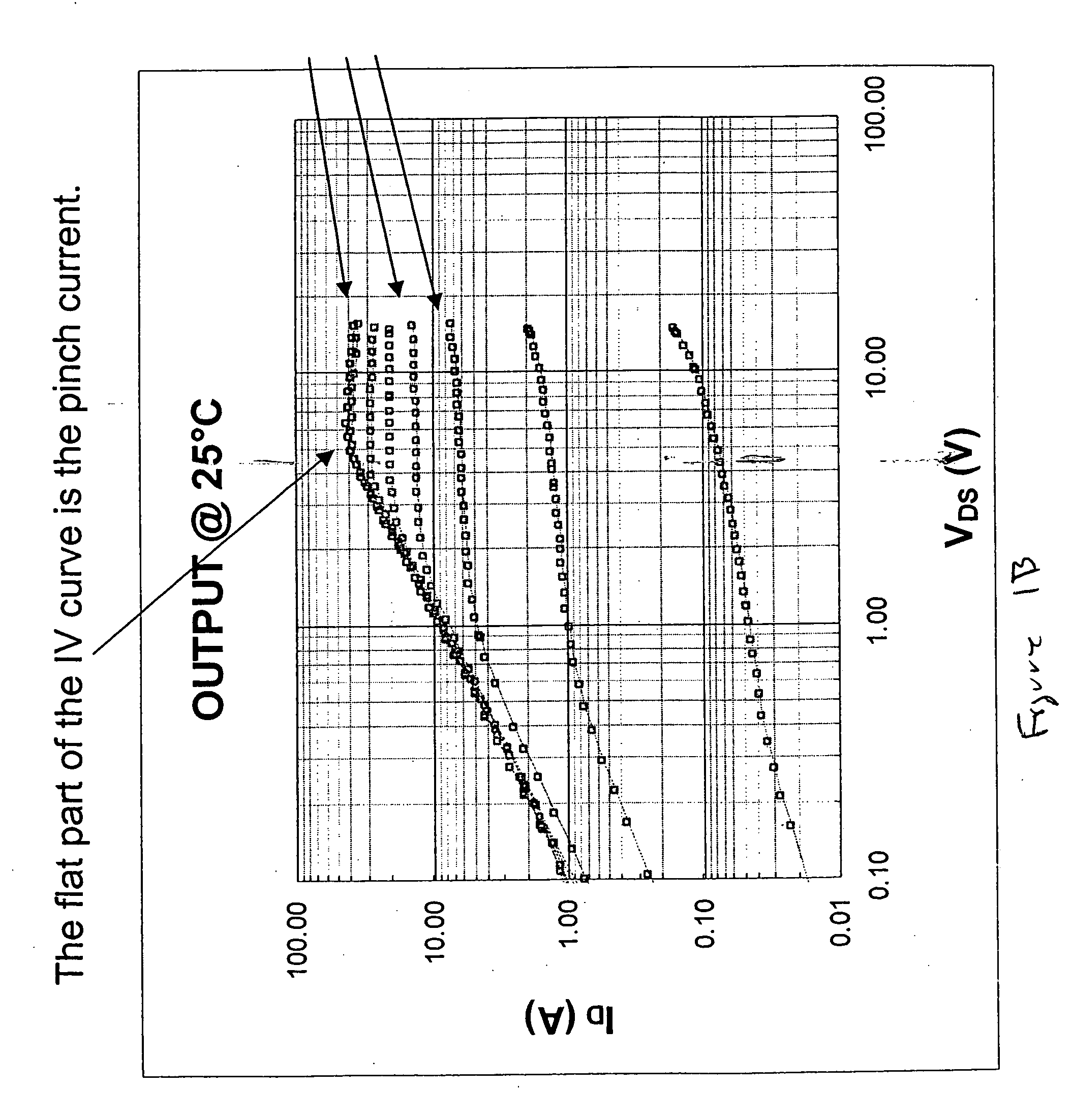

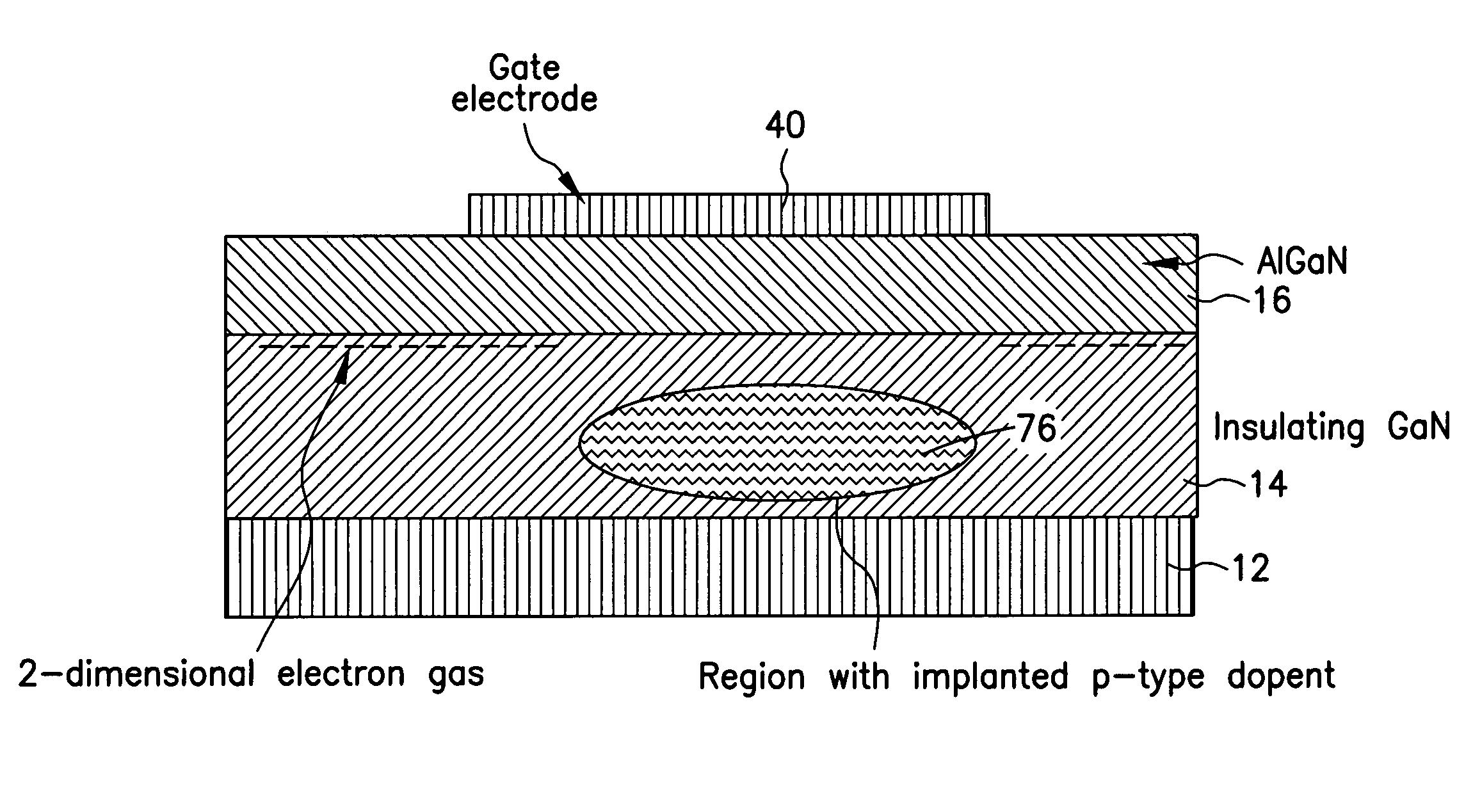

A III-nitride device includes a recessed electrode to produce a nominally off, or an enhancement mode, device. By providing a recessed electrode, a conduction channel formed at the interface of two III-nitride materials is interrupted when the electrode contact is inactive to prevent current flow in the device. The electrode can be a schottky contact or an insulated metal contact. Two ohmic contacts can be provided to form a rectifier device with nominally off characteristics. The recesses formed with the electrode can have sloped sides. The electrode can be formed in a number of geometries in conjunction with current carrying electrodes of the device. A nominally on device, or pinch resistor, is formed when the electrode is not recessed. A diode is also formed by providing non-recessed ohmic and schottky contacts through an insulator to an AlGaN layer.

Owner:INFINEON TECH AMERICAS CORP

Enhancement mode III-nitride FET

ActiveUS7382001B2Lower resistanceReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNitride

A III-nitride switch includes a recessed gate contact to produce a nominally off, or an enhancement mode, device. By providing a recessed gate contact, a conduction channel formed at the interface of two III-nitride materials is interrupted when the gate electrode is inactive to prevent current flow in the device. The gate electrode can be a schottky contact or an insulated metal contact. Two gate electrodes can be provided to form a bi-directional switch with nominally off characteristics. The recesses formed with the gate electrode can have sloped sides. The gate electrodes can be formed in a number of geometries in conjunction with current carrying electrodes of the device.

Owner:INFINEON TECH AMERICAS CORP

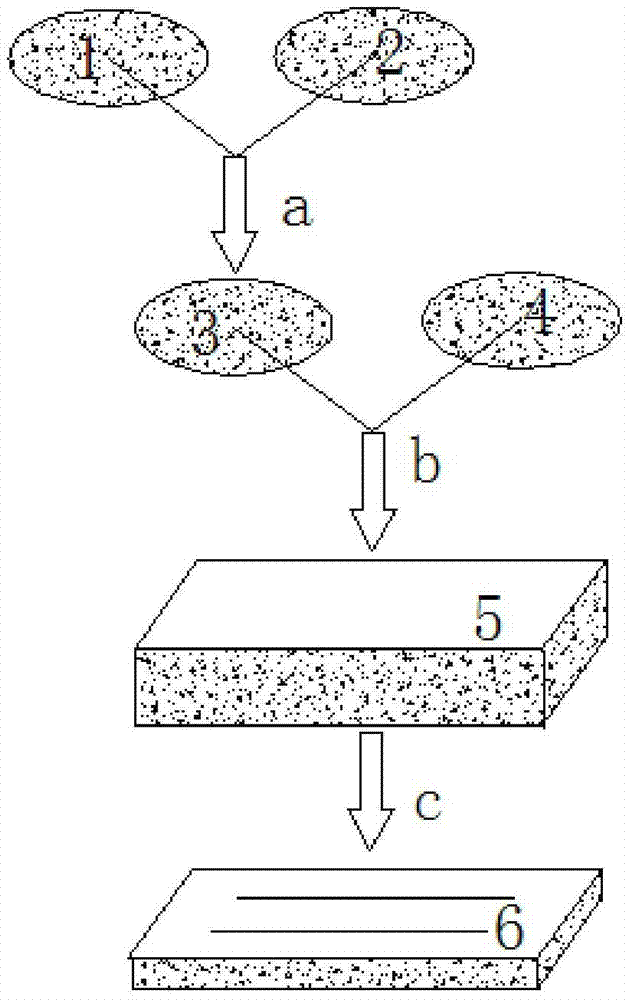

Surface-modification three-dimensional-network-carbon-fiber-reinforced composite material and preparing method

ActiveCN105818476AMitigating Galvanic CorrosionImprove resilienceLamination ancillary operationsLaminationCarbon nanotubeFiber-reinforced composite

The invention discloses a surface-modification three-dimensional-network-carbon-fiber-reinforced composite material and a preparing method.Three-dimensional carbon fiber frameworks with different bore diameters are prepared as required, and after surface pretreatment, diamond, carbon nanometer tubes and graphene are subjected to chemical vapor deposition; then the mixture and matrix materials are compounded, wherein the matrix materials are metal or polymers; the carbon-fiber-reinforced metal-based or polymer-based composite material with the three-dimensional net-shaped framework structure is obtained.A three-dimensional continuous heat conduction channel is formed in the composite material through the surface-modification three-dimensional net-shaped carbon fibers, and therefore the heat conduction performance of the composite material is greatly improved; meanwhile, according to space distribution of carbon fibers in the matrix material, the mechanical performance of the composite material can also be improved, and the density and the thermal expansion coefficient can be decreased; the thermal expansion coefficient, the mechanical performance and the thermal performance can be further regulated and controlled by adding zero-dimensional particle reinforcement.

Owner:CENT SOUTH UNIV

Bi-layer pseudo-spin field-effect transistor

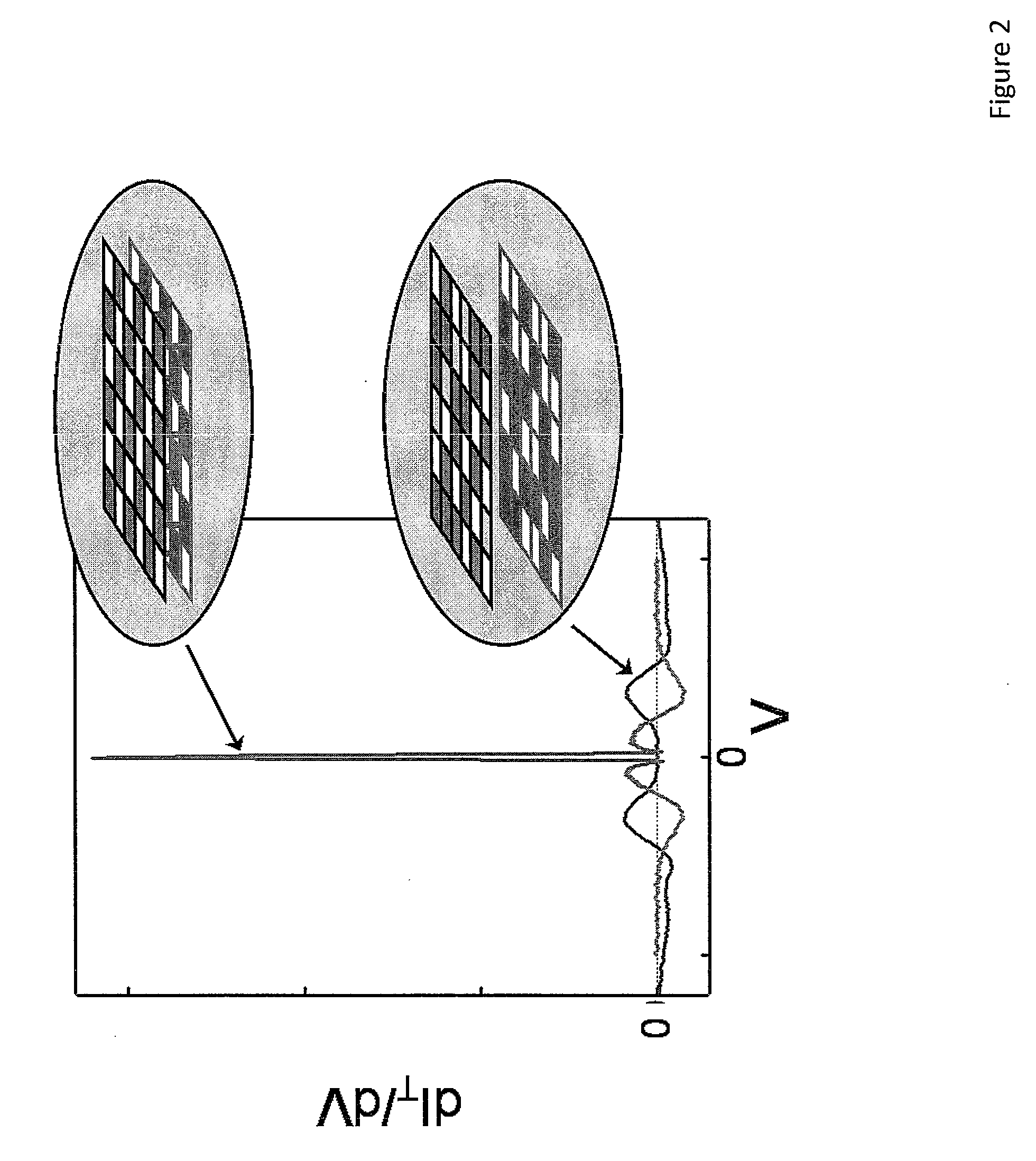

InactiveUS20100127243A1Low gate and interlayer biasesNanoinformaticsSemiconductor/solid-state device manufacturingEngineeringPeak value

A bi-layer pseudo-spin field-effect transistor (BiSFET) is disclosed. The BiSFET includes a first and second conduction layers separated by a tunnel dielectric. The BiSFET transistor also includes a first gate separated from the first conduction layer by an insulating dielectric layer, and a second gate separated from the second conduction layer by an insulating layer. These conduction layers may be composed of graphene. The voltages applied to the first and / or second gates can control the peak current and associated voltage value for current flow between top and bottom conduction channels, and interlayer current voltage characteristic exhibiting negative differential resistance. BiSFETs may be used to make a variety of logic gates. A clocked power supply scheme may be used to facilitate BiSFET-based logic.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

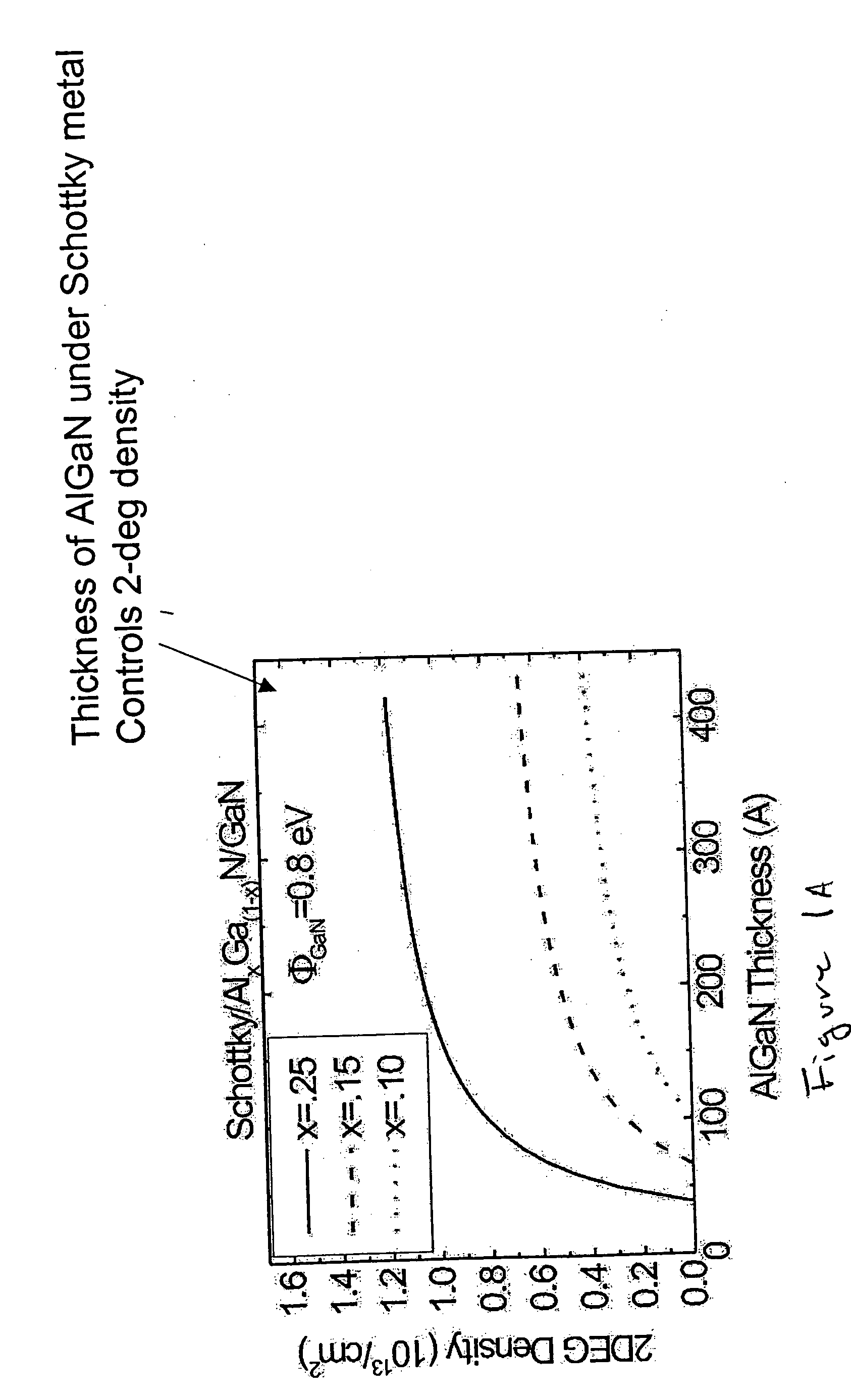

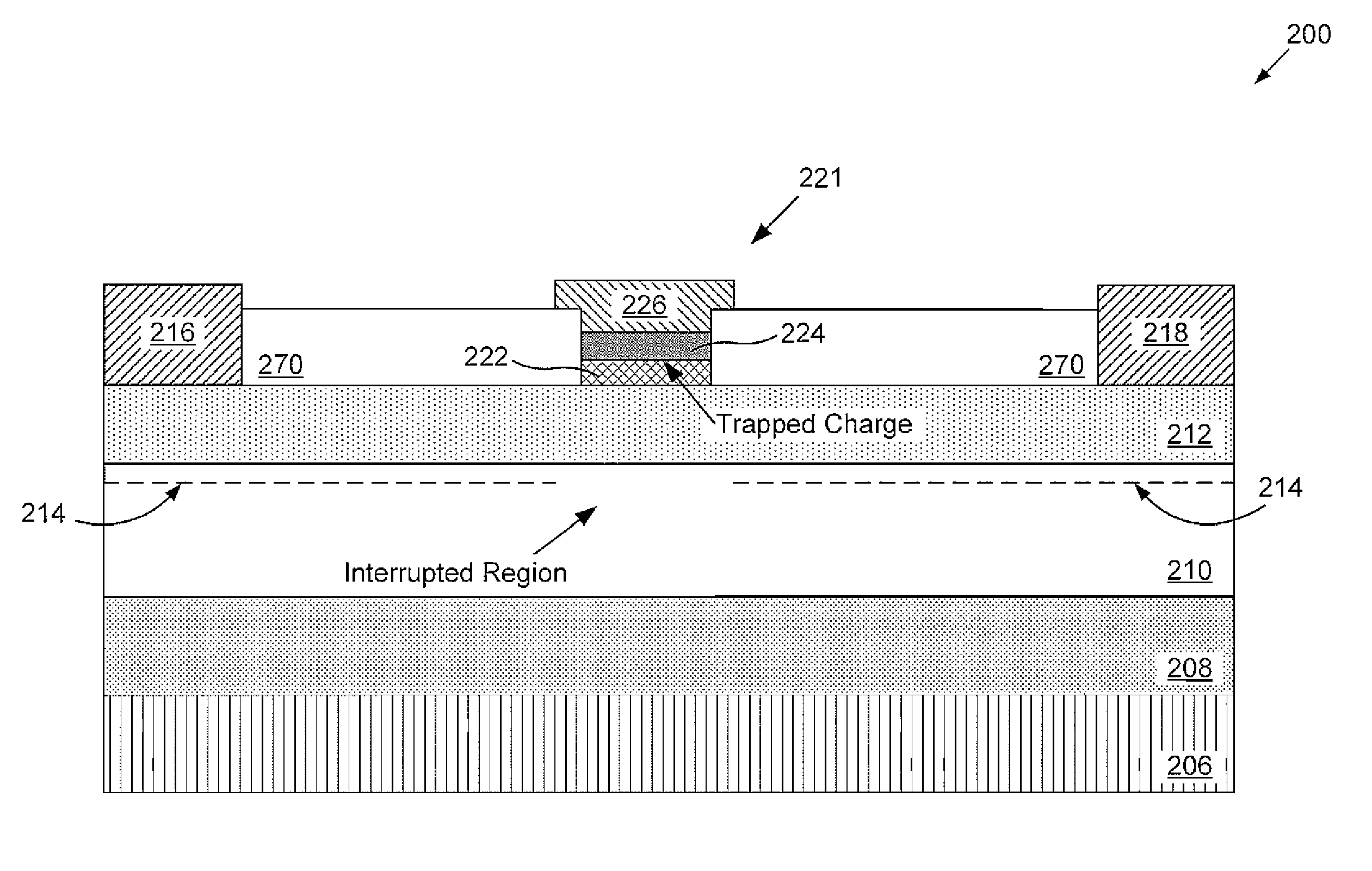

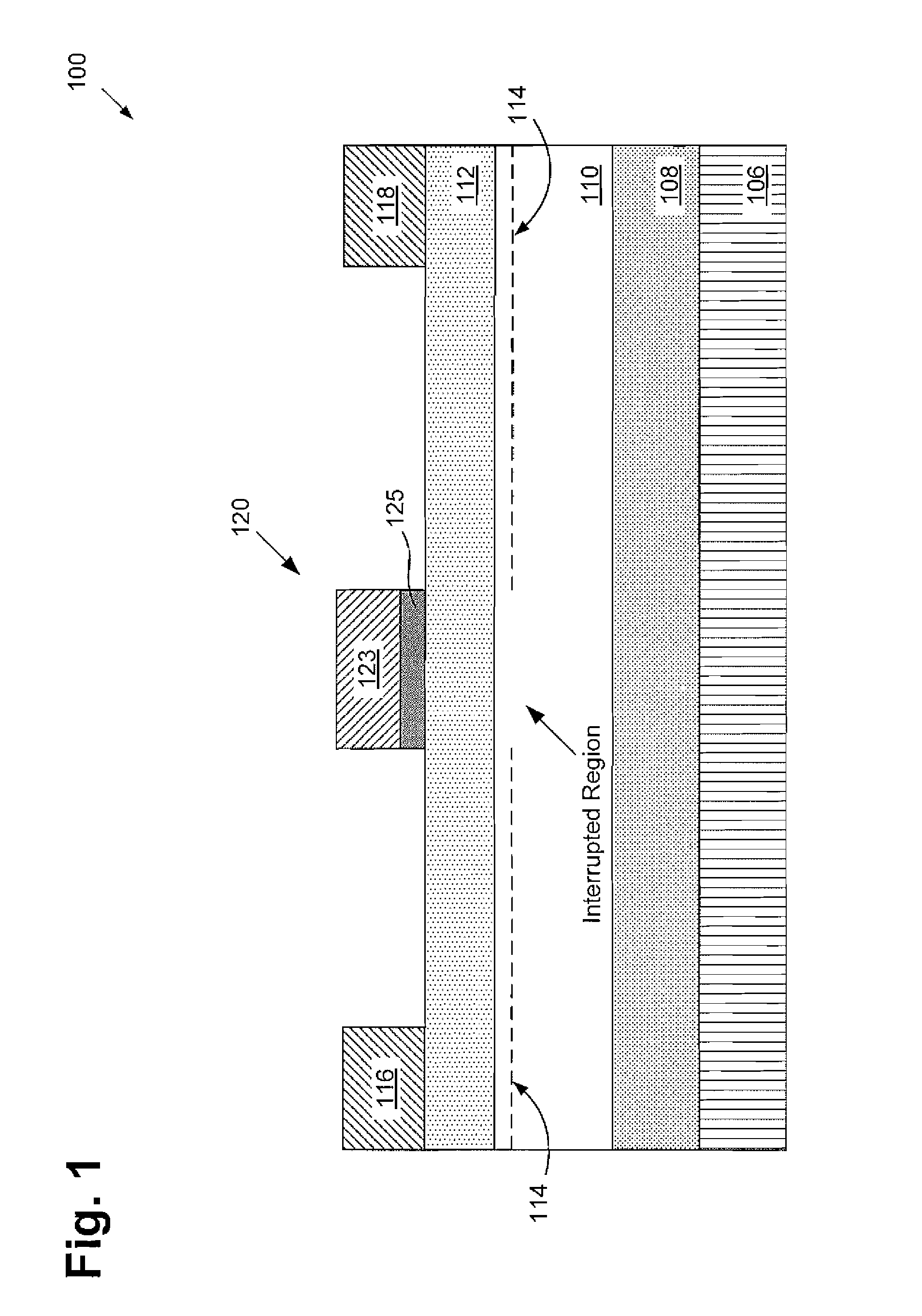

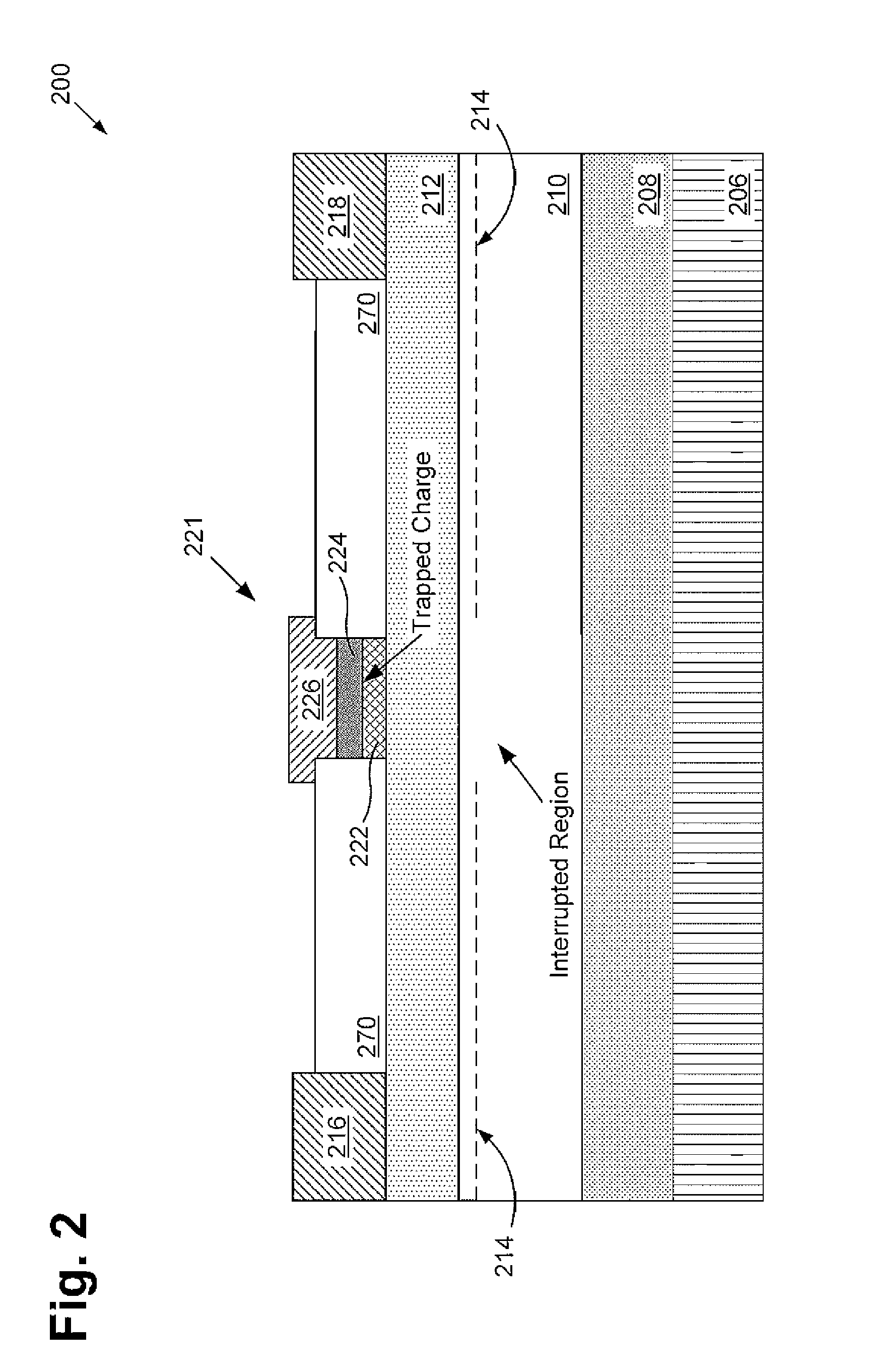

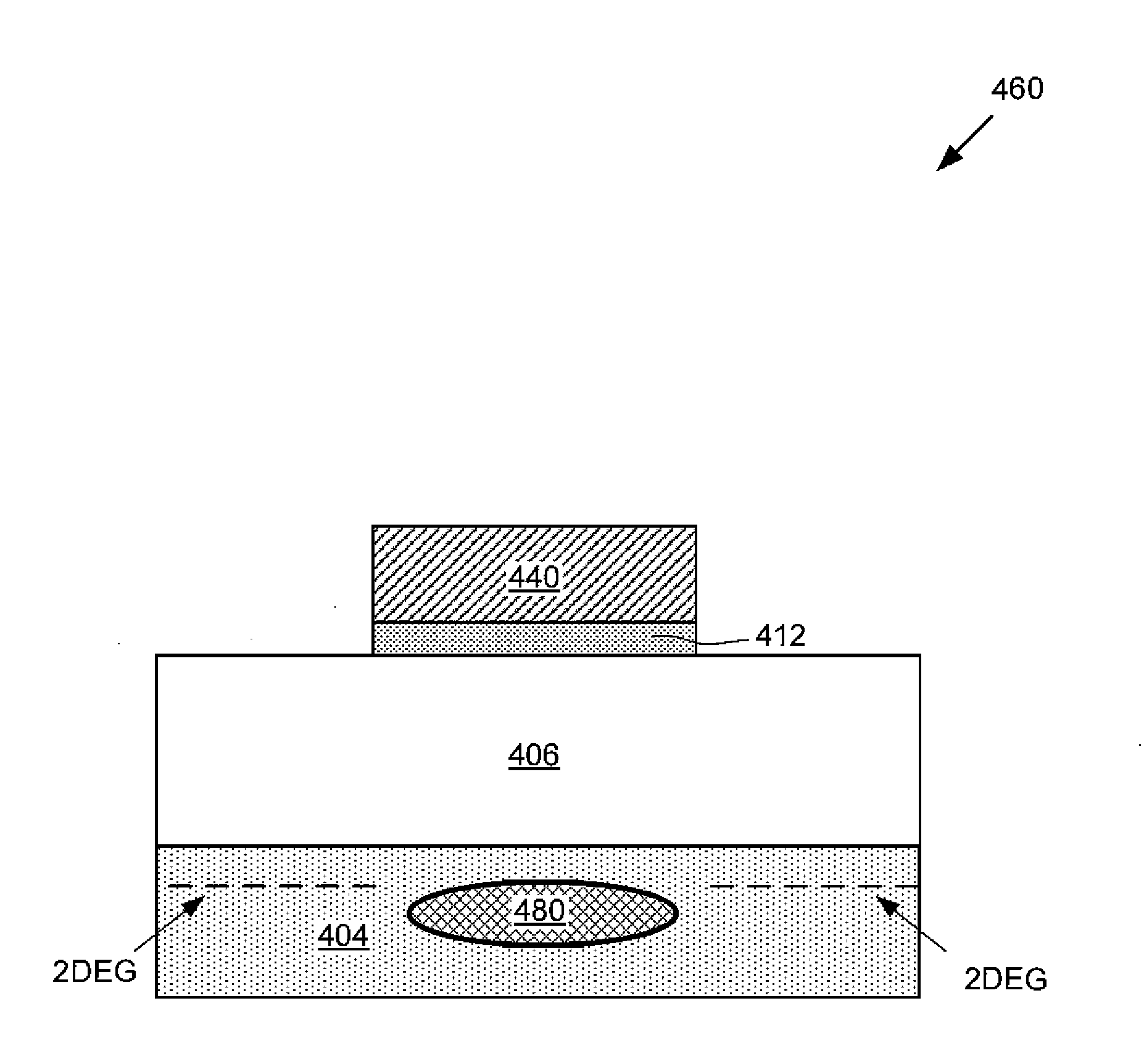

Enhancement Mode III-Nitride Transistors with Single Gate Dielectric Structure

ActiveUS20110121313A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSilicon oxide

According to one embodiment, a III-nitride transistor includes a conduction channel formed between first and second III-nitride bodies, the conduction channel including a two-dimensional electron gas. The transistor also includes at least one gate dielectric layer having a charge confined within to cause an interrupted region of the conduction channel and a gate electrode operable to restore the interrupted region of the conduction channel. The transistor can be an enhancement mode transistor. In one embodiment, the gate dielectric layer is a silicon nitride layer. In another embodiment, the at least one gate dielectric layer is a silicon oxide layer. The charge can be ion implanted into the at least one gate dielectric layer. The at least one gate dielectric layer can also be grown with the charge.

Owner:INFINEON TECH AMERICAS CORP

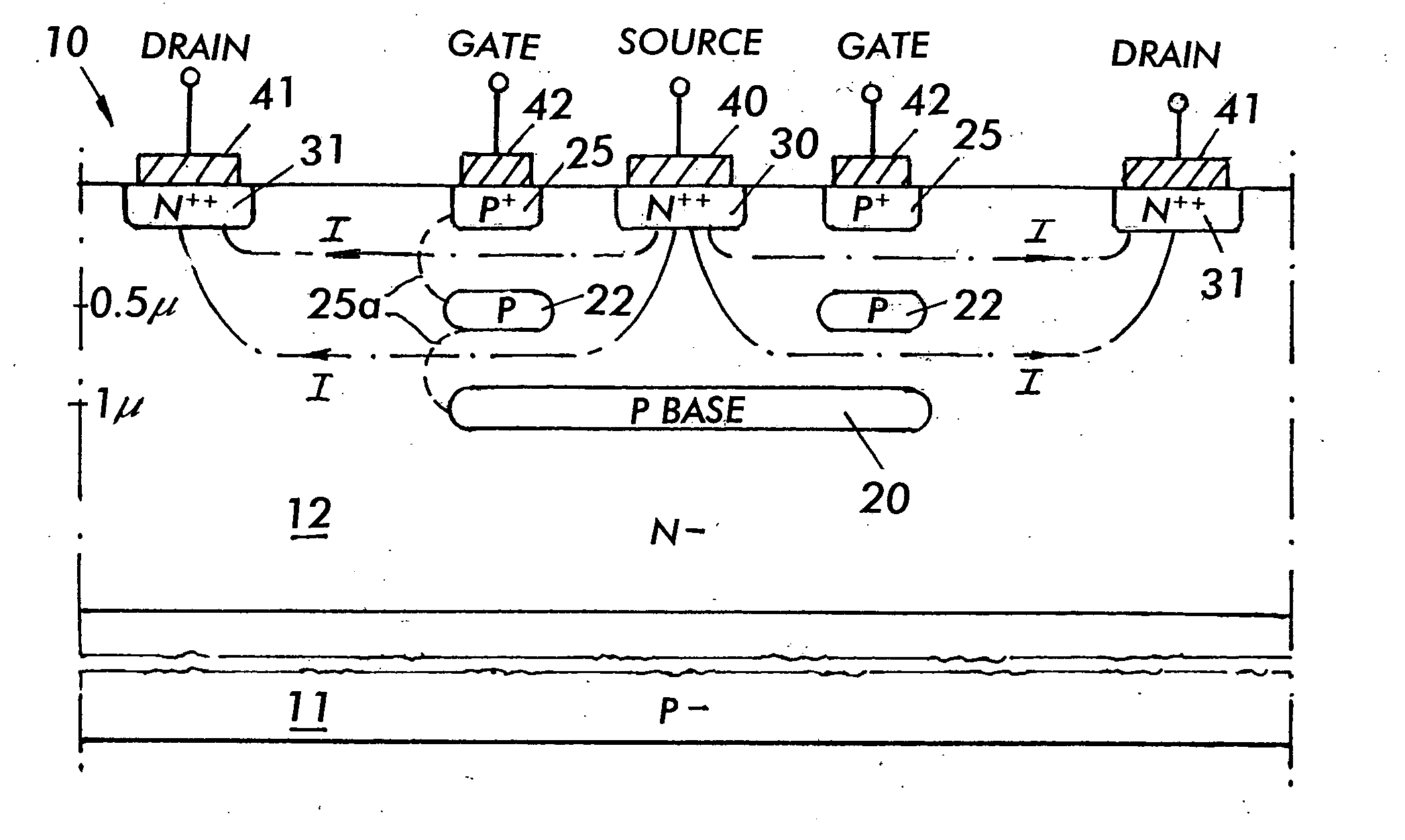

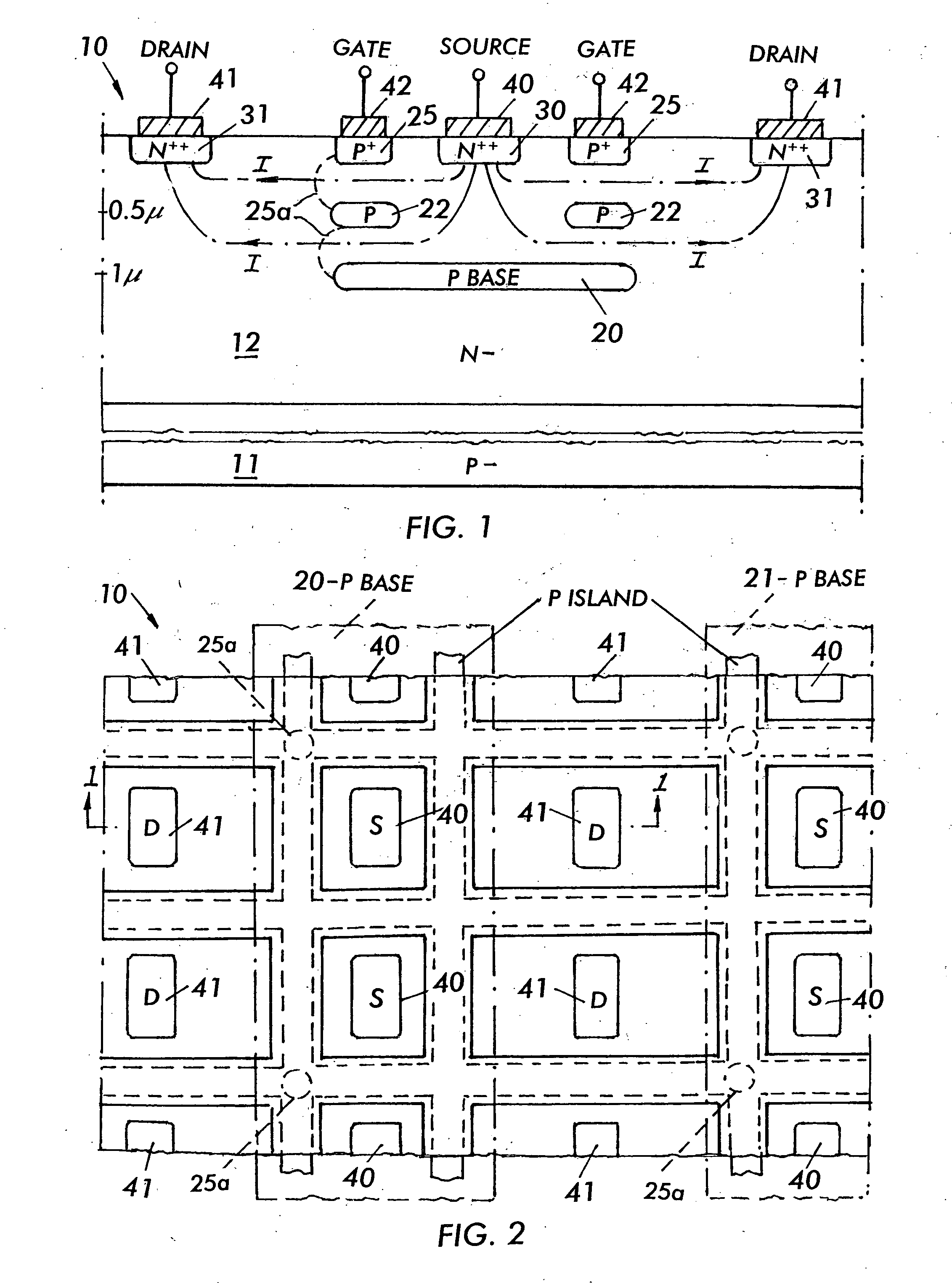

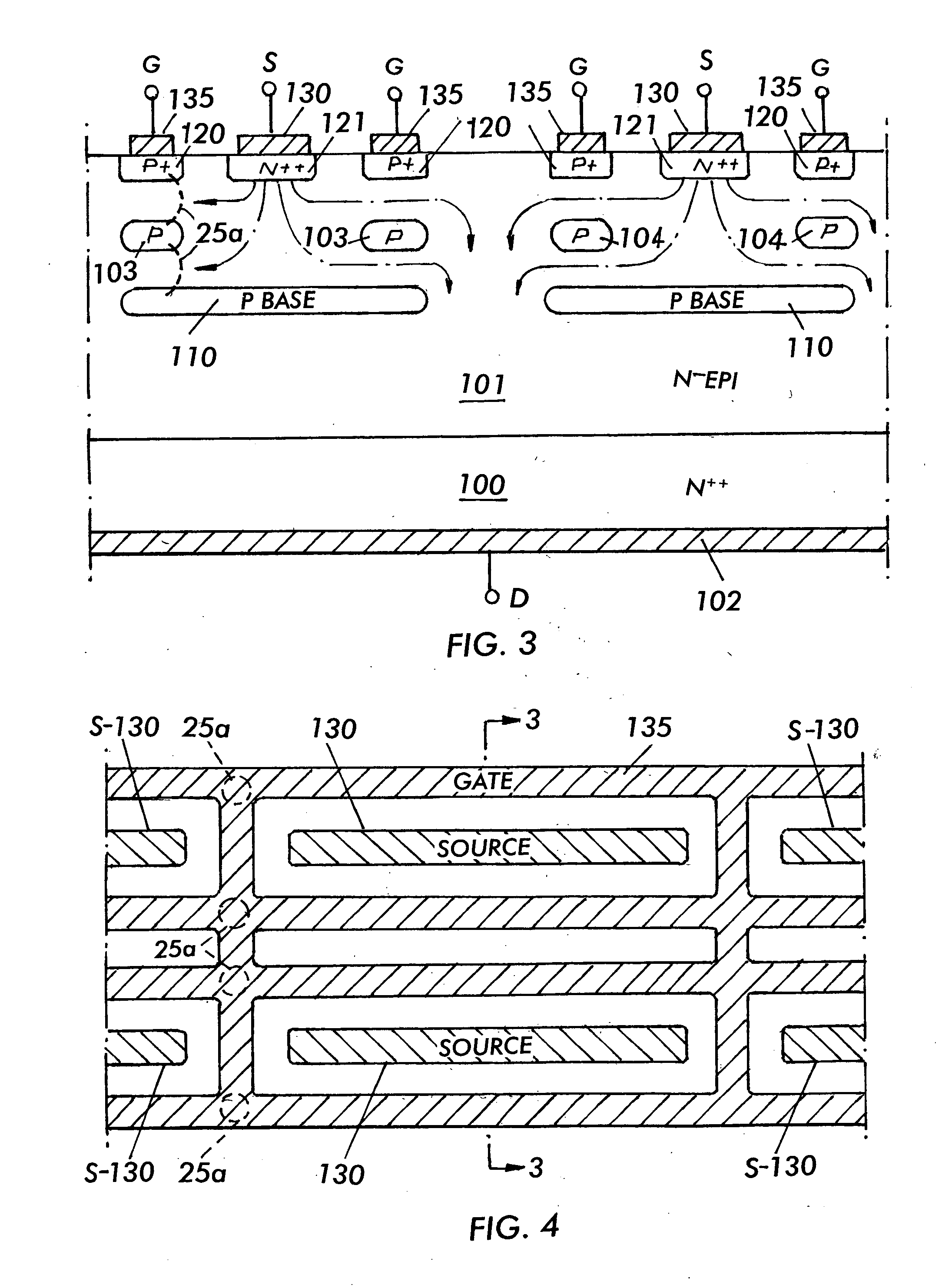

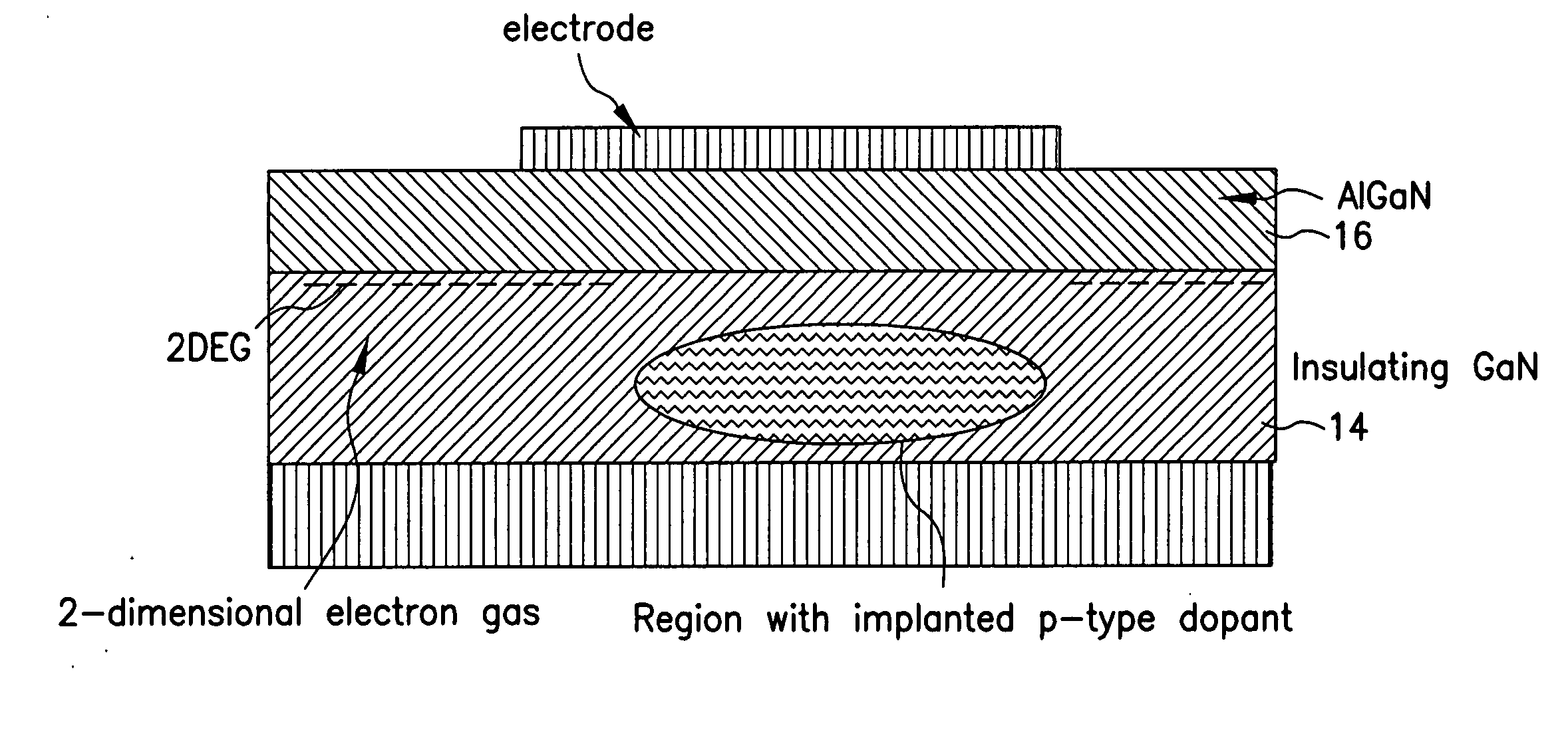

Normally off JFET

ActiveUS20050173726A1Reduce concentrationSimple processTransistorSemiconductor/solid-state device manufacturingJFETGate voltage

A normally off JFET is formed by the implantation of a P base; and a shallower P island atop the P base, forming a narrow lateral conduction channel between the two and a shallow gate implant in the device top surface which forms a second lateral conduction channel with the island. The two channels are each less than 0.5 microns thick and have an impurity concentration such that the channels are depleted at zero gate voltage and are turned on when the gate is forward biased. The gate surrounds a source implant region and a remote drain is provided which is connected to the top surface of the device for a lateral JFET or the bottom of the device for a vertical conduction JFET.

Owner:INFINEON TECH AMERICAS CORP

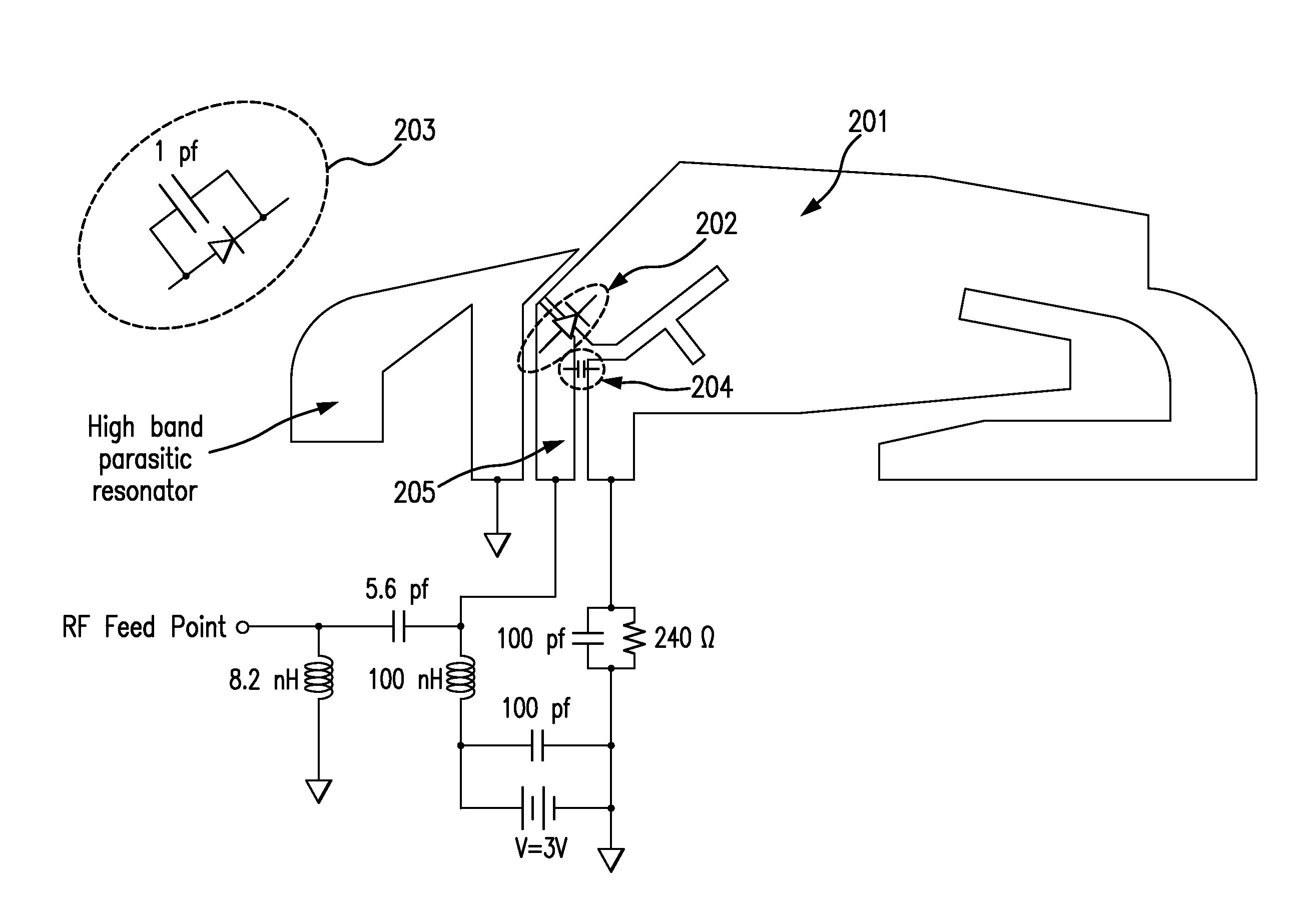

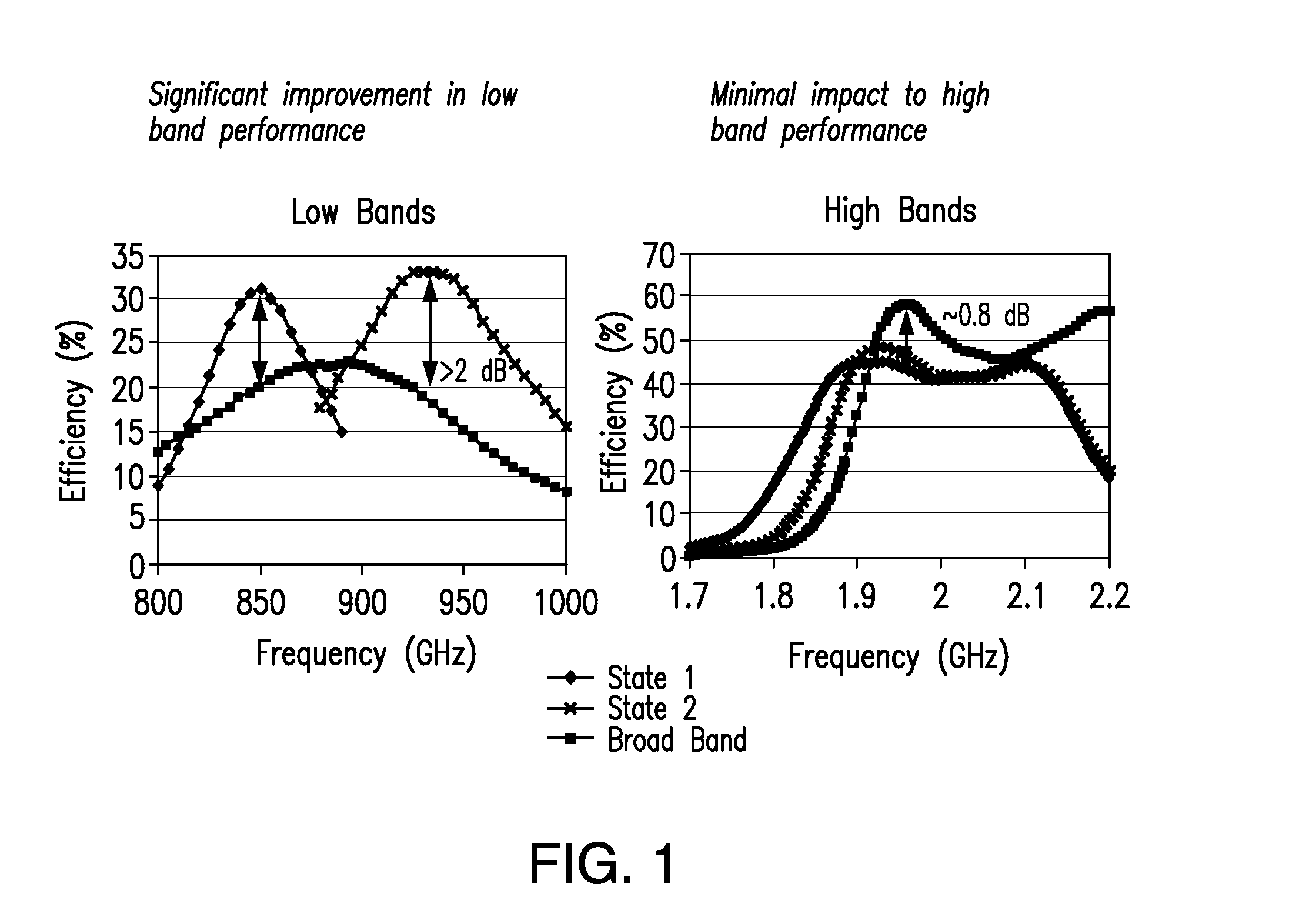

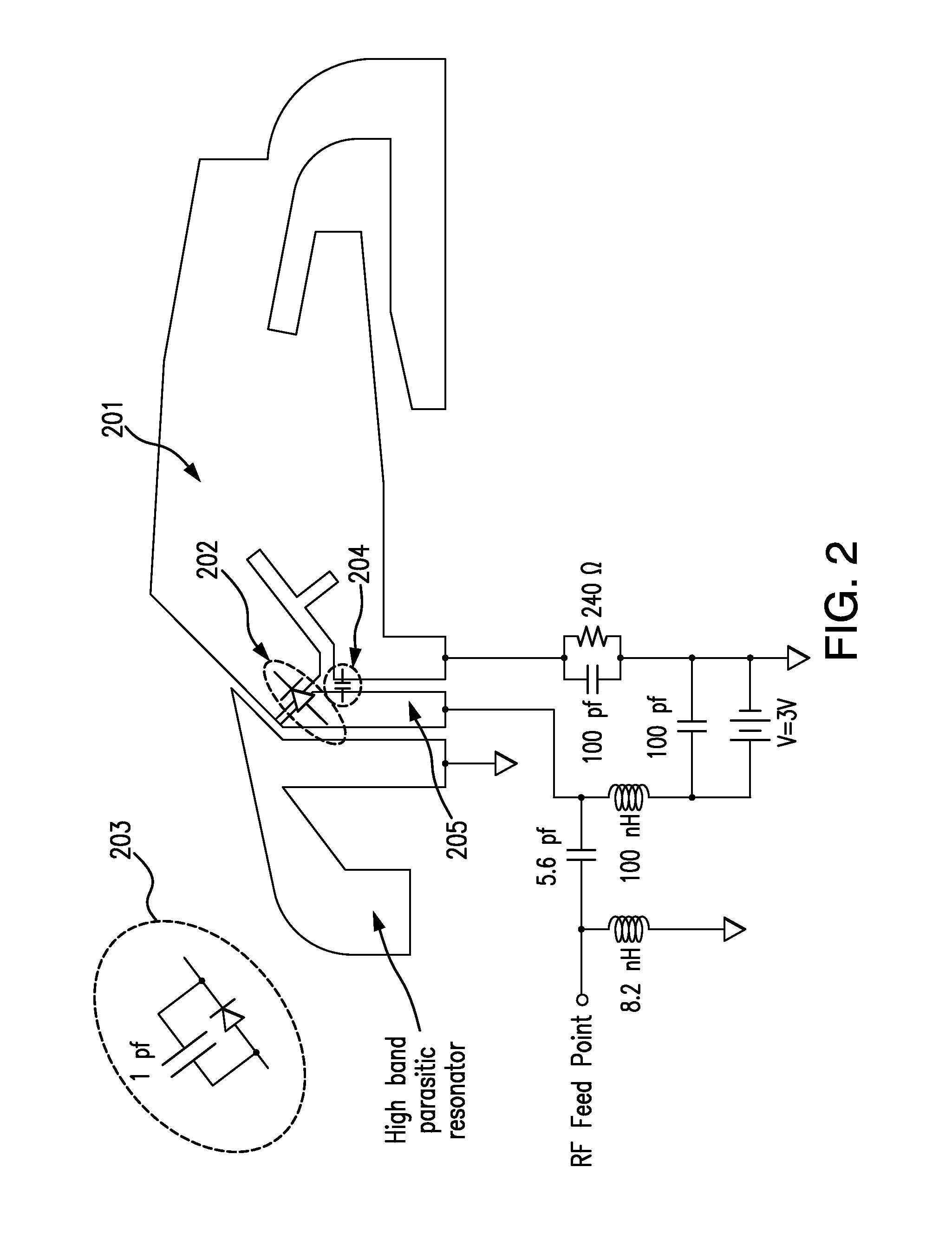

Method and apparatus for controlling an antenna

A system that incorporates the subject disclosure may include, for example, a method for coupling a primary antenna to an auxiliary antenna portion with a current-controlled switch. The method further includes generating a unidirectional direct current or a first bias voltage having a first polarity to cause the current-controlled switch to substantially form a conduction channel between the primary antenna and the auxiliary antenna portion. While the conduction channel is present, a first resonance frequency range of the primary antenna is frequency shifted to a second resonance frequency range. The method can also include removing the unidirectional direct current or generating a second bias voltage having a second polarity to cause the current-controlled switch to form an open circuit between the primary antenna and the auxiliary antenna portion. While the open circuit is present, the first resonance frequency range of the primary antenna is restored. Other embodiments are disclosed.

Owner:SKYCROSS INC

Enhancement mode iii-nitride fet

ActiveUS20080248634A1Lower resistanceReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesNitrideMetal

A III-nitride switch includes a recessed gate contact to produce a nominally off, or an enhancement mode, device. By providing a recessed gate contact, a conduction channel formed at the interface of two III-nitride materials is interrupted when the gate electrode is inactive to prevent current flow in the device. The gate electrode can be a schottky contact or an insulated metal contact. Two gate electrodes can be provided to form a bi-directional switch with nominally off characteristics. The recesses formed with the gate electrode can have sloped sides. The gate electrodes can be formed in a number of geometries in conjunction with current carrying electrodes of the device.

Owner:INFINEON TECH AMERICAS CORP

Quasi-one-dimensional metal oxide nano-material biosensor and method for manufacturing same

ActiveCN101592626AHigh sensitivityQuick responseTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesQuasi one dimensionalField-effect transistor

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

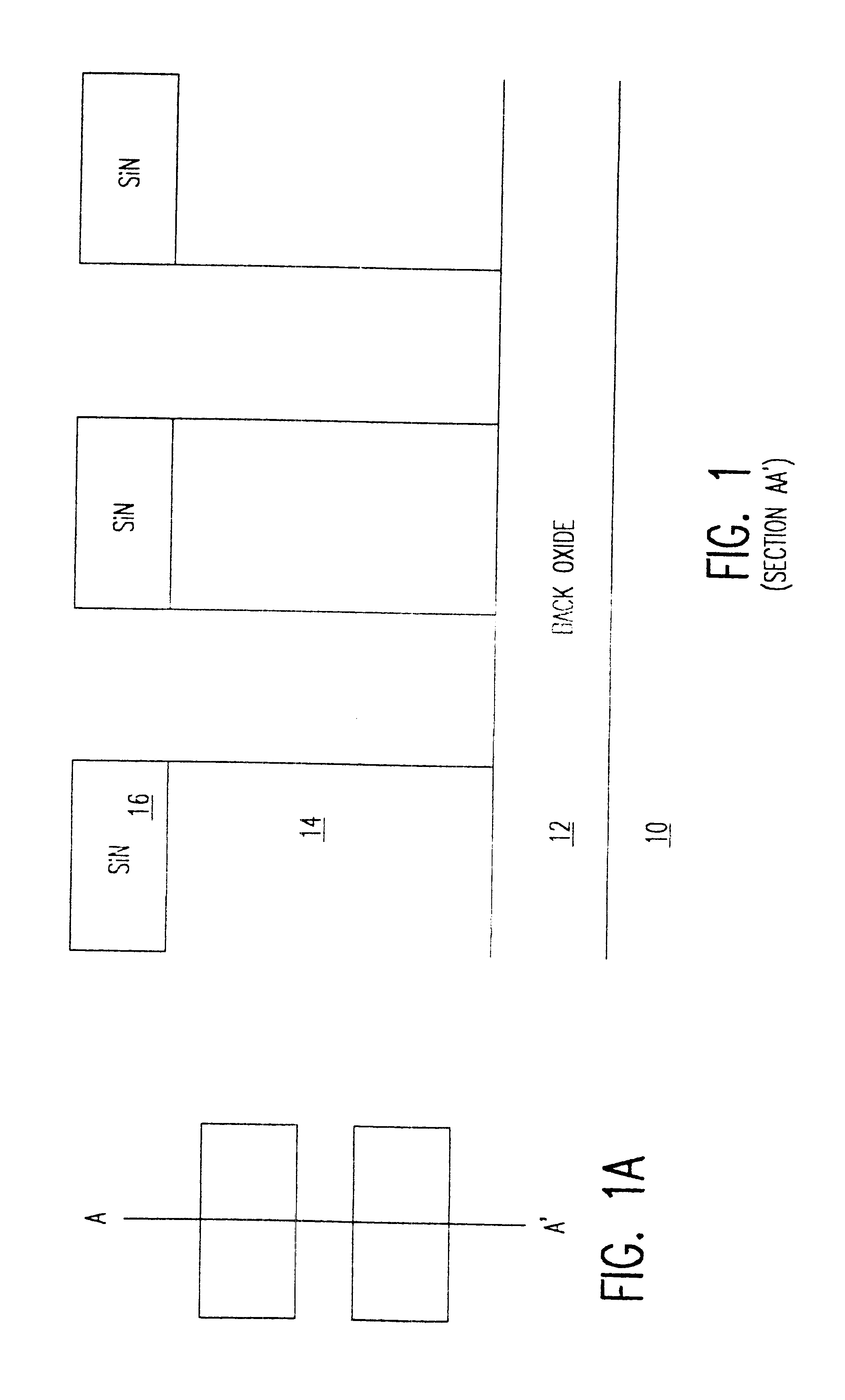

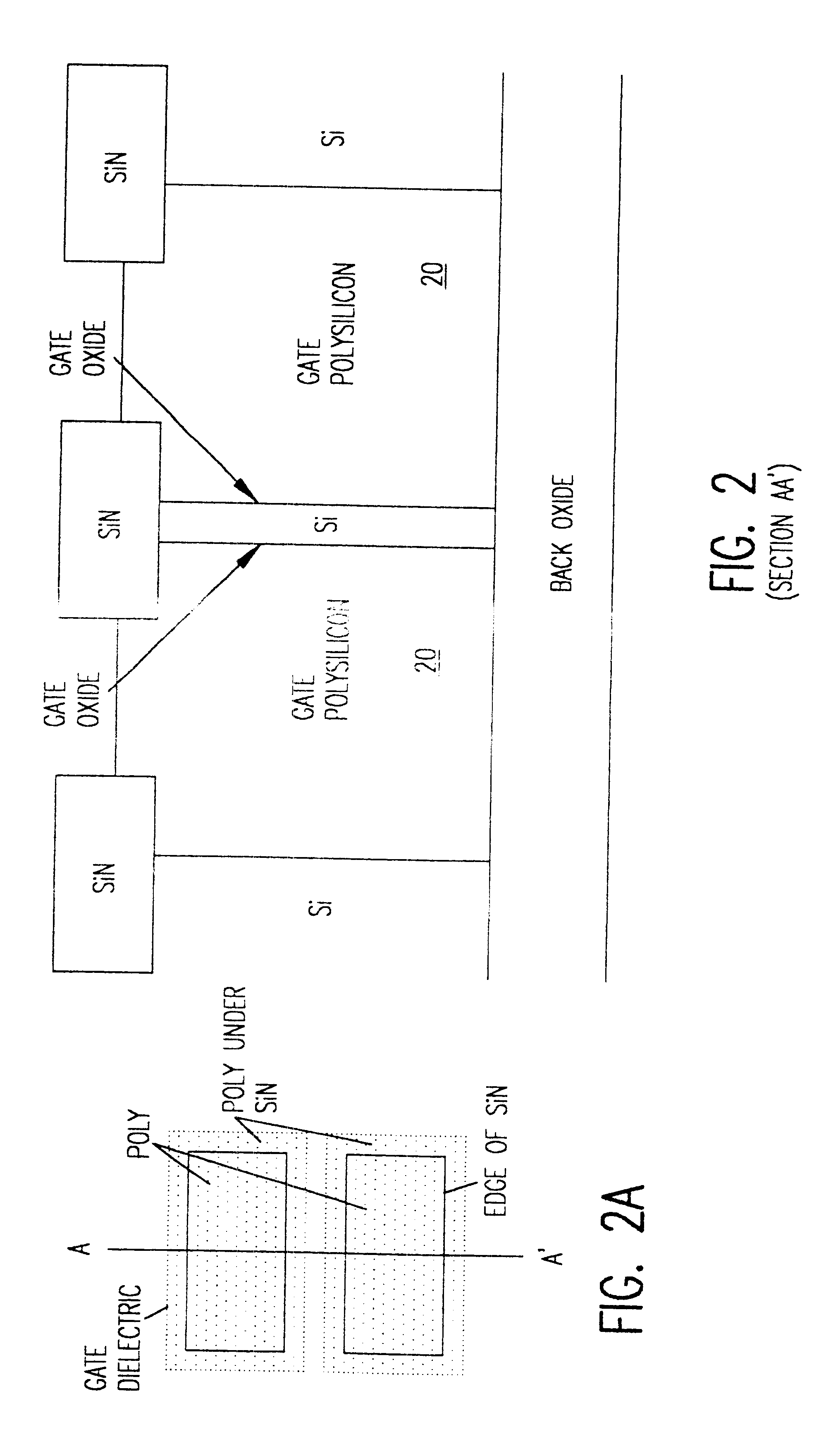

SOI transistor with polysilicon seed

InactiveUS6521949B2High density integrationHigh precisionTransistorSolid-state devicesPath lengthConcentration gradient

Short channel effects are effectively suppressed by steep impurity concentration gradients which can be placed with improved accuracy of location and geometry while relaxing process tolerances by implanting impurities in a polysilicon seed adjacent a conduction channel of a transistor and diffusing impurities therefrom into the conduction channel. The polysilicon seed also allows the epitaxial growth of polysilicon source / drain contacts therefrom having a configuration which minimizes current density and path length therein while providing further mechanical advantages.

Owner:GLOBALFOUNDRIES US INC

Mobile terminal

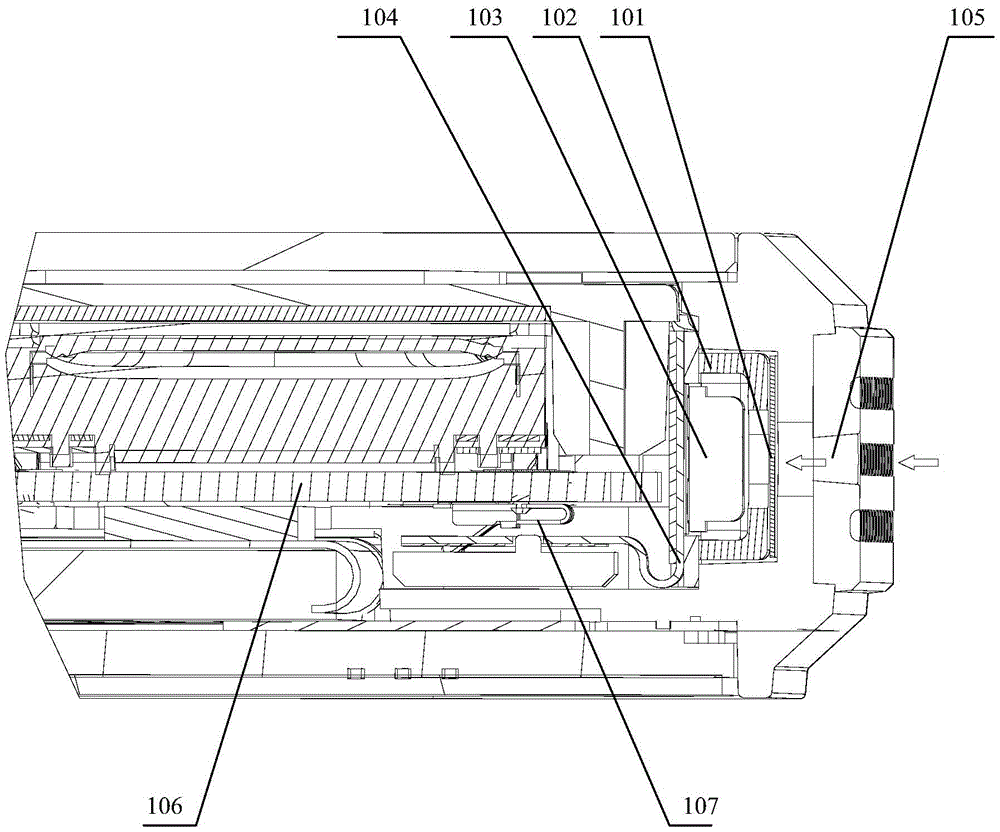

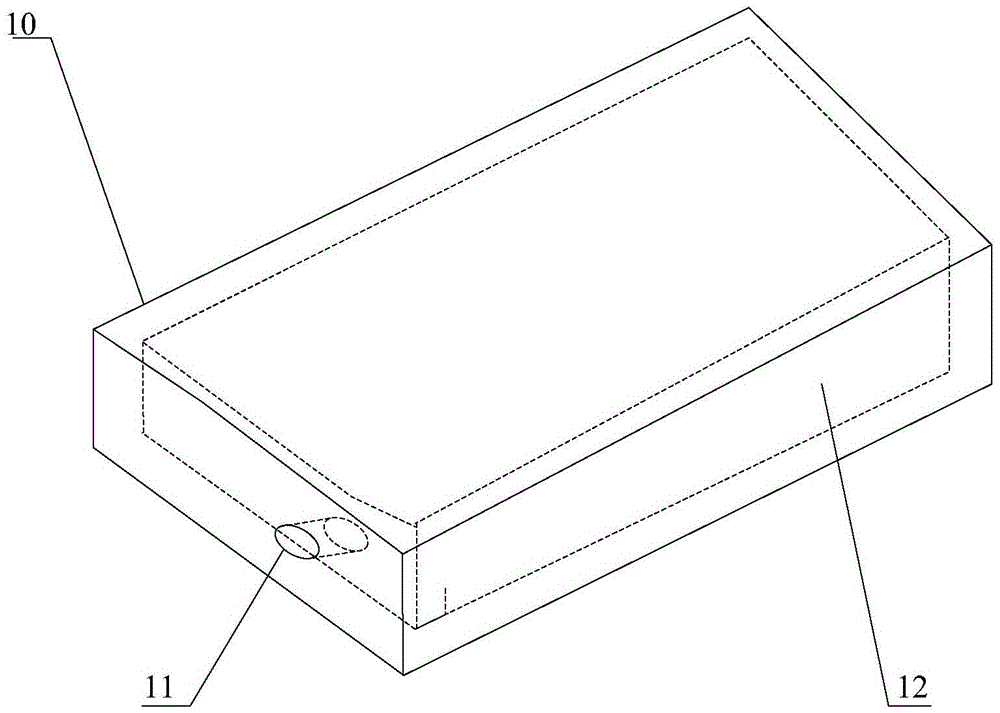

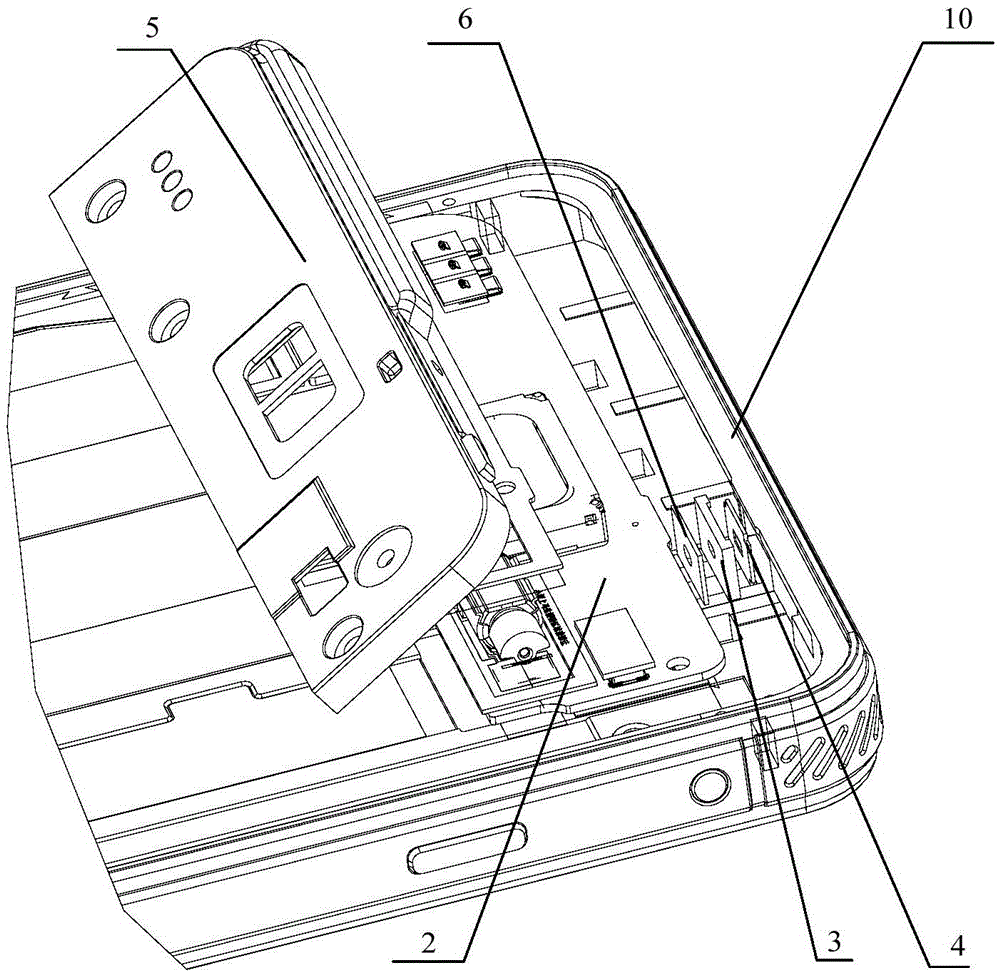

ActiveCN105611012AEasy to fixFlatten outMouthpiece/microphone attachmentsTelephone set constructionsComputer terminalEngineering

The invention provides a mobile terminal. The mobile terminal provided by the invention comprises a shell; a pickup hole is formed in the shell; a microphone, a circuit board, a waterproof membrane bracket, a waterproof membrane and a sound receiving bracket are arranged in the inner cavity of the shell; the waterproof membrane is stuck on the waterproof membrane bracket and is supported against the pickup hole which is located at the inner sidewall of the shell; the microphone is arranged on the circuit board; a sound receiving through hole which is opposite to the waterproof membrane is formed in the waterproof membrane bracket; the sound receiving bracket is connected with the shell; the sound receiving bracket is provided with a through hole; one end of the through hole is opposite to the sound receiving through hole of the waterproof membrane bracket while the other end thereof is opposite to the receiving end of the microphone, so that a sound conduction channel is formed between the pickup hole and the receiving end of the microphone; and the circuit board is electrically connected with the microphone to drive the microphone to receive sound. According to the mobile terminal, a microphone sealing and waterproof structure with good sealing and high reliability can be realized.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

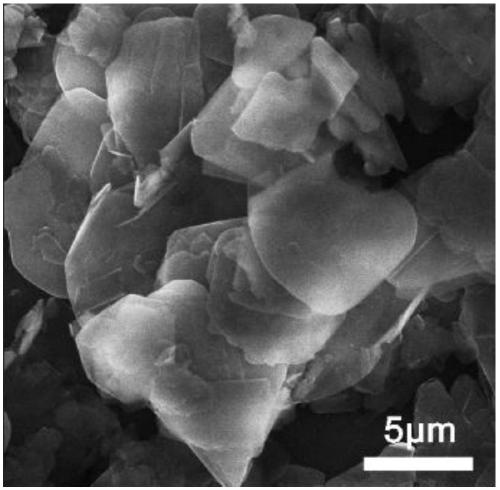

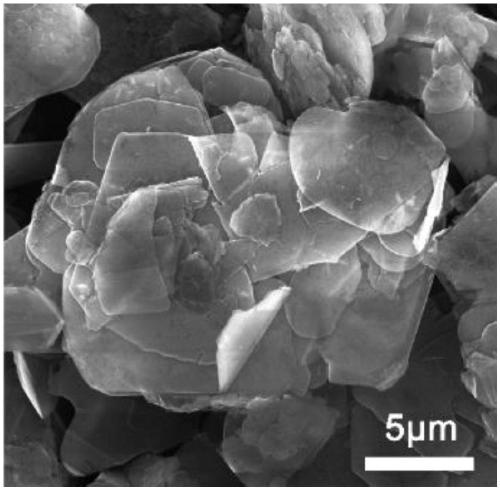

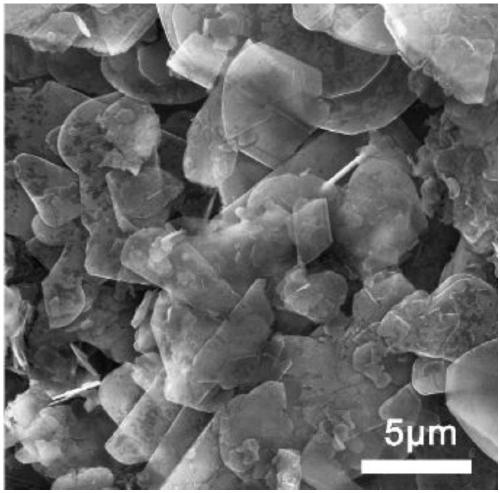

Preparation method of BN/epoxy resin heat conductive insulation composite material

The invention provides a preparation method of a BN / epoxy resin heat conductive insulation composite material and belongs to the field of preparation of heat conductive insulation composite materials.The method includes: firstly, performing annealing pretreatment to BN powder and then surface modification with a silane coupling agent; then according to certain ratio, filling an epoxy resin matrixwith the modified hexagonal BN micropowder and the modified cubic BN micropowder. The method is simple process, wherein by adding the BN in different appearances, dimensions and phase structures, effective heat conduction channels are formed to finally improve the heat conductivity of the epoxy resin. After modification, the interface combination between the HBN and the resin is strong, wherein the sheet-like HBN and bulk CBN are overlapped in the epoxy resin to form excellent heat conductive network, thus effectively reducing interfacial thermo-resistance. The composite material is beneficial to quick transmission of heat, improves heat conductivity of the epoxy resin, has excellent insulation performance, and is improved in mechanical property.

Owner:JILIN UNIV

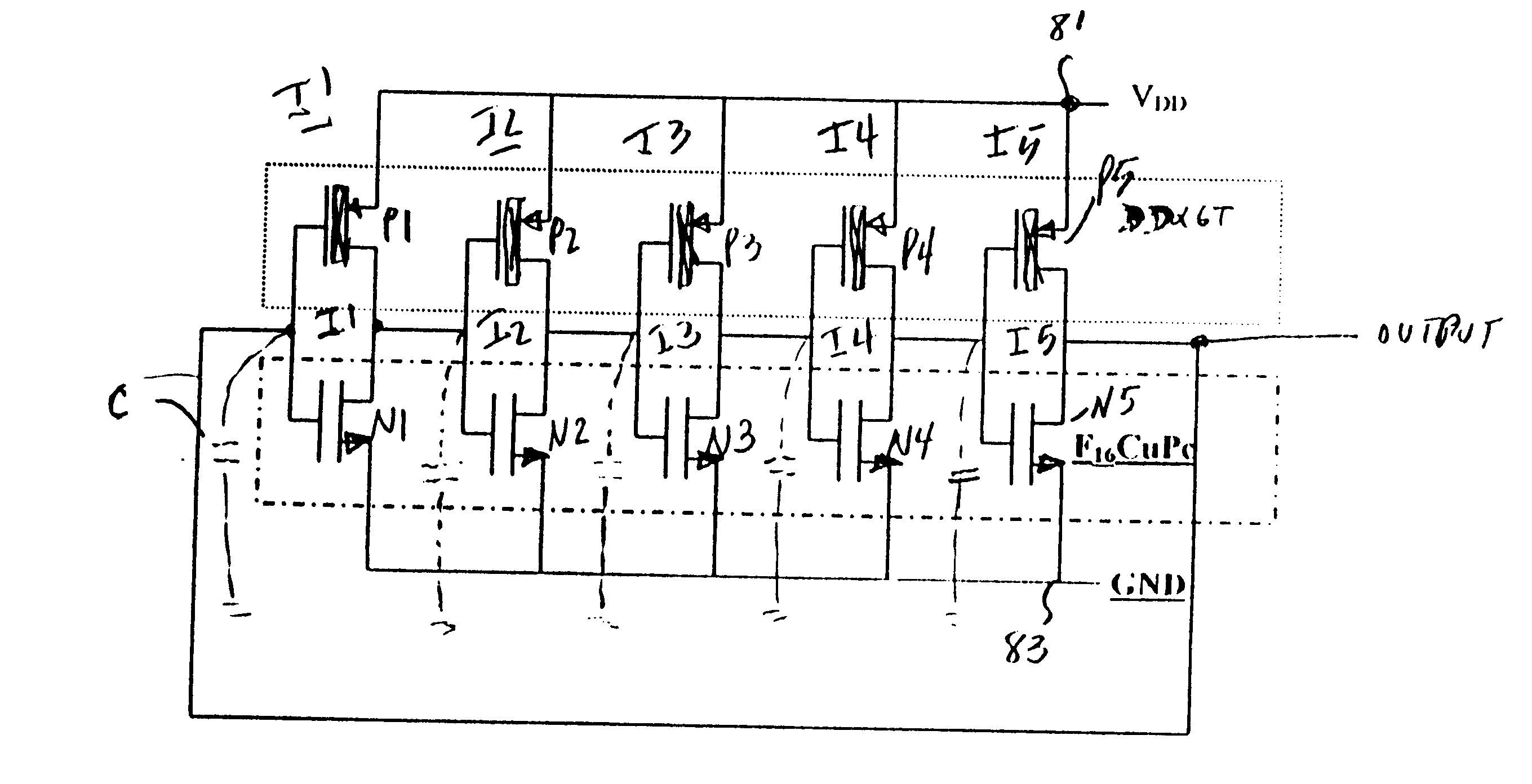

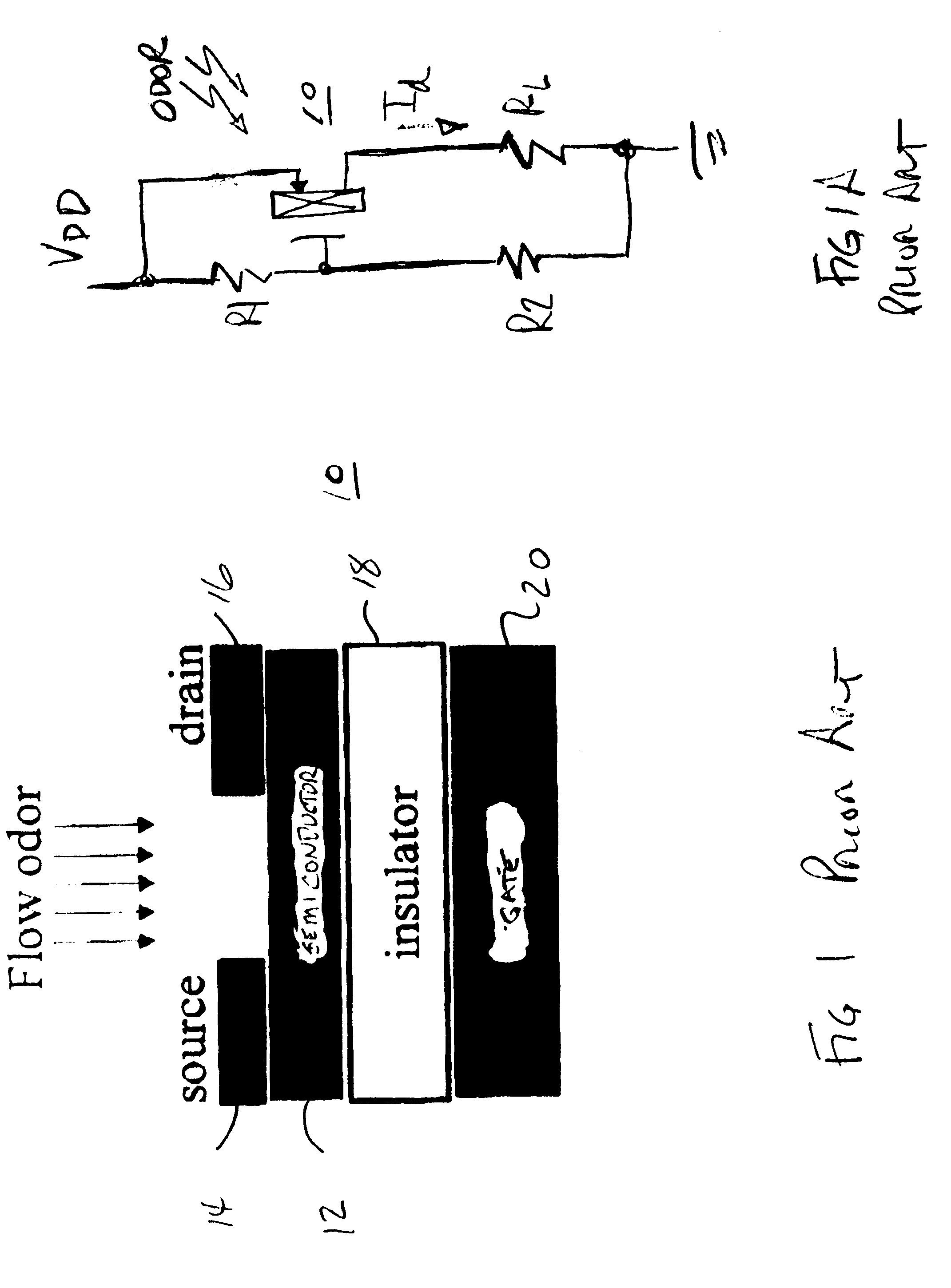

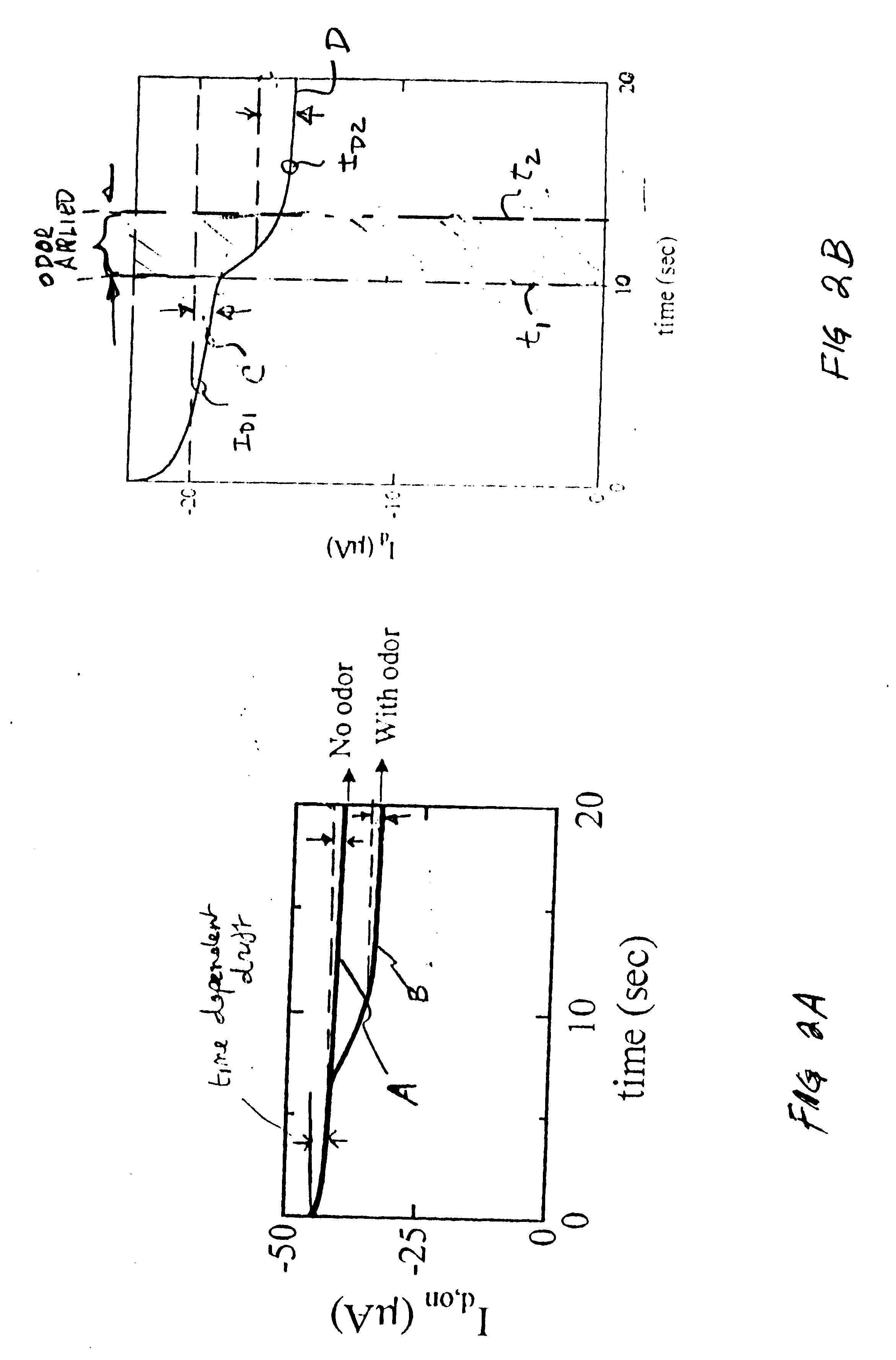

Odor sensor with organic transistor circuitry

InactiveUS6661299B2Improve responsePromote recoveryAnalysing fluids using sonic/ultrasonic/infrasonic wavesSemiconductor/solid-state device detailsConduction channelSignal enhancement

Circuits include at least one-odor sensitive organic transistor having a conduction channel whose conductivity changes in response to certain odors. The organic transistors are interconnected to increase their response to selected odor signals. The organic transistors may be interconnected to form a ring oscillator whose frequency of oscillation changes in response to an odor signal and in which the alternating signal applied to the gate electrodes of the organic transistors enhances their recovery and reduces their drift.

Owner:ALCATEL-LUCENT USA INC

Manufacturing technique of bipolar plate for fuel battery

The invention discloses a manufacturing technique of a bipolar plate for a fuel battery. By using expanded graphite as a carbon base material and resin powder as an adhesive, carbon black is added in the composite material preparation process, so that small carbon black particles help to form conduction channels among the graphite particles, thereby enhancing the electric conductivity; and carbon fibers merged into the composite bipolar plate can generate favorable bending strength. Thus, the bipolar plate for a fuel battery, which has the advantages of favorable corrosion resistance, favorable electric and thermal conductivity, high gas barrier property, high mechanical strength and low cost, and can be prepared by a reasonable compounding process.

Owner:KUSN FUERSAI ENERGY

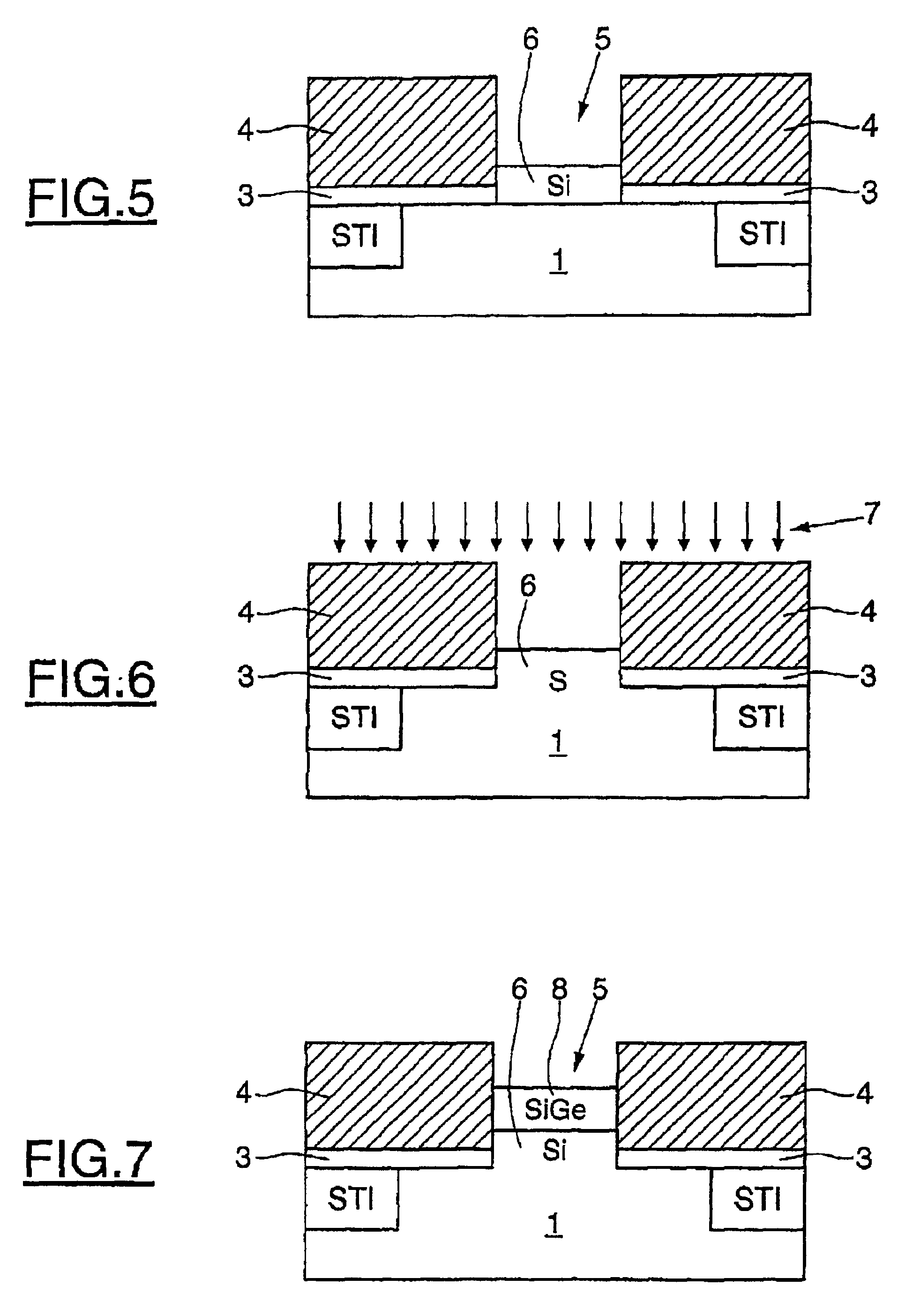

Structure and method of applying stresses to PFET and NFET transistor channels for improved performance

InactiveUS7193254B2TransistorSemiconductor/solid-state device manufacturingElectrical conductorEngineering

A semiconductor device structure is provided which includes a first semiconductor device; a second semiconductor device; and a unitary stressed film disposed over both the first and second semiconductor devices. The stressed film has a first portion overlying the first semiconductor device, the first portion imparting a first magnitude compressive stress to a conduction channel of the first semiconductor device, the stressed film further having a second portion overlying the second semiconductor device, the second portion not imparting the first magnitude compressive stress to a conduction channel of the second semiconductor device, the second portion including an ion concentration not present in the second portion such that the second portion imparts one of a compressive stress having a magnitude much lower than the first magnitude, zero stress, and a tensile stress to the conduction channel of the second semiconductor device.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING +1

Semiconductor device with a vertical channel

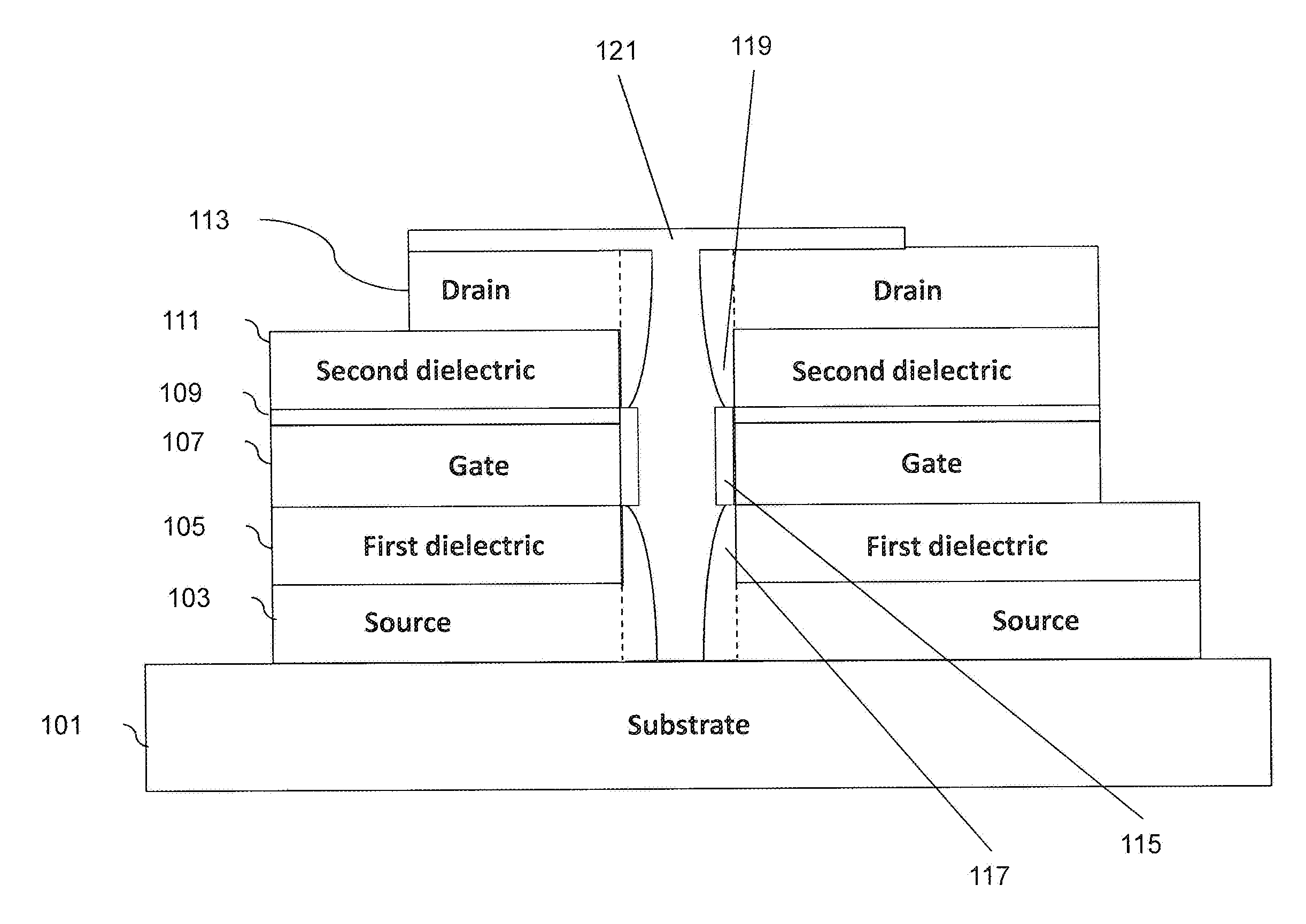

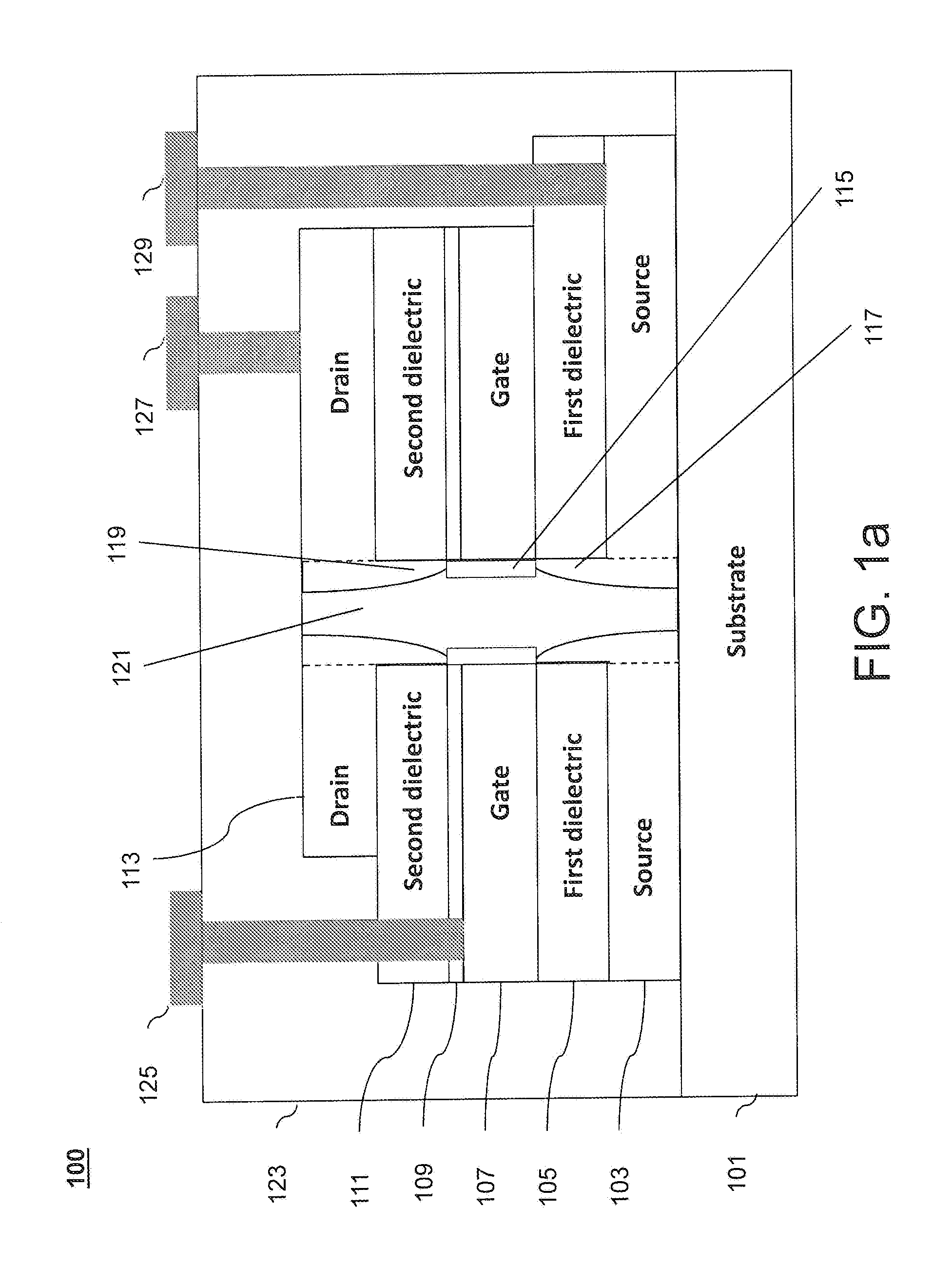

Semiconductor devices and manufacturing methods are provided for making channel and gate lengths independent from lithography. Also, semiconductor devices and manufacturing methods are provided for increasing resistivity between drain and channel to allow for higher voltage operation. For example, a semiconductor device includes a first doped layer implanted in a semiconductor substrate forming one of a source or a drain and a gate metal layer disposed over the first doped layer. The semiconductor device further includes a second doped layer disposed over the gate metal forming the other the source or the drain, where the first doped layer, the gate metal layer and the second doped layer form a vertical stack of layers of the semiconductor device. The semiconductor device further includes a conduction channel formed in a trench that extends vertically through the vertical stack of layers and terminates at the semiconductor substrate.

Owner:AVAGO TECH INT SALES PTE LTD

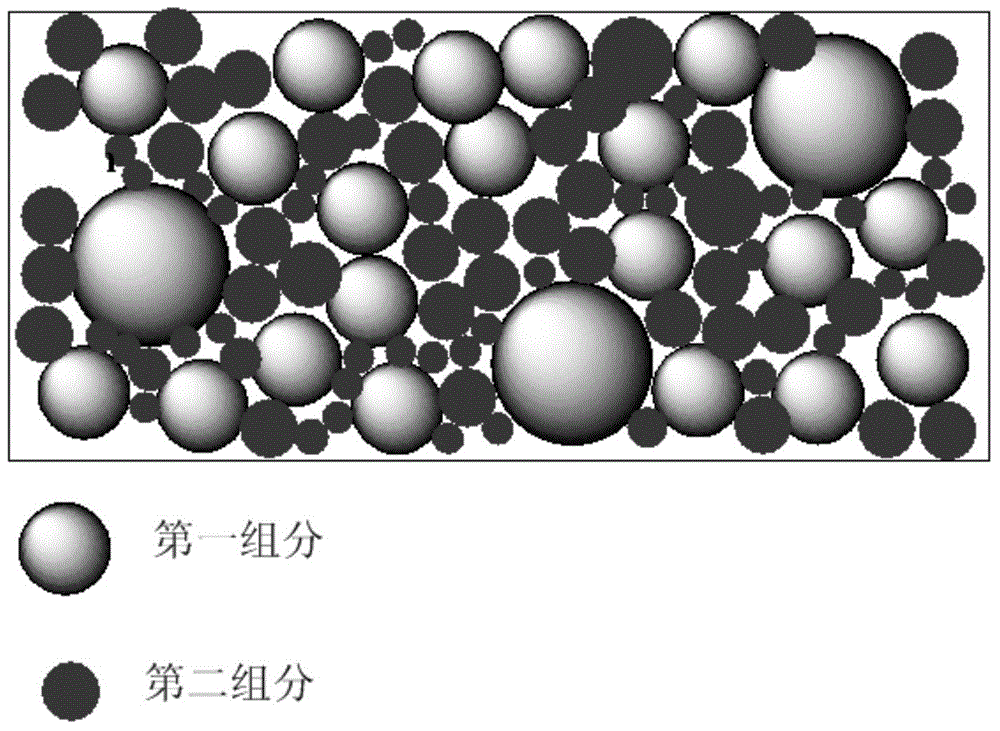

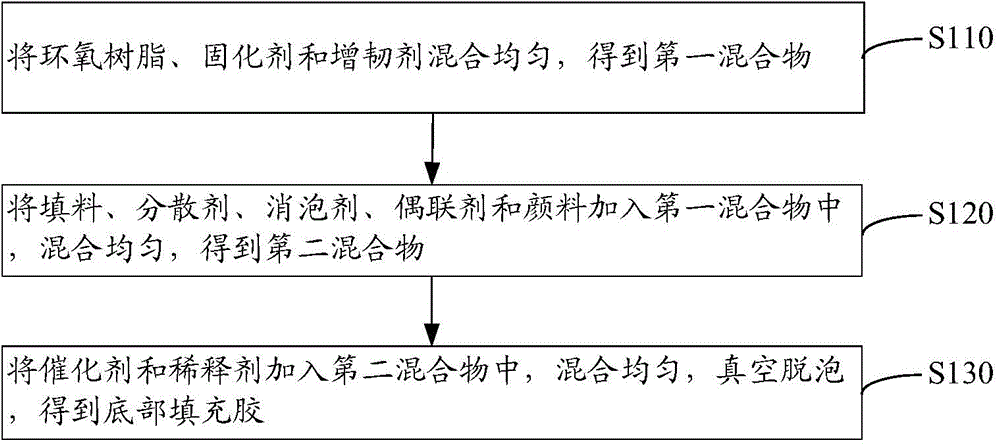

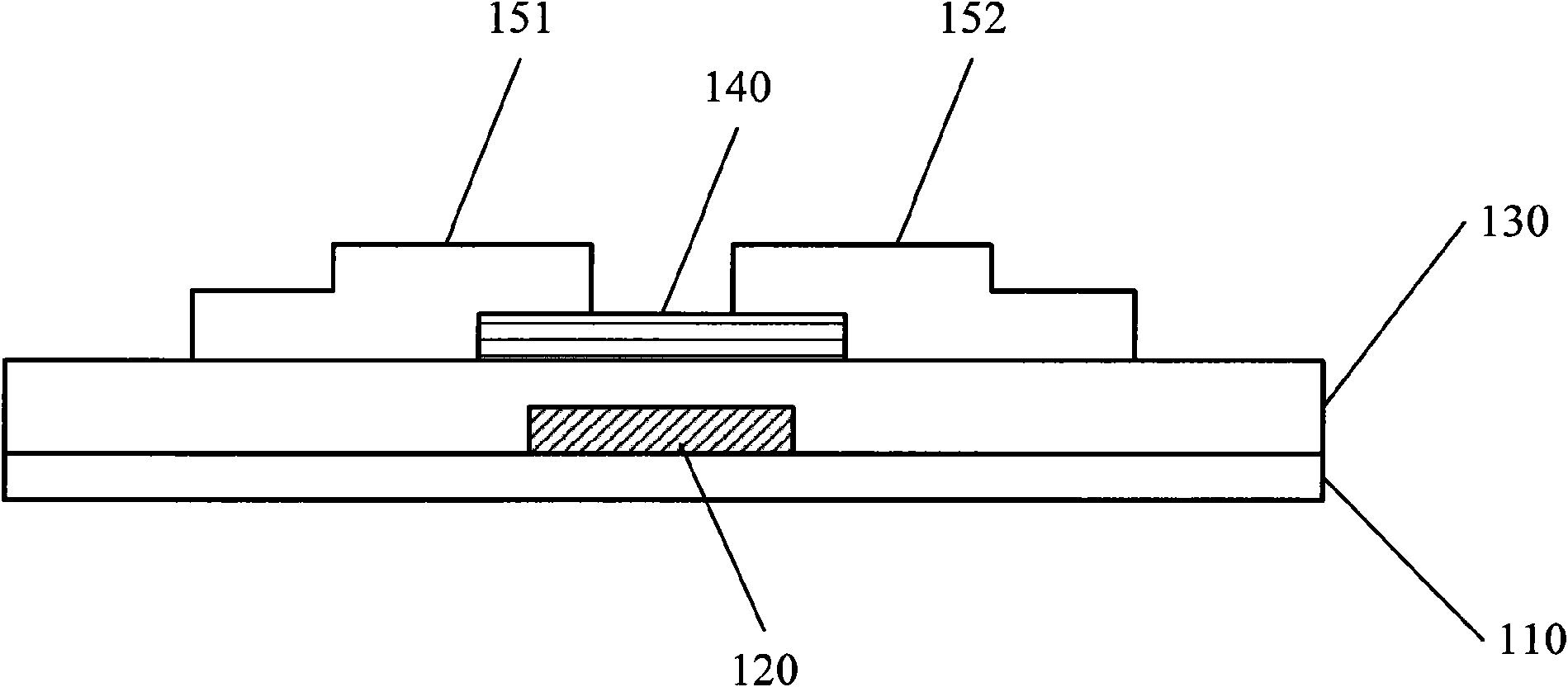

Underfill adhesive and preparation method thereof

ActiveCN104910845AImprove thermal conductivityHigh thermal conductivityNon-macromolecular adhesive additivesEpoxy resin adhesivesEpoxyAdhesive

The invention relates to an underfill adhesive and a preparation method thereof. The underfill adhesive comprises the following ingredients by weight percent: 30 to 70 percent of filler, 10 to 50 percent of epoxy resin, 2 to 20 percent of curing agent, 0.1 to 0.5 percent of catalyst, 1 to 15 percent of flexibilizer, 1 to 25 percent of diluting agent, 0.1 to 3 percent of dispersing agent, 0.05 to 1 percent of defoaming agent, 0.1 to 1 percent of coupling agent and 0.1 to 0.5 percent of pigment; the filler comprises a first component and a second component, wherein the first component is spherical silicon dioxide, and the second component is selected from one of spherical nano aluminum oxide, spherical nano boron nitride, spherical nano aluminum nitride, spherical nano silicon carbide, spherical nano silicon nitride and spherical nano diamond powder. The filler comprises the first component and the second component, and a heat conduction channel can be formed in the underfill adhesive, so that the heat conduction coefficient can be increased; and the underfill adhesive has high heat conductivity and can be widely applied to high-density systematic encapsulation.

Owner:SHENZHEN INST OF ADVANCED ELECTRONICS MATERIALS

III-nitride current control device and method of manufacture

InactiveUS20070066020A1Easy to controlImprove current carrying capacitySemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactEngineering

A III-nitride device includes a recessed electrode to produce a nominally off, or an enhancement mode, device. By providing a recessed electrode, a conduction channel formed at the interface of two III-nitride materials is interrupted when the electrode contact is inactive to prevent current flow in the device. The electrode can be a schottky contact or an insulated metal contact. Two ohmic contacts can be provided to form a rectifier device with nominally off characteristics. The recesses formed with the electrode can have sloped sides. The electrode can be formed in a number of geometries in conjunction with current carrying electrodes of the device. A nominally on device, or pinch resistor, is formed when the electrode is not recessed. A diode is also formed by providing non-recessed ohmic and schottky contacts through an insulator to an AlGaN layer.

Owner:INFINEON TECH AMERICAS CORP

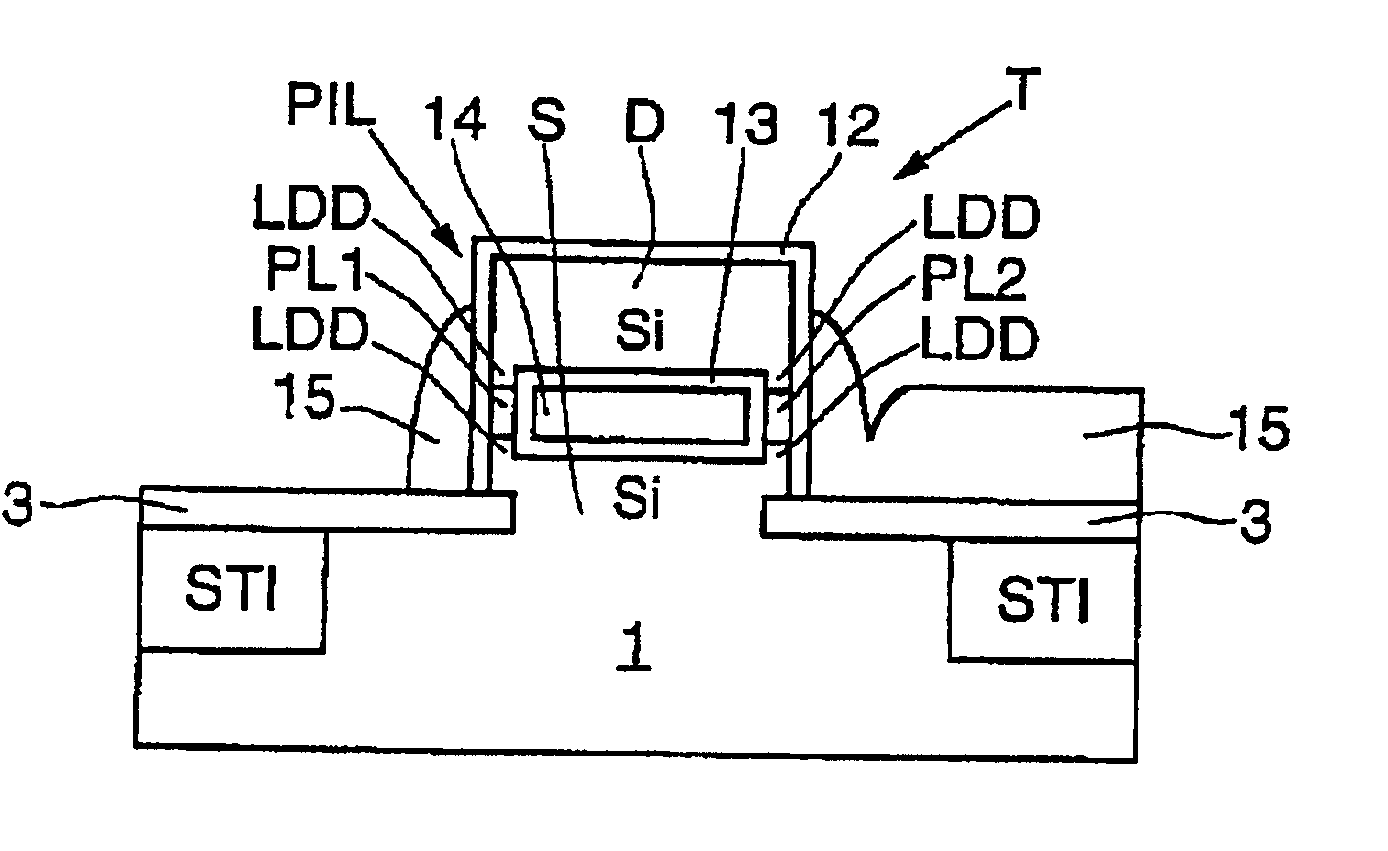

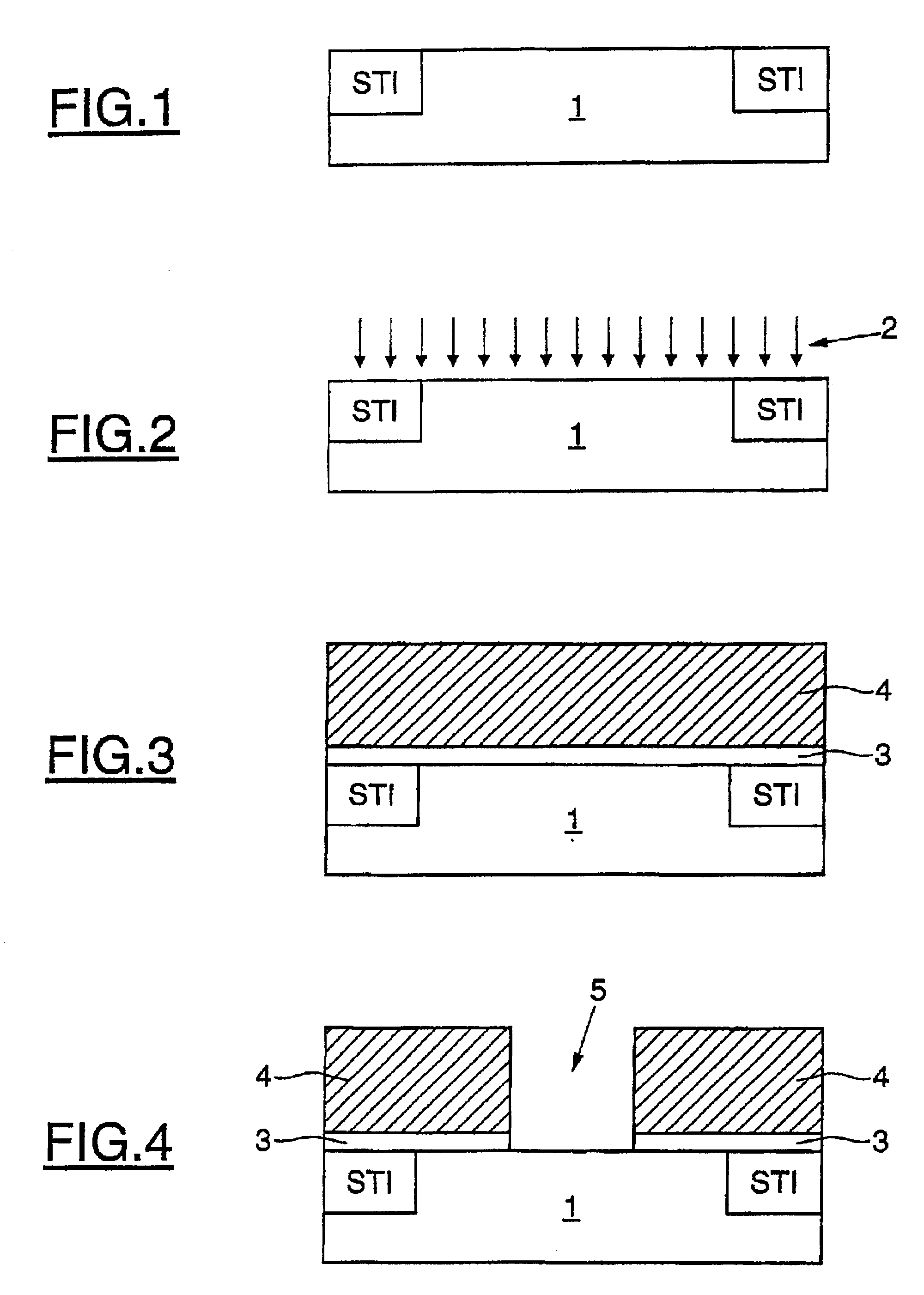

Method of fabricating a vertical quadruple conduction channel insulated gate transistor

The vertical insulated gate transistor includes, on a semiconductor substrate, a vertical pillar incorporating one of the source and drain regions at the top, a gate dielectric layer situated on the flanks of the pillar and on the top surface of the substrate, and a semiconductor gate resting on the gate dielectric layer. The other of the source and drain regions is in the bottom part of the pillar PIL and the insulated gate includes an isolated external portion 15 resting on the flanks of the pillar and an isolated internal portion 14 situated inside the pillar between the source and drain regions. The isolated internal portion is separated laterally from the isolated external portion by two connecting semiconductor regions PL1, PL2 extending between the source and drain regions, and forming two very fine pillars.

Owner:STMICROELECTRONICS SRL

Programmable III-Nitride Transistor with Aluminum-Doped Gate

Disclosed is a III-nitride heterojunction device that includes a conduction channel having a two dimensional electron gas formed at an interface between a first III-nitride material and a second III-nitride material. A modification including a contact insulator, for example, a gate insulator formed under a gate contact, is disposed over the conduction channel, wherein the contact insulator includes aluminum to alter formation of the two dimensional electron gas at the interface. The contact insulator can include AlSiN, or can be SiN doped with aluminum. The modification results in programming the threshold voltage of the III-nitride heterojunction device to, for example, make the device an enhancement mode device. The modification can further include a recess, an ion implanted region, a diffused region, an oxidation region, and / or a nitridation region. In one embodiment, the first III-nitride material comprises GaN and the second III-nitride material comprises AlGaN.

Owner:INFINEON TECH AMERICAS CORP

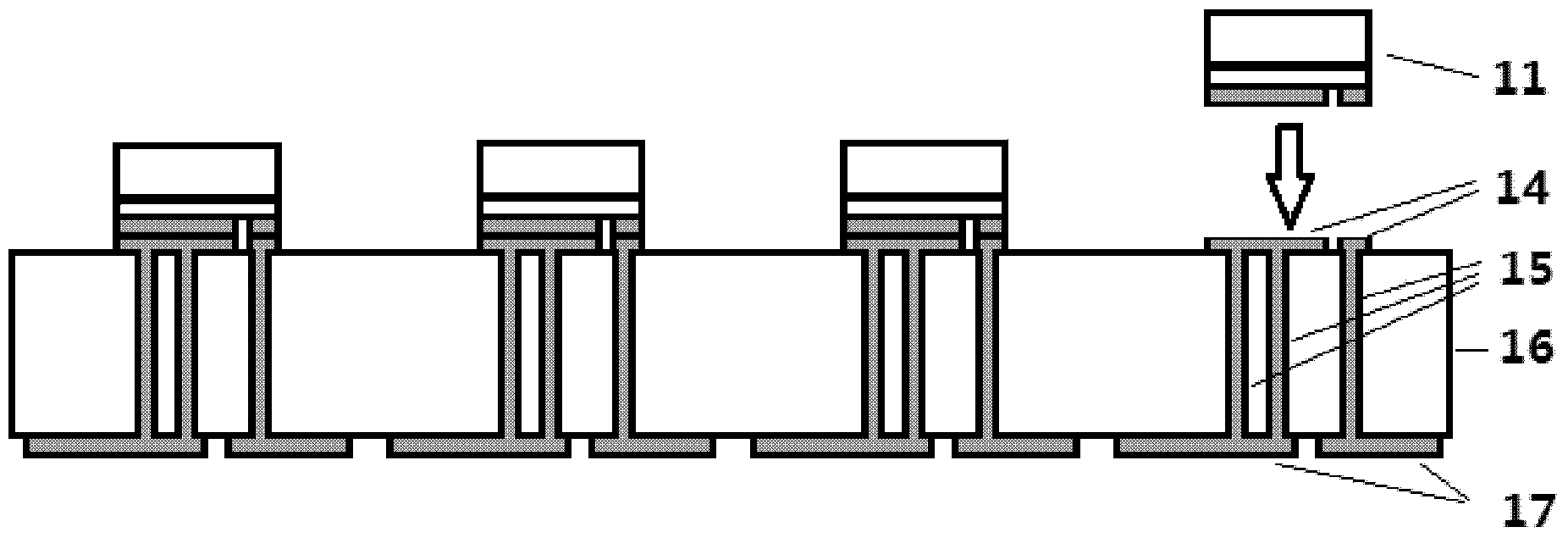

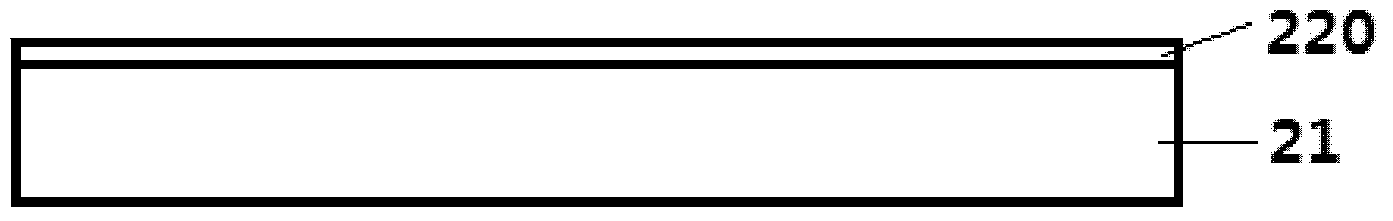

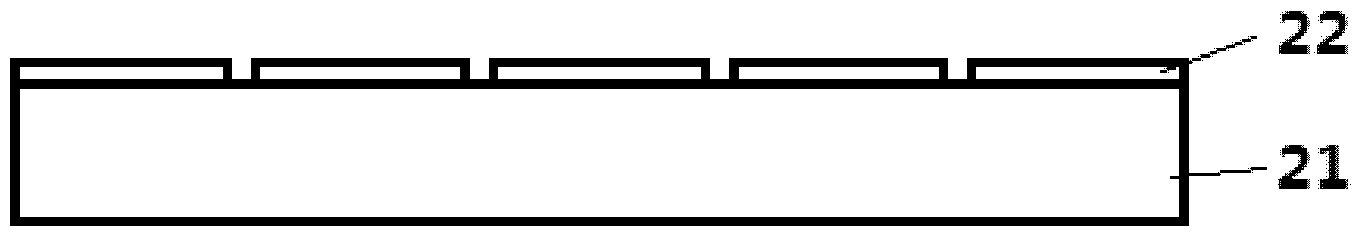

Chip transfer method for LED (light-emitting diode) wafer level package

ActiveCN103647012AImprove automationIncrease productivitySemiconductor/solid-state device manufacturingSemiconductor devicesLed arrayUnit device

A chip transfer method for LED (light-emitting diode) wafer level package includes the steps: manufacturing an LED unit device array on an LED epitaxial wafer, manufacturing metal layers on parts of unit devices of the unit device array to serve as middle metal layers in bonding, and forming a unit device array to be bonded; manufacturing metal patterns corresponding to electrodes of the unit device array to be bonded on the front surface of a base plate, forming heat conduction channels and electric conduction channels below the metal patterns, and connecting electrodes of an LED unit device with a metal bonding pad on the back surface of the base plate through the electric conduction channels; conversely mounting the unit device array to be bonded on the base plate in a bonding mode; finally, sequentially stripping the unit devices to be bonded in a laser stripping mode, separating the epitaxial layers of the unit devices to be bonded from a substrate, and forming a whole film LED array by the separated epitaxial layers and the base plate. The chip transfer method can be used for wafer level package of the LED devices, package efficiency is improved, and cost is reduced.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

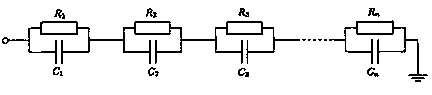

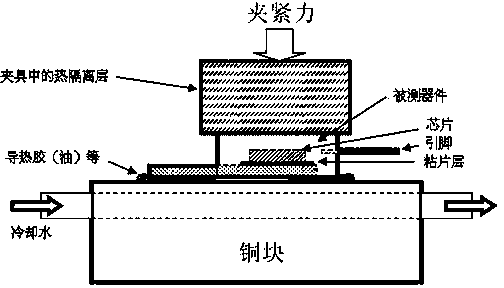

Thermal resistance measuring method for semiconductor device

ActiveCN103792476AMaterial heat developmentIndividual semiconductor device testingJunction temperatureHeat balance

The invention relates to a thermal resistance measuring method for a semiconductor device. The thermal resistance measuring method includes the following steps that (1) according to the structure of the semiconductor device, a main heat conduction channel is determined, and a constant temperature plane good in contact is arranged on the surface of a shell of the main heat conduction channel; (2) certain power is loaded to the semiconductor device, after the semiconductor device reaches heat balance, it is switched to the situation that measuring power is loaded to the semiconductor device, temperature-sensitive parameters of the semiconductor device are measured in real time to obtain the junction temperature for measuring the semiconductor device, and accordingly a transient thermal response curve of the semiconductor device is obtained; (3) according to the transient thermal response curve, the thermal resistance from a junction of the semiconductor device to the shell is determined. According to the thermal resistance measuring method for the semiconductor device, heating power is loaded through a P zone and an N zone of a substrate of the semiconductor device, the junction temperature is measured by the utilization of a PN junction assembly existing in the semiconductor device, and therefore the transient thermal resistance of integrated circuit products without temperature-sensitive diodes and the transient thermal resistance of non-power integrated circuit products can be measured accurately.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

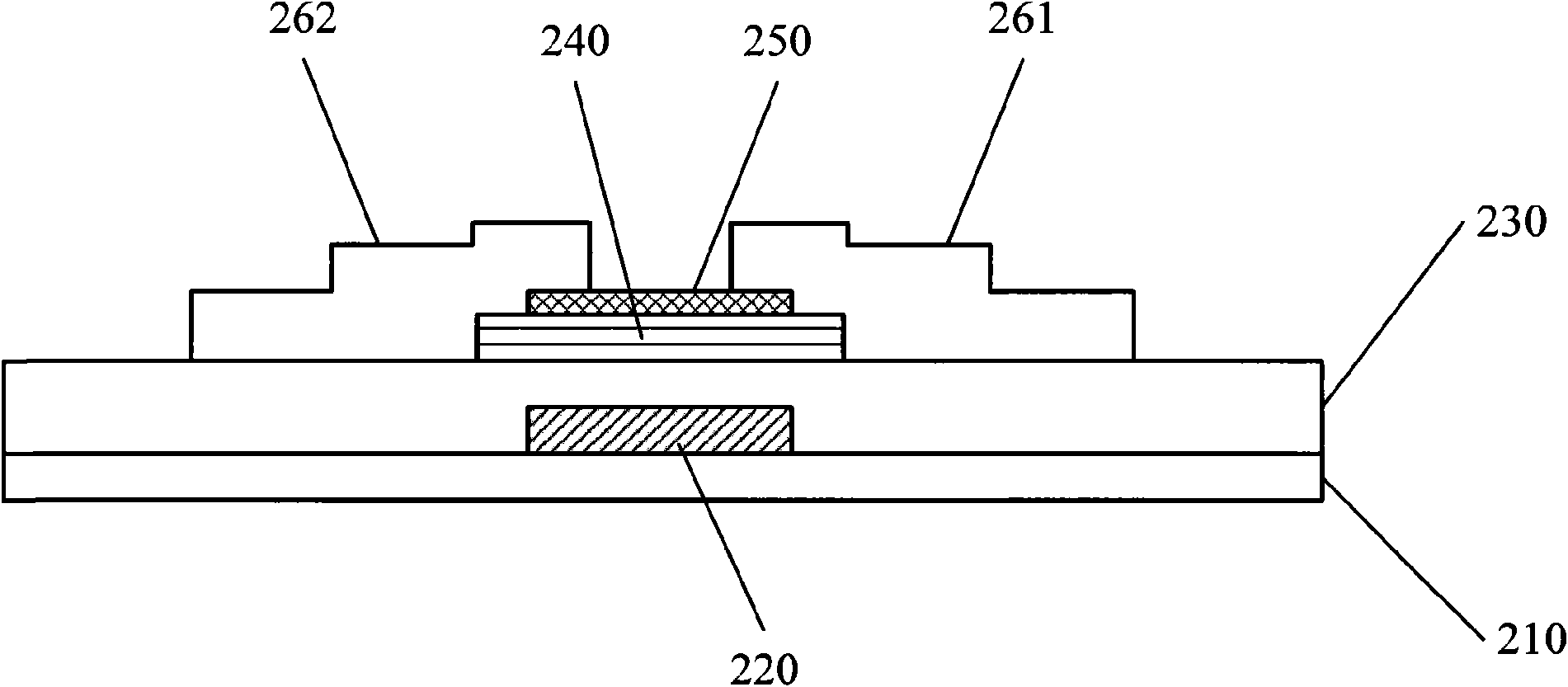

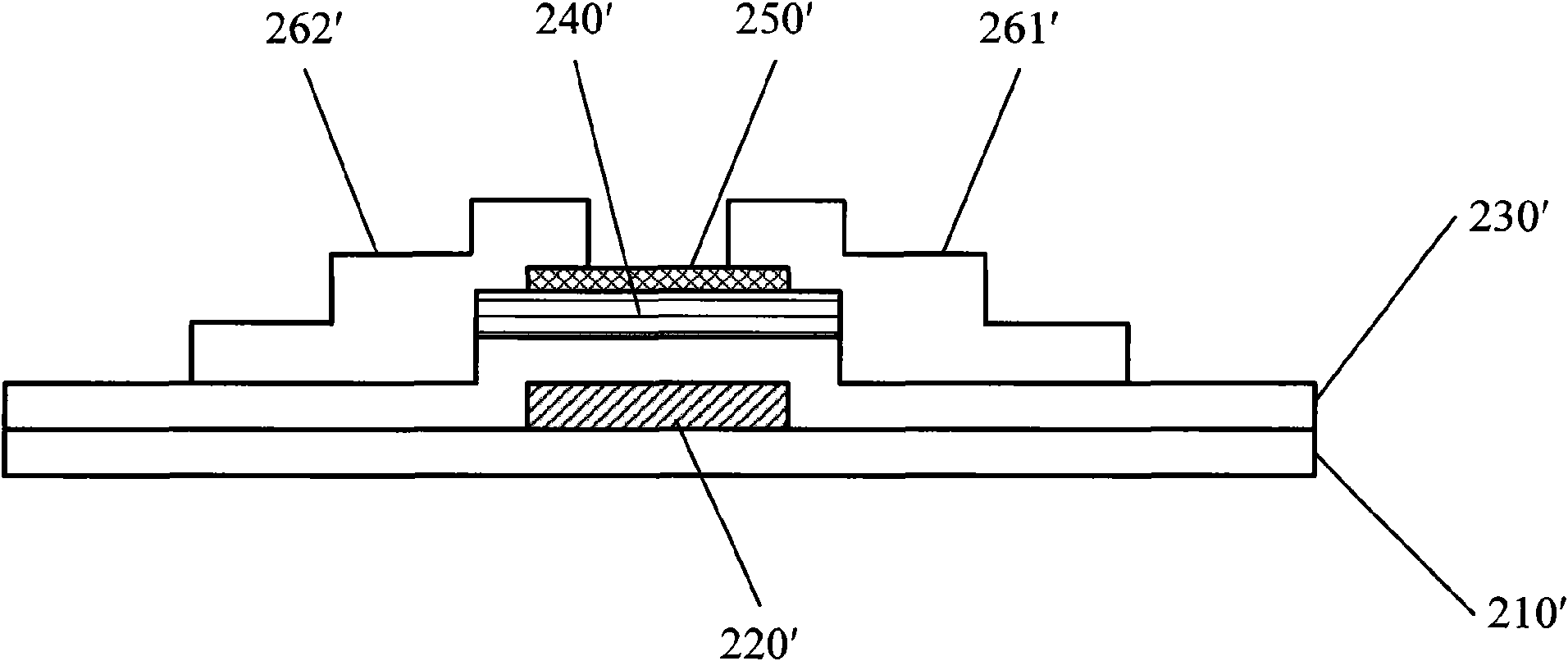

Sull transistor with etching barrier layer and preparation method thereof

InactiveCN101572274AAvoid influenceStable electrical propertiesTransistorSemiconductor/solid-state device manufacturingOxide thin-film transistorConduction channel

The invention relates to a sull transistor with an etching barrier layer, which comprises a substrate, a grid, an insulating barrier, an electric conduction channel, a source electrode and a drain electrode; the electric conduction channel is arranged on the surface of the insulating barrier far from the grid and is corresponding to the grid; the etching barrier layer wholly covers the electric conduction channel and the surface of the insulating layer and is provided with a through hole on a position corresponding to the surface of the electric conduction channel; the source electrode and the drain electrode are connected with the electric conduction channel by the through hole in the etching barrier layer. The invention also provides a method for preparing the transistor. The invention has the advantages that the etching barrier layer is adopted for wholly covering the insulating layer and the surface of the electric conduction channel, the through hole is only manufactured on a position needing the connection forming, thus avoiding the influence of a plasma etching technique on the insulating layer and the electric conduction channel and ensuring the stability of the electrical property of the sull transistor.

Owner:AU OPTRONICS CORP

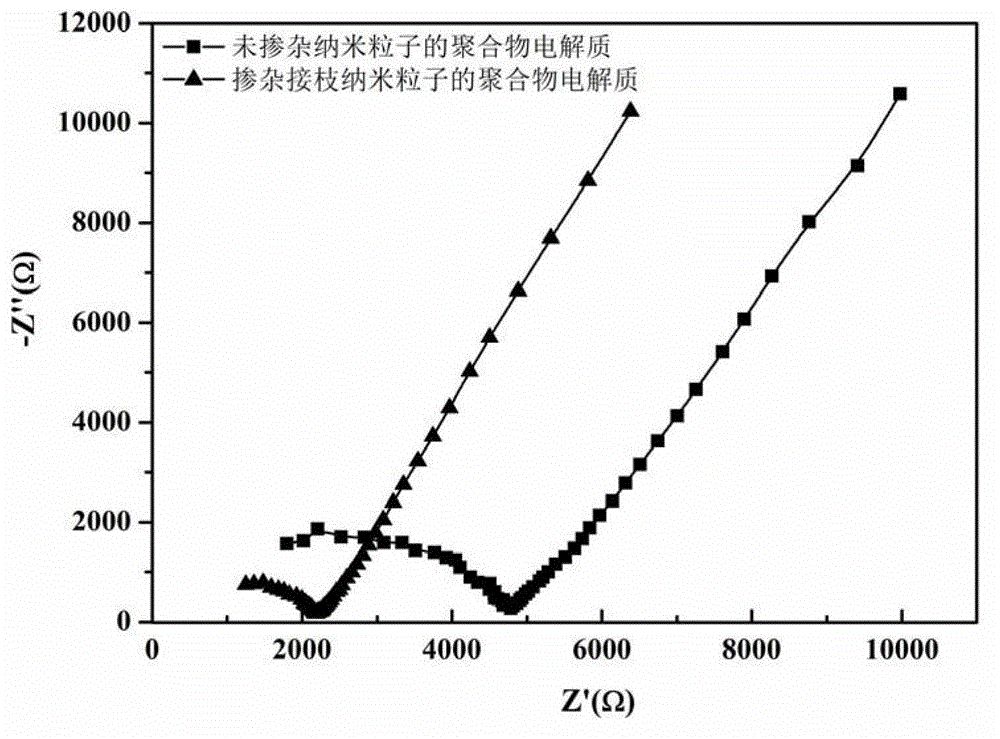

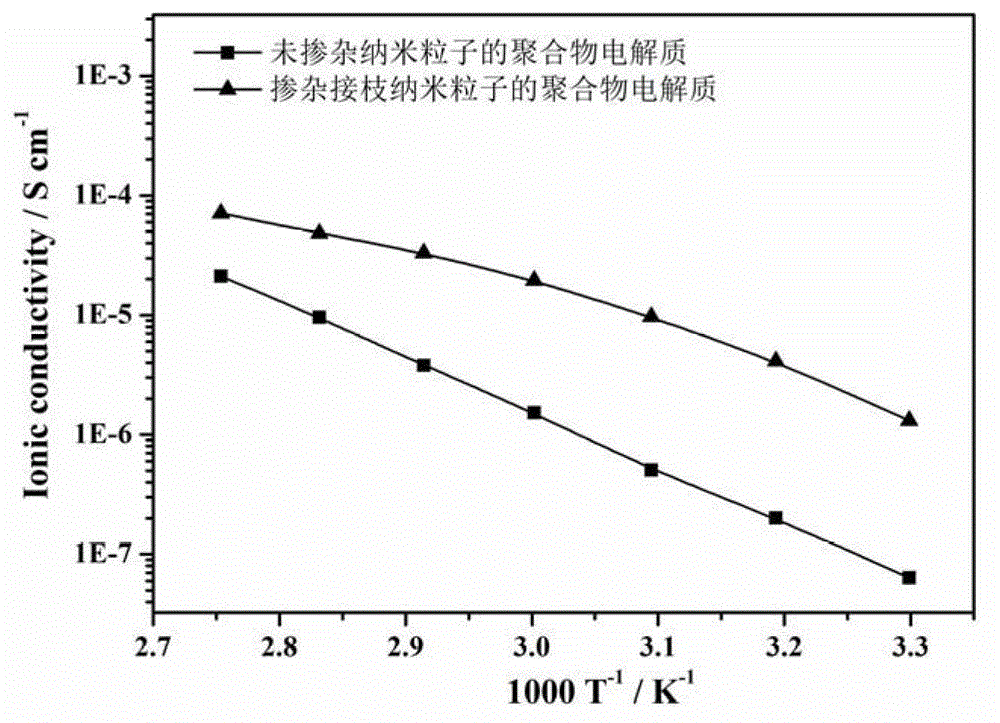

Inorganic nanometer particle modified polymer electrolyte and preparation method thereof

ActiveCN103066323AHigh crystallinityHigh lithium ion conductivitySecondary cellsQuaternary ammonium cationIon exchange

By aiming at the characteristics of high crystallization of a main polymer and low lithium-ion conductivity of the current lithium-ion battery polymer electrolyte, the invention provides an ethyoxyl-containing ionic type compound grafted inorganic nanometer particle modified polymer electrolyte and a preparation method thereof. The preparation method comprises the steps of: firstly activating nanometer particles; then reacting the activated nanometer particles with silane coupling agent having one end per se as quaternary ammonium salt; then performing ion exchange with sulfonate containing an ethyoxyl chain so as to obtain ionic type compound modified nanometer particles; and finally adding the obtained nanometer particles into a polymer electrolyte. For one aspect, the ionic type compound modified nanometer particles can inhibit crystallization of the polymer; and for the other aspect, the grafted ethyoxyl-containing compound also can serve as a new ion conduction channel to improve ionic conductivity. The prepared polymer electrolyte can be applied to preparation of high-performance solid lithium-ion polymer batteries.

Owner:HUAZHONG UNIV OF SCI & TECH

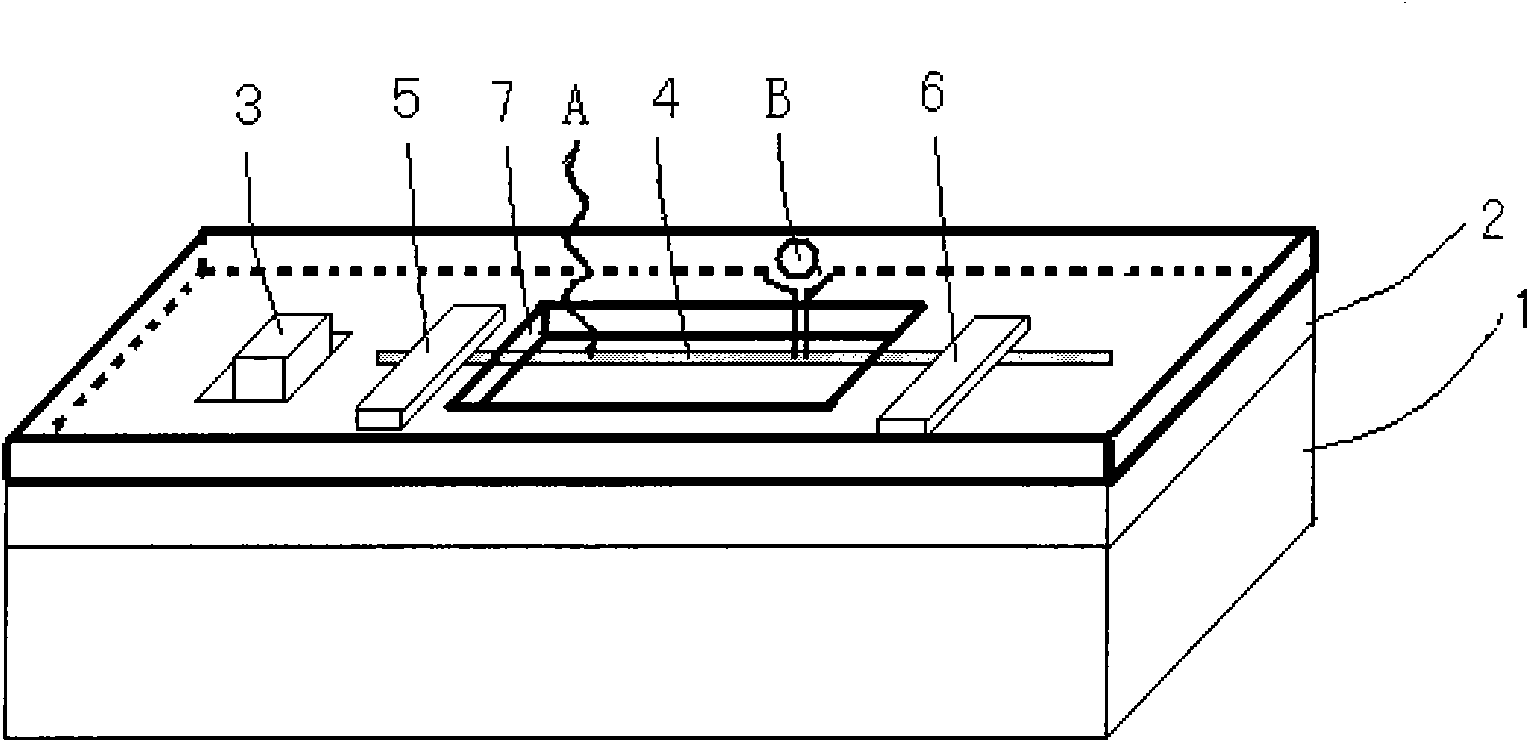

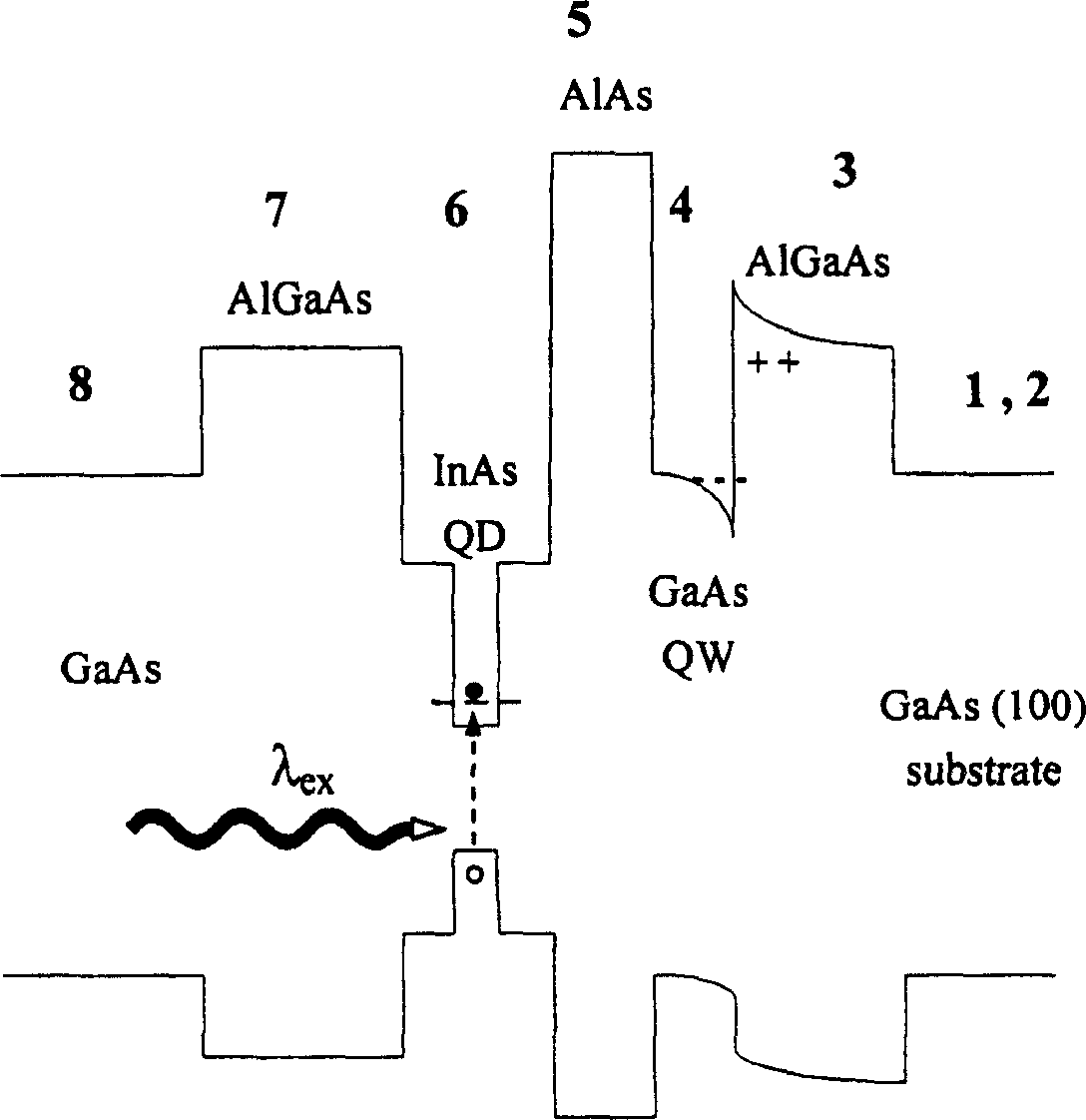

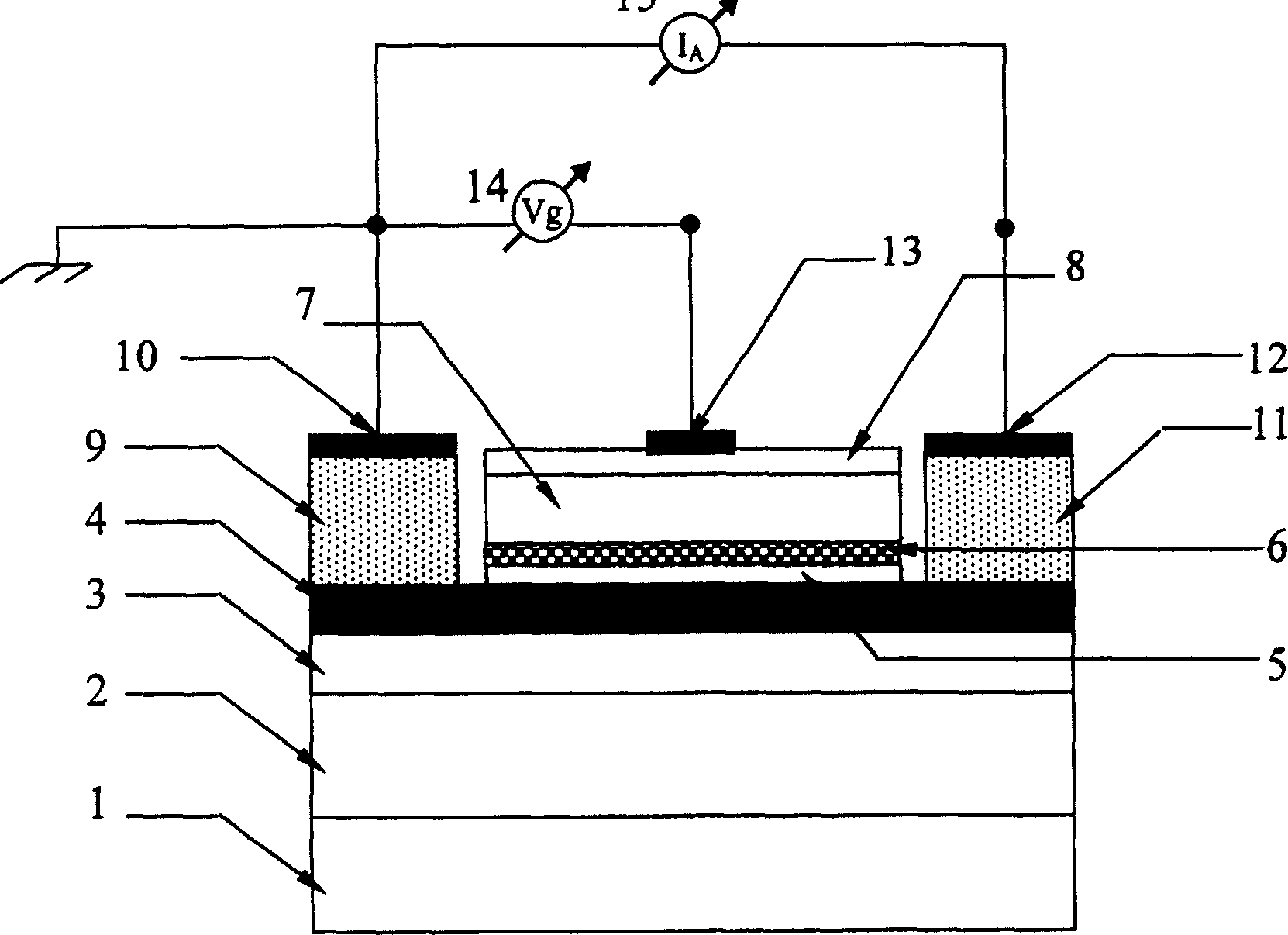

Optical detection field effect transistor containing quantum point and manufacturing method

InactiveCN1832208AImprove response efficiencySimple structureFinal product manufactureSemiconductor devicesGratingIndium arsenide

This invention relates to an optical detection field effect transistor containing quantum points and its manufacturing method characterizing: 1, longitudinally integrating a compound semiconductor optical detector and a metal-semiconductor field effect transistor to grow on a same substrate material, 2, separating the active region mesa of InAs quantum points under the grating and the source / drain region to connect the modulated conduction channel under the quantum points with the source / drain to constitute a conducting loop to realize the effective integration of optical devices and electric appliances.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

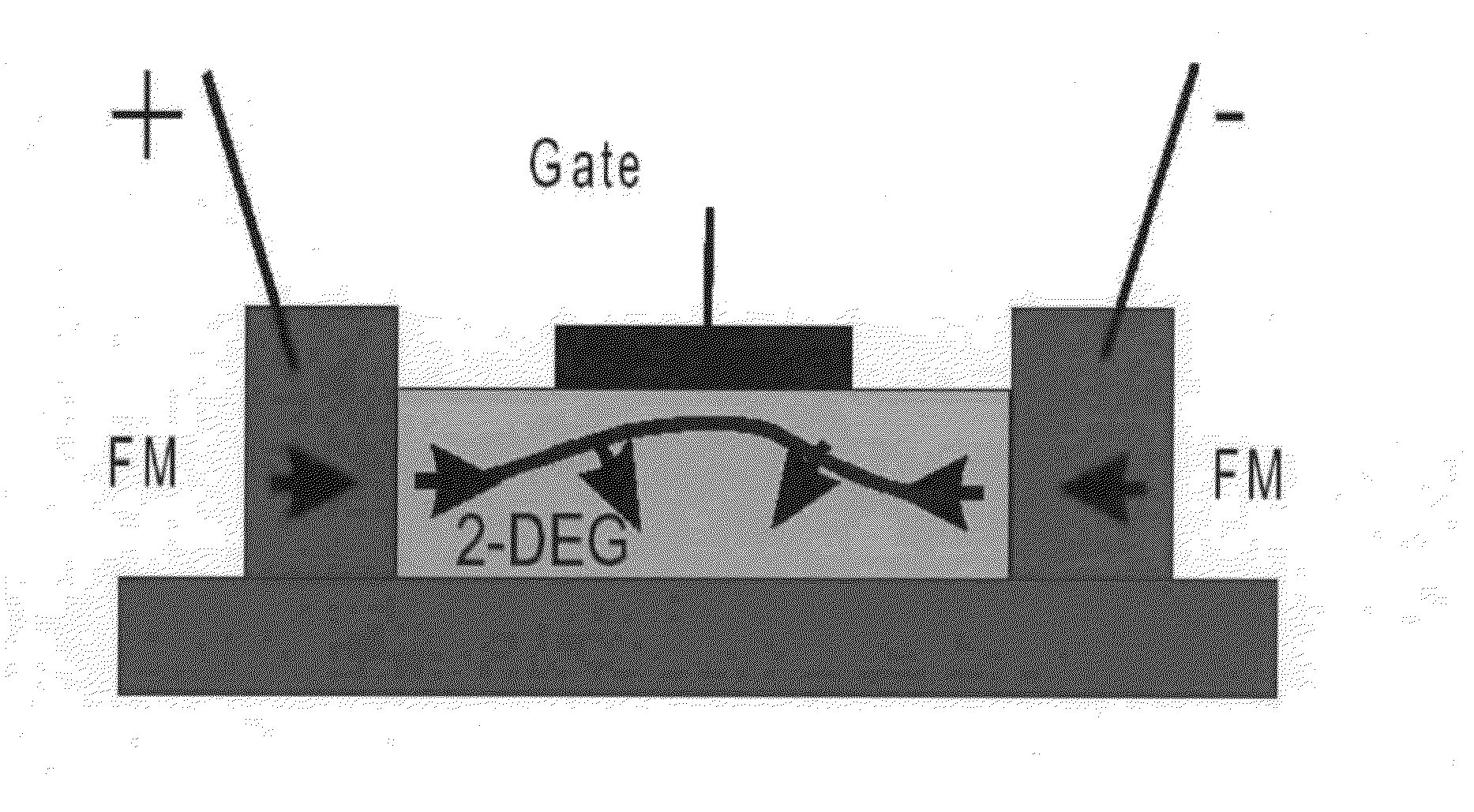

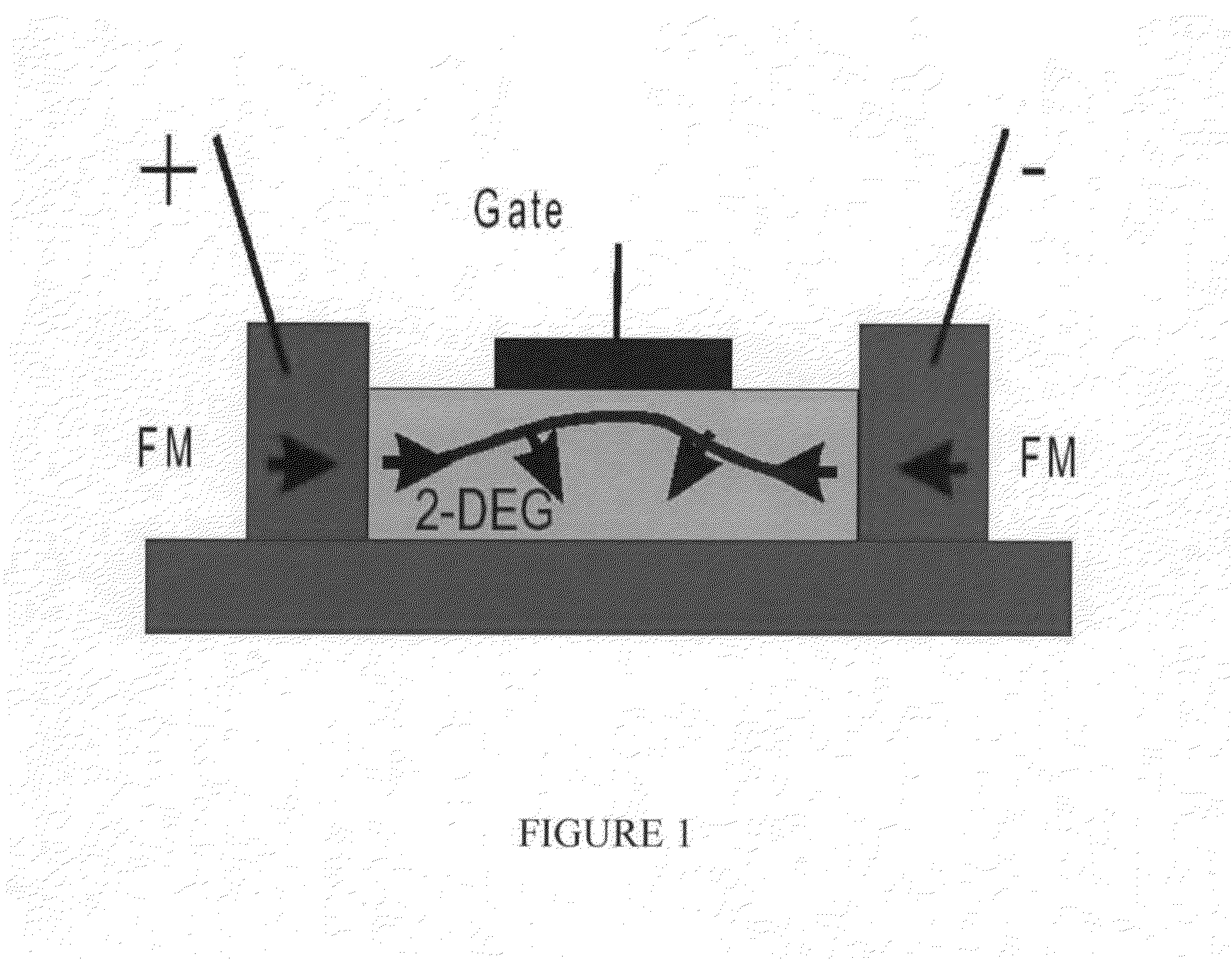

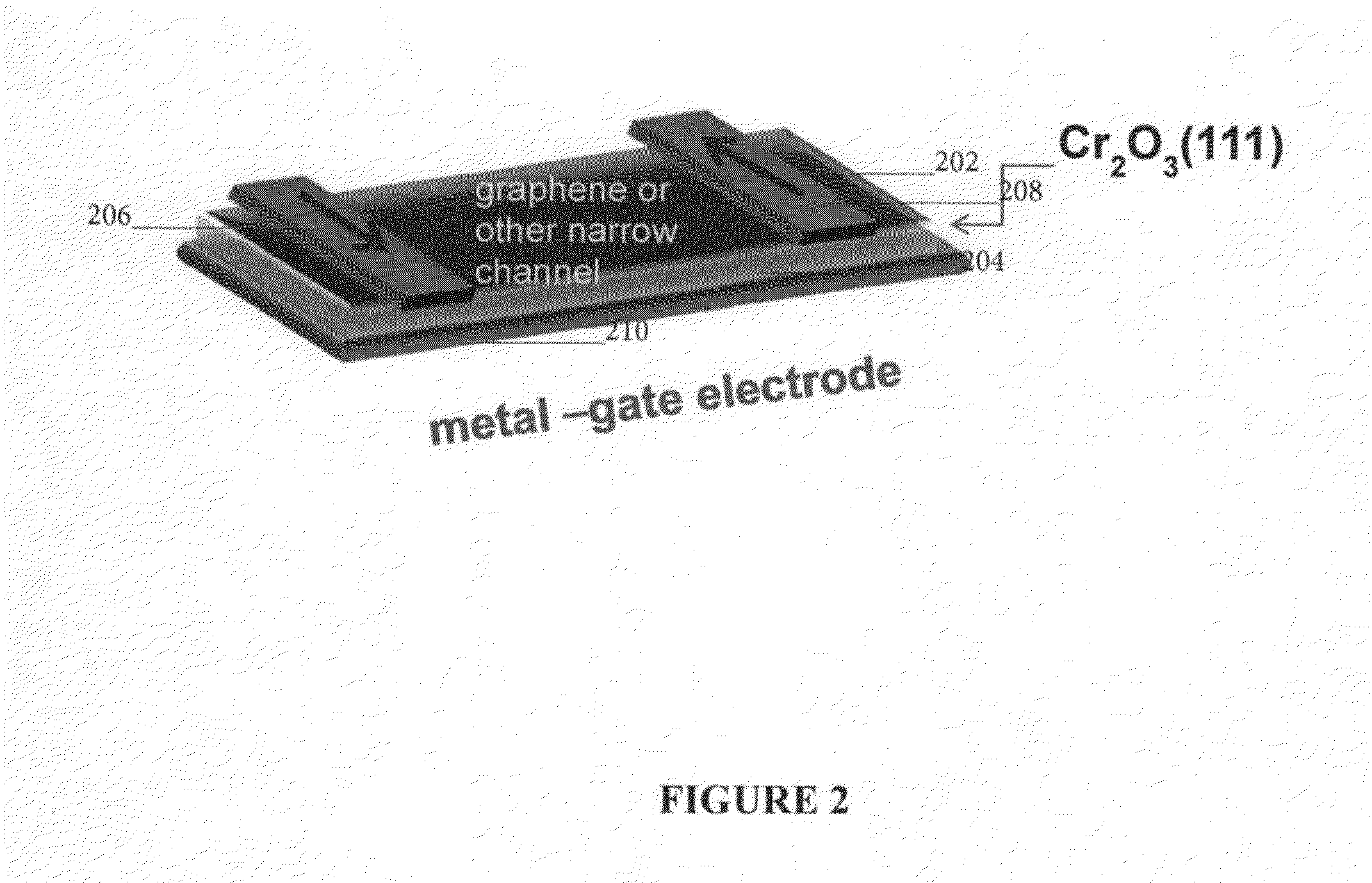

Magneto-Electric Voltage Controlled Spin Transistors

The invention relates to a magneto-electric spin-FET including a gate film of chromia and a thin film of a conductive channel material which may be graphene, InP, GaAs, GaSb, PbS, MoS2, WS2, MoSe2, WSe2 and mixtures thereof. The chromia, or other magneto-electric, and conduction channel material are in intimate contact along an interface there between. The resulting magneto-electric device may be voltage-controlled and provide non-volatile memory.

Owner:QUANTUM DEVICES +1

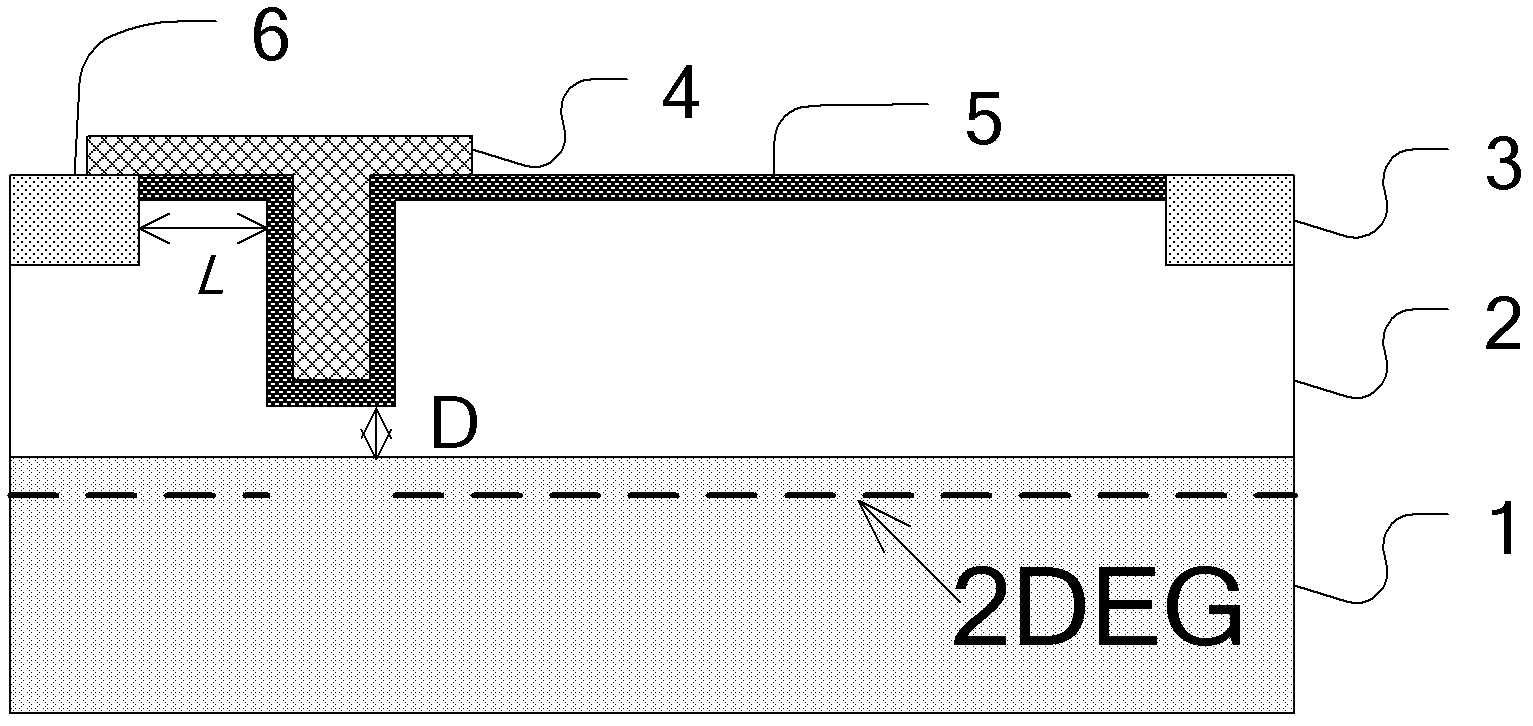

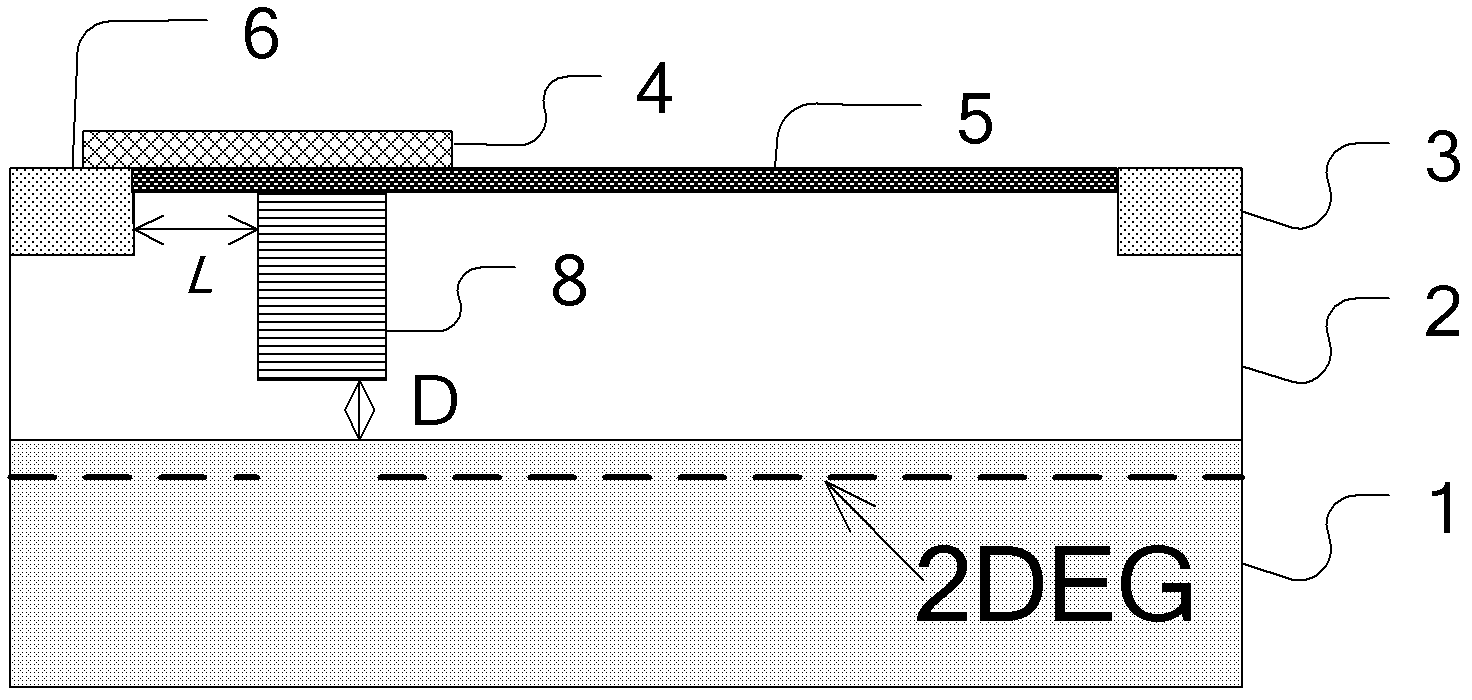

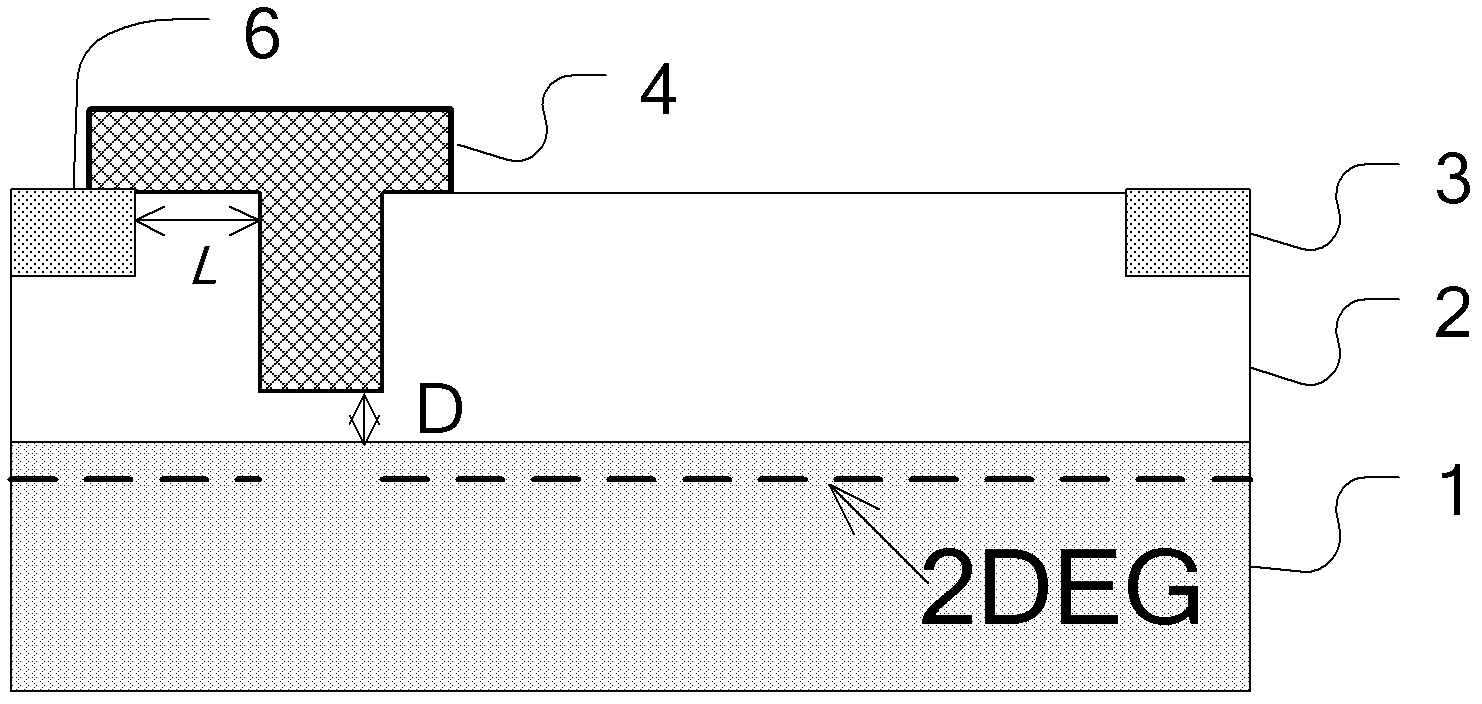

Normally-off field-controlled channel gan heterojunction diode

InactiveCN102280494AImplement field control featuresEfficient use ofSemiconductor devicesControl channelPositive power

A normally-off type field-controlled channel GaN heterojunction diode belongs to the technical field of semiconductor devices. The invention adopts the technology of combining insulating layer-groove, modulation doping and groove-modulation doping to change the conductive channel structure of the existing GaN heterojunction diode, and convert the original normally-on spontaneously polarized GaN heterojunction The junction conductive channel is changed into a normally-off field-controlled conductive channel combining spontaneous polarization and piezoelectric polarization in the present invention, which realizes the field-controlled characteristics of the GaN heterojunction diode conductive channel and reduces the forward conduction resistance and enhanced reverse cut-off capability. The invention has lower forward conduction resistance and power consumption, stronger reverse cut-off ability, and is compatible with AlGaN / GaN HEMT power switching device technology, which is beneficial to the application of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

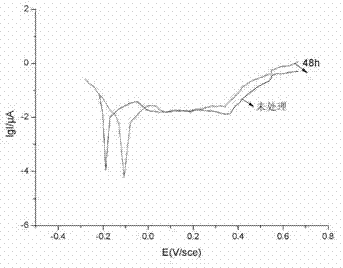

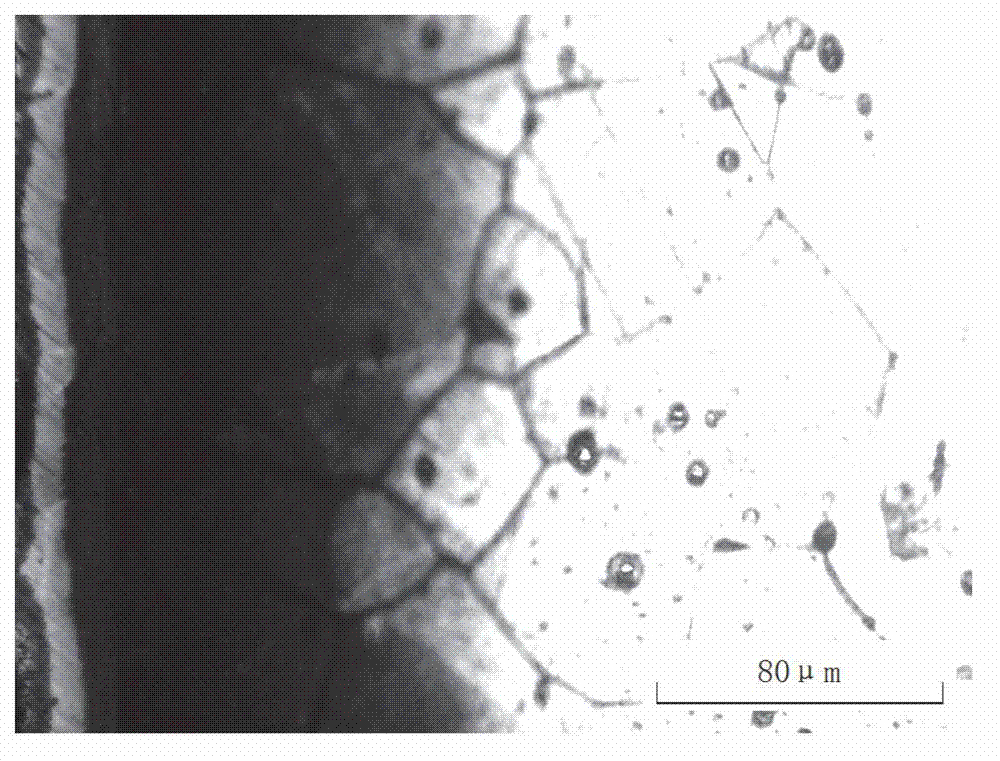

Low temperature gas carburizing method for realizing reinforcement and corrosion resistance of austenitic stainless steel

InactiveCN102828145ANo damage to corrosion resistanceImprove corrosion resistanceSolid state diffusion coatingChromium carbideNitrogen

The invention provides a low temperature gas carburizing method for realizing reinforcement and corrosion resistance of austenitic stainless steel, which belongs to the field of chemical heat treatment. The method comprises the following steps: disposing a clean and dry austenitic stainless steel part in a carburizing furnace which is filled with a PTFE activator with an amount in proportion to the mass of the austenitic stainless steel part and tightly covering the cover of the carburizing furnace; blowing in protective nitrogen, powering on and heating the carburizing furnace to a temperature of 550 DEG C so as to allow PTFE to undergo pyrolysis, and activating a passivation film on the surface of austenitic stainless steel in the furnace by using pyrolysis products of PTFE so as to form a conduction channel which is beneficial for diffusion of carbon atoms on the surface of the austenitic stainless steel; and then, pumping out gas in the furnace, blowing in mixed gas of CO, H2 and N2 into the carburizing furnace, carrying out carburizing at a temperature of 460 to 480 DEG C which is lower than the formation temperature of a chromium carbide and carrying out insulation for 48 to 72 hours to complete carburizing. According to the invention, the purpose of realizing reinforcement of the austenitic stainless steel through low temperature carburizing and maintaining excellent corrosion resistance of the austenitic stainless steel are achieved, and the method is simple to implement and has high production efficiency.

Owner:WUHAN RES INST OF MATERIALS PROTECTION