Patents

Literature

787 results about "Oxide thin-film transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

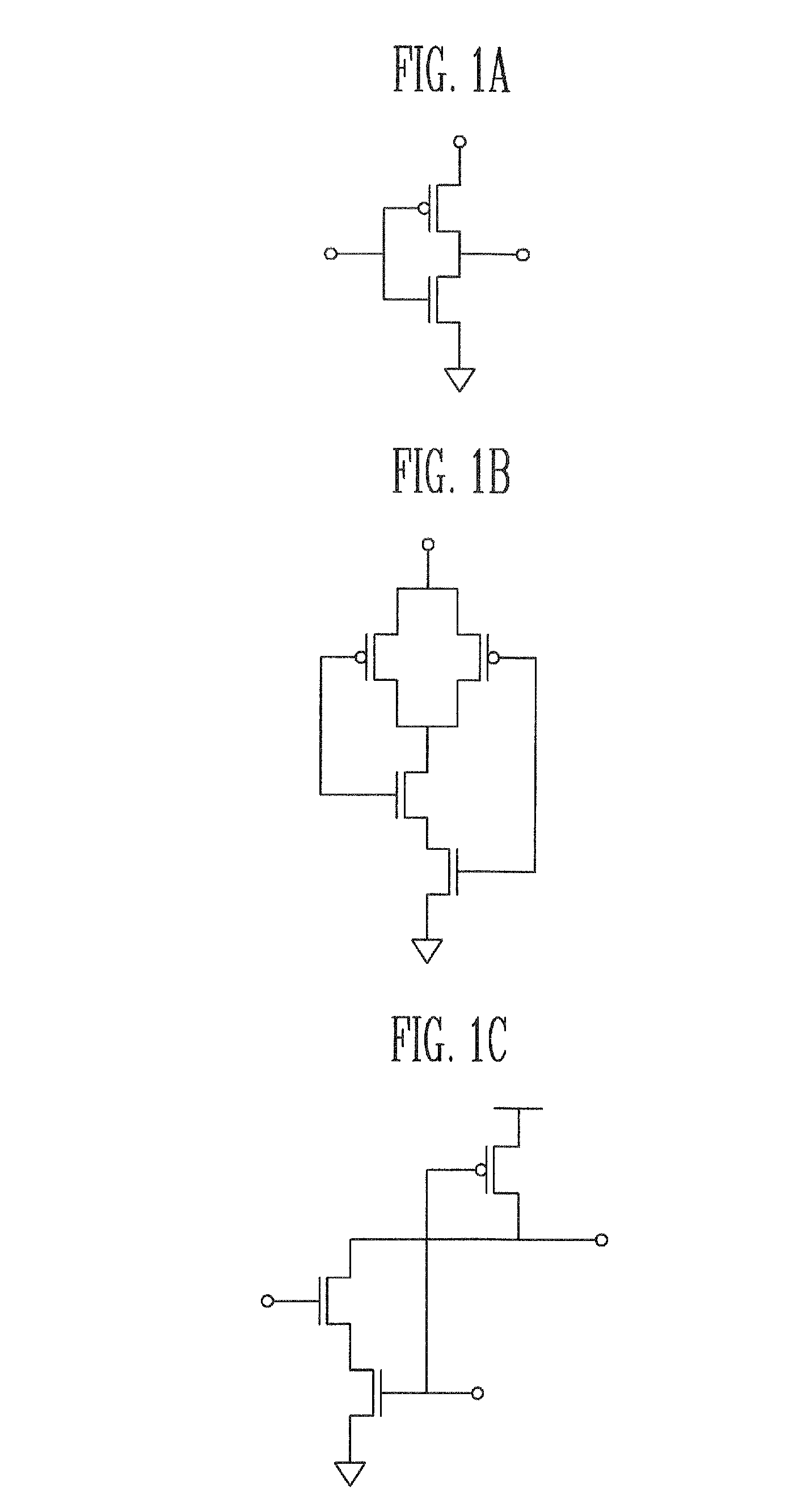

An oxide thin-film transistor (TFT) is a particular kind of field-effect transistor made by depositing thin films of a semiconductor active layer as well as the dielectric layer and metallic contacts over a supporting substrate. The principal difference between amorphous silicon TFT and Oxide TFT is that the material of the electron channel is oxide or amorphous silicon. A common substrate is glass, since the primary application of TFTs is in liquid crystal displays and organic light emitting displays (OLEDs). This differs from the conventional transistor where the semiconductor material typically is the substrate, such as a silicon wafer. TFT electrical performance is dramatically degraded if a zinc–tin–oxide TFT is covered with a dielectric layer and does not undergo both types of annealing. In addition to silicon dioxide, successful passivation of zinc–tin–oxide TFTs is accomplished using thermally evaporated calcium fluoride, germanium oxide, strontium fluoride, or antimony oxide as passivation.

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS7994500B2Improve featuresAvoid chargingSemiconductor/solid-state device detailsSolid-state devicesTrappingOxide thin-film transistor

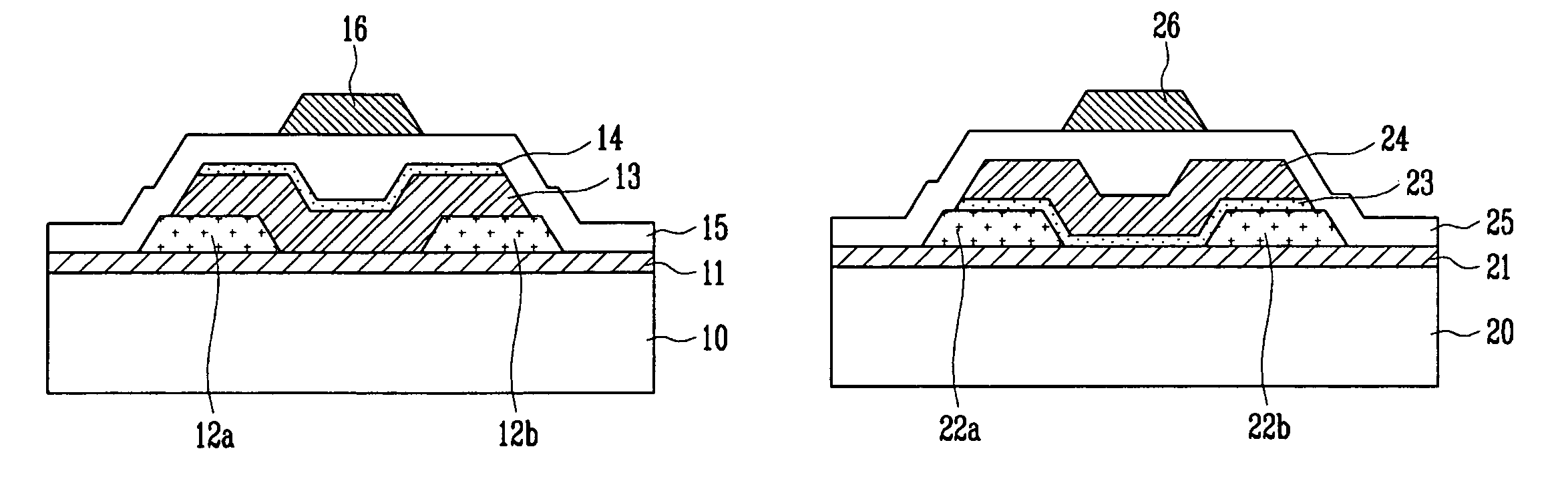

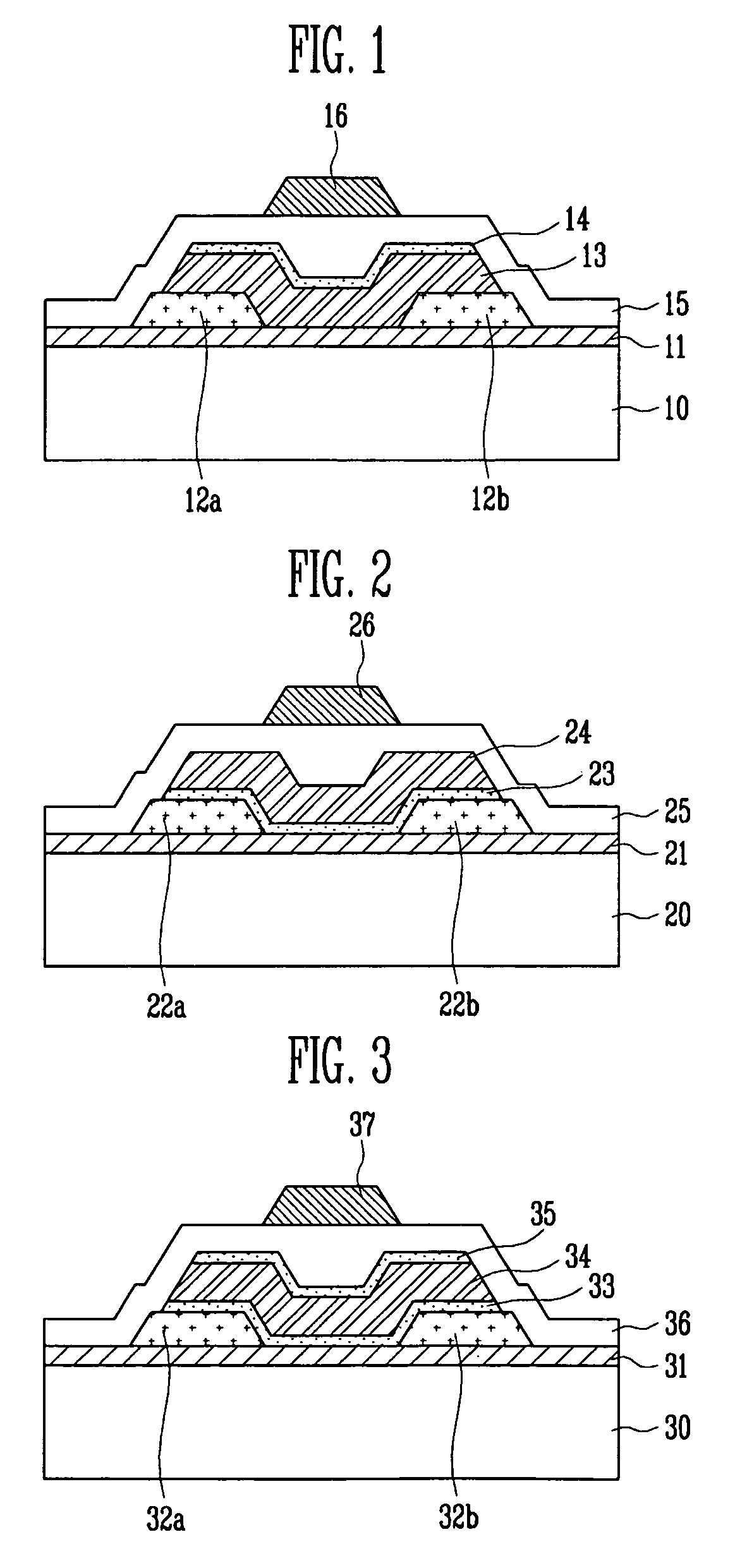

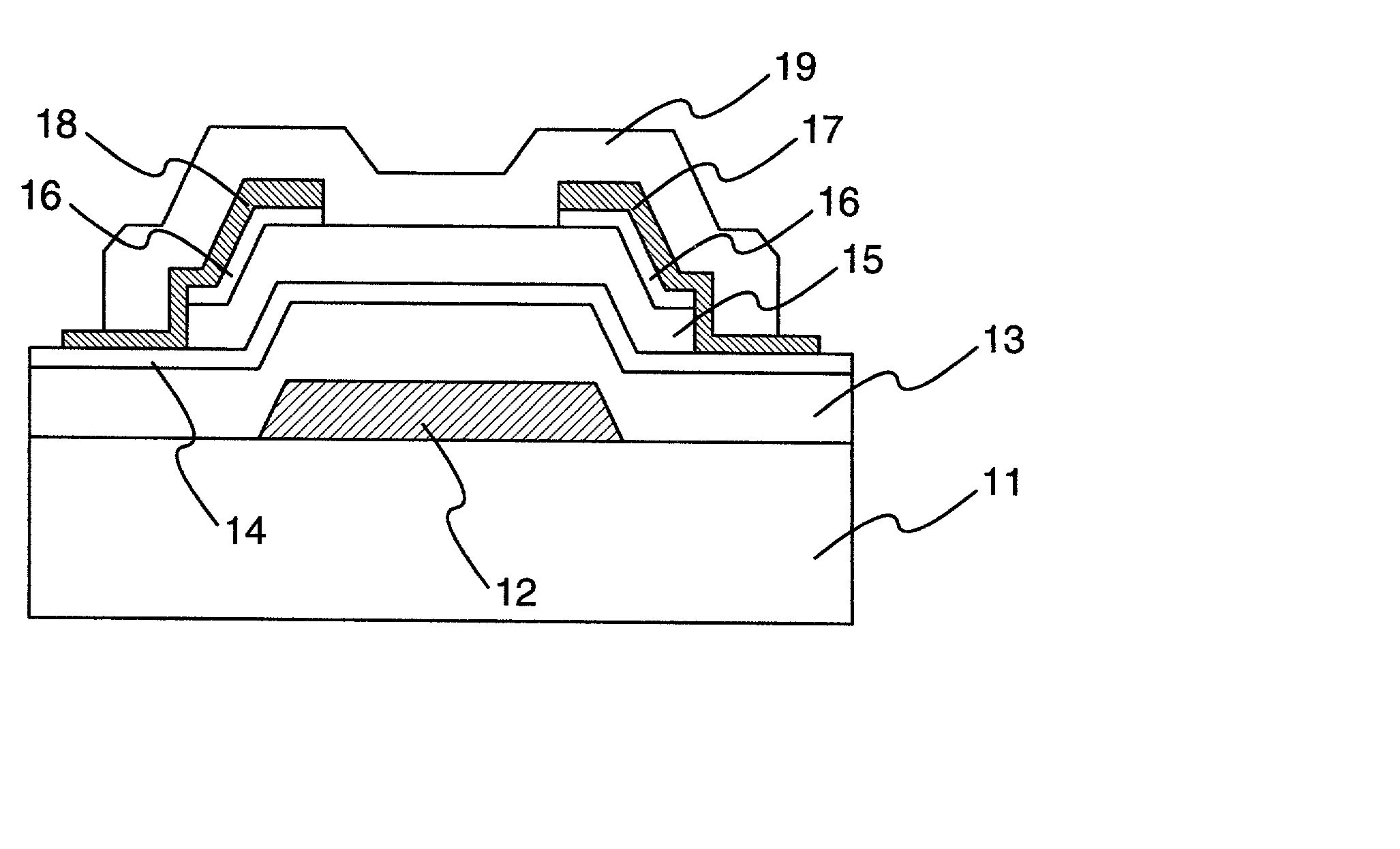

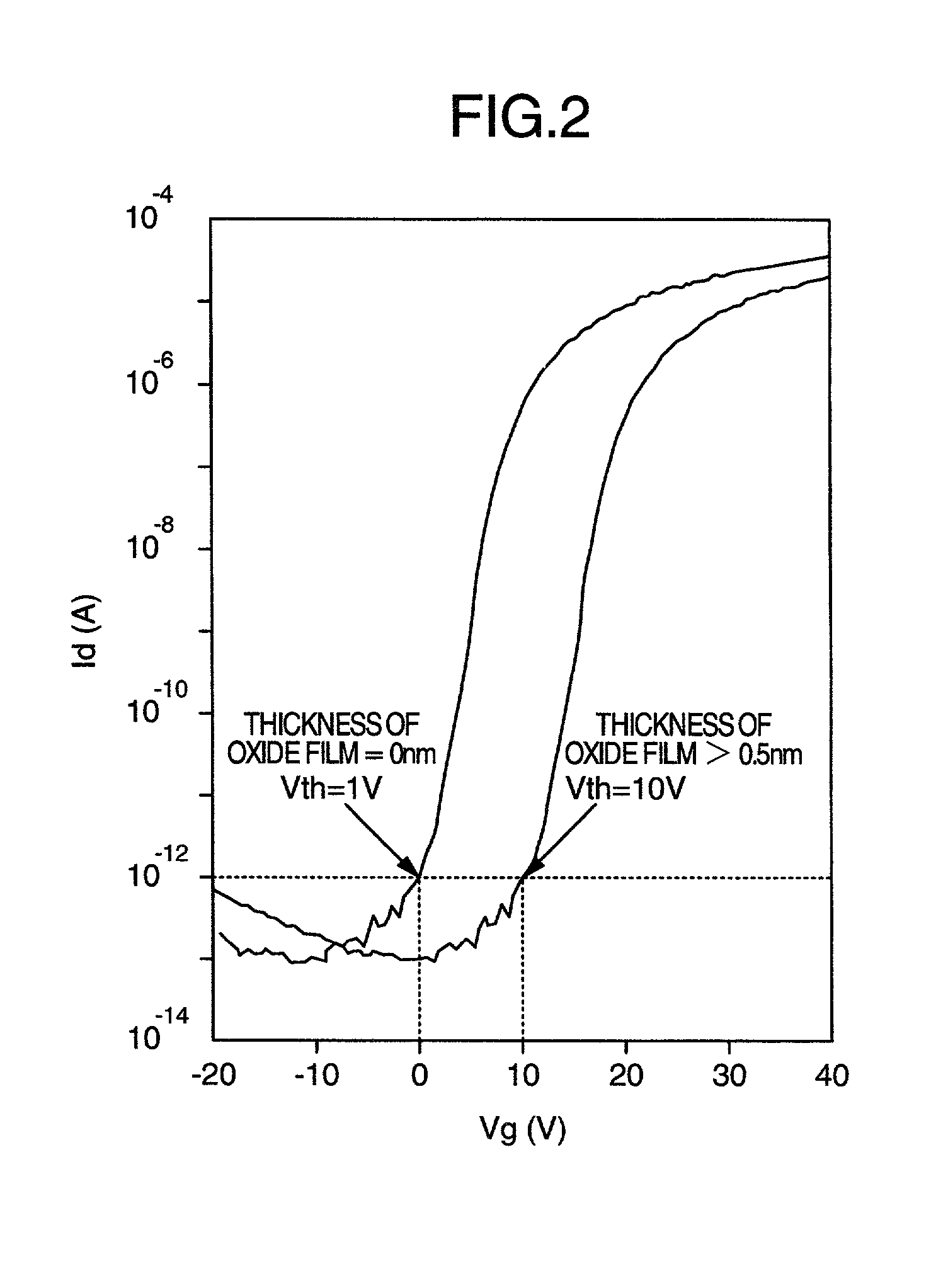

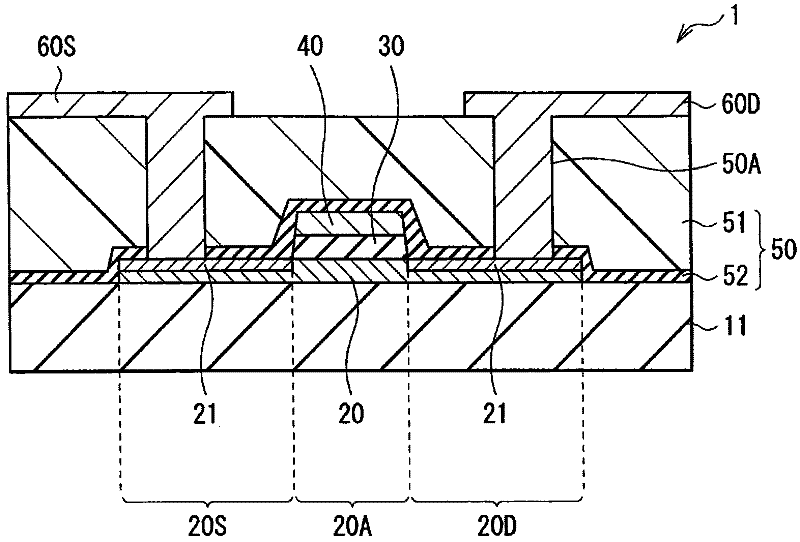

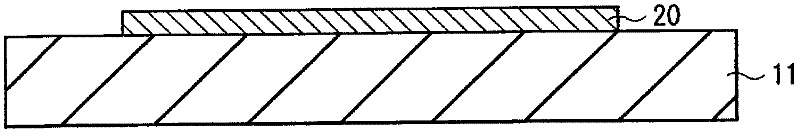

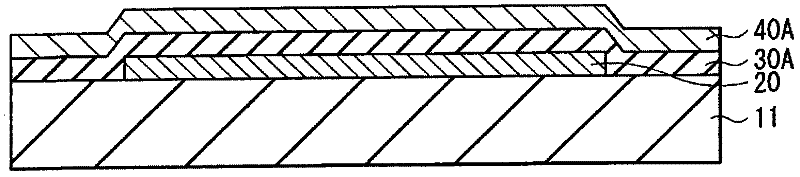

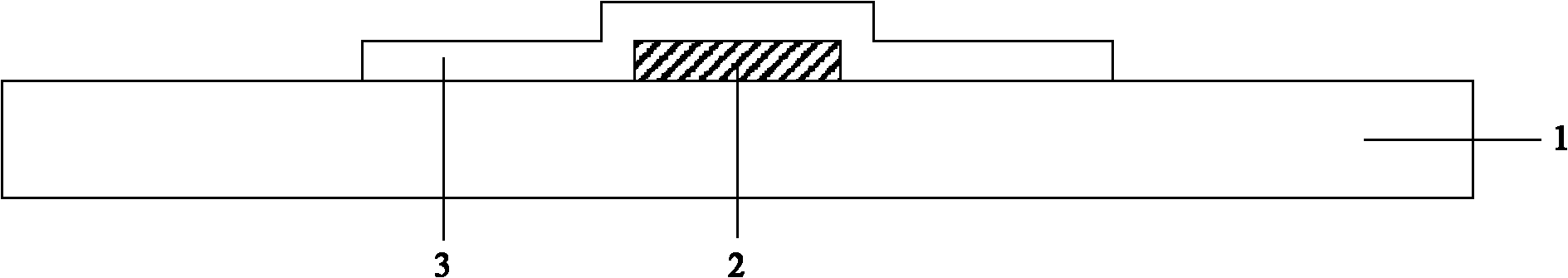

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

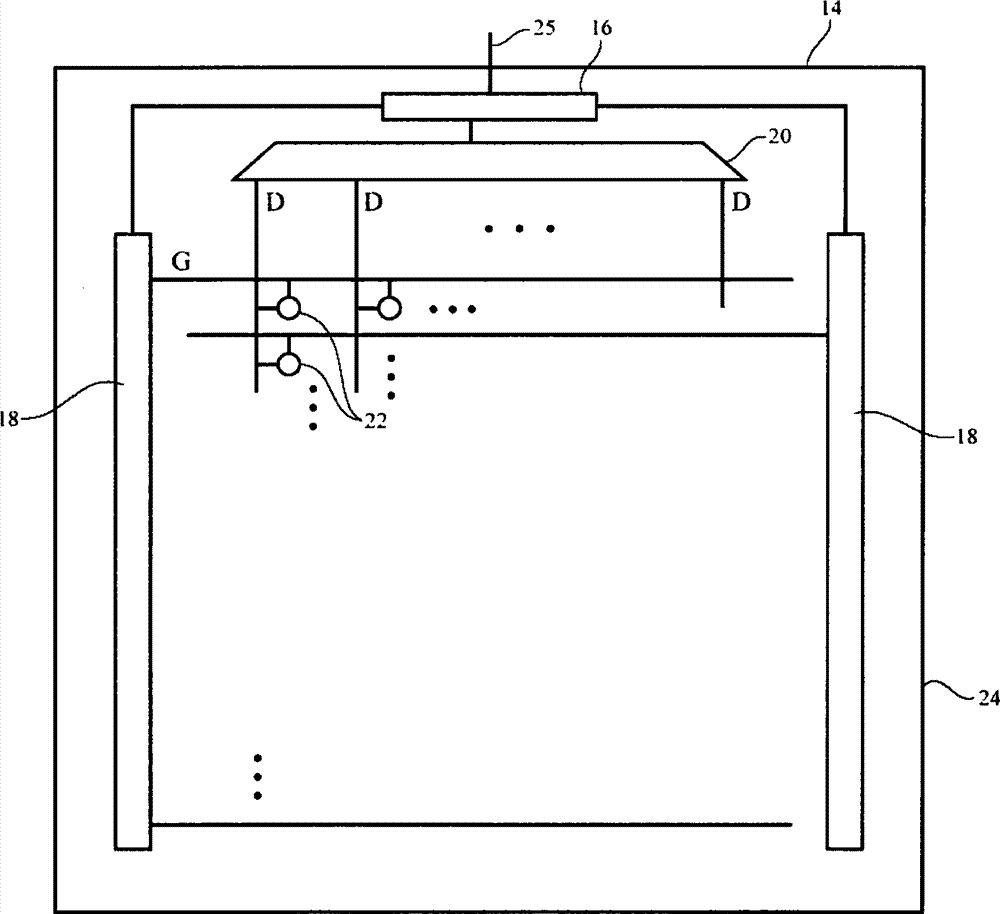

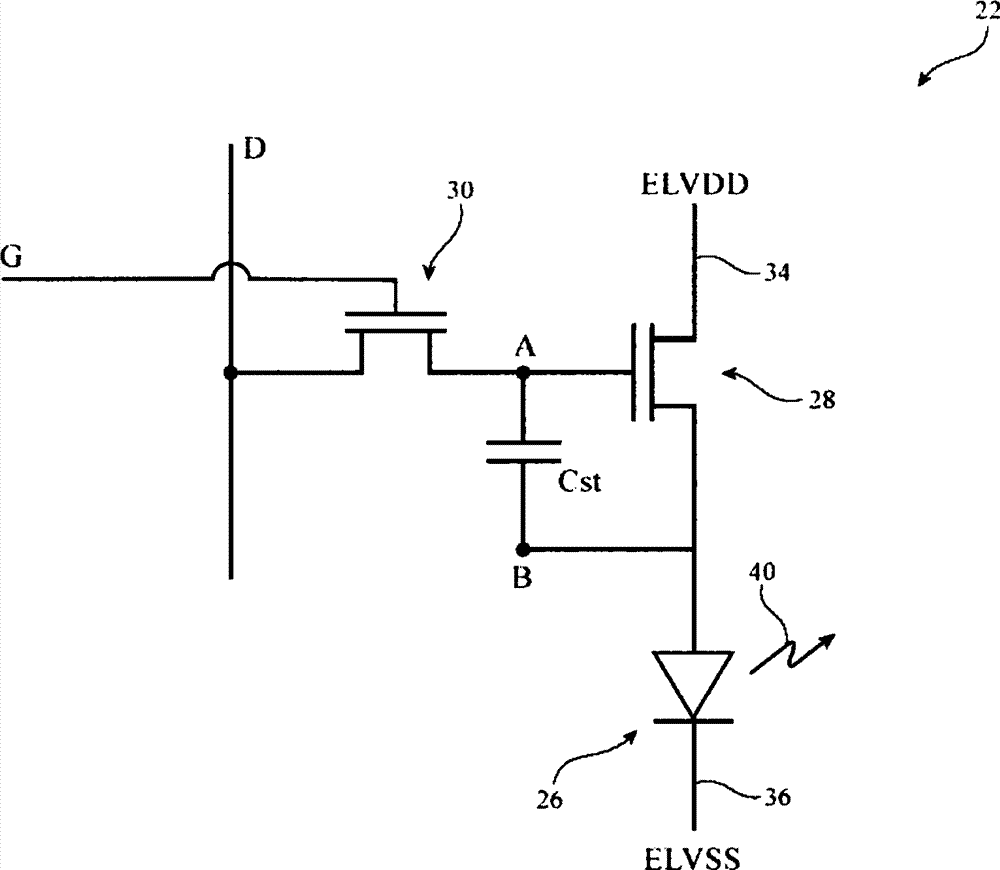

Display apparatuses and methods of operating the same

InactiveUS20100149138A1Solid-state devicesCathode-ray tube indicatorsLiquid-crystal displayOxide thin-film transistor

Provided are display apparatuses and methods of operating the same. In a display apparatus, a display image may be continuously held for longer than about 10 msec after the power of the display panel is turned off. The display apparatus may indicate a liquid crystal display (LCD) apparatus including an oxide thin film transistor (TFT). Off leakage current of the oxide TFT may be less than about 10−14 A.

Owner:SAMSUNG ELECTRONICS CO LTD

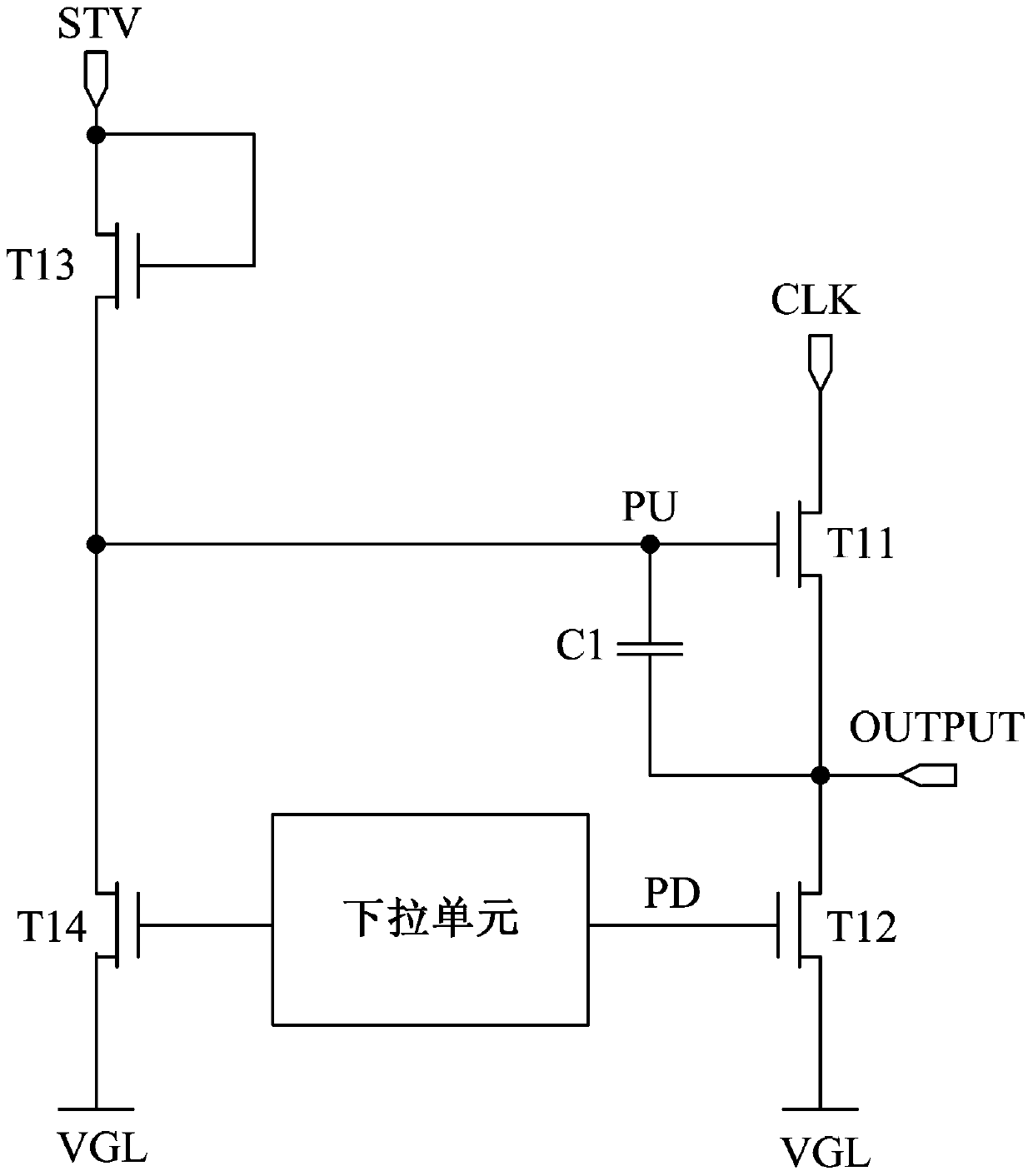

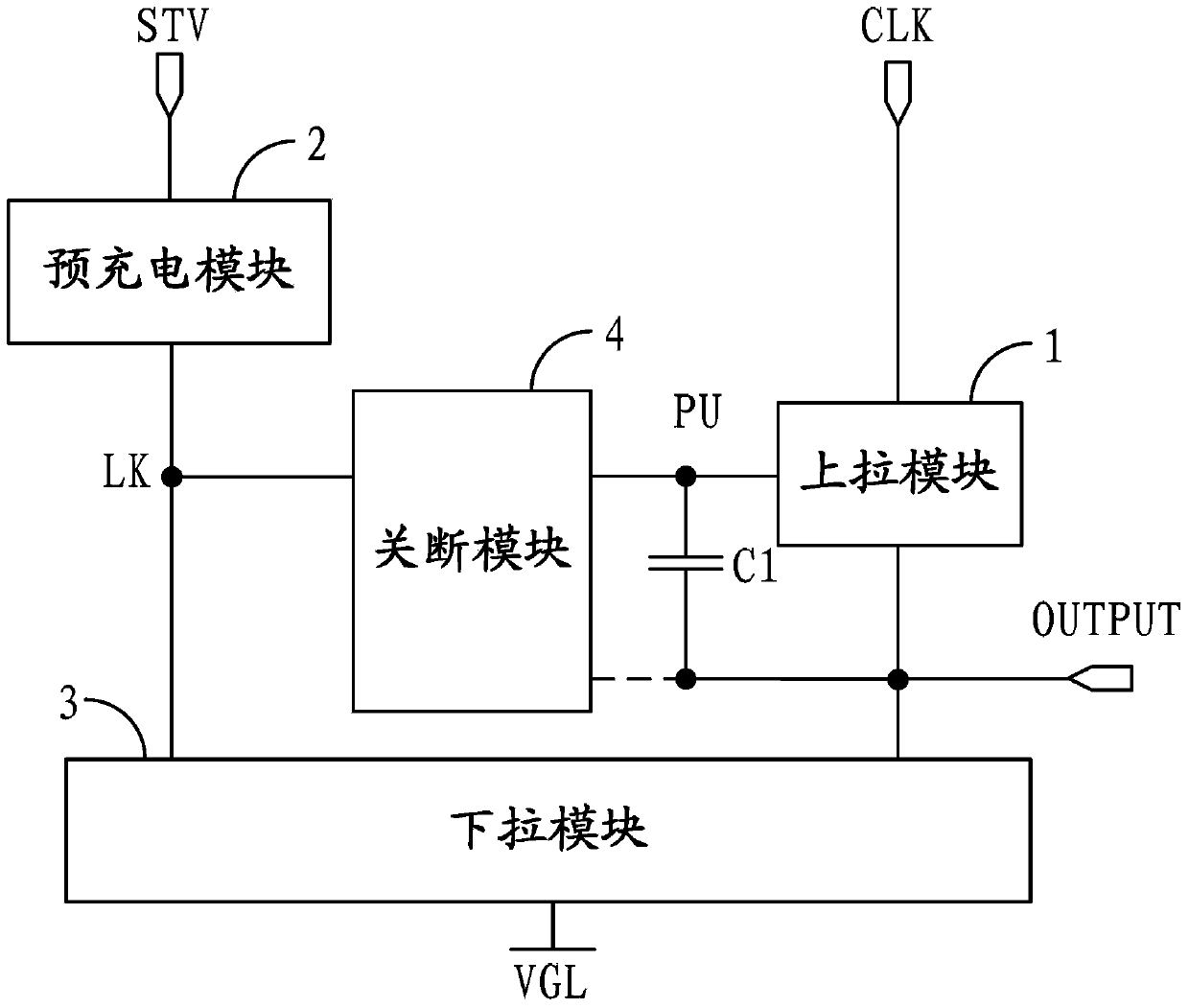

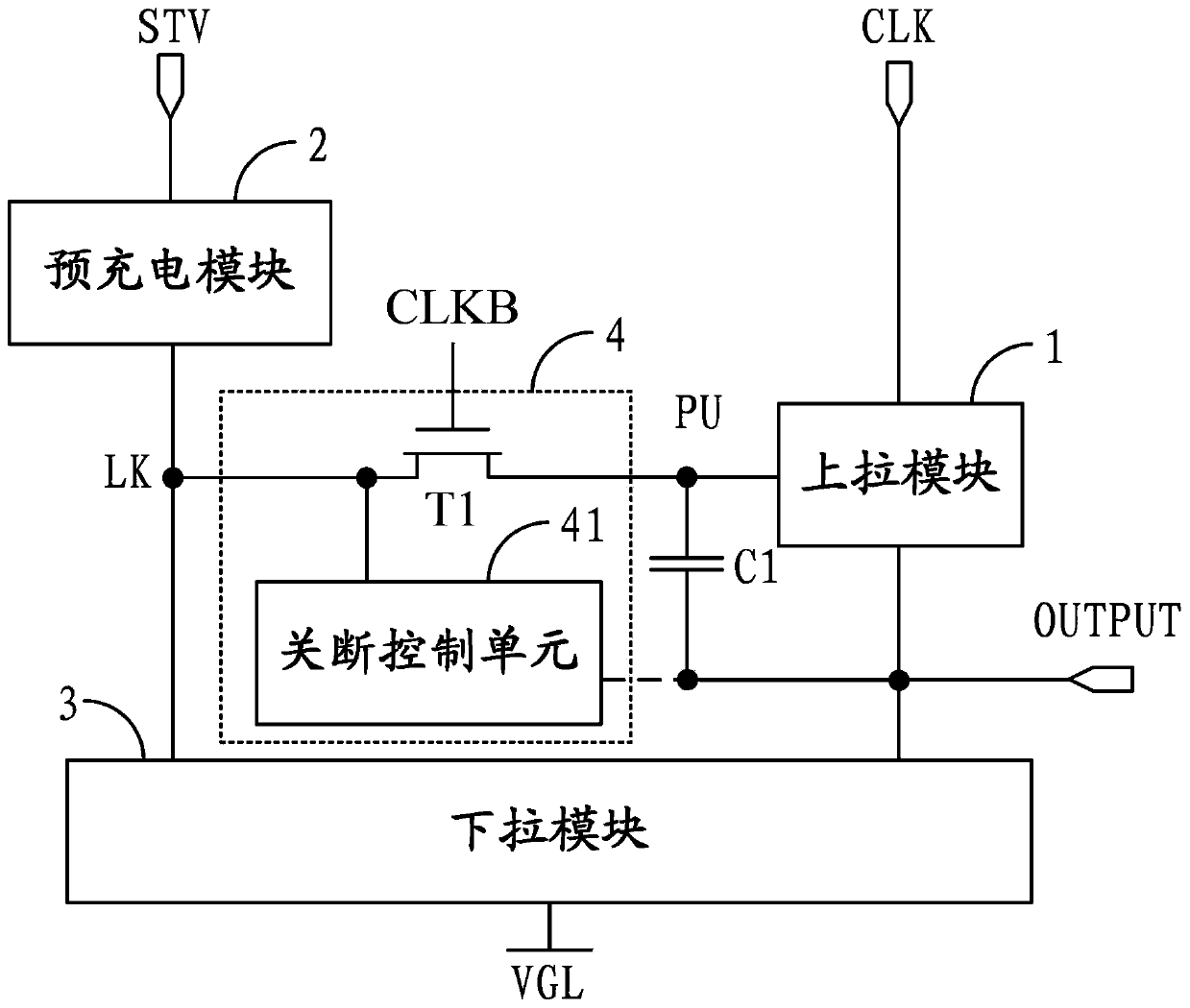

Shift register unit and driving method thereof, shift register, and display device

ActiveCN103474038ASolve the problem of excessive leakageAddress reliabilityStatic indicating devicesDigital storageShift registerOxide thin-film transistor

The invention provides a shift register unit and a driving method thereof, a shift register, and a display device. A turn-off module is arranged for breaking the electrical connection among a pulling-up node PU, a pre-charge module and a pulling-down module at a pulling-up stage so that the over-large electric leakage problem of a GOA circuit can be solved, and the reliability and power consumption problem of the adopted GOA circuit applying an oxide film transistor can be effectively solved.

Owner:BOE TECH GRP CO LTD +1

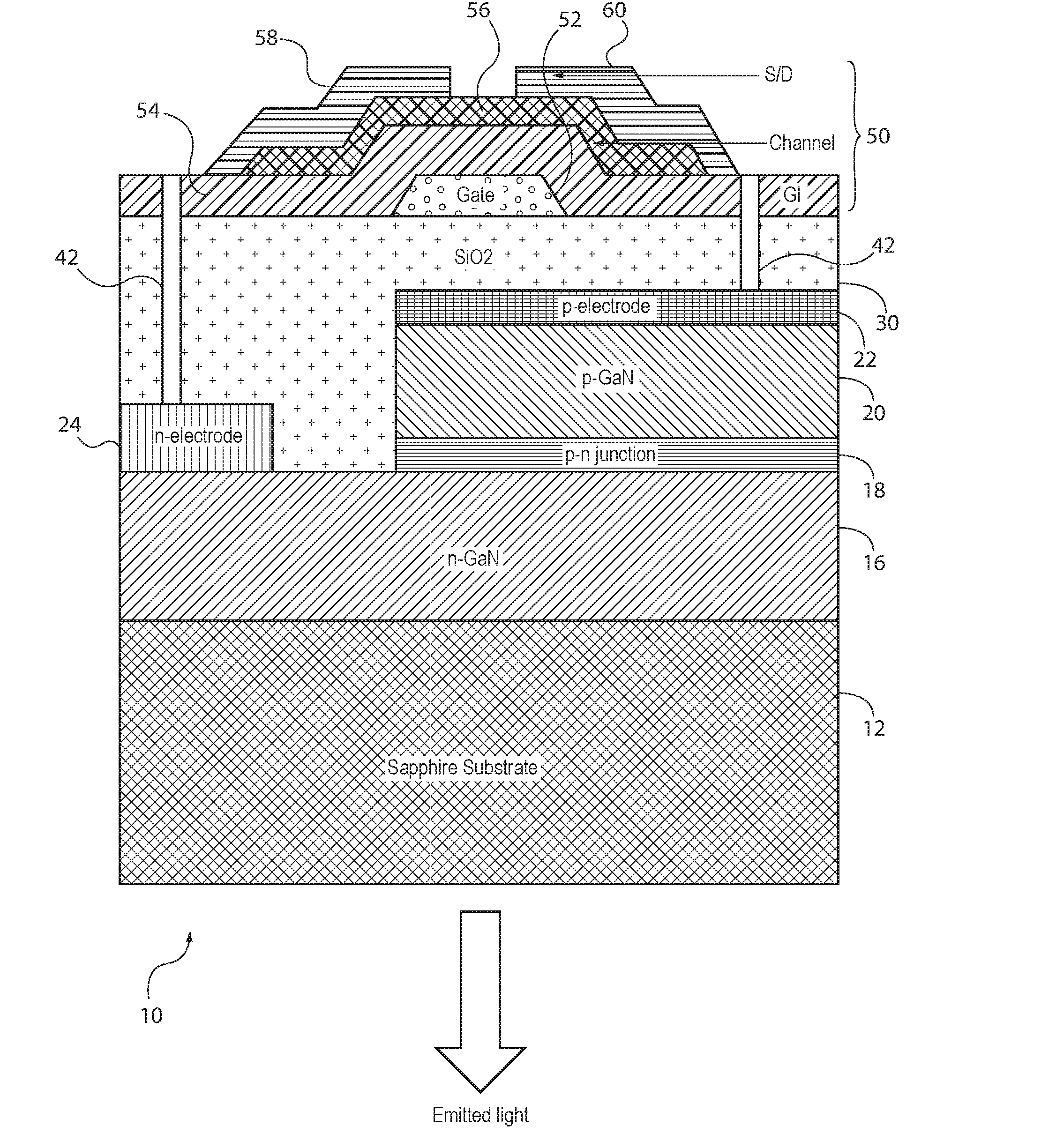

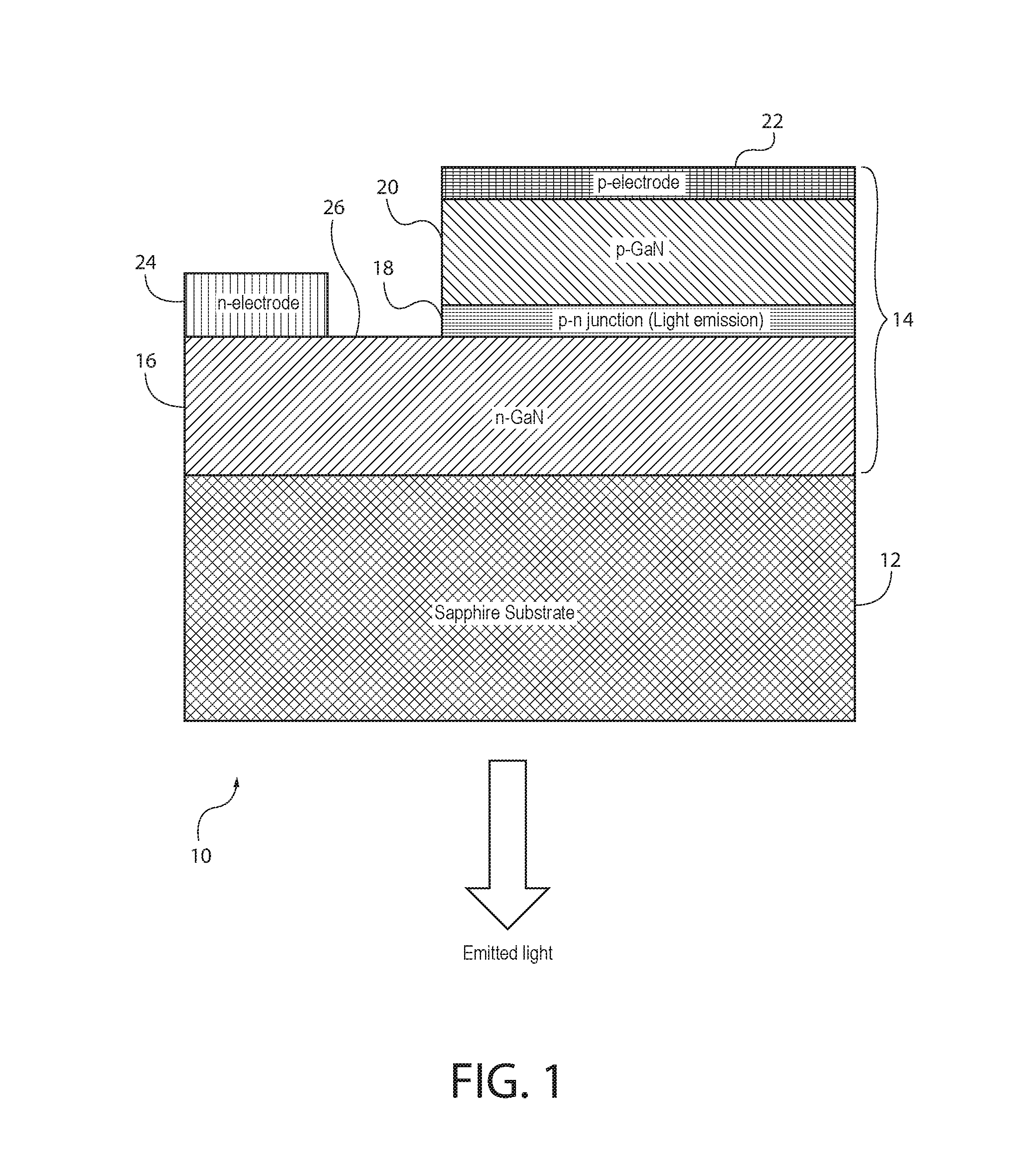

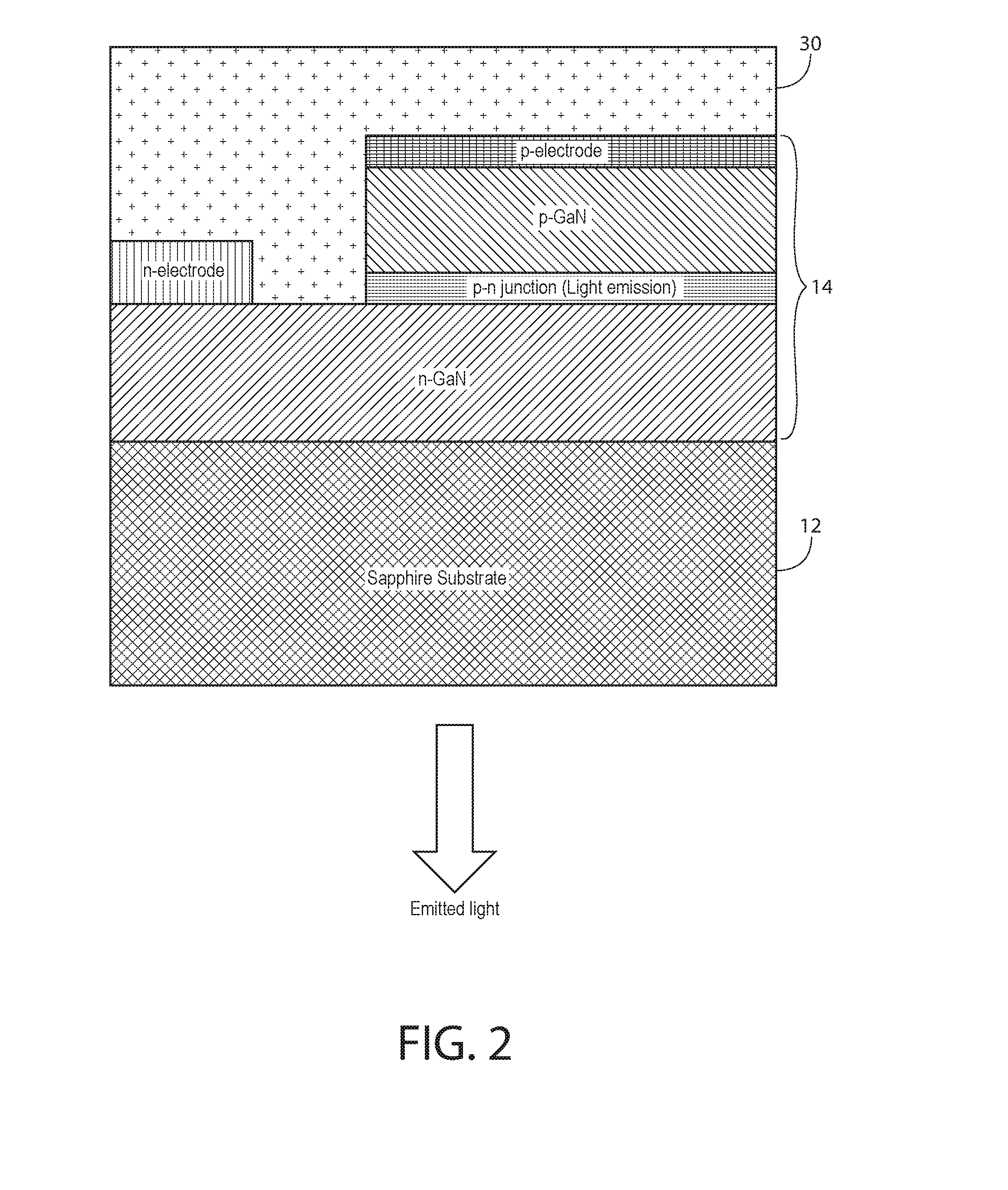

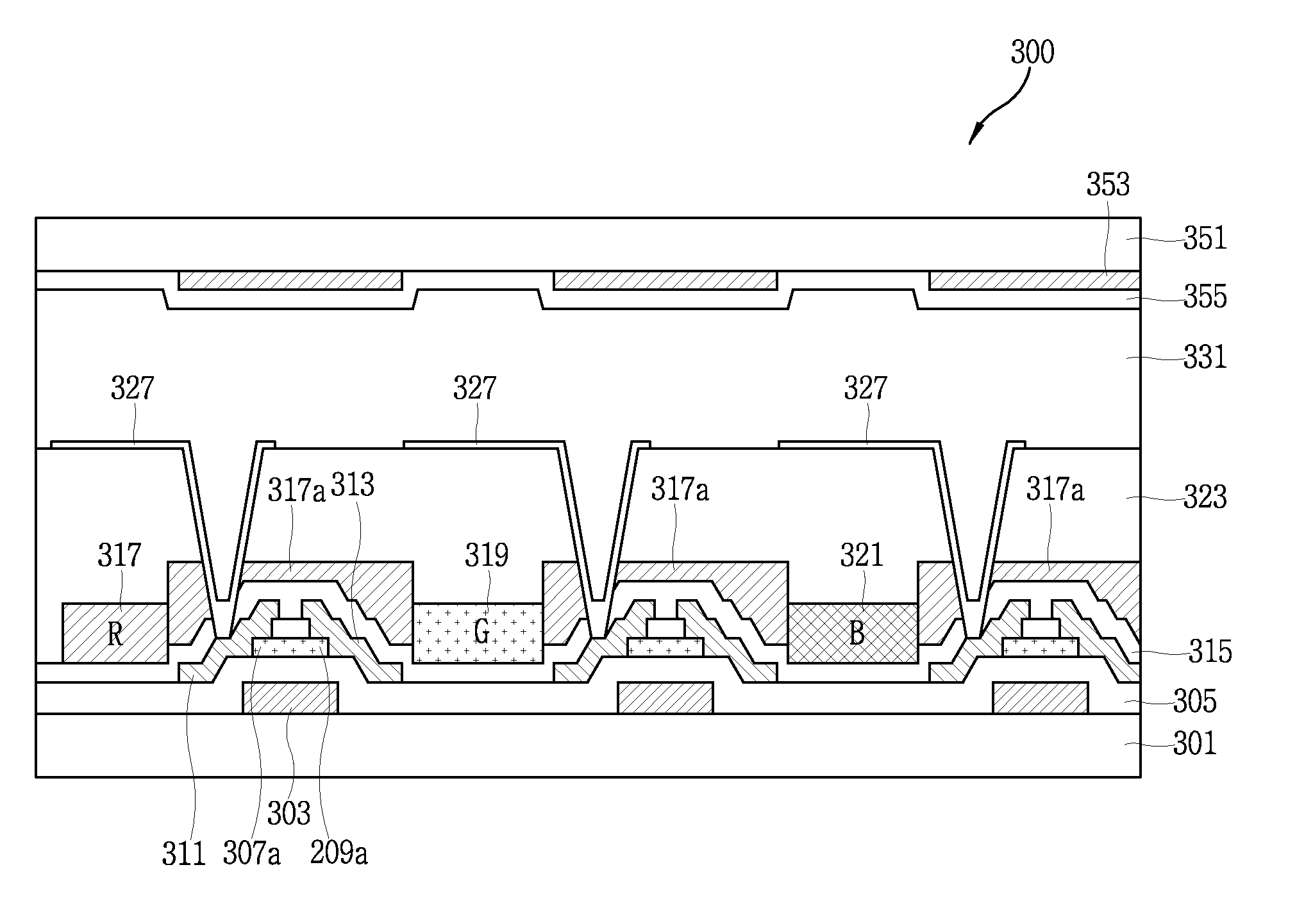

Method of integrating inorganic light emitting diode with oxide thin film transistor for display applications

ActiveUS20160293586A1Cure deficiencyIncrease brightnessTransistorSolid-state devicesDriver circuitInorganic lead

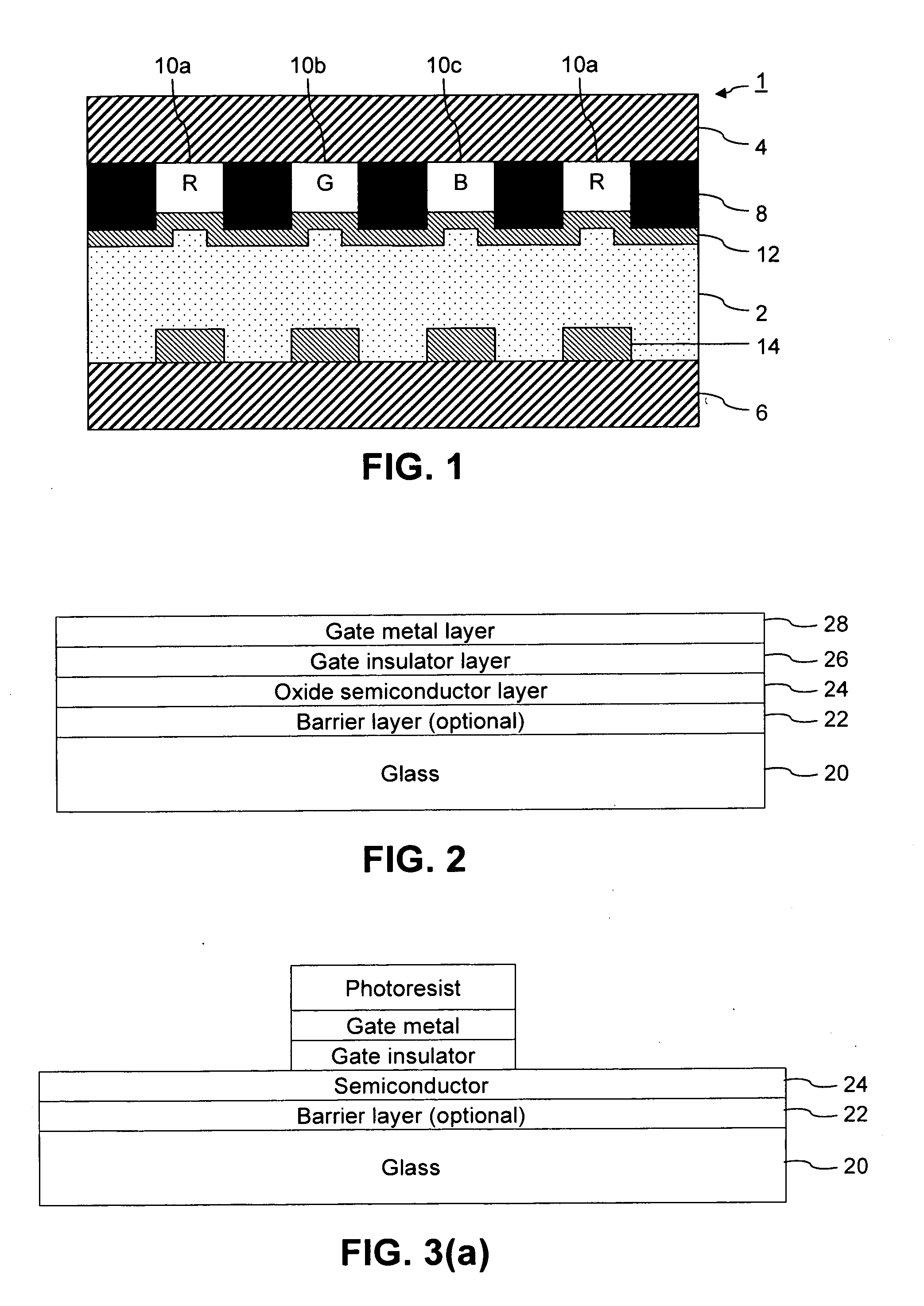

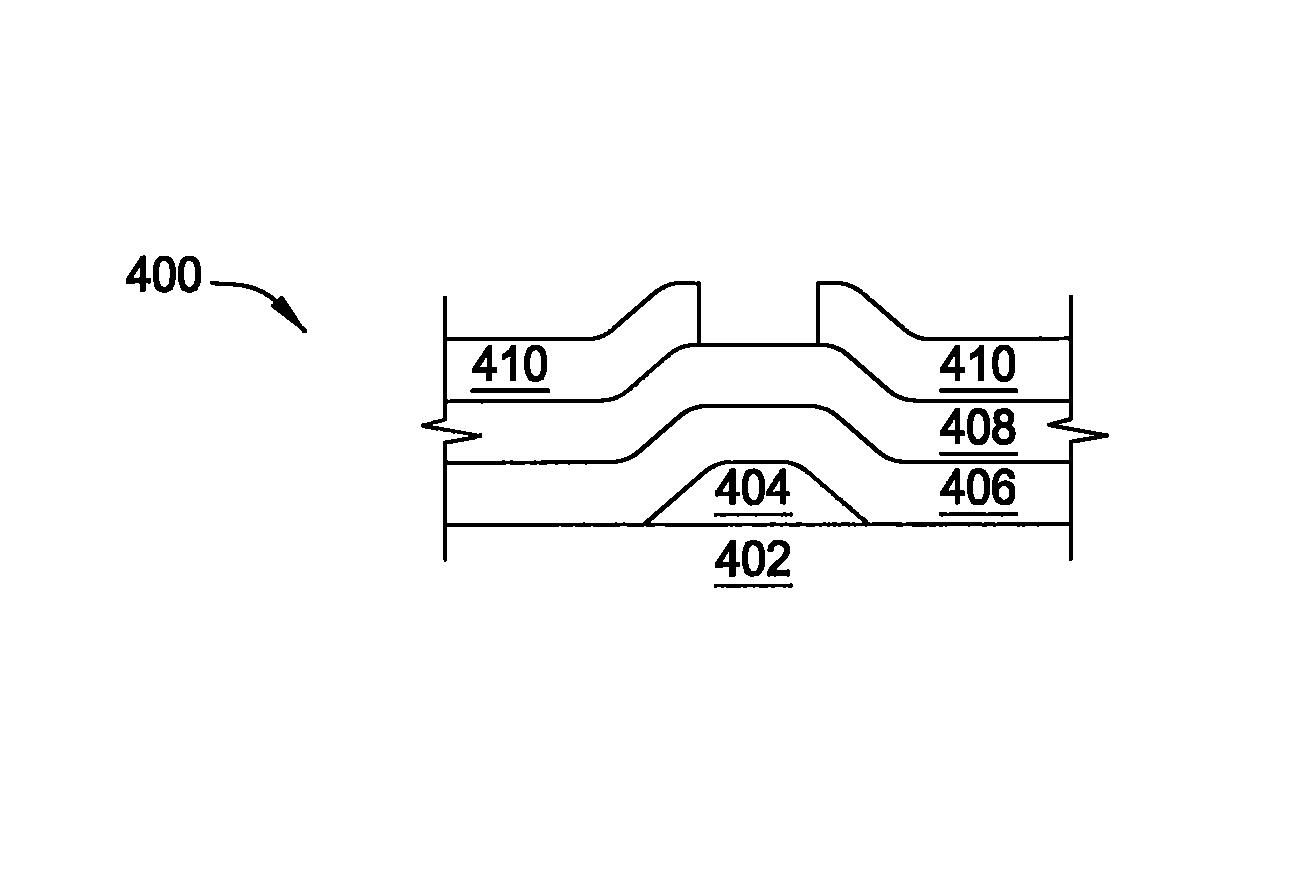

A method of fabricating an active matrix display is disclosed in which one or more oxide thin film transistors is monolithically integrated with an inorganic light emitting diode structure. The method comprises forming an array of inorganic light emitting diodes over a substrate defining a plurality of sub-pixels, depositing an insulating layer over the inorganic LED array, forming conductive vias through the insulating layer, one via for each LED in the LED array, and forming a metal oxide thin film transistor backplane, including an array of pixel driver circuits, over the dielectric layer and conductive vias, wherein one driver circuit electrically controls each sub-pixel through the dielectric layer.

Owner:EMAGIN CORP

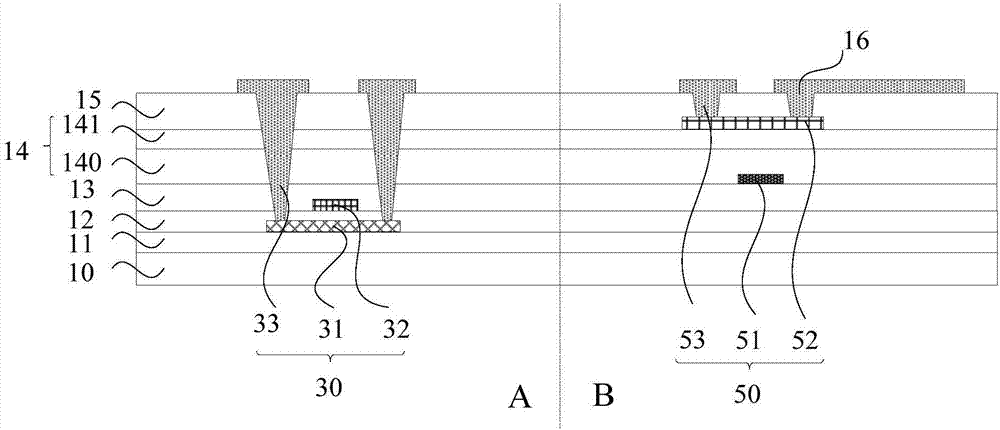

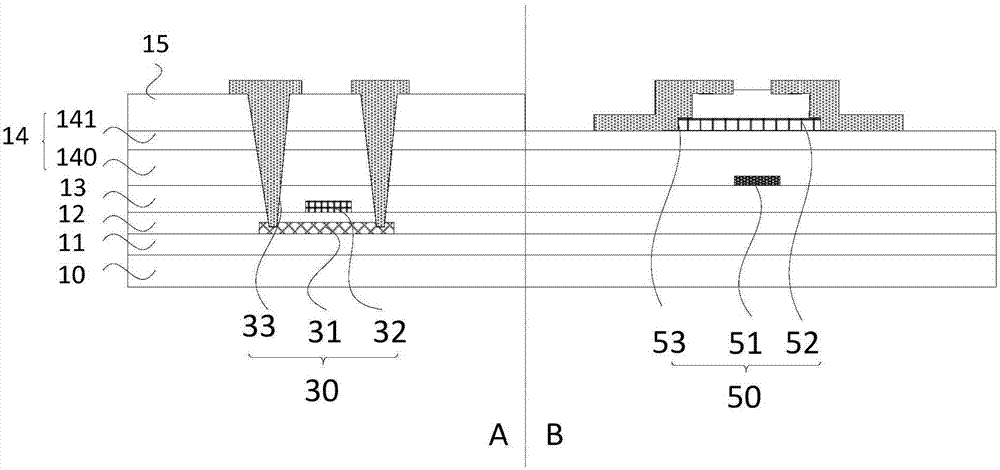

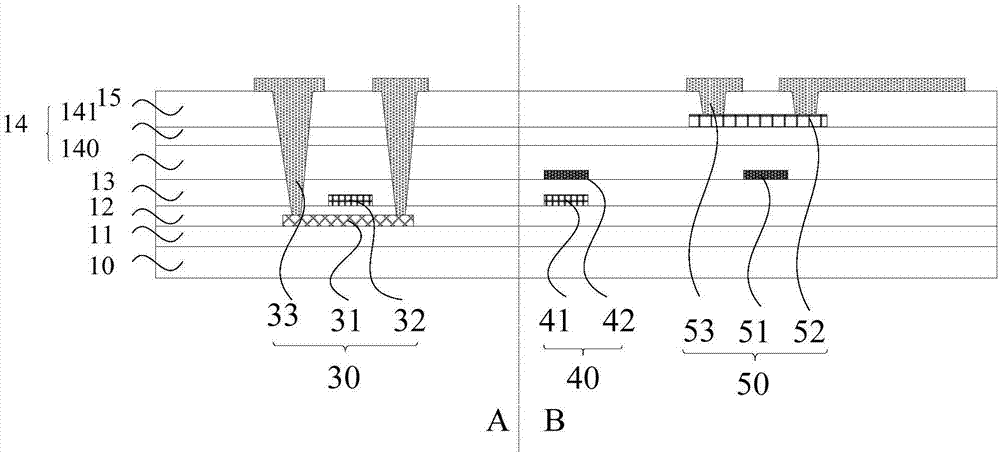

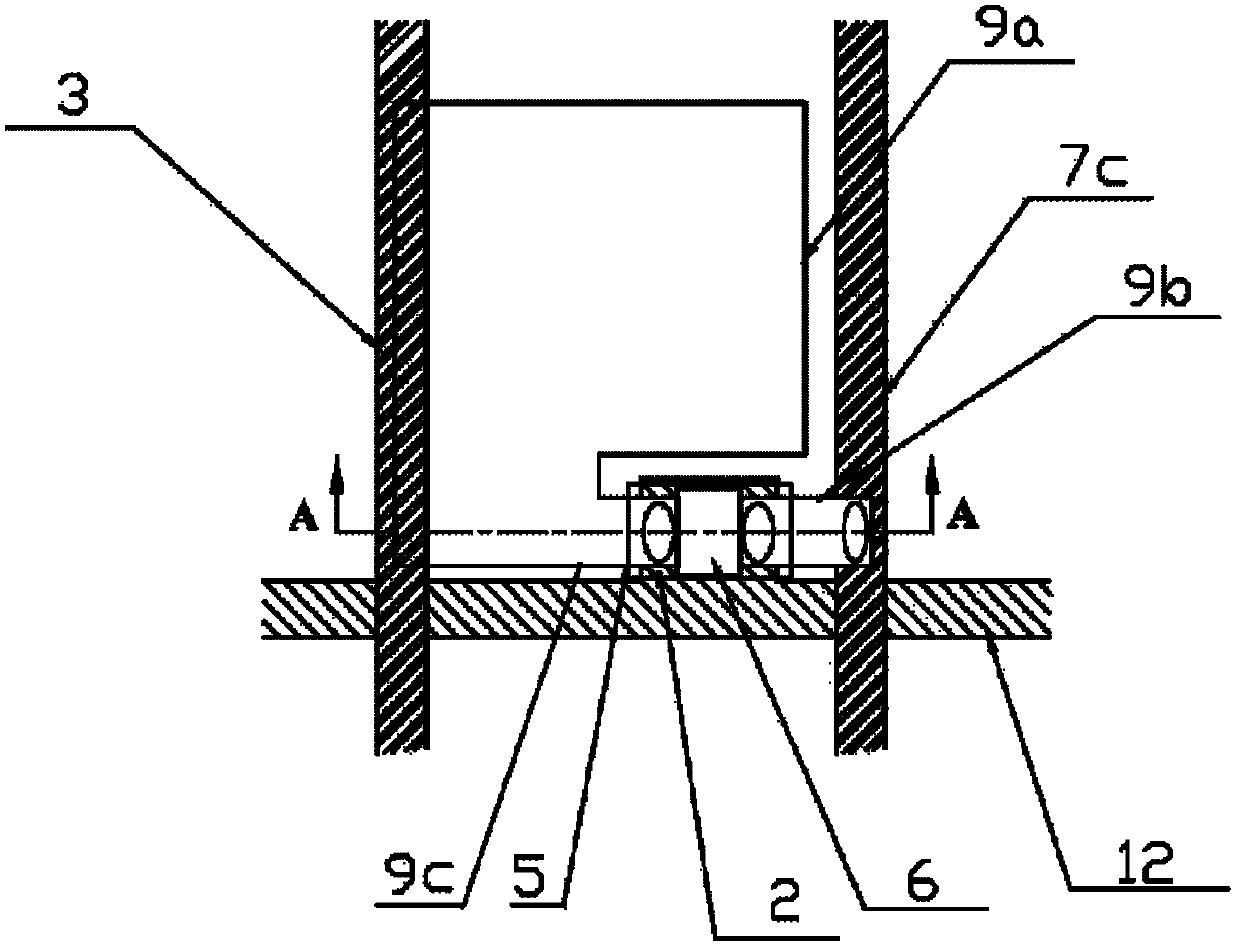

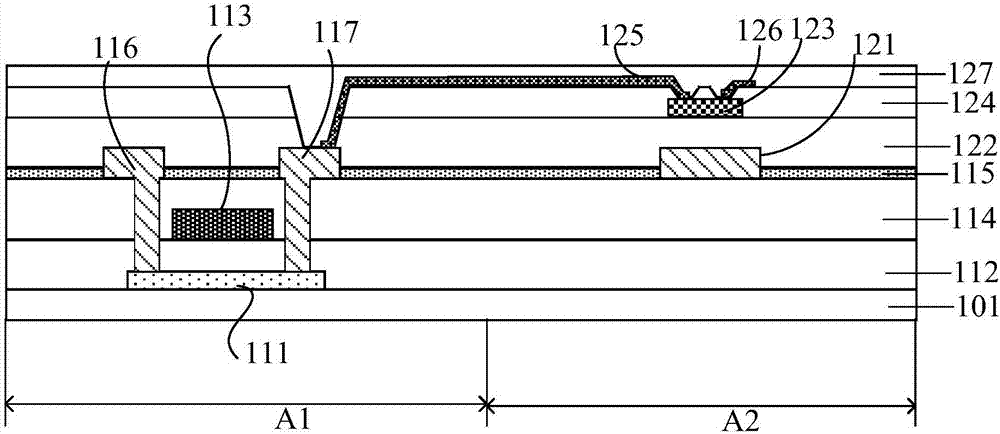

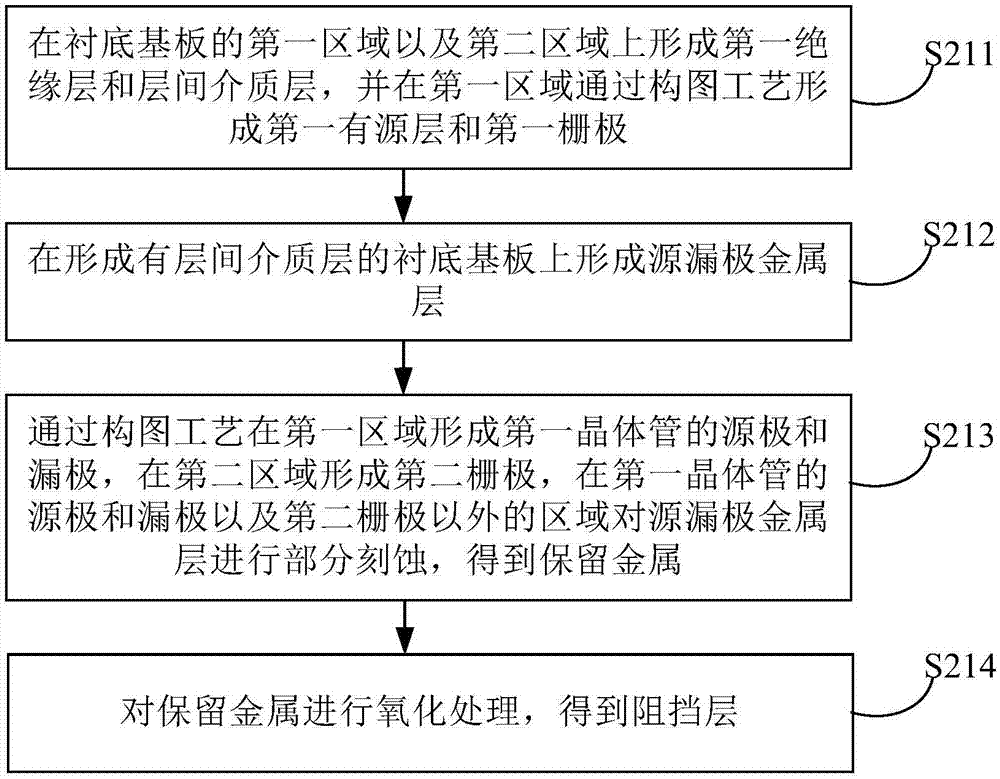

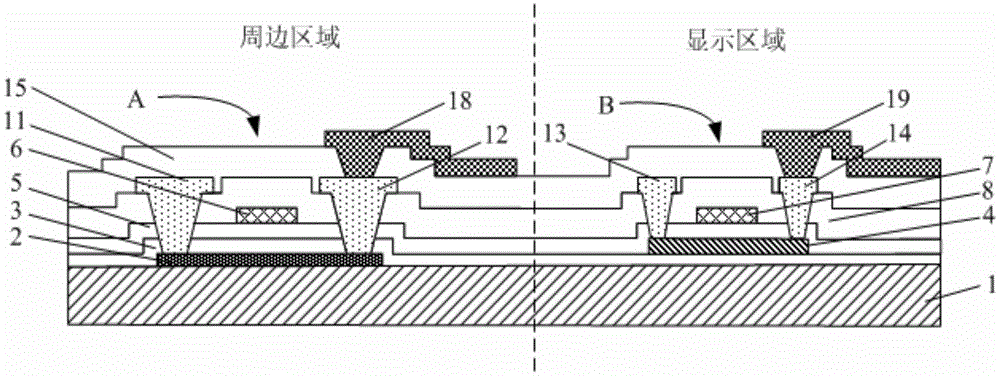

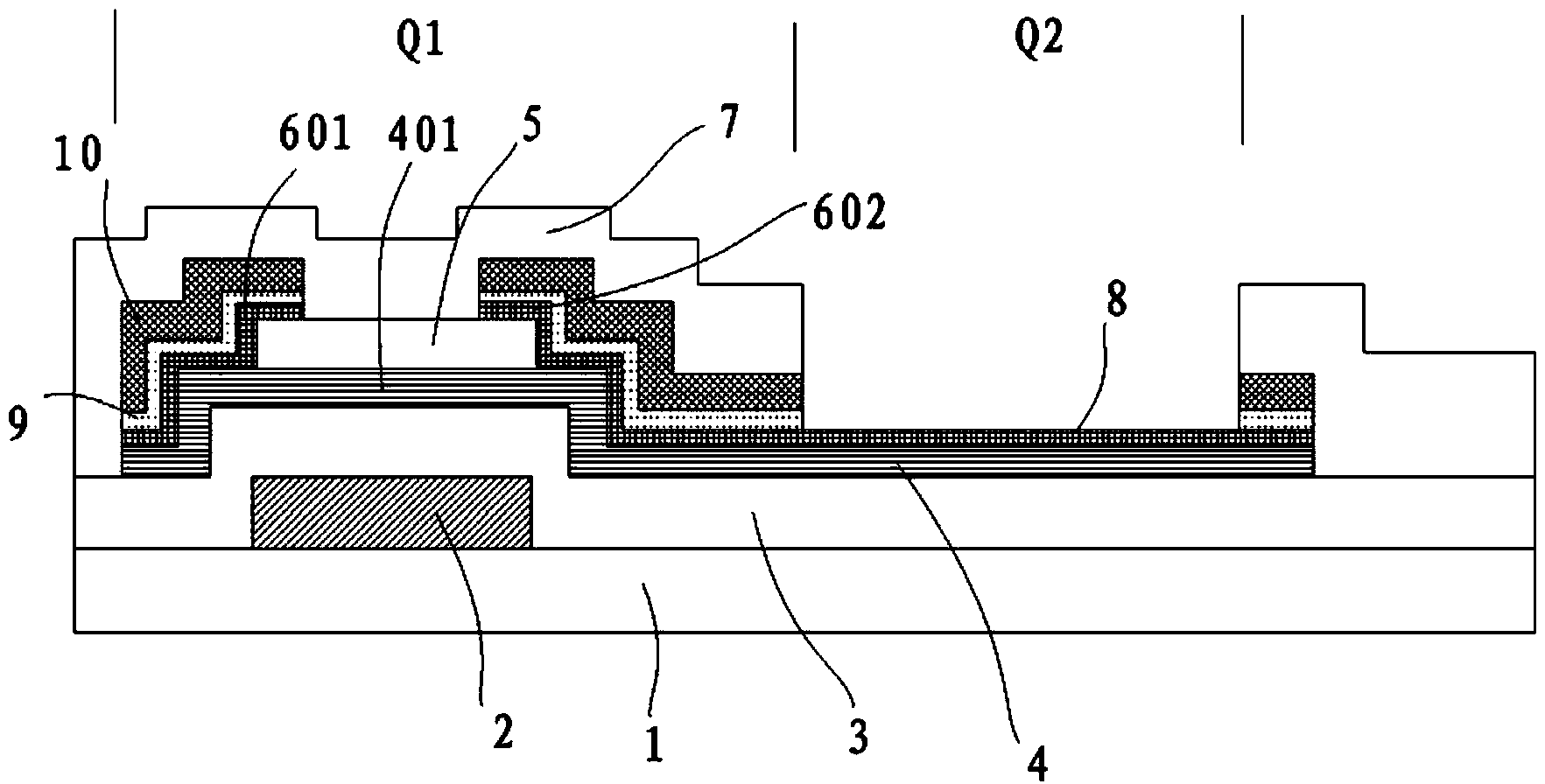

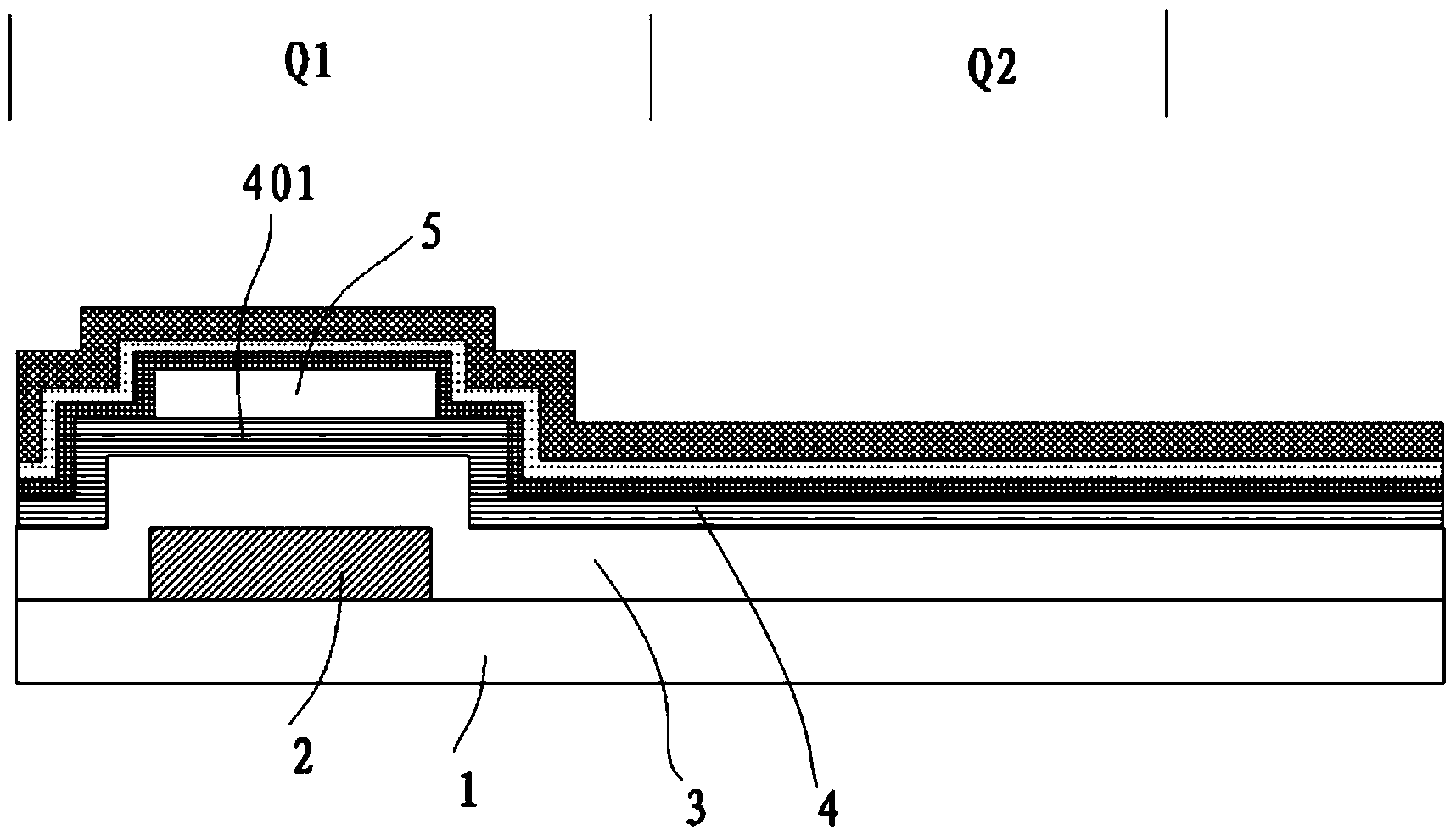

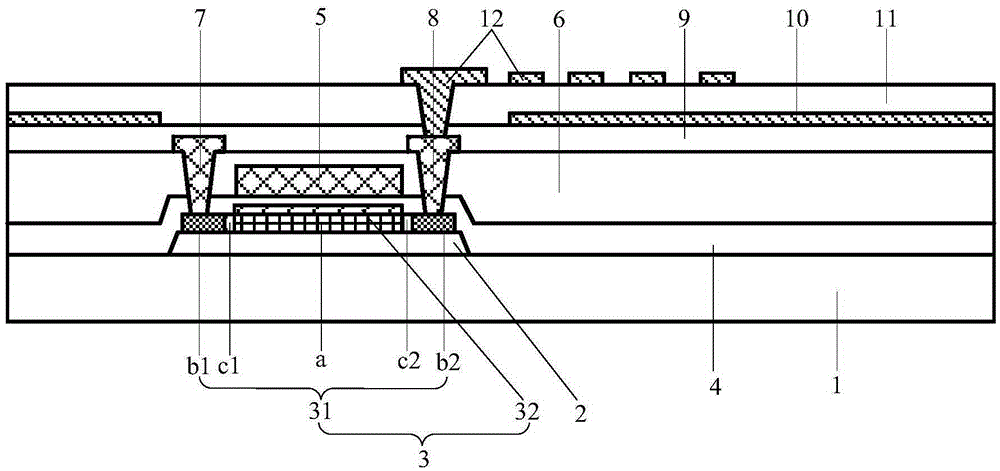

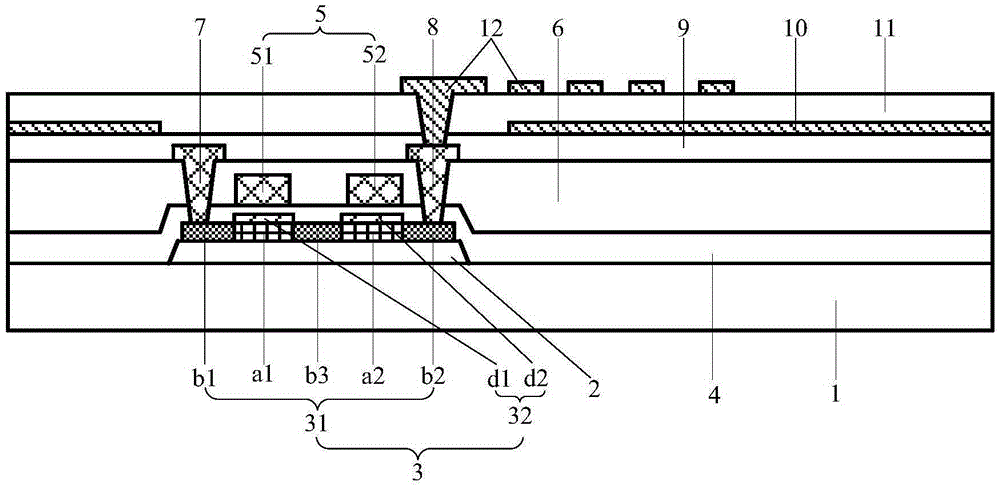

Array substrate and manufacturing method therefor

InactiveCN106876412AImprove electrical performanceImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingOxide thin-film transistorElectrical performance

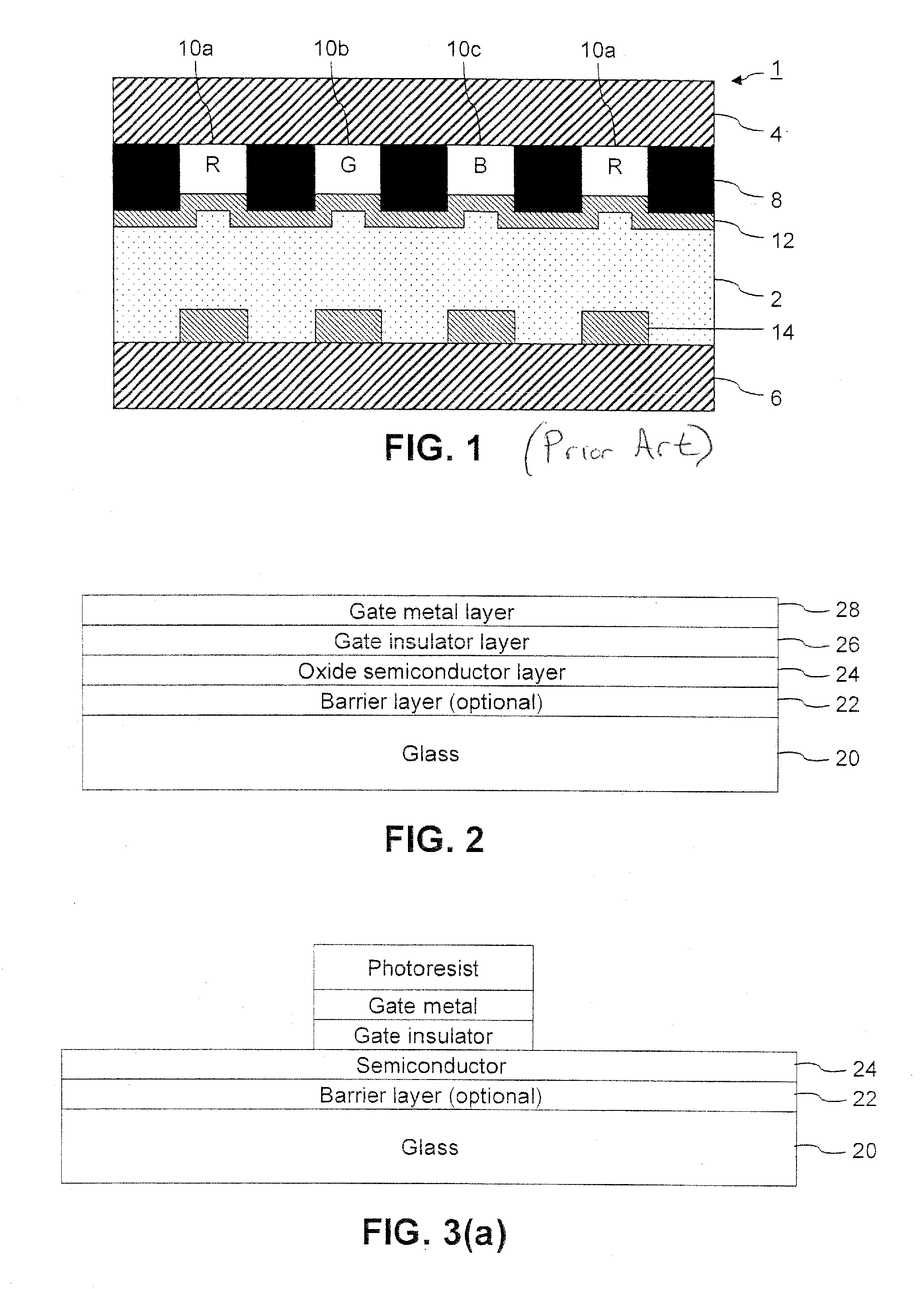

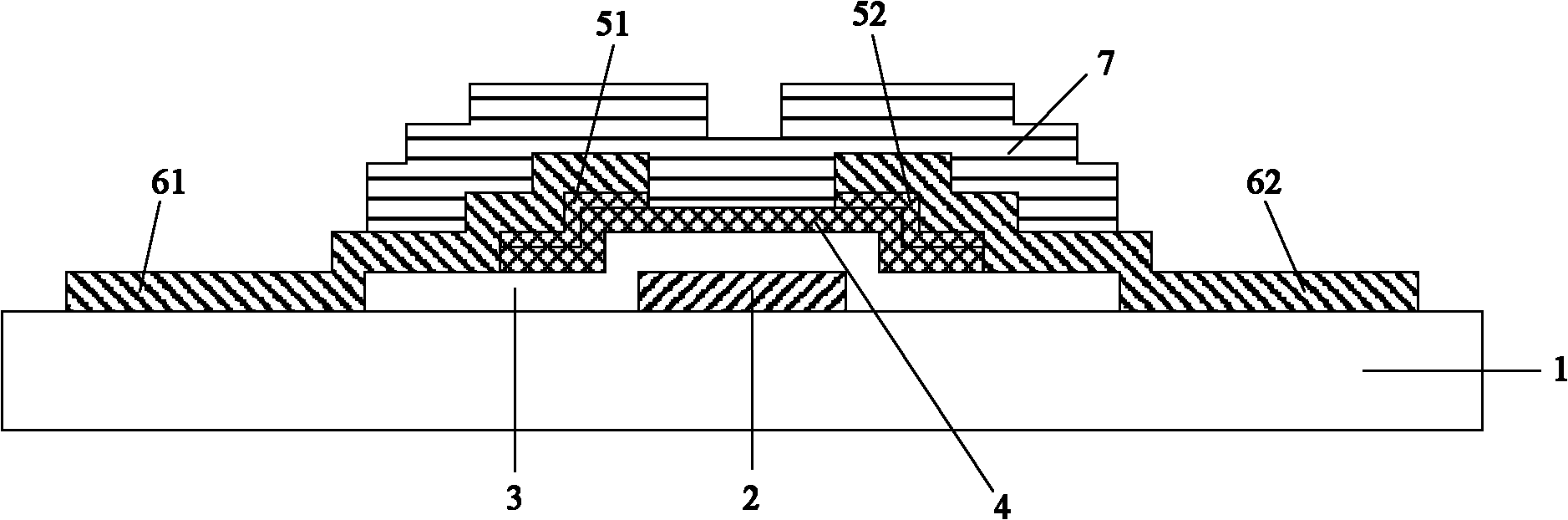

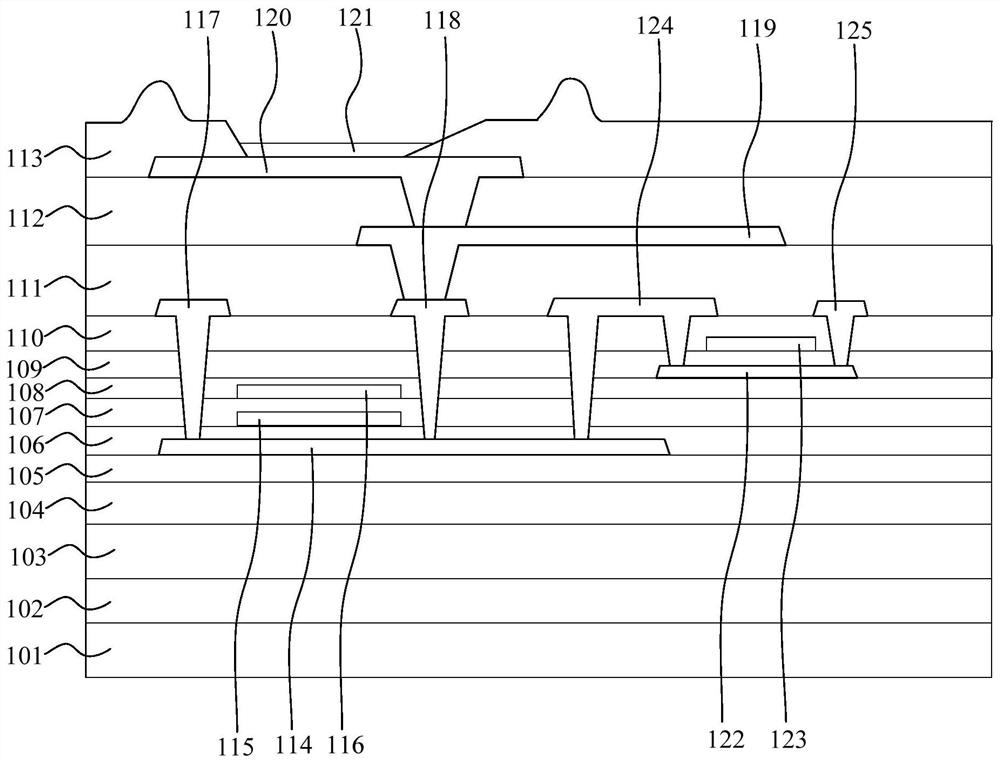

Embodiments of the invention disclose an array substrate and a manufacturing method therefor. The array substrate comprises a plurality of first thin film transistors and a plurality of second thin film transistors; the first thin film transistors and the second thin film transistors are formed above a substrate; the active layer of each first thin film transistor is low-temperature polysilicon; the active layer of each second thin film transistor is an oxide semiconductor; the first thin film transistors are positioned in a peripheral circuit region of the array substrate; the second thin film transistors are positioned in a display region of the array substrate; the grid electrodes of the first thin film transistors and the second thin film transistors are positioned on different layers; and the source and drain electrodes of the first thin film transistors and the source and drain electrodes of the second thin film transistors are positioned on the same layer. By adoption of the array substrate and the manufacturing method therefor, the problem of incompatibility of two film layers of two types of thin film transistors when the metal oxide thin film transistors and the low-temperature polysilicon thin film transistors are formed in a display panel at the same time is solved, so that the electrical performance and the stability of the display panel are improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

CMOS thin film transistor, method of fabricating the same and organic light emitting display device having the same

ActiveUS20100176395A1Simple manufacturing processMaintain electrical performanceTransistorSolid-state devicesCMOSOxide thin-film transistor

Owner:SAMSUNG DISPLAY CO LTD

Method of making oxide thin film transistor array

InactiveUS8530273B2Improve economyImprove conductivitySolid-state devicesSemiconductor/solid-state device manufacturingOxide thin-film transistorRoom temperature

Owner:GUARDIAN GLASS LLC

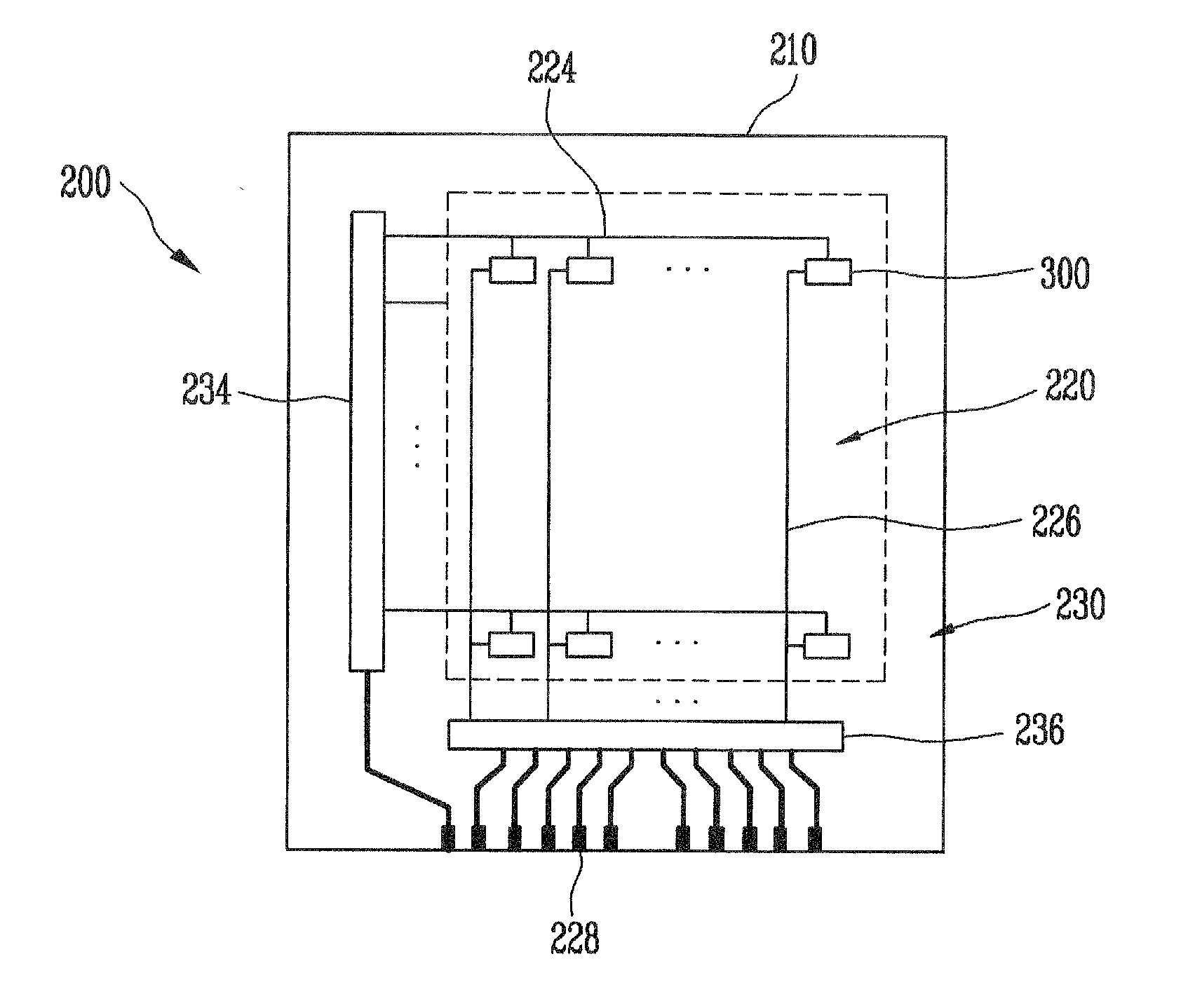

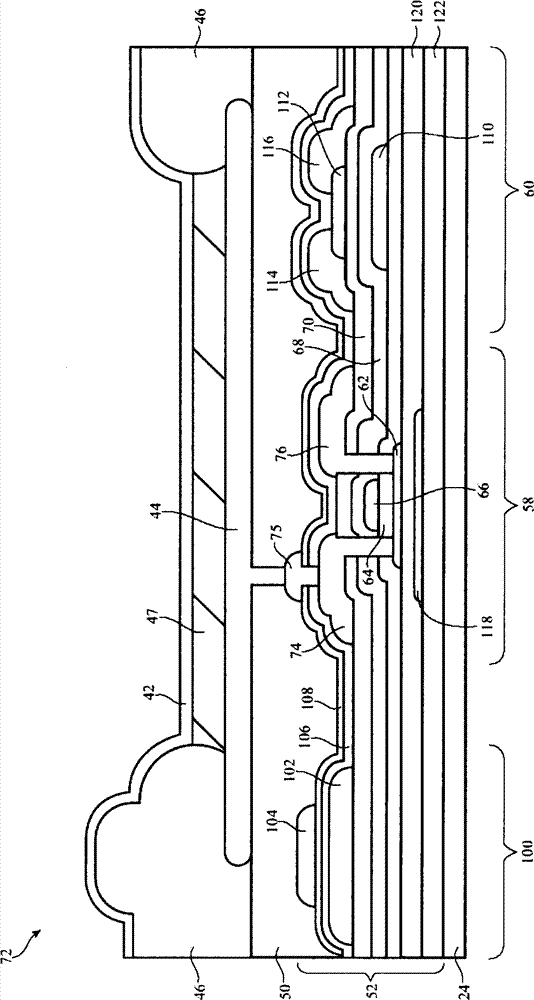

Displays with silicon and semiconducting oxide thin-film transistors

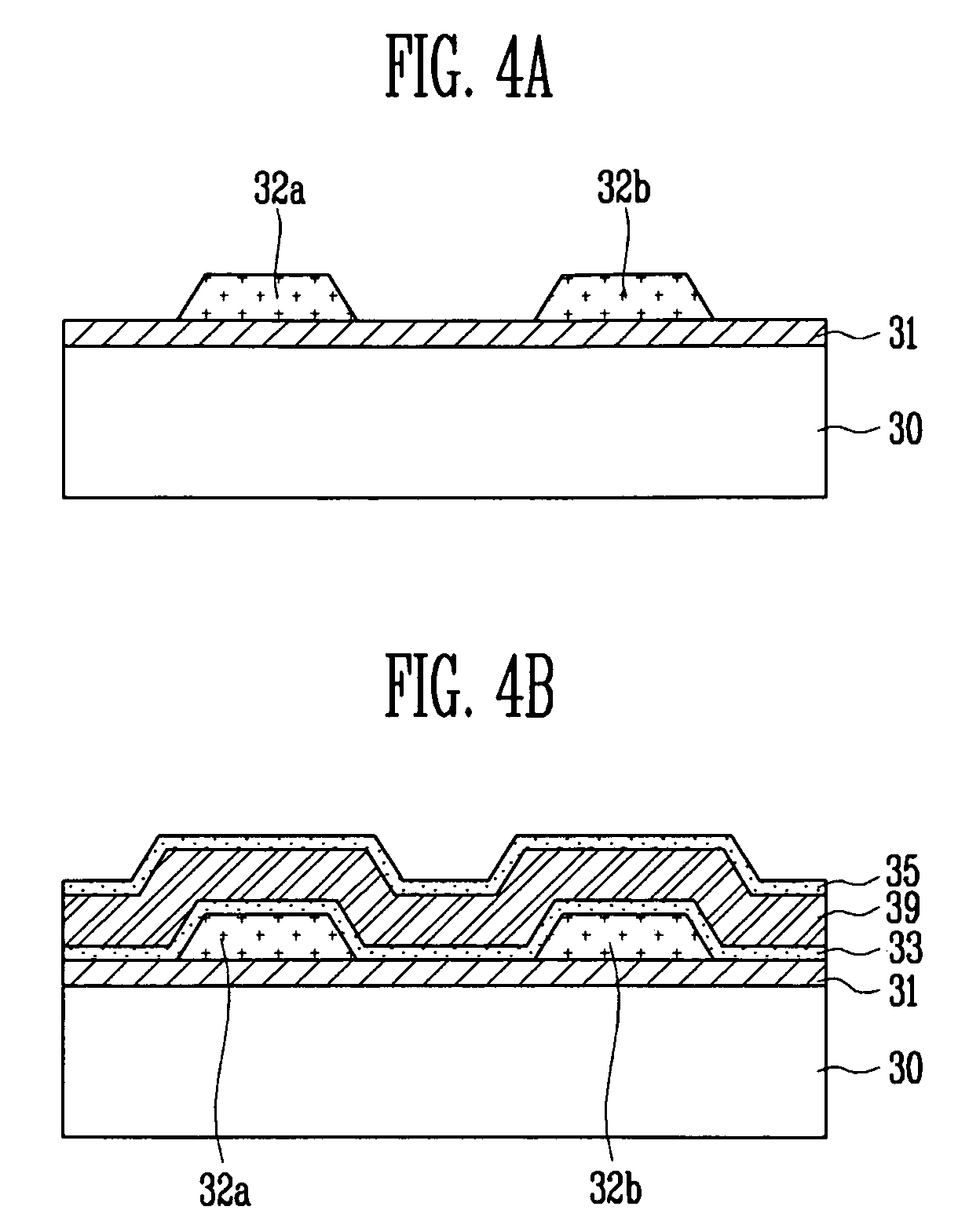

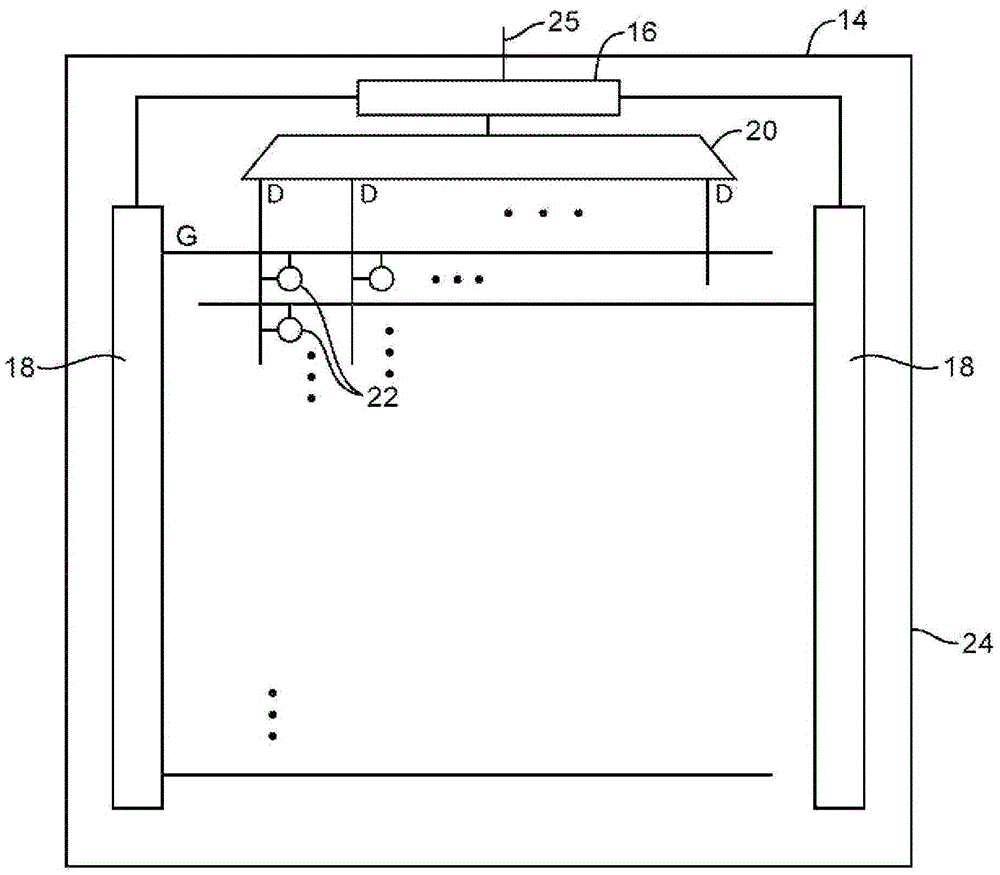

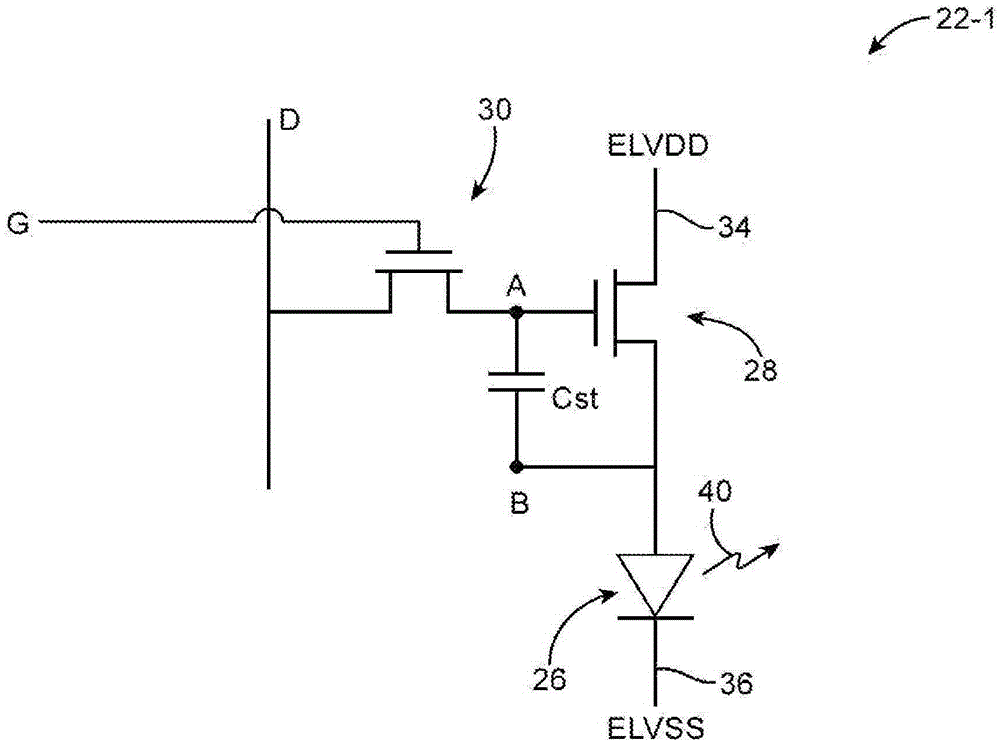

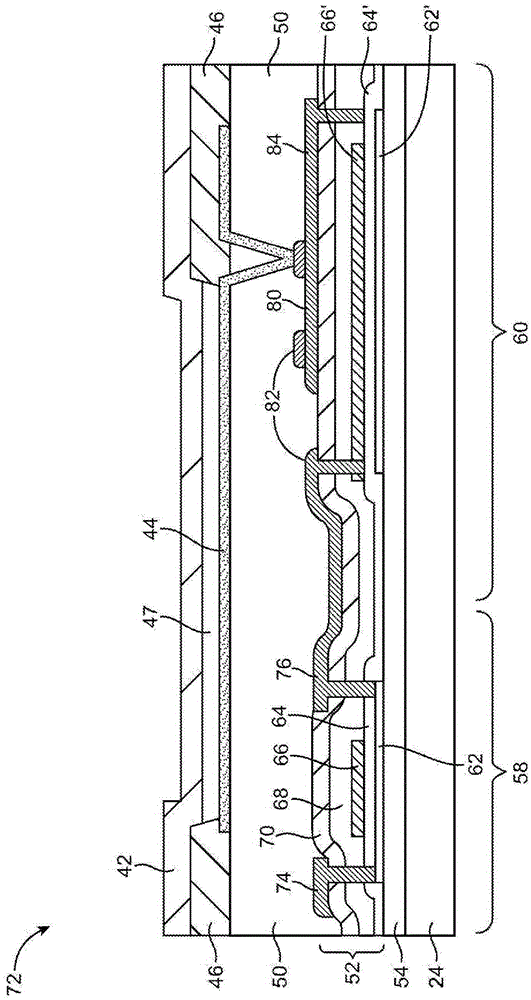

An electronic device may include a display having an array of display pixels on a substrate. The display pixels may be organic light-emitting diode display pixels or display pixels in a liquid crystal display. In an organic light-emitting diode display, hybrid thin-film transistor structures may be formed that include semiconducting oxide thin-film transistors, silicon thin-film transistors, and capacitor structures. The capacitor structures may overlap the semiconducting oxide thin-film transistors. Organic light-emitting diode display pixels may have combinations of oxide and silicon transistors. In a liquid crystal display, display driver circuitry may include silicon thin-film transistor circuitry and display pixels may be based on oxide thin-film transistors. A single layer or two different layers of gate metal may be used in forming silicon transistor gates and oxide transistor gates. A silicon transistor may have a gate that overlaps a floating gate structure.

Owner:APPLE INC

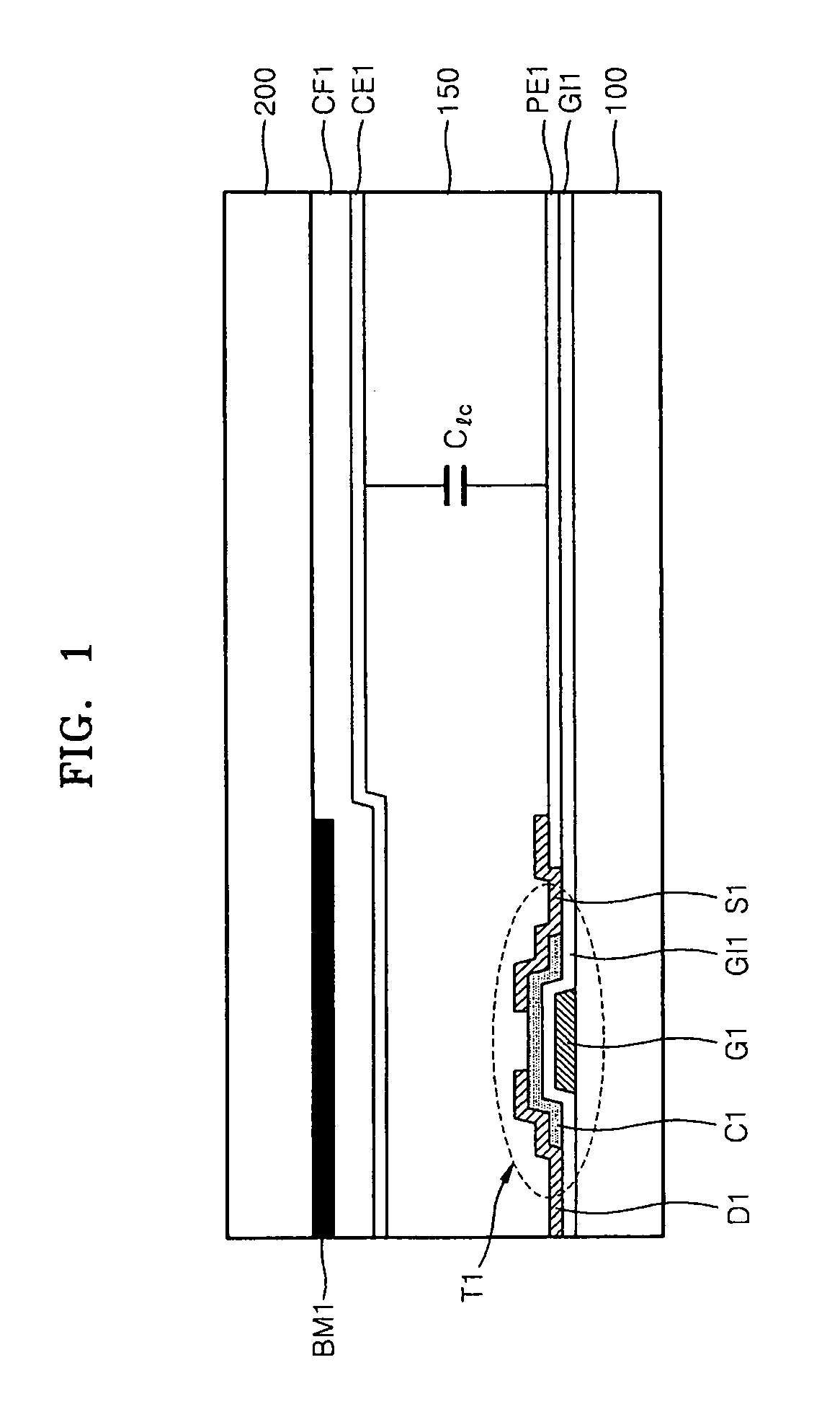

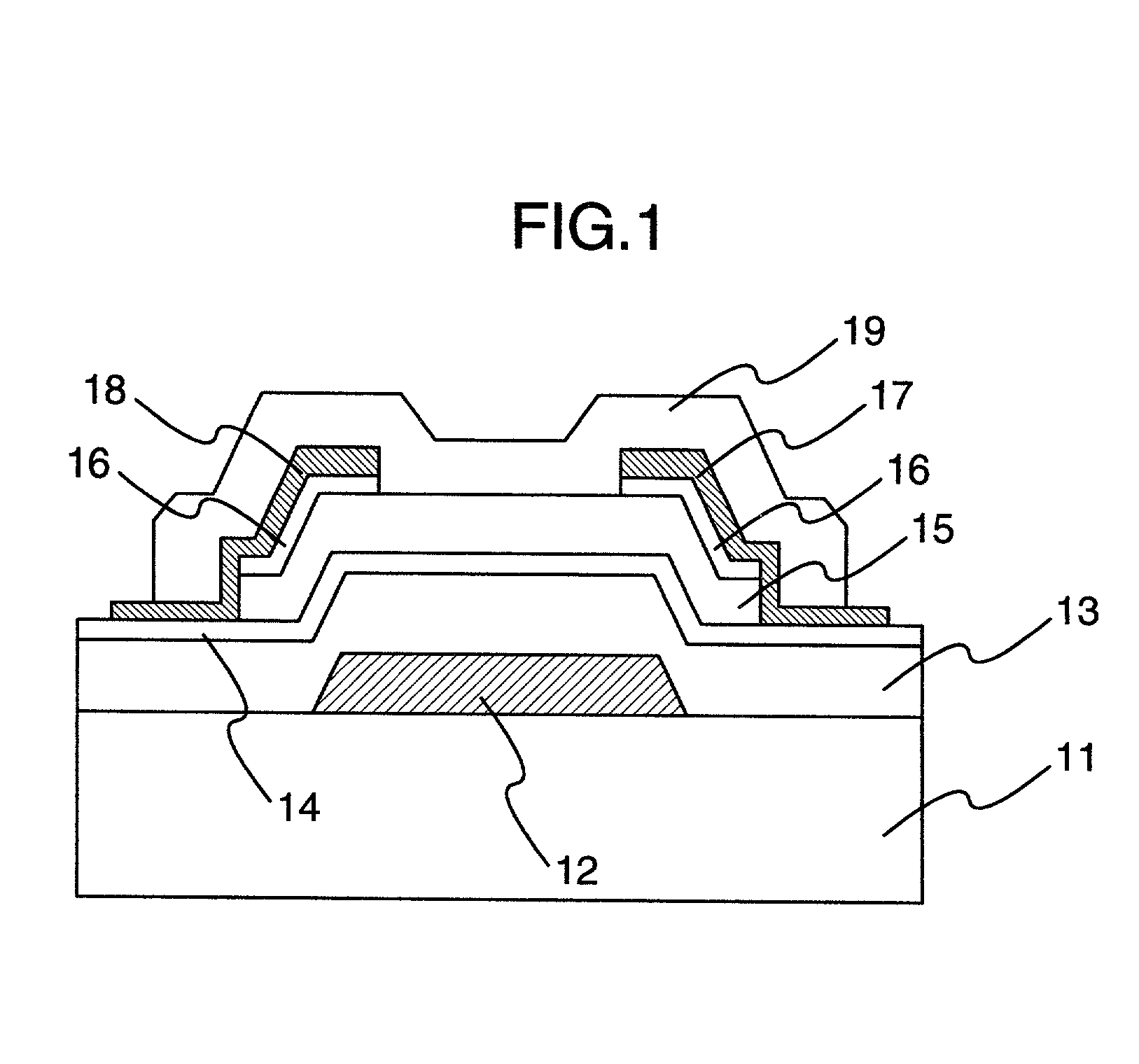

Thin film transistor and active matrix type liquid crystal display device

A gate electrode, a gate insulating layer, a semiconductor layer, a drain electrode, a source electrode and a passivation insulating layer are fabricated in turn on an insulating substrate, thereby forming a thin film transistor. The thin film transistor is designed in such a way that a silicon oxide film is employed as a second gate insulating layer adjacent to the semiconductor layer; a thickness of the silicon oxide film is set to the range of 0.5 to 3.0 nm; and it shows the characteristics in which when a stress voltage which is negative with respect to the drain electrode and the source electrode is applied to the gate electrode, the operating threshold voltage is reduced.

Owner:HITACHI LTD

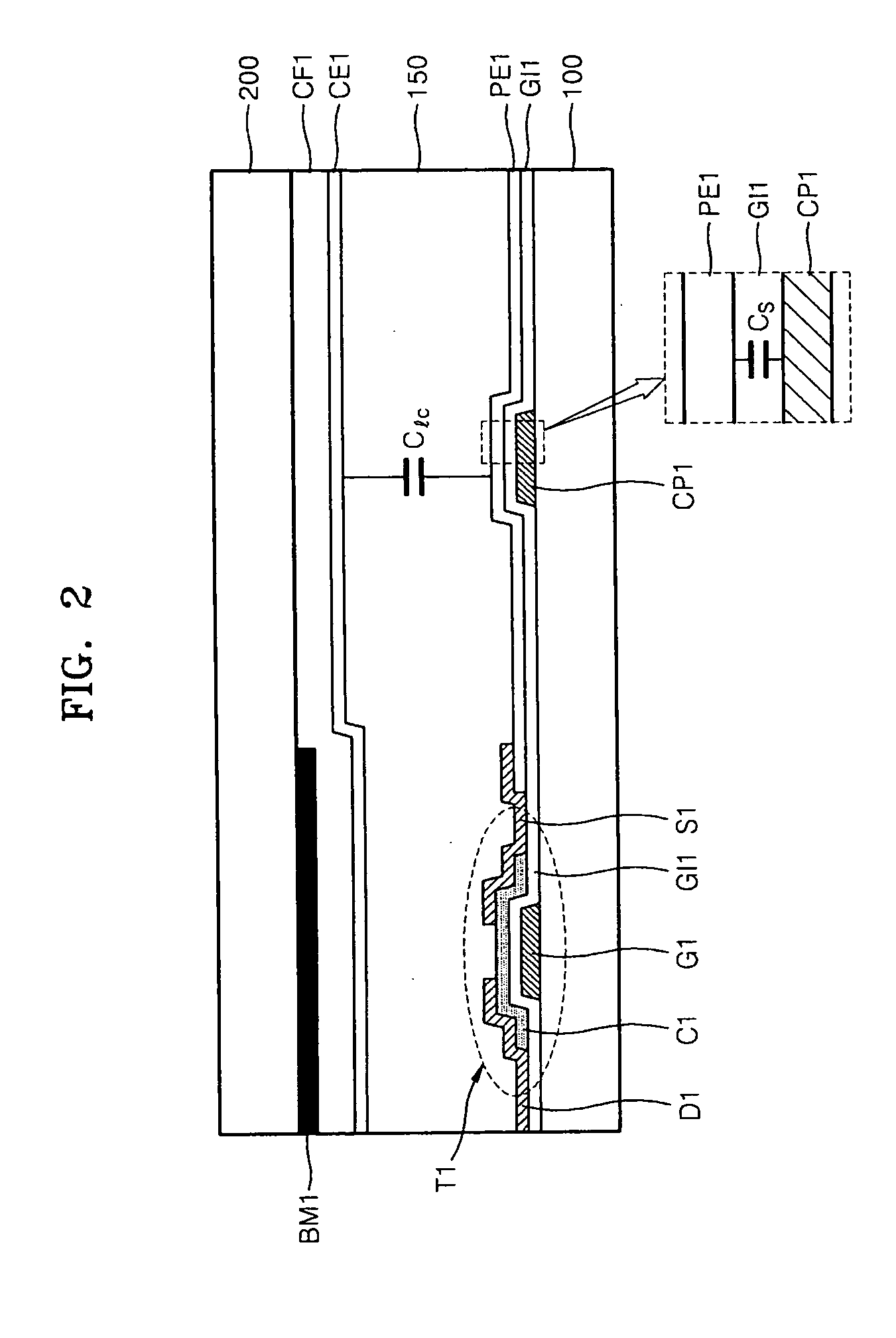

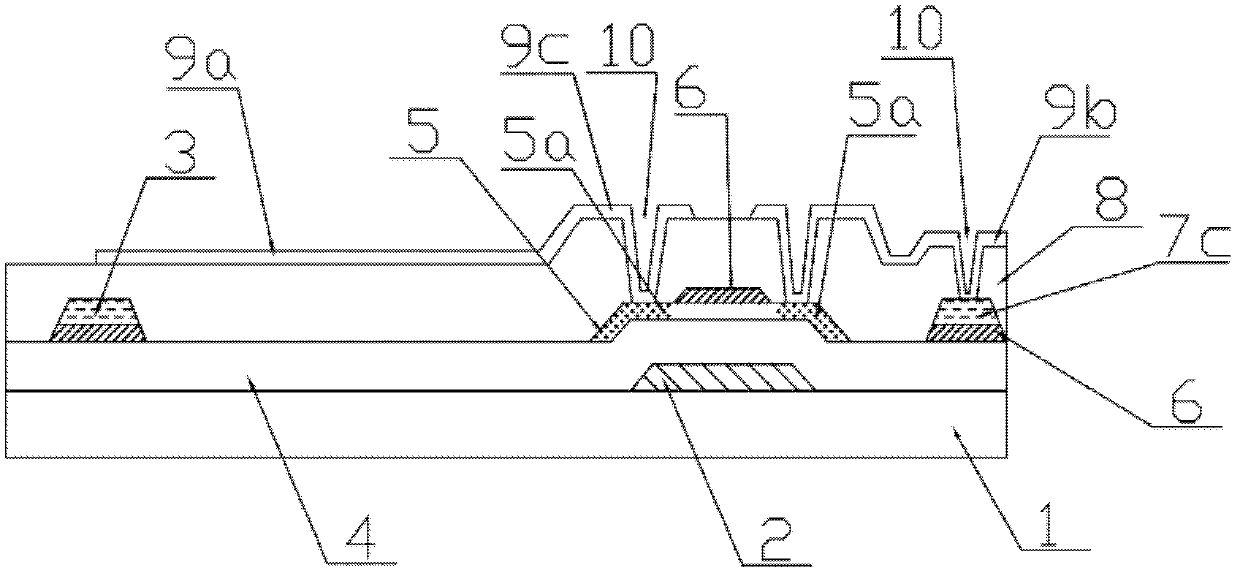

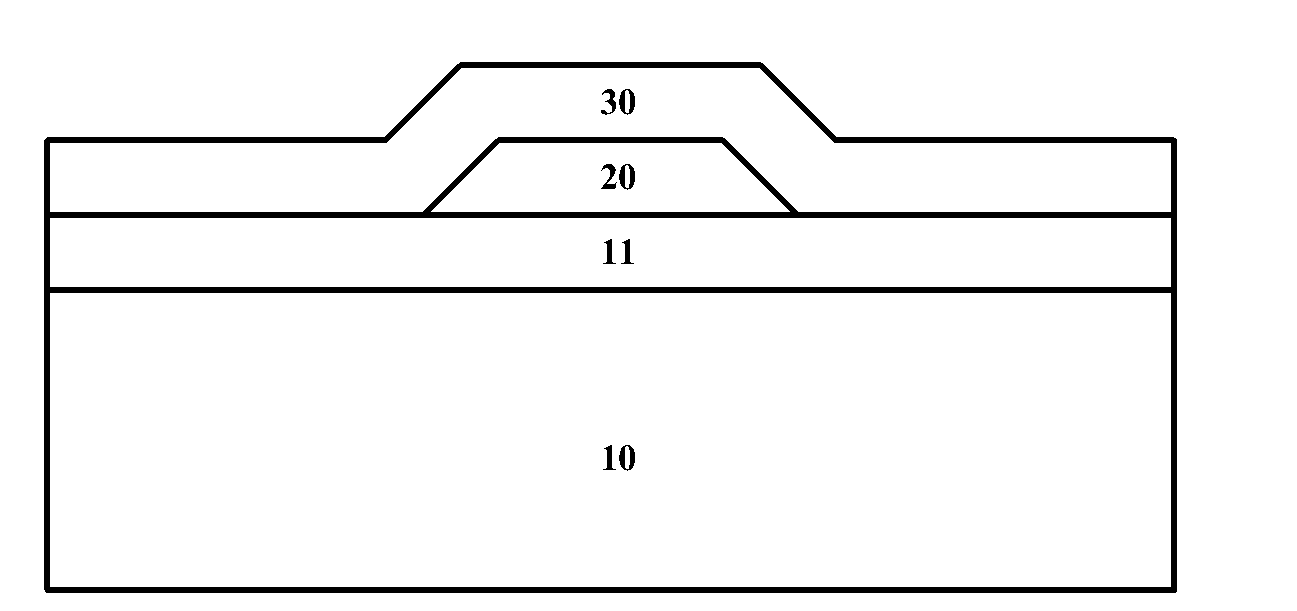

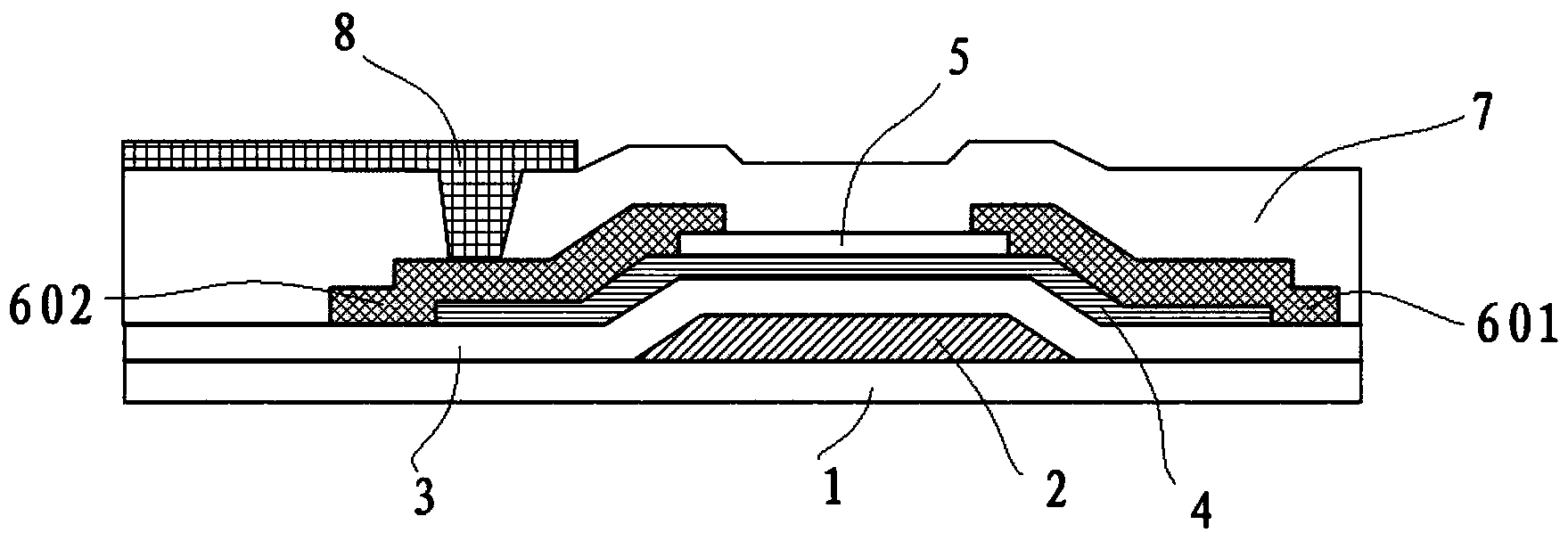

Array substrate and method for manufacturing same

ActiveCN102636927ASimple structureIncrease opening ratioSemiconductor/solid-state device manufacturingNon-linear opticsCapacitanceTransistor array

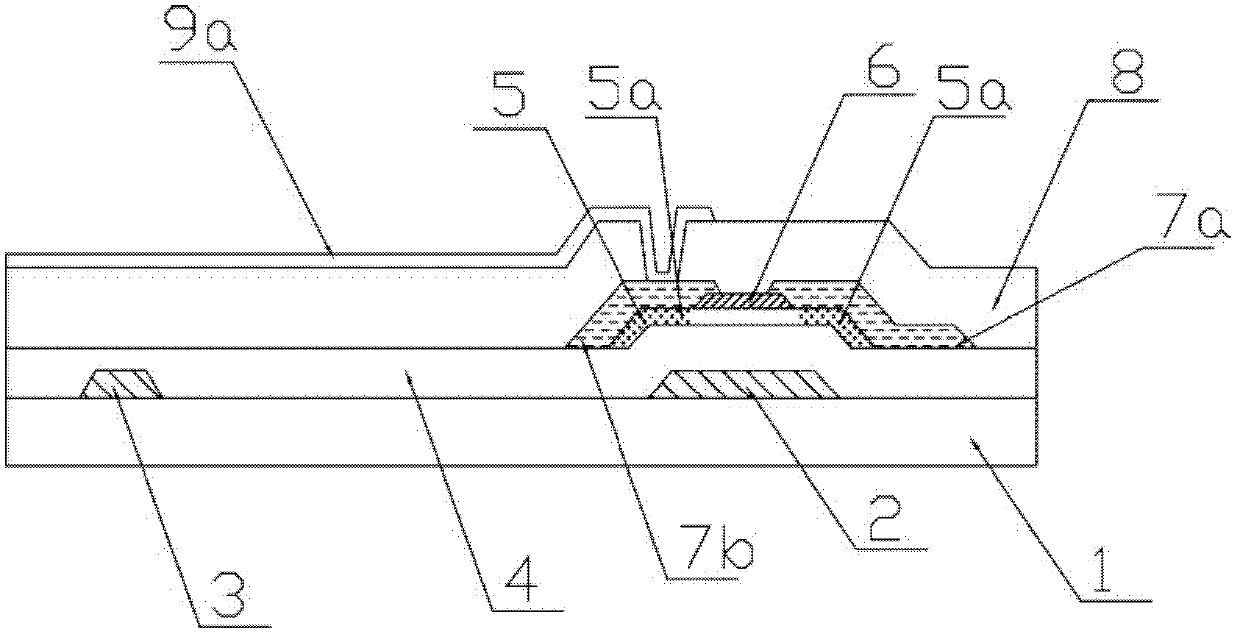

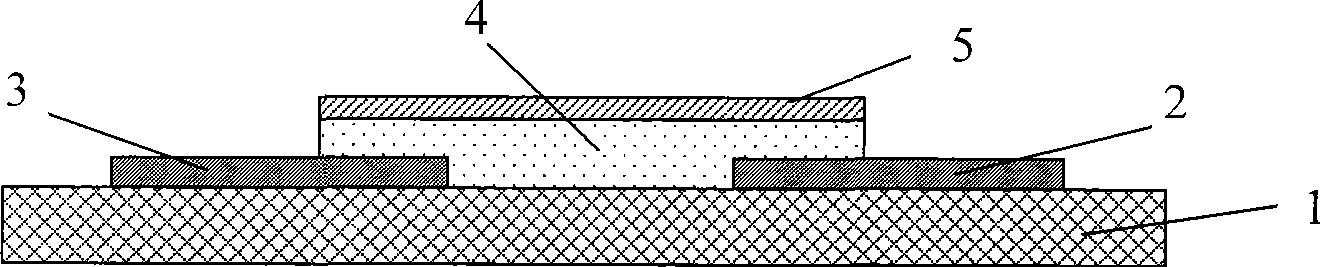

The invention belongs to the technical field of liquid crystal display, and particularly relates to an array substrate and a method for manufacturing the same. The oxide film transistor array substrate is provided with a source electrode and / or a drain electrode made of transparent conductive materials, a thin film transistor structure is simplified, and the aperture opening of a liquid crystal display device using the array substrate is increased. A common electrode wire and a data line are arranged on the same layer, the distance between the common electrode wire and a pixel electrode is shortened, storage capacitance is increased, and the performance of the array substrate is improved. When the array substrate is manufactured, by the aid of a half gray-level mask multi-step etching method, an etching protective film and the data line are obtained by means of mask exposure once, only five times of mask exposure are needed during manufacture of the array substrate, the process is simplified, and the manufacturing cost is reduced.

Owner:BOE TECH GRP CO LTD

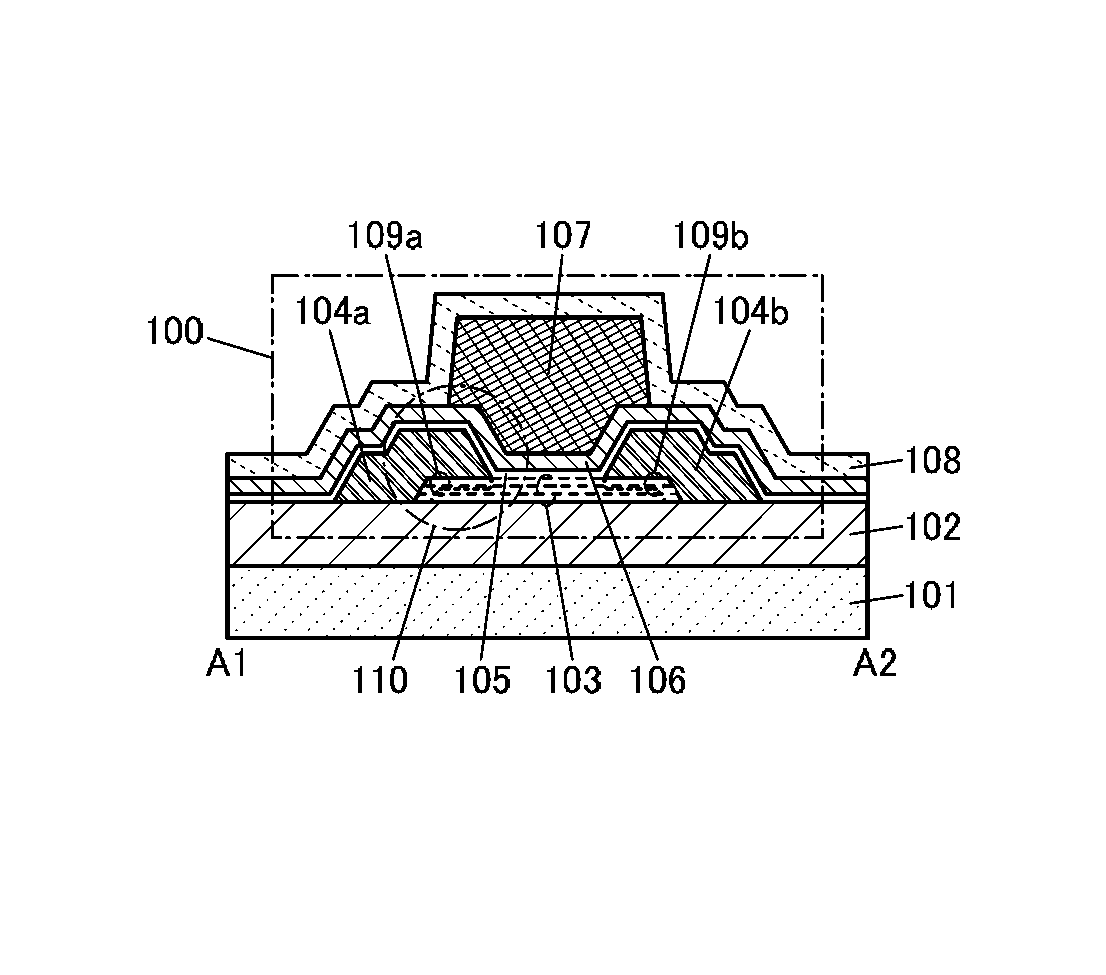

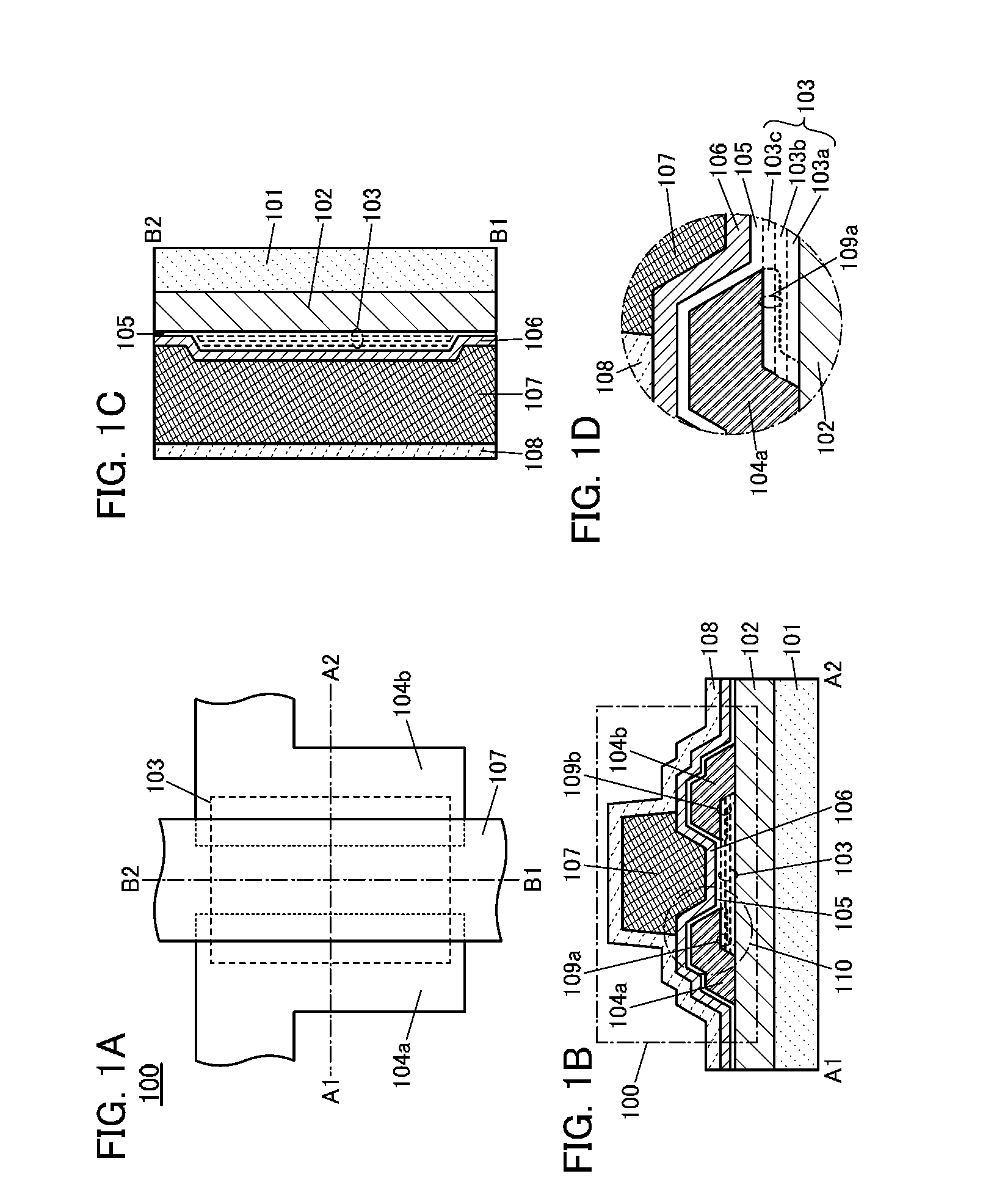

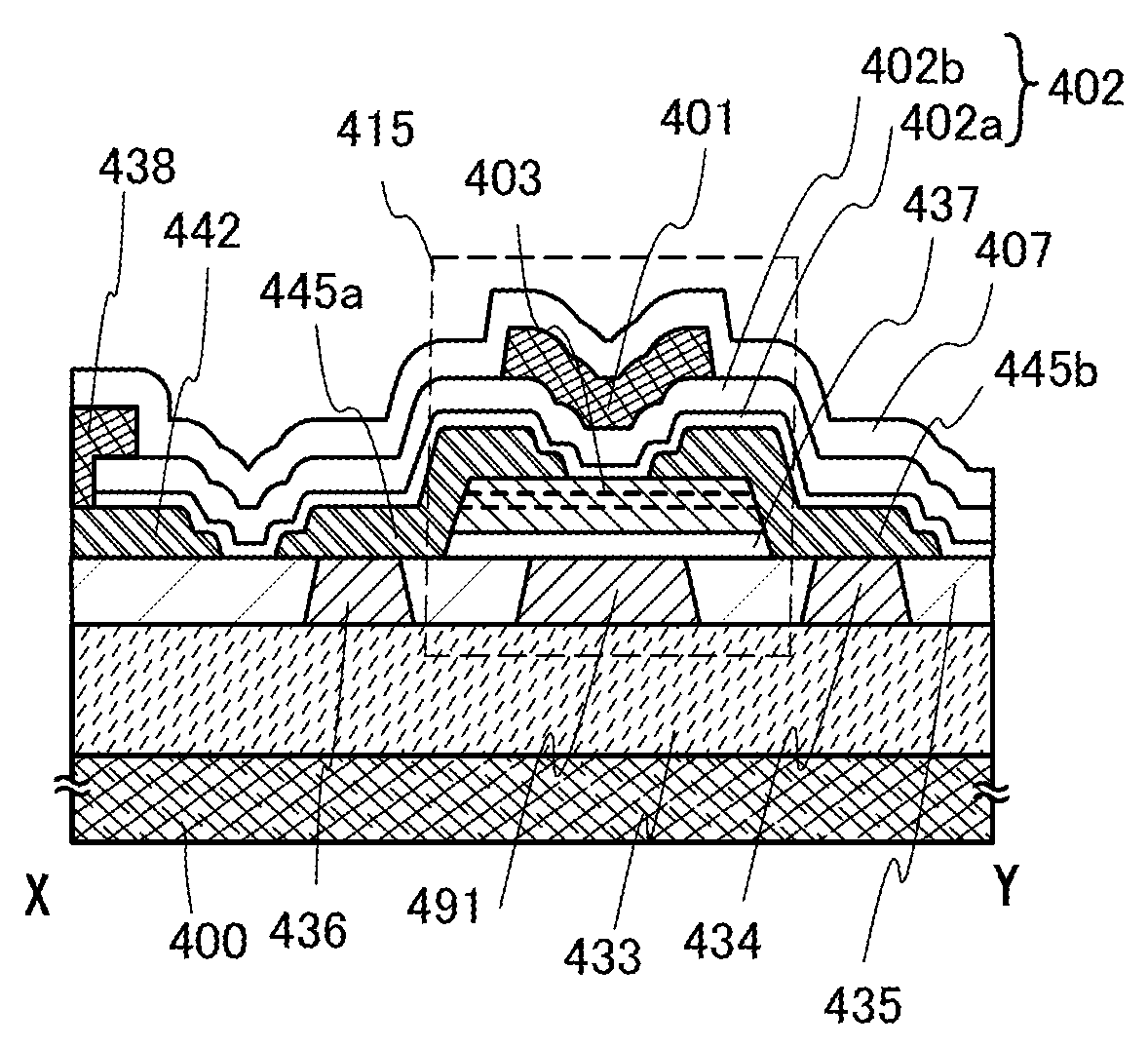

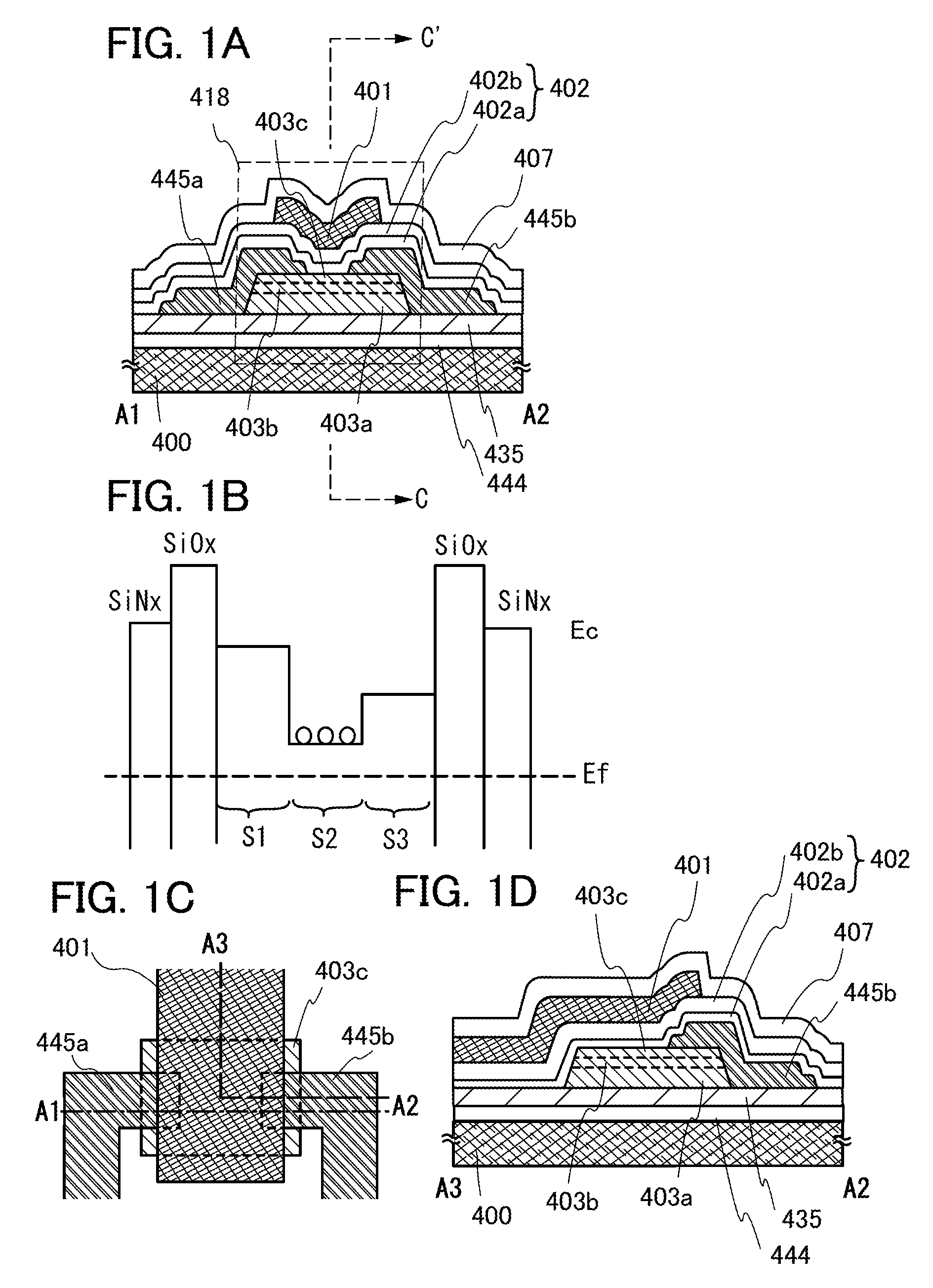

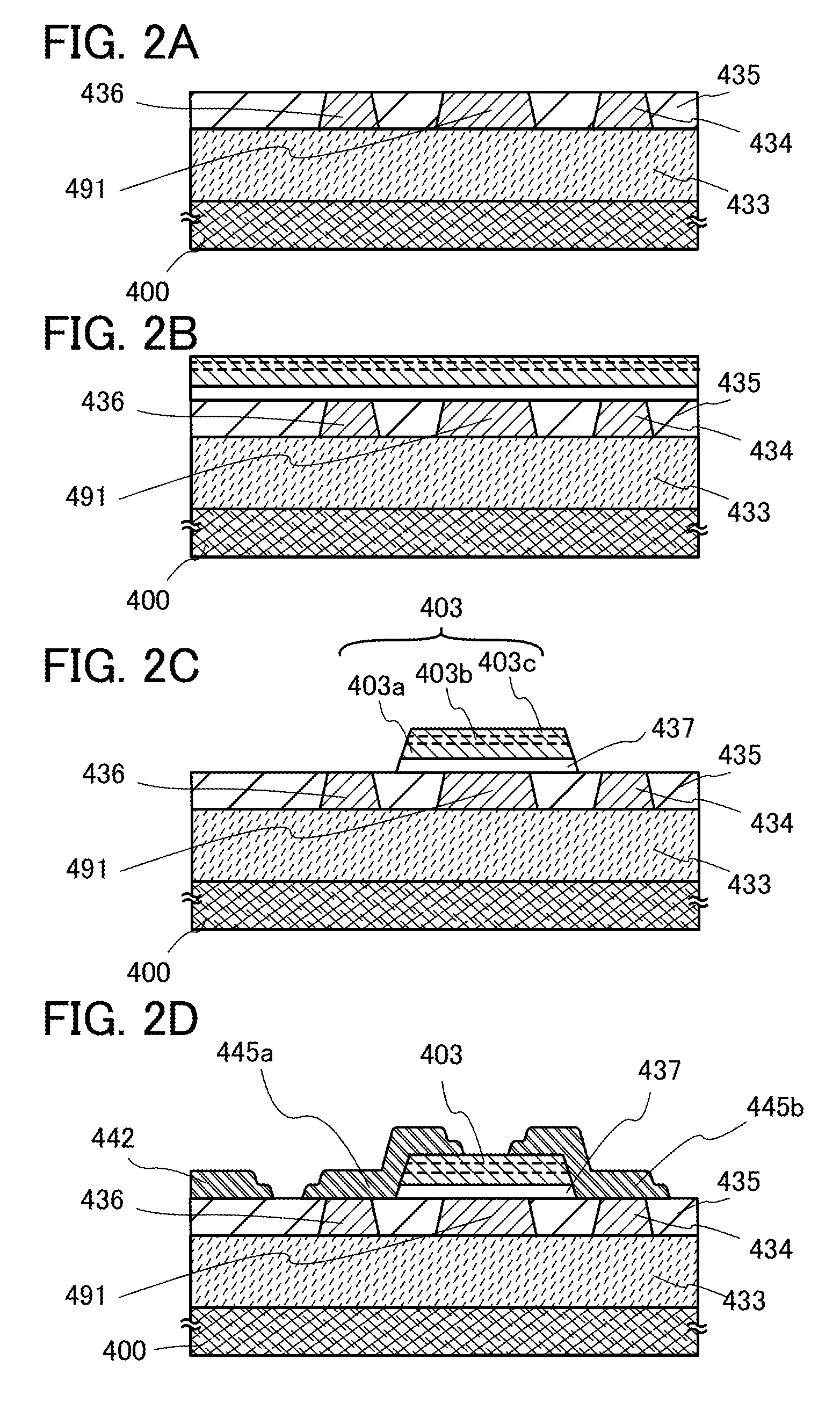

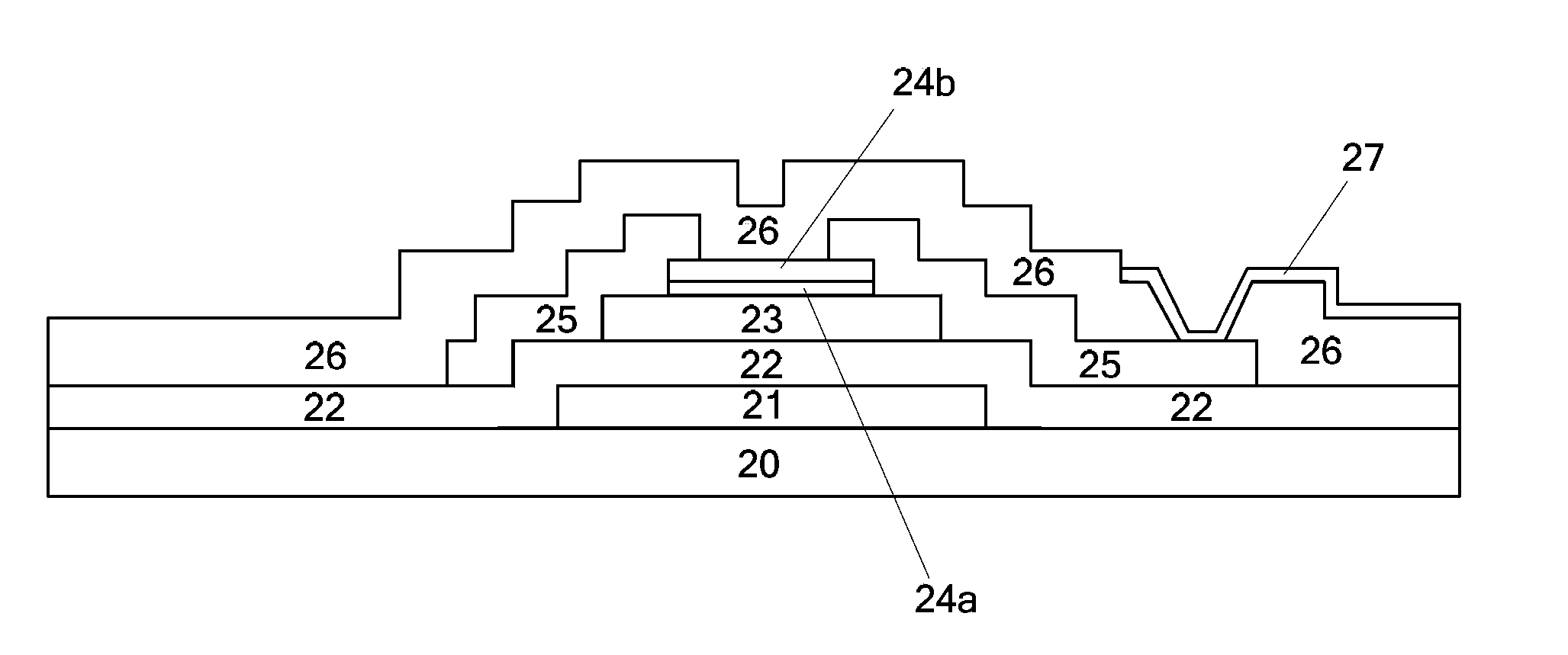

Thin film transistor having oxide semiconductor layer

ActiveUS8921853B2Low densityStable electrical characteristicsTransistorSolid-state devicesOxide thin-film transistorElectron

Oxide layers which contain at least one metal element that is the same as that contained in an oxide semiconductor layer including a channel are formed in contact with the top surface and the bottom surface of the oxide semiconductor layer, whereby an interface state is not likely to be generated at each of an upper interface and a lower interface of the oxide semiconductor layer. Further, it is preferable that an oxide layer, which is formed using a material and a method similar to those of the oxide layers be formed over the oxide layers Accordingly, the interface state hardly influences the movement of electrons.

Owner:SEMICON ENERGY LAB CO LTD

Transistors and methods of manufacturing the same

ActiveUS20110168993A1Semiconductor/solid-state device manufacturingSemiconductor devicesOxide thin-film transistorEngineering

Transistors and methods of manufacturing the same. A transistor may be an oxide thin film transistor (TFT) with a self-aligned top gate structure. The transistor may include a gate insulating layer between a channel region and a gate electrode that extends from two sides of the gate electrode. The gate insulating layer may cover at least a portion of source and drain regions.

Owner:SAMSUNG ELECTRONICS CO LTD

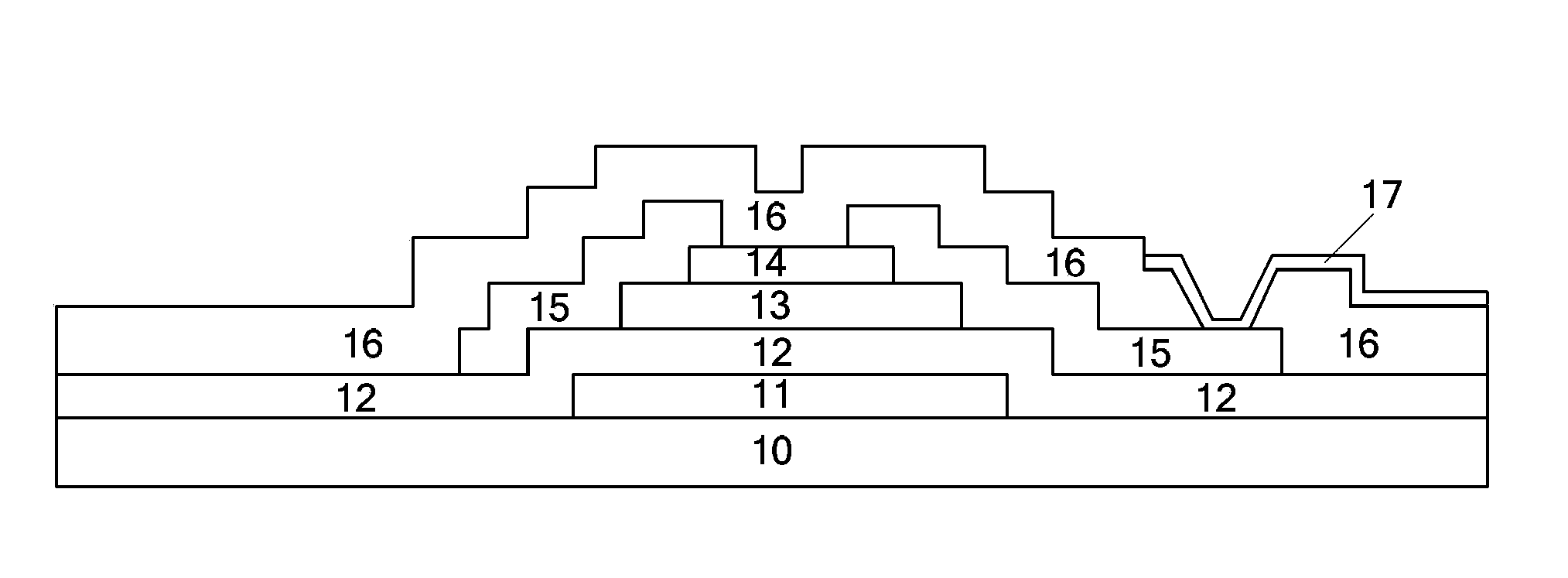

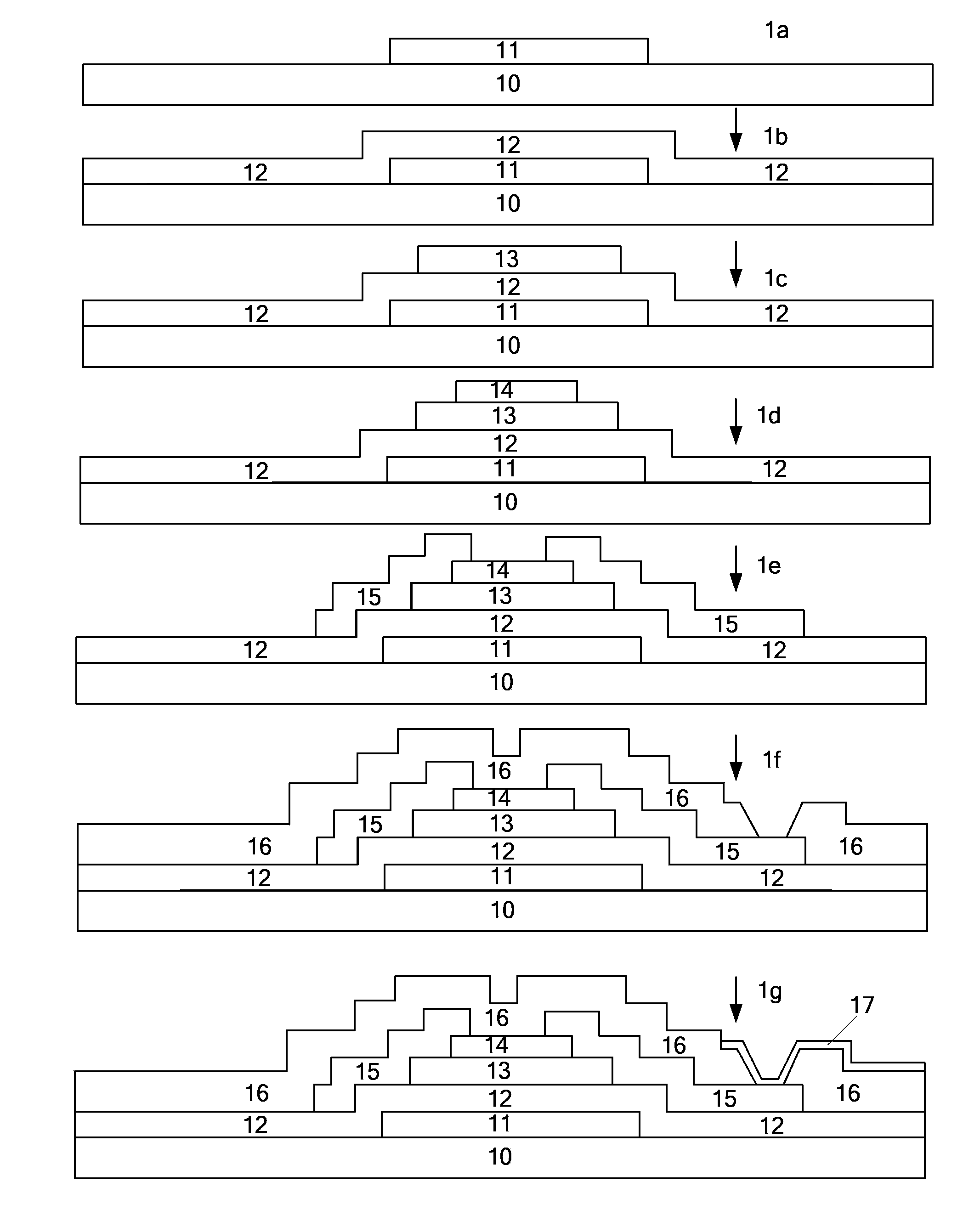

Thin film transistor with multiple oxide semiconductor layers

A transistor having high field-effect mobility is provided. In order that an oxide semiconductor layer through which carriers flow is not in contact with a gate insulating film, a buried channel structure in which the oxide semiconductor layer through which carriers flow is separated from the gate insulating film is employed. Specifically, an oxide semiconductor layer having high conductivity is provided between two oxide semiconductor layers. Further, an impurity element is added to the oxide semiconductor layer in a self-aligned manner so that the resistance of a region in contact with an electrode layer is reduced. Further, the oxide semiconductor layer in contact with the gate insulating layer has a larger thickness than the oxide semiconductor layer having high conductivity.

Owner:SEMICON ENERGY LAB CO LTD

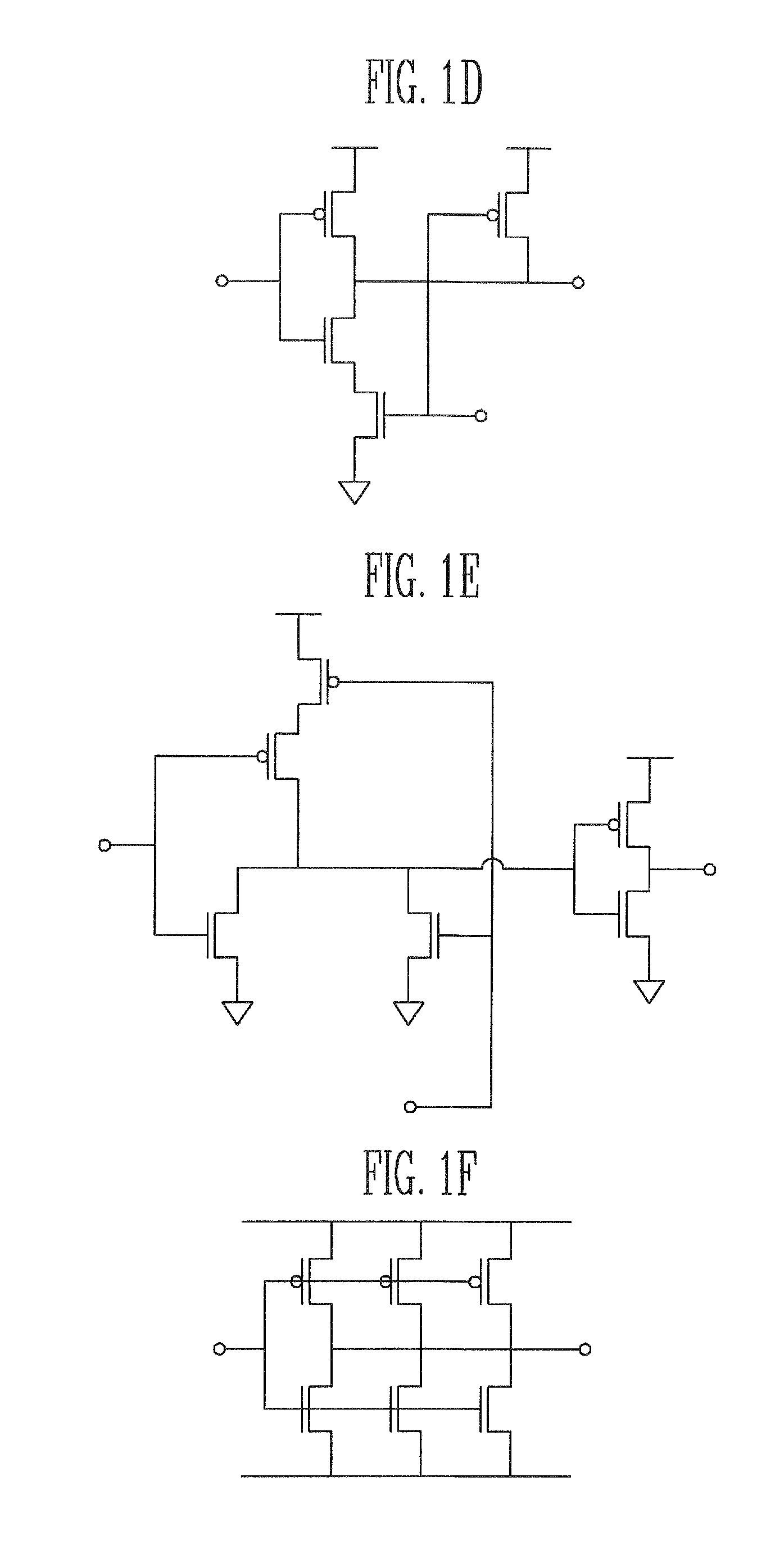

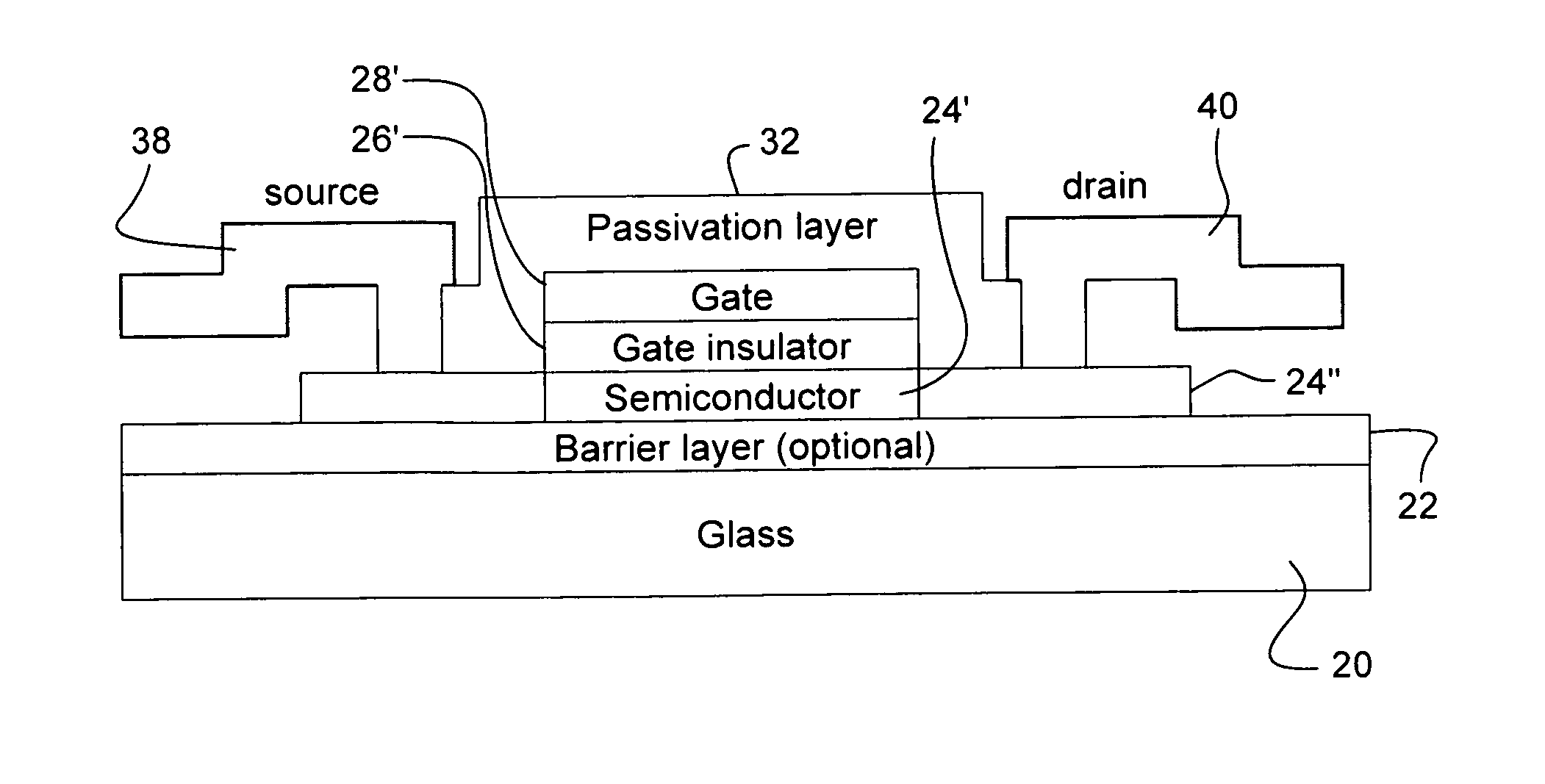

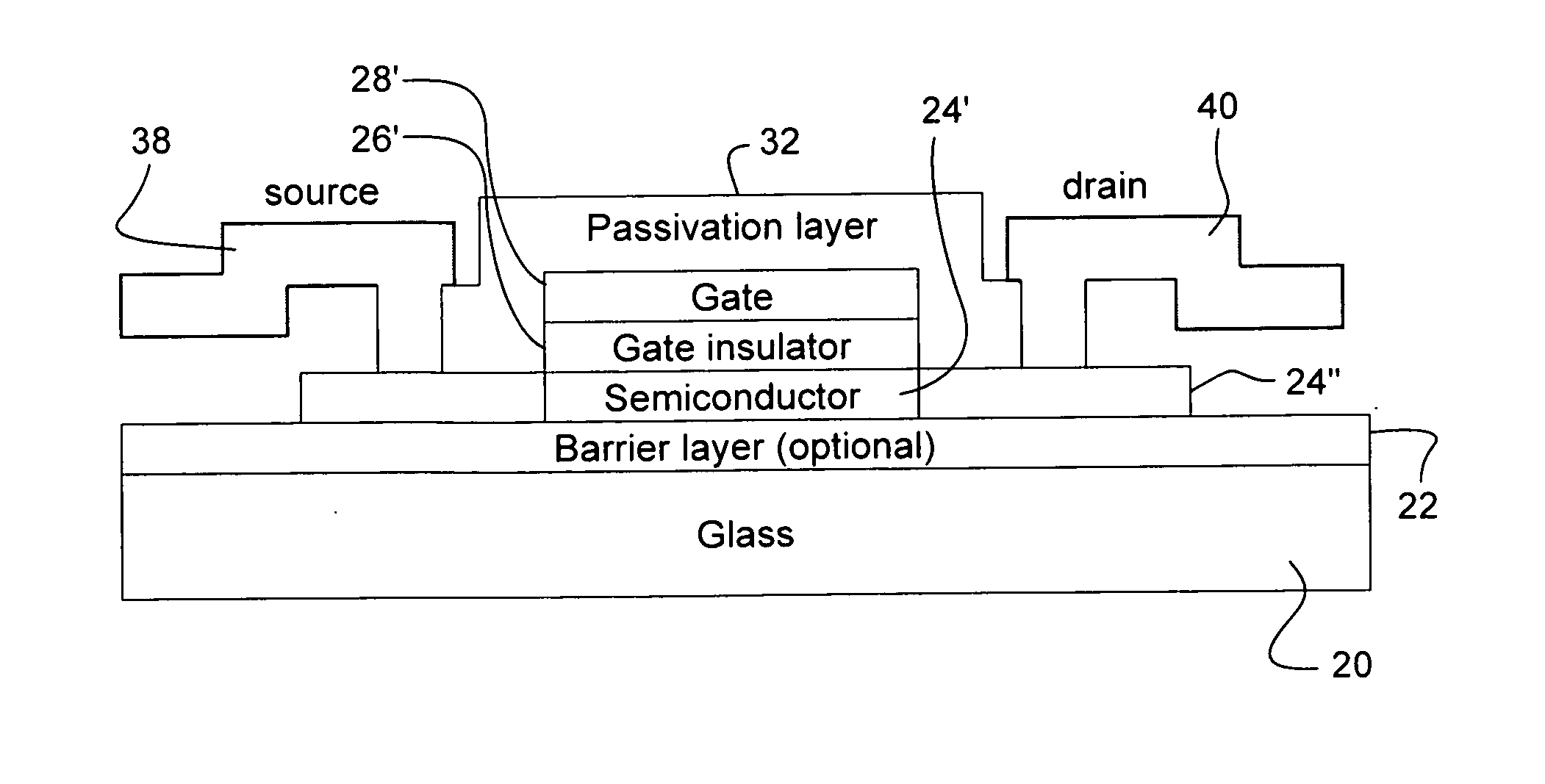

Method of making oxide thin film transistor array, and device incorporating the same

InactiveUS20120074399A1Improve conductivityImprove economyTransistorSolid-state devicesOxide thin-film transistorRoom temperature

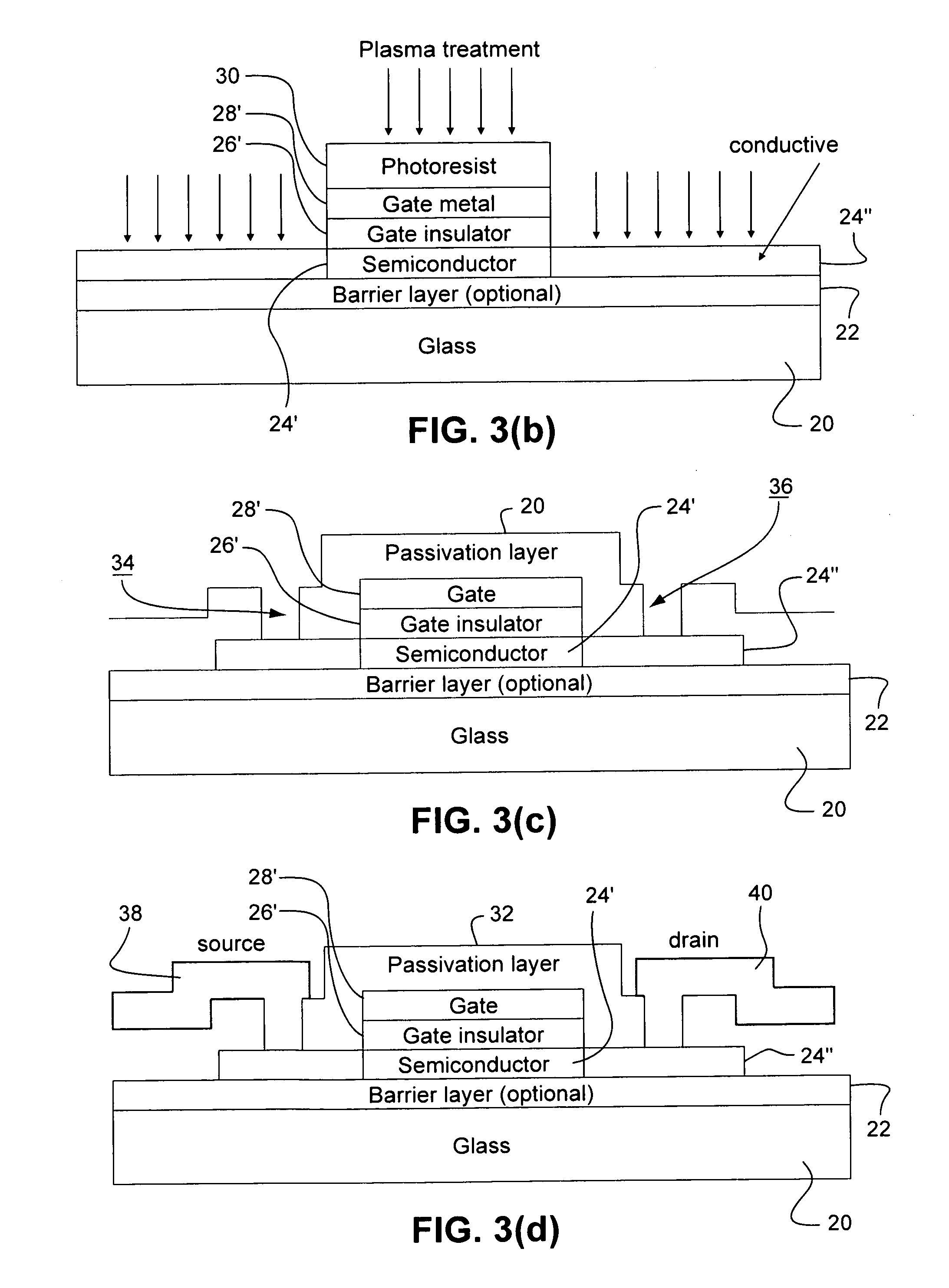

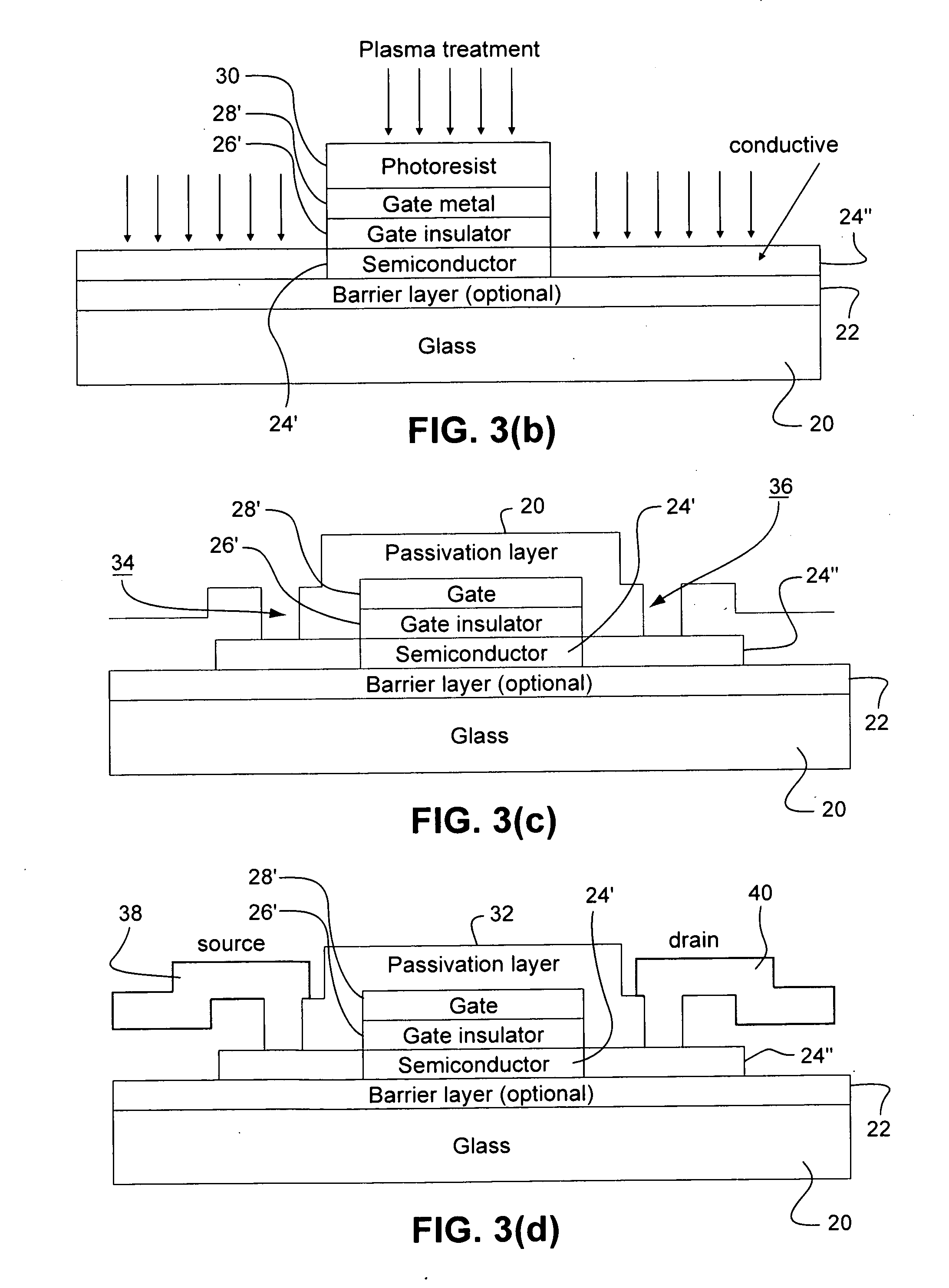

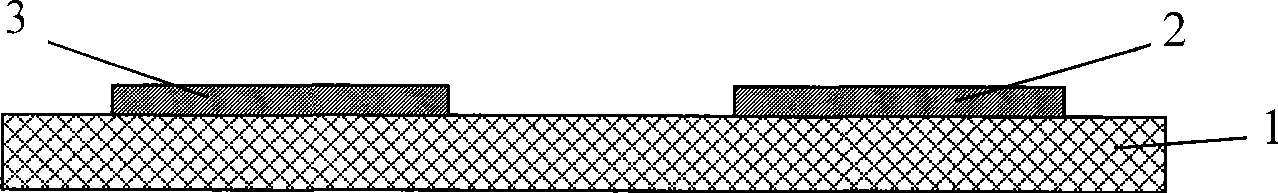

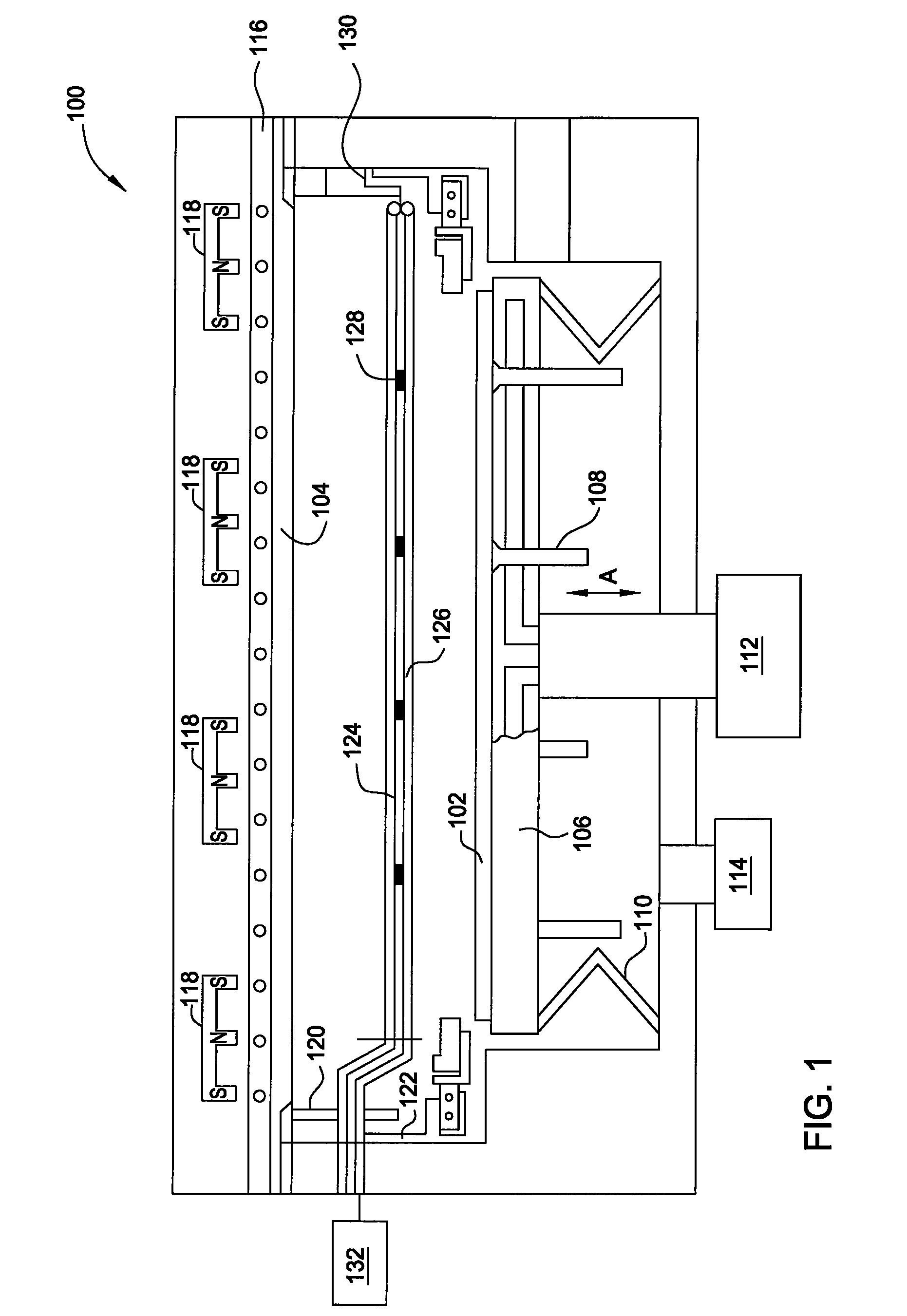

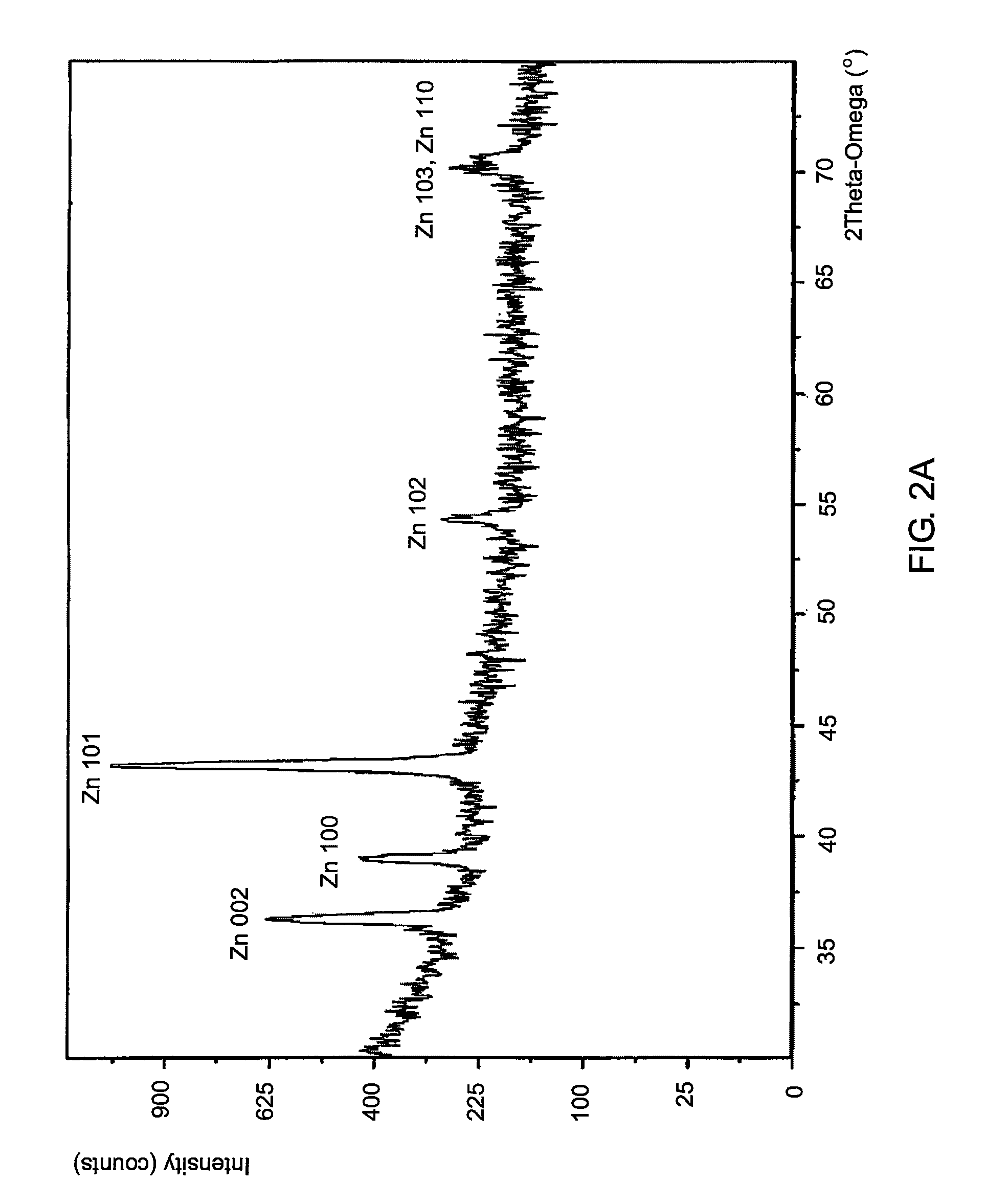

Certain example embodiments relate to methods of making oxide thin film transistor arrays (e.g., IGZO, amorphous or polycrystalline ZnO, ZnSnO, InZnO, and / or the like), and devices incorporating the same. Blanket layers of an optional barrier layer, semiconductor, gate insulator, and / or gate metal are disposed on a substrate. These and / or other layers may be deposited on a soda lime or borosilicate substrate via low or room temperature sputtering. These layers may be later patterned and / or further processed in making a TFT array according to certain example embodiments. In certain example embodiments, all or substantially all TFT processing may take place at a low temperature, e.g., at or below 150 degrees C., until a post-annealing activation step, and the post-anneal step may take place at a relatively low temperature (e.g., 200-250 degrees C.).

Owner:GUARDIAN GLASS LLC

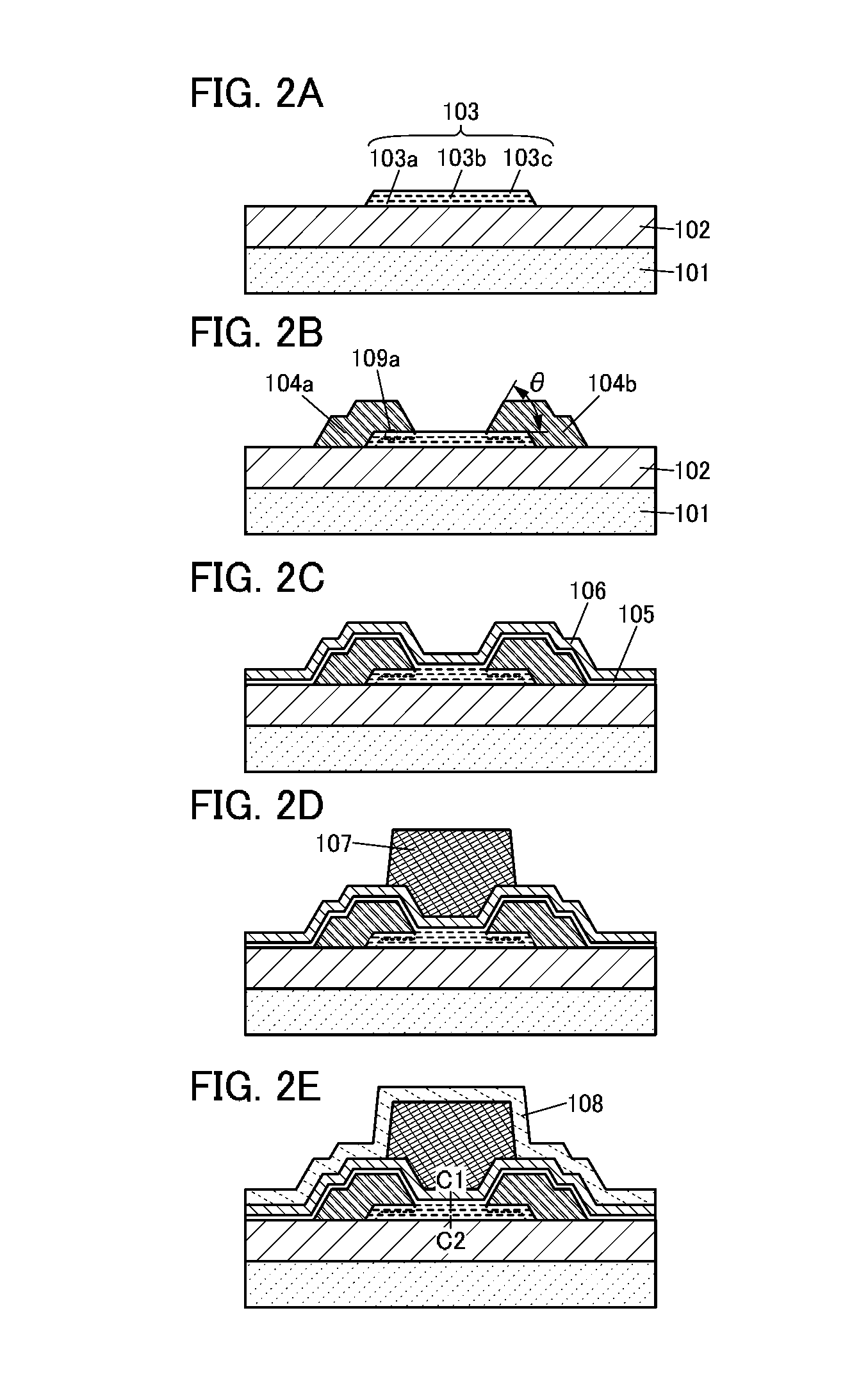

Production method for self-aligned metallic oxide thin-film transistor

ActiveCN101488459AIncreased complexityAvoid parasitic effectsSemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingOxide thin-film transistor

The invention provides a method for manufacturing a self-aligned metal-oxide film transistor. First, a metal source drain region, a metal-oxide semiconductor channel region and a transparent gate medium layer are sequentially arranged on a glass substrate, then positive photoresist is coated on the gate medium layer, after pre-baking is carried out, exposure, developing and hardbaking are carried out from the back of the glass substrate, afterwards, a layer of conductive film develops with glue, then a gate electrode is obtained after stripping the photoresist and the conductive film, photoetching and etching. The method of the invention can ensure self alignment between the gate electrode and the source drain region of a component, namely, the gate electrode is symmetrically arranged right above between the source and the drain, while, length of the gate electrode is determined by the distance between the source and the drain instead of size of a mask, thus effectively avoiding ghost effect.

Owner:BOE TECH GRP CO LTD

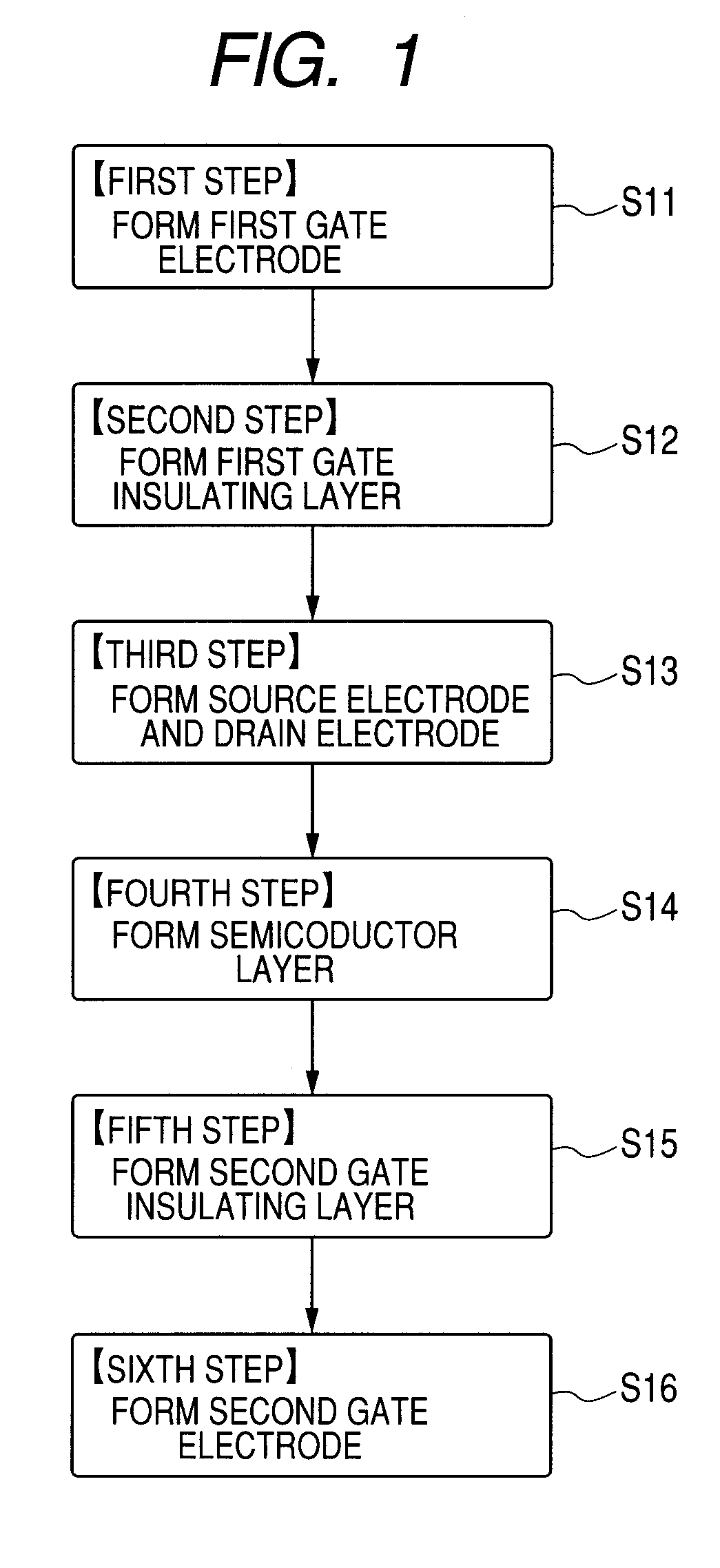

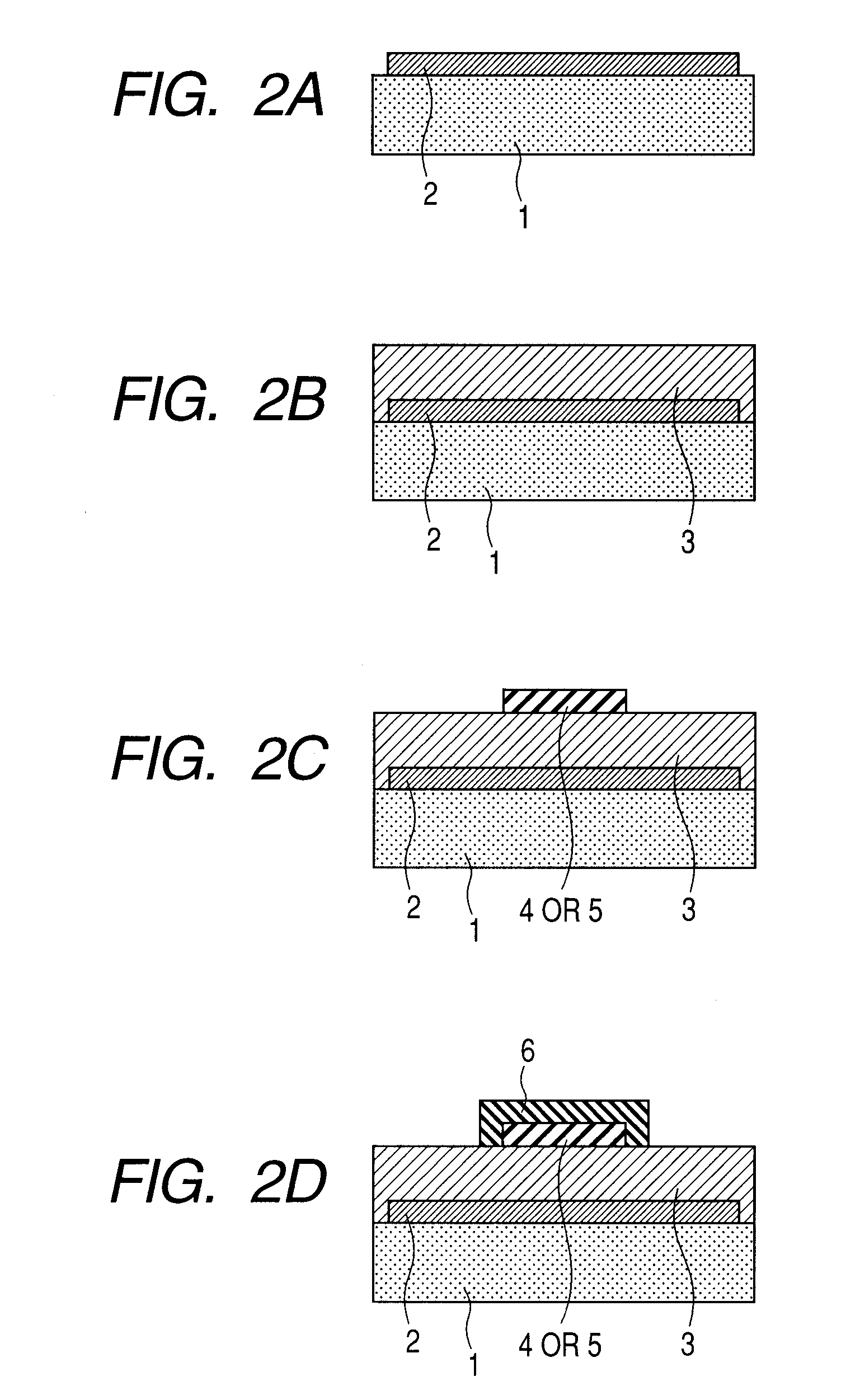

Thin film transistor, display device using thin film transistor, and production method of thin film transistor

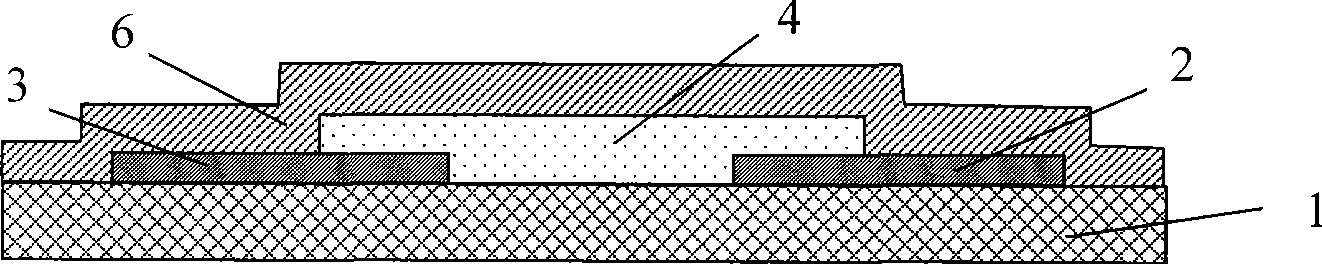

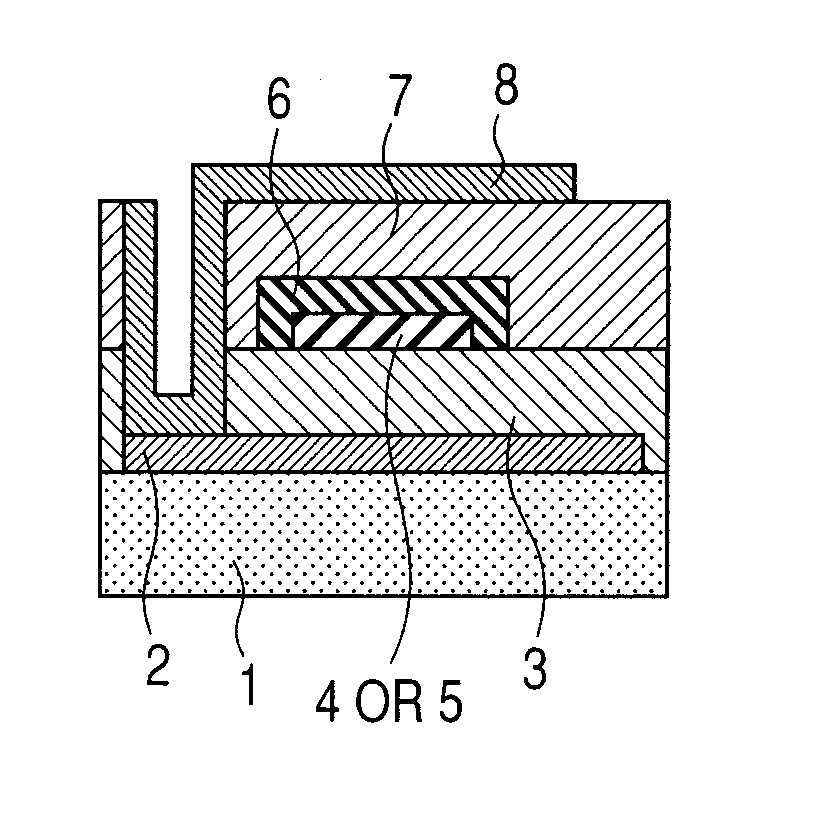

Provided is a thin film transistor including: a first gate electrode; a first gate insulating layer covering the first gate electrode; a semiconductor layer on the first gate insulating layer; a second gate insulating layer on the semiconductor layer; a second gate electrode on the second gate insulating layer; and a drain electrode and a source electrode electrically connected to the semiconductor layer, in which: the semiconductor layer is an amorphous oxide semiconductor containing at least one of Zn, Ga, In, and Sn; the first gate electrode shields light entering the semiconductor layer from below, and the second gate electrode shields light entering the semiconductor layer from above; and the second gate electrode is electrically connected to the first gate electrode by penetrating the first gate insulating layer and the second gate insulating layer, to thereby shield light entering the semiconductor layer from at least one of sides thereof.

Owner:CANON KK

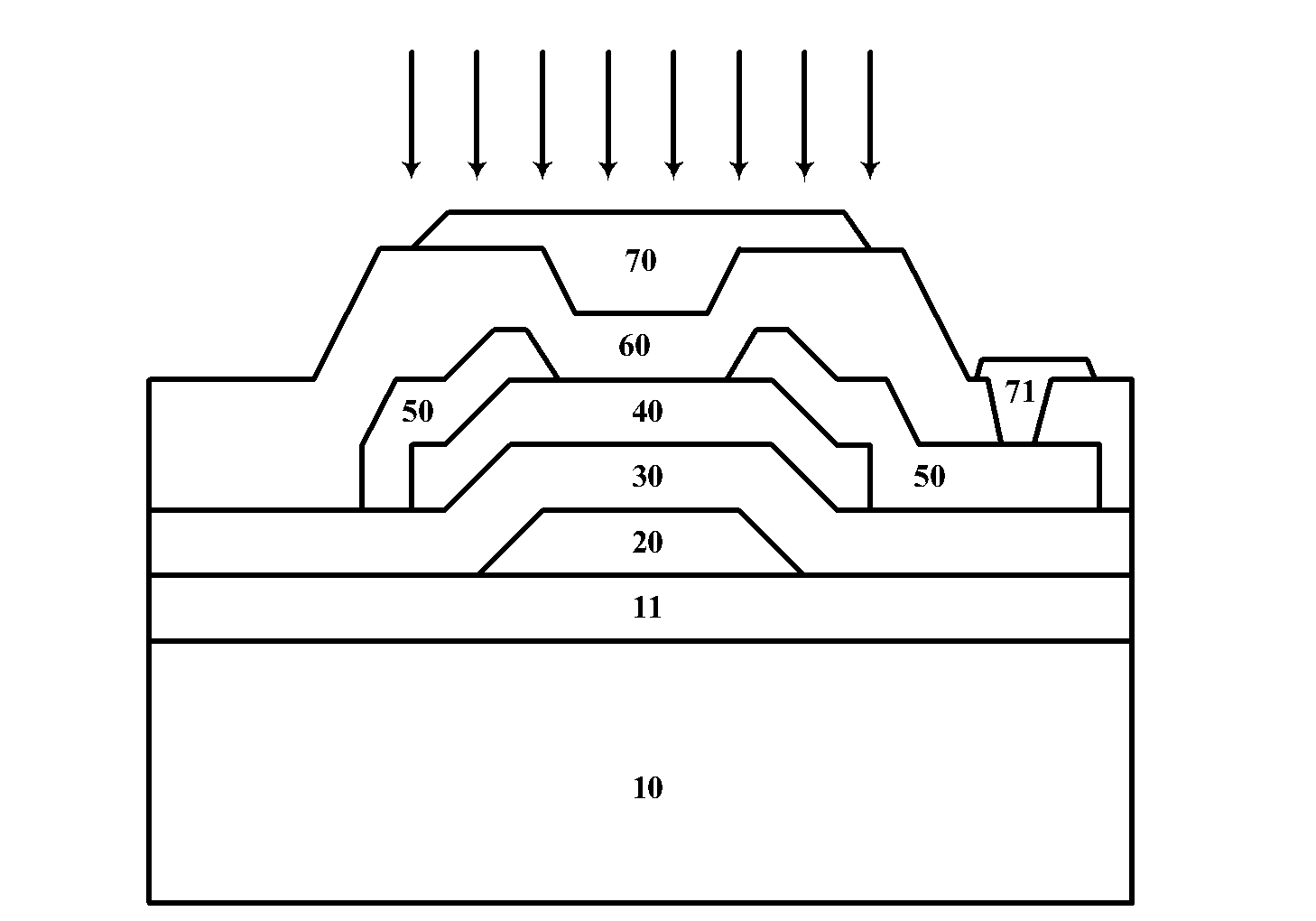

Illumination stability amorphous metallic oxide thin film transistor (TFT) device and display device

ActiveCN102969361AImprove long-term stabilityEffective filtering of conductive effectsTransistorSemiconductor/solid-state device detailsOxide thin-film transistorDisplay device

The invention provides an illumination stability amorphous metallic oxide thin film transistor (TFT) device which comprises a substrate, a reverse gate electrode, a gate insulating medium layer, a channel layer formed by amorphous metallic oxide, a source electrode and drain electrode, a passivation layer and a driving electrode which penetrates through the passivation layer to be contacted with the source electrode and drain electrode. The illumination stability amorphous metallic oxide TFT device is characterized in that a top gate protective electrode capable of greatly absorbing ultraviolet light is further arranged on the top portion of the passivation layer. By means of the TFT device, a transparent conducting material capable of greatly absorbing ultraviolet light is formed on the top portion of an active area of the device to effectively filter environment and reduce conductive influences of the ultraviolet light of an active light source on a channel, long-term stability of the device is improved, simultaneously electrostatic potential produced by consumption difference of the top gate protective electrode is used for repelling electric conduction charge of a back channel, surface damage of the back channel is weakened, and influences of defects on the long-term stability of the device are reduced. Simultaneously, an indium tin oxide (ITO) top gate electrode and an ITO lower electrode for driving organic light emitting diode share one layer of Mask, and no extra additional material electrode and imaging technology exist.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

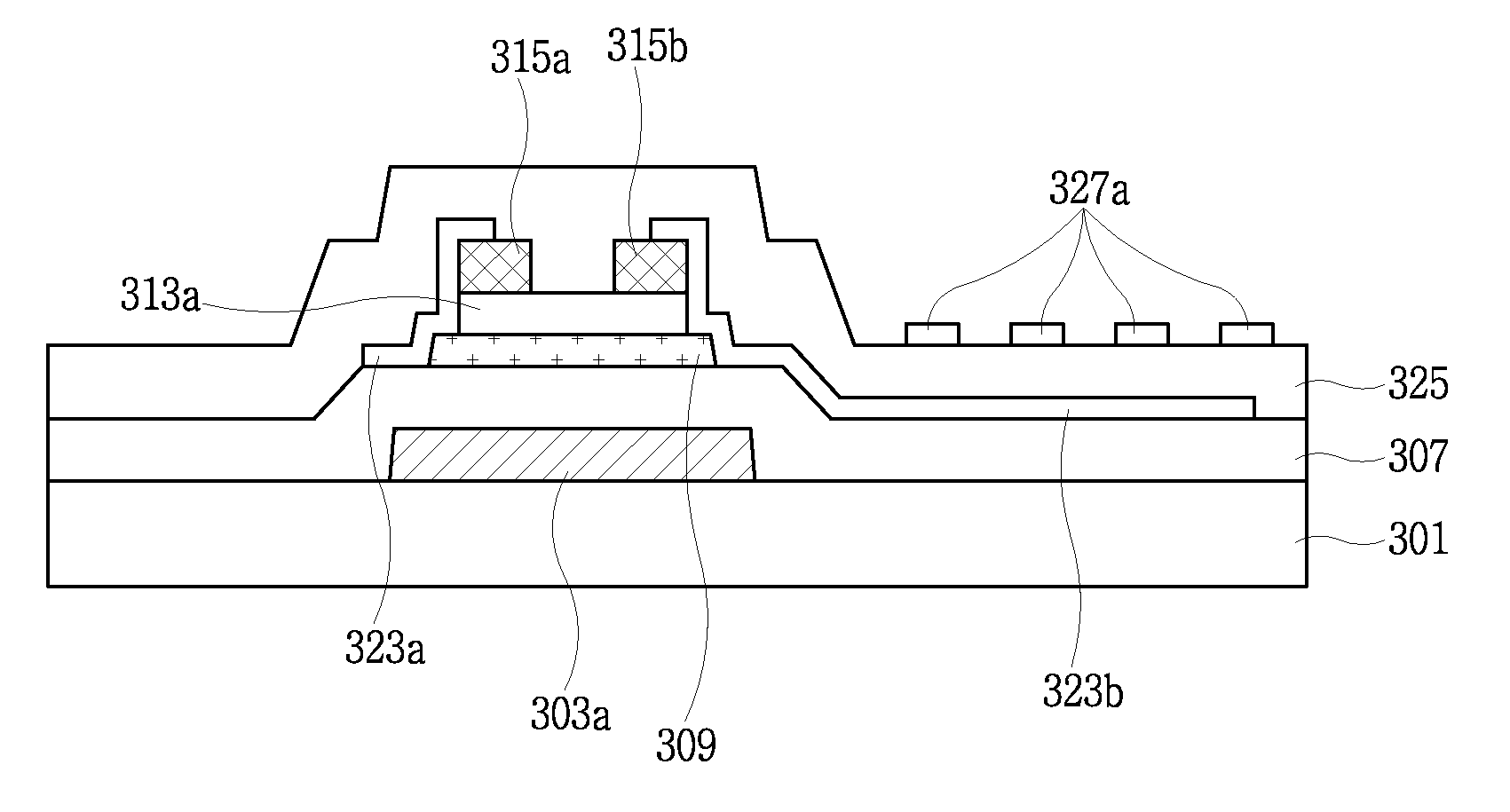

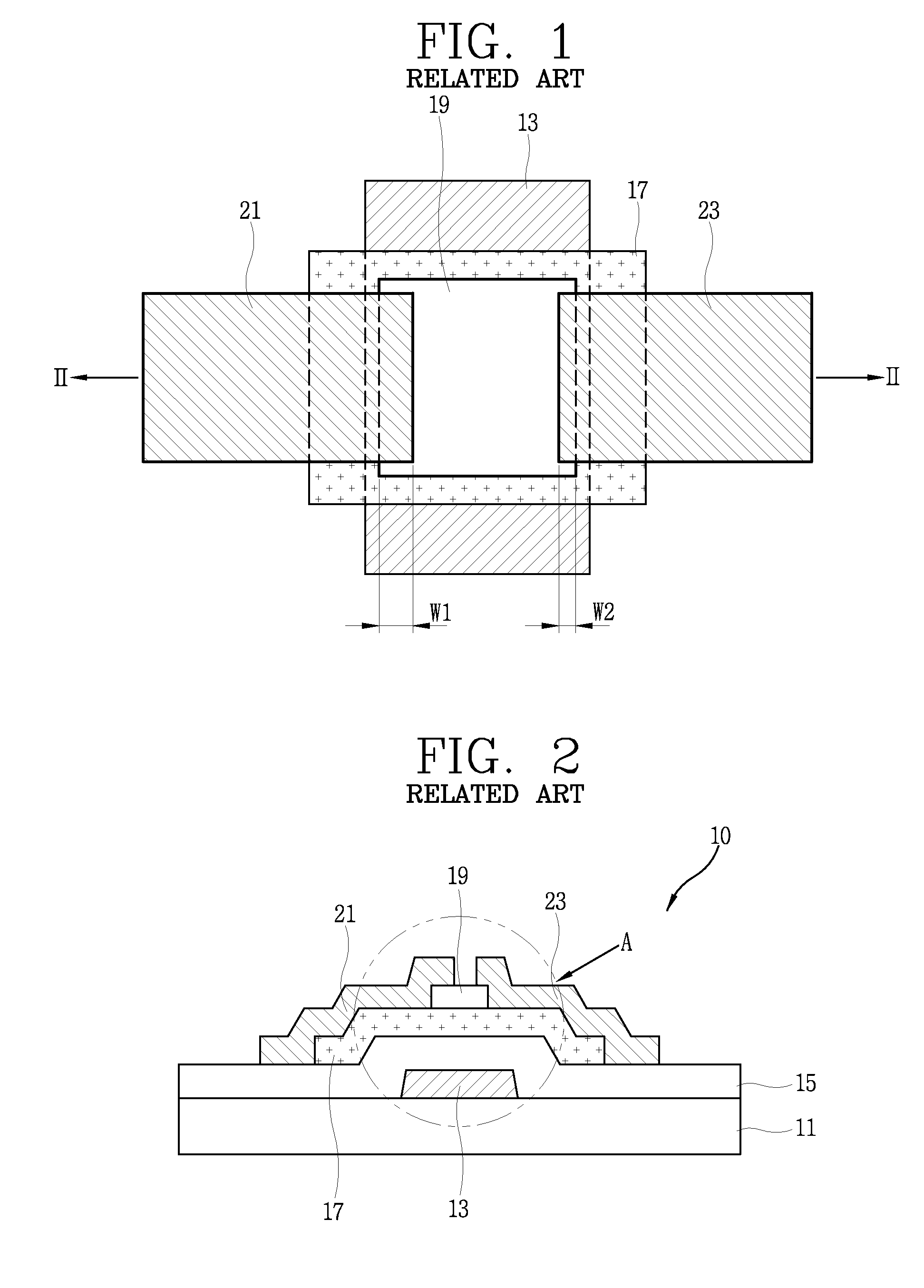

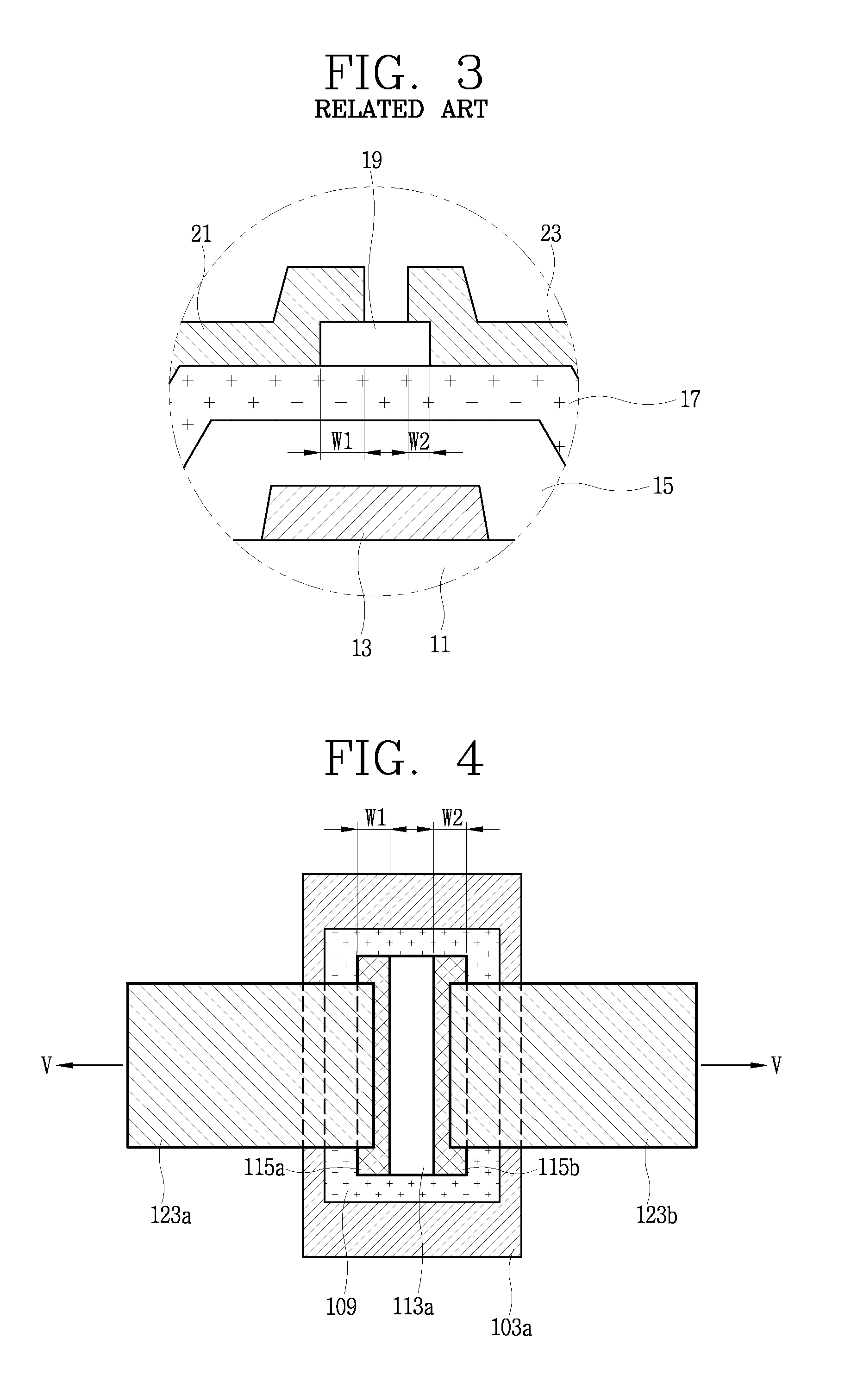

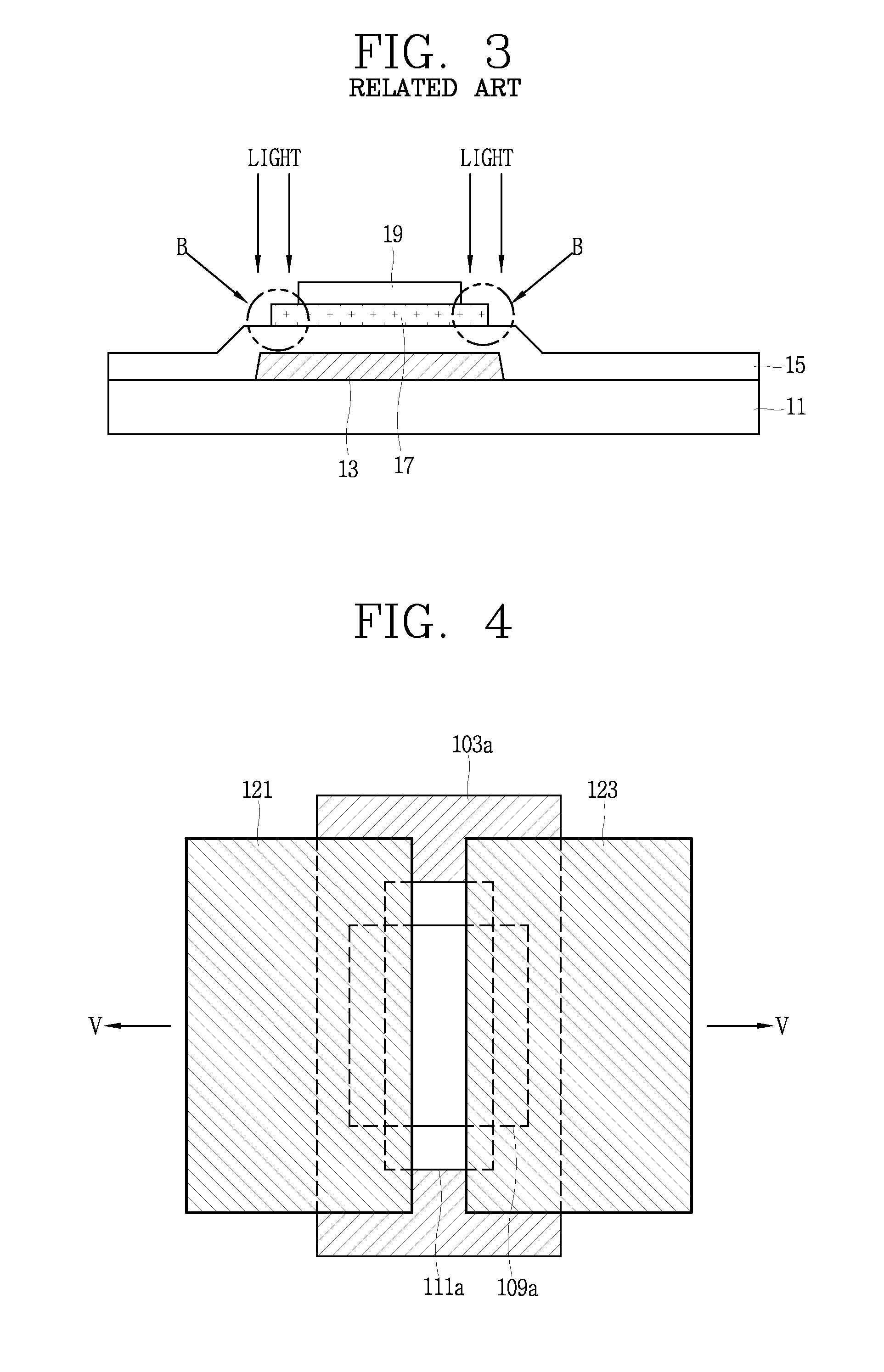

Oxide Thin Film Transistor, Method for Fabricating TFT, Array Substrate for Display Device and Method for Fabricating the Same

ActiveUS20130313546A1Enhancing element uniformity characteristicAvoid misalignmentTransistorSolid-state devicesOxide thin-film transistorDisplay device

Owner:LG DISPLAY CO LTD

Silicon and semiconductor oxide thin film transistor display device

ActiveCN104332485AEasy to bendSolid-state devicesPhotovoltaic energy generationOxide thin-film transistorSemiconductor structure

The invention discloses an electronic equipment display device having pixel circuit arrays. Each pixel circuit can comprise organic light emitting diodes and driving transistors, each driving transistor can be adjusted to control the magnitude of a current flowing through the organic light emitting diodes, each pixel circuit can comprise a storage capacitor and one or more additional transistors such as switch transistors. Semiconductor oxide transistors and silicon transistors are used for forming pixel circuits. Storage capacitor and transistors can be formed through use of metal layers, semiconductor structures and dielectric layers. Some of the layers can be removed along the edge of a display device and therefore the display device can bend conveniently. The dielectric layers can have a multistep shape where data wires in the arrays are allowed to gradually lower toward the surface of a substrate when the data wires extend to an invalid edge area.

Owner:APPLE INC

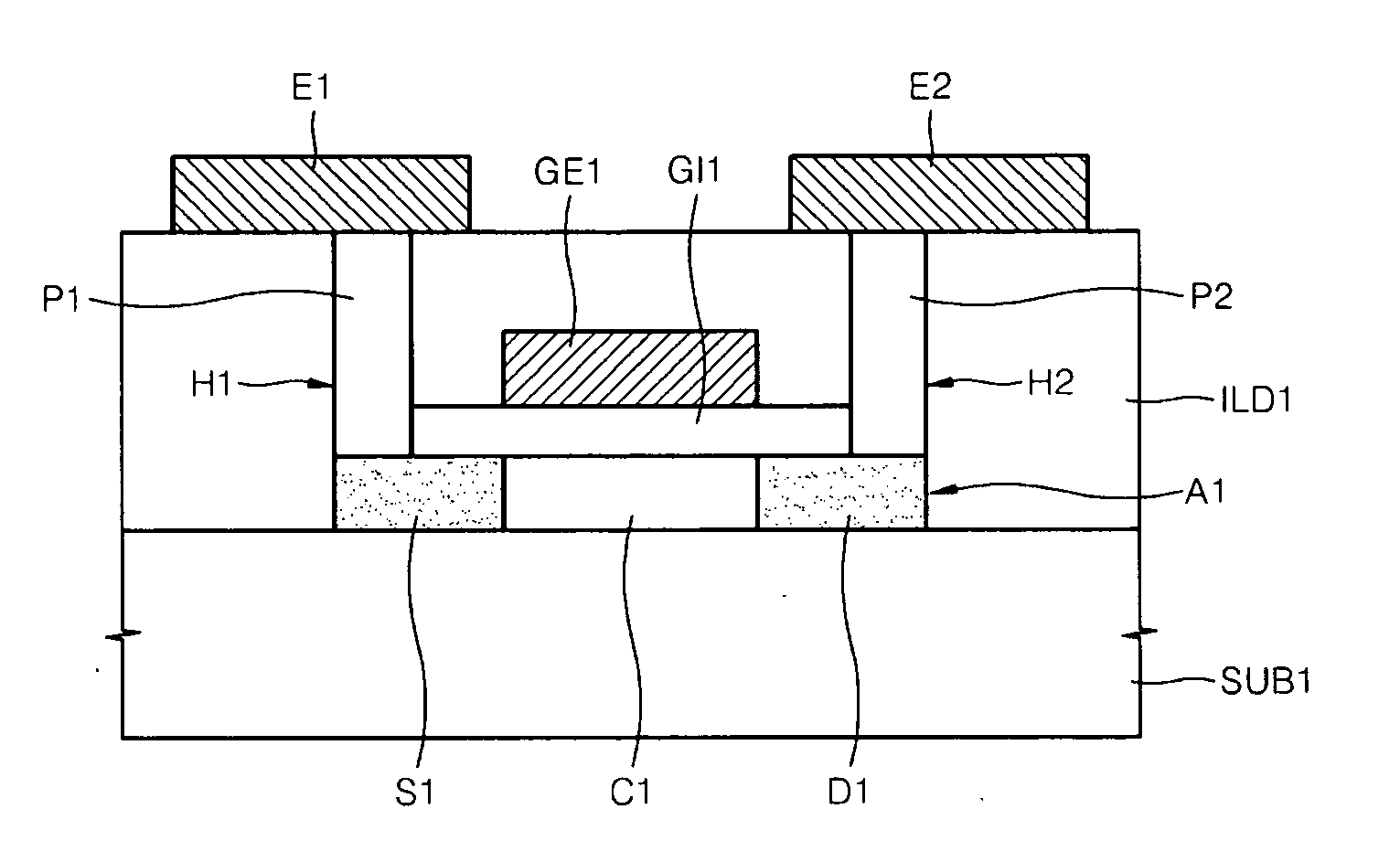

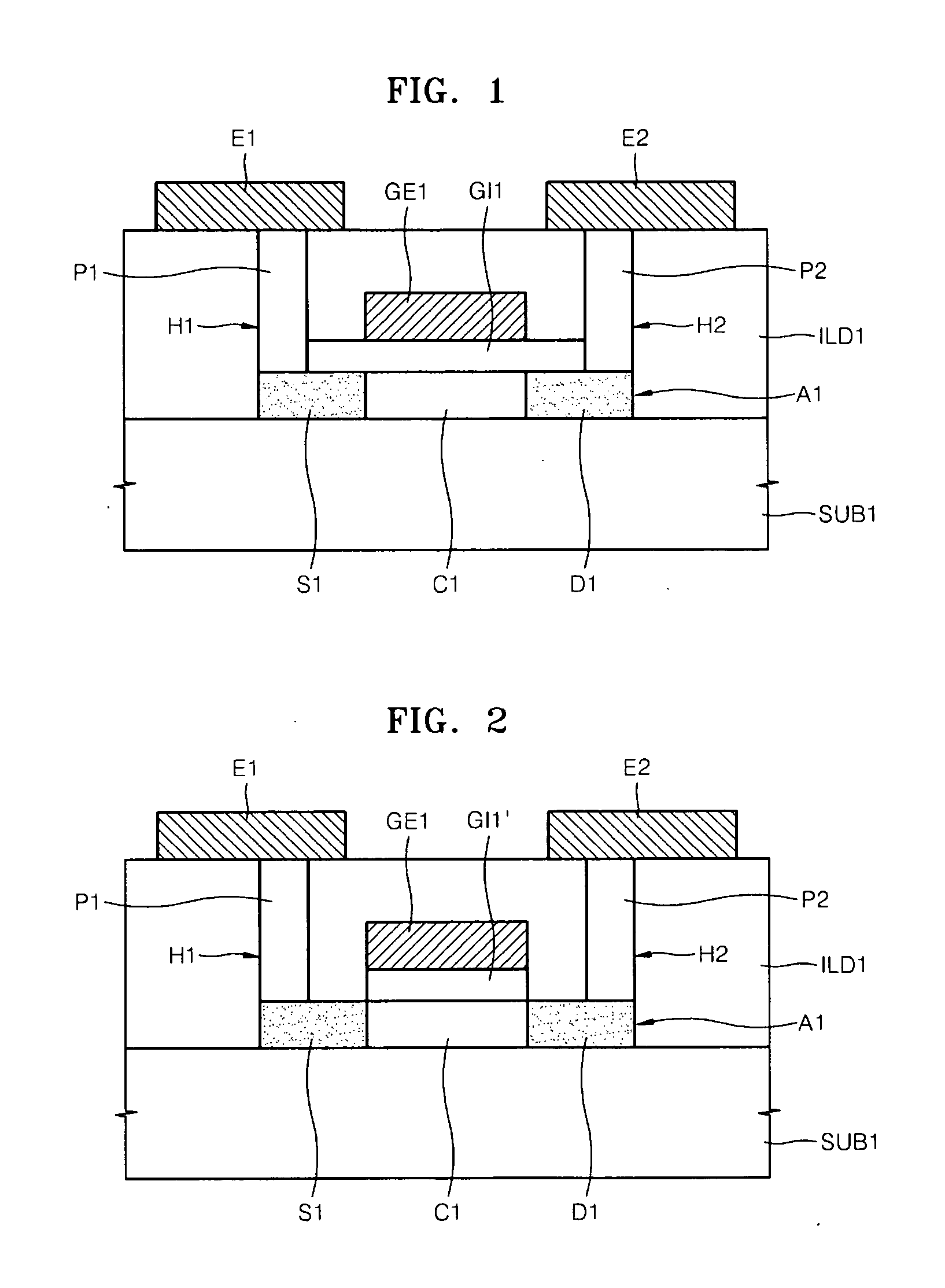

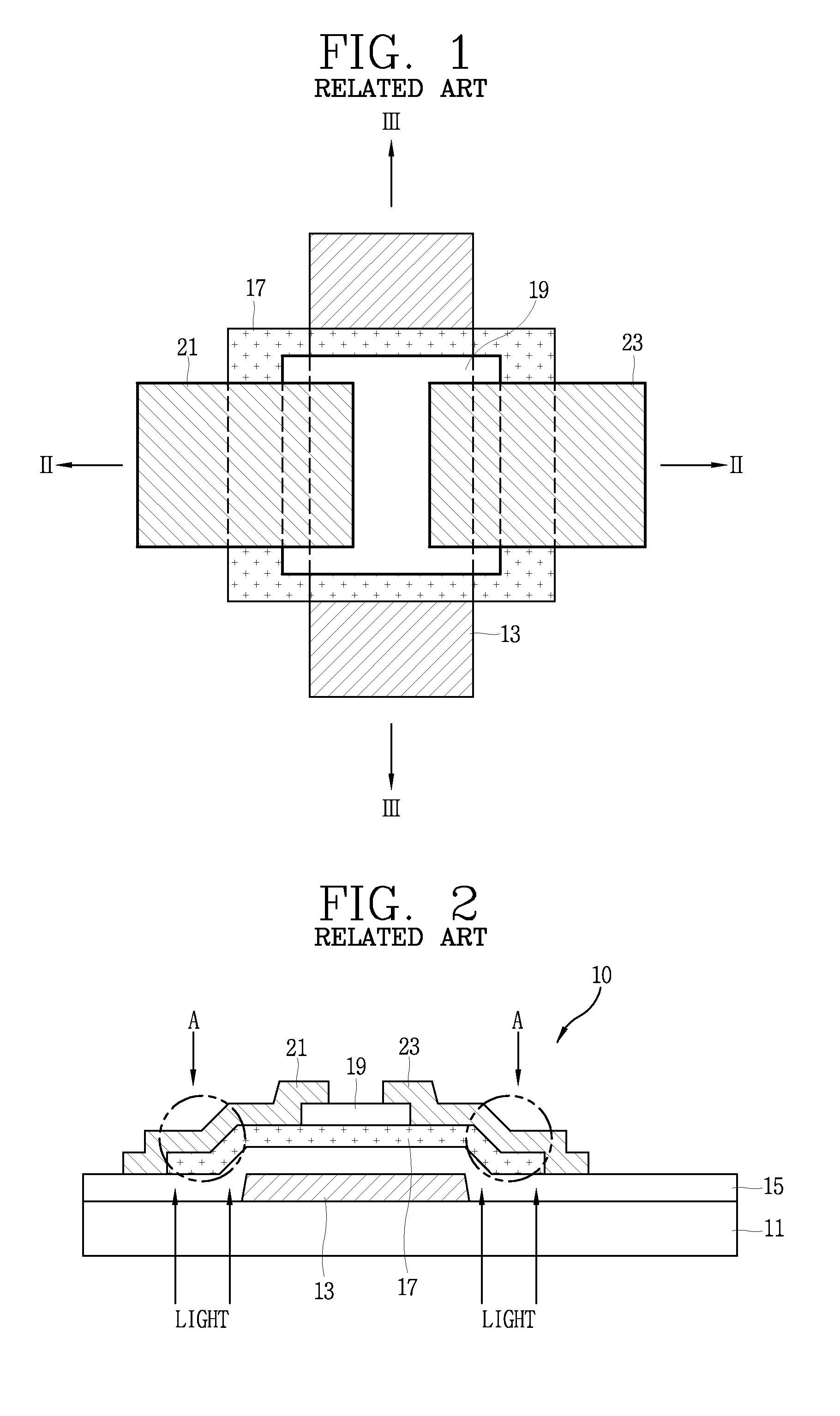

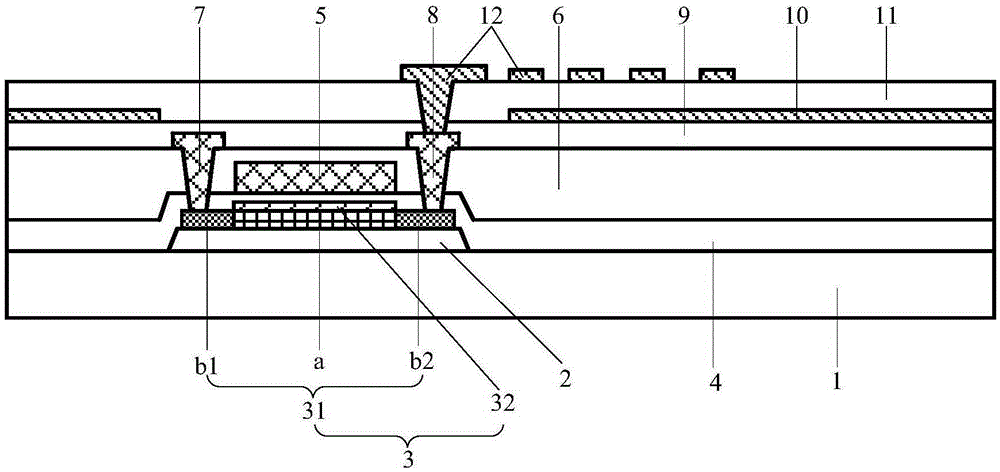

Oxide thin film transistor, method for fabricating tft, display device having tft, and method for fabricating the same

ActiveUS20130313530A1Improve component reliabilityReduce lightTransistorSolid-state devicesOxide thin-film transistorDisplay device

There are provided an oxide TFT, a method for fabricating a TFT, an array substrate for a display device having a TFT, and a method for fabricating the display device. The oxide thin film transistor includes: a gate electrode formed on a substrate; a gate insulating layer formed on the entire surface of the substrate including the gate electrode; an active layer pattern formed on the gate insulating layer above the gate electrode and completely overlapping the gate electrode; an etch stop layer pattern formed on the active layer pattern and the gate insulating layer; and a source electrode and a drain electrode formed on the gate insulating layer including the etch stop layer pattern and the active layer pattern and spaced apart from one another, and overlapping both sides of the etch stop layer pattern and the underlying active layer pattern.

Owner:LG DISPLAY CO LTD

Thin film transistor and display device

InactiveCN102315277AIncreasing the thicknessSuppress failureTransistorElectroluminescent light sourcesOxide thin-film transistorDisplay device

A thin film transistor allowed to suppress a failure caused by an interlayer insulating film and improve reliability of a self-alignment structure, and a display device including this thin film transistor are provided. The thin film transistor includes: a gate electrode; an oxide semiconductor film having a channel region facing the gate electrode, and having a source region on one side of the channel region, and a drain region on the other side of the channel region; an interlayer insulating film provided in contact with the oxide semiconductor film as well as having a connection hole, and including an organic resin film; and a source electrode and a drain electrode connected to the source region and the drain region, respectively, via the connection hole.

Owner:JOLED INC

Thin film transistors using thin film semiconductor materials

ActiveUS7994508B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsIndium

The present invention generally comprises TFTs having semiconductor material comprising oxygen, nitrogen, and one or more element selected from the group consisting of zinc, tin, gallium, cadmium, and indium as the active channel. The semiconductor material may be used in bottom gate TFTs, top gate TFTs, and other types of TFTs. The TFTs may be patterned by etching to create both the channel and the metal electrodes. Then, the source-drain electrodes may be defined by dry etching using the semiconductor material as an etch stop layer. The active layer carrier concentration, mobility, and interface with other layers of the TFT can be tuned to predetermined values. The tuning may be accomplished by changing the nitrogen containing gas to oxygen containing gas flow ratio, annealing and / or plasma treating the deposited semiconductor film, or changing the concentration of aluminum doping.

Owner:APPLIED MATERIALS INC

Amorphous-oxide thin-film transistor, manufacturing method thereof, and display panel

ActiveCN102655165AReduce parasitic resistanceImprove driving abilityTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceOxide thin-film transistor

The embodiment of the invention discloses an amorphous-oxide thin-film transistor, a manufacturing method thereof, and a display panel, relates to the field of design and manufacture of the thin-film transistor and the display panel, which are used for reducing parasitic resistance of a source and a drain. The amorphous-oxide thin-film transistor is characterized in that the substrate comprises a grid electrode, a grid insulating layer, a semiconductor active layer, a source electrode, a drain electrode and a passivation protecting layer, wherein the semiconductor active layer is of a two-layer structure with a channel layer and an ohmic contact layer, and the oxygen content of the channel layer is higher than that of the ohmic contact layer; and in addition, the channel layer and the ohmic contact layer are attached, and the ohmic contact layer is divided into two independent ohmic contact areas which are respectively attached with the source electrode and the drain electrode.

Owner:BOE TECH GRP CO LTD

Array substrate and display panel

ActiveCN111863837APrevent feature driftImprove stabilitySolid-state devicesSemiconductor devicesOxide thin-film transistorHemt circuits

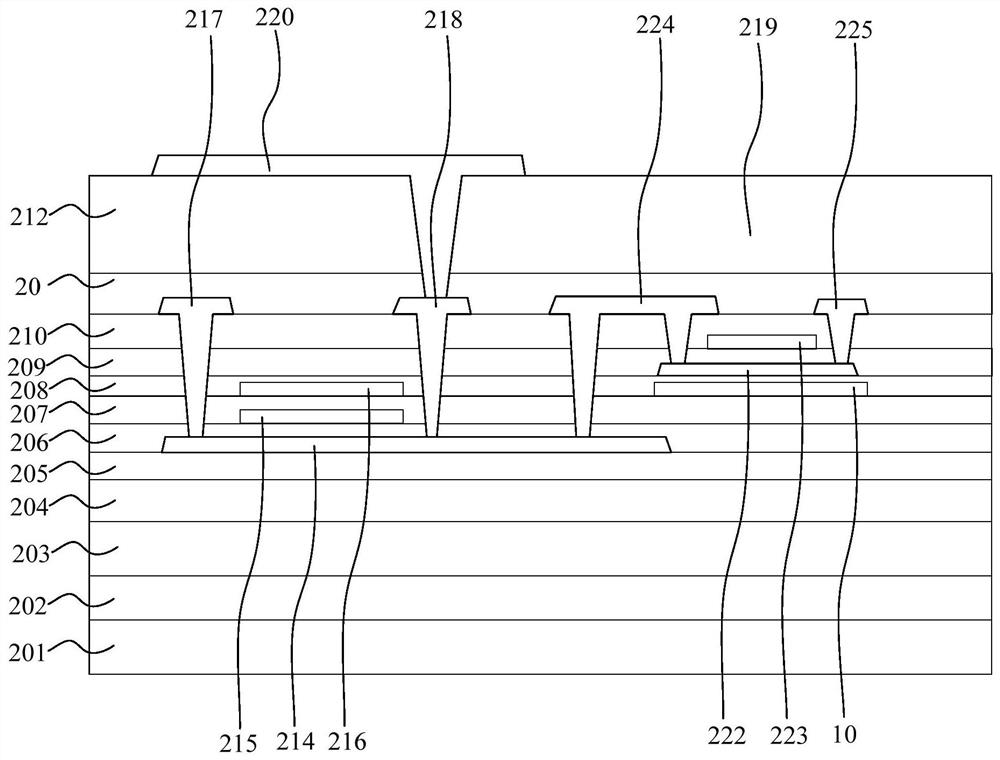

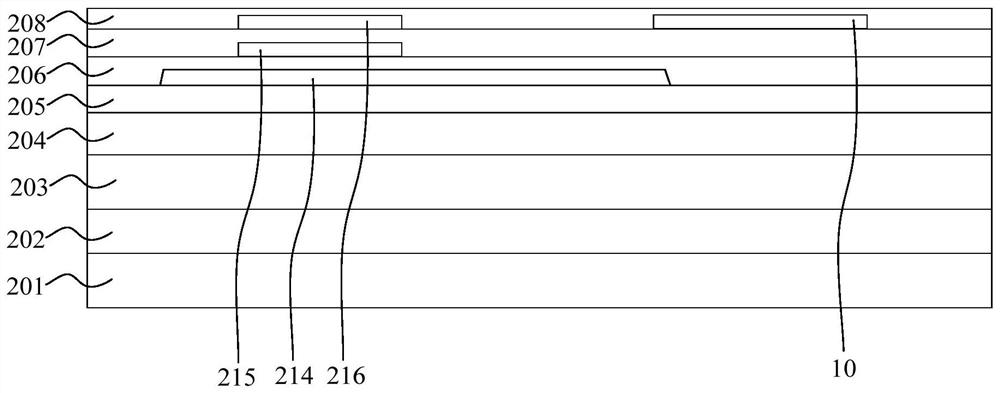

The invention provides an array substrate and a display panel. A driving circuit layer in the array substrate is formed on one side of a substrate, and the driving circuit layer comprises a low-temperature polycrystalline silicon thin film transistor and a low-temperature polycrystalline oxide thin film transistor which are electrically connected. The low-temperature polycrystalline silicon thin film transistor sequentially comprises a polycrystalline silicon active layer, a first grid electrode, a first source electrode and a first drain electrode in the direction away from the low-temperature polycrystalline silicon thin film transistor, and the low-temperature polycrystalline oxide thin film transistor sequentially comprises an oxide active layer, a second grid electrode, a second source electrode and a second drain electrode; a hydrogen barrier layer is formed on at least one side of the upper side or the lower side of the oxide active layer; a pixel electrode layer is formed on the side, away from the substrate, of the drive circuit layer, a pixel electrode is formed through patterning, and the pixel electrode is connected with the first source electrode or the first drain electrode. The hydrogen barrier layer can prevent hydrogen ions in other film layers from invading the oxide active layer to cause device characteristic drift, so that the performance of the transistorsis improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Thin film transistor and manufacturing method thereof, array substrate and display device

ActiveCN103887343AIncrease deposition rateReduce hydrogen contentTransistorSolid-state devicesInsulation layerHydrogen

The invention provides a thin film transistor and a manufacturing method thereof, an array substrate and a display device. The thin film transistor comprises a substrate, a gate electrode, an active layer, a source drain electrode, a pixel electrode and one or more insulation layers, wherein at least one insulation layer comprises a bottom insulation layer and an upper insulation layer, and the content of the hydrogen in the upper insulation layer is higher than the content of the hydrogen in the bottom insulation layer. The thin film transistor is produced by the double-layer etching barrier layer process, the content of the hydrogen in a silicon oxide thin film in an etching barrier layer is effectively reduced, the hydrogen ion generated by silicane decomposition is prevented from reacting with the metal oxide in the active layer, thus the oxide thin film transistor keeps better characteristics, and the thin film deposition rate of the etching barrier layer is increased.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

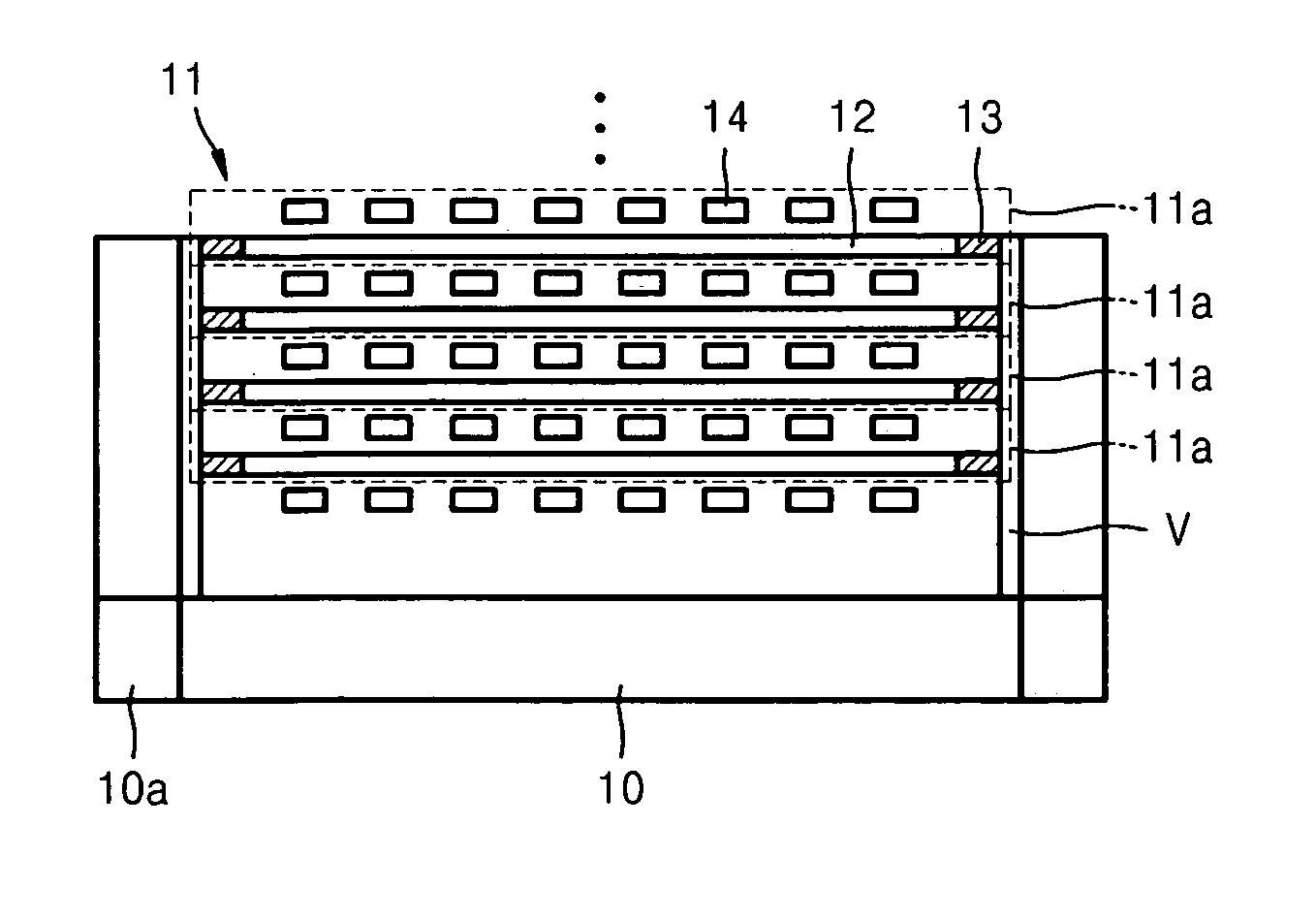

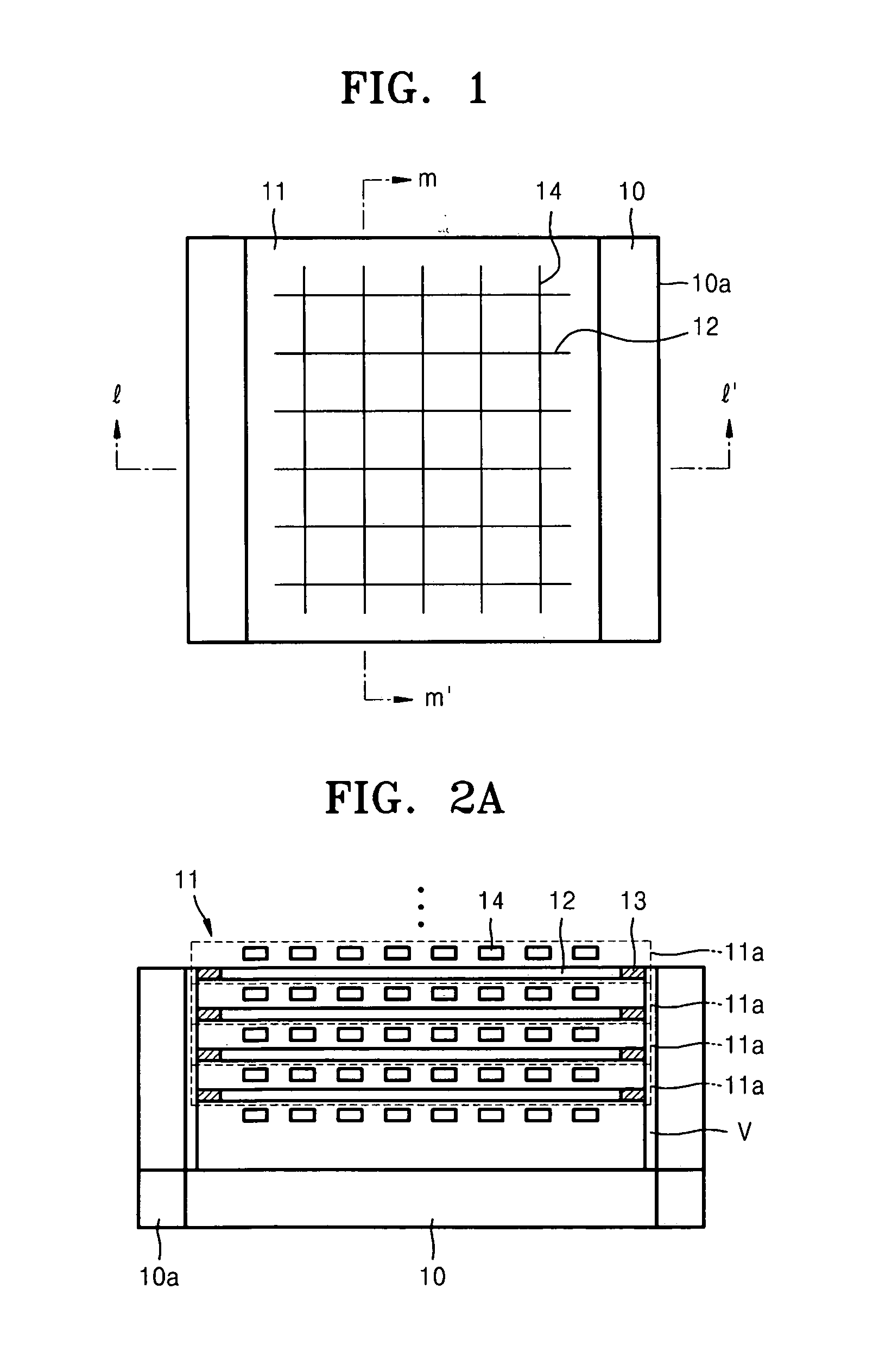

Multi-layered memory apparatus including oxide thin film transistor

InactiveUS20100096628A1Minimized in sizeTransistorSolid-state devicesOxide thin-film transistorElectrical and Electronics engineering

Provided is a multi-layered memory apparatus including an oxide thin film transistor. The multi-layered memory apparatus includes an active circuit unit and a memory unit formed on the active circuit unit. A row line and a column line are formed on memory layers. A selection transistor is formed at a side end of the row line and the column line.

Owner:SAMSUNG ELECTRONICS CO LTD

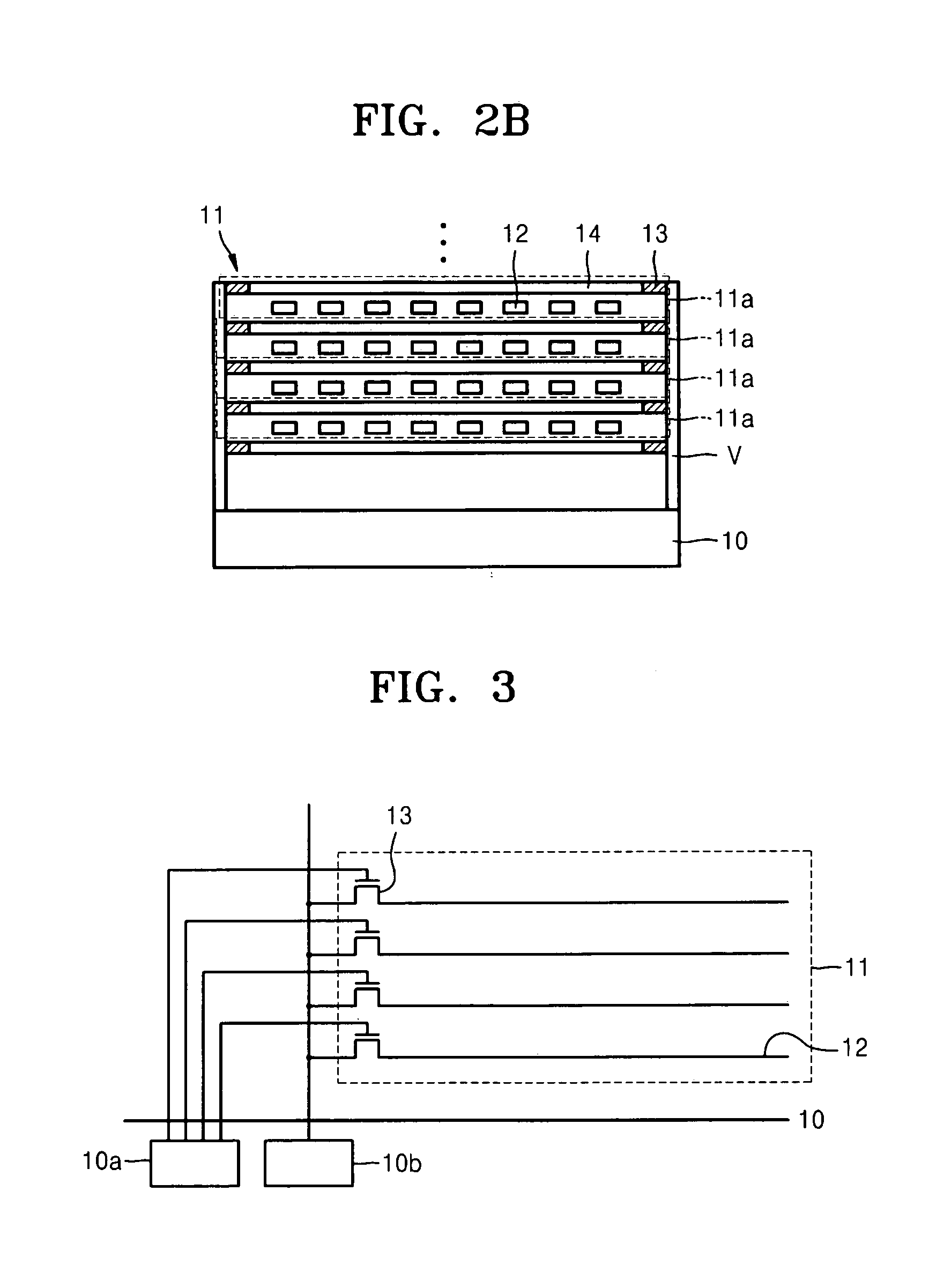

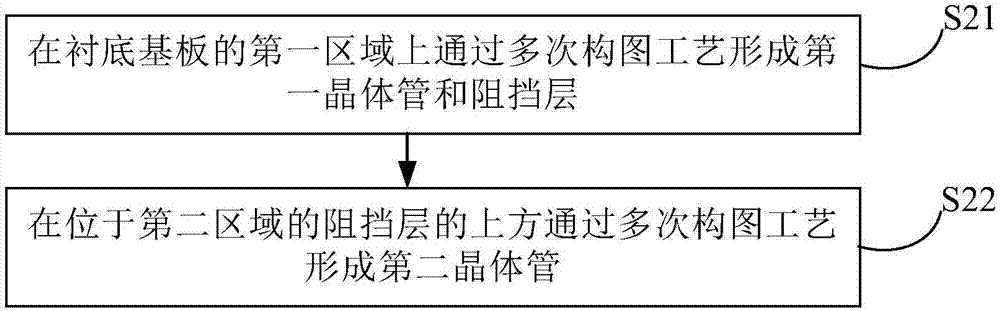

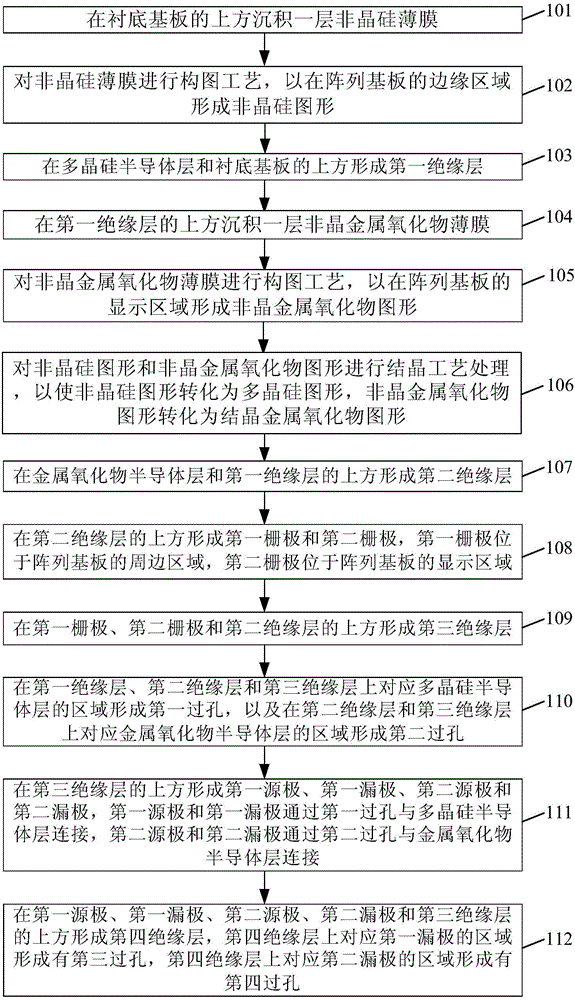

Array substrate and manufacturing method thereof, and display device

ActiveCN107275350ACharacteristic impactPrevent hydrogen permeationTransistorSolid-state devicesHydrogenOxide thin-film transistor

The invention discloses an array substrate and a manufacturing method thereof, and a display device. The array substrate comprises a substrate, wherein a first region and a second region of the substrate are respectively provided with a first transistor and a second transistor, the first transistor has a first active layer, the first active layer is low temperature polysilicon, the second transistor has a second active layer, the second active layer is metal-oxide semiconductor, the first active layer, an interlayer dielectric layer and the second active layer are sequentially arranged on the substrate, and a blocking layer is arranged between the interlayer dielectric layer and the second active layer. The array substrate is advantaged in that through arranging the blocking layer, the insulation and hydrogen blocking effect between the interlayer dielectric layer of the low temperature polysilicon film transistor and the active layer of the oxide film transistor is realized, hydrogen penetration in the subsequent heat treatment technology between the low temperature polysilicon film transistor and the oxide film transistor can be prevented, and bad influence of transistor characteristics of the low temperature polycrystalline silicon film transistor and the oxide film transistor can be prevented.

Owner:BOE TECH GRP CO LTD

Array substrate, manufacturing method thereof and display device

InactiveCN104538352ASolid-state devicesSemiconductor/solid-state device manufacturingOxide thin-film transistorDisplay device

The invention discloses an array substrate, a manufacturing method of the array substrate and a display device. The array substrate comprises a first thin film transistor and a second thin film transistor. The first thin film transistor and the second thin film transistor are formed above an underlayer substrate. The first thin film transistor is a polycrystalline silicon thin film transistor. The second thin film transistor is a metallic oxide thin film transistor or an amorphous silicon thin film transistor. The first thin film transistor is located on the peripheral region of the array substrate, and the second thin film transistor is located on the display region of the array substrate. By means of the technical scheme, the problem that the polycrystalline silicon thin film transistor cannot be applied to production of large display panels with the ram being over 6 G is solved, the limit of the excimer laser crystallization process bottleneck is broken through thoroughly, and the array substrate, the manufacturing method and the display device have very high application value.

Owner:BOE TECH GRP CO LTD

Array substrate, manufacturing method thereof, and display device

ActiveCN103354218ASimple preparation processReduce manufacturing costTransistorSolid-state devicesLiquid-crystal displayOxide thin-film transistor

The invention provides an array substrate, a manufacturing method thereof, and a display device, and belongs to the technical field of liquid crystal display, and problems that an existing manufacturing process of oxide thin film transistor array substrates is complex and relatively high in manufacturing cost. The manufacturing method for the array substrate comprises: forming a pattern including a grid electrode on a substrate through a composition technology, and forming a grid insulating layer; forming a pattern including an active area and an etching blocking area on the substrate which has processed by the above step through the composition technology; forming a transparent conducting layer film, and using the transparent conducting layer film to form a pattern including a source electrode and a drain electrode through the composition technology; and using the transparent conducting layer film to form a pattern including a pixel electrode through the composition technology. The array substrate comprises a thin film transistor area and a display area, and comprises the transparent conducting layer. The transparent conducting layer forms the source electrode and the drain electrode of the thin film transistor on the thin film transistor area, and forms the pixel electrode in the display area. The display device comprises the above array substrate.

Owner:BOE TECH GRP CO LTD

Thin film transistor, manufacturing method thereof, array substrate, and display device

ActiveCN105390551ATransistorSemiconductor/solid-state device manufacturingElectrical conductorOxide thin-film transistor

The present invention provides a manufacturing method of a thin film transistor, an array substrate and a display device, relating to the technical field of display. The invention is used for solving the problems of large current, high power consumption of a low-temperature polysilicon thin film transistor. The thin film transistor comprises semiconductor layers comprising a first semiconductor layer and a second semiconductor layer, and the first semiconductor layer and the second semiconductor layer are laminated. The material of the first semiconductor layer is low-temperature polysilicon, and the carrier mobility of the second semiconductor layer is smaller than the carrier mobility of the first semiconductor layer. The above thin film transistor is used in the array substrate, and pixels are driven.

Owner:BOE TECH GRP CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com