Patents

Literature

1479results about How to "Low mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

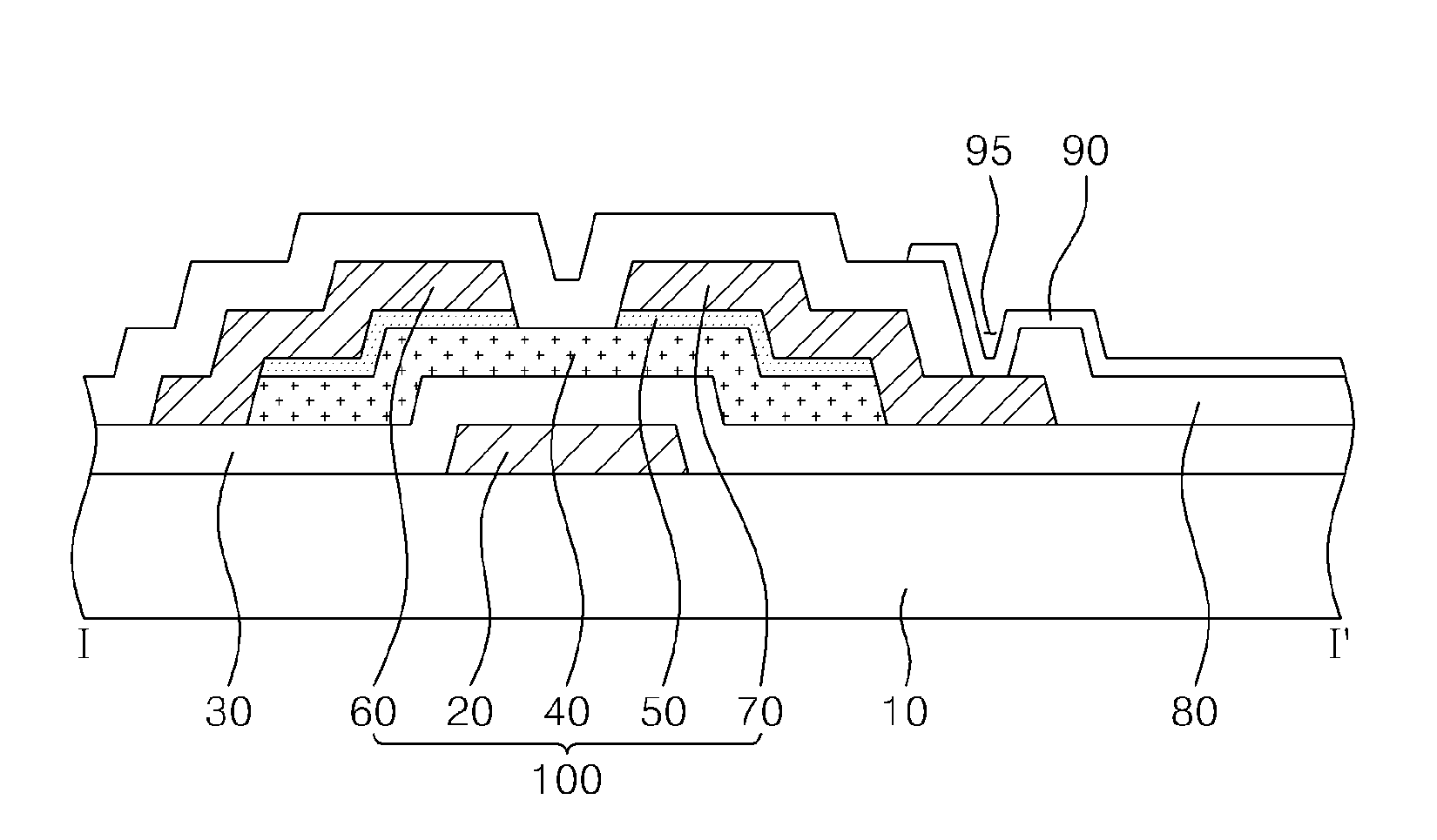

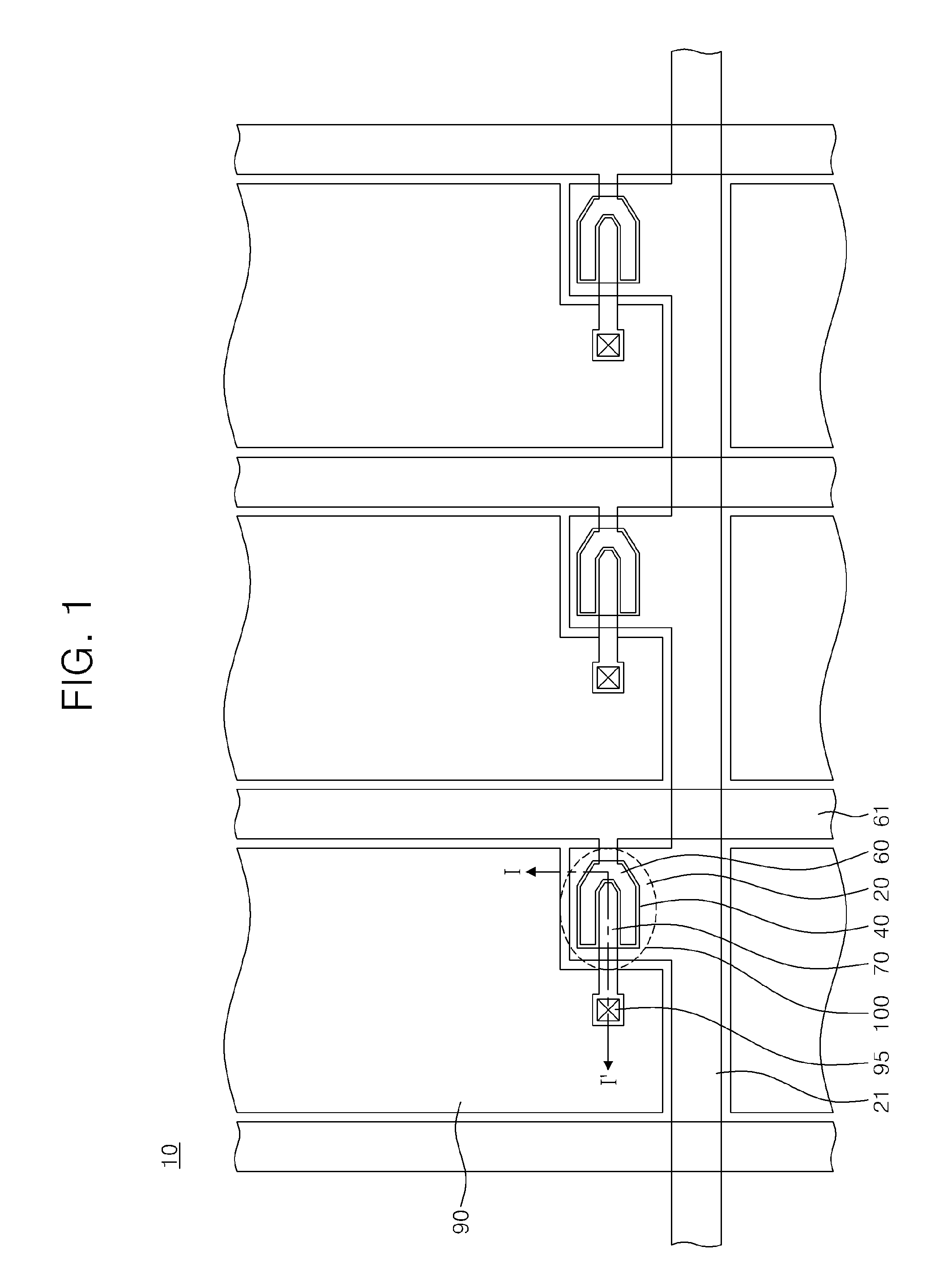

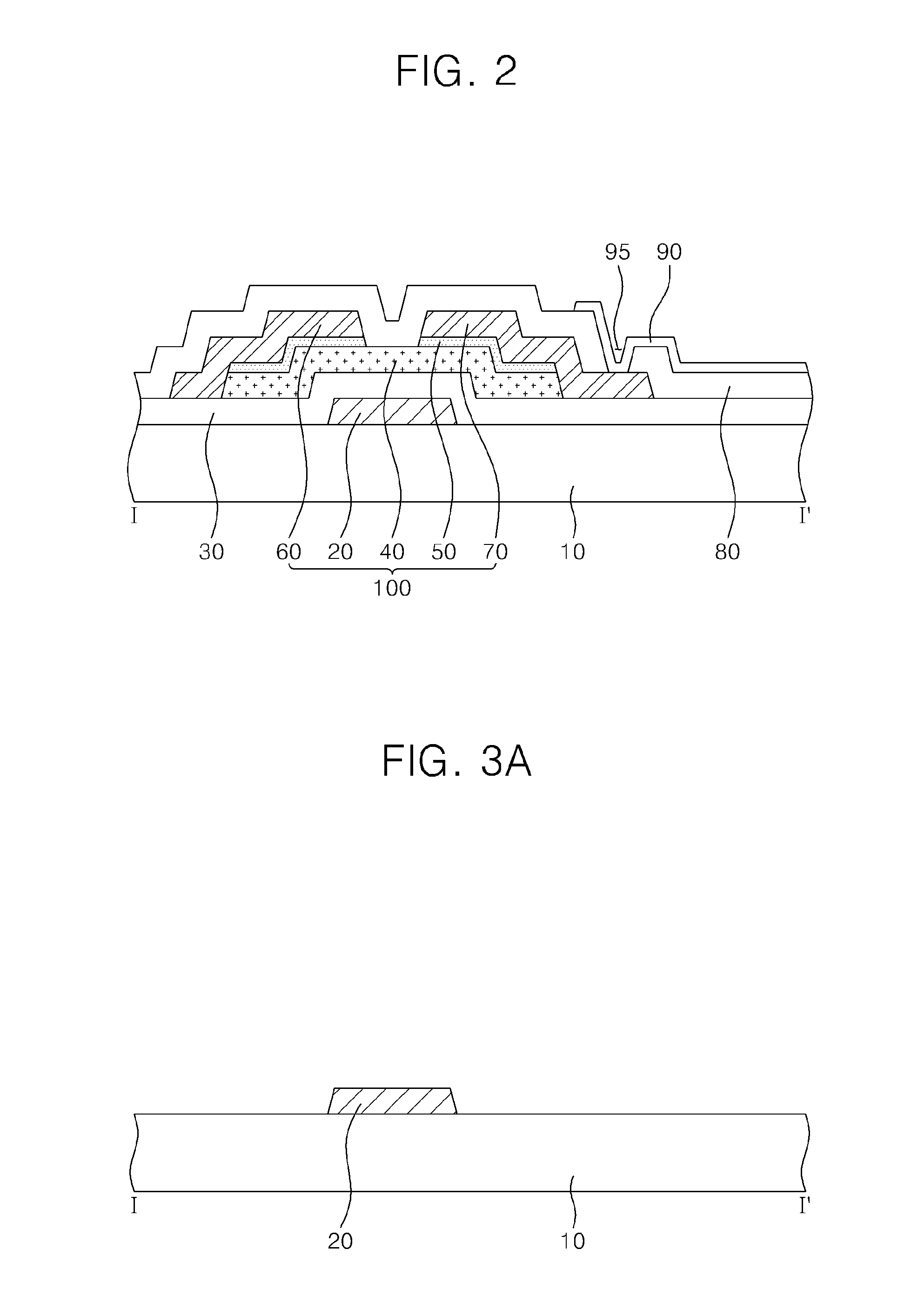

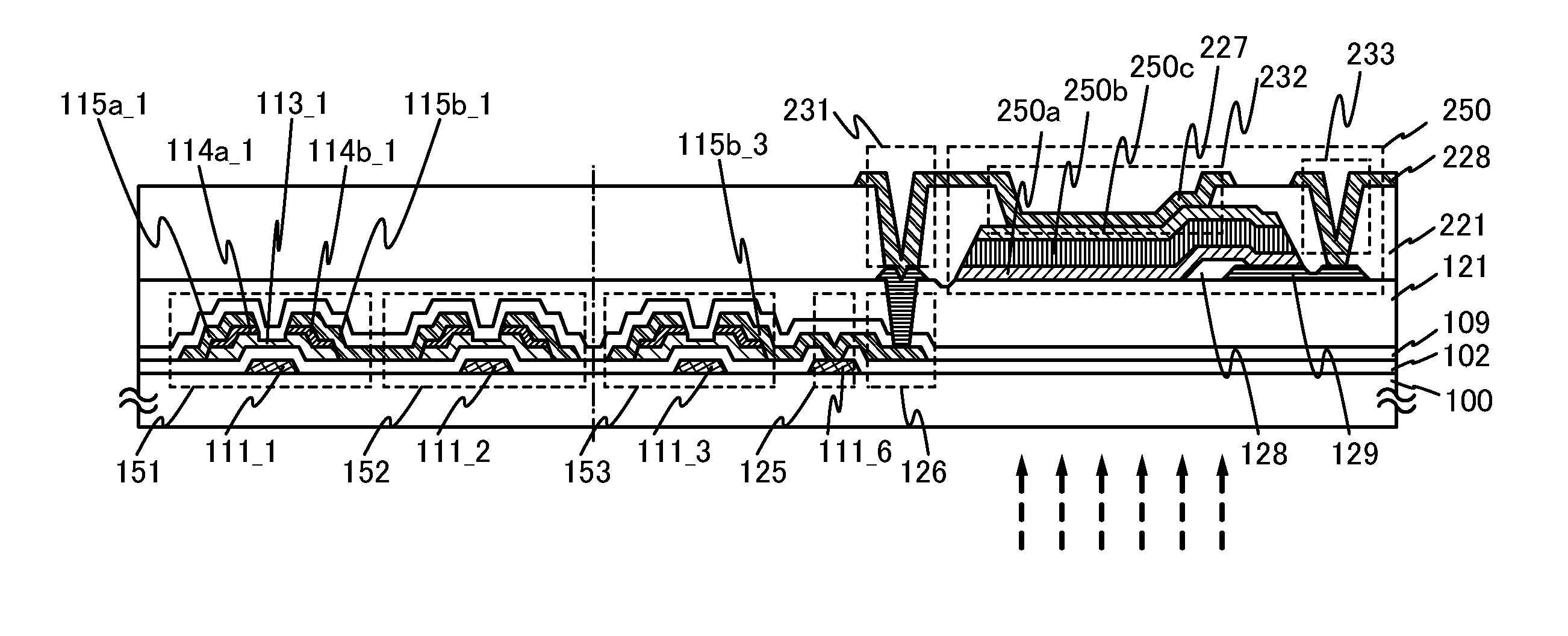

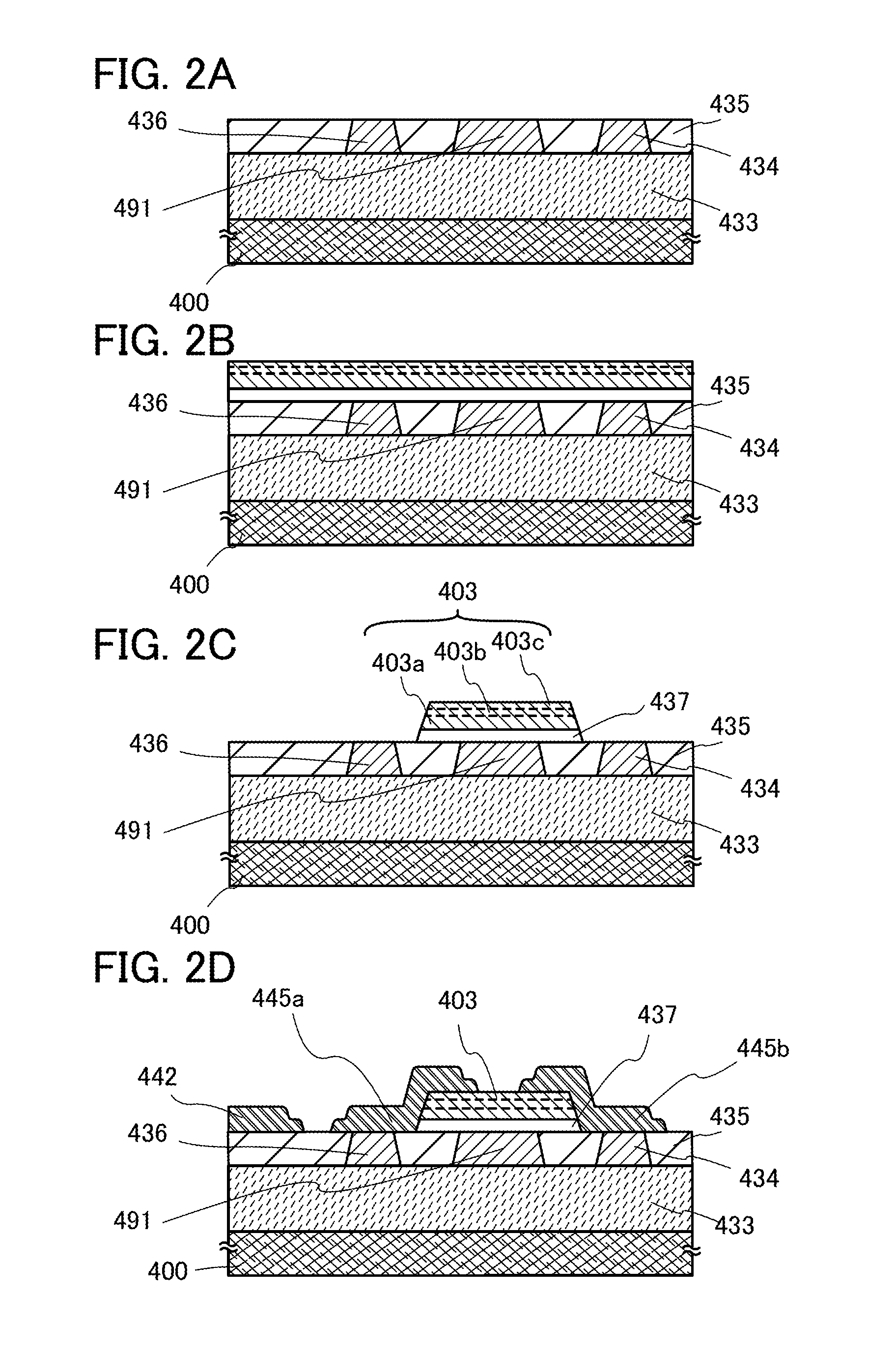

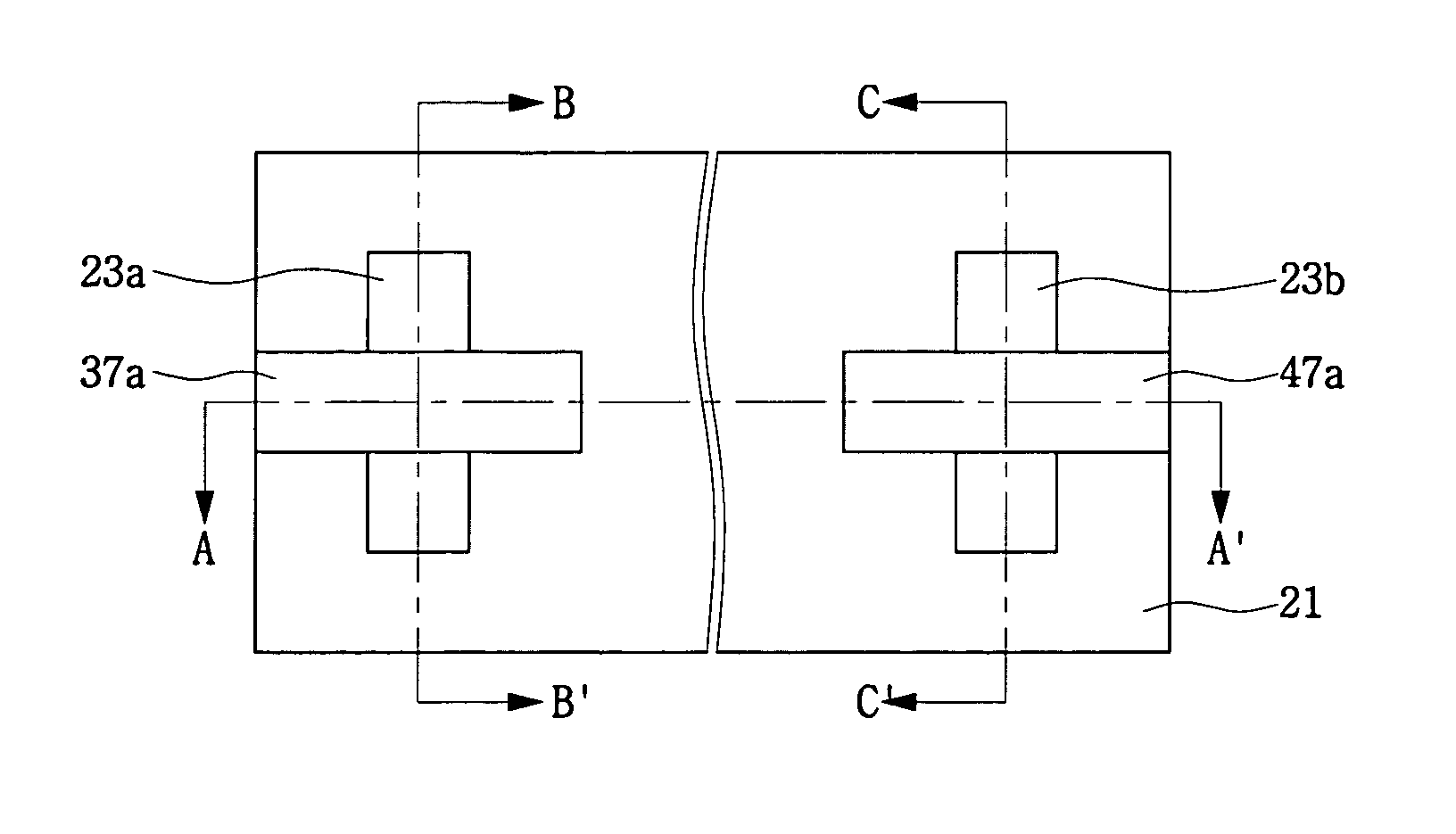

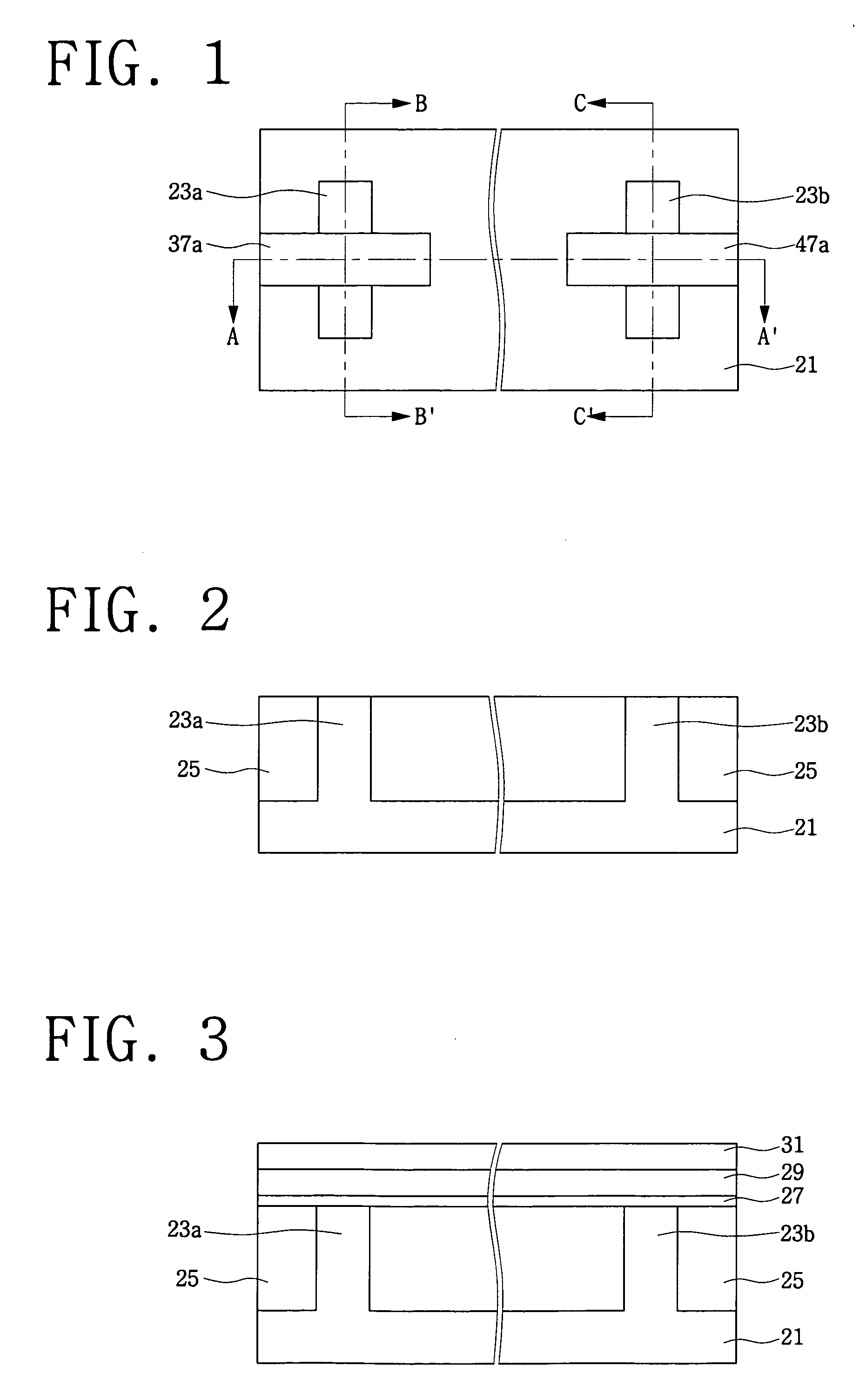

Thin film transitor substrate and method of manufacturing the same

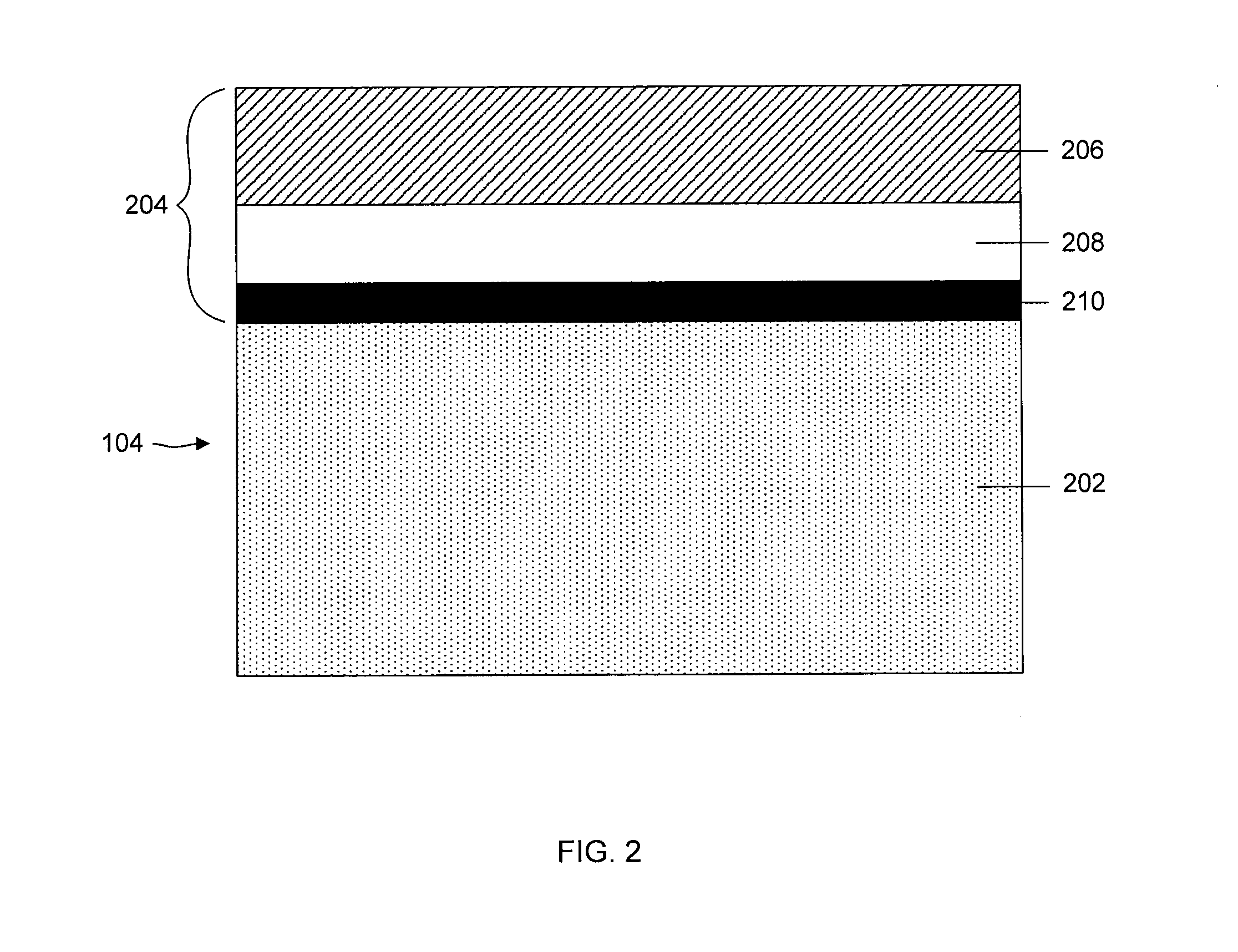

InactiveUS20080258143A1Increases process time and leakage current and serial contact resistanceDegrading property of TFTTransistorSemiconductor/solid-state device manufacturingOxide semiconductorOxide

A method of manufacturing a thin film transistor (“TFT”) substrate includes forming a first conductive pattern group including a gate electrode on a substrate, forming a gate insulating layer on the first conductive pattern group, forming a semiconductor layer and an ohmic contact layer on the gate insulating layer by patterning an amorphous silicon layer and an oxide semiconductor layer, forming a second conductive pattern group including a source electrode and a drain electrode on the ohmic contact layer by patterning a data metal layer, forming a protection layer including a contact hole on the second conductive pattern group, and forming a pixel electrode on the contact hole of the protection layer. The TFT substrate including the ohmic contact layer formed of an oxide semiconductor is further provided.

Owner:SAMSUNG ELECTRONICS CO LTD

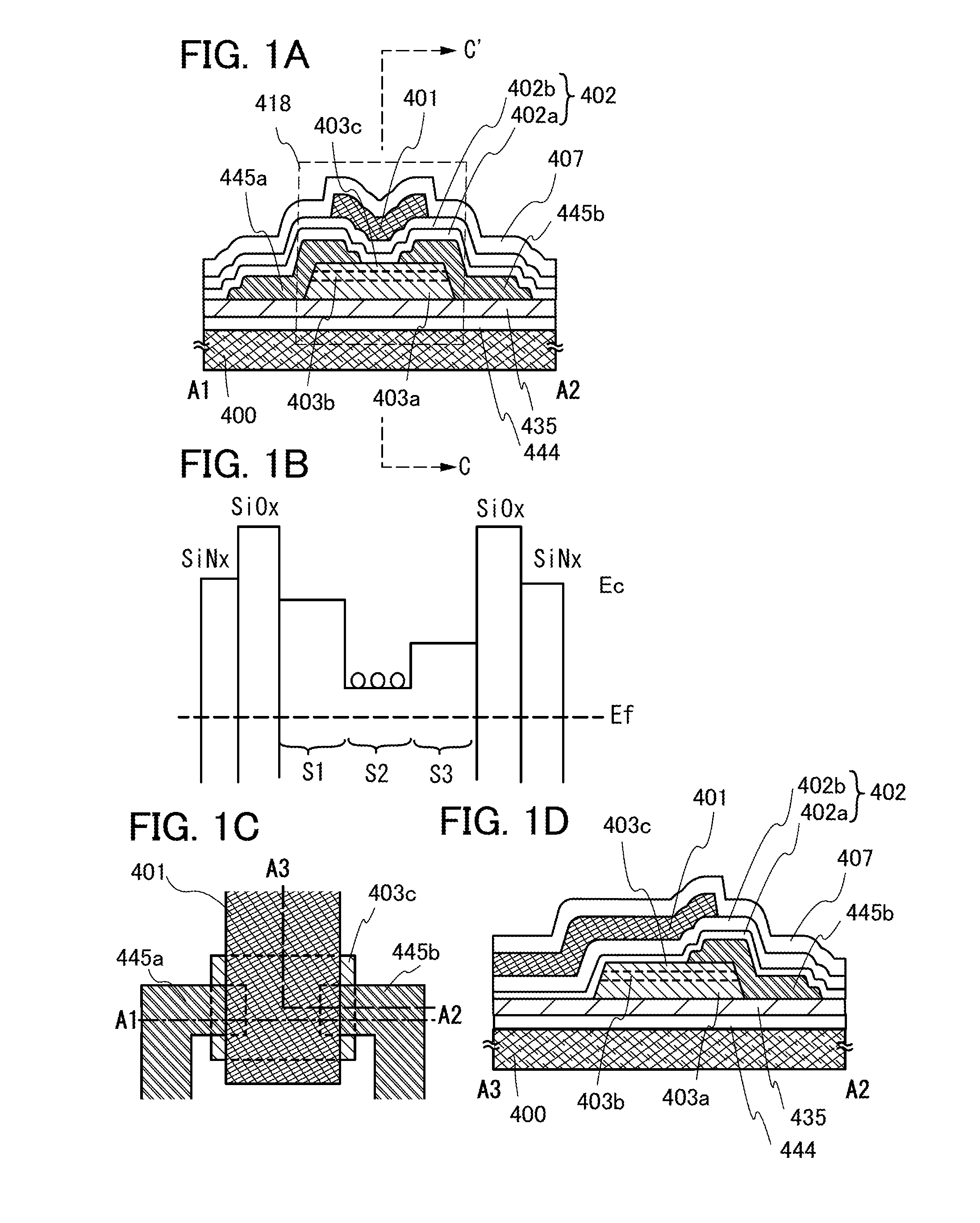

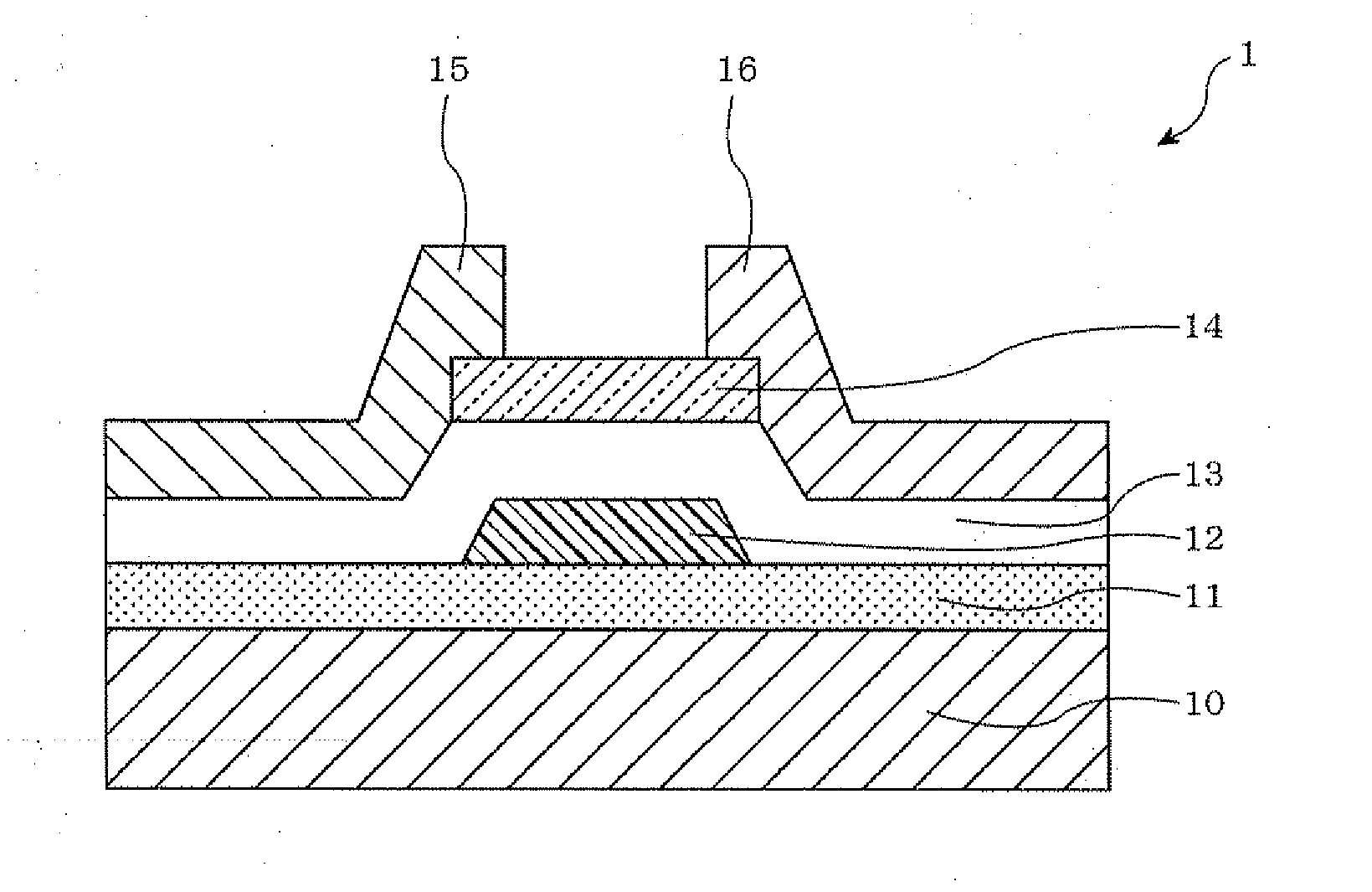

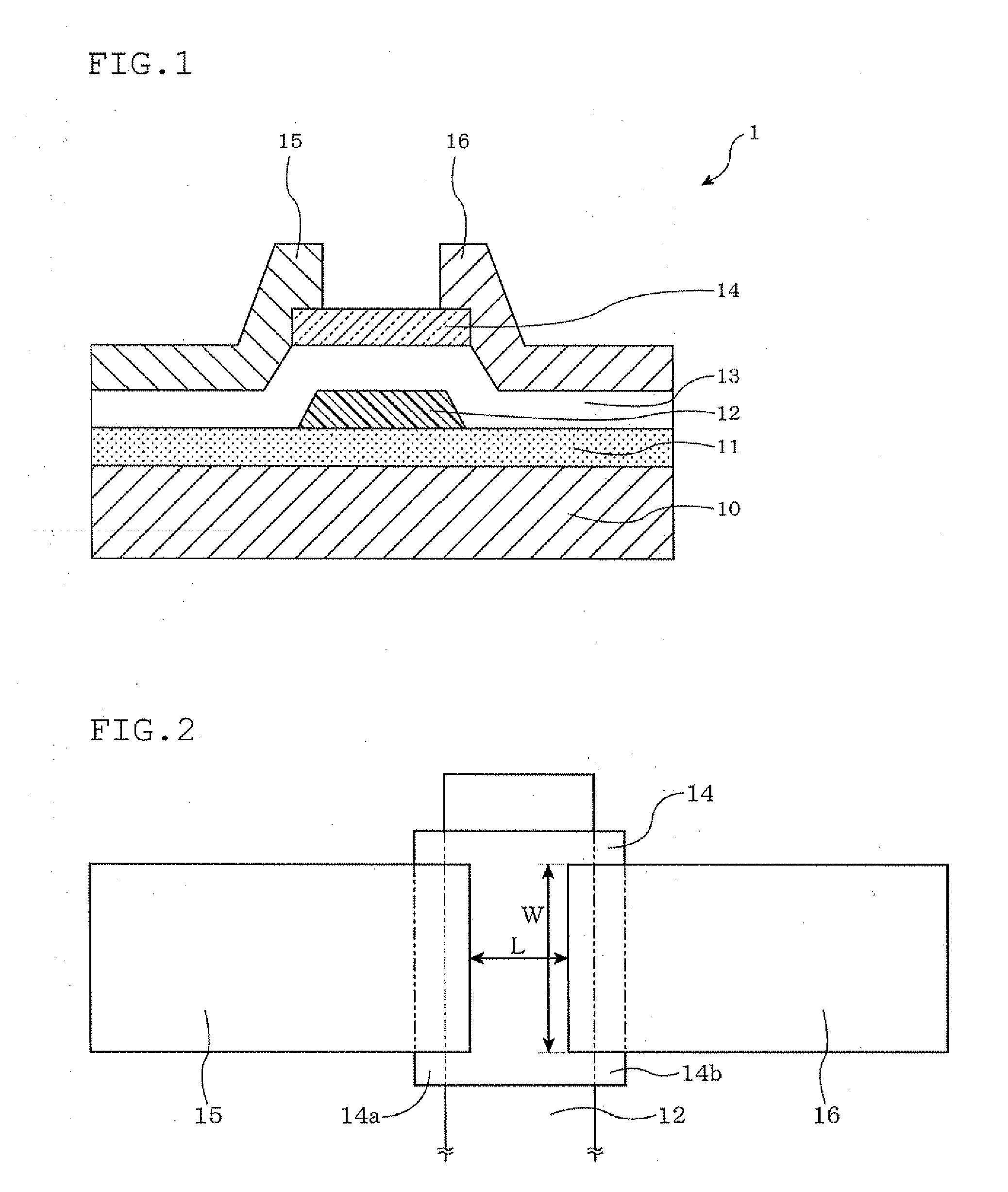

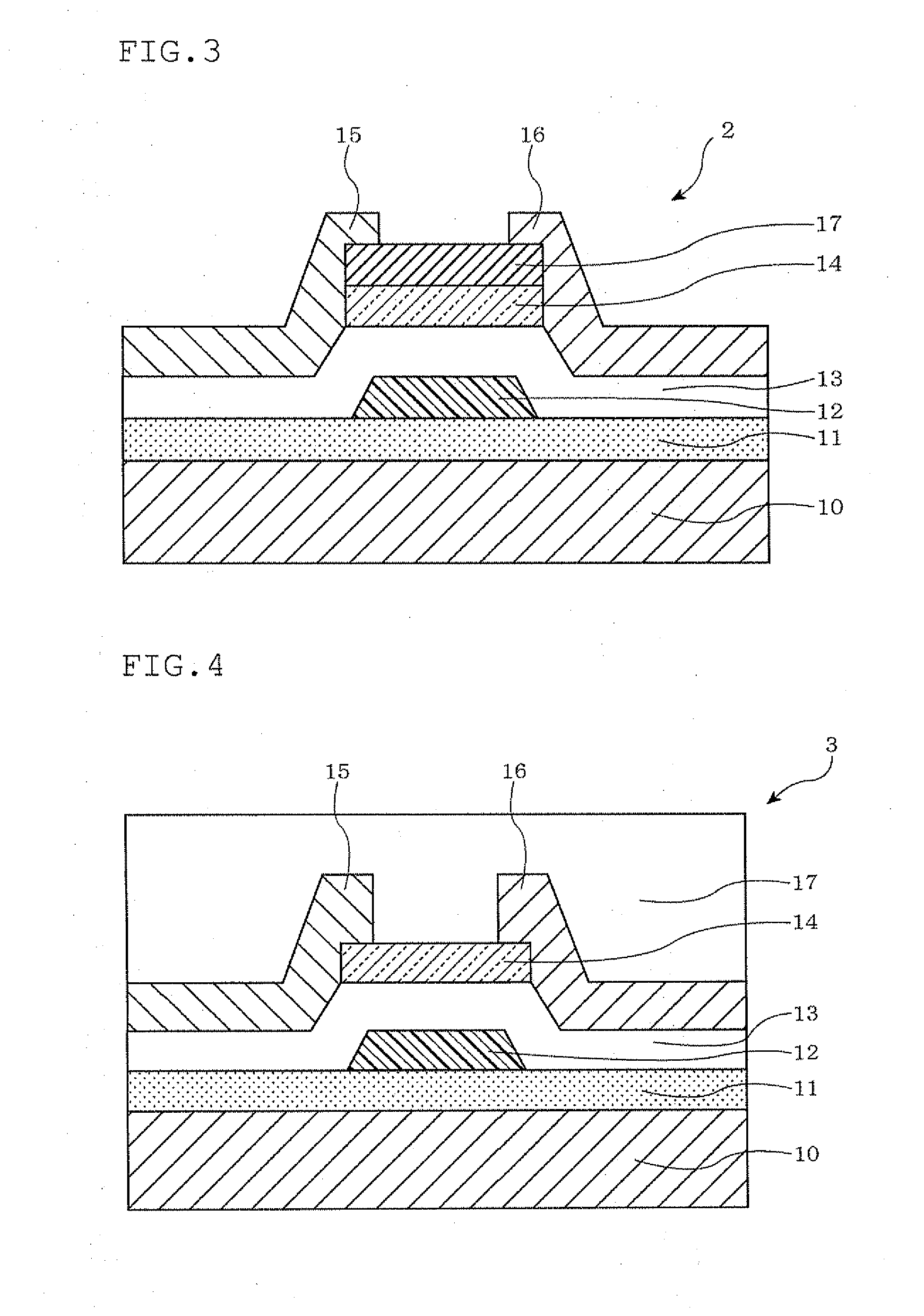

Thin-film transistor, method of producing the same, and devices provided with the same

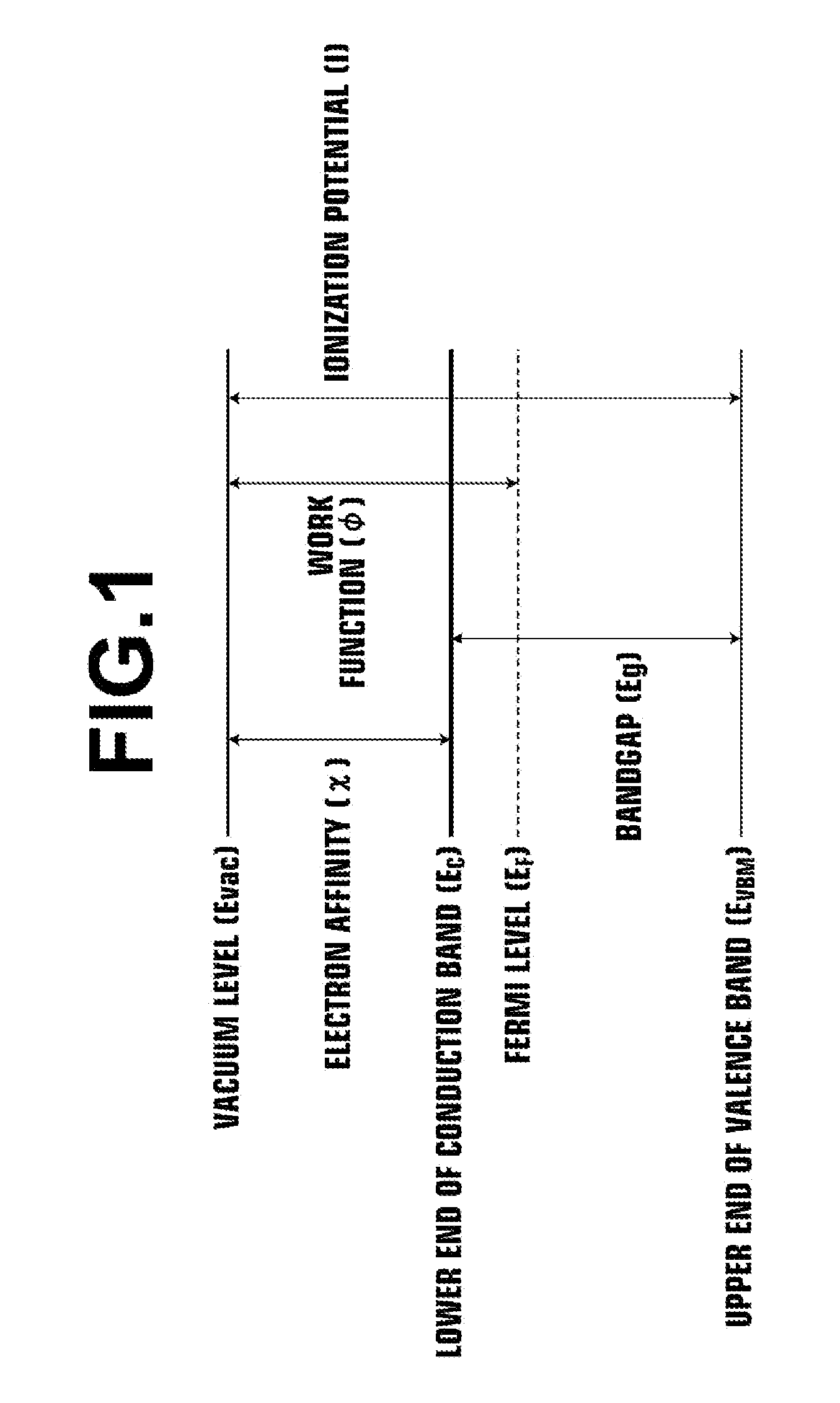

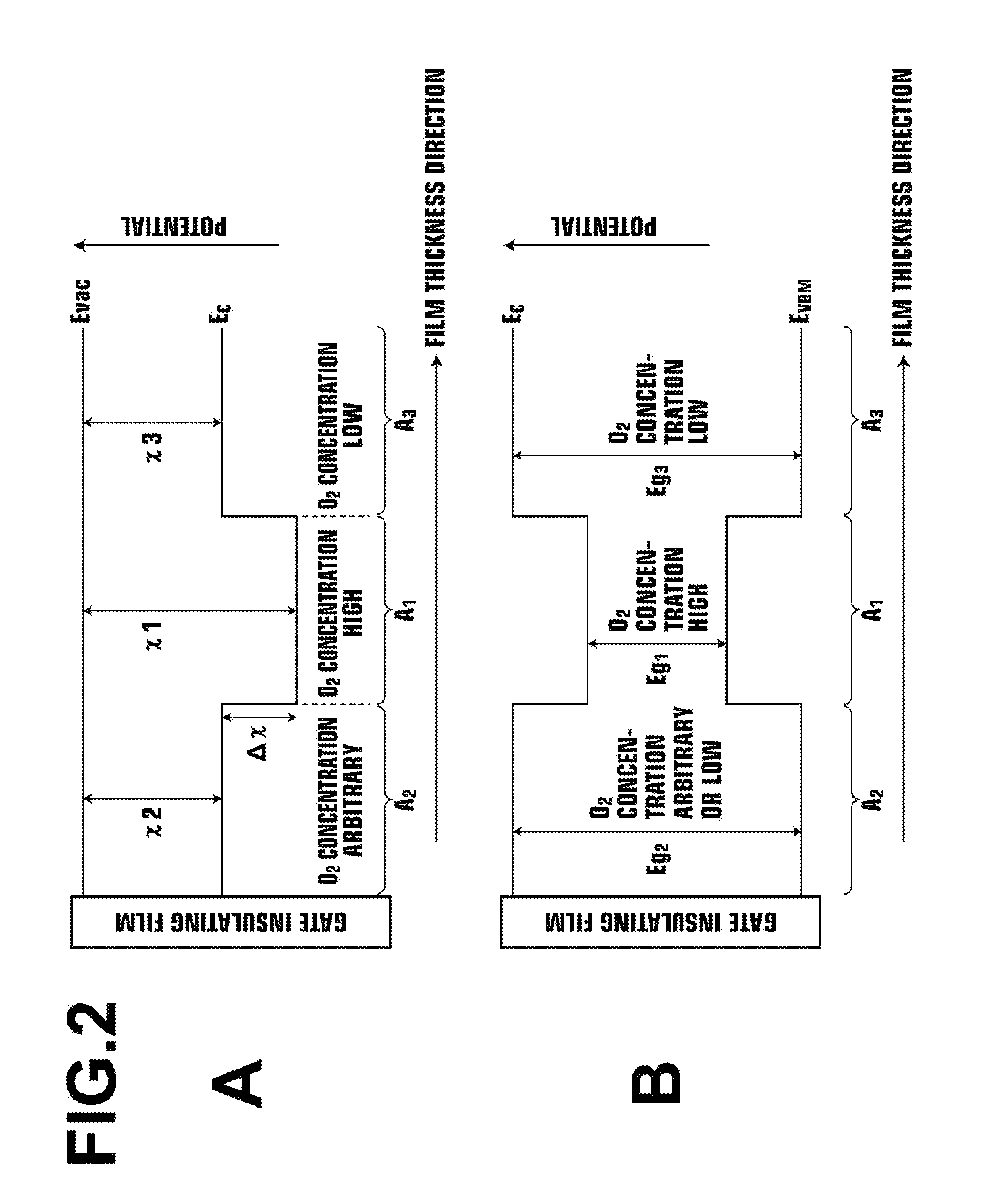

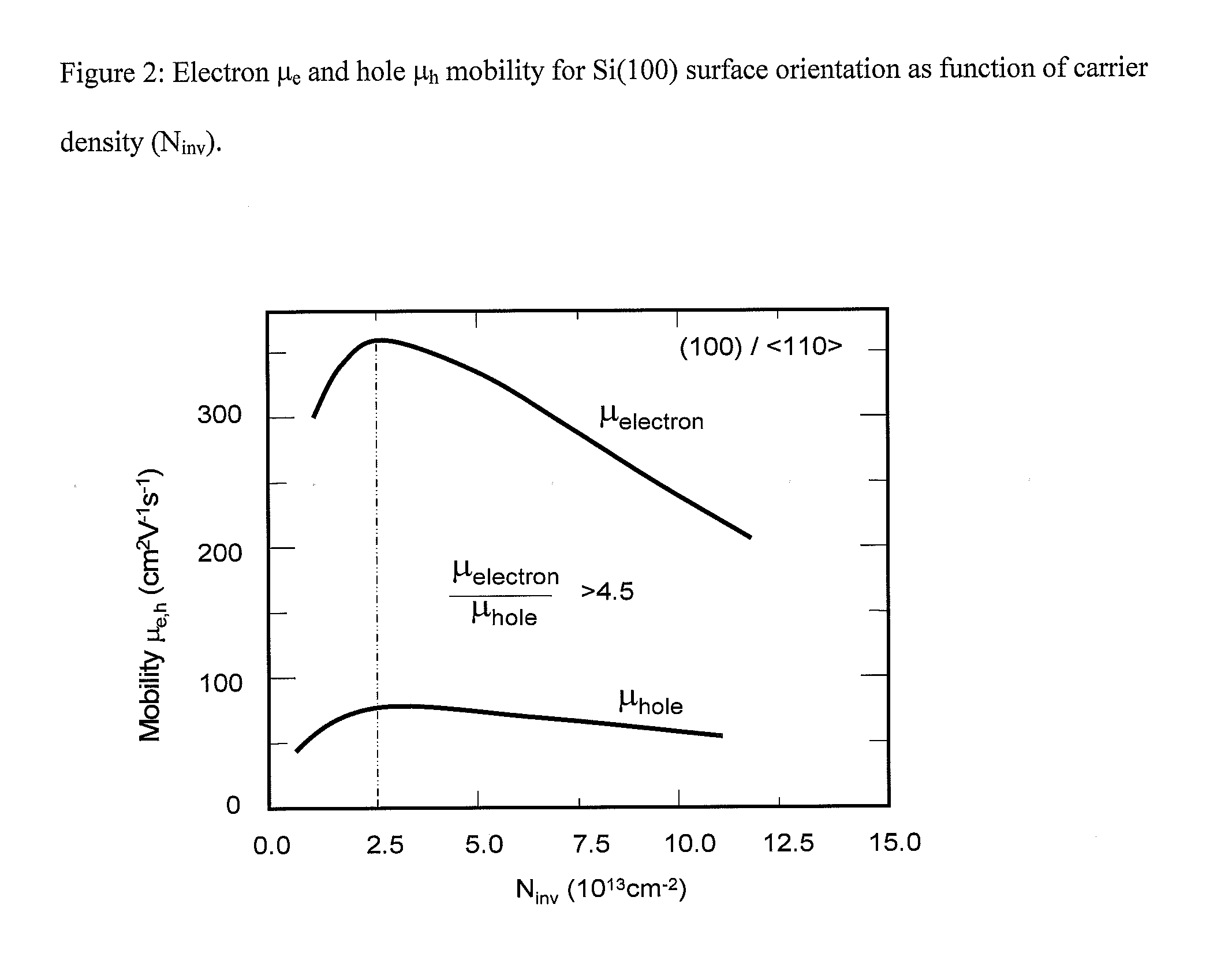

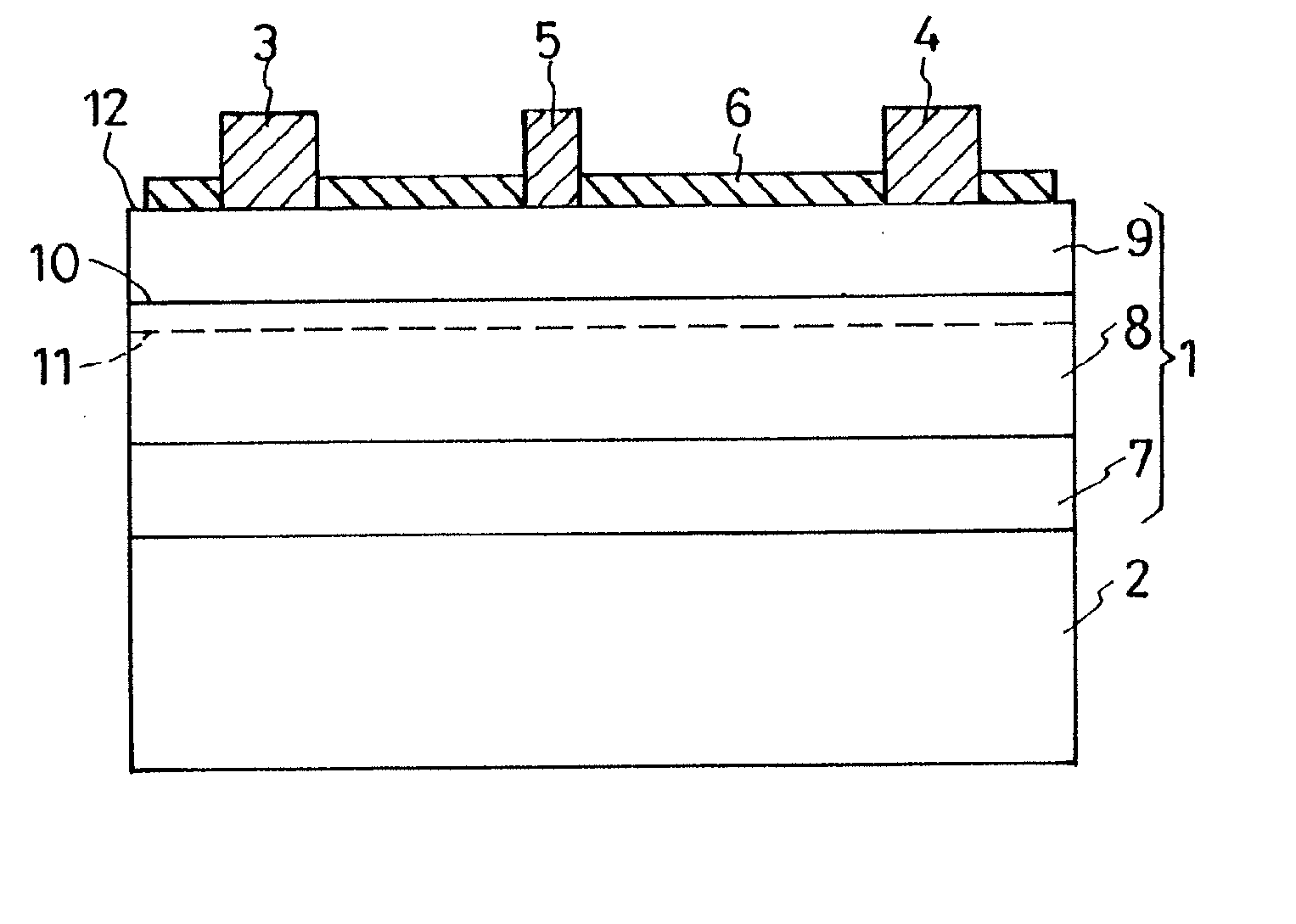

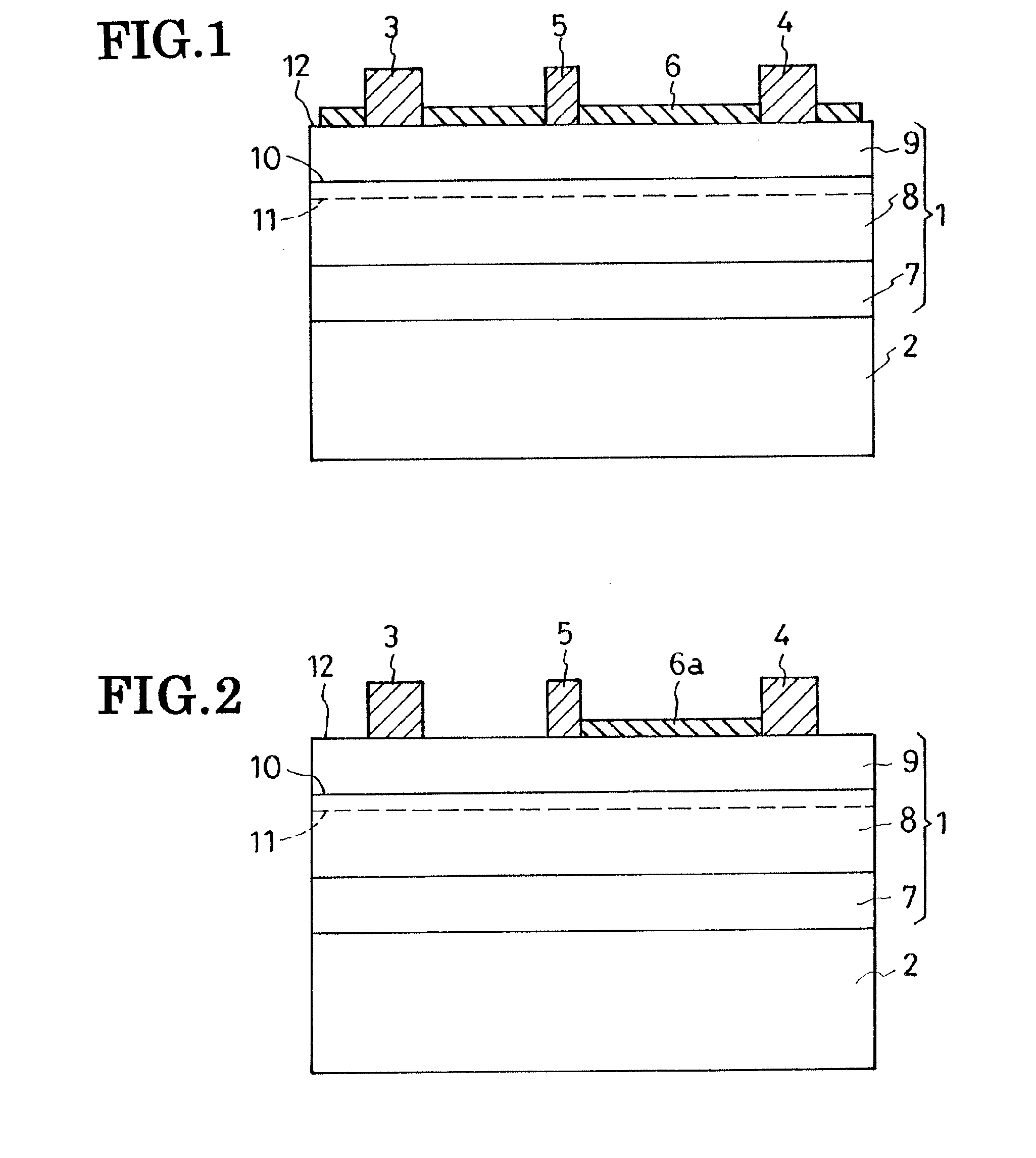

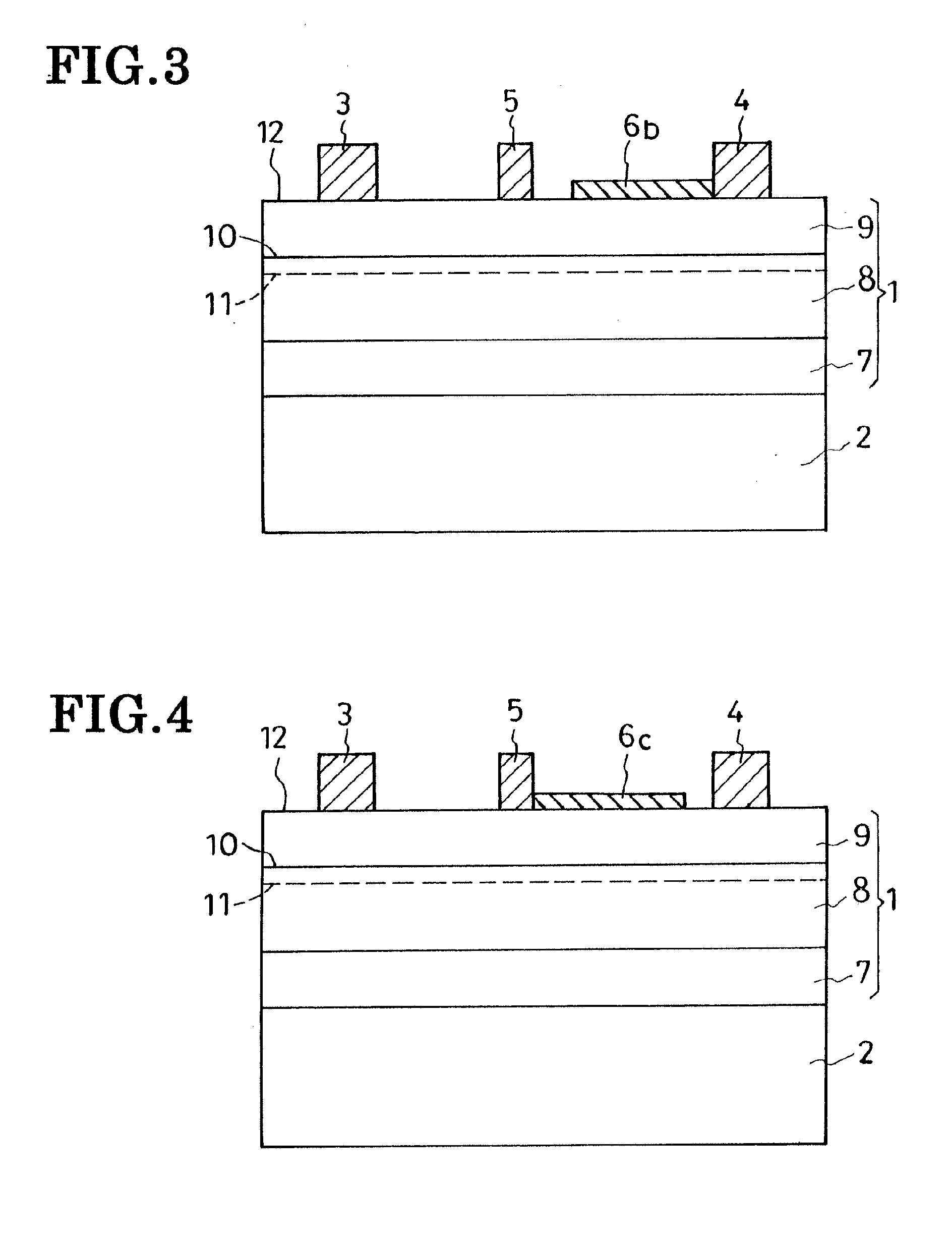

ActiveUS20110140100A1Low mobilityIncrease carrier densityTransistorSemiconductor/solid-state device manufacturingOxygenSemiconductor

A thin-film transistor including an oxide semiconductor layer is disclosed. The oxide semiconductor layer includes a first area, a second area and a third area forming a well-type potential in the film-thickness direction. The first area forms a well of the well-type potential and has a first electron affinity. The second area is disposed nearer to the gate electrode than the first area and has a second electron affinity smaller than the first electron affinity. The third area is disposed farther from the gate electrode than the first area and has a third electron affinity smaller than the first electron affinity. At least an oxygen concentration at the third area is lower than an oxygen concentration at the first area.

Owner:SAMSUNG DISPLAY CO LTD

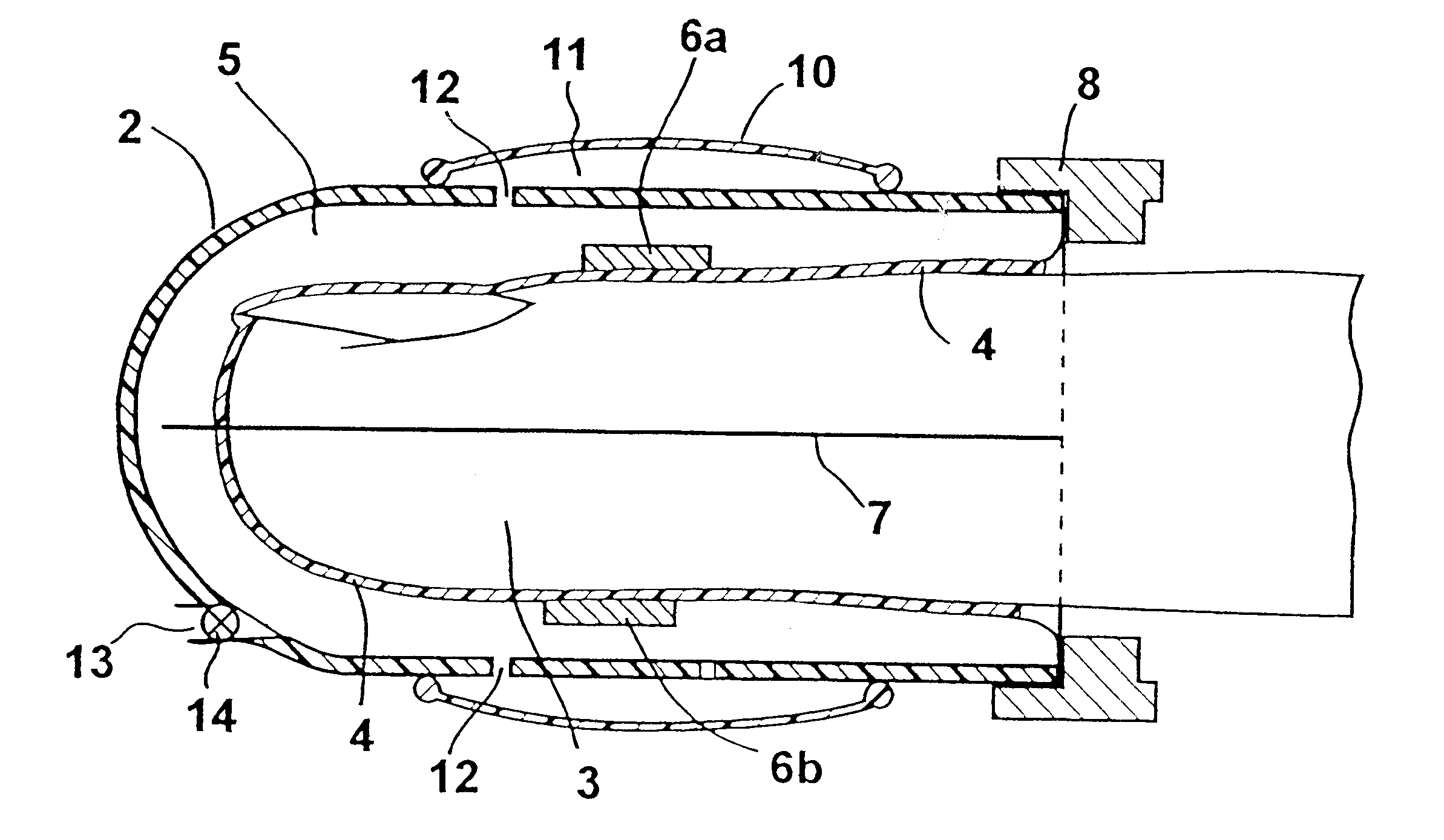

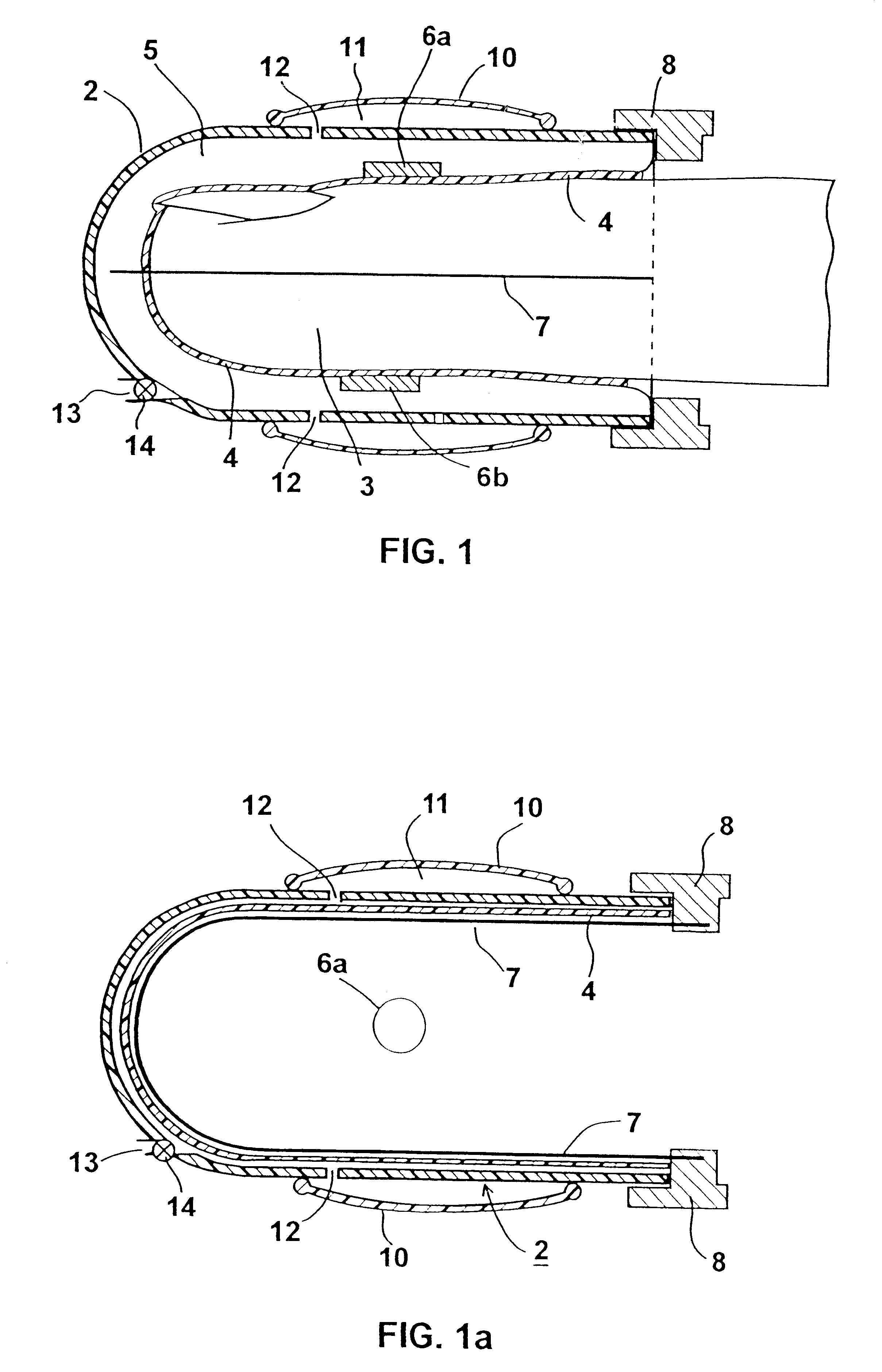

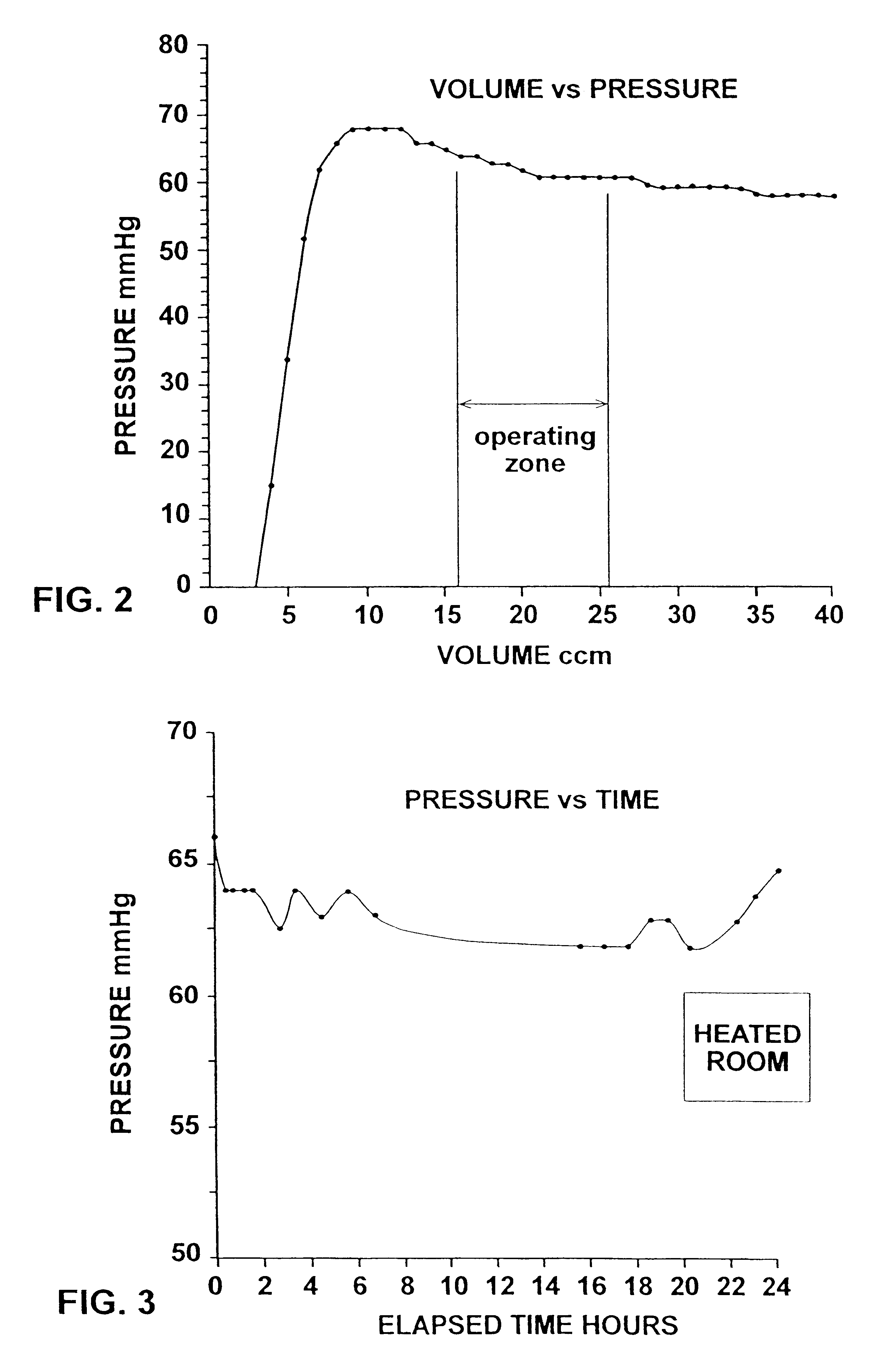

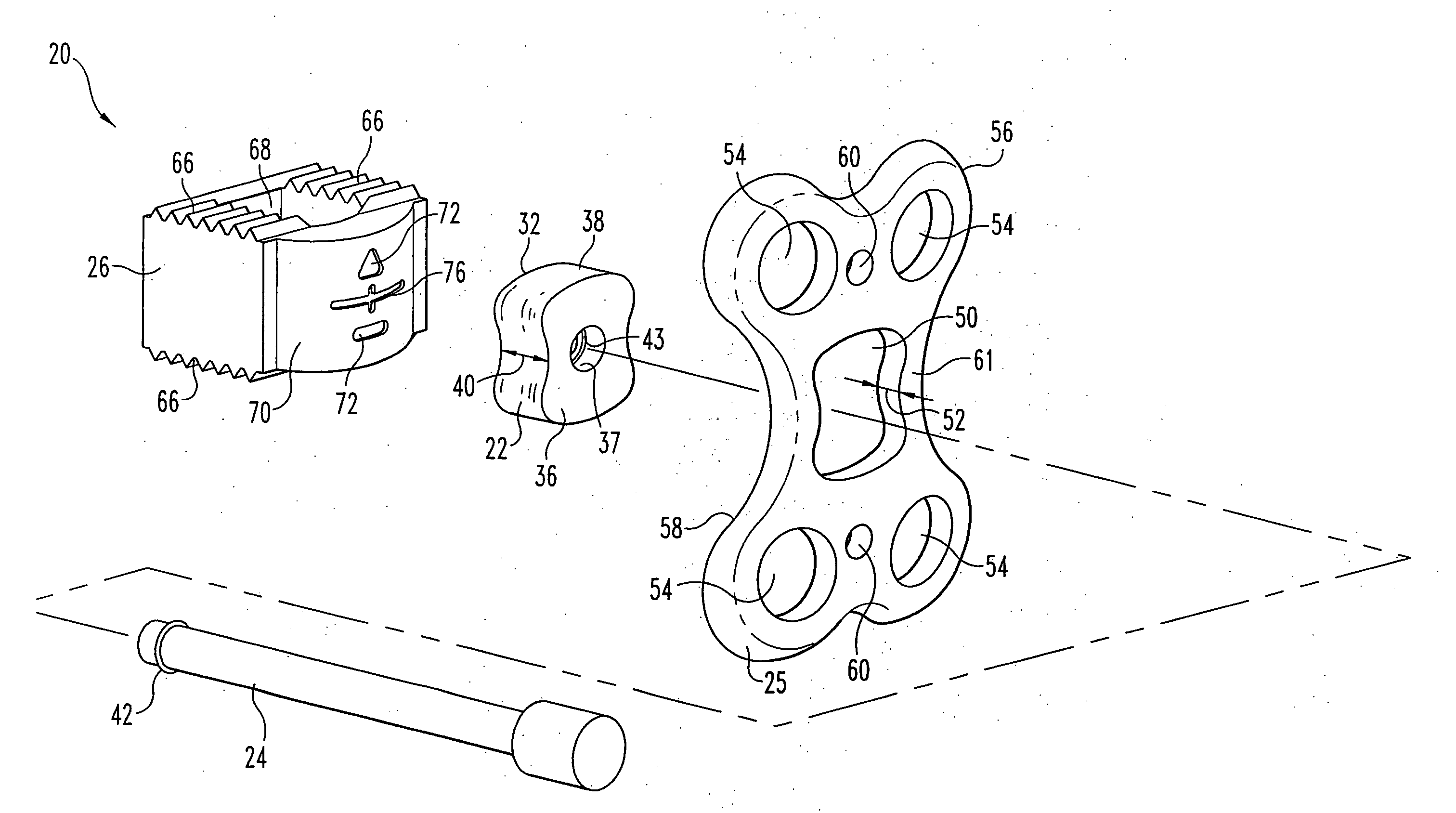

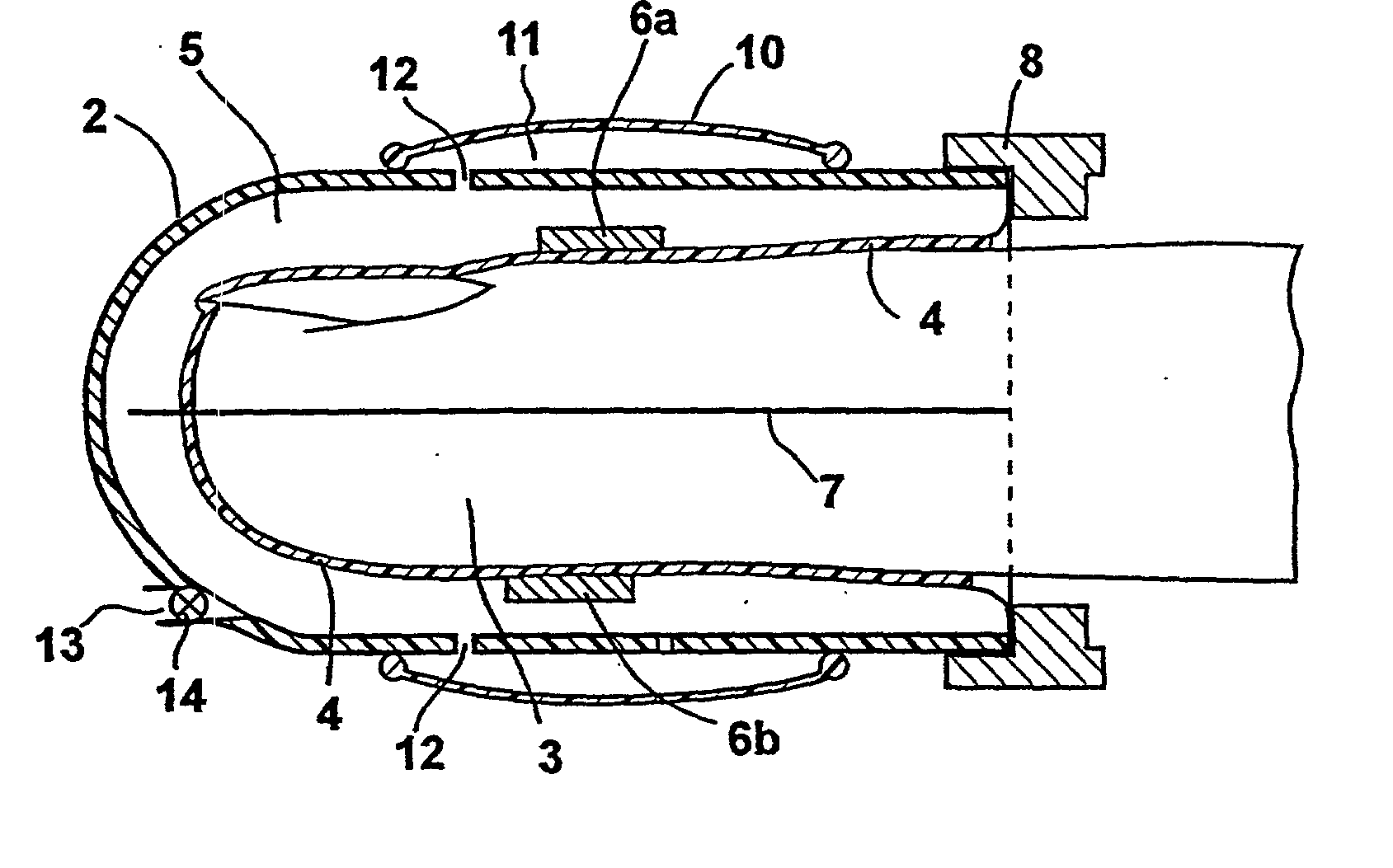

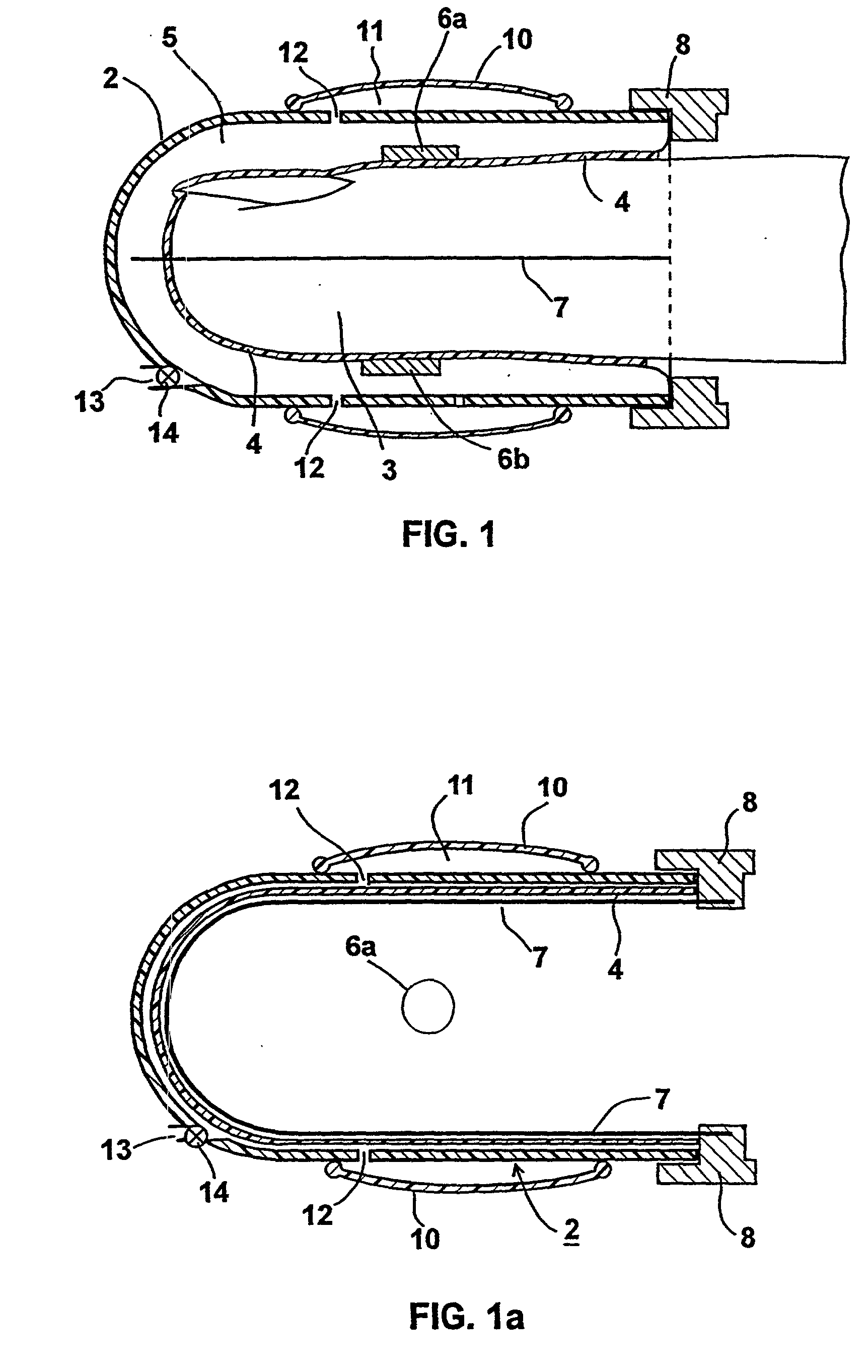

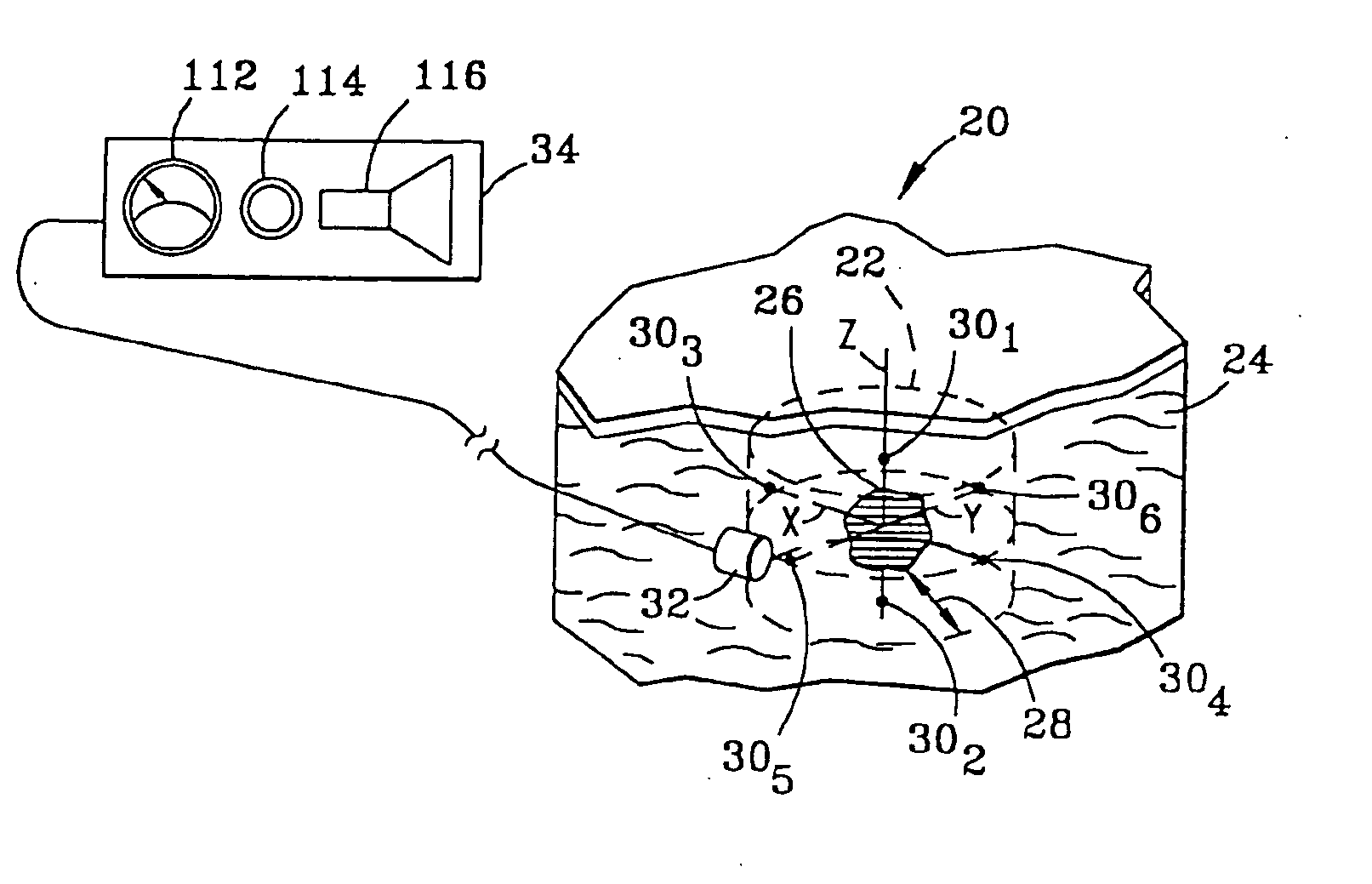

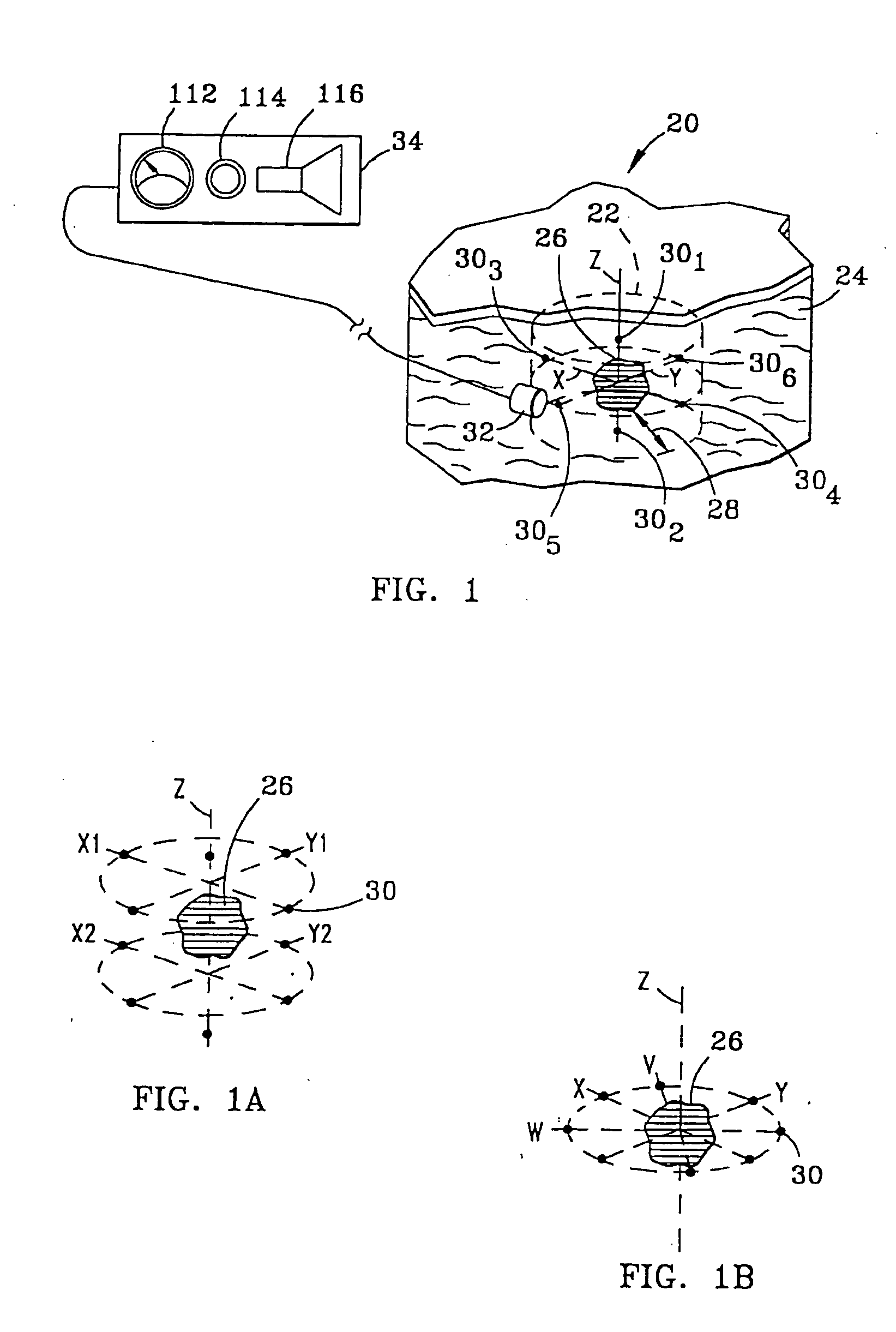

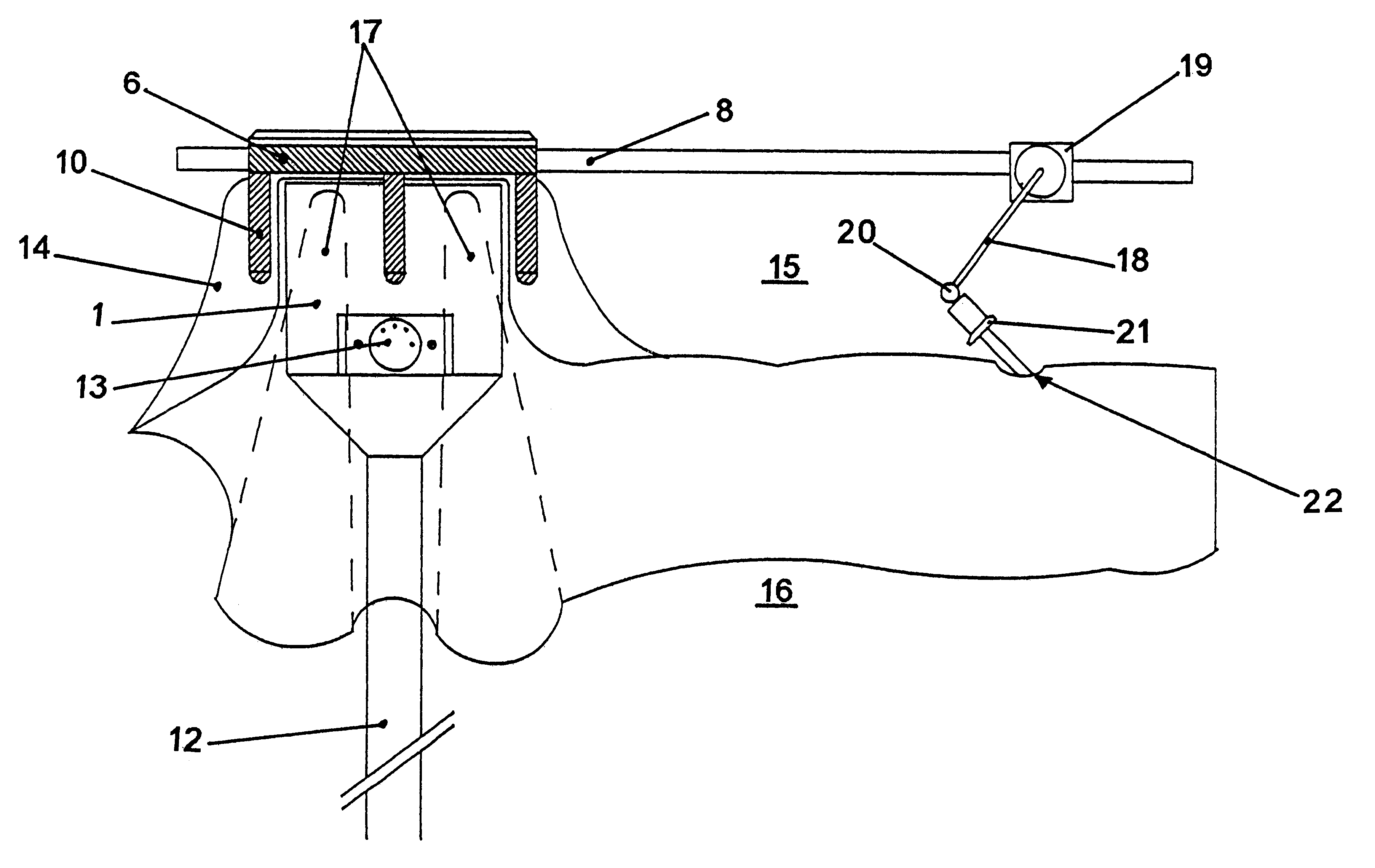

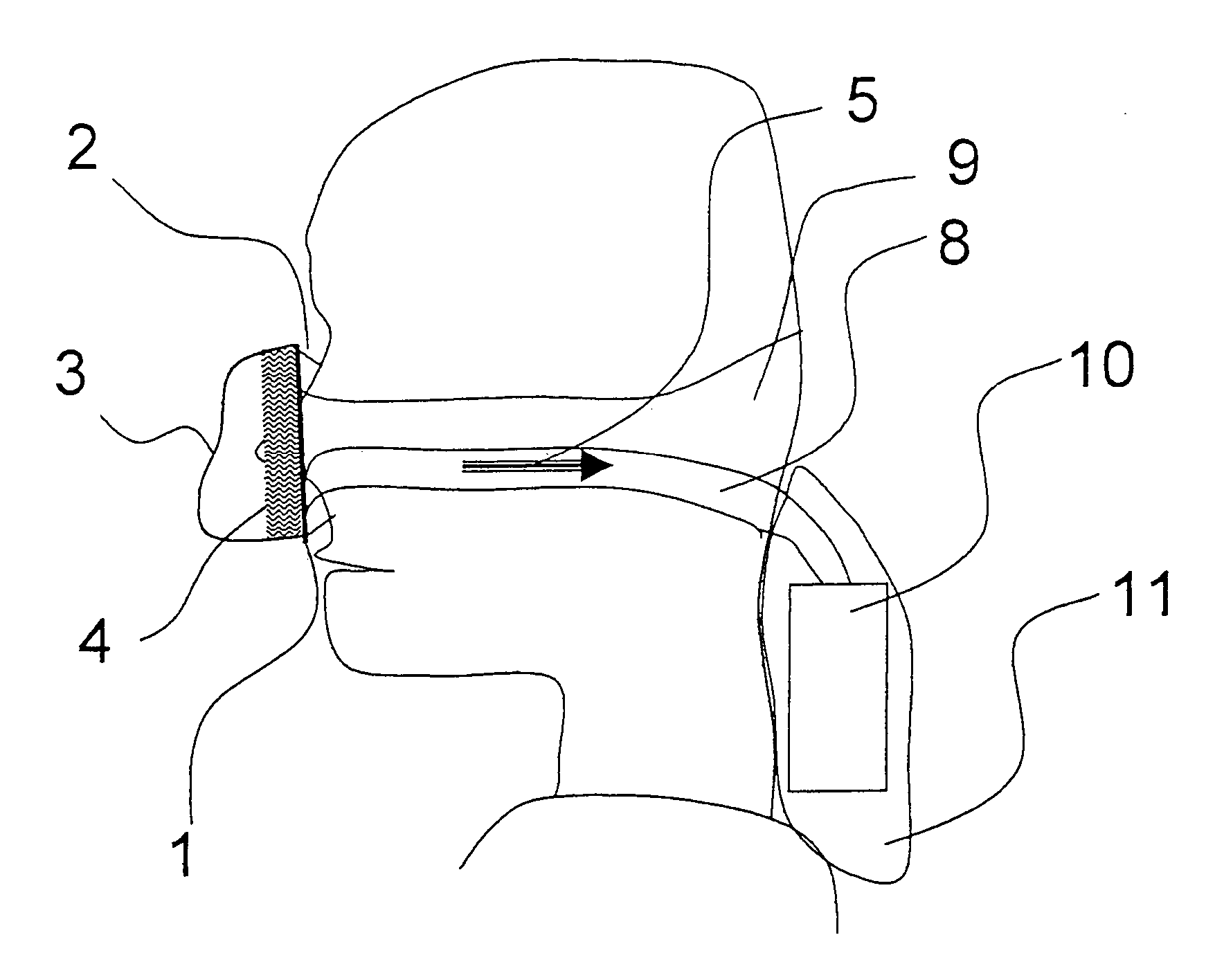

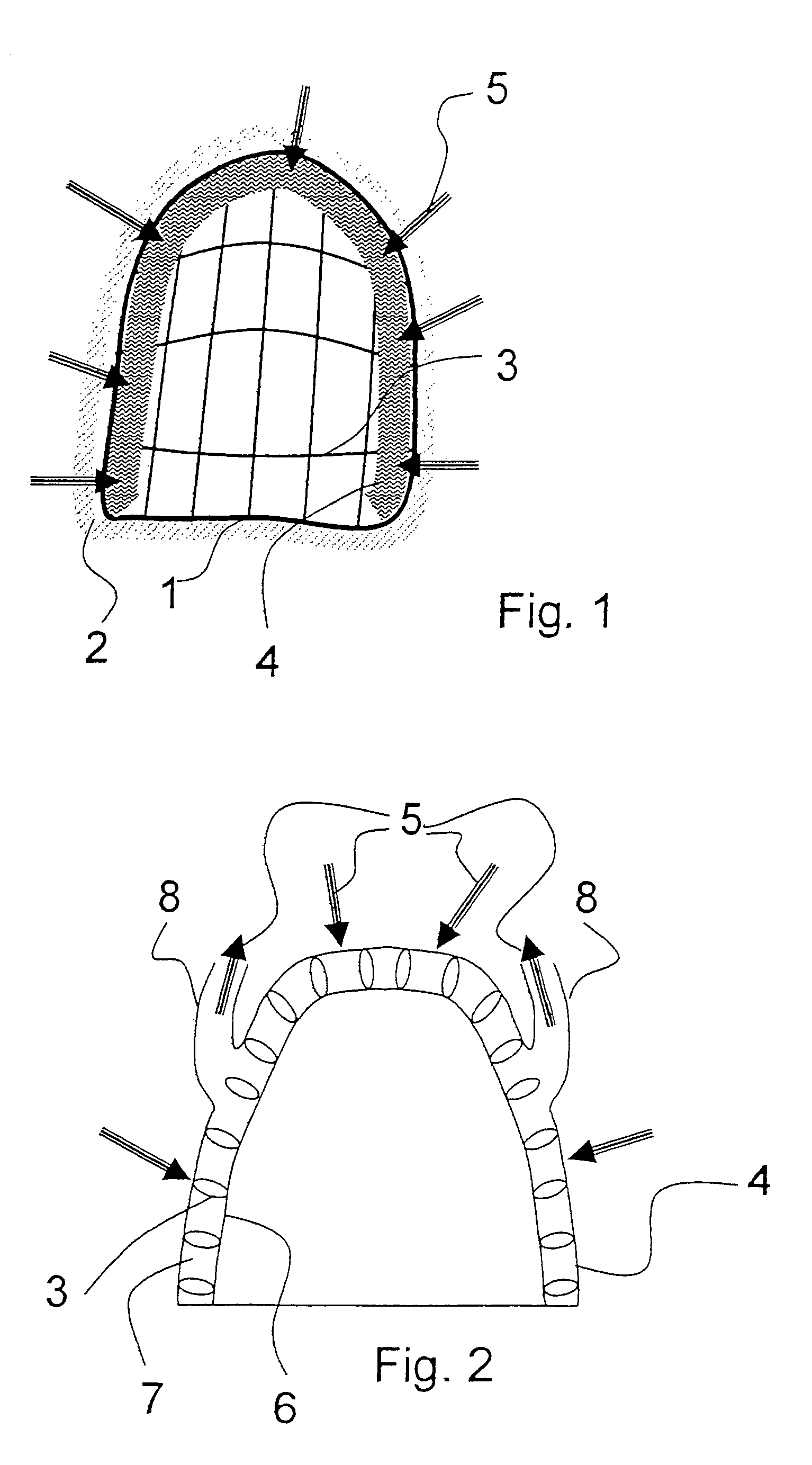

Pressure applicator devices particularly useful for non-invasive detection of medical conditions

InactiveUS6461305B1Low mobilityEasy constructionEvaluation of blood vesselsCatheterVeinBlood arterial

A probe for application to a body part particularly a finger of a patient to detect a change in the physical condition of the patient includes a housing defining a compartment closed at one end and open at the opposite end for receiving the distal end of the patient's finger and a medium wholly self-contained within the probe for applying a static pressure field substantially uniformly around the distal end of the patient's finger, of a predetermined magnitude sufficient to substantially prevent distention of the venous vasculature, uncontrolled venous backflow, and retrognade shockwave propagation into the distal end, and to partially unload the wall tension of, but not to occlude, the arteries in the distal end when at heart level or below. A sensor senses changes in the distal end of the patient's finger related to changes in arterial blood volume therein.

Owner:ITAMAR MEDICAL LTD

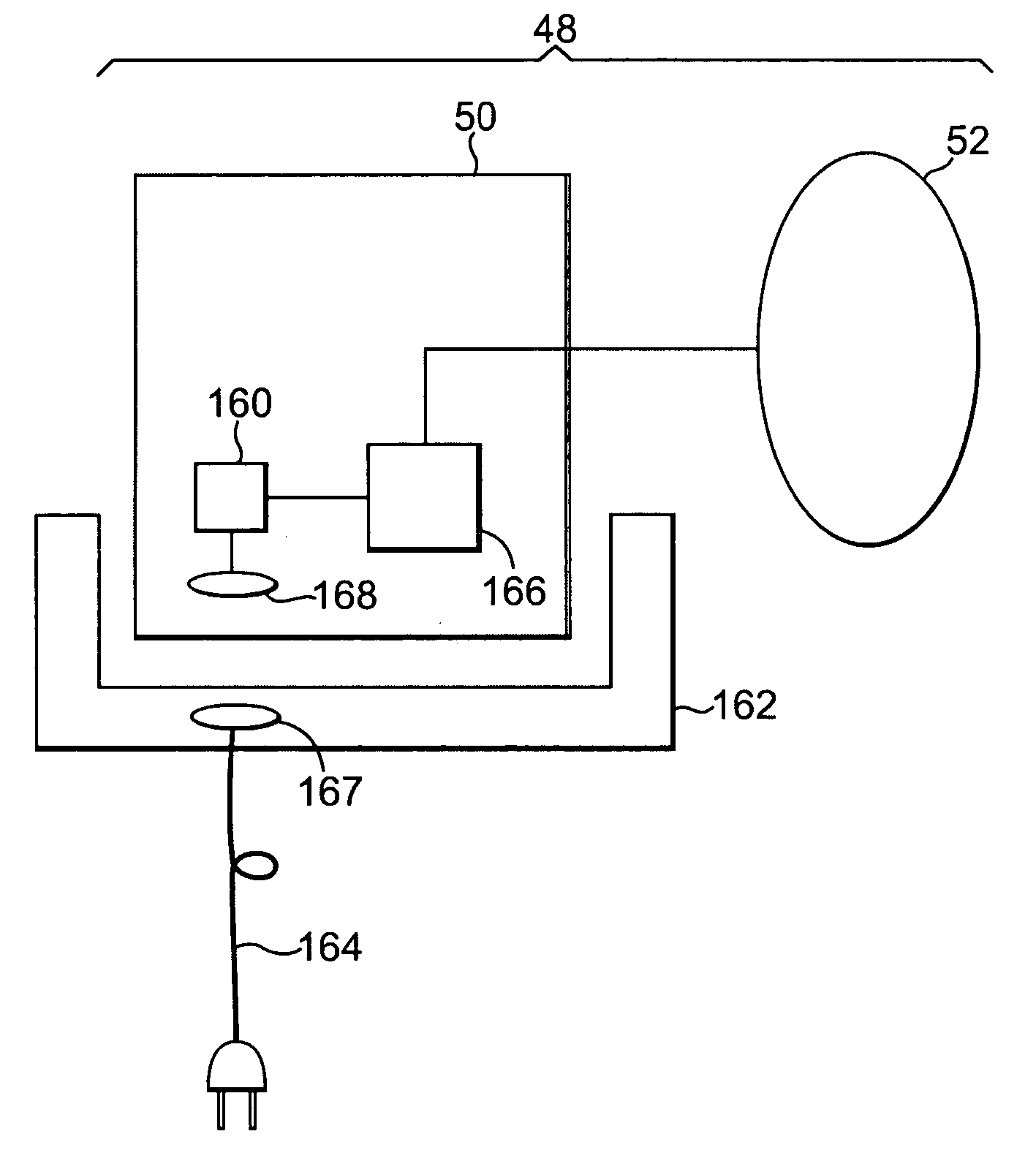

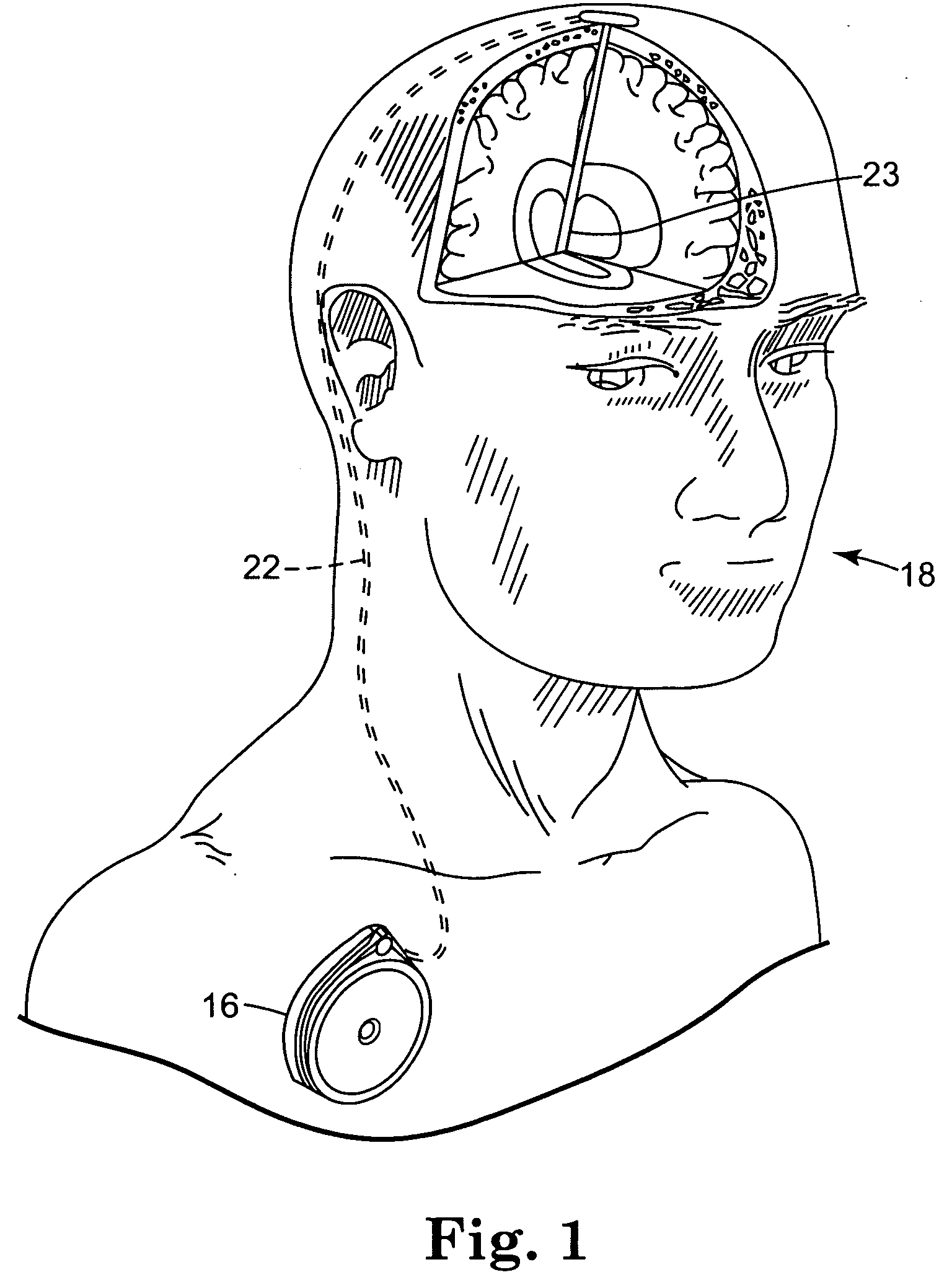

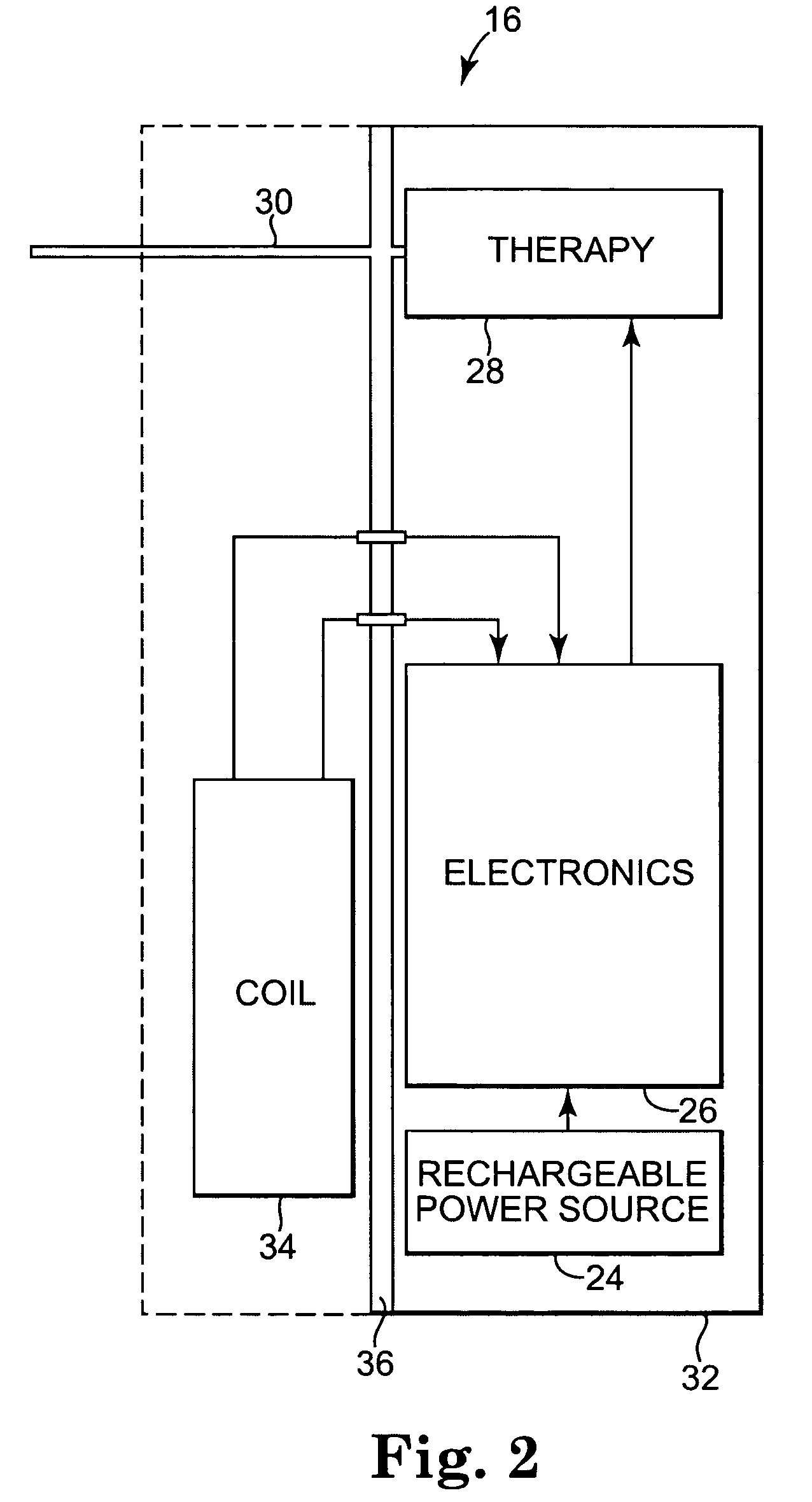

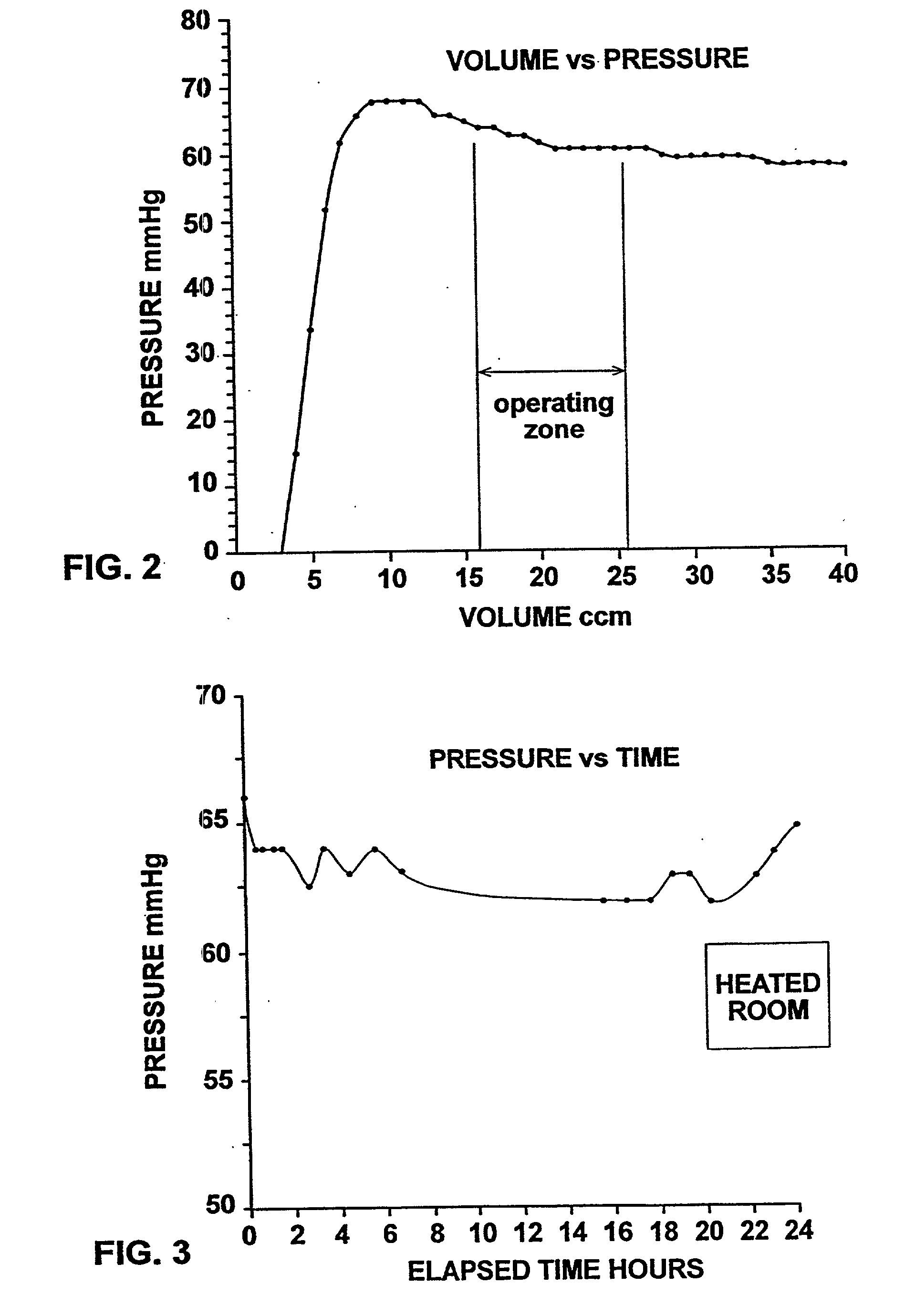

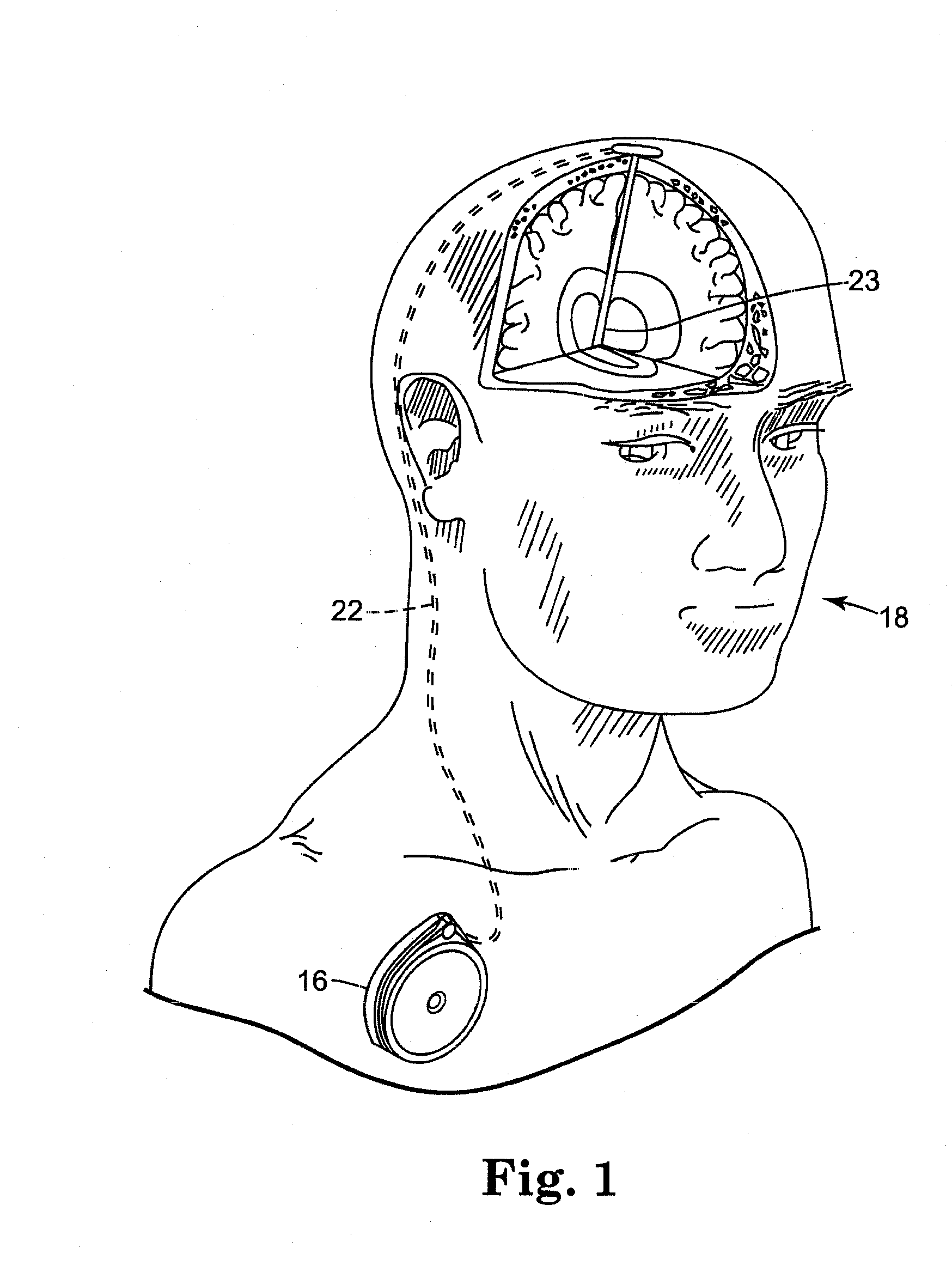

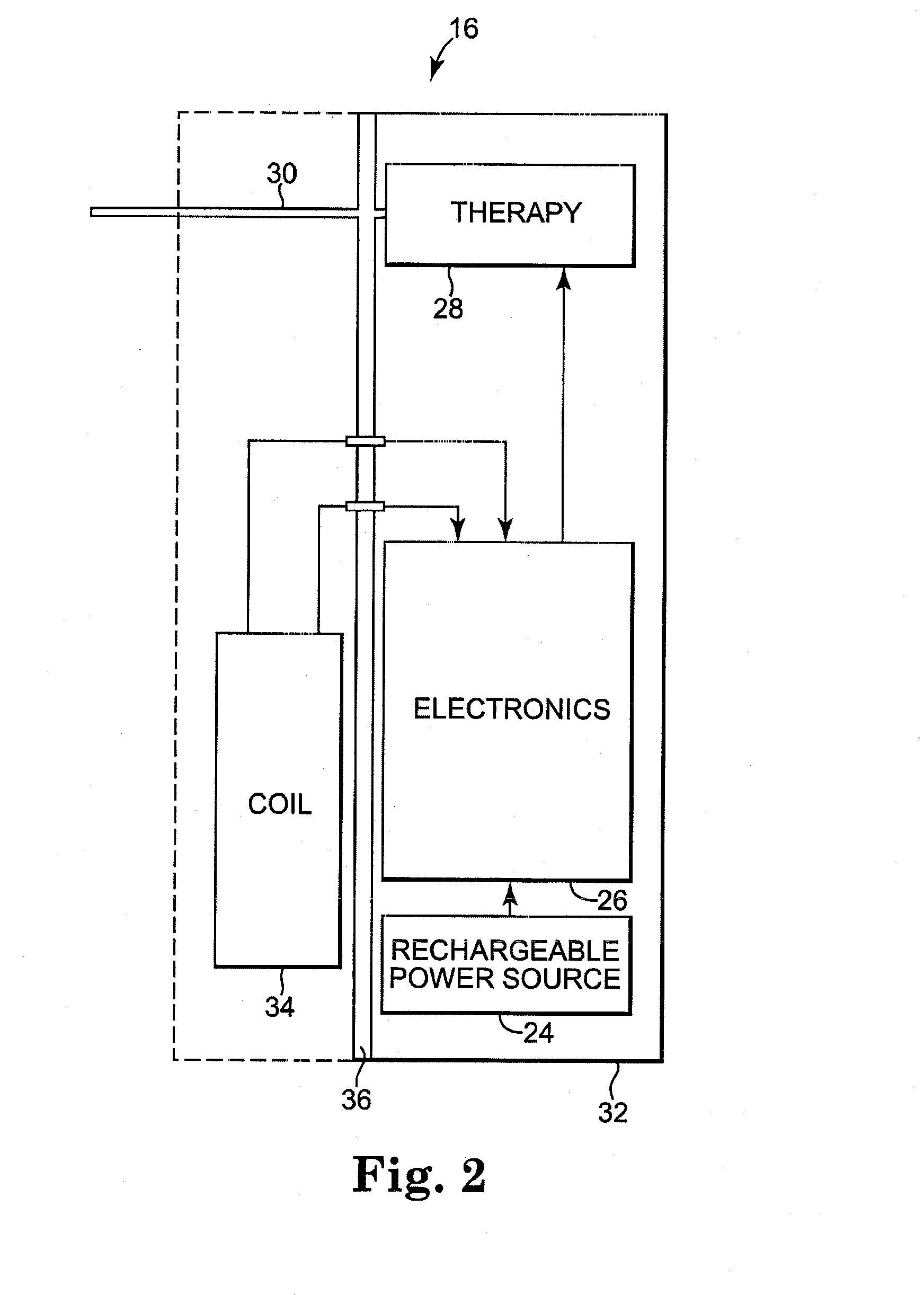

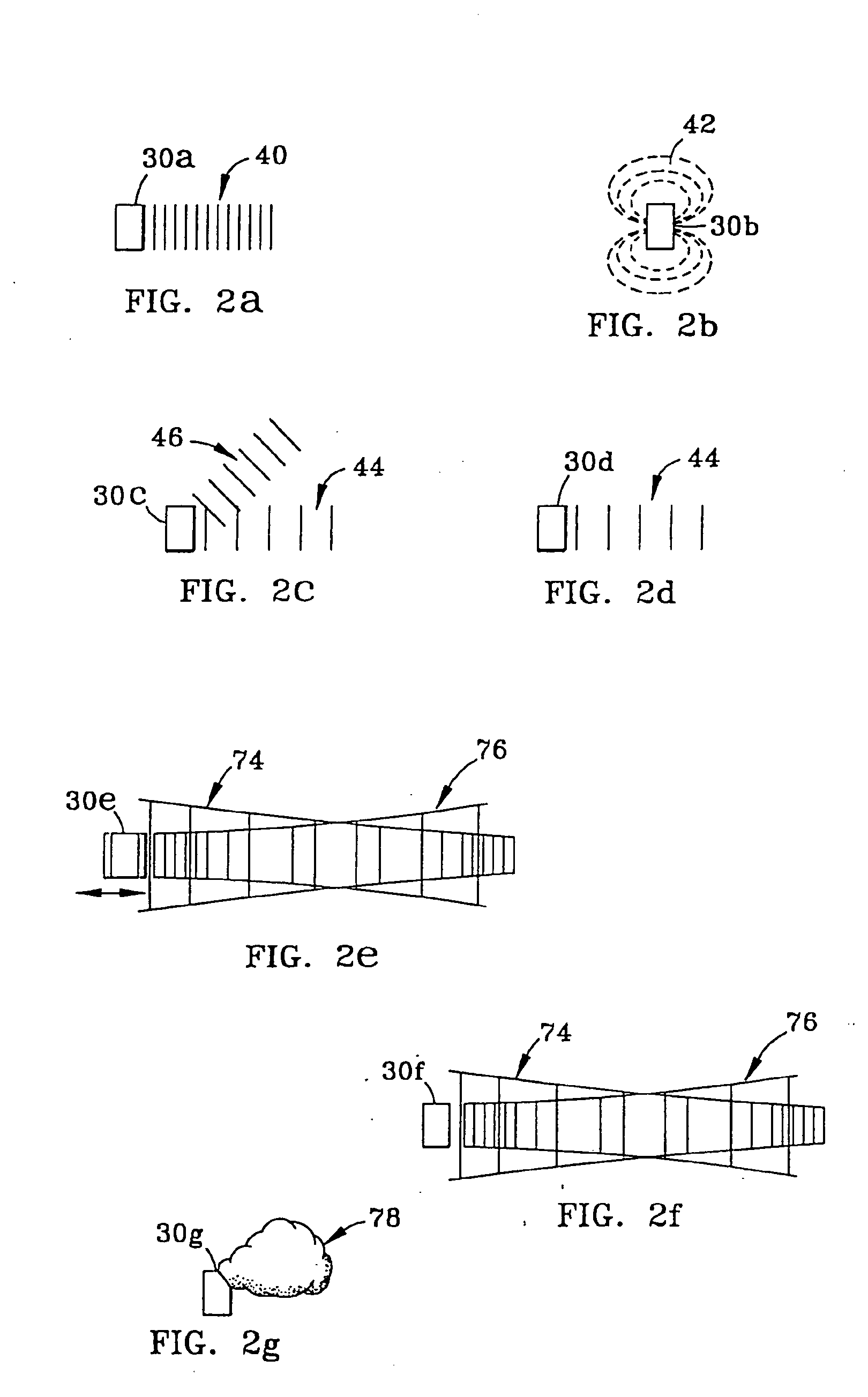

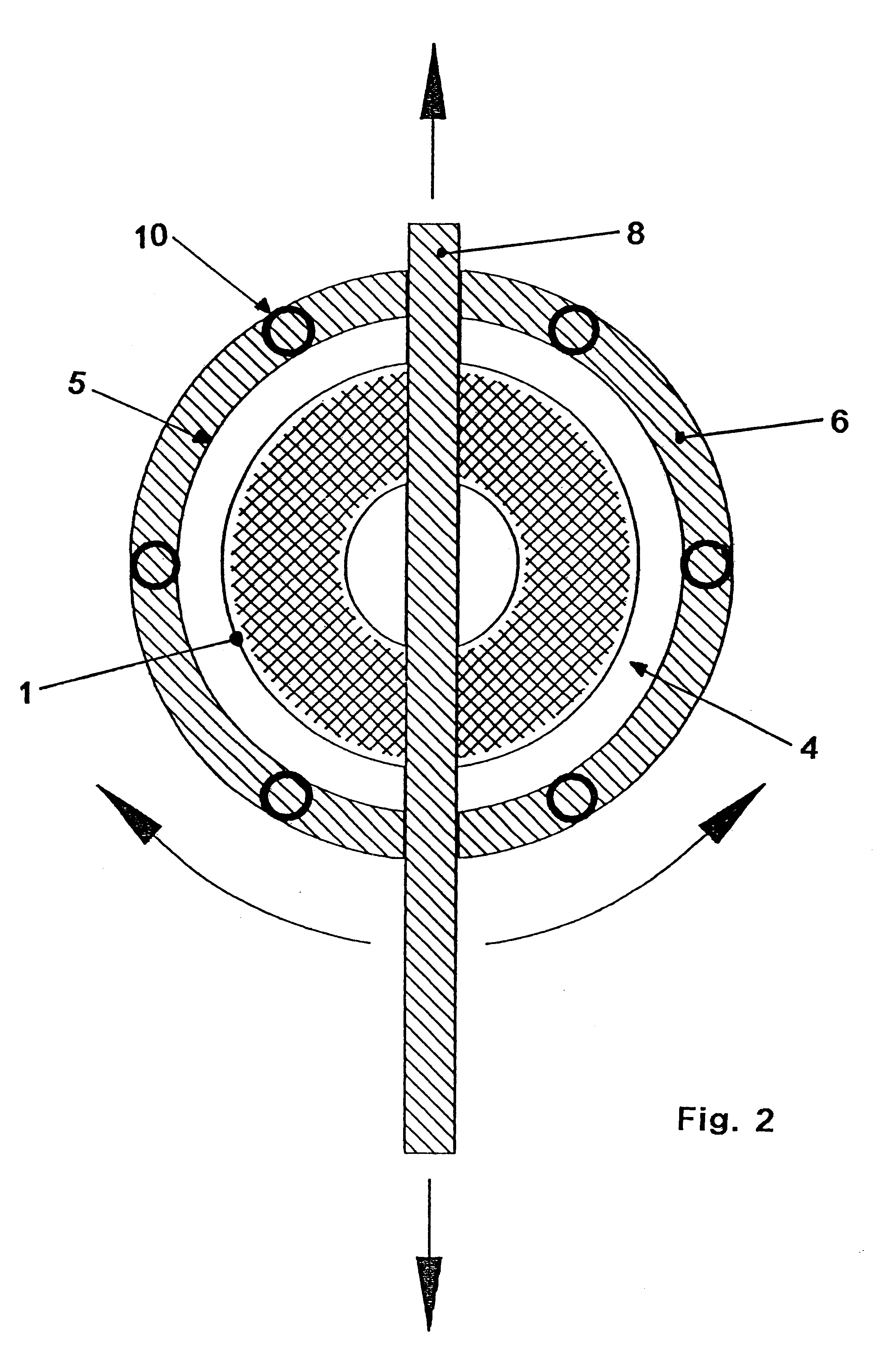

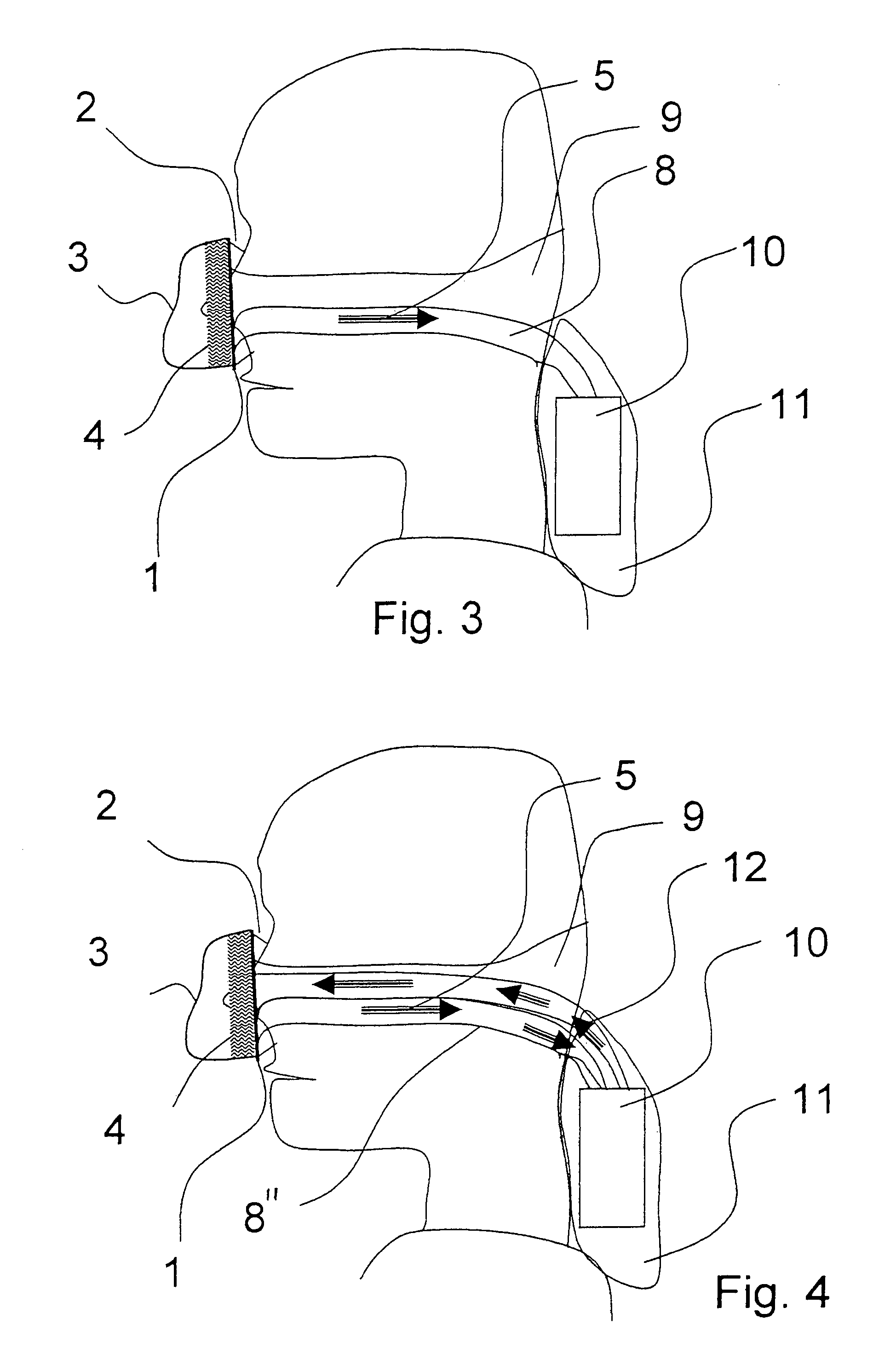

Inductively rechargeable external energy source, charger, system and method for a transcutaneous inductive charger for an implantable medical device

InactiveUS20050075696A1Low mobilityAmount of power availableBatteries circuit arrangementsElectrotherapyExternal energyEngineering

External power source, charger, system and method for an implantable medical device having therapeutic componentry and a secondary coil operatively coupled to the therapeutic componentry. A primary charging coil is capable of transcutaneously inductively energizing the secondary coil when externally placed in proximity of the secondary coil. Drive circuitry is operatively coupled to the primary charging coil for exciting the primary charging coil. A rechargeable power source is operatively coupled to the drive circuitry. A secondary recharging coil is operatively coupled to the rechargeable power source. A primary recharging coil is adapted to be coupled to a source of AC power which when placed in proximity of the secondary recharging coil can inductively energize the secondary recharging coil in order to charge the rechargeable power source.

Owner:MEDTRONIC INC

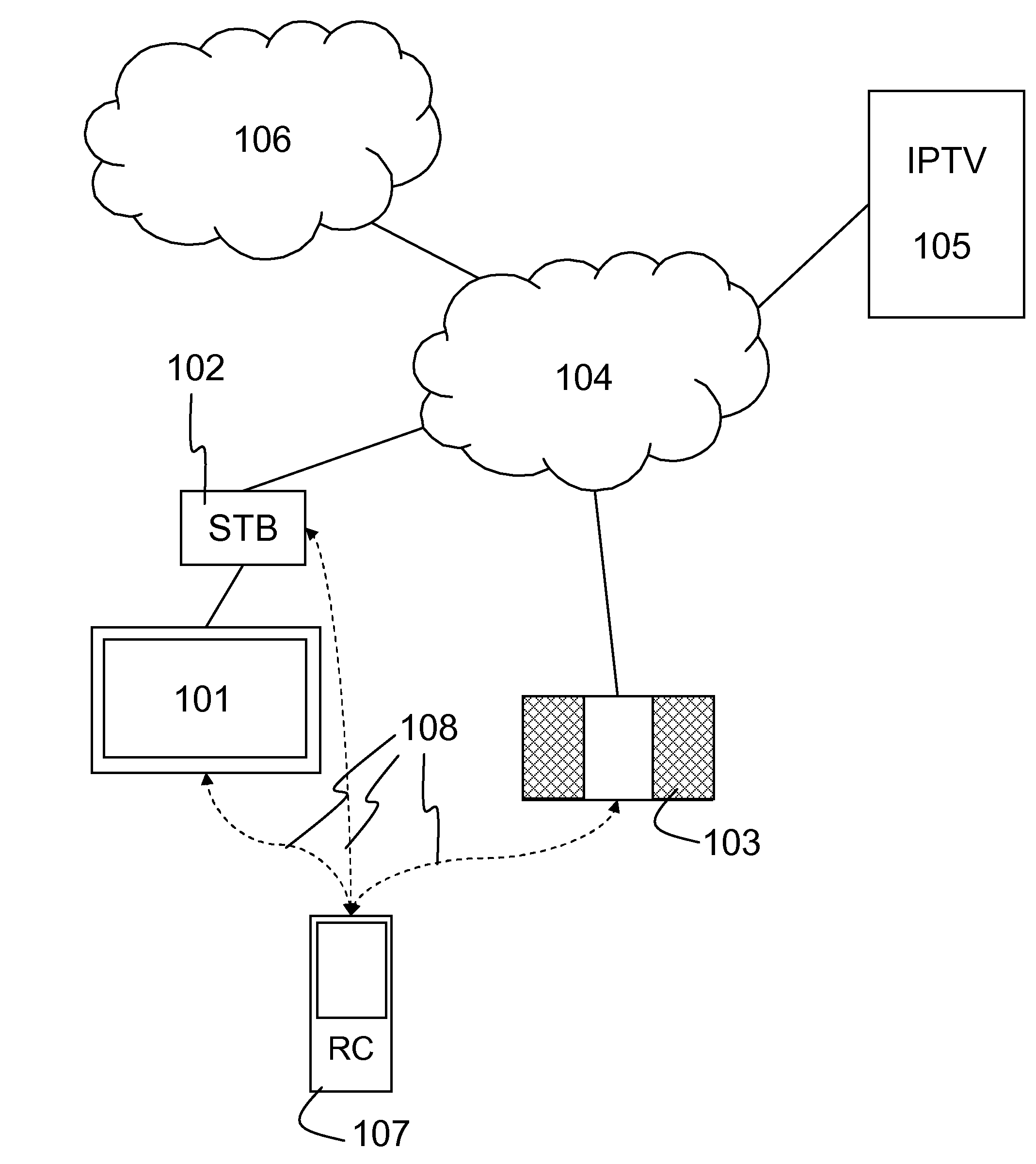

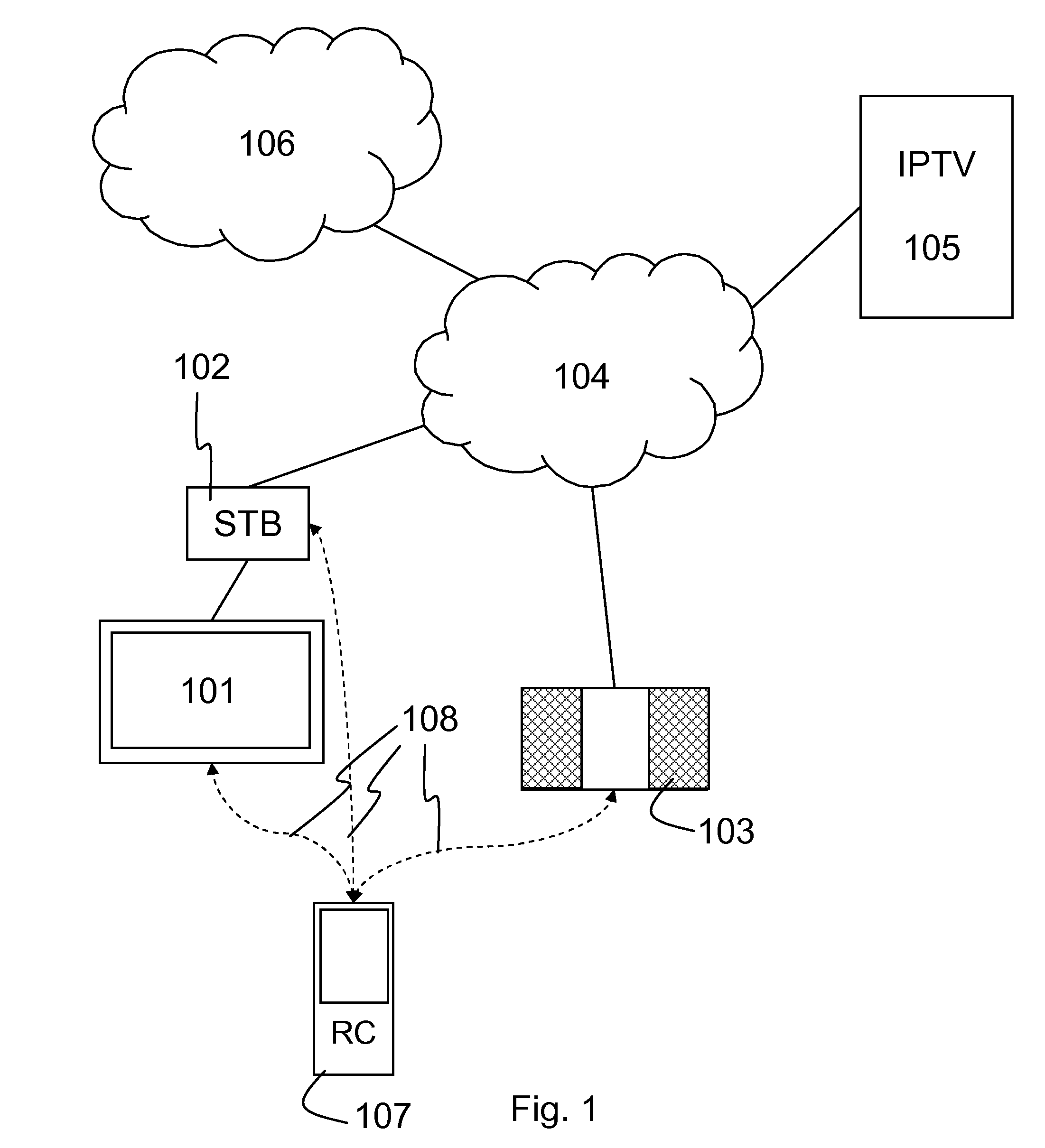

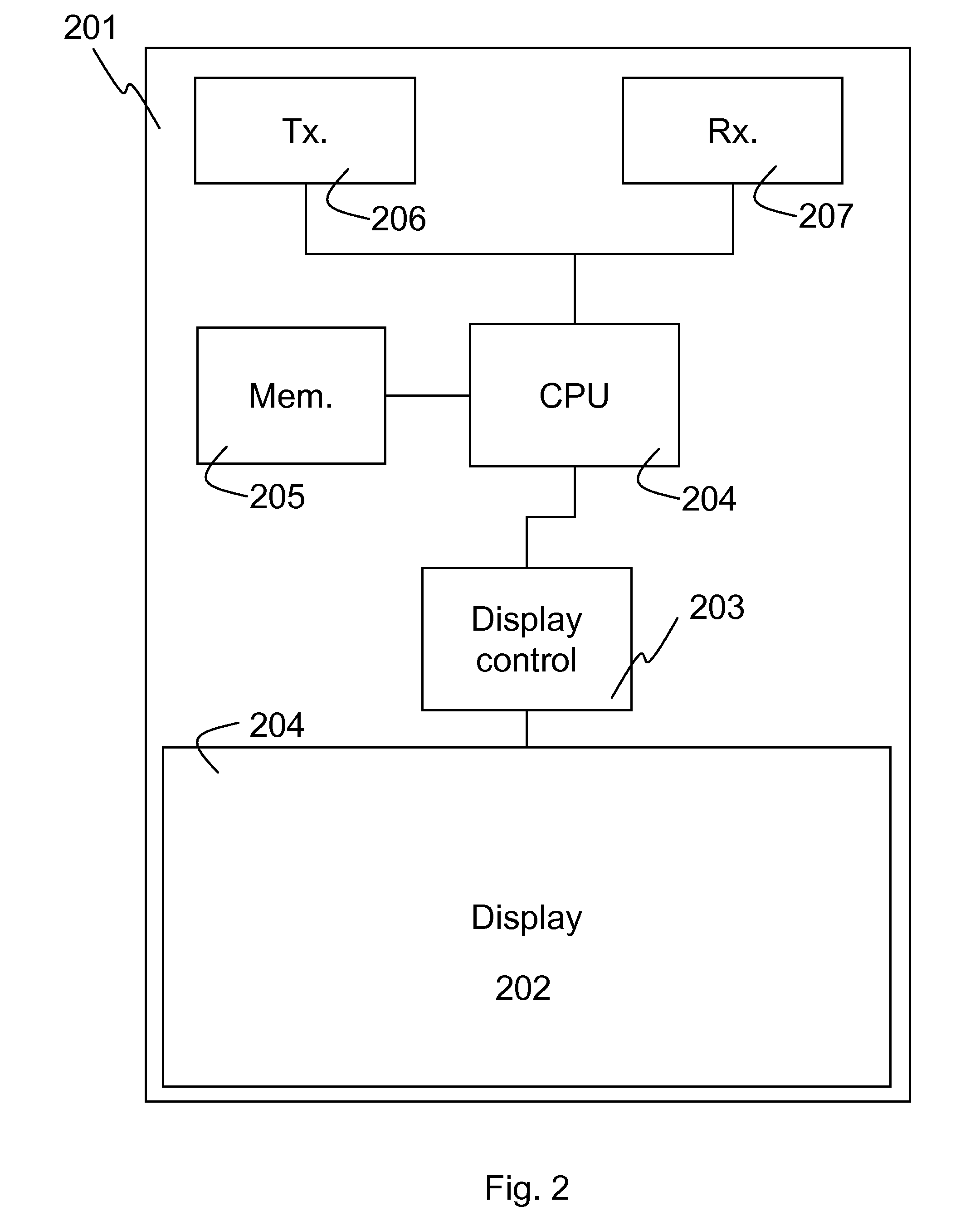

Remote control for devices with connectivity to a server delivery platform

InactiveUS20080301729A1Limited bandwidthRaise the possibilityTelevision system detailsResonant circuit detailsComputer networkRemote control

The present invention relates to a remote control (107; 201; 301) for controlling at least one device (101, 102, 103; 302) with connectivity to a service delivery network (105, 106). The remote control (107; 201; 301) comprising one or more displays (202) for showing display items which are indicative for one or more control instructions and the remote control (107; 201; 301) is able to adapt the display items and / or the control instructions in real-time depending on a selected service (303).

Owner:ALCATEL LUCENT SAS

Photosensor and display device

ActiveUS20100134735A1Good reproducibilitySmall display unevennessTransistorStatic indicating devicesDriver circuitIndium

Thin film transistors including an oxide semiconductor containing indium, gallium, and zinc are easily arranged in a matrix over a large substrate and have small characteristic variations. With amplifier circuits and driver circuits of display elements which include the thin film transistors including an oxide semiconductor containing indium, gallium, and zinc with small characteristic variations, intensity distribution of light received by the photodiodes arranged in a matrix is converted into electrical signals with high reproducibility and output, and the display elements arranged in a matrix can be uniformly driven.

Owner:SEMICON ENERGY LAB CO LTD

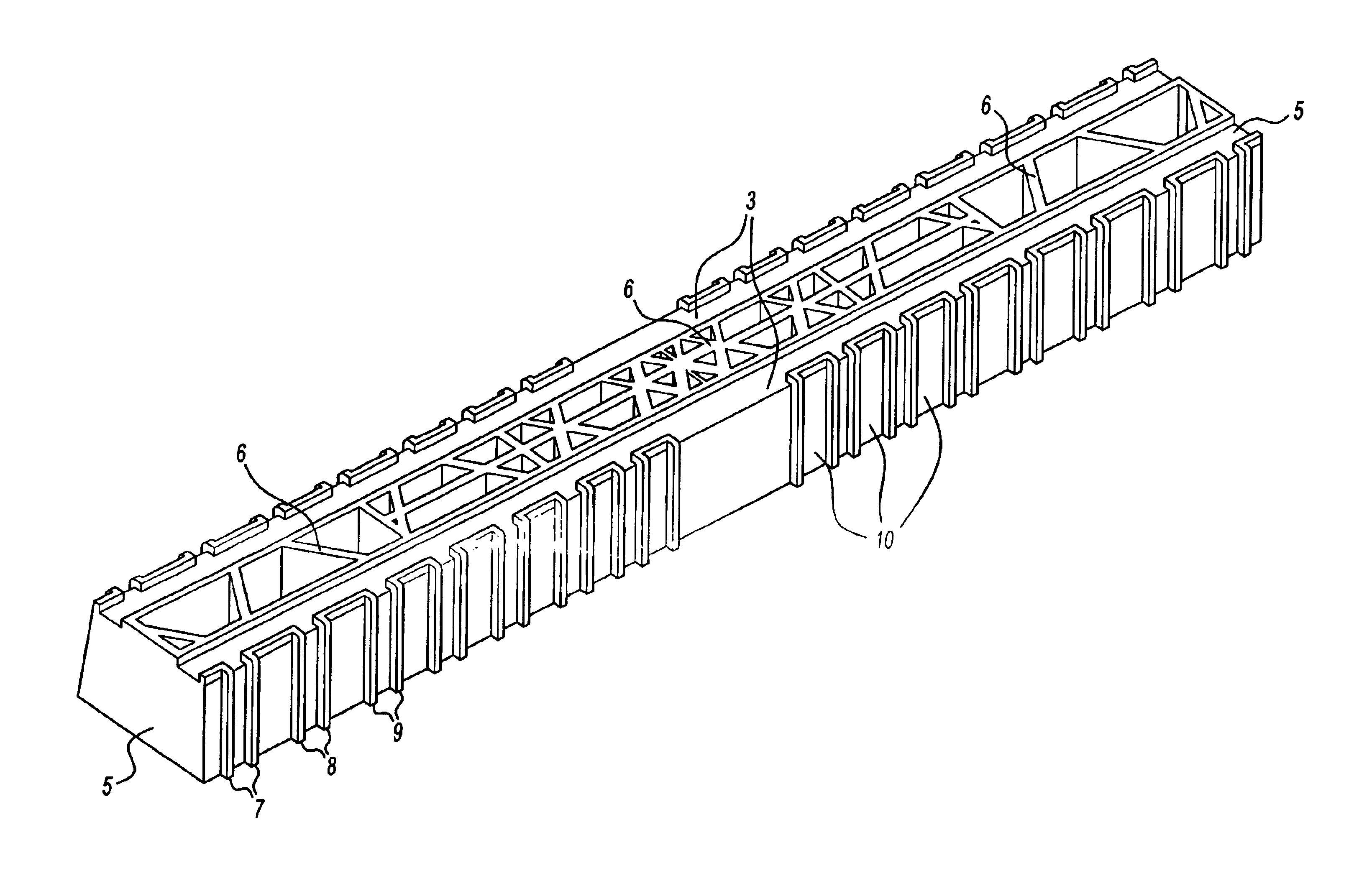

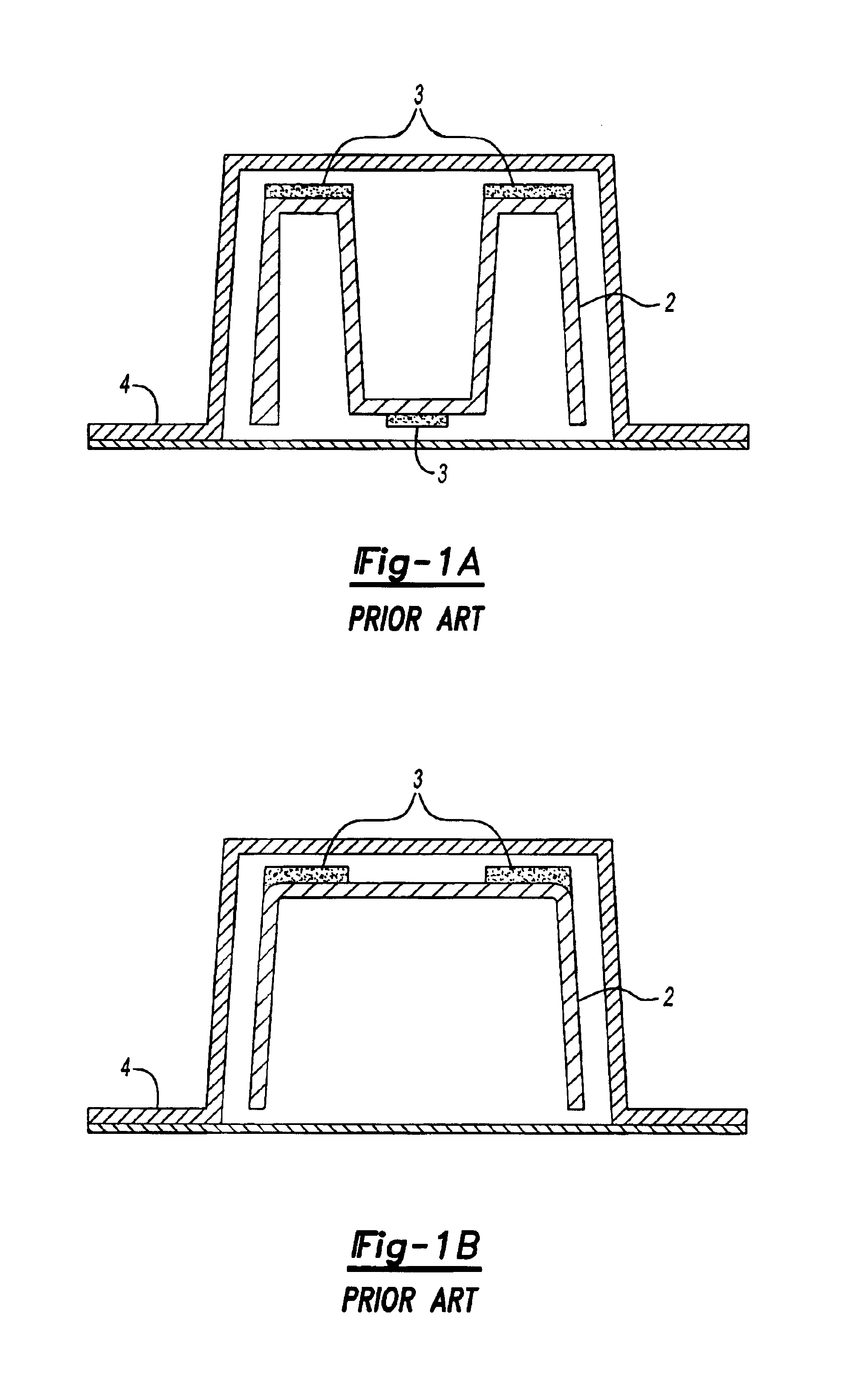

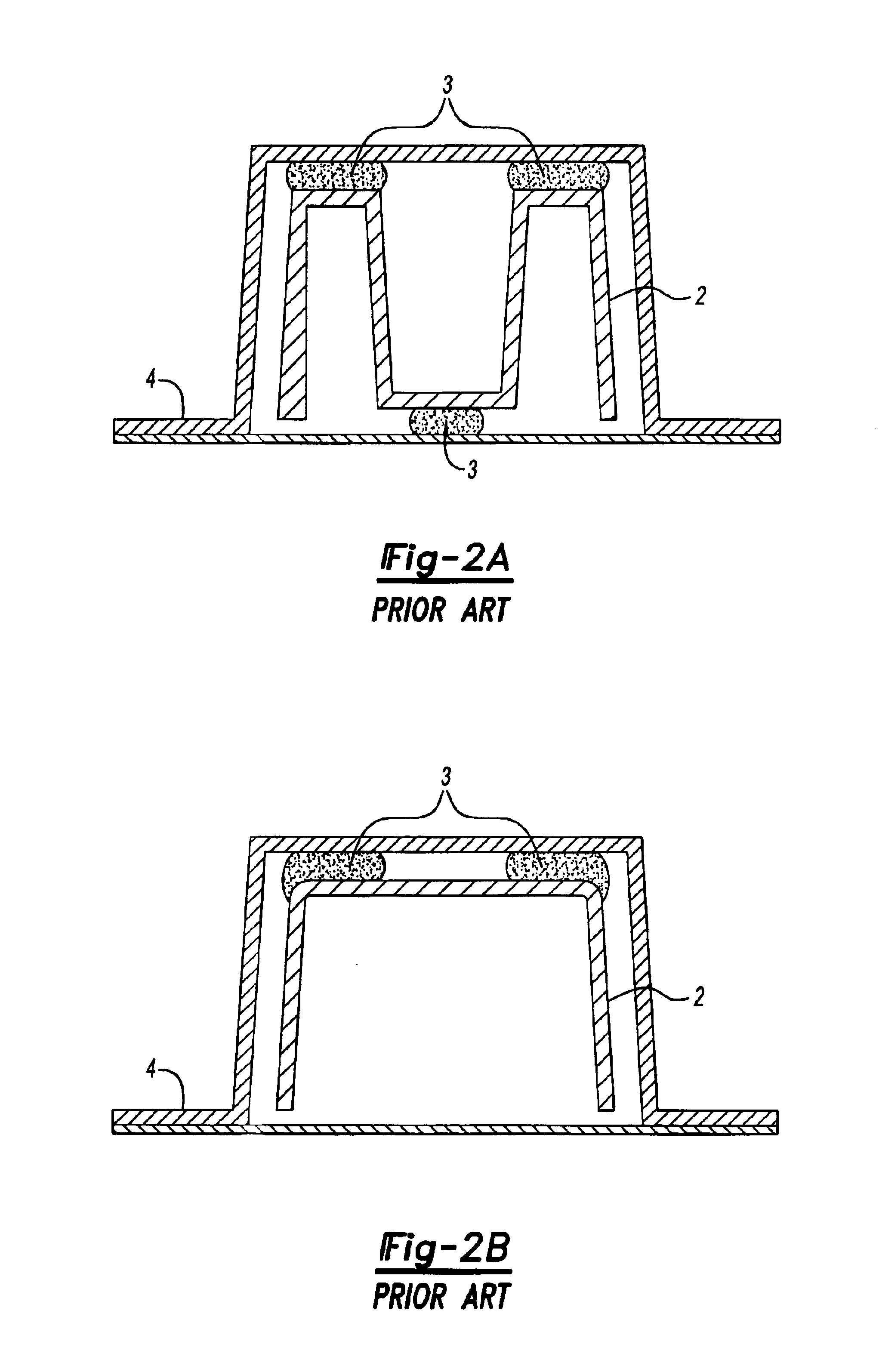

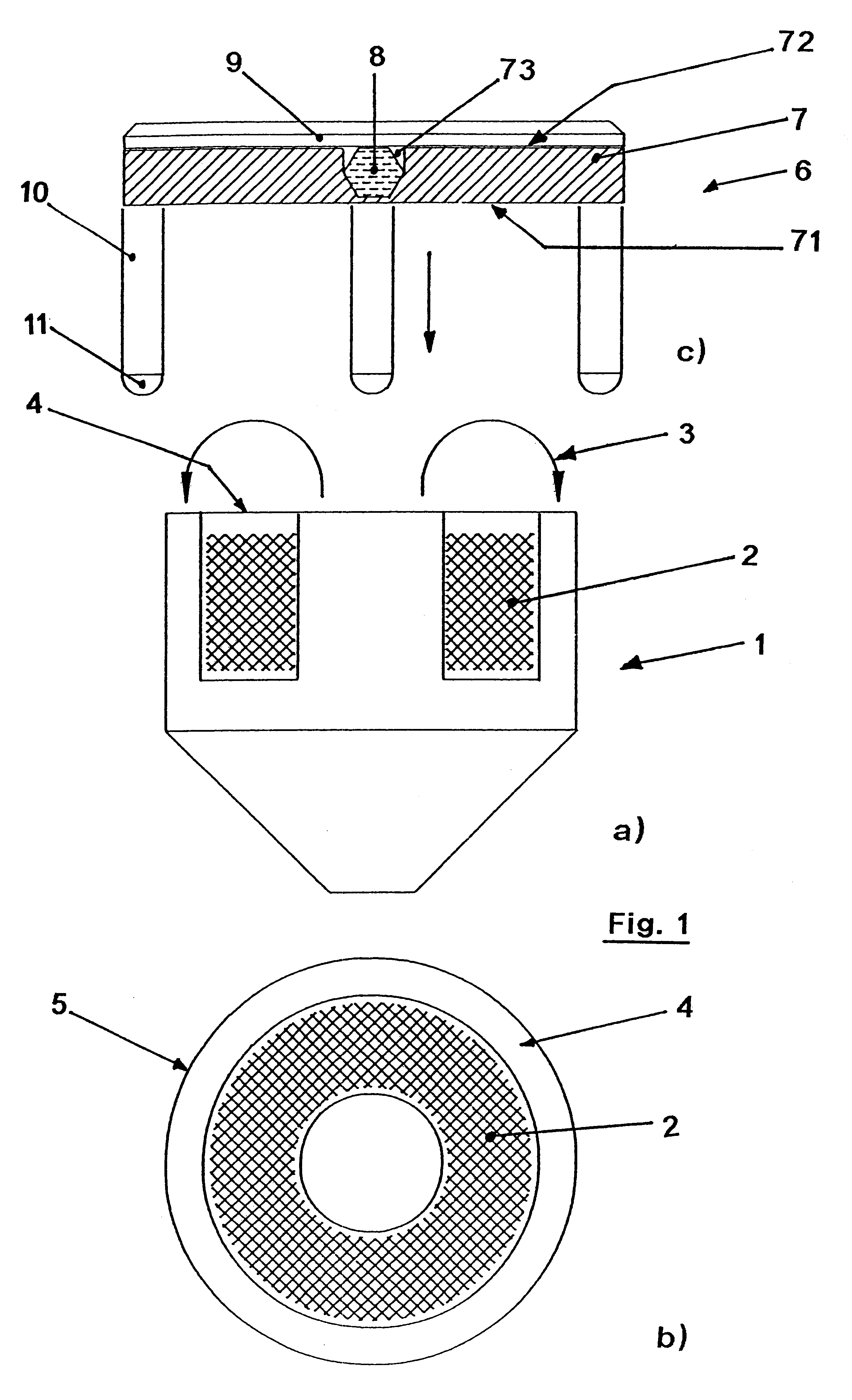

Structural reinforcement

InactiveUS6941719B2Reduced strengthSatisfies requirementVehicle seatsStructural elementsAdhesive materialsBiomedical engineering

A structural reinforcement for a hollow member comprising a rigid reinforcing member having a shape that substantially conforms to the cross section of the hollow member to be reinforced with an expandable adhesive material over at least a portion of the surface of the structural reinforcement having one or more extensions on its external surface which control and direct the direction in which the adhesive material expands to bond the reinforcing member to the internal surface of the hollow member, some of the extensions also provide improved reinforcement.

Owner:ZEPHYROS INC

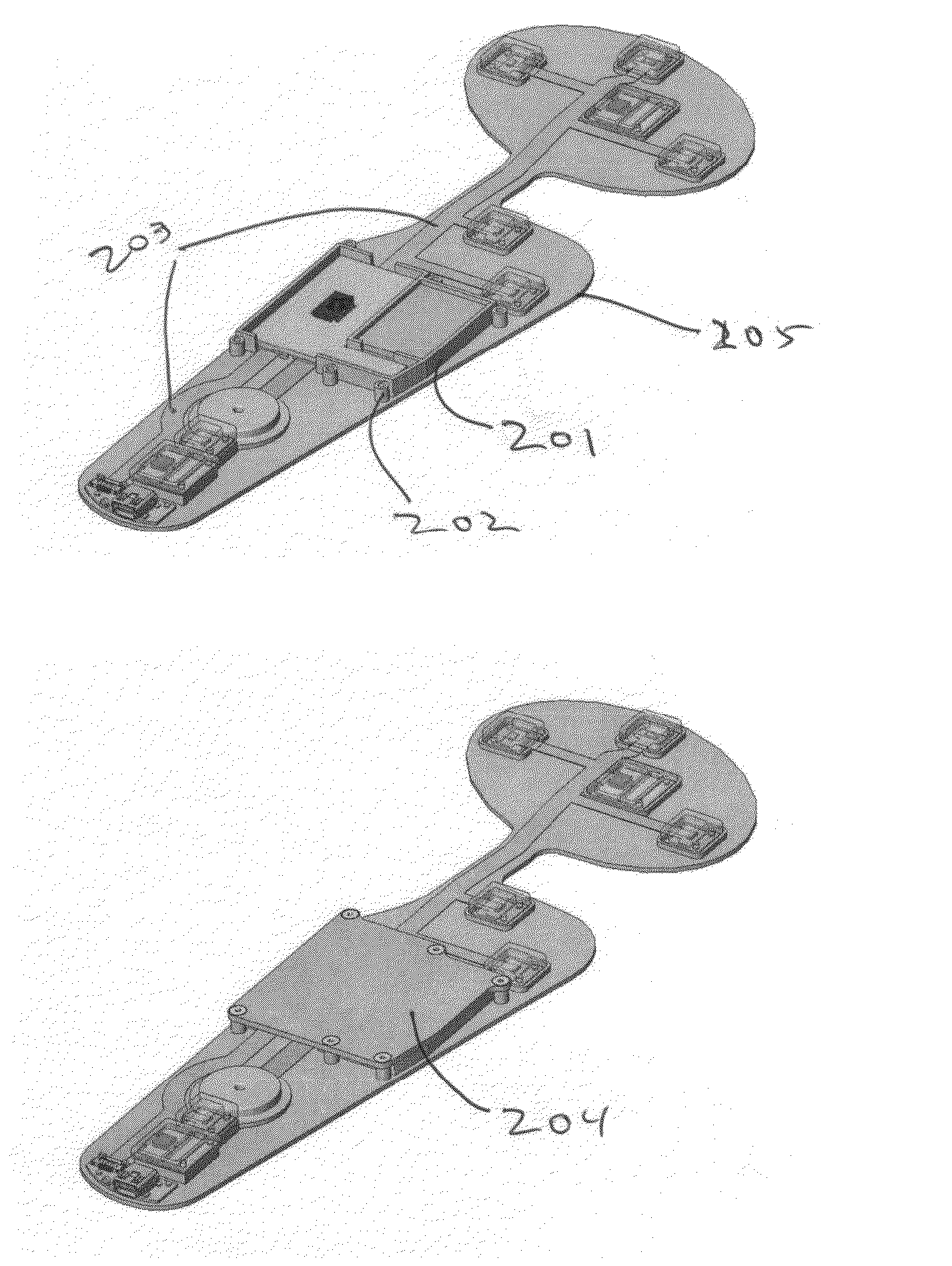

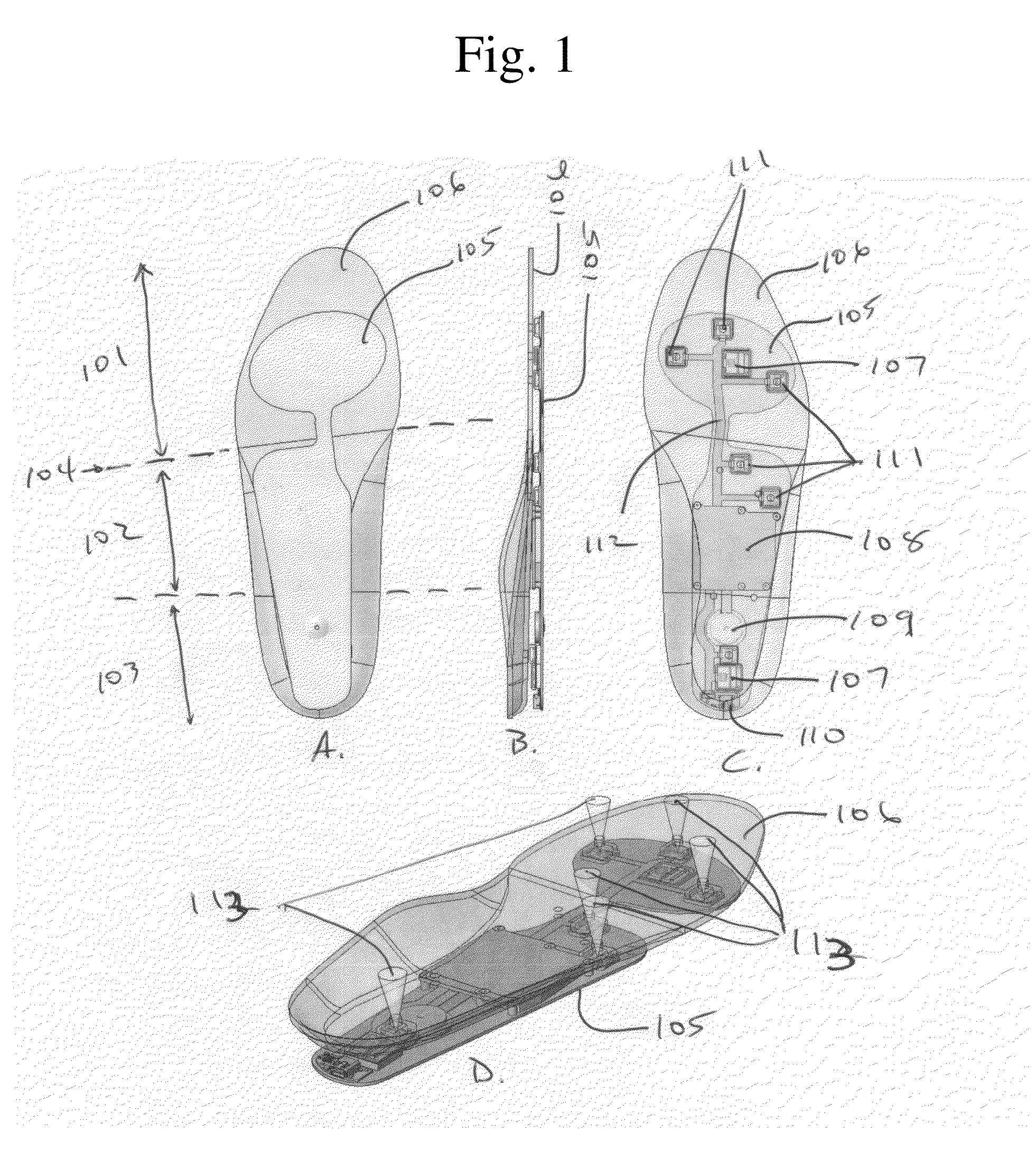

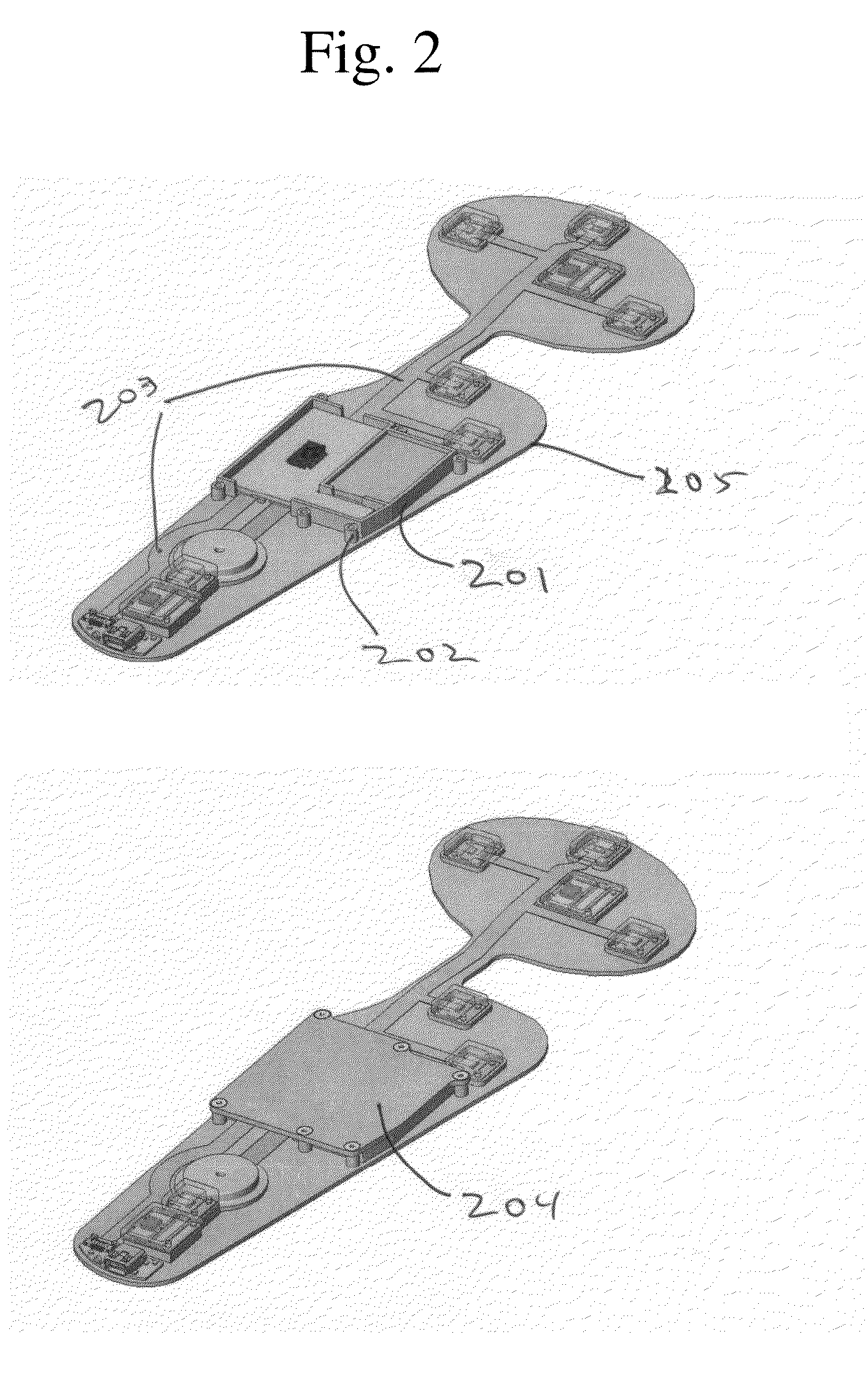

Devices for management of foot injuries and methods of use and manufacture thereof

The present invention provides orthotic devices for use in managing the treatment and prevention of lower extremity injuries, including foot ulcers. In various aspects, the present invention provides foot-worn orthotics which provide for improved compliance monitoring, and methods of their manufacture and use.

Owner:LASERCURE SCI

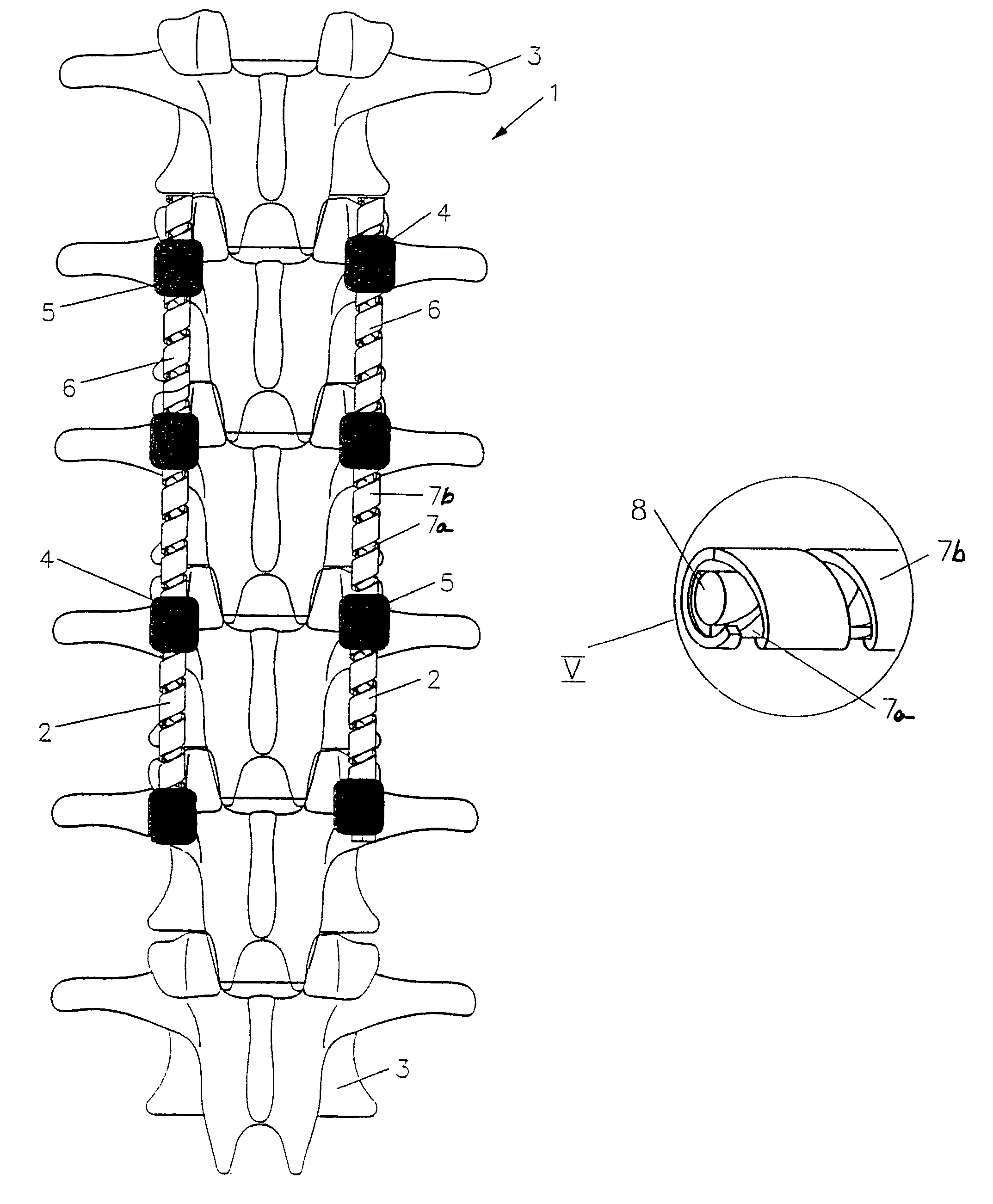

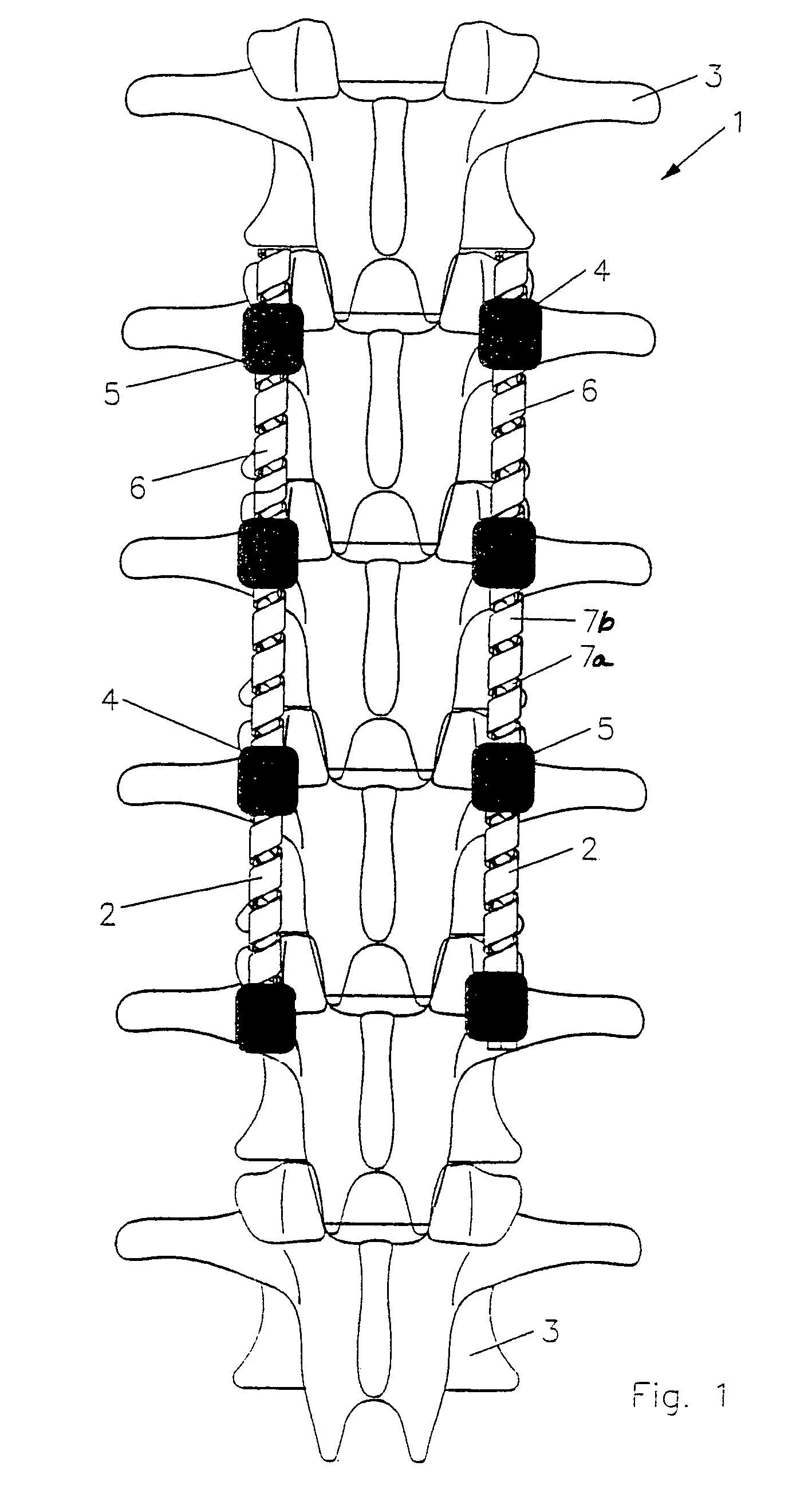

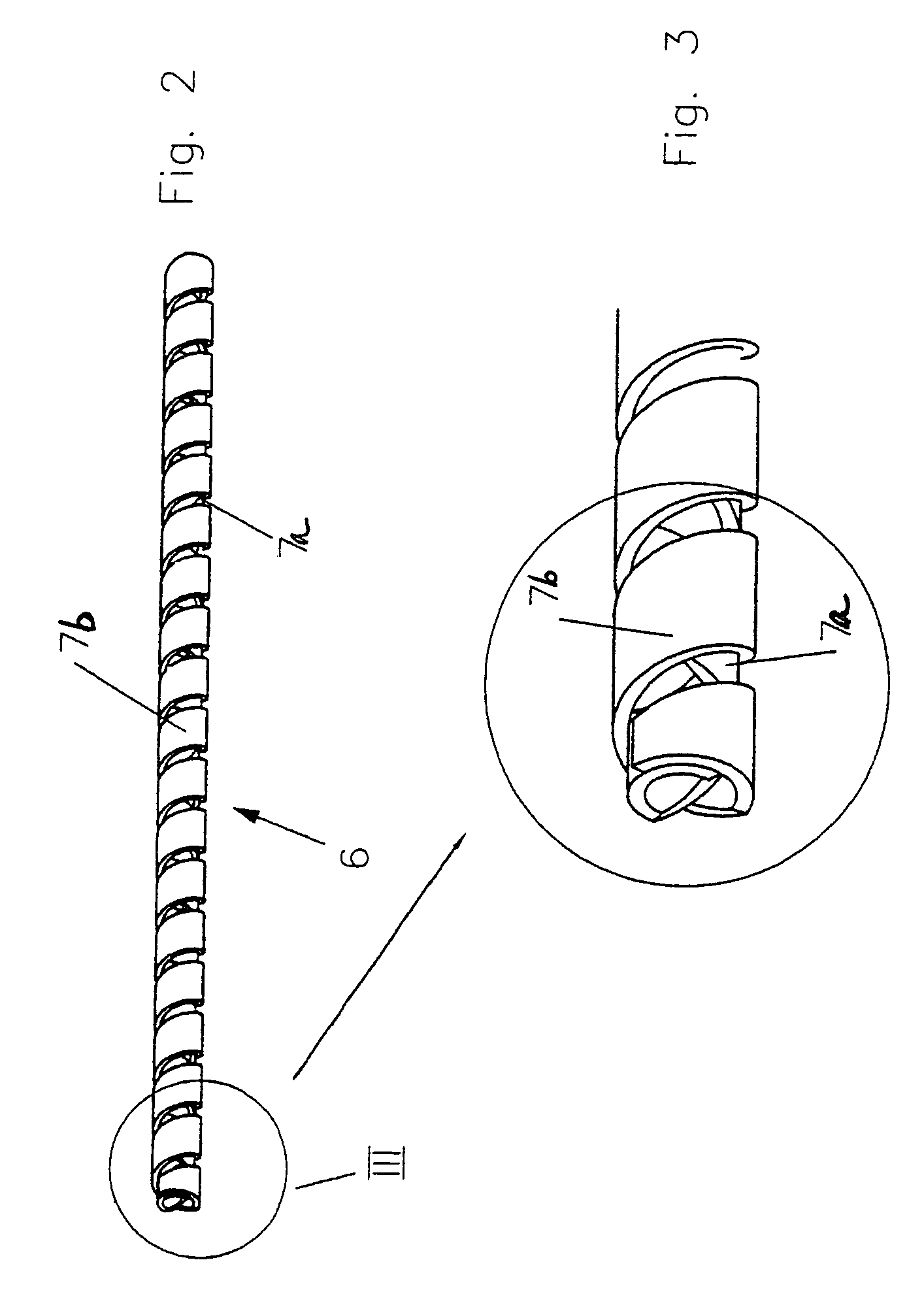

Implant for correction and stabilization of the spinal column

InactiveUS7651515B2Improve approximationLow mobilityInternal osteosythesisJoint implantsSpinal columnIliac screw

An implant for the correction and stabilization of the spinal column, comprising pedicle screws that can be screwed into the vertebrae of a spine, and of at least one connection element that connects the pedicle screws at the screw heads. This connection element is formed by a spiral whose spiral windings are arranged offset in the axial direction, following a screw line.

Owner:ULRIKH GMBKH & KO KG

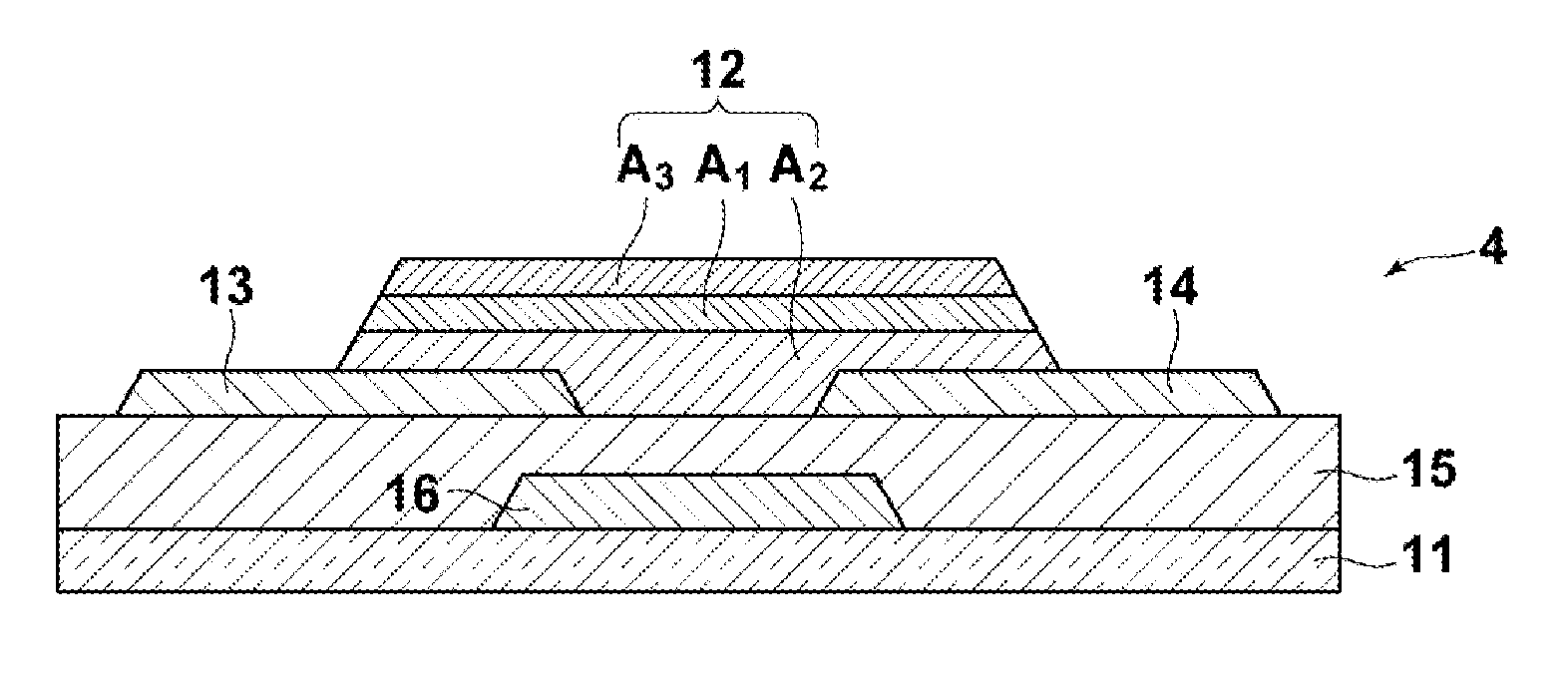

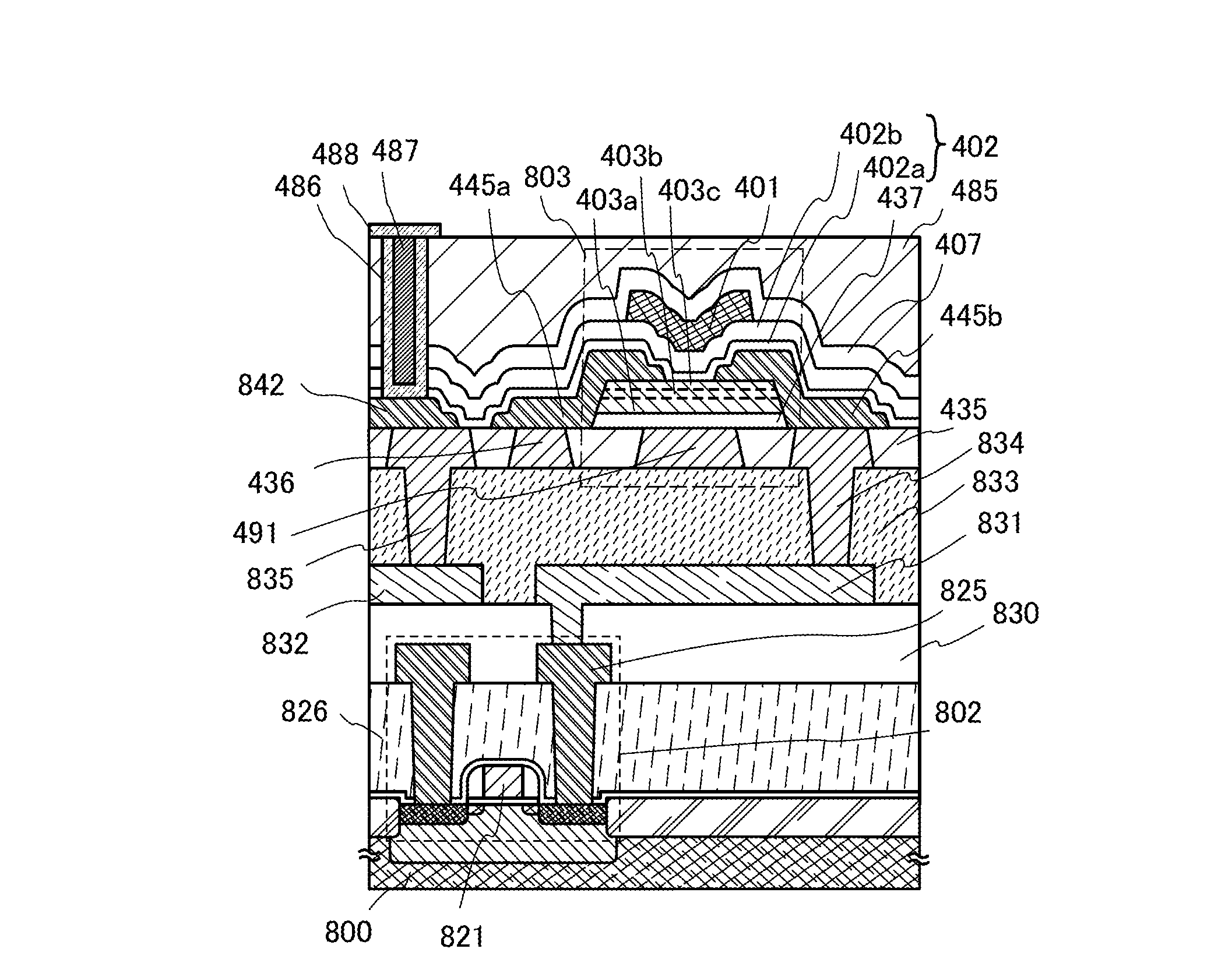

Semiconductor device

ActiveUS20130334533A1Improve reliabilityHigh field-effect mobilityTransistorOxide semiconductorCharge carrier

A transistor having high field-effect mobility is provided. In order that an oxide semiconductor layer through which carriers flow is not in contact with a gate insulating film, a buried channel structure in which the oxide semiconductor layer through which carriers flow is separated from the gate insulating film is employed. Specifically, an oxide semiconductor layer having high conductivity is provided between two oxide semiconductor layers. Further, an impurity element is added to the oxide semiconductor layer in a self-aligned manner so that the resistance of a region in contact with an electrode layer is reduced. Further, the oxide semiconductor layer in contact with the gate insulating layer has a larger thickness than the oxide semiconductor layer having high conductivity.

Owner:SEMICON ENERGY LAB CO LTD

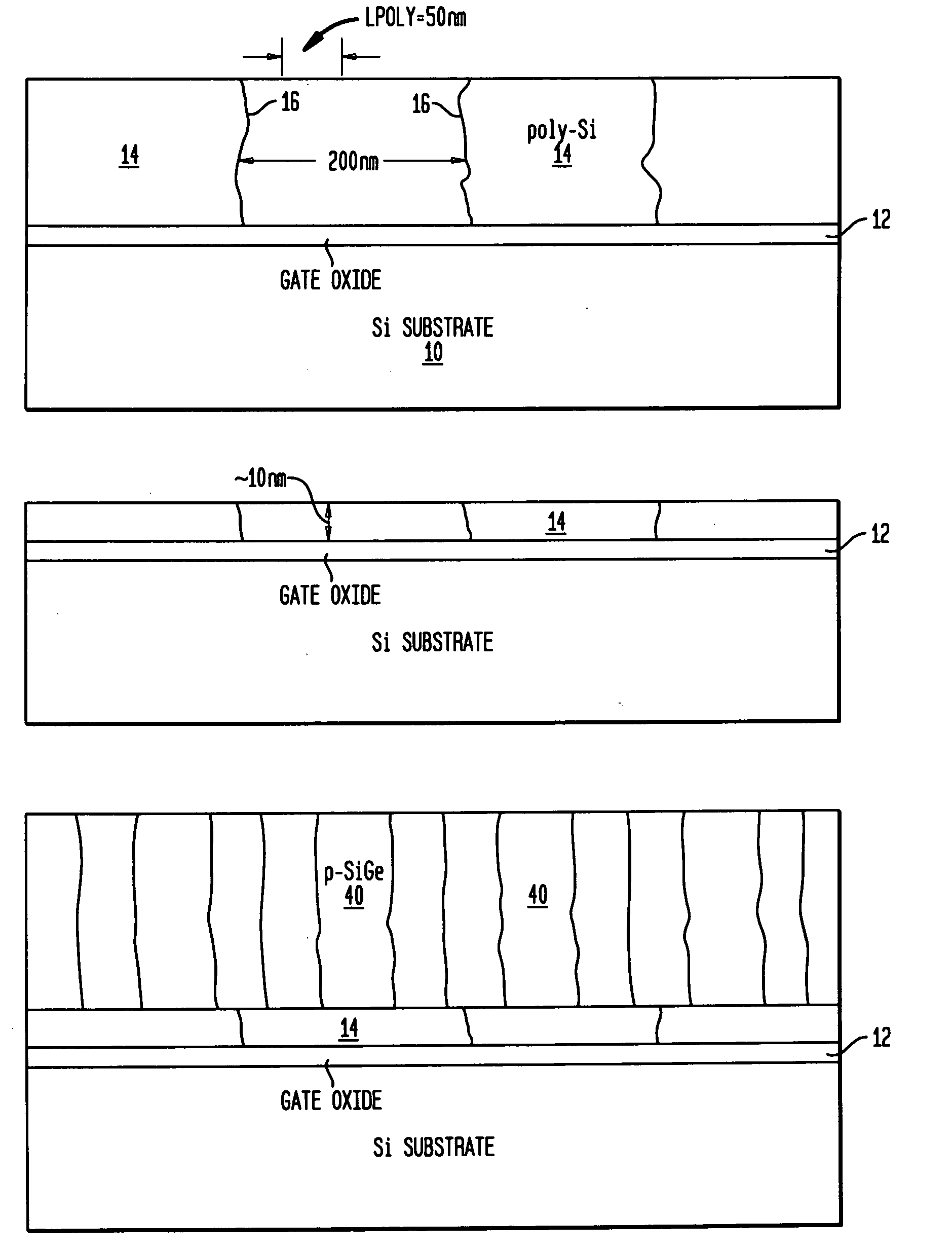

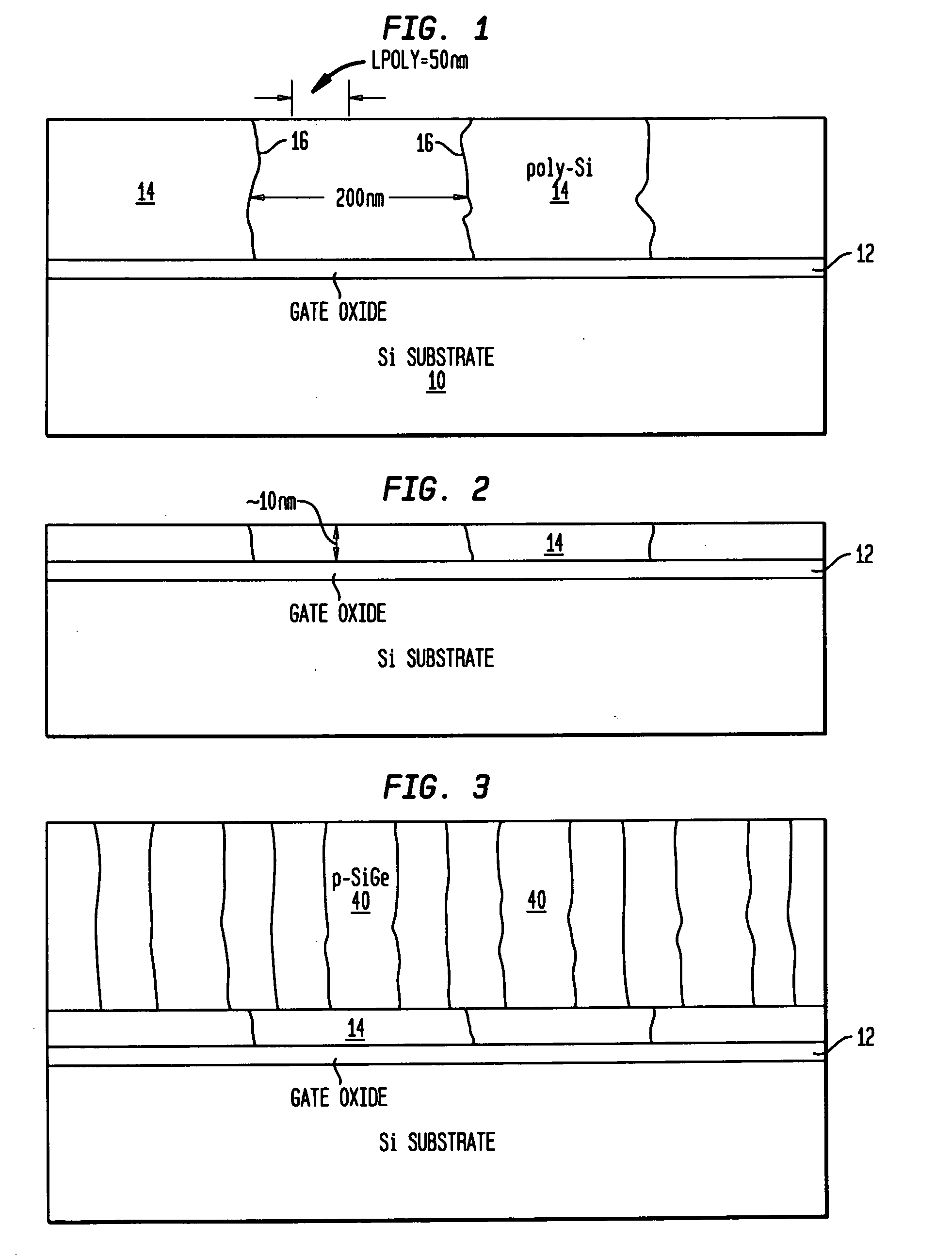

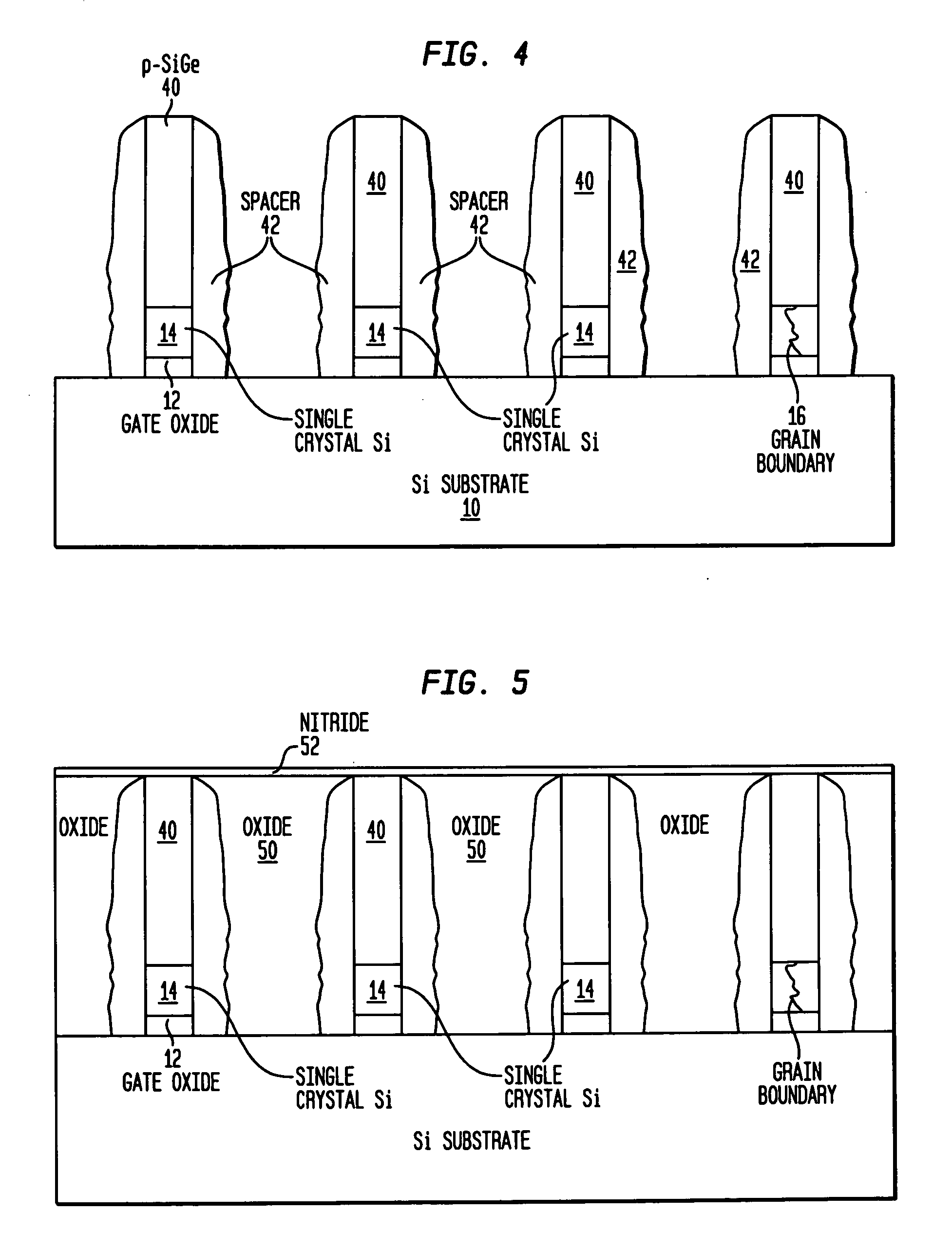

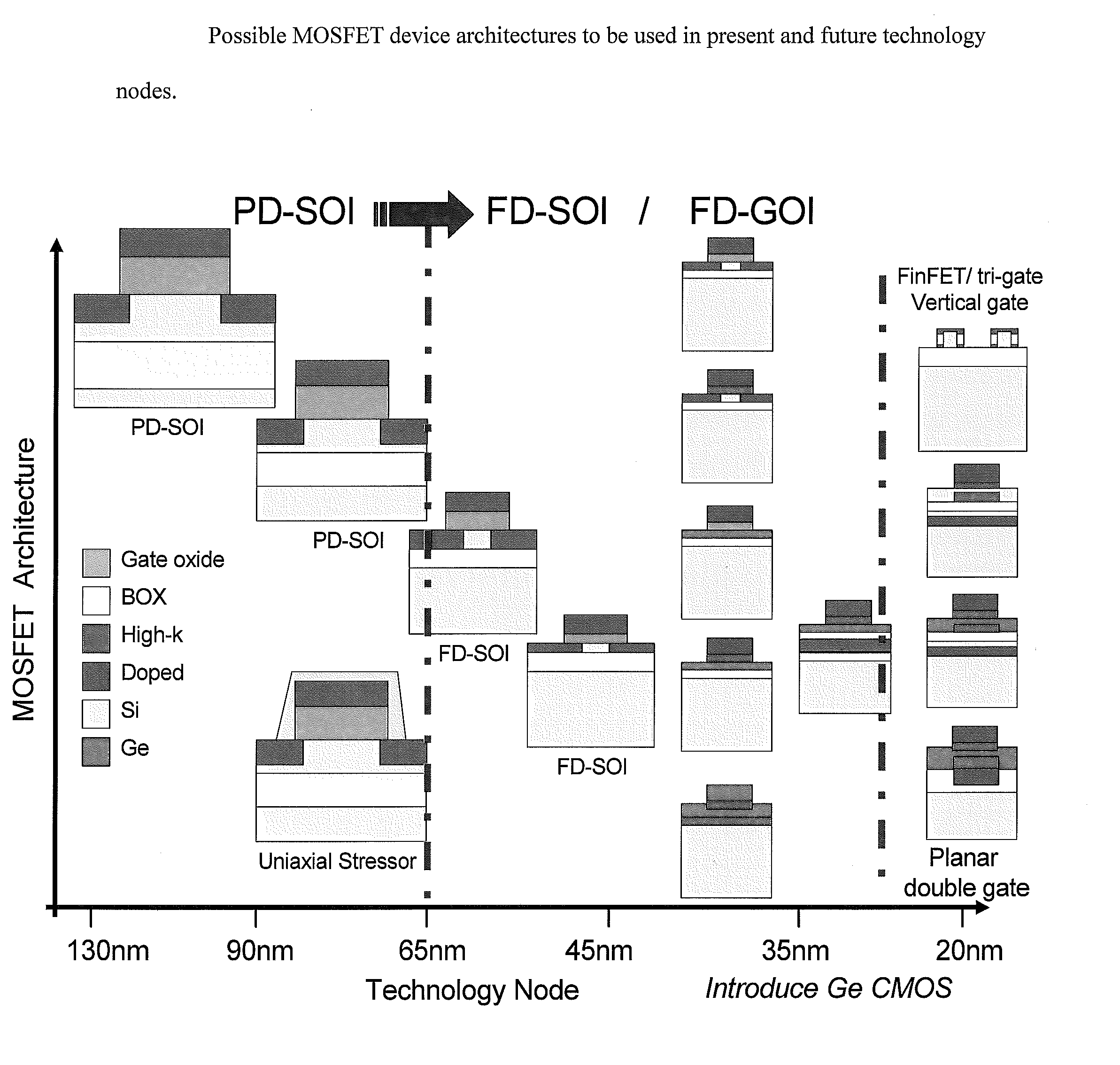

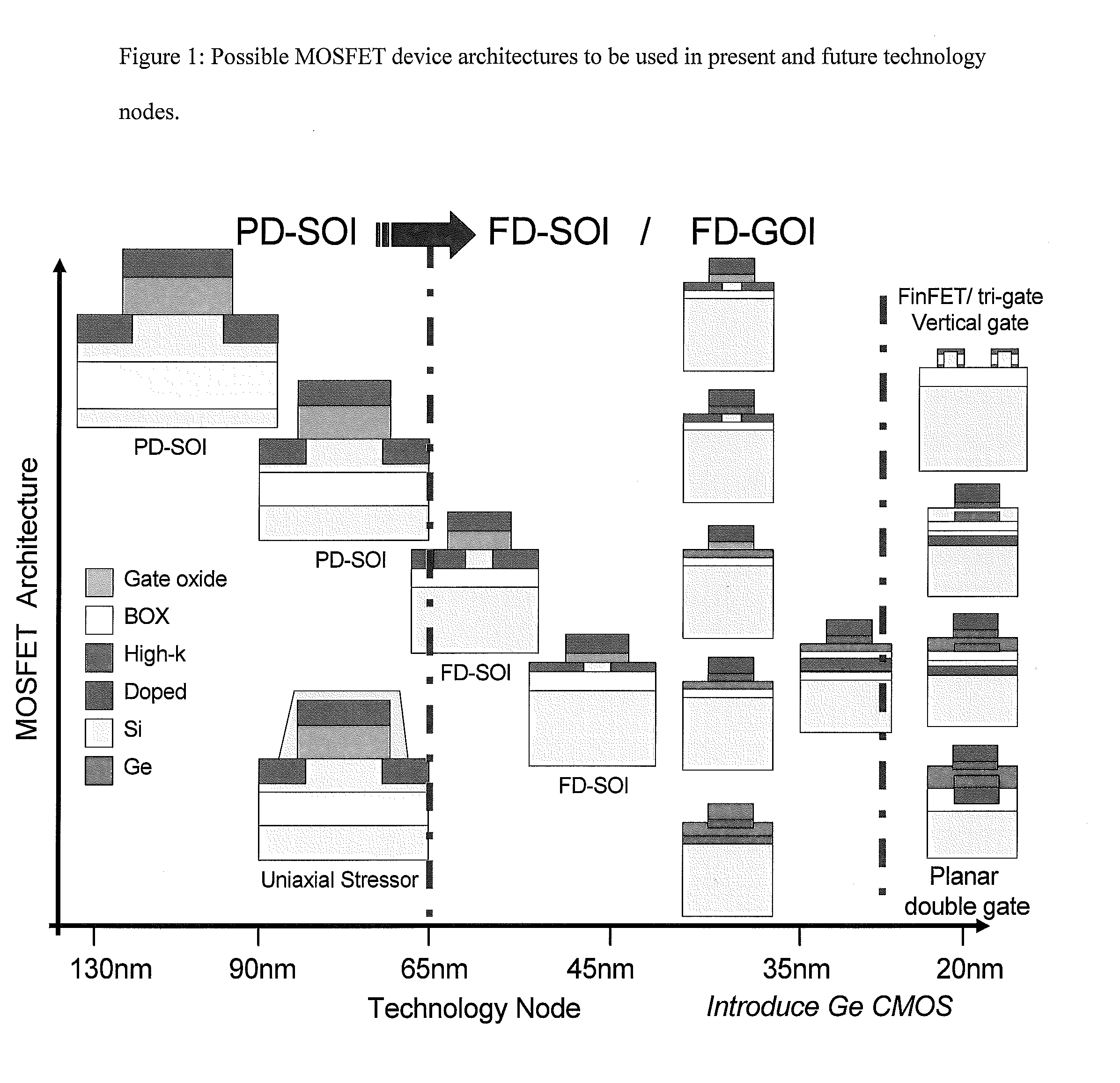

STRUCTURES AND METHODS FOR MANUFACTURING OF DISLOCATION FREE STRESSED CHANNELS IN BULK SILICON AND SOI CMOS DEVICES BY GATE STRESS ENGINEERING WITH SiGe AND/OR Si:C

ActiveUS20050236668A1Avoid misalignmentReduce generationTransistorSemiconductor/solid-state device detailsSoi cmosCMOS

Structures and methods of manufacturing are disclosed of dislocation free stressed channels in bulk silicon and SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) devices by gate stress engineering with SiGe and / or Si:C. A CMOS device comprises a substrate of either bulk Si or SOI, a gate dielectric layer over the substrate, and a stacked gate structure of SiGe and / or Si:C having stresses produced at the interfaces of SSi(strained Si) / SiGe or SSi / Si:C in the stacked gate structure. The stacked gate structure has a first stressed film layer of large grain size Si or SiGe over the gate dielectric layer, a second stressed film layer of strained SiGe or strained Si:C over the first stressed film layer, and a semiconductor or conductor such as p(poly)-Si over the second stressed film layer.

Owner:GLOBALFOUNDRIES US INC

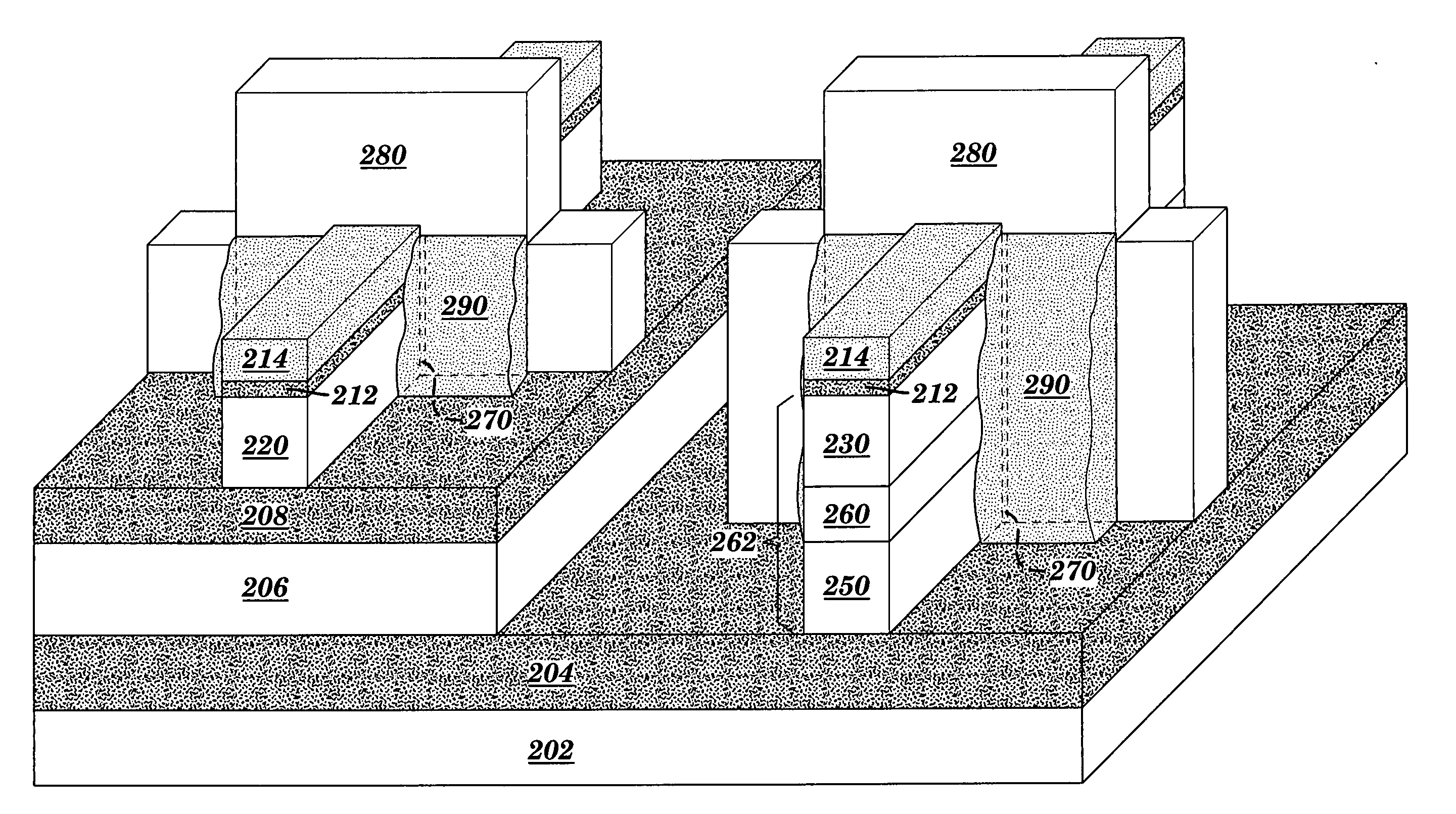

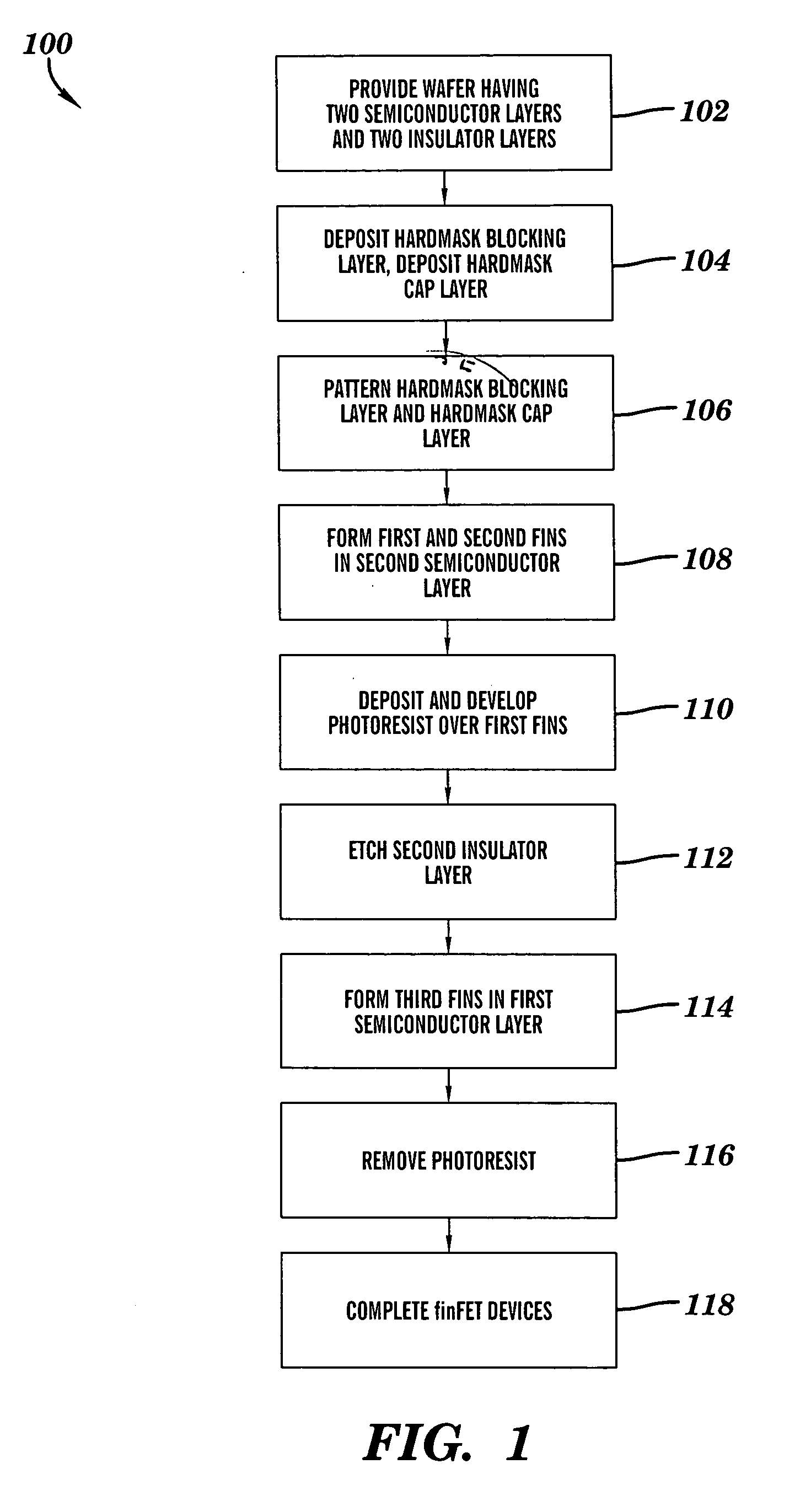

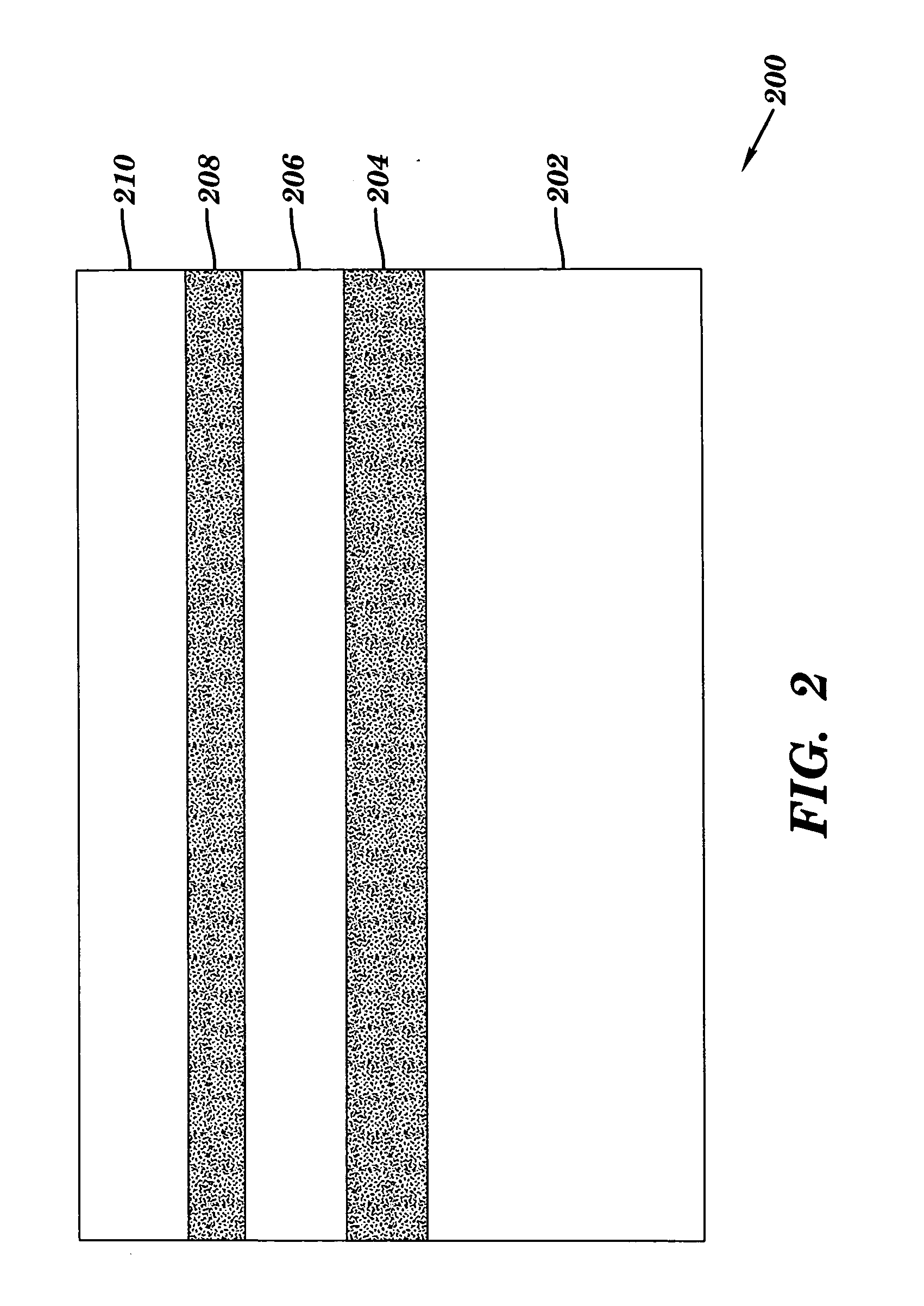

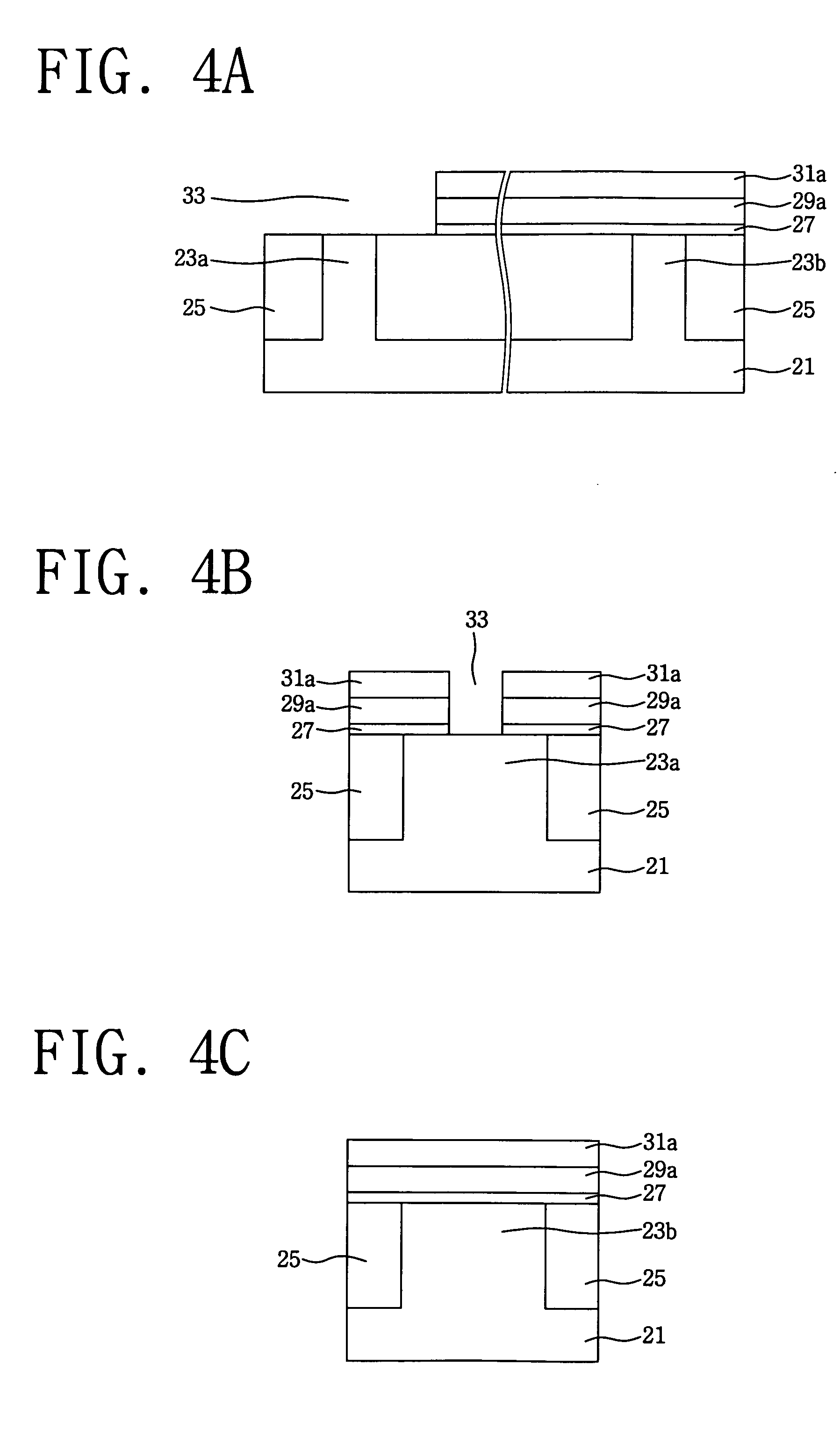

structure and method of manufacturing a finFet device having stacked fins

InactiveUS20050239242A1Improve circuit densityOptimize mobilityTransistorSolid-state devicesEngineeringElectrical conductor

The present invention provides a device structure and method of forming a finFet device having stacked fins. The method of the present invention comprises: providing a substrate with a first semiconductor layer on a first insulator layer, a second insulator layer on the first semiconductor layer, and a second semiconductor layer on the second insulator layer; forming a first fin and a second fin in the second semiconductor layer; masking the first fin; and forming a third fin in the first semiconductor layer, where the second fin is stacked on the third fin. The structure of the present invention comprises: a semiconductor substrate having a first semiconductor layer on a first insulator layer, a second insulator layer on the first semiconductor layer, and a second semiconductor layer on the second insulator layer; a first and second fin formed in the second semiconductor layer; and a third fin formed in the first semiconductor layer, where the second fin is stacked on the third fin.

Owner:IBM CORP

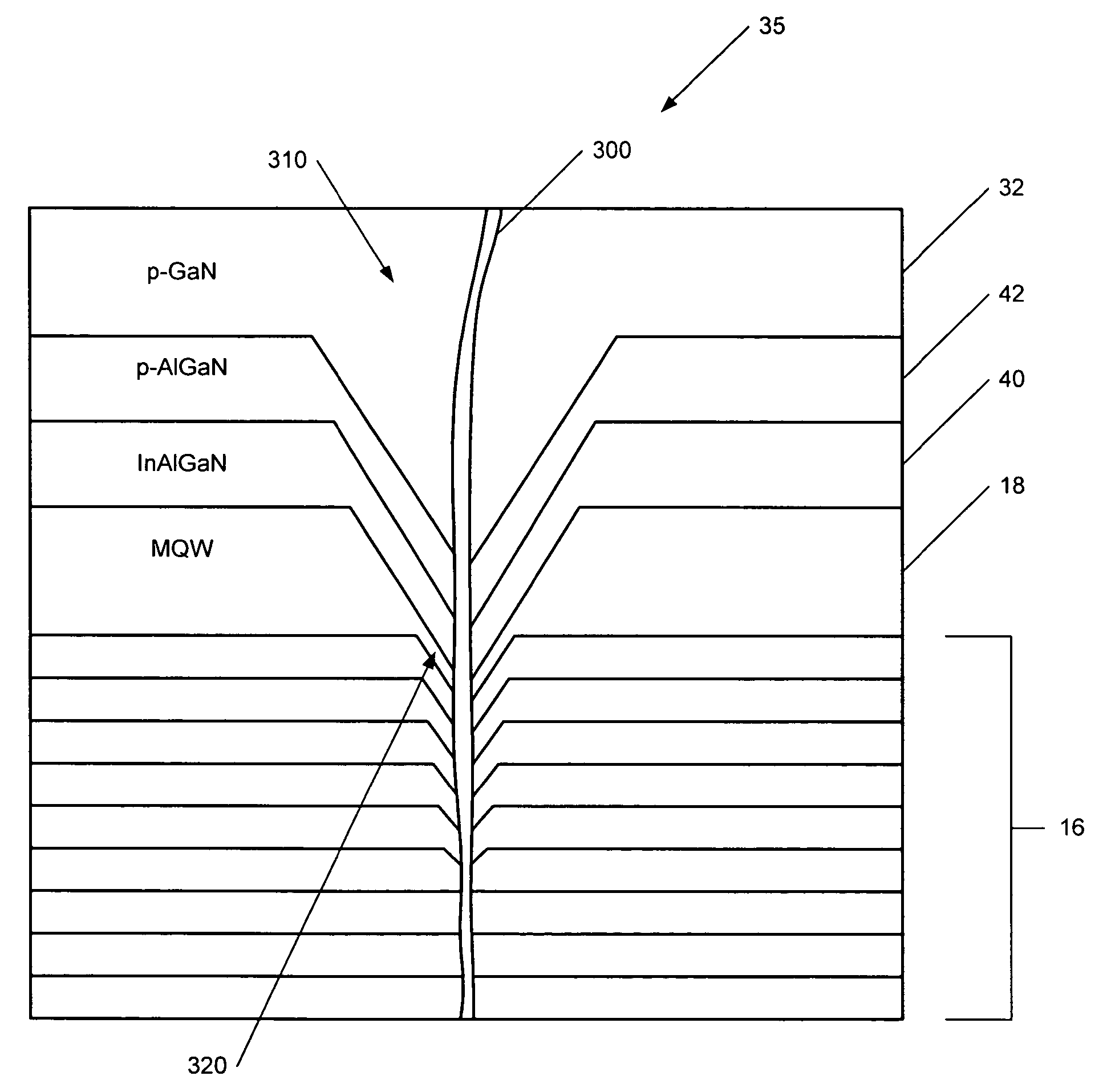

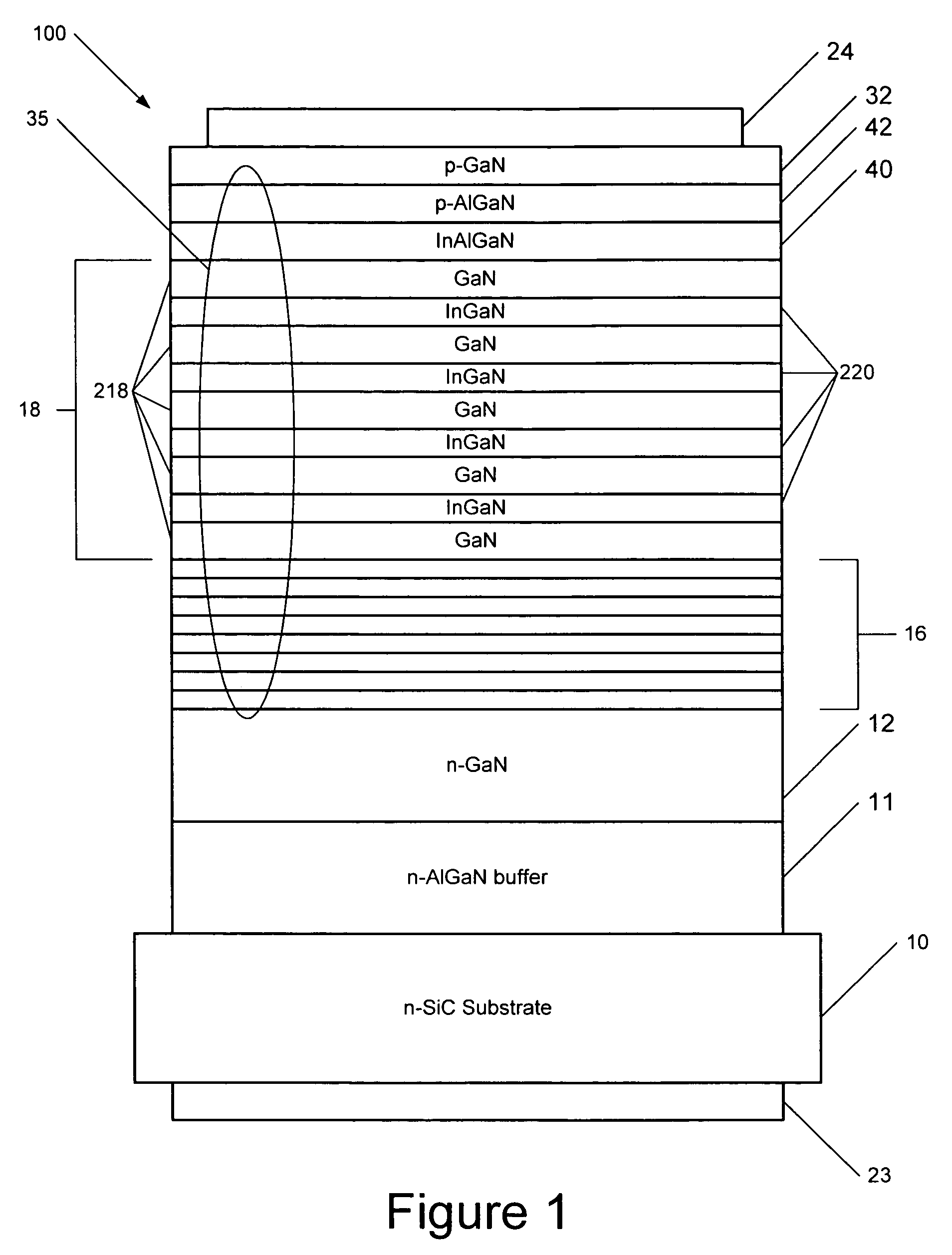

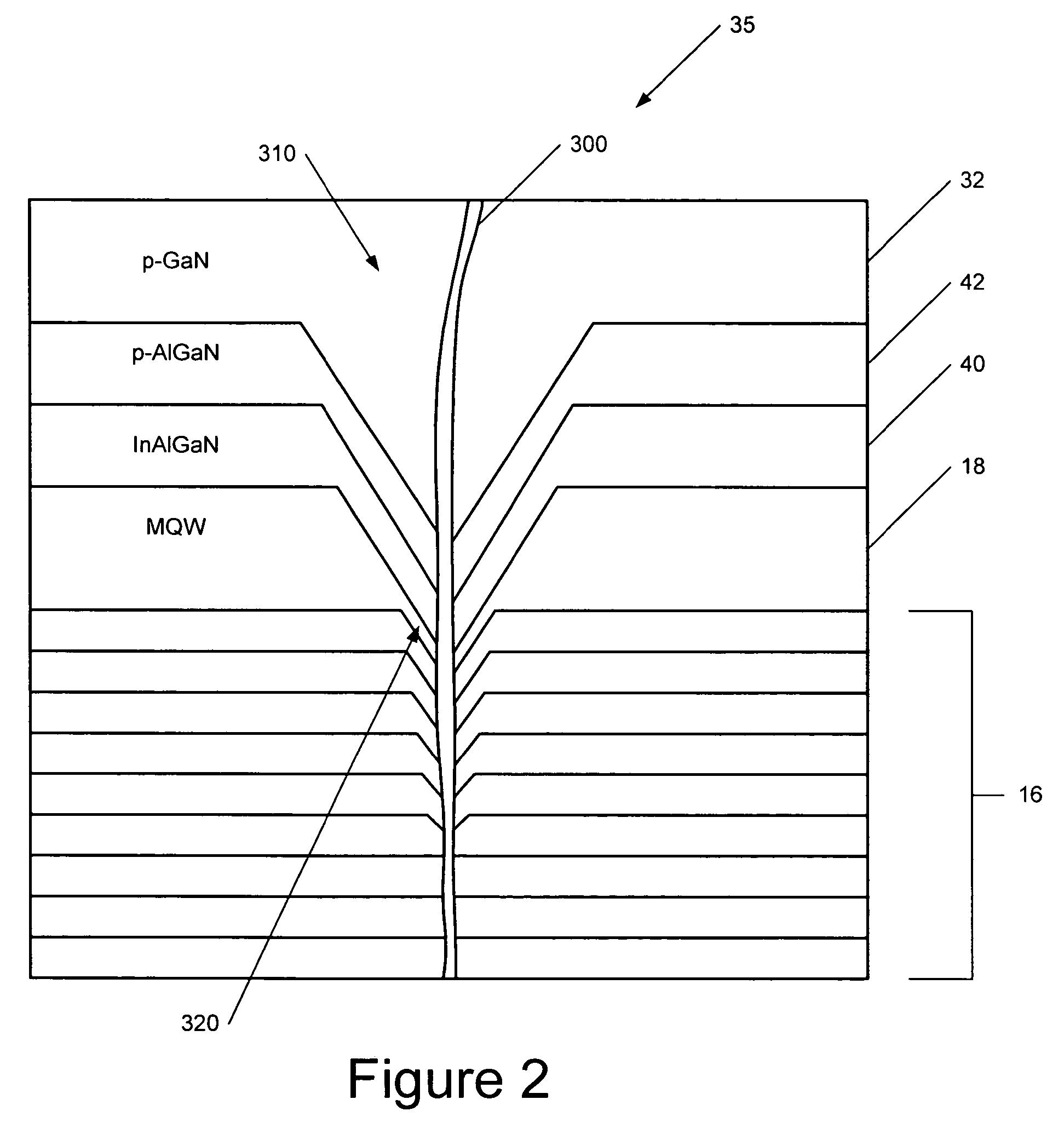

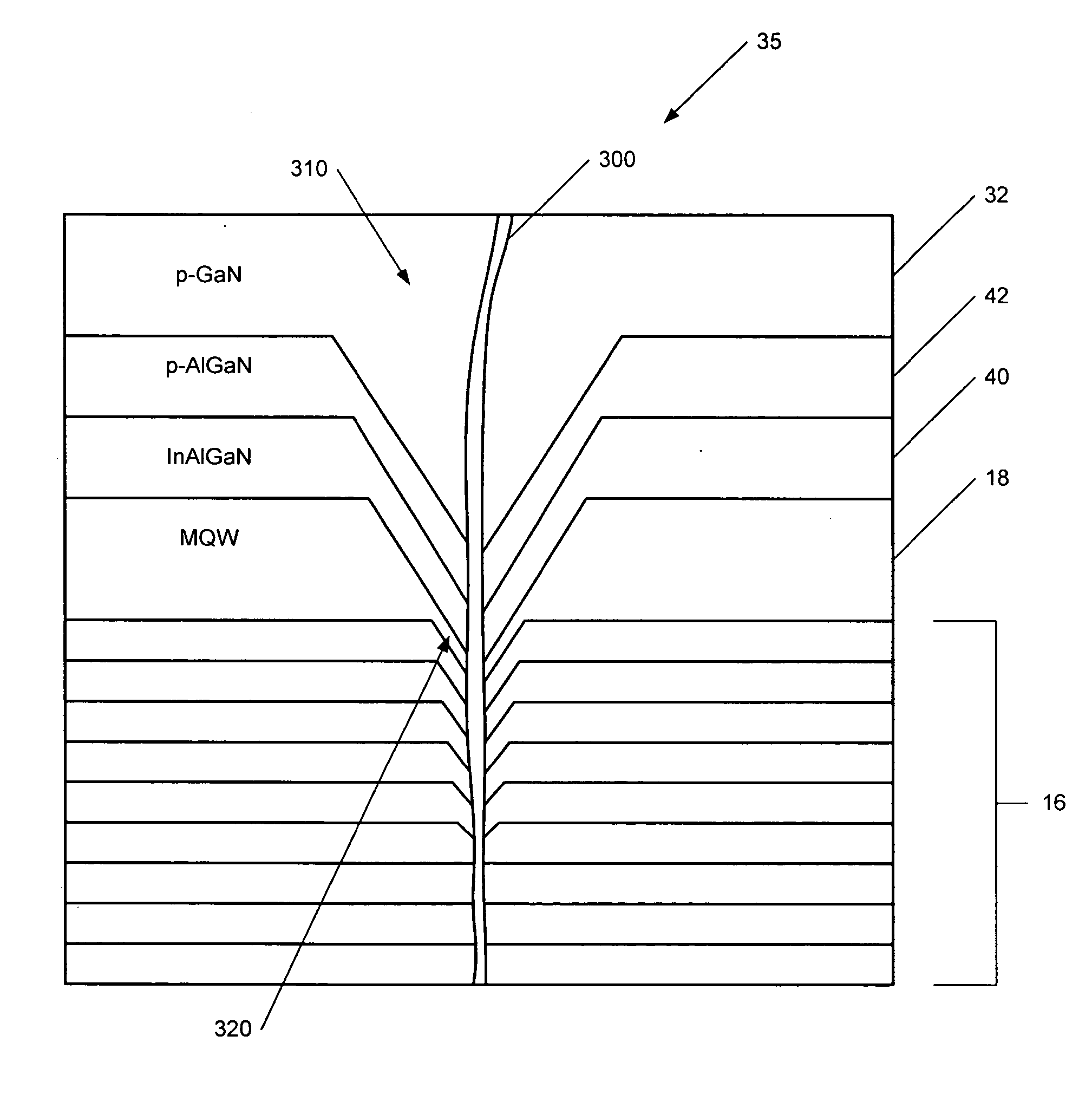

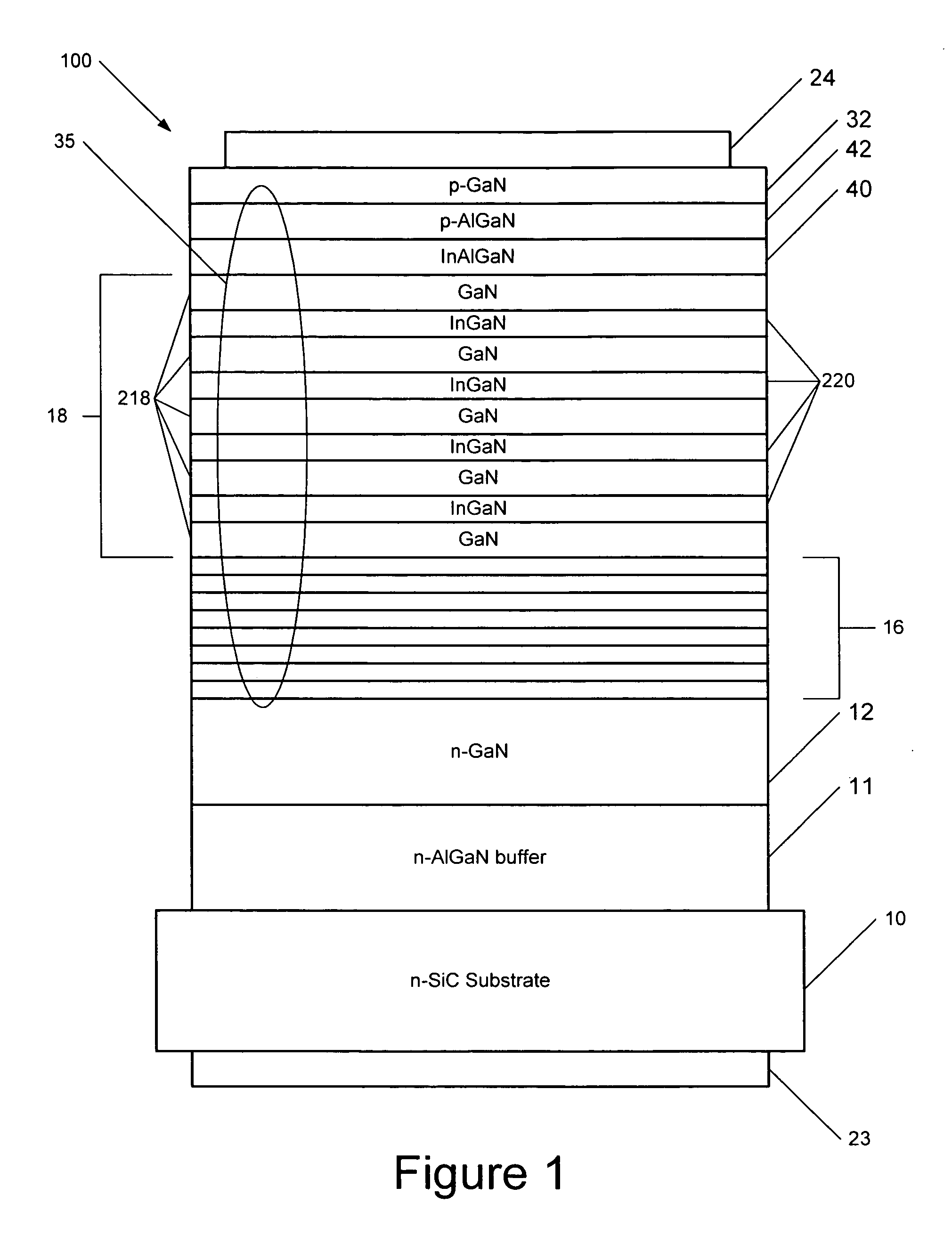

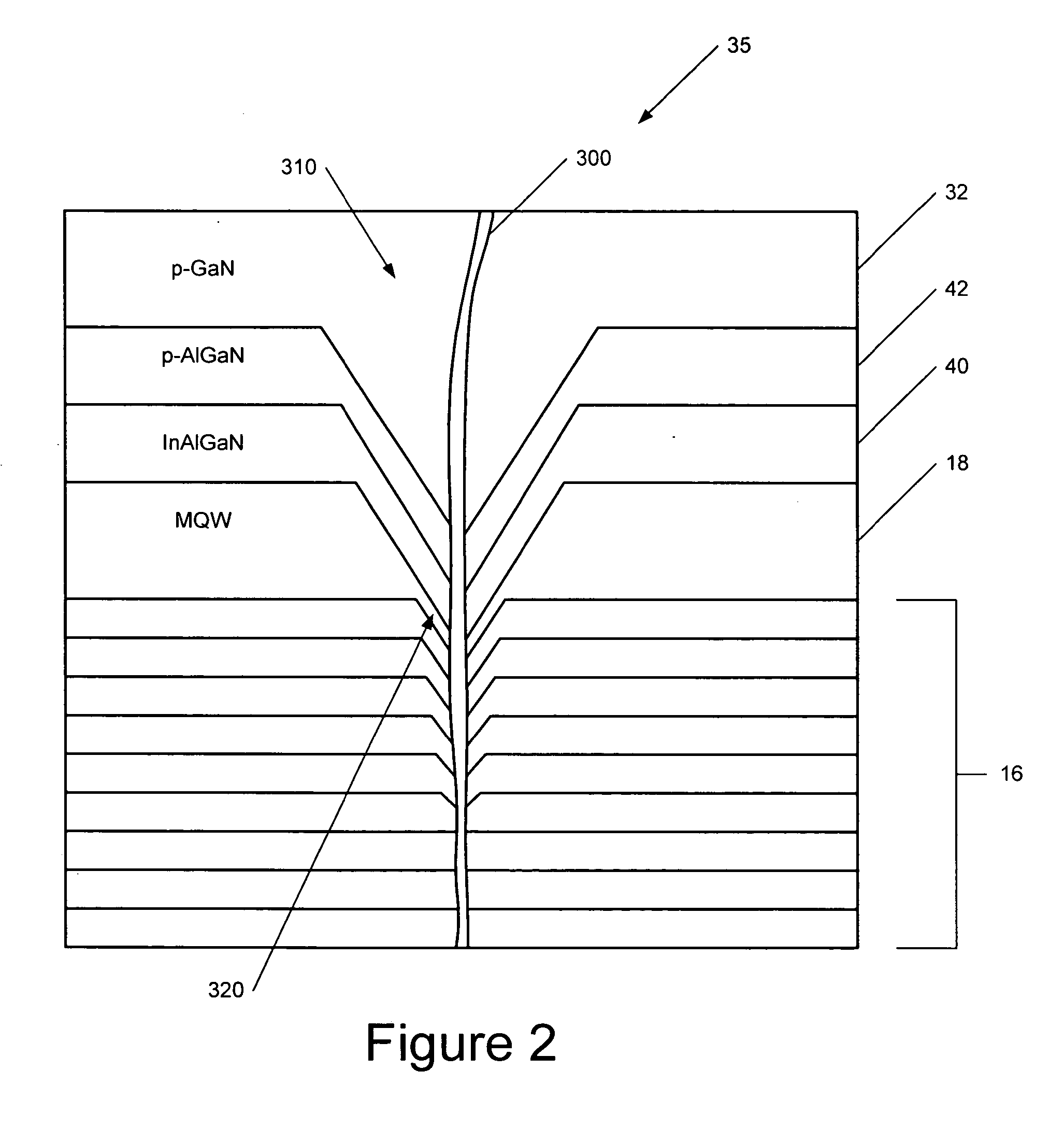

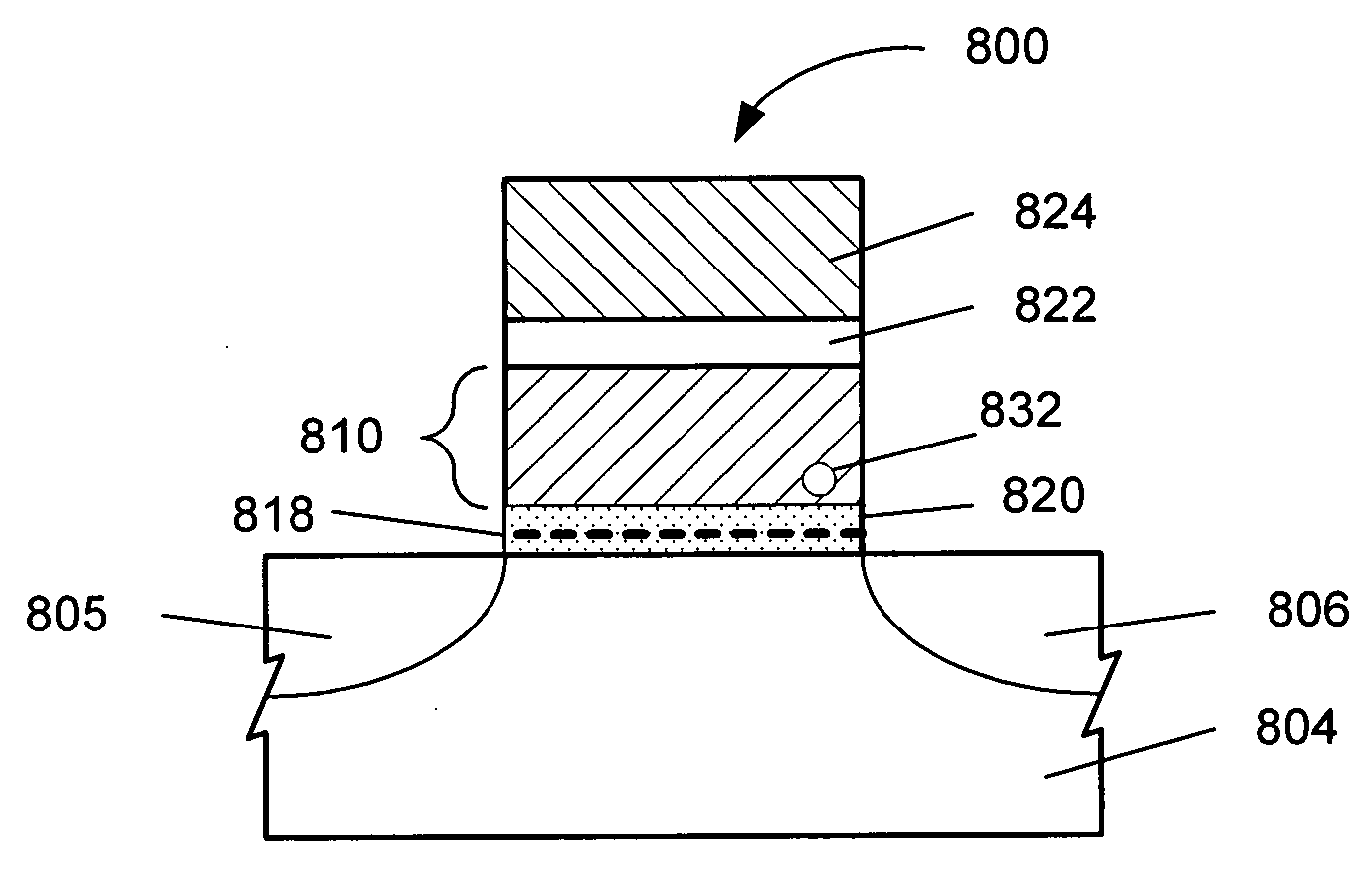

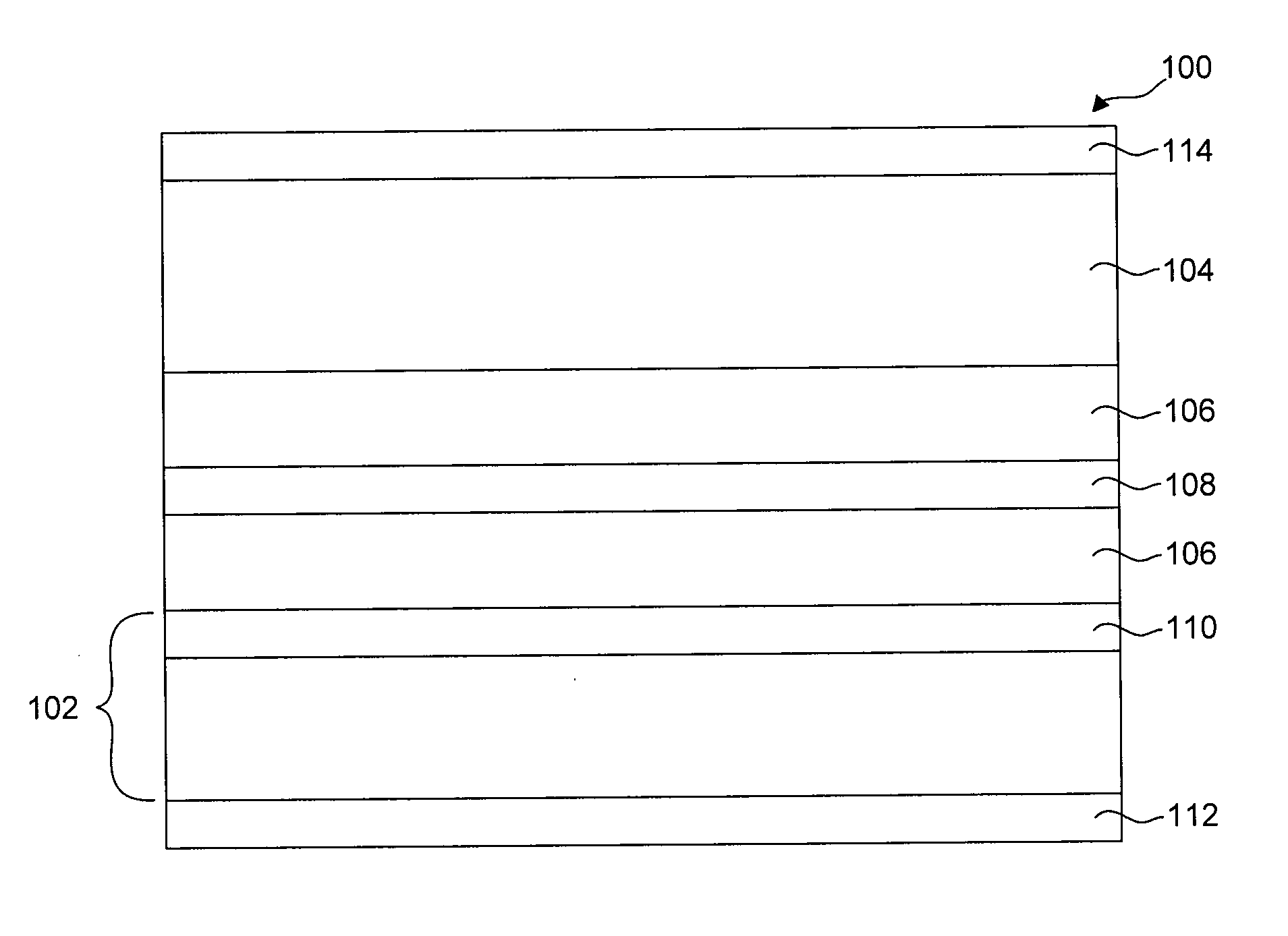

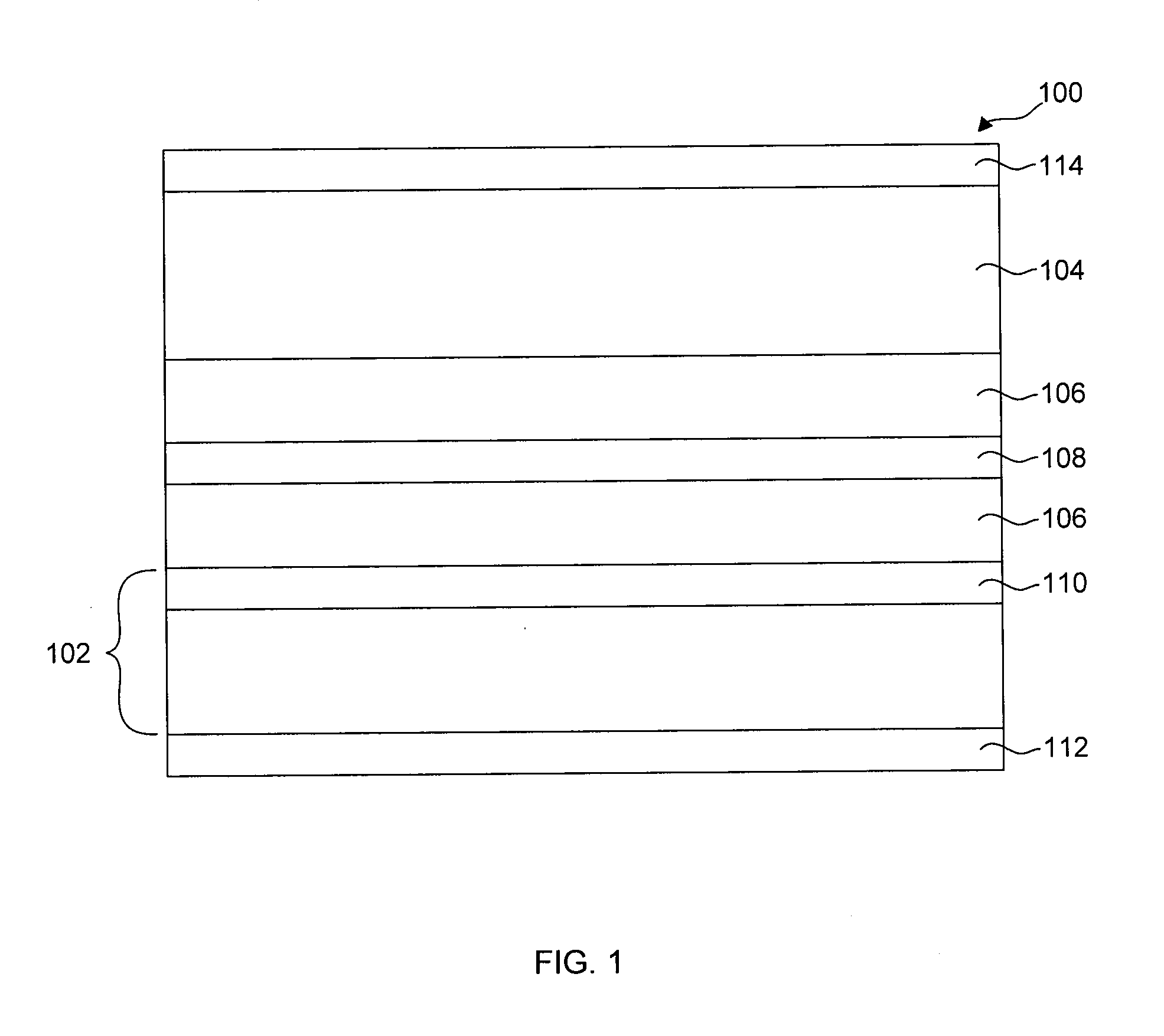

Light emitting devices with active layers that extend into opened pits

ActiveUS7446345B2Low mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringActive layer

Light emitting devices include an active region comprising a plurality of layers and a pit opening region on which the active region is disposed. The pit opening region is configured to expand a size of openings of a plurality of pits to a size sufficient for the plurality of layers of the active region to extend into the pits. In some embodiments, the active region comprises a plurality of quantum wells. The pit opening region may comprise a superlattice structure. The pits may surround their corresponding dislocations and the plurality of layers may extend to the respective dislocations. At least one of the pits of the plurality of pits may originate in a layer disposed between the pit opening layer and a substrate on which the pit opening layer is provided. The active region may be a Group III nitride based active region. Methods of fabricating such devices are also provided.

Owner:CREELED INC

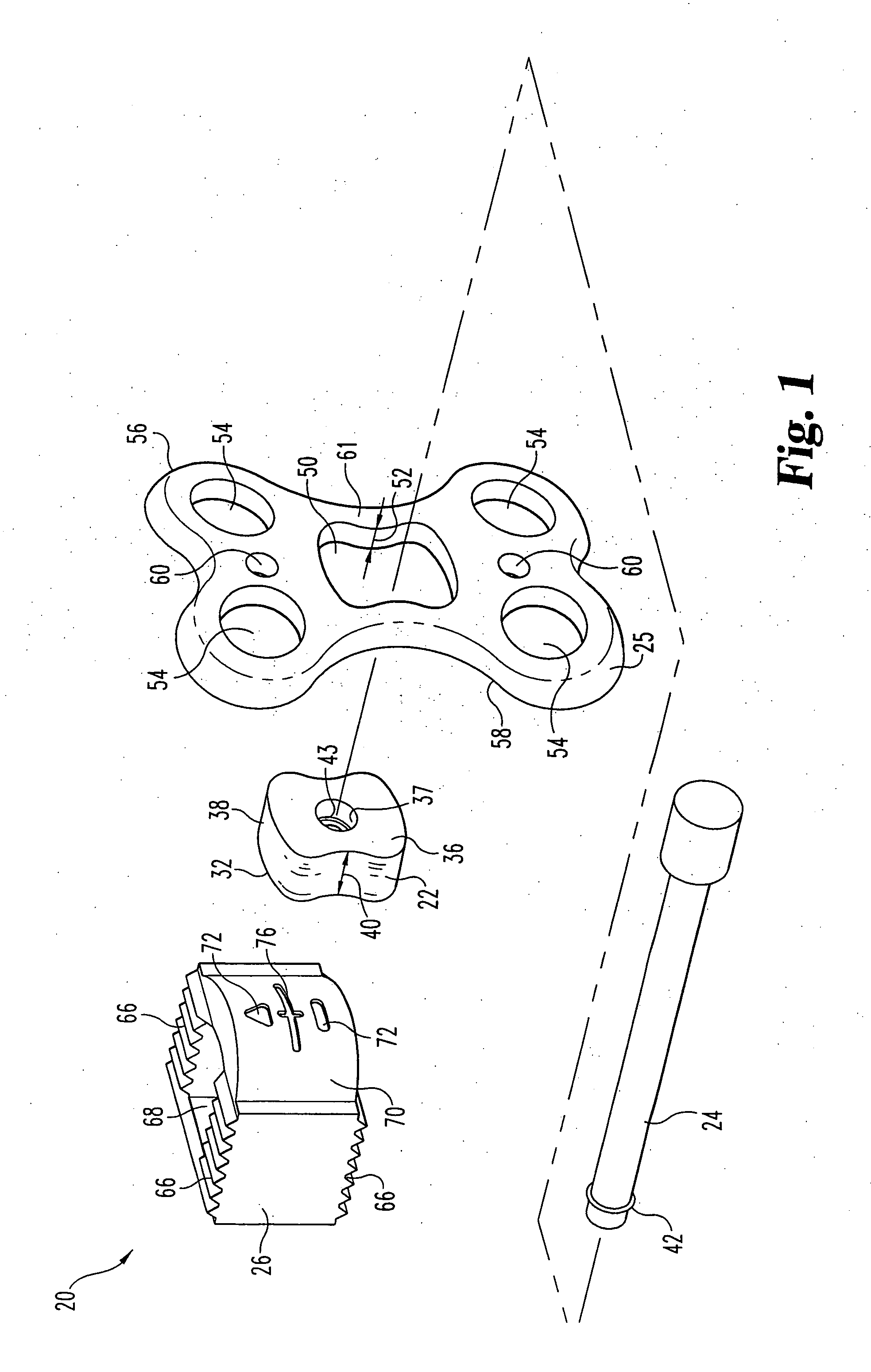

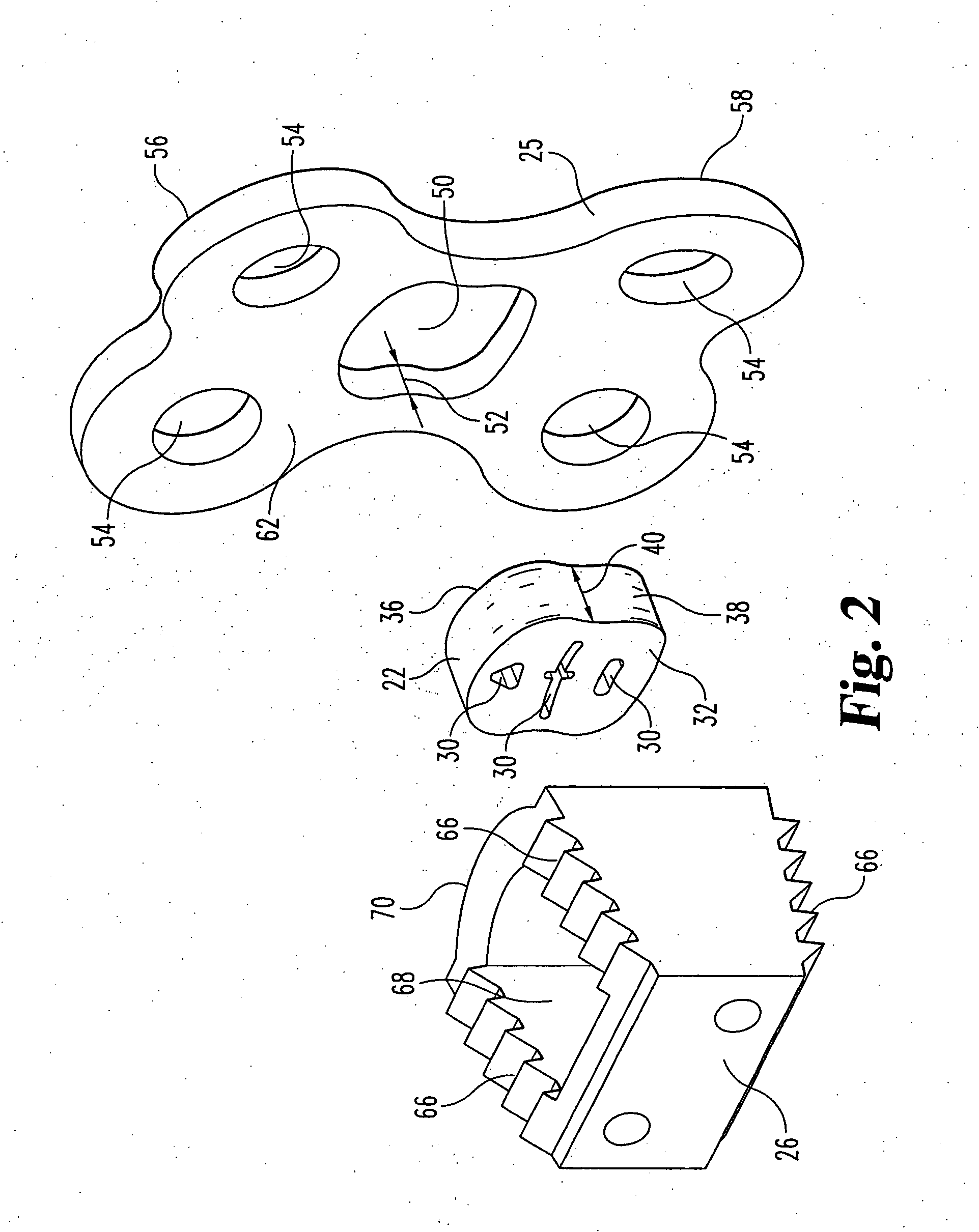

Orthopedic support locating or centering feature and method

ActiveUS20070270965A1Stabilize spineDistributes forceInternal osteosythesisJoint implantsIntervertebral spaceCentring

Spinal plate positioning system including a spinal plate, centering member and implant, is used to position and center a spinal plate over an implant in an intervertebral space. Implant may include a centering feature which may engage a surface of centering member or spinal plate to aid in placement of spinal plate.

Owner:WARSAW ORTHOPEDIC INC

Light emitting devices with active layers that extend into opened pits

ActiveUS20060246612A1Low mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDislocationEngineering

Light emitting devices include an active region comprising a plurality of layers and a pit opening region on which the active region is disposed. The pit opening region is configured to expand a size of openings of a plurality of pits to a size sufficient for the plurality of layers of the active region to extend into the pits. In some embodiments, the active region comprises a plurality of quantum wells. The pit opening region may comprise a superlattice structure. The pits may surround their corresponding dislocations and the plurality of layers may extend to the respective dislocations. At least one of the pits of the plurality of pits may originate in a layer disposed between the pit opening layer and a substrate on which the pit opening layer is provided. The active region may be a Group III nitride based active region. Methods of fabricating such devices are also provided.

Owner:CREELED INC

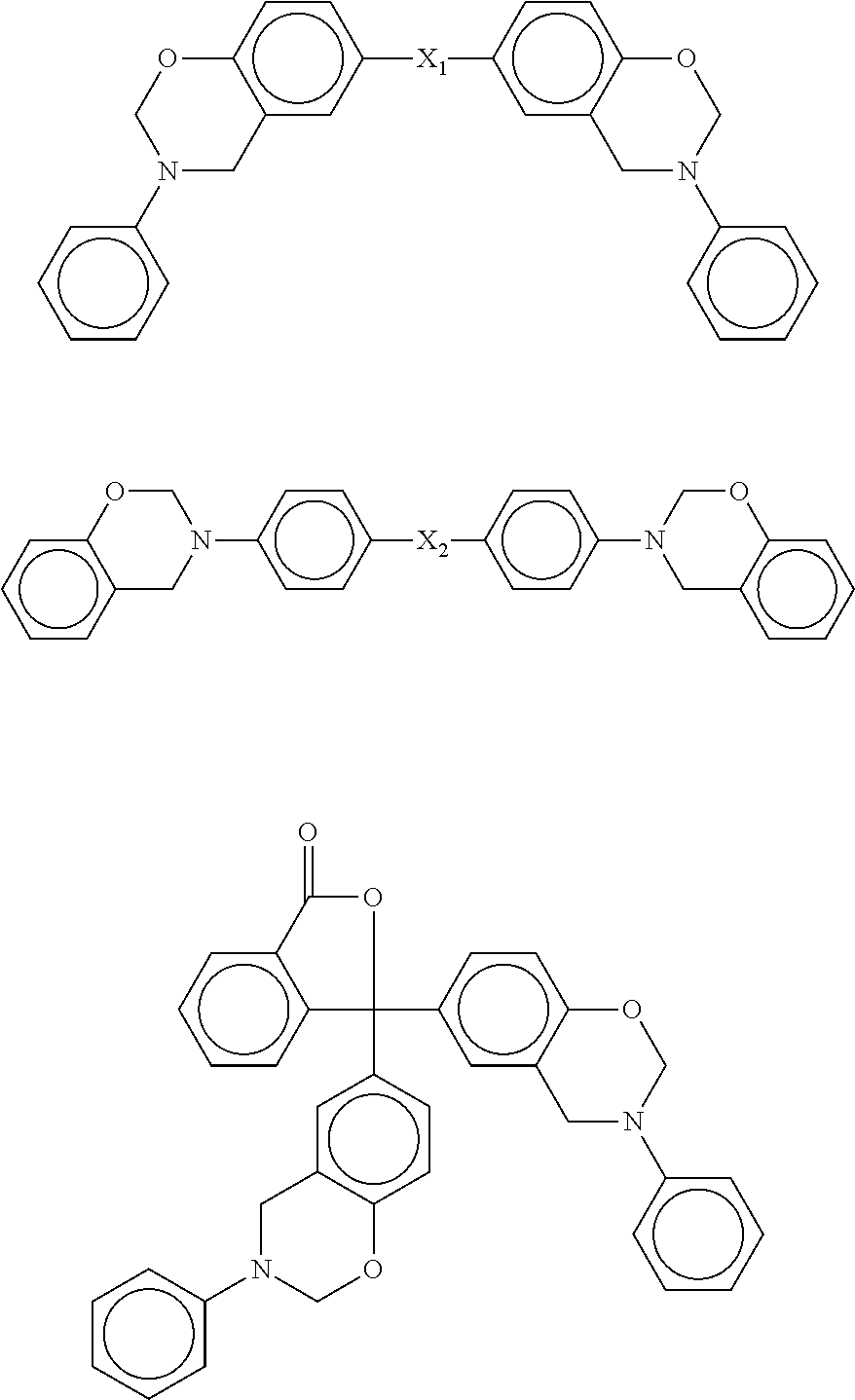

Halogen-free resin composition and its application for copper clad laminate and printed circuit board

ActiveUS20130161080A1Low dielectric constantImprove heat resistancePlastic/resin/waxes insulatorsGroup 5/15 element organic compoundsEpoxyLow dissipation

A halogen-free resin composition includes (A) 100 parts per hundred resin of epoxy resin; (B) 1 to 100 parts per hundred resin of benzoxazine resin; (C) 1 to 100 parts per hundred resin of styrene-maleic anhydride; (D) 0.5 to 30 parts per hundred resin of amine curing agent; and (E) 5 to 150 parts per hundred resin of halogen-free flame retardant. The composition obtains properties of low dielectric constant, low dissipation factor, high heat resistance and flame retardancy by specific composition and ratio. Thus, a prepreg or a resin film, which can be applied to a copper clad laminate and a printed circuit board, is formed.

Owner:ELITE MATERIAL

Complementary metal oxide semiconductor (CMOS) transistors having three-dimensional channel regions and methods of forming same

ActiveUS20050215014A1Unique and even optimum characteristicMobilityTransistorSolid-state devicesCMOSEngineering

An integrated circuit device containing complementary metal oxide semiconductor transistors includes a semiconductor substrate and an NMOS transistor having a first fin-shaped active region that extends in the semiconductor substrate. The first fin-shaped active region has a first channel region therein with a first height. A PMOS transistor is also provided. The PMOS transistor has a second fin-shaped active region that extends in the semiconductor substrate. This second fin-shaped active region has a second channel region therein with a second height unequal to the first height.

Owner:SAMSUNG ELECTRONICS CO LTD

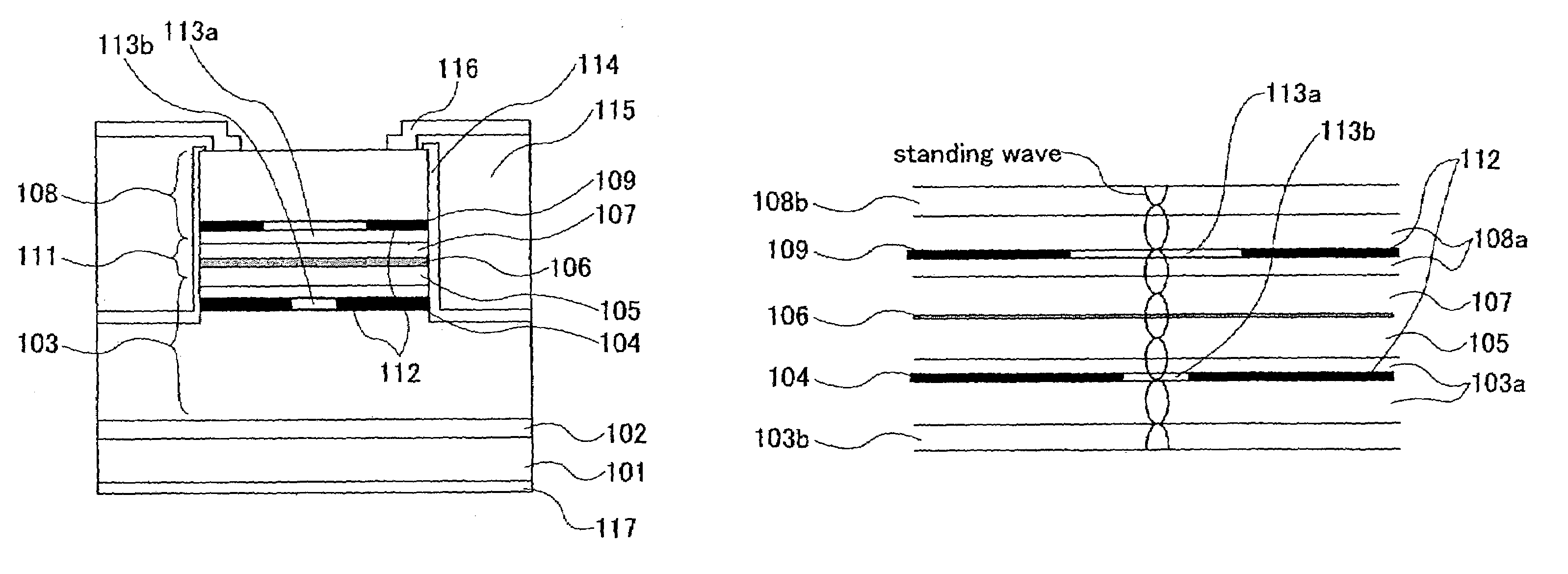

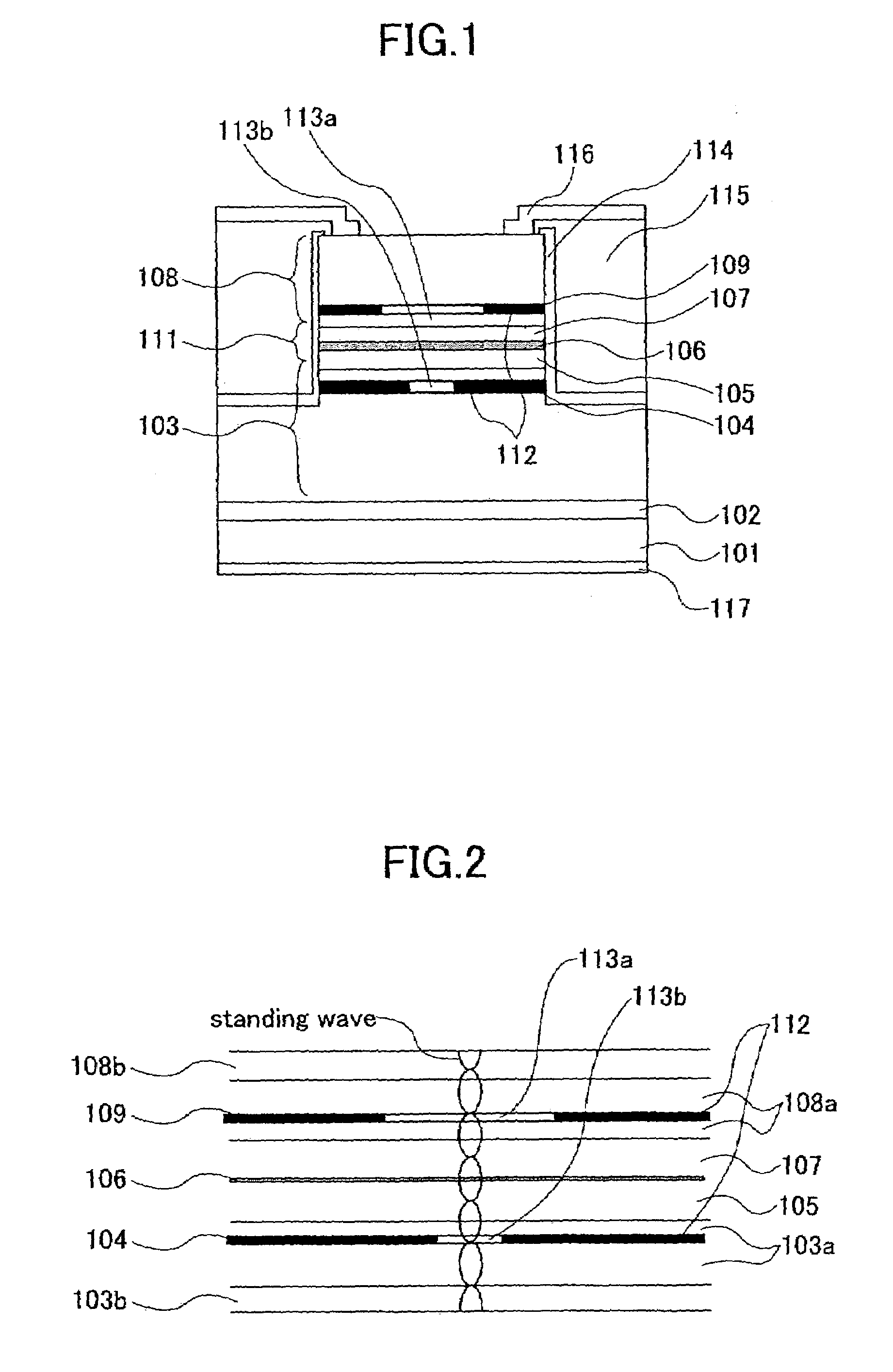

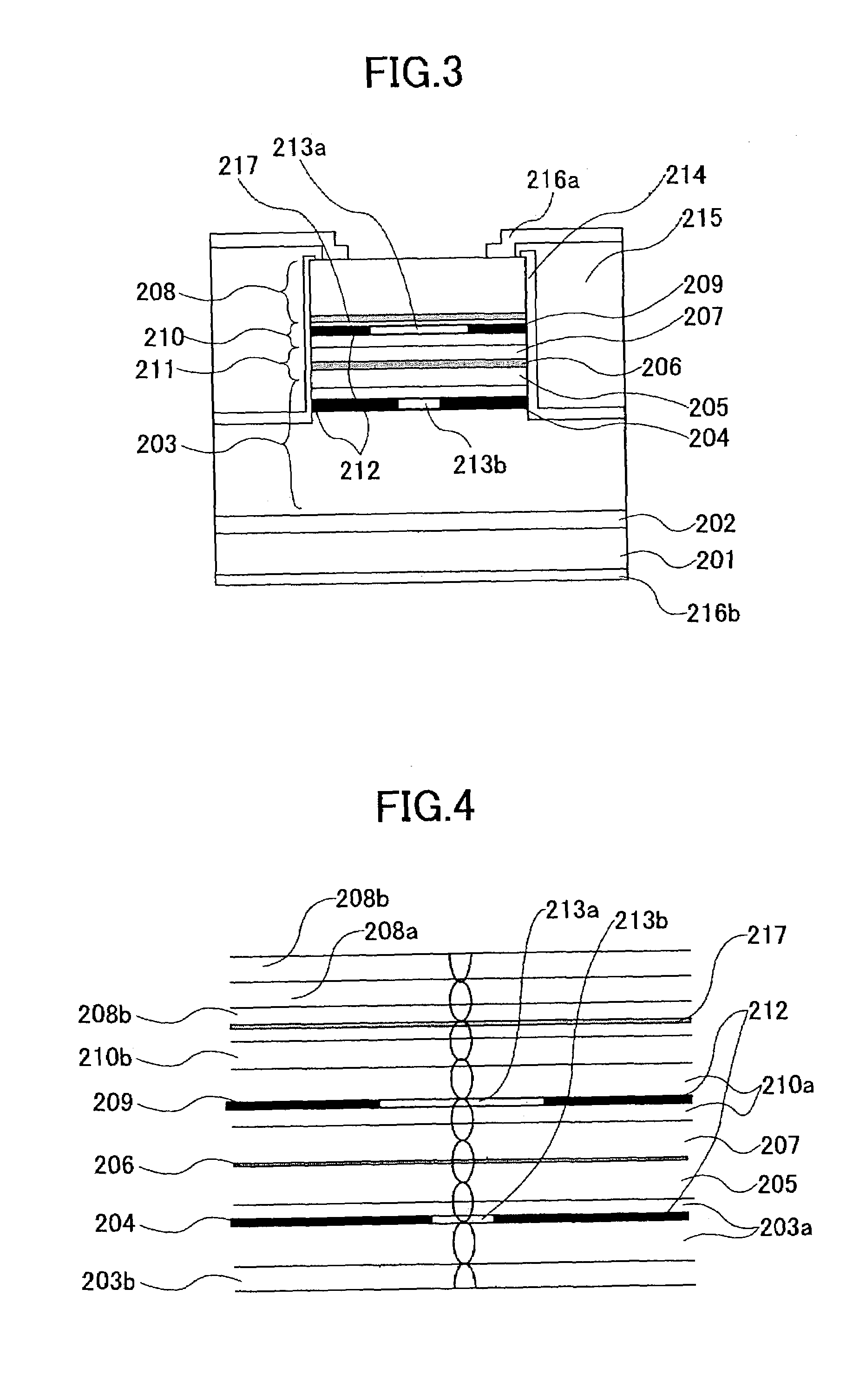

Surface-emitting laser diode having reduced device resistance and capable of performing high output operation, surface-emitting laser diode array, electrophotographic system, surface-emitting laser diode module, optical telecommunication system, optical interconnection system using the surface-emitting laser diode, and method of fabricating the surface-emitting laser diode

ActiveUS6959025B2Lower resistanceHigh-output operationOptical wave guidanceOptical resonator shape and constructionMode controlDistributed Bragg reflector

A surface-emitting laser diode device that oscillates in a direction perpendicular to the substrate is provided. This surface-emitting laser diode device includes: an active layer; a resonator structure including a first distributed Bragg reflector and a second distributed Bragg reflector that face each other and sandwich the active layer; a hole passage that extends from a first electrode to the active layer; an electron passage that extends from a second electrode to the active layer; a hole restricting structure that is located in the hole passage and defines a region for confining holes to the active layer; and an optical mode control structure that includes a non-oxide region provided in the resonator structure and an oxide region surrounding the non-oxide region, each region containing Al as a constituent element. In this surface-emitting laser diode, the area of the non-oxide region is smaller than the area of the hole restricting structure.

Owner:RICOH KK

Pressure applicator devices particularly useful for non-invasive detection of medical conditions

InactiveUS20020072681A1Low mobilityEasy constructionEvaluation of blood vesselsCatheterVeinBlood arterial

A probe for application to a body part particularly a finger of a patient to detect a change in the physical condition of the patient includes a housing defining a compartment closed at one end and open at the opposite end for receiving the distal end of the patient's finger and means consituted of a medium wholly self-contained within the probe for applying a static pressure field substantially uniformly around the distal end of the patient's finger, of a predetermined magnitude sufficient to substantially prevent distention of the venous vasculature, uncontrolled venous backflow, and retrognade shockwave propagation into the distal end, and to partially unload the wall tension of, but not to occlude, the arteries in the distal end when at heart level or below. A sensor senses changes in the distal end of the patient's finger related to changes in arterial blood volume therein.

Owner:ITAMAR MEDICAL LTD

Method of Energy Transfer to an Implantable Medical Device While Coupling Energy to Charging Unit

InactiveUS20070167997A1Low mobilityAmount of power availableElectrotherapyBatteries circuit arrangementsEnergy transferEnergy coupling

External power source, charger, system and method for an implantable medical device having therapeutic componentry and a secondary coil operatively coupled to the therapeutic componentry. A primary charging coil is capable of transcutaneously inductively energizing the secondary coil when externally placed in proximity of the secondary coil. Drive circuitry is operatively coupled to the primary charging coil for exciting the primary charging coil. A rechargeable power source is operatively coupled to the drive circuitry. A secondary recharging coil is operatively coupled to the rechargeable power source. A primary recharging coil is adapted to be coupled to a source of AC power which when placed in proximity of the secondary recharging coil can inductively energize the secondary recharging coil in order to charge the rechargeable power source.

Owner:MEDTRONIC INC

System and method for bracketing and removing tissue

Owner:VARIAN MEDICAL SYSTEMS

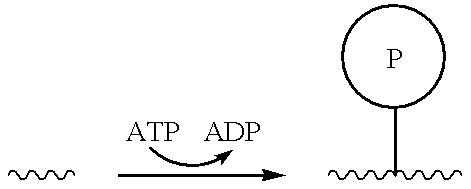

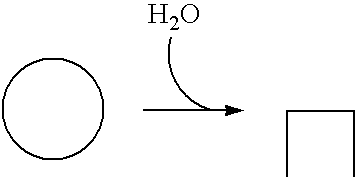

Molecular modification assays

InactiveUS7070921B2Increase brightnessLow mobilityBioreactor/fermenter combinationsBiological substance pretreatmentsPhosphateEnzyme

Assays for detecting molecular modifications such as phosphate modifications and the presence and / or activity of enzymes and other agents involved in facilitating or otherwise regulating such modifications.

Owner:MOLECULAR DEVICES

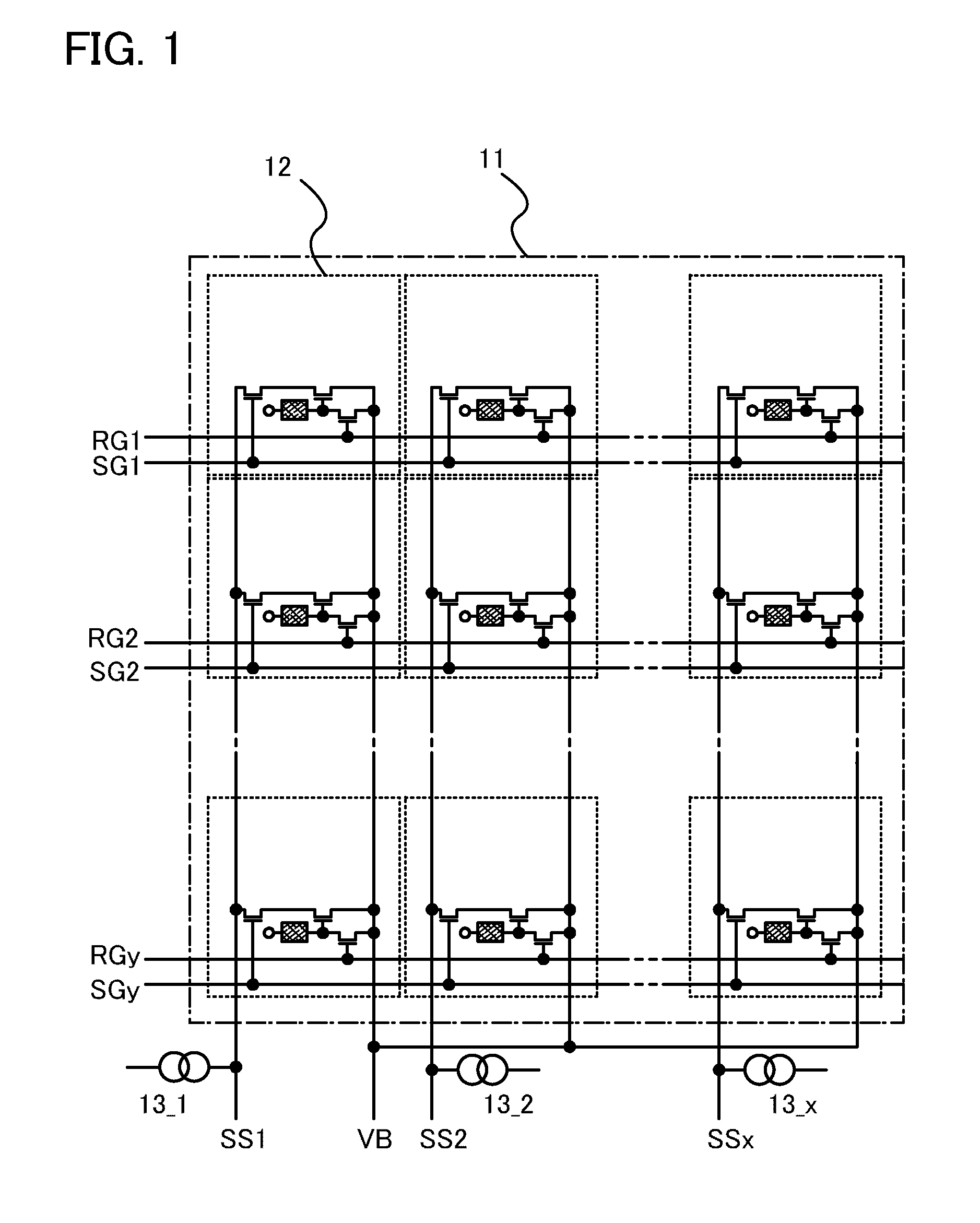

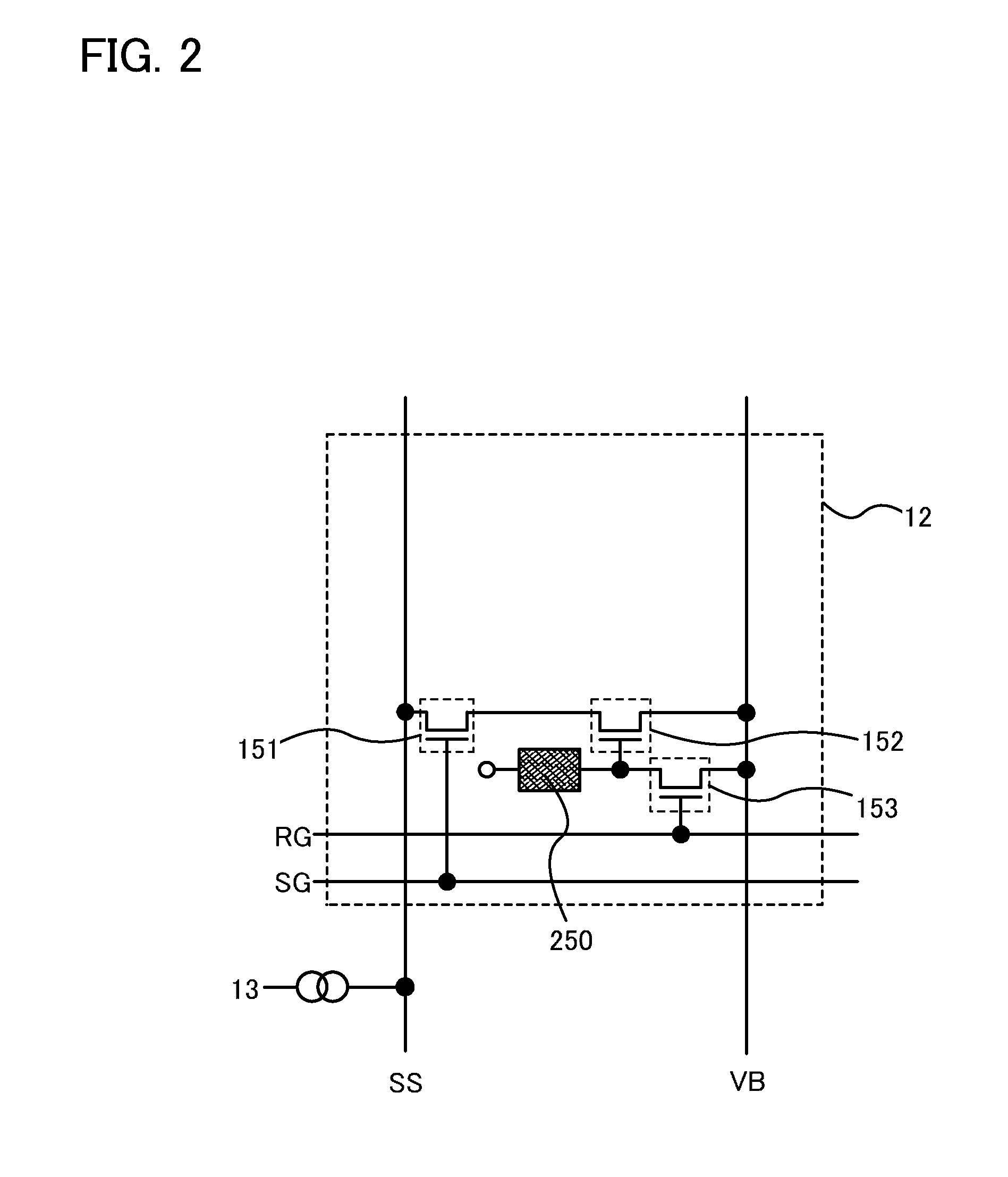

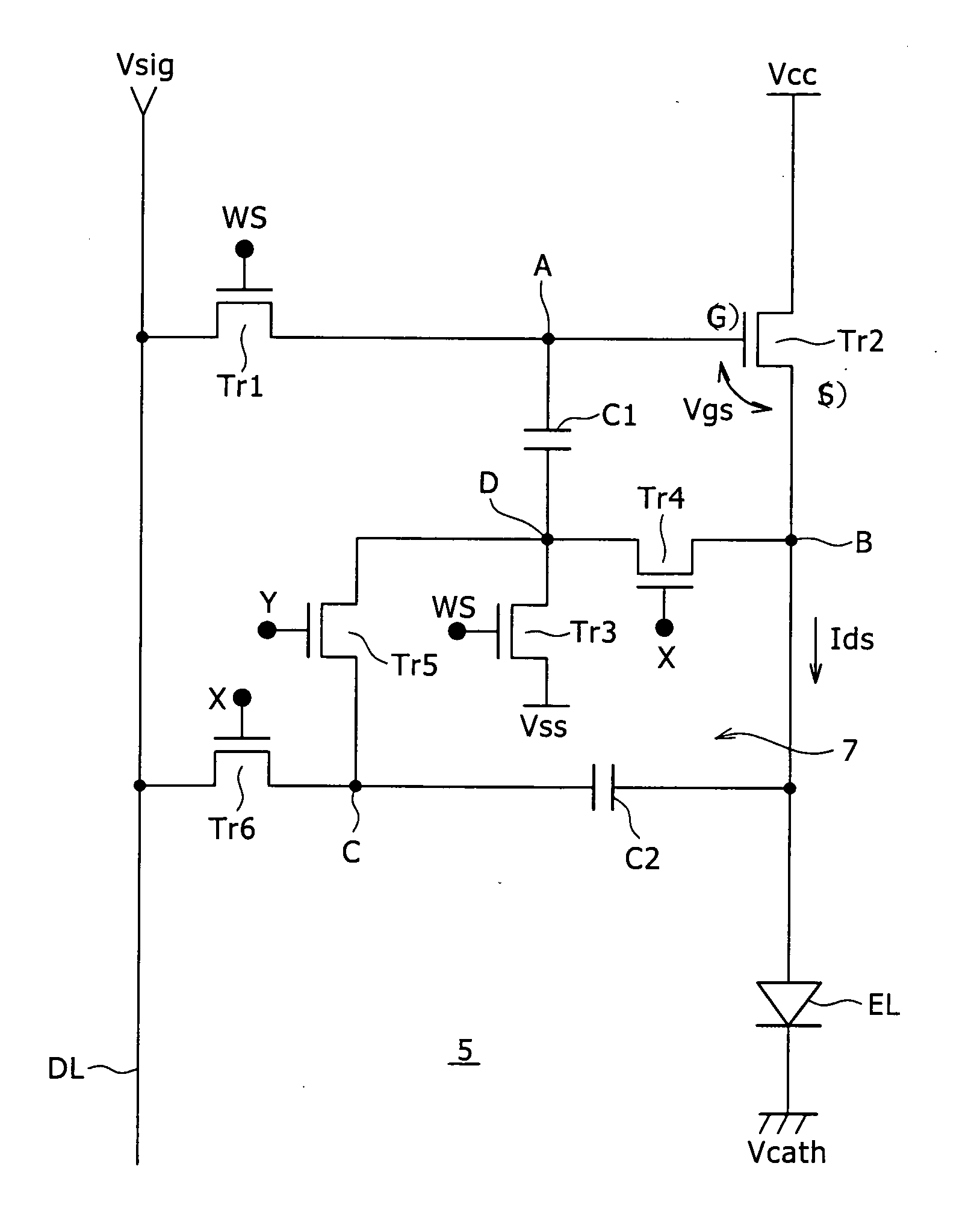

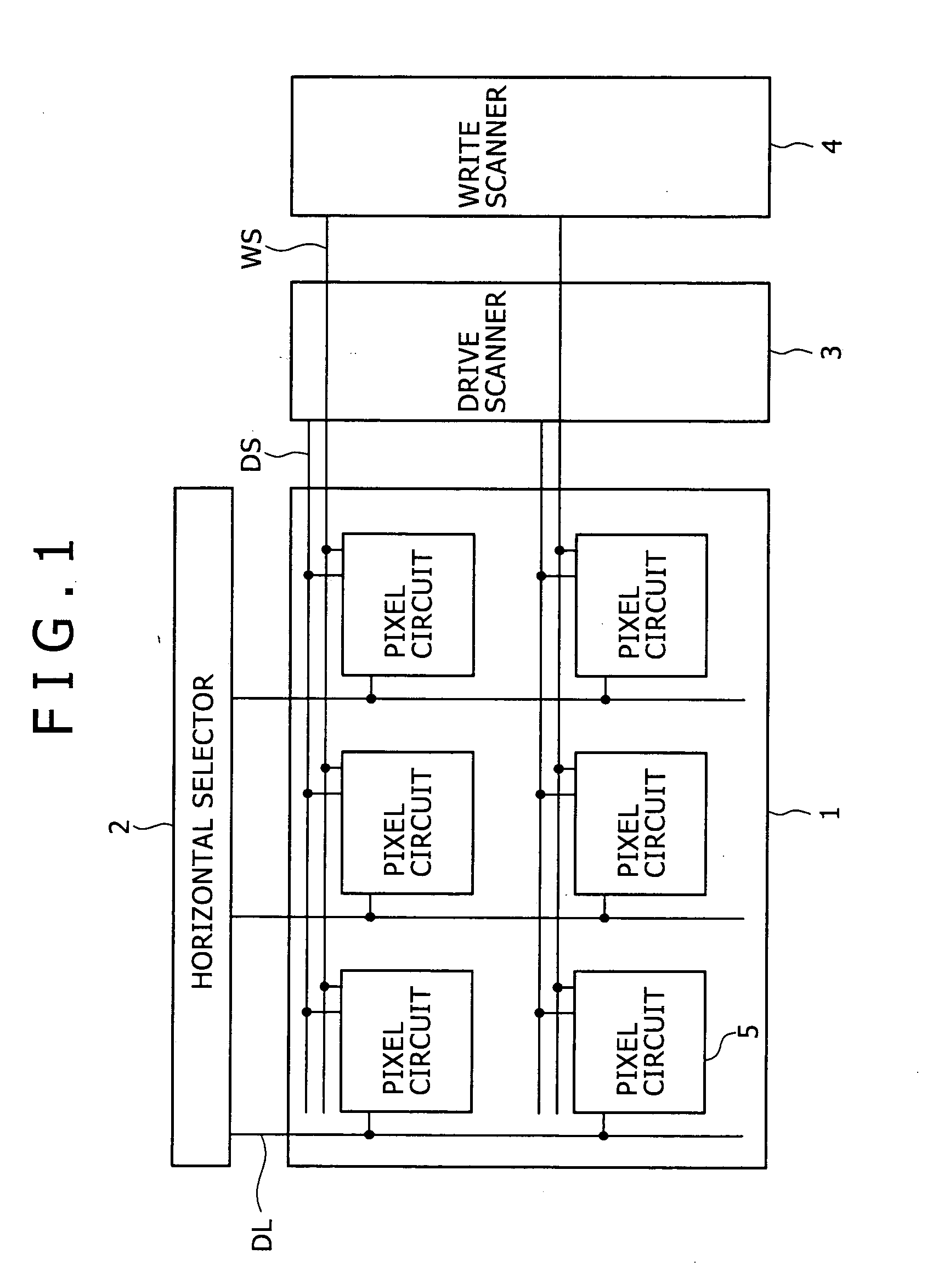

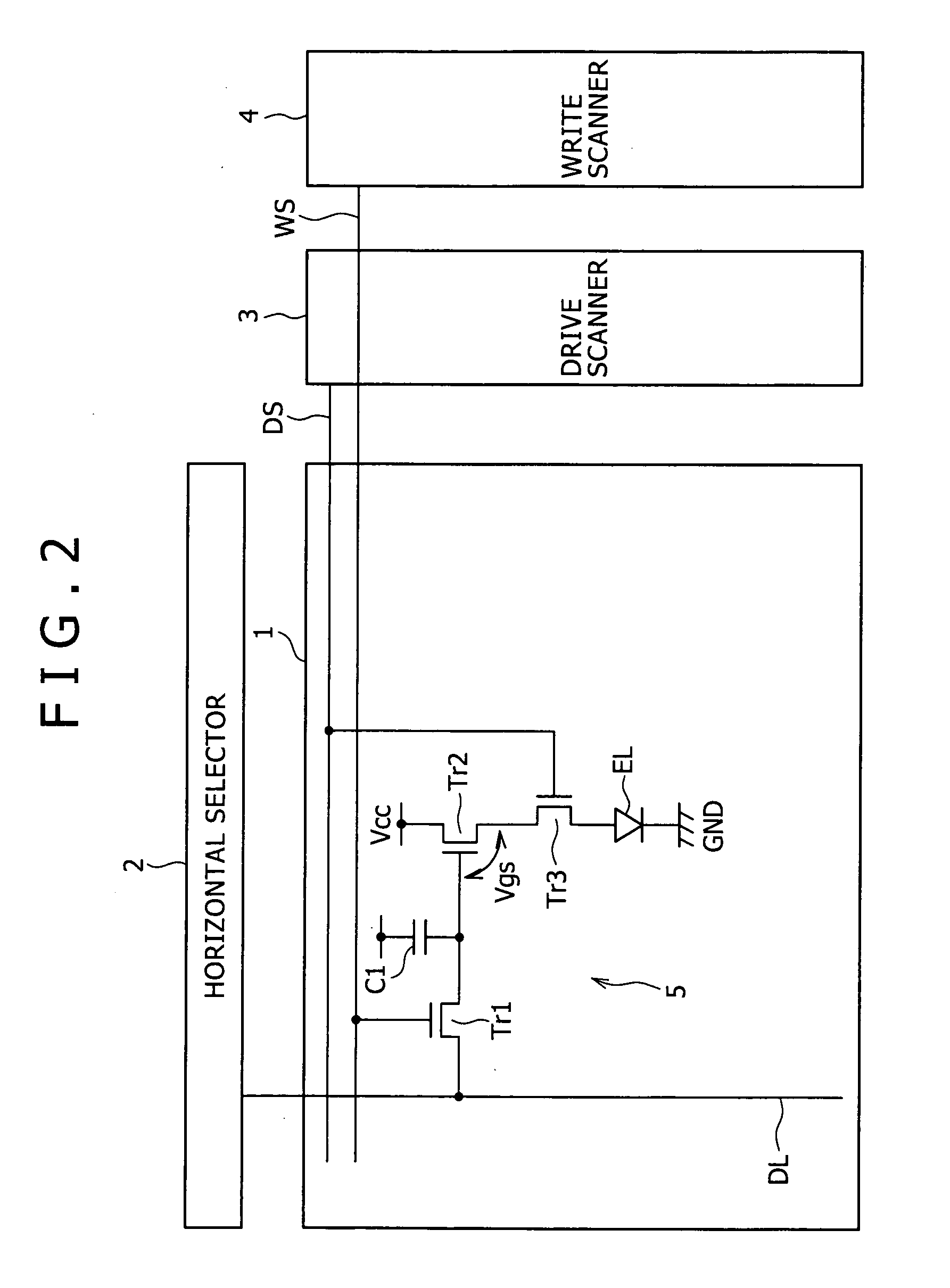

Pixel circuit, display device, driving method of pixel circuit, and driving method of display device

InactiveUS20060022907A1Increase brightnessLow mobilityStatic indicating devicesCapacitanceDriving current

A pixel circuit disposed at a part where a scanning line and a signal line intersect each other includes at least an electrooptic element, a drive transistor, a sampling transistor, and a retaining capacitance. The drive transistor has a gate connected to an input node, a source connected to an output node, and a drain connected to a predetermined power supply potential and supplies a driving current to the electrooptic element according to a signal potential retained in the retaining capacitance. The electrooptic element has one terminal connected to the output node and another terminal connected to a predetermined potential. The sampling transistor is connected between the input node and the signal line and operates when selected by the scanning line, samples an input signal from the signal line, and retains the input signal in the retaining capacitance. The retaining capacitance is connected to the input node. The pixel circuit further includes a compensating circuit which detects a decrease in the driving current from a side of the output node, and feeds back a result of detection to a side of the input node, for compensating for a decrease in the driving current which decrease is attendant on a secular change of the drive transistor.

Owner:SONY CORP

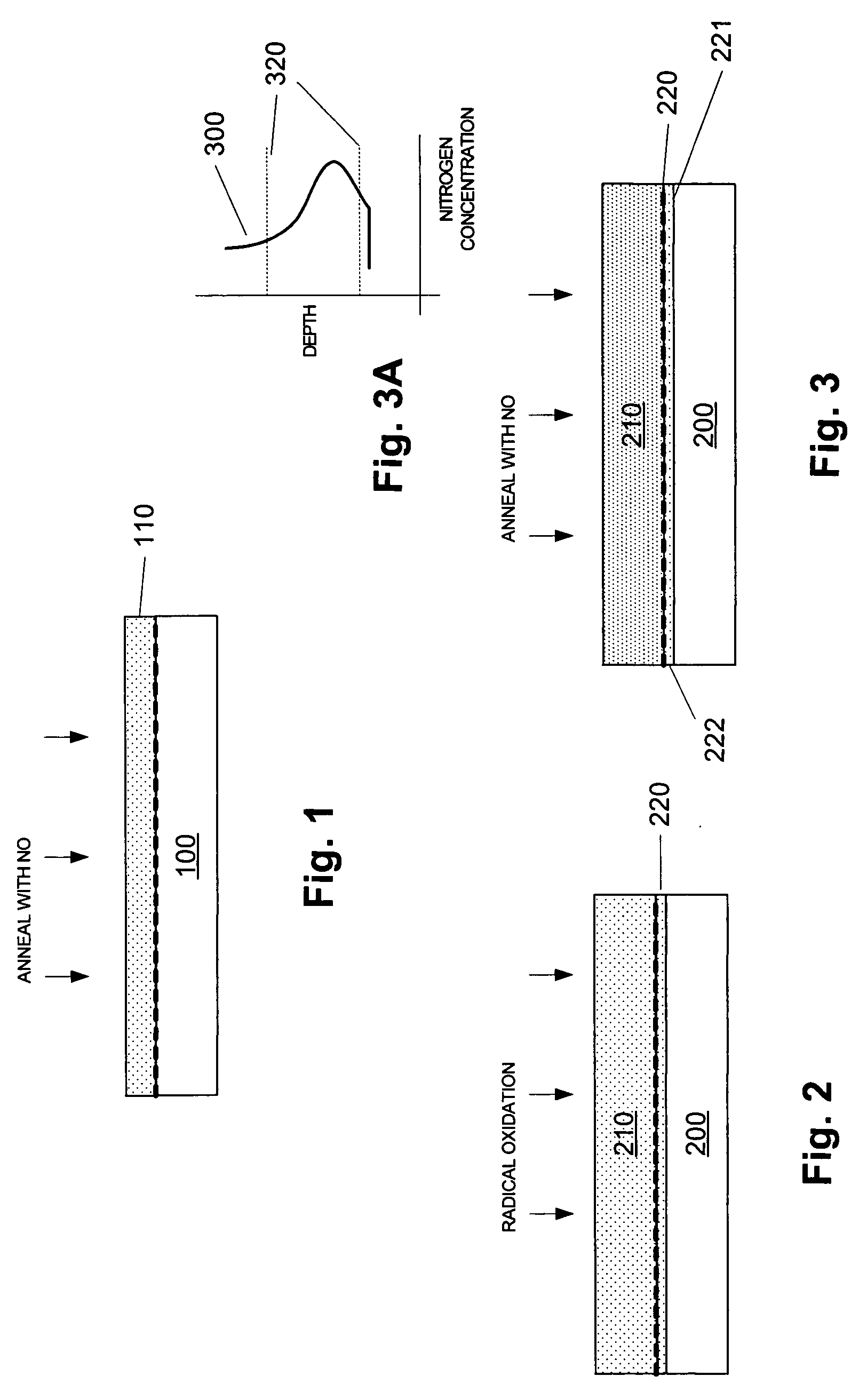

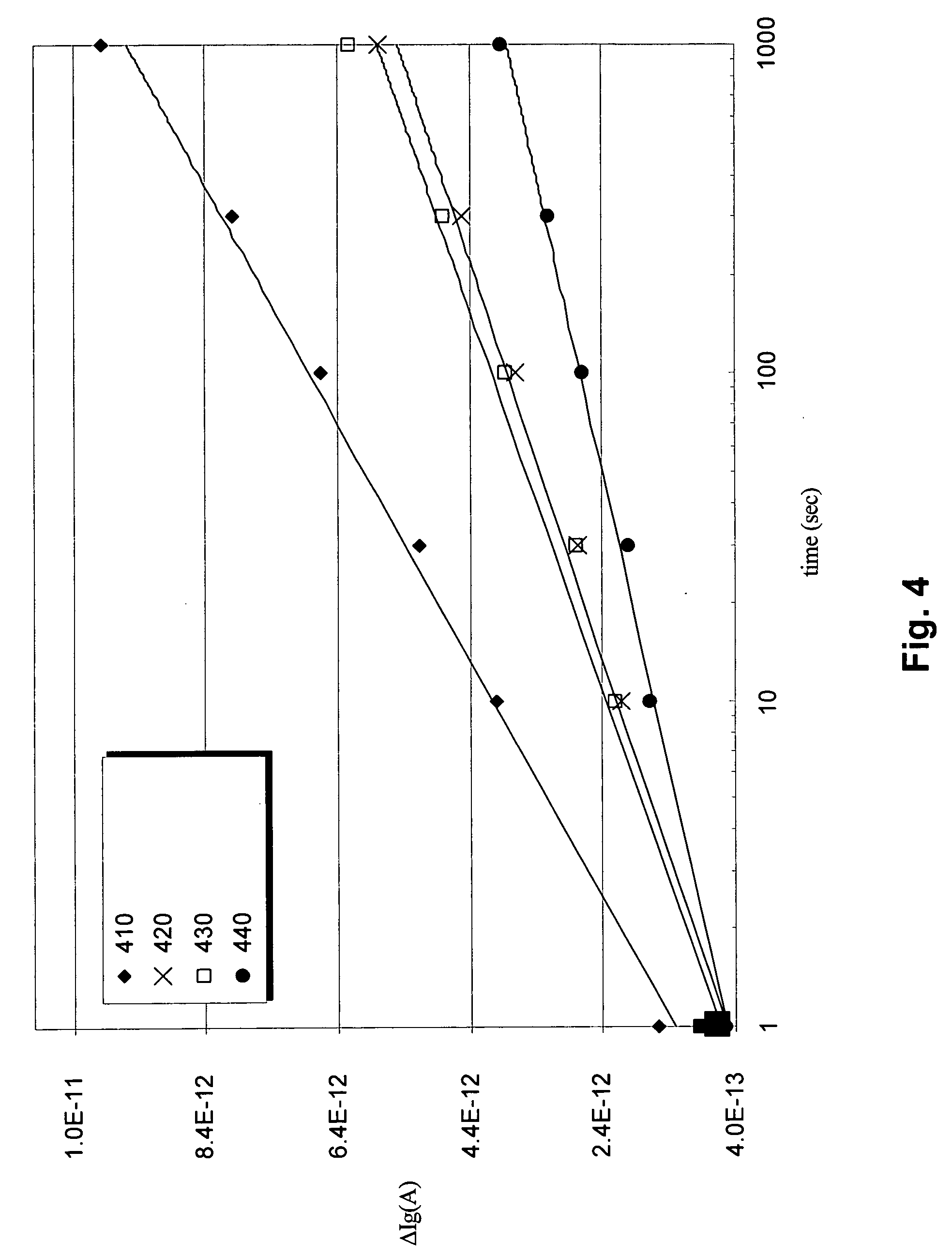

Tunnel oxynitride in flash memories

ActiveUS20050266637A1Avoids decreased mobility of chargeReduce stress induced leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenNitrogen oxide

Methods for forming a tunnel oxide structure device and methods for forming the structure are described. A structure comprising nitrogen is formed on a semiconductor substrate. The structure is oxidized. Nitrogen of the oxide structure is redistributed to form a region of concentrated nitrogen. Oxidizing the structure and redistributing the nitrogen is performed via radical oxidation. Nitrogen is added to the oxide structure. The region of concentrated nitrogen helps to regulate the depth of the added nitrogen.

Owner:MACRONIX INT CO LTD

Electrochemical cell, components thereof, and methods of making and using same

ActiveUS20110287305A1Increase electrochemical performanceReduce self dischargeAlkaline accumulatorsCell electrodesElectrochemical cellNitrogen

An electrochemical cell including at least one nitrogen-containing compound is disclosed. The at least one nitrogen-containing compound may form part of or be included in: an anode structure, a cathode structure, an electrolyte and / or a separator of the electrochemical cell. Also disclosed is a battery including the electrochemical cell.

Owner:SION POWER CORP

Fixing device for at least one operating element suitable for application in sterile areas in surgical operations, such as a surgical instrument

InactiveUS6471172B1Risk of formationControlled rotational mobility of the cap elementDiagnosticsSurgical drapesSurgical operationEngineering

A fixing device is disclosed for at least one operating element or fixing element suitable for application in sterile areas in surgical operations, which is largely freely positioned in three dimensions and supported for fixing, while the sterile area is separated from the non-sterile area substantially by a sheet-like covering. A holding device is provided which is located in the non-sterile area and which, while being at least separated by the covering, enters into an operative connection via an active surface with the operating or fixing element, with the operative connection being based on magnetic forces.

Owner:LEMKE NORBERT +1

Oxide semiconductor field effect transistor and method for manufacturing the same

ActiveUS20100276688A1Easy to producePoor smoothnessTransistorVacuum evaporation coatingLanthanideField-effect transistor

A field effect transistor including a semiconductor layer including a composite oxide which contains In, Zn, and one or more elements X selected from the group consisting of Zr, Hf, Ge, Si, Ti, Mn, W, Mo, V, Cu, Ni, Co, Fe, Cr, Nb, Al, B, Sc, Y and lanthanoids in the following atomic ratios (1) to (3):In / (In+Zn)=0.2 to 0.8 (1)In / (In+X)=0.29 to 0.99 (2)Zn / (X+Zn)=0.29 to 0.99 (3).

Owner:IDEMITSU KOSAN CO LTD

Breathing mask with integrated suction area

InactiveUS7481221B2High wearing comfortImprove securityBreathing filtersRespiratory masksEngineeringAmbient air

A breathing mask for breathing support devices (10) to guide the breathing support gas to the patient. The mask includes a mask body including a material that is permeable to air at least in partial areas. A gas guiding structure is provided which can be connected to suction openings of the breathing support device (10). The gas guiding structure extends through the interior of the mask body. The gas guiding structure for the transport / delivery of gas is limited partially by air-permeable areas of the wall of the mask body, through which ambient air can be drawn in. The mask is characterized by high wear comfort and improved safety against accidental coverage of the suction areas.

Owner:DRAGERWERK AG

Semiconductor Structures with Rare-earths

ActiveUS20090236595A1Improve device performanceQuality improvementTransistorSolid-state devicesSemiconductor materialsSemiconductor structure

The present invention discloses structures to increase carrier mobility using engineered substrate technologies for a solid state device. Structures employing rare-earth compounds enable heteroepitaxy of different semiconductor materials of different orientations.

Owner:IQE

Surface-stabilized semiconductor device

InactiveUS20080121876A1Economical and reliableImprove pressure resistanceSemiconductor/solid-state device detailsSolid-state devicesHigh-electron-mobility transistorOrganic semiconductor

A high electron mobility transistor is disclosed which has a main semiconductor region formed on a silicon substrate. The main semiconductor region is a lamination of a buffer layer on the substrate, an electron transit layer on the buffer layer, and an electron supply layer on the electron transit layer. A source, drain, and gate overlie the electron supply layer. Also formed on the electron supply layer is a surface-stabilizing organic semiconductor overlay which is of p conductivity type in contrast to the n type of the electron supply layer.

Owner:SANKEN ELECTRIC CO LTD