Patents

Literature

3987results about How to "Increase current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

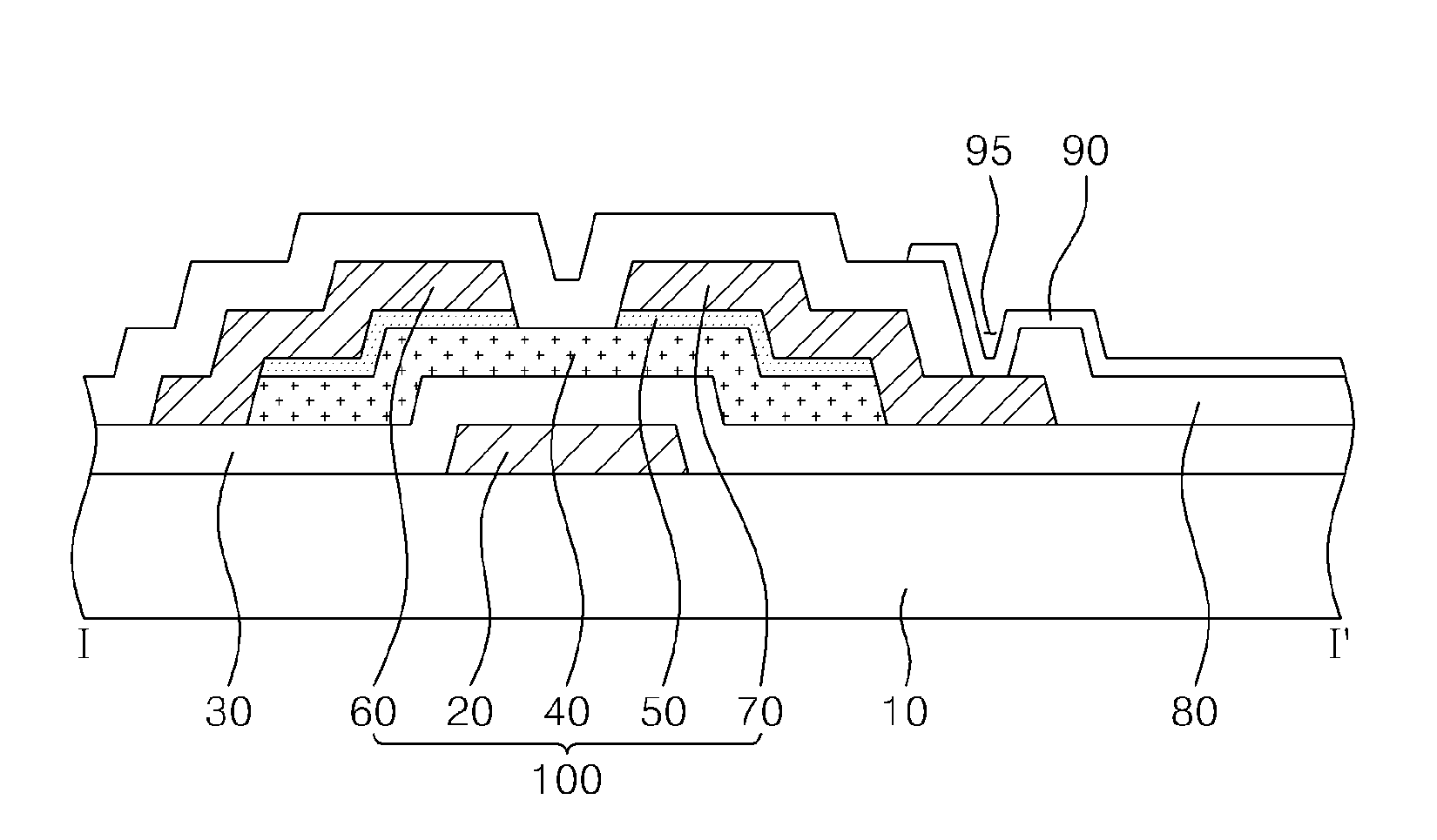

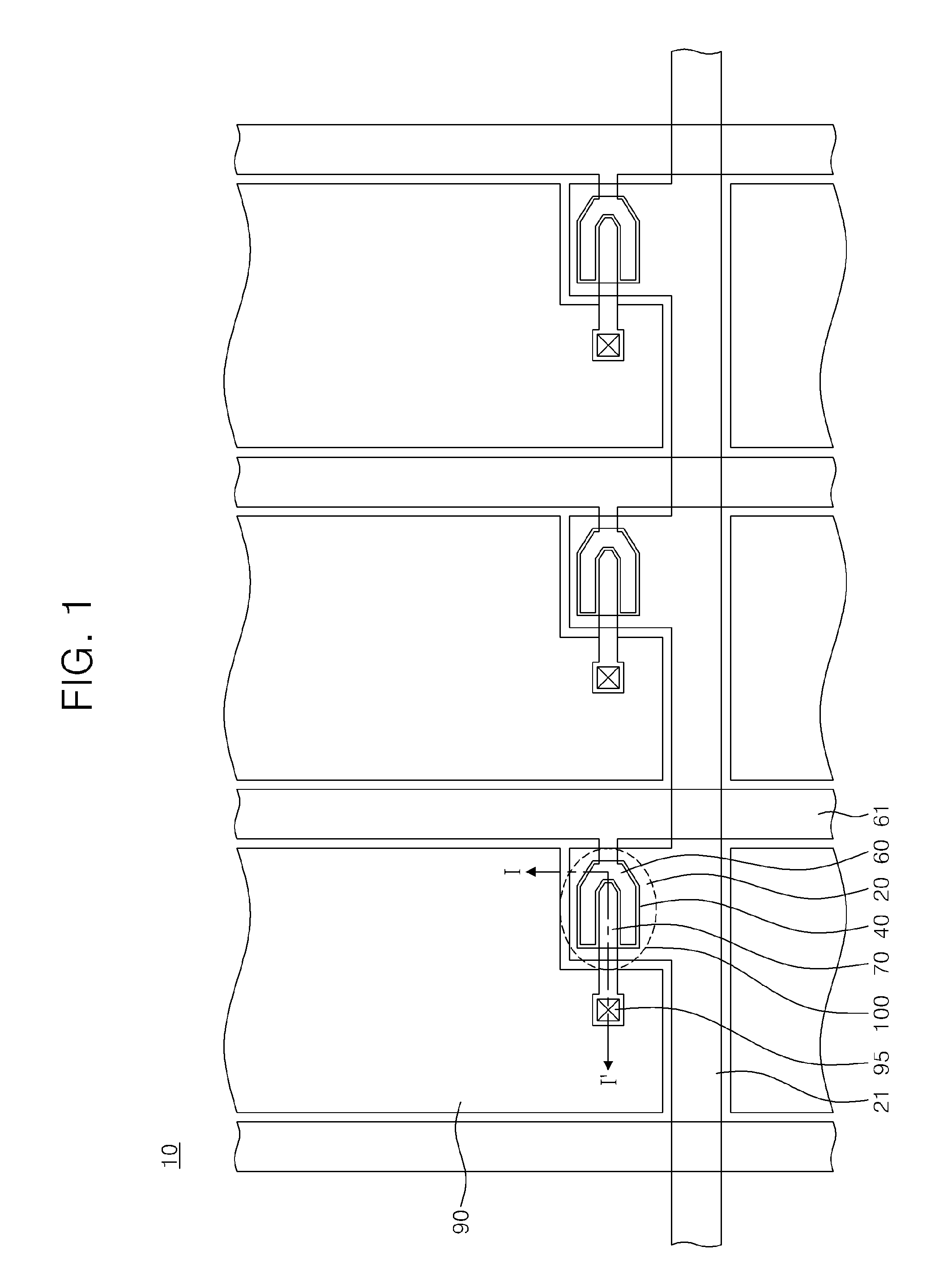

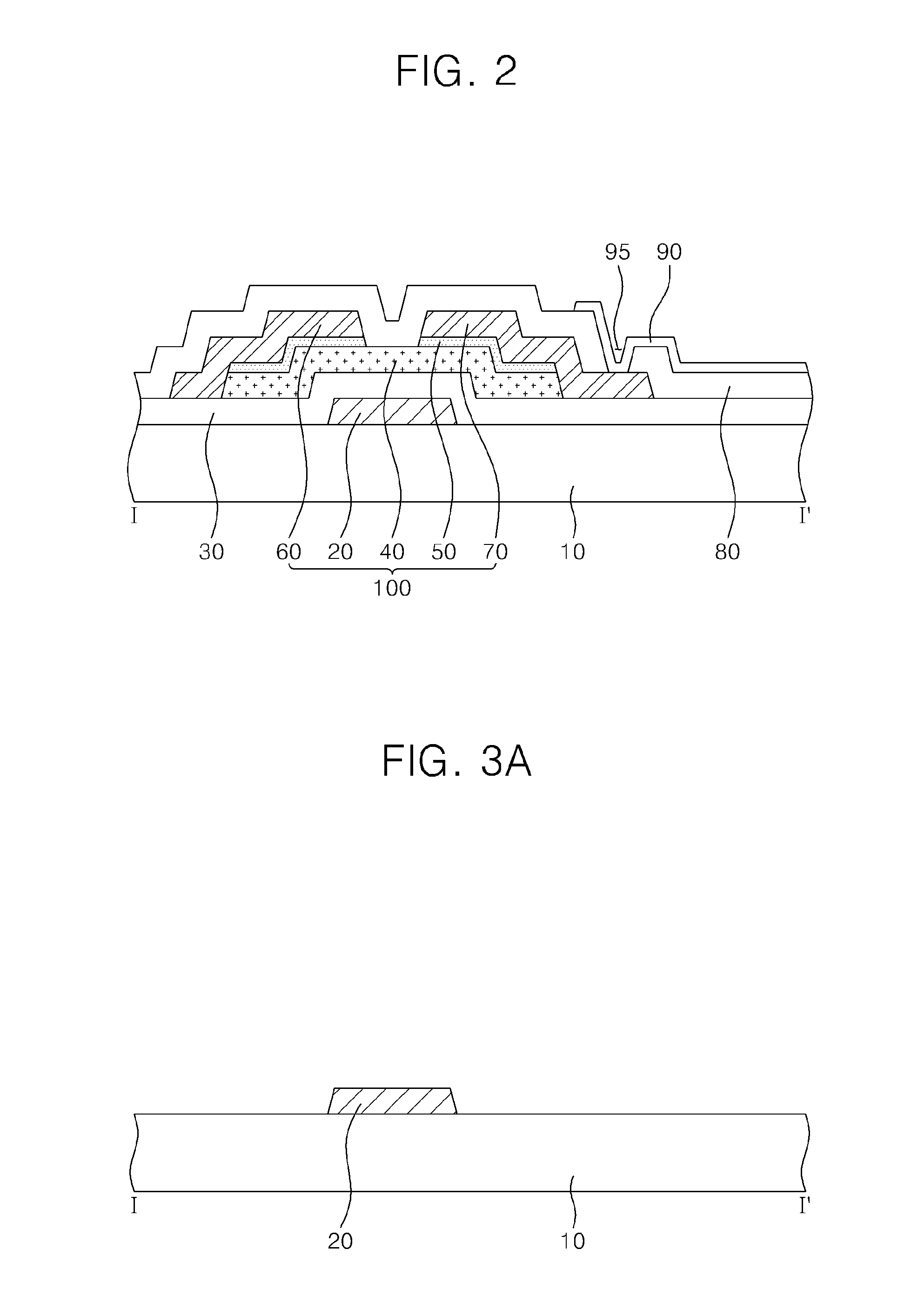

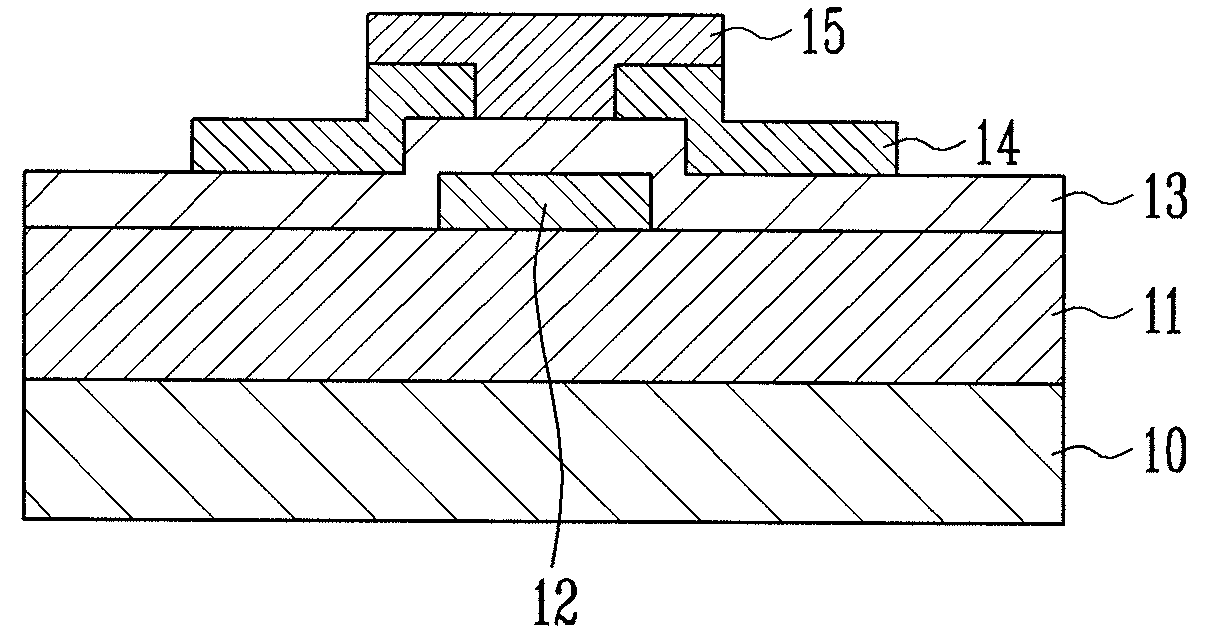

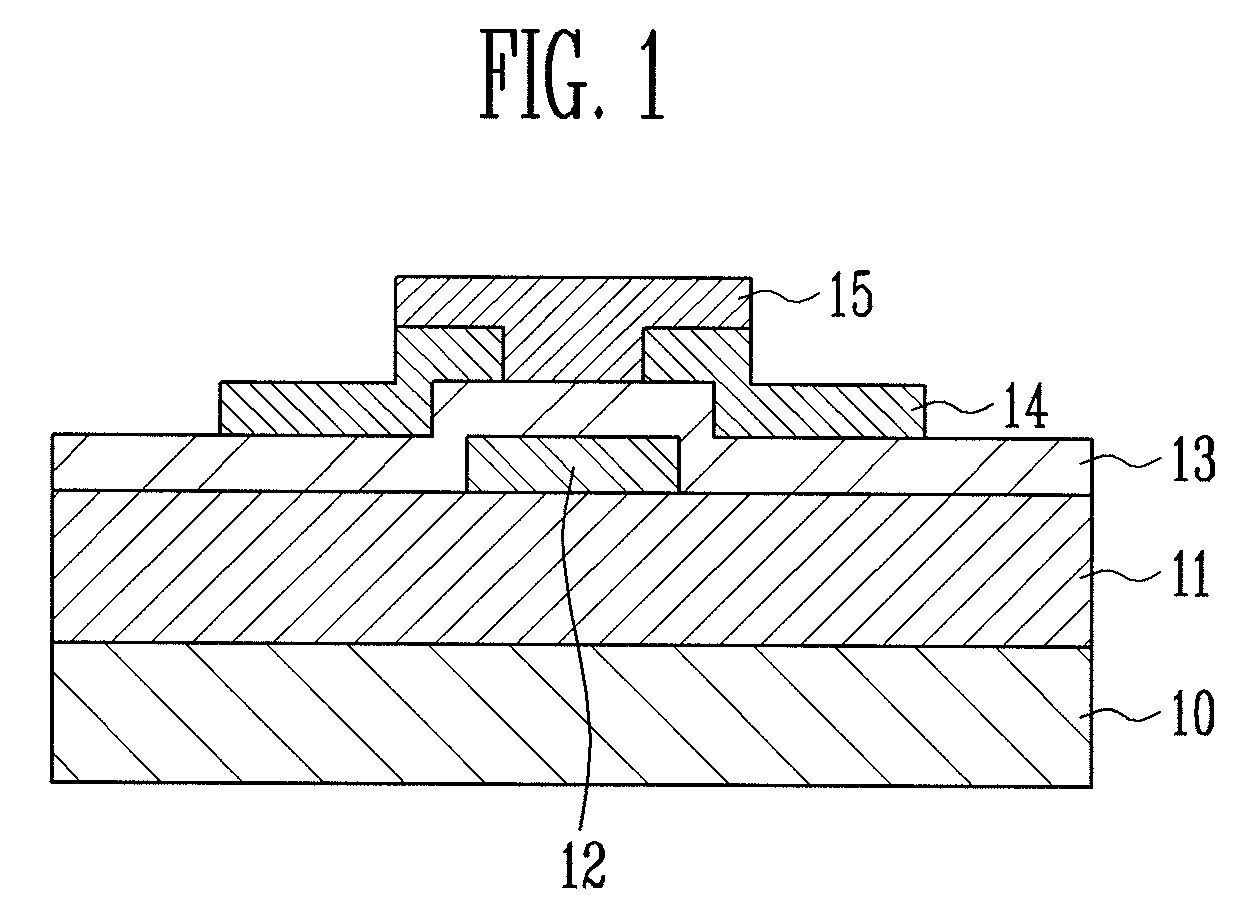

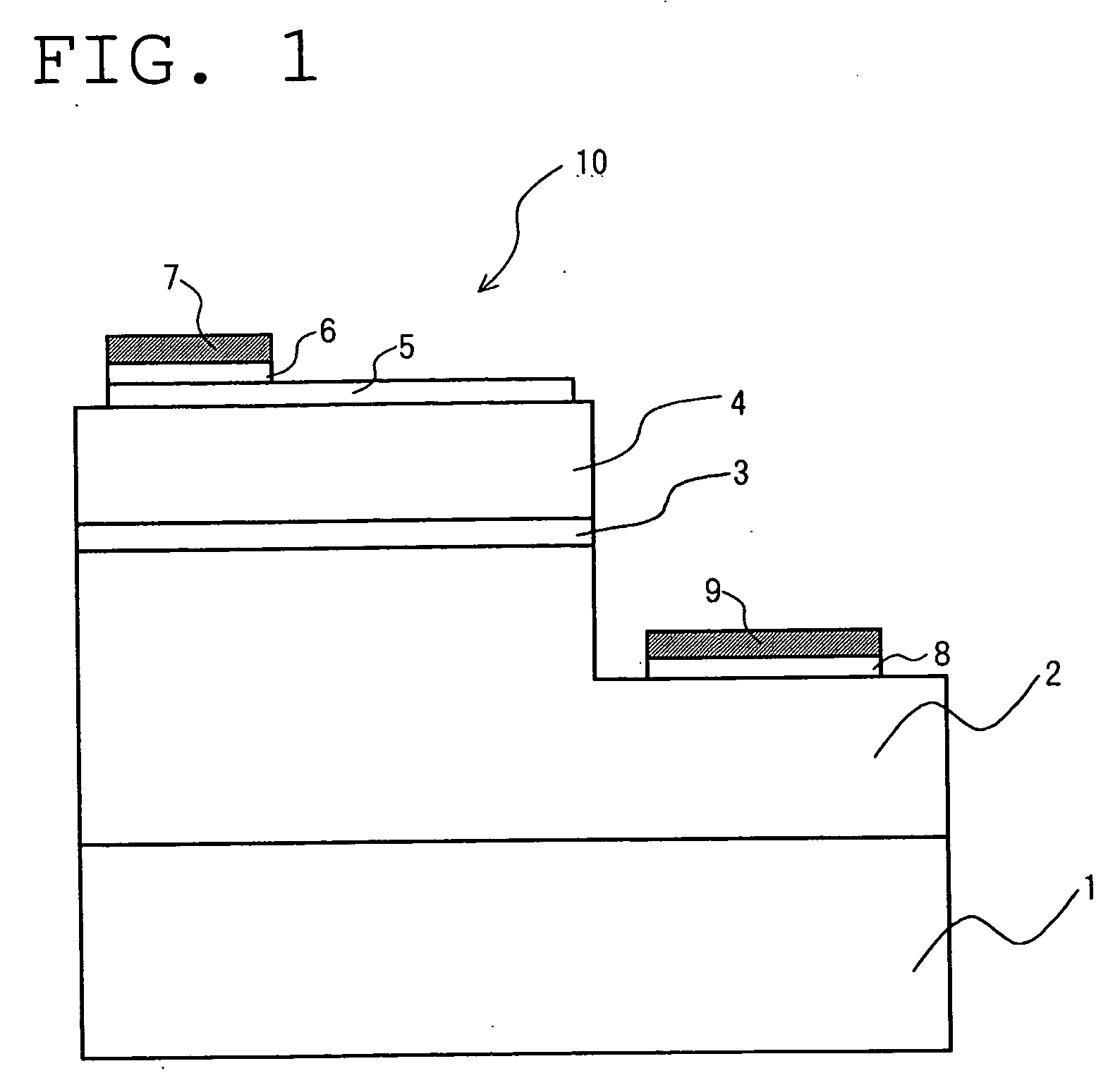

Thin film transitor substrate and method of manufacturing the same

InactiveUS20080258143A1Increases process time and leakage current and serial contact resistanceDegrading property of TFTTransistorSemiconductor/solid-state device manufacturingOxide semiconductorOxide

A method of manufacturing a thin film transistor (“TFT”) substrate includes forming a first conductive pattern group including a gate electrode on a substrate, forming a gate insulating layer on the first conductive pattern group, forming a semiconductor layer and an ohmic contact layer on the gate insulating layer by patterning an amorphous silicon layer and an oxide semiconductor layer, forming a second conductive pattern group including a source electrode and a drain electrode on the ohmic contact layer by patterning a data metal layer, forming a protection layer including a contact hole on the second conductive pattern group, and forming a pixel electrode on the contact hole of the protection layer. The TFT substrate including the ohmic contact layer formed of an oxide semiconductor is further provided.

Owner:SAMSUNG ELECTRONICS CO LTD

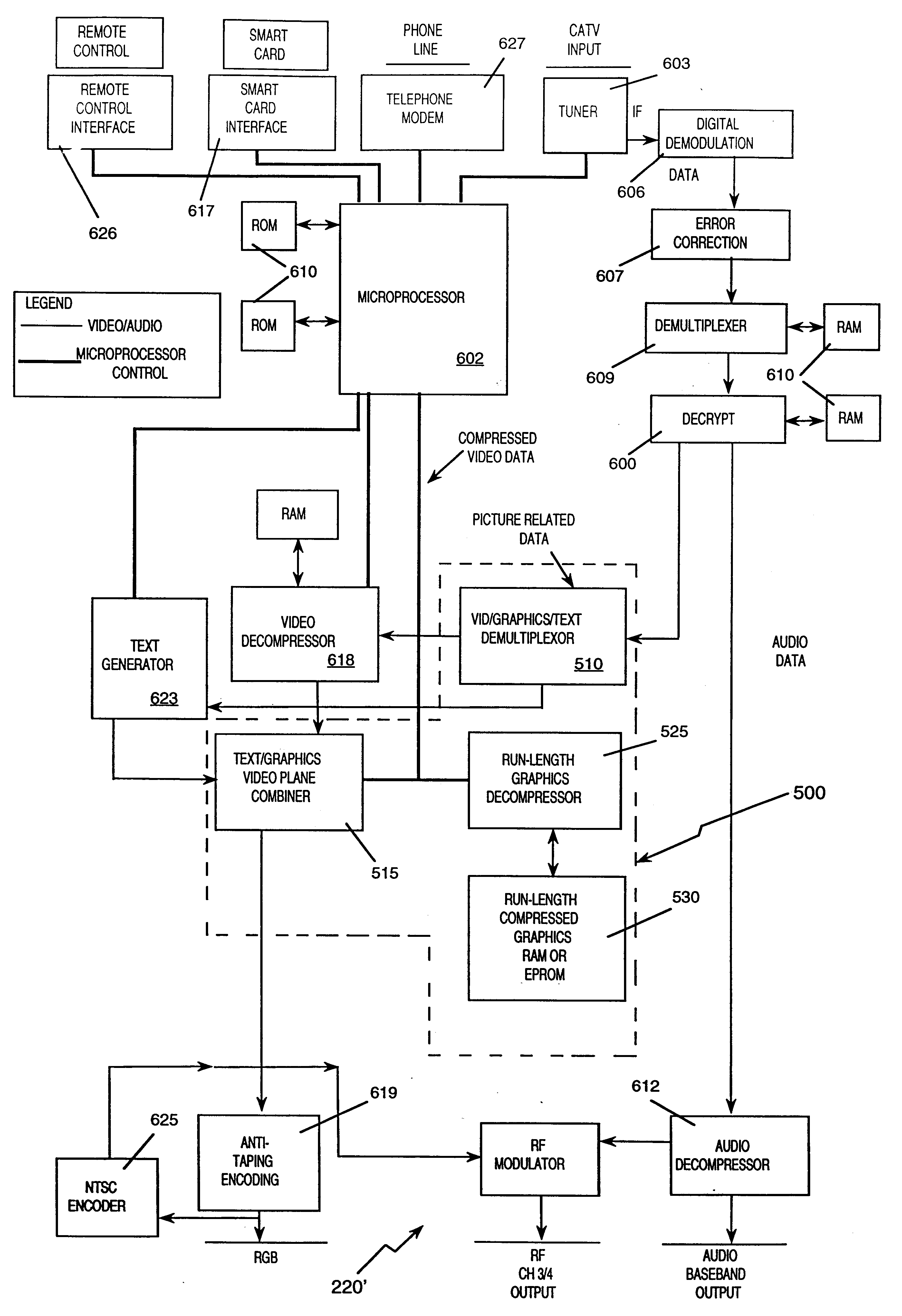

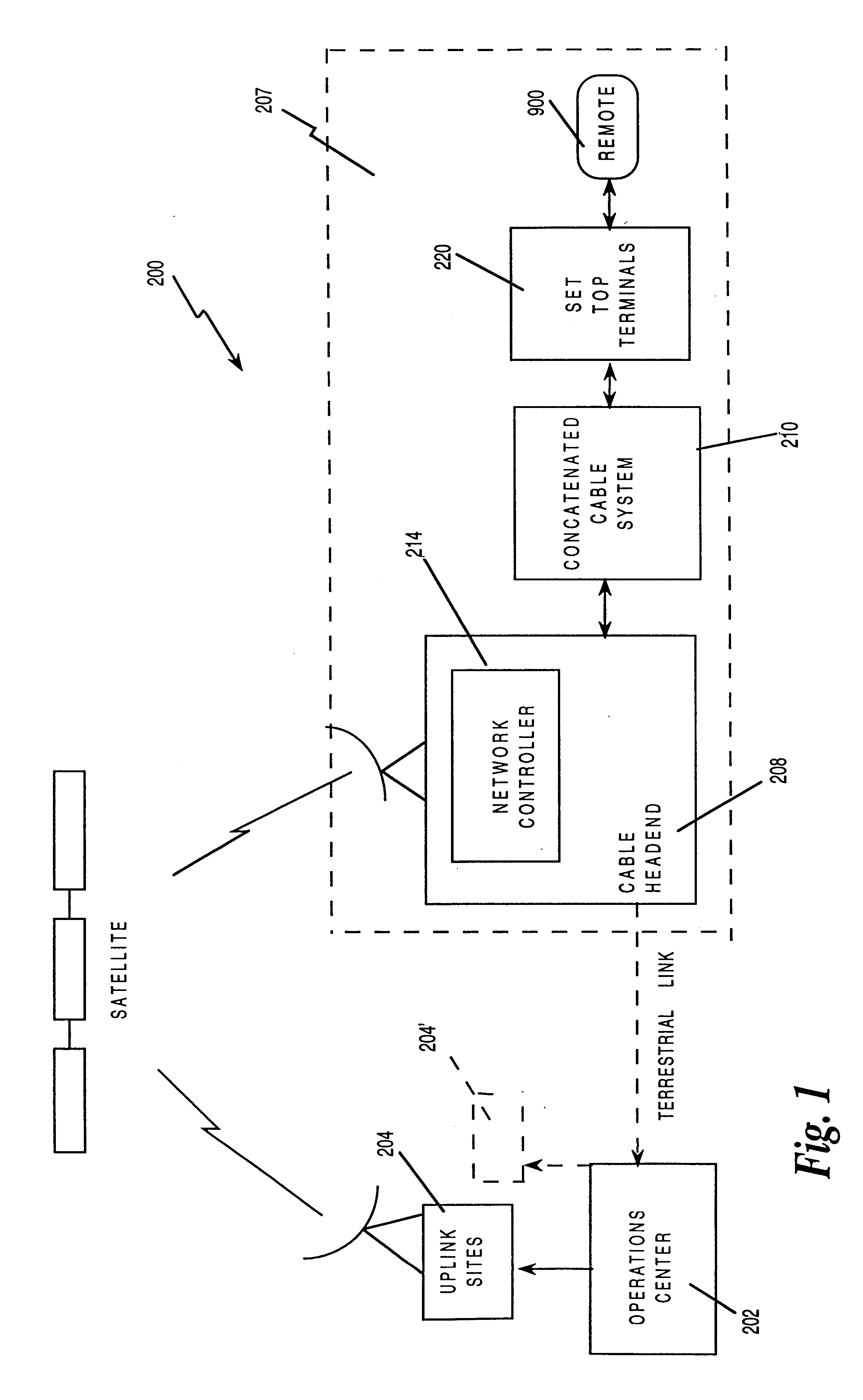

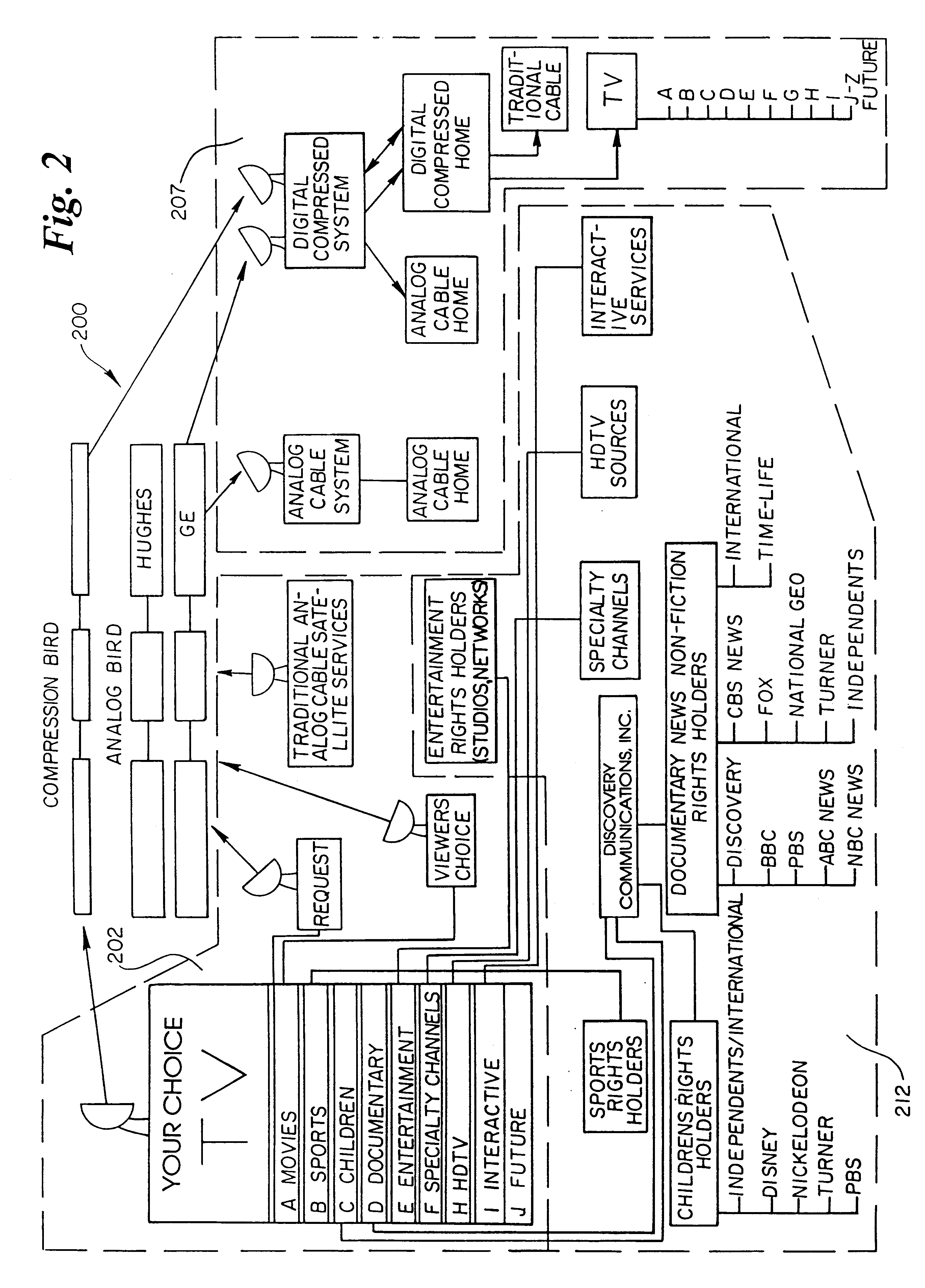

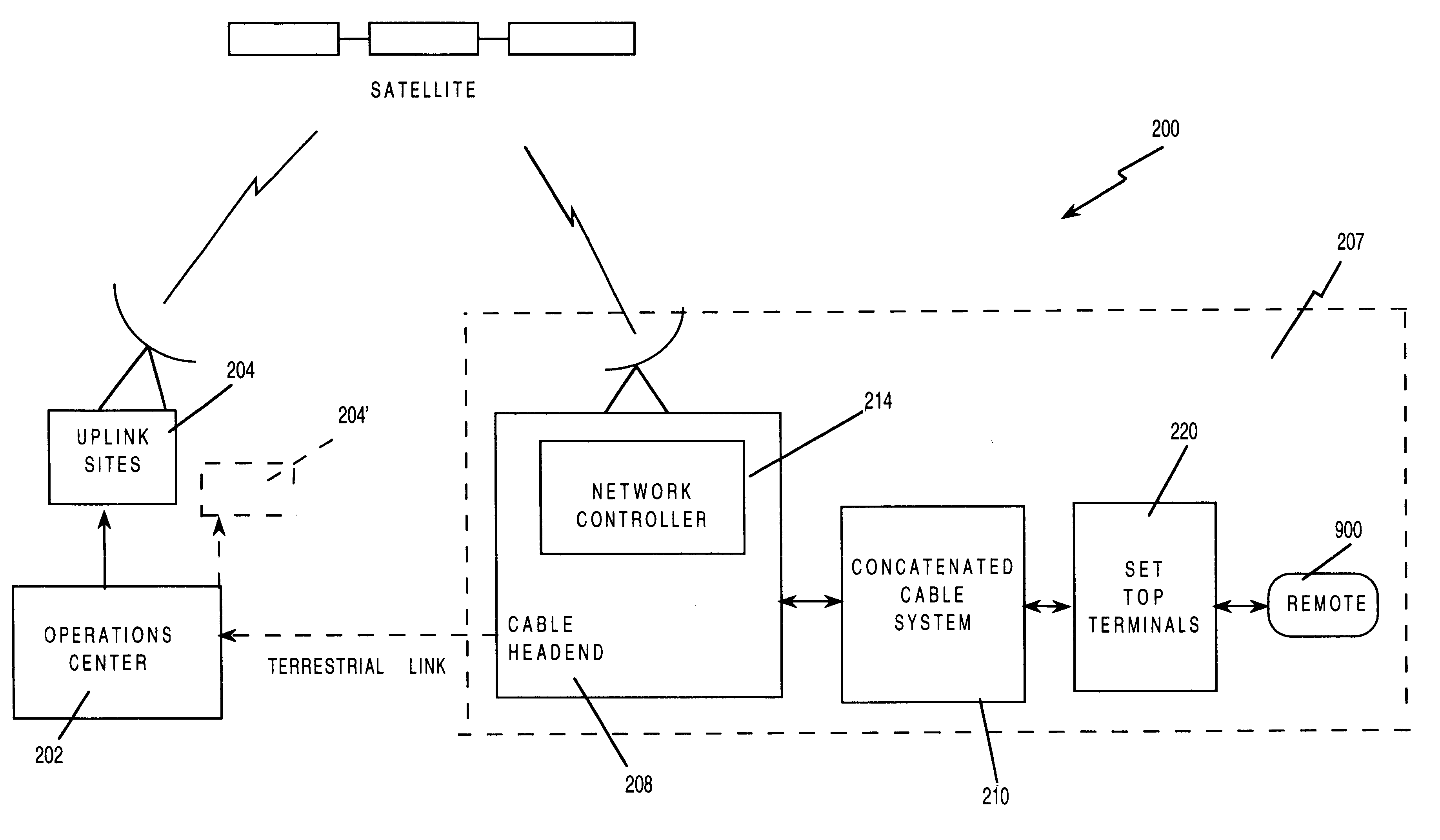

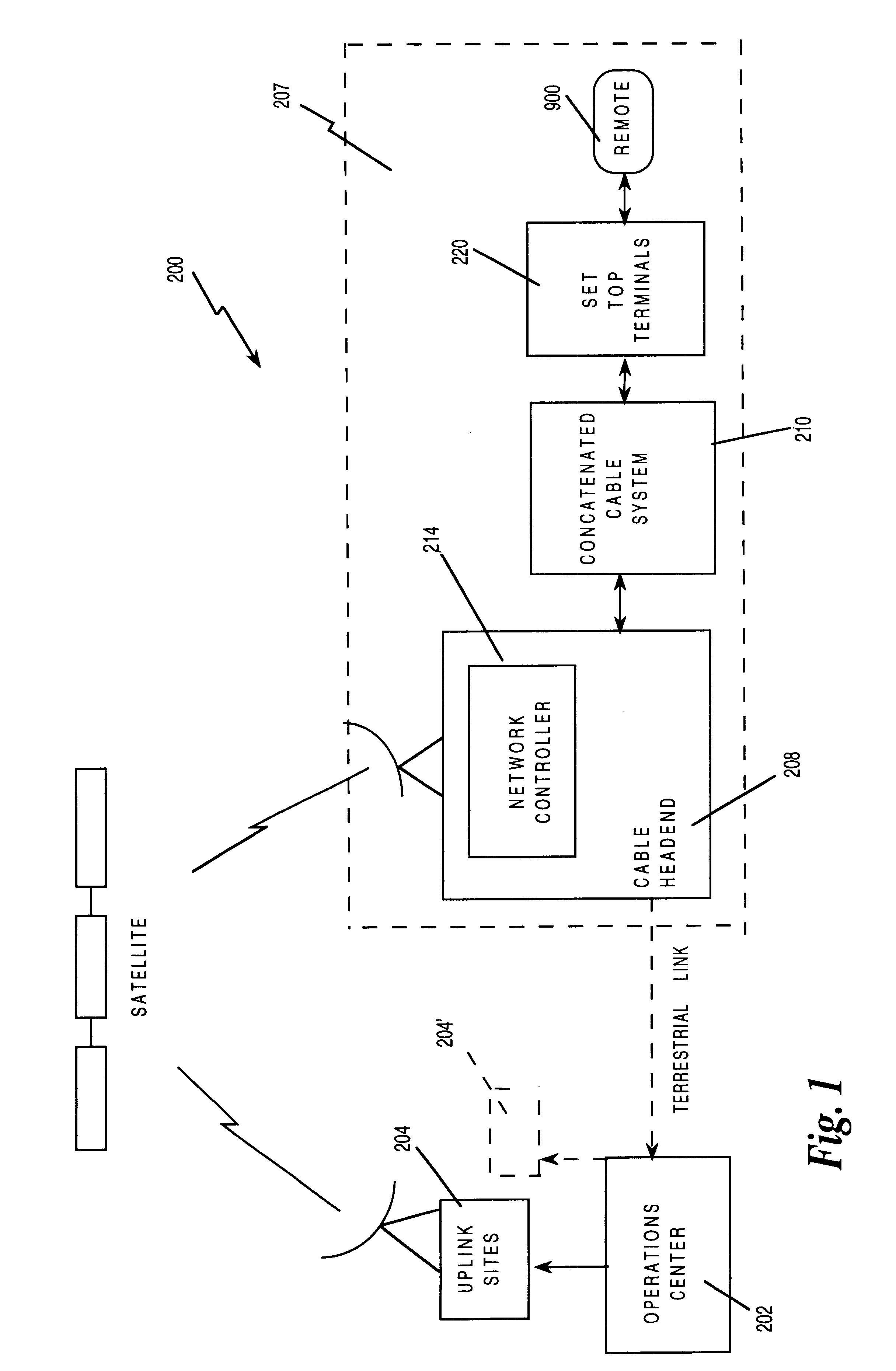

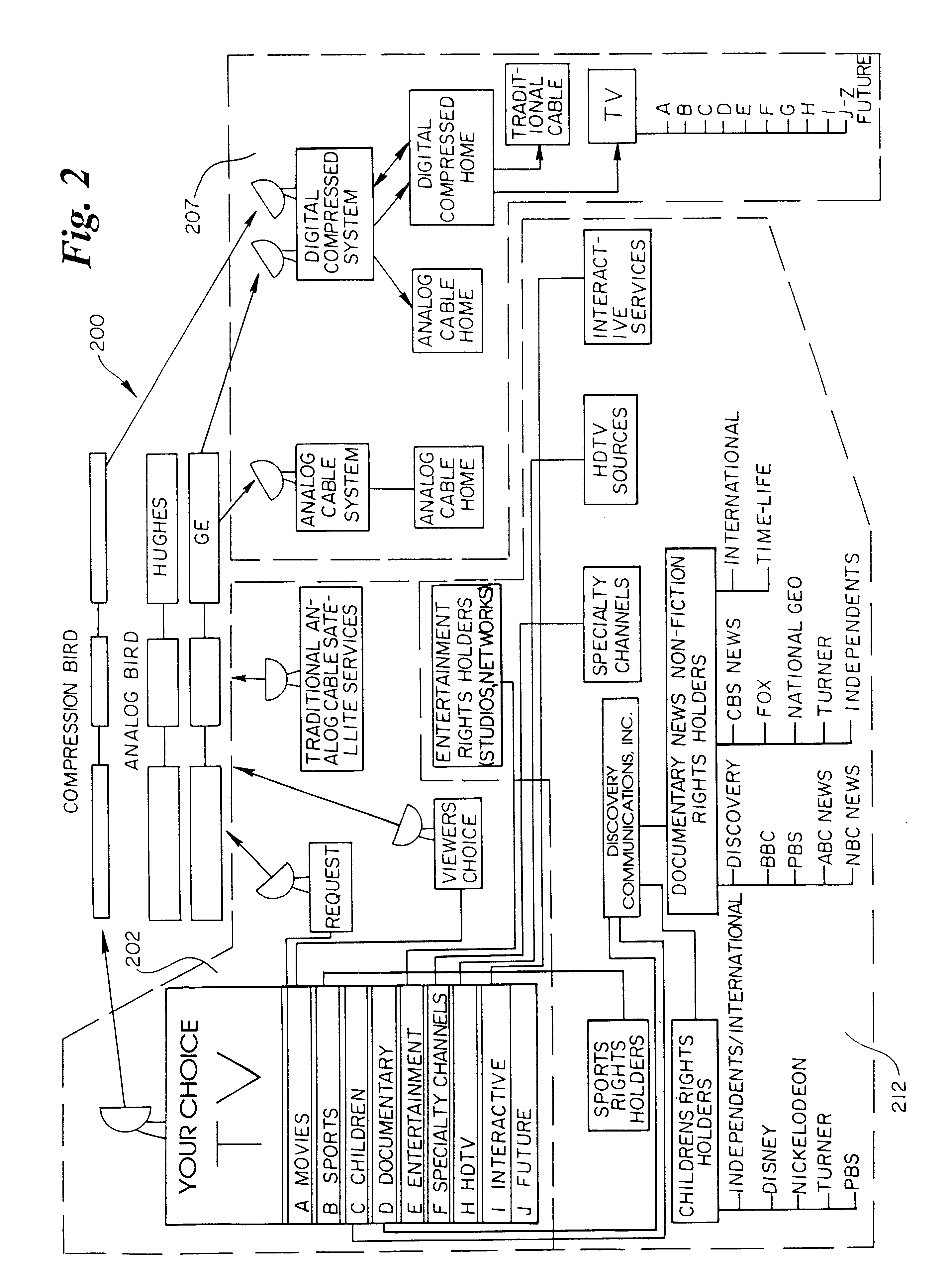

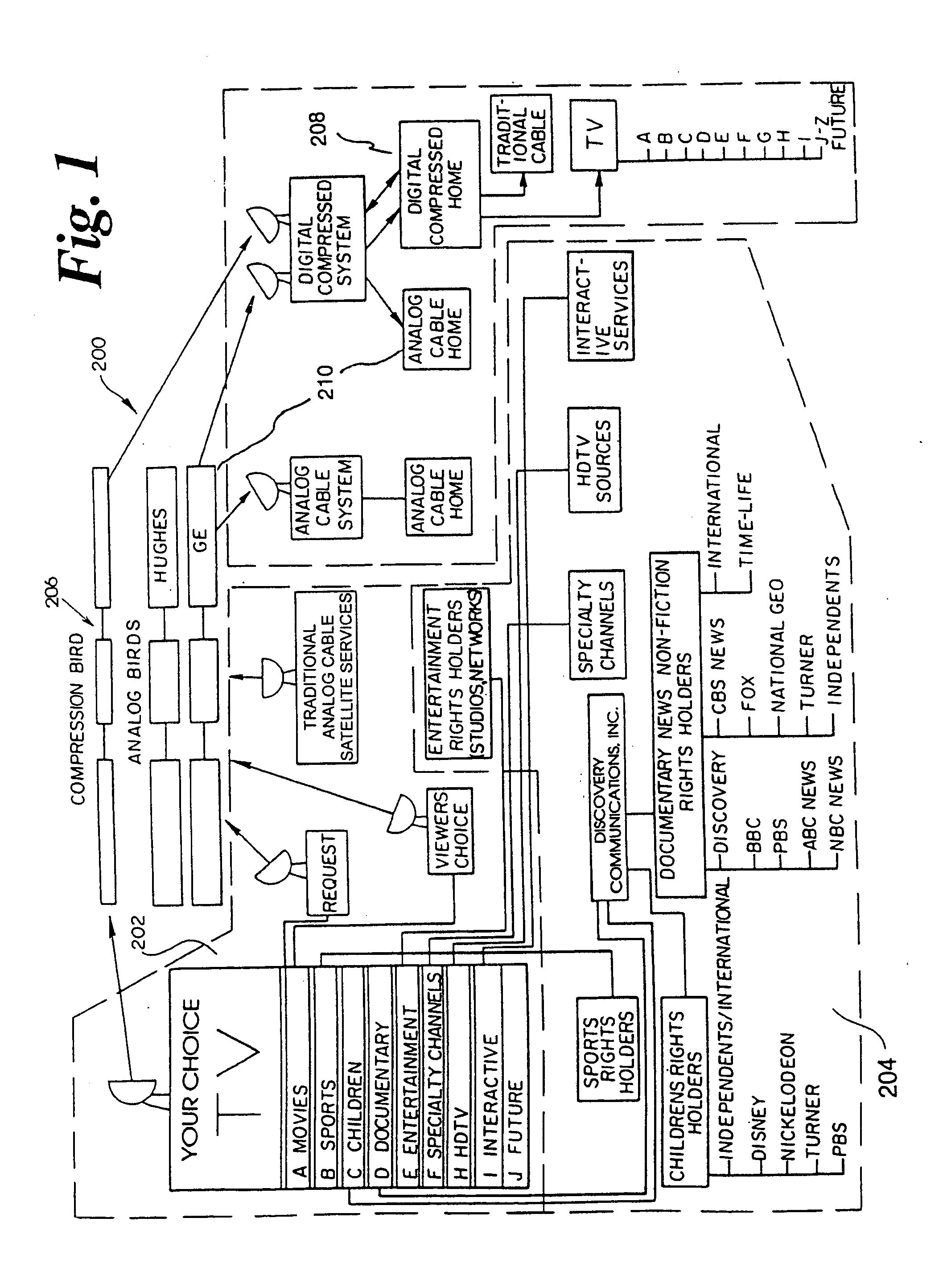

Card for a set top terminal

InactiveUS6181335B1Speed up searchImprove throughputTelevision system detailsPulse modulation television signal transmissionData signalUser Friendly

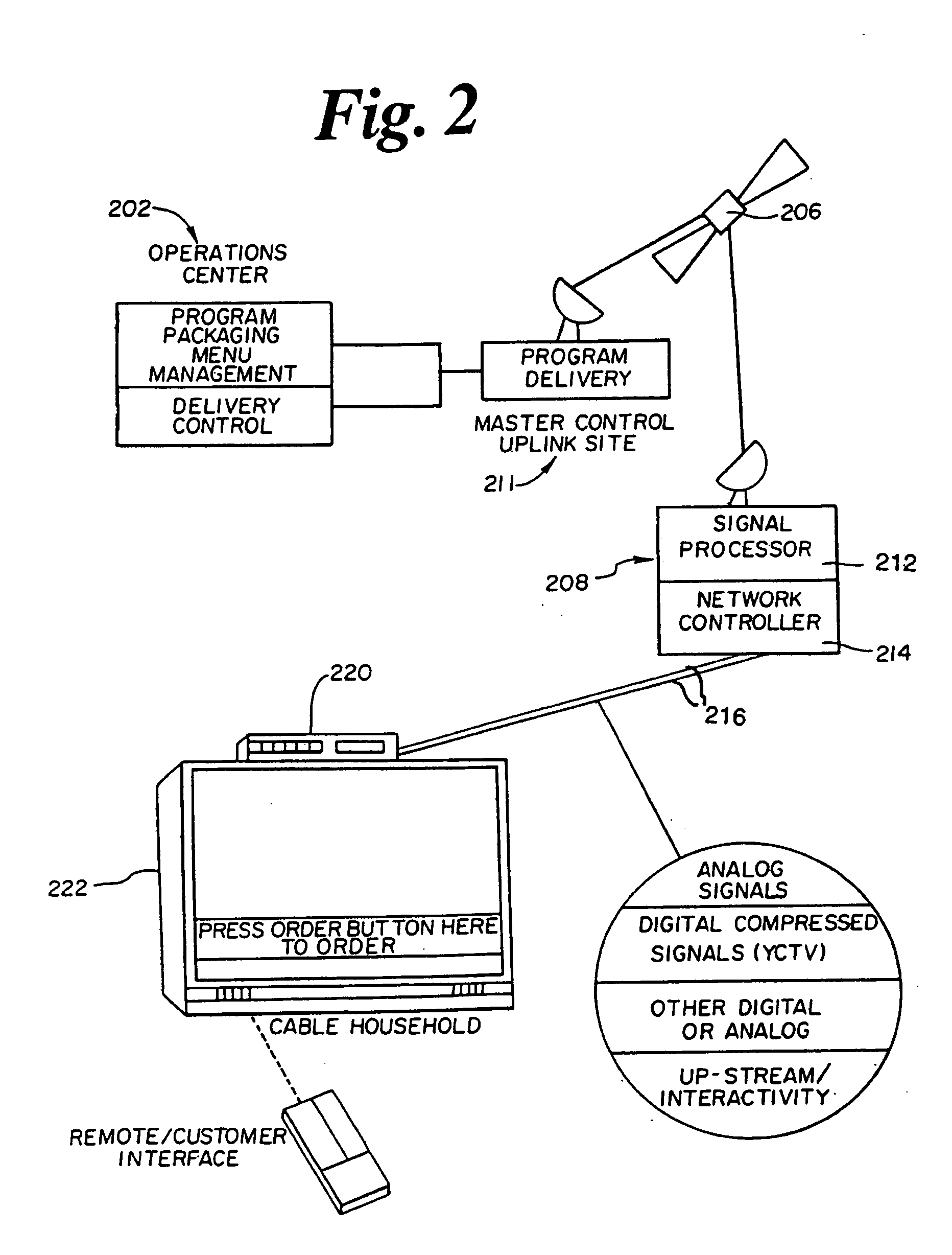

An apparatus for upgrading a viewer interface for a television program delivery system (200) is described. The invention relates to methods and devices for viewer pathways to television programs and services. Specifically, the apparatus involves hardware and software used in conjunction with the interface and a television at the viewer home to create a user friendly menu based approach to accessing programs and services. The apparatus is particularly useful in a program delivery system (200) with hundreds of programs and a data signal carrying program information. The disclosure describes menu generation and menu selection of television programs.

Owner:COMCAST IP HLDG I

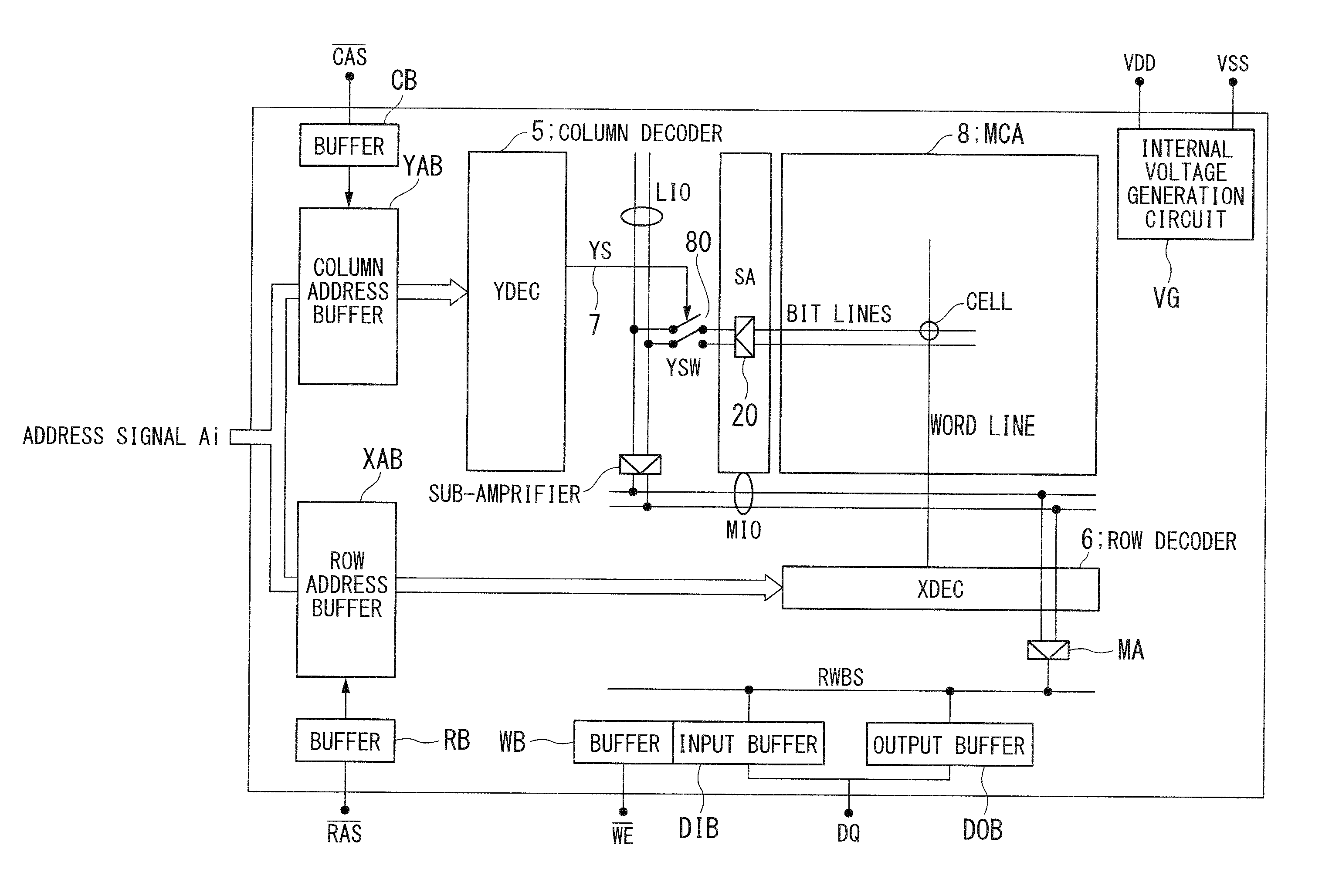

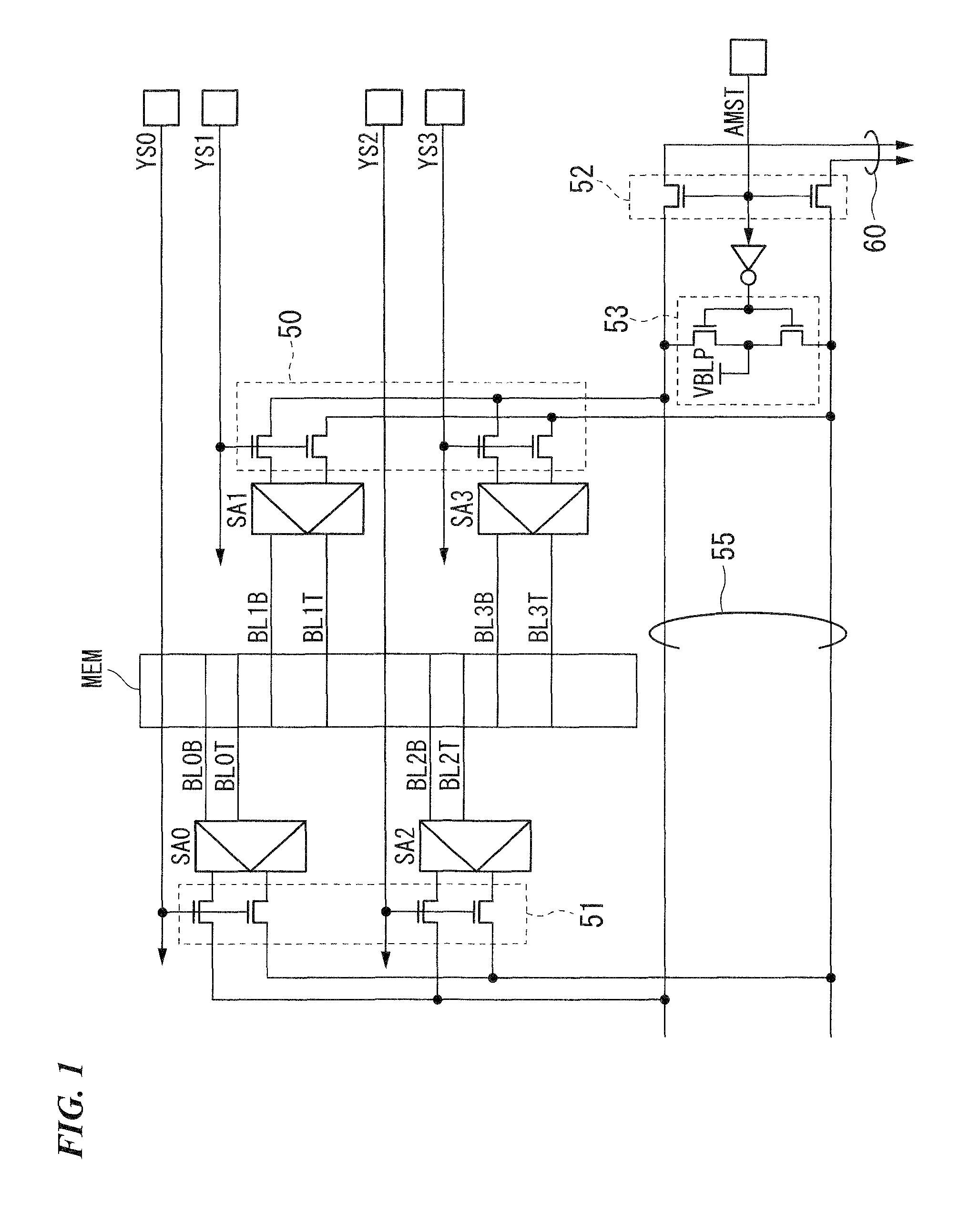

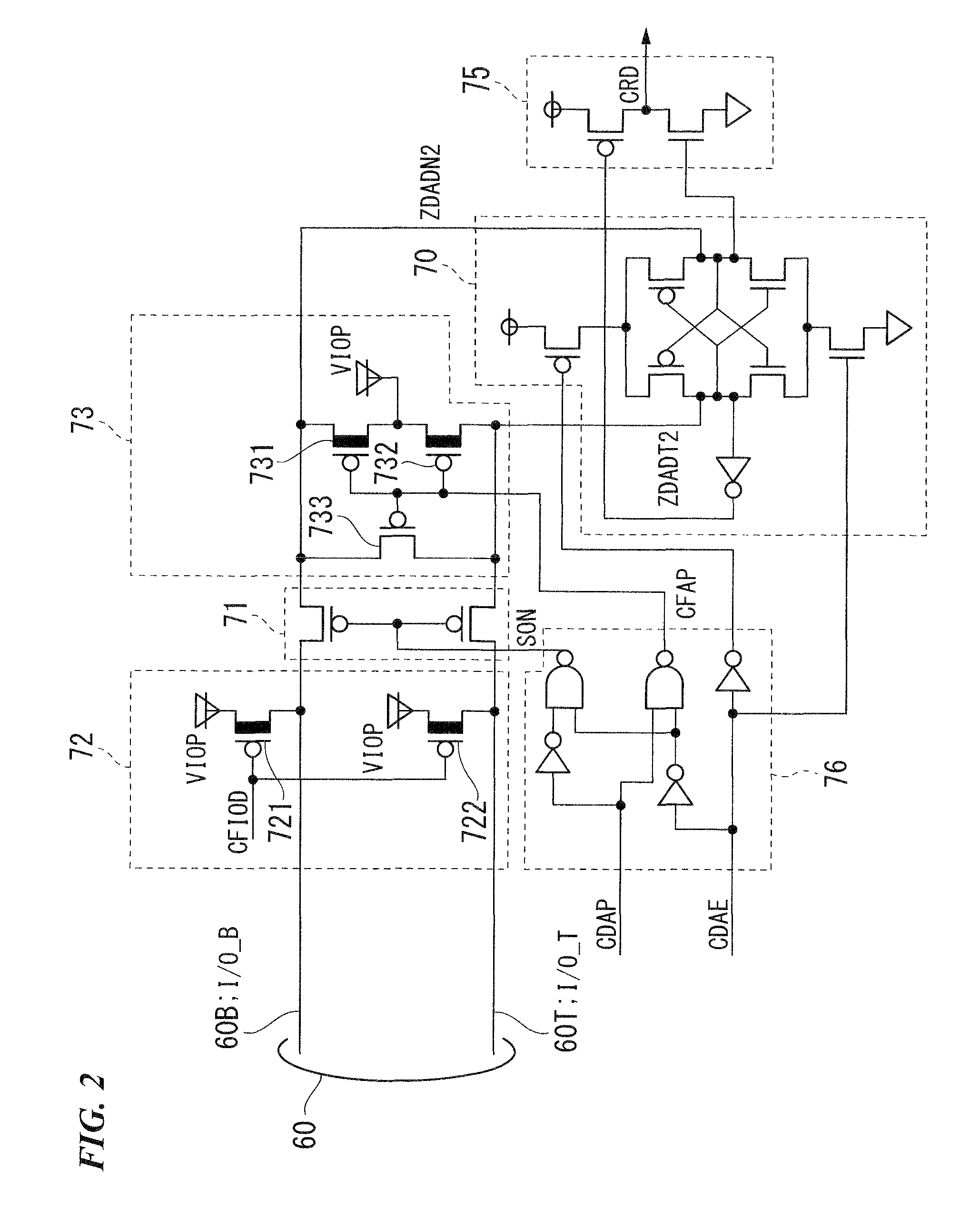

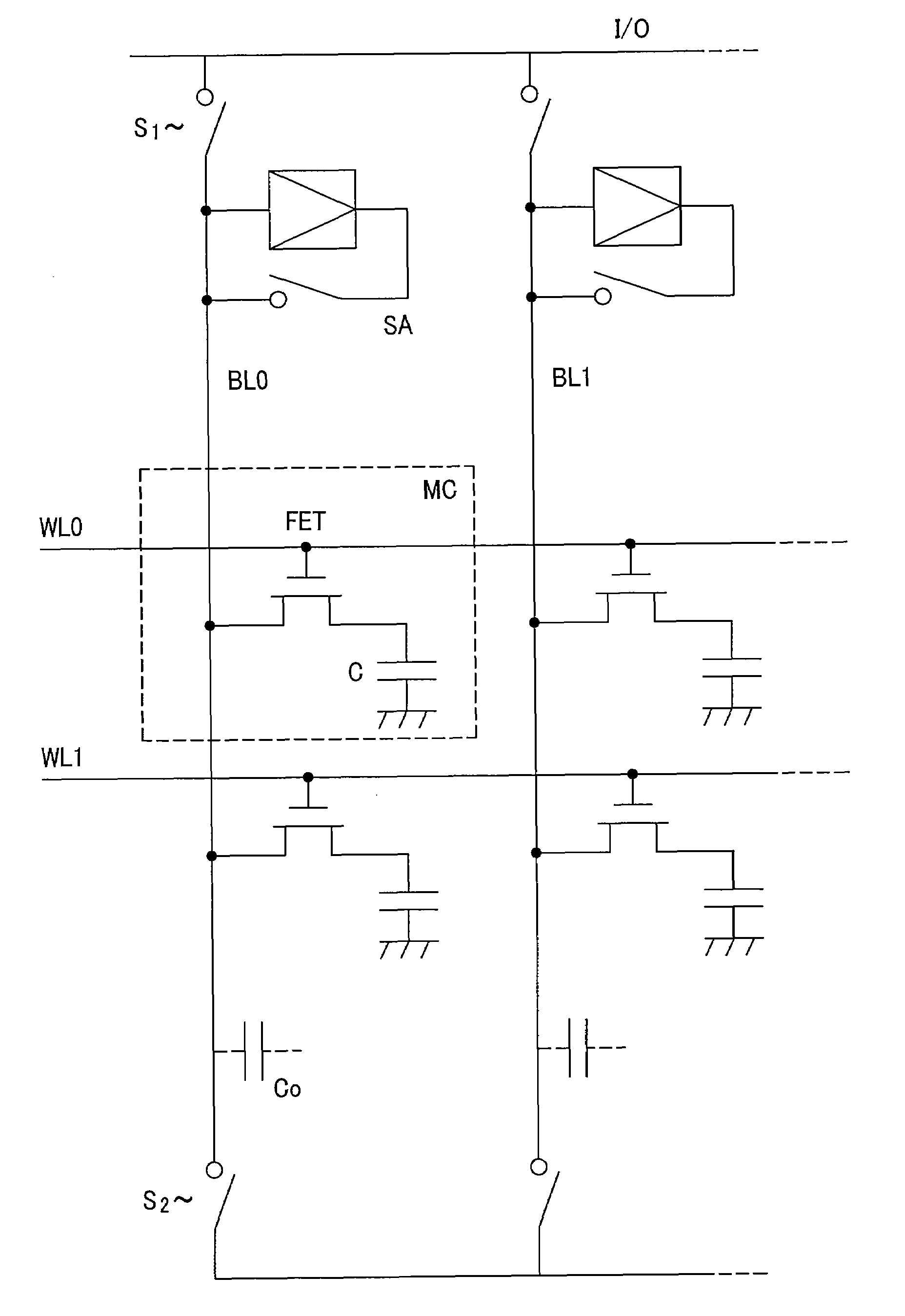

Semiconductor device

A semiconductor device includes a column decoder that generates a column selecting signal that selects any of a plurality of bit line pairs to which memory cells are connected according to a column address that is input; a bit line selecting switch that connects by the column selecting signal any of a plurality of bit line pairs and a data I / O line pair that outputs data that has been read from a memory cell to the outside; a data amplifier that amplifies a voltage differential of a data I / O line pair and outputs data that has been read to an output buffer; a data I / O line switch that is provided in the data I / O lines; an I / O line precharge circuit that precharges a data I / O line pair that is not on the side of the data amplifier; and an amplifier precharge circuit that precharges a data I / O line pair that is on the side of the data amplifier.

Owner:LONGITUDE LICENSING LTD

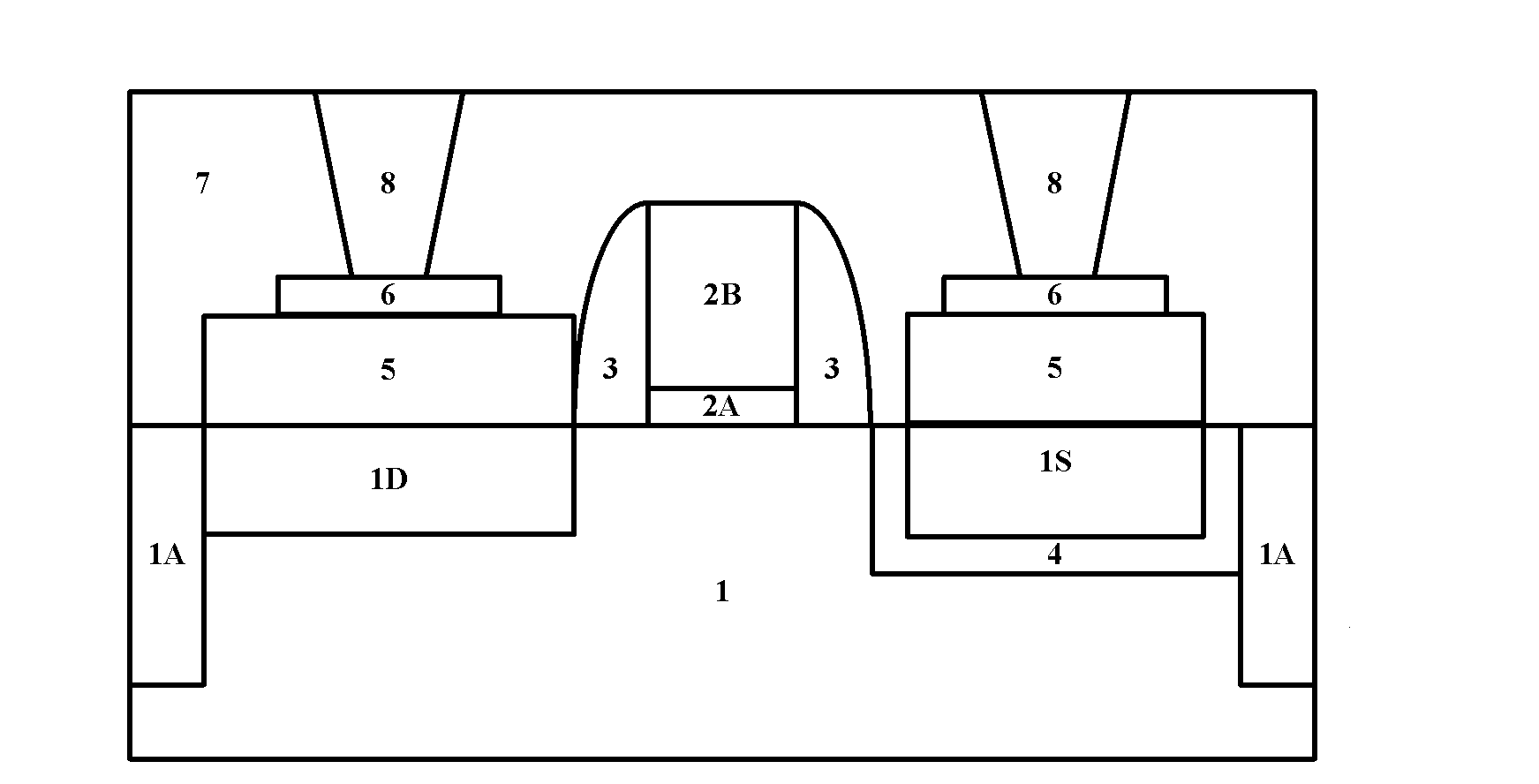

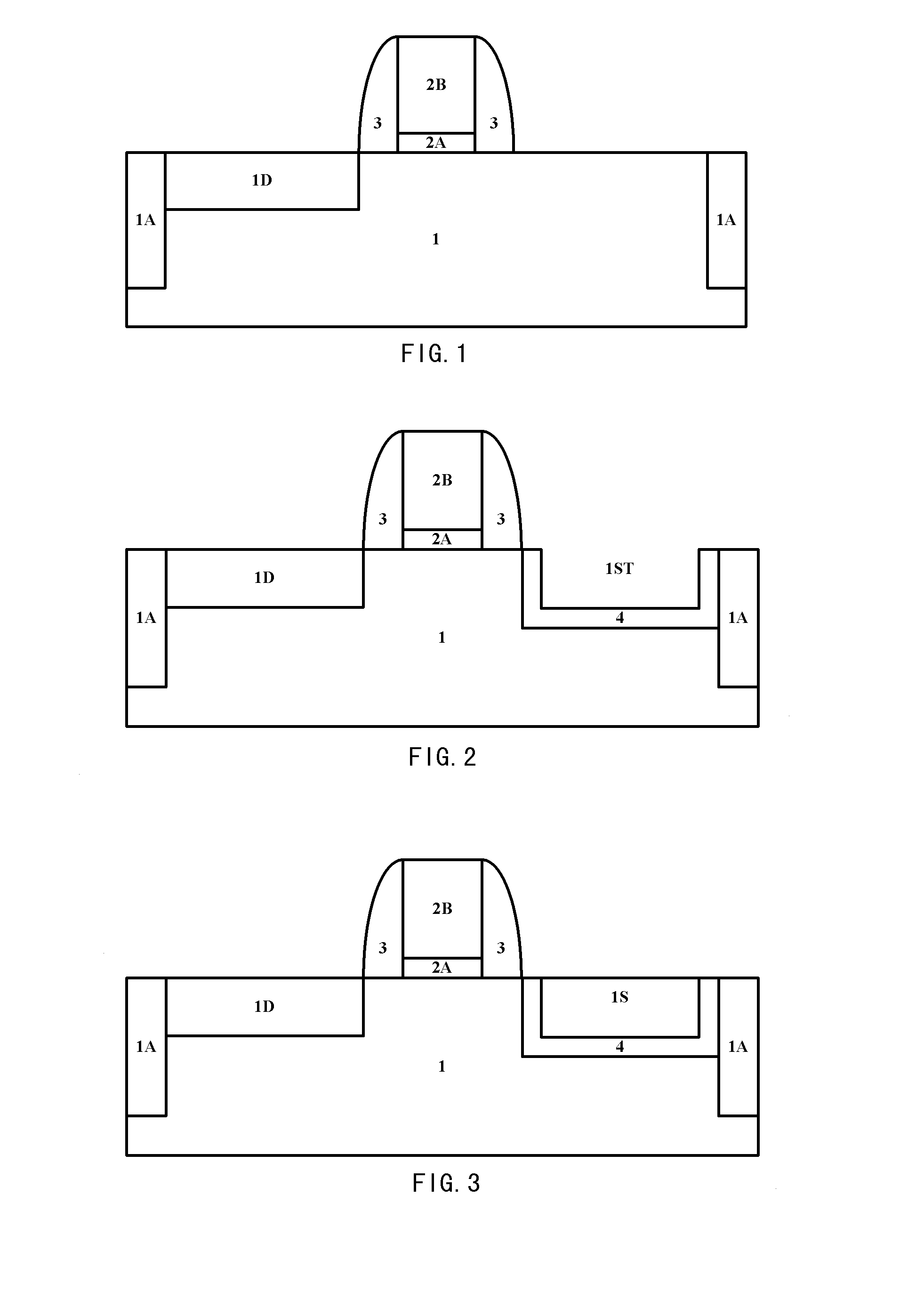

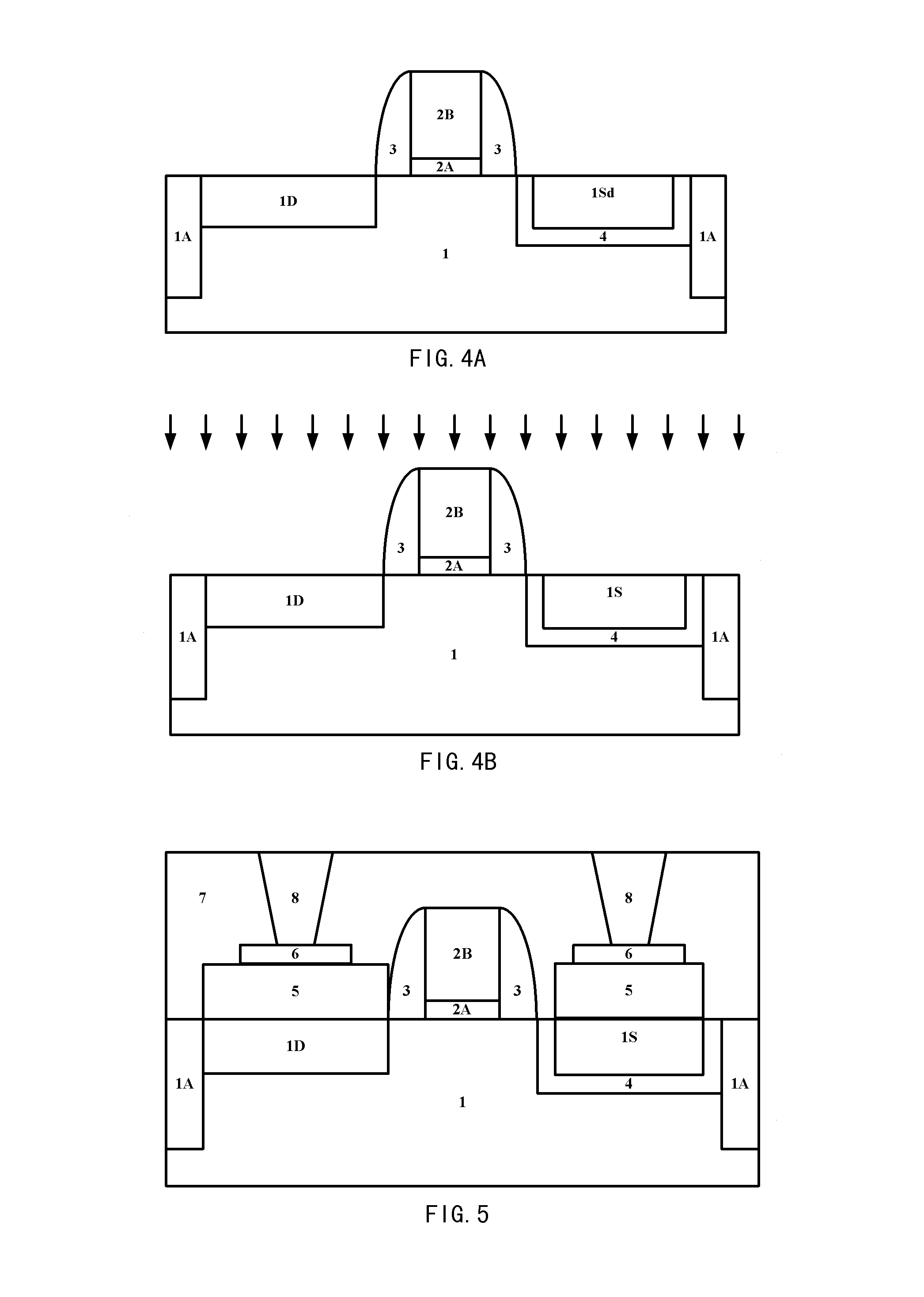

Semiconductor device and method for manufacturing the same

ActiveUS20140048765A1Increase currentReduce power consumptionSemiconductor/solid-state device manufacturingDiodeAlloyGate stack

The present invention discloses a semiconductor device, comprising: a substrate, a gate stack structure on the substrate, source and drain regions in the substrate on both sides of the gate stack structure, and a channel region between the source and drain regions in the substrate, characterized in that the source region in the source and drain regions comprises GeSn alloy, and a tunnel dielectric layer is optionally comprised between the GeSn alloy of the source region and the channel region. In accordance with the semiconductor device and method for manufacturing the same of the present invention, GeSn alloy having a narrow band gap is formed by implanting precursors and performing a laser rapid annealing, the on-state current of TFET is effectively enhanced, accordingly it has an important application prospect in a high performance low power consumption application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

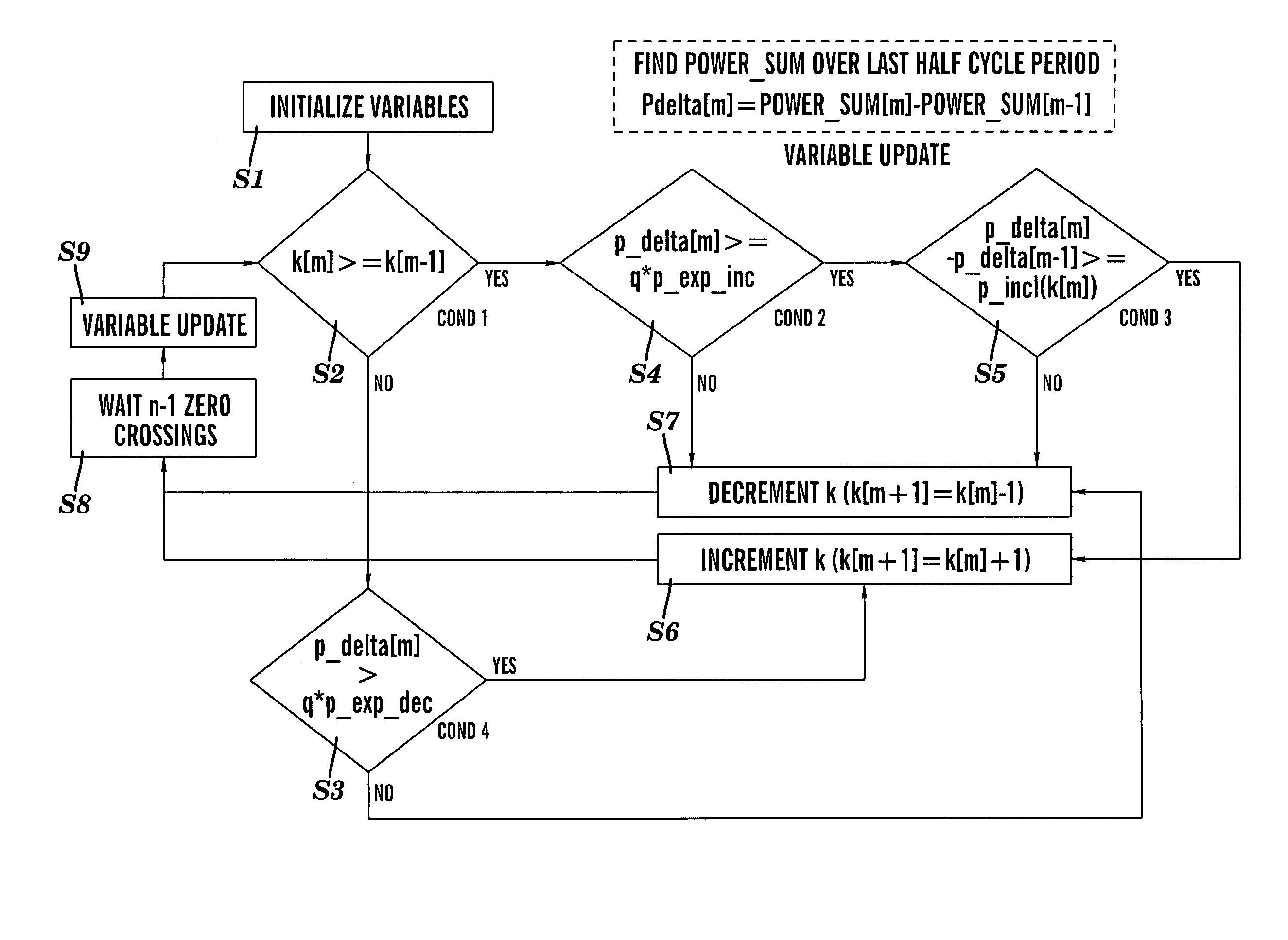

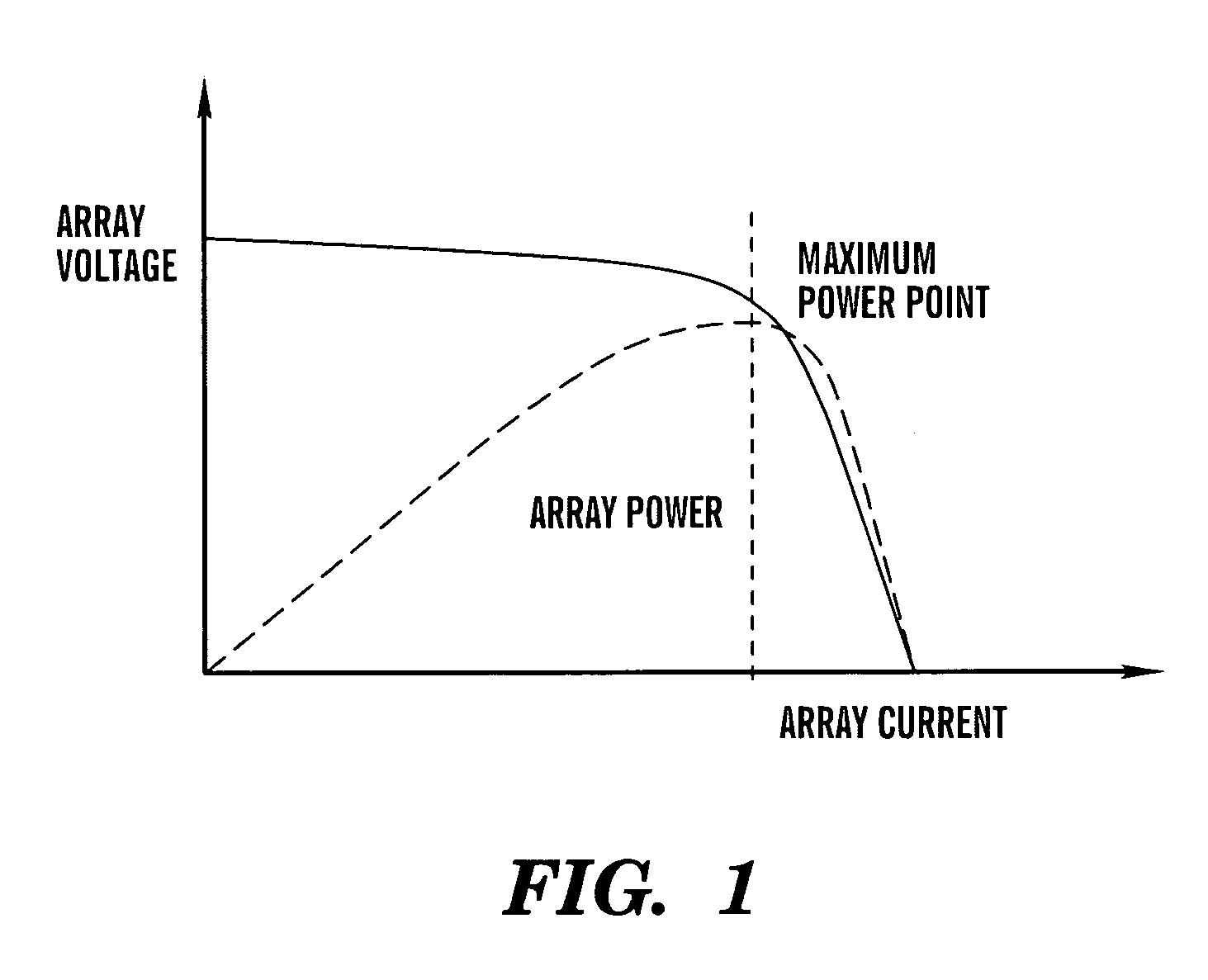

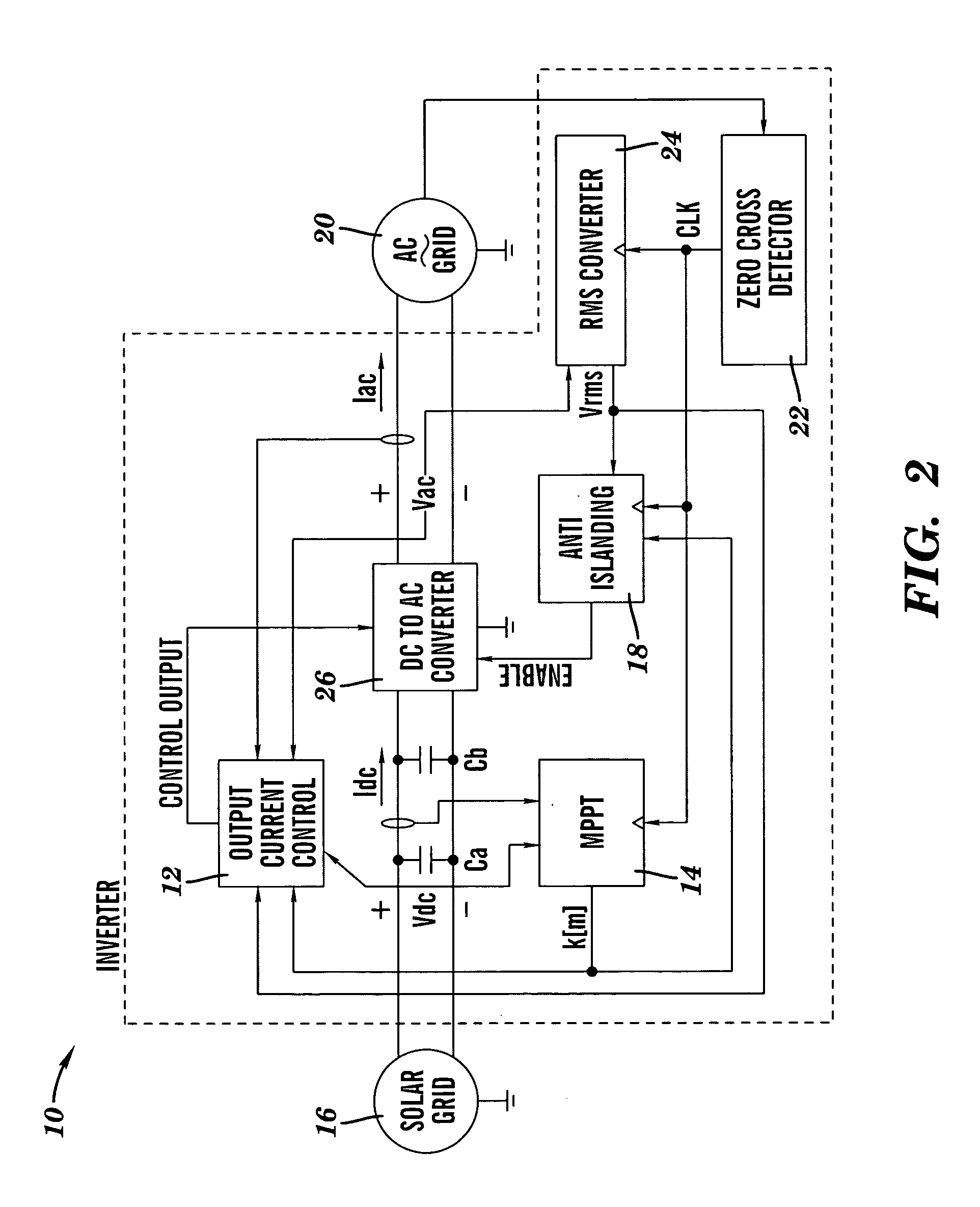

Inverter control methodology for distributed generation sources connected to a utility grid

InactiveUS7248946B2Improvement in MPPTEasy to controlMechanical power/torque controlLevel controlIslandingMppt algorithm

Owner:ADVANCED ENERGY CONVERSION

Semiconductor integrated circuit device

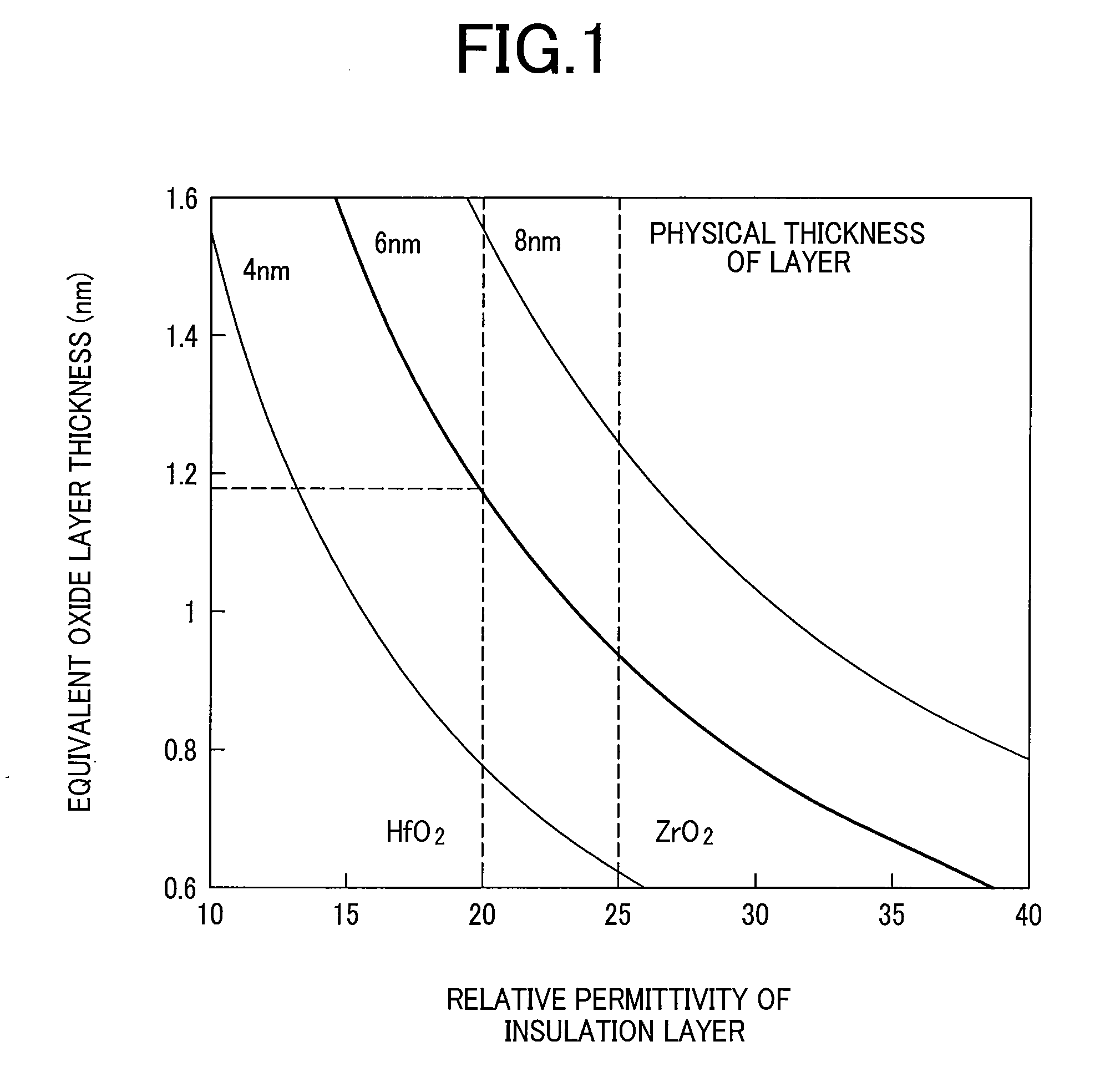

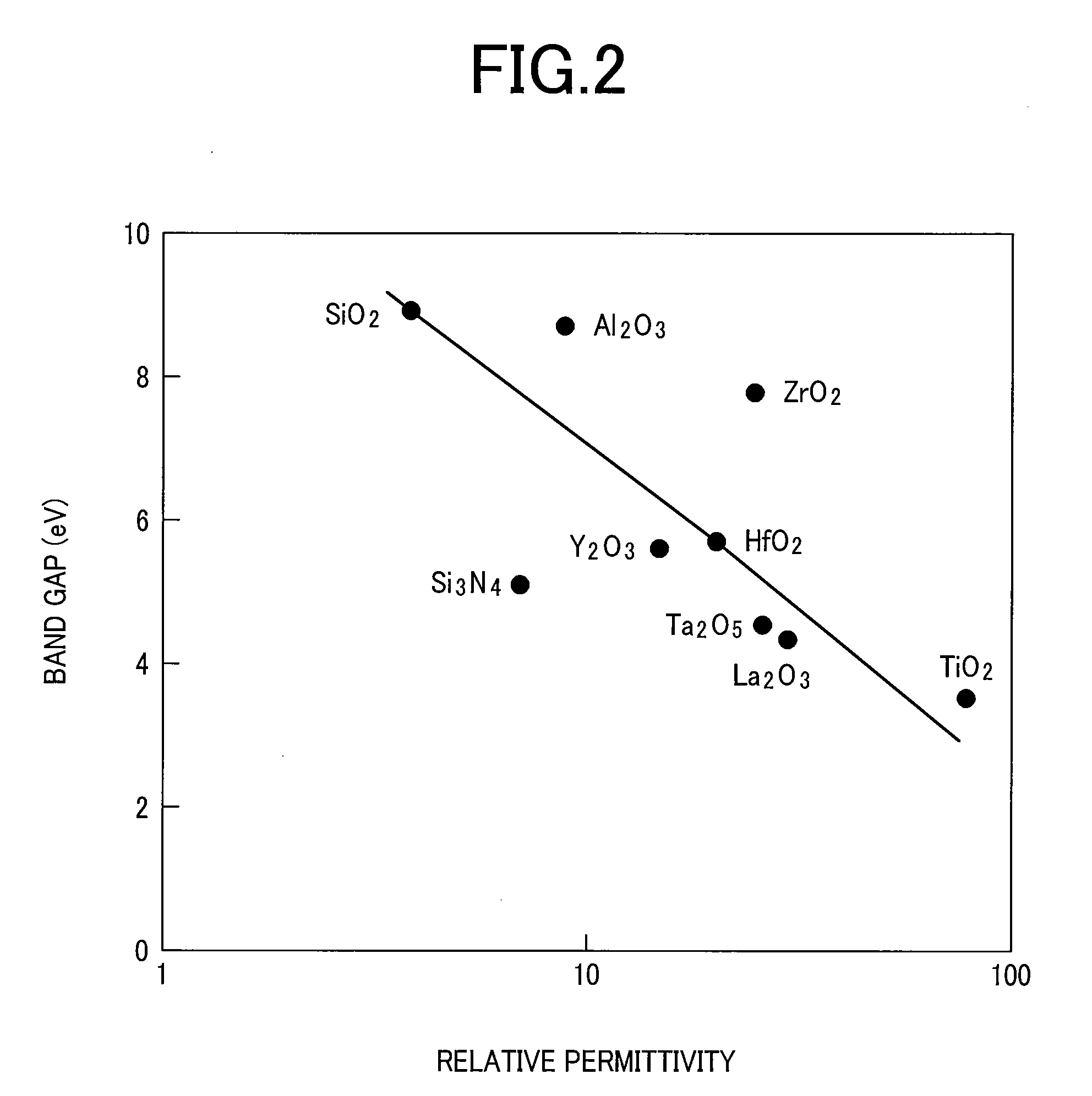

InactiveUS20080157157A1High operation speedLow power consumptionTransistorSolid-state devicesPhysicsSulfur dioxide

A DRAM capacitor uses ruthenium or ruthenium oxide as an upper electrode and hafnium dioxide or zirconium oxide as an insulation layer. The DRAM capacitor is intended to suppress diffusion of ruthenium, etc. into hafnium dioxide. Tantalum pentoxide or niobium oxide having a higher permittivity than that of the insulation layer is inserted as a cap insulation layer to the boundary between the upper electrode of ruthenium or ruthenium oxide and the insulation layer of hafnium dioxide or zirconium oxide to thereby suppress diffusion of ruthenium, etc. into hafnium dioxide, etc.

Owner:HITACHI LTD

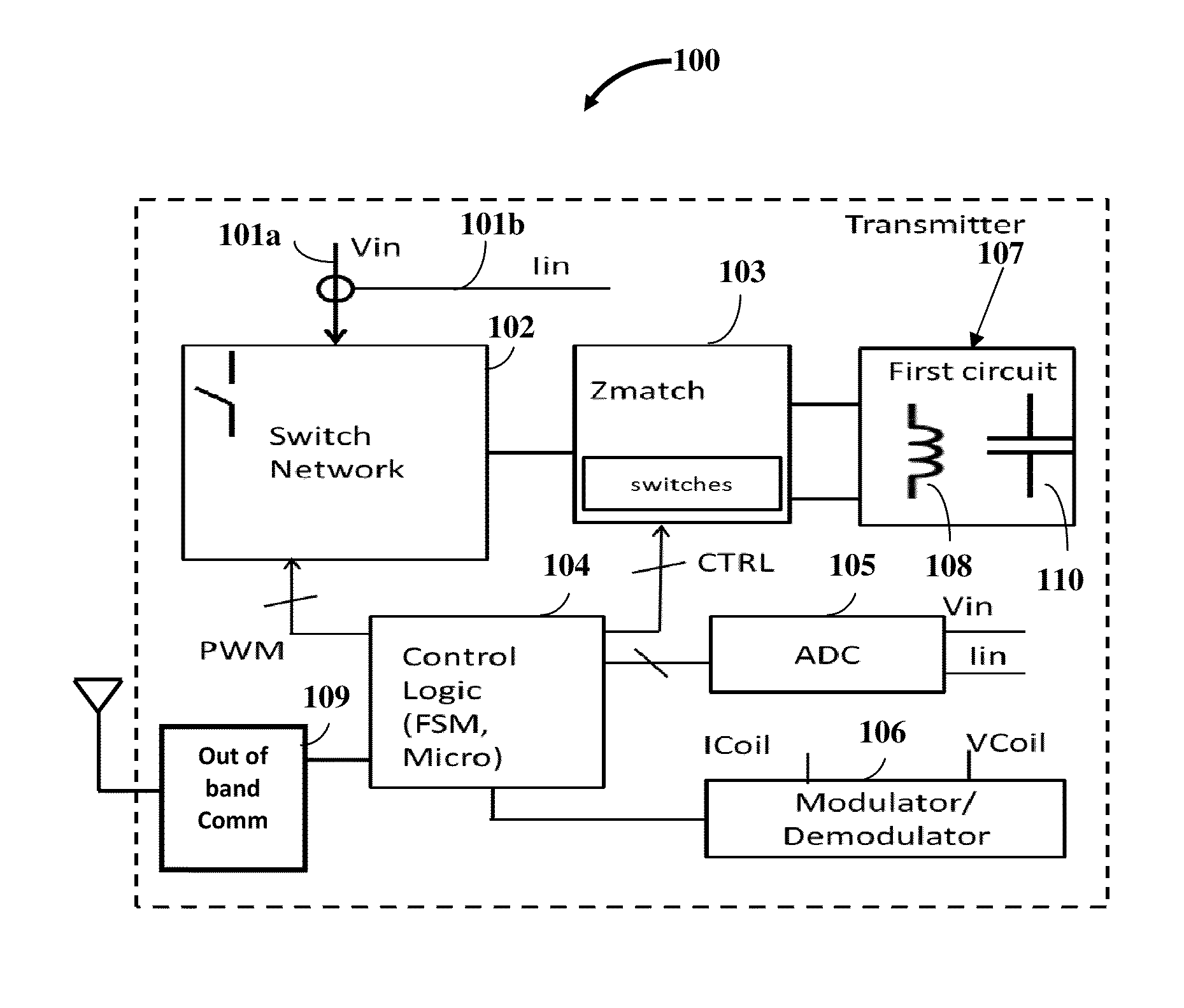

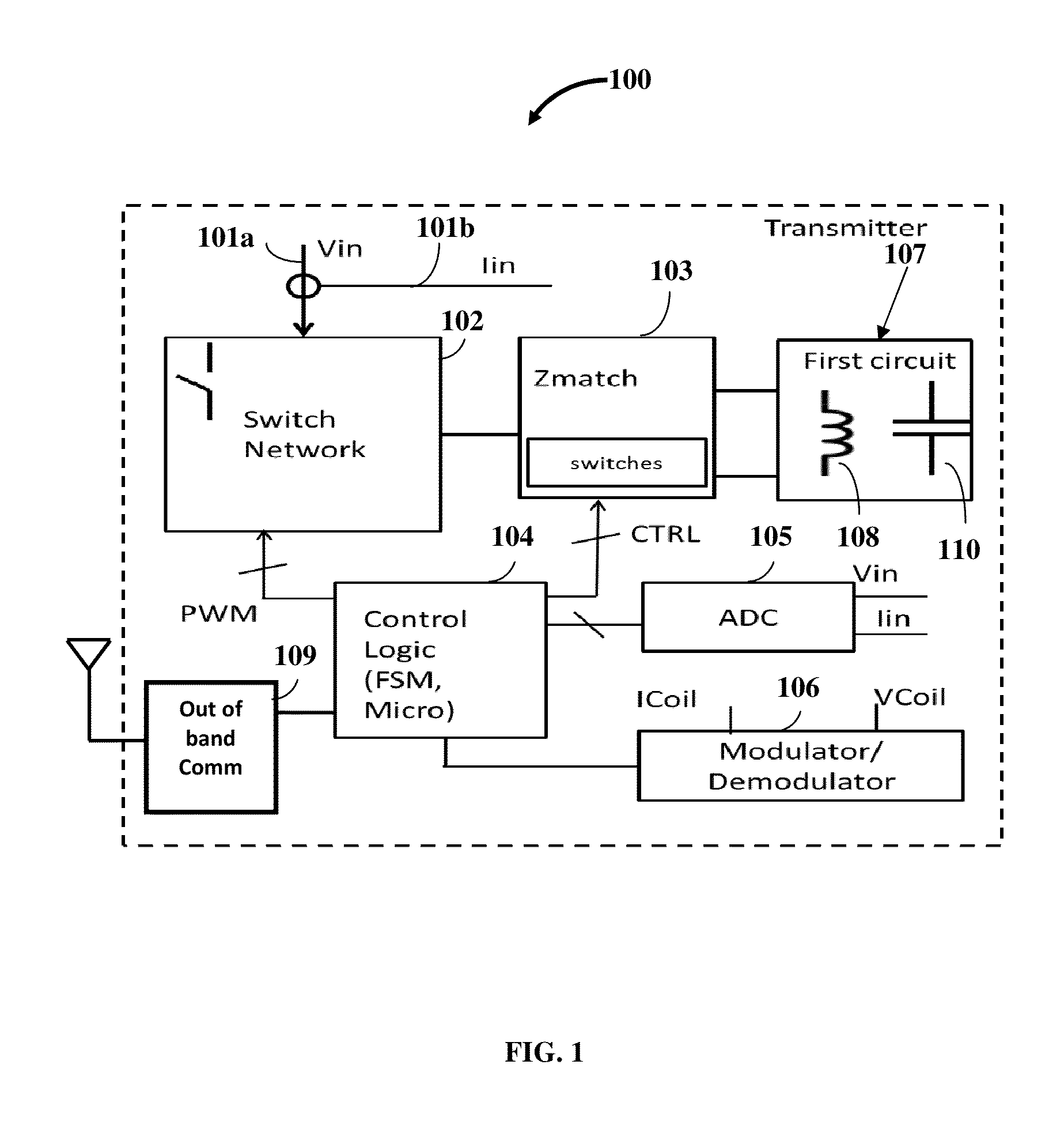

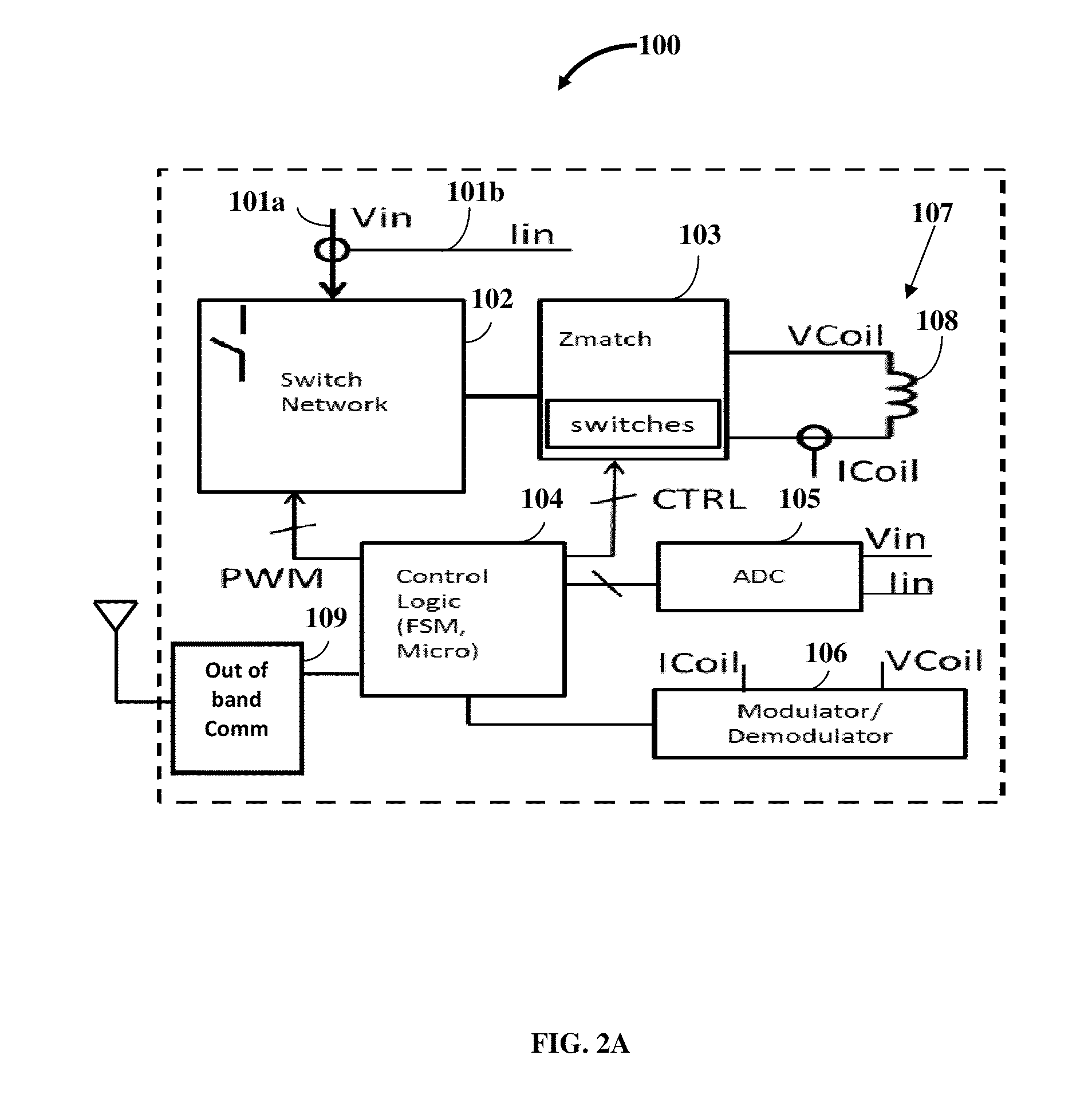

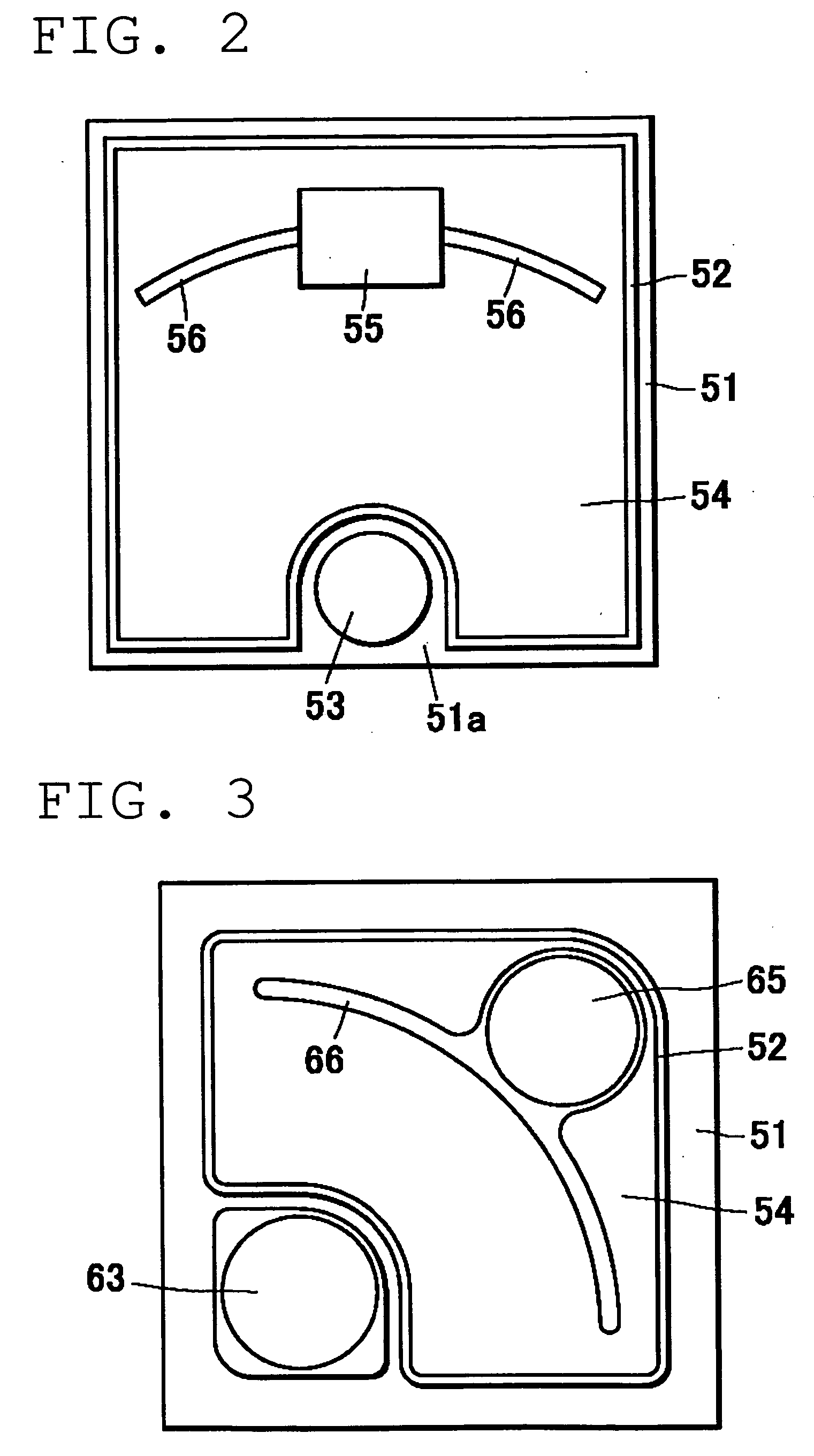

Multi-mode Multi-coupling Multi-protocol Ubiquitous Wireless Power Transmitter

InactiveUS20140139034A1Transmit power can be effectivelyGuaranteed normal transmissionBatteries circuit arrangementsElectromagnetic wave systemExchange networkTransmitted power

A multi-mode multi-coupling multi-protocol wireless power transmitter (WPT) and its embodiments transmit power to a wireless power receiver (WPR) in a power transfer mode (PTM) and a wireless power protocol (WPP) of the WPR. A first circuit of the WPT includes inductors or capacitors emanating power via a magnetic field or electric field PTM respectively. The WPT sequentially parses a test condition to identify a PTM, a power coupling linkage (PCL) between the WPT and the WPR, and a WPP of the WPR. The WPT identifies a match if the PTM of the first circuit and the WPP of the switch network, the variable matching circuit, a modulator / demodulator block or an out-of-band communication block, and a control logic circuit of the WPT match the PTM and the WPP of the WPR to transmit power to the WPR based on the match.

Owner:WIPQTUS

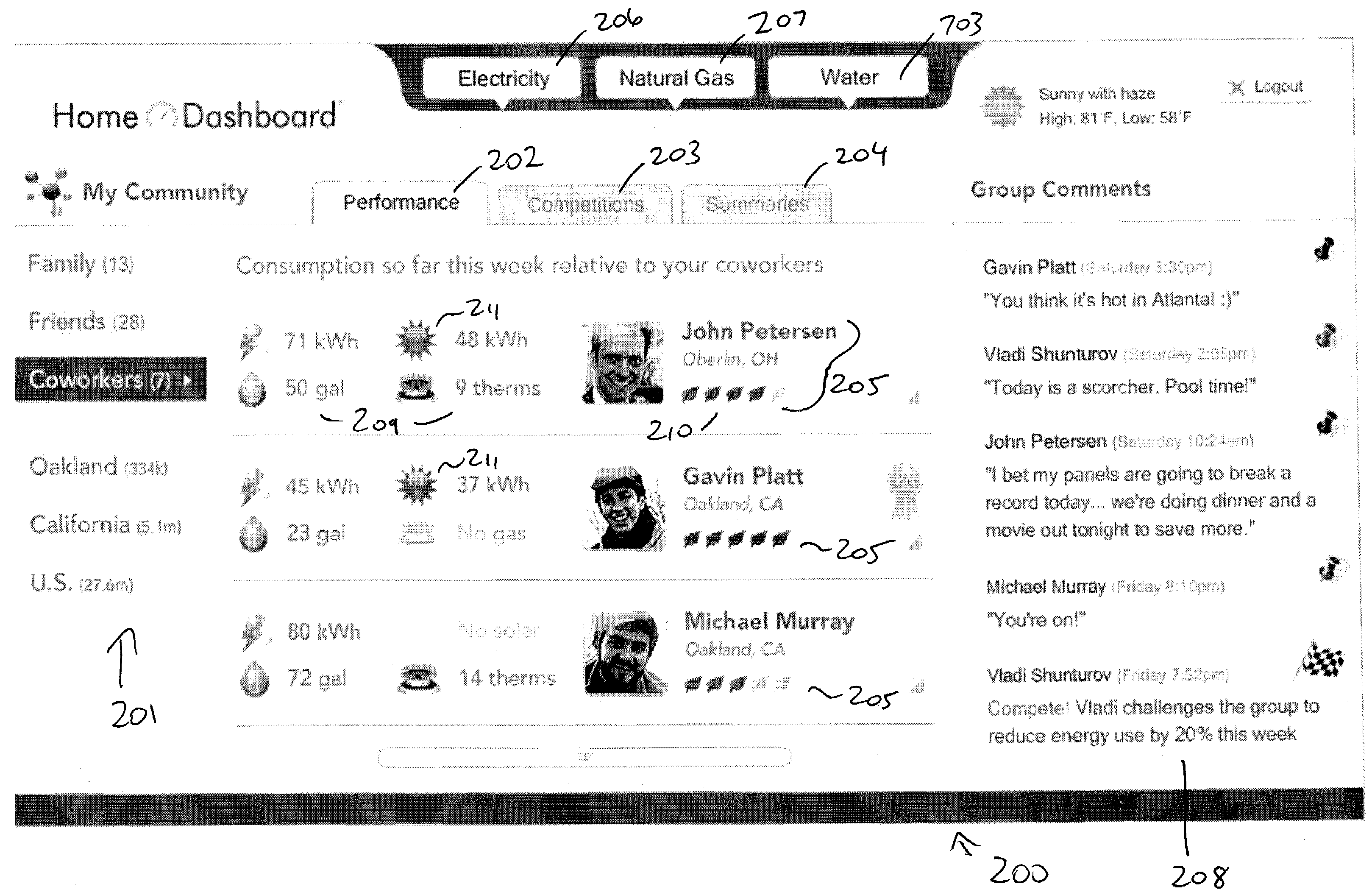

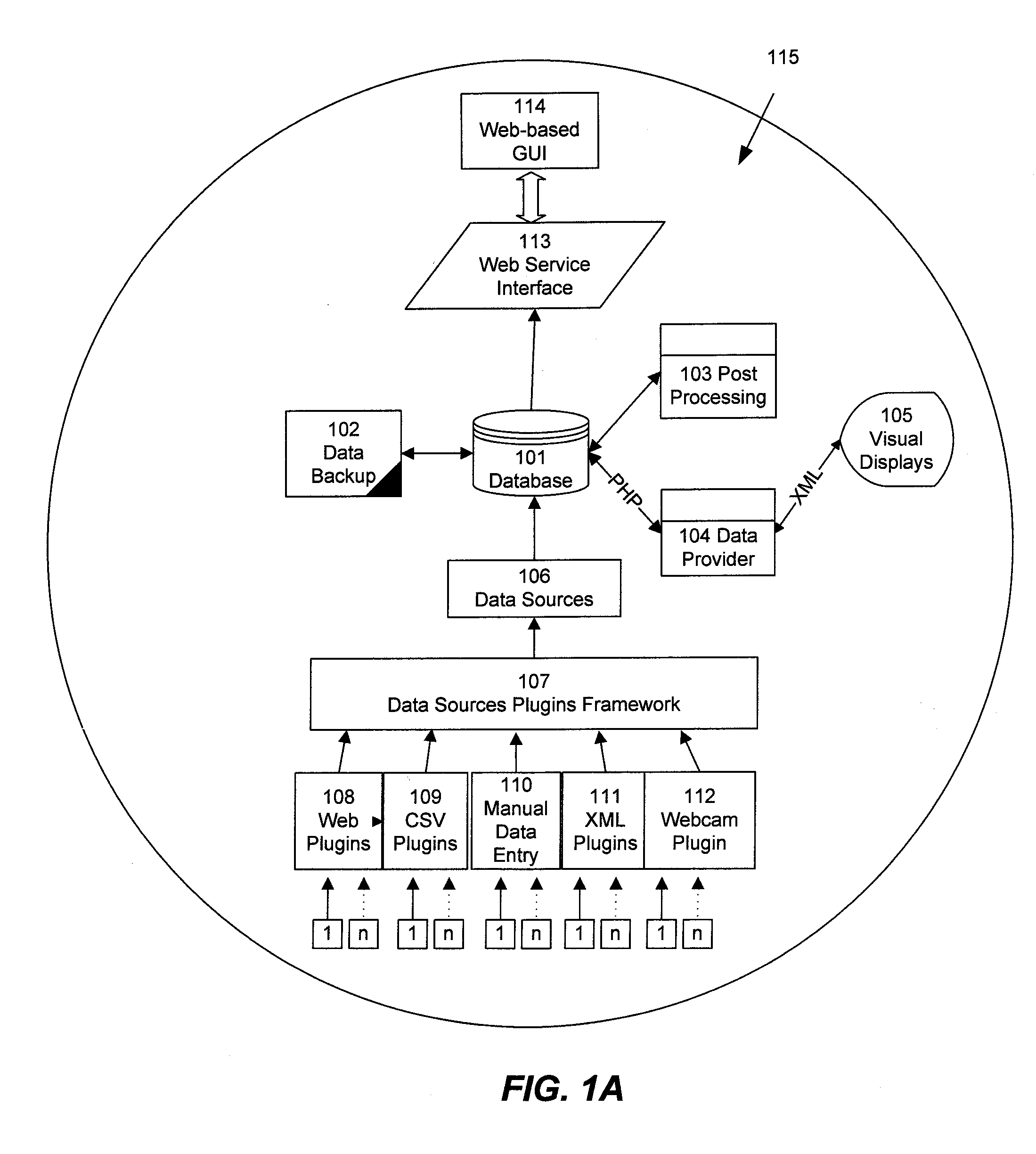

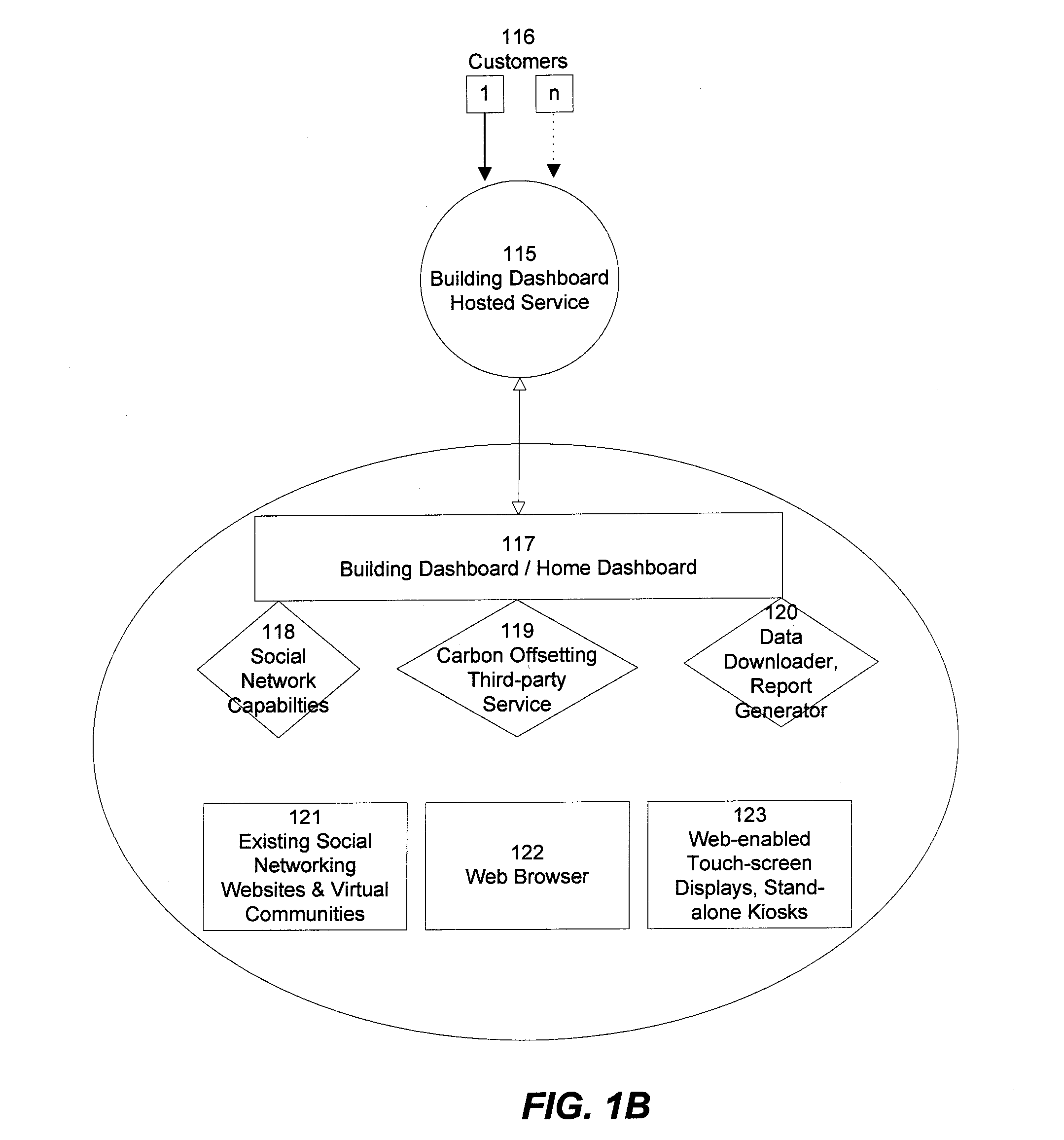

Collecting, sharing, comparing, and displaying resource usage data

ActiveUS20080306985A1Easy to compareThe effect is highlightedOffice automationCommerceGraphicsInteractive displays

Resource usage data is automatically collected for an individual, house-hold, family, organization, or other entity. The collected data is transmitted to a central repository, where it is stored and compared with real-time and / or historical usage data by that same entity and / or with data from other sources. Graphical, interactive displays and reports of resource usage data are then made available. These displays can include comparisons with data representing any or all of community averages, specific entities, historical use, representative similarly-situated entities, and the like. Resource usage data can be made available within a social networking context, published, and / or selectively shared with other entities.

Owner:ABL IP HLDG

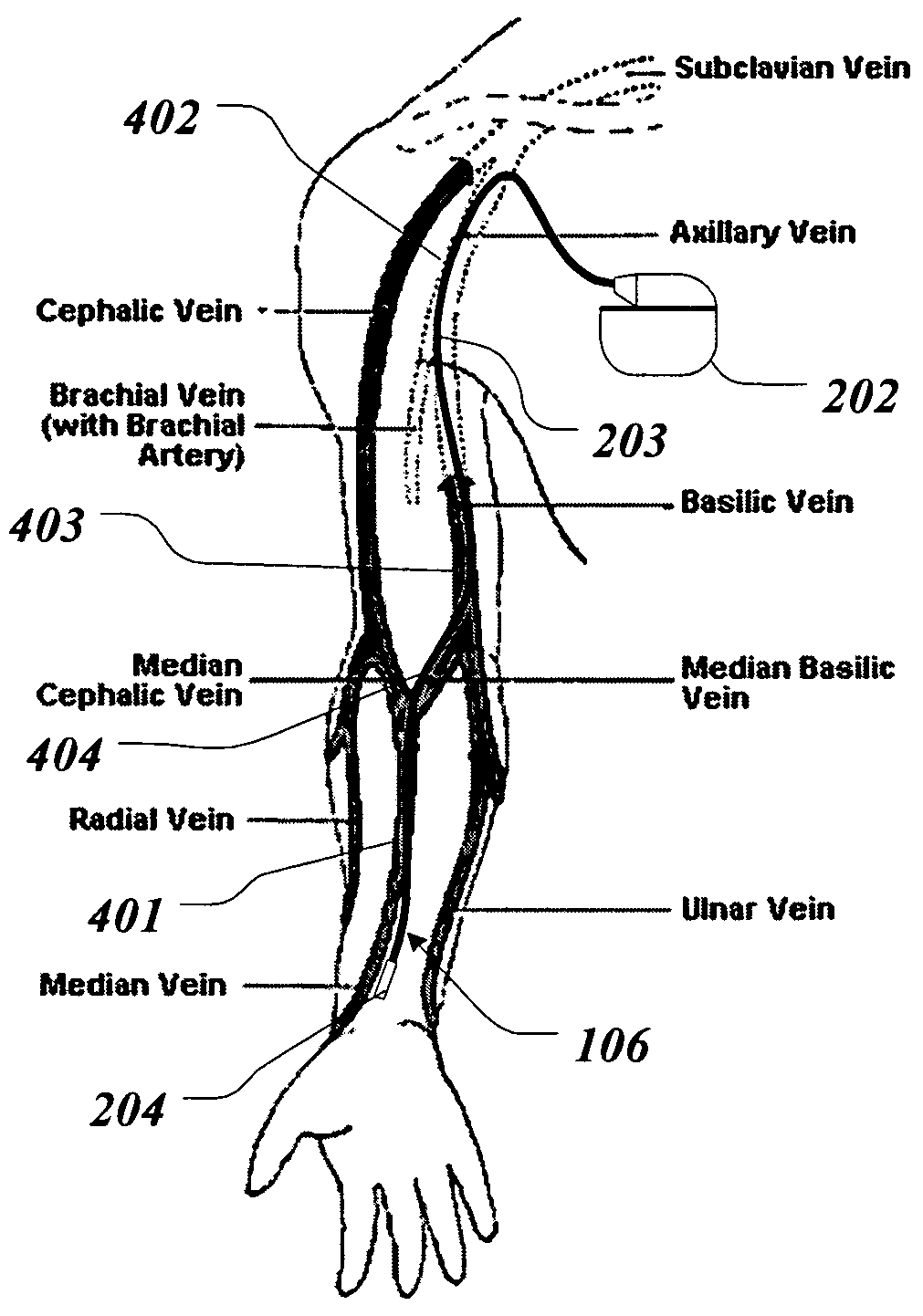

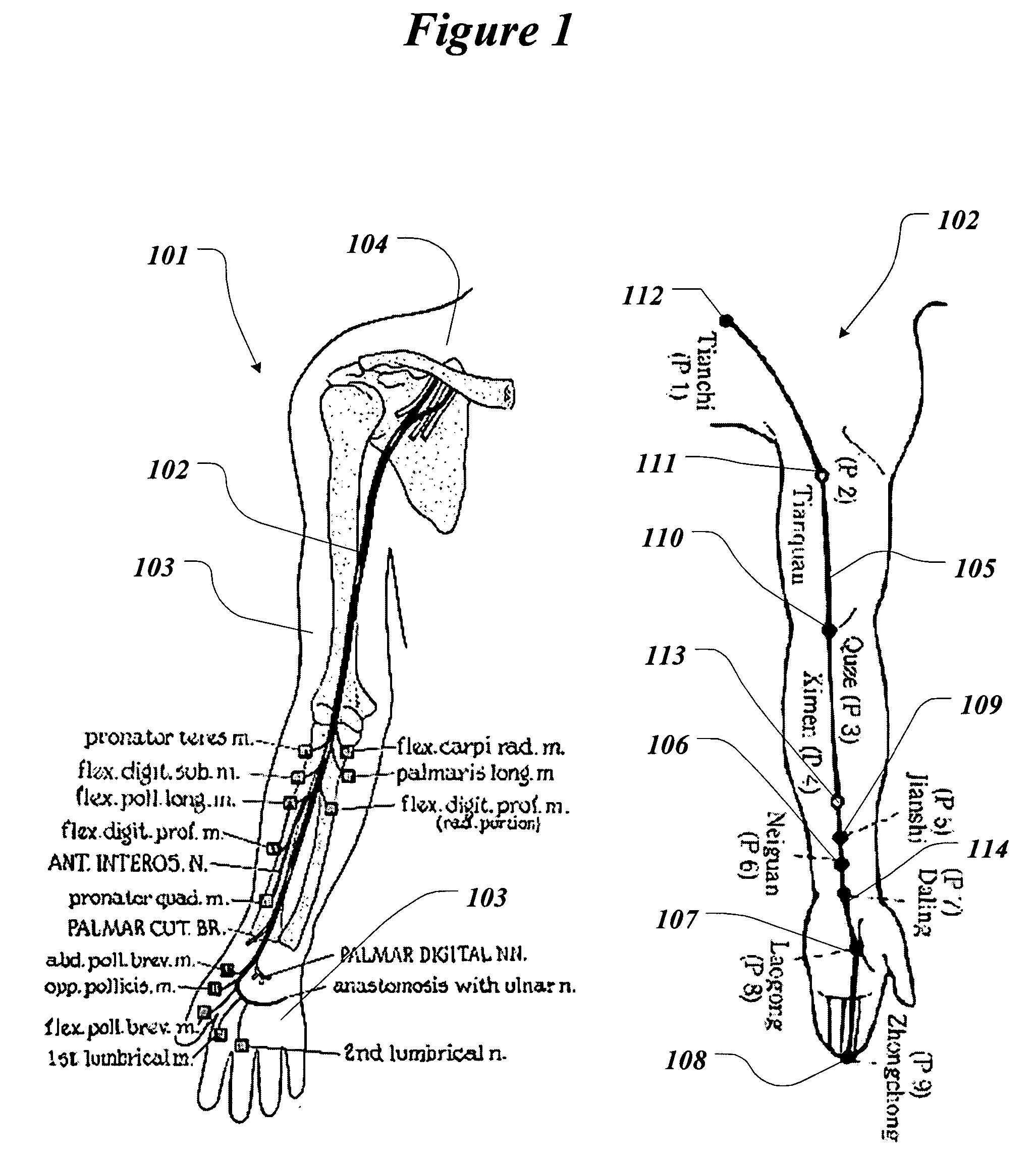

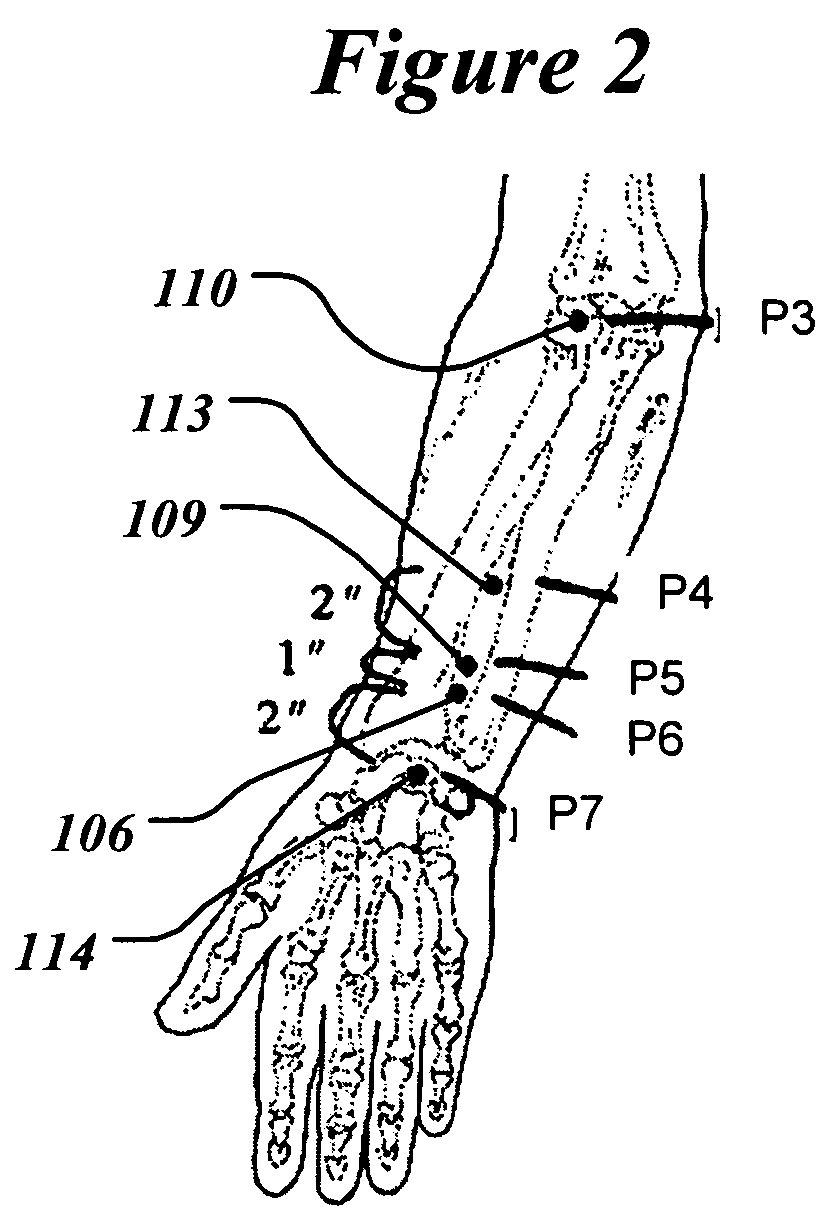

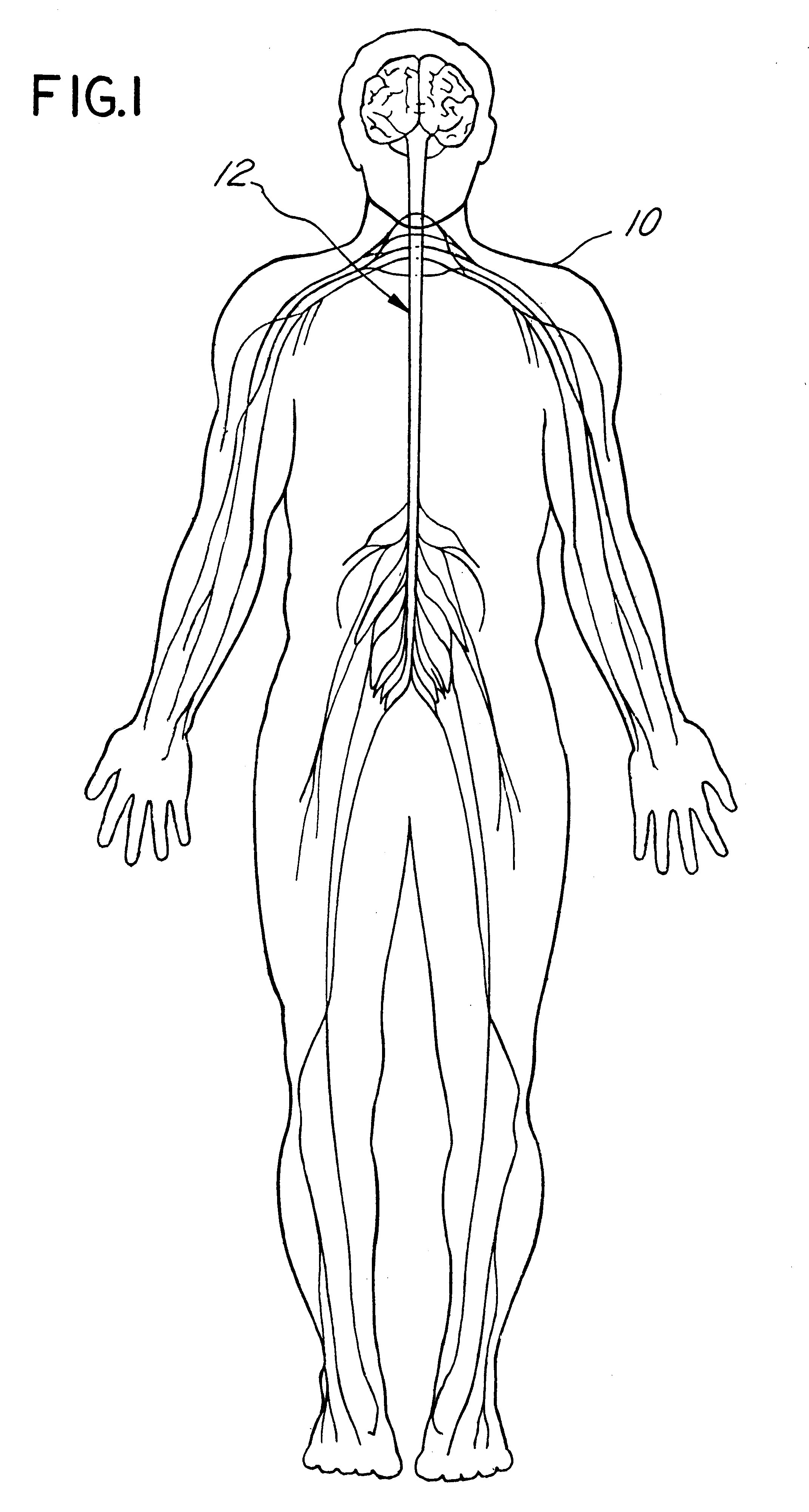

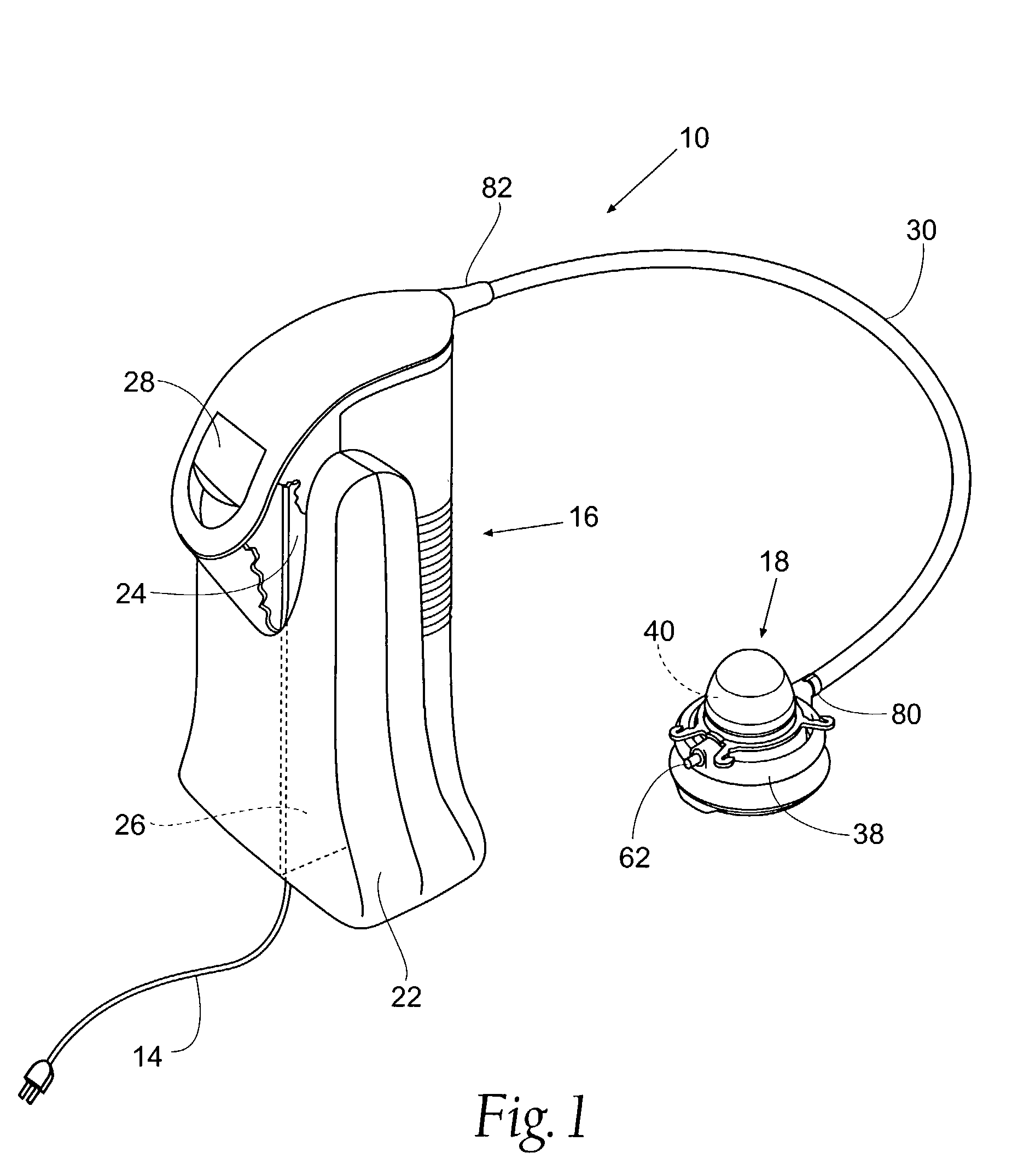

Implantable device and method for treatment of hypertension

ActiveUS7373204B2Improve dysfunctionIncrease probabilityElectrotherapySurgeryPower flowImplanted device

A method and apparatus for treatment of hypertension with electrostimulation of peripheral nerves. Treatment is performed by periodically stimulating a nerve such as a median nerve. Apparatus for stimulation is permanently implanted in the body. The nerve is stimulated by electric current applied to electrodes that are placed near the target nerve or the muscle innervated by the target nerve.

Owner:LIFESTIM

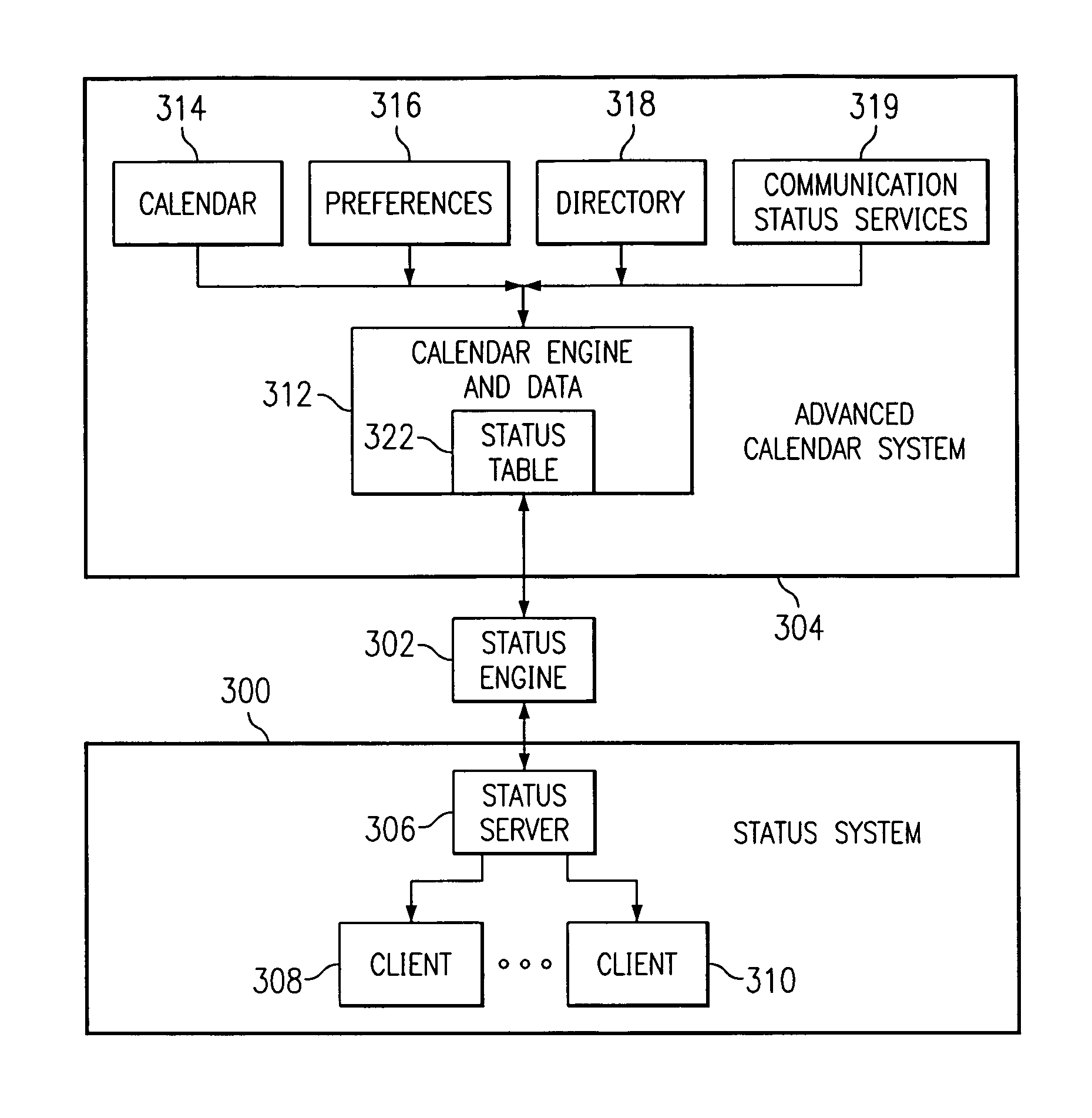

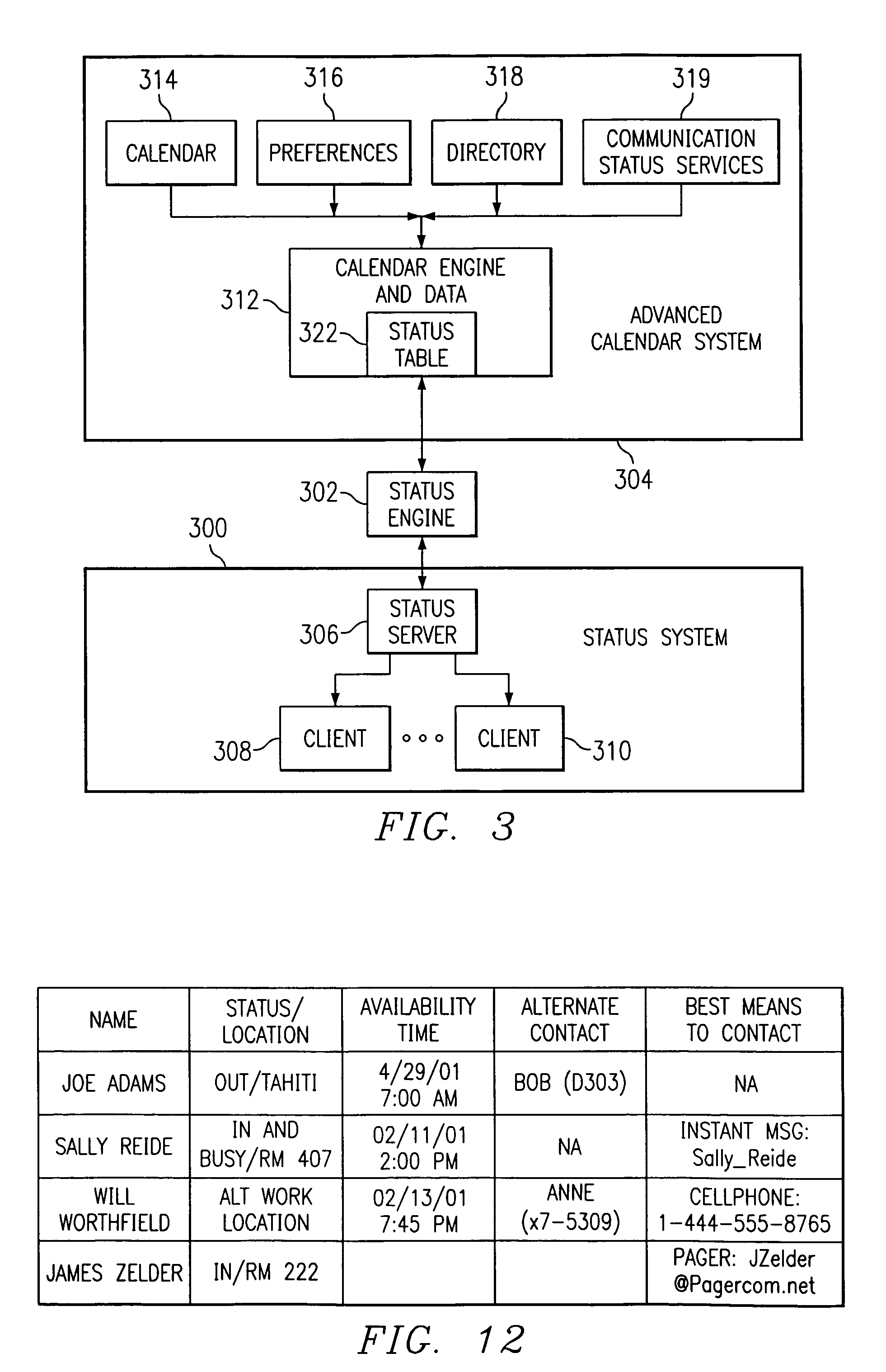

Calendar-enhanced awareness for instant messaging systems and electronic status boards

ActiveUS7035865B2Automate processIncrease currentOffice automationData switching networksPagerElectronic states

A method, system, and product are disclosed for providing calendar-enhanced awareness / presence information for instant messaging systems and electronic status boards. This invention automates status transitions, enhances and automates status messages, and automates and extends the IM “who can see me” function. Additionally, this invention extends awareness to dimensions other than IM status, to include availability in-person, via telephone, via wireless device or wireless messaging device (e.g., pager).

Owner:IBM CORP

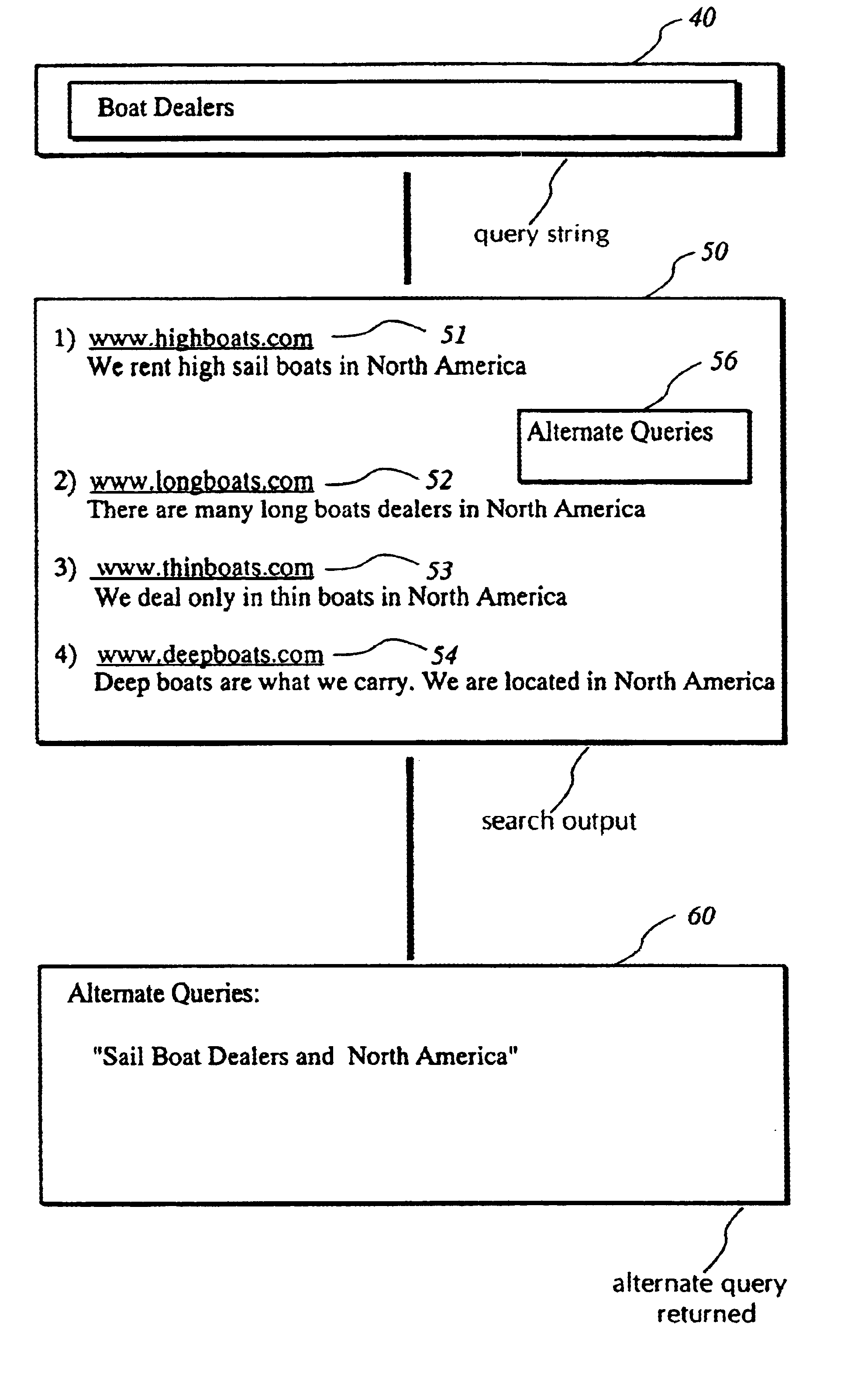

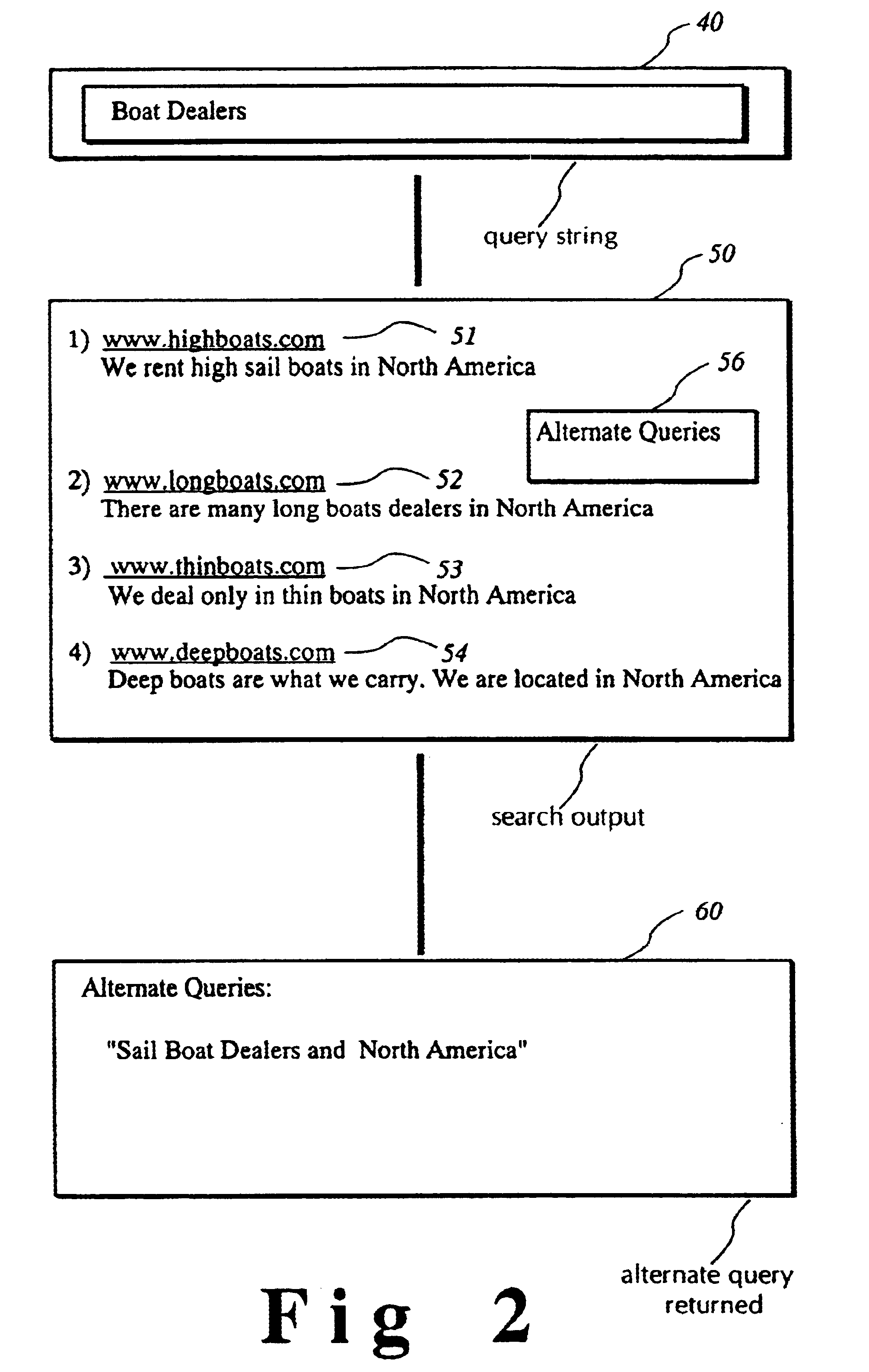

System and technique for suggesting alternate query expressions based on prior user selections and their query strings

InactiveUS6671681B1Increase currentData processing applicationsDigital data information retrievalGraphicsGraphical user interface

An invention for monitoring user choices and selections on a search result web page and providing alternative query expressions to further narrow and enhance the user's search. Monitoring and recording user choices and selections is achieved by a query manager. Query strings are then standardized. The search is performed on an Internet search engine, and each search result item in the result output set is then associated with a list of alternative standardized queries by an alternate query matching manager. Each search result item in the result output set that is associated with the alternate queries is then flagged. The resulting flagged list of alternative queries is displayed to the user by a page presentation manager using a graphical user interface for subsequent user selection. Upon selection of the graphical user interface for alternate query expressions, an alternate query selection manager retrieves and displays each alternate query to the user.

Owner:IBM CORP

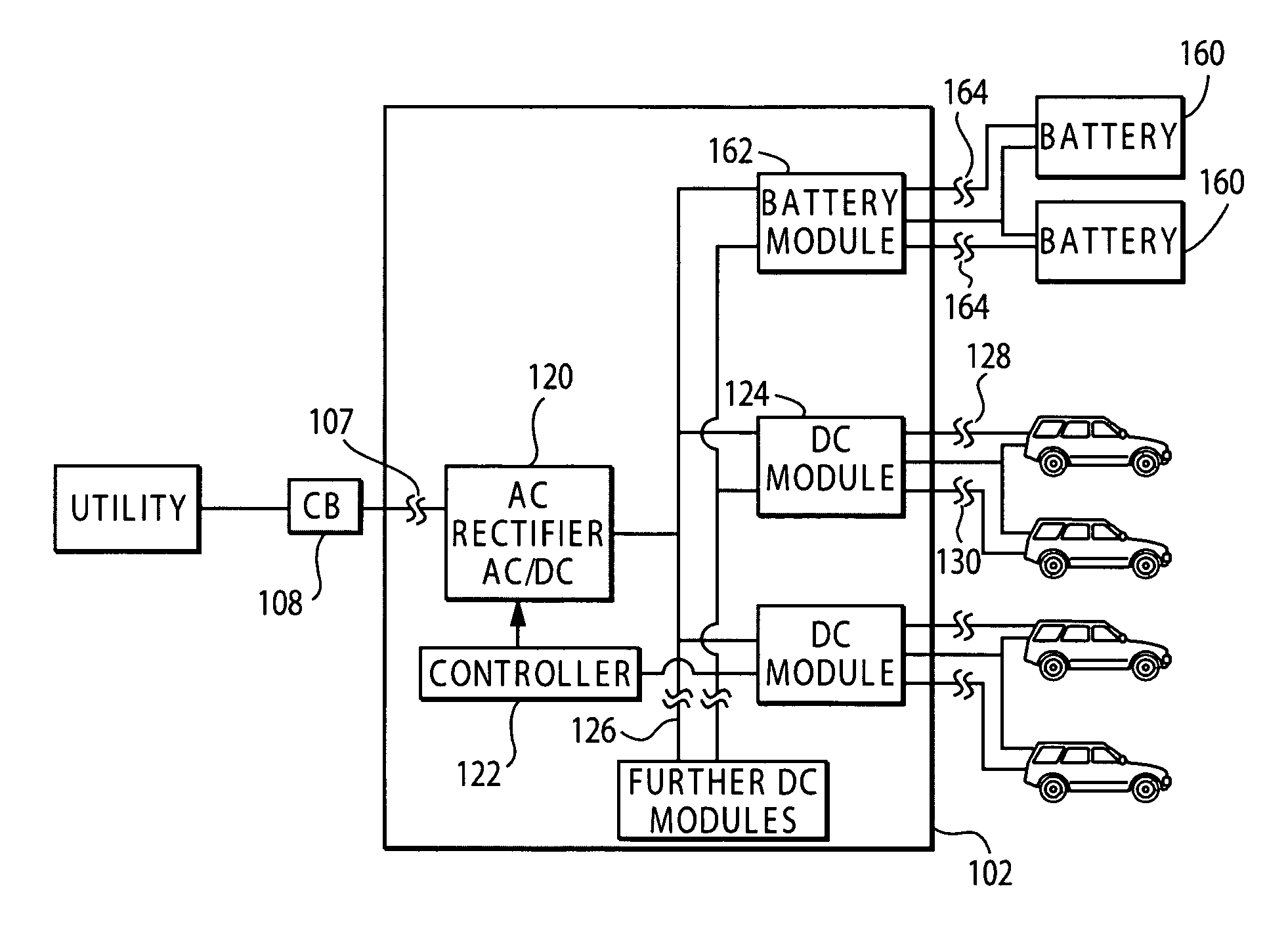

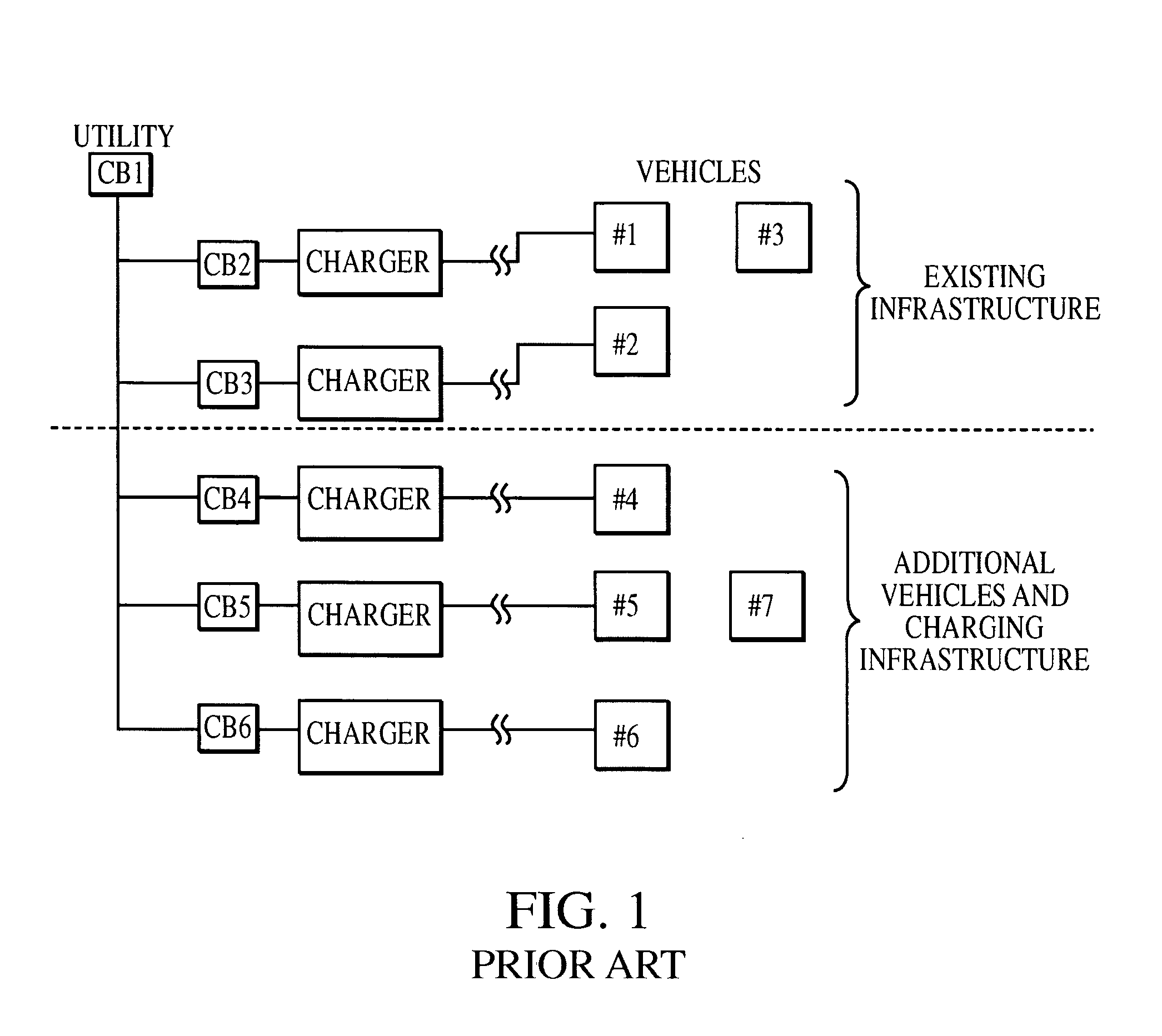

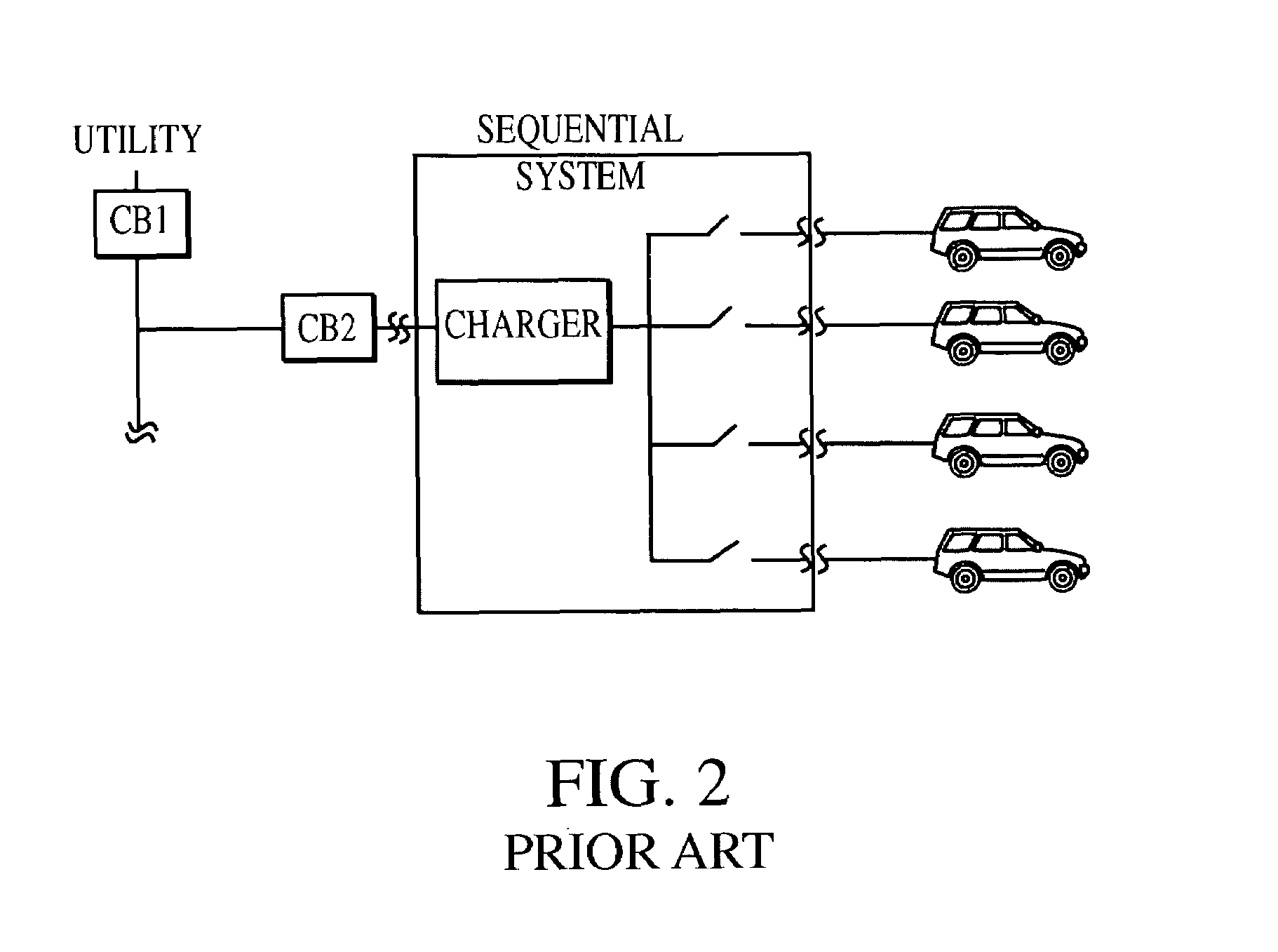

Battery charging system and method

InactiveUS7256516B2Meet system requirementsMeet power requirementsLoad balancing in dc networkDc source parallel operationEngineeringAC power

A charging system for simultaneously charging the batteries of a plurality of battery powered vehicles. The charging includes one or more DC-DC power converters having one or more charging ports configured to plug into the batteries. The DC-DC power converters are each configured to selectively connect to more than one charging port to selectively provide for higher port power levels. The DC-DC power converters connect to an AC rectifier through a DC bus. The AC rectifier connects to an AC power source having a limited power rating. The AC charging system also has a controller that controls the operation of the DC-DC power converters such that the total power draw on the AC rectifier does not exceed the power rating. The system is further configured such that the DC-DC power converters can drain selected batteries to obtain power for charging other batteries, thus allowing for batteries to be cycled.

Owner:WEBASTO CHARGING SYST INC

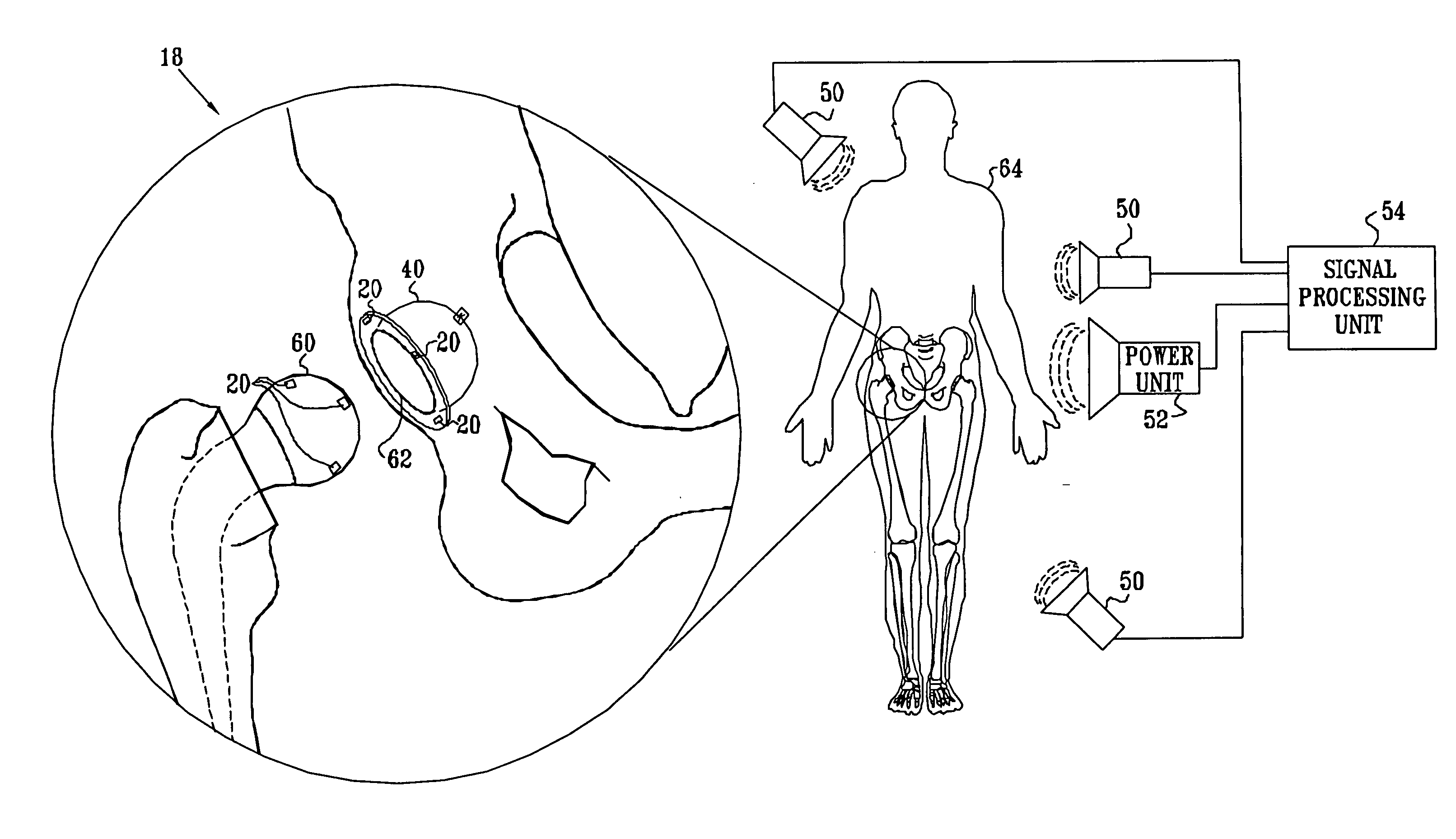

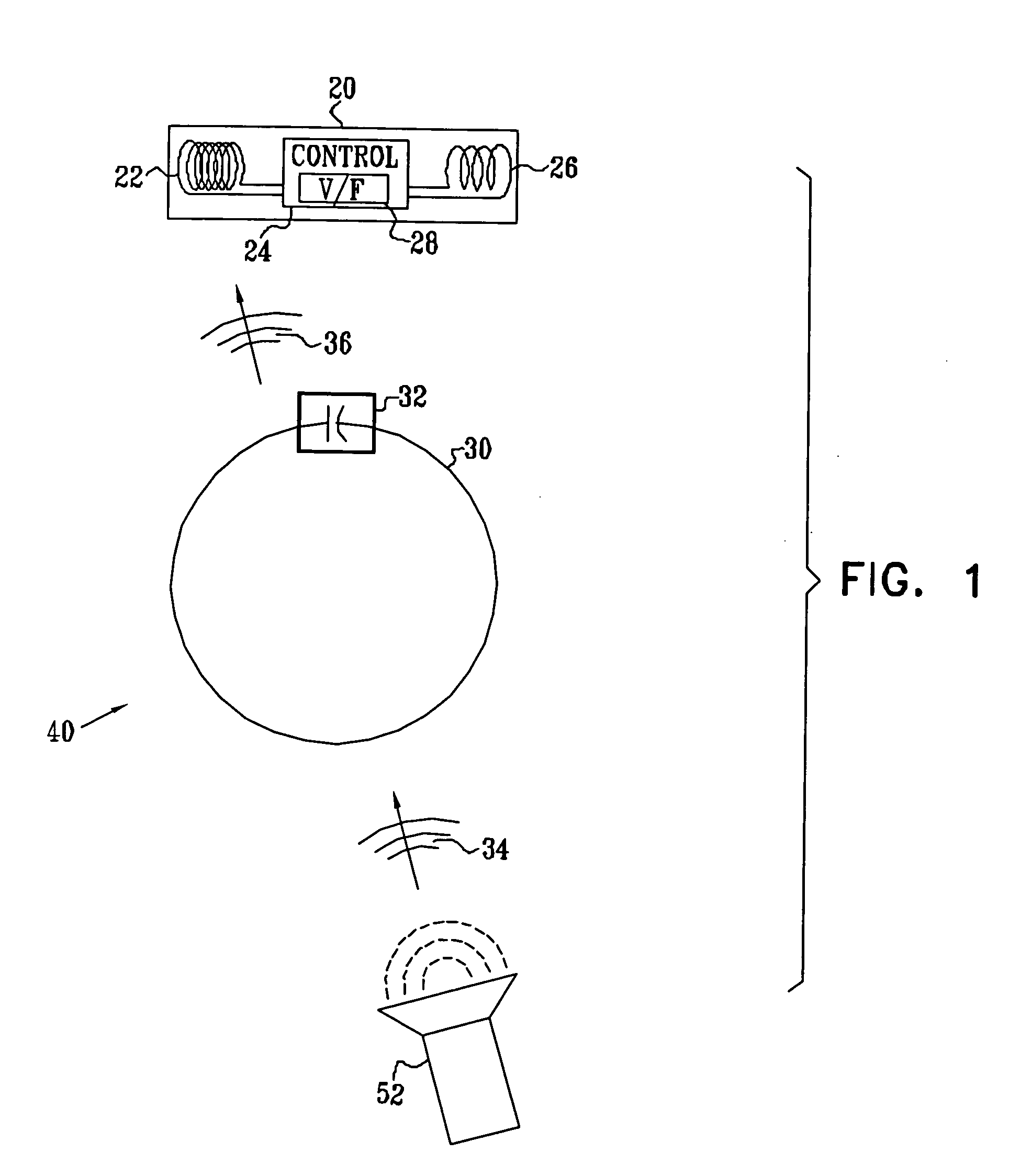

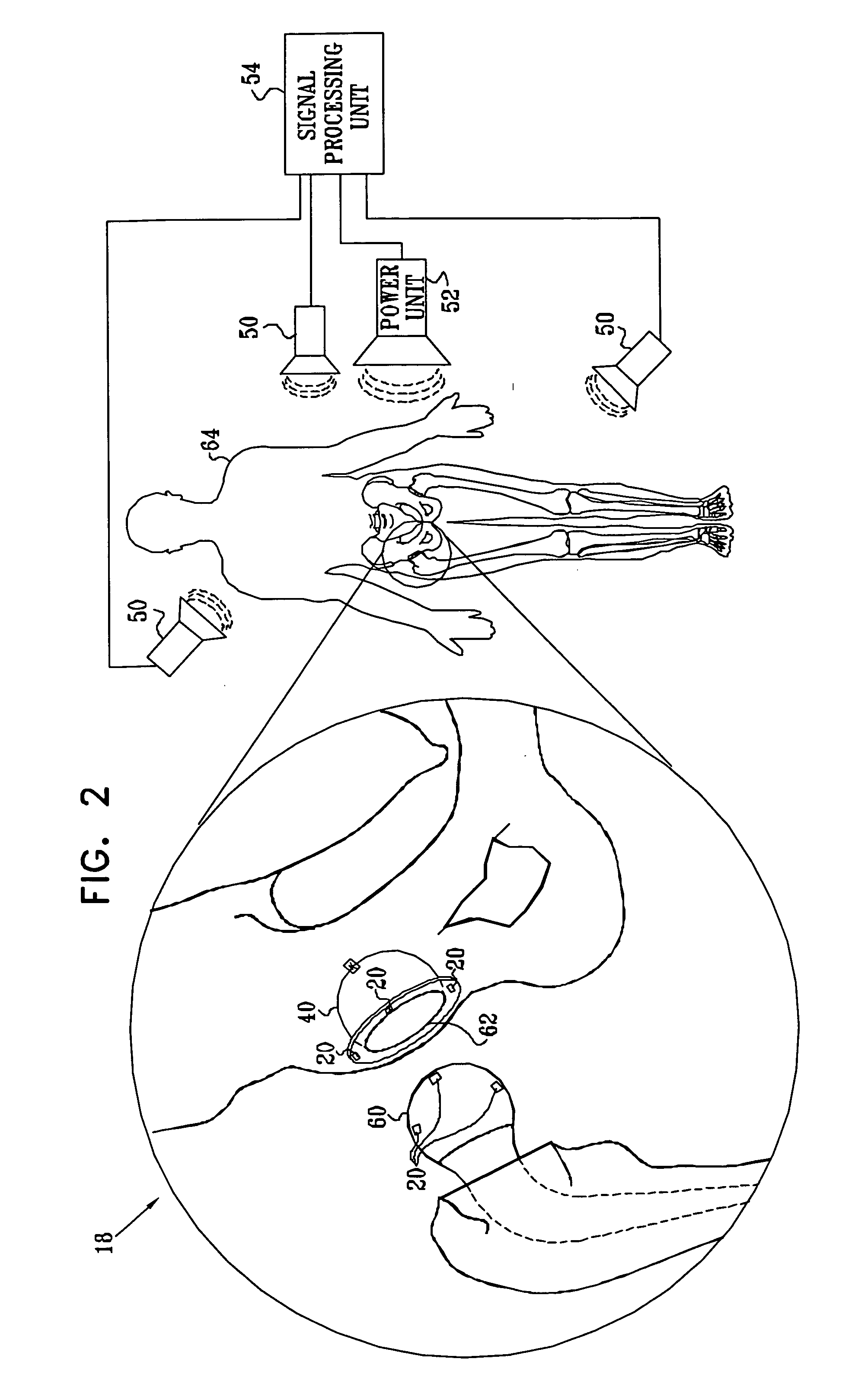

Energy transfer amplification for intrabody devices

InactiveUS20050027192A1Improved power transferImprove wireless transferSurgeryJoint implantsPower circuitsEngineering

Apparatus for driving current in a power circuit of a medical device inserted into a body of a subject includes a power transmitter, which is adapted to generate, in a vicinity of the body, an electromagnetic field having a predetermined frequency capable of inductively driving the current in the power circuit. A passive energy transfer amplifier, having a resonant response at the frequency of the electromagnetic field is placed in proximity to the medical device so as to enhance the current driven in the power circuit by the electromagnetic field.

Owner:BIOSENSE WEBSTER INC

Set top terminal that stores programs locally and generates menus

InactiveUS6828993B1Improve throughputImprove programming performanceTelevision system detailsPulse modulation television signal transmissionData signalComputer science

A viewer interface for a television program delivery system is described. The innovation relates to methods and devices for viewer pathways to television programs. Specifically, the interface involves hardware and software used in conjunction with a television at the viewer home to create a user friendly menu based approach to television program access. The device is particularly useful in a program delivery system with hundreds of programs and a data signal carrying program information. The disclosure describes menu generation and menu selection of television programs.

Owner:COMCAST IP HLDG I

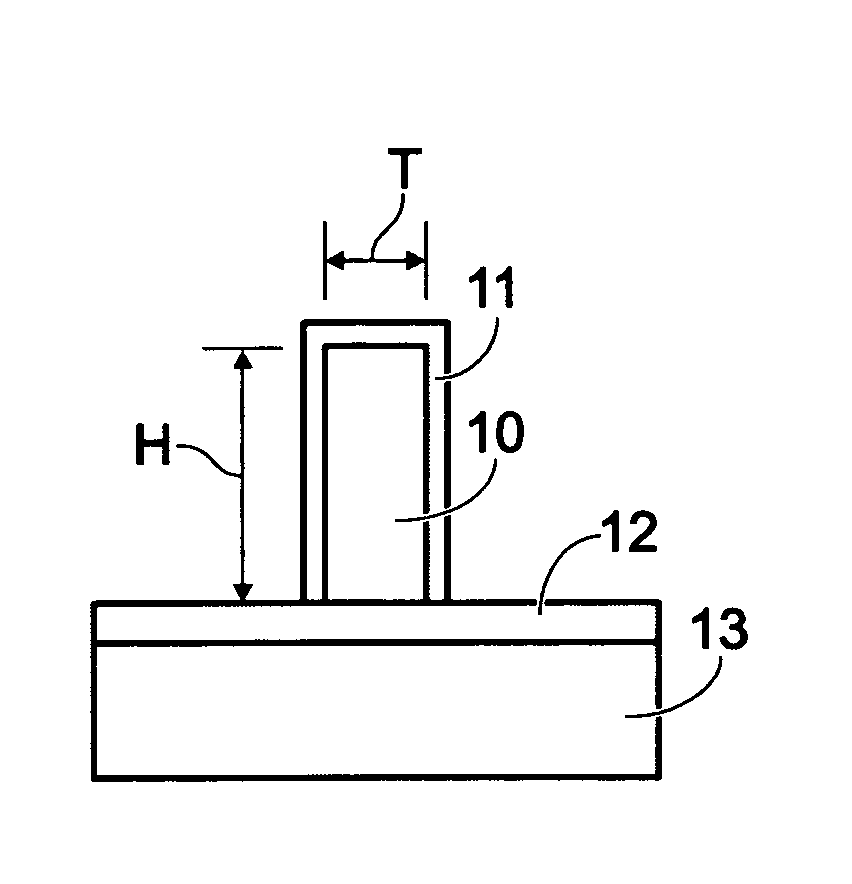

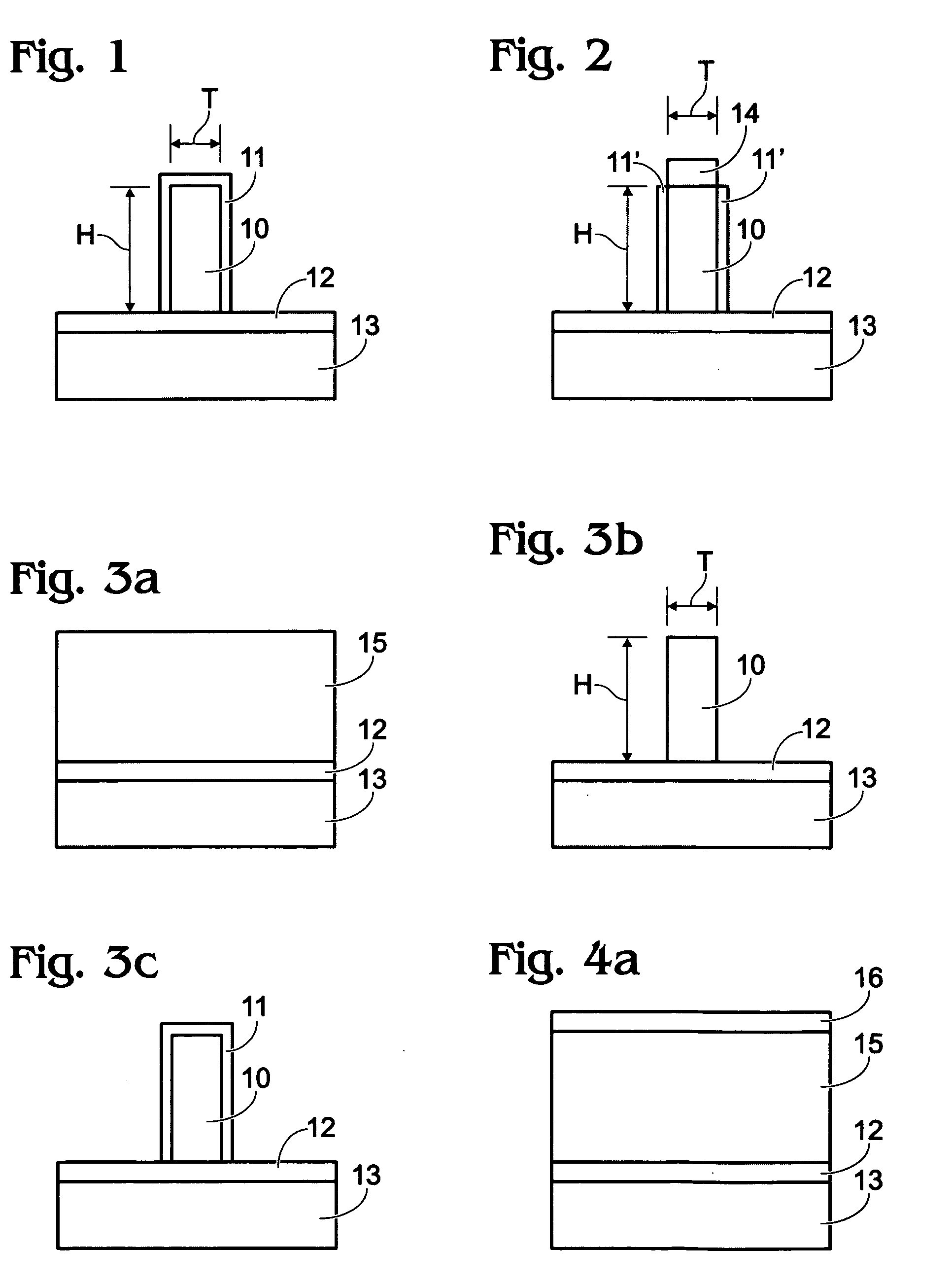

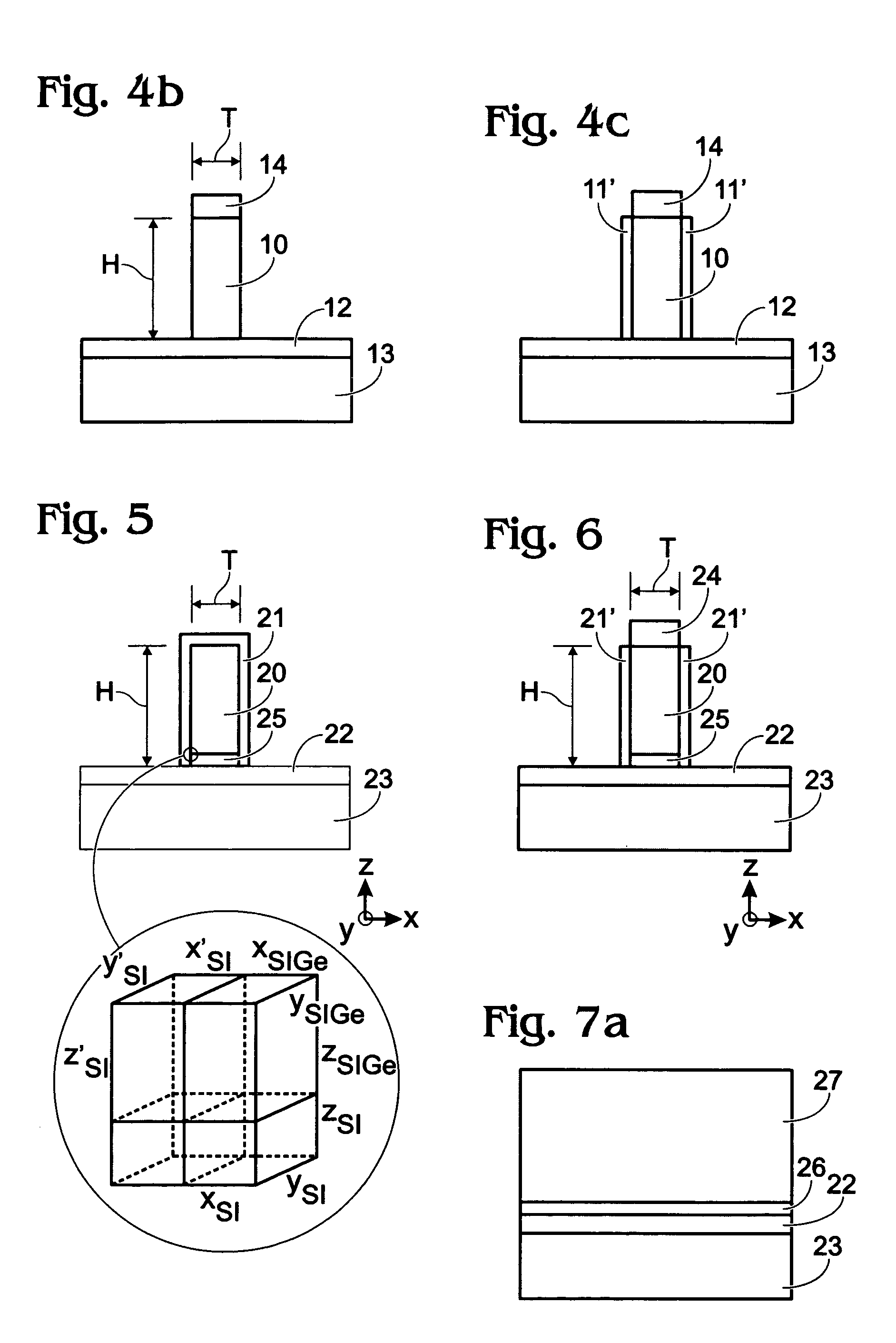

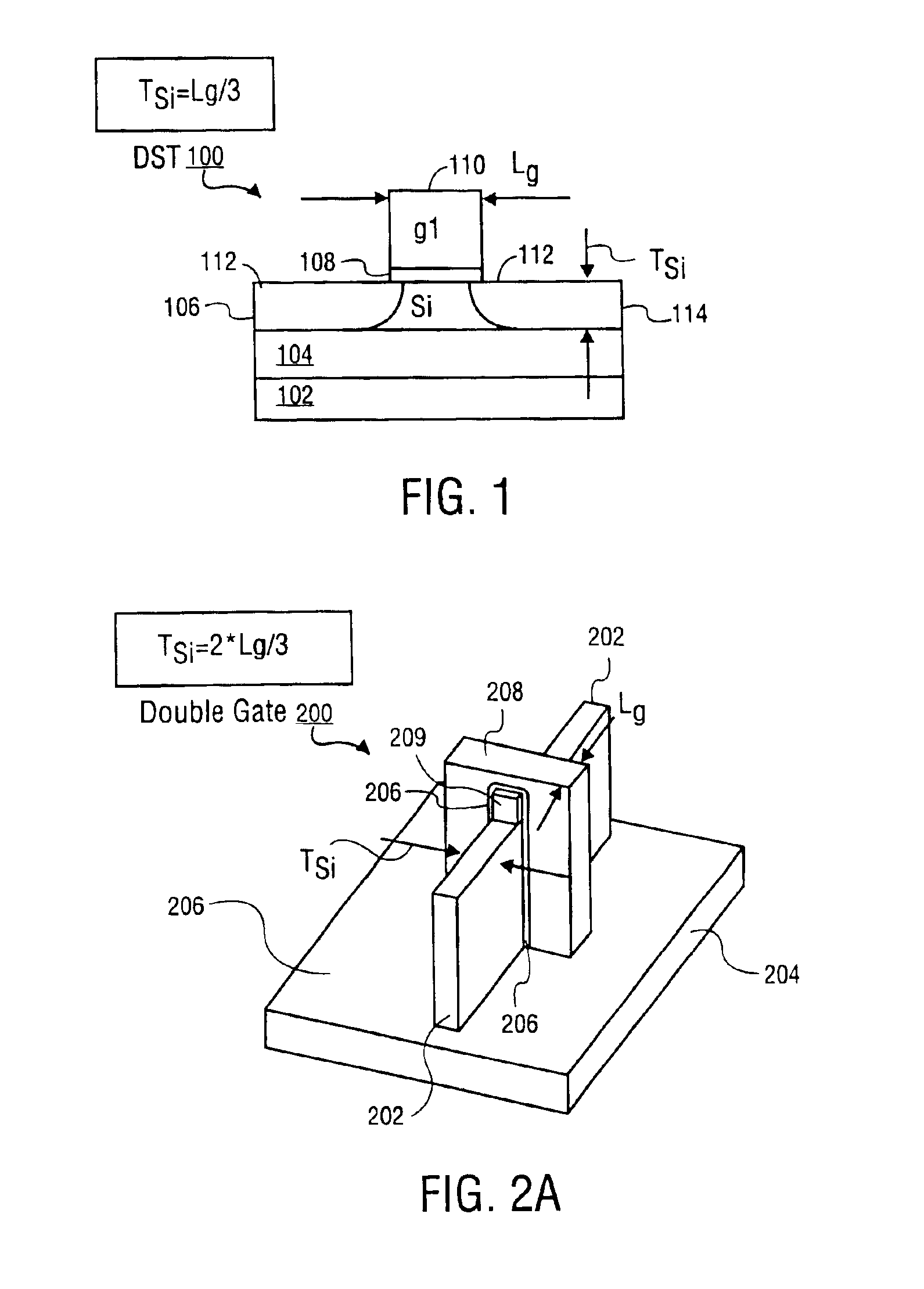

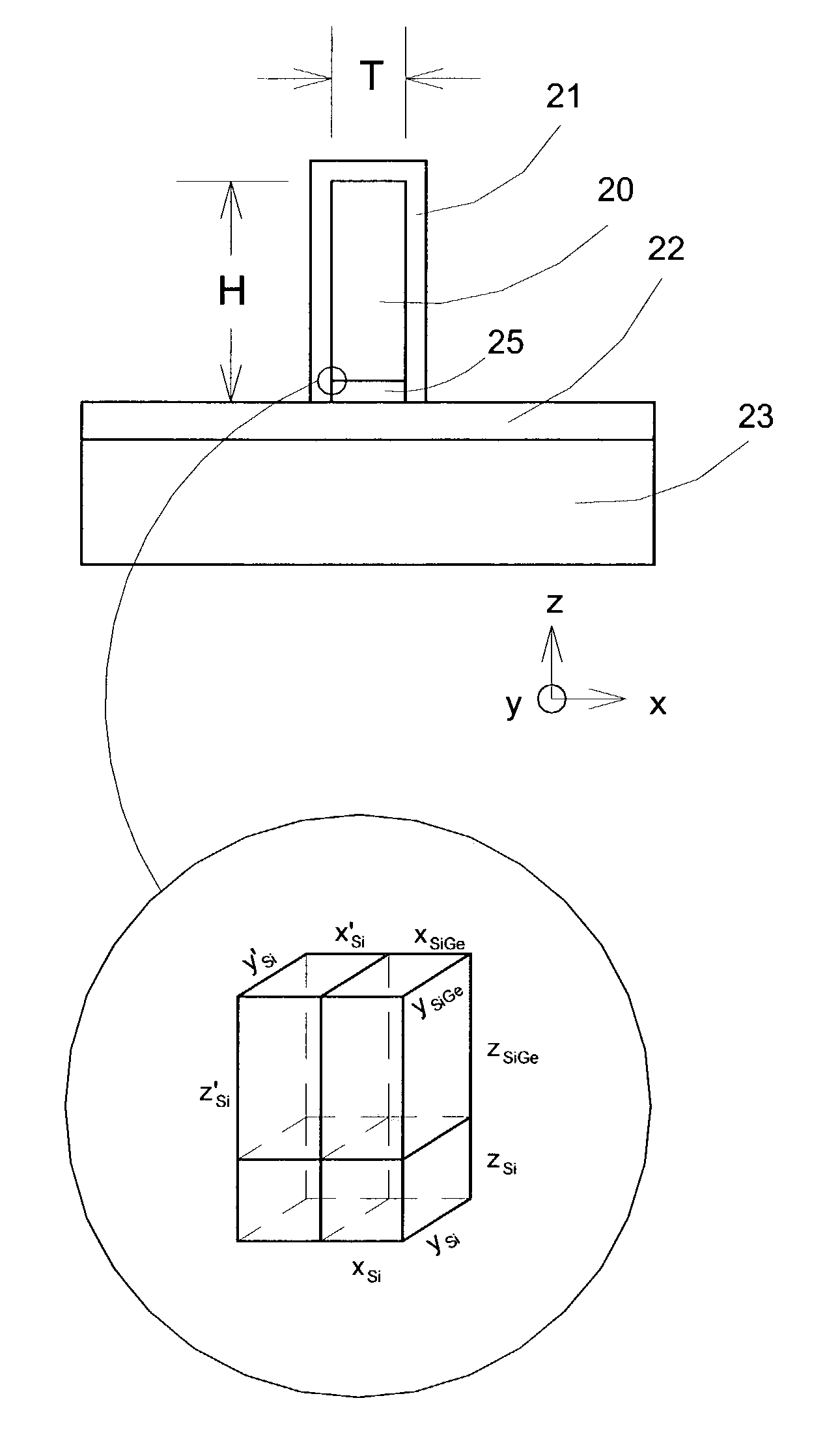

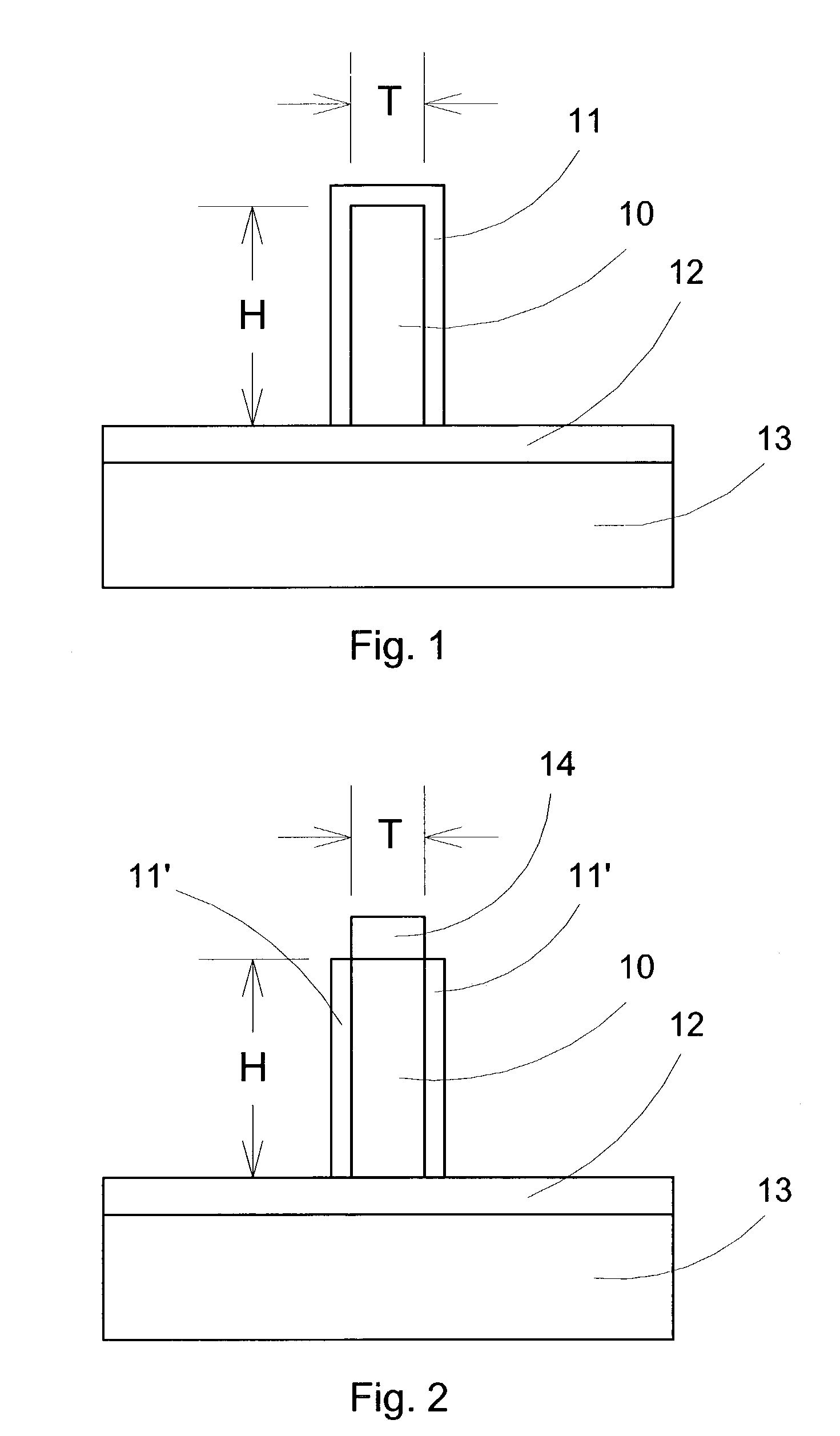

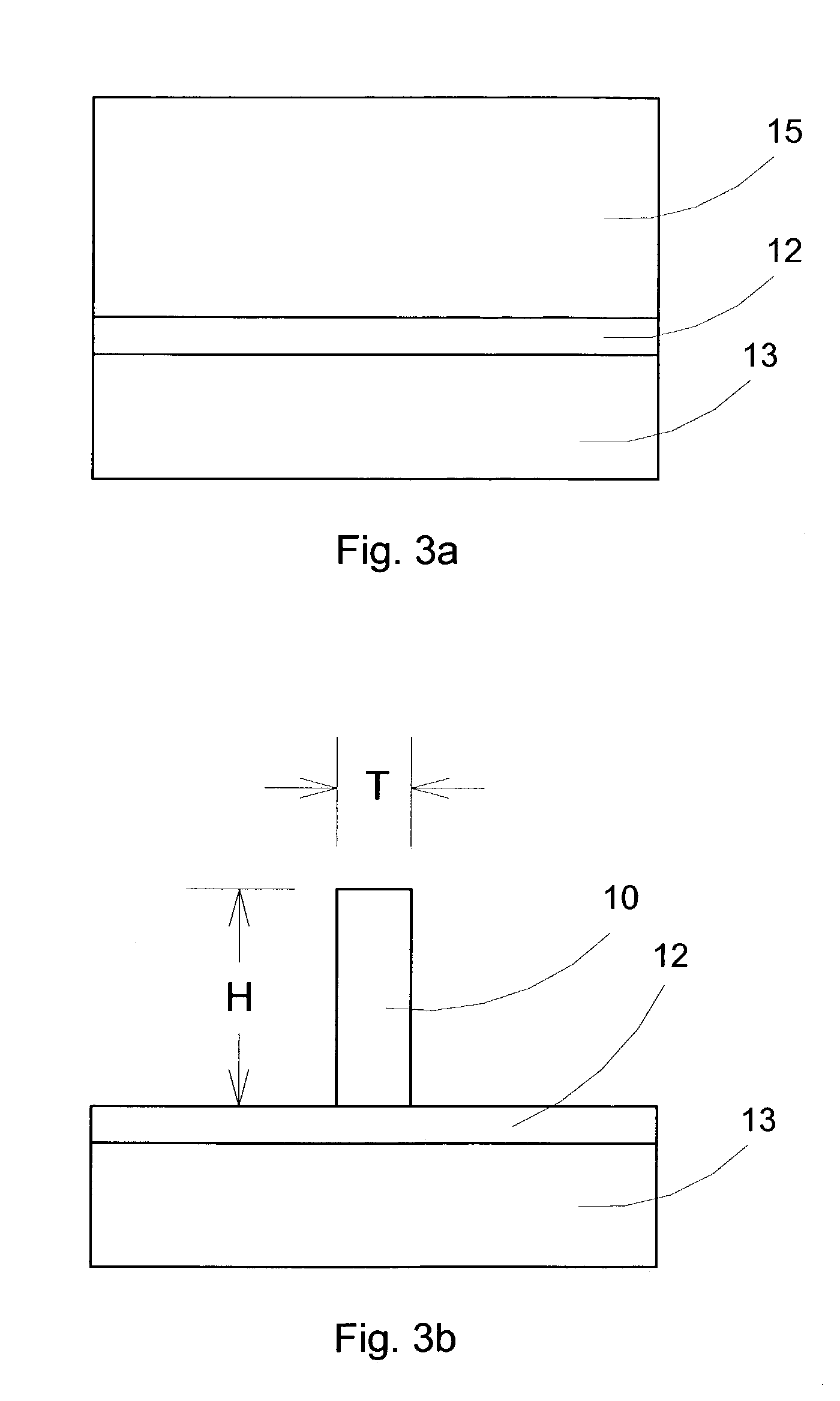

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

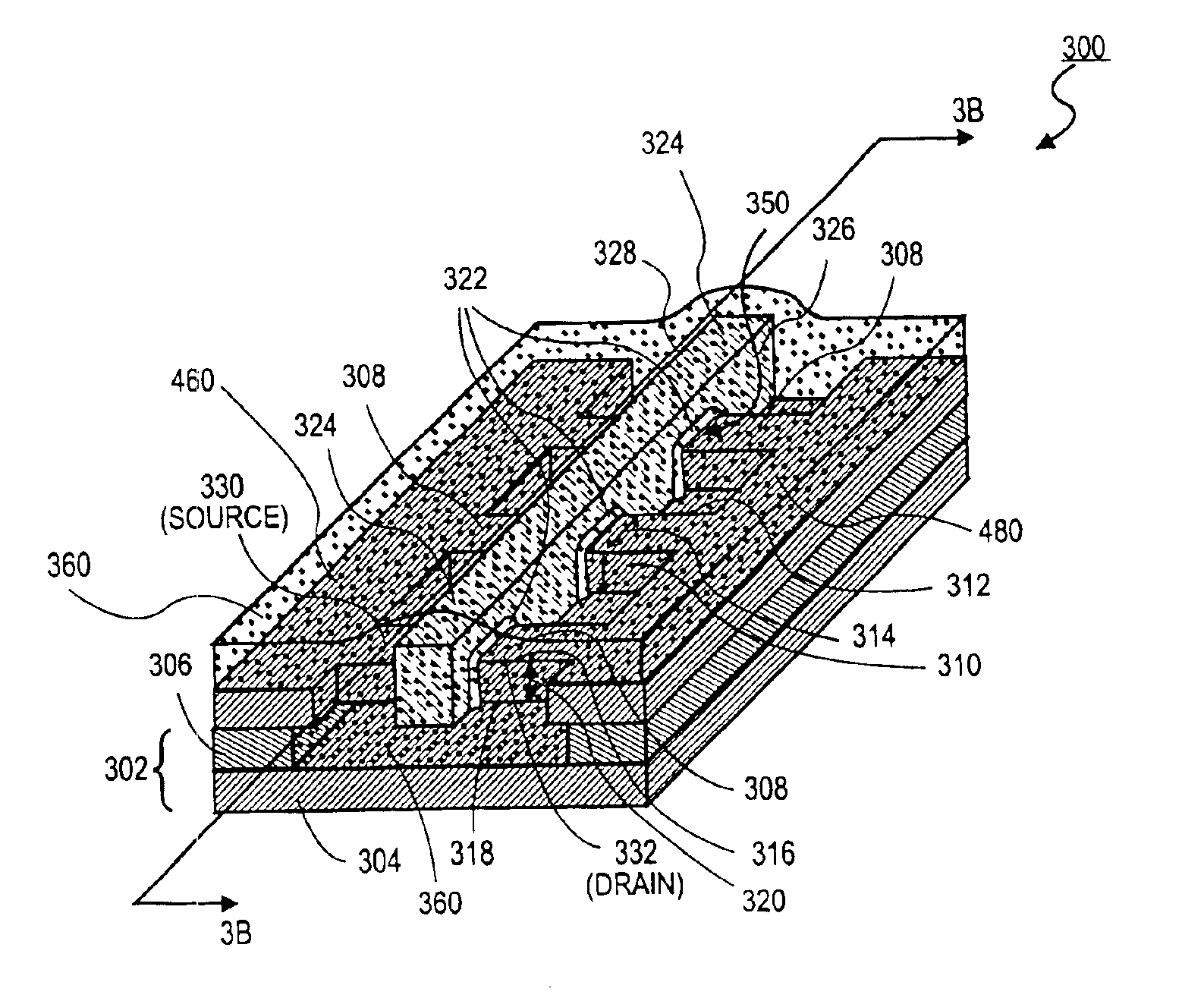

Nonplanar device with stress incorporation layer and method of fabrication

InactiveUS6909151B2Improve performanceHigh carrier mobilityTransistorSolid-state devicesGate dielectricSemiconductor

A semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls is formed on an insulating substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and is formed adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body. A thin film is then formed adjacent to the semiconductor body wherein the thin film produces a stress in the semiconductor body.

Owner:INTEL CORP

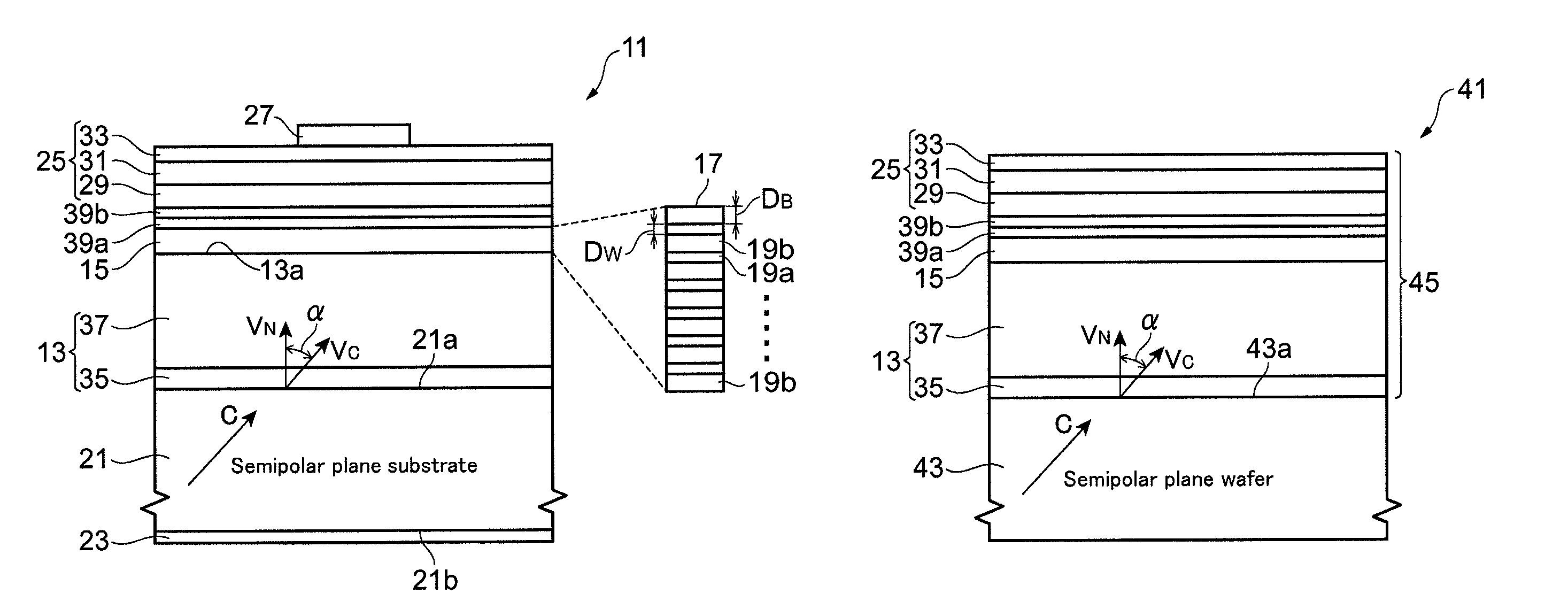

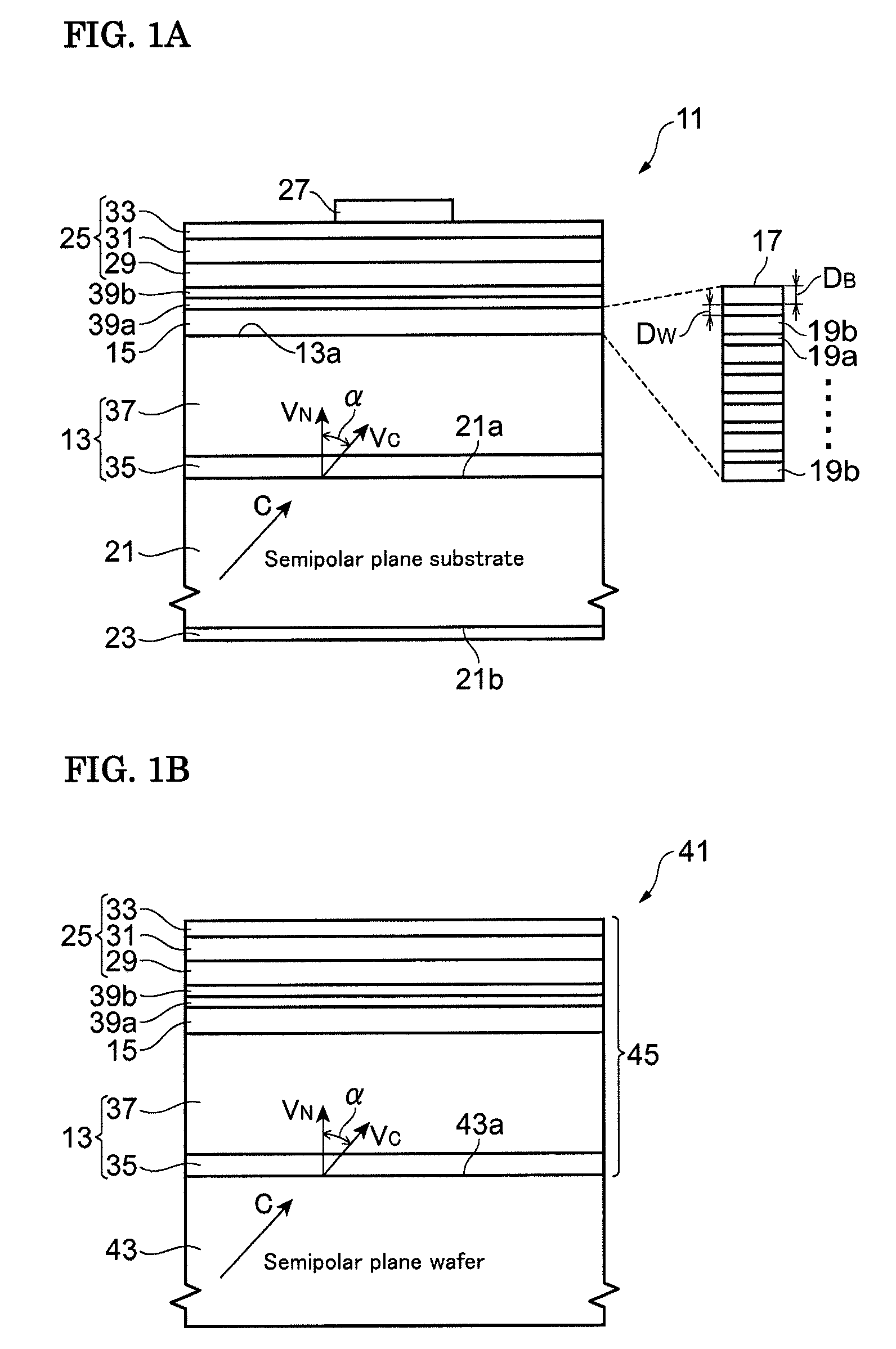

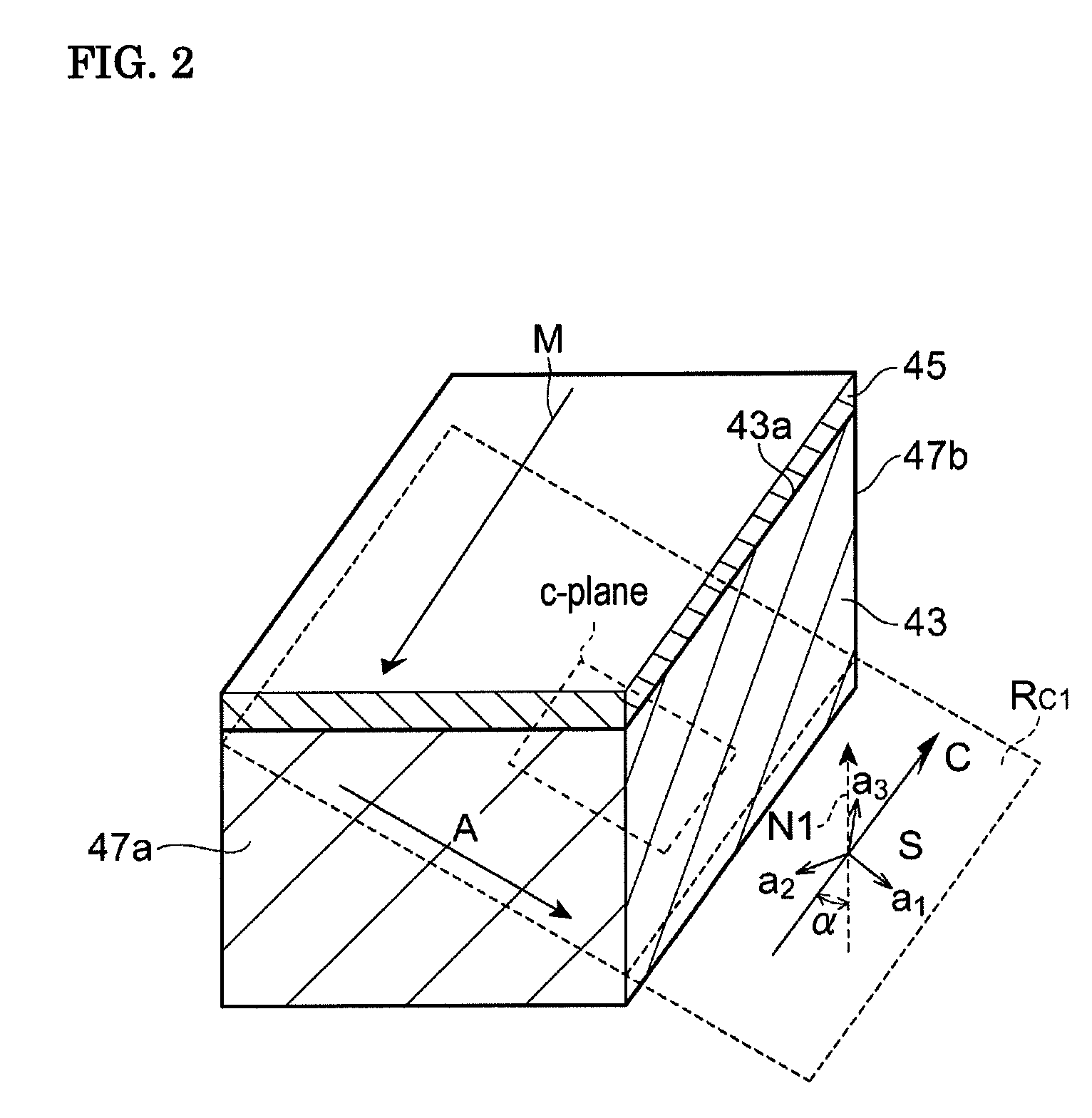

Group-III nitride light-emitting device

ActiveUS7968864B2Piezoelectric field is reducedLow efficiencyThyristorSolid-state devicesQuantum wellLength wave

A group-III nitride light-emitting device is provided. An active layer having a quantum well structure is grown on a basal plane of a gallium nitride based semiconductor region. The quantum well structure is formed in such a way as to have an emission peak wavelength of 410 nm or more. The thickness of a well layer is 4 nm or more, and 10 nm or less. The well layer is composed of InXGa1-XN (0.15≦X<1, where X is a strained composition). The basal plane of the gallium nitride based semiconductor region is inclined at an inclination angle within the range of 15 degrees or more, and 85 degrees or less with reference to a {0001} plane or a {000-1} plane of a hexagonal system group III nitride. The basal plane in this range is a semipolar plane.

Owner:SUMITOMO ELECTRIC IND LTD

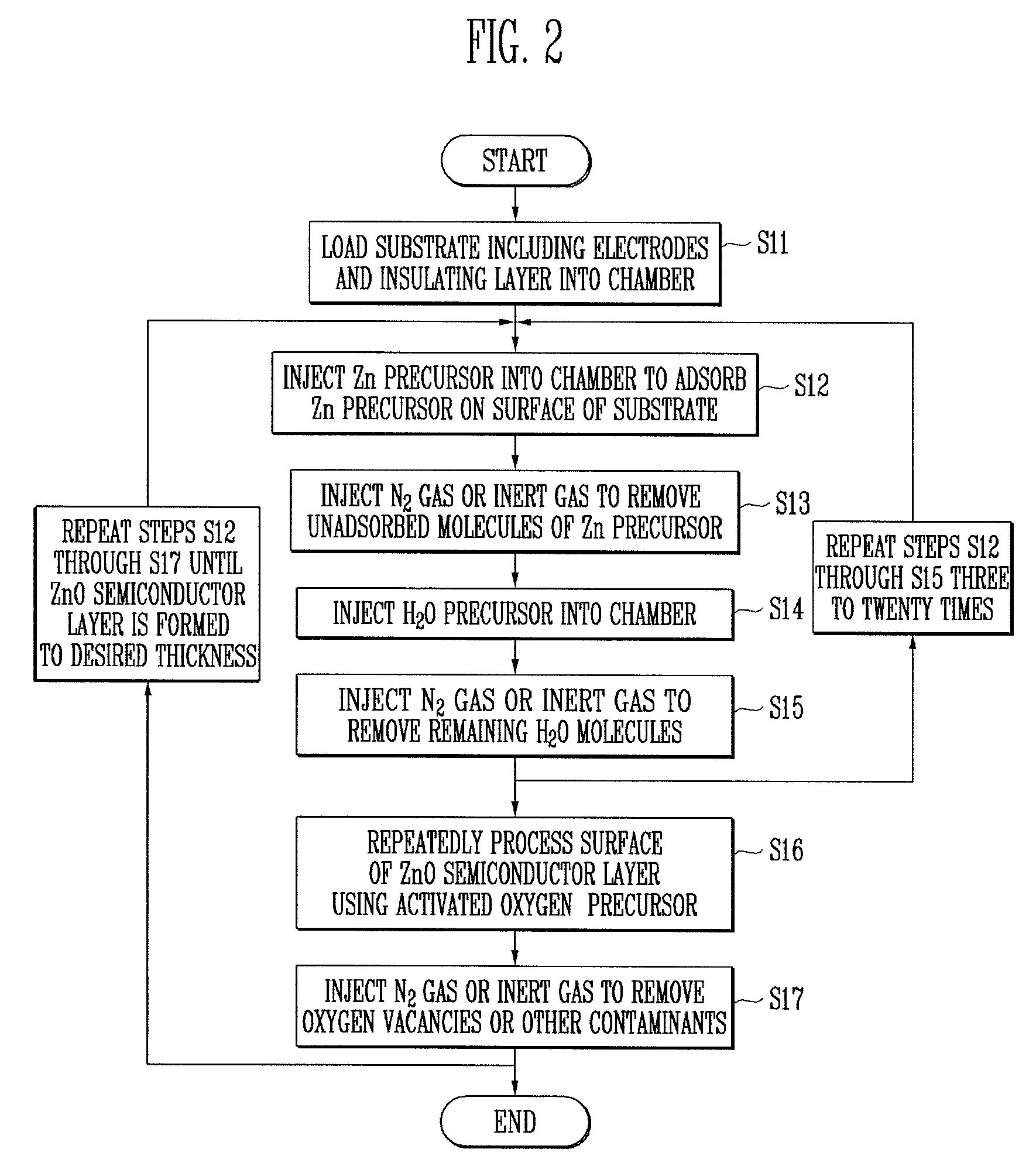

METHOD OF MANUFACTURING ZnO SEMICONDUCTOR LAYER FOR ELECTRONIC DEVICE AND THIN FILM TRANSISTOR INCLUDING THE ZnO SEMICONDUCTOR LAYER

InactiveUS20080277656A1Improve mobilityIncrease currentTransistorSemiconductor/solid-state device manufacturingCrystallinitySemiconductor

Provided are a method of manufacturing a ZnO semiconductor layer for an electronic device, which can control the size of crystals of the ZnO semiconductor layer and the number of carriers using a surface chemical reaction between precursors, and a thin film transistor (TFT) including the ZnO semiconductor layer. The method includes: (a) loading a substrate into a chamber; (b) injecting a Zn precursor into the chamber to adsorb the Zn precursor on the substrate; (c) injecting an inert gas or N2 gas into the chamber to remove the remaining Zn precursor; (d) injecting an oxygen precursor into the chamber to cause a reaction between the oxygen precursor and the Zn precursor adsorbed on the substrate to form the ZnO semiconductor layer; (e) injecting the N2 gas or inert gas into the chamber to remove the remaining oxygen precursor; (f) repeating steps (a) through (e); (g) repeatedly processing the surface treatment of the ZnO semiconductor layer using O2 plasma or O3; (h) injecting the N2 gas or inert gas into the chamber to remove the remaining oxygen and Zn precursors; and (i) repeating steps (a) through (h) to control the thickness of the ZnO semiconductor layer. In this method, a transparent TFT is formed using a transparent substrate to enable manufacture of a transparent display device, and a flexible display device can be manufactured using a flexible substrate. Also, the crystallinity of the ZnO semiconductor layer can be increased to improve the mobility of a TFT, and the number of carriers can be controlled to reduce a leakage current. Therefore, a ZnO semiconductor having excellent characteristics can be manufactured.

Owner:ELECTRONICS & TELECOMM RES INST

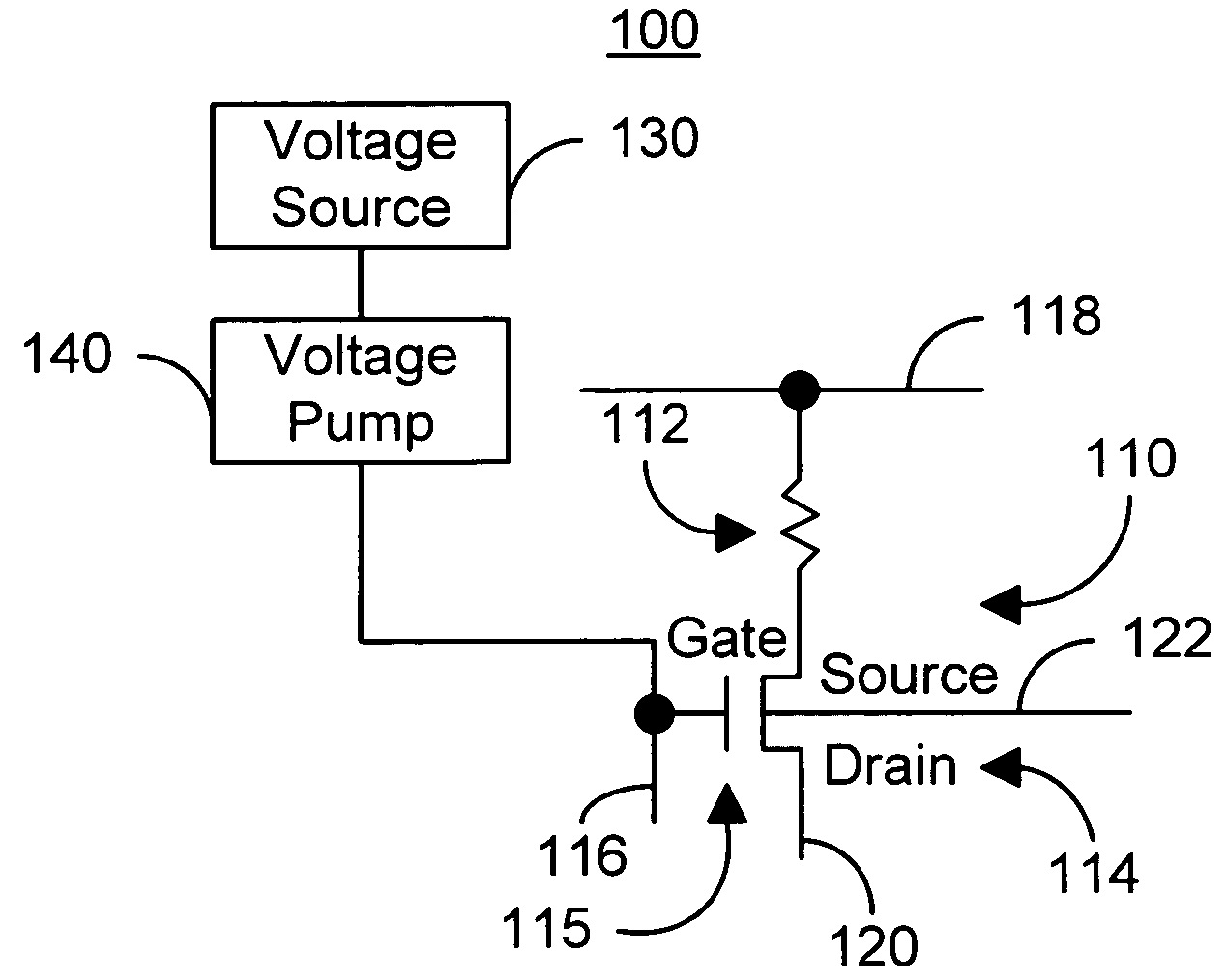

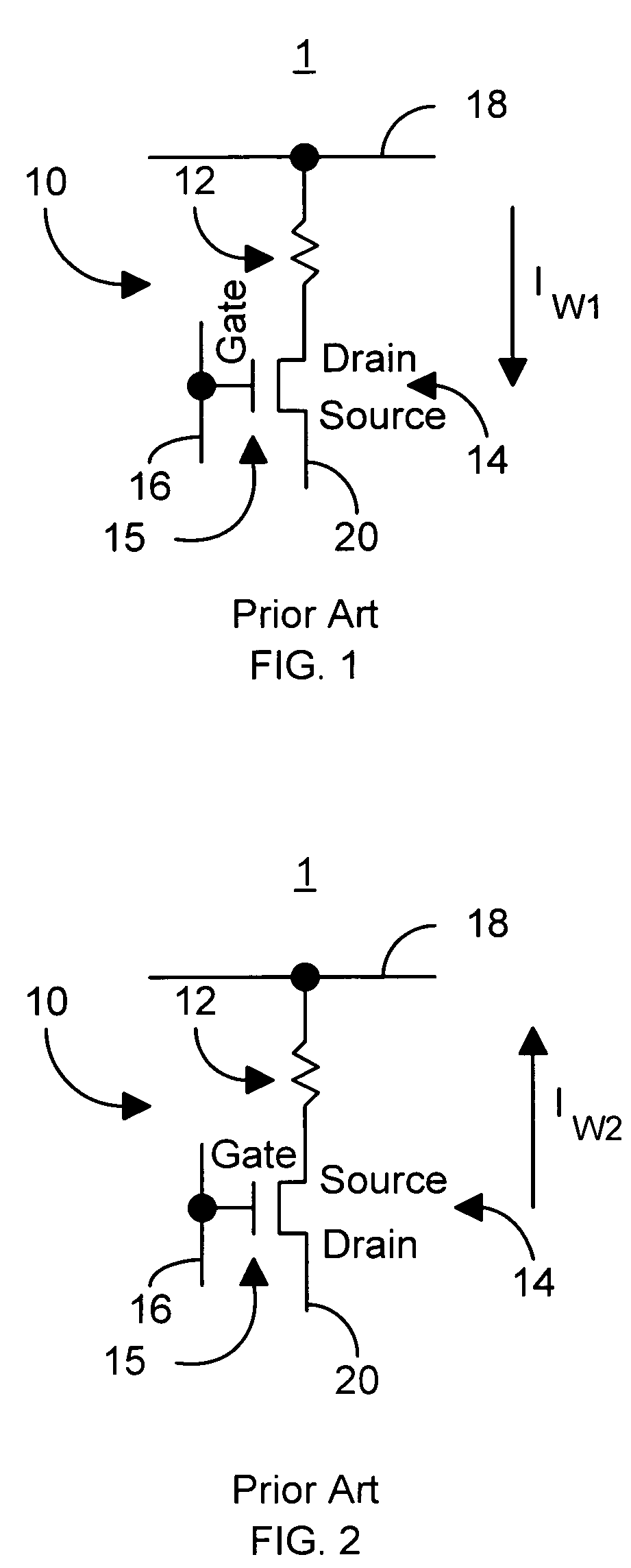

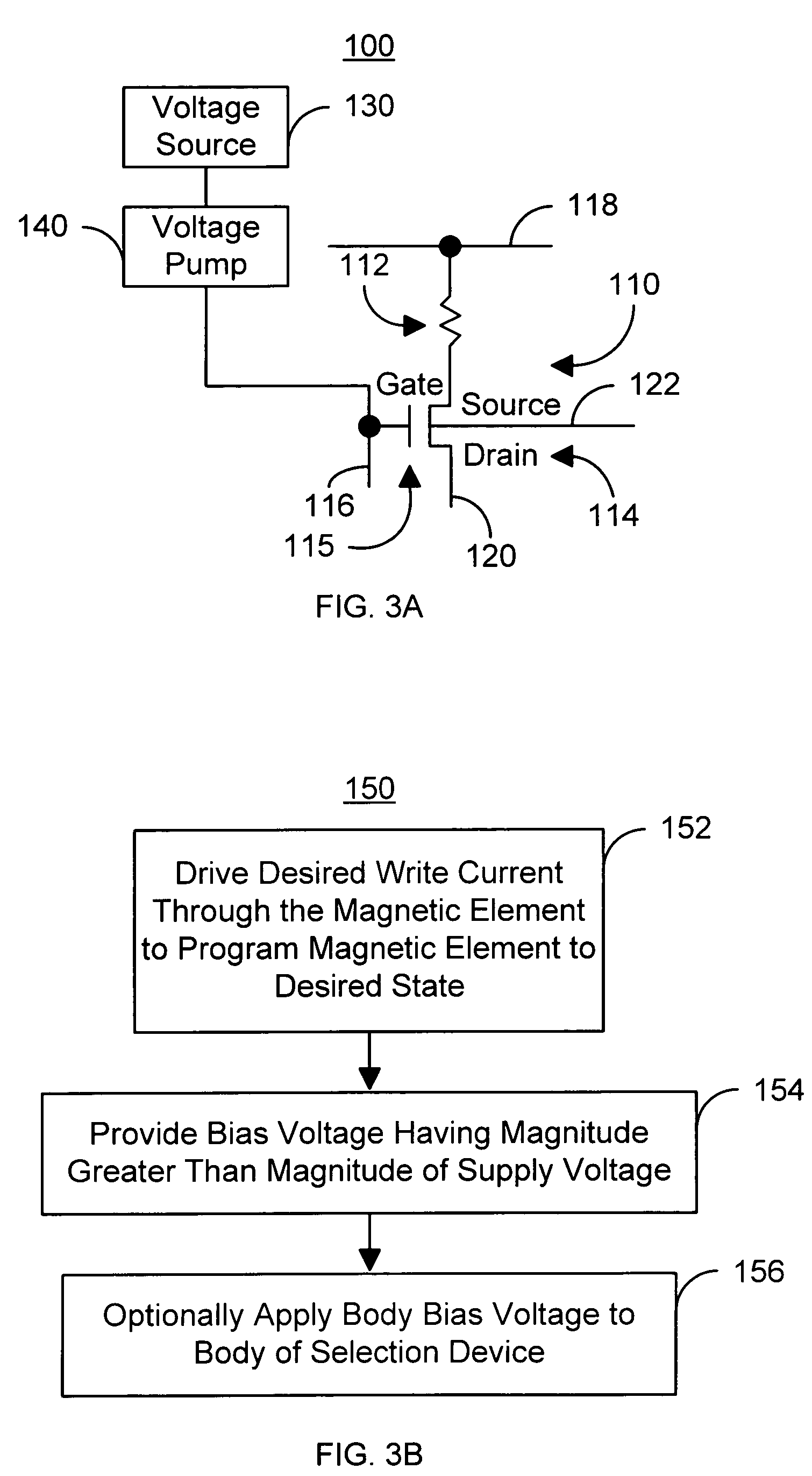

Current driven memory cells having enhanced current and enhanced current symmetry

A method and system for providing and using a magnetic memory is described. The method and system include providing a plurality of magnetic storage cells. Each magnetic storage cell includes a magnetic element and a selection device coupled with the magnetic element. The magnetic element is programmed by write currents driven through the magnetic element in a first or second direction. In one aspect, the method and system include providing a voltage supply and a voltage pump coupled with the magnetic storage cells and the voltage supply. The voltage supply provides a supply voltage. The voltage pump provides to the selection device a bias voltage having a magnitude greater than the supply voltage. Another aspect includes providing a silicon on oxide transistor as the selection device. Another aspect includes providing to the body of the transistor a body bias voltage that is a first voltage when the transistor is off and a second voltage when the transistor is on.

Owner:SAMSUNG SEMICON

Strained silicon finFET device

ActiveUS7045401B2Short effectEnhance carrier mobilityTransistorSemiconductor/solid-state device manufacturingCarbon dopedElectron mobility

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

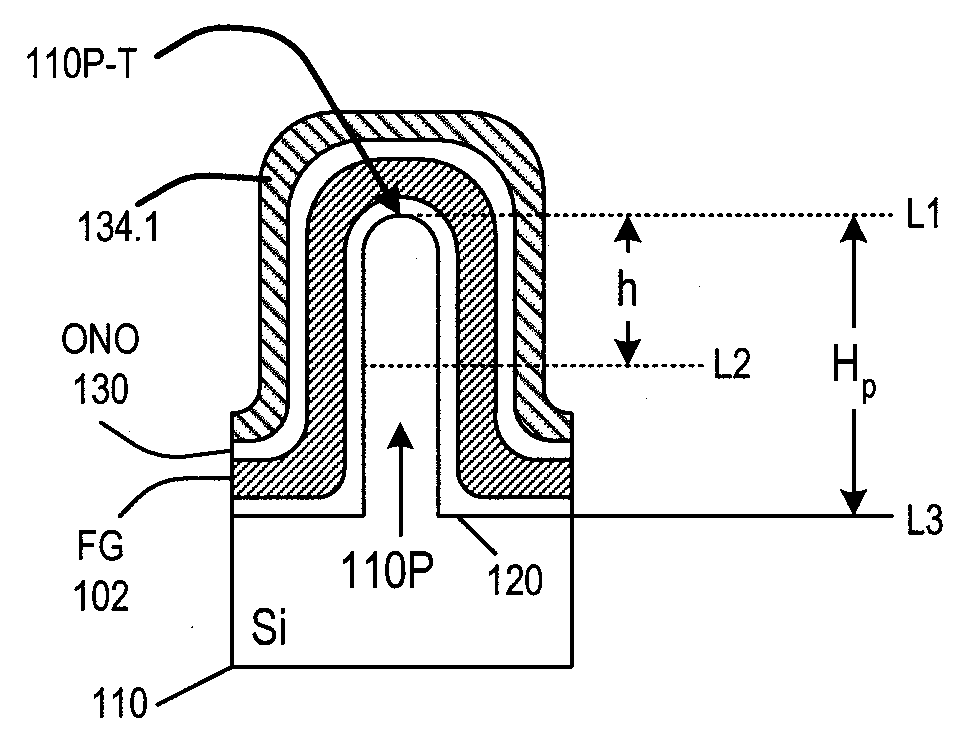

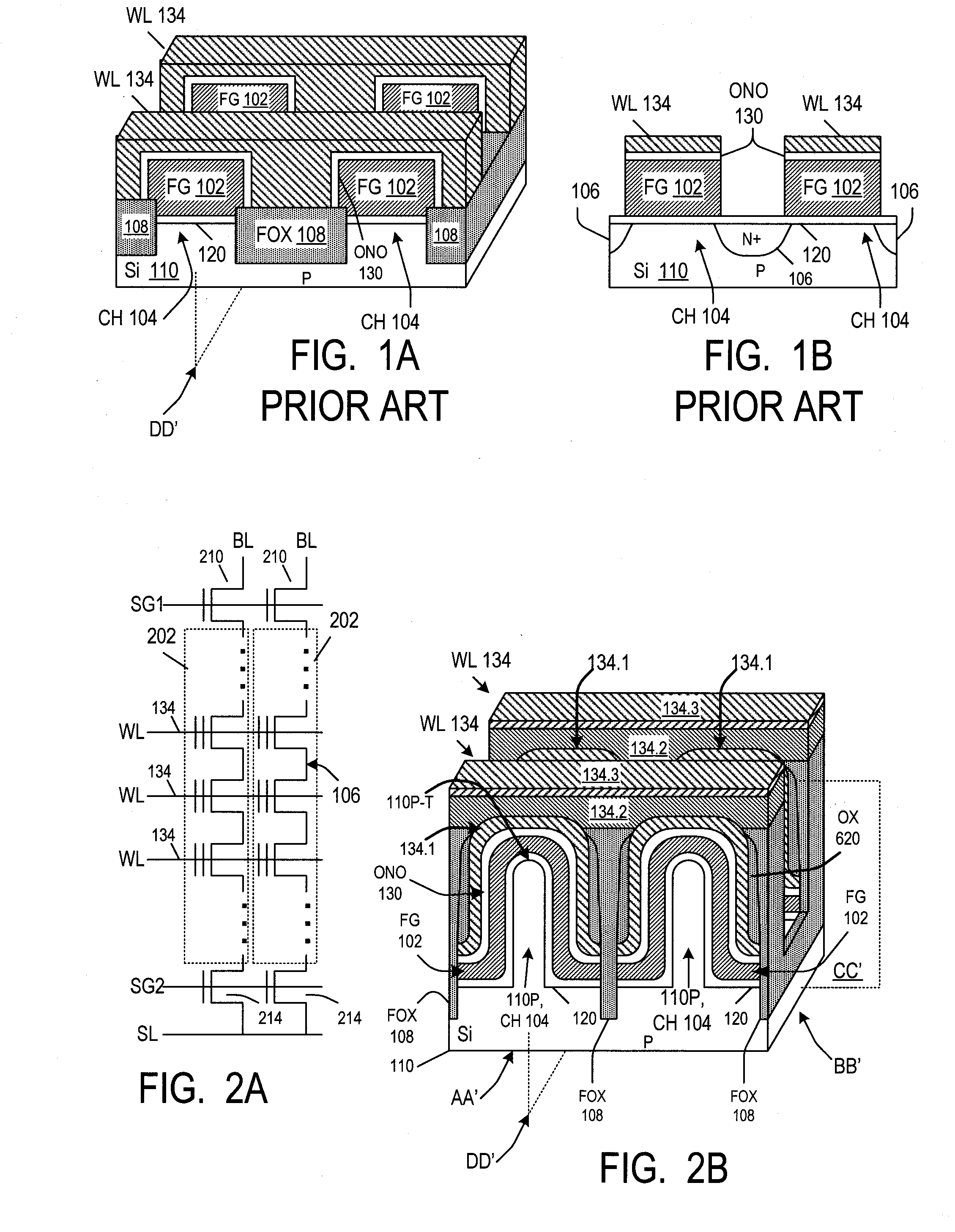

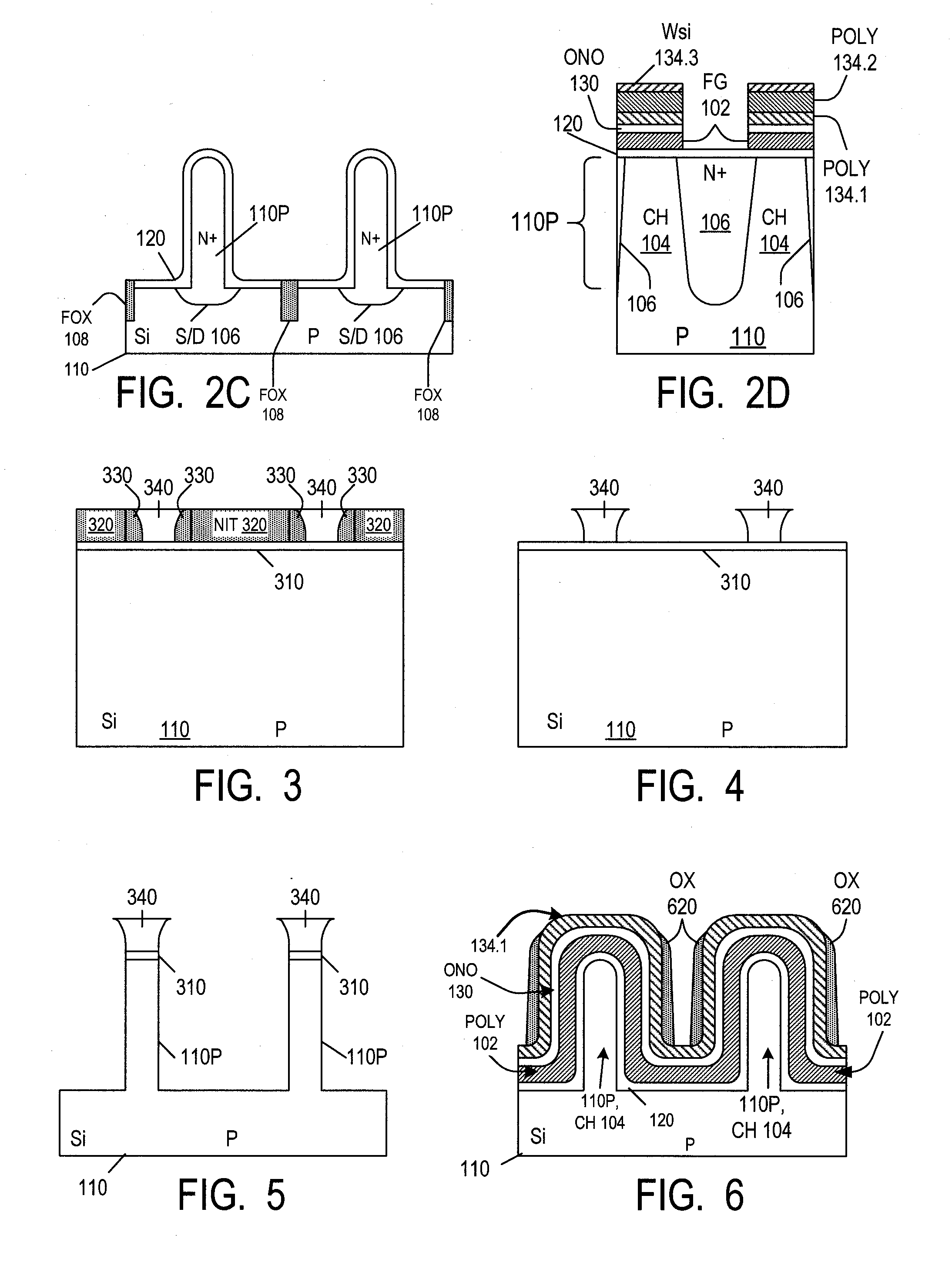

Integrated circuits with substrate protrusions, including (but not limited to) floating gate memories

ActiveUS20080265305A1Enhanced couplingIncrease currentTransistorSolid-state devicesDielectricPhotonic integrated circuit

A floating gate memory cell's channel region (104) is at least partially located in a fin-like protrusion (110P) of a semiconductor substrate. The floating gate's top surface may come down along at least two sides of the protrusion to a level below the top (110P-T) of the protrusion. The control gate's bottom surface may also comes down to a level below the top of the protrusion. The floating gate's bottom surface may comes down to a level below the top of the protrusion by at least 50% of the protrusion's height. The dielectric (120) separating the floating gate from the protrusion can be at least as thick at the top of the protrusion as at a level (L2) which is below the top of the protrusion by at least 50% of the protrusion's height. A very narrow fin or other narrow feature in memory and non-memory integrated circuits can be formed by providing a first layer (320) and then forming spacers (330) from a second layer without photolithography on sidewalls of features made from the first layer. The narrow fin or other feature are then formed without further photolithography in areas between the adjacent spacers. More particularly, a third layer (340) is formed in these areas, and the first layer and the spacers are removed selectively to the third layer. The third layer is used as a mask to form the narrow features.

Owner:PROMOS TECH INC

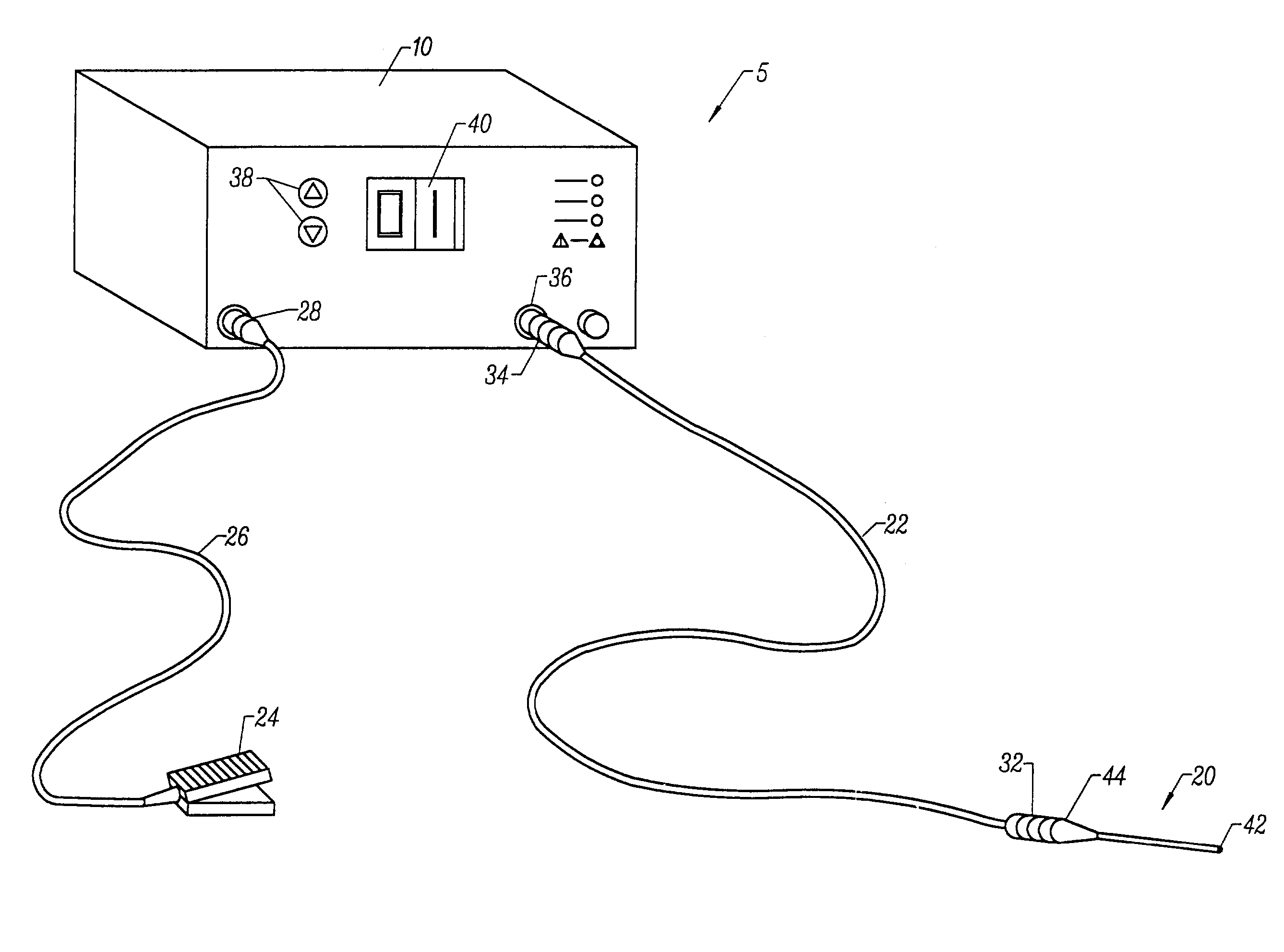

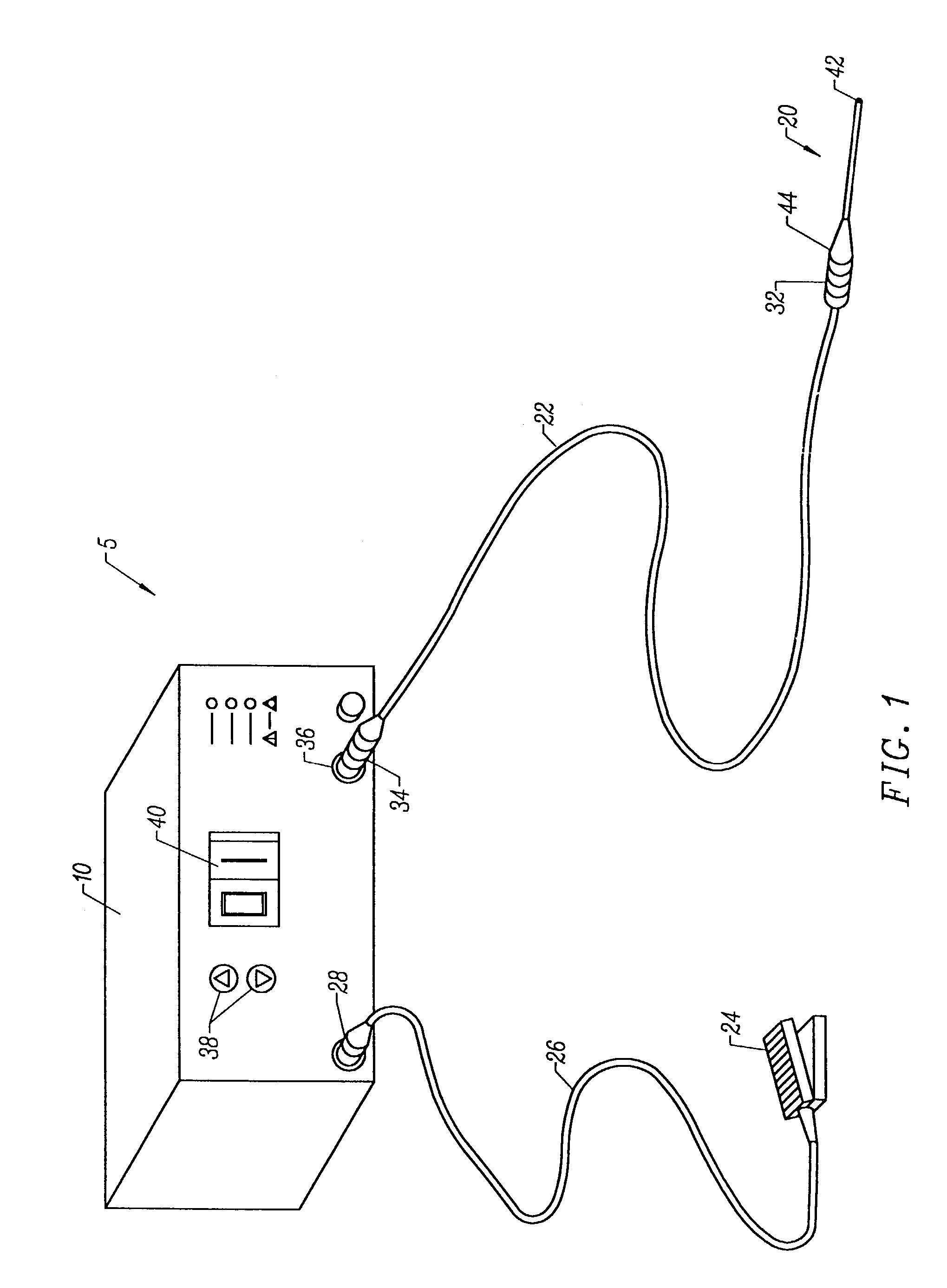

Systems and methods for electrosurgical tissue contraction

InactiveUS7094215B2Limiting thermal damage and dissociationSuppress thermal damageEye treatmentSurgical instruments for heatingSacroiliac jointSurgical department

Systems and methods are provided for performing electrosurgical interventions, such as selectively contracting soft collagen tissue and other body structures, while limiting thermal damage or molecular dissociation of such tissue and limiting the thermal damage to tissue adjacent to and underlying the treatment site. The systems and methods of the present invention are particularly useful for surgical procedures in electrically conducting environments, such as arthroscopic procedures in the joints, e.g., shoulder, knee, hip, hand, foot, elbow or the like. The present invention is also useful in relatively dry environments, such as treating and shaping the cornea, and dermatological procedures involving surface tissue contraction of tissue underlying the surface of the skin for tissue rejuvenation, wrinkle removal and the like.

Owner:ARTHROCARE

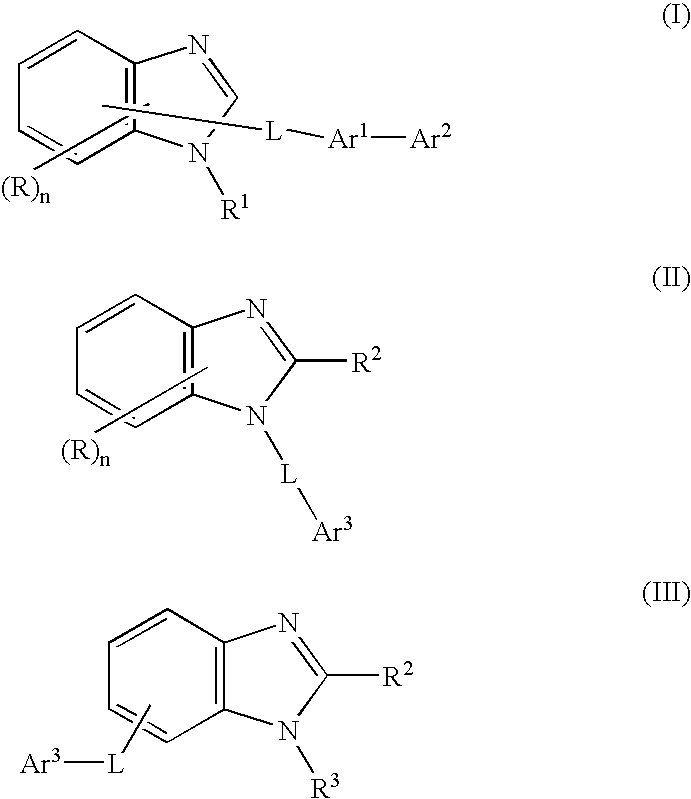

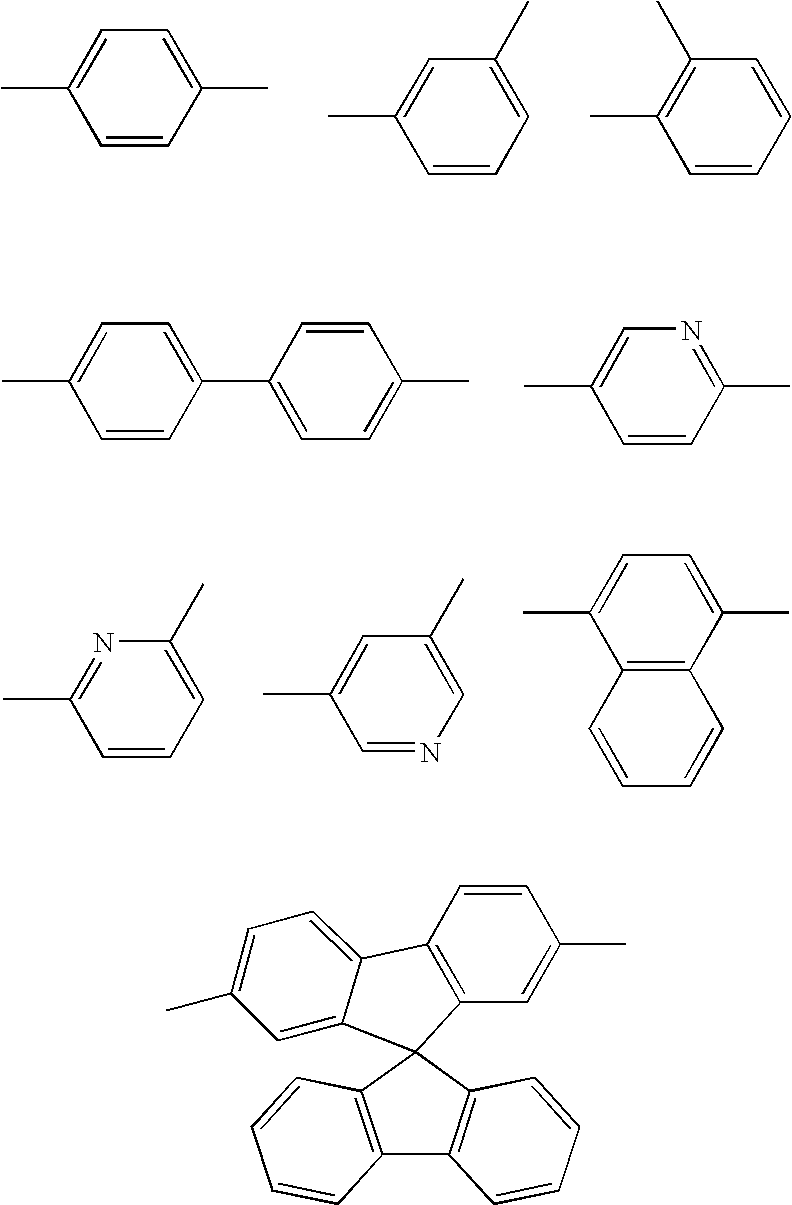

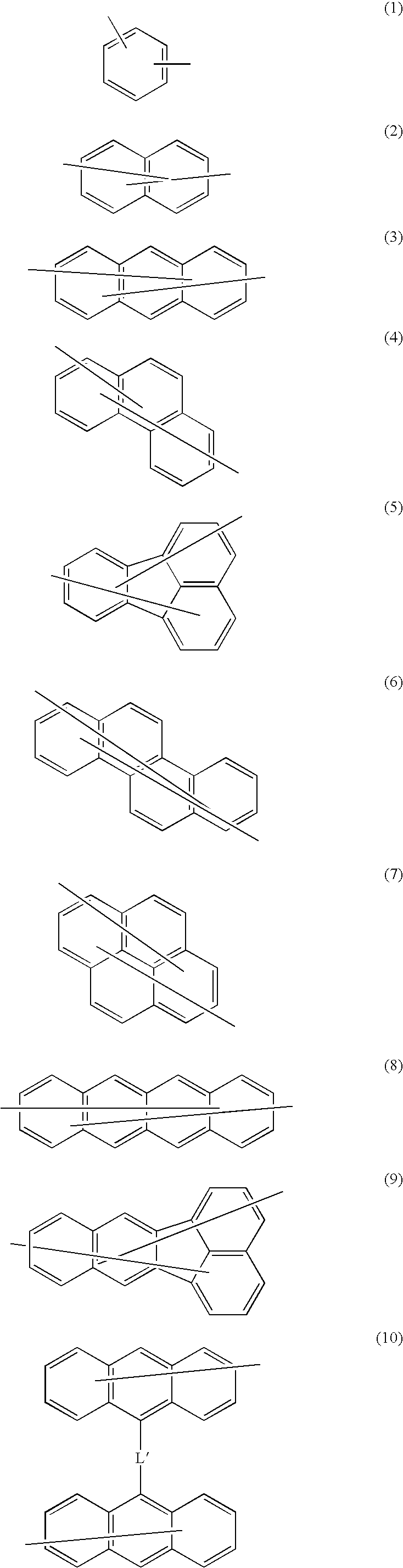

Nitrogen-containing heterocycle derivative and organic electroluminescent element using the same

ActiveUS20060147747A1Improve luminanceElevation of of efficiencyOrganic chemistryDischarge tube luminescnet screensNitrogenOrganic electroluminescence

A novel derivative of heterocyclic compound having nitrogen atom with a structure made by bonding special groups to benzimidazole, a material for an organic electroluminescence (EL) device comprising the derivative of heterocyclic compound having nitrogen atom and an organic electroluminescence device comprising at least one organic compound layer containing a light emitting layer sandwiched between a pair of electrodes, wherein the device contains the derivative of heterocyclic compound having nitrogen atom. An organic EL device achieving elevation of luminance and of efficiency in light emission even under low driving voltage is obtainable by an employment of the derivative of heterocyclic compound having nitrogen atom for at least one layer composing organic compound layers of the EL device.

Owner:IDEMITSU KOSAN CO LTD

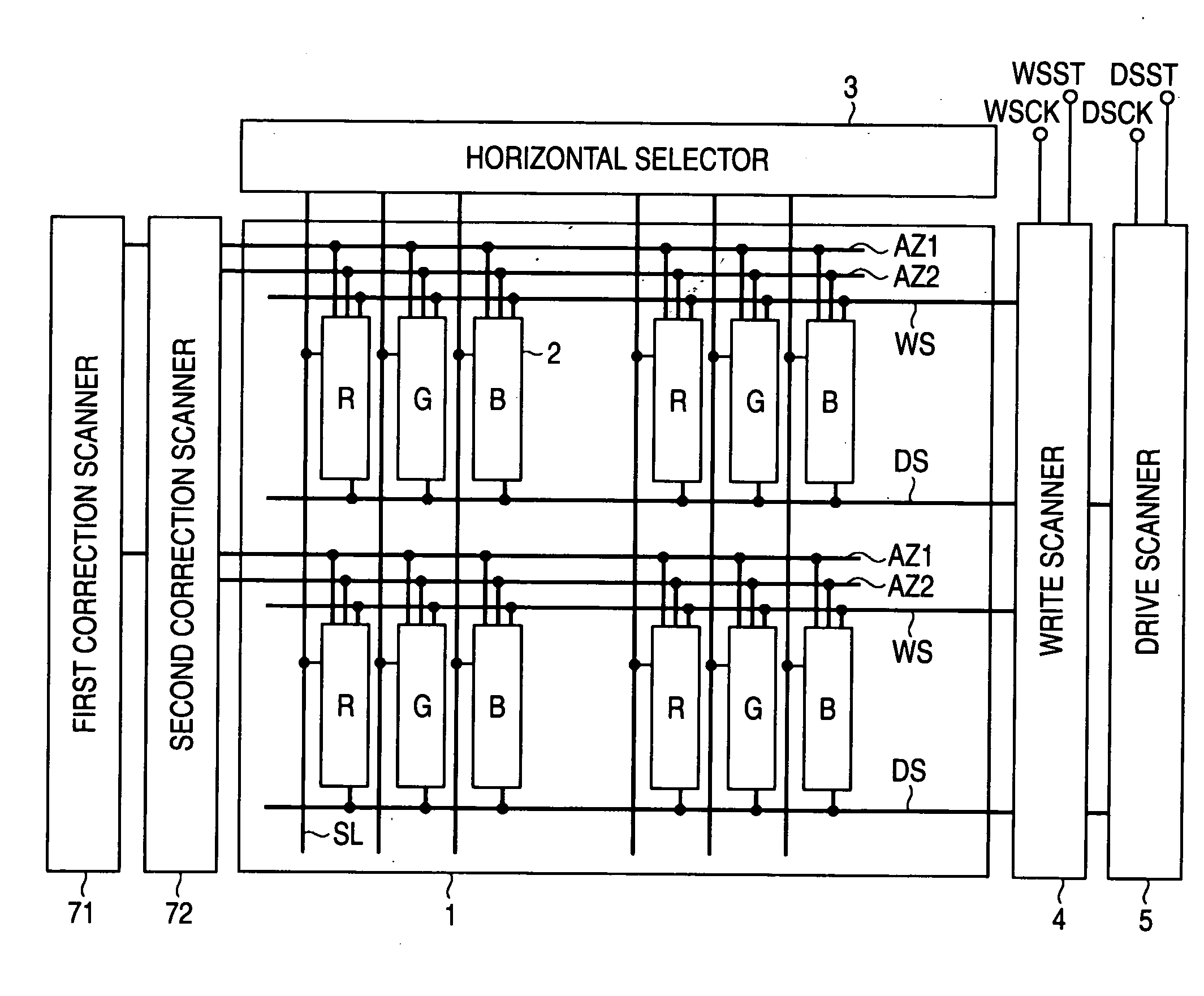

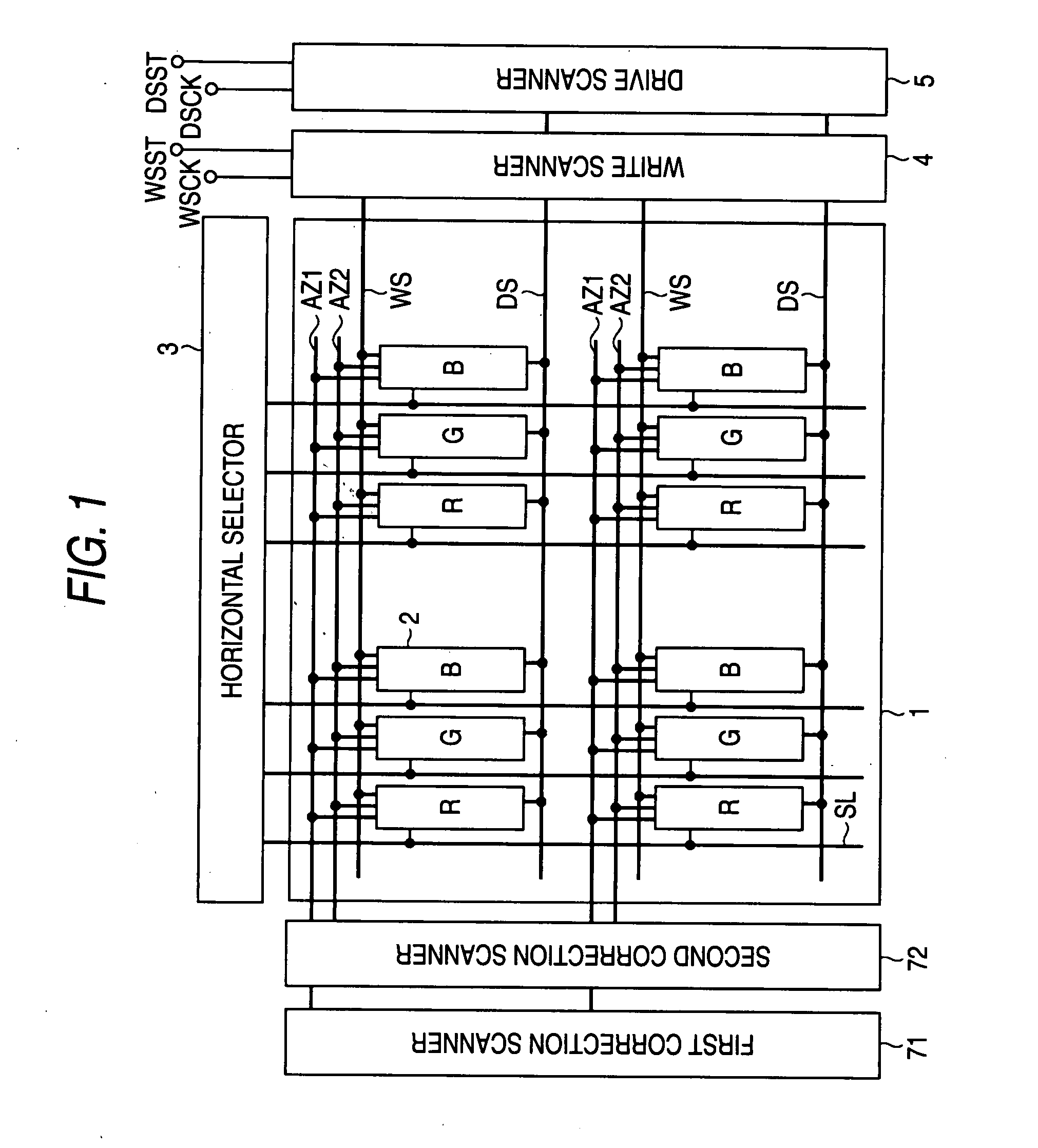

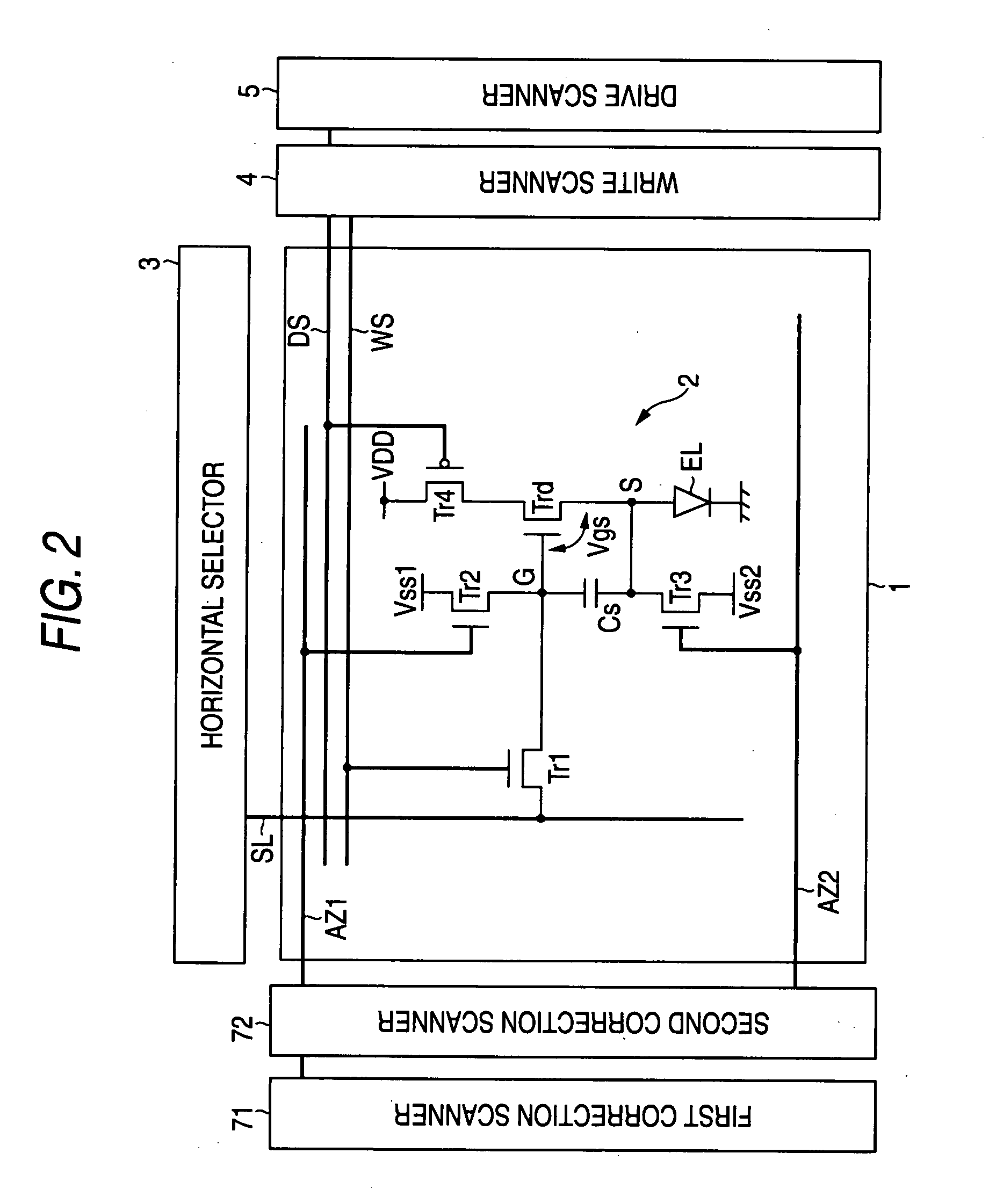

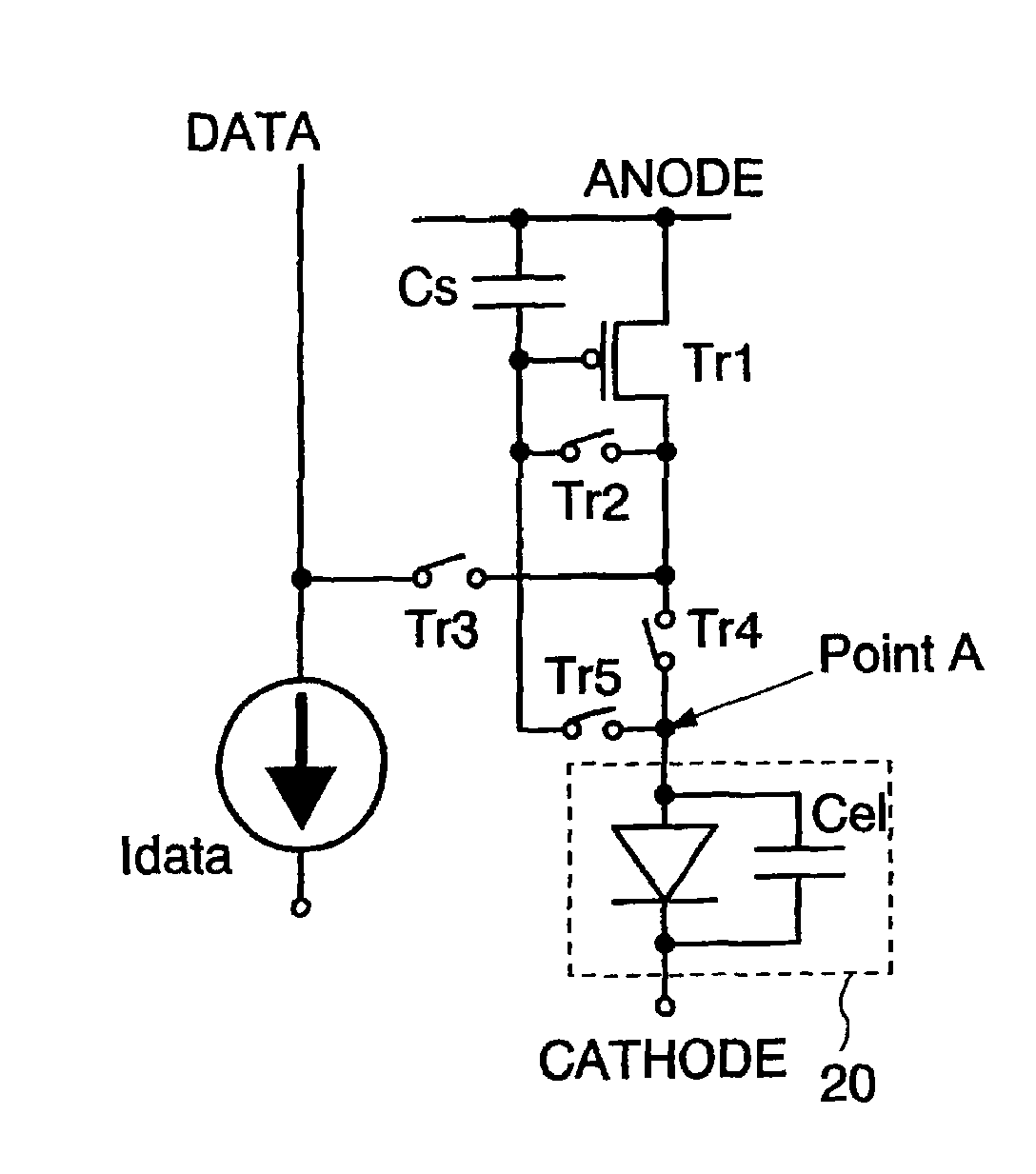

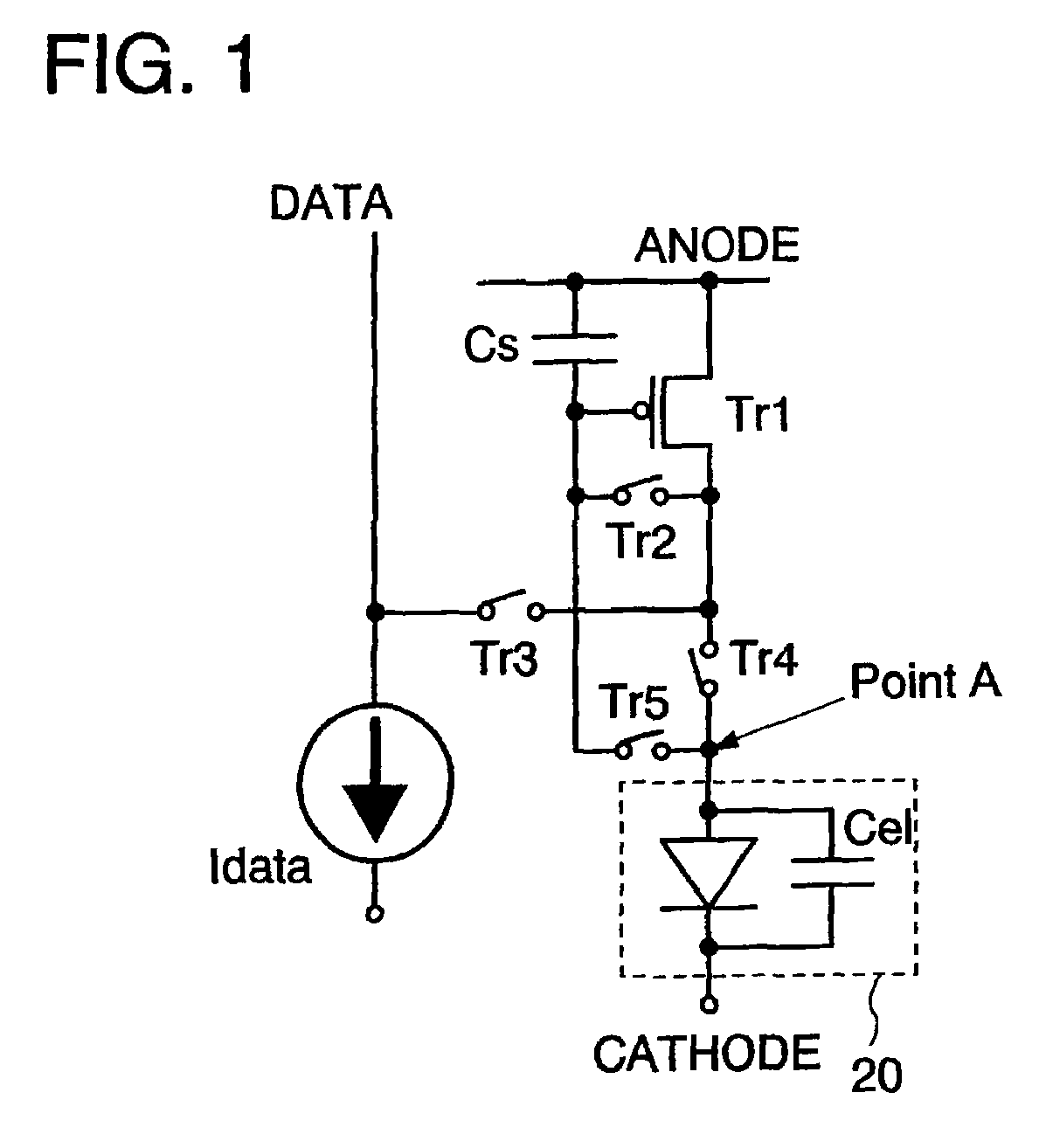

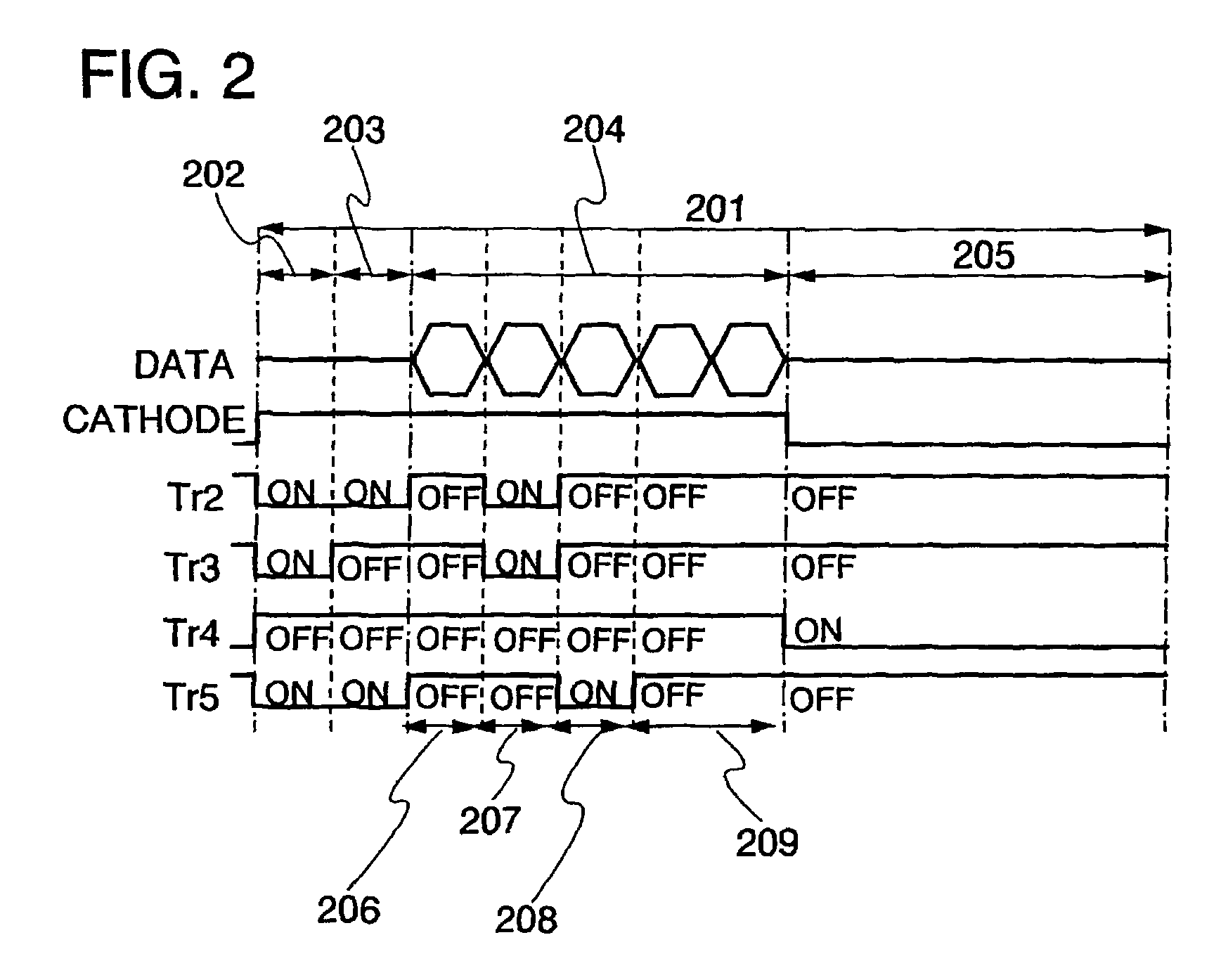

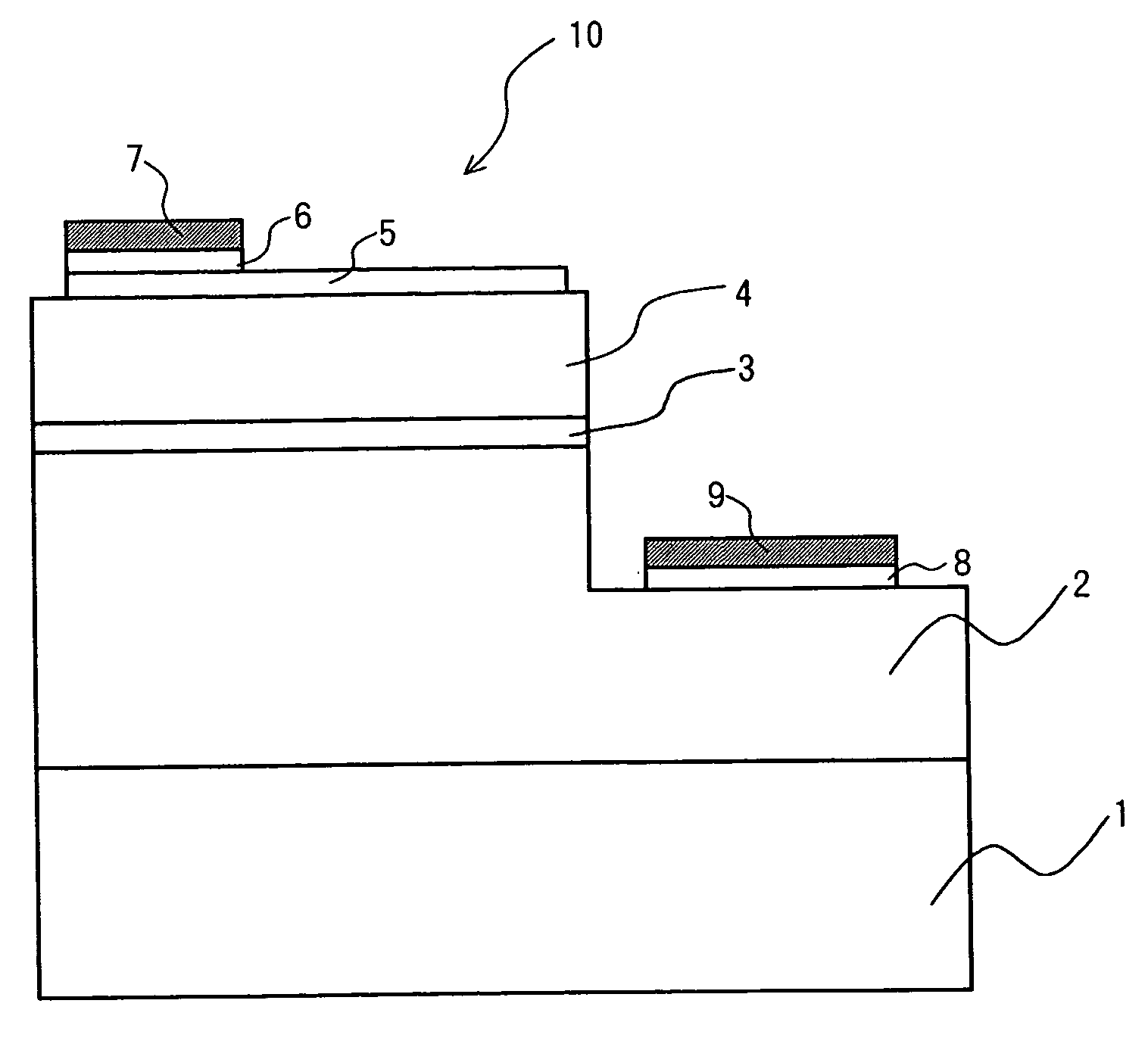

Display device and electronic equipment

ActiveUS20080042948A1Amount of signal becomes smallReduce semaphoreElectrical apparatusStatic indicating devicesScan lineControl signal

A display device is disclosed. The display device includes: a pixel array part; and a drive part that drives the pixel array part. The pixel array part includes row-wise first scan lines and second scan lines, column-wise signal lines, pixels arranged in a matrix form on parts where the lines intersect, and power supply lines and ground lines that supply power to the respective pixels. The drive part includes a first scanner that sequentially supplies first control signals to the respective first scan lines and line-sequentially scans the pixels in units of rows, a second scanner that sequentially supplies second control signals to the respective second scan lines according to the line-sequential scan, and a signal selector that supplies video signals to the column-wise signal lines according to the line-sequential scan.

Owner:JOLED INC

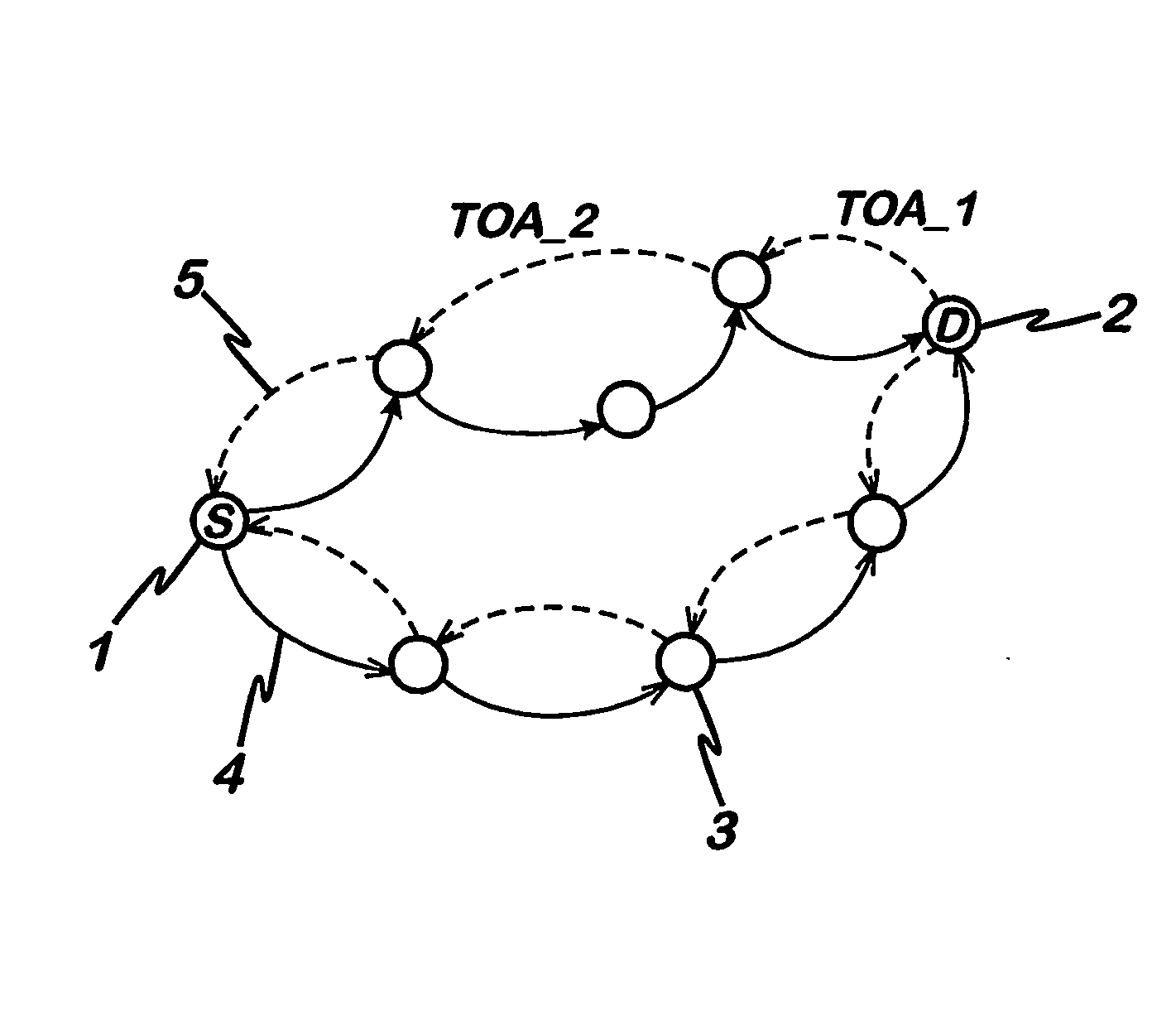

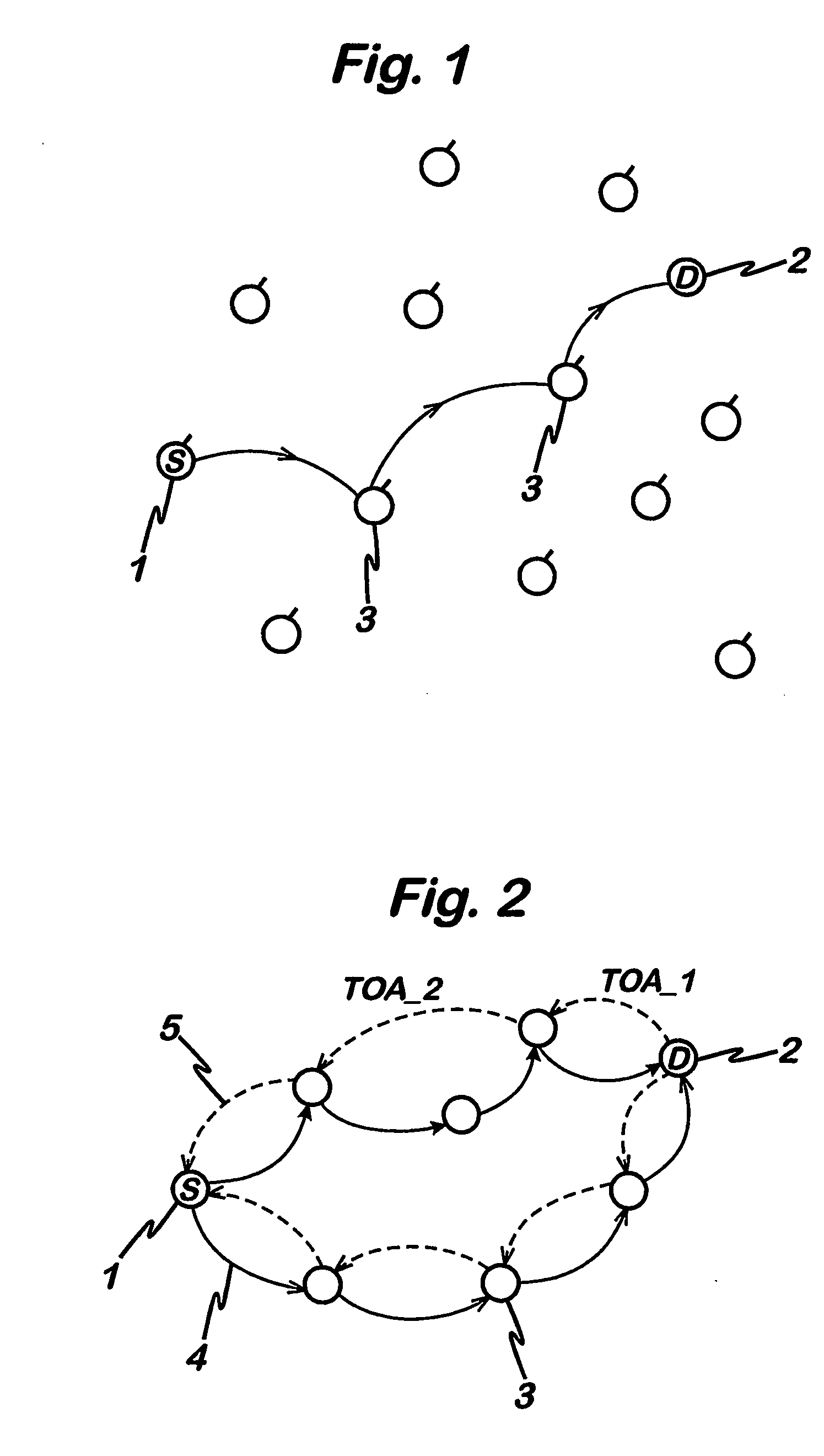

Signal propagation delay routing

ActiveUS20060007863A1Improving current routing algorithmIncrease currentEnergy efficient ICTError prevention/detection by using return channelSignal propagation delayWireless network

A method of routing a message from a source node to a destination node in an adhoc wireless network comprising a plurality of nodes, comprising the steps of; transmitting a first message from the source node to the destination node, receiving said first message at said destination node, transmitting a second message from said destination node in response to the first message and, wherein at least one of said first message and said second message is sent between the source and destination nodes via a plurality of paths comprising at least one intermediate node, selecting a path for communication between the source node and the destination node using an indication of the time taken for at least one of said second and first messages to propagate between each node on each path.

Owner:MANITOBA UNIV OF THE +1

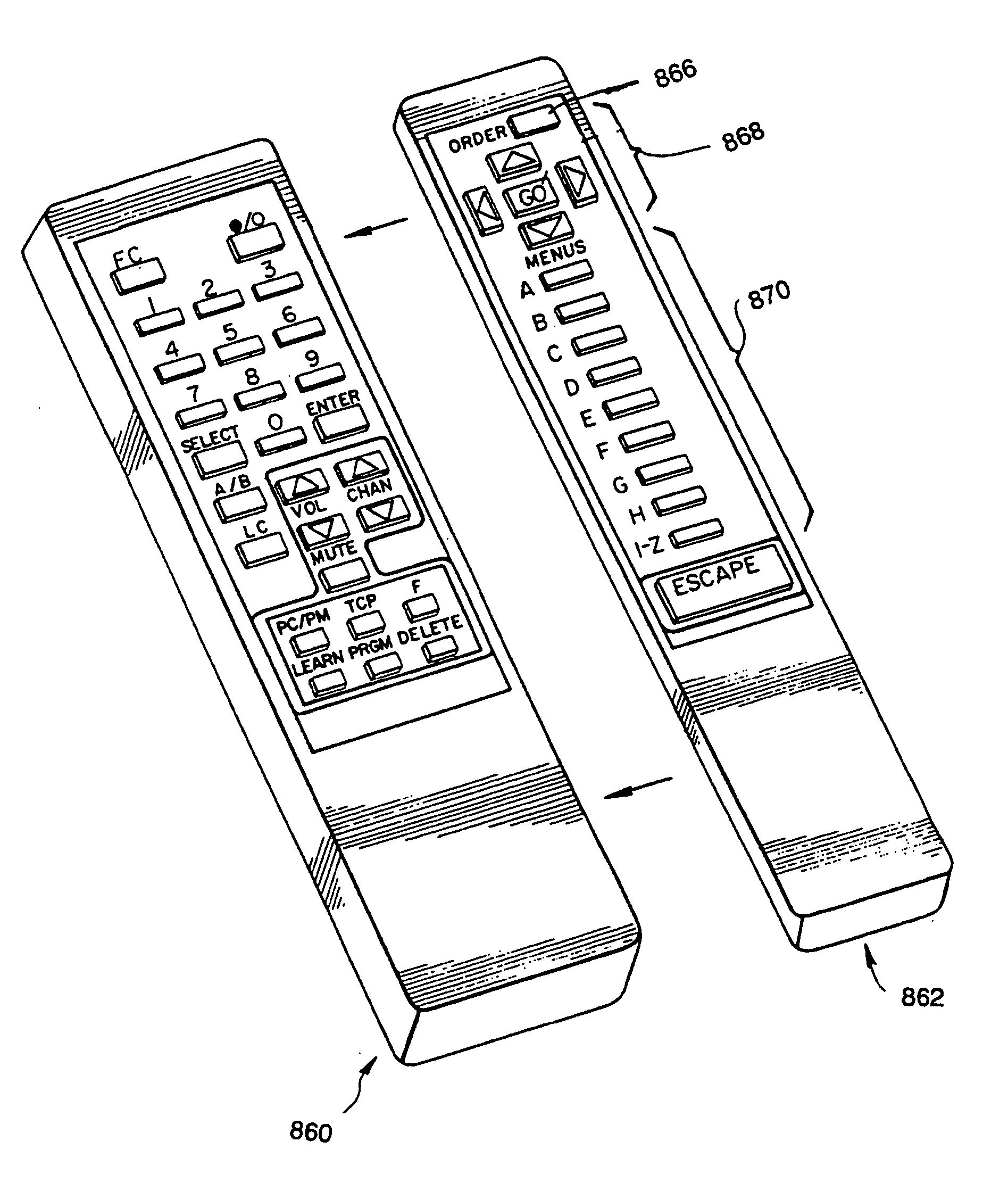

Remote control for menu driven subscriber access to television programming

InactiveUS20050157217A1Improve throughputImprove programming performancePulse modulation television signal transmissionBroadcast information characterisationMultiplexingRemote control

An expanded television program delivery system is disclosed which allows viewers to select television and audio program choices from a series of menus. Menus are partially stored in a set-top terminal in each subscriber's home. The menus may be reprogrammed by signals sent from a headend or from a central operations center. The system allows for a great number of television signals to be transmitted by using digital compression techniques. An operations center with computer-assisted packaging allows various television, audio and data signals to be combined, compressed and multiplexed into signals transmitted on various channels to a cable headend which distributes the signals to individual set-top terminals. Various types of menus may be used and the menus may incorporate information included within the video / data signal received by the set-top terminal. A remote control unit with icon buttons allows a subscriber to select programs based upon a series of major menus, submenus, and during program menus. Various billing and statistics gathering methods for the program delivery system are also disclosed.

Owner:COMCAST IP HLDG I

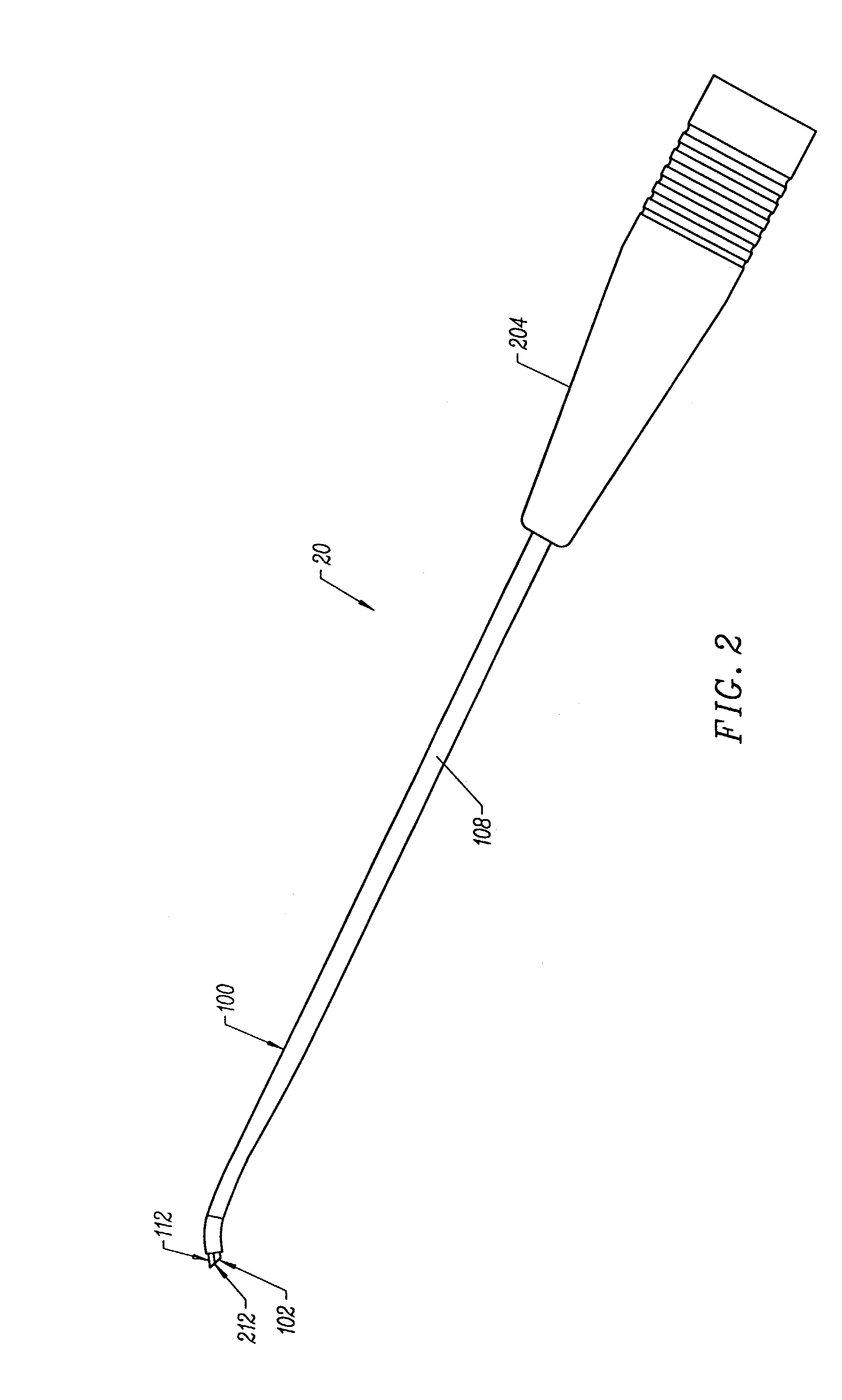

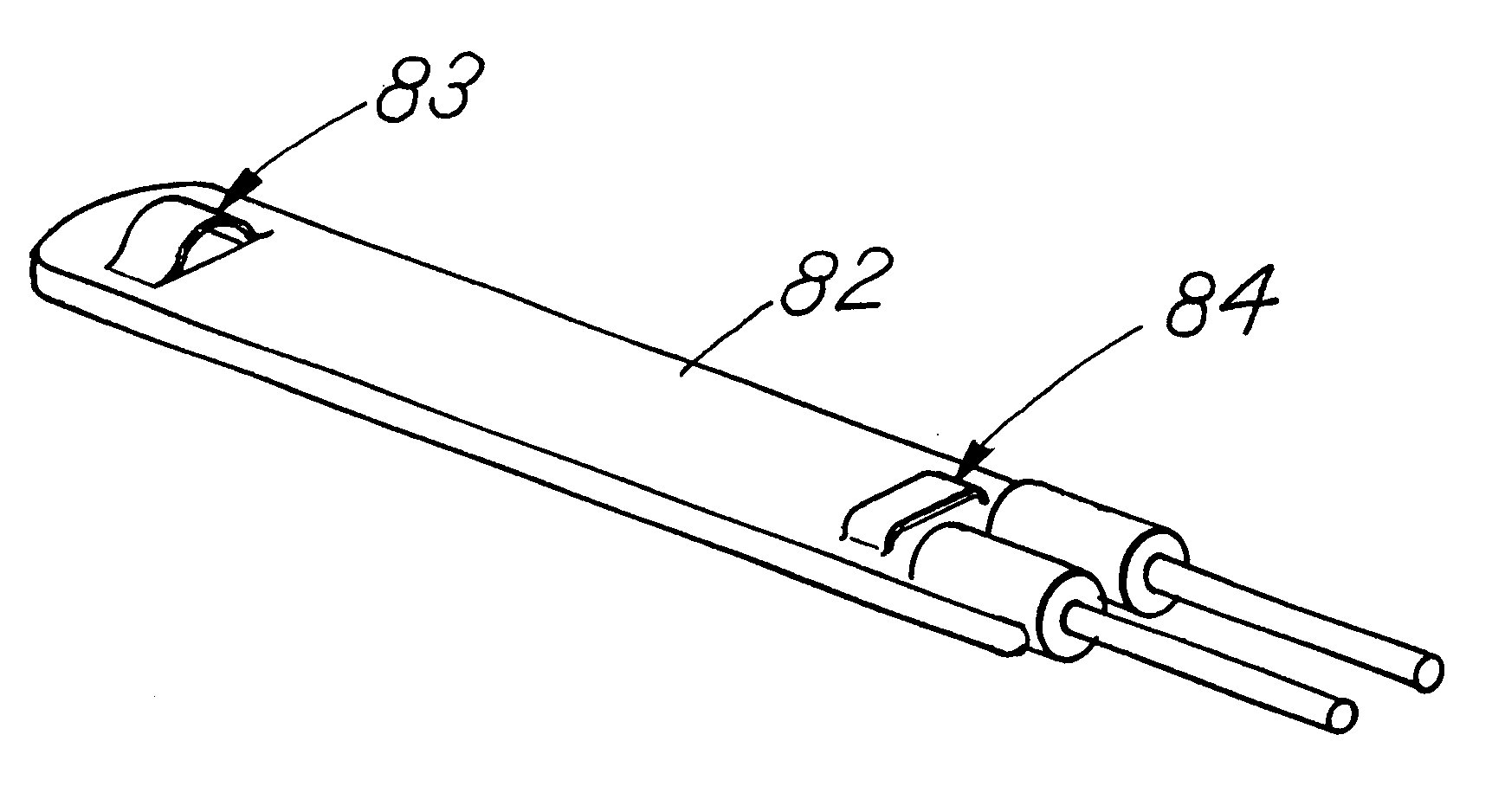

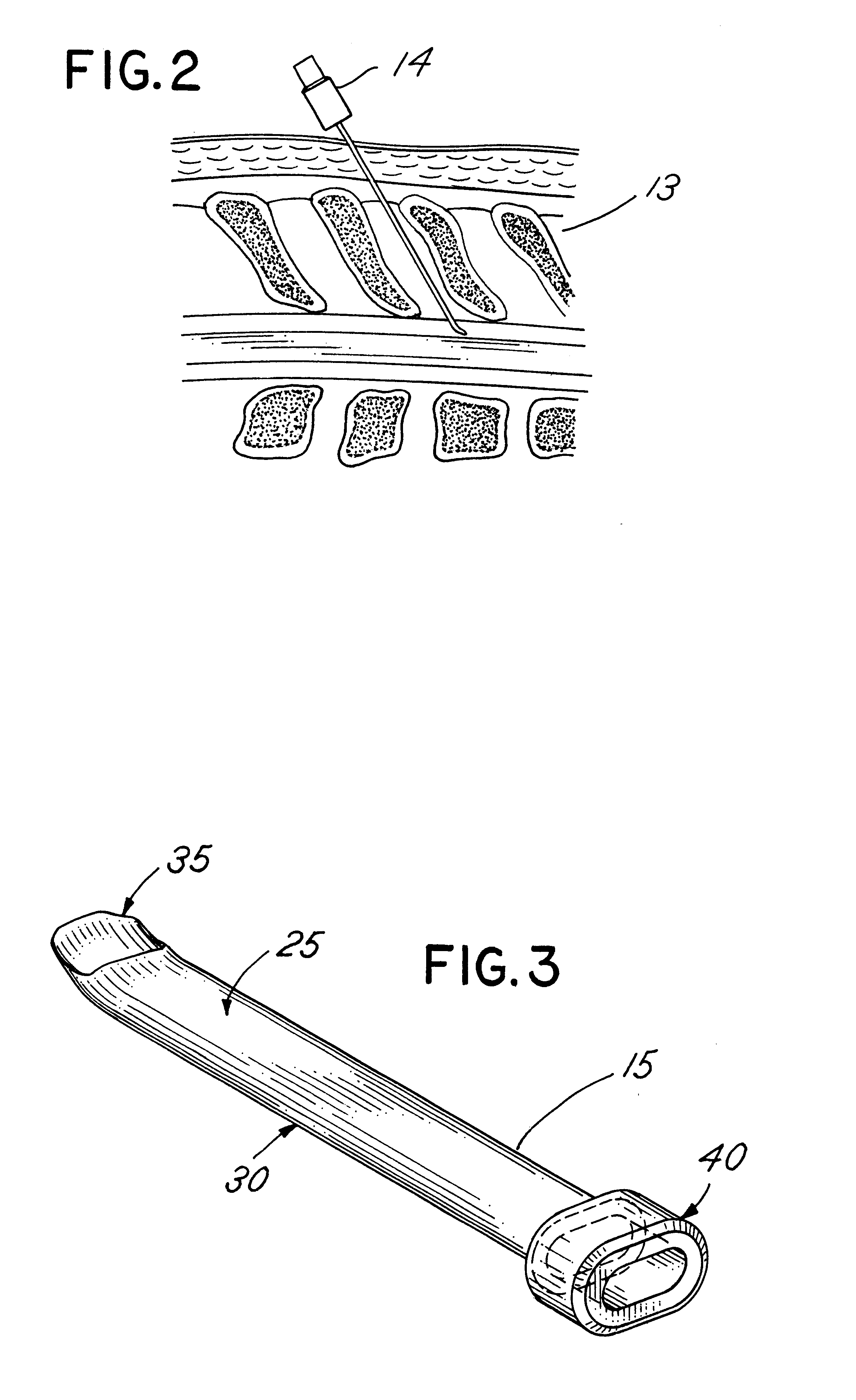

Apparatus and method for percutaneous implant of a paddle style lead

InactiveUS6249707B1Less traumaticIncrease currentSpinal electrodesGuide needlesSpinal columnBiomedical engineering

A needle assembly for introduction of a paddle style lead near a spinal column of a patient includes a body having a proximal end and a distal end, a lumen with a continuous oblong cross section, and a paddle style lead adapted to accept a stiffening member. The distal end of the body has an introducer portion where the top side of the introducer has an orifice to allow for protrusion of the paddle style lead from the lumen into the spinal column area. The needle has a hub affixed to the proximal end of the body which is adapted to receive a stylet. The needle may also have a stylet that is inserted within the lumen. The introducer of the needle has a curvature extending from the bottom side toward the top side at the distal end and guides the introduction of the paddle style lead near the spinal column.

Owner:MEDTRONIC INC

Display device and driving method thereof

ActiveUS7969390B2Short timeIncrease opening ratioStatic indicating devicesSolid-state devicesDisplay deviceAperture ratio

To solve the lack of program time, which is a problem of a display device including an EL element, and to provide a display device including a pixel circuit with a high aperture ratio and a driving method thereof. In a circuit including a driving transistor, a capacitor, a display element which can be used as a capacitor, a first power supply line and a second power supply line, potentials of the first power supply line and the second power supply line are set to be almost the same, thereby a threshold voltage of the driving transistor is held in the display element, and after that, a charge is divided into the display element and the capacitor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor light emitting device

A semiconductor light emitting device with improved efficiency in extracting light is provided. The semiconductor light emitting device comprises a first conductive type semiconductor layer, a light emitting layer, and a second conductive semiconductor layer stacked in this order, electrodes respectively connected to the first and second conductive semiconductor layers, the electrode connected to the second conductive type semiconductor layer comprising a lower conductive oxide film and an upper conductive oxide film disposed on the lower conductive oxide film, and a metal film disposed only on the upper conductive oxide film. The upper and lower conductive oxide films comprise an oxide including at least one element selected from the group consisting of zinc (Zn), indium (In), tin (Sn), and magnesium (Mg).

Owner:NICHIA CORP

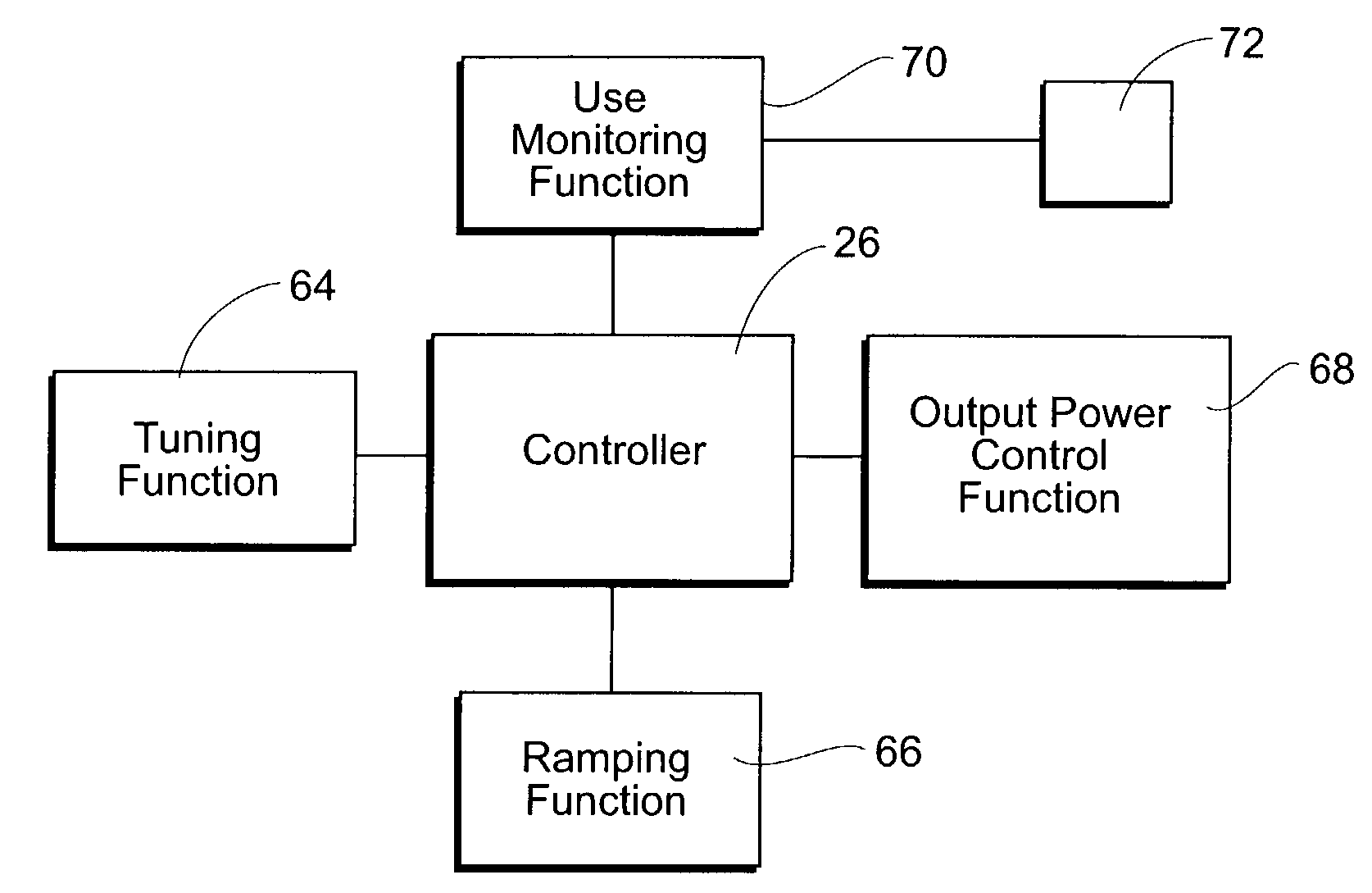

Systems and methods for delivering ultrasound energy at an output power level that remains essentially constant despite variations in transducer impedance

InactiveUS7335169B2Increase the output voltageImproving impedanceUltrasonic/sonic/infrasonic diagnosticsUltrasound therapySonificationTransducer

Systems and methods deliver ultrasound energy to an ultrasound transducer having an impedance subject to variations. The systems and methods electrically couple an ultrasound generator to the ultrasound transducer to deliver ultrasound energy. The systems and methods deliver ultrasound energy to the ultrasound transducer at a set output frequency and at an output power level that remains essentially constant, despite variations in the impedance, based upon preprogrammed rules.

Owner:TIMI 3 SYST