Patents

Literature

5468results about How to "Enhanced coupling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

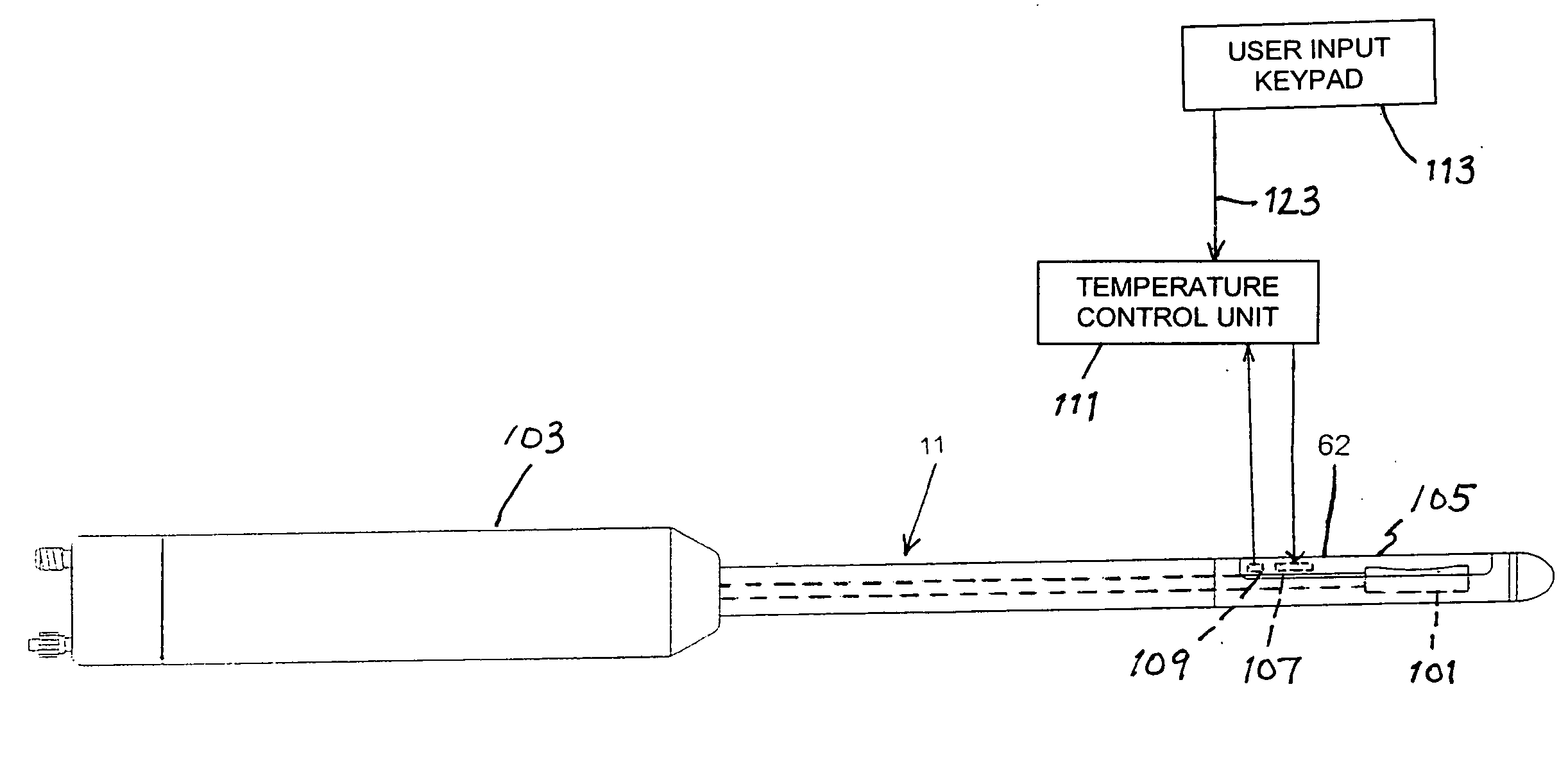

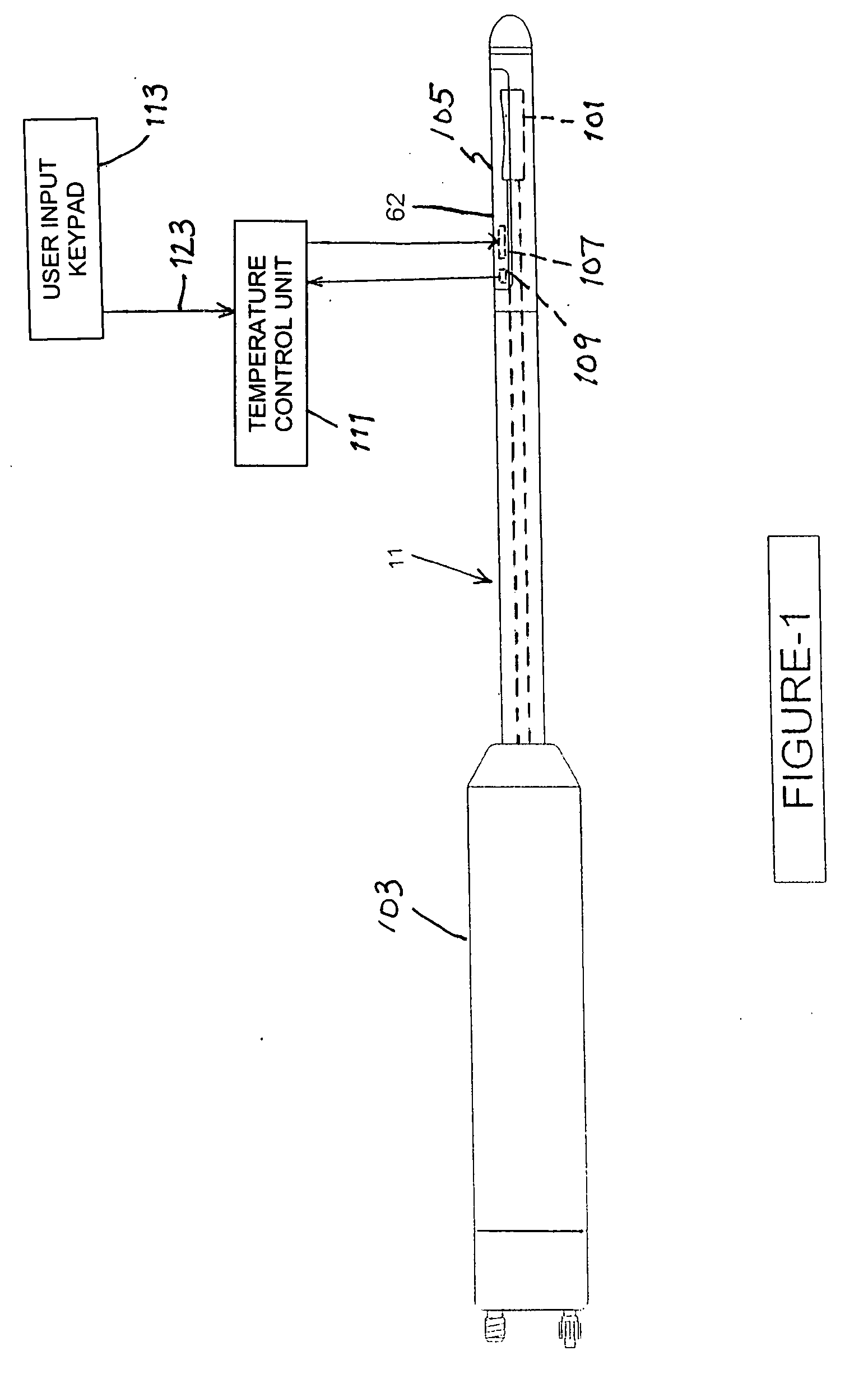

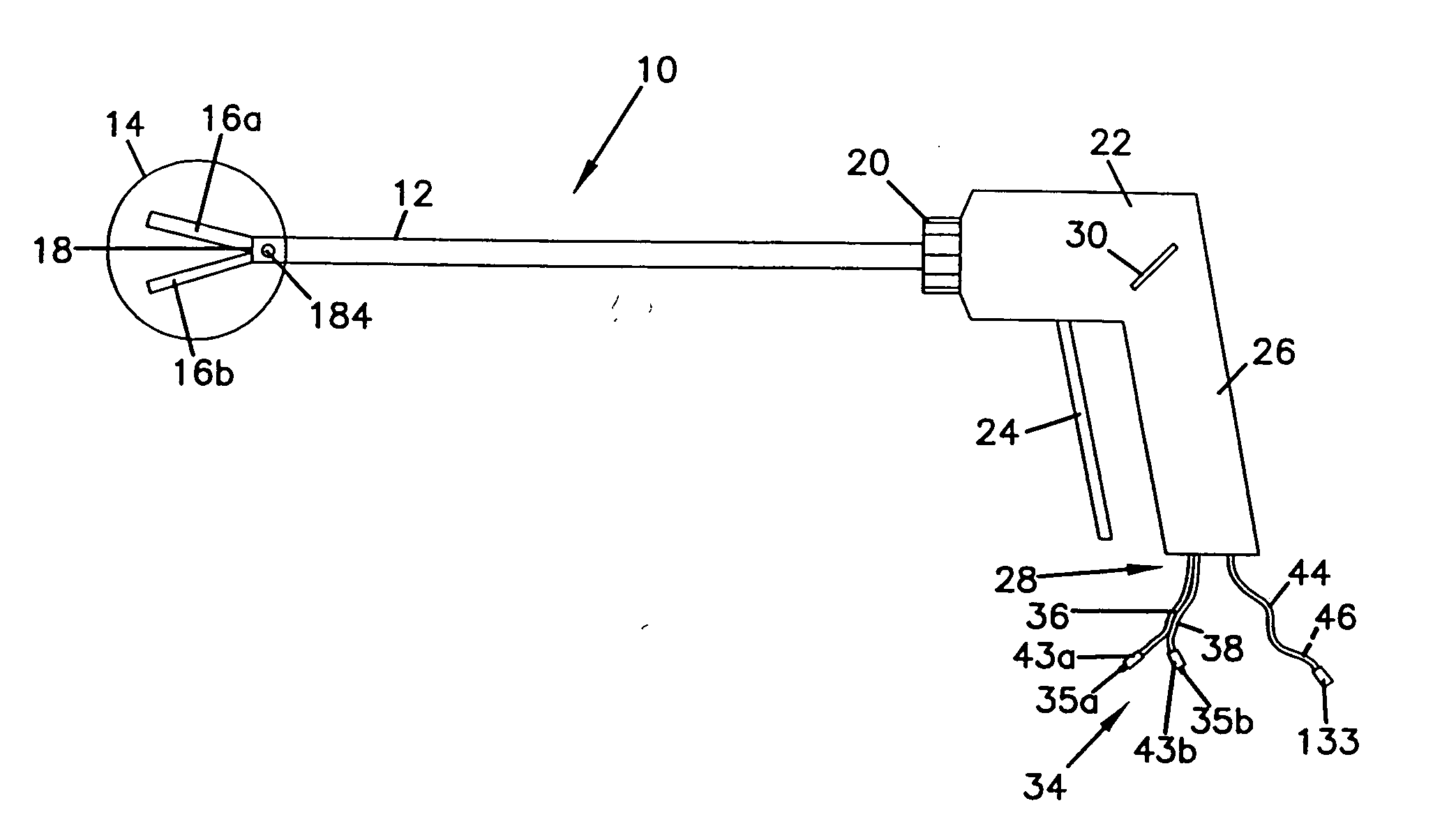

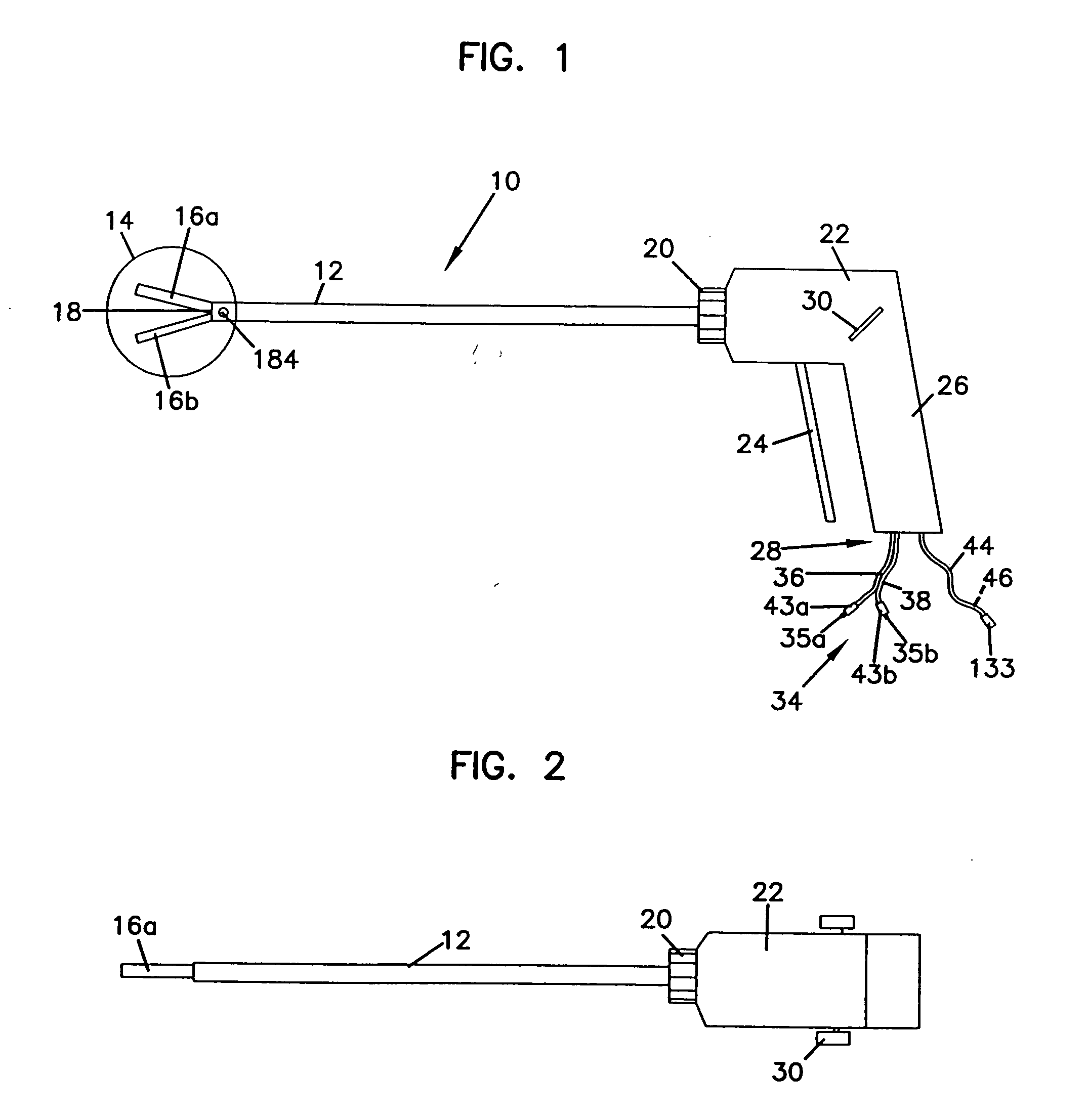

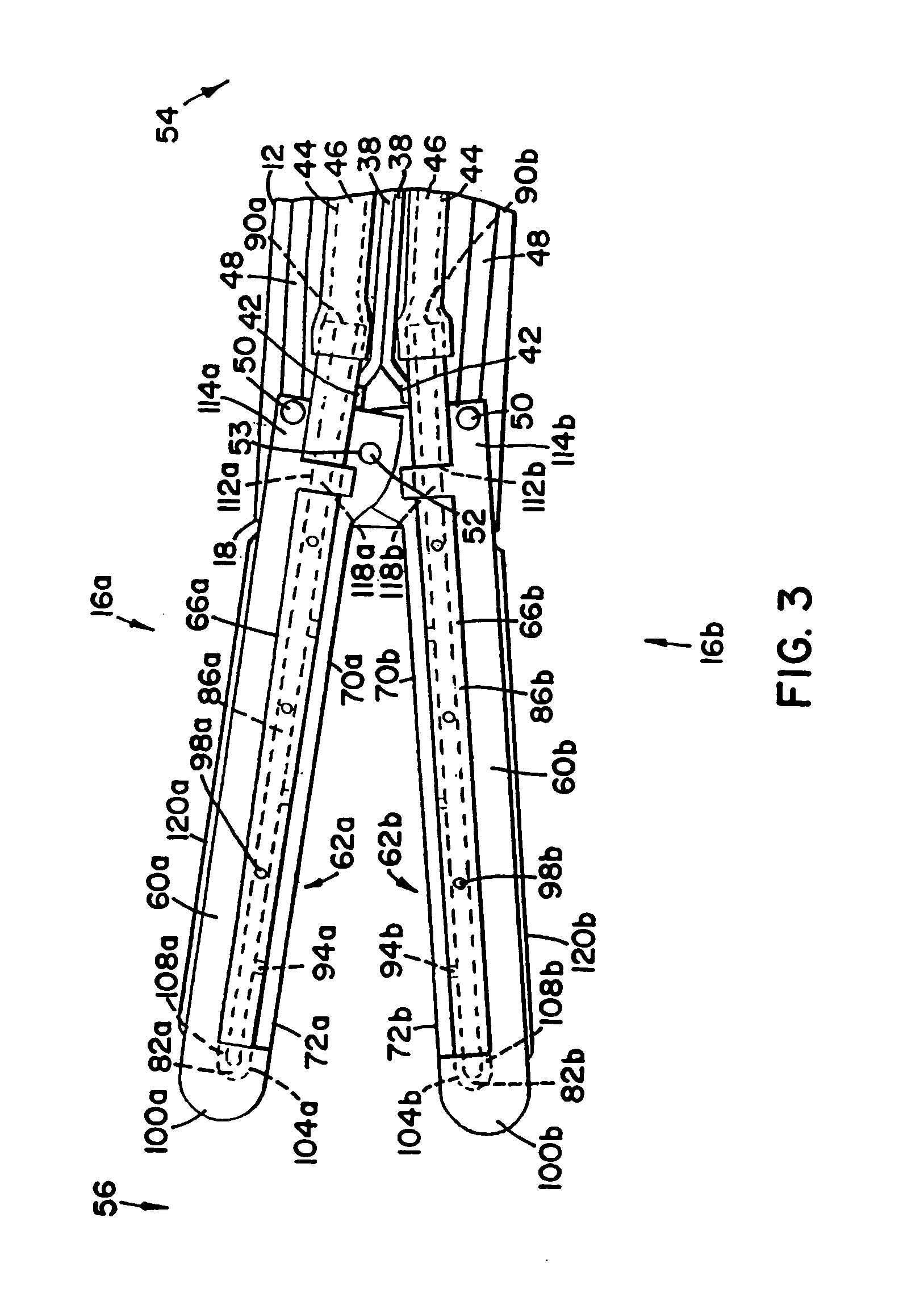

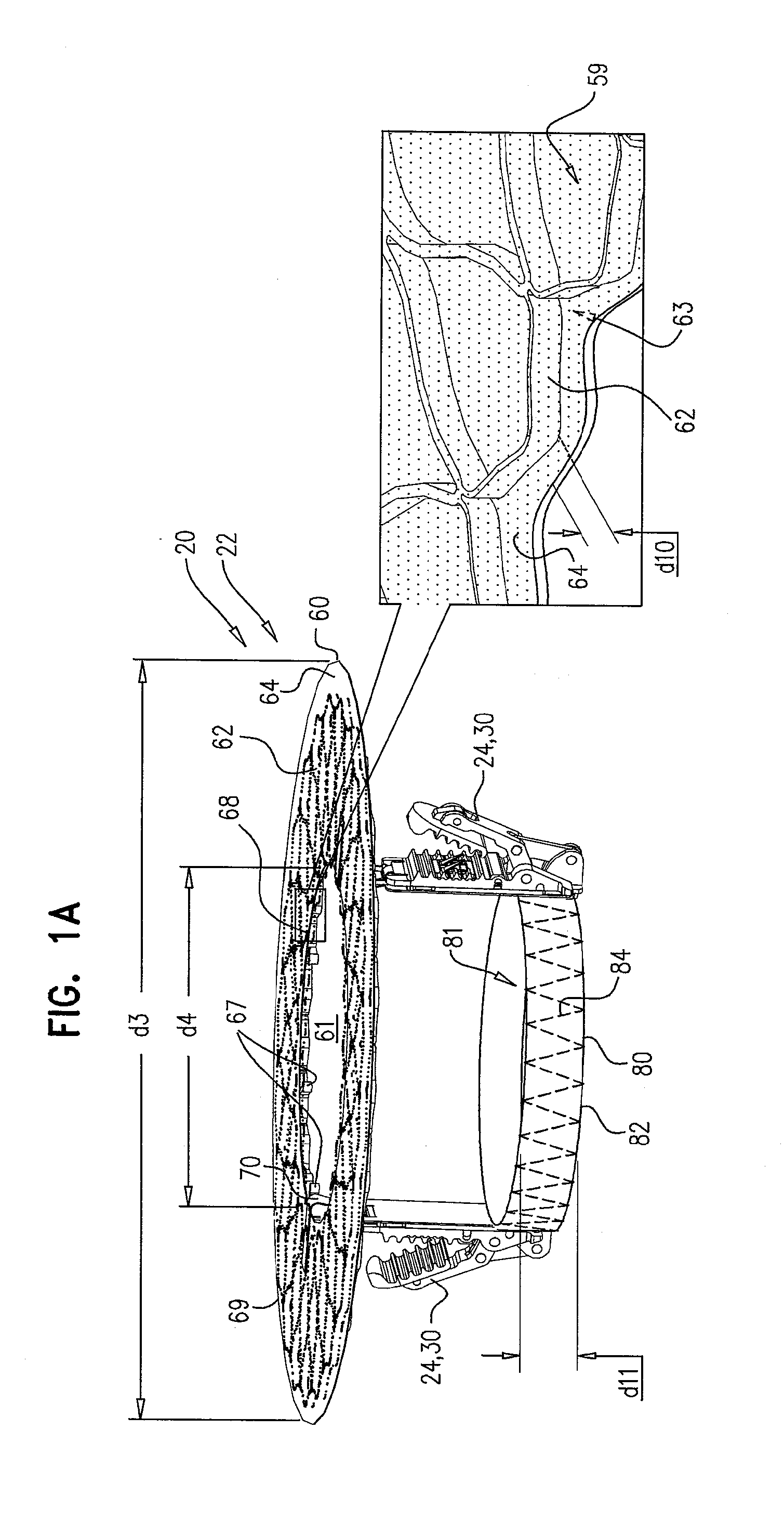

Fluid-assisted medical devices, systems and methods

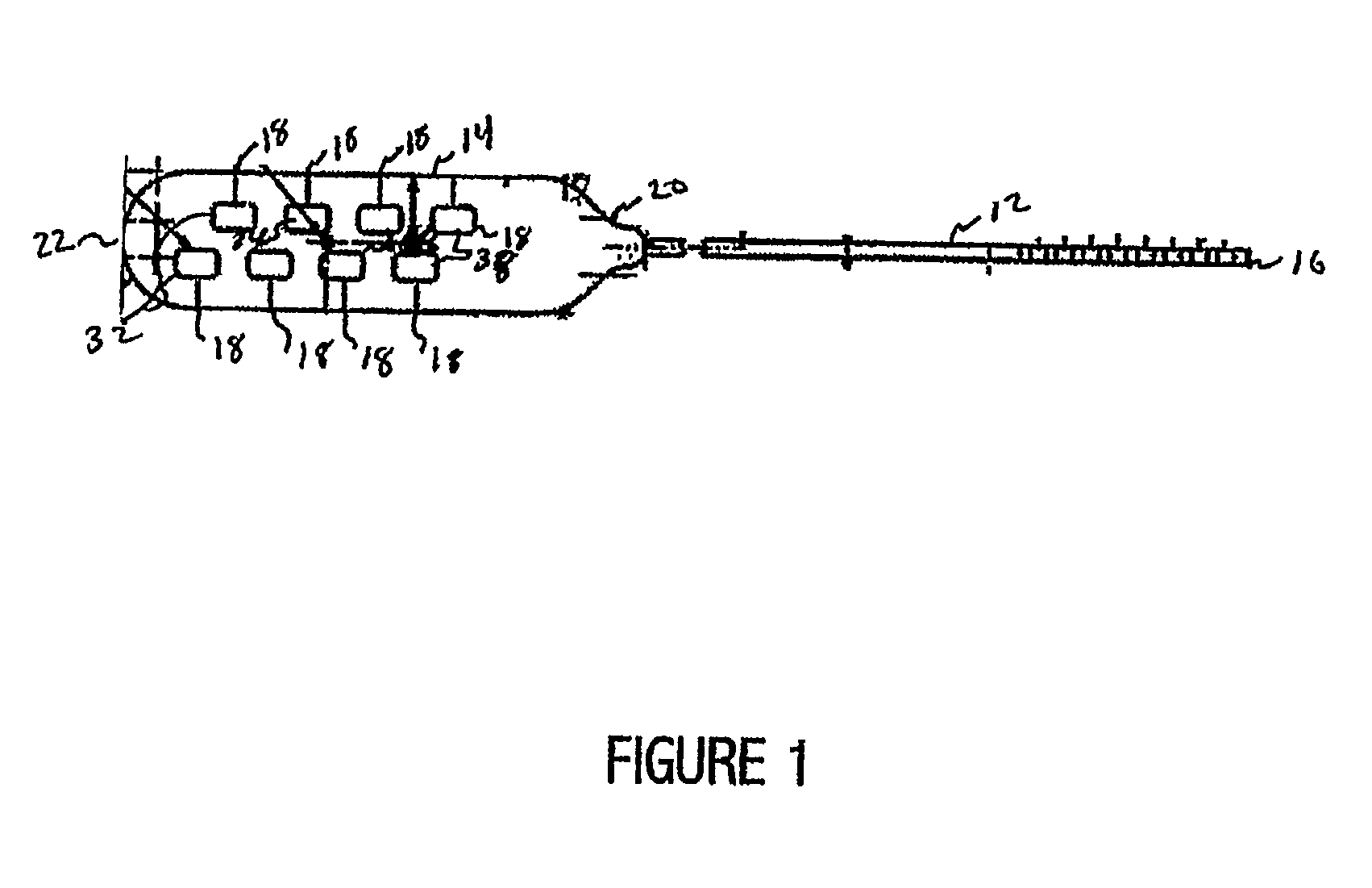

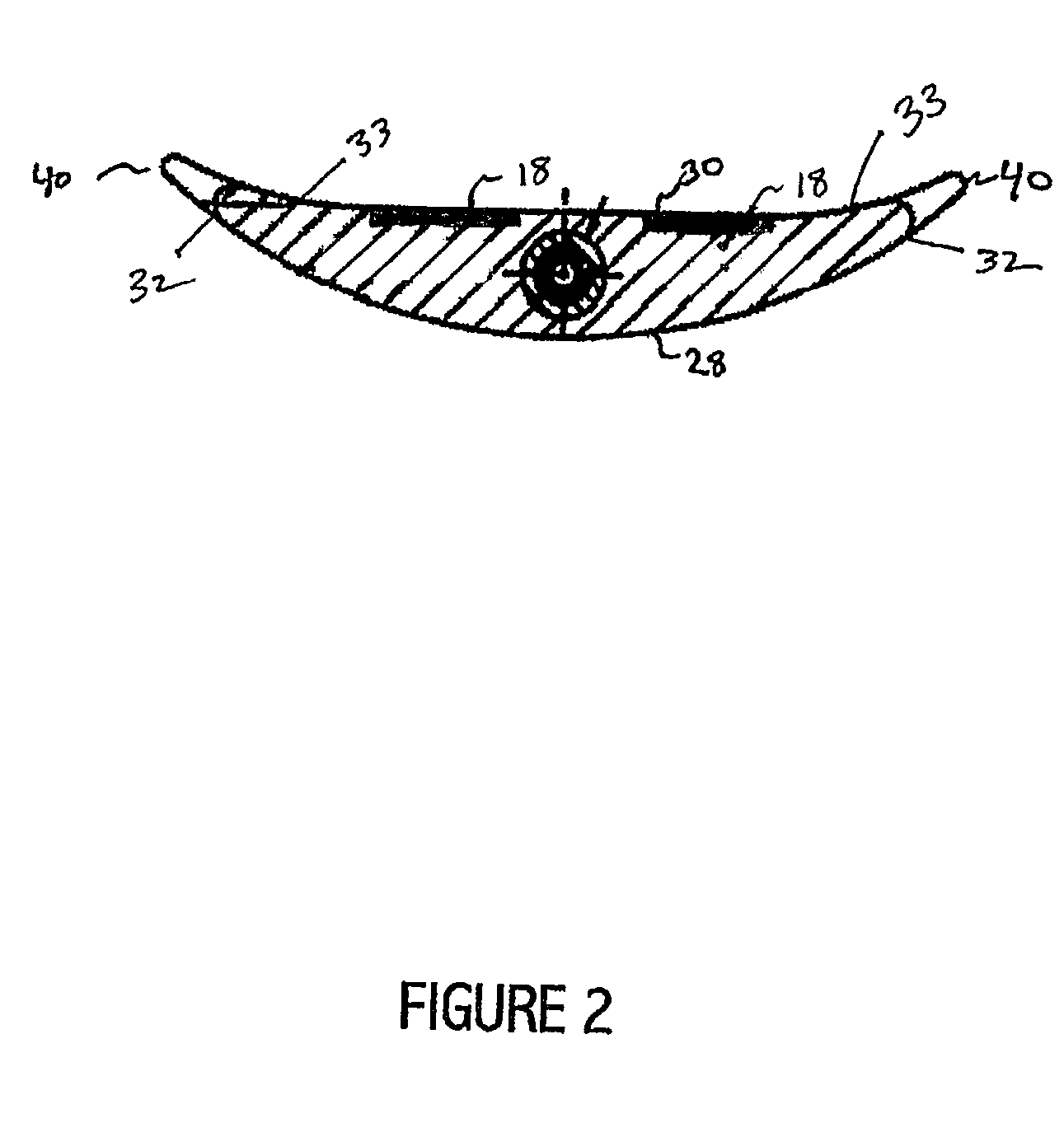

Surgical devices, systems and methods for treating tissue are provided. An exemplary surgical device comprises a tip portion including first and second jaws each having a tissue grasping surface, at least one of the jaws being movable toward the other jaw. The tissue grasping surface of each jaw has includes an electrically insulative surface. The device also includes first and second electrodes connectable to different terminals of an RF generator to generate electrical current flow therebetween, with each of the electrodes having an electrode surface. One of the electrode surfaces is located on one of the jaws separated from one edge of the tissue grasping surface, and the other of the electrode surfaces is located on one or the other of the jaws separated from the other edge of the tissue grasping surface. The device also includes at least one fluid passage being connectable to a fluid source.

Owner:MEDTRONIC ADVANCED ENERGY

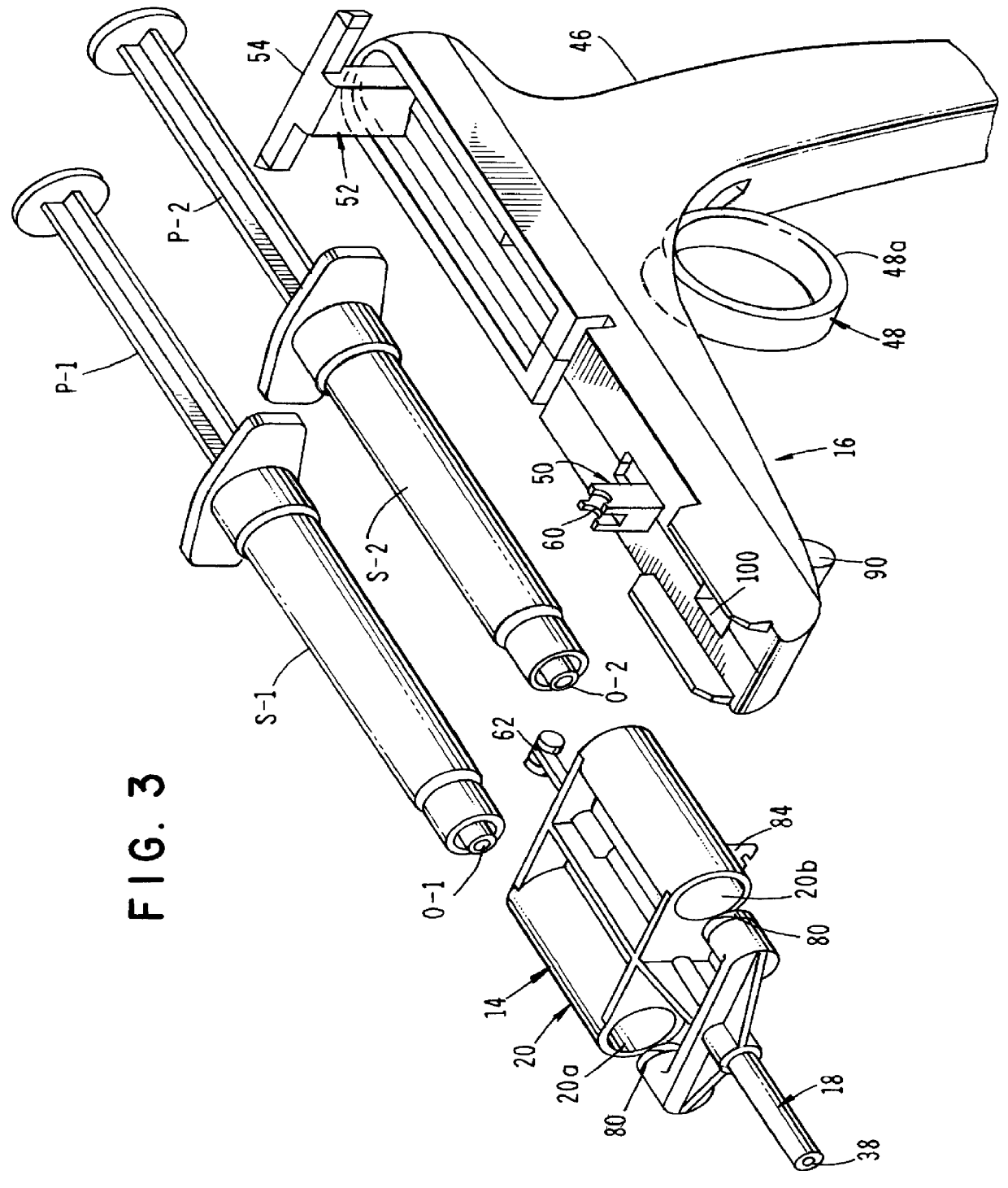

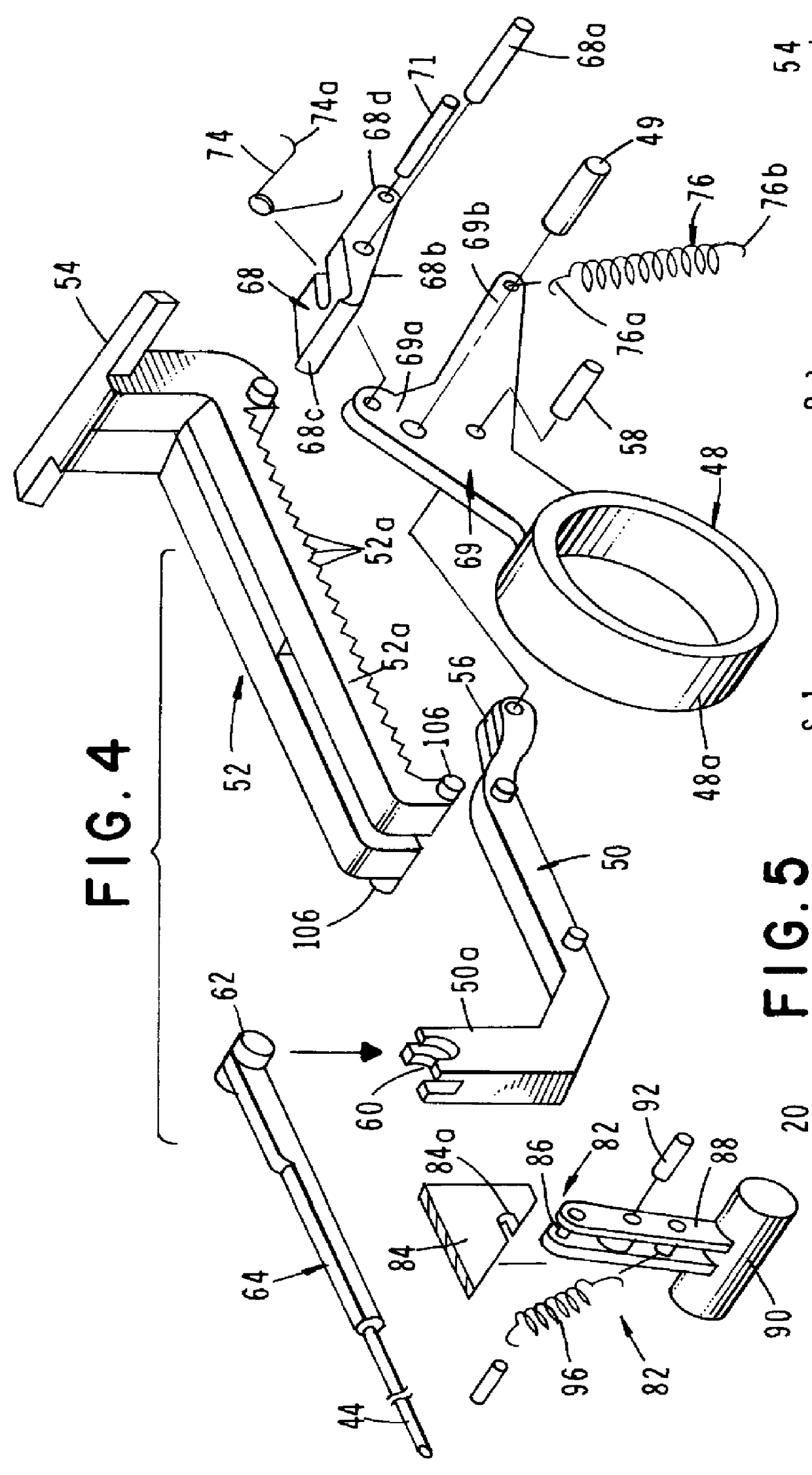

Two component fluid dispenser

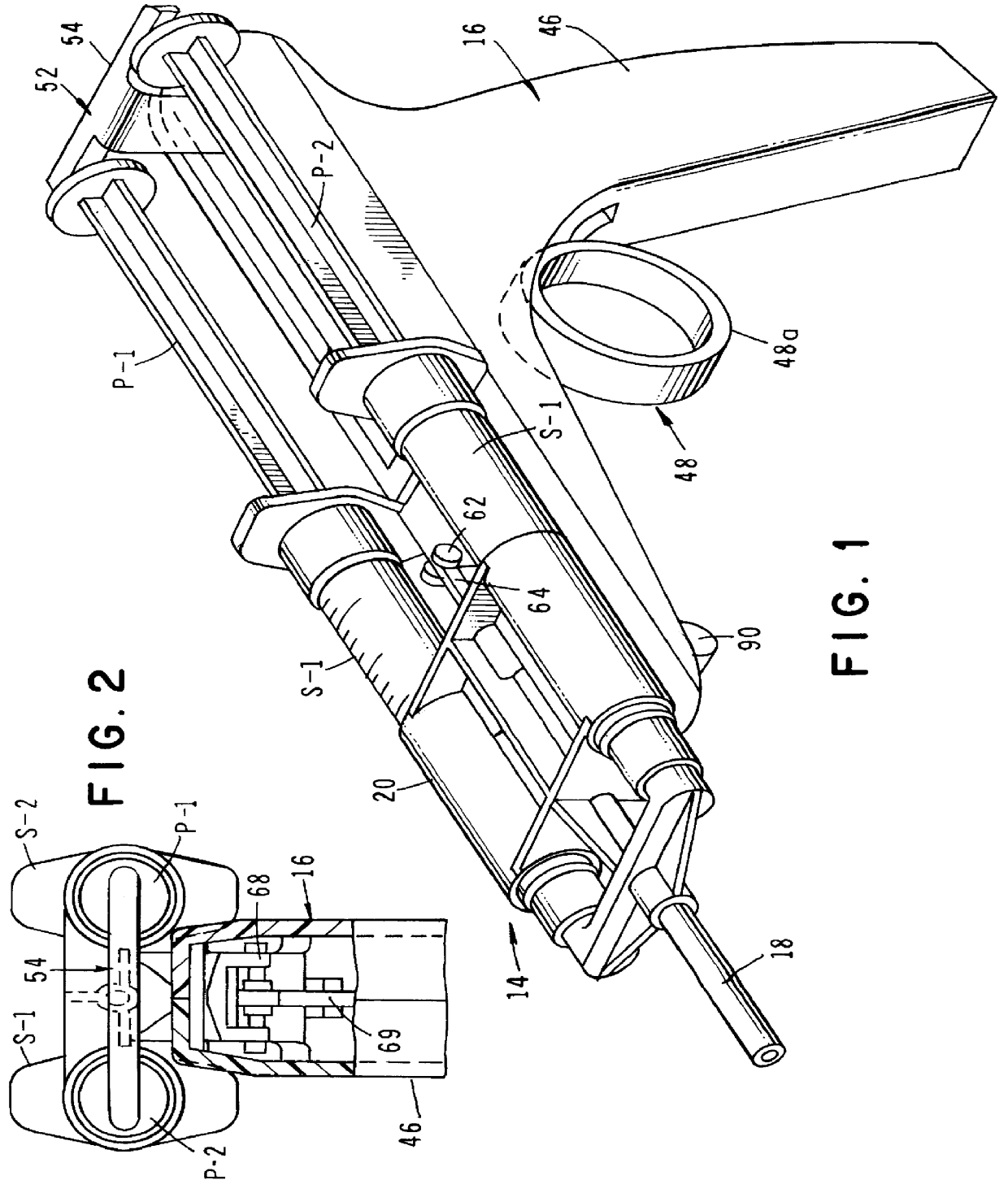

InactiveUS6047861AEnhanced couplingSecurely holdLiquid surface applicatorsSurgeryEngineeringViscosity

A two-component fluid dispenser which can accurately mix two liquids of varying viscosity and then precisely deliver the mixture formed in discrete amounts. The mixture of the two components is delivered from a single delivery tube in a manner such that none of the mixture remains within the delivery tube at the completion of each mixing and delivery cycle. In one form of the apparatus, the single delivery tube of the apparatus is operably coupled with conventional hypodermic syringes of various sizes so that different fluids can be mixed in different ratios.

Owner:BAXTER INT INC

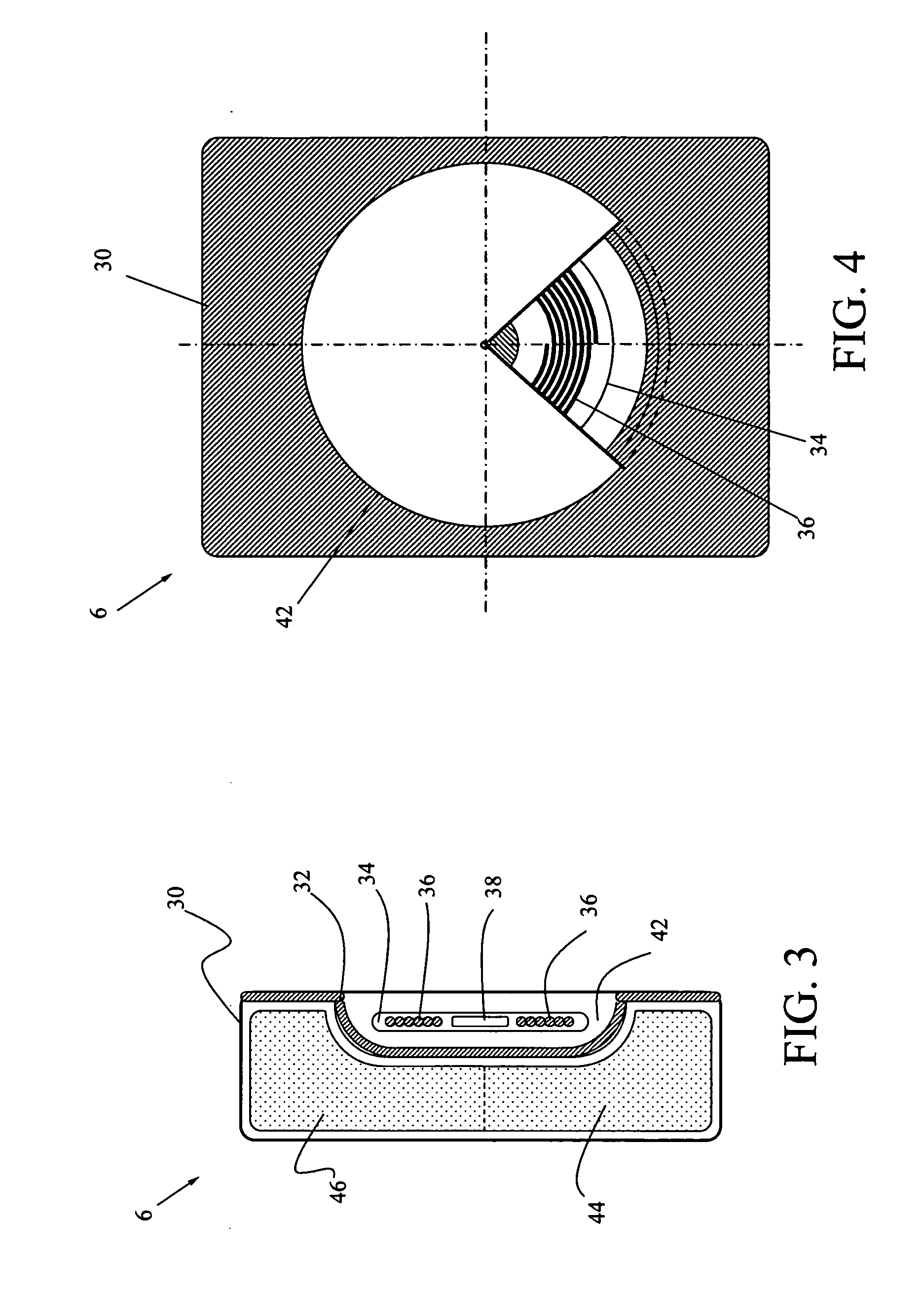

Vacuum assisted wound dressing

ActiveUS8715256B2Small and lightImprove portabilityPlastersAdhesive dressingsTopical Negative-Pressure TherapyVacuum assisted

Owner:SMITH & NEPHEW PLC

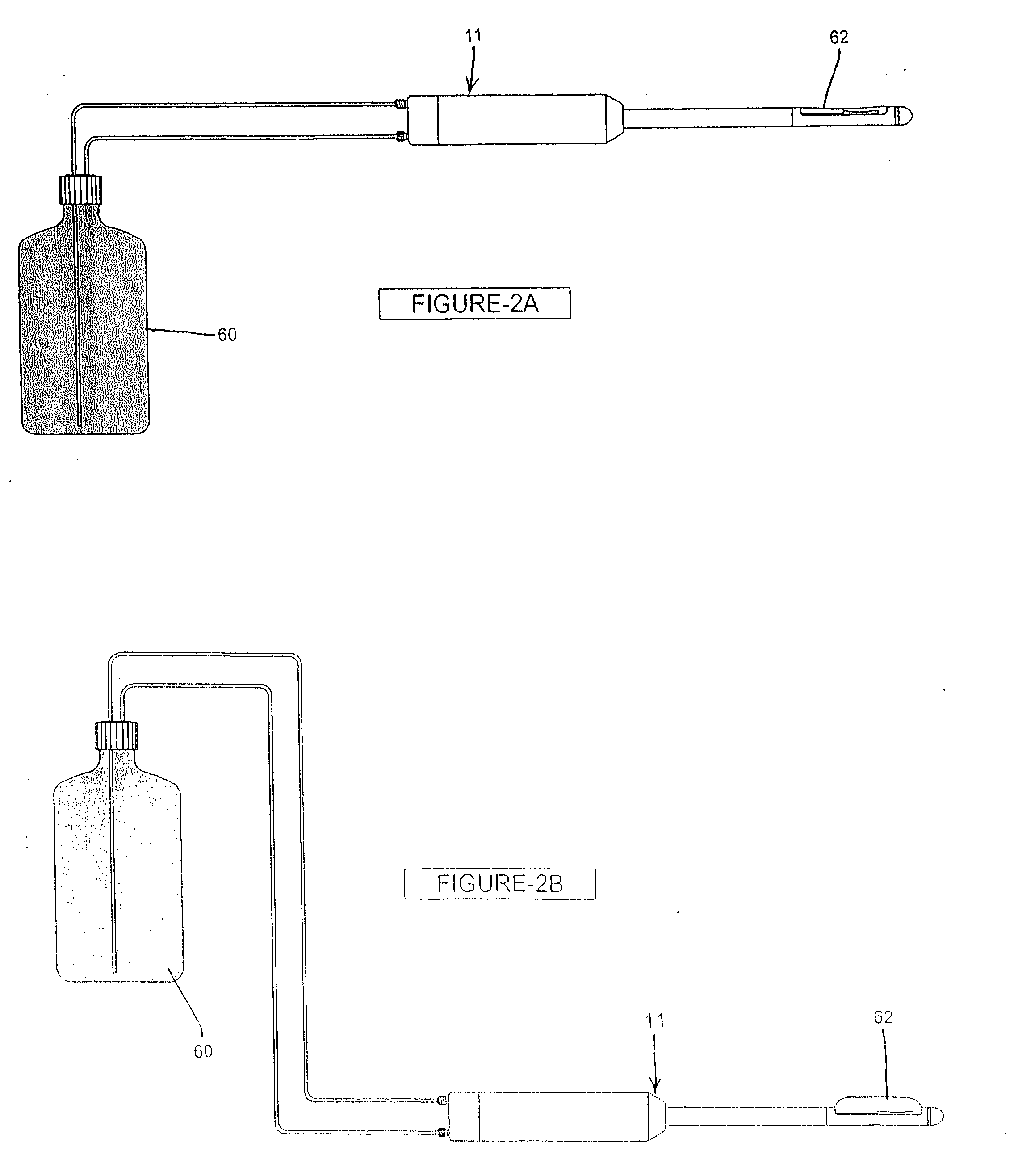

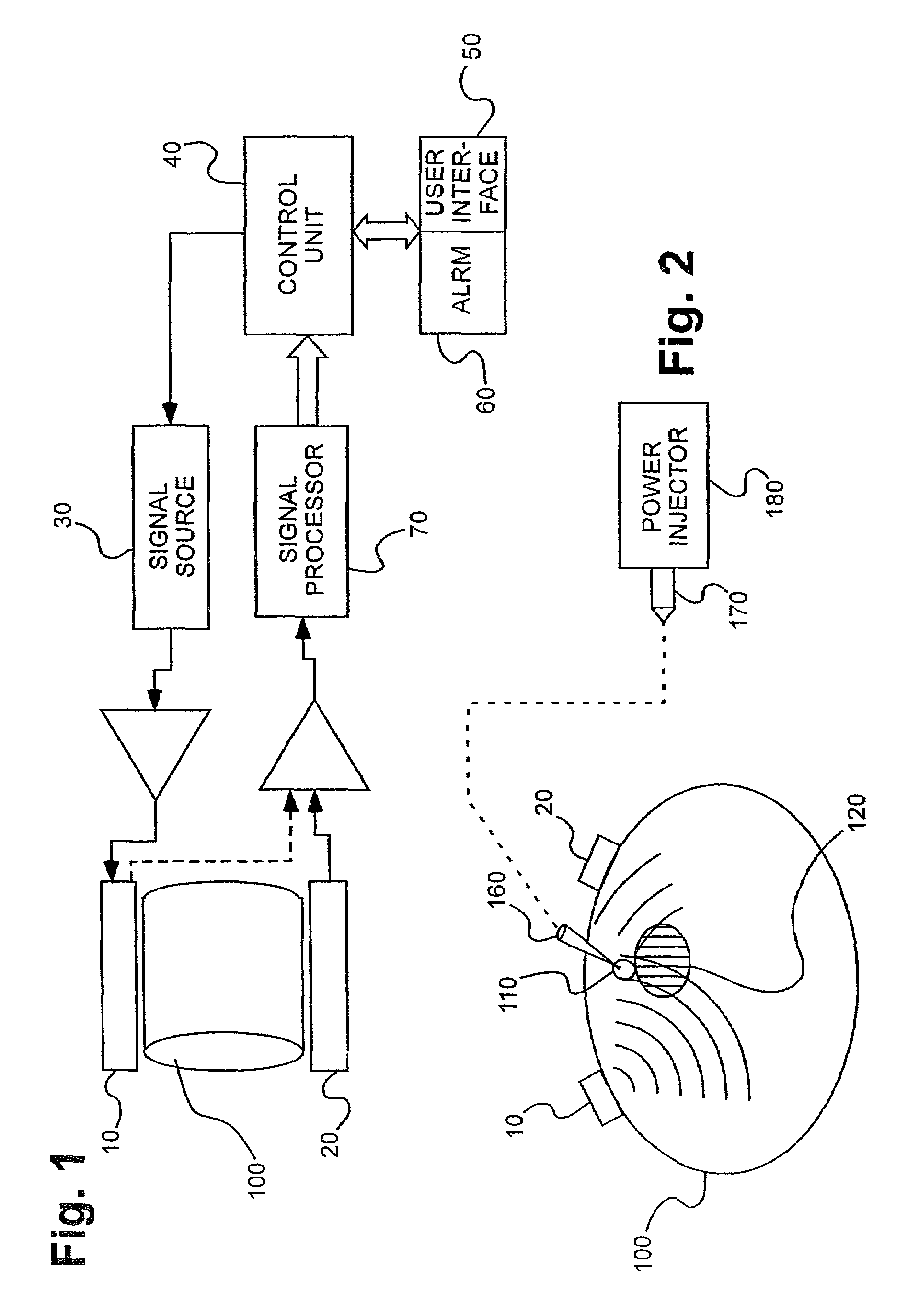

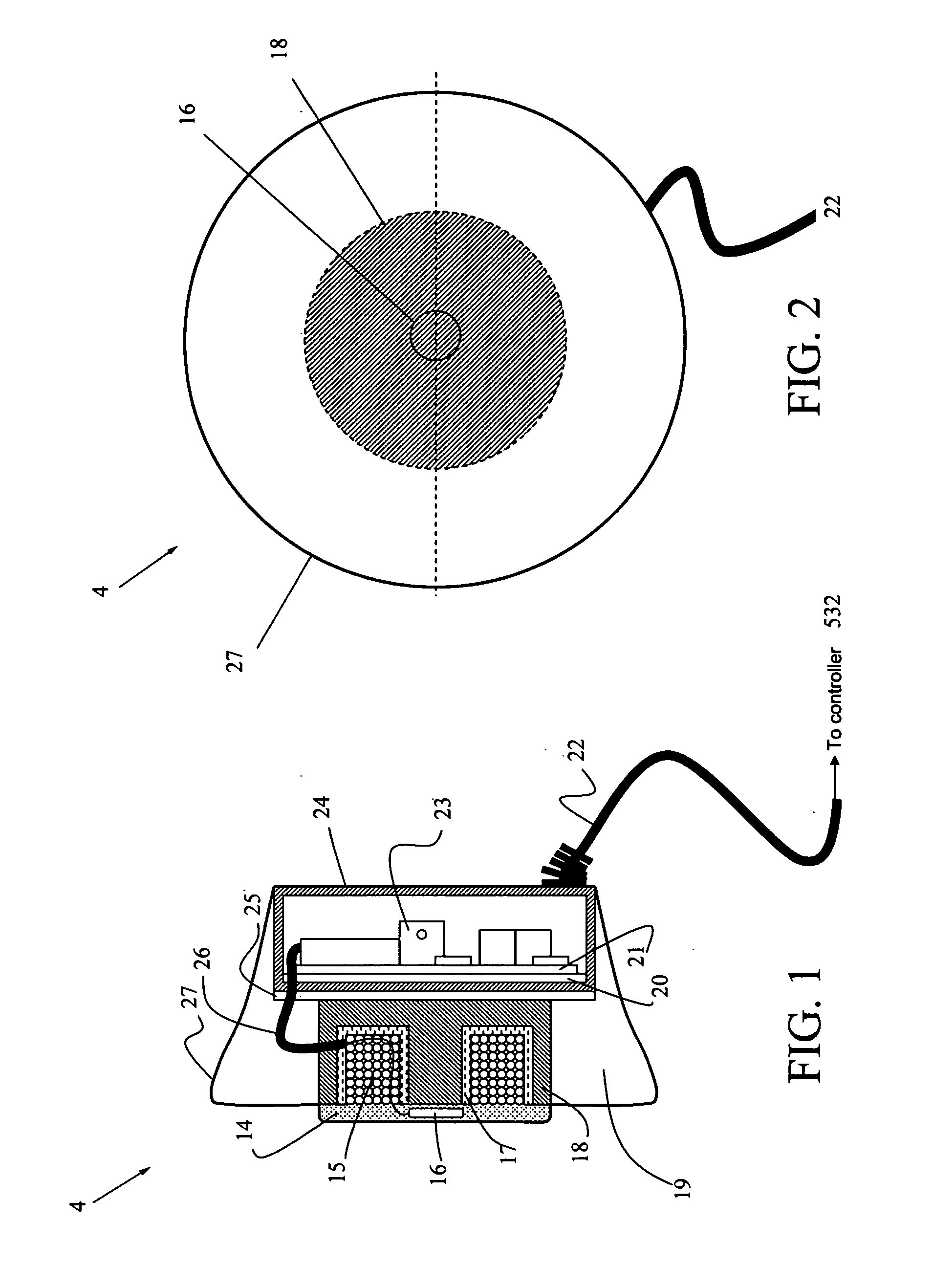

Elevated coupling liquid temperature during HIFU treatment method and hardware

InactiveUS20080281200A1Avoid necrosisEnhanced couplingUltrasonic/sonic/infrasonic diagnosticsUltrasound therapyLiquid temperatureUltrasonic vibration

A medical procedure utilizes a high-intensity focused ultrasound instrument having an applicator surface, a liquid-containing bolus or expandable chamber acting as a heat sink, and a source of ultrasonic vibrations, the applicator surface being a surface of a flexible wall of the bolus, the source of ultrasonic vibrations being in operative contact with the bolus. The applicator surface is placed in contact with an organ surface of a patient, the source is energized to produce ultrasonic vibrations focused at a predetermined focal region inside the organ, and a temperature of liquid in the bolus is controlled while the applicator surface is in contact with the organ surface to control temperature elevation in tissues of the organ between the focal region and the organ surface to necrose the tissues to within a desired distance from the organ surface.

Owner:US HIFU

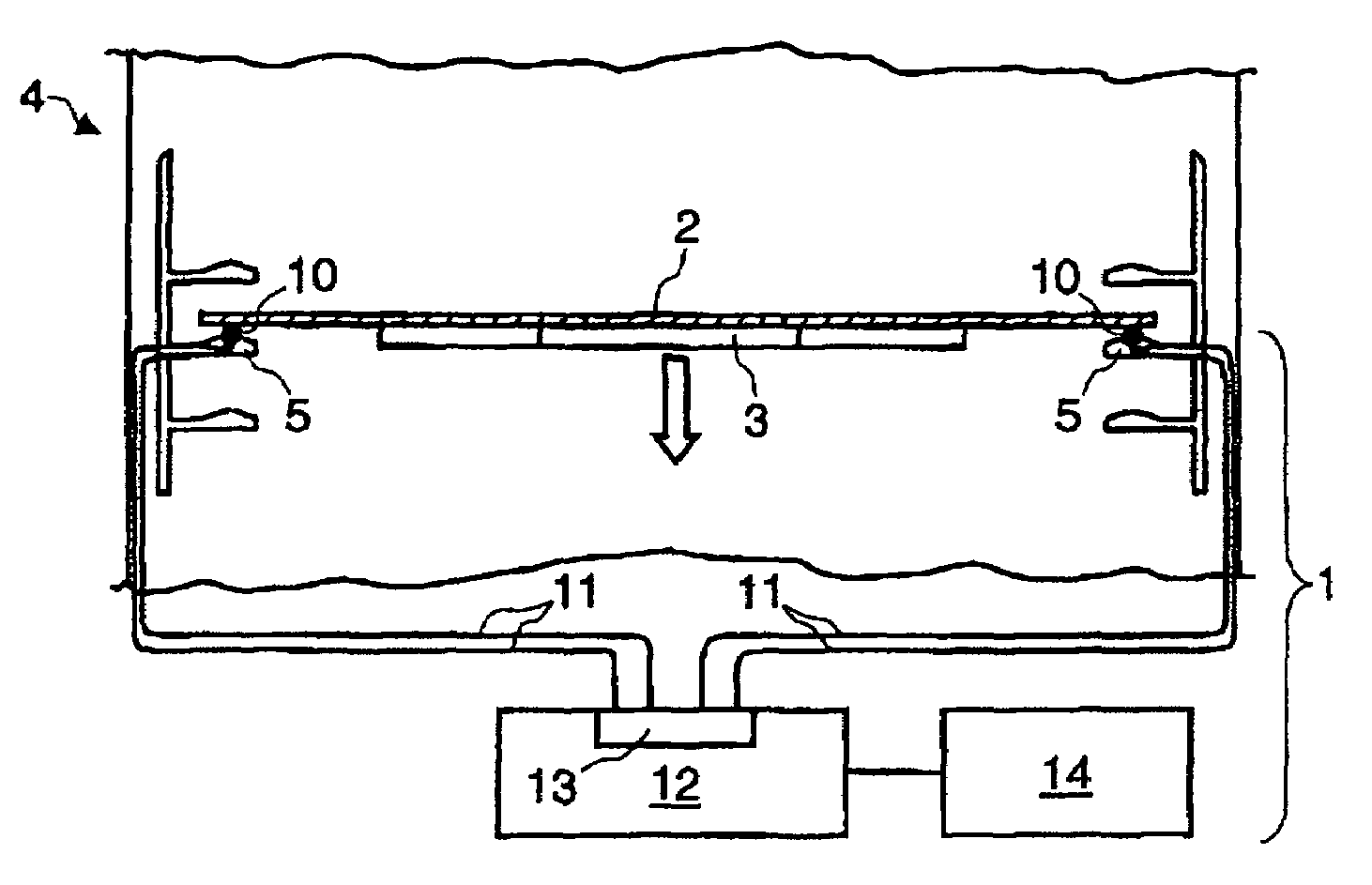

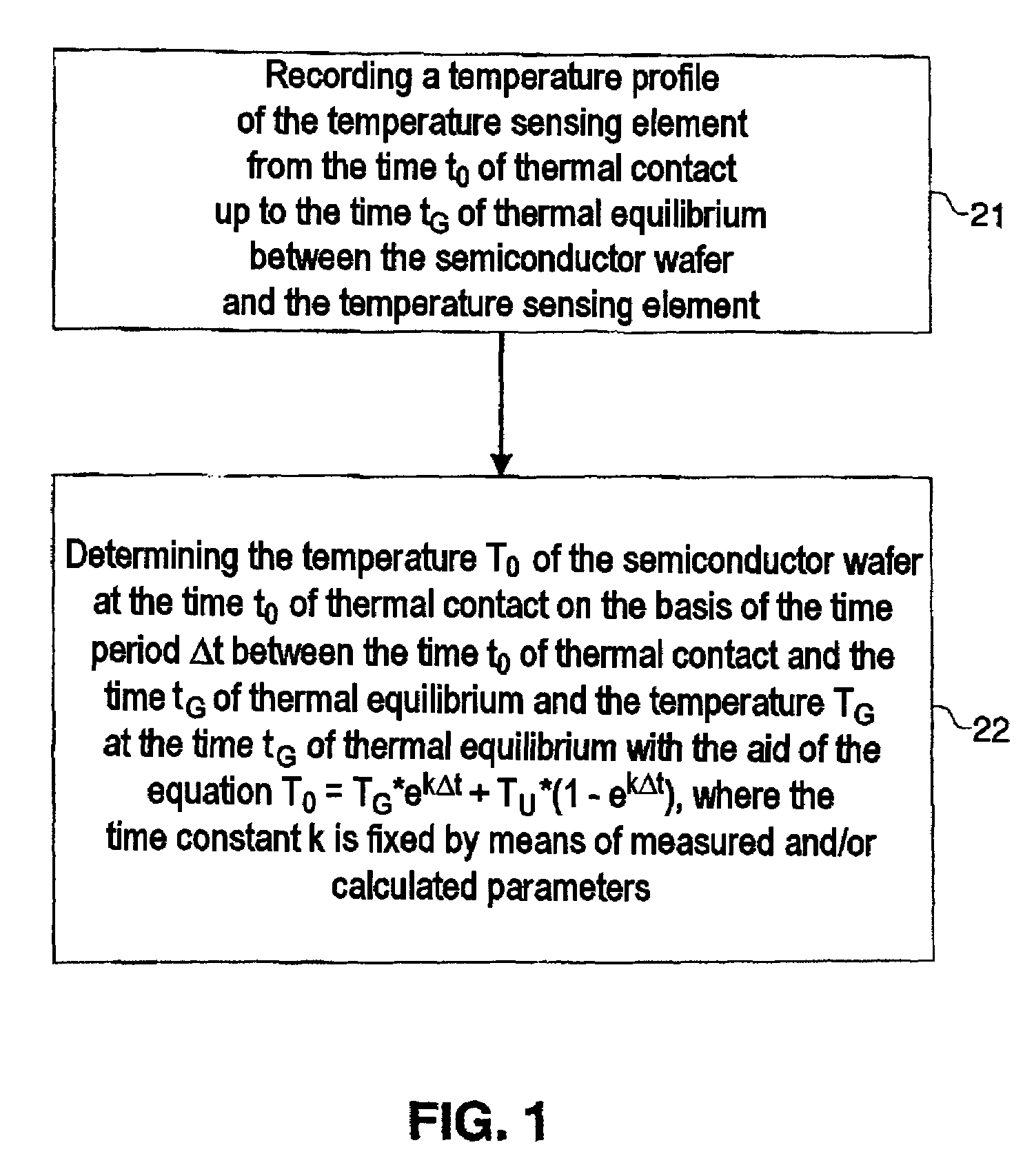

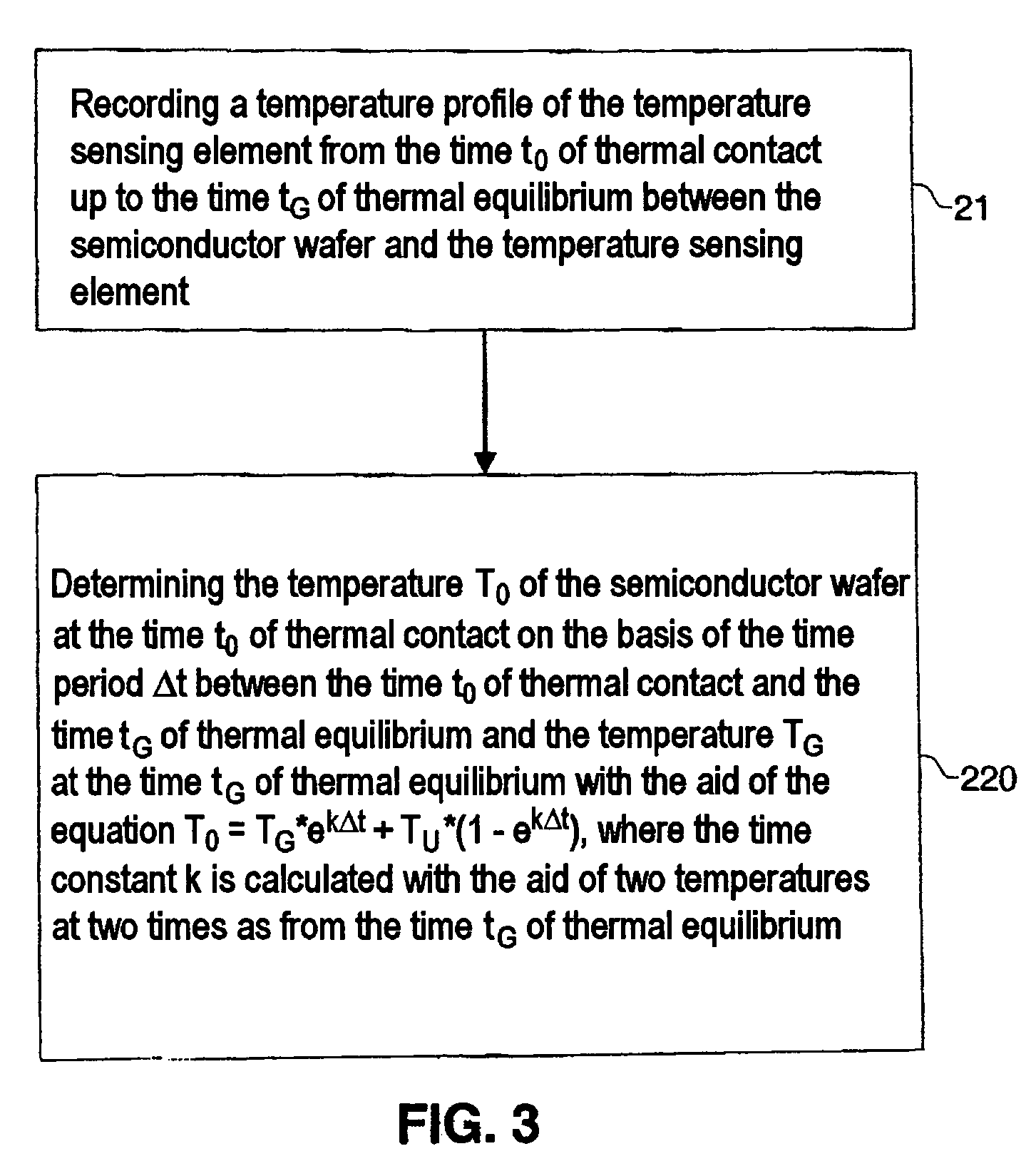

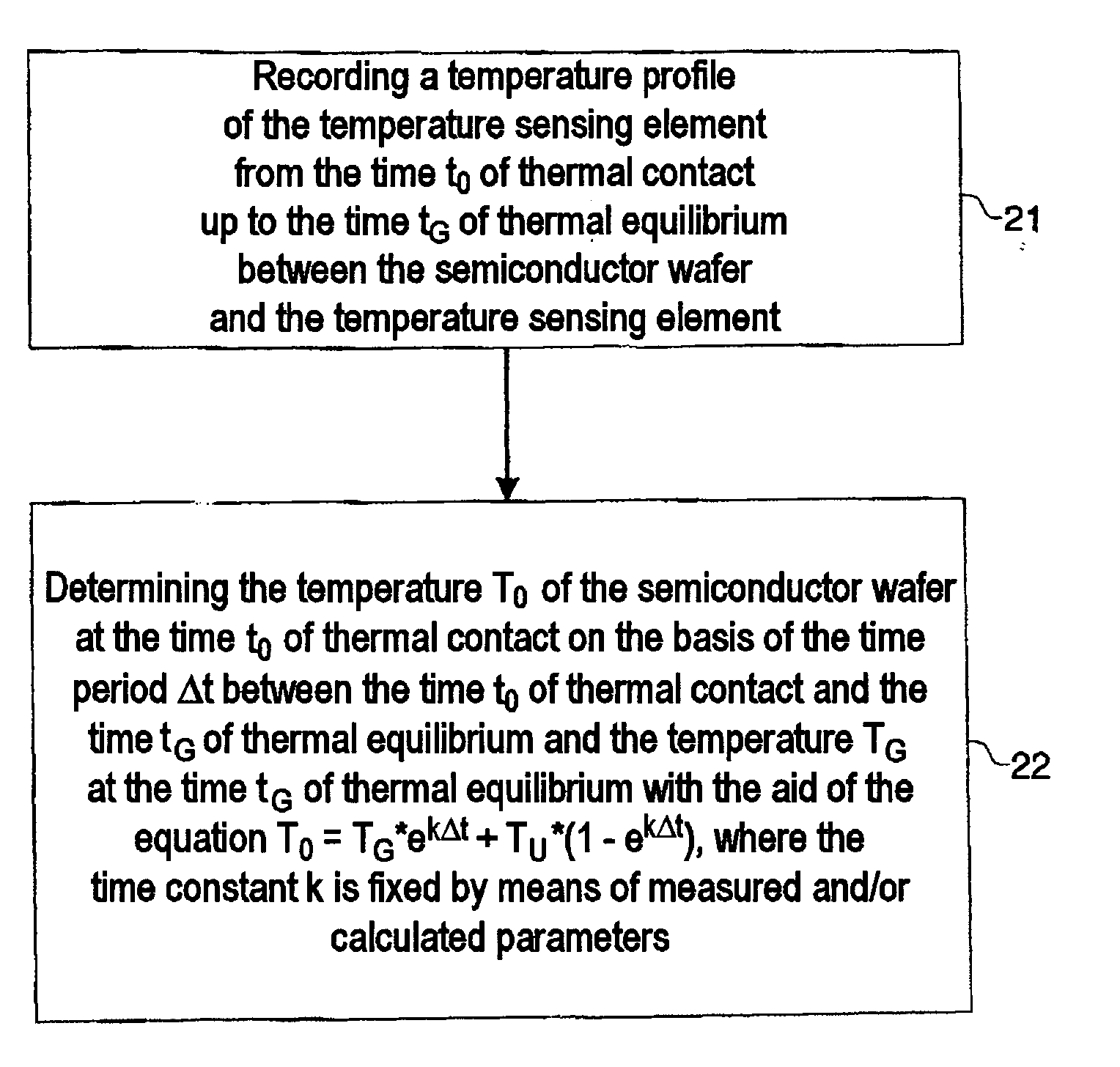

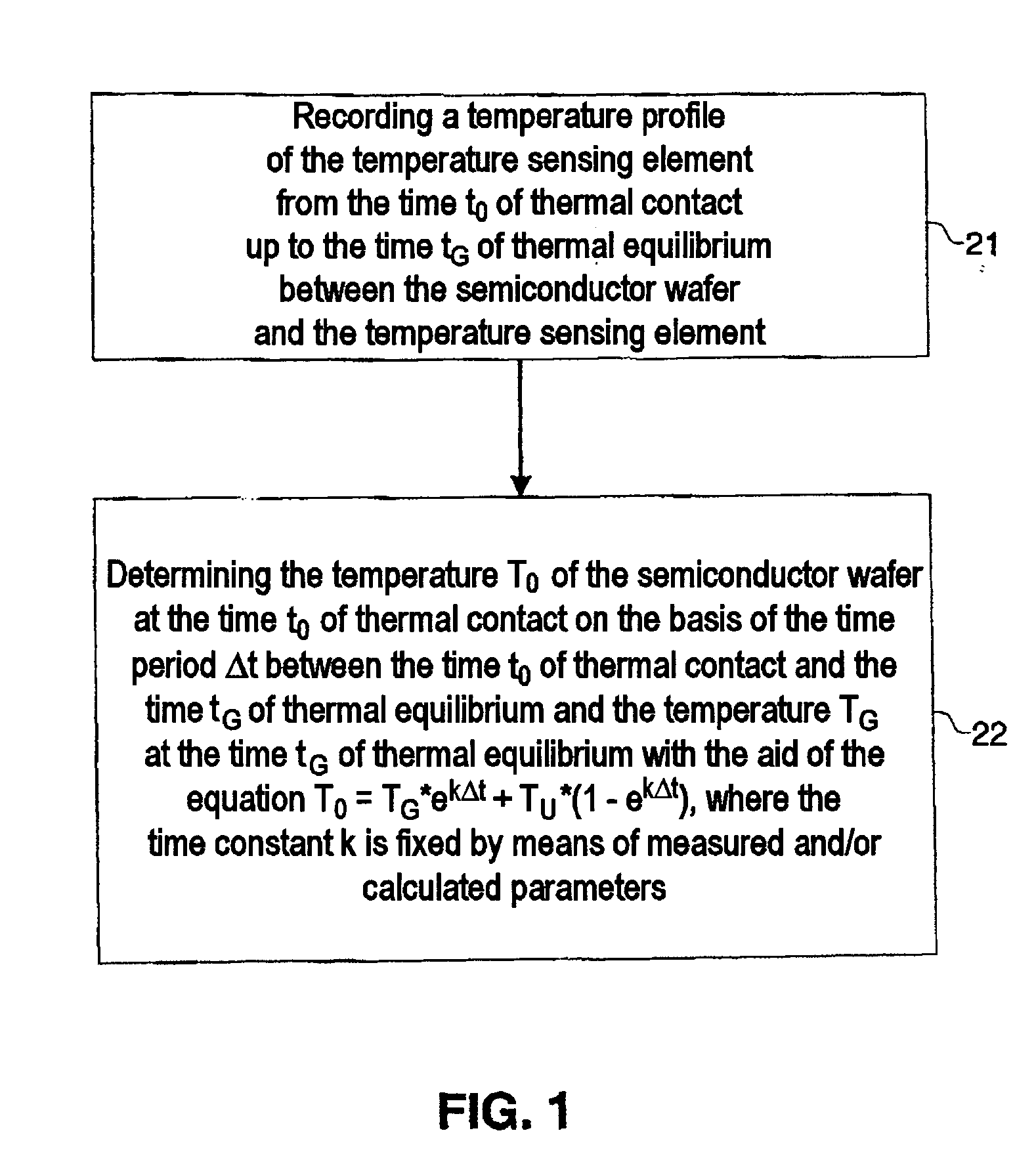

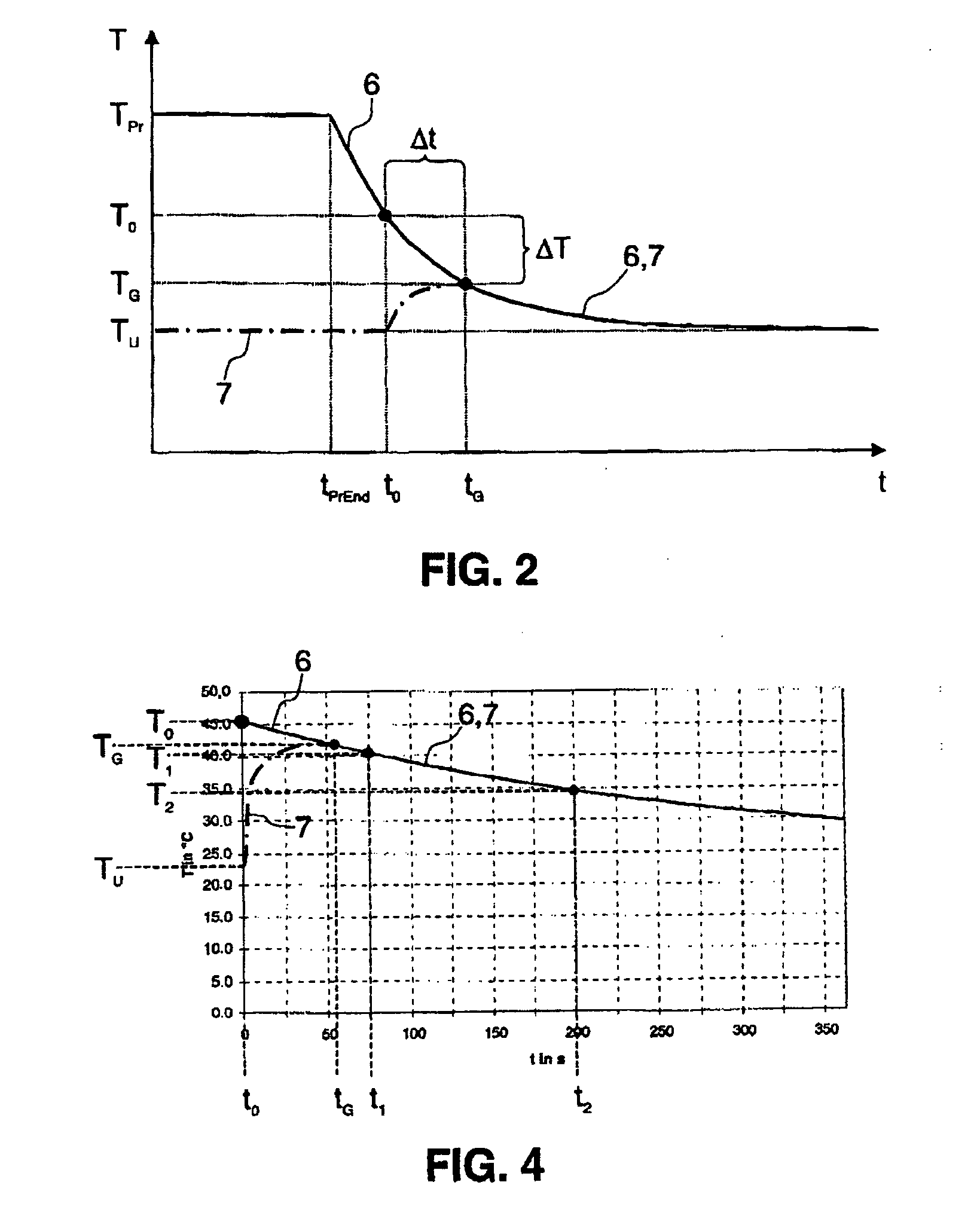

System and method for determining the temperature of a semiconductor wafer

InactiveUS7274867B2High precisionImprove convenienceDrying solid materials with heatSemiconductor/solid-state device testing/measurementTime segmentBack calculation

A system and method for determining the temperature of a semiconductor wafer at the time of thermal contact of the semiconductor wafer with a temperature sensing element. According to the invention, a temperature profile of the temperature sensing element is recorded from the time of thermal contact up to the time of thermal equilibrium between the semiconductor wafer and the temperature sensing element and the temperature of the semiconductor wafer at the time of thermal contact is determined on the basis of a time period between the time of thermal contact and the time of thermal equilibrium and the temperature TG of the semiconductor wafer reached at the time tG of thermal equilibrium is determined by back calculation with the aid of an equation derived from Newton's law of cooling.

Owner:POLARIS INNOVATIONS LTD

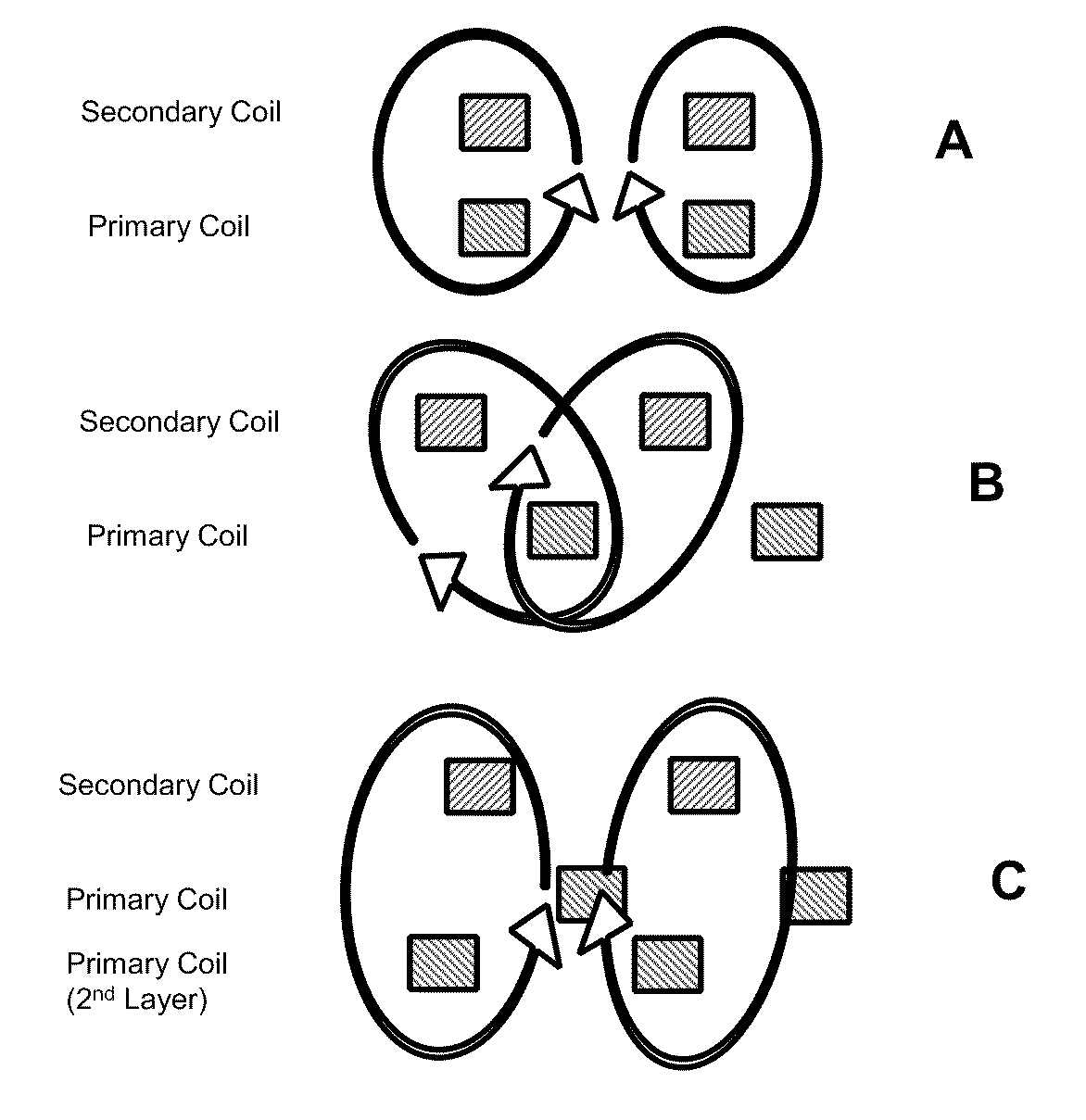

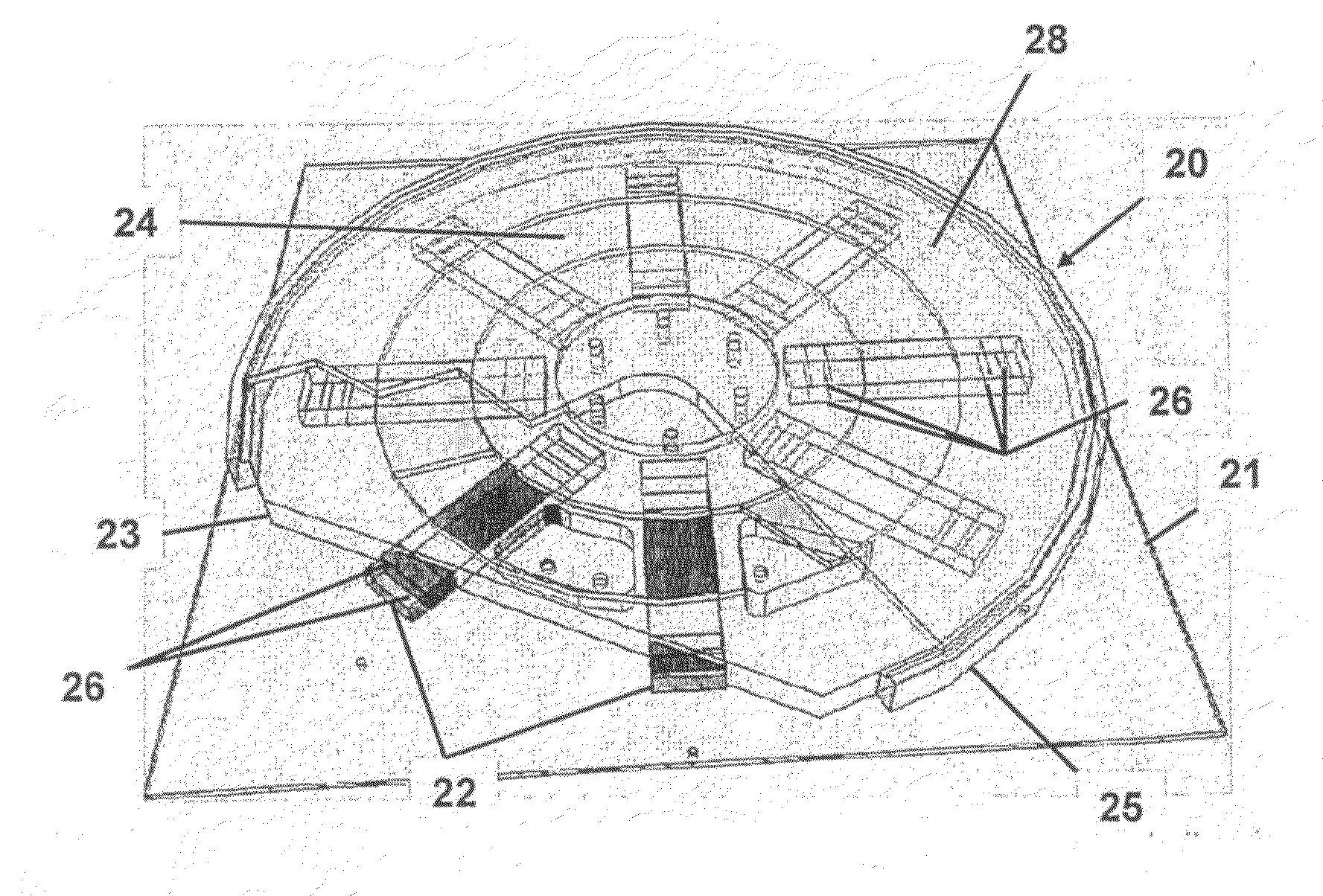

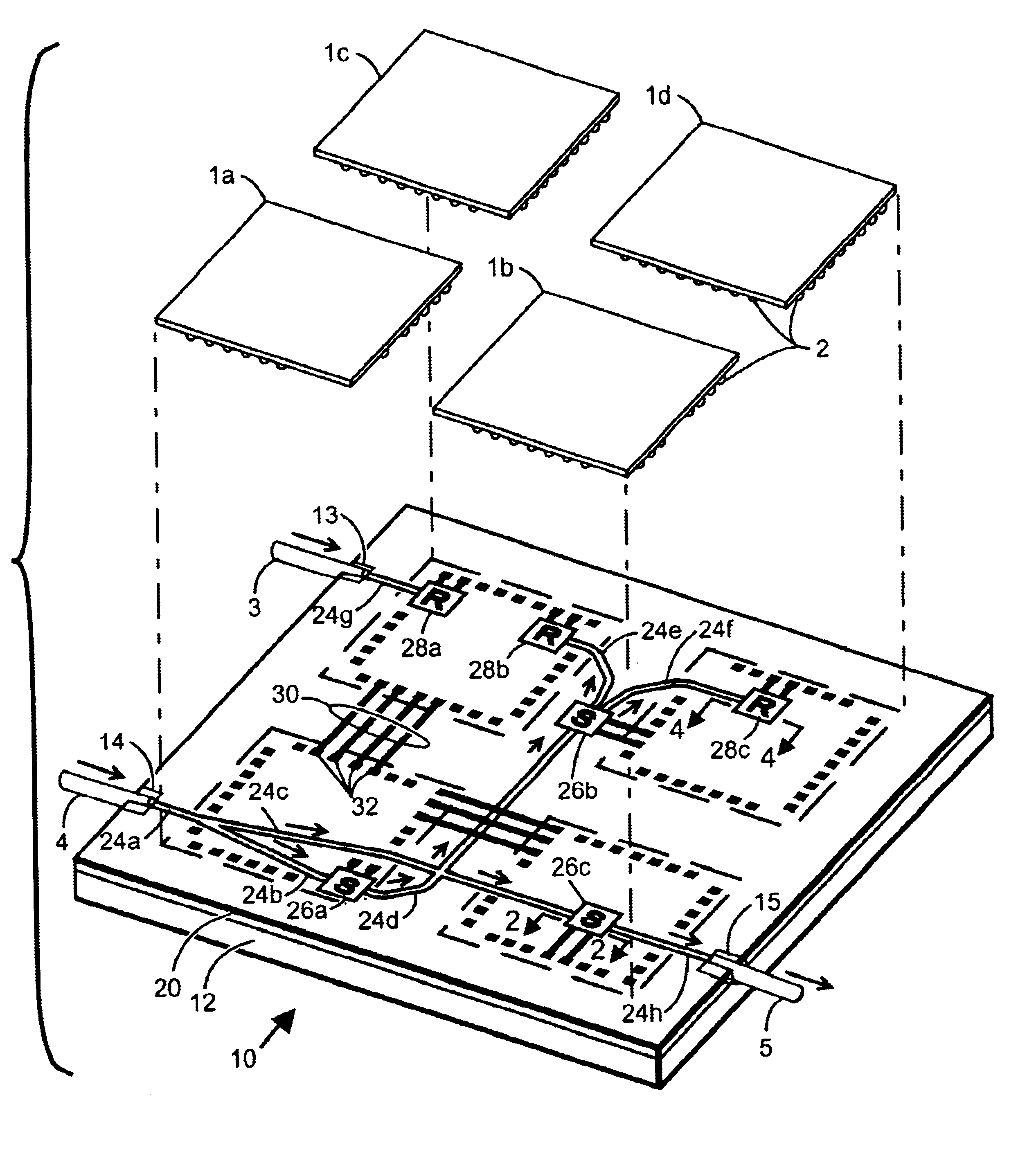

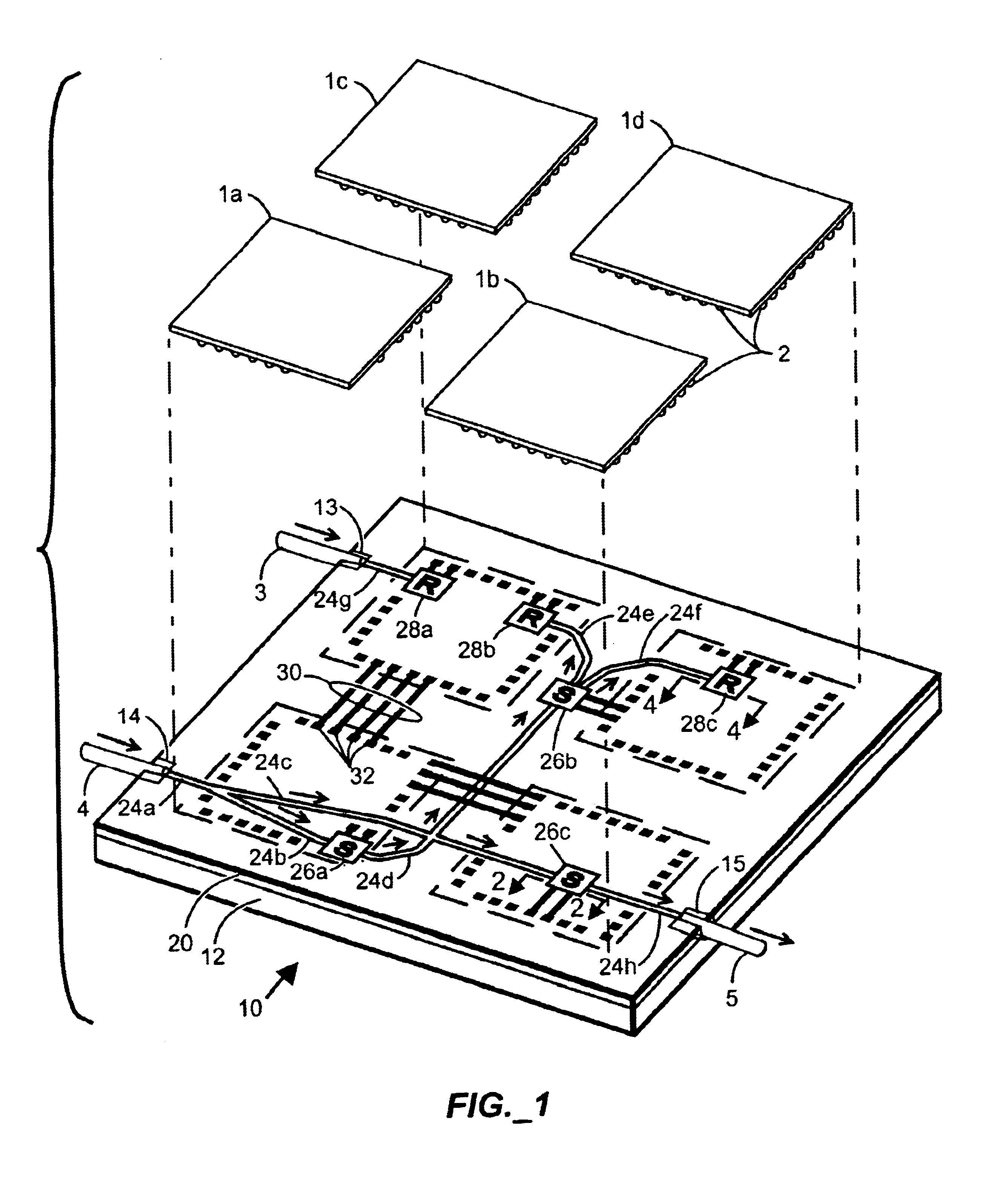

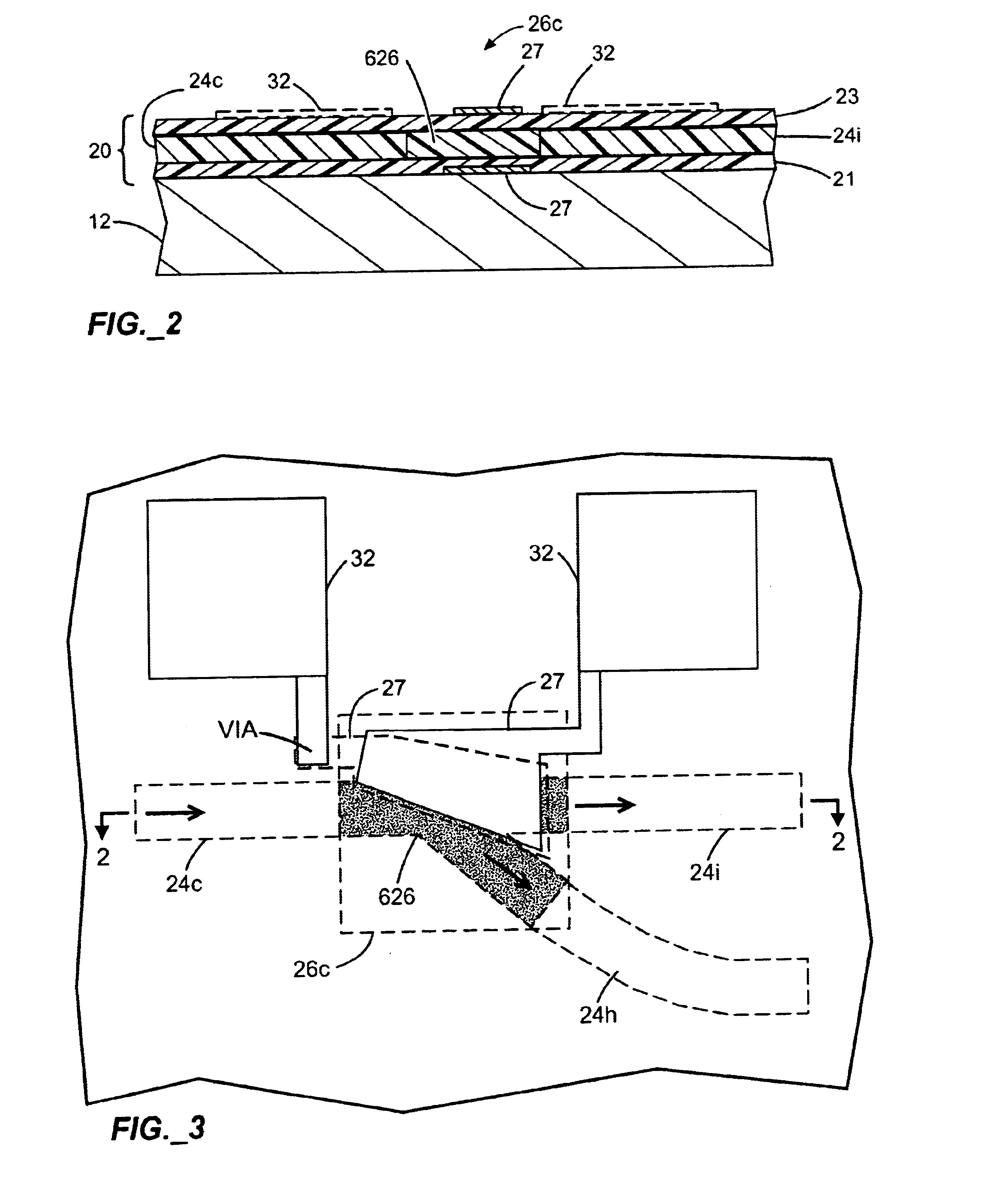

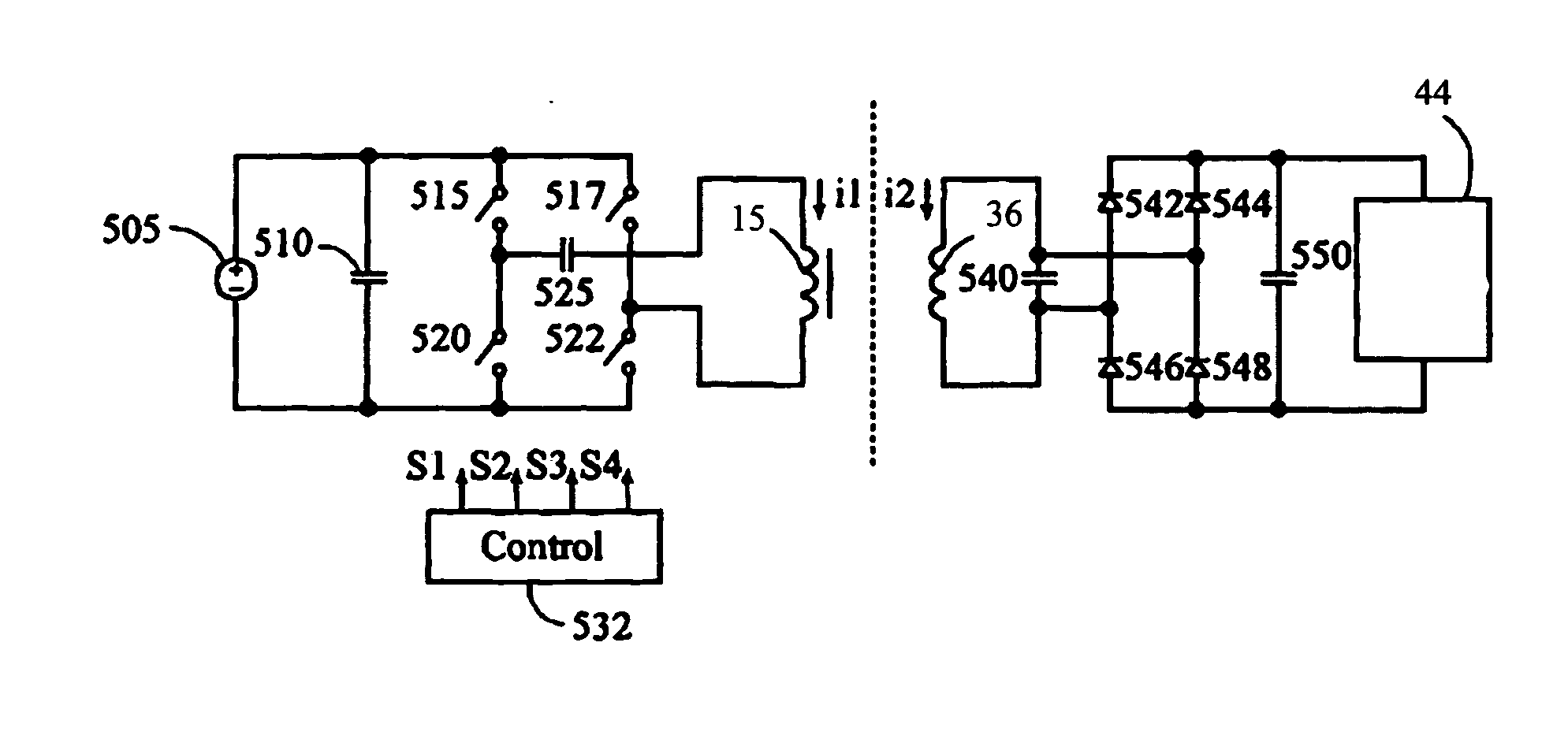

Selectable coil array

ActiveUS20100259217A1Reduce lossesImprove efficiencyImpedence networksMobile unit charging stationsCoil arrayElectric power system

An inductive wireless power system using an array of coils with the ability to dynamically select which coils are energized. The coil array can determine the position of and provide power to one or more portable electronic devices positioned on the charging surface. The coils in the array may be connected with series resonant capacitors so that regardless of the number of coils selected, the resonance point is generally maintained. The coil array can provide spatial freedom, decrease power delivered to parasitic loads, and increase power transfer efficiency to the portable electronic devices.

Owner:PHILIPS IP VENTURES BV

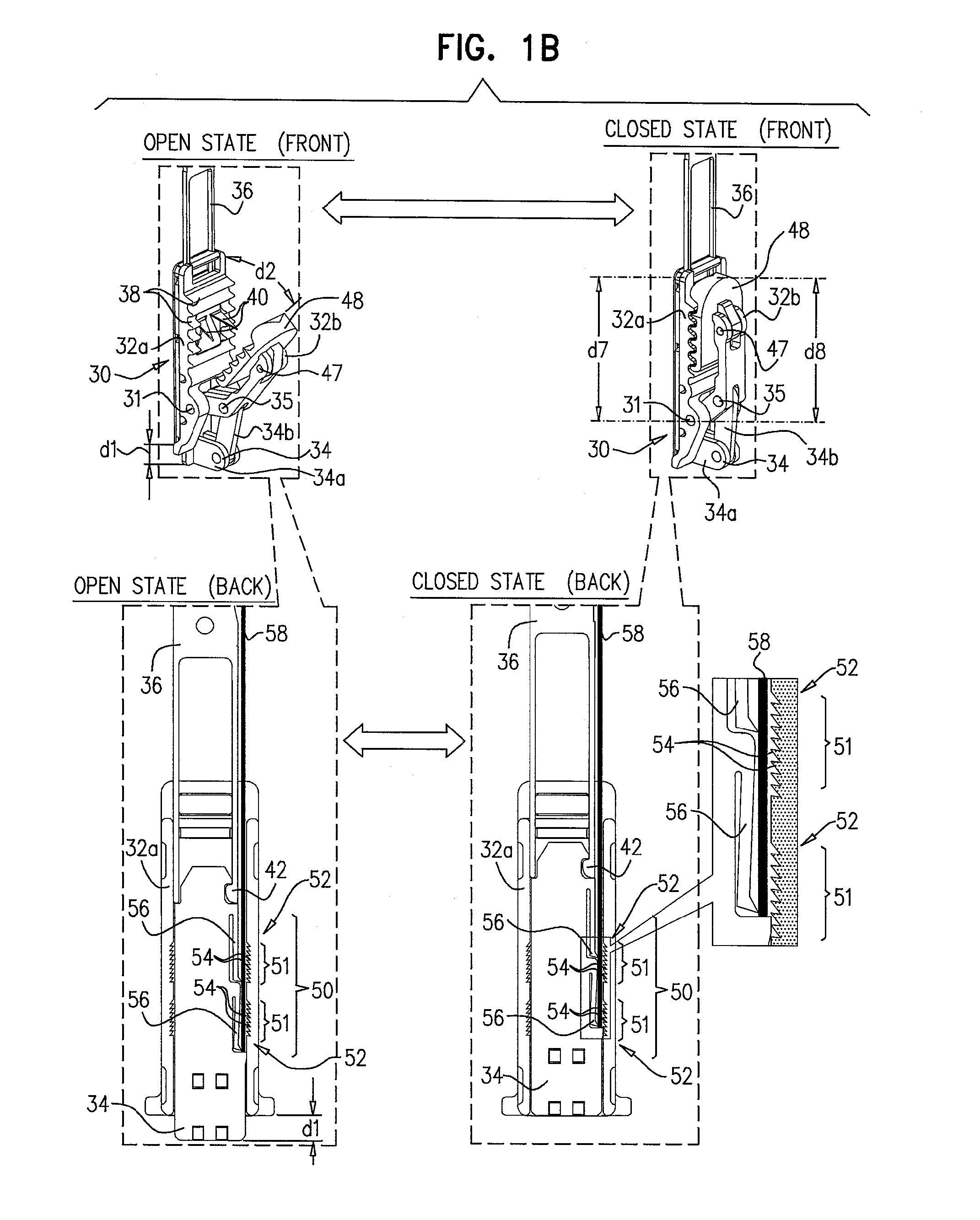

Tissue anchor for annuloplasty device

ActiveUS20110106247A1Facilitate implantationFacilitate couplingSuture equipmentsBone implantBiomedical engineeringFar lateral

Apparatus is provided for use with an implant, the apparatus including a tissue anchor, which comprises a distal tissue coupling element, which is configured to penetrate cardiac tissue, and a proximal implant-penetrating element configured to penetrate the implant. The proximal implant-penetrating element is shaped so as to define a passage therethrough, which passage has at least two openings that are within 1 mm of a proximal end of the implant-penetrating element. The apparatus also comprises a cord configured to be removably passed through the passage. Other applications of the present invention are also described.

Owner:VALTECH CARDIO LTD

System and method for determining the temperature of a semiconductor wafer

InactiveUS20050042778A1High precisionImprove convenienceDrying solid materials with heatSemiconductor/solid-state device testing/measurementBack calculationThermal contact

A system and method for determining the temperature of a semiconductor wafer at the time of thermal contact of the semiconductor wafer with a temperature sensing element. According to the invention, a temperature profile of the temperature sensing element is recorded from the time of thermal contact up to the time of thermal equilibrium between the semiconductor wafer and the temperature sensing element and the temperature of the semiconductor wafer at the time of thermal contact is determined on the basis of a time period between the time of thermal contact and the time of thermal equilibrium and the temperature TG of the semiconductor wafer reached at the time tG of thermal equilibrium is determined by back calculation with the aid of an equation derived from Newton's law of cooling.

Owner:POLARIS INNOVATIONS LTD

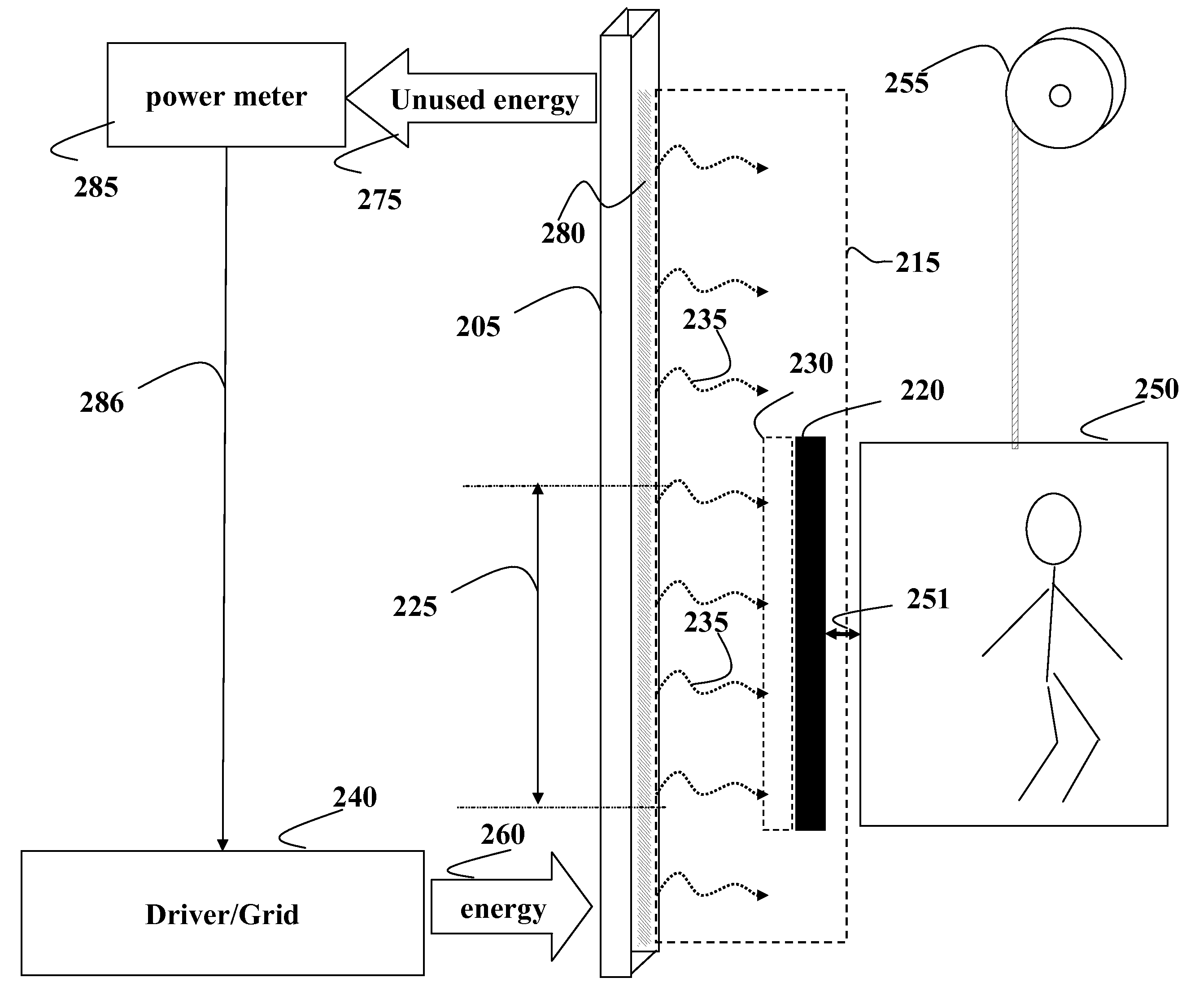

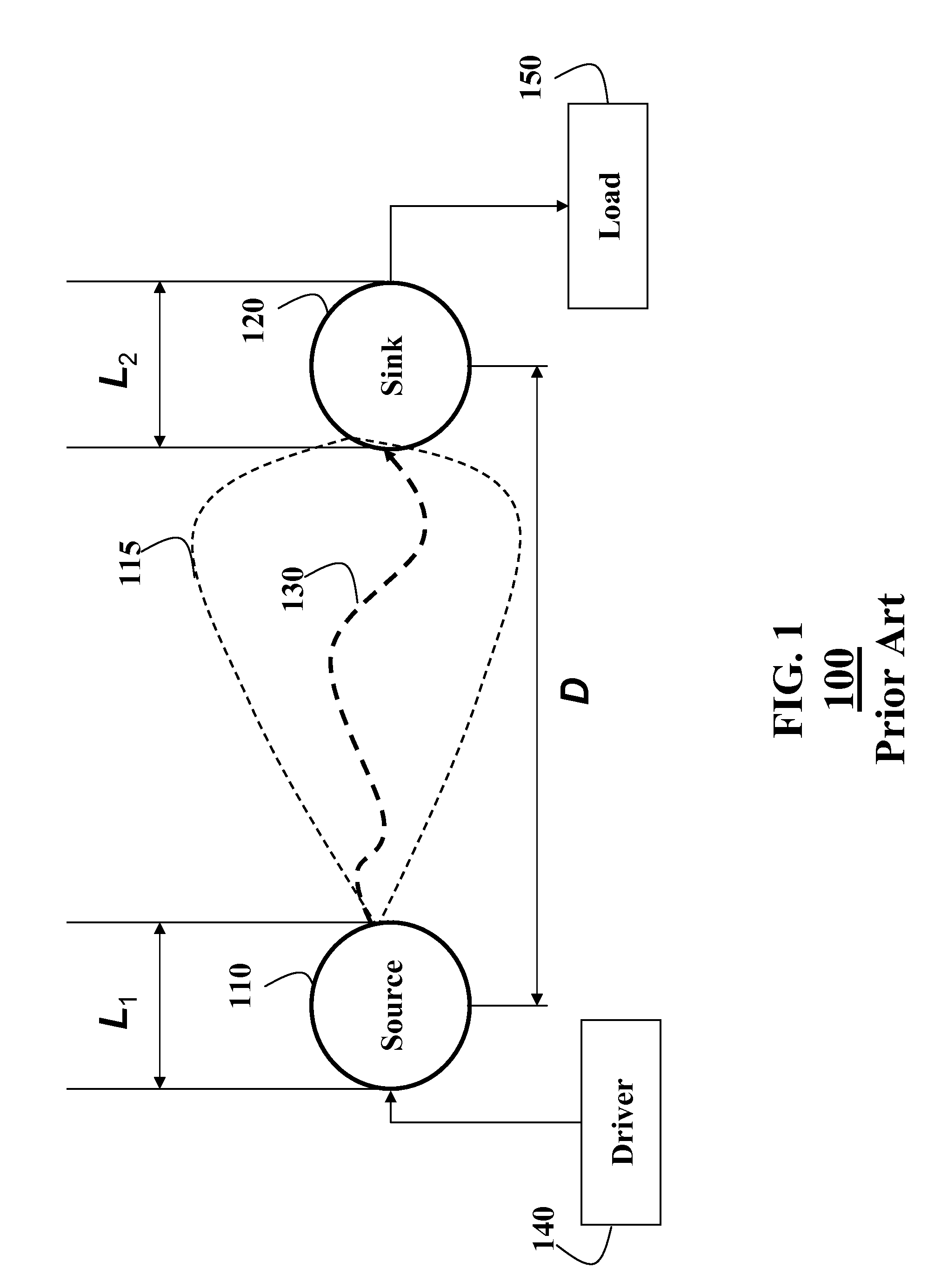

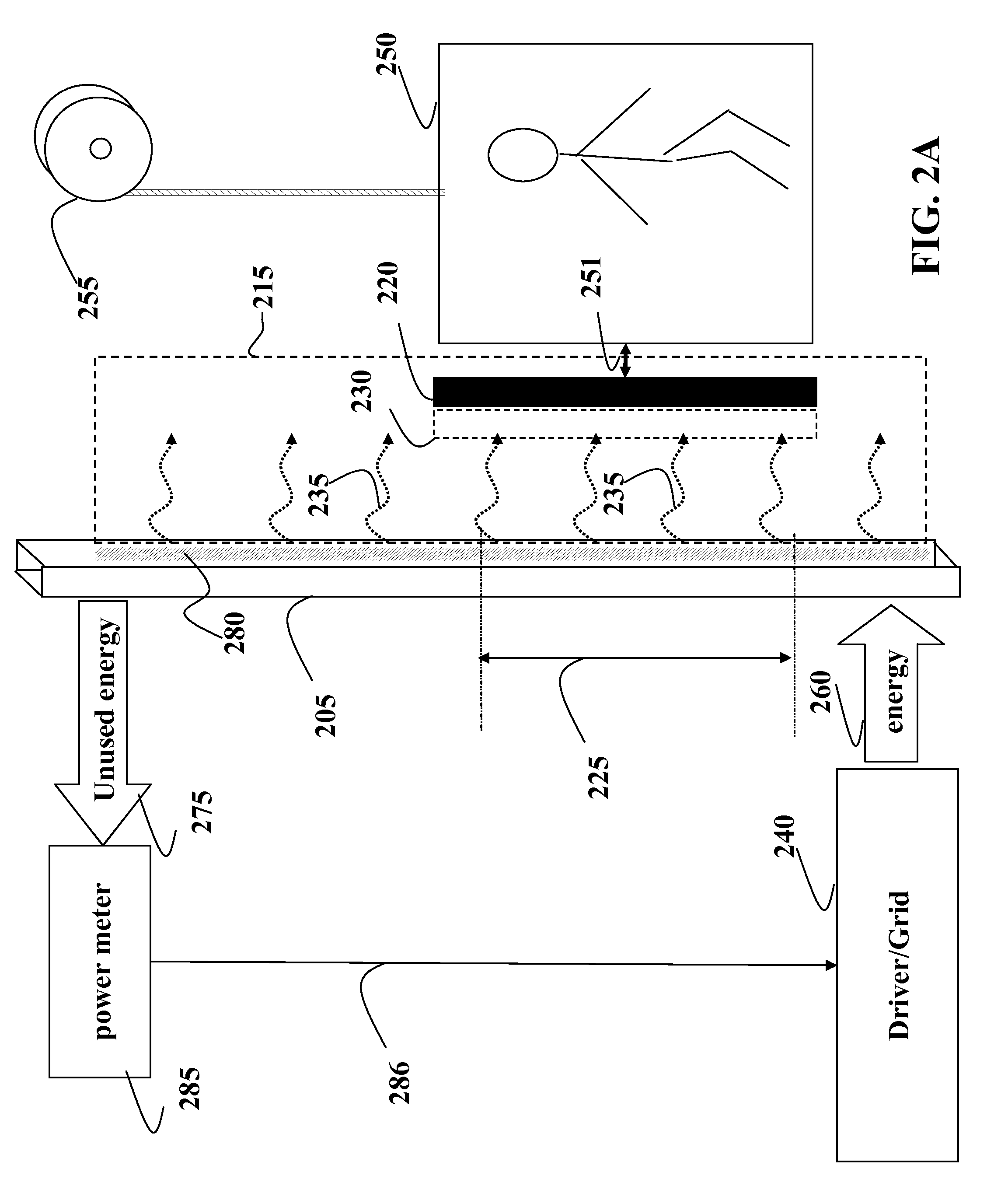

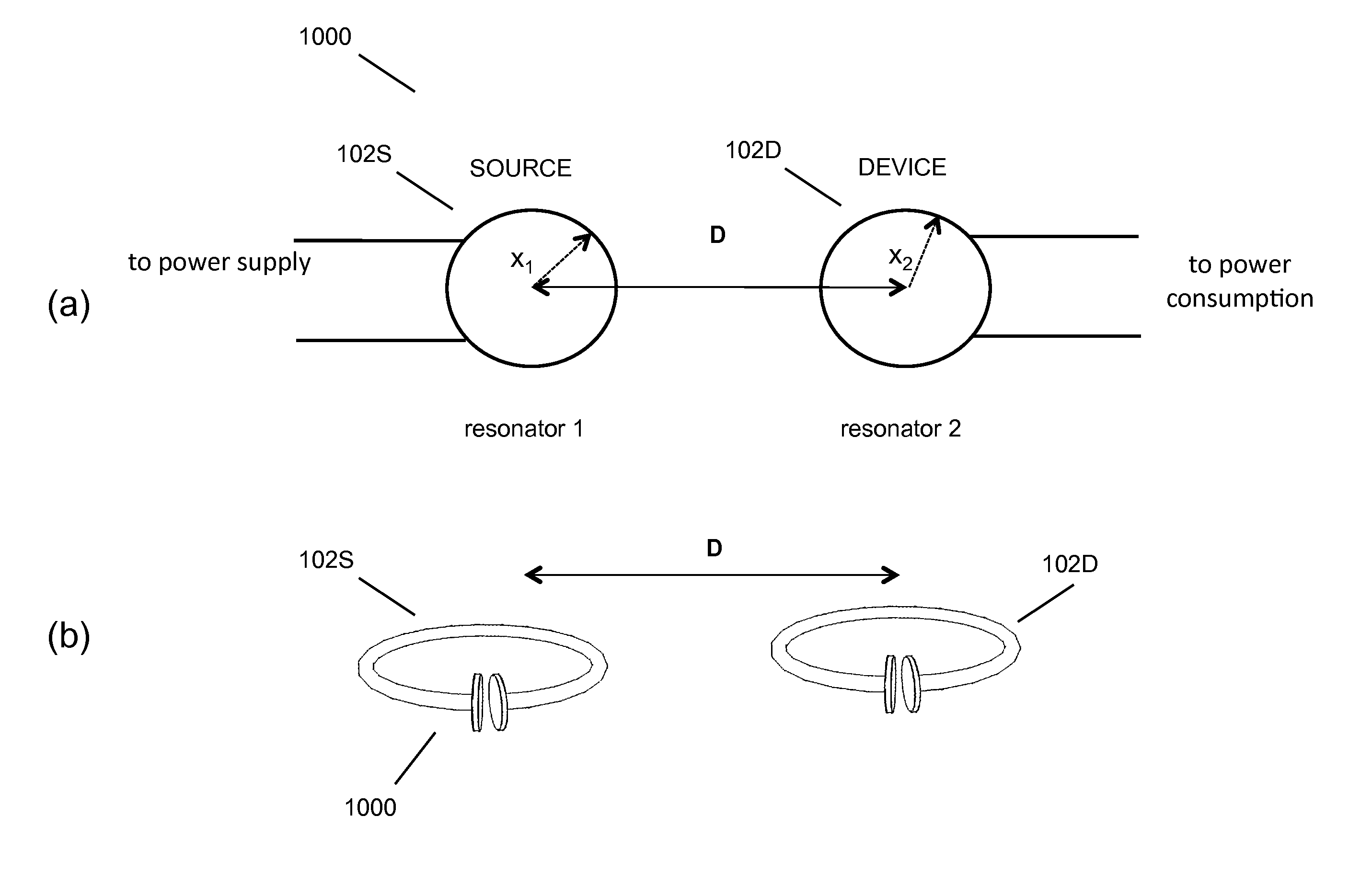

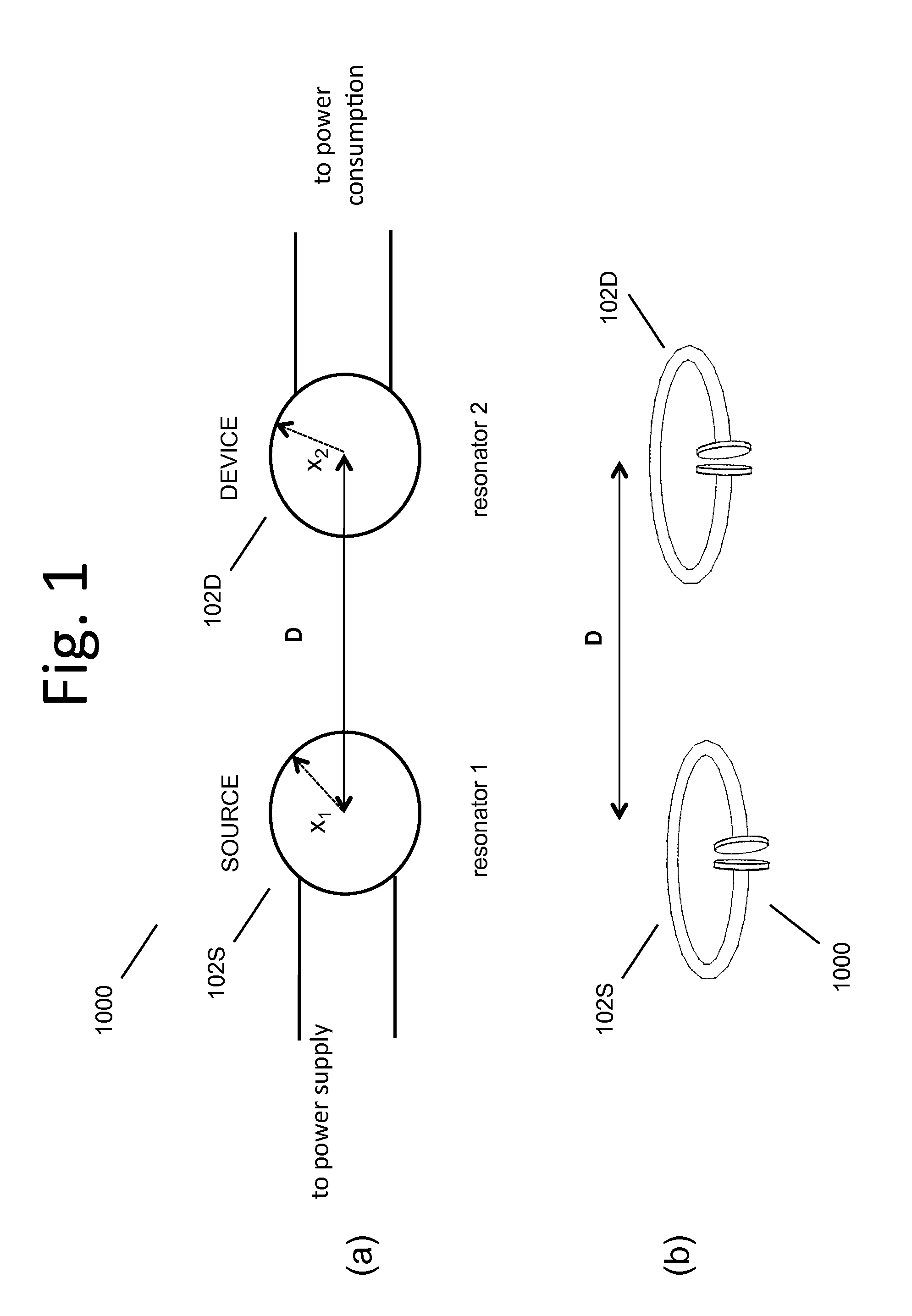

Wireless Energy Transfer to Moving Devices

ActiveUS20110169336A1Enhanced couplingElectromagnetic wave systemTransformersEnergy transferCoupling

Embodiments of the invention disclose a method and a system configured to transfer energy wirelessly, comprising: a source configured to generate evanescent waves, in response to receiving the energy, on at least part of a surface of the source; a sink configured to receive the energy wirelessly from the source via a coupling of the at least part of the evanescent waves; and a load configured to receive the energy from the sink, wherein the load and the sink are configured to move along the surface of the source such that the at least a part of the evanescent waves are coupled between the source and the sink within an energy transfer area.

Owner:MITSUBISHI ELECTRIC RES LAB INC

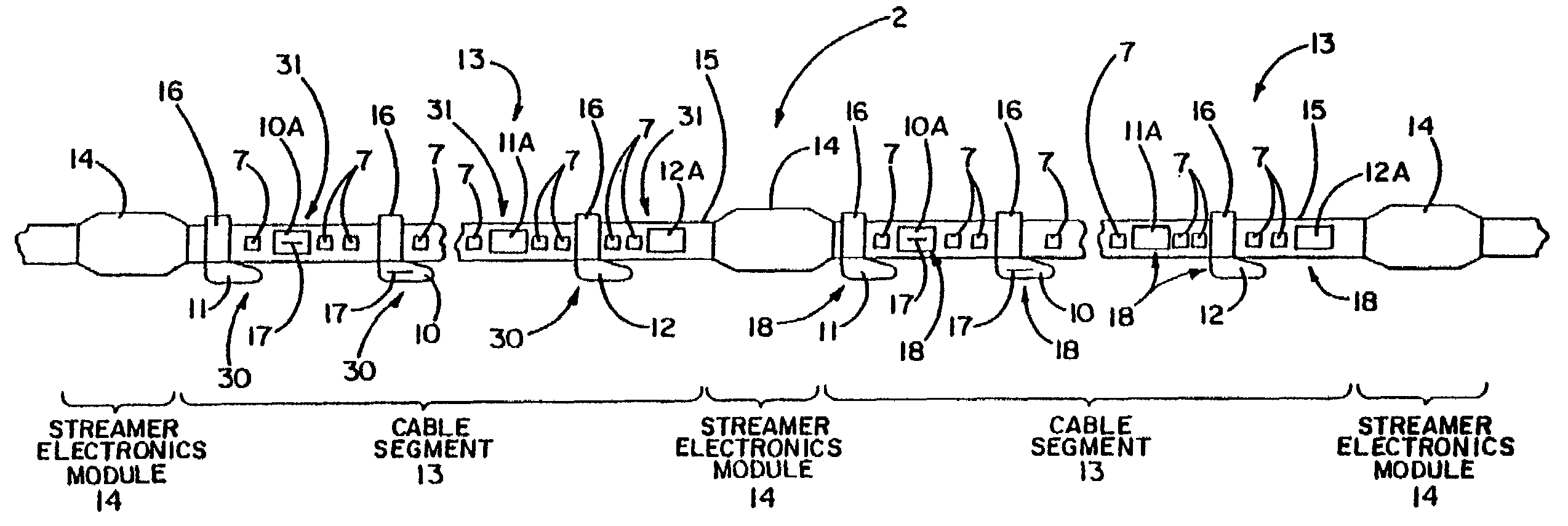

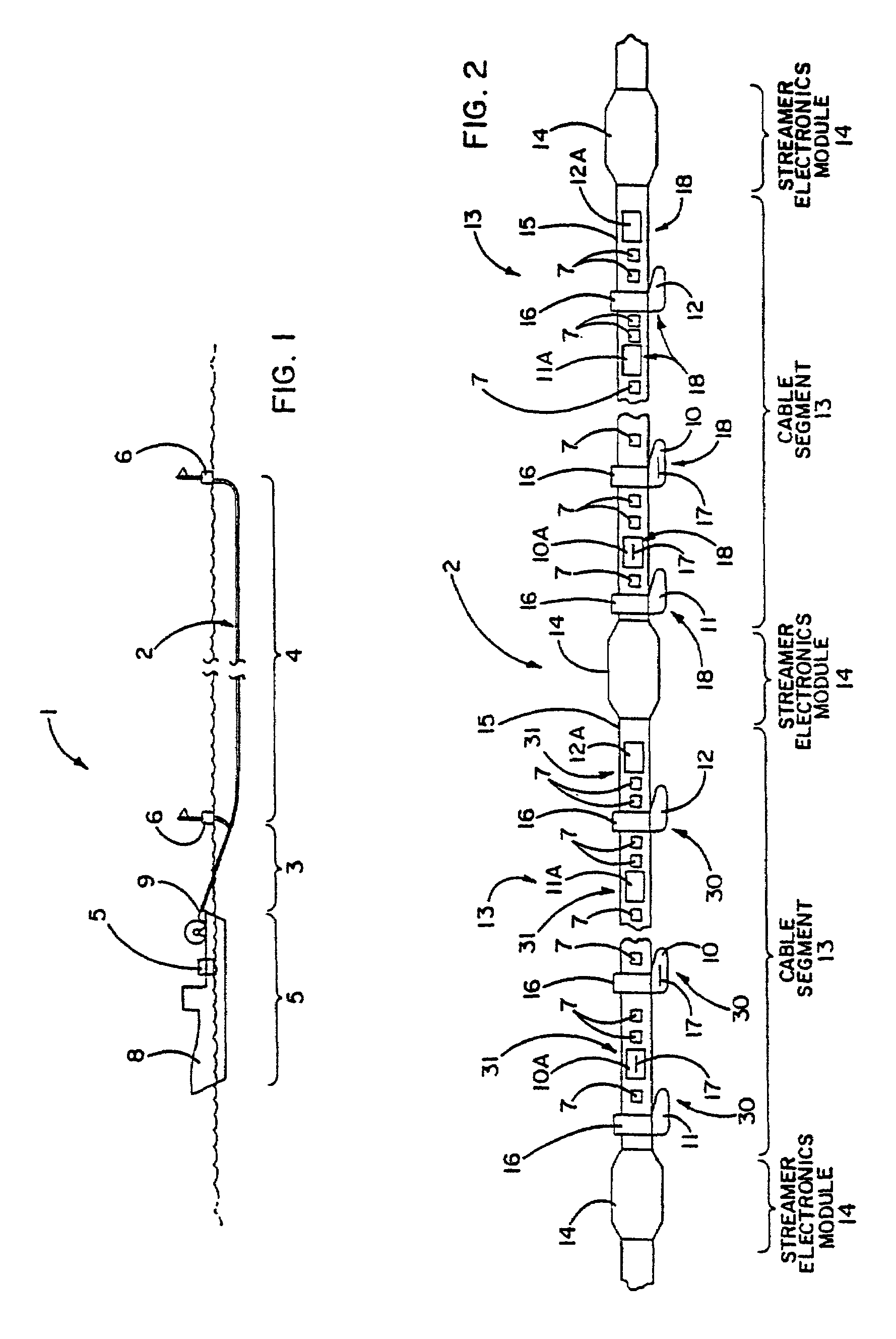

Electrical power distribution and communication system for an underwater cable

ActiveUS7176589B2Improve reliabilityImprove operationBus-bar/wiring layoutsInsulated cablesCommunications systemElectrical devices

An underwater cable arrangement includes systems and method for distributing and / or transferring power and / or data to internal devices and external devices disposed along an underwater cable. Under water coupling systems and underwater electrical devices may be used in the distribution and / or transfer of the power and / or data.

Owner:INPUT OUTPUT INC

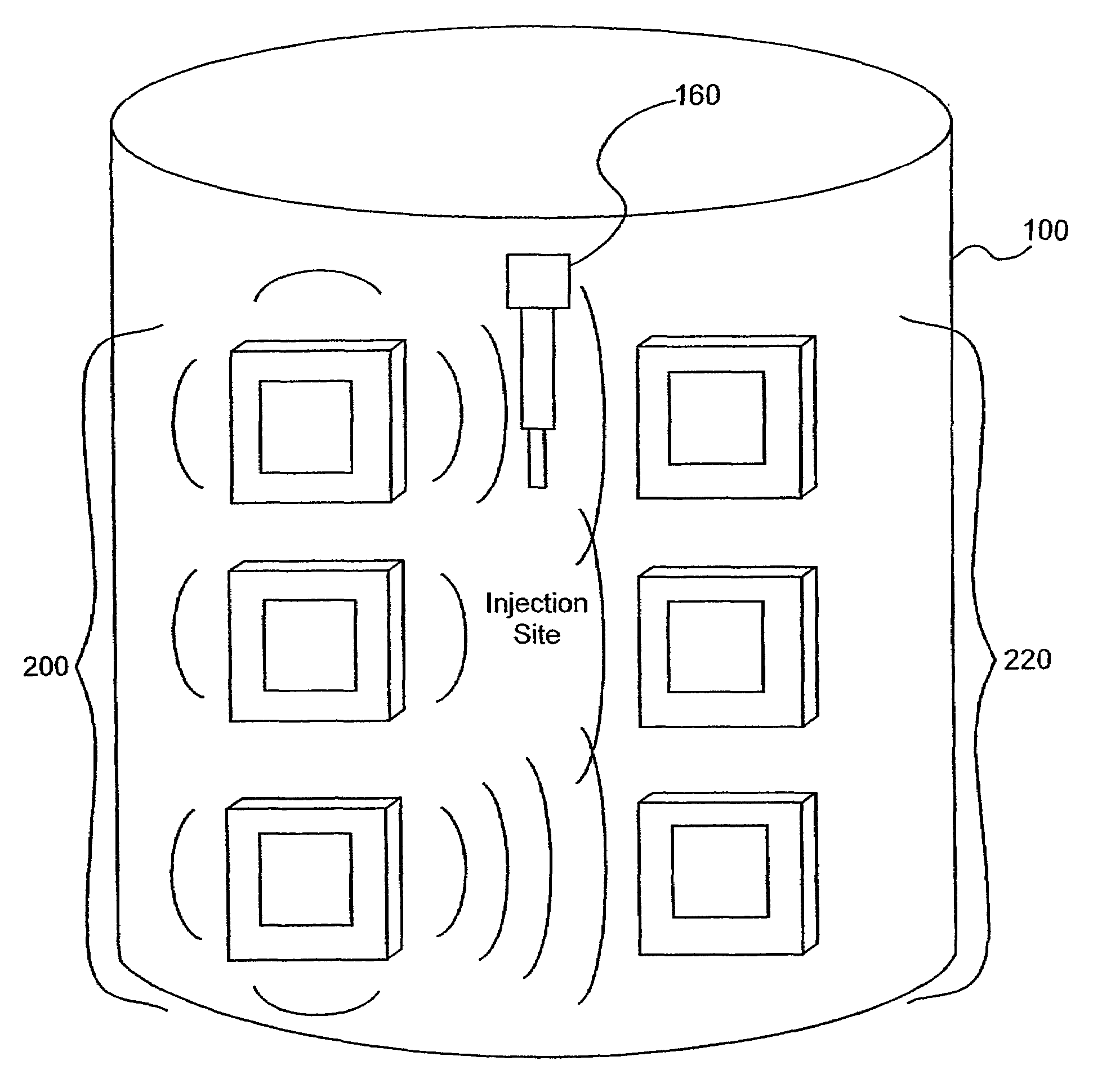

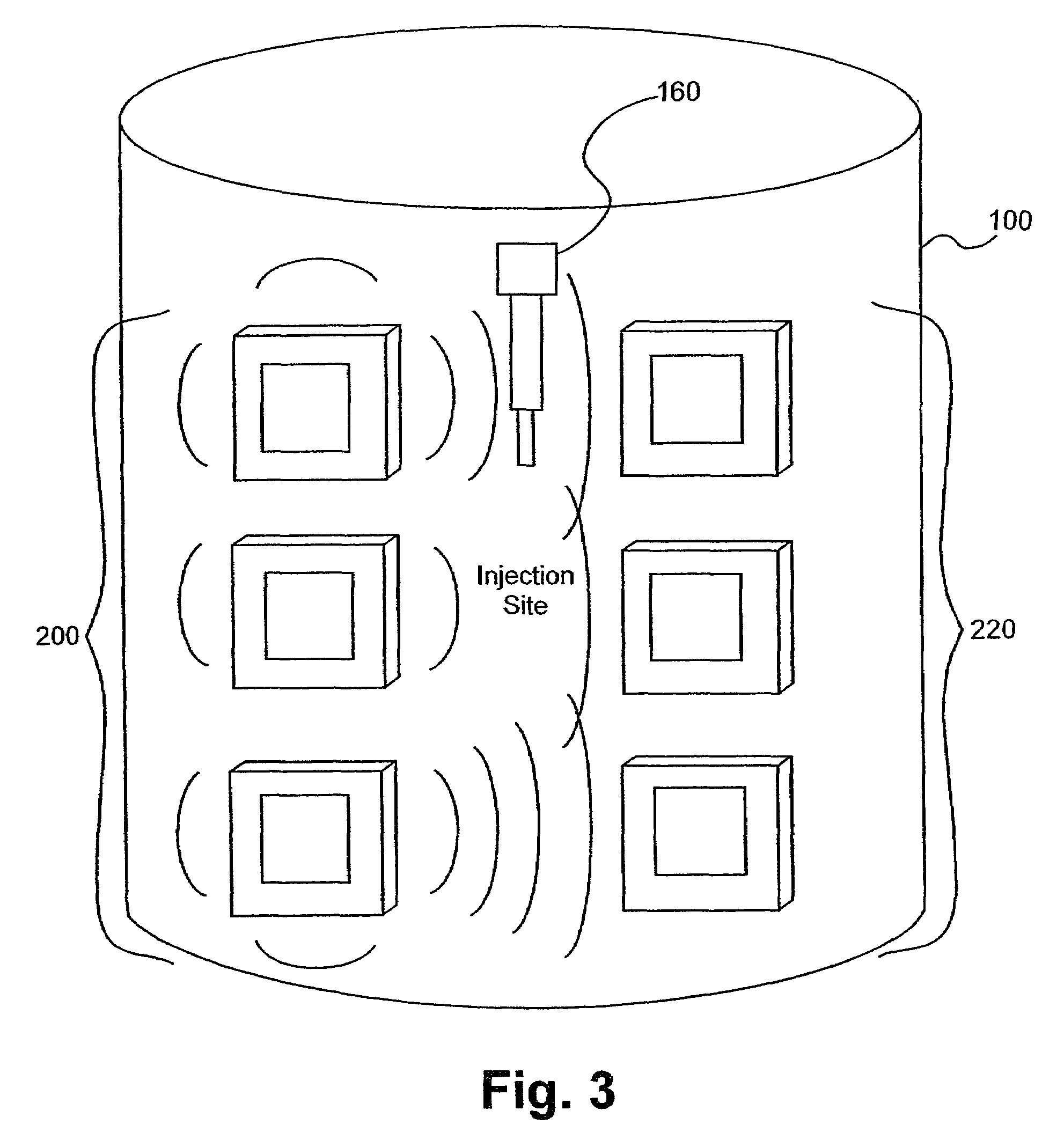

Electromagnetic sensors for biological tissue applications and methods for their use

ActiveUS7591792B2Improves signal couplingImproves resulting measurementElectrotherapyAntenna supports/mountingsMeasurement pointEngineering

Tissue sensors house one or more sensor elements. Each element has a housing mounted substrate and a superstrate with a planar antenna between. A transitional periphery (TP) of a superstrate outer surface interconnects a base to a plateau. At least some of the TP has a generally smooth transition. Plural elements are spaced by the housing. Alternately, the superstrate TP is flat, the housing extends to the outer superstrate surface and a shield surrounds the element. The housing is flush with or recessed below the superstrate and defines a TP between the housing and superstrate. A method converts a reference signal to complex form; plots it in a complex plane as a reference point (RP); converts a measurement signal to complex form; plots it in the complex plane as a measurement point (MP); determine a complex distance between the MP and the RP; and compares complex distance to a threshold.

Owner:BAYER HEALTHCARE LLC

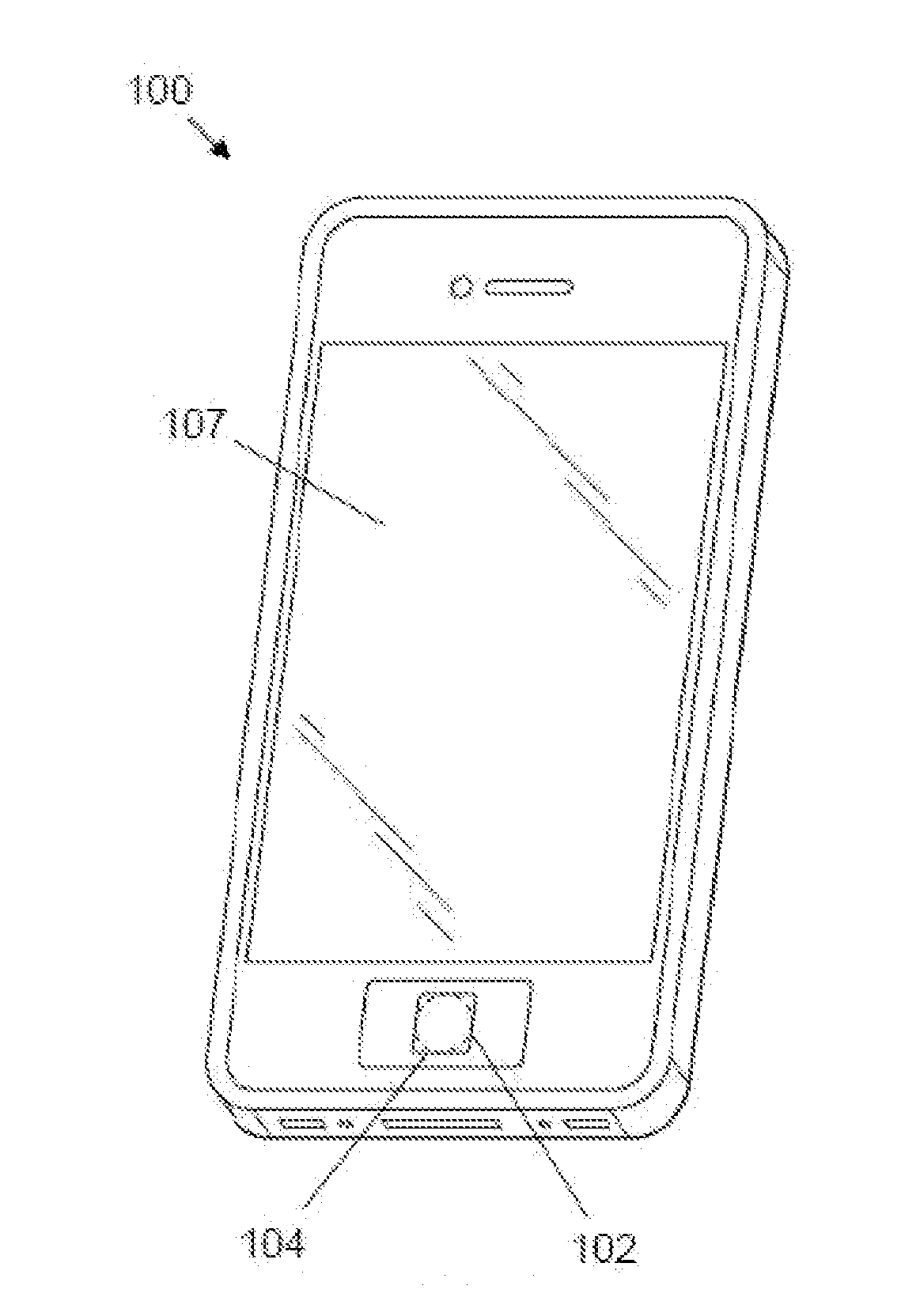

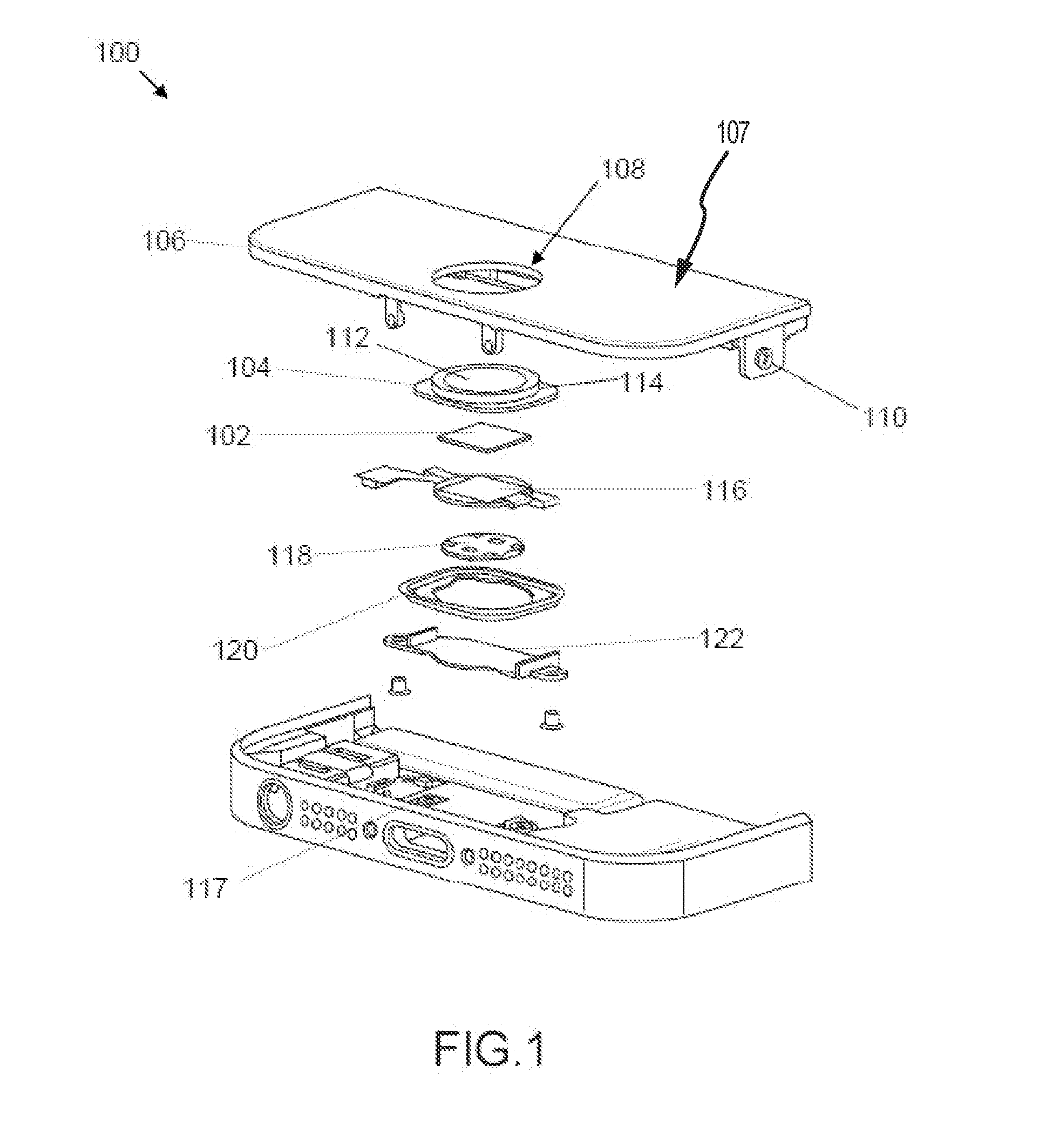

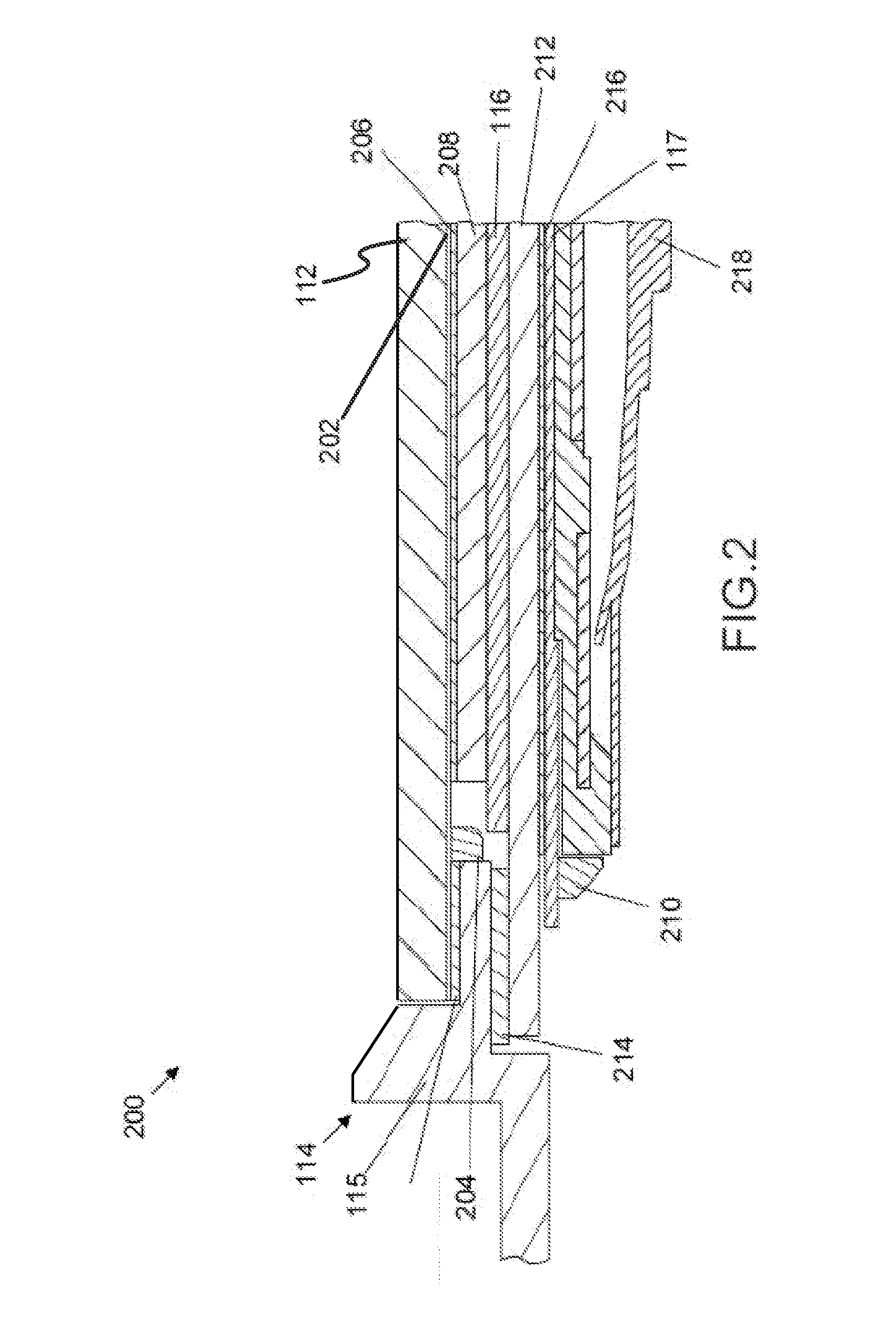

Capacitive Sensor Packaging

ActiveUS20130307818A1Enhanced couplingPrint image acquisitionMatching and classificationCapacitanceDielectric

An apparatus comprises a fingerprint sensor having a set of capacitive elements configured for capacitively coupling to a user fingerprint. The fingerprint sensor may be disposed under a control button or display element of an electronic device, for example one or more of a control button and a display component. A responsive element is responsive to proximity of the user fingerprint, for example one or both of a first circuit responsive to motion of the control button, and a second circuit responsive to a coupling between the fingerprint and a surface of the display element. The fingerprint sensor is disposed closer to the fingerprint than the responsive element. The control button or display component may include an anisotropic dielectric material, for example sapphire.

Owner:APPLE INC

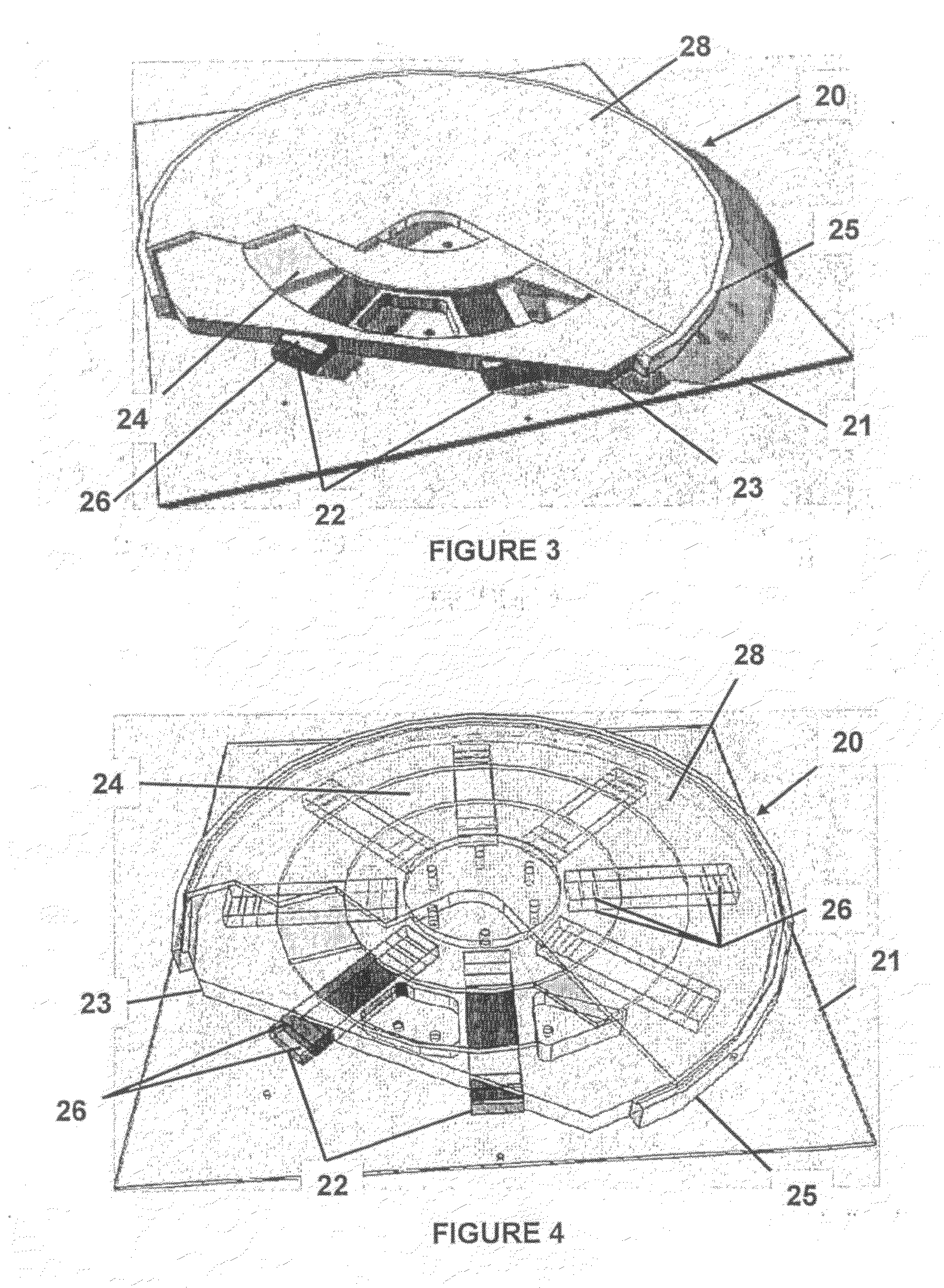

Multi power sourced electric vehicle

ActiveUS20100109604A1Increasing and reducing power consumedAvoid crackingHybrid vehiclesNear-field transmissionElectrical batteryHigher Power

An inductive power transfer (IPT) pad and system for the charging of electric and hybid electric vehicles. The batter of such a vehicle can be selectively coupled to a high power electrical supply for fast charging or a lower power electrical supply for charging using IPT. The batteries of the vehicles are used in a system to control the load demand in an electricity network through variations of the frequency of power supplied.

Owner:AUCKLAND UNISERVICES LTD

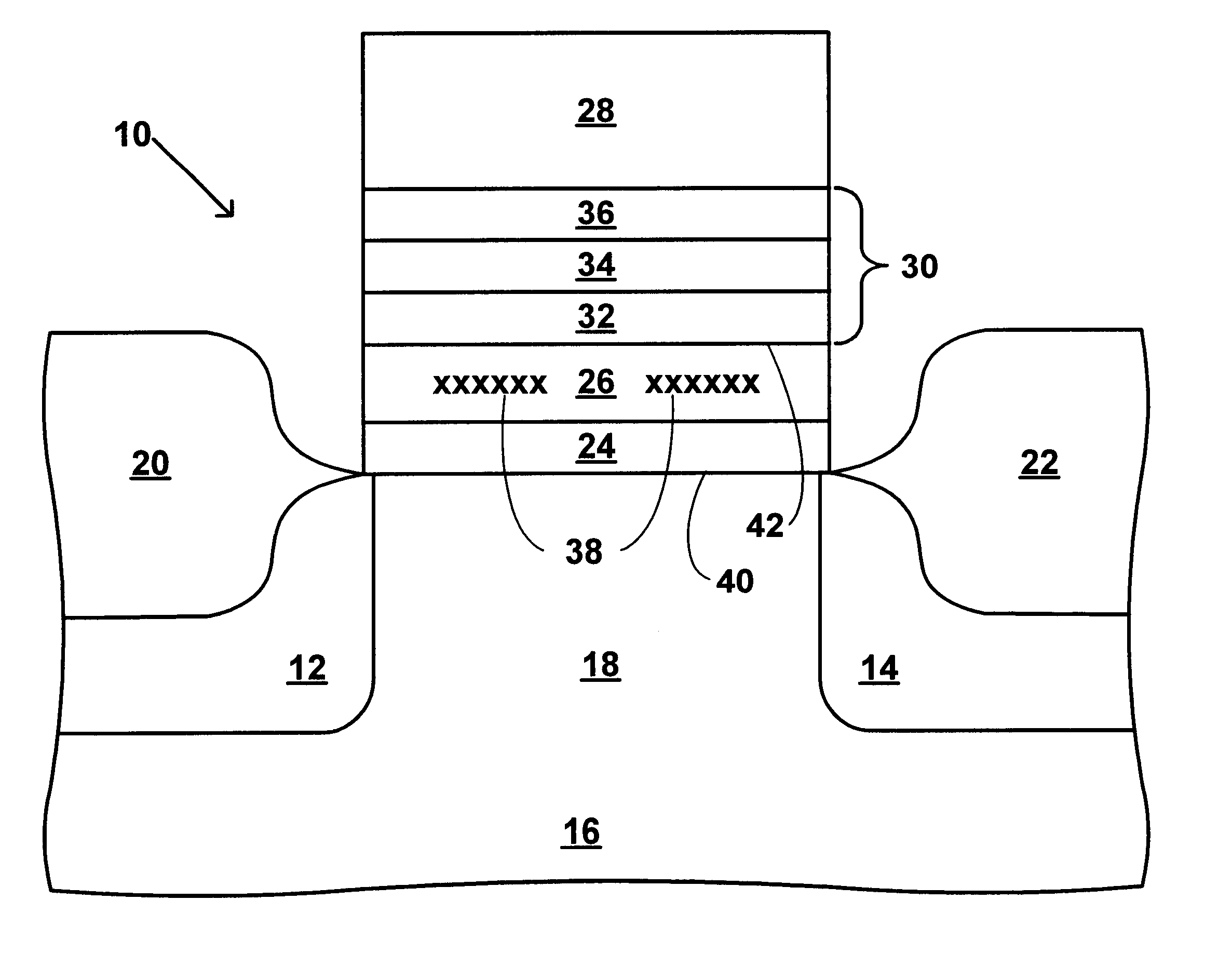

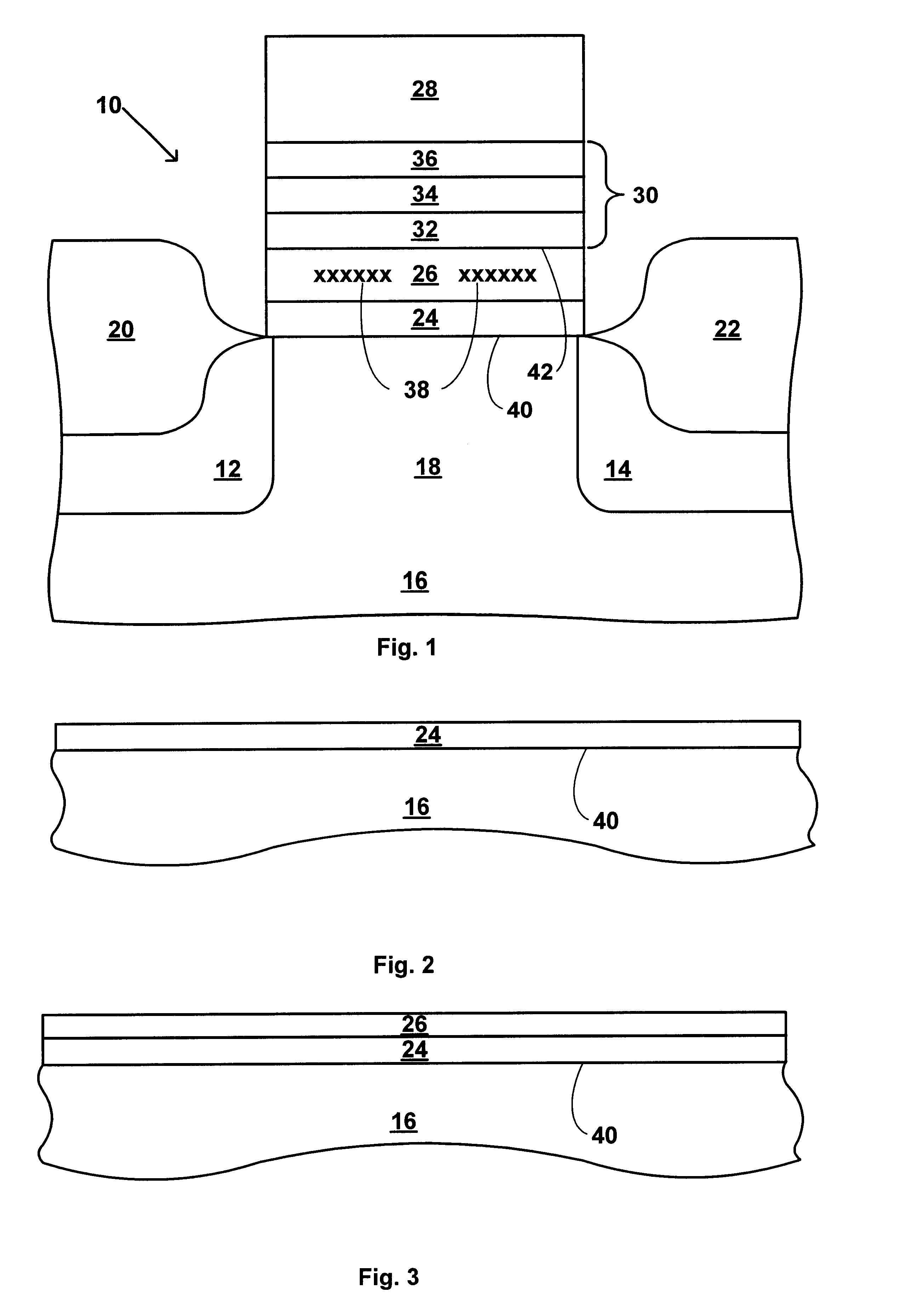

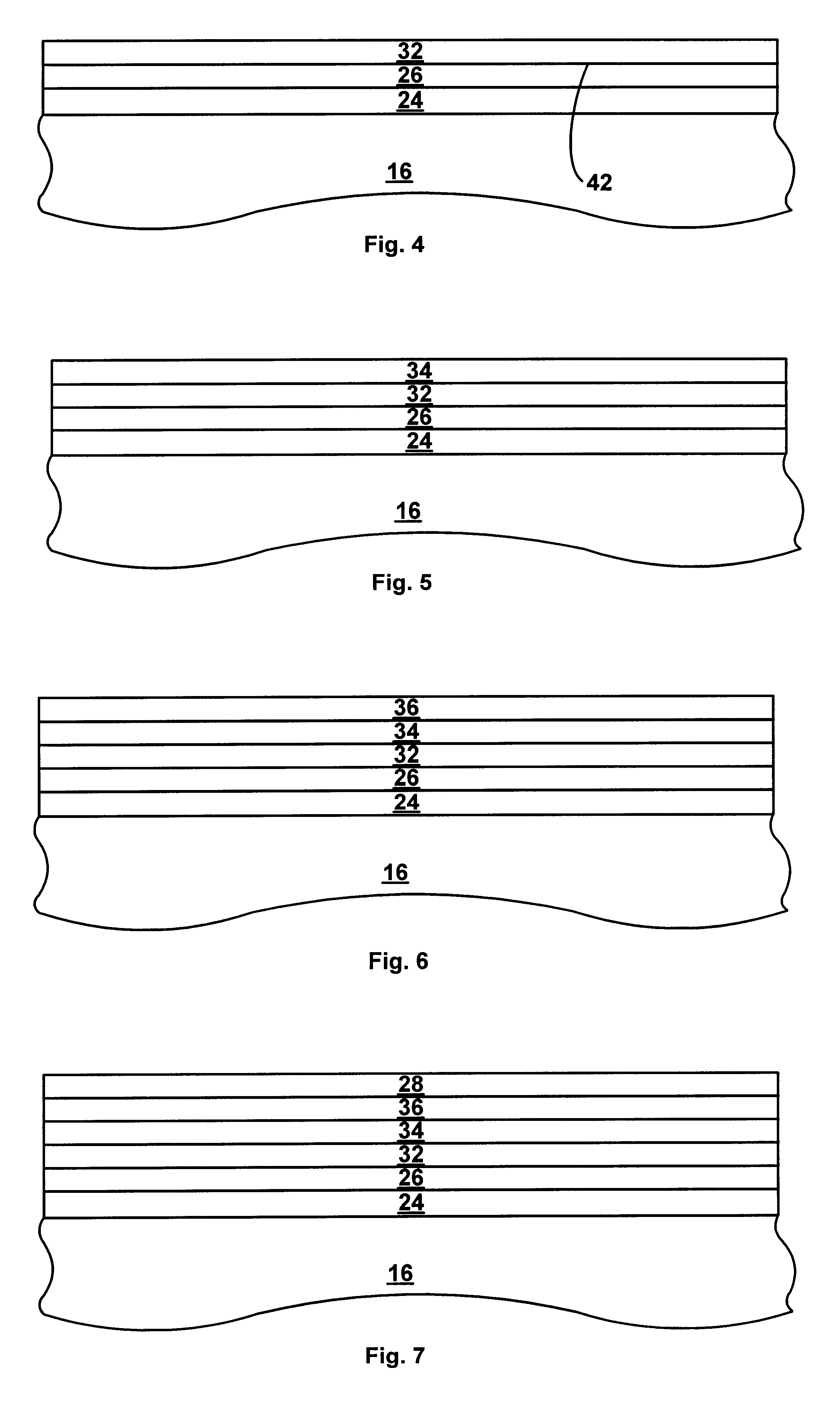

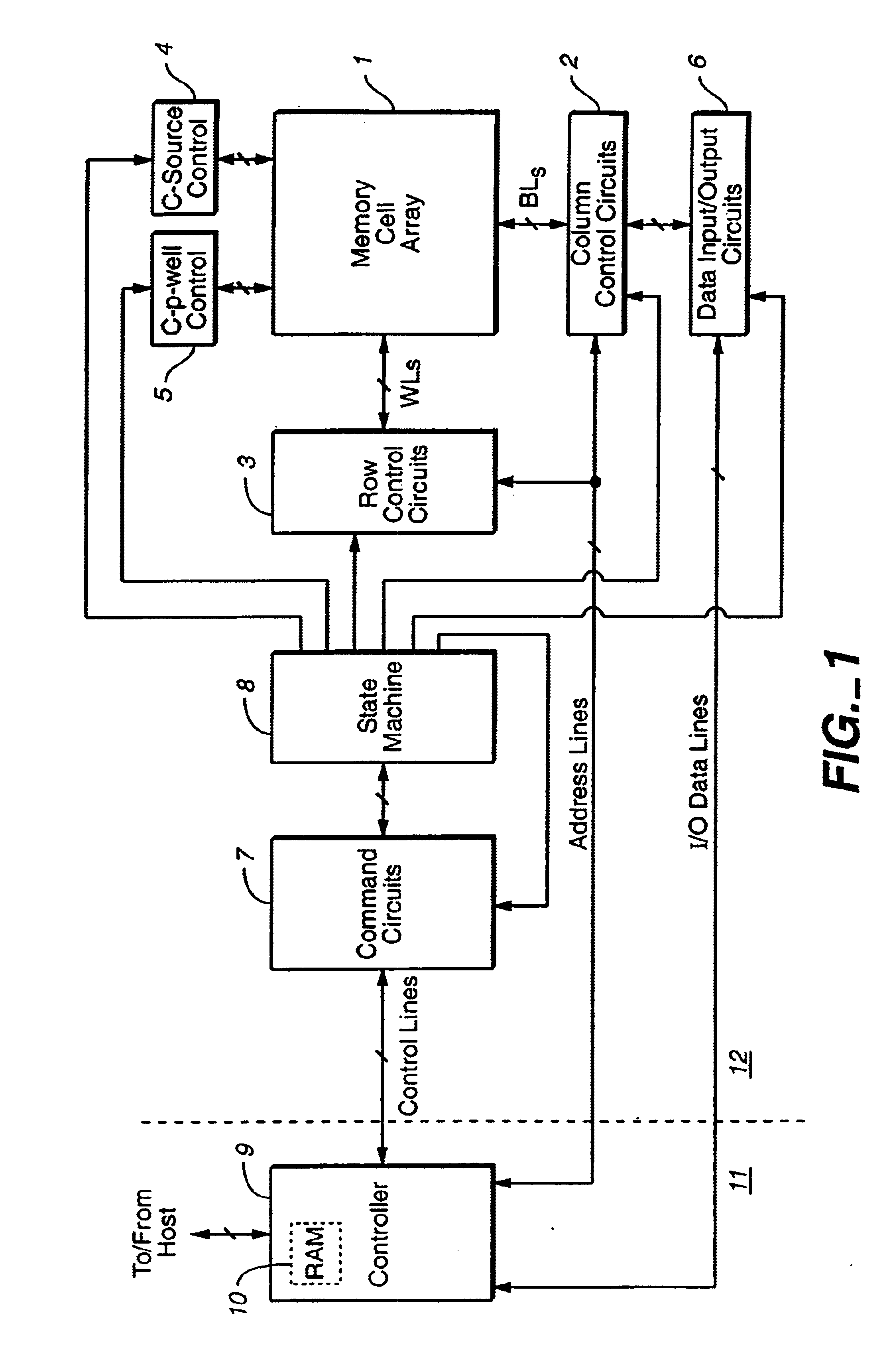

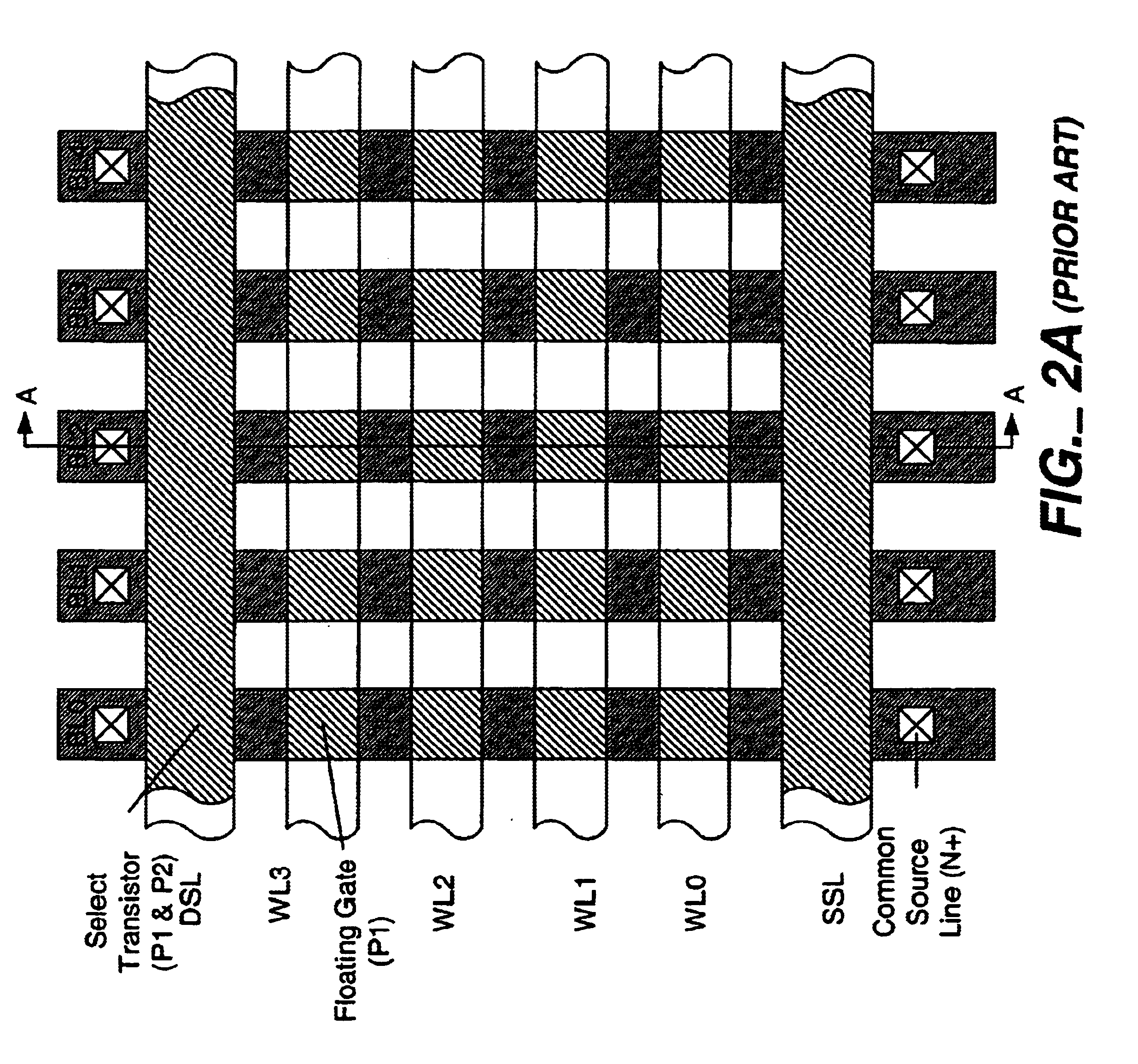

Use of high-K dielectric material for ONO and tunnel oxide to improve floating gate flash memory coupling

InactiveUS6617639B1Enhanced couplingReduce equivalent oxide thicknessTransistorSemiconductor/solid-state device manufacturingCouplingDielectric layer

A floating gate flash memory device including a substrate comprising a source region, a drain region, and a channel region positioned therebetween; a floating gate electrode positioned above the channel region and separated from the channel region by a tunnel dielectric material layer; and a control gate electrode positioned above the floating gate electrode and separated from the floating gate electrode by an interpoly dielectric layer, the interpoly dielectric layer comprising a modified ONO structure having a bottom dielectric material layer adjacent to the floating gate electrode, a top dielectric material layer adjacent to the control gate electrode, and a center layer comprising a nitride and positioned between the bottom dielectric material layer and the top dielectric material layer, in which the tunnel dielectric material layer, and at least one of the bottom dielectric material layer and the top dielectric material layer, comprise a high-K dielectric material.

Owner:MONTEREY RES LLC

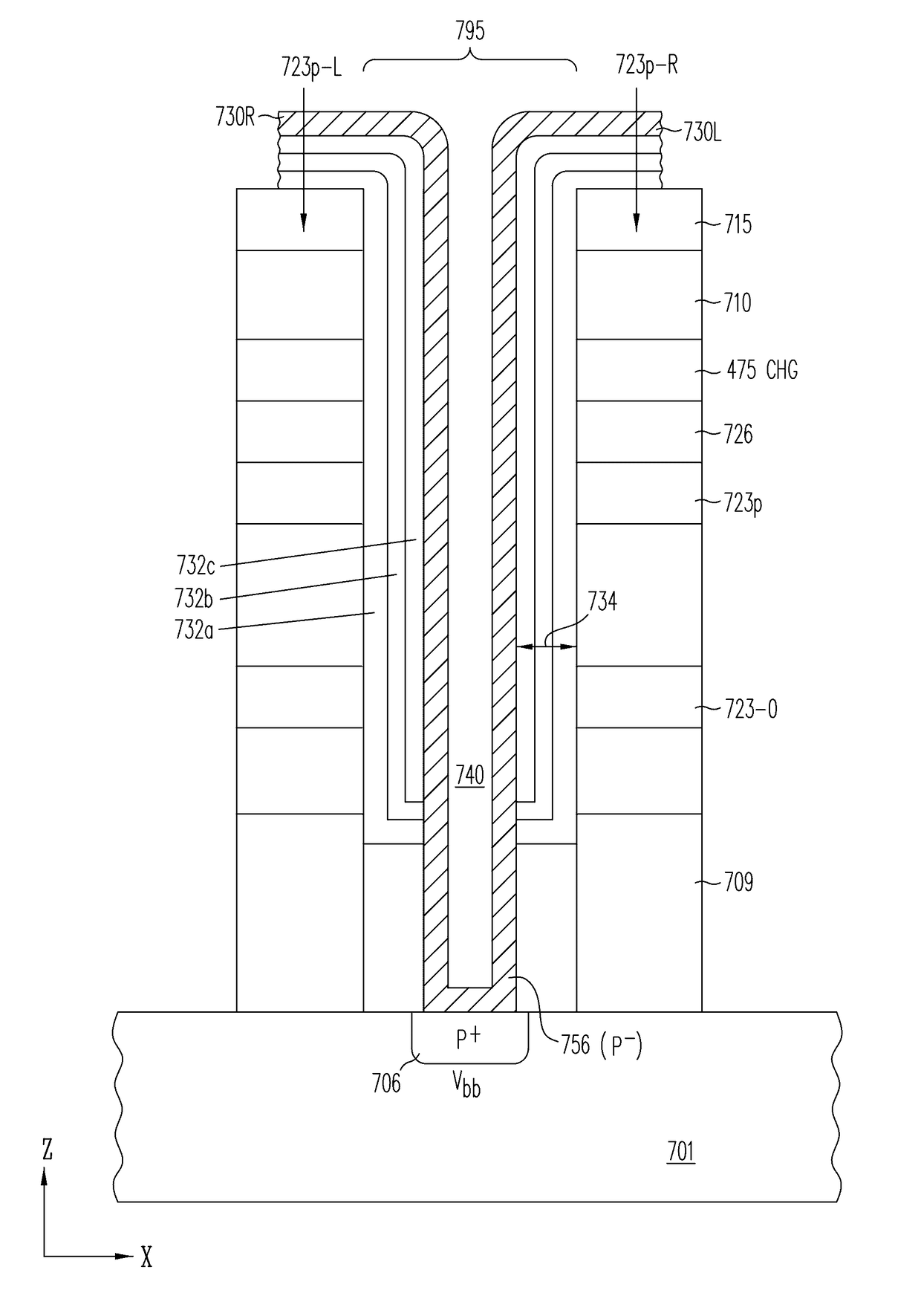

Three-dimensional vertical nor flash thin film transistor strings

ActiveUS20170148517A1Less resistanceFaster senseTransistorSemiconductor/solid-state device detailsEngineeringPolycrystalline silicon

A memory structure, includes (a) active columns of polysilicon formed above a semiconductor substrate, each active column extending vertically from the substrate and including a first heavily doped region, a second heavily doped region, and one or more lightly doped regions each adjacent both the first and second heavily doped region, wherein the active columns are arranged in a two-dimensional array extending in second and third directions parallel to the planar surface of the semiconductor substrate; (b) charge-trapping material provided over one or more surfaces of each active column; and (c) conductors each extending lengthwise along the third direction. The active columns, the charge-trapping material and the conductors together form a plurality of thin film transistors, with each thin film transistor formed by one of the conductors, a portion of the lightly doped region of an active column, the charge-trapping material between the portion of the lightly doped region and the conductor, and the first and second heavily doped regions. The thin film transistors associated with each active column are organized into one or more vertical NOR strings.

Owner:SUNRISE MEMORY CORP

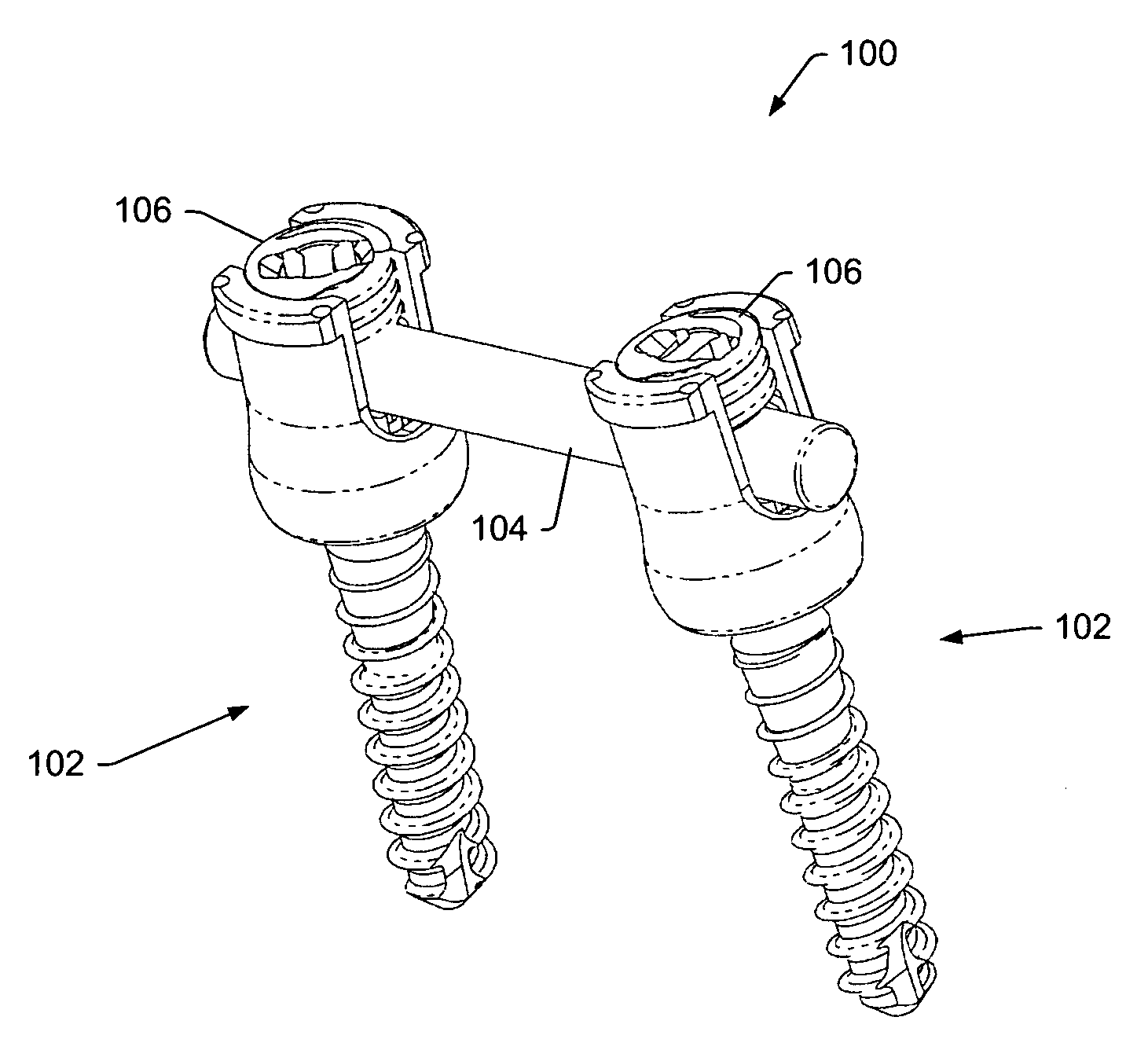

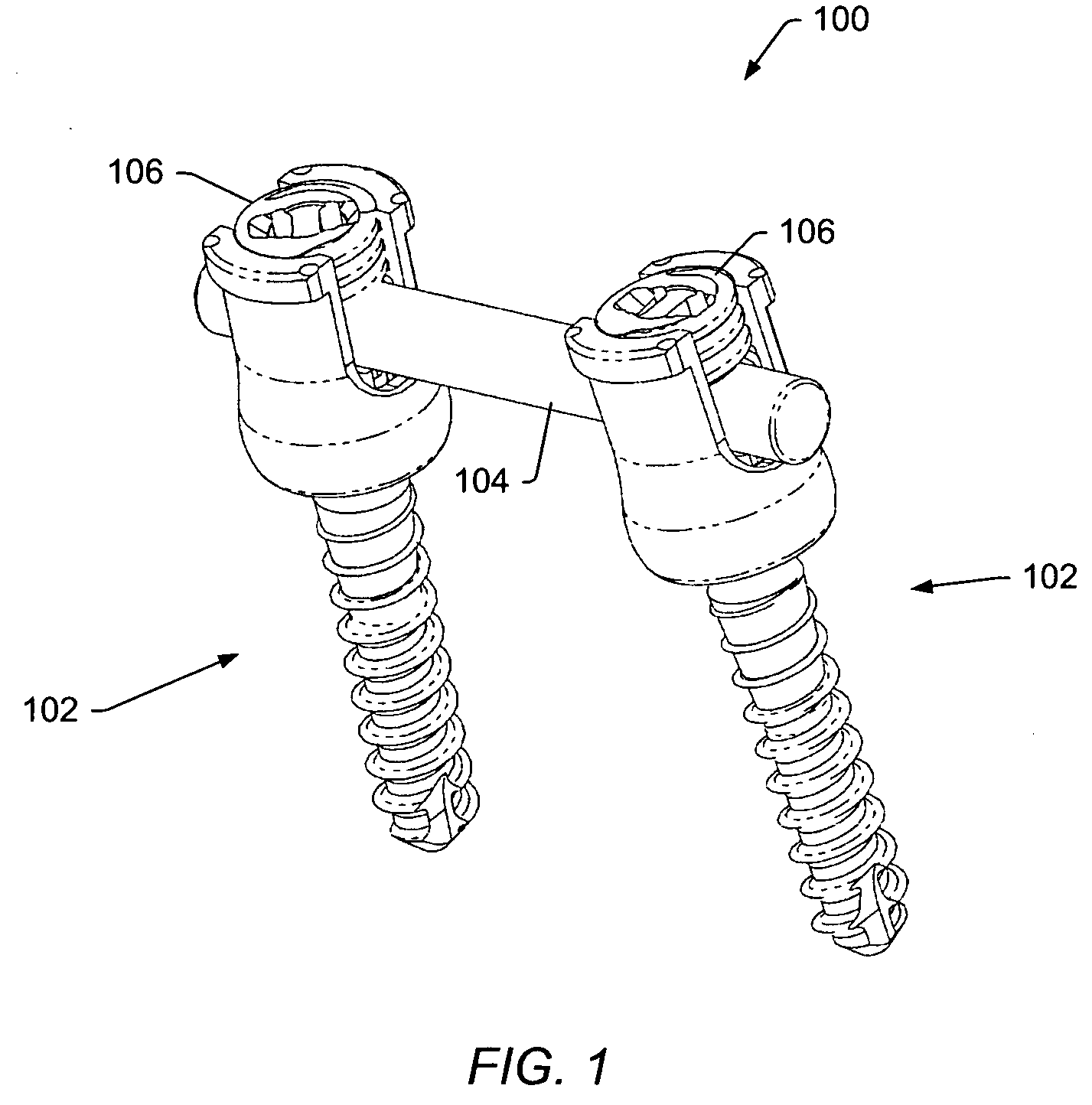

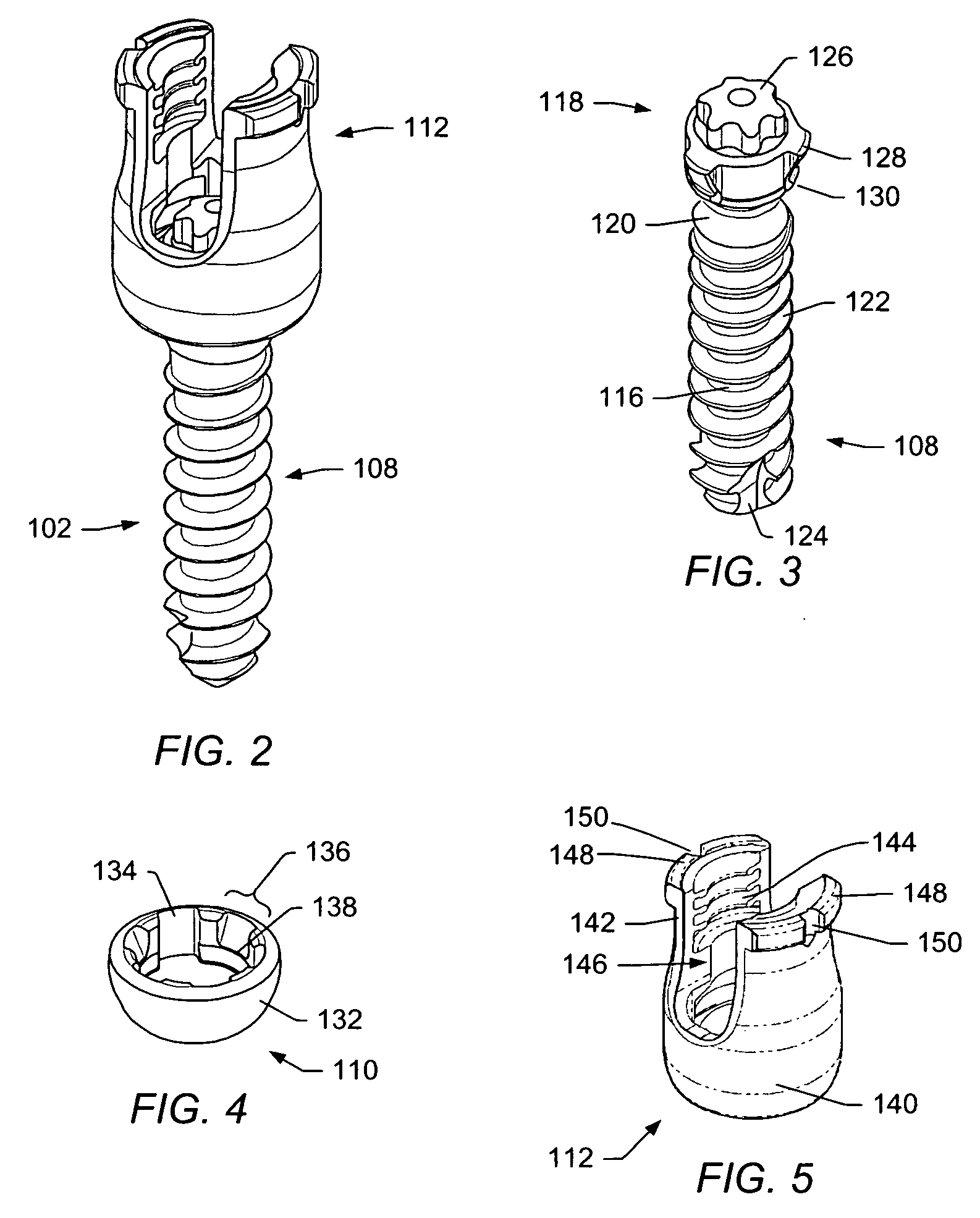

Instruments and methods for adjusting separation distance of vertebral bodies with a minimally invasive spinal stabilization procedure

ActiveUS20060122597A1Enhanced couplingInhibition of translationInternal osteosythesisDiagnosticsMinimally invasive proceduresCombined use

A spinal stabilization system may be formed in a patient. In some embodiments, a minimally invasive procedure may be used to form a spinal stabilization system in a patient. Bone fastener assemblies may be coupled to vertebrae. Each bone fastener assembly may include a bone fastener and a collar. Extenders may be coupled to the collar to allow for formation of the spinal stabilization system through a small skin incision. The extenders may allow for alignment of the collars to facilitate insertion of an elongated member in the collars. An elongated member may be positioned in the collars and a closure member may be used to secure the elongated member to the collars. An adjuster may be used in conjunction with the extenders to change a separation distance between the bone fastener assemblies.

Owner:ZIMMER BIOMET SPINE INC

Multi-layer opto-electronic substrates with electrical and optical interconnections and methods for making

InactiveUS6845184B1Reduce area requirementsOptical coupling efficiency improvementSemiconductor/solid-state device detailsSolid-state devicesElectricityThin layer

Opto-electrical systems having electrical and optical interconnections formed in thin layers are disclosed. In one set of preferred embodiments, optical signals are conveyed between layers by respective vertical optical couplers disposed on the layers. In other preferred embodiments, optical signals are conveyed by stack optical waveguide coupling means. Yet other preferred embodiments have electrical via means formed in one or more layers to covey electrical signals between two or more layers.

Owner:FUJITSU LTD

Implantable medical device with contactless power transfer housing

InactiveUS20050288743A1Minimizing surgeryMinimizing subsequent treatmentElectrotherapyElectromagnetic wave systemTransmitted powerElectrical battery

A transcutaneous recharging system for providing power to an implantable medical device comprises a primary side circuit for transmitting power in the form of magnetic flux; and a secondary side circuit integral to the implantable medical device for receiving the power transmitted from the primary side circuit and for providing the received power to recharge a battery in the implantable medical device, wherein the primary and secondary side circuits are not physically coupled. A variety of attachment configurations are disclosed for attaching and shielding the secondary circuit directly onto the housing of the implantable medical device, inclusive of flexible printed circuit coils and wire coils recessed into helical notches.

Owner:AHN IN +2

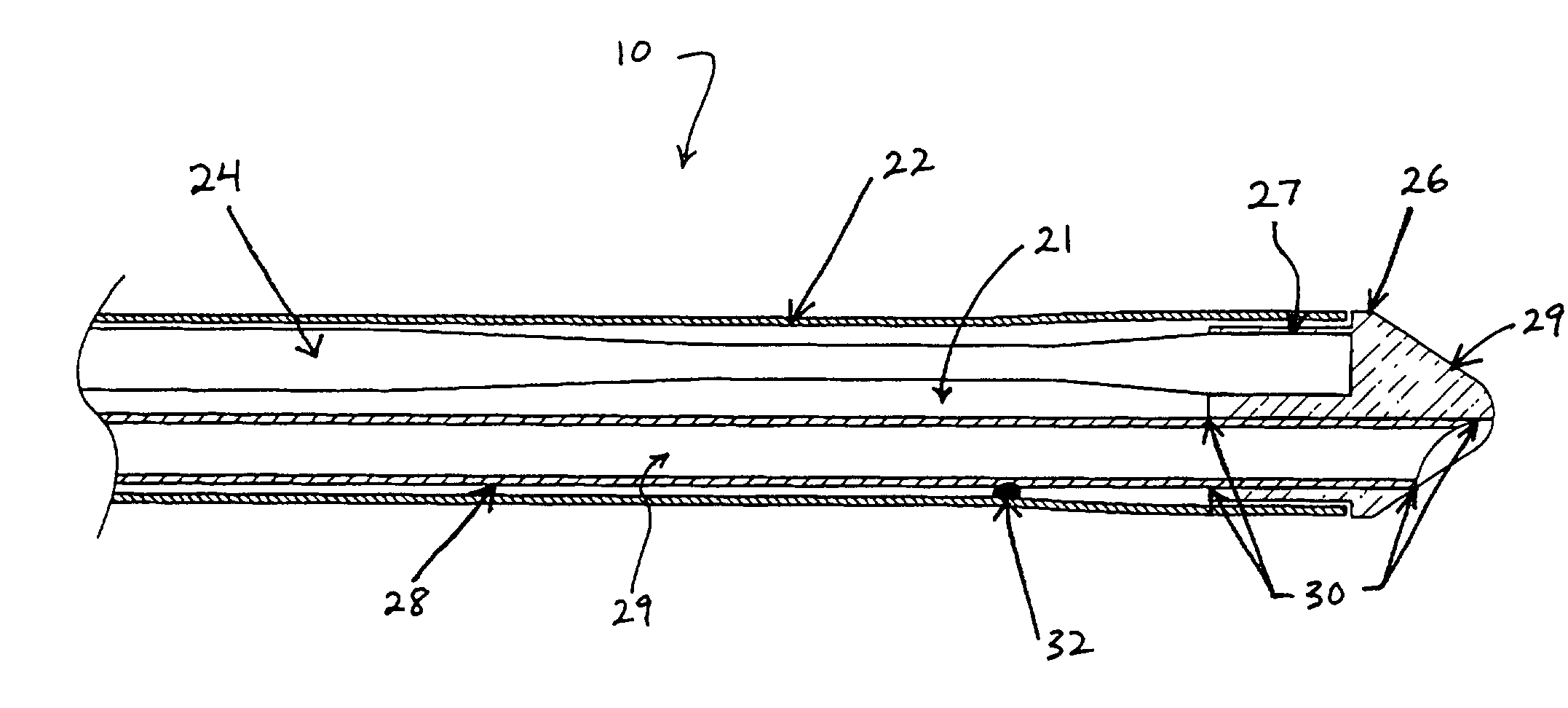

Fluid-assisted medical devices, systems and methods

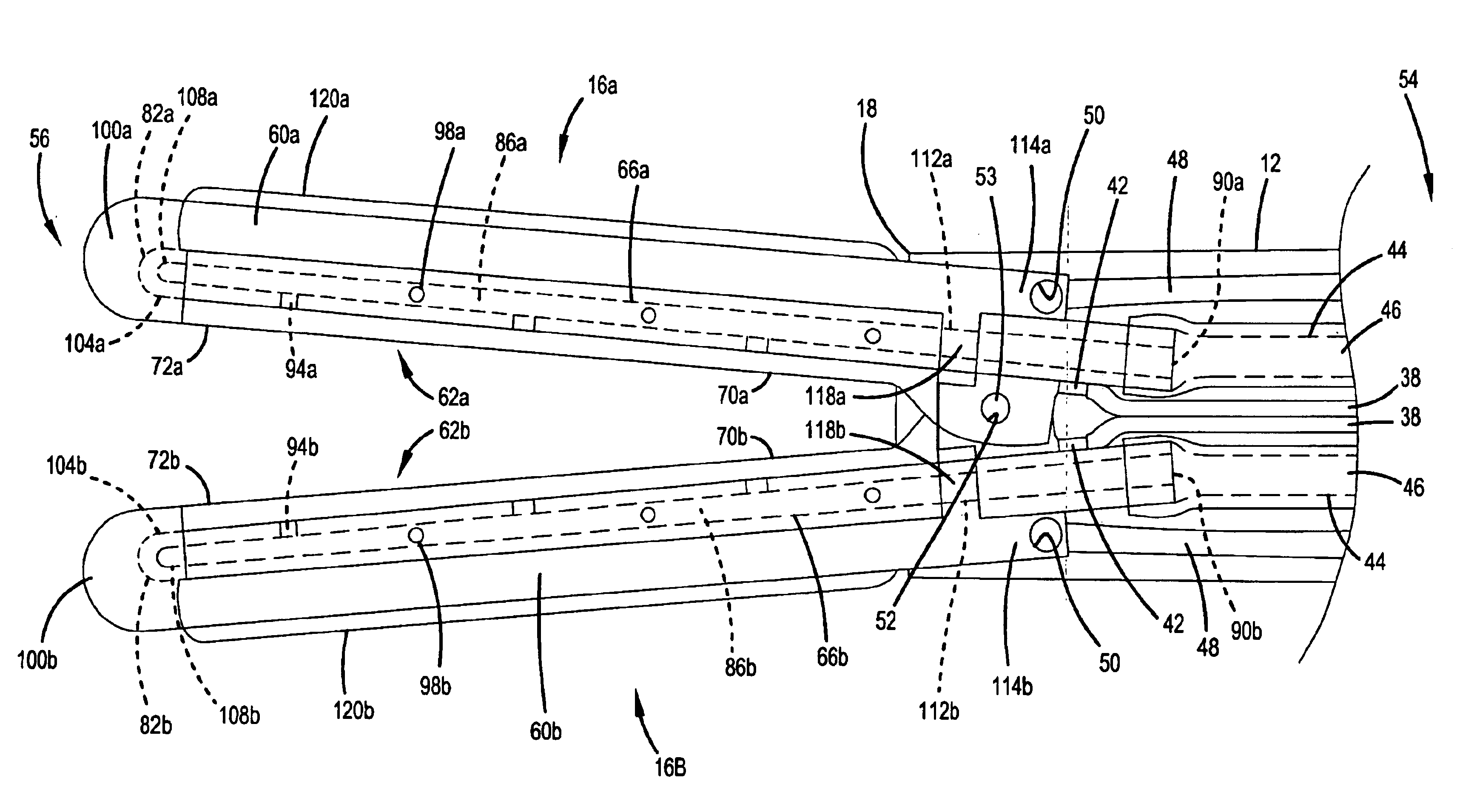

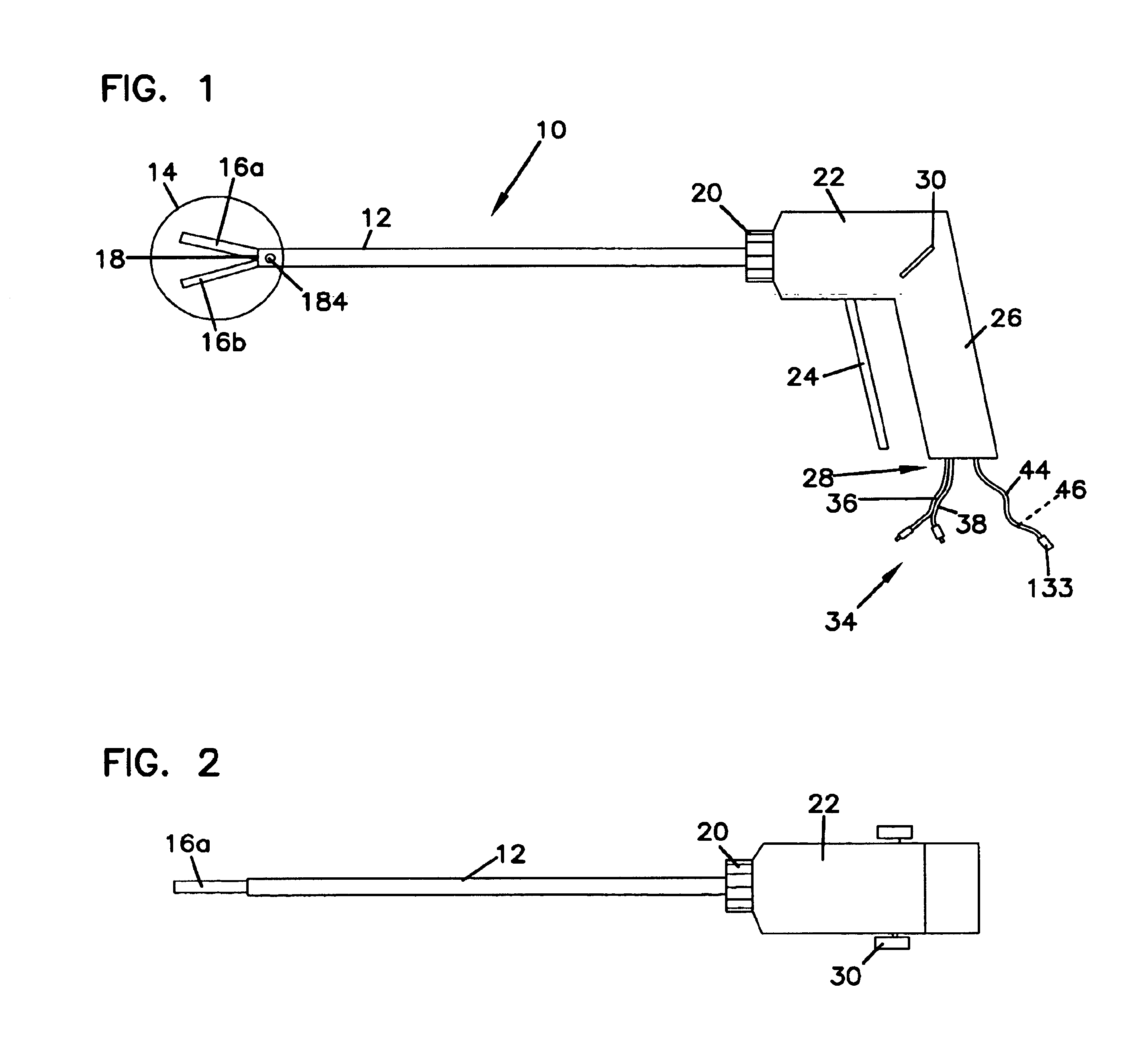

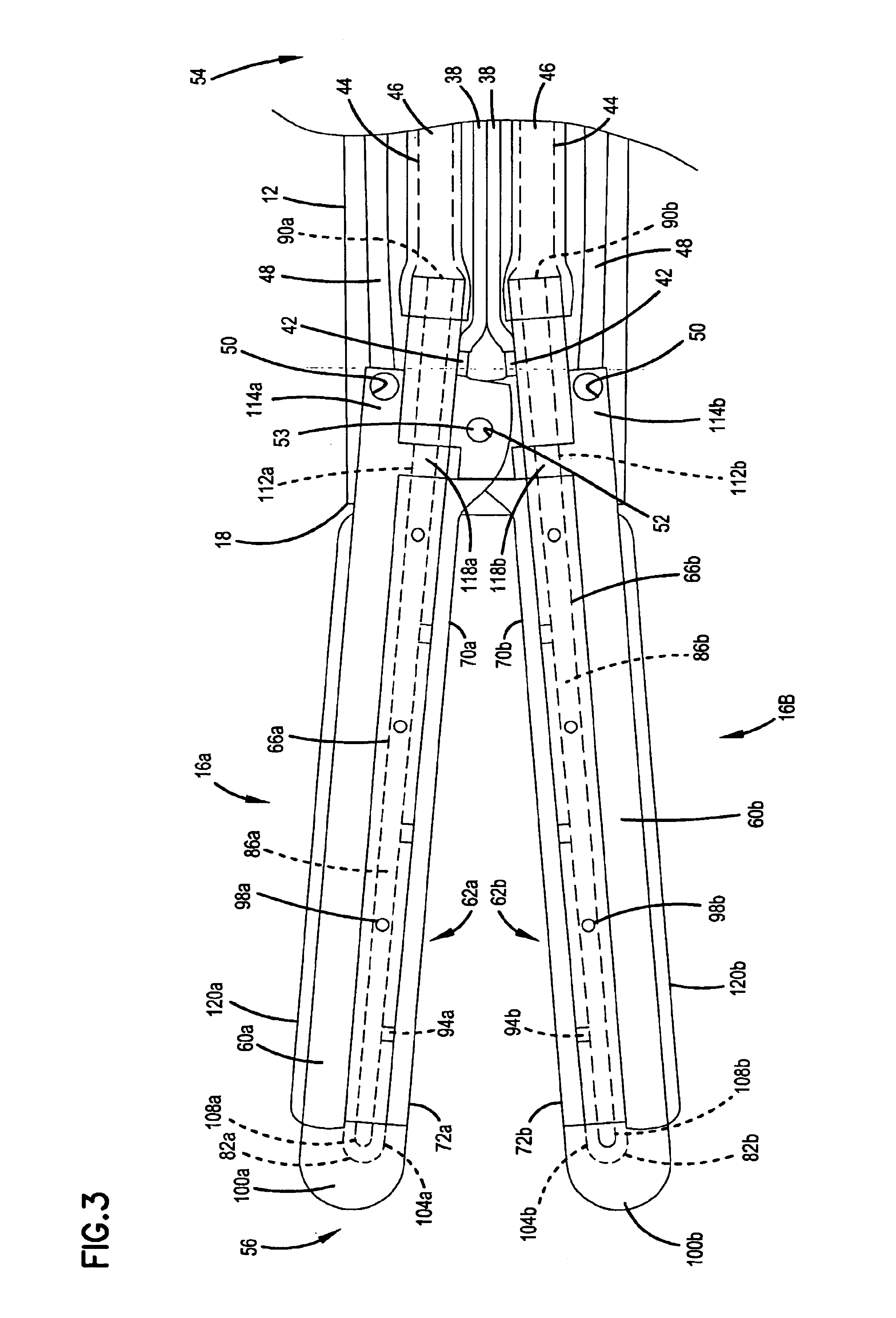

InactiveUS20060116675A1Improve uniformityEnhanced couplingDiagnosticsCatheterElectricityMedical device

Surgical devices, systems and methods for treating tissue are provided. An exemplary surgical device comprises a tip portion including first and second jaws each having a tissue grasping surface, at least one of the jaws being movable toward the other jaw. The tissue grasping surface of each jaw has includes an electrically insulative surface. The device also includes first and second electrodes connectable to different terminals of an RF generator to generate electrical current flow therebetween, with each of the electrodes having an electrode surface. One of the electrode surfaces is located on one of the jaws separated from one edge of the tissue grasping surface, and the other of the electrode surfaces is located on one or the other of the jaws separated from the other edge of the tissue grasping surface. The device also includes at least one fluid passage being connectable to a fluid source.

Owner:MEDTRONIC ADVANCED ENERGY

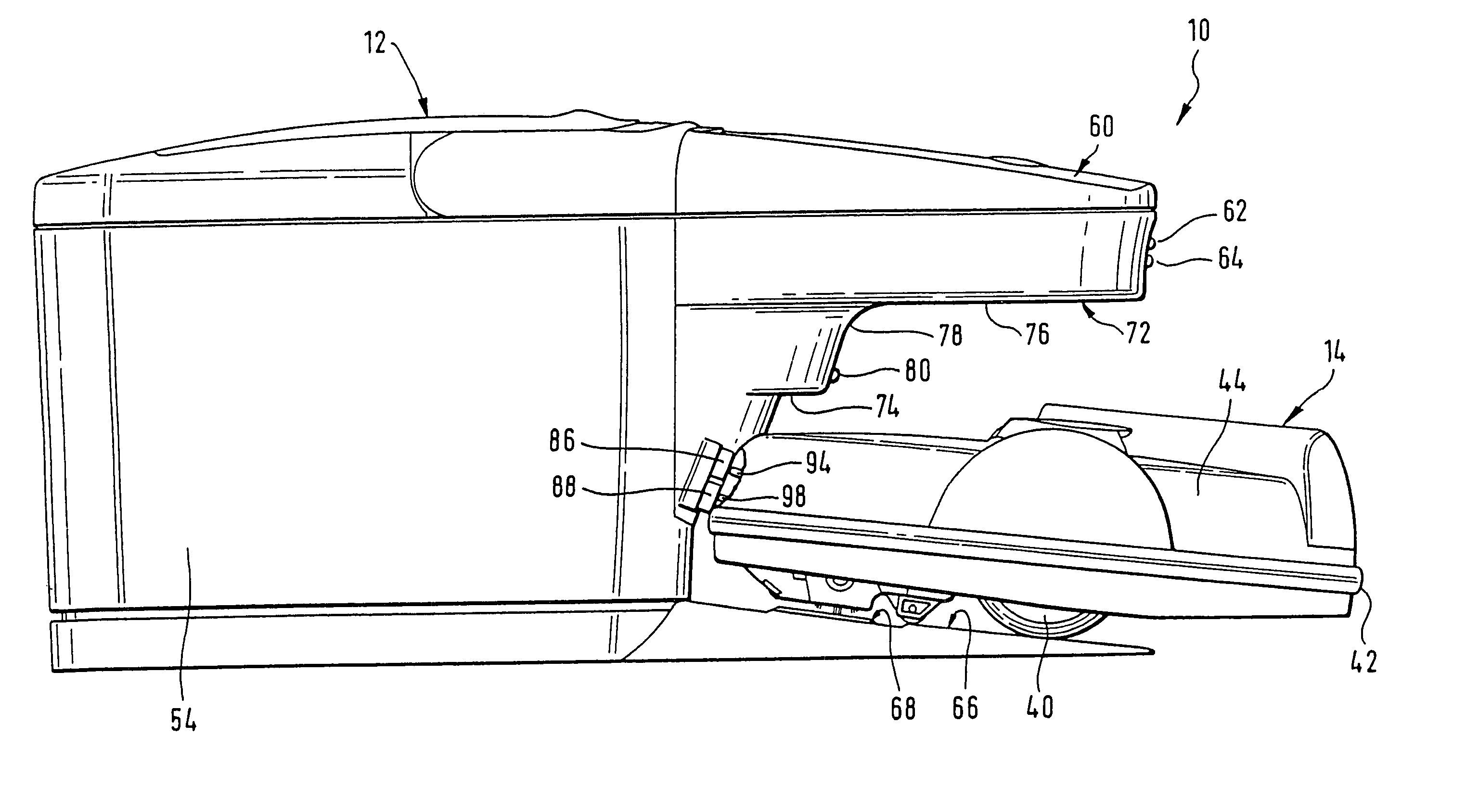

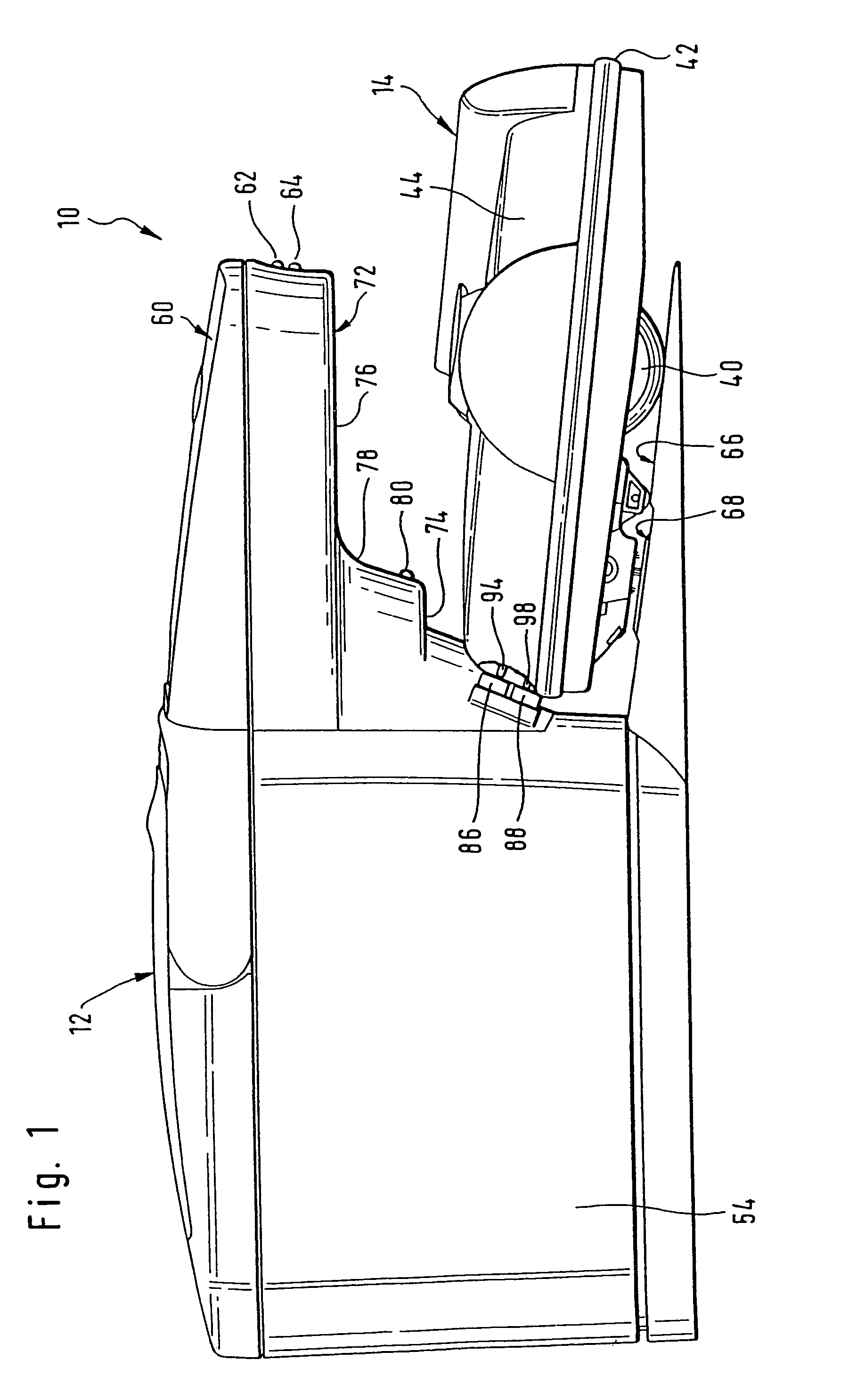

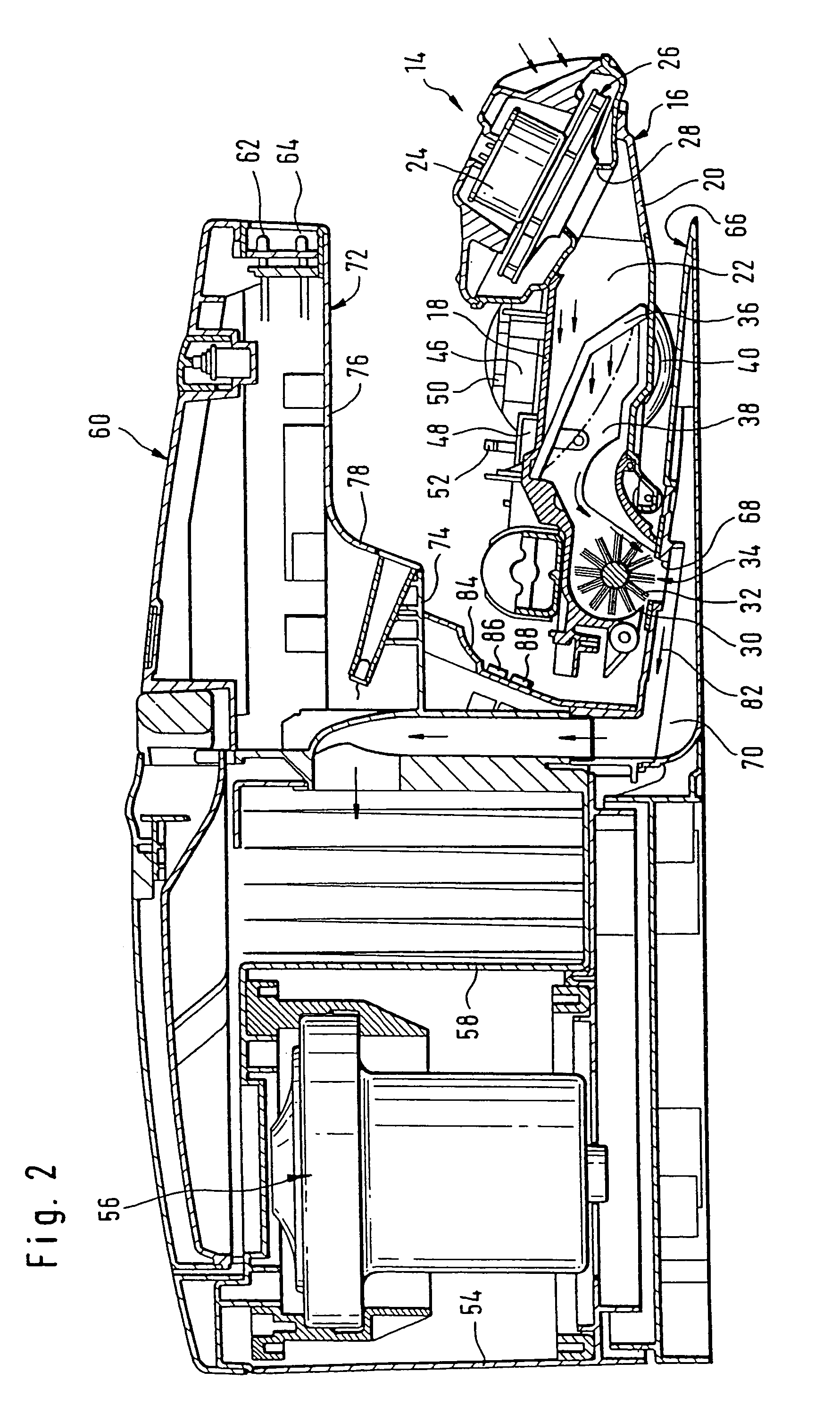

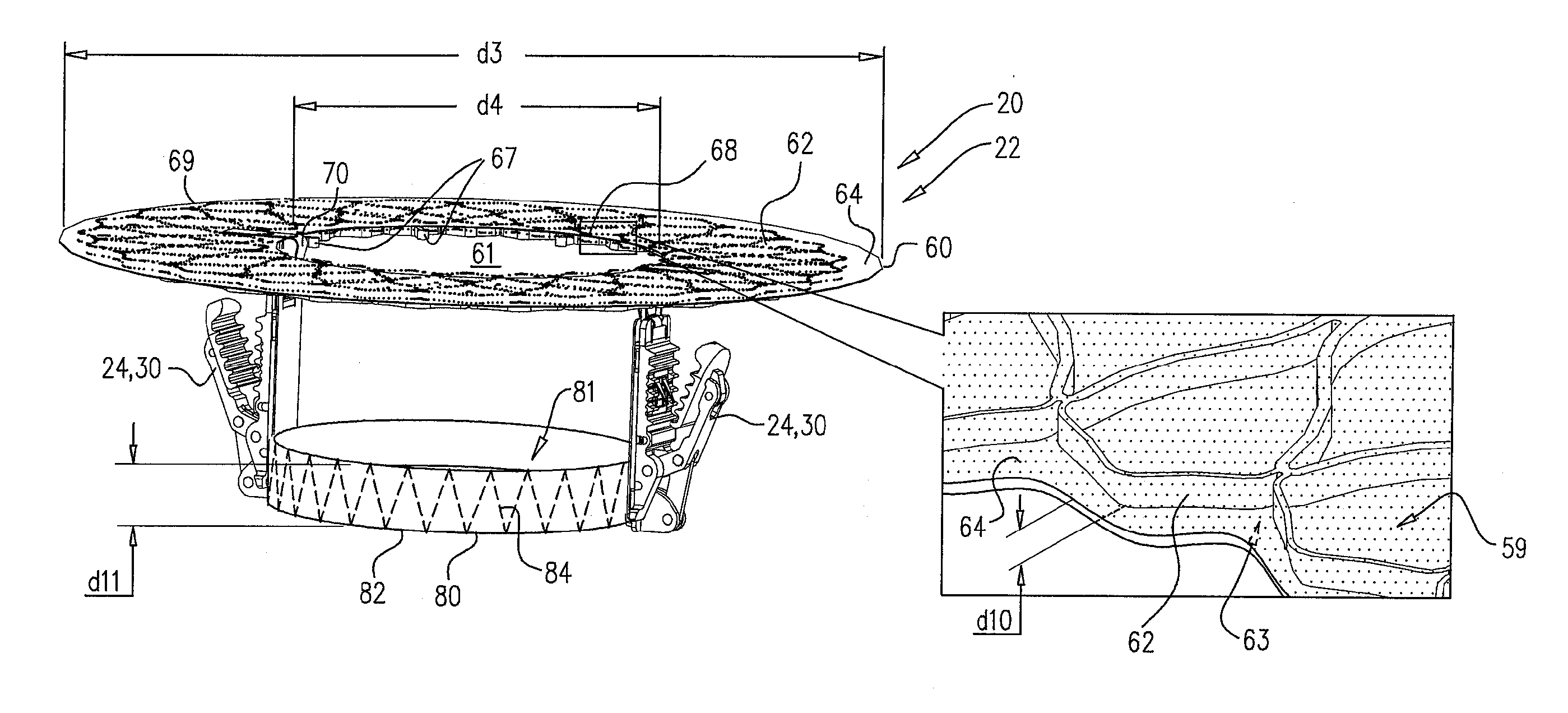

Floor treatment system with self-propelled and self-steering floor treatment unit

InactiveUS7055210B2Efficient transferEnhanced couplingSuction filtersCoupling contact membersElectricityCoupling

Owner:ALFRED KARCHER GMBH & CO KG

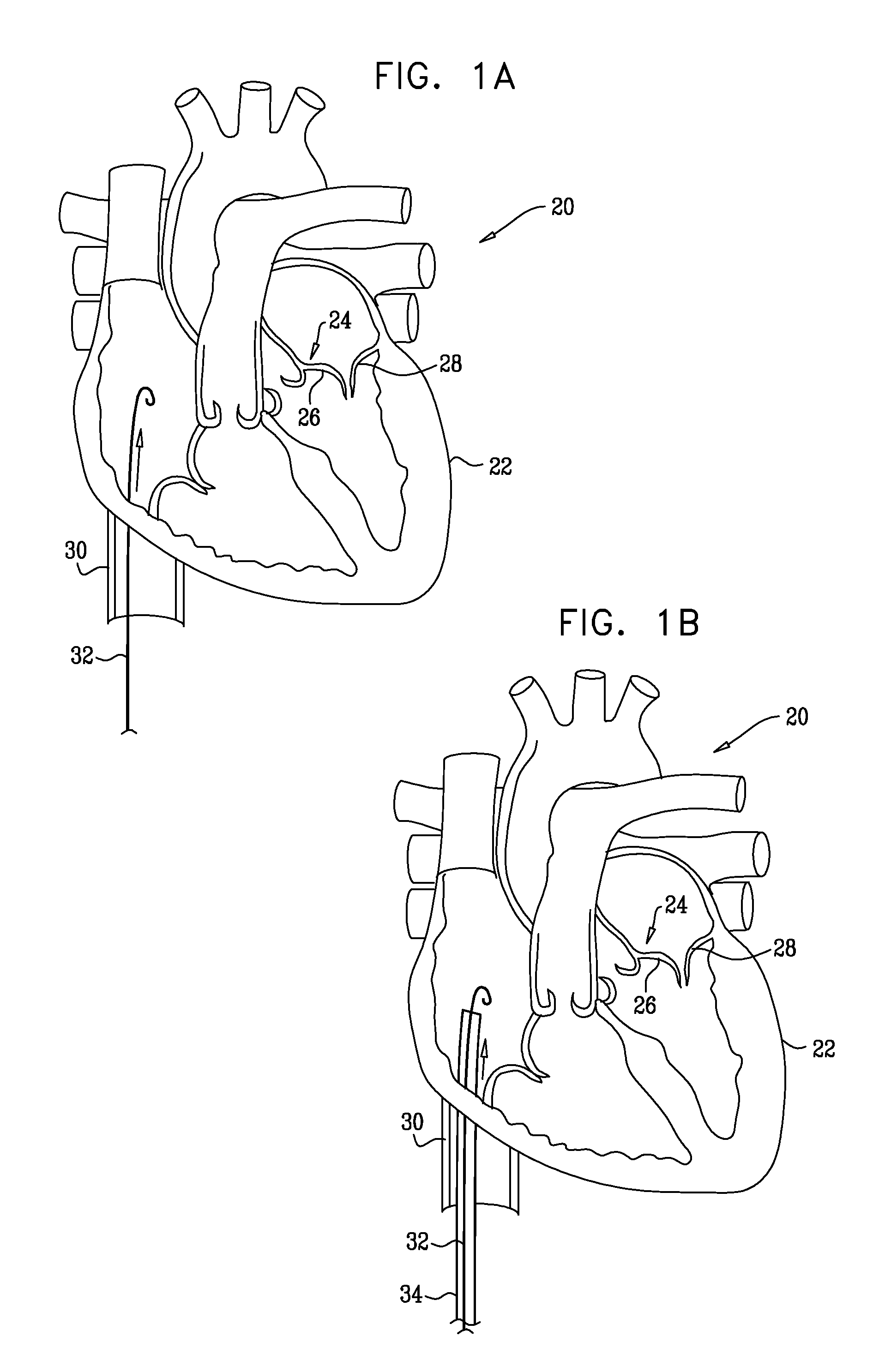

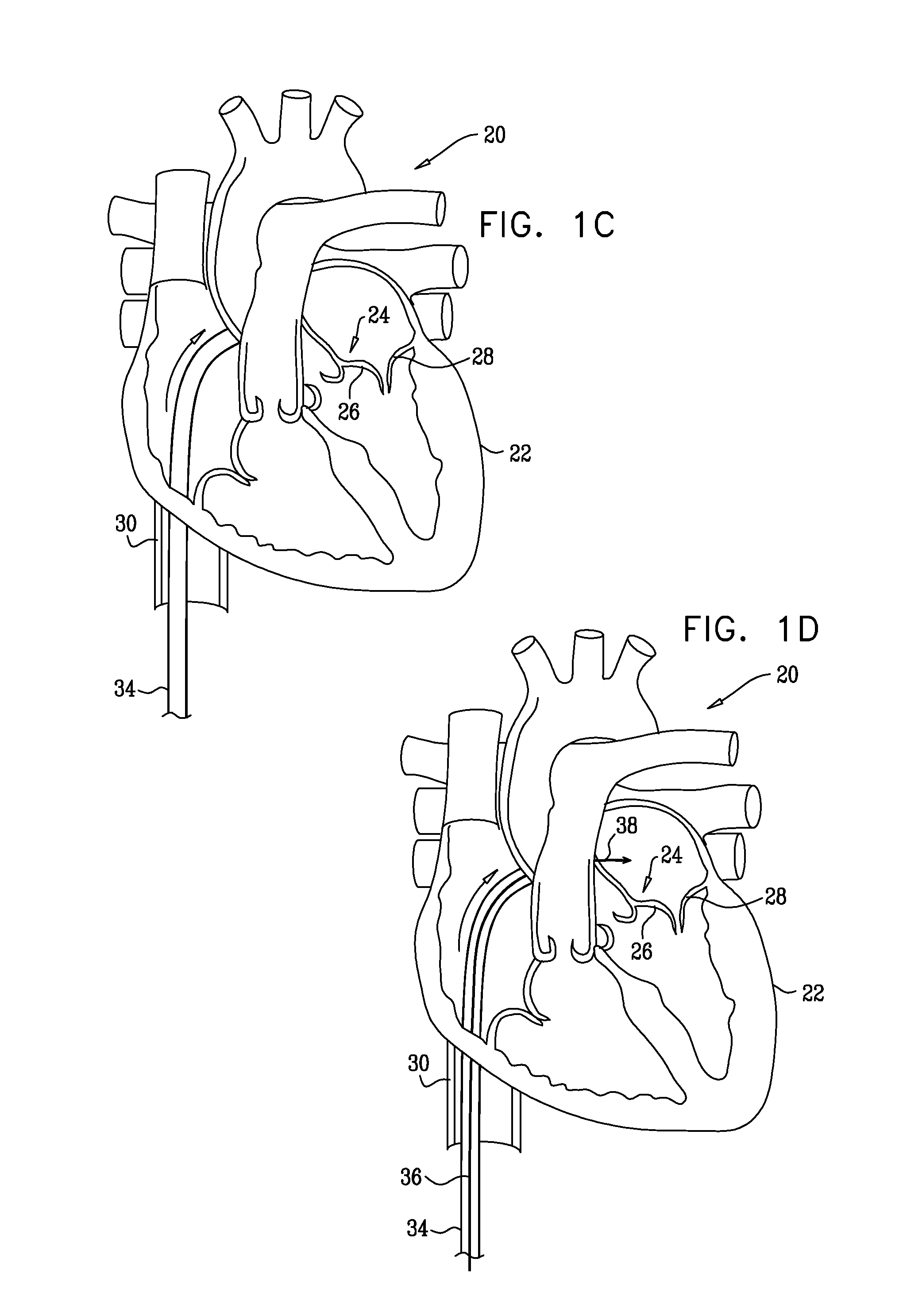

Percutaneous mitral valve replacement and sealing

ActiveUS20140257475A1Enhanced couplingStentsAnnuloplasty ringsBioprosthetic mitral valve replacementBiomedical engineering

Apparatus is provided for use with a prosthetic valve for implantation at a native valve of a subject, the native valve including at least one native leaflet, the apparatus including (1) a prosthetic valve support, including (a) an upstream support portion, being configured to be placed against an upstream side of the native valve, and having an inner perimeter that defines an opening that is configured to receive the prosthetic valve, and (b) at least one clip (i) comprising at least two clip arms and a clip-controller interface, the clip-controller interface being coupled to at least one of the clip arms, and (ii) being configured to be coupled to a native leaflet of the native valve; and (2) at least one clip controller, reversibly couplable to the clip-controller interface, and configured to facilitate opening and closing of the clip. Other embodiments are also described.

Owner:CARDIOVALVE LTD

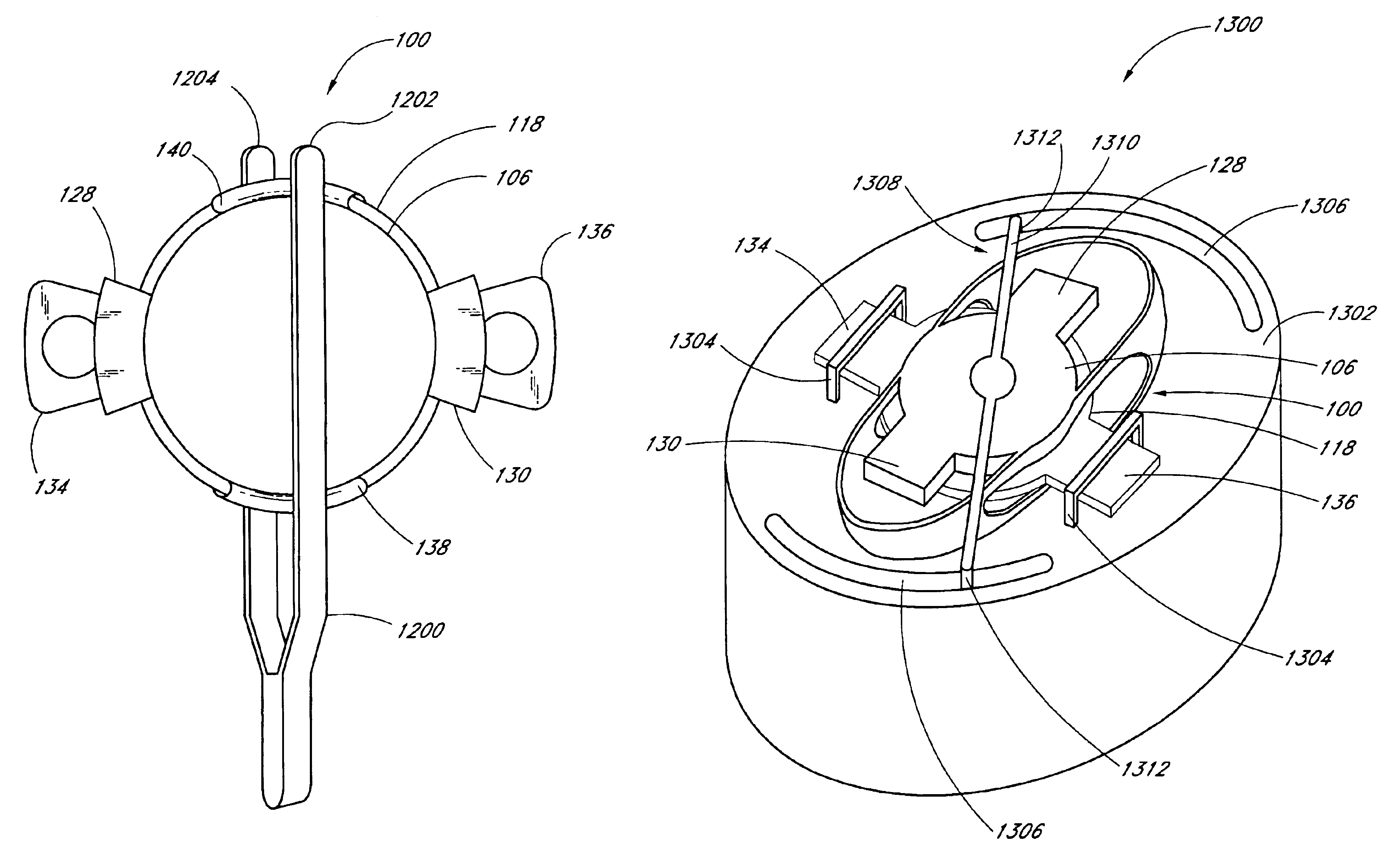

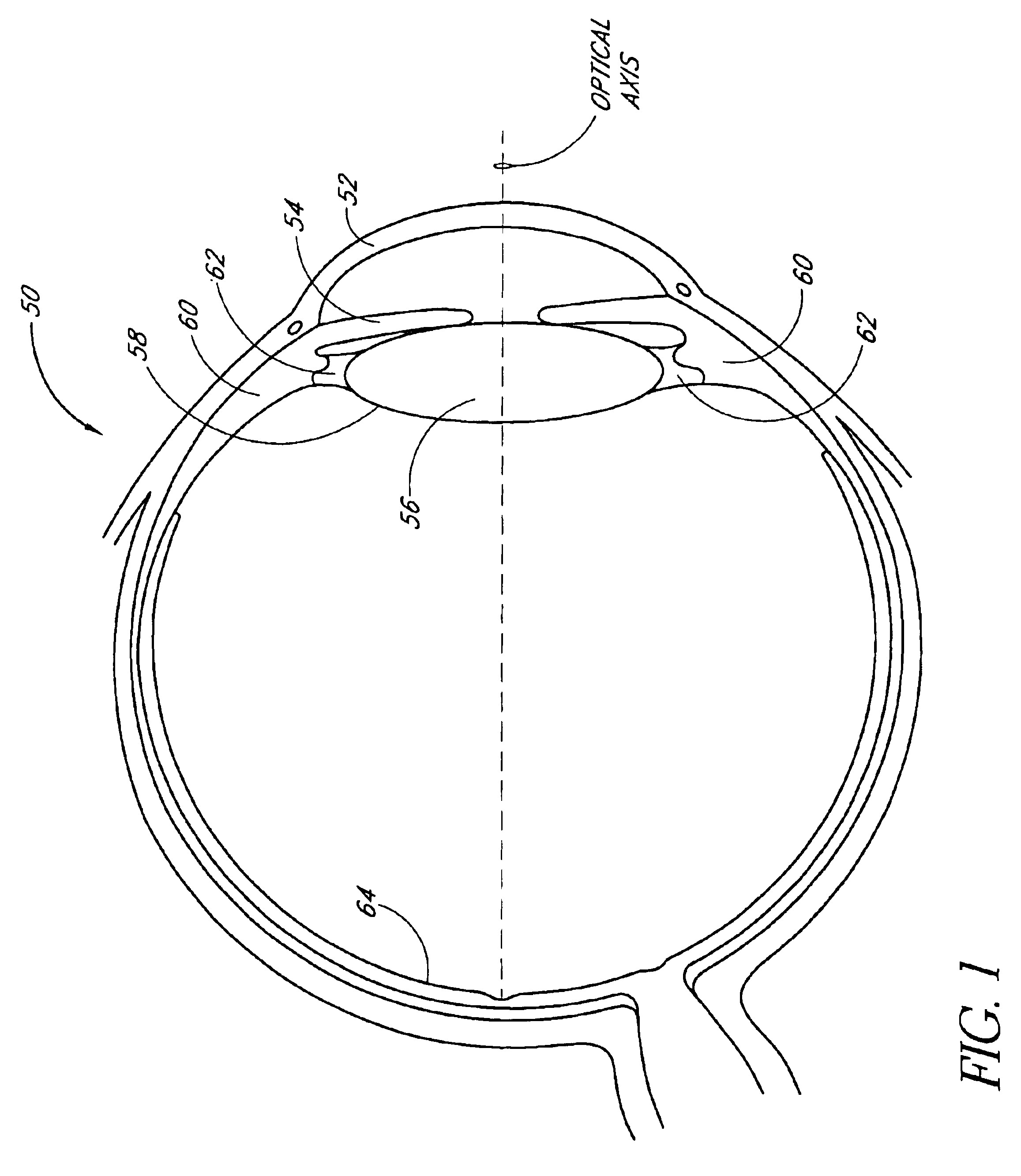

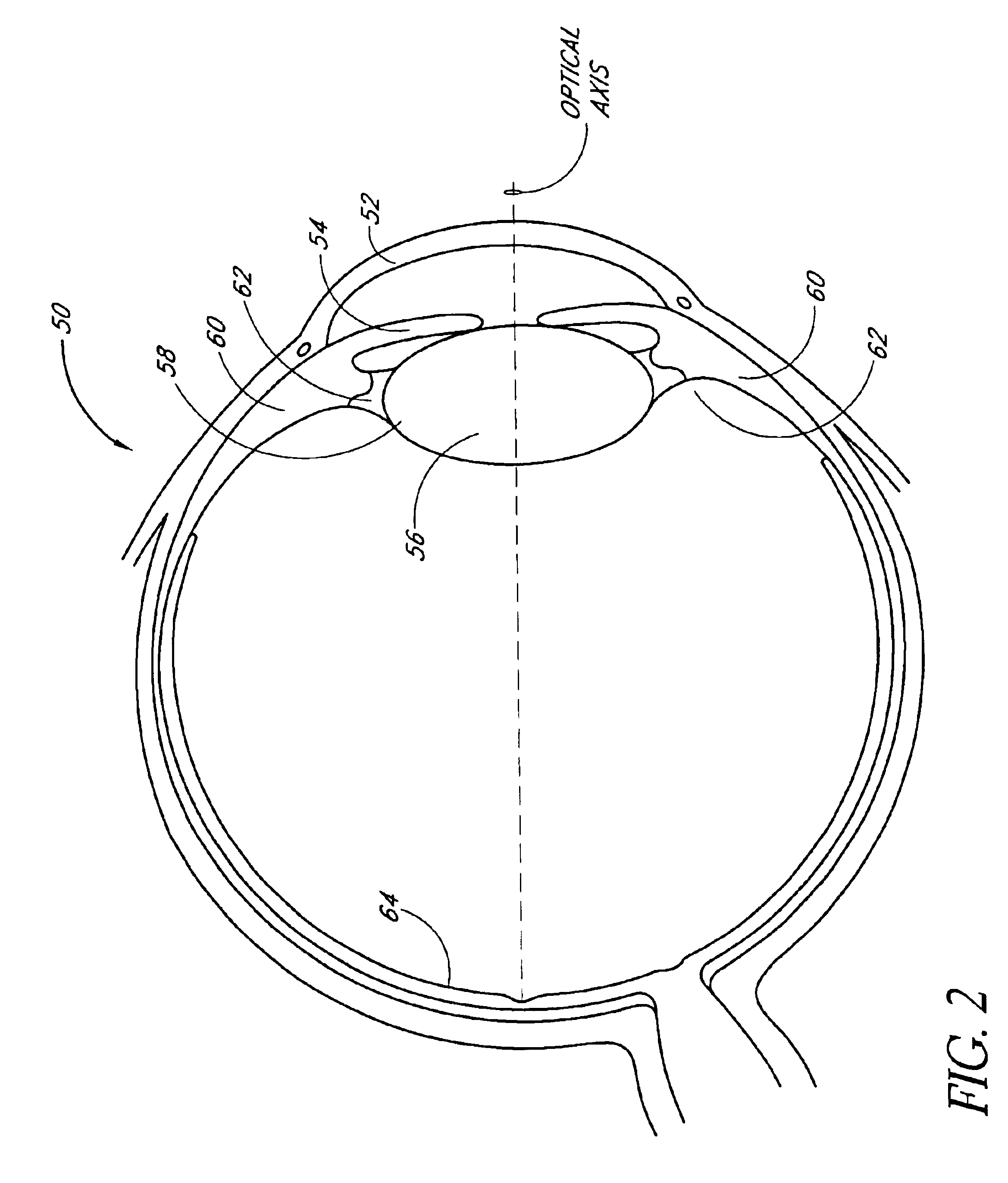

Method of preparing an intraocular lens for implantation

InactiveUS6884261B2SeparationEasy to separateEye surgeryOptical articlesIntraocular lensOptical axis

There is disclosed a method of preparing an accommodating intraocular lens having an optical axis for subsequent implantation. The method comprises providing an intraocular lens having first and second viewing elements interconnected by plural members. At least a portion of the members are disposed from the optical axis by a distance greater than a periphery of at least one of the viewing elements. The distance is measured orthogonal to the optical axis. The method further comprises drawing the members inwardly toward the optical axis by relatively rotating the first and second viewing elements. The method further comprises increasing the separation between the viewing elements along the optical axis while drawing the members inwardly.

Owner:VISIOGEN

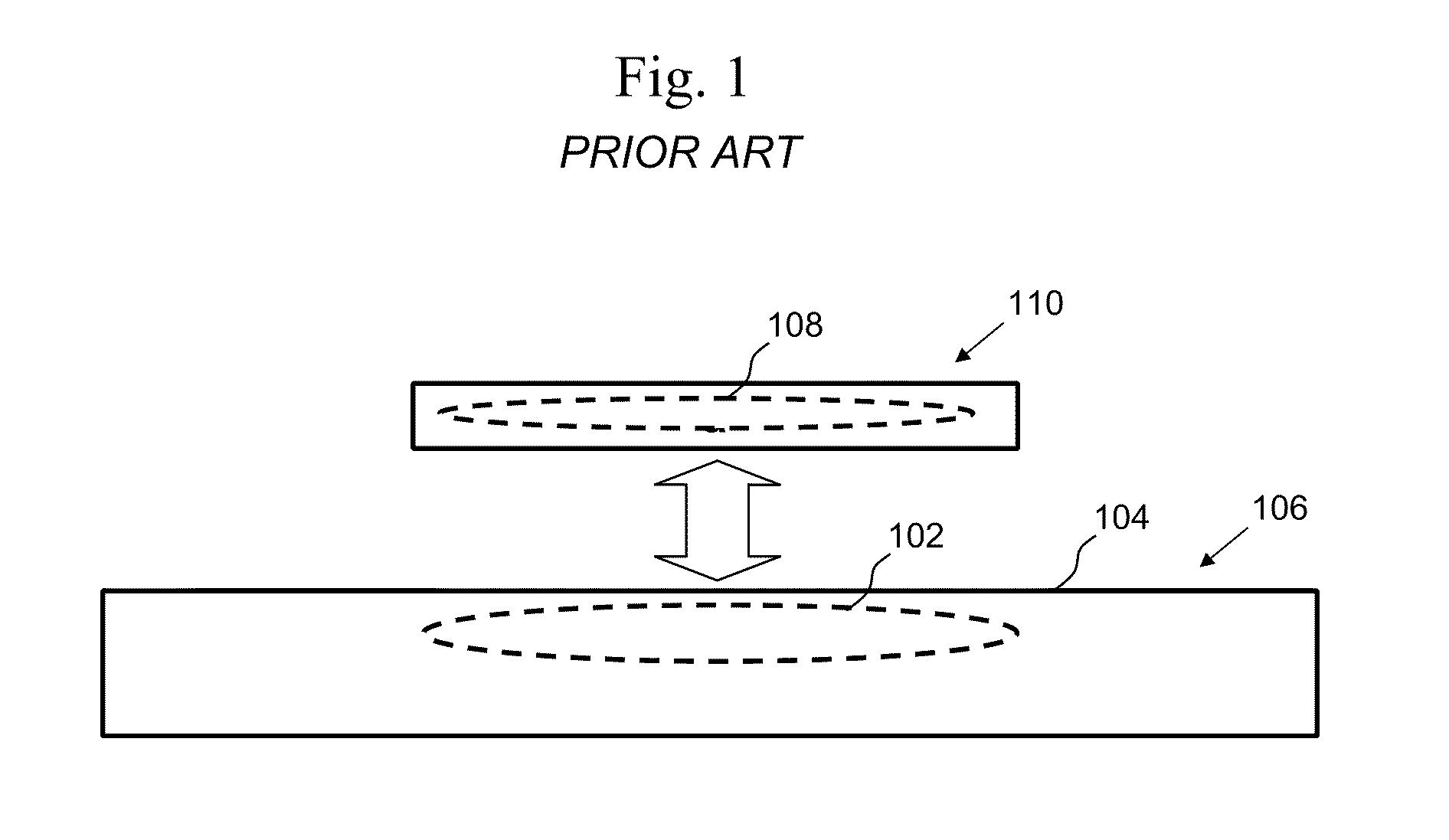

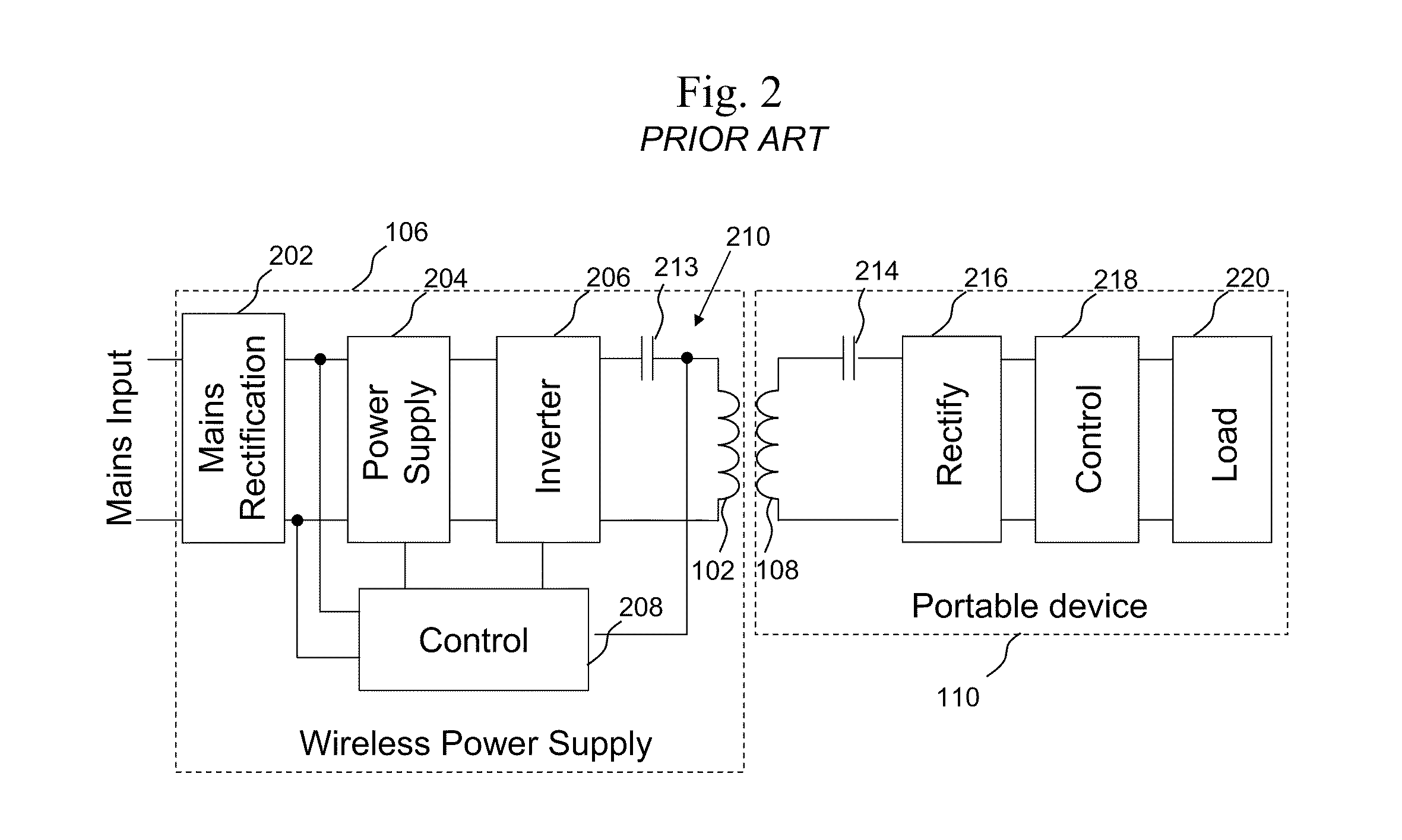

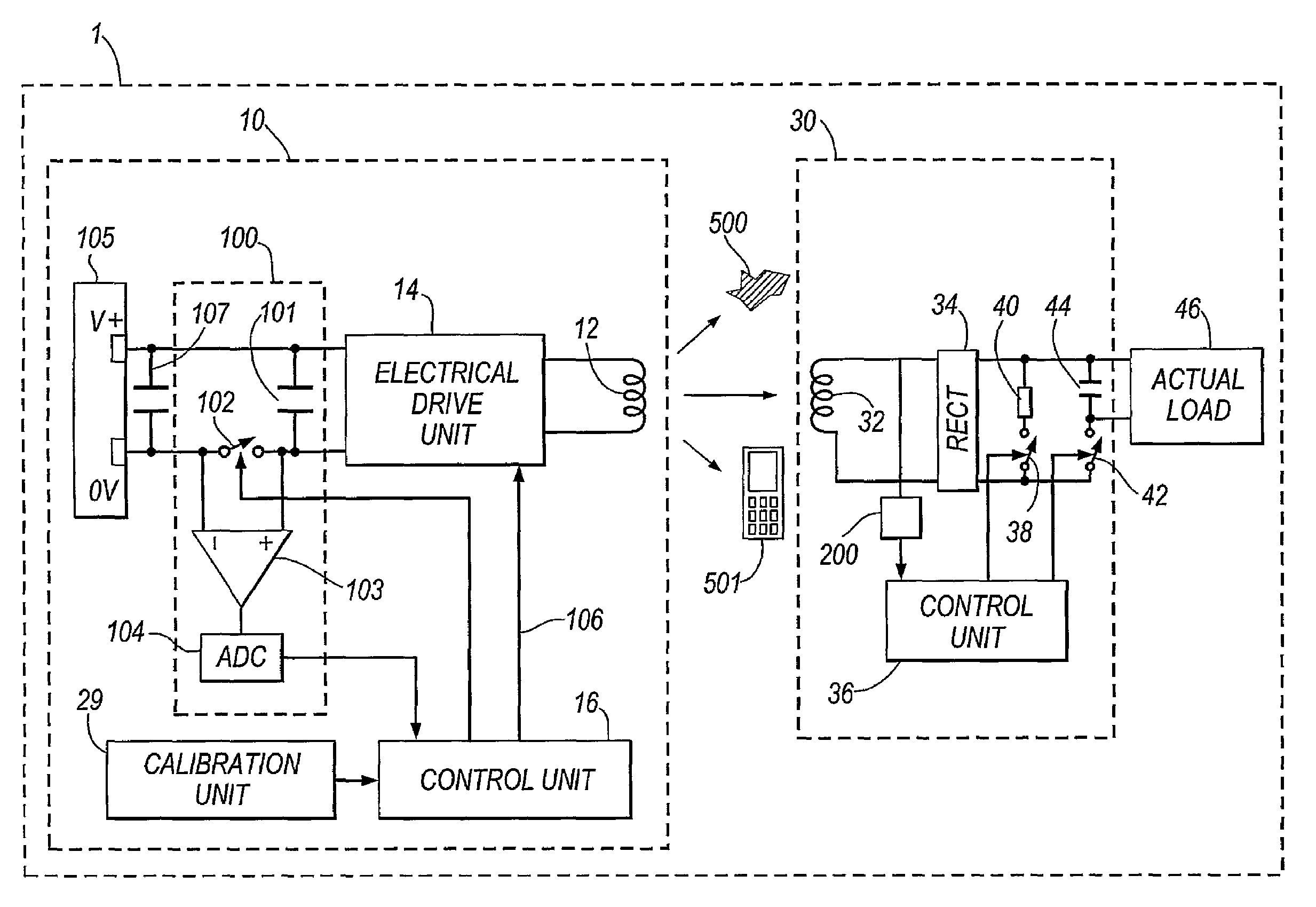

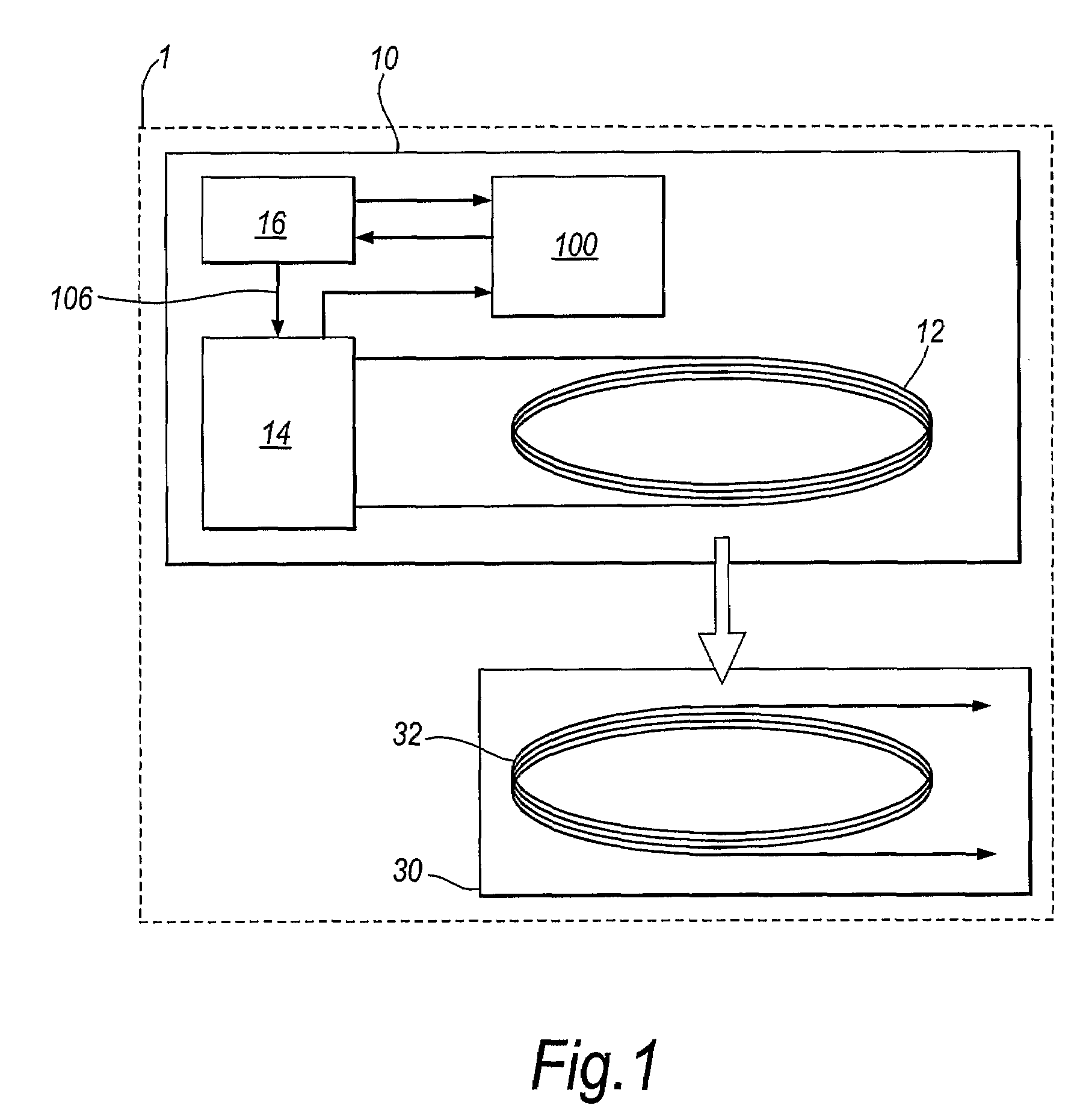

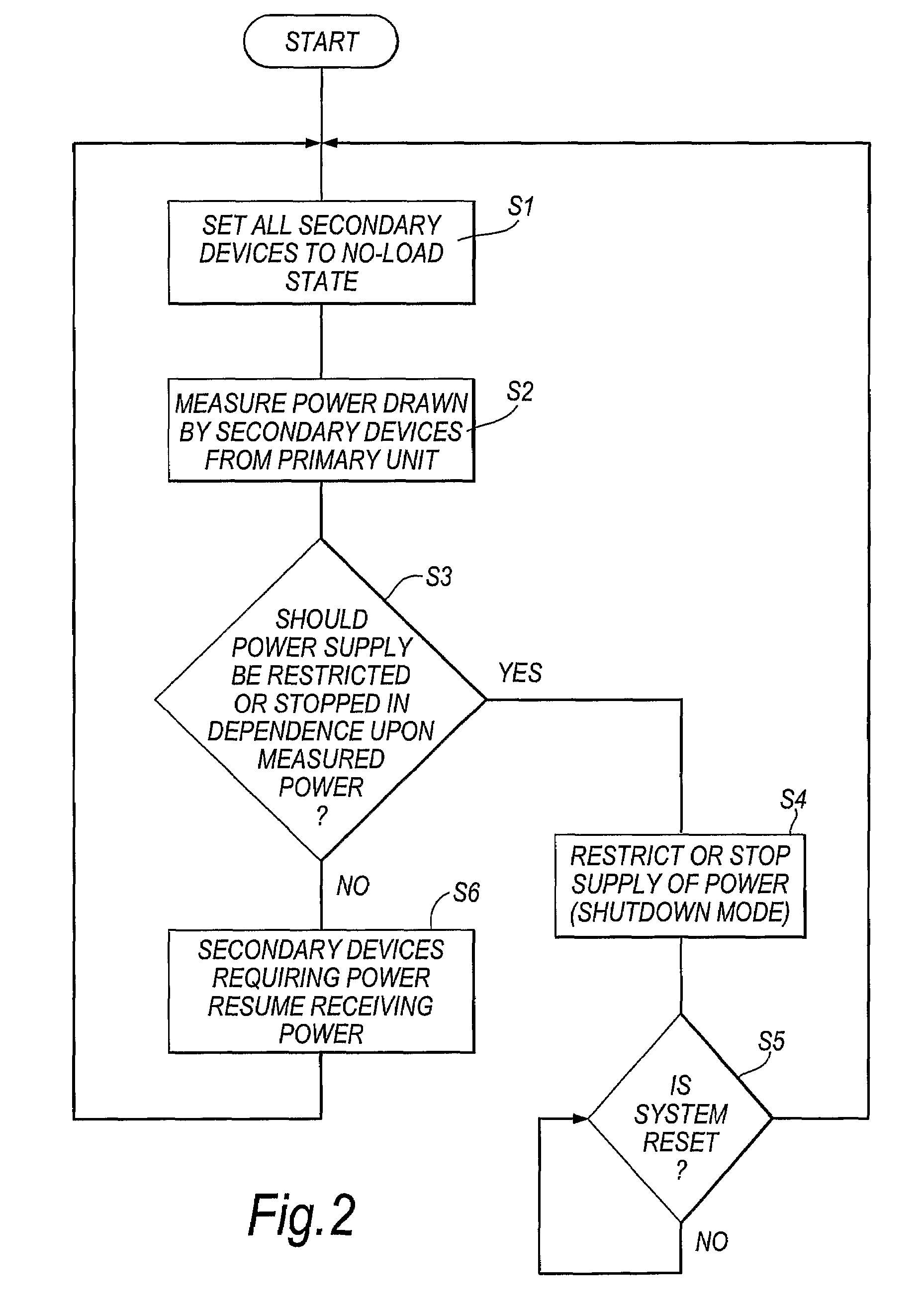

Controlling inductive power transfer systems

ActiveUS7605496B2Enhanced couplingBatteries circuit arrangementsElectromagnetic wave systemTransfer systemEngineering

An inductive power transfer system (1) comprises a primary unit (10) operable to generate an electromagnetic field and at least one secondary device (30), separable from the primary unit, and adapted to couple with the field when the secondary device is in proximity to the primary unit so that power can be received inductively by the secondary device from the primary unit without direct electrical conductive contacts therebetween. The system detects if there is a substantial difference between, on the one hand, a power drawn from the primary unit and, on the other hand, a power required by the secondary device or, if there is more than one secondary device, a combined power required by the secondary devices. Following such detection, the system restricts or stops the inductive power supply from the primary unit. Such a system can detect the presence of unwanted parasitic loads in the vicinity of the primary unit reliably.

Owner:PHILIPS IP VENTURES BV

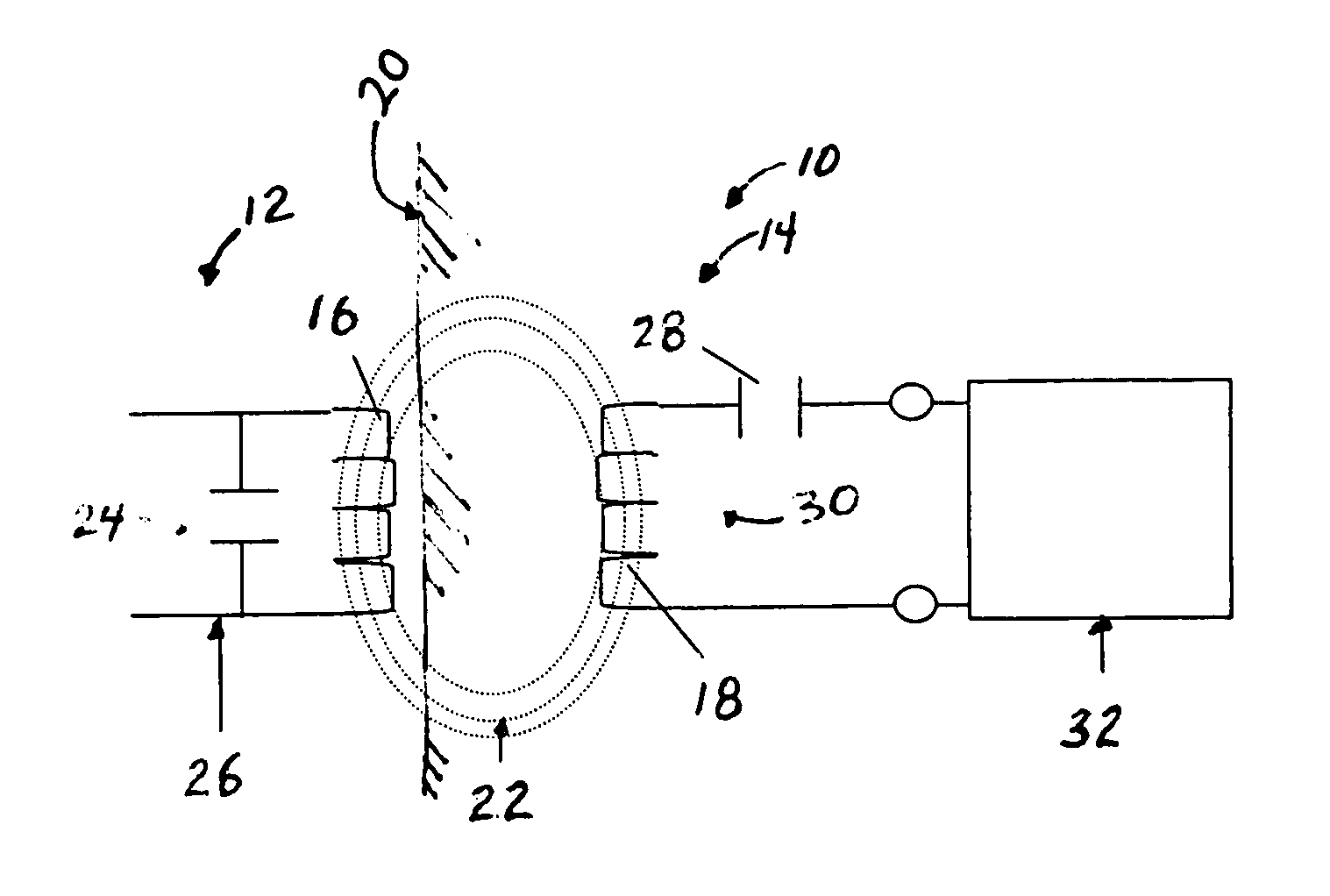

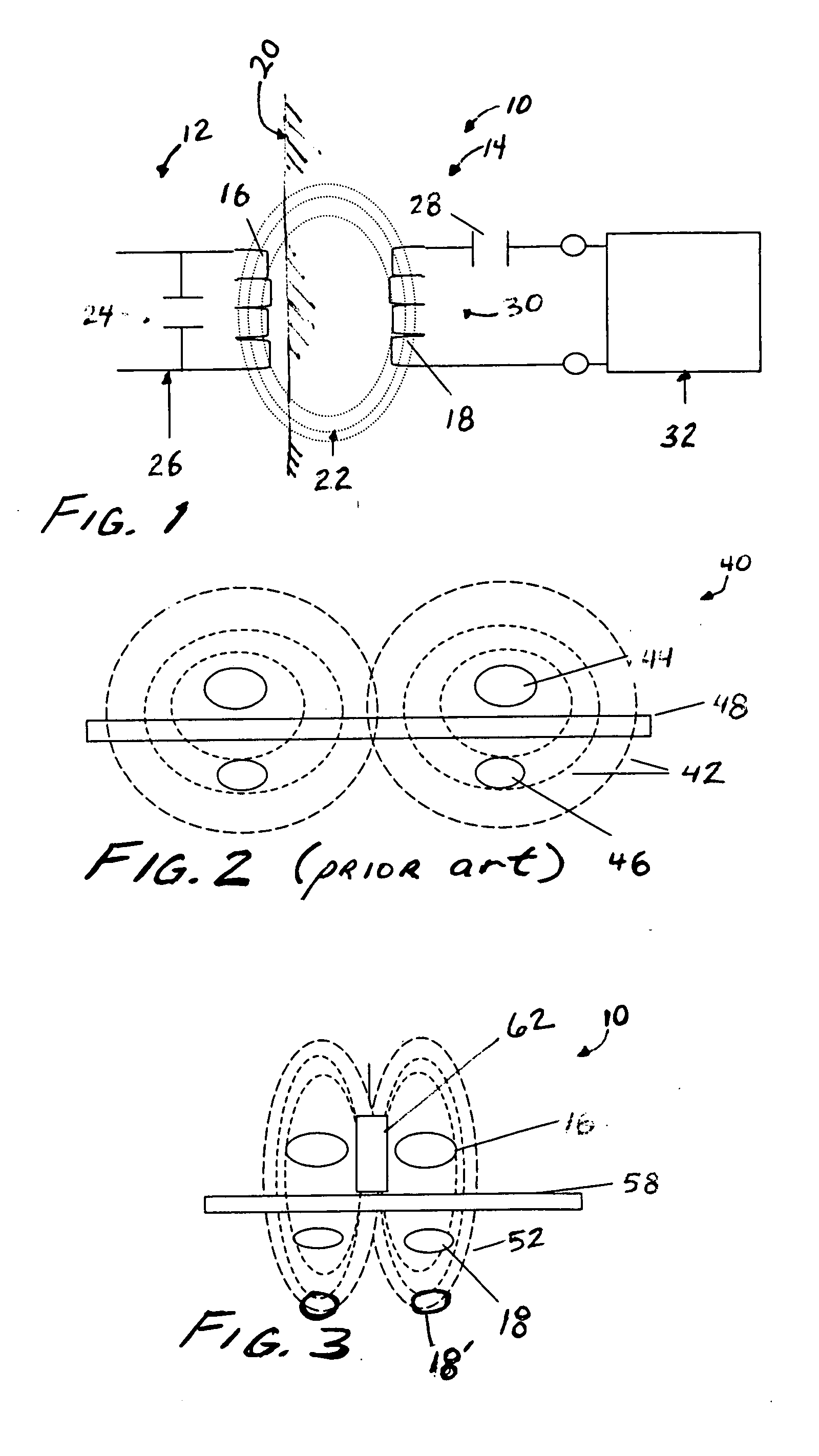

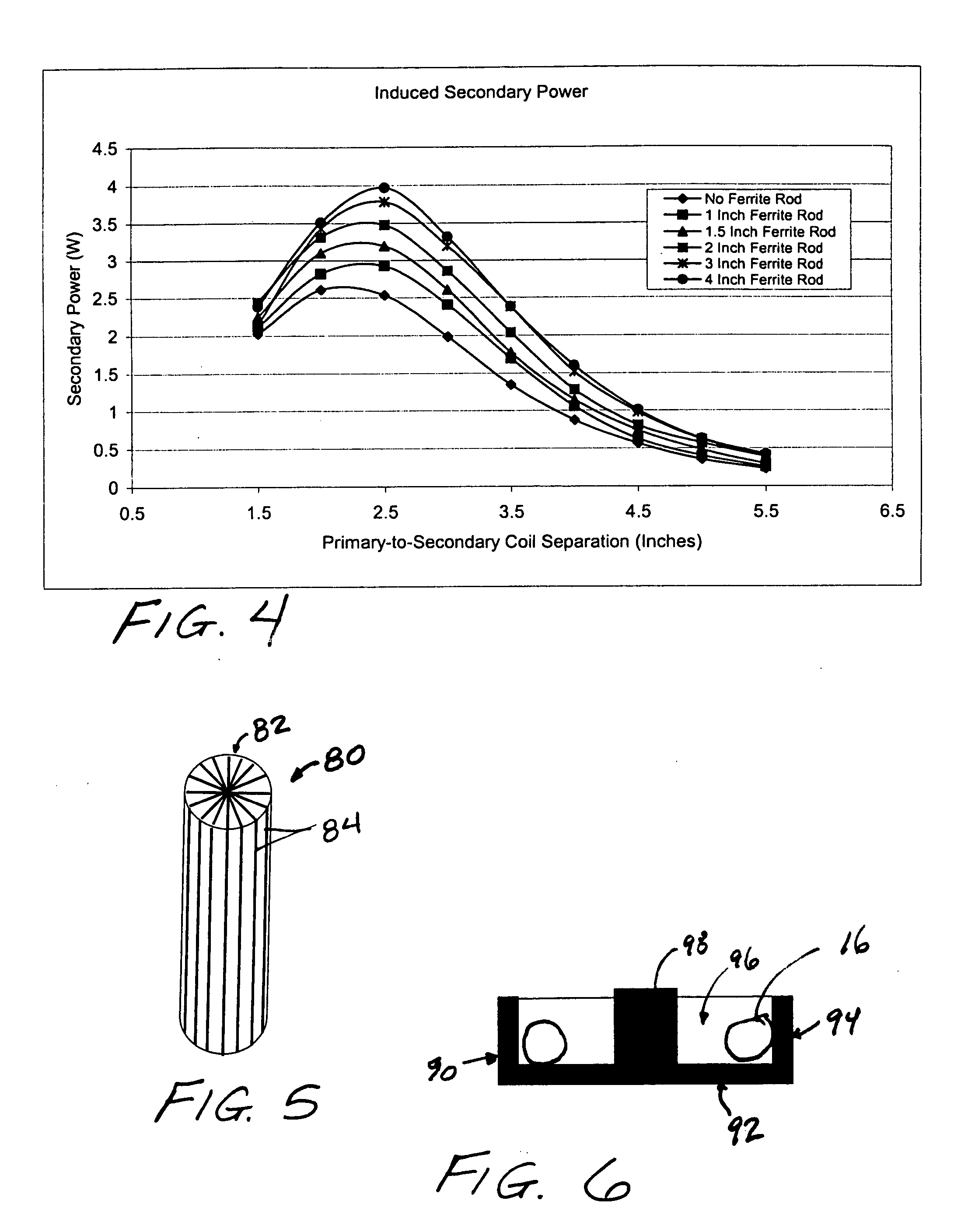

Transcutaneous energy transfer primary coil with a high aspect ferrite core

InactiveUS20050288742A1Enhanced couplingElectrotherapyCoilsLaparoscopic adjustable gastric bandingFerrite core

Adjustable gastric band implants contain a hollow elastomeric balloon with fixed end points encircling a patient's stomach just inferior to the esophago-gastric junction. These balloons can expand and contract through the introduction of saline solution into the balloon. In current bands, this saline solution must be injected into a subcutaneous port with a needle to reach the port located below the skin surface. The port communicates hydraulically with the band via a catheter. As an alternative to using a percutaneously accessed injection port, a system for regulating the flow of saline that is totally implanted may rely upon bi-directionally pumping fluid from an implant device. This system instead transfers AC magnetic flux energy from an external primary coil to a secondary coil that powers the pump in the implanted reservoir. A magnetically permeable rod centered within the primary coil increases power coupled to the secondary coil.

Owner:ETHICON ENDO SURGERY INC

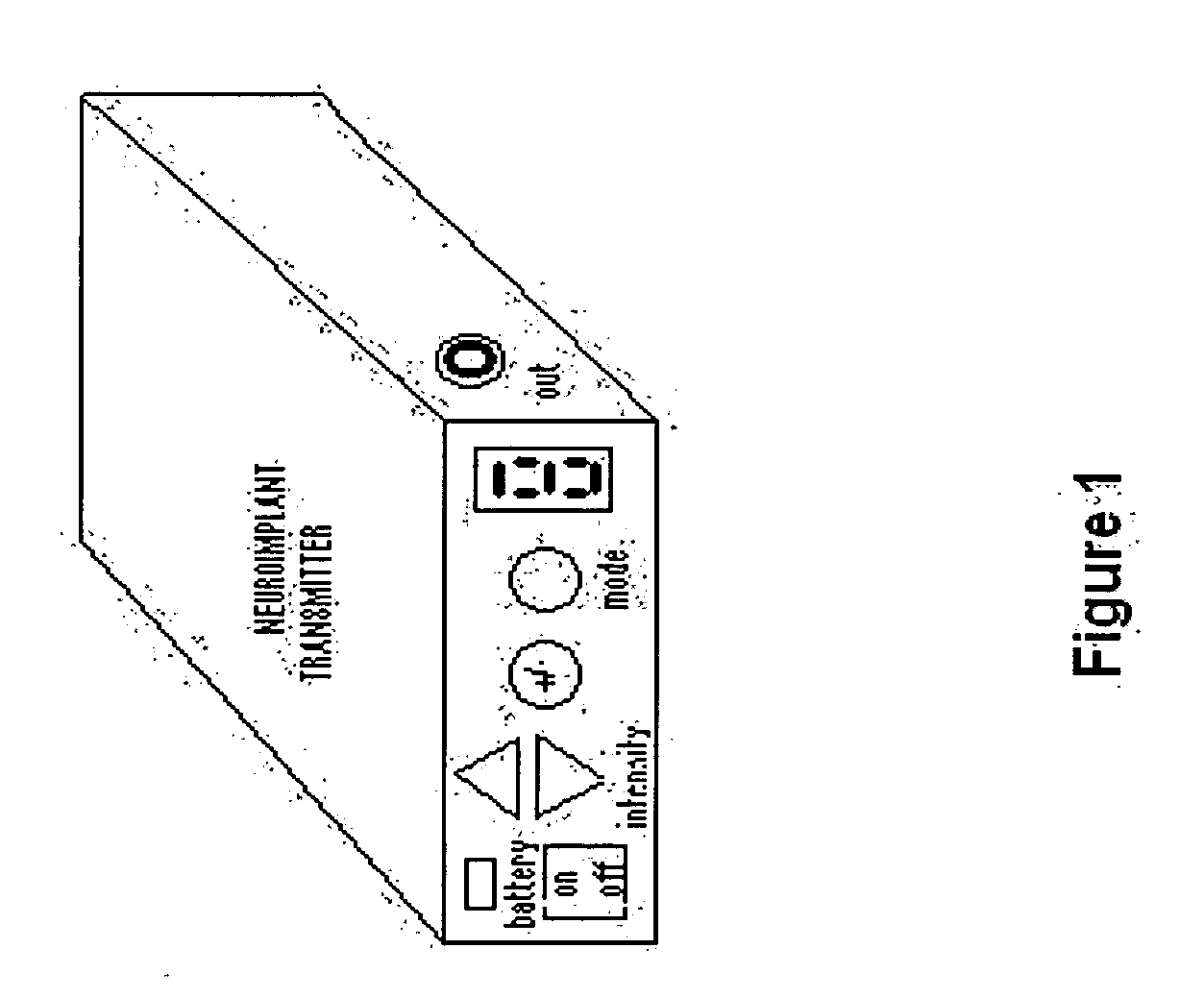

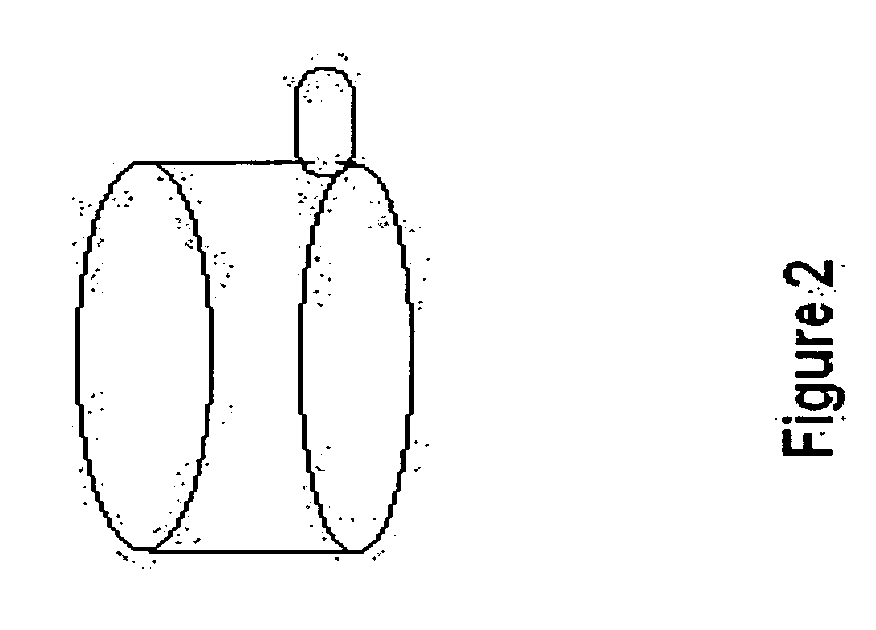

Externally activated neuro-implant which directly transmits therapeutic signals

InactiveUS20060142822A1Enhances inductive couplingMinimized in sizeElectrotherapyArtificial respirationImplantable ElectrodesElectrical stimulations

An externally powered and controlled neuro-implant system for transmission of stimulating therapeutic signals to an implantable electrode. The system basically consists of two coils, one external active coil and one internal passive coil each housed in a ferrite pot core which enhances inductive coupling and minimizes the coils in size, thus facilitating the construction of a passive coils array to enable the usage of multi-contact electrodes for swithching of the electrical stimulation between a number of sites along the target neurons. The implanted part of the system, comprising only a coil housed in a ferrite pot core, is fully passive. The passive coil, that is implanted under the skin, is connected with the electrode placed in neighbouring of the target neural tissue via implanted thin medical grade wires. The active coil is placed on the skin overlying the passive coil. Therapeutic signals produced by the transmitter outside the body are transmitted through the coils by inductive coupling across the skin of the patient.

Owner:TULGAR METIN

Mechanically removable wireless power vehicle seat assembly

ActiveUS20130221744A1Efficient deliveryEfficient energy transferMultiple-port networksCircuit monitoring/indicationHigh conductivityElectric power

Described herein are improved capabilities for a system and method for wireless energy distribution to a mechanically removable vehicle seat, comprising a source resonator coupled to an energy source of a vehicle, the source resonator positioned proximate to the mechanically removable vehicle seat, the source resonator generating an oscillating magnetic field with a resonant frequency and comprising a high-conductivity material adapted and located between the source resonator and a vehicle surface to direct the oscillating magnetic field away from the vehicle surface, and a receiving resonator integrated into the mechanically removable vehicle seat, the receiving resonator having a resonant frequency similar to that of the source resonator, and receiving wireless energy from the source resonator, and providing power to electrical components integrated with the mechanically removable vehicle seat.

Owner:WITRICITY CORP

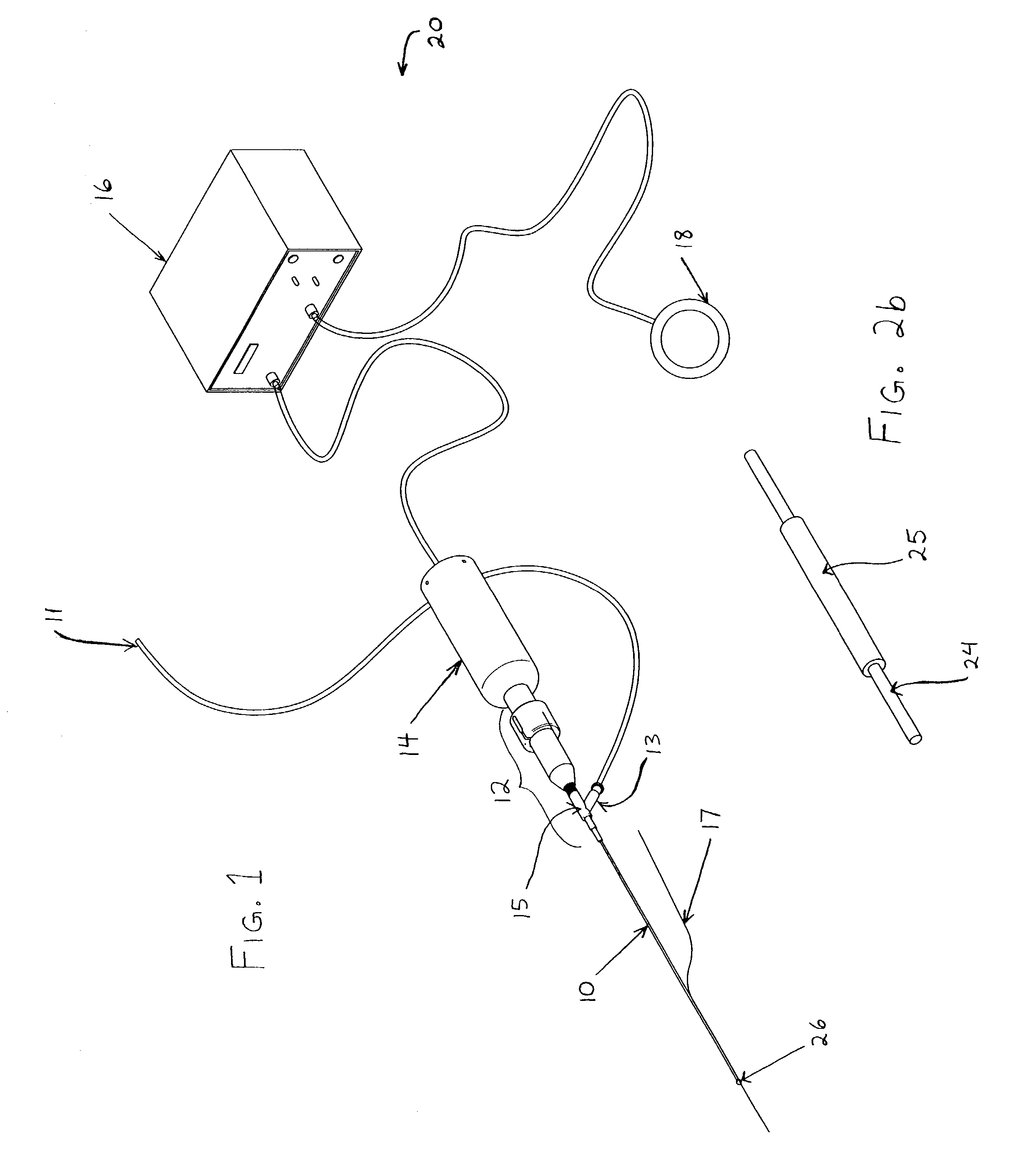

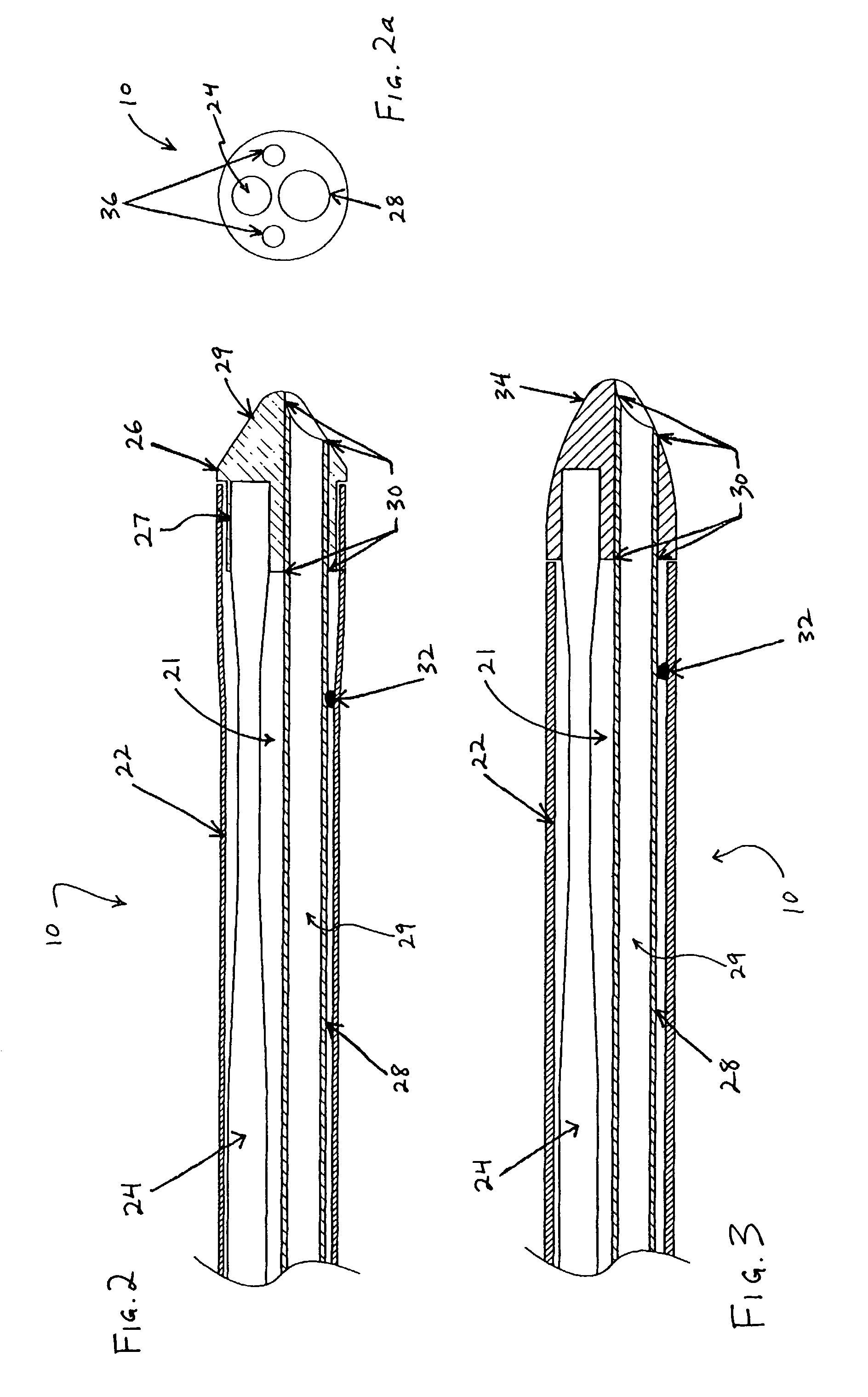

Ultrasound catheter for disrupting blood vessel obstructions

InactiveUS7137963B2Accelerated destructionImprove abilitiesChiropractic devicesMedical devicesBlood vessel occlusionGuide wires

Ultrasound catheter devices and methods provide enhanced disruption of blood vessel obstructions. Generally, an ultrasound catheter includes an elongate flexible catheter body with one or more lumens. An ultrasound transmission member or wire extends longitudinally through the catheter body lumen and, in many embodiments, a guide wire tube also extends through the same lumen. A distal head is fixed to or otherwise mechanically coupled with the distal end of the ultrasound transmission member or wire and is positioned adjacent the distal end of the catheter body. Although the distal end of the catheter body overlaps the distal head, the distal head is not directly affixed to the distal end of the catheter body. Thus, the distal tip may move freely, relative to the distal end of the catheter body when ultrasonic energy is applied through the ultrasound transmission member. Such a freely floating distal head enhances the efficiency of an ultrasound catheter, enabling the catheter to ablate calcific occlusions and increasing the useful life of the ultrasound transmission member and catheter.

Owner:FLOWCARDIA

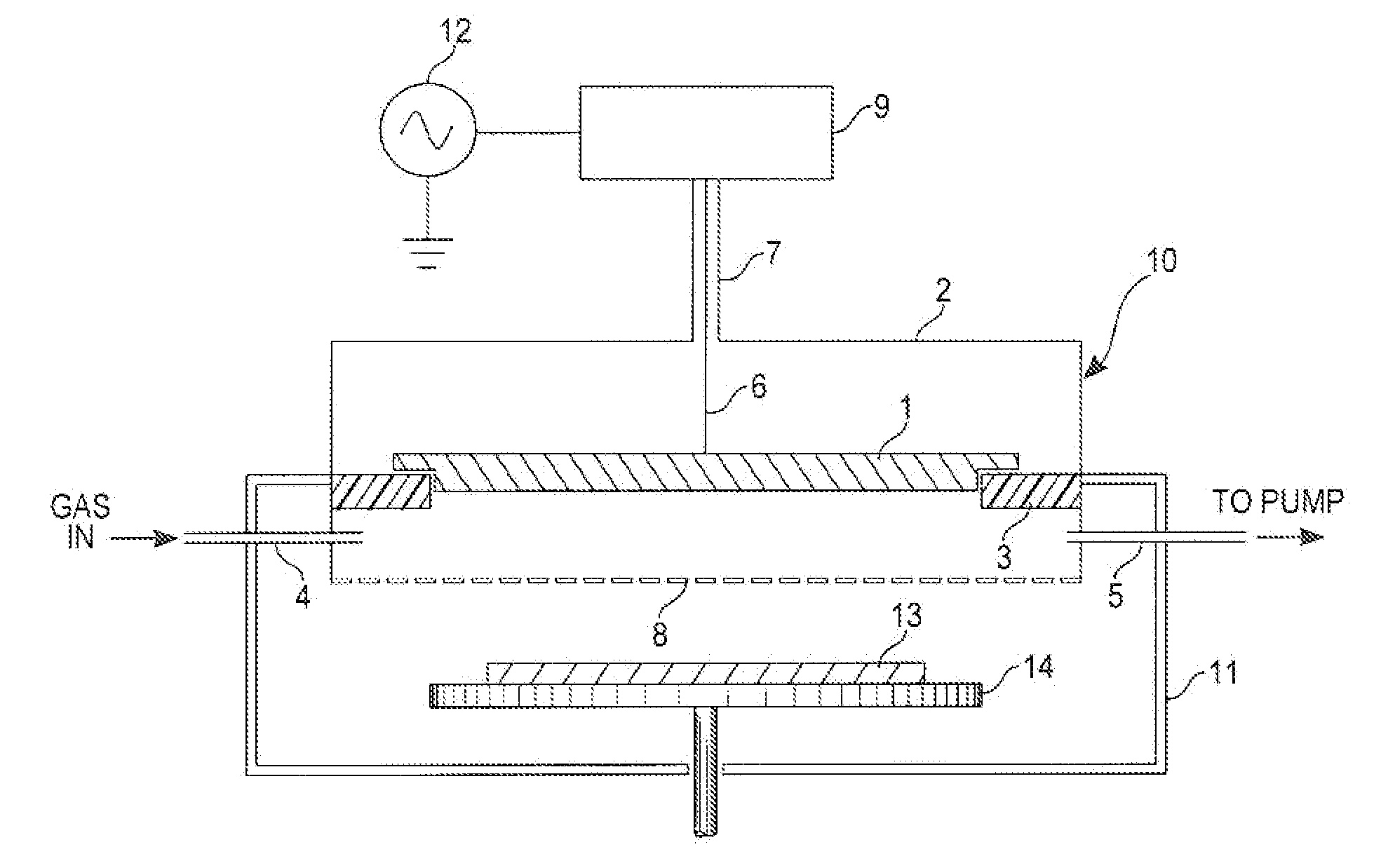

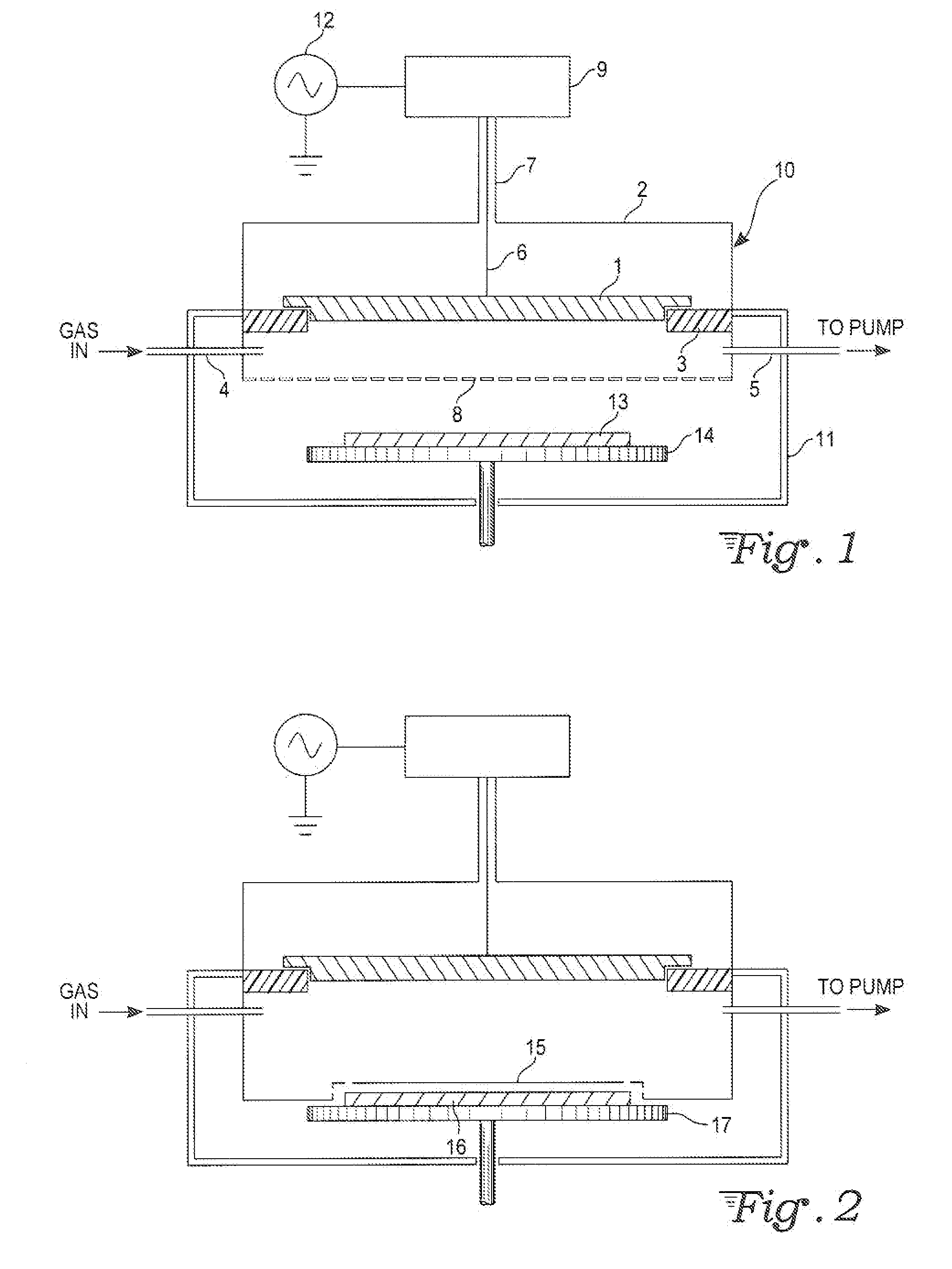

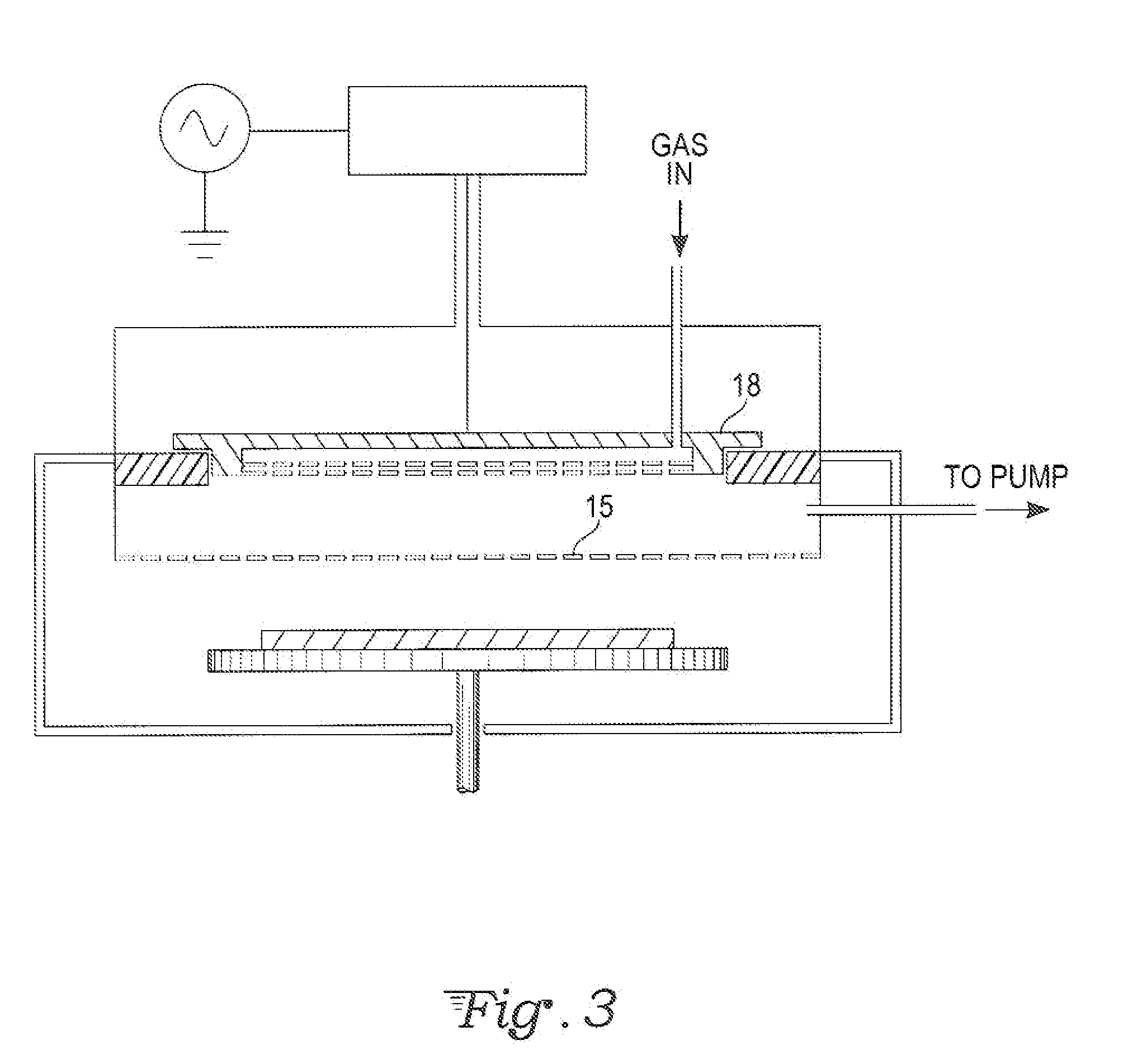

Capacitively coupled remote plasma source with large operating pressure range

InactiveUS20100101727A1System costExtension of timeElectric discharge tubesSemiconductor/solid-state device manufacturingCapacitanceRadio frequency

A radio frequency (RF) coaxial resonator feeding a saltshaker-like gas distributing electrode assembly forms a capacitively coupled plasma source. This apparatus can generate plasma of high density over a wide pressure range and large process window. The system may be used as a remote radical-rich plasma source for materials surface processing.

Owner:JI HELIN

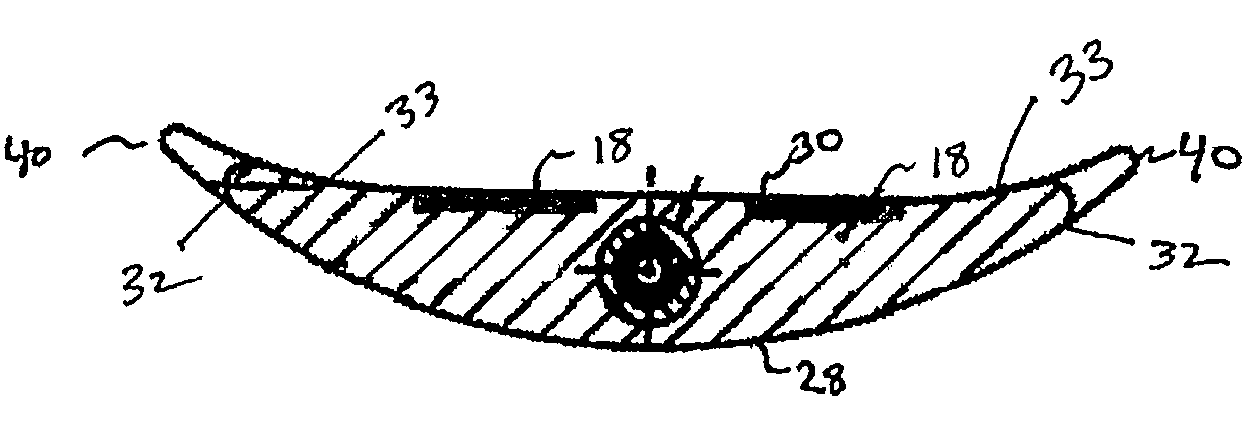

Winged electrode body for spinal cord stimulation

ActiveUS6999820B2Prevent axial movementOptimize couplingSpinal electrodesExternal electrodesSpinal cord stimulationTarget fibers

An implantable stimulation system including epidural lead for spinal cord stimulation that includes a paddle having a curved proximal end and lateral winged tips and an array of electrodes coupled to conductors within a lead body. The conductors couple to a pulse generator or other stimulation device. The curved and winged paddle provides more complete electrical stimulation coverage to targeted human tissue by minimizing the potential gap between electrodes and targeted fibers.

Owner:ADVANCED NEUROMODULATION SYST INC

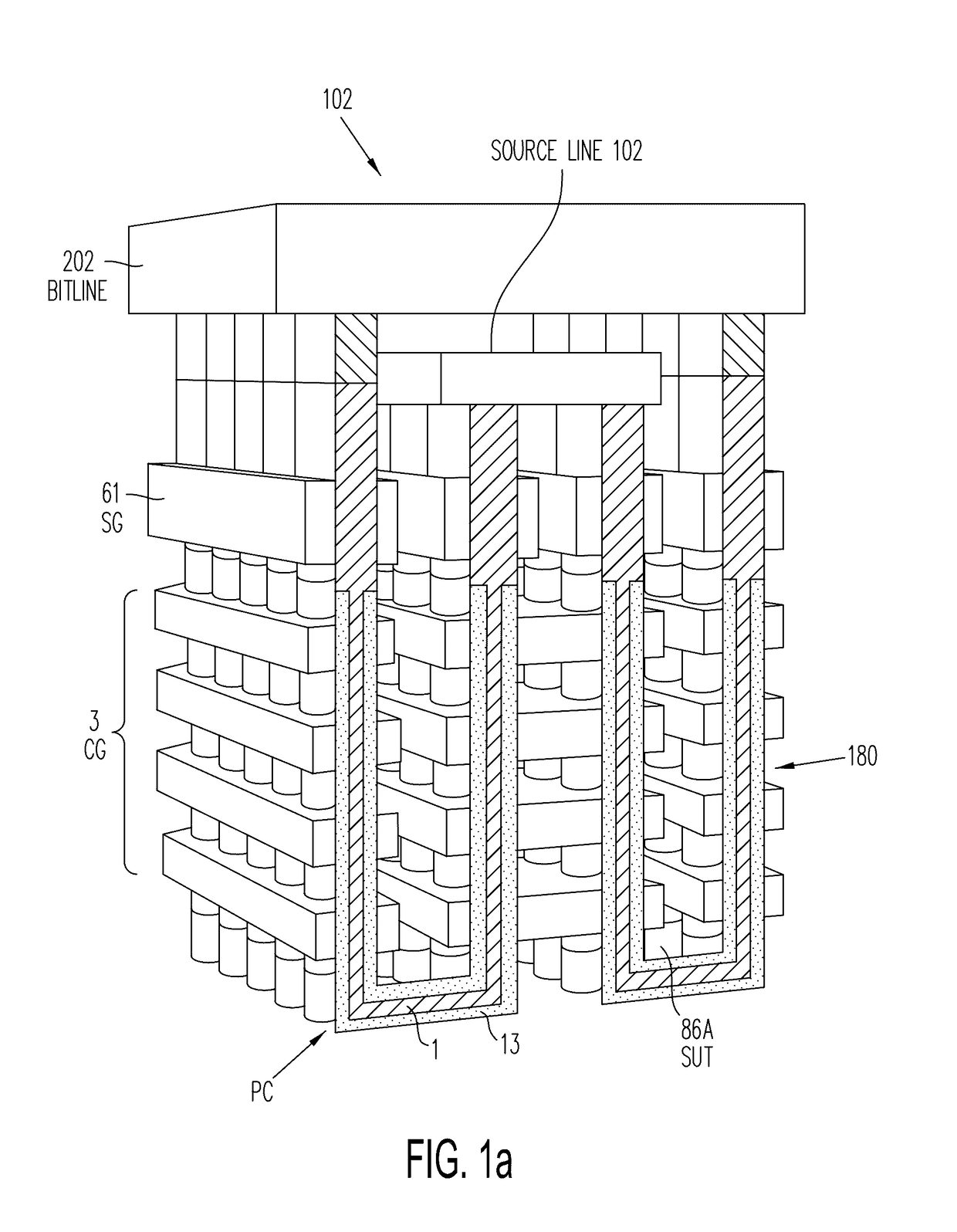

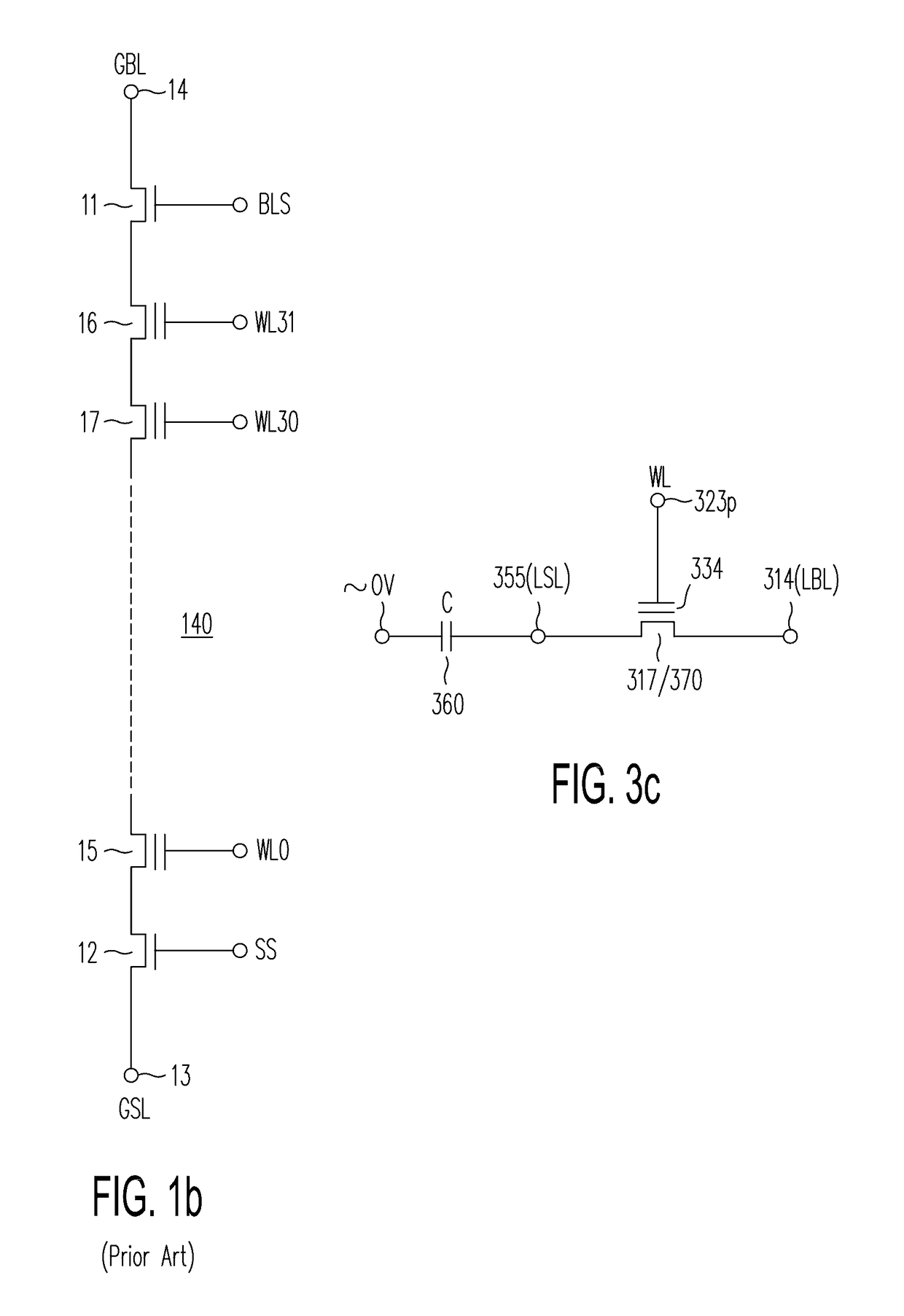

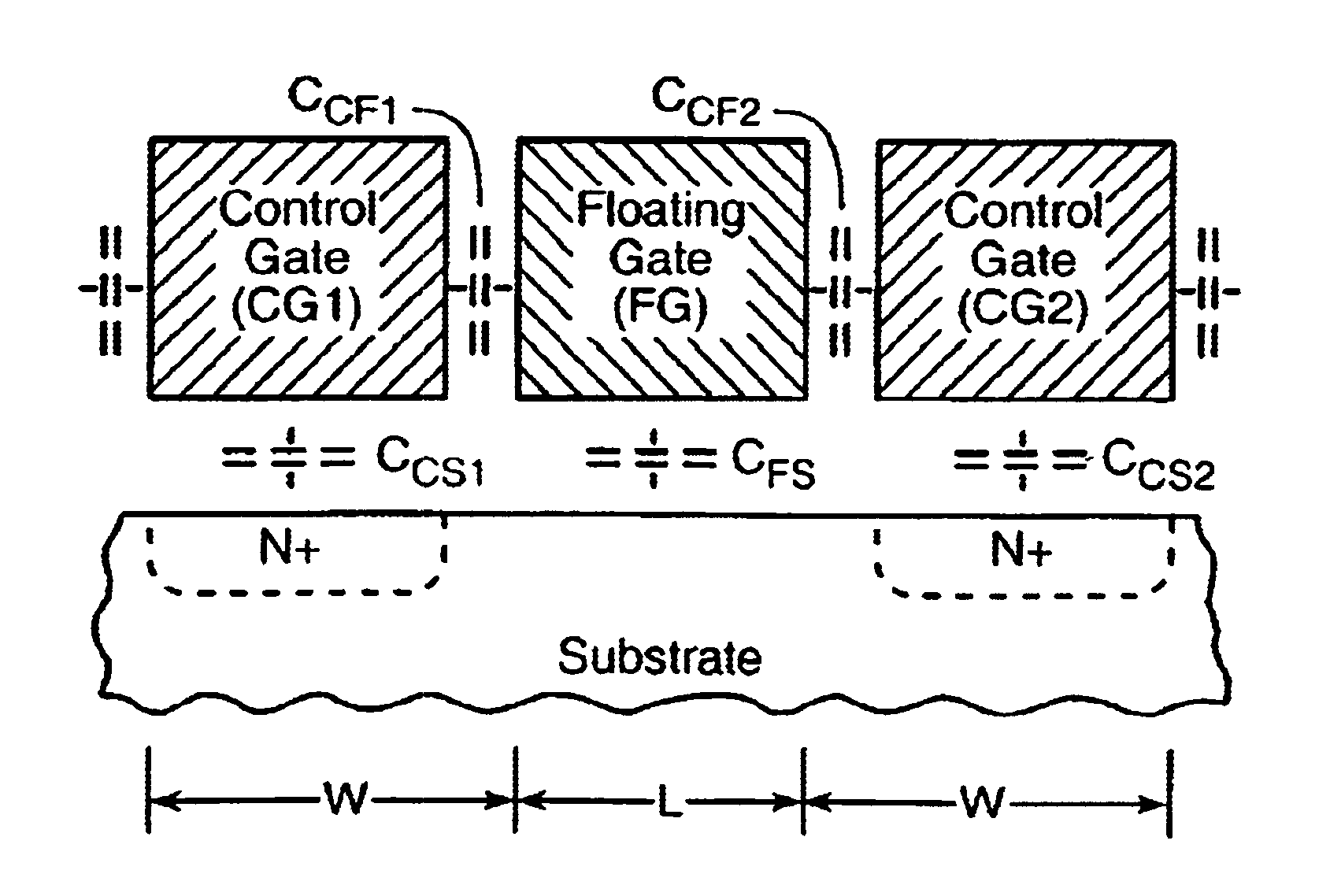

Flash memory cell arrays having dual control gates per memory cell charge storage element

InactiveUS6888755B2Increase coupling areaImprove the coupling ratioTransistorSolid-state devicesCapacitanceImage resolution

A flash NAND type EEPROM system with individual ones of an array of charge storage elements, such as floating gates, being capacitively coupled with at least two control gate lines. The control gate lines are preferably positioned between floating gates to be coupled with sidewalls of floating gates. The memory cell coupling ratio is desirably increased, as a result. Both control gate lines on opposite sides of a selected row of floating gates are usually raised to the same voltage while the second control gate lines coupled to unselected rows of floating gates immediately adjacent and on opposite sides of the selected row are kept low. The control gate lines can also be capacitively coupled with the substrate in order to selectively raise its voltage in the region of selected floating gates. The length of the floating gates and the thicknesses of the control gate lines can be made less than the minimum resolution element of the process by forming an etch mask of spacers.

Owner:SANDISK TECH LLC