Patents

Literature

216results about How to "Reduce area requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

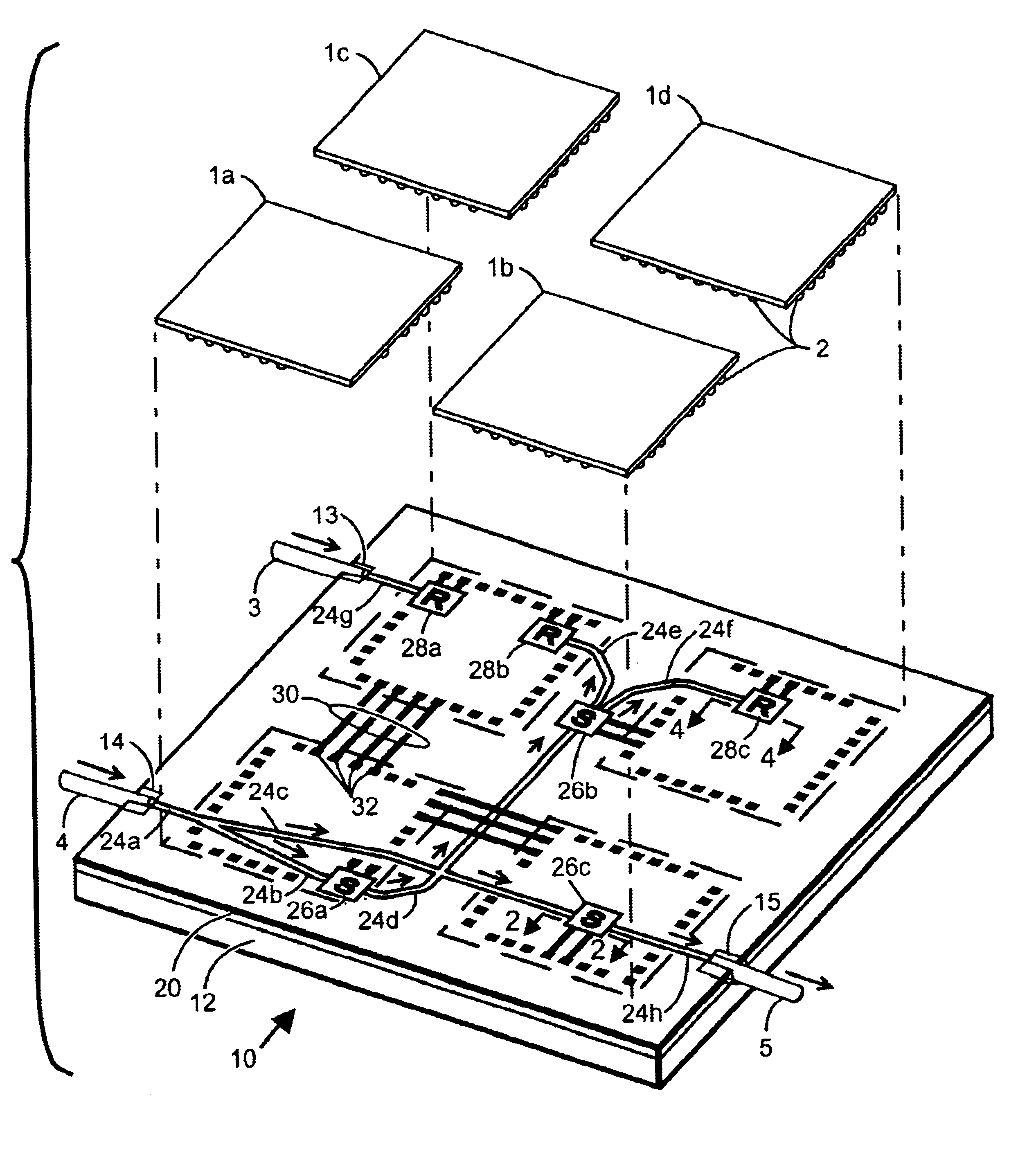

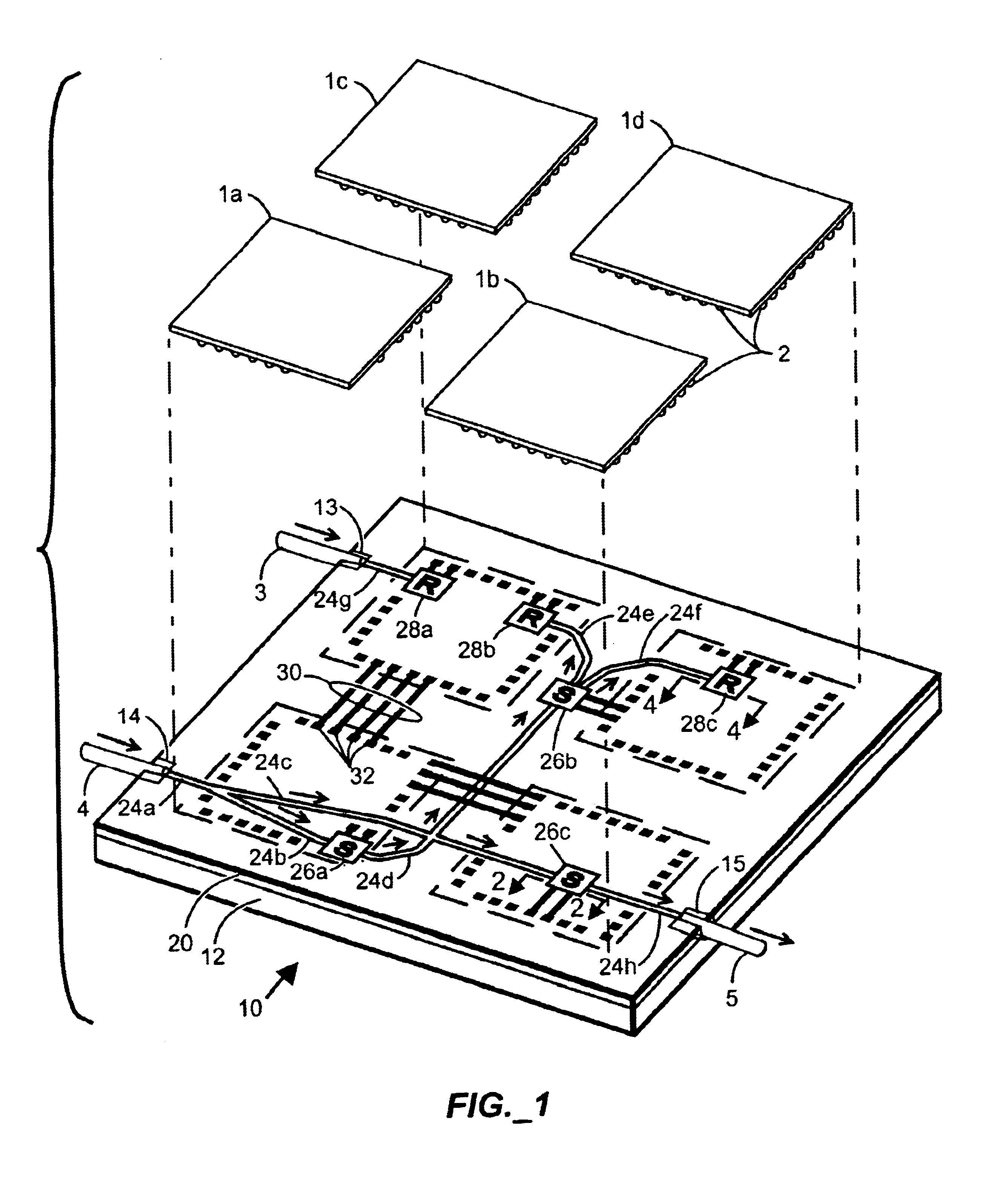

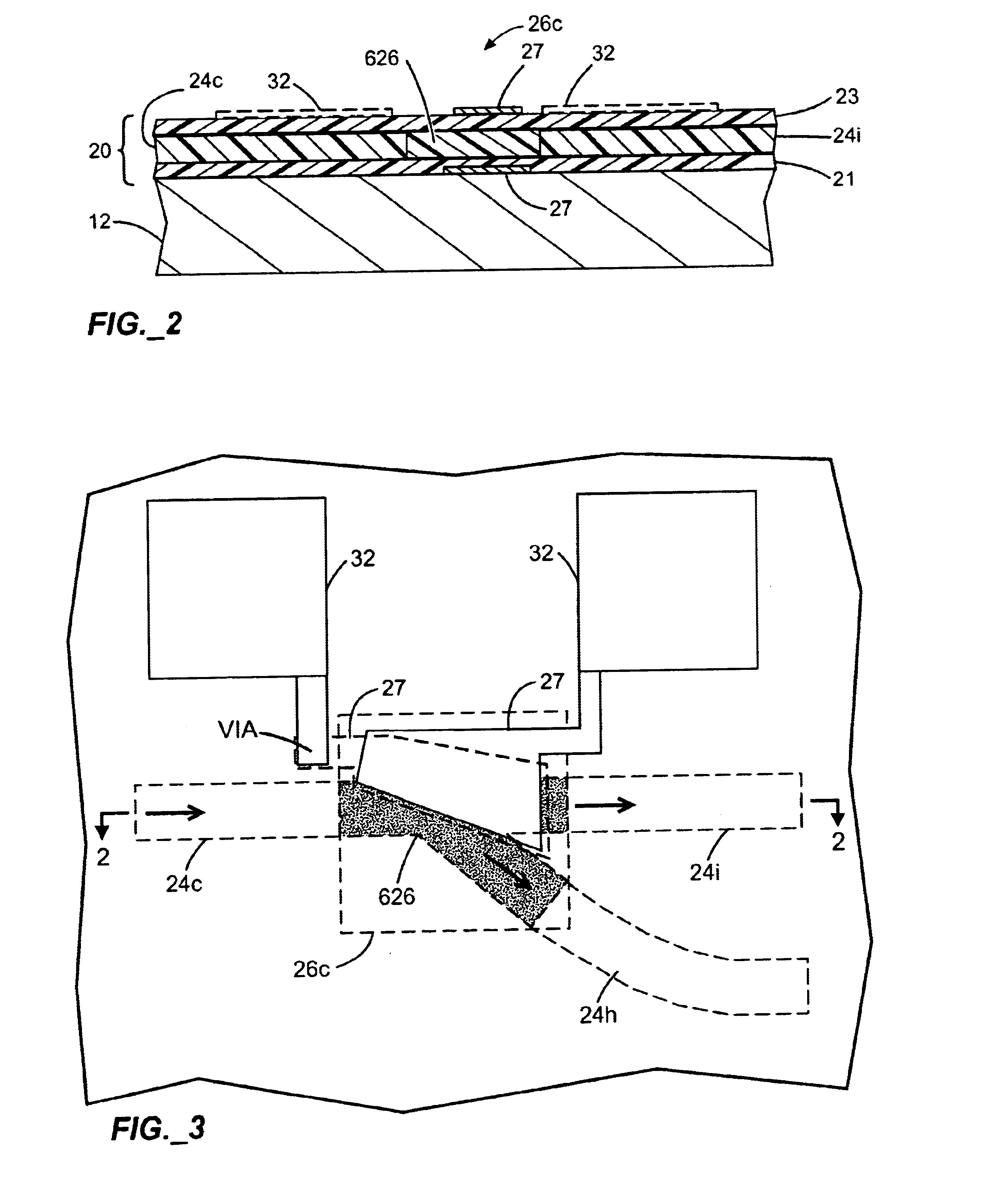

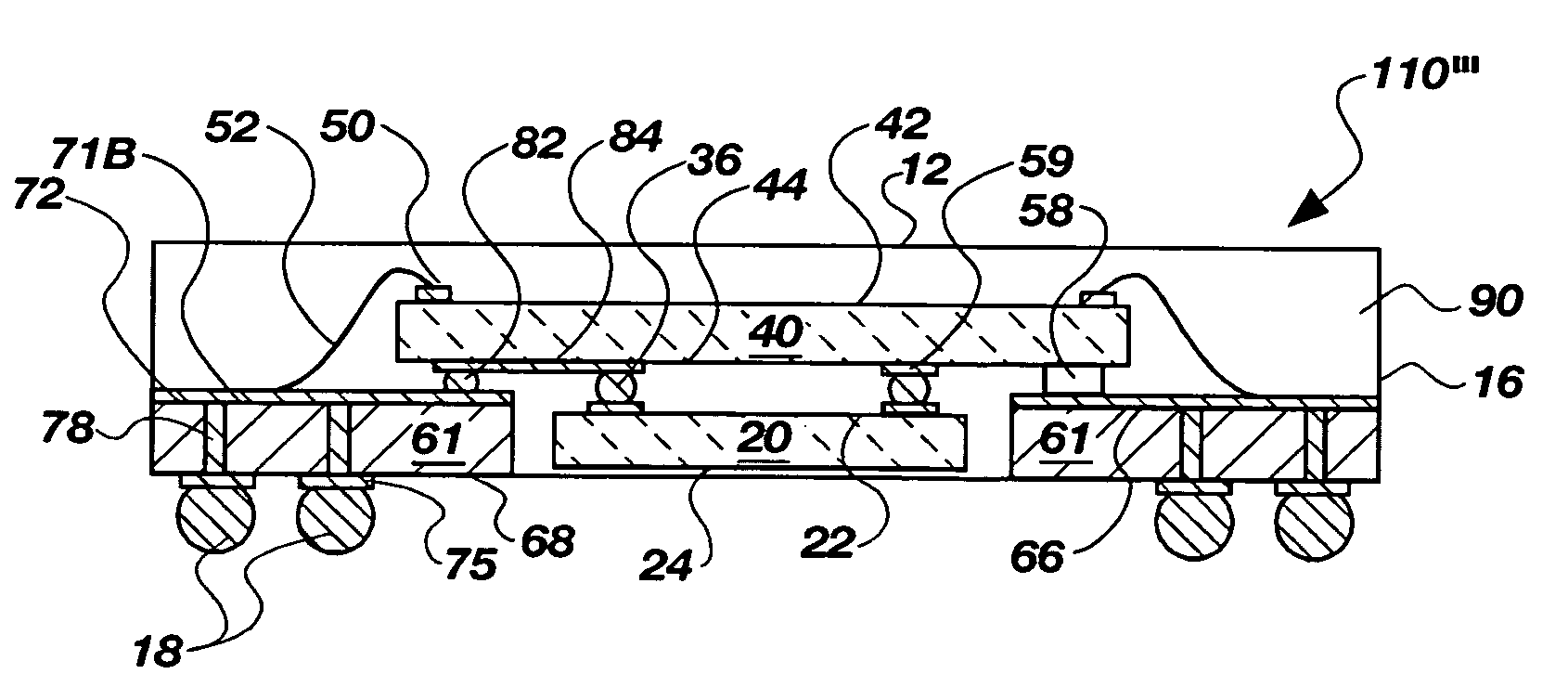

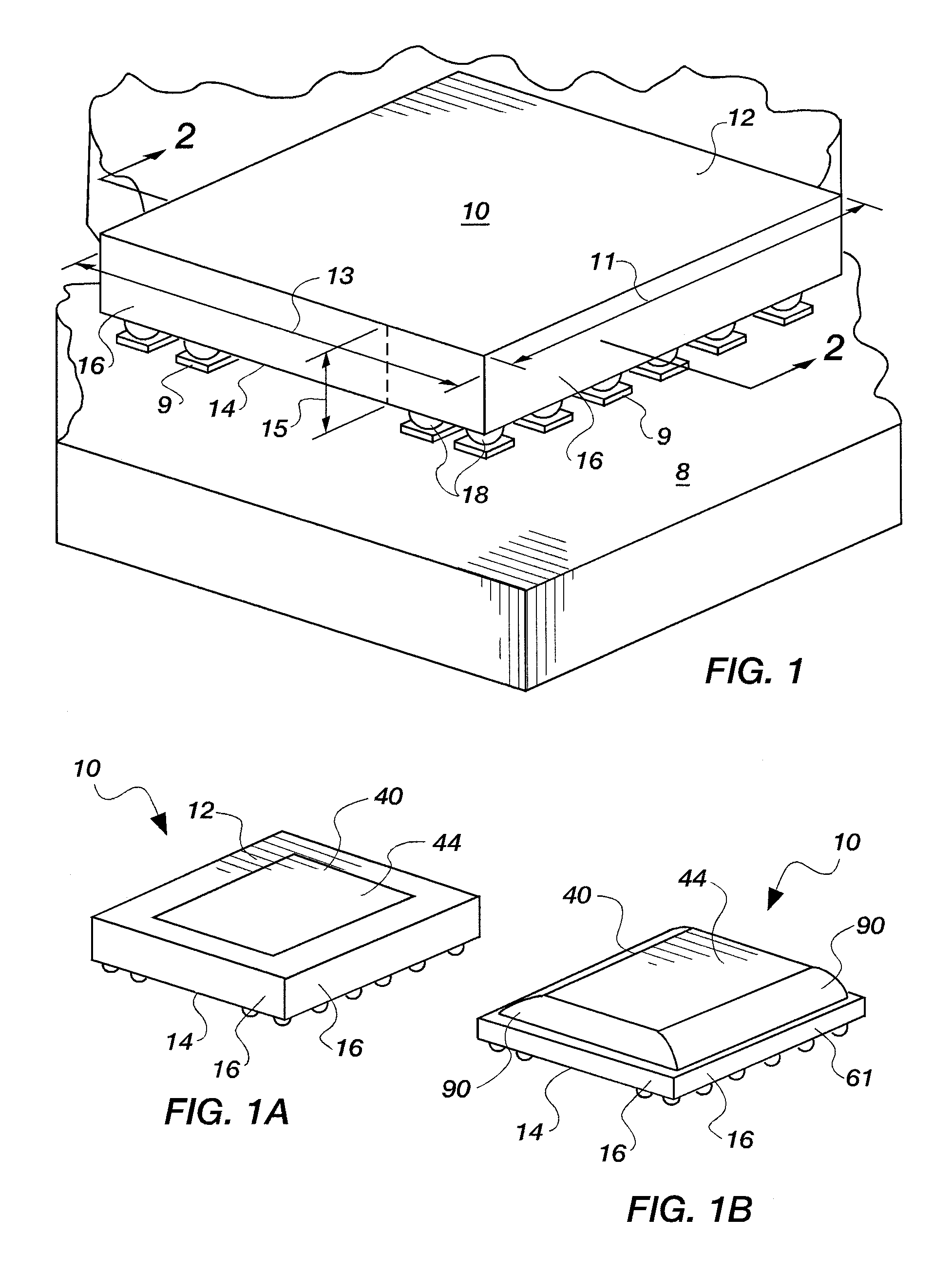

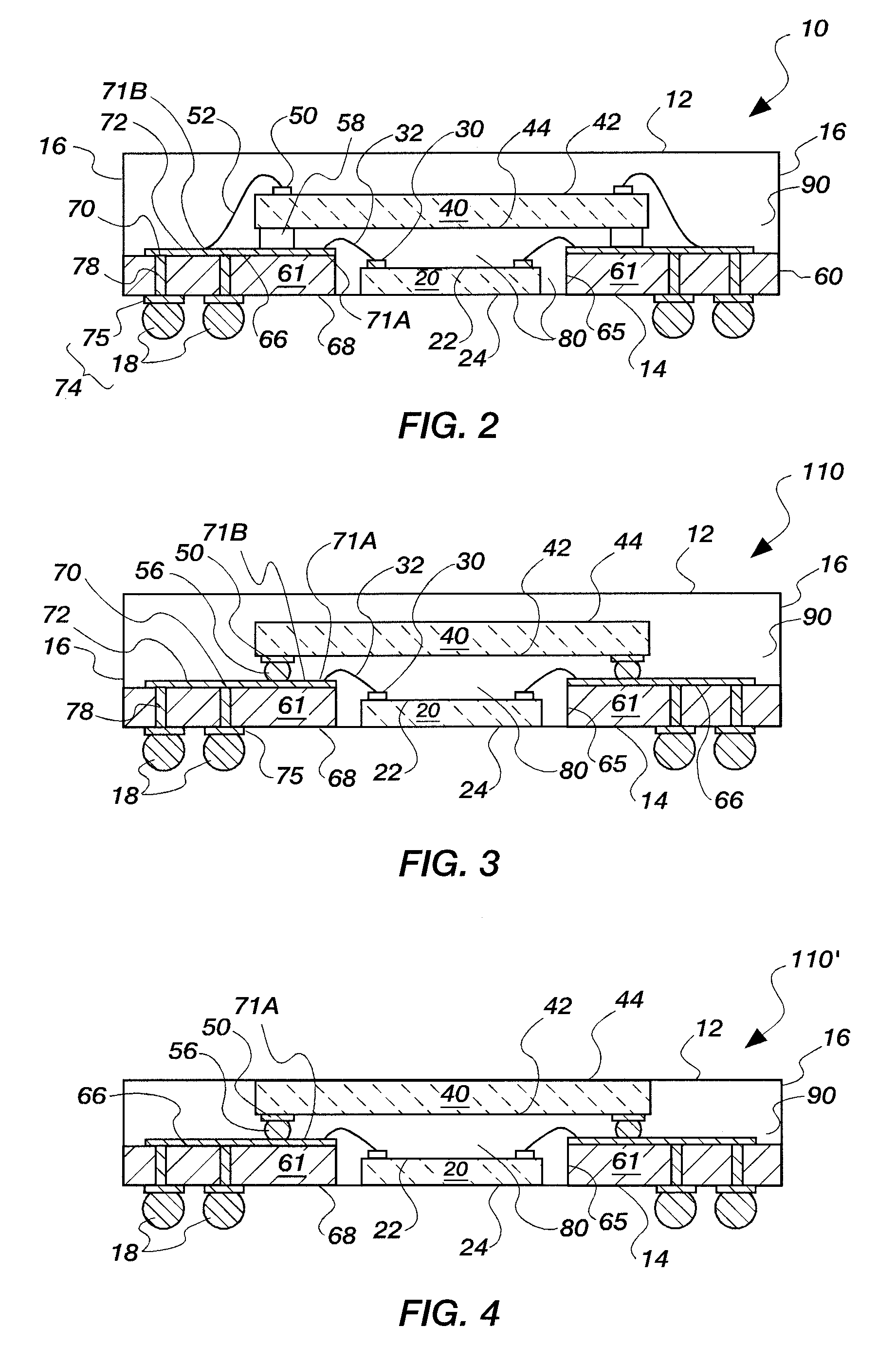

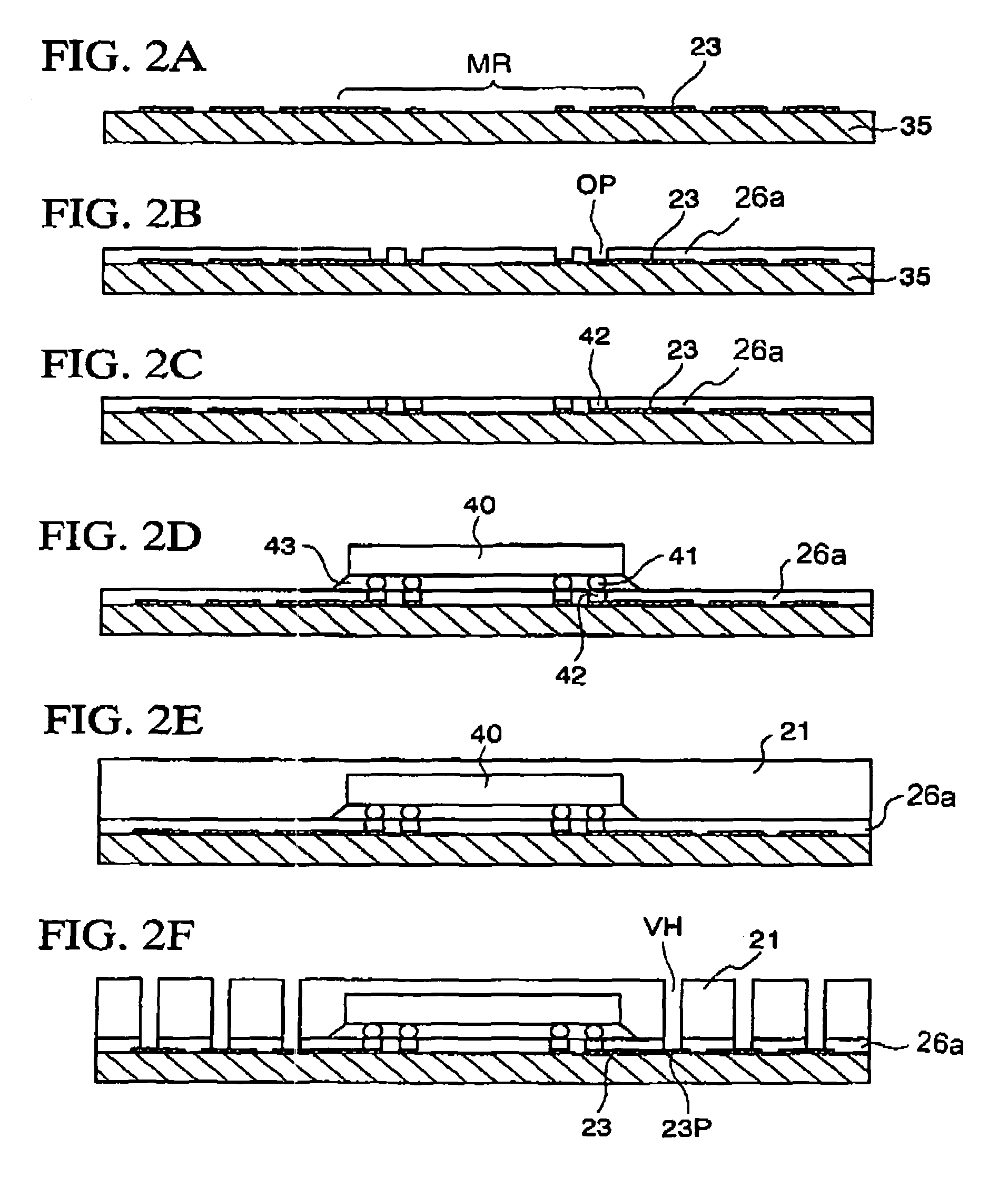

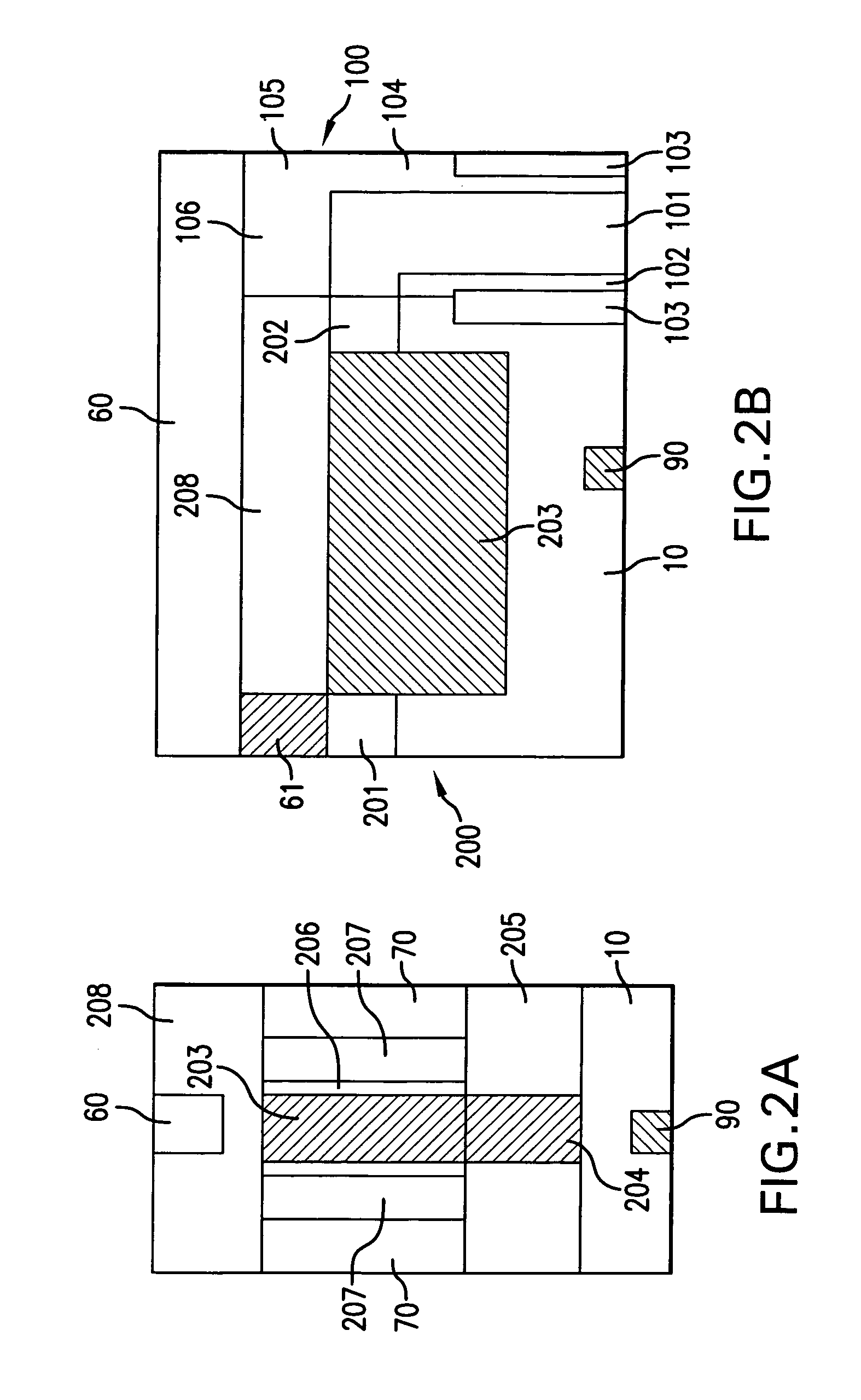

Multi-layer opto-electronic substrates with electrical and optical interconnections and methods for making

InactiveUS6845184B1Reduce area requirementsOptical coupling efficiency improvementSemiconductor/solid-state device detailsSolid-state devicesElectricityThin layer

Opto-electrical systems having electrical and optical interconnections formed in thin layers are disclosed. In one set of preferred embodiments, optical signals are conveyed between layers by respective vertical optical couplers disposed on the layers. In other preferred embodiments, optical signals are conveyed by stack optical waveguide coupling means. Yet other preferred embodiments have electrical via means formed in one or more layers to covey electrical signals between two or more layers.

Owner:FUJITSU LTD

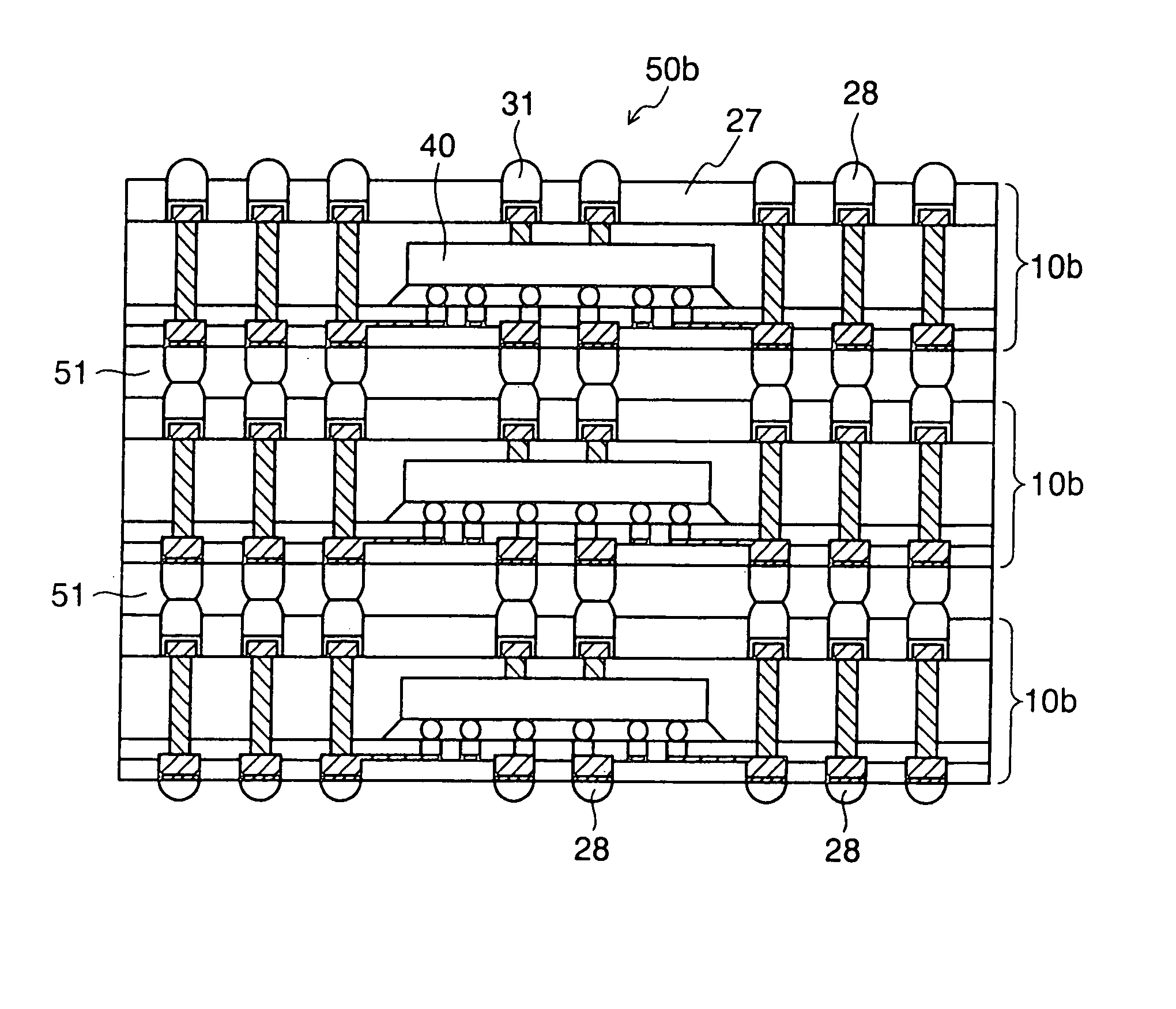

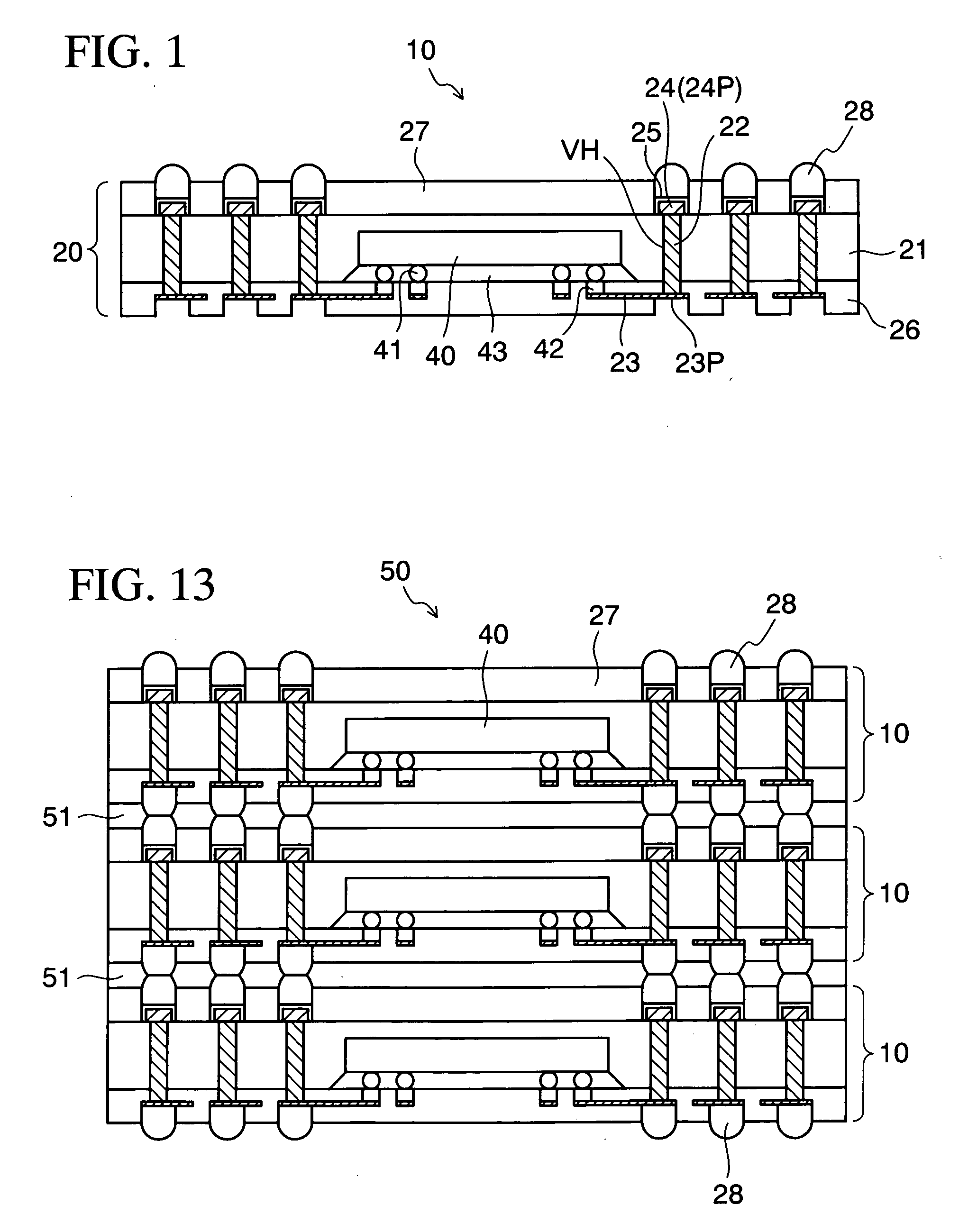

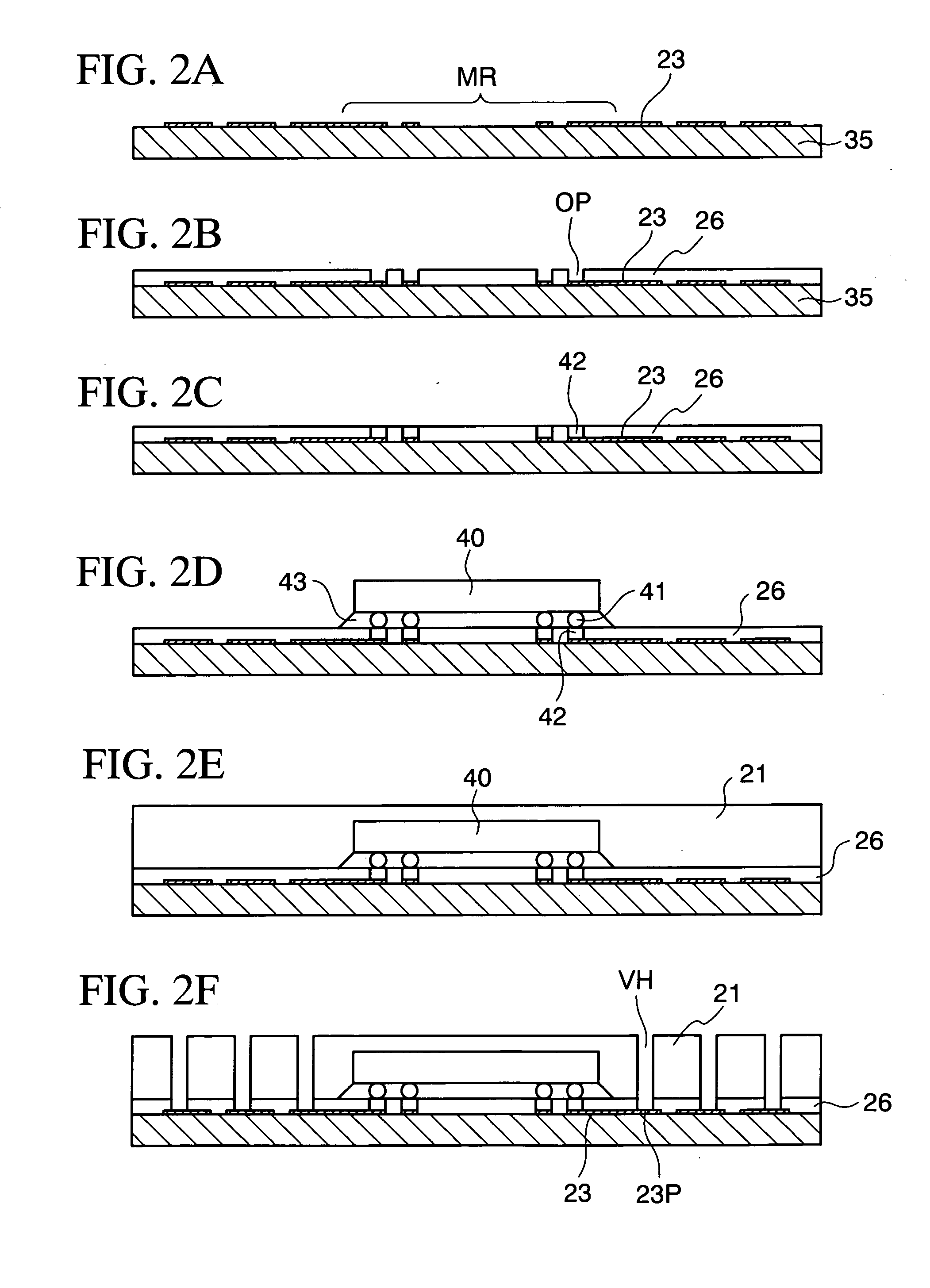

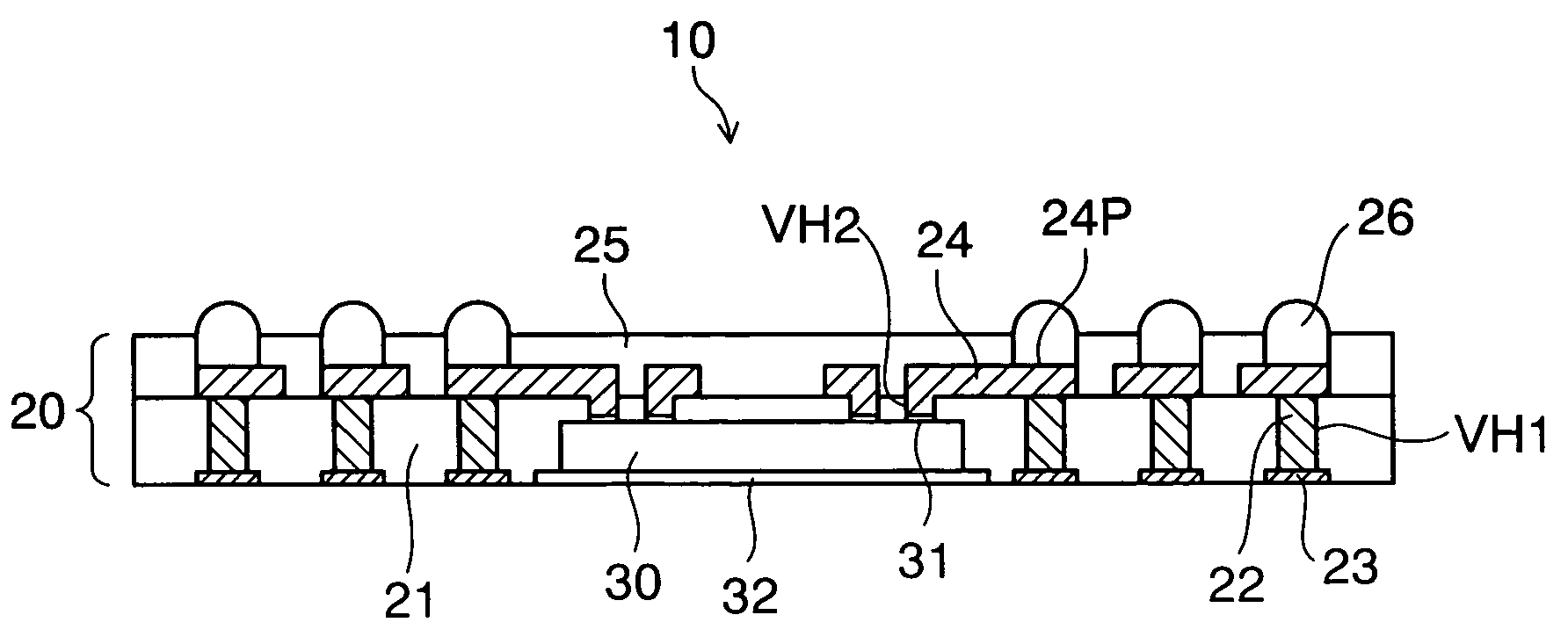

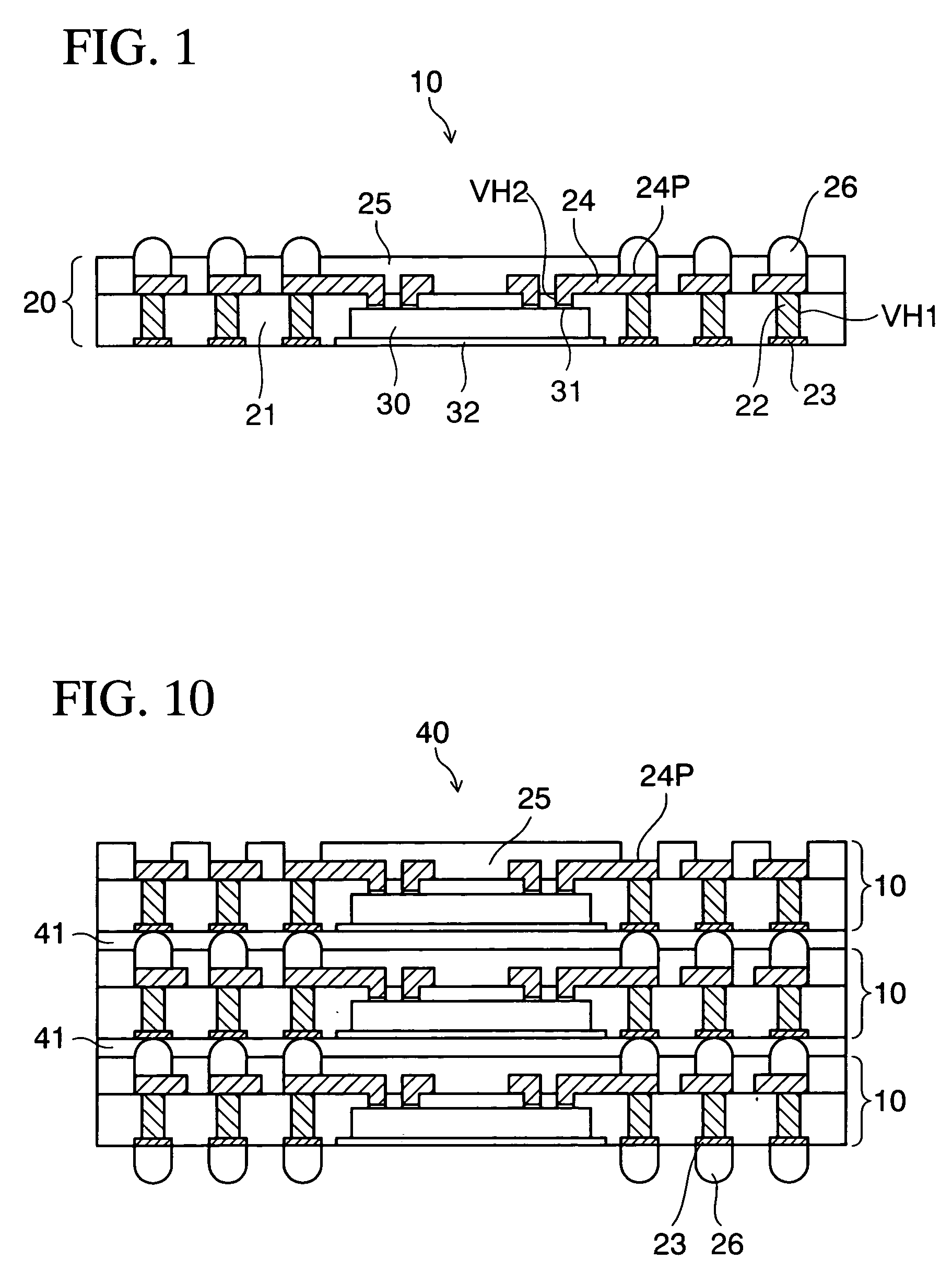

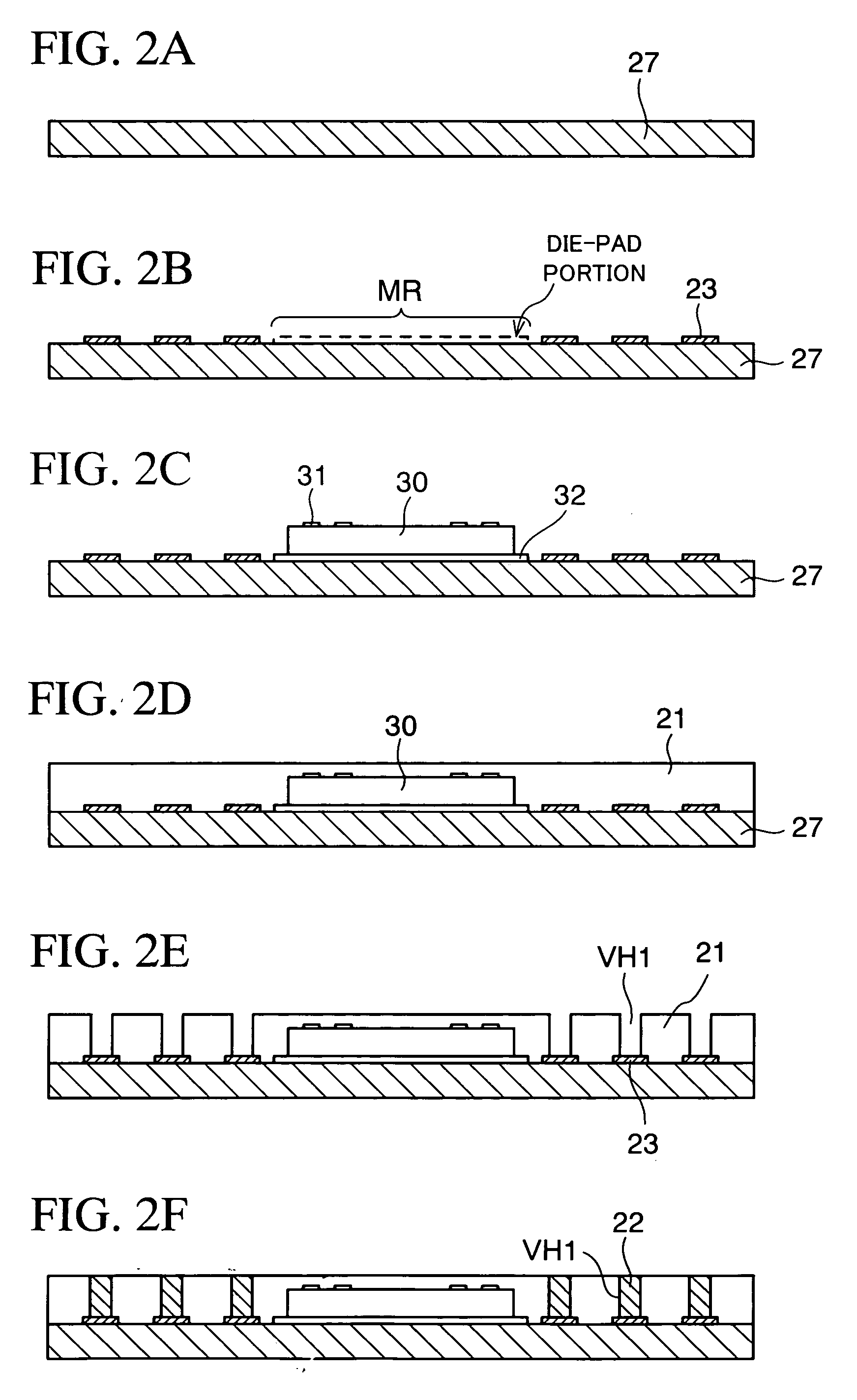

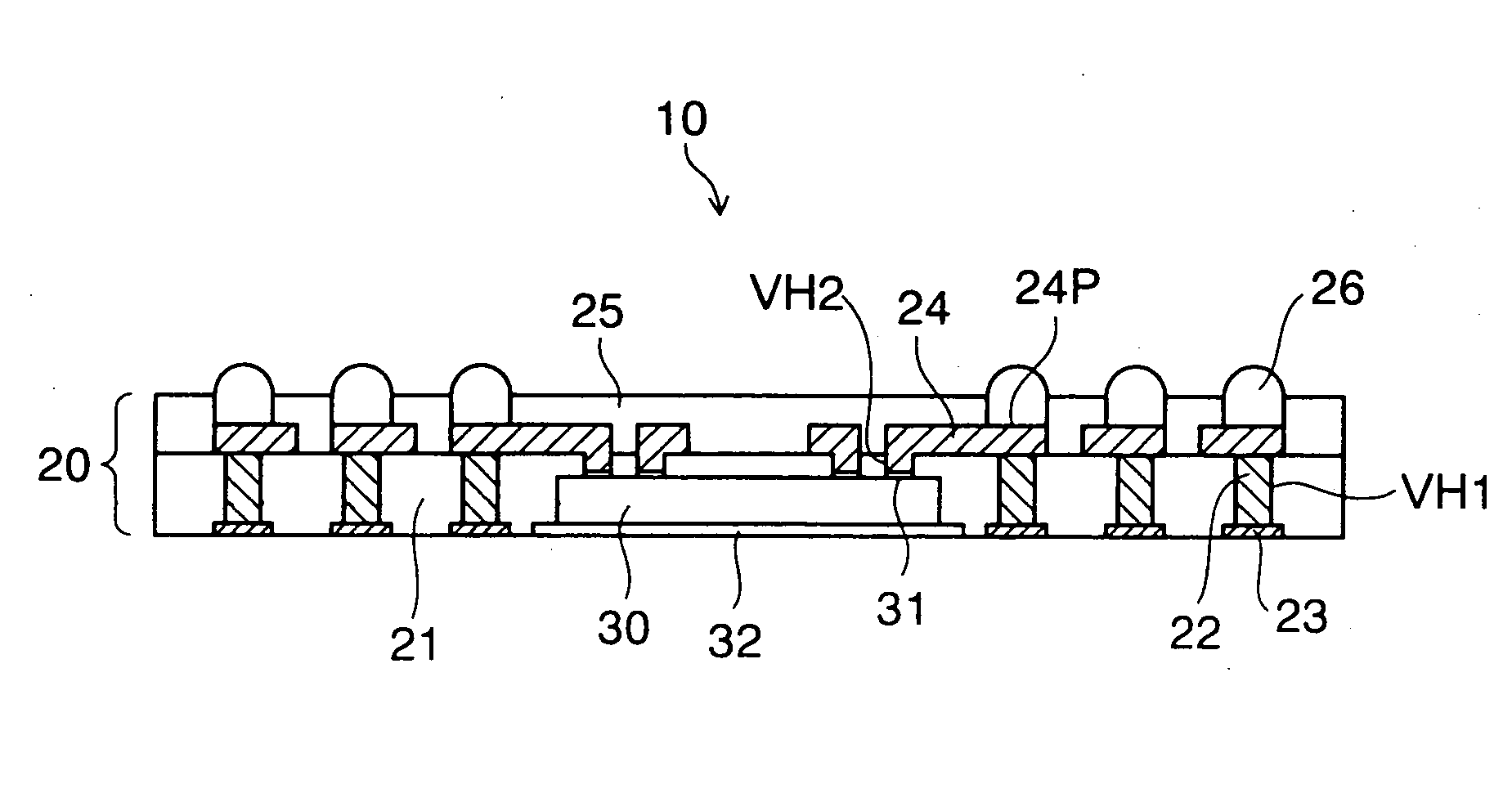

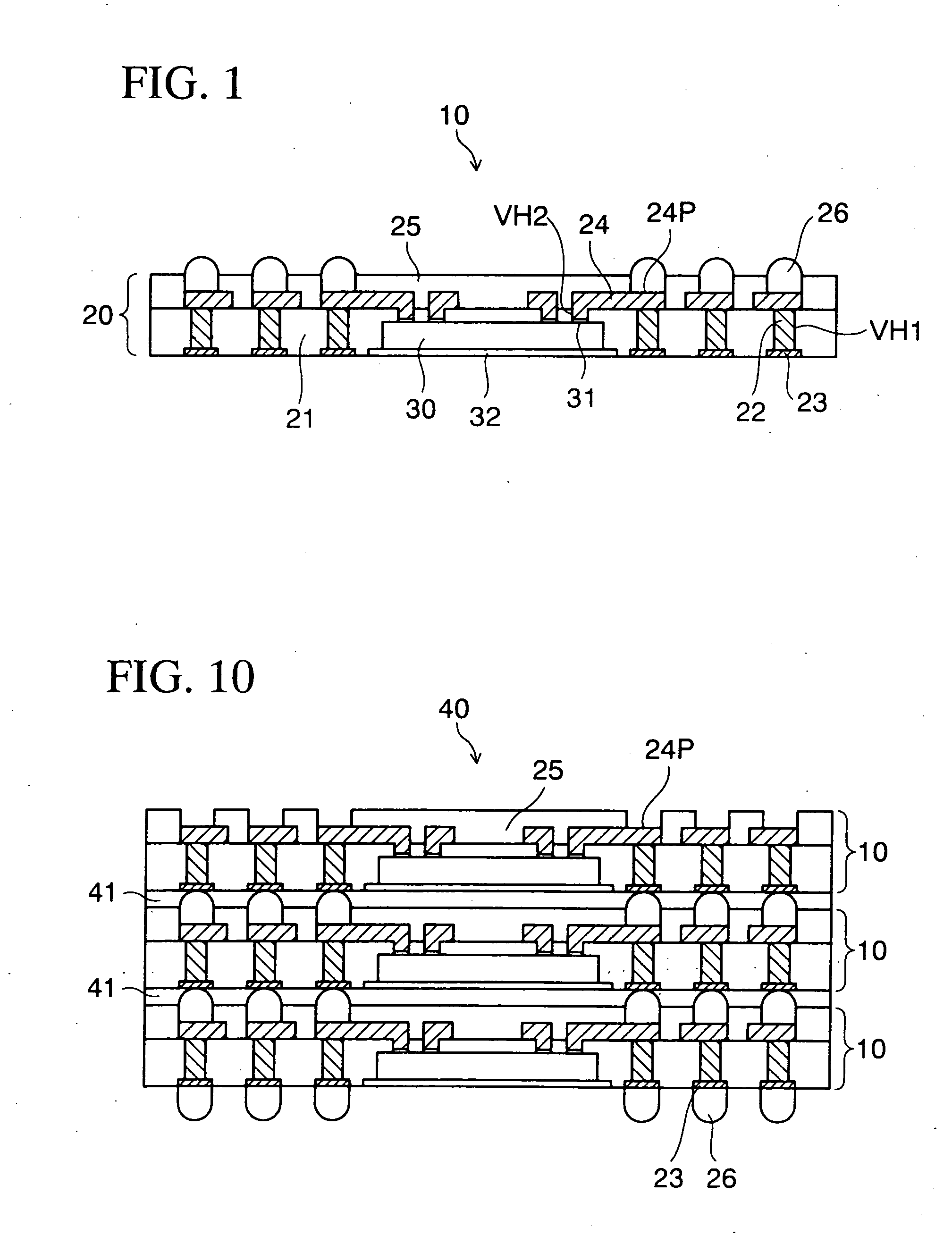

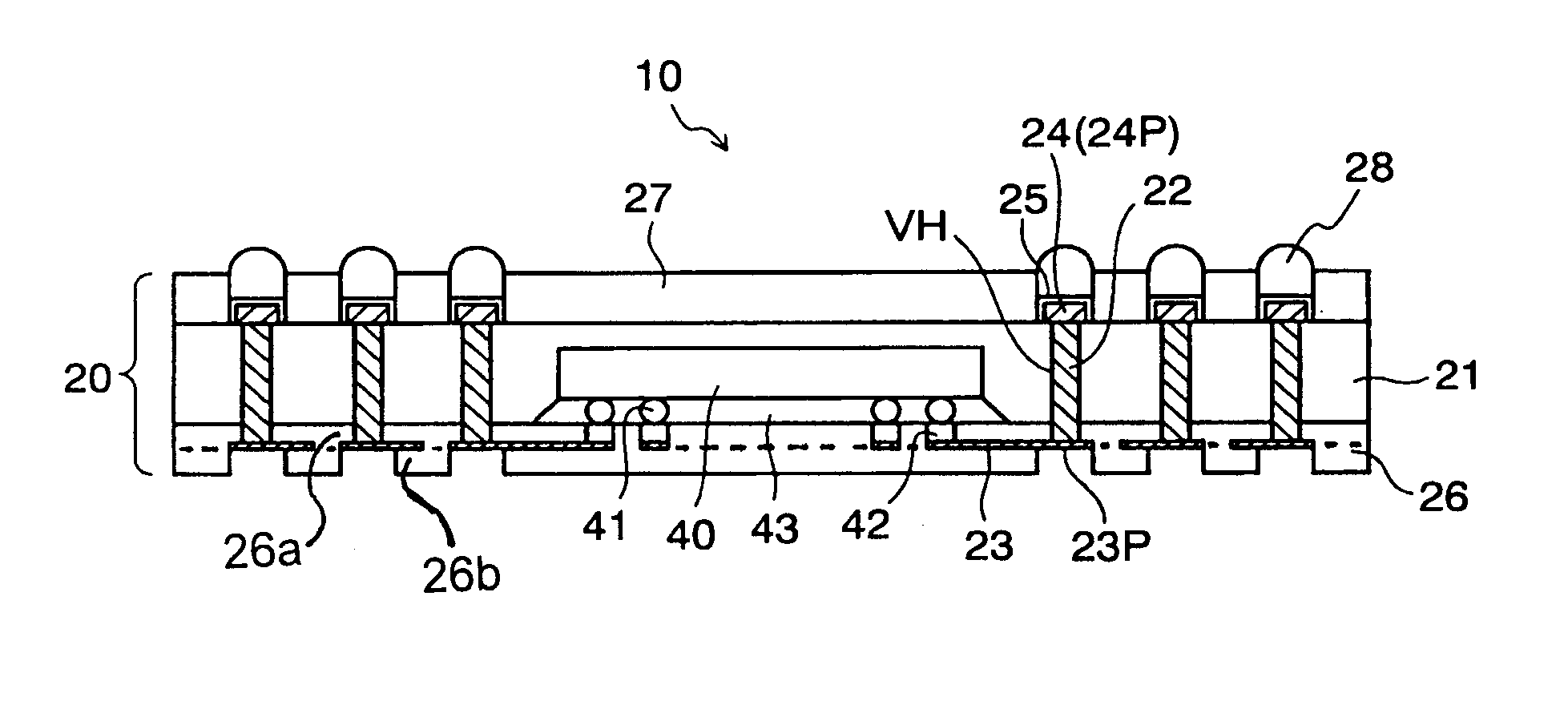

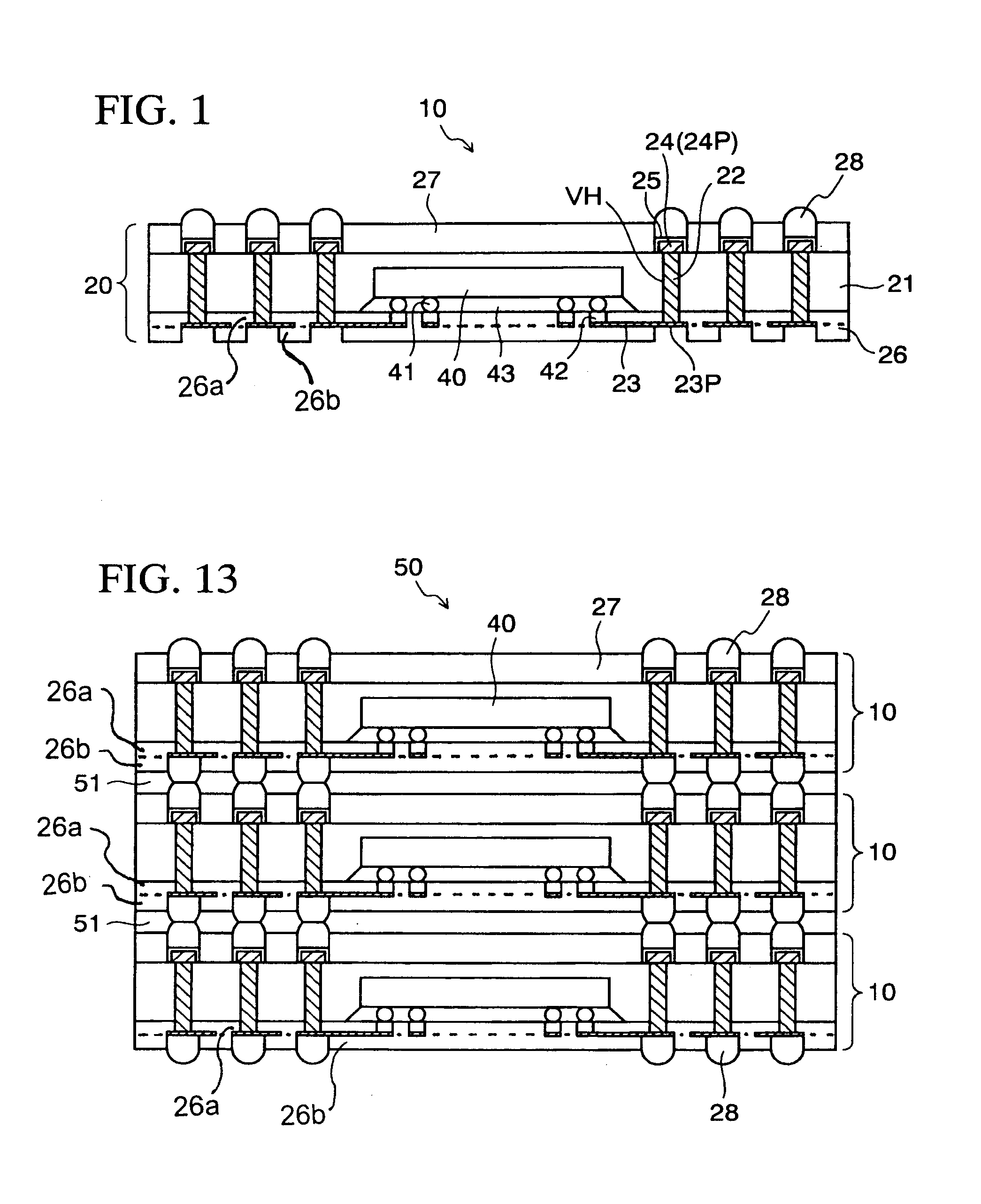

Semiconductor device and method of manufacturing the same

InactiveUS20050184377A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, and conductor layers are respectively formed to be connected to one end and another end of the conductor filled in the individual via hole. Portions (pad portions) of the conductor layers which correspond to the conductors are exposed from protective films, or external connection terminals are bonded to the pad portions. The chip is mounted with flip-chip technology so that at least some of electrode terminals thereof are electrically connected to the conductor layers.

Owner:SHINKO ELECTRIC IND CO LTD

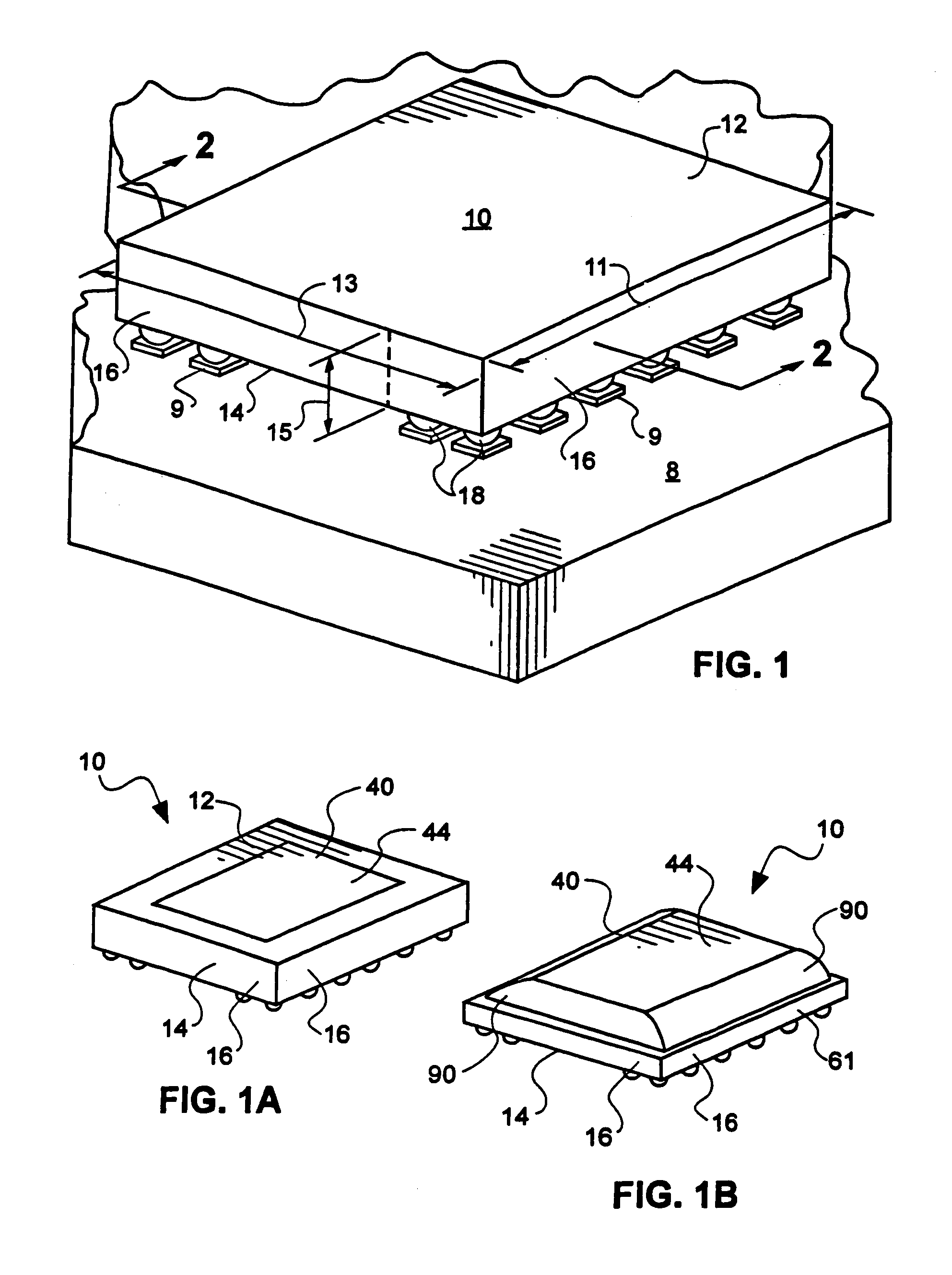

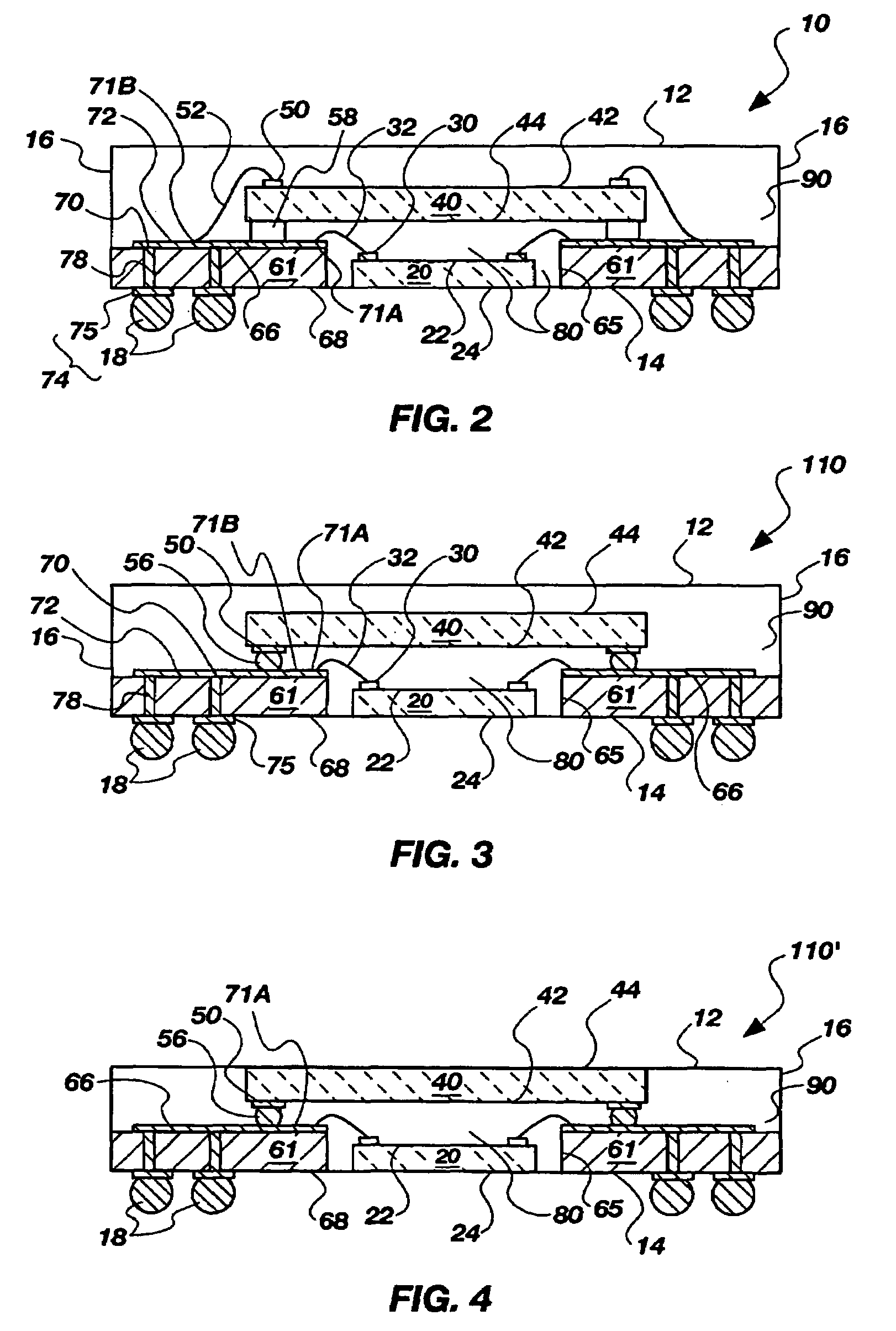

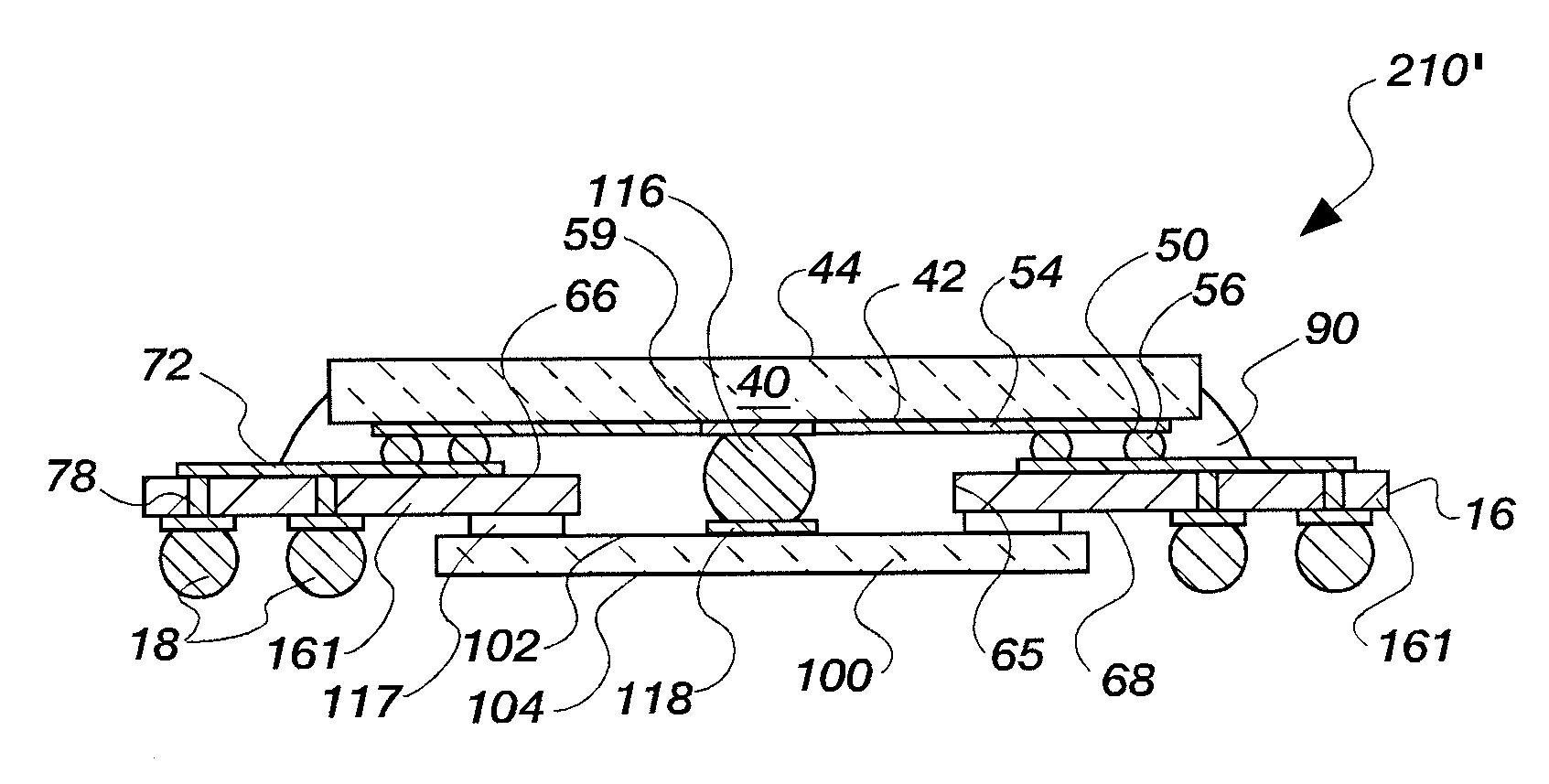

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

Semiconductor device and method of manufacturing the same

ActiveUS20050161833A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, one end of a conductor filled in the via hole is covered with a pad portion exposed to the outside, and a wiring layer connected to the other end of the conductor is formed. The portion (pad portion) of the wiring layer which correspond to the conductor is exposed from a protective film, or an external connection terminal is bonded to the top of the pad portion. Electrode terminals of the chip are connected to the wiring layer, and the opposite surface of the chip is exposed to the outside.

Owner:SHINKO ELECTRIC IND CO LTD

Semiconductor device assemblies and packages including multiple semiconductor device components

InactiveUS7573136B2Reduce area requirementsHelp positioningSemiconductor/solid-state device detailsSolid-state devicesContact padInterposer

A multidie semiconductor device assembly or package includes an interposer comprising a substrate with at least one receptacle therethrough. A plurality of semiconductor device components (e.g., semiconductor devices) may be assembled with the interposer. For example, at least one contact pad of a semiconductor device component adjacent to one surface of the interposer may be electrically connected to a corresponding contact pad of another semiconductor device component positioned adjacent to an opposite surface of the interposer. As another example, multiple semiconductor device components may be at least partially superimposed relative to one another and at least partially disposed within a receptacle of the interposer.

Owner:MICRON TECH INC

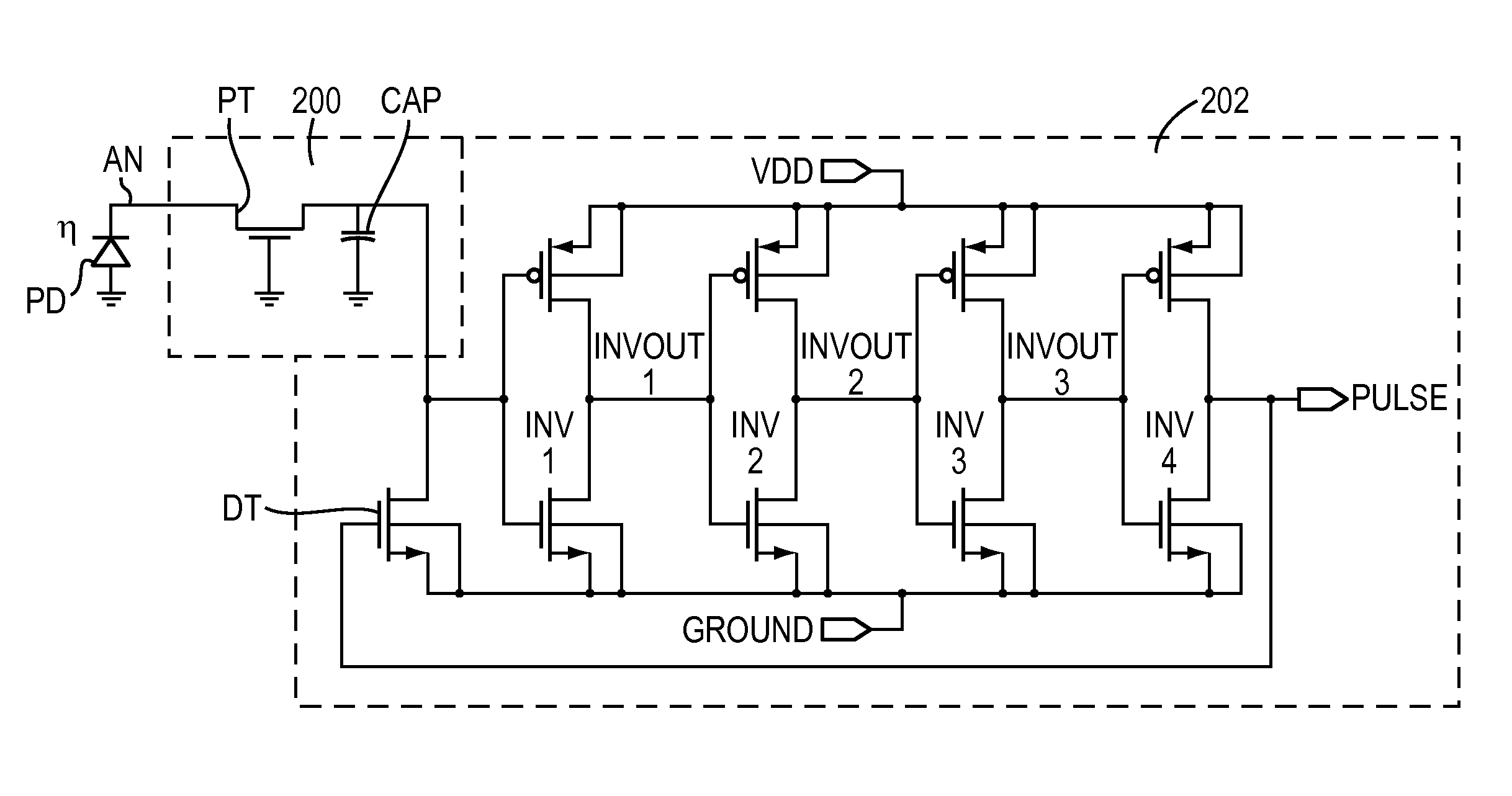

Digital readout method and apparatus

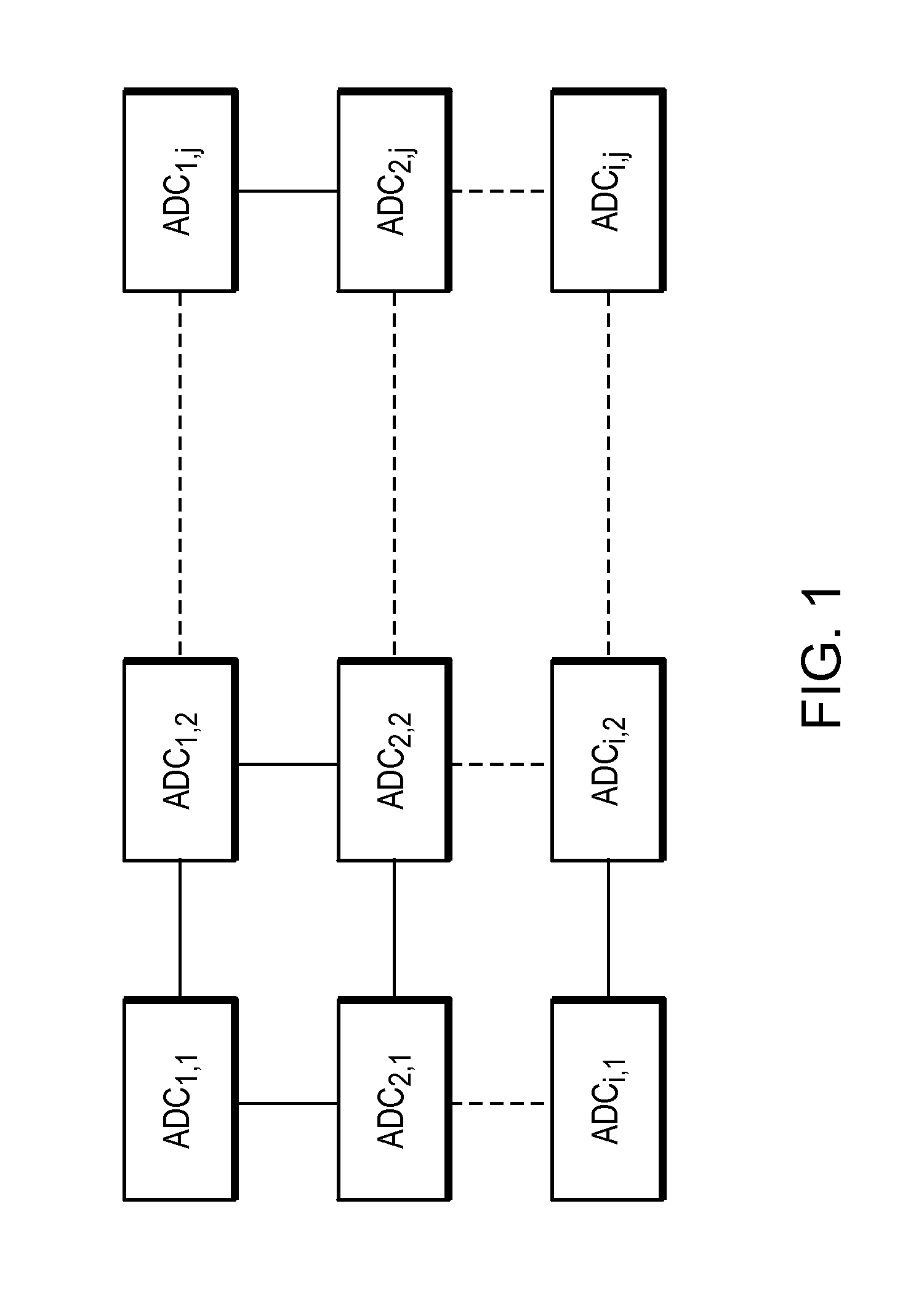

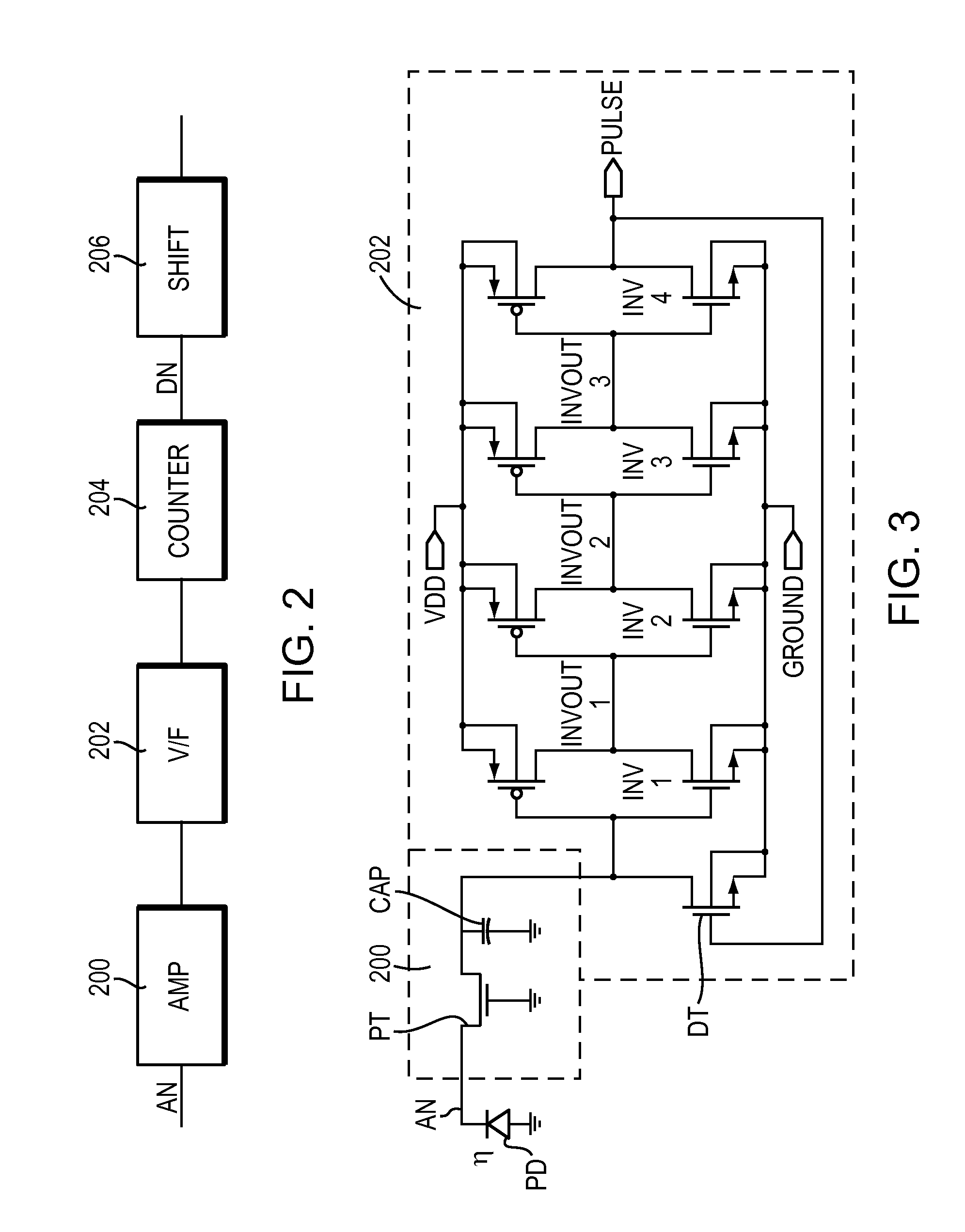

ActiveUS8179296B2Large chargeHighly linear analog electronics can be eliminatedTelevision system detailsElectric signal transmission systemsSensor arrayDigital signal processing

Autonomously operating analog to digital converters are formed into a two dimensional array. The array may incorporate digital signal processing functionality. Such an array is particularly well-suited for operation as a readout integrated circuit and, in combination with a sensor array, forms a digital focal plane array.

Owner:MASSACHUSETTS INST OF TECH

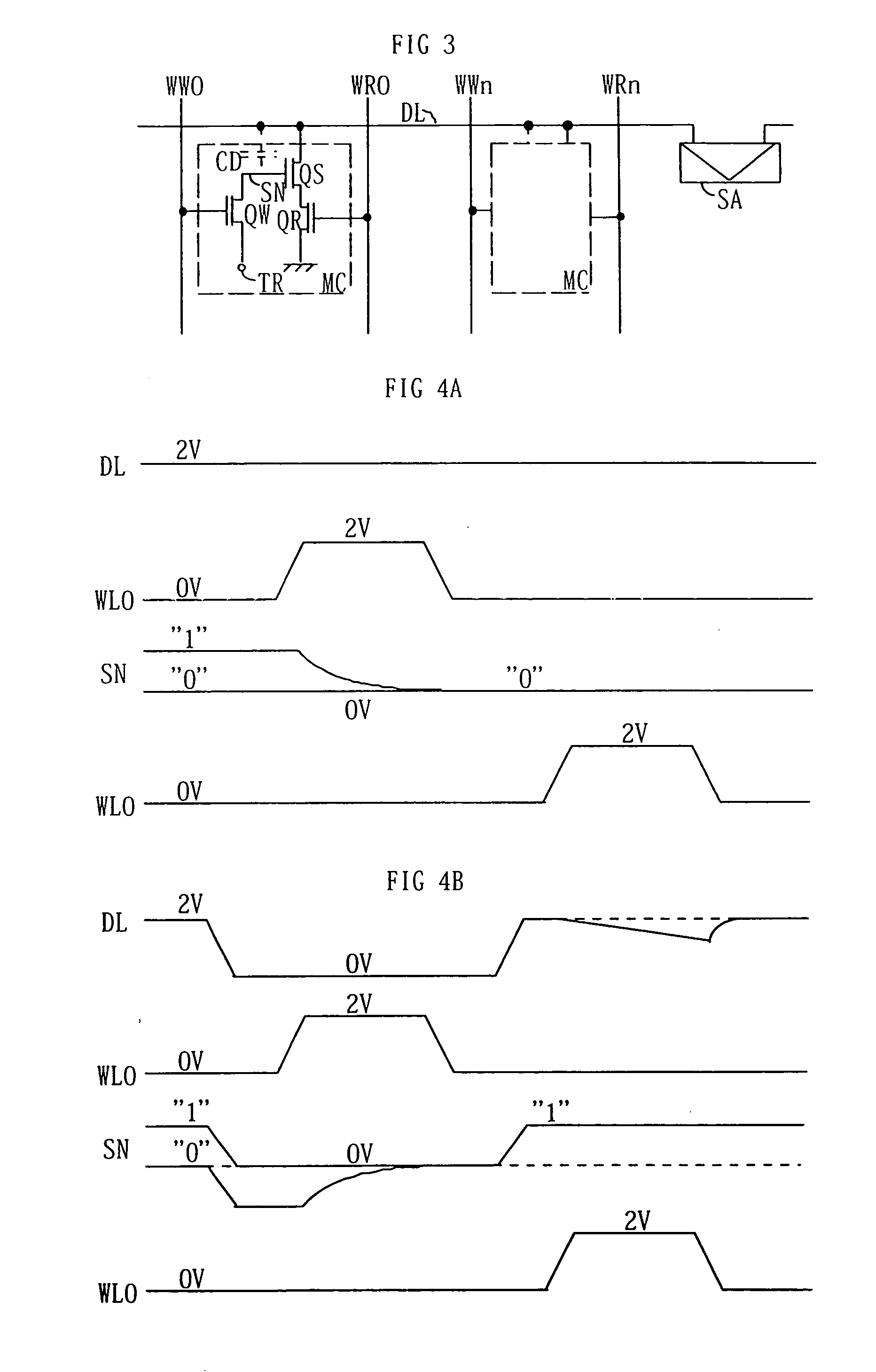

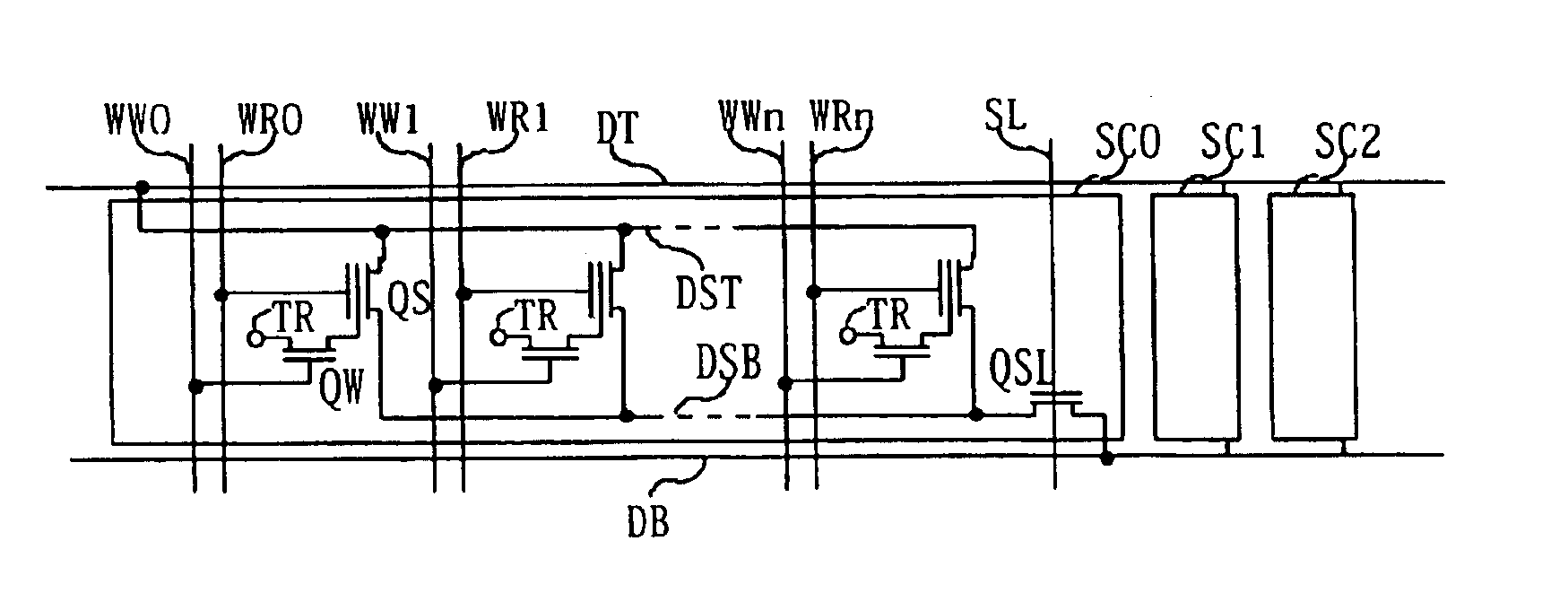

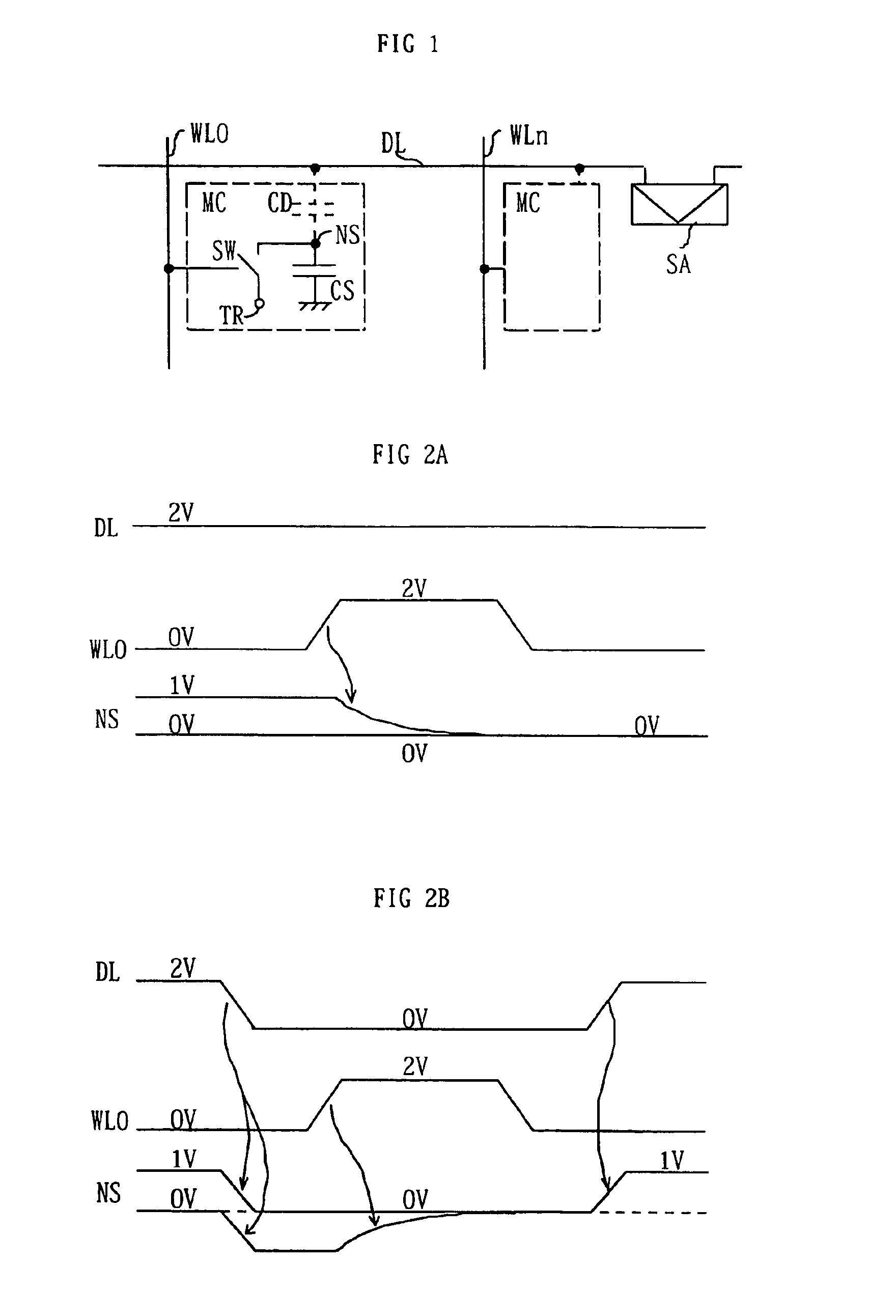

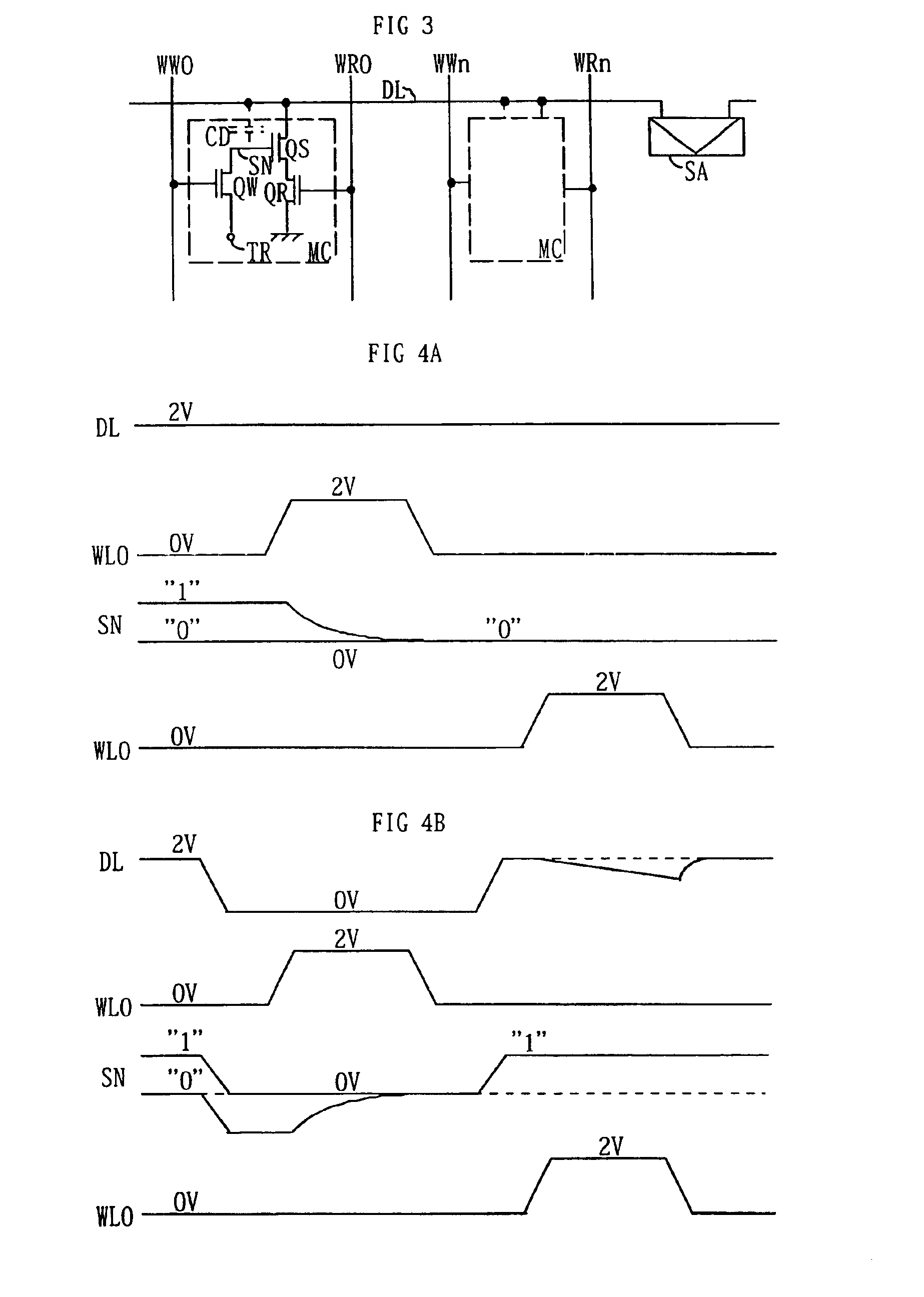

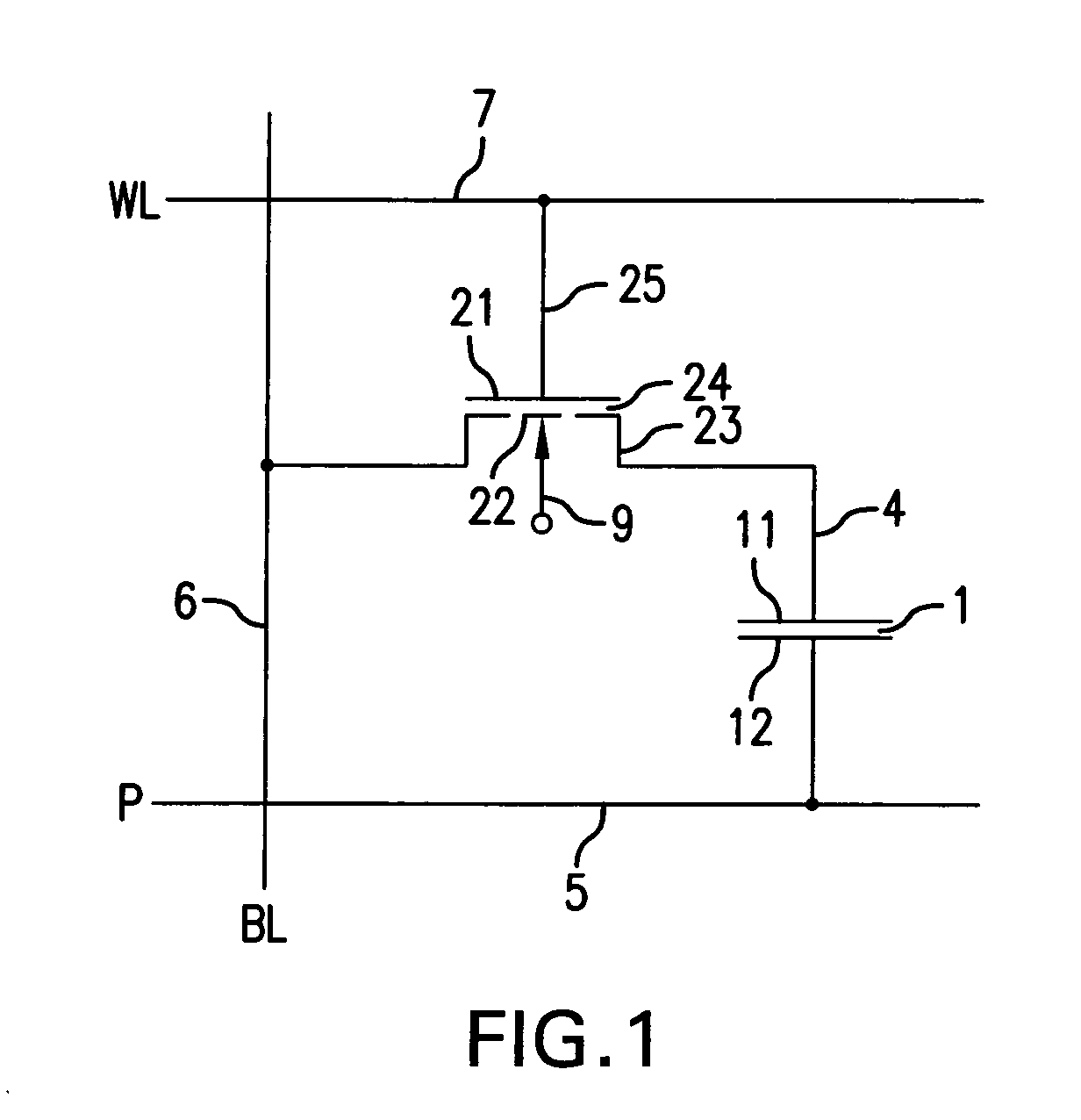

Semiconductor memories

InactiveUS20050237786A1Reduce areaReduce area requirementsTransistorSolid-state devicesHigh densityComputer science

A high integration dynamic random access memory is provided by this invention. Furthermore, a write method is provided such that cell size of two-and three-transistor gain cell memories is reduced. A dynamic memory incorporating a thin-channel transistor as the write element such that long data storage retention is achieved in the memory devices of this invention. A dynamic memory cell having low operating power and high density is also realized by this invention.

Owner:HITACHI LTD +1

Semiconductor device and method of manufacturing the same

InactiveUS20090246909A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, one end of a conductor filled in the via hole is covered with a pad portion exposed to the outside, and a wiring layer connected to the other end of the conductor is formed. The portion (pad portion) of the wiring layer which correspond to the conductor is exposed from a protective film, or an external connection terminal is bonded to the top of the pad portion. Electrode terminals of the chip are connected to the wiring layer, and the opposite surface of the chip is exposed to the outside.

Owner:SHINKO ELECTRIC IND CO LTD

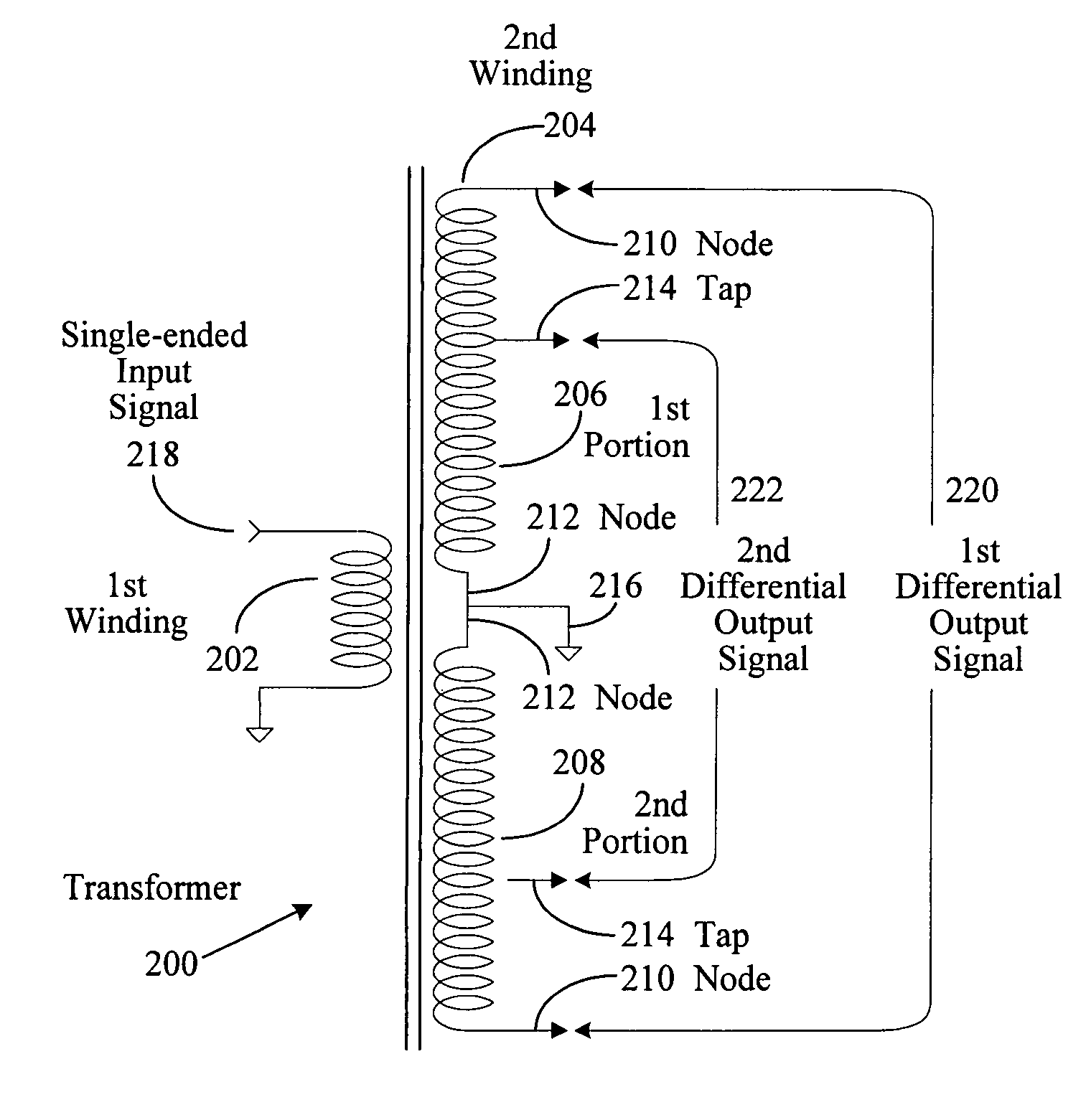

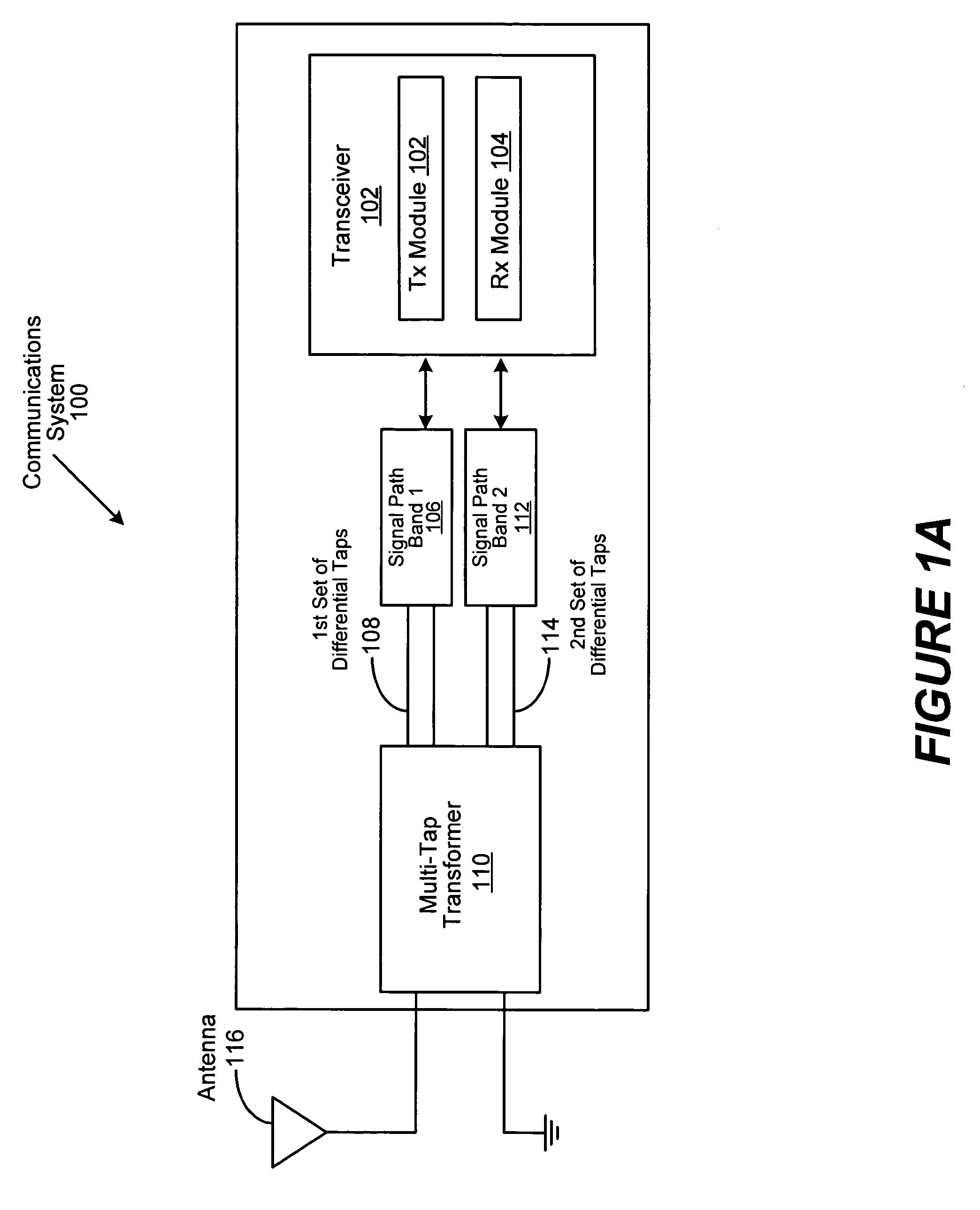

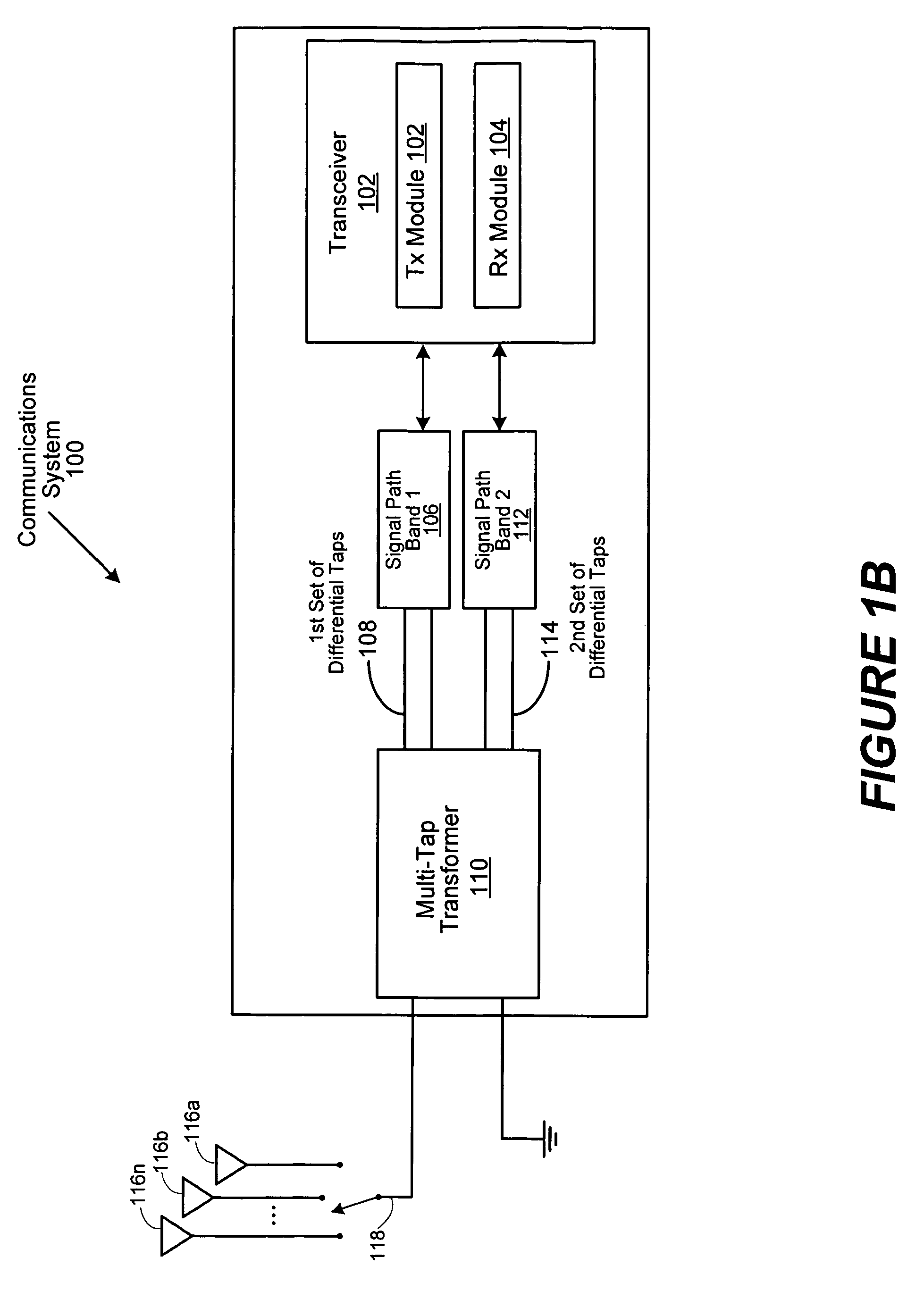

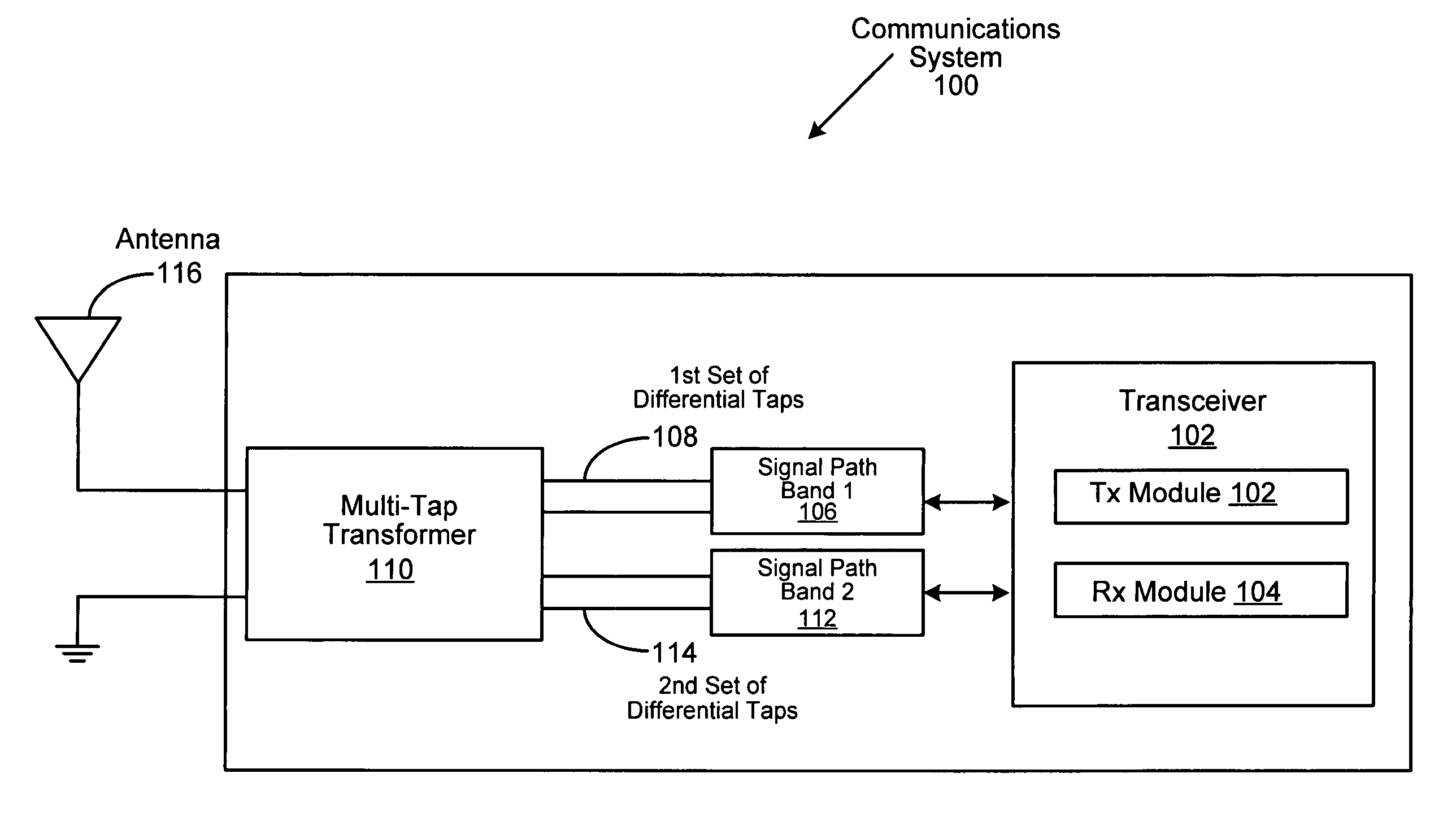

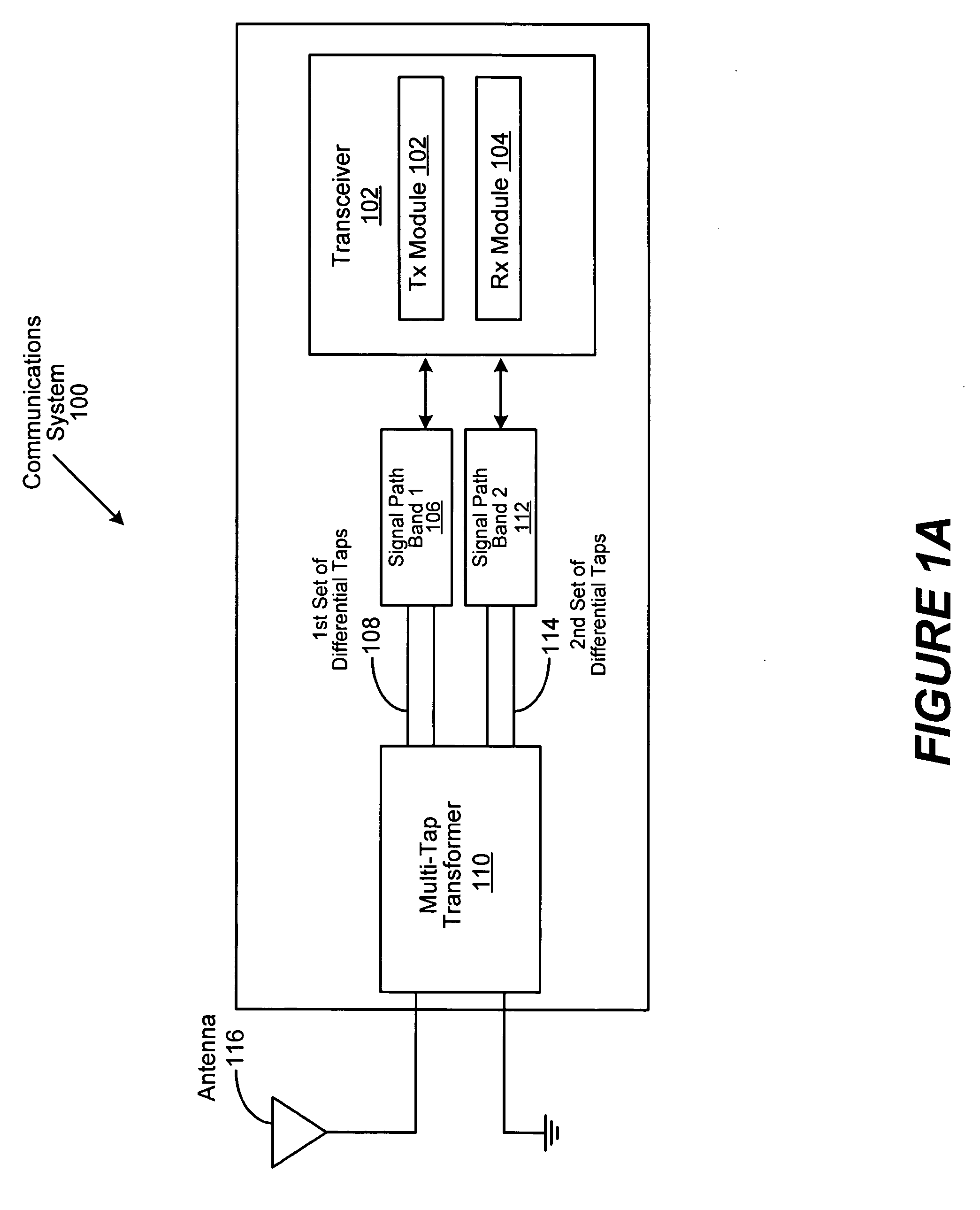

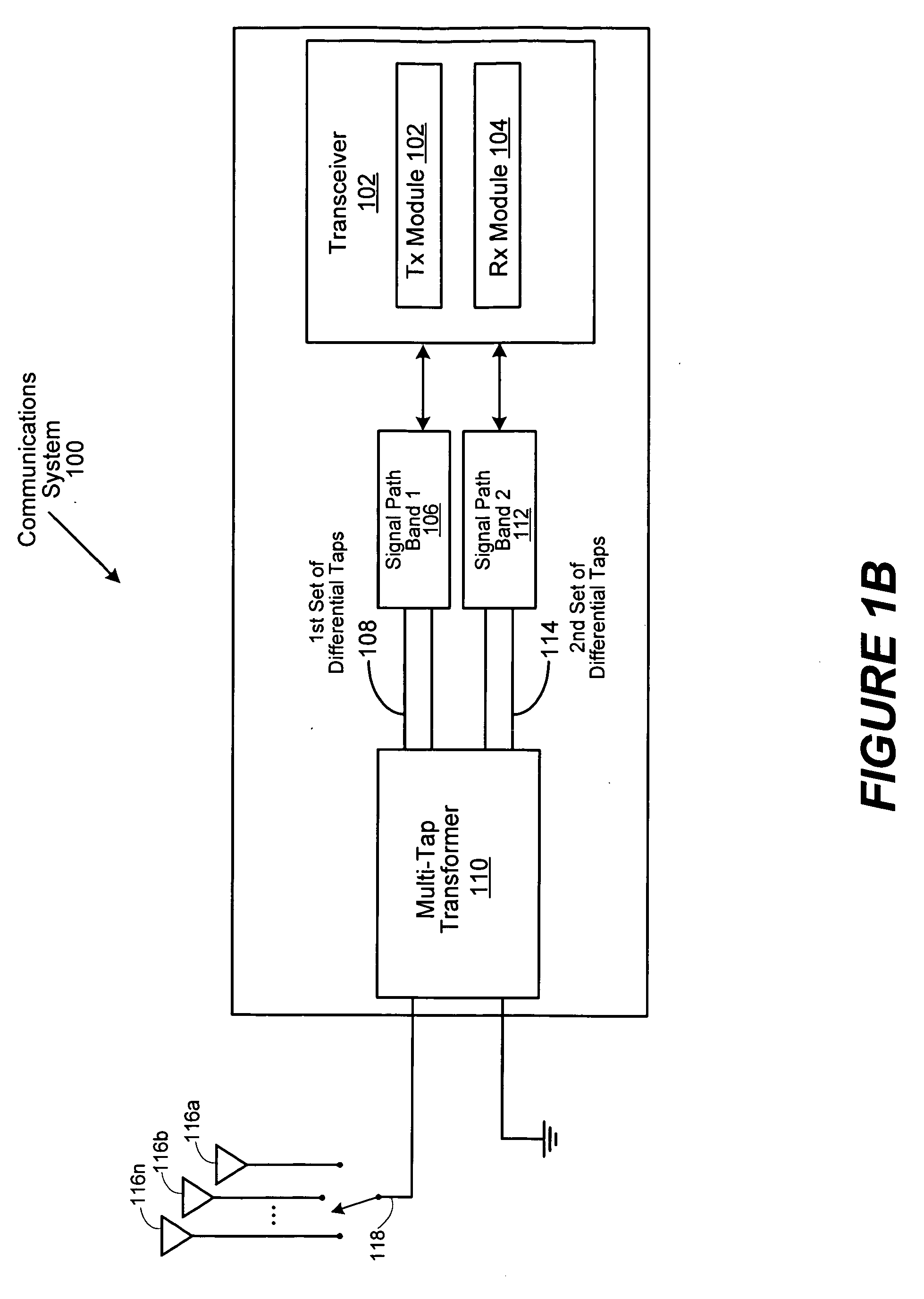

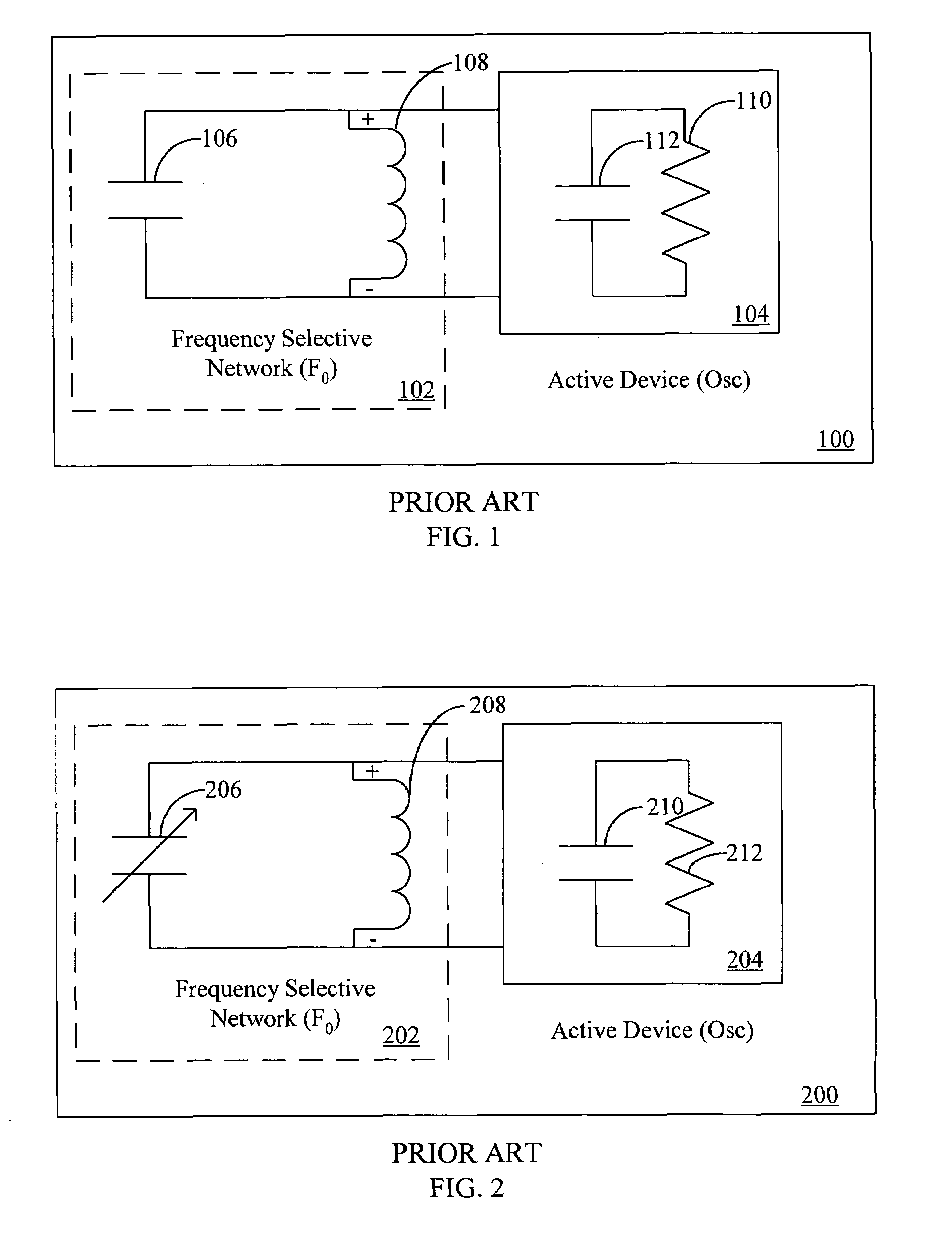

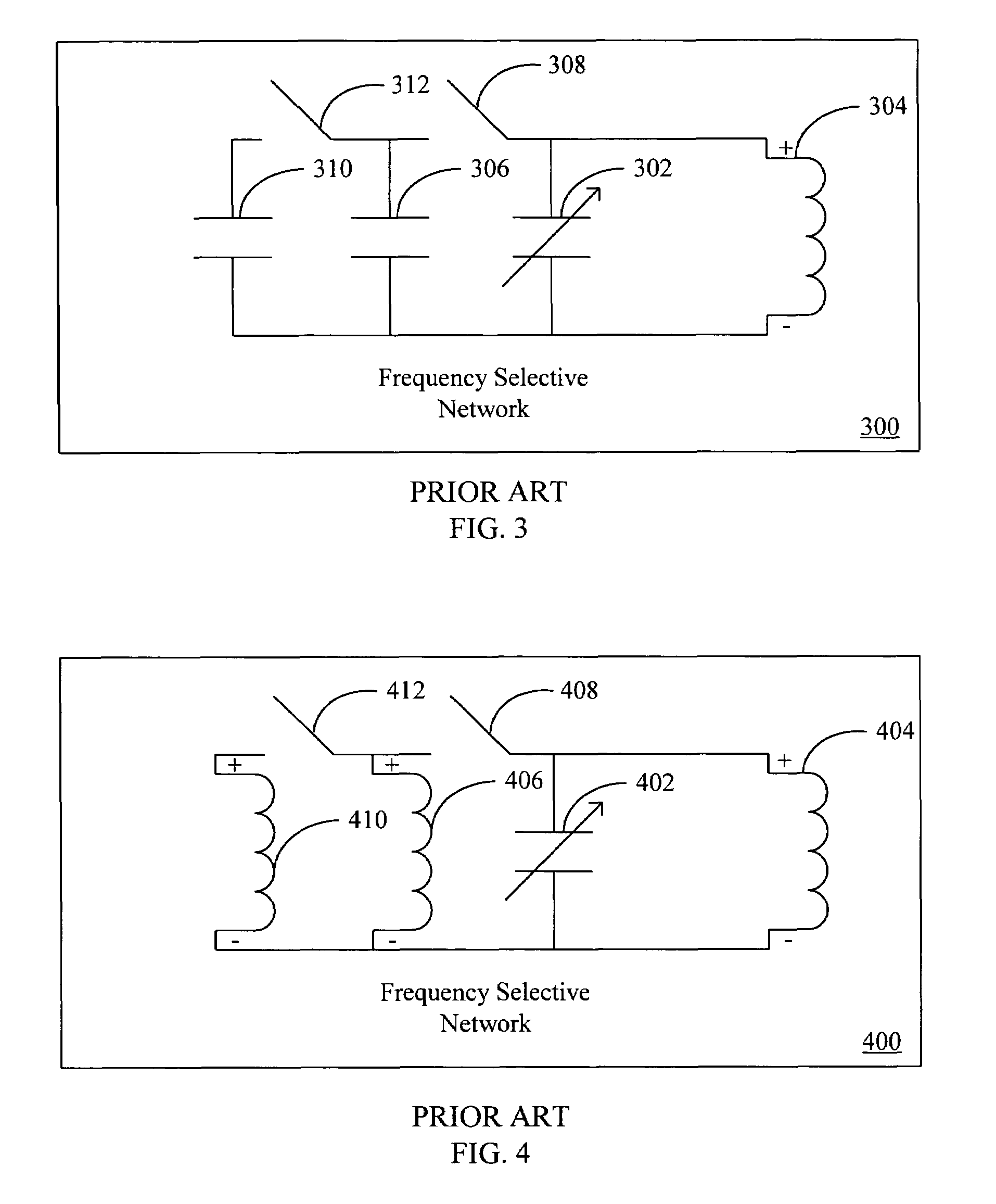

Transformer-based multi-band RF front-end architecture

InactiveUS7526256B2Reduce area requirementsOne-port networksDc level restoring means or bias distort correctionMulti bandTransformer

Owner:AVAGO TECH INT SALES PTE LTD

Transformer-based multi-band RF front-end architecture

InactiveUS20060270377A1Reduce area requirementsOne-port networksDc level restoring means or bias distort correctionMulti bandRF front end

An apparatus and method for allowing two different signal paths to be coupled to a multi-tap transformer balun. The multi-tap transformer has a first port, which is coupled to a single antenna, and two or more differential secondary ports. Each port has one or more taps, which are optimized separately for each of the signal paths, allowing each of the two or more signal paths to operate in different frequency bands. Use of the method of the invention can decrease the number of external components and integrated circuit package pins, and reduce the area required for each signal path on an integrated circuit die, a printed circuit board, or the like.

Owner:AVAGO TECH INT SALES PTE LTD

Semiconductor device and method of manufacturing the same

InactiveUS7791206B2Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

Owner:SHINKO ELECTRIC IND CO LTD

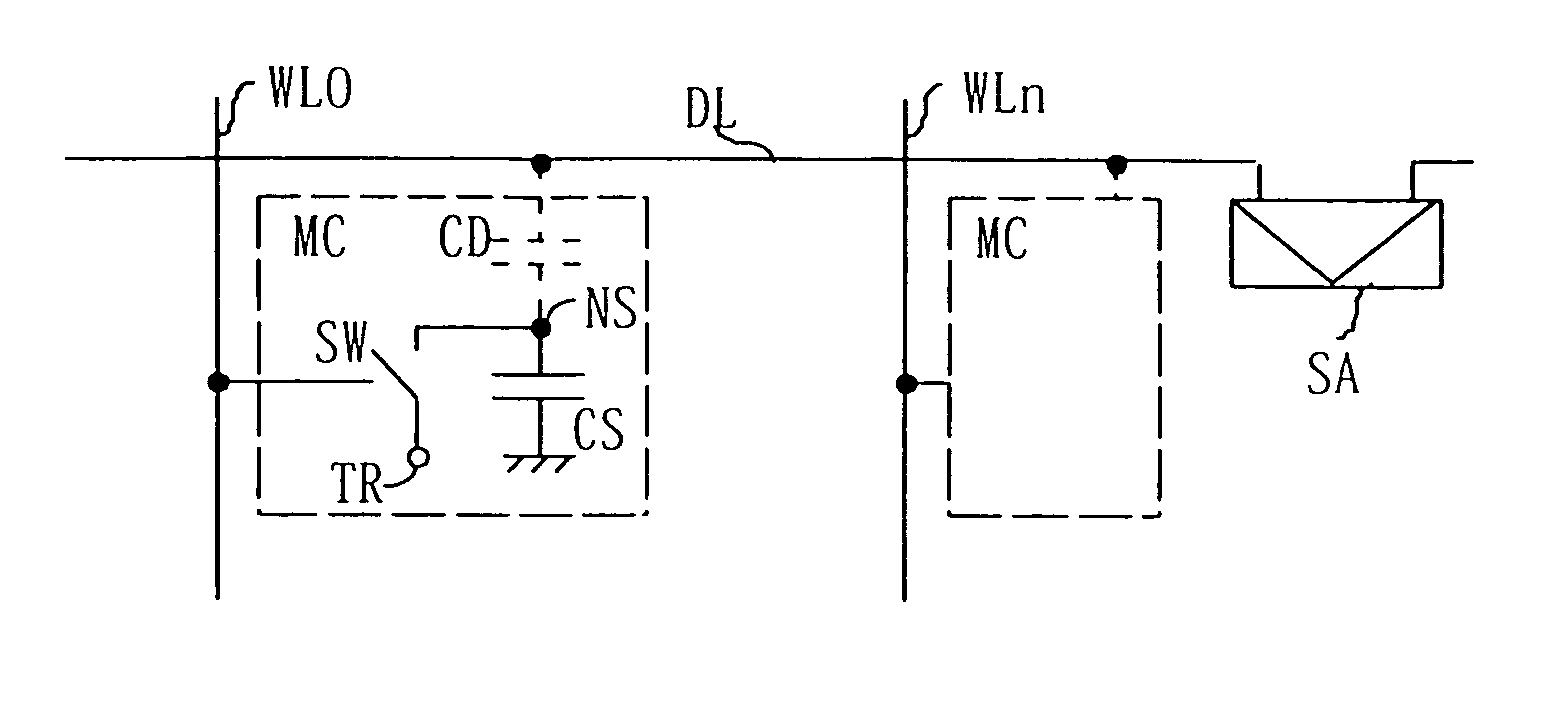

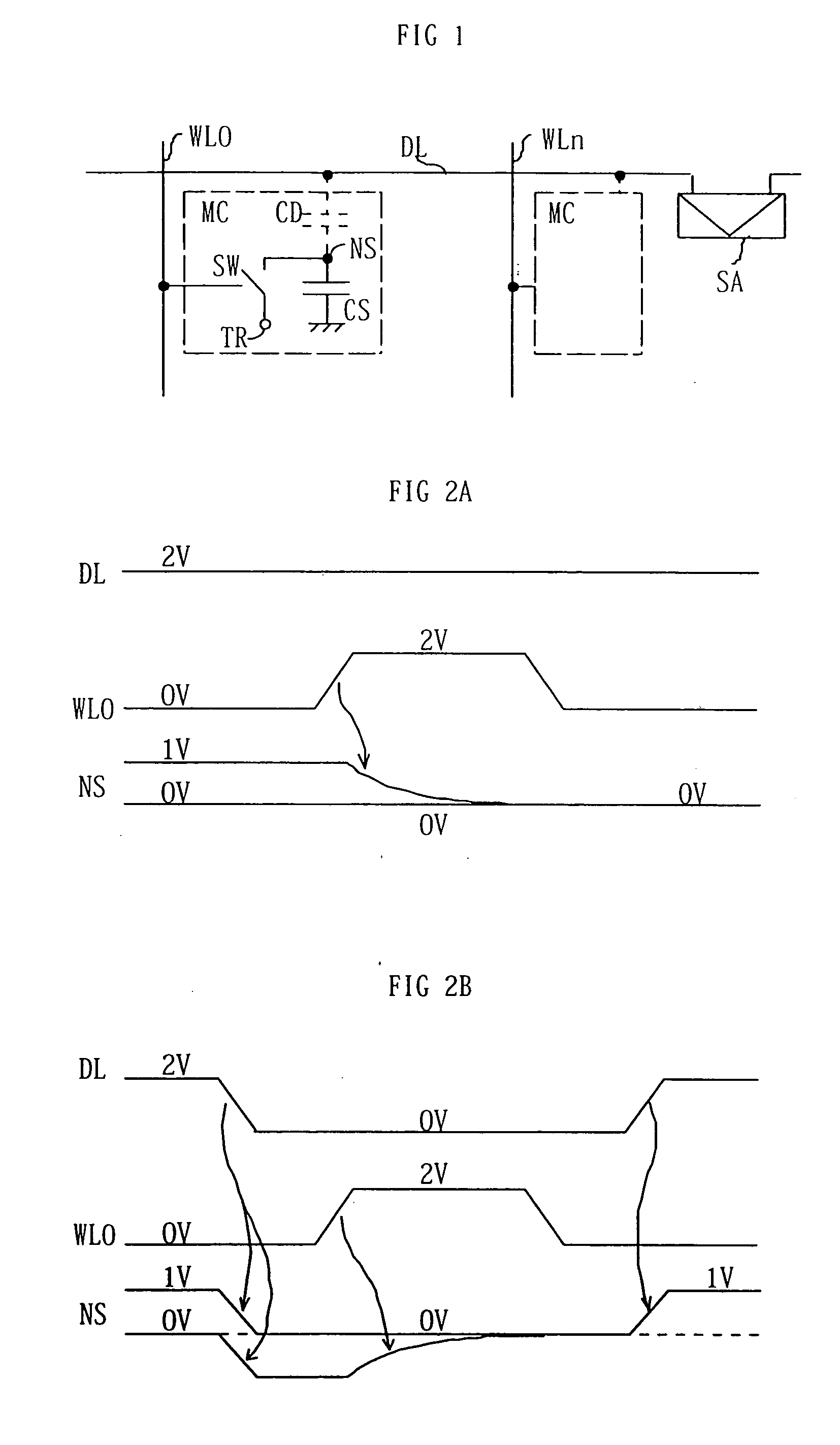

Semiconductor memories

InactiveUS6949782B2Reduce areaReduce area requirementsTransistorSolid-state devicesHigh densityComputer science

A high integration dynamic random access memory is provided by this invention. Furthermore, a write method is provided such that the cell size of two-and three-transistor gain cell memories is reduced. A dynamic memory incorporating a thin-channel transistor as the write element such that long data storage retention is achieved in the memory devices of this invention. A dynamic memory cell having low operating power and high density is also realized by this invention.

Owner:HITACHI LTD

Lateral high-Q inductor for semiconductor devices

InactiveUS6292086B1Reduce area requirementsSimple modelSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsInductorEngineering

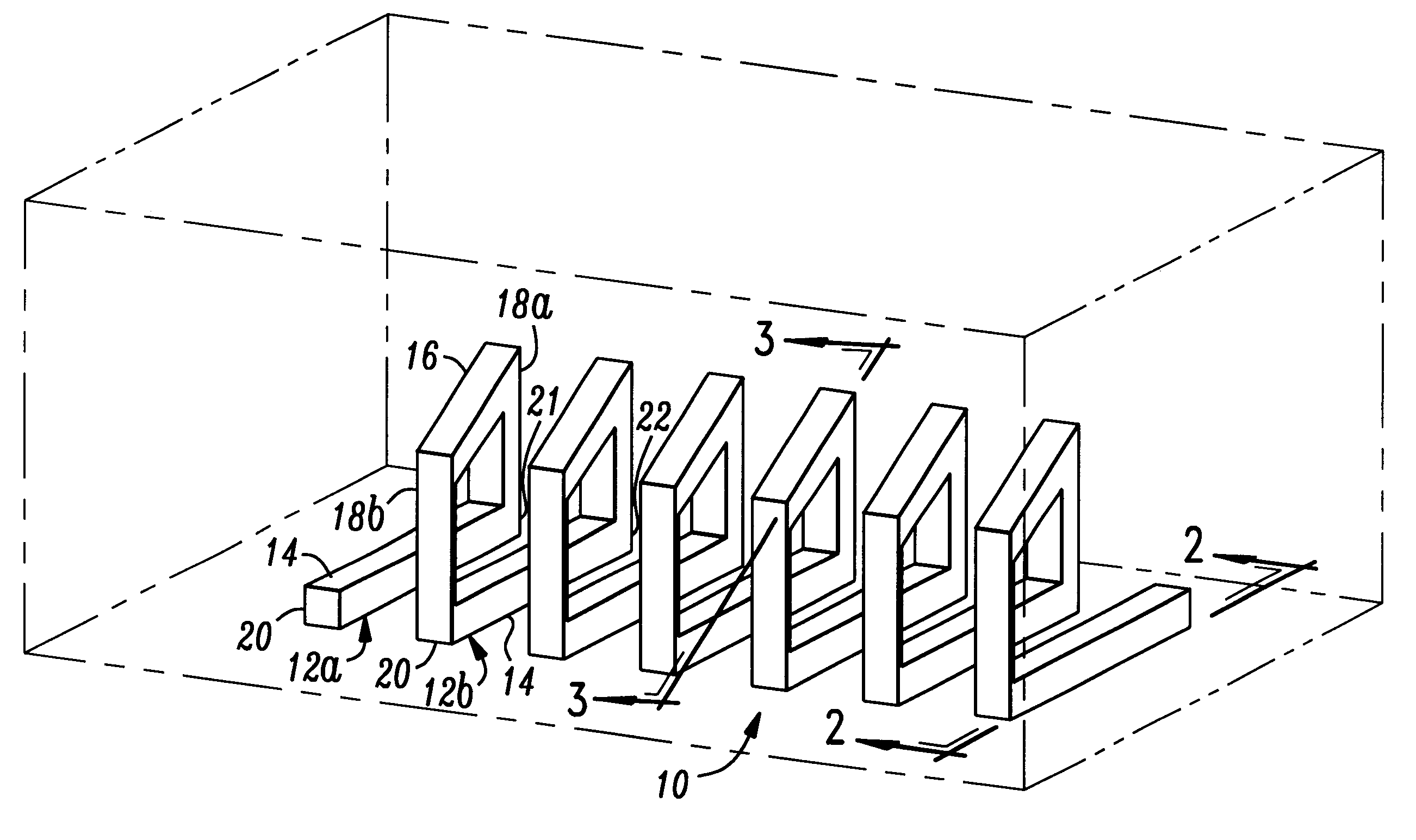

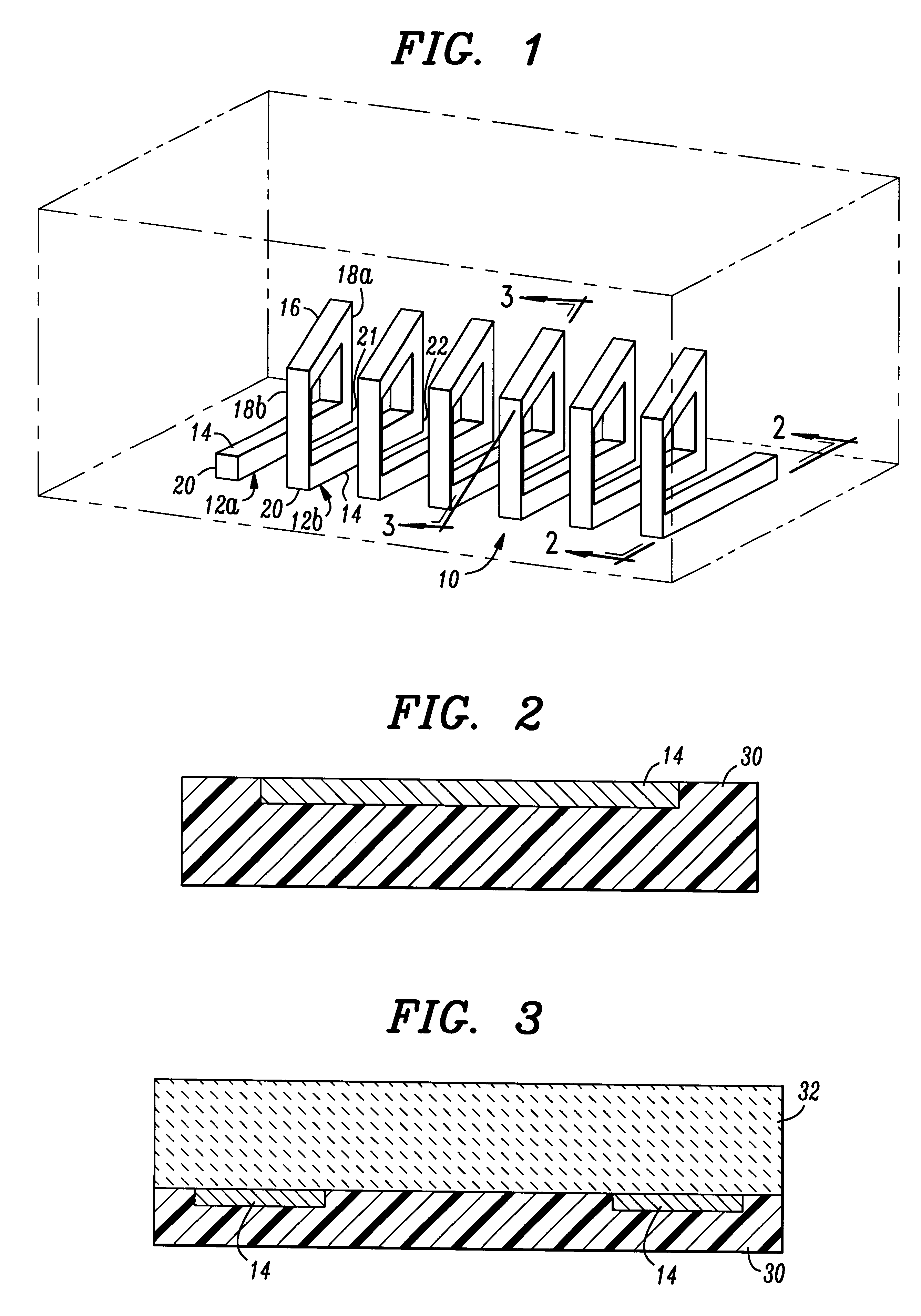

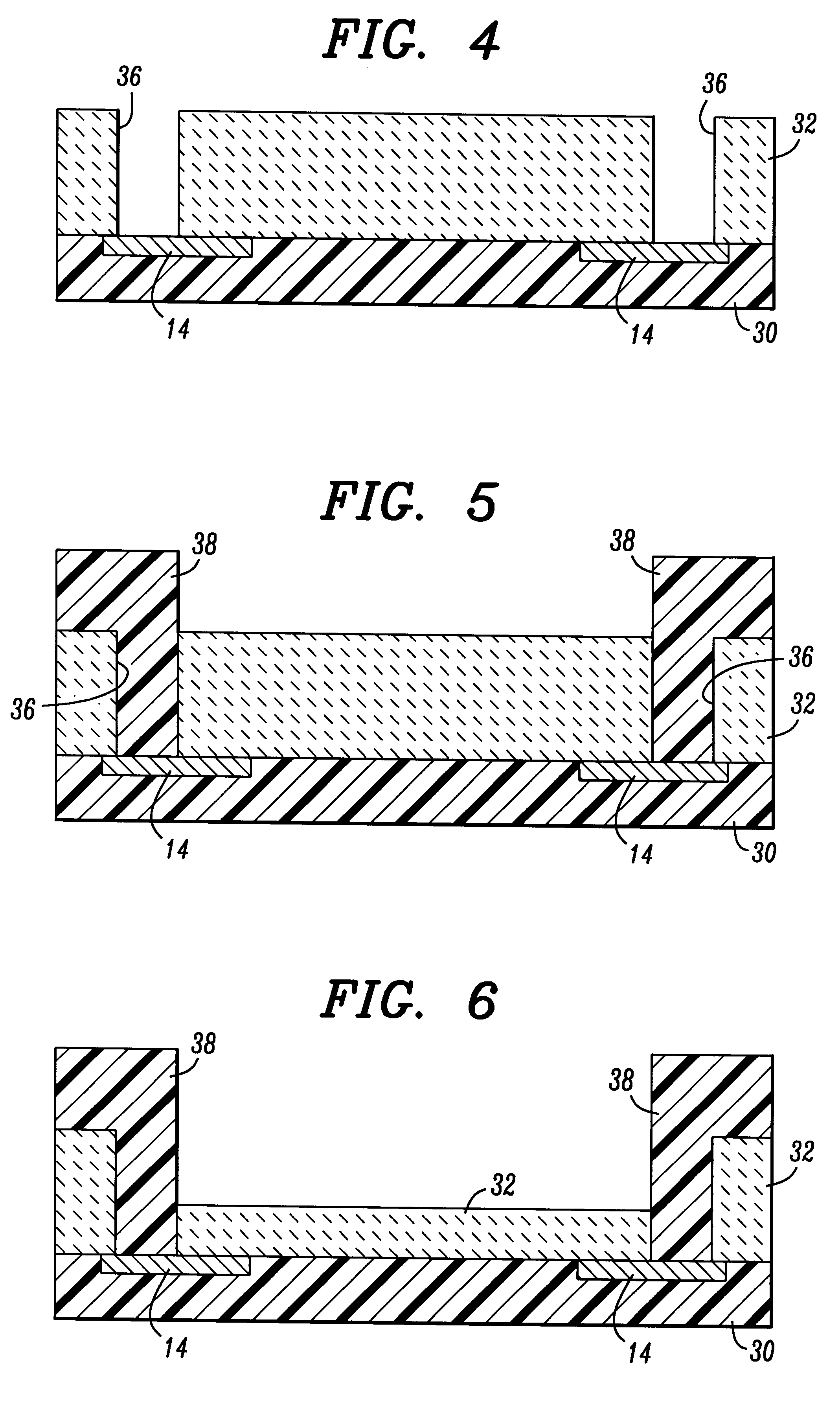

An inductor for a semiconductor device comprises a plurality of loops connected in series and formed along a lateral axis of the semiconductor device. Each loop comprises a bottom leg, a top leg, and a pair of side legs. The bottom legs are parallel and extend along a first plane. The top legs are also parallel and extend along a second plane. The second plane is parallel to and separate from the first plane. The first and second planes are parallel to said lateral axis, and the side legs are perpendicular to the first and second planes. The top and side legs can be formed from copper. A barrier layer between the top legs and a substrate layer adjacent the top legs and between the side legs and the bottom legs and the substrate layer can also be provided. The barrier can be formed from tantalum.

Owner:BELL SEMICON LLC +1

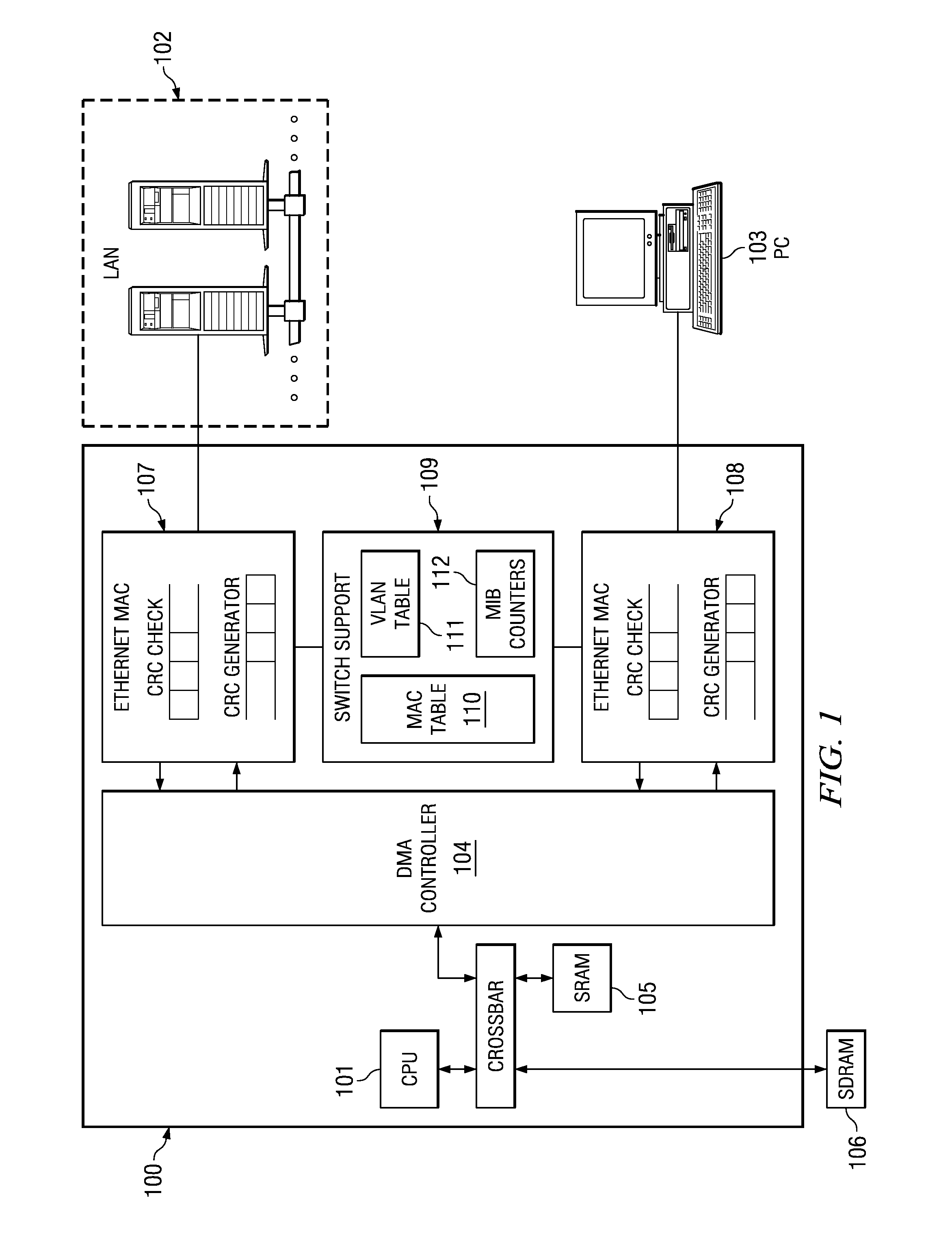

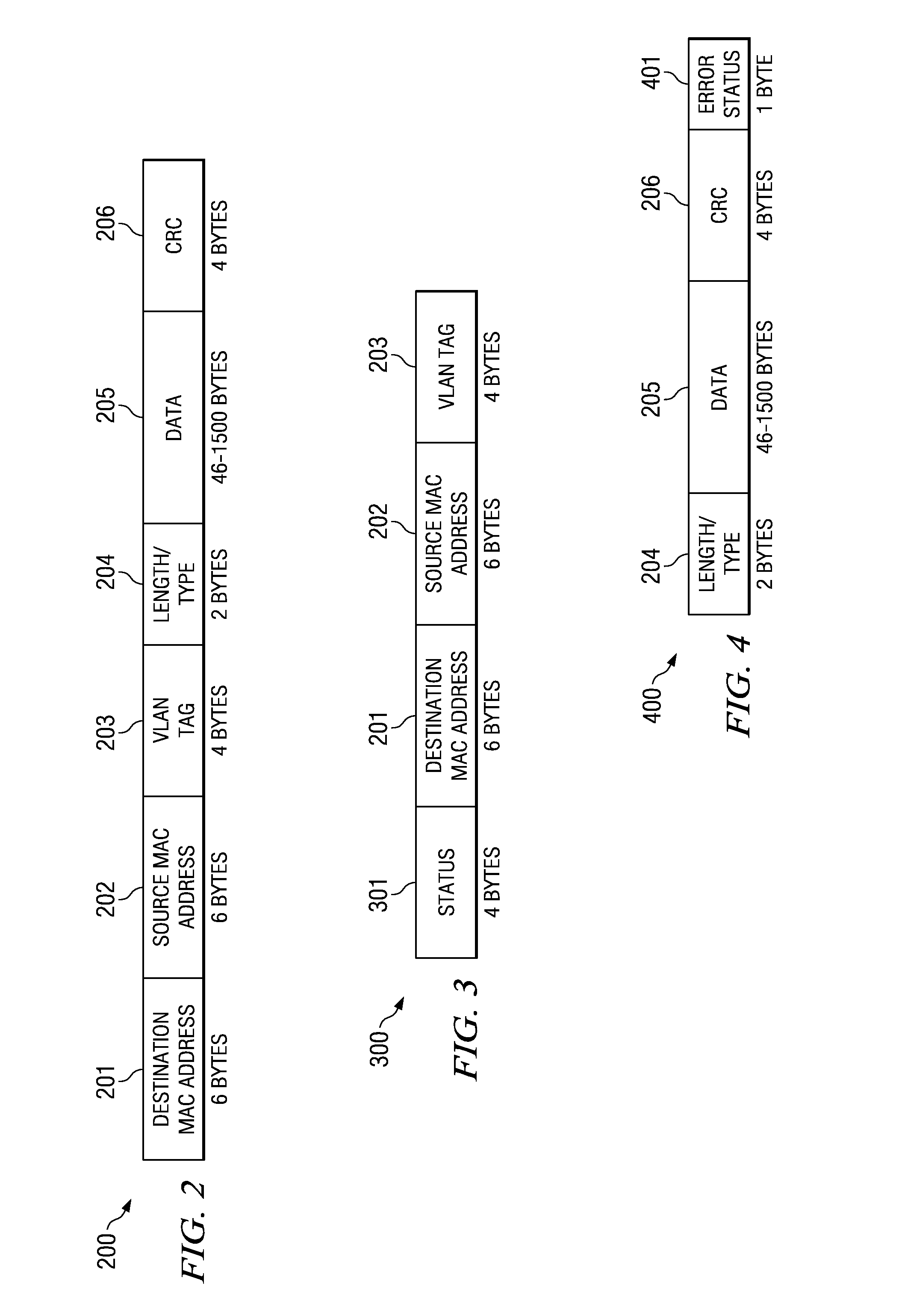

Three-port ethernet switch with external buffer

InactiveUS20080240103A1Reduce chip areaReduce area requirementsData switching by path configurationData bufferPayload

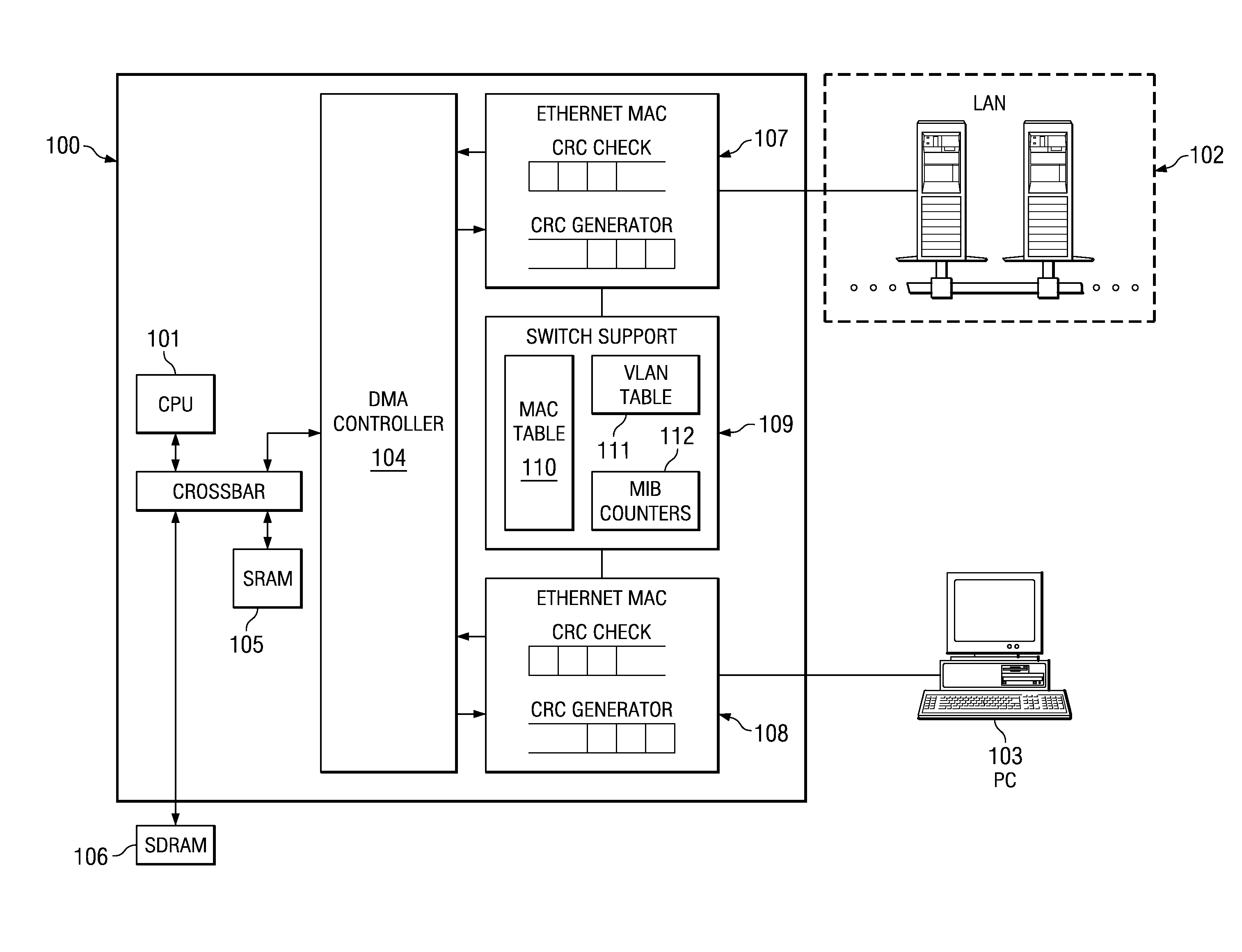

System and method for routing data packets in an Ethernet switch. A preferred embodiment comprises receiving a data frame at a first port, wherein the data frame comprises a header portion and payload portion. The header portion is analyzed to determine a destination port for the data frame. A destination status is added to the header portion to create a modified header portion. The modified header portion is stored in an on-chip memory. The payload portion is stored in an off-chip memory. An on-chip CPU instructs a DMA controller how to route the data frame.

Owner:LANTIQ BET GMBH & CO KG

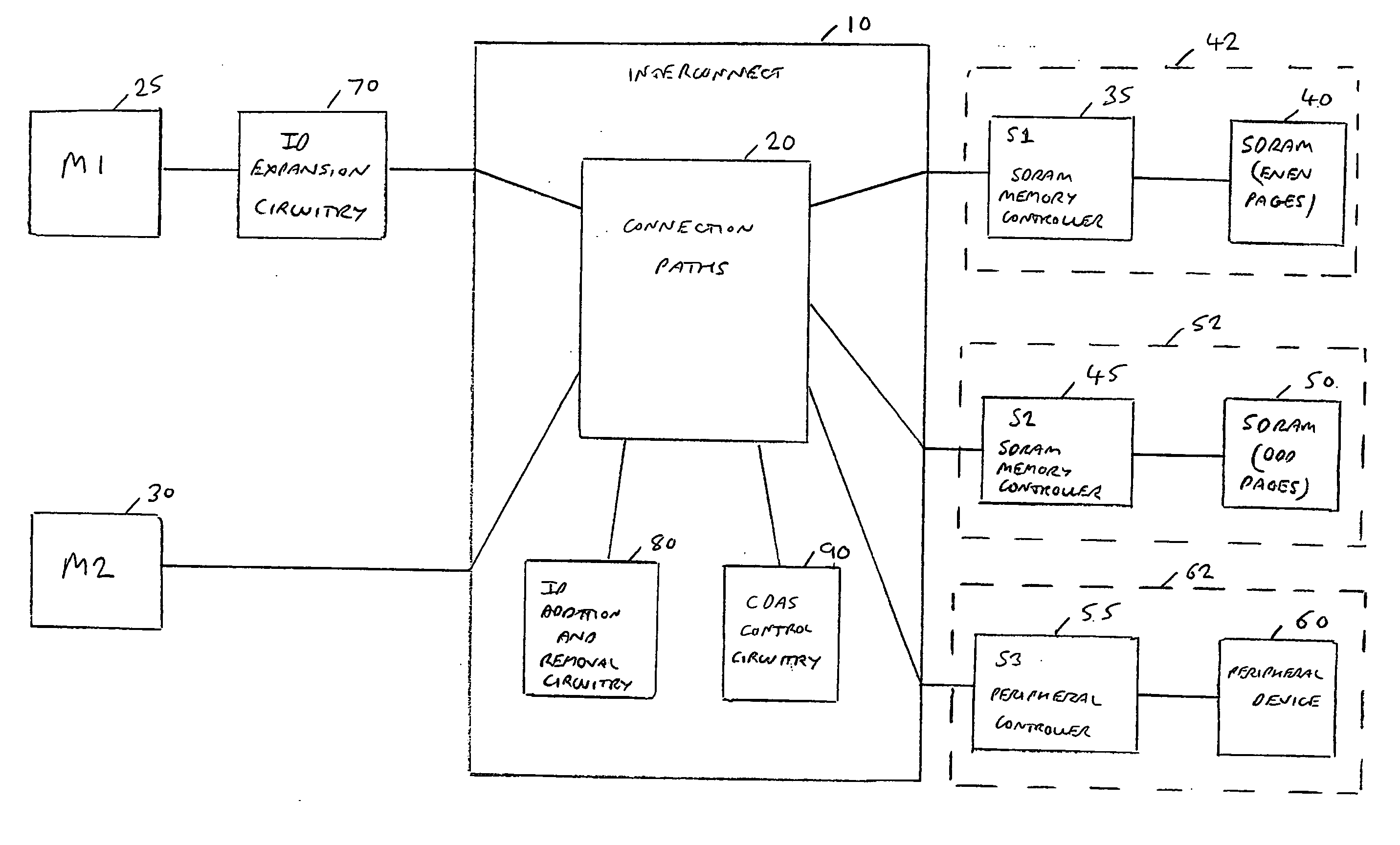

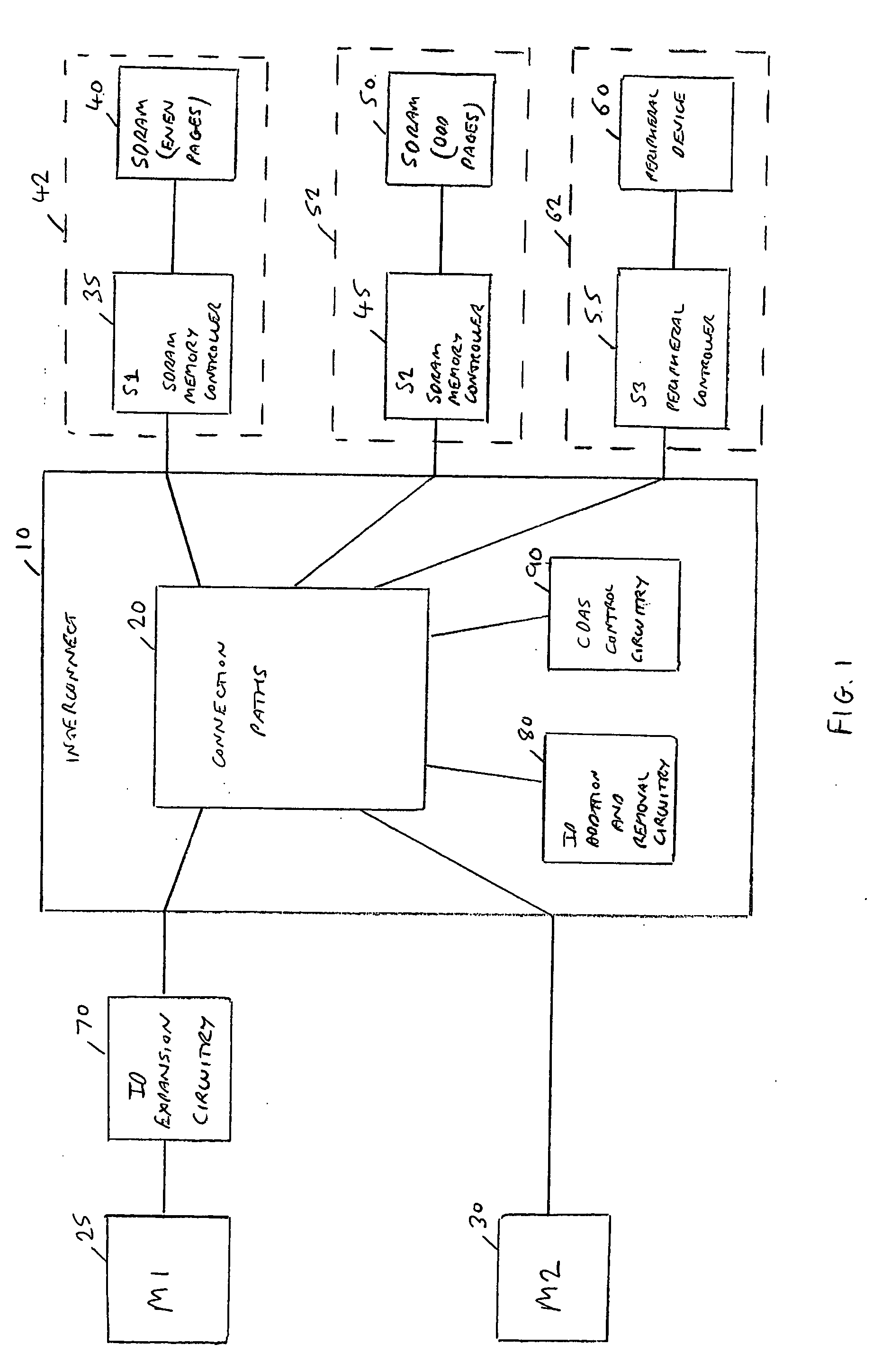

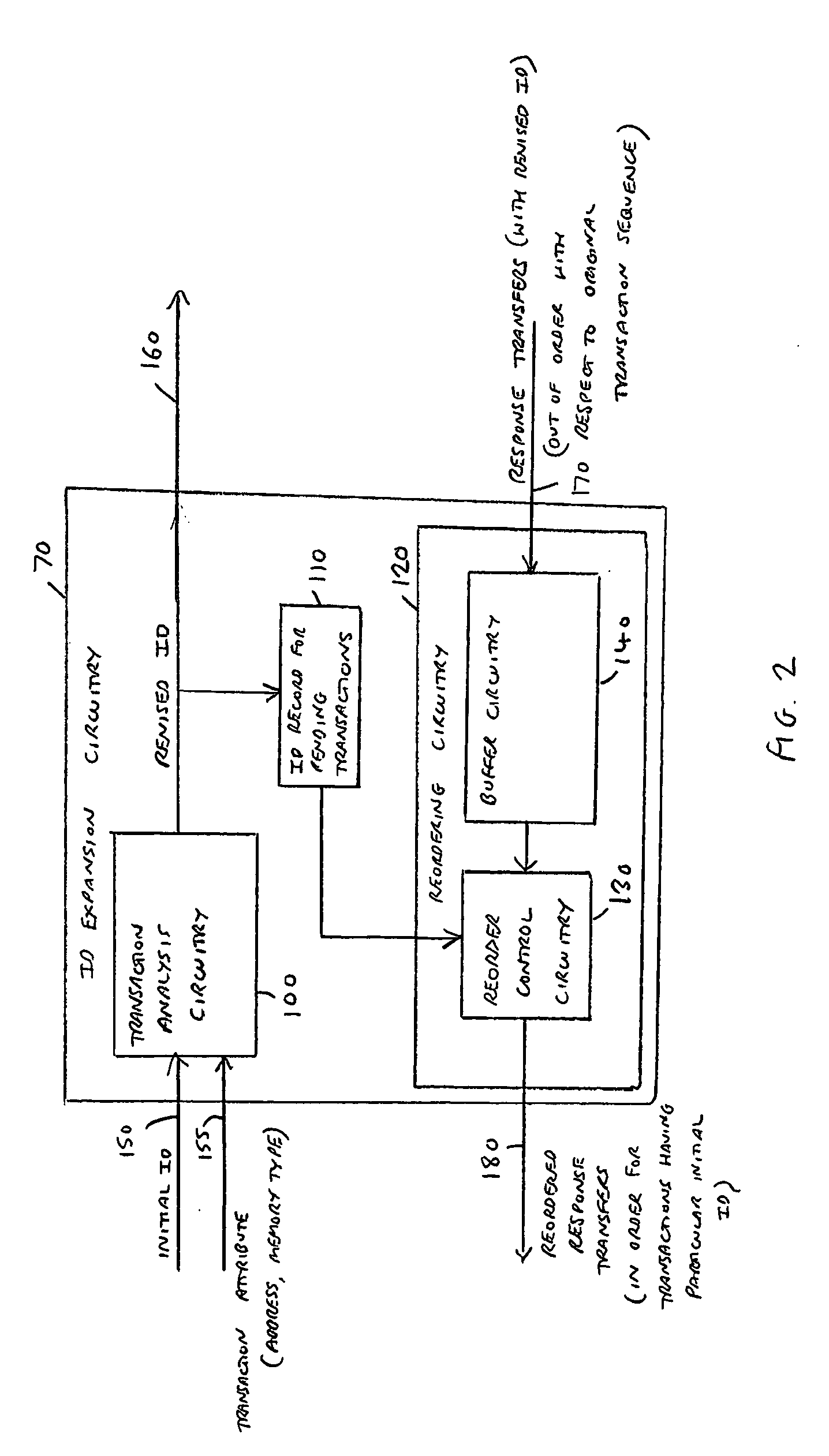

Transaction indentifier expansion circuitry and method of operation of such circuitry

ActiveUS20120290752A1Work wellSimple techniqueElectric digital data processingIdentifier ExtensionDeadlock

Transaction identifier expansion circuitry is provided, along with a method of operating such circuitry. The transaction identifier expansion circuitry interfaces between a master device and interconnect circuitry used to couple the master device with a plurality of slave devices to enable transactions to be performed. Transaction analysis circuitry is responsive to each transaction in a sequence of transactions initiated by the master device, to compare at least one attribute of the transaction with predetermined attributes indicative of the target slave device for that transaction. Based on the comparison, an initial transaction identifier is then mapped to one of a plurality of revised transaction identifiers, such that the revised transaction identifier is dependent on the target slave device. Reordering circuitry is then arranged to buffer response transfers received from the interconnect circuitry destined for the master device, with each response transfer having the revised transaction identifier associated therewith. The reordering circuitry then re-orders the response transfers having regard to the original transaction order of those transactions within the sequence of transactions that had the same initial transaction identifier, prior to provision of each response transfer to the master device. By such an approach, the performance of a high performance master device can be maintained, by ensuring that for at least the transactions targeted to a particular subset of the slave devices, no intervention by deadlock avoidance circuitry within the interconnect is required when routing transactions to those slave devices, due to the use of different transaction identifiers when accessing those slave devices.

Owner:ARM LTD

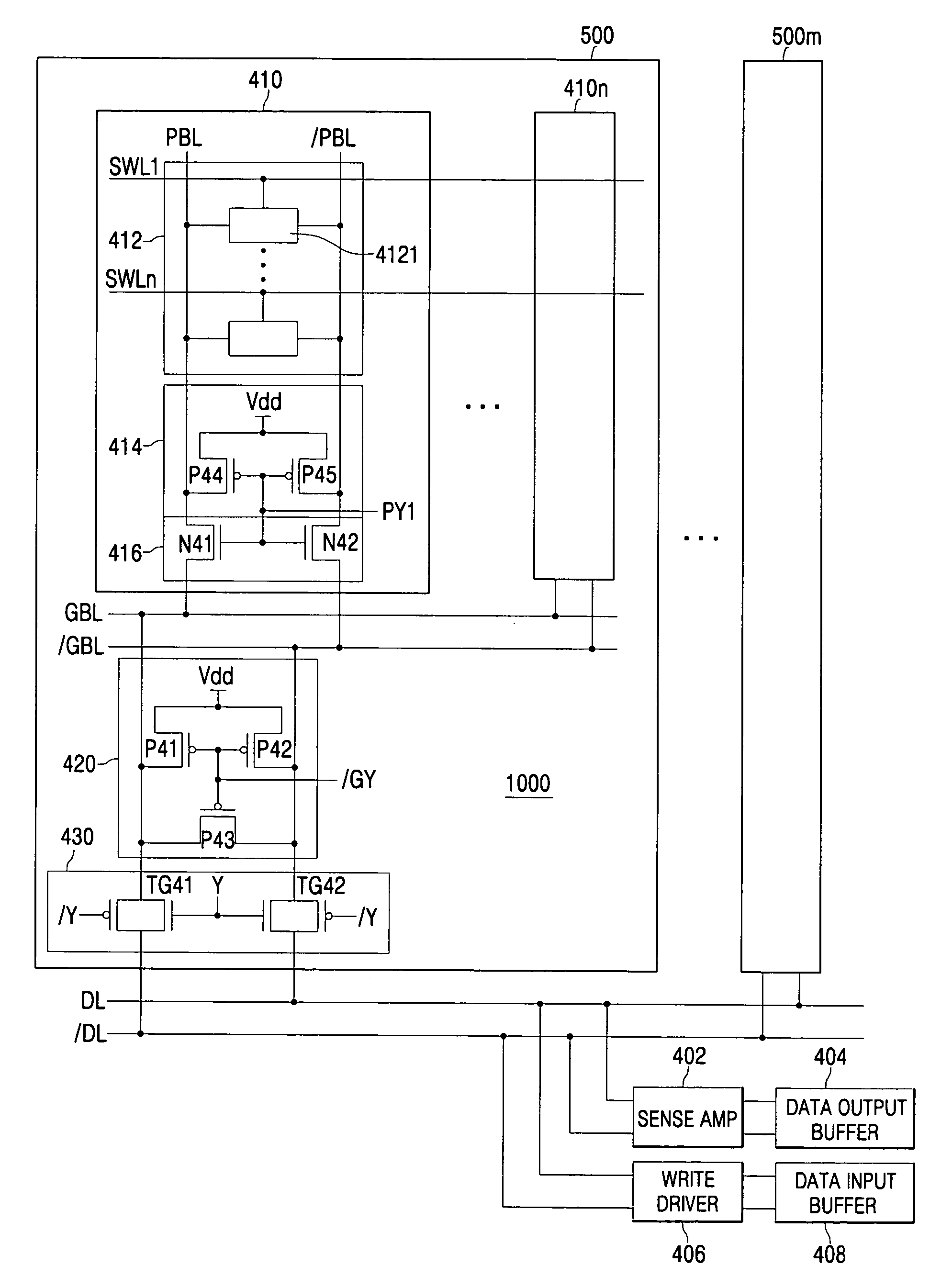

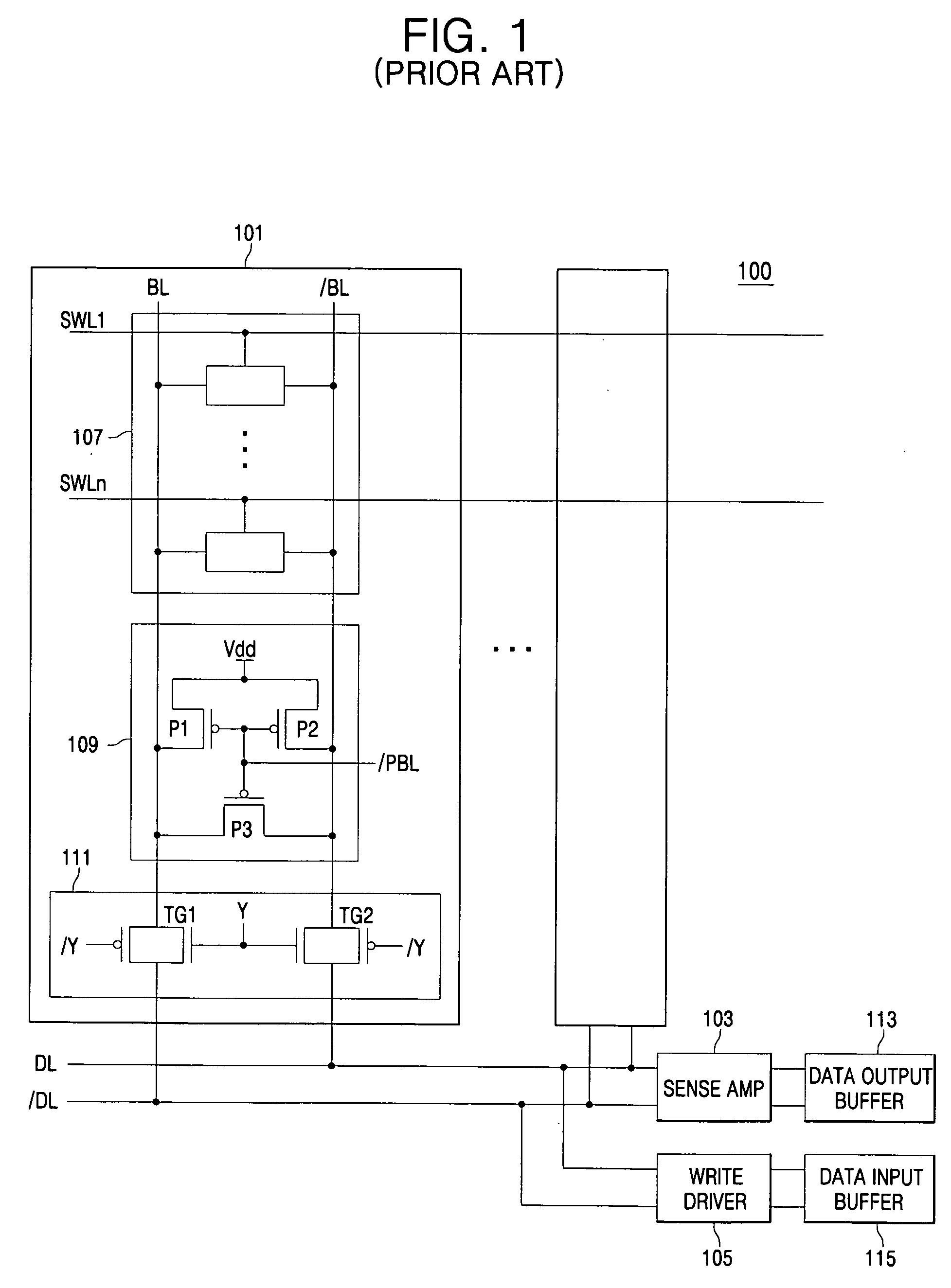

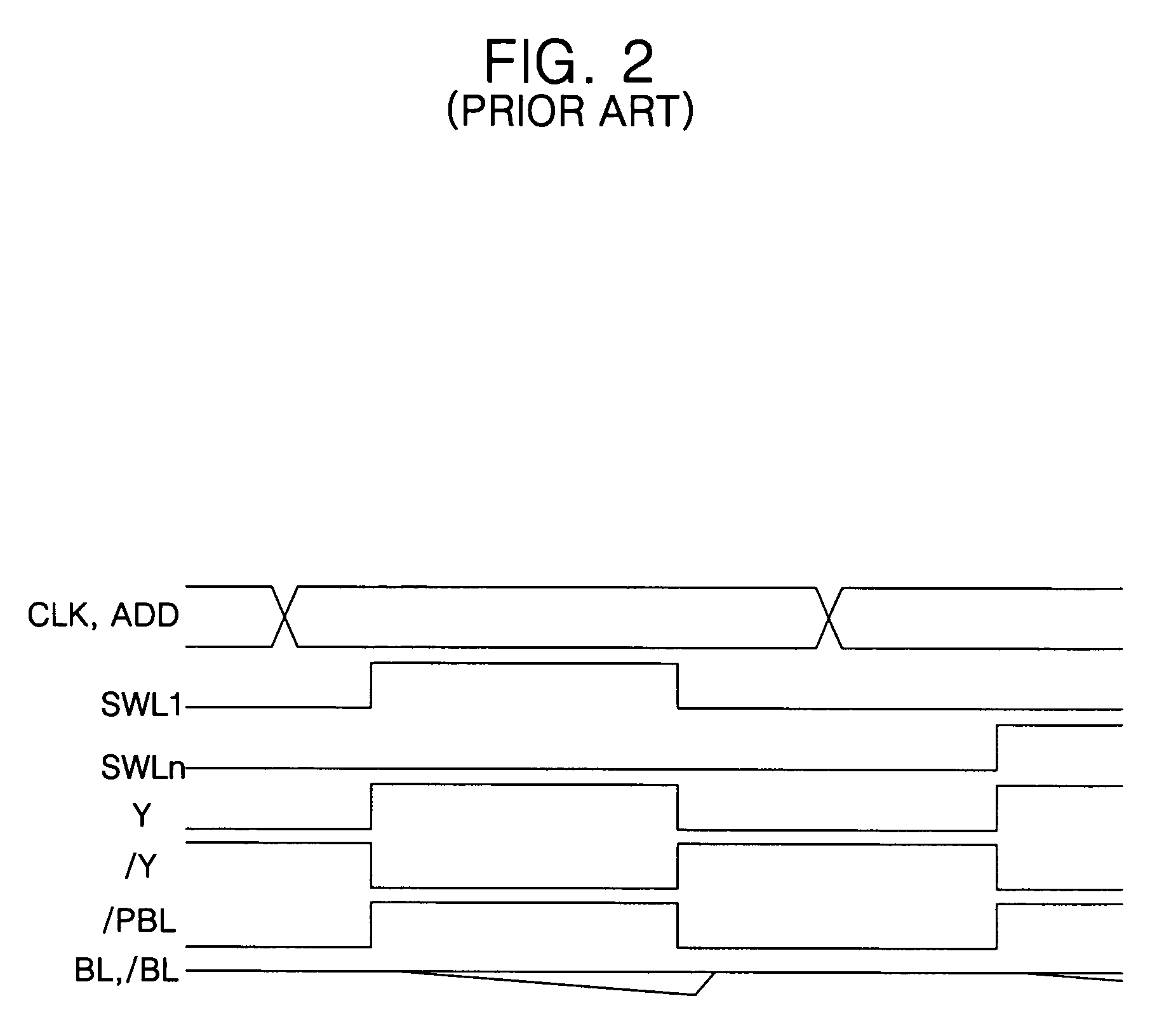

Integrated circuit memory devices having hierarchical bit line selection circuits therein

InactiveUS20060062061A1Reduce active power requirementLine capacitance is decreasedTransistorSolid-state devicesBit lineElectricity

Integrated circuit memory devices include a first column of memory cells electrically coupled to a first pair of bit lines and a bit line precharge and selection circuit. This bit line precharge and selection circuit includes at least one stacked arrangement of thin-film transistors. These thin-film transistors include a first PMOS thin-film pull-up transistor and a first NMOS thin-film pass transistor. These thin-film transistors are electrically coupled to one of the first pair of bit lines. The first column of memory cells includes a column of TFT SRAM cells.

Owner:SAMSUNG ELECTRONICS CO LTD

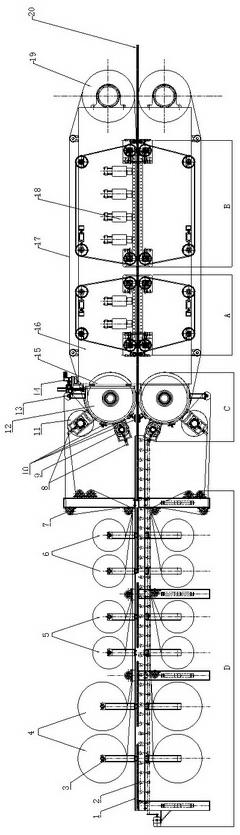

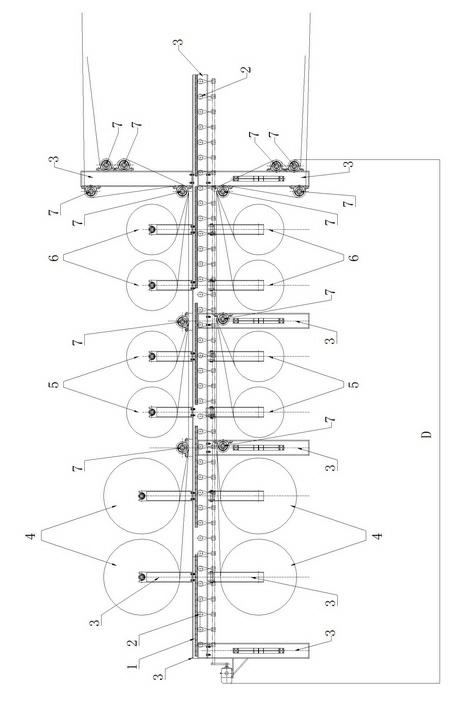

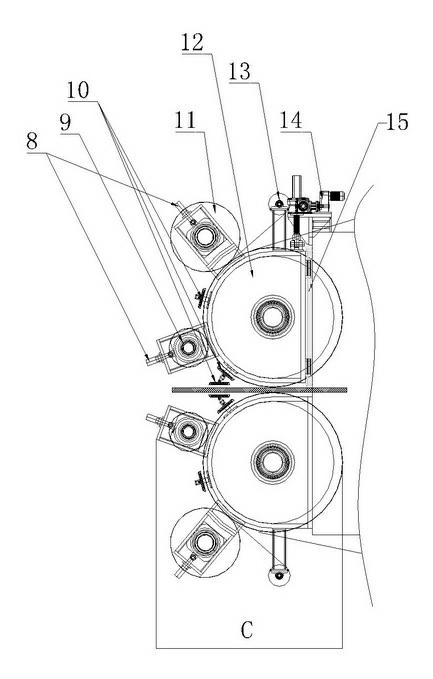

Method for producing thermoplastic composite material and double steel-belt continuous press

ActiveCN102615917AReduce area requirementsIncrease profitLaminationLamination apparatusComposite plateThermoplastic composites

The invention provides a method for producing a thermoplastic composite material and a double steel-belt continuous press. The double steel-belt continuous press mainly comprises a set of paper and board feed system D, a set of preheating and prepressurizing system C which is arranged on driven rollers at an inlet of the press, a group of driving rollers, a group of driven rollers, and steel belts which are wound on the driving rollers and the driven rollers, wherein the inner part of the press is divided into a heating section A and a cooling section B. Raw materials (core boards and paper) of a product enter the preheating and prepressurizing system C through the paper and board feed system and are combined between the two driven rollers through heating and pressurization, enter the heating section for constant-temperature setting along with the traction of the steel belts, and are cooled and molded through the cooling section to produce finished sheets and strips. The defects of the conventional production machinery for composite boards are overcome; the press has a simple structure and reliable performance, and is relatively low in cost; the finished sheets and strips are pressed by a production process that the internal gluing is not required and the raw materials are combined after being molten; and products in corresponding sizes are processed according to requirements.

Owner:DUNHUA YALIAN MACHINEY

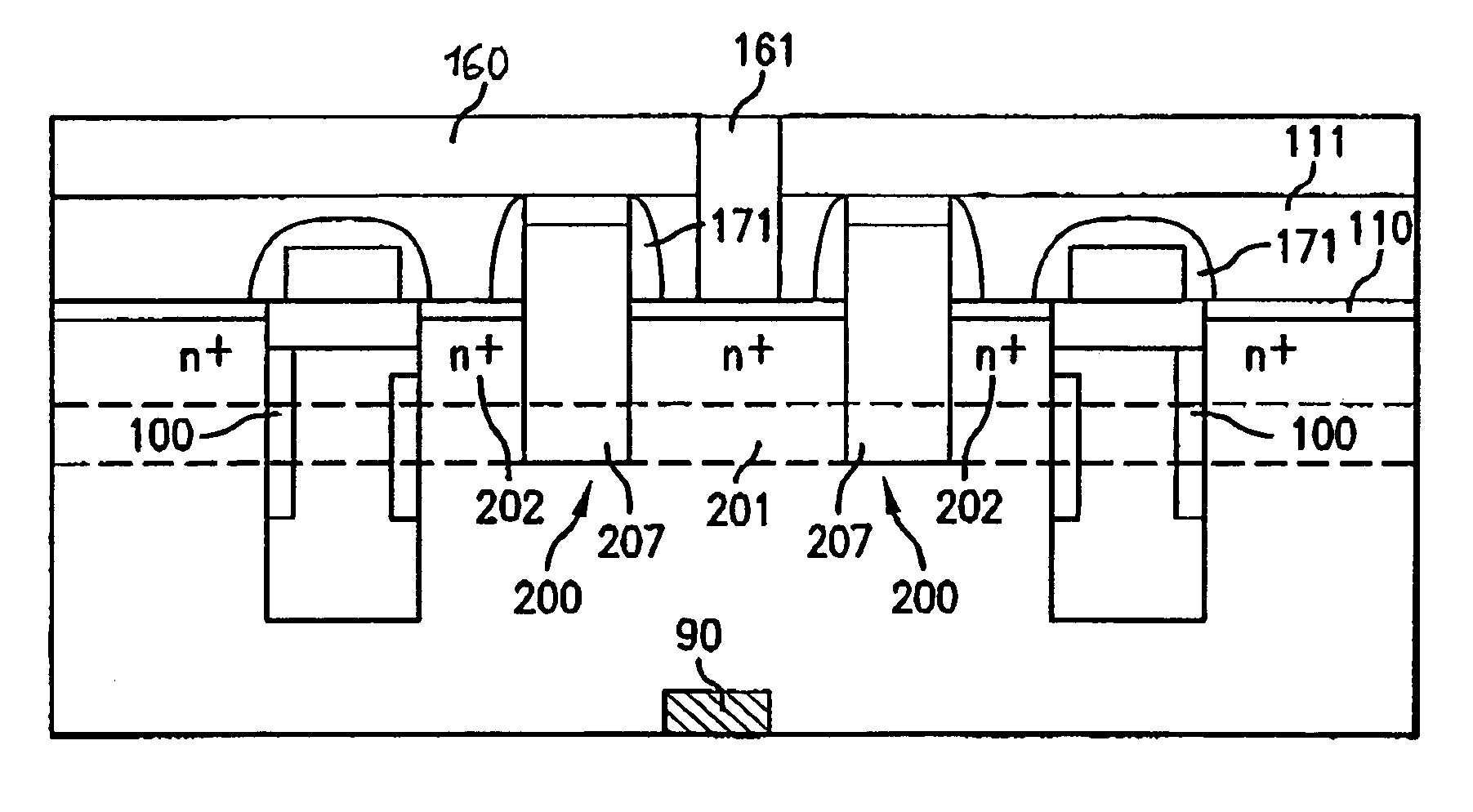

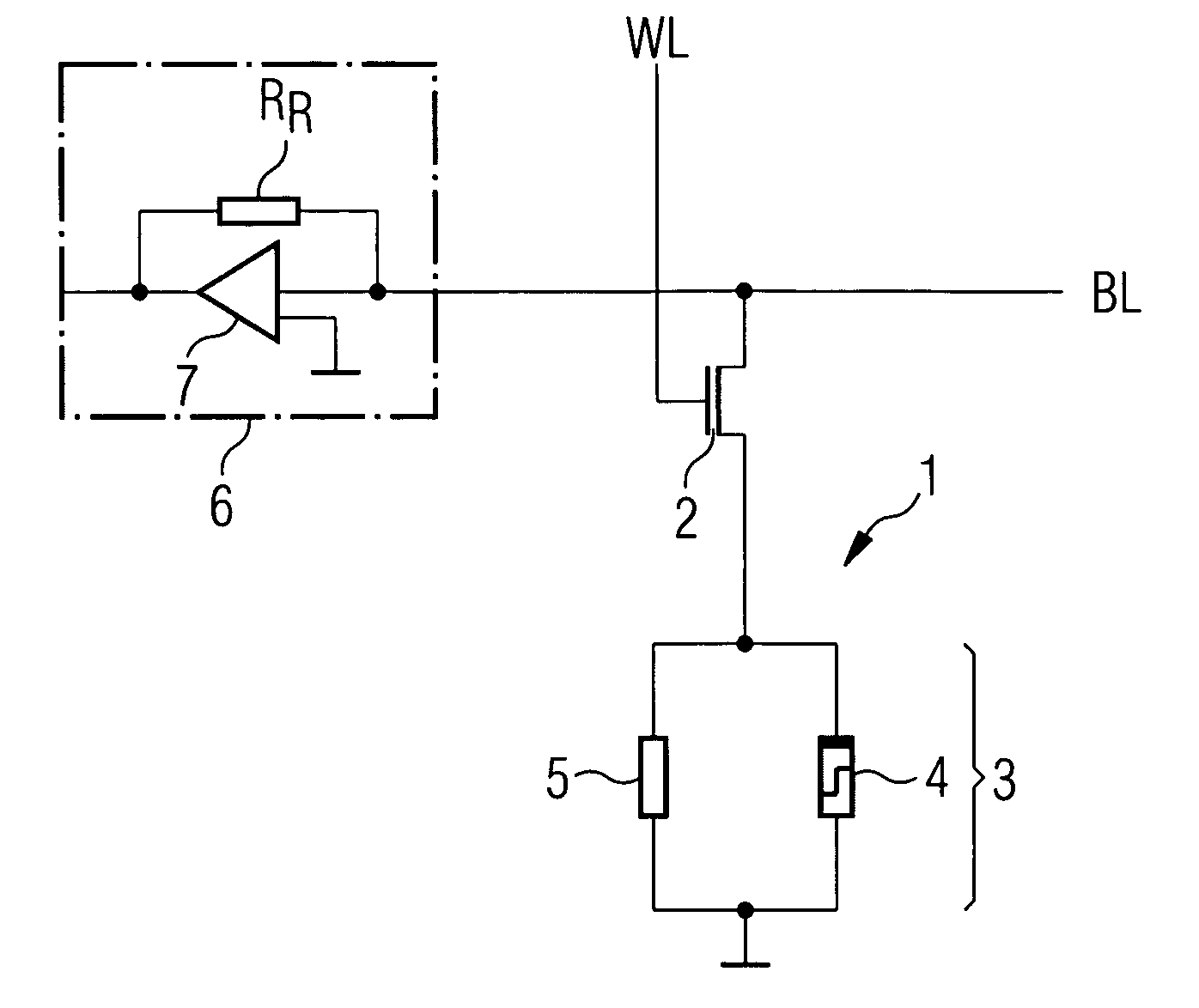

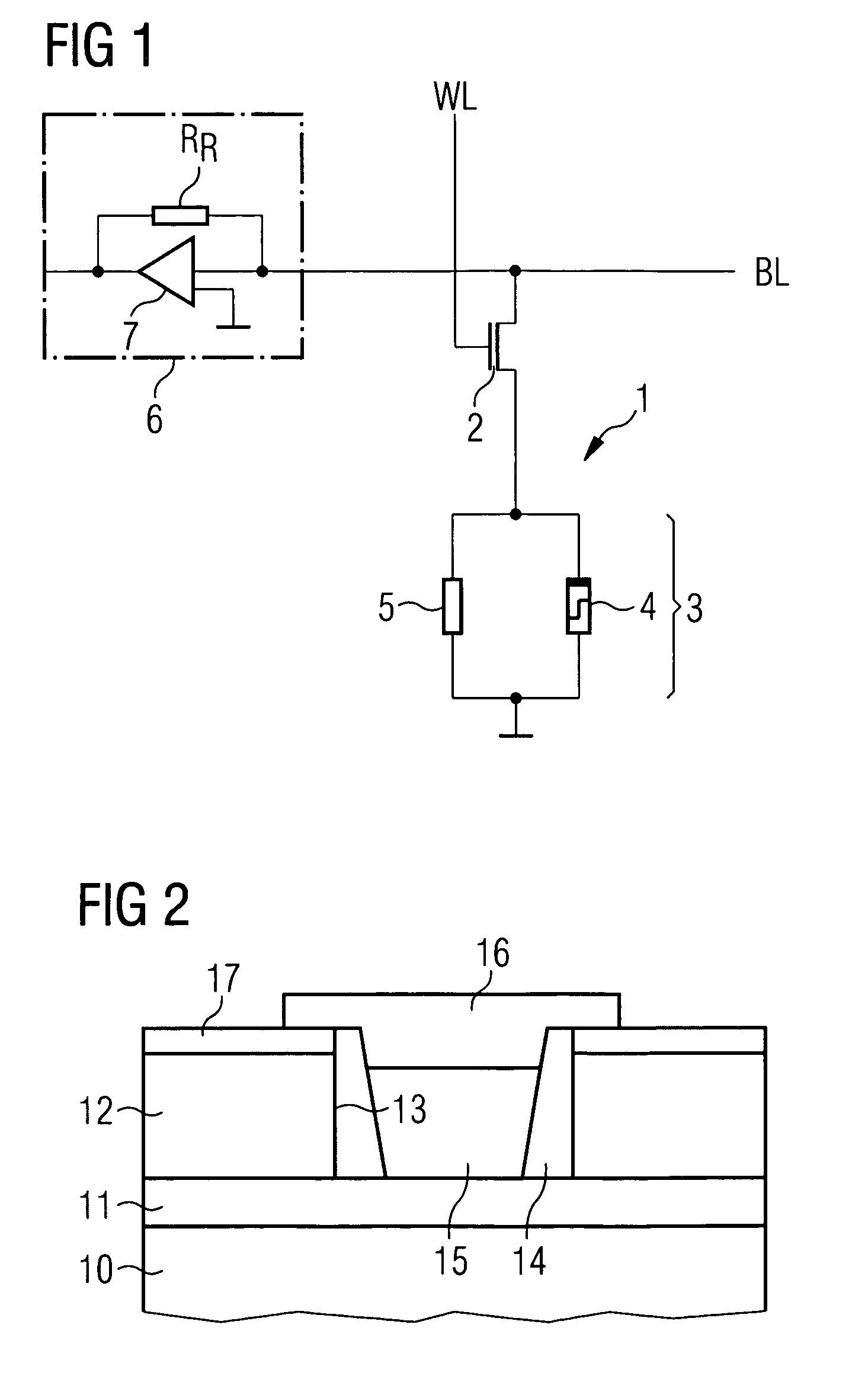

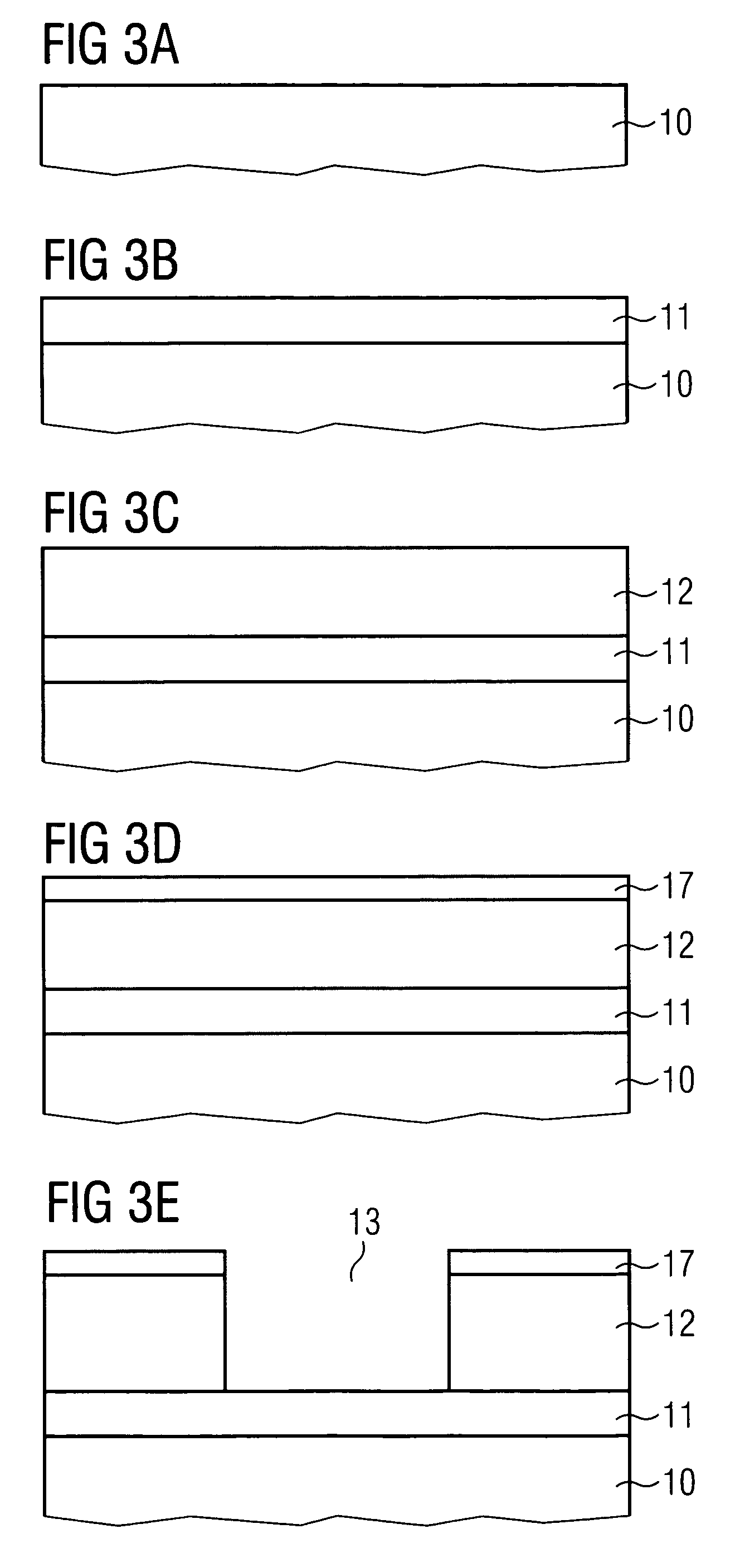

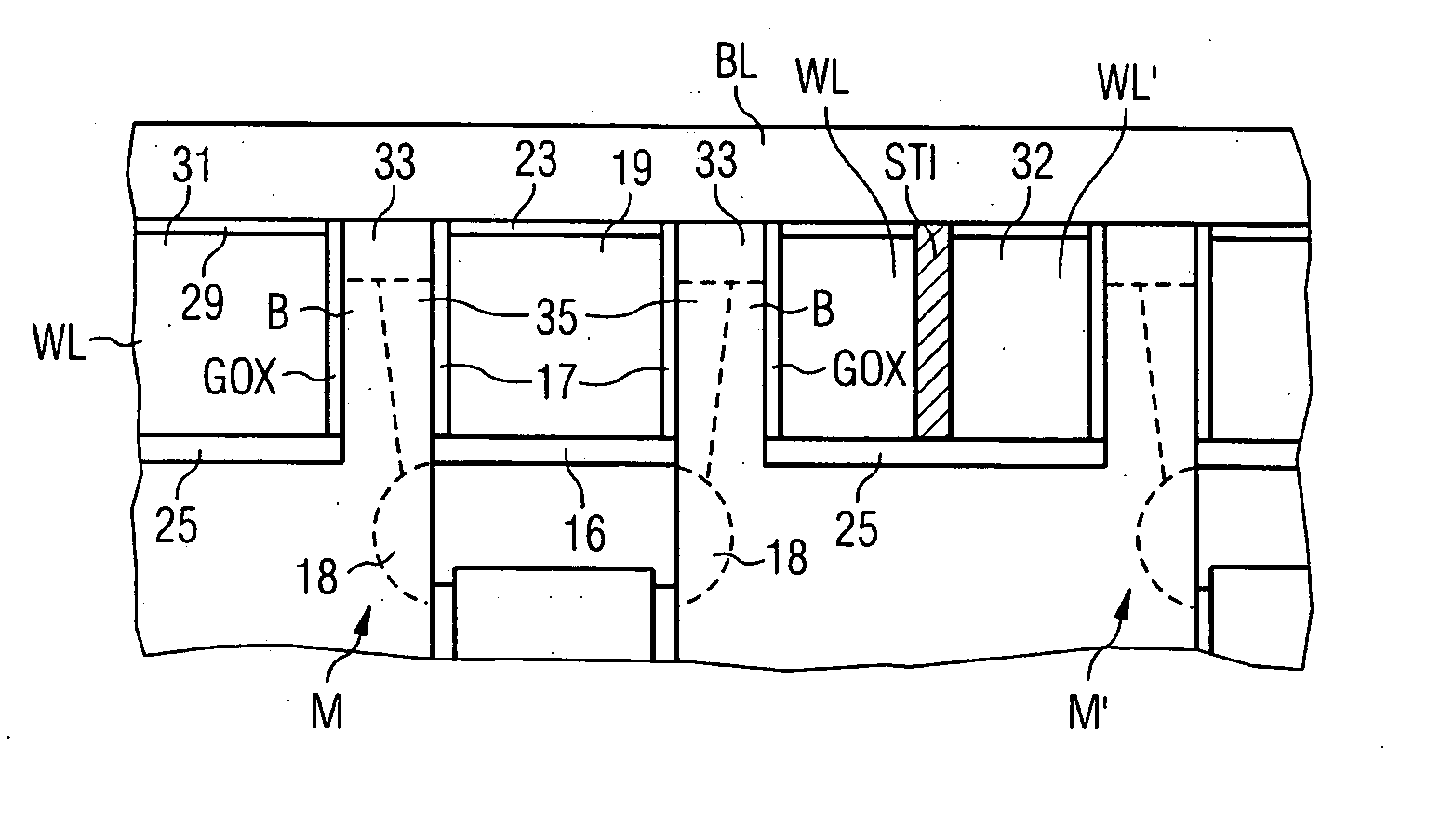

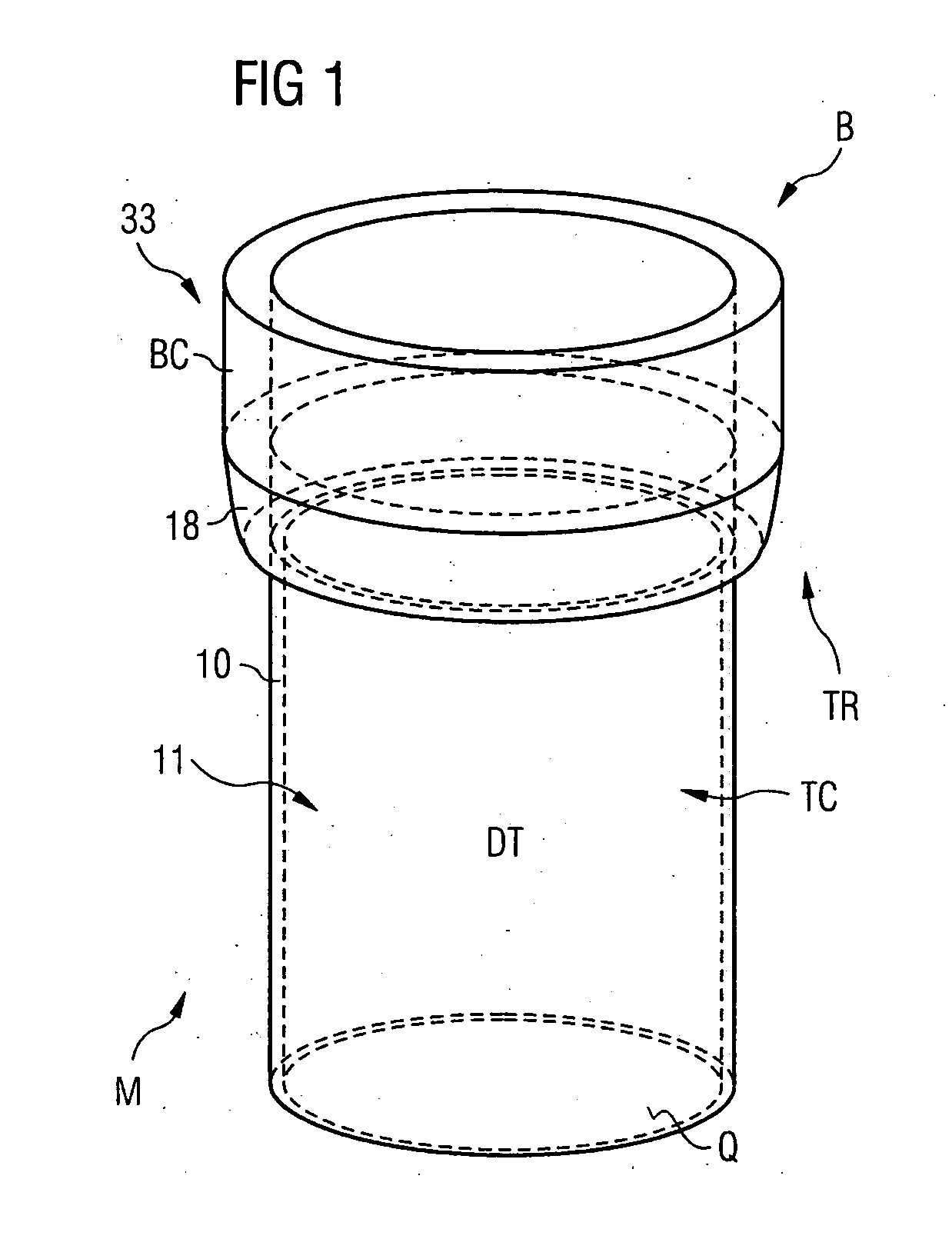

DRAM memory cell

InactiveUS7368752B2Reduce area requirementsImprove abilitiesTransistorSolid-state devicesDram memoryEngineering

A DRAM memory cell is provided with a selection transistor, which is arranged horizontally at a semiconductor substrate surface and has a first source / drain electrode, a second source / drain electrode, a channel layer arranged between the first and the second source / drain electrode in the semiconductor substrate, and a gate electrode, which is arranged along the channel layer and is electrically insulated from the channel layer, a storage capacitor, which has a first capacitor electrode and a second capacitor electrode, insulated from the first capacitor electrode, one of the capacitor electrodes of the storage capacitor being electrically conductively connected to one of the source / drain electrodes of the selection transistor, and a semiconductor substrate electrode on the rear side, the gate electrode enclosing the channel layer at at least two opposite sides.

Owner:POLARIS INNOVATIONS LTD

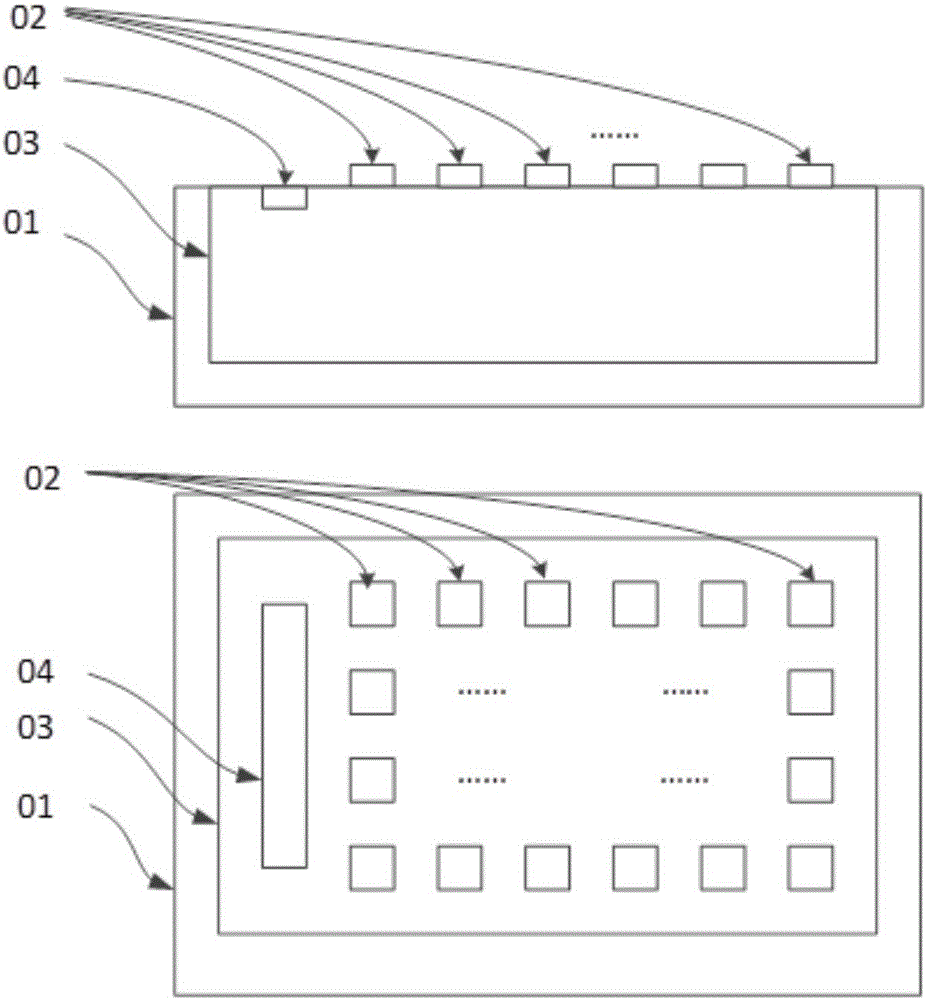

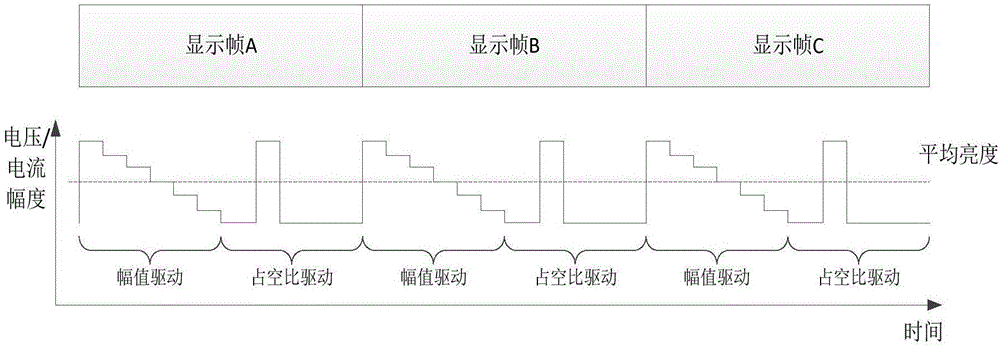

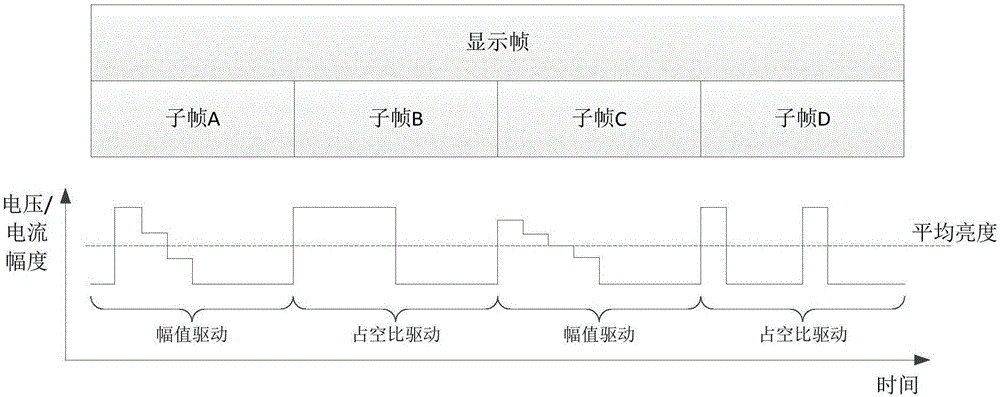

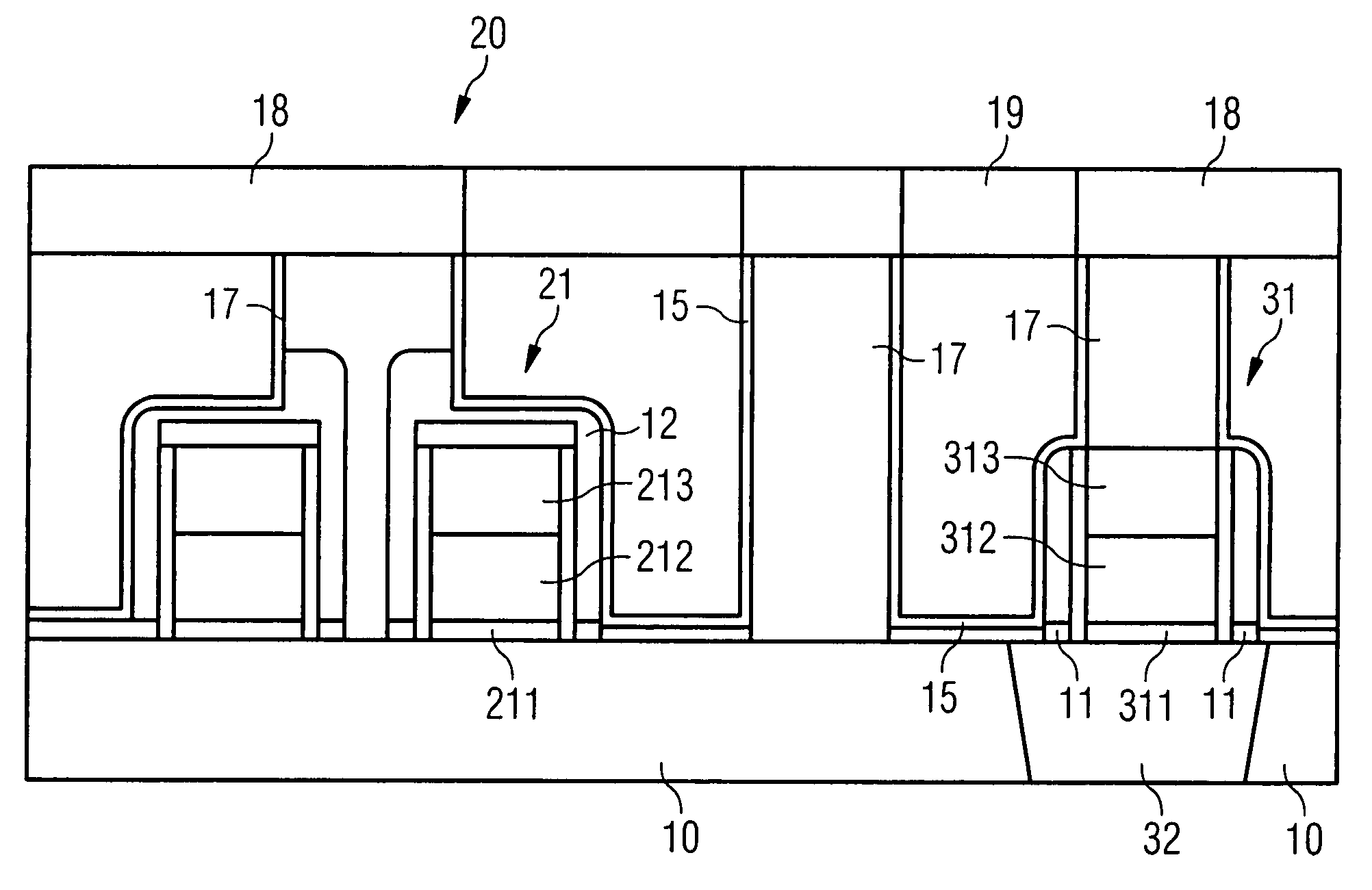

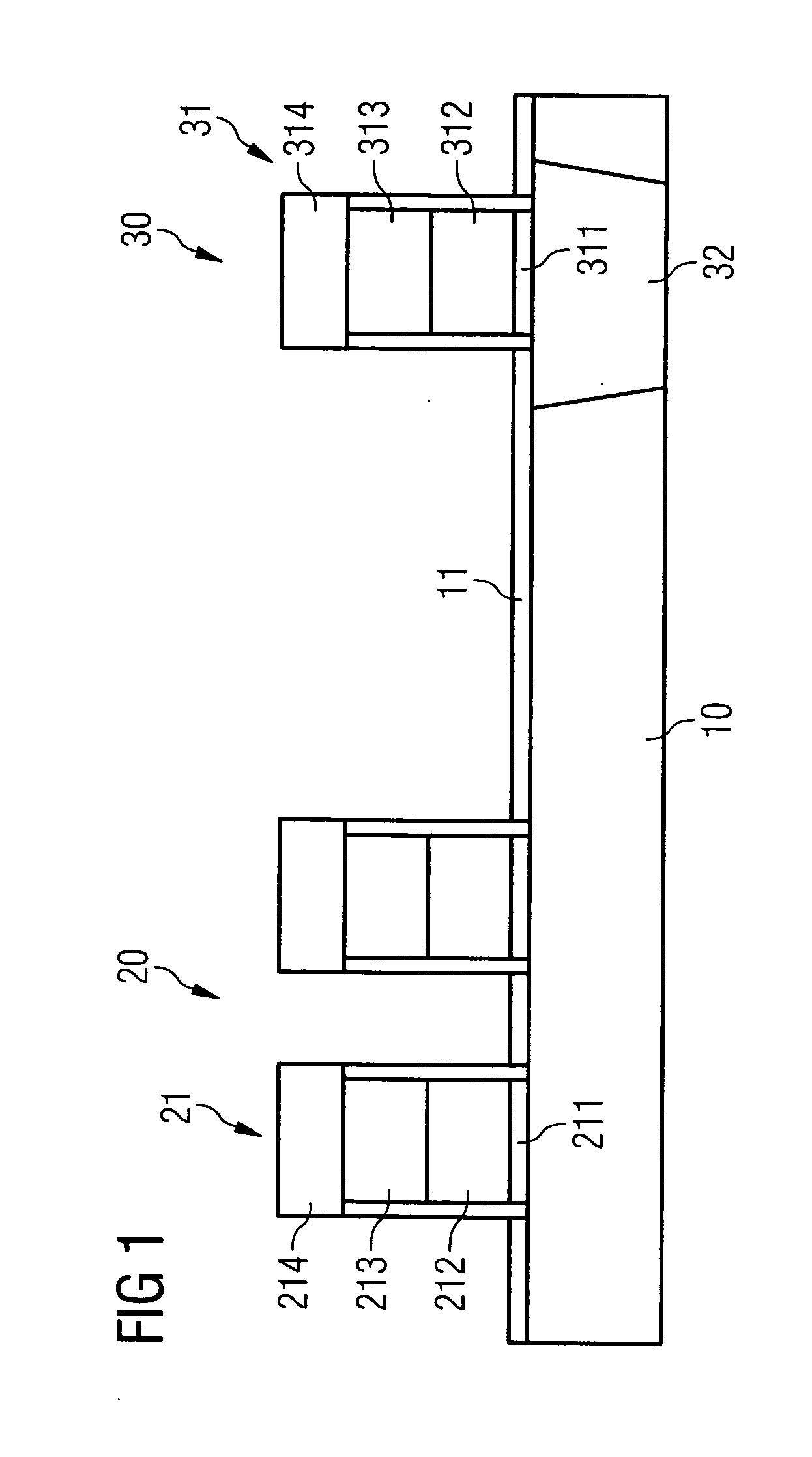

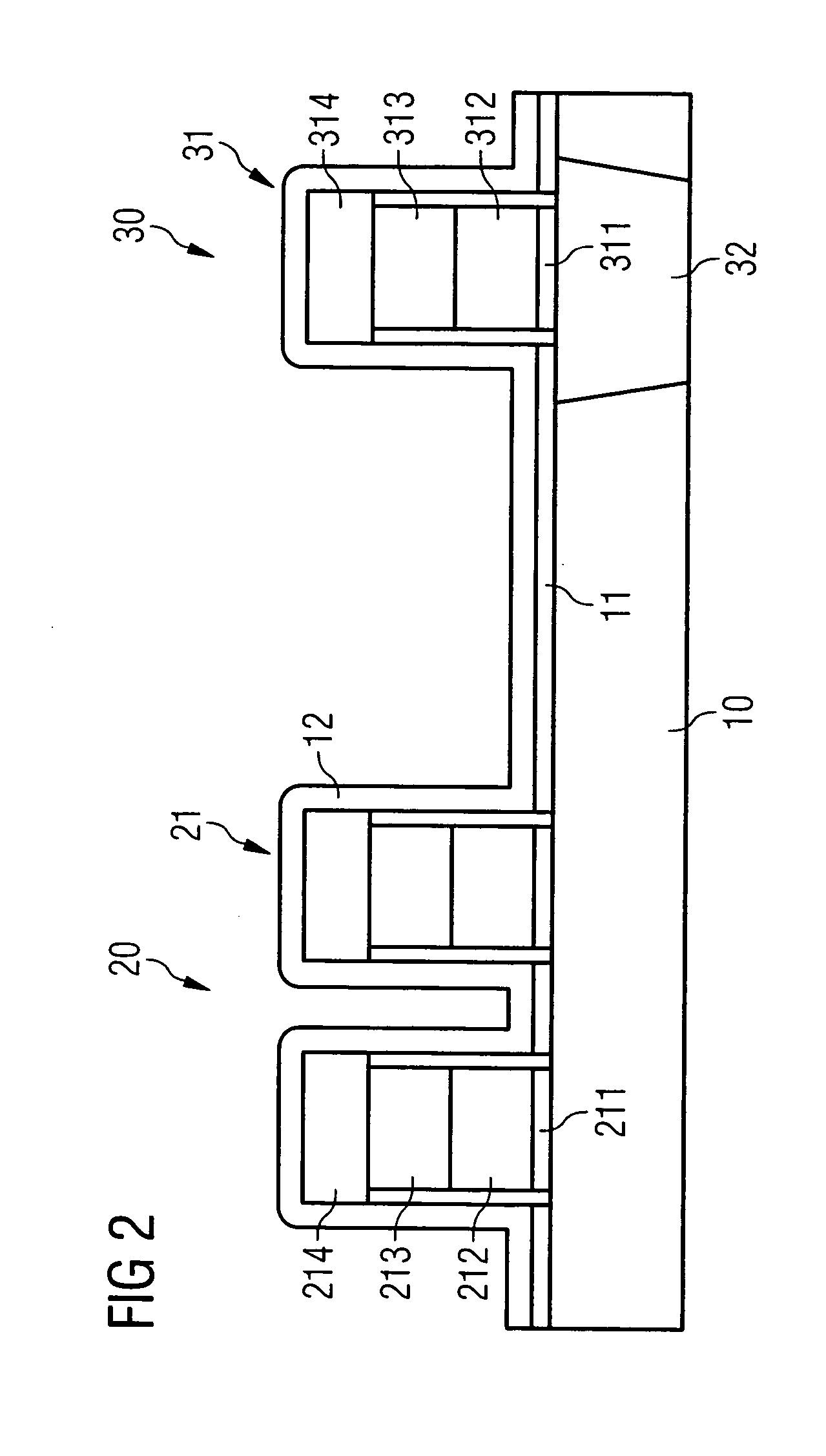

Silicon-based display adopting digital-analog hybrid drive

ActiveCN106652963AReduced precision requirementsImprove conversion accuracyStatic indicating devicesVoltage amplitudeDigital analog converter

The invention discloses a silicon-based display adopting digital-analog hybrid drive. Pixels are driven to emit light through the method of combining the simulation amplitude modulation drive strategy and a digital pulse width modulation drive strategy, wherein the luminance of the pixels is determined by output current or voltage amplitude of the pixels in the subframe and the duty ratio of time of the output current or voltage of the pixels in the subframe, the frame of image is divided into a plurality of different digital subframes and simulation subframes, the digital drive strategy is adopted for the digital subframes, the time proportionable drive mode or luminance proportionable drive mode is adopted, the simulation drive strategy is adopted for the simulation subframes, many digital-analog converters with few digits are adopted, input data is converted into amplitude quantity of voltage or current, so that the pixels emit light, and the simulation subframes and the digital subframes are combined to generate the final display frame. The requirements of the simulation amplitude modulation drive strategy for the digital-analog converter and the requirements of the pixel circuit for the precision of analog quantity are reduced, and the conversion speed of the digital-analog converter and the contrast of the pixel luminance are improved.

Owner:南京昀光科技有限公司

Method for fabricating a first contact hole plane in a memory module

InactiveUS20060148227A1Simple and reliable processSimple processSolid-state devicesSemiconductor/solid-state device manufacturingBit lineConductive materials

A silicon dioxide layer is formed and a mask layer is deposited and then patterned to produce openings in the mask layer in the region around the gate contacts onto the gate electrode tracks in the logic region. The surface is uncovered around the gate contacts to the gate electrode tracks in the logic region, reducing the silicon dioxide layer. A sacrificial layer covering the gate electrode tracks is formed and patterned to form sacrificial layer blocks above the contact openings for the bit line contacts between the mutually adjacent gate electrode tracks in the cell array region and above the contact openings for the substrate contacts to the semiconductor surface and the gate contacts onto the gate electrode tracks in the logic region. A filling layer is formed between the sacrificial layer blocks, and the sacrificial layer blocks are removed. The contact opening regions are filled with conductive material.

Owner:INFINEON TECH AG

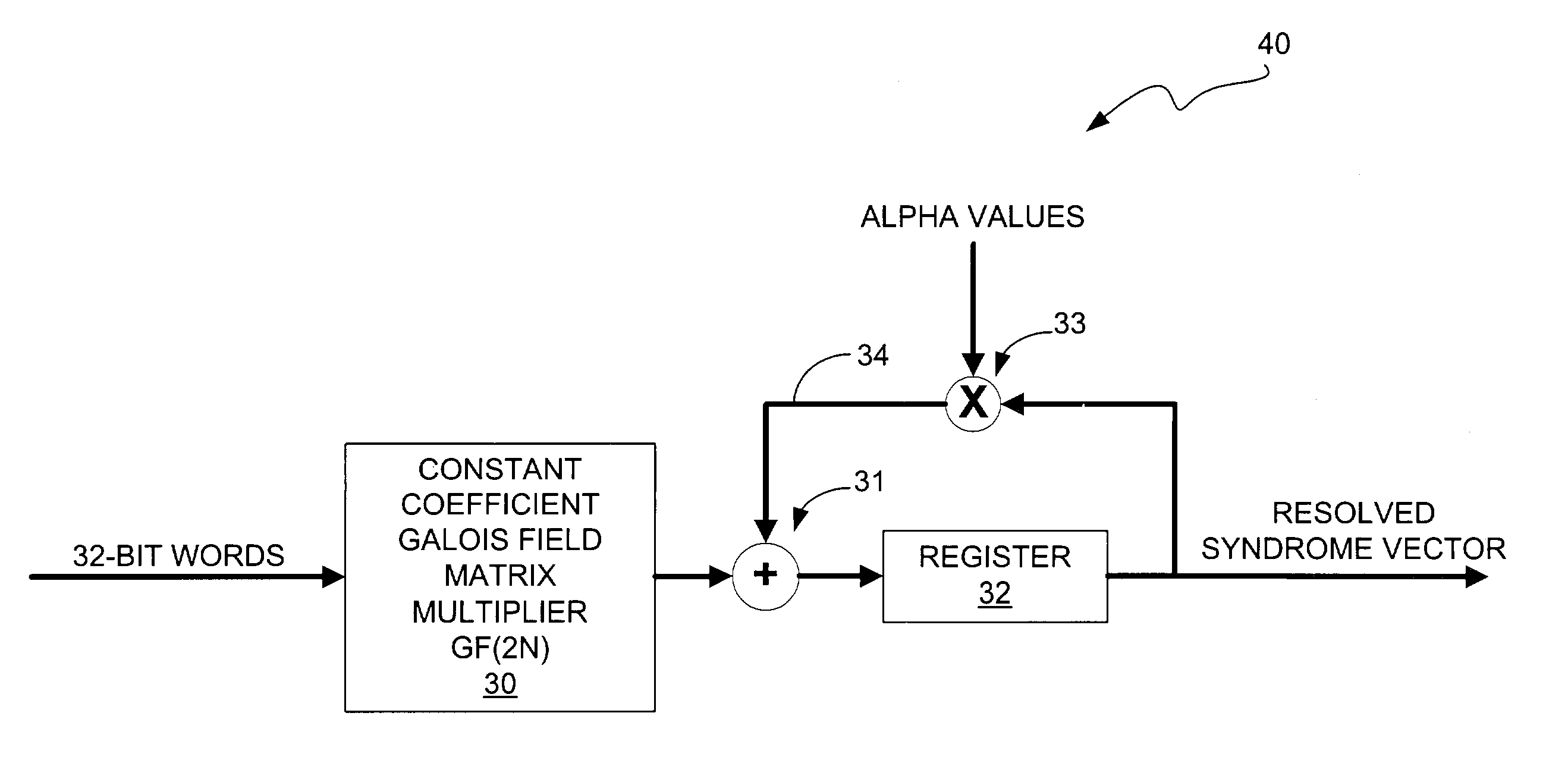

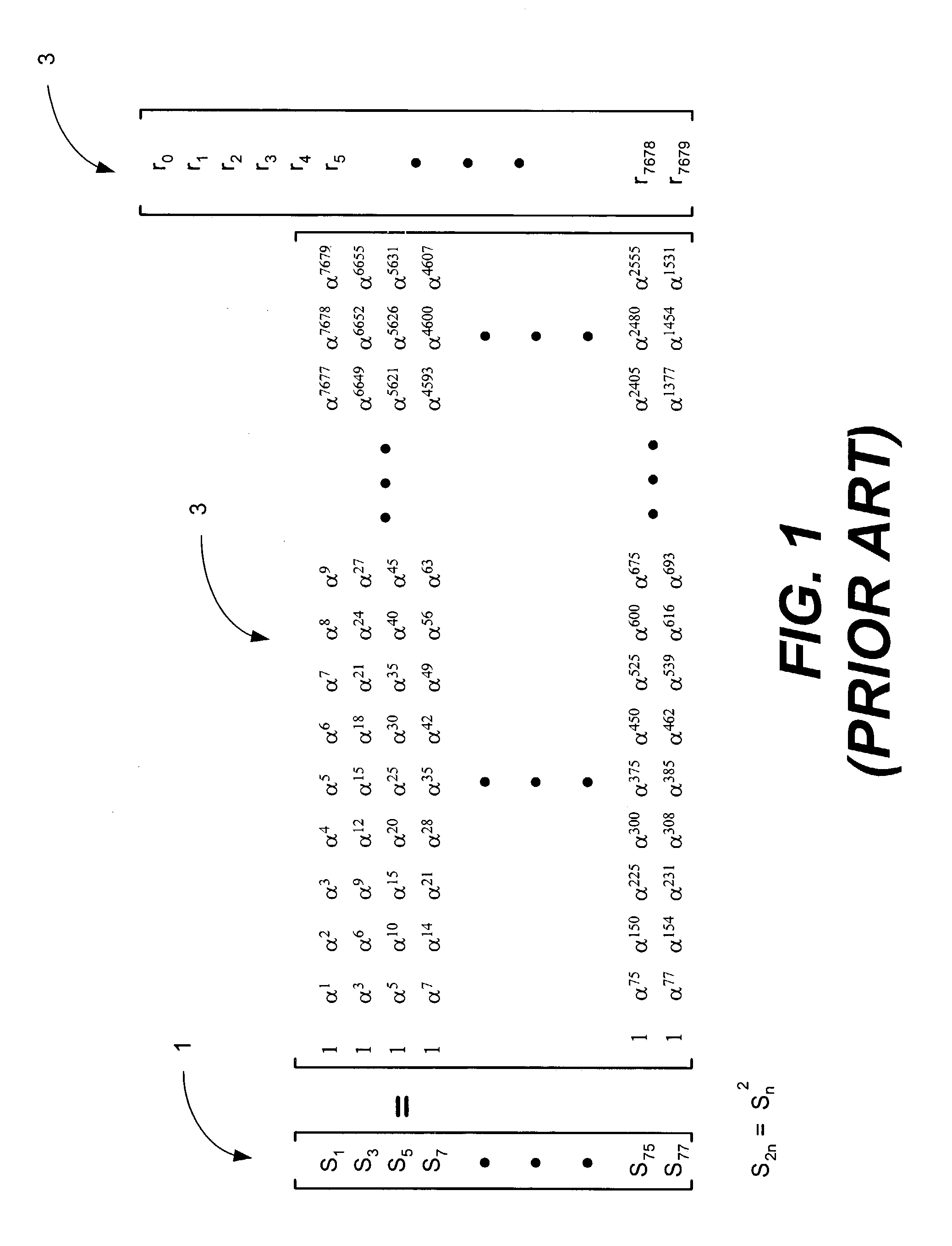

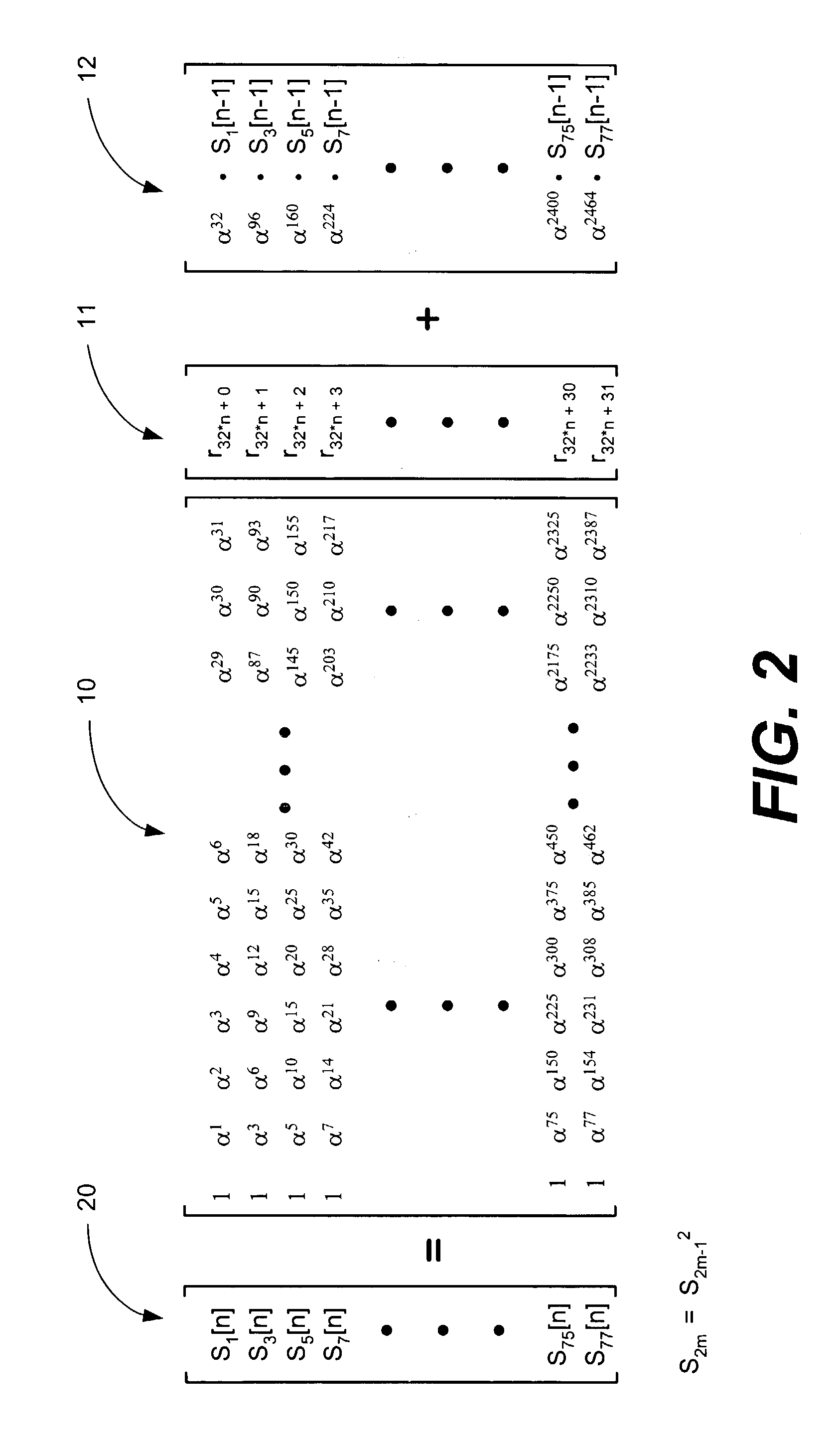

Method and apparatus for performing syndrome computation in a decoder of a forward error correction (FEC) system

ActiveUS7039854B1Reduce the amount requiredReduce area requirementsDigital data processing detailsDigital computer detailsParity-check matrixForward error correction

A method and apparatus for performing syndrome computation in a decoder of a forward error correction (FEC) system. Syndrome computation logic of the decoder uses a partial parity-check matrix to recursively generate intermediate syndrome vectors based on a code word received by the decoder and to modulo-2 add the recursively generated intermediate syndrome vectors together until a final resolved syndrome vector has been generated. This recursive use of the partial parity-check matrix enables the syndrome computations to be performed very quickly so that the decoder is suitable for use in high data rate systems and provides a very large reduction in the amount of logic needed to perform the syndrome vector computations. The reduction in the syndrome computation logic results in reduced area requirements for the logic as well as reduced power requirements.

Owner:CIENA

Optimum RF VCO structure

ActiveUS6943635B1Reduce area requirementsReduce in quantityAngle modulation by variable impedenceElectric pulse generatorInductorCapacitor

Owner:NXP BV

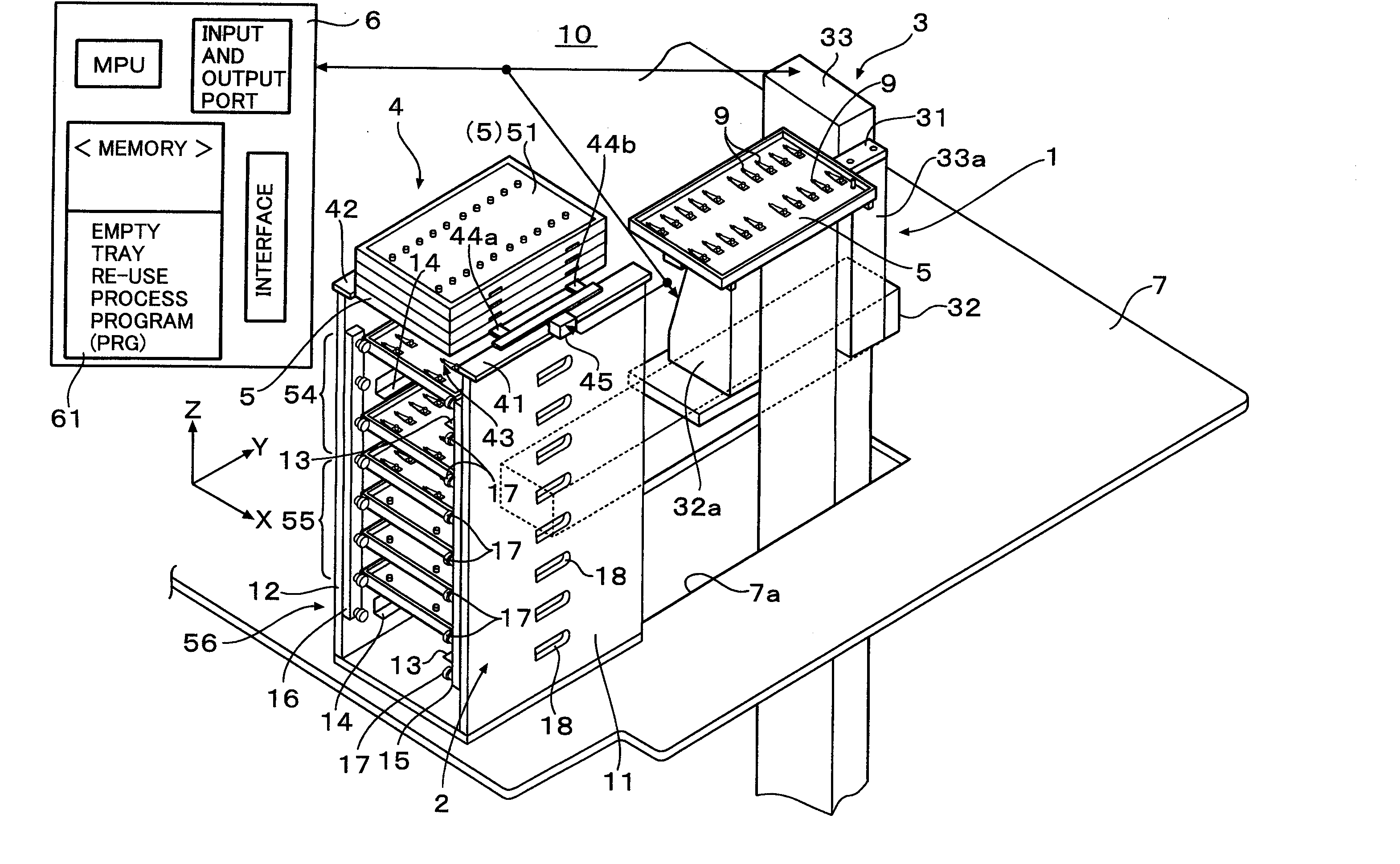

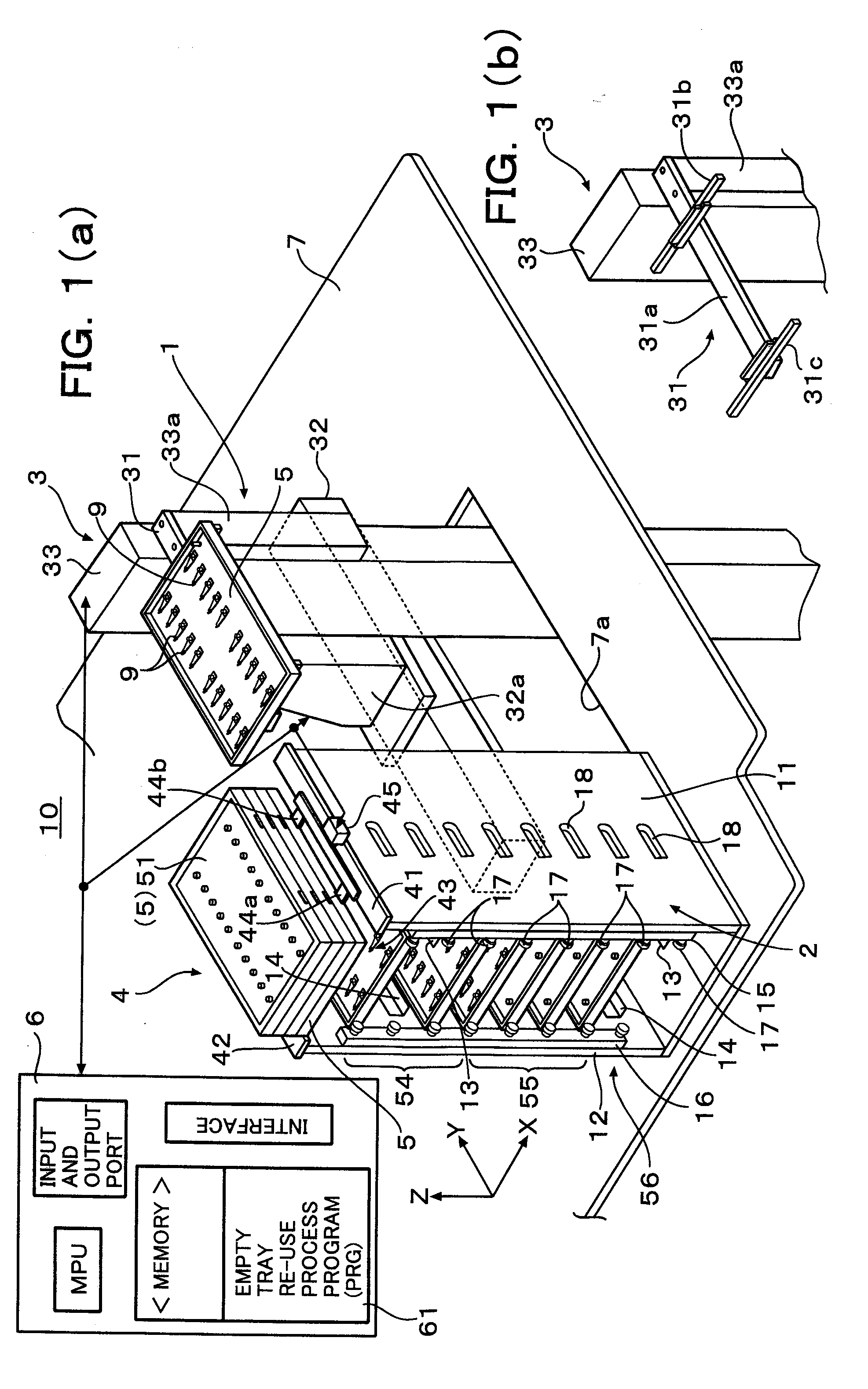

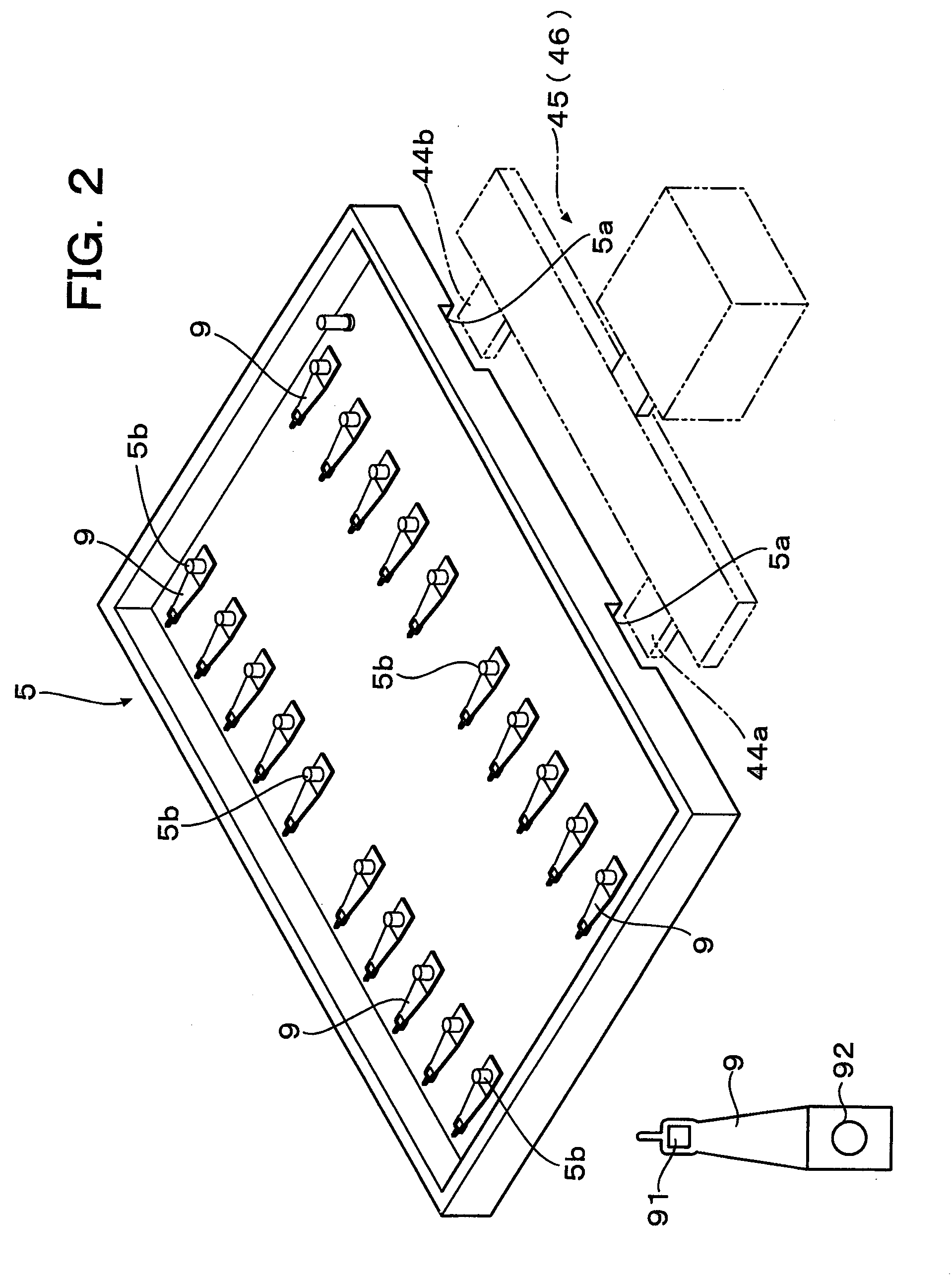

Handling mechanism of trays with which electronic parts are fed and inspection device of the electronic parts using the mechanism

InactiveUS20090035119A1Small sizeReduce exchange frequencyArticle unpackingFunctional testing of recording headsEngineeringMechanical engineering

In the present invention, through the provision of a tray placing rack for storing trays in multi steps, the trays accommodating electronic parts after inspection are received in the racks and through the provision of a tray stacking rack above the tray placing rack, an empty tray emptied by having been inspected of the electronic parts before inspection at an inspection stage is stacked on the tray stacking rack. When a certain tray is filled with electronic parts after inspection and is discharged, an empty ray is taken out from the tray stacking rack and the empty tray is fed to the rack position of the discharged tray to permit re-use of empty trays

Owner:HITACHI HIGH-TECH CORP

Memory cell for storing an information item, memory circuit and method for producing a memory cell

InactiveUS20050243596A1Reduce noiseLess to signal crosstalkElectrical apparatusRead-only memoriesMemory circuitsElectrolyte

The invention relates to a memory cell for providing an information item, having a memory element, which has a PMC resistance component with a solid electrolyte material. The solid electrolyte material may be put into a first state with a high electrical resistance and into a second state with a low electrical resistance. The memory element has a resistance element which is connected up to the PMC resistance component in such a way as to reduce the total resistance of the memory element in the first state.

Owner:POLARIS INNOVATIONS

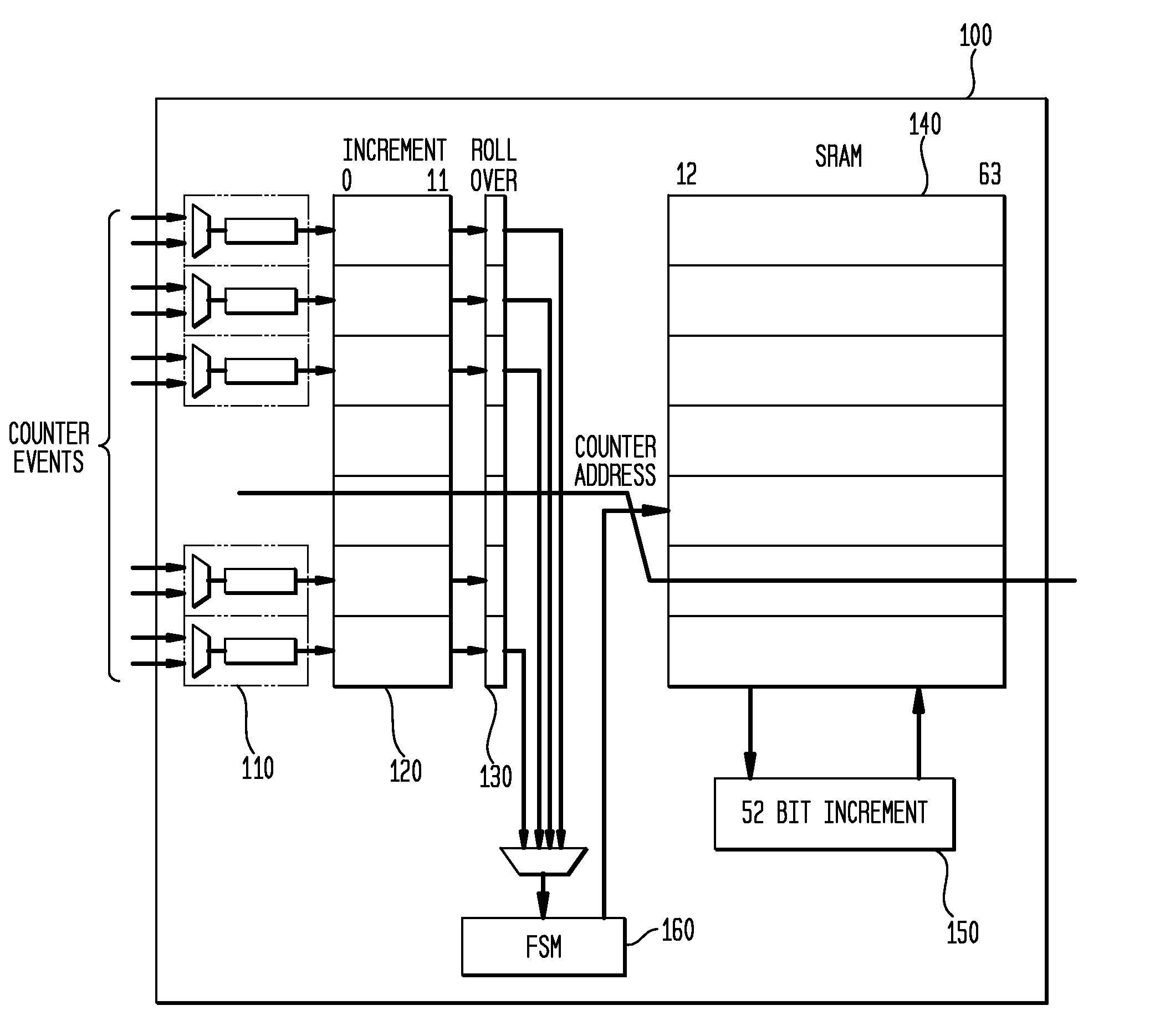

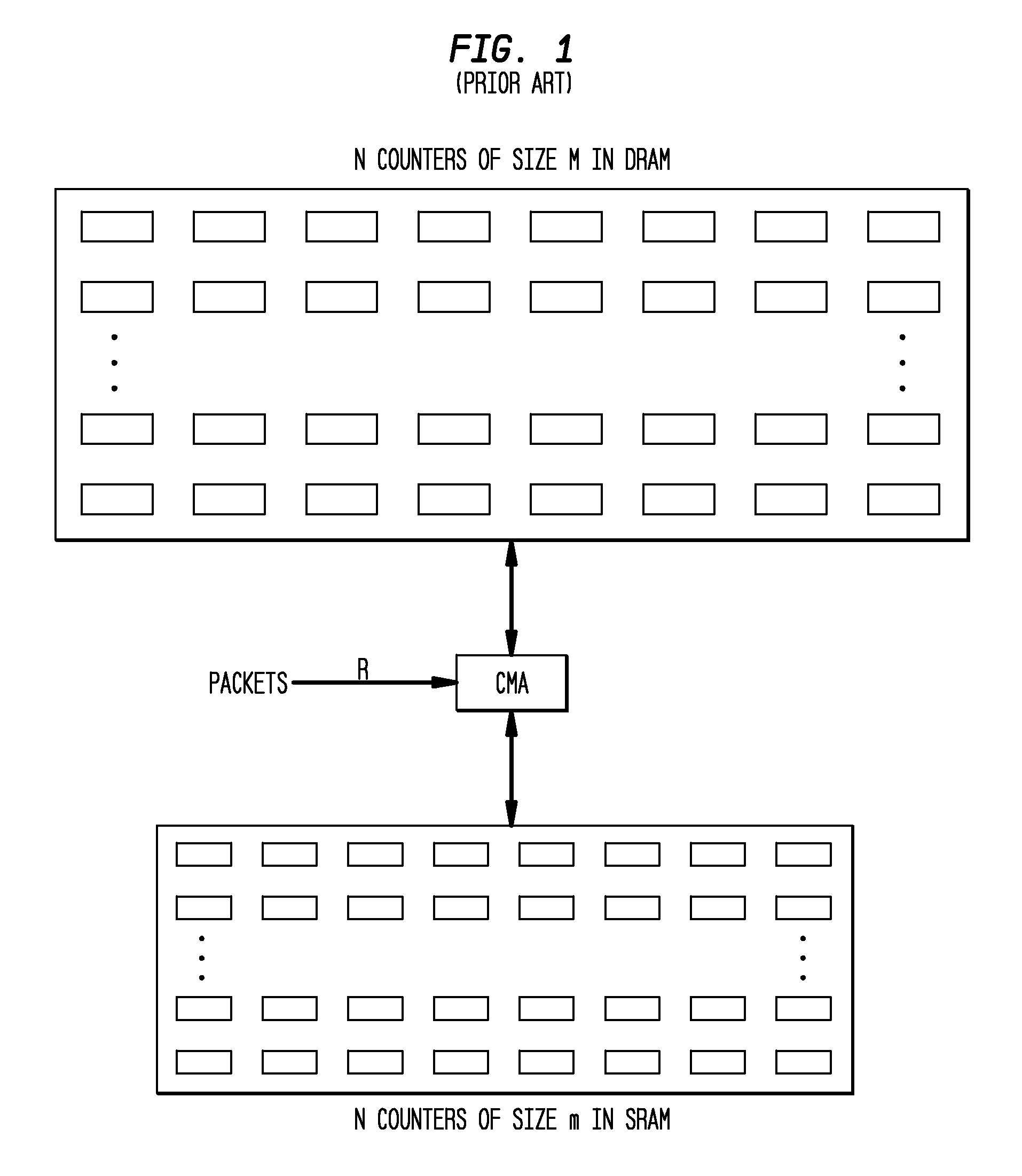

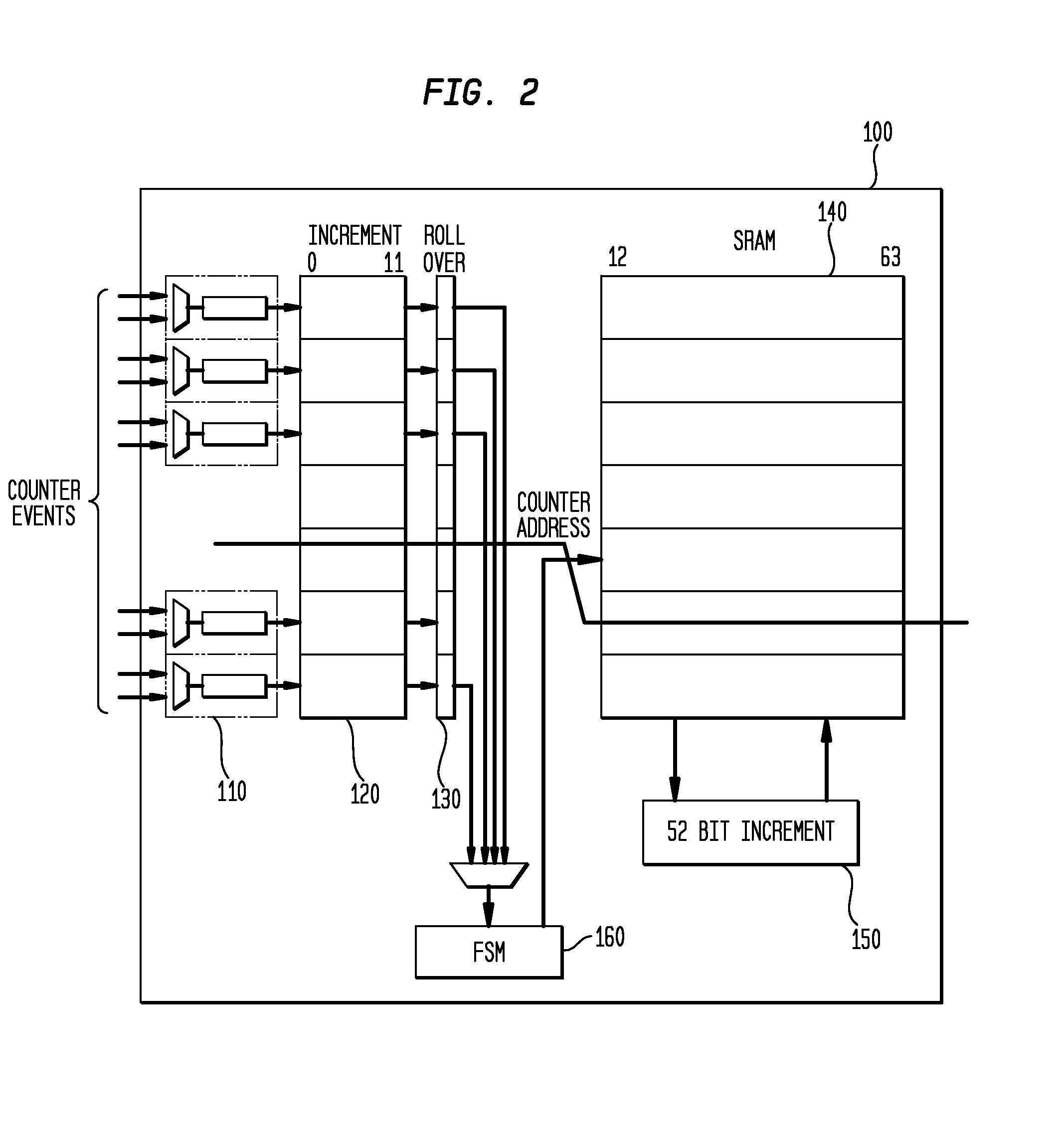

Method and apparatus for efficient performance monitoring of a large number of simultaneous events

InactiveUS7461383B2Reduce area requirementsReduce the required powerEnergy efficient ICTError detection/correctionEvent typeDevice Monitor

A system for monitoring a large number of simultaneous events implements a hybrid counter array device having a first counter portion comprising counter devices, each counter device for receiving signals representing occurrences of events from an event source and providing a first count value corresponding to a lower order bits of the hybrid counter array. A second counter portion comprises a memory array device having addressable memory locations in correspondence with the counter devices, each addressable memory location for storing a second count value representing higher order bits. A control device monitors each of the counter devices and initiates updating a value of a corresponding second count value stored at the corresponding addressable memory location. The system includes interrupt pre-indication for providing fast interrupt trigger to a processor device when a count value related to an event equals a threshold value. A data transfer sub-system additionally enables one or more of: read access or write access to both the count values in the first and second counter portions over a narrow bus, the read / write access for purposes of initializing and determining status of the count values for a monitored event type in response to a processor device request.

Owner:IBM CORP

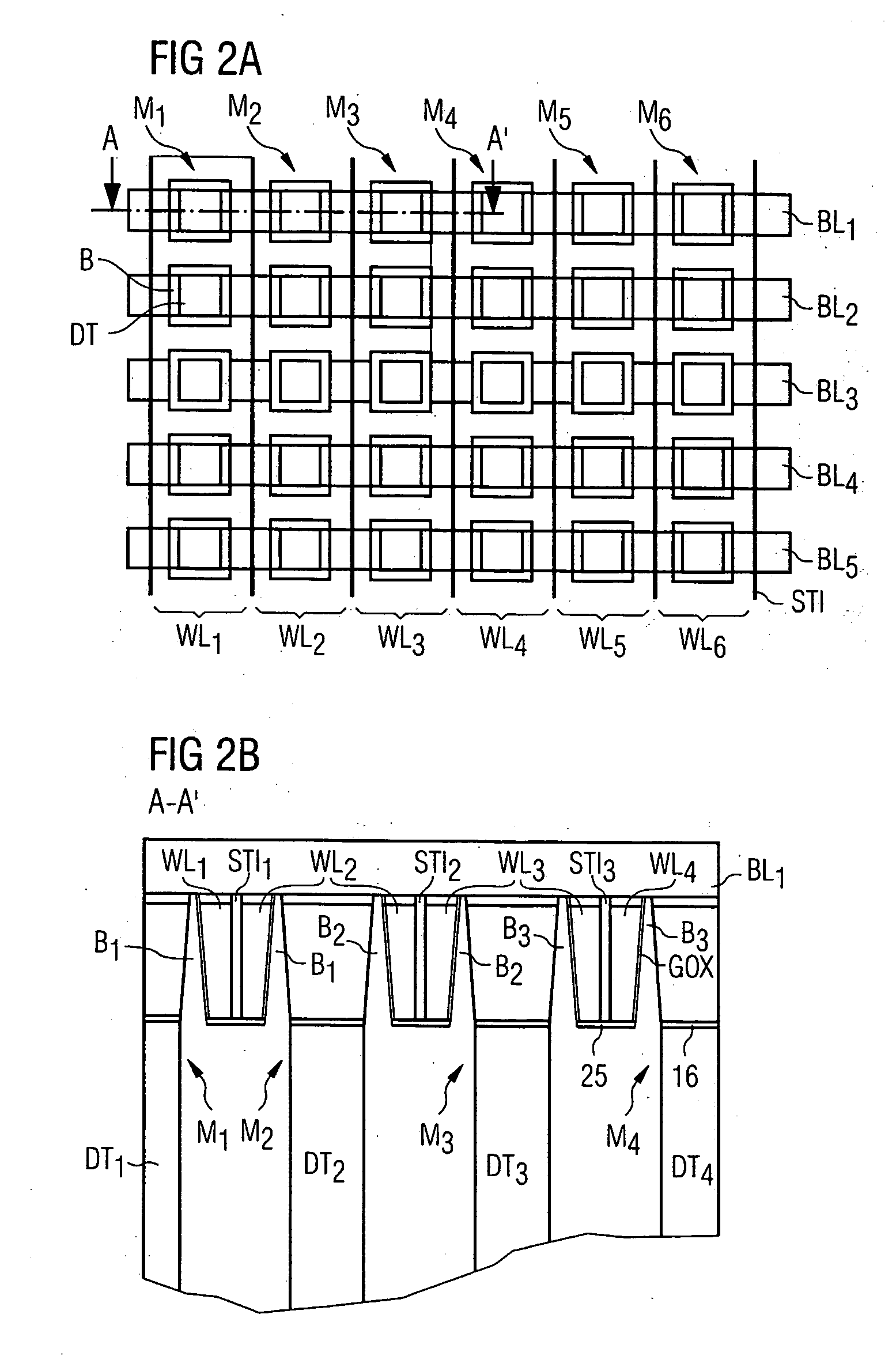

DRAM memory with vertically arranged selection transistors

InactiveUS20050056873A1Increase capacitySimple processTransistorSolid-state devicesBit lineDram memory

The invention relates to a semiconductor memory, particularly a DRAM, in which the memory cells in each case have a trench capacitor arranged in a lower area of a trench hole and a vertical selection transistor which is formed adjoining an upper area of the trench hole and which connects an inner electrode of the trench capacitor to a bit line, a conductive channel being capable of being formed in dependence on the potential of a word line in the channel area, the channel area completely enclosing the trench hole in its upper area, and the associated word line at least partially enclosing the channel area.

Owner:QIMONDA

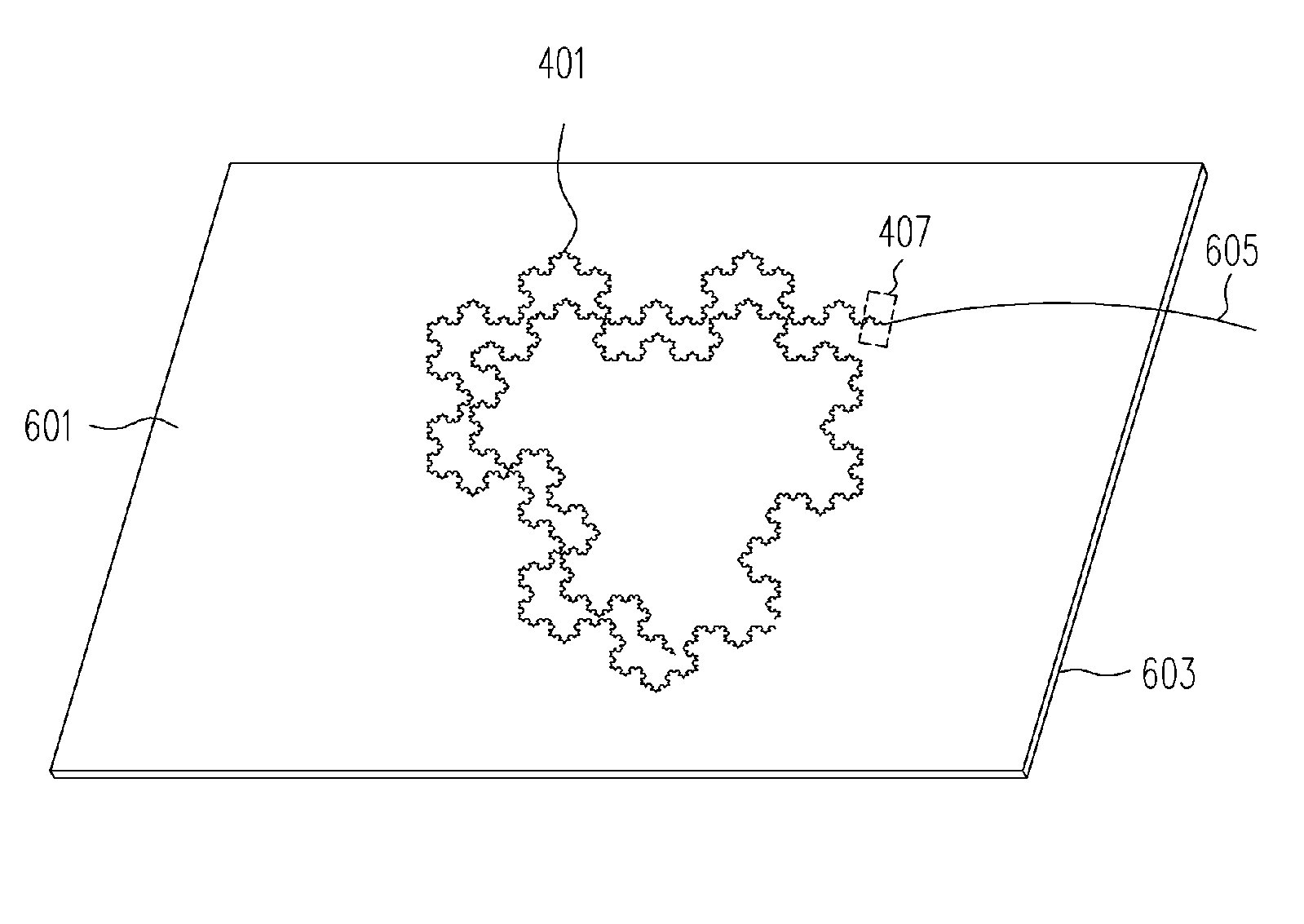

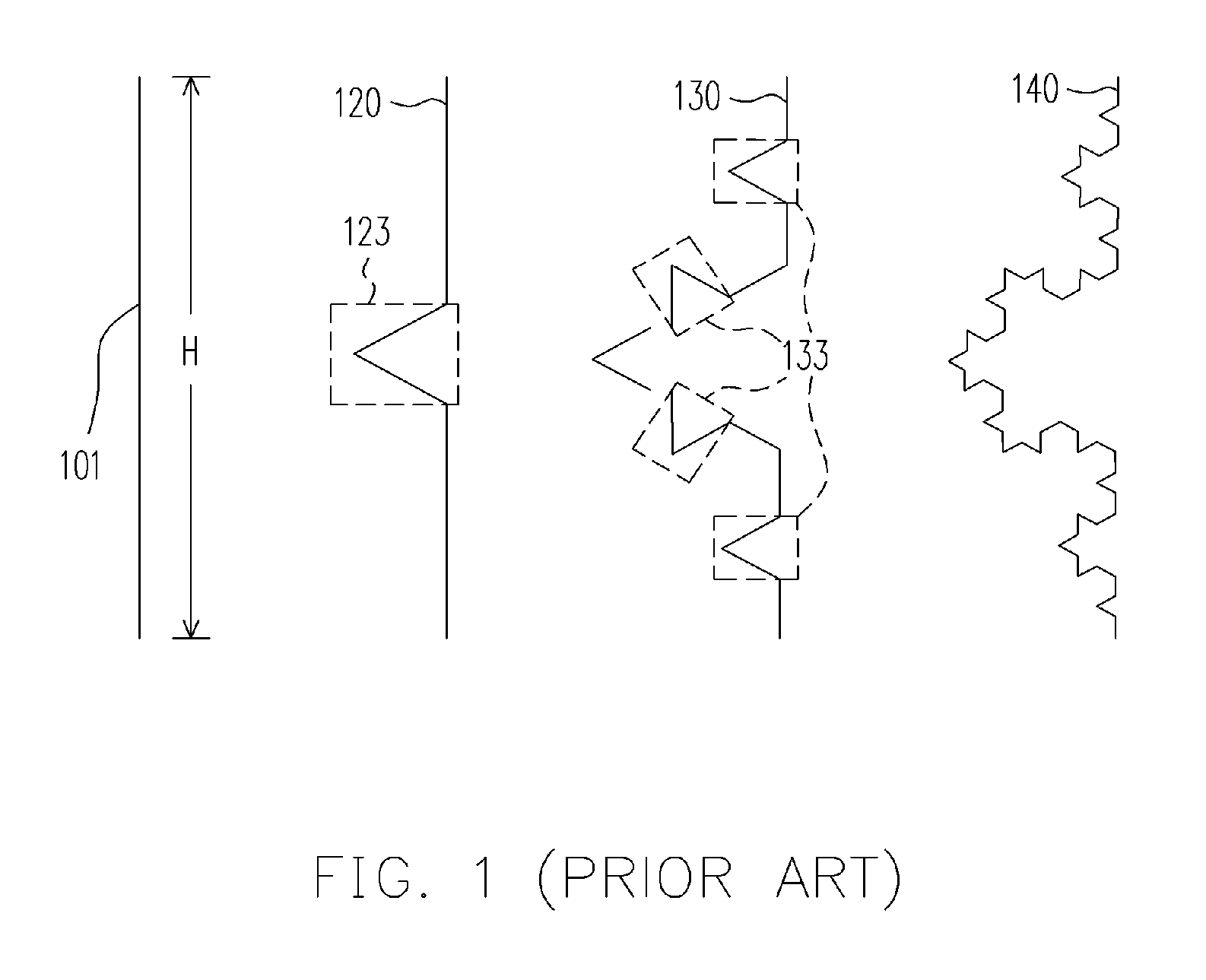

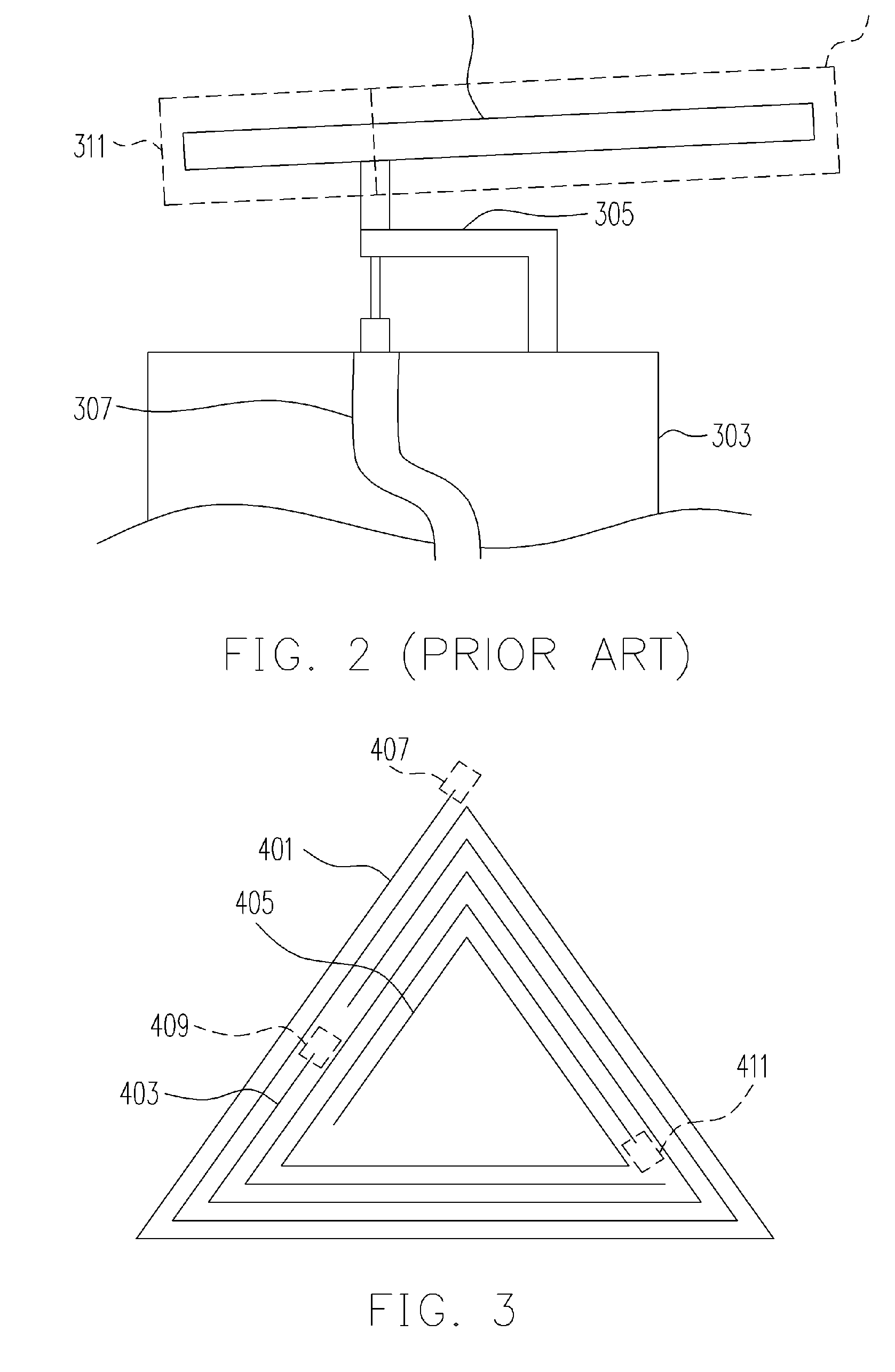

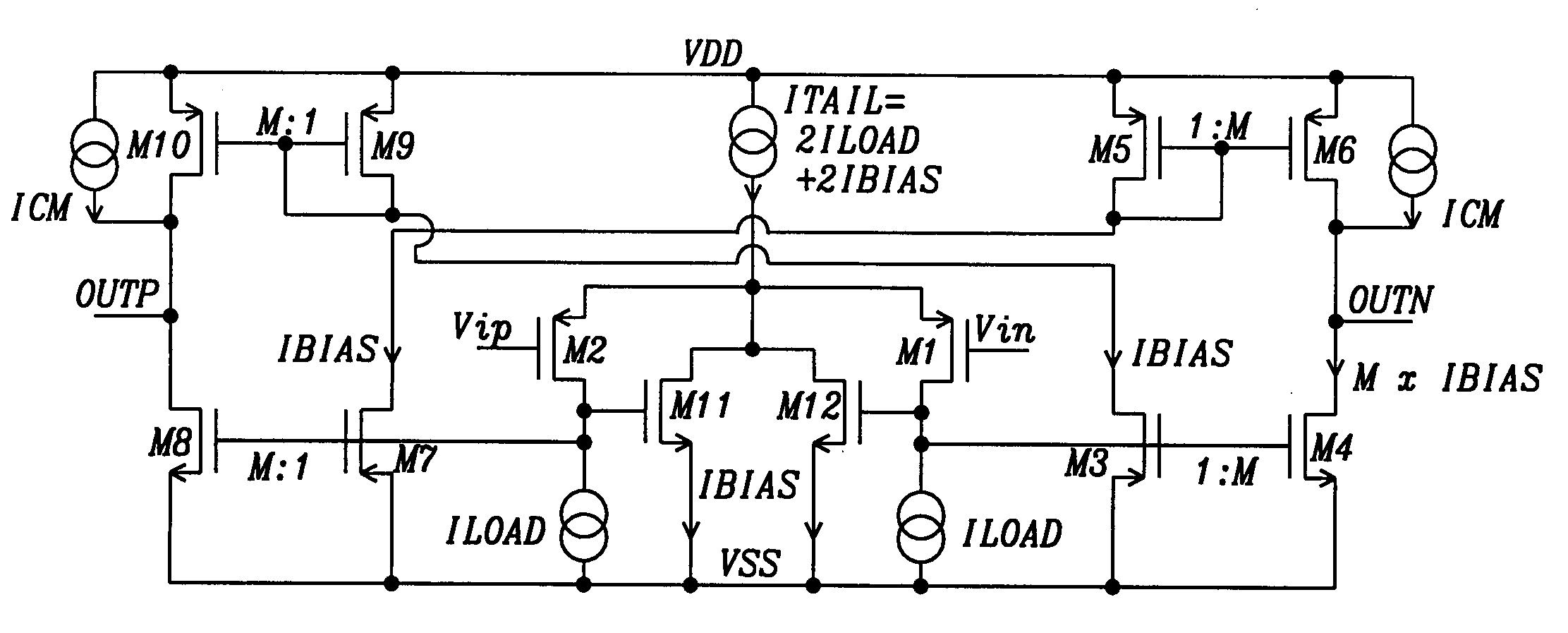

Multi-band antenna and design method thereof

ActiveUS20060164306A1Reduce area requirementsReduced footprintSimultaneous aerial operationsRadiating elements structural formsMulti bandAntenna design

The present invention provides a multi-band antenna to which the arrangement of Koch fractal antenna is applied. The multi-band antenna is designed in triangular shape whose area is smaller than the general antenna structure. By using the arrangement of Koch fractal antenna, the area of the inverted-F dual-band antenna can be reduced efficiently, so as to enhance more usability.

Owner:WISTRON NEWEB

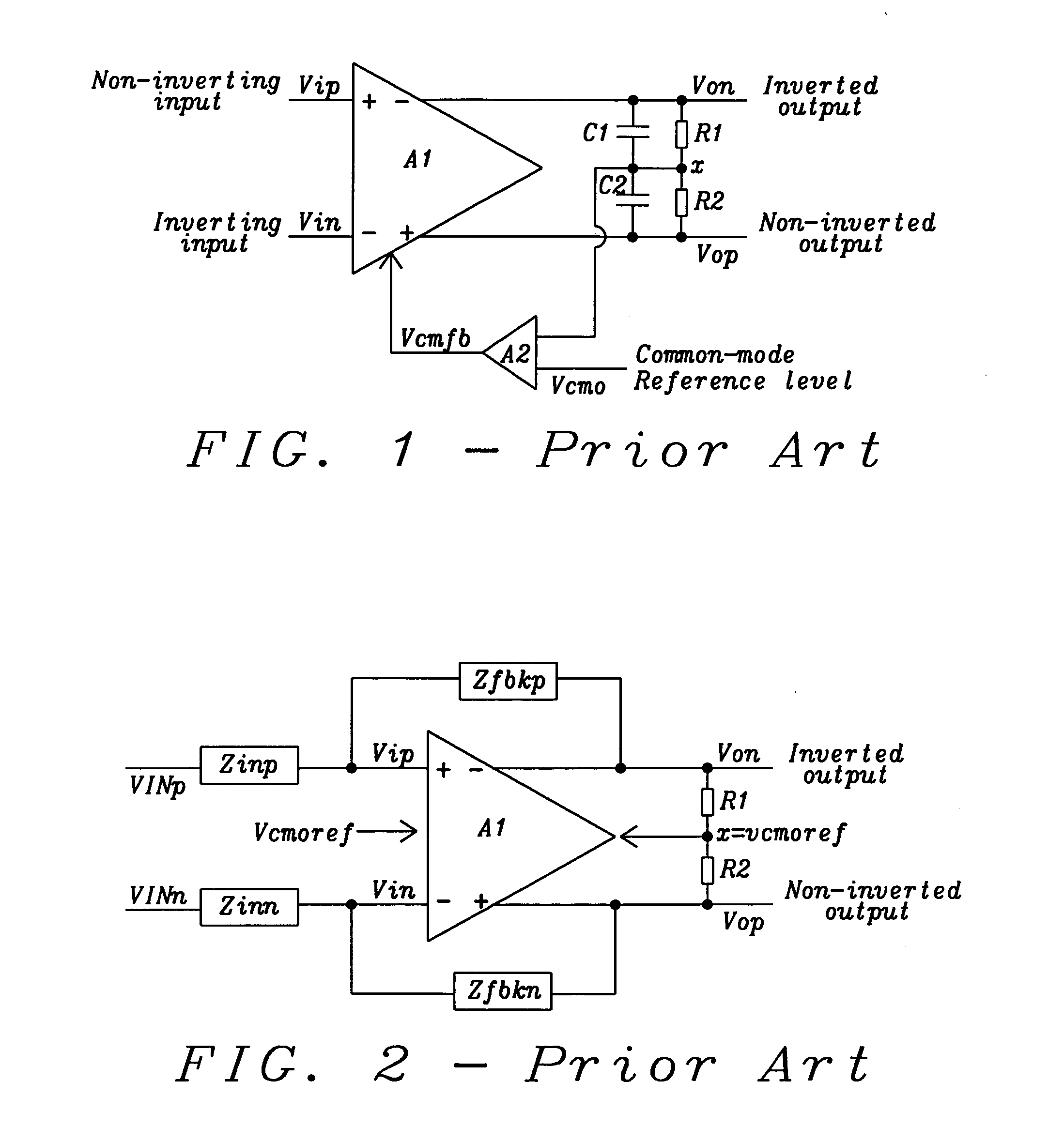

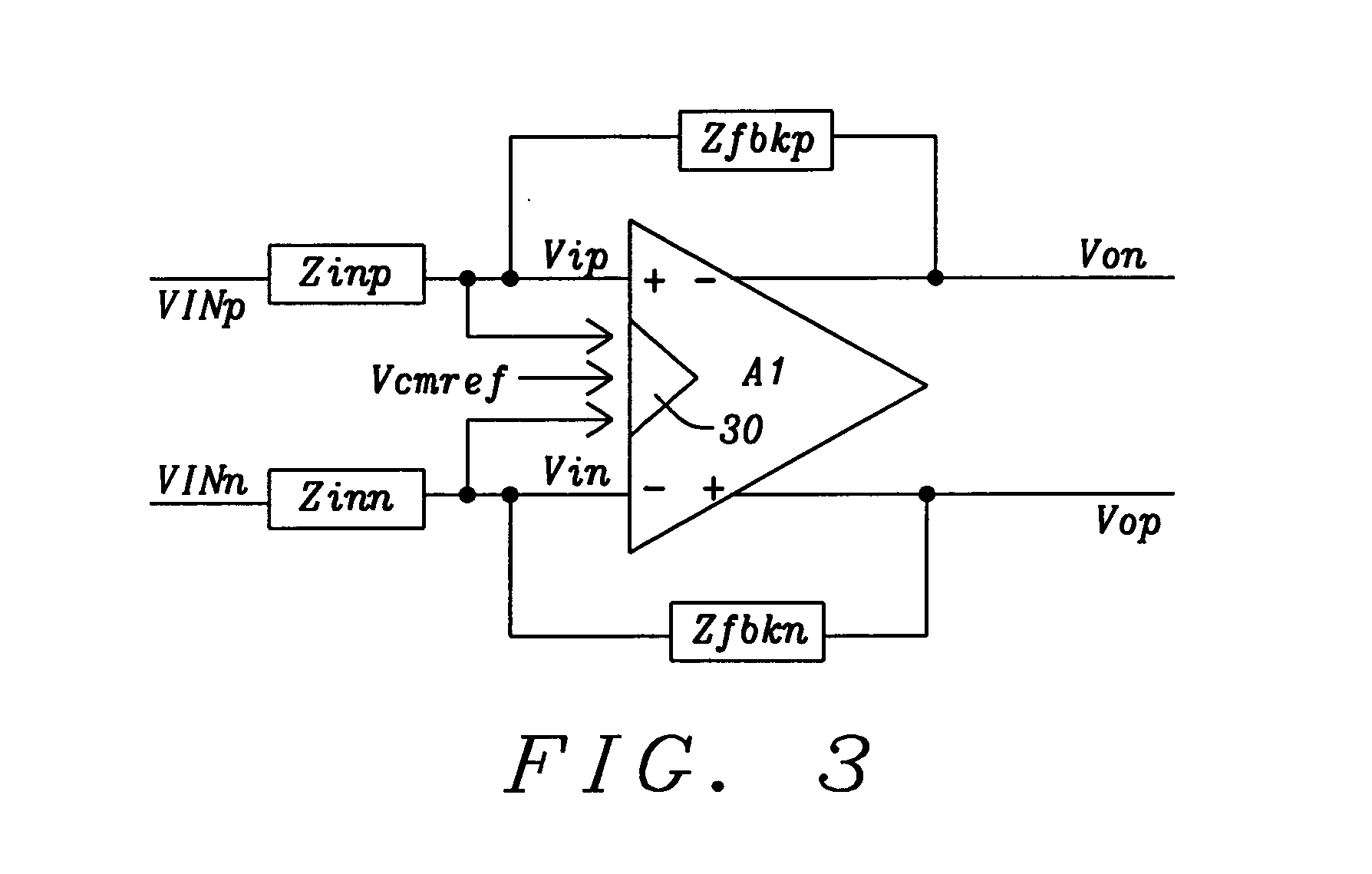

Amplifier common-mode control methods

InactiveUS20120154048A1Save powerSave areaNegative-feedback-circuit arrangementsDifferential amplifiersAudio power amplifierMode control

Systems and methods for providing a fully differential amplifier performing common-mode voltage control having reduced area and power requirements are disclosed. The amplifier disclosed comprises an additional input stage at the amplifier input which senses the common mode voltage of the amplifier's inputs and applies internal feedback control to adjust the output common-mode voltage until the input common-mode voltage matches a target voltage and thereby indirectly set the output common-mode voltage. Furthermore the internal common-mode control can be implemented in such a manner as to provide a feed-forward transconductance function in addition to common-mode control if desired. Moreover it is possible to use feedback from other amplifier stages in an amplifier chain to implement common-mode feedback.

Owner:DIALOG SEMICONDUCTOR GMBH

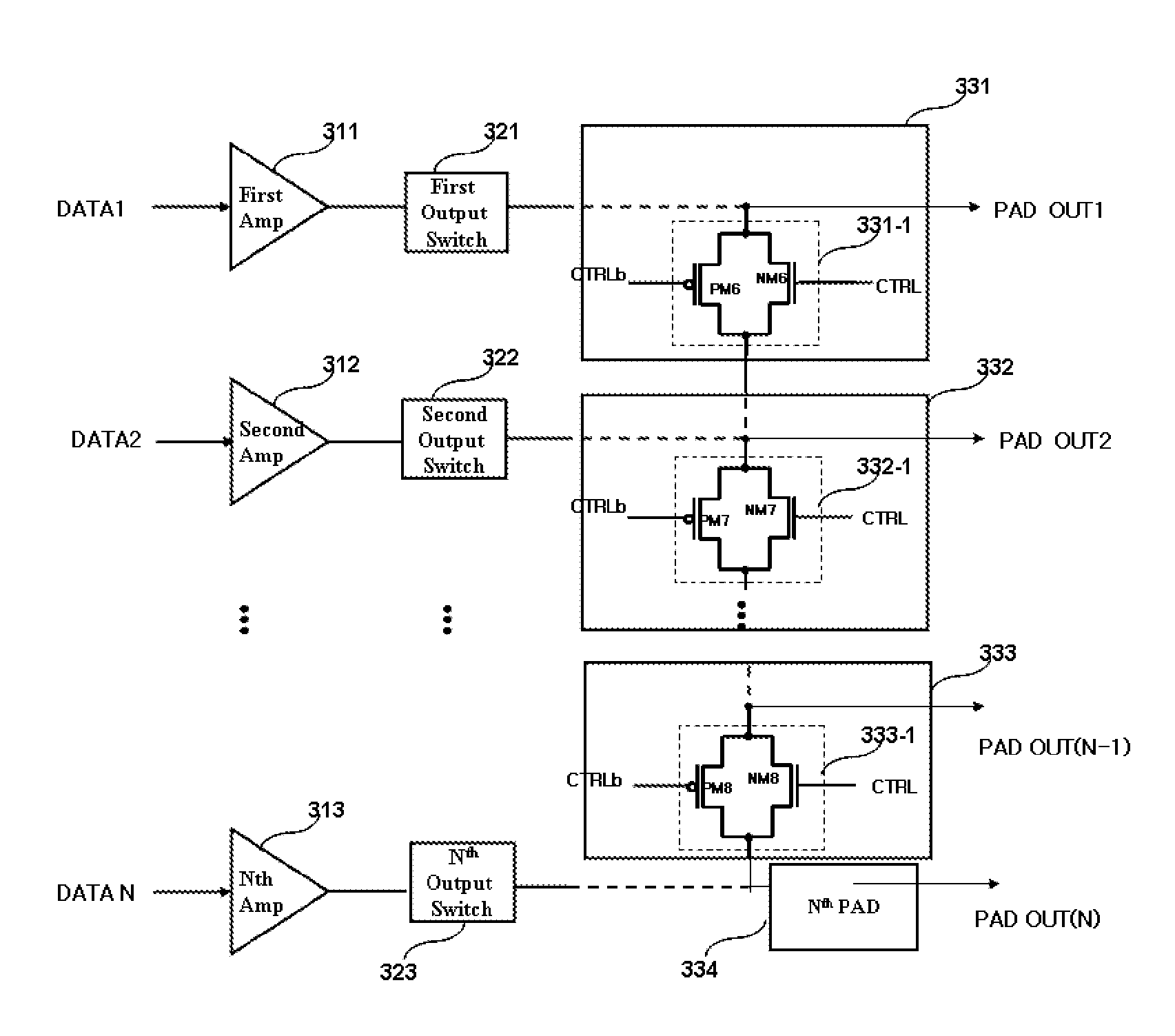

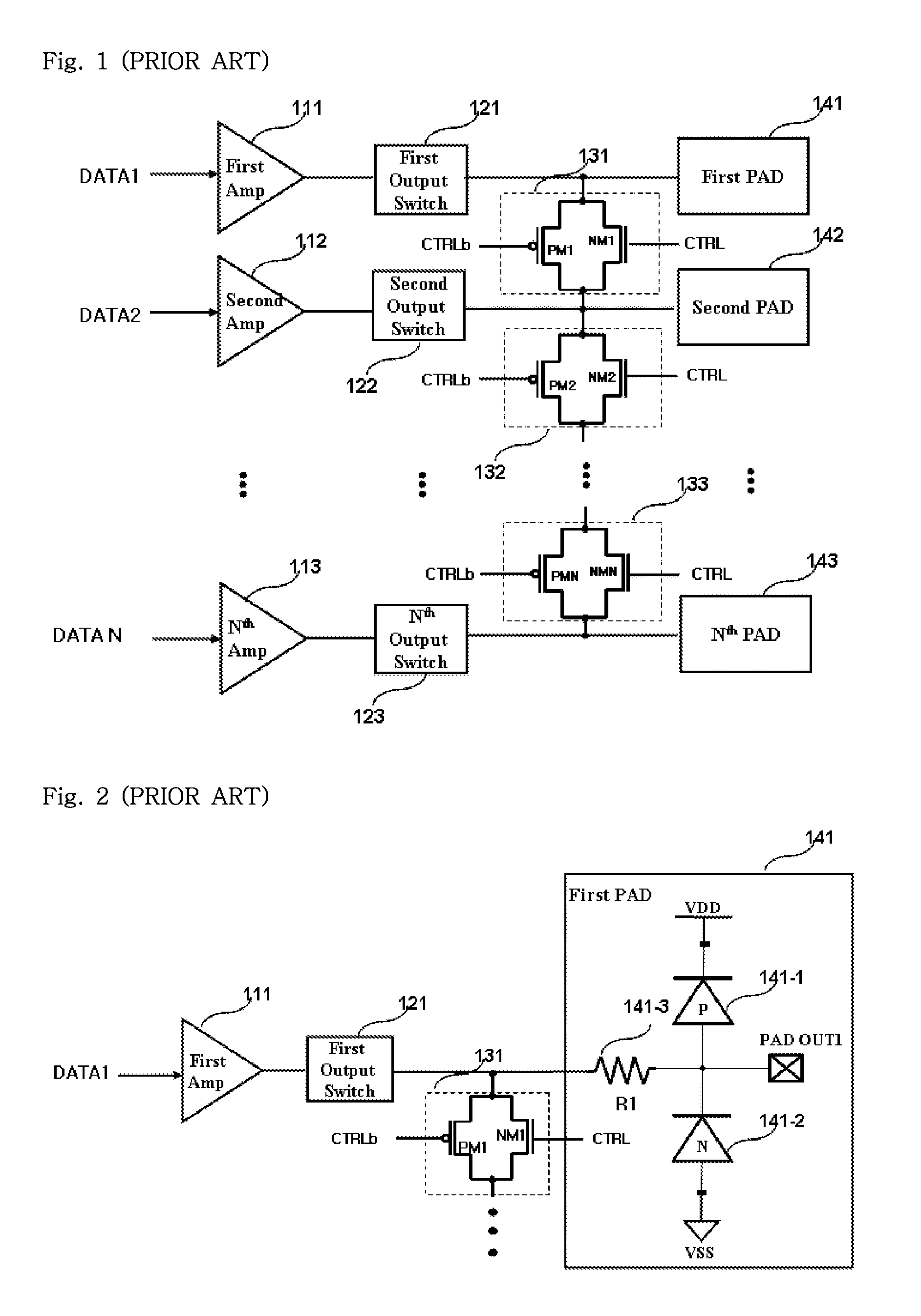

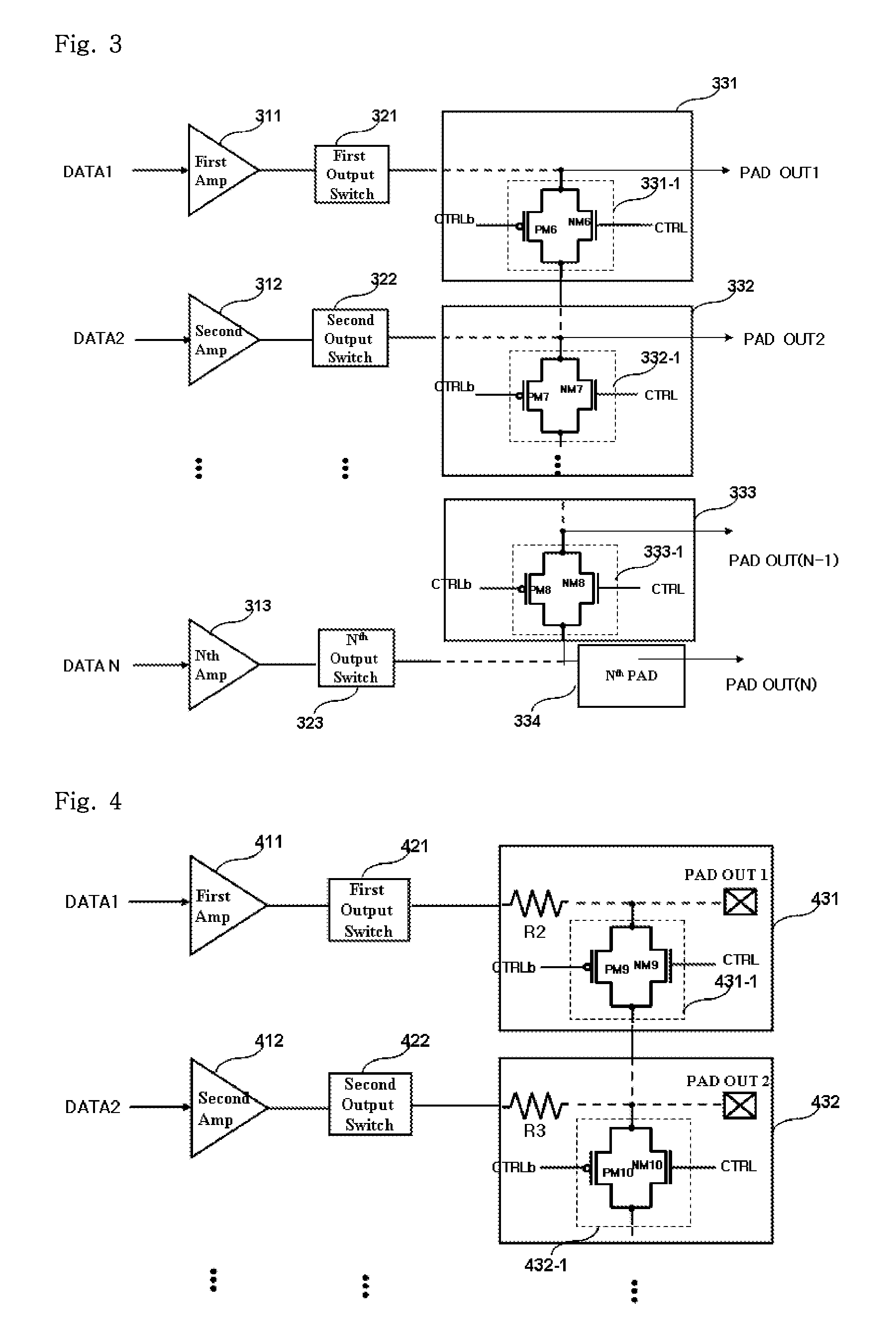

Display panel driving circuit having charge sharing switch formed in pad

InactiveUS20110169813A1Reduce decreaseReduce power consumptionCathode-ray tube indicatorsInput/output processes for data processingAudio power amplifierCharge sharing

A display panel driving circuit includes N number of amplifiers configured to supply N number of output voltages to a display panel; N number of output switches configured to transmit output signals from the N number of amplifiers through N number of pads to the display panel; and a plurality of charge sharing switches configured to share charges among the N number of pads, wherein the charge sharing switches are formed in the pads.

Owner:SILICON WORKS CO LTD

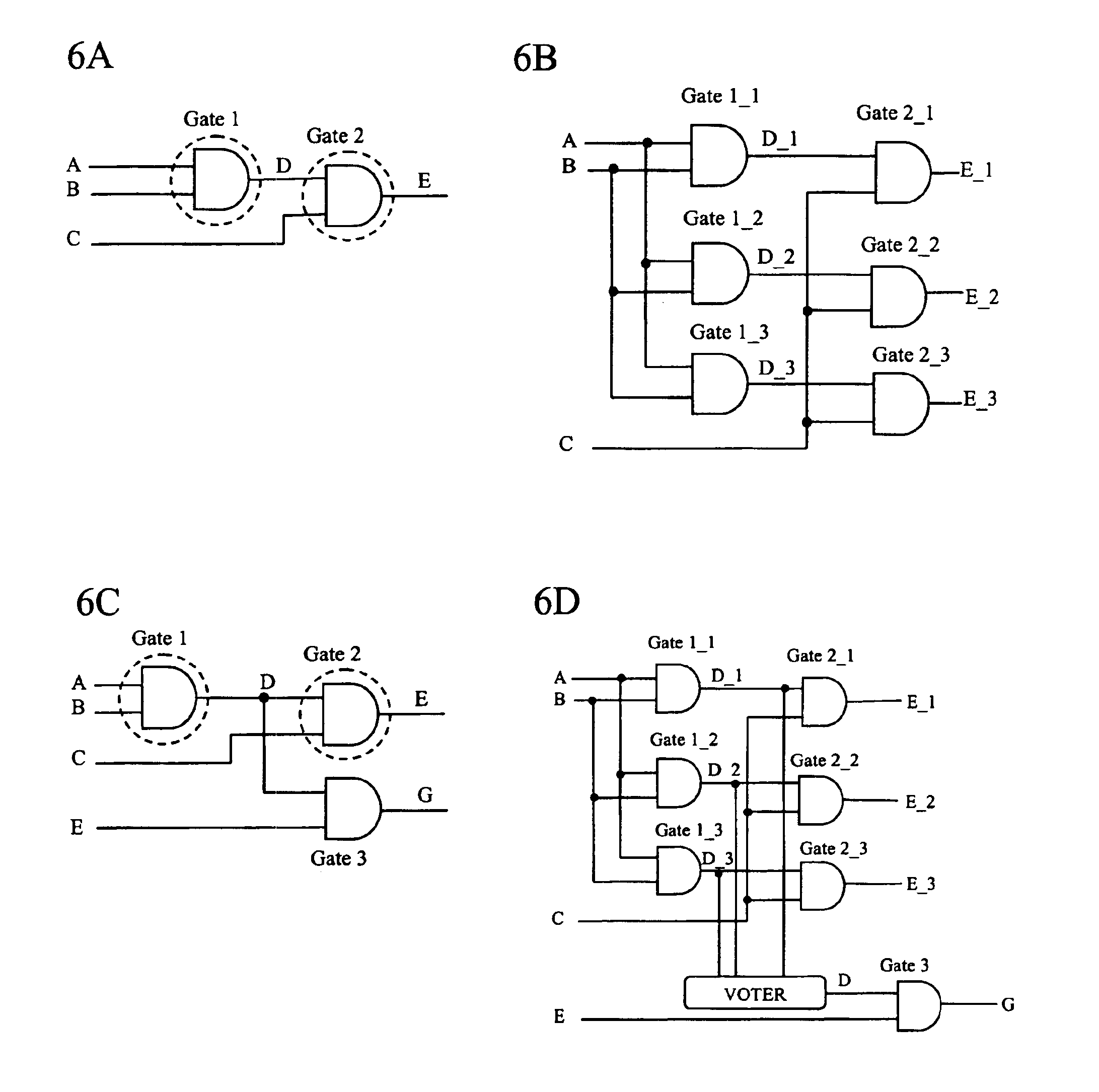

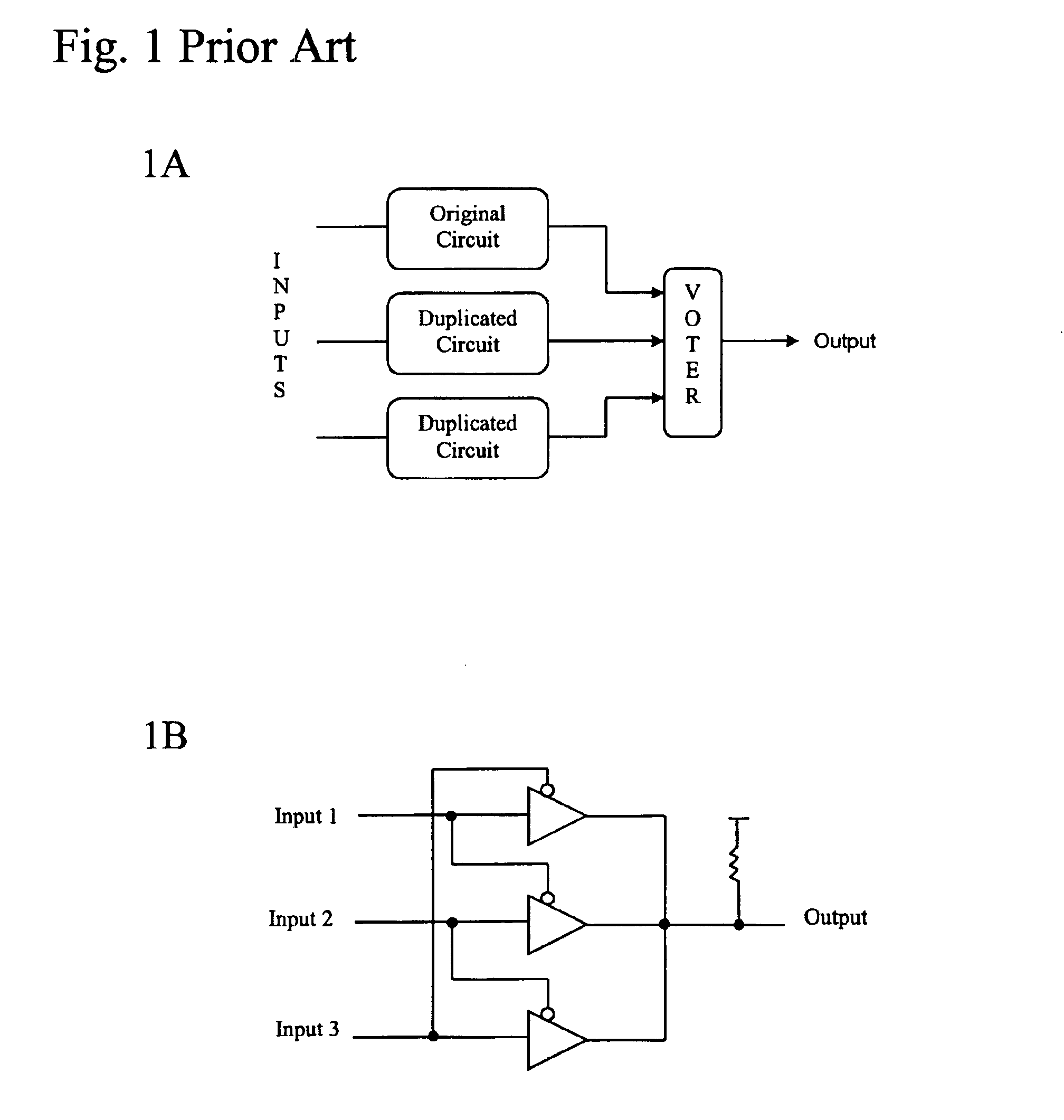

Method and apparatus for creating circuit redundancy in programmable logic devices

InactiveUS6963217B2Reduces area requireReduce payloadReliability increasing modificationsElectronic circuit testingProgrammable logic deviceErasable programmable logic device

A method for reducing circuit sensitivity to single event upsets in programmable logic devices, involves identifying single event upset sensitive gates within a single event upset sensitive sub-circuit of a programmable logic device as determined by the input environment and introducing triple modular redundancy and voter circuits for each single event upset sensitive sub-circuit so identified.

Owner:UNIV OF SOUTH FLORIDA +1