Patents

Literature

409results about How to "Save area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

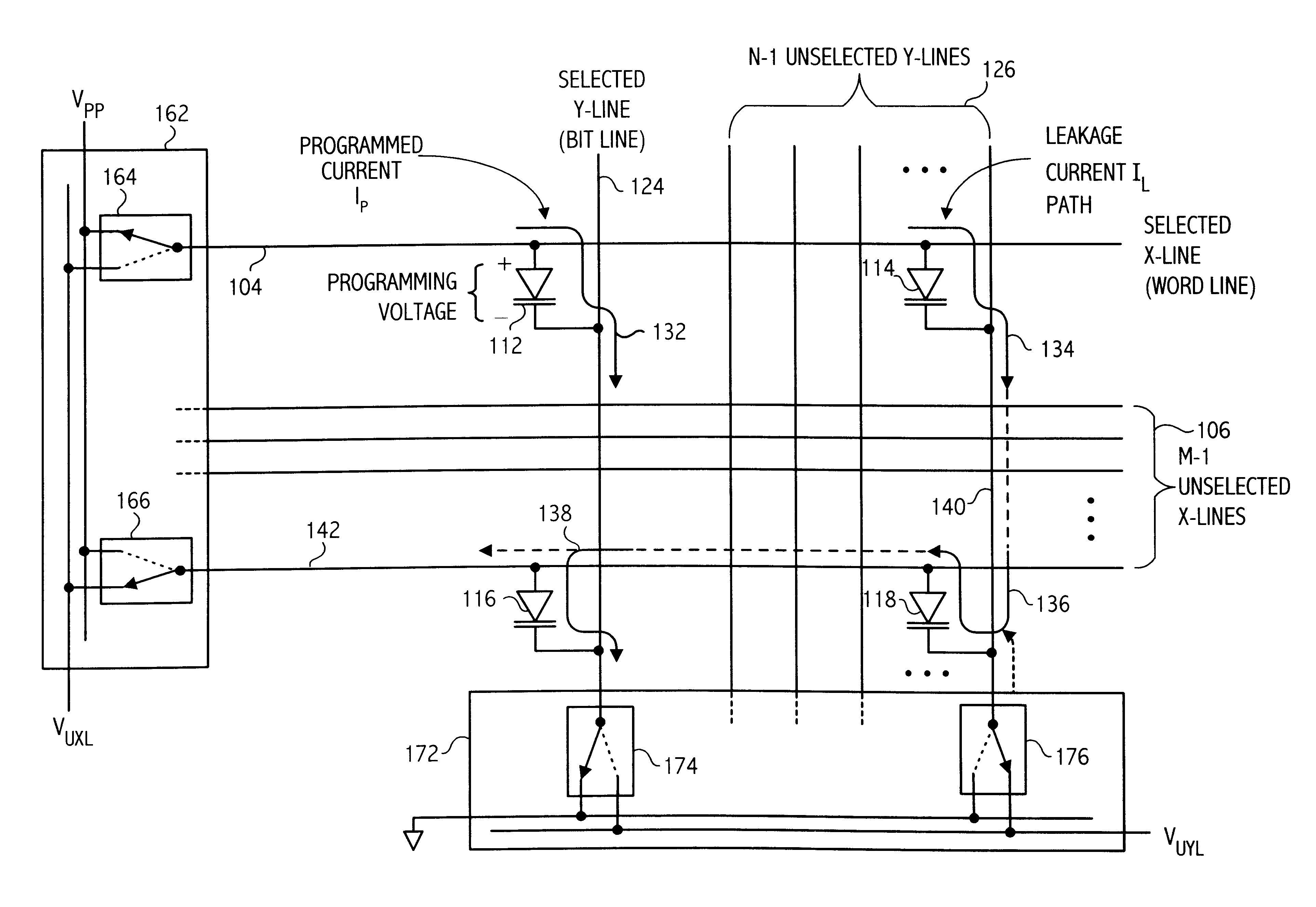

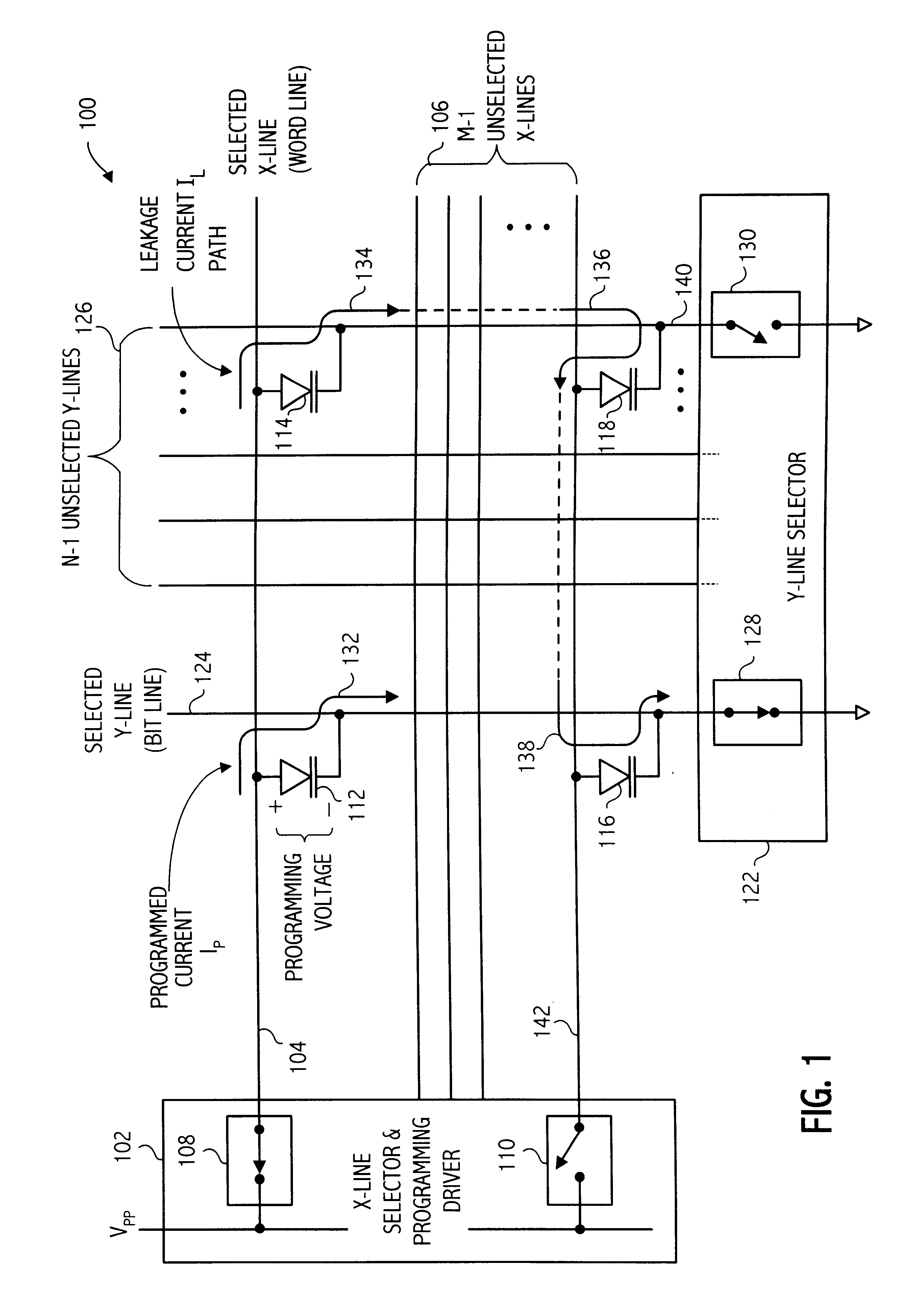

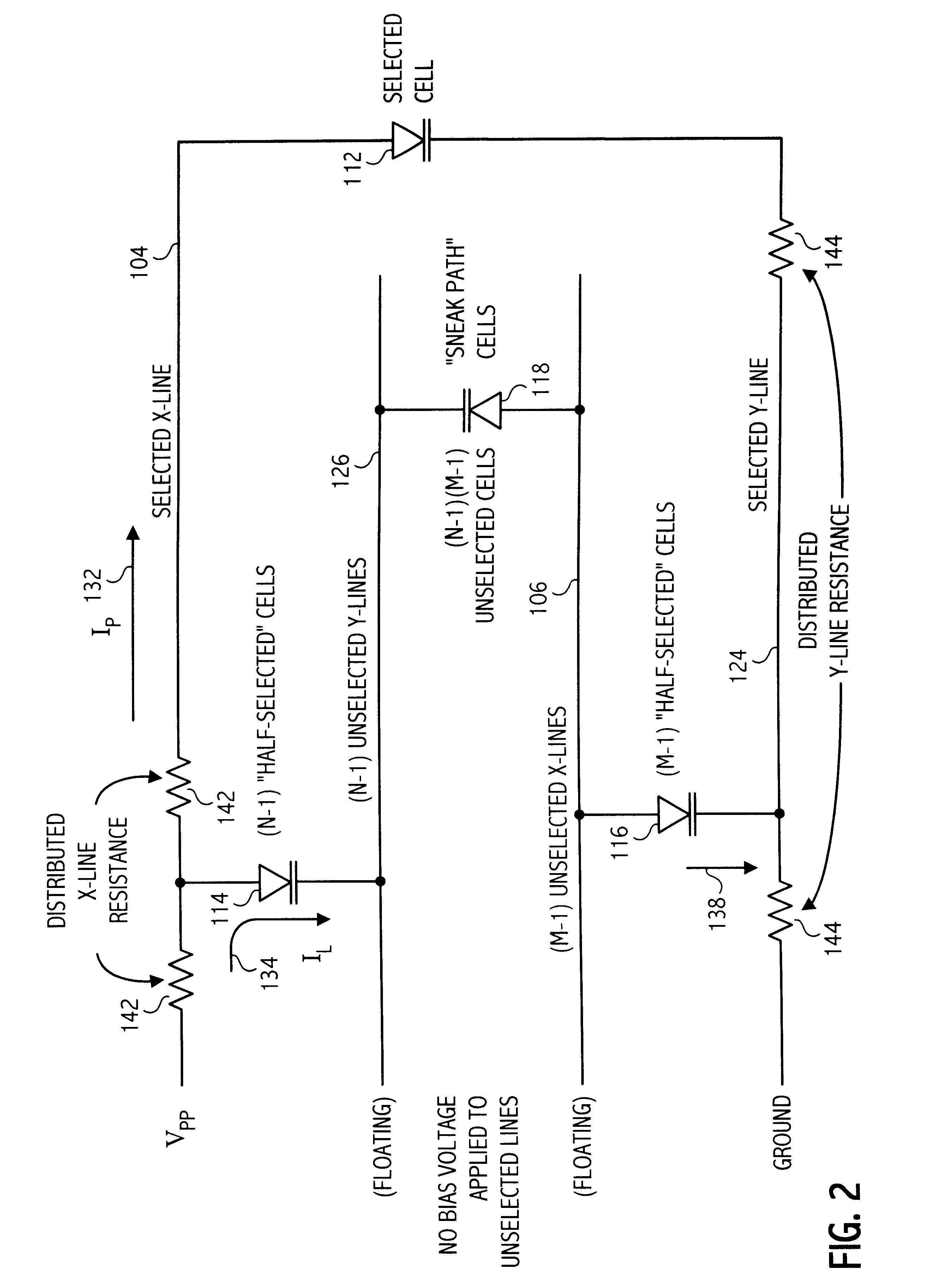

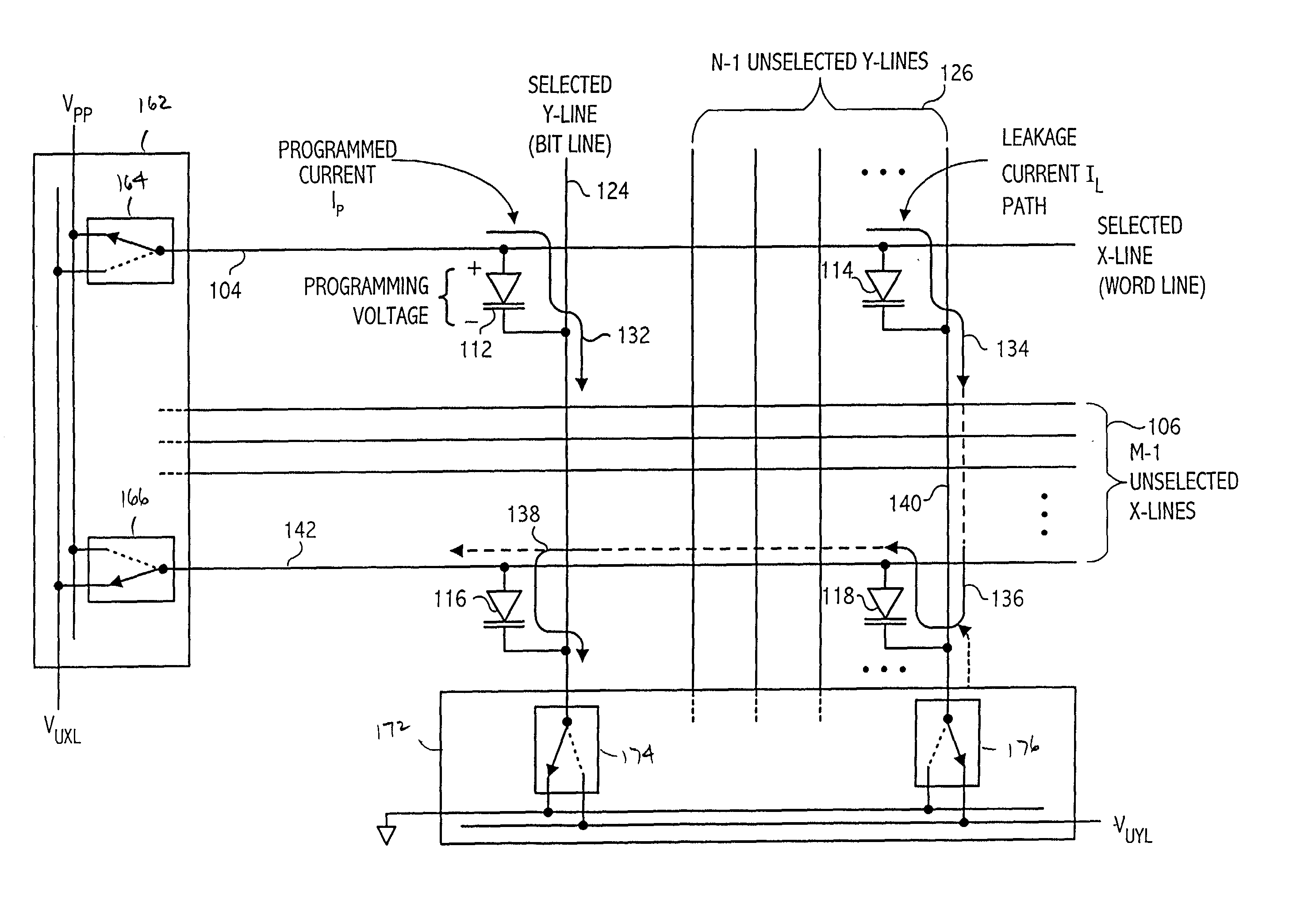

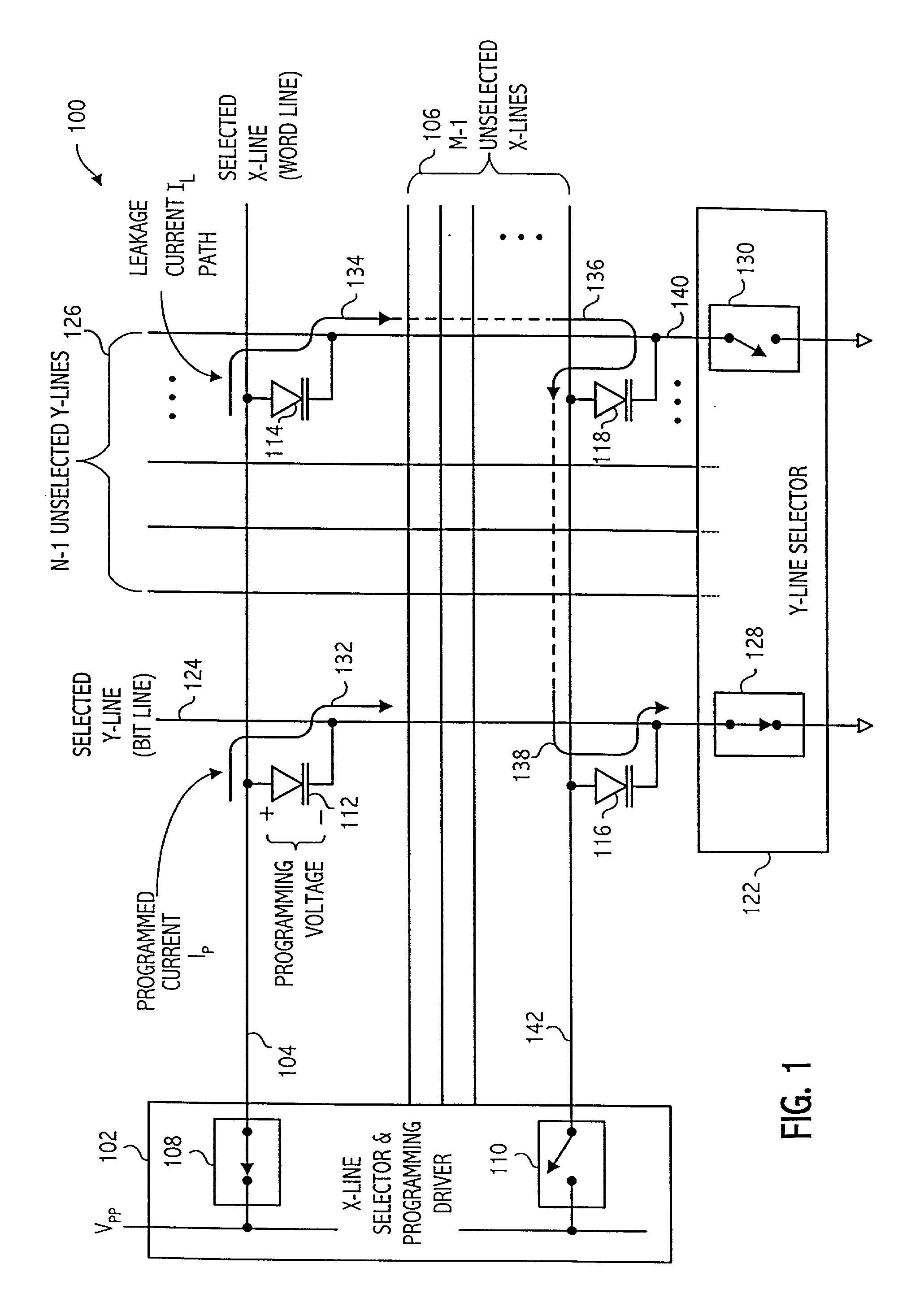

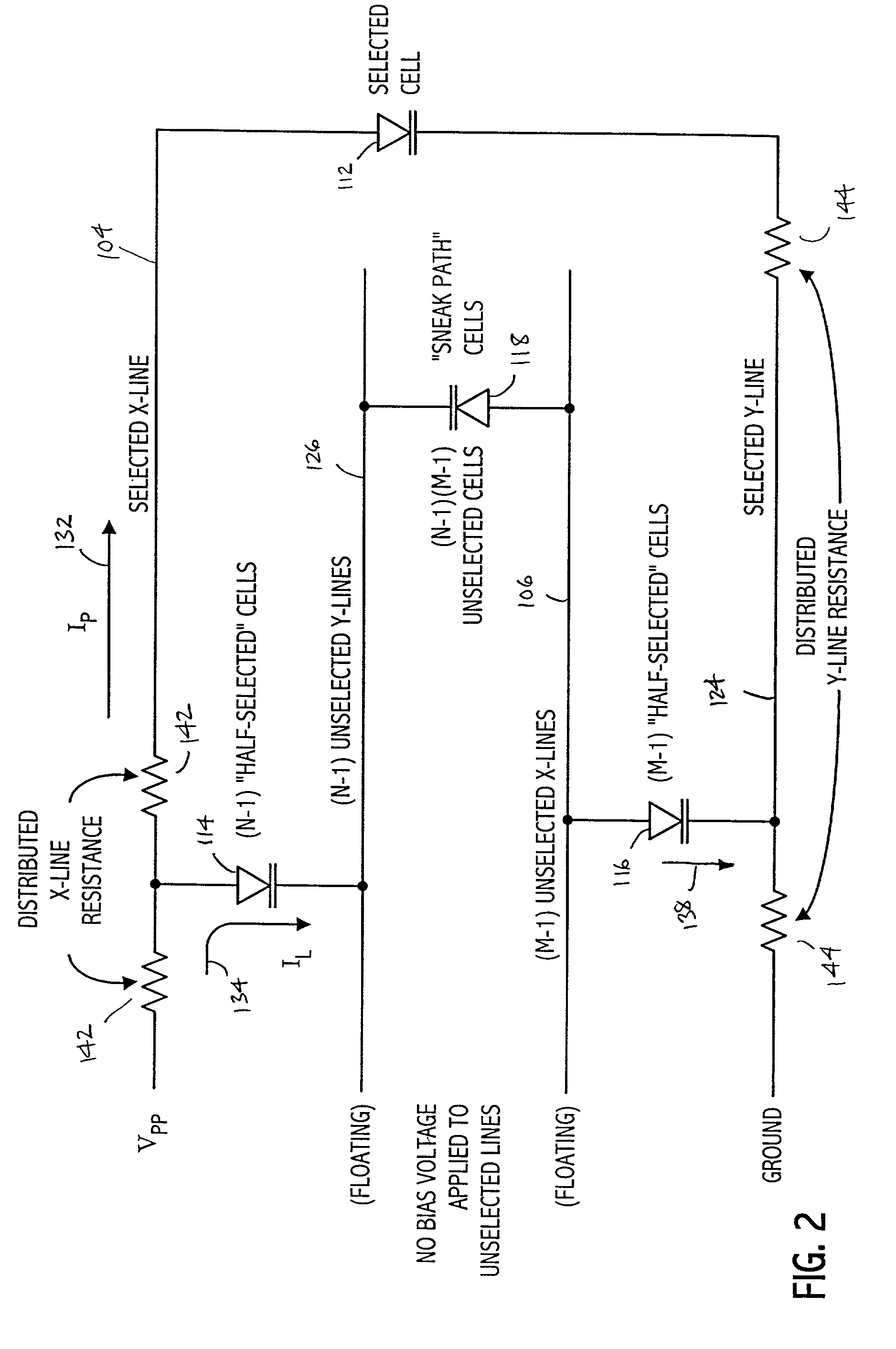

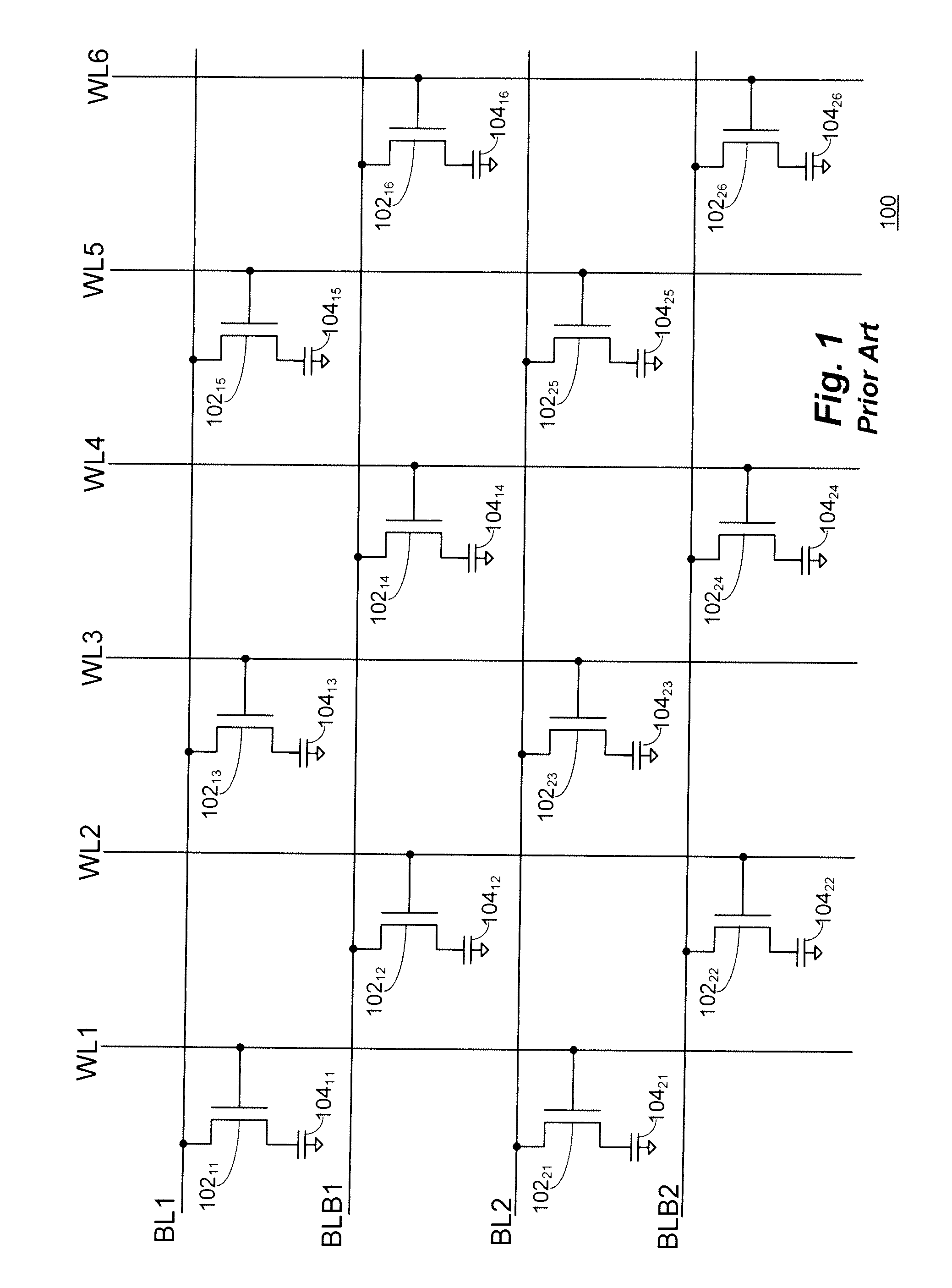

Method and apparatus for biasing selected and unselected array lines when writing a memory array

InactiveUS6618295B2Much faster programmingVoltage requirementRead-only memoriesDigital storageCapacitanceEngineering

A passive element memory array preferably biases selected X-lines to an externally received VPP voltage and selected Y-lines to ground. Unselected Y-lines are preferably biased to VPP minus a first offset voltage, and unselected X-lines biased to a second offset voltage (relative to ground). The first and second offset voltages preferably are identical and have a value of about 0.5 to 2 volts. The VPP voltage depends upon the memory cell technology used, and preferably falls within the range of 5 to 20 volts. The area otherwise required for an on-chip VPP generator and saves the power that would be consumed by such a generator. In addition, the operating temperature of the integrated circuit during the programming operation decreases, which further decreases power dissipation. When discharging the memory array, the capacitance between layers is preferably discharged first, then the layers are discharged to ground.

Owner:SANDISK TECH LLC

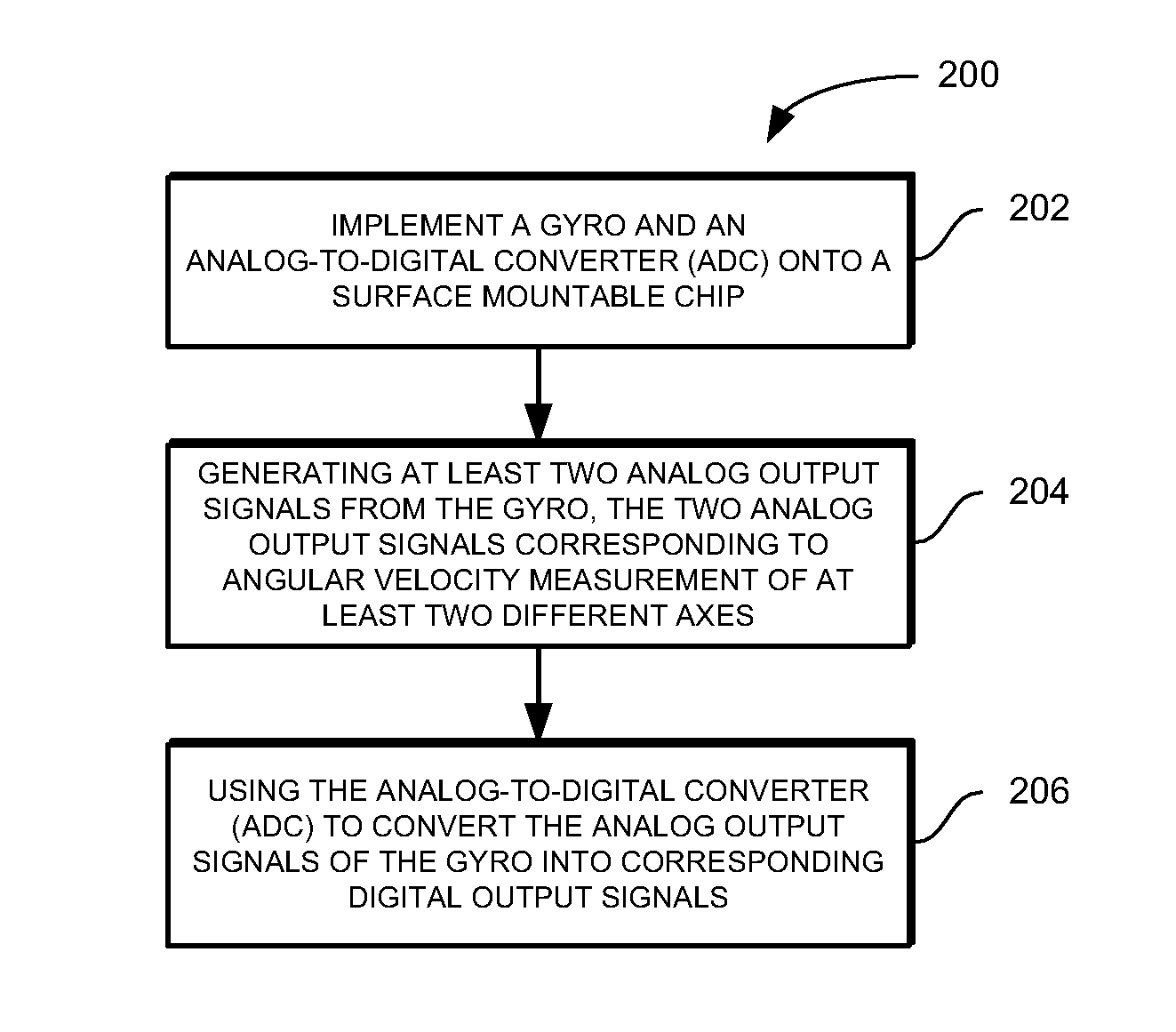

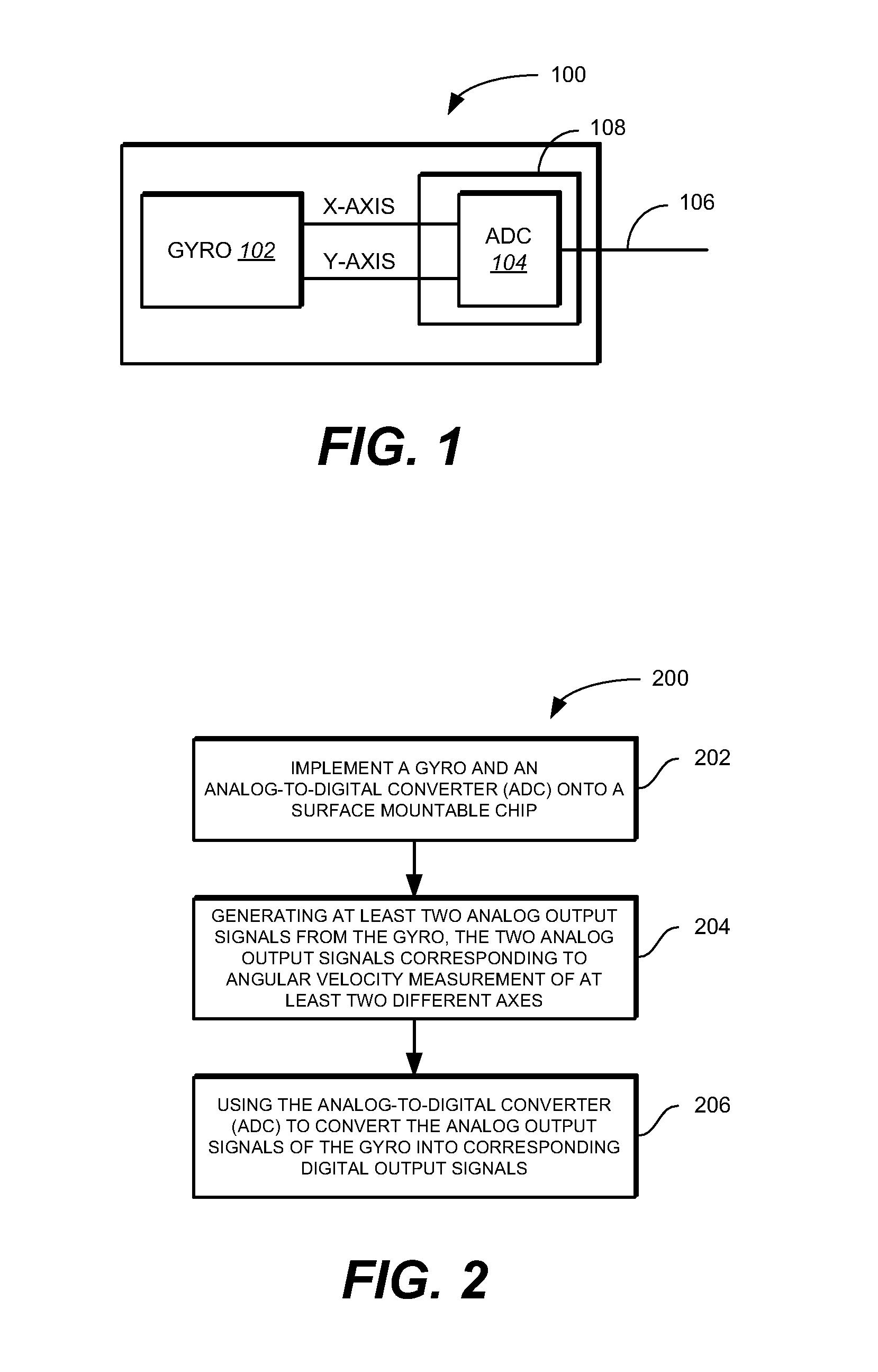

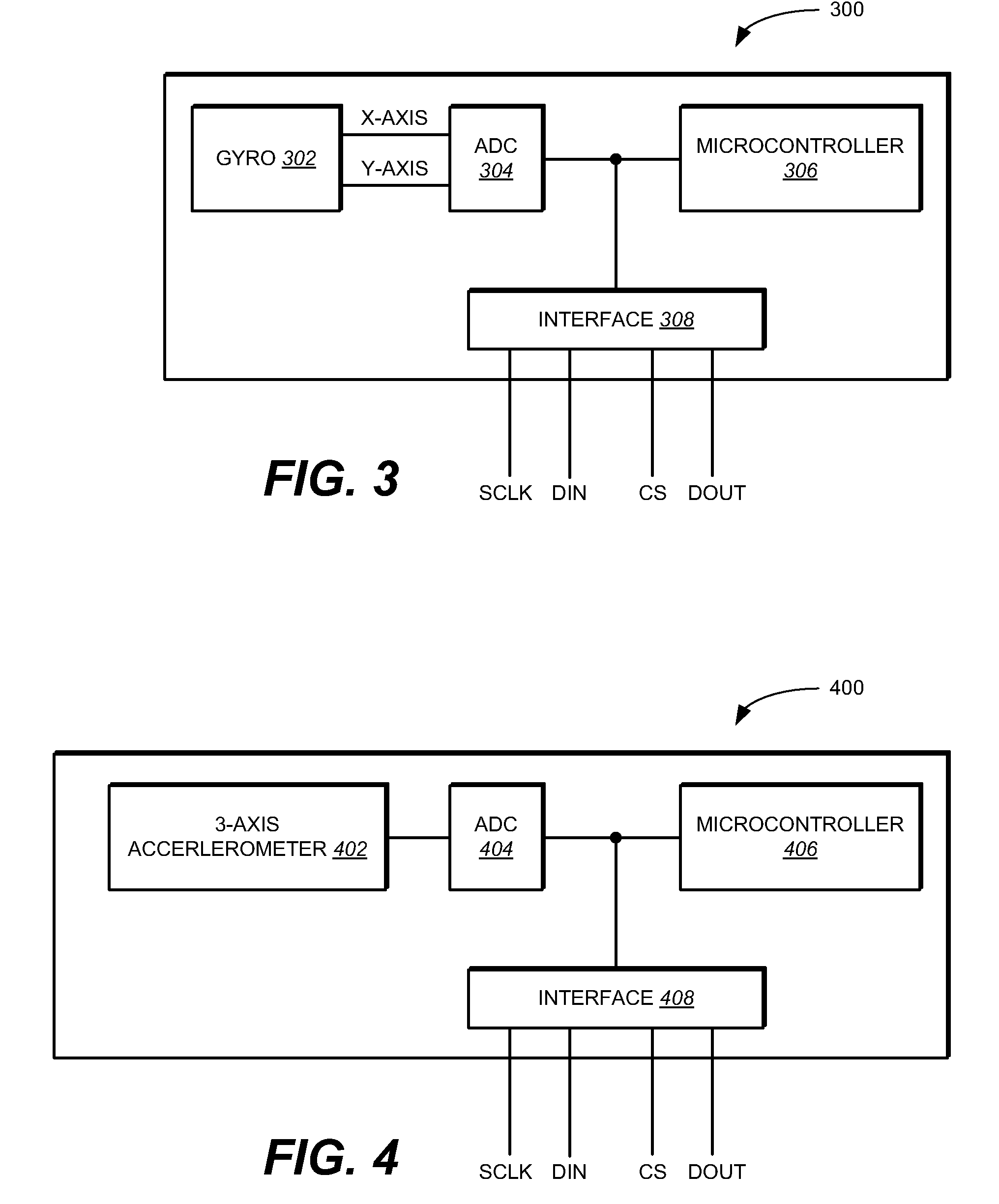

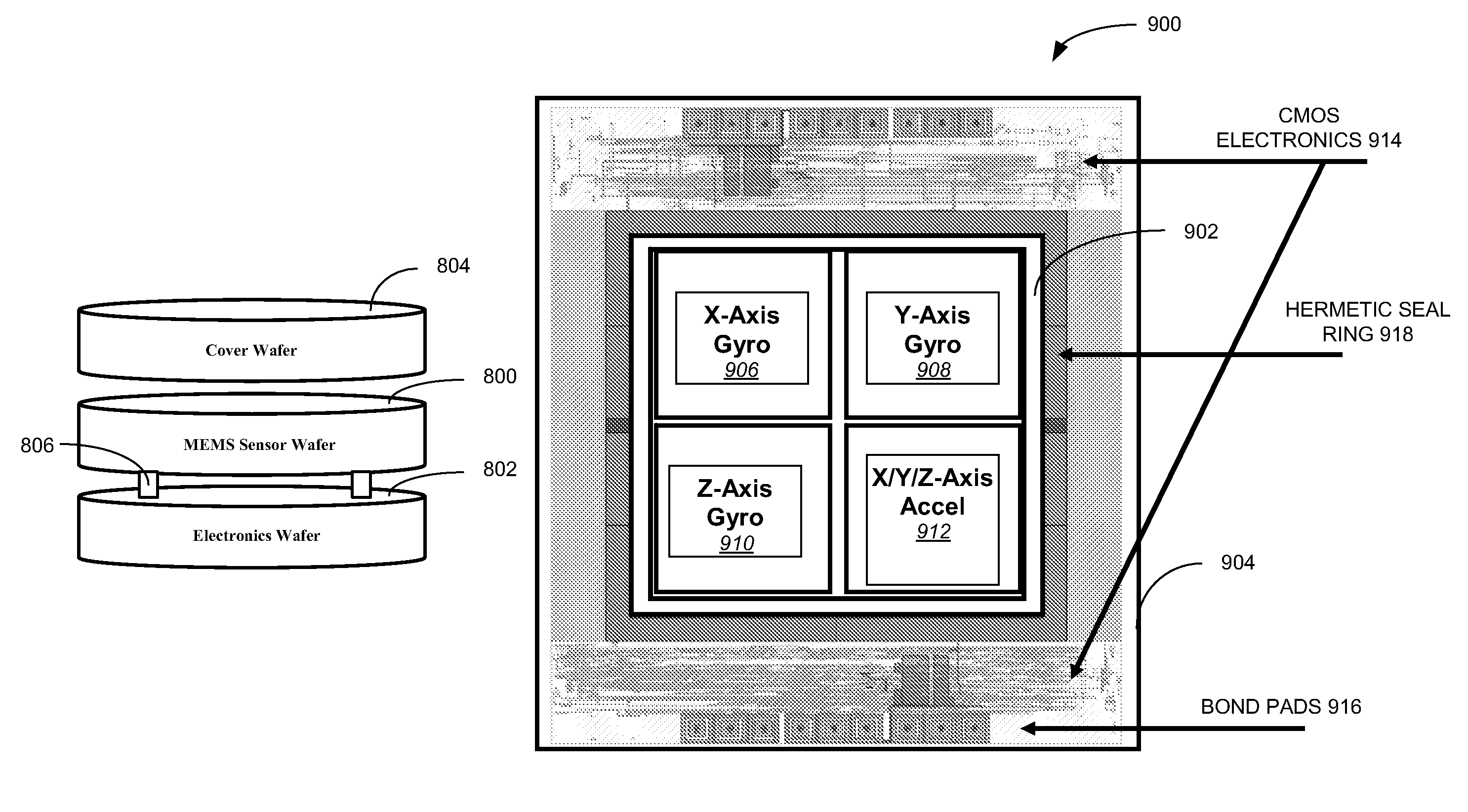

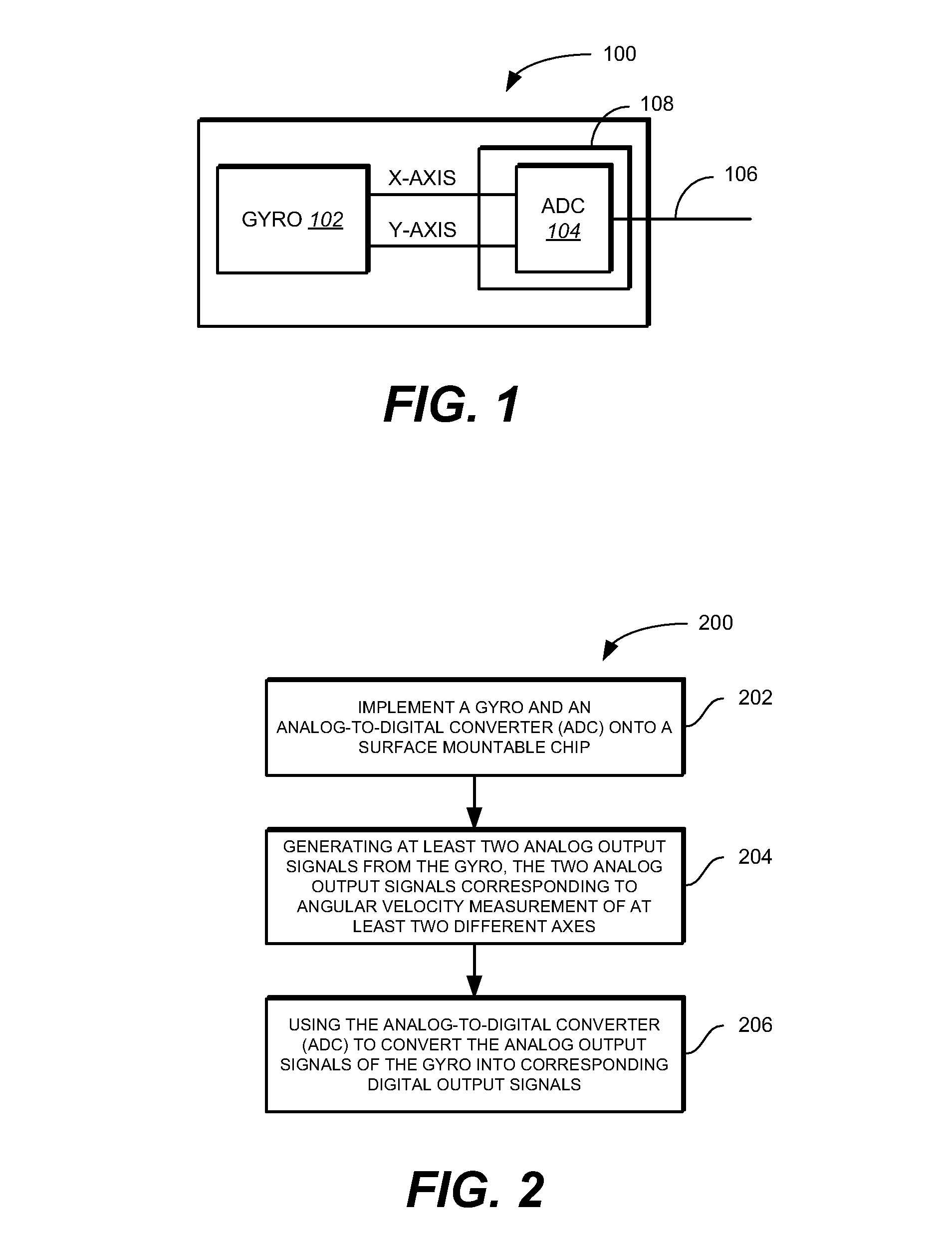

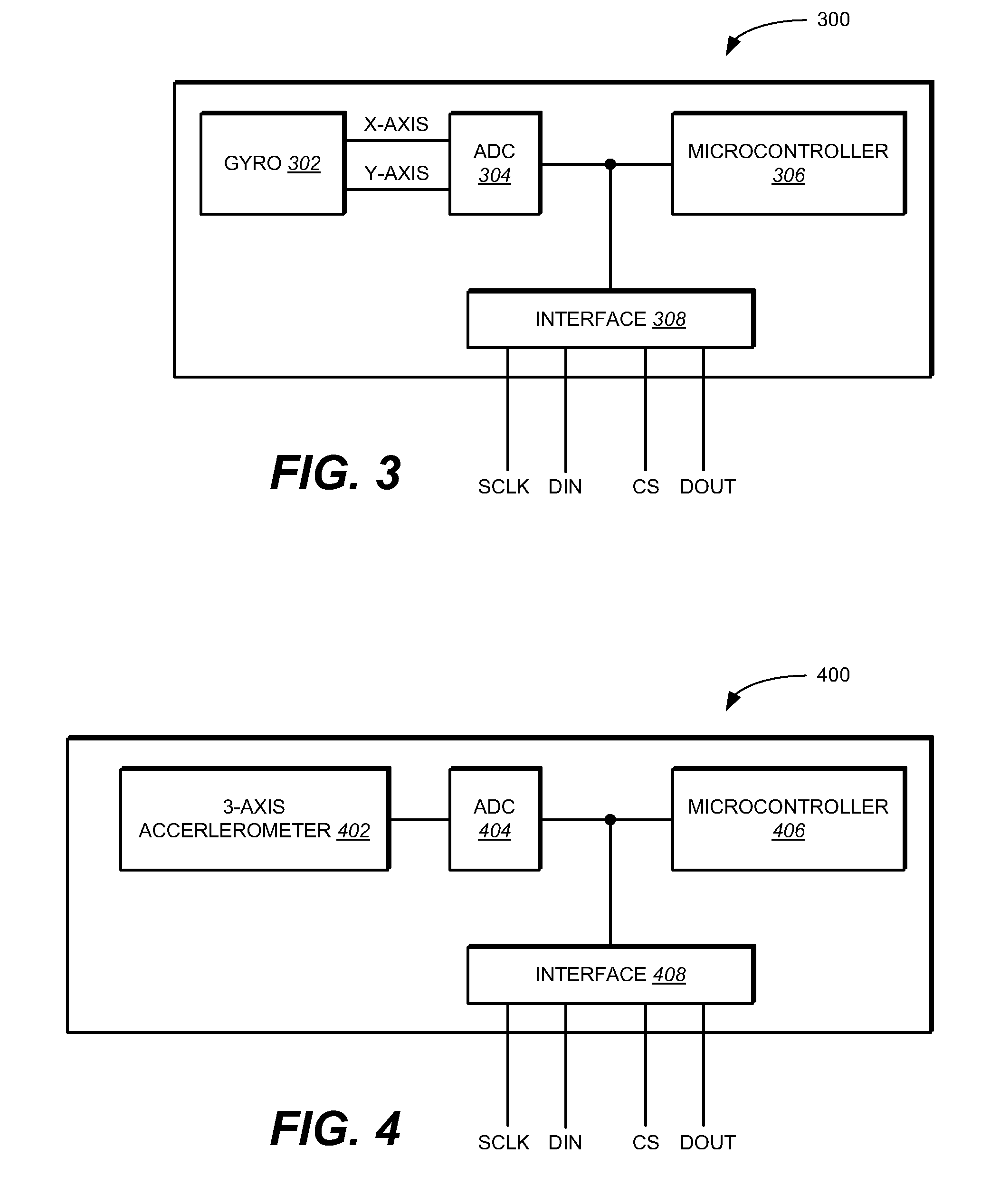

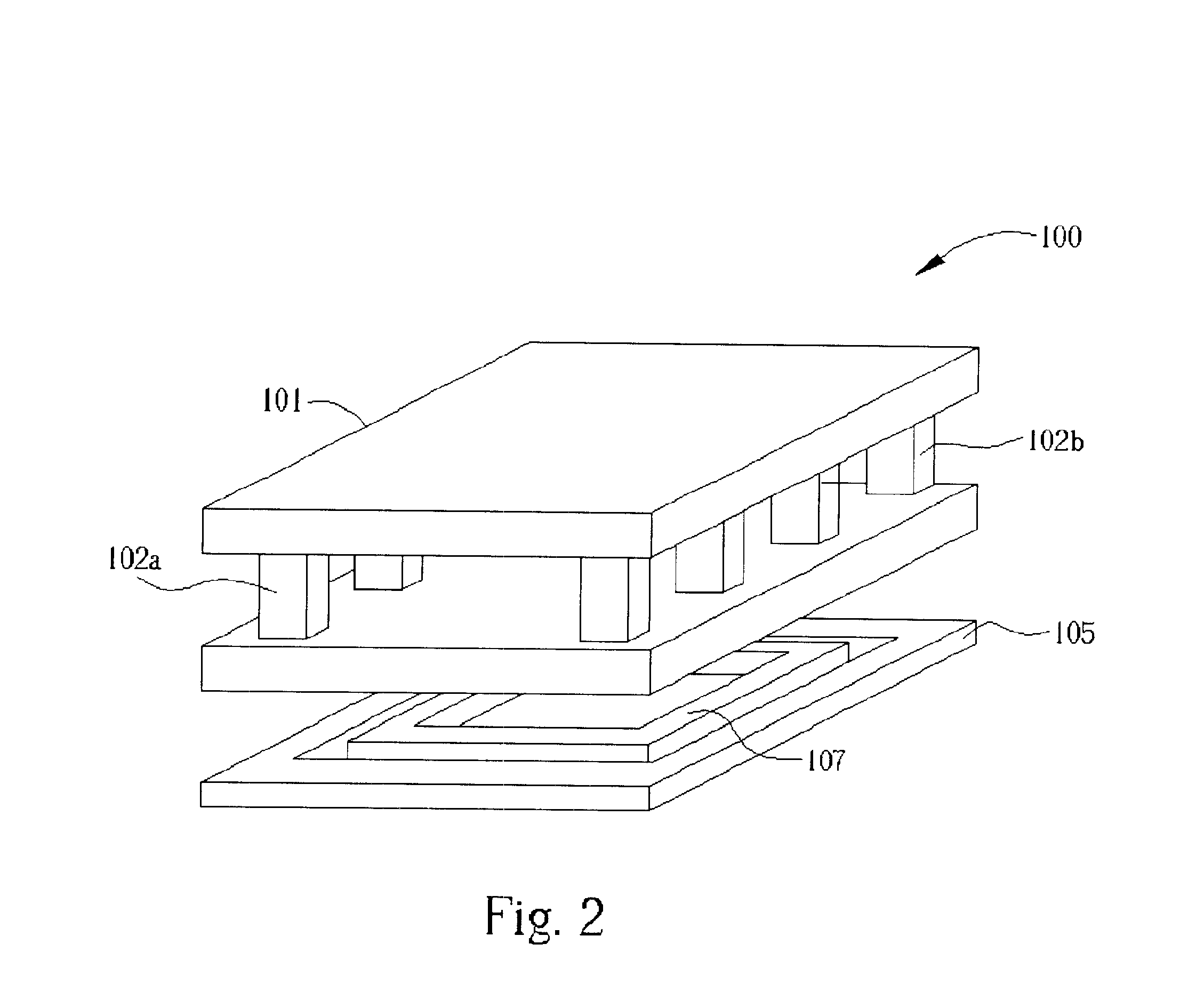

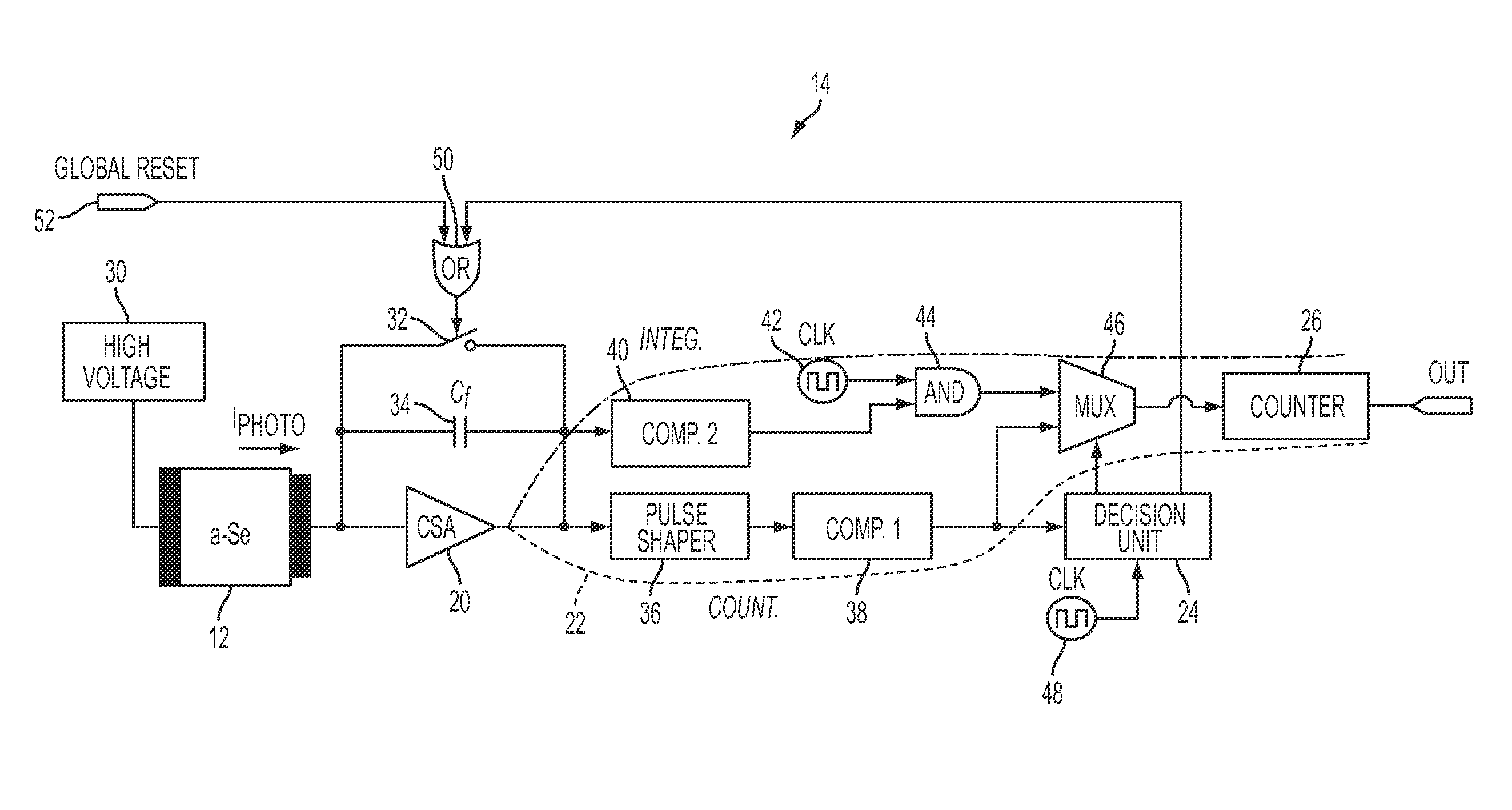

Integrated Motion Processing Unit (MPU) With MEMS Inertial Sensing And Embedded Digital Electronics

ActiveUS20090007661A1Small packageLower performance requirementsElectric signal transmission systemsAcceleration measurement using interia forcesMotion processingAccelerometer

A module operable to be mounted onto a surface of a board. The module includes a linear accelerometer to provide a first measurement output corresponding to a measurement of linear acceleration in at least one axis, and a first rotation sensor operable to provide a second measurement output corresponding to a measurement of rotation about at least one axis. The accelerometer and the first rotation sensor are formed on a first substrate. The module further includes an application specific integrated circuit (ASIC) to receive both the first measurement output from the linear accelerometer and the second measurement output from the first rotation sensor. The ASIC includes an analog-to-digital converter and is implemented on a second substrate. The first substrate is vertically bonded to the second substrate.

Owner:INVENSENSE

Integrated motion processing unit (MPU) with MEMS inertial sensing and embedded digital electronics

ActiveUS8250921B2Low costSmall packageElectric signal transmission systemsSpeed/acceleration/shock instrument detailsMotion processingAccelerometer

Owner:INVENSENSE

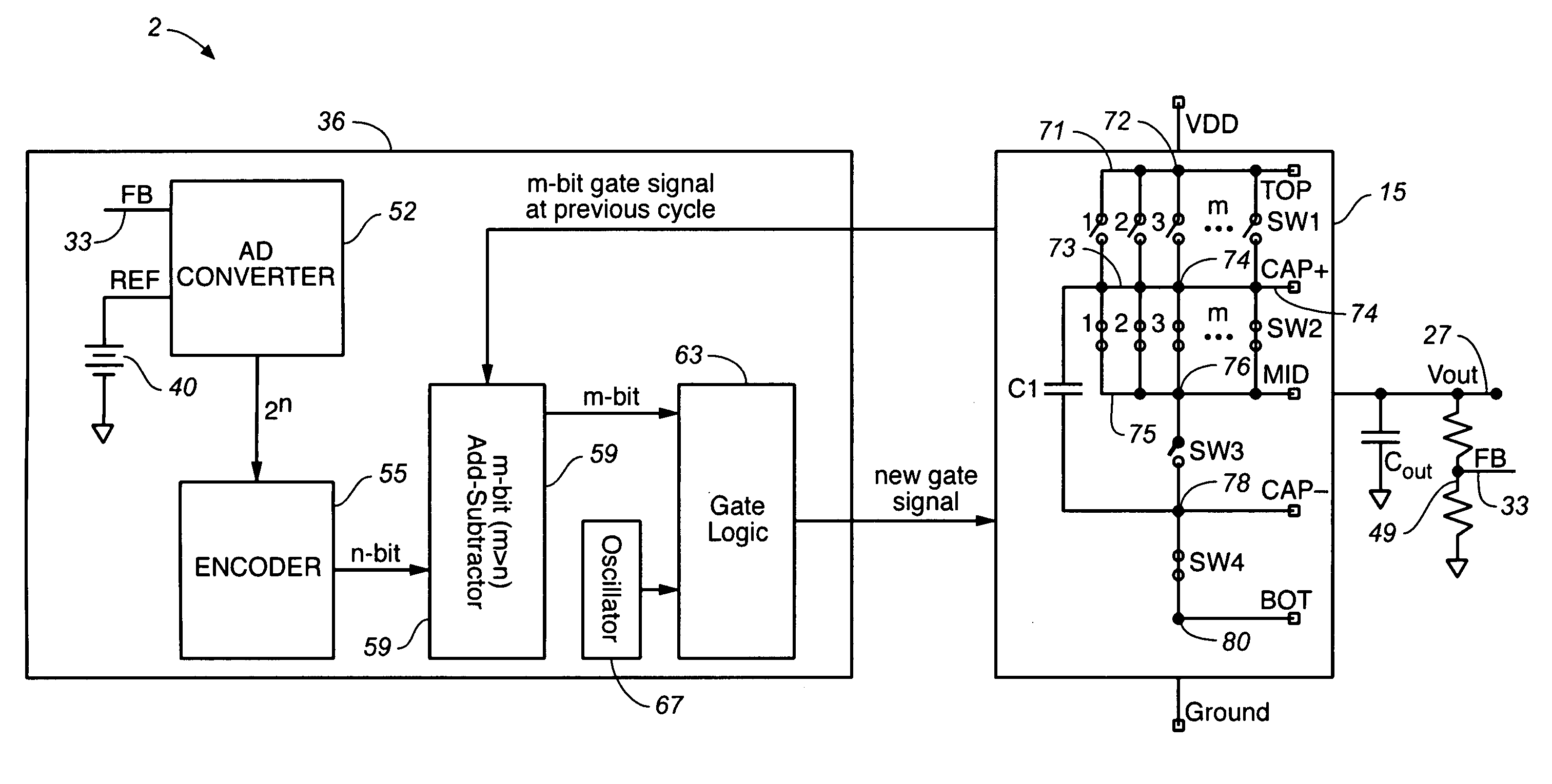

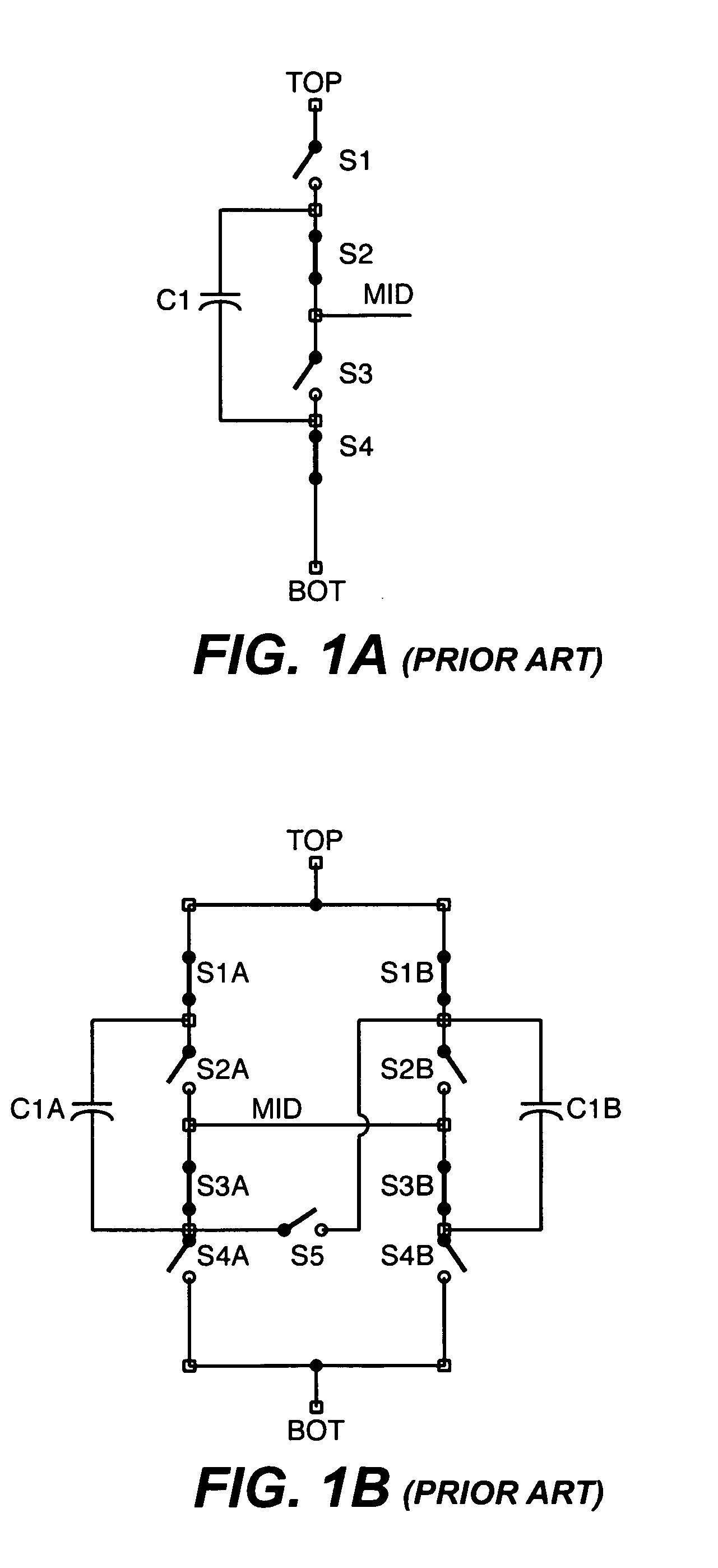

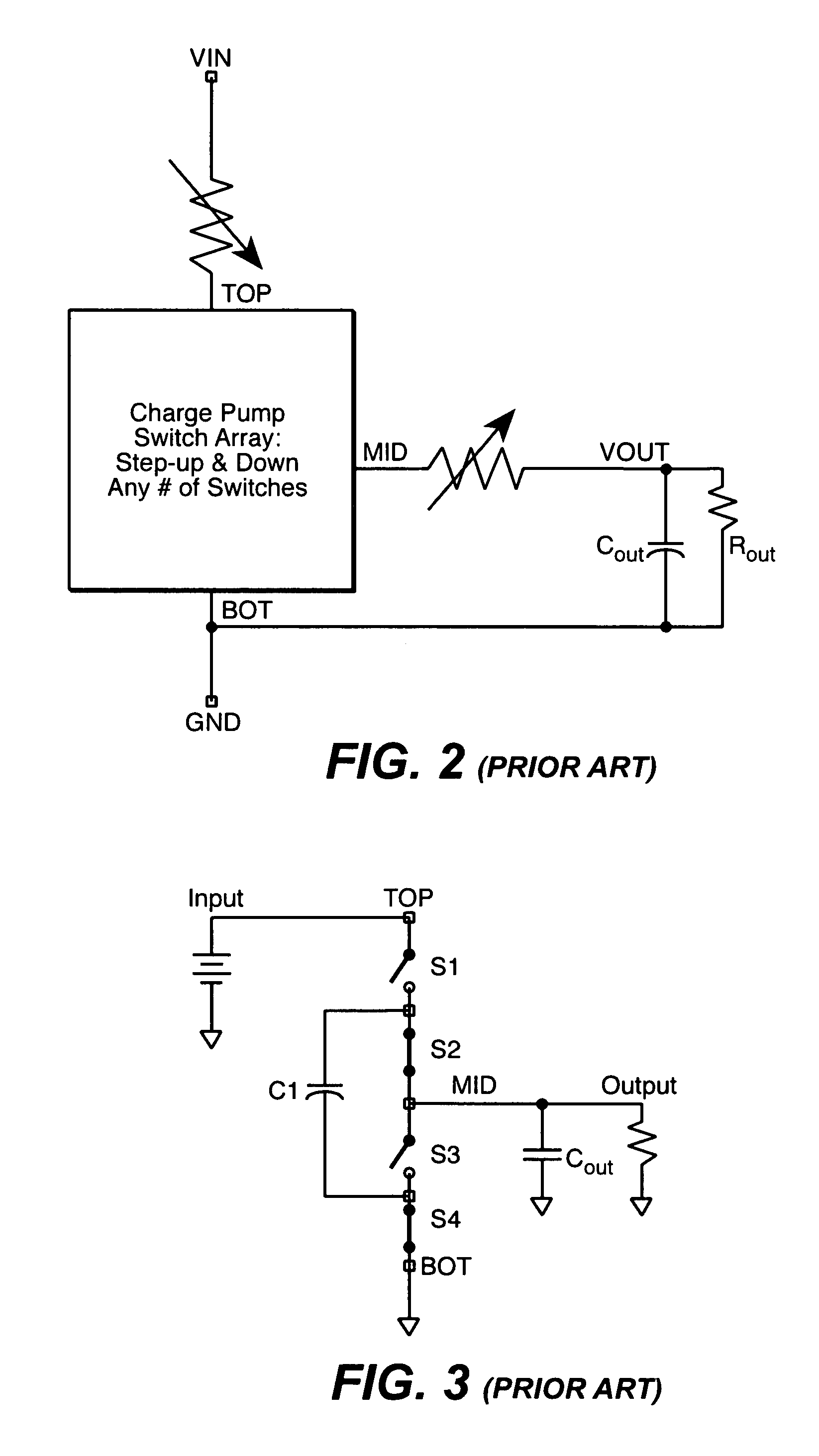

Digital loop for regulating DC/DC converter with segmented switching

InactiveUS6995995B2Save areaReduce rippleEmergency protective circuit arrangementsAc-dc conversionA d converterVoltage regulation

A power control circuit is provided containing a switch array, which includes segmented switches, a flying capacitor, an output voltage terminal, a feedback loop, and a digital voltage regulator block. The digital voltage regulator block includes an A / D converter, an encoder, an add-subtractor, and a gate logic. These power control circuits do not include pass transistors. A method is also provided, where the charge pumps of the power control circuit are operated in two-phase cycles including a charging phase and a pumping phase. The power control circuit is controlled in both of these phases, thereby reducing the ripple of the output voltage.

Owner:SEMICON COMPONENTS IND LLC

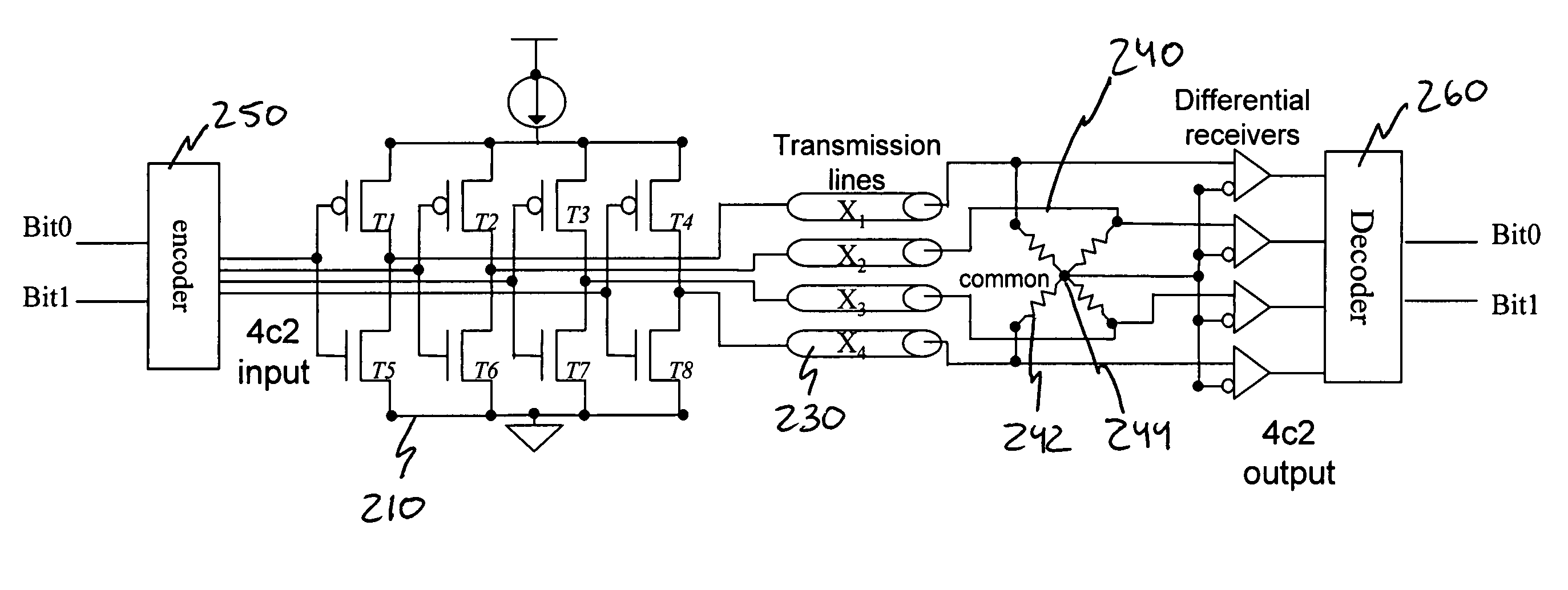

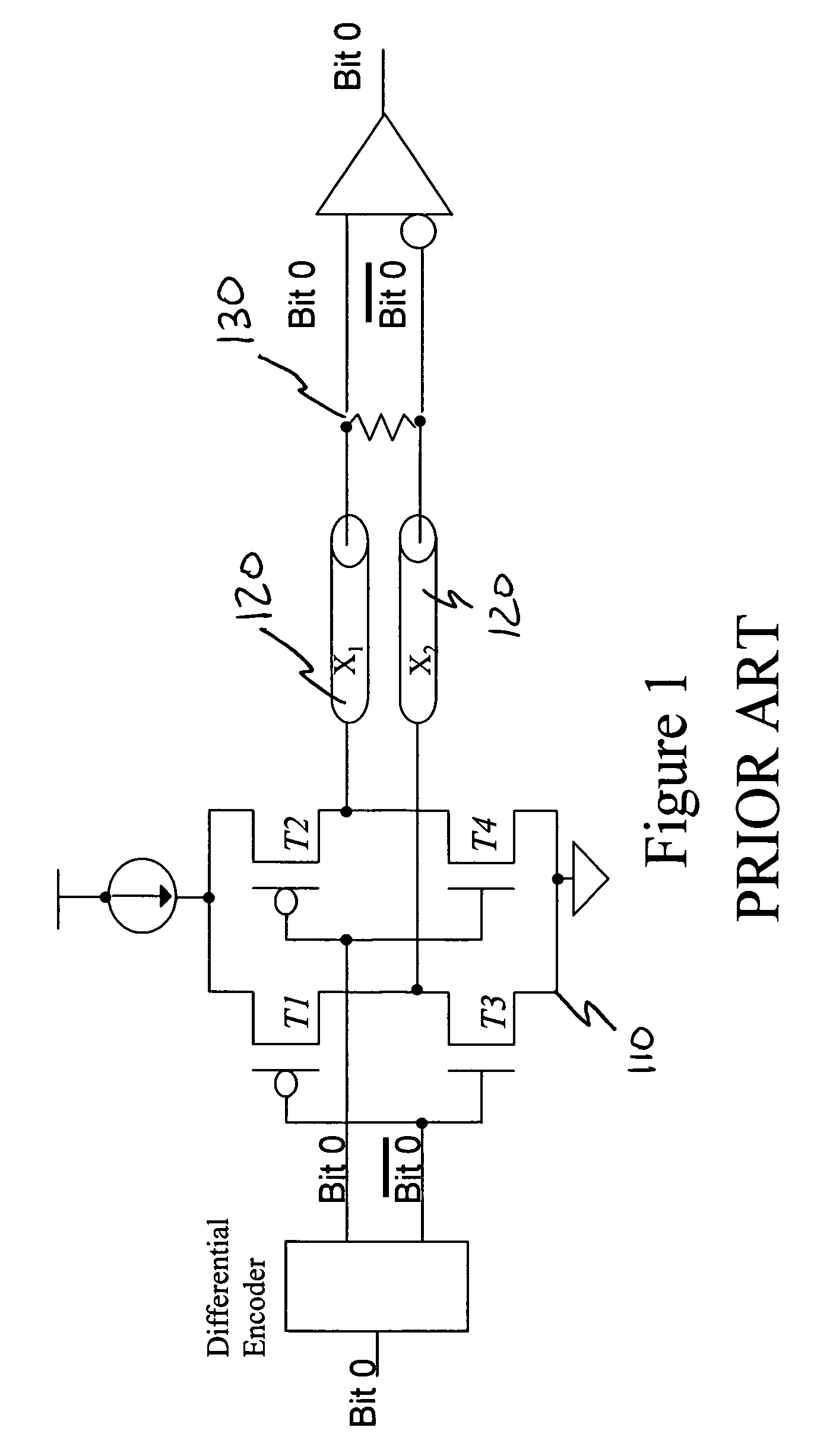

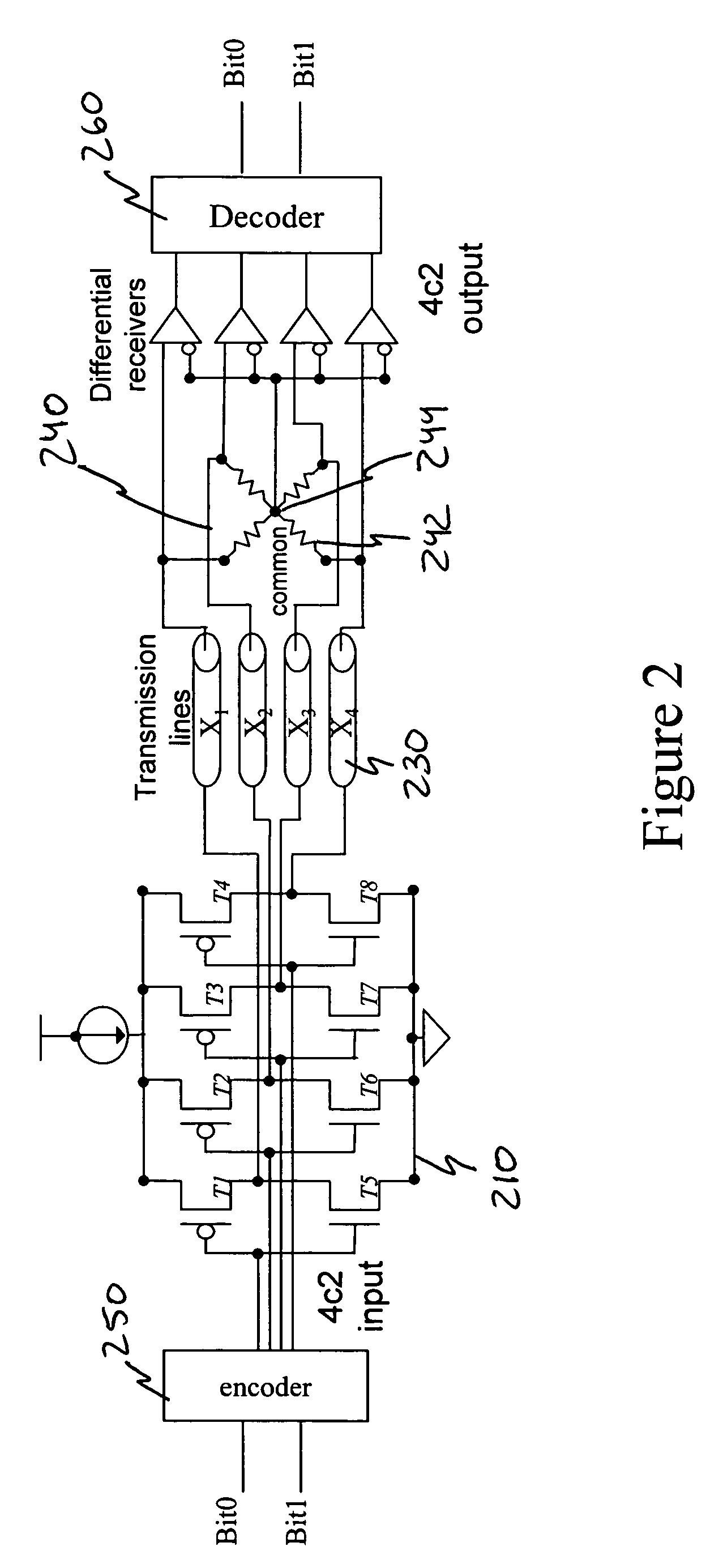

Power efficient, high bandwidth communication using multi-signal-differential channels

ActiveUS7358869B1High coding densitySave areaAnalogue conversionIndividual digits conversionPower efficientHigh bandwidth

A low-power, area and pin efficient signaling alternative to serial differential links used for chip-to-chip, backplane, optical and other signaling applications. The multi-bit differential signaling (MBDS) generally comprises a driver and link termination network design coupled with a coding system based on n choose M (nCm) coding. MBDS has comparable electrical characteristics to conventional low-voltage differential signaling (LVDS) and is fully compatible with existing LVDS receivers in point-to-point and multi-point bus topologies. However, MBDS uses up to 40% less power, with up to 33% fewer I / O pads than equivalent LVDS links.

Owner:PITTSBURGH UNIV OF

Method and apparatus for biasing selected and unselected array lines when writing a memory array

InactiveUS20020136047A1Much faster programmingVoltage requirementRead-only memoriesDigital storageCapacitanceEngineering

A passive element memory array preferably biases selected X-lines to an externally received VPP voltage and selected Y-lines to ground. Unselected Y-lines are preferably biased to VPP minus a first offset voltage, and unselected X-lines biased to a second offset voltage (relative to ground). The first and second offset voltages preferably are identical and have a value of about 0.5 to 2 volts. The VPP voltage depends upon the memory cell technology used, and preferably falls within the range of 5 to 20 volts. The area otherwise required for an on-chip VPP generator and saves the power that would be consumed by such a generator. In addition, the operating temperature of the integrated circuit during the programming operation decreases, which further decreases power dissipation. When discharging the memory array, the capacitance between layers is preferably discharged first, then the layers are discharged to ground.

Owner:SANDISK TECH LLC

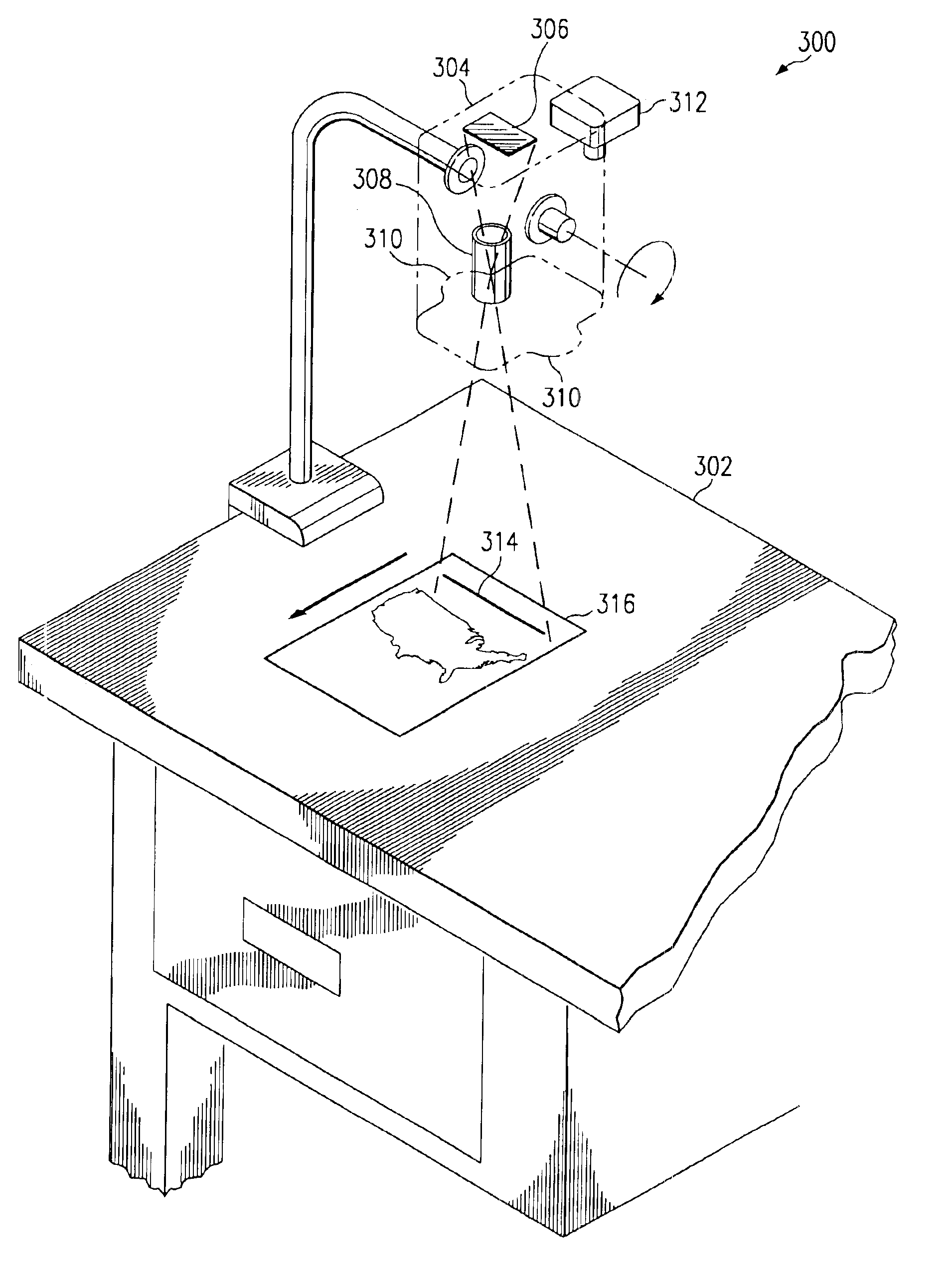

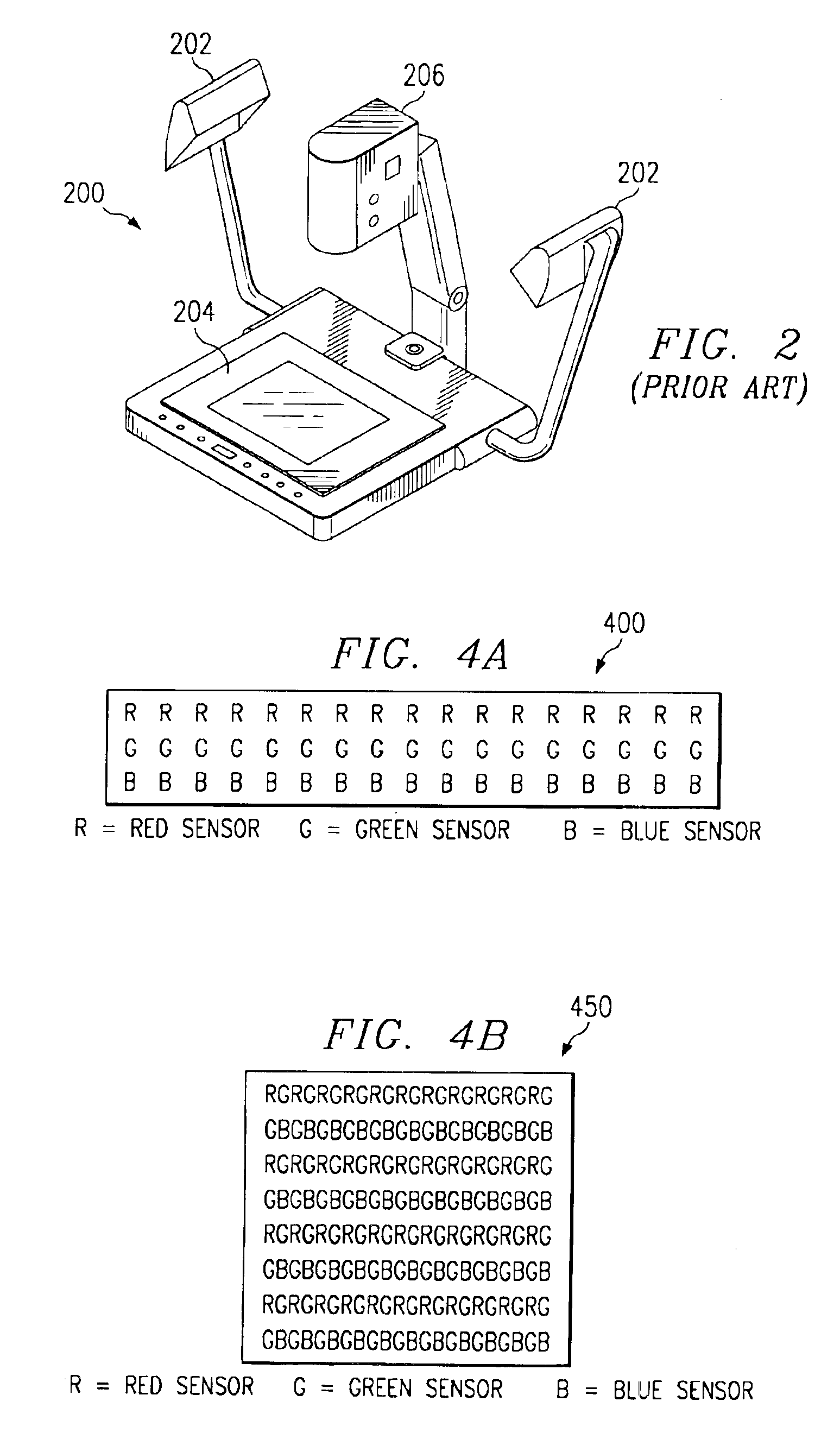

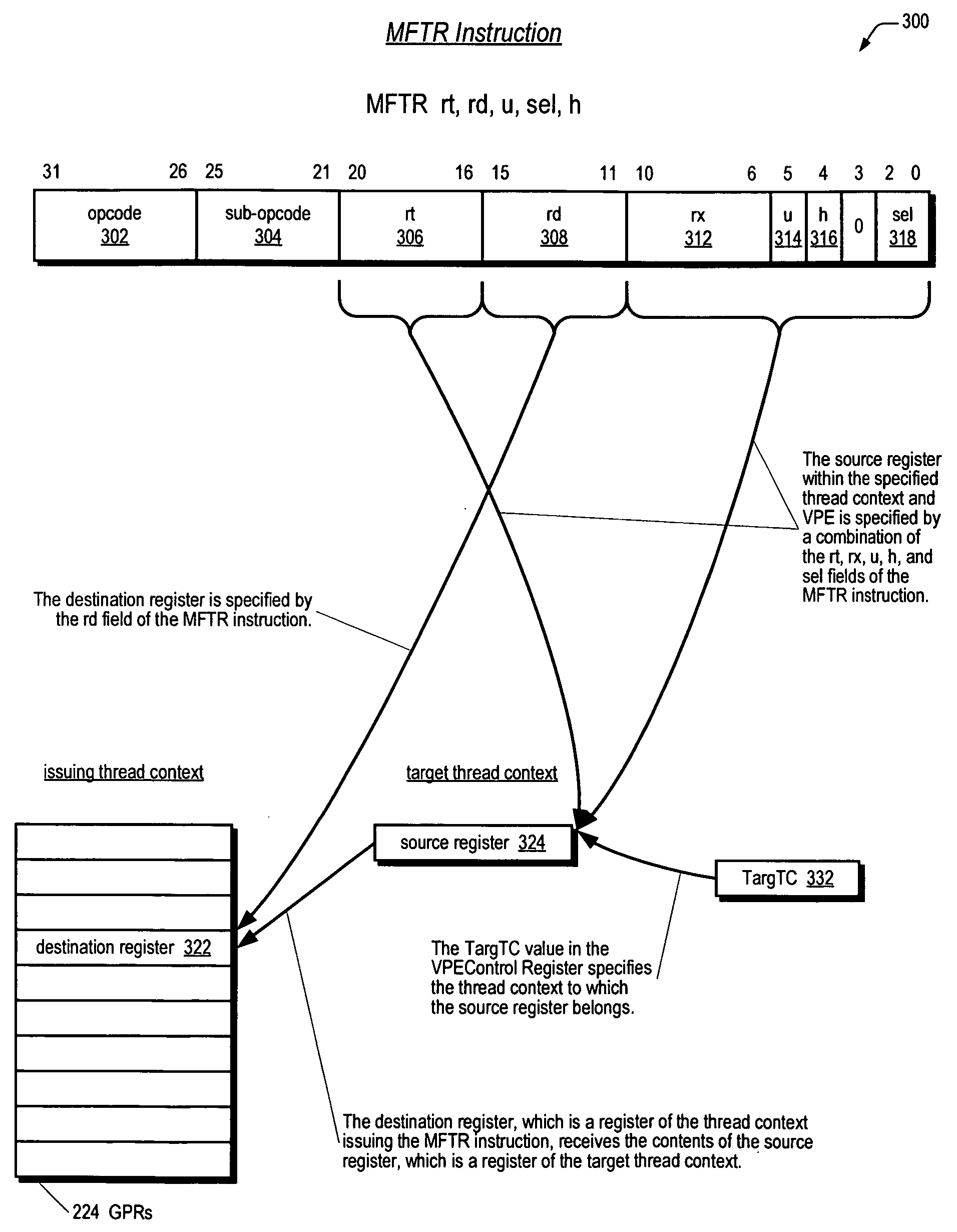

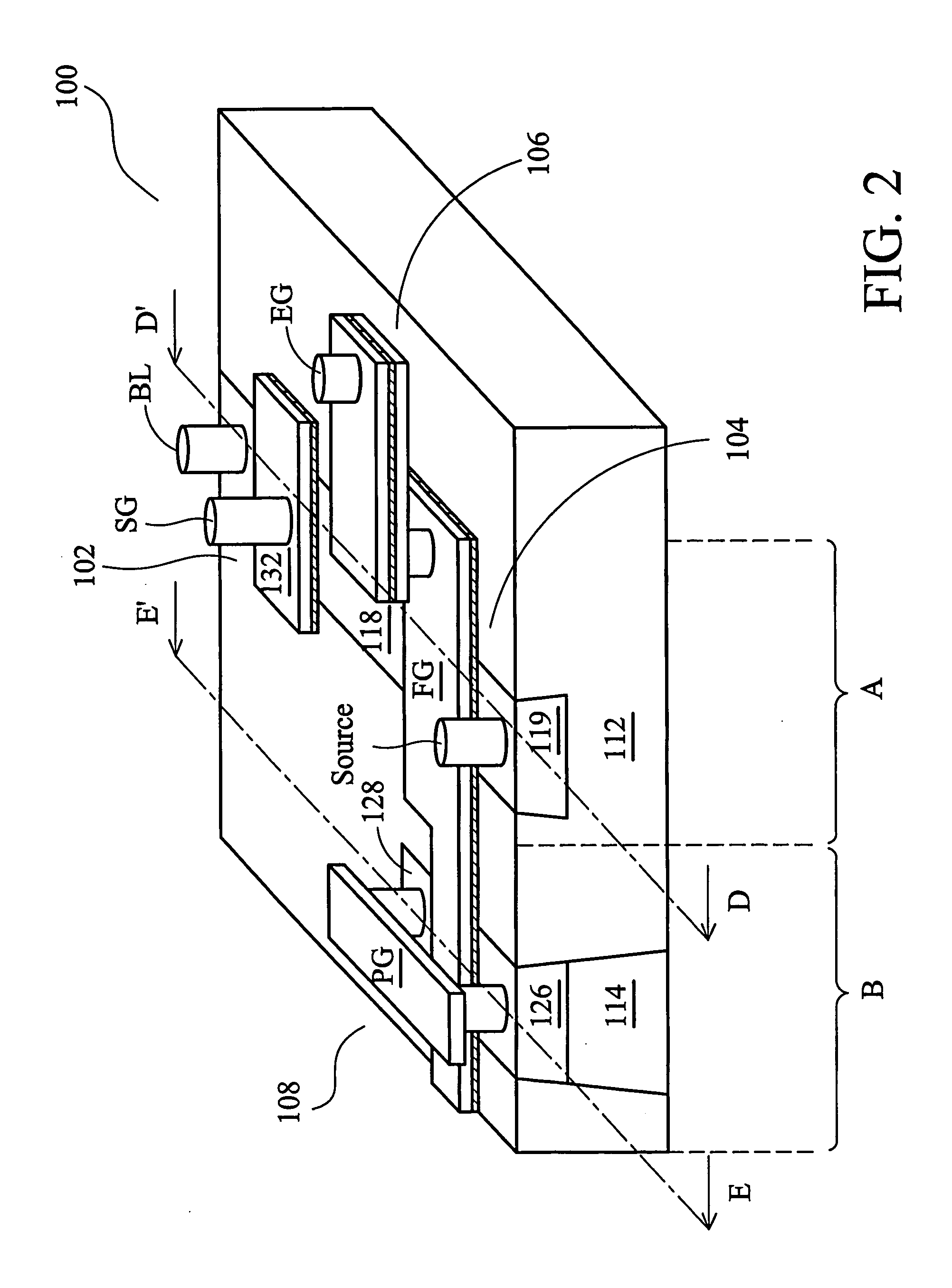

Method and system for scanning an image using a look-down linear array scanner

InactiveUS6965460B1Precise alignmentHigh resolutionImage data processing detailsPictoral communicationDigital videoDigital imaging

A system and method are disclosed which provide a look-down digital imaging device capable of capturing relatively high resolution digital images (e.g., comparable to traditional flatbed scanners). A preferred embodiment provides a look-down digital imaging device comprising a linear sensor for imaging a raster line of an original image placed substantially below the look-down digital imaging device, and a lens for focusing reflected light from the original to such linear sensor. The linear sensor functions much as in traditional flatbed scanners in that it captures a single, congruent digital image of a scanned original. Most preferably, the linear sensor is a high resolution sensor that enables a digital image to be captured having resolution comparable to that of traditional flatbed scanners. For instance, the linear sensor preferably enables capture of a digital image having a resolution no less than approximately 300 dpi. As a result, such linear sensor most preferably captures a digital image having sufficient resolution to permit optical character recognition operations to be performed on such captured image. In a most preferred embodiment, the look-down digital imaging device further comprises a digital video camera for capturing video data of a target scan area. Such video data may be fed in substantially real-time to a display (either included within the look-down digital imaging device or included on a device to which the look-down digital imaging device is coupled), which may aid a user in properly aligning an original within the target scan area.

Owner:HEWLETT PACKARD DEV CO LP

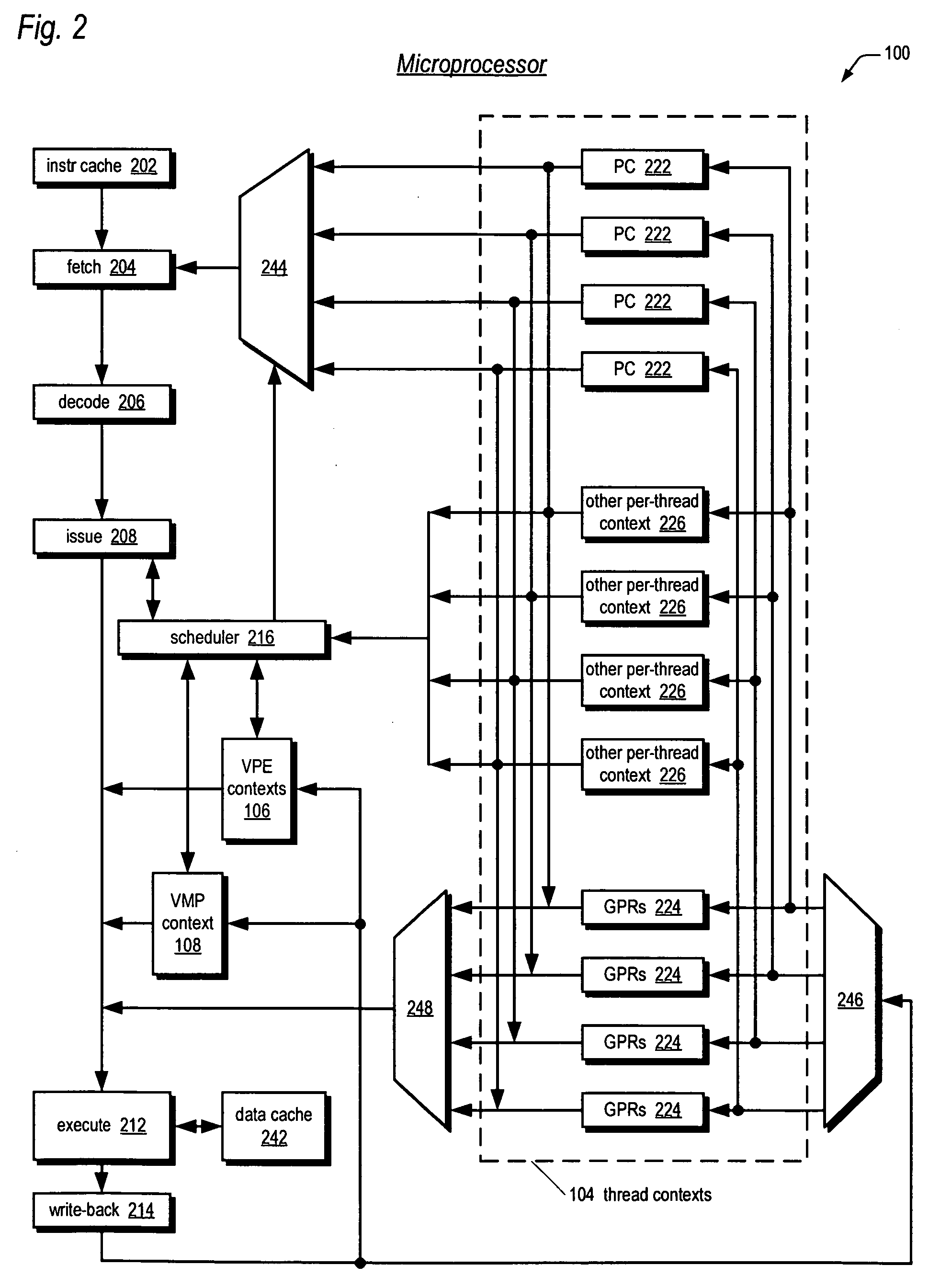

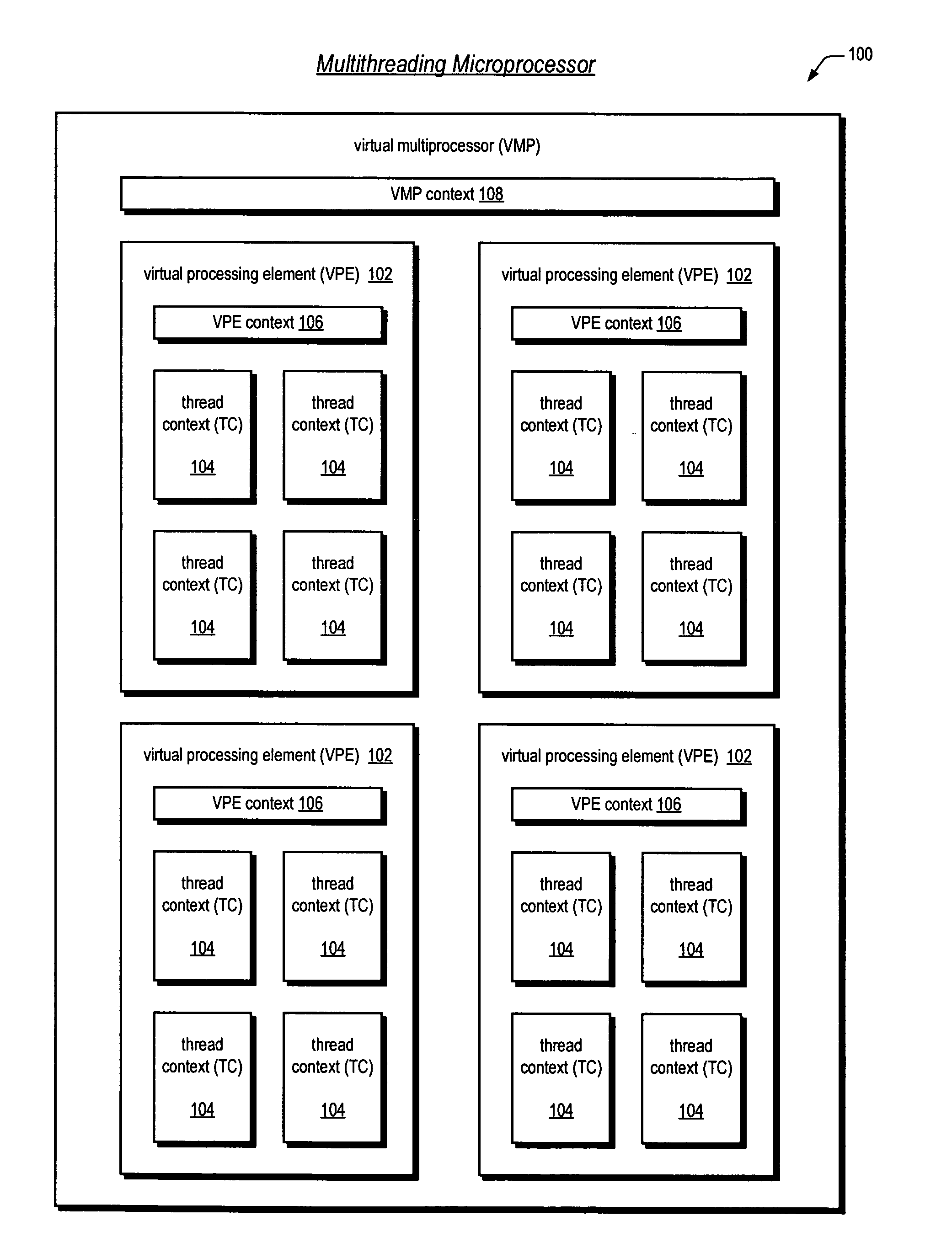

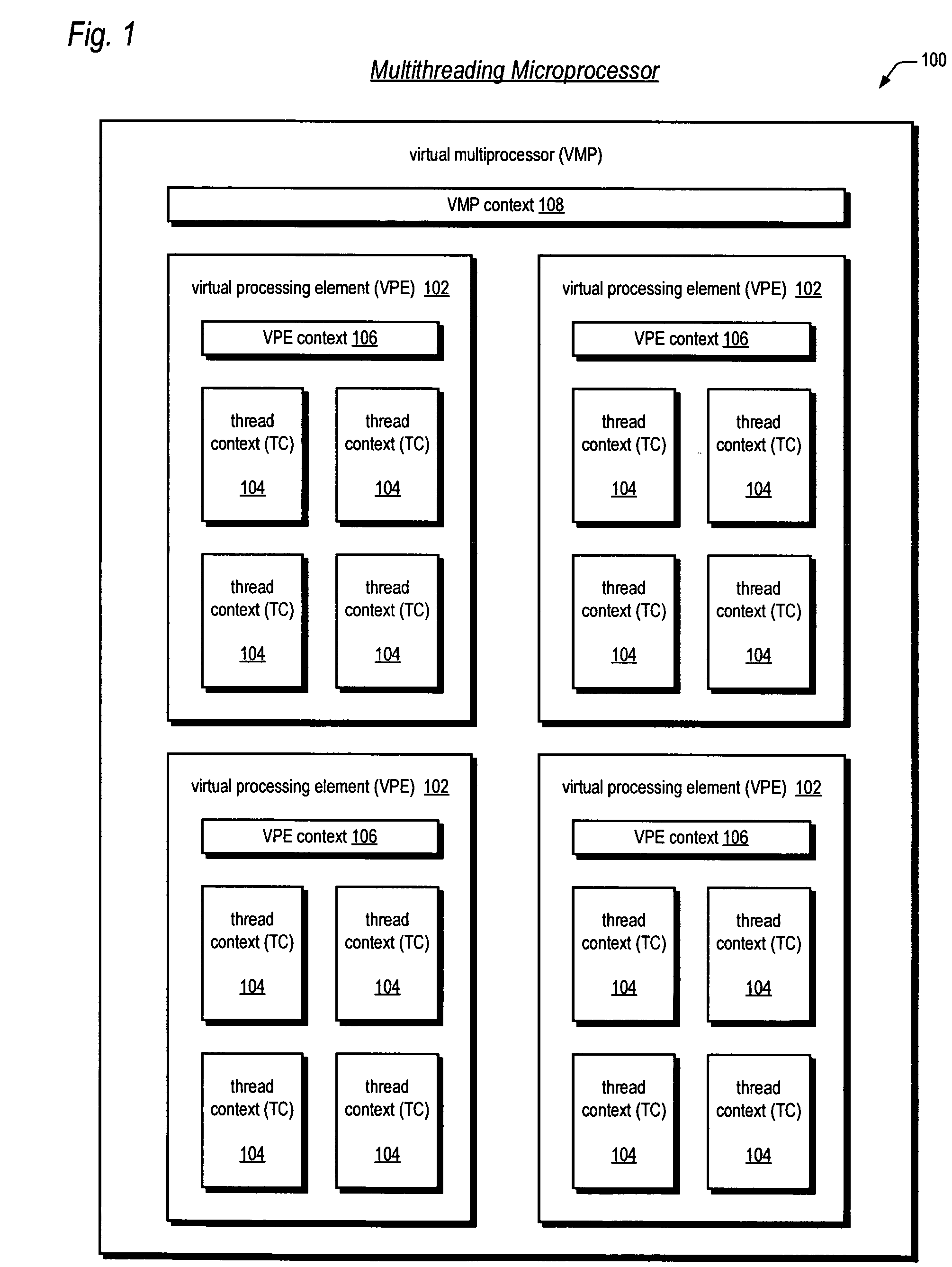

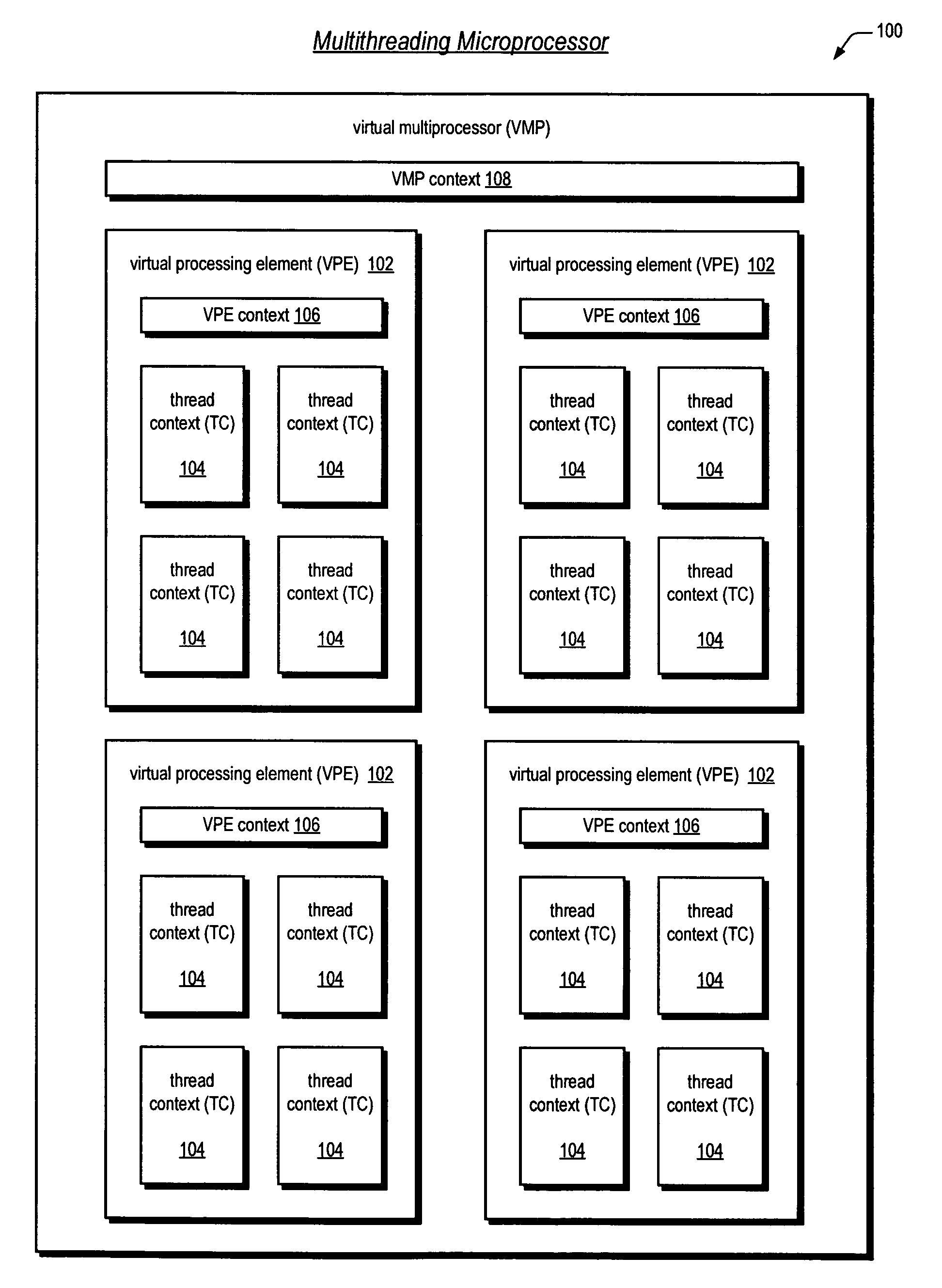

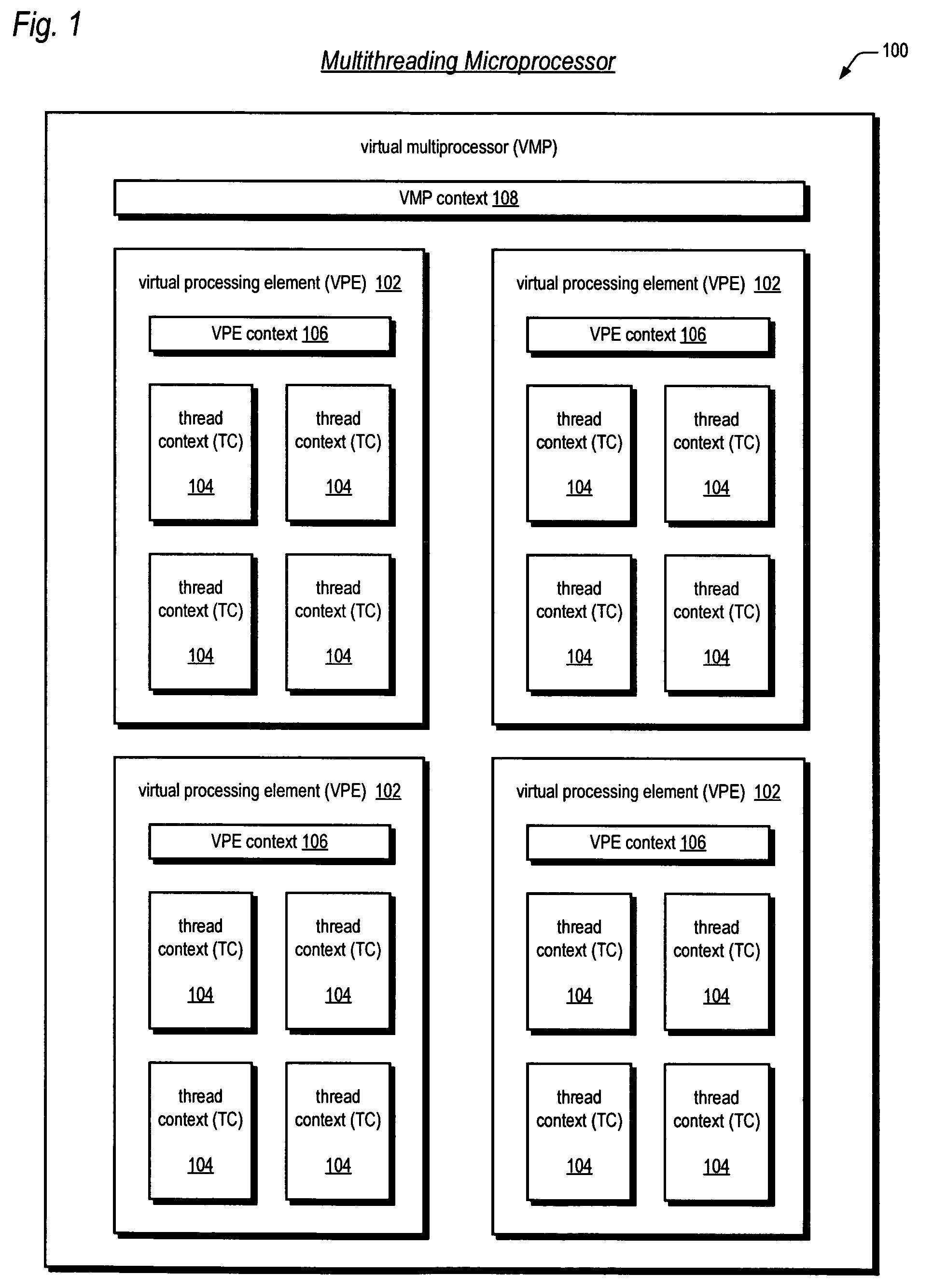

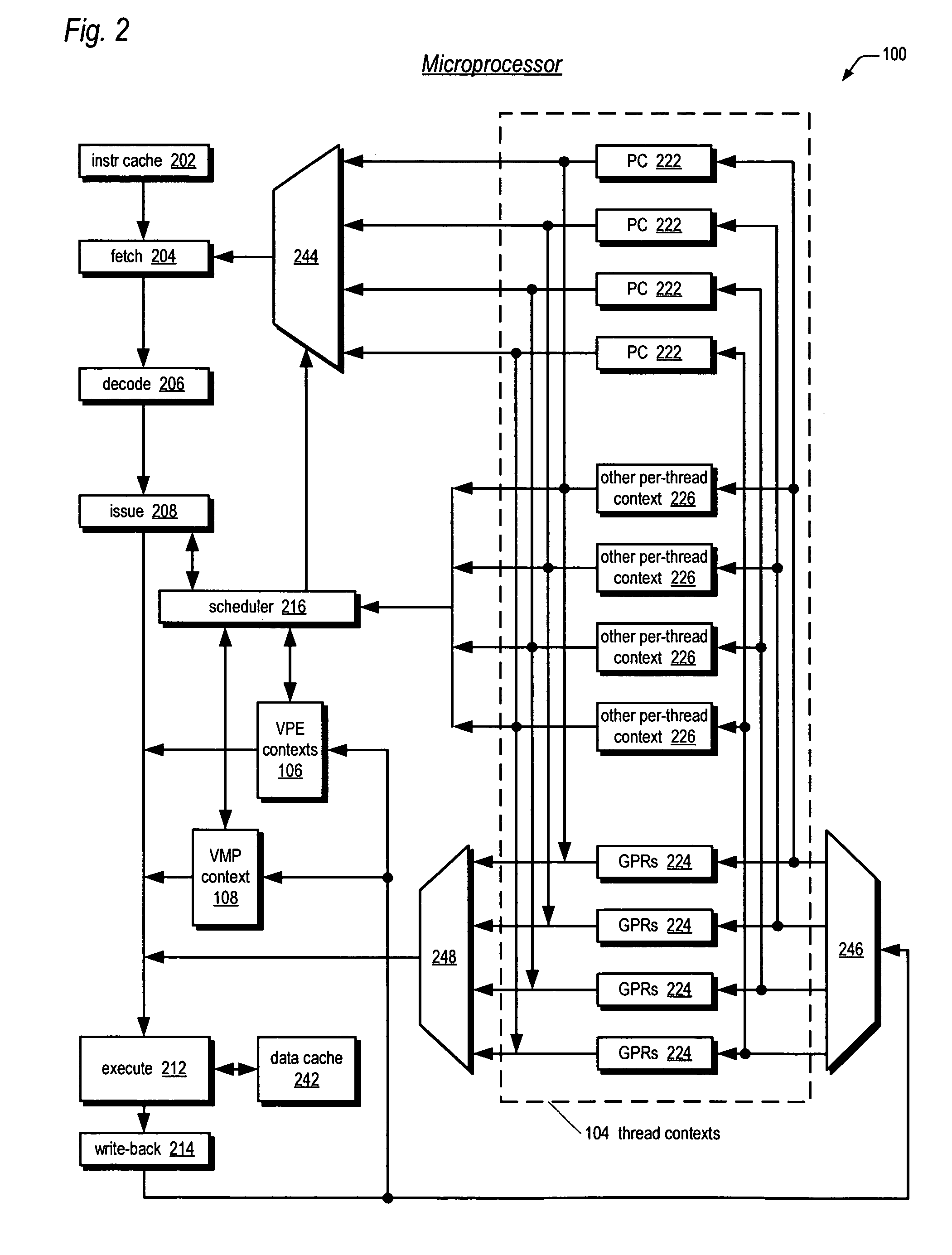

Preemptive multitasking employing software emulation of directed exceptions in a multithreading processor

ActiveUS20060161921A1Save chip area and powerHigh performanceSoftware engineeringRuntime instruction translationNon specificTimer

A multiprocessor computer system includes an exception domain having multiple thread contexts (TCs) each having a restart address register, and a timer that generates a periodic interrupt request to the exception domain. The exception domain selects an eligible TC to service the interrupt request, which is non-specific regarding which TC to select. A first interrupt handler executes on the selected TC to service the interrupt request to schedule a set of processes assigned by the SMP OS for execution on the selected TC, and write an address of a second interrupt handler to the restart address register of each TC other than the selected TC. The second interrupt handler schedules a plurality of sets of processes assigned by the SMP OS for execution on respective ones of the TCs other than the selected TC.

Owner:MIPS TECH INC

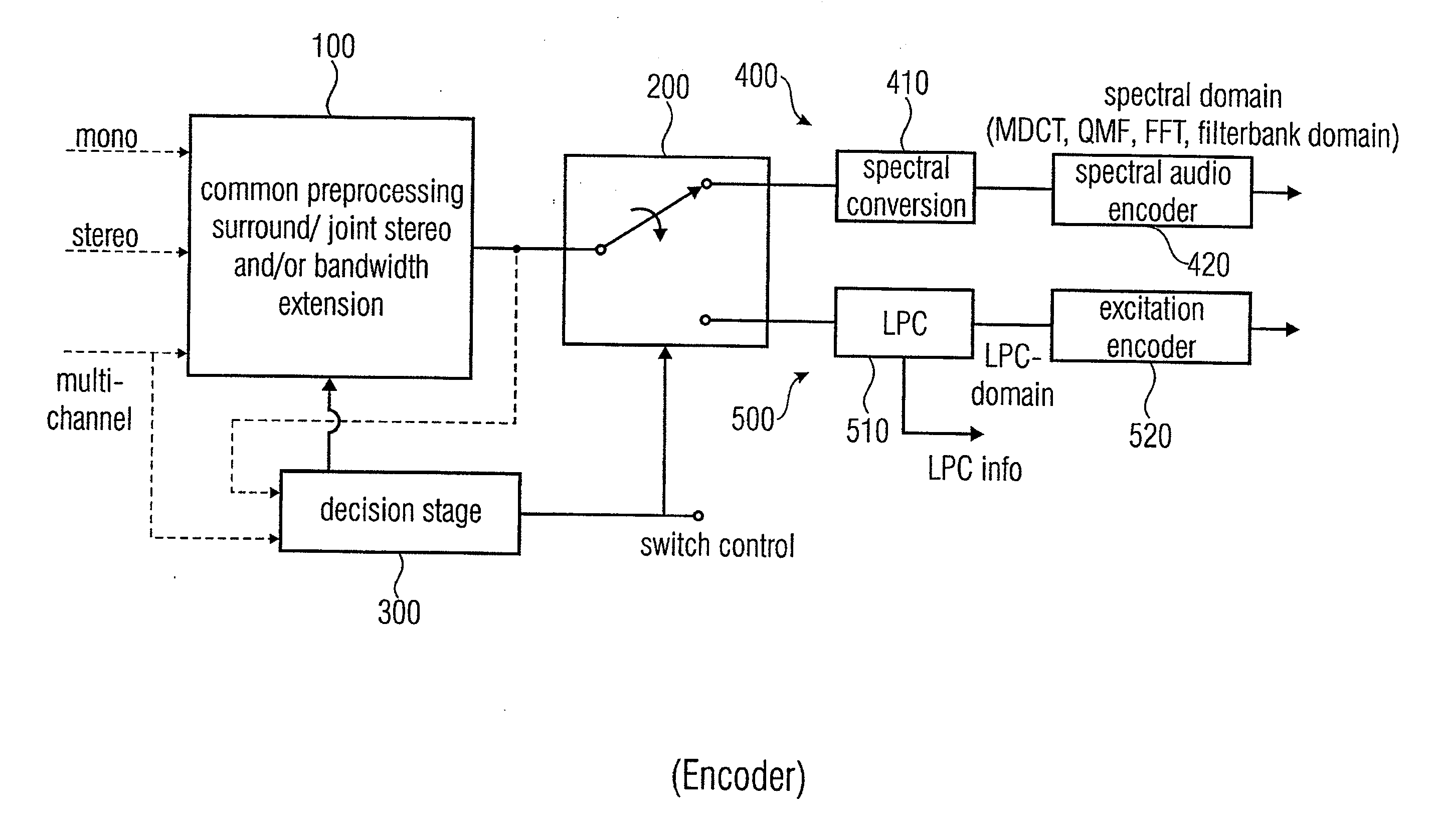

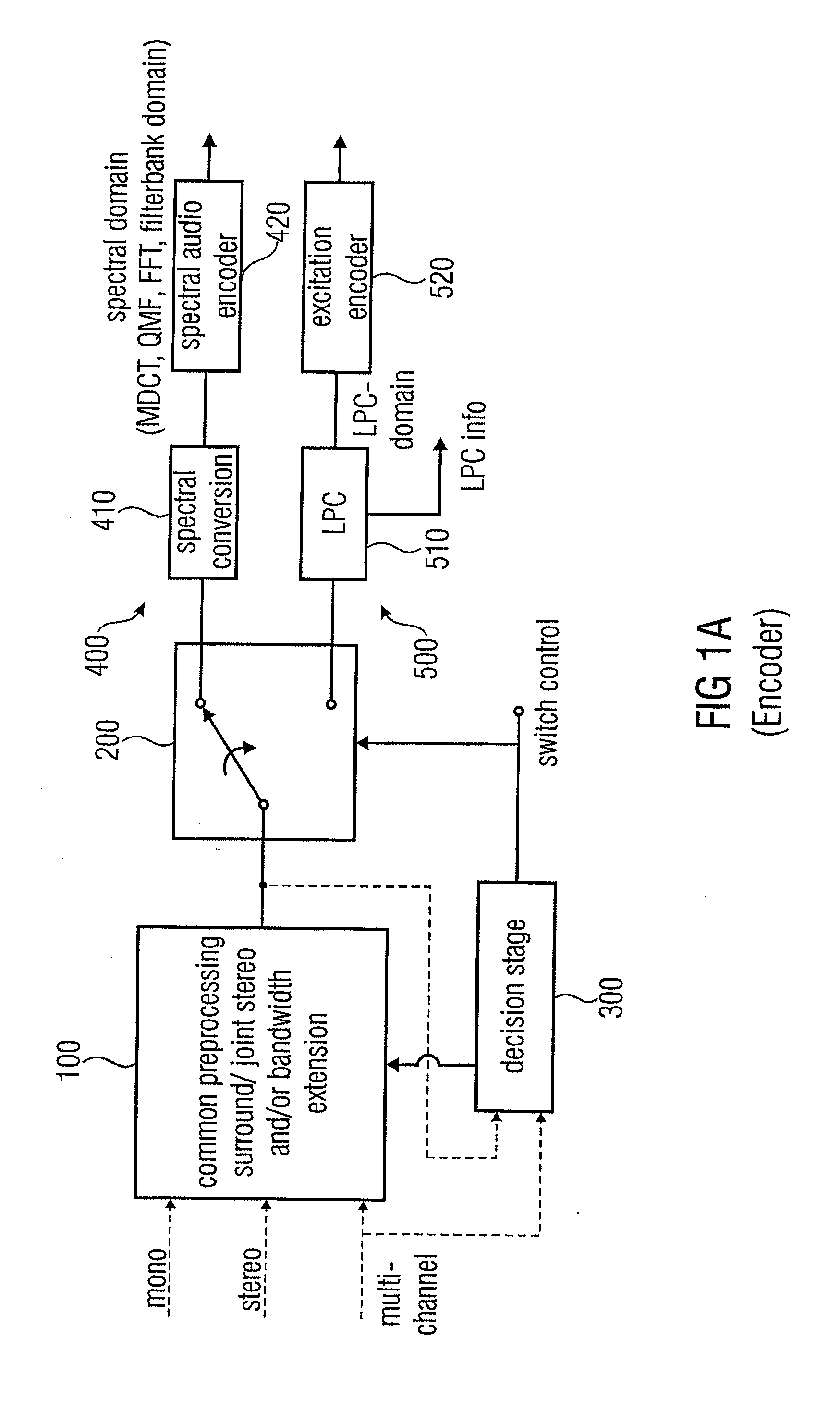

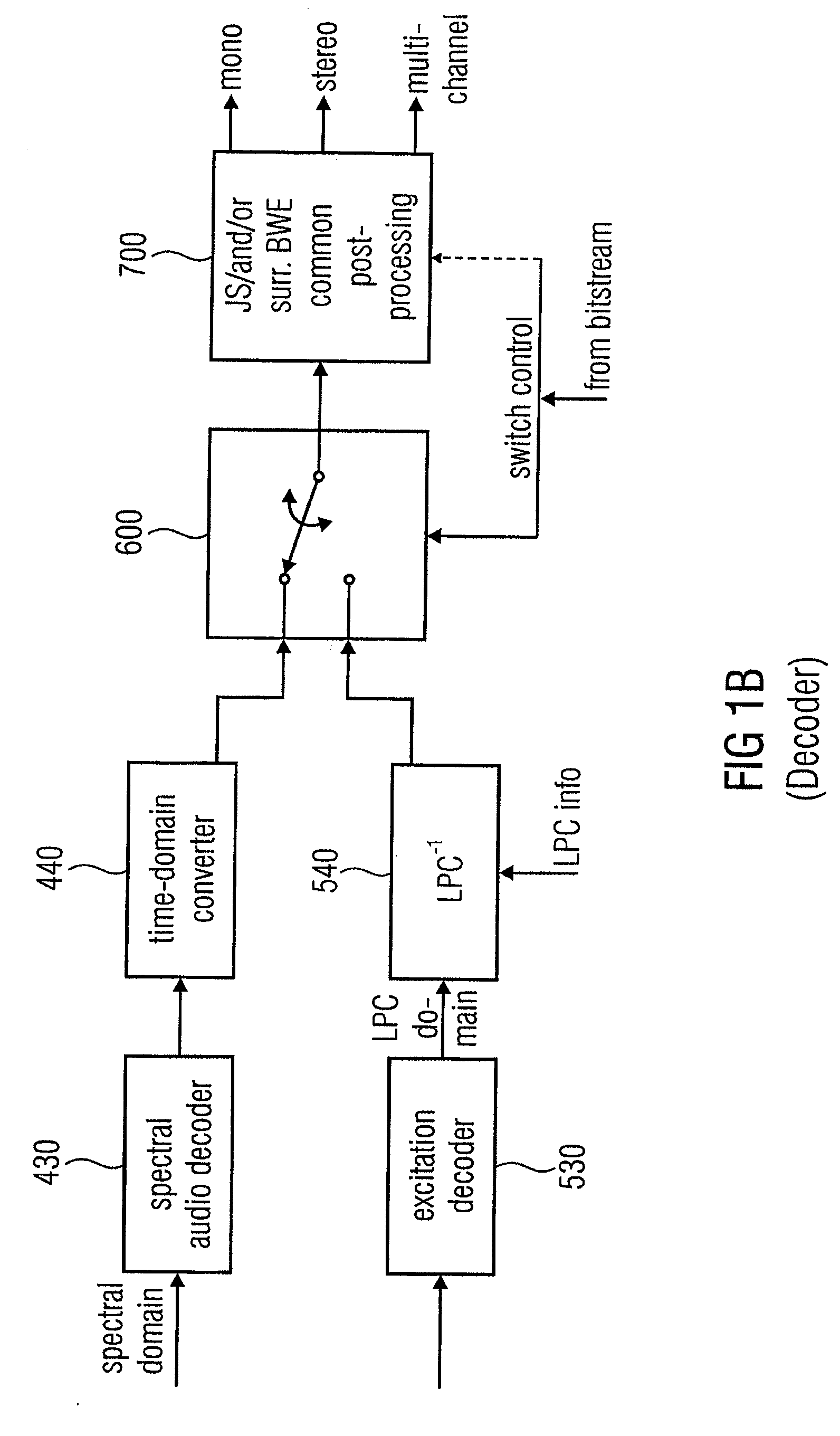

Low Bitrate Audio Encoding/Decoding Scheme with Common Preprocessing

ActiveUS20110200198A1Save amountSave of area consumptionSpeech analysisStereophonic arrangmentsTime domainFrequency spectrum

An audio encoder has a common preprocessing stage, an information sink based encoding branch such as spectral domain encoding branch, a information source based encoding branch such as an LPC-domain encoding branch and a switch for switching between these branches at inputs into these branches or outputs of these branches controlled by a decision stage. An audio decoder has a spectral domain decoding branch, an LPC-domain decoding branch, one or more switches for switching between the branches and a common post-processing stage for post-processing a time-domain audio signal for obtaining a post-processed audio signal.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

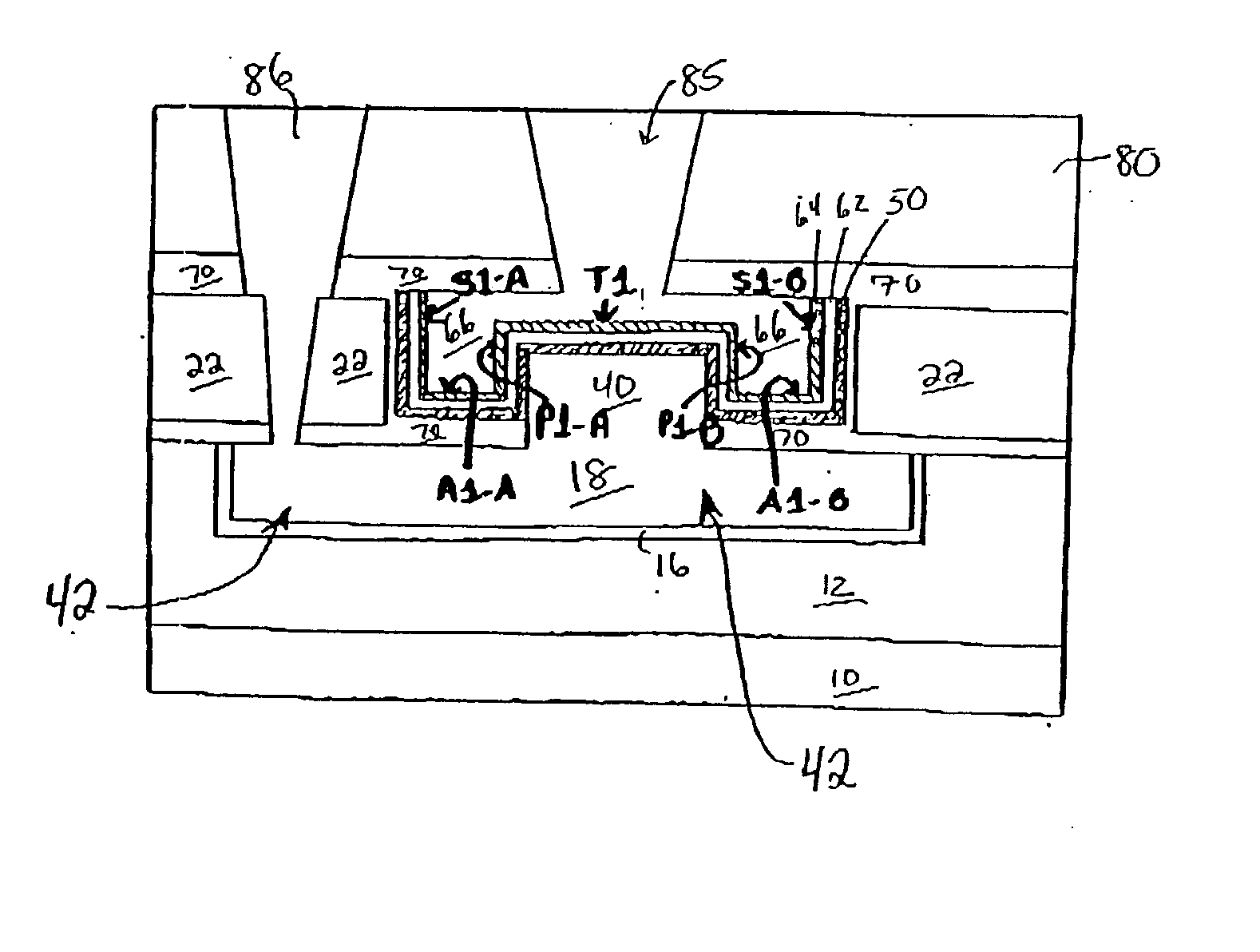

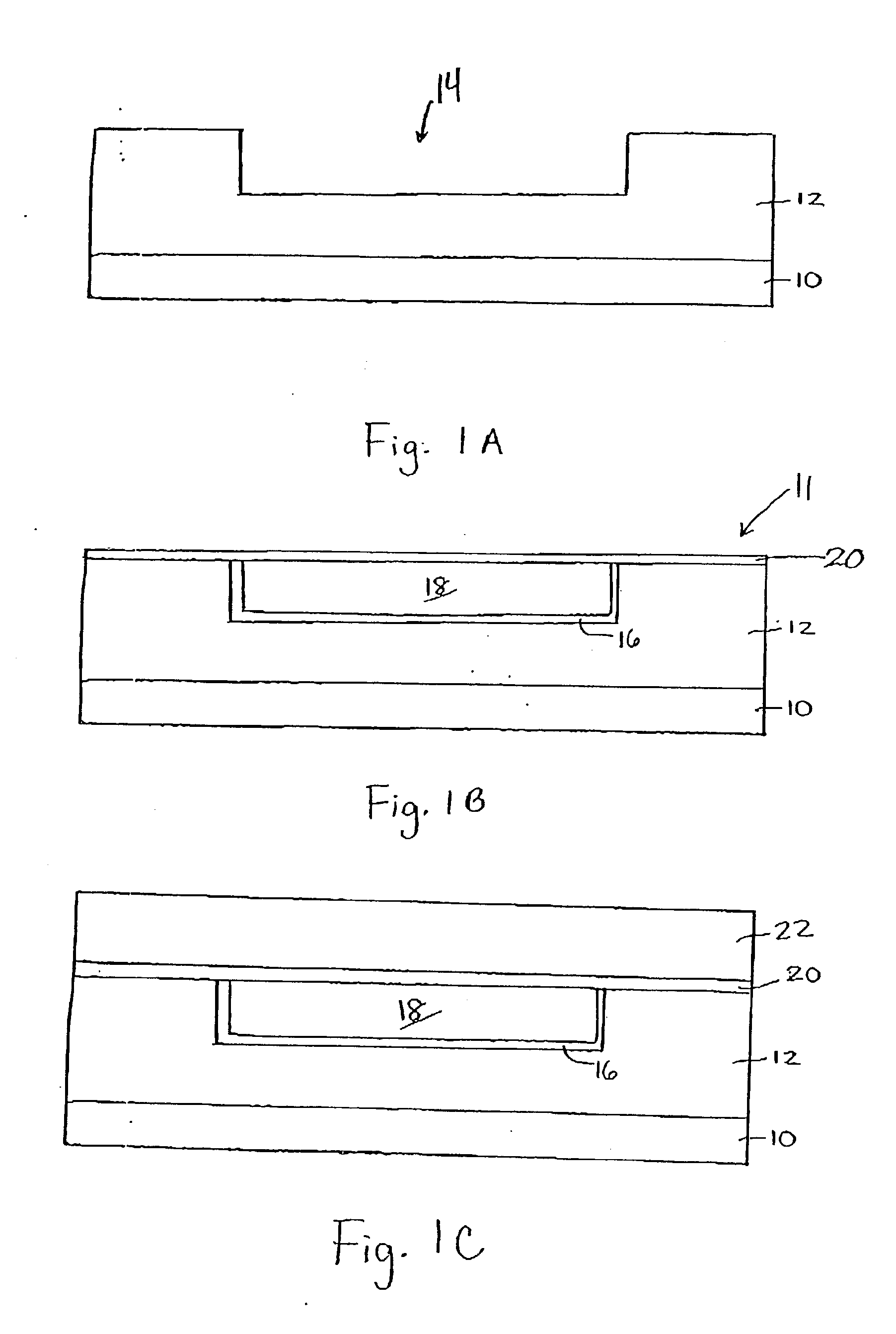

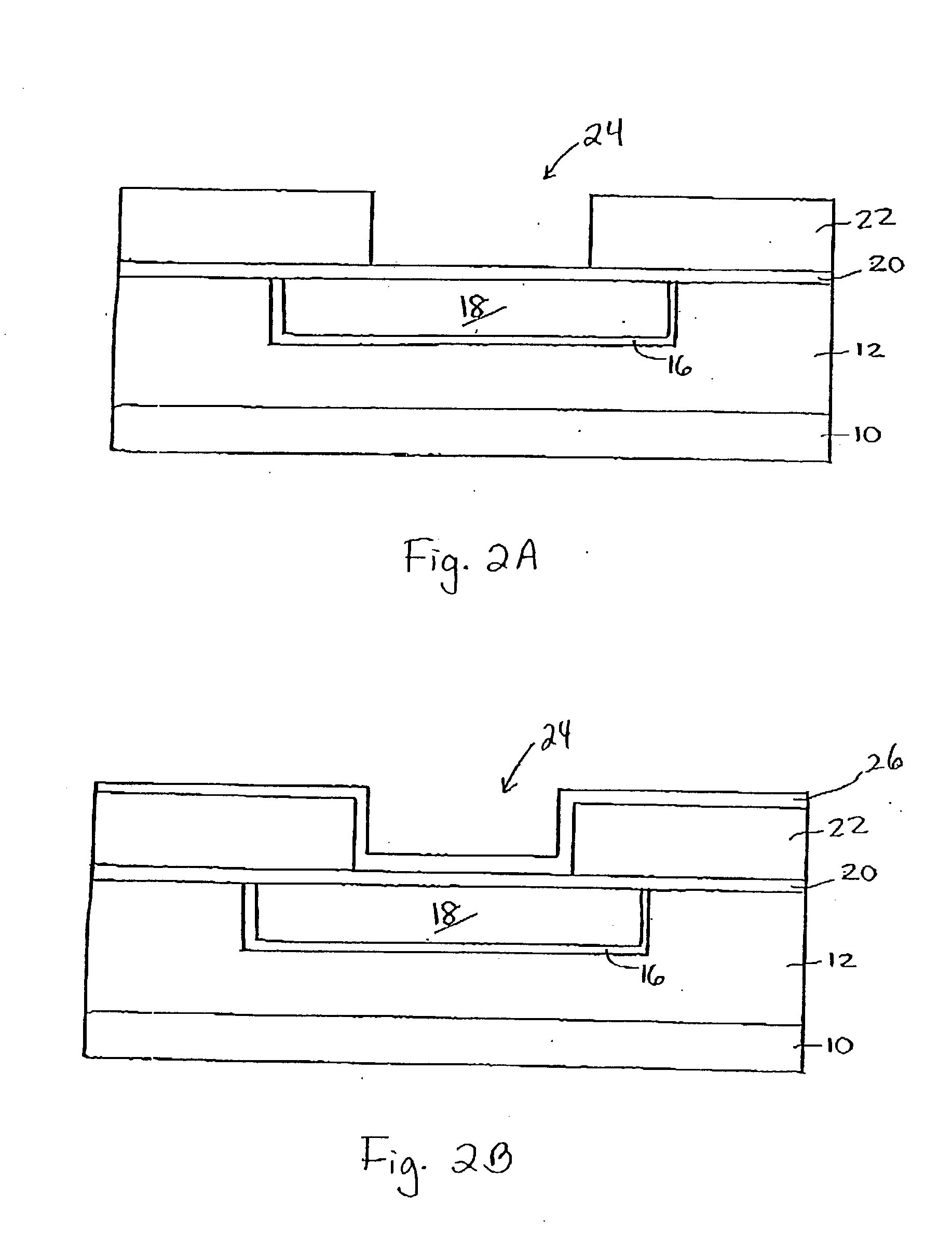

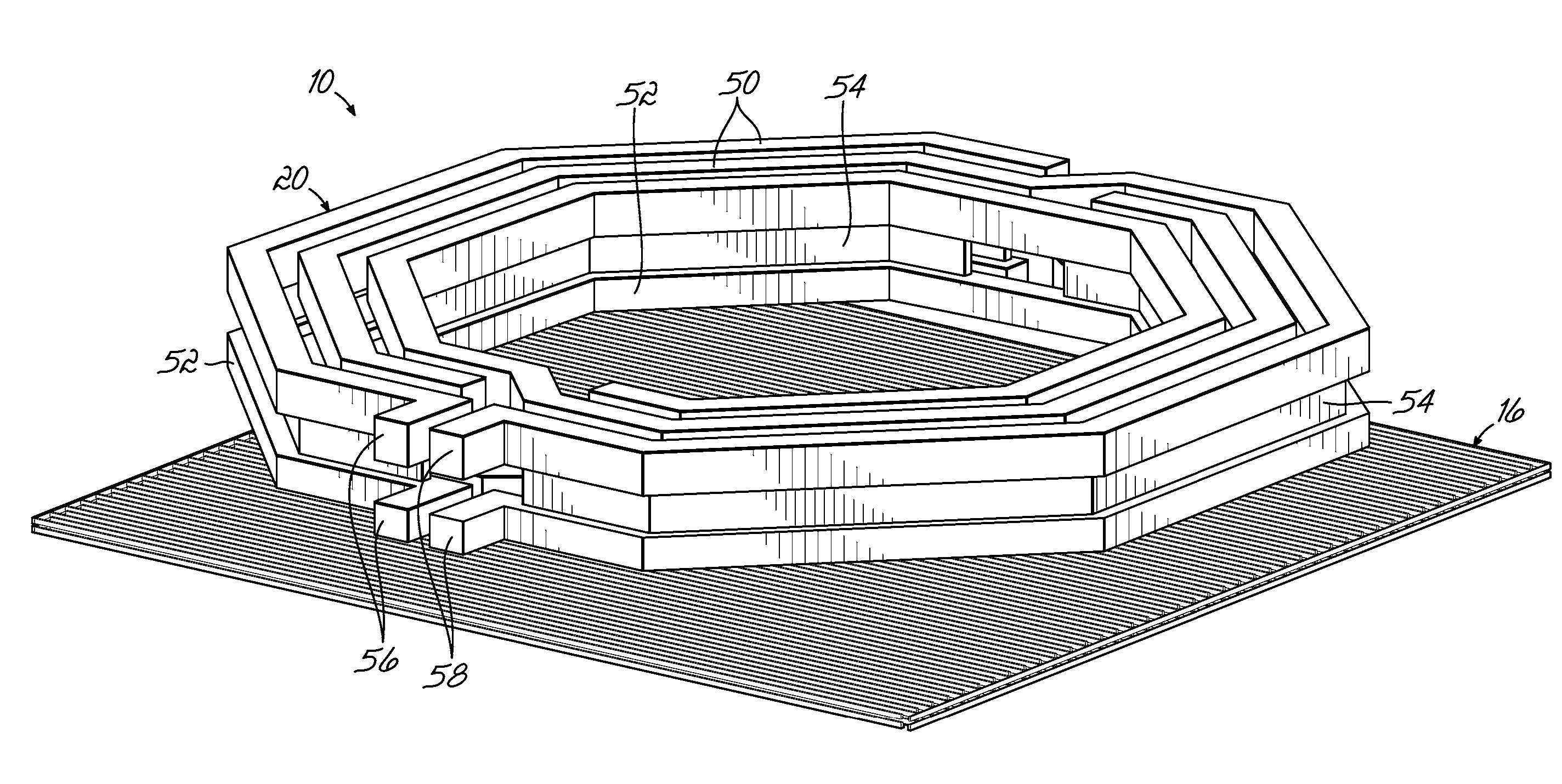

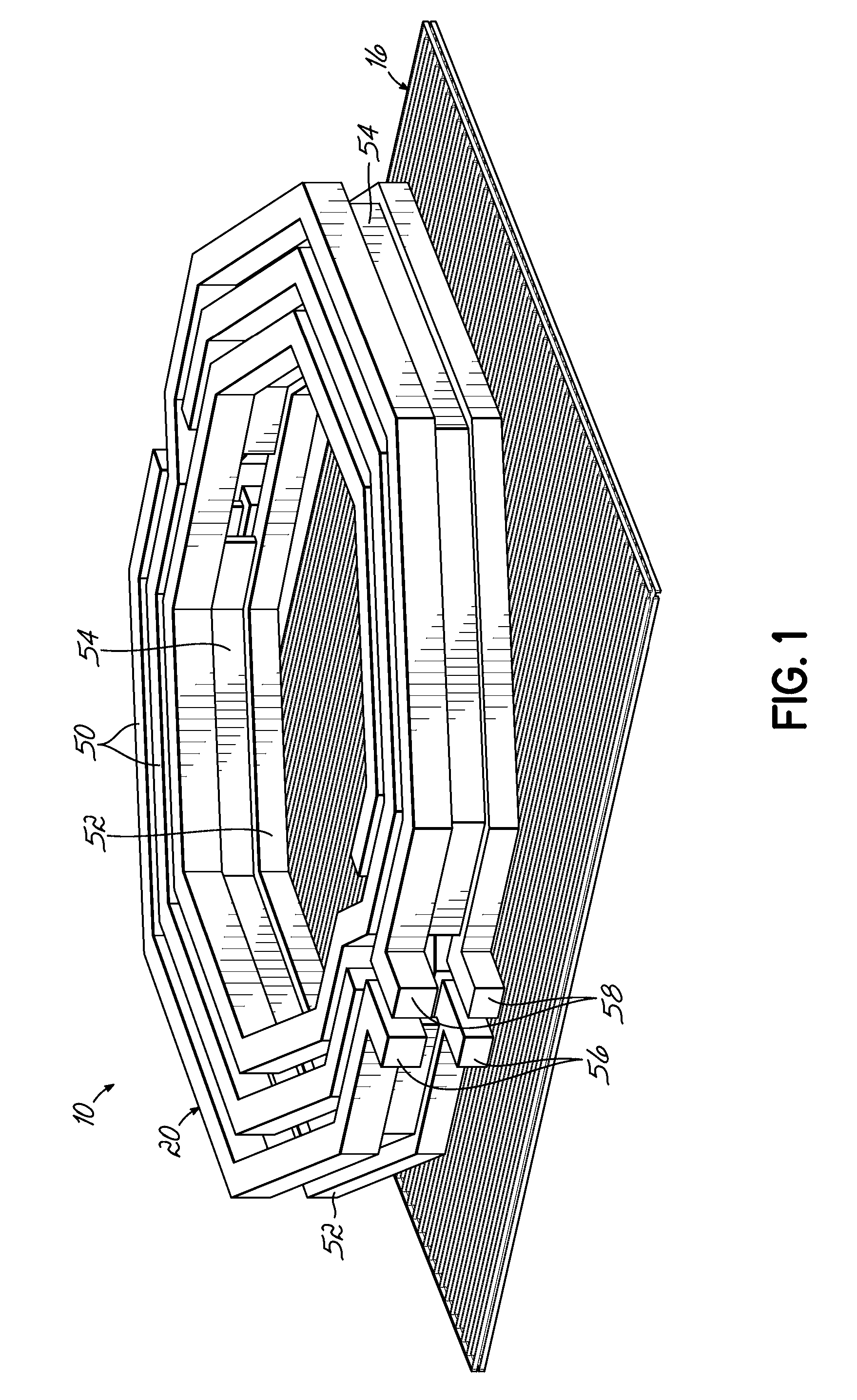

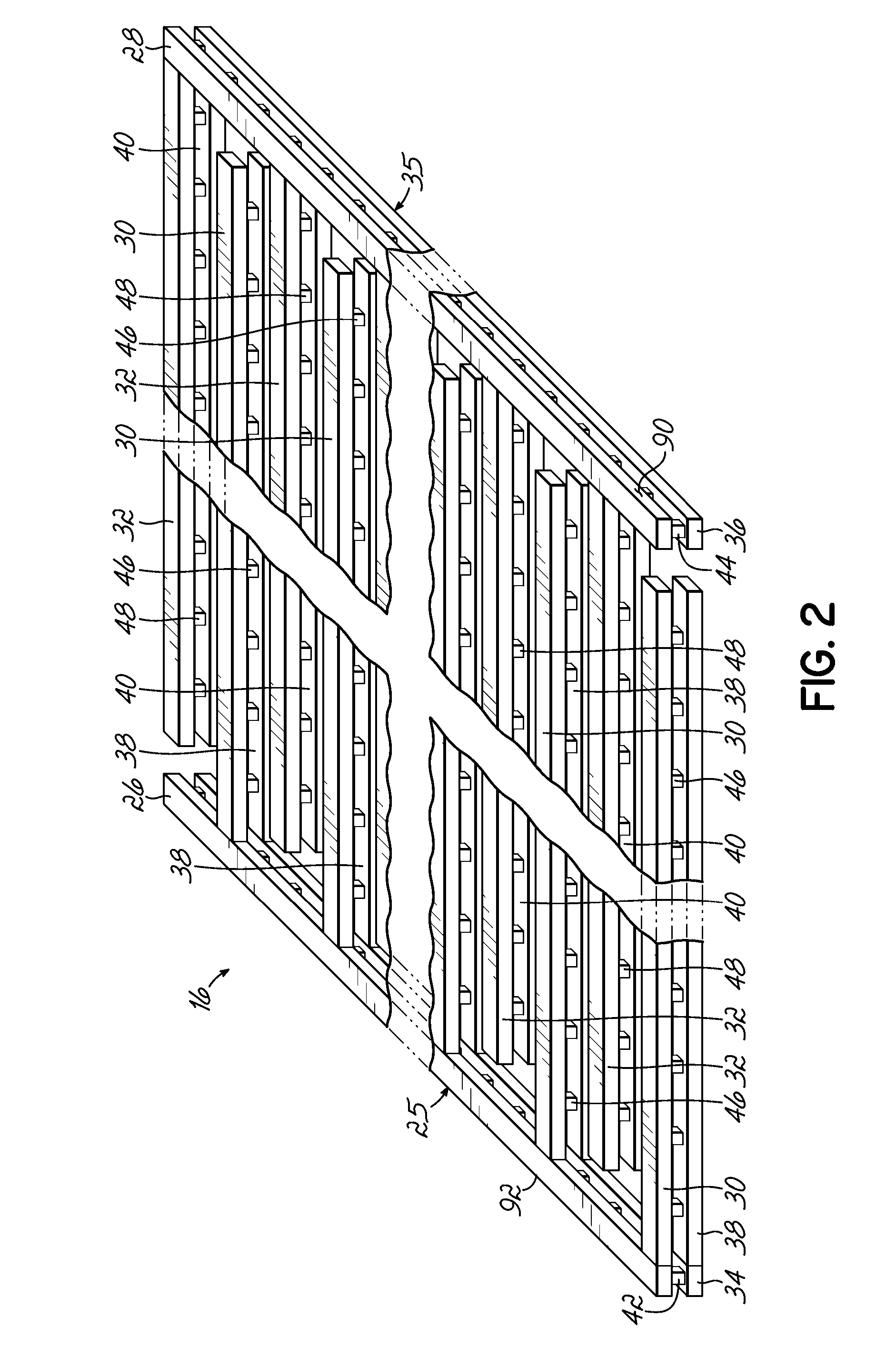

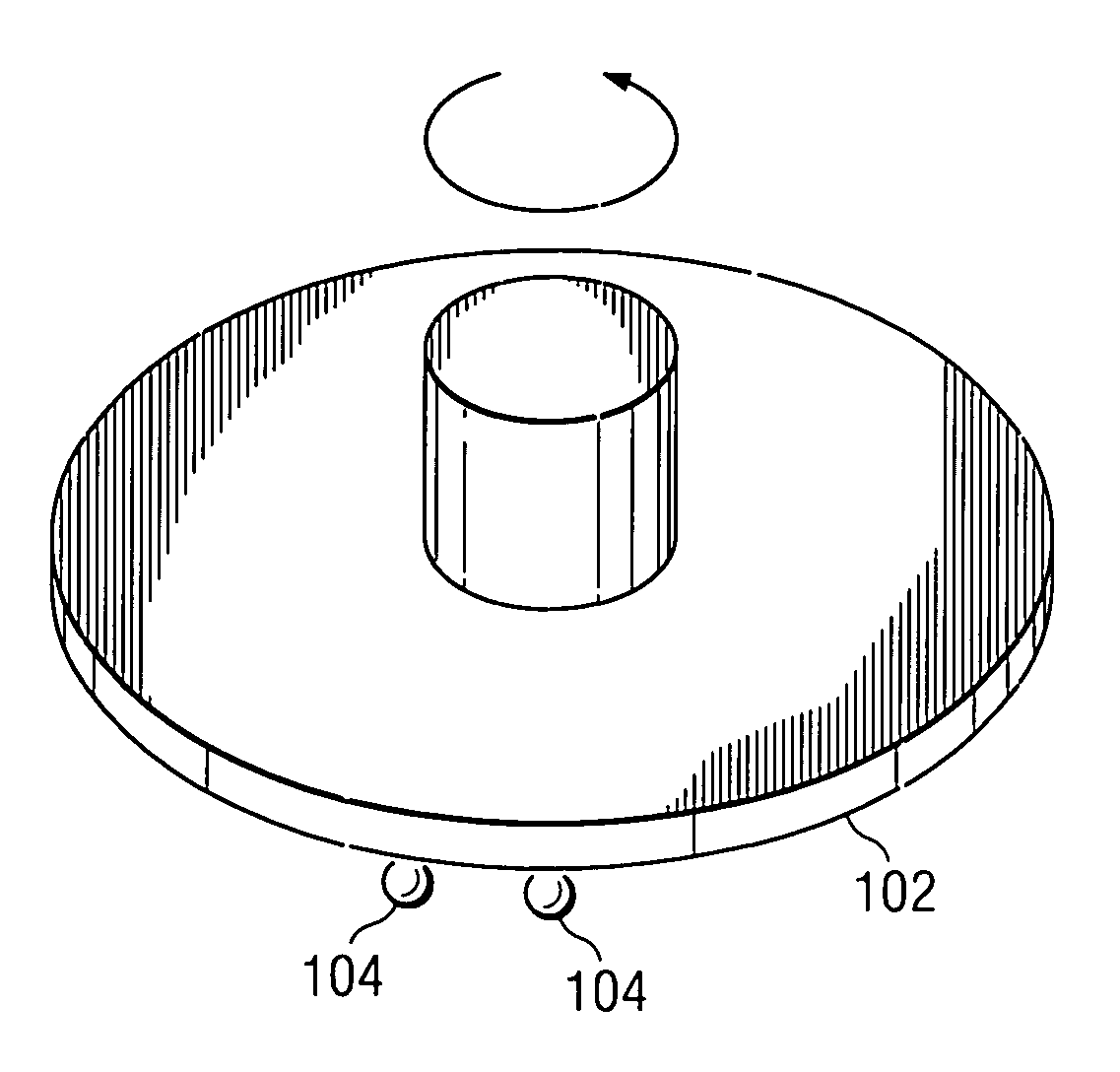

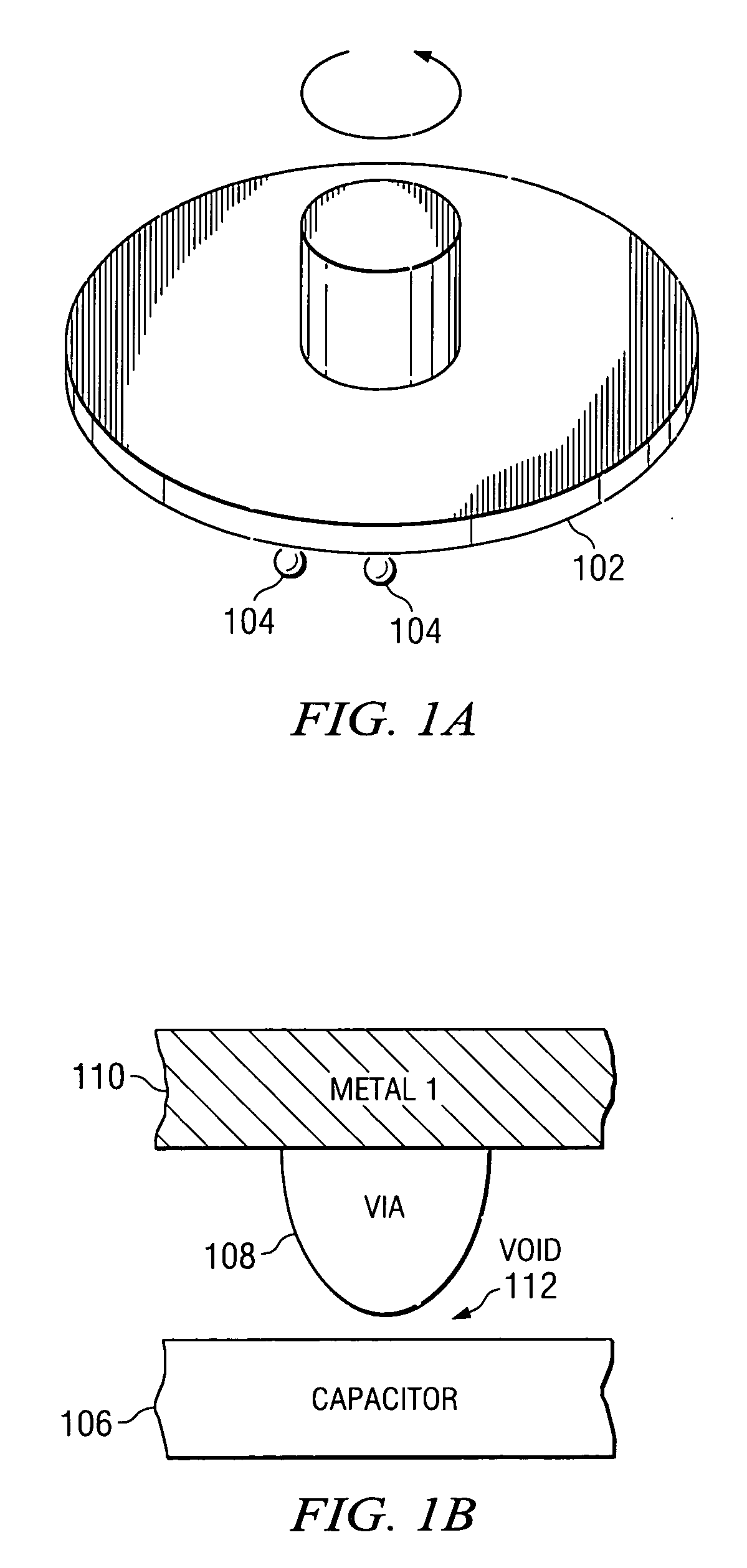

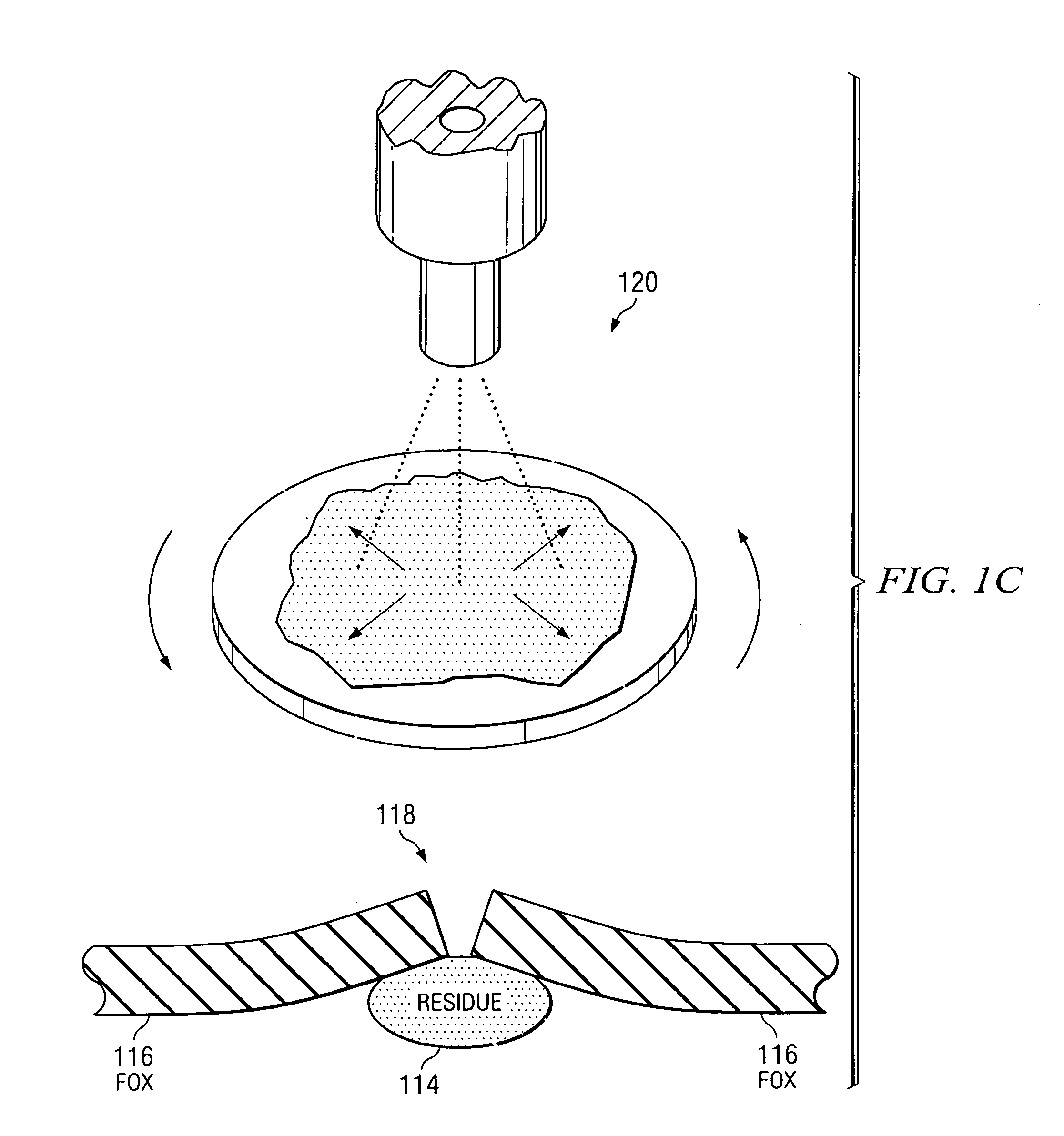

Damascene integration scheme for developing metal-insulator-metal capacitors

InactiveUS20040113235A1Increase capacitanceSave chip areaTransistorSolid-state devicesMetal-insulator-metalGas phase

The invention is directed to unique high-surface area BEOL capacitor structures with high-k dielectric layers and methods for fabricating the same. These high-surface area BEOL capacitor structures may be used in analog and mixed signal applications. The capacitor is formed within a trench with pedestals within the trench to provide additional surface area. The top and bottom electrodes are created using damascene integration scheme. The dielectric layer is created as a multilayer dielectric film comprising for instance Al2O3, Al2O3 / Ta2O5, Al2O3 / Ta2O5 / Al2O3 and the like. The dielectric layer may be deposited by methods like atomic layer deposition or chemical vapor deposition. The dielectric layer used in the capacitor may also be produced by anodic oxidation of a metallic precursor to yield a high dielectric constant oxide layer.

Owner:GLOBALFOUNDRIES US INC

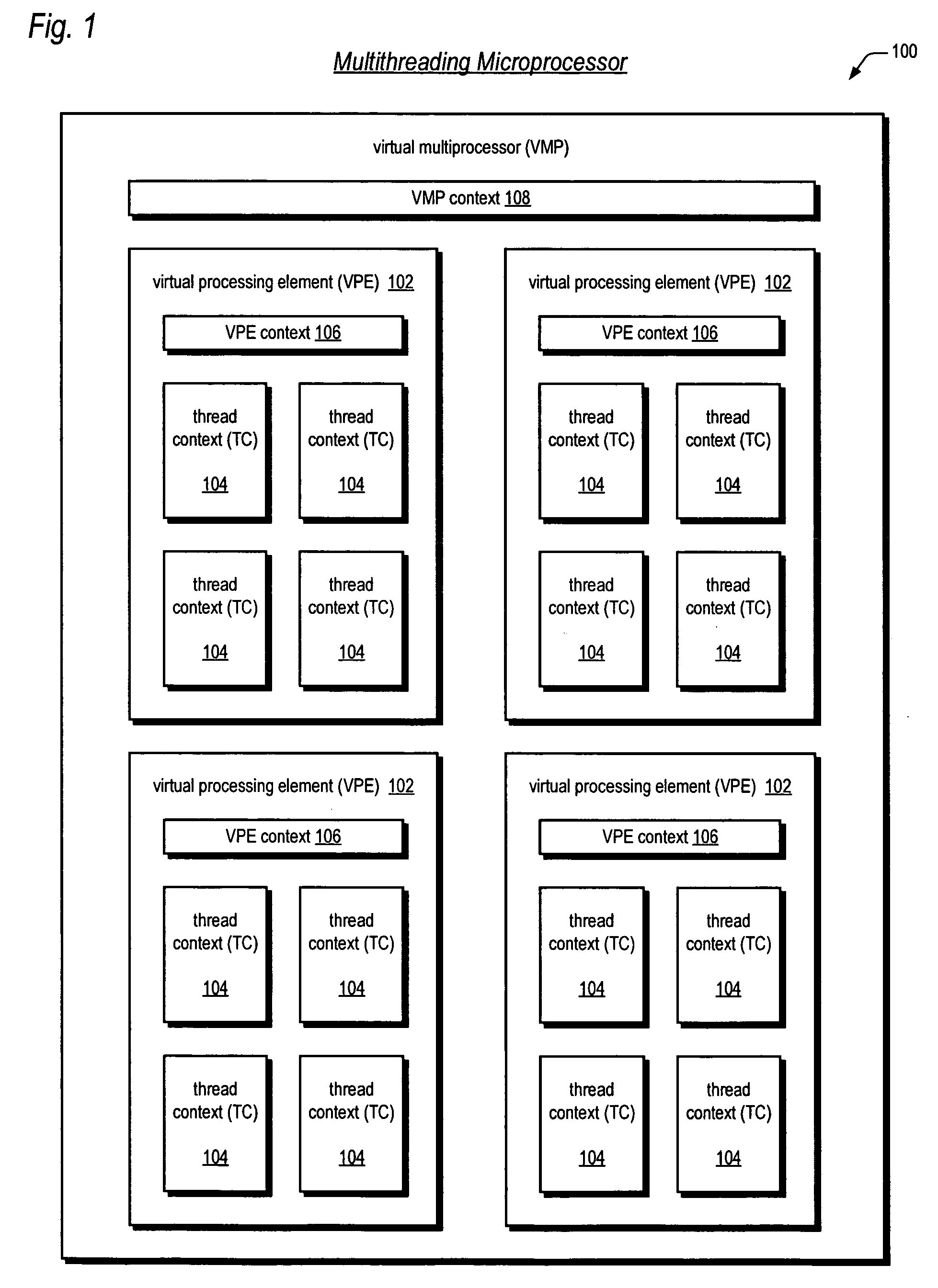

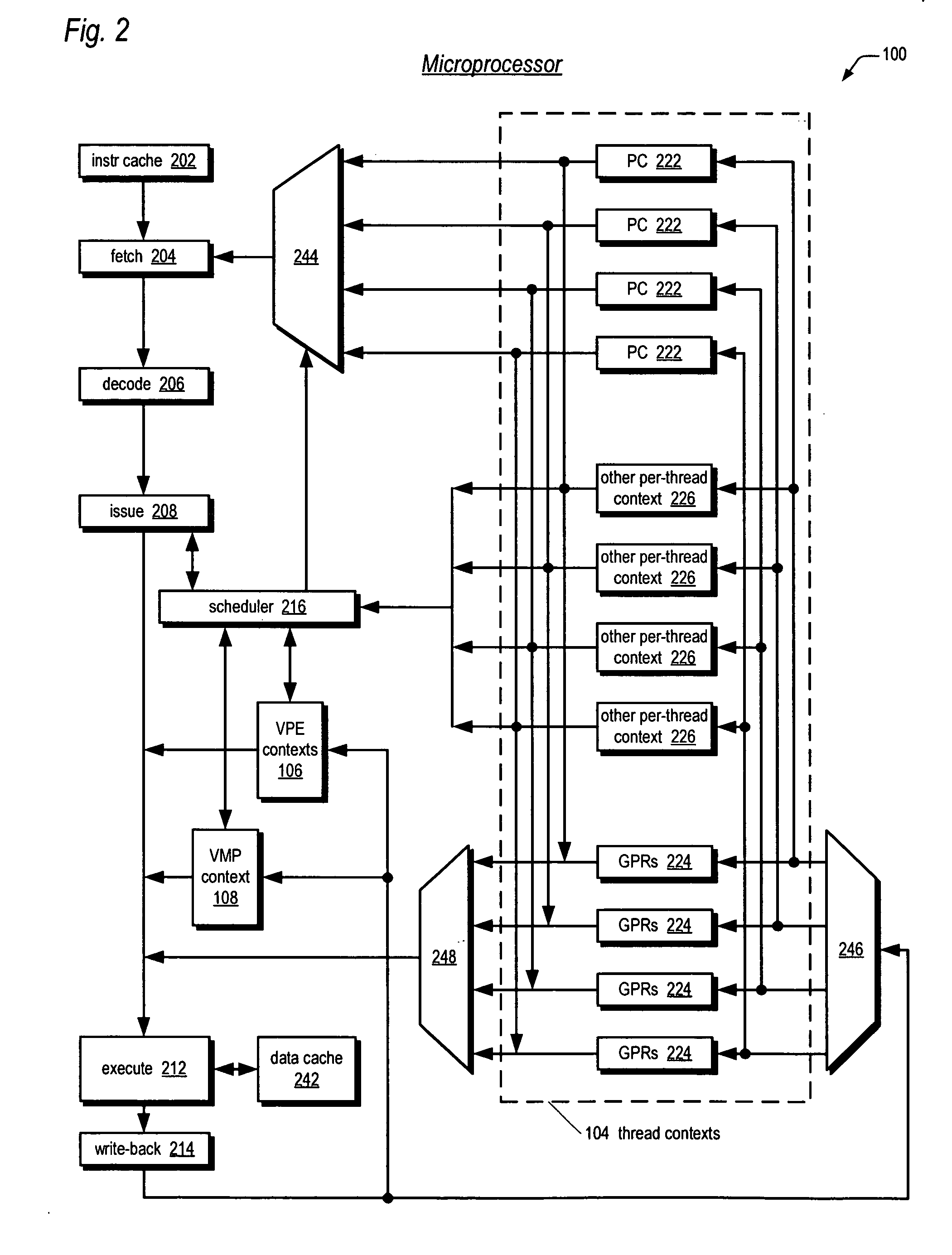

Software emulation of directed exceptions in a multithreading processor

ActiveUS20060161421A1More scalableSave areaDigital computer detailsSoftware simulation/interpretation/emulationGeneral purposeSoftware emulation

A multithreading microprocessor has a plurality of thread contexts (TCs) each including sufficient state, such as general purpose registers and program counter, to execute a separate thread of execution as one of a plurality of symmetric processors controlled by a multiprocessor operating system. However, the microprocessor hardware does not support the ability for one TC to direct an exception to another TC, i.e., to specify to which of the other TCs the exception is directed. A first thread running on a first TC of the operating system executes architected instructions to halt a second thread (either user or kernel thread) running on a second TC, save state of the second TC, write the second TC state to emulate an exception—including writing a restart register with the address of an exception handler, and unhalt the second TC to execute the exception hander.

Owner:MIPS TECH INC

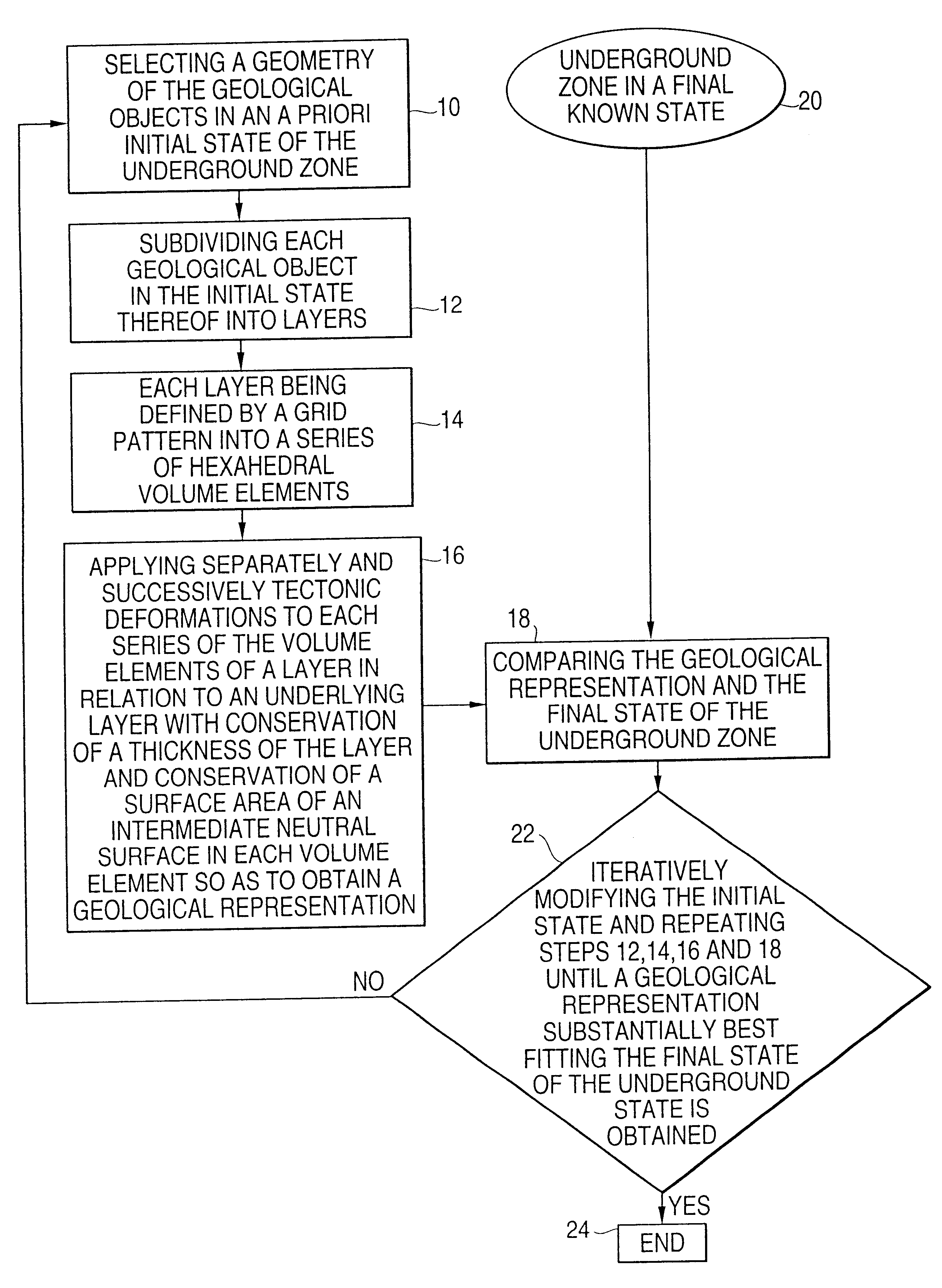

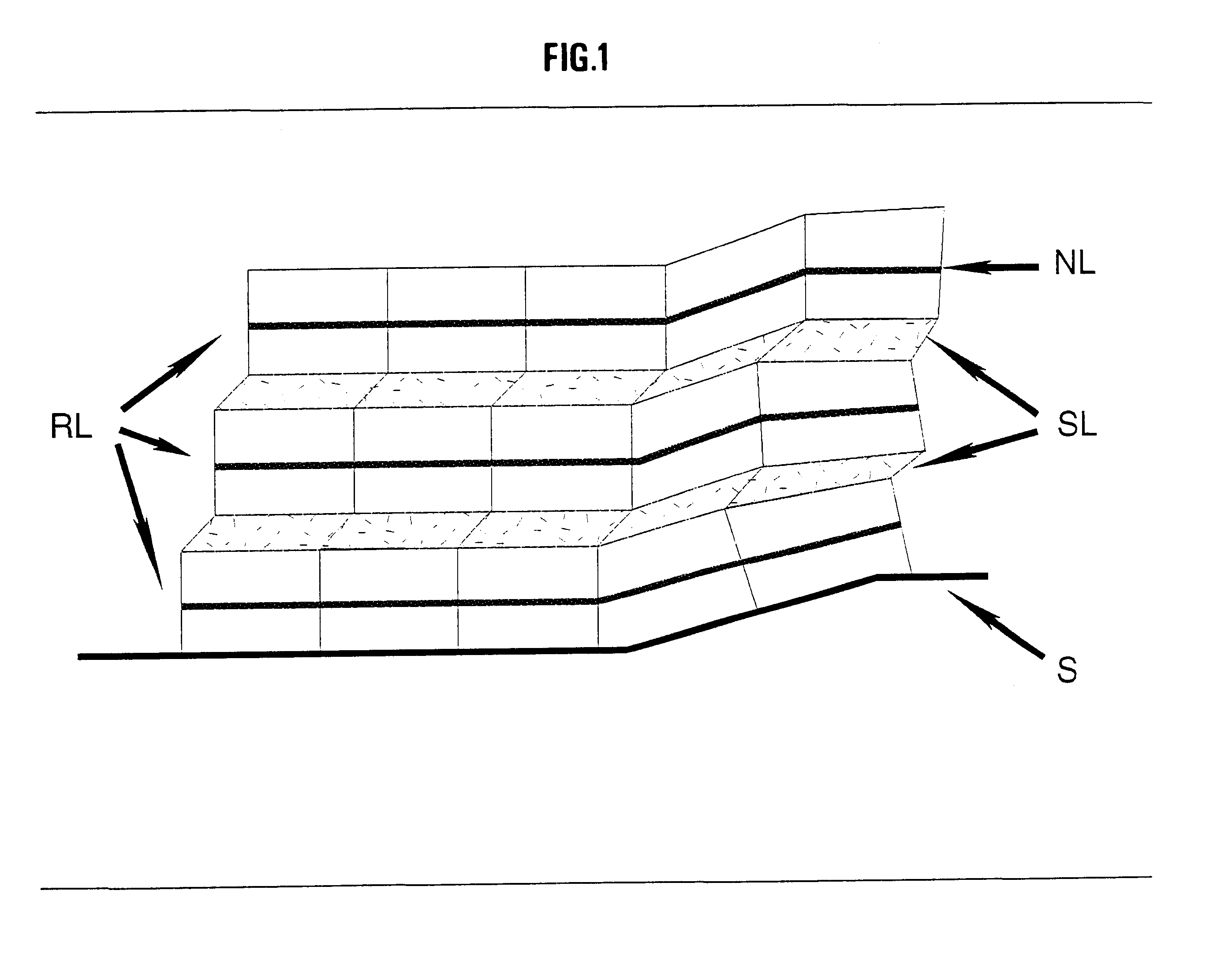

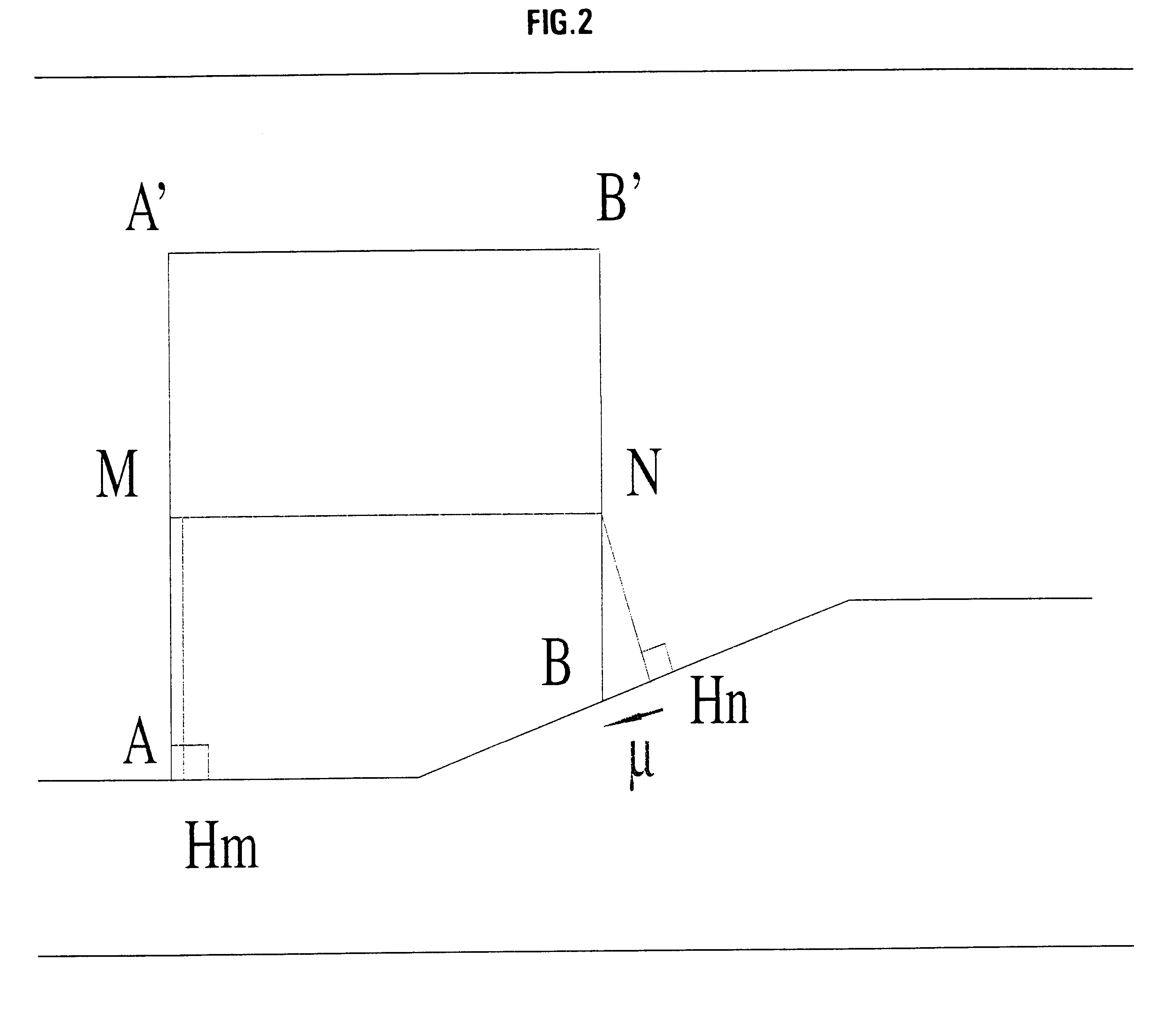

Method for forming a 3D kinematic deformation model of a sedimentary basin

InactiveUS6597995B1Easy to implementSave areaSeismic signal processingSpecial data processing applicationsGrid patternGeomorphology

A method for forming a prograde kinematic model allowing reproduction in 3D intermediate geometries of geologic objects of an underground zone such as a sedimentary basin, from an initial state to a current state. A representation of the current geometry of the geologic objects of the zone is formed by interpretation of acquired data obtained by seismic exploration, by in-situ measurements and by observations, then each geologic object is subdivided into layers separated by deformation interfaces. Each one of the layers is defined by means of a grid pattern into a series of hexahedral volume elements. Tectonic deformations are then applied separately and successively to each series of volume elements of a layer in relation to an underlying layer while conserving the thickness and the surface area of an intermediate neutral surface in each volume element. Then the tectonic deformations are iteratively modified until a geologic representation substantially in accordance with the known final state of the underground zone is obtained.

Owner:INST FR DU PETROLE

BEOL Wiring Structures That Include an On-Chip Inductor and an On-Chip Capacitor, and Design Structures for a Radiofrequency Integrated Circuit

ActiveUS20090322447A1Save chip areaSave areaTransformers/reacts mounting/support/suspensionMultiple-port networksLc resonatorResonance

Back-end-of-line (BEOL) wiring structures that include an on-chip inductor and an on-chip capacitor, as well as design structures for a radiofrequency integrated circuit. The on-chip inductor and an on-chip capacitor, which are fabricated as conductive features in different metallization levels, are vertically aligned with each other. The on-chip capacitor, which is located between the on-chip inductor and the substrate, may serve as a Faraday shield for the on-chip inductor. Optionally, the BEOL wiring structure may include an optional Faraday shield located vertically either between the on-chip capacitor and the on-chip inductor, or between the on-chip capacitor and the top surface of the substrate. The BEOL wiring structure may include at least one floating electrode capable of being selectively coupled with the electrodes of the on-chip capacitor to permit tuning, during circuit operation, of a resonance frequency of an LC resonator that further includes the on-chip inductor.

Owner:GLOBALFOUNDRIES US INC

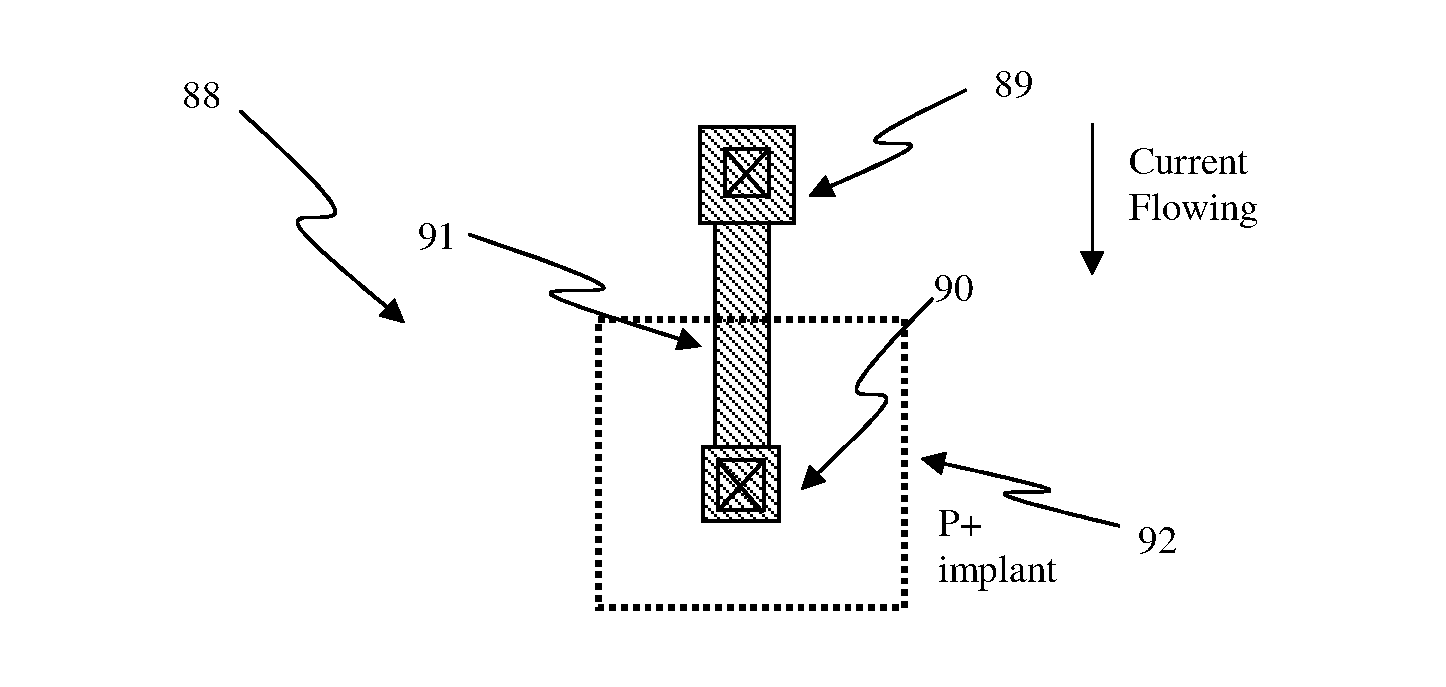

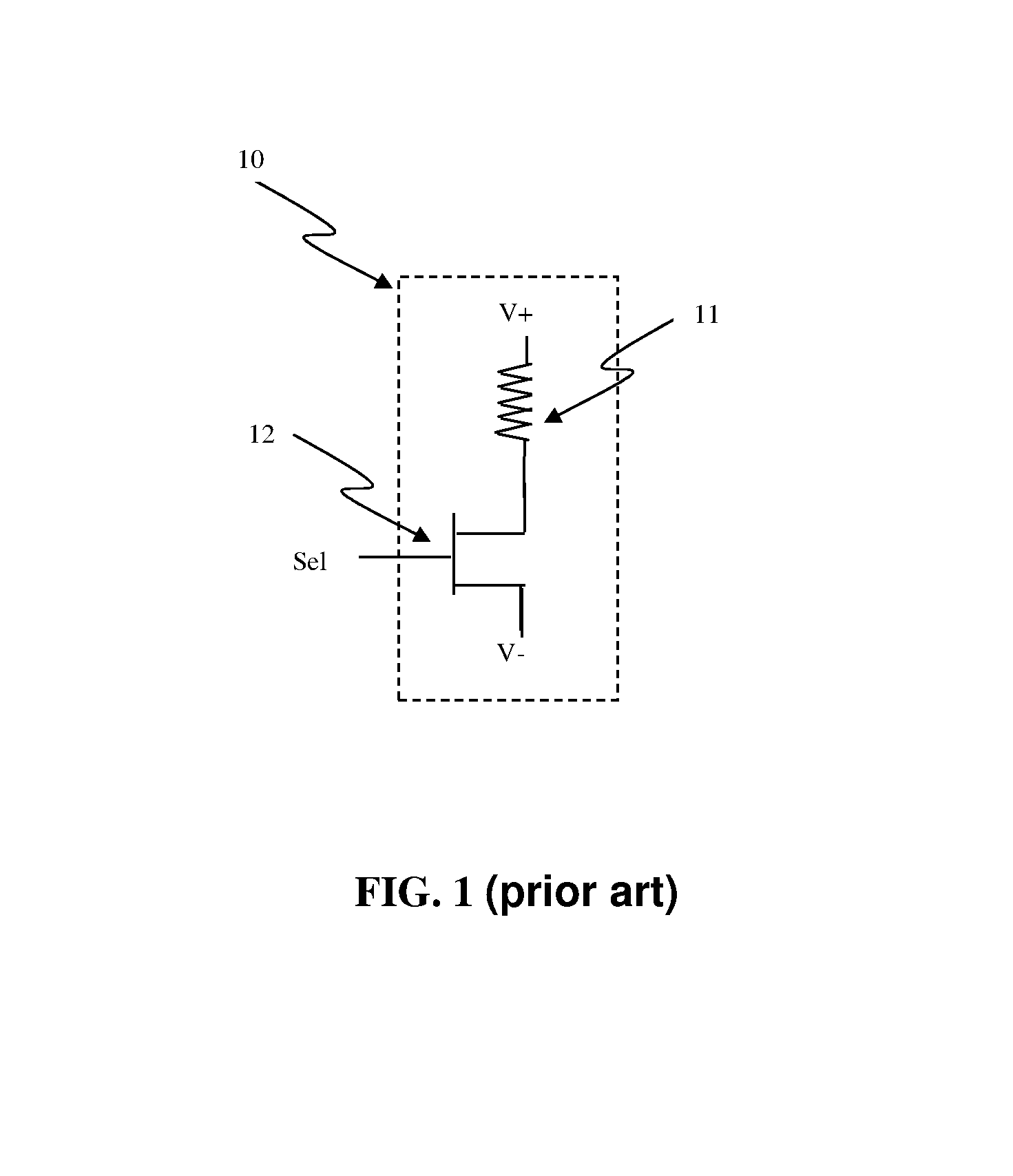

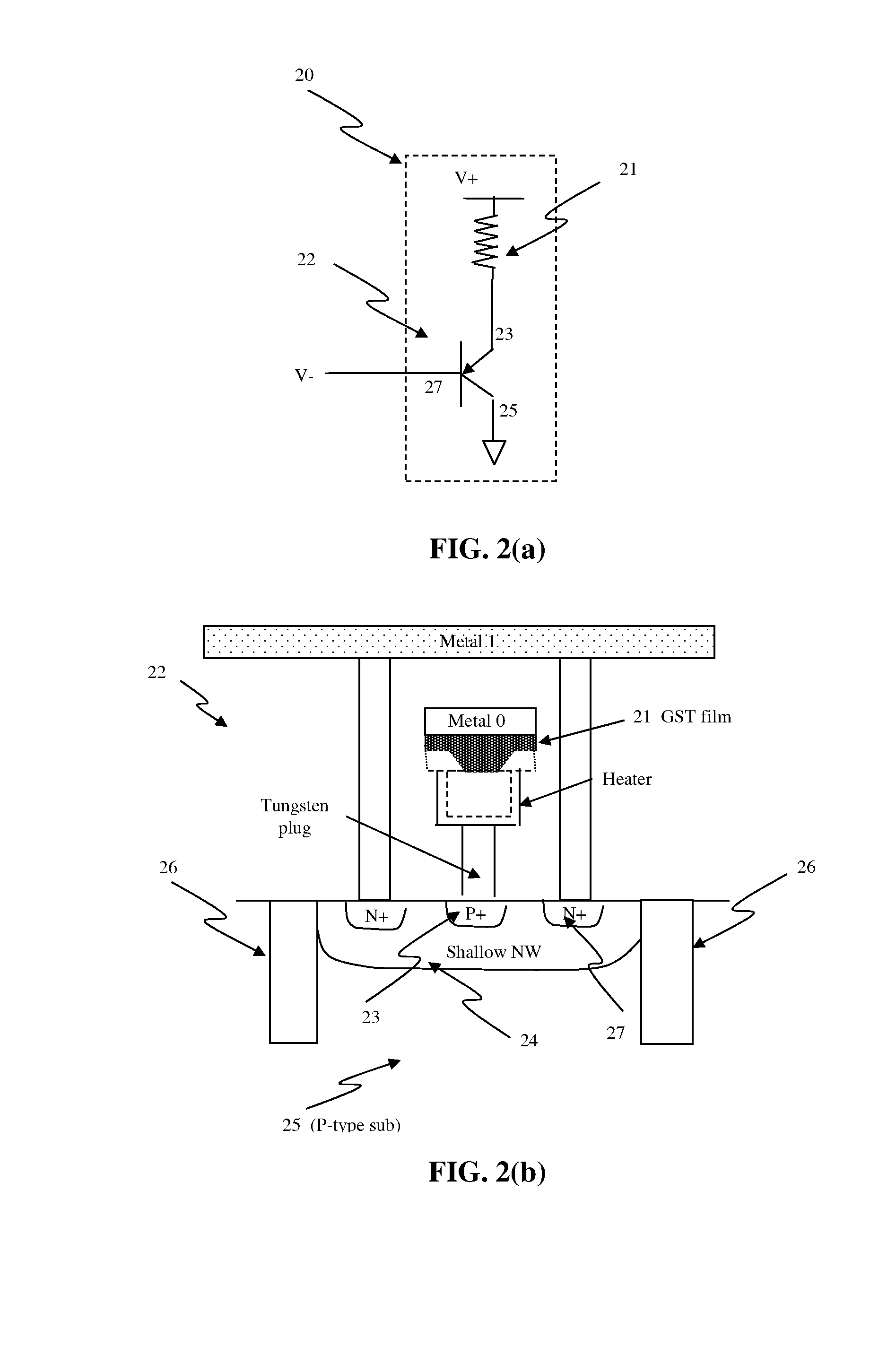

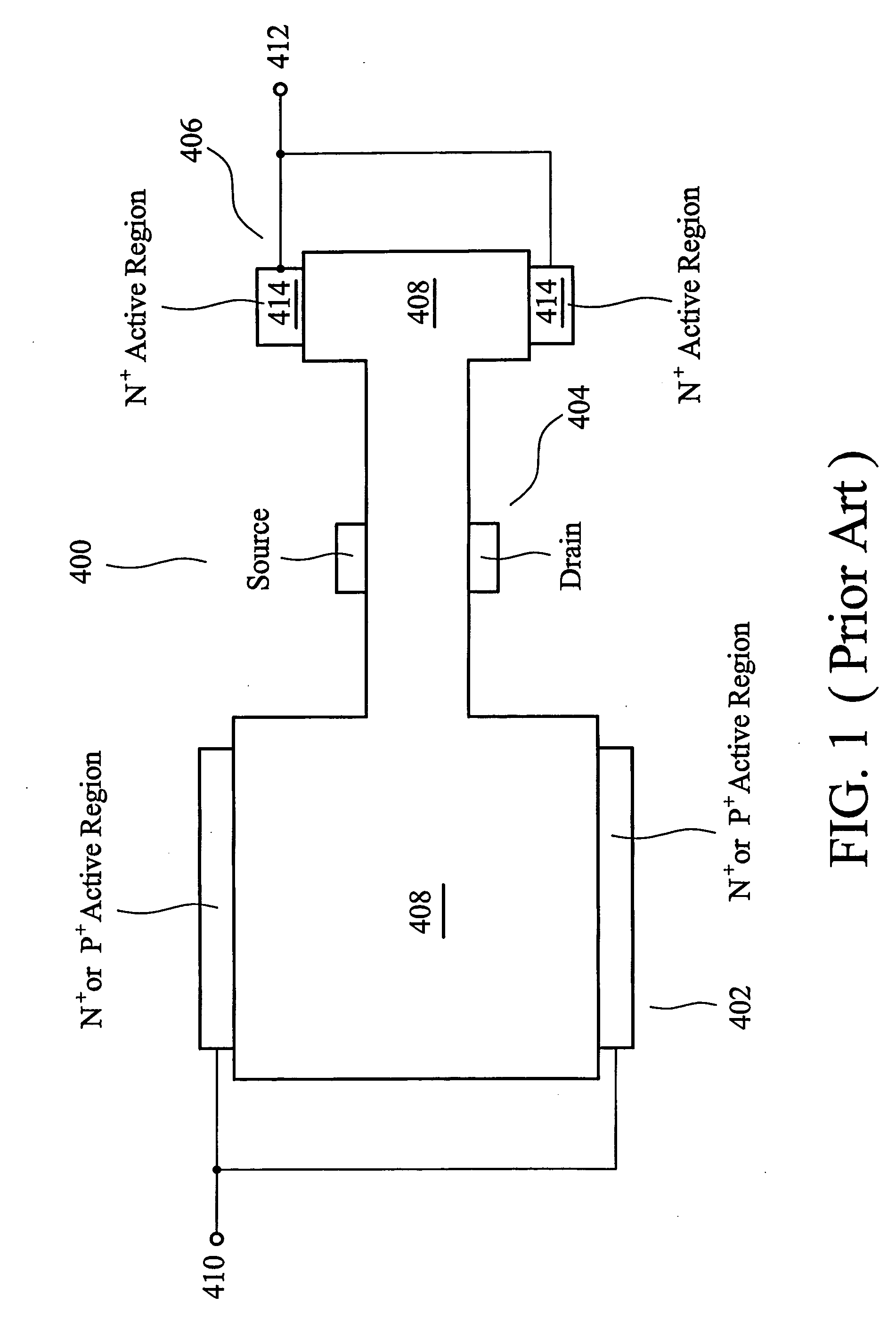

Circuit and system of using polysilicon diode as program selector for one-time programmable devices

ActiveUS20120044737A1Avoid shortingSave extra spaceSolid-state devicesRead-only memoriesLow voltageHemt circuits

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has an OTP element coupled to a diode in a memory cell. The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a high voltage to an OTP element coupled to the P-terminal of a diode and switching the N-terminal of a diode to a low voltage for suitable duration of time, a current flows through the OTP element may change the resistance state. On the polysilicon diode, the spacing and doping level of a gap between the P- and N-implants can be controlled for different breakdown voltages and leakage currents. The Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting. If the OTP element is a polysilicon electrical fuse, the fuse element can be merged with the polysilicon diode in one piece to save area.

Owner:ATTOPSEMI TECH CO LTD

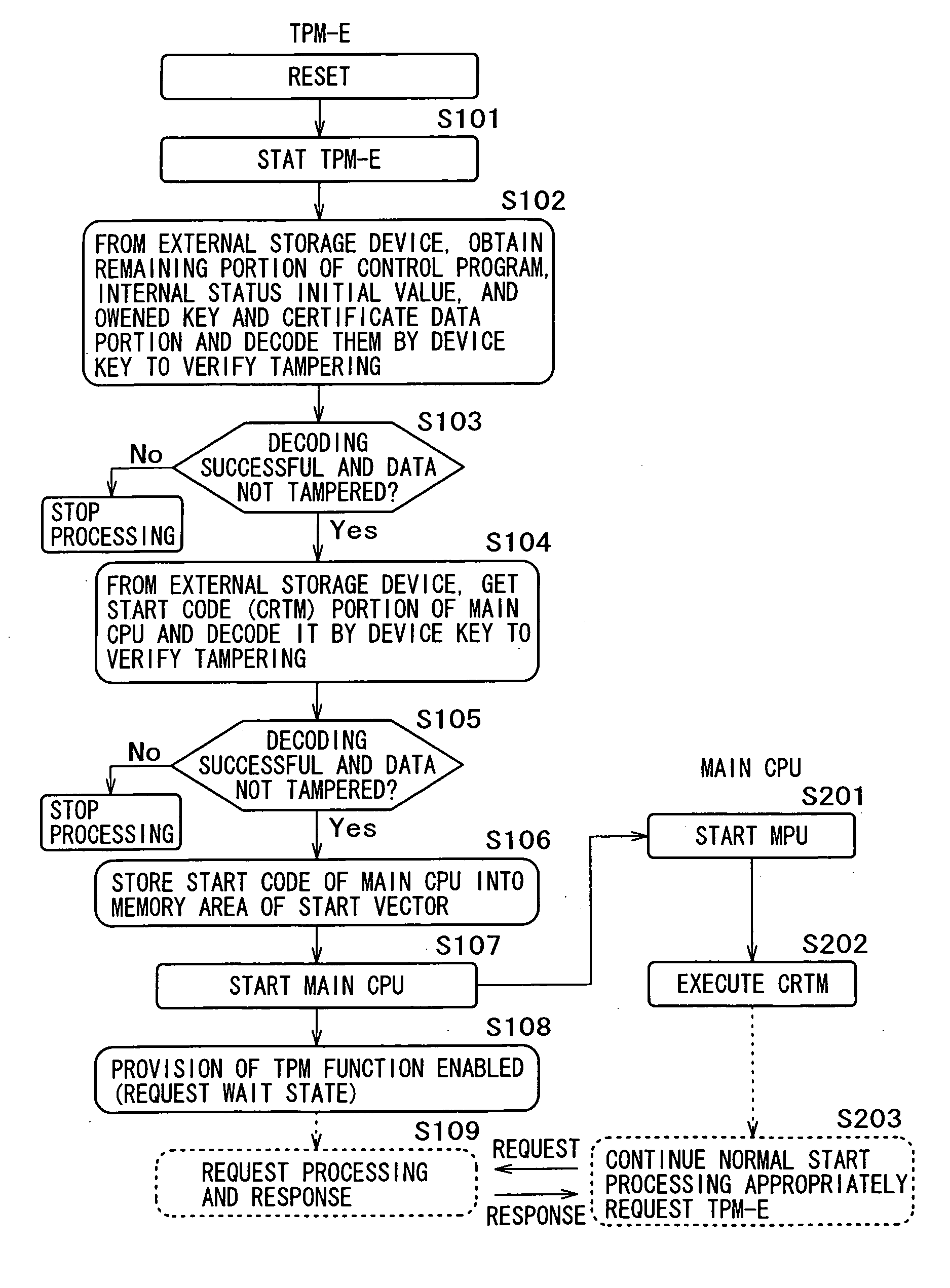

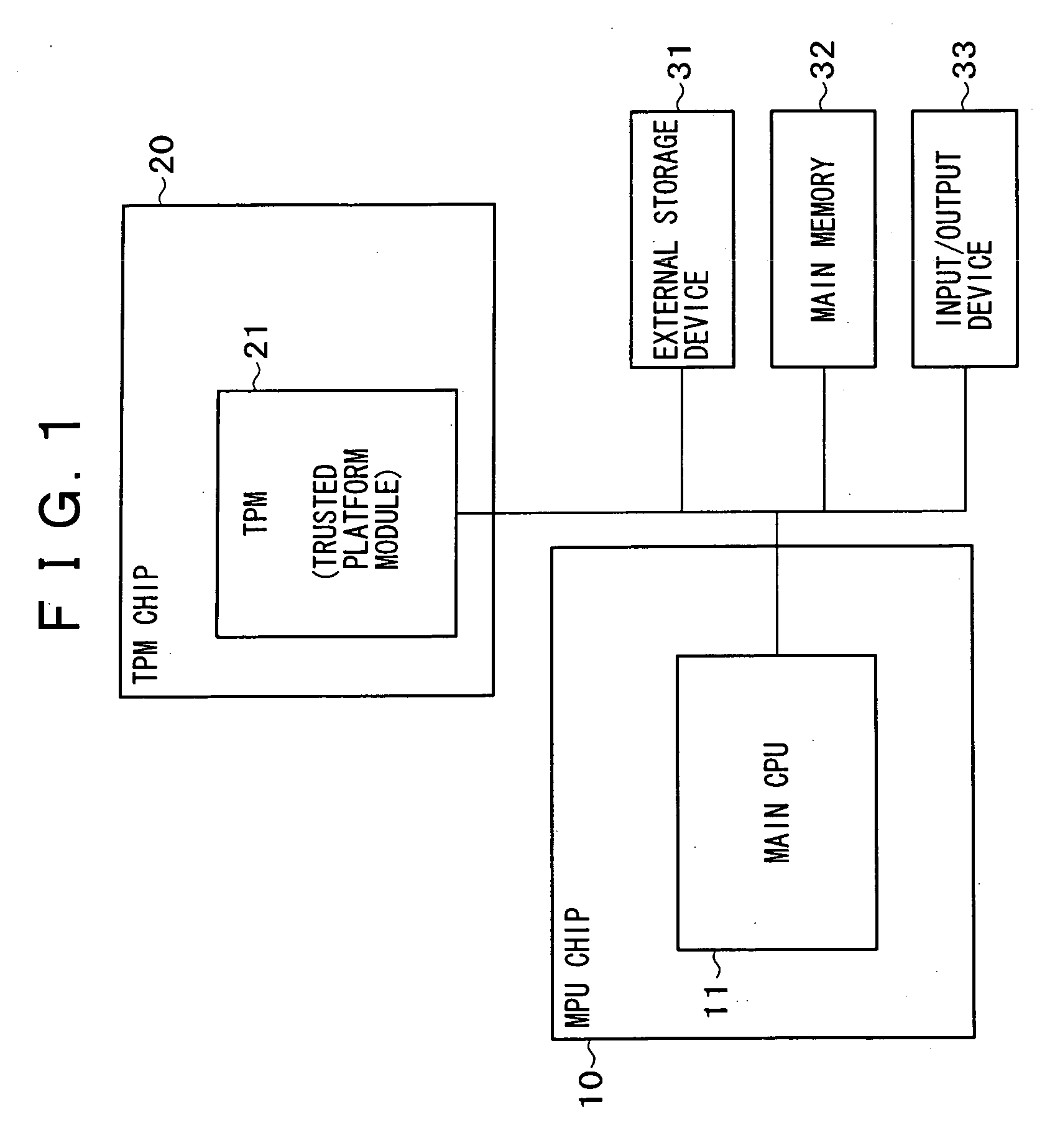

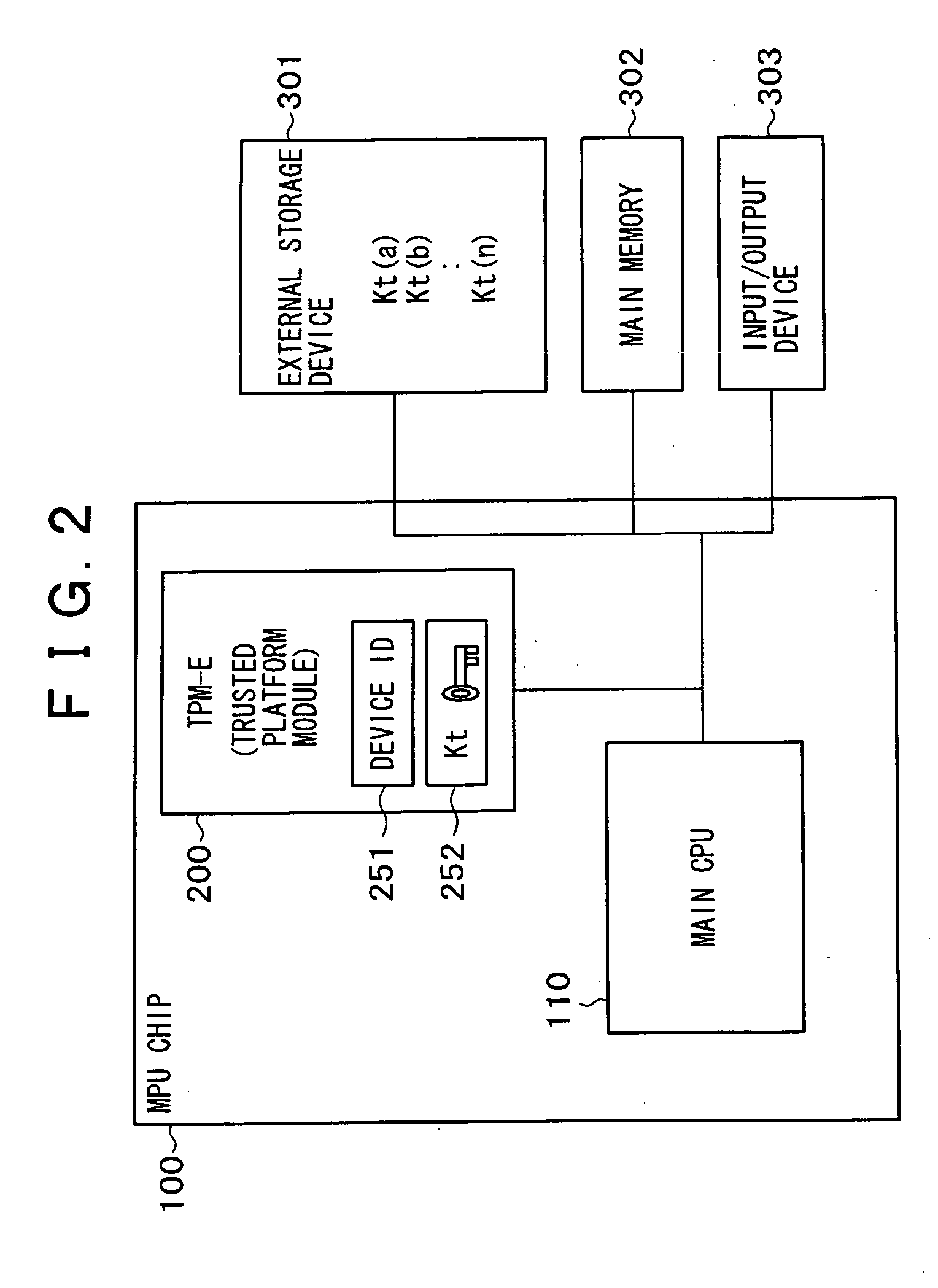

Information processing apparatus and method and computer program

InactiveUS20050182952A1Reduced package areaReduce the amount requiredUnauthorized memory use protectionHardware monitoringInformation processingExternal storage

The present invention provides an information processing apparatus of space-saved type that can execute the processing corresponding to a security function module. A security function module storing a device key is integrally arranged in an MPU chip, the secret data including programs and data to be applied to the data processing to be executed in the security function module are encrypted with the device key or attached with a falsification verification value and the resultant programs and data are stored in an external storage section. This novel configuration can significantly reduce the amount of data to be stored in the security function module and therefore eliminate the necessity for a large-capacity flash memory. Consequently, the security function module can be integrally arranged in the MPU chip having the main CPU, thereby significantly reducing the packaging area and the production cost.

Owner:SONY CORP

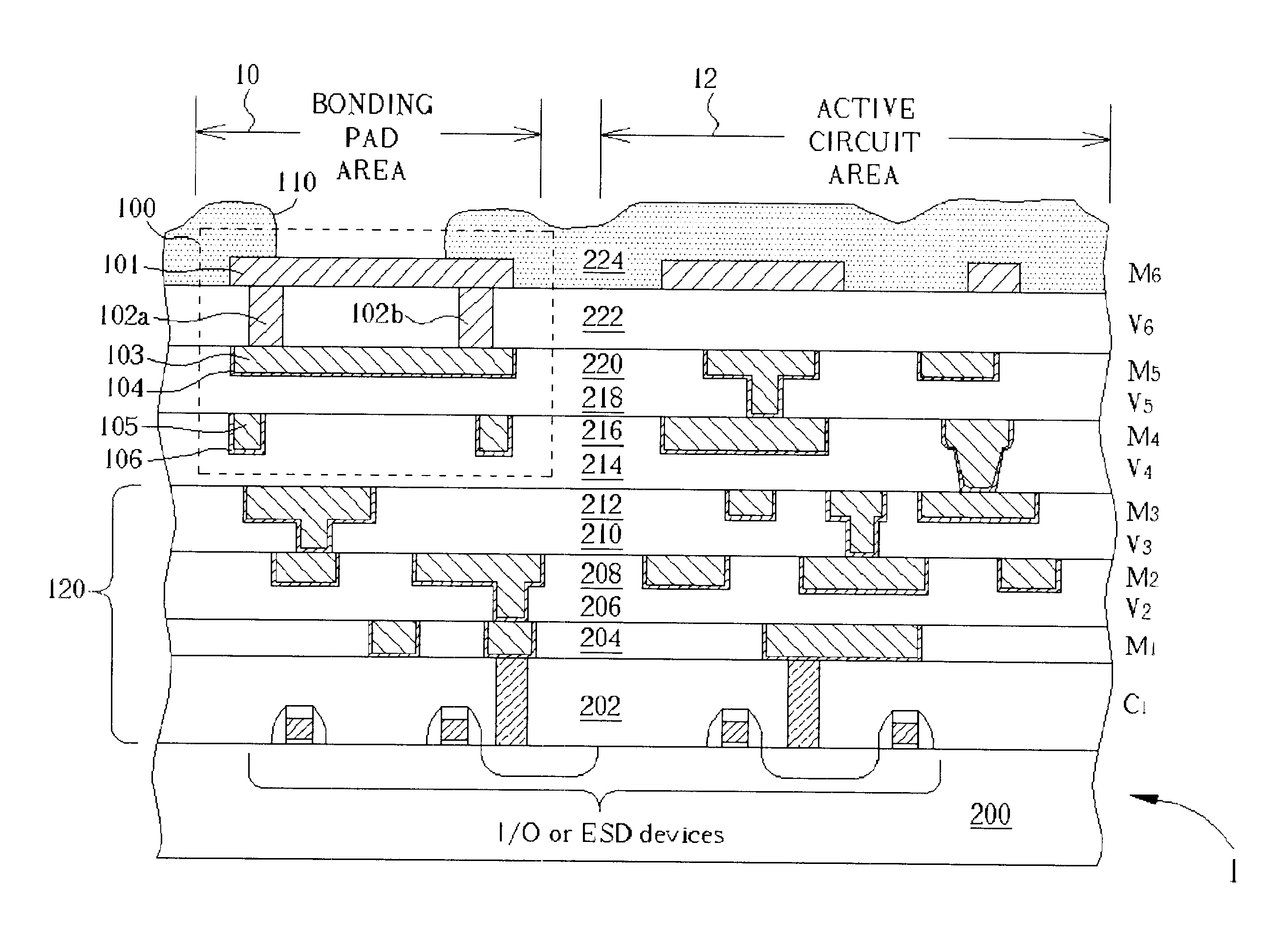

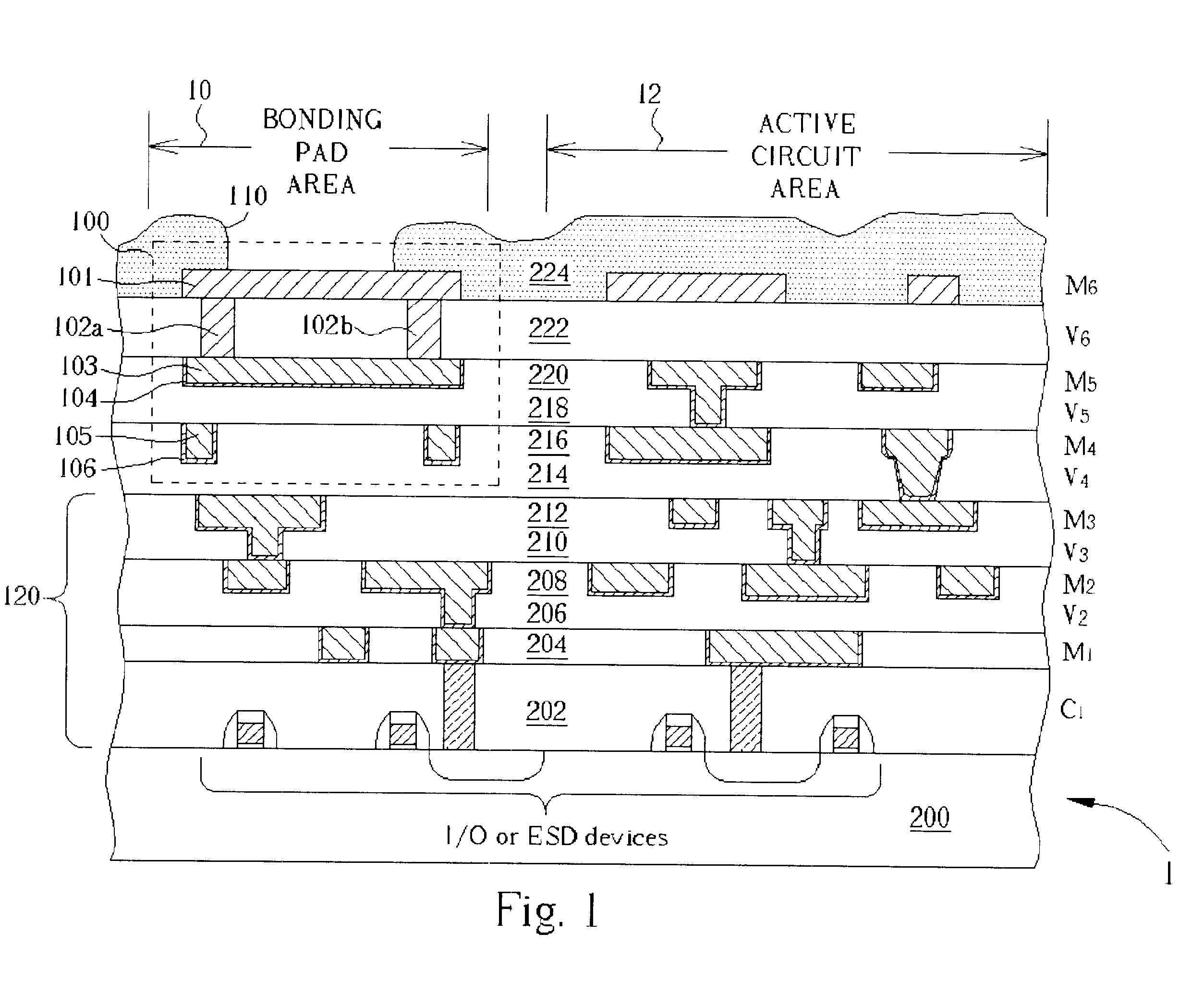

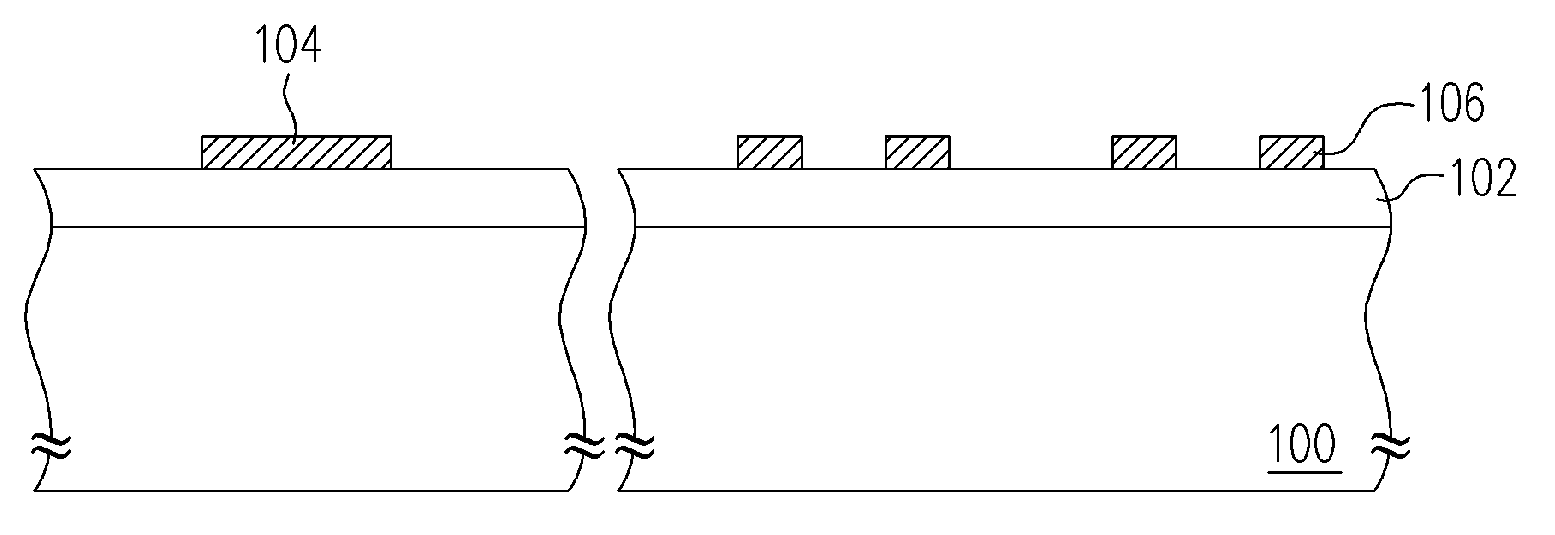

Semiconductor chip capable of implementing wire bonding over active circuits

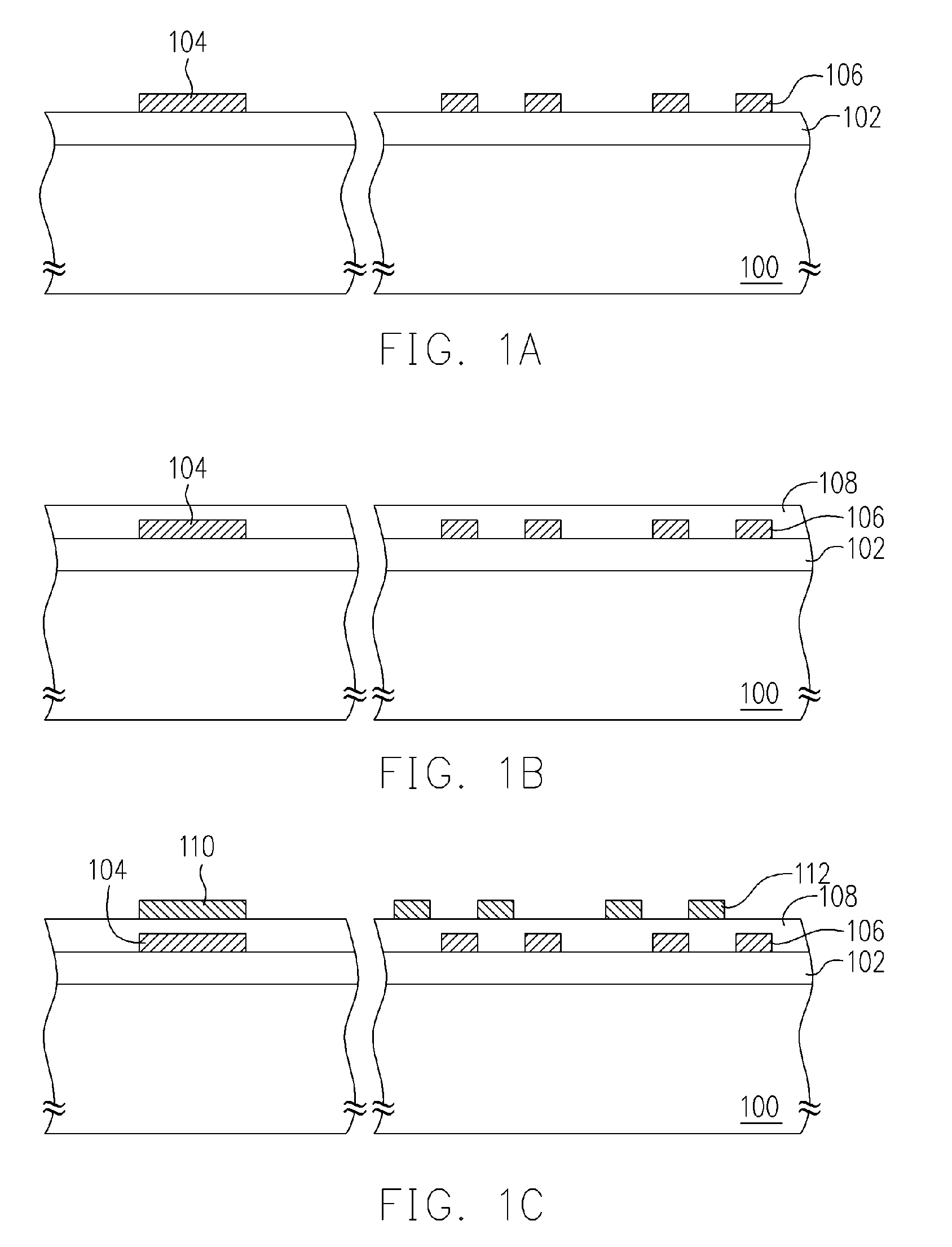

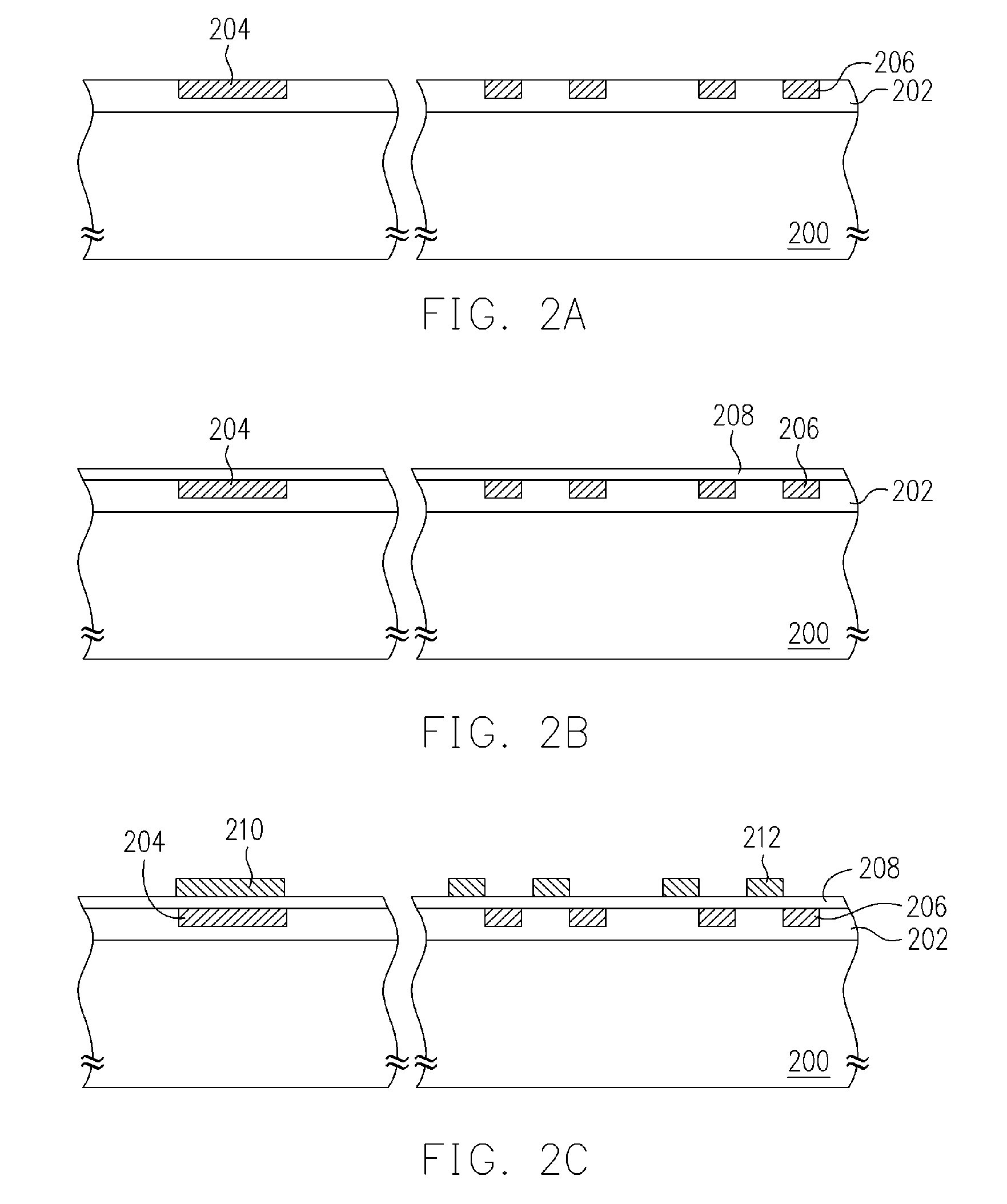

ActiveUS6900541B1Save areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipDielectric layer

An integrated circuit including a reinforced bonding pad structure is disclosed. The reinforced bonding pad structure includes a bondable metal layer defined on a stress-buffering dielectric layer, and an intermediate metal layer damascened in a first inter-metal dielectric (IMD) layer disposed under the stress-buffering dielectric layer. The intermediate metal layer is situated directly under the bondable metal layer and is electrically connected to the bondable metal layer with a plurality of via plugs integrated with the bondable metal layer. At least one metal frame is damascened in a second IMD layer under the first IMD layer. The metal frame is situated directly under the intermediate metal layer for counteracting mechanical stress exerted on the bondable metal layer during bonding. An active circuit portion including active circuit components of the integrated circuit is situated directly under the metal frame of the reinforced bonding pad structure.

Owner:UNITED MICROELECTRONICS CORP

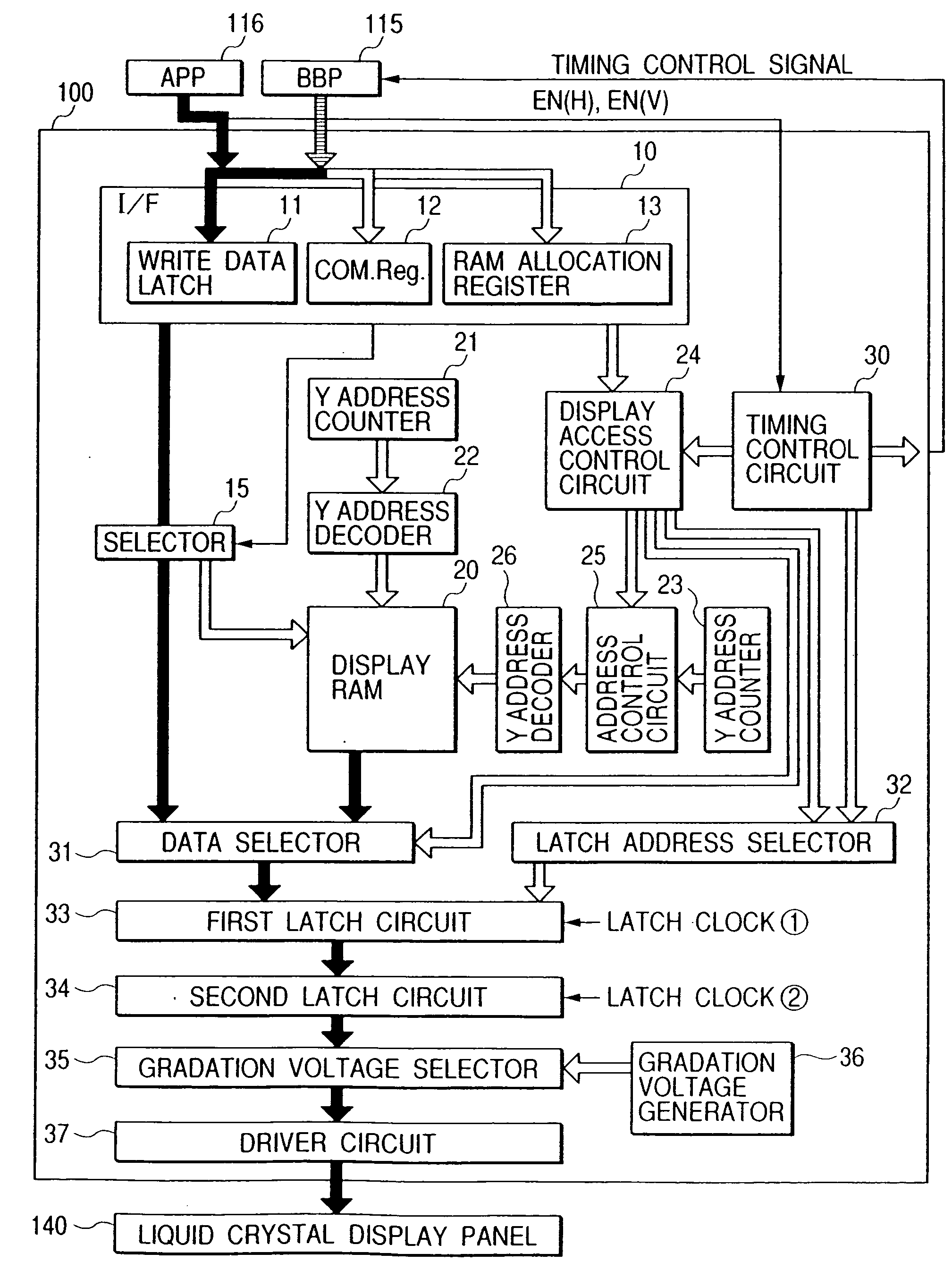

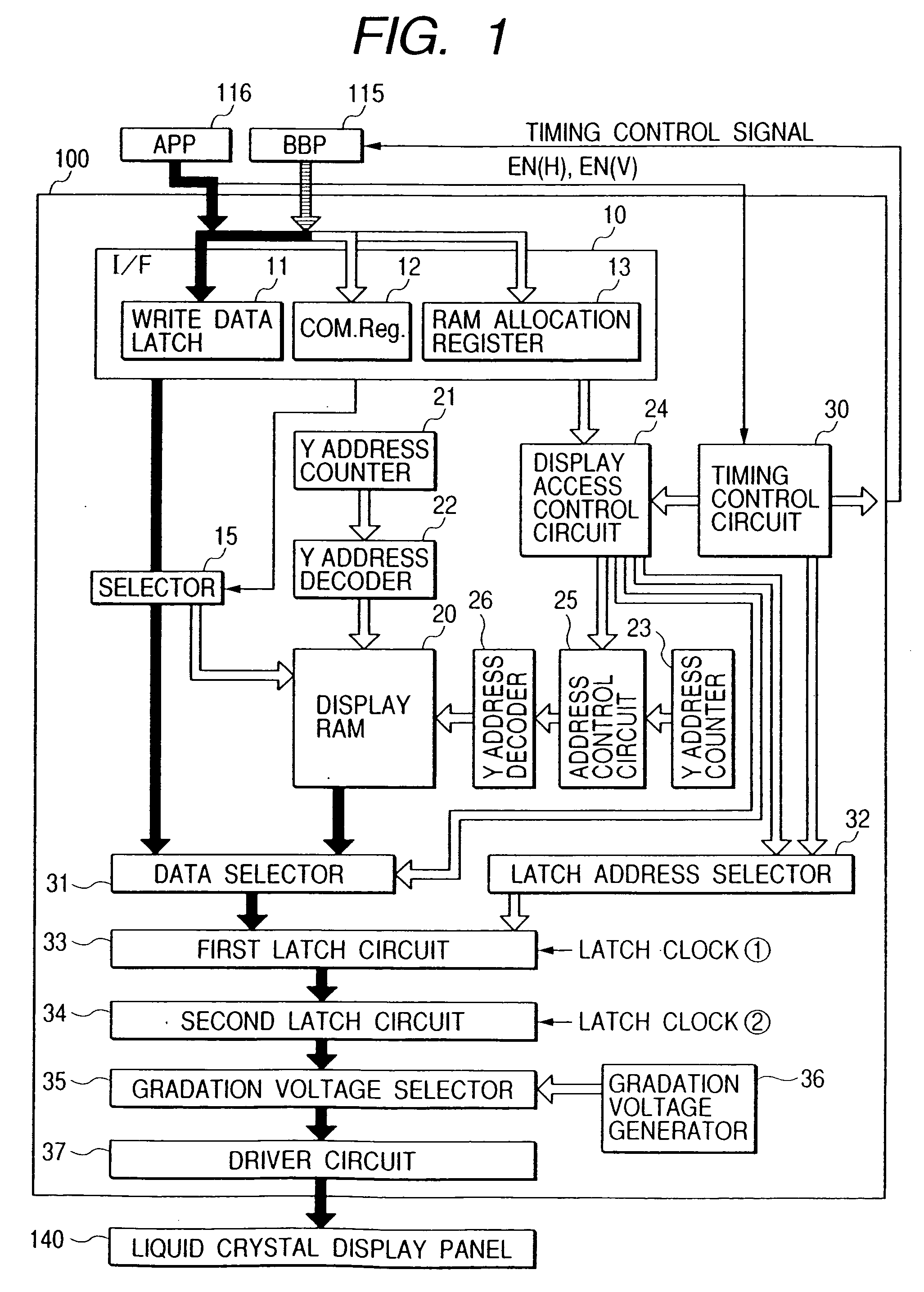

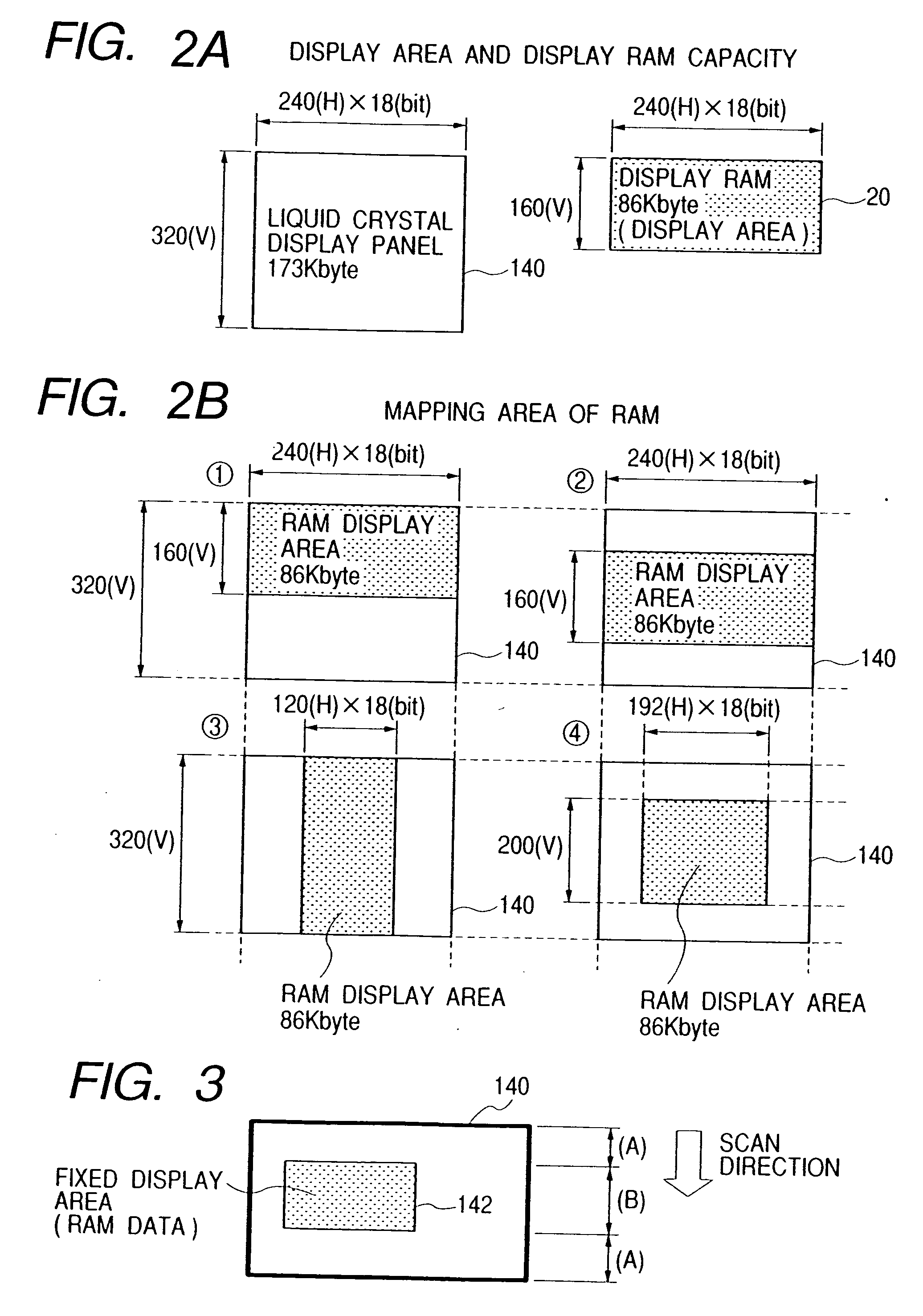

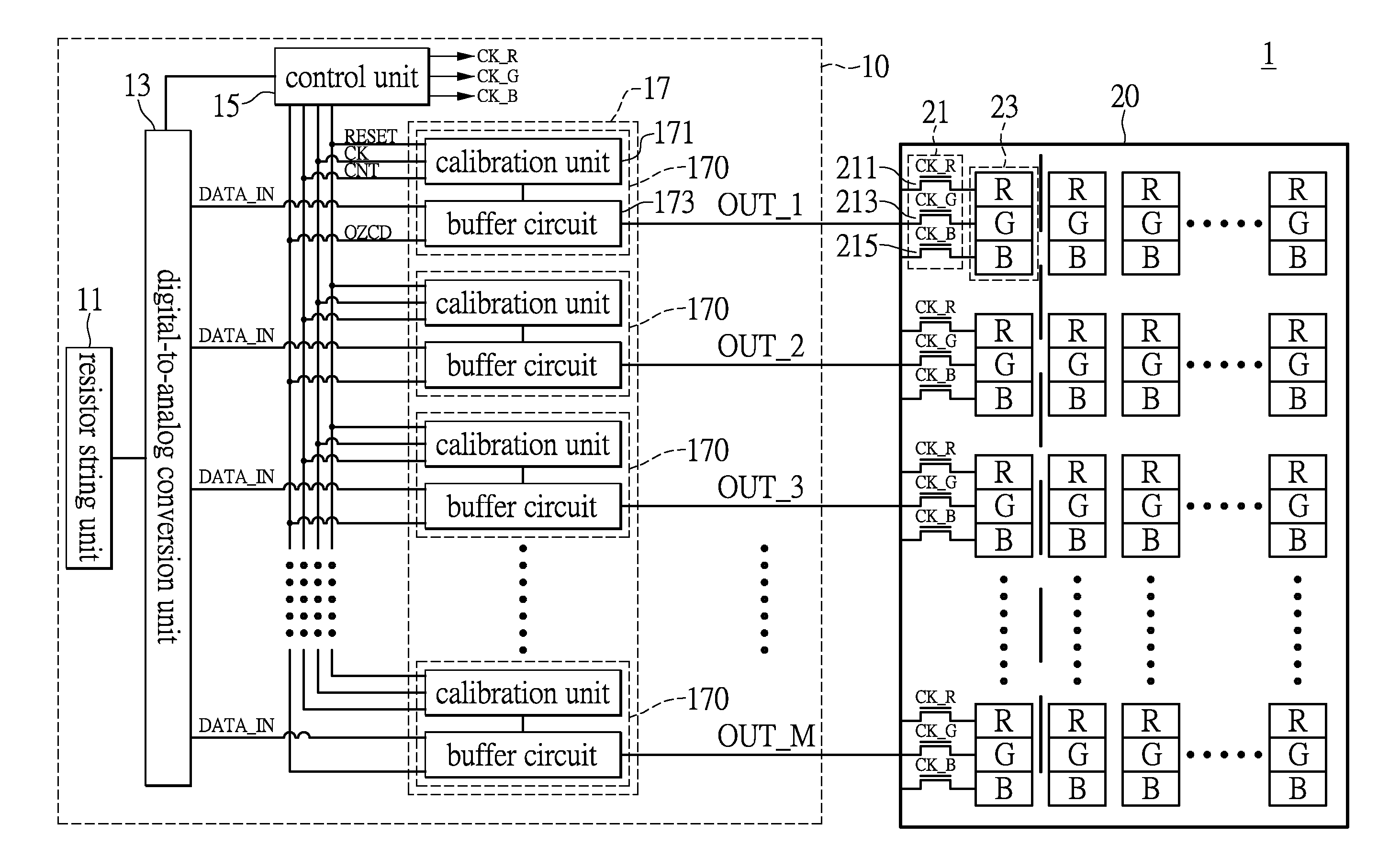

Display driver control circuit and electronic equipment with display device

InactiveUS20070035503A1Large capacityNumber of display colors are more and more increasingCathode-ray tube indicatorsControl circuitComputer science

There is provided a display driver control circuit which is just suitable for display drive including display with a small amount of change and display with a large amount of change and can realize saving of chip area and reduction of power consumption and cost. In this display driver control circuit, memory capacity of an internal display memory is set smaller than amount of data of one display picture of a display panel as the drive object, and the display data can be transferred with the system in which externally inputted display data is once stored in the display memory and is then sent of a drive circuit to output a drive signal and with the system in which the display data is sent in direct to the drive circuit by way of no display memory to output a drive signal. Moreover, both transfer methods can be executed on the time division basis.

Owner:KUROKAWA YASUHITO +4

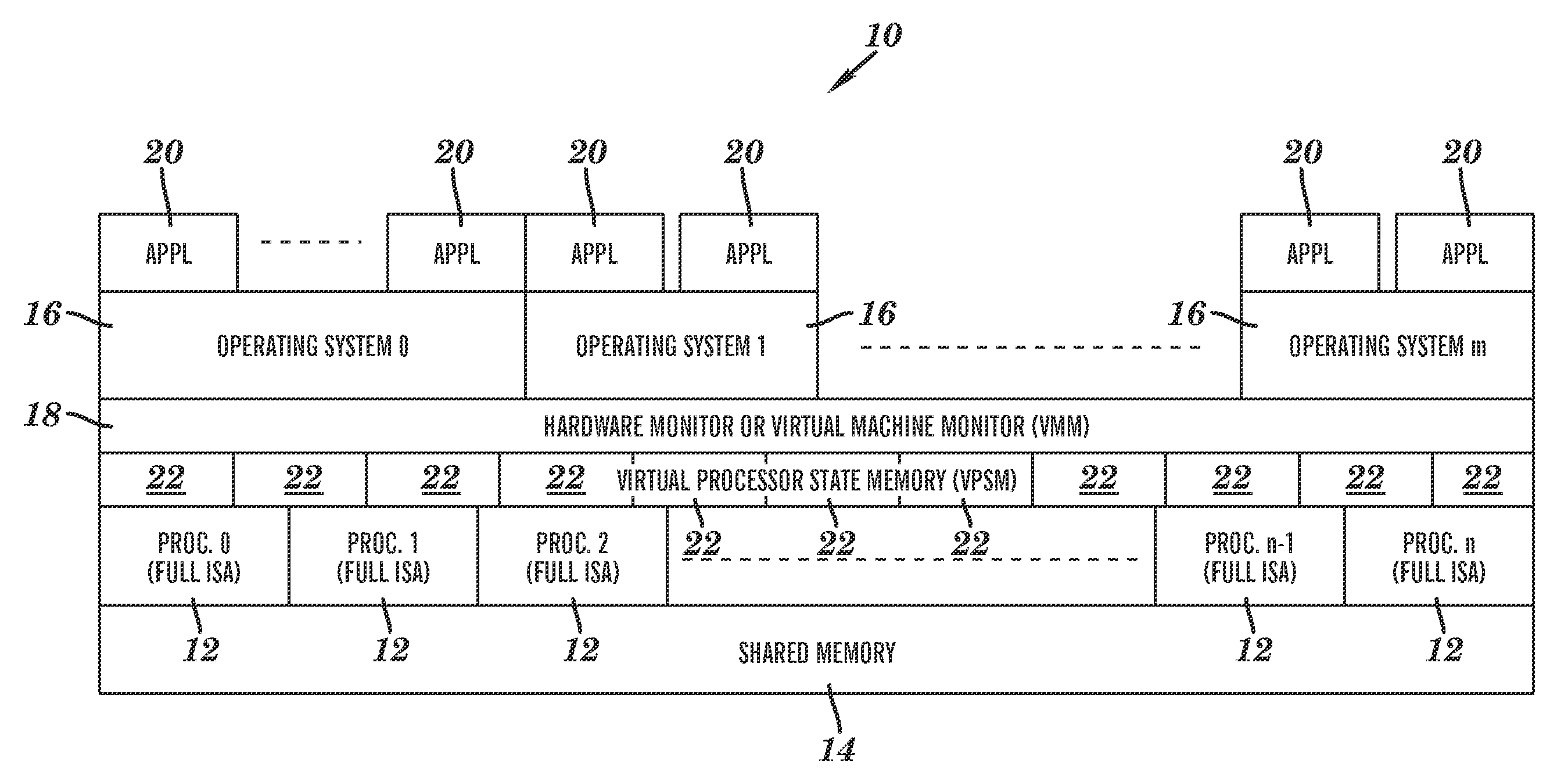

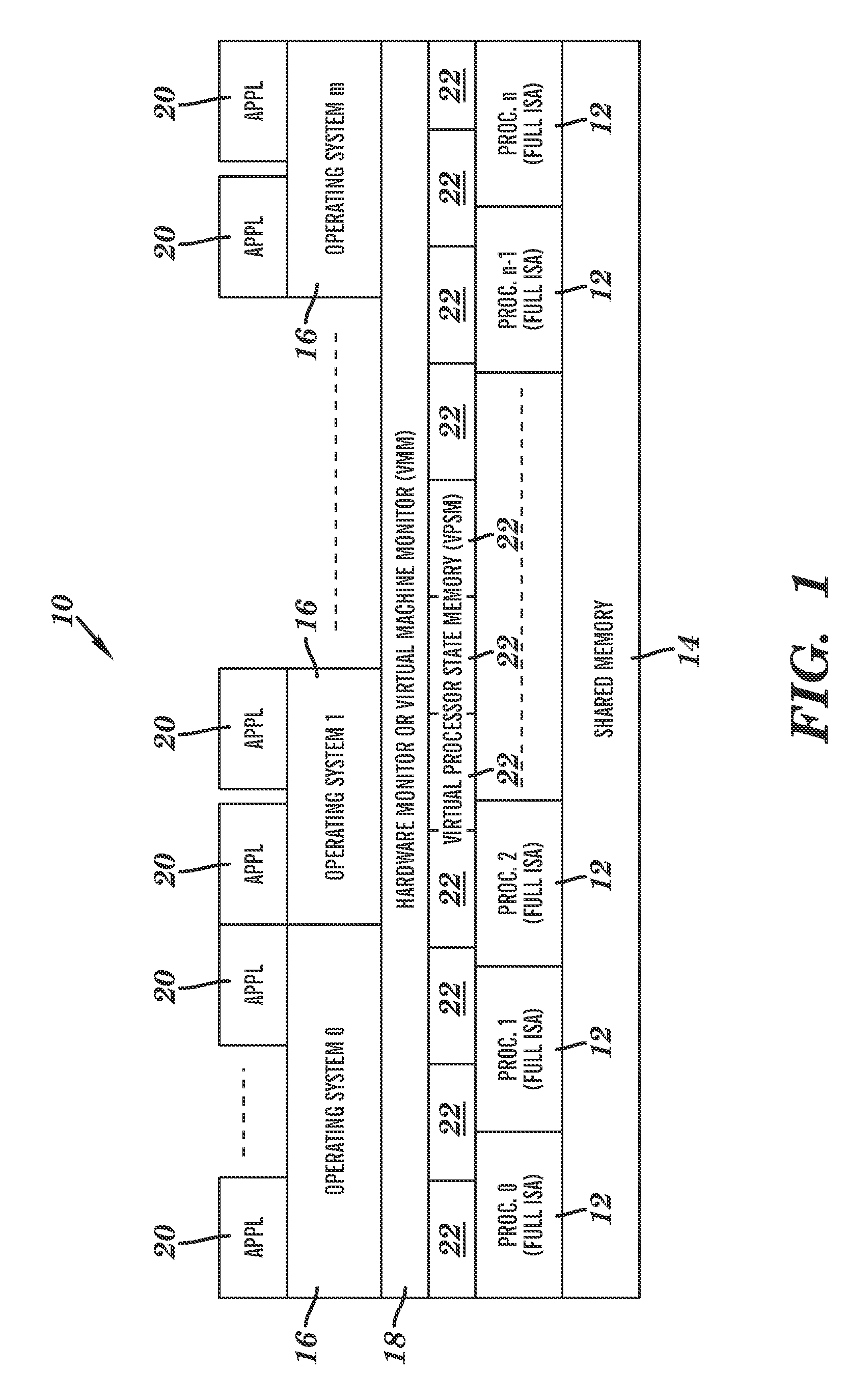

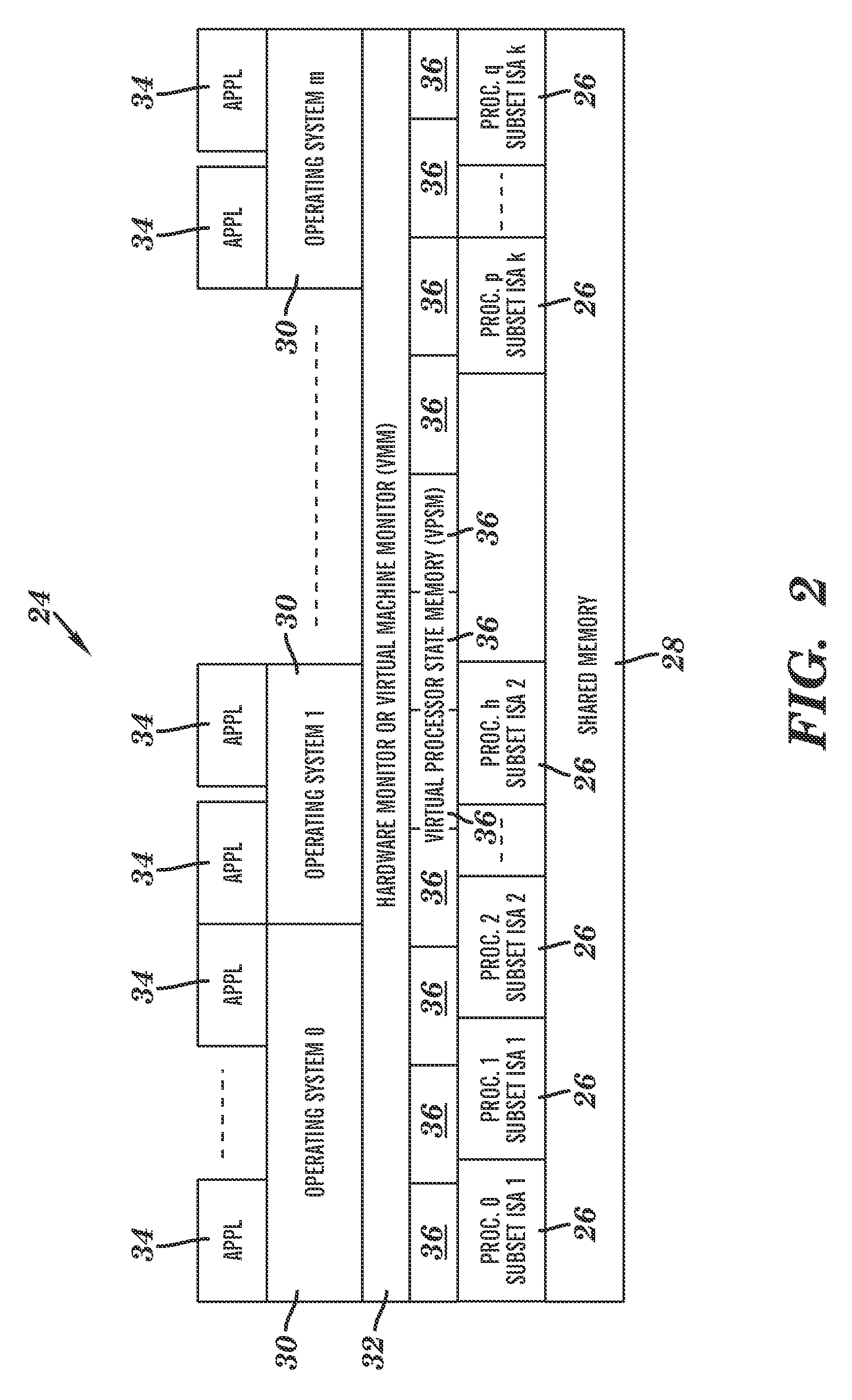

Virtualizing the execution of homogeneous parallel systems on heterogeneous multiprocessor platforms

InactiveUS20080163206A1SavingClosely matchedEnergy efficient ICTError detection/correctionVirtualizationPhysics processing unit

A method of virtual processing includes running a virtual processor (1), which when the virtual processor (1) encounters a faulting instruction unmaps the virtual processor (1) from the physical processor (A), and generates a list of other of the physical processors that could execute the instruction. Then determines if one of the other of the physical processors in the list is currently idle, and when one of the other of the physical processors in the list is determined to be currently idle, maps the virtual processor (1) to a physical processor (B) which is the one of the other of the physical processors in the list that was determined to be currently idle.

Owner:IBM CORP

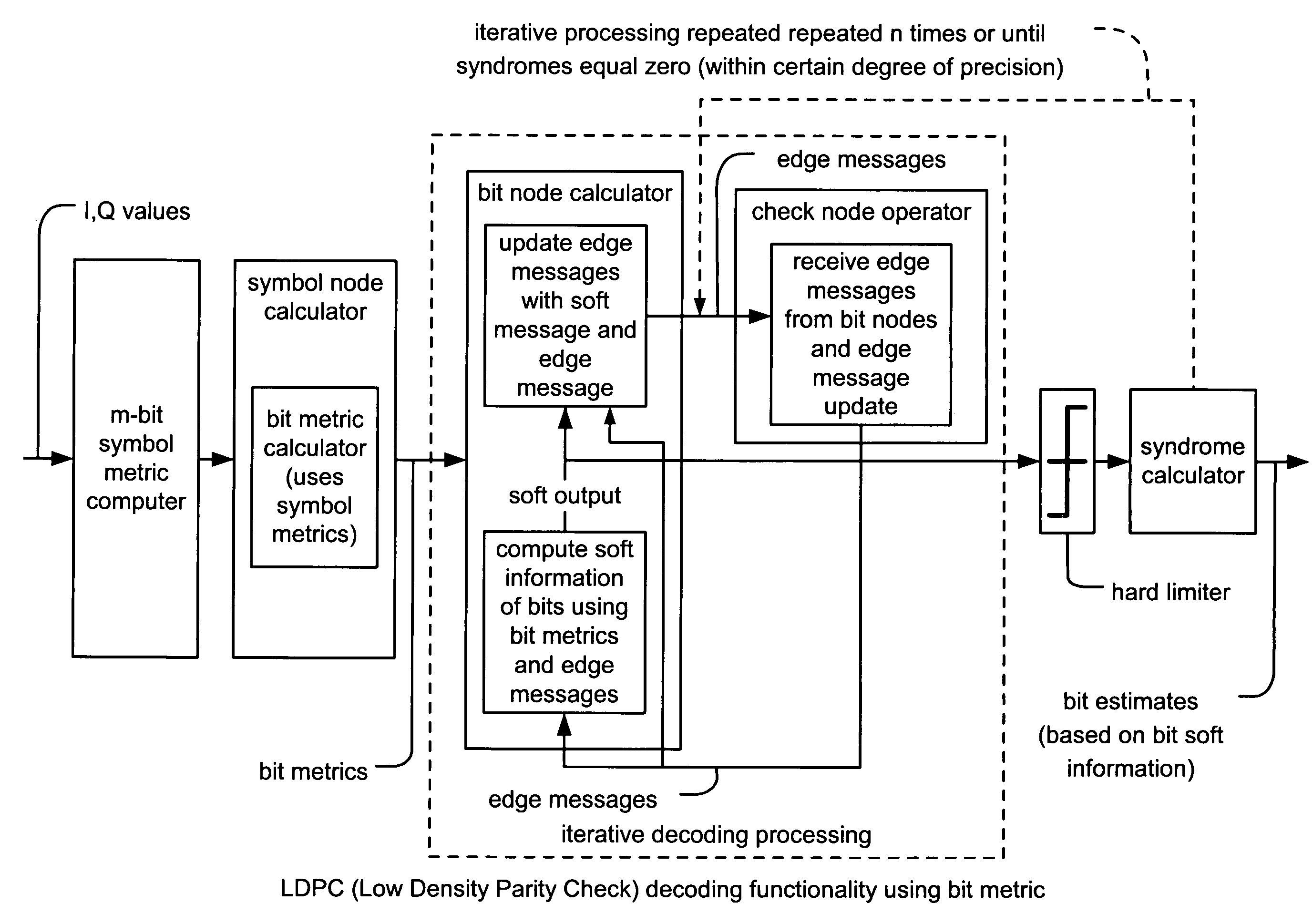

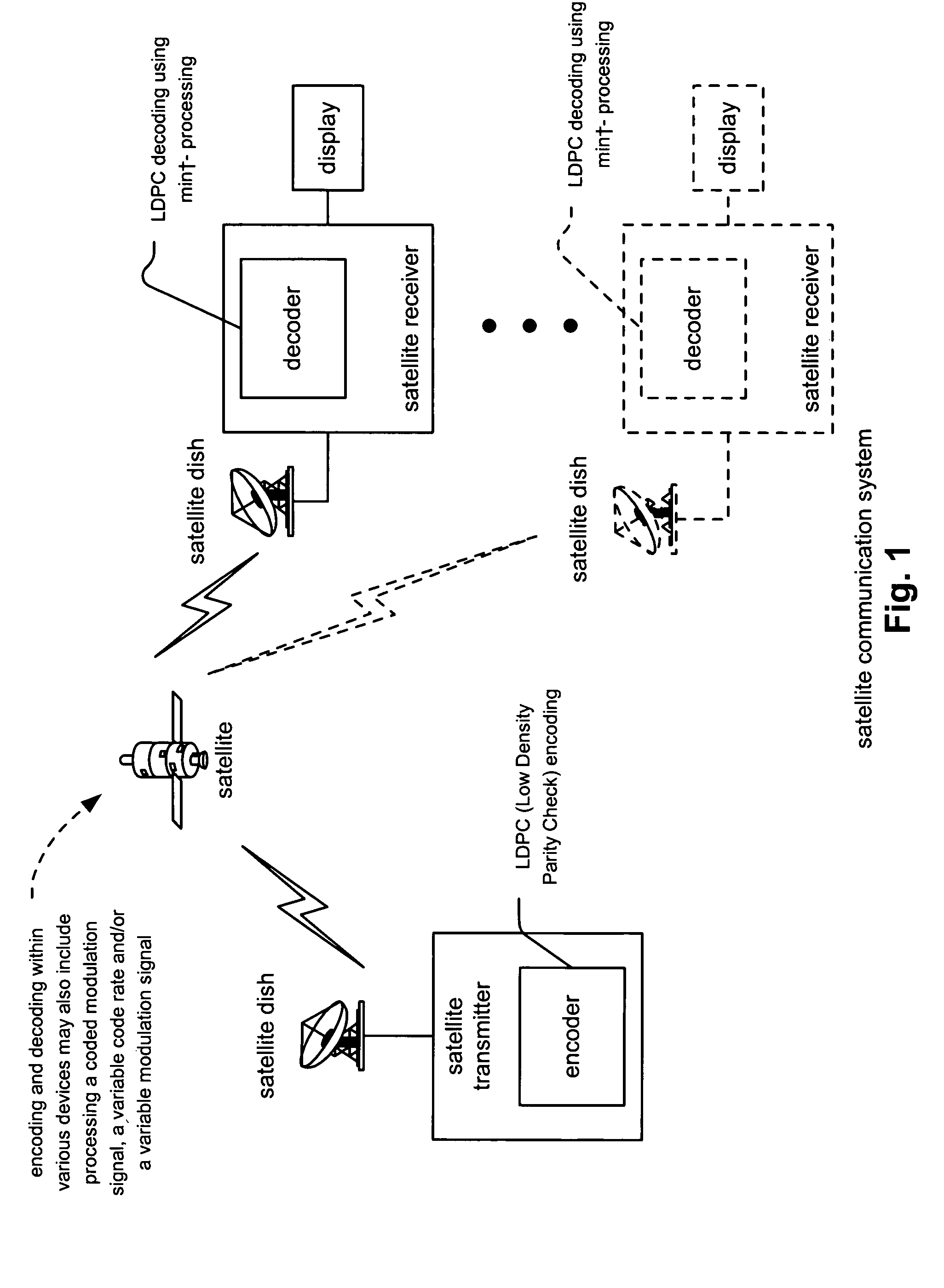

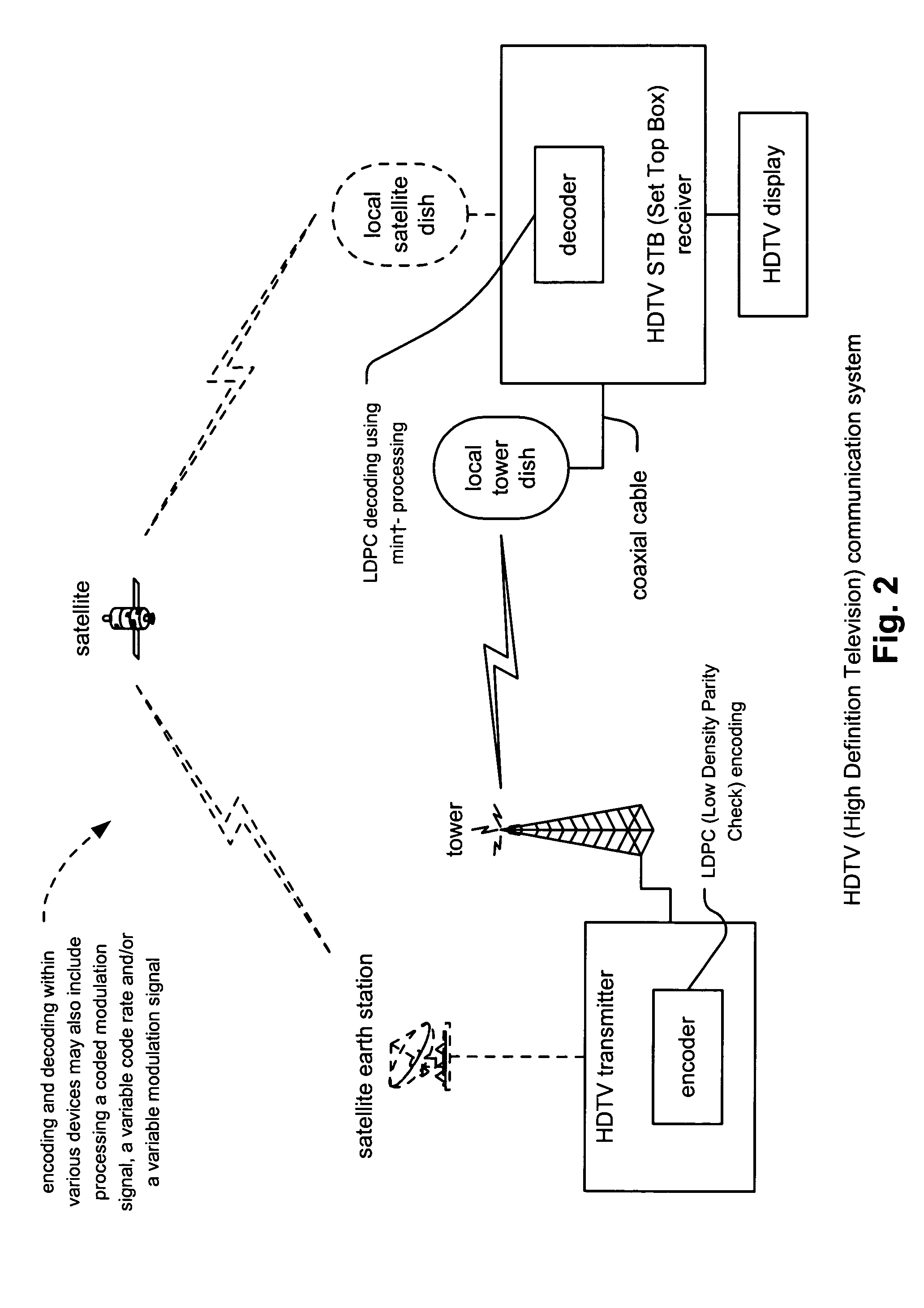

Efficient LDPC code decoding with new minus operator in a finite precision radix system

InactiveUS7149953B2Easy to implementLower latencyError detection/correctionError correction/detection using LDPC codesMathematical OperatorsTheoretical computer science

Efficient LDPC code decoding with new minus operator in a finite precision radix system. A new mathematical operator is introduced and applied to the decoding of LDPC coded signals. This new operator is referred to as the min†− (min-dagger minus) operator herein. This min†− processing is appropriately applied during the updating of the edge messages with respect to the variable nodes. In a bit level decoding approach to decoding LDPC coded signals, the updating of the edge messages with respect to the bit nodes is performed using the new min†− operator. This approach provides very comparable performance to min** processing as also applied to updating of the edge messages with respect to the bit nodes and may also provide for a significant savings in hardware. Also, within finite precision radix systems, the new min†− operator provides a means by which always meaningful results may be achieved during the decoding processing.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Set associative repair cache systems and methods

InactiveUS20060080572A1Reduce sizeLessError detection/correctionStatic storageMemory addressParallel computing

The present invention facilitates scaling of memory devices and operation thereof by employing a set associative repair cache system to correct or repair identified faulty memory cells. A repair cache region router 602 compares a repair region portion of a memory address to repair cache regions to identify a matching repair cache region. Then, a local repair location router 603 compares a repair address portion of the memory address to a local repair location addresses particular to the matching repair cache region to identify a matching local repair address. If a matching local repair address is identified, a repair component 606 provides access to a repair data location according to the matching local repair address and the matching repair cache region. Otherwise, a main memory 604 provides access to a memory location according to the memory address. Other systems and methods are disclosed.

Owner:TEXAS INSTR INC

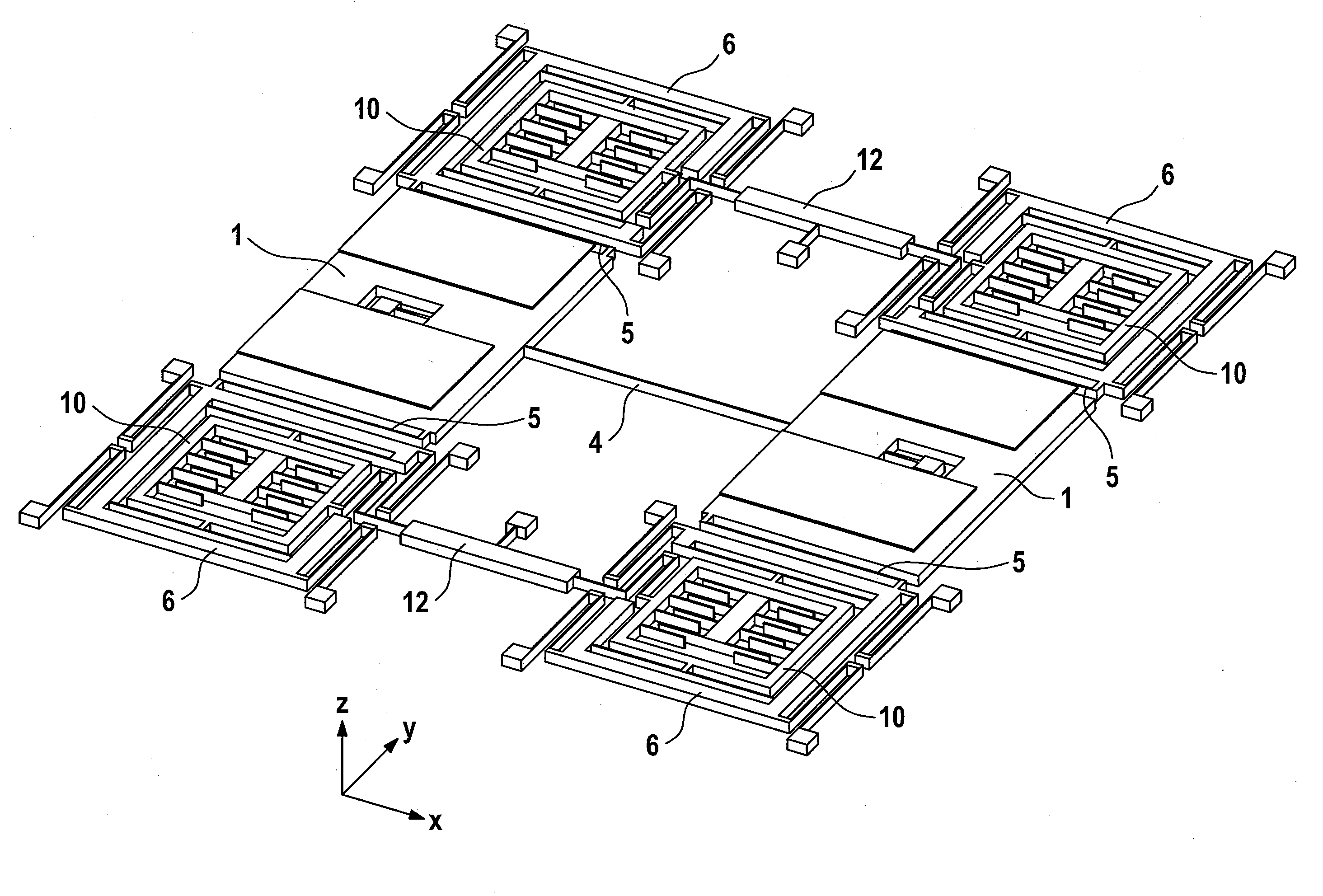

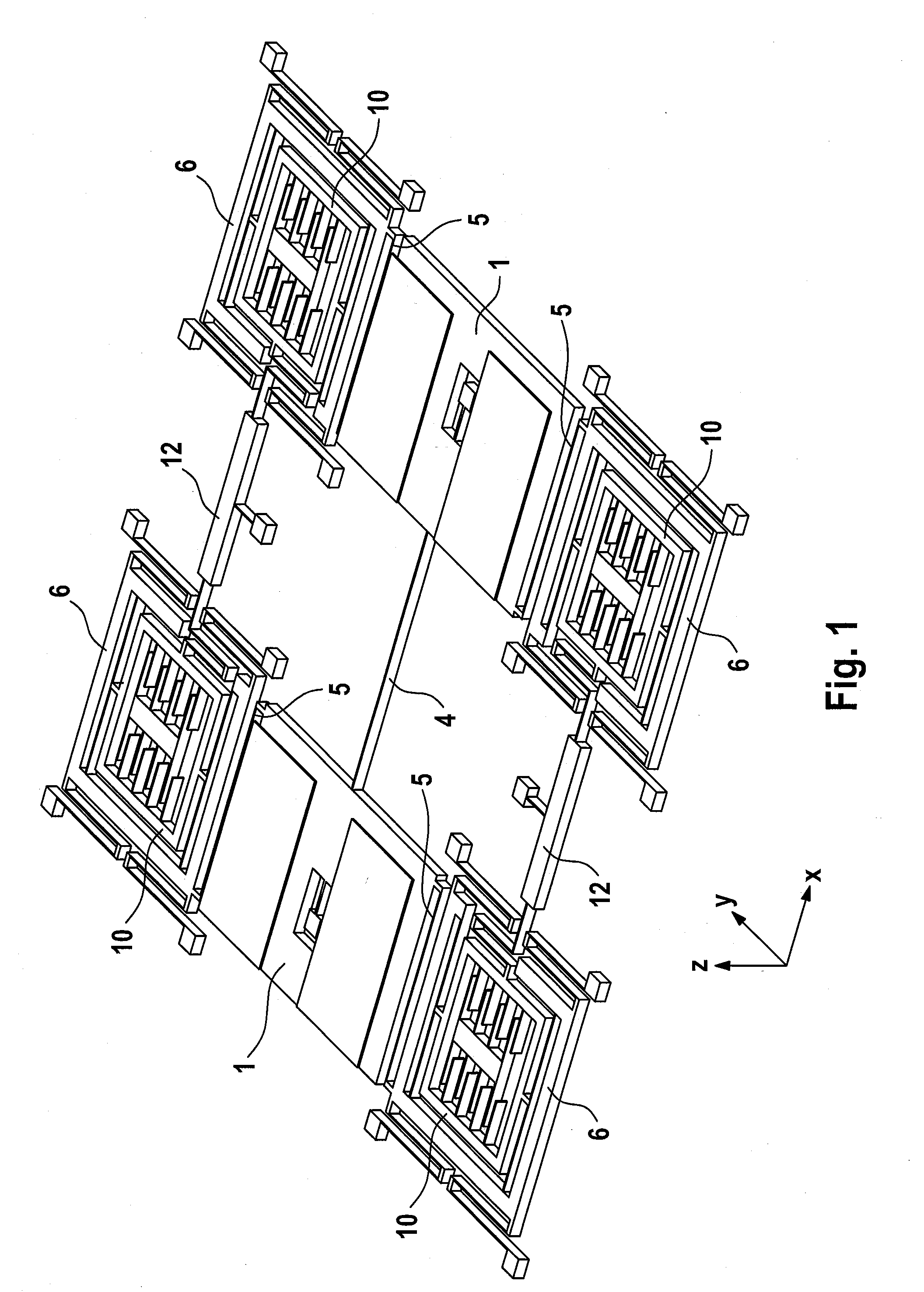

Double-axle, shock-resistant rotation rate sensor with linear and rotary seismic elements

ActiveUS20120210788A1Precise alignmentEasy to operateAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsSeismic massClassical mechanics

A micromechanical rotation rate sensor has at least one first and one second seismic mass coupled to at least one first drive device and are suspended such that the first and second seismic masses are driven such that they are deflected in antiphase in one drive mode, with the rotation rate sensor being designed such that it can detect rotation rates about at least two mutually essentially orthogonal sensitive axes, wherein at least the first and second seismic masses are designed and suspended such that they oscillate in antiphase in a first read mode when a first rotation rate about the first sensitive axis is detected, and the first and second seismic masses and / or additional seismic masses are designed and suspended such that they oscillate in antiphase in a second read mode when a second rotation rate about the second sensitive axis is detected.

Owner:CONTINENTAL TEVES AG & CO OHG

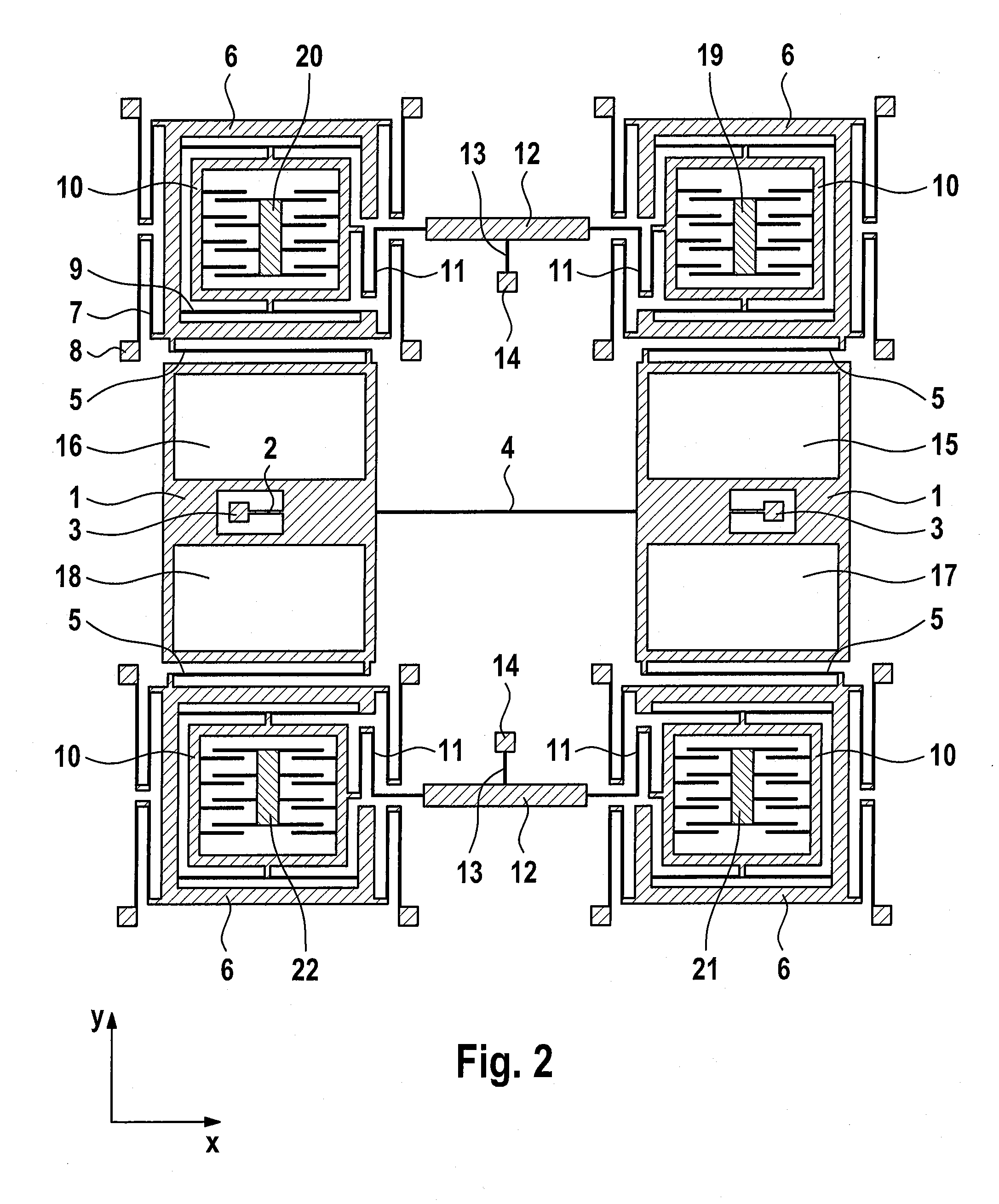

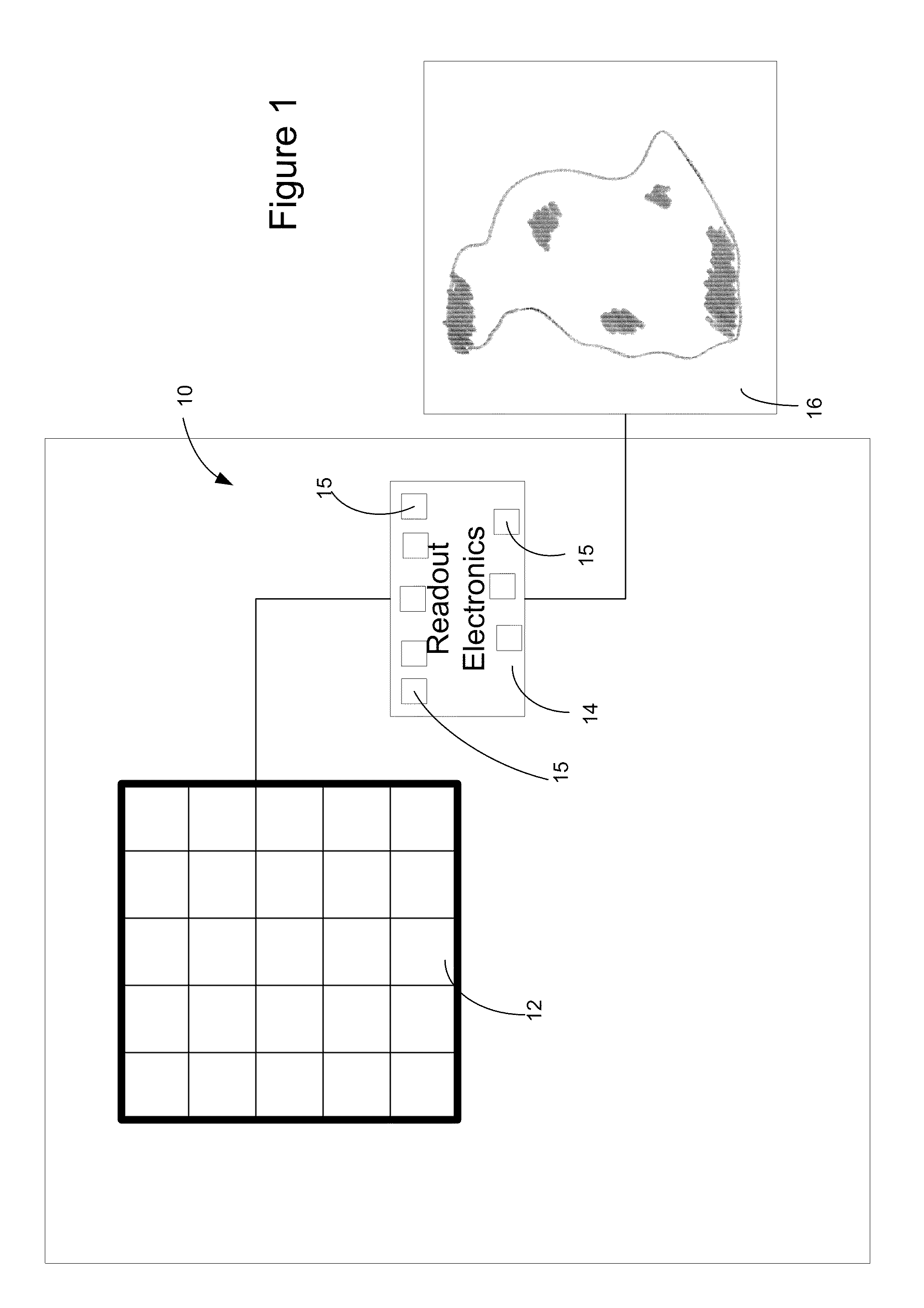

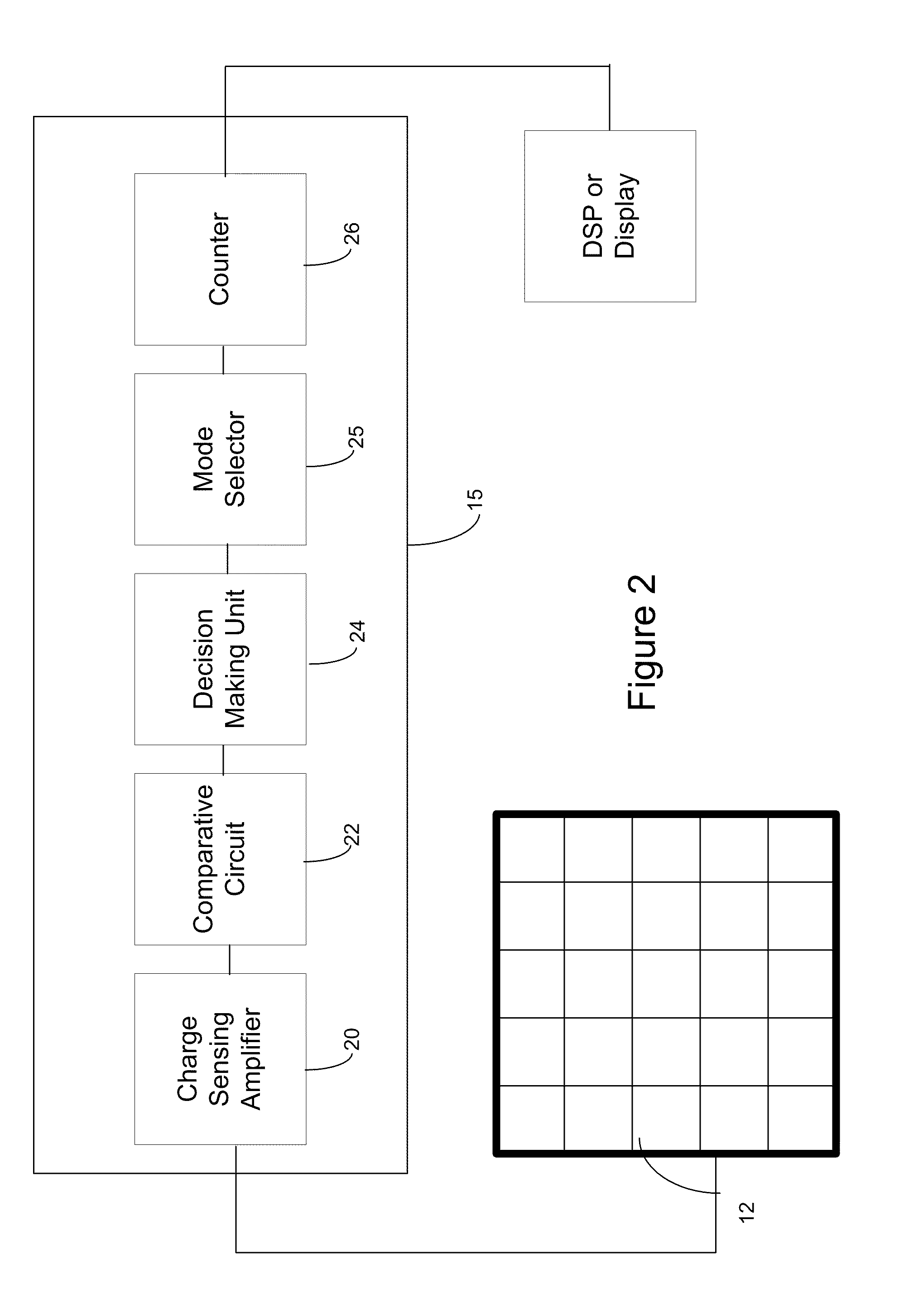

Digitizer for a digital imaging system

InactiveUS20100181491A1Excellent contrast ratioImprove signal-to-noise ratioTelevision system detailsMaterial analysis by optical meansPhysicsPhoton flux

The disclosure is directed at a method of digital imaging comprising sensing photons on at least one pixel within a pixel array of a radiation detector; counting the photons using photon counting to produce a digital signal representative of the sensed photons; monitoring a photon flux associated with the sensed photons; and using photon integration to produce a digital signal representative of the sensed photons when the photon flux is higher than a predetermined photon flux.

Owner:KARIM KARIM S +2

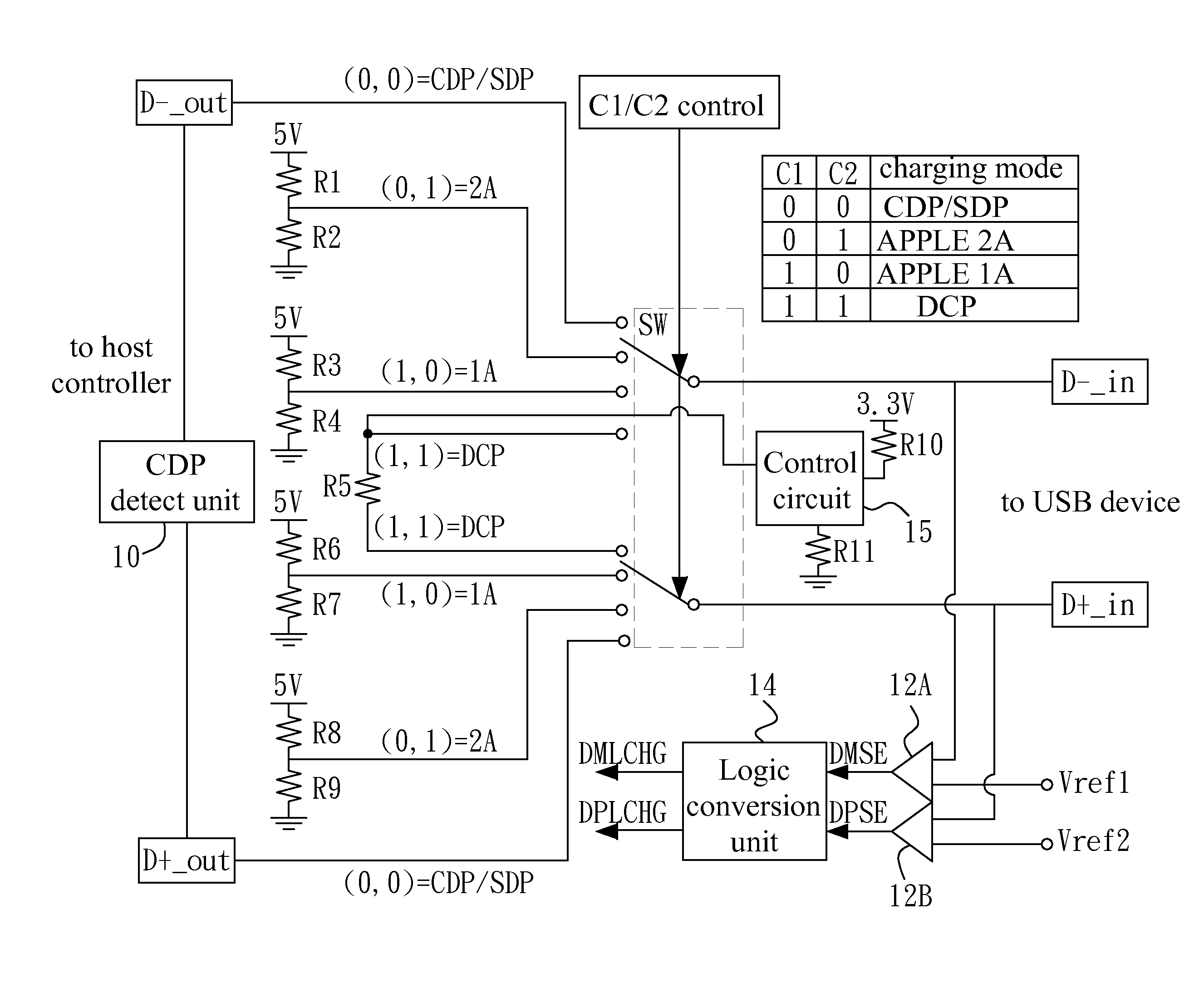

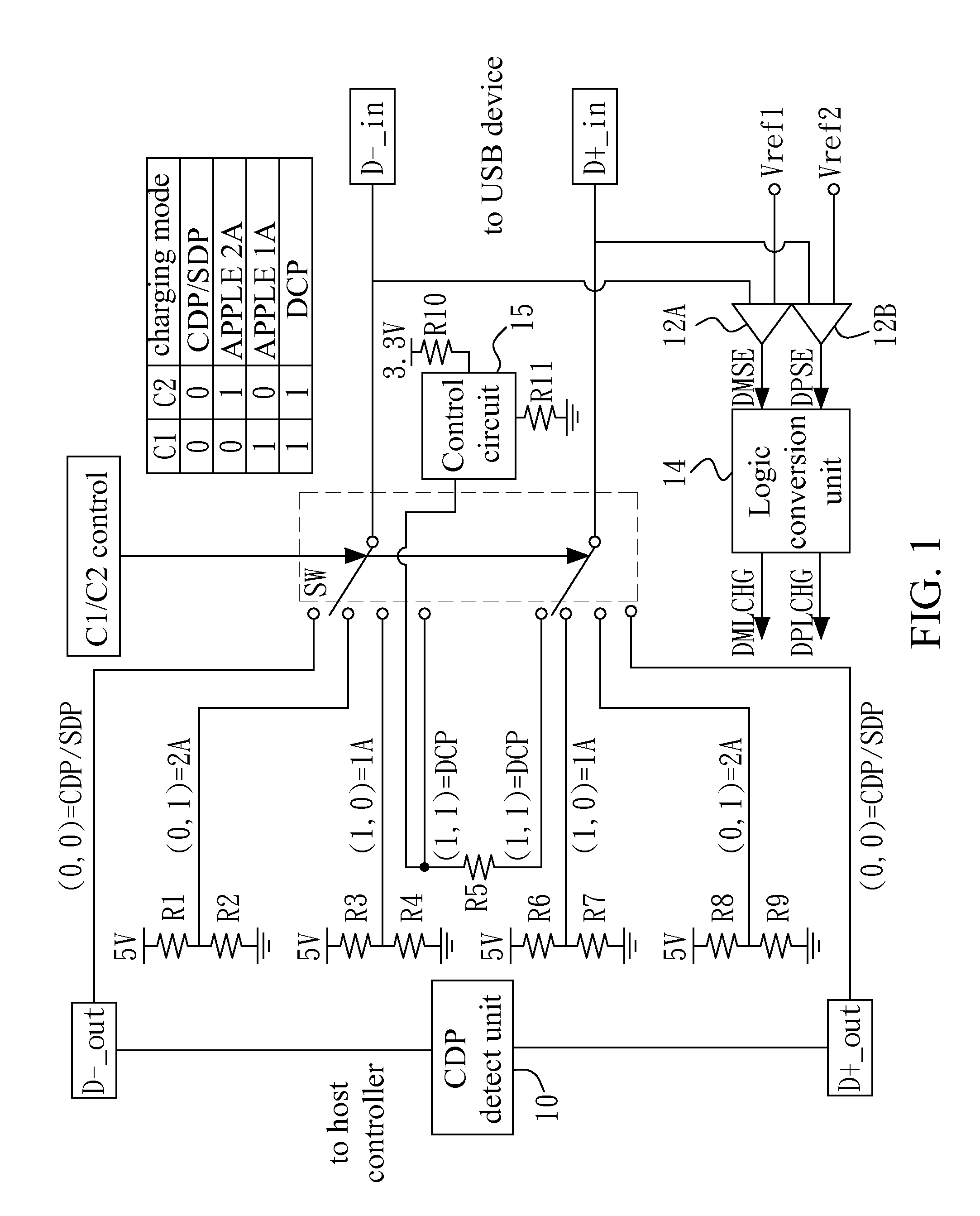

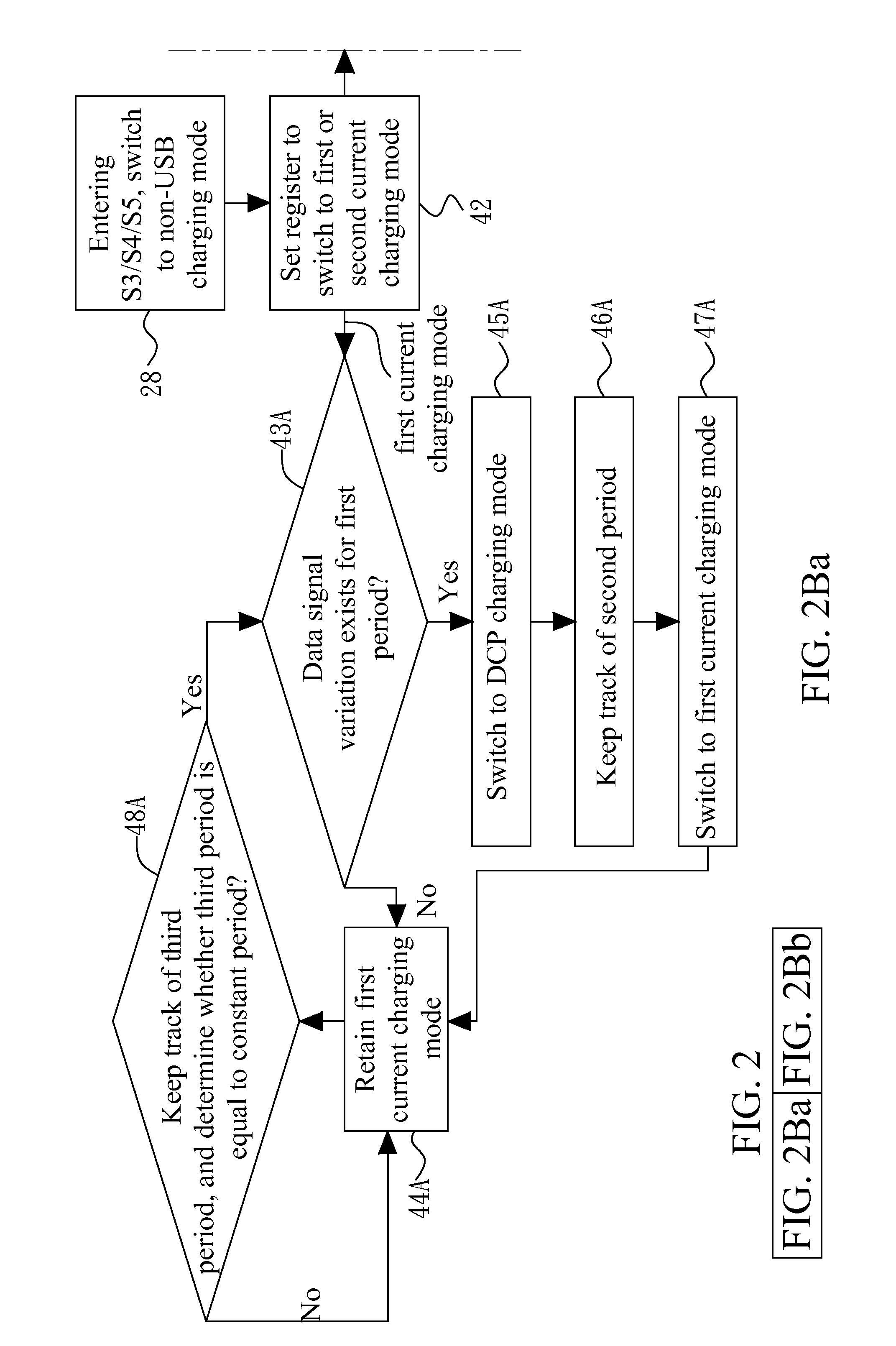

Adaptive USB charging method and system

ActiveUS20120210146A1Saving circuit areaSaving associated manufacturing costVolume/mass flow measurementPower supply for data processingData signalUSB

An adaptive universal serial bus (USB) charging method and system are disclosed. In a low-power state, a USB device is charged with a non-USB charging mode. The non-USB charging mode is retained when no variation of a data signal coupled to the USB device is detected. When the data signal possesses variation for a first period, it is switched to a third proprietary charging mode.

Owner:VIA LABS INC

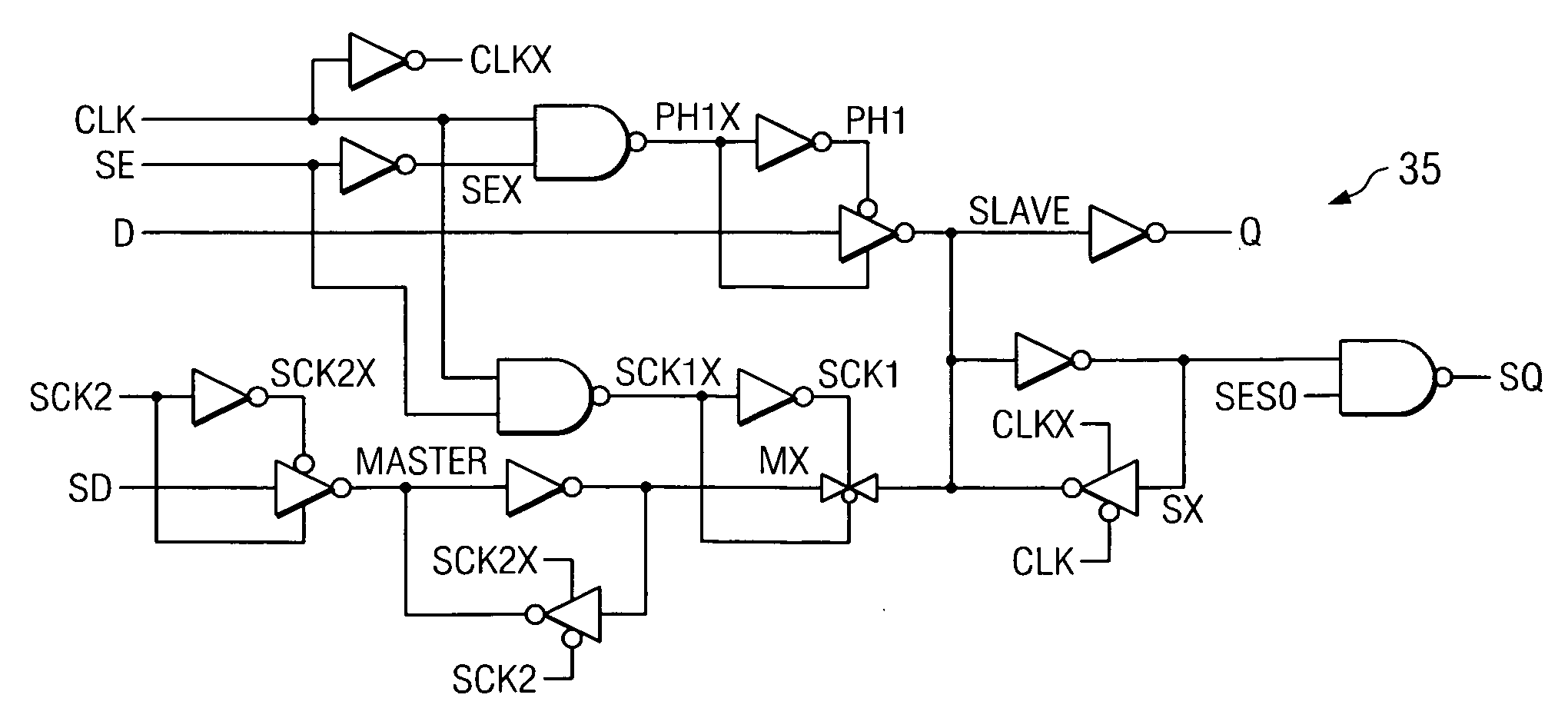

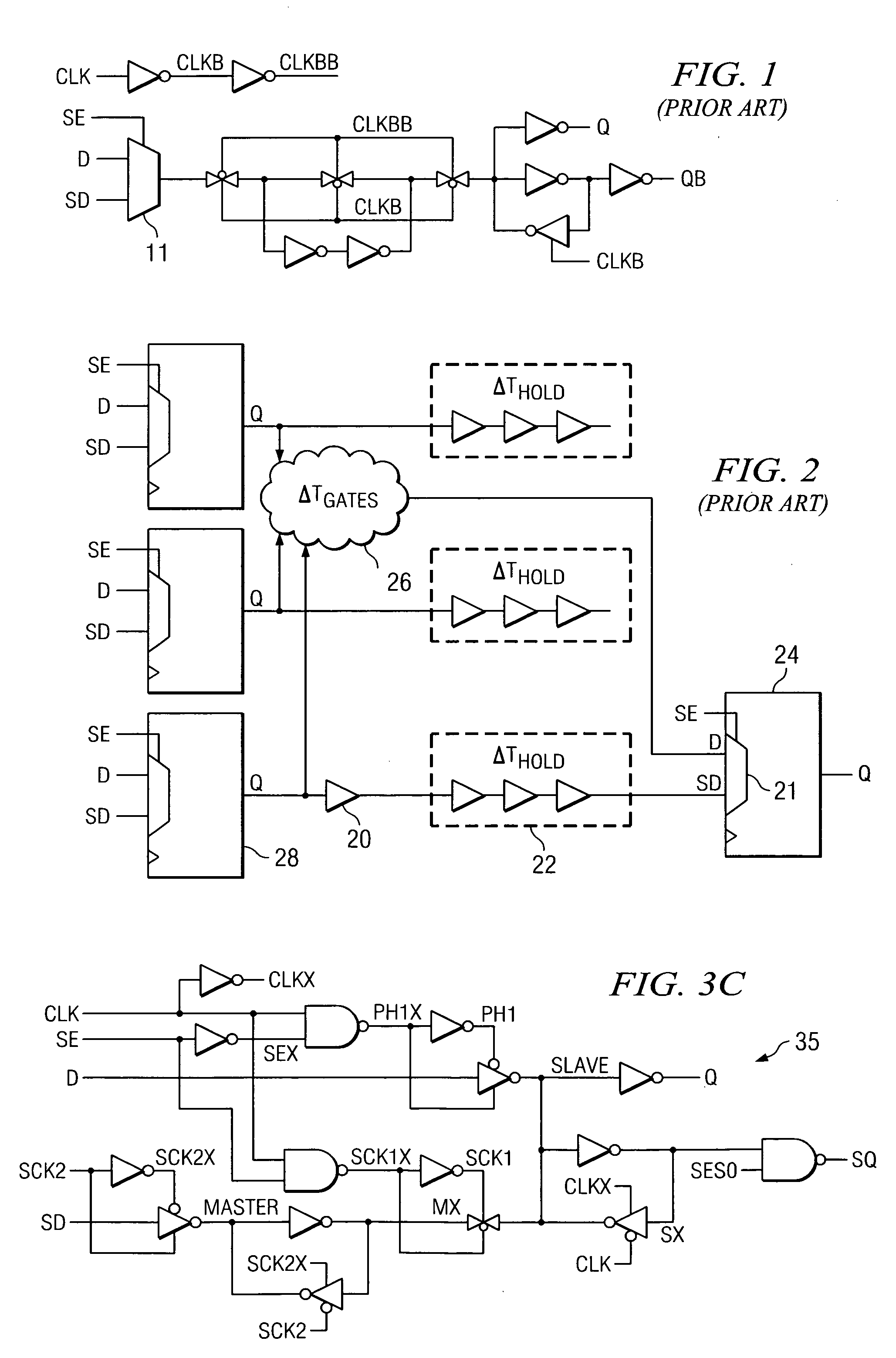

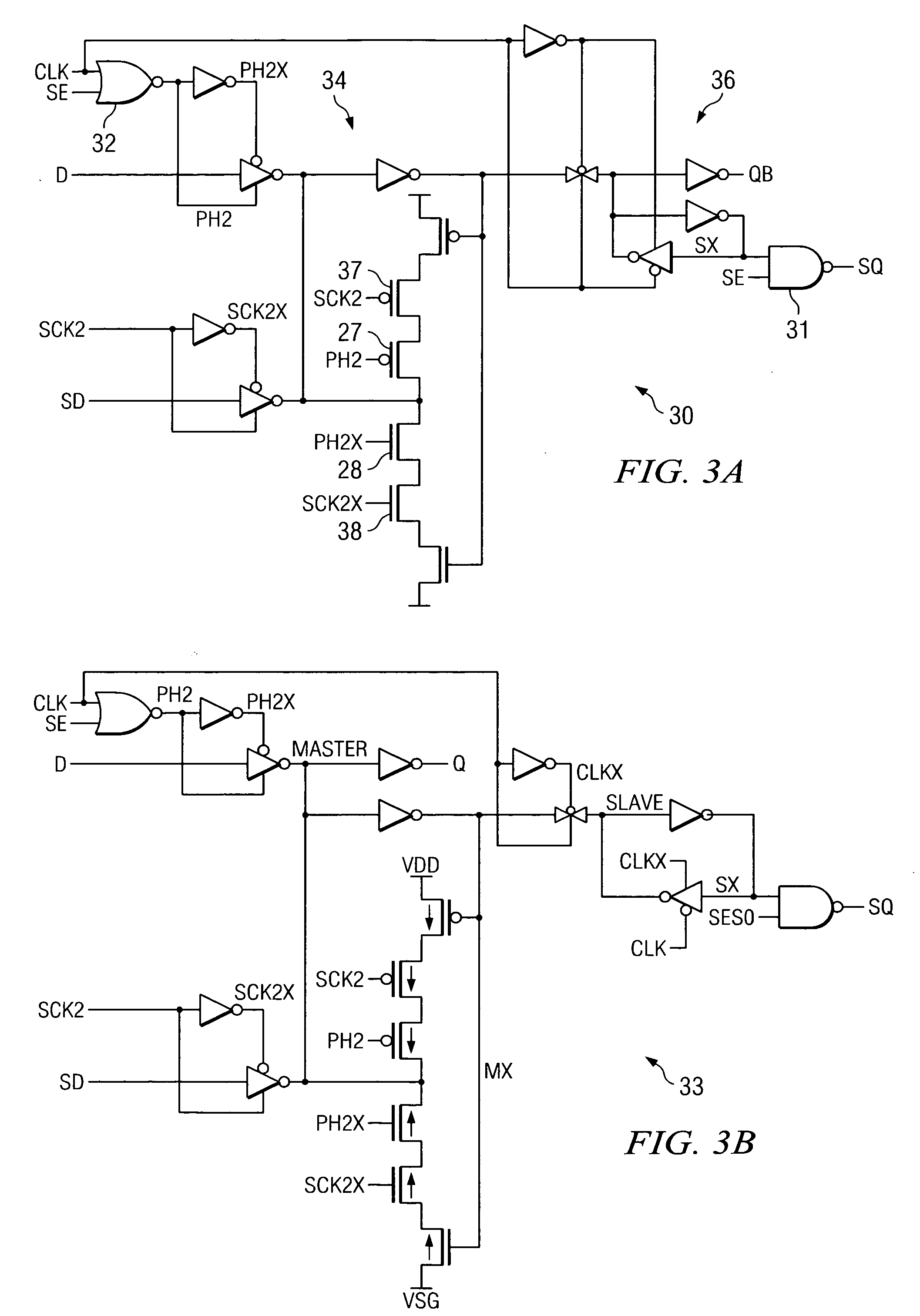

Digital design component with scan clock generation

A master and a slave stage of a flip-flop are each separately clocked with non-overlapping clock signals during scan mode to eliminate a data input scan mode multiplexer. Separate, non-overlapping clocking permits the elimination of hold violations in scan mode for scan mode flip flop chains, permitting the elimination of delay buffers in the scan mode data paths. Resulting application circuits have reduced circuit area, power consumption and noise generation. A clock generator for scan mode clocking is provided to obtain the separate, non-overlapping scan mode clocks. Scan mode clocks may be generated with a toggle flip flop, a pulse generator or a clock gating circuit.

Owner:TEXAS INSTR INC

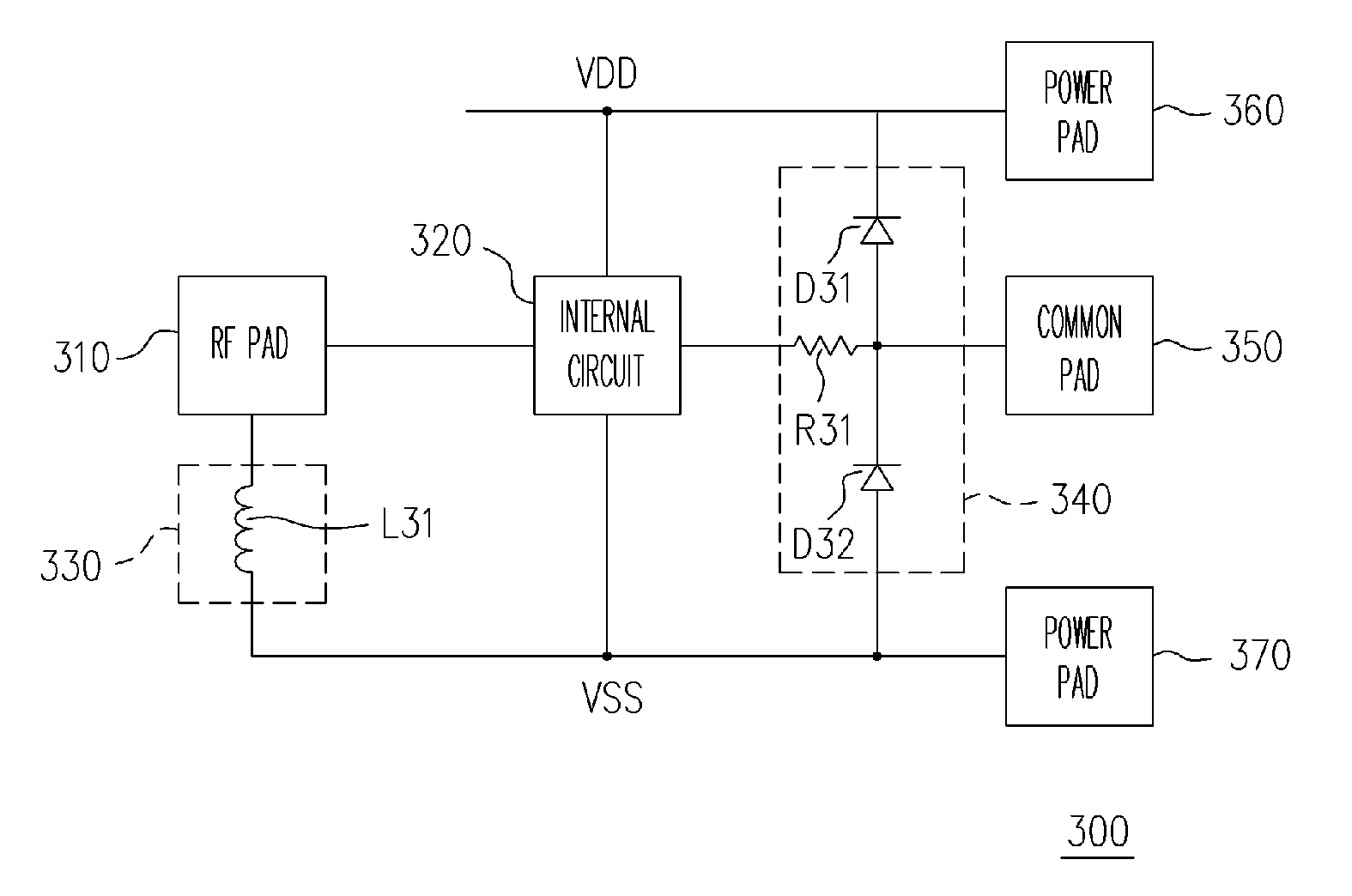

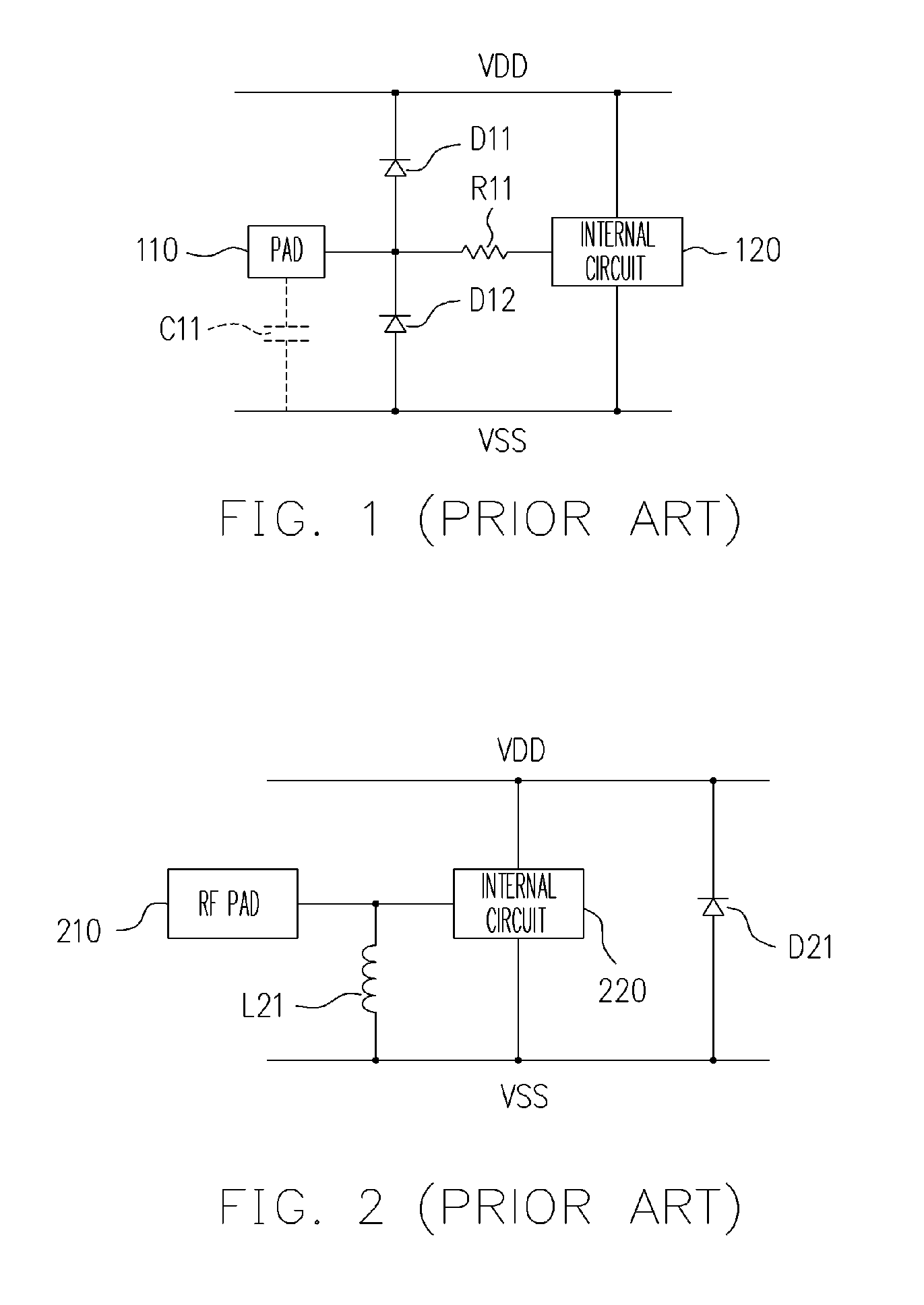

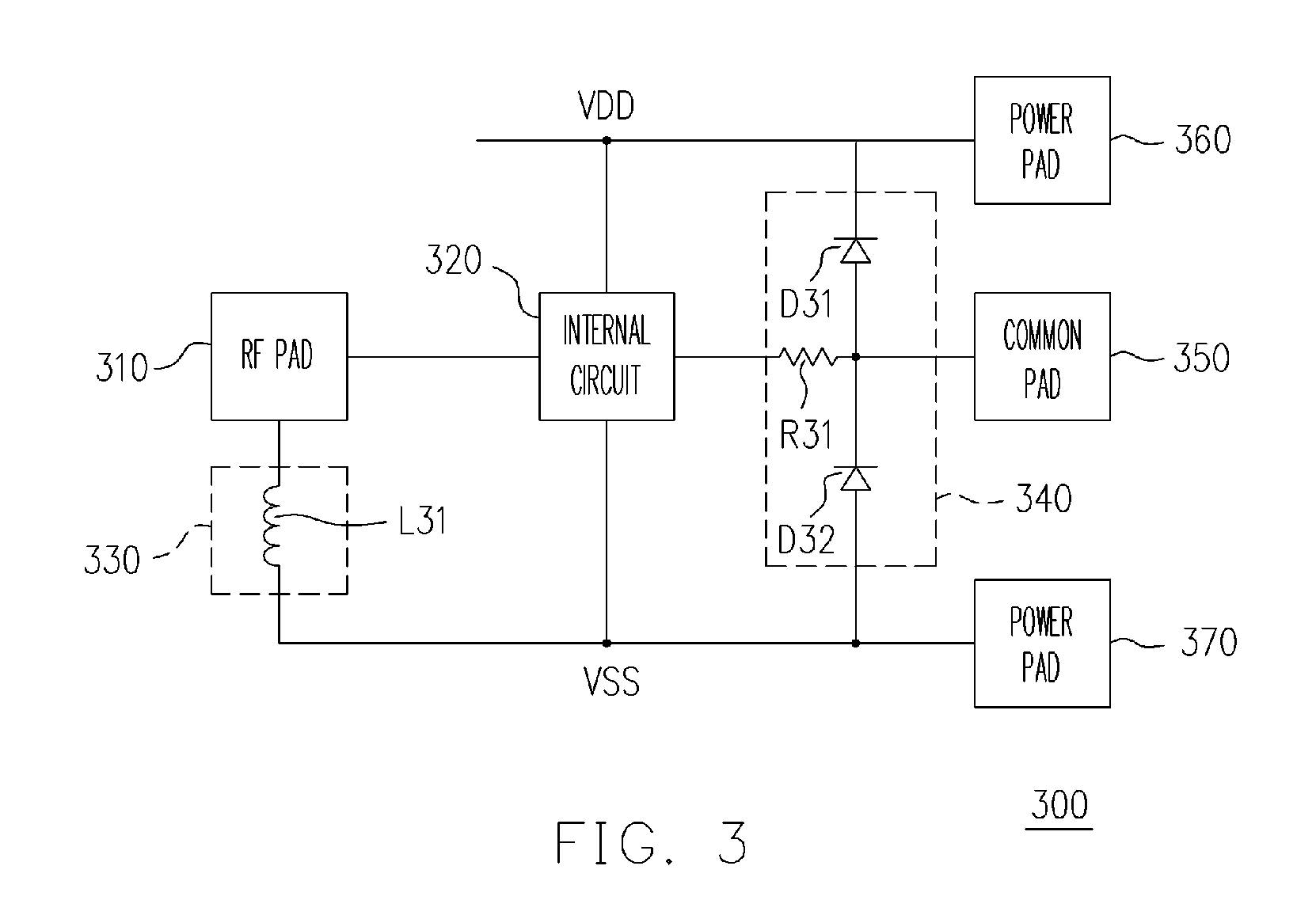

RF integrated circuit with ESD protection and ESD protection apparatus thereof

InactiveUS20070296055A1Save chip areaReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesEngineeringInductor

A radio frequency (RF) integrated circuit with electrostatic discharge (ESD) protection and an ESD protection apparatus thereof are provided. The ESD protection apparatus includes a substrate, an RF bonding pad, and an ESD protection unit. The RF bonding pad for transmitting RF signal is disposed upon the substrate. The ESD protection unit is disposed under the RF bonding pad. Wherein, The ESD protection unit includes an inductor electrically connected between the RF bonding pad and the power rail.

Owner:UNITED MICROELECTRONICS CORP

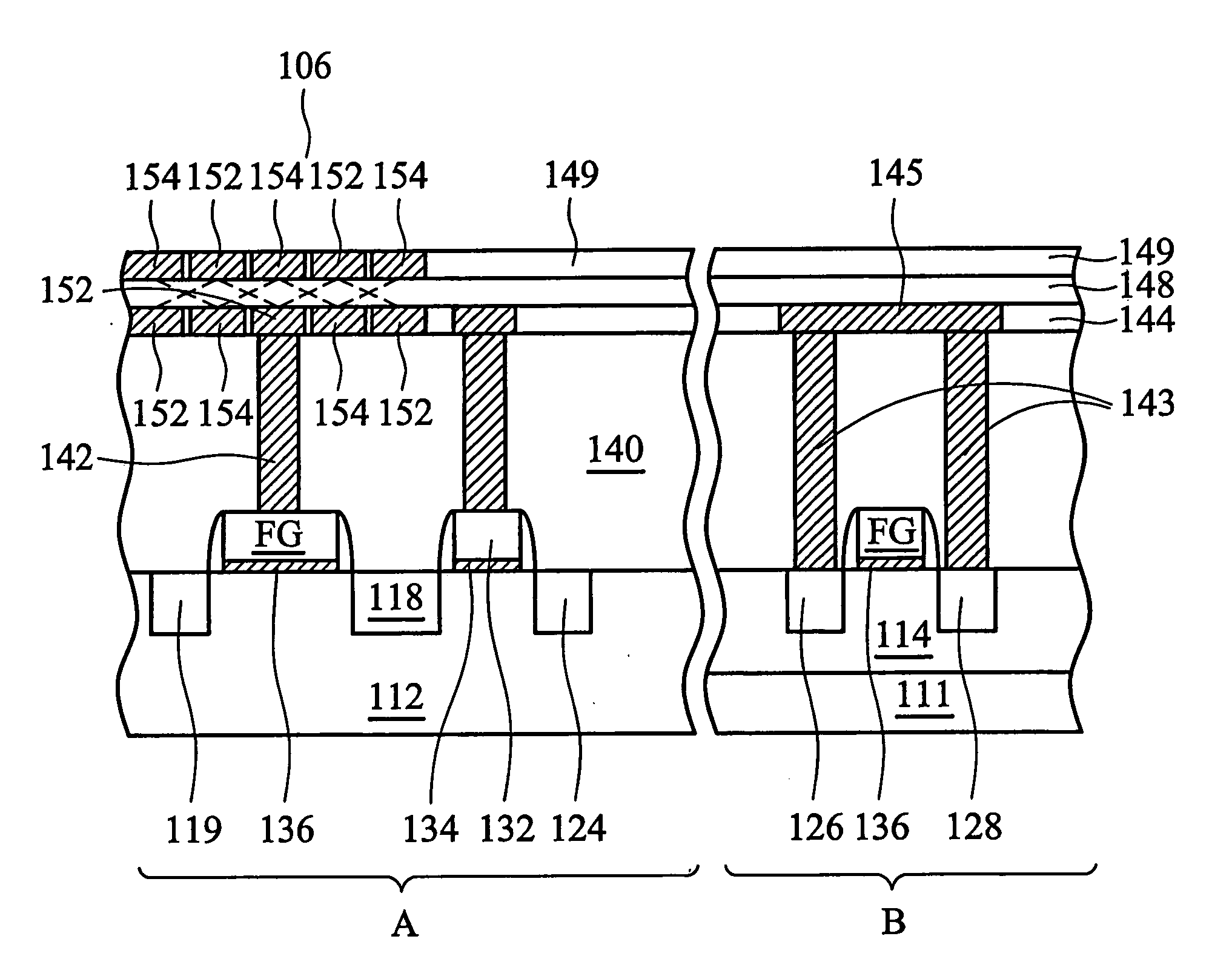

Logic compatible storage device

InactiveUS20080006868A1Save chip areaTotal current dropSolid-state devicesRead-only memoriesCapacitorSemiconductor

A non-volatile memory cell and a method of manufacturing the same are provided. The non-volatile memory cell includes a floating gate over a semiconductor substrate, a first capacitor comprising a first plate, the floating gate, and a dielectric therebetween, a second capacitor comprising a second plate, the floating gate, and a dielectric therebetween, a third capacitor comprising a third plate connected to the floating gate, and a fourth plate, wherein the third and fourth plates are formed in metallization layers over the semiconductor substrate. The first plate of the first capacitor includes a first doped region and a second doped region in the semiconductor substrate. The non-volatile memory cell further includes a transistor comprising a gate electrode over the semiconductor substrate, wherein a source / drain region of the transistor is connected to the first doped region of the first capacitor.

Owner:TAIWAN SEMICON MFG CO LTD

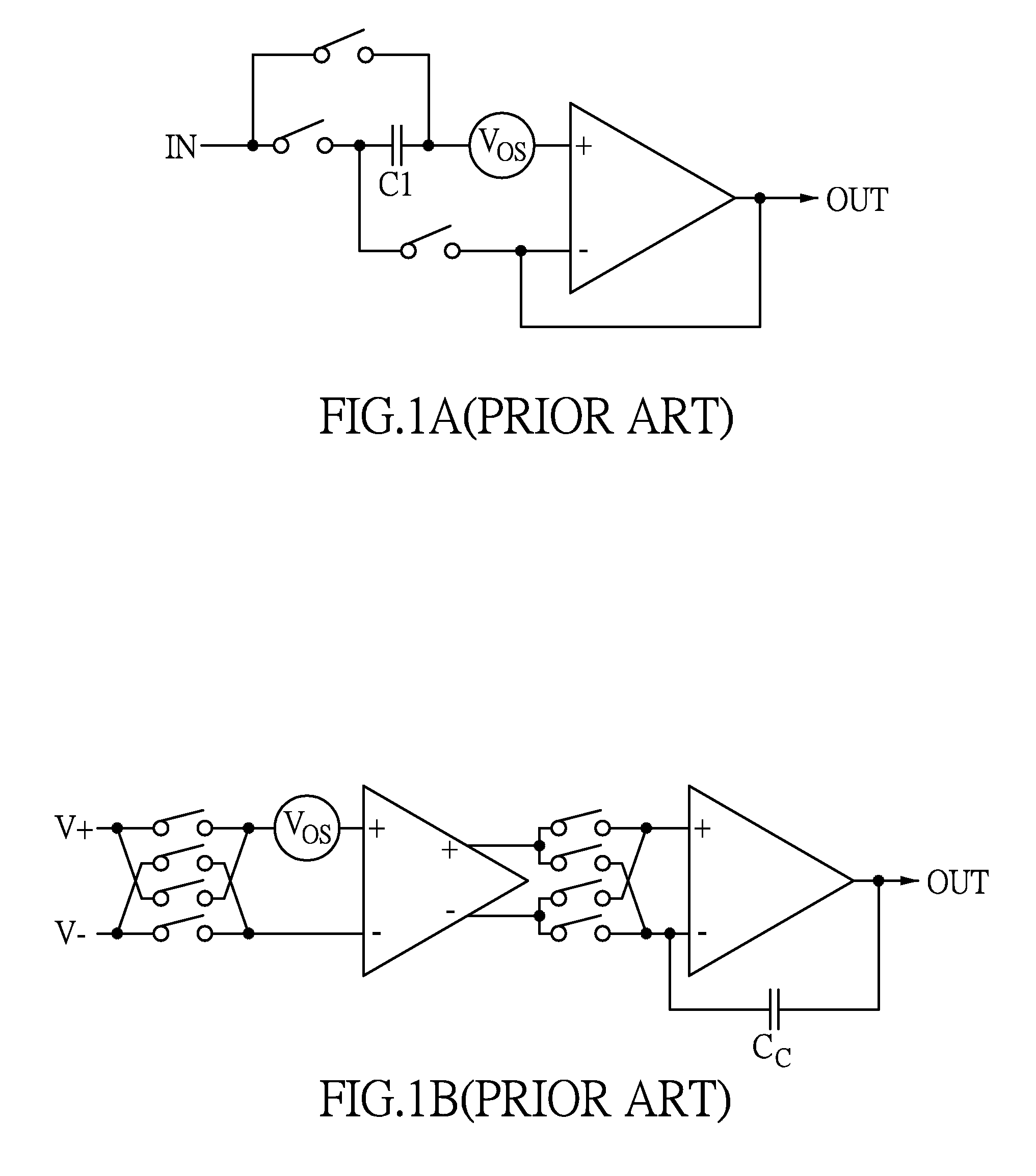

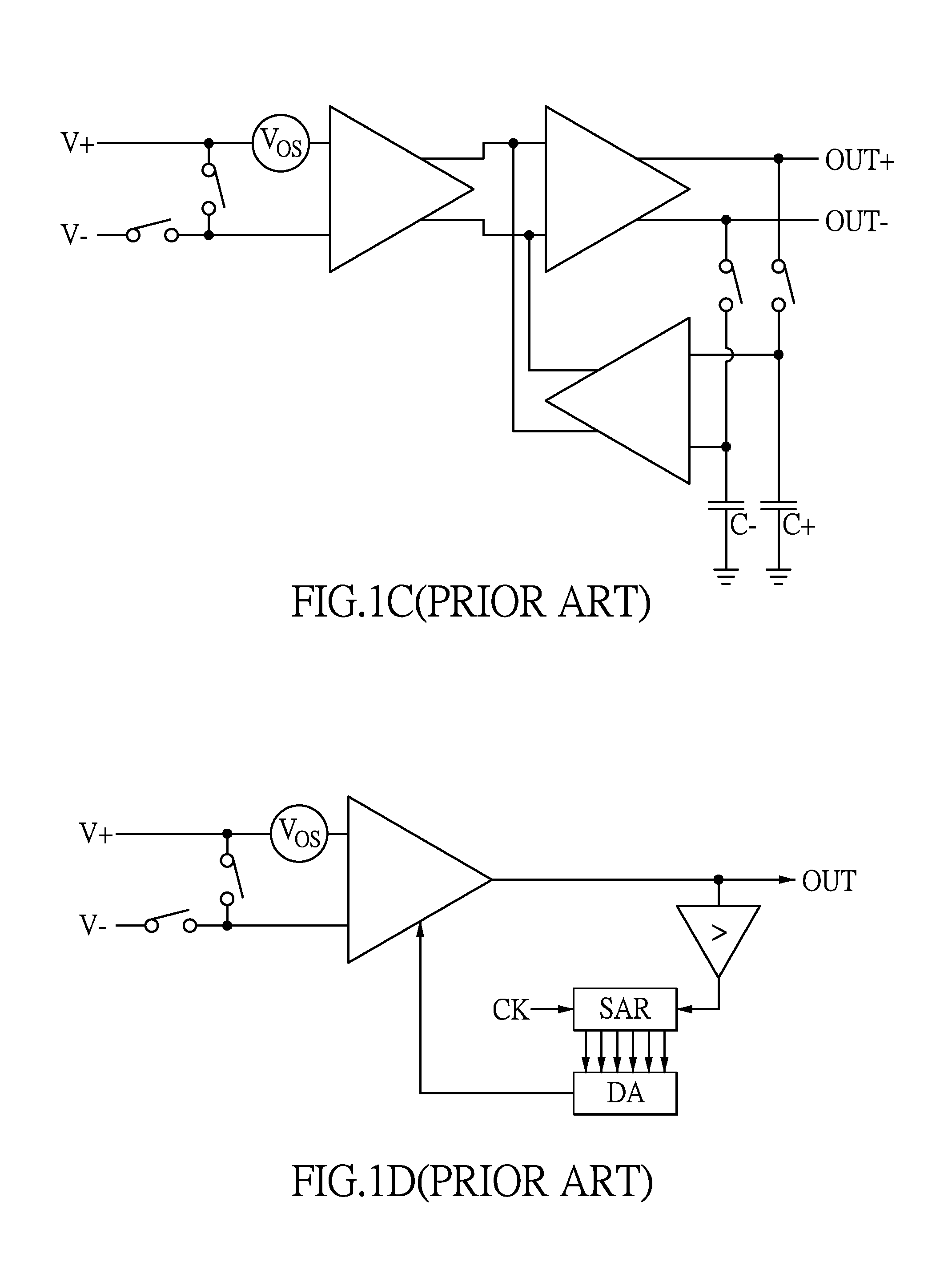

Drive circuit of organic light emitting display and offset voltage adjustment unit thereof

InactiveUS20150035813A1Improve display qualitySave chip areaCathode-ray tube indicatorsDifferential amplifiersDriver circuitAudio power amplifier

A drive circuit of an organic light emitting display and an offset voltage adjustment unit thereof are provided. The offset voltage adjustment unit can be used in an operational amplifier of the drive circuit having a differential input stage, a bias stage, and an output stage. The offset voltage adjustment unit coupled between the bias stage and a ground including a resistor string and a plurality of latch units. The resistor string has a first-end, a second-end, and a plurality of resistors series-connected between the first-end and the second-end forming a plurality of junctions. The latch units are coupled between the junctions and the ground, respectively. The latch units are sequentially conducted to adjust a bias current of the bias stage according to a control signal. The latch units enter a latch state upon receiving a latch signal to calibrate an output offset voltage of the operational amplifier.

Owner:INTEGRATED SOLUTIONS TECH

Software emulation of directed exceptions in a multithreading processor

ActiveUS7849297B2More scalableSave areaDigital computer detailsProgram loading/initiatingGeneral purposeSoftware emulation

A multithreading microprocessor has a plurality of thread contexts (TCs) each including sufficient state, such as general purpose registers and program counter, to execute a separate thread of execution as one of a plurality of symmetric processors controlled by a multiprocessor operating system. However, the microprocessor hardware does not support the ability for one TC to direct an exception to another TC, i.e., to specify to which of the other TCs the exception is directed. A first thread running on a first TC of the operating system executes architected instructions to halt a second thread (either user or kernel thread) running on a second TC, save state of the second TC, write the second TC state to emulate an exception—including writing a restart register with the address of an exception handler, and unhalt the second TC to execute the exception hander.

Owner:MIPS TECH INC

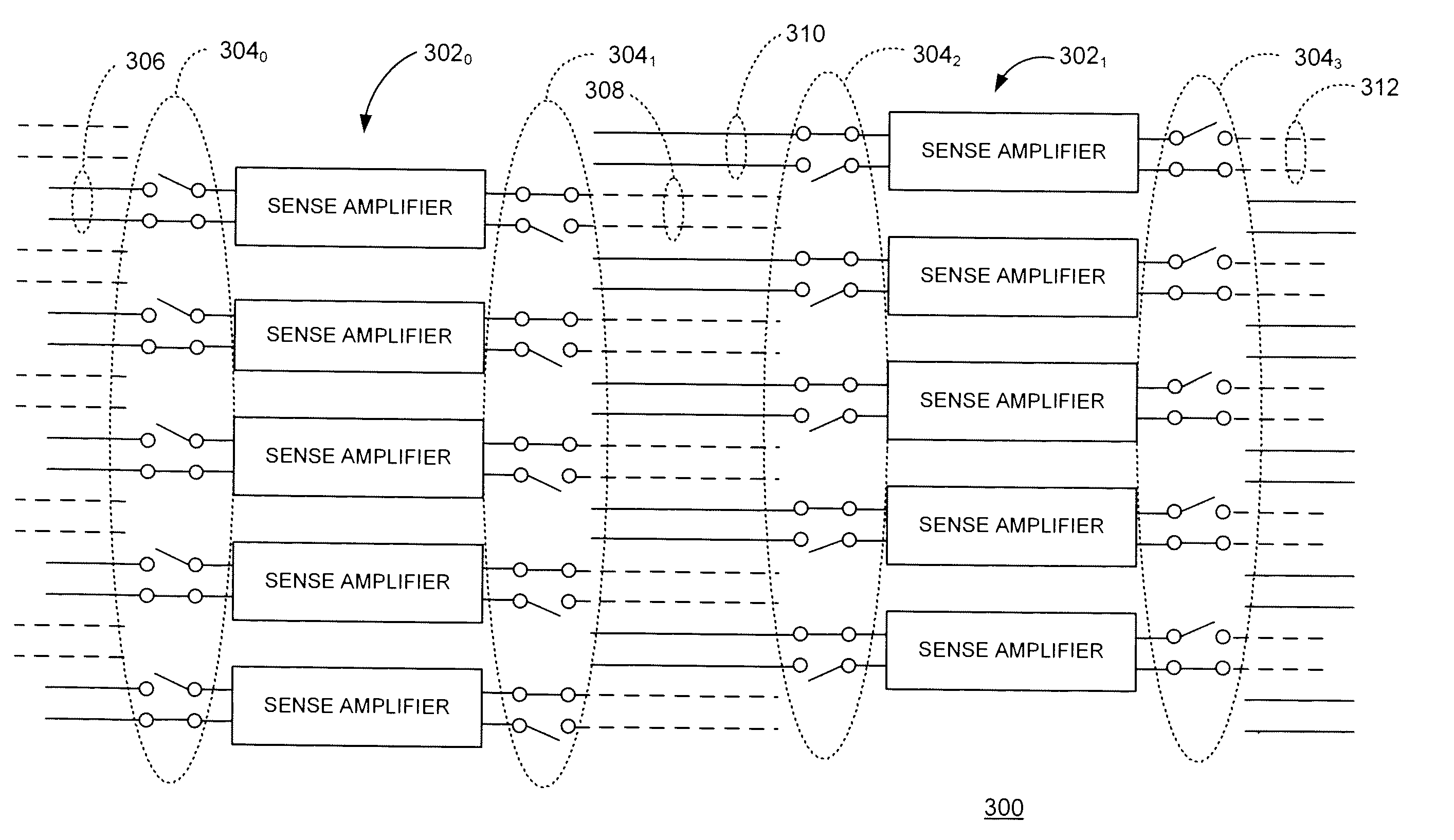

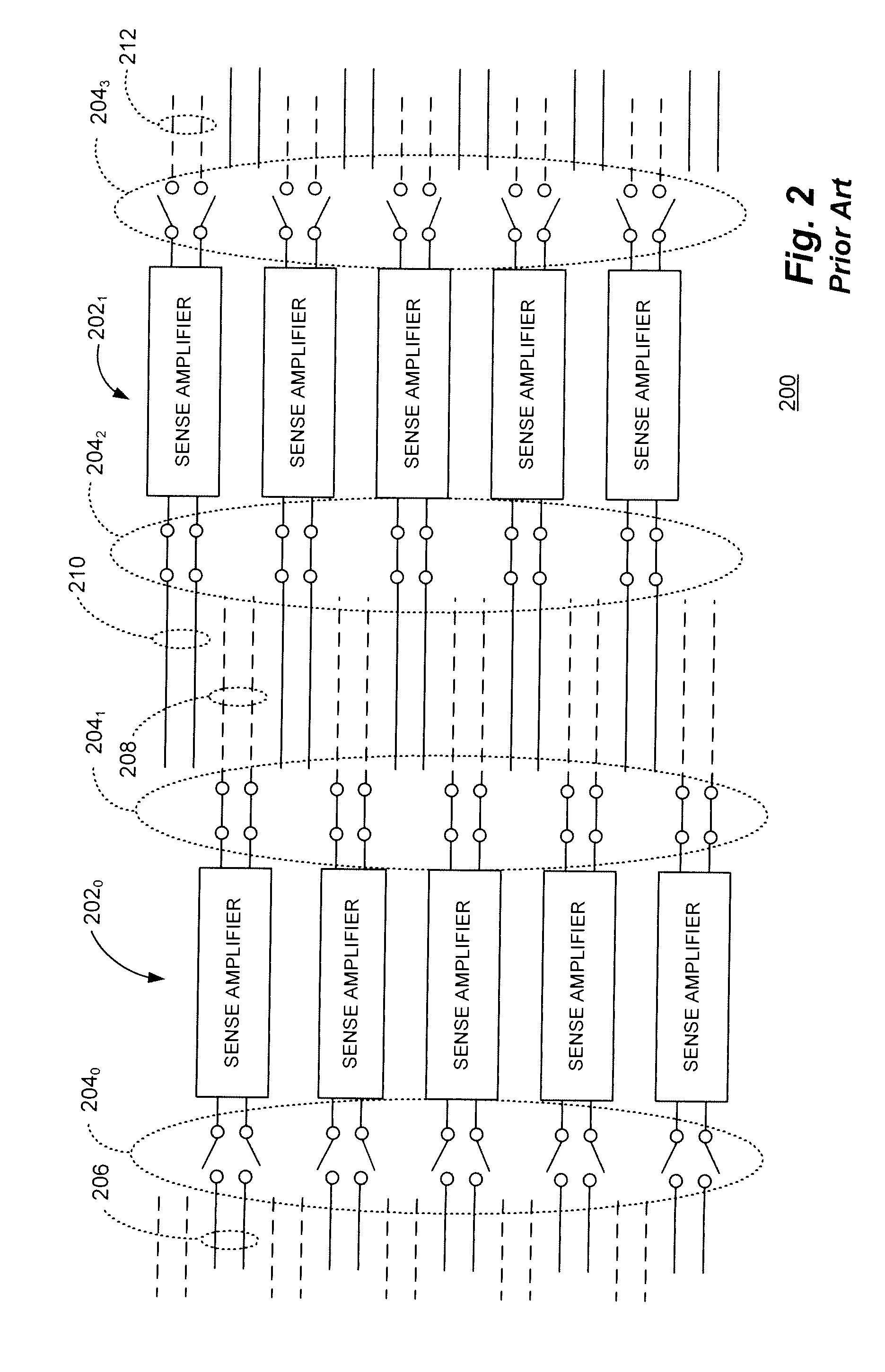

Shielded bitline architecture for dynamic random access memory (DRAM) arrays

A shielded bitline architecture for DRAM memories and integrated circuit devices incorporating embedded DRAM is disclosed herein which comprises a shared sense amplifier, folded bitline array using a bitline from an adjacent, non-active subarray as a reference for a bitline in an active array.

Owner:PROMOS TECH PTE LTD

Metal-insulator-metal transformer and method for manufacturing the same

ActiveUS7365627B2Save areaReduce spacingSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsMetal-insulator-metalTransformer

The invention is directed to a method for manufacturing a metal-insulator-metal transformer together with a capacitor. The method comprises steps of providing a substrate having at least a dielectric layer formed thereon and then forming a first metal layer of the metal-insulator-metal capacitor together with a first metal coil of the transformer over the substrate. An insulating layer is formed to cover the substrate, the first metal layer and the first metal coil. A second metal layer of the metal-insulator-metal capacitor is formed together with a second metal coil of the transformer on the insulating layer.

Owner:UNITED MICROELECTRONICS CORP