Patents

Literature

634results about How to "Avoid shorting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

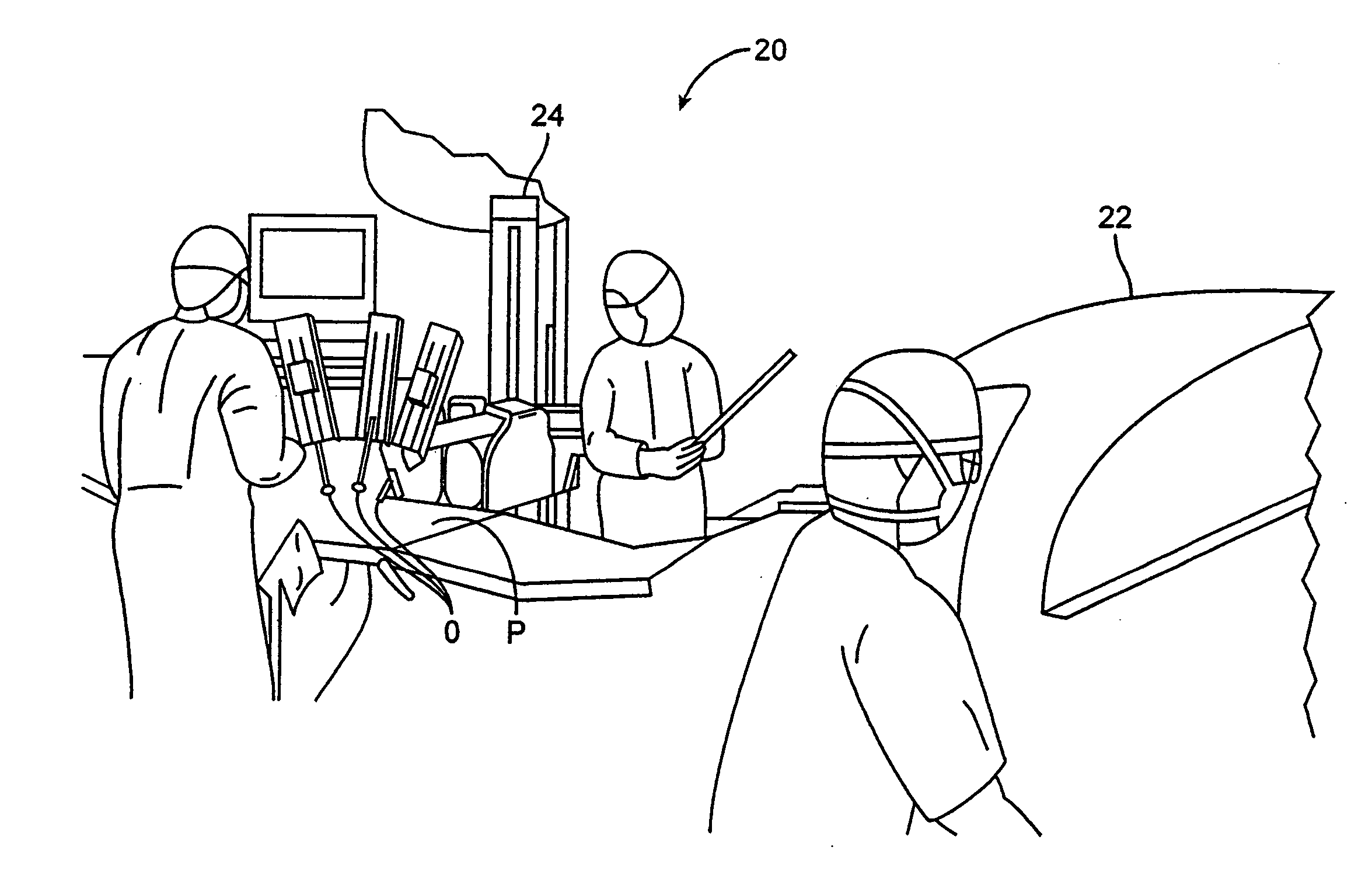

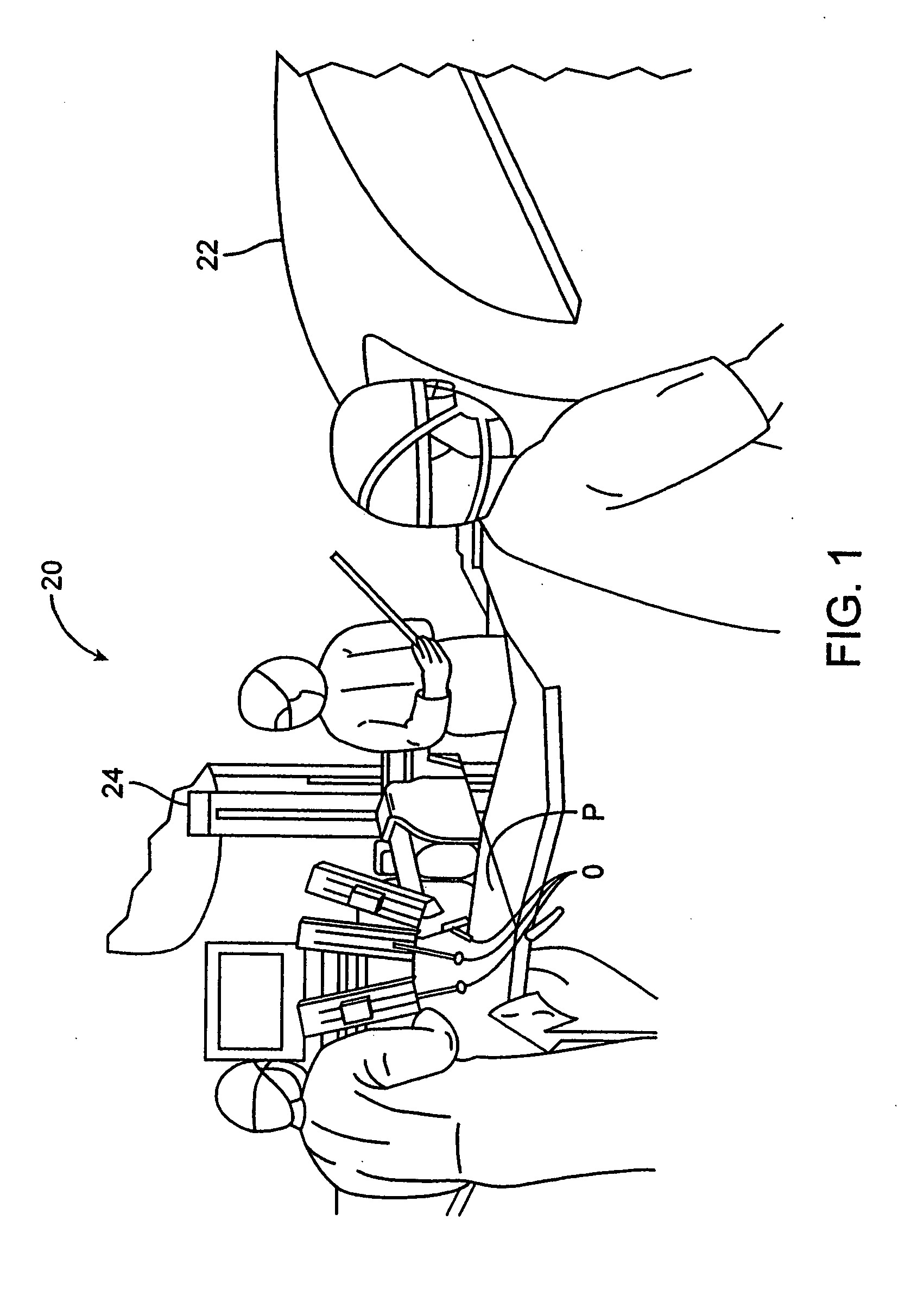

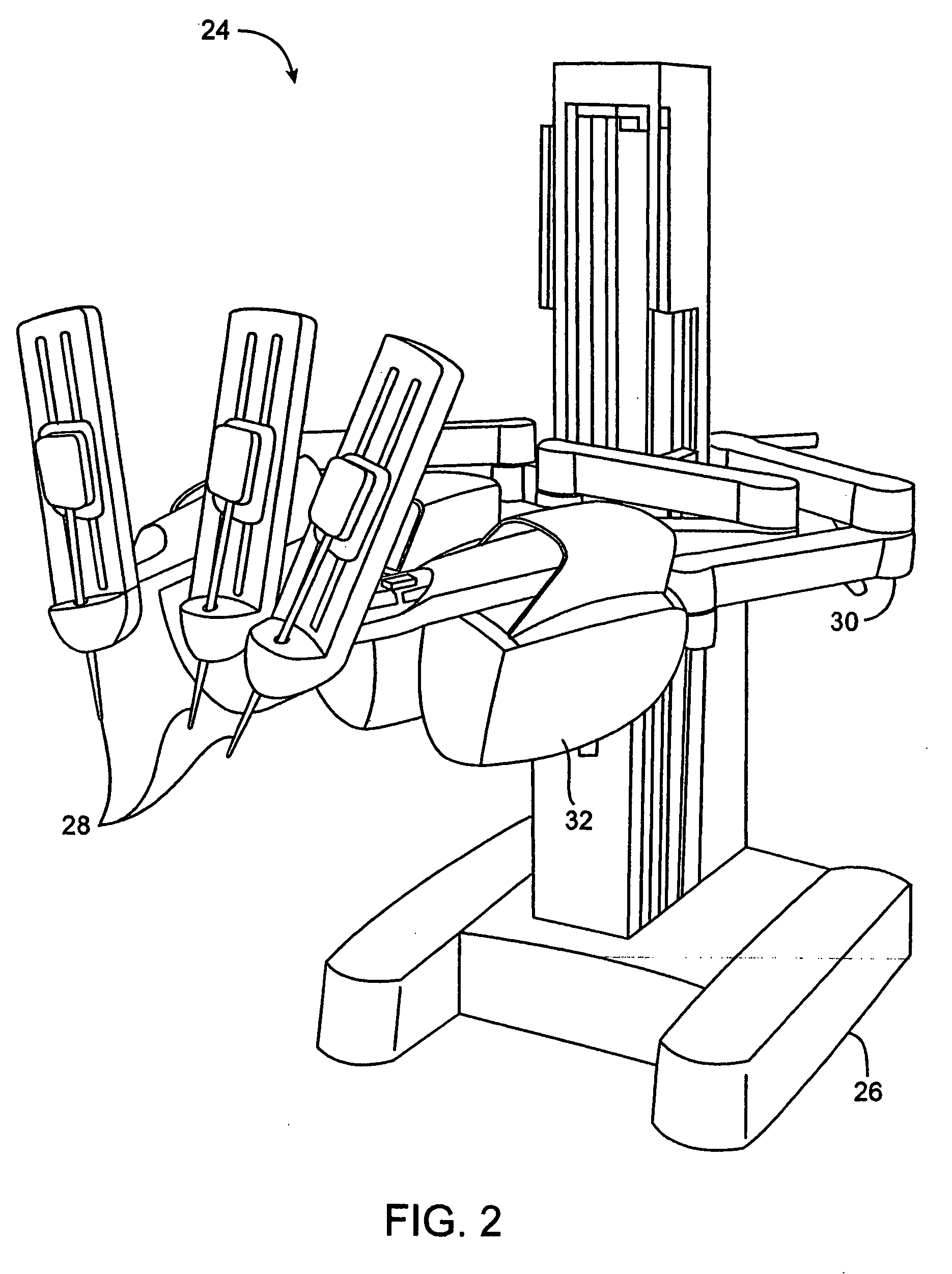

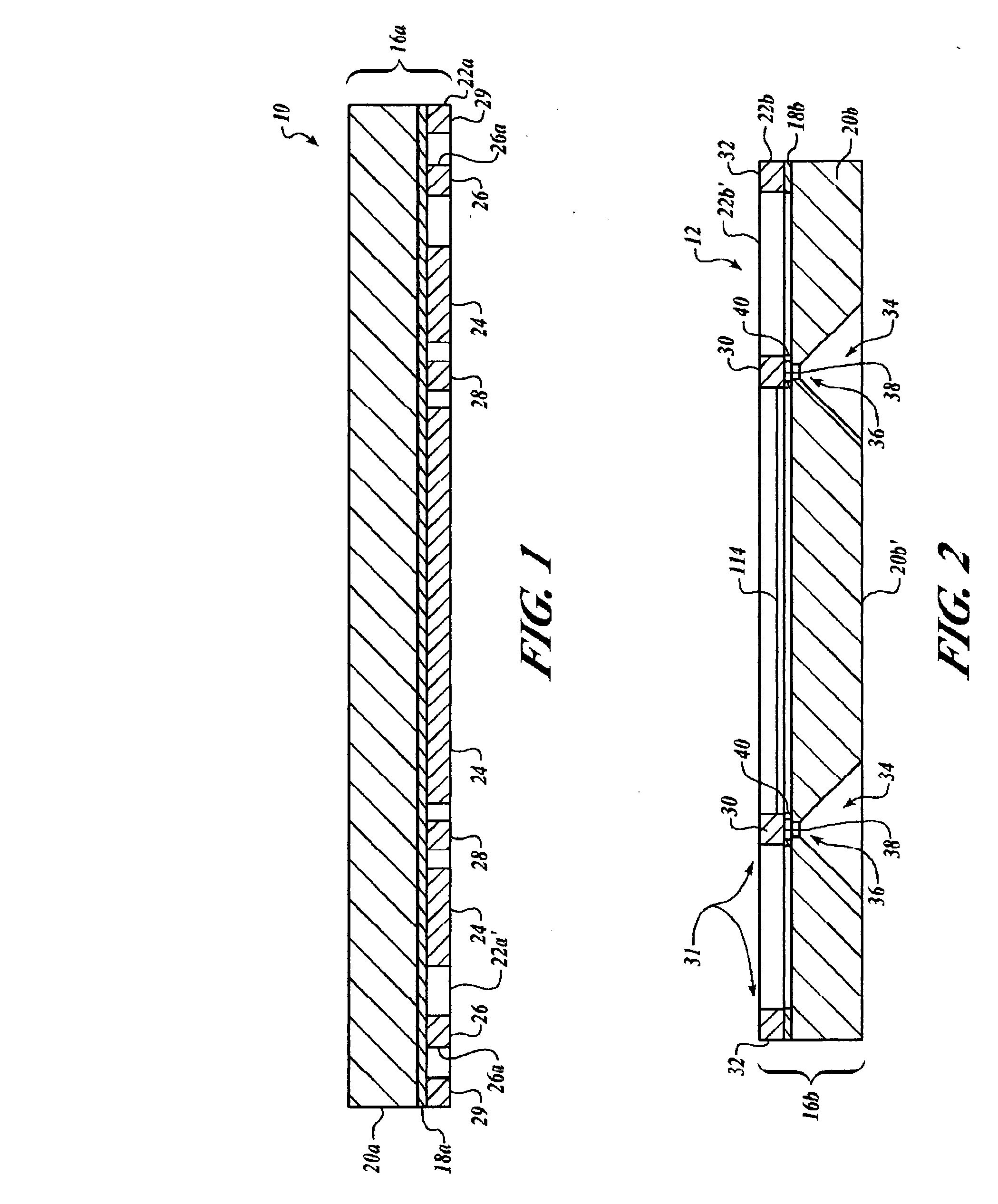

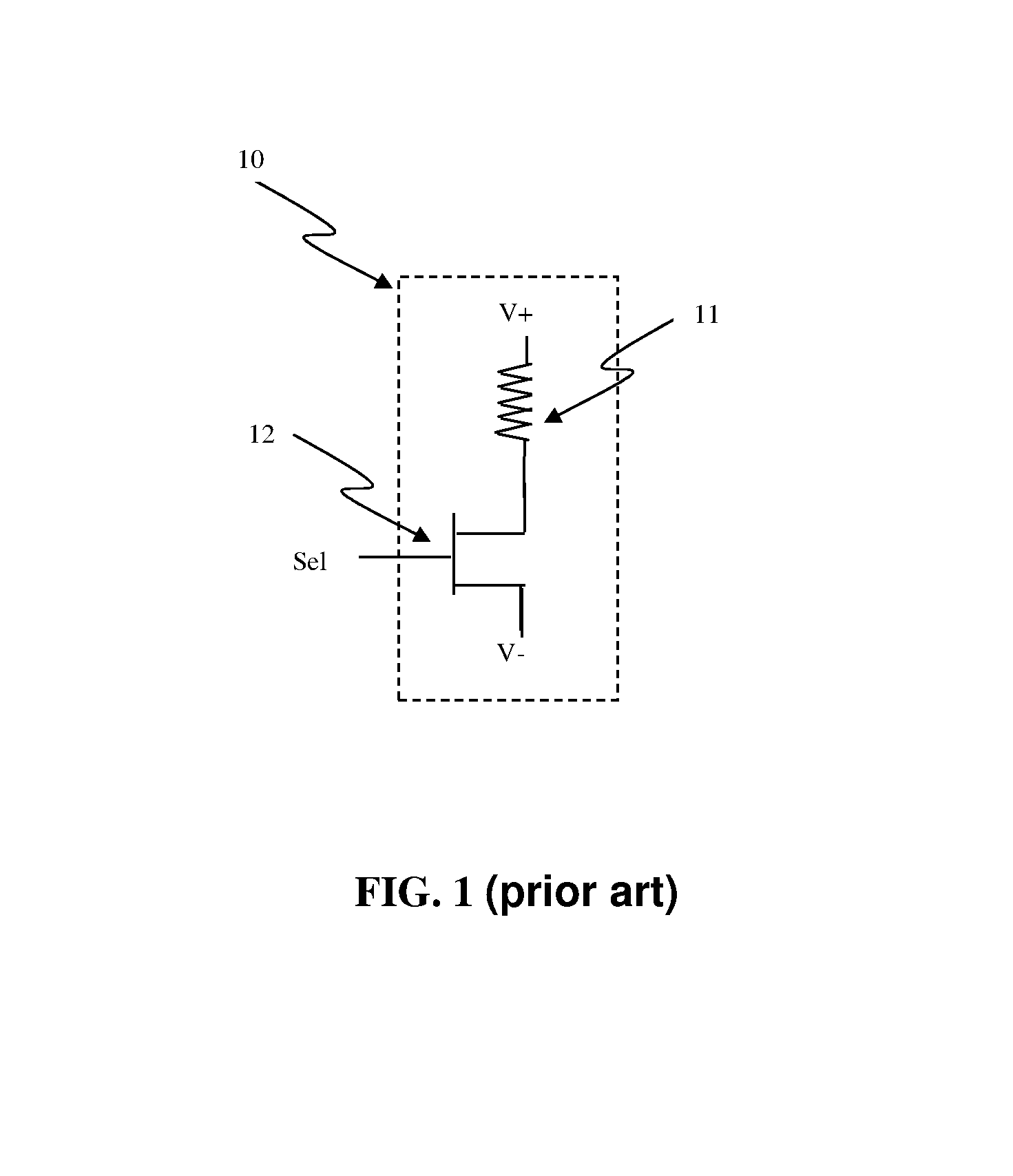

Bipolar cauterizing instrument

A bipolar surgical instrument that includes opposing grips that can engage the tissue. A current is delivered from an electrosurgical power source to electrodes disposed on the grips to cauterize the tissue. The electrode configurations provide efficient cauterization of the tissue. In some embodiments, the positive and negative electrodes will be offset from each other to prevent shorting and to provide a thin line of coagulation heating to the gripped tissue. In some embodiments the electrodes are removably coupled to the grips through nonconductive sleeves. In some embodiments, the first electrode is disposed in a groove and the second electrode is disposed on a boss.

Owner:INTUITIVE SURGICAL

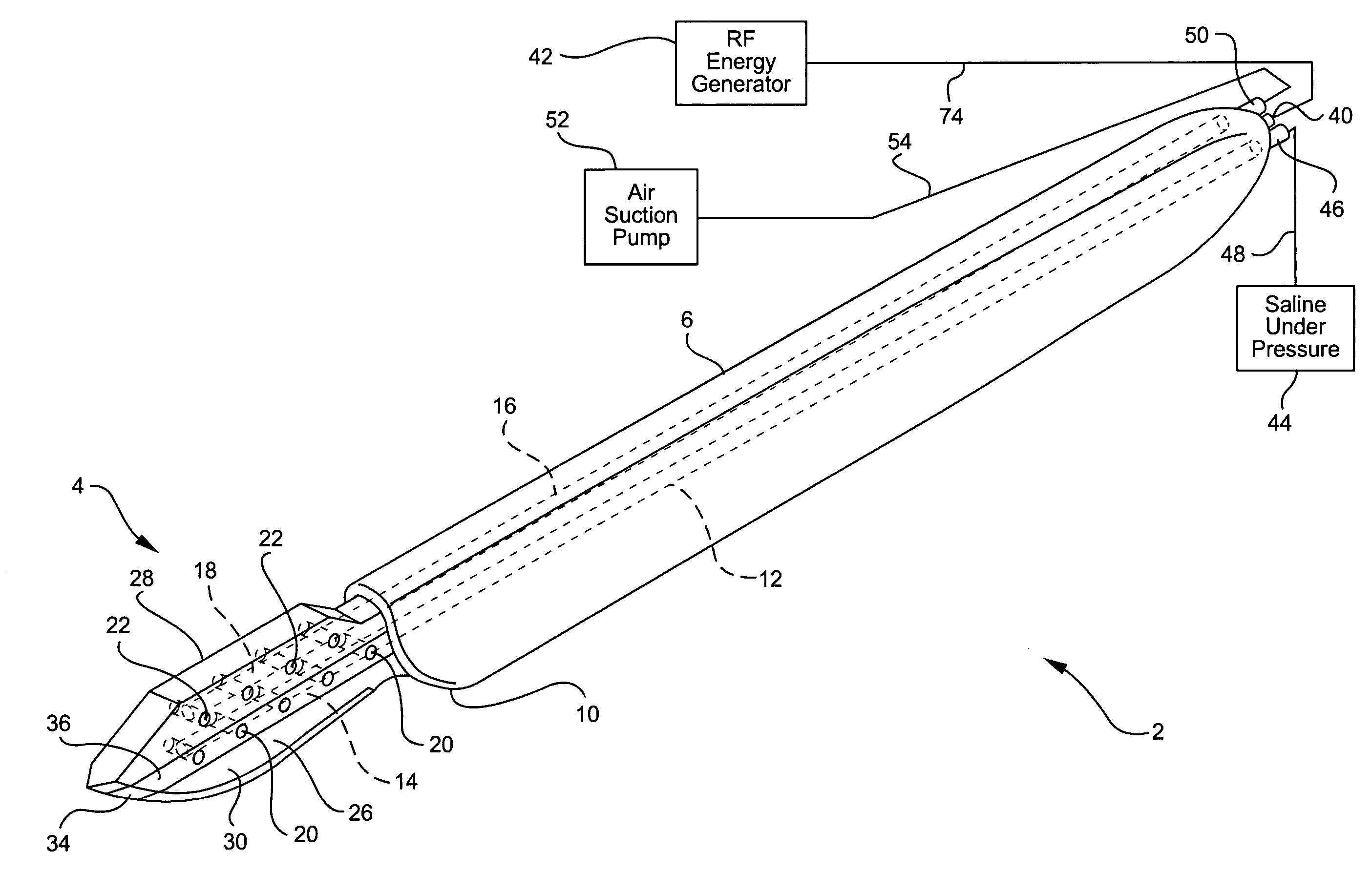

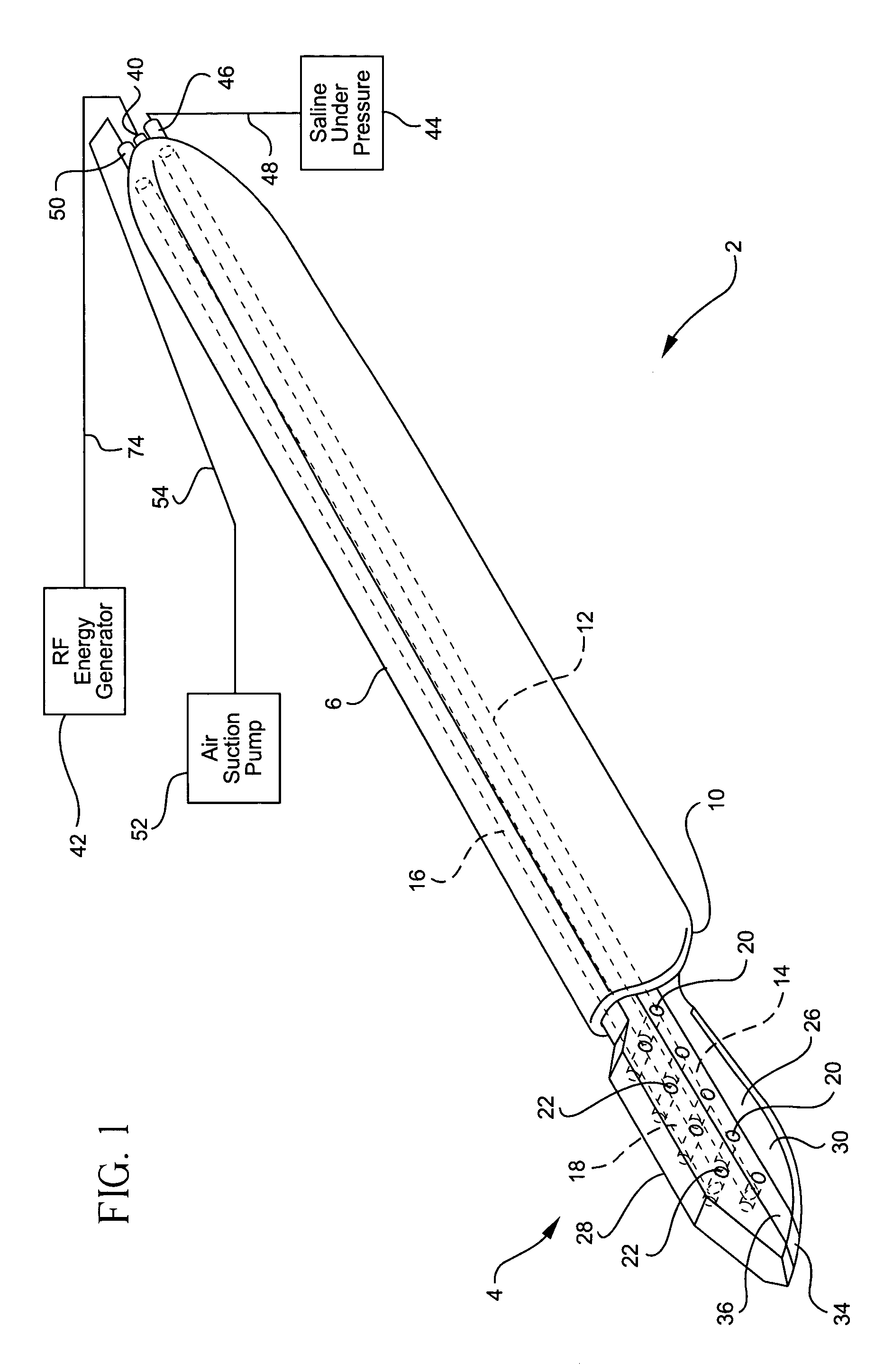

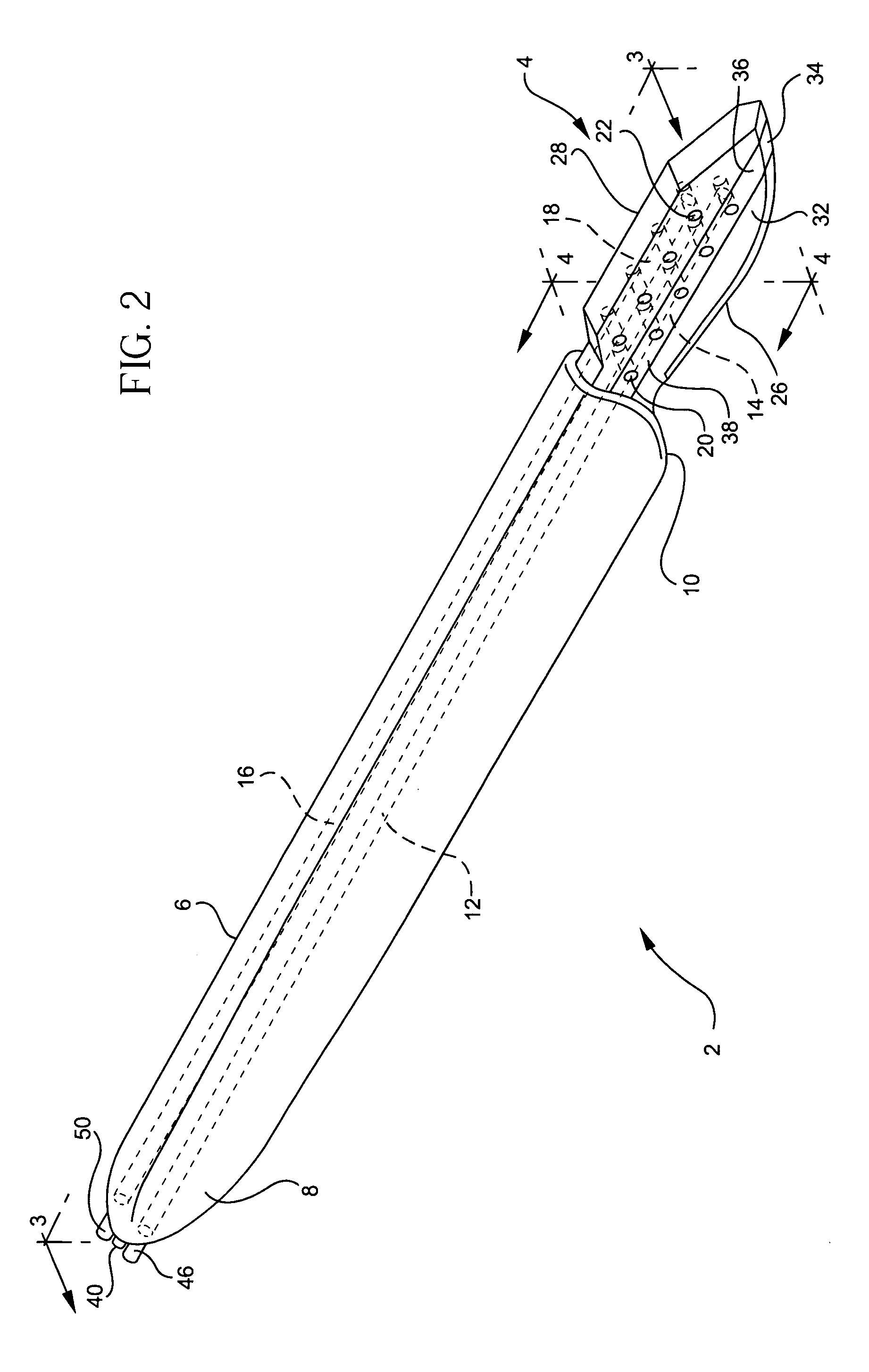

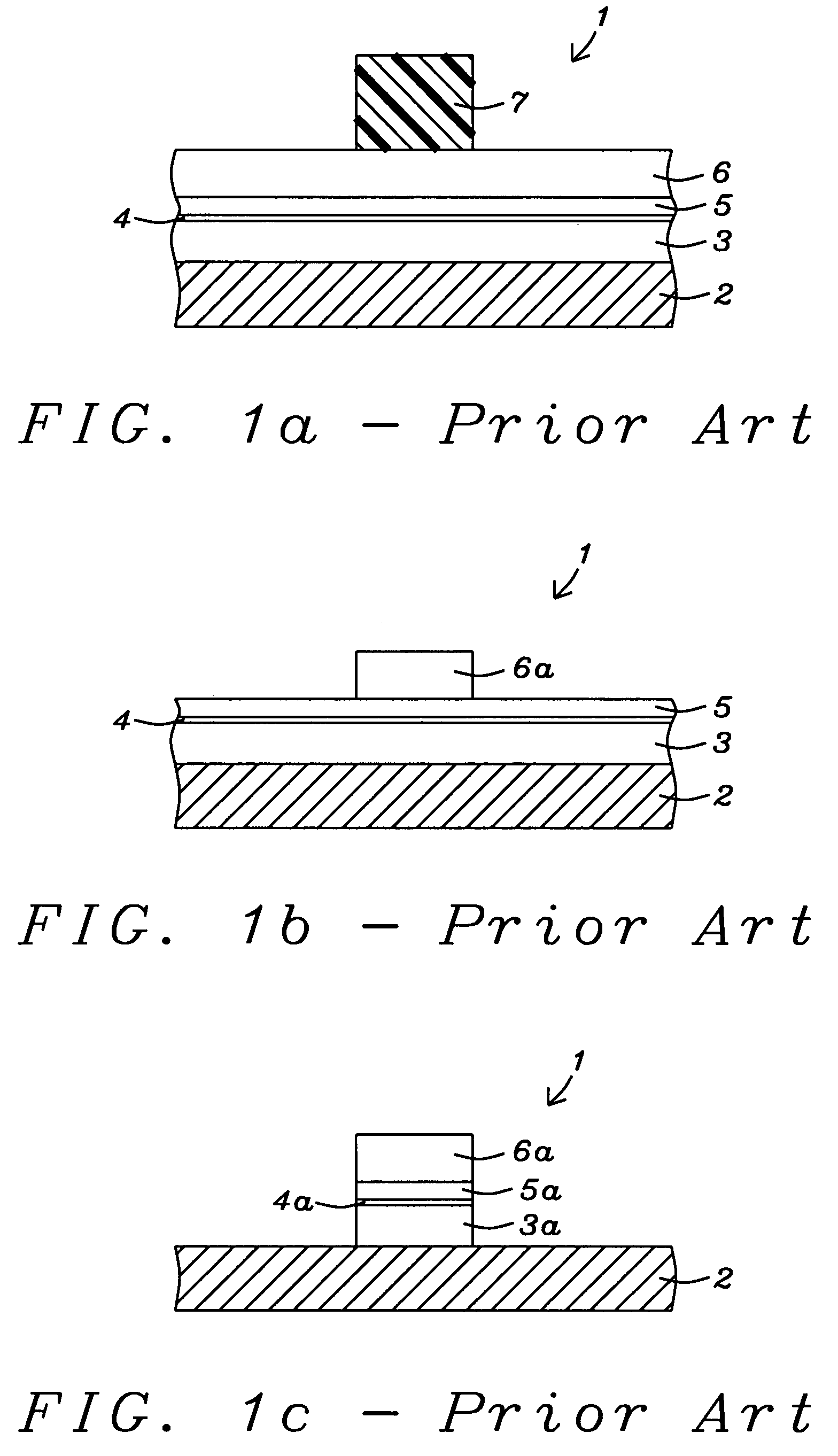

Surgical cutting and tissue vaporizing instrument

ActiveUS7066936B2Inherent disadvantageAvoid shortingSurgical instruments for heatingSurgical instruments for aspiration of substancesActive electrodeSurgical department

A surgical cutting and tissue vaporizing instrument, also referred to as an electrosurgical instrument, is in the form of a scalpel or scissors. The scalpel has a handle portion and a blade portion mounted on the handle portion. The blade portion has a smaller front section which acts as an active electrode, a larger rear section which acts as a return electrode, and an insulating middle section separating the two electrodes. A plurality of ports and conduits are formed in the blade portion, with the conduits extending through the handle portion, so that saline may be supplied to the handle and blade portions and out of the ports to the targeted area for tissue transection, and so that excess saline may be drawn by suction through other ports formed on the blade portion. The scissors include two cross-pivotally joined blades, each having a tip portion functioning as either an active electrode or as a return electrode. Ports and conduits are formed in each blade to elute saline onto the targeted area for tissue transection and to remove by suction excess saline from the targeted area.

Owner:ETHICON INC

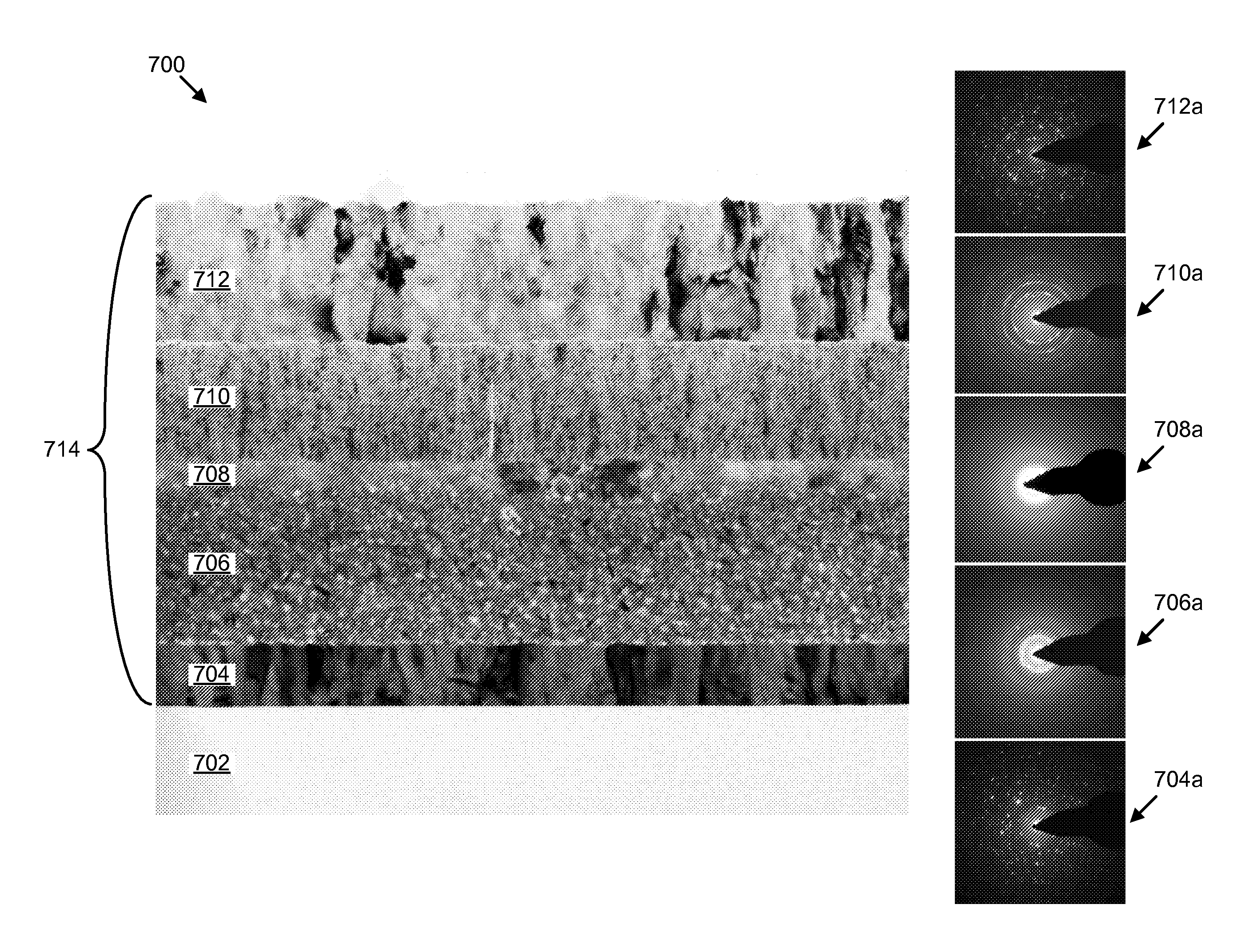

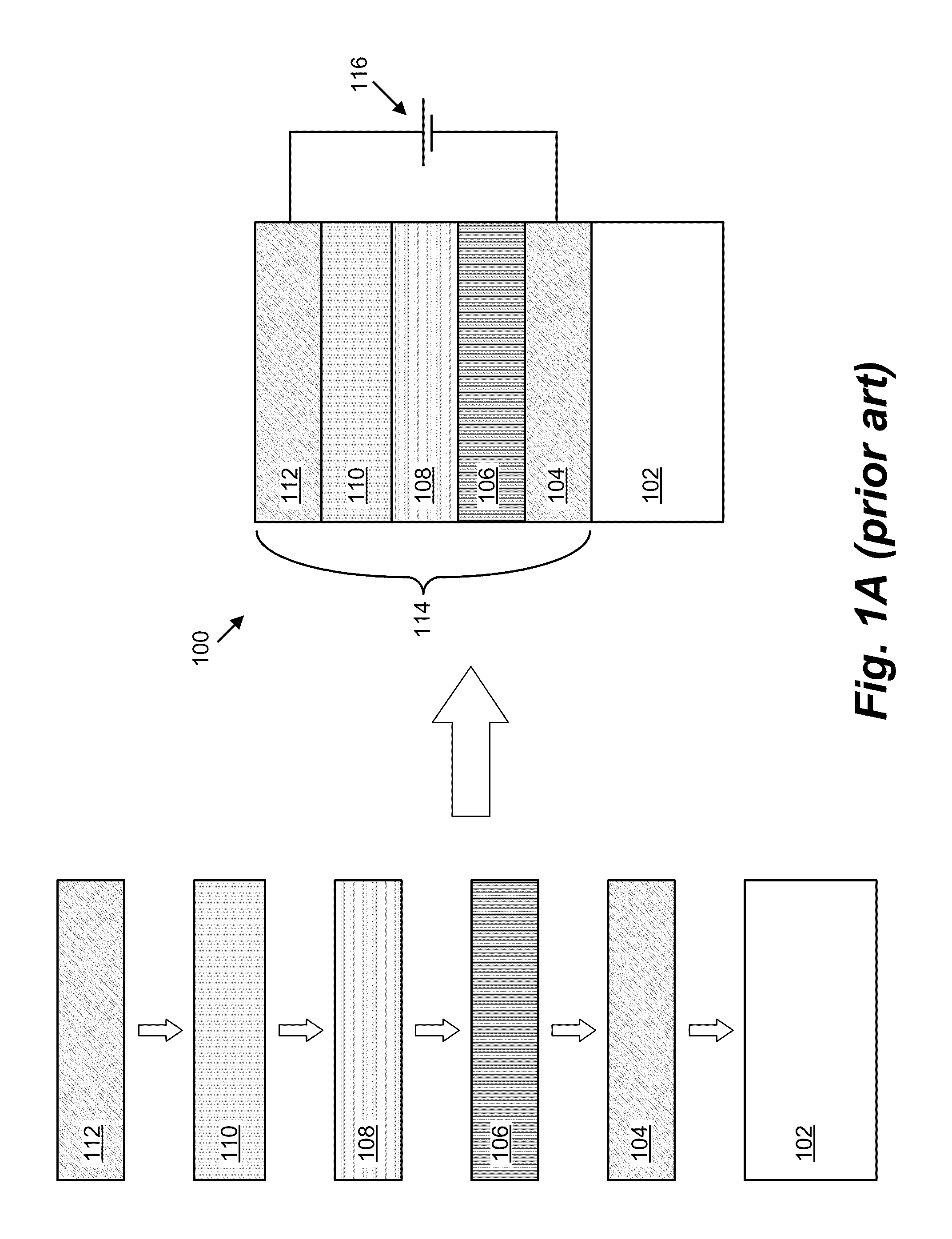

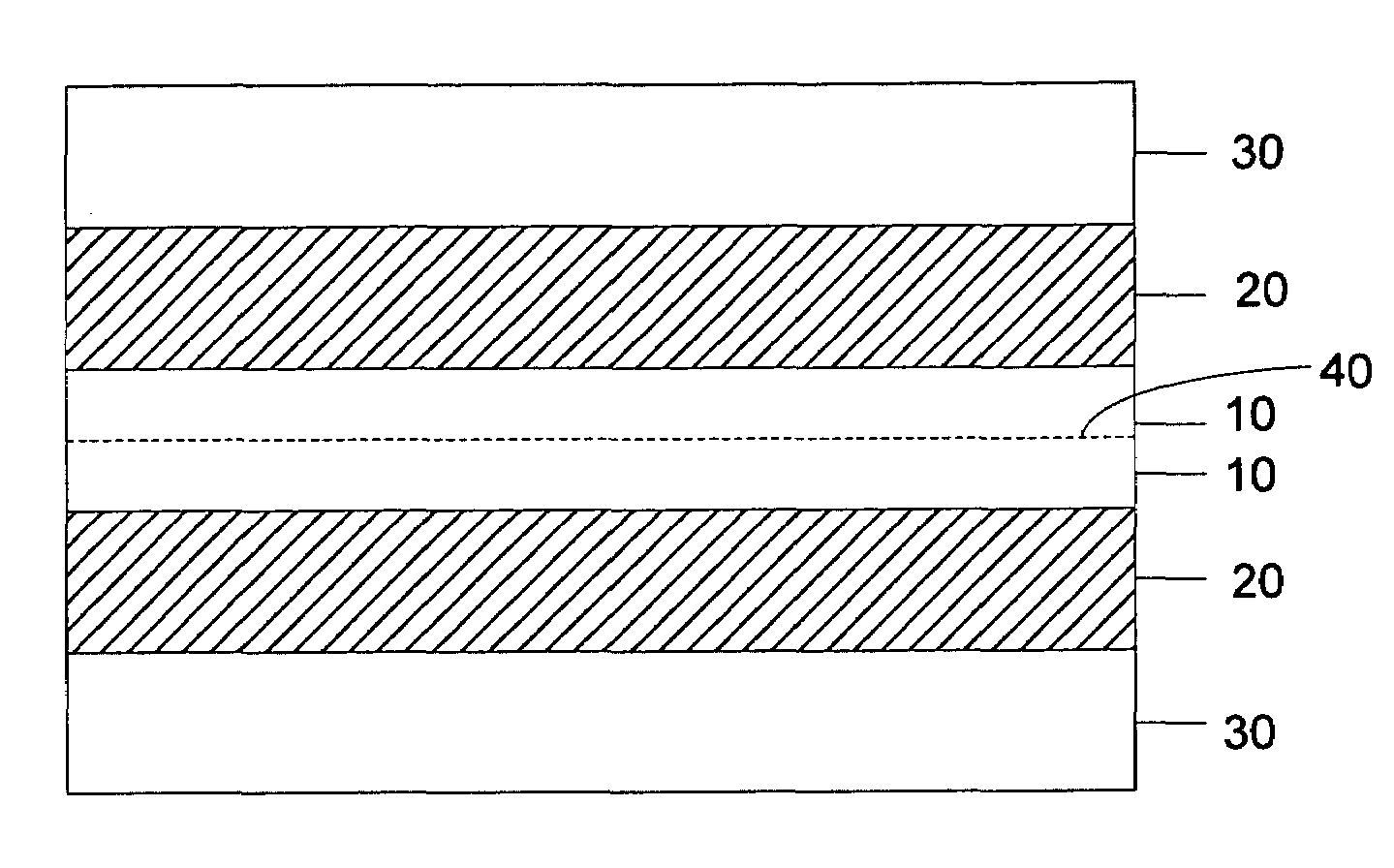

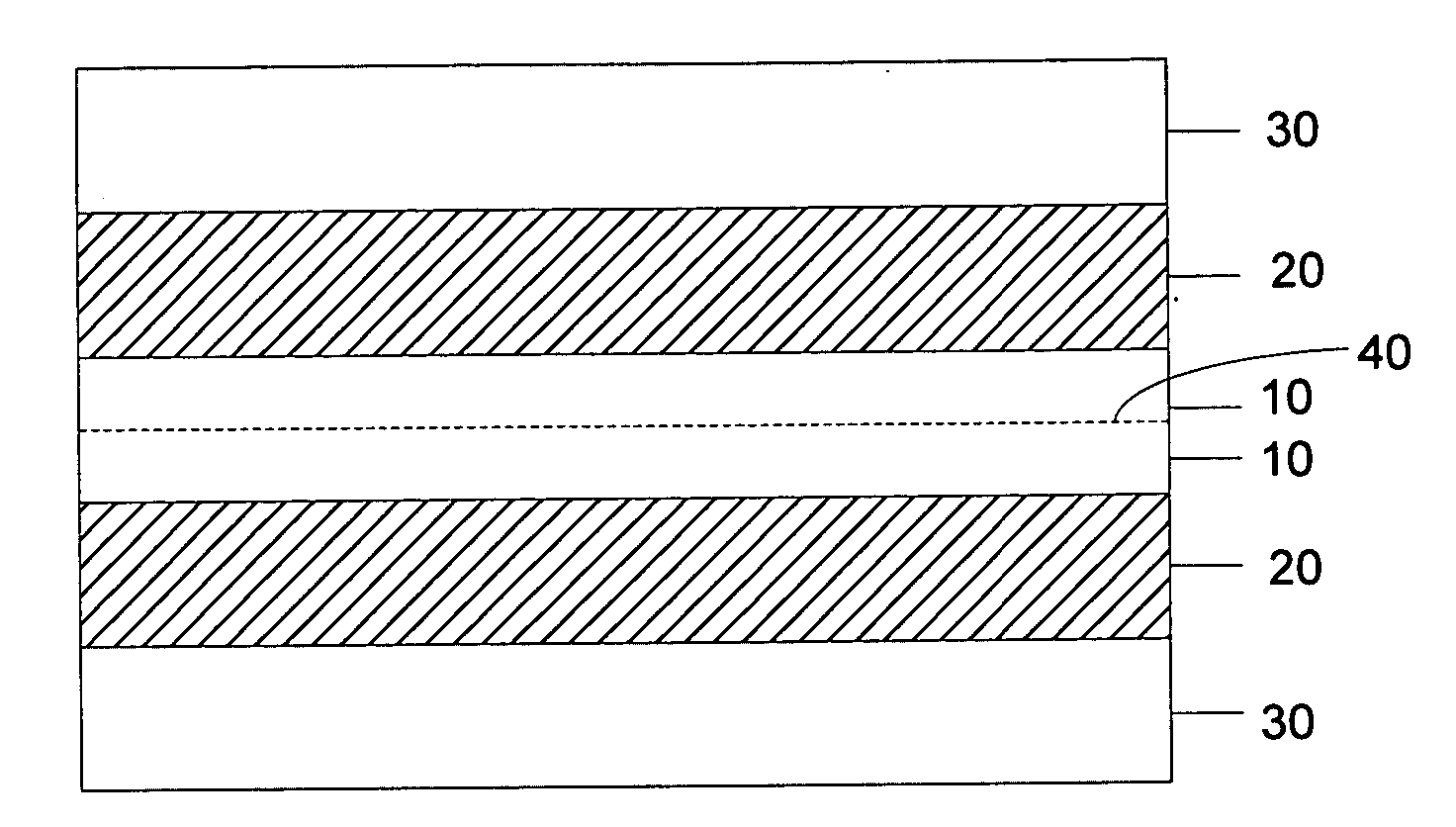

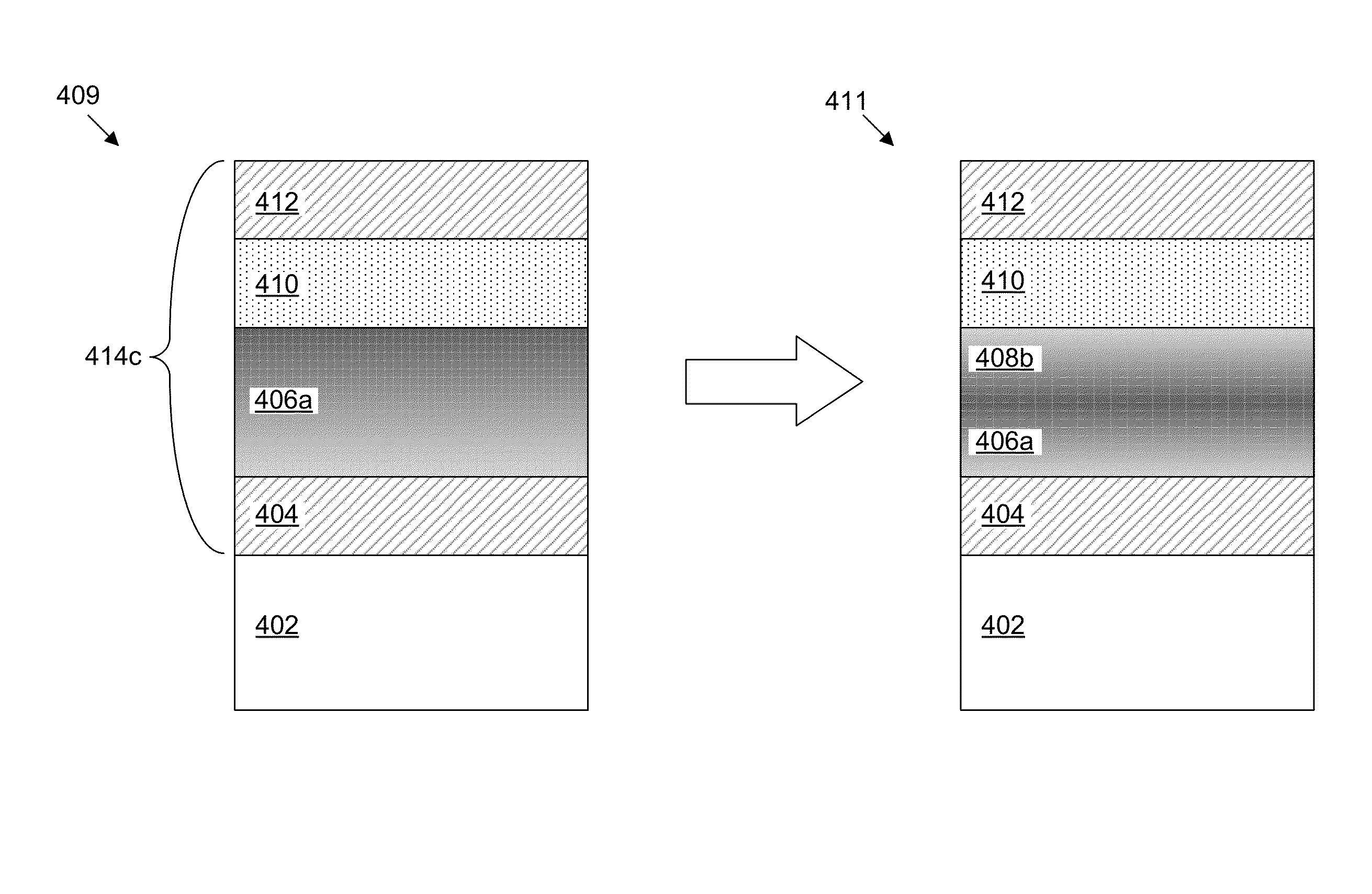

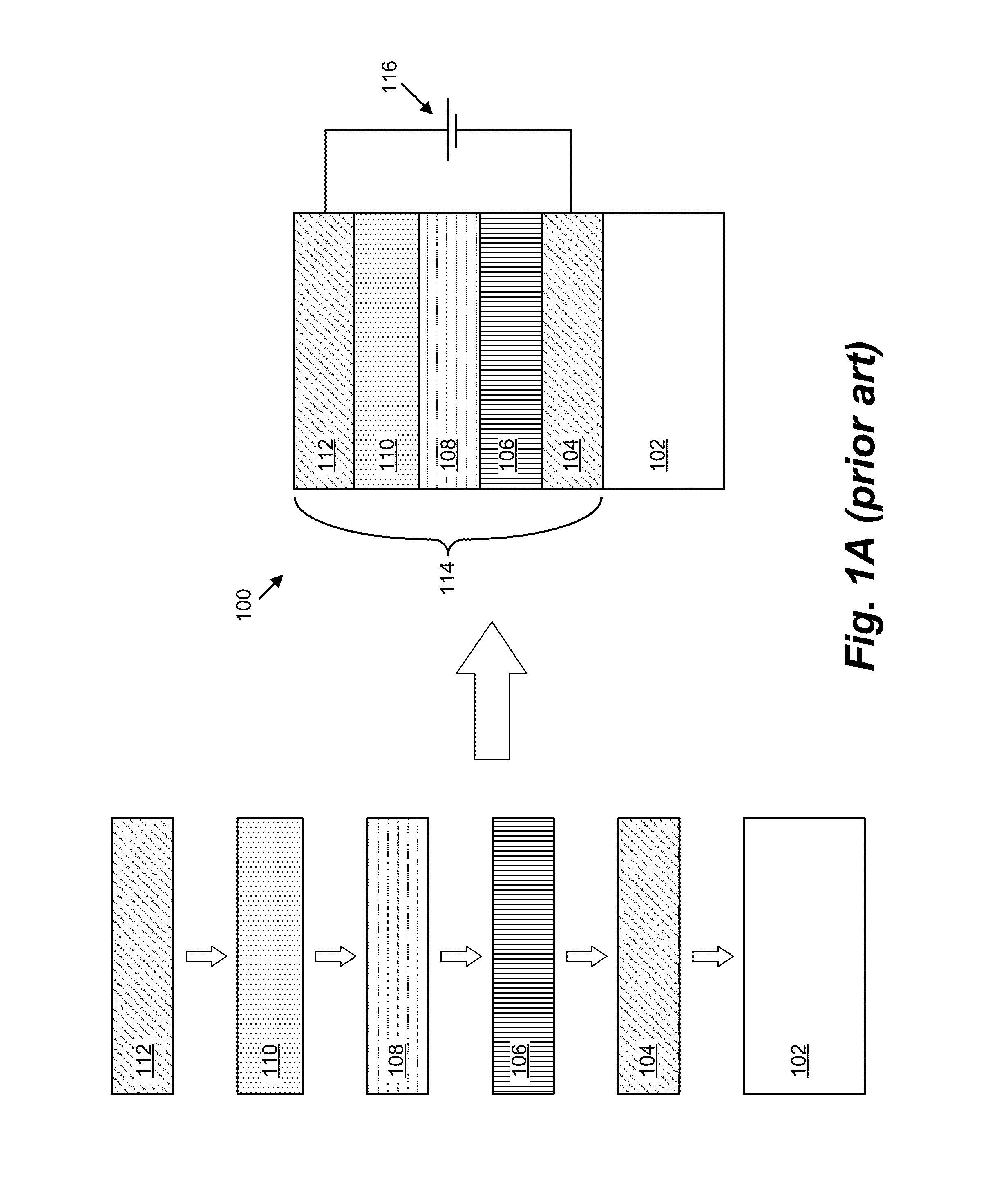

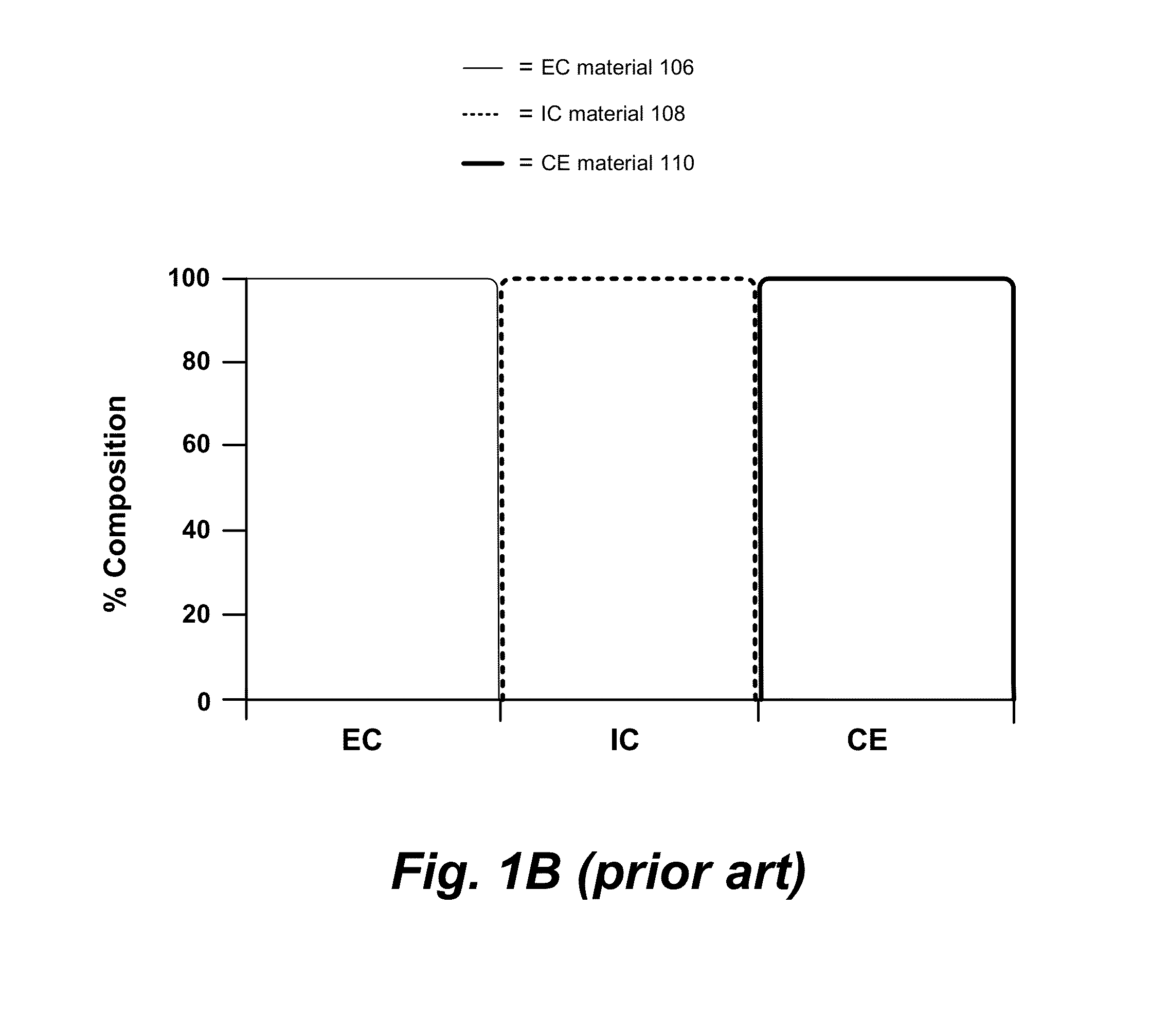

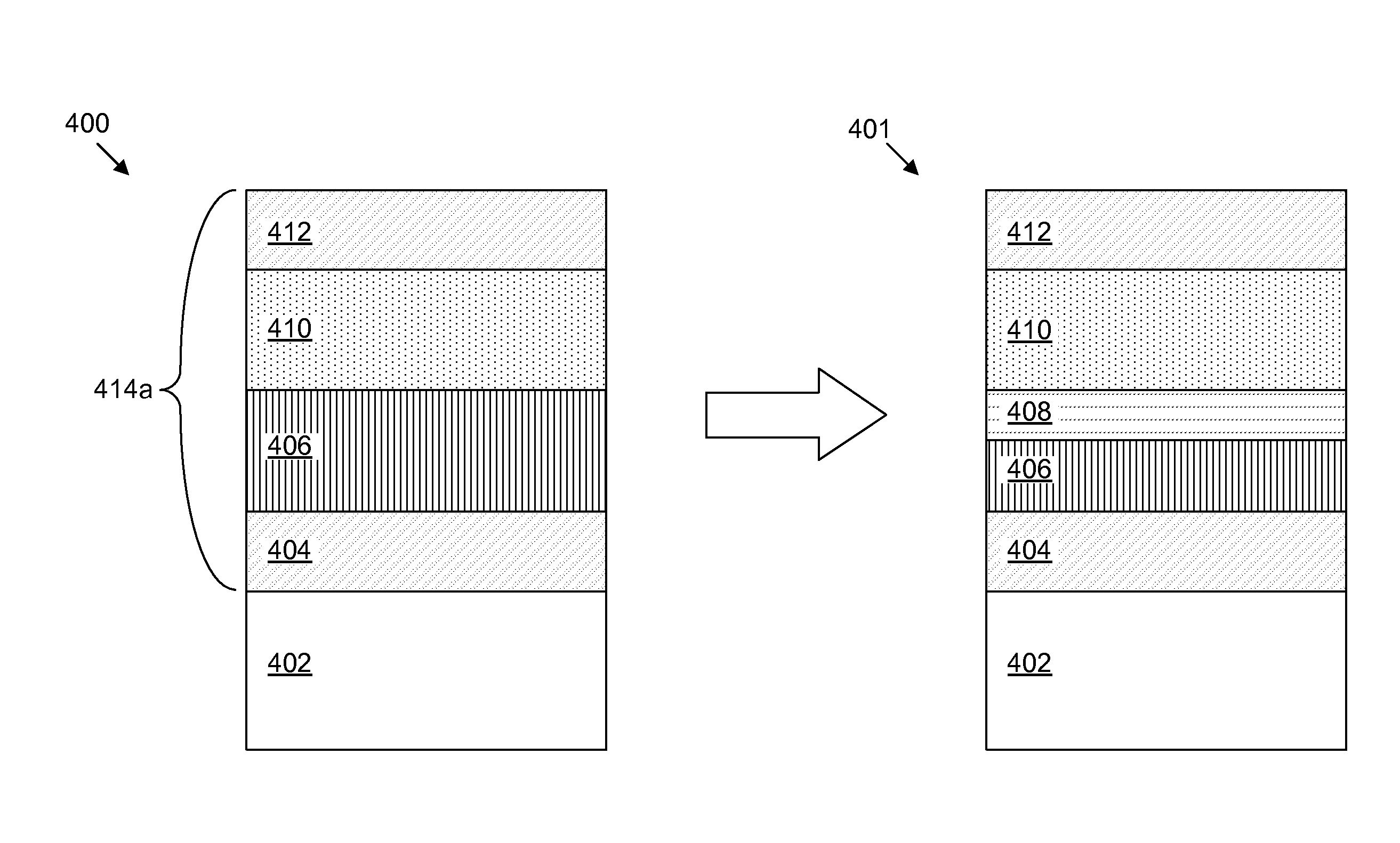

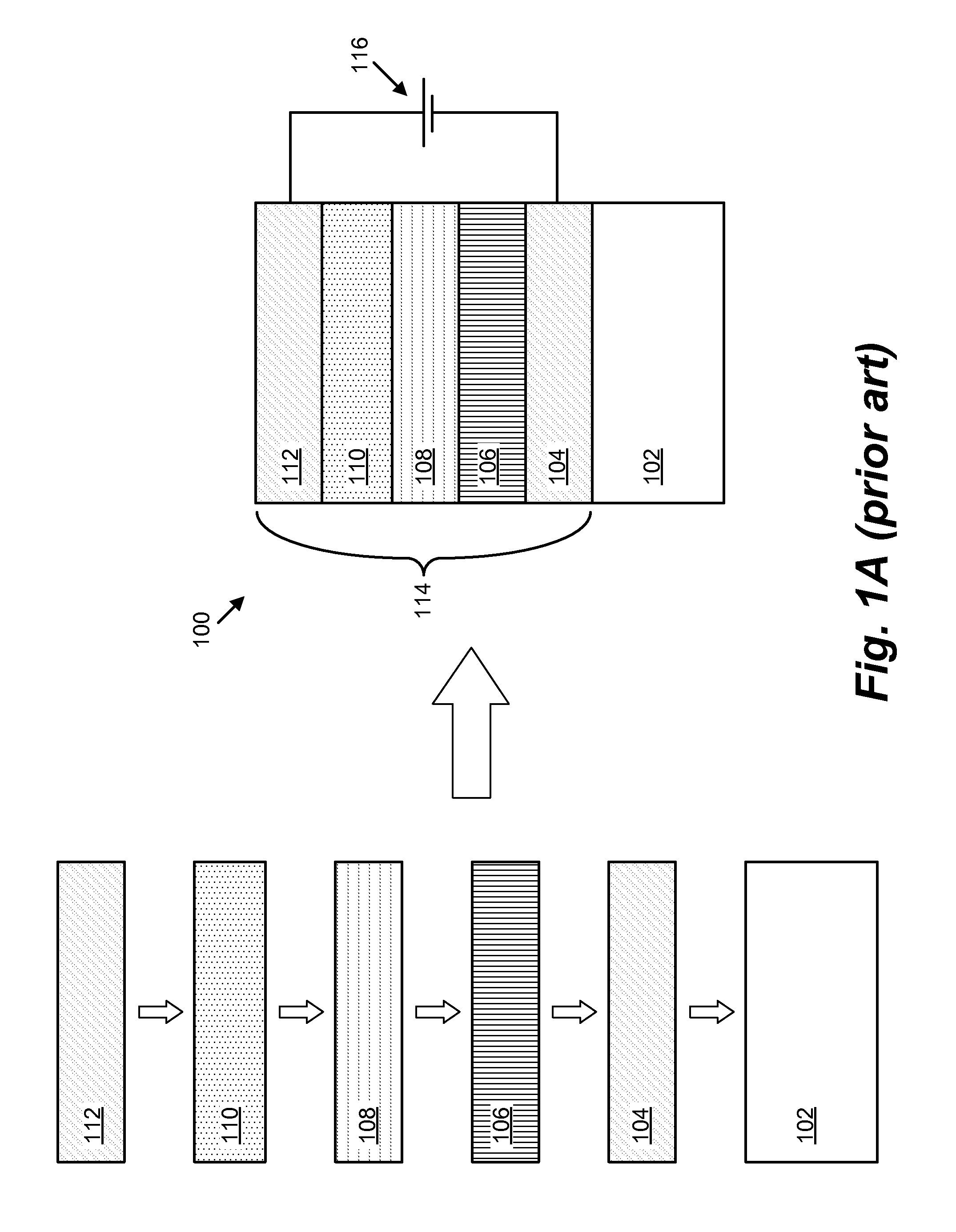

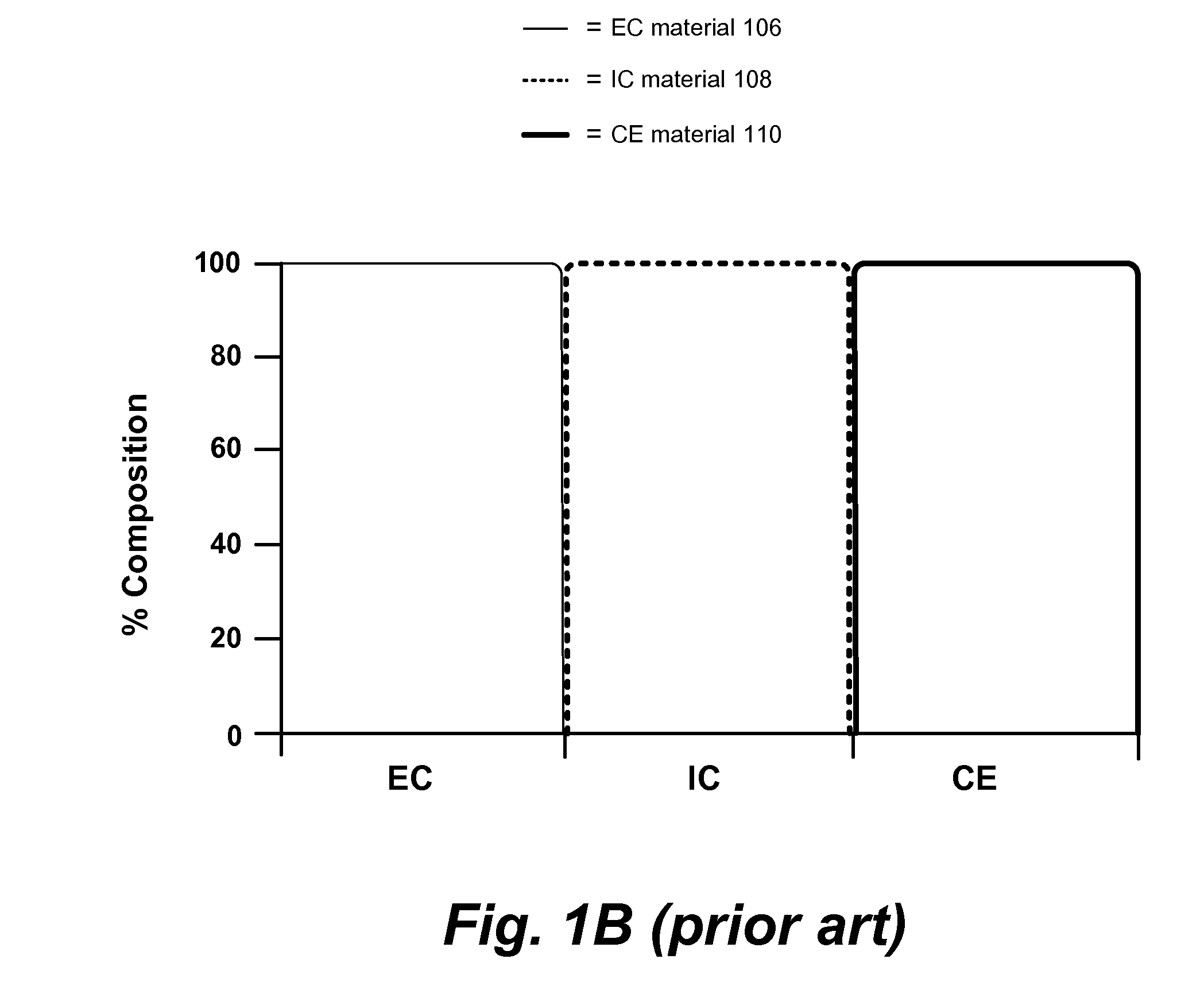

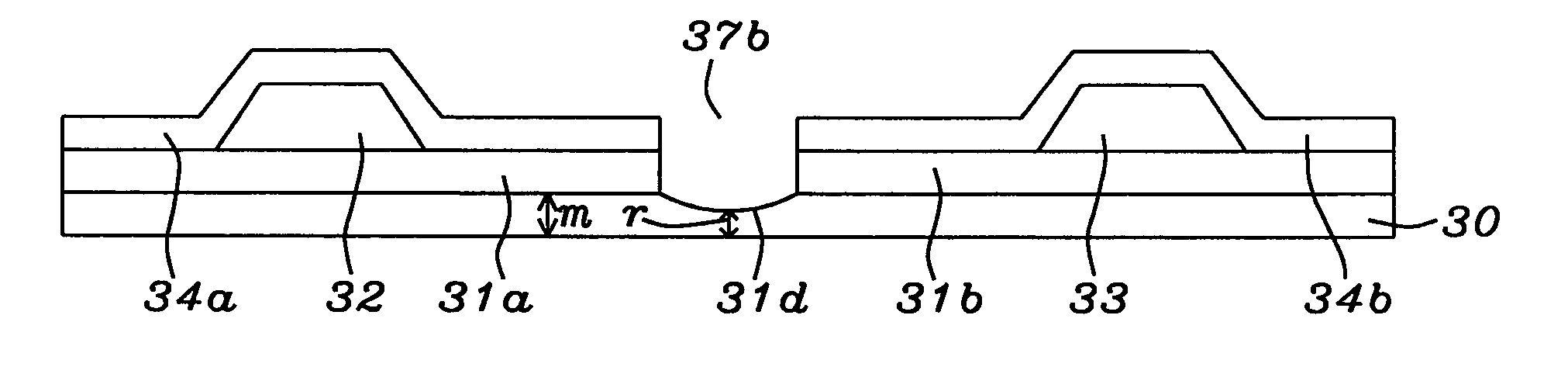

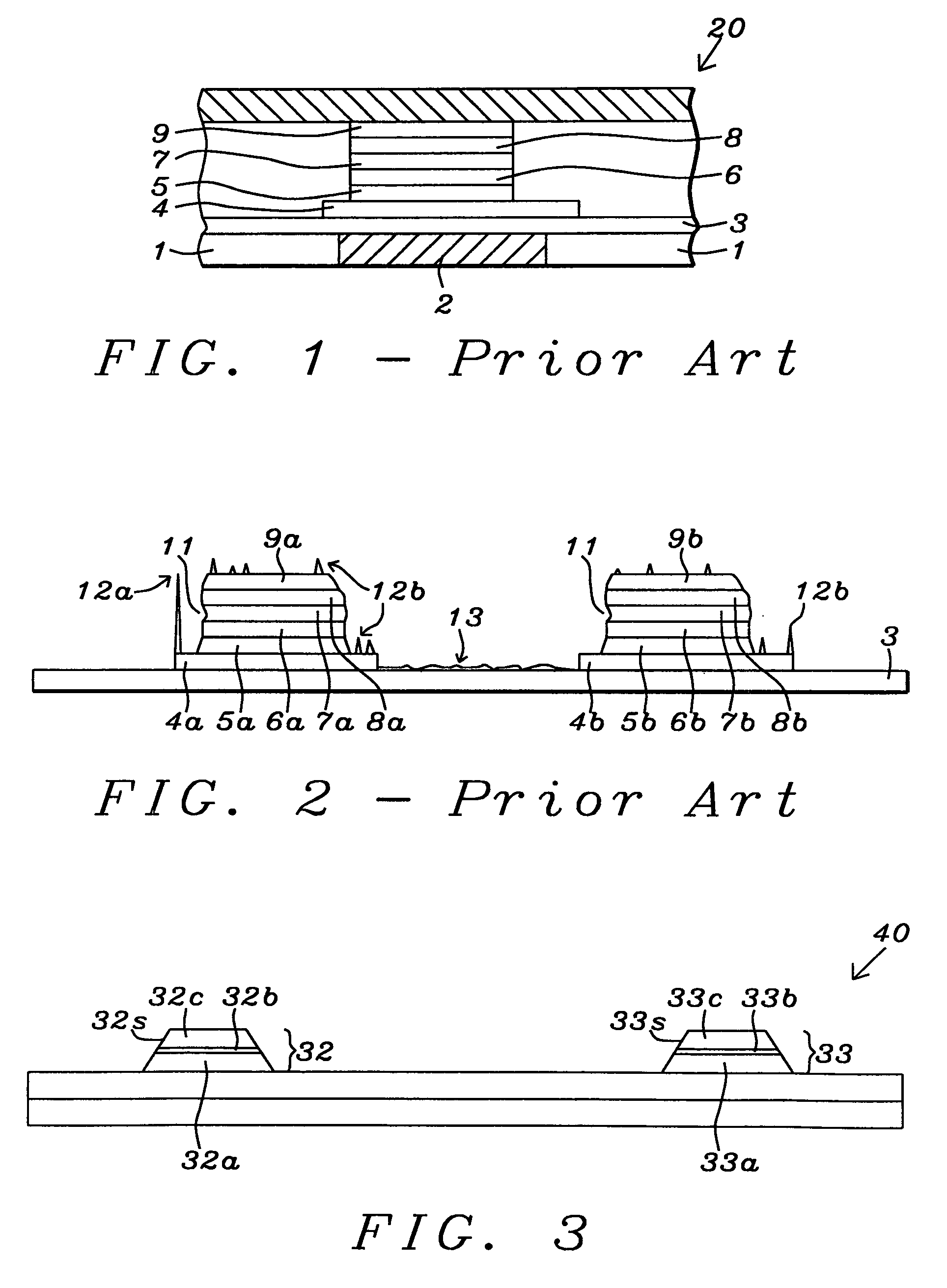

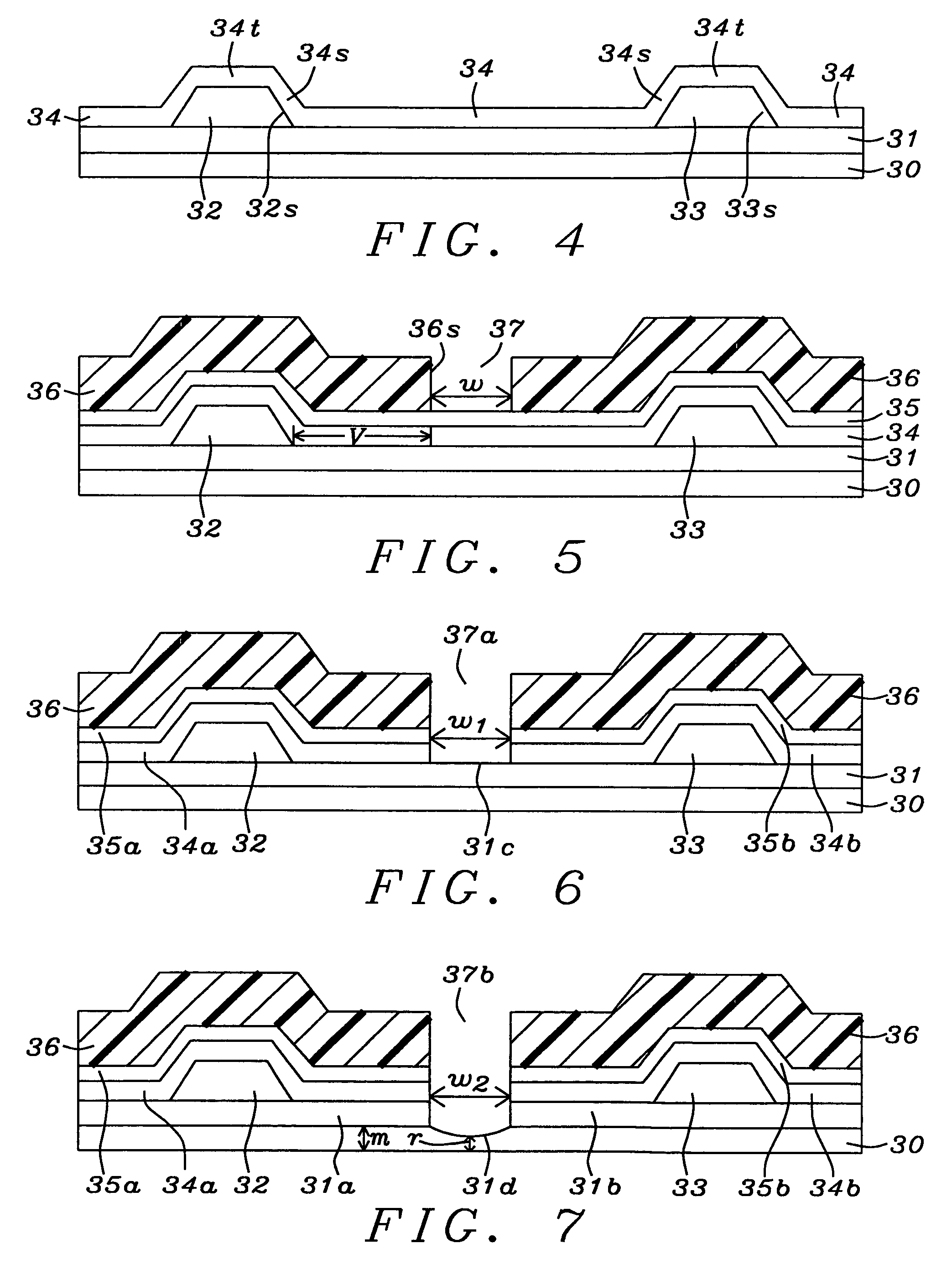

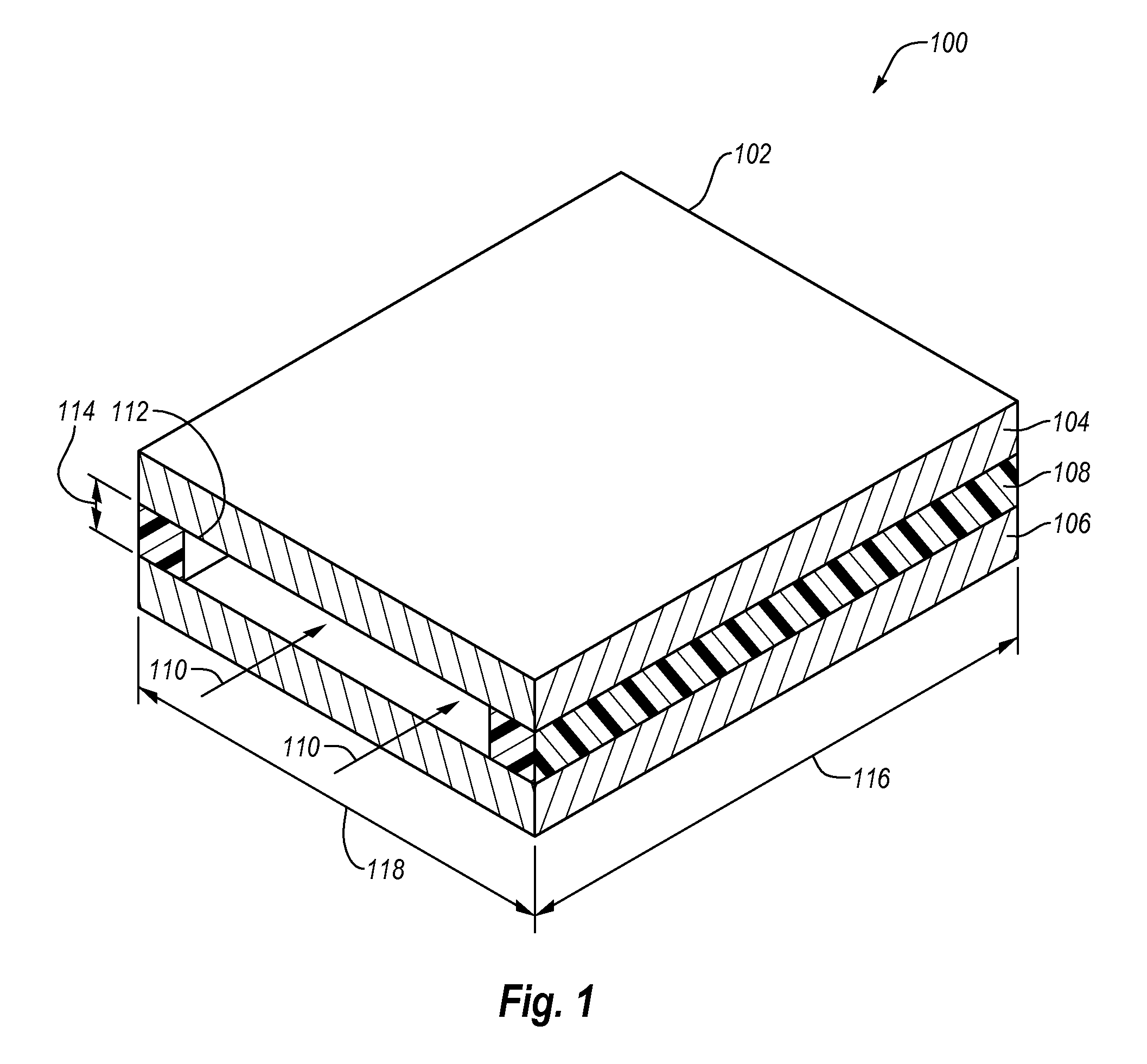

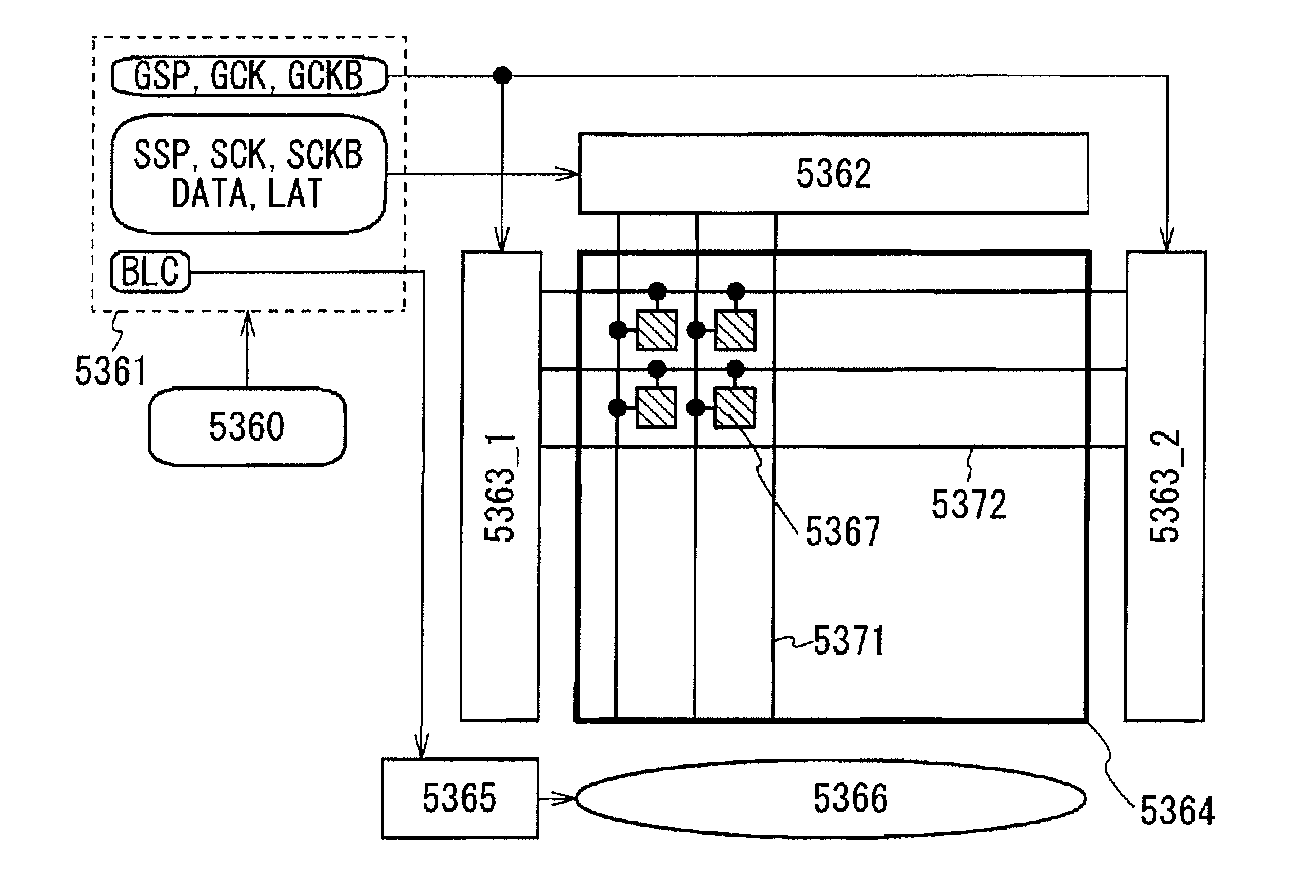

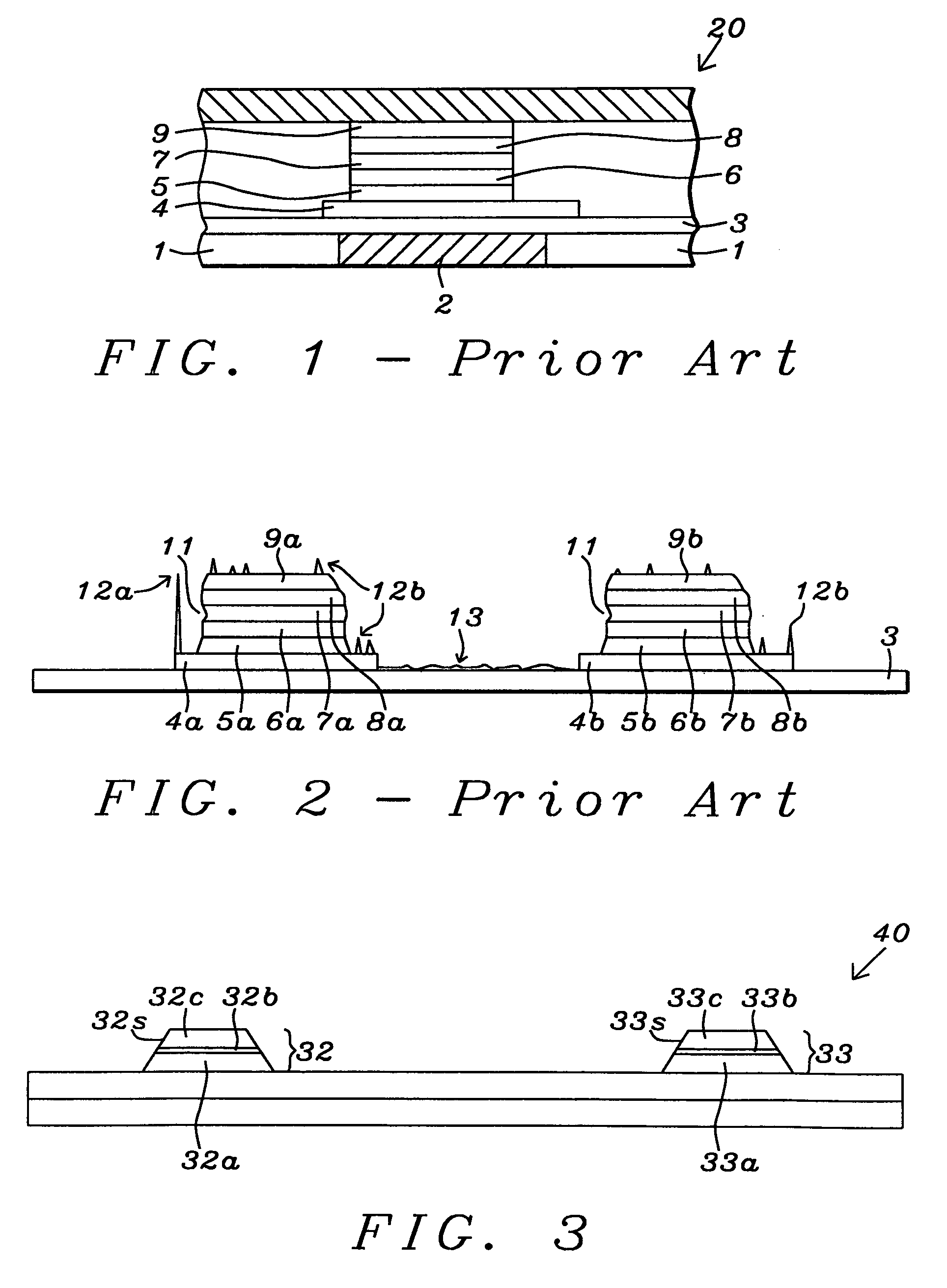

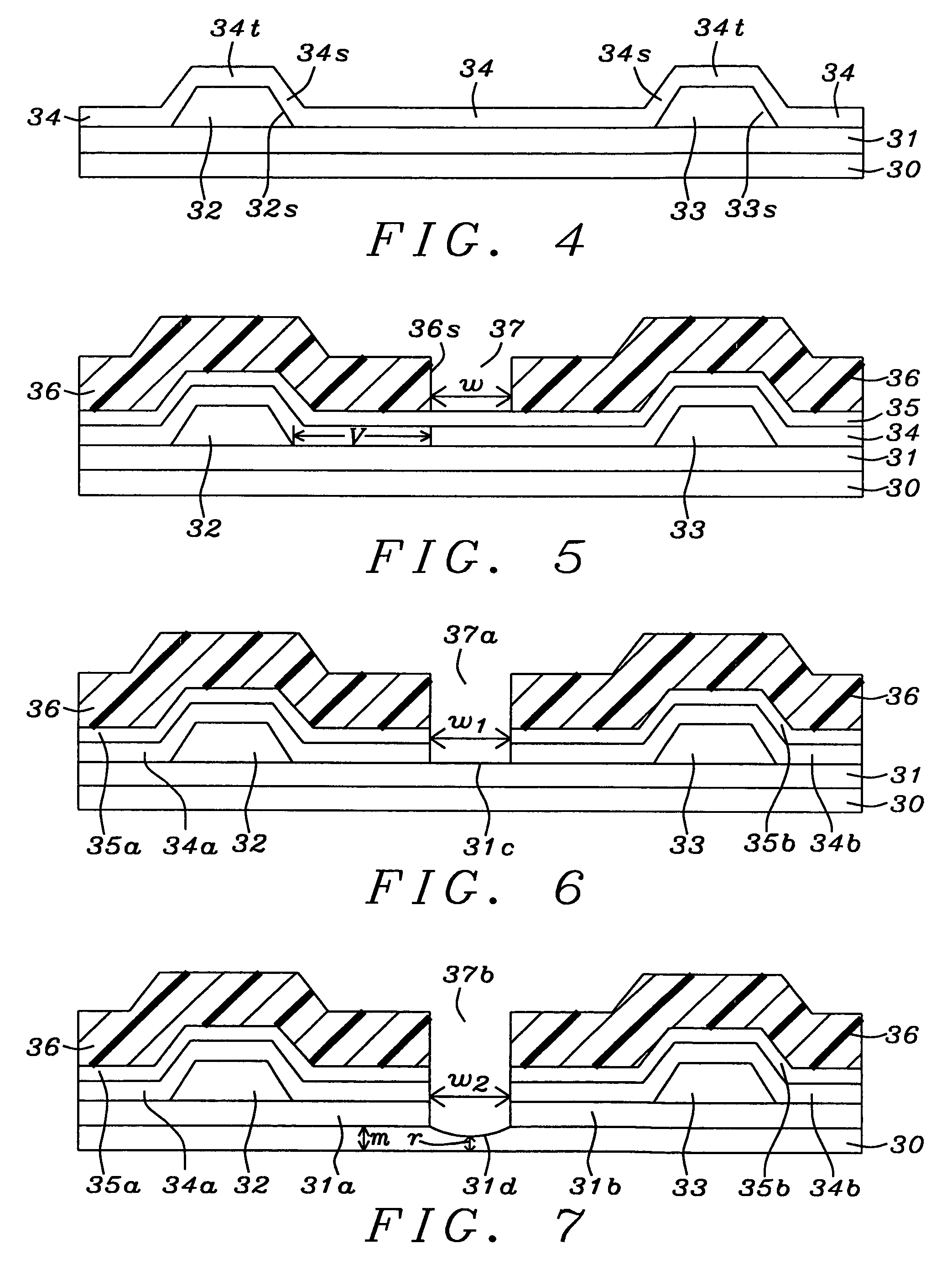

Electrochromic devices

ActiveUS20110267674A1Highly conductiveHigh resistanceDoors/windowsVacuum evaporation coatingIonElectricity

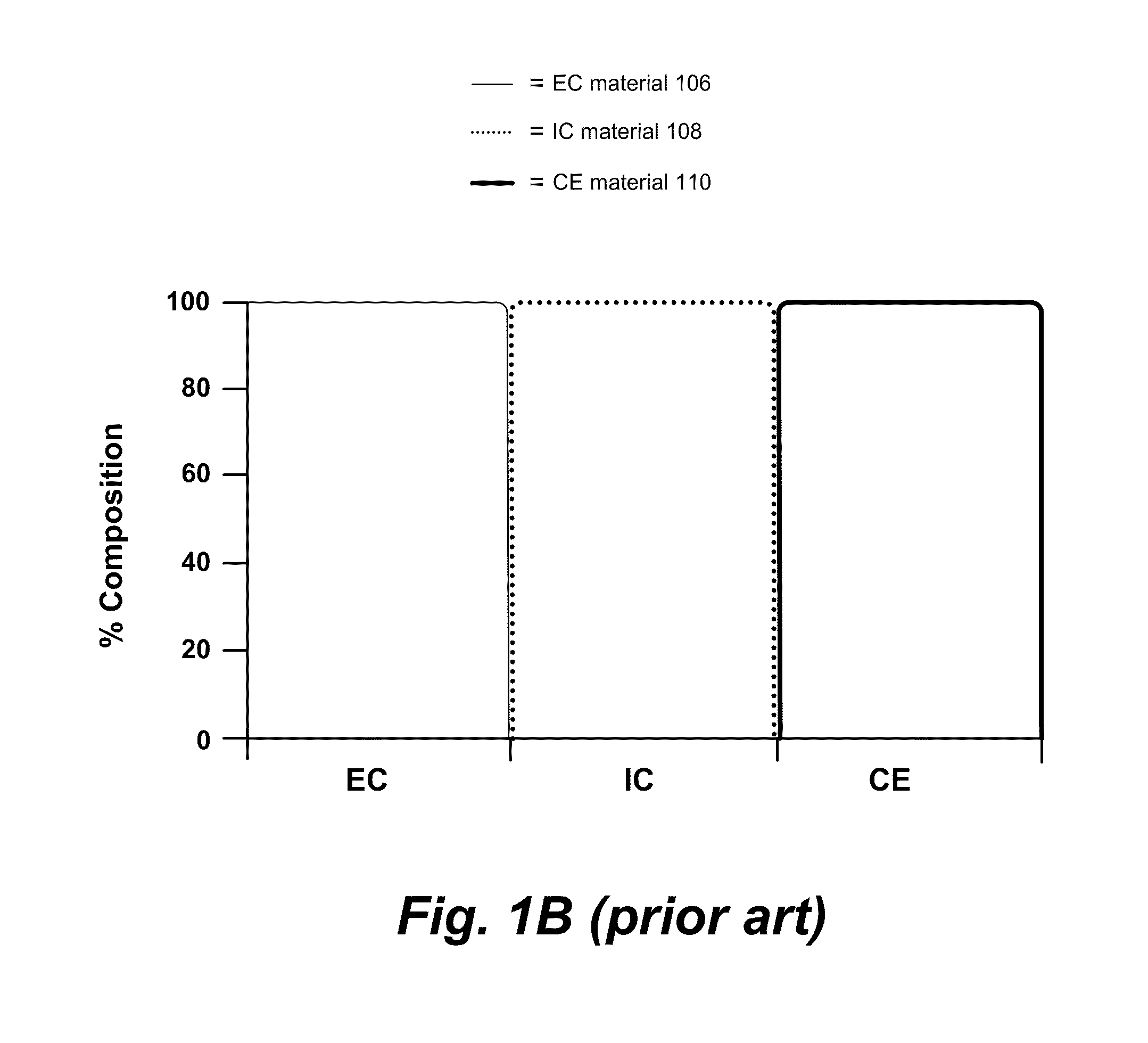

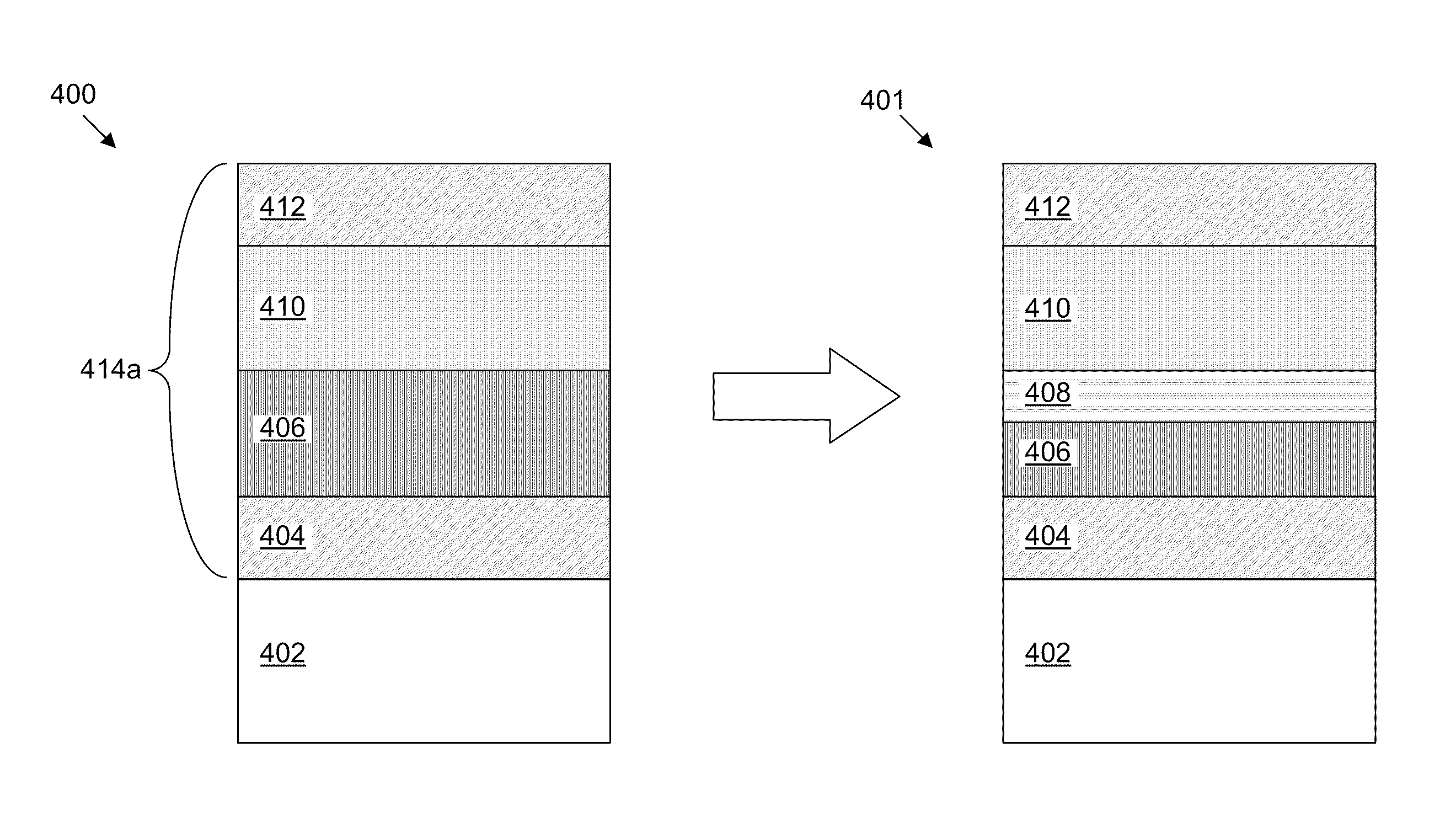

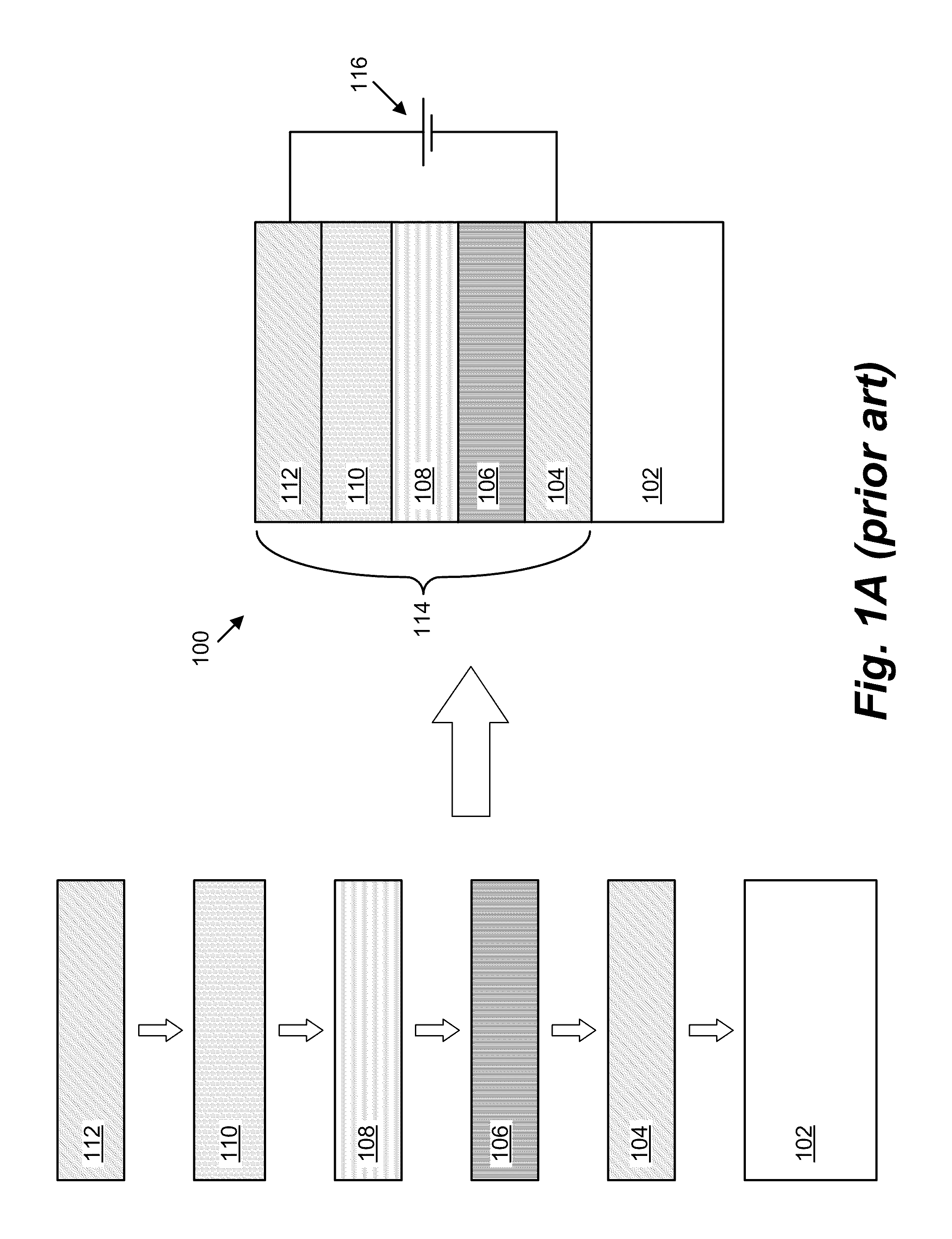

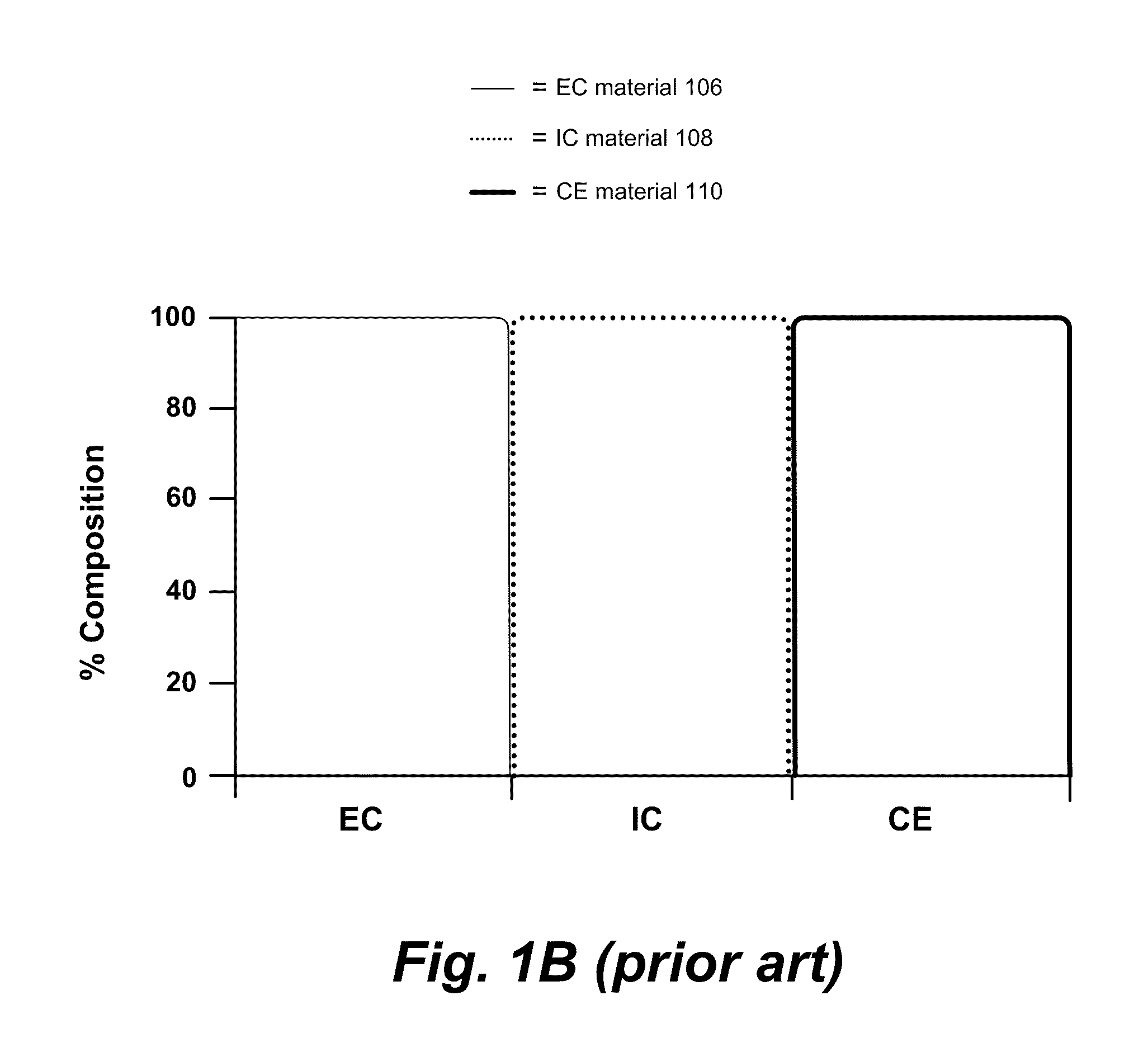

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

Electrochromic devices

ActiveUS8300298B2Improve conductivityIncrease resistanceDoors/windowsVacuum evaporation coatingElectricityOptoelectronics

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

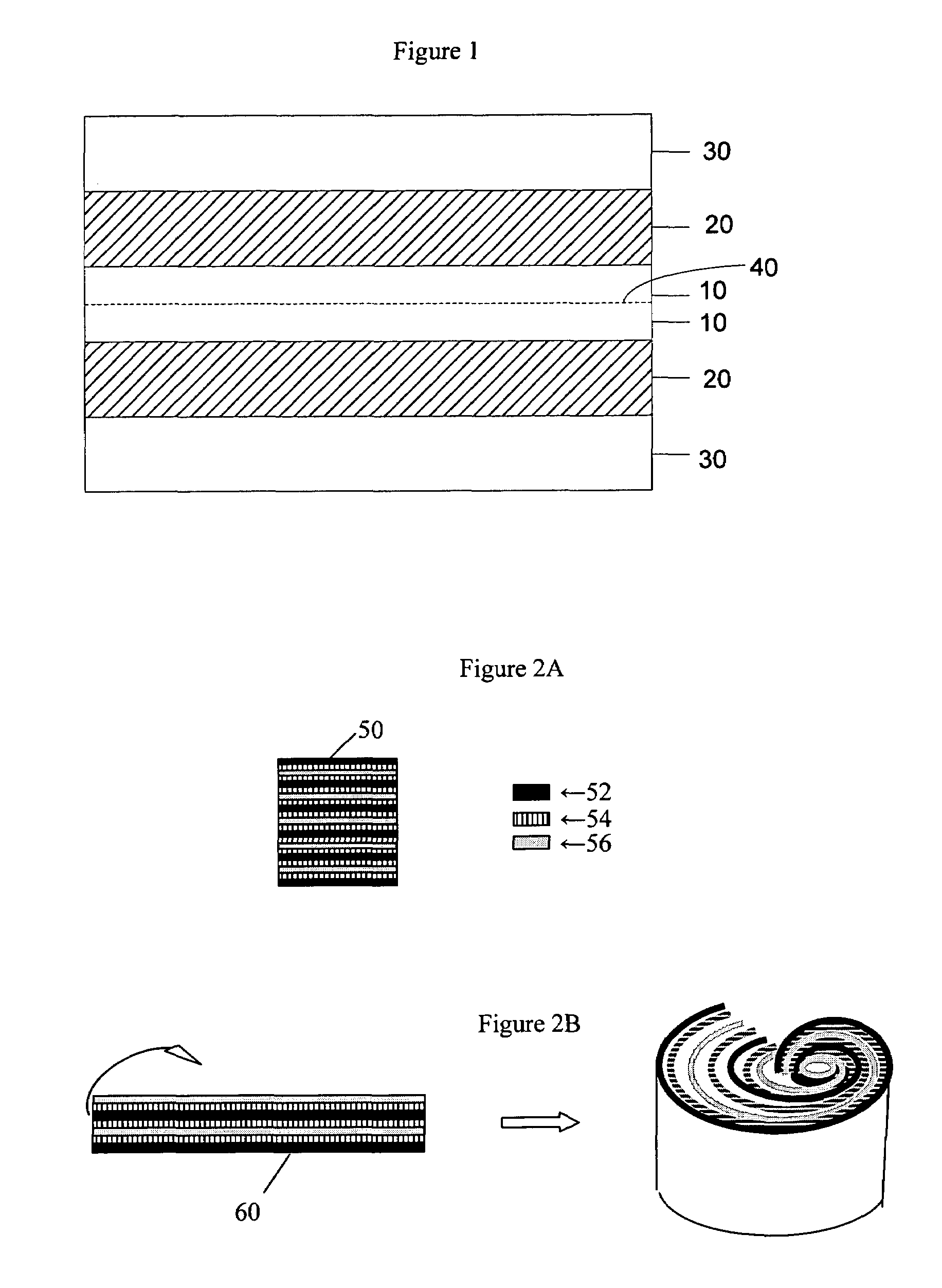

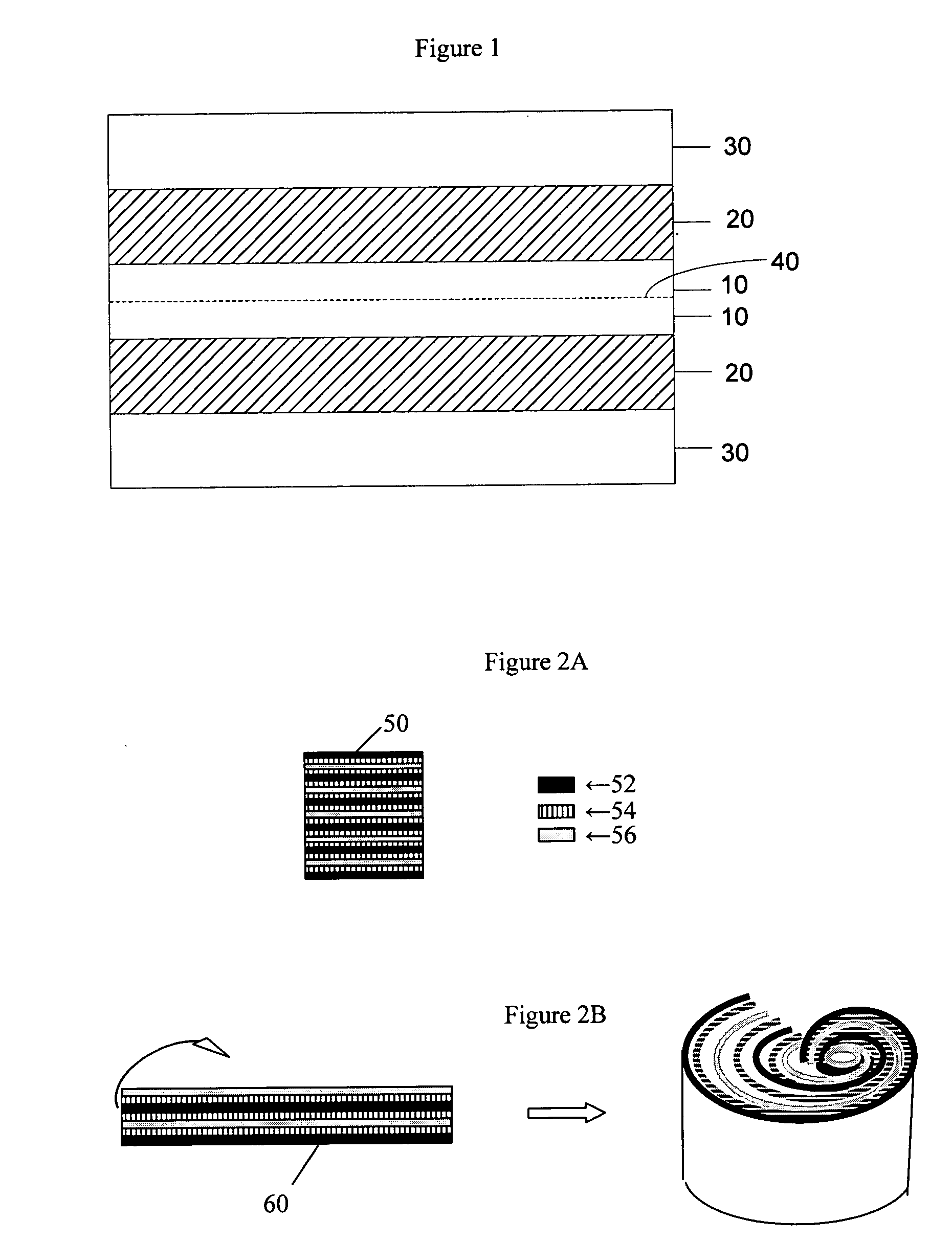

Supercapacitor having electrode material comprising single-wall carbon nanotubes and process for making the same

InactiveUS7061749B2Avoid shortingHybrid capacitor electrolytesHybrid capacitor electrodesSupercapacitorNanotube

The present invention relates to a supercapacitor, also known as an electrical double-layer capacitor or ultracapacitor, having electrode material comprising single-wall carbon nanotubes. The carbon nanotubes can be derivatized with functional groups. The electrode material is made by preparing a polymer-nanotube suspension comprising polymer and nanotubes, forming the polymer-nanotube suspension into a polymer-nanotube composite of the desired form, carbonizing the polymer-nanotube composite to form a carbonaceous polymer-nanotube material, and activating the material. The supercapacitor includes electrode material comprising activated carbonaceous polymer-nanotube material in contact with current collectors and permeated with an electrolyte, which may be either fluid or solid. In the case of a fluid or compressible electrolyte, an electrolyte-permeable separator or spacer is interposed between the electrodes to keep the electrodes from shorting. The supercapacitor made with electrodes comprising underivatized single-wall carbon nanotubes and polymer that has been carbonized and activated appears to operate as a non-Faradaic supercapacitor.

Owner:GEORGIA TECH RES CORP

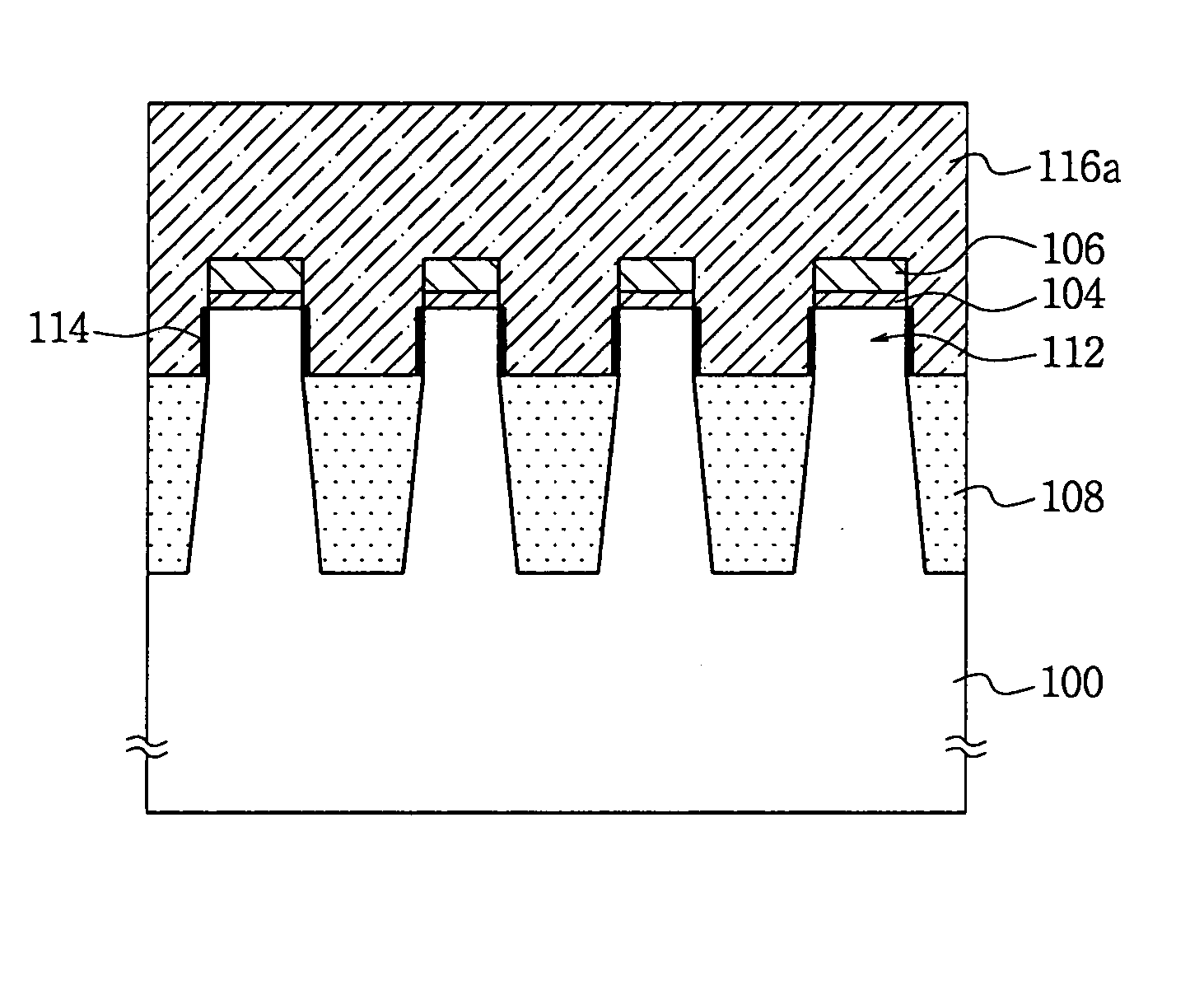

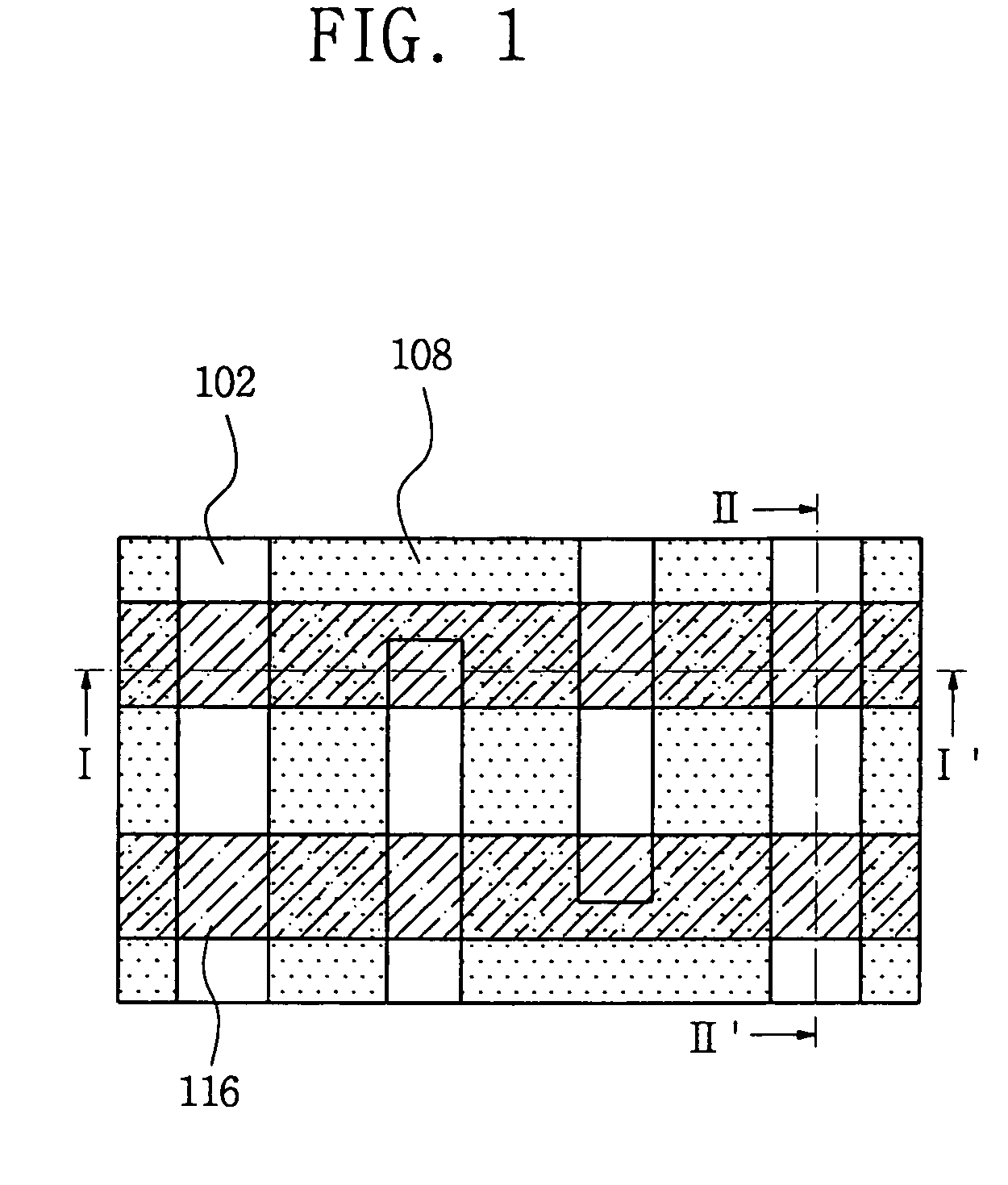

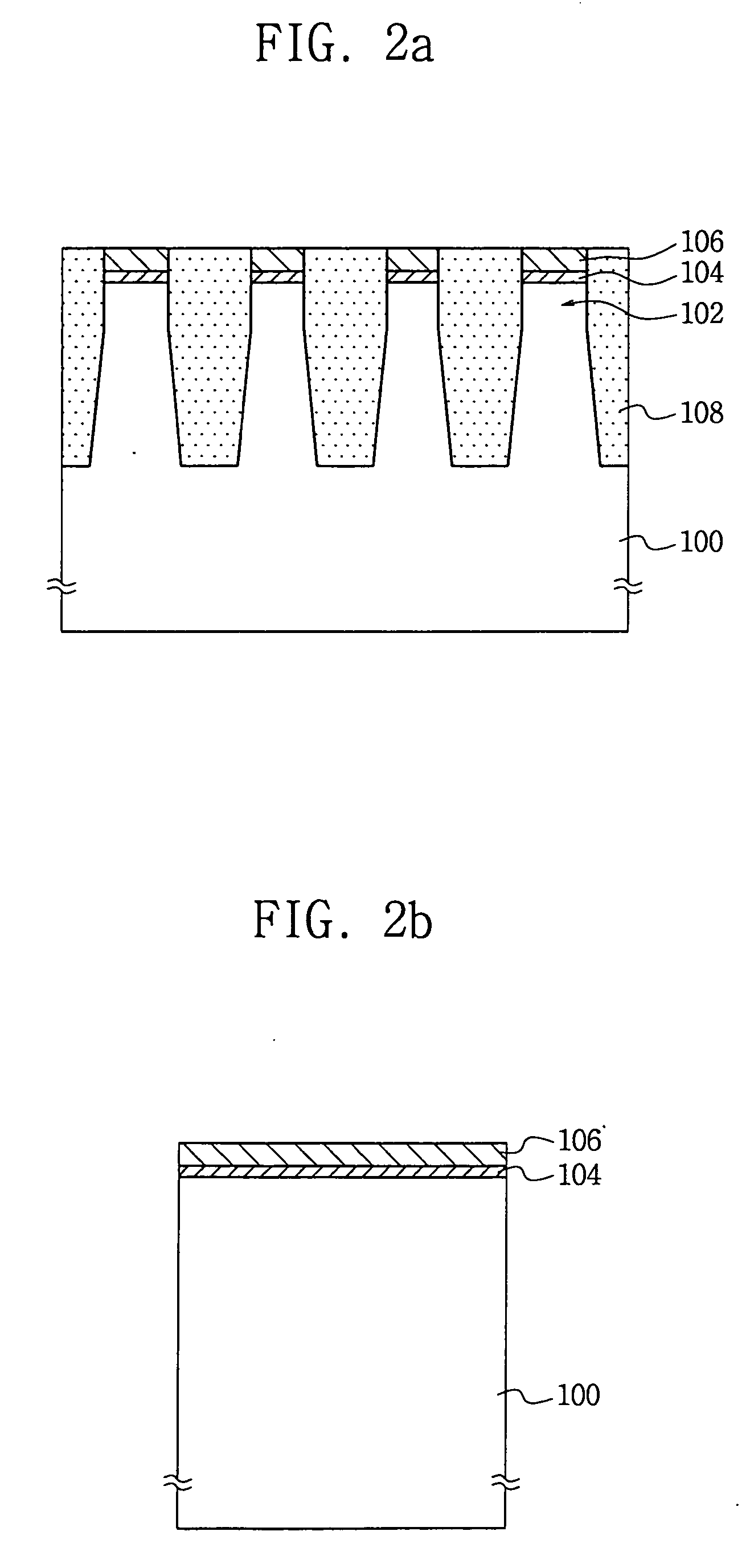

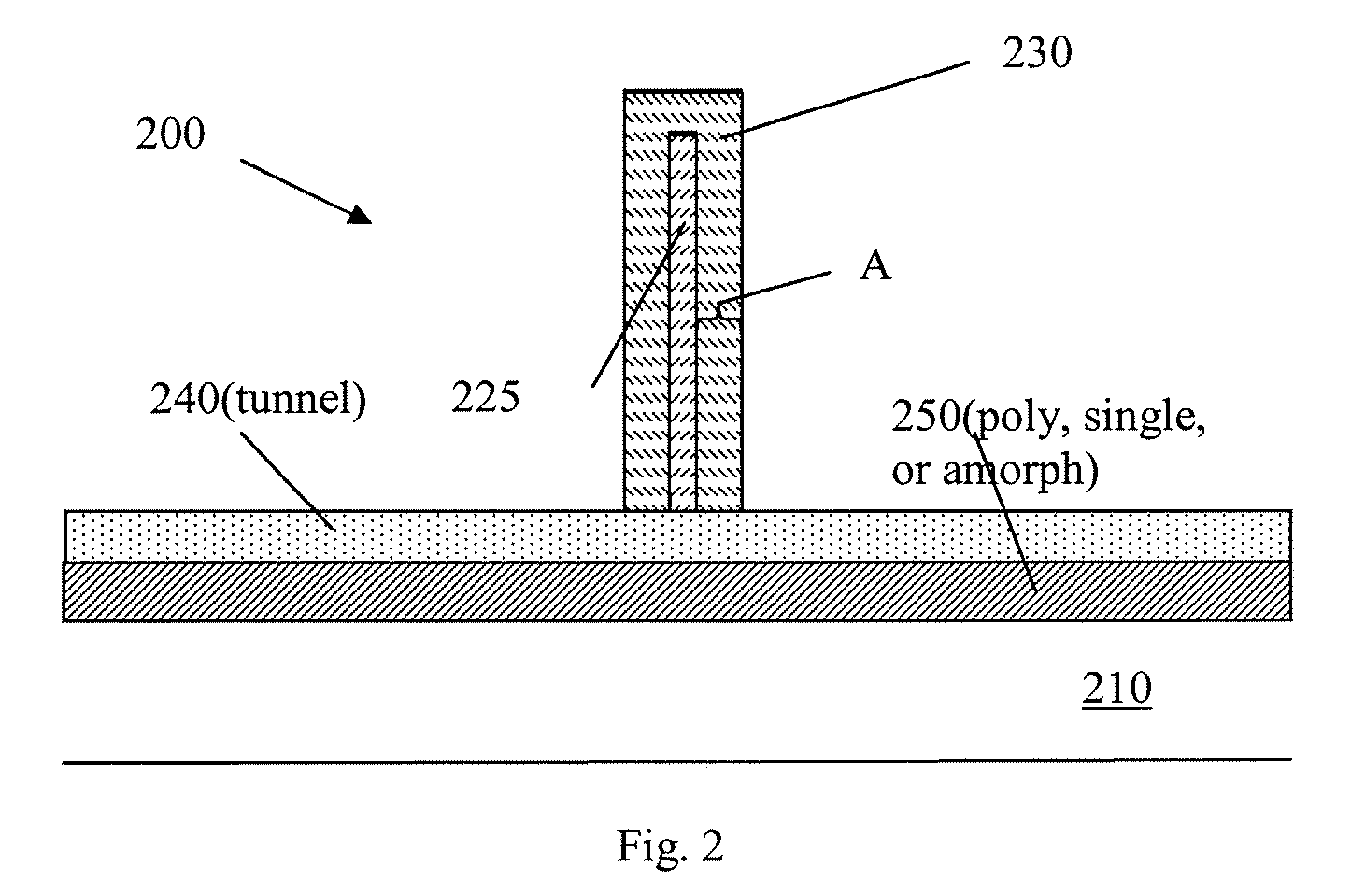

Method for forming a FinFET by a damascene process

ActiveUS20050170593A1Low costAvoid shortingTransistorBrushesManufacturing cost reductionInsulation layer

A device isolation film and an active region are formed on a semiconductor substrate, using a first mask pattern to expose only a formation region of the device isolation film. Only the device isolation film is selectively etched by using the first mask pattern and a second mask pattern as an etch mask, to form a fin only on a gate formation region, the second mask pattern to expose only a gate electrode formation region. A gate insulation layer is formed on both sidewalls of the fin and a gate electrode covering the first mask pattern and the gate insulation layer is formed. Source and drain regions are formed on the remaining portion of the active region where the gate electrode was not formed. Gate electrode separation becomes adequate and manufacturing costs can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

Fabrication process for a magnetic tunnel junction device

InactiveUS20050051820A1Avoid shortingMagnetic-field-controlled resistorsSolid-state devicesEngineeringOxygen

A method of fabricating a magnetic tunnel junction (MTJ) device is provided. A patterned hard mask is oxidized to form a surface oxide thereon. An MTJ stack is etched in alignment with the patterned hard mask after the oxidizing of the patterned hard mask. Preferably, the MTJ stack etch recipe includes chlorine and oxygen. Etch selectivity between the hard mask and the MTJ stack is improved.

Owner:INFINEON TECH AG +1

Supercapacitor having electrode material comprising single-wall carbon nanotubes and process for making the same

InactiveUS20060098389A1Avoid shortingHybrid capacitor electrolytesHybrid capacitor electrodesSupercapacitorNanotube

The present invention relates to a supercapacitor, also known as an electrical double-layer capacitor or ultracapacitor, having electrode material comprising single-wall carbon nanotubes. The carbon nanotubes can be derivatized with functional groups. The electrode material is made by preparing a polymer-nanotube suspension comprising polymer and nanotubes, forming the polymer-nanotube suspension into a polymer-nanotube composite of the desired form, carbonizing the polymer-nanotube composite to form a carbonaceous polymer-nanotube material, and activating the material. The supercapacitor includes electrode material comprising activated carbonaceous polymer-nanotube material in contact with current collectors and permeated with an electrolyte, which may be either fluid or solid. In the case of a fluid or compressible electrolyte, an electrolyte-permeable separator or spacer is interposed between the electrodes to keep the electrodes from shorting. The supercapacitor made with electrodes comprising underivatized single-wall carbon nanotubes and polymer that has been carbonized and activated appears to operate as a non-Faradaic supercapacitor.

Owner:GEORGIA TECH RES CORP

Electrochromic devices

ActiveUS8764951B2Improve conductivityIncrease resistanceVacuum evaporation coatingSputtering coatingEngineeringInorganic materials

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically-insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically-insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

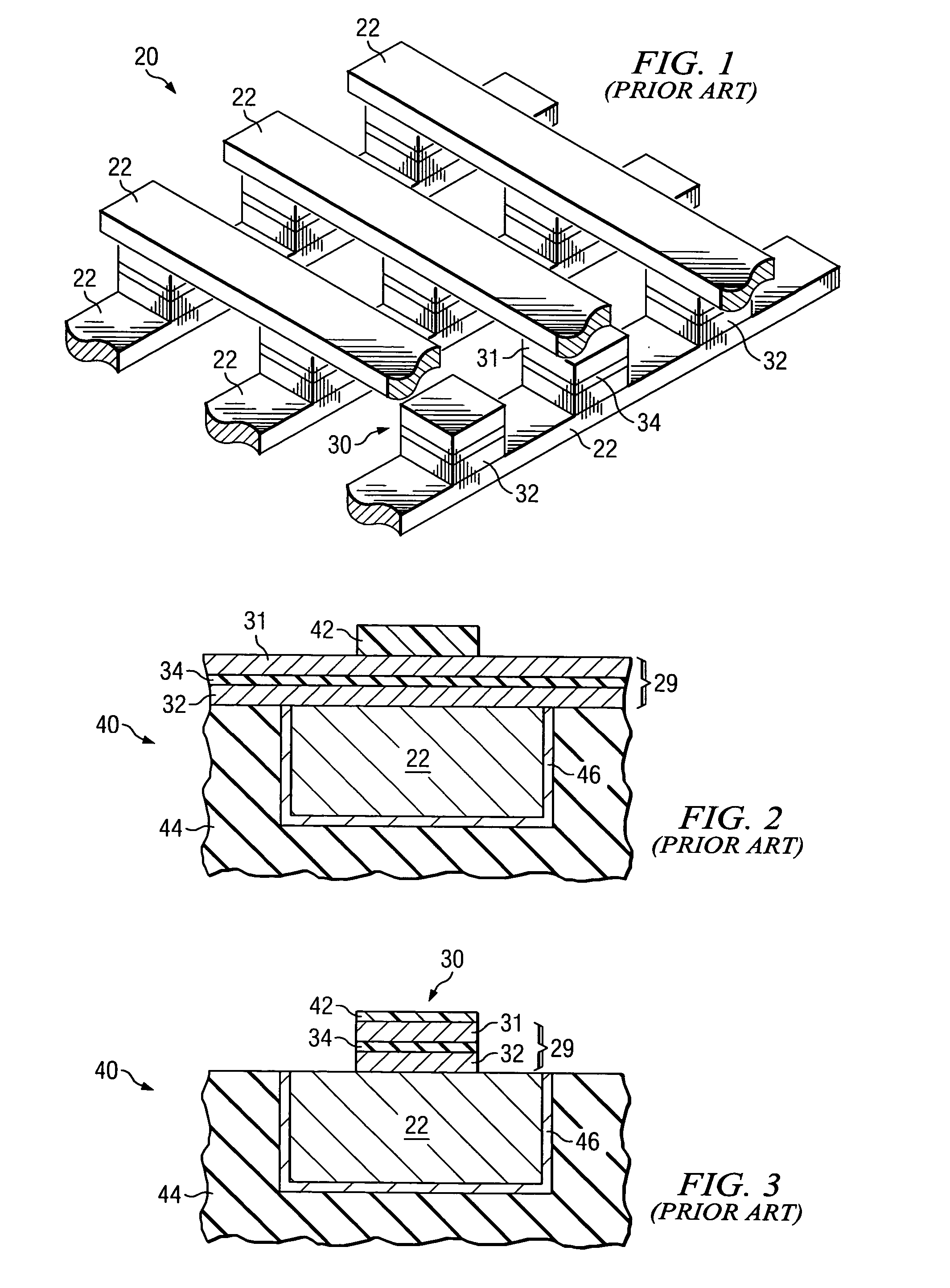

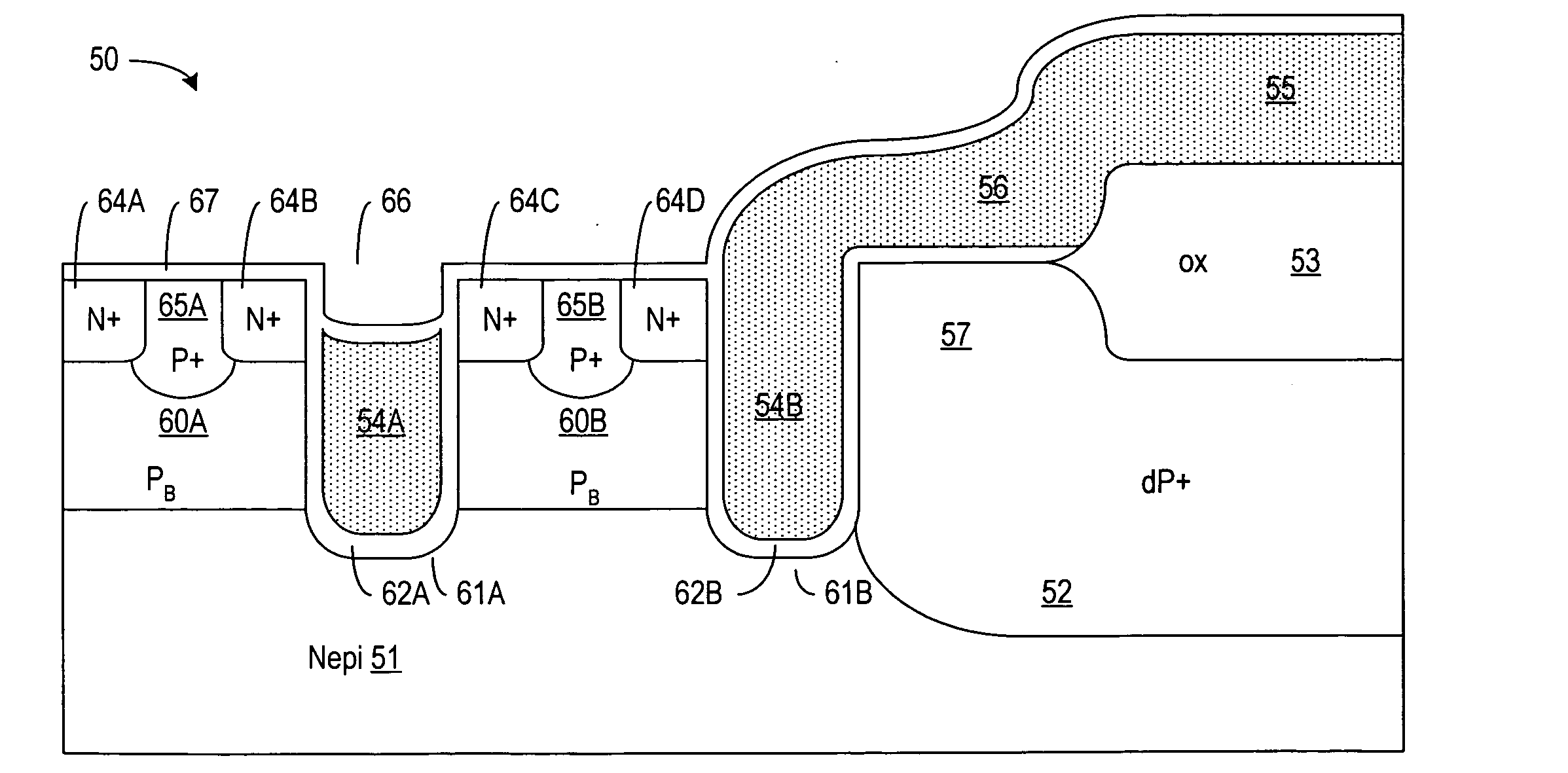

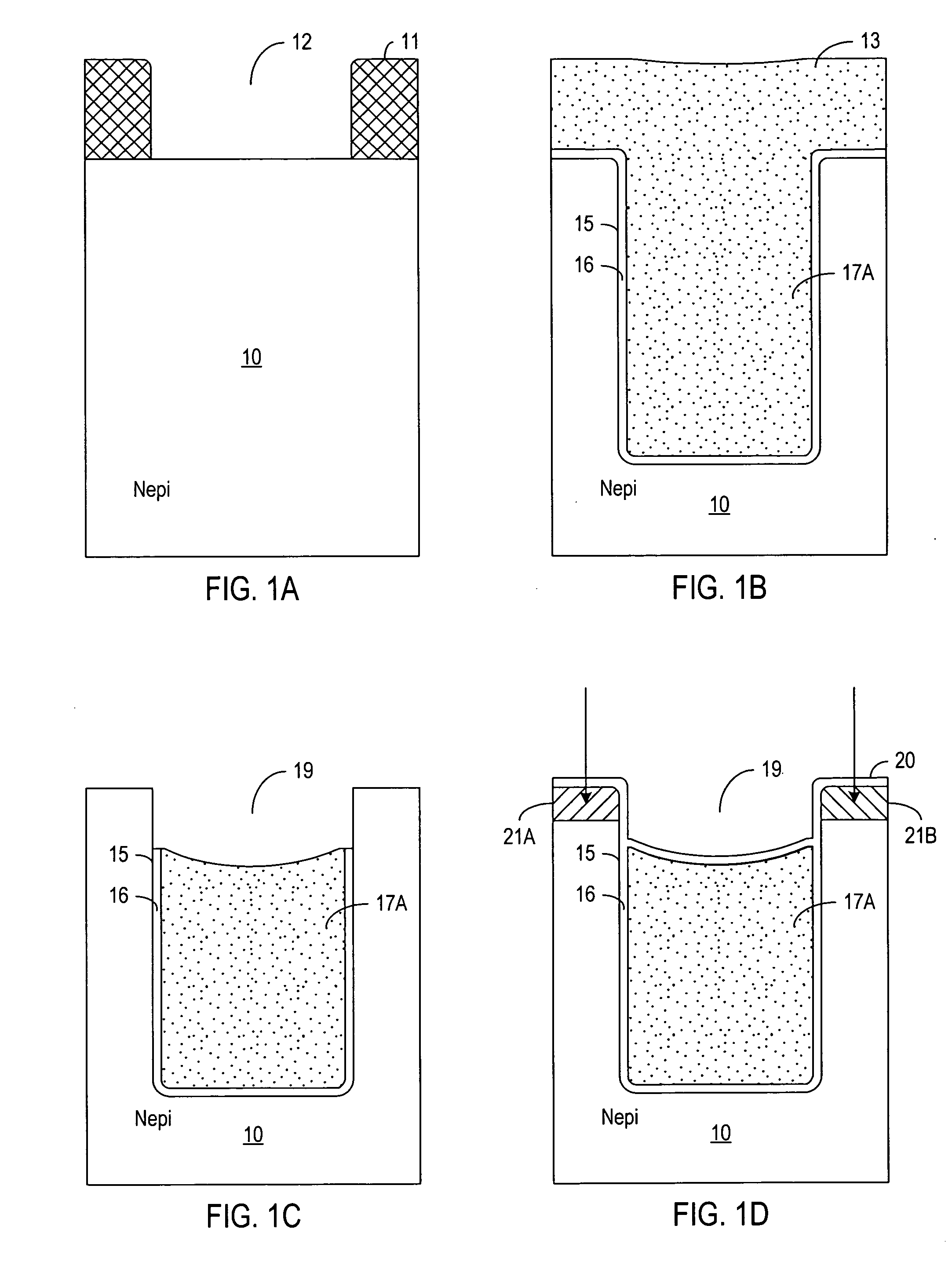

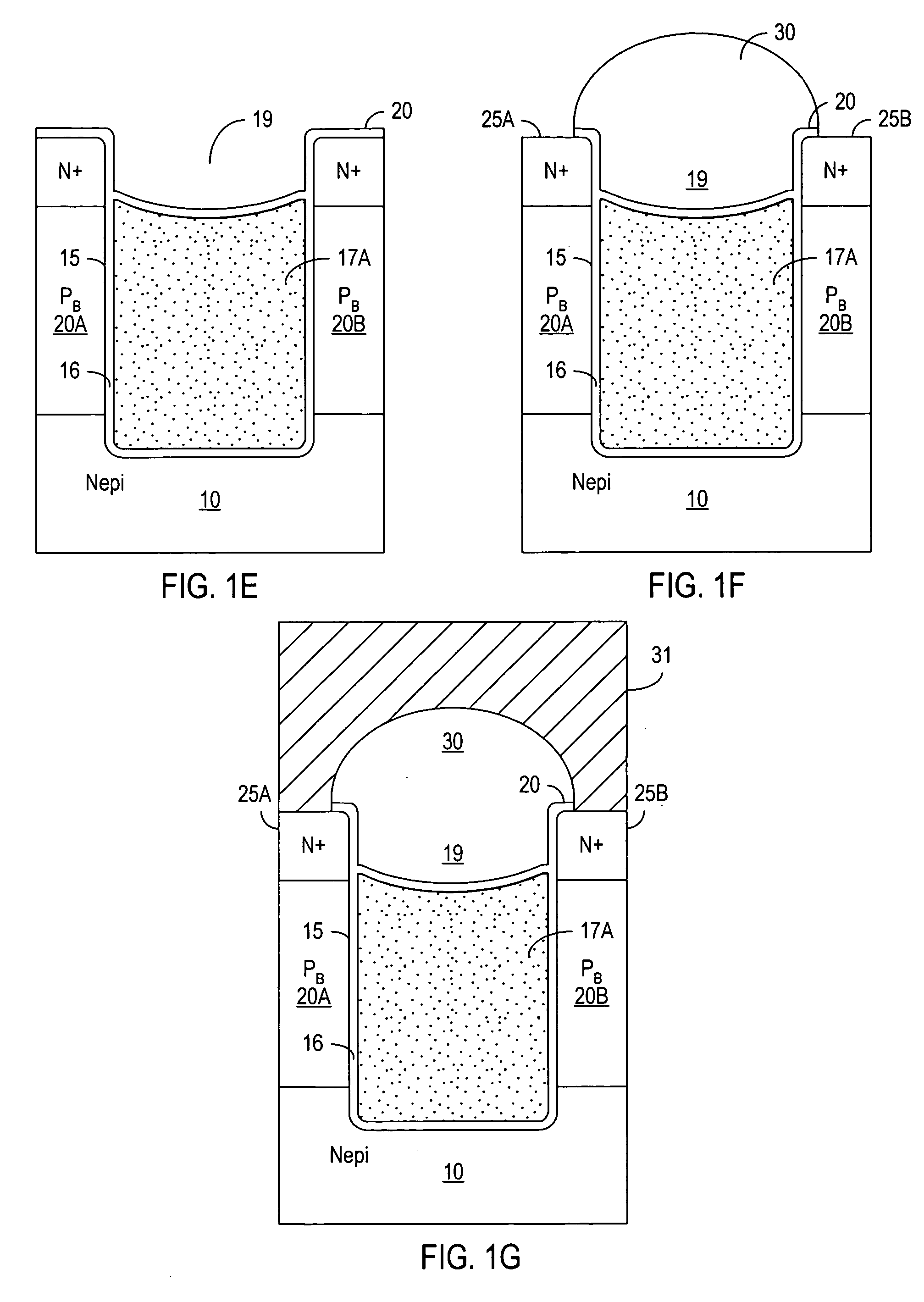

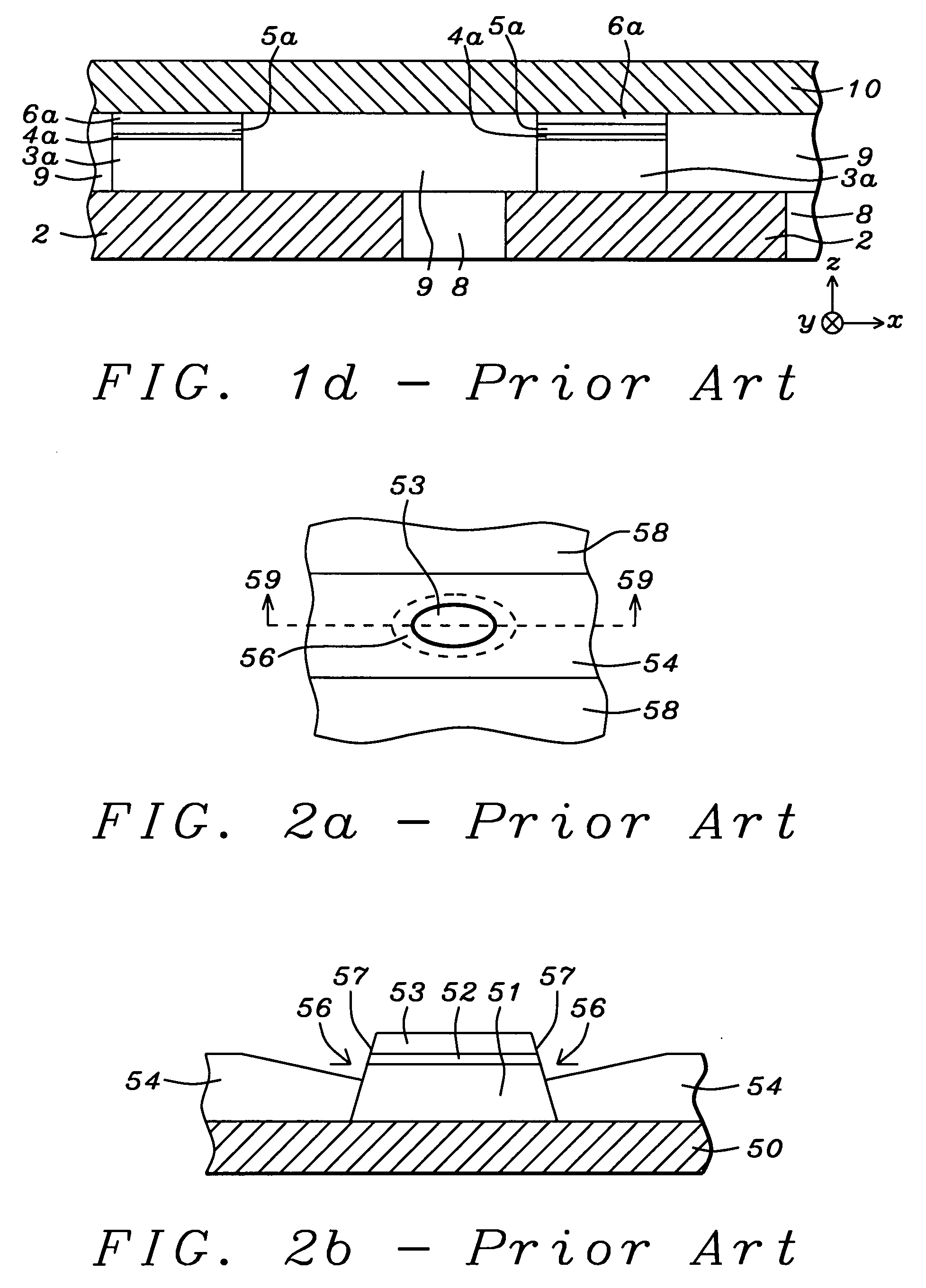

Trench power MOSFET with planarized gate bus

InactiveUS20040173844A1Increase contactMaximize device densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower MOSFETSubstrate surface

Power MOSFETs and fabrication processes for power MOSFETs use a continuous conductive gate structure within trenches to avoid problems arising from device topology caused when a gate bus extends above a substrate surface. The conductive gate structure forms gates in device trenches in an active device region and forms a gate bus in a gate bus trench. The gate bus trench that connects to the device trenches can be wide to facilitate forming a gate contact to the gate bus, while the device trenches can be narrow to maximize device density. CMP process can be used to planarize the conductive gate structure and / or overlying insulating layers. The processes are compatible with processes forming self-aligned or conventional contacts in the active device region.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

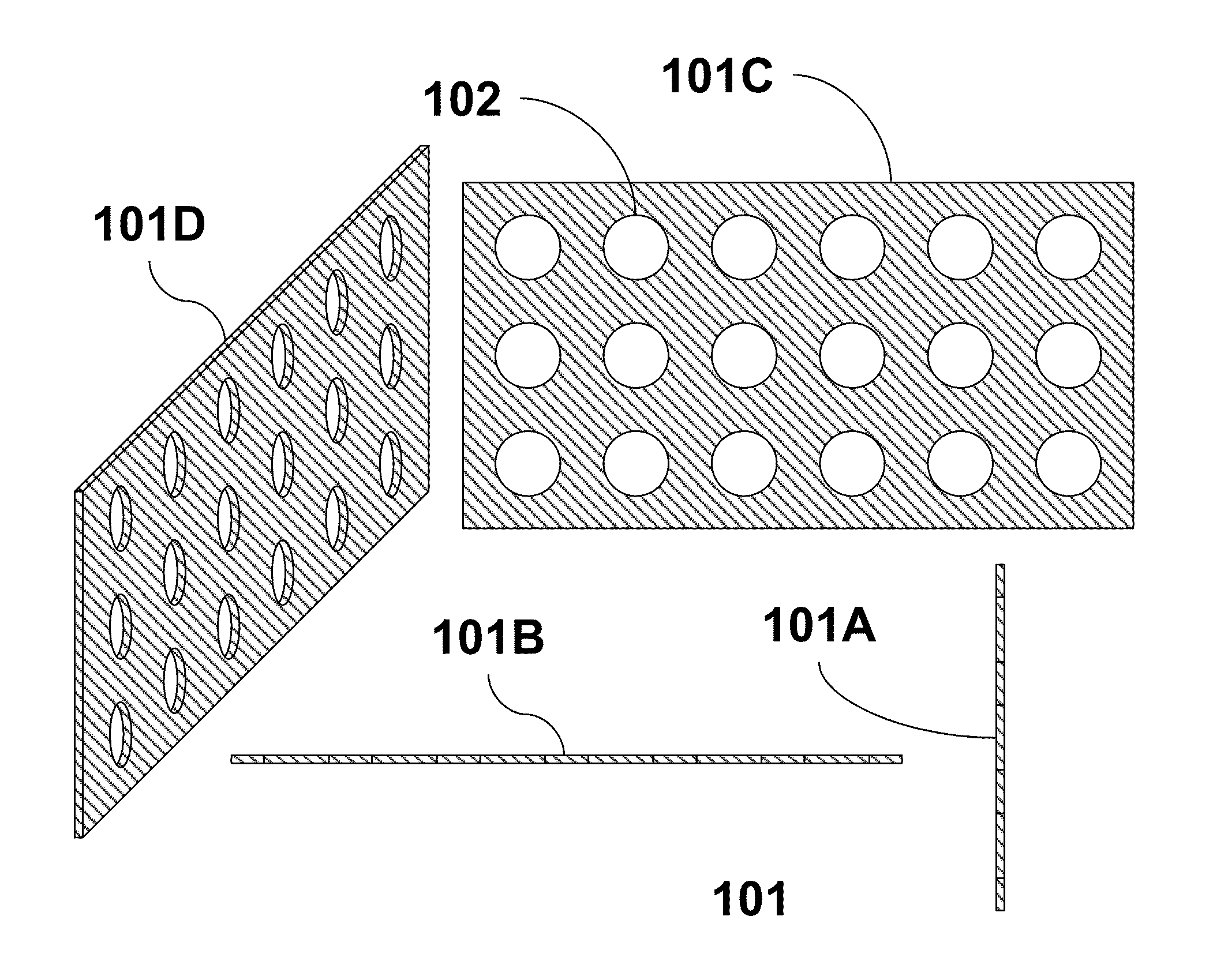

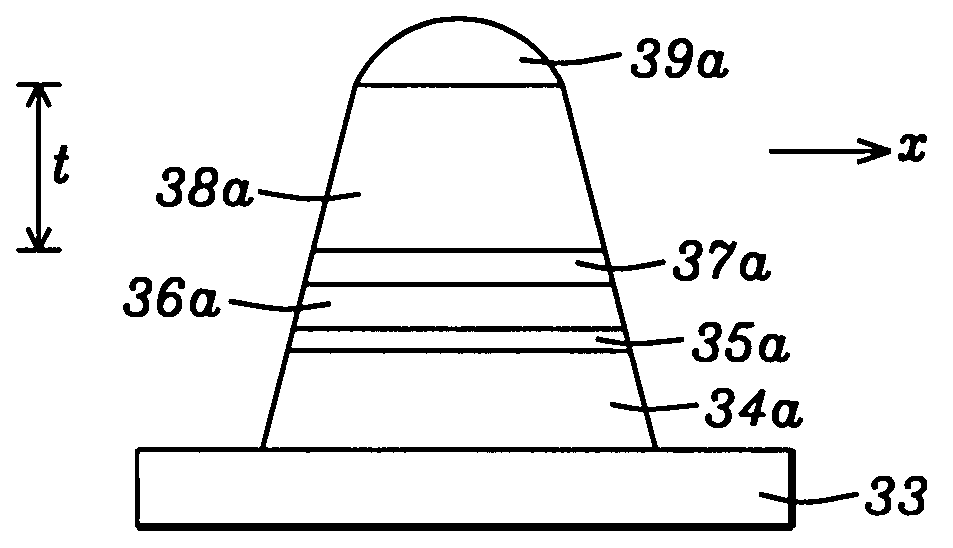

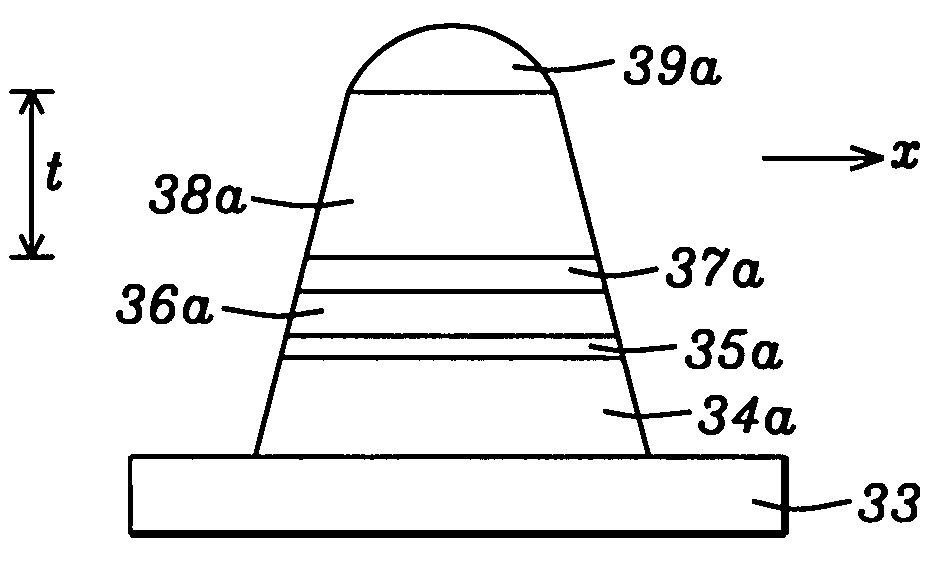

Multilayered Film-Nanowire Composite, Bifacial, and Tandem Solar Cells

A photovoltaic device includes a substrate having at least two surfaces and a multilayered film disposed on at least a portion of at least one surface of the substrate. Elongated nanostructures are disposed on the multilayered film. The device incorporates a top layer of the multilayered film contacting the elongated nanostructures that is a tunnel junction. The device has at least one layer deposited over the elongated nanostructures defining a portion of a photoactive junction. A solar panel includes at least one photovoltaic device. The solar panel isolates each such devices from its surrounding atmospheric environment and permits the generation of electrical power.

Owner:GENERAL ELECTRIC CO

Part solid, part fluid and flow electrochemical cells including metal-air and li-air battery systems

PendingUS20130189592A1Provide integrityAvoid shortingPrimary cell to battery groupingFuel and primary cellsLithium–air batteryEngineering

Owner:CALIFORNIA INST OF TECH

Electrochromic devices

ActiveUS20110249314A1Improve conductivityIncrease resistanceElectric discharge tubesVacuum evaporation coatingElectricityOptoelectronics

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

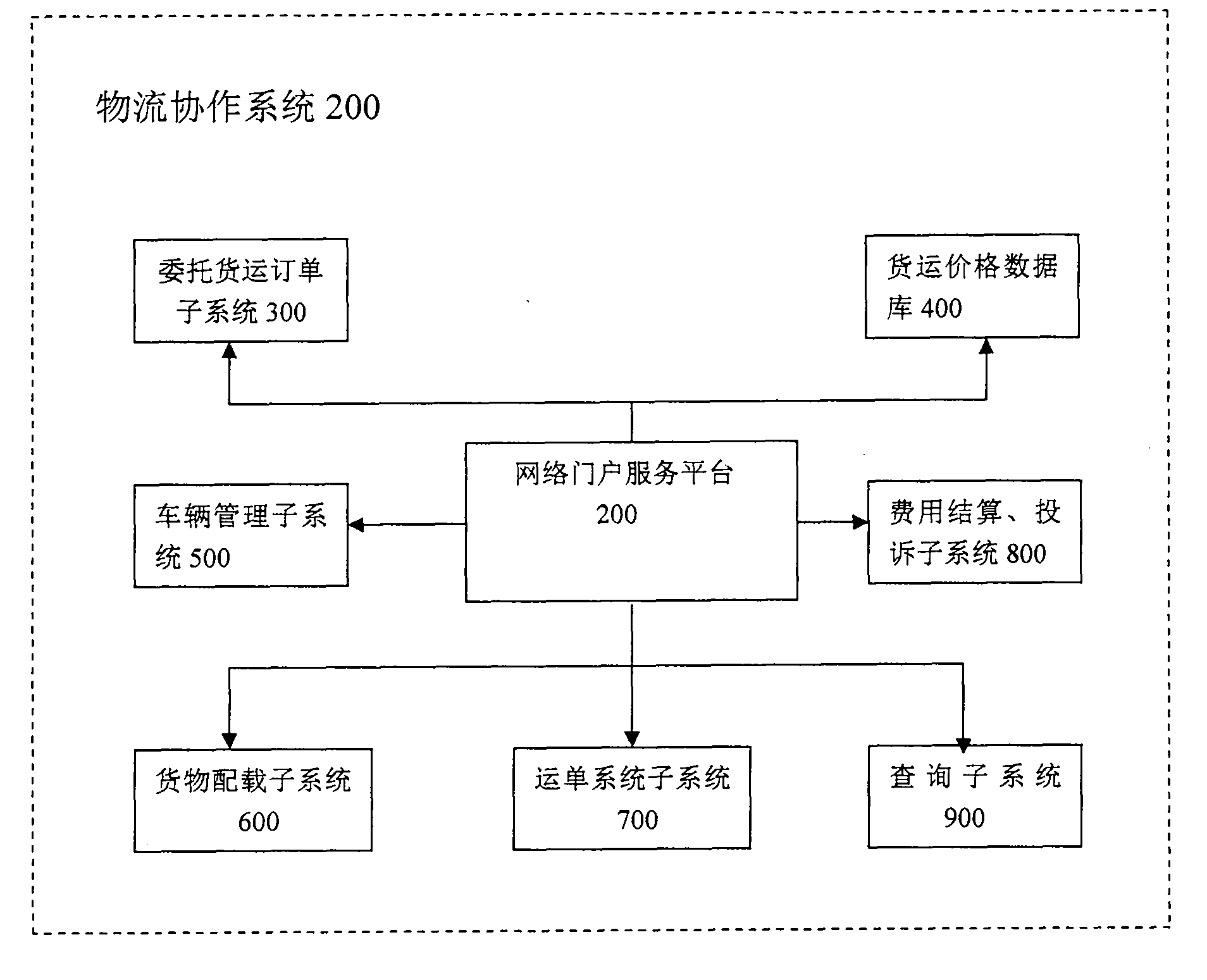

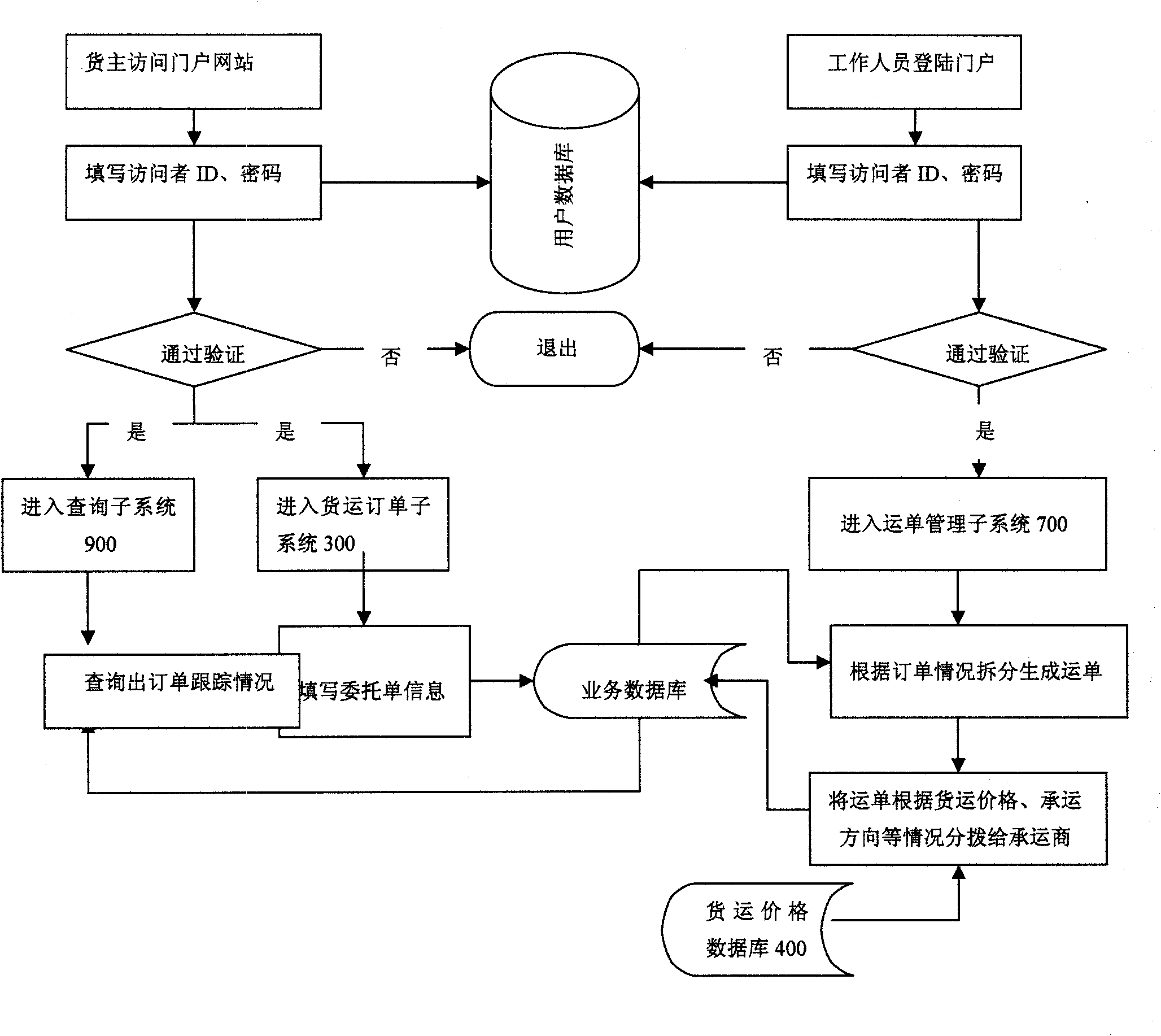

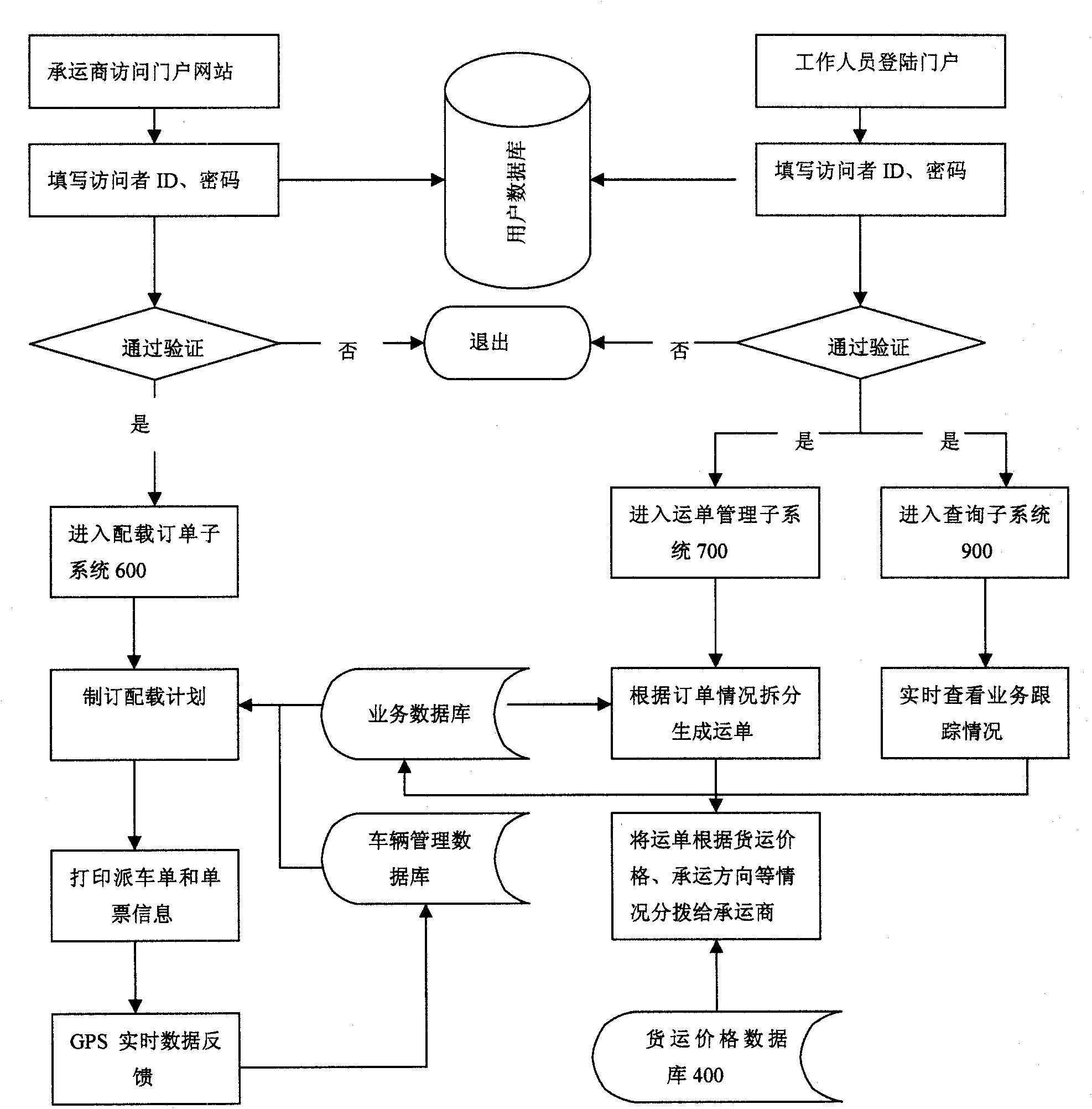

Transportation management method based on joint collaboration of logistics company, shipper and carrier

InactiveCN101923666AHigh transparencyImprove tightnessLogisticsLogistics managementNetworking protocol

The invention relates to a transportation management method based on the joint collaboration of a logistics company, a shipper and a carrier. The transportation management method comprises the following steps: the logistics company creates a transportation management system network platform; the shipper and the carrier visit the system network platform through the network protocol, and the logistics company signs a contract with the shipper and the carrier and delivers order information with forwarding order number according to the contract to the carrier and the shipper; the carrier adjusts according to the vehicle scheduling plan and single vote information and feedbacks the information to the system network platform; the logistics company performs expense settlement based on the information, accepts complaints and settles claims; and the network platform provides a real-time query system, so that the relevant information of accepted goods and the account statement can be checked in real time. The invention has the advantages that the shipper, the logistics company and the carrier share the total process of forwarding transportation, so that the competitiveness of a supply chain is increased; the information asymmetry caused by regional difference is solved, a supply of goods can be organized at different places, so that return vehicles of the carrier can be avoided from being empty, and benefits are brought for three parties of supplier, customer and service provider.

Owner:上海美华系统有限公司

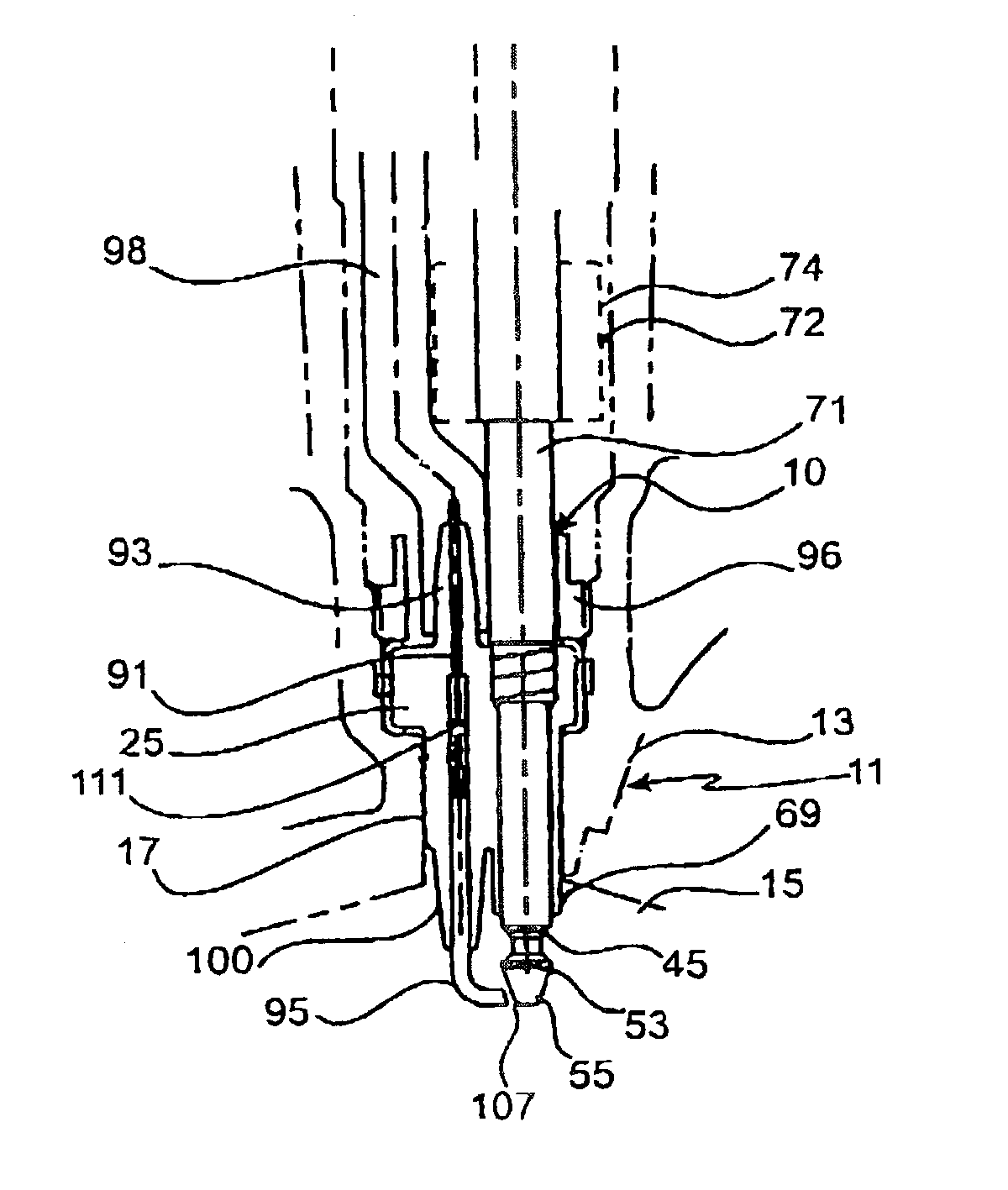

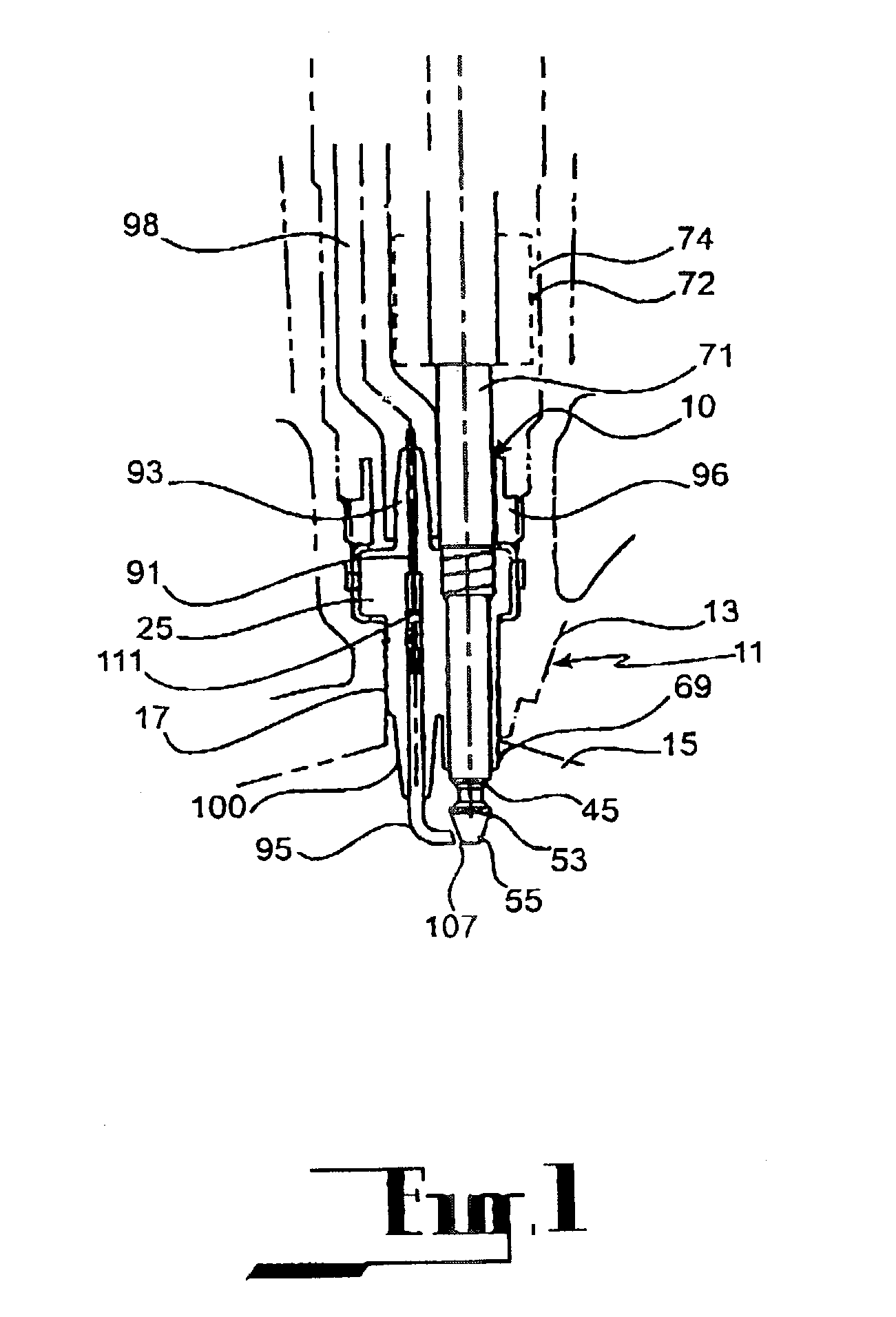

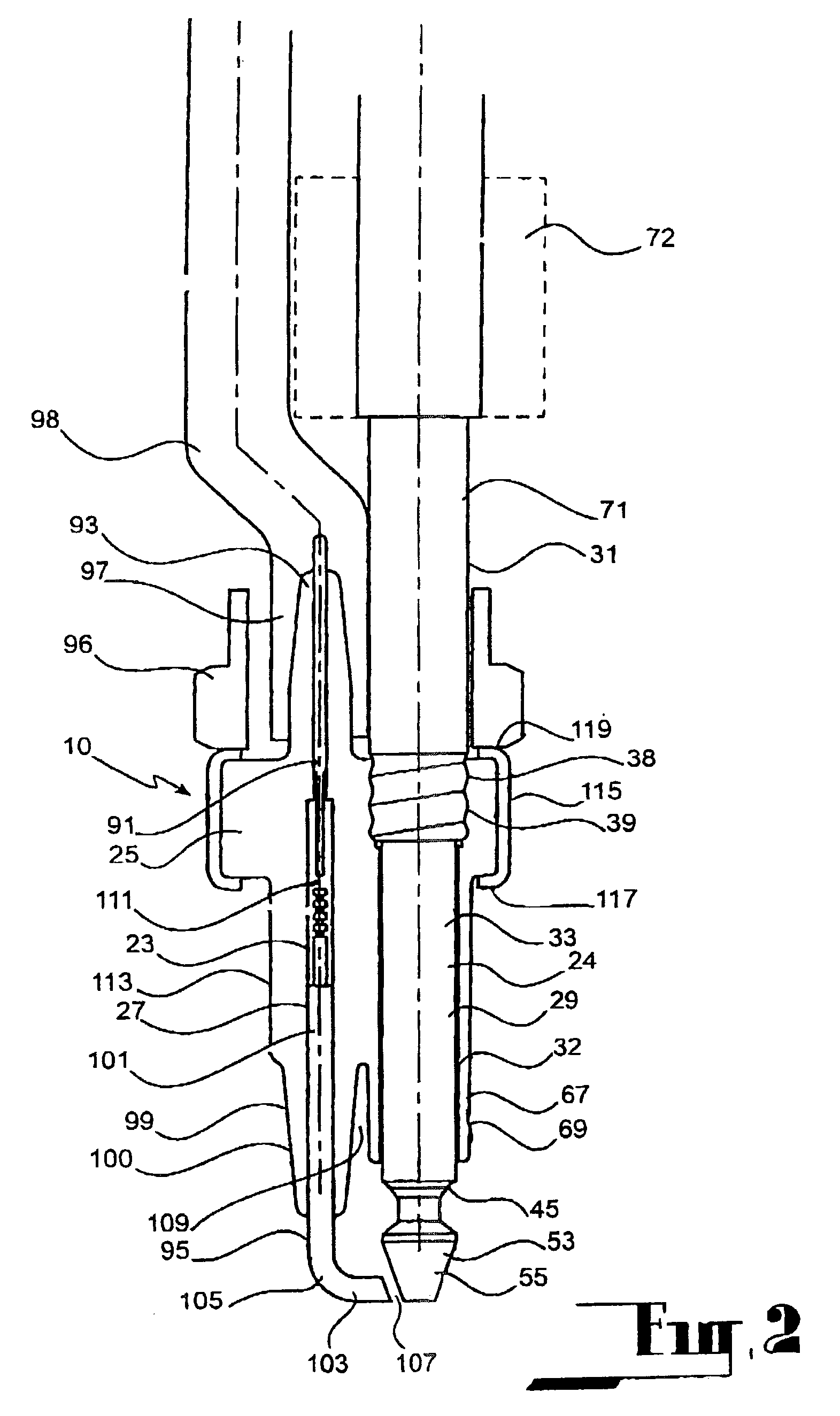

Combined fuel injection and ignition means

InactiveUS7086376B2Reduce capacityConstruction is difficultHigh pressure gas fuel injectionMachines/enginesEngineeringInternal combustion engine

A device (10) providing a combined fuel injection and ignition means for a spark-ignition internal combustion engine. The device (10) comprises a insulator body (25) of ceramic material, a fuel flow path (24) having a section thereof encased in the insulator body (25) and terminating at a delivery port (45) disposed outwardly of the insulator body (25), and, an ignition path (23) having a section encased in the insulator body (25) in a spaced apart relationship with respect to the section of the fuel path (24). The fuel path (24) is defined within a valve structure (33) detachably secured to the insulator body (25) so as to be selectively removable therefrom. The ignition path (23) terminates at an electrode (95) disposed outwardly of the insulator body (25). The insulator body has a nose portion (100) and a skirt portion (69) beyond the delivery port (45). The nose (100) and the delivery port (45) are positioned relative to each other such that all or at least part of the fuel spray issuing from the delivery port (45) avoids impingement on the nose (100).

Owner:ORBITAL ENGINE CO PTY LTD

Bottom electrode etching process in MRAM cell

ActiveUS8334213B2Not to damageImprove device yieldDecorative surface effectsSolid-state devicesBit lineWater based

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

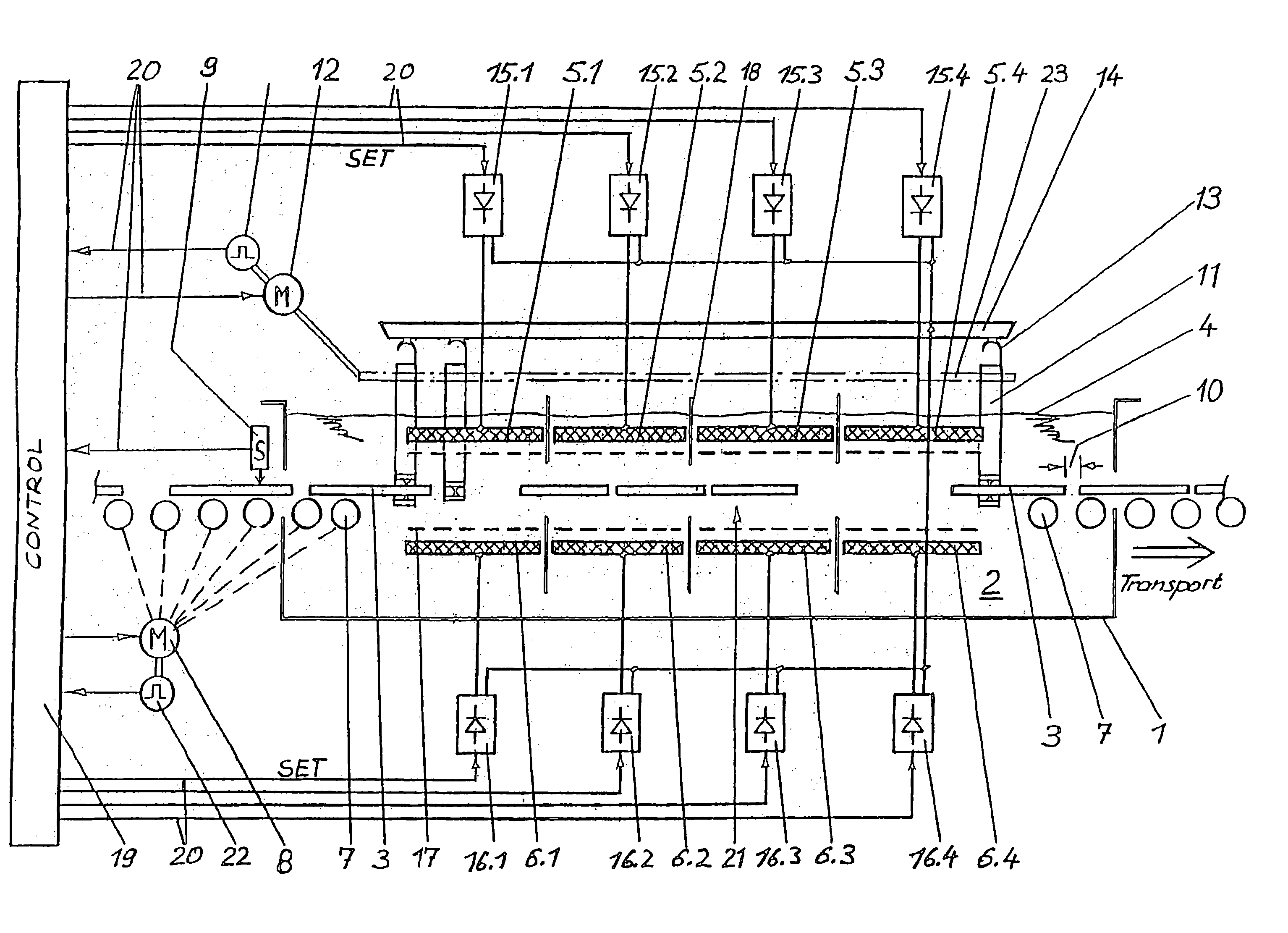

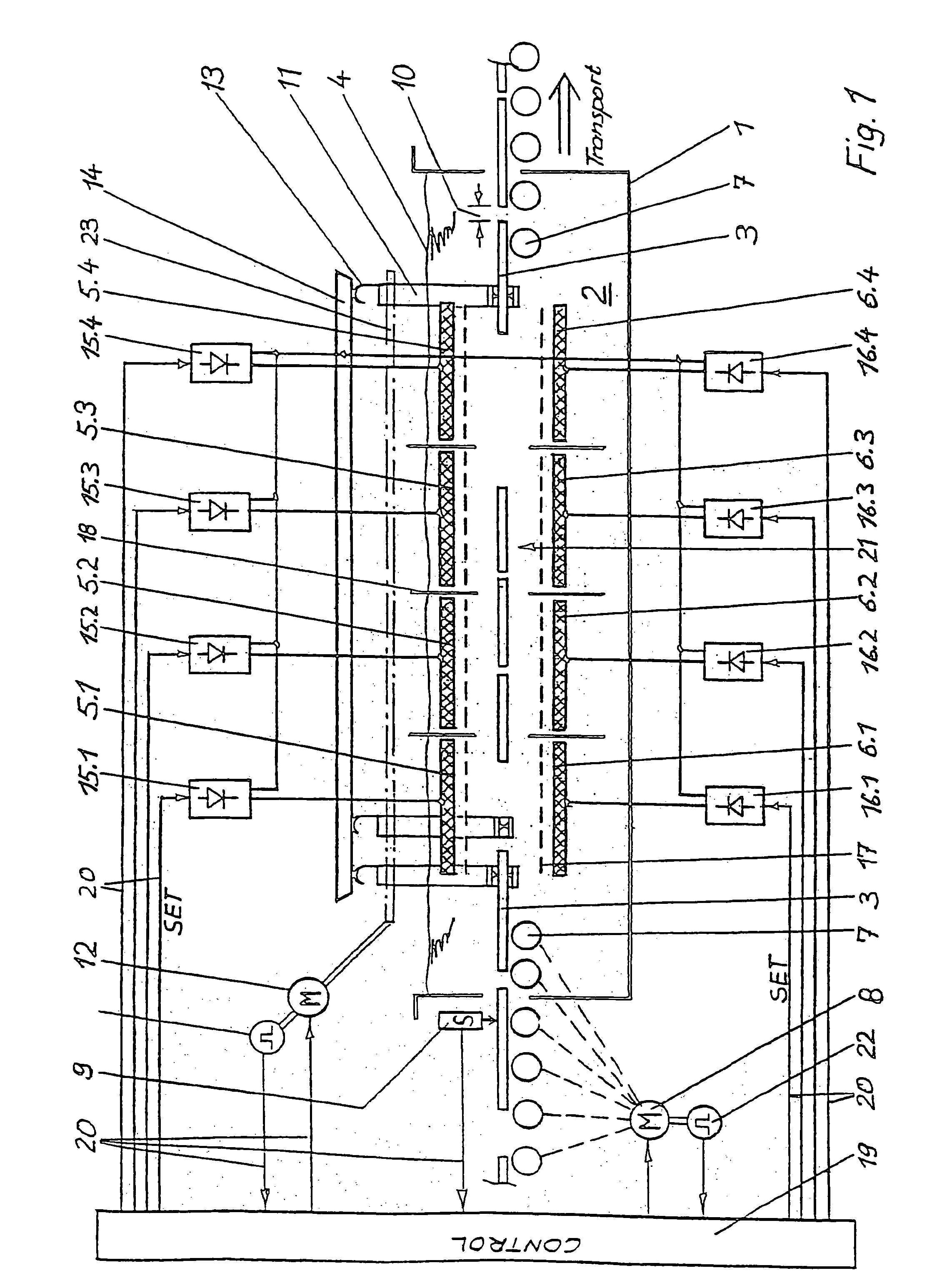

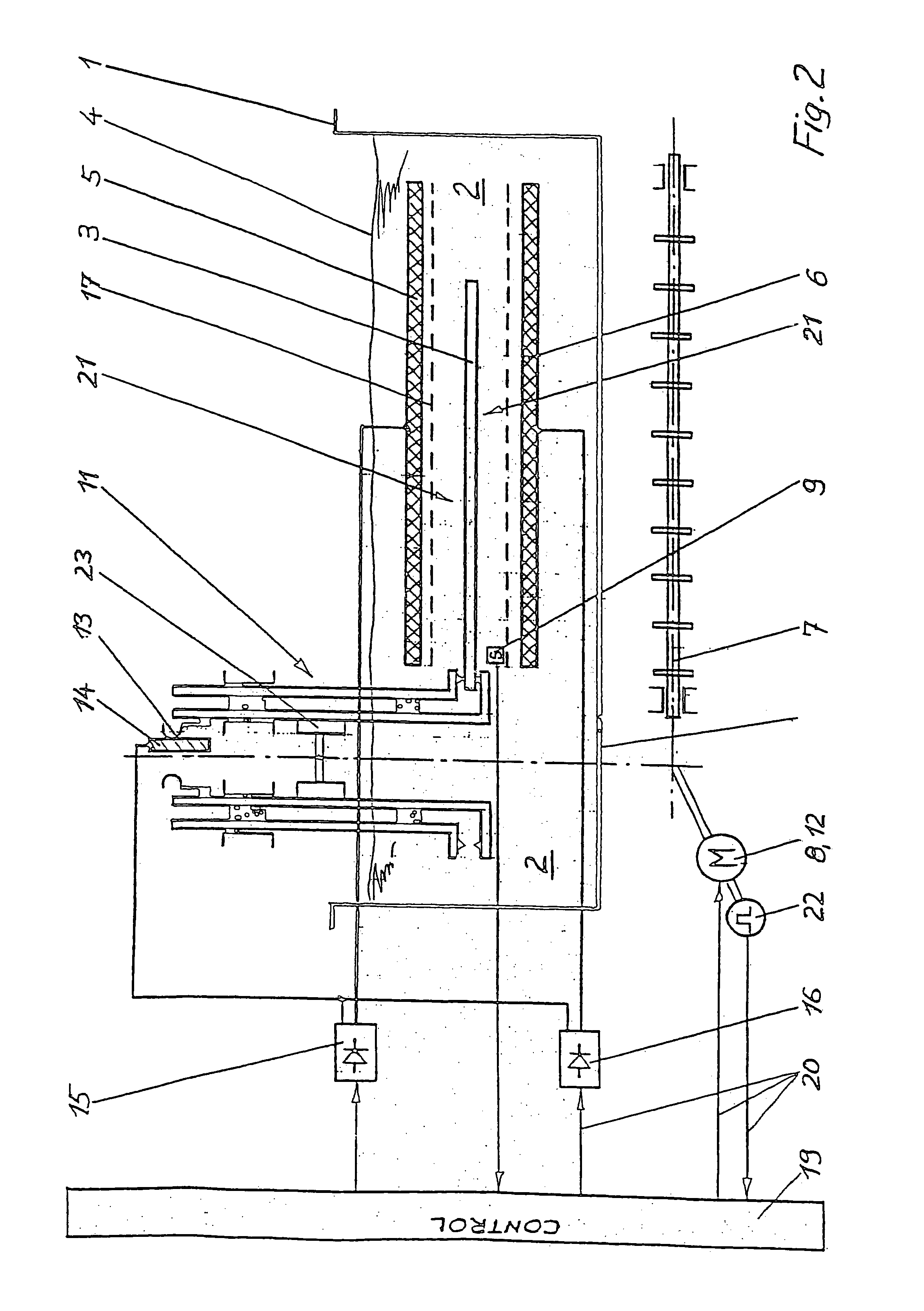

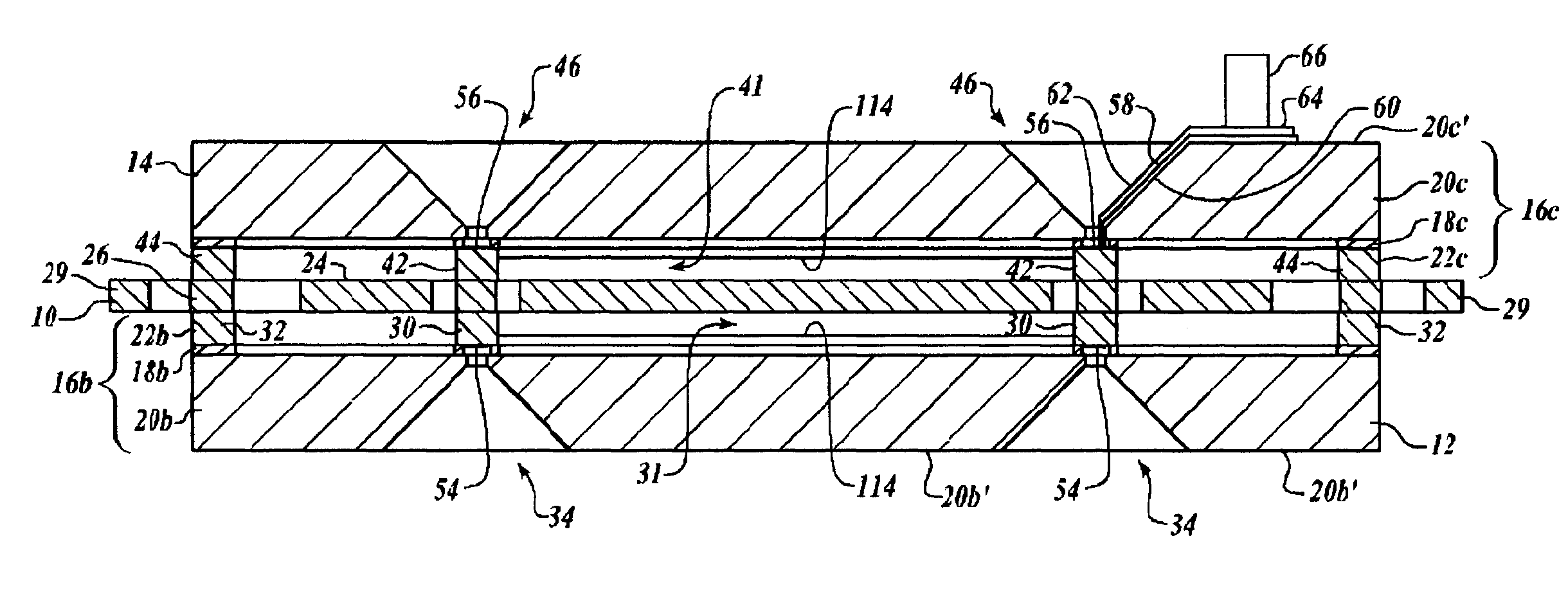

Method and conveyorized system for electrolytically processing work pieces

ActiveUS7563352B2Avoid disadvantagesEasy to adjustCellsConductive pattern reinforcementVolumetric Mass DensityEngineering

In order to avoid an edge-effect (increased electrical field line density at the edges of electrolytically to be processed work pieces) during the electrolytic processing of work pieces 3.x in a conveyorized system, the electric currents originating from various counter electrodes 5.x in the plant are set to values in function of the electrolytically to be processed surface areas of the work pieces 3.x as far as they are located directly opposite the respective ones of the various counter electrodes 5.x. Moreover, the distance between the work pieces 3.x and the counter electrodes 5.x is chosen to be 50 mm maximum. Means 19 for individually controlling and adjusting every single current supply unit 15.x of the counter electrodes 5.x are provided for this purpose. Said means 19 are configured in such a manner that the respective electric currents originating from the various counter electrodes 5.x are settable to values in function of the electrolytically to be processed surface areas of the work pieces 3.x, as far as they are located directly opposite the respective various counter electrodes 5.x.

Owner:ATOTECH DEUT GMBH

Systems, apparatuses, and methods for extracting non-polar lipids from an aqueous algae slurry and lipids produced therefrom

InactiveUS20110095225A1Increase volume flowEasy extractionLiquid separation by electricityMicroorganism lysisLipid formationPhospholipid

Methods, systems, and apparatuses for extracting non-polar lipids from microalgae are achieved using a lipid extraction device having an anode and a cathode that forms a channel and defines a fluid flow path through which an aqueous slurry is passed. An electromotive force is applied across the channel at a gap distance in a range from 0.5 mm to 200 mm to cause the non-polar lipids to be released from the algae cells. The non-polar lipids can be extracted at a high throughput rate and with low concentrations of polar lipids such as phospholipids and chlorophyll.

Owner:ORGINOIL INC

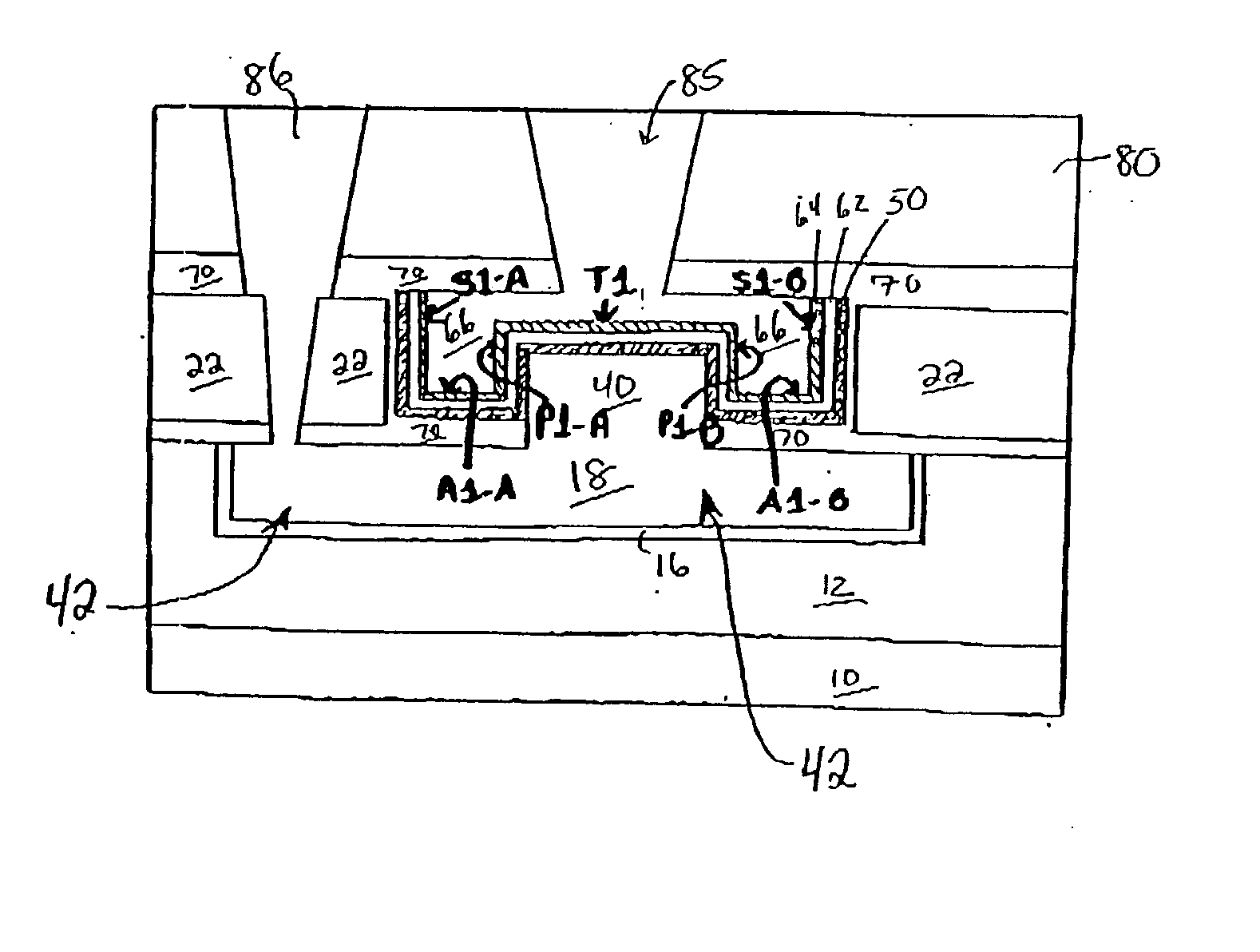

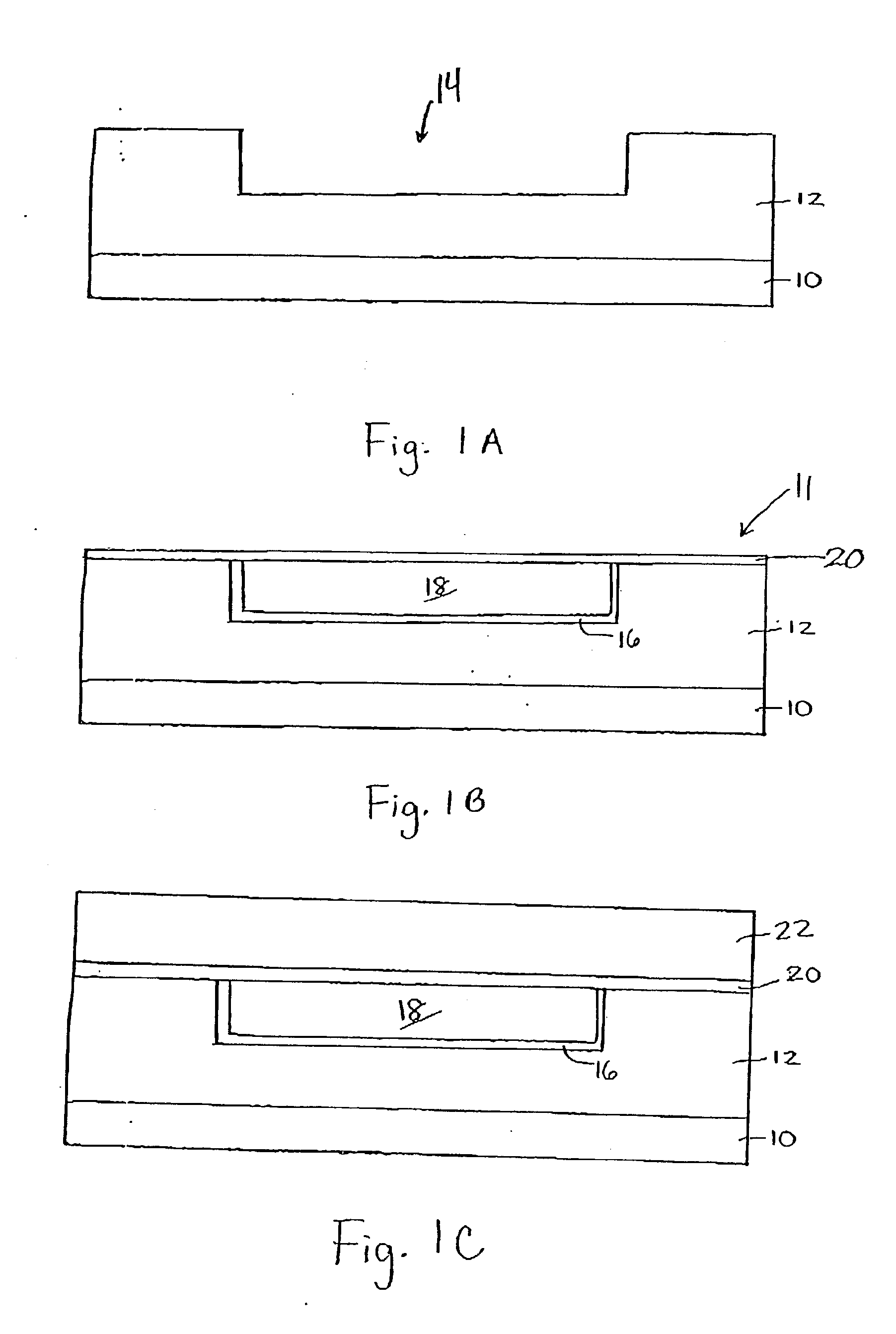

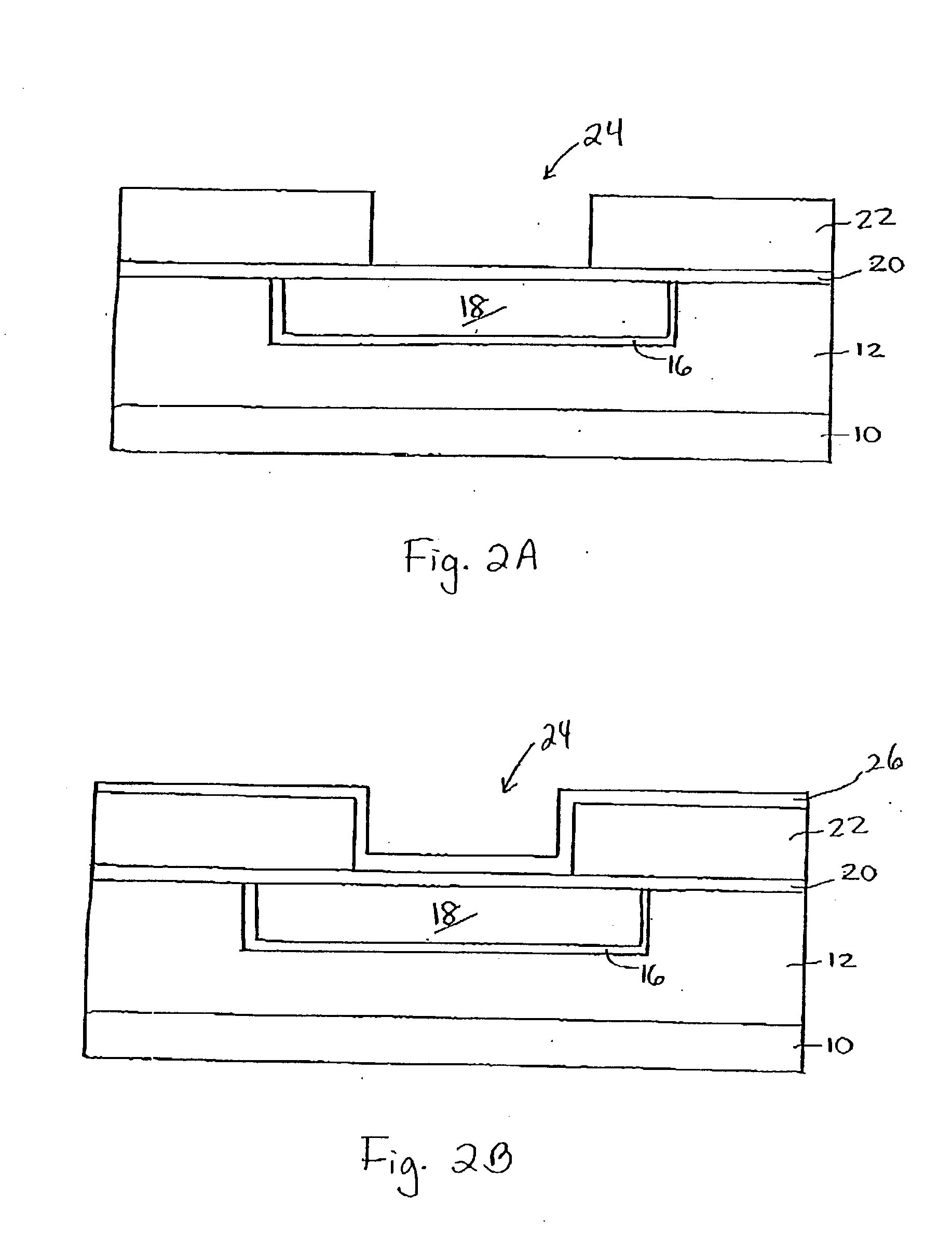

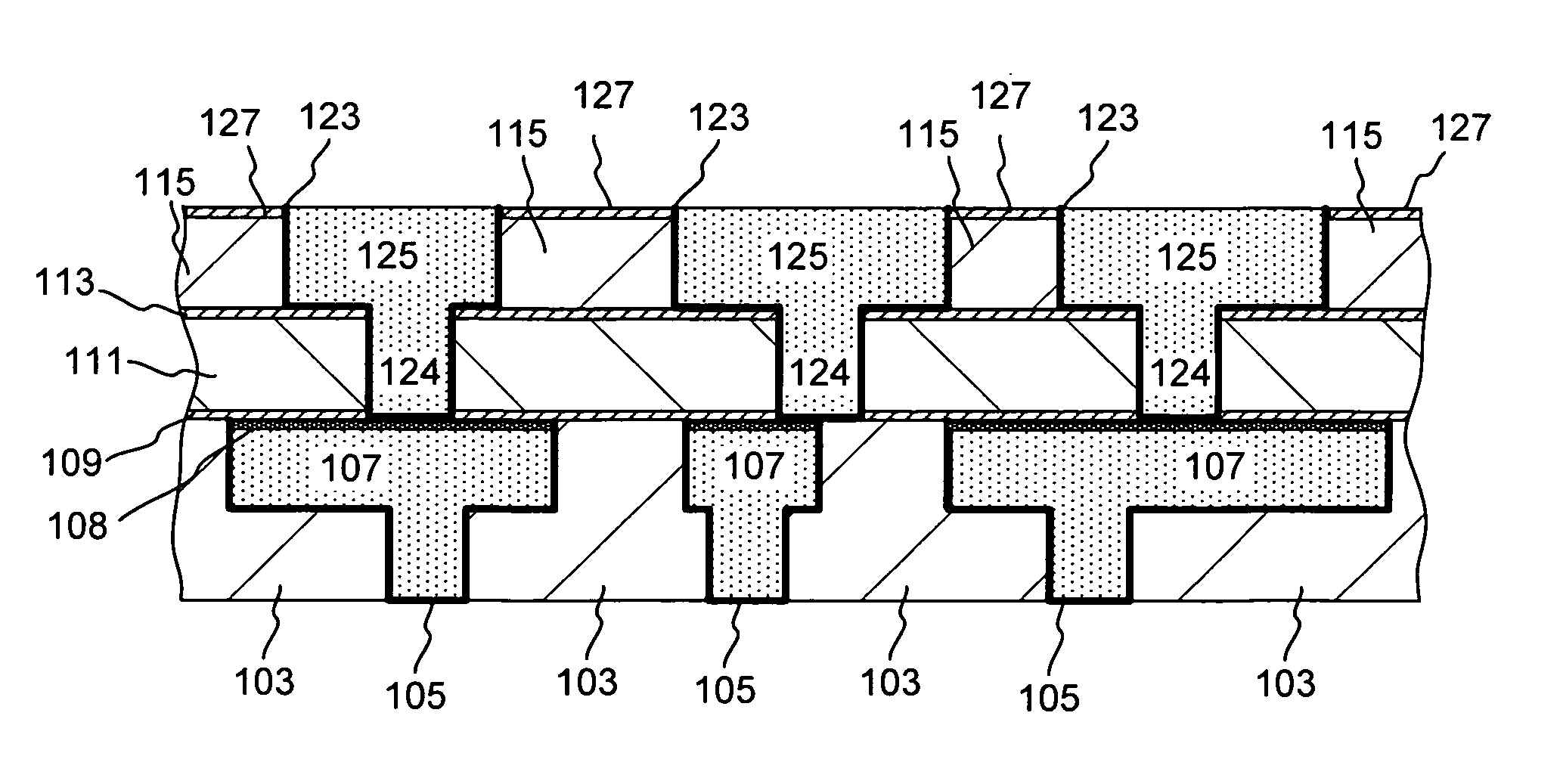

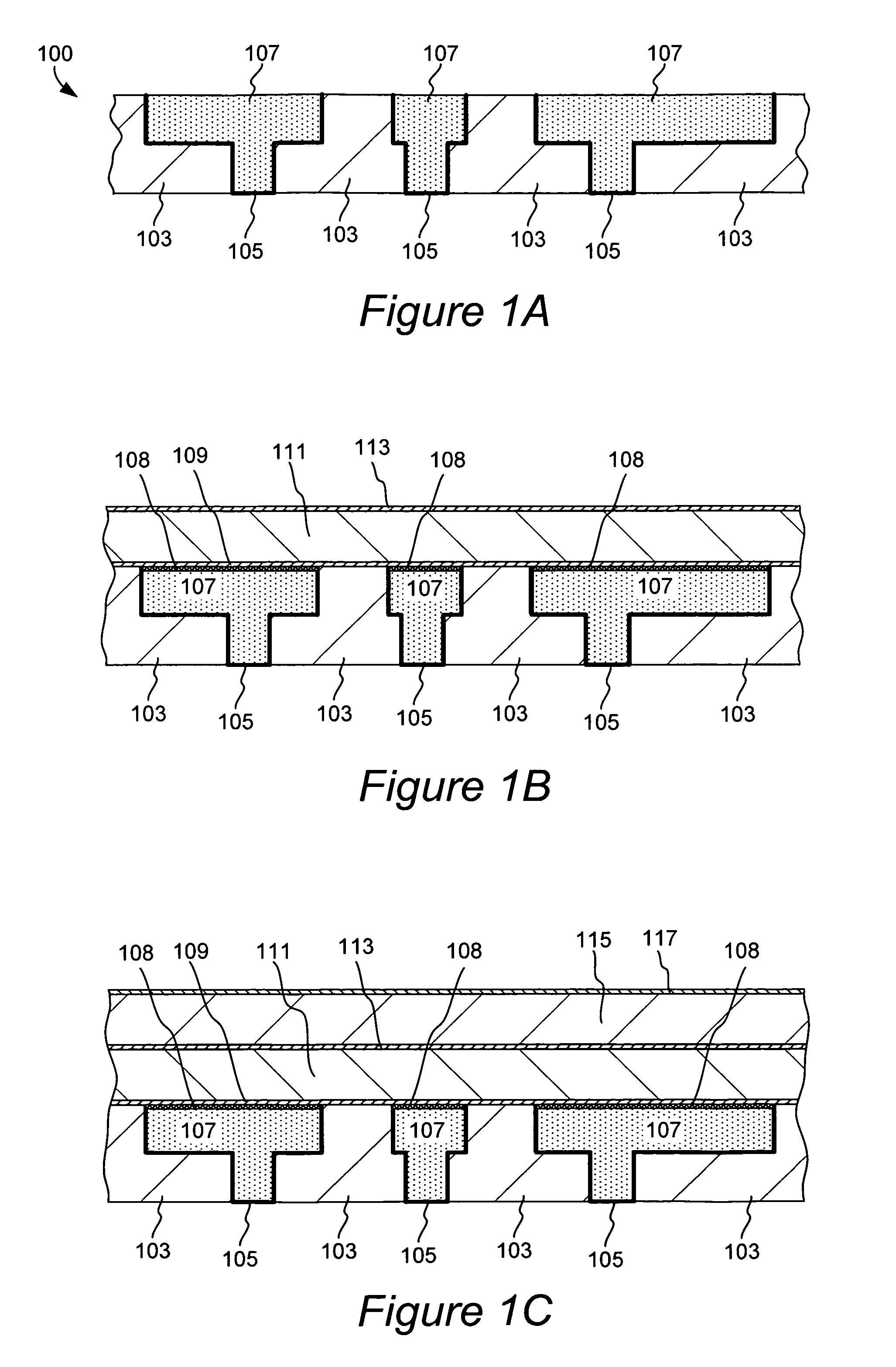

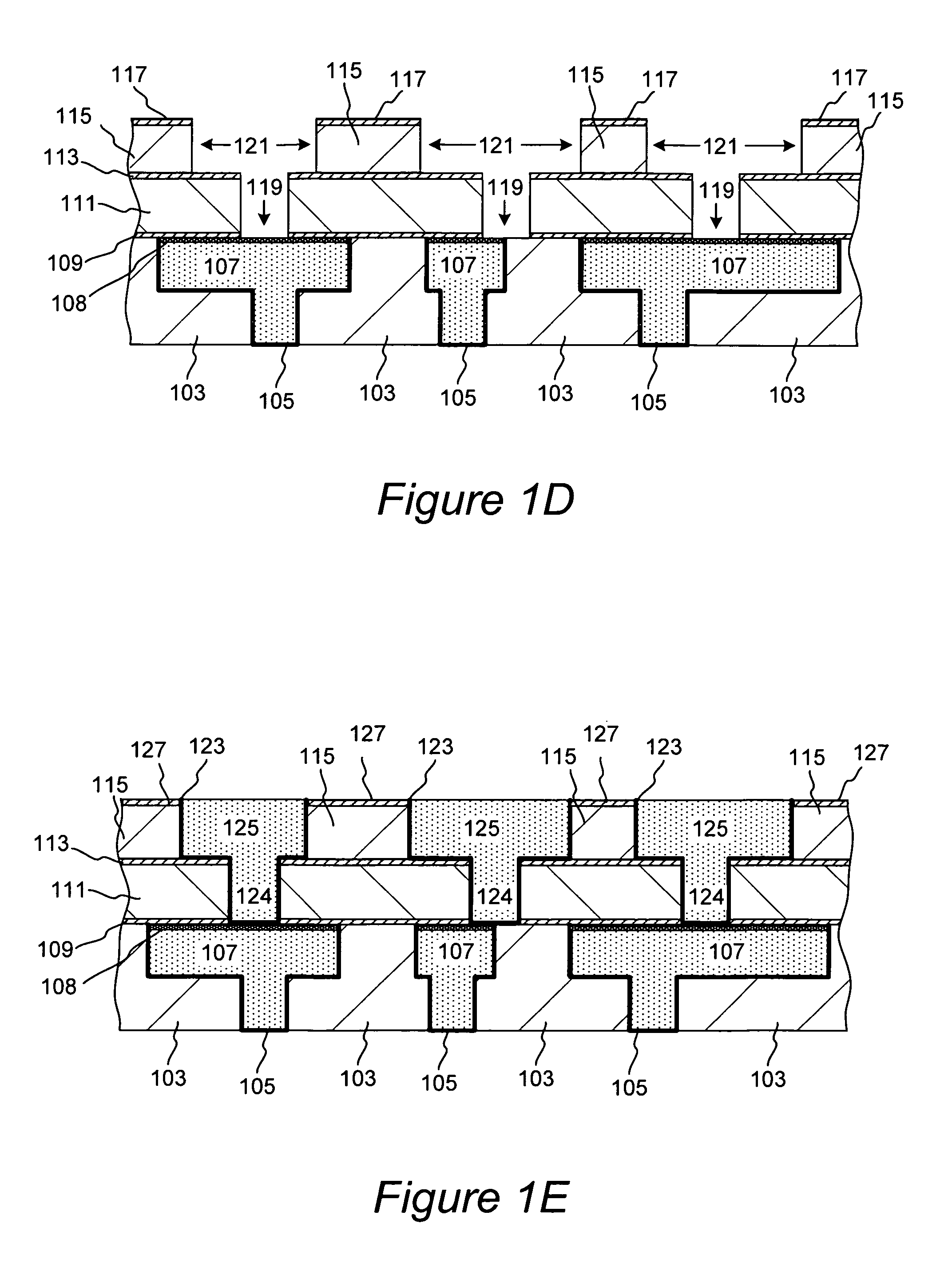

Damascene integration scheme for developing metal-insulator-metal capacitors

InactiveUS20040113235A1Increase capacitanceSave chip areaTransistorSolid-state devicesMetal-insulator-metalGas phase

The invention is directed to unique high-surface area BEOL capacitor structures with high-k dielectric layers and methods for fabricating the same. These high-surface area BEOL capacitor structures may be used in analog and mixed signal applications. The capacitor is formed within a trench with pedestals within the trench to provide additional surface area. The top and bottom electrodes are created using damascene integration scheme. The dielectric layer is created as a multilayer dielectric film comprising for instance Al2O3, Al2O3 / Ta2O5, Al2O3 / Ta2O5 / Al2O3 and the like. The dielectric layer may be deposited by methods like atomic layer deposition or chemical vapor deposition. The dielectric layer used in the capacitor may also be produced by anodic oxidation of a metallic precursor to yield a high dielectric constant oxide layer.

Owner:GLOBALFOUNDRIES US INC

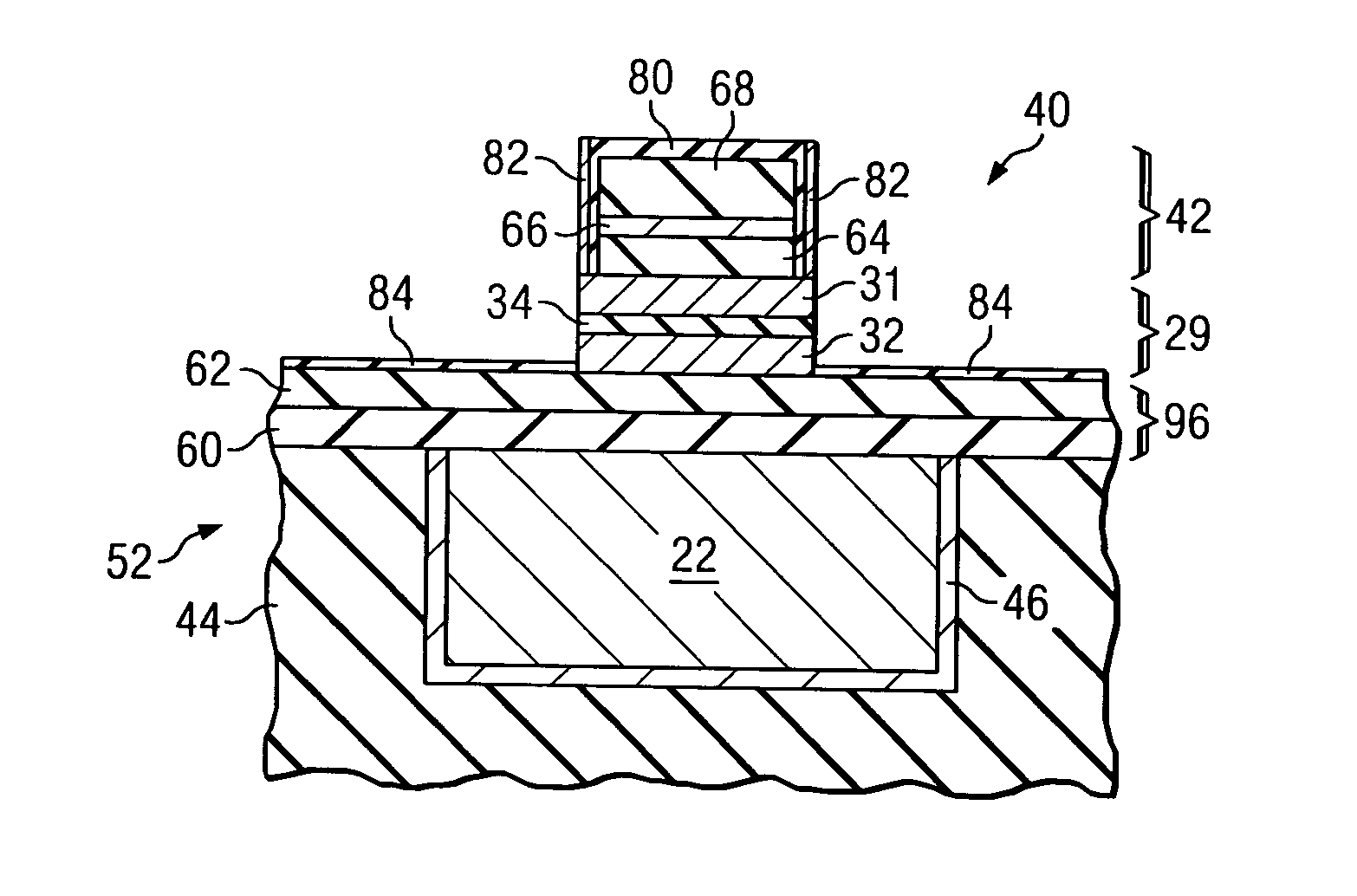

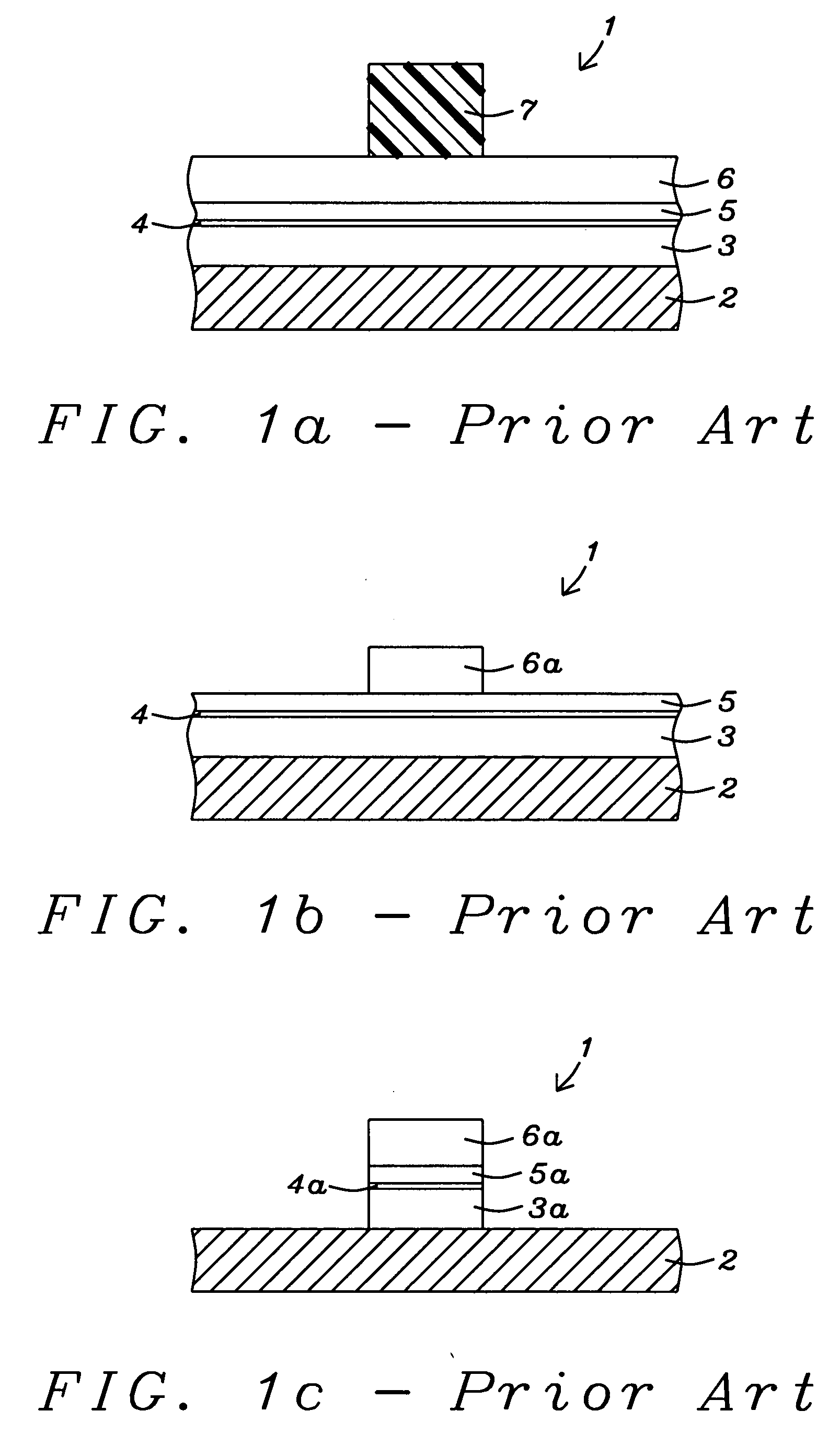

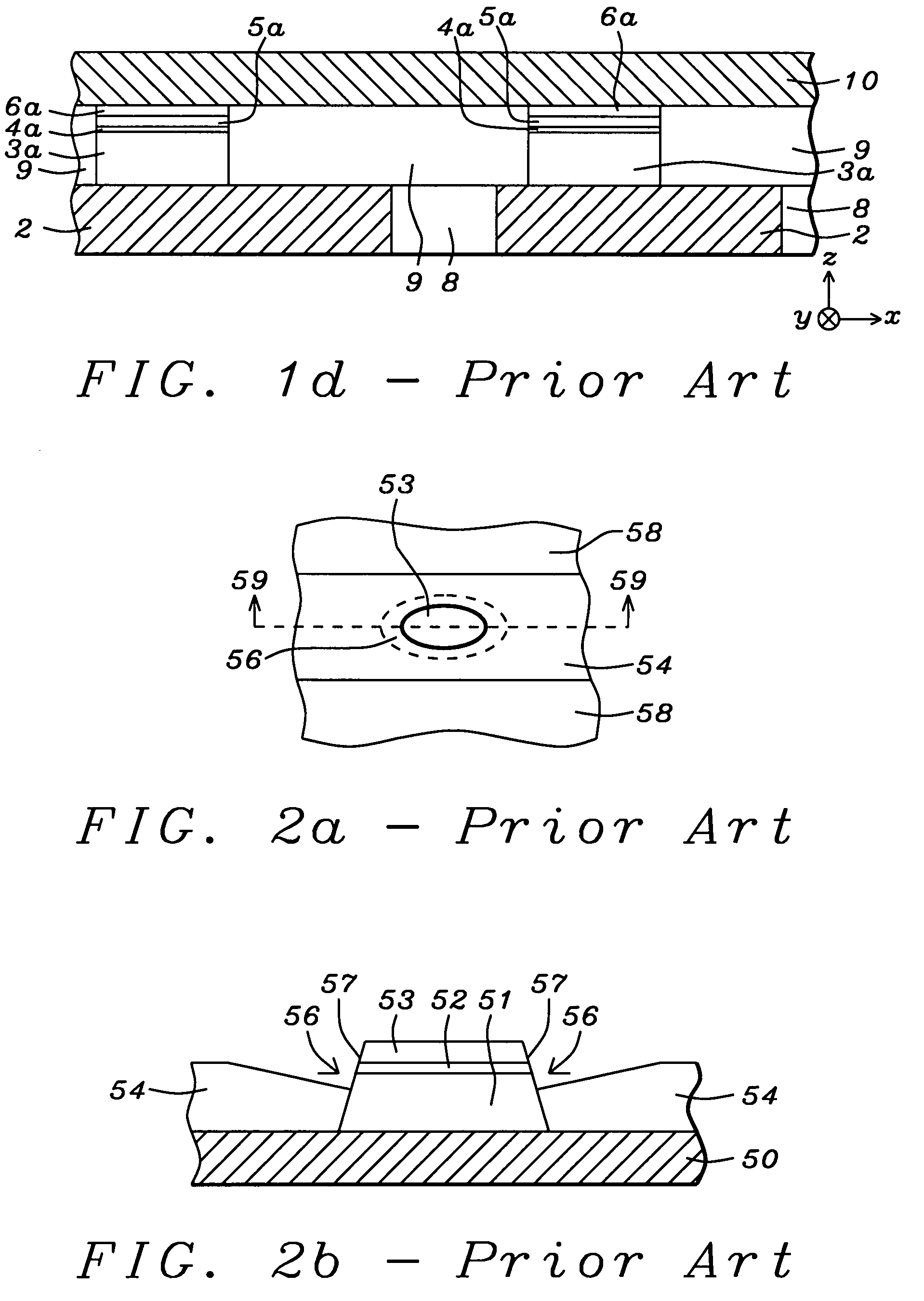

Composite hard mask for the etching of nanometer size magnetic multilayer based device

ActiveUS20090078927A1Prevent electrical shortingAvoid shortingLayered productsSemiconductor/solid-state device manufacturingBit lineEtching

A composite hard mask is disclosed that enables sub-100 nm sized MTJ cells to be formed for advanced devices such as spin torque MRAMs. The hard mask has a lower non-magnetic metallic layer such as Ru to magnetically isolate an overlying middle metallic spacer such as MnPt from an underlying free layer. The middle metallic spacer provides a height margin during subsequent processing to avoid shorting between a bit line and the MTJ cell in the final device. An upper conductive layer may be made of Ta and is thin enough to allow a MTJ pattern in a thin overlying photoresist layer to be transferred through the Ta during a fluorocarbon etch without consuming all of the photoresist. The MTJ pattern is transferred through the remaining hard mask layers and underlying MTJ stack of layers with a second etch step using a C, H, and O etch gas composition.

Owner:TAIWAN SEMICON MFG CO LTD

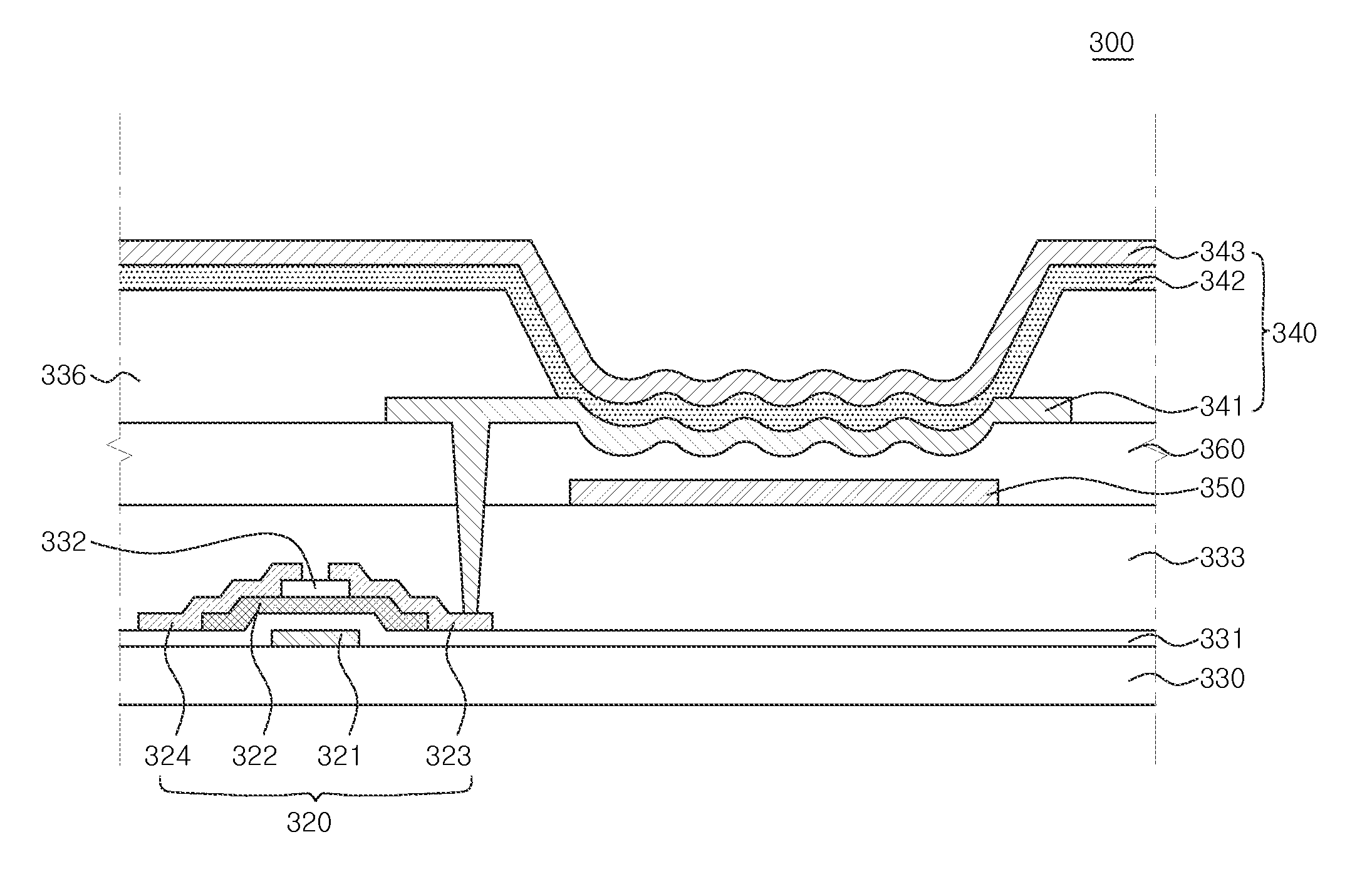

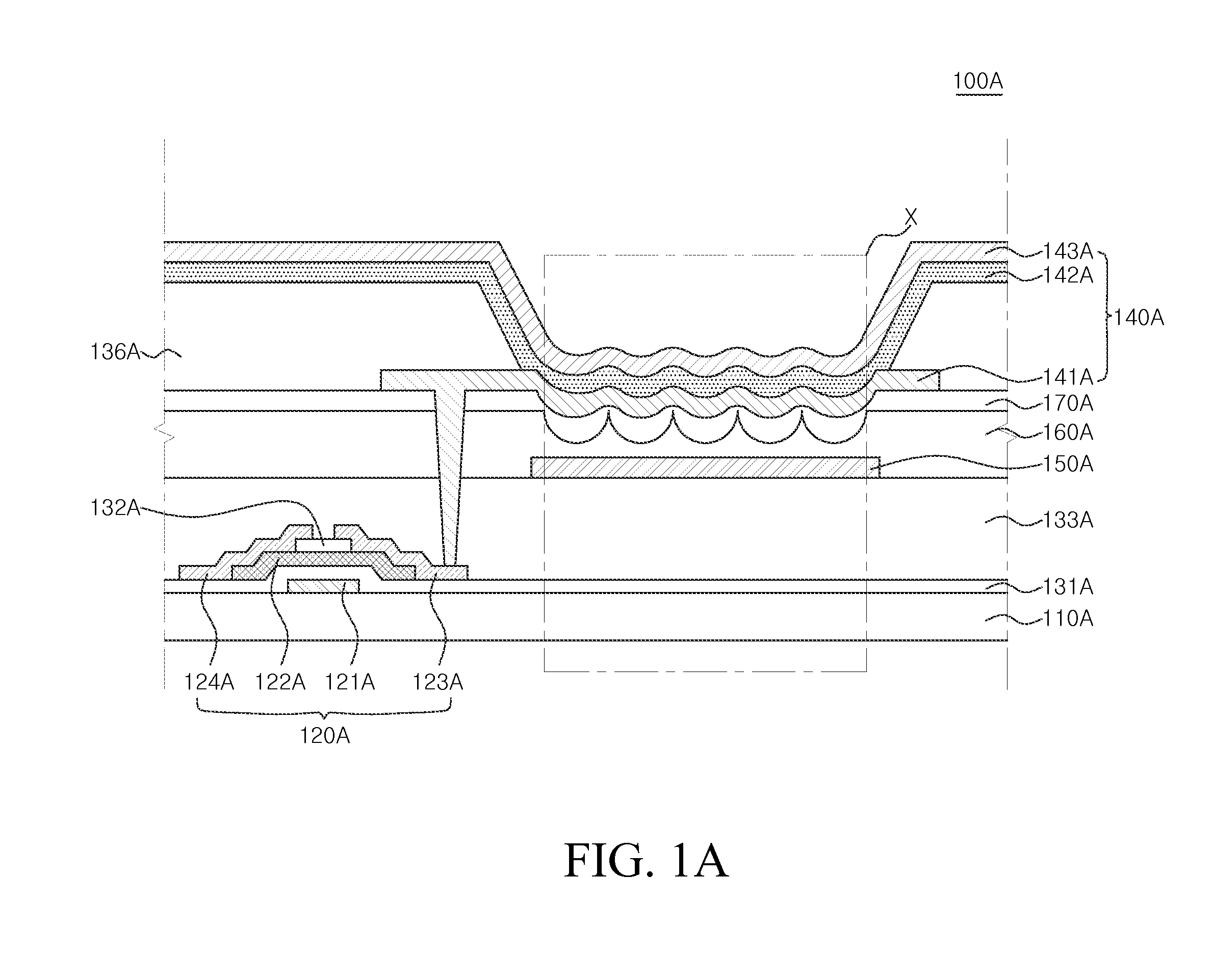

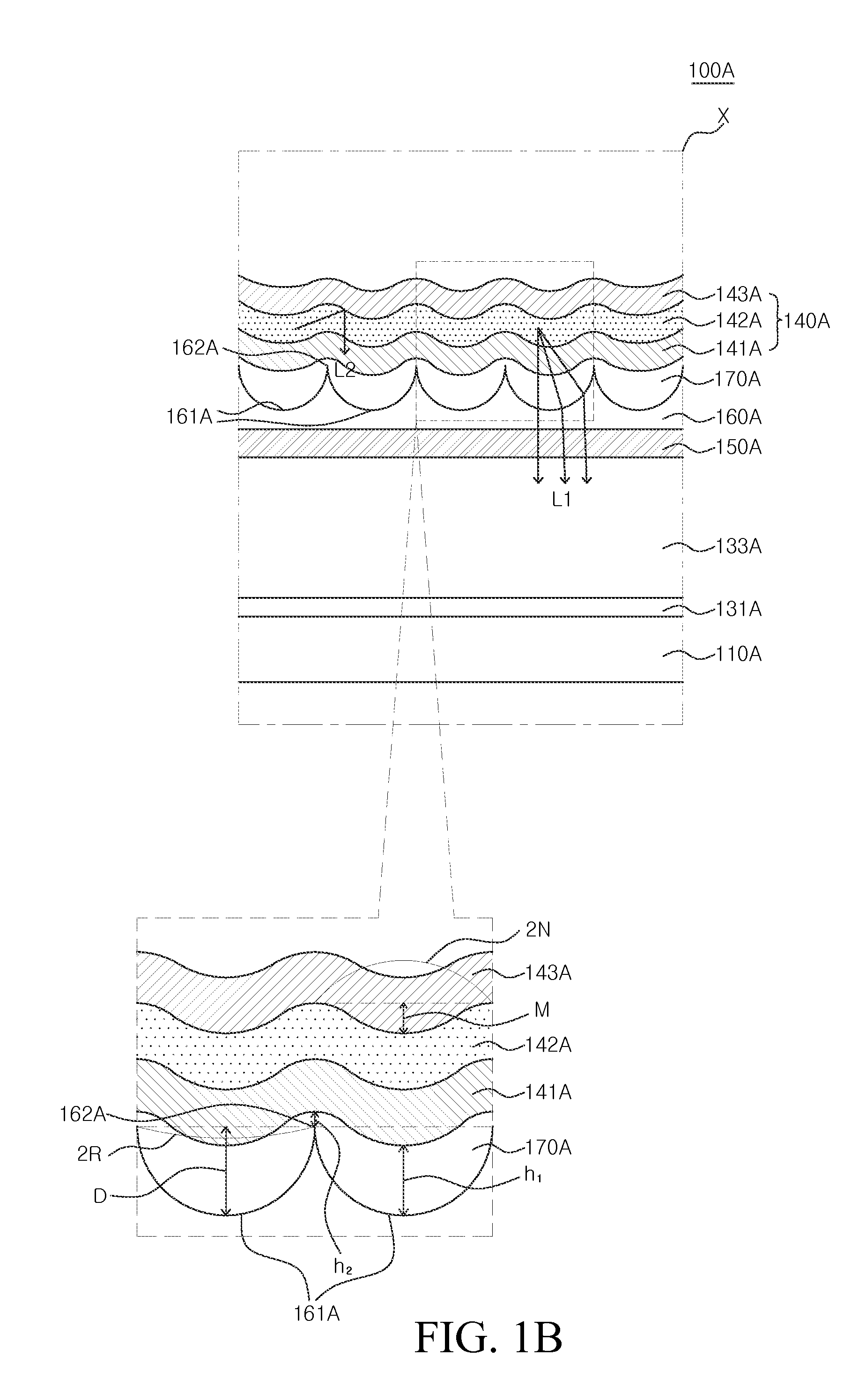

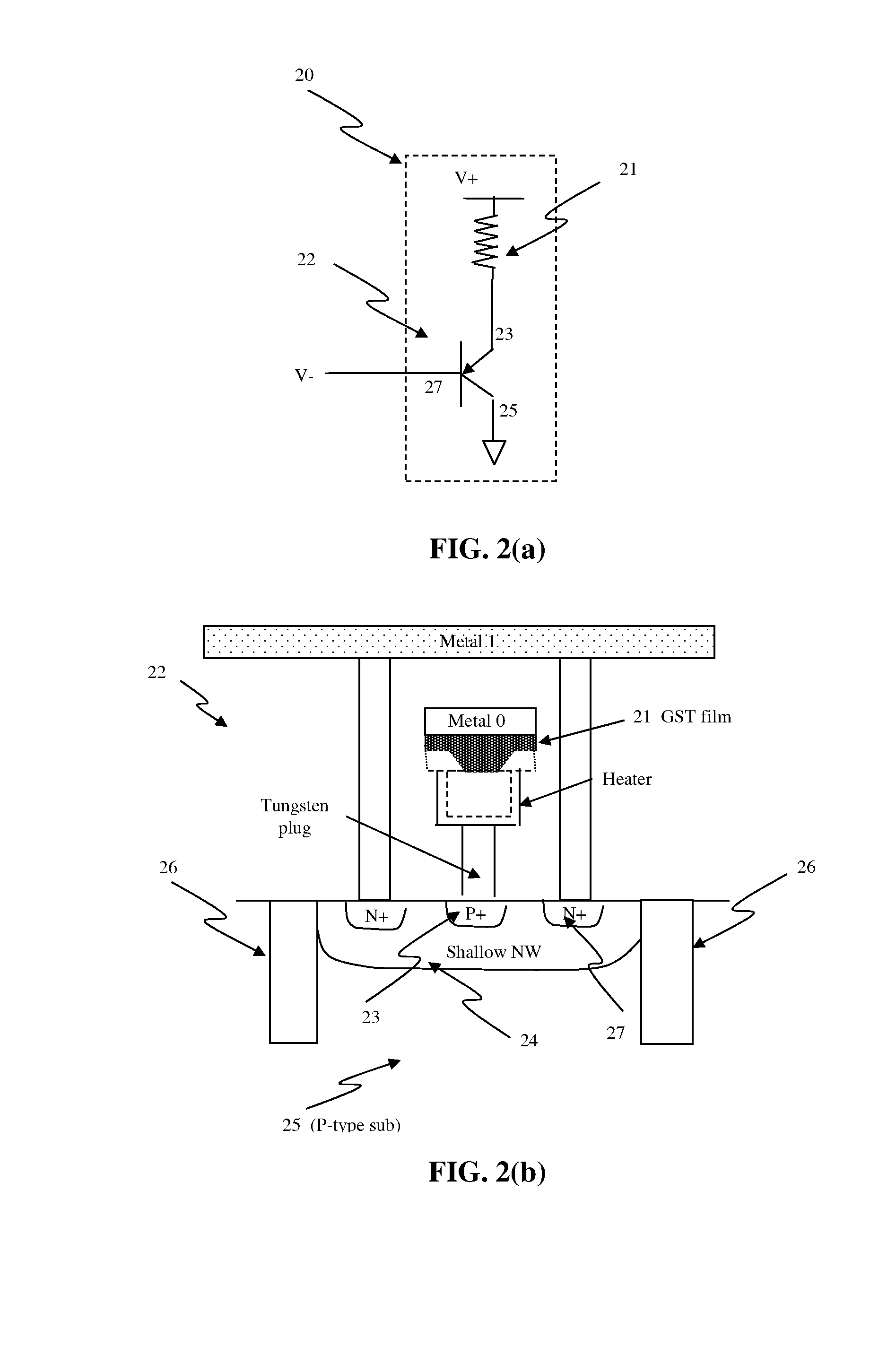

Organic light emitting display device and method for manufacturing the same

ActiveUS20150380466A1Reduce step differenceHigh refractive indexSolid-state devicesSemiconductor/solid-state device manufacturingRefractive indexDisplay device

Provided are an organic light emitting display device and a method for manufacturing the same. A color filter is disposed on a substrate. An overcoating layer is disposed on the color filter and includes a plurality of protrusions or a plurality of recesses. The plurality of protrusions and the plurality of recesses are disposed on the color filter to be overlapped with the color filter. A buffer layer for reducing step difference is disposed on the overcoating layer. The buffer layer has a higher refractive index than the overcoating layer and reduces a step difference caused by the plurality of protrusions and the plurality of recesses. An organic light emitting element including an anode, an organic light emitting layer, and a cathode is disposed on the buffer layer. Since the buffer layer has a higher refractive index than the overcoating layer, light extraction efficiency can be increased.

Owner:LG DISPLAY CO LTD

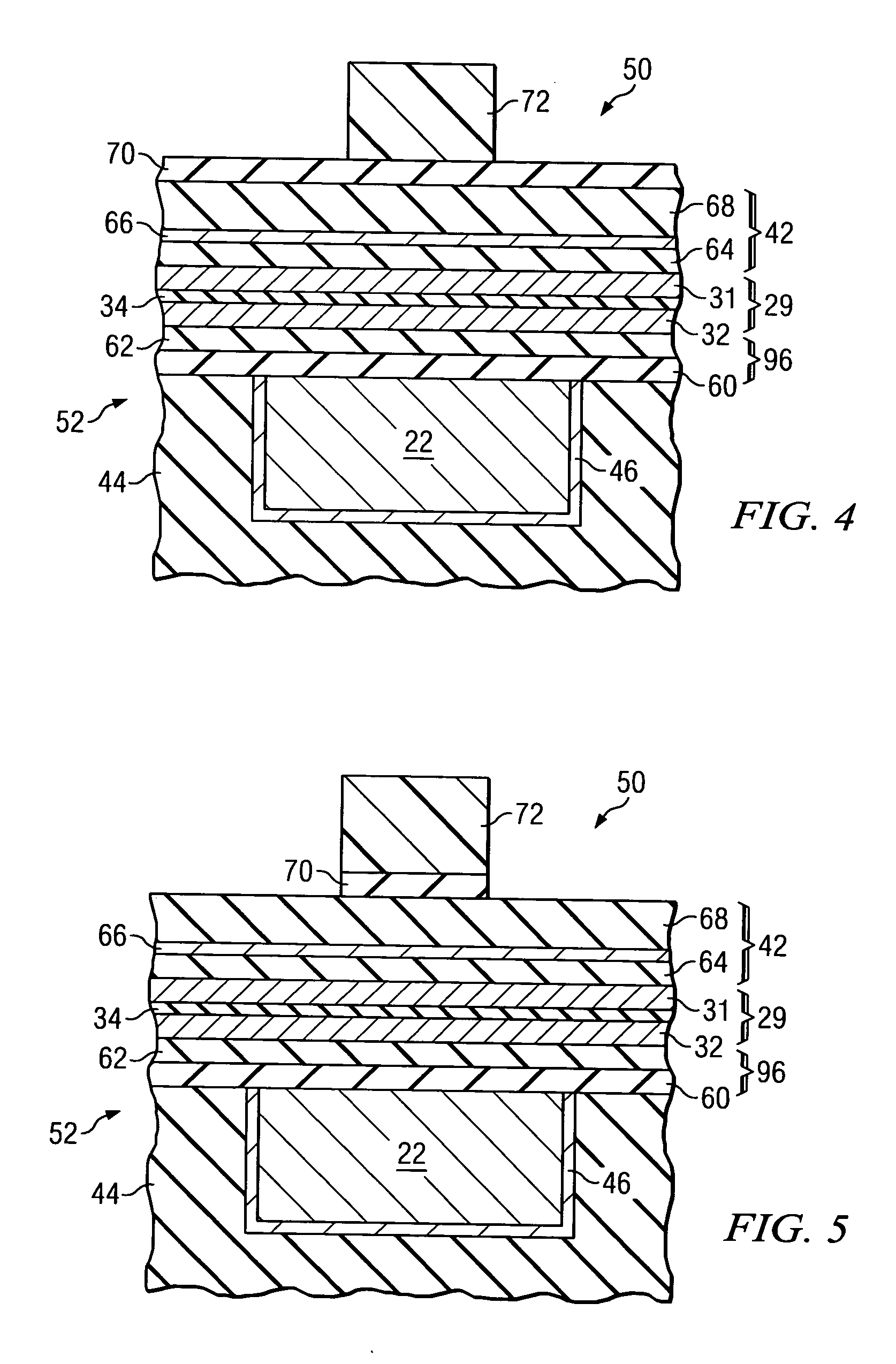

High performance MEMS packaging architecture

InactiveUS20060163679A1Reduce the impactWeakening rangeAcceleration measurement using interia forcesSolid-state devicesHermetic sealActive layer

An apparatus and method for sensor architecture based on bulk machining of Silicon-On-Oxide wafers and fusion bonding that provides a symmetric, nearly all-silicon, hermetically sealed MEMS device having a sensor mechanism formed in an active semiconductor layer, and opposing silicon cover plates each having active layers bonded to opposite faces of the sensor mechanism. The mechanism is structured with sensor mechanical features structurally supported by at least one mechanism anchor. The active layers of the cover plates each include interior features structured to cooperate with the sensor mechanical features and an anchor structured to cooperate with the mechanism anchor. A handle layer of each cover plate includes a pit extending there through in alignment with the cover plate anchor. An unbroken rim of dielectric material forms a seal between the cover plate anchor and the pit and exposes an external surface of the cover plate anchor.

Owner:HONEYWELL INT INC

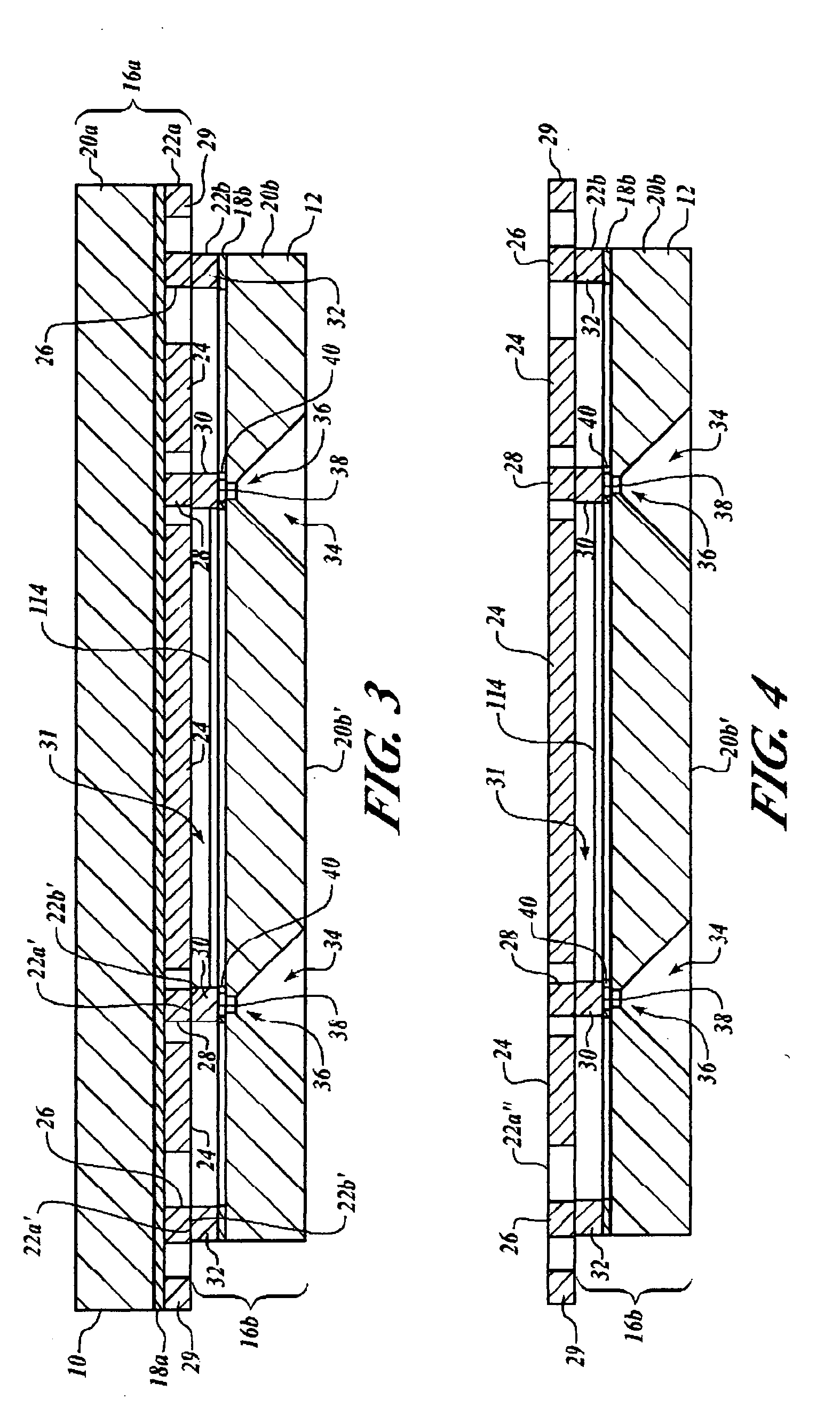

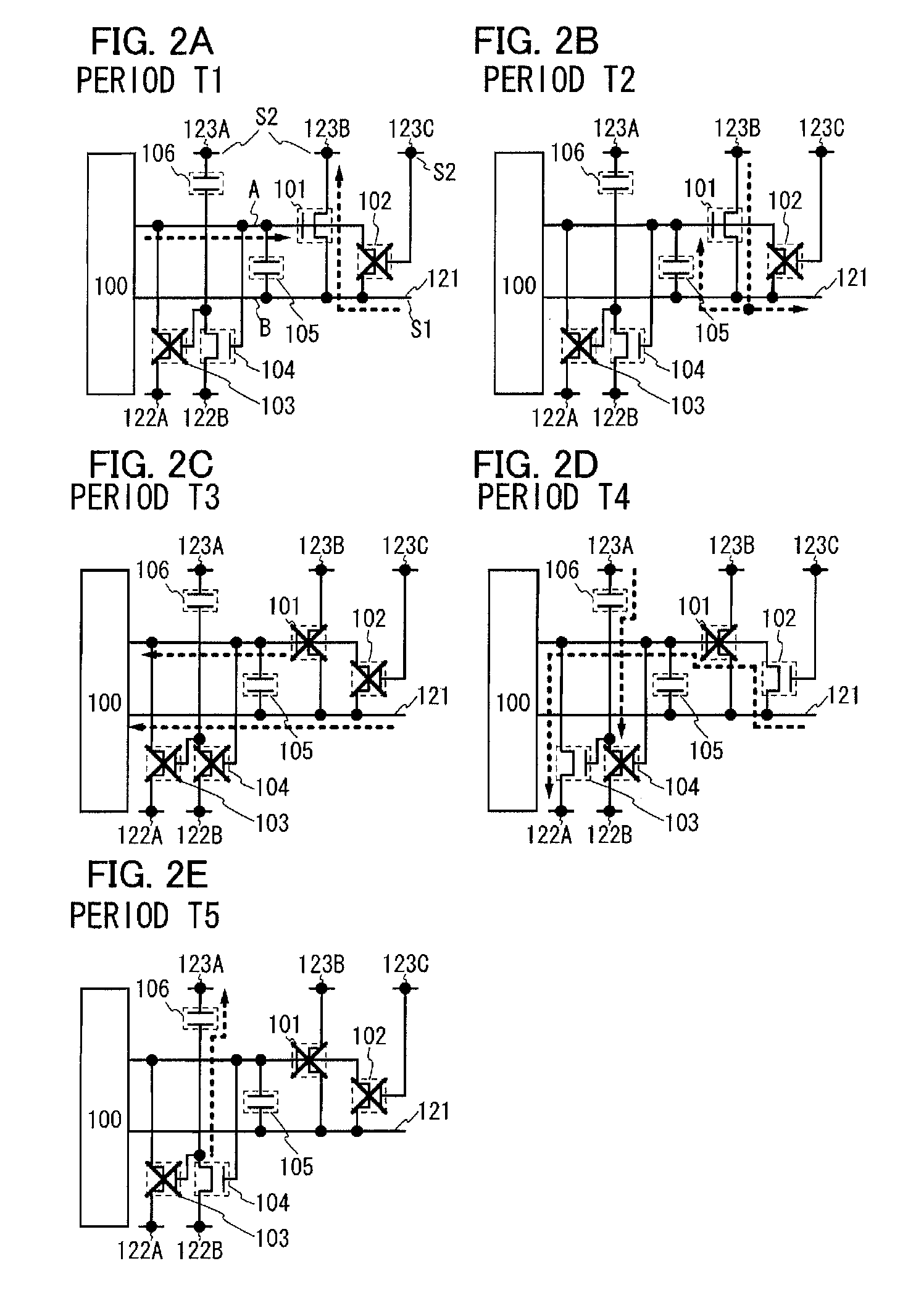

Display device and electronic device including the same

ActiveUS20100134396A1Reduce in quantityReduce parasitic capacitanceTransistorStatic indicating devicesDisplay deviceCapacitor

It is an object to decrease the number of transistors connected to a capacitor. In a structure, a capacitor and one transistor are included, one electrode of the capacitor is connected to a wiring, and the other electrode of the capacitor is connected to a gate of the transistor. Since a clock signal is input to the wiring, the clock signal is input to the gate of the transistor through the capacitor. Then, on / off of the transistor is controlled by a signal which synchronizes with the clock signal, so that a period when the transistor is on and a period when the transistor is off are repeated. In this manner, deterioration of the transistor can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

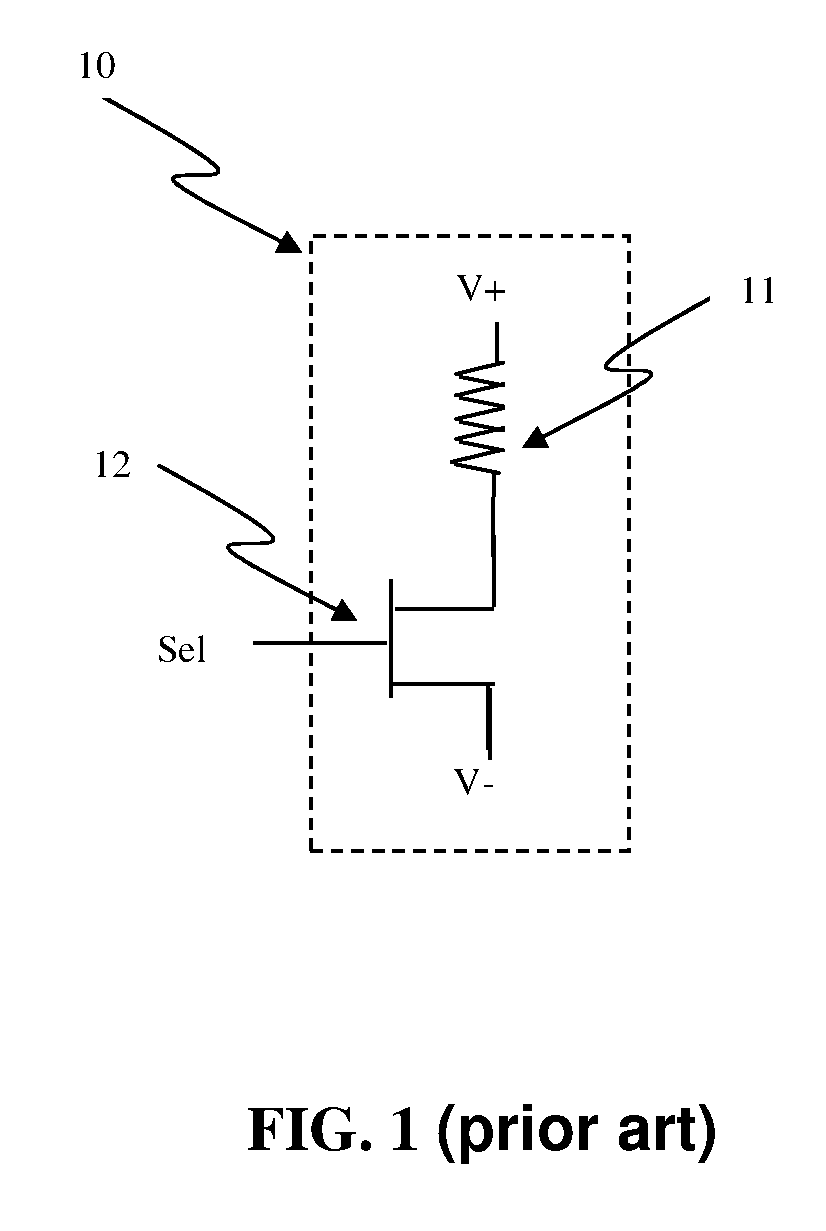

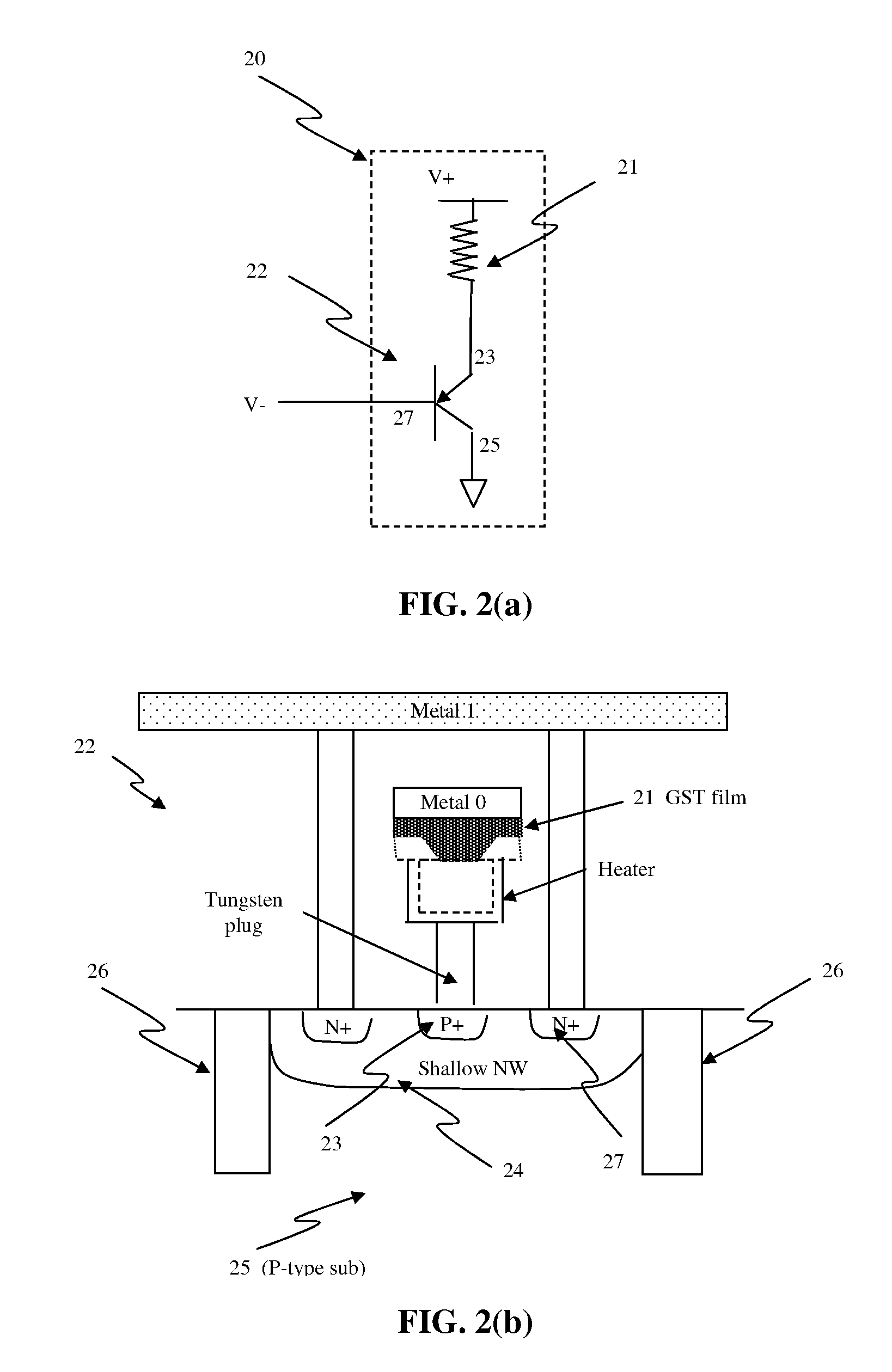

Circuit and system of using polysilicon diode as program selector for one-time programmable devices

ActiveUS20120044737A1Avoid shortingSave extra spaceSolid-state devicesRead-only memoriesLow voltageHemt circuits

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has an OTP element coupled to a diode in a memory cell. The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a high voltage to an OTP element coupled to the P-terminal of a diode and switching the N-terminal of a diode to a low voltage for suitable duration of time, a current flows through the OTP element may change the resistance state. On the polysilicon diode, the spacing and doping level of a gap between the P- and N-implants can be controlled for different breakdown voltages and leakage currents. The Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting. If the OTP element is a polysilicon electrical fuse, the fuse element can be merged with the polysilicon diode in one piece to save area.

Owner:ATTOPSEMI TECH CO LTD

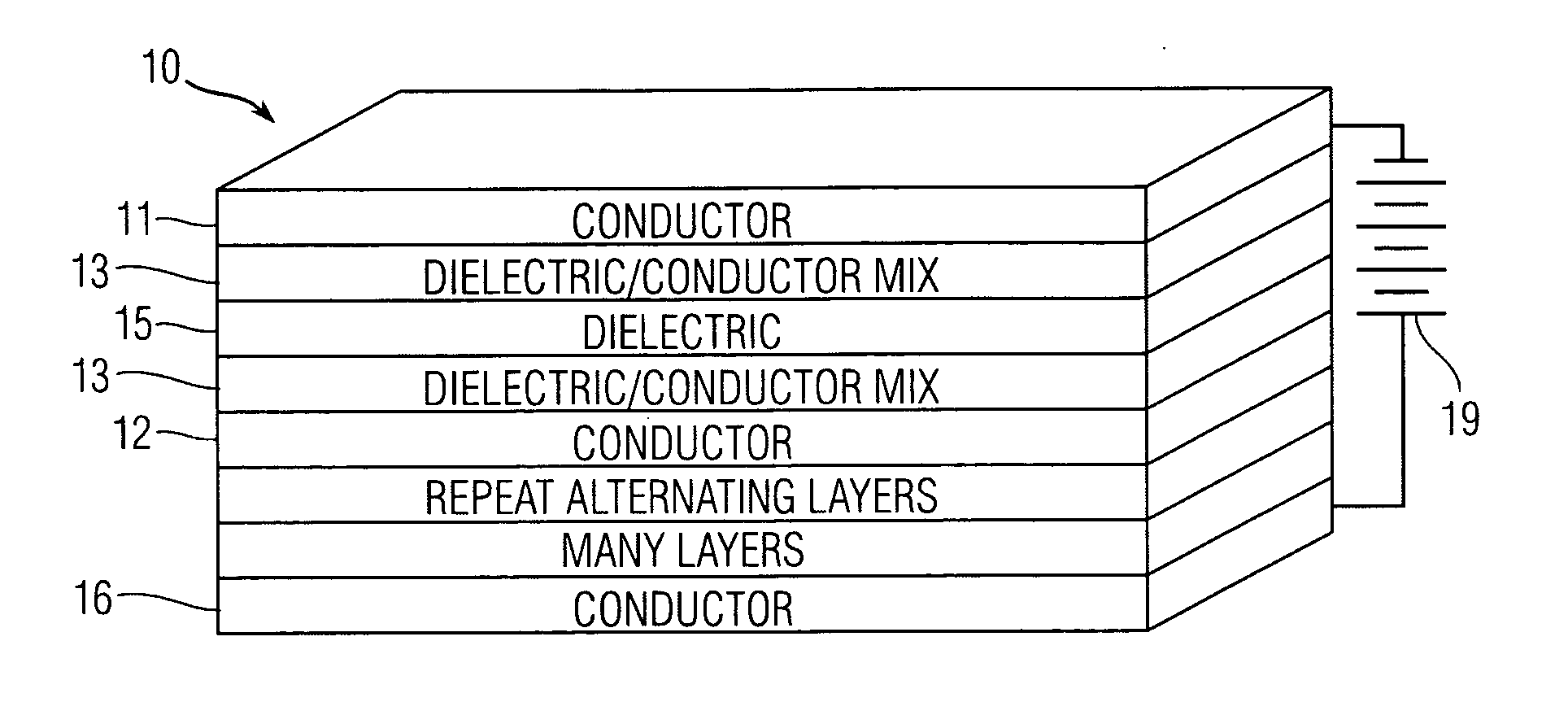

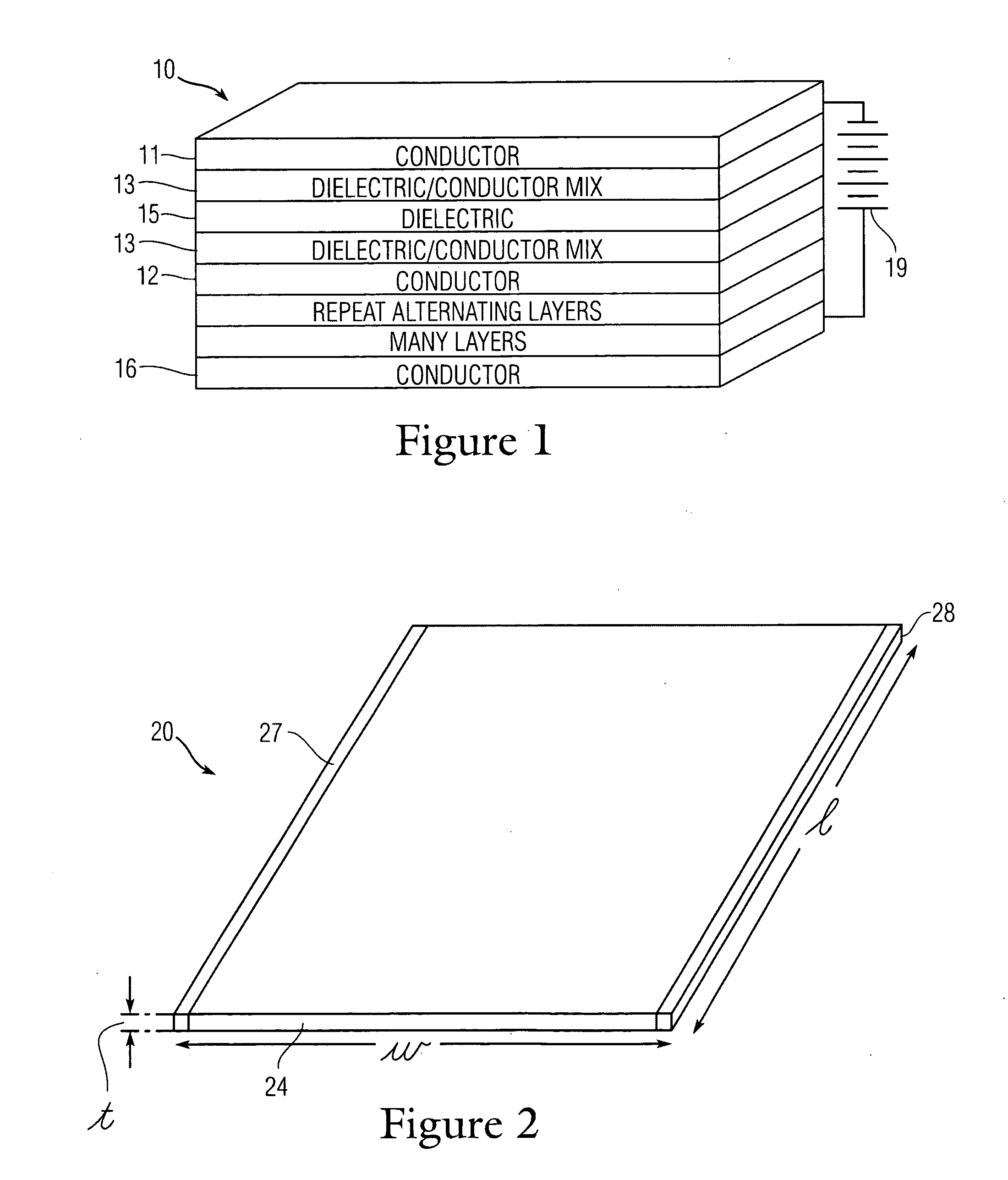

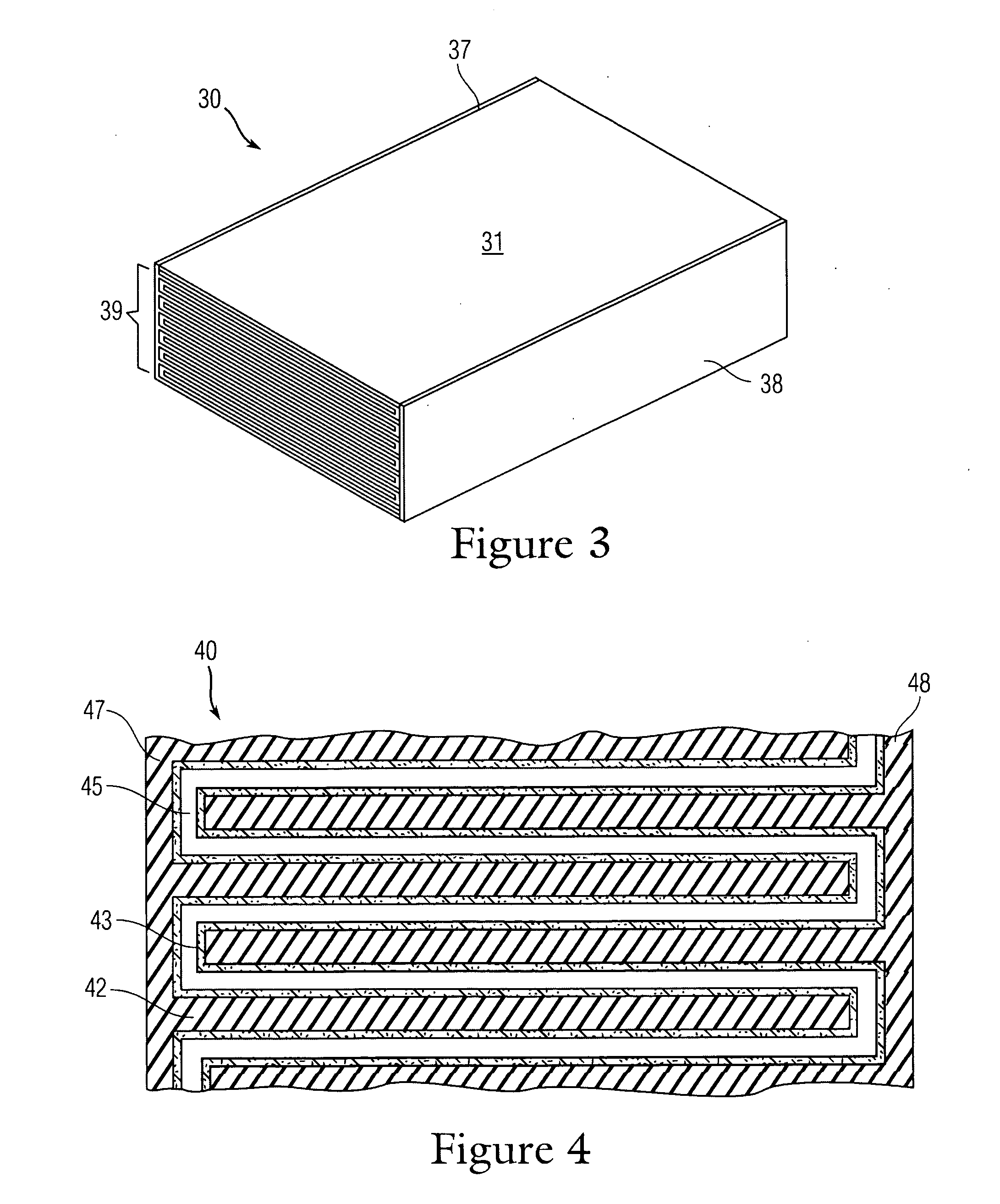

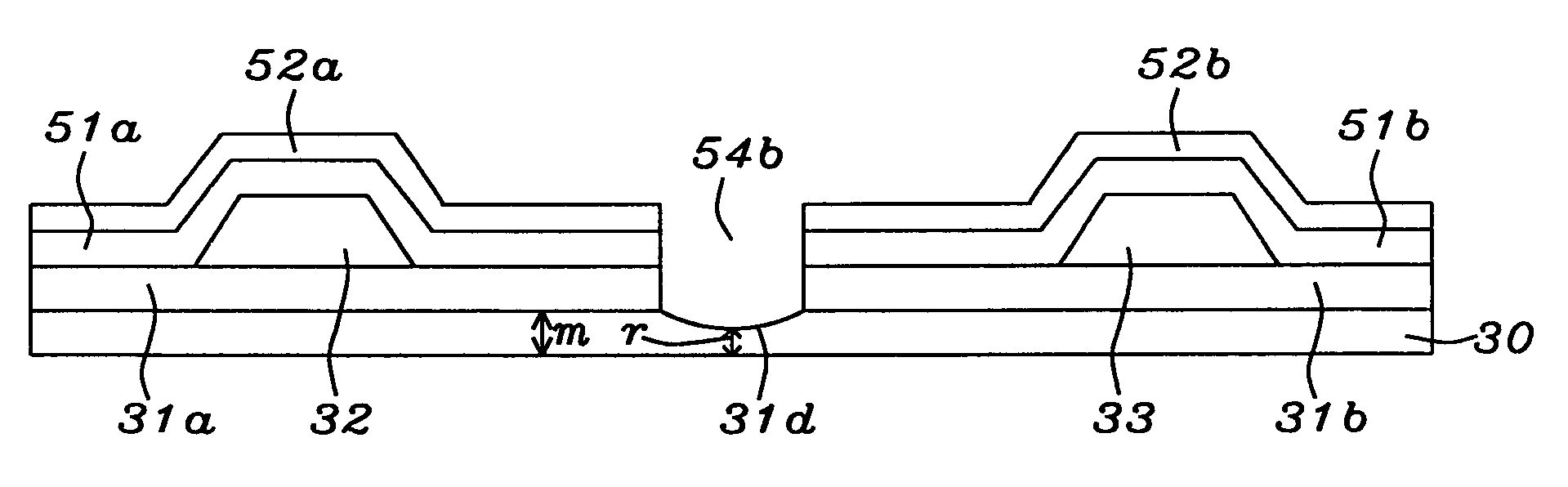

High performance capacitor with high dielectric constant material

InactiveUS20060120020A1Improve performanceHigh energy-density capacitorFixed capacitor dielectricStacked capacitorsElectrical conductorVolumetric Mass Density

A multilayered high performance capacitor formed of two or more conductors with a dielectric layer and one or more a dielectric-conductor interface layer sandwiched in between the conductors. The capacitor may be fabricated using many thin layers, at the nano level, providing a nanocapacitor. The capacitor may employ an interleaved structured where numerous conductor layers are interleaved with other conductor layers. The dielectric layers may be multilayered or a single layer and may consist of materials with high dielectric constants ranging from 800 to over 1 million, including materials in the perovskite-oxide family. The capacitor can be shaped, sized and the appropriate materials selected to obtain breakdown voltages within the range of 0.1 to over 11 MV / cm and to obtain specific energies and energy densities equivalent to or exceeding the power characteristics of known capacitors, fuel cells, and batteries. The nanocapacitor may be combined with other nanocapacitors to form stacks, packs, or grids of cells where the cells may be connected in series, parallel or both to provide increased energy or power characteristics

Owner:DOWGIALLO JR EDWARD J

Bottom electrode etching process in MRAM cell

ActiveUS20100311243A1Not to damageImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingWater basedResist

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

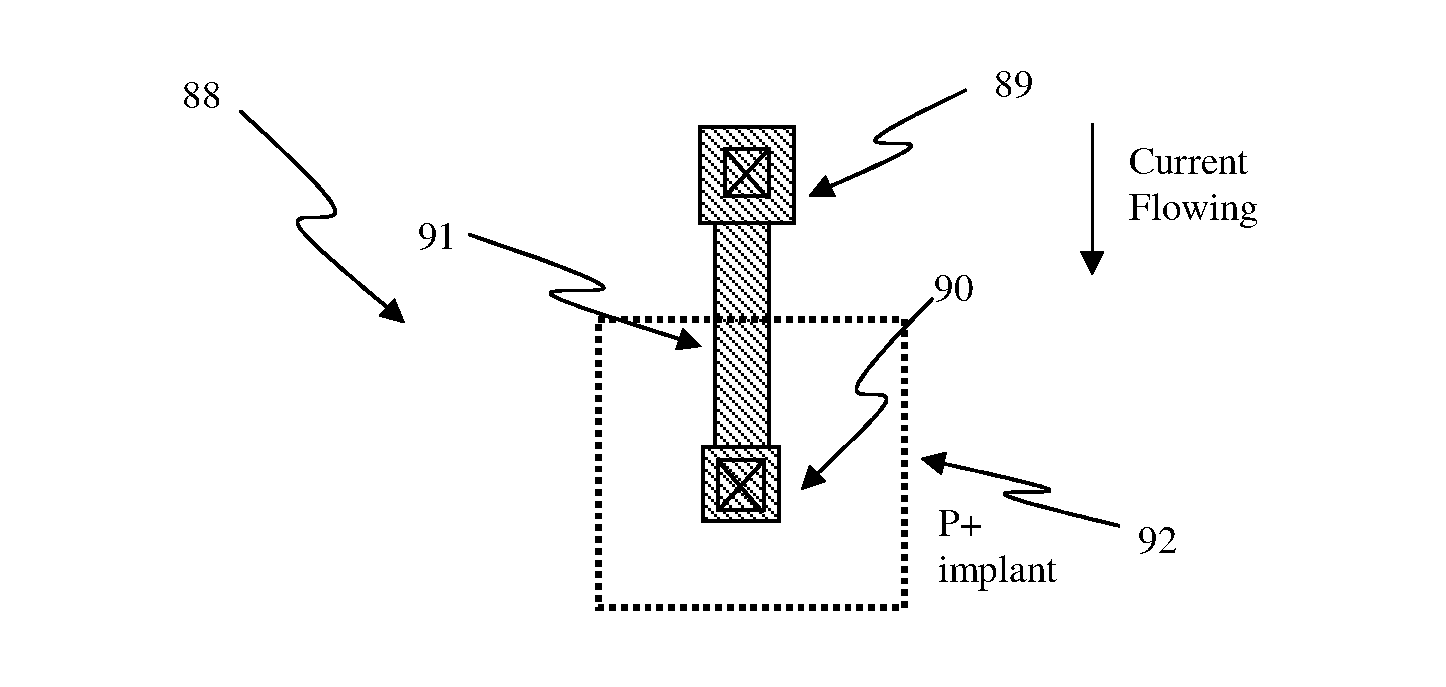

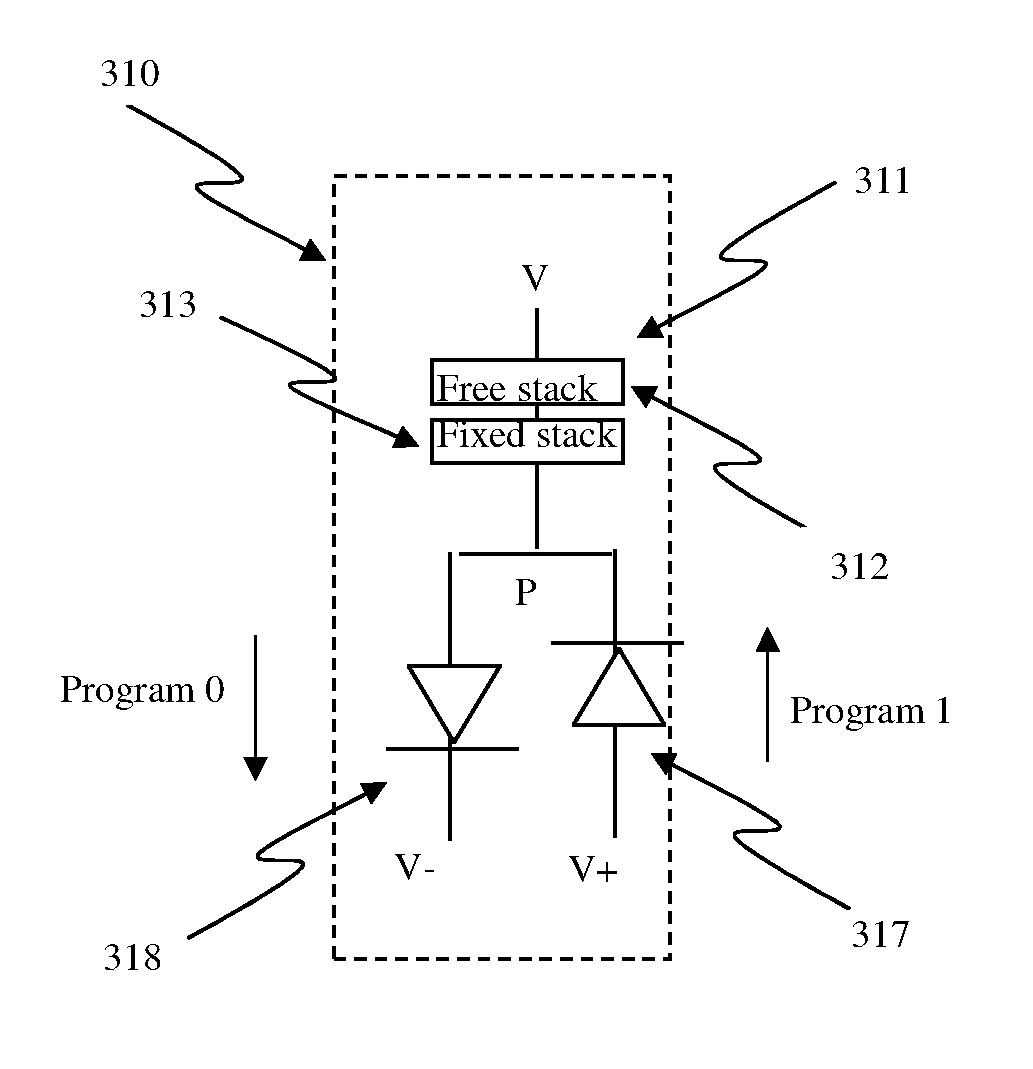

Memory devices using a plurality of diodes as program selectors with at least one being a polysilicon diode

ActiveUS8482972B2Avoid shortingSmall cell sizeSolid-state devicesRead-only memoriesPower flowCmos process

Embodiments of programmable memory cells using a plurality of diodes as program selectors are disclosed for memory cells that can be programmed based on direction of current flow. These memory cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to the P-terminal of a first diode and to the N-terminal of a second diode. At least one of the diodes can be a polysilicon diode fabricated using standard CMOS processes. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon substrate as a program selector.

Owner:ATTOPSEMI TECH CO LTD

Composite hard mask for the etching of nanometer size magnetic multilayer based device

ActiveUS7696551B2Avoid shortingImprove etch selectivitySemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentBit lineEtching

A composite hard mask is disclosed that enables sub-100 nm sized MTJ cells to be formed for advanced devices such as spin torque MRAMs. The hard mask has a lower non-magnetic metallic layer such as Ru to magnetically isolate an overlying middle metallic spacer such as MnPt from an underlying free layer. The middle metallic spacer provides a height margin during subsequent processing to avoid shorting between a bit line and the MTJ cell in the final device. An upper conductive layer may be made of Ta and is thin enough to allow a MTJ pattern in a thin overlying photoresist layer to be transferred through the Ta during a fluorocarbon etch without consuming all of the photoresist. The MTJ pattern is transferred through the remaining hard mask layers and underlying MTJ stack of layers with a second etch step using a C, H, and O etch gas composition.

Owner:TAIWAN SEMICON MFG CO LTD

Interfacial layers for electromigration resistance improvement in damascene interconnects

ActiveUS7648899B1Improve performanceIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesDielectricDopant

Protective caps residing at an interface between metal lines and dielectric diffusion barrier (or etch stop) layers are used to improve electromigration performance of interconnects. Protective caps are formed by depositing a source layer of dopant-generating material (e.g., material generating B, Al, Ti, etc.) over an exposed copper line, converting the upper portion of the source layer to a passivated layer (e.g., nitride or oxide) while allowing an unmodified portion of a dopant-generating source layer to remain in contact with copper, and, subsequently, allowing the dopant from the unmodified portion of source layer to controllably diffuse into and / or react with copper, thereby forming a thin protective cap within copper line. The cap may contain a solid solution or an alloy of copper with the dopant.

Owner:NOVELLUS SYSTEMS

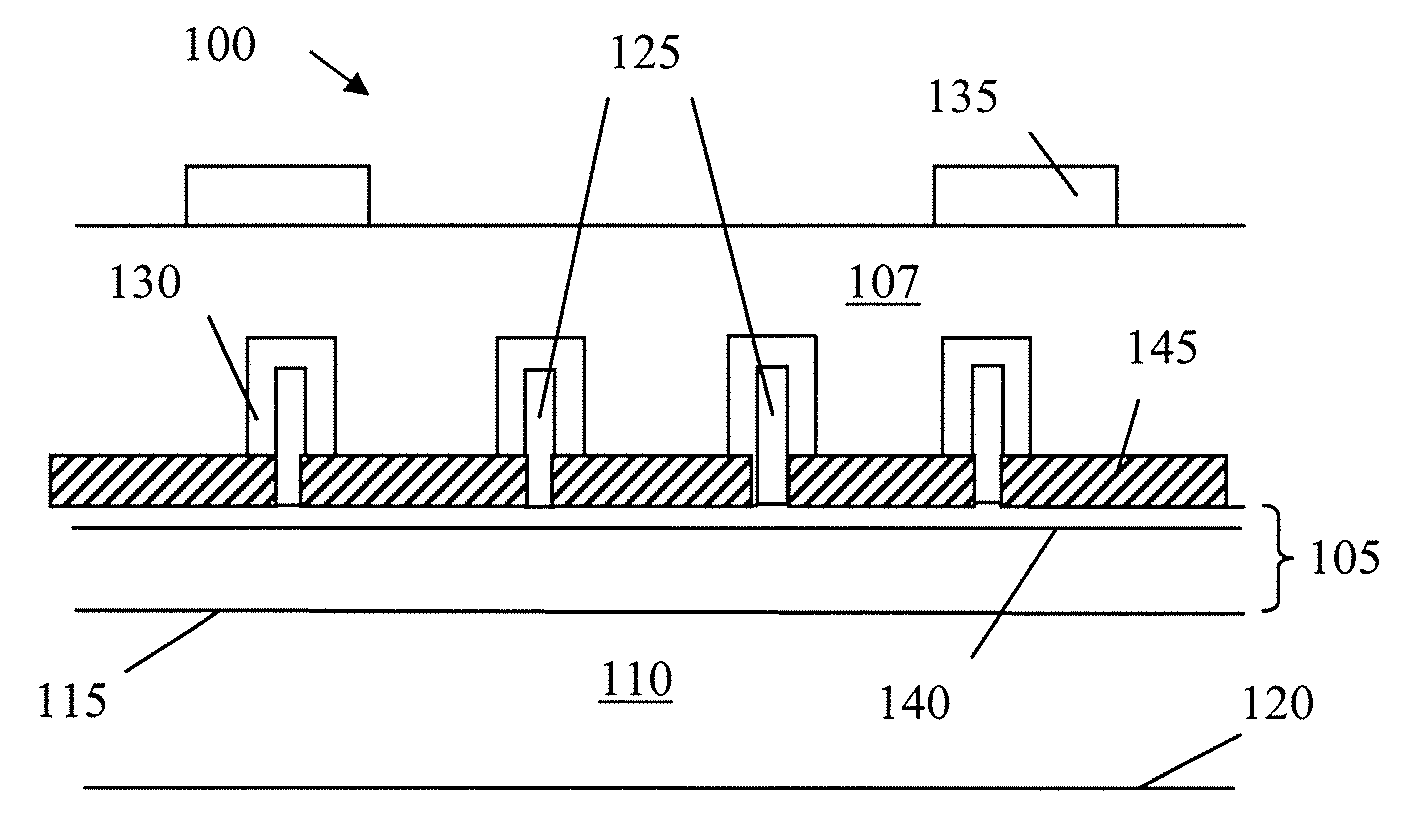

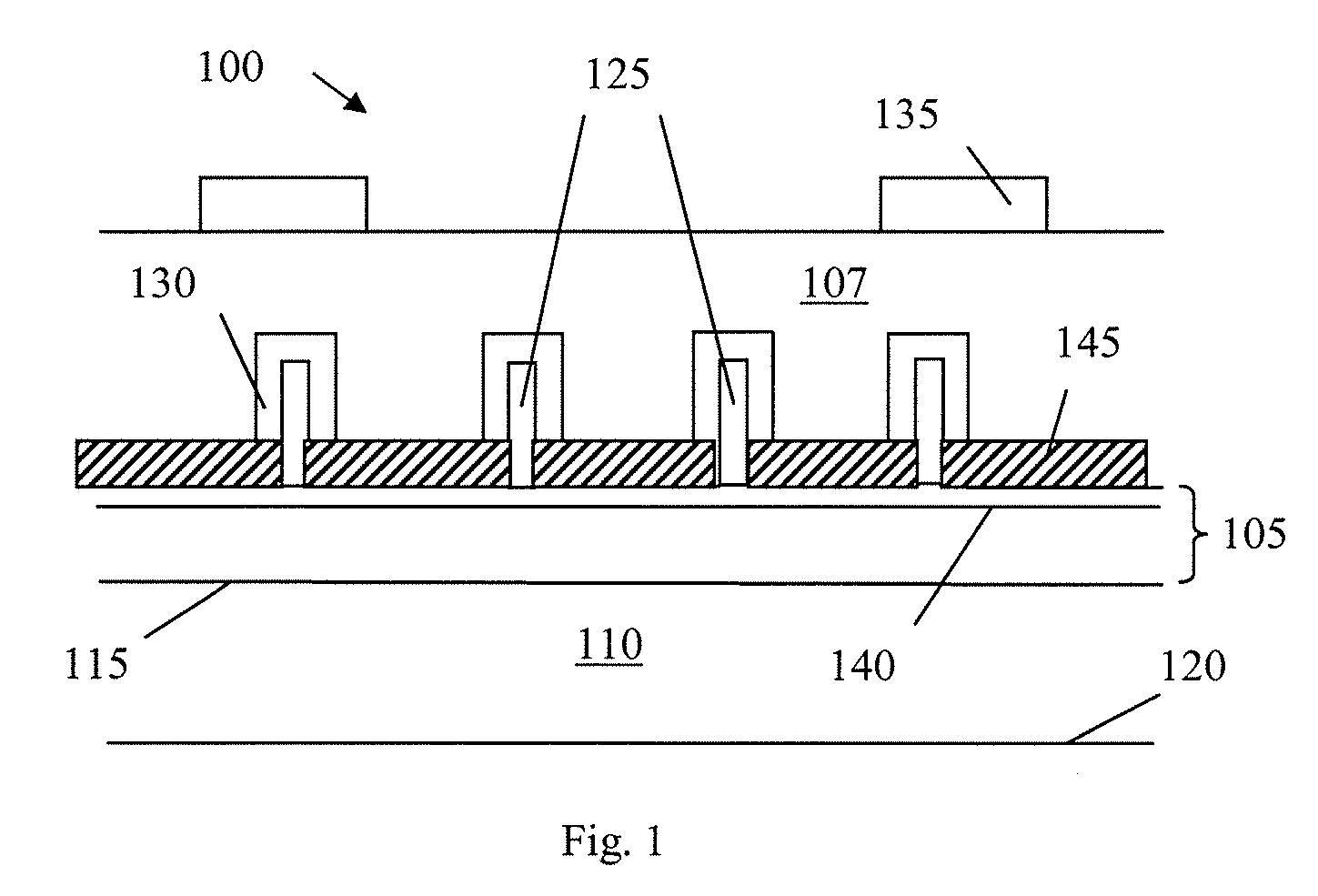

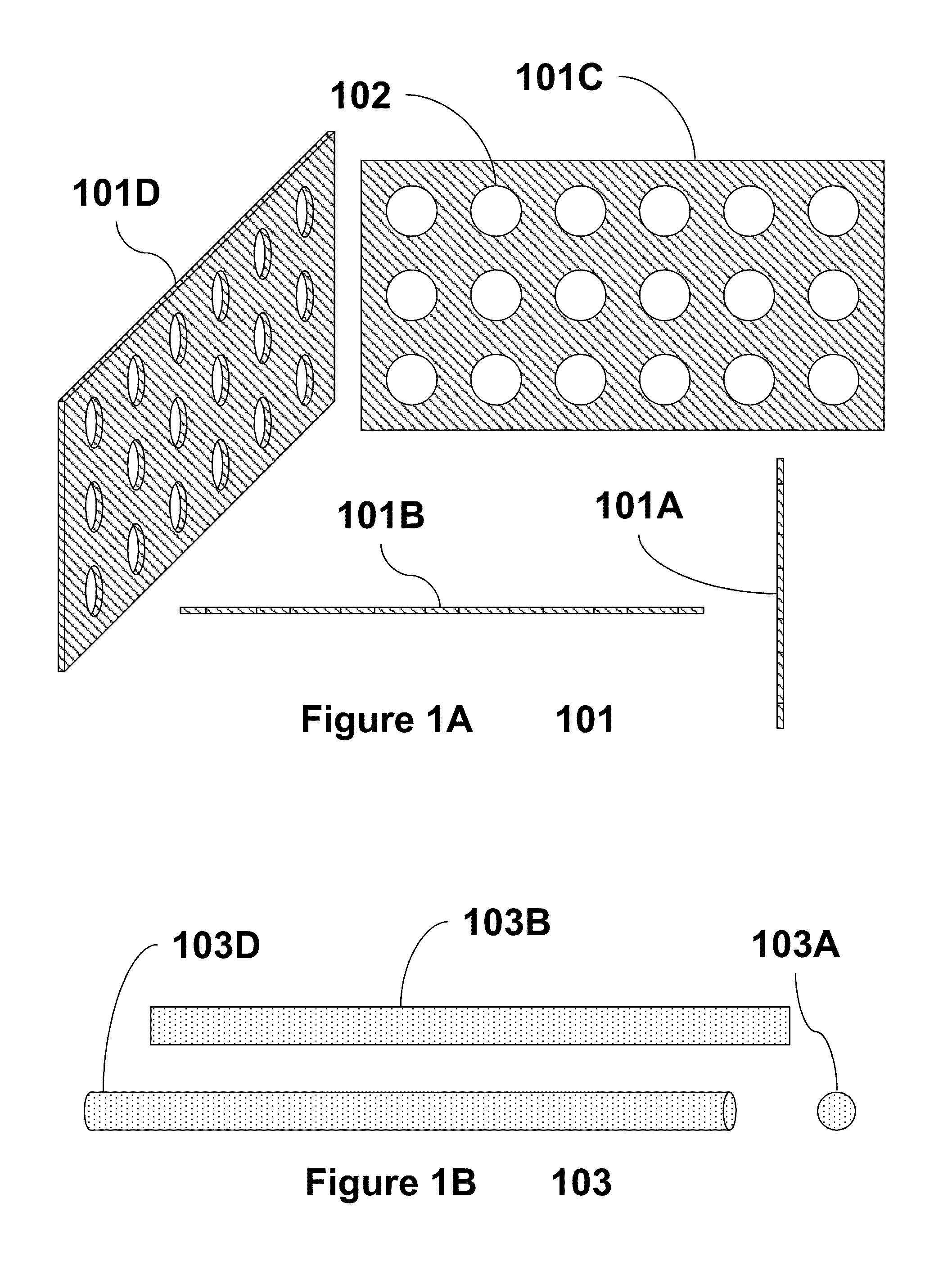

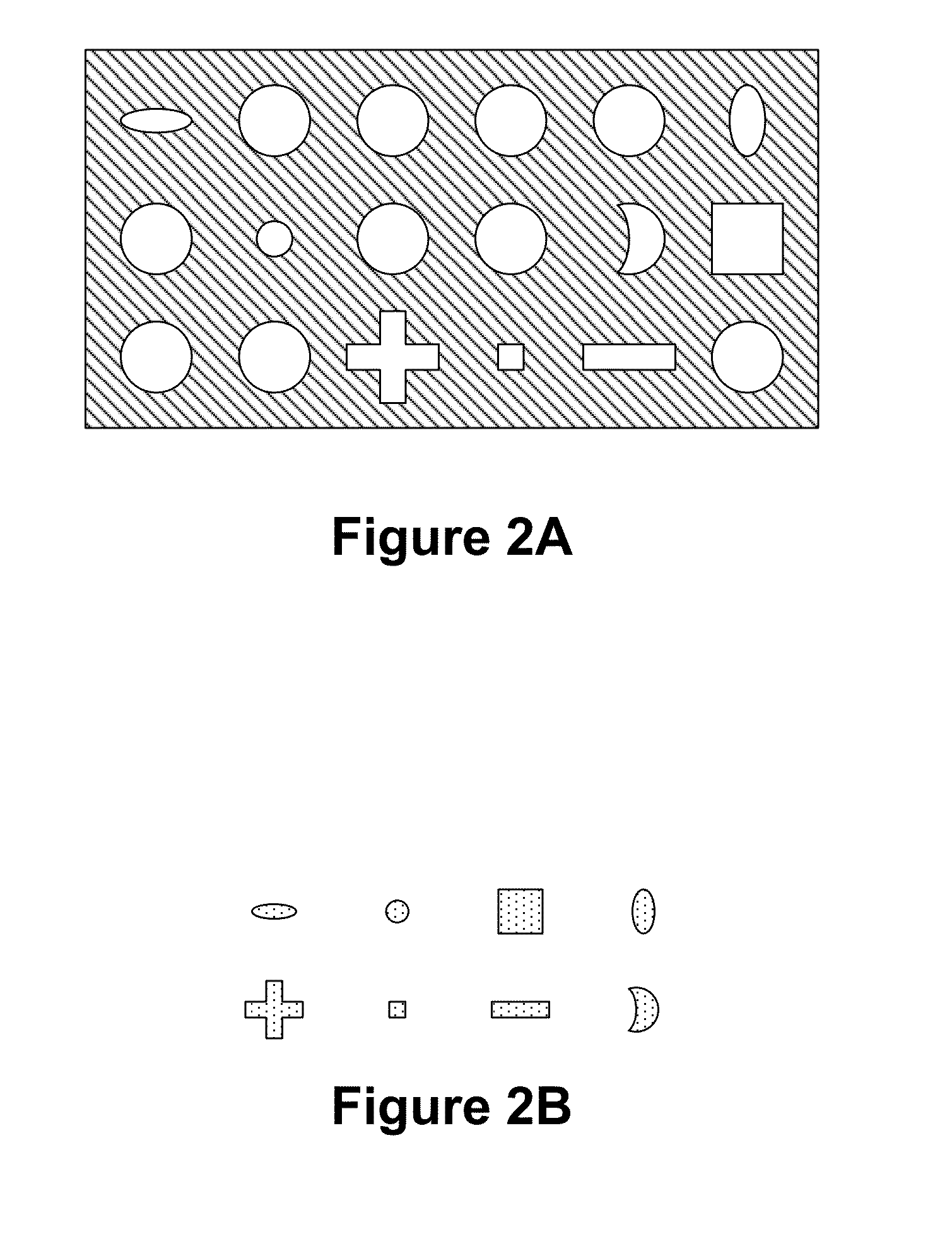

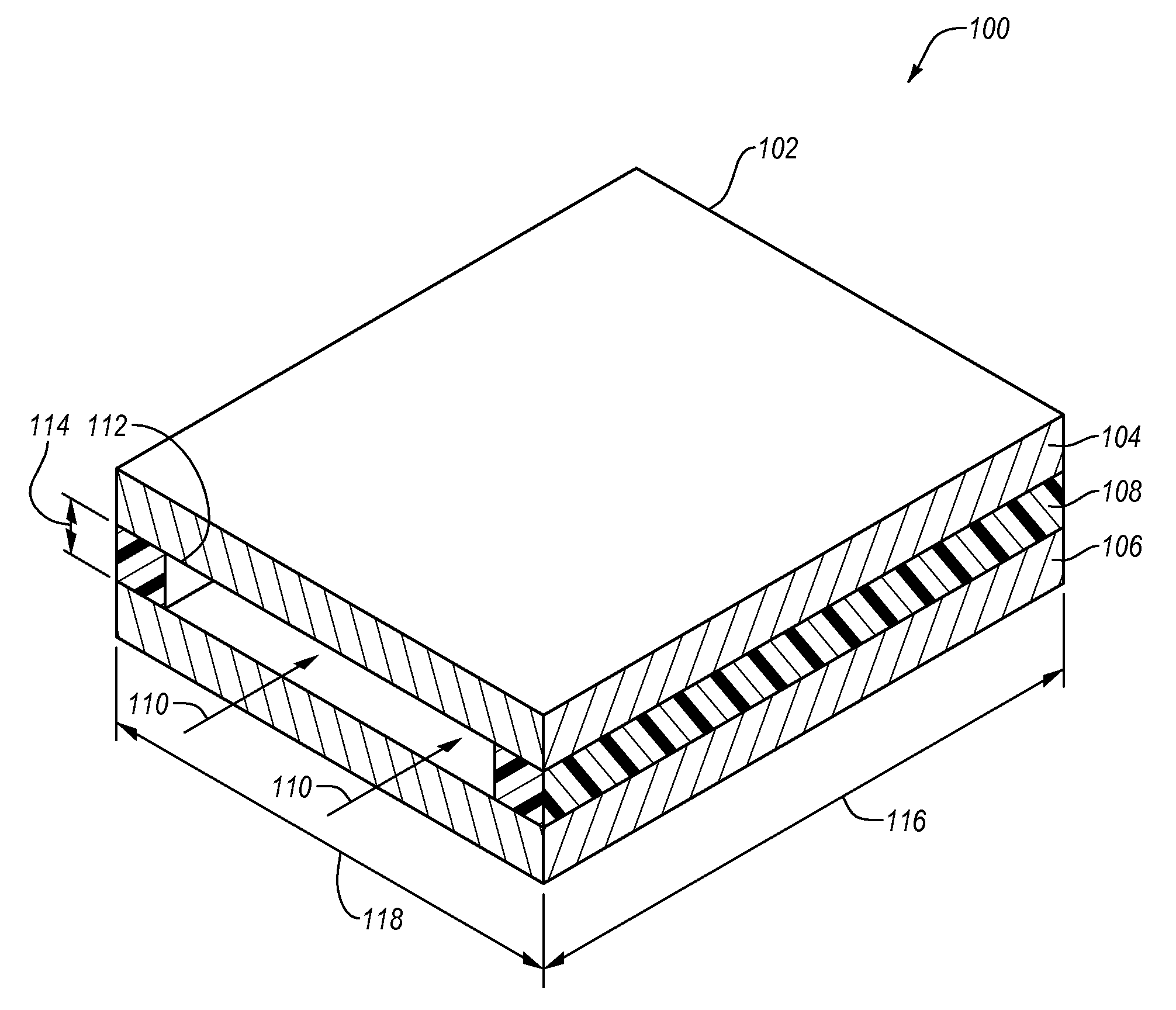

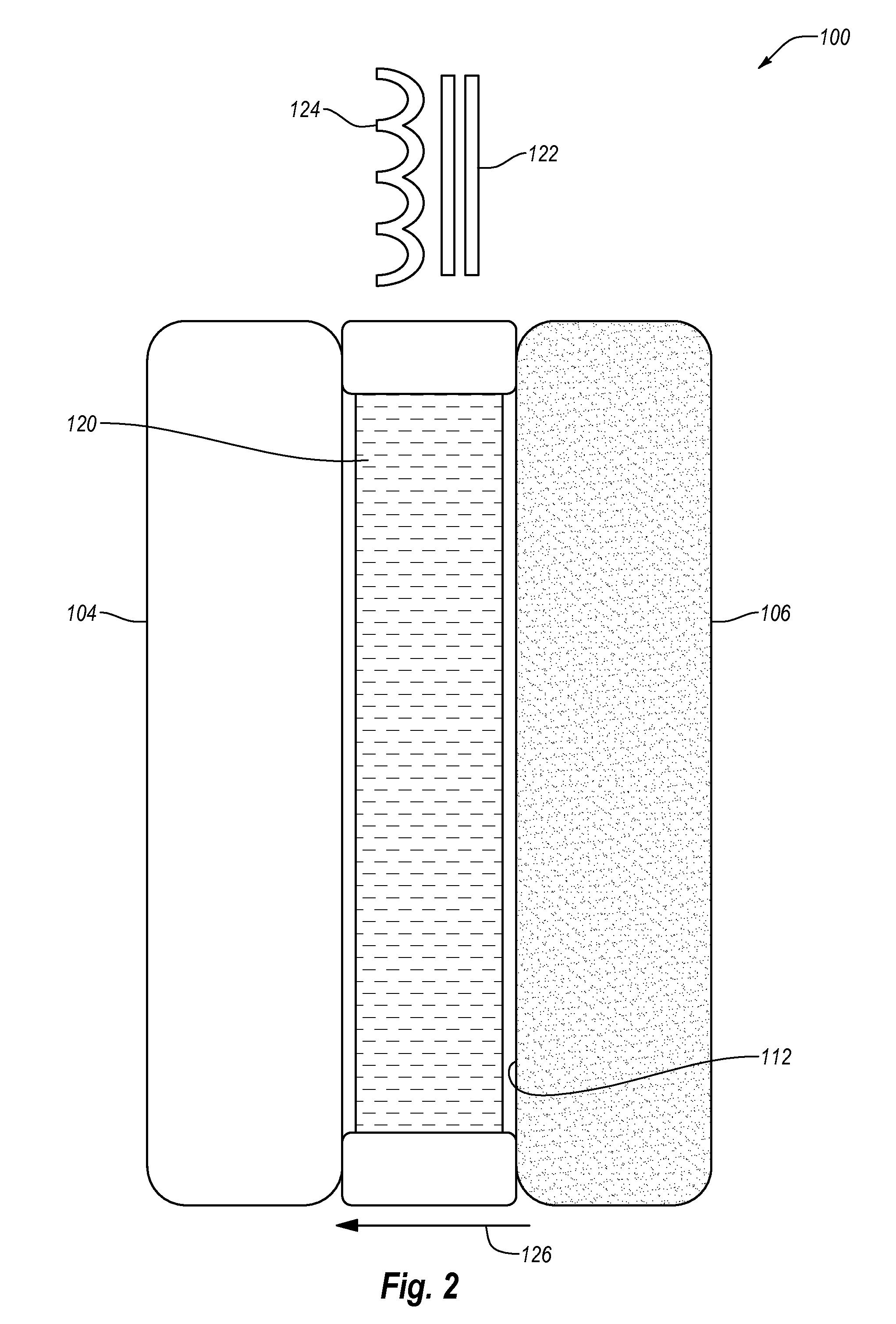

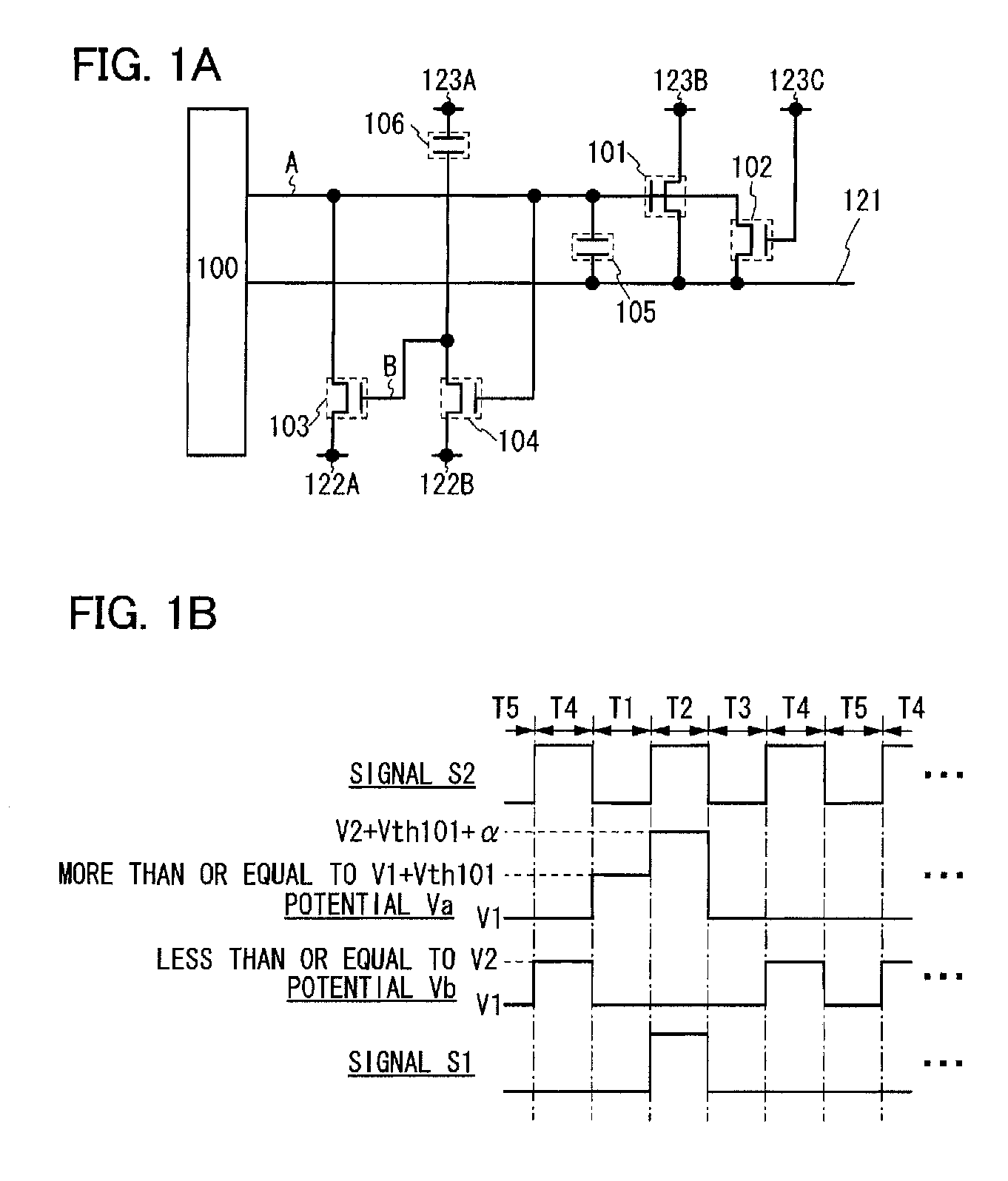

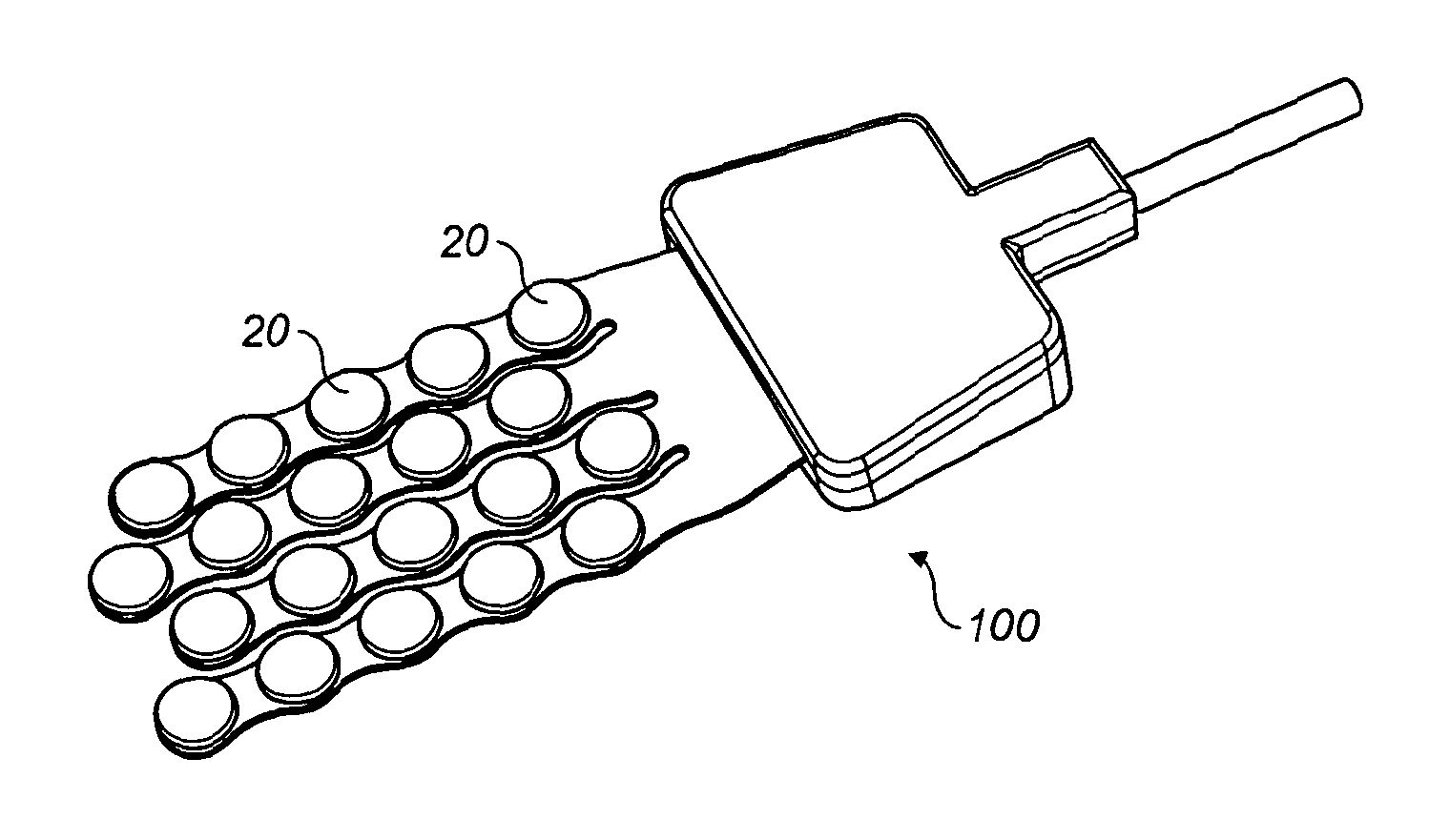

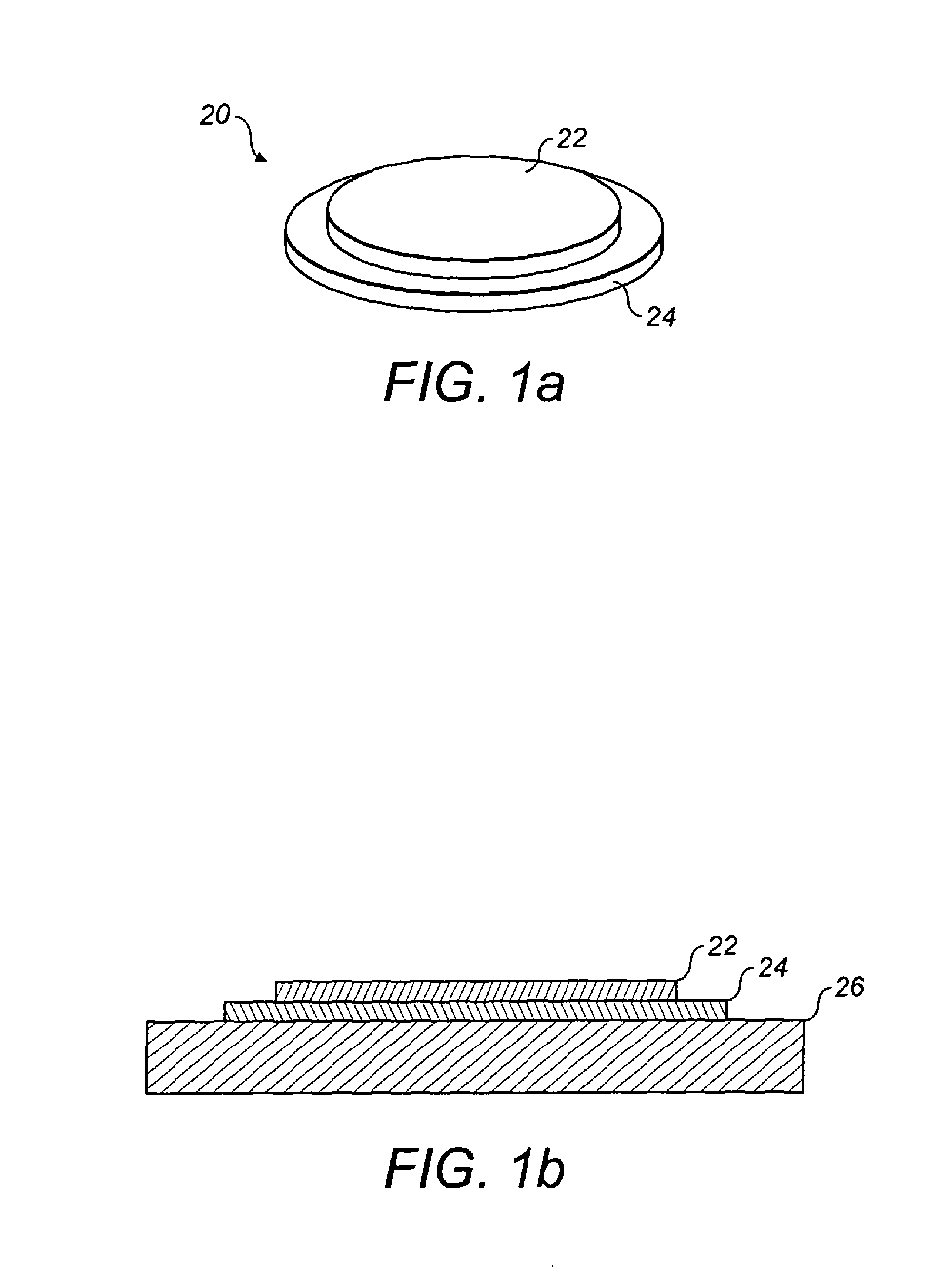

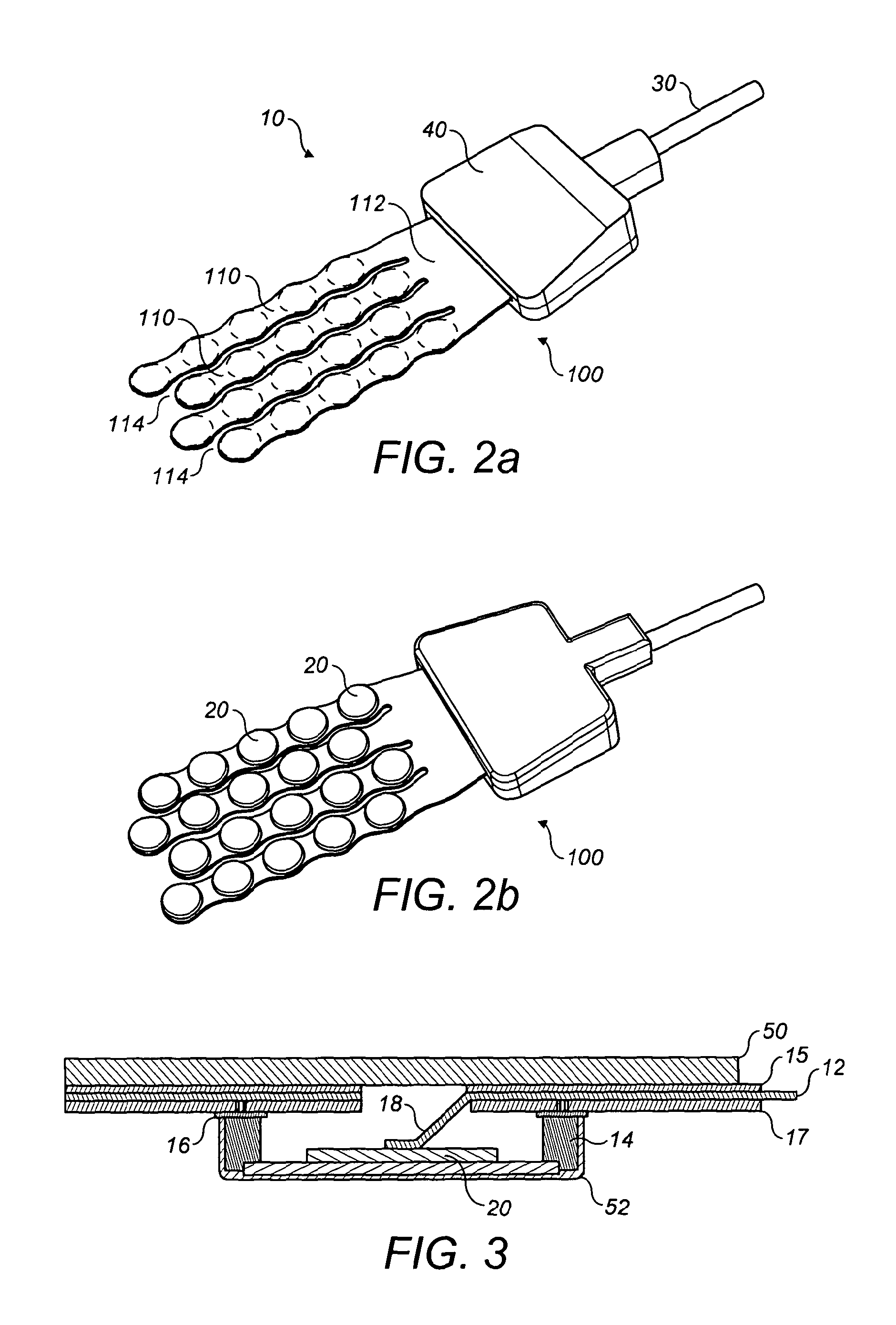

Flexi-PCB Mounting of Ultrasonic Transducers for Enhanced Dermal and Transdermal Applications

ActiveUS20120277639A1Deliver ultrasound efficientlyEfficient deliveryUltrasonic/sonic/infrasonic diagnosticsUltrasound therapyElectricityTransducer

An ultrasound transducer patch (100) comprises an array of ultrasound transducers (20) mounted to a flexi-PCB (10) containing multiple tracks (12). Each transducer (20), or a sub-group of the transducers is electrically connected to first and second of the multiple tracks. The flexi-PCB (10) is configured, such as by virtue of cut-out portions (114, 414) or by inherent elasticity, to be bendable a out non-parallel axes. The enables the patch (100) to readily conform to a complex 3D surface such as a portion of a patient's face to ensure efficient transmission of ultrasound energy to a desired area of treatment.

Owner:CAREWEAR CORP