Patents

Literature

811results about How to "High resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

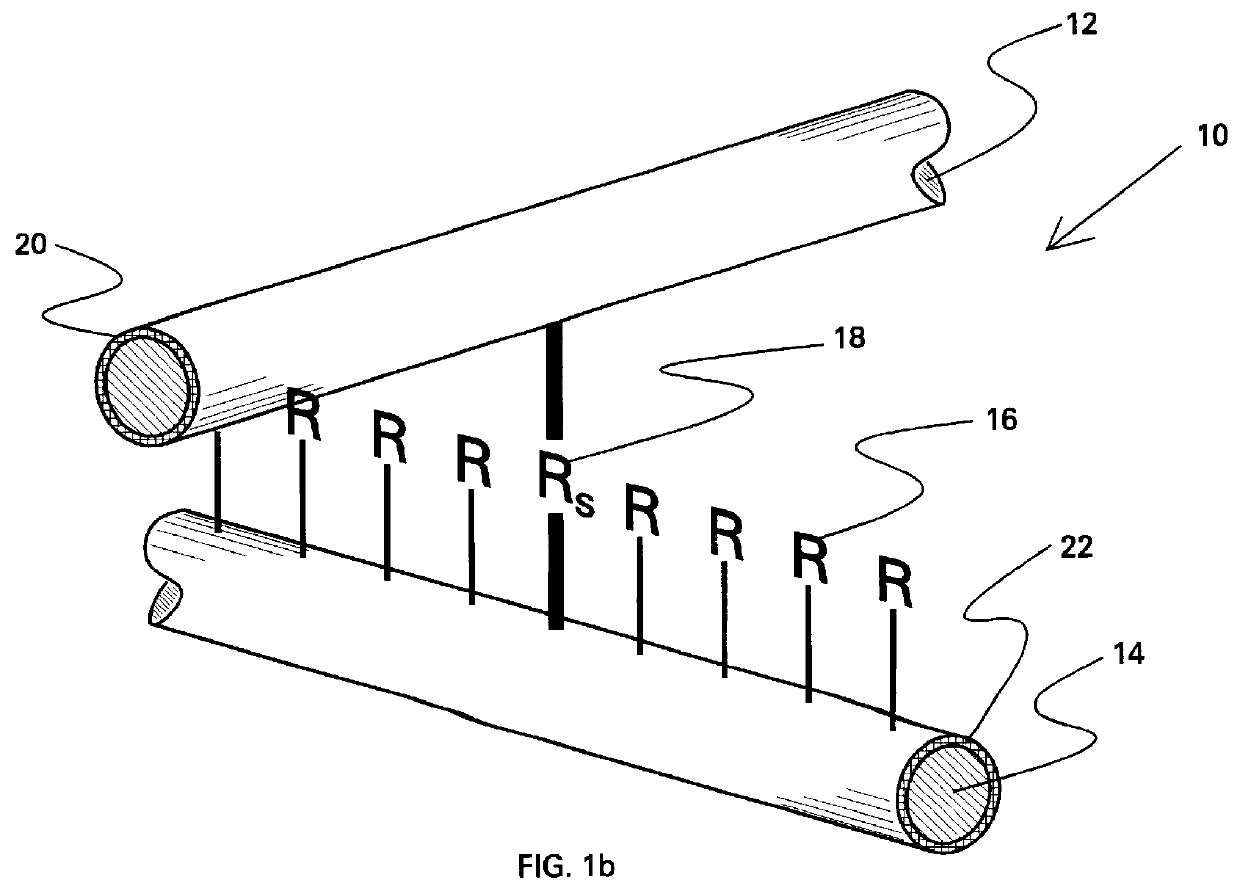

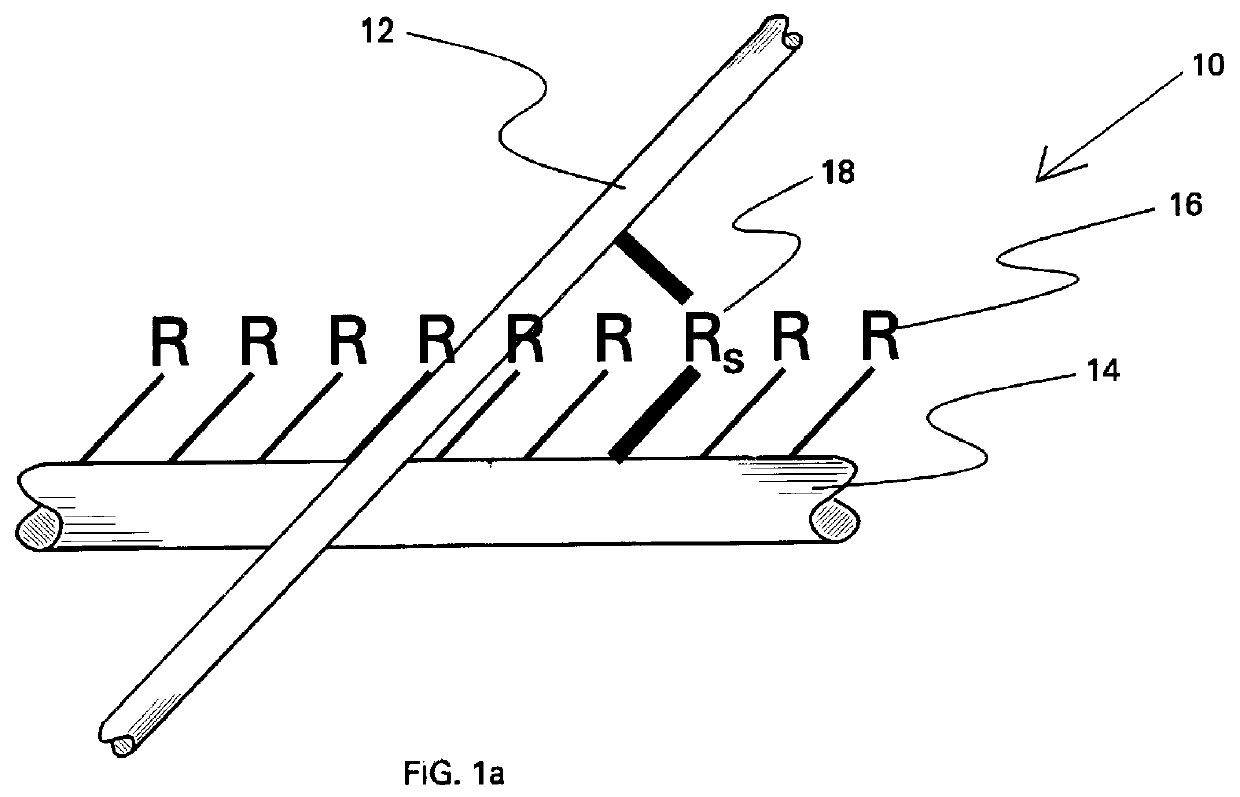

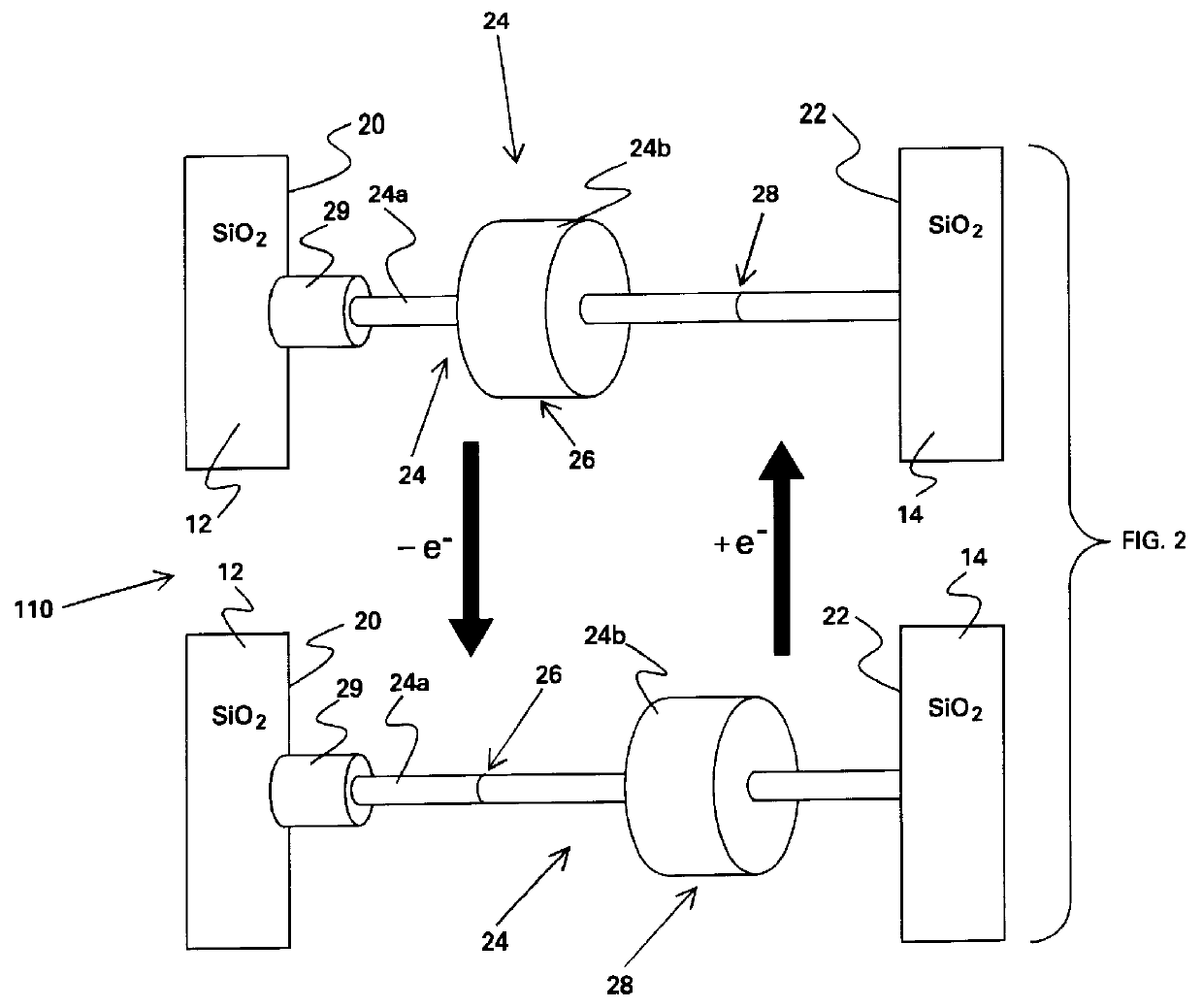

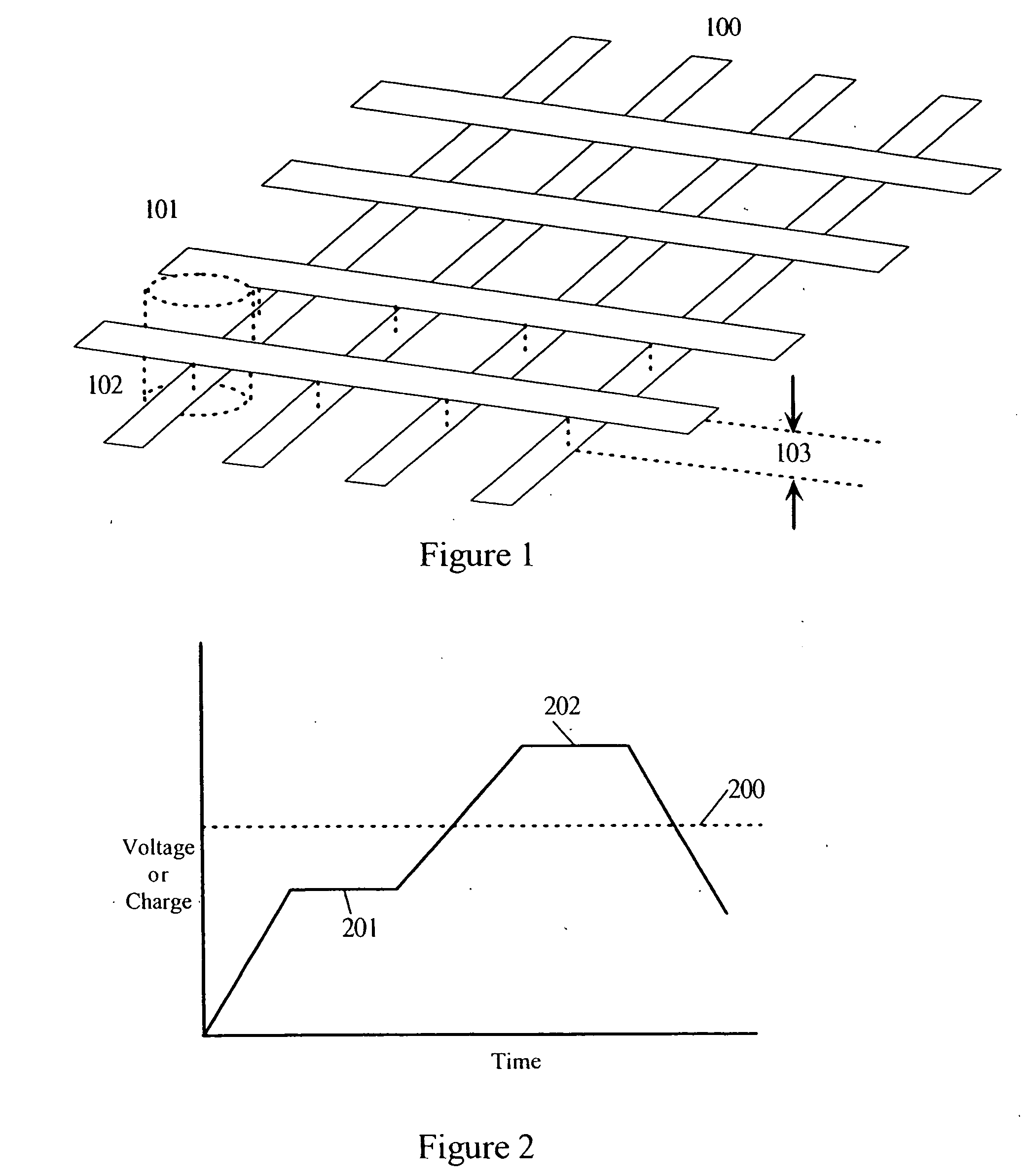

Molecular wire crossbar memory

InactiveUS6128214AAvoid switchingReduce power consumptionNanoinformaticsSolid-state devicesResistorNon symmetric

A molecular wire crossbar memory (MWCM) system is provided. The MWCM comprises a two-dimensional array of a plurality of nanometer-scale devices, each device comprising a junction formed by a pair of crossed wires where one wire crosses another and at least one connector species connecting the pair of crossed wires in the junction. The connector species comprises a bi-stable molecular switch. The junction forms either a resistor or a diode or an asymmetric non-linear resistor. The junction has a state that is capable of being altered by application of a first voltage and sensed by application of a second, non-destructive voltage.

Owner:RGT UNIV OF CALIFORNIA +1

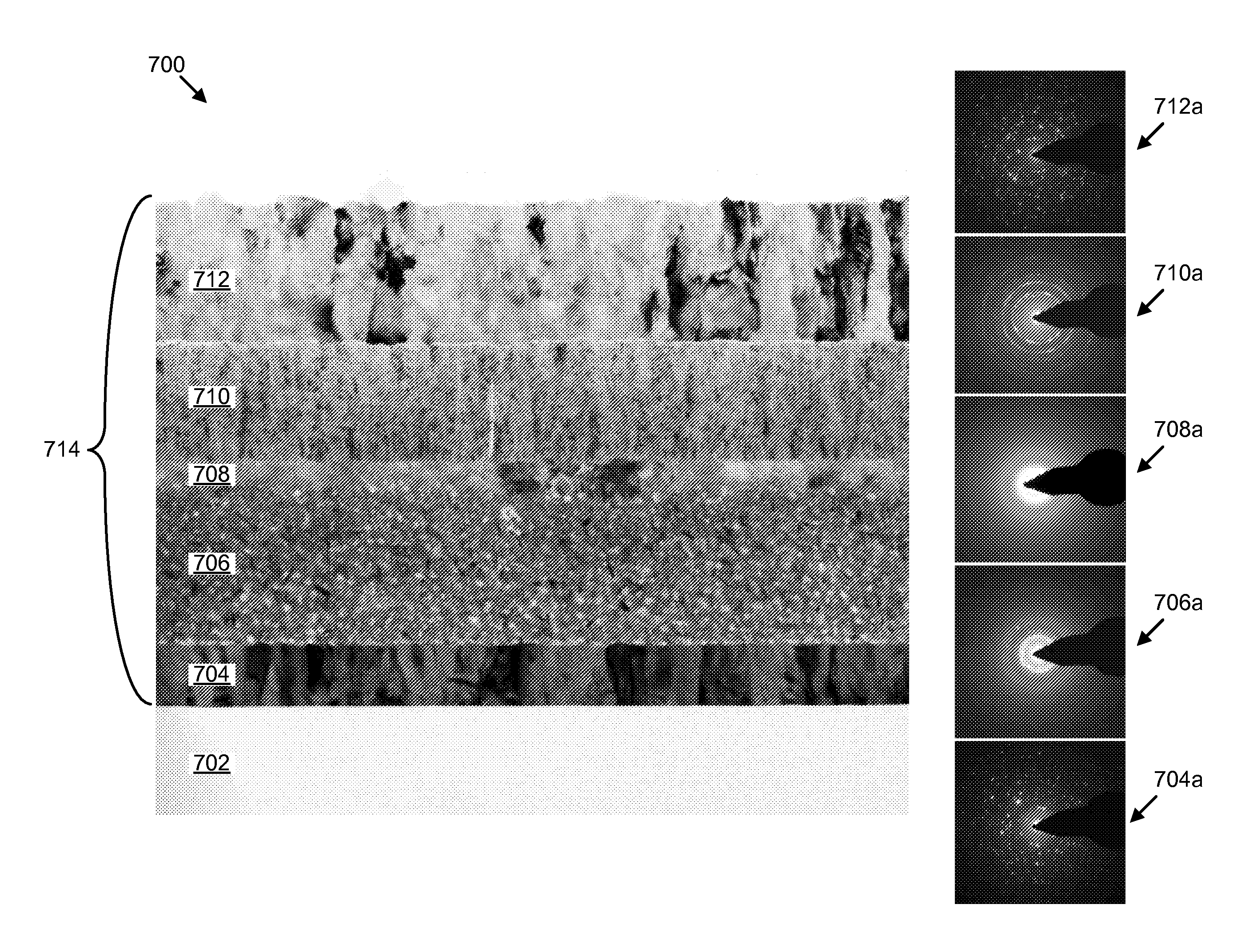

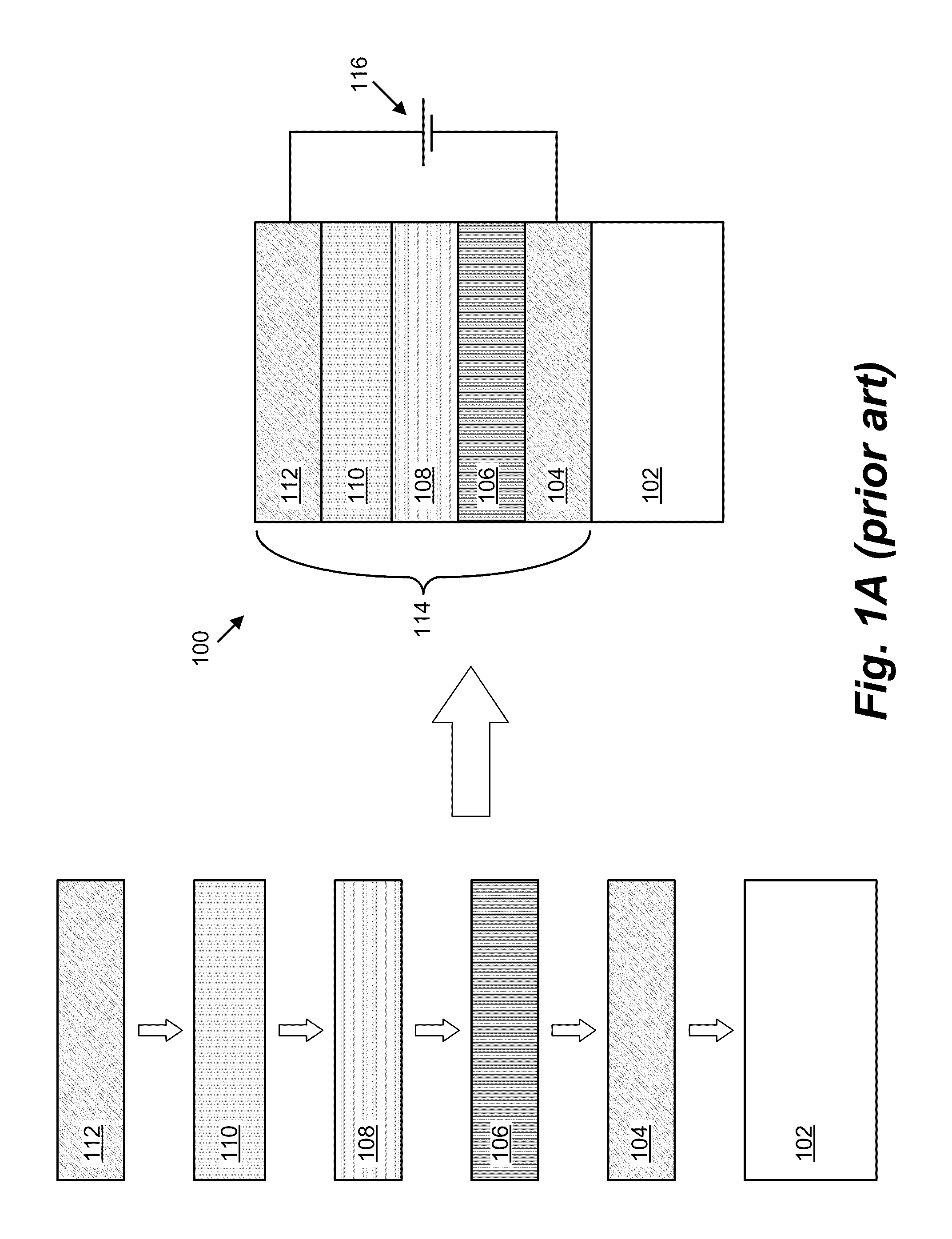

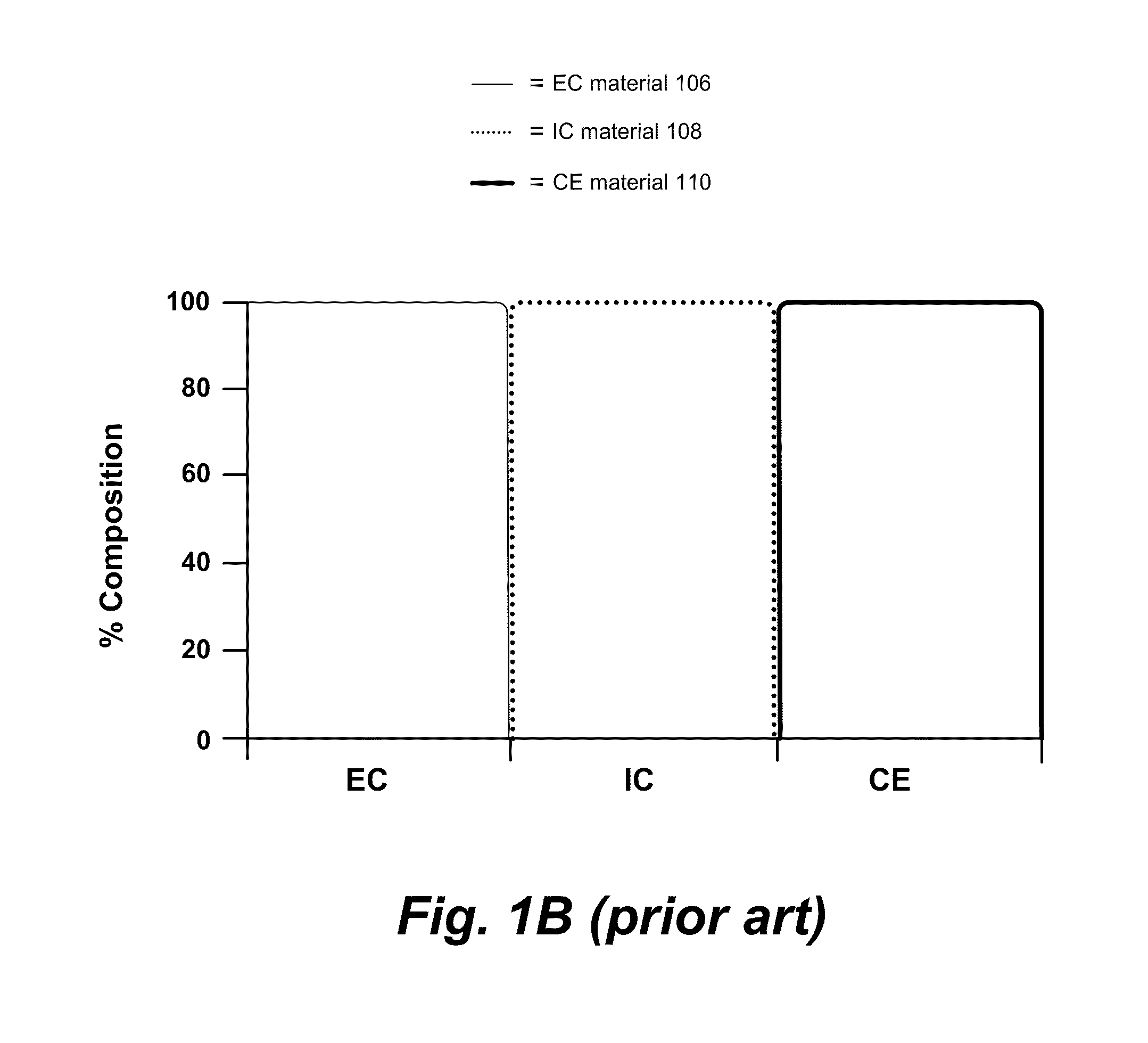

Electrochromic devices

ActiveUS20110267674A1Highly conductiveHigh resistanceDoors/windowsVacuum evaporation coatingIonElectricity

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

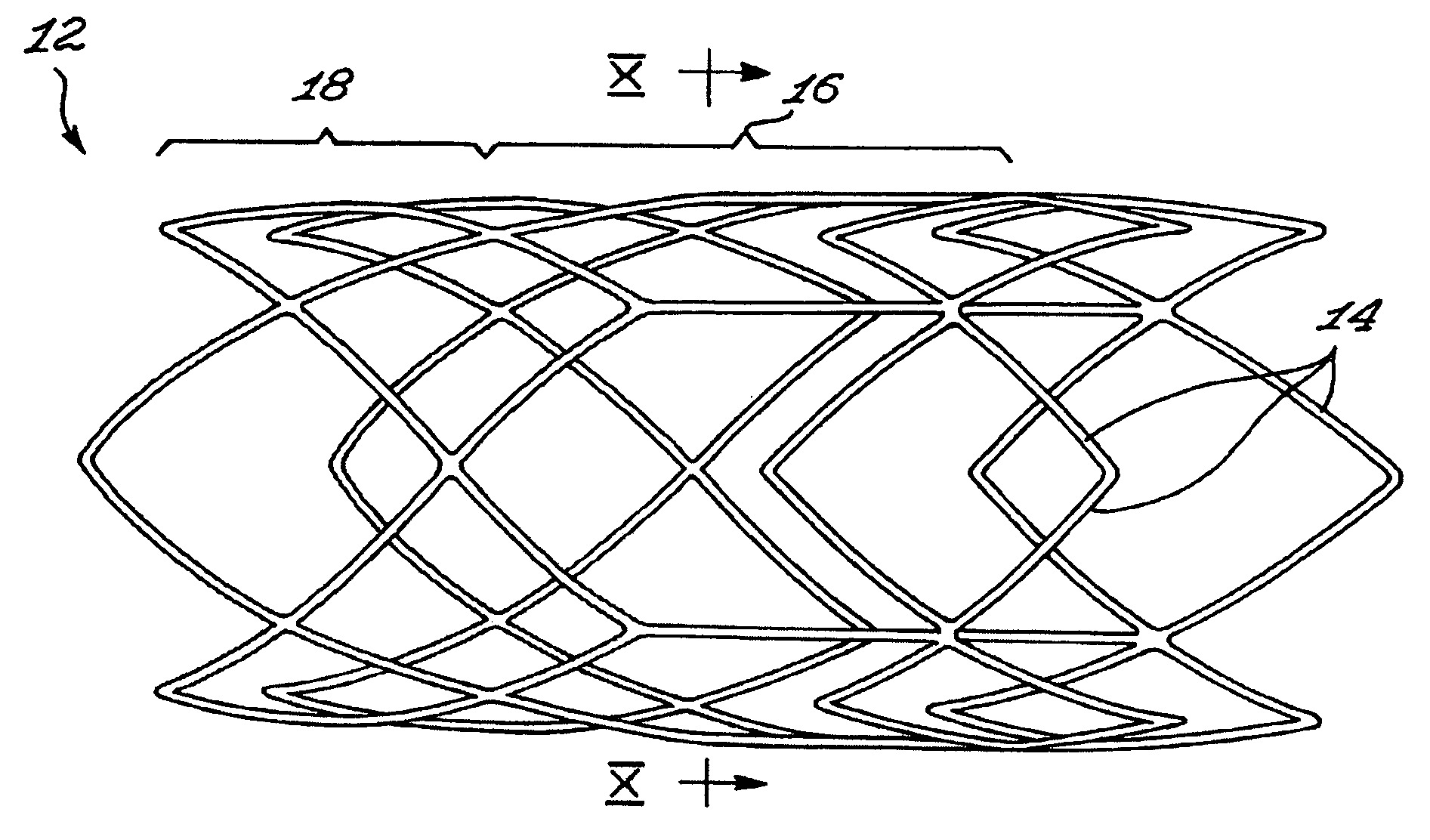

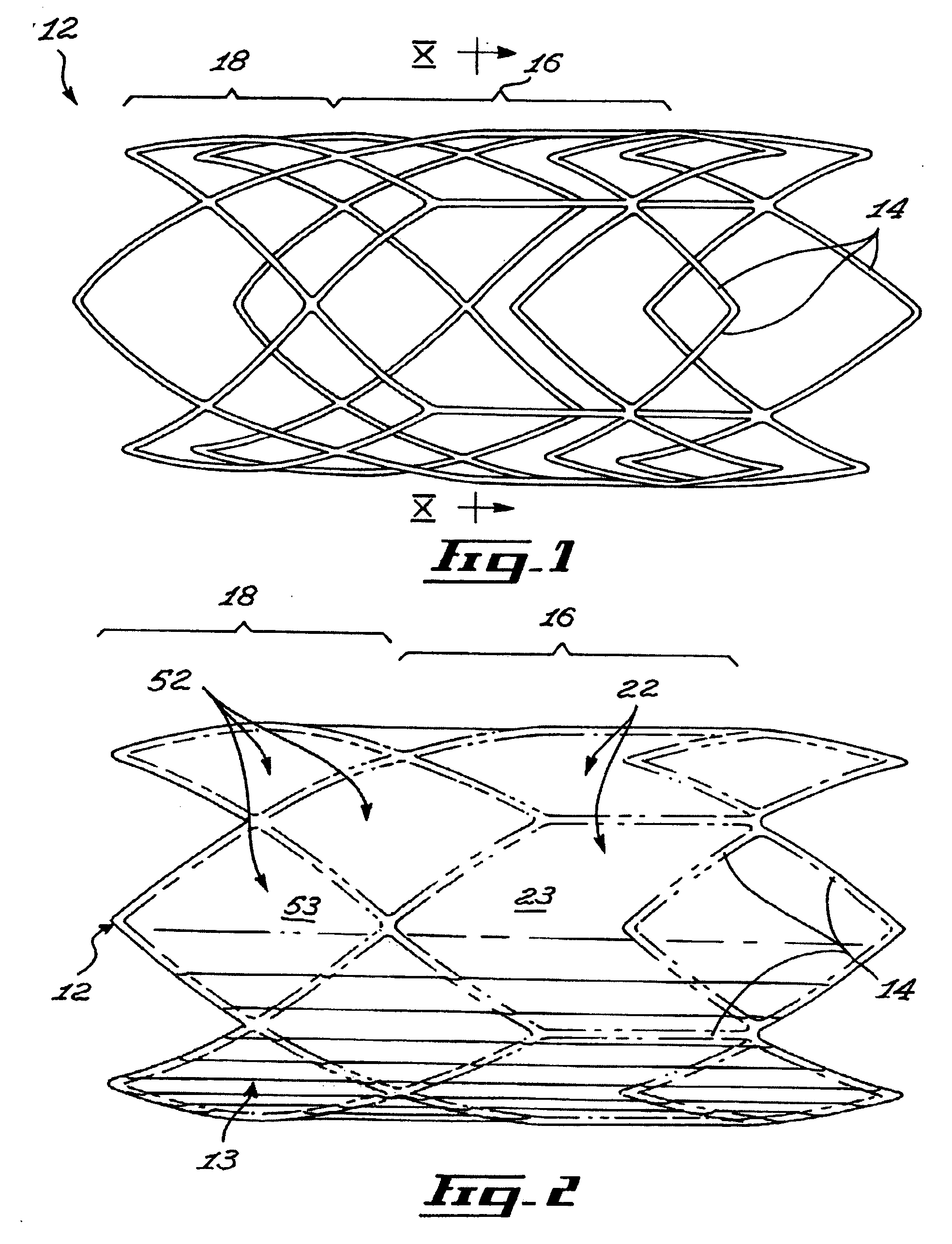

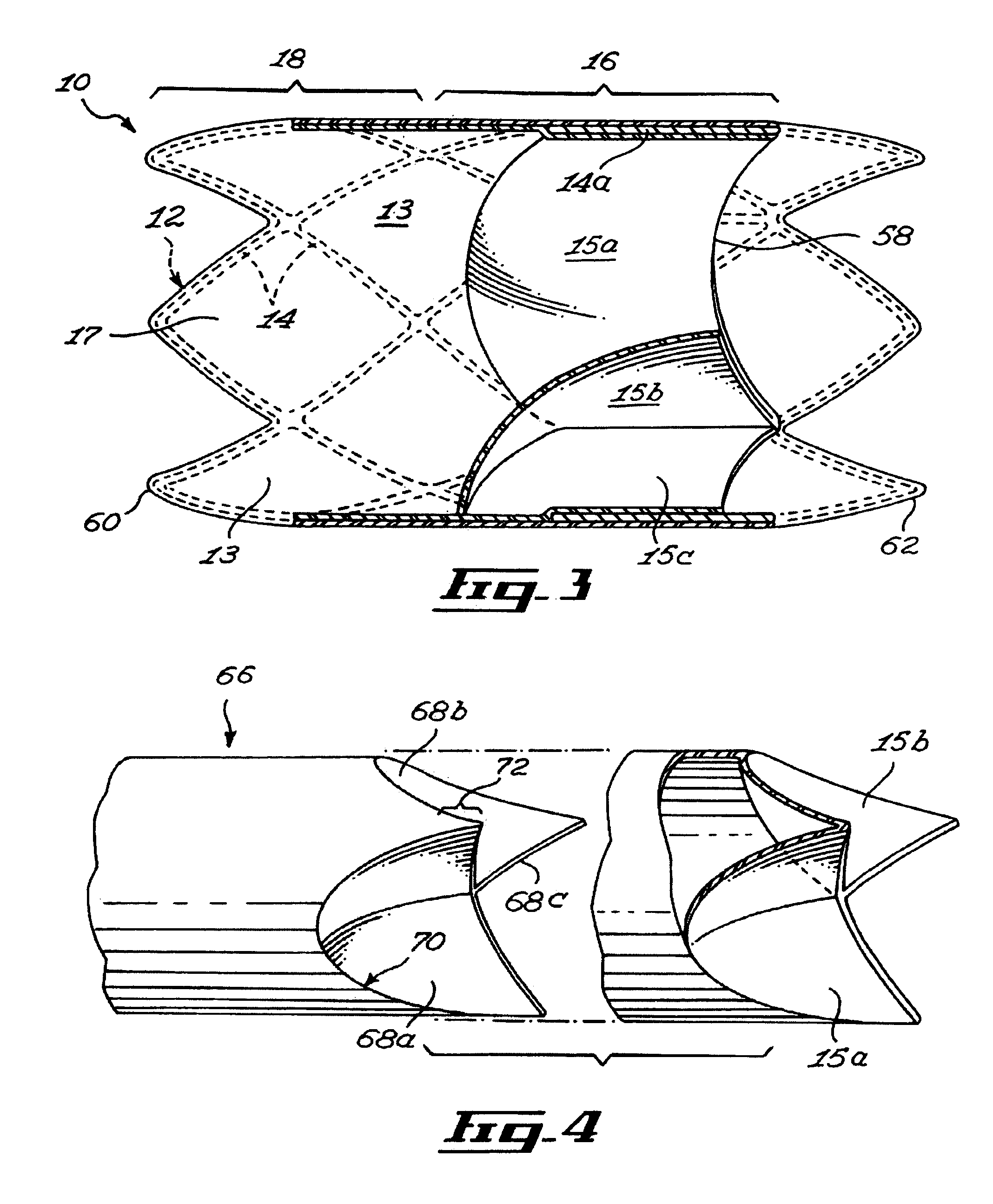

Stent and method of manufacturing same

A stent insertable in a body lumen. The stent includes a scaffold having interlinked struts forming a scaffold first section and a scaffold second section, the scaffold being deformable substantially radially between a scaffold retracted configuration and a scaffold expanded configuration. The struts are configured and sized such that the coefficient of radial compressibility of the scaffold second section is greater than the coefficient of radial compressibility of the scaffold first section and the coupling coefficient between radial and longitudinal strains of the scaffold second section is greater than the coupling coefficient between radial and longitudinal strains of the scaffold first section.

Owner:BAYLIS MEDICAL

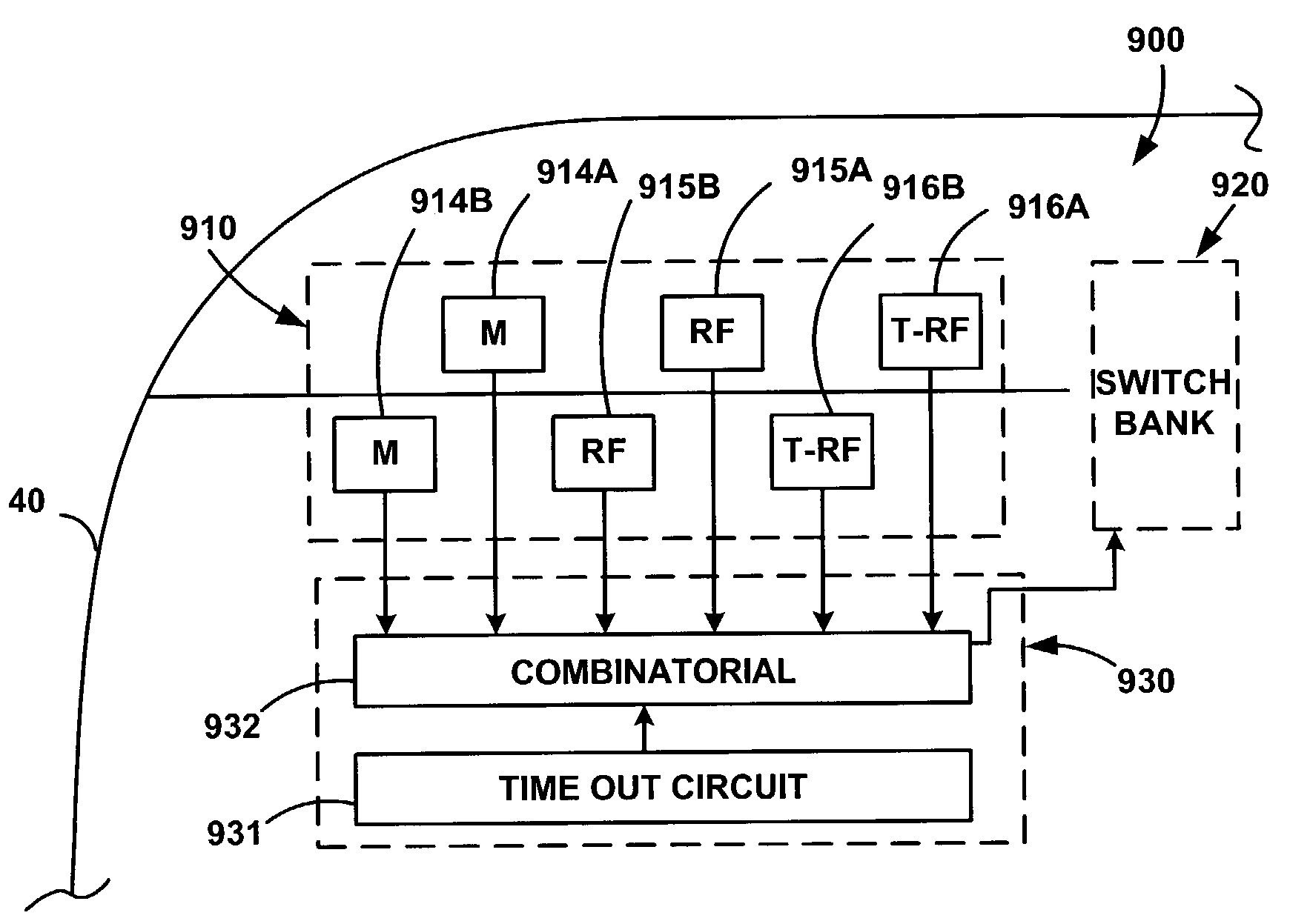

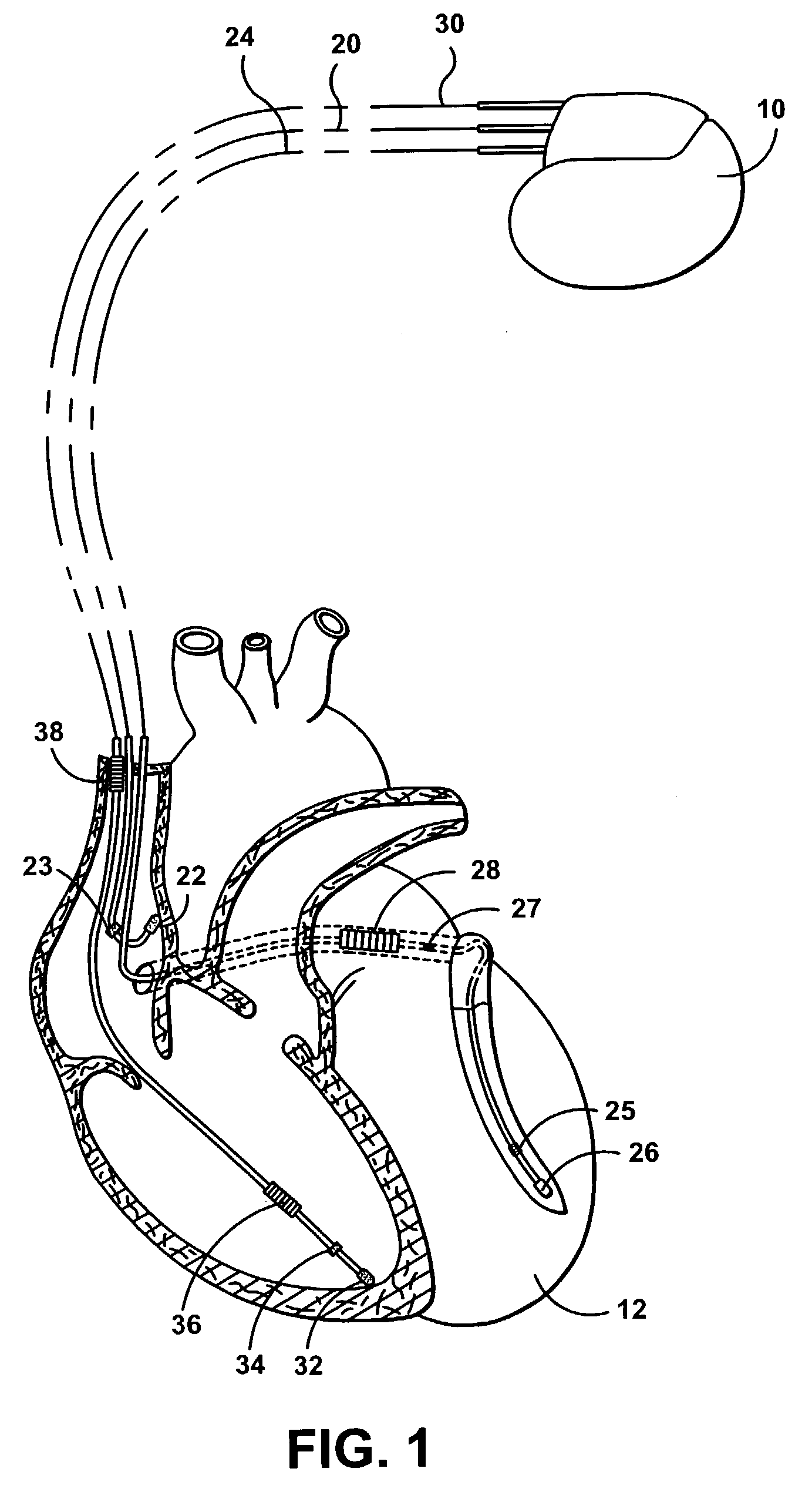

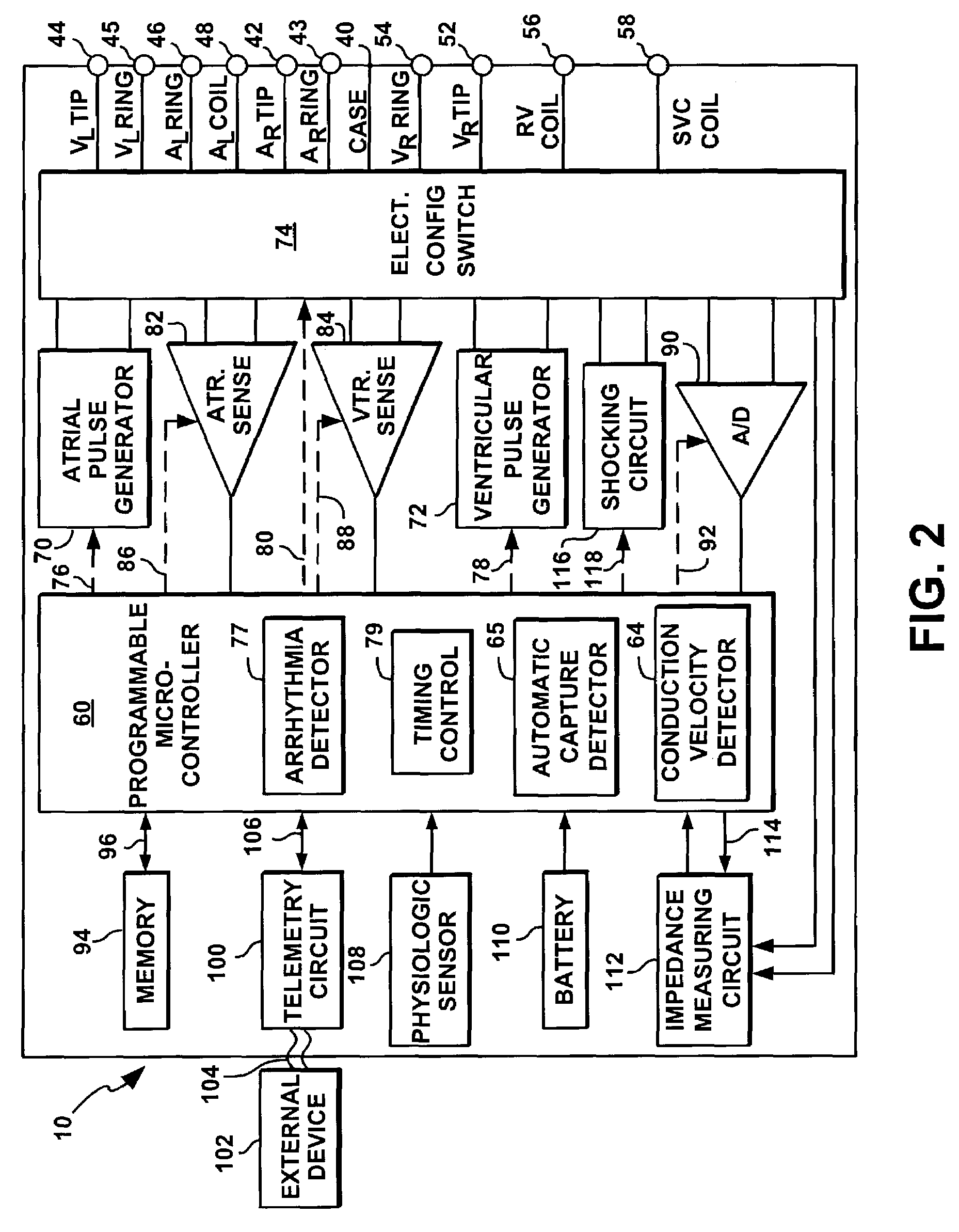

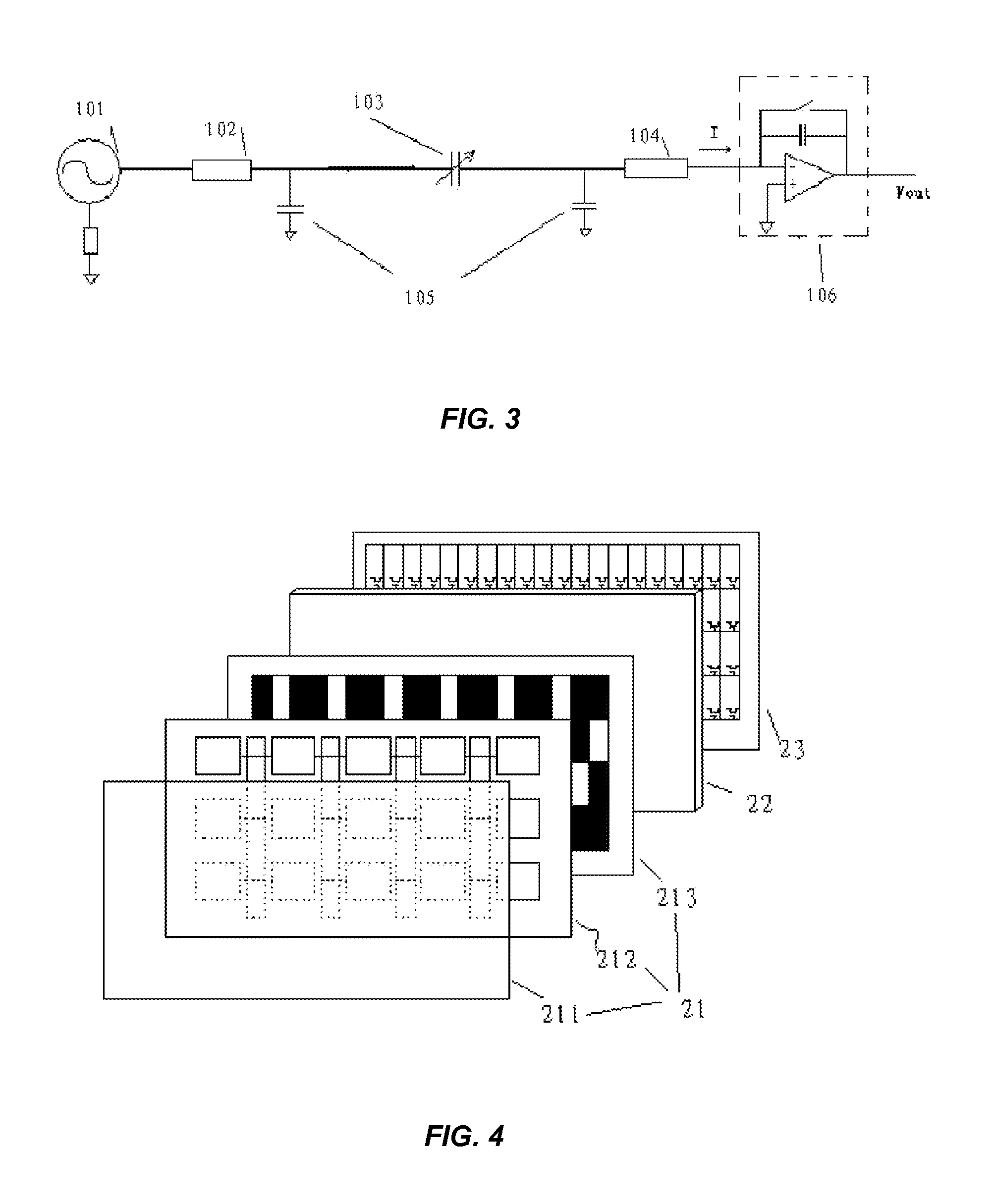

Implantable stimulation device with isolating system for minimizing magnetic induction

An implantable cardiac stimulation device is equipped with an isolation system capable of attenuating or eliminating induction currents flowing through the stimulation device by eliminating induction loops. The isolation system comprises a magnetic insulator configured to shield selected components of the stimulation device from external magnetic fields or radio-frequency (RF) signals. The magnetic insulator comprises a plurality of sensors that are configured to detect the intensity of the external magnetic fields and / or RF signals, and a switch bank that electrically isolates certain components of the stimulation device to eliminate the induction loops. The isolation system further comprises an attenuation system comprised of at least one magnetoresistor disposed along potential induction loops to attenuate induction currents when subjected to undesirable external magnetic fields and / or RF signals.

Owner:PACESETTER INC

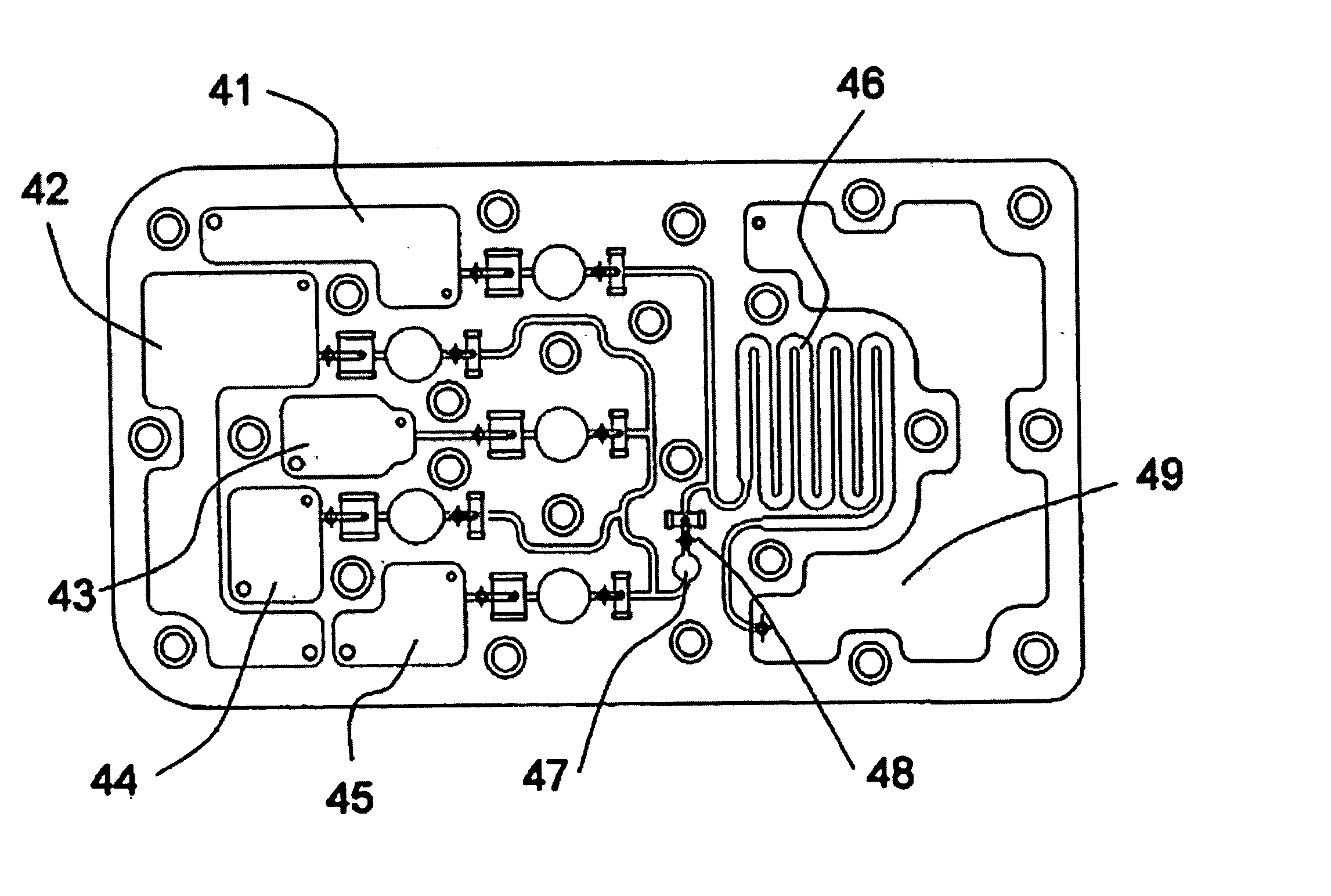

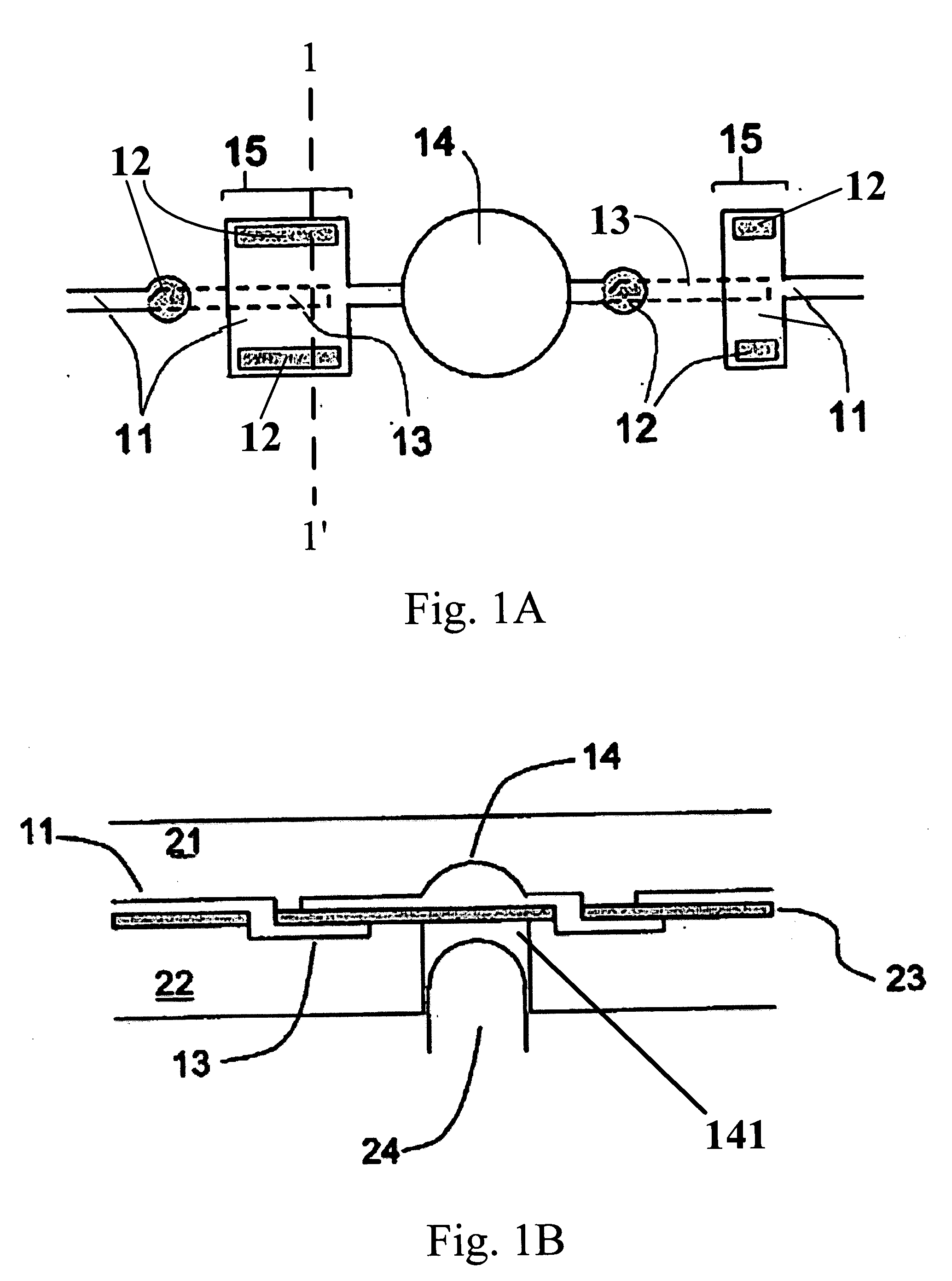

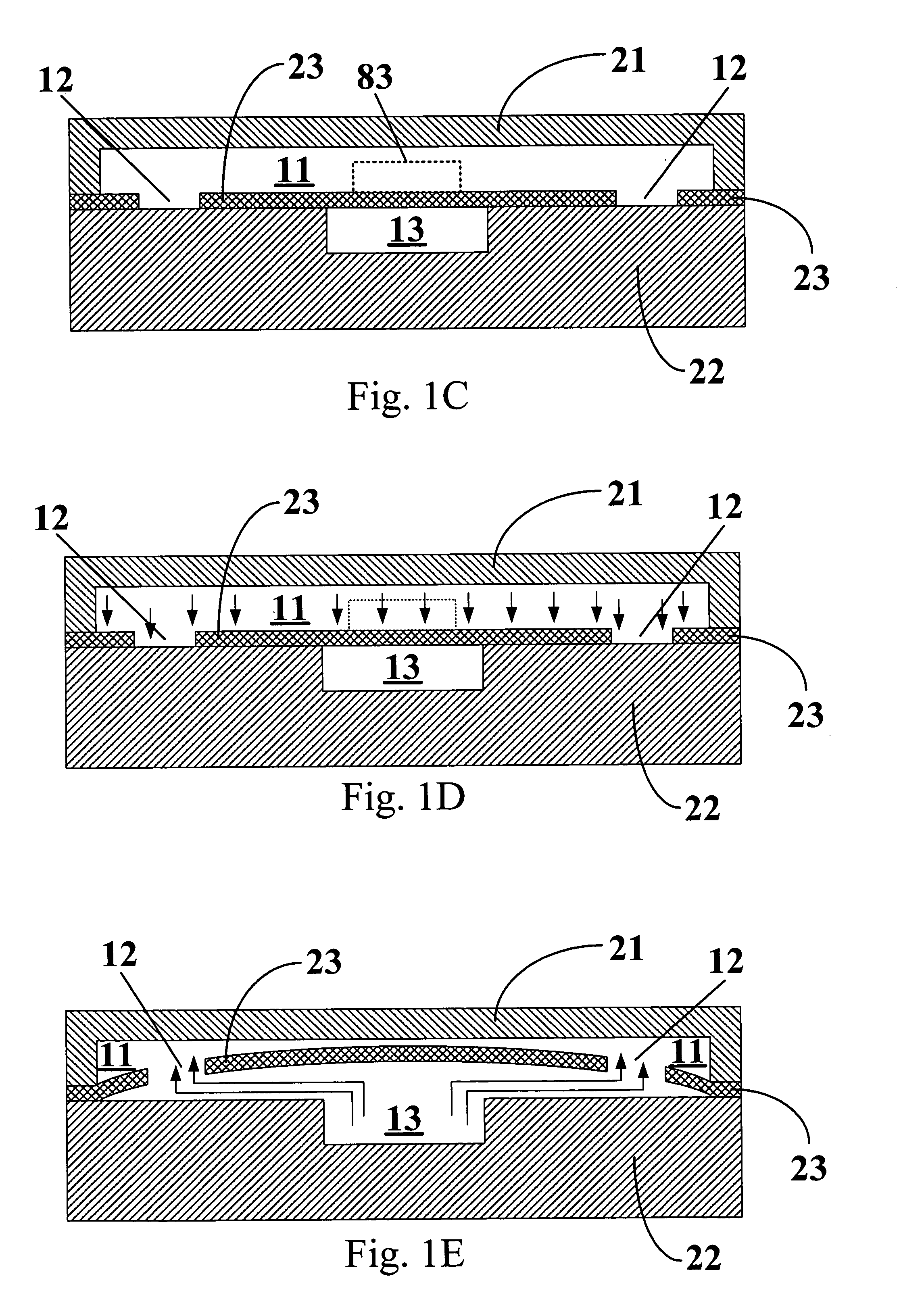

Miniaturized fluid delivery and analysis system

ActiveUS20050180891A1Low resistanceHigh resistanceBioreactor/fermenter combinationsBiological substance pretreatmentsLinear actuatorEngineering

An apparatus comprising a fluidic cartridge including a first and second substrate and an intermediate interlayer is provided. The intermediate interlayer is sealedly interfaced between the first and second substrates to form therein a plurality of channels of capillary dimensions. The apparatus further includes an open reservoir, a pump chamber and a reaction chamber. The open reservoir and reaction chamber are each connected to the pump chamber through the channels. The open reservoir and reaction chamber are in fluid communication with each other via the channels. The apparatus further comprises a fluid flow controlling structure, formed in the fluidic cartridge, which restricts a flow of a fluid through the reaction chamber to one direction. The apparatus further comprises a linear actuator for providing a pumping action in the pump chamber to pump the fluid to flow between the open reservoir and reaction chamber via the plurality of channels and pump chamber.

Owner:AST MANAGEMENT

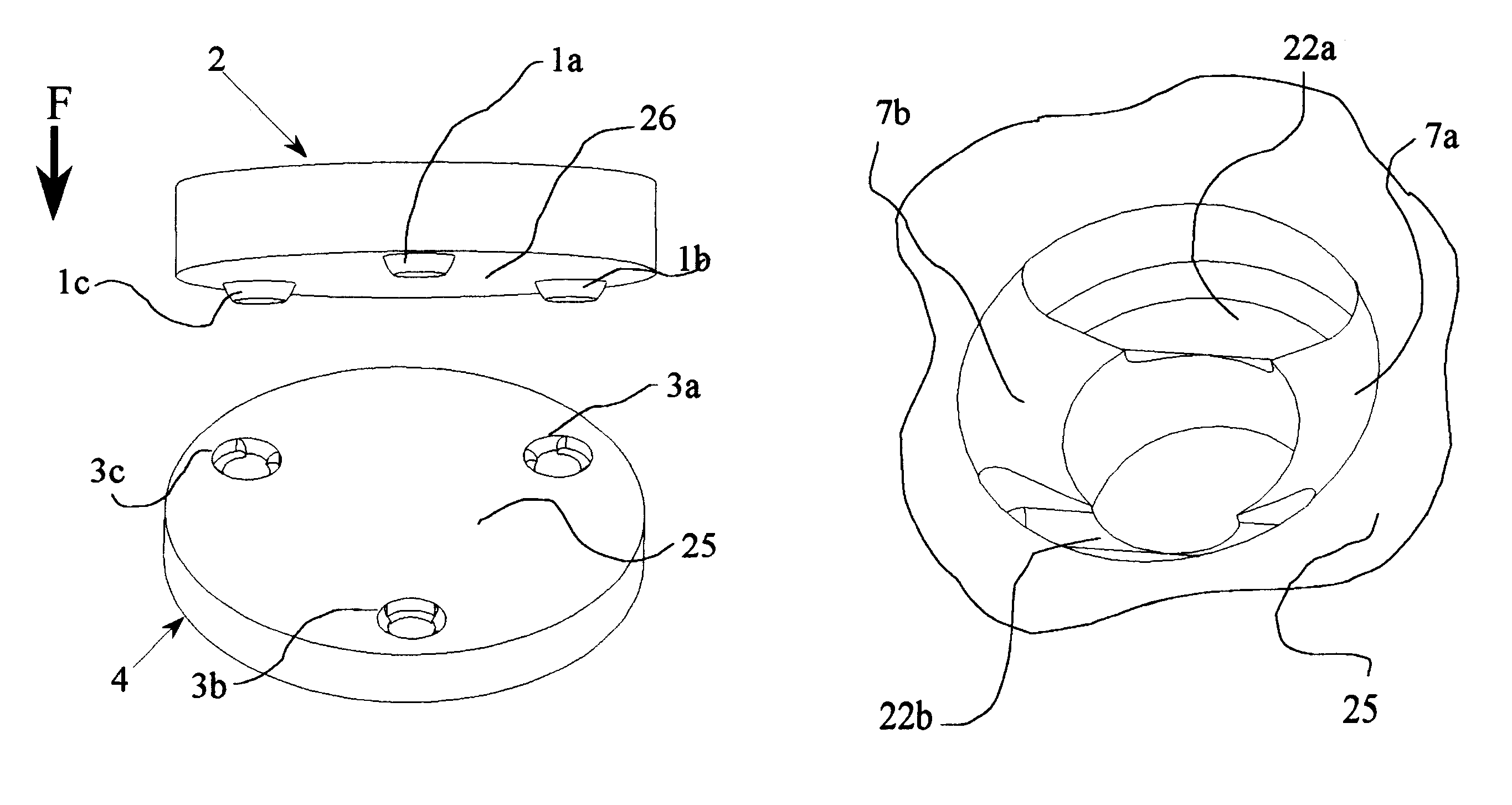

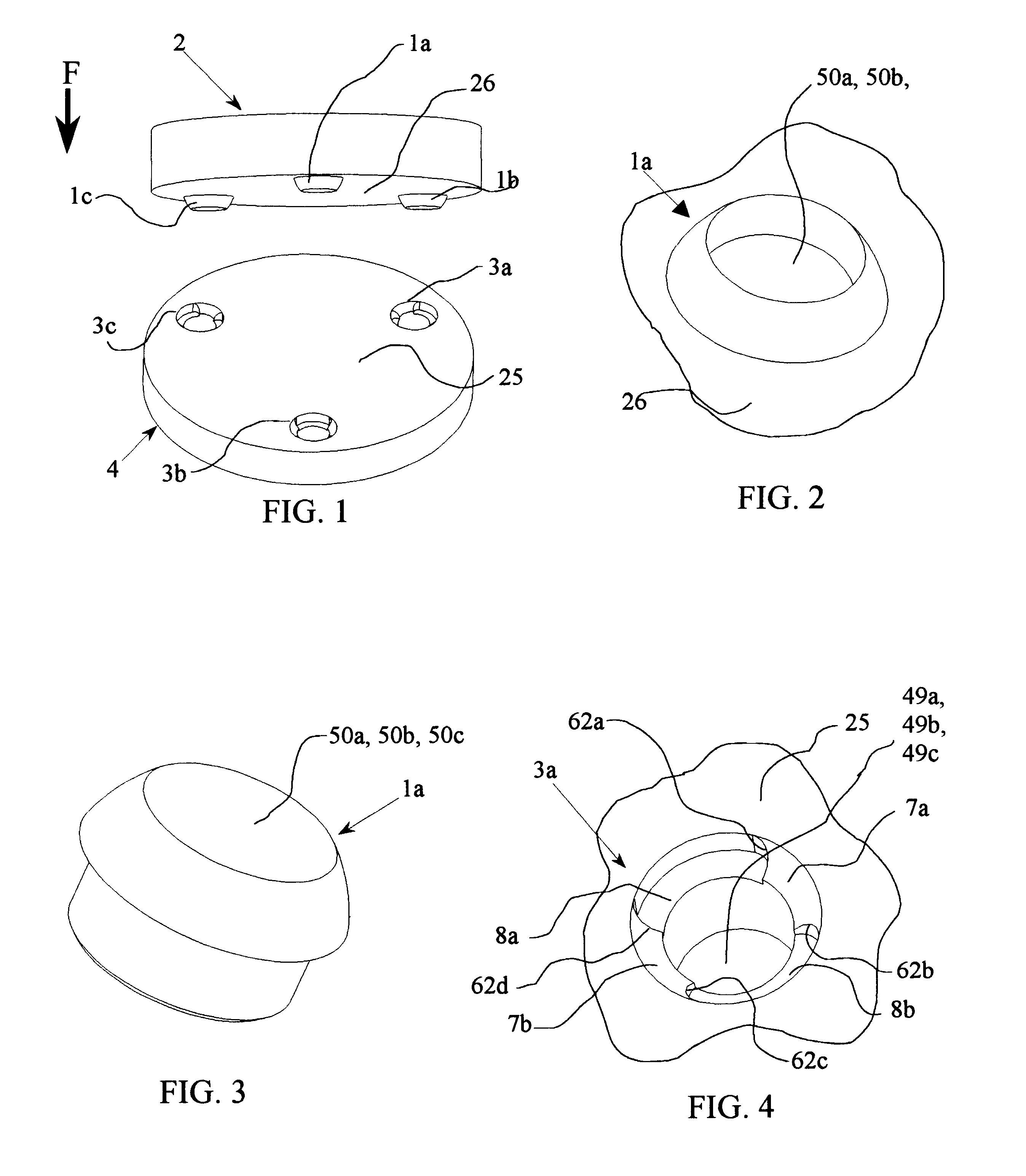

Quasi-kinematic coupling and method for use in assembling and locating mechanical components and the like

InactiveUS6193430B1Low costLess repeatabilityControlling membersRopes and cables for vehicles/pulleyKinematic couplingMechanical components

A quasi-kinematic coupling for mating components (mechanical parts, surfaces, assemblies and the like) employing mating sets of surface of revolution, (conical) grooves and cooperative surface of revolution (spherical / conical) protrusions for establishing six lines (not just prior points) of contact at the kinematic interfaces, and with elastic compliance therebetween and preferably with relief features to define the effective orientation as a clamping force seats the protrusions in the grooves and seals the component mating surfaces into contact.

Owner:AESOP

Methods of making, positioning and orienting nanostructures, nanostructure arrays and nanostructure devices

InactiveUS20050230356A1Easy to controlHigh resistanceMaterial nanotechnologyNanostructure manufactureNanostructure fabricationNanostructure

Nanostructure manufacturing methods and methods for assembling nanostructures into functional elements such as junctions, arrays and devices are provided. Systems for practicing the methods are also provided.

Owner:ONED MATERIAL INC

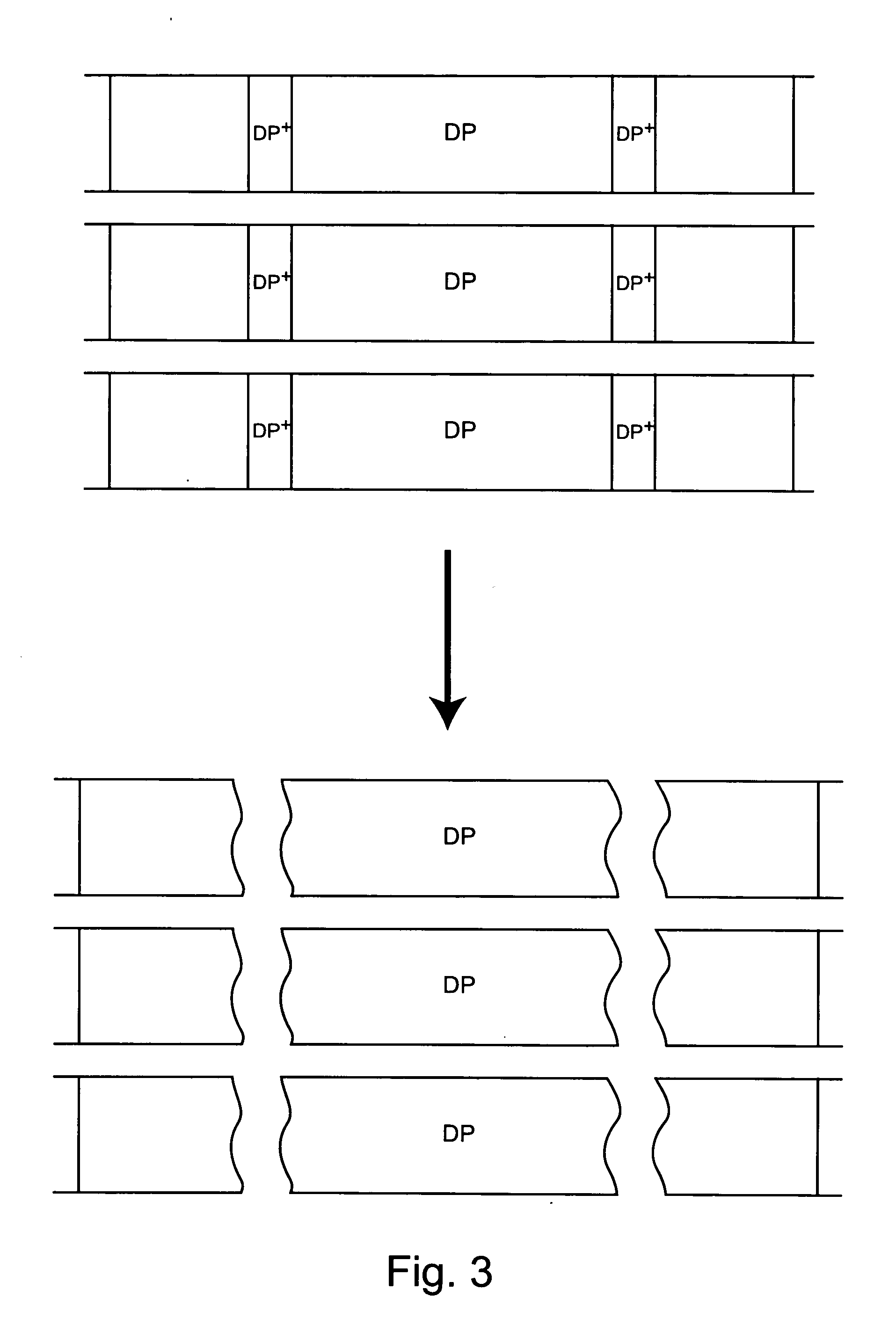

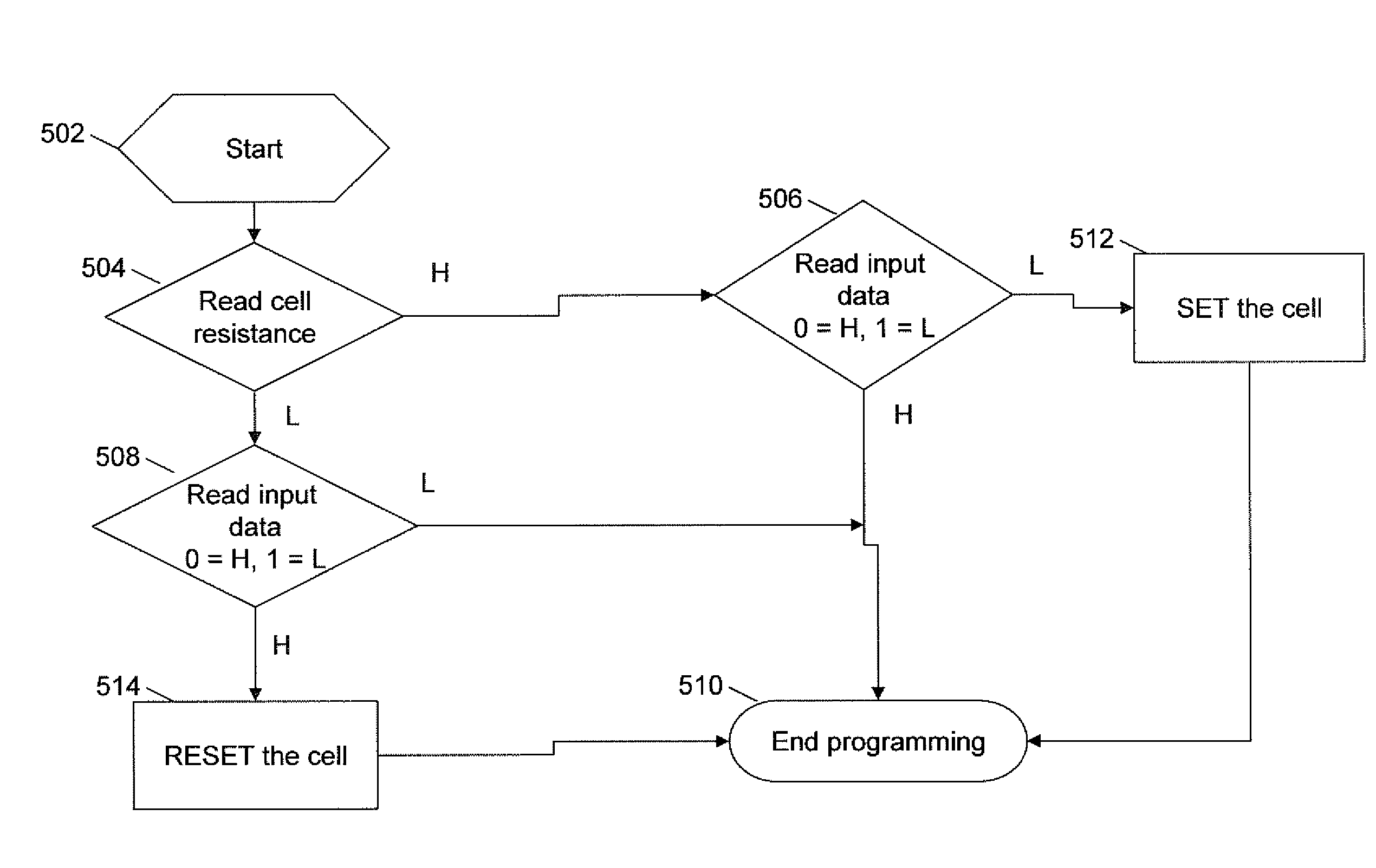

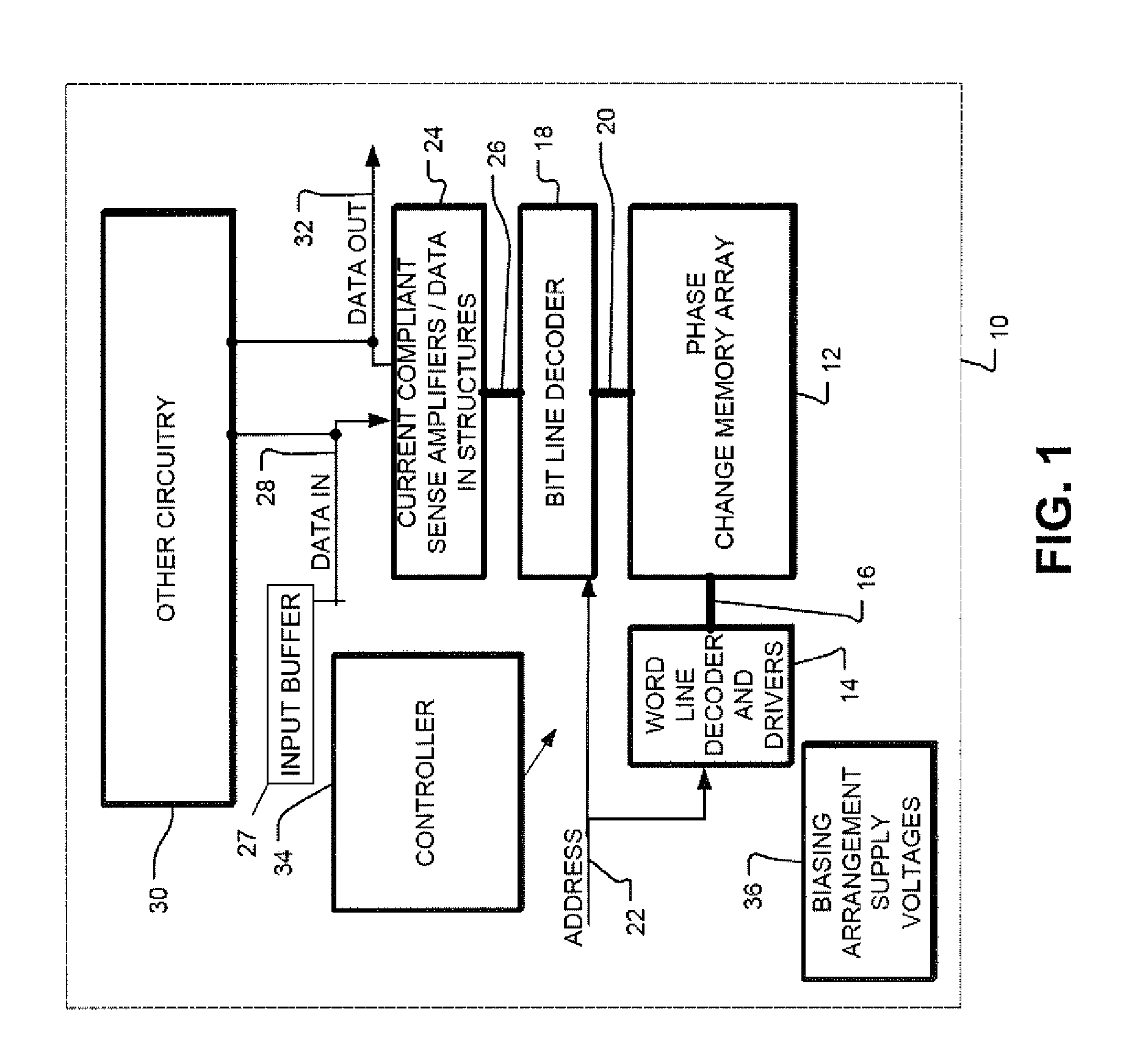

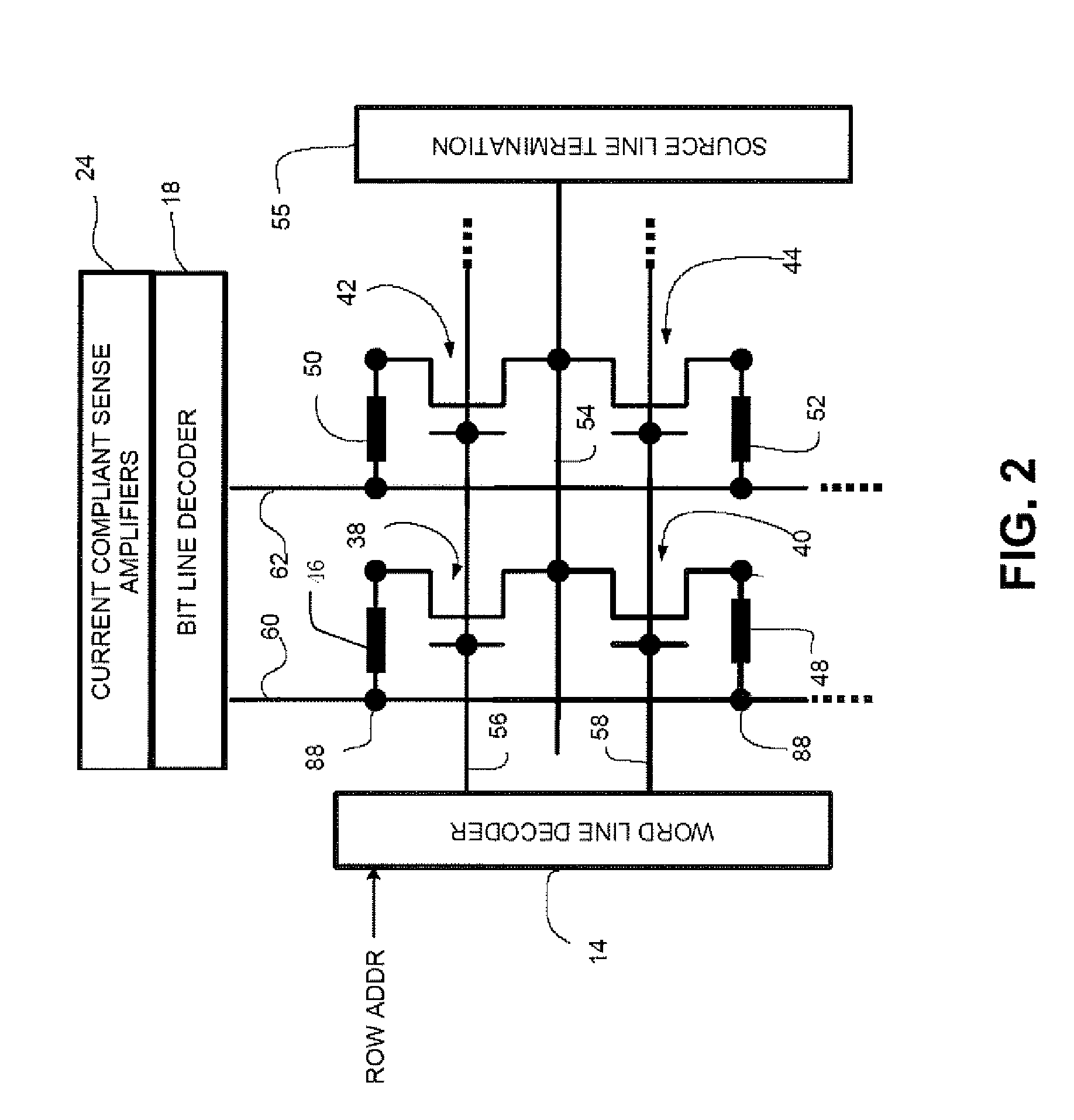

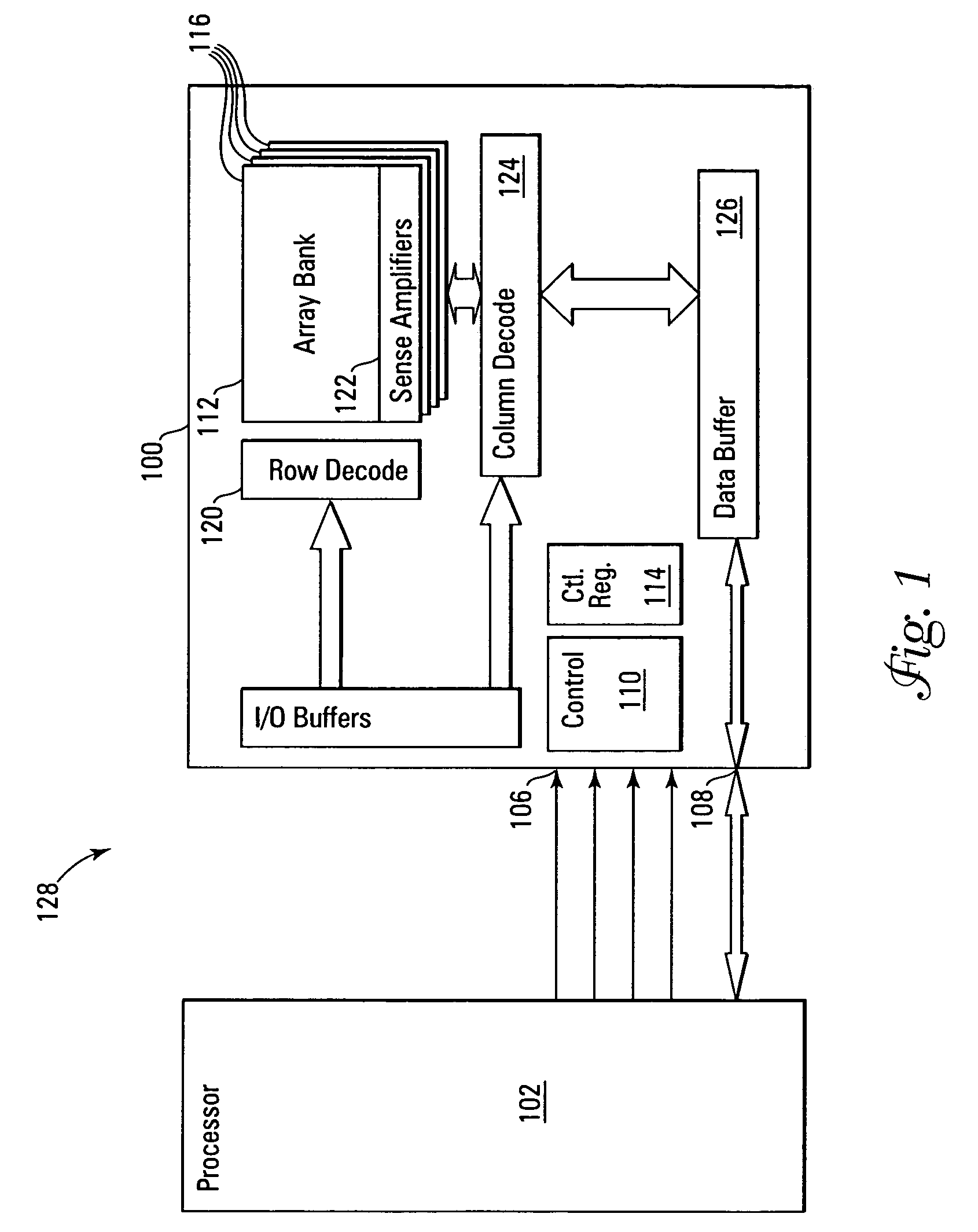

Method, Apparatus and Computer Program Product for Stepped Reset Programming Process on Programmable Resistive Memory Cell

ActiveUS20080165572A1High voltageHigh resistanceRead-only memoriesDigital storageBit linePhase-change memory

A method, system and computer program product for resetting a phase change memory cell having a memory cell threshold voltage is disclosed. The method includes reading a resistance of the memory cell. If the resistance is larger than a chosen resistance, the resetting of the memory cell ends. Otherwise, the method proceeds by applying a voltage, larger than the memory cell threshold voltage, to the bit line, and applying a voltage VWL, larger than the access device threshold voltage, to the word line. The resistance of the memory cell is again read. If the resistance is larger than the chosen resistance, the resetting of the memory cell ends. Otherwise, the method proceeds by applying a voltage, larger than the memory cell threshold voltage, to the bit line, increasing voltage VWL by a voltage ΔV and applying the increased voltage VWL to the word line.

Owner:MACRONIX INT CO LTD

Method of improving adhesion of carbon fibers with a polymeric matrix

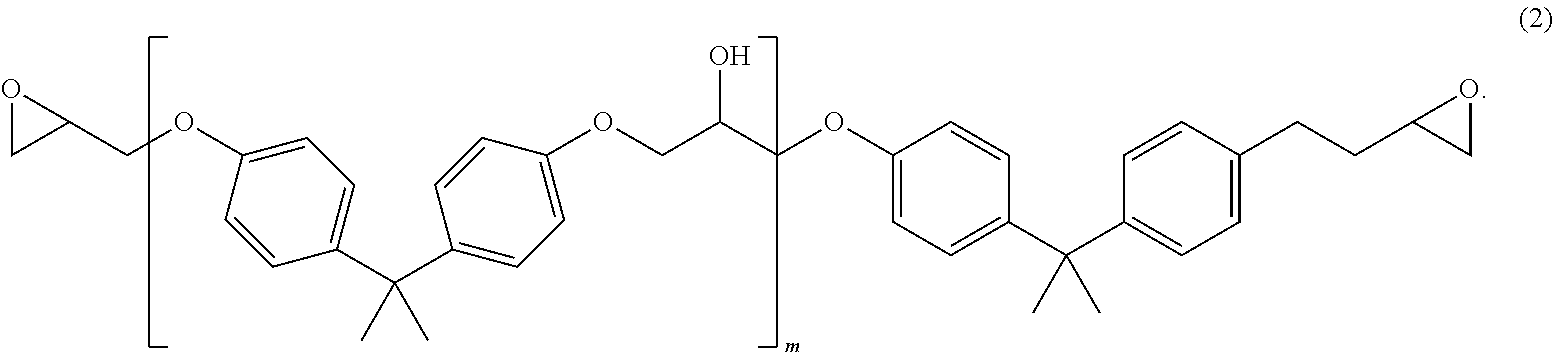

ActiveUS20130224470A1Large resistanceEasy to processSynthetic resin layered productsWood working apparatusEpoxyFiber

A functionalized carbon fiber having covalently bound on its surface a partially cured epoxy or amine-containing sizing agent, wherein at least a portion of epoxide or amine groups in the sizing agent are available as uncrosslinked epoxide or amine groups, which corresponds to a curing degree of epoxide or amine groups of no more than about 0.6. Composites comprised of these functionalized carbon fibers embedded in a polymeric matrix are also described. Methods for producing the functionalized carbon fibers and composites thereof are also described.

Owner:UT BATTELLE LLC

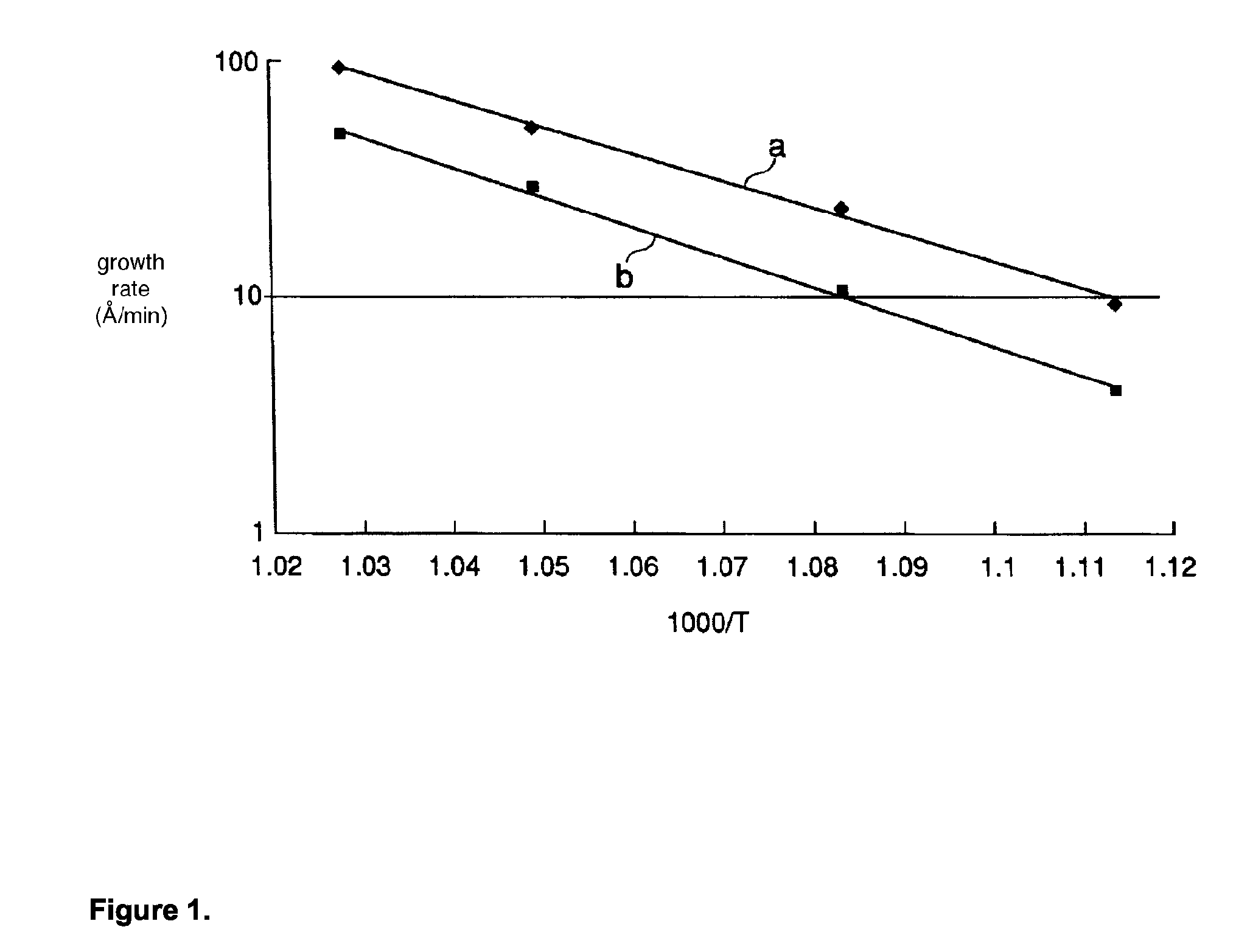

Method for Producing Silicon Nitride Films

ActiveUS20080260969A1Excellent film propertyHigh resistanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingTrisilylamineSilicon nitride

(Problem) To provide a method for producing silicon nitride films by vapor deposition that, while employing trisilylamine as precursor, can produce silicon nitride films that exhibit excellent film properties and can do so at relatively low temperatures and relatively high growth rates. (Solution) Method for producing silicon nitride film, said method being characterized by feeding gaseous trisilylamine and gaseous nitrogen source comprising at least two amine-type compounds selected from amine-type compounds with formula (1) NR1R2R3 (R1, R2, and R3 are each independently selected from hydrogen and C1-6 hydrocarbyl) into a reaction chamber that holds at least one substrate and forming silicon nitride film on said at least one substrate by reacting the trisilylamine and said nitrogen source.

Owner:LAIR LIQUIDE SA POUR LETUDE & LEXPLOITATION DES PROCEDES GEORGES CLAUDE

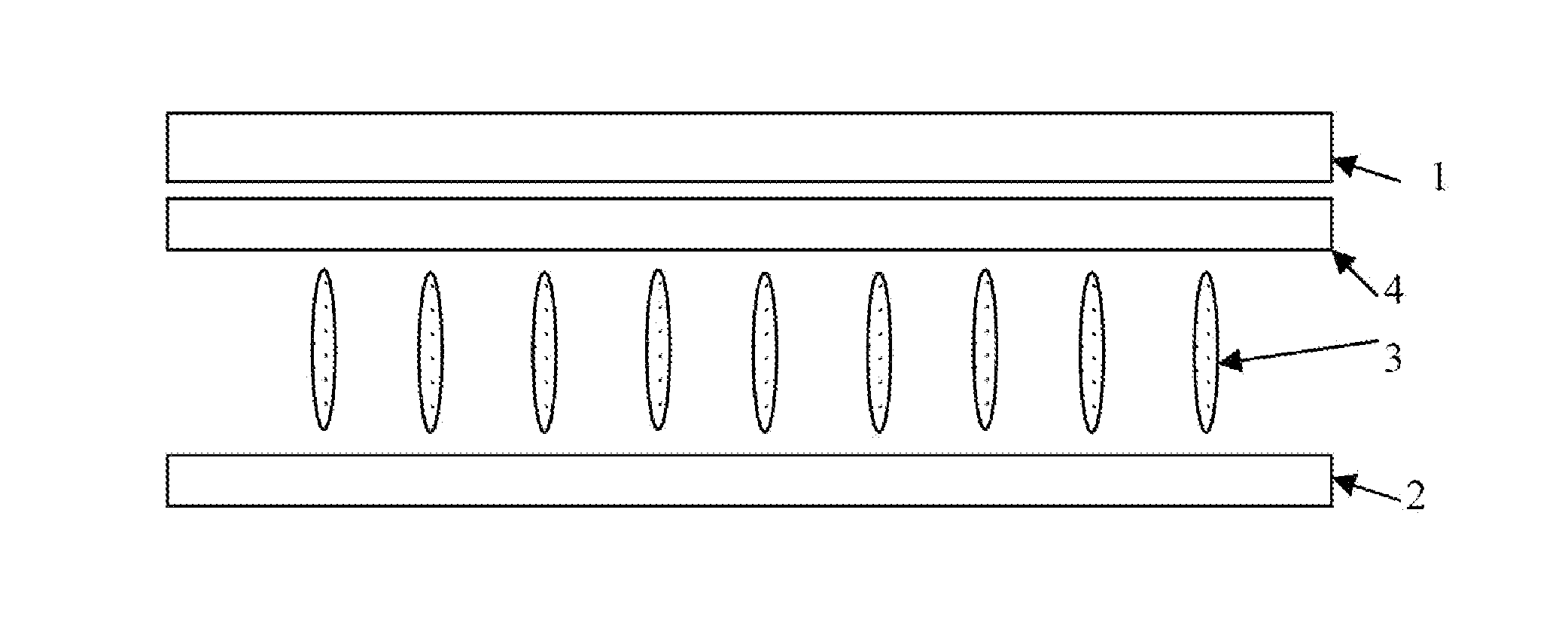

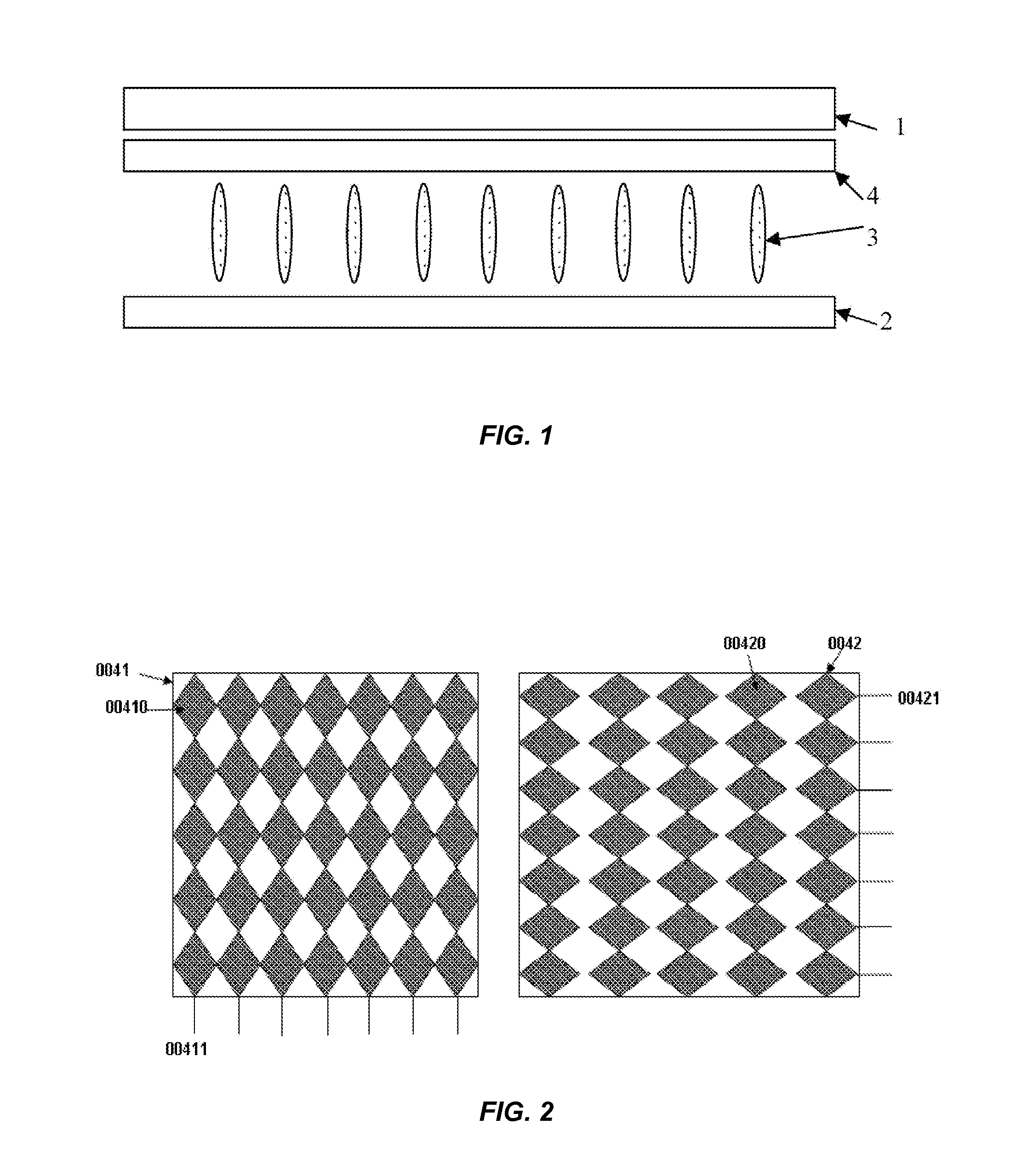

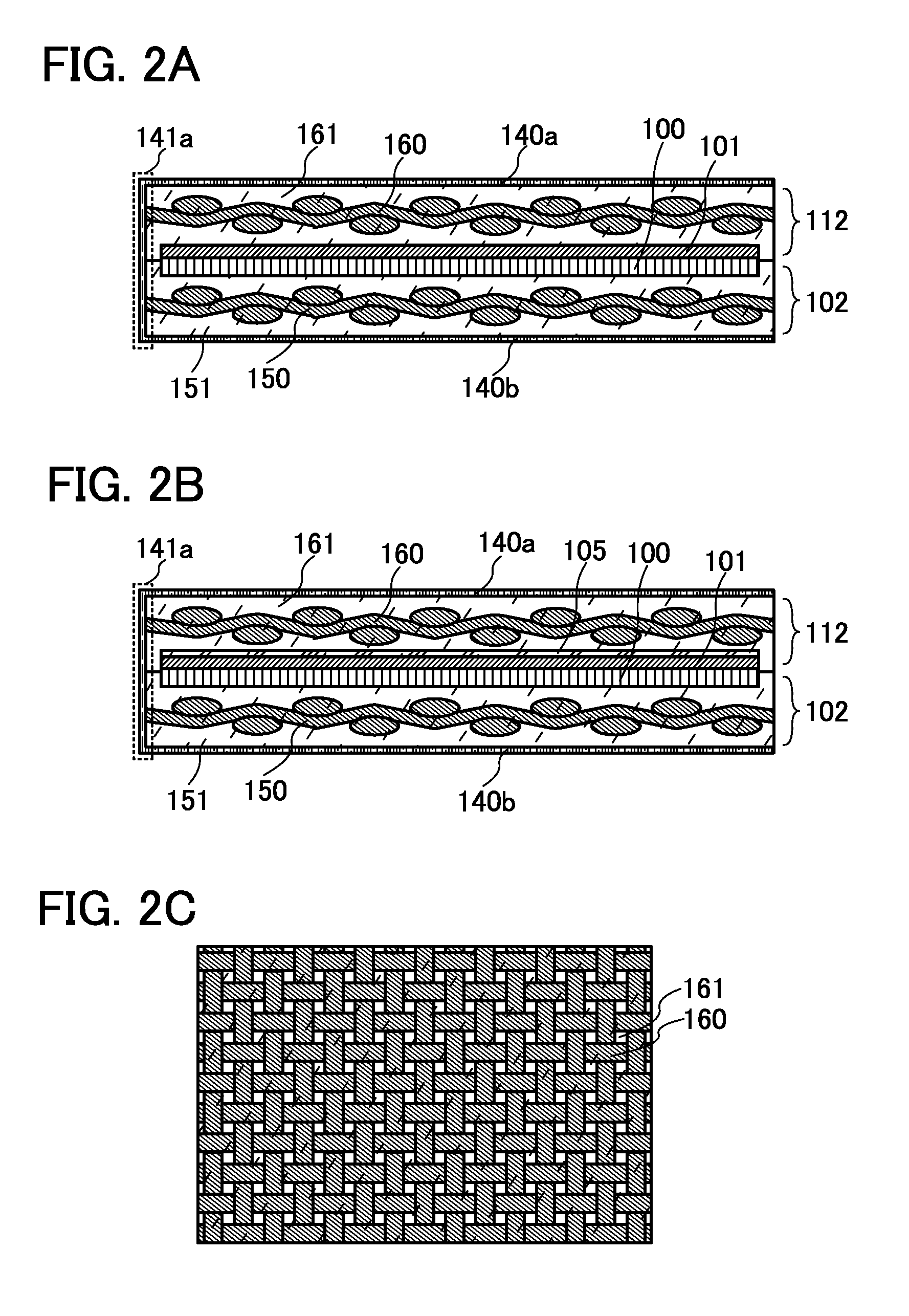

Touch control liquid crystal display device

ActiveUS20140168540A1Low detection sensitivityControl loadNon-linear opticsInput/output processes for data processingMetal gridLiquid-crystal display

One inventive aspect is a touch control liquid crystal display device. The device includes a color film substrate, a thin film transistor array substrate, and a liquid crystal layer between the color film substrate and the thin film transistor array substrate. The color film substrate includes a grid-shaped black matrix layer, a touch control layer, and a color film layer. The touch control layer includes metal grid electrodes in a rectangle, where the metal grid electrodes include metal lines intersecting transversely and vertically. In addition, the metal grid electrodes include drive electrodes and sense electrodes. The drive electrodes are connected together through first metal connection lines in a first direction, and the sense electrodes are connected together through second metal connection lines in a second direction. In addition, the projection of the metal grid electrodes falls into the projection of the black matrix layer in the light transmission direction.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

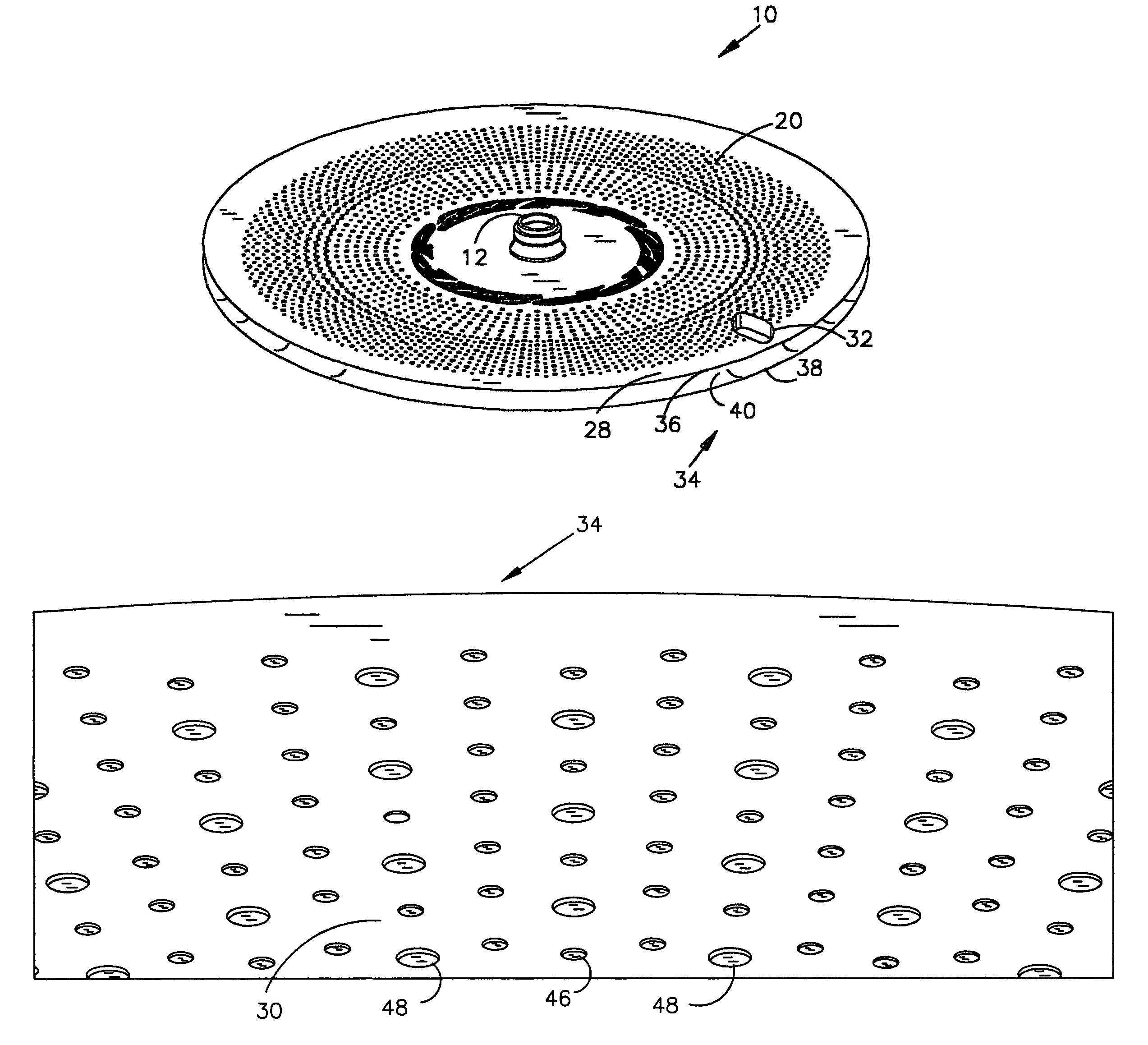

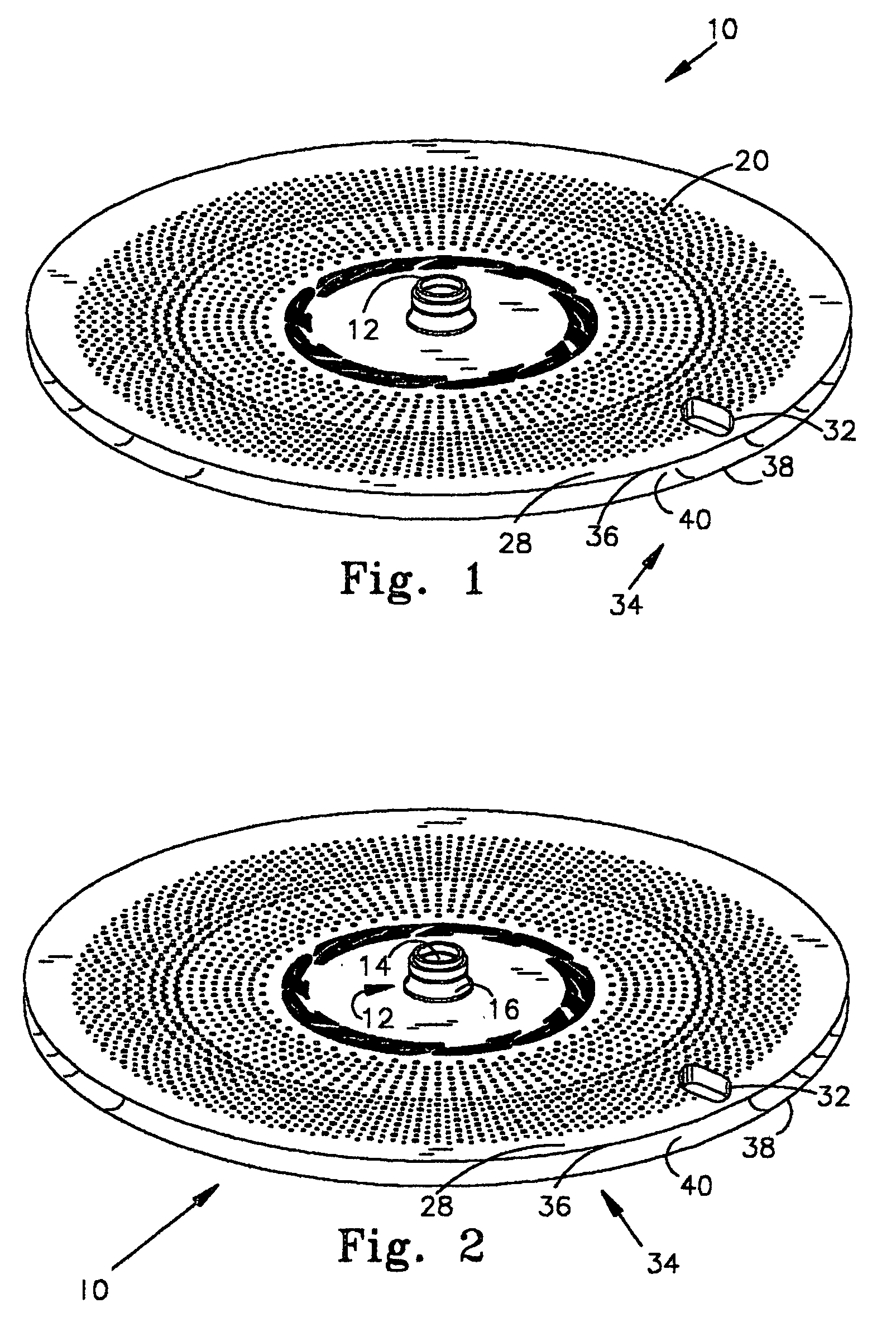

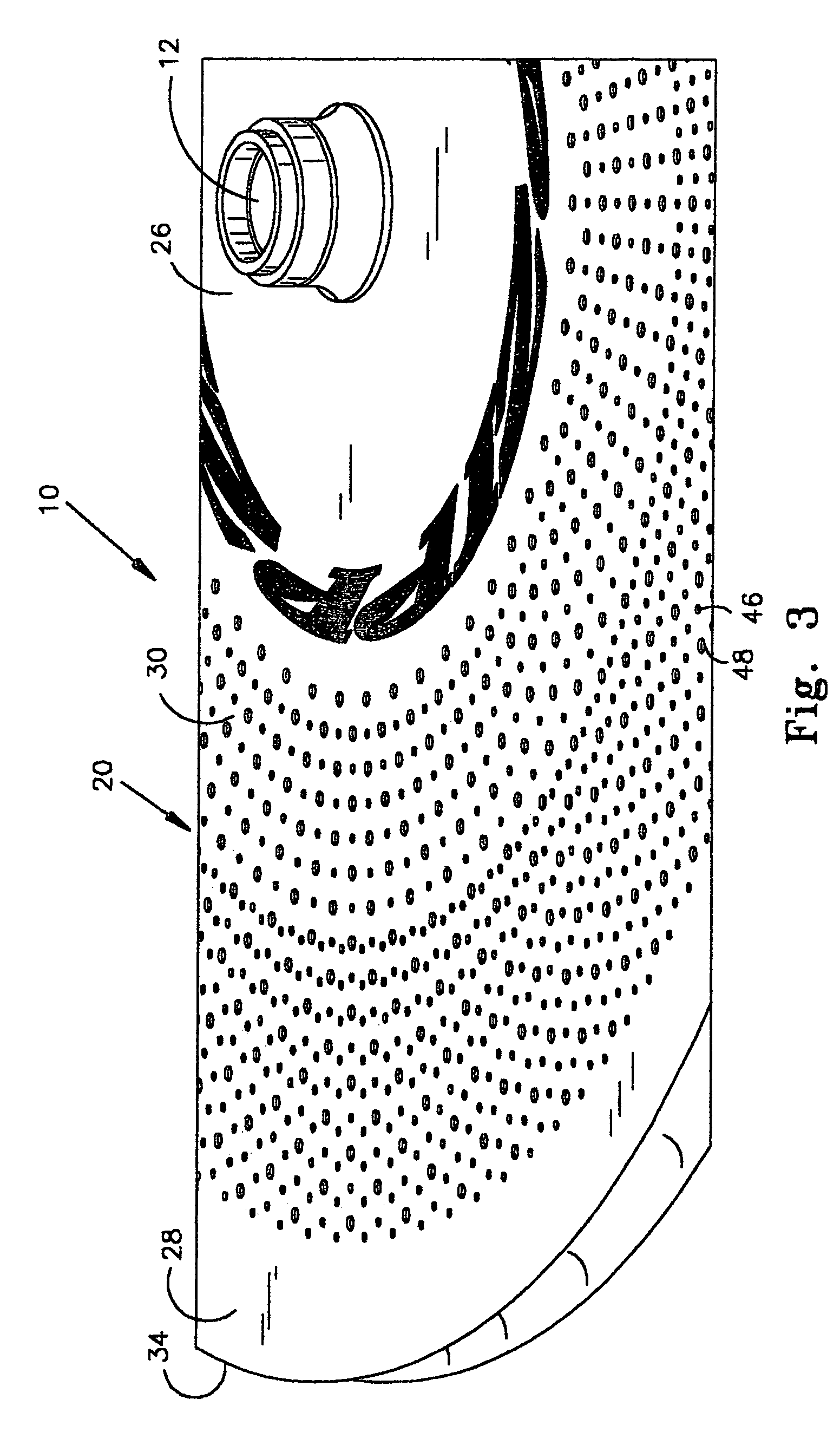

Aerodynamic surfaced bicycle wheel

InactiveUS7114785B2Reduce air resistanceHigh speedNon-metallic wheel bodyWheel protectionAerodynamic dragEngineering

A bicycle wheel includes a tire engaging portion located at the outward perimeter of the wheel, an inner portion located radially inward from the tire engaging portion A pair of air engaging side surfaces extend radially between the inner portion and the tire engaging portion forming the sides of the wheel. The air engaging side surfaces contain a plurality of surface features designed to create a turbulent boundary layer when the wheel travels through air to reduce aerodynamic drag on the wheel.

Owner:COMPOSITECH

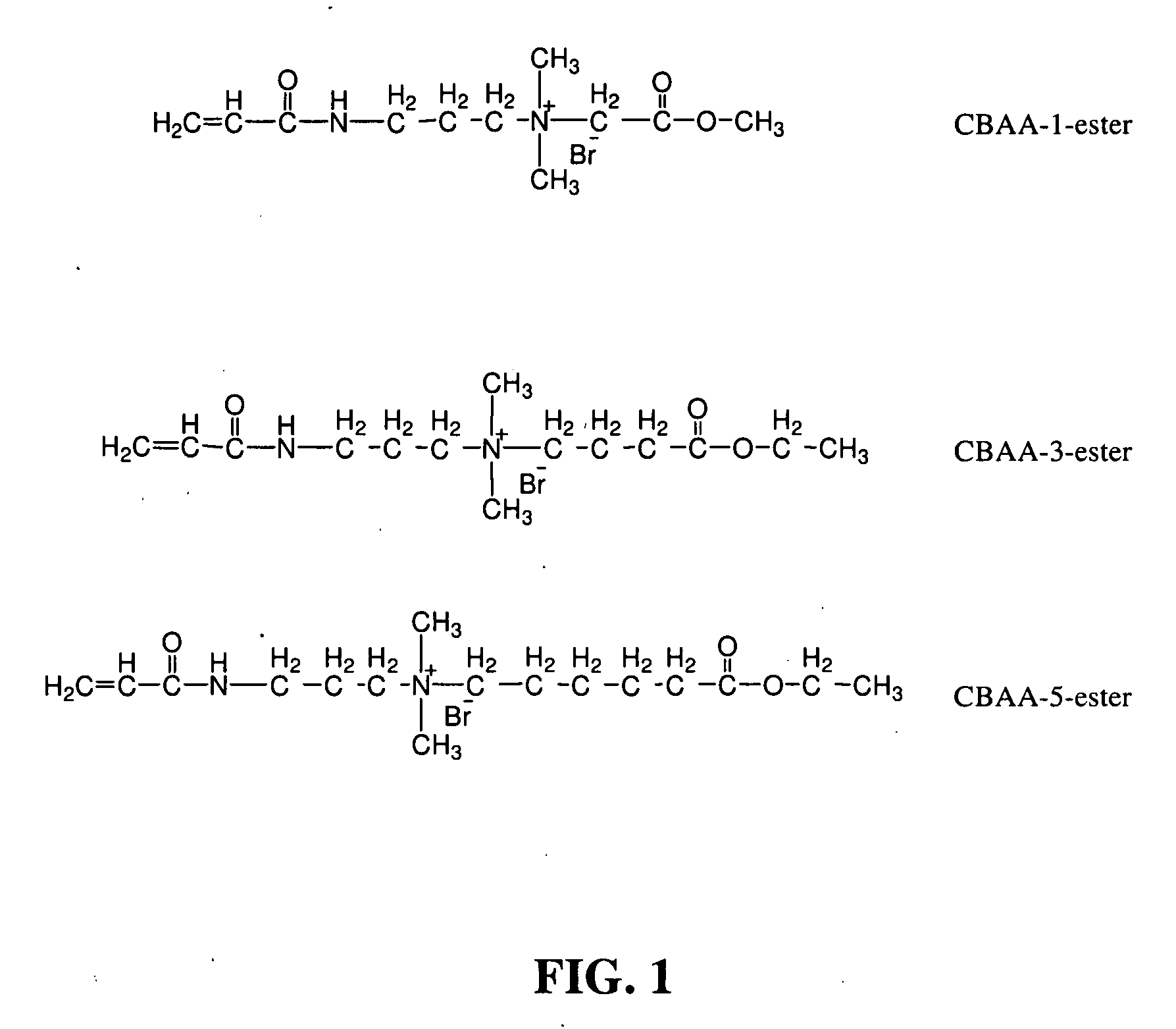

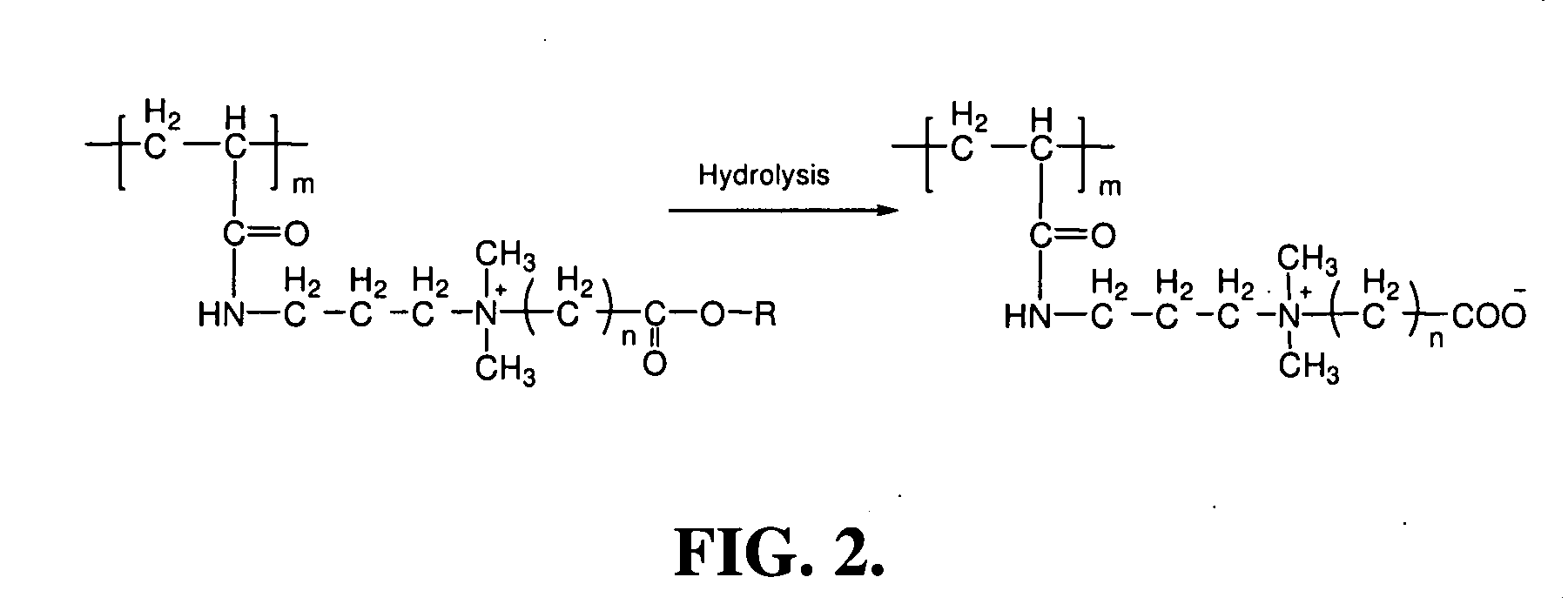

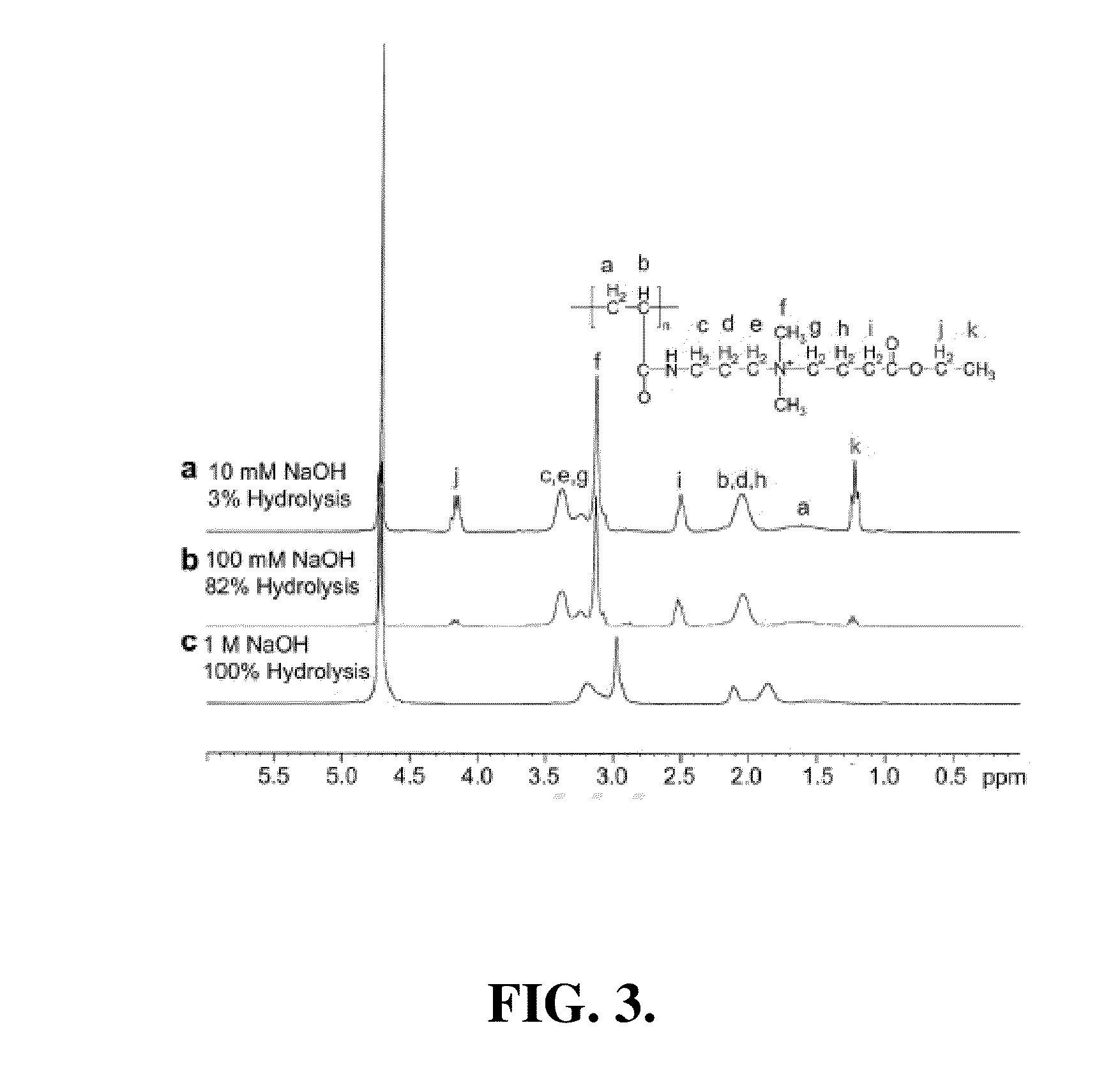

Cationic betaine precursors to zwitterionic betaines having controlled biological properties

Owner:UNIV OF WASHINGTON

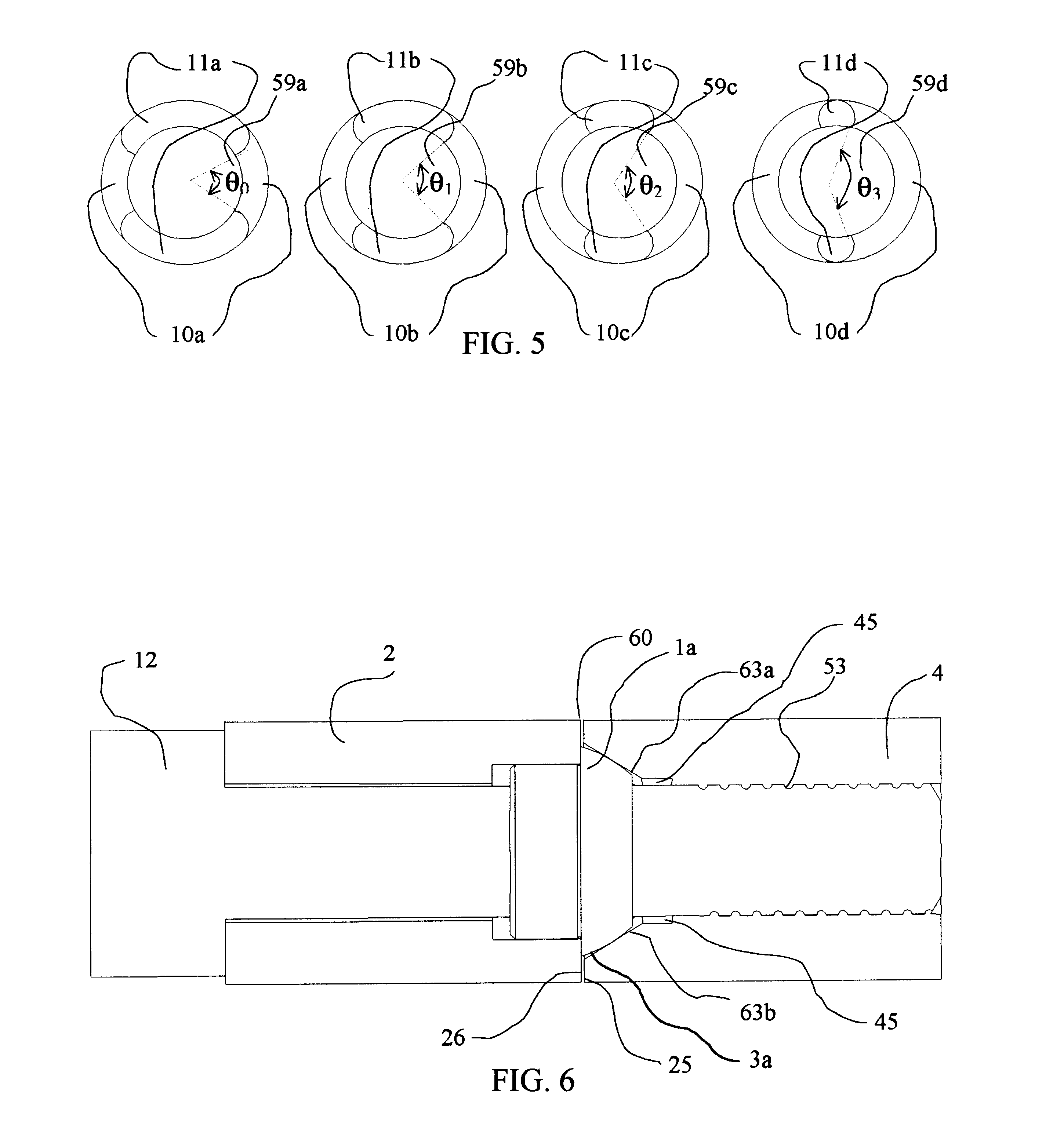

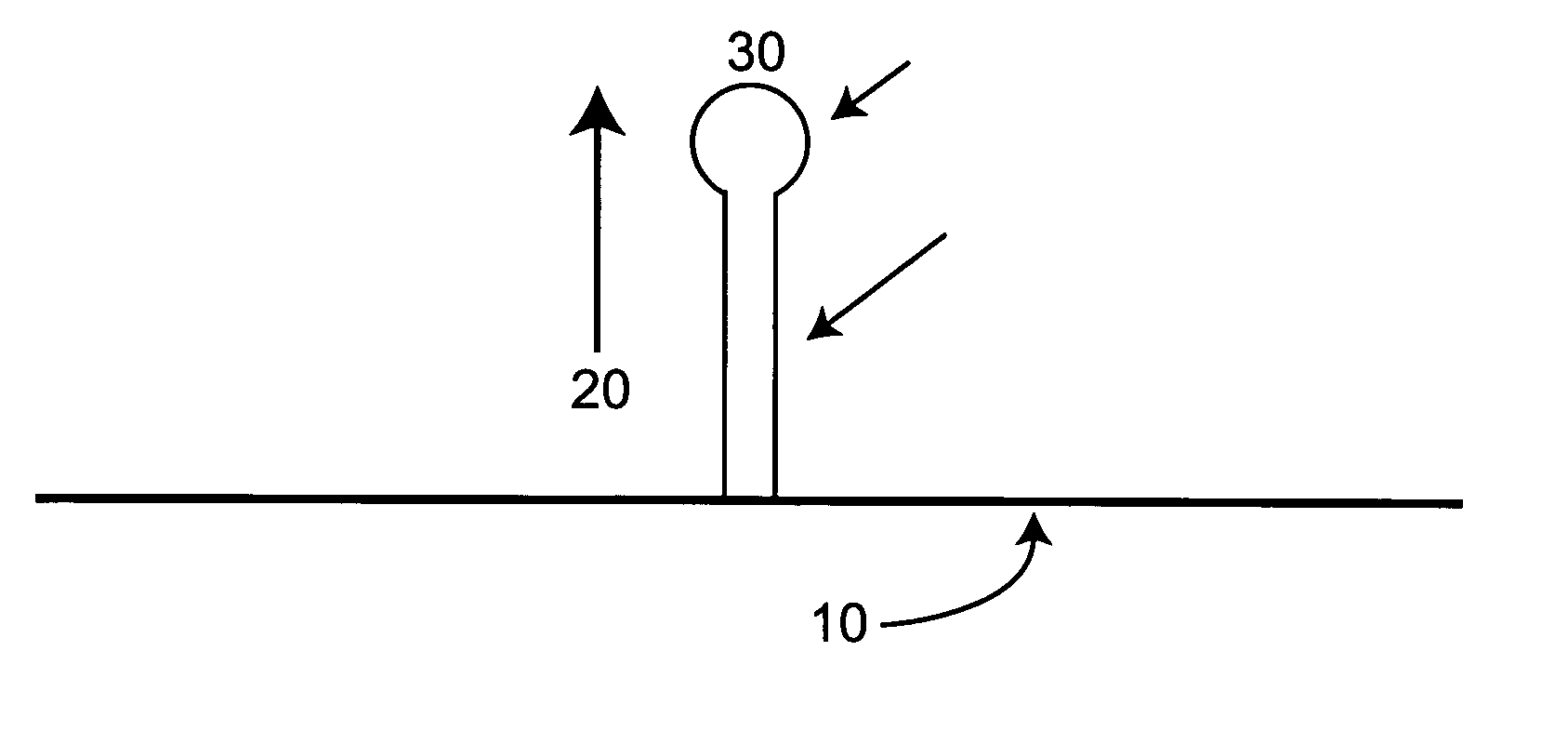

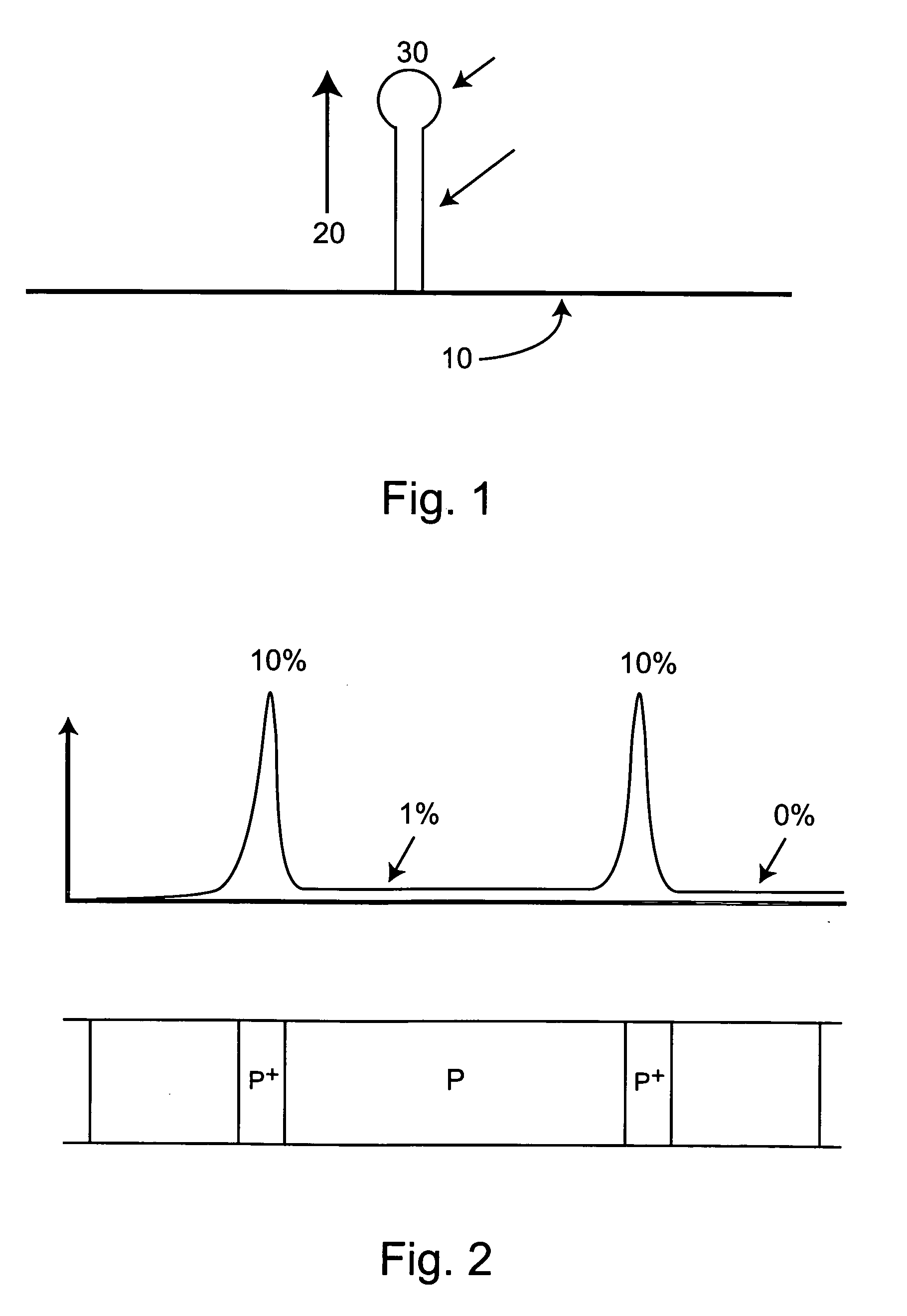

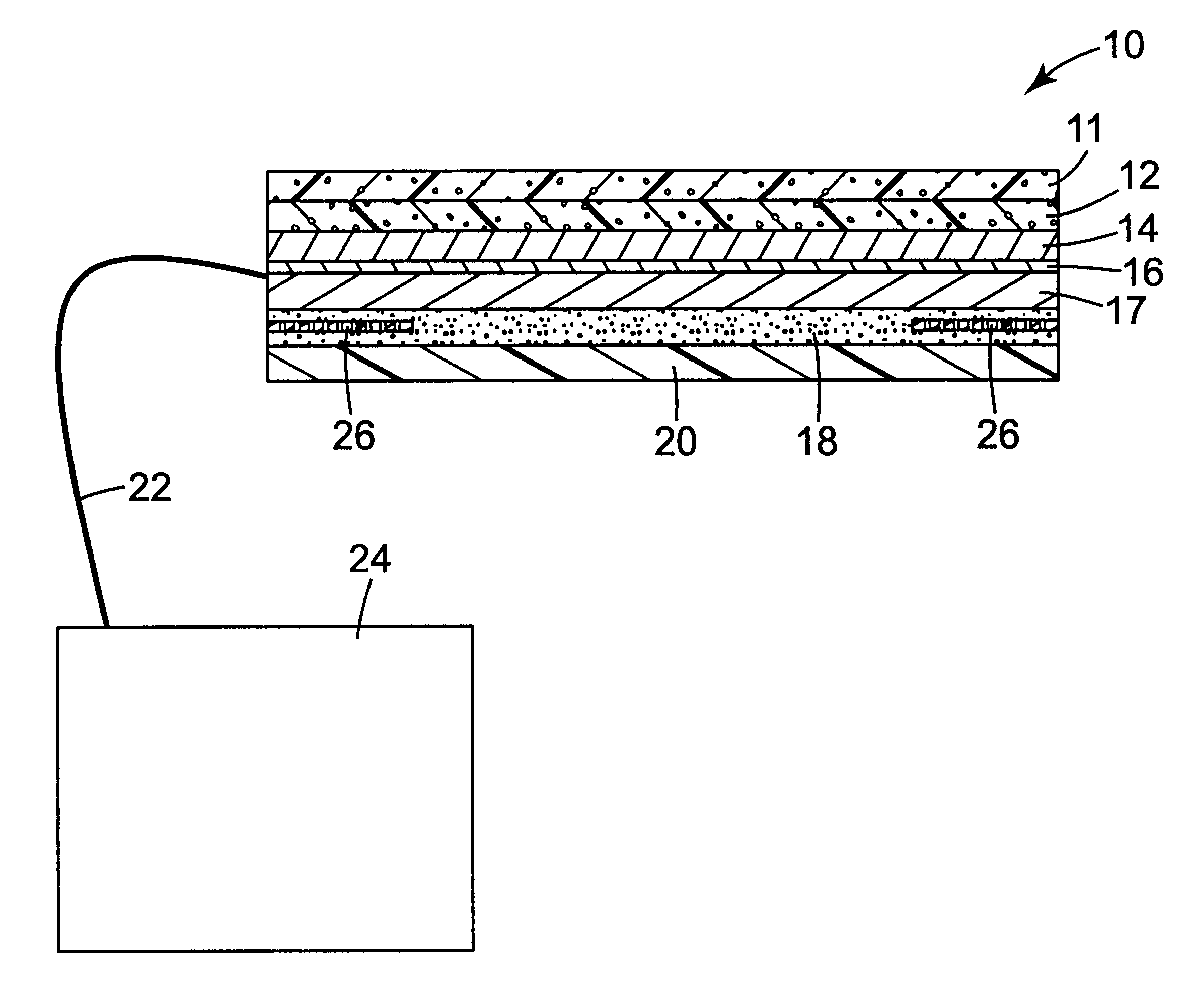

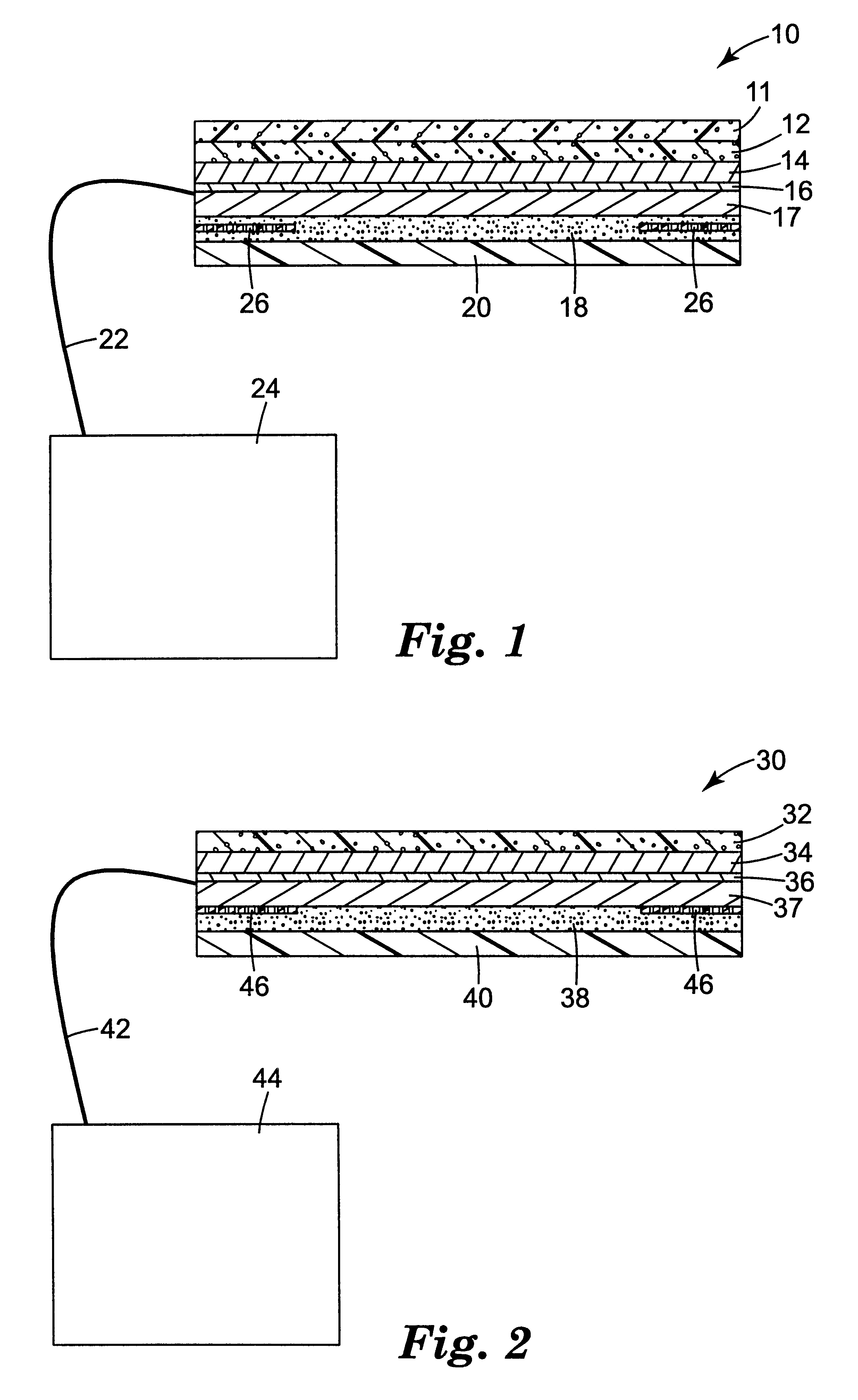

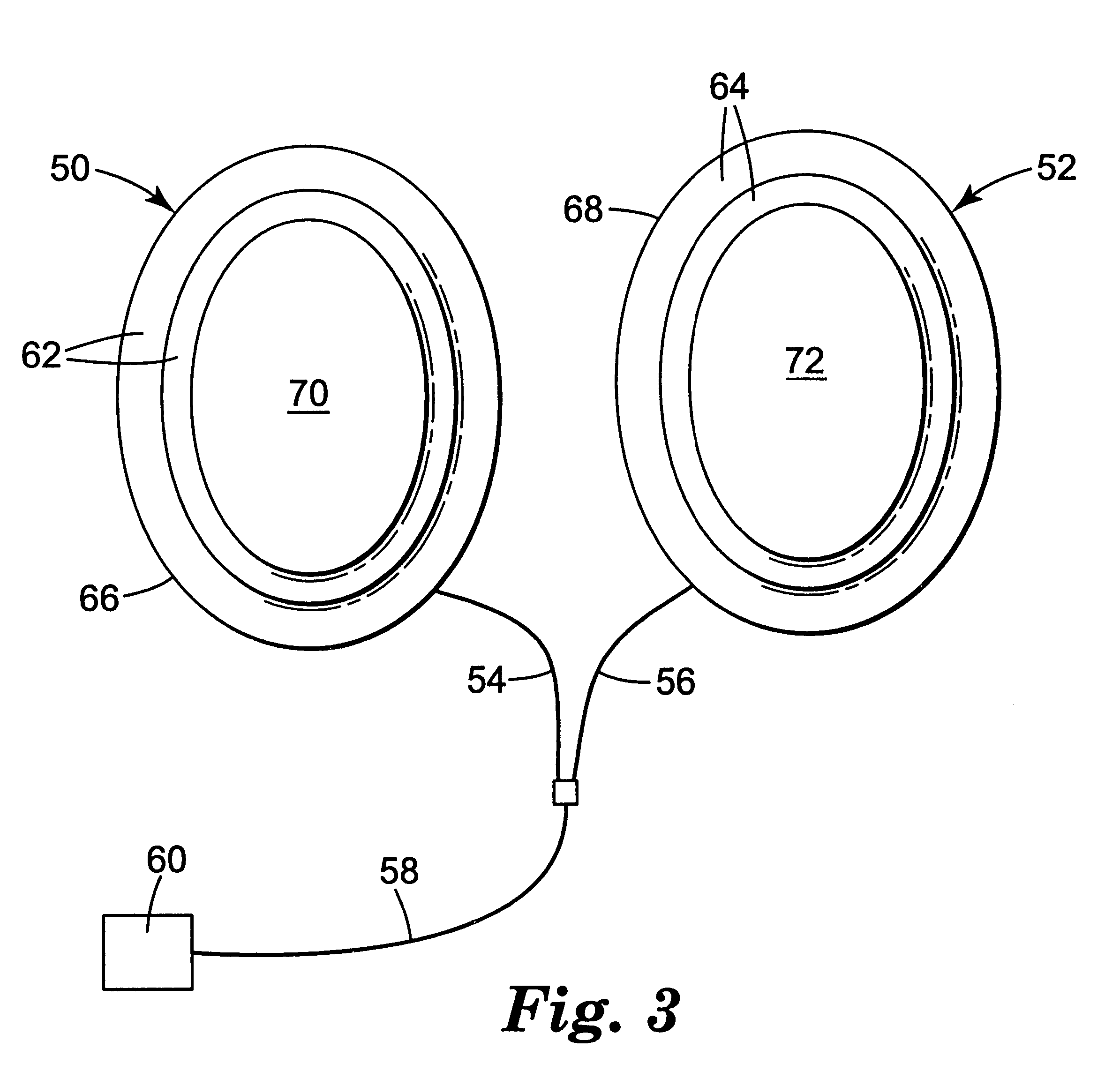

Universally functional biomedical electrode

InactiveUS6356779B1High resistanceReduce effectHeart defibrillatorsInternal electrodesResistive elementBiomedical instrumentation

A universally functional biomedical electrode is disclosed, where the electrode has a resistive element that reduces edge effect by a redistribution of current within the electrode and in mammalian tissue contacting the electrode. In one embodiment, the electrode has at its perimeter in one layer the resistive element that provides a cross-sectional area to reduce edge effect regardless of the type of biomedical instrumentation connected thereto. With the construction of other layers suitable for multifunctional electrode usage, this electrode can serve as a single item in inventory at health facilities.

Owner:3M INNOVATIVE PROPERTIES CO

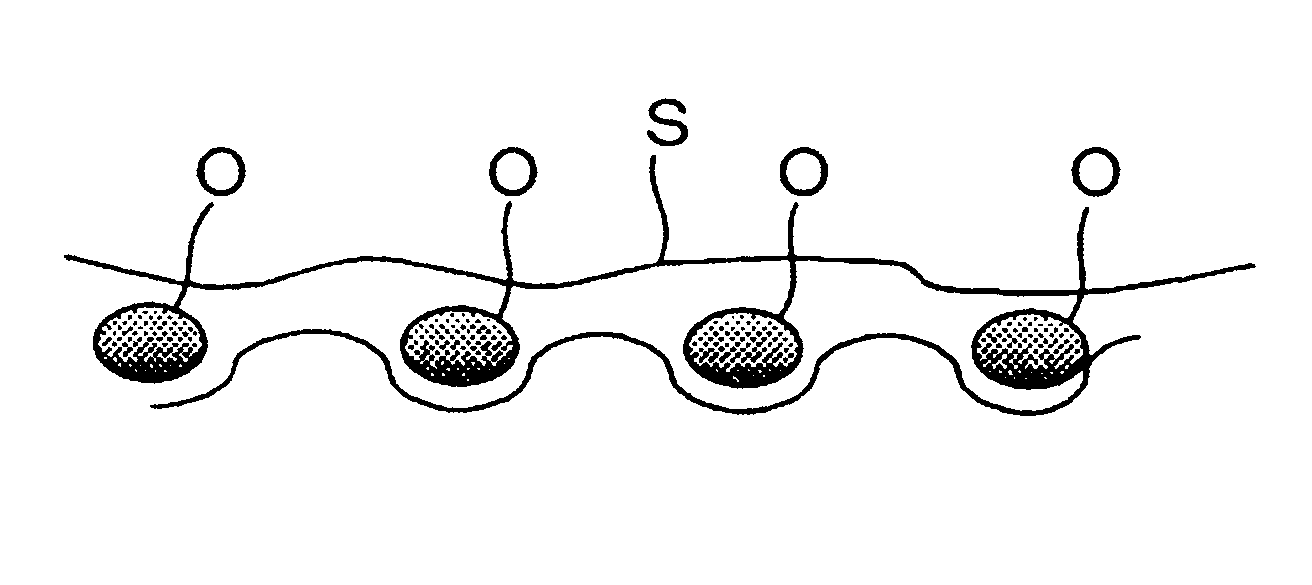

Particles for electro-rheological fluid

The present invention can provide particles for electro-rheological fluid for providing a high electro-rheological effect over a wide temperature range at low electric power consumption, and having high strength and excellent durability, not being susceptible to break-up due to the load of stress. Particles for an electro-rheological fluid of the present invention comprise spherical carbonaceous particles, obtained substantially from a solvent and a condensation product of a methylene type bond of aromatic sulfonic acid or a salt thereof.

Owner:NIPPON COKE & ENG

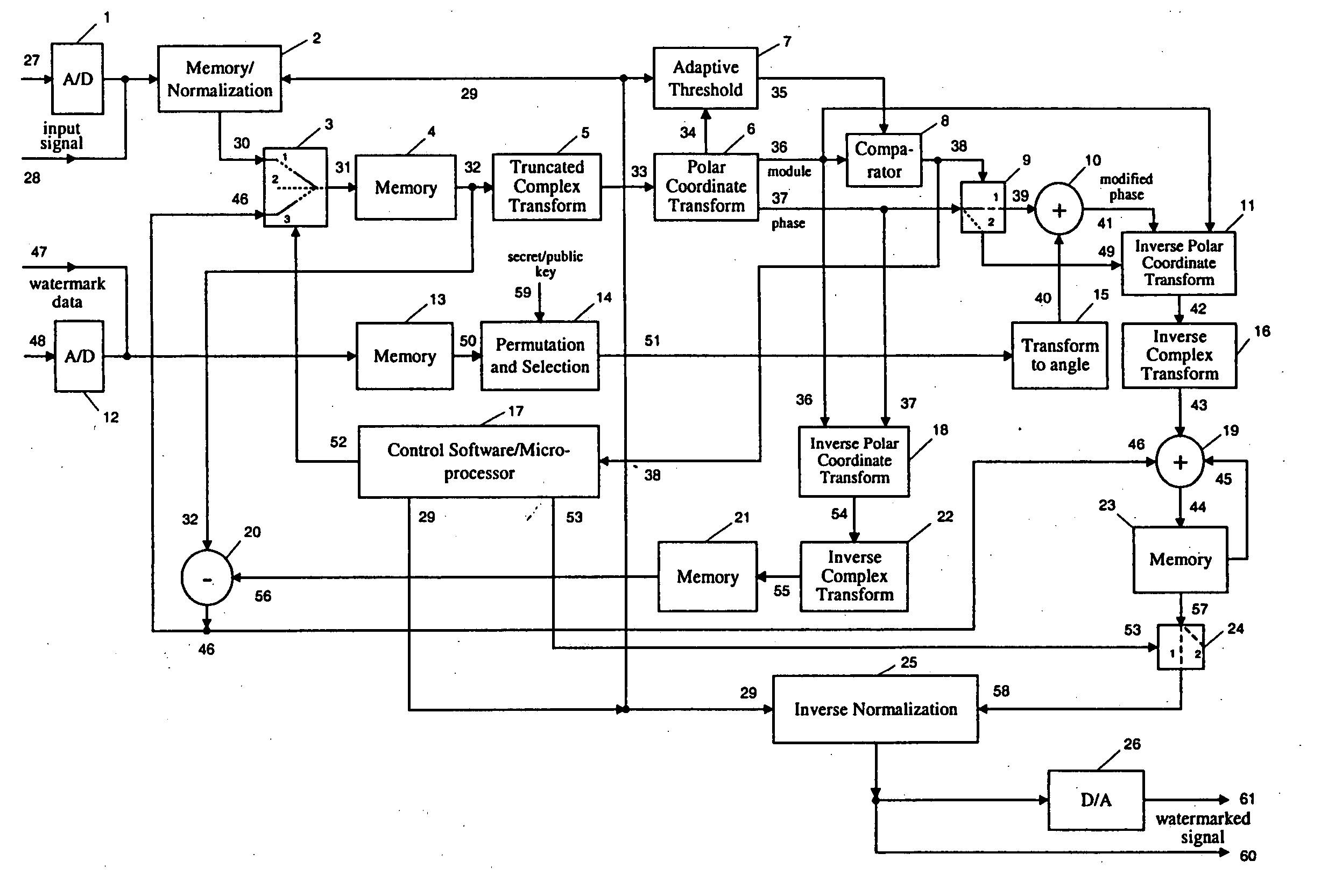

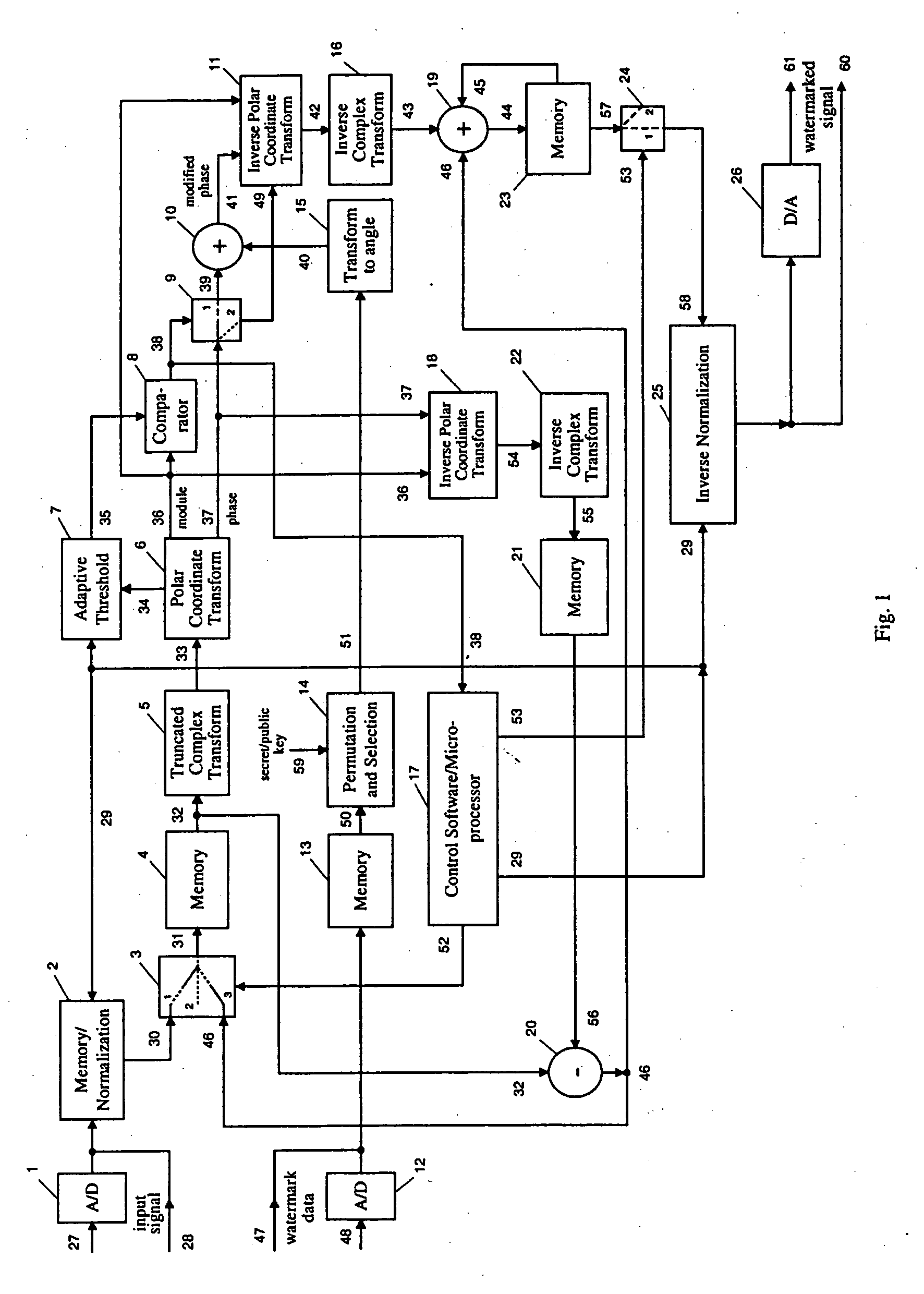

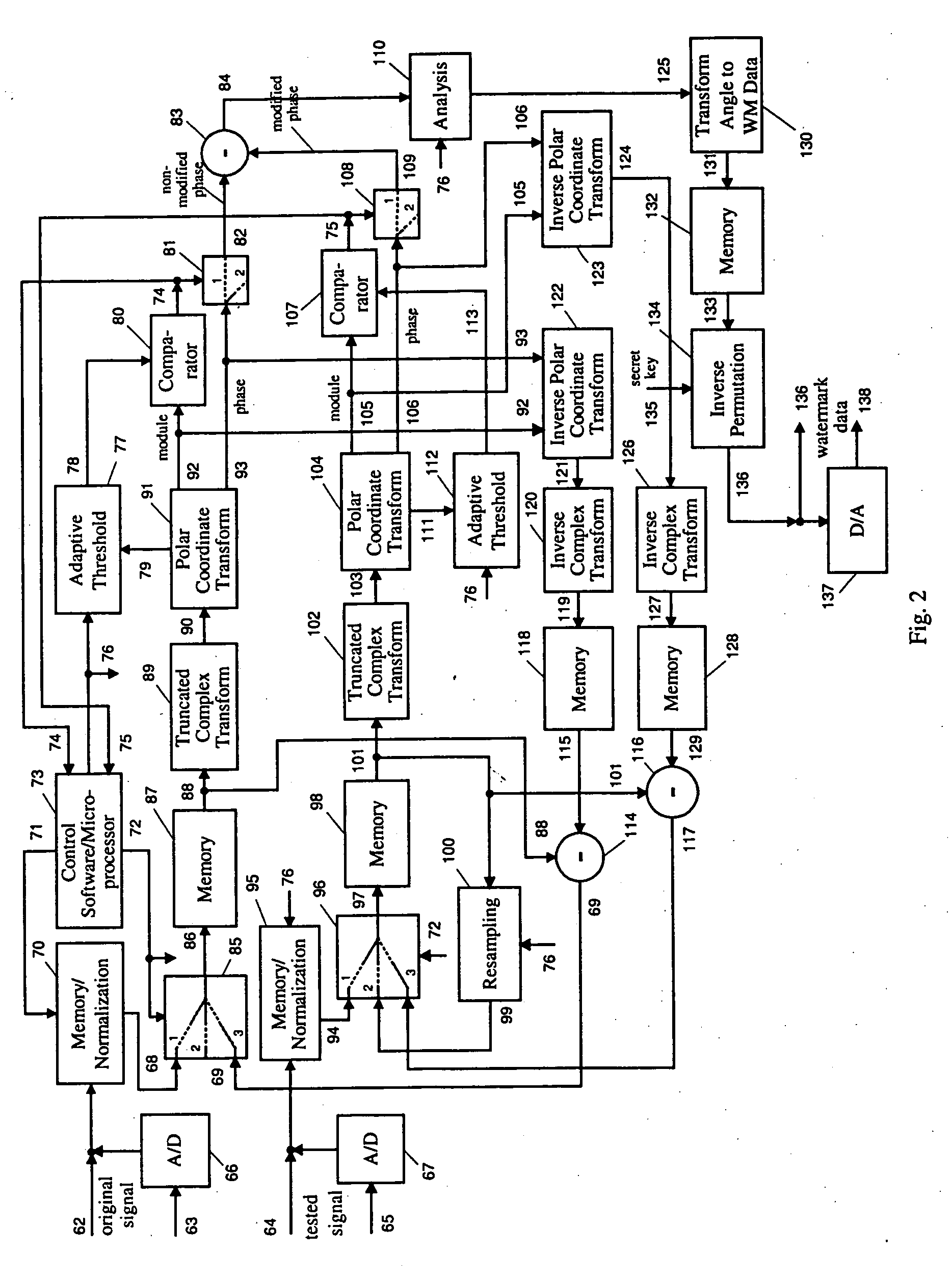

Method and system for digital watermarking of multimedia signals

InactiveUS20070014428A1High resistanceResistant to noiseCharacter and pattern recognitionImage data processing detailsDecompositionPyramid

Disclosed is a method and system for digital watermarking of multimedia signals. The input multimedia signal is represented using an inverse difference pyramid decomposition. Spectrum coefficients may be calculated for each level of the pyramid using a new kind of complex Hadamard transform, the matrix of which is distinguished from the known ones by the fact that only one-fourth of its coefficients are complex numbers. The phases of a previously selected part of the low-frequency coefficients are modified with the watermark data, limiting the angles of the phase changes in a gap of several degrees only. After an inverse complex Hadamard Transform, the values of the coefficients from all pyramid levels are summed up and the result is the watermarked signal. The watermark can contain multiple independent levels for each level of the pyramid.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

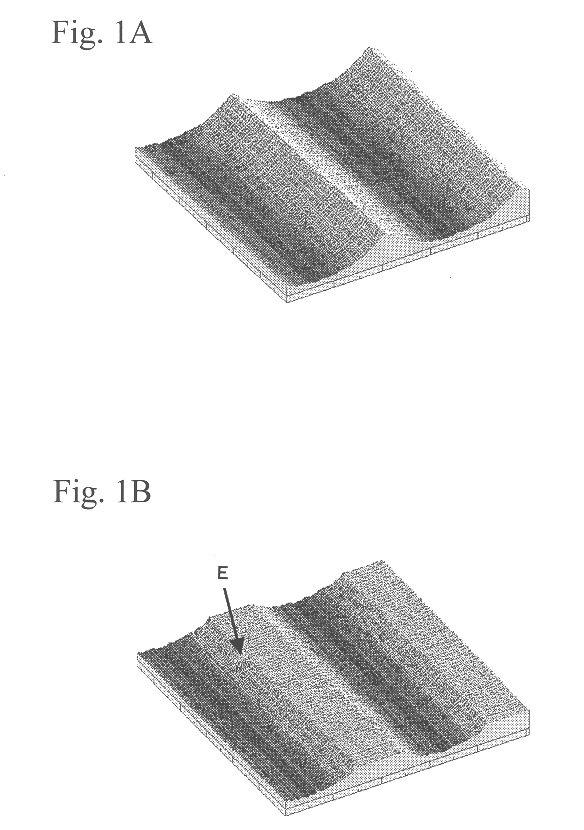

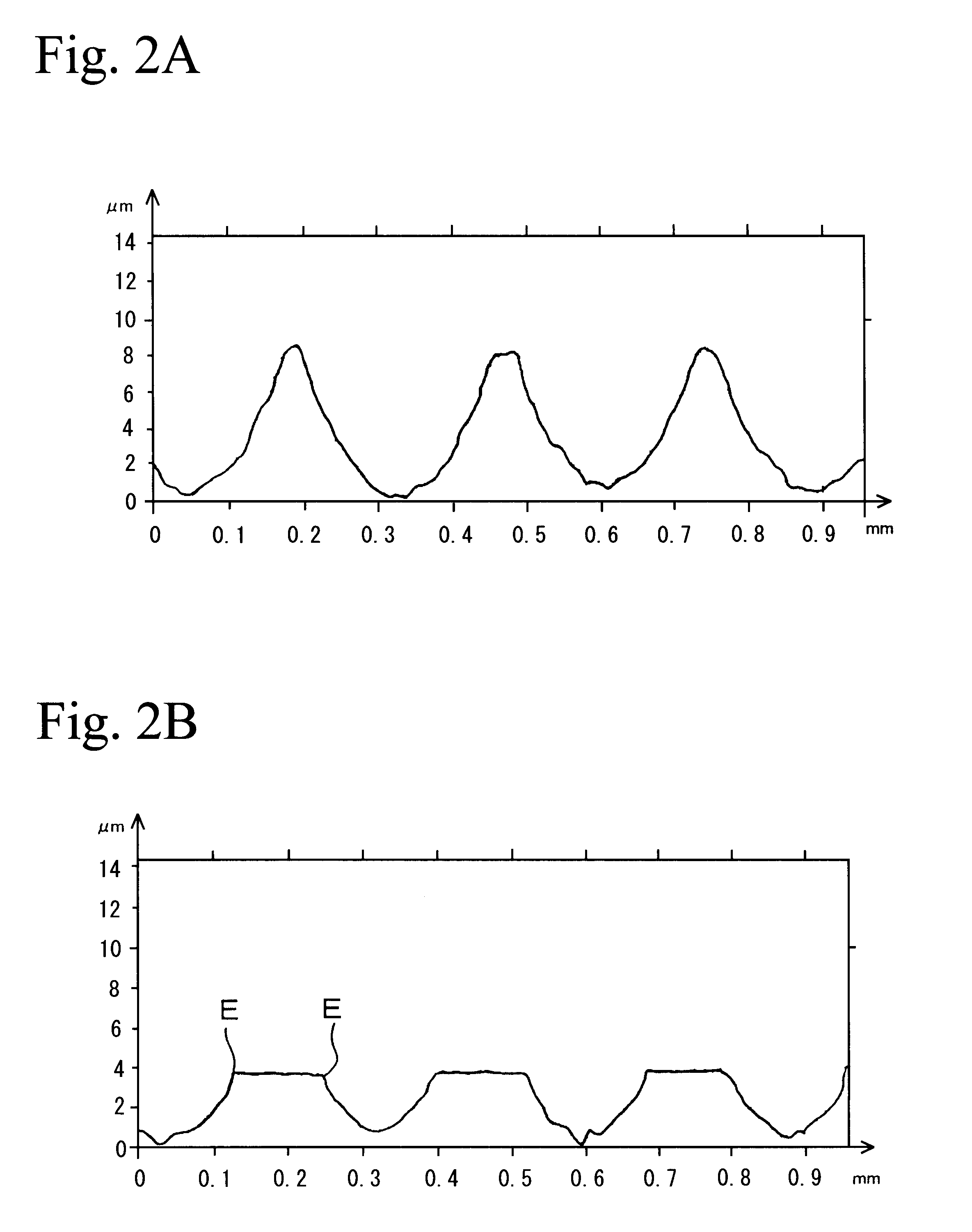

Sliding members and piston for internal combustion engine

InactiveUS6523456B1Avoid unusual noiseClearanceCylindersMachines/enginesInternal combustion enginePiston

A sliding surface of at least one of sliding members sliding with respect to each other in a sliding direction comprises a protrusion extending along a direction intersecting the sliding direction and fine dimples provided on a surface of the protrusion. In the sliding members, lubricating oil is accumulated in the dimples, and is easily extracted through a drain portion formed by dimple in a running-in operation.

Owner:HONDA MOTOR CO LTD

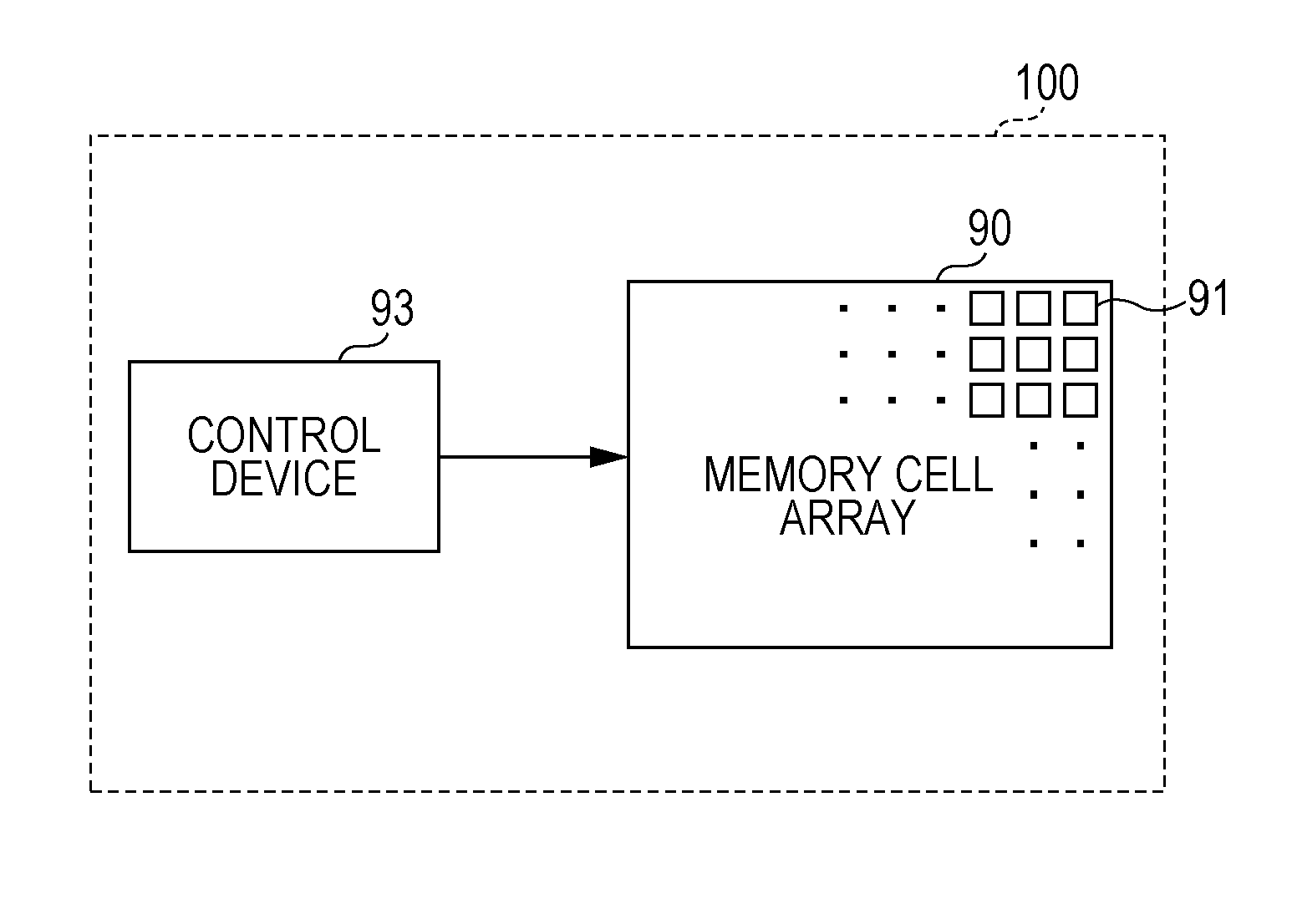

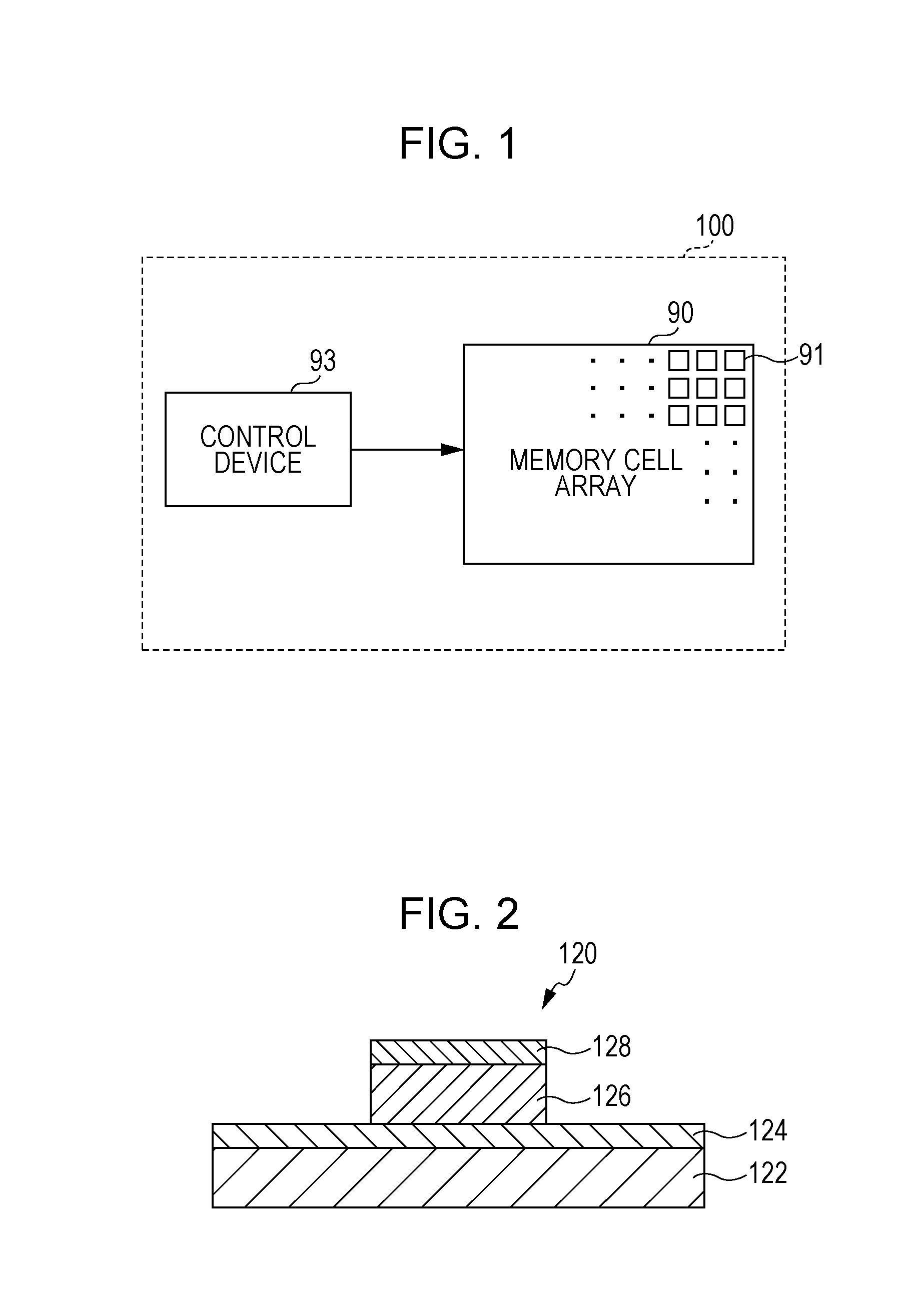

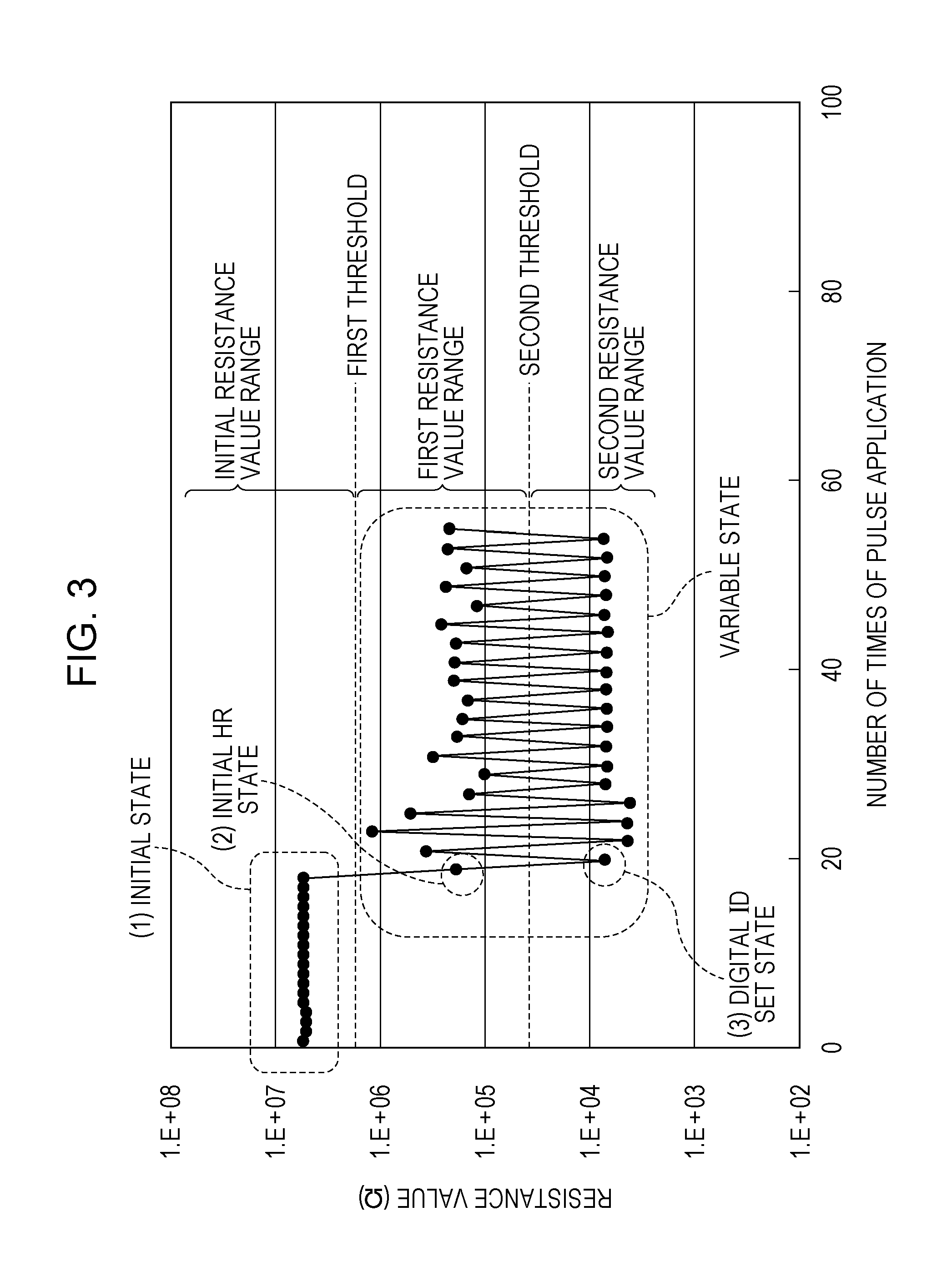

Tamper-resistant non-volatile memory device

ActiveUS20160148679A1Difficult to duplicateHigh resistanceRead-only memoriesDigital storageData AdjustmentsDigital data

A non-volatile memory device includes a memory cell array including memory cells, a read circuit that, in operation, obtains pieces of resistance value information each relating to the resistance value of one of the memory cells, an arithmetic circuit that, in operation, calculates a binary reference value based on at least a part of the pieces of resistance value information, and a data adjustment circuit. In operation, the read circuit assigns, based on the binary reference value, 0 or 1 to each of the pieces of resistance value information. In operation, the data adjustment circuit determines whether to adjust the binary reference value, in accordance with a difference between the numbers of pieces of digital data “0” and digital data “1” in the pieces of digital data.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

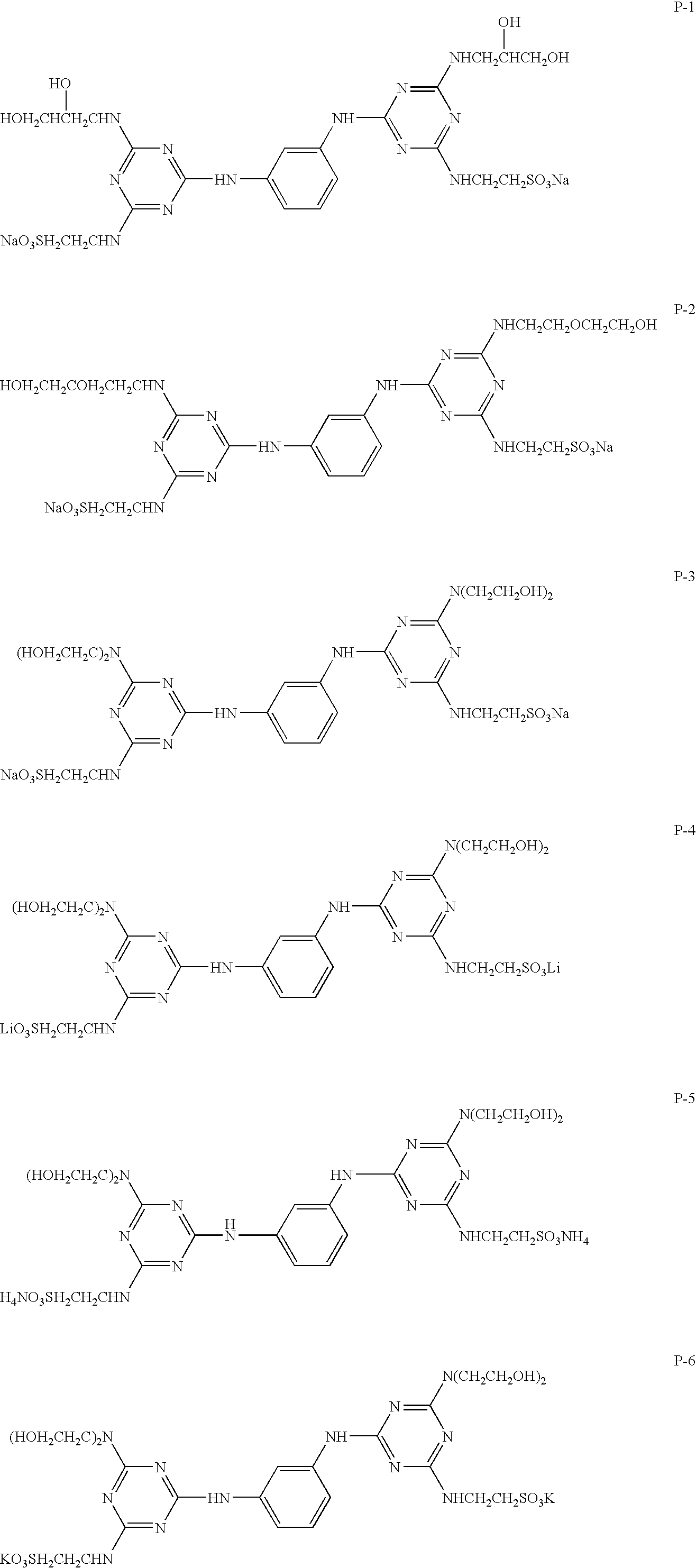

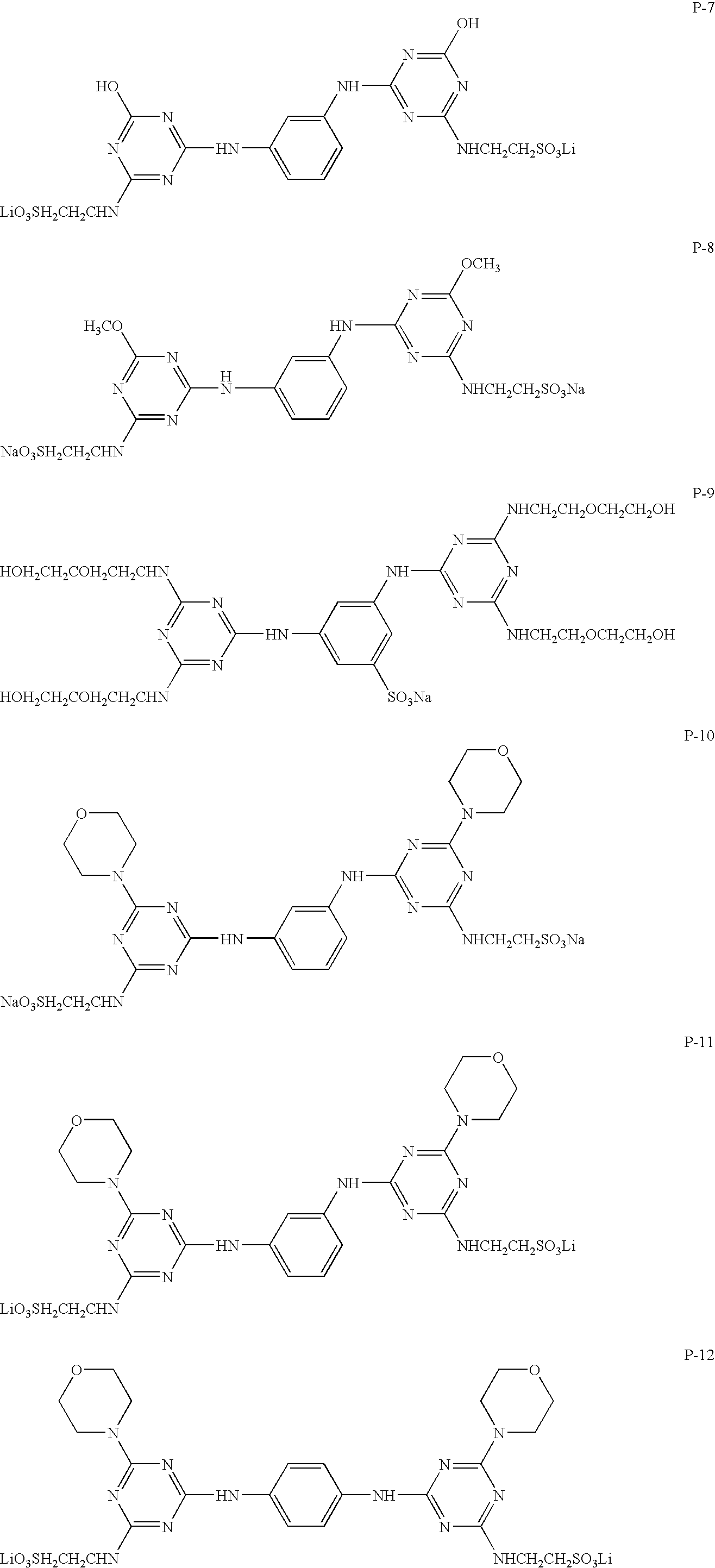

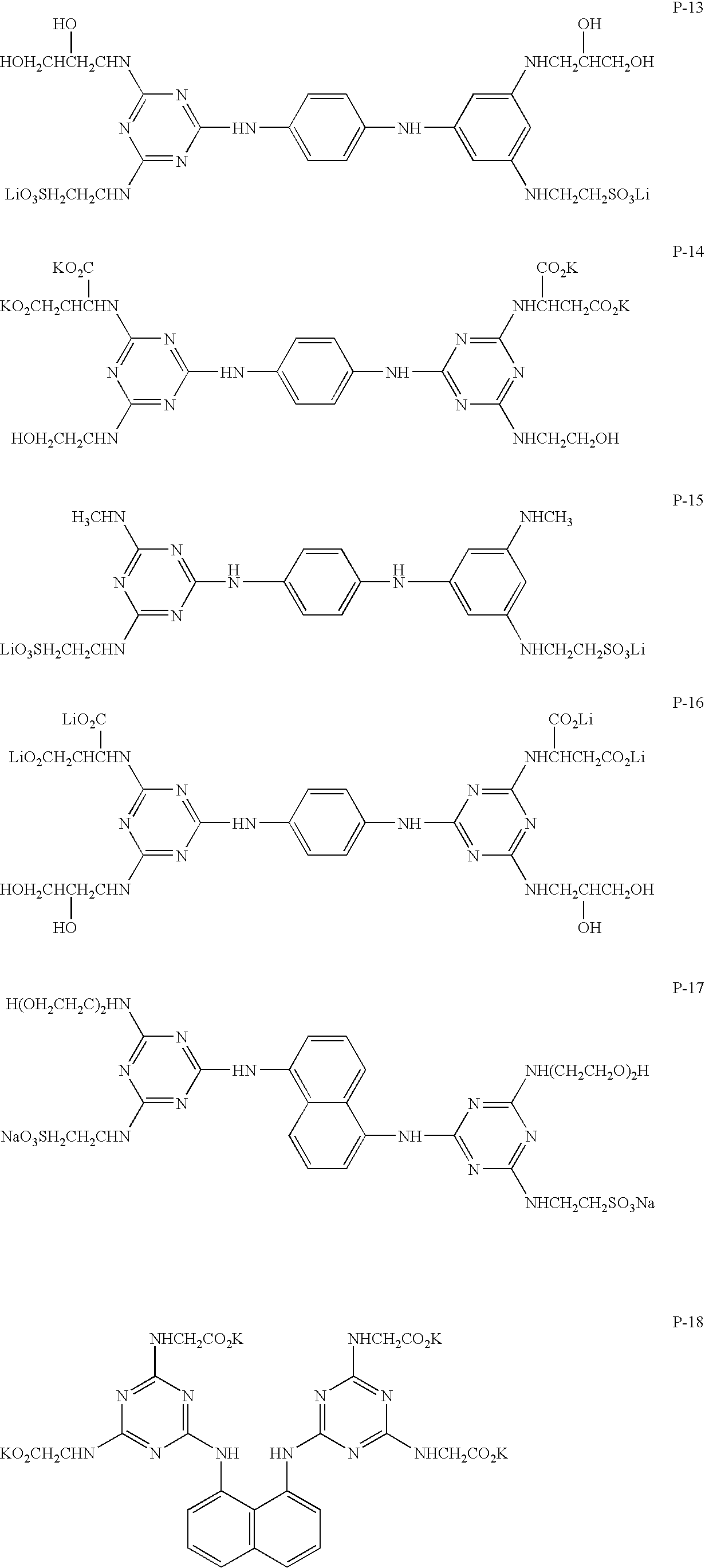

Recording medium, ink composition and recording method using the same

InactiveUS20050233097A1High resistanceExcellent propertyInksThermographyFluorescenceColor difference

A recording medium containing a substantially colorless compound in which at least 10 atoms having conjugate π electrons are present on a per-molecule basis, wherein it is especially preferable that the compound has at least two aromatic ring groups and / or shows no fluorescence. An ink composition used for printing in image form on media, with the composition containing a dye and controlling a hue change caused in the printed images over a period of one hour immediately after the printing to 5 or below in color-difference terms. And a method of recording images on media by printing an ink composition in image form, wherein the ink composition contains a dye and a hue change caused in the printed images over a period of one hour immediately after the printing is controlled to 5 or below in color-difference terms.

Owner:FUJIFILM HLDG CORP +1

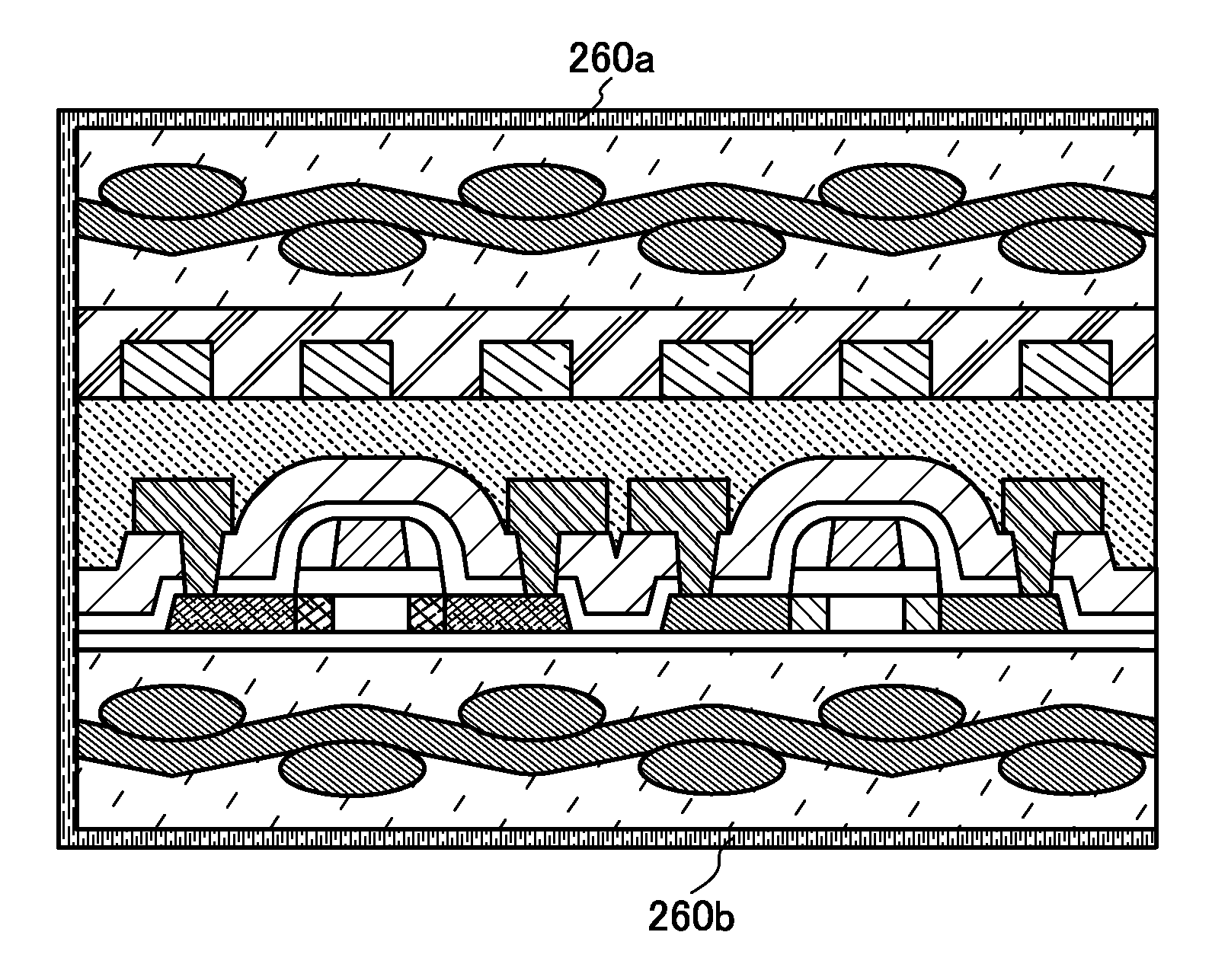

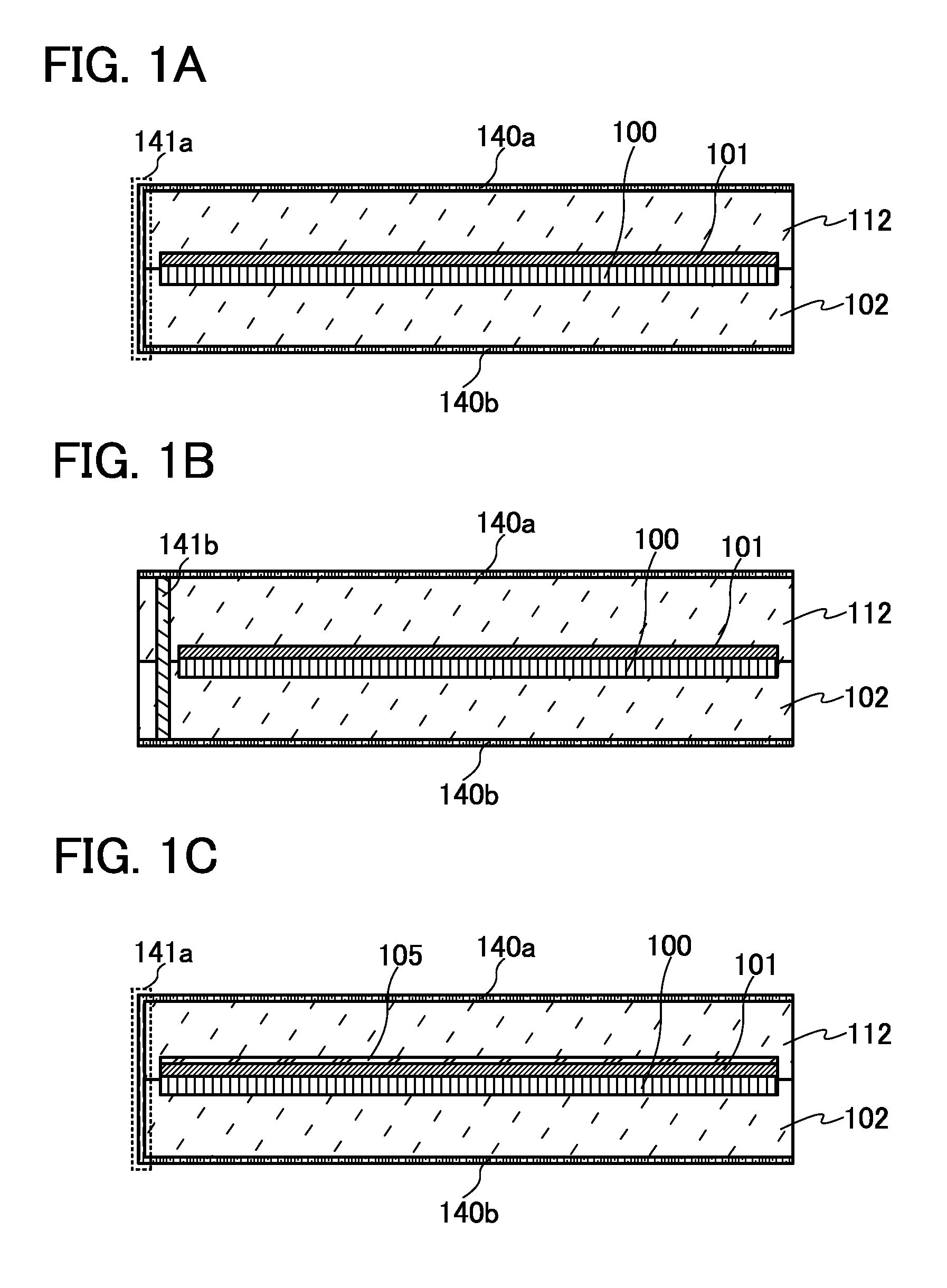

Semiconductor device

InactiveUS20090289341A1Reduction in thickness and sizeHigh resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrostatic dischargeElectrically conductive

An object is to provide a highly reliable semiconductor device having resistance to external stress and electrostatic discharge while achieving reduction in thickness and size. Another object is to prevent defective shapes and deterioration in characteristics due to external stress or electrostatic discharge in a manufacture process to manufacture a semiconductor device with a high yield. A first insulator and a second insulator facing each other, a semiconductor integrated circuit and an antenna provided between the first insulator and the second insulator facing each other, a conductive shield provided on one surface of the first insulator, and a conductive shield provided on one surface of the second insulator are provided. The conductive shield provided on one surface of the first insulator and the conductive shield provided on one surface of the second insulator are electrically connected.

Owner:SEMICON ENERGY LAB CO LTD

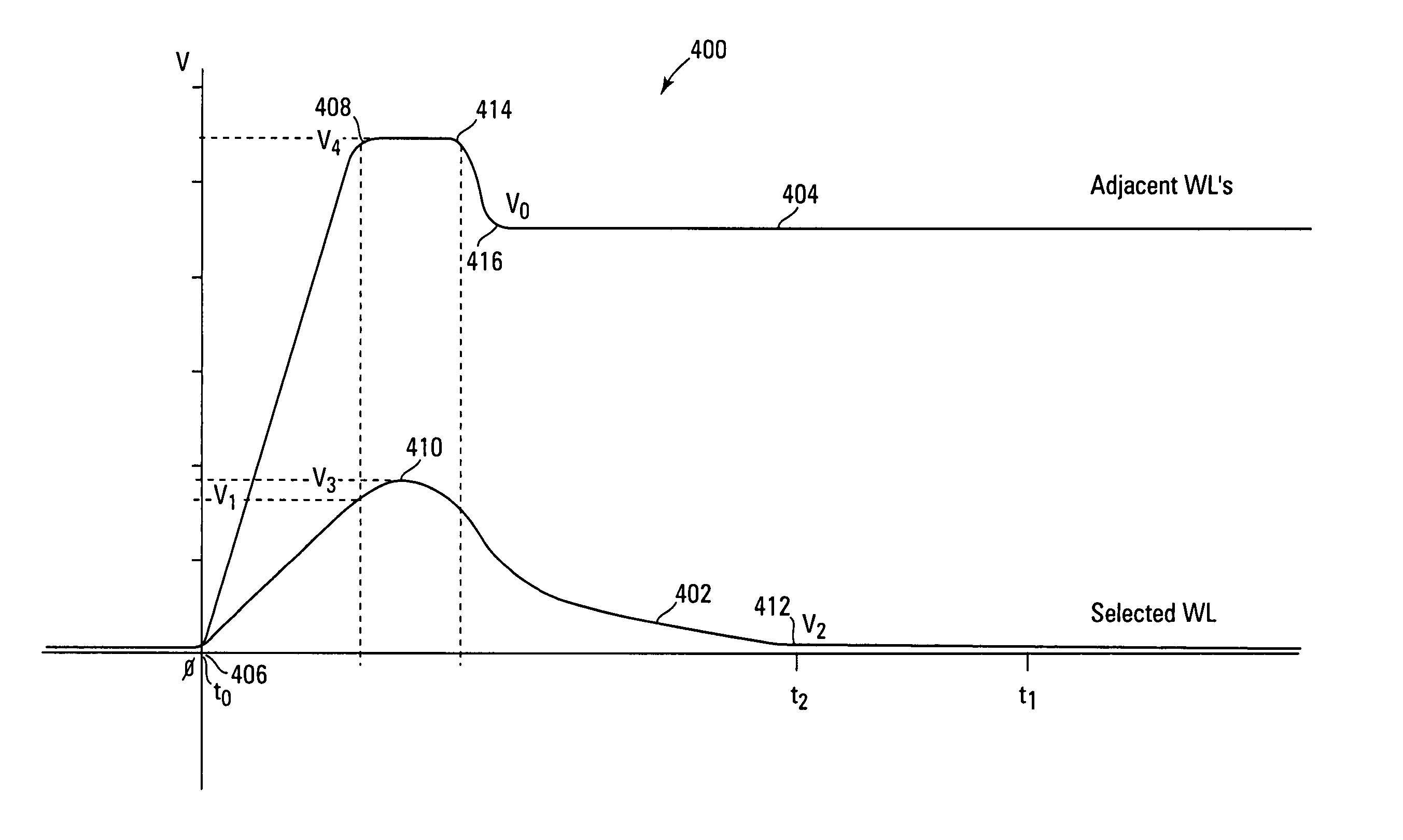

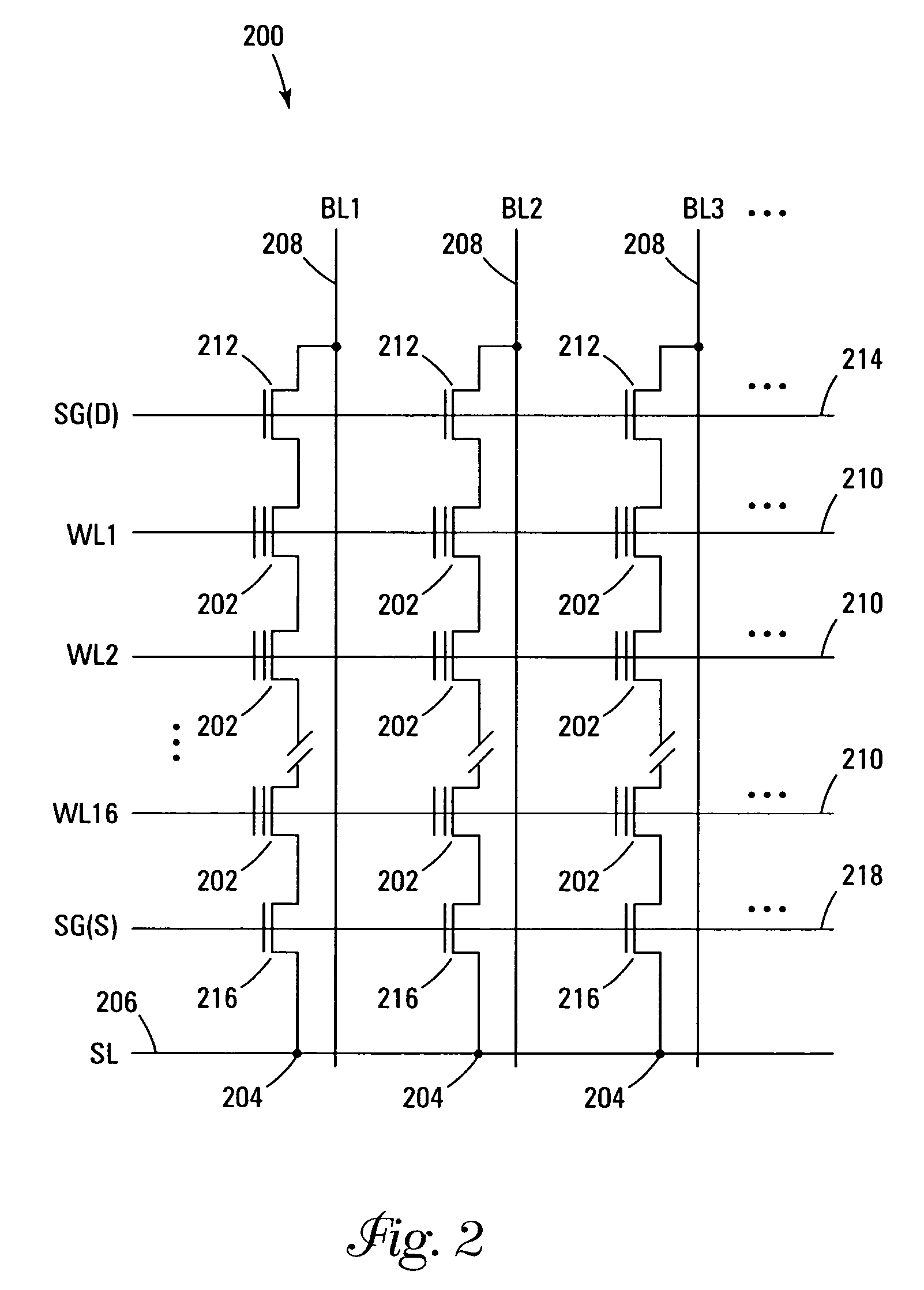

NAND string wordline delay reduction

ActiveUS7064981B2Extension of timeEnhancing Capacitive CouplingRead-only memoriesDigital storageCapacitanceLow voltage

An improved NAND Flash memory and word line selection method has been described, that takes advantage of the asymmetric nature of the word line to word line capacitive coupling to reduce word line selection delay by driving the adjacent word lines to a higher initial voltage and then reducing it to the final target voltage. As the capacitive coupling in between the NAND word lines is a larger effect when the voltages are being lowered, this has the effect of damping out the voltage initially induced in the lower voltage word line by the rising voltages on the adjacent word lines, reducing the overall selection time.

Owner:MICRON TECH INC

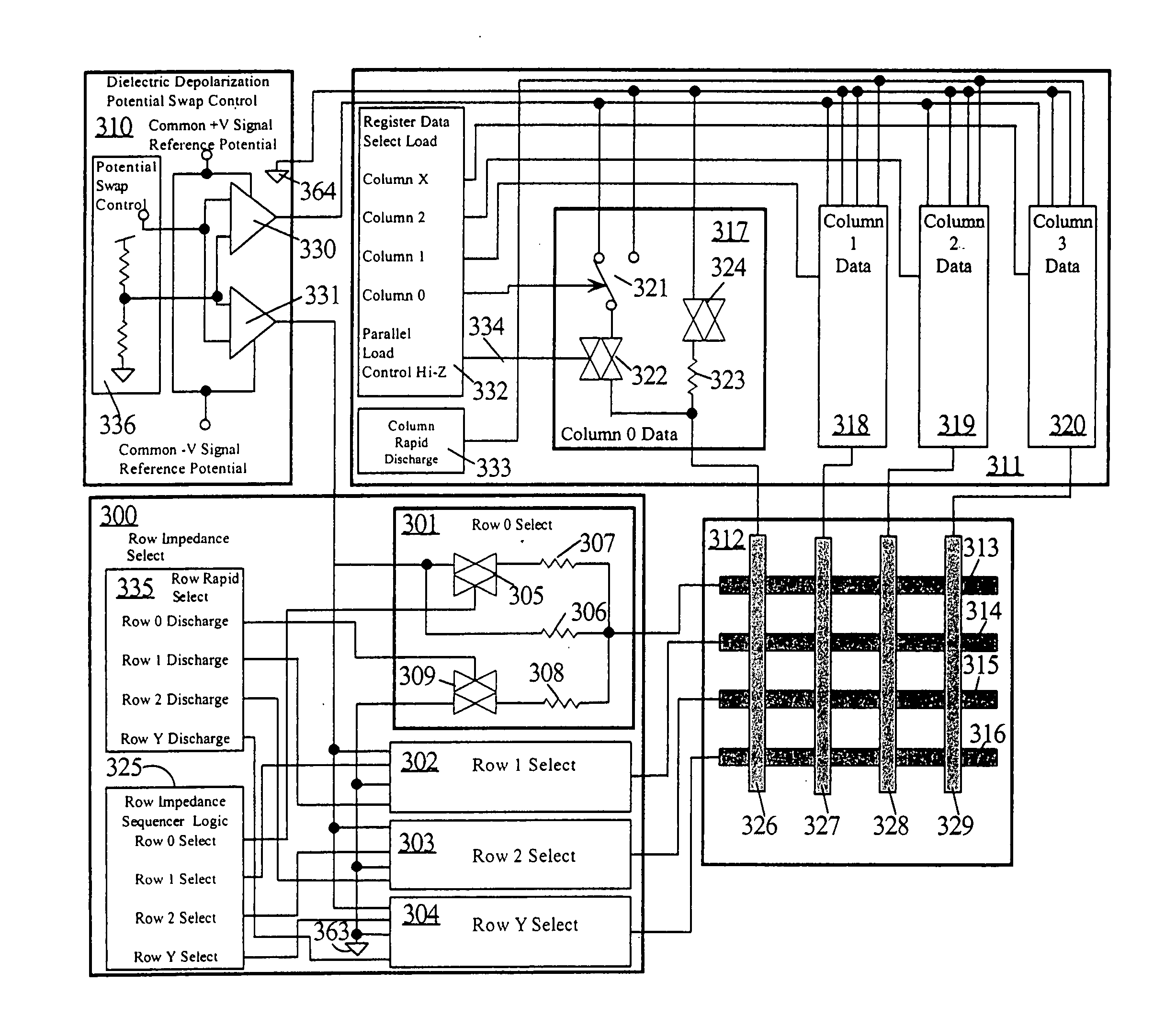

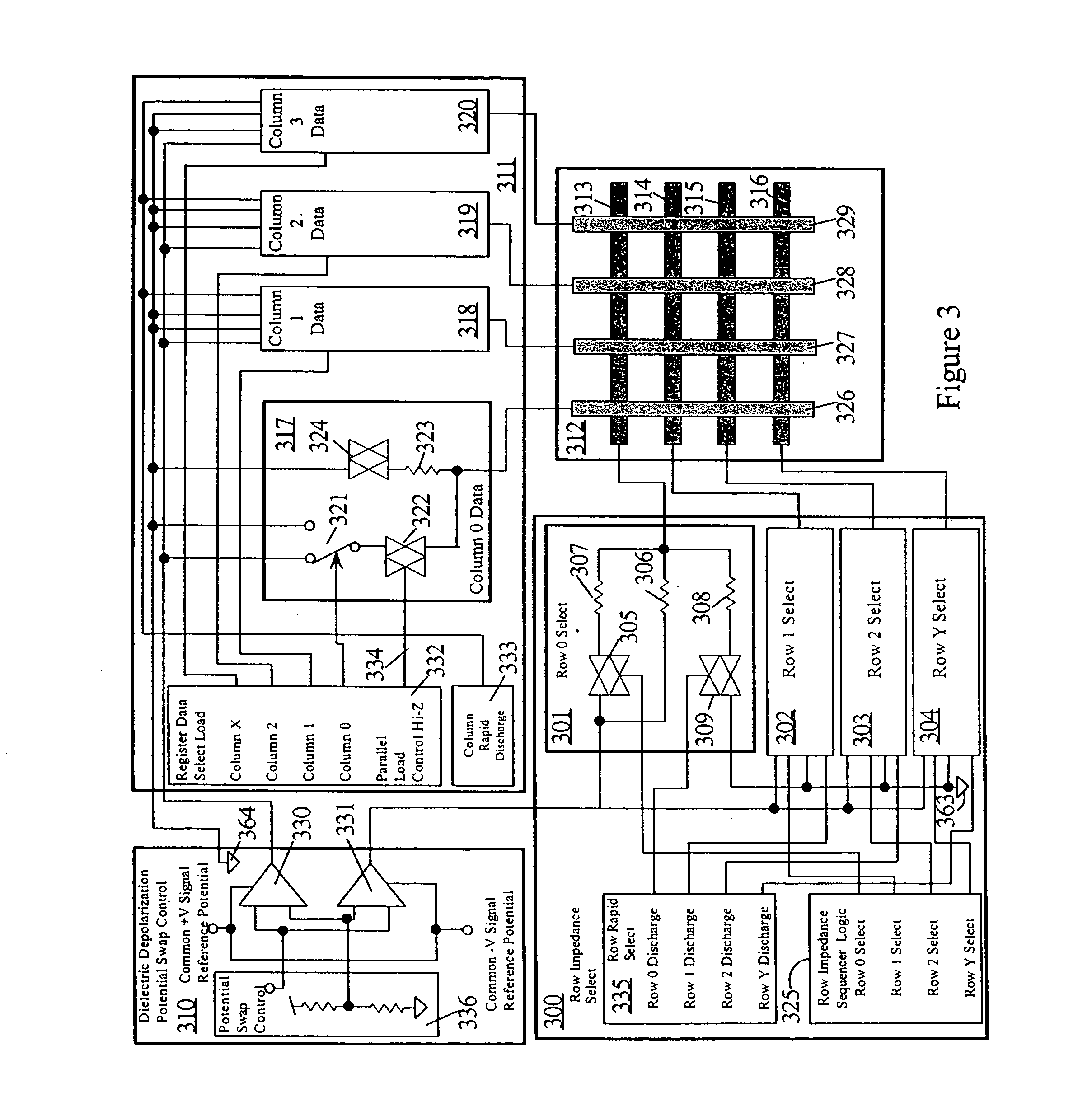

Simple matrix addressing in a display

InactiveUS20060238443A1High resistanceEnsure persistenceBioreactor/fermenter combinationsBiological substance pretreatmentsCapacitanceHysteresis

An addressing mechanism for charging and discharging quasi-capacitive elements in an X-Y matrix. The addressing mechanism may be configured to toggle a resistor-capacitor (RC) time constant between large and small values such as by opening or closing a circuit path to a low impedance resistor disposed in parallel with a higher impedance in-line resistor. When this occurs, elements in the X-Y matrix can be addressed and controlled. The X-Y matrix may be comprised of multiple “rows” and “columns” of conductors where crosstalk may occur along the columns and rows. Crosstalk may be curtailed by using either hysteresis management or global control of the row's impedance along its entire length. The resulting control obviates the need for active devices at each matrix element to perform the switching functions.

Owner:RAMBUS DELAWARE

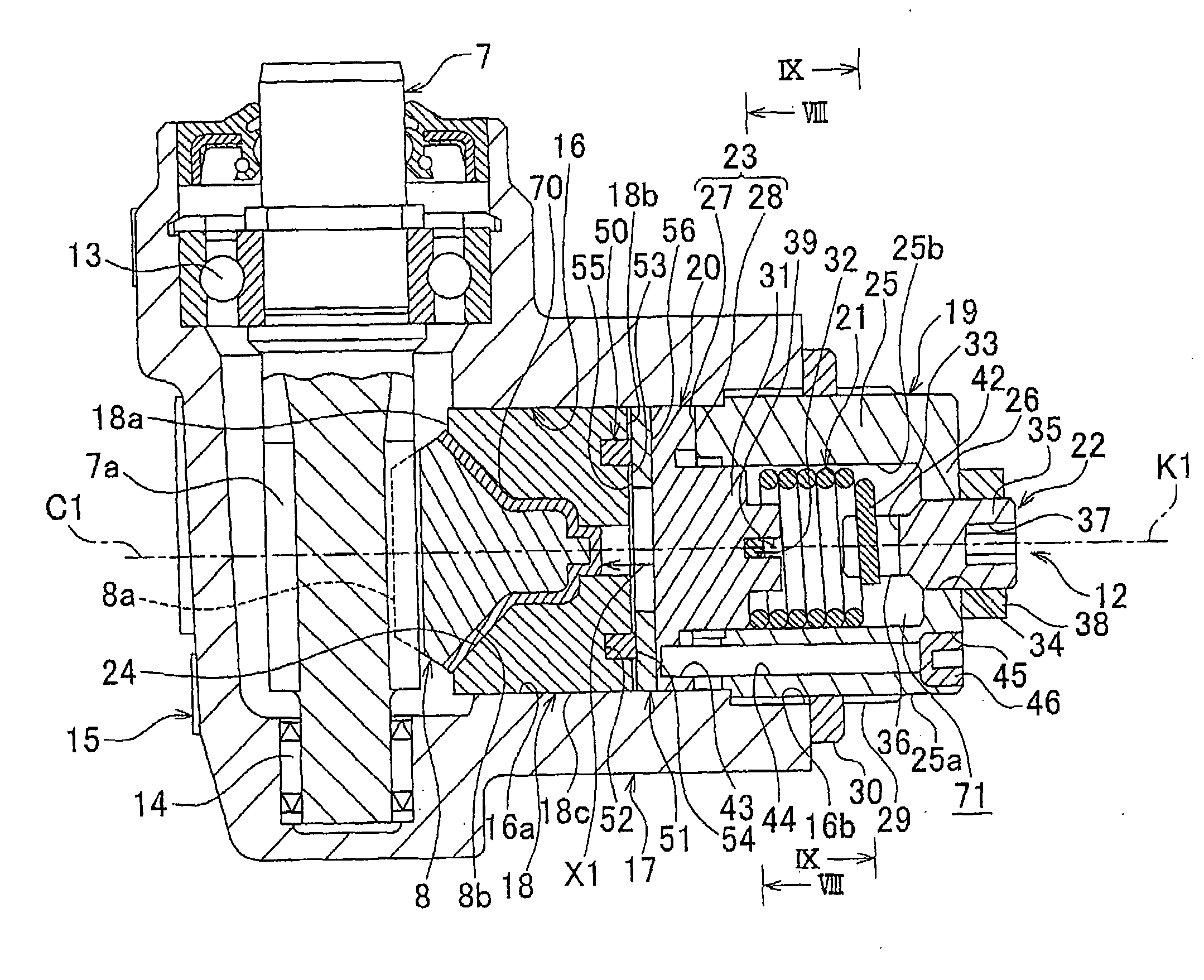

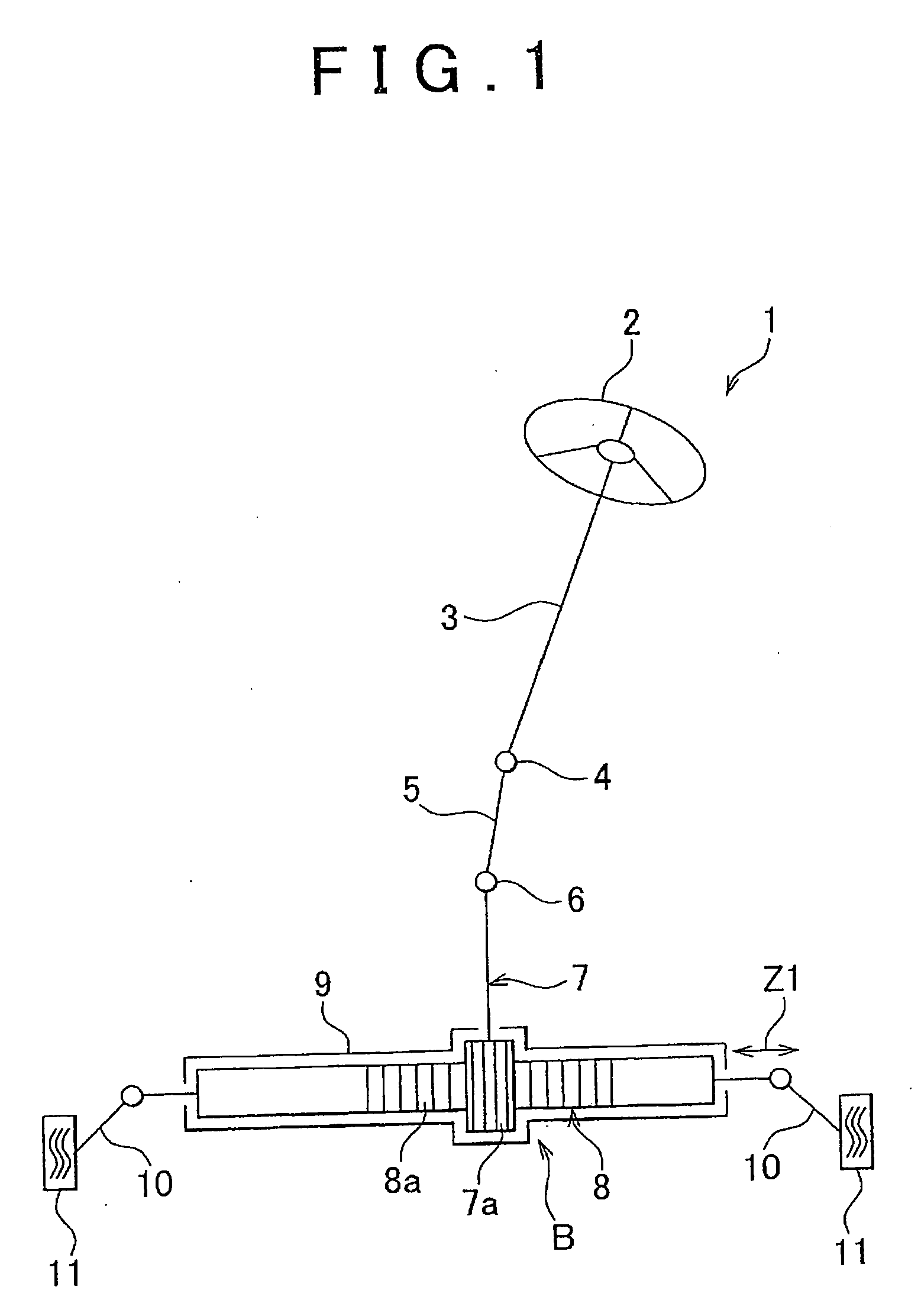

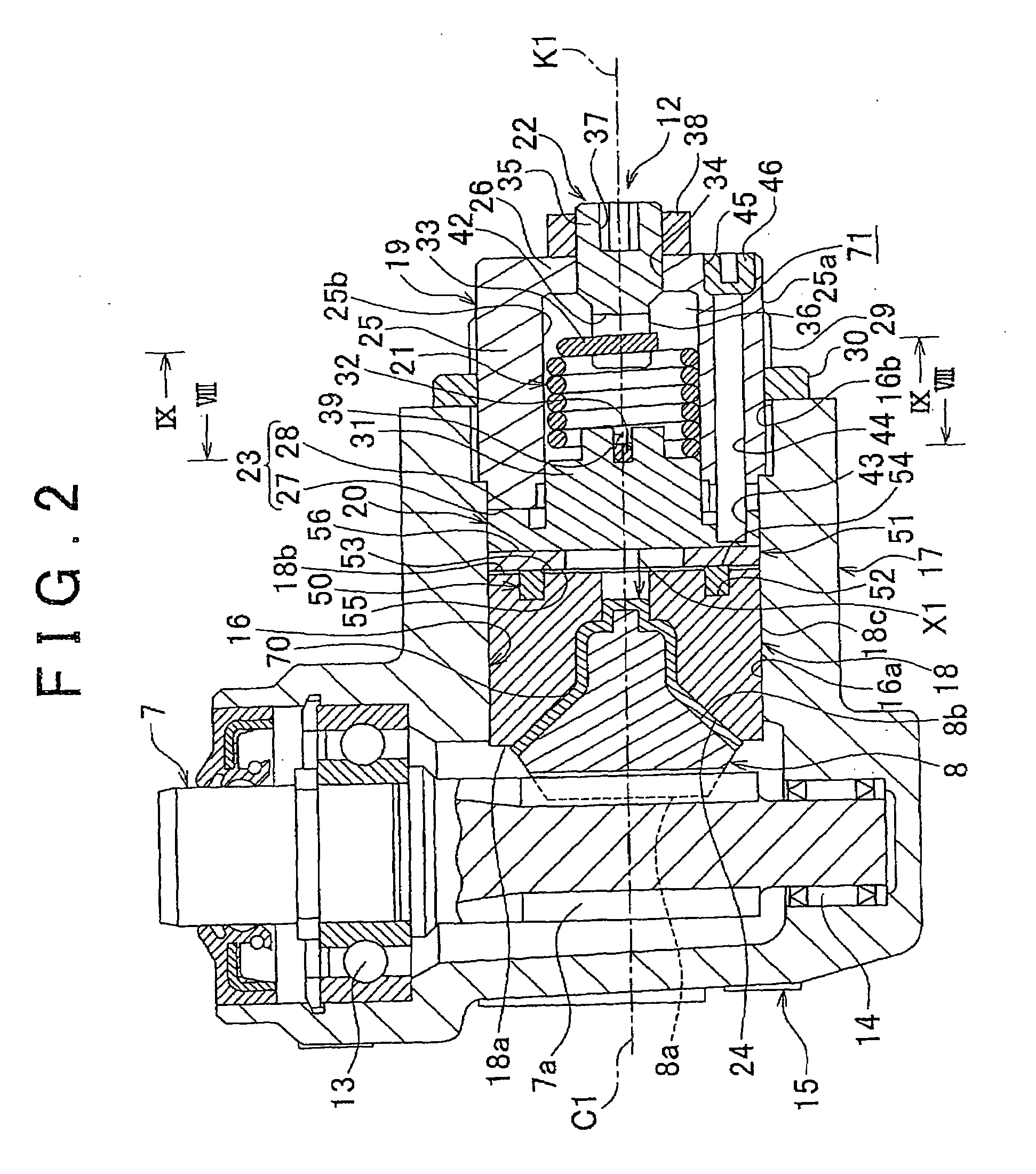

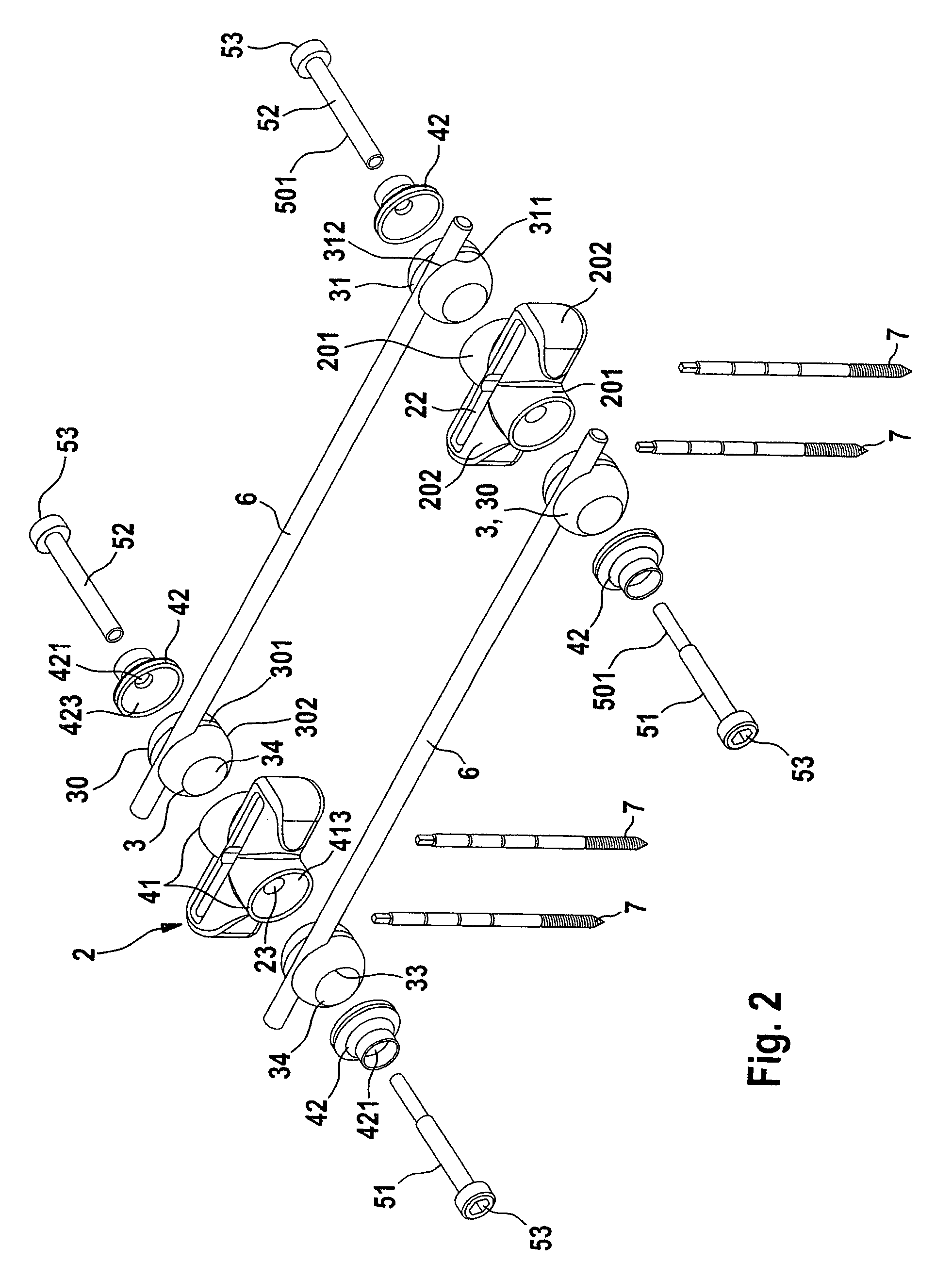

Rack shaft support device

ActiveUS20100024583A1Small frictional forceSmooth rotationPortable liftingToothed gearingsEngineeringCam

A rack shaft support device includes: a rack shaft support member that is accommodated inside a retention hole formed in a housing so as to slide in an axial direction of the retention hole, and slidably supports a rack shaft; a sealing member fixed to an inlet port of the retention hole; an intermediate member that is interposed between the rack shaft support member and the sealing member; a torsion spring that couples the sealing member and the intermediate member; a cam mechanism that converts a rotational force of the intermediate member induced by untwisting of the torsion spring to a force by which the intermediate member pushes the rack shaft support member; an opposing portion that opposes a rear surface of the rack shaft support member; and an annular elastic member that is interposed between the rear surface of the rack shaft support member and the opposing portion.

Owner:JTEKT CORP

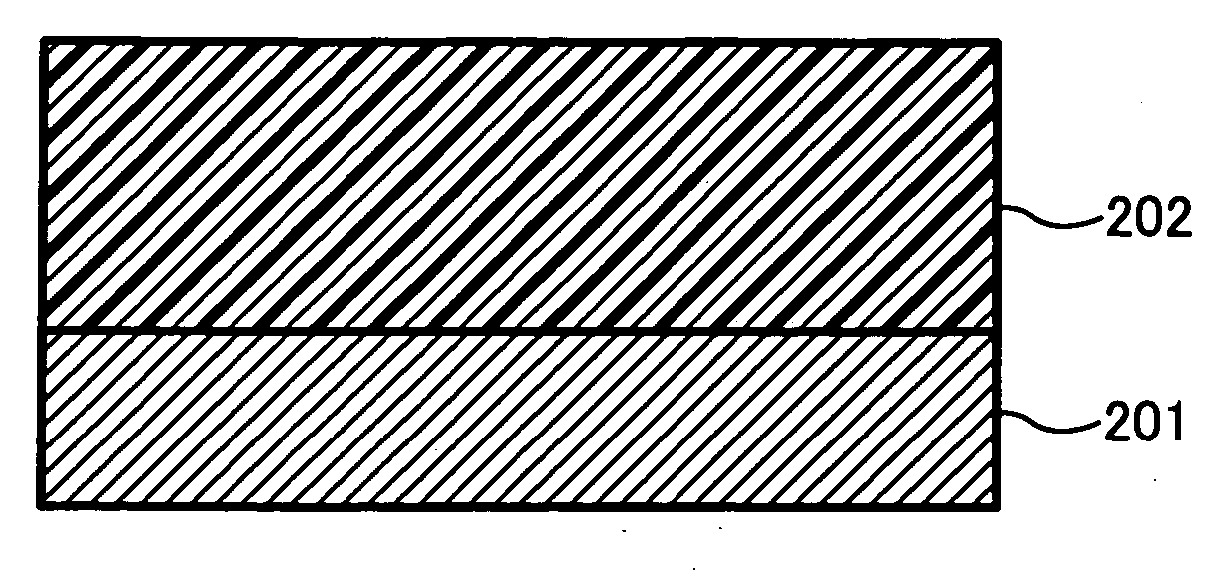

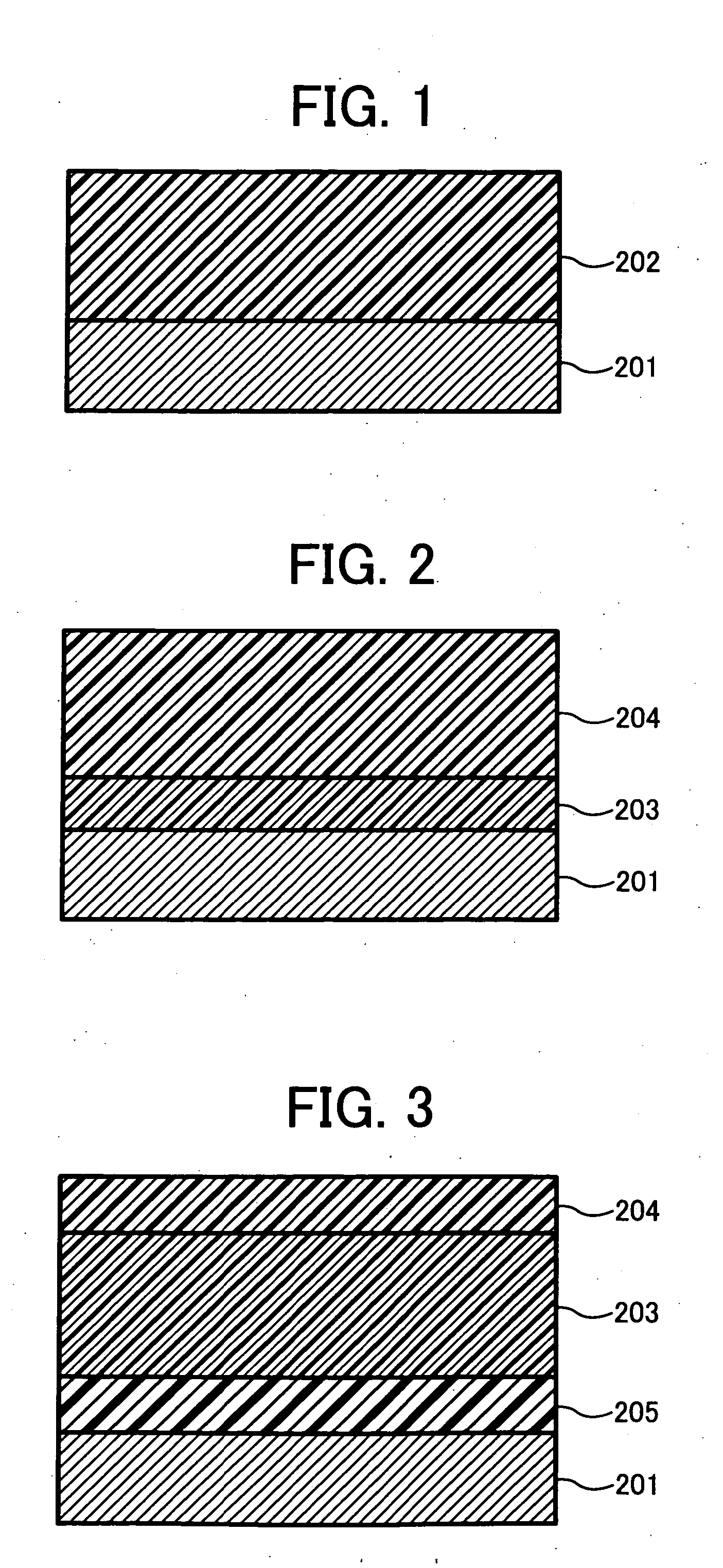

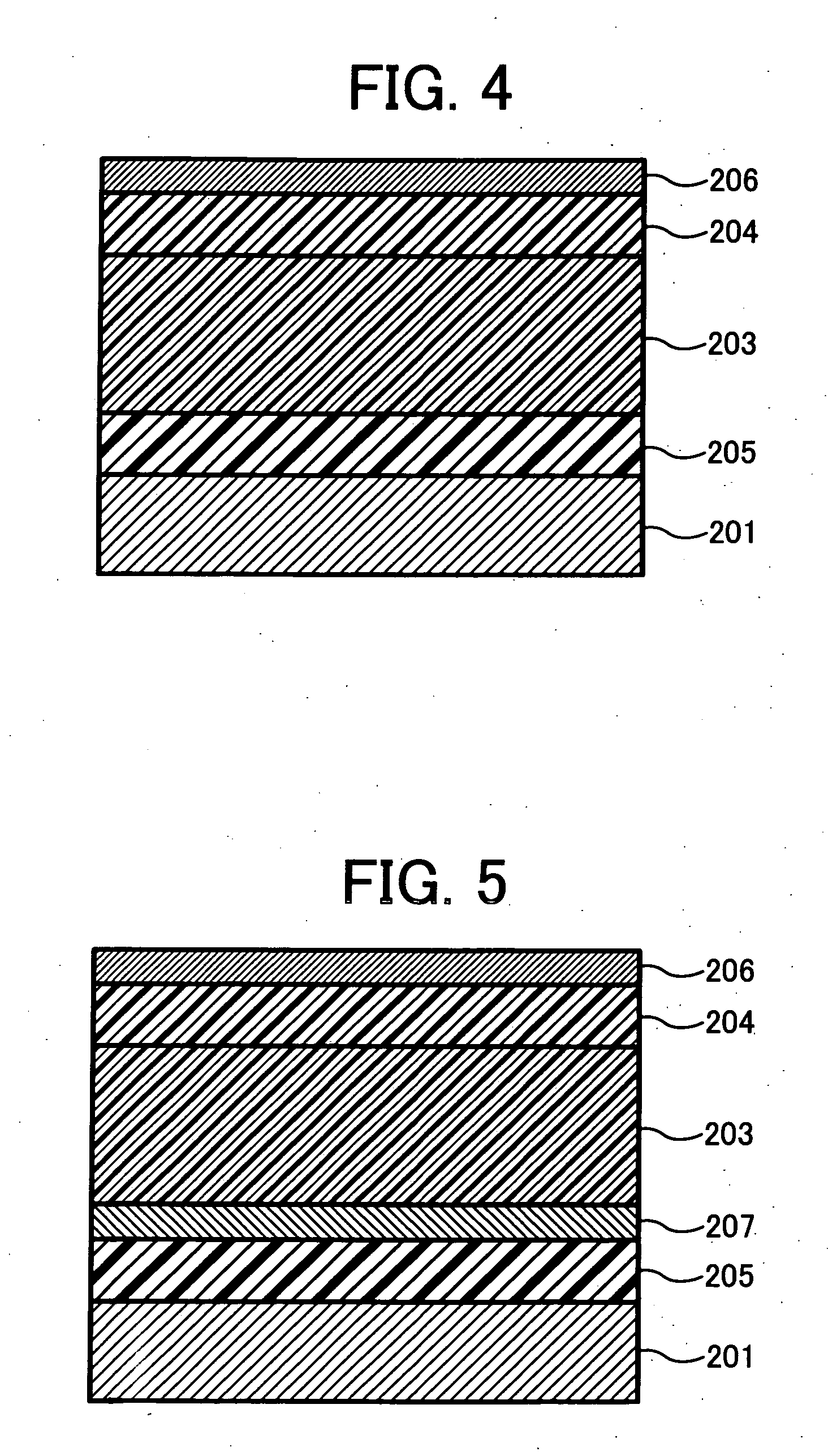

Electrostatic latent image bearer, and image forming method, image forming apparatus and process cartridge using the electrostatic latent image bearer

InactiveUS20060199092A1High resistanceGood electrophotographic image formabilityElectrographic process apparatusElectrographic processes using charge patternEngineeringParticulate material

An electrostatic latent image bearer, including a substrate and a photosensitive layer located overlying the substrate, wherein an outermost layer of the electrostatic latent image bearer includes a binder resin and an electroconductive particulate material, wherein the electroconductive particulate material has the following formula: MxSbyOz wherein M represents a metallic element; and x, y and z represent molar ratios for respective elements.

Owner:RICOH KK

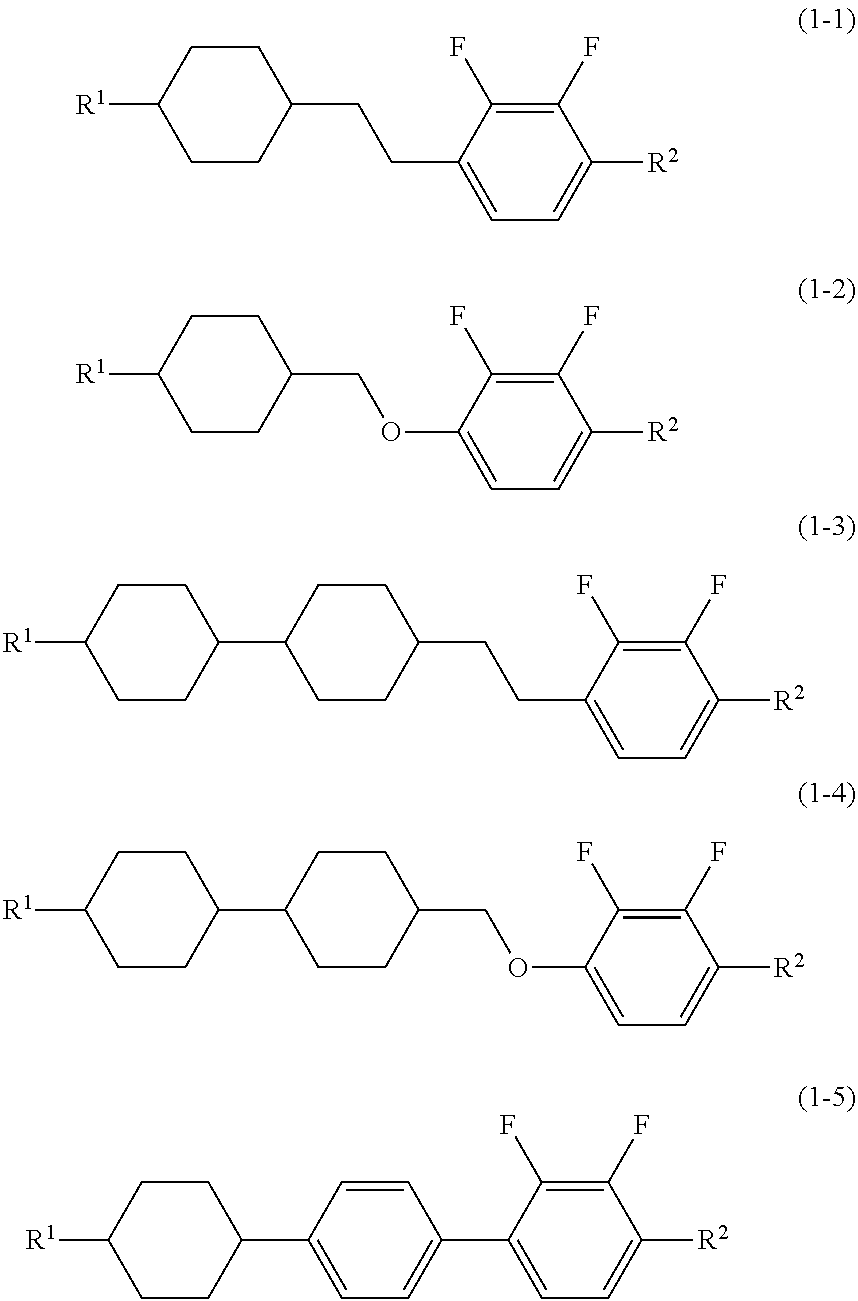

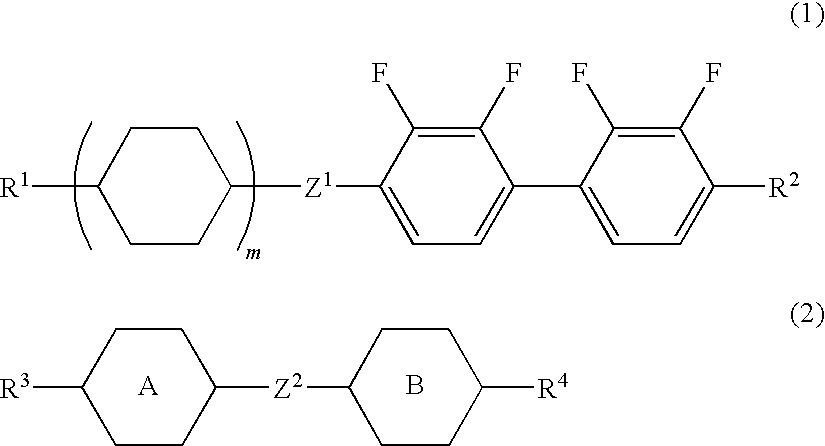

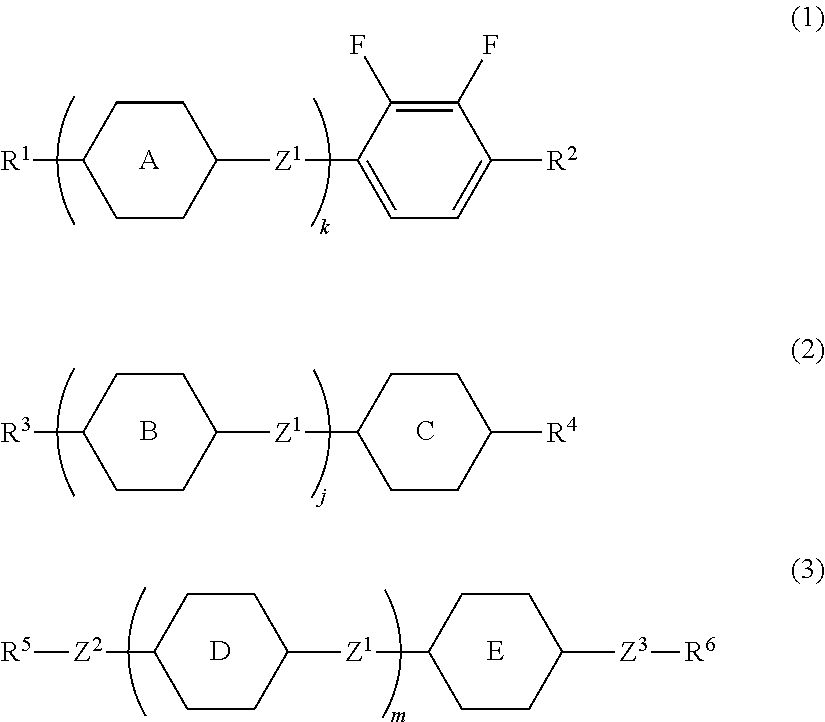

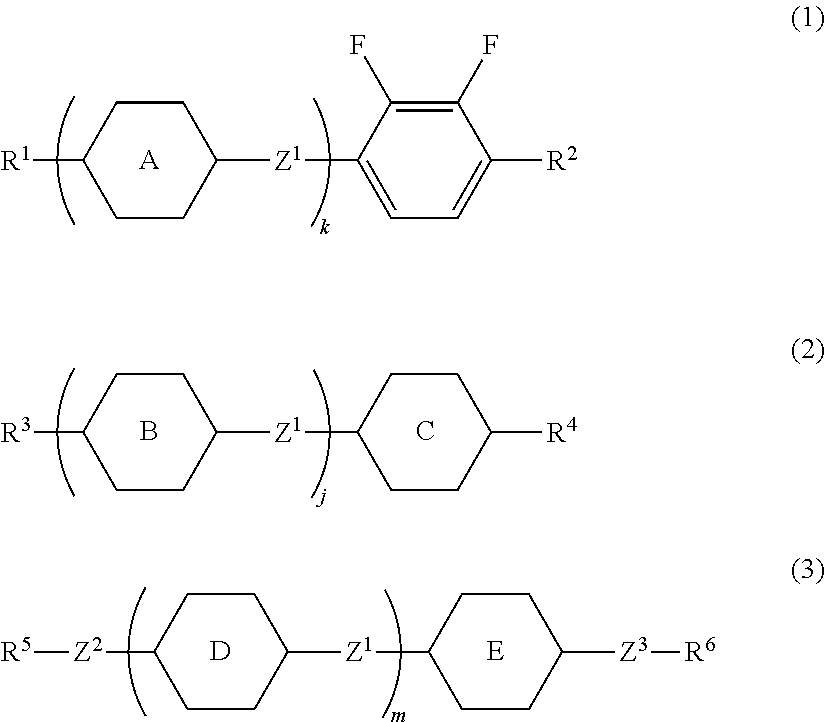

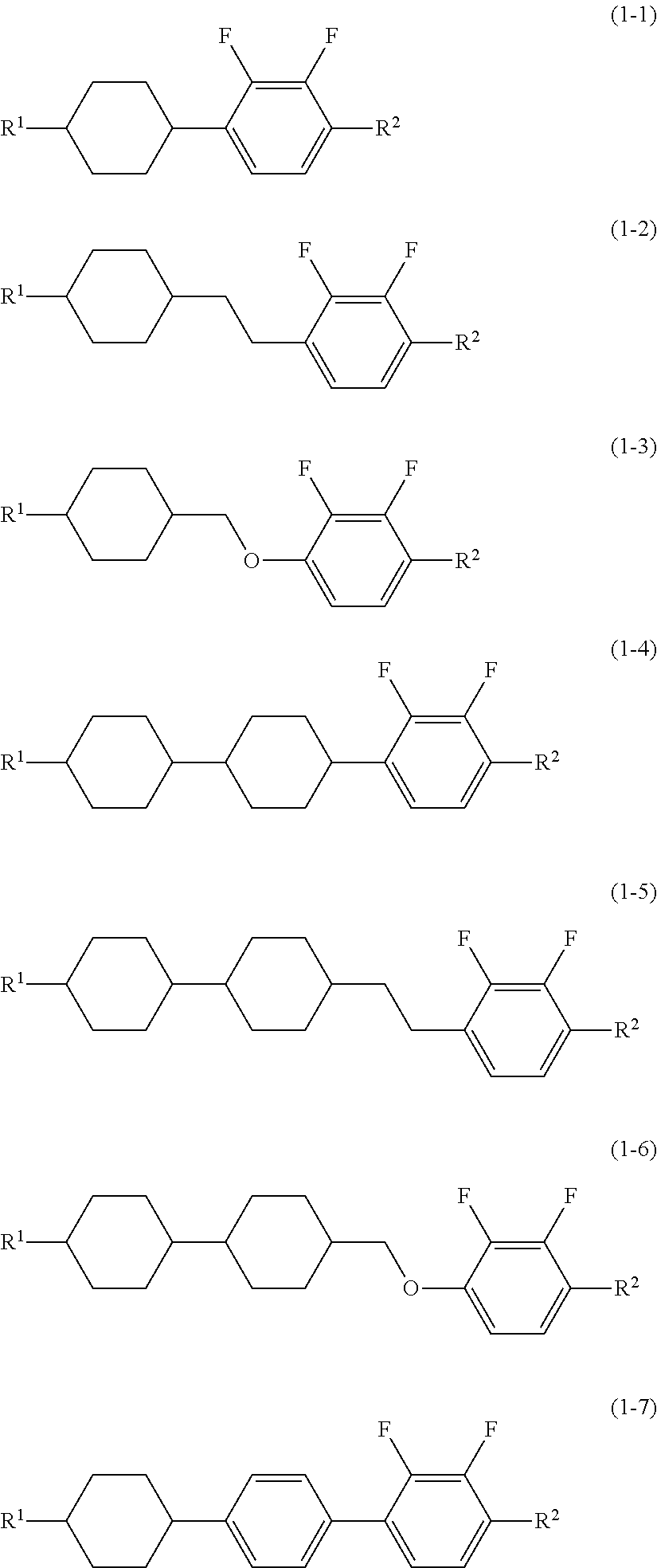

Liquid crystal composition and liquid crystal display device

ActiveUS20110096285A1Short response timeSmall viscosityLiquid crystal compositionsThin material handlingCrystallographyDielectric anisotropy

The subject is to provide a liquid crystal composition that satisfies at least one of characteristics such as a high maximum temperature of a nematic phase, a low minimum temperature of a nematic phase, a small viscosity, a suitable optical anisotropy, a large dielectric anisotropy, a large specific resistance, a high stability to ultraviolet light and a high stability to heat, or that is suitably balanced regarding at least two characteristics. The subject is to provide an AM device that has a short response time, a large voltage holding ratio, a large contrast ratio, a long service life and so forth. The invention provides a liquid crystal composition having a negative dielectric anisotropy that contains a specific compound having negatively large dielectric anisotropy as the first component, and has a specific two ring compound having a low viscosity as the second component, and provides a liquid crystal display device containing the composition.

Owner:JNC CORP +1

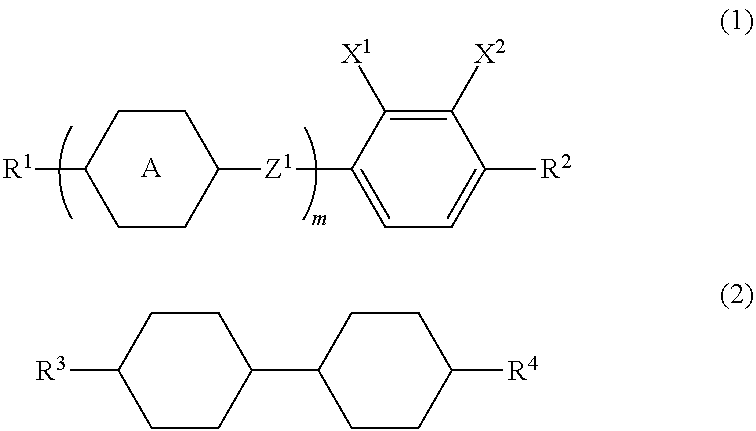

Liquid crystal composition and liquid crystal display device

InactiveUS20090278089A1High stability to ultraviolet lightShort response timeLiquid crystal compositionsOrganic chemistryDielectric anisotropyUltraviolet lights

A liquid crystal composition is provided that satisfies at least one characteristic among the characteristics such as a high maximum temperature of a nematic phase, a low minimum temperature of a nematic phase, a small viscosity, a large optical anisotropy, a large dielectric anisotropy, a large specific resistance, a high stability to ultraviolet light and a high stability to heat, or is properly balanced regarding at least two characteristics. An AM device is provided that has a short response time, a large voltage holding ratio, a large contrast ratio, a long service life and so forth. The liquid crystal composition contains a specific compound having especially negatively large dielectric anisotropy as the first component,a specific bicyclic compound having a small viscosity as the second component, a specific compound having a high maximum temperature as the third component, a specific compound having a negatively large dielectric anisotropy, a low minimum temperature as the fourth component. The liquid crystal composition has a negative dielectric anisotropy. The liquid crystal display device contains the liquid crystal composition.

Owner:JNC PETROCHEM +1

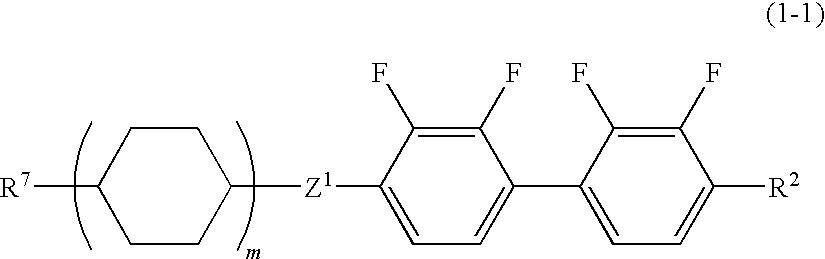

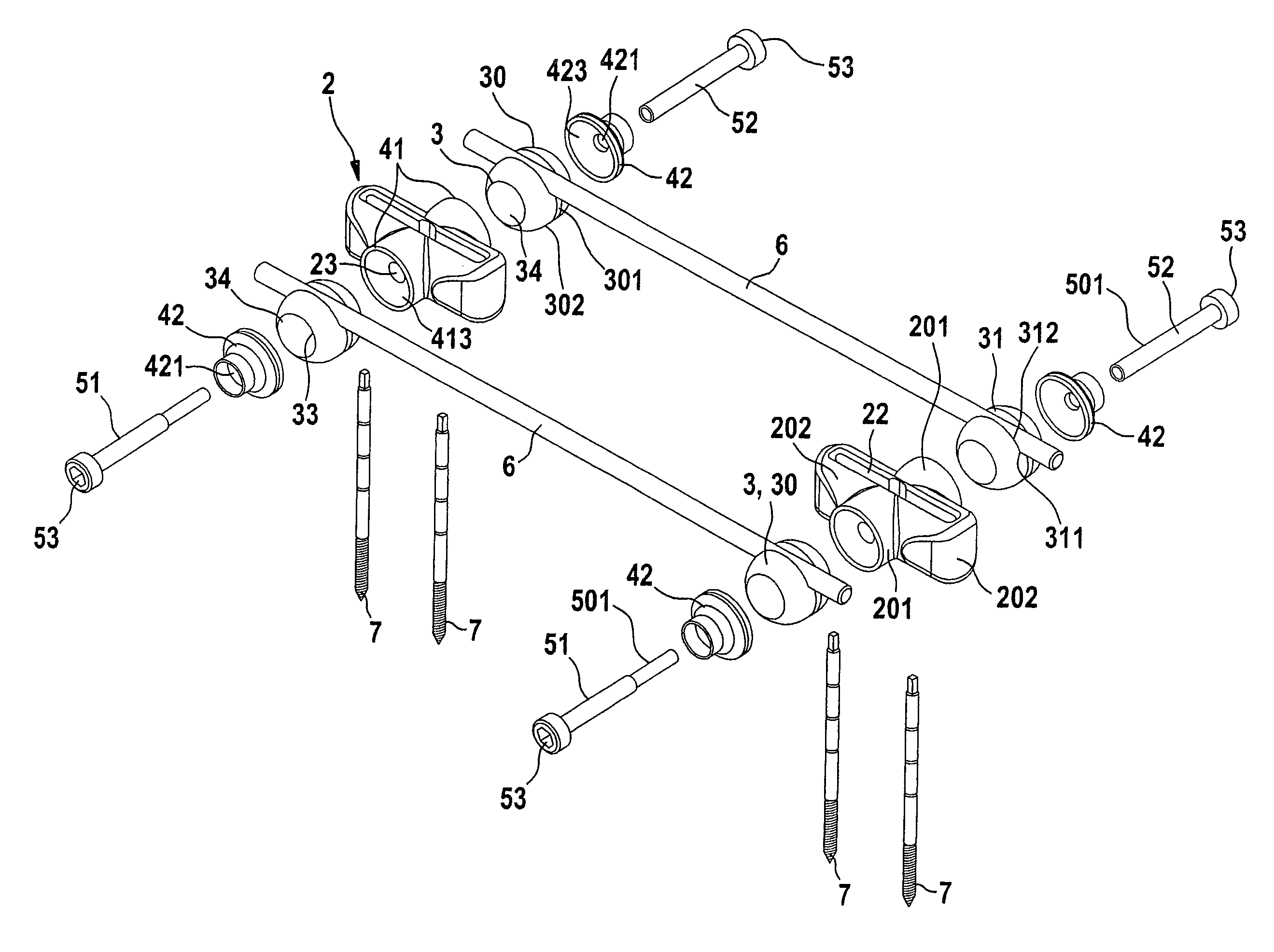

Fixation device for stably interlinking at least two bone fragments of a broken bone and corresponding fixation element and kit

InactiveUS8147490B2Reduce the numberEasy to handleInvalid friendly devicesFractureBone fragmentBone staple

Owner:TANTUM AG

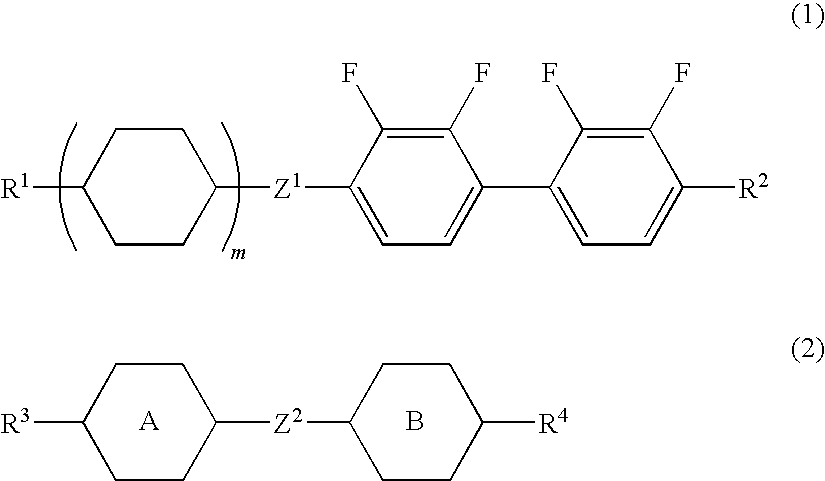

Liquid crystal composition and liquid crystal display device

ActiveUS20110272631A1High stability to ultraviolet lightShort response timeLiquid crystal compositionsThin material handlingLower limitDielectric anisotropy

Described is a liquid crystal composition which satisfies at least one of such characteristics as high upper limit temperature of the nematic phase, low lower limit temperature of the nematic phase, low viscosity, adequate optical anisotropy, large negative dielectric anisotropy, high resistivity, high stability to ultraviolet light and high stability to heat, or which has an adequate balance between at least two of the above-mentioned characteristics. Also described is an AM element having a short response time, high voltage holding ratio, high contrast ratio, long life and the like. The liquid crystal composition contains a specific compound having a large negative dielectric anisotropy and a low lower limit temperature as a first component, a specific compound having a low viscosity or a high upper limit temperature as a second component, and a specific compound having a polymerizable group as a third component. The AM element contains the composition.

Owner:JNC CORP +1

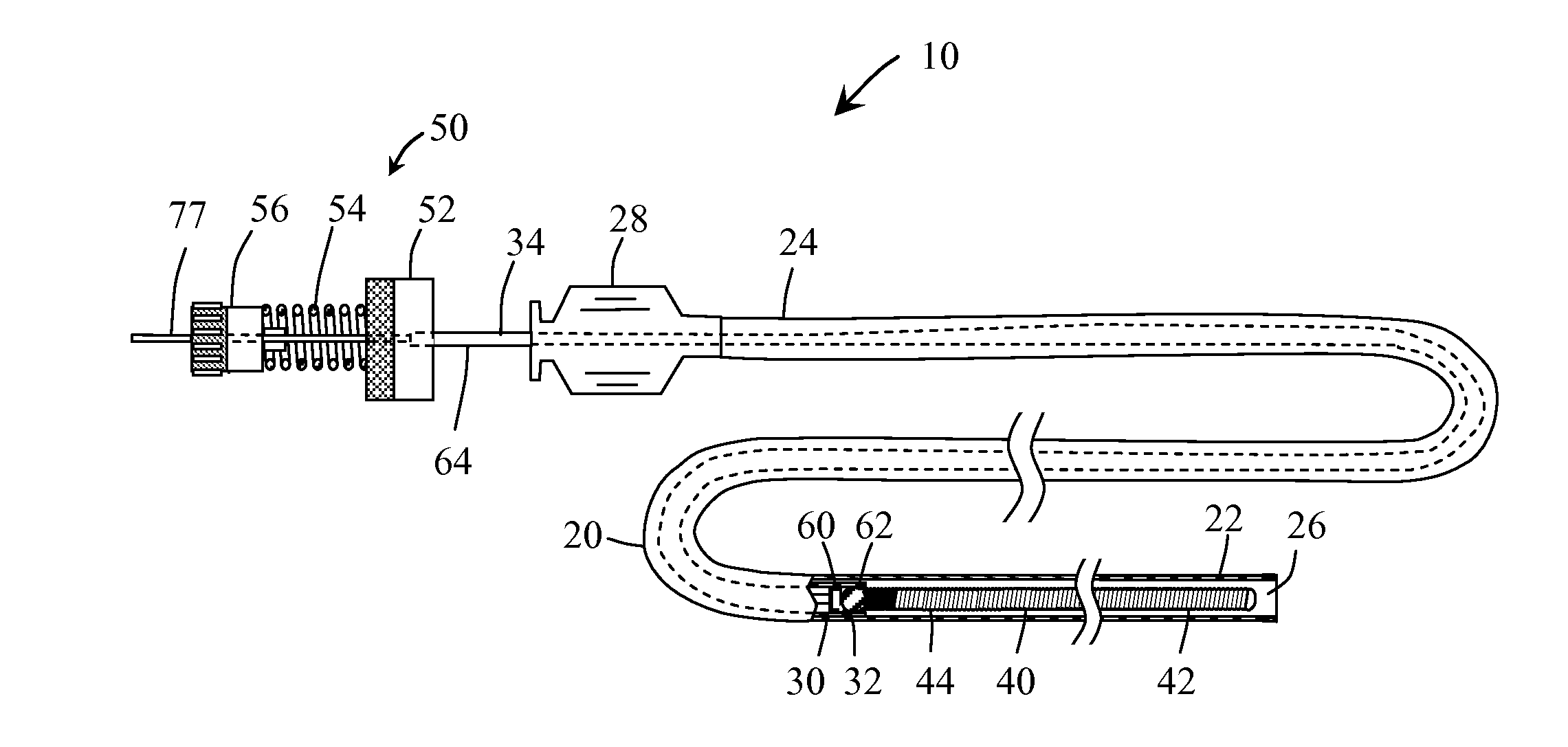

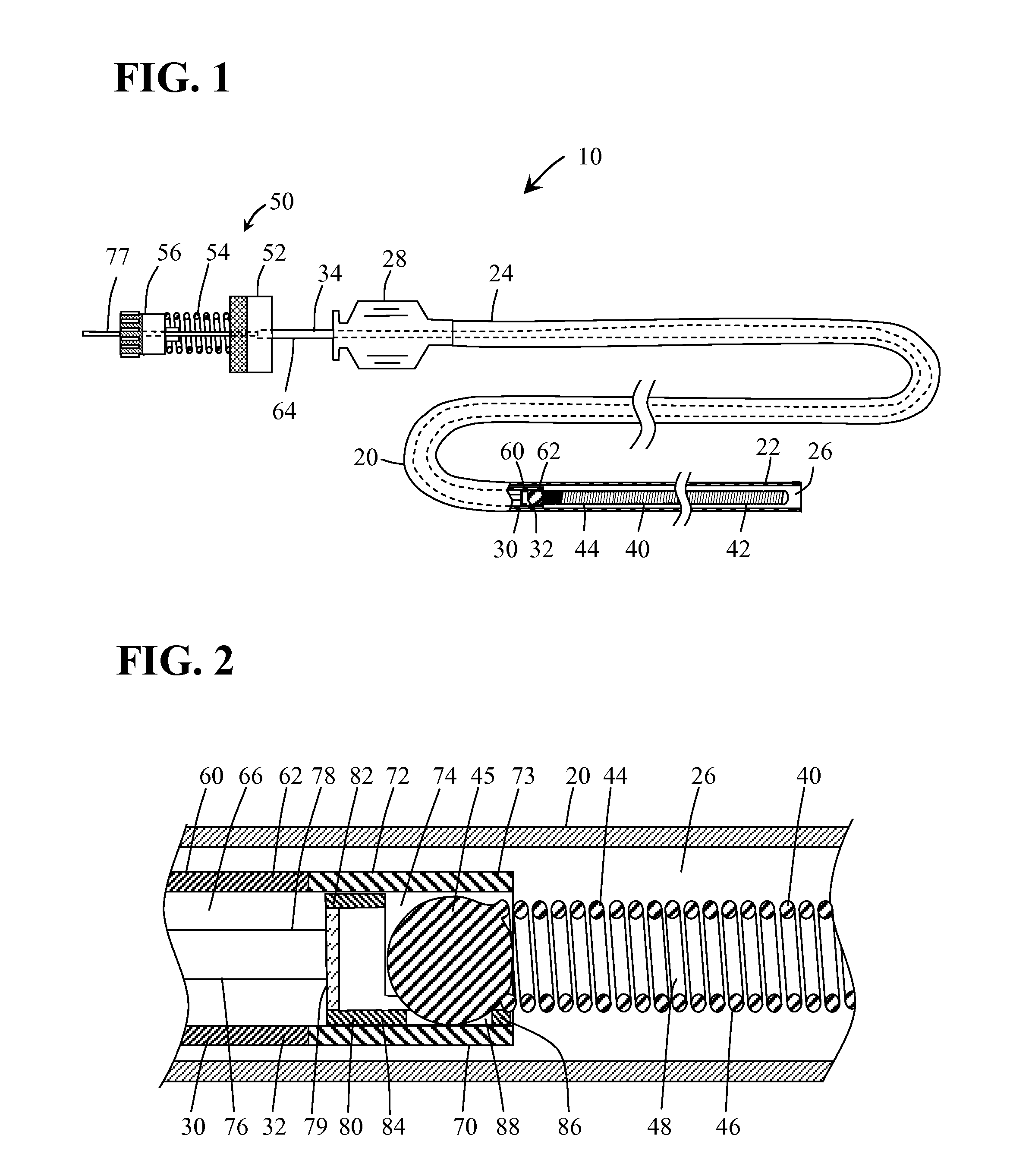

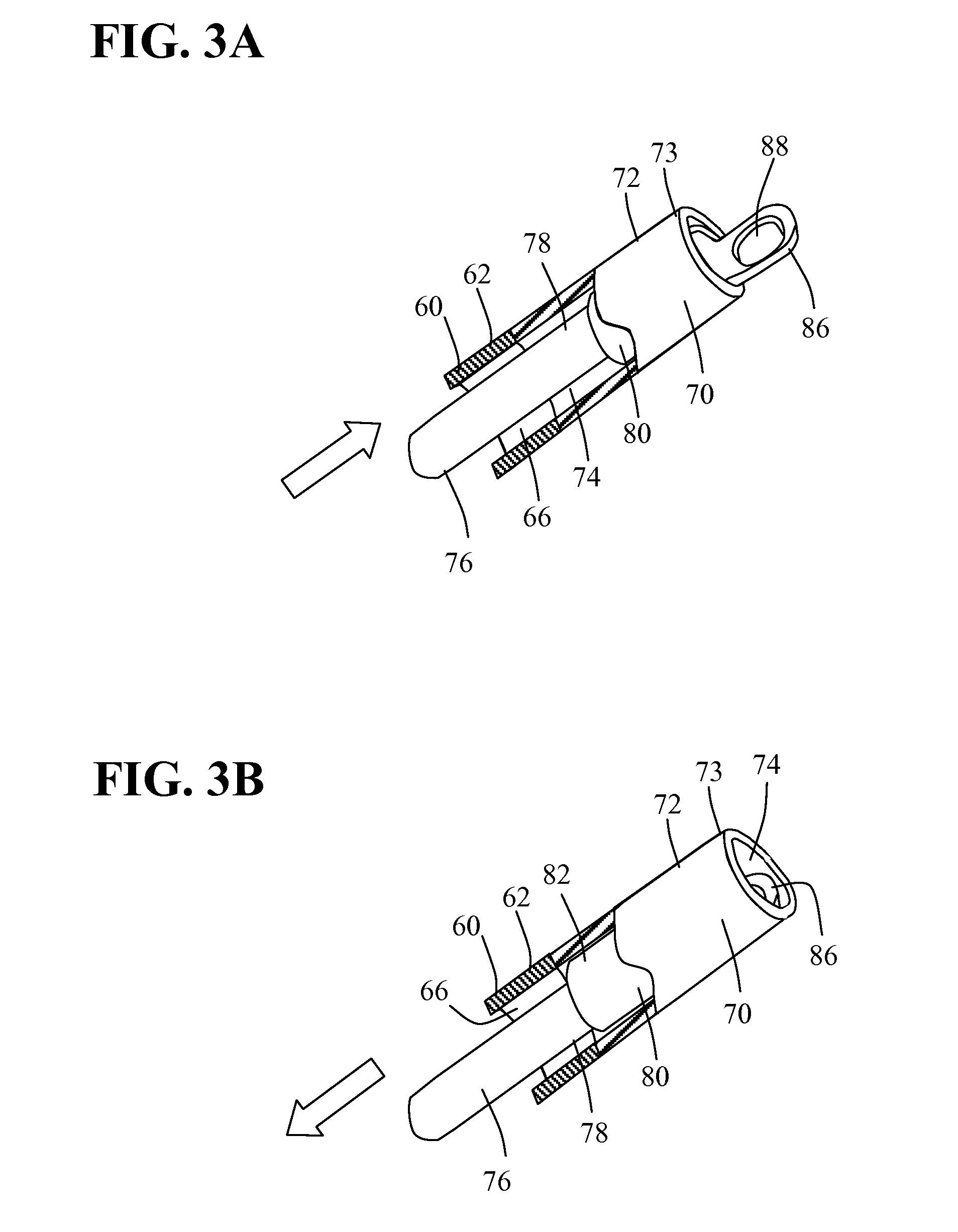

Implant delivery and release system

InactiveUS20140058435A1Minimal resistanceFacilitate couplingDilatorsOcculdersBiomedical engineeringMedical treatment

A medical implant deployment system for placing an implant at a preselected site within a vessel, duct or body lumen of a mammal comprising a reloadable deployment system includes a mechanical coupling assembly at the distal end of a delivery member, having an extended configuration in which the coupling assembly is adapted to receive or release the implant proximal end and a retracted configuration where the coupling assembly distal end is interlockingly engaged with the implant proximal end. Once the implant is properly positioned the coupling assembly is actuated, thereby releasing the implant at a desired position within the body.

Owner:JONES DONALD K +1

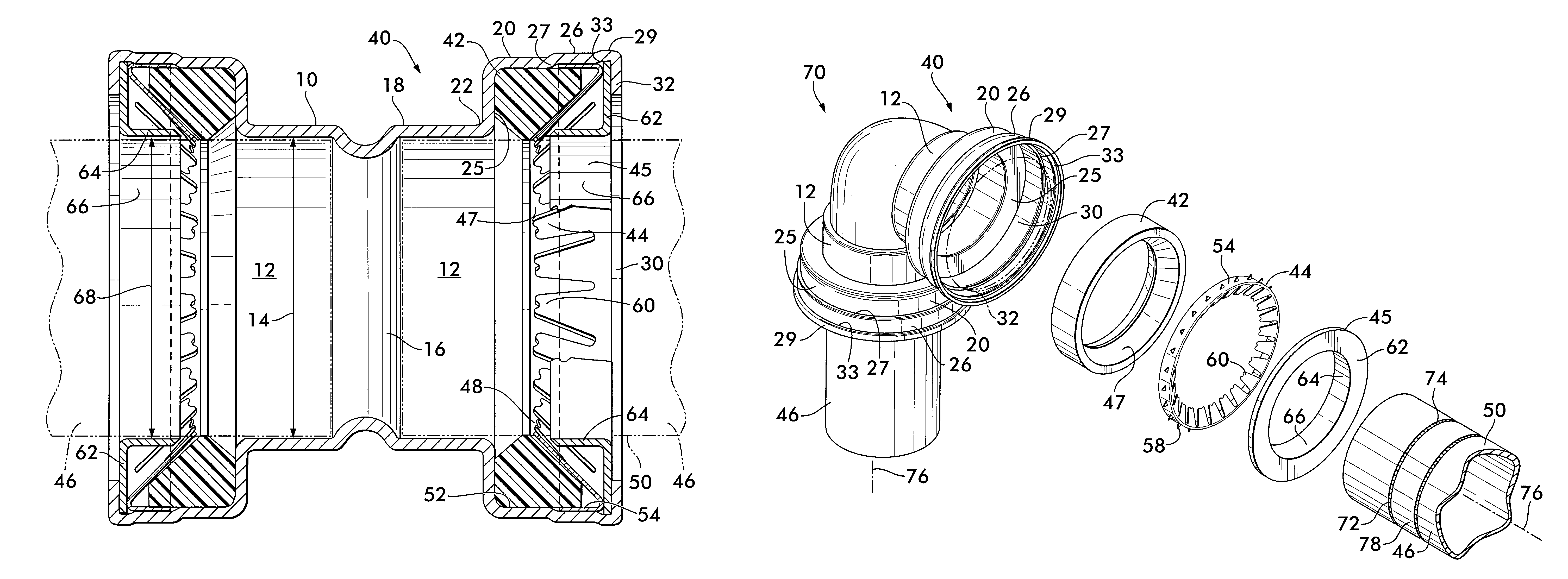

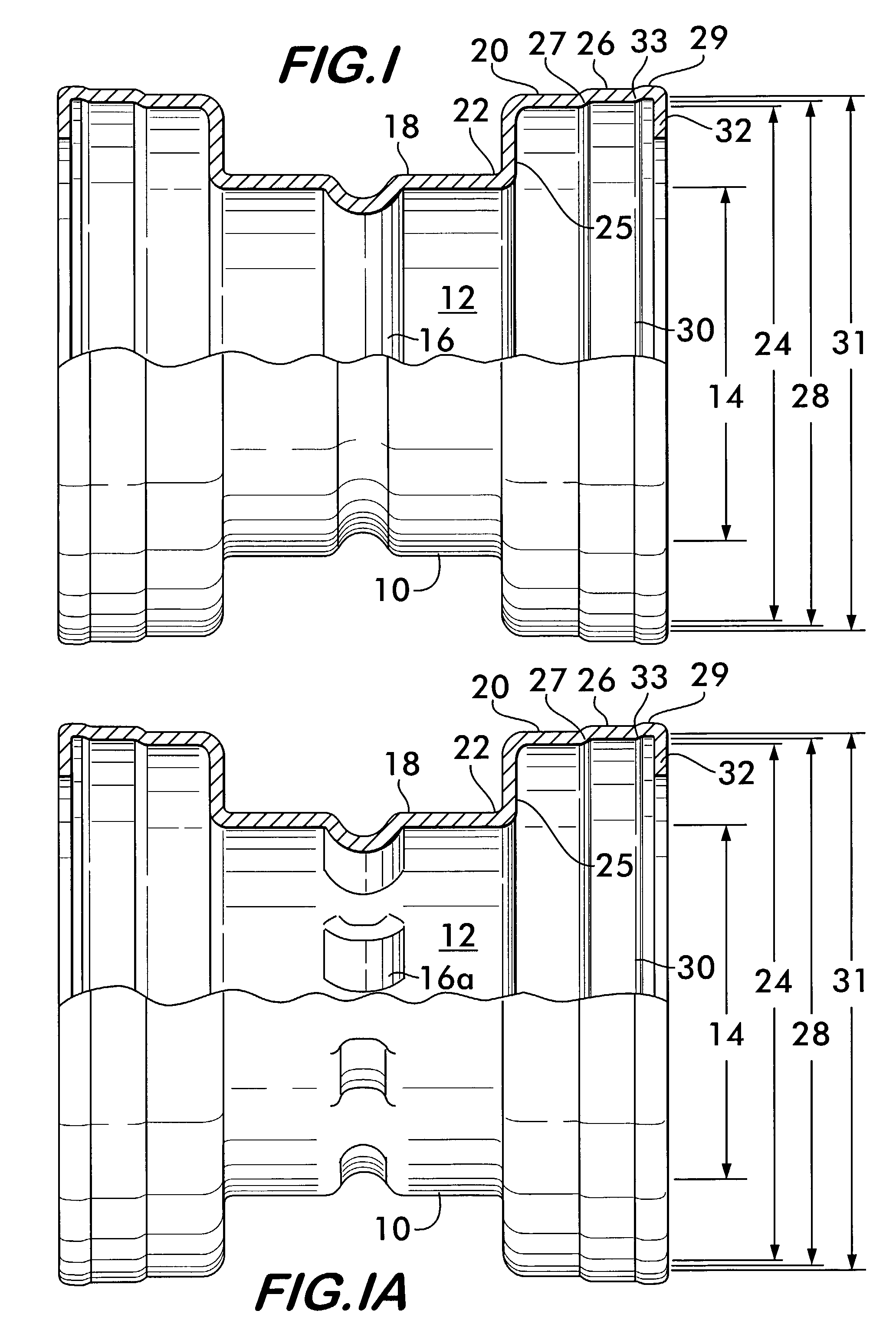

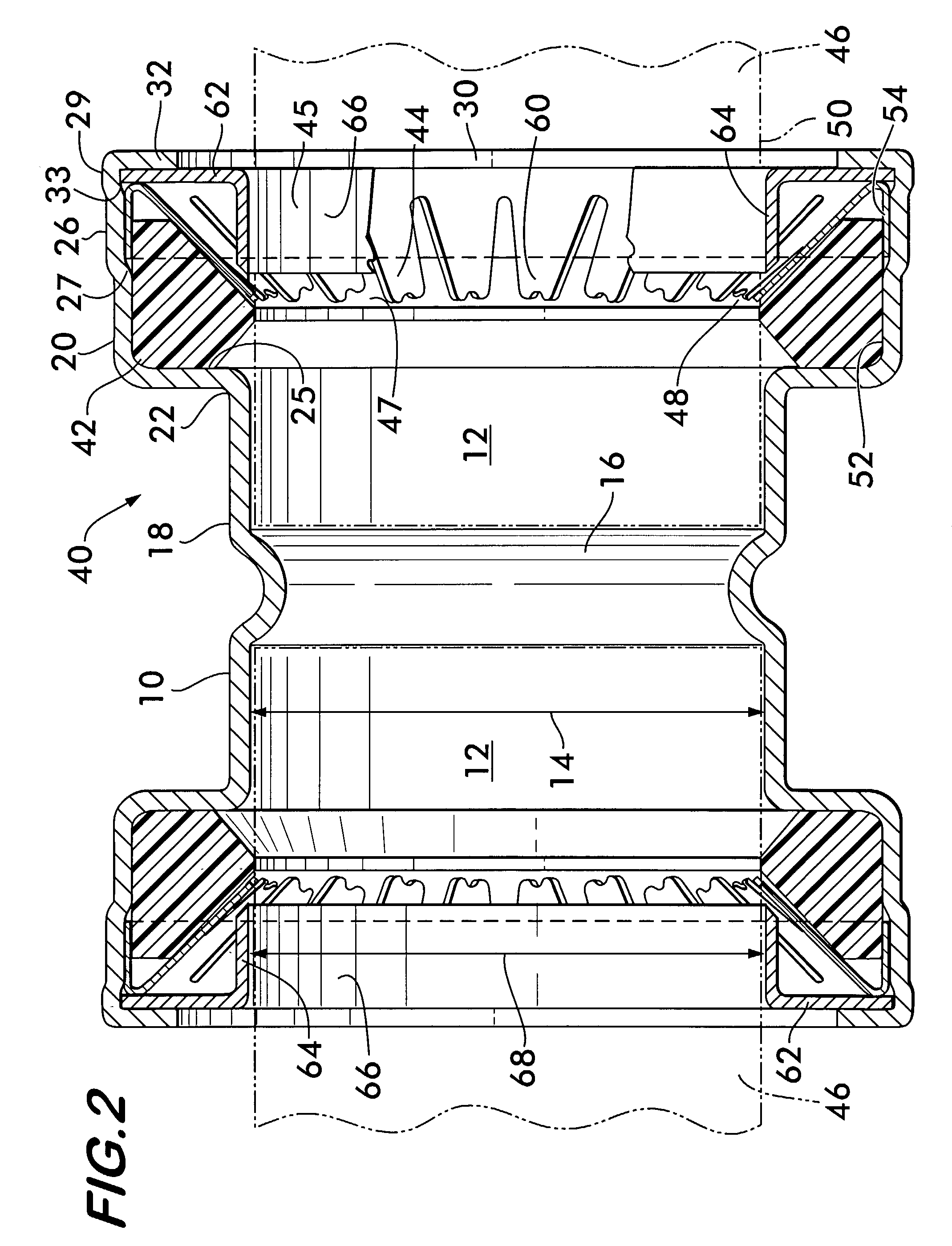

Triple-expanded mechanical pipe coupling derived from a standard fitting

InactiveUS7121593B2Increase economyImprove fluid flow and compactnessSleeve/socket jointsFluid pressure sealed jointsEngineeringFlange

A coupling for joining pipe segments together is disclosed. The coupling is derived from a standard fitting and has a housing with a socket and a first expanded region adjacent to the socket, a second expanded region adjacent to the first expanded region and a third expanded region adjacent to the second. A sealing member is positioned in the first expanded region, a retainer is positioned in the second expanded region and a support washer having transversely oriented radial and coaxial flanges is positioned adjacent to the retainer in the third expanded region. A lip turned inwardly on the second expanded region overlaps the radial flange and captures the support washer, retainer and sealing member within the coupling. The retainer has a plurality of radial teeth angularly oriented to engage a pipe and prevent its removal from the coupling.

Owner:VICTAULIC