Patents

Literature

1828 results about "Nand flash memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

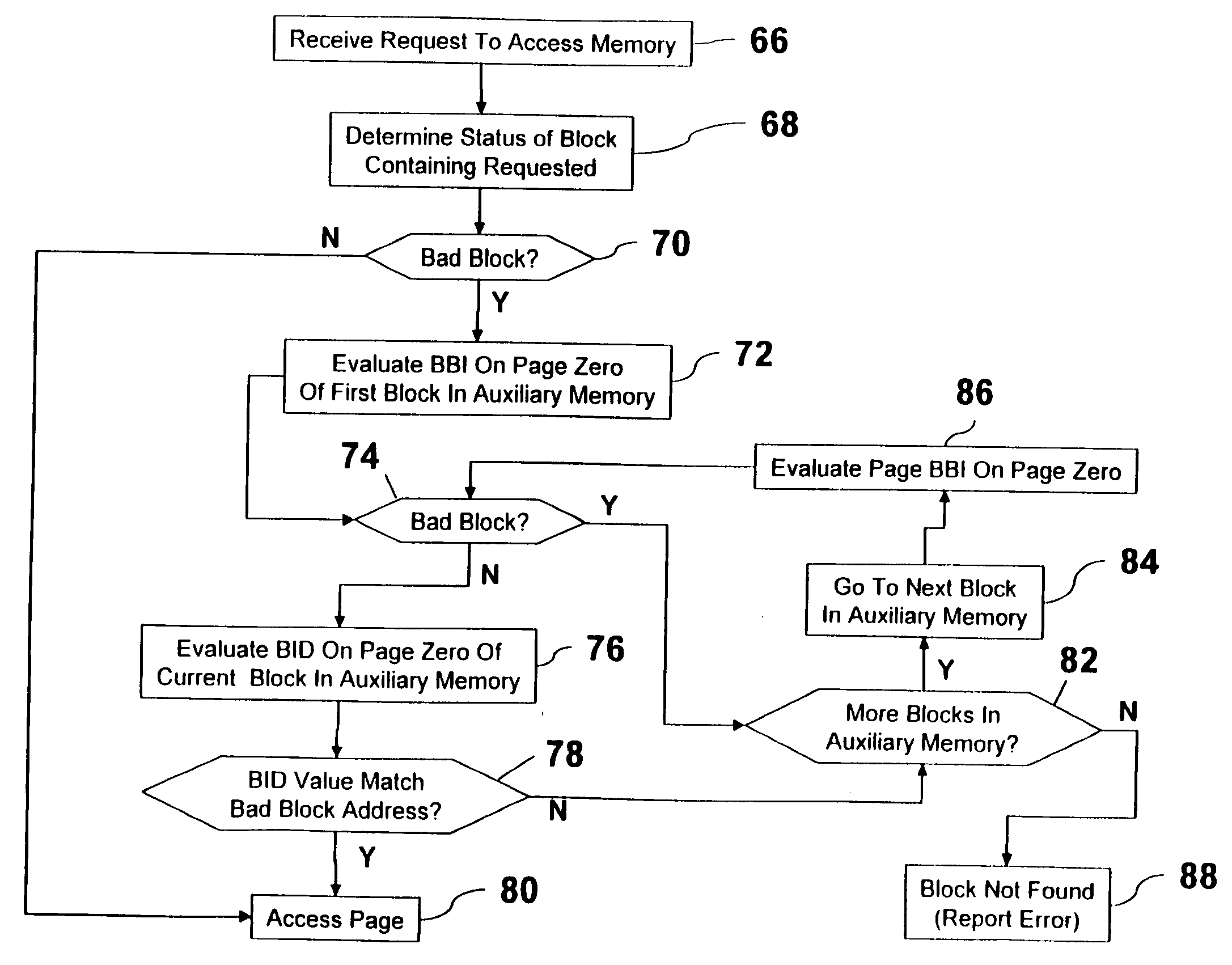

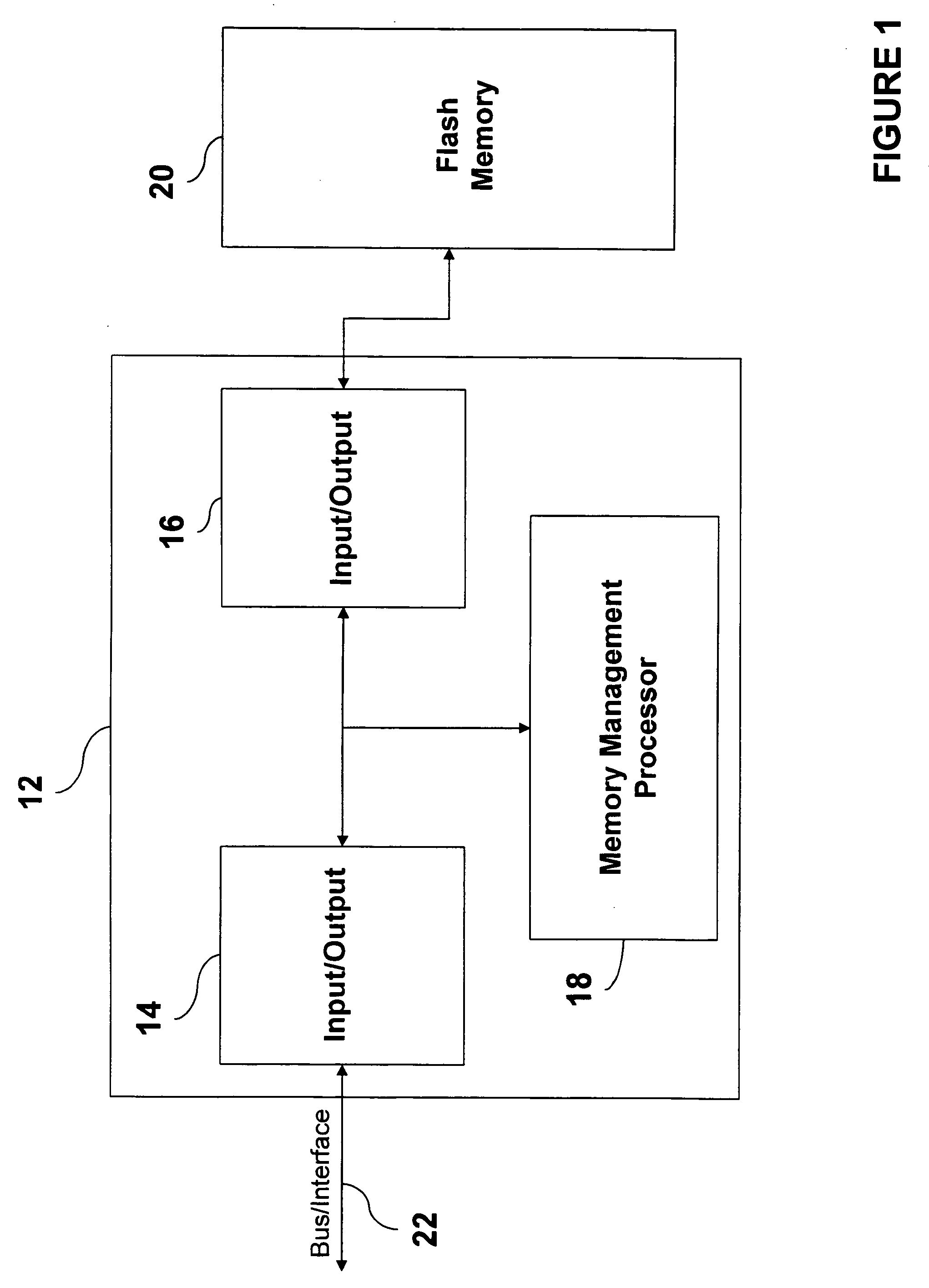

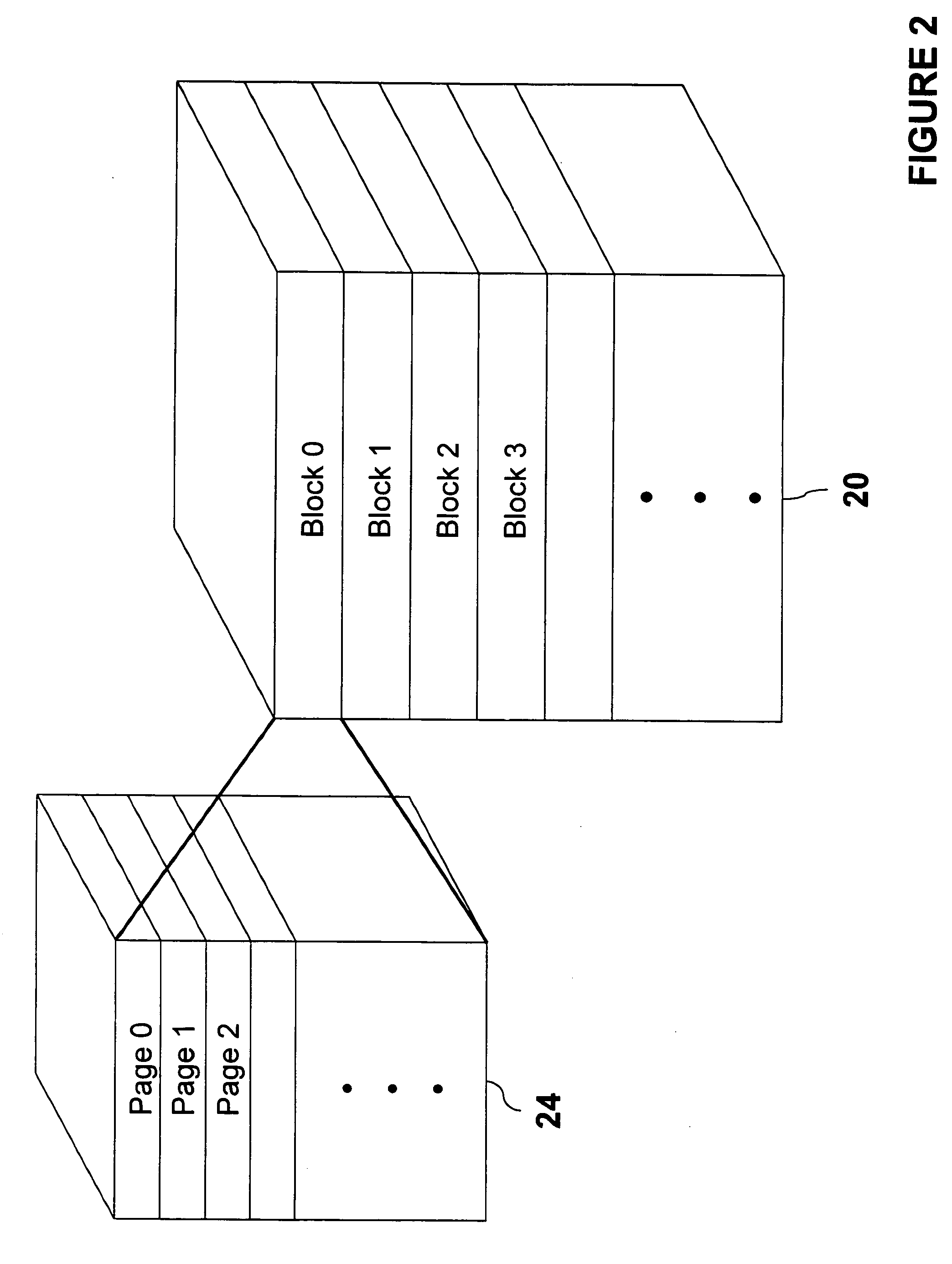

NAND flash memory management

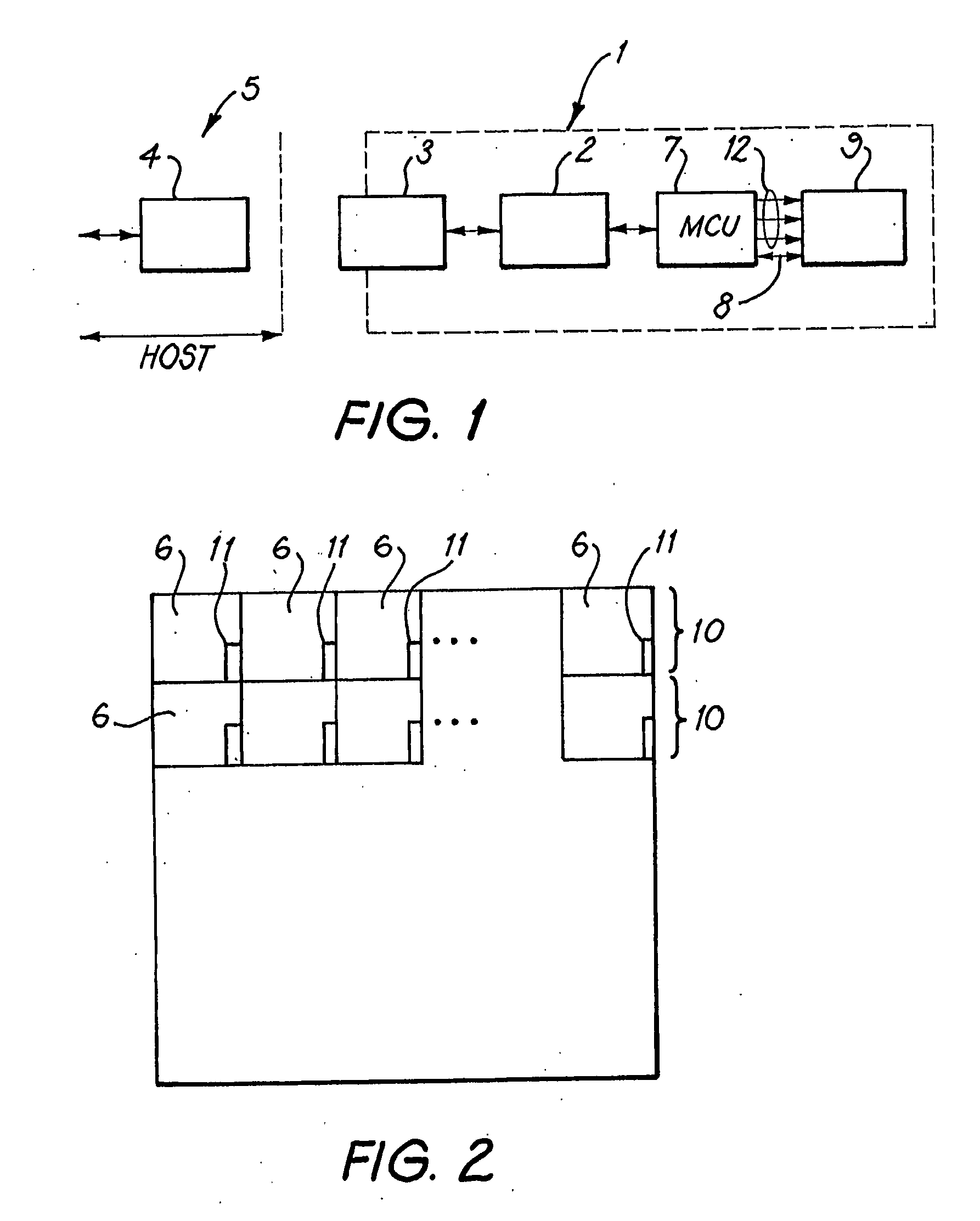

A memory controller is utilized to overcome NAND flash memory's propensity for comprising bad blocks of memory. The memory controller utilizes minimal hardware and is essentially transparent to a device requesting access to the NAND memory. A NAND flash memory device is configured to comprise a set of main blocks of memory and a set of auxiliary blocks of memory. Each block is divided into pages of memory and each page includes metadata. The metadata includes a block status indicator, indicating whether a block is good or bad. When receiving a request to access a page in the NAND flash memory, if the block in which the page resides is good, that block is accessed. If the block is bad, auxiliary memory is searched until a block containing the address of the bad block in its metadata is found. The found block is accessed in lieu of the bad block.

Owner:MICROSOFT TECH LICENSING LLC

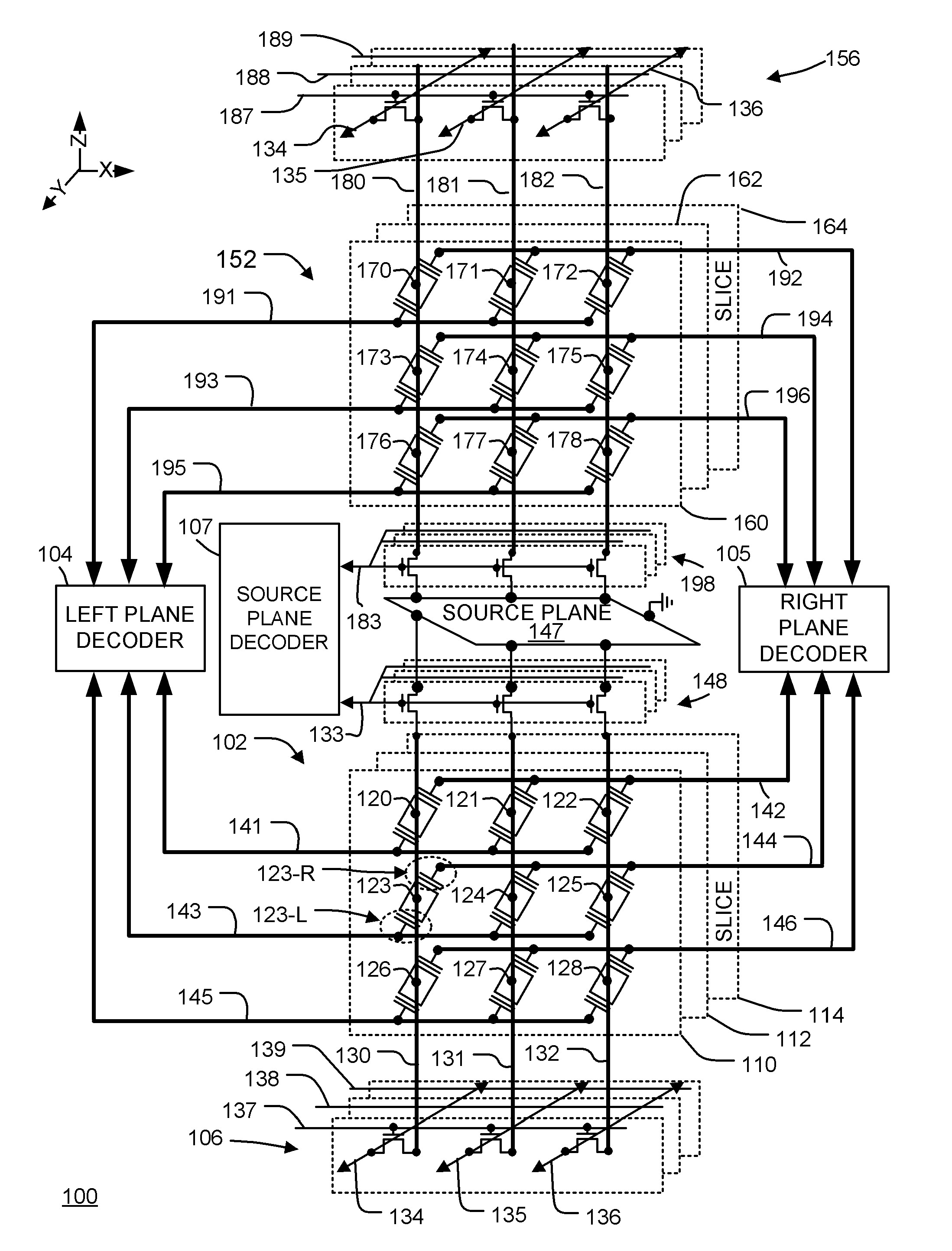

3D two-bit-per-cell NAND flash memory

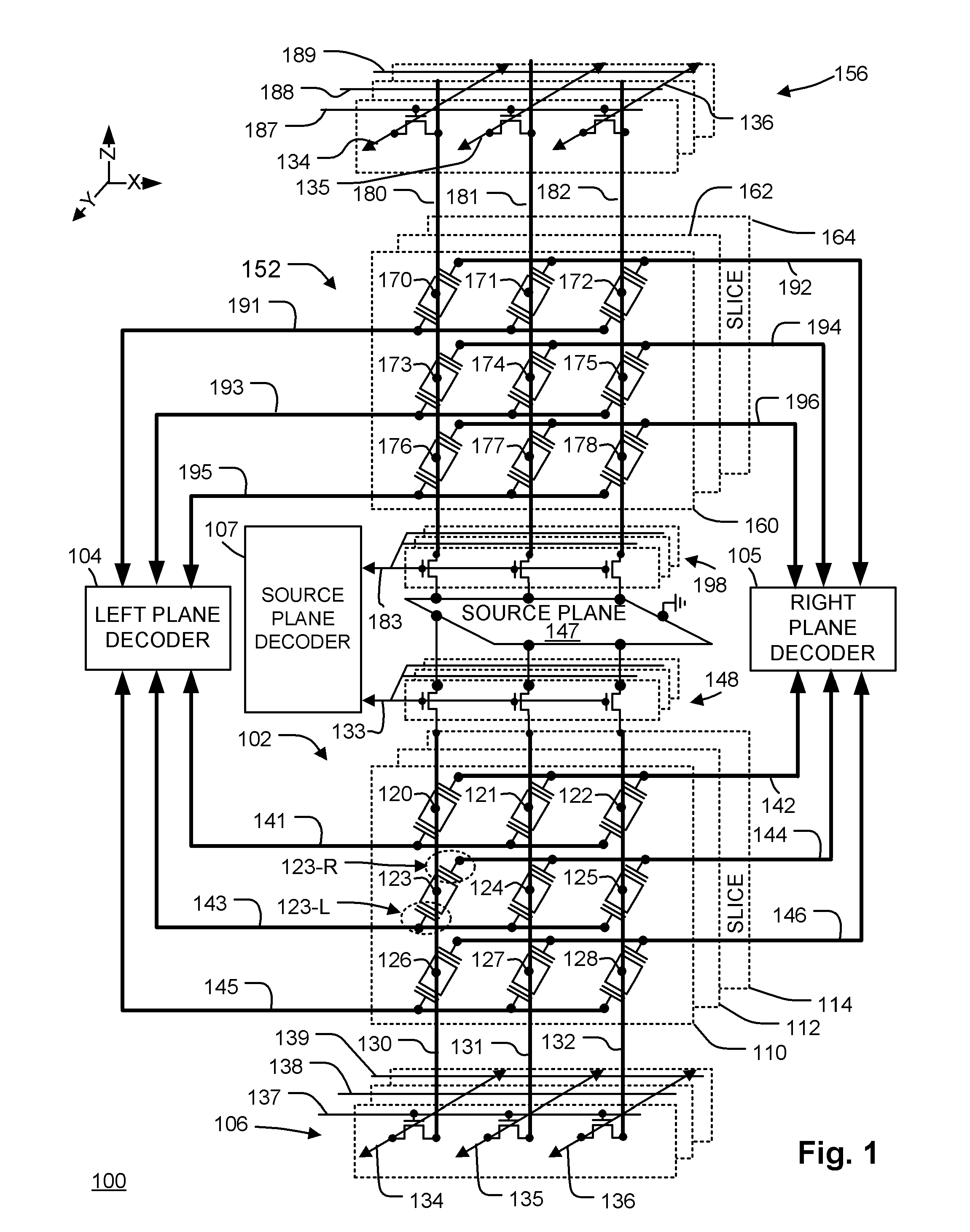

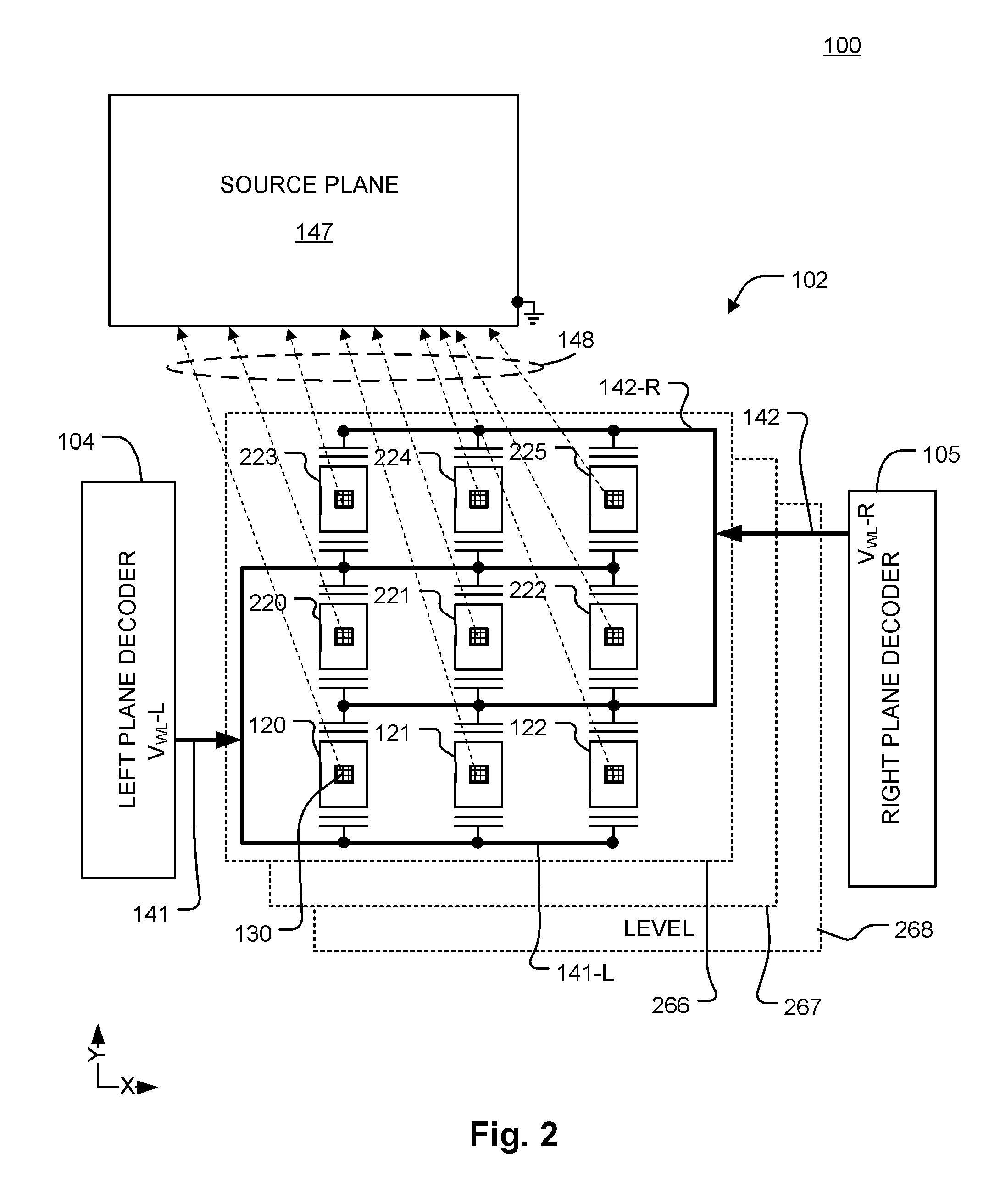

ActiveUS20110286283A1Few stepsHigh densitySolid-state devicesRead-only memoriesSource planePower flow

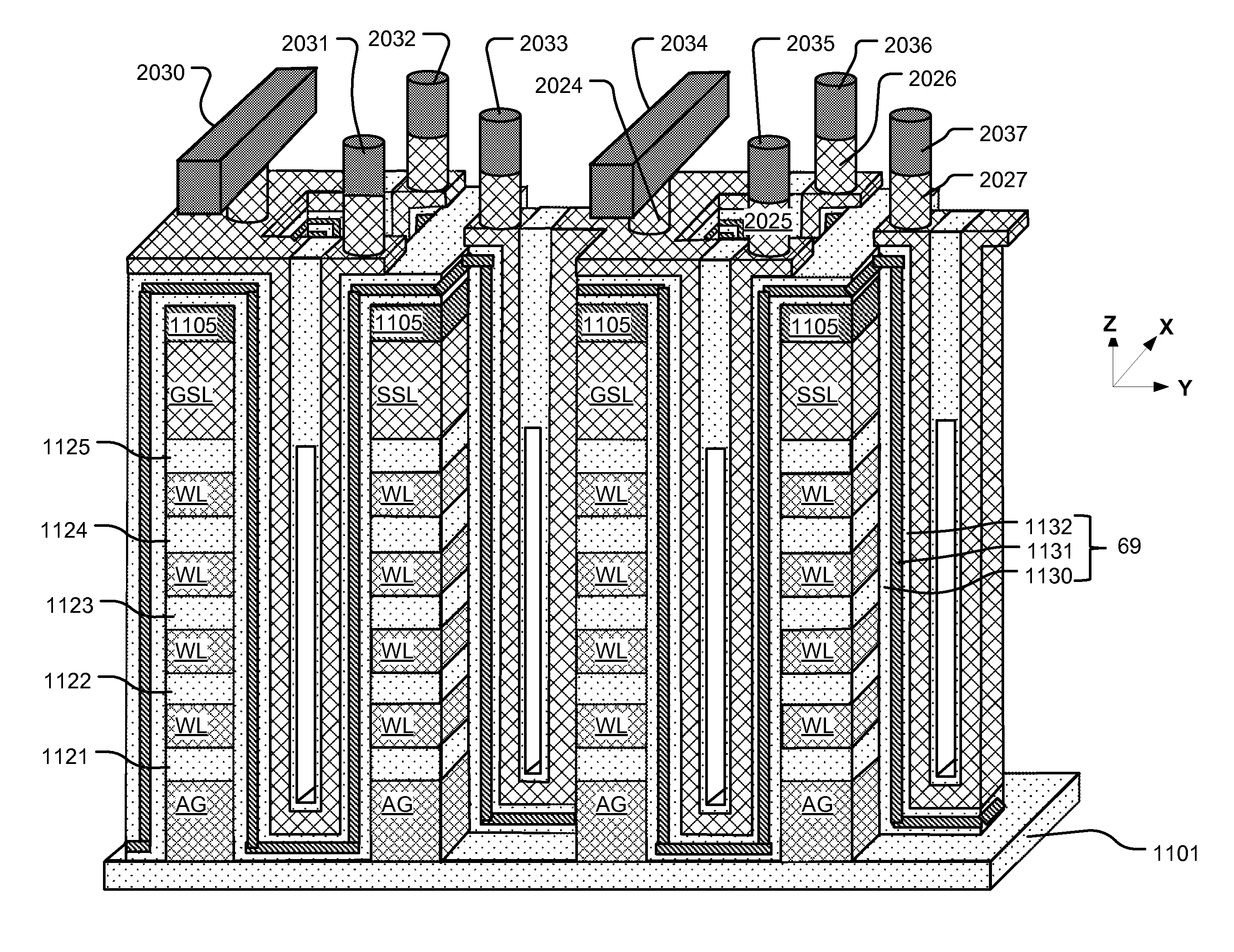

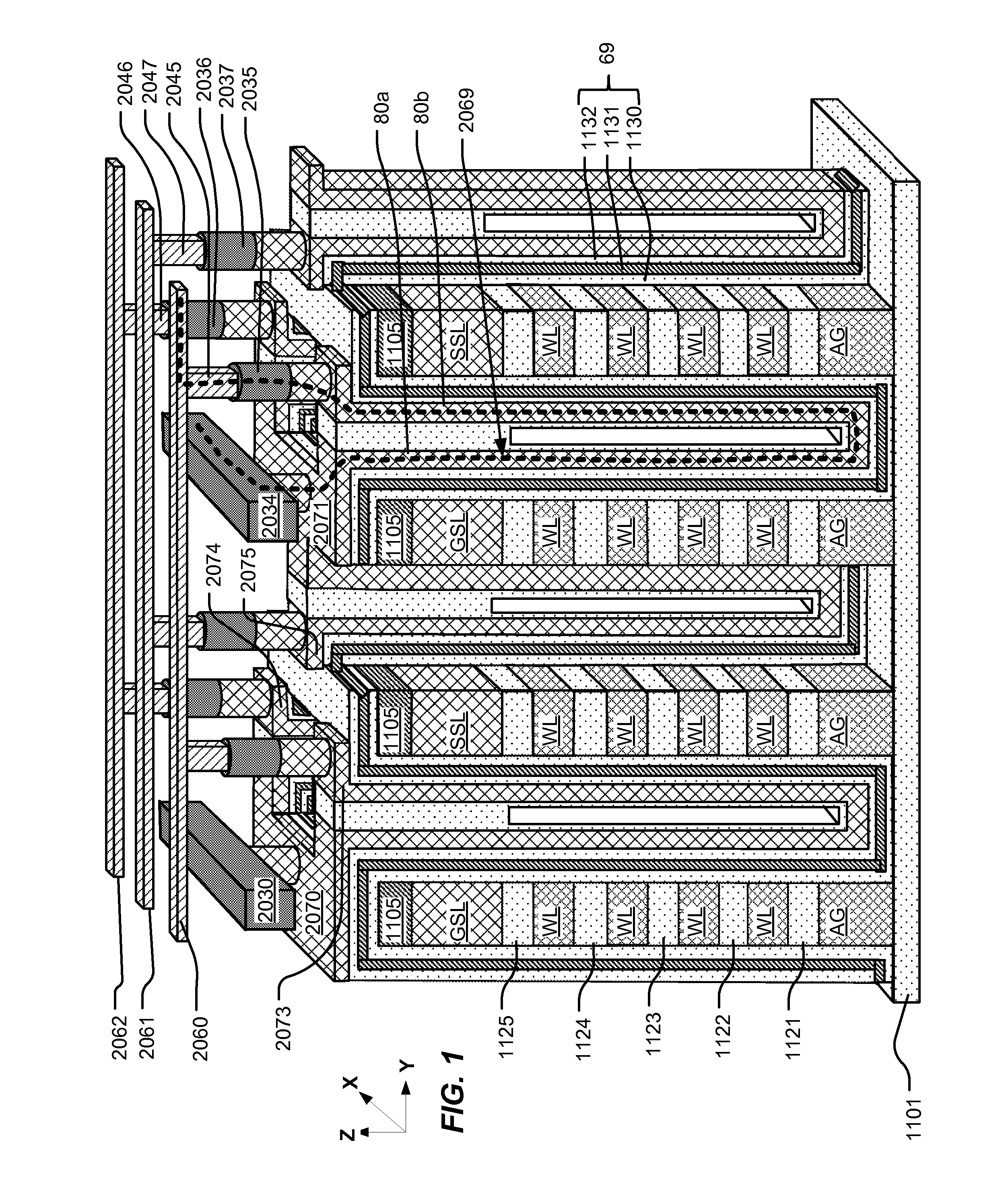

A 3D memory device is described which includes bottom and top memory cubes having respective arrays of vertical NAND string structures. A common source plane comprising a layer of conductive material is between the top and bottom memory cubes. The source plane is supplied a bias voltage such as ground, and is selectively coupled to an end of the vertical NAND string structures of the bottom and top memory cubes. Memory cells in a particular memory cube are read using current through the particular vertical NAND string between the source plane and a corresponding bit line coupled to another end of the particular vertical NAND string.

Owner:MACRONIX INT CO LTD

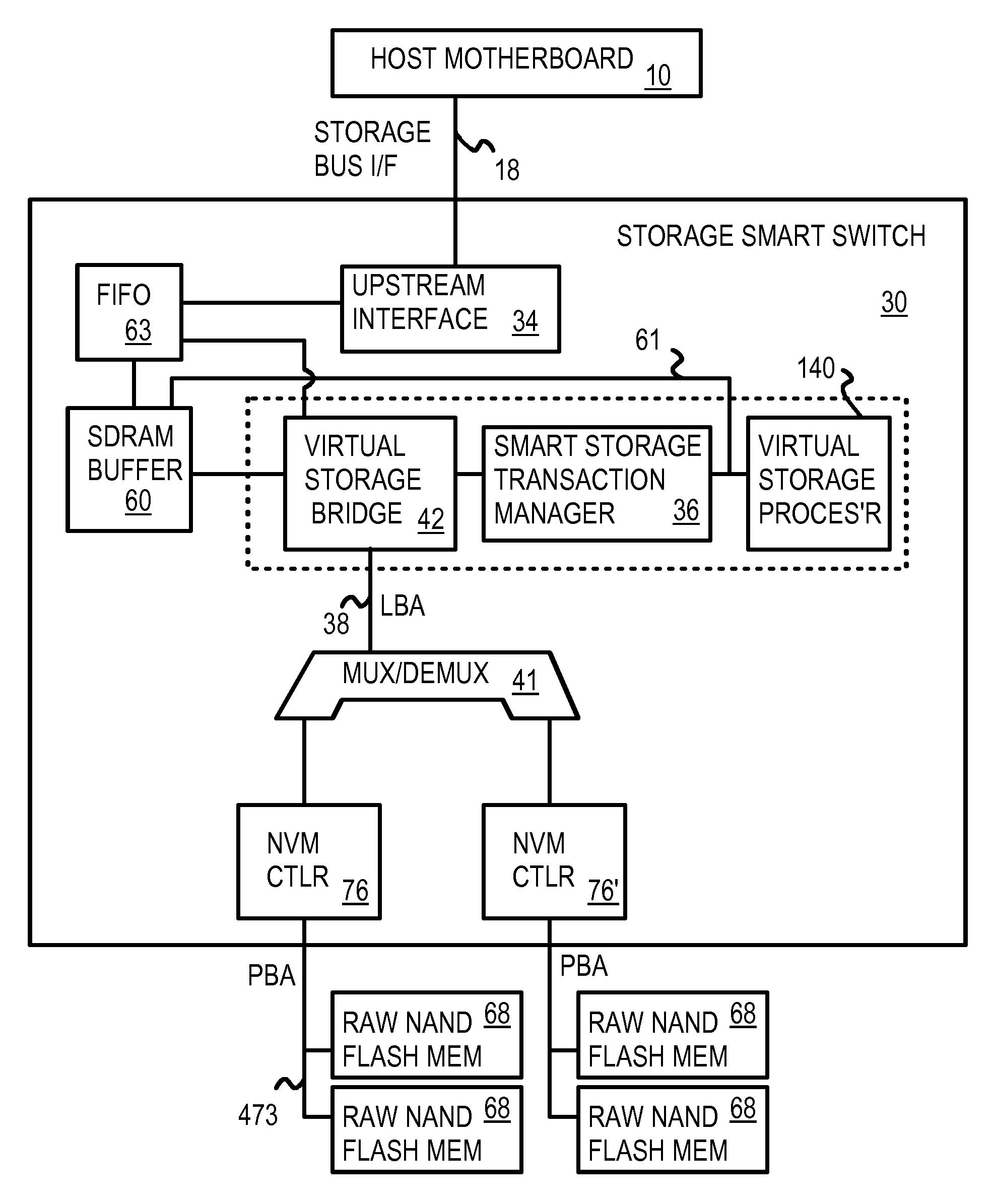

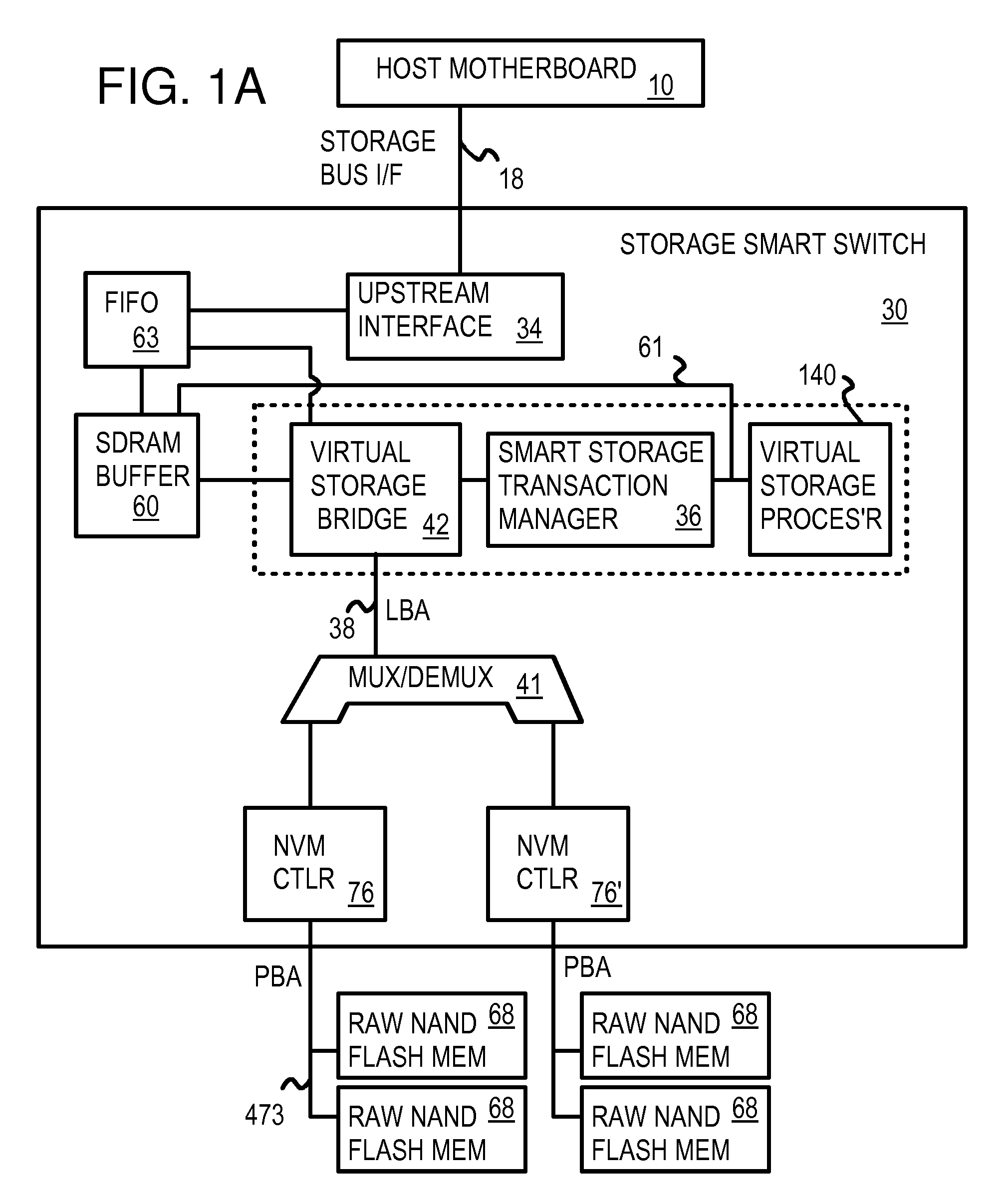

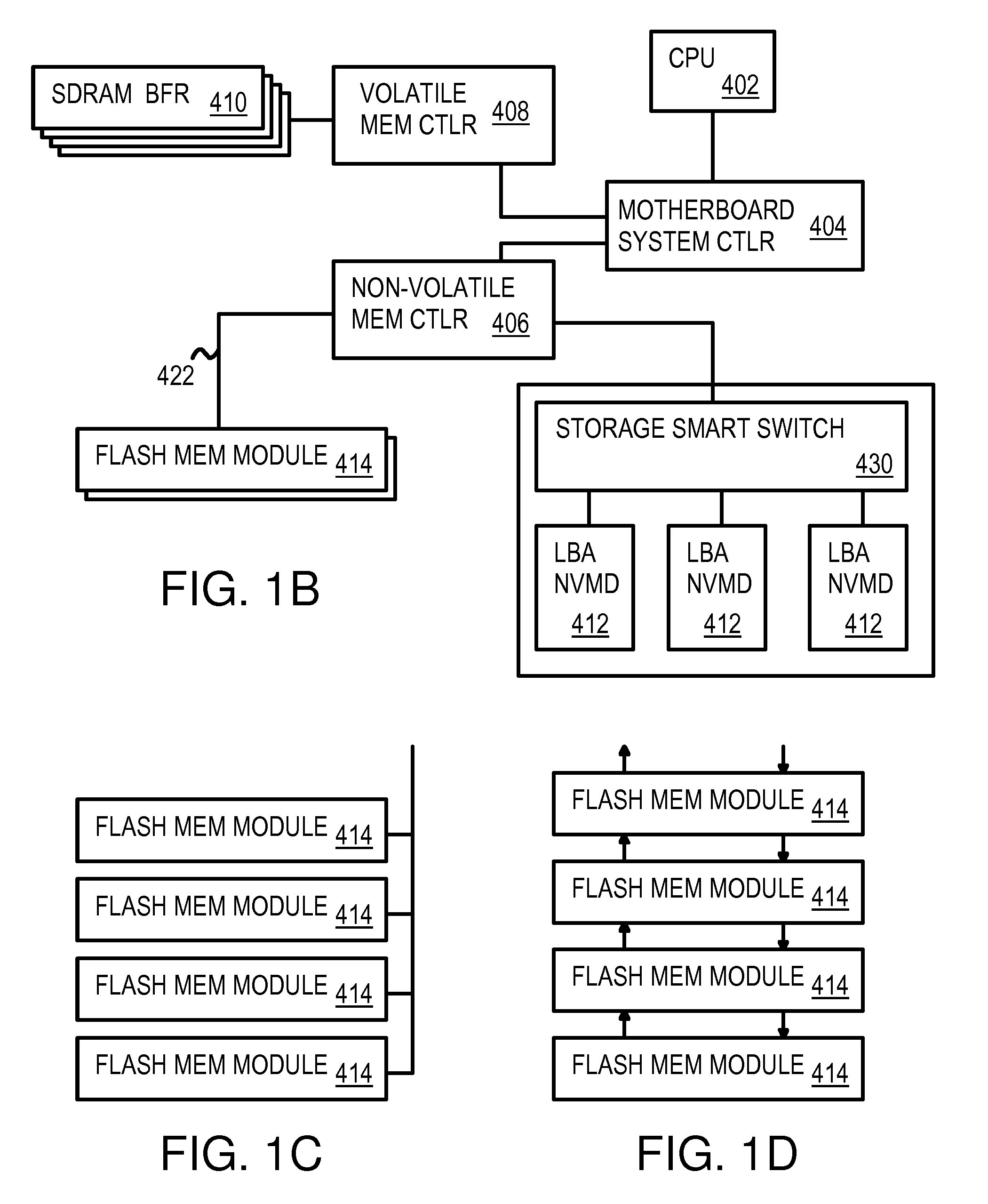

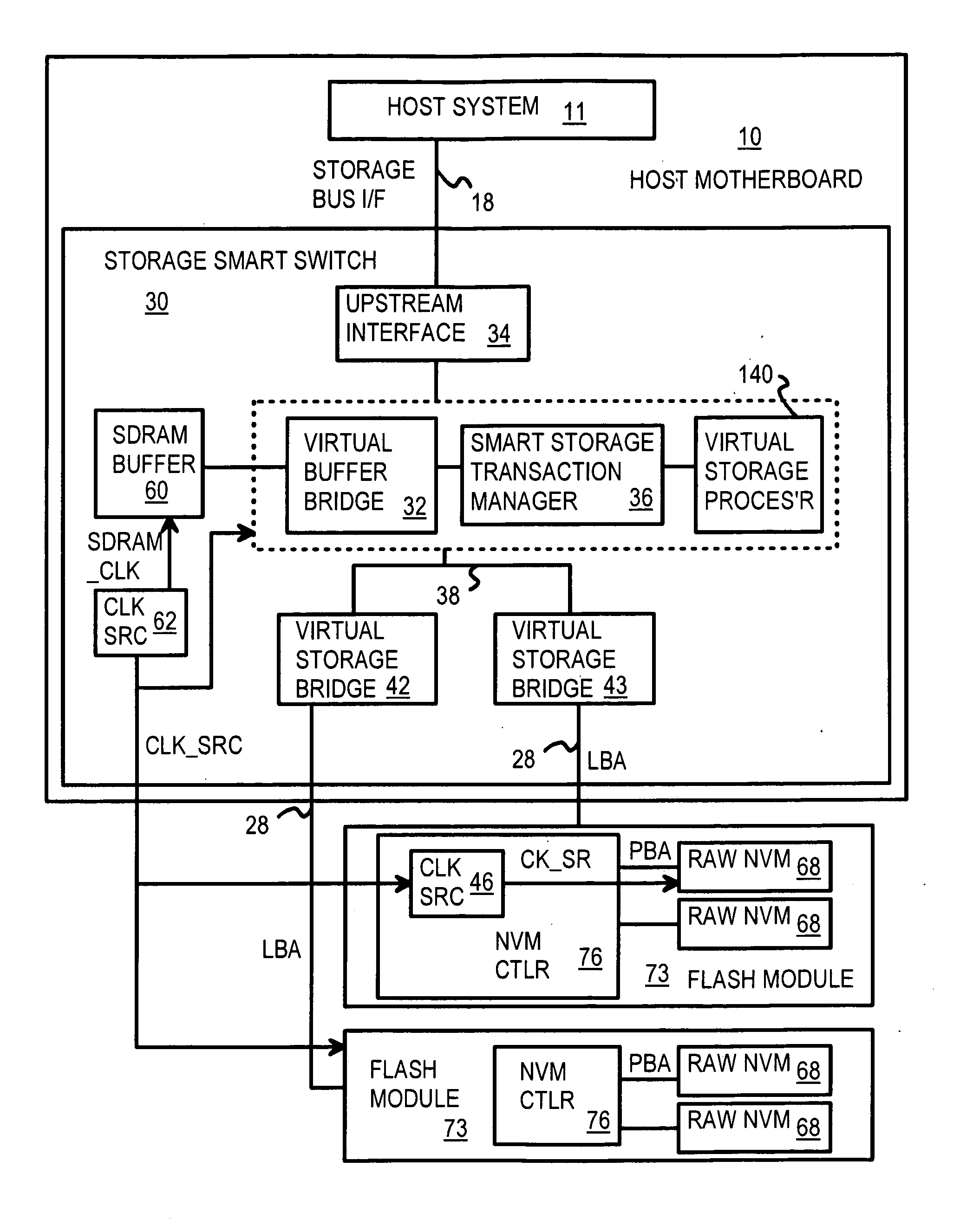

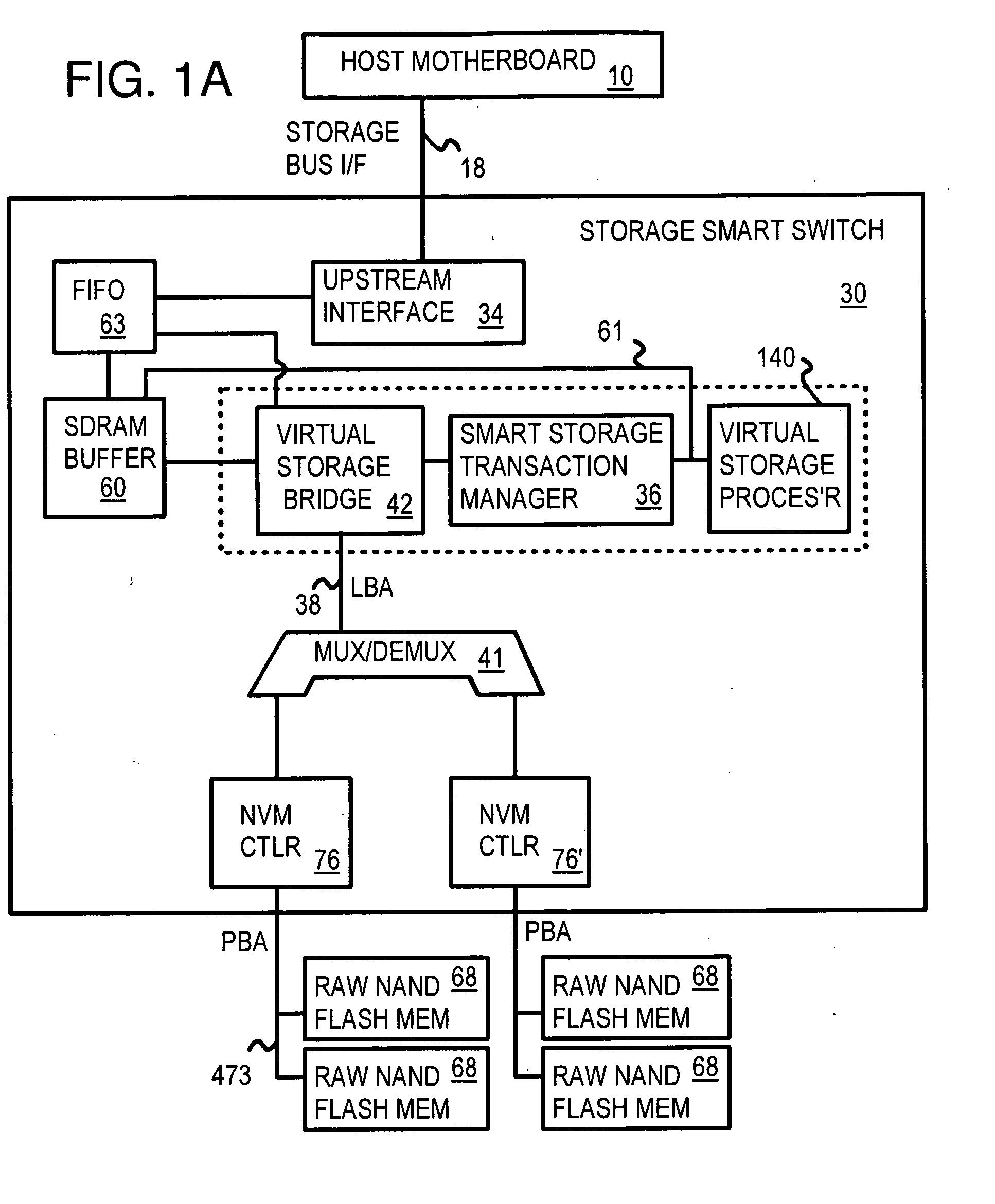

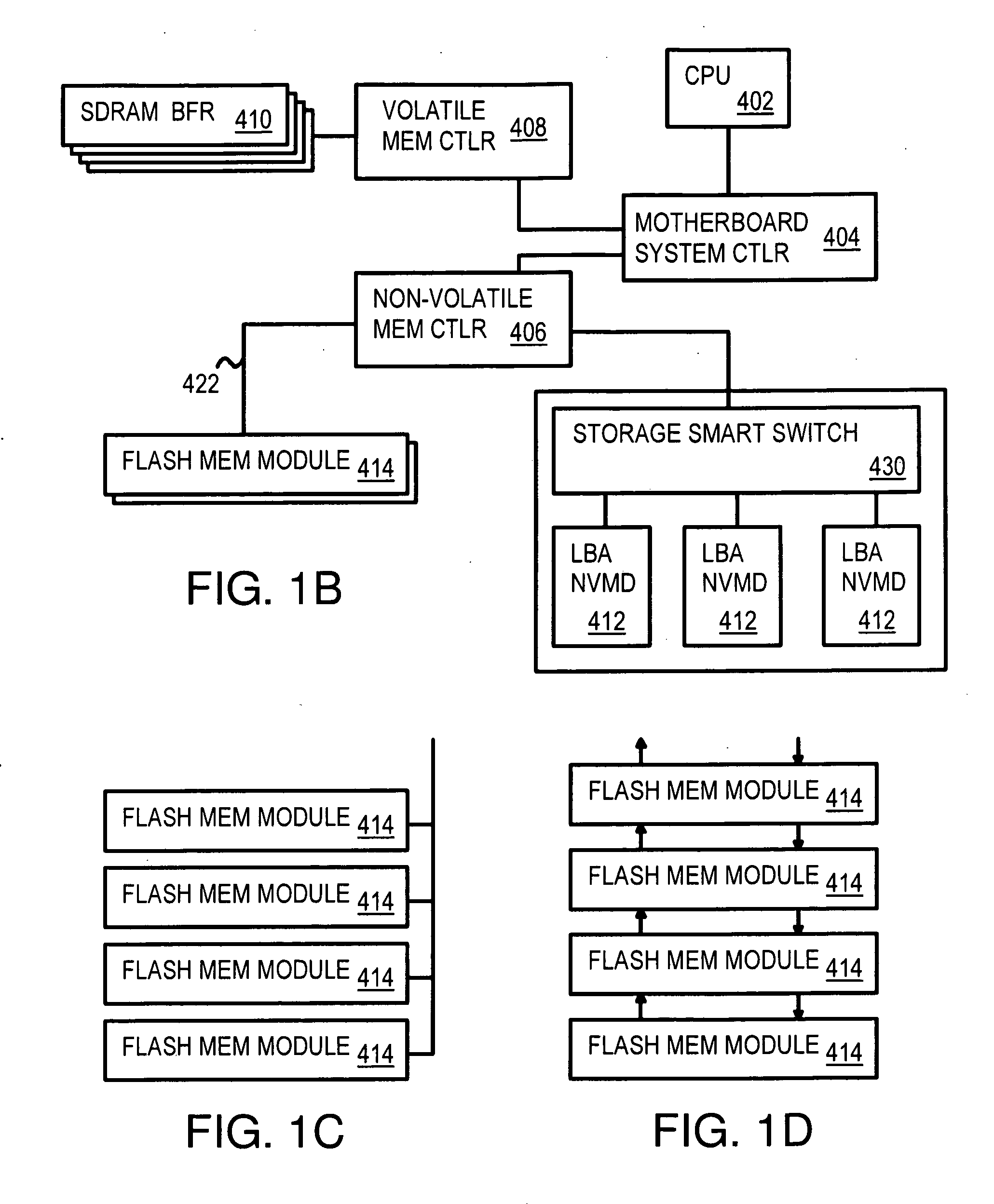

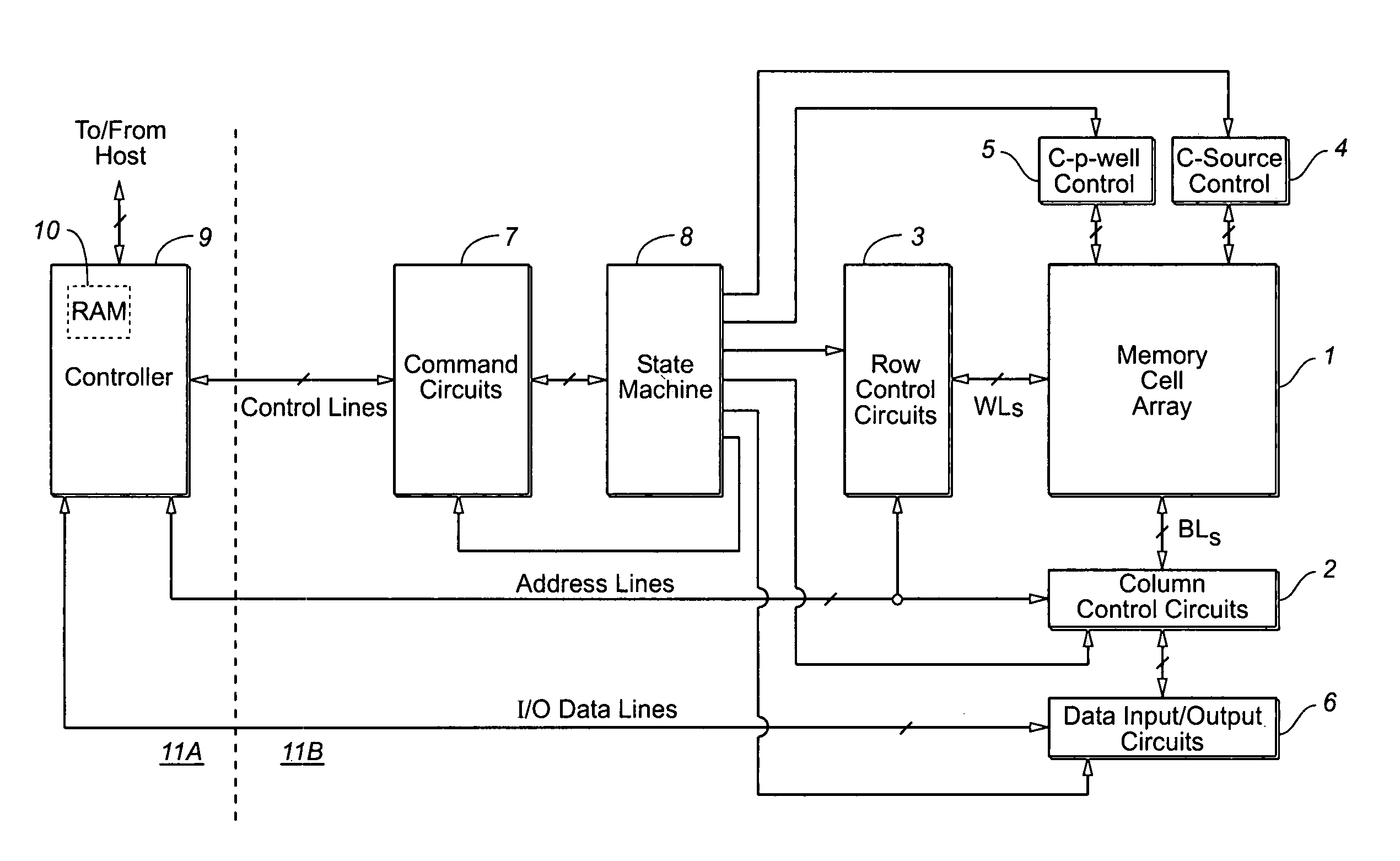

Command Queuing Smart Storage Transfer Manager for Striping Data to Raw-NAND Flash Modules

ActiveUS20090037652A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingHost machine

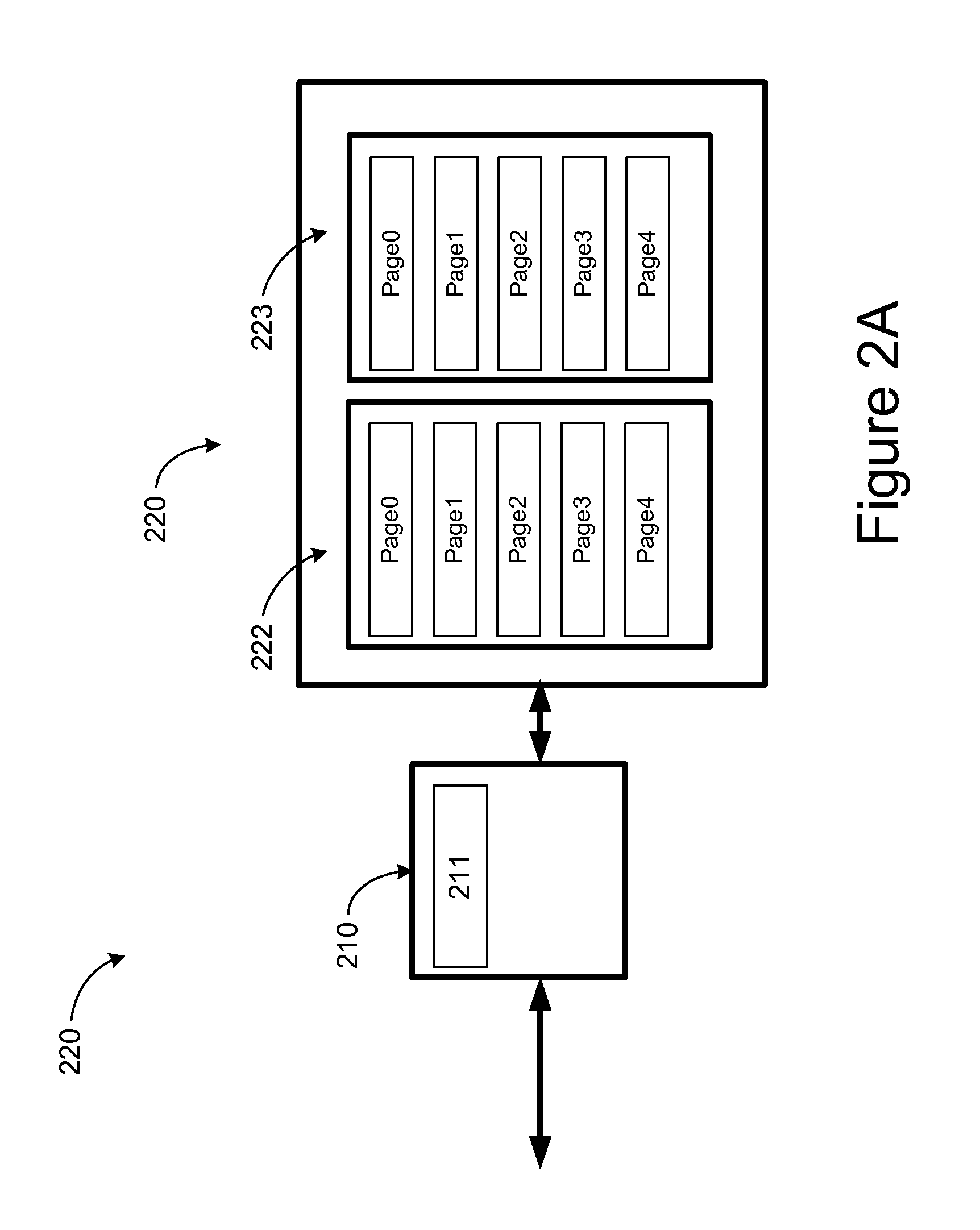

A flash module has raw-NAND flash memory chips accessed over a physical-block address (PBA) bus by a NVM controller. The NVM controller is on the flash module or on a system board for a solid-state disk (SSD). The NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Data striping and interleaving among multiple channels of the flash modules is controlled at a high level by a smart storage transaction manager, while further interleaving and remapping within a channel may be performed by the NVM controllers. A SDRAM buffer is used by a smart storage switch to cache host data before writing to flash memory. A Q-R pointer table stores quotients and remainders of division of the host address. The remainder points to a location of the host data in the SDRAM. A command queue stores Q, R for host commands.

Owner:SUPER TALENT TECH CORP

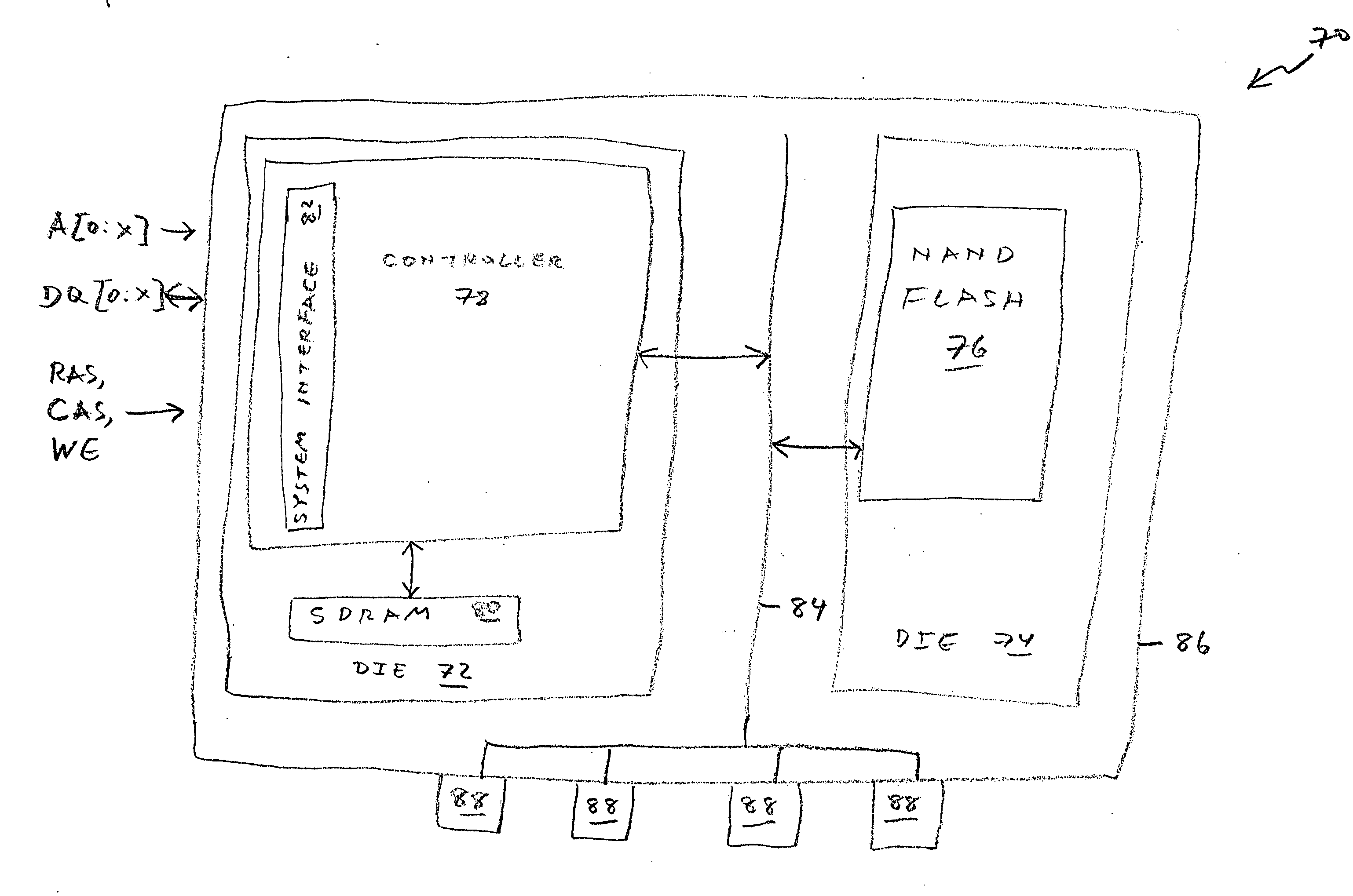

SDRAM memory device with an embedded NAND flash controller

A memory device includes two dies. A first memory is fabricated on one die. A controller of the first memory is fabricated on the other die. Also fabricated on the other die is another component, such as a second memory, that communicates with a host system using a plurality of signals different from the signals used by the first memory. The device includes a single interface for communicating with the host system using only the respective signals of the second component. In a most preferred embodiment, the first memory is a NAND flash memory and the second memory is a SDRAM.

Owner:INNOVATIVE MEMORY SYST INC

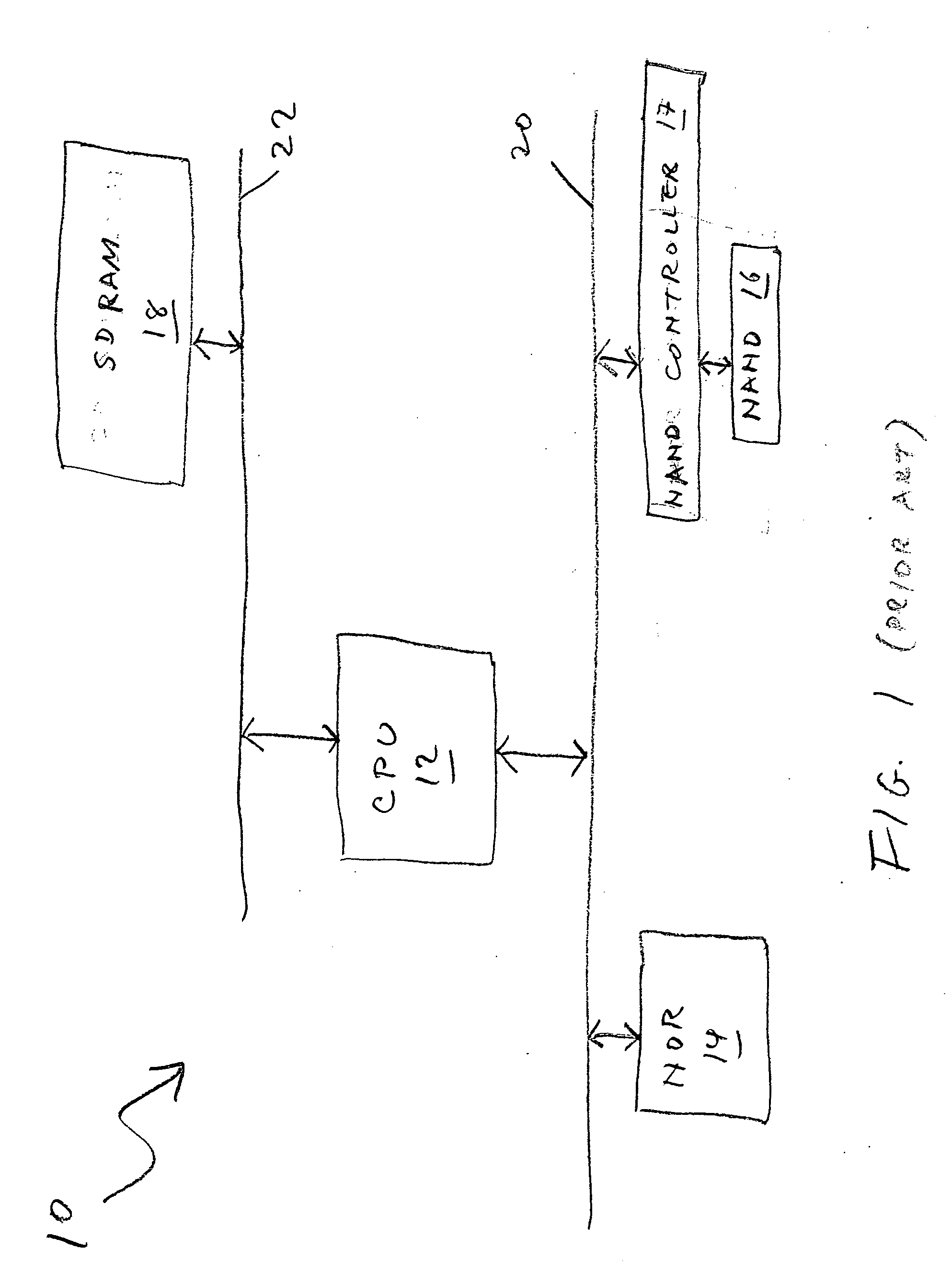

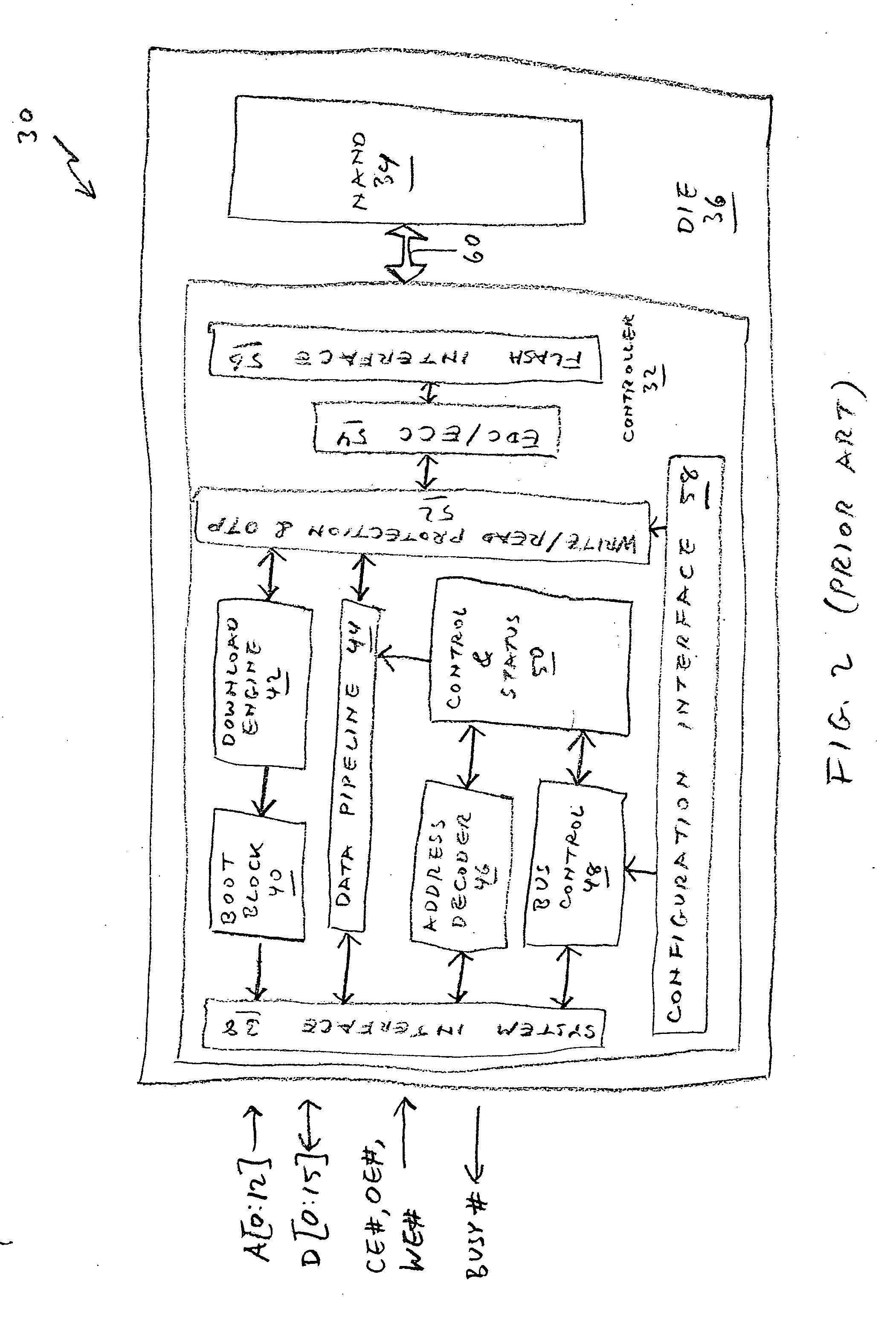

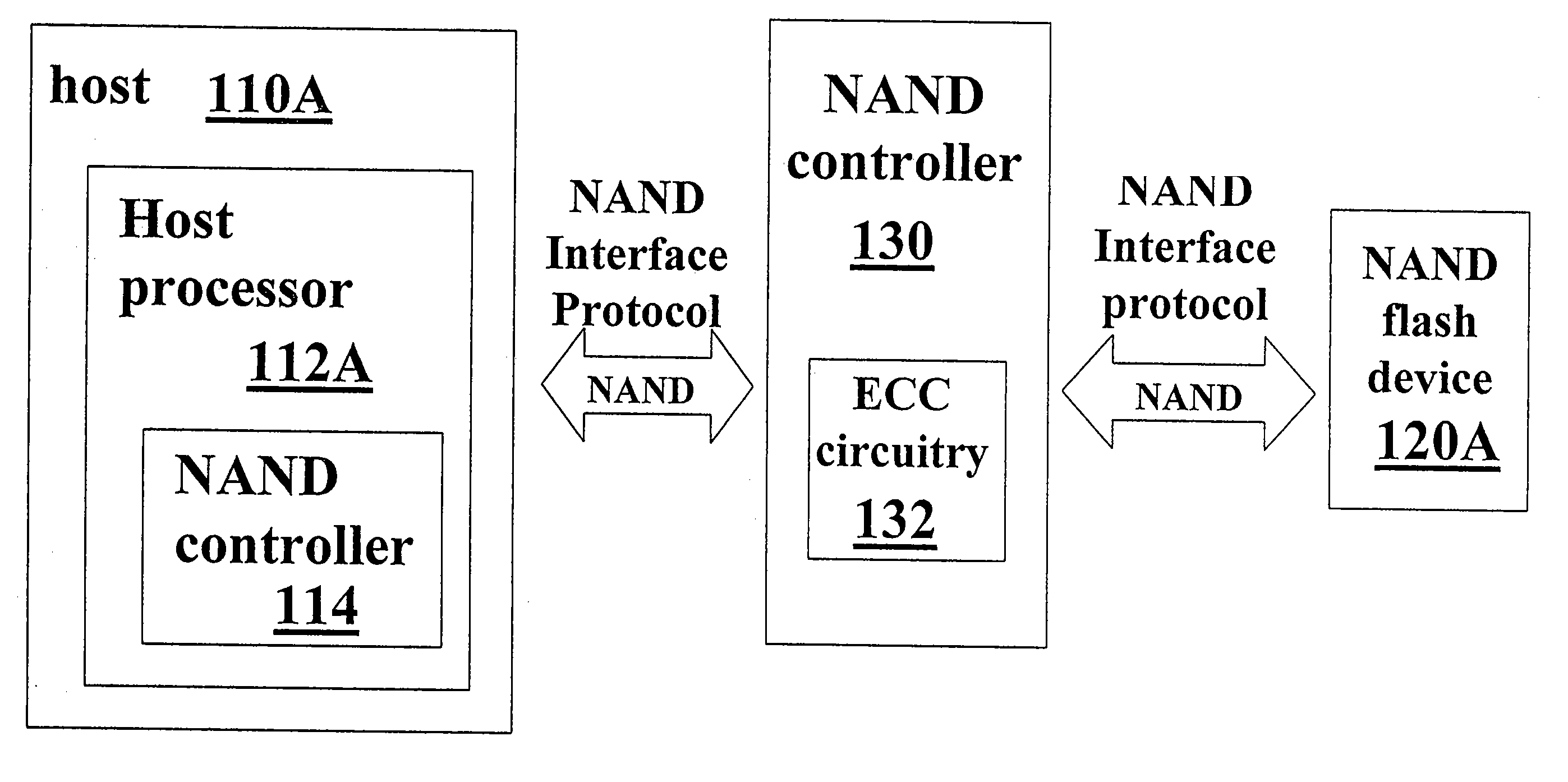

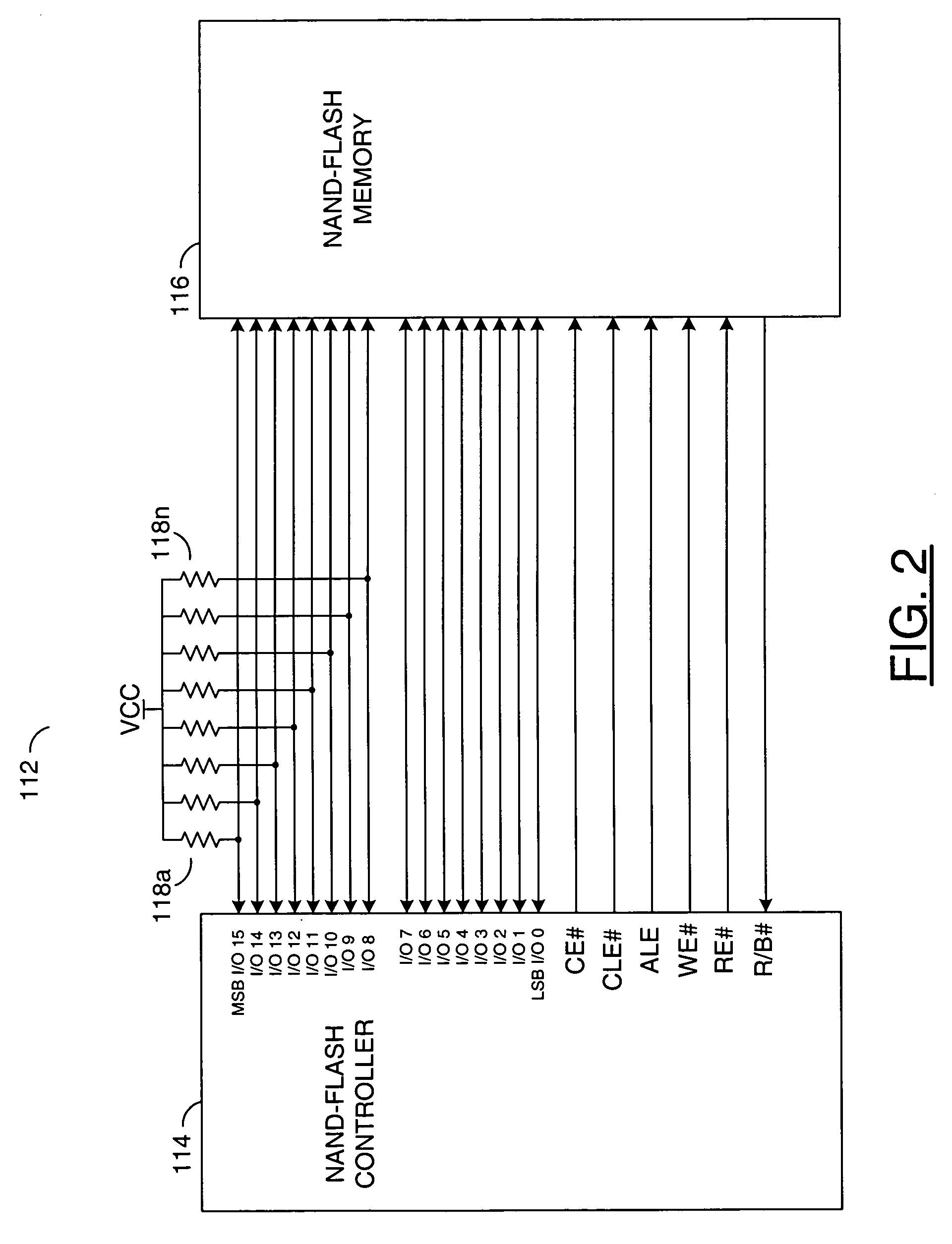

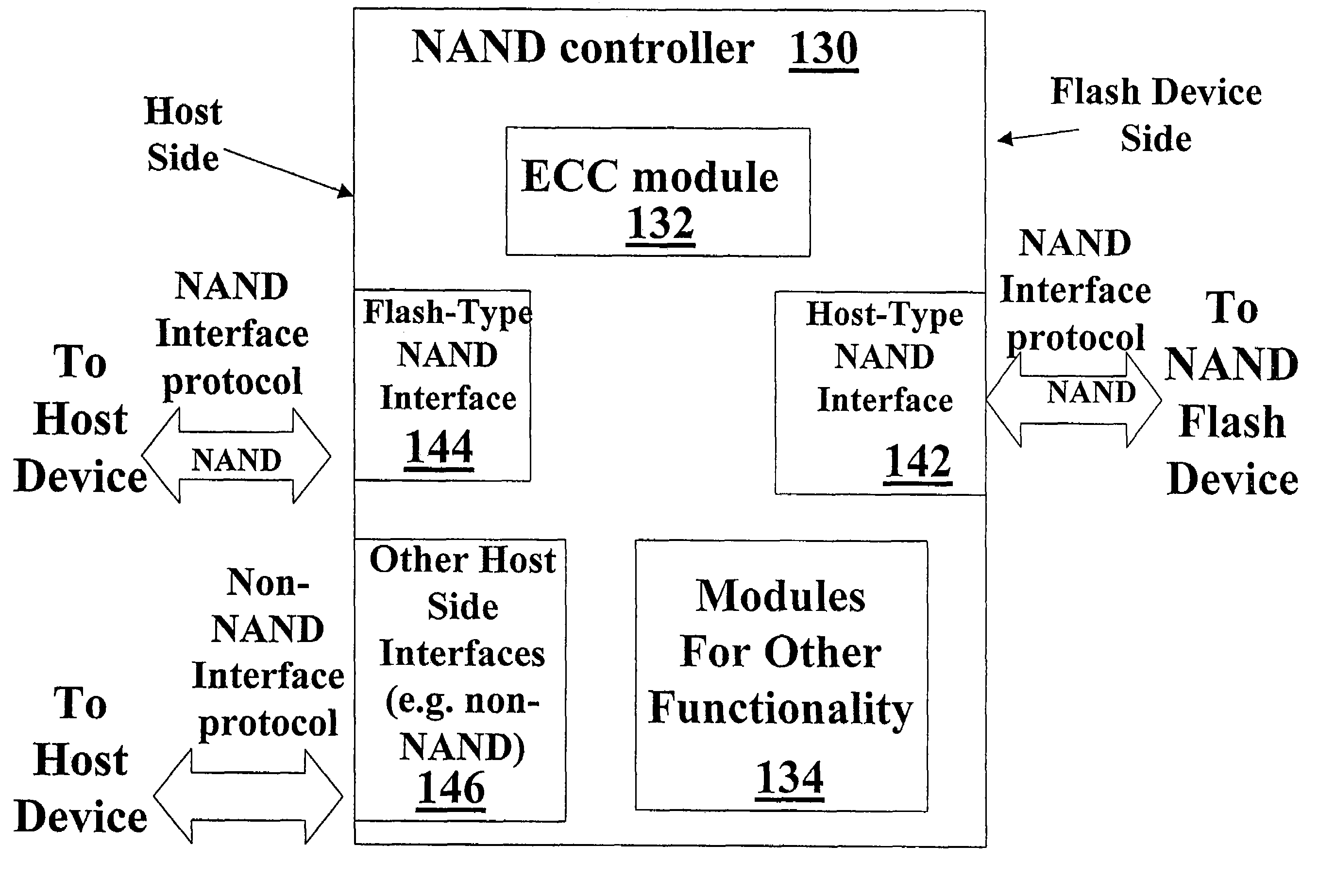

NAND Flash Memory Controller Exporting a NAND Interface

ActiveUS20100023800A1Satisfies needMemory architecture accessing/allocationData representation error detection/correctionHost typeHost machine

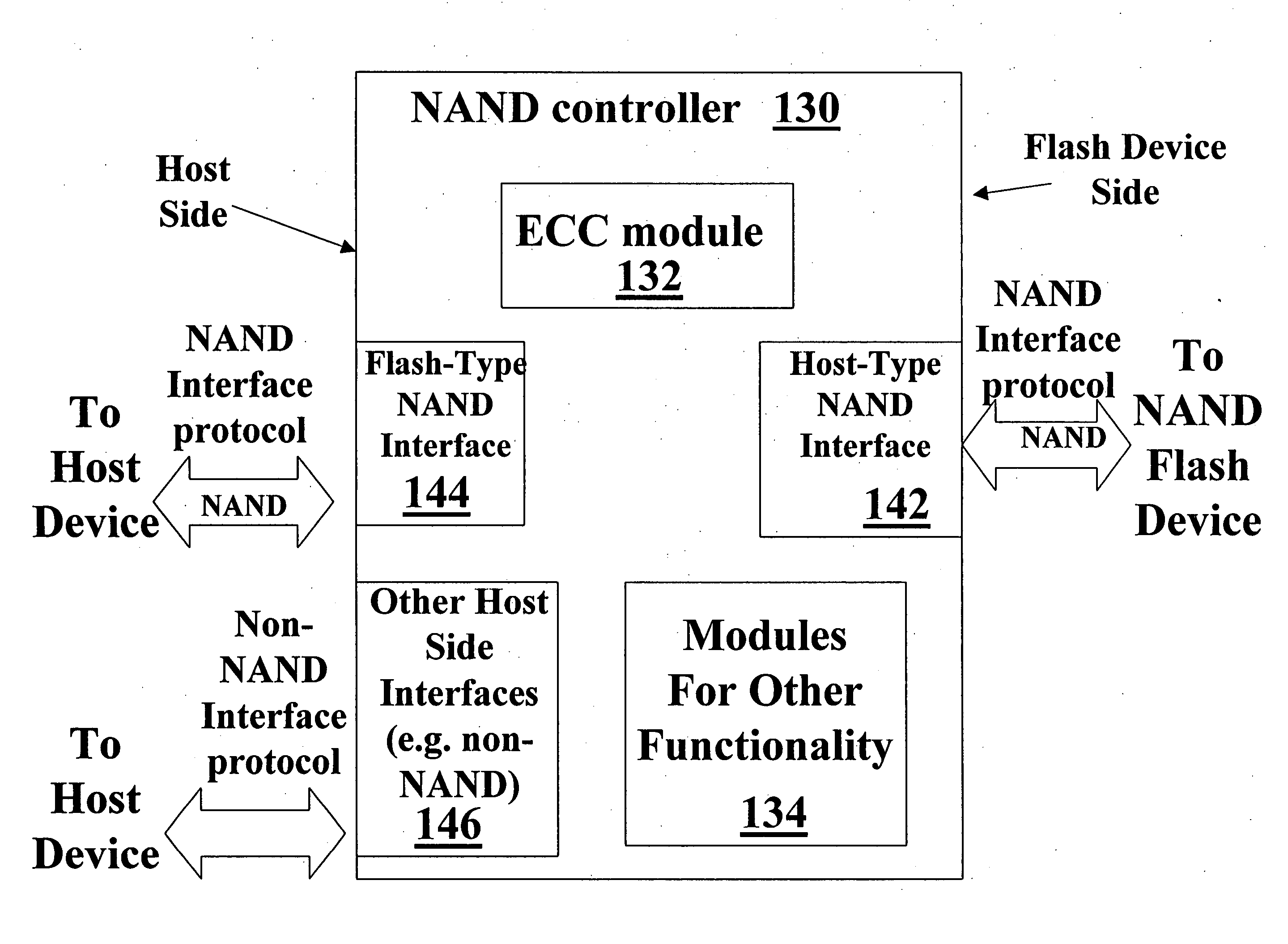

A NAND controller for interfacing between a host device and a flash memory device (e.g., a NAND flash memory device) fabricated on a flash die is disclosed. In some embodiments, the presently disclosed NAND controller includes electronic circuitry fabricated on a controller die, the controller die being distinct from the flash die, a first interface (e.g. a host-type interface, for example, a NAND interface) for interfacing between the electronic circuitry and the flash memory device, and a second interface (e.g. a flash-type interface) for interfacing between the controller and the host device, wherein the second interface is a NAND interface. According to some embodiments, the first interface is an inter-die interface. According to some embodiments, the first interface is a NAND interface. Systems including the presently disclosed NAND controller are also disclosed. Methods for assembling the aforementioned systems, and for reading and writing data using NAND controllers are also disclosed.

Owner:INNOVATIVE MEMORY SYST INC

Command Queuing Smart Storage Transfer Manager for Striping Data to Raw-NAND Flash Modules

InactiveUS20090204872A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingComputer module

A flash module has raw-NAND flash memory chips accessed over a physical-block address (PBA) bus by a NVM controller. The NVM controller is on the flash module or on a system board for a solid-state disk (SSD). The NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Data striping and interleaving among multiple channels of the flash modules is controlled at a high level by a smart storage transaction manager, while further interleaving and remapping within a channel may be performed by the NVM controllers. A SDRAM buffer is used by a smart storage switch to cache host data before writing to flash memory. A Q-R pointer table stores quotients and remainders of division of the host address. The remainder points to a location of the host data in the SDRAM. A command queue stores Q, R for host commands.

Owner:SUPER TALENT ELECTRONICS

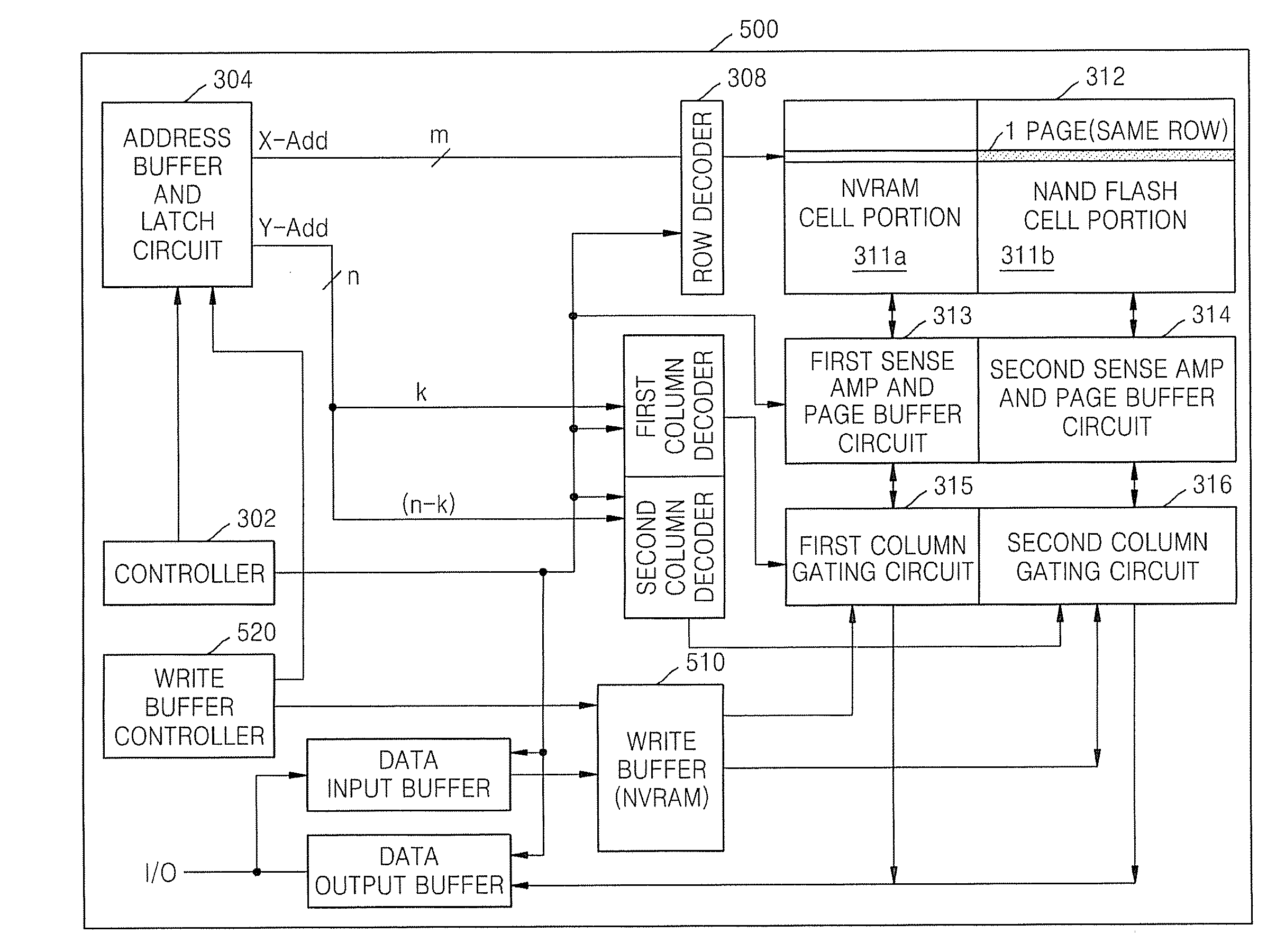

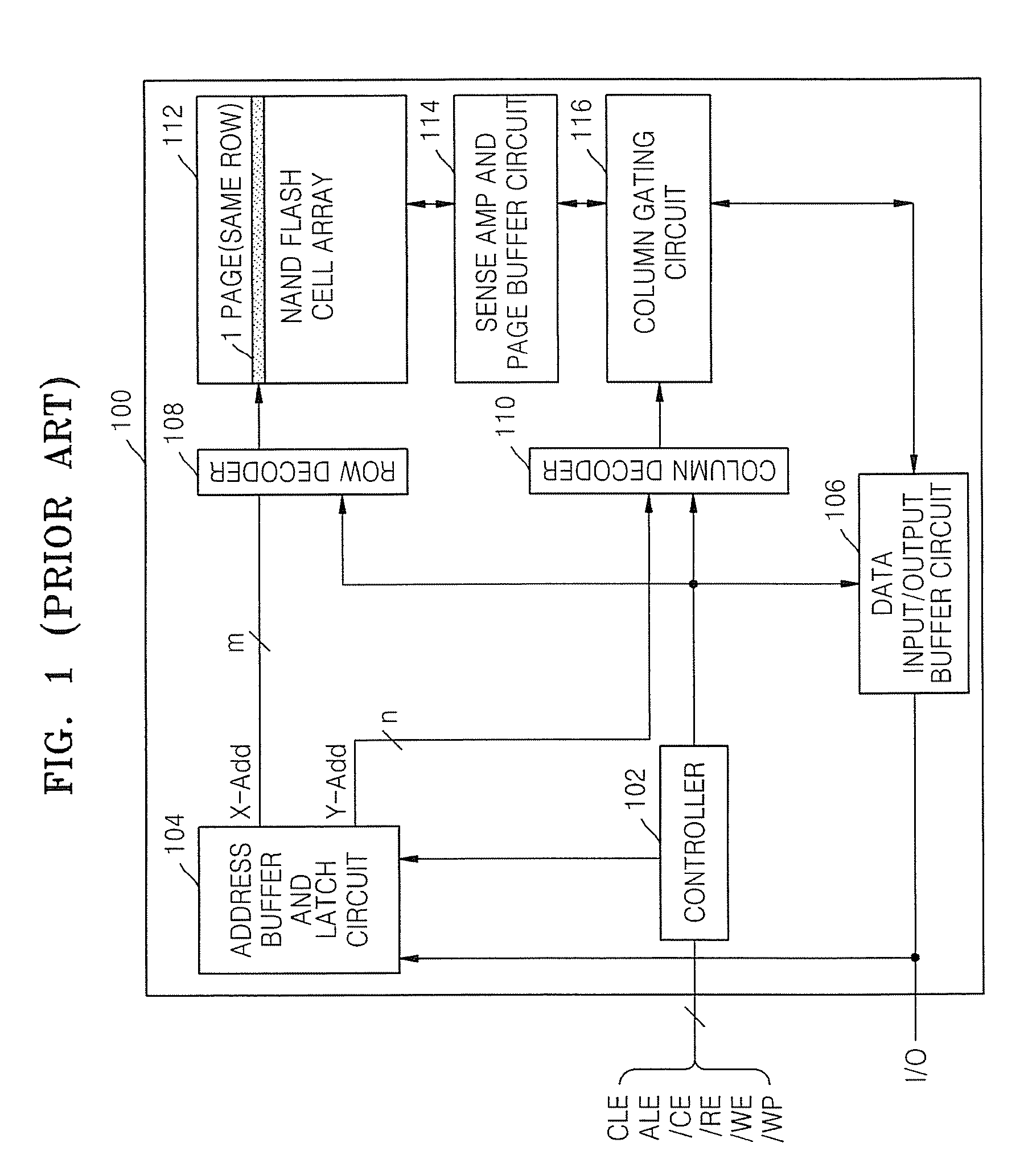

Memory device employing NVRAM and flash memory cells

A memory device includes a memory cell array including a NAND flash cell portion including a plurality of first columns of serially-connected flash memory cells and a non-volatile random access memory (NVRAM) cell portion including a plurality of second columns of NVRAM cells. The flash memory cells and the NVRAM cells are arranged such that respective word lines are connected to flash memory cells and NVRAM cells in each of respective rows, which may correspond to page units including flash memory cells and NVRAM cells.

Owner:SAMSUNG ELECTRONICS CO LTD

NAND flash memory controller exporting and NAND interface

A NAND controller for interfacing between a host device and a flash memory device (e.g. a NAND flash memory device) fabricated on a flash die is disclosed. In some embodiments, the presently disclosed NAND controller includes electronic circuitry fabricated on a controller die, the controller die being distinct from the flash die, a first interface (e.g. a host-type interface, for example, a NAND interface) for interfacing between the electronic circuitry and the flash memory device, and a second interface (e.g. a flash-type interface) for interfacing between the controller and the host device, wherein the second interface is a NAND interface. According to some embodiments, the first interface is an inter-die interface. According to some embodiments, the first interface is a NAND interface. Systems including the presently disclosed NAND controller are also disclosed. Methods for assembling the aforementioned systems, and for reading and writing data using NAND controllers are also disclosed.

Owner:INNOVATIVE MEMORY SYST INC

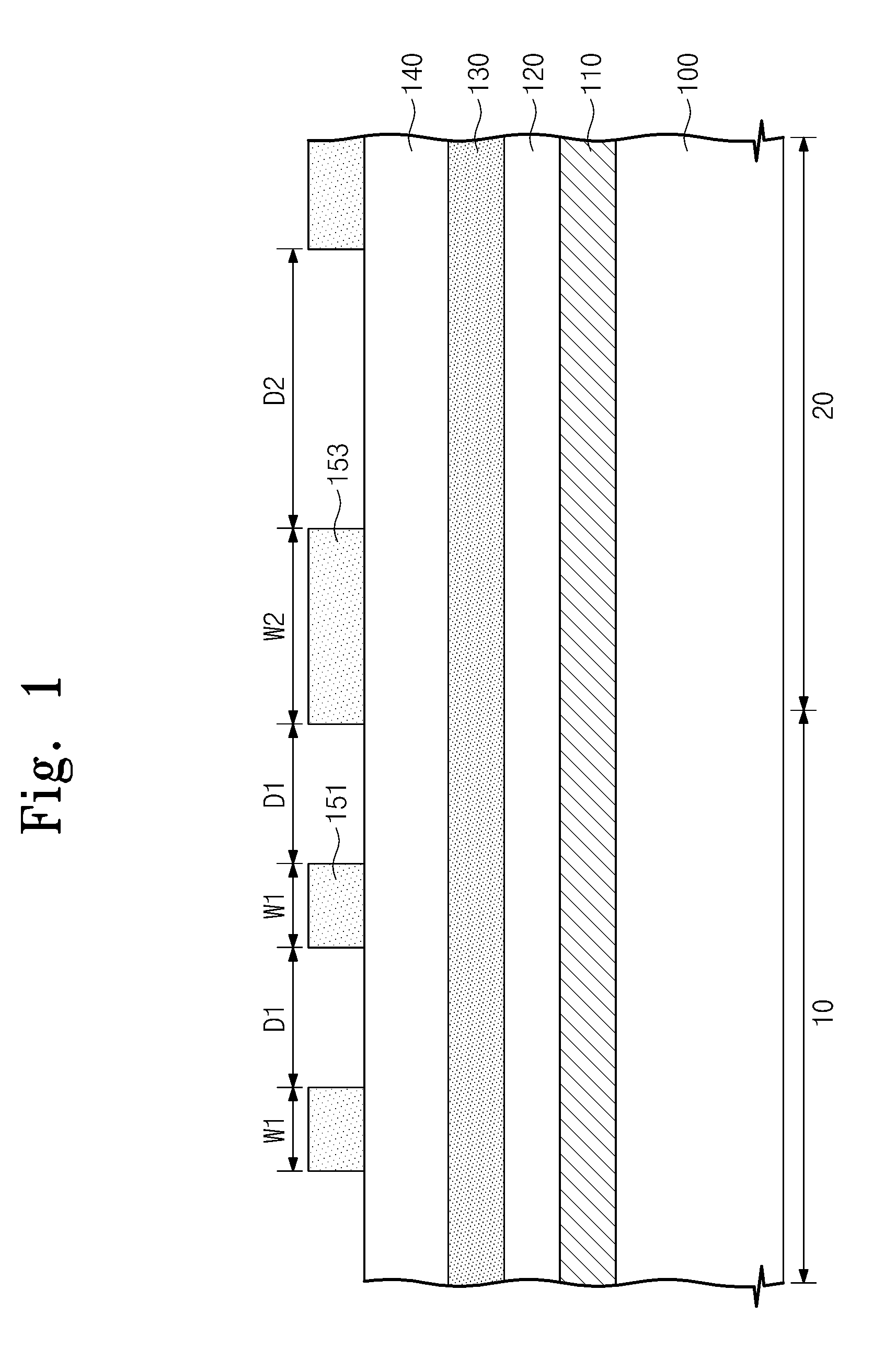

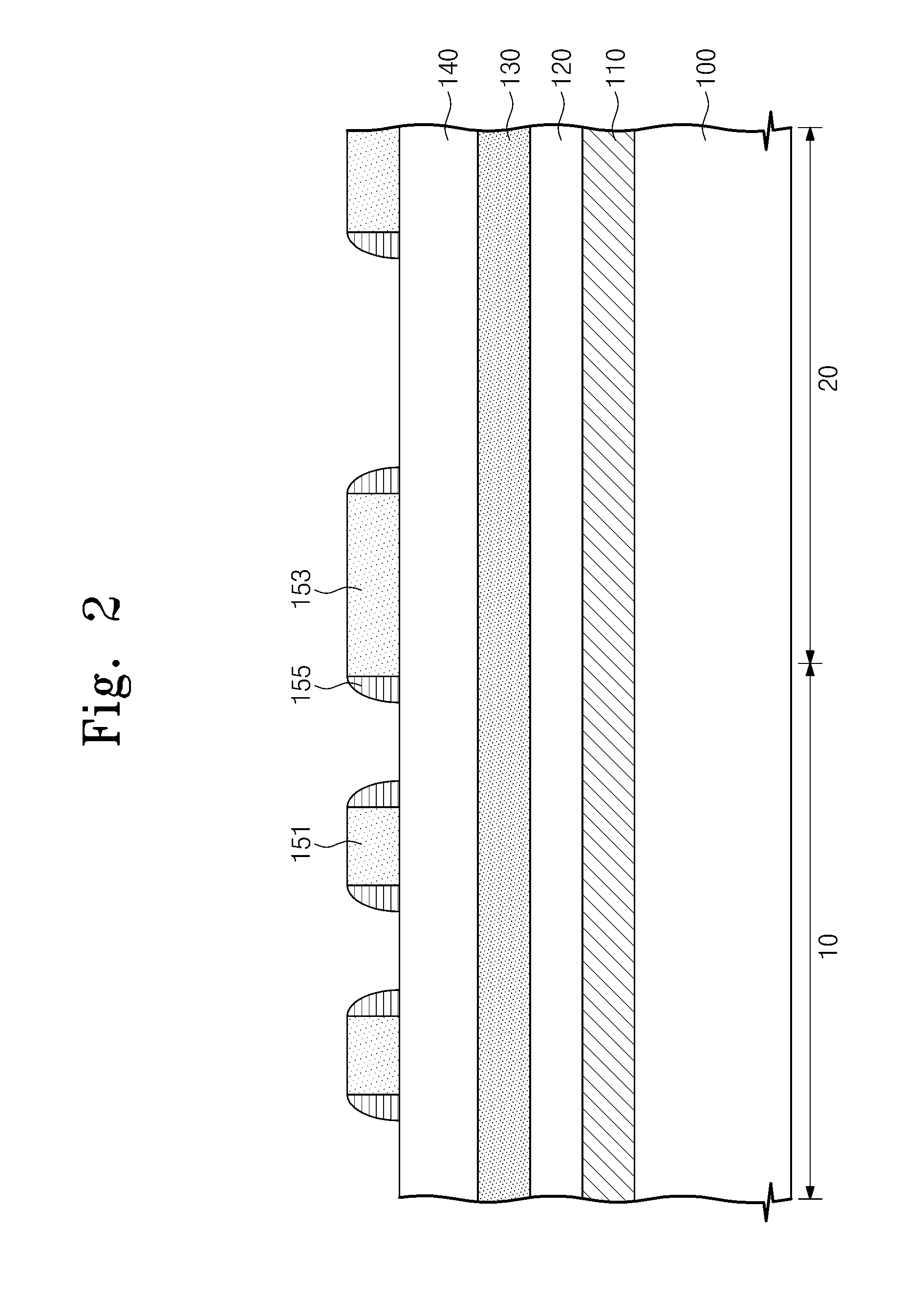

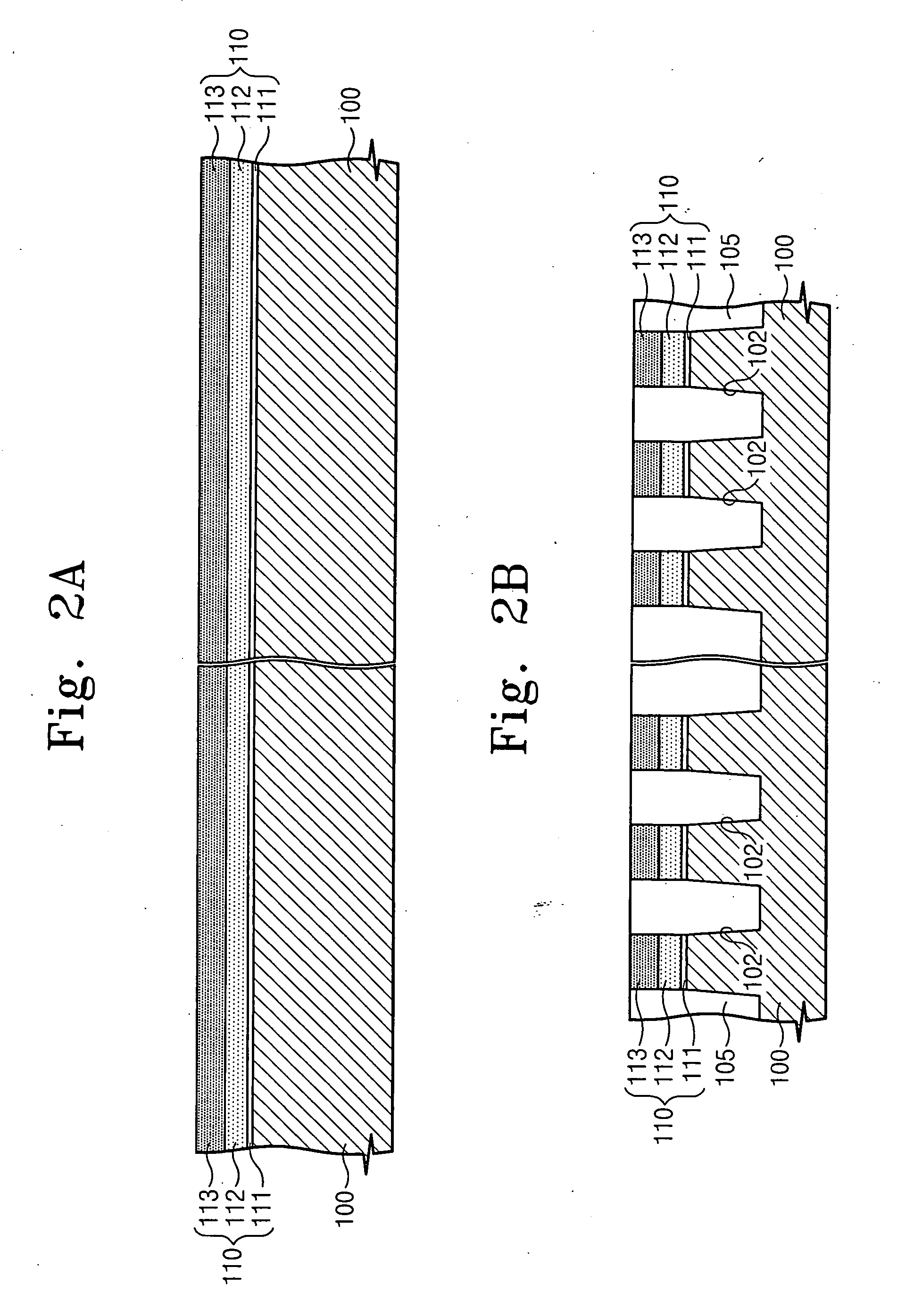

Method for forming fine patterns of a semiconductor device

ActiveUS20120208361A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialImage resolution

A method of forming fine patterns in a semiconductor device includes forming narrow-width patterns in a first region and wide-width patterns in a second region, where the widths of the narrow-width patterns are smaller than the resolution limitations in a photolithography process used to make the semiconductor device. The first and second regions may comprise cell array regions, with memory cells in the first region and peripheral circuits for operating the memory cells in the second region. The semiconductor device can be, for example, a NAND FLASH memory device. The semiconductor memory device can be variously classified according to the type of memory cells to be integrated in the cell array region, e.g., a DRAM, an SRAM, a PRAM, a RRAM, an MRAM, and a FRAM. In other embodiments, a MEMS device, an optoelectronic device, or a processor, such as CPU or DSP, may be provided on the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

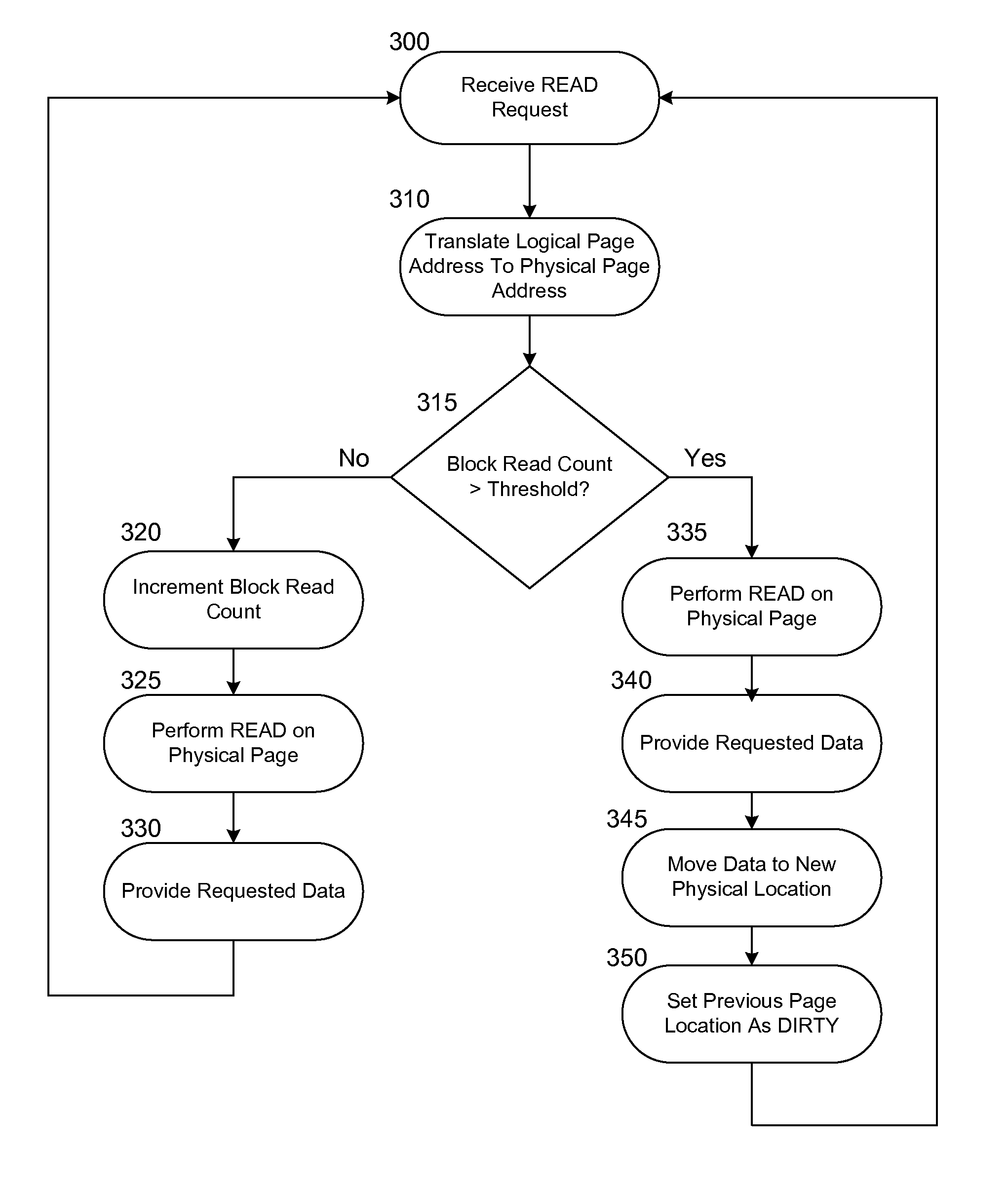

Efficient reduction of read disturb errors in NAND FLASH memory

InactiveUS7818525B1Disturb errorEfficient reduction of Read Disturb errorMemory architecture accessing/allocationRead-only memoriesPhysical addressTranslation table

Methods and apparatuses for reduction of Read Disturb errors in a NAND FLASH memory system comprise a controller configured to organize FLASH memory devices into blocks, each block having a plurality of pages, and each page defining an individually addressable physical memory location. The controller is further configured to accumulate a Block READ Count corresponding to the number of times any pages in a first block of pages have been read since the first block was last erased. Once the READ count reaches a predetermined number, the controller responds to subsequent READ requests for pages within the first block by moving data associated with a requested page to a page in a second, different block without moving data associated with other pages in the first block, and modifying a logical-to-physical translation table to associate the moved data with the physical address of the page in the second block.

Owner:IBM CORP

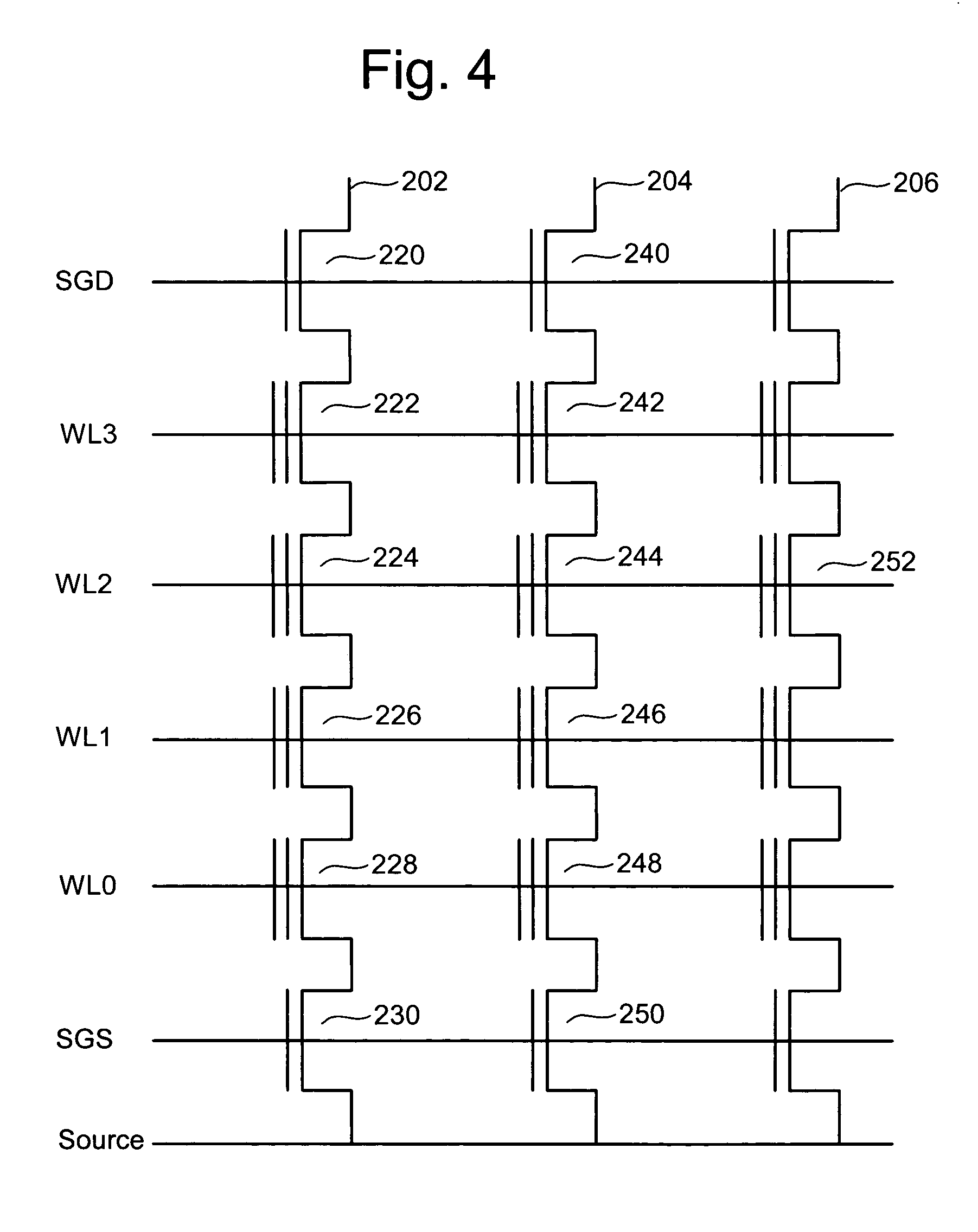

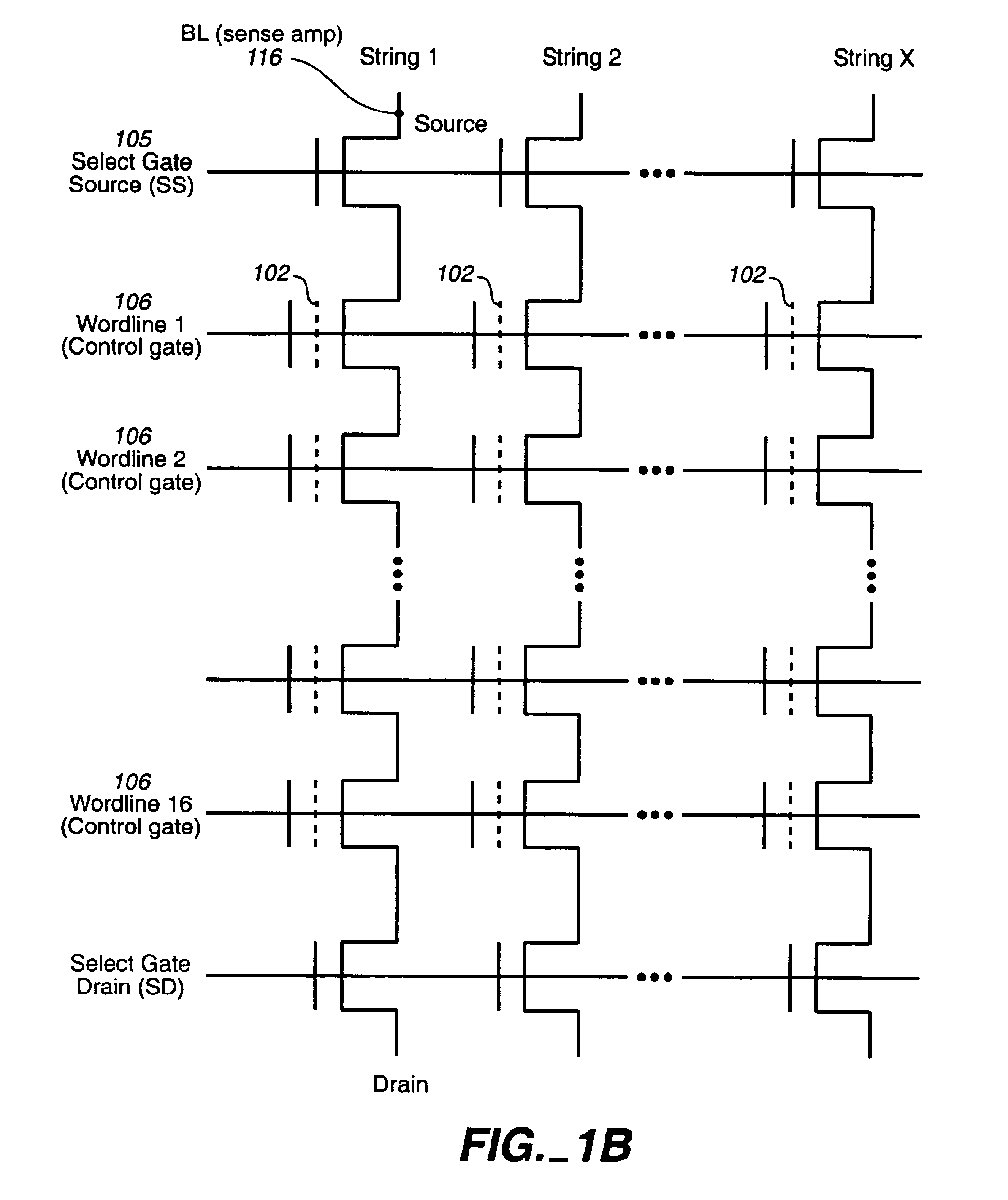

Operating non-volatile memory without read disturb limitations

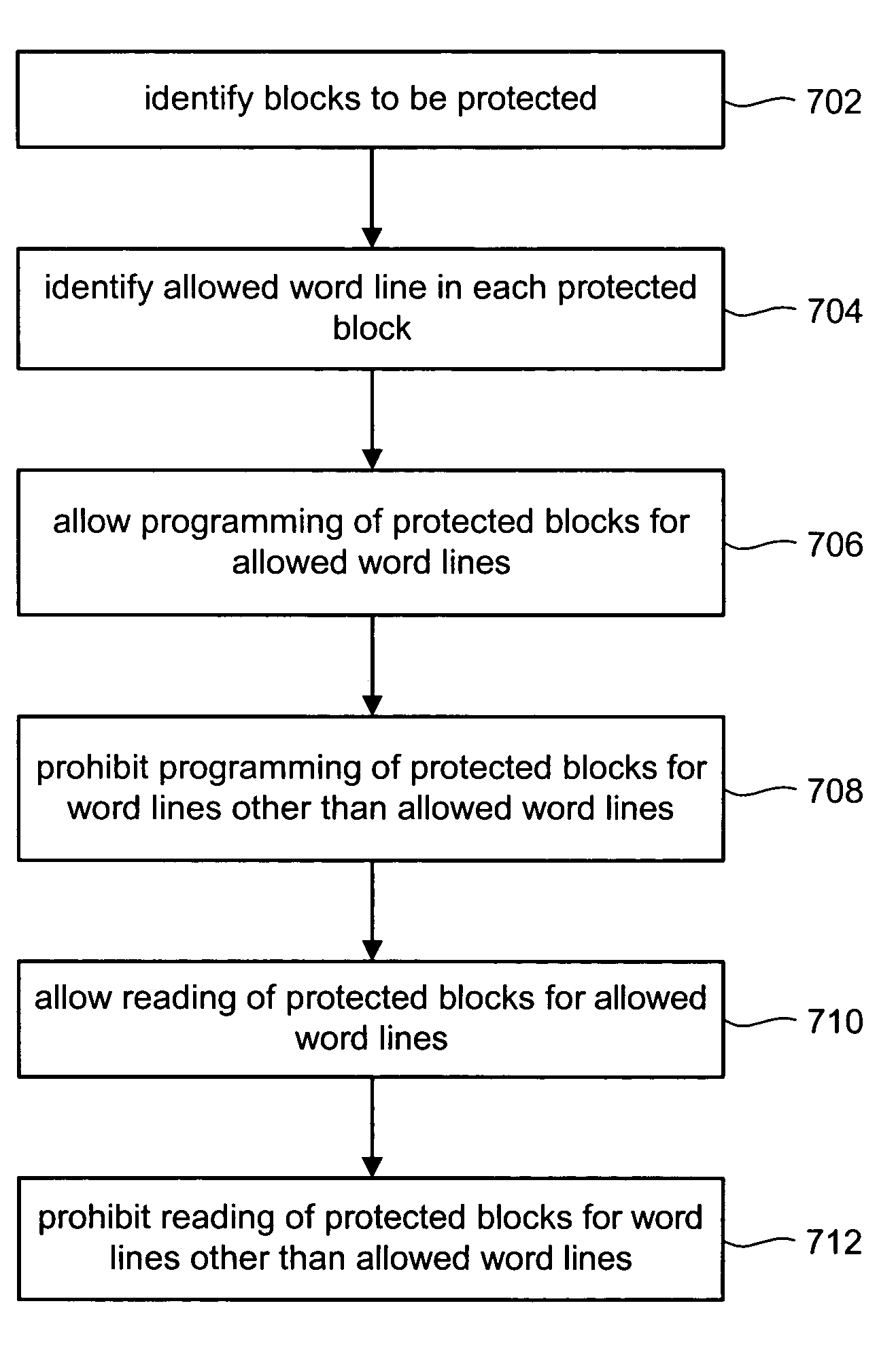

When reading a memory cell on a NAND string, the word lines for the memory cells not being read will receive a voltage so that those memory cells operate as pass gates. Over time, if there are a lot of read operations without any program operations, the cells not being read may suffer from Read Disturb because the voltage applied to the word lines may cause electrons to accumulate in the floating gates of the non-selected cells. The accumulation of charge in the floating gates raises the threshold voltage. To avoid the limitations of Read Disturb, only one word line of a block (or other grouping) is used to program and read data. In a system using NAND flash memory, the word line being read is not typically subjected to read disturb. Thus, a NAND flash memory that restricts programming and reading to one word line of a block is not likely to exhibit read disturb in that block.

Owner:SANDISK TECH LLC

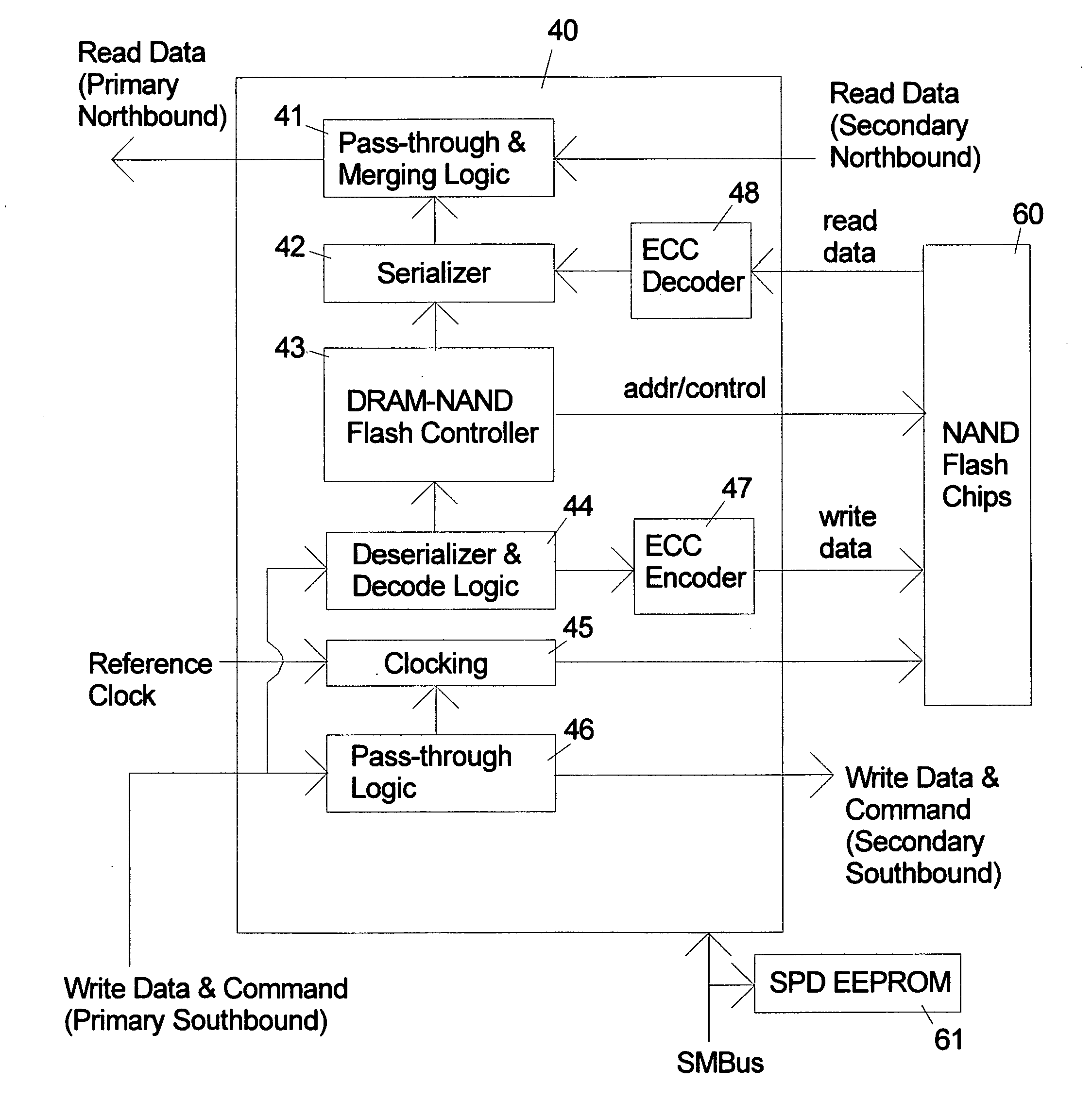

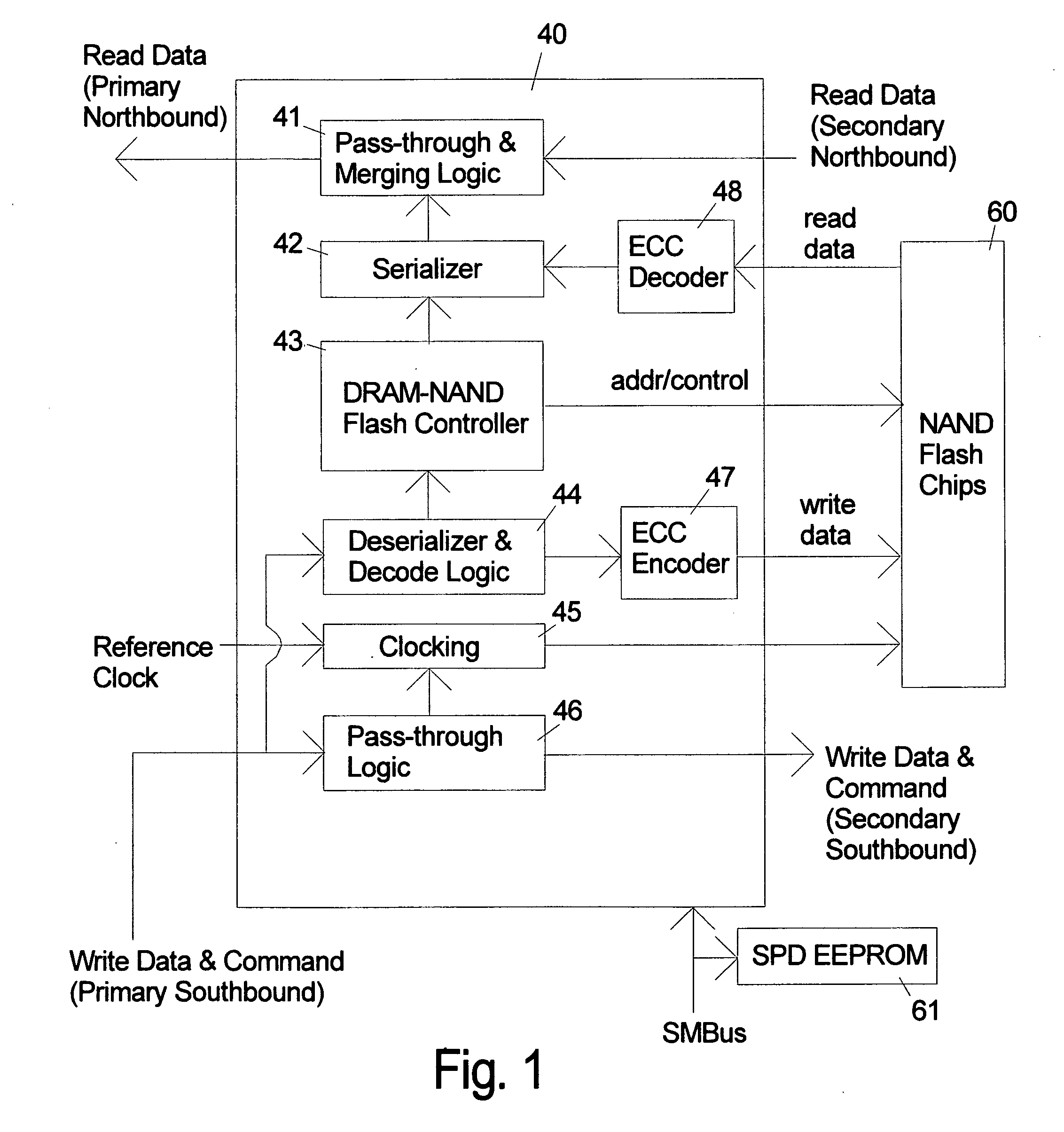

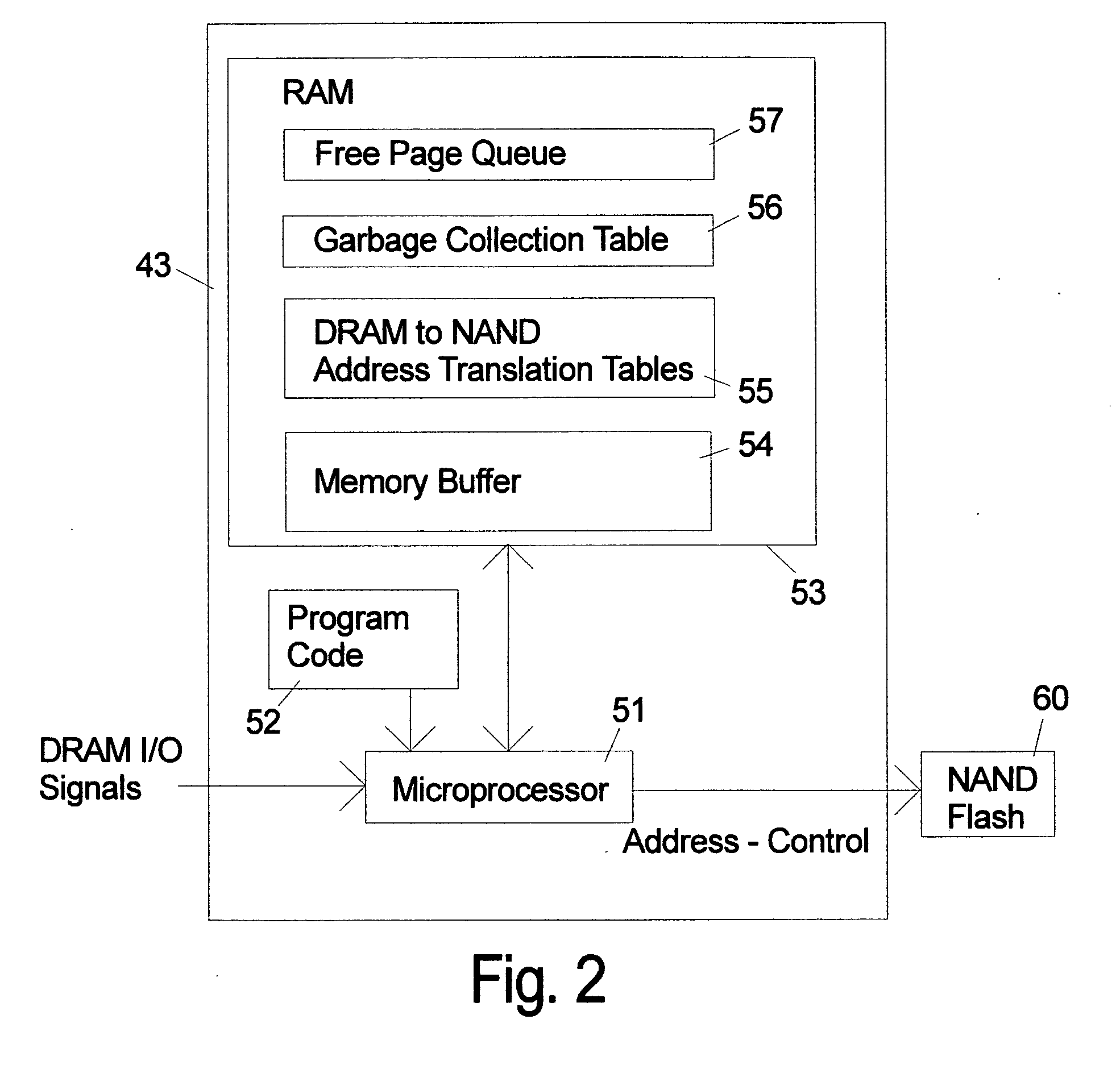

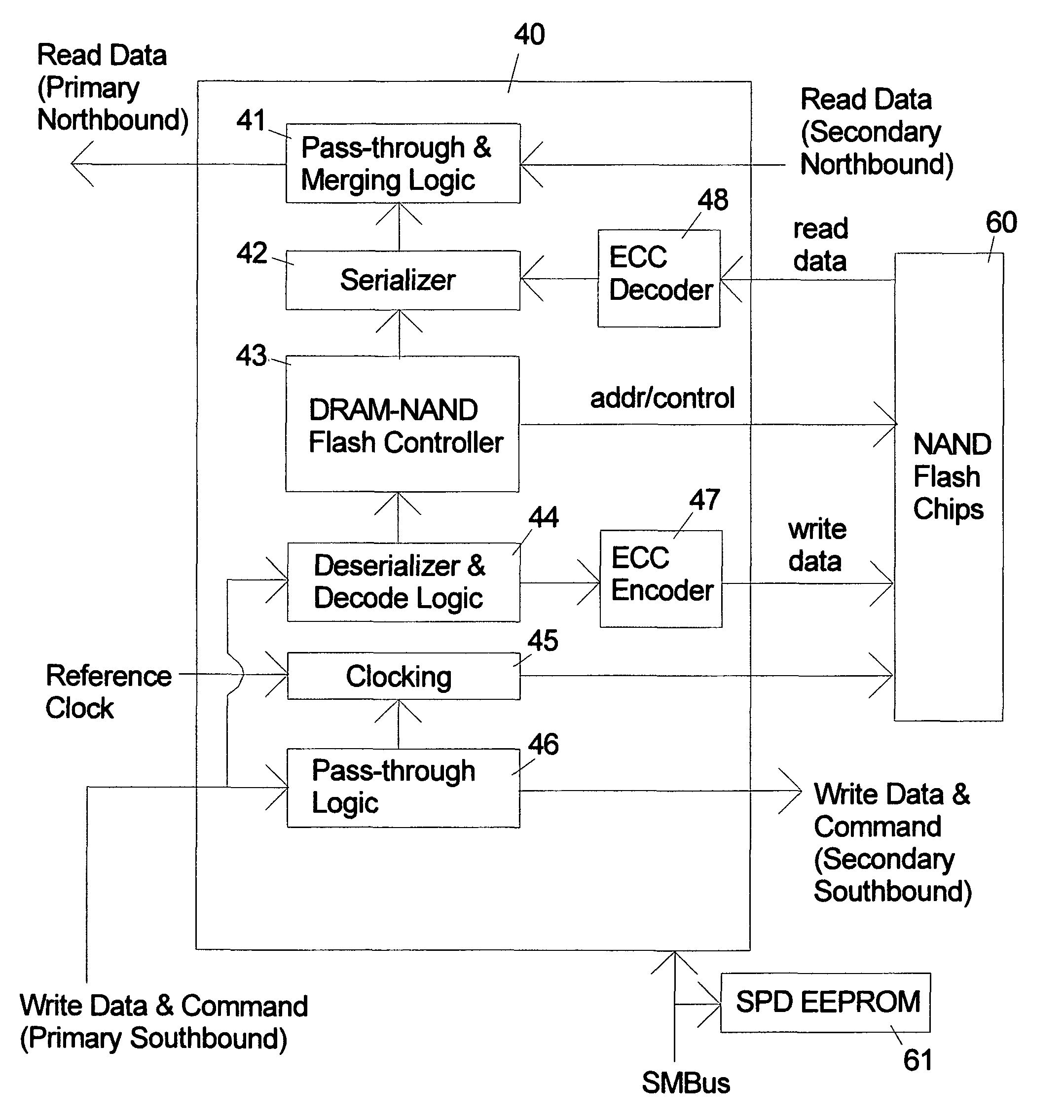

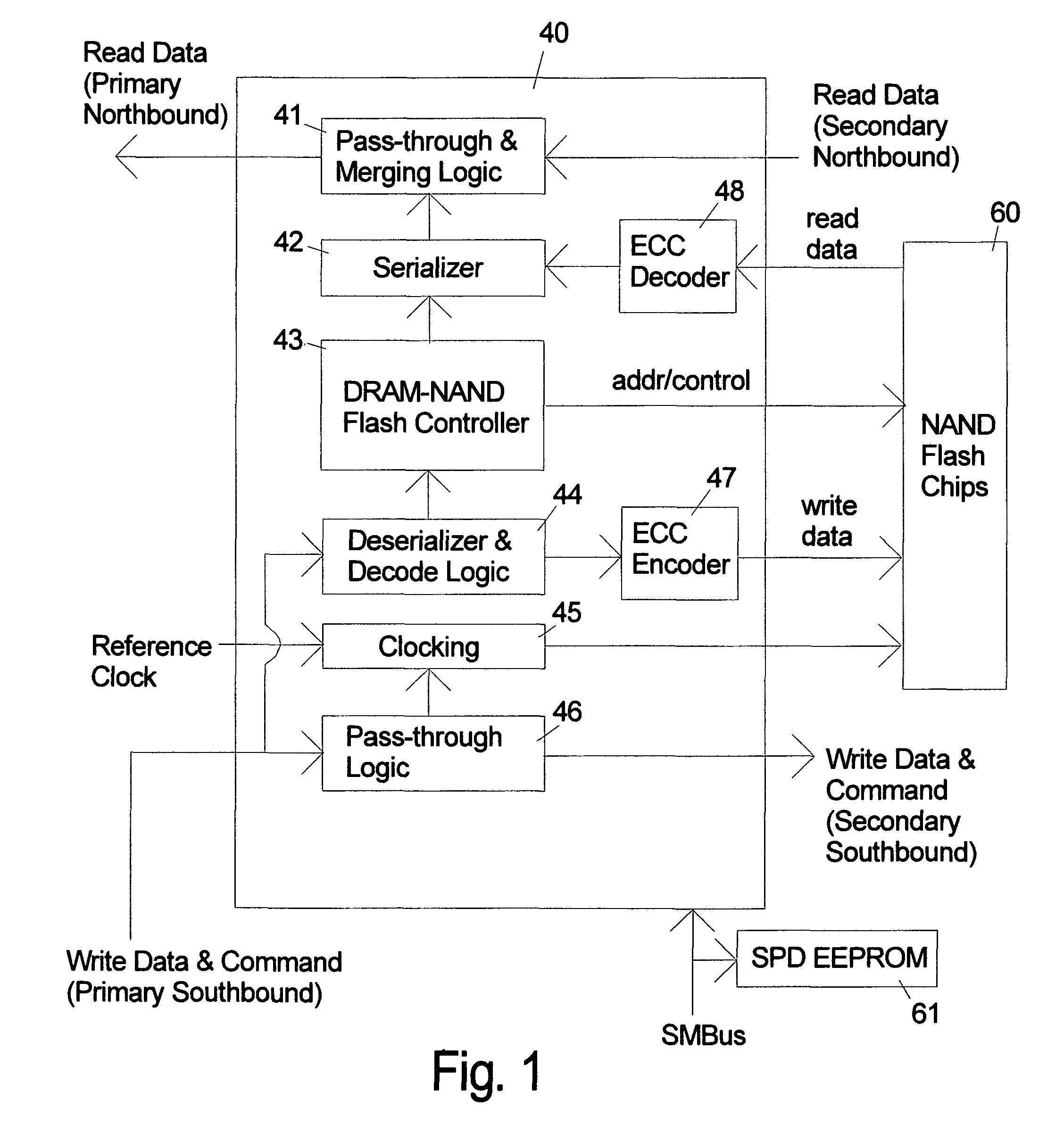

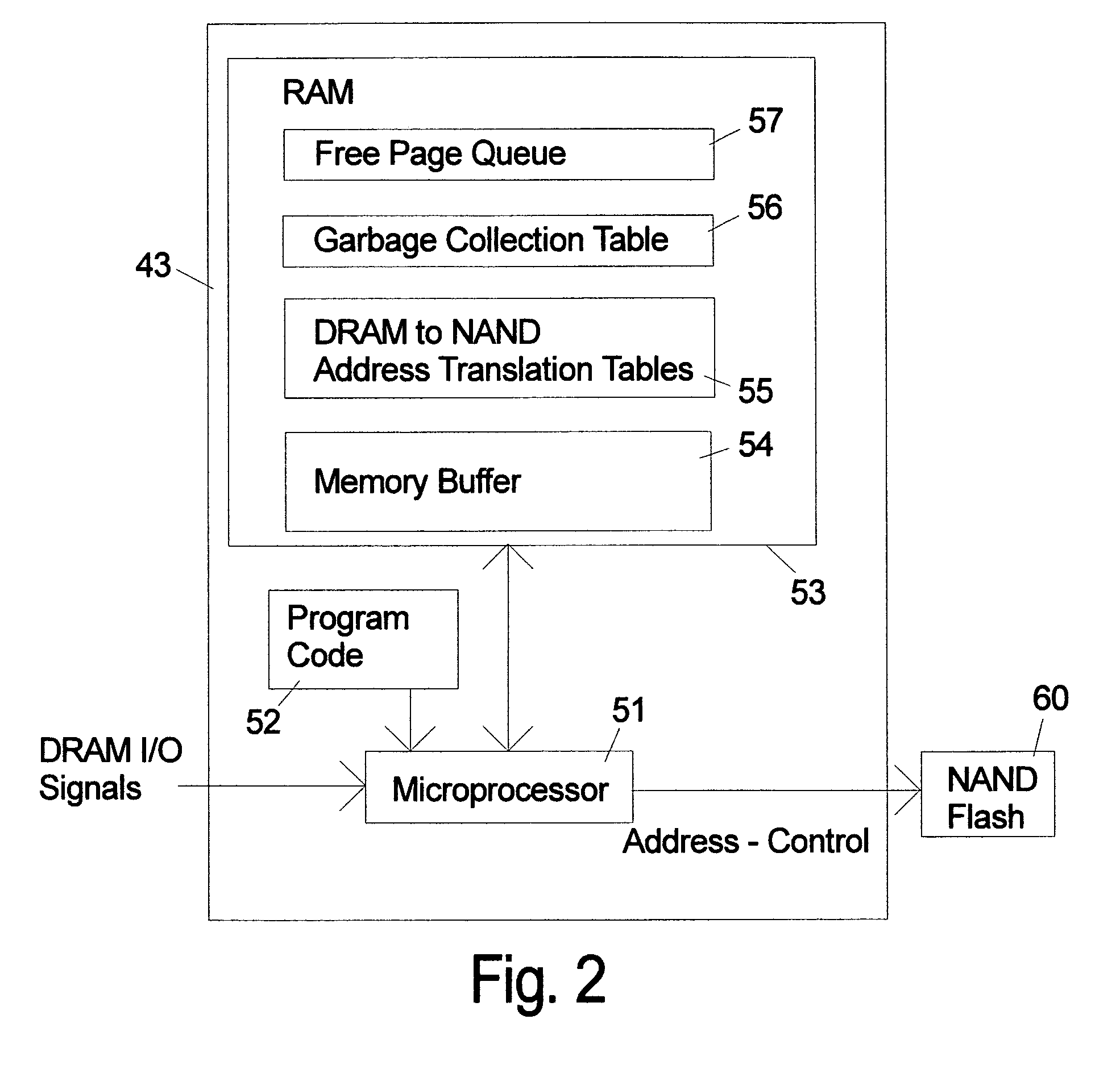

NAND flash module replacement for DRAM module

ActiveUS20090157950A1Most efficientAddressing slow performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationControl signalFlash memory controller

An electronic memory module according to the invention provides non-volatile memory that can be used in place of a DRAM module without battery backup. An embodiment of the invention includes an embedded microprocessor with microcode that translates the FB-DIMM address and control signals from the system into appropriate address and control signals for NAND flash memory. Wear-leveling, bad block management, garbage collection are preferably implemented by microcode executed by the microprocessor. The microprocessor, additional logic, and embedded memory provides the functions of a flash memory controller. The microprocessor memory preferably contains address mapping tables, free page queue, and garbage collection information.

Owner:WESTERN DIGITAL TECH INC

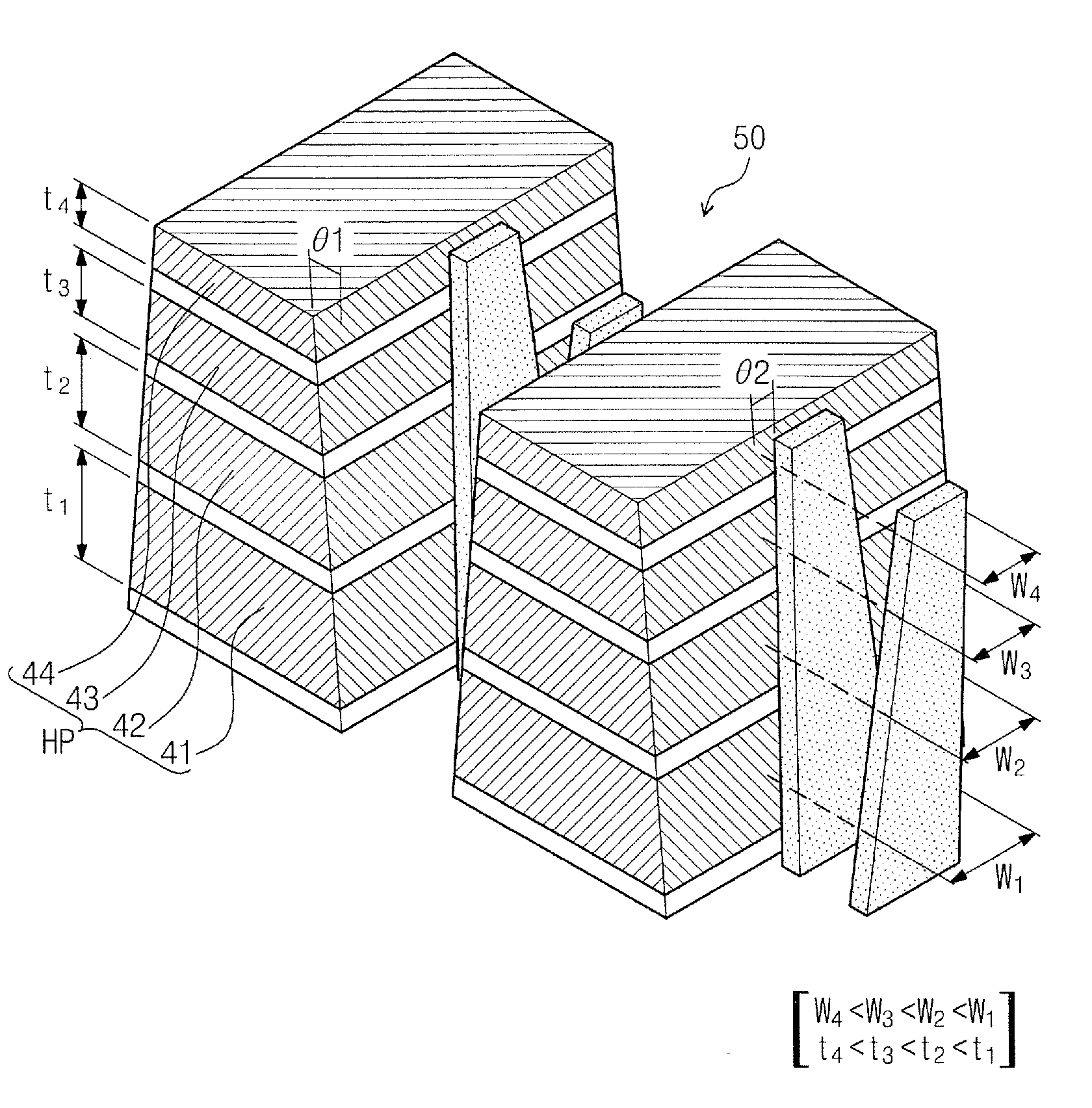

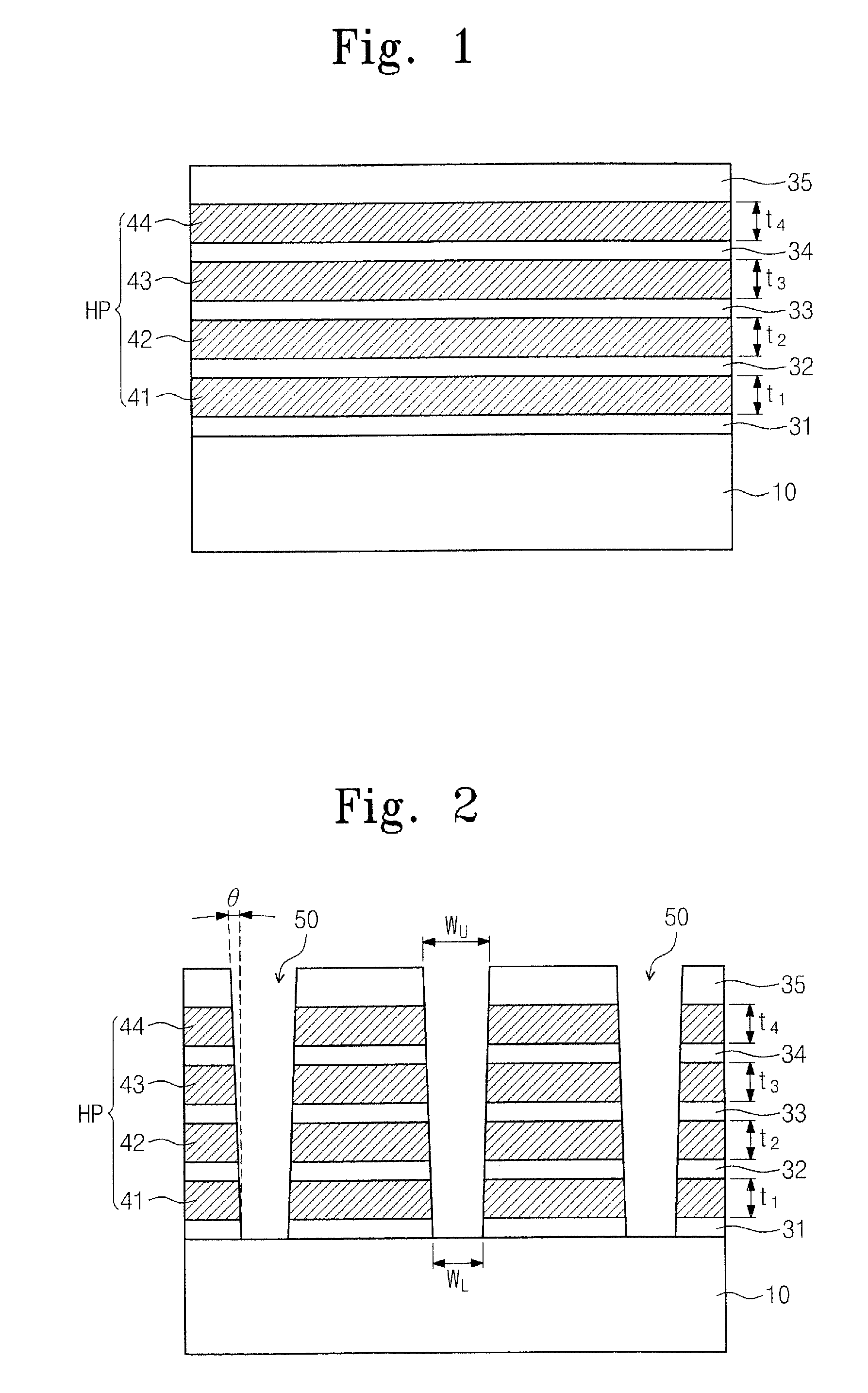

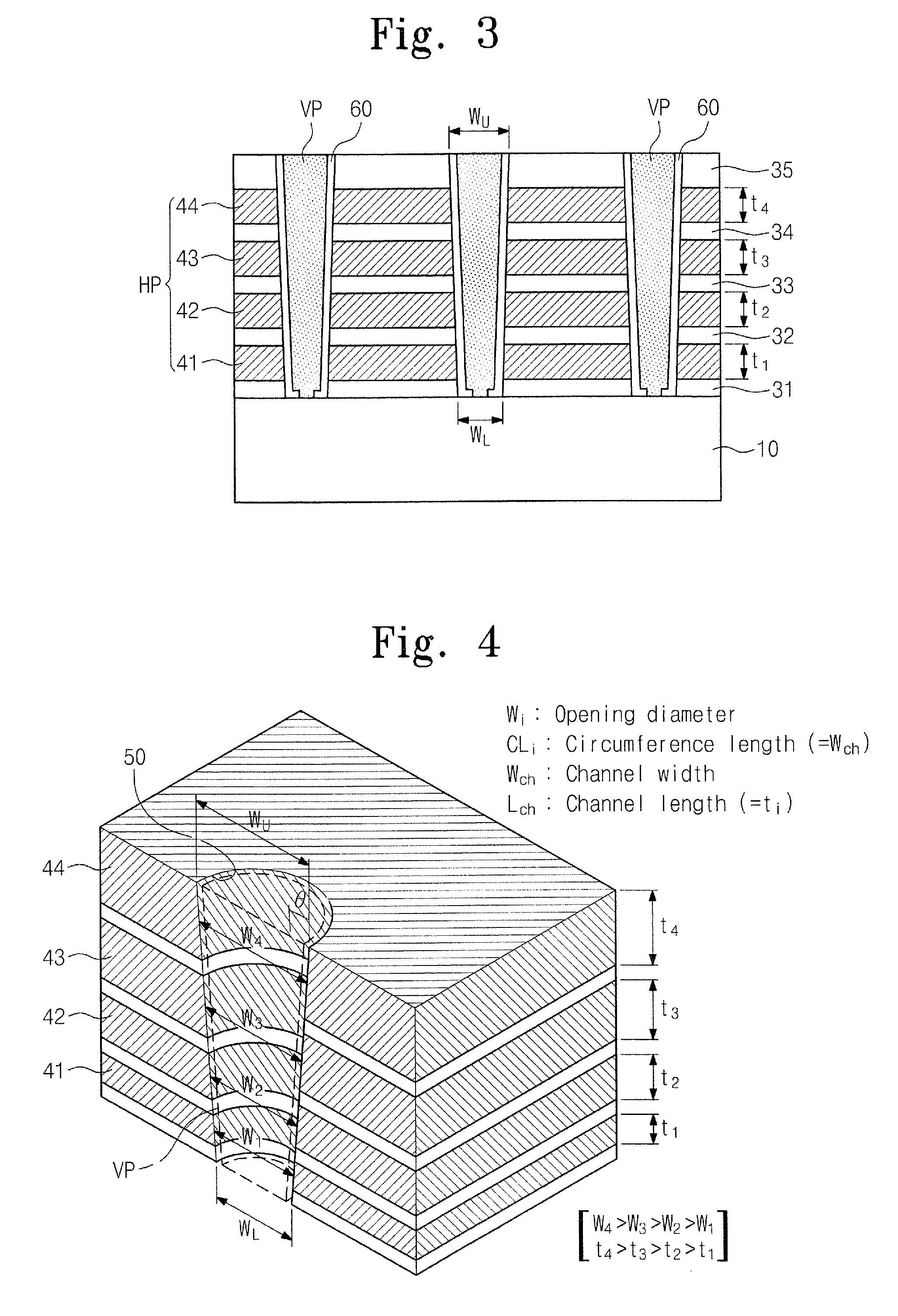

Three-dimensional microelectronic devices including repeating layer patterns of different thicknesses

ActiveUS20100078701A1Reduce drive current variationIncreasing the thicknessTransistorSolid-state devicesEngineeringComputational physics

A vertical NAND flash memory device includes a substrate having a face and a string of serially connected flash memory cells on the substrate. A first flash memory cell is adjacent the face, and a last flash memory cell is remote from the face. The flash memory cells include repeating layer patterns that are stacked on the face, and a pillar that extends through the series of repeating layer patterns. The pillar includes at least one oblique wall. At least two of the series of repeating layer patterns in the string are of different thicknesses. Other vertical microelectronic devices and related fabrication methods are also described.

Owner:SAMSUNG ELECTRONICS CO LTD

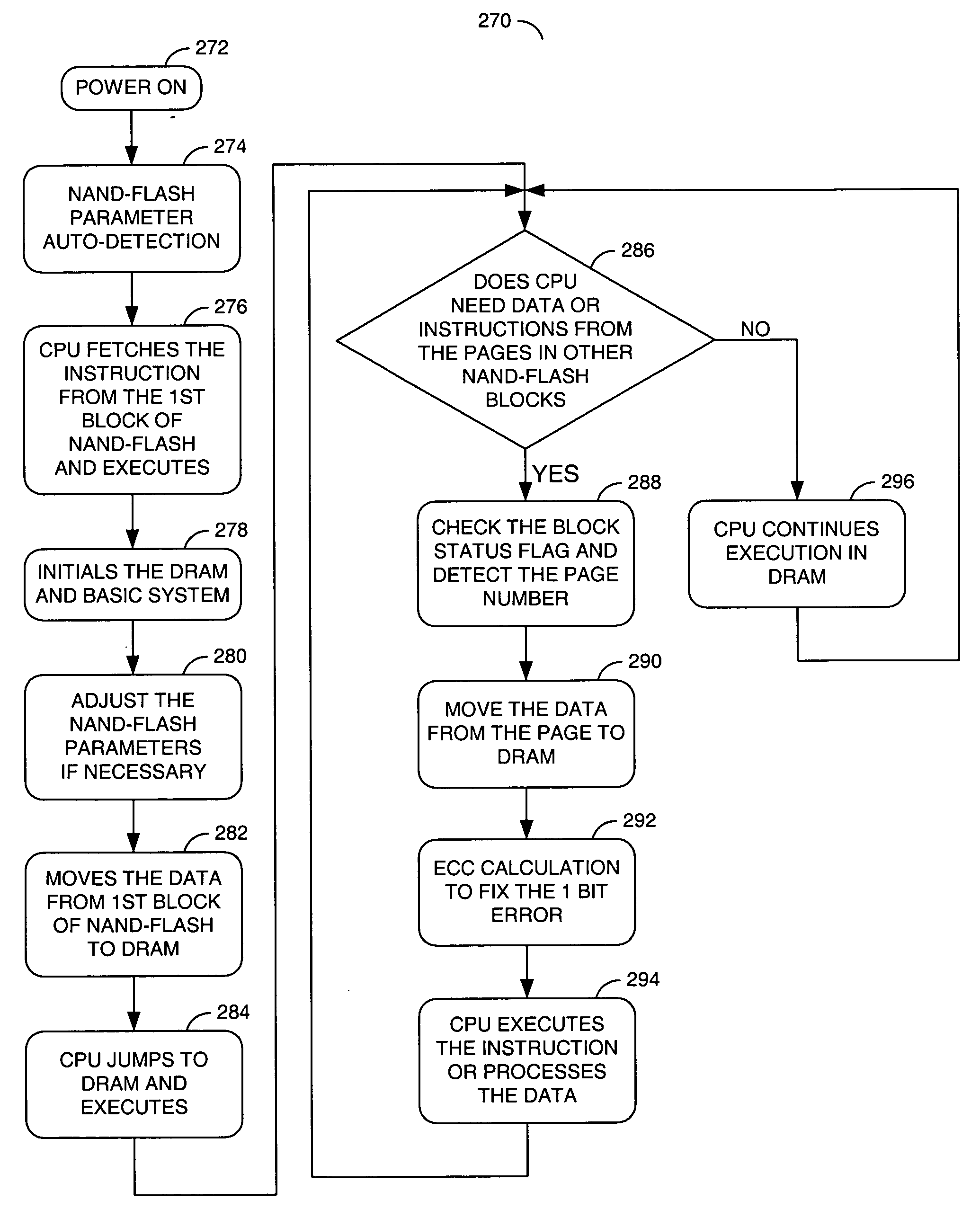

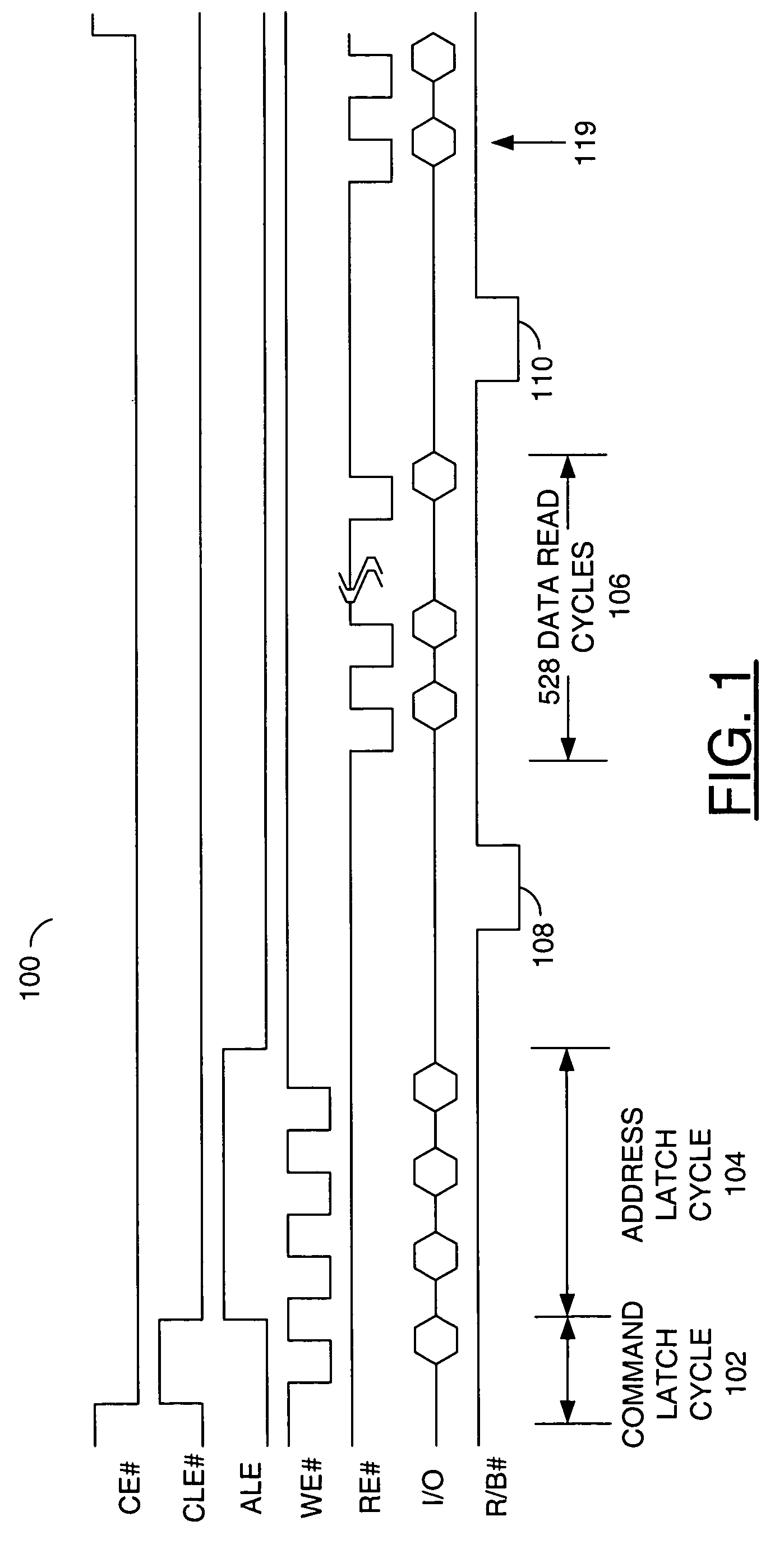

Method to detect NAND-flash parameters by hardware automatically

InactiveUS20060195650A1Reduce areaLow costRead-only memoriesDigital computer detailsSize parameterReal-time computing

Owner:AVAGO TECH INT SALES PTE LTD

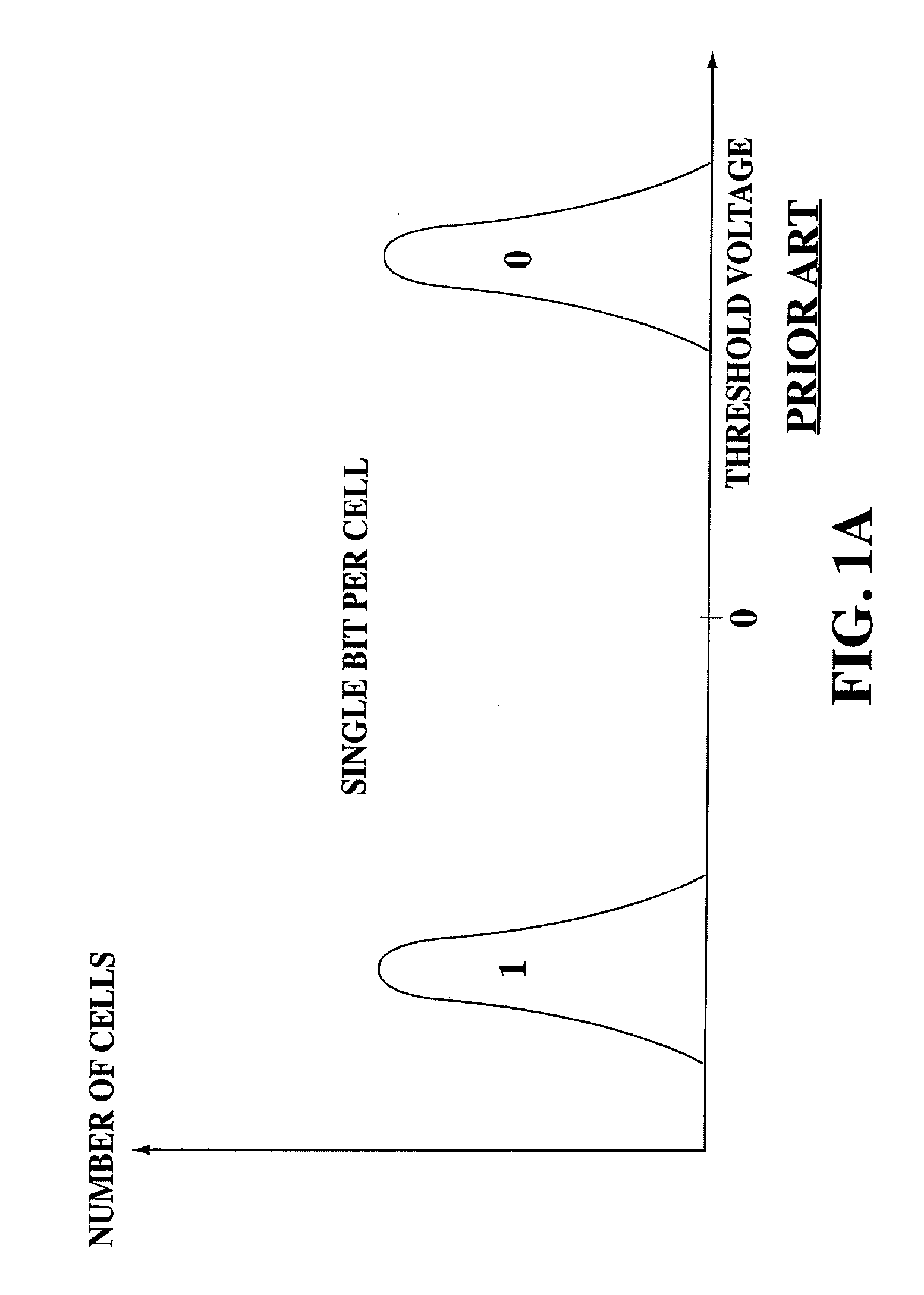

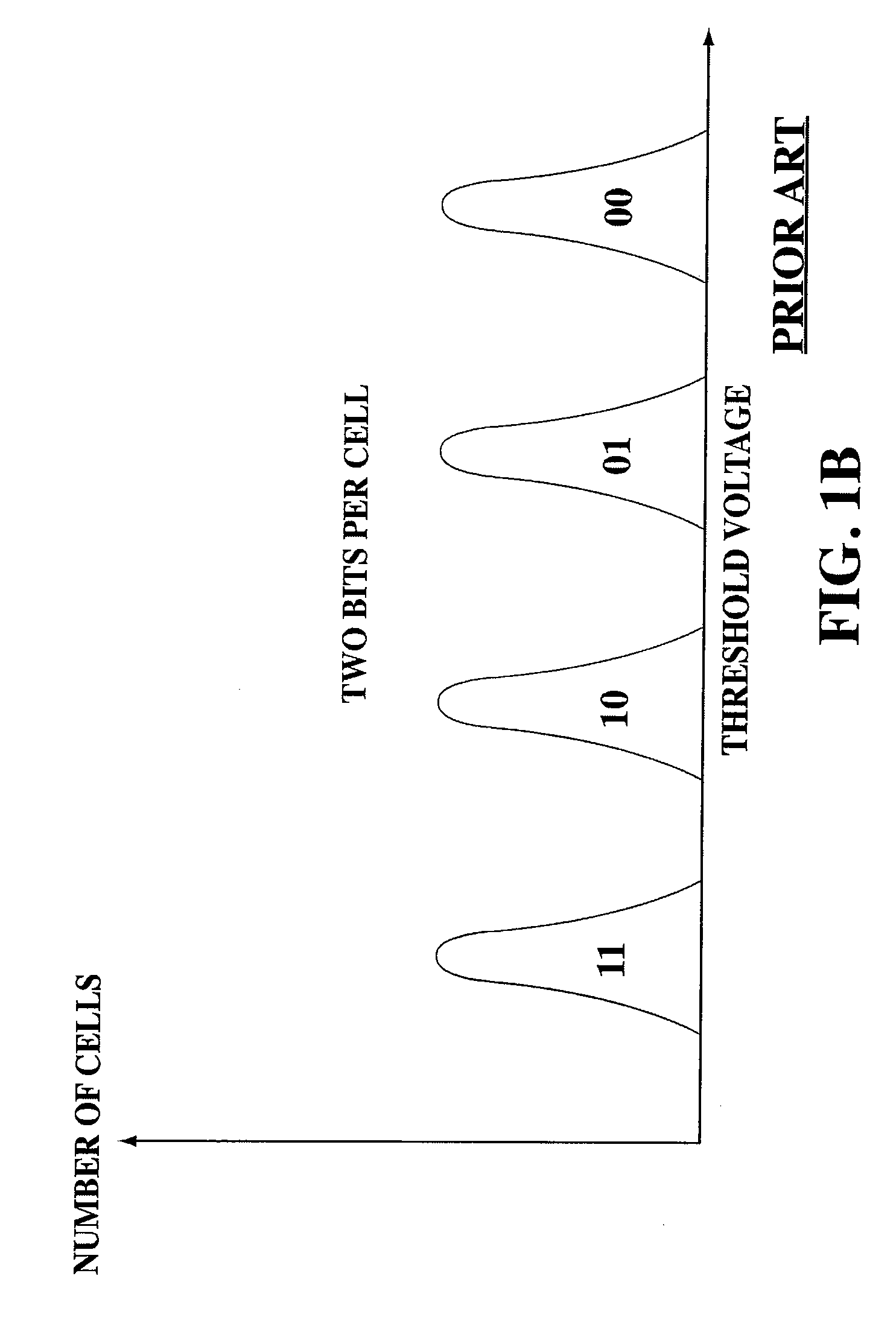

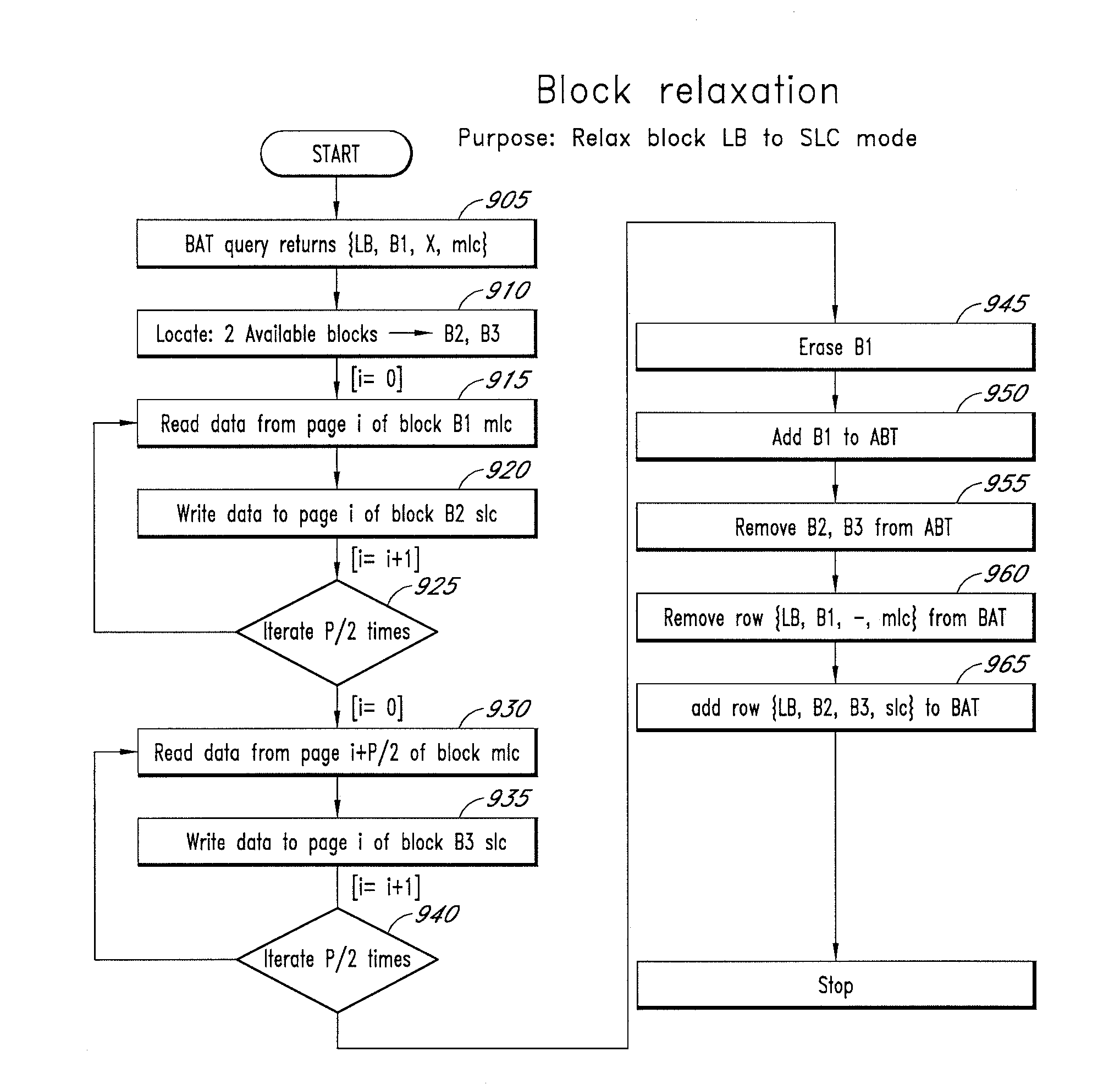

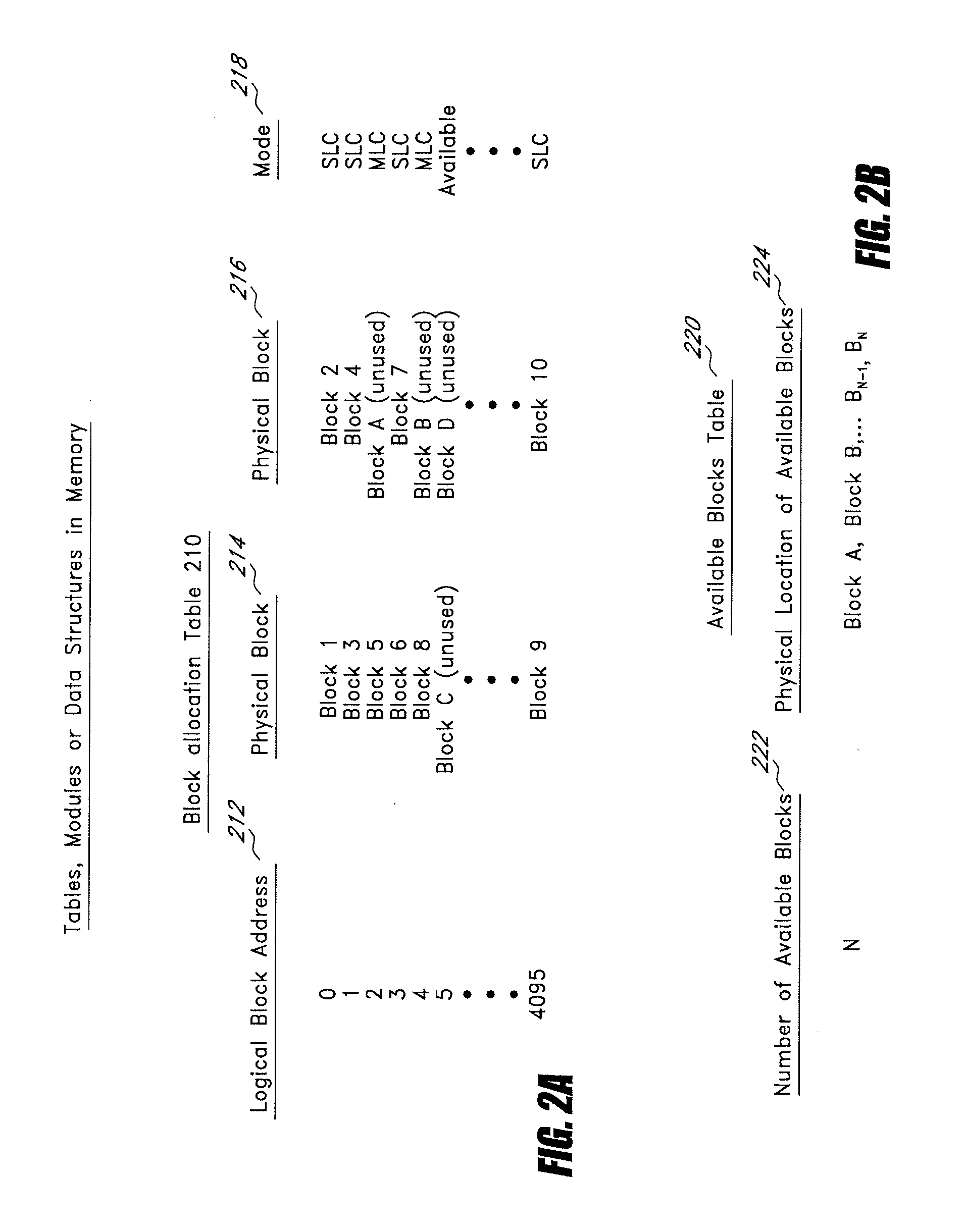

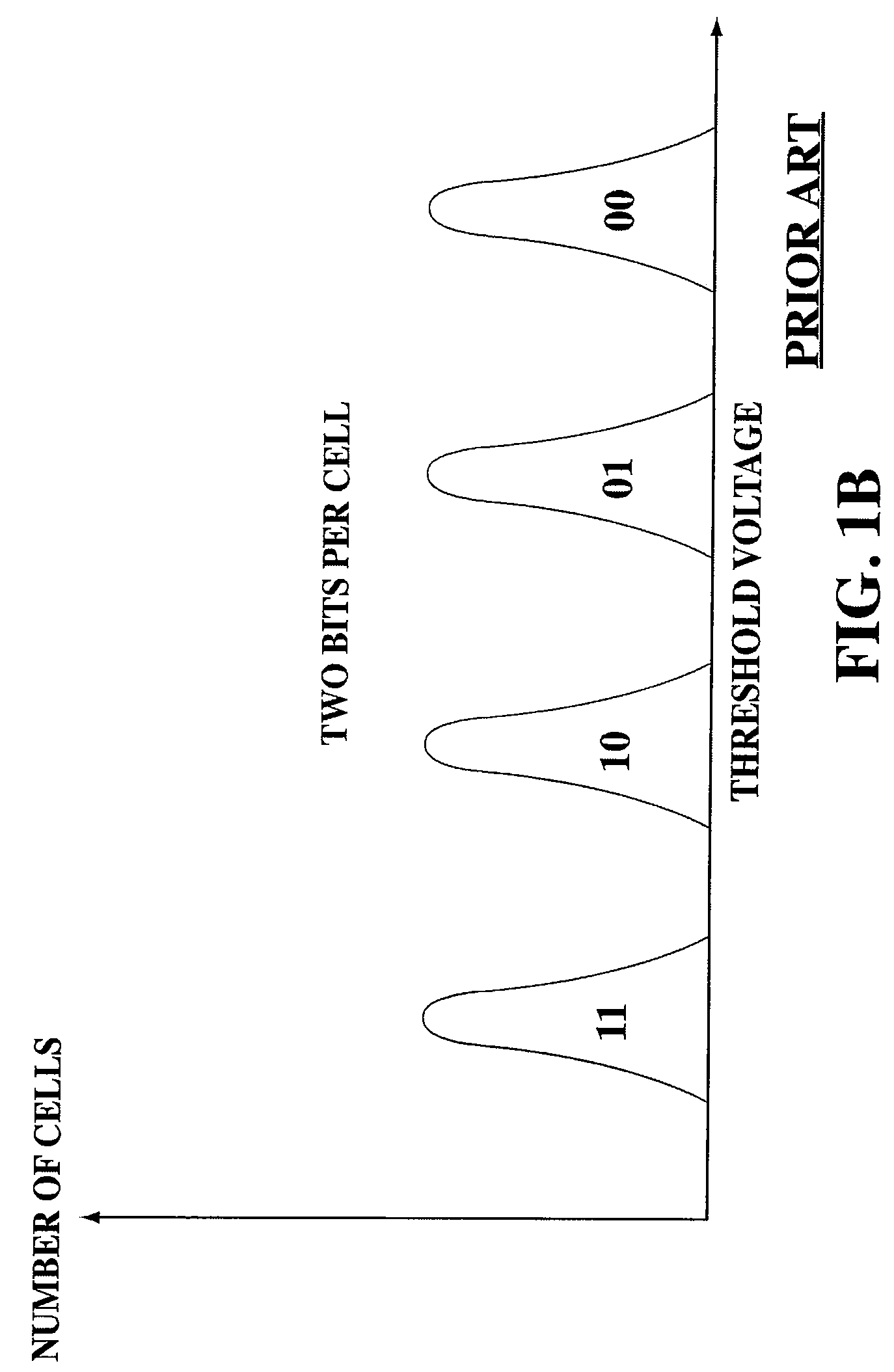

Dynamic slc/mlc blocks allocations for non-volatile memory

InactiveUS20100122016A1Memory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingSingle level

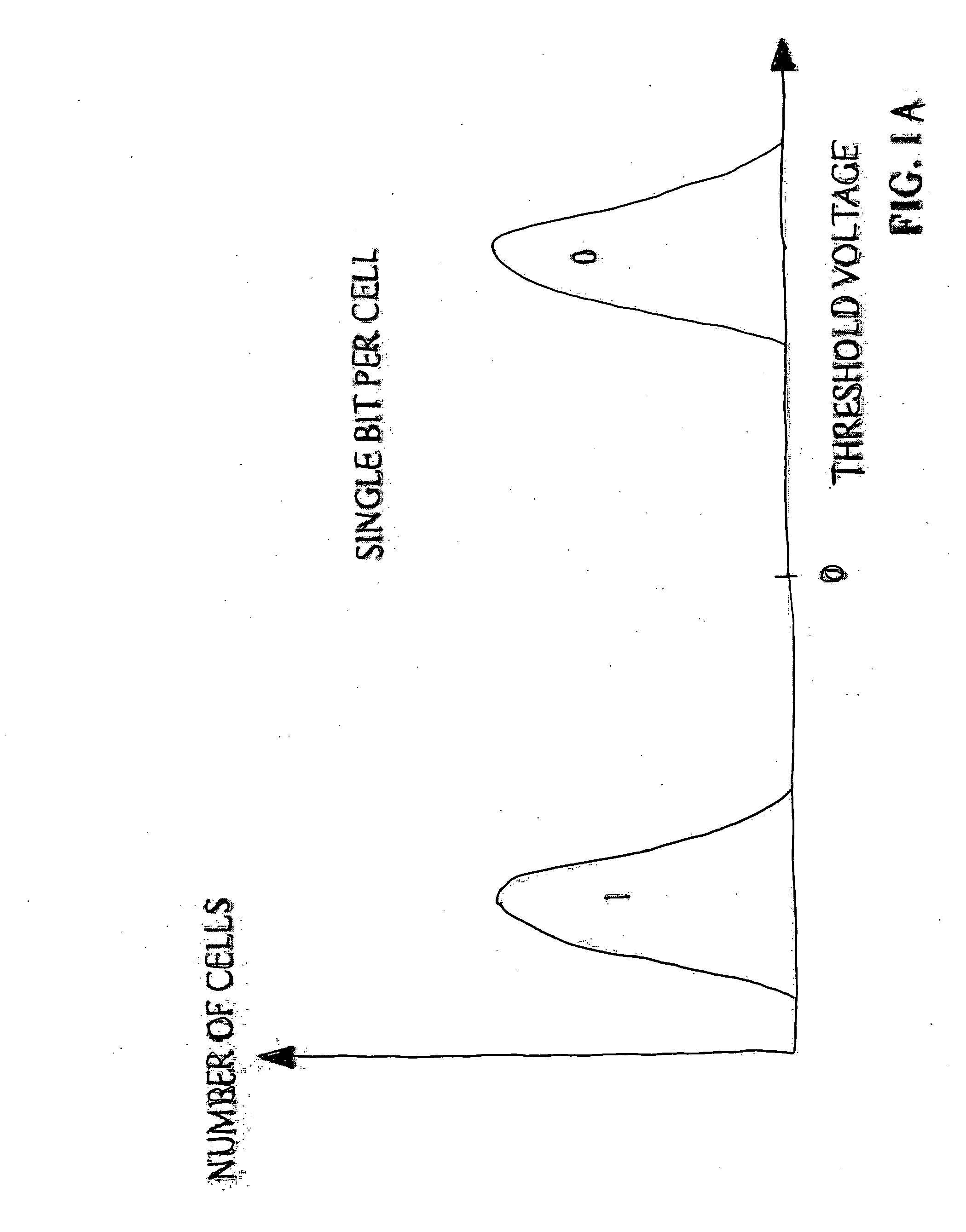

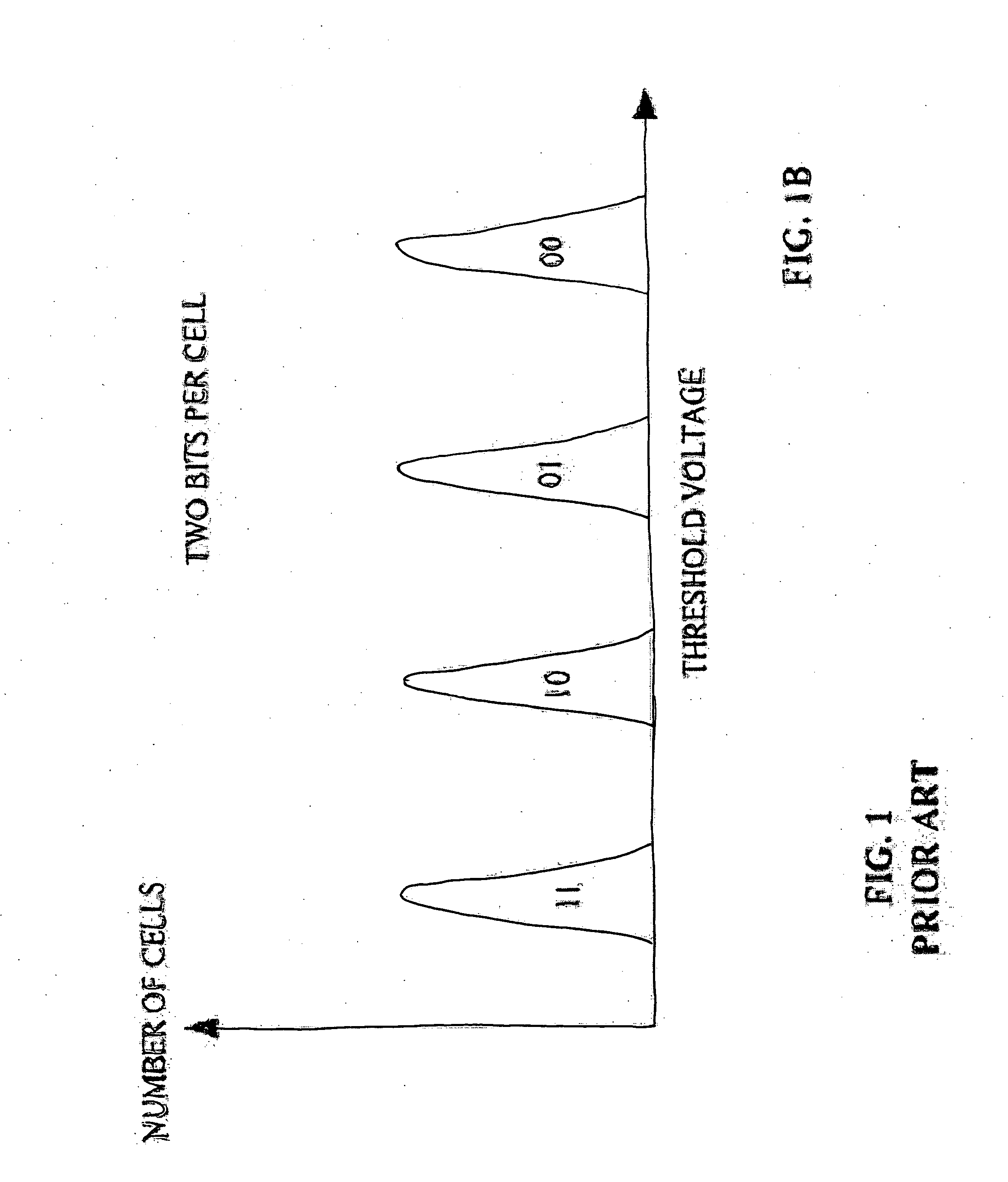

Apparatus and methods are disclosed, such as those that provide dynamic block allocations in NAND flash memory between single-level cells (SLC) and multi-level cells (MLC) based on characteristics. In one embodiment, a memory controller dynamically switches between programming and / or reprogramming blocks between SLC mode and MLC mode based on the amount of memory available for use. When memory usage is low, SLC mode is used. When memory usage is high, MLC mode is used. Dynamic block allocation allows a memory controller to obtain the performance and reliability benefits of SLC mode while retaining the space saving benefits of MLC mode.

Owner:ROUND ROCK RES LLC

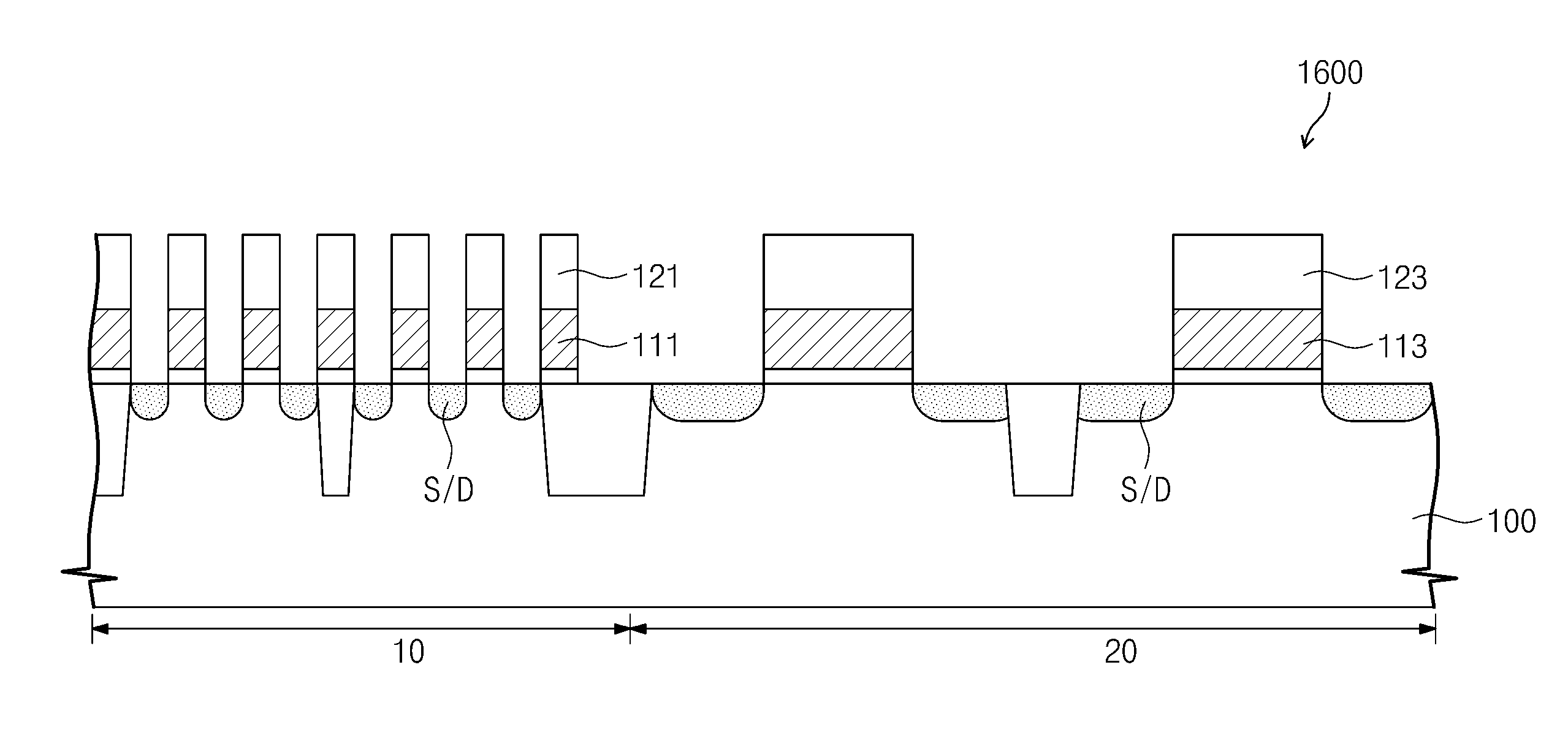

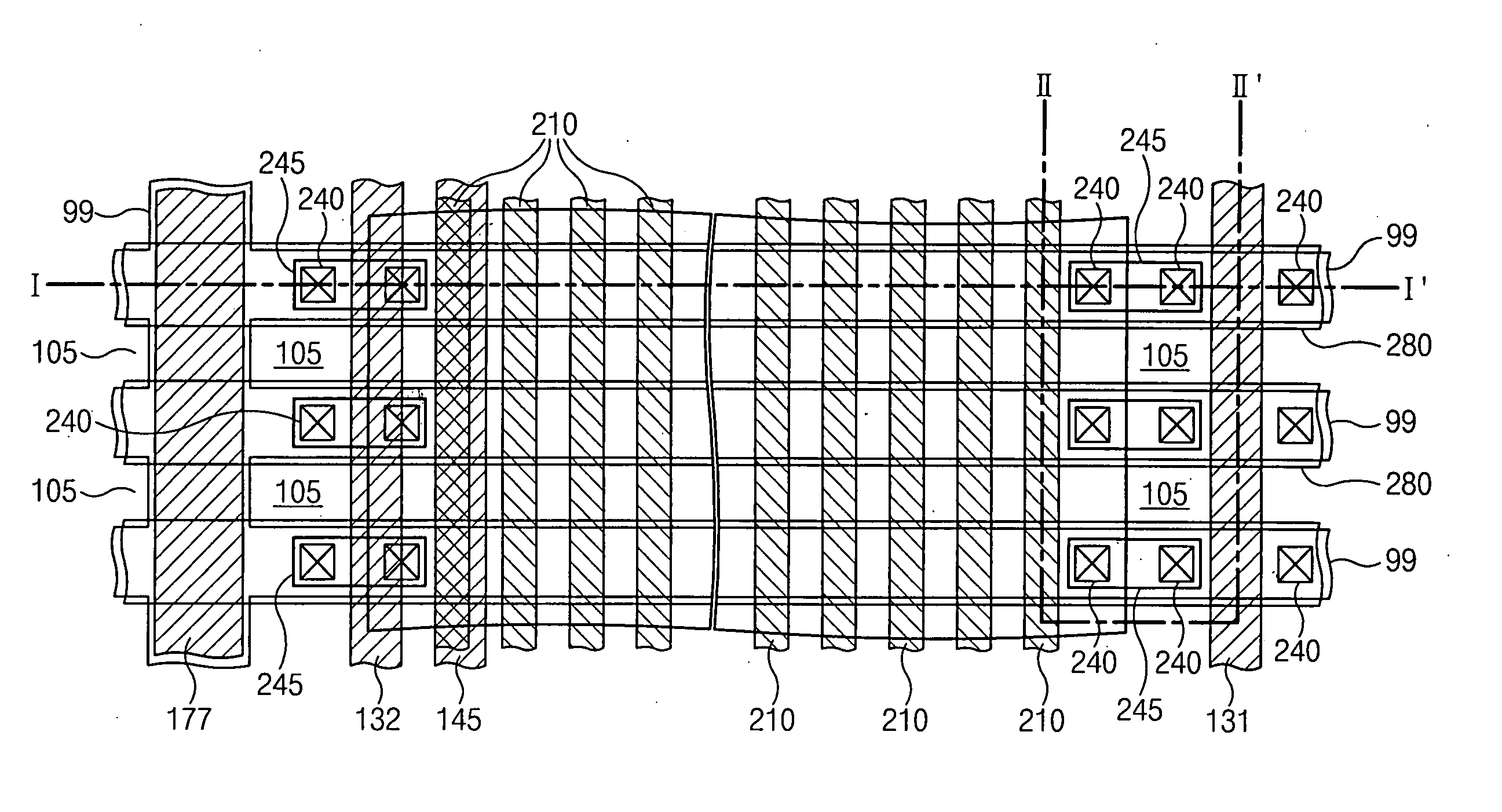

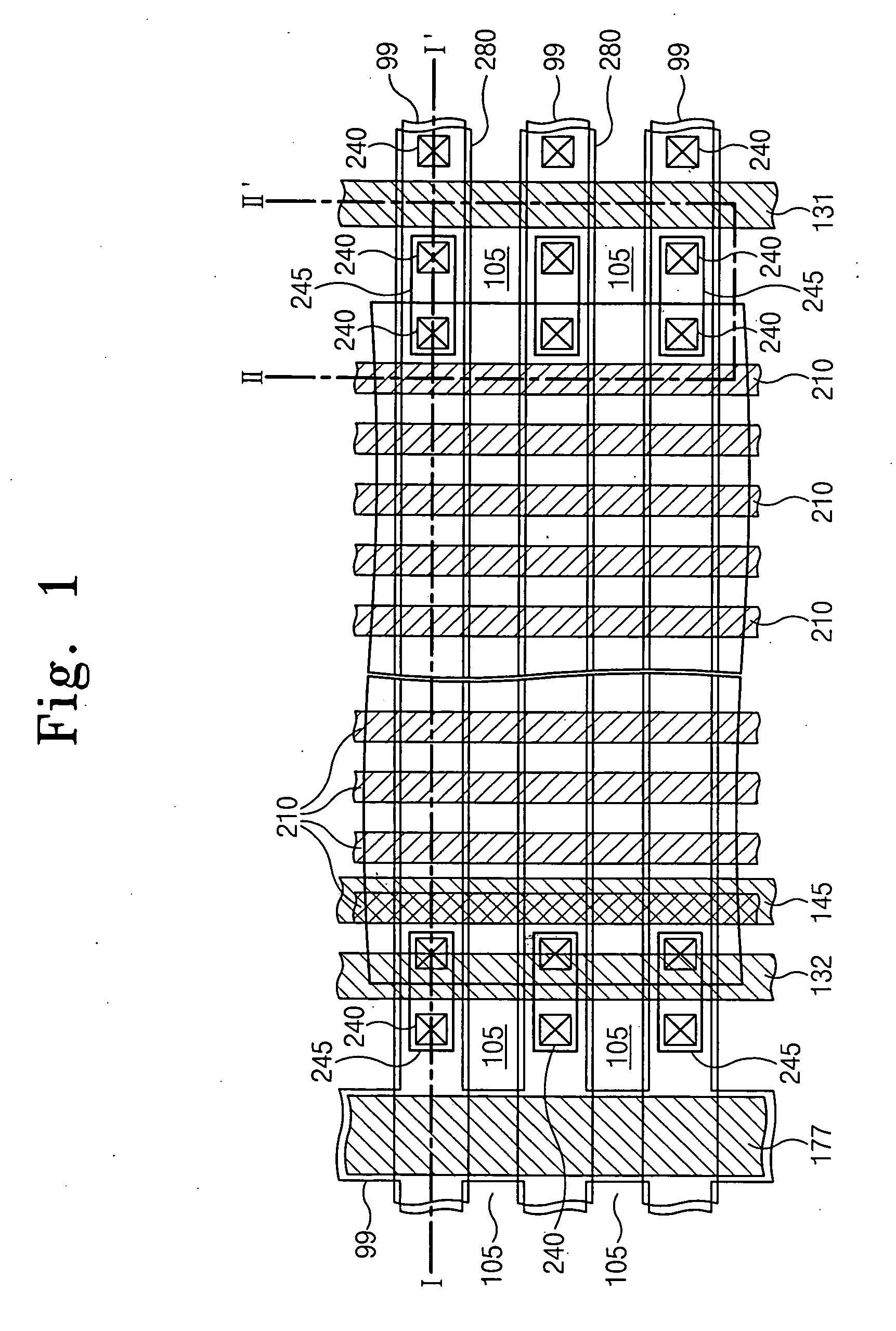

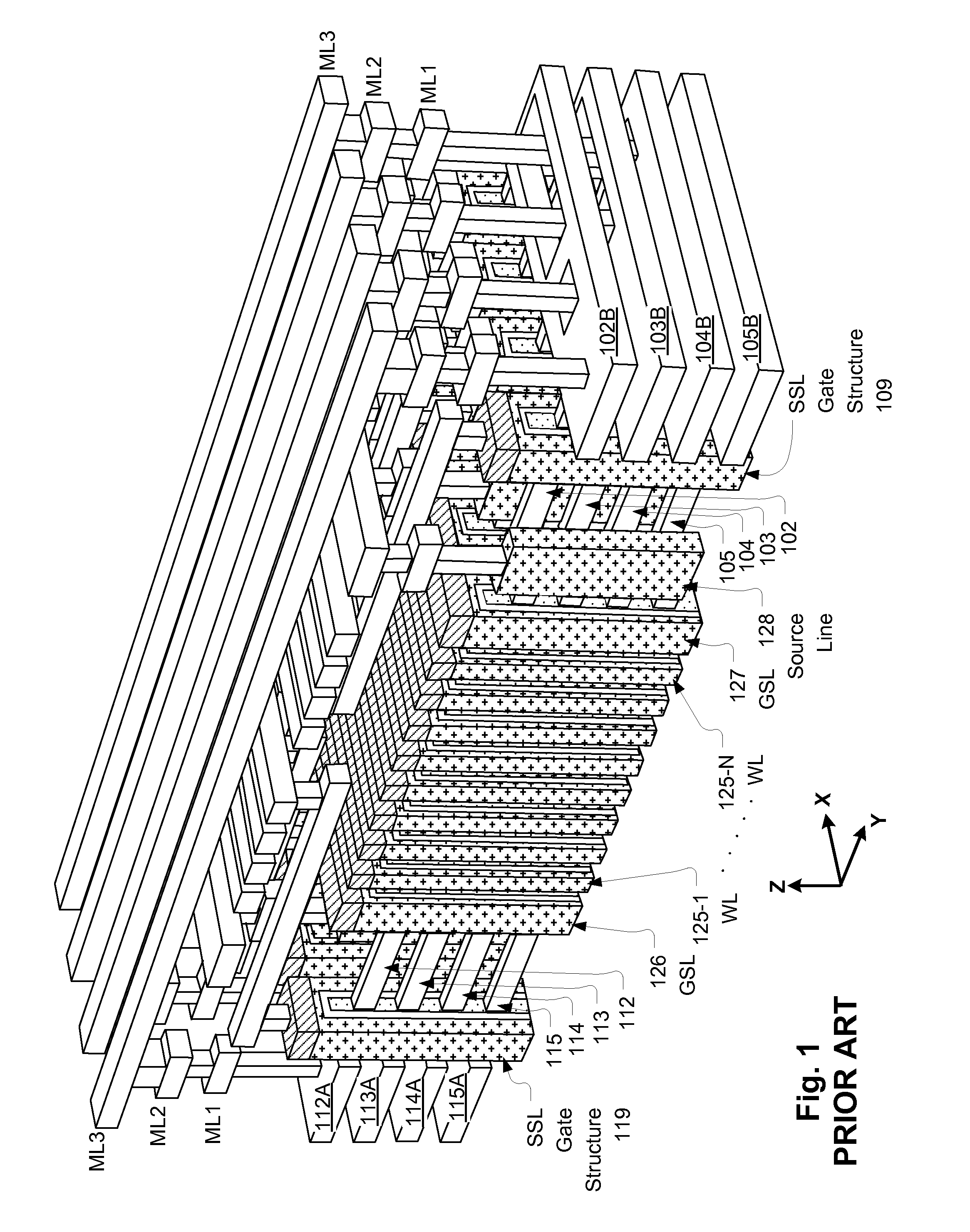

NAND flash memory devices including multi-layer memory cell transistor structures and methods of fabricating the same

InactiveUS20060108627A1Solid-state devicesSemiconductor/solid-state device manufacturingIntegrated circuitTransistor

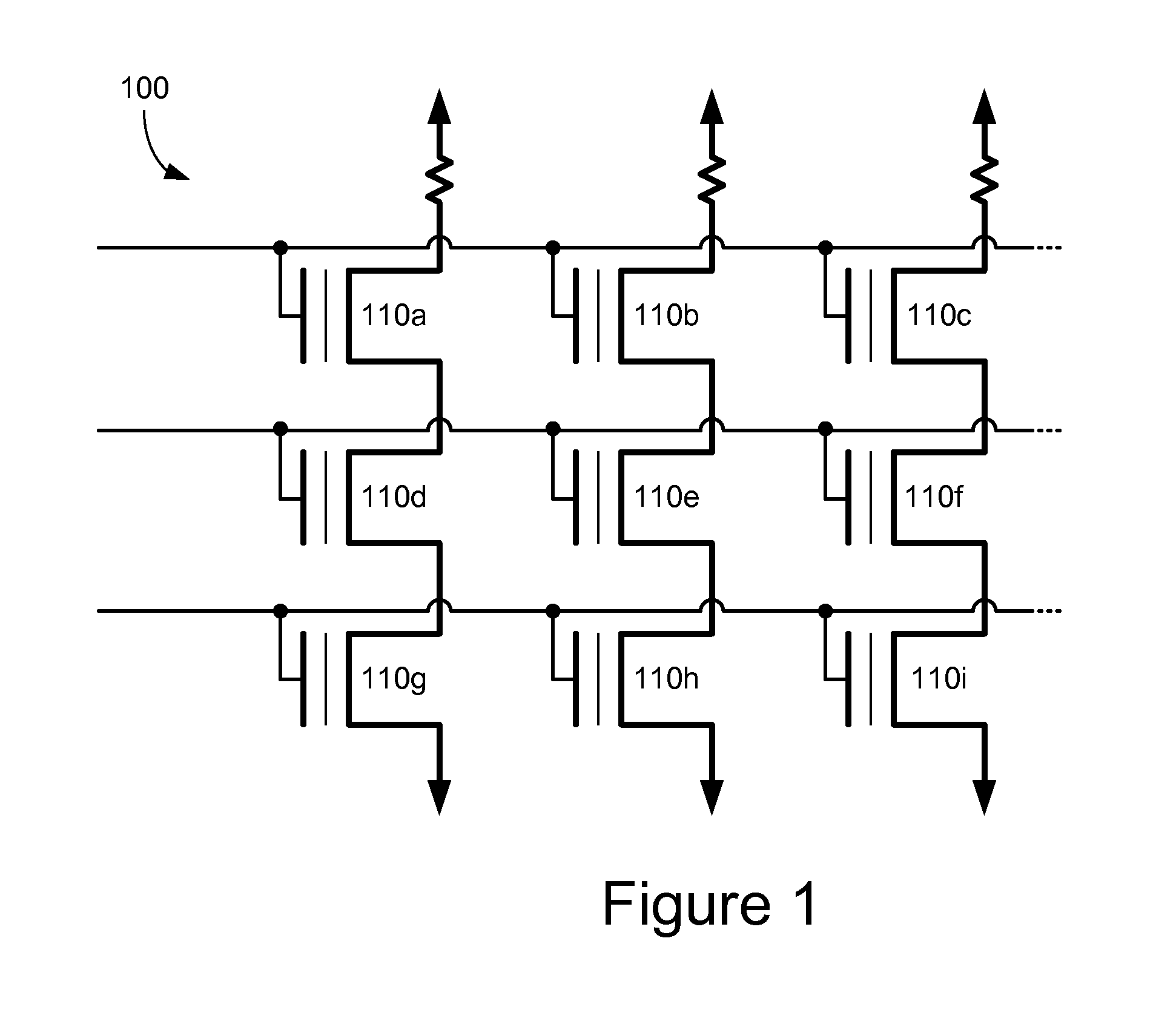

An integrated circuit memory device on a multi-layer substrate includes first and second selection transistors, a first plurality of serially connected memory cell transistors on a first substrate layer, and a second plurality of serially connected memory cell transistors on a second substrate layer. The first plurality of serially connected memory cell transistors are serially connected between the first and second selection transistors. The second plurality of serially connected memory cell transistors are also serially connected between the first and second selection transistors.

Owner:SAMSUNG ELECTRONICS CO LTD

NAND flash memory controller exporting a NAND interface

A NAND controller for interfacing between a host device and a flash memory device (e.g. a NAND flash memory device) fabricated on a flash die is disclosed. In some embodiments, the presently disclosed NAND controller includes electronic circuitry fabricated on a controller die, the controller die being distinct from the flash die, a first interface (e.g. a host-type interface, for example, a NAND interface) for interfacing between the electronic circuitry and the flash memory device, and a second interface (e.g. a flash-type interface) for interfacing between the controller and the host device, wherein the second interface is a NAND interface. According to some embodiments, the first interface is an inter-die interface. According to some embodiments, the first interface is a NAND interface. Systems including the presently disclosed NAND controller are also disclosed. Methods for assembling the aforementioned systems, and for reading and writing data using NAND controllers are also disclosed.

Owner:INNOVATIVE MEMORY SYST INC

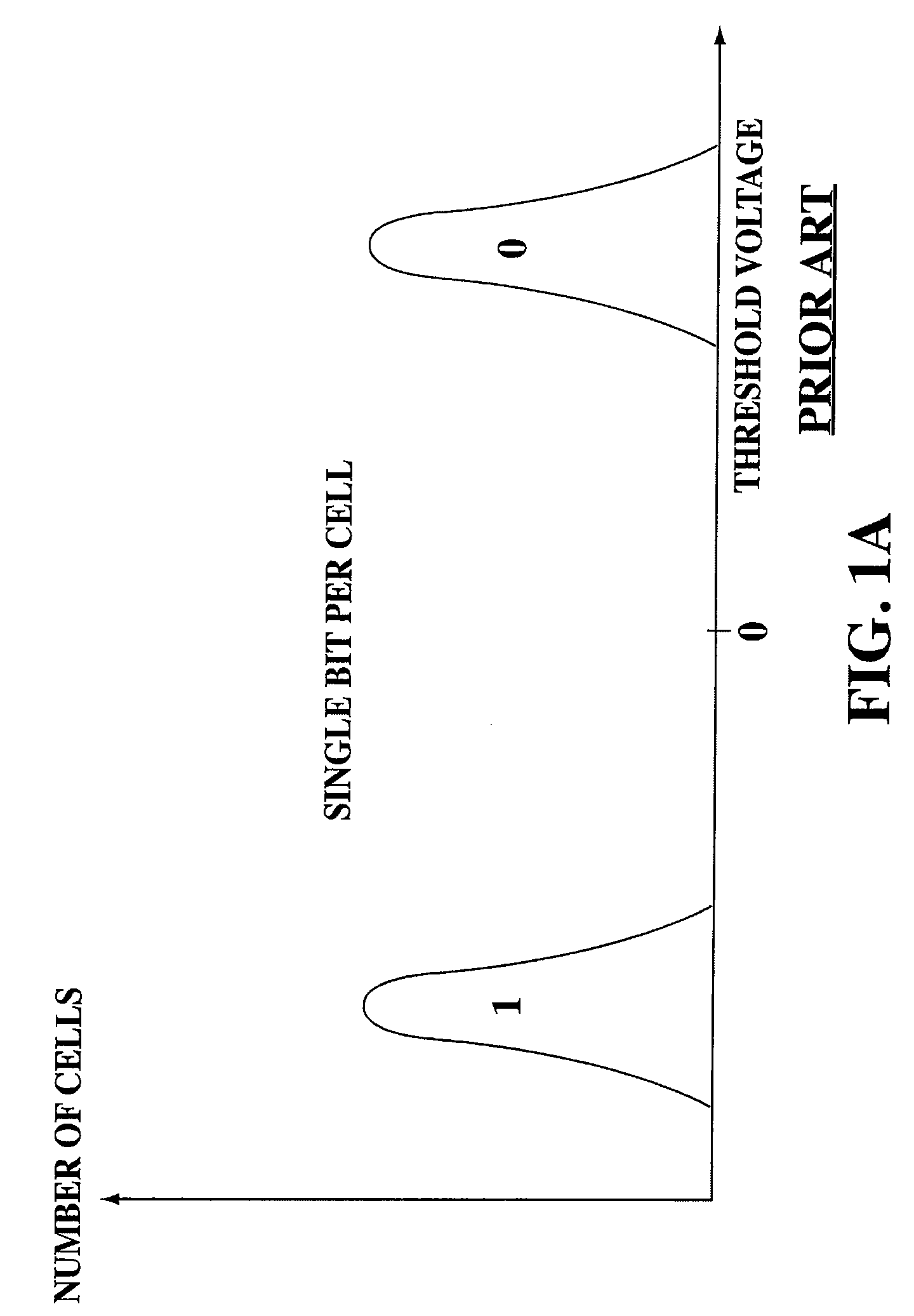

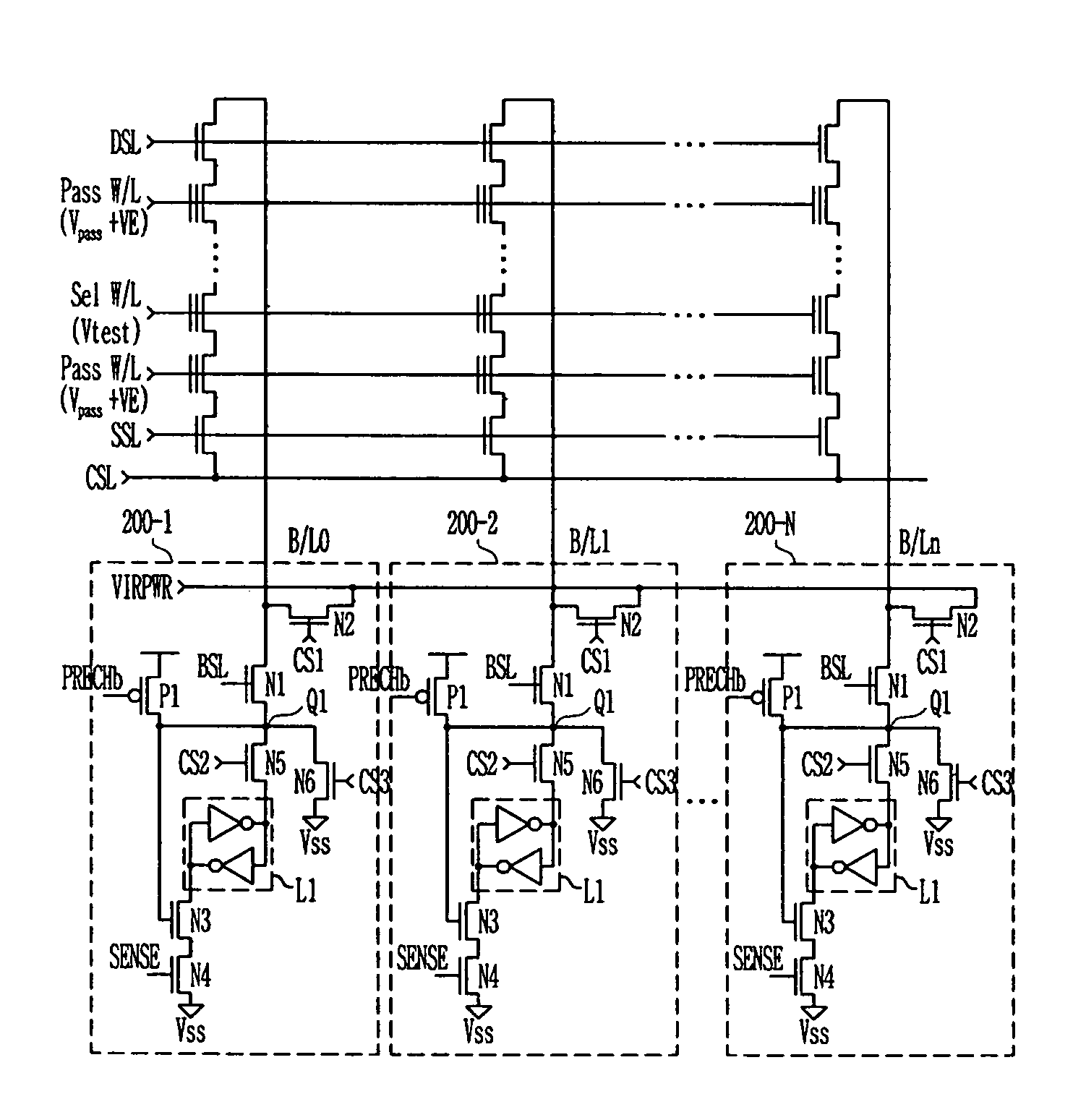

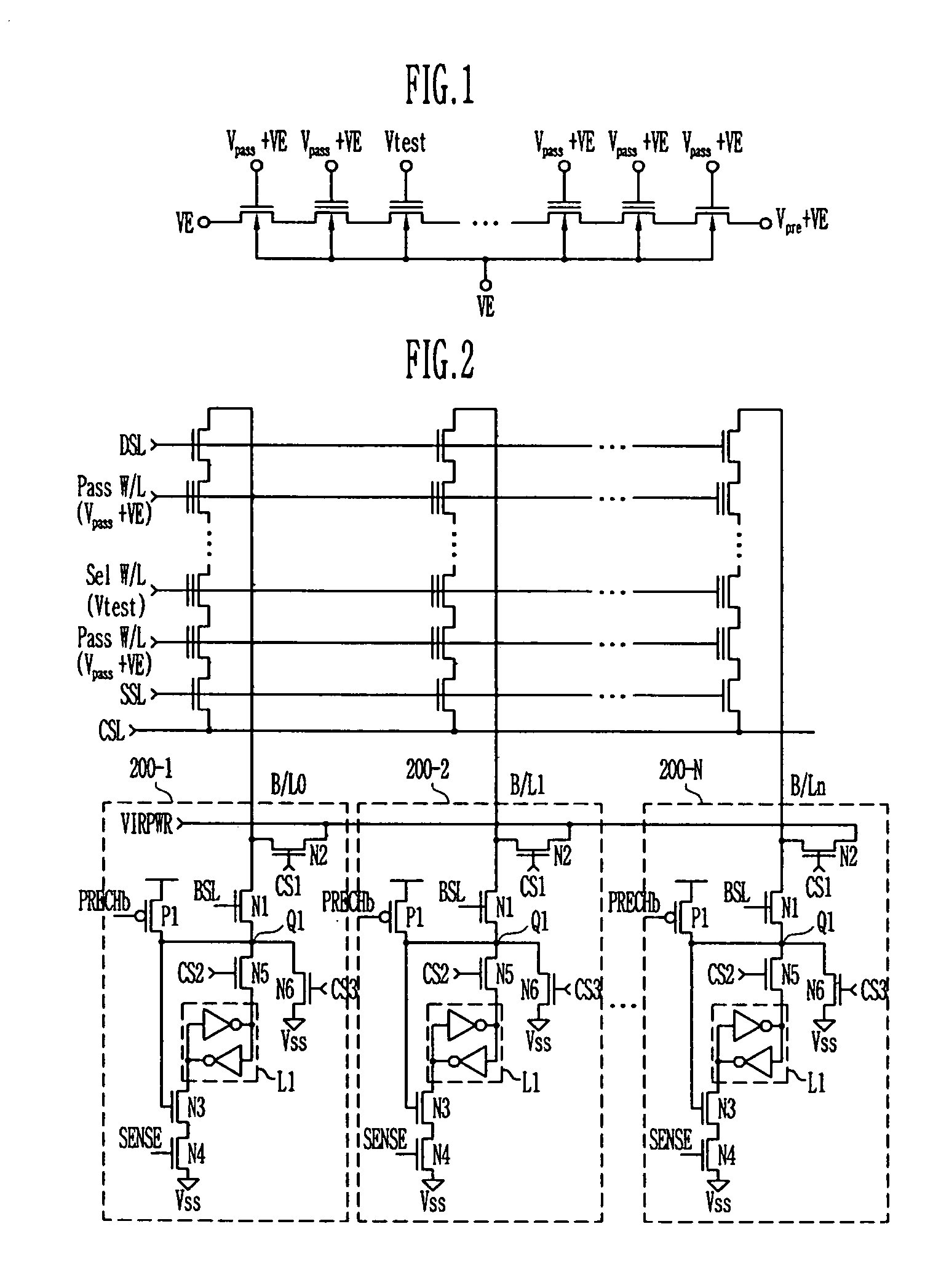

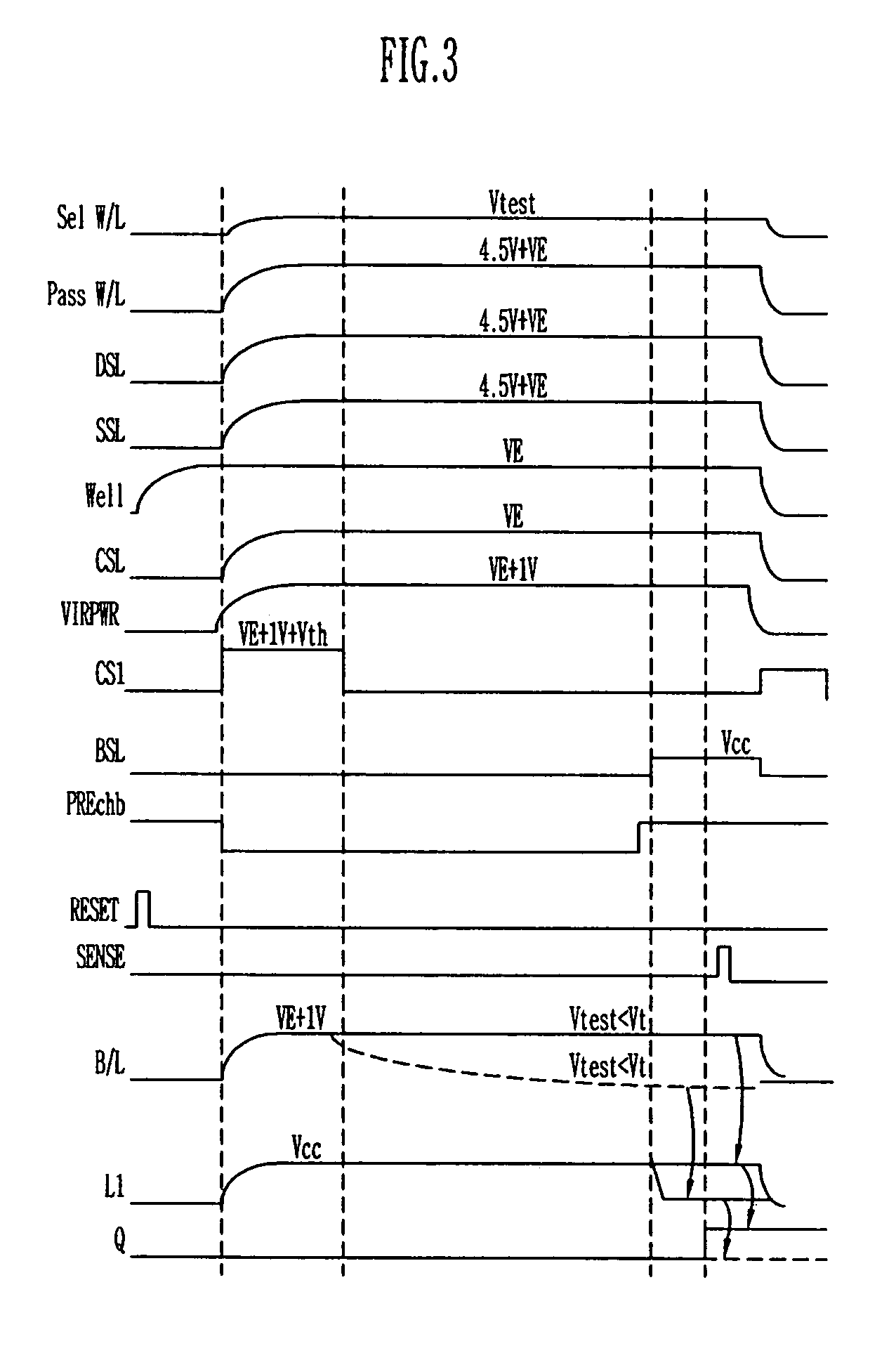

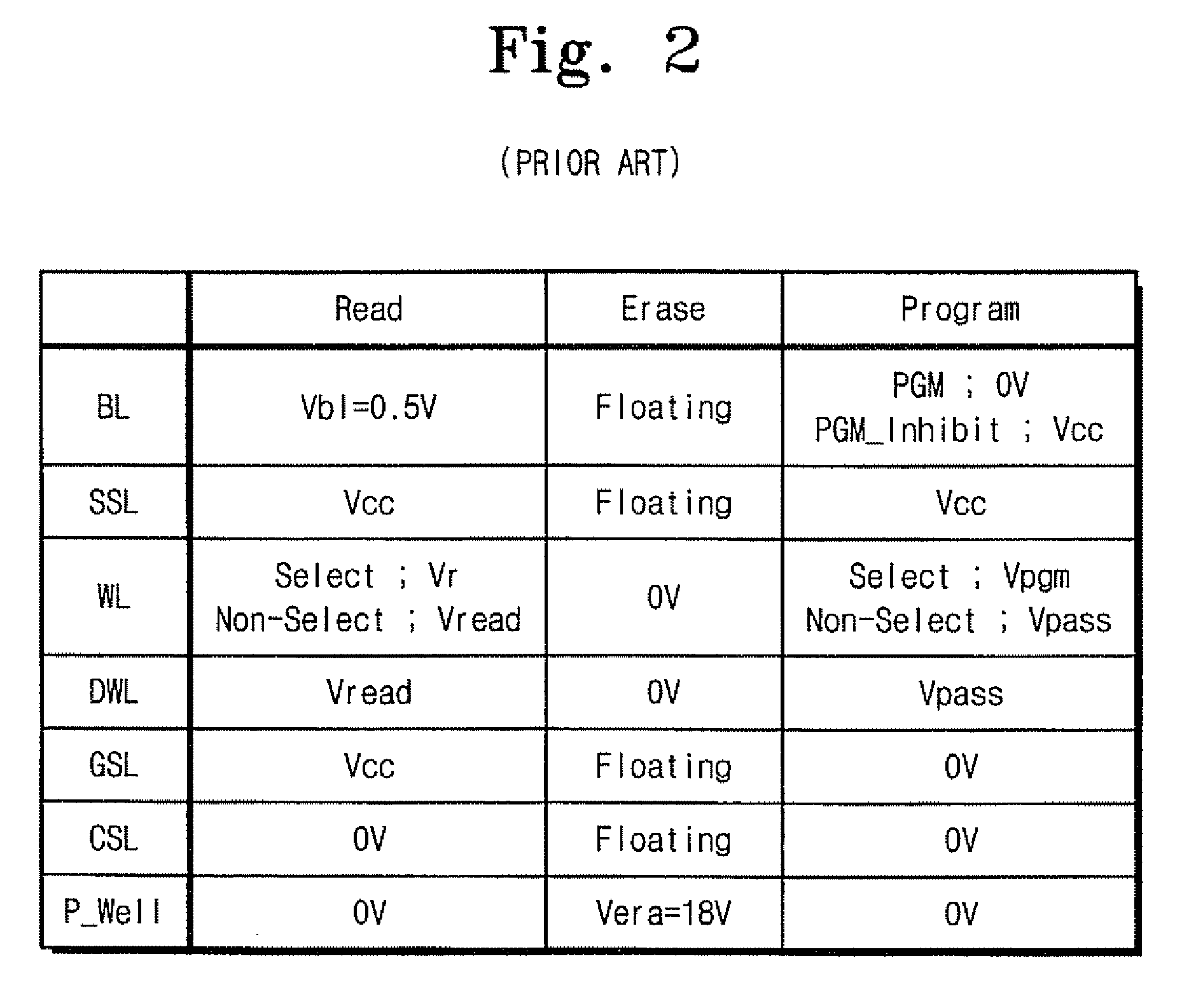

Method of measuring threshold voltage for a NAND flash memory device

Provided is a method of measuring threshold voltages in a NAND flash memory device. In the method, a test voltage is applied to a wordline of selected memory cells to measure a distribution profile of threshold voltages of memory cells. A voltage summing up a pass voltage and an operation voltage is applied to wordlines of deselected cells. The operation voltage is applied to a well and a common source line. A voltage summing up a precharge voltage and the operation voltage is applied to a bitline. After then, a voltage variation on the bitline can be detected to measure a threshold voltage of a memory cell. A negative threshold voltage can be measured by applying a positive voltage with reference to a voltage, as the threshold voltage of the memory cell, set by subtracting the operation voltage from the test voltage in accordance with the bitline voltage variation.

Owner:STMICROELECTRONICS SRL +1

NAND flash module replacement for DRAM module

ActiveUS8185685B2Reduce speedMost efficientMemory architecture accessing/allocationMemory adressing/allocation/relocationProcess memoryControl signal

An electronic memory module according to the invention provides non-volatile memory that can be used in place of a DRAM module without battery backup. An embodiment of the invention includes an embedded microprocessor with microcode that translates the FB-DIMM address and control signals from the system into appropriate address and control signals for NAND flash memory. Wear-leveling, bad block management, garbage collection are preferably implemented by microcode executed by the microprocessor. The microprocessor, additional logic, and embedded memory provides the functions of a flash memory controller. The microprocessor memory preferably contains address mapping tables, free page queue, and garbage collection information.

Owner:WESTERN DIGITAL TECH INC

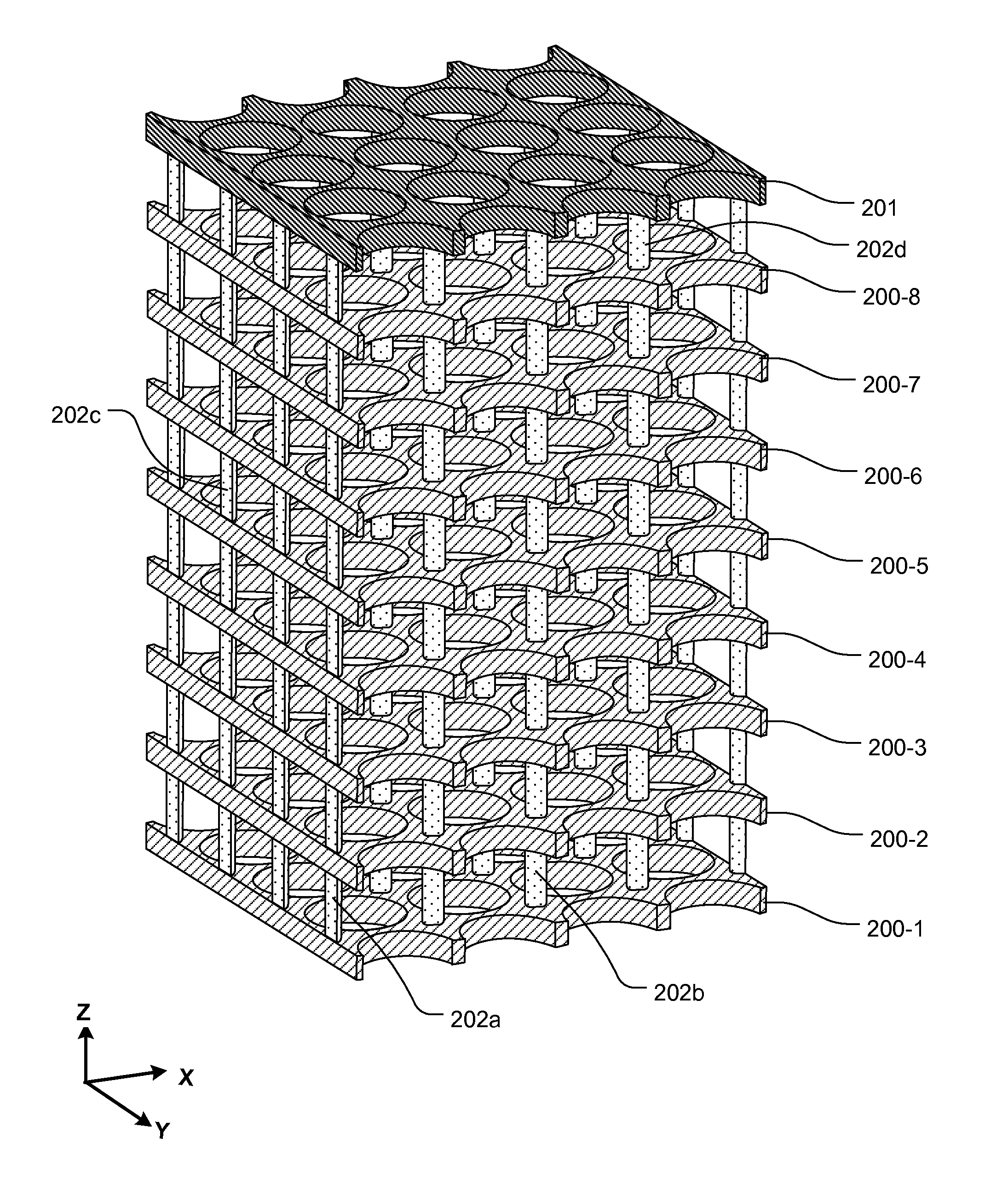

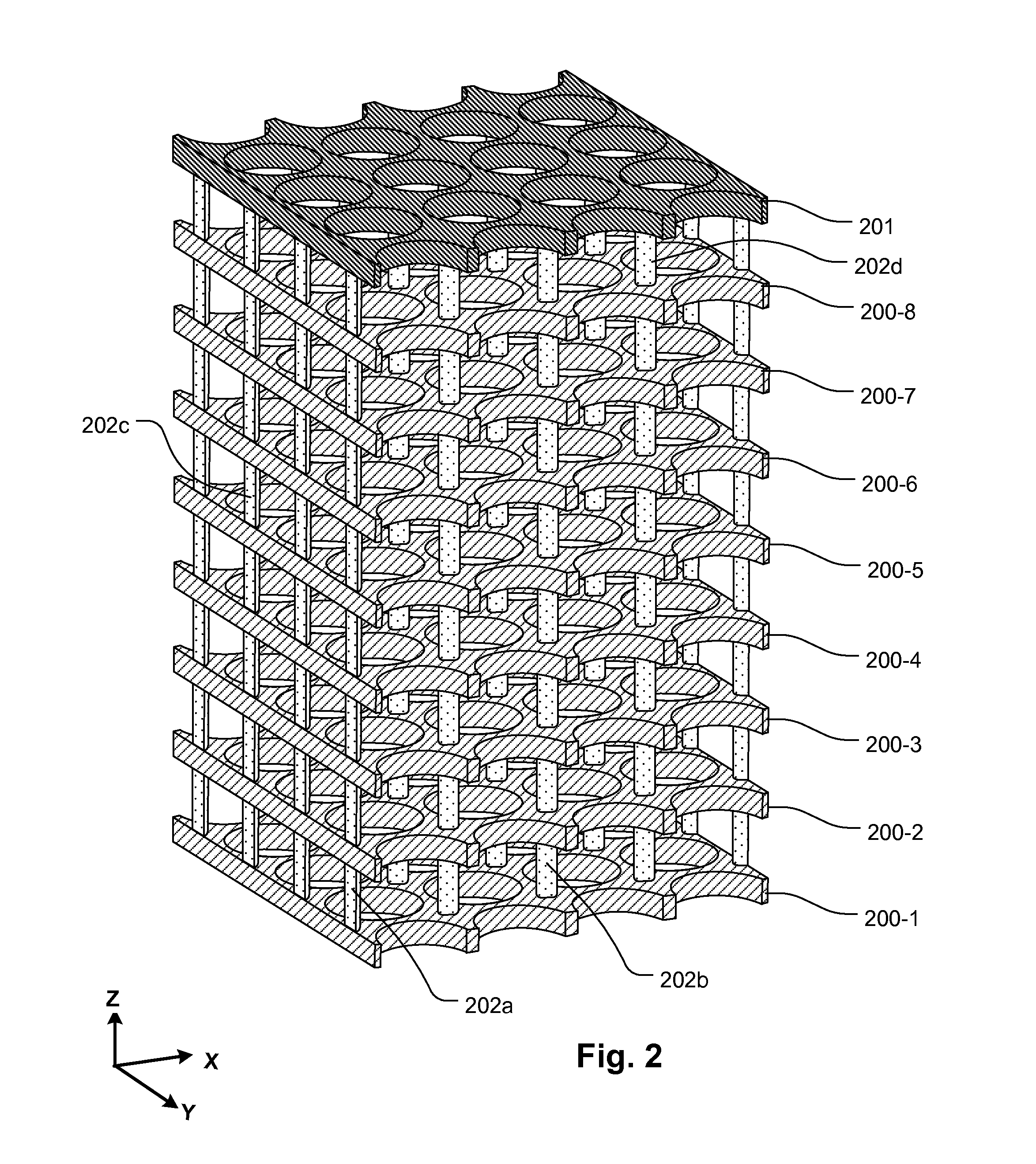

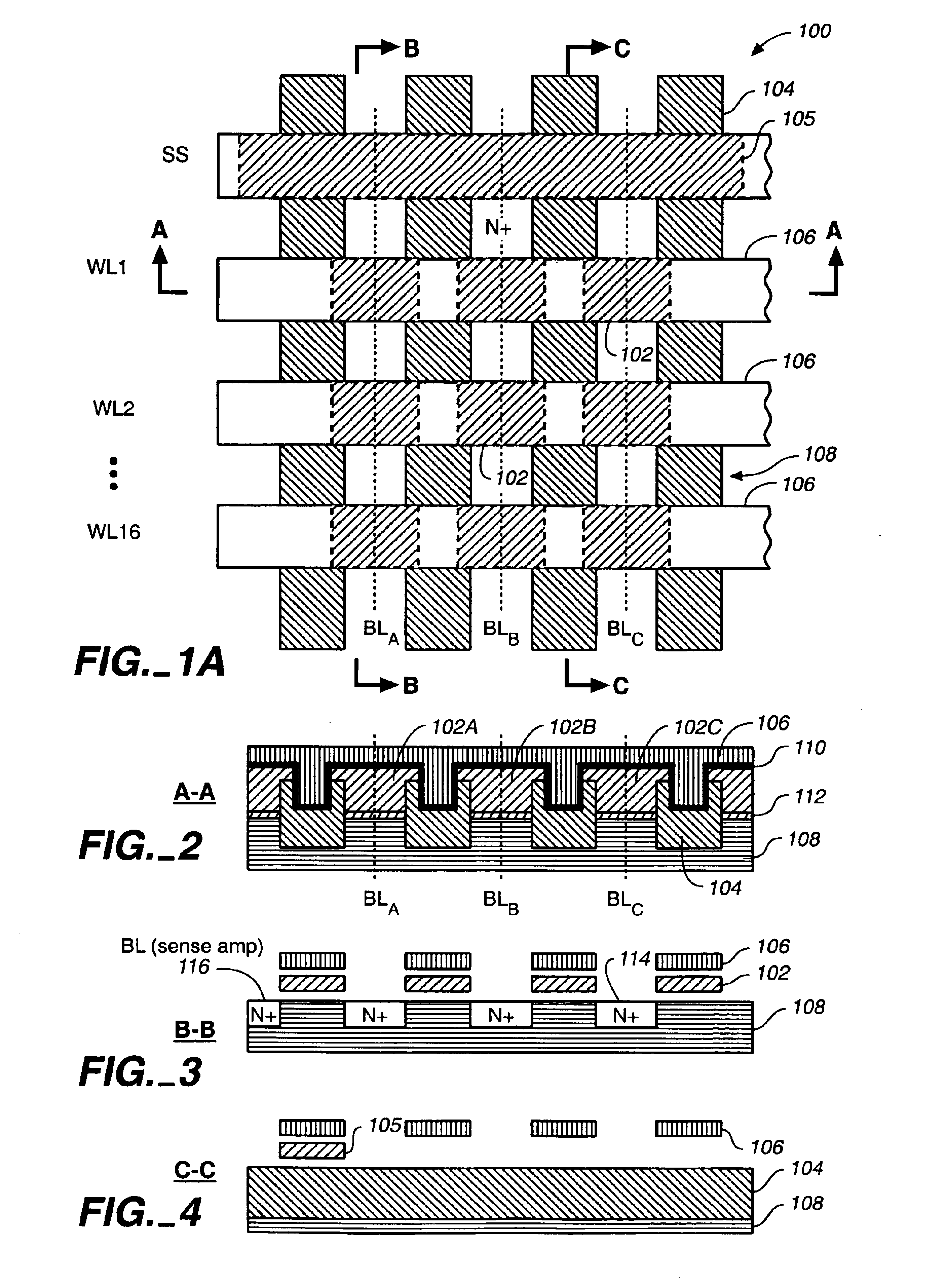

Vertical and 3D memory devices and methods of manufacturing the same

ActiveUS20160141299A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical slice

A memory device is described, which includes a block of memory cells comprising a plurality of stacks of horizontal active lines such as NAND string channel lines, with a plurality of vertical slices penetrated by, and surrounding, the horizontal active lines to provide a gate-all-around structure. A memory film is disposed between the horizontal active lines in the plurality of stacks and the vertical slices in the plurality of vertical slices. A 3D, horizontal channel, gate-all-around NAND flash memory is provided. A method for manufacturing a memory involves a buttress process. The buttress process enables horizontal channel, gate-all-around structures.

Owner:MACRONIX INT CO LTD

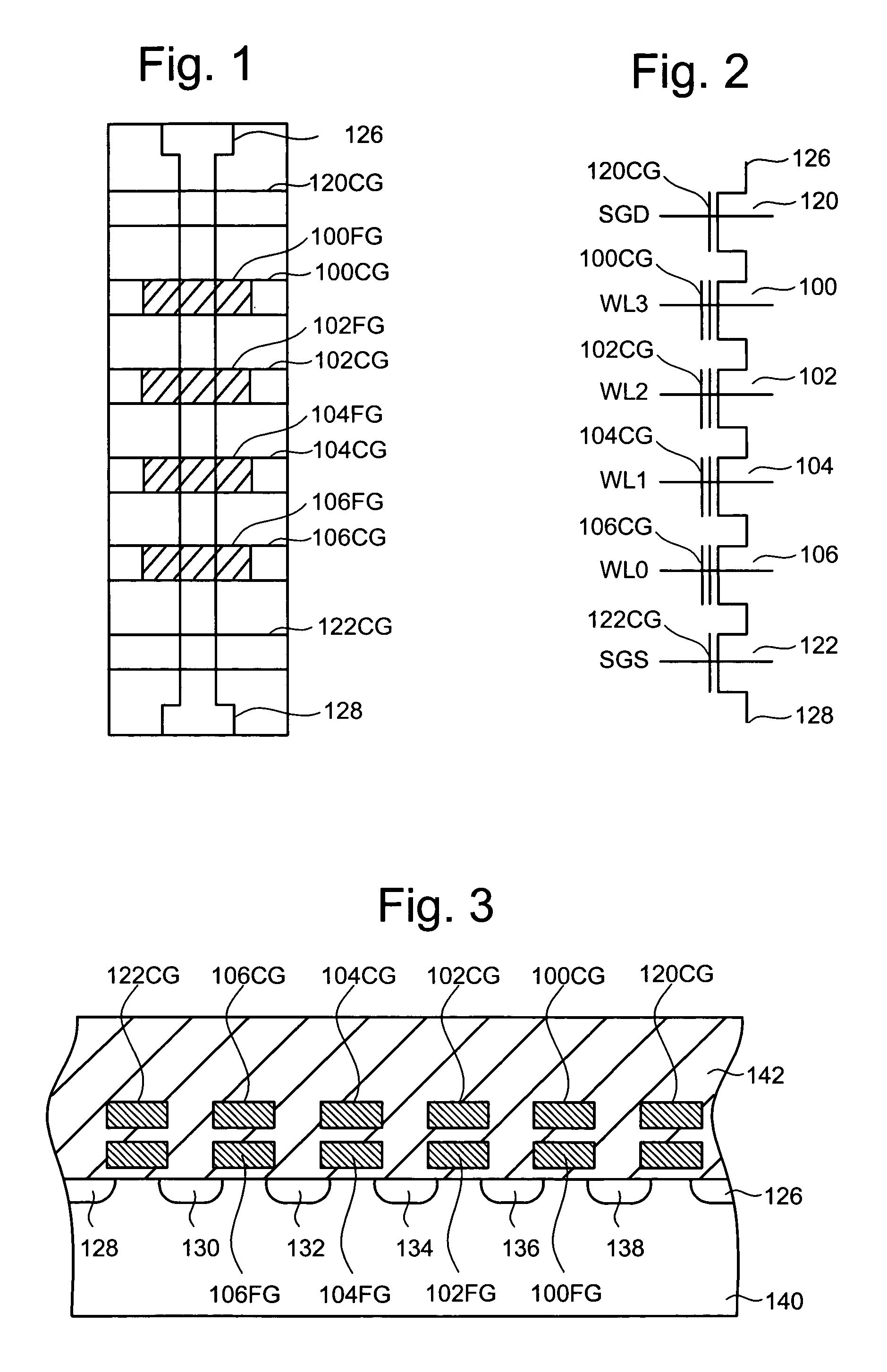

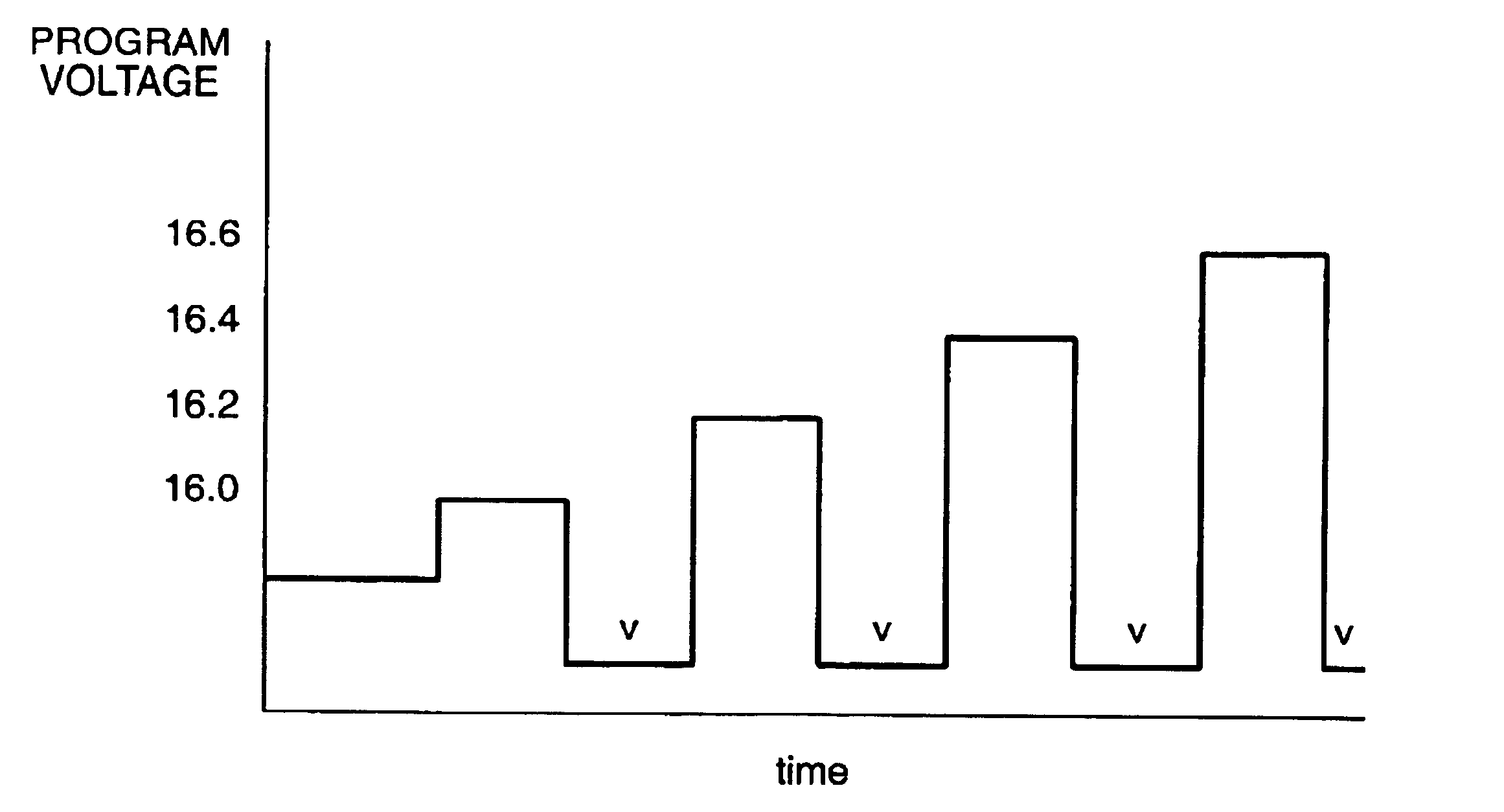

Self-boosting system for flash memory cells

ActiveUS20050174852A1Reduce leakageLowering drain side area boosted voltageRead-only memoriesDigital storageLow voltageThreshold voltage

A low voltage of the order of or one to three volts instead of an intermediate VPASS voltage (e.g. of the order of five to ten volts) is applied to word line zero immediately adjacent to the source or drain side select gate of a NAND flash device to reduce or prevent the shifting of threshold voltage of the memory cells coupled to word line zero during the programming cycles of the different cells of the NAND strings. This may be implemented in any one of a variety of different self boosting schemes including erased areas self boosting and local self boosting schemes. In a modified erased area self boosting scheme, low voltages are applied to two or more word lines on the source side of the selected word line to reduce band-to-band tunneling and to improve the isolation between two boosted channel regions. In a modified local self boosting scheme, zero volt or low voltages are applied to two or more word lines on the source side and to two or more word lines on the drain side of the selected word line to reduce band-to-band tunneling and to improve the isolation of the channel areas coupled to the selected word line.

Owner:SANDISK TECH LLC

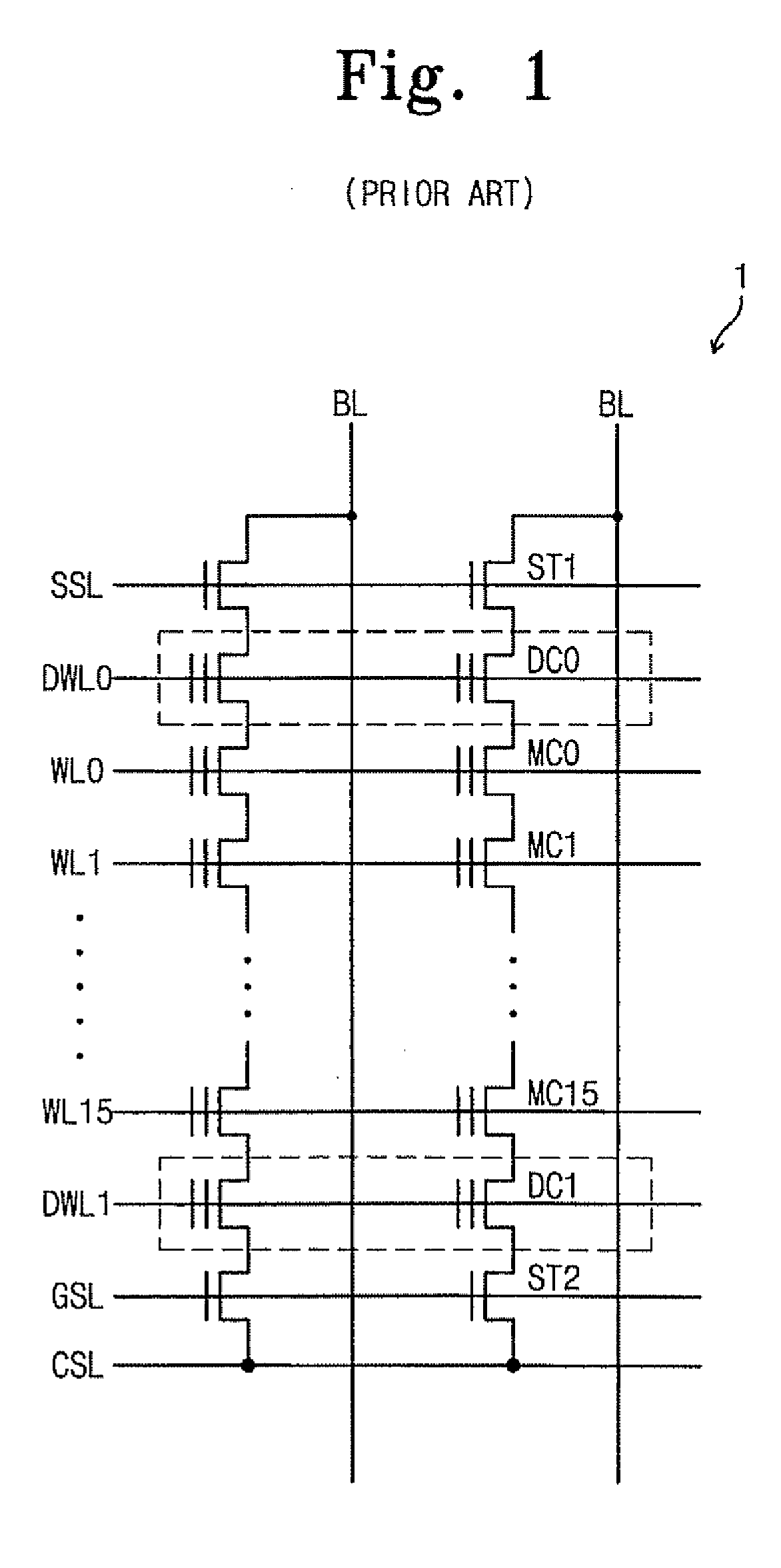

NAND Flash Memory Device Having Dummy Memory cells and Methods of Operating Same

A NAND flash memory device includes a control circuit configured to apply, during a program operation, a first word line voltage to non-selected ones of a plurality of serially-connected memory cells, a second word line voltage greater than the first word line voltage to a selected one of the plurality of memory cells, and a third word line voltage lower than the first word line voltage to a dummy memory cell connected in series with the plurality of memory cells. In other embodiments, a control circuit is configured to program a dummy memory cell before and / or after each erase operation on a plurality of memory cells connected in series therewith. In still other embodiments, a control circuit is configured to forego erasure of a dummy memory cell while erasing a plurality of memory cells connected in series therewith.

Owner:SAMSUNG ELECTRONICS CO LTD

Deep wordline trench to shield cross coupling between adjacent cells for scaled NAND

InactiveUS6898121B2Minimize impactHigh density NAND typeTransistorSolid-state devicesCouplingParallel computing

A NAND flash memory structure with a wordline or control gate that provides shielding from Yupin effect errors and generally from potentials in adjacent strings undergoing programming operations with significant variations in potential.

Owner:SANDISK TECH LLC

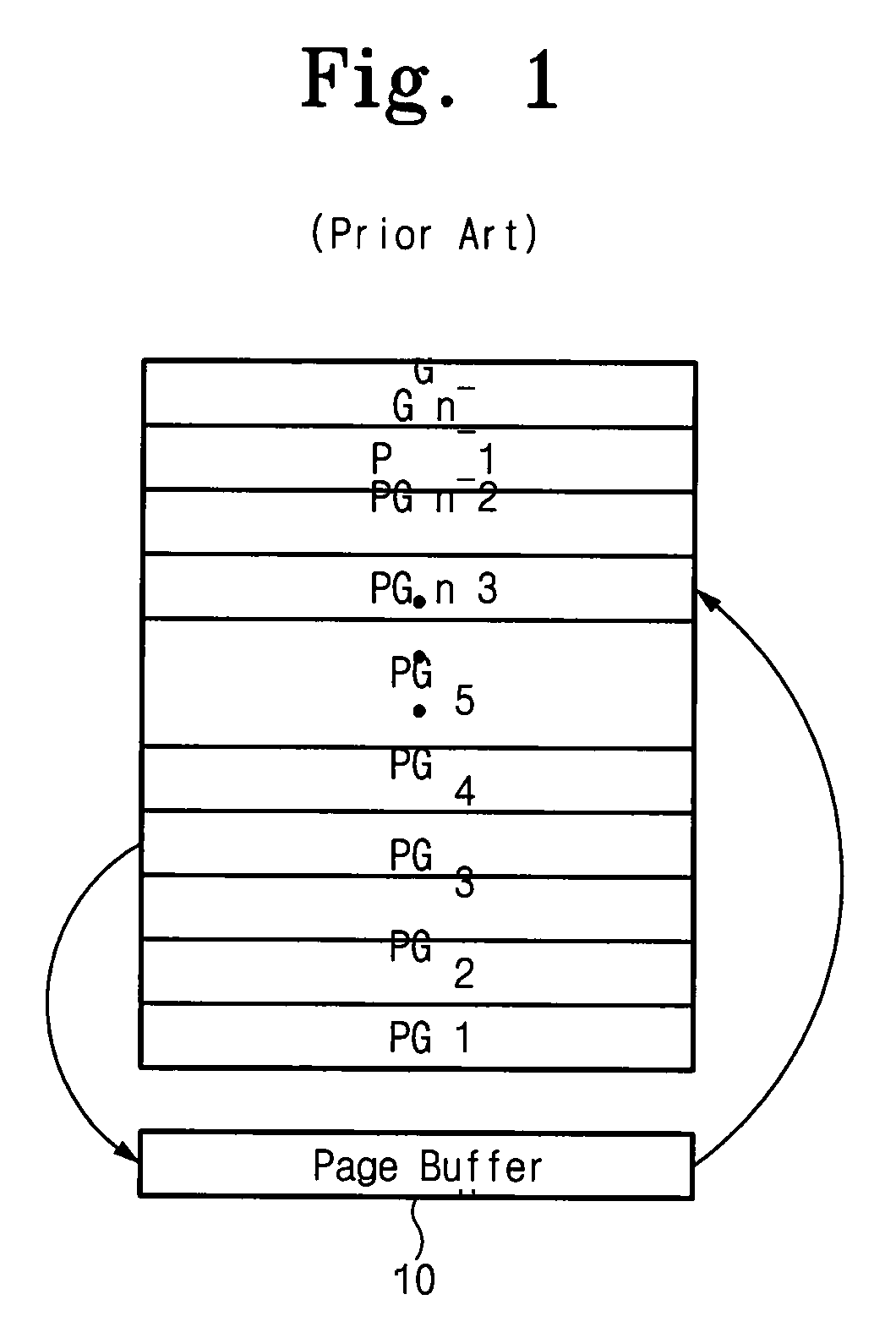

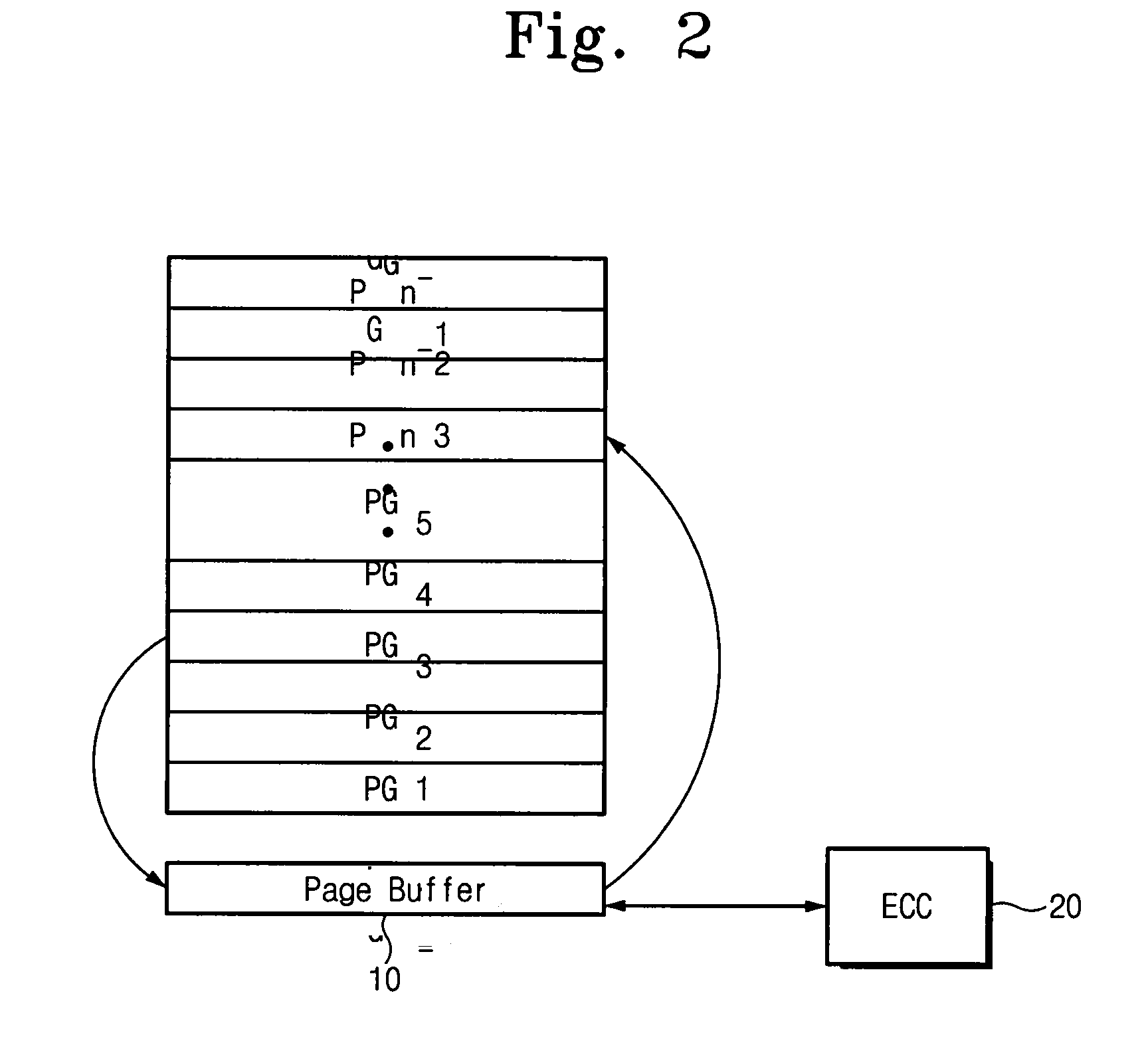

Nonvolatile memory with error correction for page copy operation and method thereof

InactiveUS20080163030A1Transcription errorMaintain integrityMemory loss protectionMemory adressing/allocation/relocationError checkingData storing

The disclosure is a NAND flash memory with the function of error checking and correction during a page copy operation. The NAND flash memory is able to prohibit transcription of erroneous bits to a duplicate page from a source page. Embodiments of the inventive flash memory include a correction circuit for correcting bit errors of source data stored in a page buffer, a circuit configured to provide the source data to the correction circuit and to provide correction data to the page buffer, and a copy circuit configured to copy the source data to the page buffer, and to store the correction data in the other page from the page buffer.

Owner:SAMSUNG ELECTRONICS CO LTD

Self-boosting system for flash memory cells

ActiveUS7161833B2Undesirable change can be preventedLower areaRead-only memoriesDigital storageLow voltageEngineering

A low voltage of the order of or one to three volts instead of an intermediate VPASS voltage (e.g. of the order of five to ten volts) is applied to word line zero immediately adjacent to the source or drain side select gate of a NAND flash device to reduce or prevent the shifting of threshold voltage of the memory cells coupled to word line zero during the programming cycles of the different cells of the NAND strings. This may be implemented in any one of a variety of different self boosting schemes including erased areas self boosting and local self boosting schemes. In a modified erased area self boosting scheme, low voltages are applied to two or more word lines on the source side of the selected word line to reduce band-to-band tunneling and to improve the isolation between two boosted channel regions. In a modified local self boosting scheme, zero volt or low voltages are applied to two or more word lines on the source side and to two or more word lines on the drain side of the selected word line to reduce band-to-band tunneling and to improve the isolation of the channel areas coupled to the selected word line.

Owner:SANDISK TECH LLC

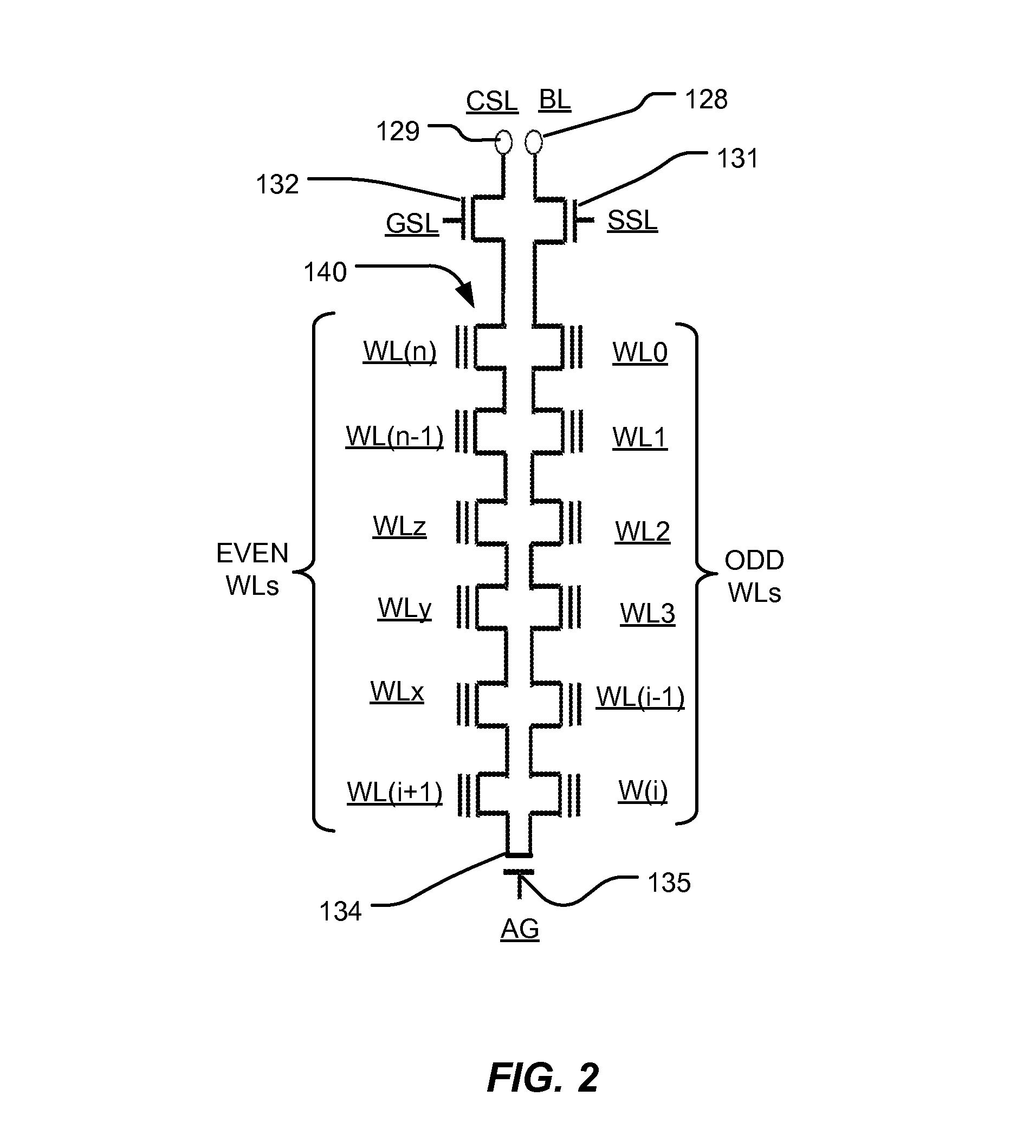

Reference line and bit line structure for 3D memory

A 3D NAND flash memory includes even and odd stacks of conductive strips. Some of the conductive strips in the stacks are configured as word lines. Data storage structures are disposed on the sidewalls of the even and odd stacks. Active pillars include even and odd semiconductor films on the data storage structures connected at the bottom ends so that the semiconductor films can be thin films having a U-shaped current path. An even pad connected to the even semiconductor film and an odd pad connected to the odd semiconductor film are disposed over the even and odd stacks respectively. A segment of a reference line is connected to the even pad, and an inter-level connector is connected to the odd pad. A segment of a bit line comprises an extension contacting the inter-level connector.

Owner:MACRONIX INT CO LTD

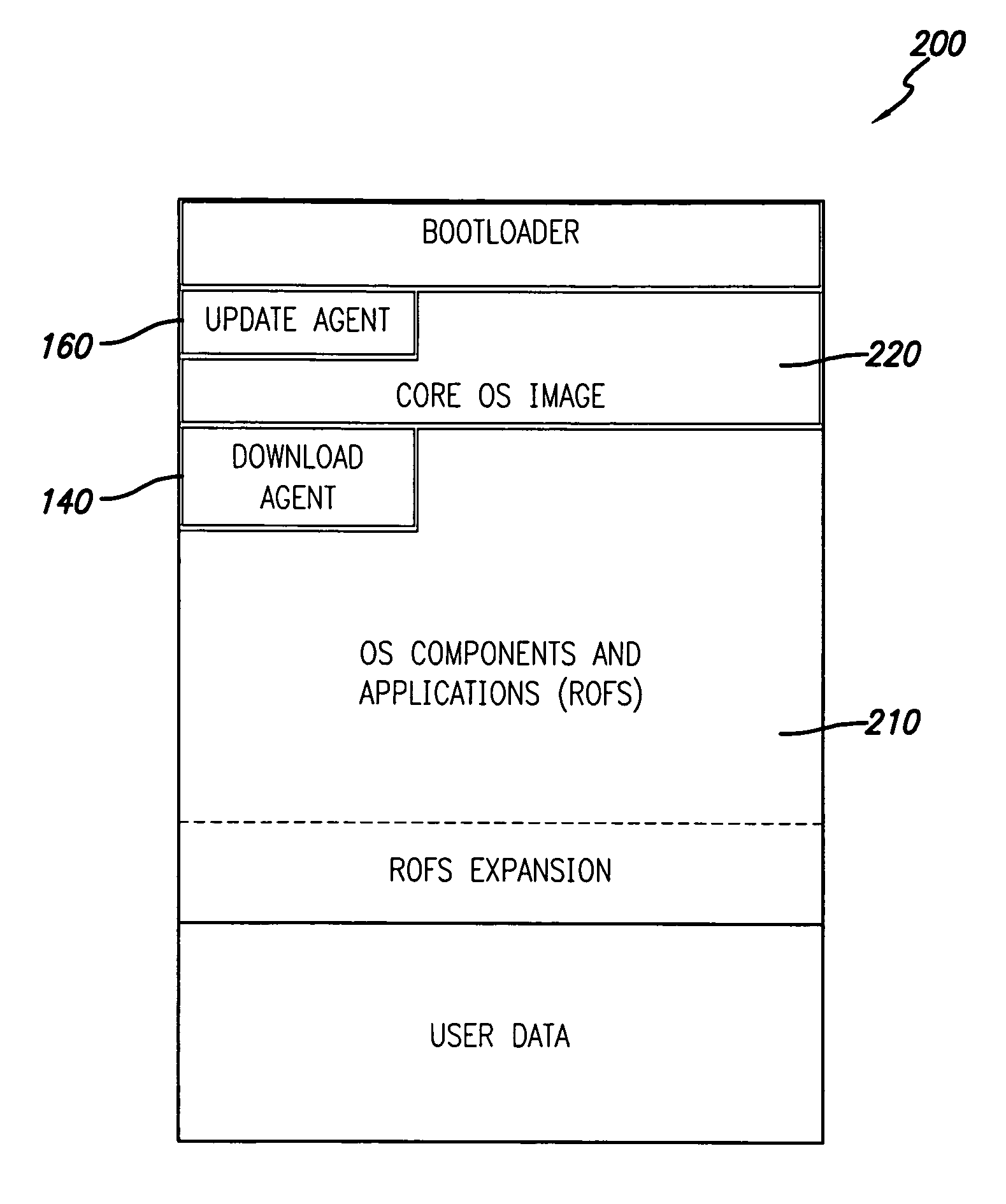

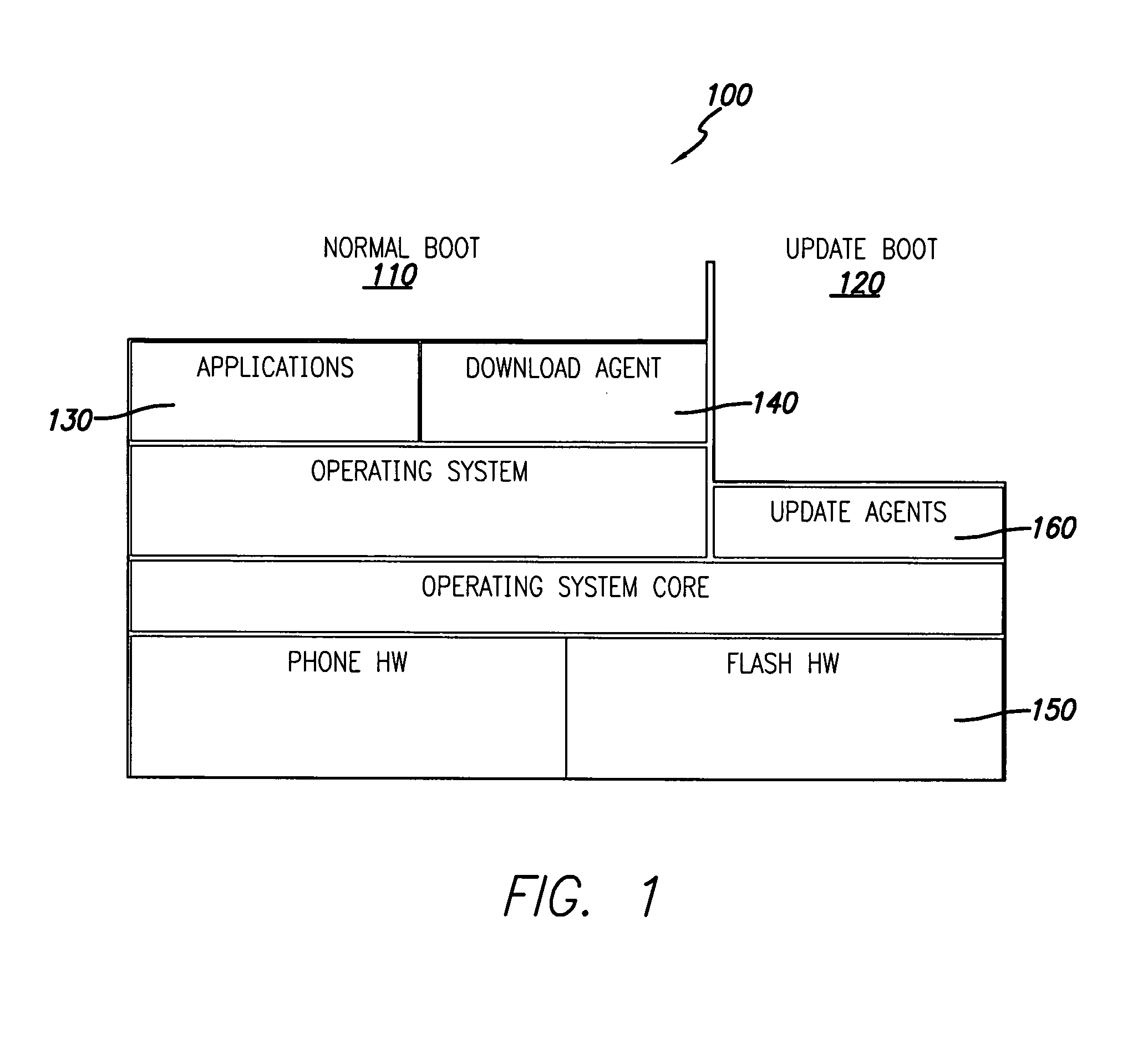

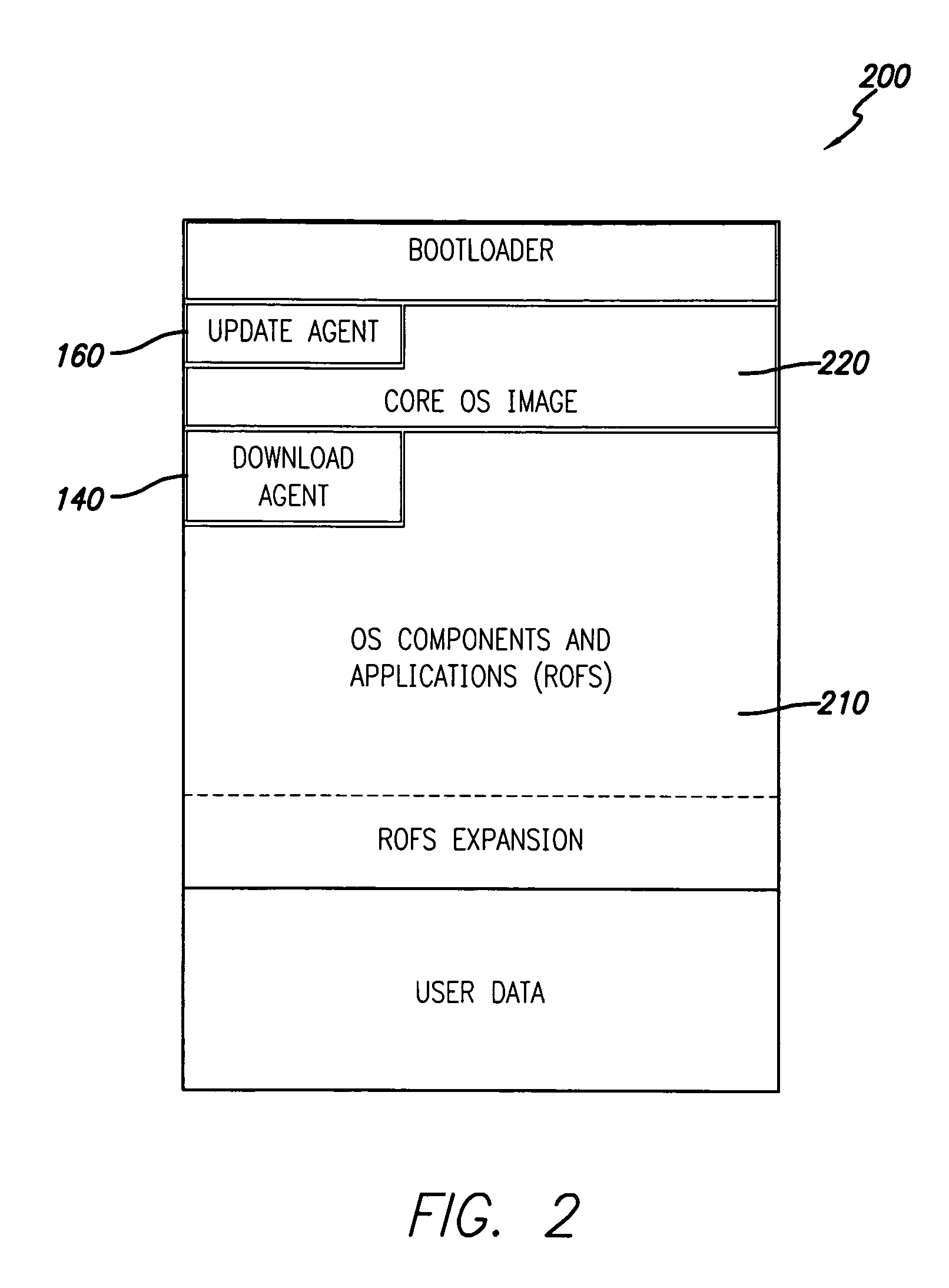

Method for over-the-air firmware update of NAND flash memory based mobile devices

ActiveUS7698698B2Easy to transplantAdvantage in code portabilityError detection/correctionSpecific program execution arrangementsOperational systemFile system

A method for receiving, storing, and applying an update package to modify an original image stored within non-volatile flash memory devices. More specifically, the present design provides a download agent responsible for communicating with a server to transfer and store the update package; and an update agent responsible for verifying, decompressing and decoding the update package. The present design separates non-essential operating system (OS) components and applications from the core OS, stores non-essential OS components, applications, and download agent as a single image in a read-only file system. This image may be updated by applying an update package created by running a binary differencing engine on two pre-built file system images representing the current and new file systems to modify the stored image. Additionally, the present design applies an update package to the core OS, which includes the update agent.

Owner:INSIGNIA SOLUTIONS

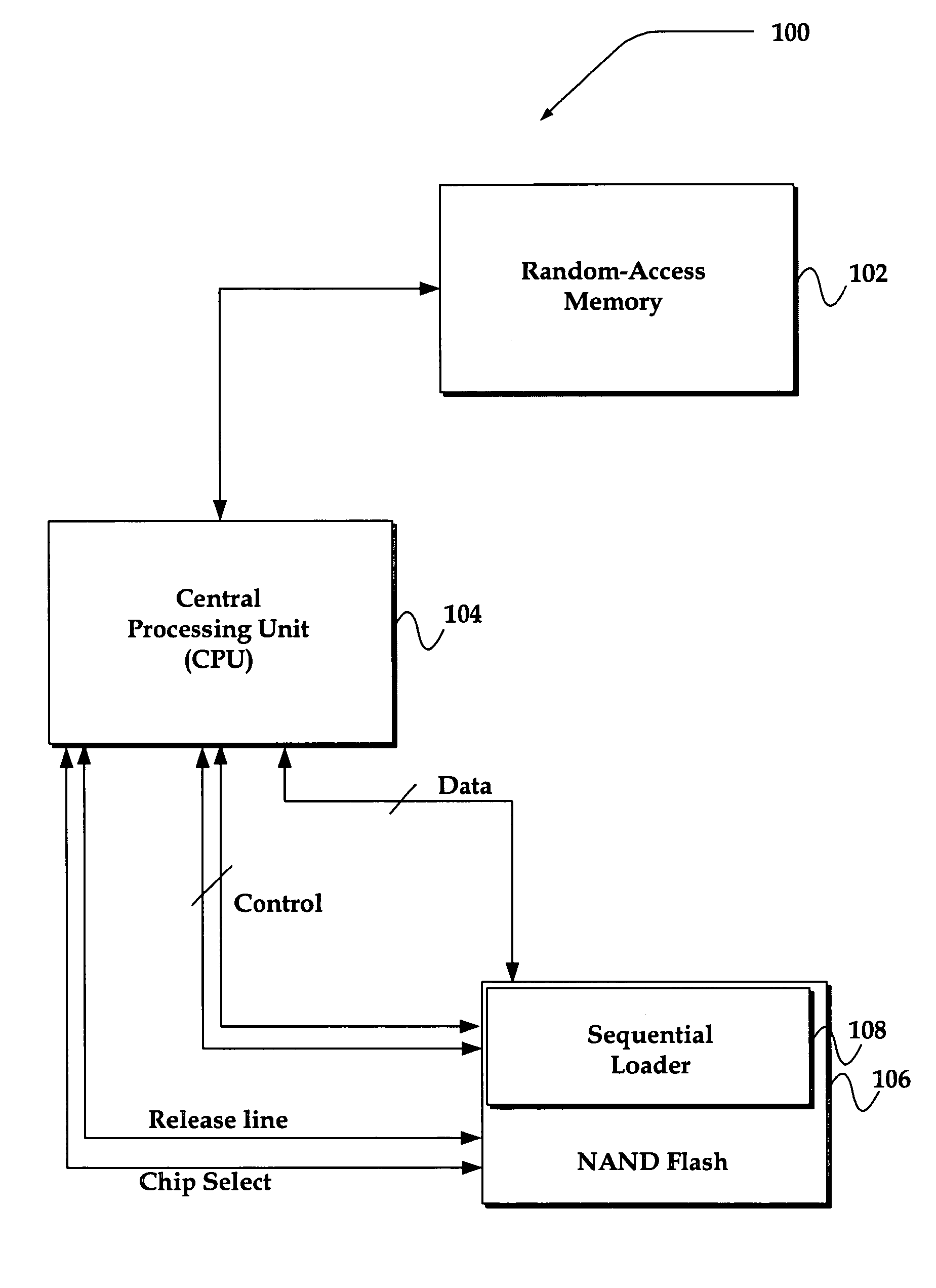

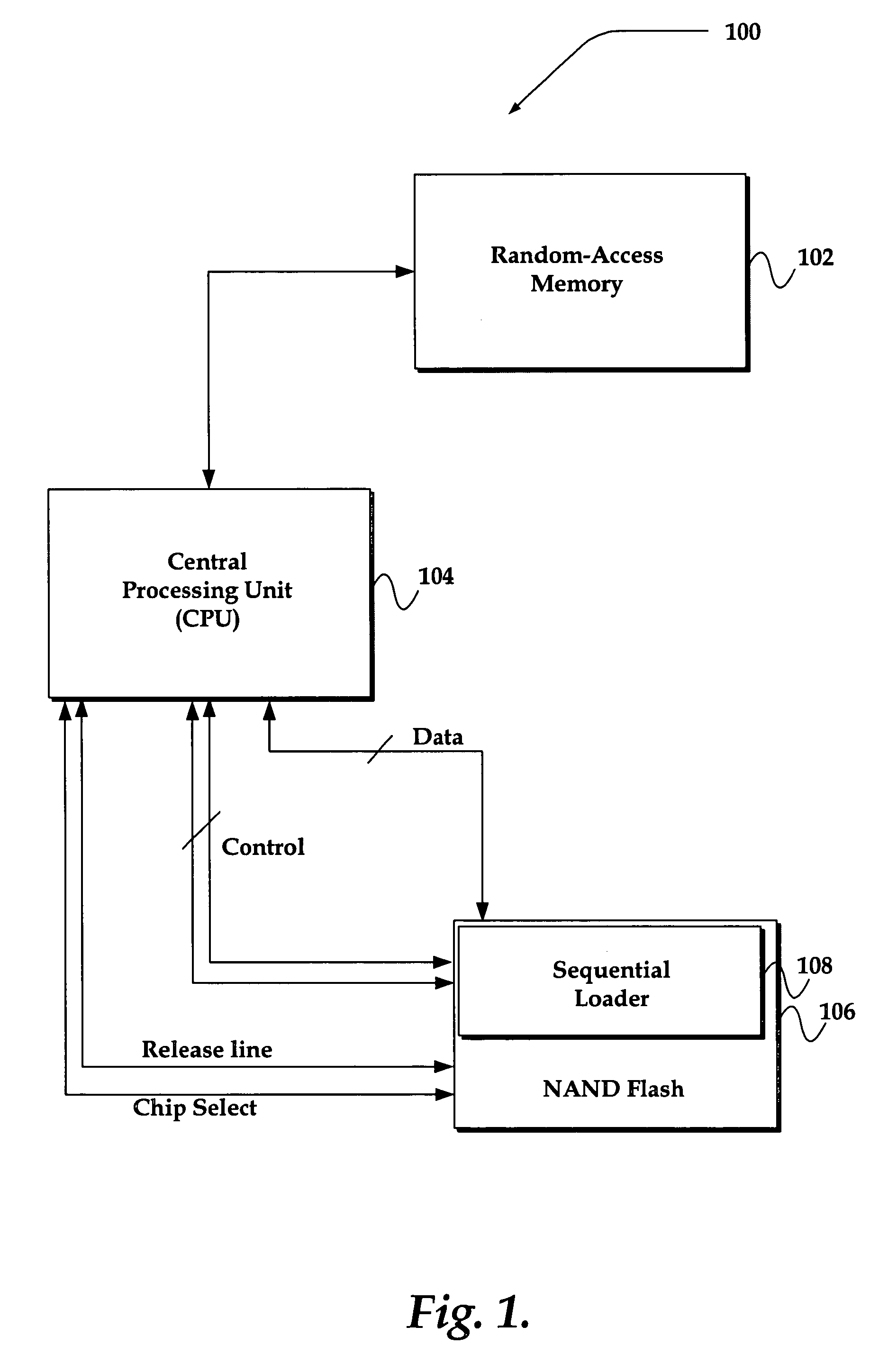

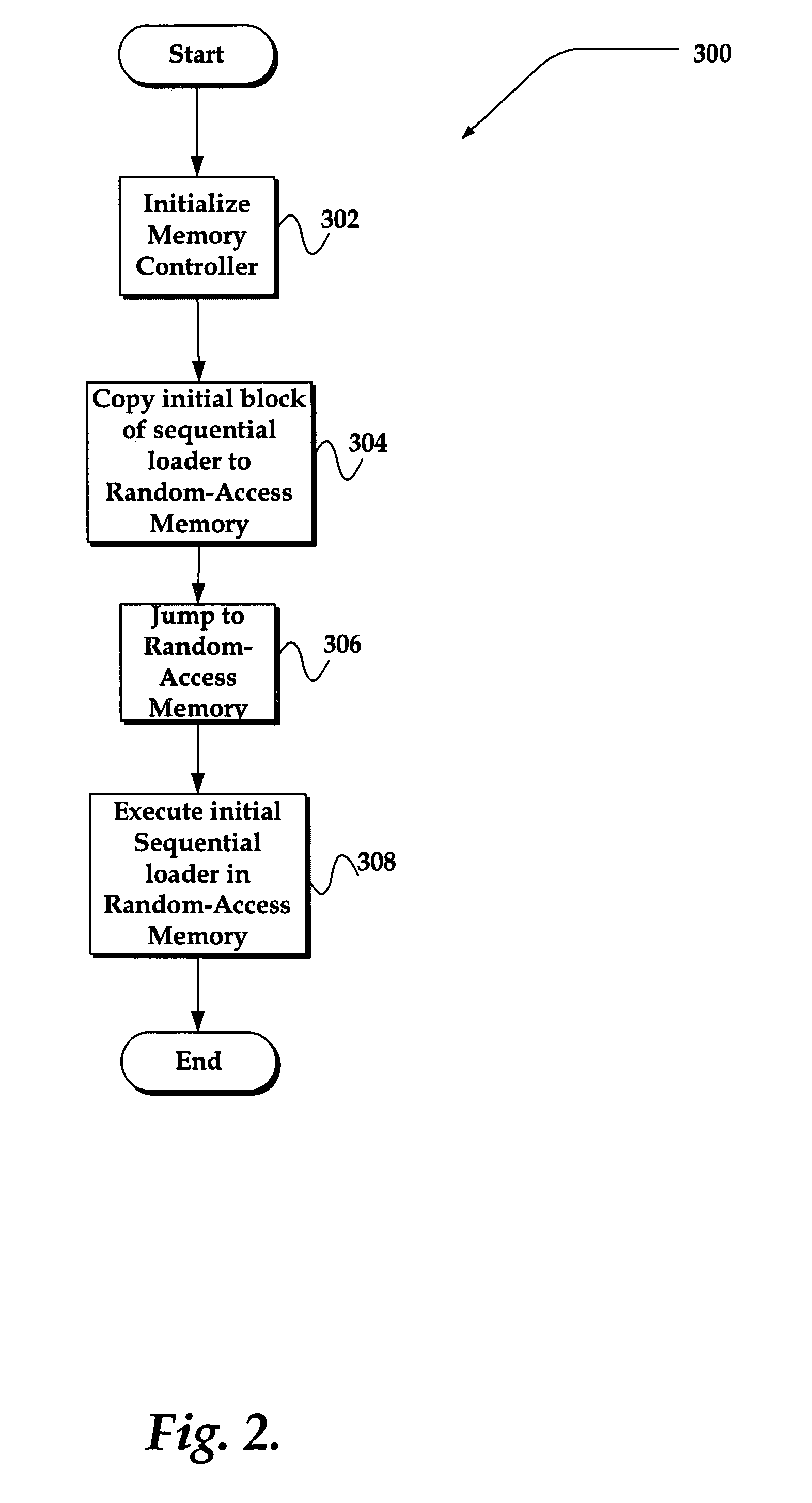

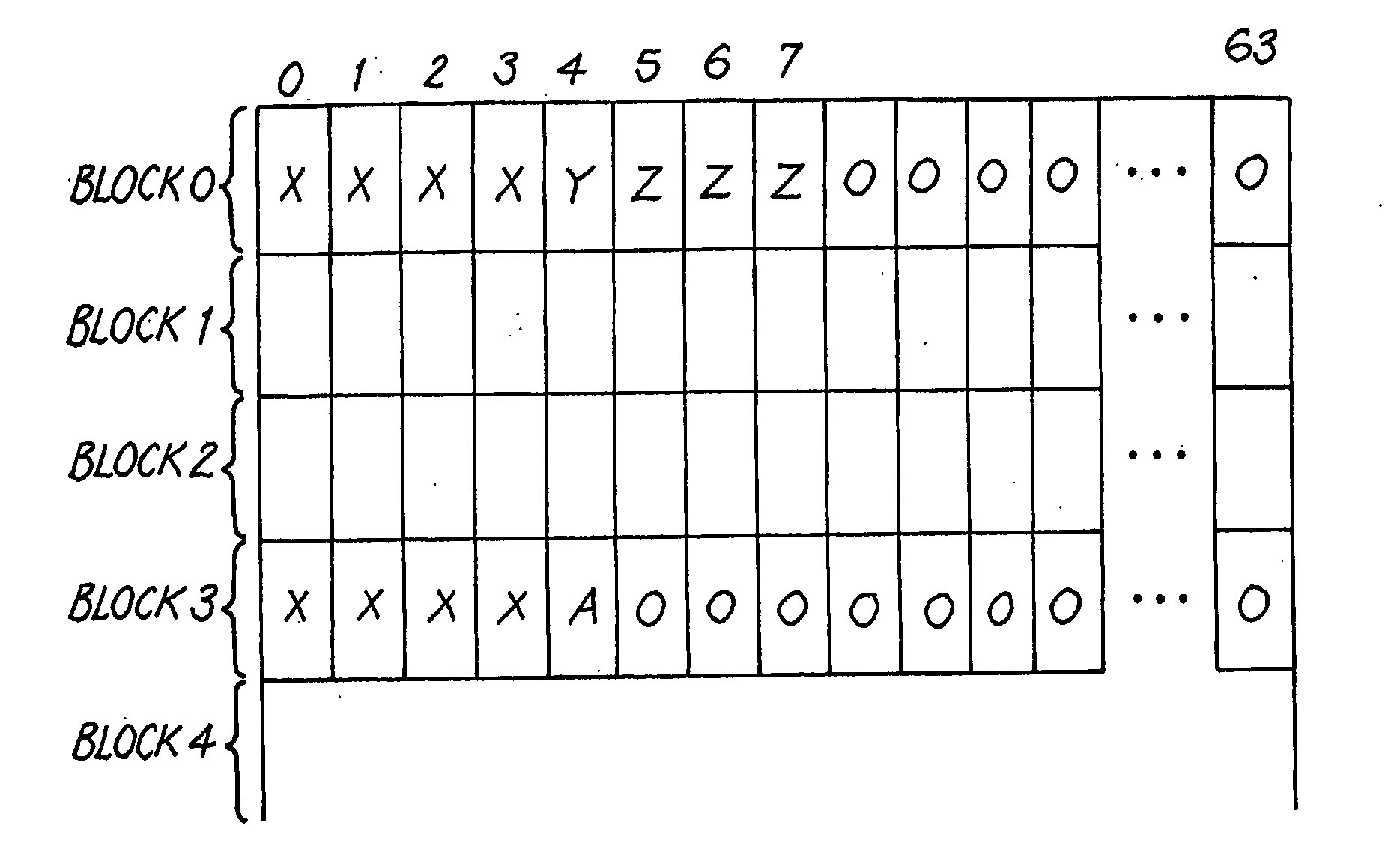

System and method for initializing a memory device from block oriented NAND flash

Described is a system and method for initializing other memory from block oriented NAND flash by central processing units (CPUs) designed for non-NAND flash. The system employs a sequential loader that avoids the use of branches, loops, and the like, to enable a portion of the sequential loader to be sequentially fetched and executed by the CPU. The fetched and executed portion of the sequential loader is configured to copy additional instructions from NAND flash into random-access memory, such that the CPU may be fully booted from the sequential loader by executing code that has been copied into the random-access memory.

Owner:MICROSOFT TECH LICENSING LLC

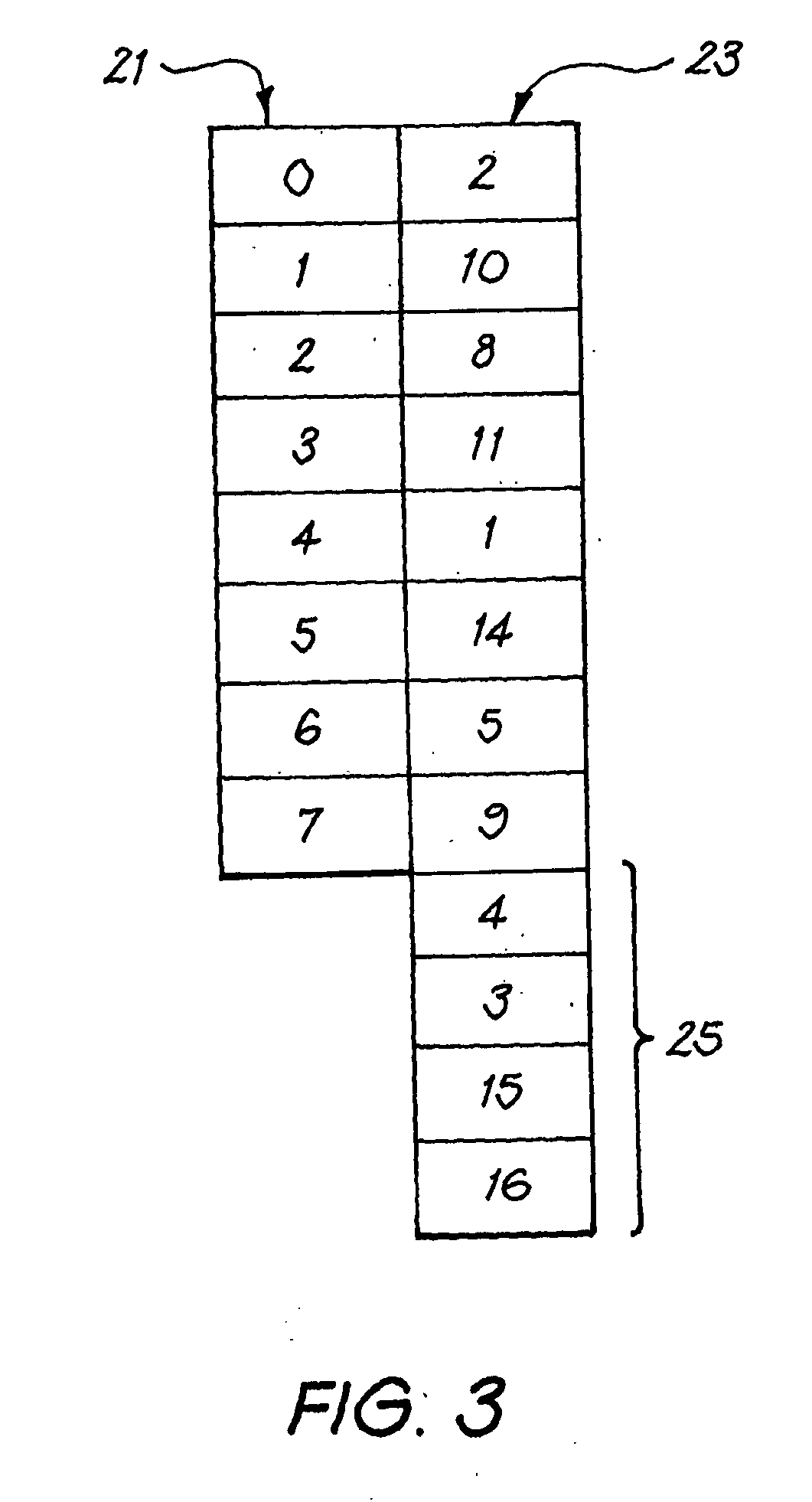

Portable Data Storage Device Using a Memory Address Mapping Table

InactiveUS20080228995A1Reduce in quantityFast operationMemory architecture accessing/allocationCombination recordingMemory addressUSB

A portable data storage device includes a USB controller, a master control unit and a NAND flash memory device. The master control unit receives data to be written to logical addresses, and instructions to read data from logical addresses. It uses a memory address mapping table to associate the logical addresses with the physical addresses in the memory device, and writes data to or reads data from the physical address corresponding to the logical address. The mapping is changed at intervals, so that different ones of the physical address regions are associated at different times with the logical addresses. This increases the speed of the device, and also means that no physical addresses are rapidly worn out by being permanently associated with logical addresses to which data is written relatively often.

Owner:TREK TECH SINGAPORE PTE

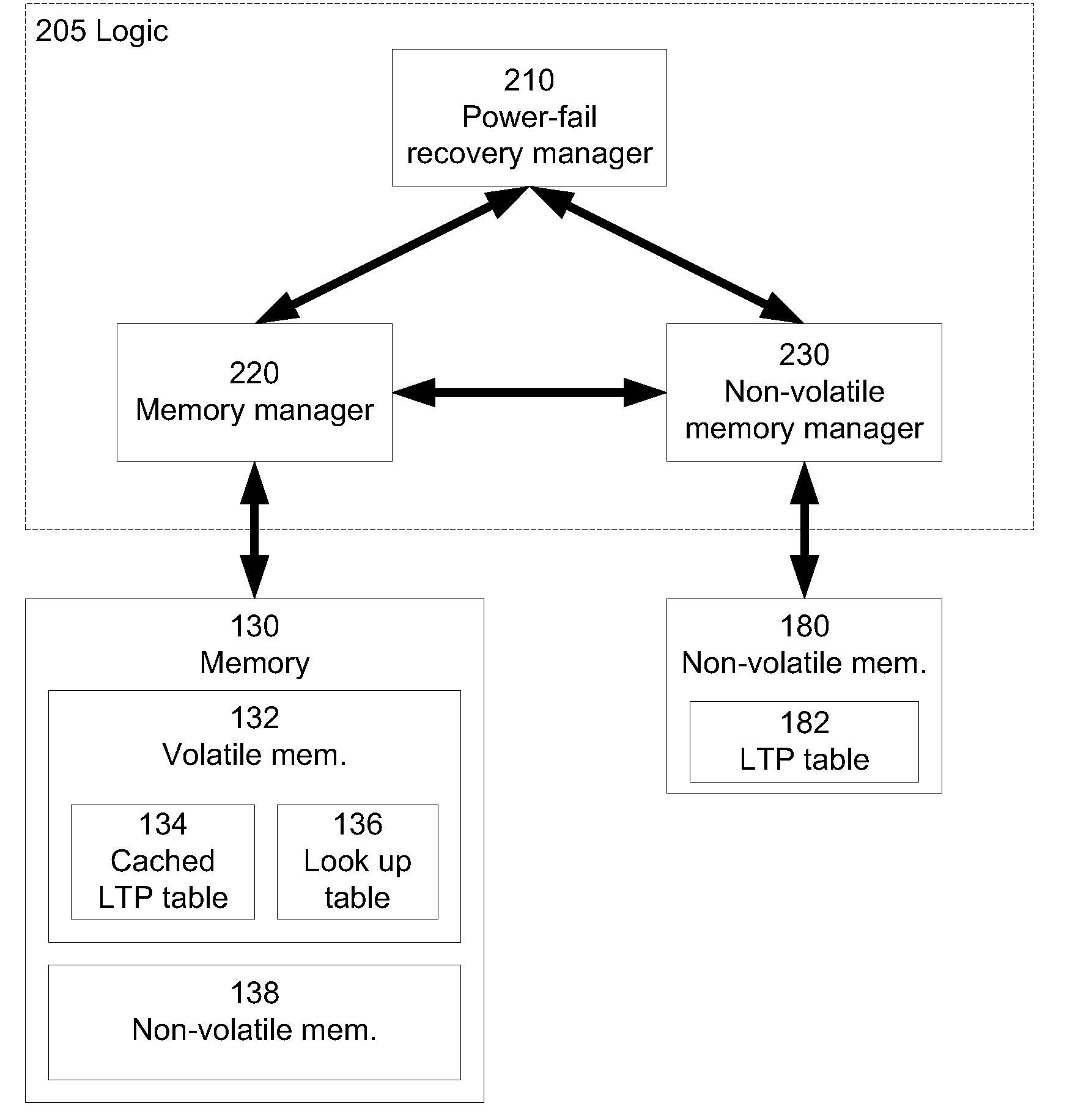

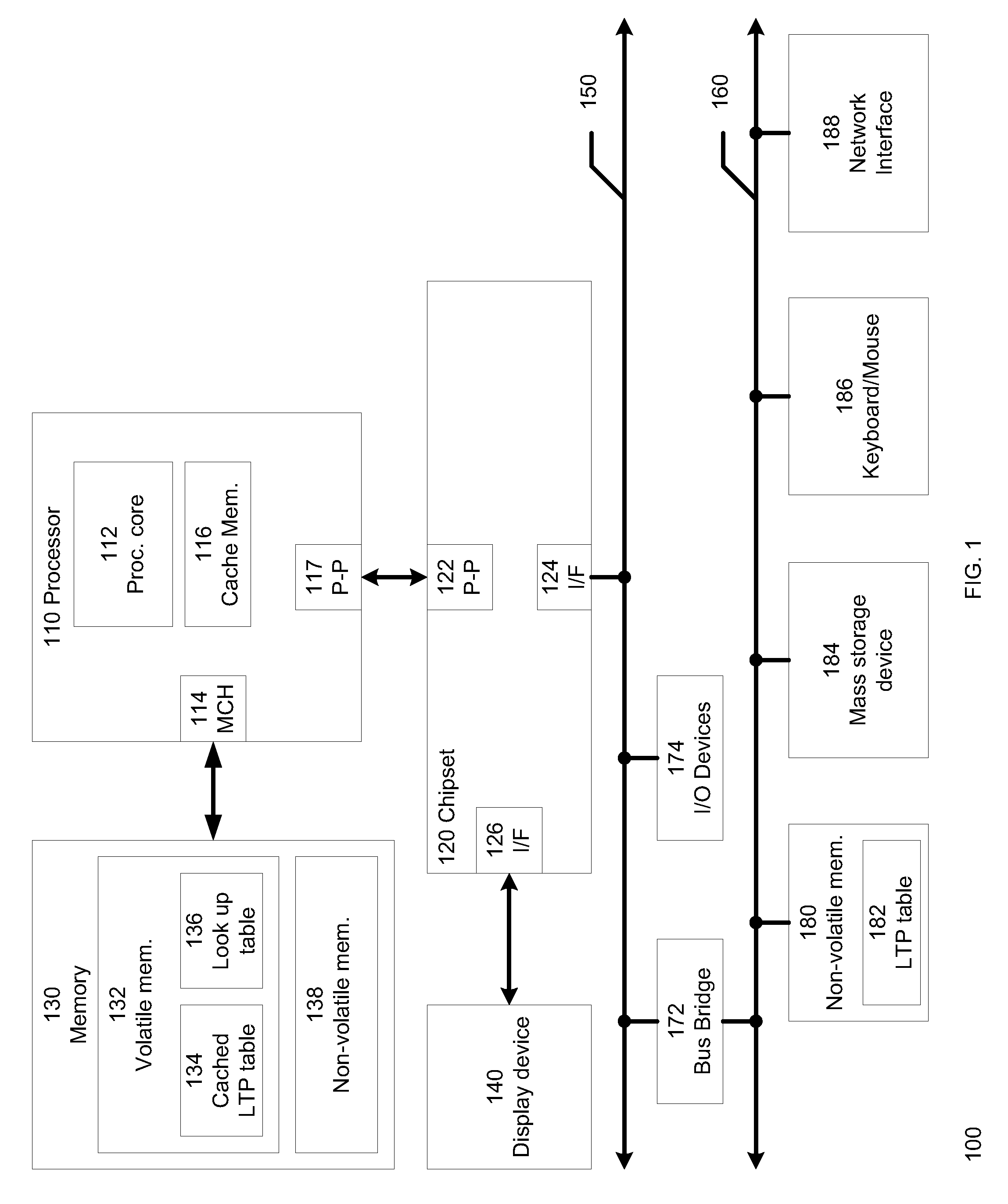

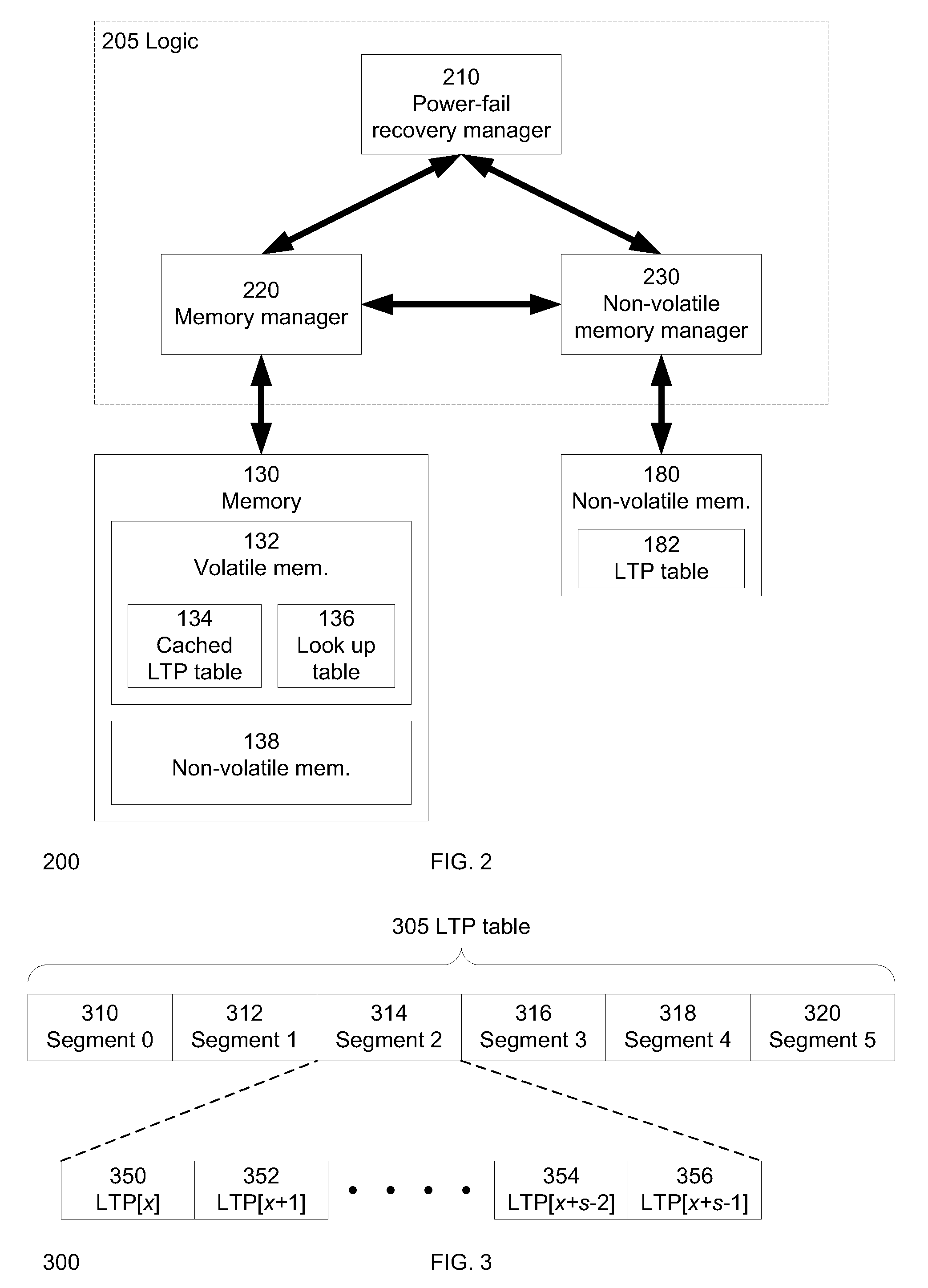

Method and system for managing a NAND flash memory

ActiveUS20100332730A1Memory architecture accessing/allocationMemory adressing/allocation/relocationPagingDatabase

A method and system to facilitate paging of one or more segments of a logical-to-physical (LTP) address mapping structure to a non-volatile memory. The LTP address mapping structure is part of an indirection system map associated with the non-volatile memory in one embodiment of the invention. By allowing one or more segments of the LTP address mapping structure to be paged to the non-volatile memory, the amount of volatile memory required to store the LTP address mapping structure is reduced while maintaining the benefits of the LTP address mapping structure in one embodiment of the invention.

Owner:SK HYNIX NAND PROD SOLUTIONS CORP