Patents

Literature

768 results about "Translation table" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Translation table A table of information stored within a processor or a peripheral that is used to convert encoded information into another form of code with the same meaning. There are a variety of codes used within the field of computing and sometimes more than one code may be used within a single system.

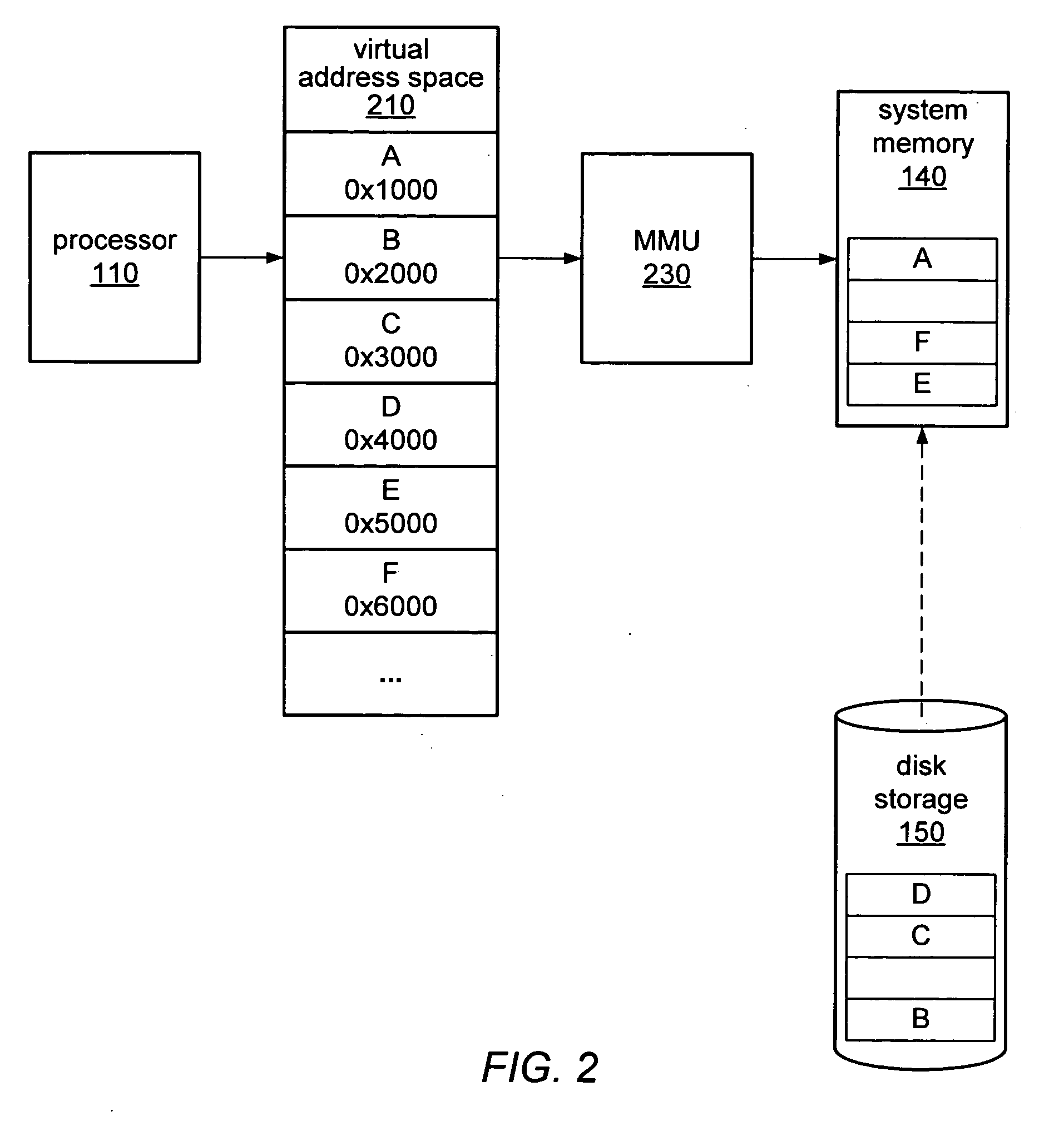

Dynamic selection of memory virtualization techniques

ActiveUS7752417B2Error detection/correctionMemory adressing/allocation/relocationVirtualizationComputerized system

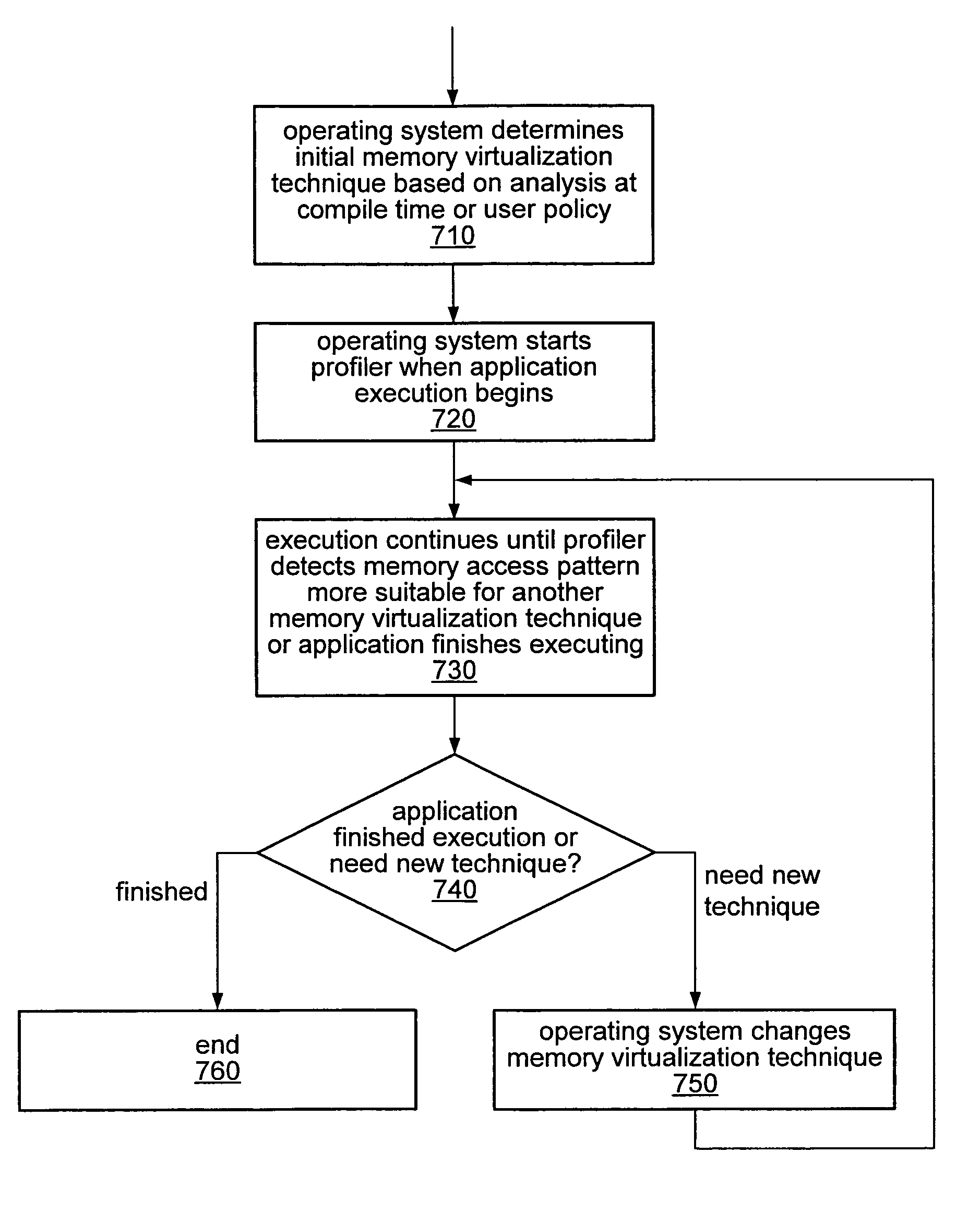

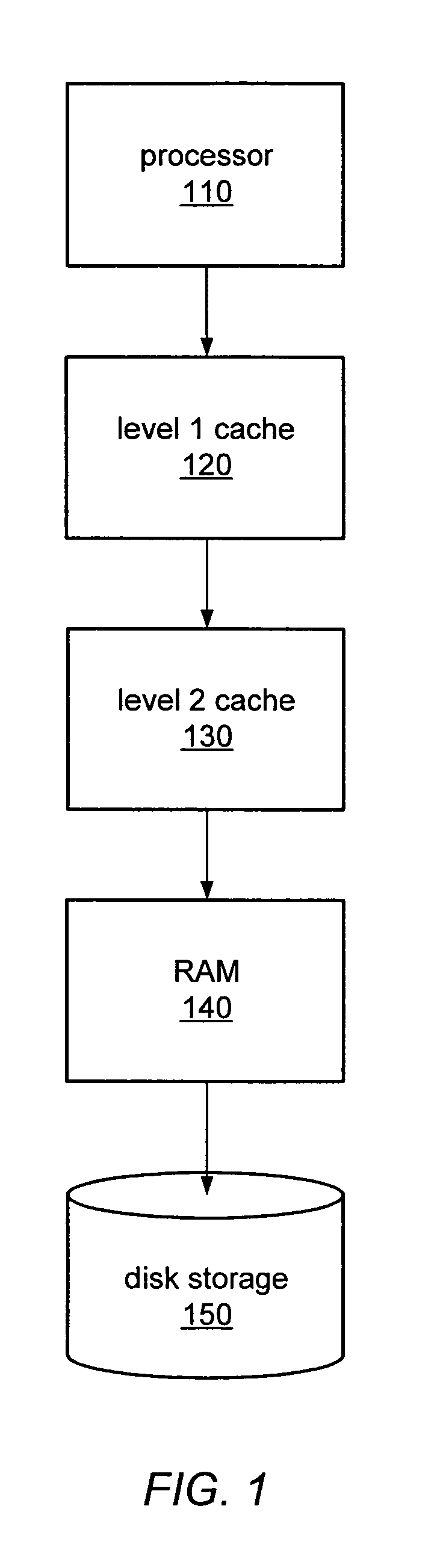

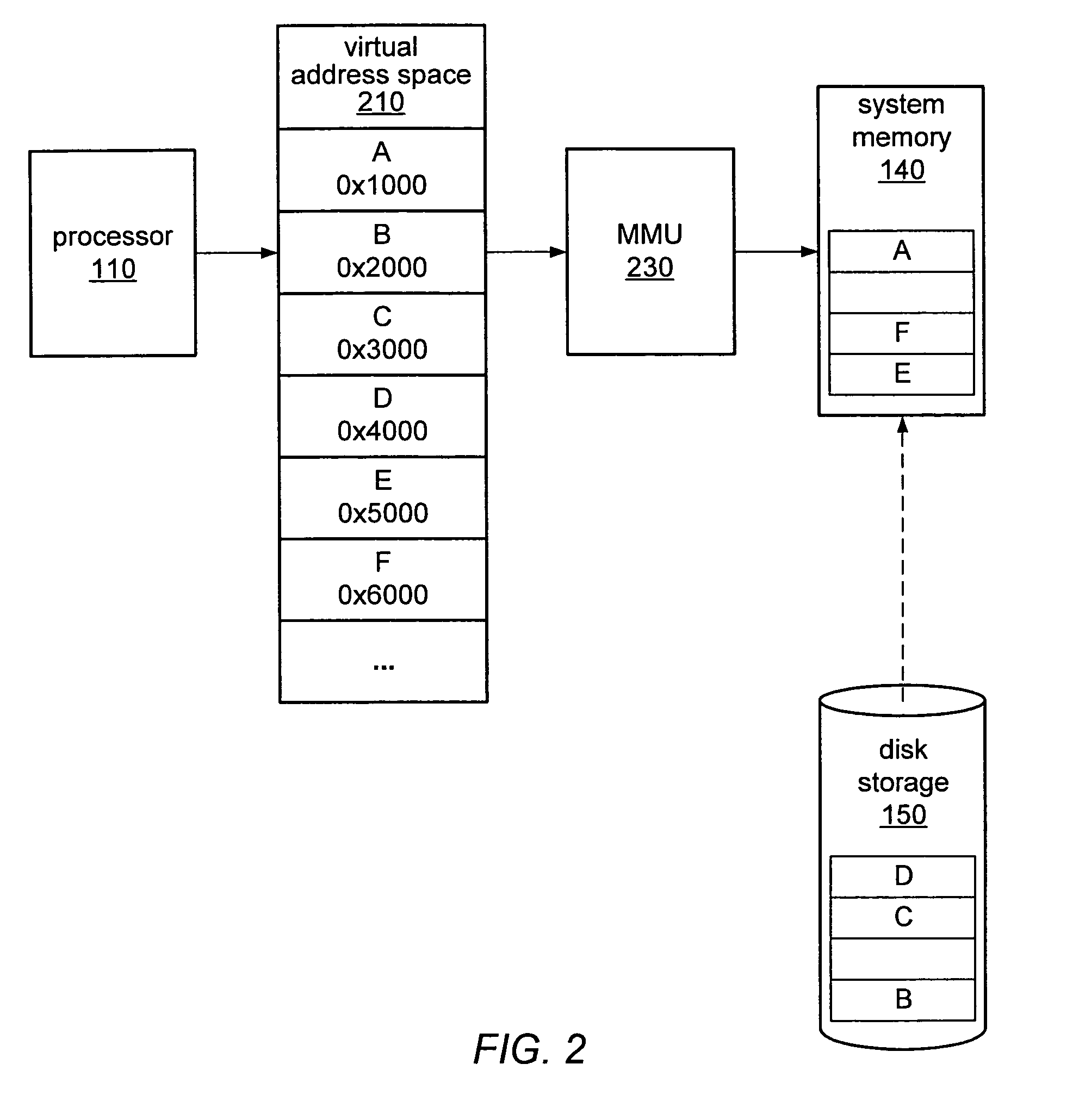

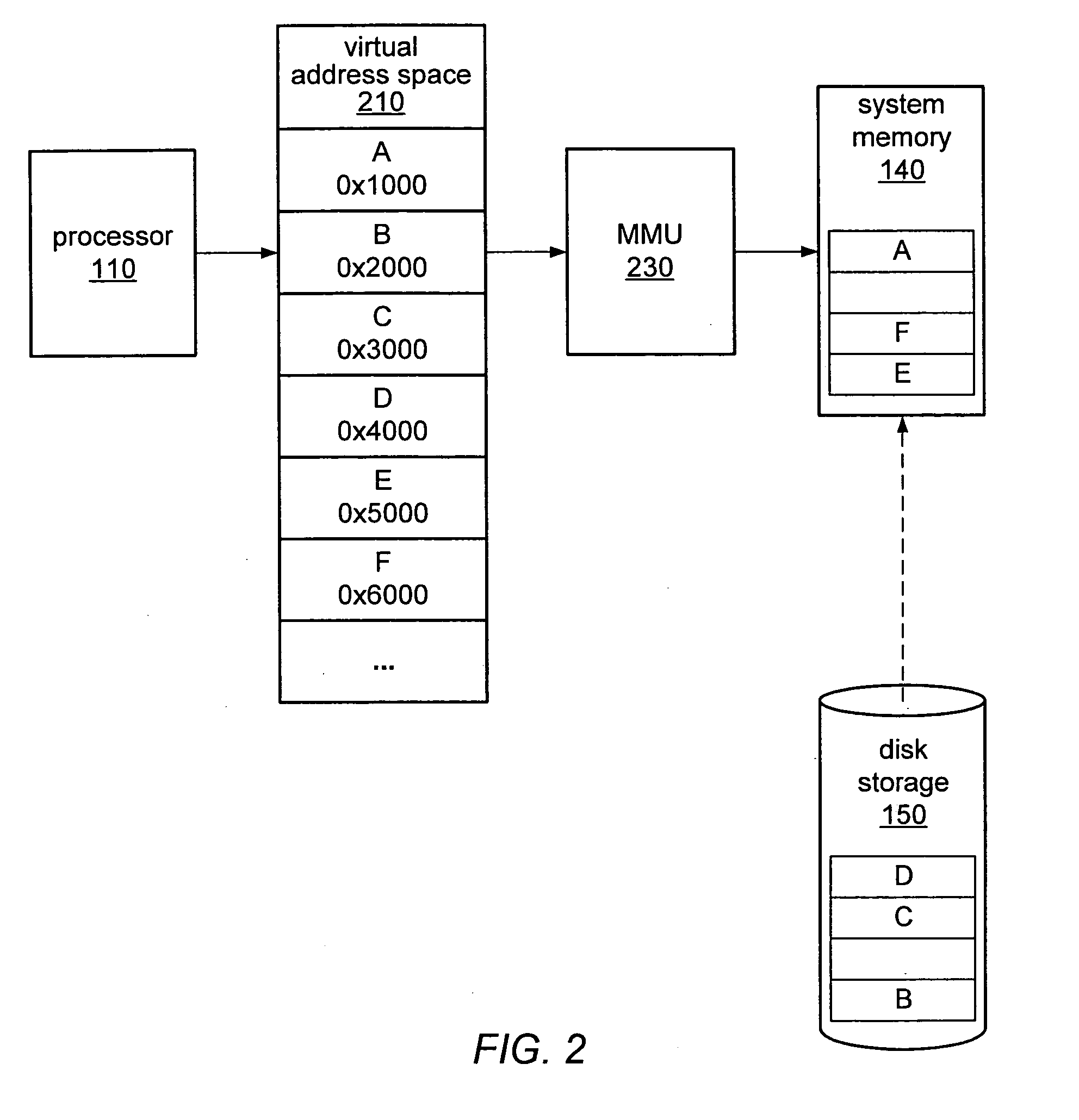

A computer system may be configured to dynamically select a memory virtualization and corresponding virtual-to-physical address translation technique during execution of an application and to dynamically employ the selected technique in place of a current technique without re-initializing the application. The computer system may be configured to determine that a current address translation technique incurs a high overhead for the application's current workload and may be configured to select a different technique dependent on various performance criteria and / or a user policy. Dynamically employing the selected technique may include reorganizing a memory, reorganizing a translation table, allocating a different block of memory to the application, changing a page or segment size, or moving to or from a page-based, segment-based, or function-based address translation technique. A selected translation technique may be dynamically employed for the application independent of a translation technique employed for a different application.

Owner:ORACLE INT CORP

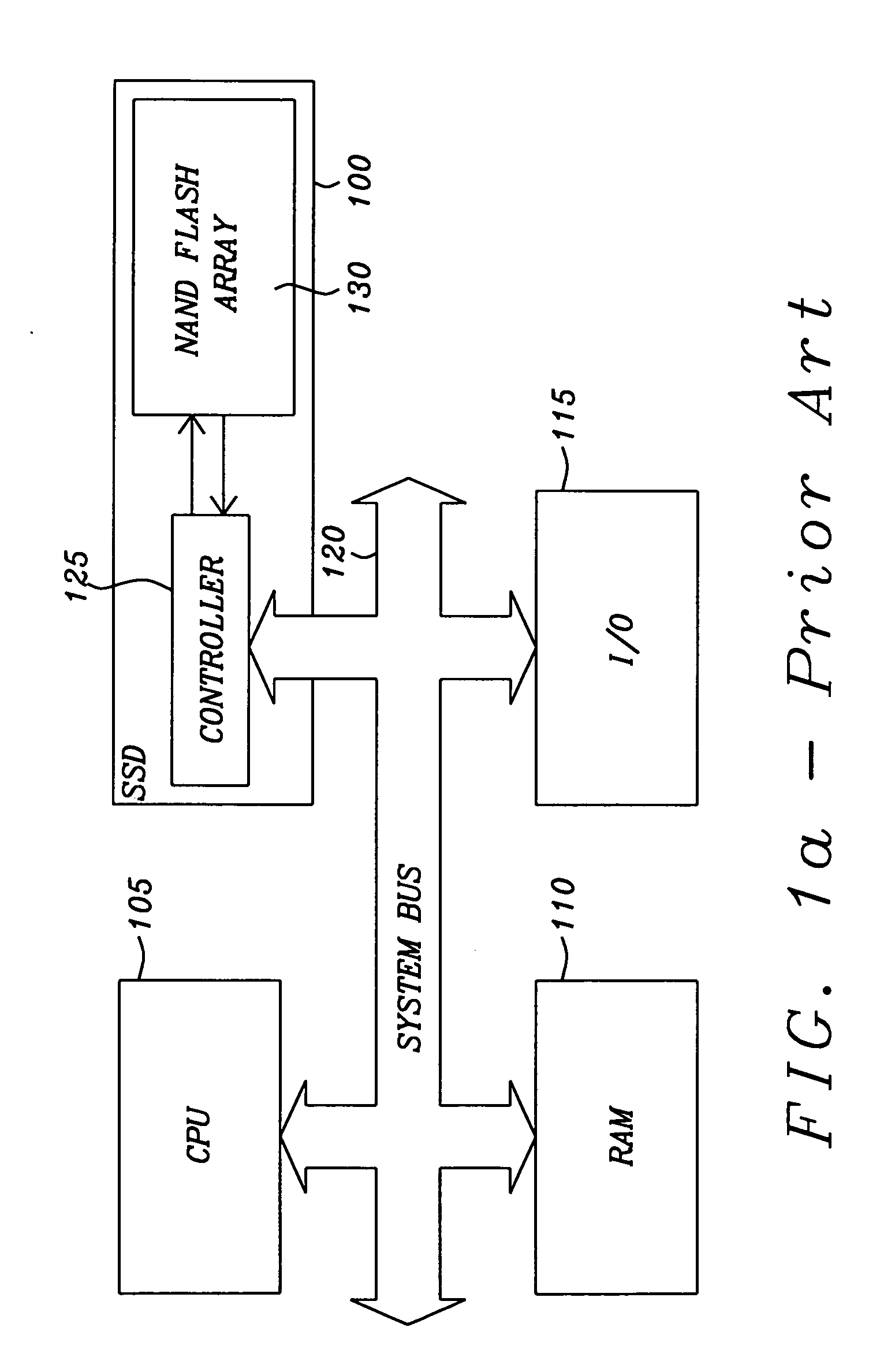

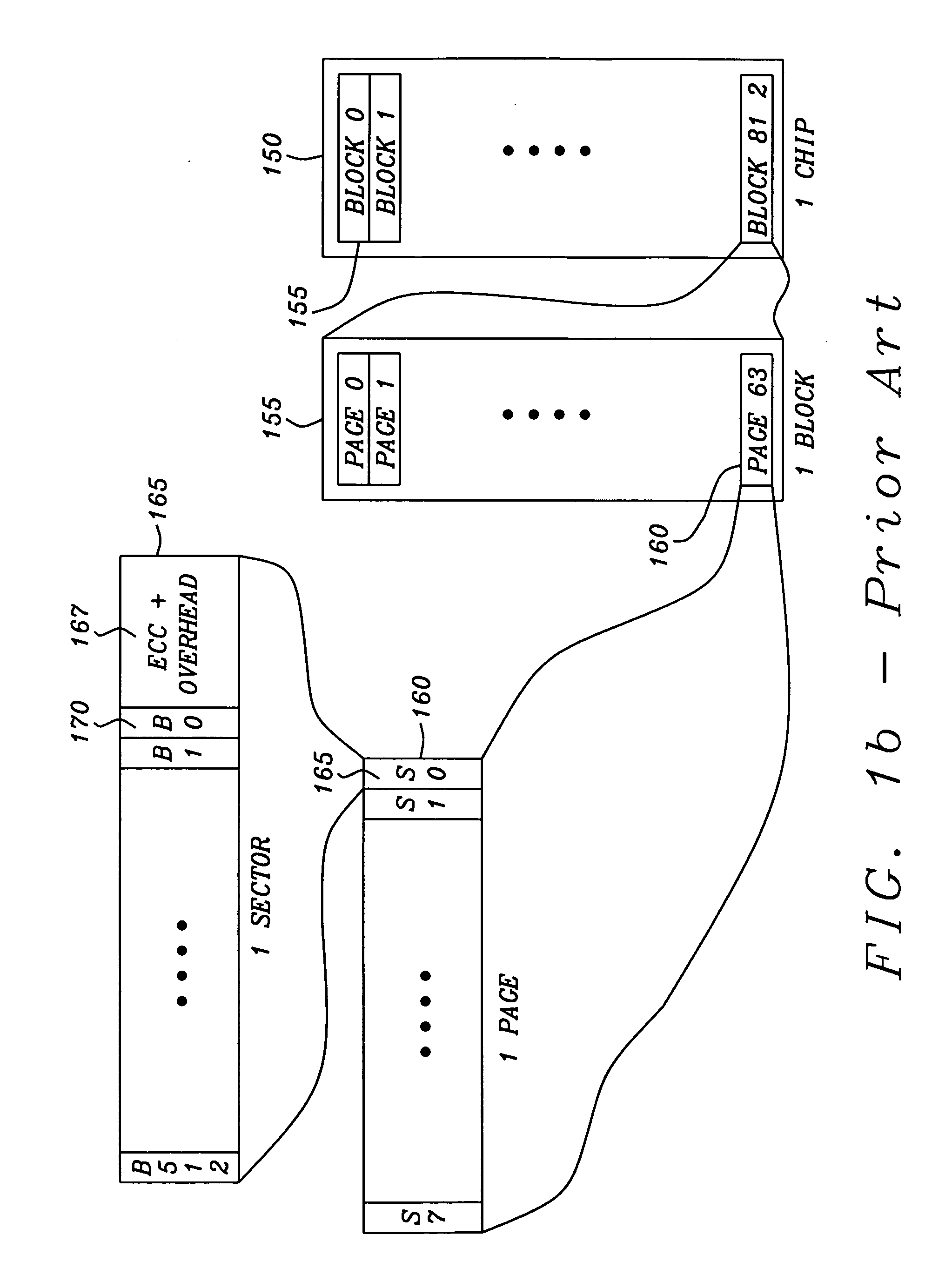

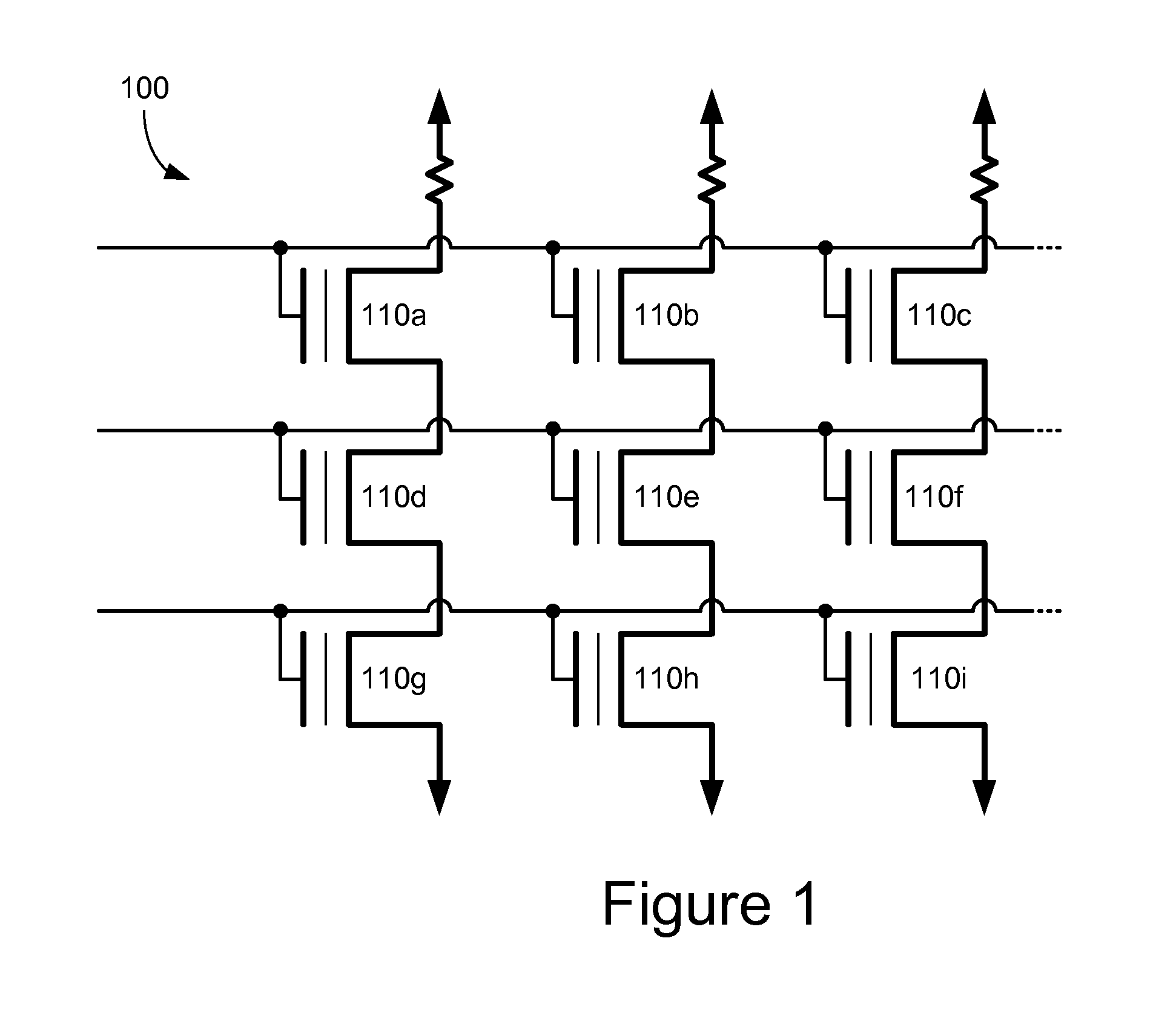

Page based management of flash storage

InactiveUS20110055458A1Memory architecture accessing/allocationMemory adressing/allocation/relocationControl signalPaging

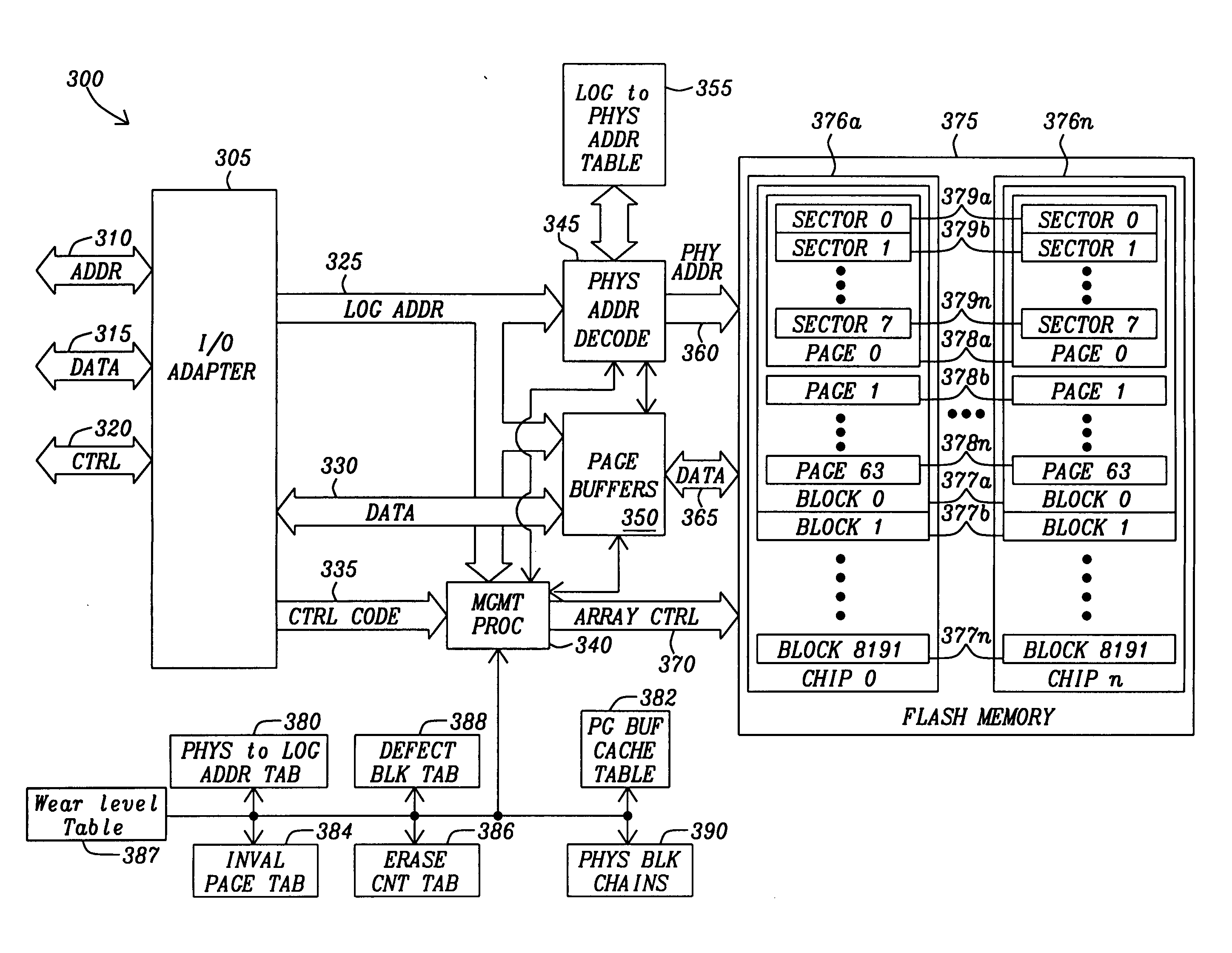

Methods and circuits for page based management of an array of Flash RAM nonvolatile memory devices provide paged base reading and writing and block erasure of a flash storage system. The memory management system includes a management processor, a page buffer, and a logical-to-physical translation table. The management processor is in communication with an array of nonvolatile memory devices within the flash storage system to provide control signals for the programming of selected pages, erasing selected blocks, and reading selected pages of the array of nonvolatile memory devices.

Owner:PIONEER CHIP TECH

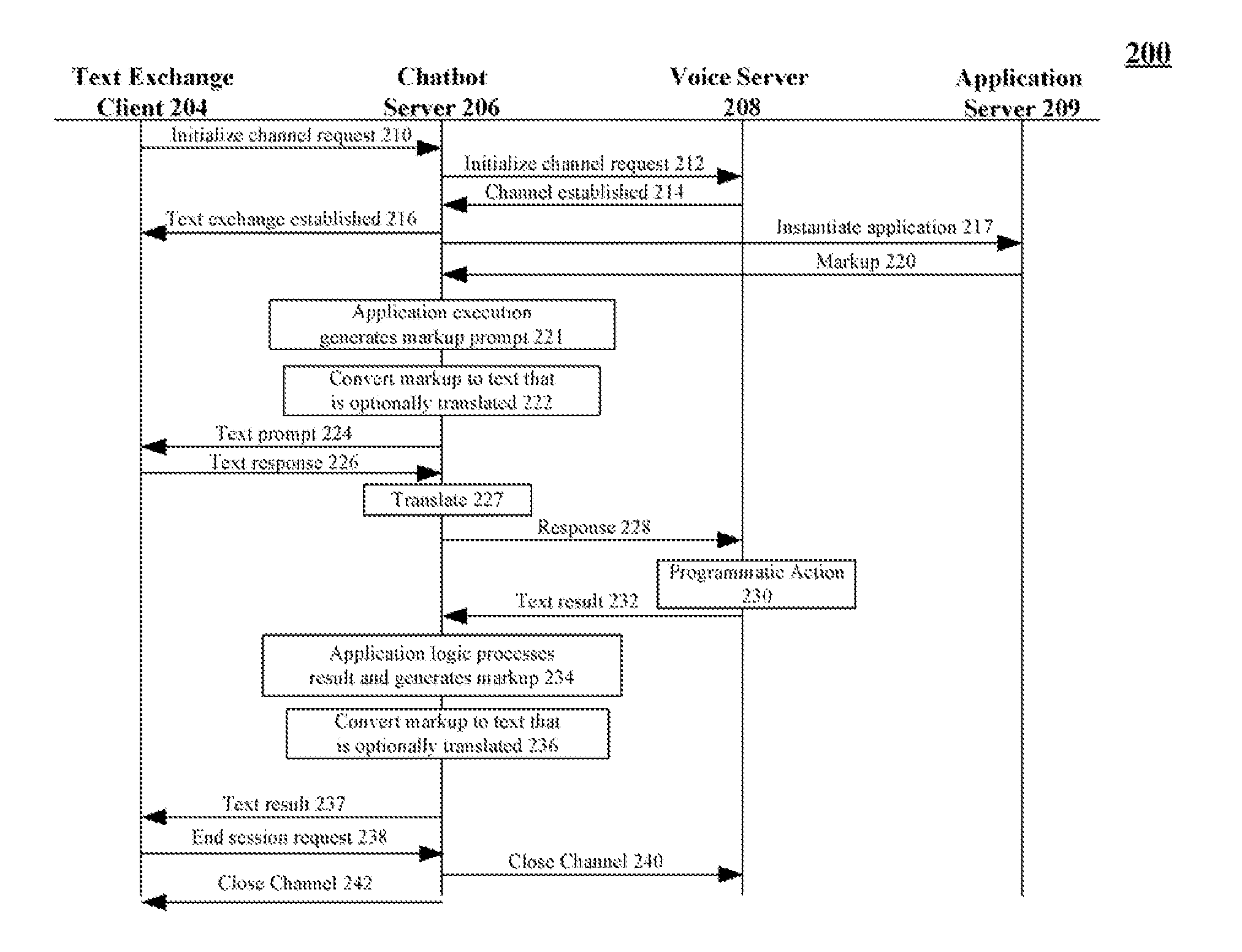

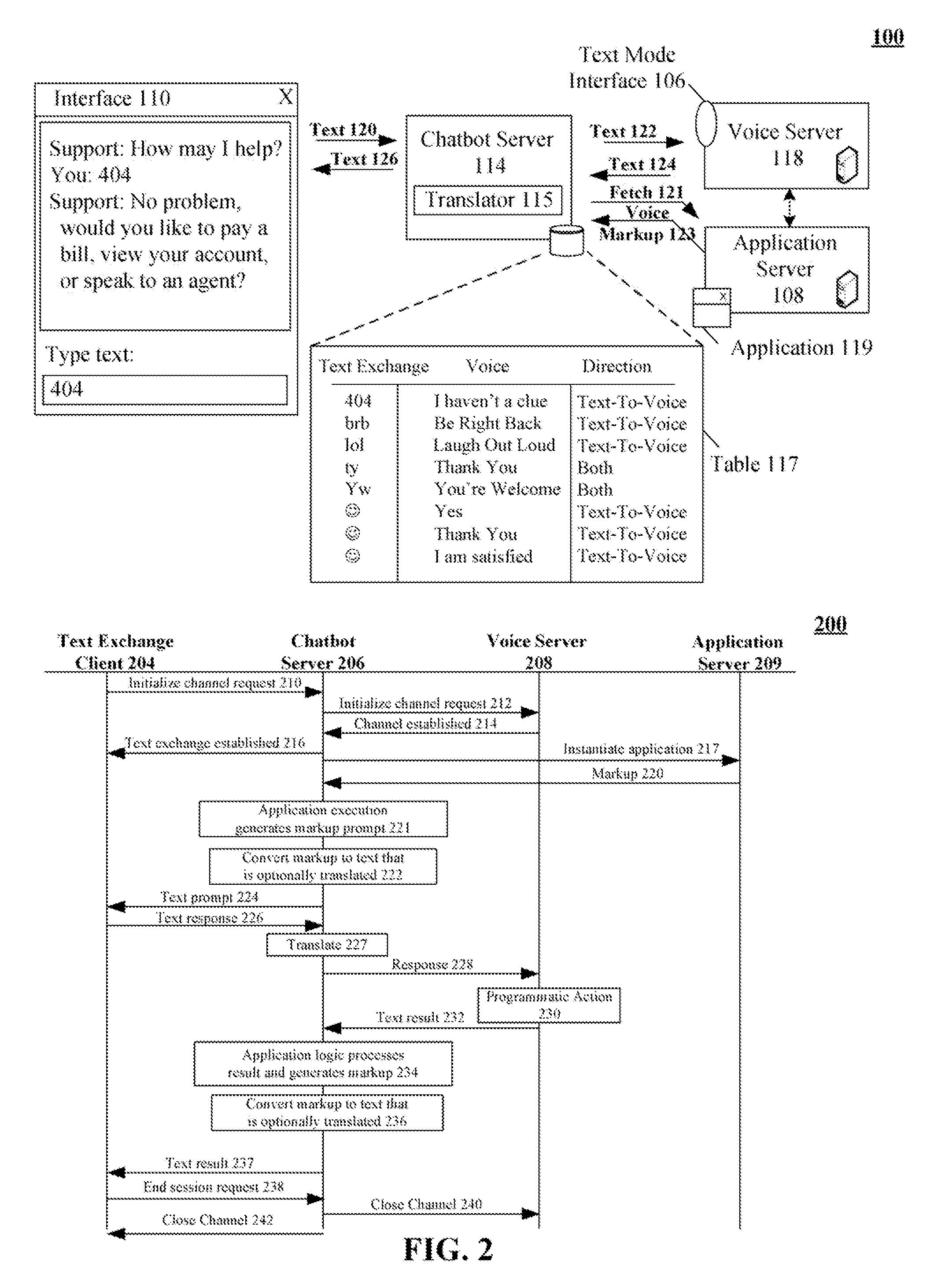

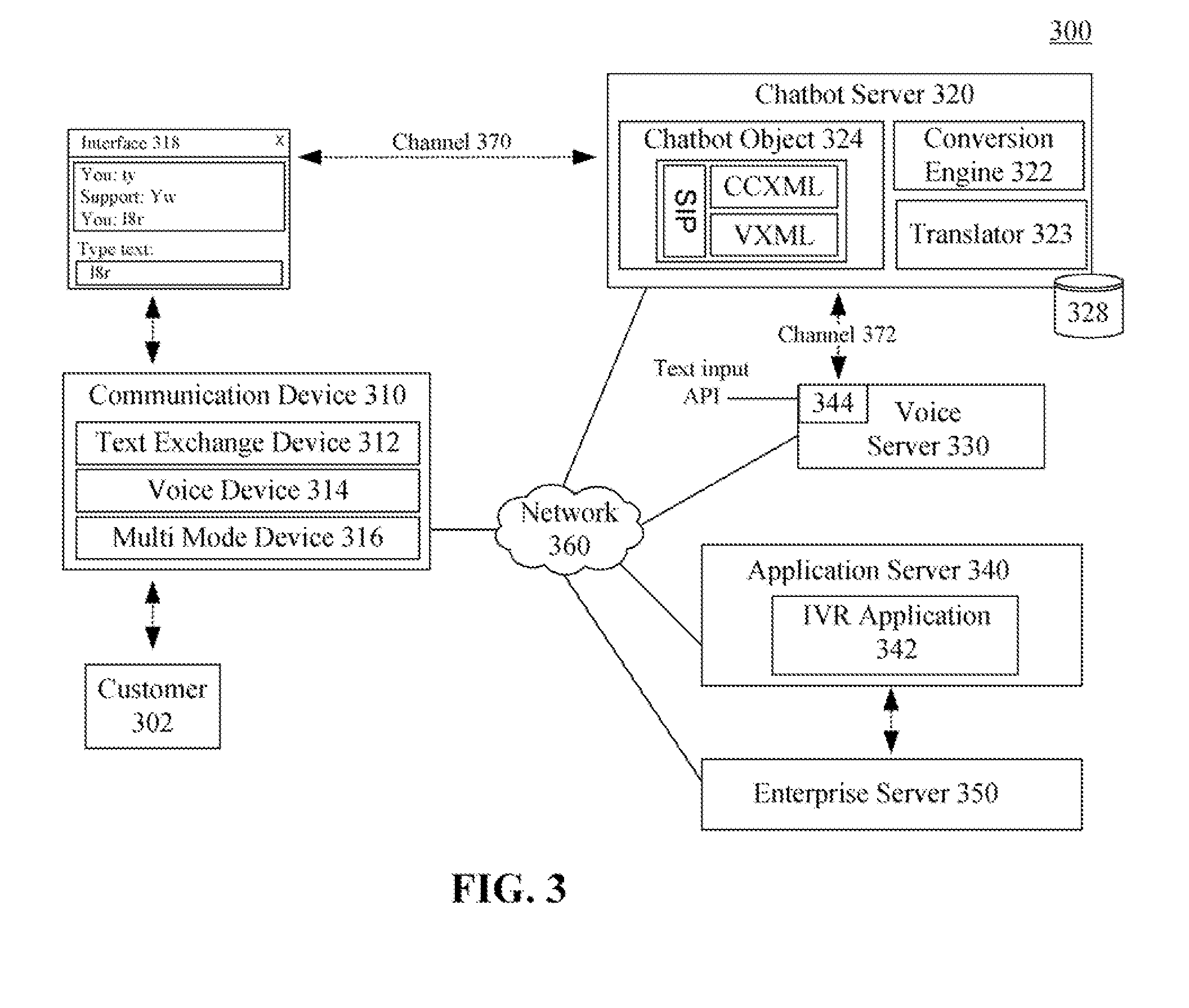

Dialect translator for a speech application environment extended for interactive text exchanges

The present solution includes a real-time automated communication method. In the method, a real-time communication session can be established between a text exchange client and a speech application. A translation table can be identified that includes multiple entries, each entry including a text exchange item and a corresponding conversational translation item. A text exchange message can be received that was entered into a text exchange client. Content in the text exchange message that matches a text exchange item in the translation table can be substituted with a corresponding conversational item. The translated text exchange message can be sent as input to a voice server. Output from the voice server can be used by the speech application, which performs an automatic programmatic action based upon the output.

Owner:NUANCE COMM INC

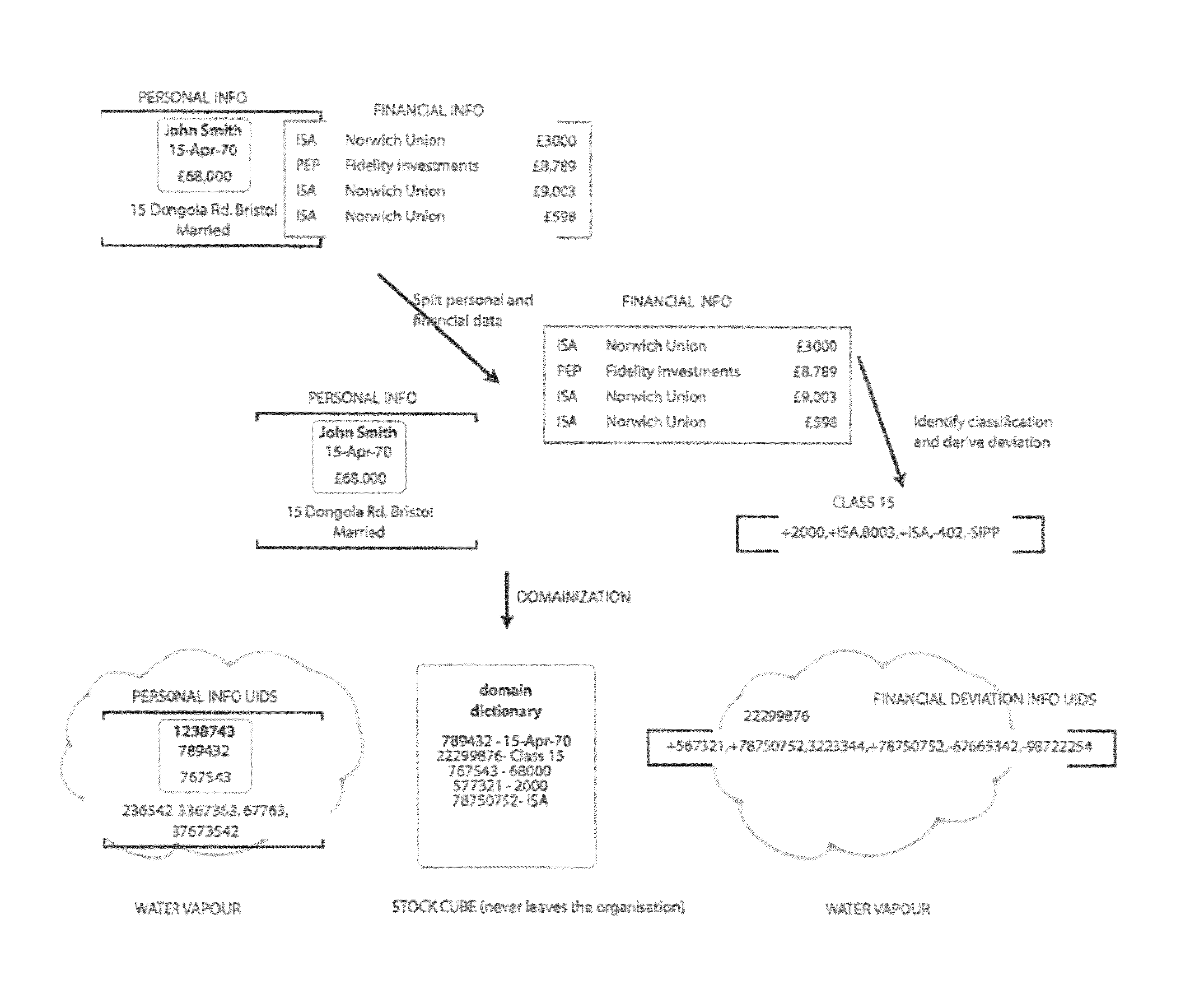

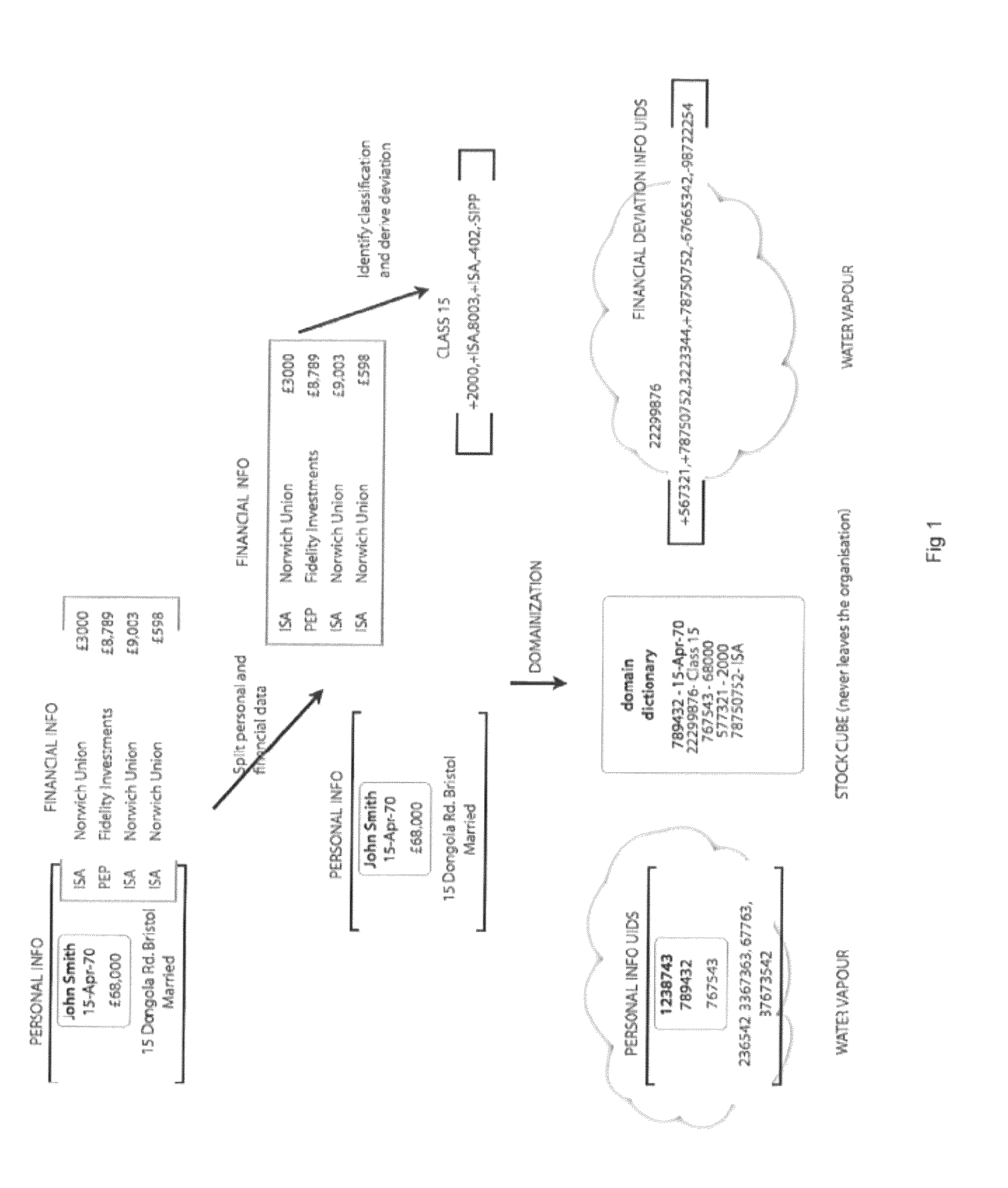

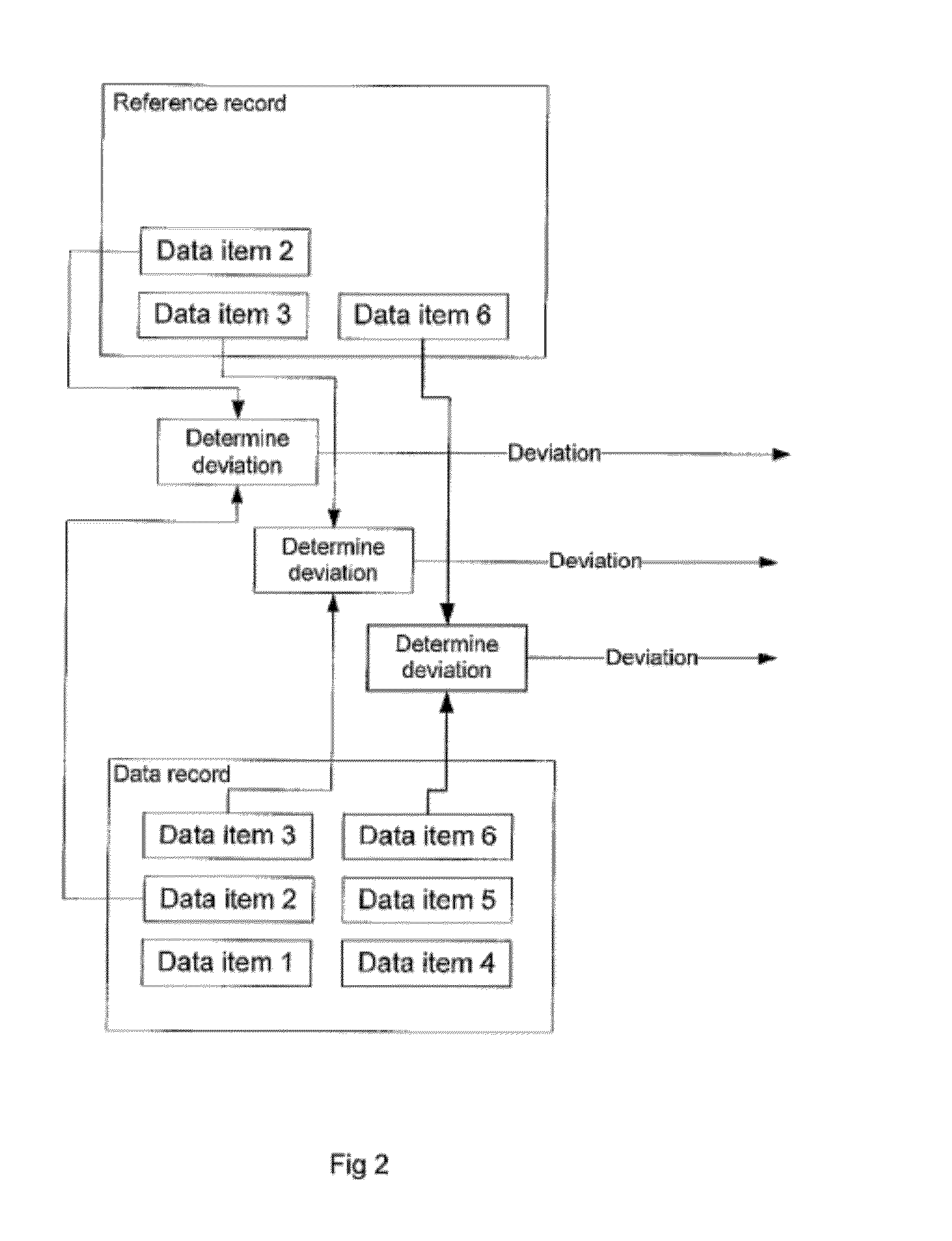

Private information storage system

This invention relates to a scheme for storage of private information on a cloud computing platform without contravention of territorial privacy laws. A method of anonymising a database of personal data is described whereby data identifiers are assigned to data items and deviation identifiers are assigned to deviations for selected data items derived from reference records. Such information can then be uploaded to a cloud based storage platform. A translation table maps the data items, data identifiers and deviation identifiers to the original data entries. This translation table is stored locally and separate to the anonymised information uploaded to the cloud. The invention further describes a method of decoding the database anonymised according to the above method.

Owner:ANZEN TECH SYST LTD

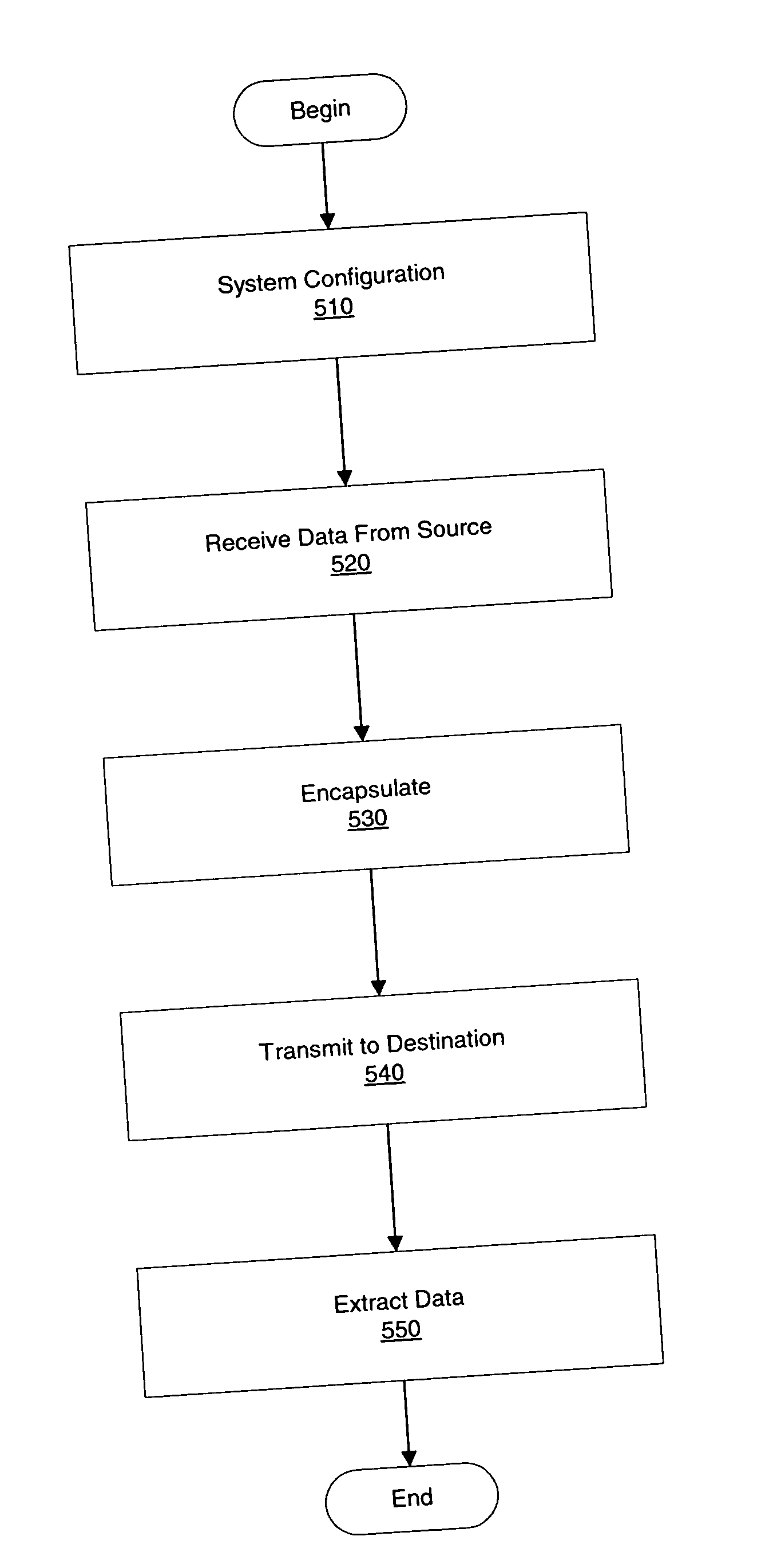

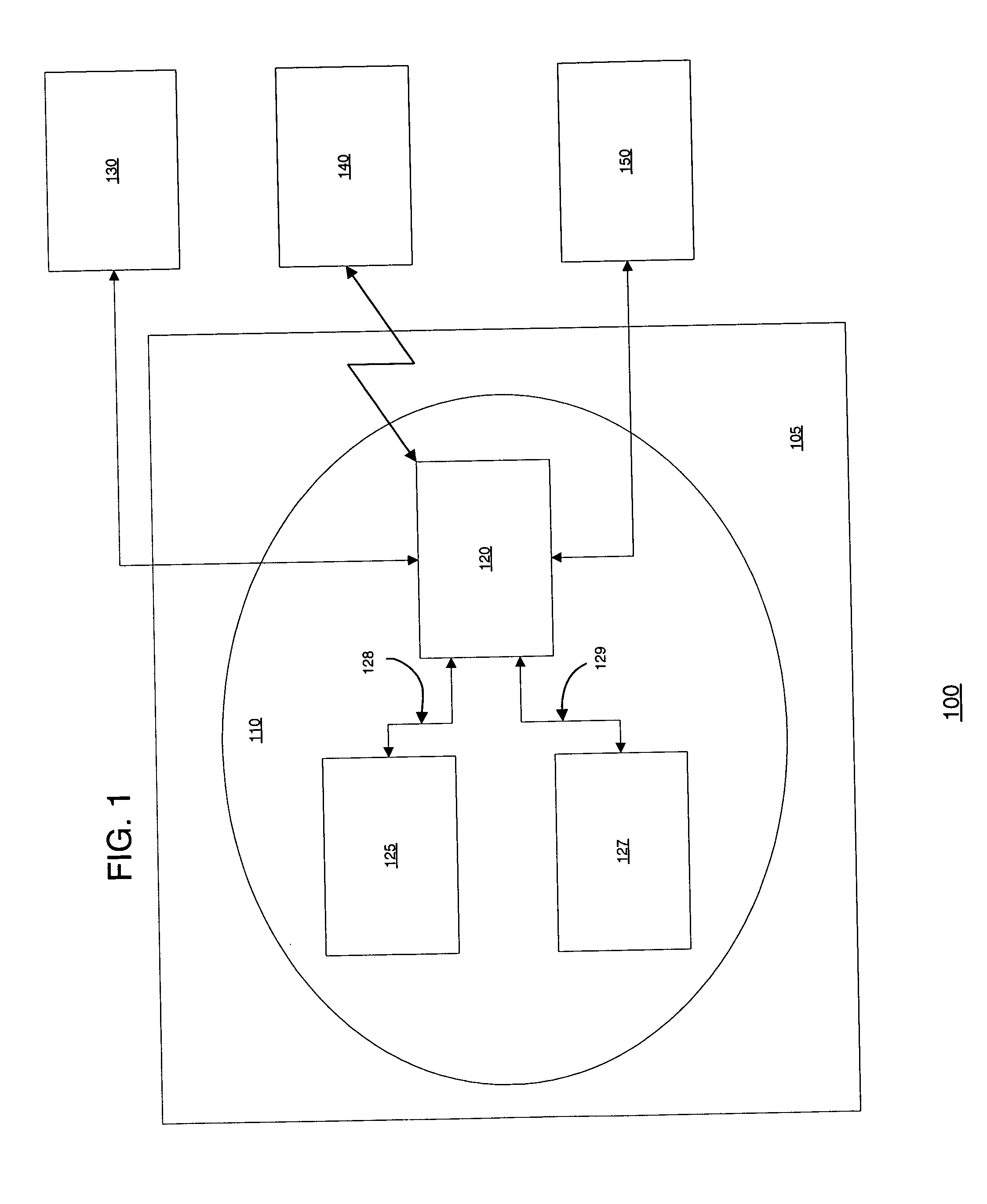

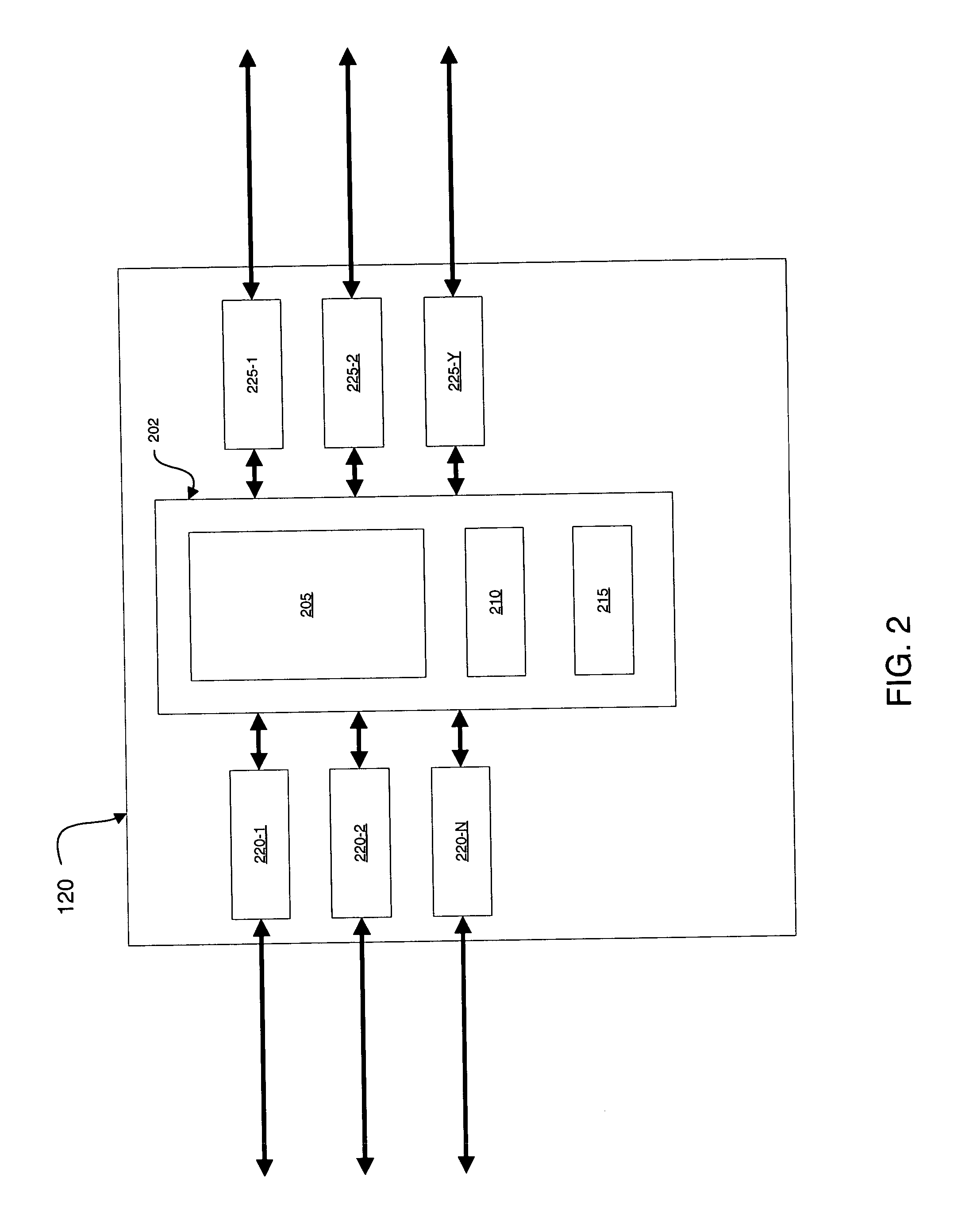

Systems and methods for performing protocol conversions in a work machine

Methods and systems are provided for performing protocol conversions in an environment including a work machine having one or more modules coupled to one or more data links. Such methods and systems may leverage one or more gateways to perform tunneling, translating, and bridging operations. Tunneling processes may include receiving a message from a source module in a first protocol, encapsulating the message within transmission units of a second protocol, and transmitting the encapsulated message via the second protocol. Translating processes may include receiving, by the gateway, a message in a first data link protocol including a parameter identifier. The gateway may match the parameter identifier with a parameter identifier included in a translation table and scale associated parameter data using a scale factor corresponding to a second data link protocol. The gateway may then provide the scaled parameter data to a module using the second data link protocol.

Owner:CATERPILLAR INC

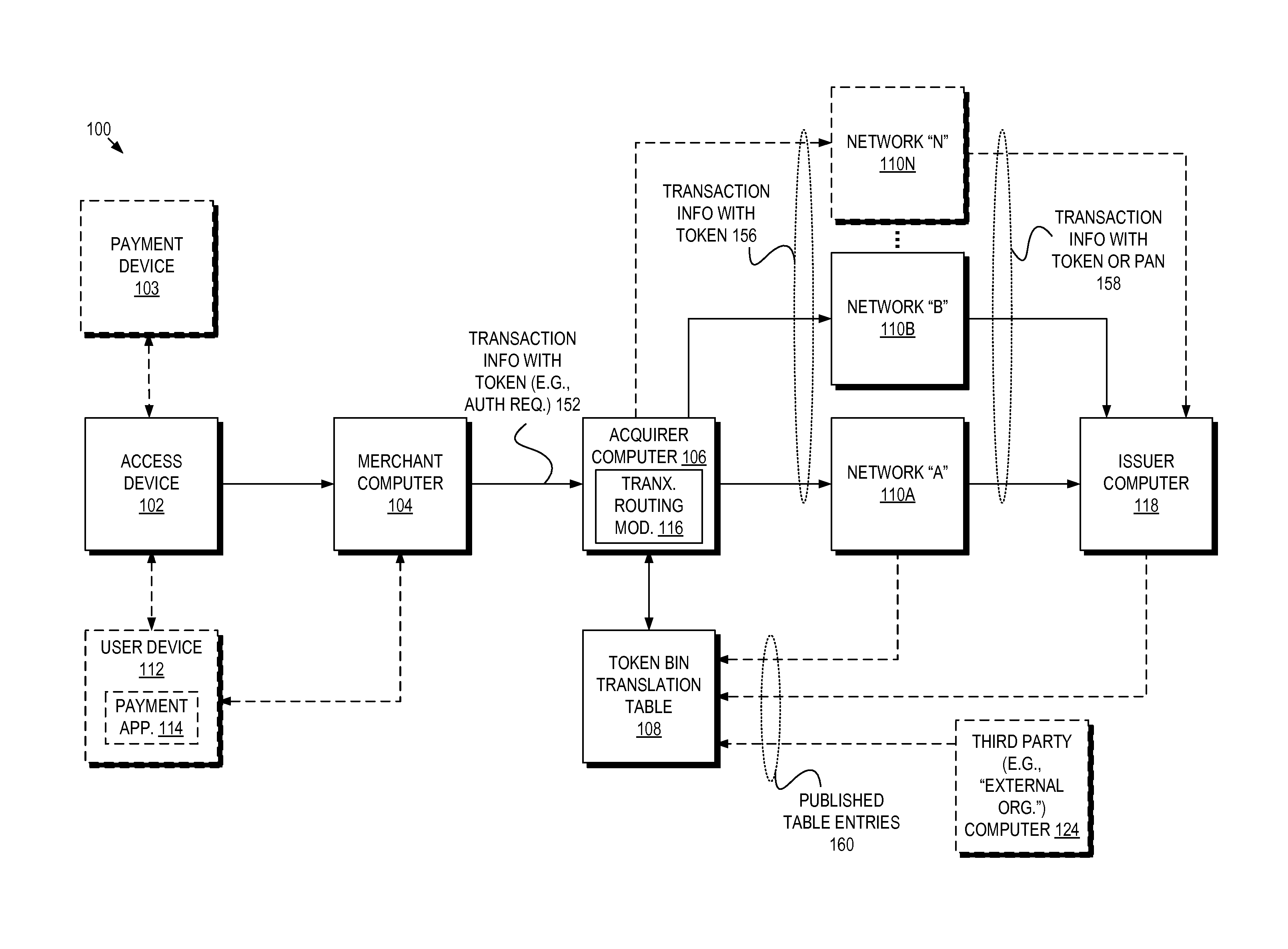

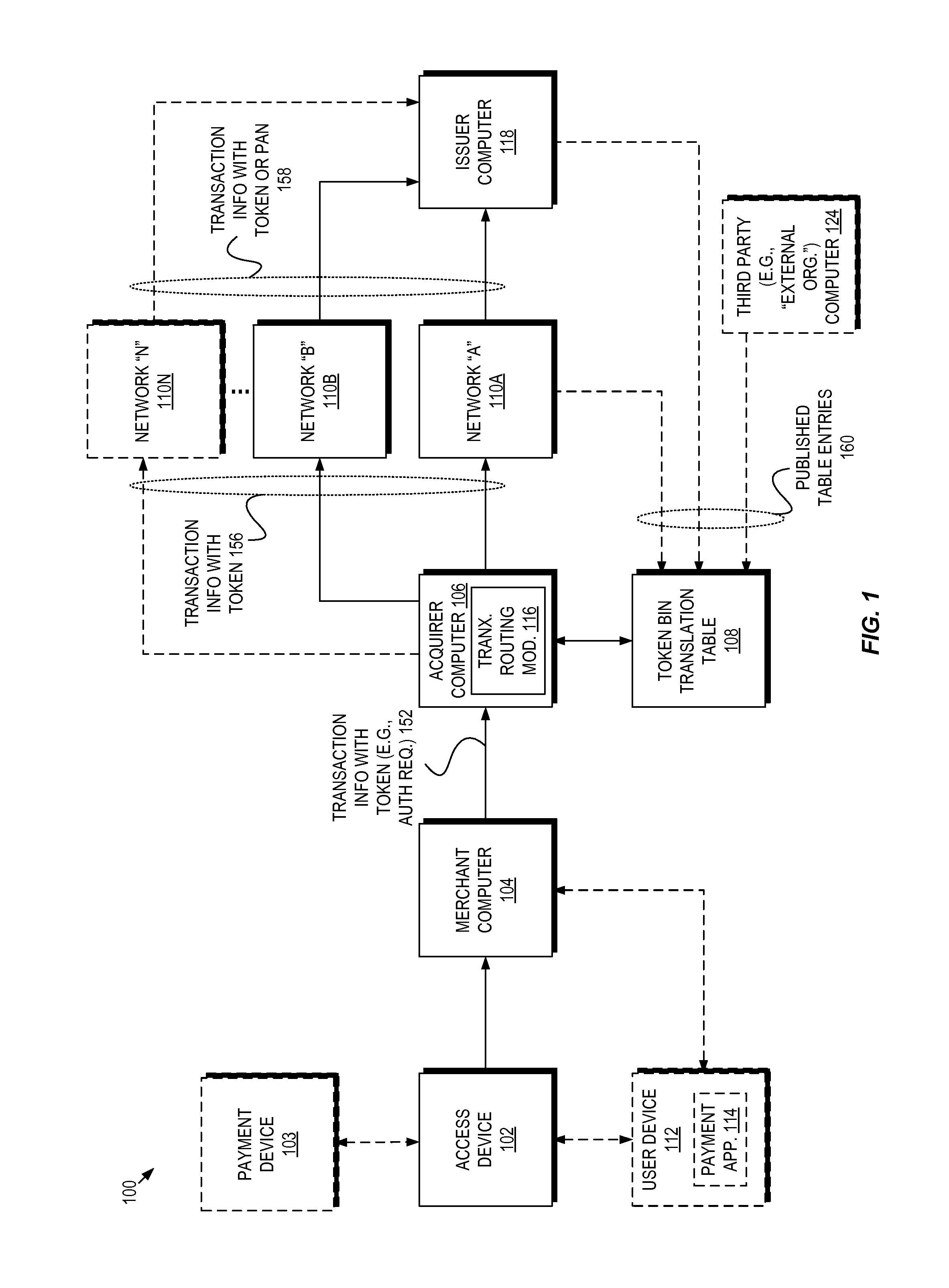

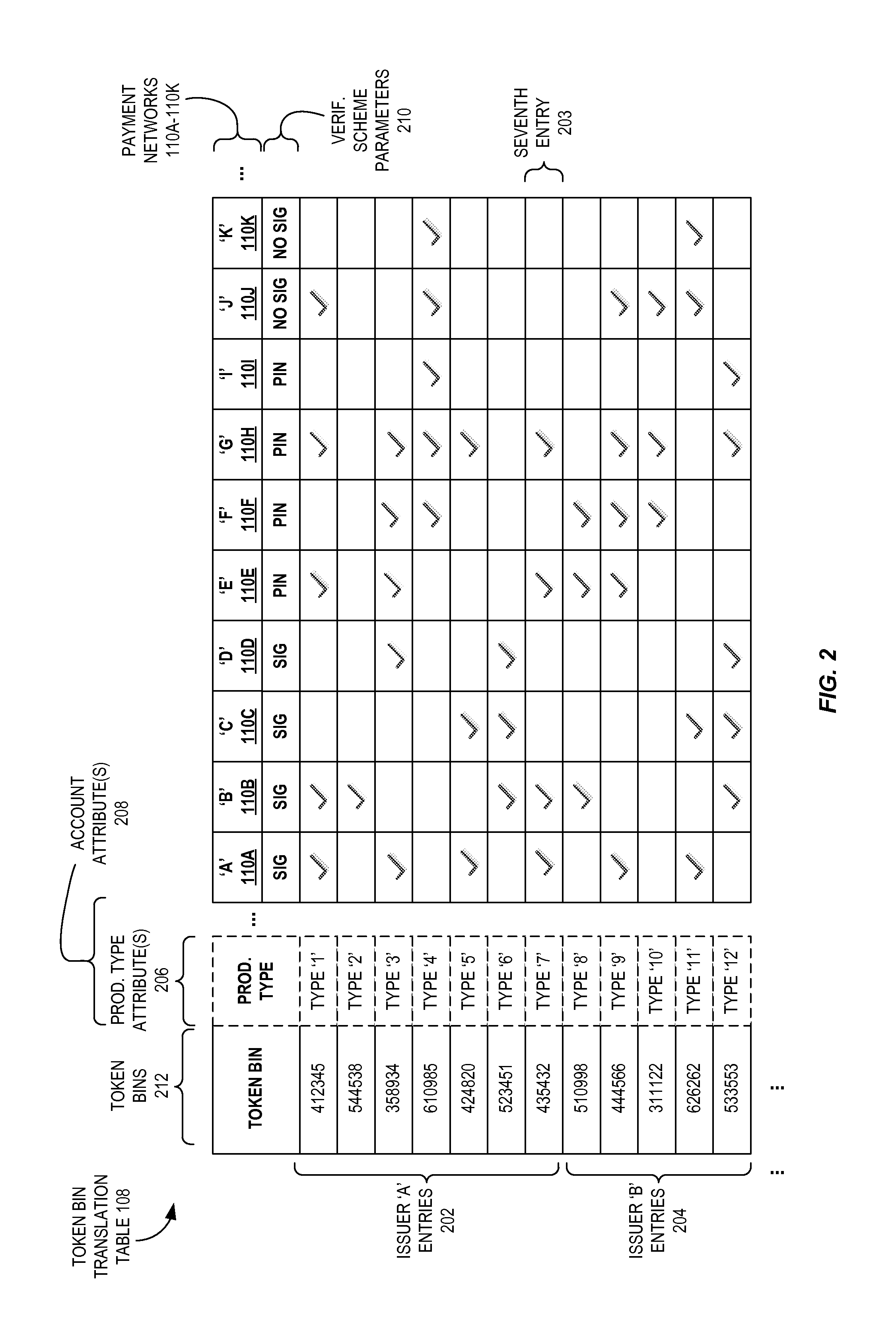

Multi-network token bin routing with defined verification parameters

Techniques described herein relate to using tokenization with BIN table routing by configuring a computer system, such as an acquirer computer, to utilize a token BIN translation table to determine which payment processing network(s) are eligible to route a transaction based upon a utilized token. In an embodiment, each token BIN translation table entry associates a token BIN with one or more payment processing networks that are eligible to route transactions. An acquirer computer, upon receiving a token for a transaction, thus may flexibly route the transaction to an eligible network from the set of payment processing networks identified by the entry corresponding to the token's BIN value. The entry may further identify verification methods for the eligible payment processing networks, and may identify product type attributes of the account associated with the token, either of which may be used in determining which payment processing network to select.

Owner:VISA INT SERVICE ASSOC

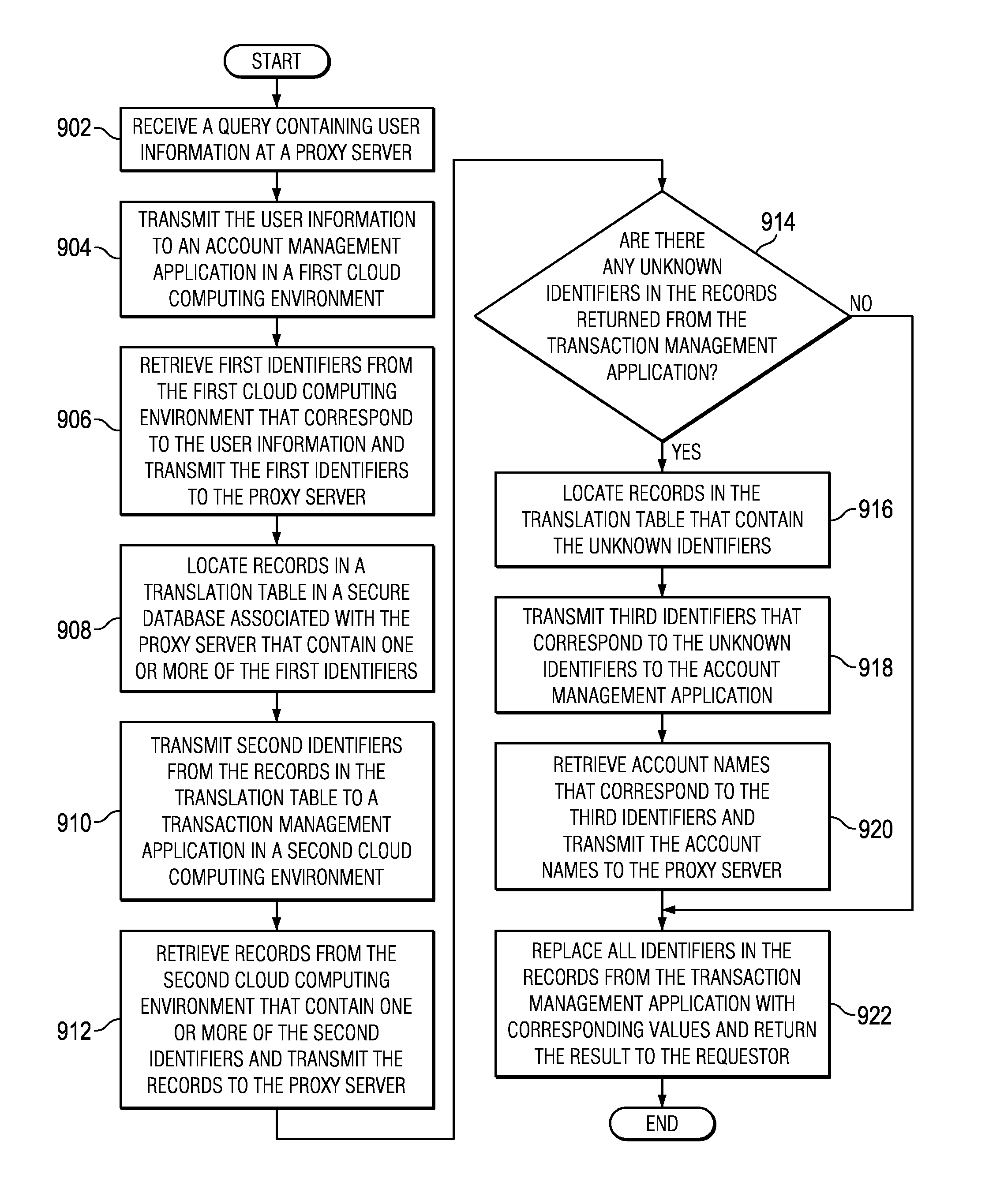

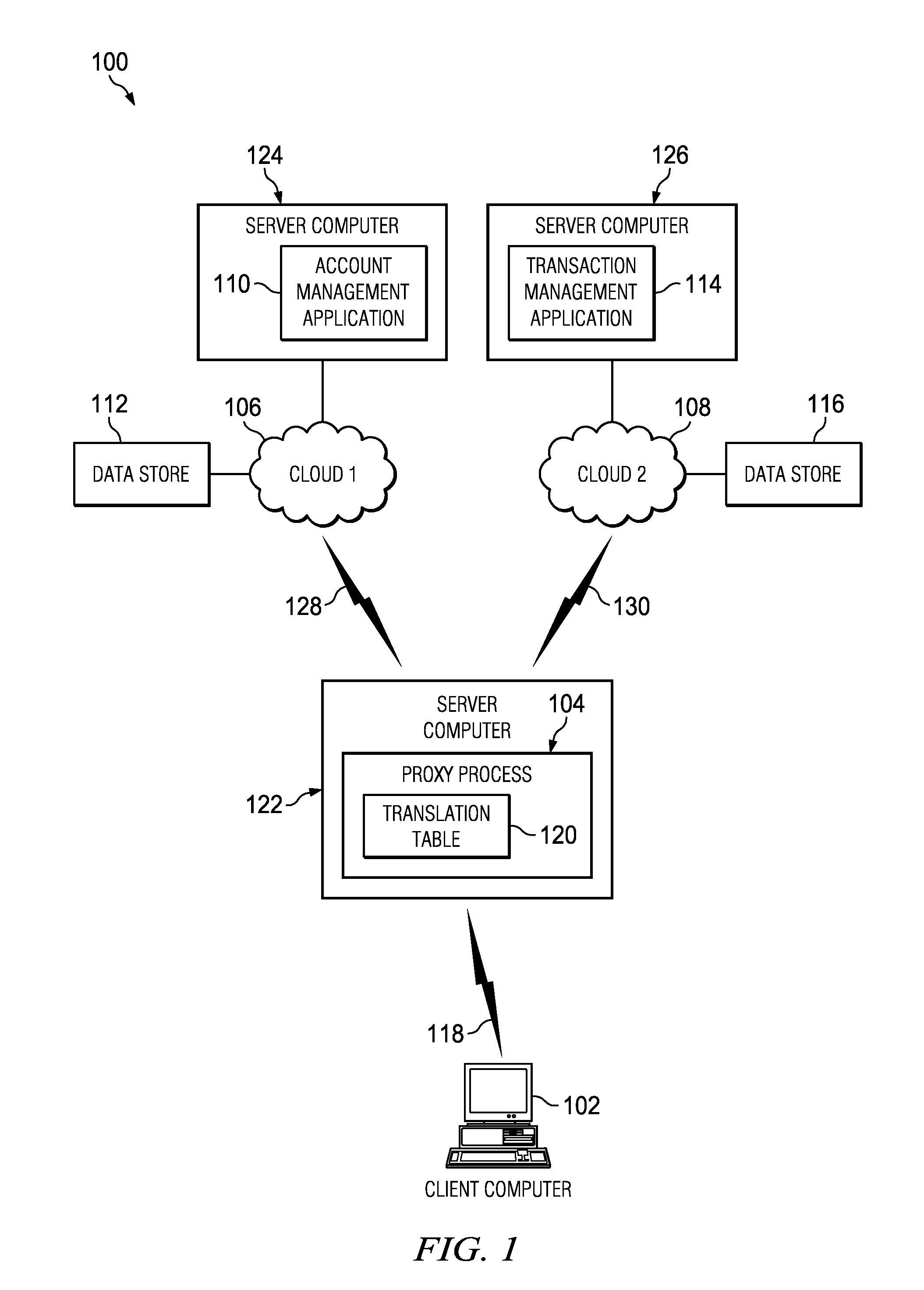

Managing sensitive data in cloud computing environments

ActiveUS9460307B2Digital data processing detailsDigital data protectionTranslation tableCloud computing

The illustrative embodiments provide a method, computer program product, and apparatus for managing collectively sensitive data. Collectively sensitive data is divided into a first partition for reassembly data, a second partition of the collectively sensitive data, and a third partition of the collectively sensitive data. Each of the second partition and the third partition are collectively nonsensitive in isolation. The first partition is stored in a translation table in a secure database. The translation table is configured for use in assembling collectively sensitive data from the second partition and the third partition. The second partition of the collectively sensitive data is stored in a first database associated with a first cloud computing environment. The third partition of collectively sensitive data is stored in a second database associated with a second cloud computing environment.

Owner:INT BUSINESS MASCH CORP

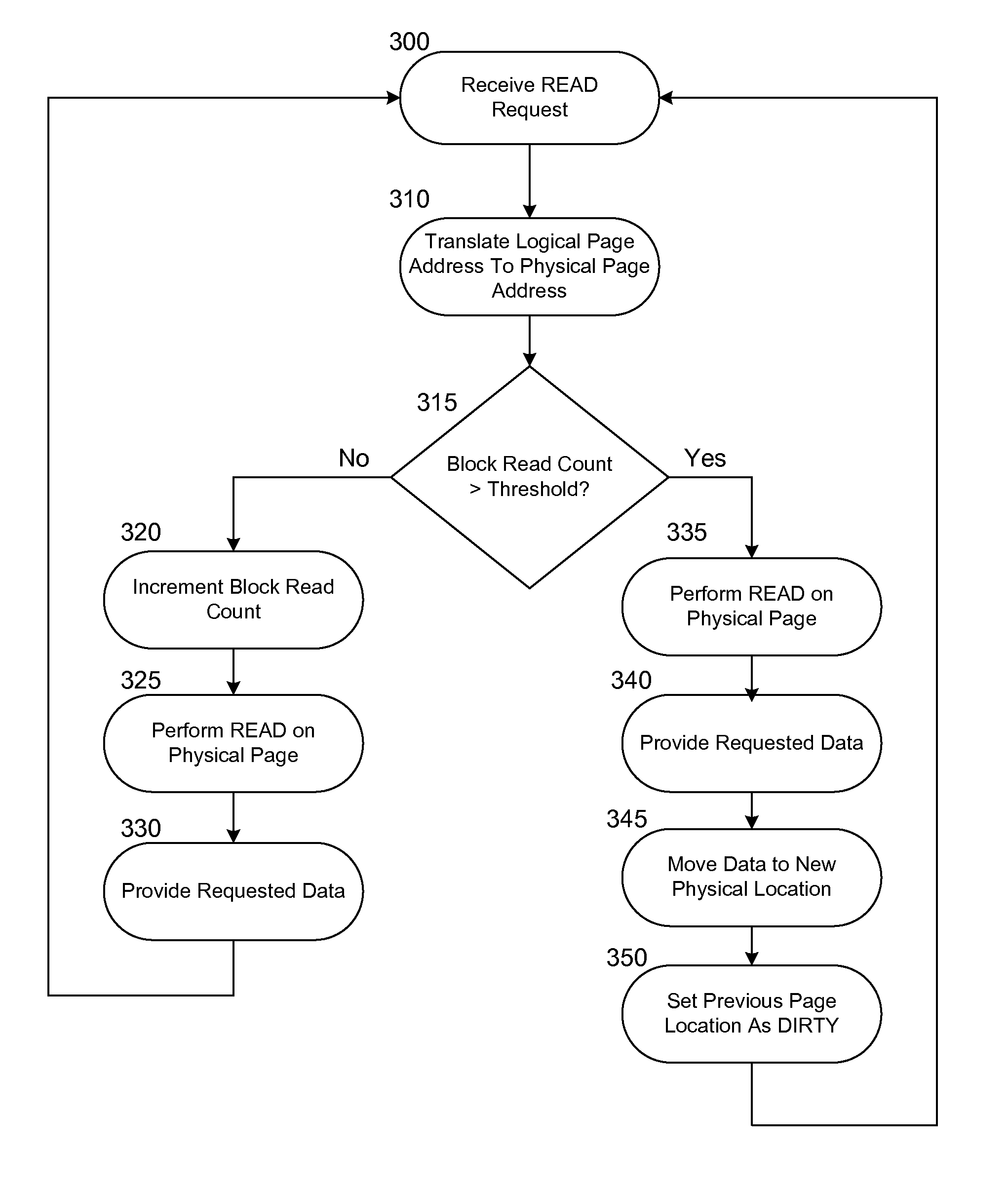

Efficient reduction of read disturb errors in NAND FLASH memory

InactiveUS7818525B1Disturb errorEfficient reduction of Read Disturb errorMemory architecture accessing/allocationRead-only memoriesPhysical addressTranslation table

Methods and apparatuses for reduction of Read Disturb errors in a NAND FLASH memory system comprise a controller configured to organize FLASH memory devices into blocks, each block having a plurality of pages, and each page defining an individually addressable physical memory location. The controller is further configured to accumulate a Block READ Count corresponding to the number of times any pages in a first block of pages have been read since the first block was last erased. Once the READ count reaches a predetermined number, the controller responds to subsequent READ requests for pages within the first block by moving data associated with a requested page to a page in a second, different block without moving data associated with other pages in the first block, and modifying a logical-to-physical translation table to associate the moved data with the physical address of the page in the second block.

Owner:IBM CORP

Dynamic selection of memory virtualization techniques

ActiveUS20070283125A1Error detection/correctionMemory adressing/allocation/relocationVirtualizationComputerized system

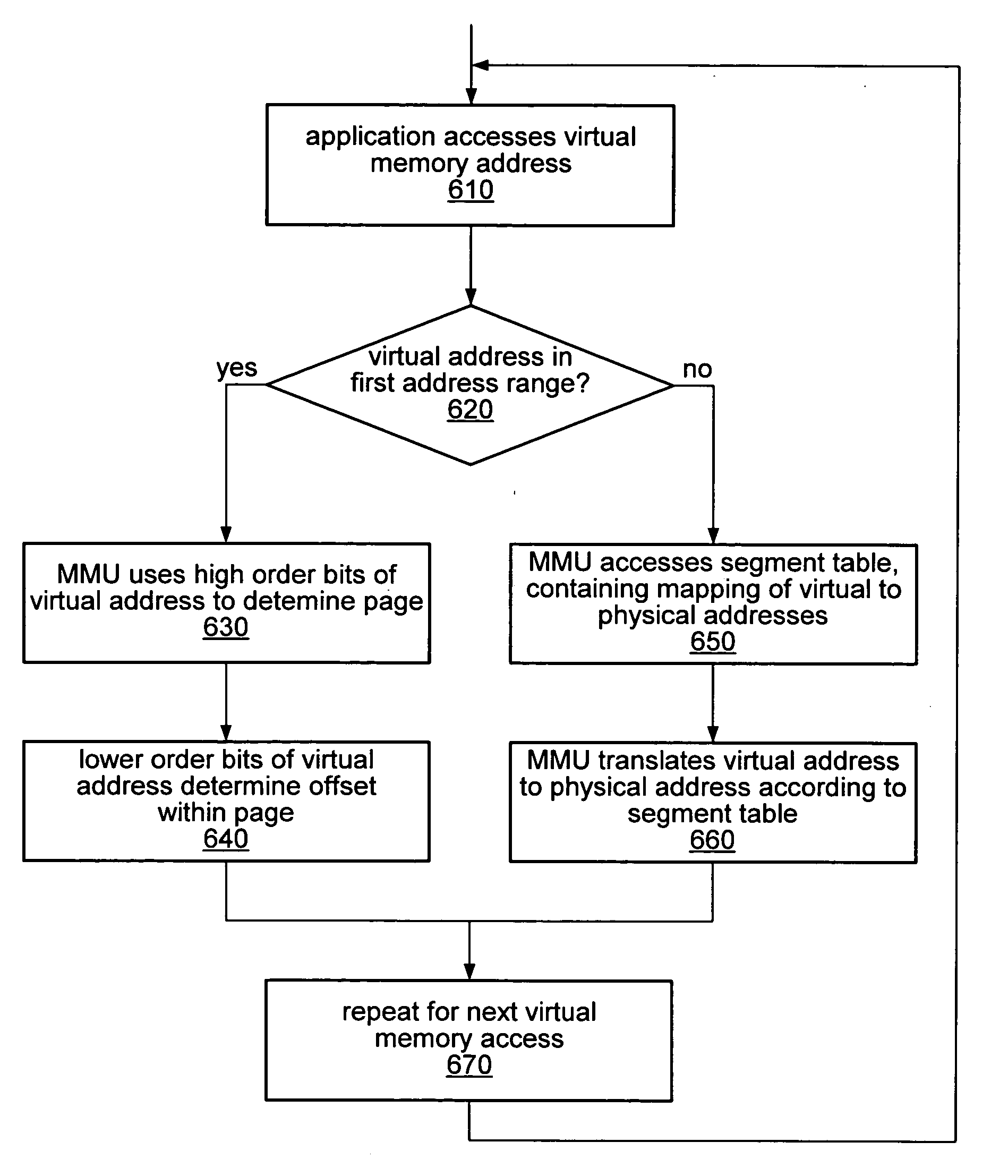

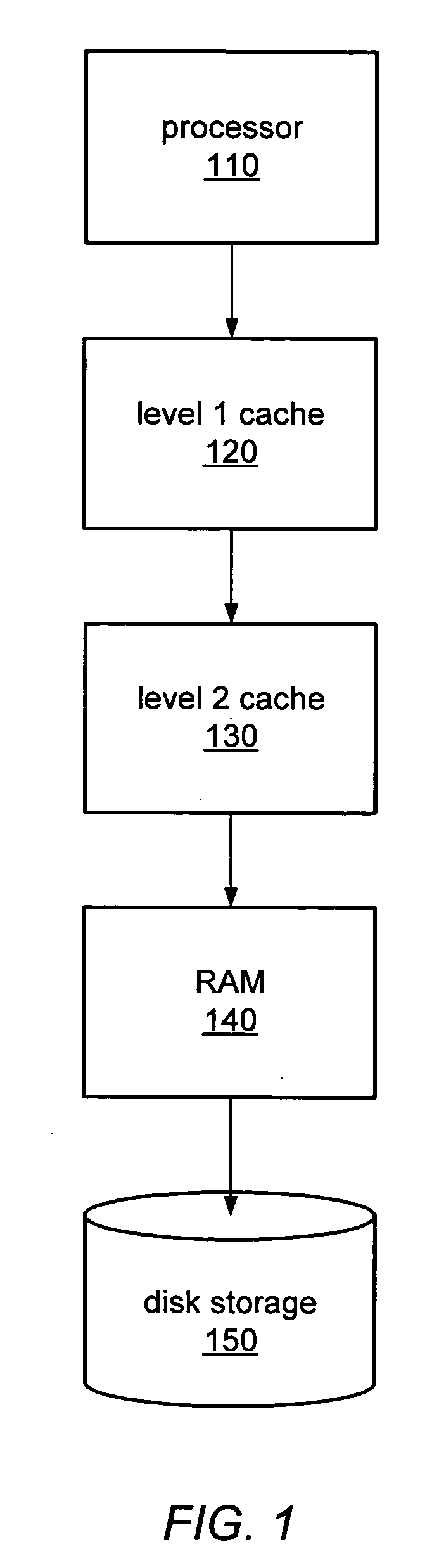

A computer system may be configured to dynamically select a memory virtualization and corresponding virtual-to-physical address translation technique during execution of an application and to dynamically employ the selected technique in place of a current technique without re-initializing the application. The computer system may be configured to determine that a current address translation technique incurs a high overhead for the application's current workload and may be configured to select a different technique dependent on various performance criteria and / or a user policy. Dynamically employing the selected technique may include reorganizing a memory, reorganizing a translation table, allocating a different block of memory to the application, changing a page or segment size, or moving to or from a page-based, segment-based, or function-based address translation technique. A selected translation technique may be dynamically employed for the application independent of a translation technique employed for a different application.

Owner:ORACLE INT CORP

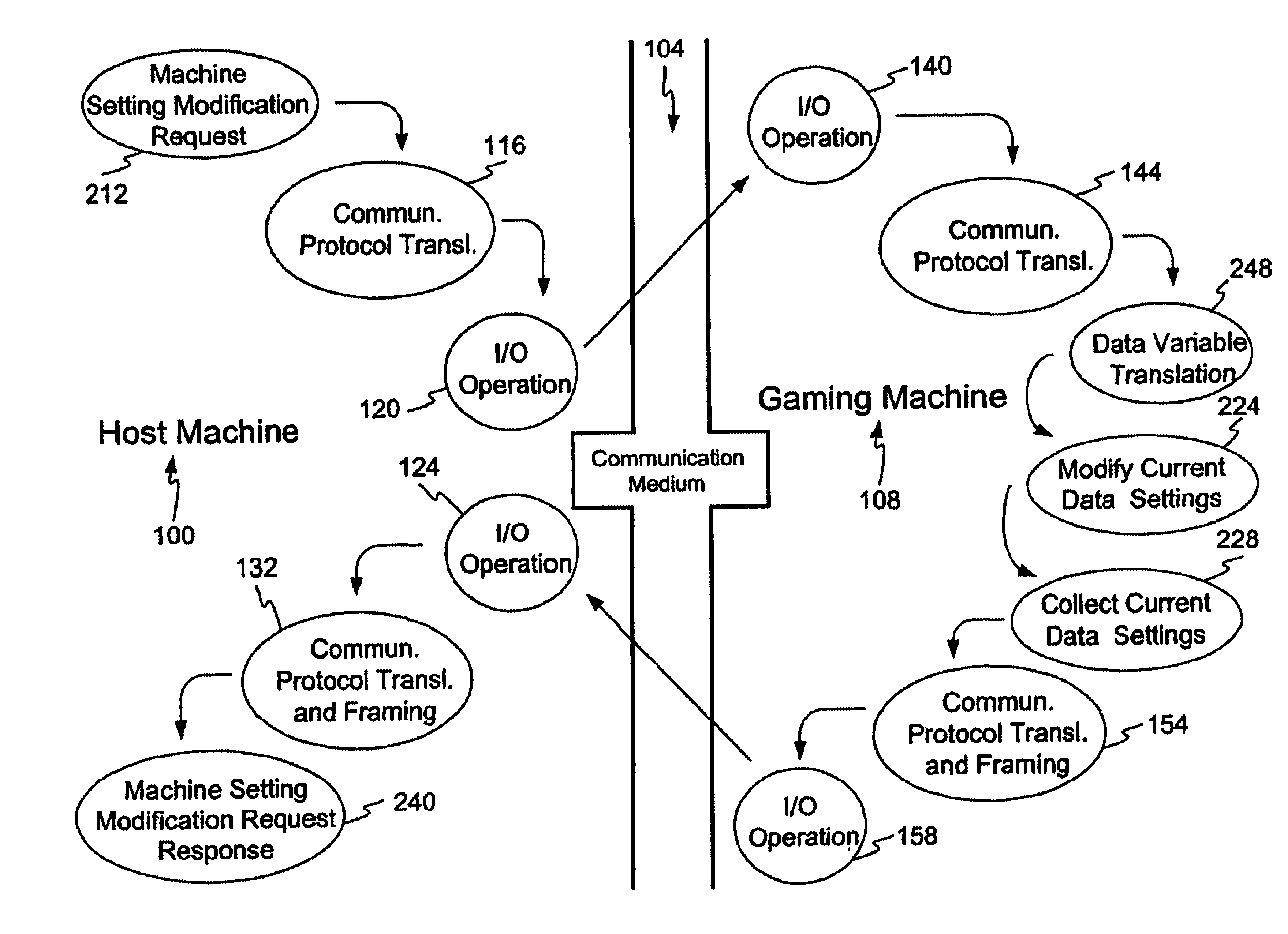

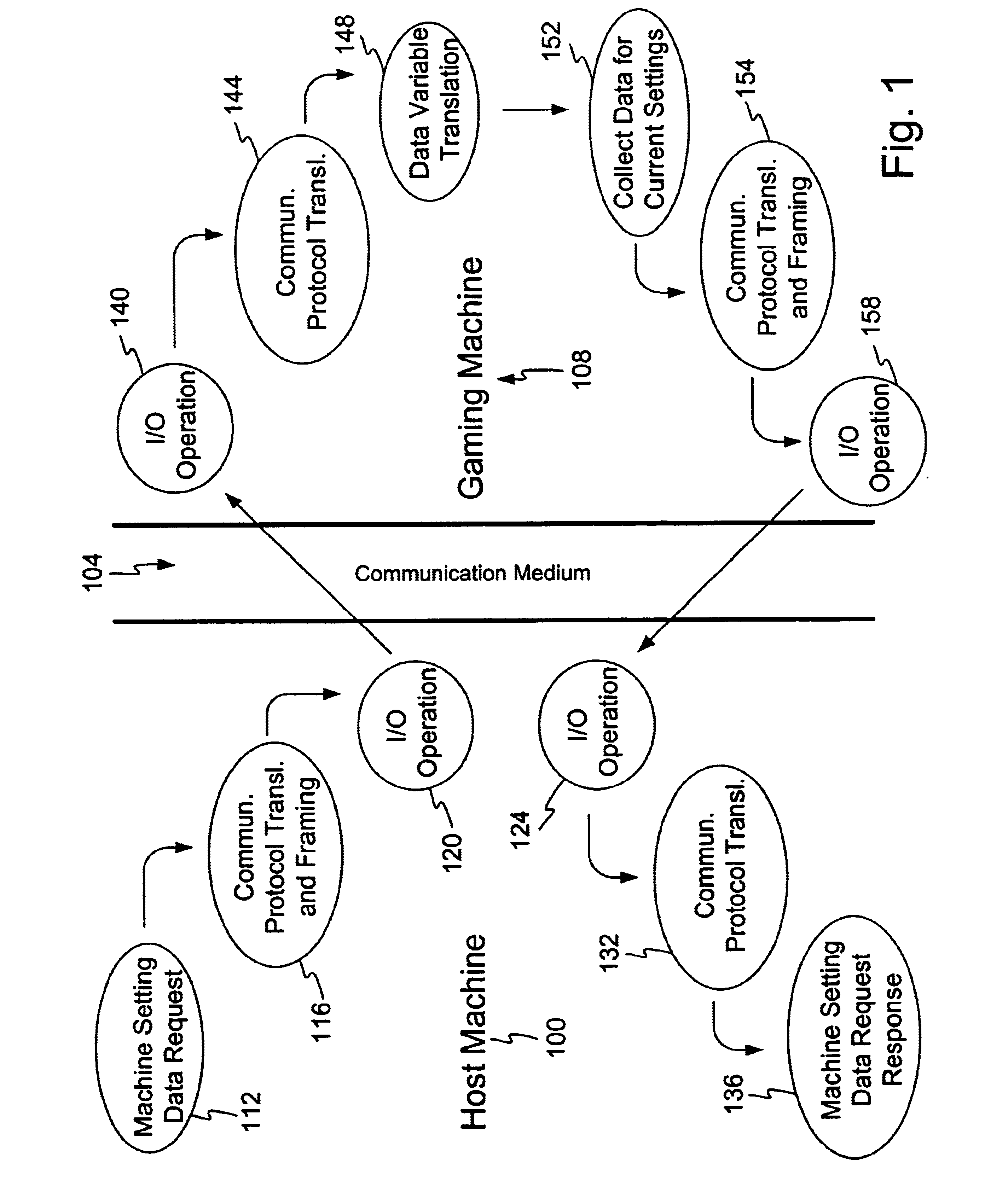

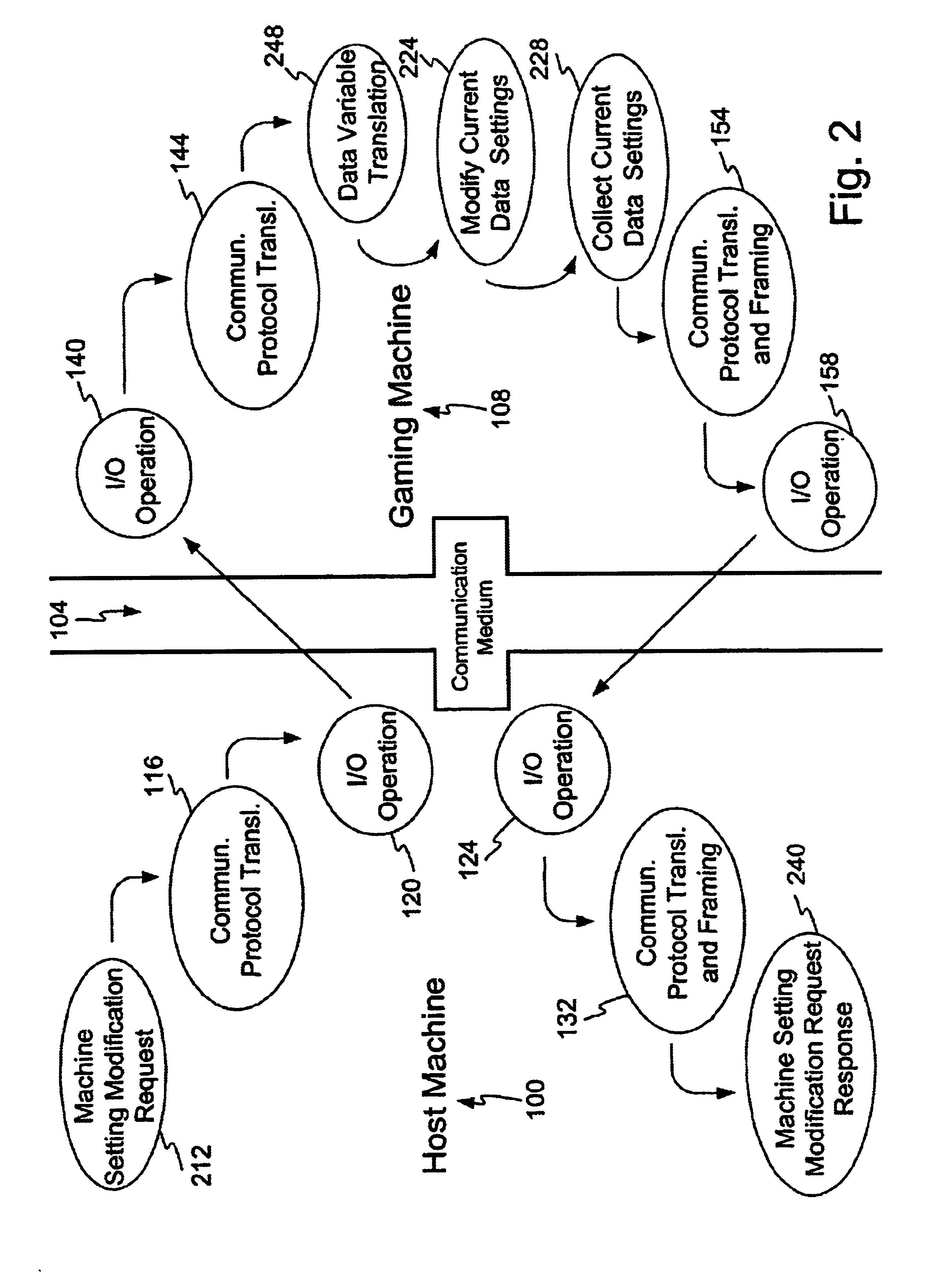

Communication protocol for gaming system configuration

InactiveUS6884174B2Overcomes drawbackApparatus for meter-controlled dispensingVideo gamesComputer hardwareNetwork Communication Protocols

A method and apparatus for communicating gaming machine settings is disclosed. In one embodiment a universal configuration communication protocol is provided for retrieving or modifying, over a network, current gaming machine setting of a remotely located gaming machine. A translation table may be implemented with the communication protocol to achieve variable translation between different gaming machine platforms. In one embodiment the gaming machine status is requested prior to activating the communication protocol to prevent interruption of game play. In one embodiment activation of the communication protocol may result in the gaming machine momentarily entering an inactive status.

Owner:IGT

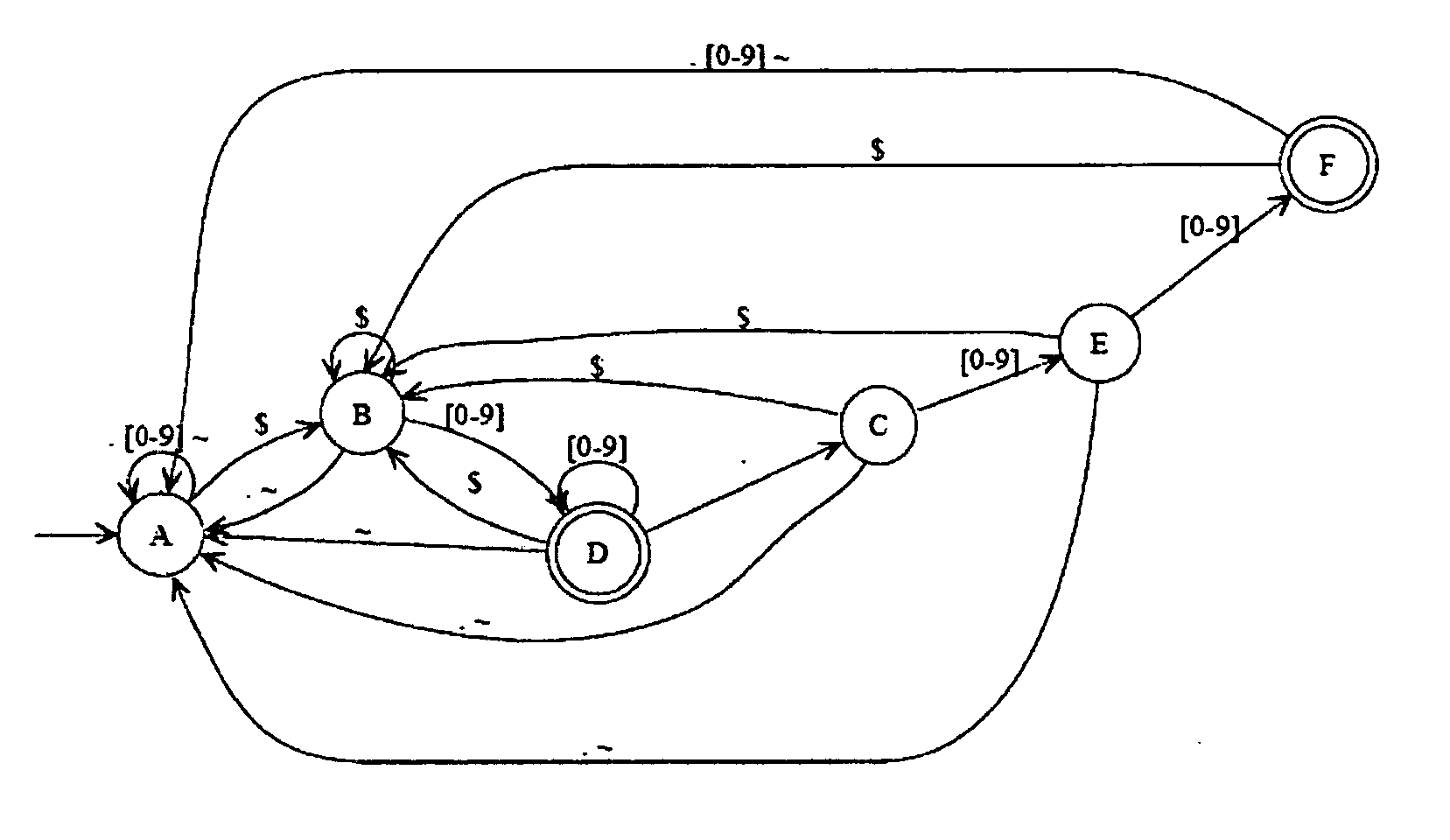

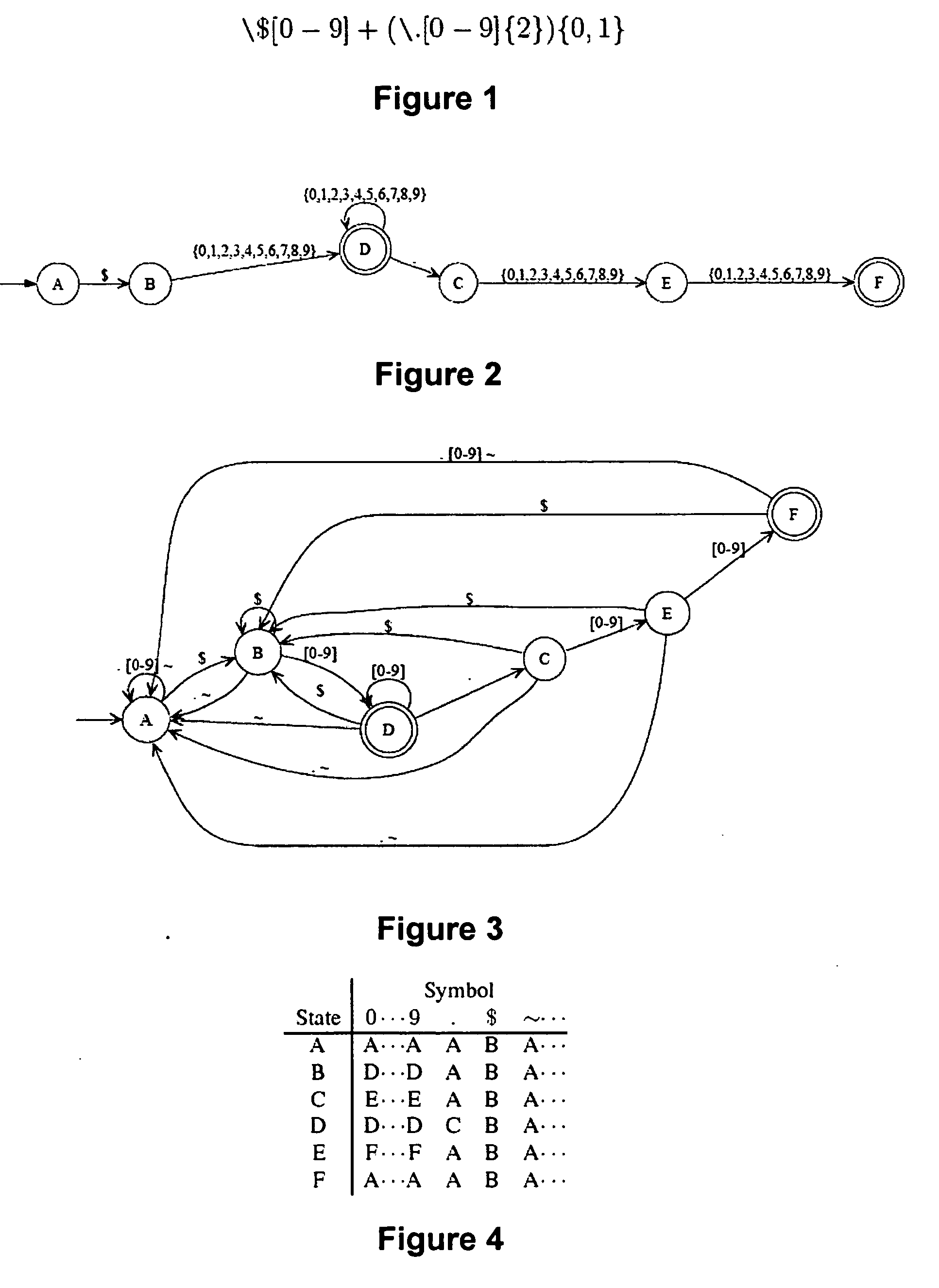

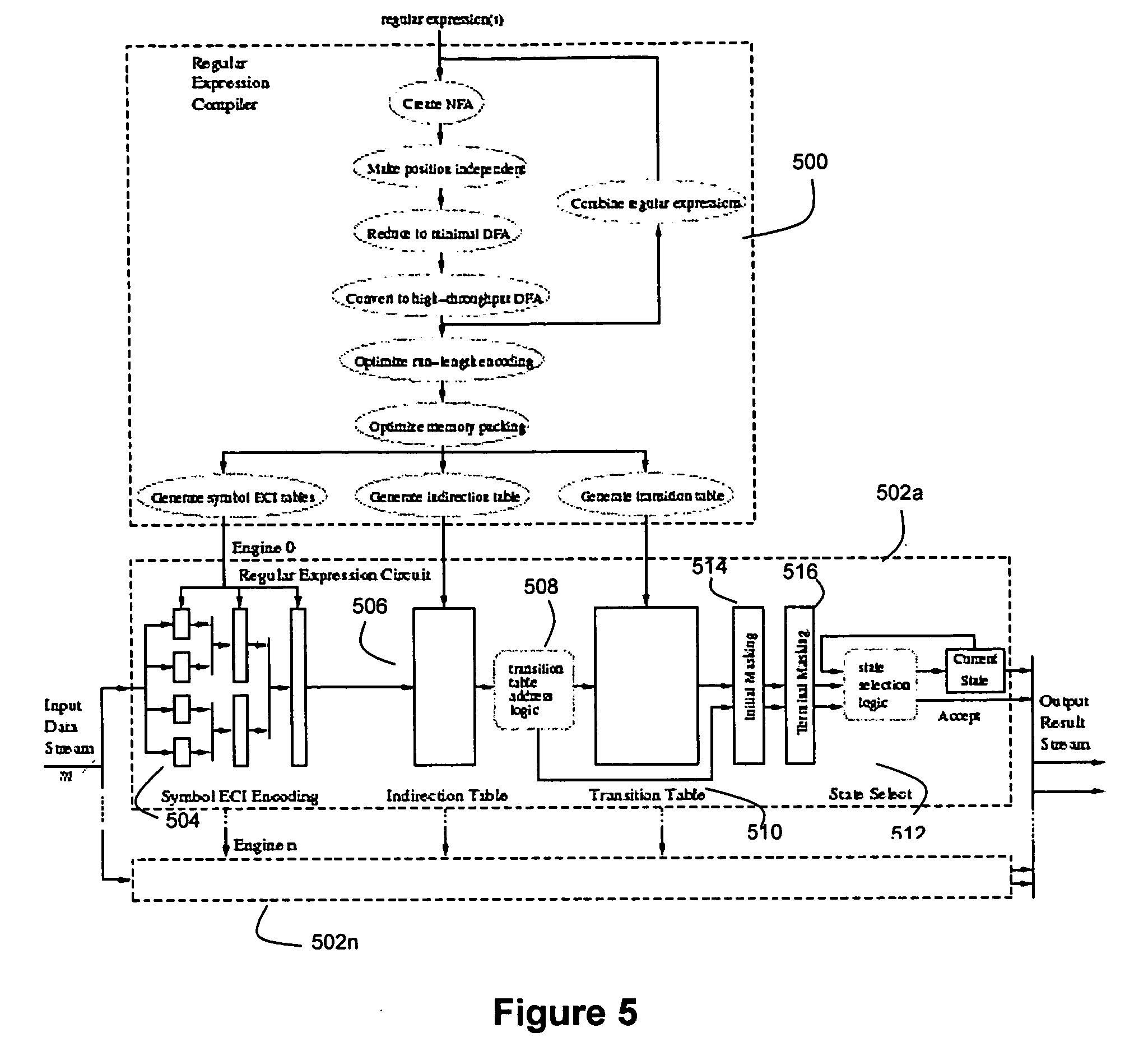

Method and device for high performance regular expression pattern matching

ActiveUS20070130140A1Minimize the numberData processing applicationsDigital data information retrievalAlgorithmPattern matching

Disclosed herein is an improved architecture for regular expression pattern matching. Improvements to pattern matching deterministic finite automatons (DFAs) that are described by the inventors include a pipelining strategy that pushes state-dependent feedback to a final pipeline stage to thereby enhance parallelism and throughput, augmented state transitions that track whether a transition is indicative of a pattern match occurring thereby reducing the number of necessary states for the DFA, augmented state transition that track whether a transition is indicative of a restart to the matching process, compression of the DFA's transition table, alphabet encoding for input symbols to equivalence class identifiers, the use of an indirection table to allow for optimized transition table memory, and enhanced scalability to facilitate the ability of the improved DFA to process multiple input symbols per cycle.

Owner:IP RESERVOIR

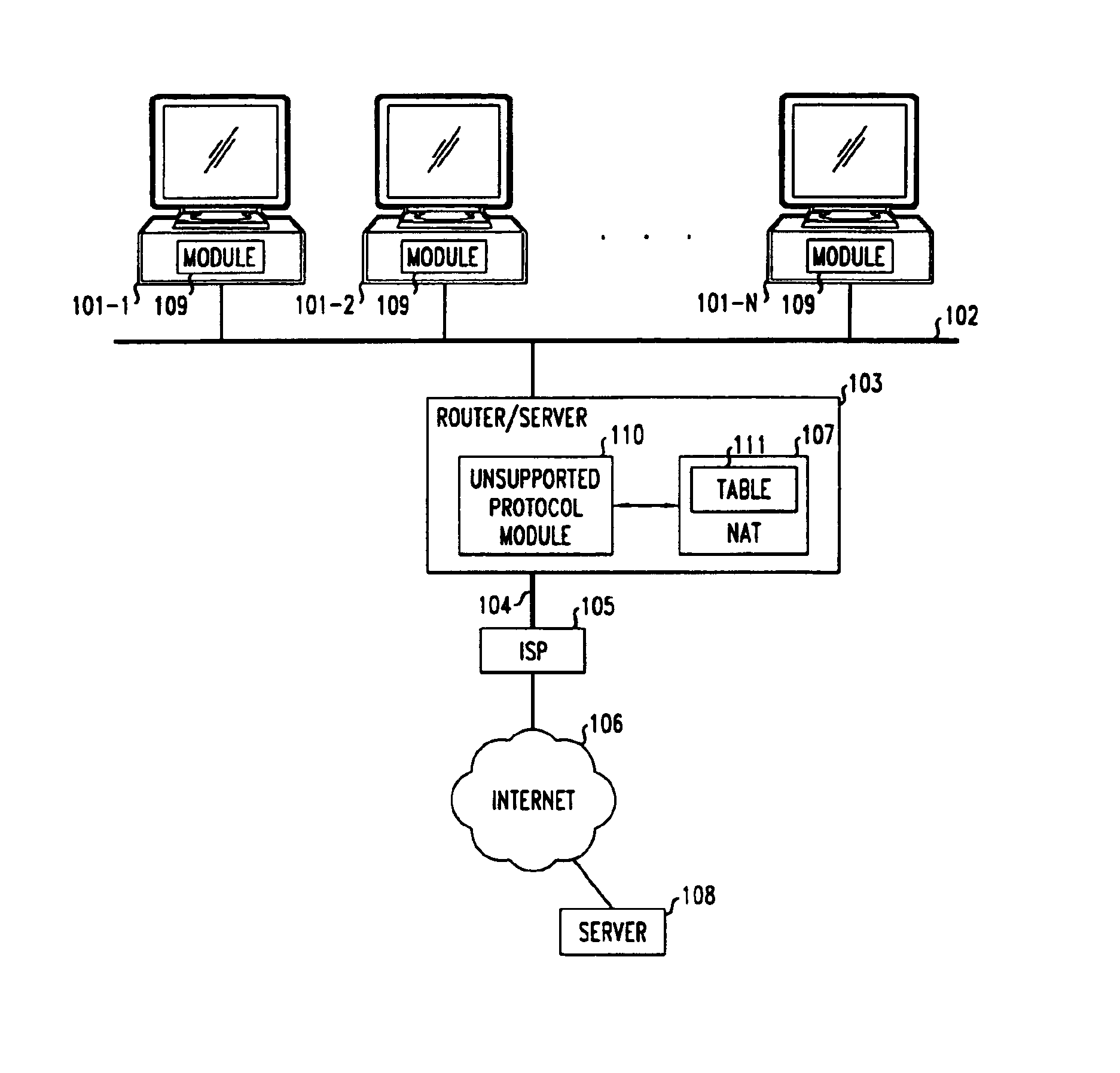

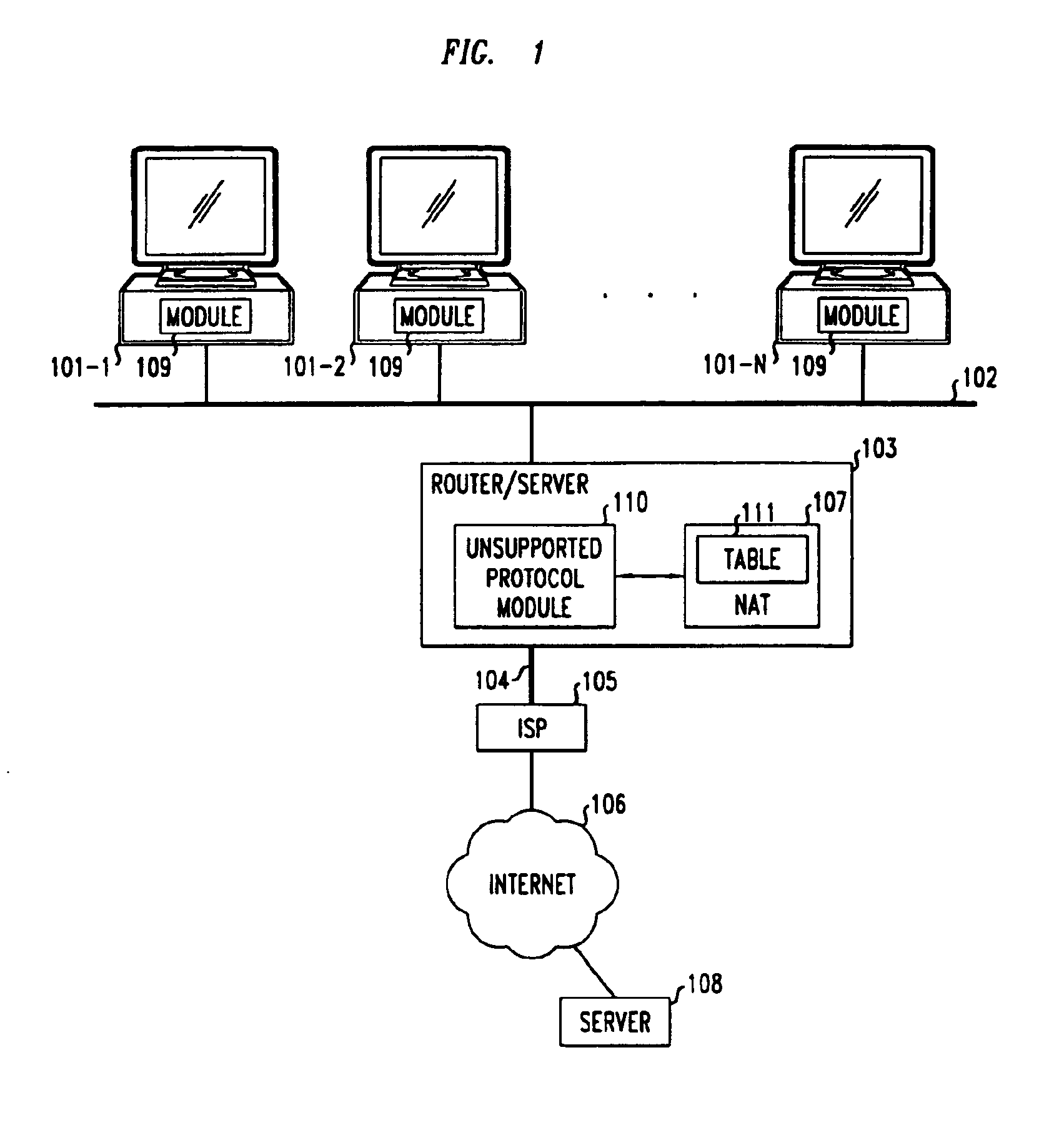

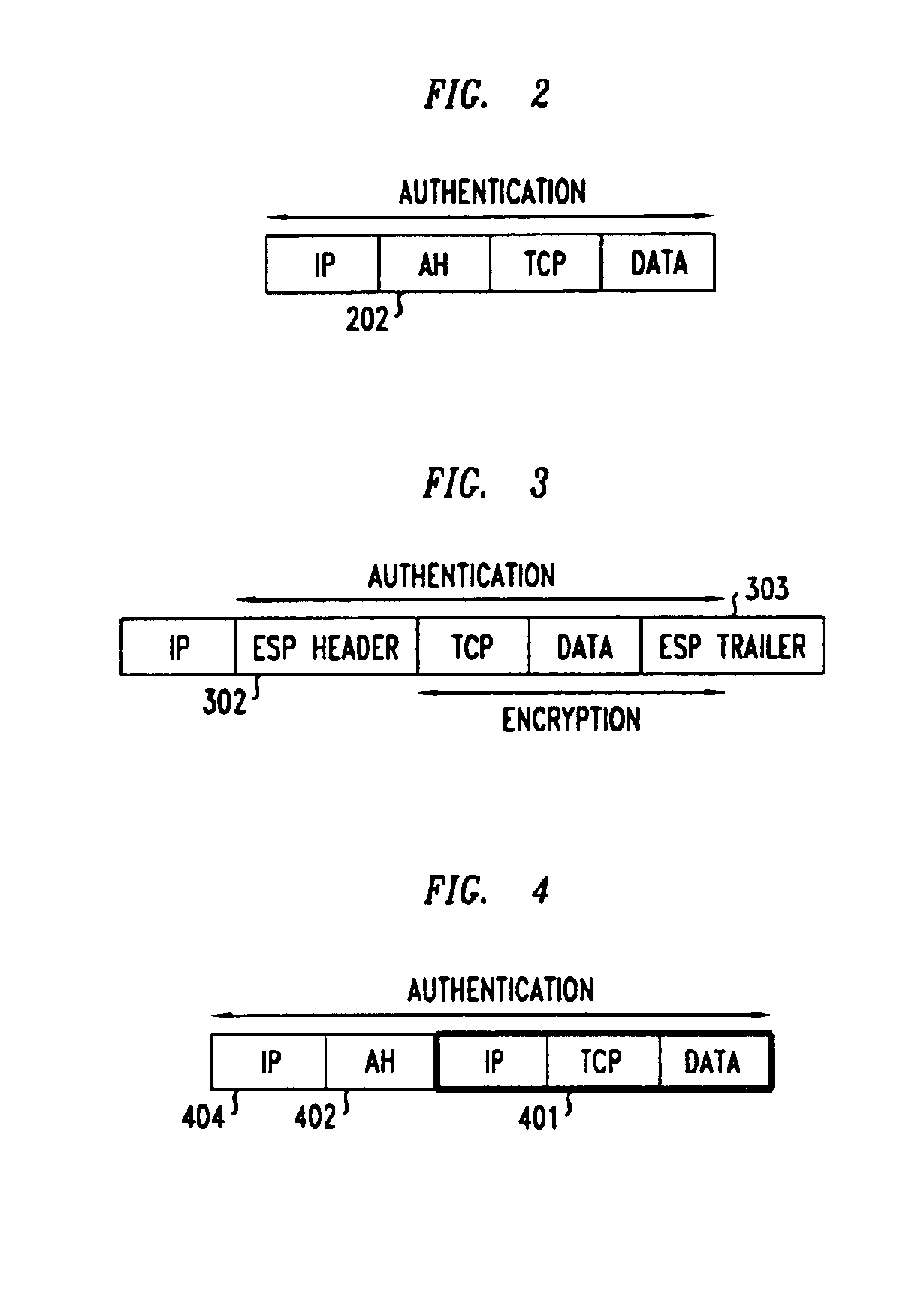

Method and apparatus for extending network address translation for unsupported protocols

InactiveUS6886103B1Ensure safetyMultiple digital computer combinationsProgram controlExpiration TimeIp address

Clients that are connected on a private network and which are assigned a private IP address that is not routable on the Internet can connect to the Internet through a router / server that includes a network address translator (NAT). For outgoing packets, the NAT translates the client's private source IP address and generalized port number (GPN) to the NAT's global IP address and GPN. For incoming packets sent to the NAT's global IP address and GPN, the NAT translates the global destination IP address and GPN to the client's private IP address and GPN. For protocols which cannot be directly supported by the NAT, such as those in the IPSec security protocol suite, the NAT is extended by creating in the NAT's translation table an entry that associates, for a specific unsupported protocol, a client's private IP address and GPN, the NAT's global IP address and GPN, and a foreign address on the Internet, that is valid until a specified or default expiration time. Outgoing packets from the client to that foreign address and incoming packets from that foreign address to the NAT's global IP address and GPN are translated according to the entry until the entry expires. In associations with these translations to outgoing and incoming packets, the client implements any Application Layer Gateway (ALG) that would otherwise be implemented at the NAT. Further, at the client, outgoing packets are modified before being transmitted so as to pre-compensate for the effects of the translations. Incoming packets at the client from the NAT are similarly modified so as to post-compensate for the effects of the translations. For the IPSec protocol, these modification include adjusting the checksum in the TCP or UDP header to account for IP address and TCP or UDP port number translations.

Owner:ALCATEL-LUCENT USA INC

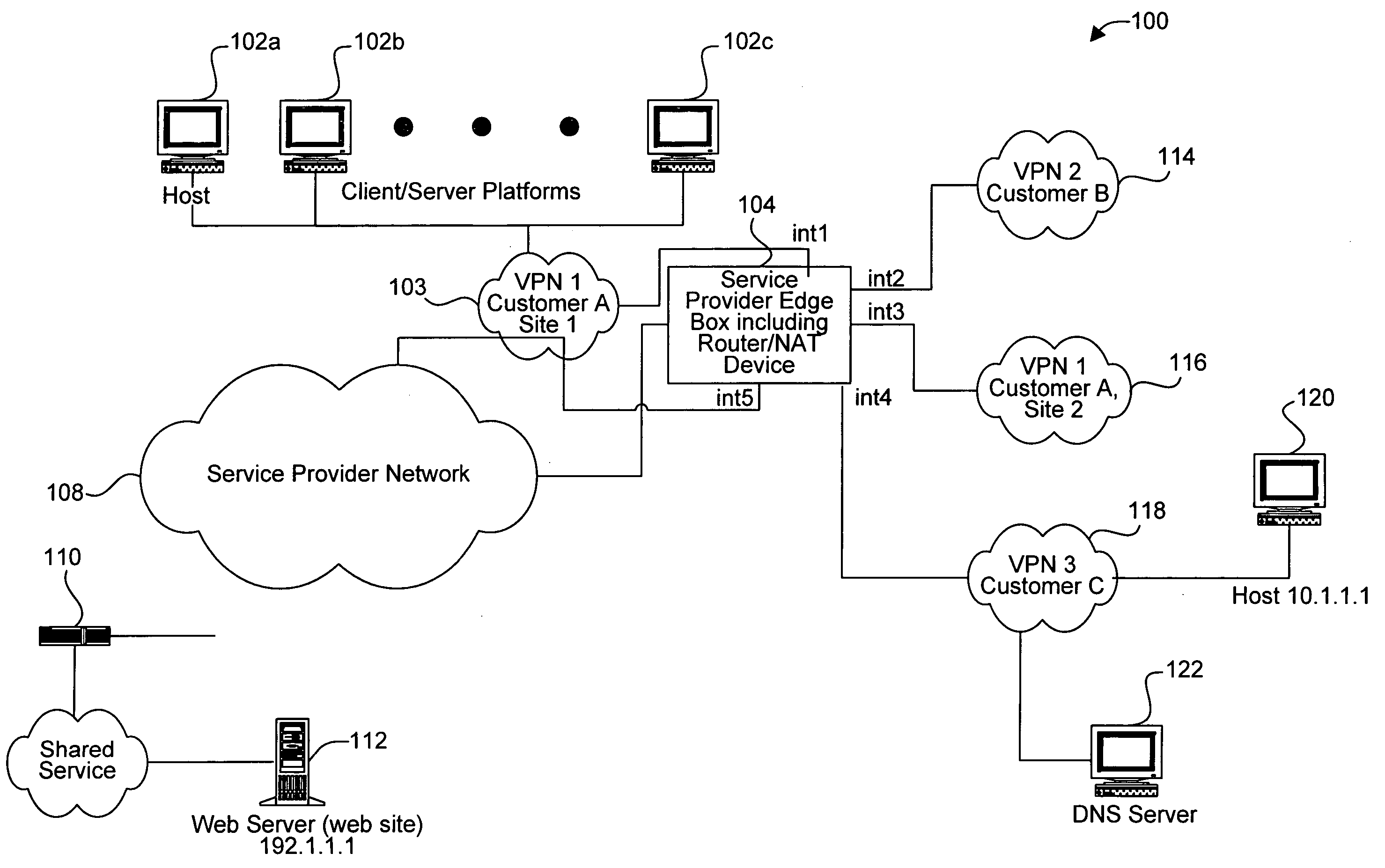

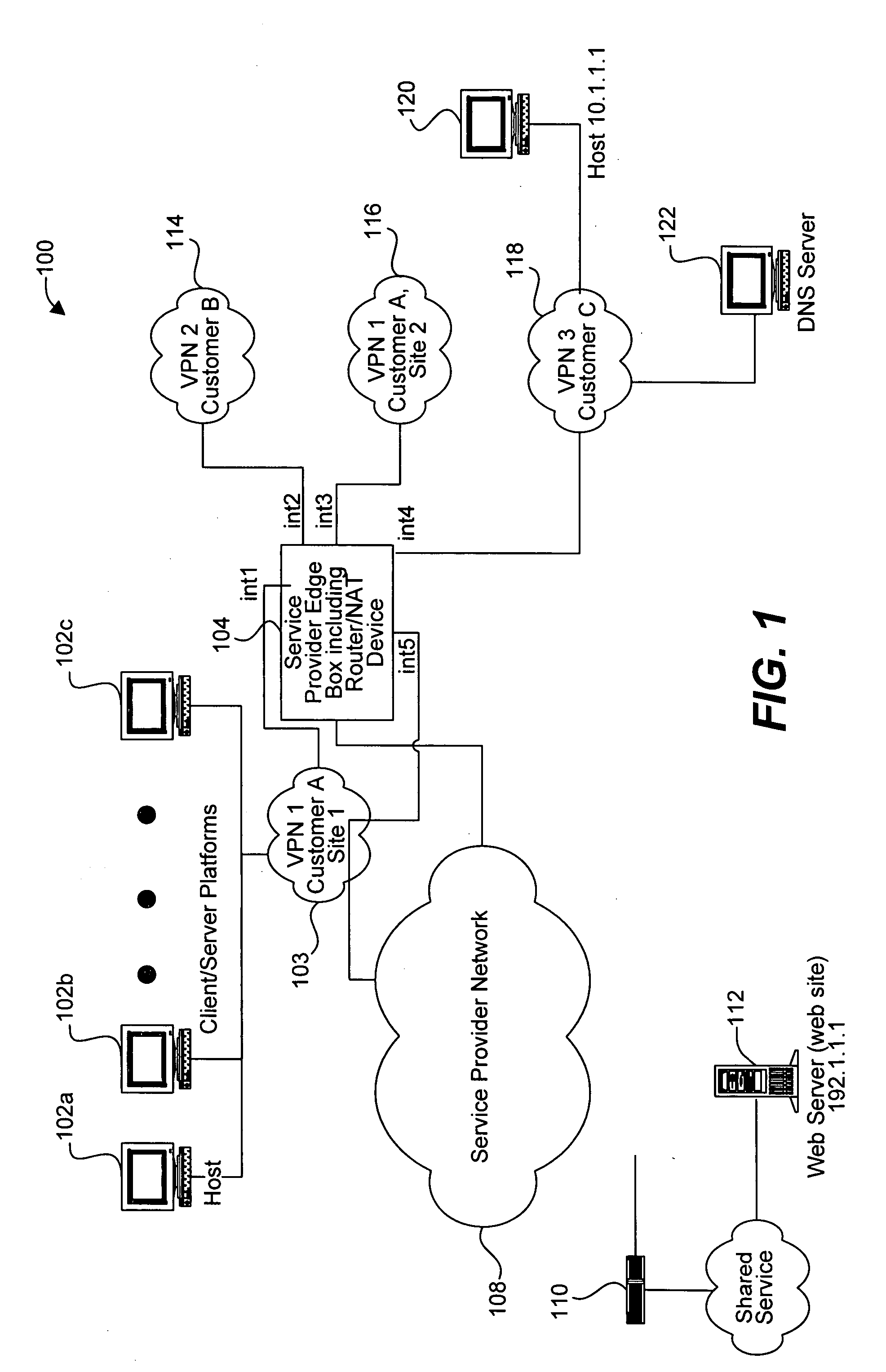

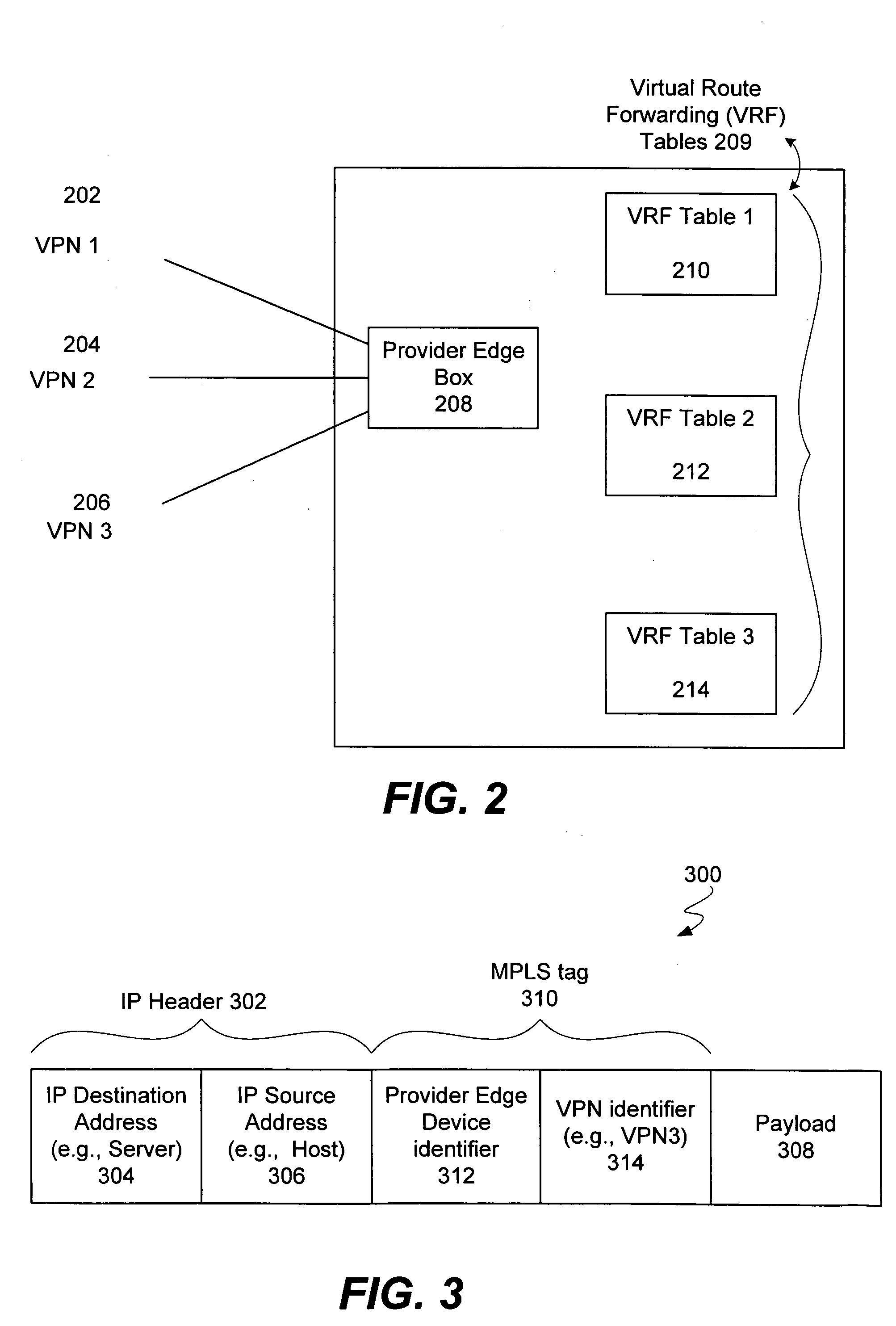

Apparatus and methods for handling shared services through virtual route forwarding(VRF) -aware- NAT

Methods and apparatus for performing NAT are disclosed. Specifically, NAT is performed at a service provider network device associated with an interface of a service provider network. When a packet is sent from a VPN to a node outside the service provider network (e.g., to access a shared service), the packet includes a VPN identifier (or VRF identifier) In accordance with various embodiments, each packet includes an MPLS tag that includes the VPN identifier. The VPN identifier is stored in a translation table entry. The storing of the VPN identifier will enable a reply packet from the shared service network to the customer VPN to be routed using a routing table identified by the VPN identifier.

Owner:CISCO TECH INC

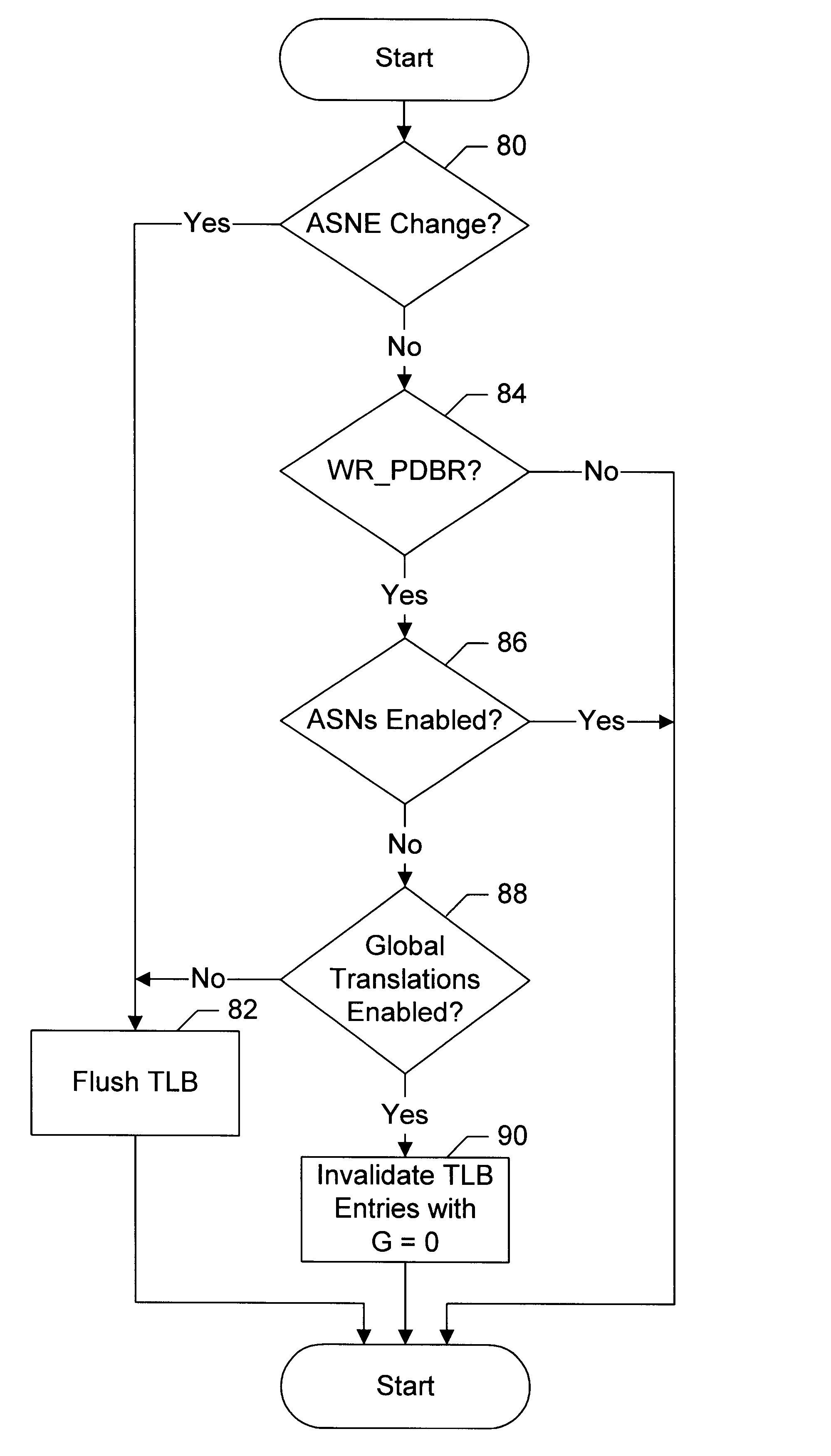

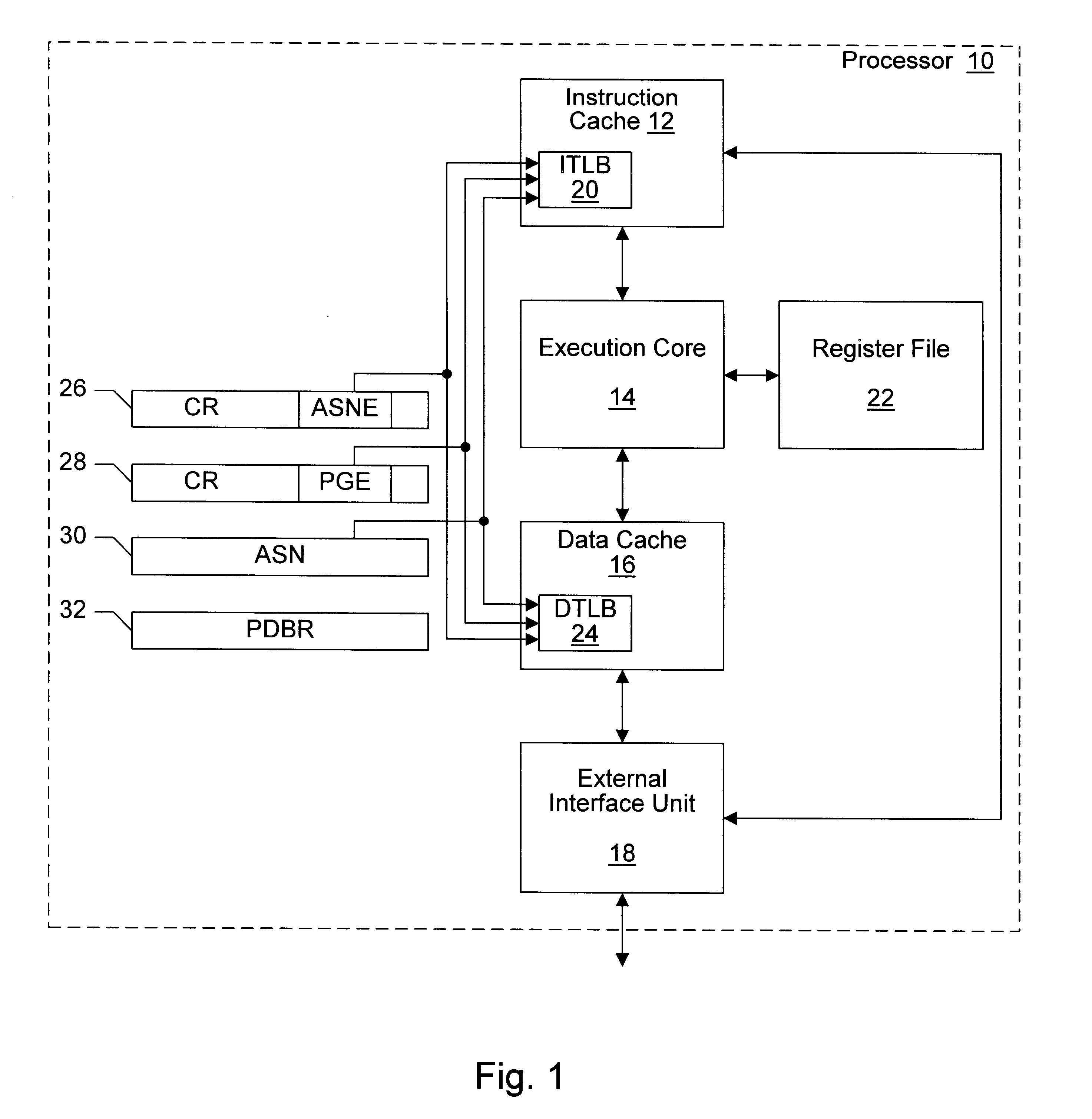

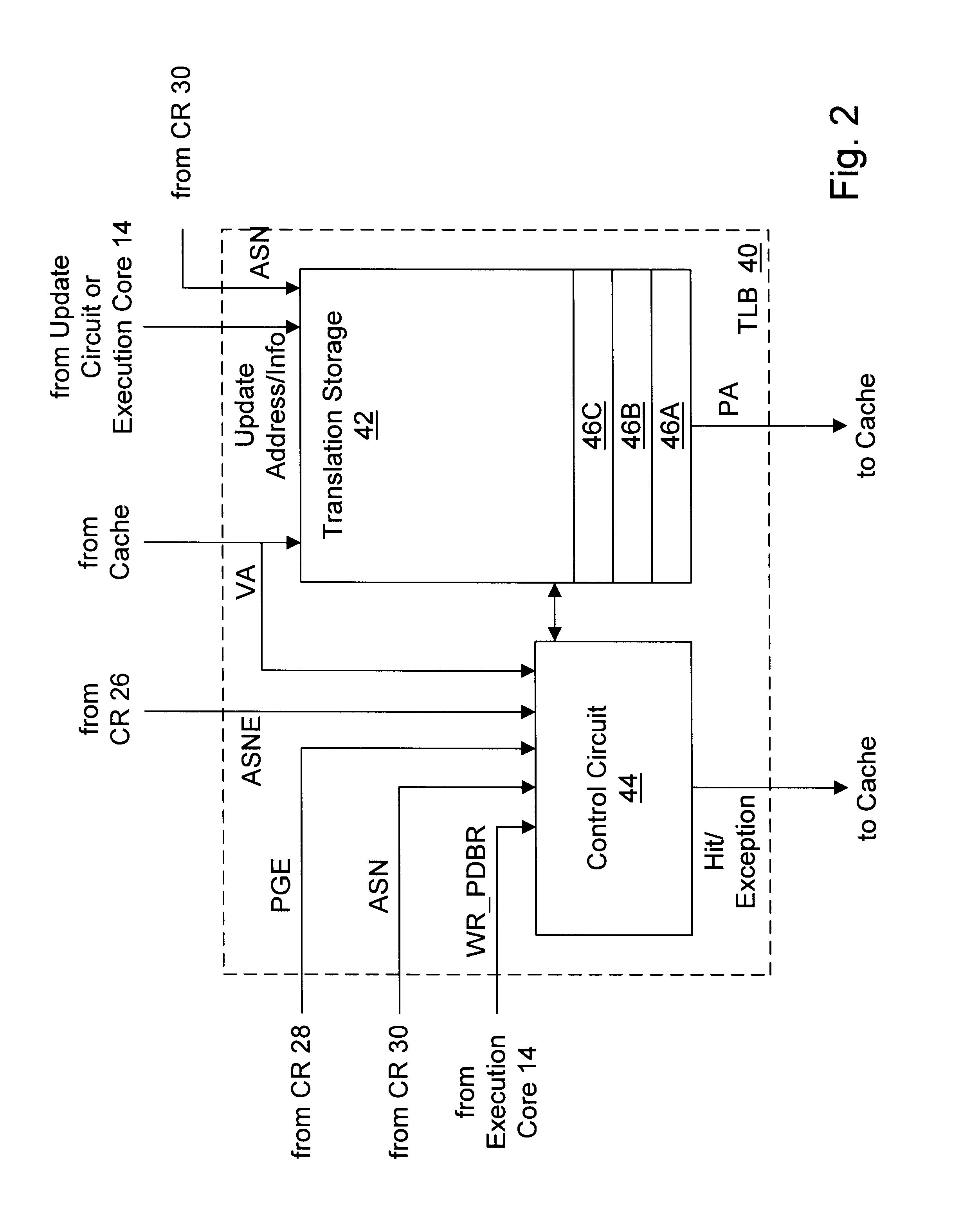

Providing global translations with address space numbers

InactiveUS6604187B1Easy to useMemory architecture accessing/allocationMemory adressing/allocation/relocationOperational systemProcessor register

A processor provides a register for storing an address space number (ASN). Operating system software may assign different ASNs to different processes. The processor may include a TLB to cache translations, and the TLB may record the ASN from the ASN register in a TLB entry being loaded. Thus, translations may be associated with processes through the ASNs. Generally, a TLB hit will be detected in an entry if the virtual address to be translated matches the virtual address tag and the ASN matches the ASN stored in the register. Additionally, the processor may use an indication from the translation table entries to indicate whether or not a translation is global. If a translation is global, then the ASN comparison is not included in detecting a hit in the TLB. Thus, translations which are used by more than one process may not occupy multiple TLB entries. Instead, a hit may be detected on the TLB entry storing the global translation even though the recorded ASN may not match the current ASN. In one embodiment, if ASNs are disabled, the TLB may be flushed on context switches. However, the indication from the translation table entries used to indicate that the translation is global may be used (when ASNs are disabled) by the TLB to selectively invalidate non-global translations on a context switch while not invalidating global translations.

Owner:GLOBALFOUNDRIES US INC

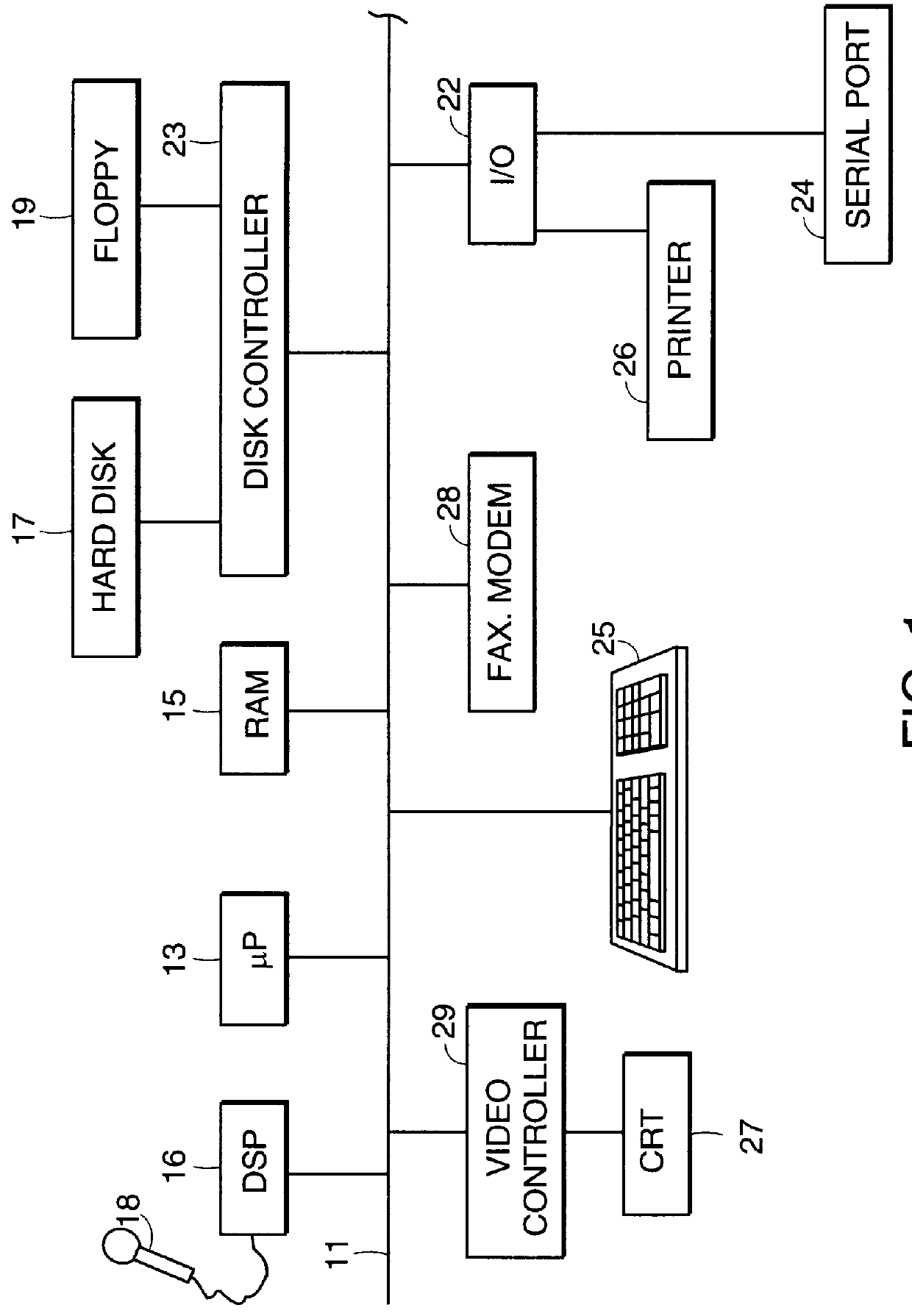

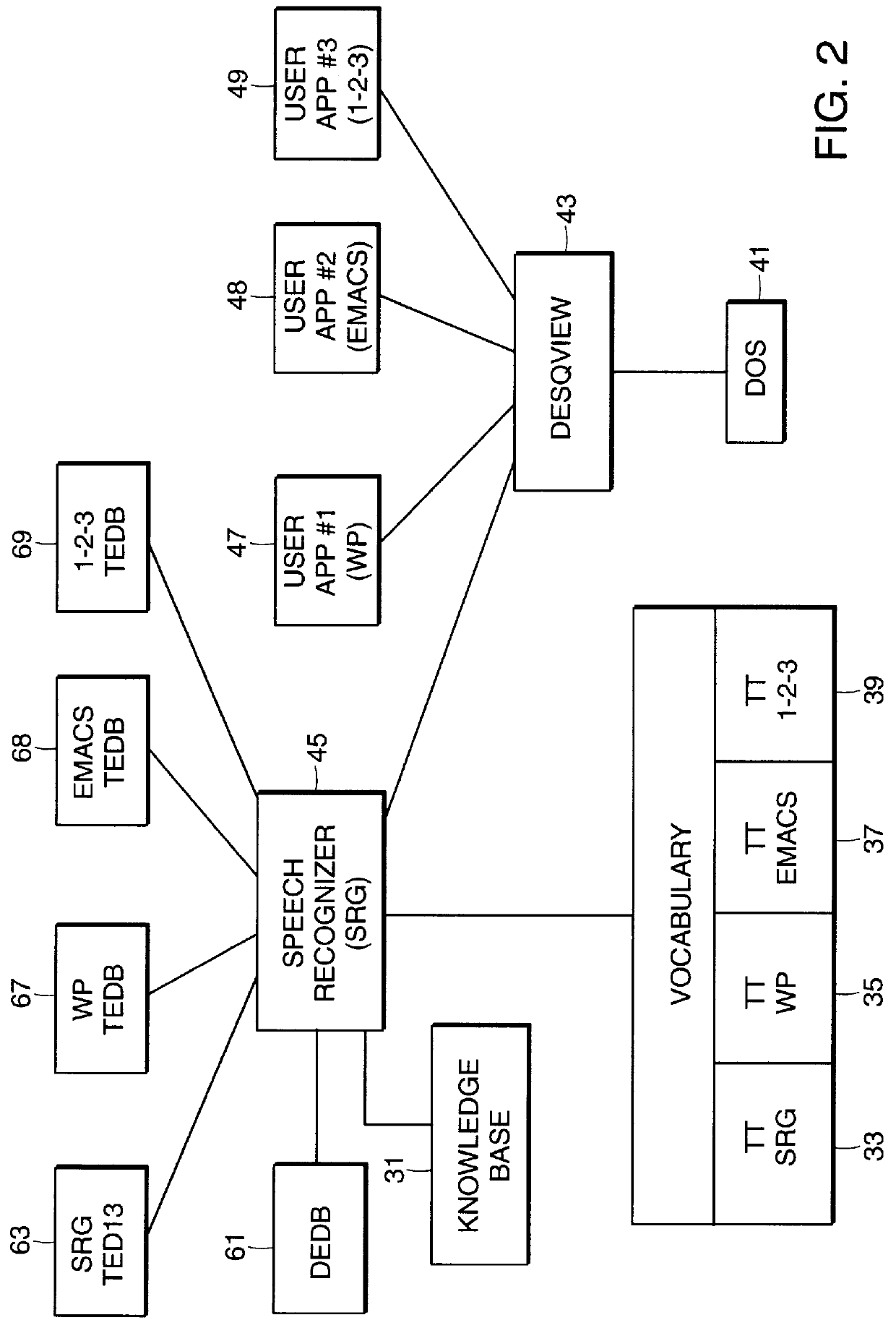

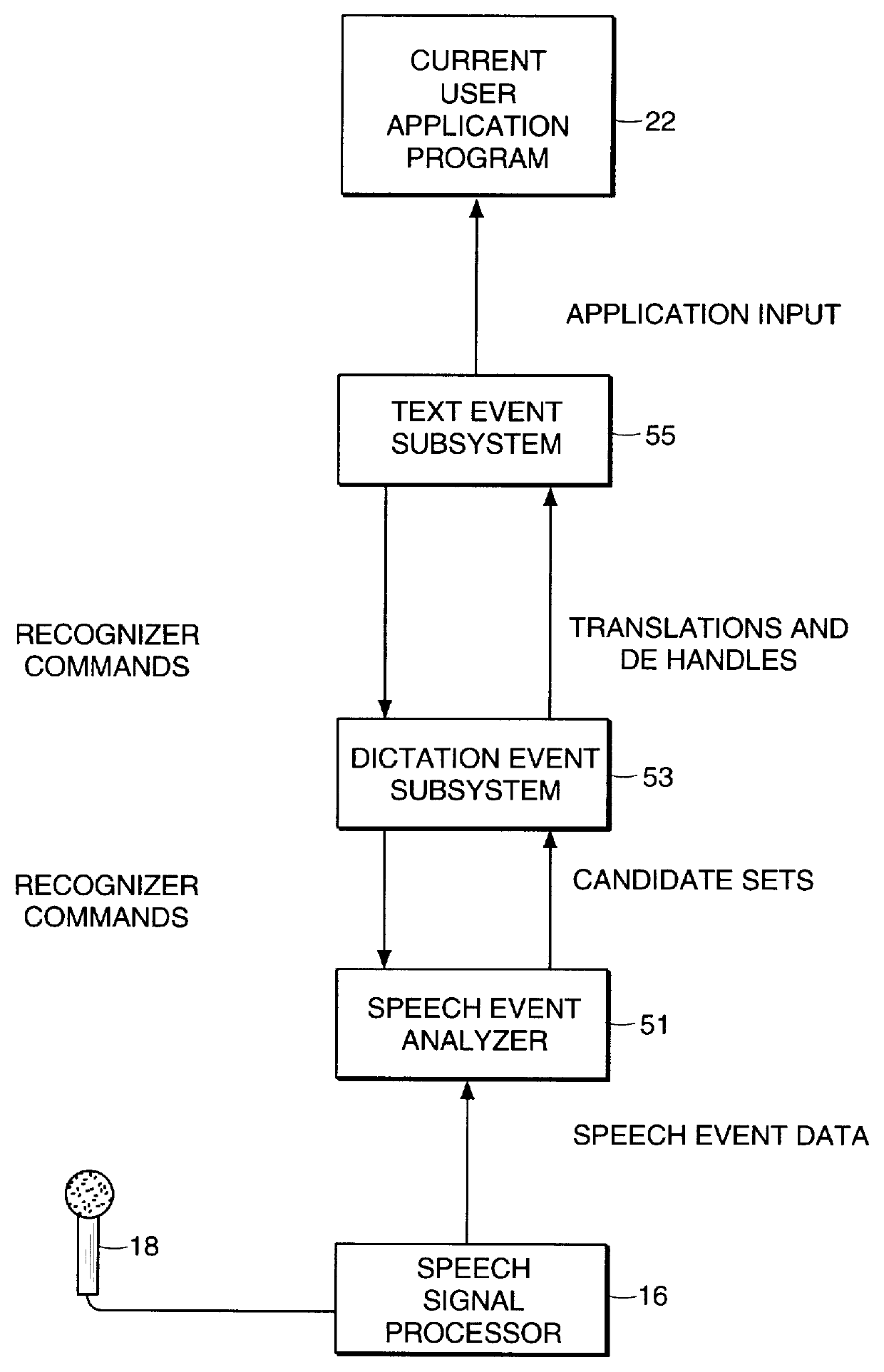

System for controlling multiple user application programs by spoken input

The system described herein facilitates the control, by spoken input, of multiple user application programs running under an operating system providing multi-tasking capability. A speech recognition program runs as one of the multi-tasked programs. The recognition program is operative to provide translation, either text or program commands, of spoken words in accordance with a translation table. Each of the other user application programs which is to be controlled is provided with a respective translation table section. In accordance with the invention, the recognition program includes means for creating a database for each of the other user application programs which is run and stores, in the respective database, a record reflecting each translation which is sent to a running one of the other application programs. These records identify the speech event which was translated and also identifies alternate possible translations of the speech event. Using the databases, the user can undo the effect of a previously sent translation, select an alternate translation and perform other editing tasks.

Owner:NUANCE COMM INC

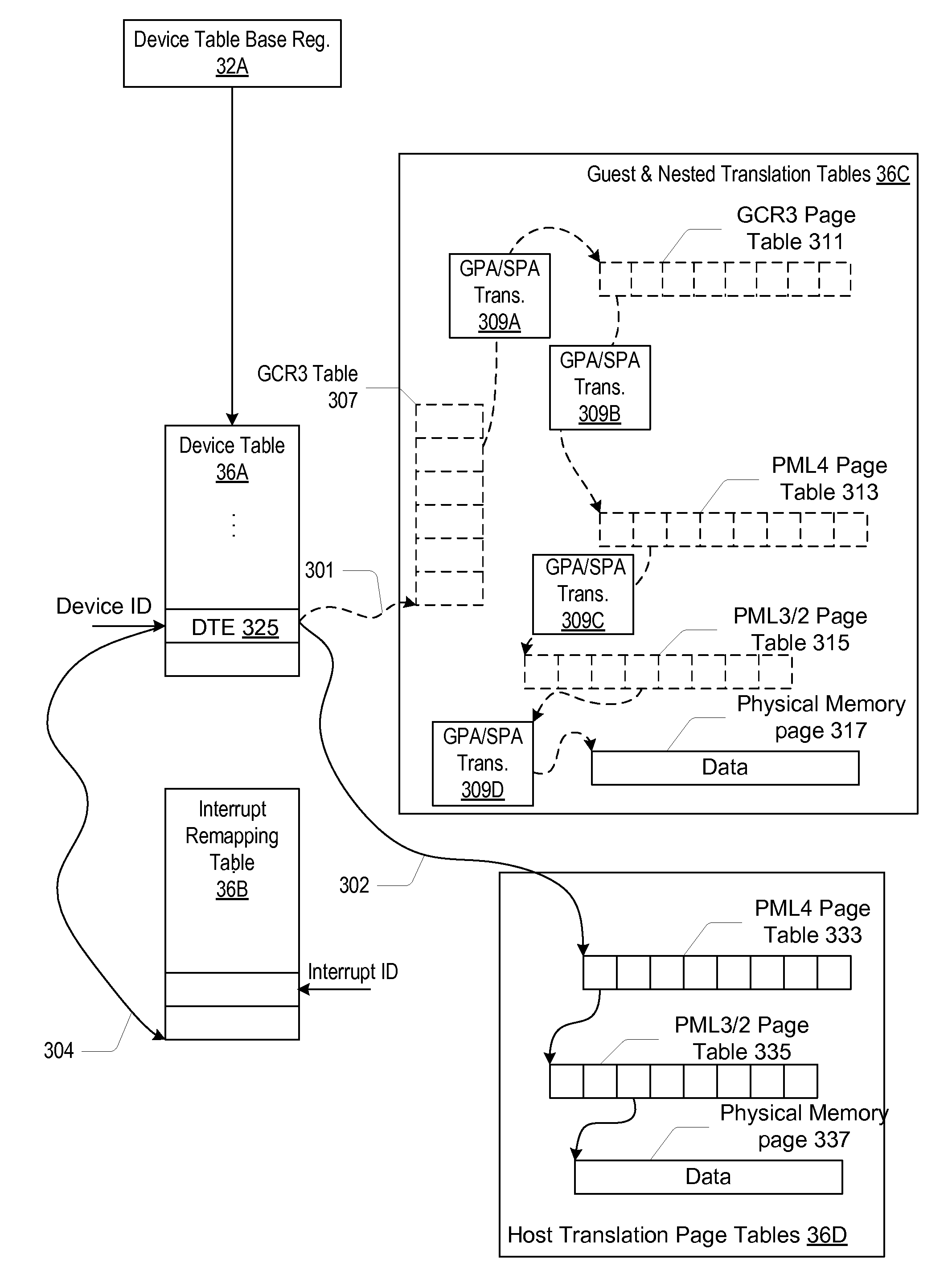

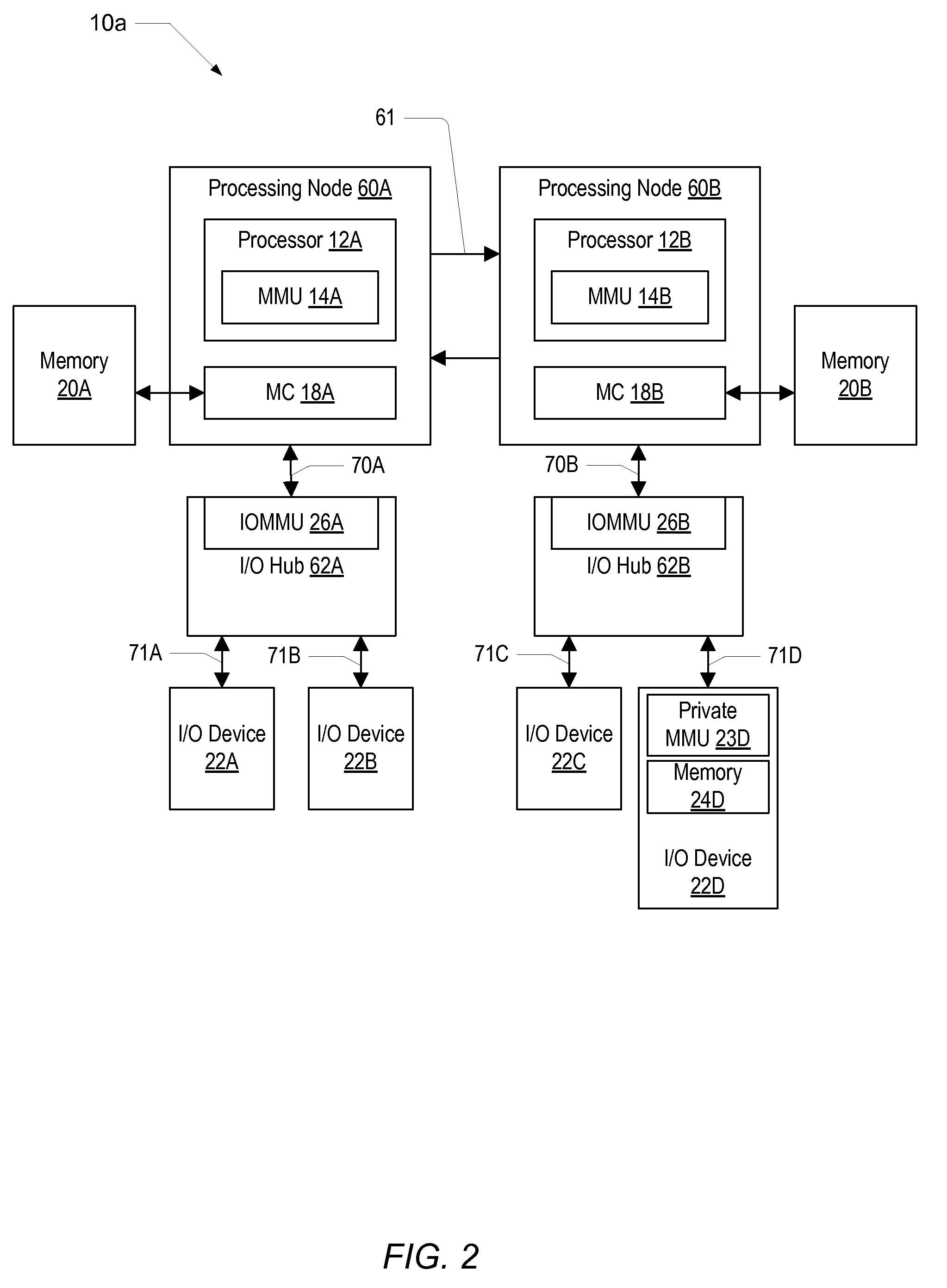

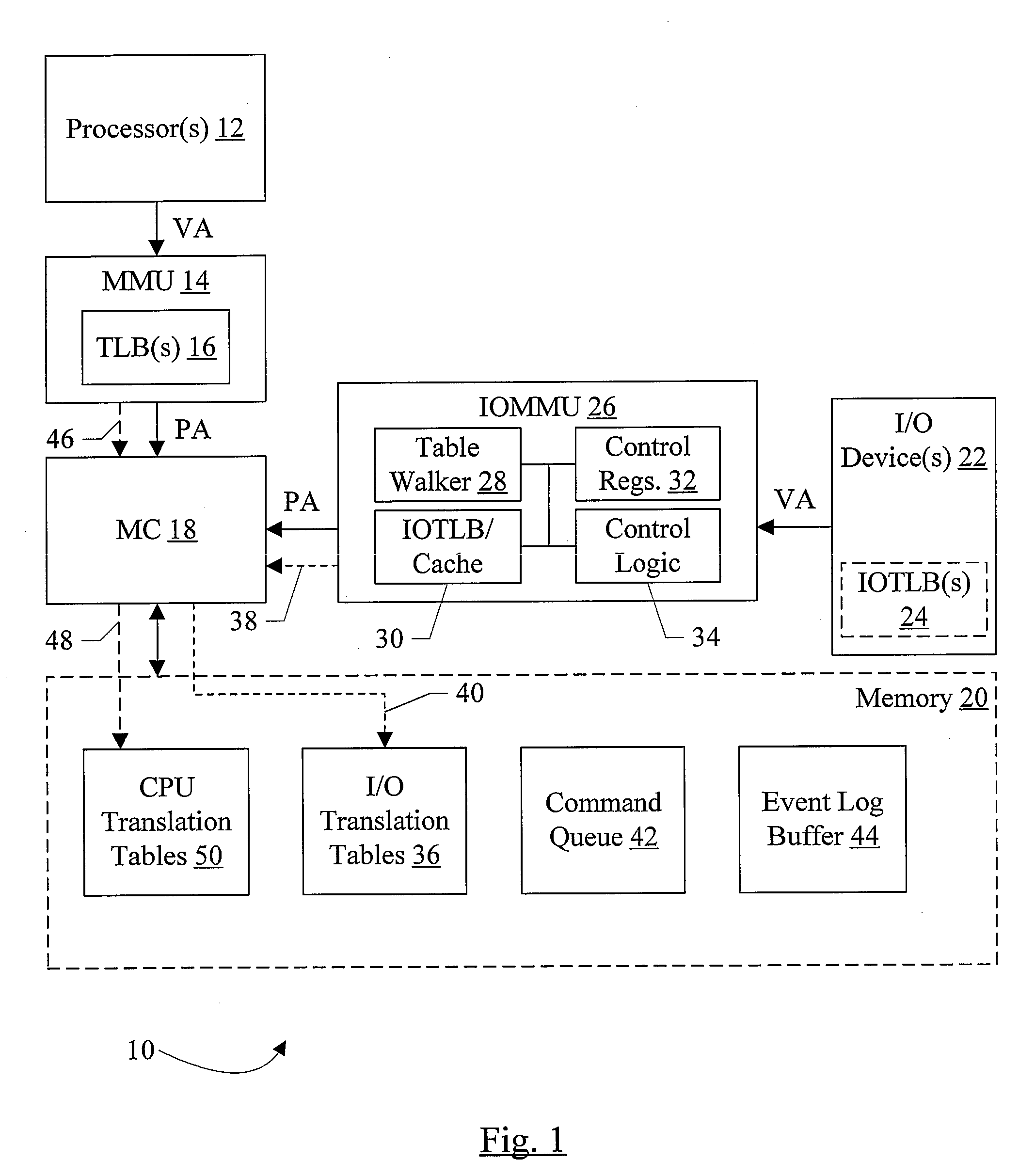

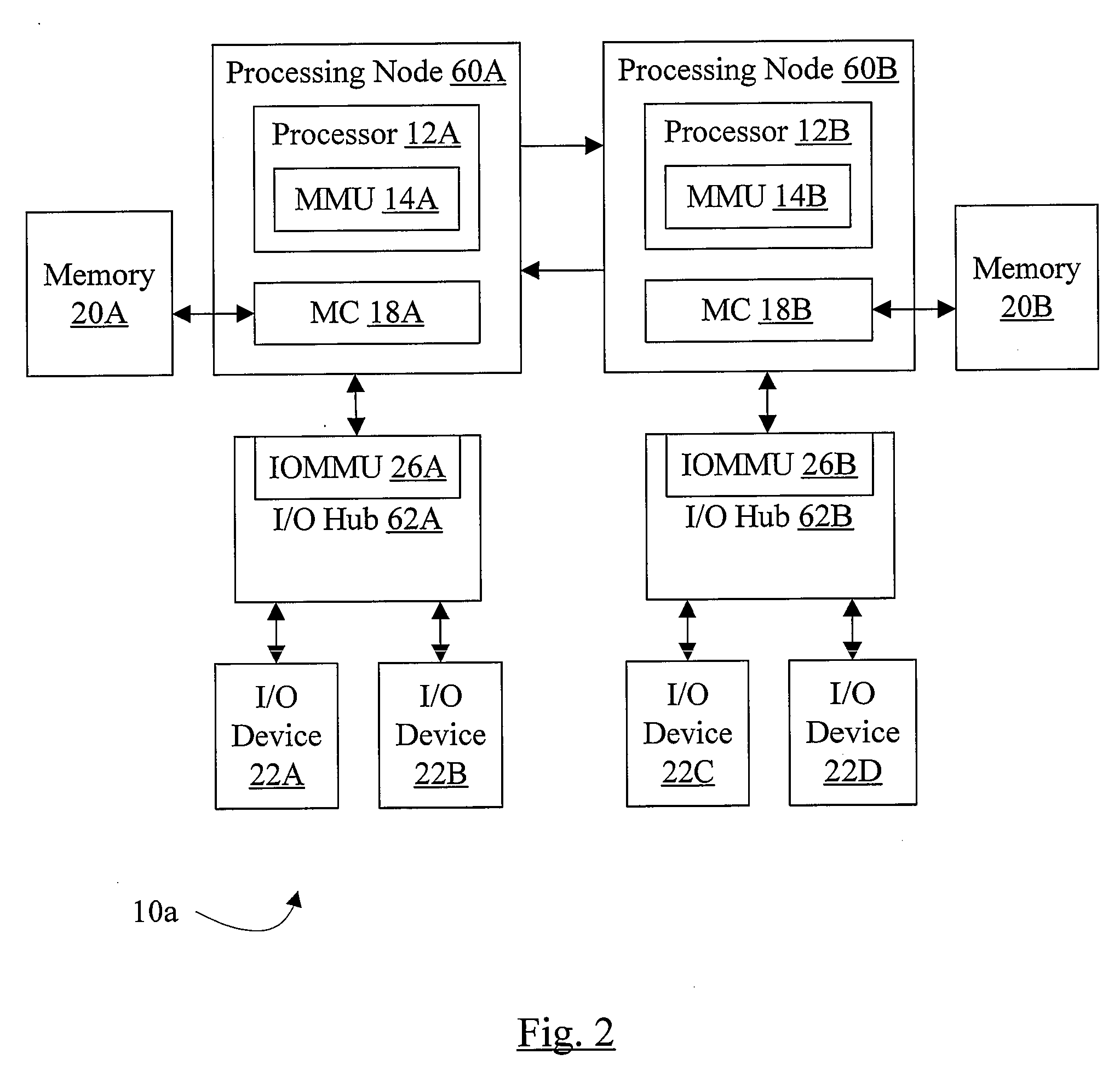

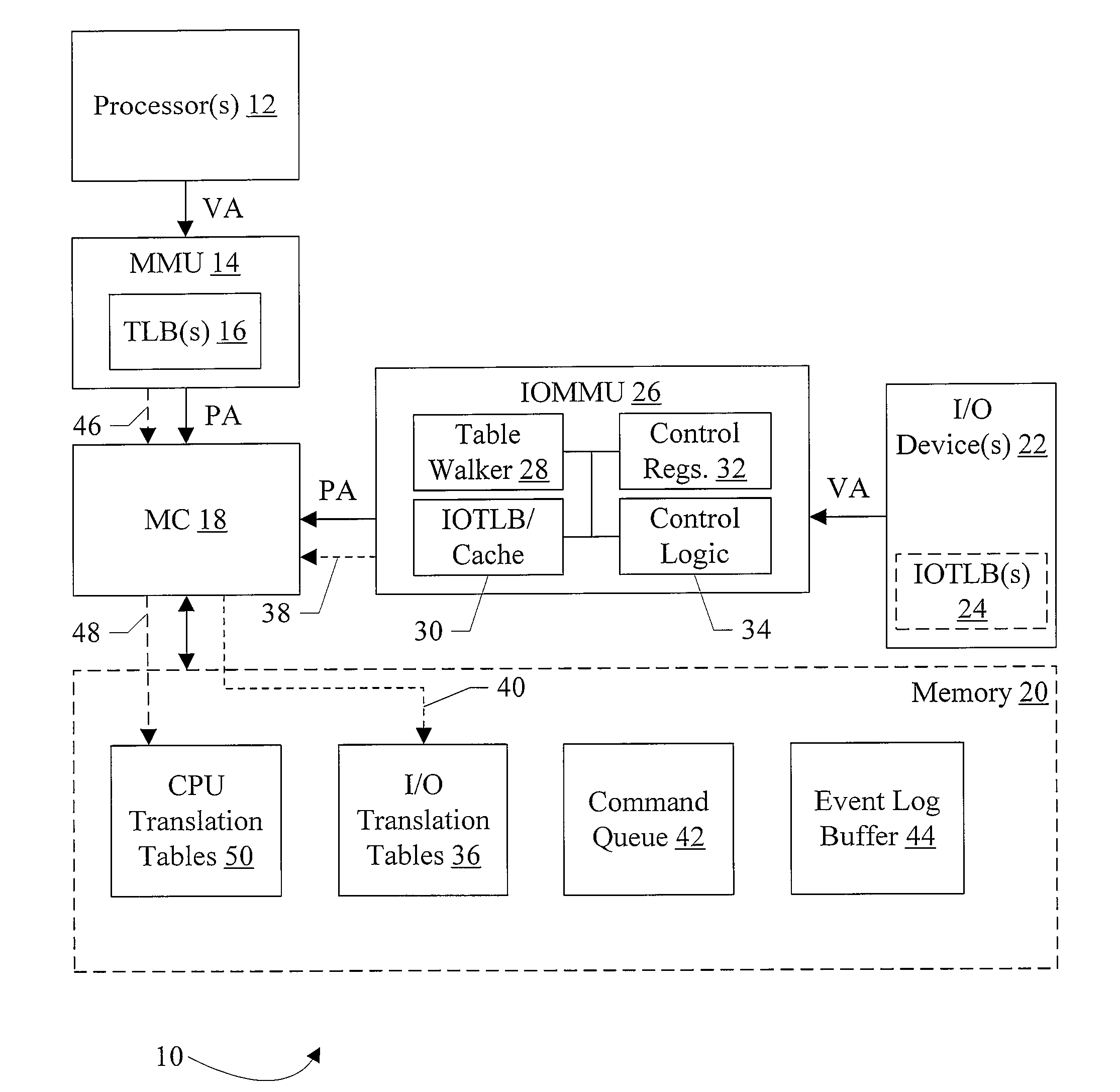

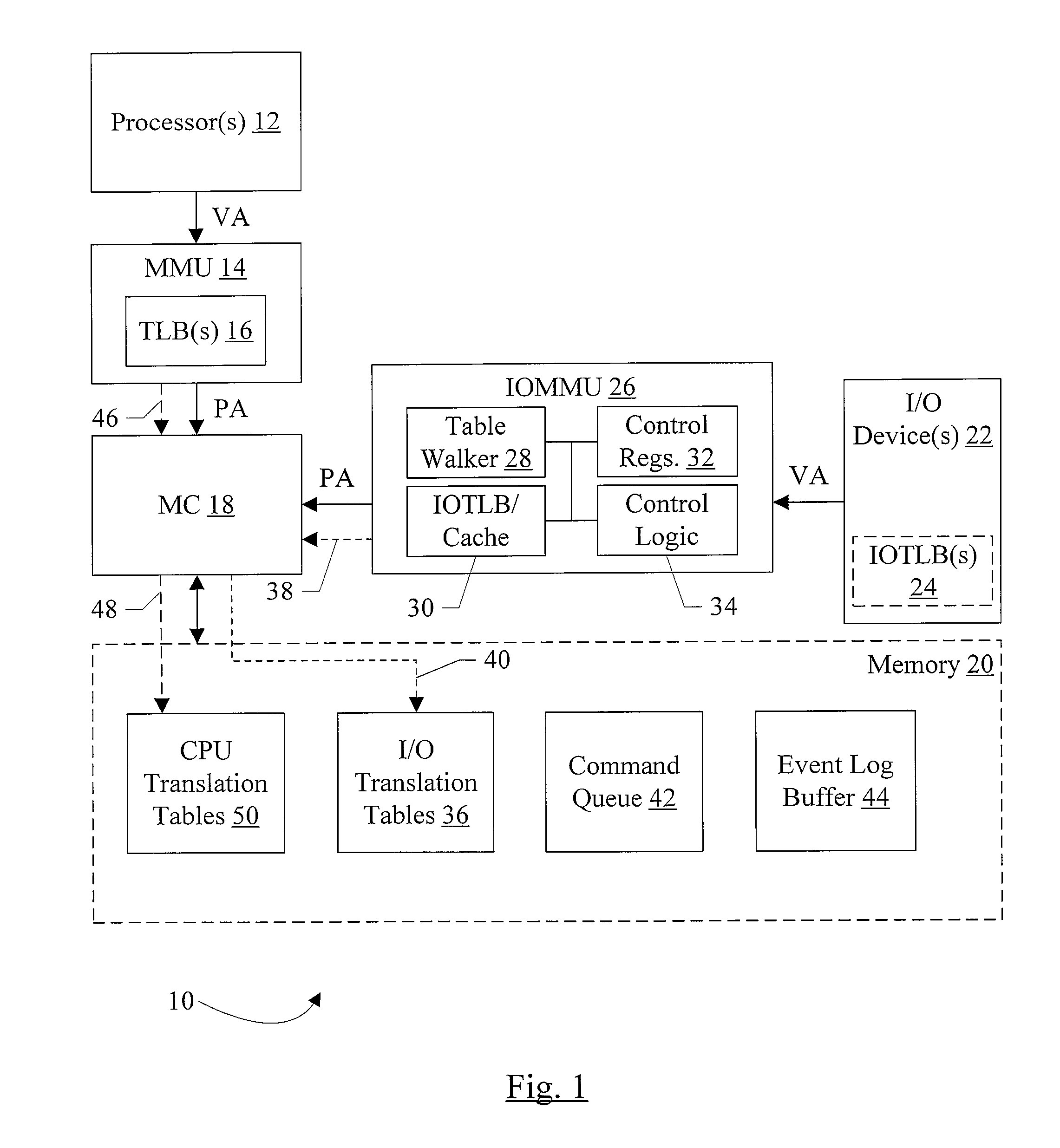

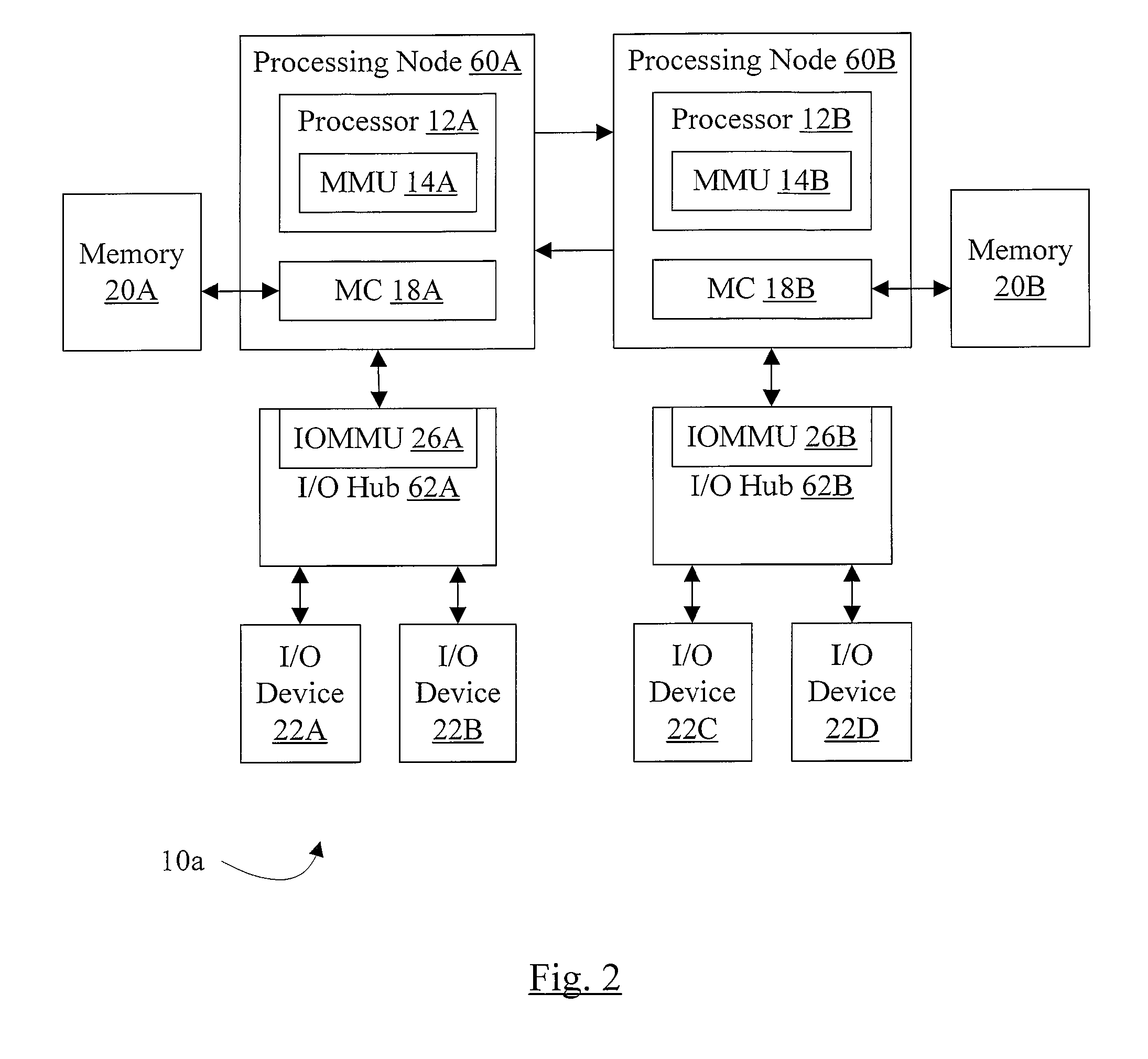

I/O memory management unit including multilevel address translation for I/O and computation offload

ActiveUS20110023027A1Memory architecture accessing/allocationMemory adressing/allocation/relocationTranslation tablePage table

An input / output memory management unit (IOMMU) configured to control requests by an I / O device to a system memory includes control logic that may perform a two-level guest translation to translate an address associated with an I / O device-generated request using translation data stored in the system memory. The translation data includes a device table having a number of entries. The control logic may select the device table entry for a given request by the using a device identifier that corresponds to the I / O device that generates the request. The translation data may also include a first set of I / O page tables including a set of guest page tables and a set of nested page tables. The selected device table entry for the given request may include a pointer to the set of guest translation tables, and a last guest translation table includes a pointer to the set of nested page tables

Owner:ADVANCED MICRO DEVICES INC

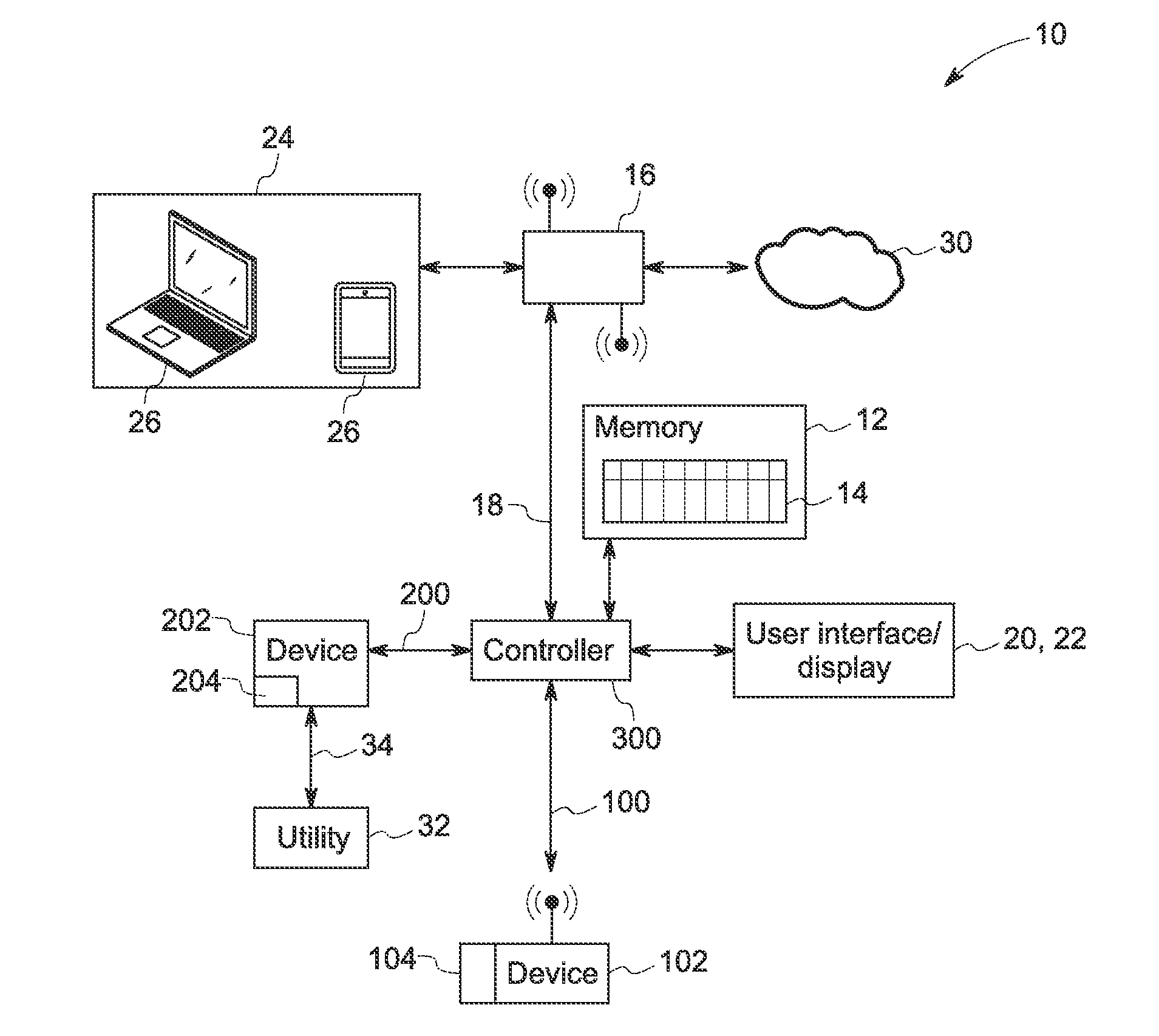

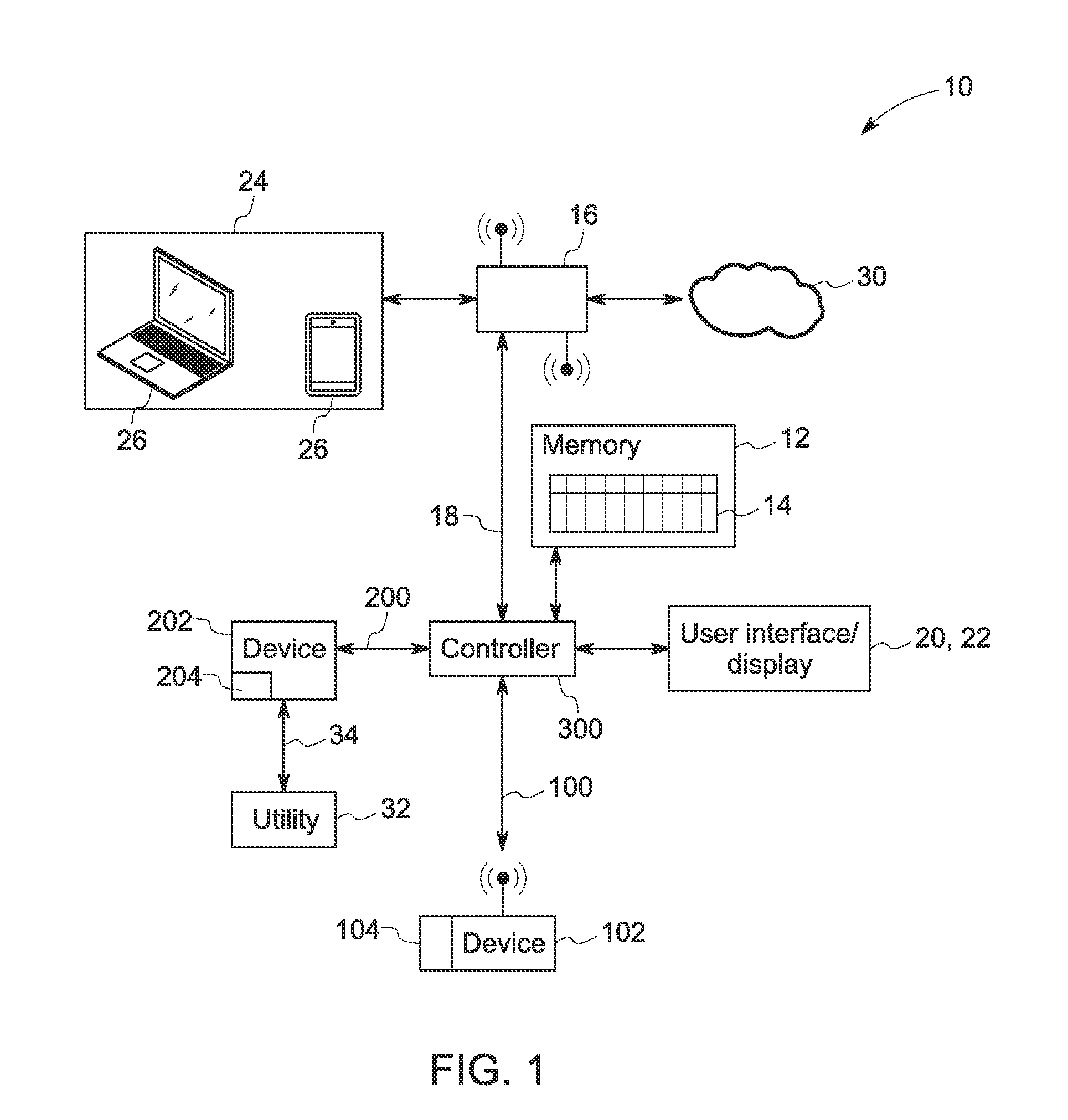

Network address translation for zigbee™ /802.15.4 bridges

ActiveUS20150074228A1Overcome disadvantagesMultiple digital computer combinationsTransmissionNetwork address translationTranslation table

A method and device for addressing between a first device on a first network and a second device on a second network using a network bridging device, the first and second networks being physically different networks. The method includes discovering the first device on the first network, creating a virtual endpoint for the first device, storing the created virtual endpoint in a network translation table, detecting, in the network bridging device, a communication packet sent from the second network, determining if an endpoint identified in the communication packet is stored as a virtual endpoint in the network translation table, and, if so, identifying an address of the device on the second network associated with the virtual endpoint stored in the network address translation table, and transmitting the communication packet to the device address on the second network.

Owner:HAIER US APPLIANCE SOLUTIONS INC

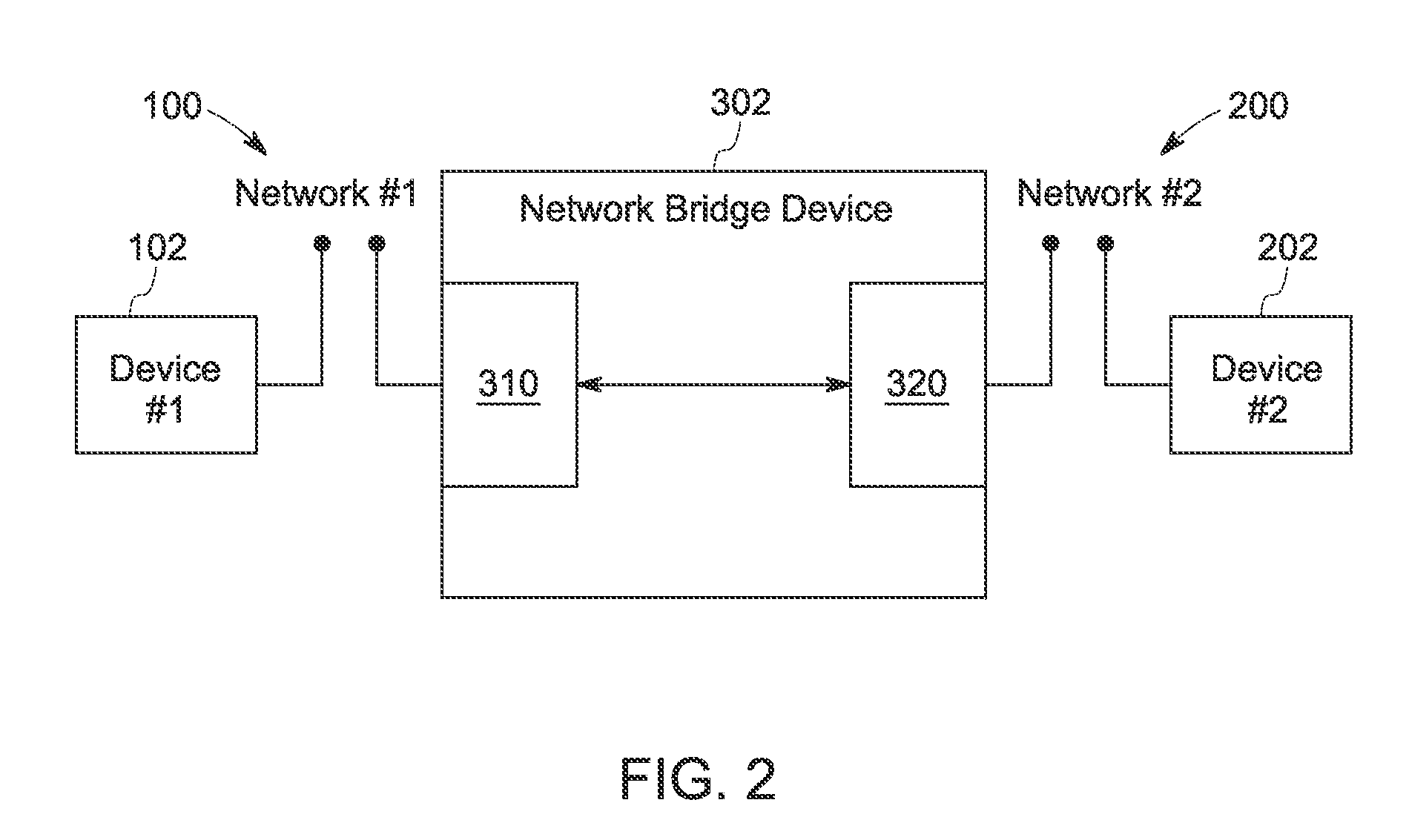

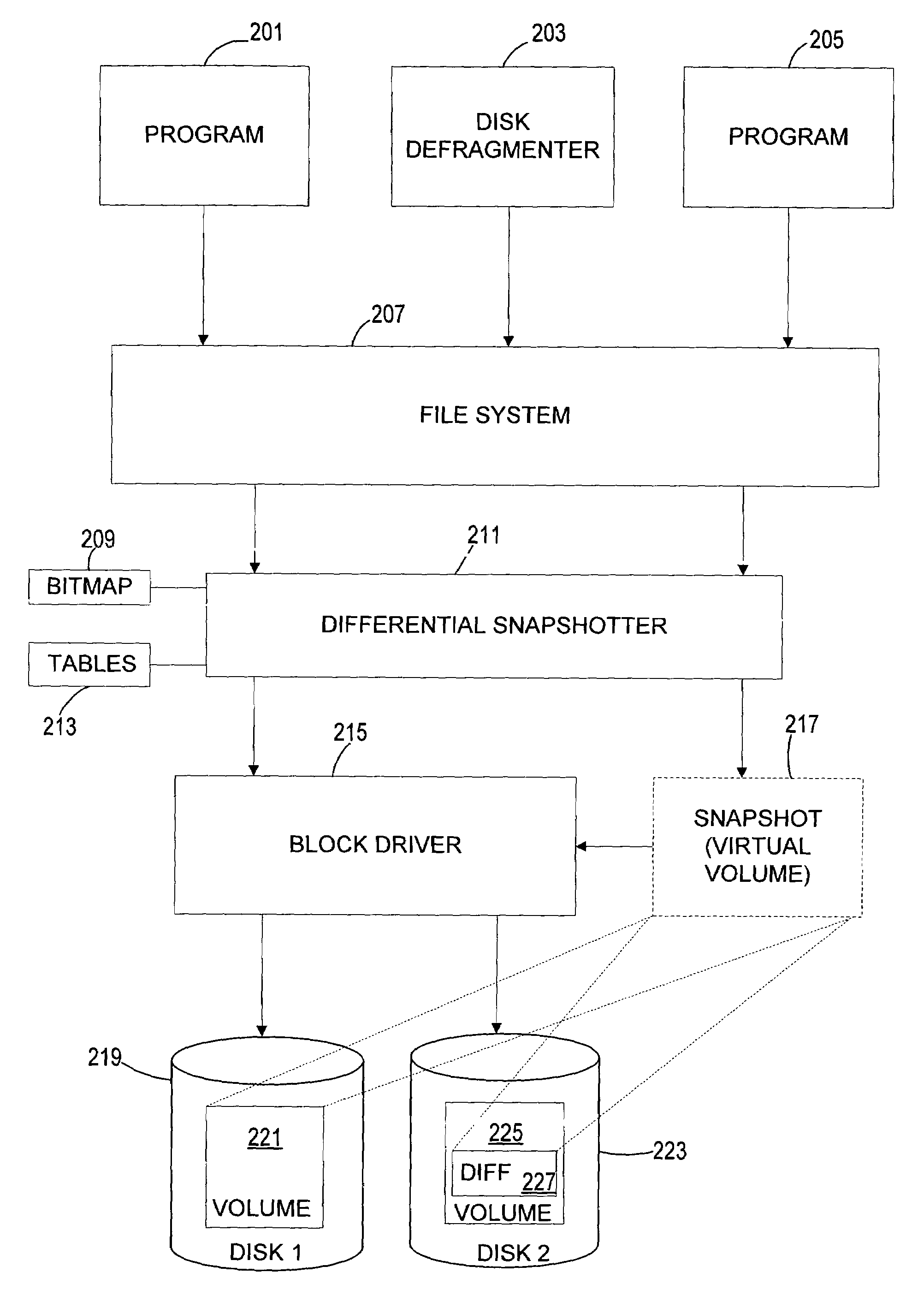

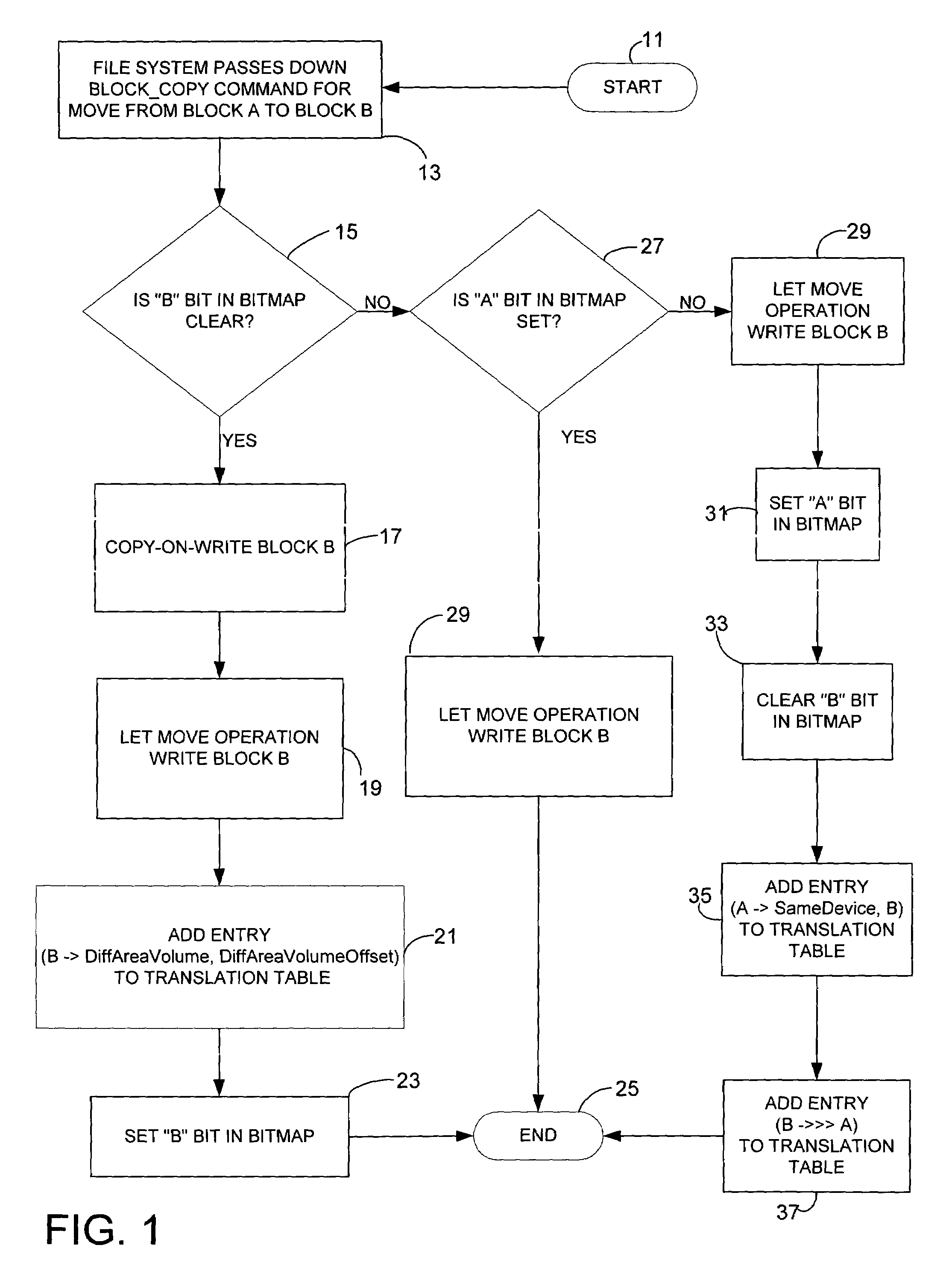

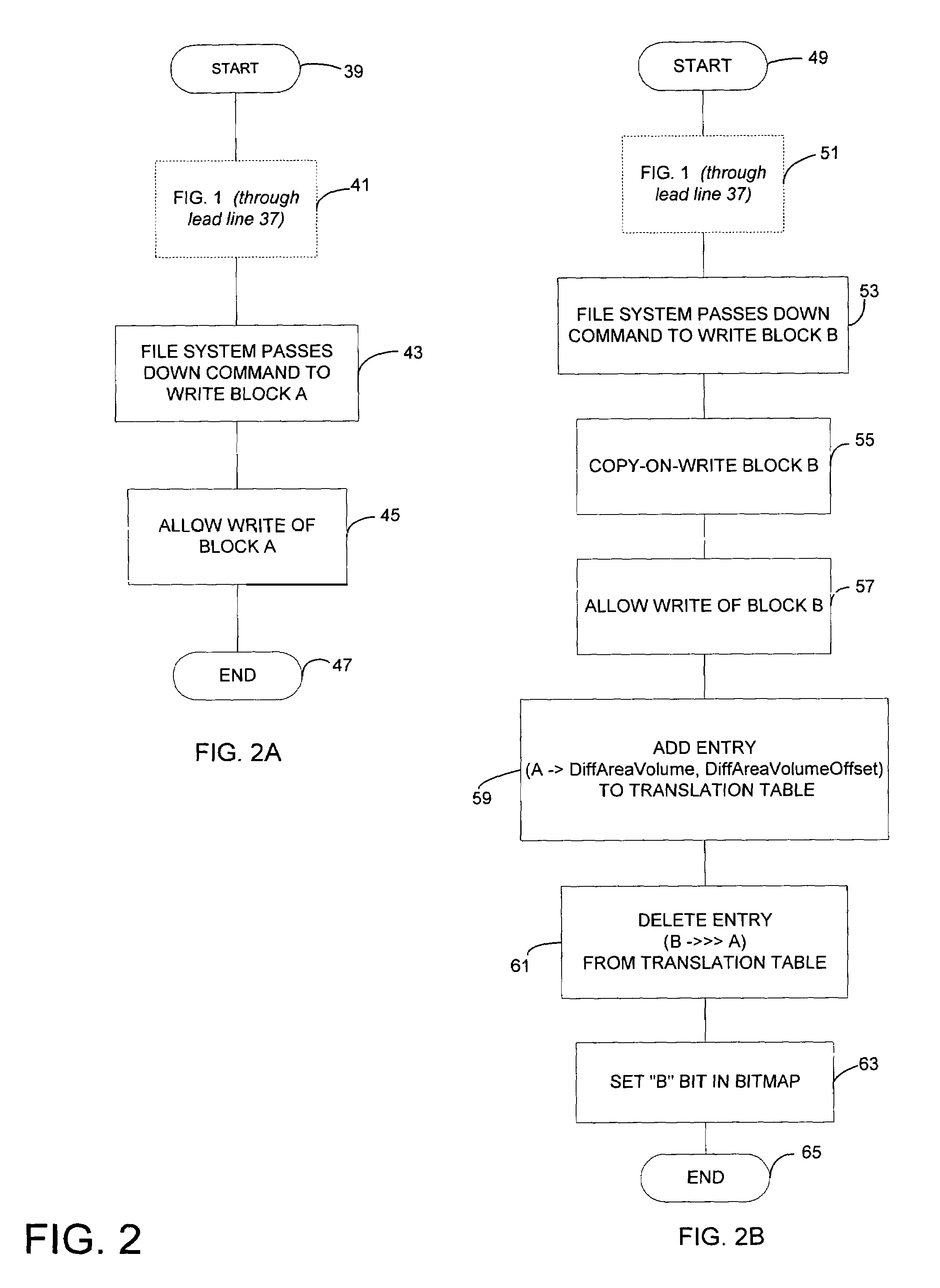

Optimizing defragmentation operations in a differential snapshotter

InactiveUS7664771B2Avoid unnecessary copy-on-write operationInput/output to record carriersDigital data processing detailsFile systemTranslation table

A differential snapshot is established and maintained for a set of files stored on a volume. Copy-on-write operations are avoided for logically insignificant moves of blocks, such as the block rearrangements characteristic of defragmentation utilities. A file system passes a block copy command to lower-level drivers that are to inform the snapshotter that a block move operation is not logically meaningful. When the logically insignificant move is of a block whose data forms part of the data captured in the snapshot virtual volume, and when the move is to a block location that is functioning as logical free space, the snapshotter can simply modify its block bitmap and update translation table entries without needing to perform a copy-on-write.

Owner:MICROSOFT TECH LICENSING LLC

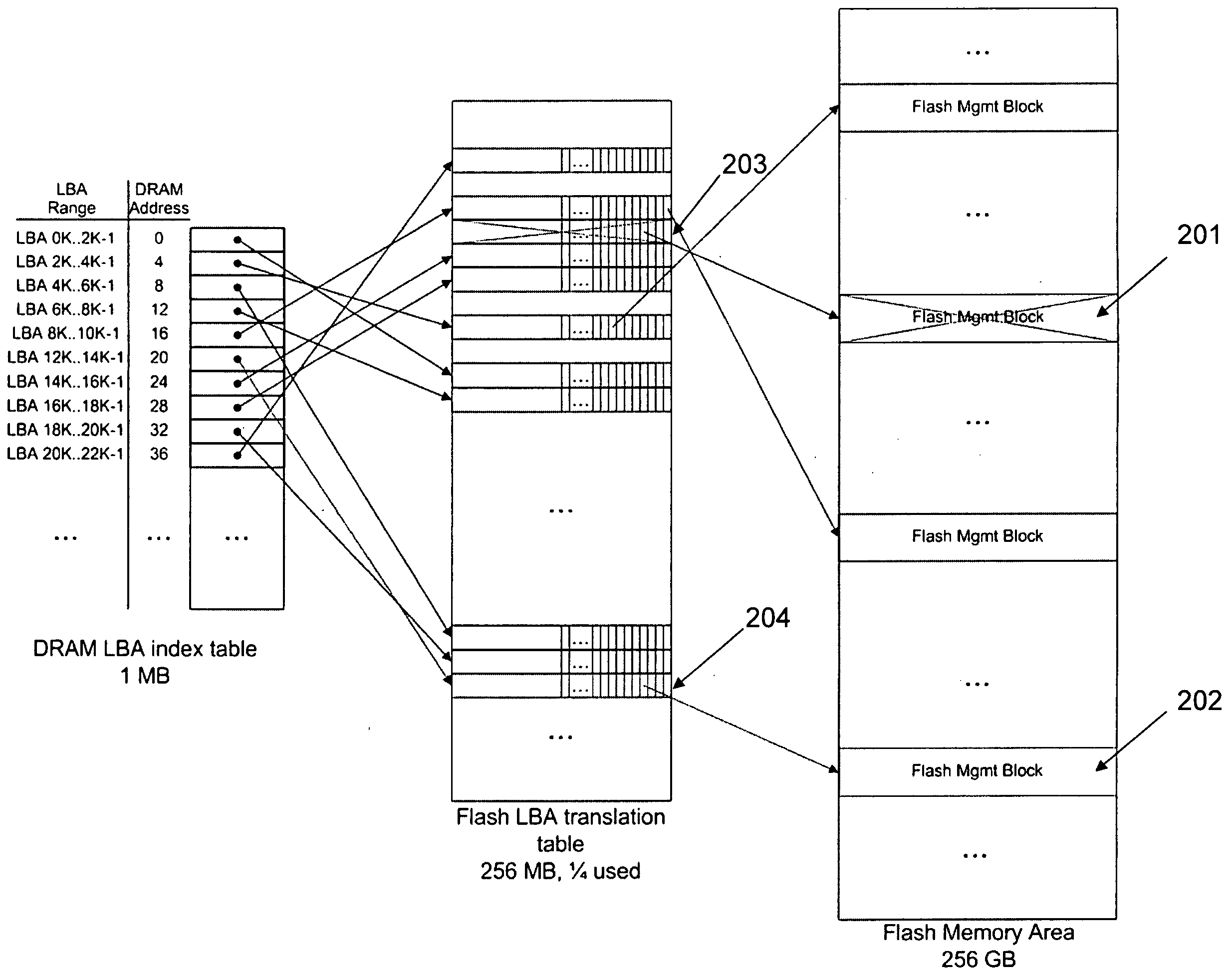

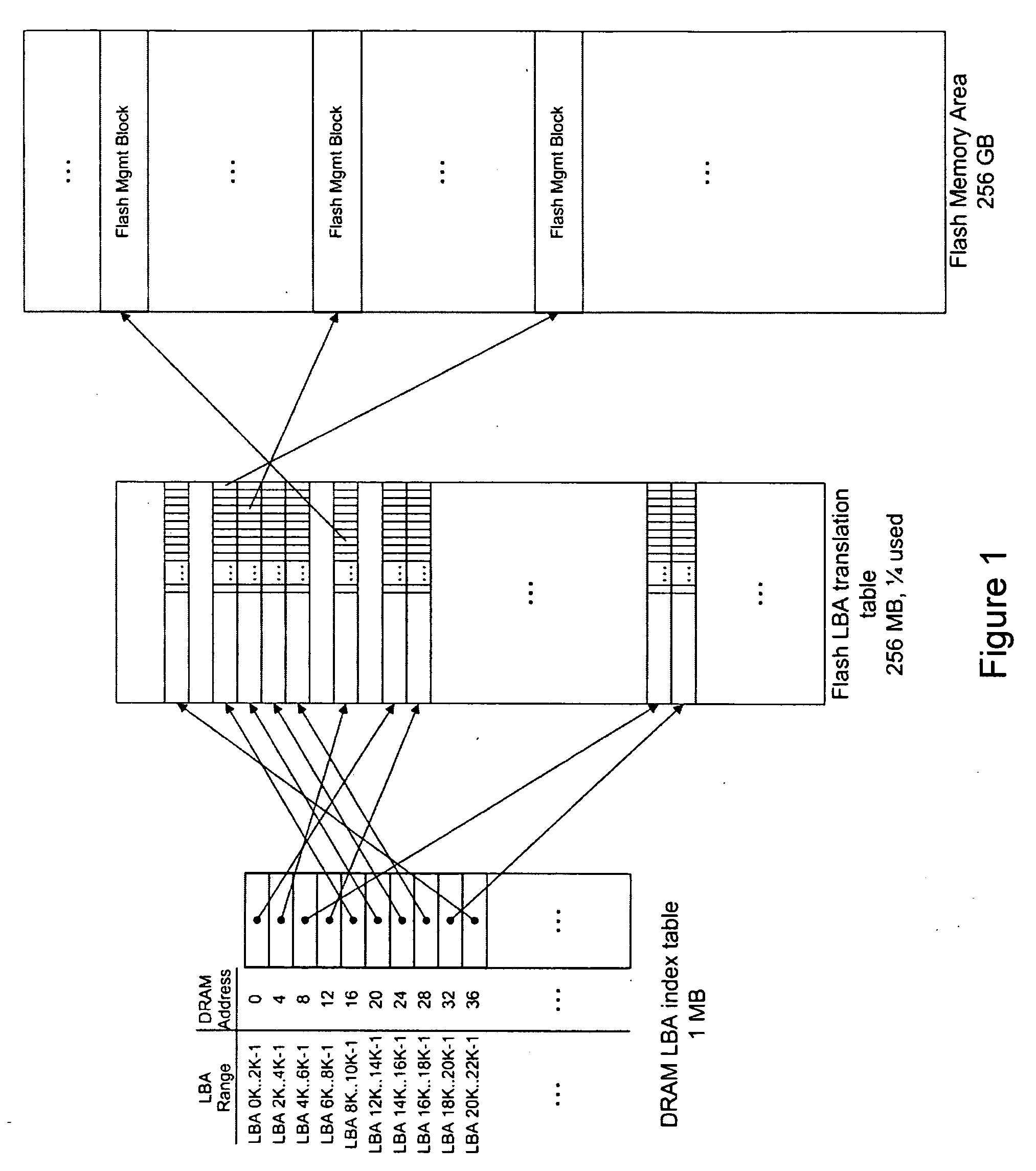

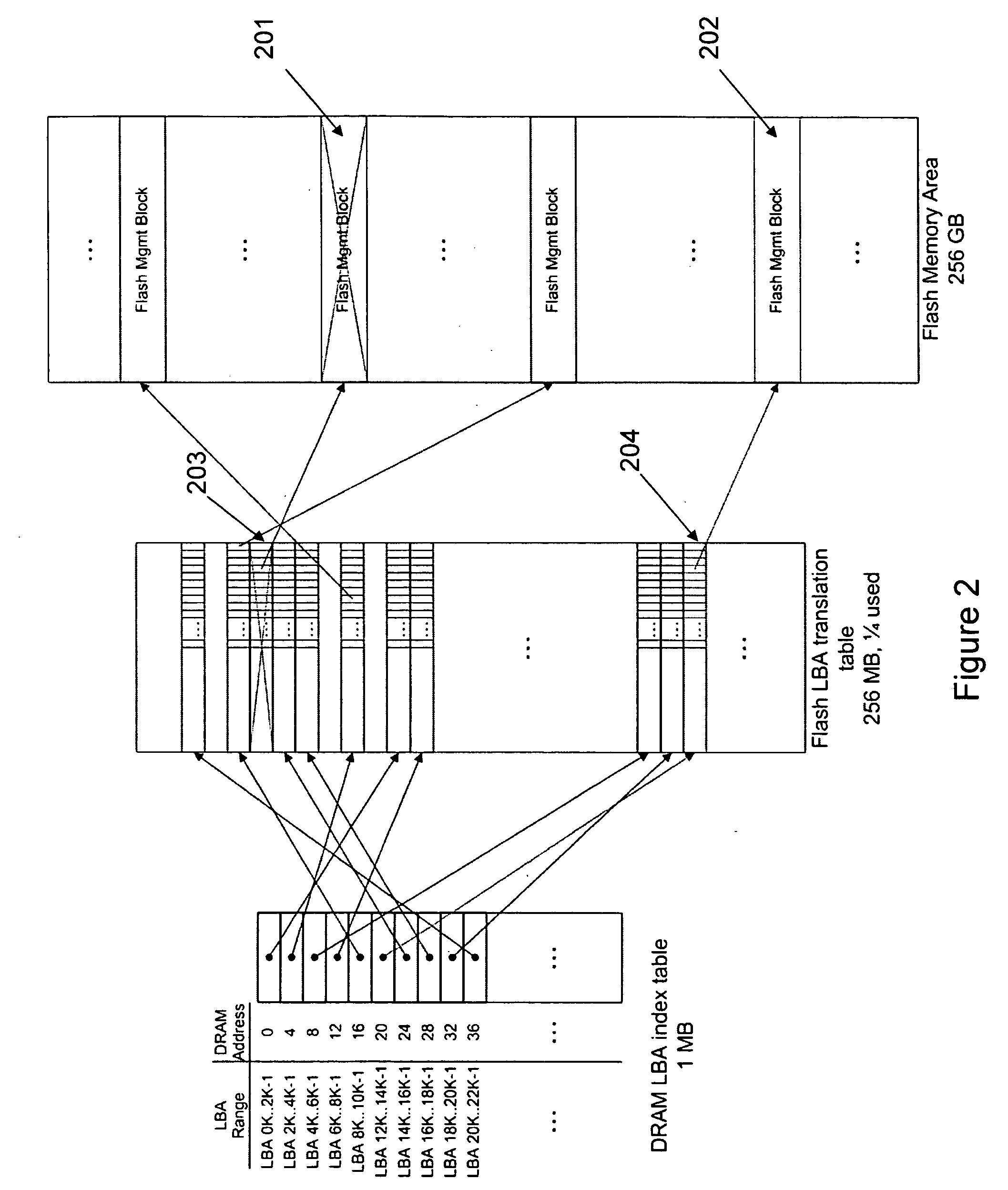

Process and Method for Logical-to-Physical Address Mapping in Solid Sate Disks

ActiveUS20100030999A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMass storageLogical block addressing

An embodiment of the invention relates to a mass storage device including a nonvolatile memory device with a plurality of memory management blocks and an address translation table formed with pointers to locations of the memory management blocks. A volatile memory device is included with an address index table formed with pointers to the pointers to the locations of the memory management blocks. The address index table is stored in the nonvolatile memory upon loss of bias voltage. Changes to the address translation table are accumulated in the volatile memory and written to the address translation table when at least a minimum quantity of the changes has been accumulated. The changes to the logical block address translation table accumulated in the volatile memory are written to a page in the address translation table after prior data in the page has been updated, written to another page, and then erased.

Owner:INFINEON TECH AG

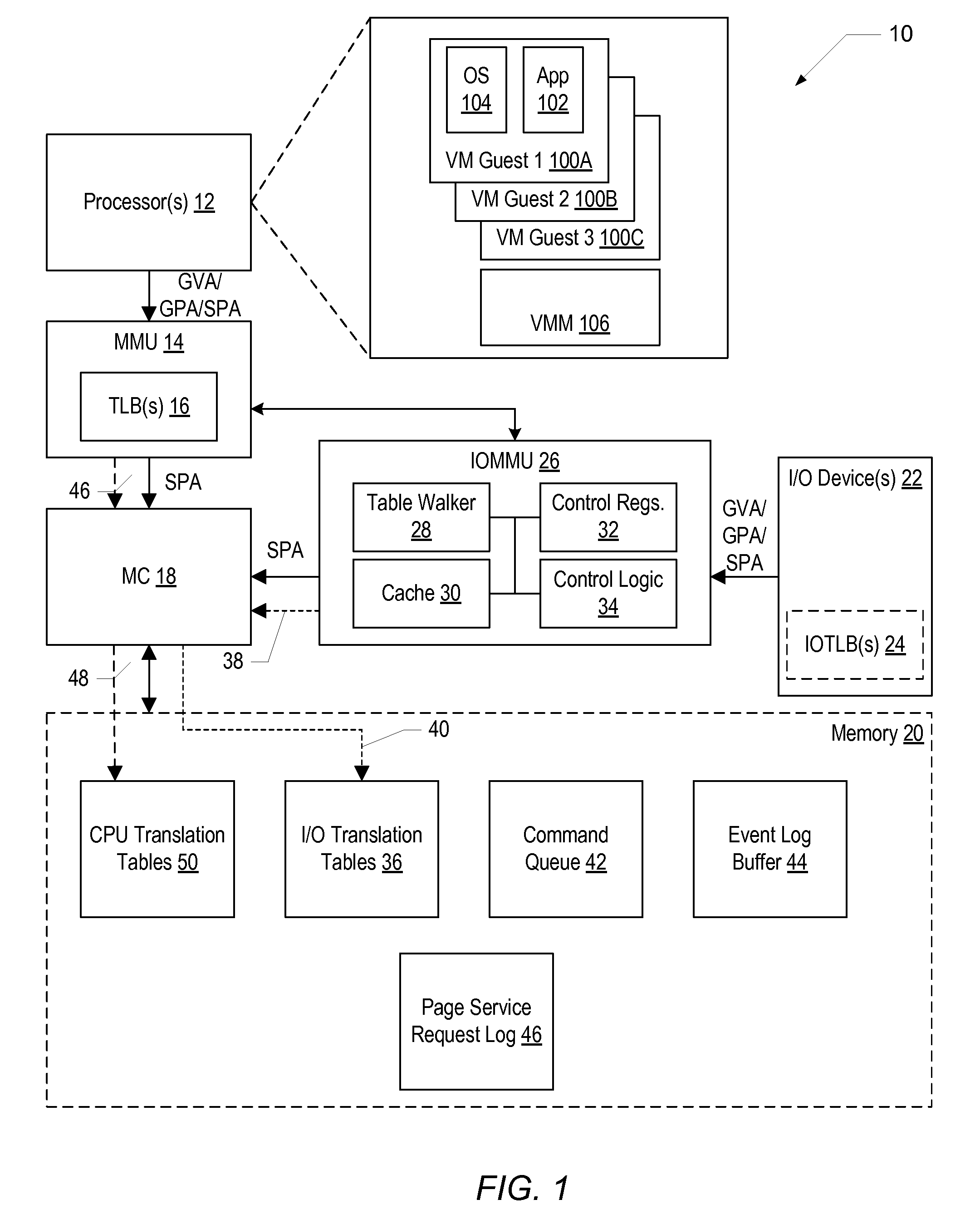

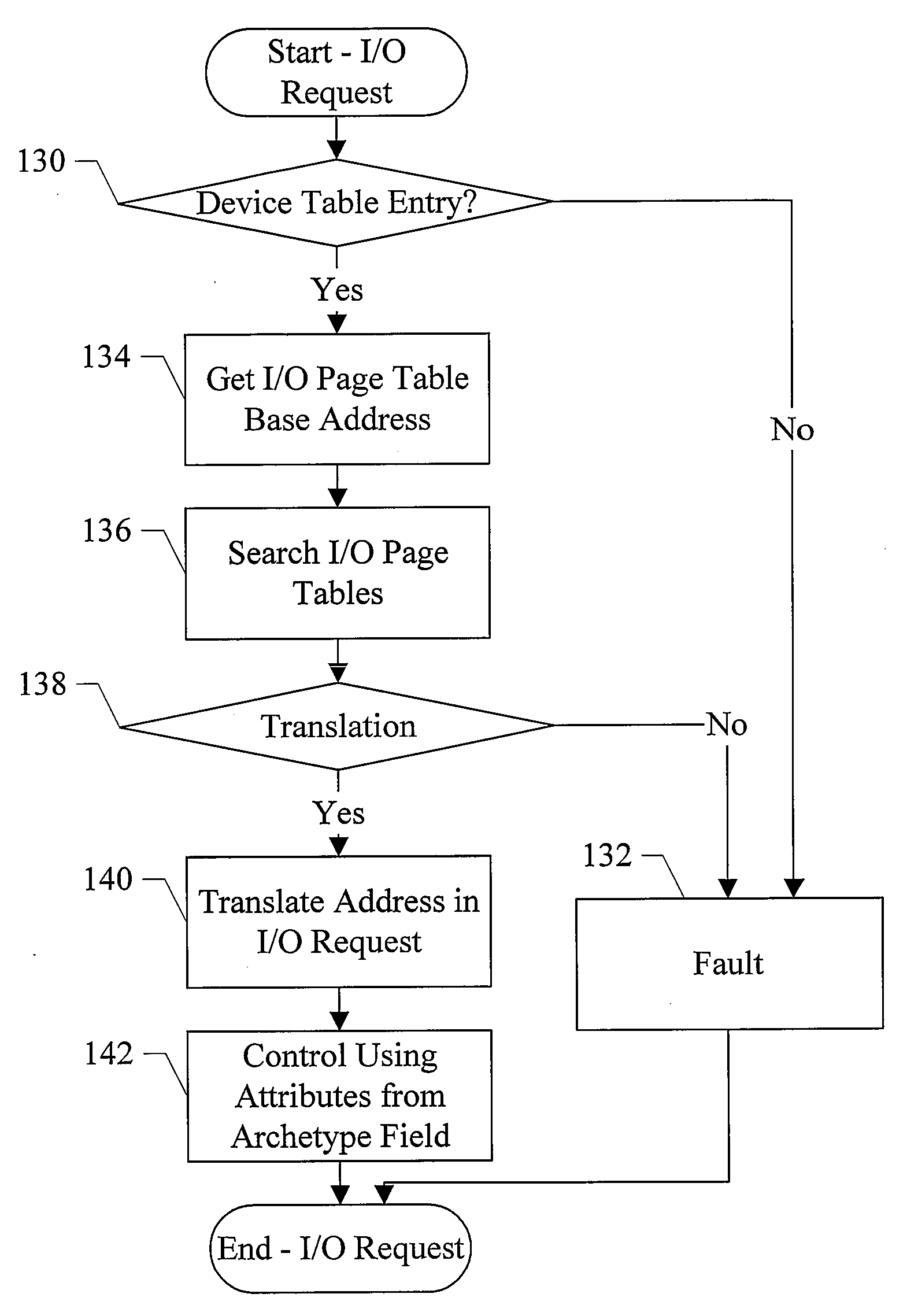

Using an IOMMU to Create Memory Archetypes

ActiveUS20070168644A1Memory architecture accessing/allocationMemory systemsManagement unitComputerized system

In one embodiment, an input / output (I / O) memory management unit (IOMMU) comprises at least one memory and control logic coupled to the memory. The memory is configured to store translation data corresponding to one or more I / O translation tables stored in a memory system of a computer system that includes the IOMMU. The control logic is configured to translate an I / O device-generated memory request using the translation data. The translation data includes a type field indicating one or more attributes of the translation, and the control logic is configured to control the translation responsive to the type field.

Owner:ADVANCED MICRO DEVICES INC

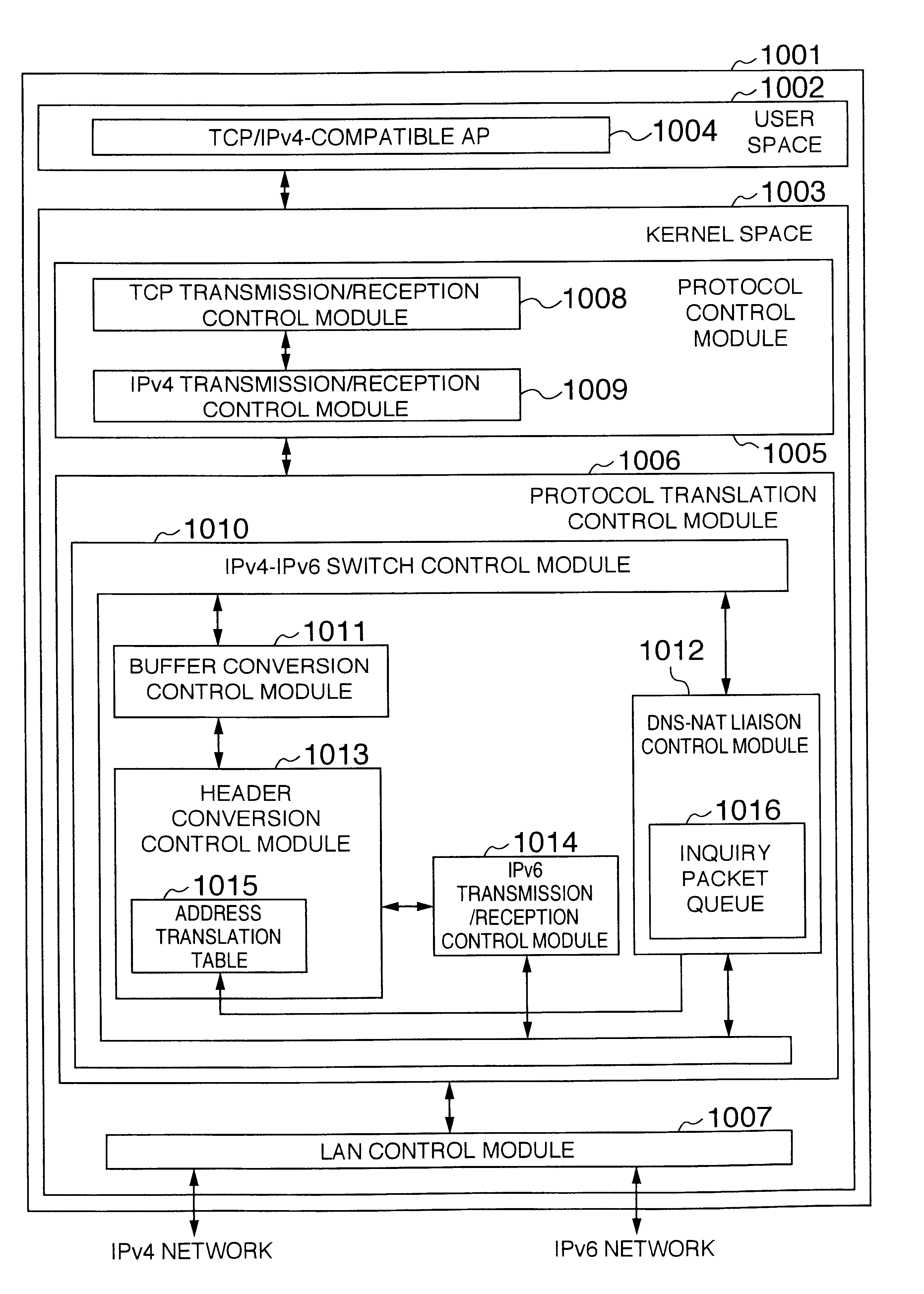

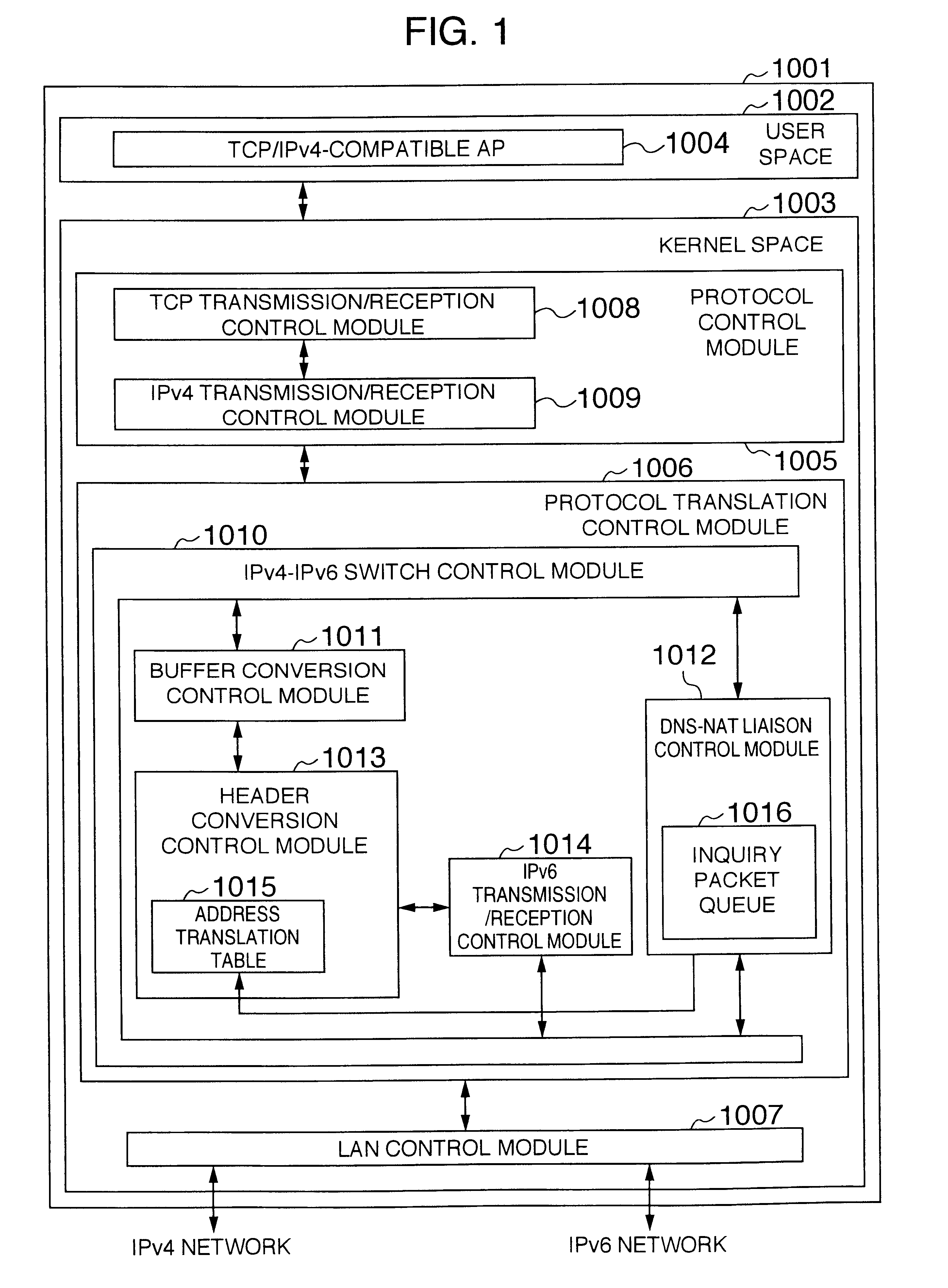

Packet communication method and apparatus and a recording medium storing a packet communication program

InactiveUS6580717B1Time-division multiplexData switching by path configurationComputer hardwareInformation processing

A packet communication method and a packet communication system capable of making an IPv4-compatible application operating on an information processing apparatus communicate with another information processing apparatus connected to an IPv6 network without using an address translation router. In the information processing apparatus connected to the IPv6 network incorporates, an IPv4-to-IPv6 protocol conversion control function is incorporated in a LAN driver. A protocol conversion control module receives an IPv4 packet from a protocol control module. When a send destination IPv4 address contained in a header of the packet is registered in an address translation table incorporated in the protocol conversion control module, an IPv6 address is generated to be sent onto a LAN. Unless the send destination IPv4 address contained in the packet header is registered in the address translation table incorporated in the protocol conversion control module, the IPv4 packet as received is intactly sent onto the LAN.

Owner:HITACHI LTD

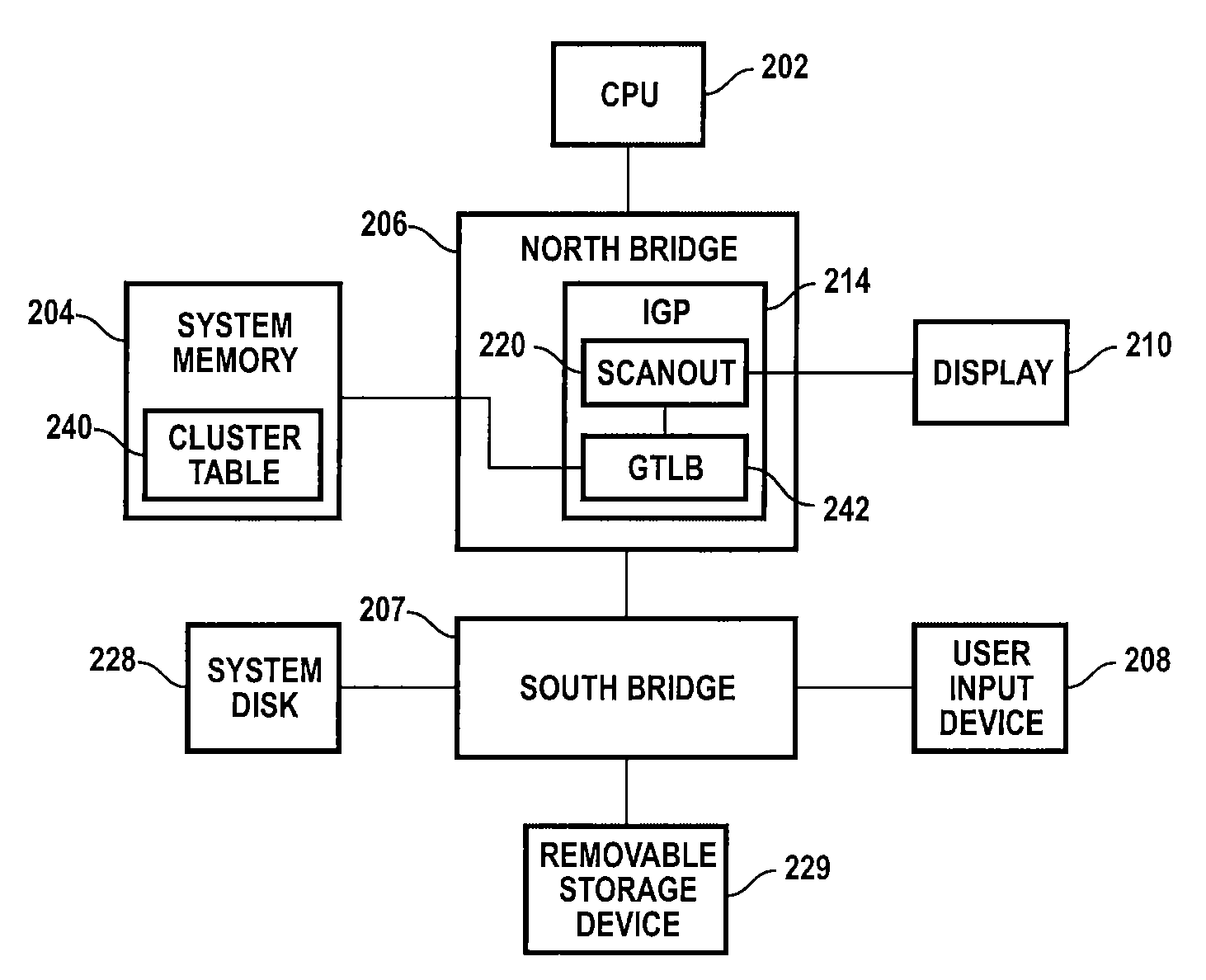

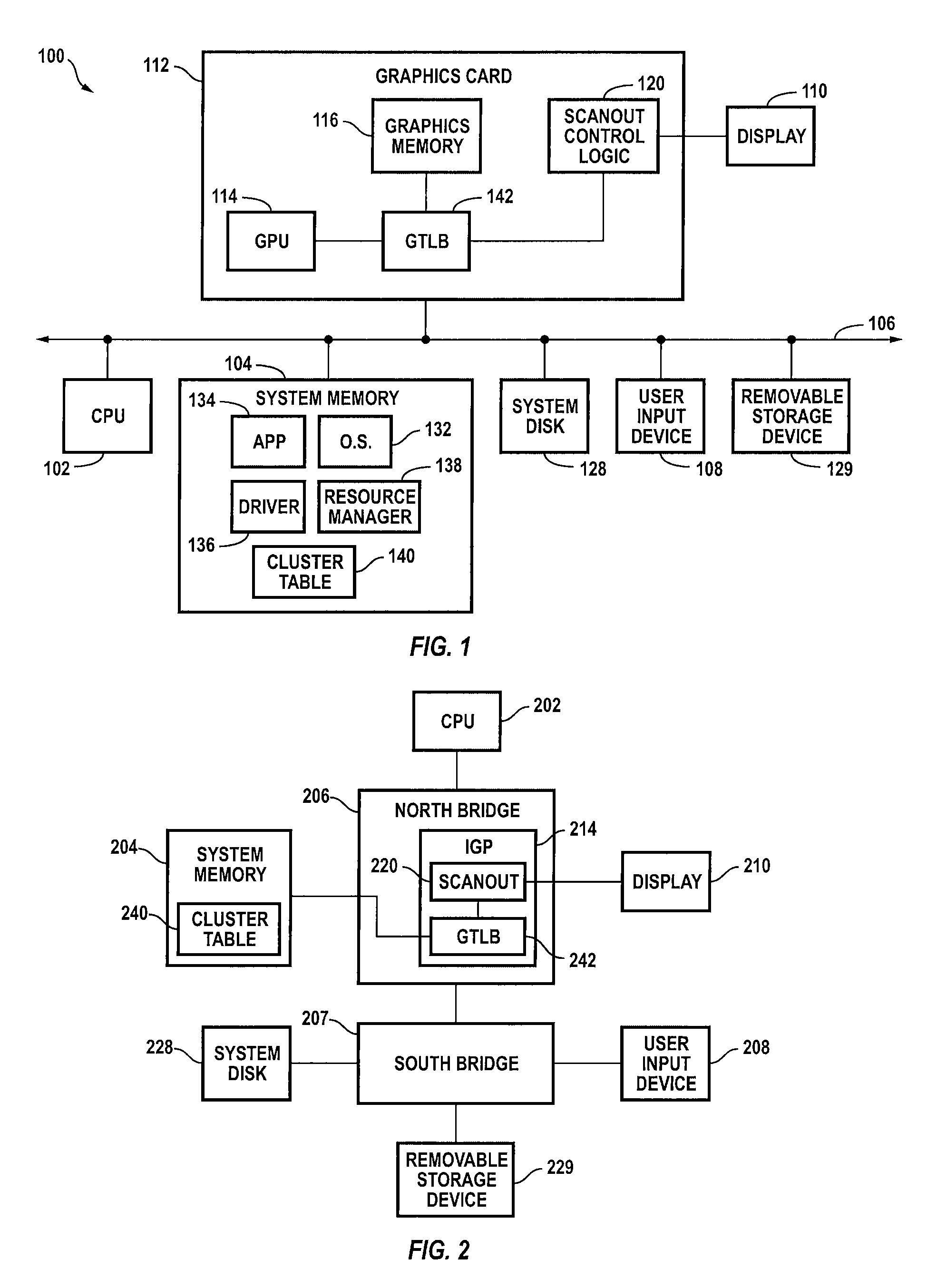

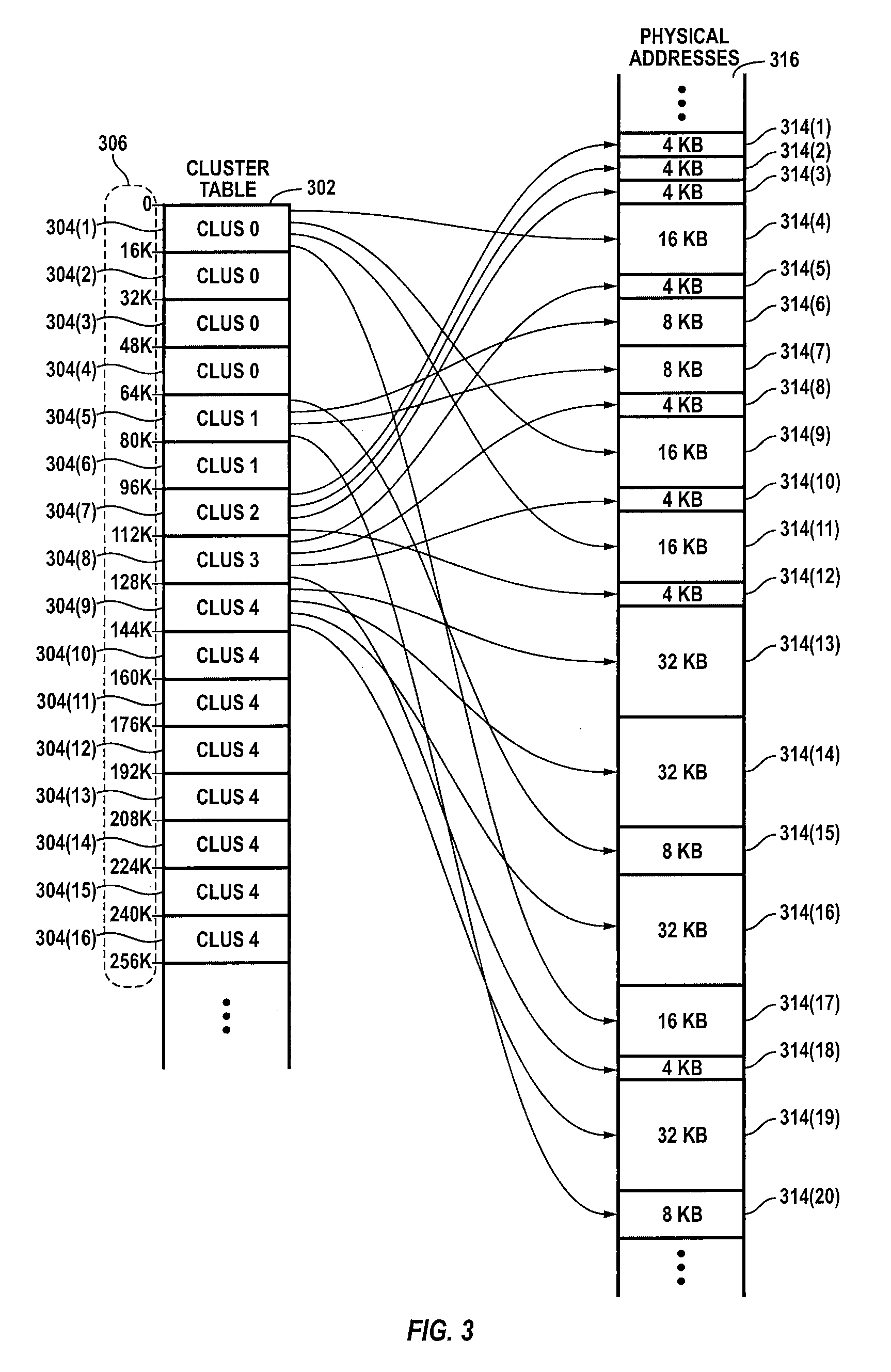

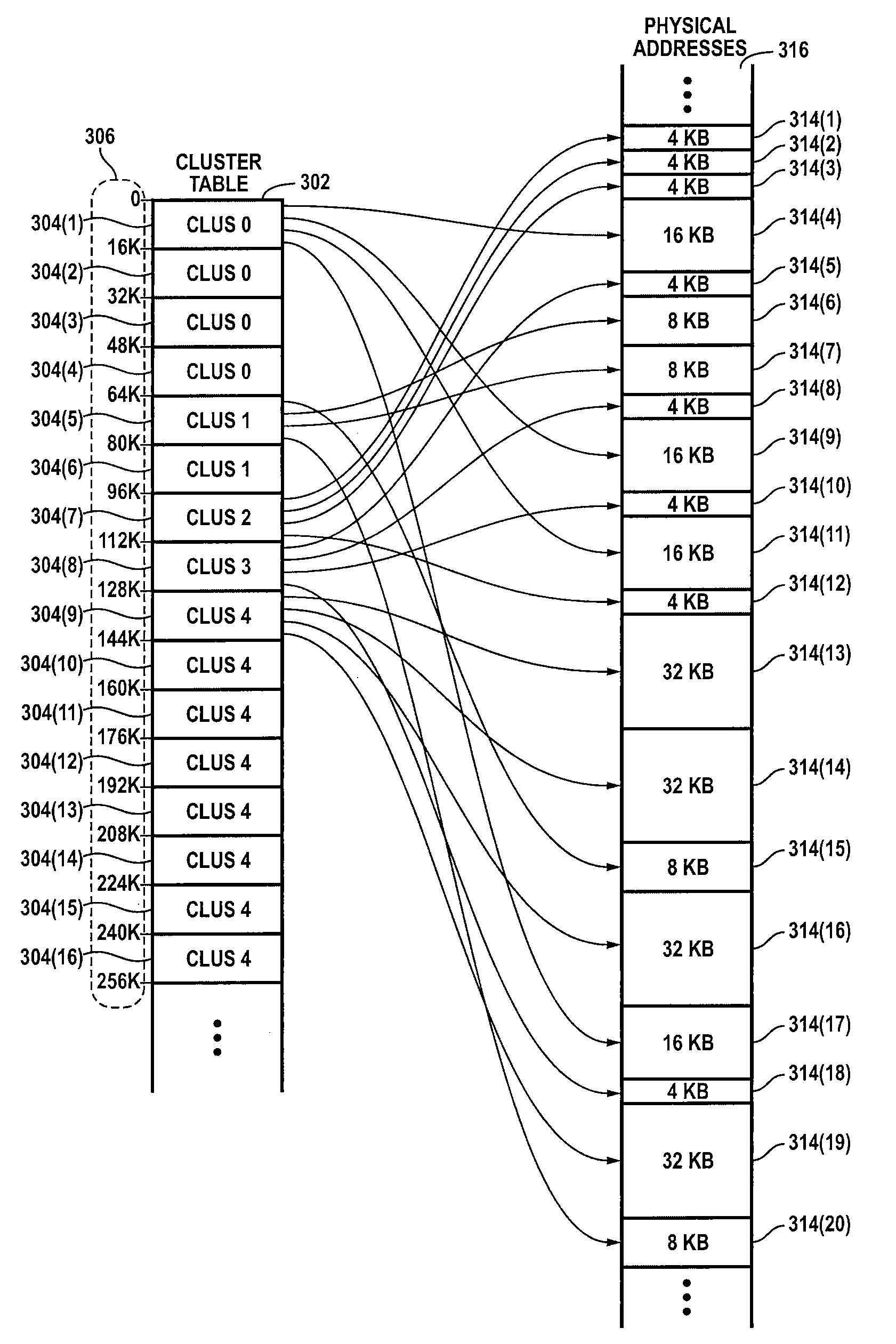

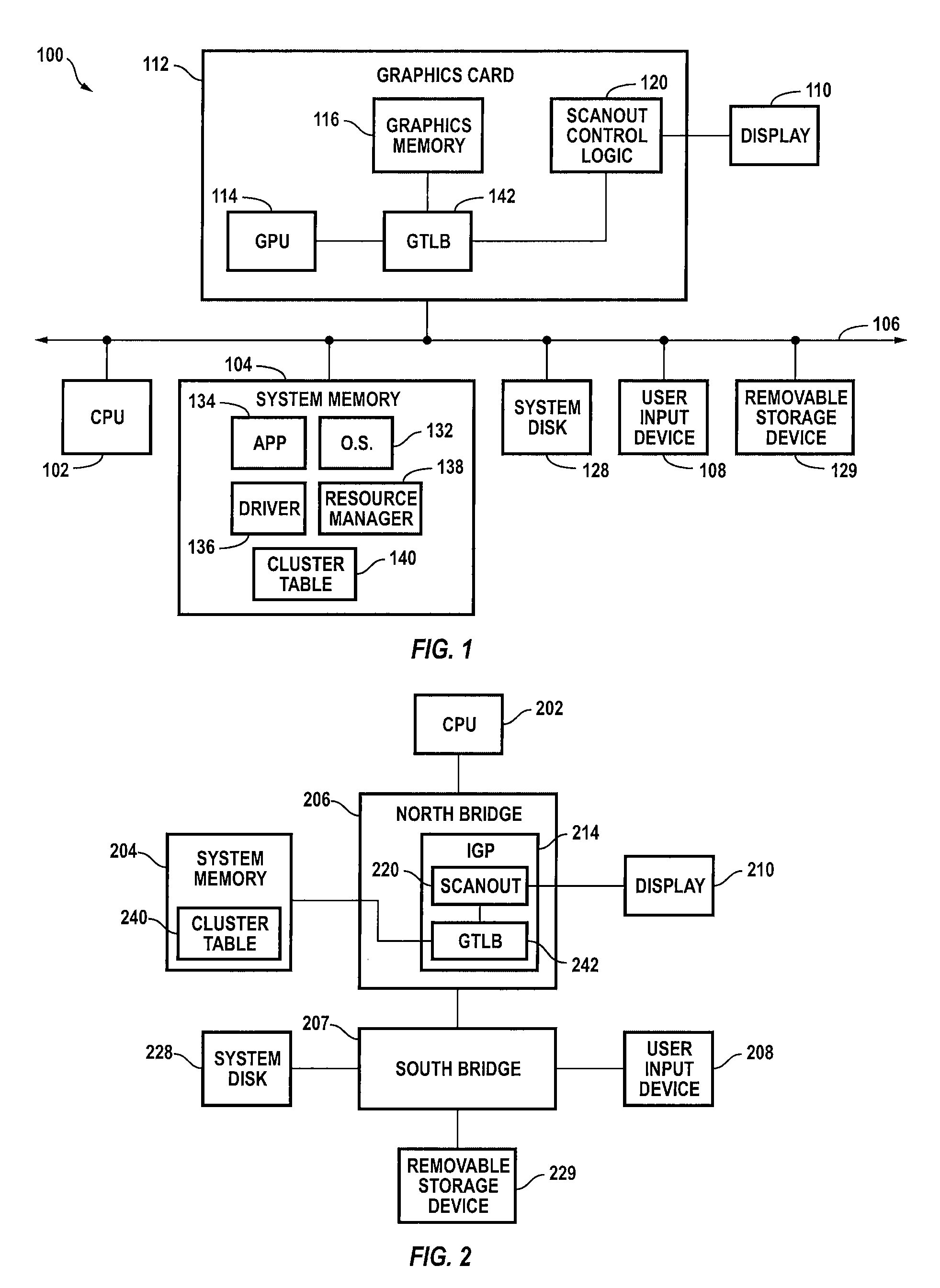

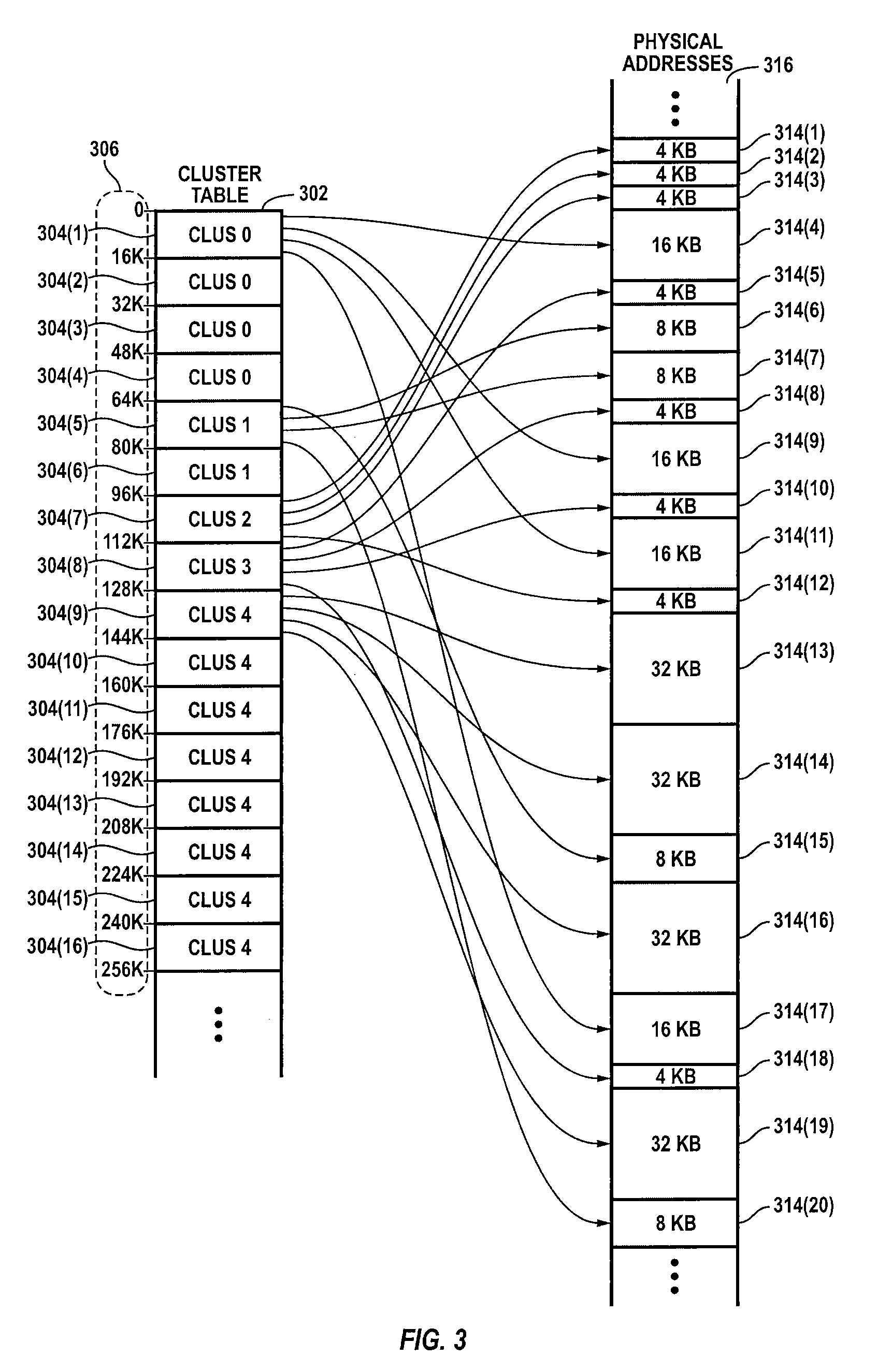

Virtual address translation system with caching of variable-range translation clusters

ActiveUS7278008B1Reduce in quantityMemory architecture accessing/allocationMemory systemsTranslation tableOperating system

A virtual address translation table and an on-chip address cache are usable for translating virtual addresses to physical addresses. Address translation information is provided using a cluster that is associated with some range of virtual addresses and that can be used to translate any virtual address in its range to a physical address, where the sizes of the ranges mapped by different clusters may be different. Clusters are stored in an address translation table that is indexed by virtual address so that, starting from any valid virtual address, the appropriate cluster for translating that address can be retrieved from the translation table. Recently retrieved clusters are stored in an on-chip cache, and a cached cluster can be used to translate any virtual address in its range without accessing the address translation table again.

Owner:NVIDIA CORP

Multi-client virtual address translation system with translation units of variable-range size

ActiveUS7334108B1Reduce in quantityMemory architecture accessing/allocationMemory adressing/allocation/relocationClient-sideTranslation table

A virtual address translation table and an on-chip address cache are usable for translating virtual addresses to physical addresses. Address translation information is provided using a cluster that is associated with some range of virtual addresses and that can be used to translate any virtual address in its range to a physical address, where the sizes of the ranges mapped by different clusters may be different. Clusters are stored in an address translation table that is indexed by virtual address so that, starting from any valid virtual address, the appropriate cluster for translating that address can be retrieved from the translation table. Recently retrieved clusters are stored in an on-chip cache, and a cached cluster can be used to translate any virtual address in its range without accessing the address translation table again.

Owner:NVIDIA CORP

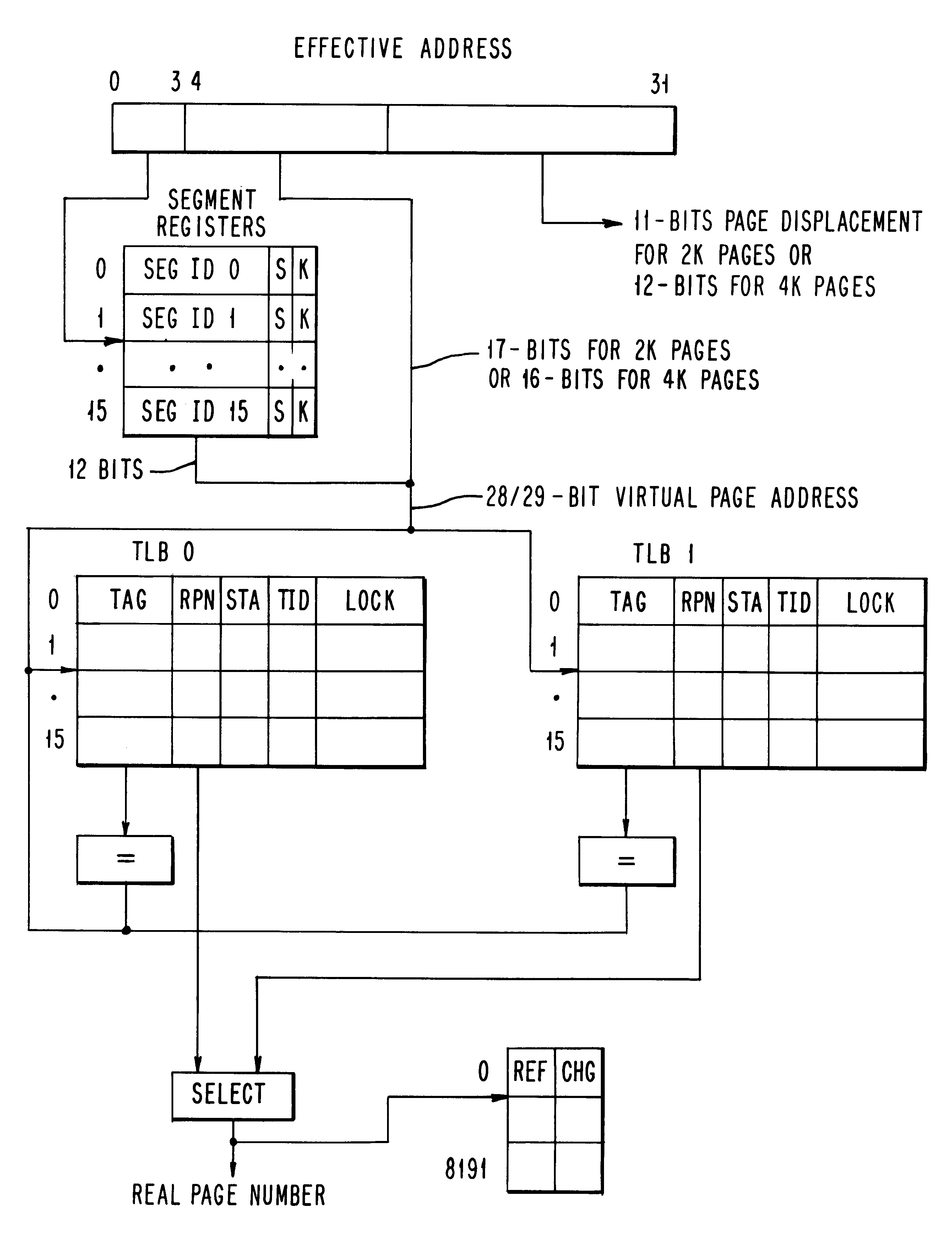

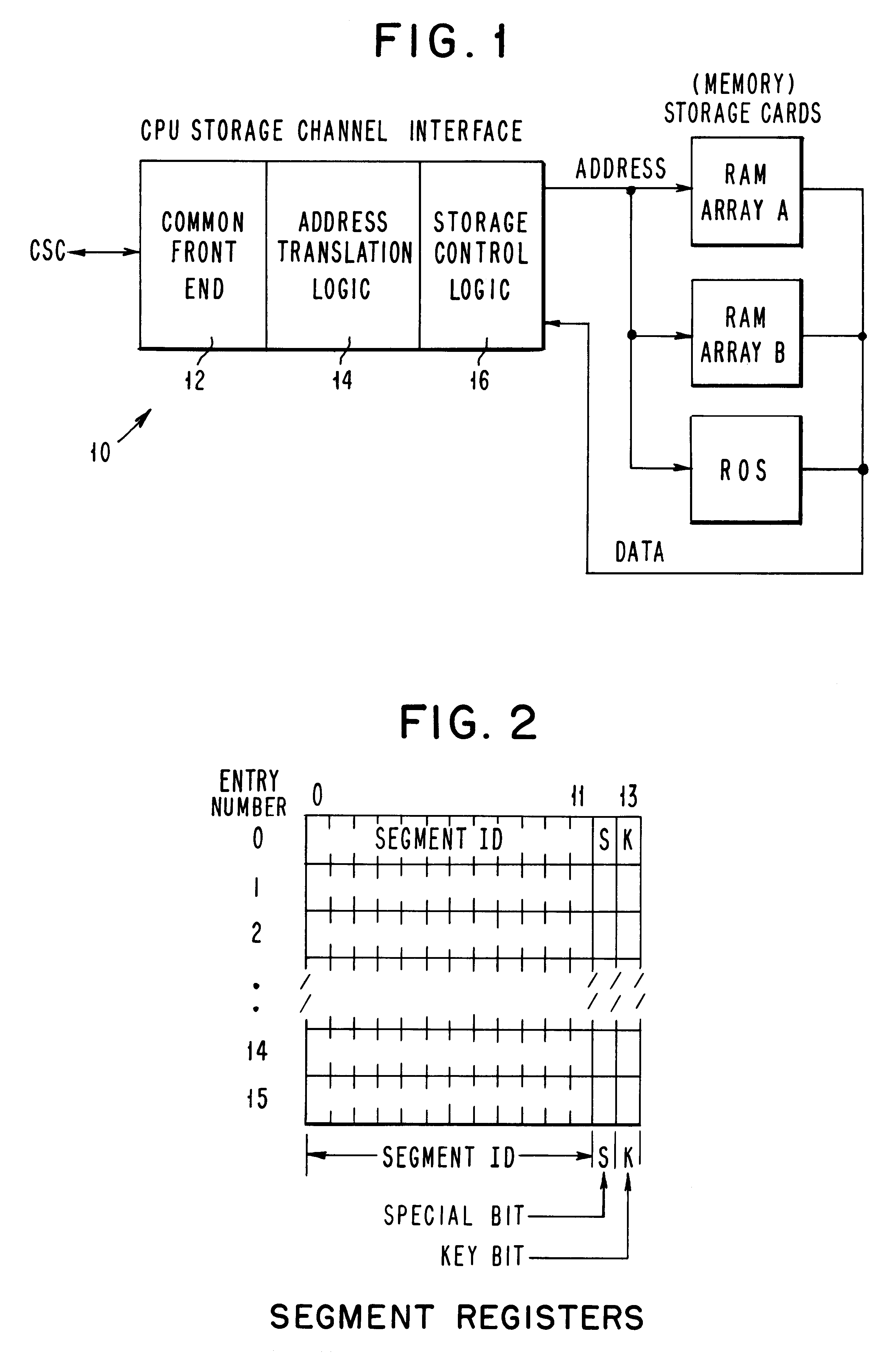

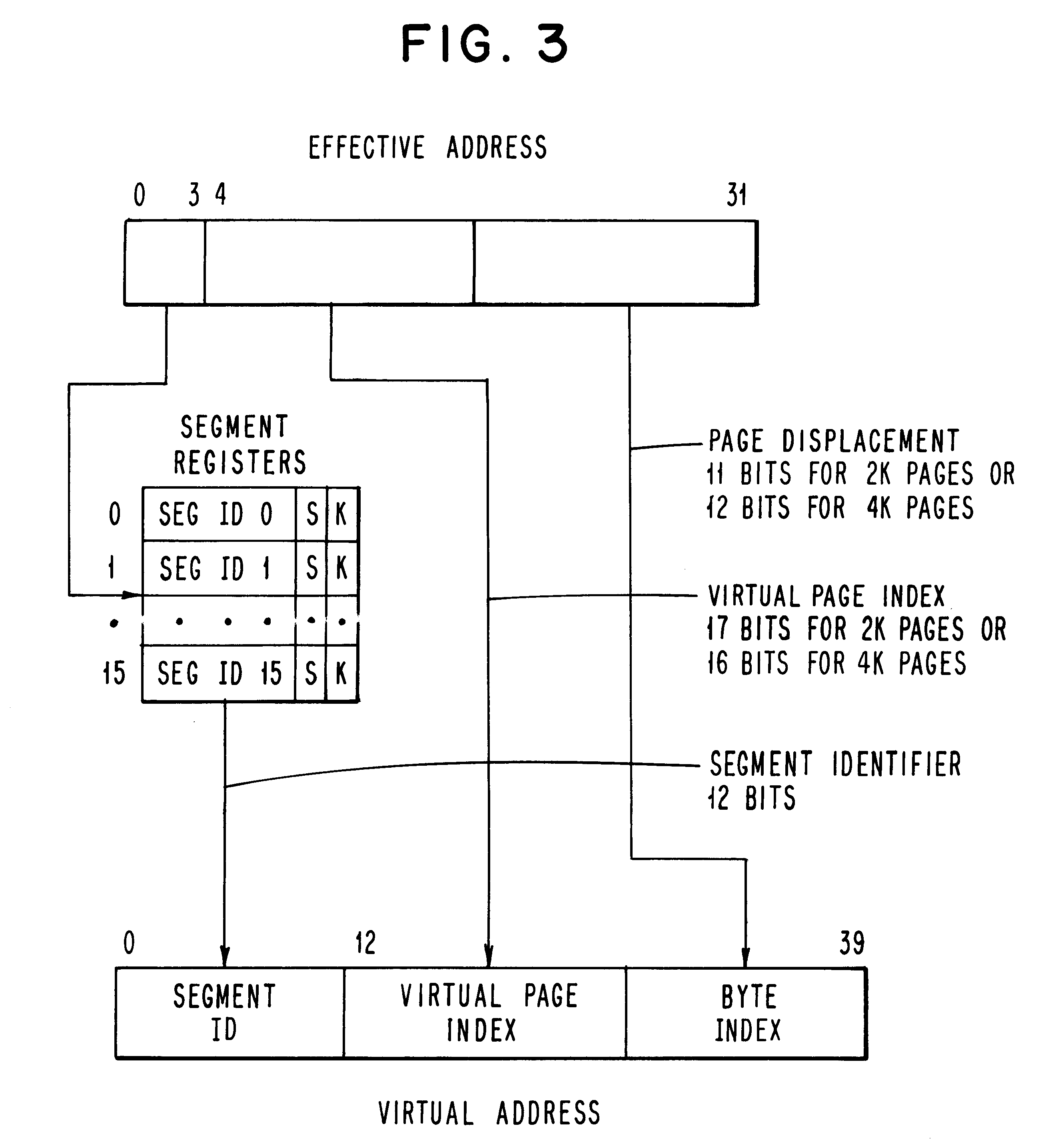

Virtual memory address translation mechanism with controlled data persistence

InactiveUSRE37305E1Less prone to errorFacilitates journallingMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressData field

A memory address translation and related control system for performing the dual functions of converting virtual memory addresses generated by the CPU into real memory addresses in a highly efficient and versatile manner and for controlling certain memory functions such as journalling. The address translation function comprises two steps, the first comprising converting the virtual address into a second virtual address or an effective address and finally the step of converting the effective address into a real memory address. The first step utilizes a set of special registers addressable by a small field to the CPU generated virtual address which converts the virtual address into an expanded form. The second or effective address is then used as the subject of the second or address translation step. To greatly enhance the translation of frequently used virtual addresses, a special set of translation tables referred to herein as a Translation Look-Aside, Buffer (TLB) contain current effective to real address translations for use where frequently referenced addresses are requested. The TLBs are addressed using a subset of the effective address whereupon the contents of the addressed TLB is examined for a match with the effective address. If the addresses match a successful address translation is possible and the real address stored in the address field of the TLB is available for system use. If the desired effective address is not present in the TLB, the page frame tables stored in main memory are accessed and searched for the desired effective address and if found the associated real address is accessed. Further a special data field is provided in both the TLBs and the page frame tables in main memory wherein a bit is provided for each line in the referenced page at a given effective to real address translation which bits may be used to indicate when a line of data has been accessed or altered.

Owner:IBM CORP

Data document generator

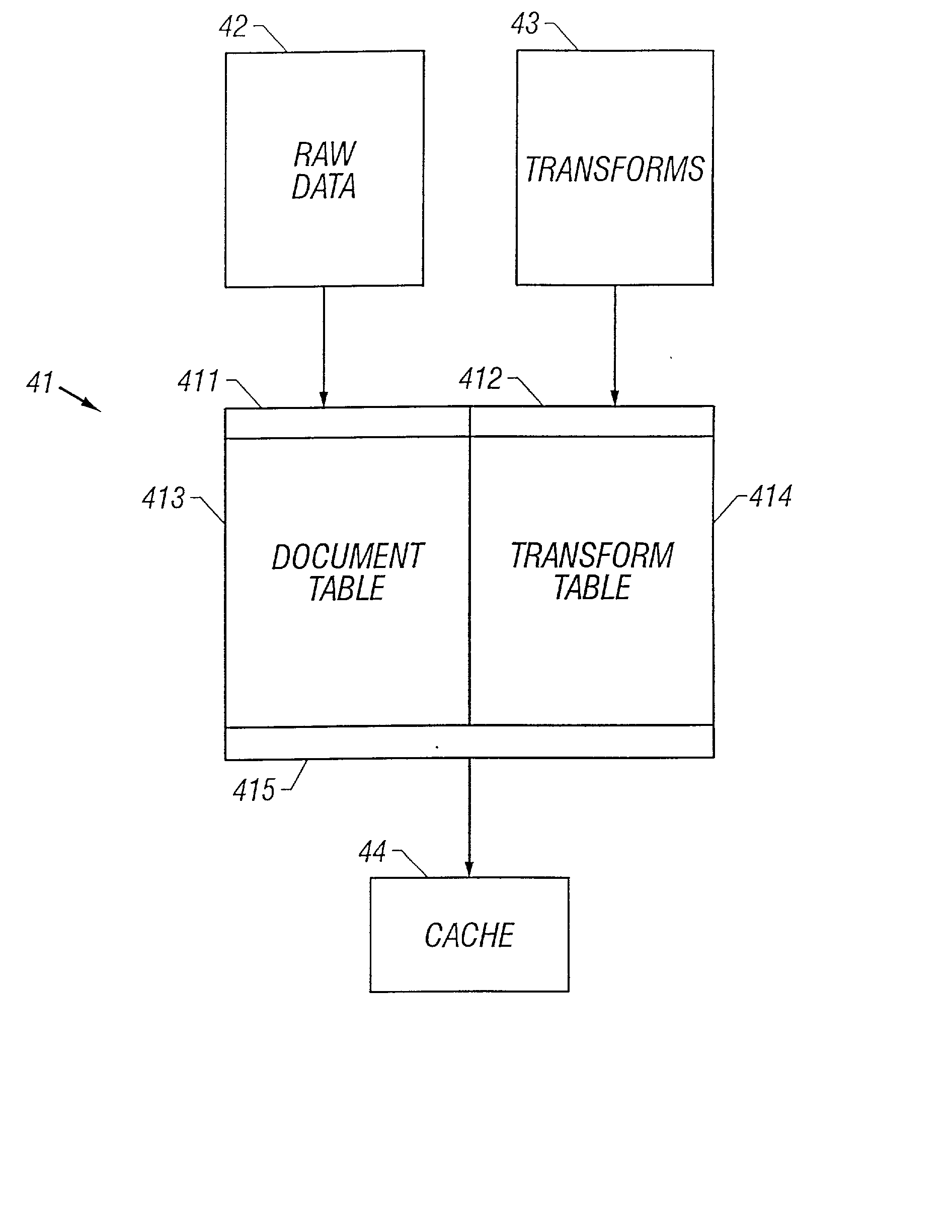

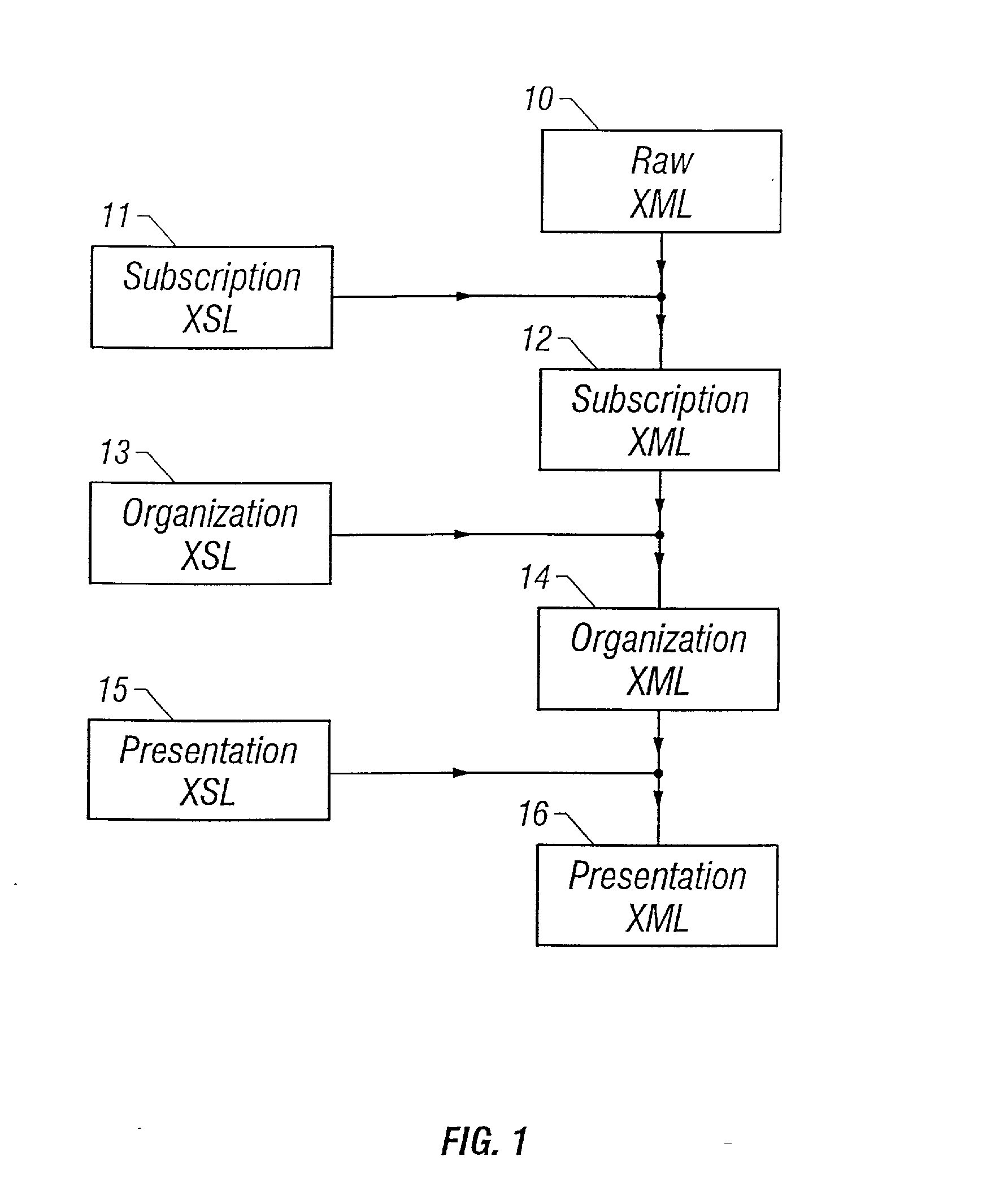

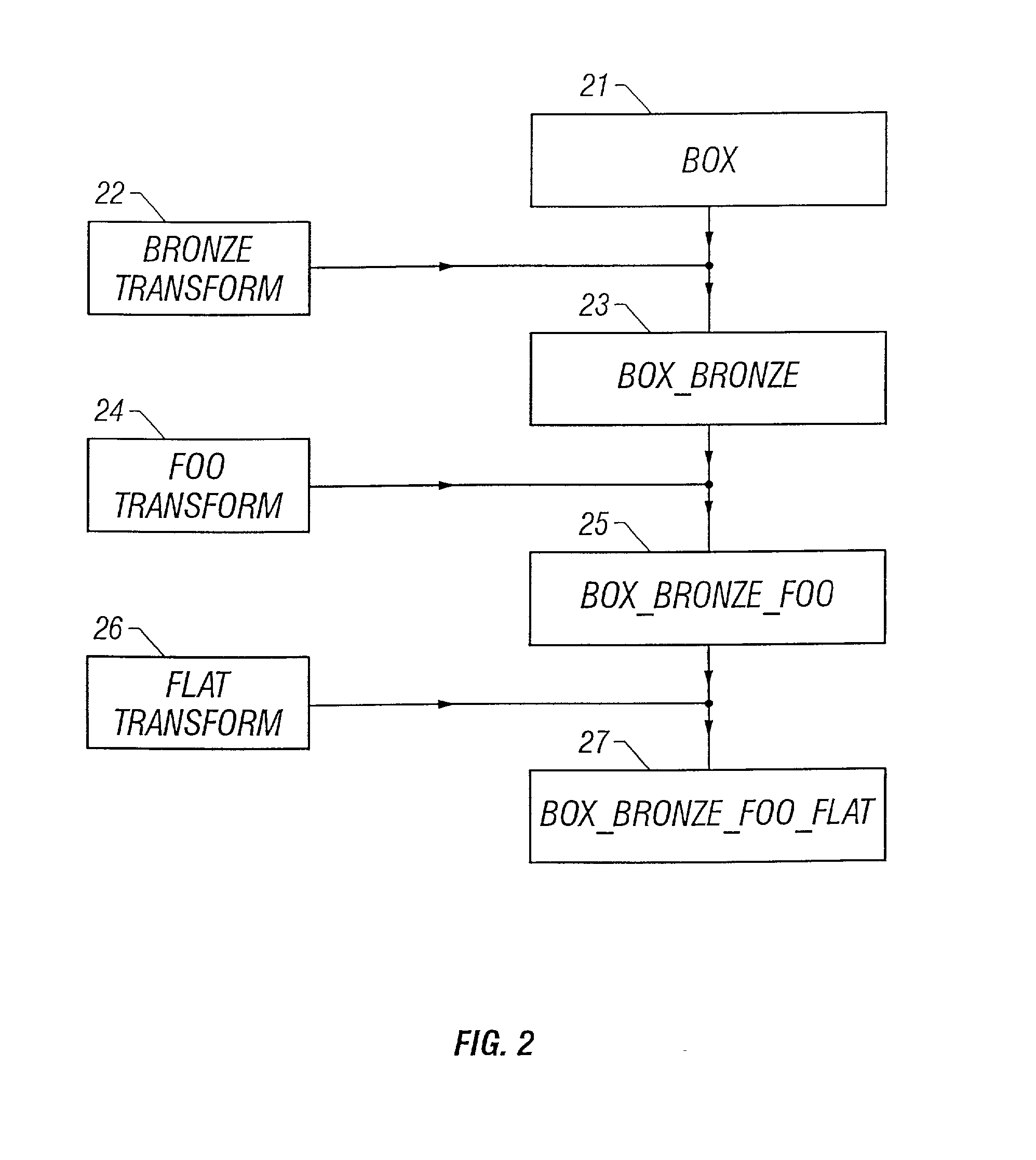

ActiveUS20030014447A1Natural language data processingSpecial data processing applicationsOriginal dataData file

A data management system for generating customized versions of data documents. Initially the document is stored as in the form of raw data, which is subsequently parsed into an internal representation of the document. In one embodiment, raw data is stored in XML form and is parsed by an XML parser. Upon the initial request for a customized version of the document, a sequence of transforms is applied to the internal representation and to subsequently transformed documents in order to create hierarchical, customized document levels. In one embodiment, transforms are implemented as either XSL stylesheets, although Java classes may also be employed. The document versions are written to cache, and subsequent requests for existing versions of the document are referred to cache. In the event that any document dependencies change, a cached version will be denoted invalid, and subsequent requests will result in the re-generation of a customized version. The data management system is implemented in the form of a document manager, a database that includes a document table and a transform table. The document manager reads raw documents from a raw-document database and reads transforms from a transform database. Requested customized documents are written to cache.

Owner:VERSATA SOFTWARE INC

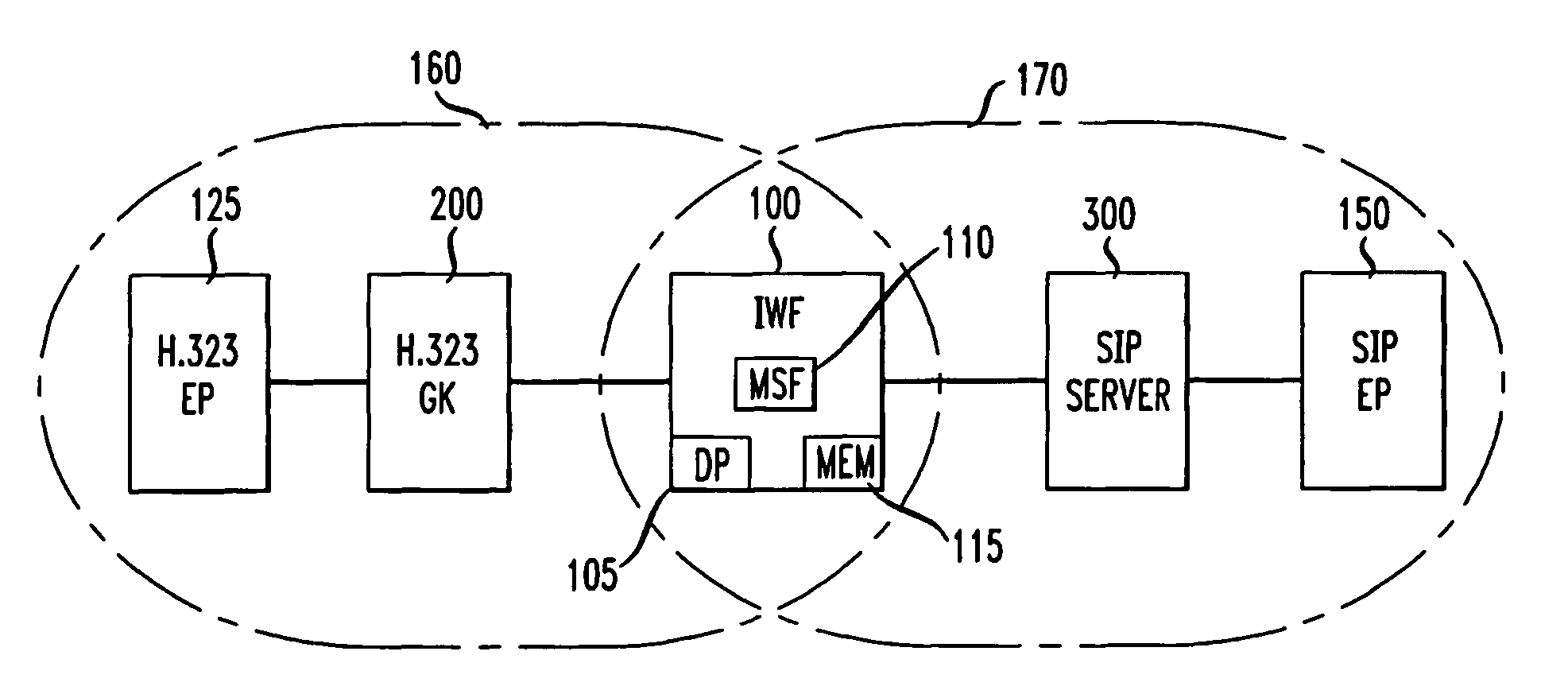

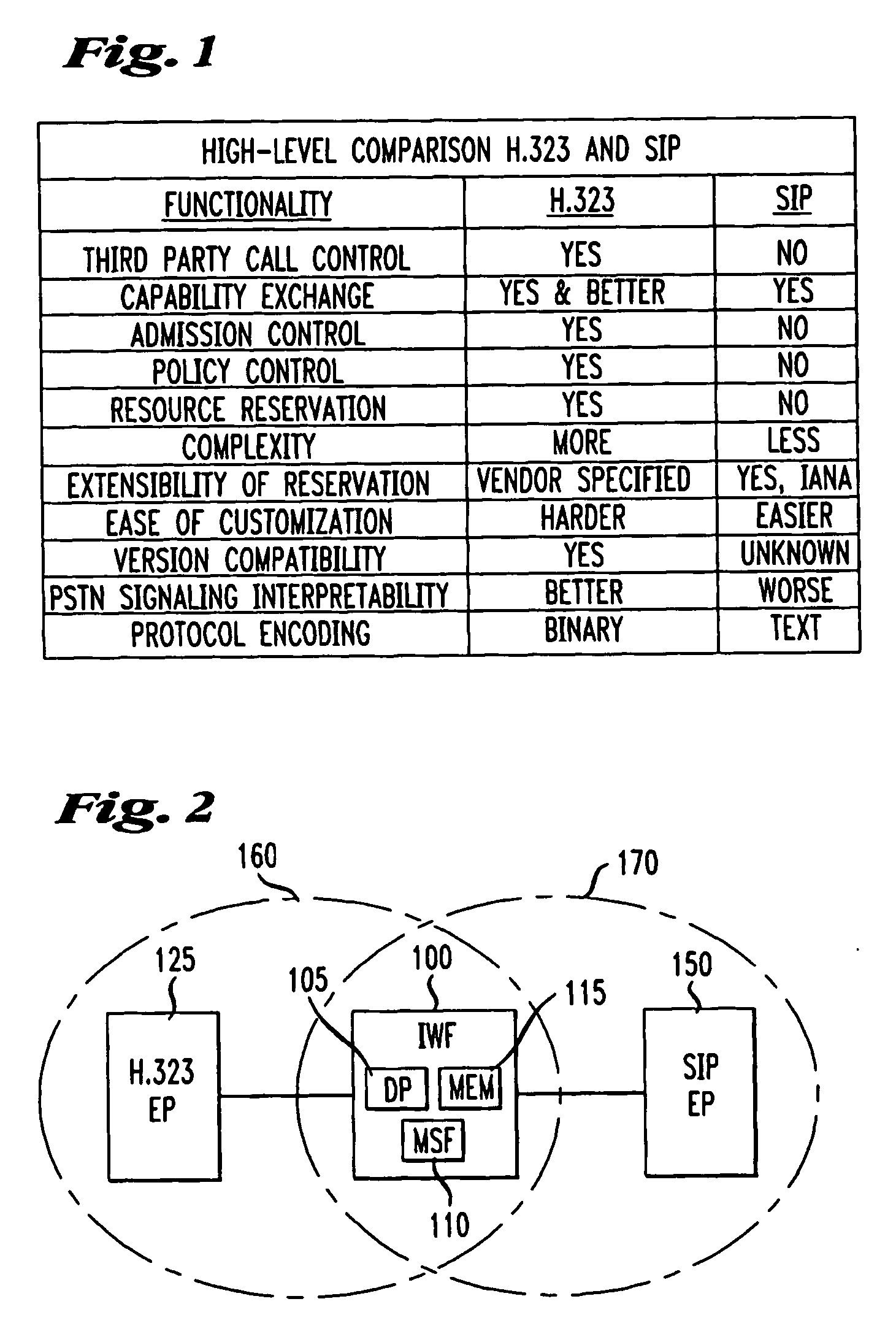

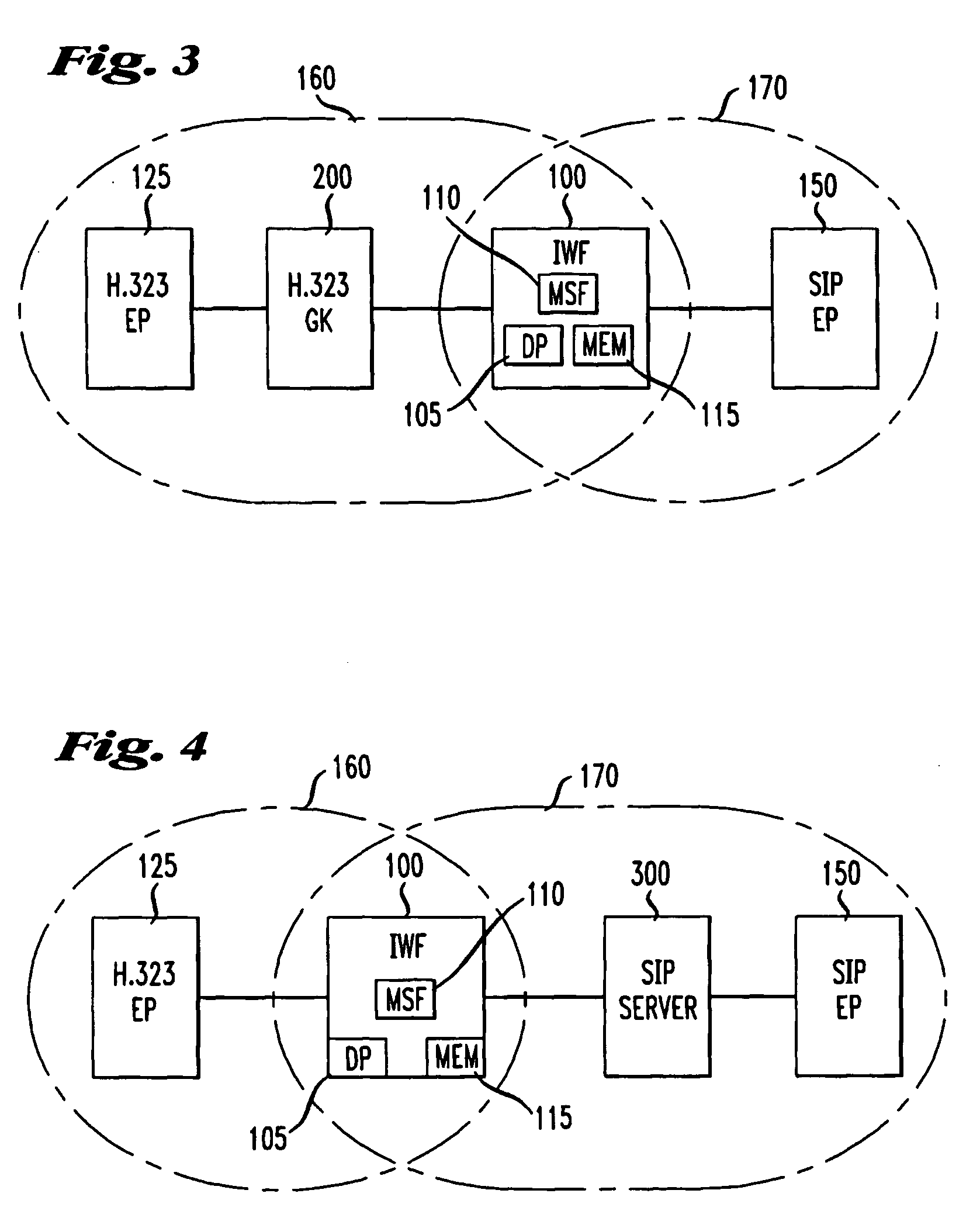

Method and apparatus for S.I.P./H.323 interworking

InactiveUS20060007954A1Time-division multiplexData switching by path configurationState dependentStructure of Management Information

An interworking function (IWF) for a first and second protocol based network, for example, an H.323 protocol based network and an SIP protocol based network comprises an interworking gateway server including a state machine for defining each call processing state and a translation table for use in translating addresses formatted in each protocol. A method of interworking for use in interworking between said first protocol based network and said second protocol based network comprises the steps of receiving at said interworking gateway server serving said first and second protocol based networks a request from an endpoint in the first or second protocol based networks, establishing a state machine in memory whereby, for each state of said state machine, a message associated with that state is categorized as one of a triggering message, a non-triggering message and an error message, establishing a translation table in said memory whereby an address formatted in said first protocol has a one-for-one correspondence with an address formatted in said second protocol, processing said request in accordance with said translation table and said state machine and permitting communication between said first and second endpoints utilizing a realtime transport protocol. In the event media is terminated at said interworking gateway server, the interworking gateway server, in one embodiment, comprises a media switching fabric for switching media terminated at the gateway to an addressed endpoint capable of receiving it.

Owner:AT&T INTPROP II L P

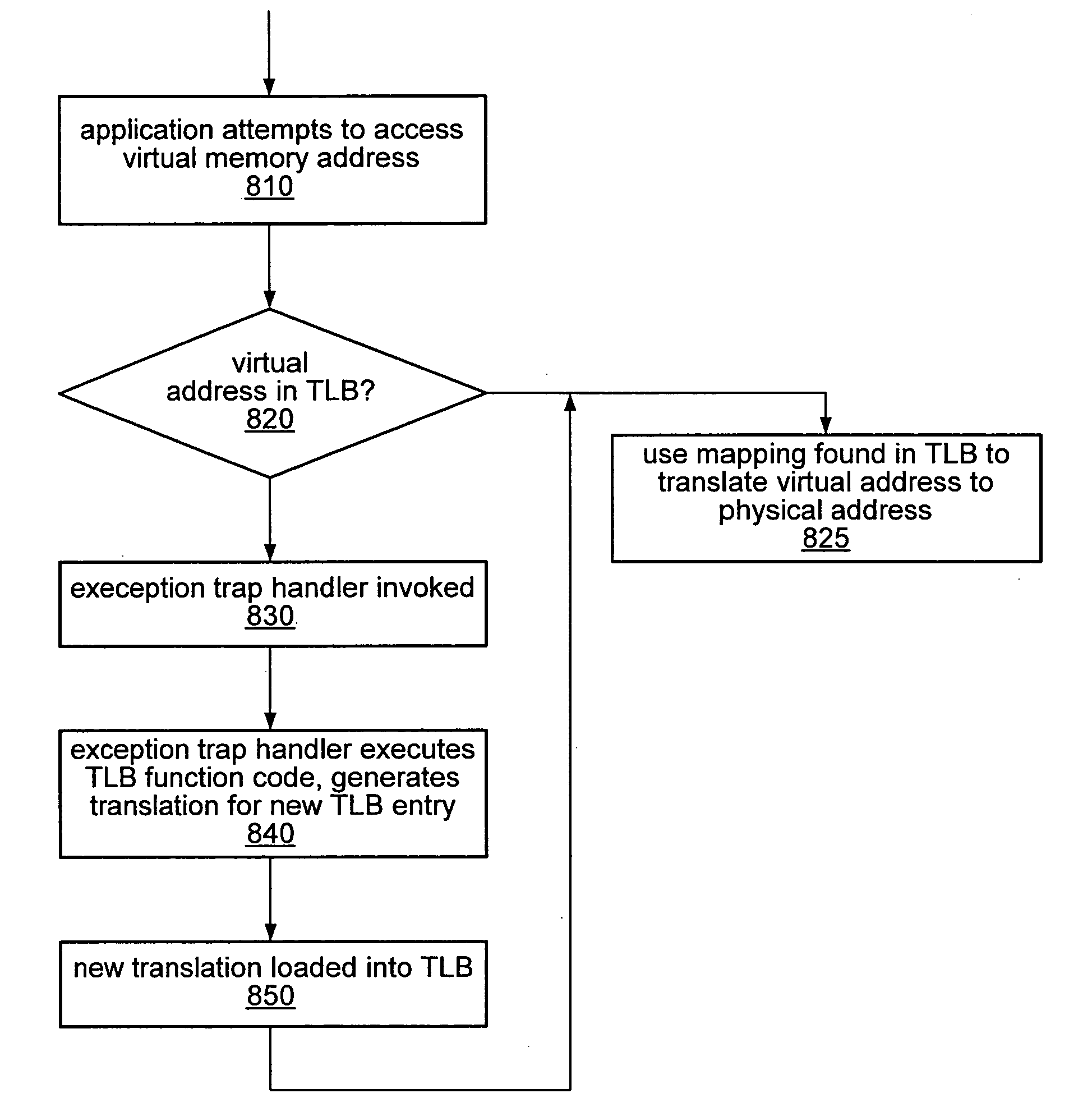

Function-based virtual-to-physical address translation

ActiveUS20070283123A1Simplify translation functionFunction increaseMemory architecture accessing/allocationMemory adressing/allocation/relocationVirtualizationComputerized system

A computer system employing memory virtualization may employ a function-based technique for virtual-to-physical address translation. A function-based translation technique may involve replacing a generic trap handler and one or more translation table look-ups with a function to compute a corresponding physical address from a given virtual address. The computer system may be configured to determine a translation function dependent on mappings in one or more translation tables. The computer system may be configured to reorganize a memory, to reorganize one or more translation tables, or to allocate different blocks of memory to an application prior to determining a translation function. Different applications or threads executing on the computer system may employ different translation functions. Different regions of memory may be accessed using different translation functions. Some virtual addresses may be translated using a function while others may be translated using one or more translation table look-ups.

Owner:ORACLE INT CORP

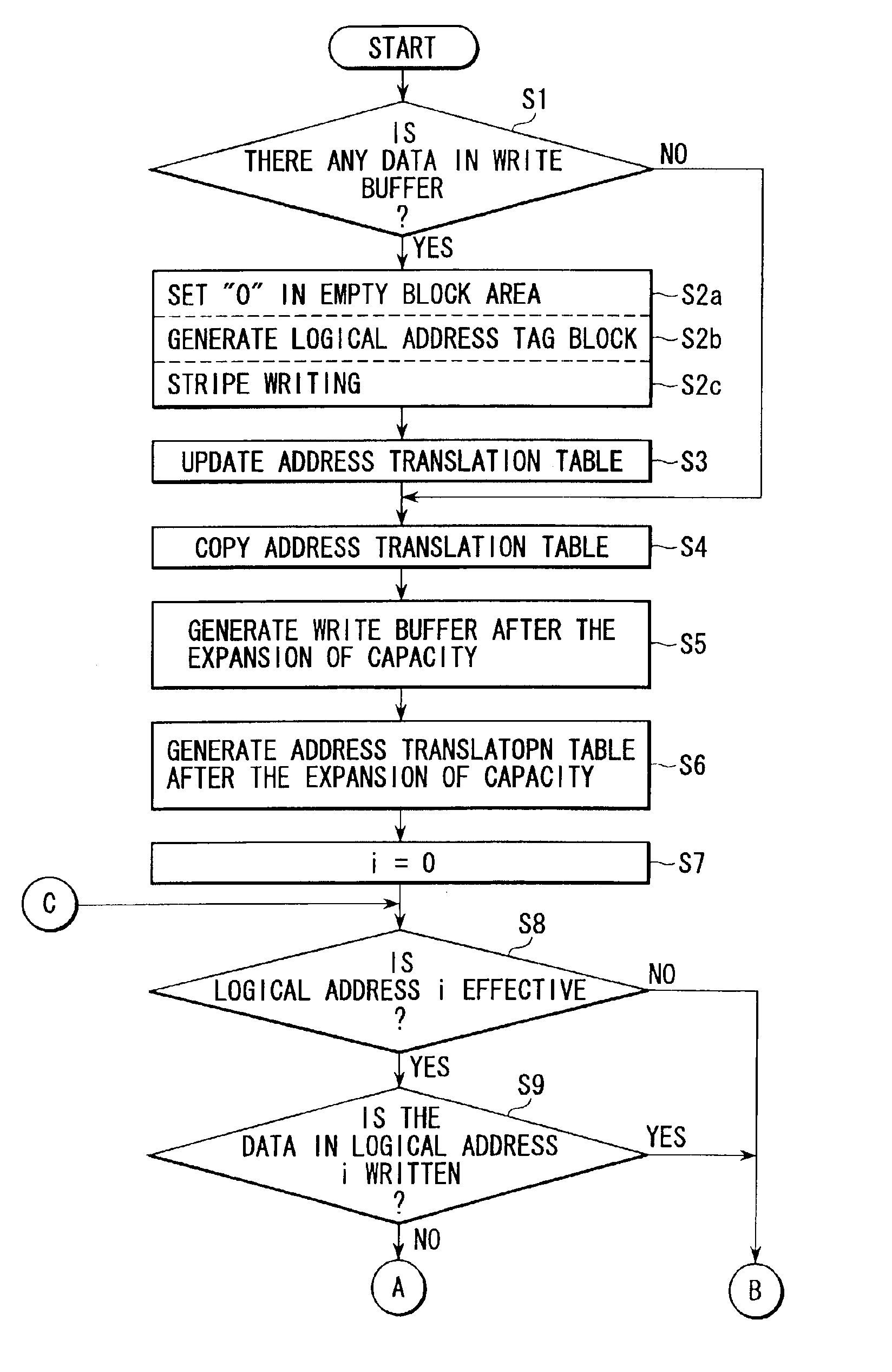

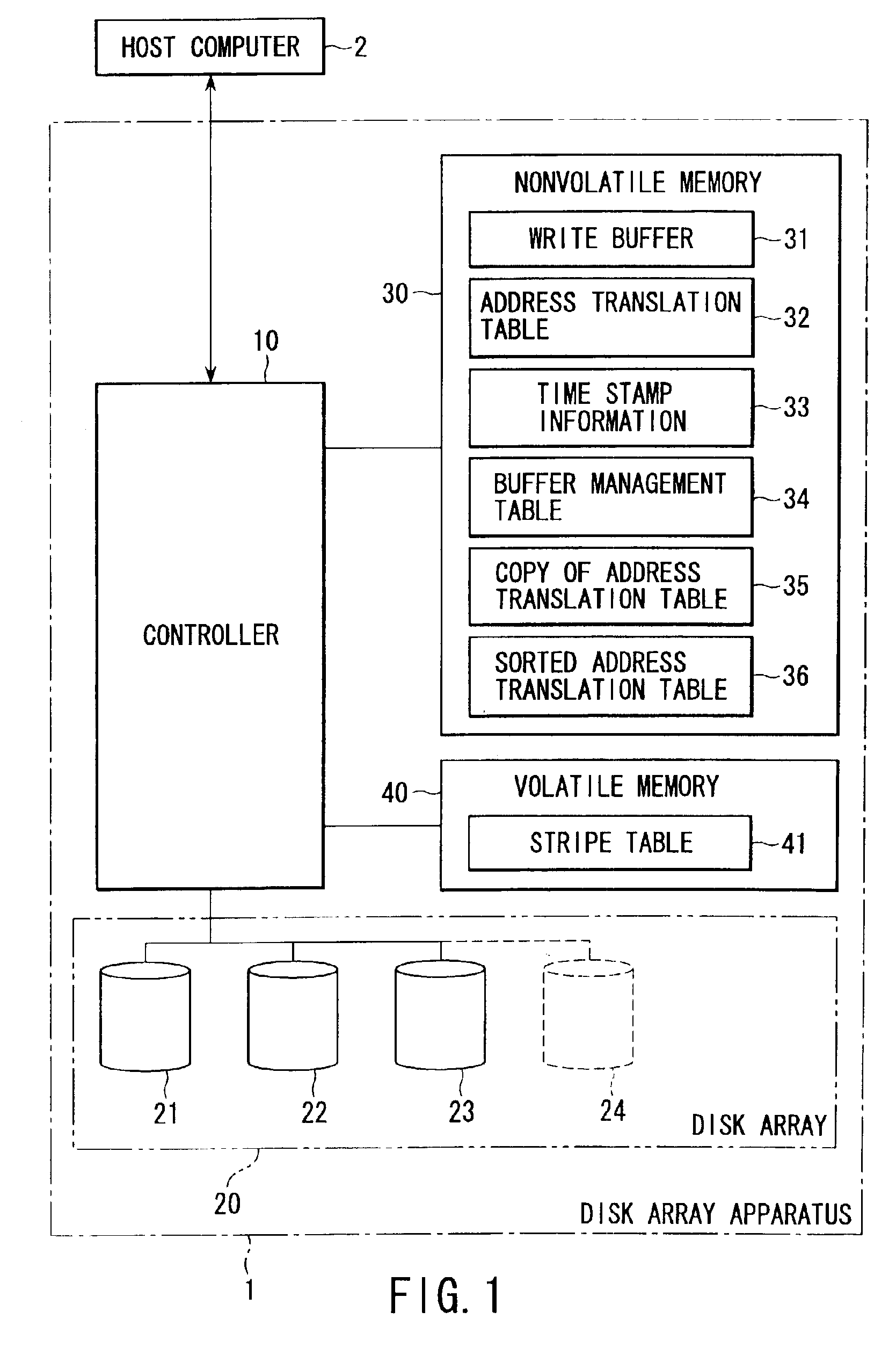

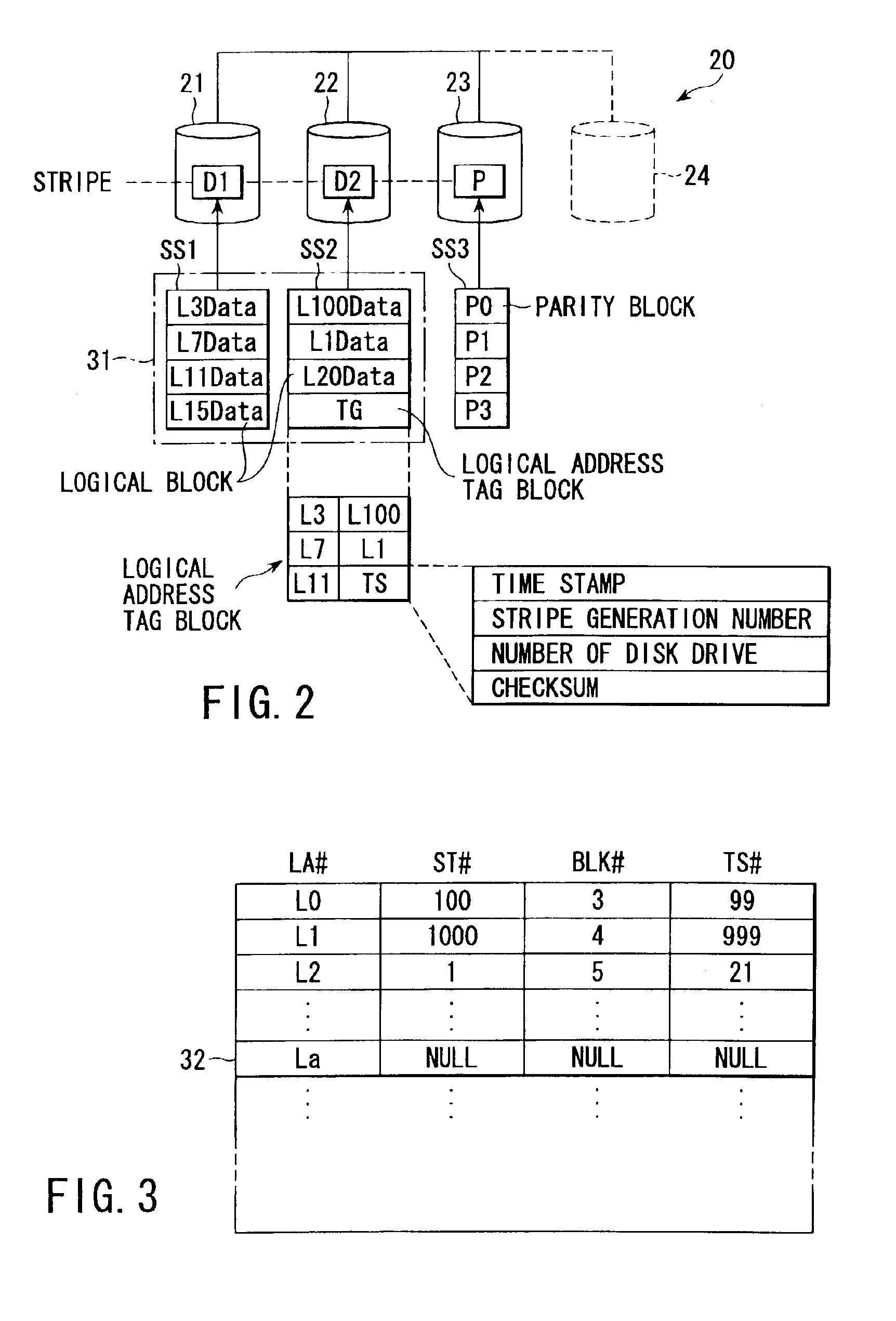

Disk array apparatus for and method of expanding storage capacity dynamically

InactiveUS6901479B2Shorten the timeIncrease storage capacityInput/output to record carriersError detection/correctionWrite bufferDisk array

A controller retrieves effective logical addresses sequentially according to a copy of an address translation table at the time of the start of storage capacity expansion in the process of expanding the storage capacity of a disk array by adding a disk drive to the disk array. The controller stores the data in the logical address into a restructured write buffer each time an effective logical address is retrieved. The controller writes one stripe worth of data blocks including one stripe of logical blocks and a logical address tag block into an empty area different from the area in which the data to be updated has been stored in the data array each time one stripe worth of logical blocks of data is accumulated in the write buffer.

Owner:KK TOSHIBA

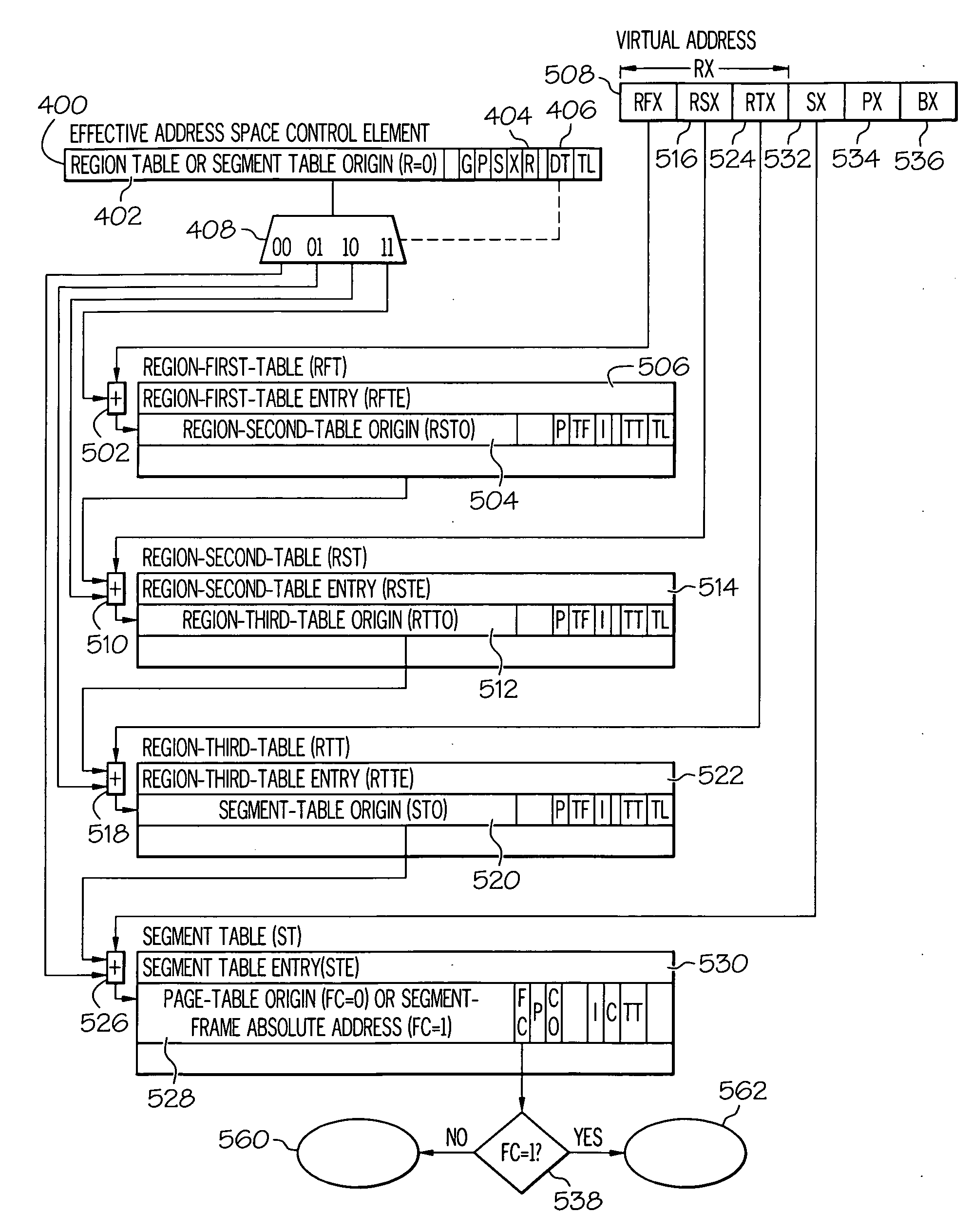

Dynamic address translation with translation exception qualifier

ActiveUS20090216992A1Small sizeMemory architecture accessing/allocationMemory adressing/allocation/relocationTranslation tableComputer science

What is provided is an enhanced dynamic address translation facility. In one embodiment, a virtual address to be translated and an initial origin address of a translation table of the hierarchy of translation tables are obtained. Dynamic address translation of the virtual address proceeds. In response to a translation interruption having occurred during dynamic address translation, bits are stored in a translation exception qualifier (TXQ) field to indicate that the exception was either a host DAT exception having occurred while running a host program or a host DAT exception having occurred while running a guest program. The TXQ is further capable of indicating that the exception was associated with a host virtual address derived from a guest page frame real address or a guest segment frame absolute address. The TXQ is further capable of indicating that a larger or smaller host frame size is preferred to back a guest frame.

Owner:IBM CORP

Translation Data Prefetch in an IOMMU

ActiveUS20080209130A1Memory architecture accessing/allocationMemory adressing/allocation/relocationDirect memory accessManagement unit

In an embodiment, a system memory stores a set of input / output (I / O) translation tables. One or more I / O devices initiate direct memory access (DMA) requests including virtual addresses. An I / O memory management unit (IOMMU) is coupled to the I / O devices and the system memory, wherein the IOMMU is configured to translate the virtual addresses in the DMA requests to physical addresses to access the system memory according to an I / O translation mechanism implemented by the IOMMU. The IOMMU comprises one or more caches, and is configured to read translation data from the I / O translation tables responsive to a prefetch command that specifies a first virtual address. The reads are responsive to the first virtual address and the I / O translation mechanism, and the IOMMU is configured to store data in the caches responsive to the read translation data.

Owner:GLOBALFOUNDRIES US INC