Patents

Literature

931 results about "Memory functions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Specific mental functions of registering and storing information and retrieving it as needed.

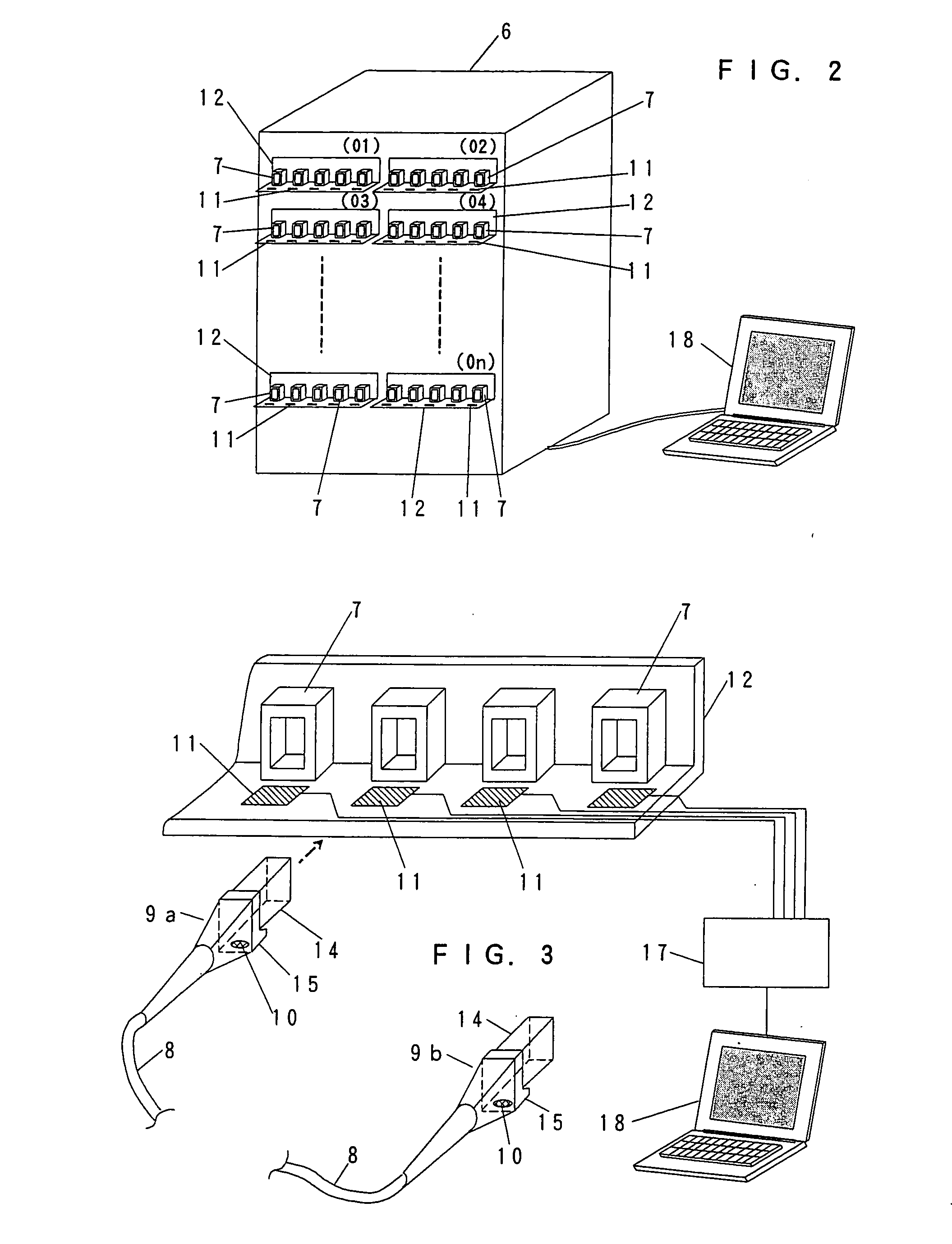

Connector adapter with memory function unit

Owner:TOKYO TSUSHINKI INDS

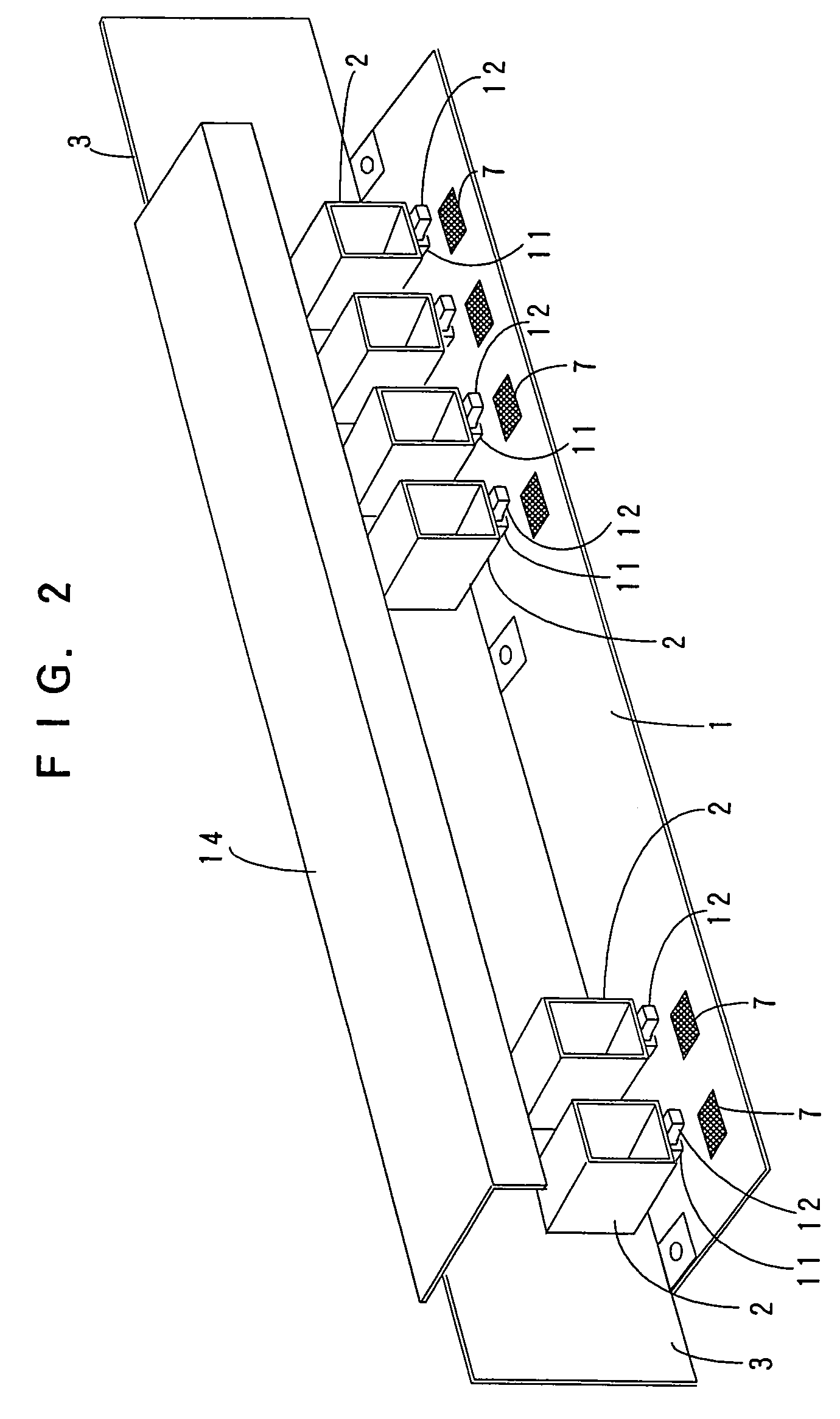

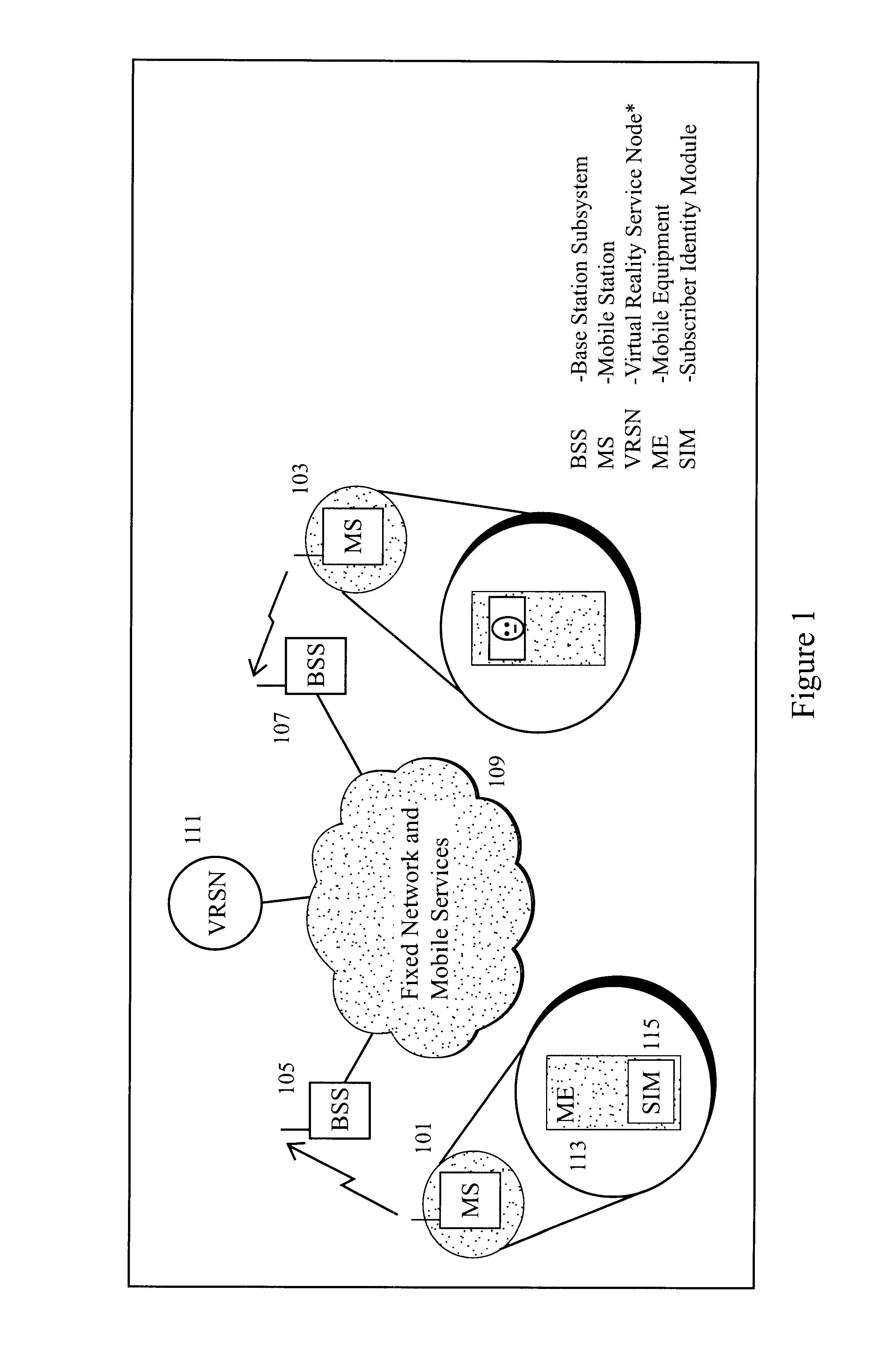

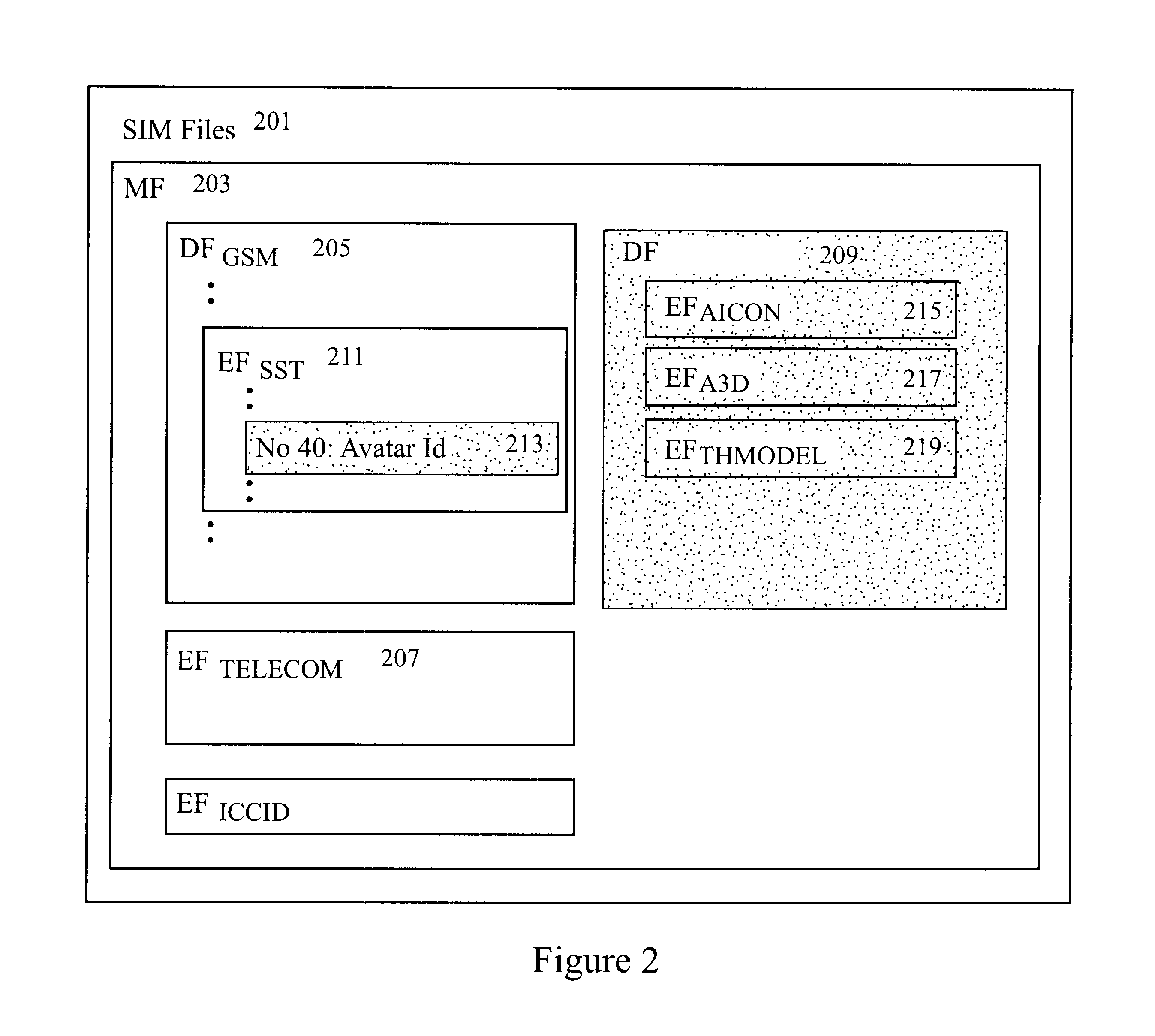

Method and a device for use in a virtual environment

InactiveUS6397080B1Payment architectureRadio/inductive link selection arrangementsVirtual worldMemory functions

Information about avatar characteristics for a user are stored in a removable memory card (115), for example in a SIM card for the GSM system. The information regarding the avatar can then be moved from one access terminal to another. A virtual world, which the avatar is designed to enter, can then be accessed from many different access terminals by means of inserting the SIM card and entering a personal identity number (PIN) code. Thus by adding such a memory function to a removable memory card (e.g. a SIM card or a Smart card), besides of making it possible to access a virtual world from different access terminals, also makes it possible to use avatars in new applications, such as in a GSM phone or another mobile phone or terminal.

Owner:TELEFON AB LM ERICSSON (PUBL)

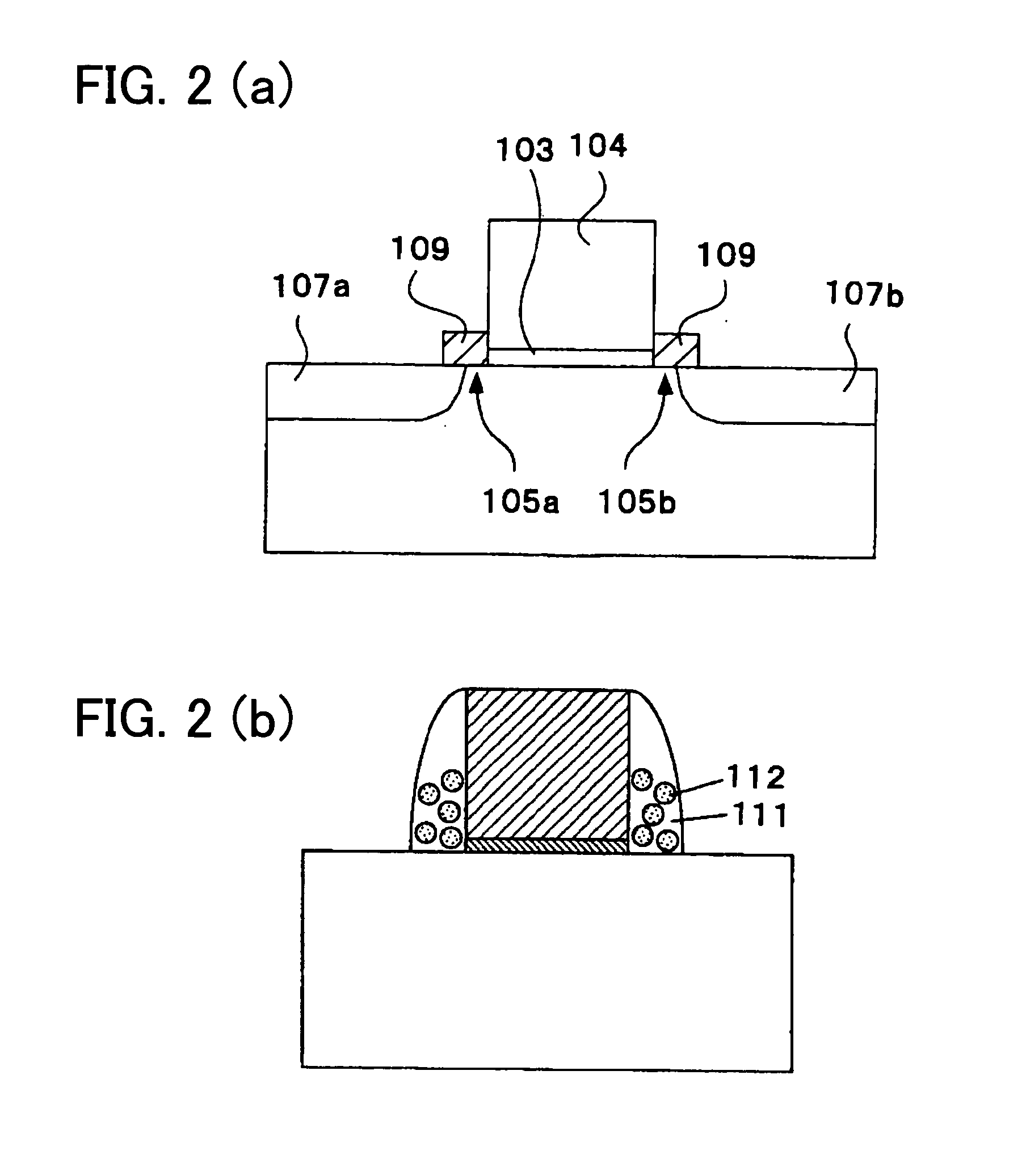

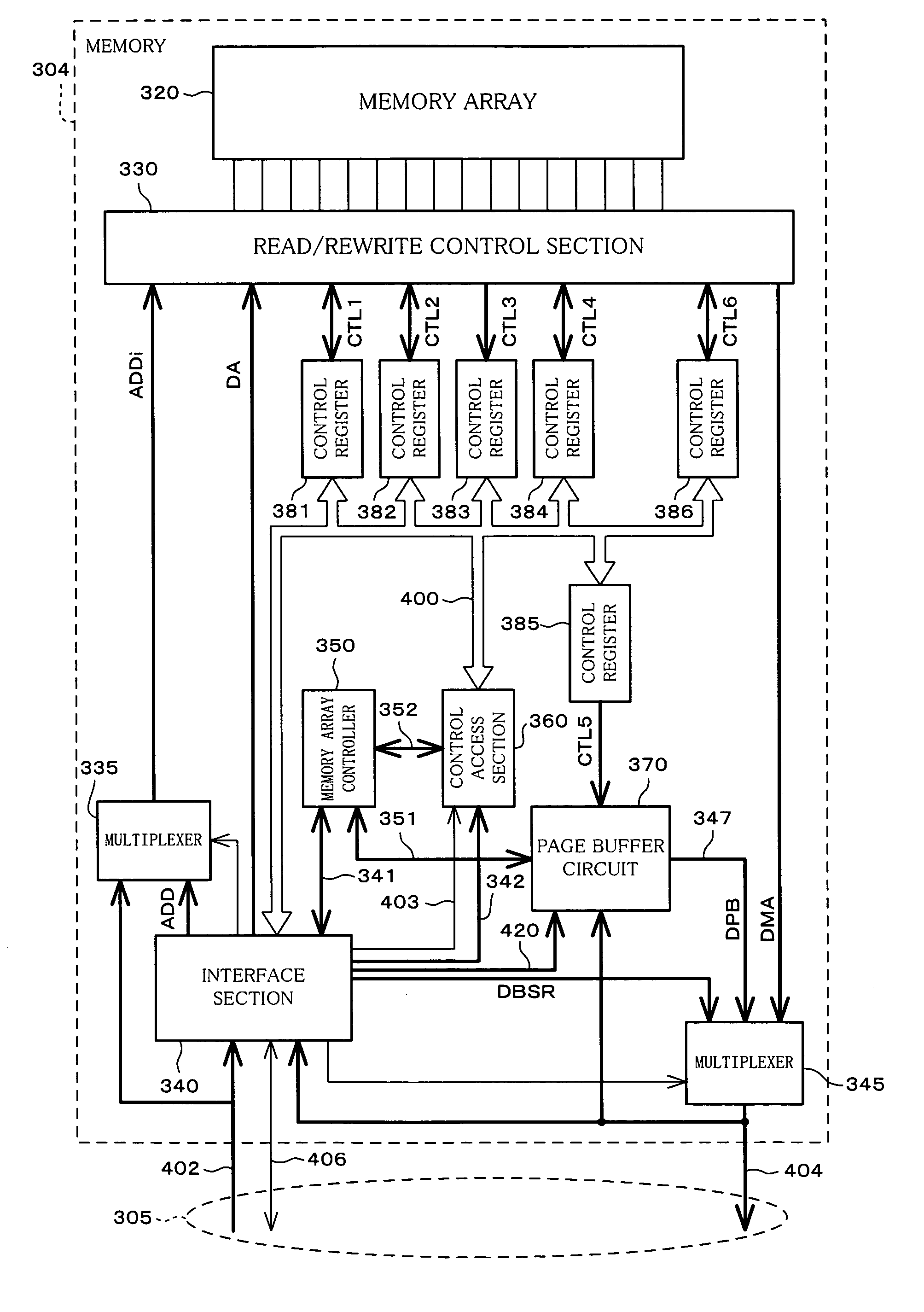

Writing control method and writing control system of semiconductor storage device, and portable electronic apparatus

InactiveUS20050002263A1Easily-realized finerSpeedup of writingTransistorSolid-state devicesSemiconductor storage devicesEngineering

A writing control system providing high-speed writing to a nonvolatile semiconductor storage device, includes (a) a plurality of memory elements each having: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion region provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member, provided on both sides of the gate electrode, having a function of holding electric charges, (b) a memory array including a page buffer circuit, and (c) CPU controlling writing to the memory array. The CPU loads a first plane of the page buffer circuit with a first byte of data and writes with the first byte of data stored in the first plane. Further, the CPU writes a second byte of data into the second plane and writes the second byte of data having been stored in the second plane while writing the first byte of data having been stored in the first plane into the memory array.

Owner:SHARP KK

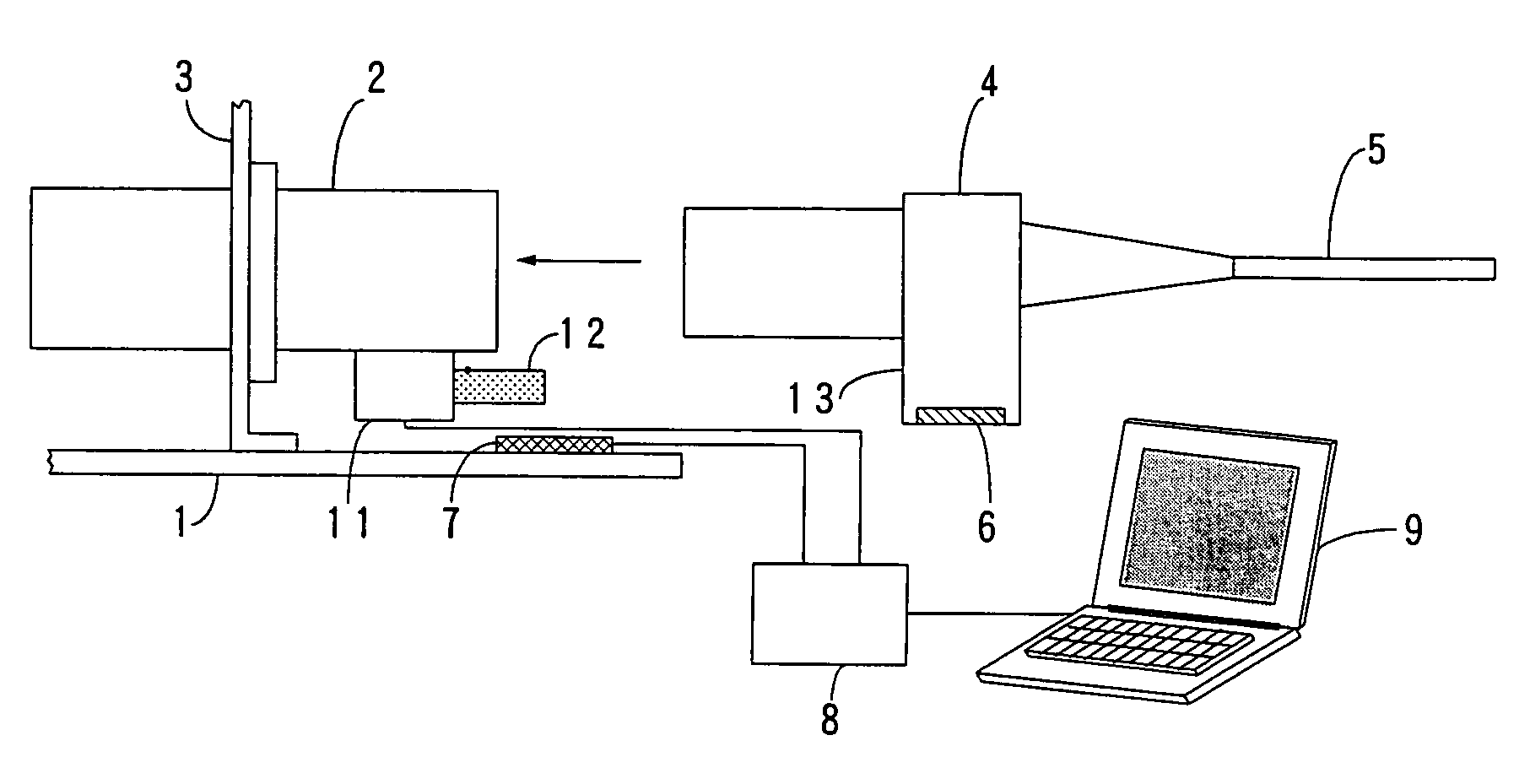

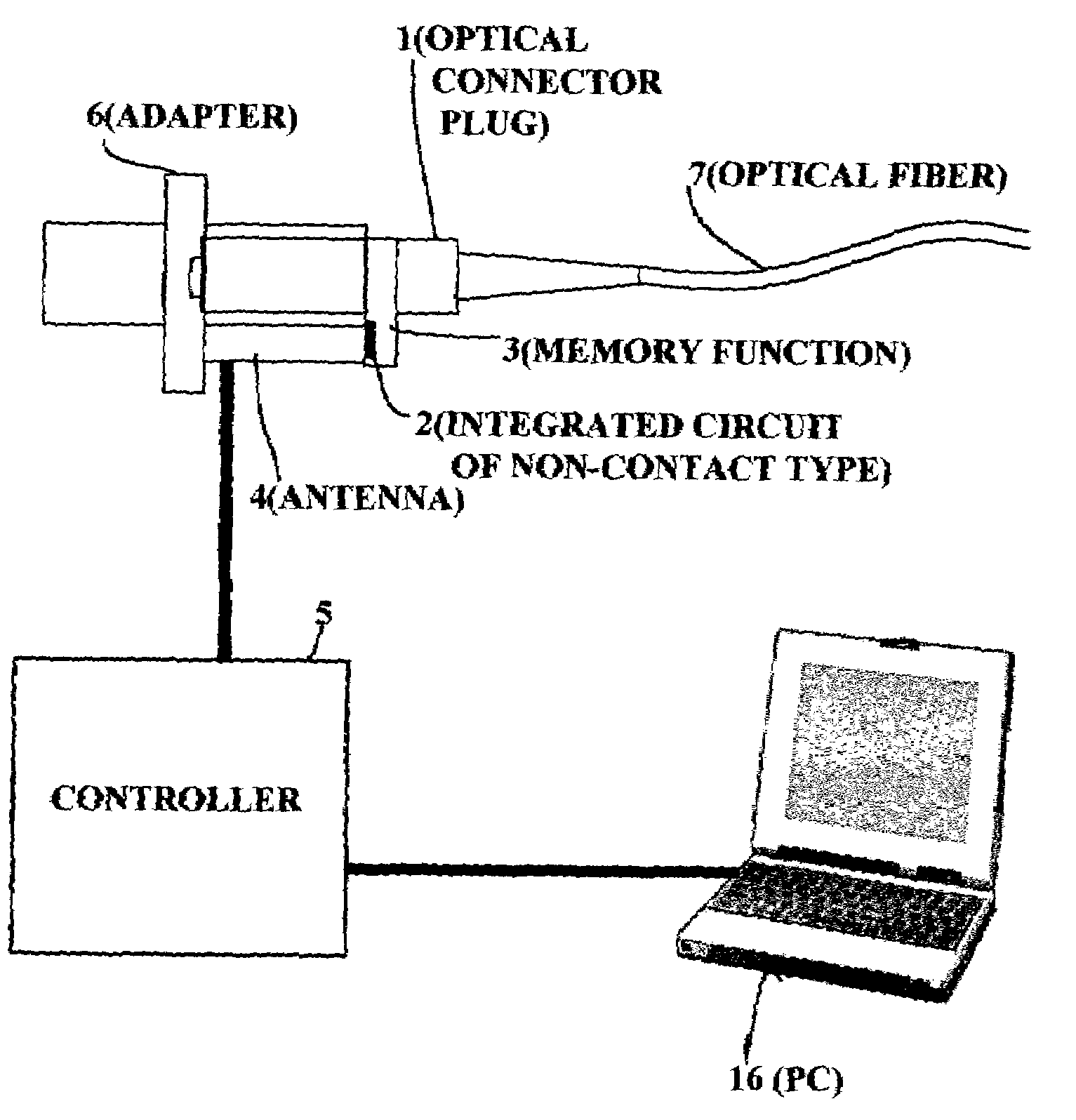

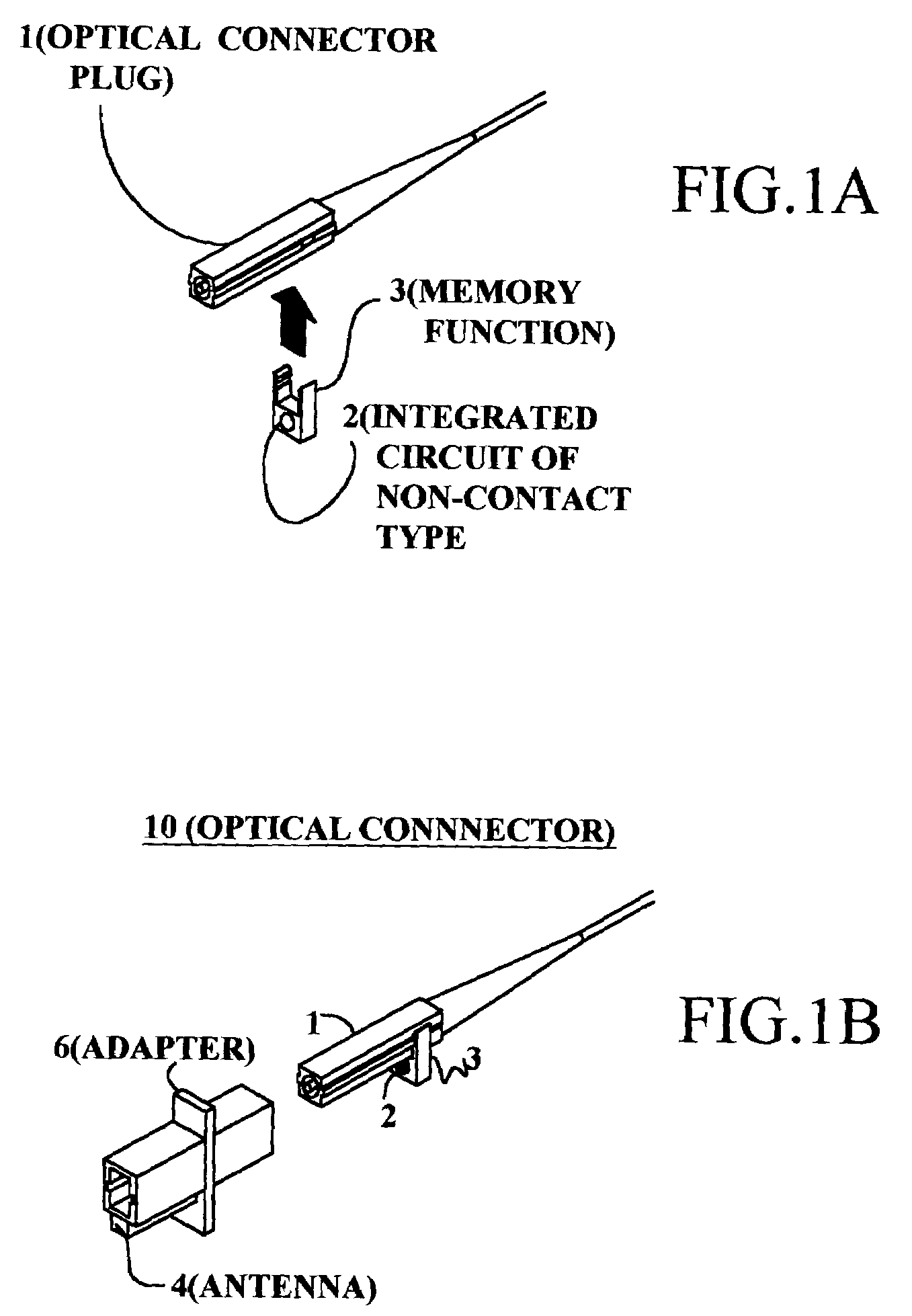

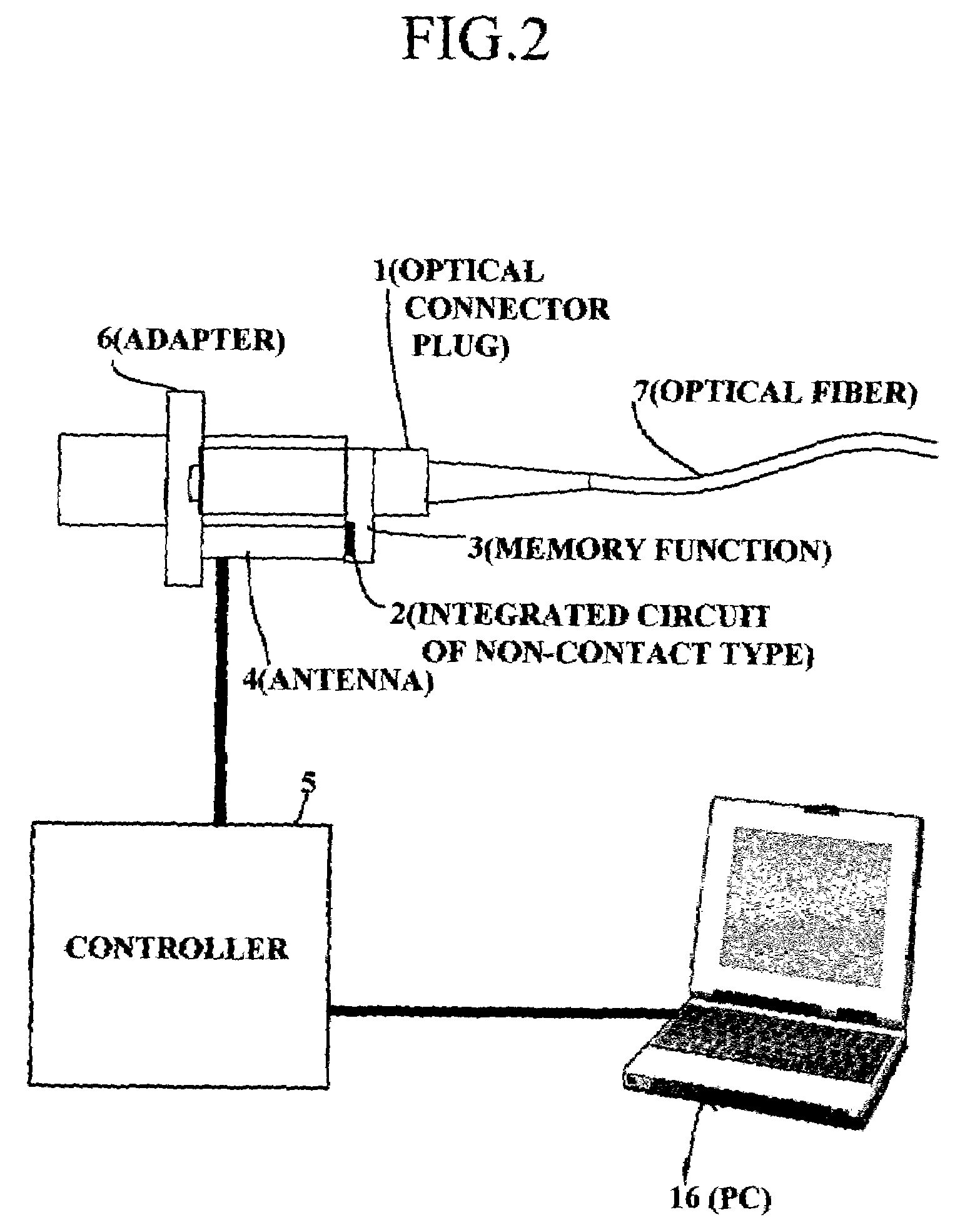

Optical connector with memory function

InactiveUS7210858B2Easy to moveSeparate controlCoupling light guidesRecord carriers used with machinesEngineeringMemory functions

An optical connector with memory function comprises memory function for storing respective identification information in order to readily and exactly perform separate control of respective control steps and further to obtain convenient handling of connectors. The optical connector with memory function 3 of the present invention is characterized by a memory function capable of untouchably performing, from outside thereof, writing-in and reading-out of necessary information. The memory function has a structure mounted on or mountable on the outer construction of a housing accommodating therein the optical connection portion of an optical connector plug in the optical connector with memory function.

Owner:TOKYO TSUSHINKI INDS

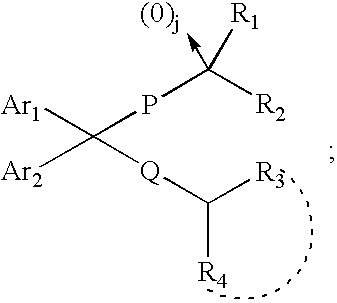

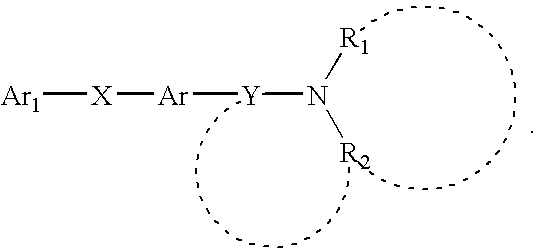

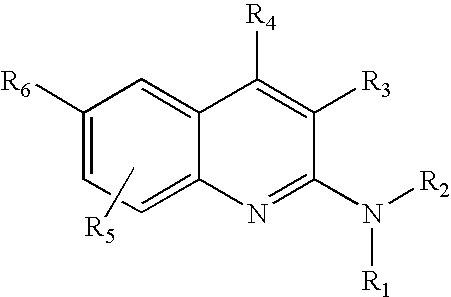

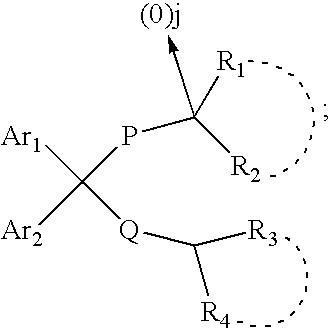

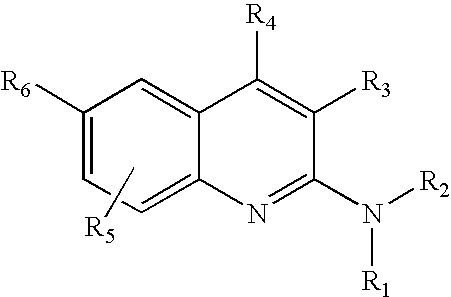

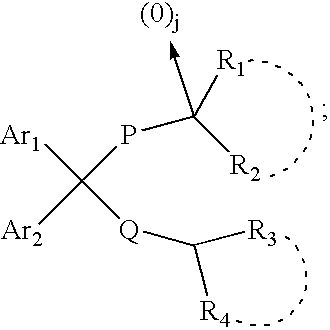

4-Aminoquinoline compounds

The present invention is concerned with compounds of the general Formula I: and pharmaceutically acceptable salts thereof, which are useful as melanin concentrating hormone receptor antagonists, particularly MCH-1R antagonists. As such, compounds of the present invention are useful for the treatment or prevention of obesity or eating disorders associated with excessive food intake and complications thereof, osteoarthritis, certain cancers, AIDS wasting, cachexia, frailty (particularly in elderly), mental disorders stress, cognitive disorders, sexual function, reproductive function, kidney function, locomotor disorders, attention deficit disorder (ADD), substance abuse disorders and dyskinesias, Huntington's disease, epilepsy, memory function, and spinal muscular atrophy. Compounds of formula I may therefore be used in the treatment of these conditions, and in the manufacture of a medicament useful in treating these conditions. Pharmaceutical formulations comprising one of the compounds of formula (I) as an active ingredient are disclosed, as are processes for preparing these compounds.

Owner:DEVITA ROBERT J +5

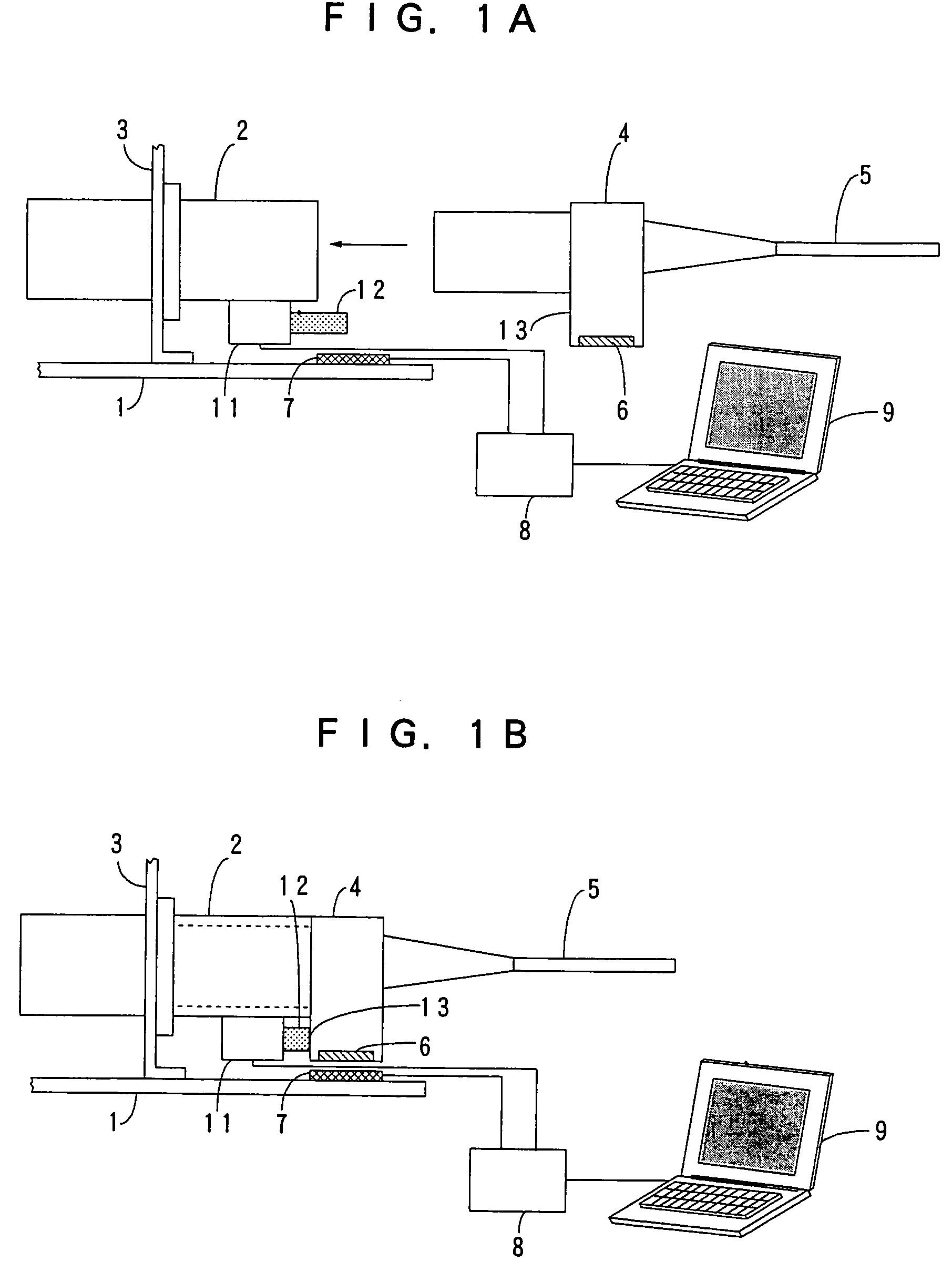

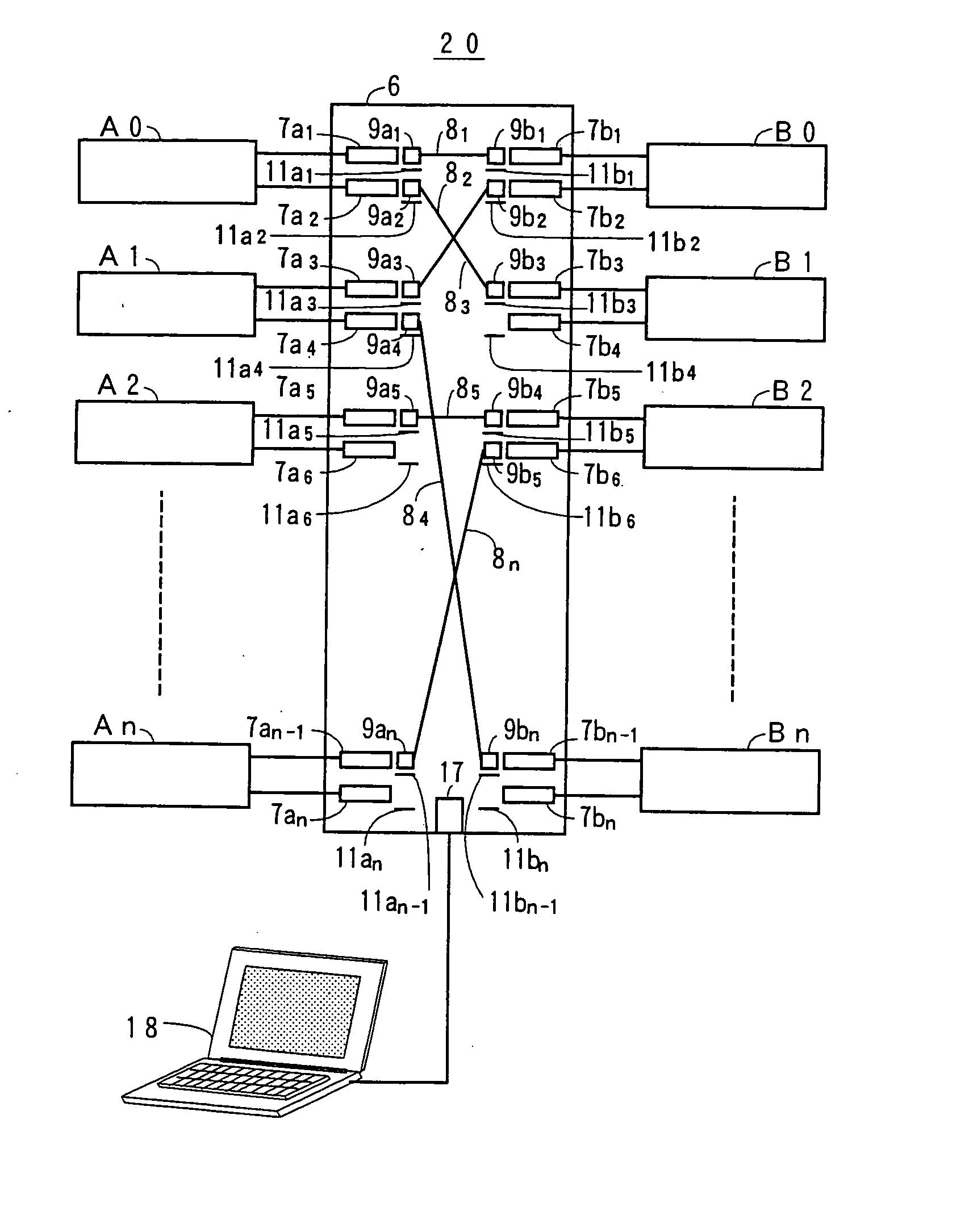

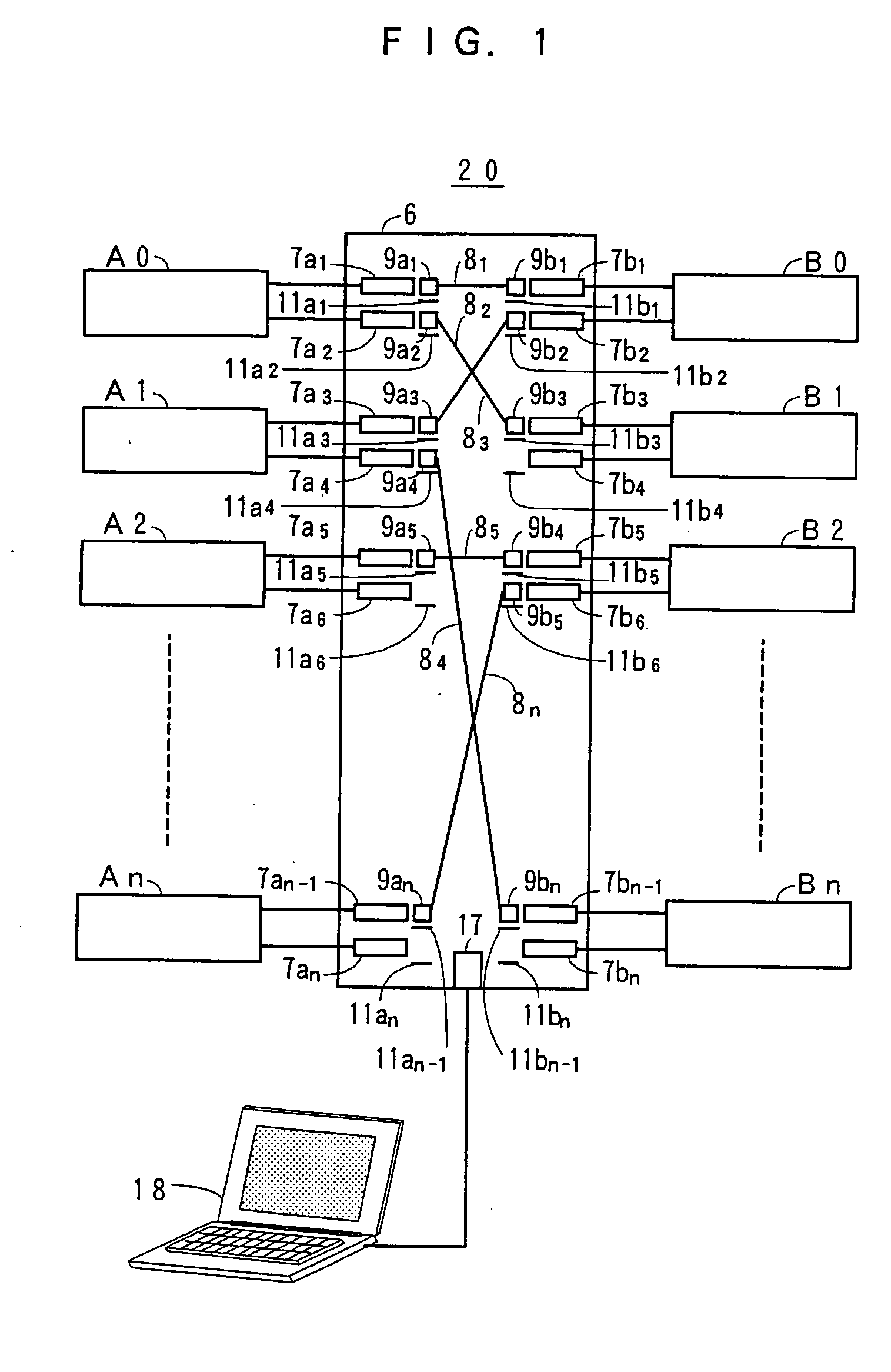

Distributing system

InactiveUS20040117515A1Incorrect coupling preventionCo-operative working arrangementsDisplay deviceEngineering

A distributing system 20, comprising: connection lines 3 to two ends of each of which connector plugs 9 with memory function unit 10 capable of untouchably performing, from the outside thereof, writing-in operation and reading-out operation of identification information of the same connector plugs are respectively connected; plug boards 6 mounted on the distributing system; adapters or receptacles 7, mounted separately on the plug boards and connected respectively to communication lines, for coupling to each of the connector plugs; antennas 11 positioned at the neighborhood of each of the adapters or receptacles for untouchably writing-in operation into and reading-out operation of the address information from the memory function unit when each of the connector plugs is coupled to desired one of the adapters or receptacles; and a data processing and display device 17,18, connected to the antennas, comprising memory means for storing a wiring table indicative of desired mutual relationship between said addresses information of said adapters or receptacles and said identification information of the connector plugs, and display means for displaying desired parts of information on the wiring table. The identification information of each of the connector plugs coupled to one of said adapters or receptacles specified from said mutual relationship is displayed on the display means and stored in the memory means.

Owner:TOKYO TSUSHINKI INDS +1

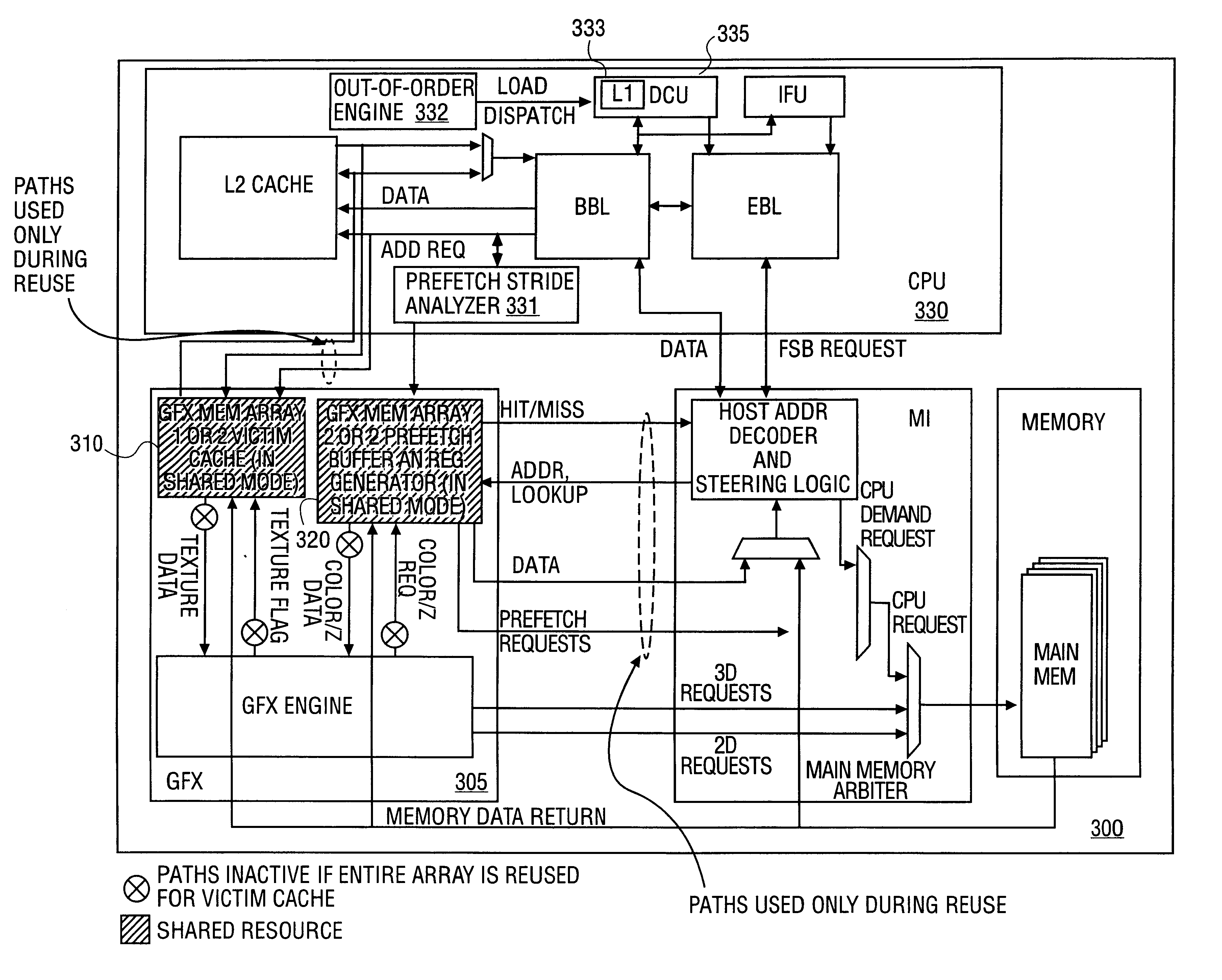

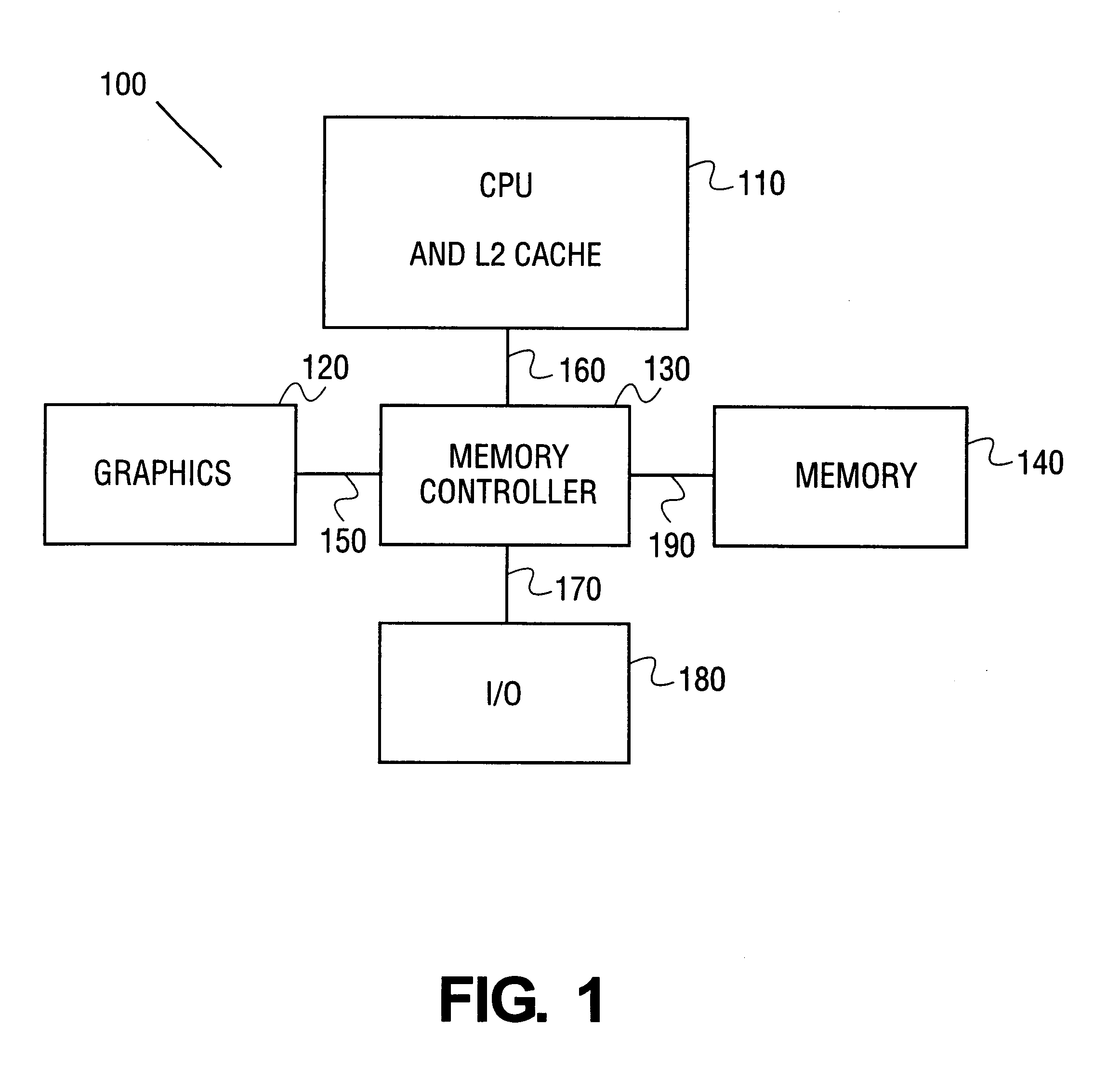

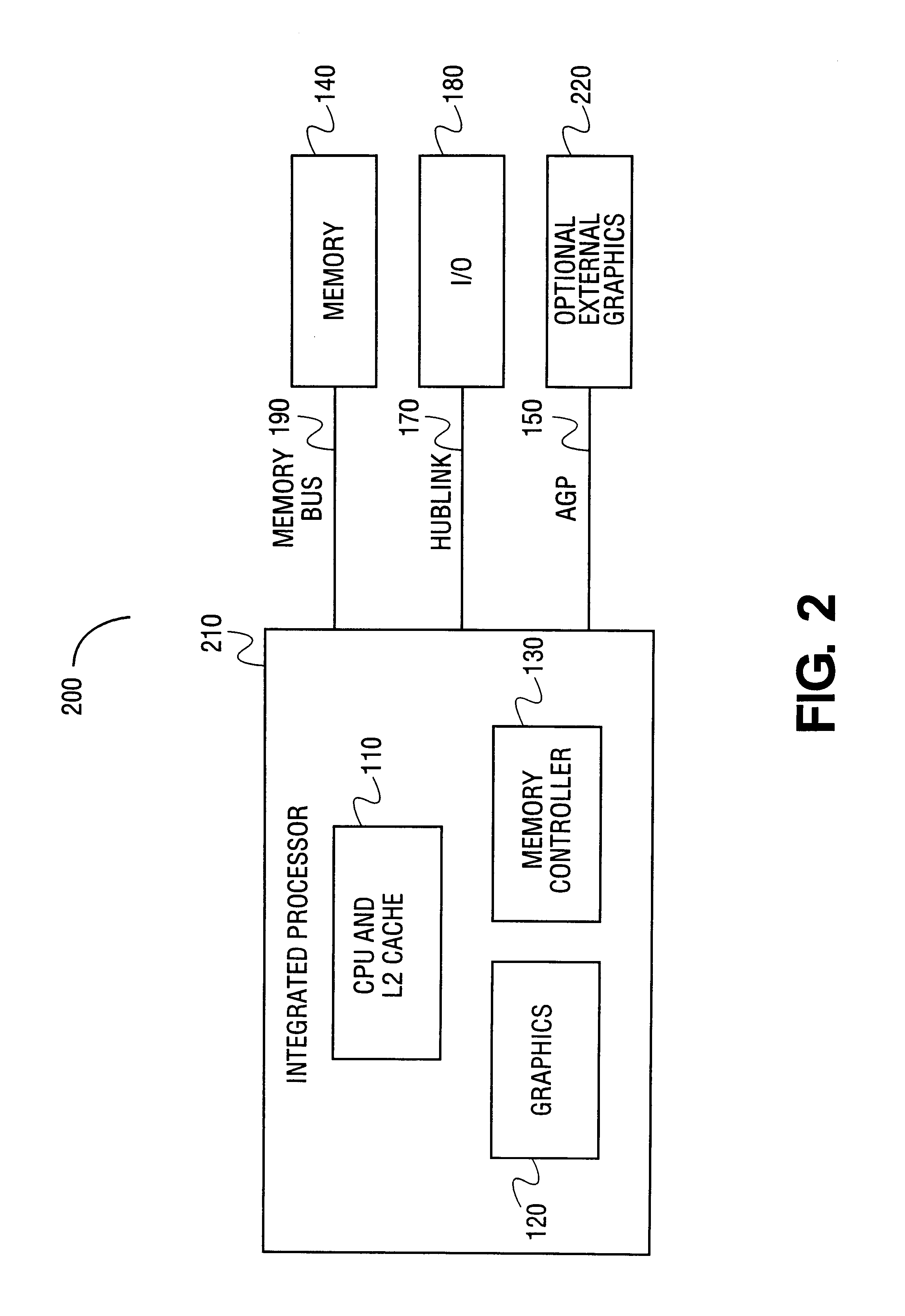

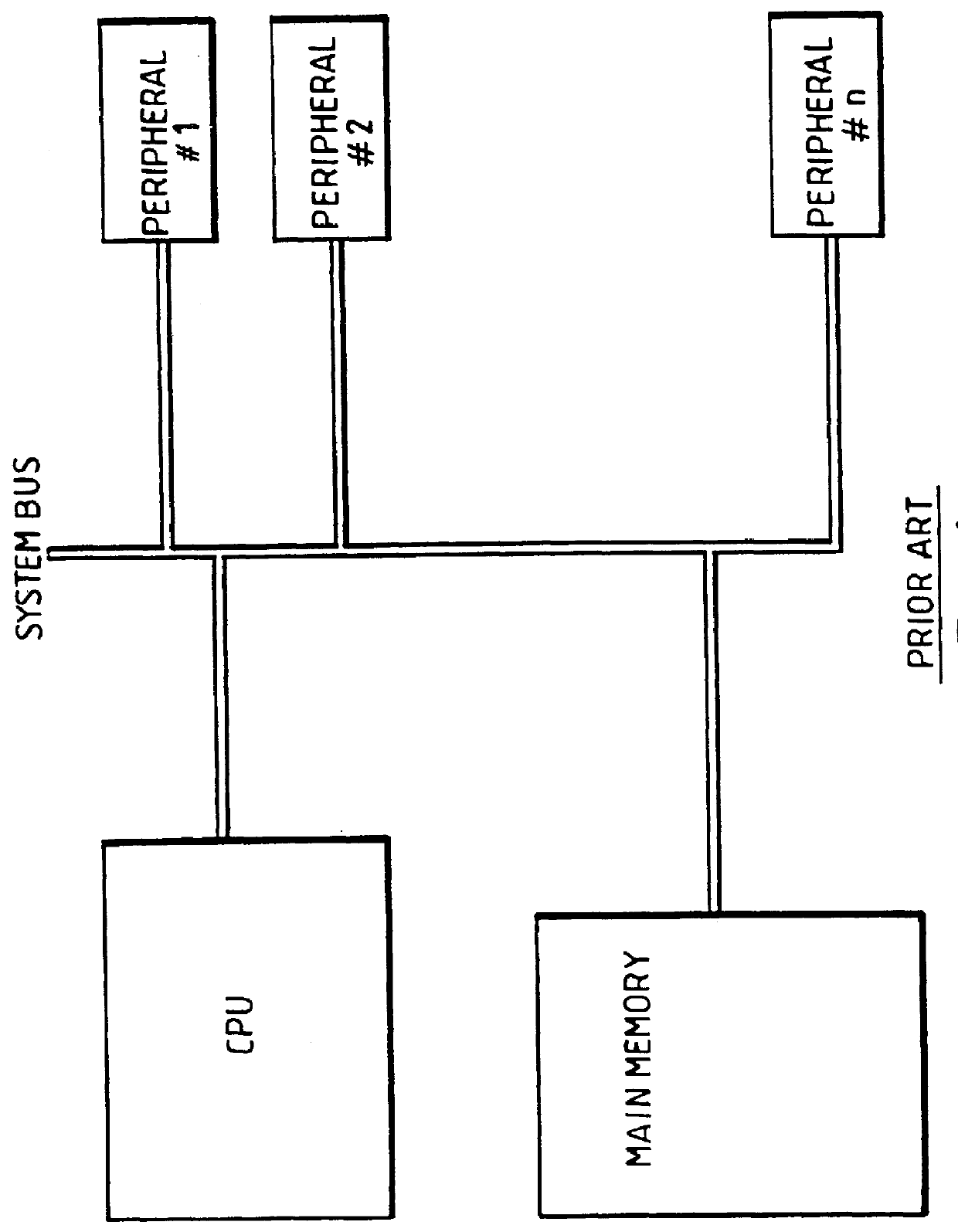

Opportunistic sharing of graphics resources to enhance CPU performance in an integrated microprocessor

InactiveUS6842180B1Memory architecture accessing/allocationMemory adressing/allocation/relocationGraphicsAddress decoder

An electronic device that has an integrated central processing unit (CPU) including a pre-fetch stride analyzer and an out-of-order engine is provided. The electronic device also has a graphics engine, having graphics memory, that is coupled to the integrated CPU. A main memory that is coupled to a memory controller is provided. The memory controller is also coupled to the CPU and the graphics engine. The device has a host address decoder coupled to the integrated CPU. A front side bus (FSB) is provided that is coupled to the integrated CPU and the host address decoder. Also provided is a plurality of memory components. Accordingly, either the plurality of memory components or the graphics memory can be shared to perform alternate memory functions. Additionally, a method is provided that determines allocation availability between memory components in an integrated computer processing unit. The method also shares an available memory component as a pre-fetch buffer and another available memory component as a victim cache.

Owner:INTEL CORP

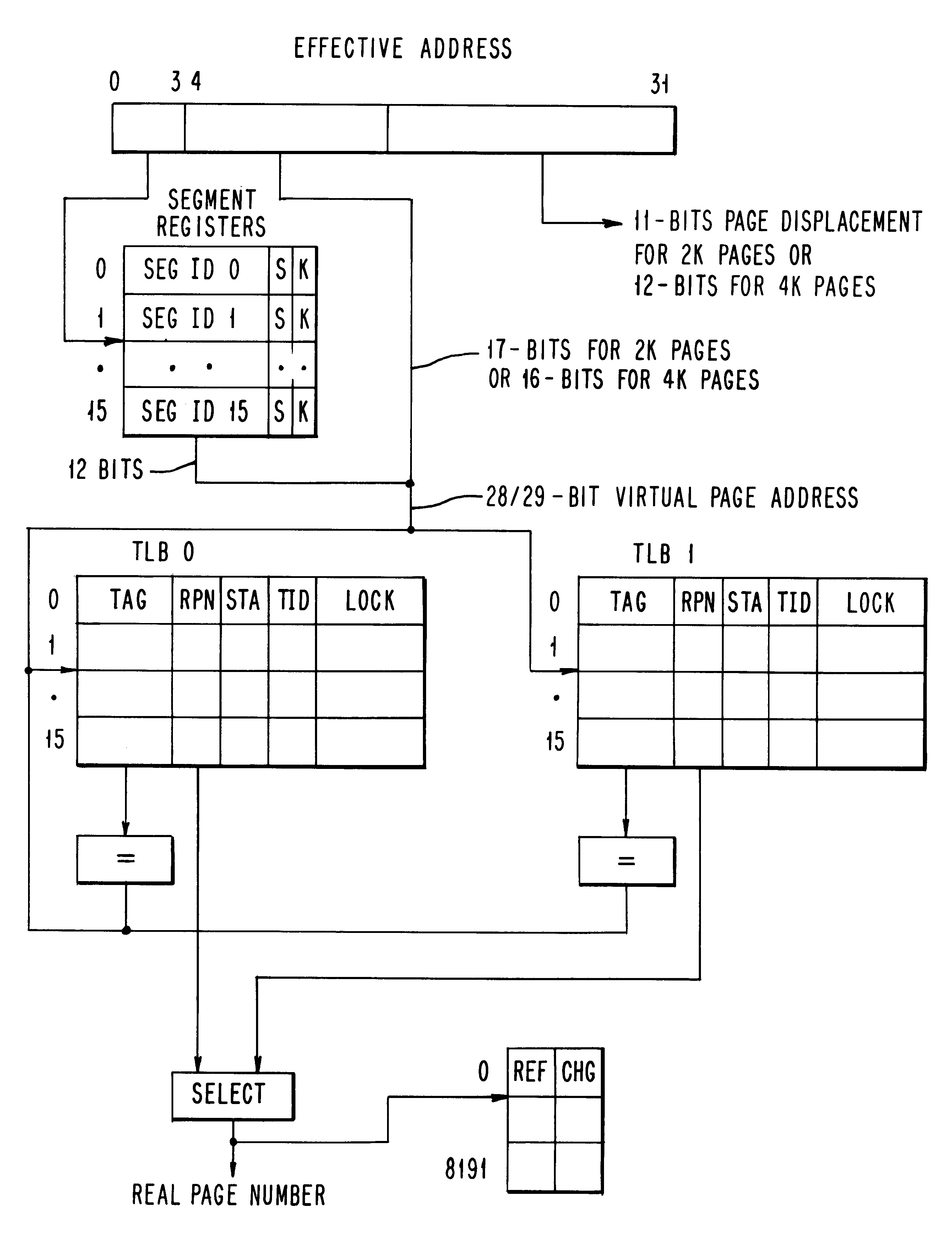

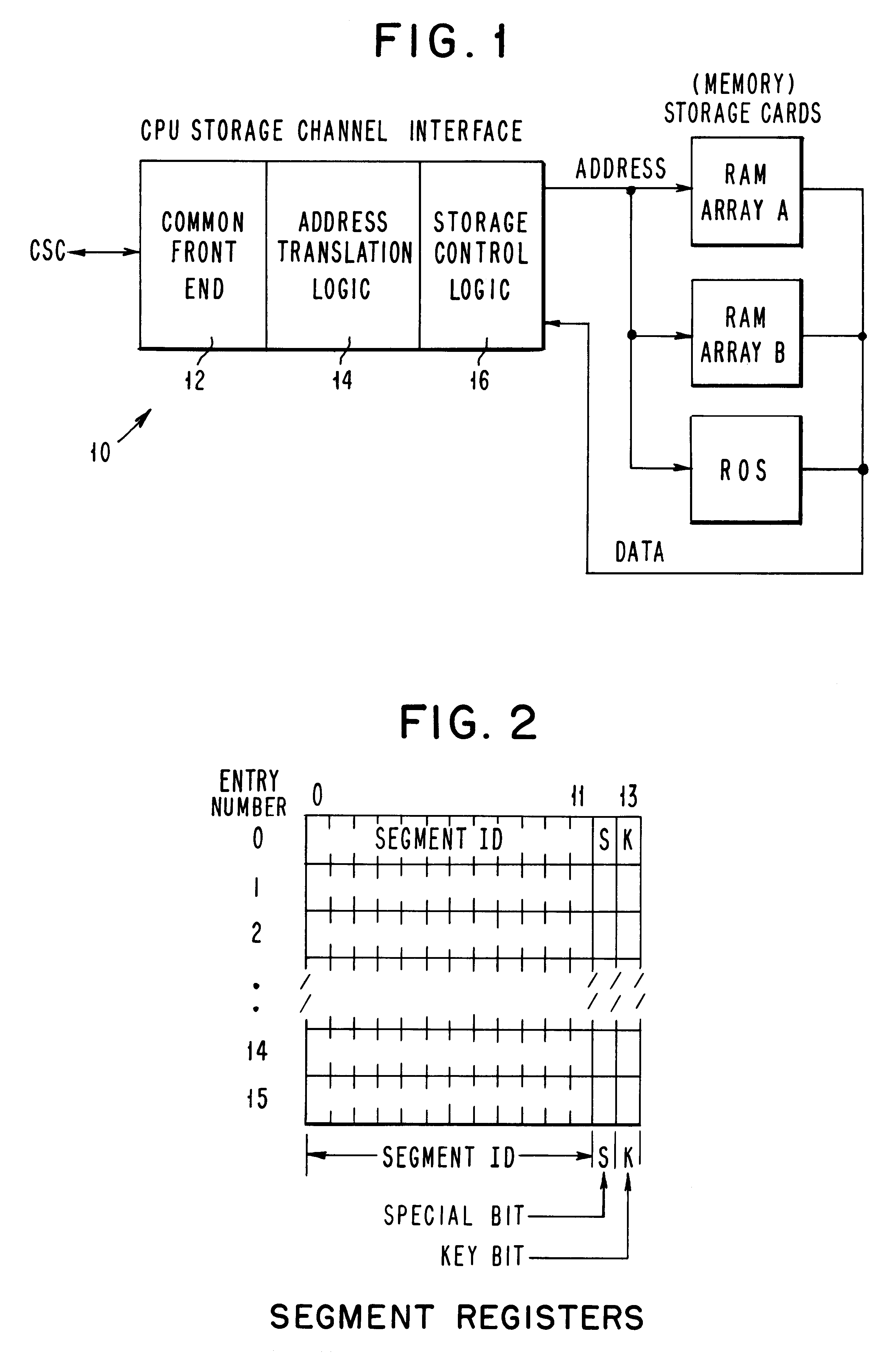

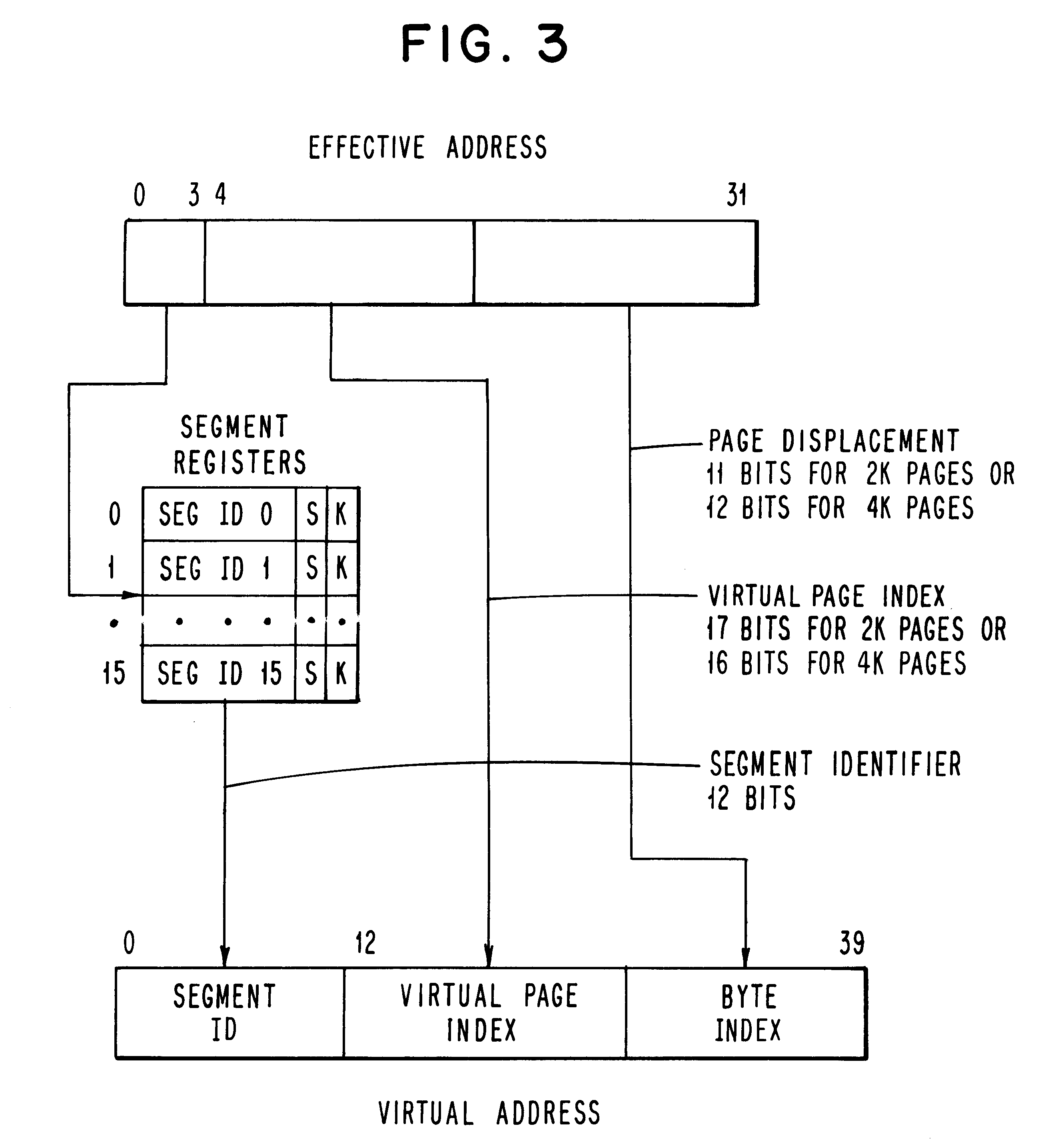

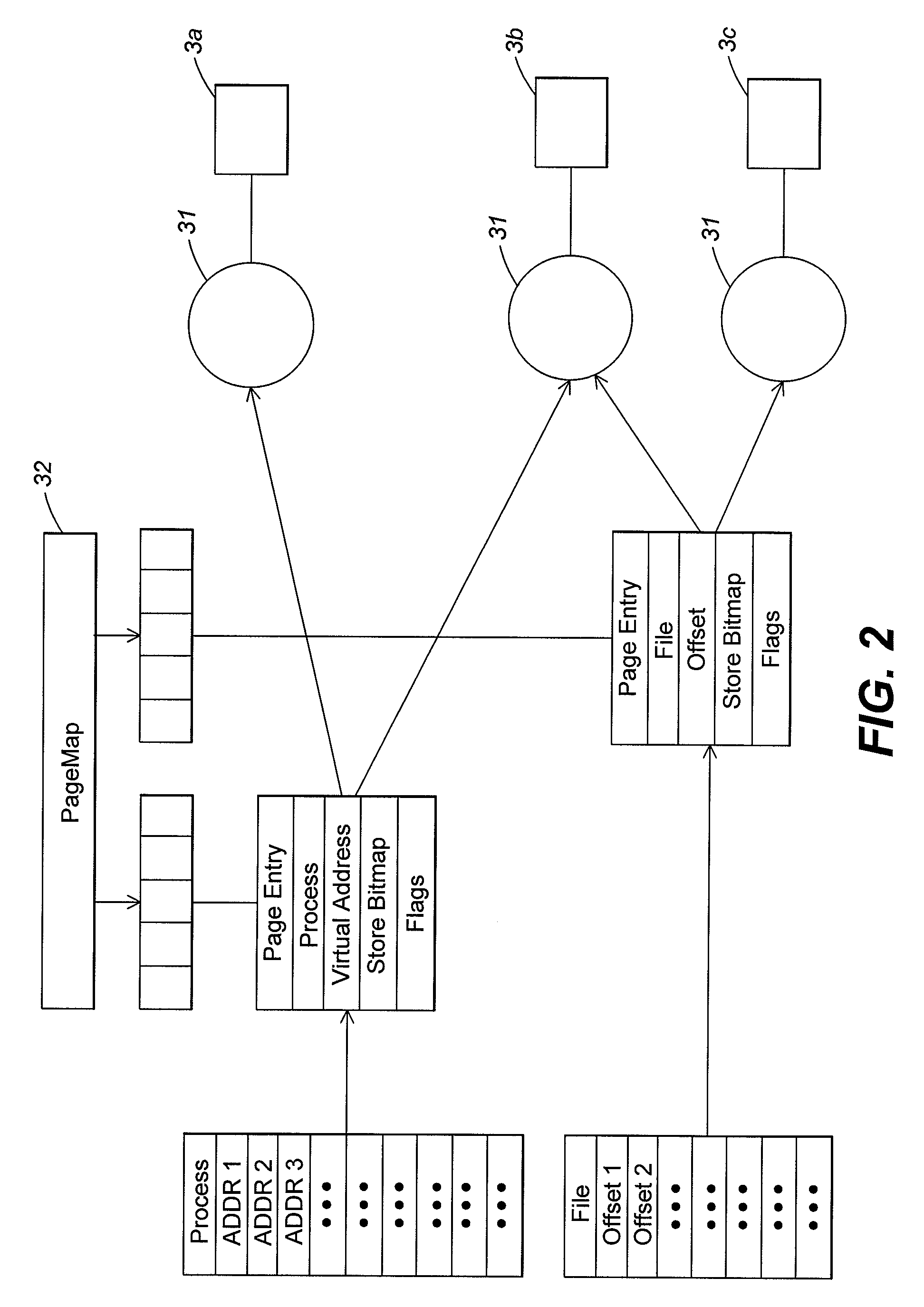

Virtual memory address translation mechanism with controlled data persistence

InactiveUSRE37305E1Less prone to errorFacilitates journallingMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressData field

A memory address translation and related control system for performing the dual functions of converting virtual memory addresses generated by the CPU into real memory addresses in a highly efficient and versatile manner and for controlling certain memory functions such as journalling. The address translation function comprises two steps, the first comprising converting the virtual address into a second virtual address or an effective address and finally the step of converting the effective address into a real memory address. The first step utilizes a set of special registers addressable by a small field to the CPU generated virtual address which converts the virtual address into an expanded form. The second or effective address is then used as the subject of the second or address translation step. To greatly enhance the translation of frequently used virtual addresses, a special set of translation tables referred to herein as a Translation Look-Aside, Buffer (TLB) contain current effective to real address translations for use where frequently referenced addresses are requested. The TLBs are addressed using a subset of the effective address whereupon the contents of the addressed TLB is examined for a match with the effective address. If the addresses match a successful address translation is possible and the real address stored in the address field of the TLB is available for system use. If the desired effective address is not present in the TLB, the page frame tables stored in main memory are accessed and searched for the desired effective address and if found the associated real address is accessed. Further a special data field is provided in both the TLBs and the page frame tables in main memory wherein a bit is provided for each line in the referenced page at a given effective to real address translation which bits may be used to indicate when a line of data has been accessed or altered.

Owner:IBM CORP

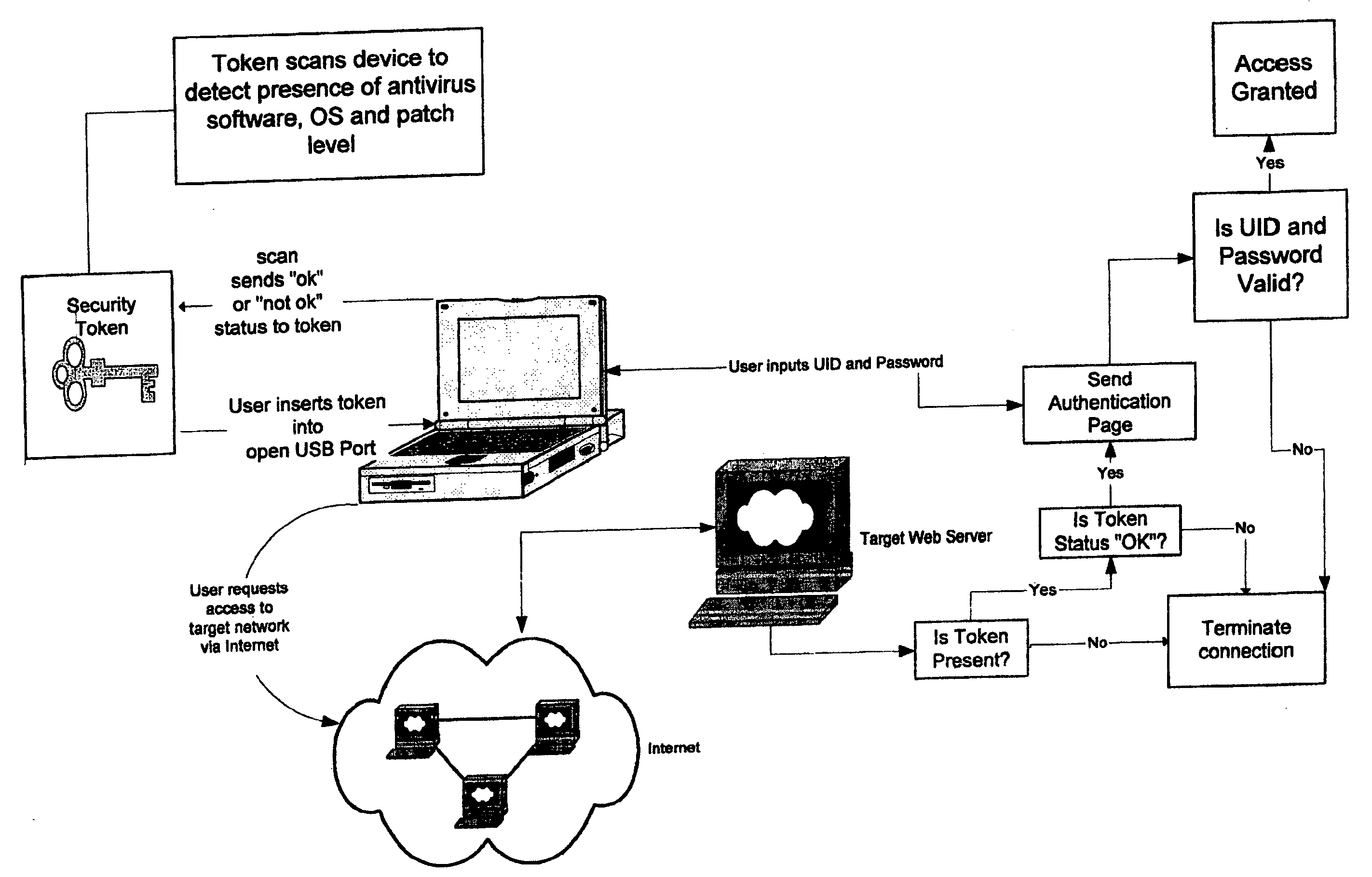

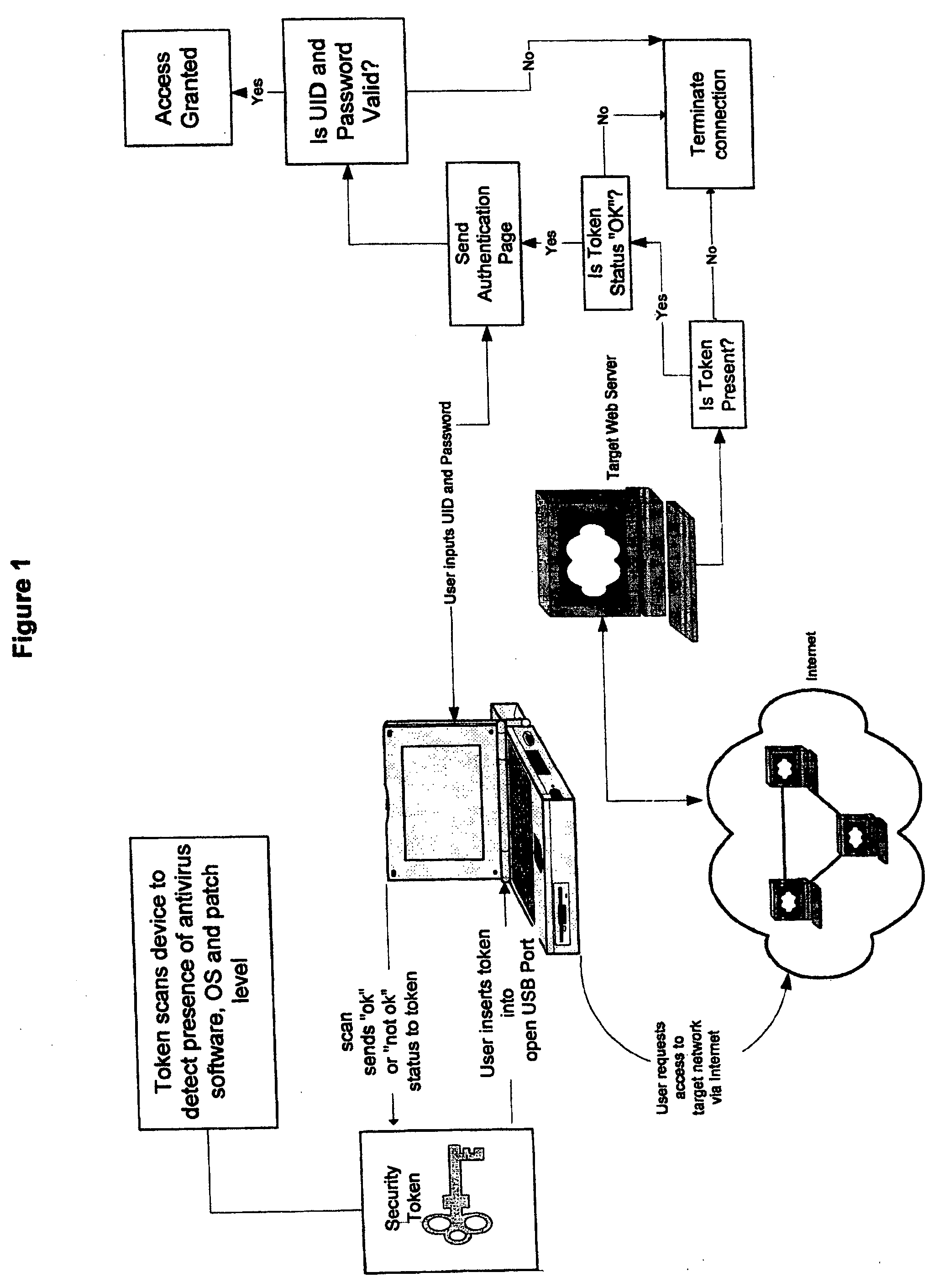

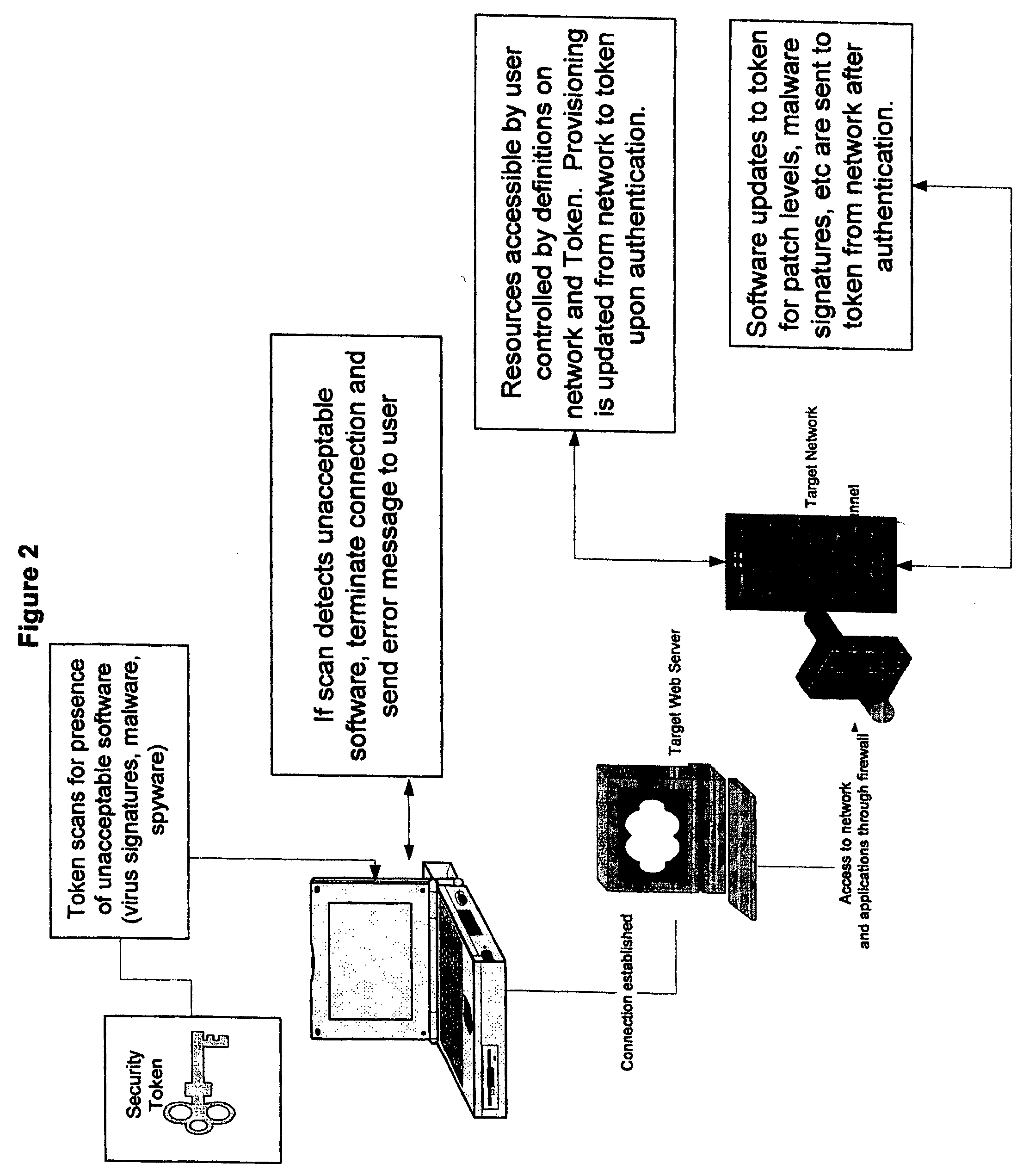

Personal network security token

InactiveUS20060168653A1Satisfies needDigital data processing detailsUser identity/authority verificationAnti virusOperational system

In general the present invention provides for a small hand held size device that is easily kept in a pocket or purse or on a key chain. The security token will contain a microprocessor having memory function and will connect to a PC or other computing device or workstation via a USB port. Upon insertion into the open USB port of the user's remote computer, the personal network security token scans the remote computer to detect the presence of at least one or more operating applications, such as the type of anti-virus software and patch level and / or the type of operating system (OS) the remote computer is running and the patch level. Upon contacting the target network, the network will send an inquiry to the user's remote computer to determine if the personal network security token is present as well as other parameters. If the condition status of the token is “OK” then the network sends an authentication page to the user for the user to enter his or her user ID and password. If the ID and password are valid, then the user is allowed access to the network.

Owner:CONTRERA SUZANNE HALL

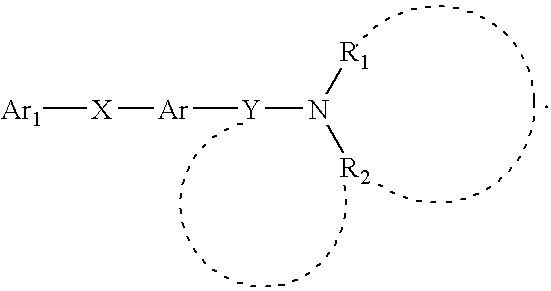

2-Aminoquinoline compounds

The present invention is concerned with compounds of the general Formula I: and pharmaceutically acceptable salts thereof, which are useful as melanin concentrating hormone receptor antagonists, particularly MCH-1R antagonists. As such, compounds of the present invention are useful for the treatment or prevention of obesity or eating disorders associated with excessive food intake and complications thereof, osteoarthritis, certain cancers, AIDS wasting, cachexia, frailty (particularly in elderly), mental disorders stress, cognitive disorders, sexual function, reproductive function, kidney function, locomotor disorders, attention deficit disorder (ADD), substance abuse disorders and dyskinesias, Huntington's disease, epilepsy, memory function, and spinal muscular atrophy. Compounds of formula I may therefore be used in the treatment of these conditions, and in the manufacture of a medicament useful in treating these conditions. Pharmaceutical formulations comprising one of the compounds of formula (I) as an active ingredient are disclosed, as are processes for preparing these compounds.

Owner:MERCK SHARP & DOHME CORP

Semiconductor memory device, page buffer resource assigning method and circuit therefor, computer system and mobile electronic device

InactiveUS7405974B2Readily scaled down in sizeReadily access page planeTransistorSolid-state devicesMode controlMobile electronics

A semiconductor memory device includes a page buffer circuit and an arrangement of memory elements each including: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion area provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member provided on both sides of the gate electrodes, having a function of storing electric charge. The page buffer circuit provides a common resource shared between a memory array controller and a user. The page buffer circuit has two planes containing random access memory arrays. The page buffer circuit also includes a mode control section to facilitate access to the planes over a main bus in user mode and access to the planes by the memory array controller in memory control mode.

Owner:SHARP KK

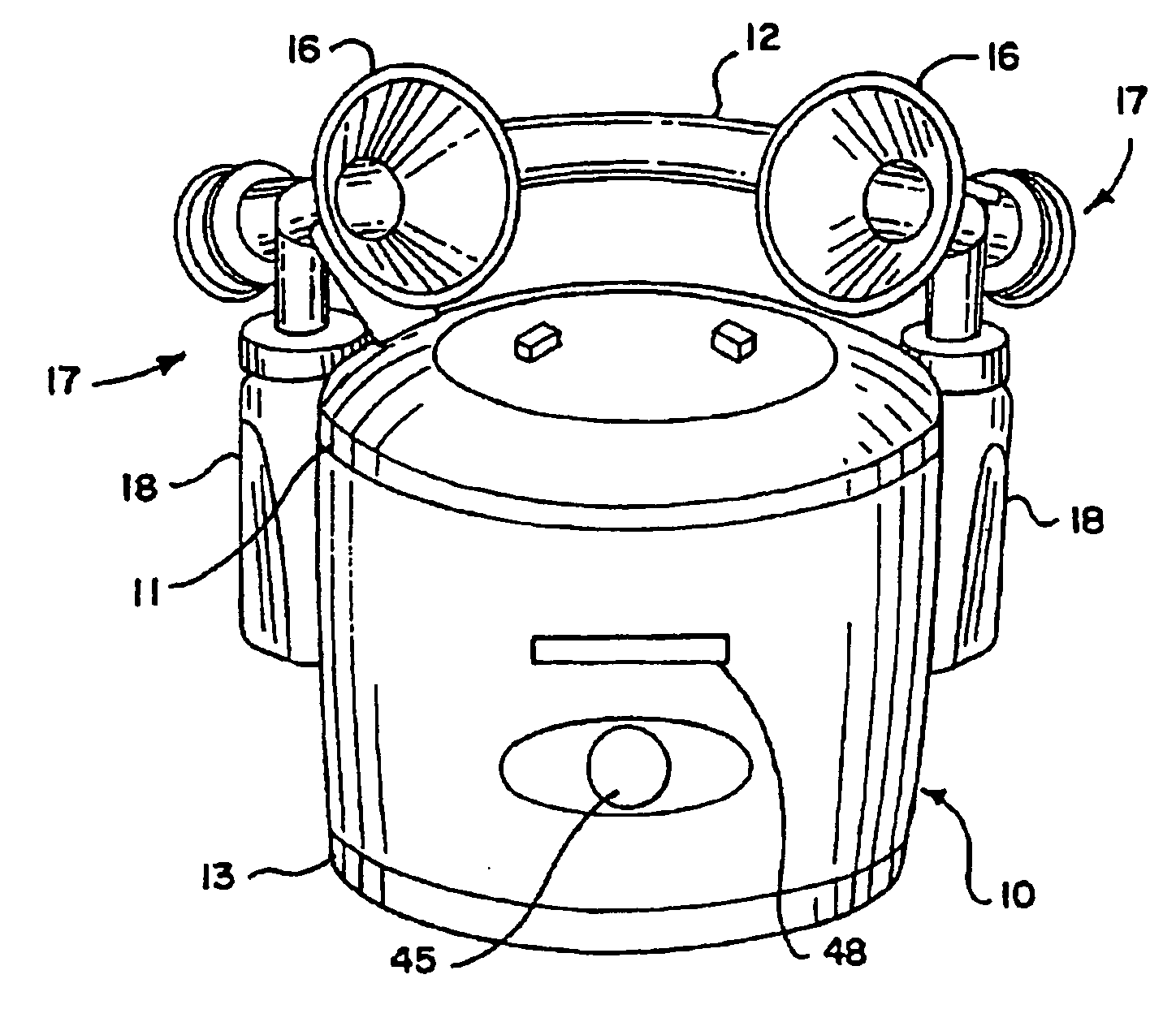

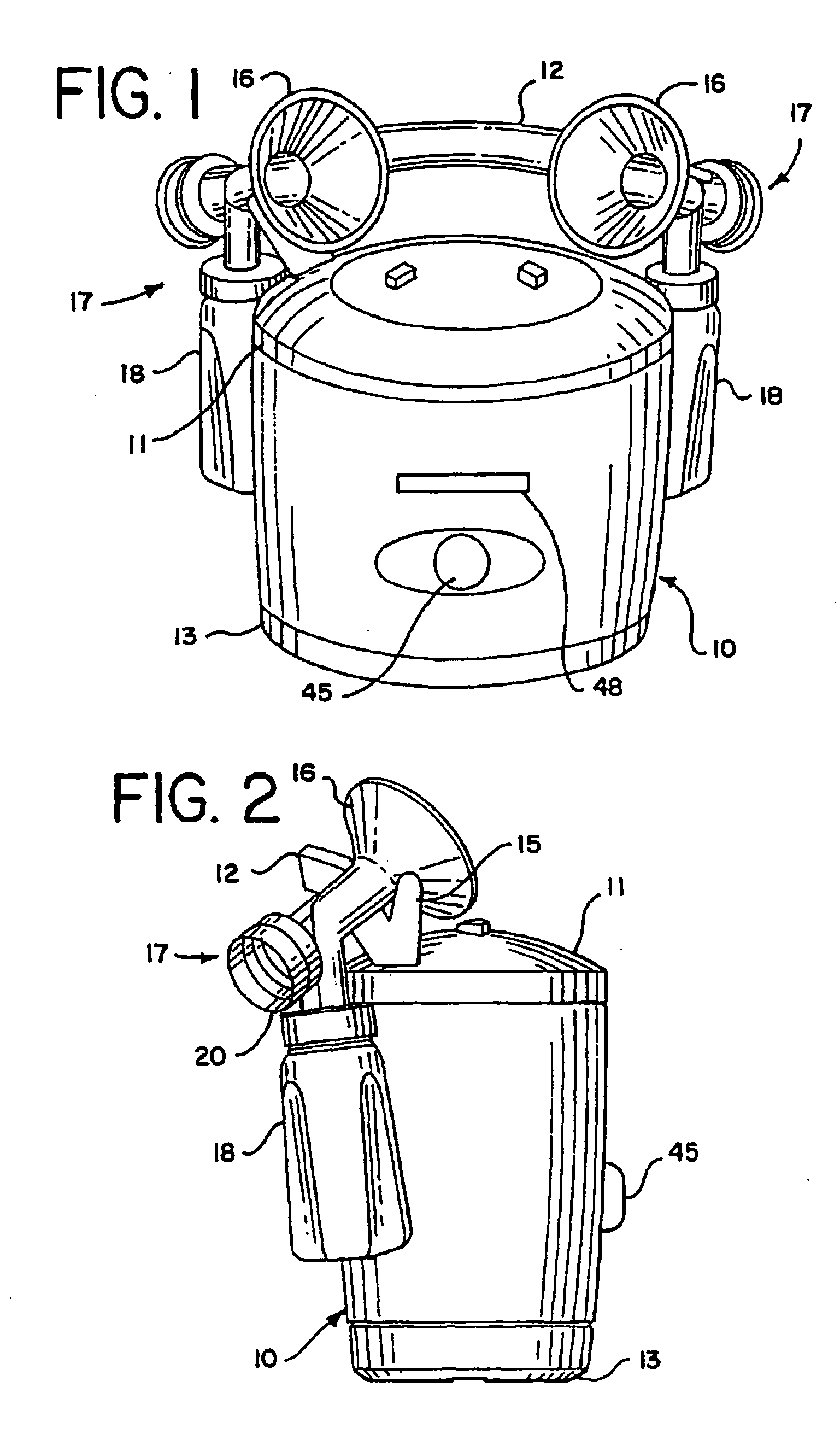

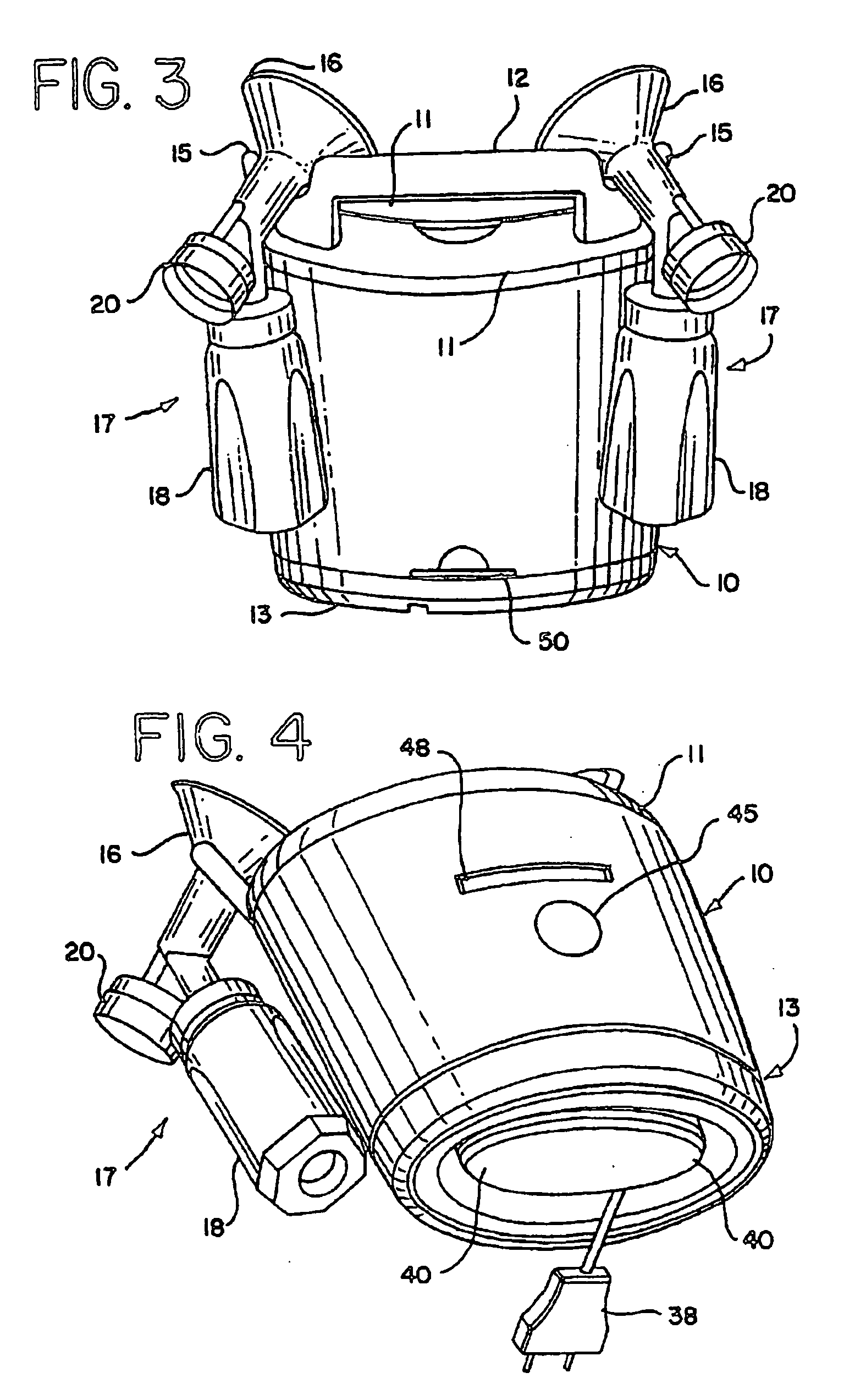

Memory function for a breastpump

InactiveUS20080045887A1Recorded dataImprove recallMilking pumpMedical devicesComputer scienceMemory functions

Owner:MEDELA HLDG AG

Multi-port internally cached DRAM system utilizing independent serial interfaces and buffers arbitratively connected under a dynamic configuration to allow access to a common internal bus

InactiveUS6108725AImprove system performanceLow costMemory adressing/allocation/relocationCathode-ray tube indicatorsGraphicsComputer architecture

A novel low cost / high performance multi-port internally cached dynamic random access memory architecture called 'AMPIC DRAM', and consequentially a unique system architecture which eliminates current serious system bandwidth limitations, providing a means to transfer blocks of data internal to the chip, orders of magnitude faster than the traditional approach, and with the chip also interconnecting significantly higher numbers of resources with substantially enhanced performance and at notably lower cost. Through use of a system configuration based on this novel architecture and working equally efficiently for both main memory functions and as graphics memory, thus providing a truly low cost, high performance unified memory architecture.

Owner:CHATTER MUKESH

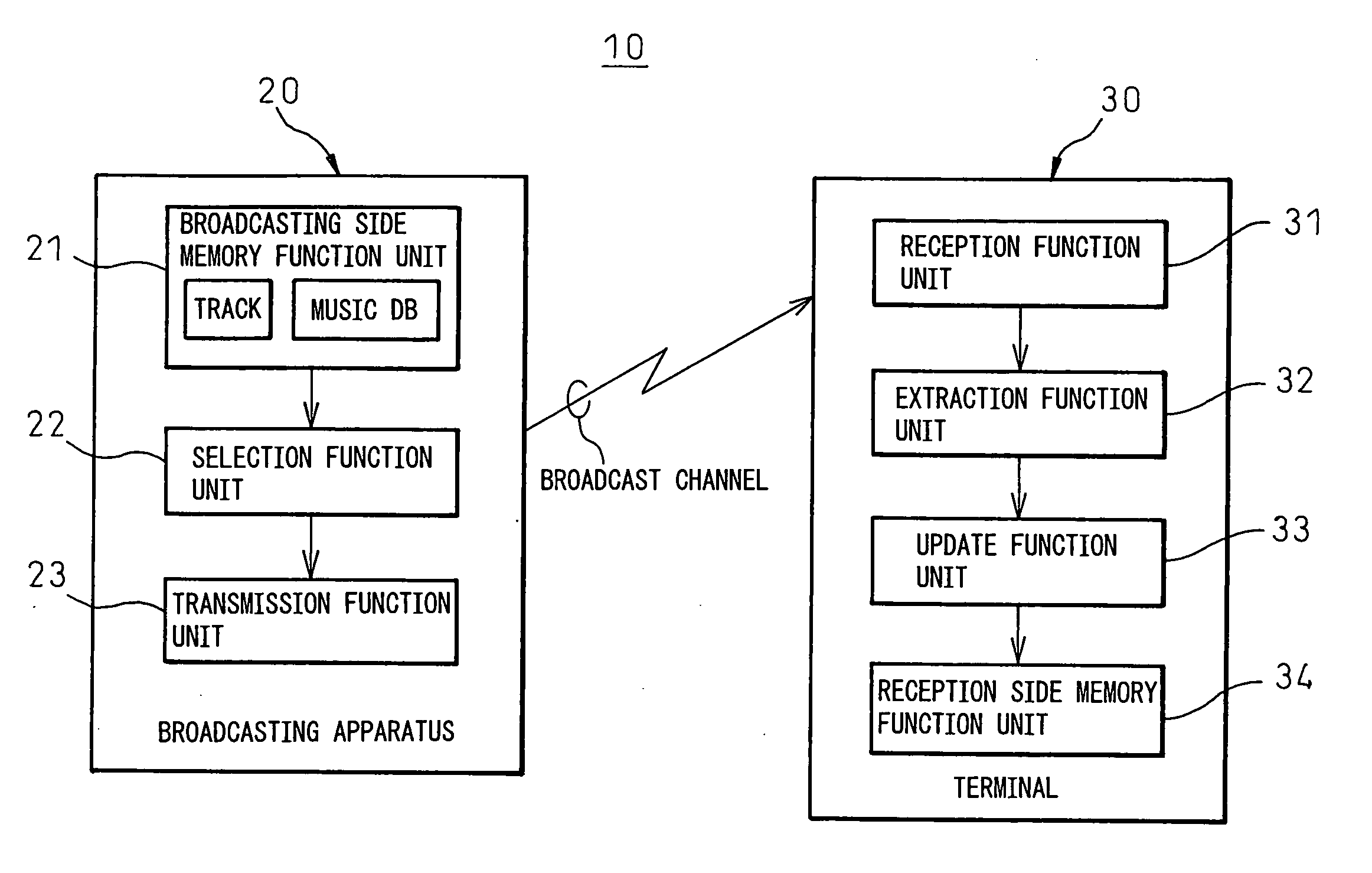

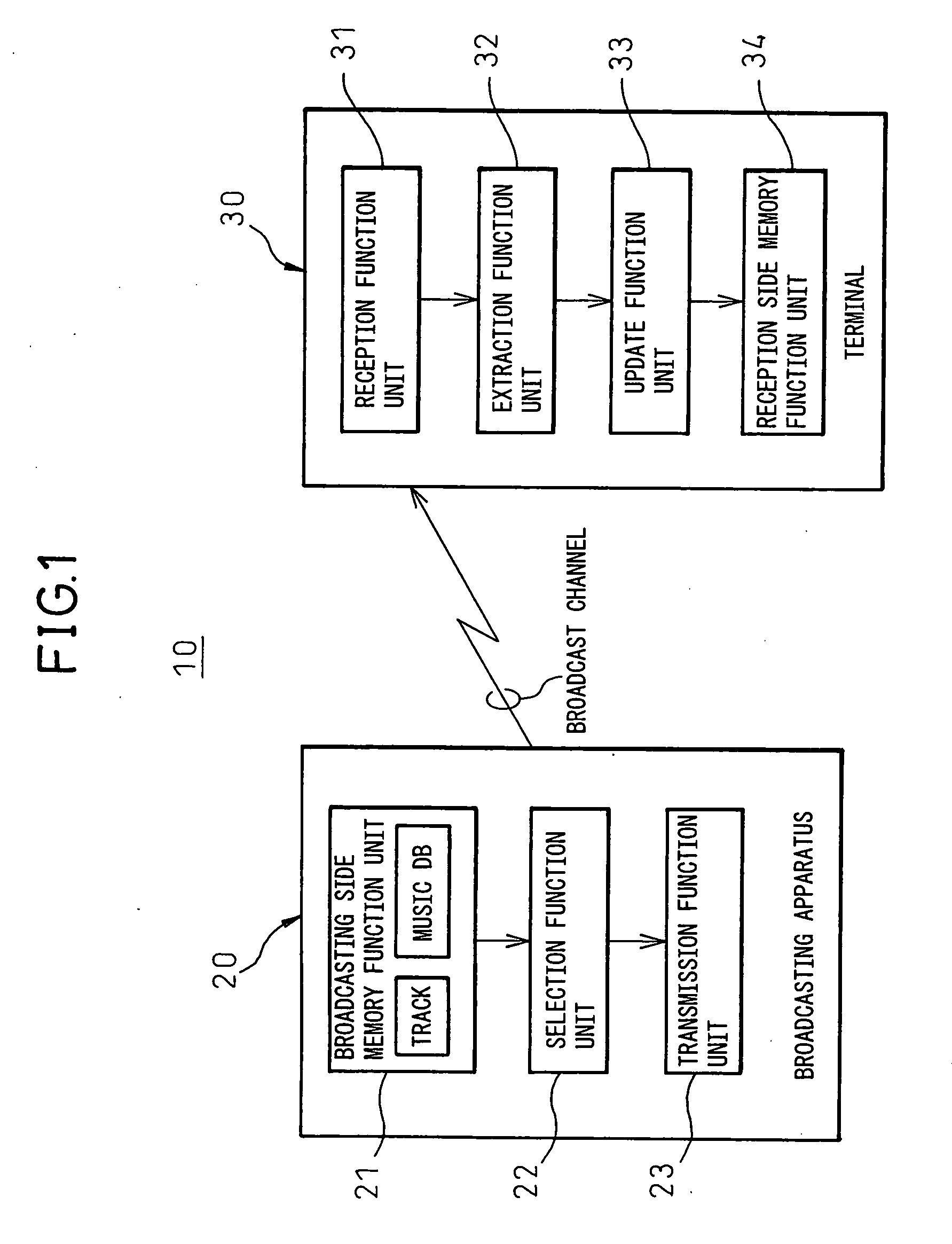

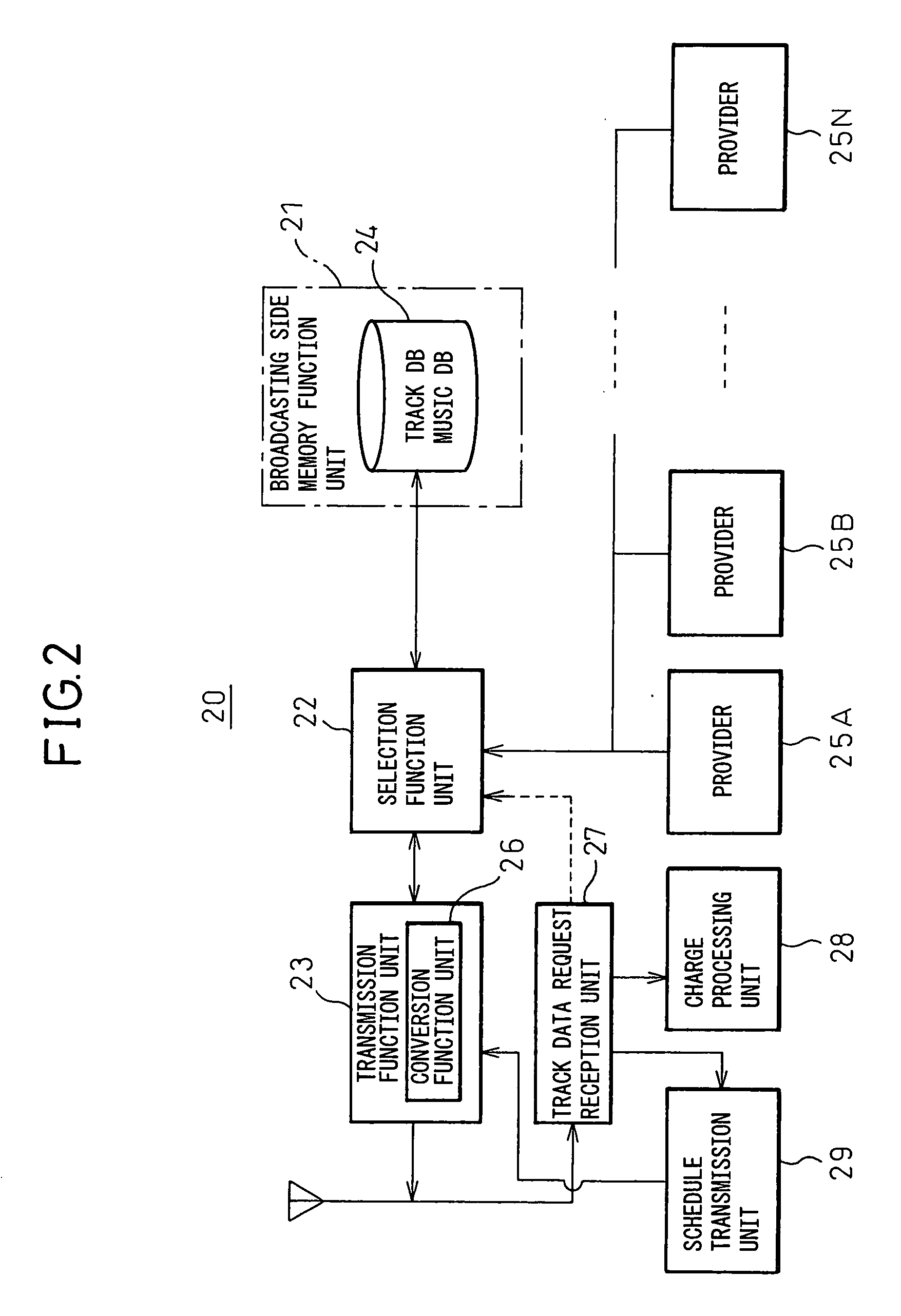

Music information,updating system, music information broadcasting apparatus, terminal apparatus having music information updating function, music information updating method, music information broadcasting method, and music information updating method of terminal apparatus

InactiveUS20060286951A1Without burdenSpecific information broadcast systemsBroadcast transmission systemsBroadcast channelsTerminal equipment

An updating system able to easily and cheaply update music information in a terminal having a memory function unit storing music information of track data and music database information. A broadcasting apparatus 20 is configured by a broadcasting side memory function unit 21 for storing music information including track data and music database information and a transmission function unit 23 for broadcasting the music information on a broadcast channel, and a terminal 30 is configured by a reception function unit 31 for receiving the broadcast wave thereof, an extraction function unit 32 for extracting the music information from the received broadcast wave, and an update function unit 33 for updating the information in the reception side memory function unit 34 with the extracted music information.

Owner:FUJITSU GENERAL LTD

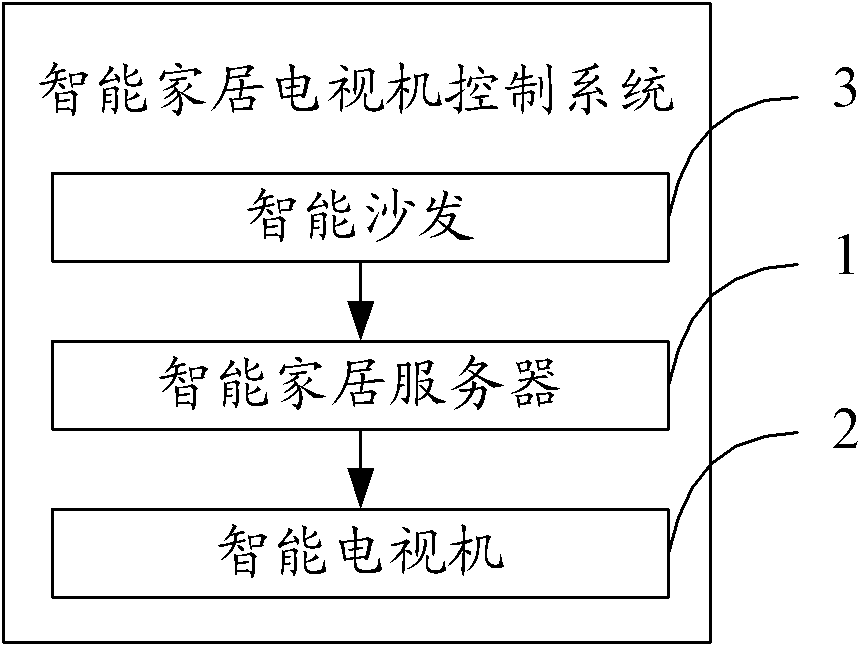

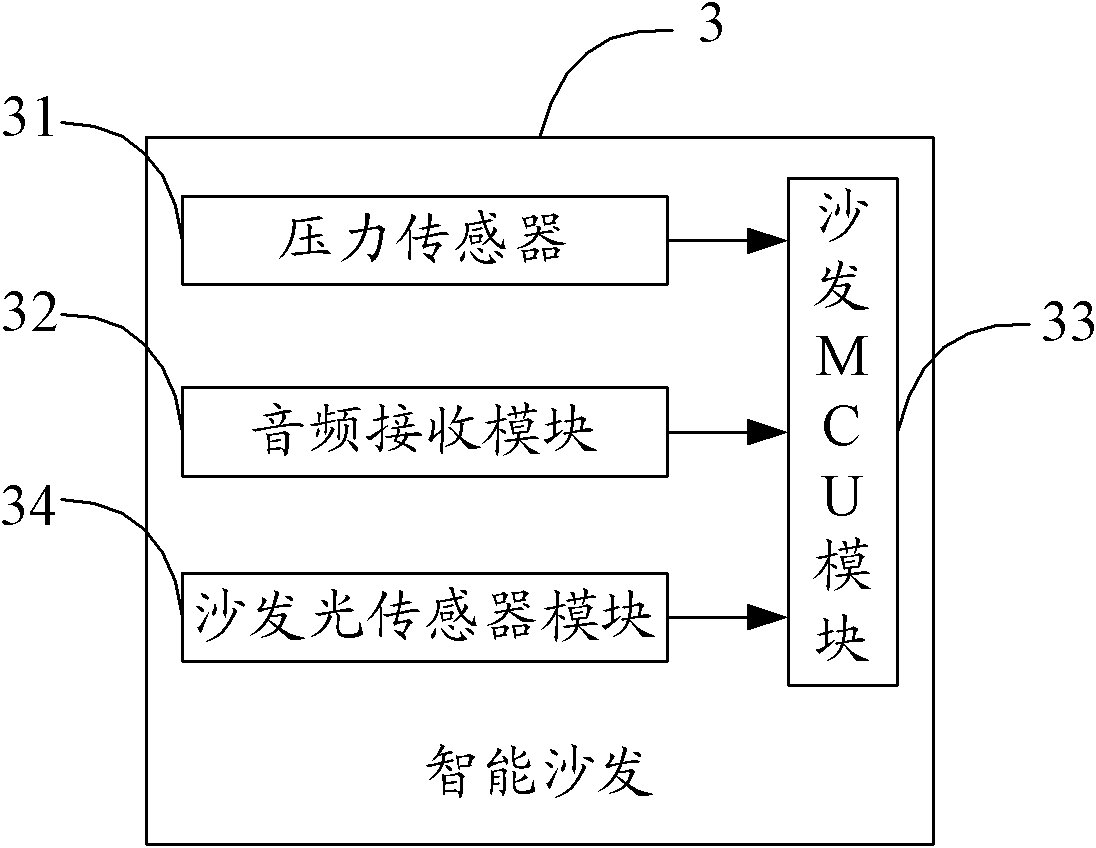

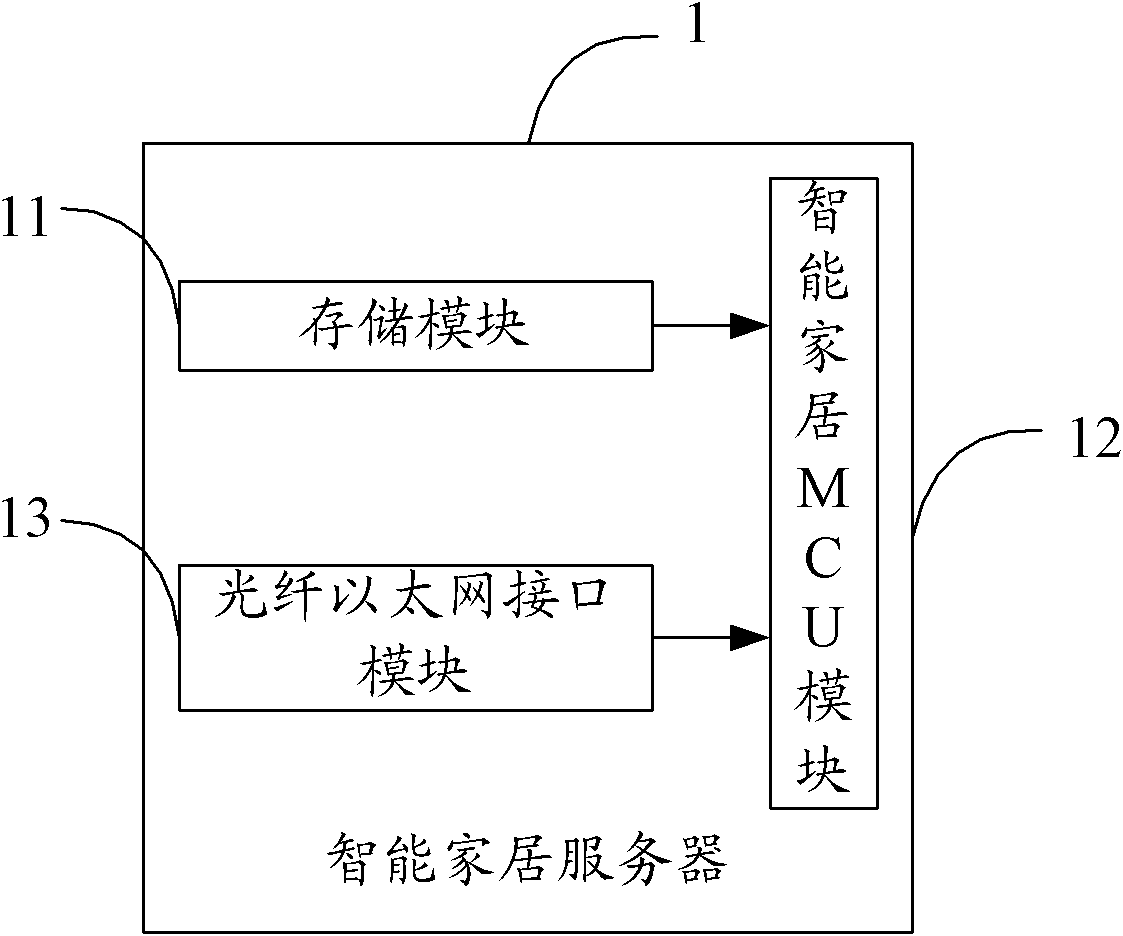

Intelligent household television control system and method thereof

ActiveCN102523401AImprove experienceImprove comfortTelevision system detailsNon-electrical signal transmission systemsAutomatic controlControl system

The invention relates to an intelligent household television control system and a method thereof. The intelligent household television control system comprises an intelligent household server, an intelligent television and an intelligent sofa facing the intelligent television. The intelligent sofa acquires information of a user side, the intelligent household server transmits television operation commands to the intelligent television according to results of matching and judging information of the user side and local-storage reference information, the intelligent television can be turned on and off, or relative parameters, such as volume and channels and the like can be adjusted according to the television operation commands. A user does not need to operate the television by hands, can control on and off of the television and adjust volume and brightness and the like automatically by patting the sofa or speaking and the like. Besides, the intelligent household television control system has study and memory functions and can record favorite programs of different users and television set parameters, such as brightness, volume and the like, so that favorite parameters or television programs of the users can be adjusted automatically, user experience is improved greatly, comfortableness of user watching the television is improved and energy sources are saved simultaneously.

Owner:SHENZHEN TCL NEW-TECH CO LTD

2-Aminoquinoline compounds

The present invention is concerned with compounds of the general Formula I:and pharmaceutically acceptable salts thereof, which are useful as melanin concentrating hormone receptor antagonists, particularly MCH-1R antagonists. As such, compounds of the present invention are useful for the treatment or prevention of obesity or eating disorders associated with excessive food intake and complications thereof, osteoarthritis, certain cancers, AIDS wasting, cachexia, frailty (particularly in elderly), mental disorders stress, cognitive disorders, sexual function, reproductive function, kidney function, locomotor disorders, attention deficit disorder (ADD), substance abuse disorders and dyskinesias, Huntington's disease, epilepsy, memory function, and spinal muscular atrophy. Compounds of formula I may therefore be used in the treatment of these conditions, and in the manufacture of a medicament useful in treating these conditions. Pharmaceutical formulations comprising one of the compounds of formula (I) as an active ingredient are disclosed, as are processes for preparing these compounds.

Owner:MERCK SHARP & DOHME CORP

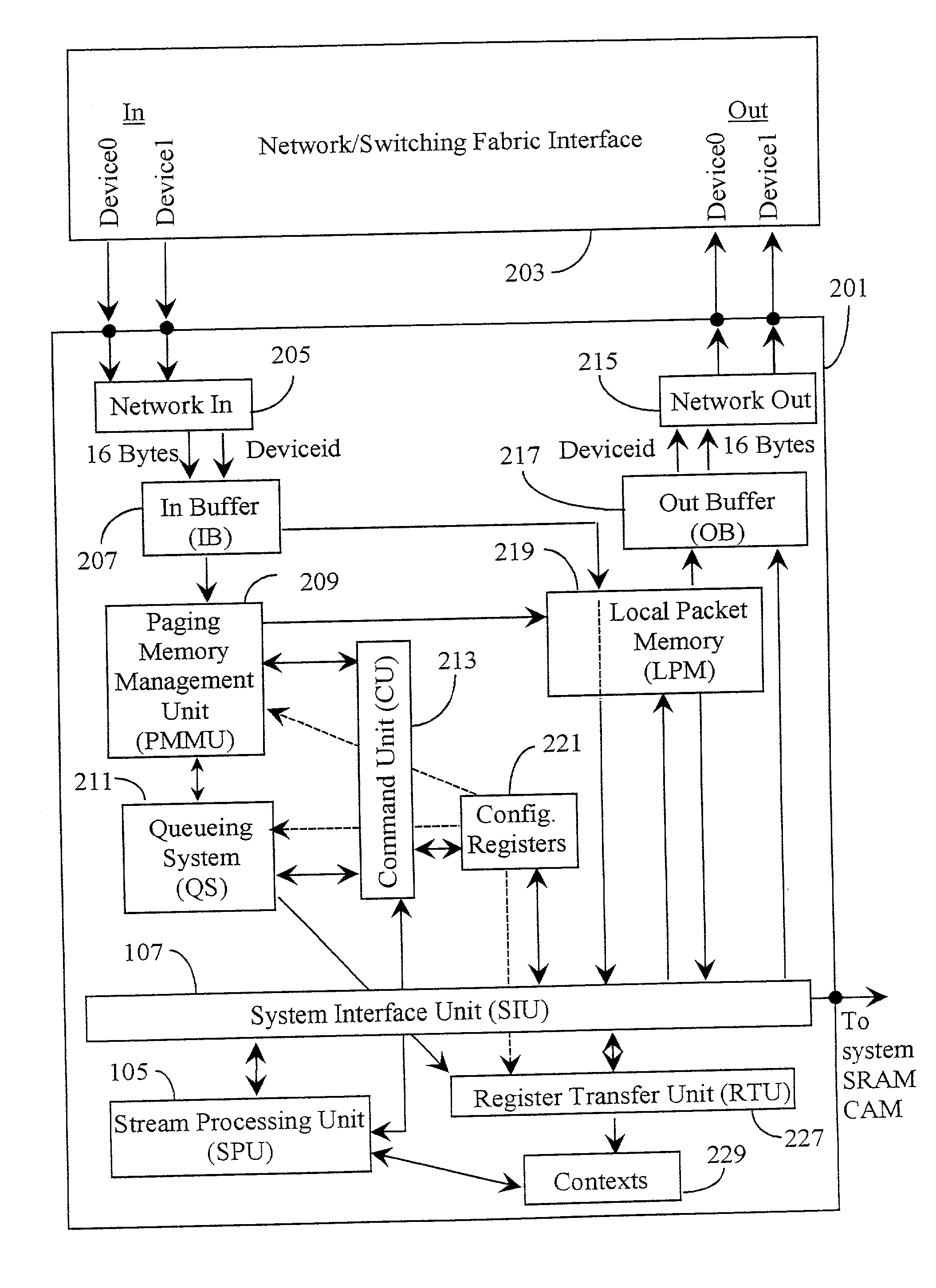

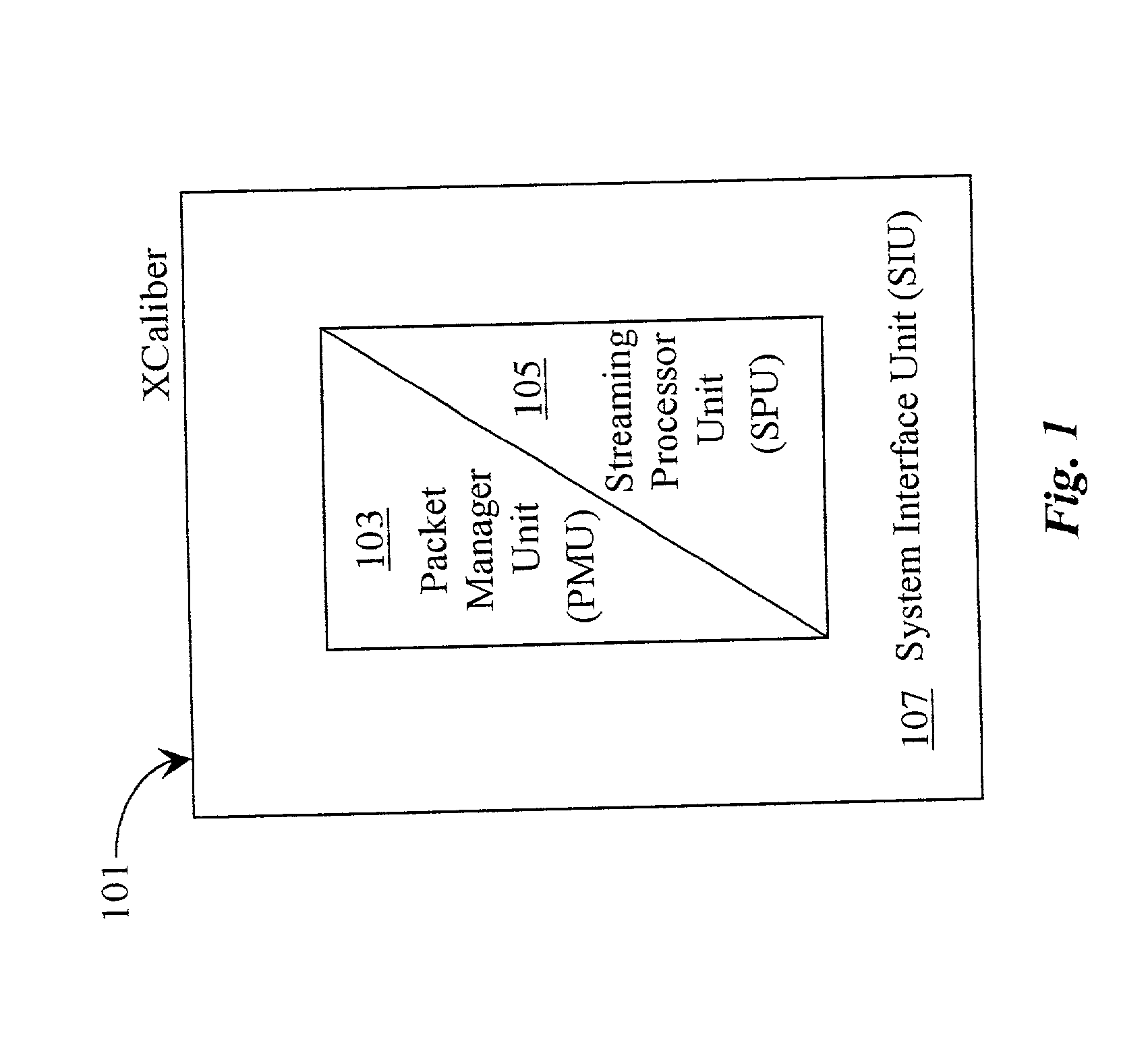

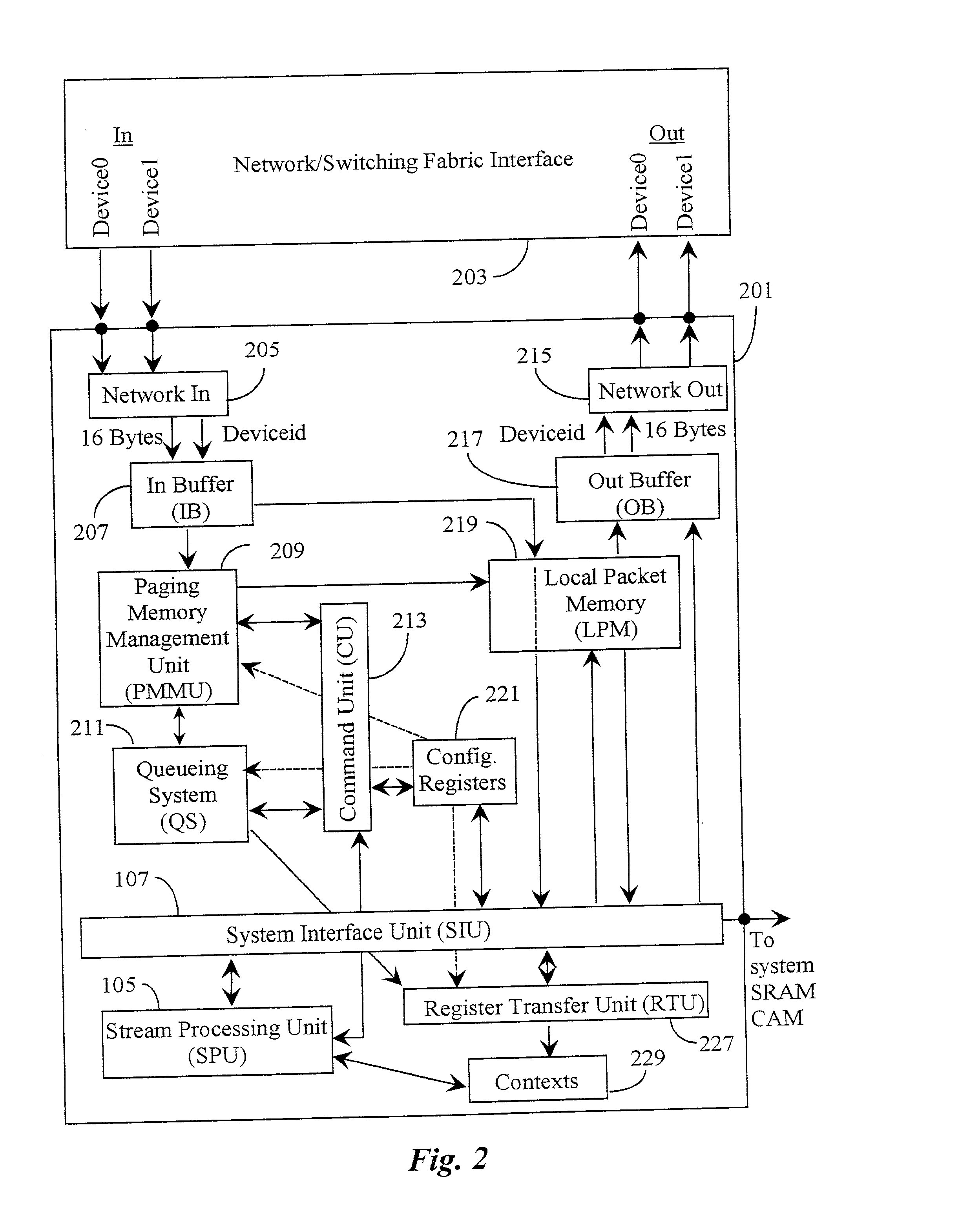

Extended instruction set for packet processing applications

InactiveUS20020054603A1Memory adressing/allocation/relocationDigital computer detailsManagement unitOut of memory

A software program extension for a dynamic multi-streaming processor is disclosed. The extension comprising an instruction set enabling coordinated interaction between a packet management component and a core processing component of the processor. The software program comprises, a portion thereof for managing packet uploads and downloads into and out of memory, a portion thereof for managing specific memory allocations and de-allocations associated with enqueueing and dequeuing data packets, a portion thereof for managing the use of multiple contexts dedicated to the processing of a single data packet; and a portion thereof for managing selection and utilization of arithmetic and other context memory functions associated with data packet processing. The extension complements standard data packet processing program architecture for specific use for processors having a packet management unit that functions independently from a streaming processor unit.

Owner:ARM FINANCE OVERSEAS LTD

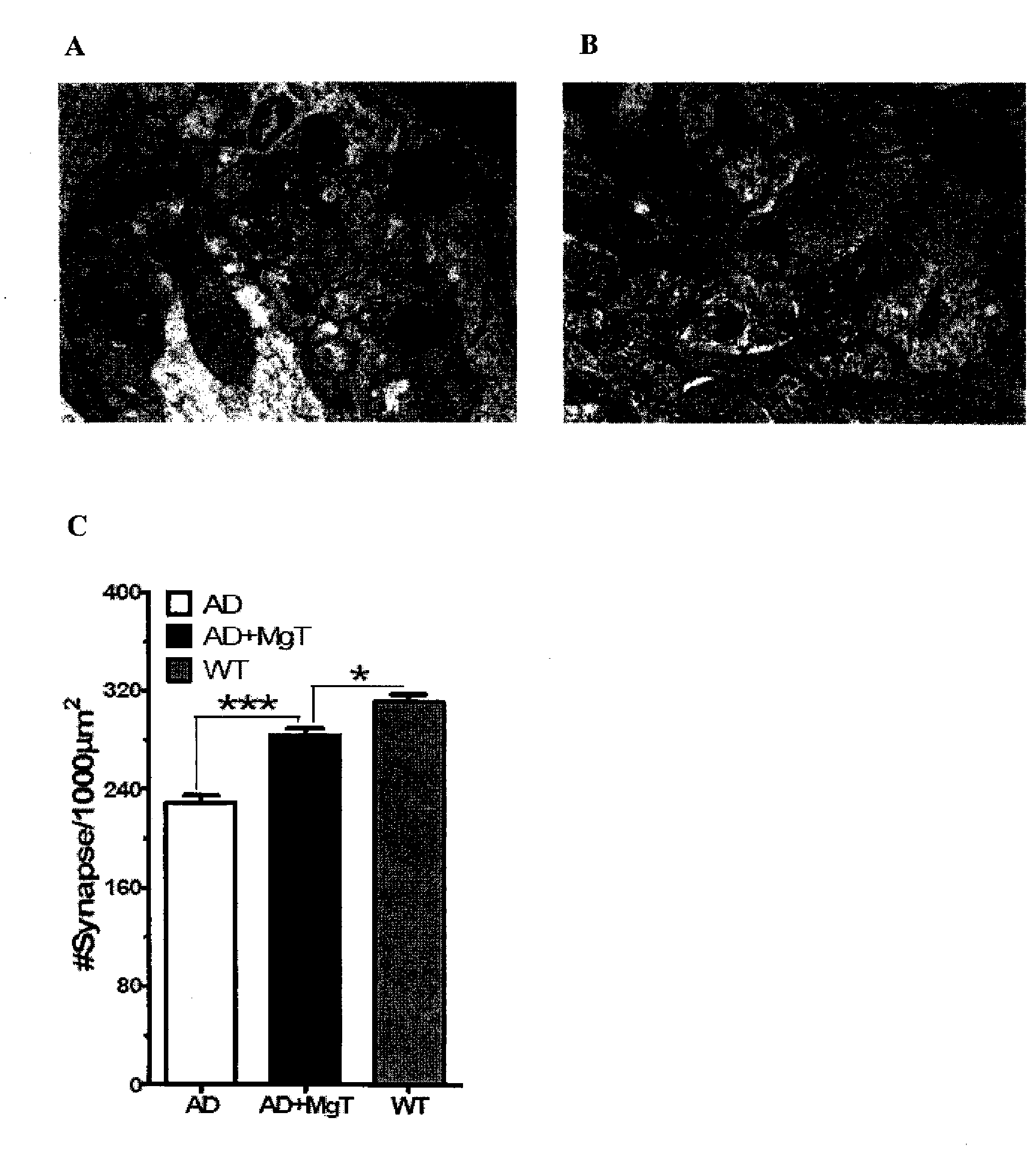

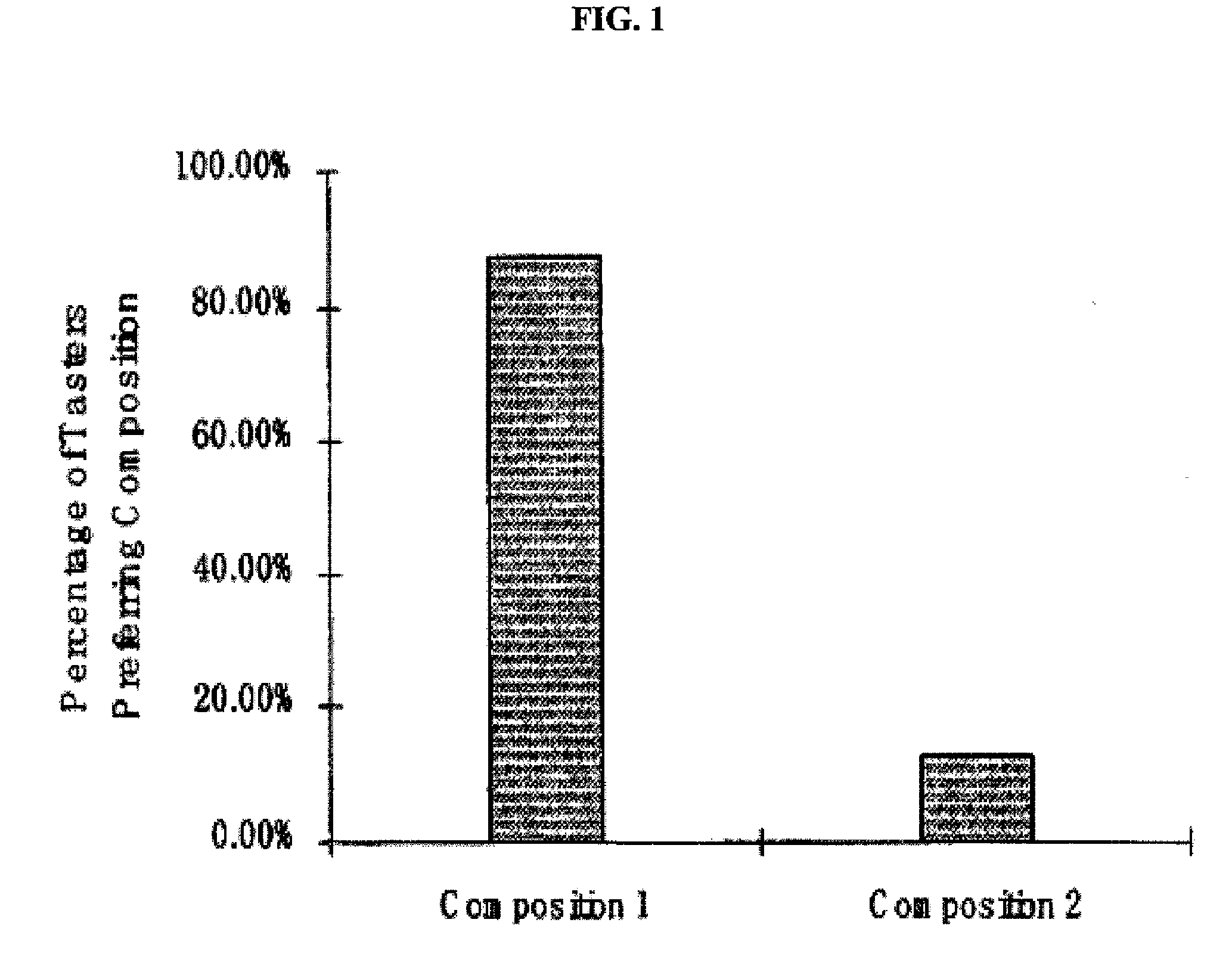

Magnesium compositions and uses thereof

ActiveUS20080248100A1Increase in physiological concentrationImprove depressionPowder deliveryBiocideAttention deficitsMigraine

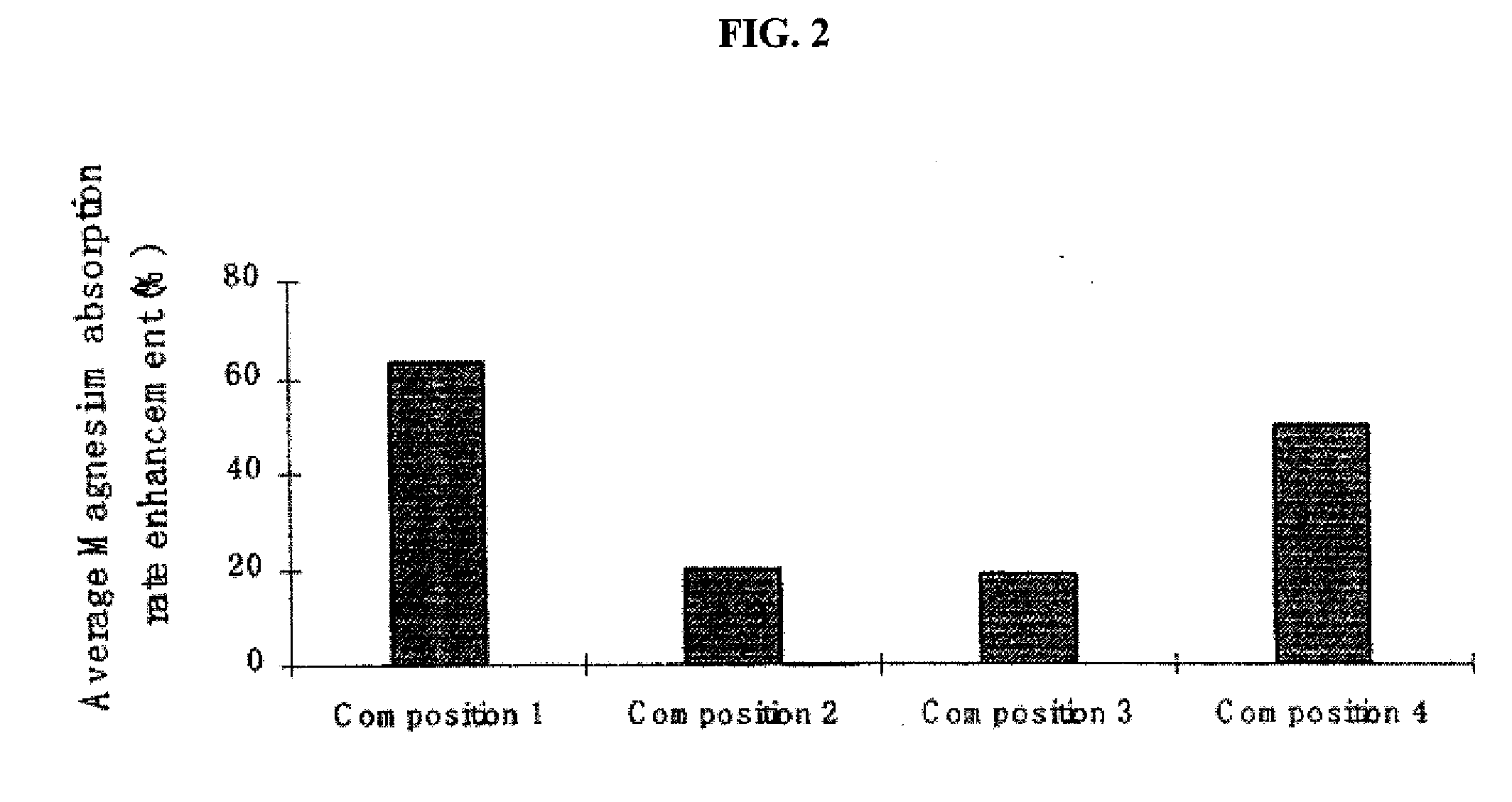

A composition for administration to a subject, such as oral administration to a subject, for example, has been provided. Such a composition may comprise at least one magnesium-counter ion compound. A magnesium-counter ion composition described herein may be useful for any of a variety of applications provided herein, such as maintaining, enhancing, and / or improving health, nutrition, and / or another condition of a subject, and / or cognitive, learning, and / or memory function. A magnesium-counter ion composition provided herein may be useful for administration to a subject presenting magnesium deficiency, mild cognitive impairment, Alzheimer's disease, attention deficit hyperactivity disorder, ALS, Parkinson's disease, diabetes, migraine, anxiety disorder, mood disorder, and / or hypertension. A kit, method, and other associated technology are also provided.

Owner:NEUROCENTRIA INC

Bidirectional shape memory polymer composite material and preparation method thereof

InactiveCN101164770ALarge deformation rateEasy to useLamination ancillary operationsSynthetic resin layered productsPolymer scienceMemory effect

The present invention relates to a polymer composite material with bidirectional shape memory effect and its preparation method. It is characterized by that said polymer composite material is made up by using polymer material with shape memory function and elastric material which can be actively reverted through a certain superimposing and binding process. Said polymer composite material has bidirectional shape memory effect. The shape memory reversion temperature range of said polymer composite material is large, the different shape memory polymers can be selected and used, the bidirectionalshape memory function with different shape reversion temperature can be obtained. The bidirectional shape memory property also can be obtained by regulating thickness of shape memory polymer and thickness of elastic material. Besides, said polymer composite material has good corrosion resistance, electroinsulating property and heat-insulating effect.

Owner:THE HONG KONG POLYTECHNIC UNIV

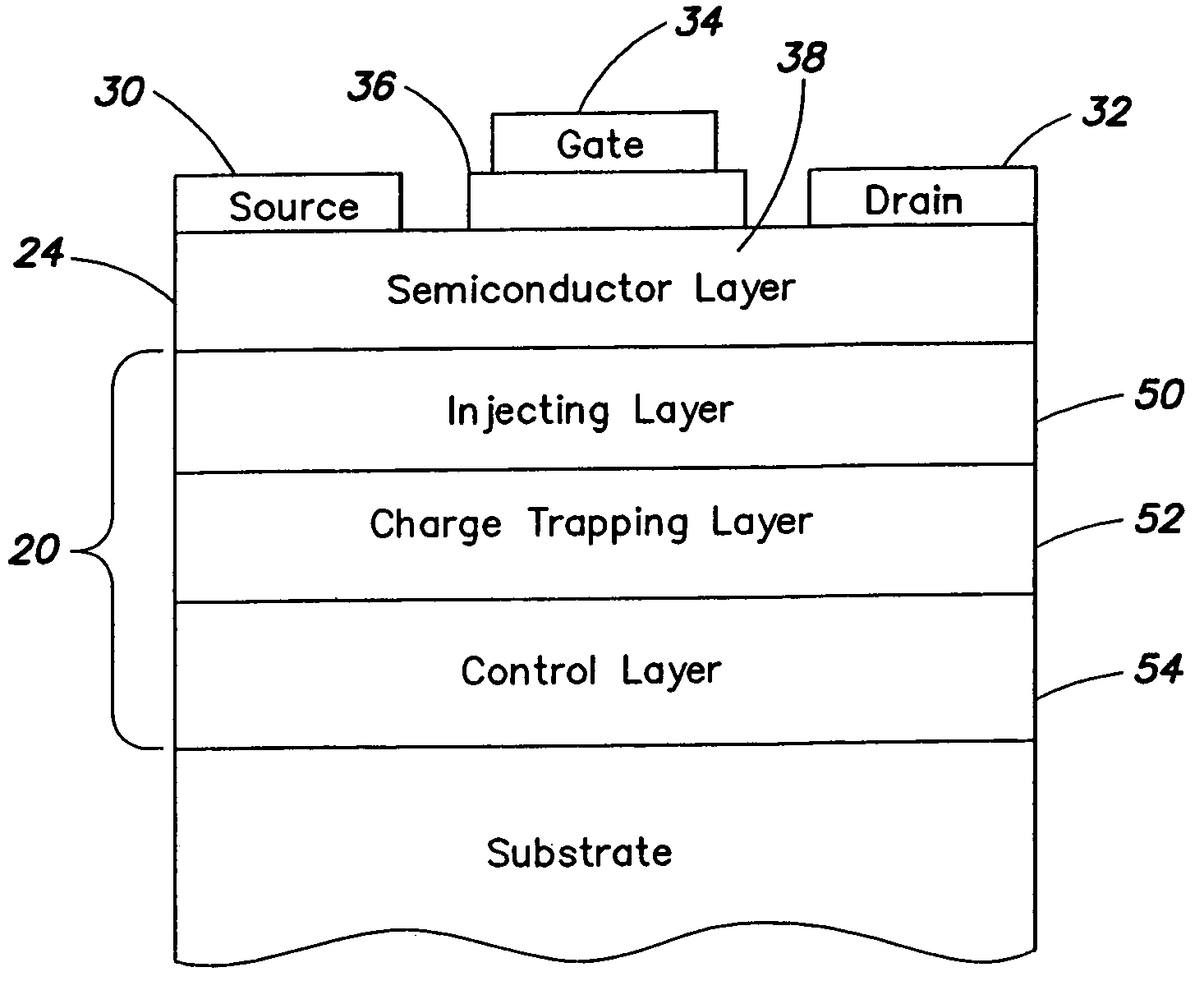

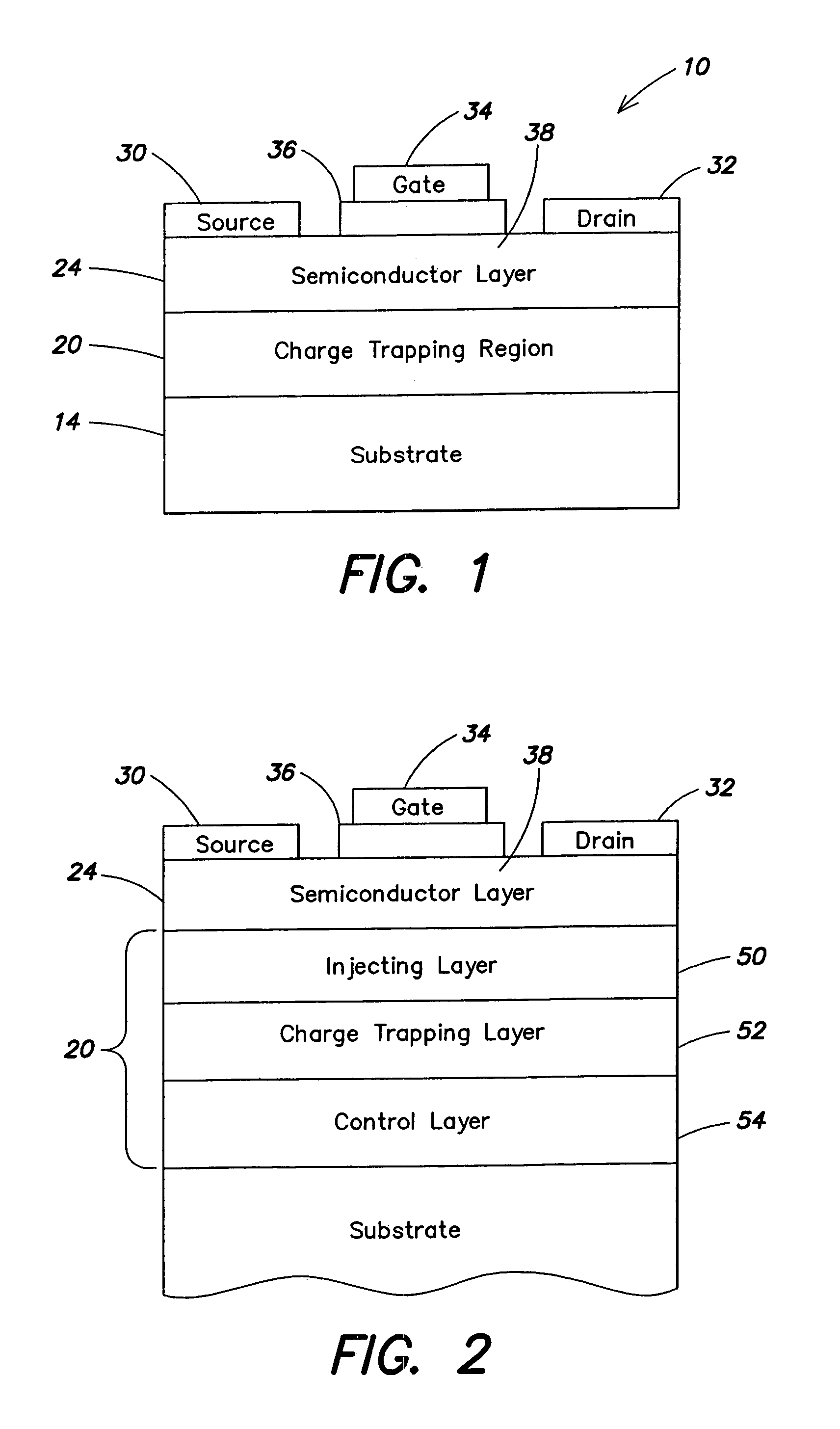

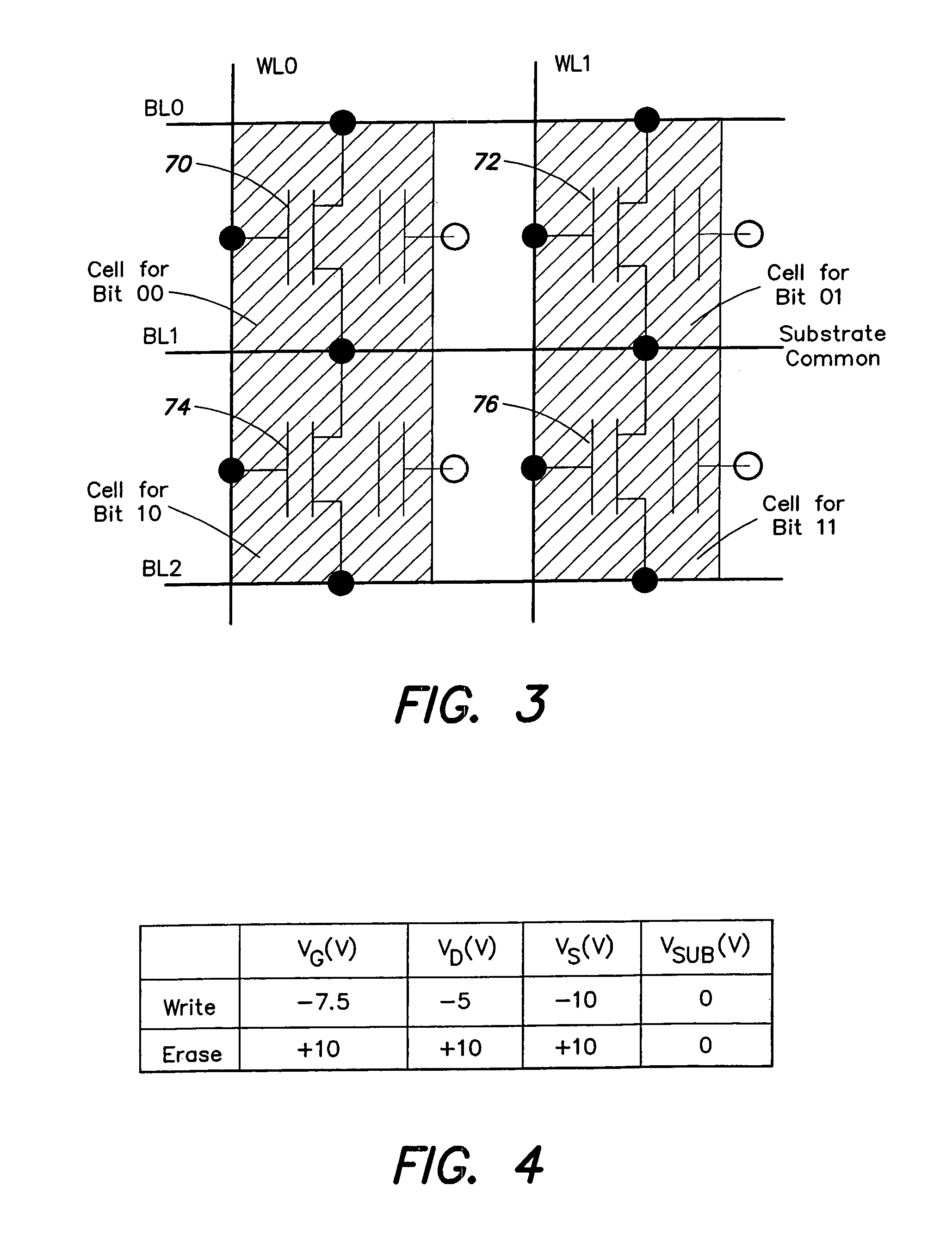

Scalable nano-transistor and memory using back-side trapping

According to an aspect of the invention, a device structure is provided where charging and discharging occur in a trapping region formed by a stack of films that is placed on the back of a thin silicon channel. Uncoupling the charging mechanisms that lead to the memory function from the front gate transistor operation allows efficient scaling of the front gate. But significantly more important is a unique character of these devices: these structures can be operated both as a transistor and as a memory. The thin active silicon channel and the thin front oxide provide the capability of scaling the structure to tens of nanometers, and the dual function of the device is obtained by using two voltage ranges that are clearly distinct. At small voltages the structure operates as a normal transistor, and at higher voltages the structure operates as a memory device.

Owner:CORNELL RES FOUNDATION INC

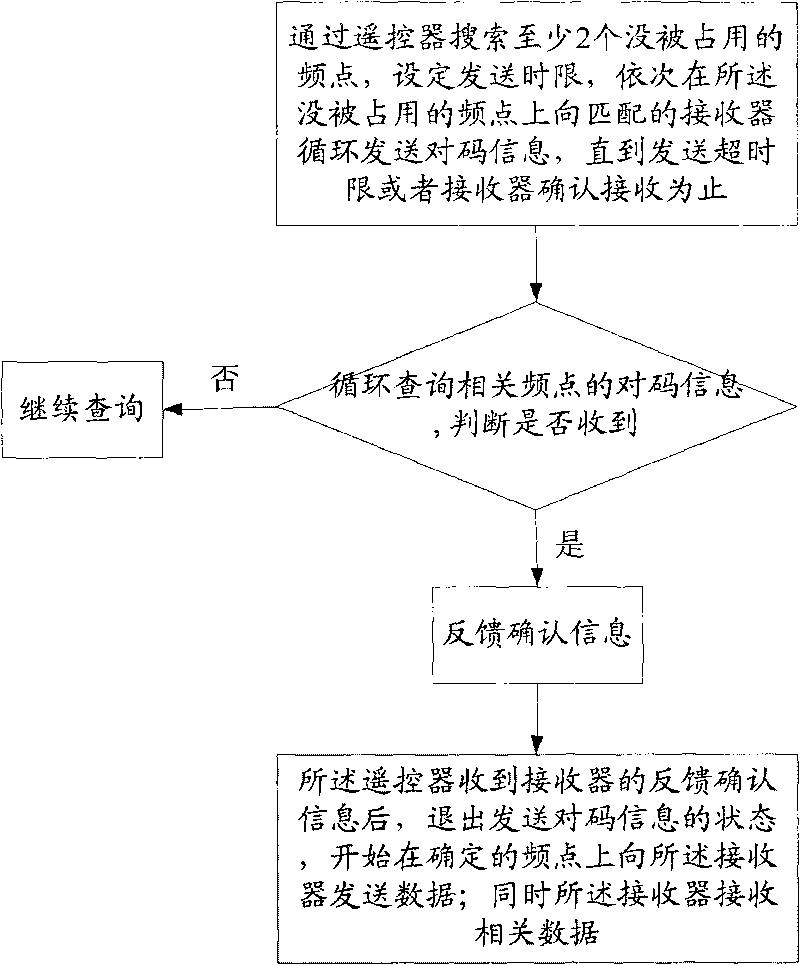

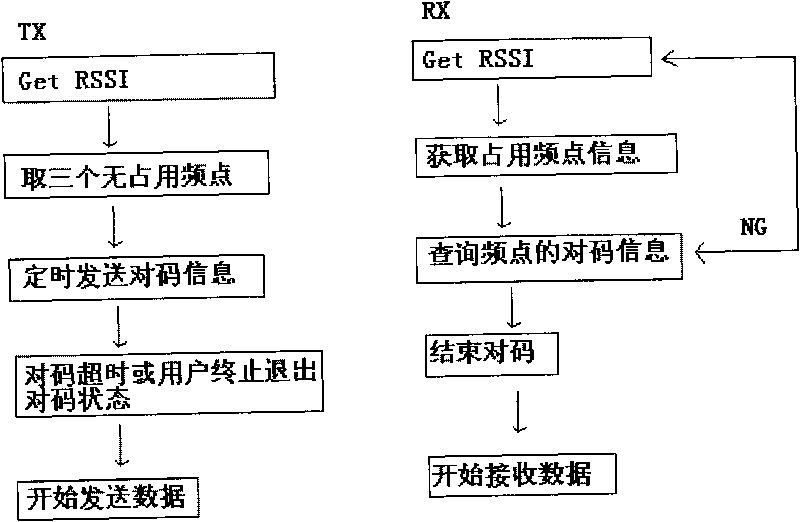

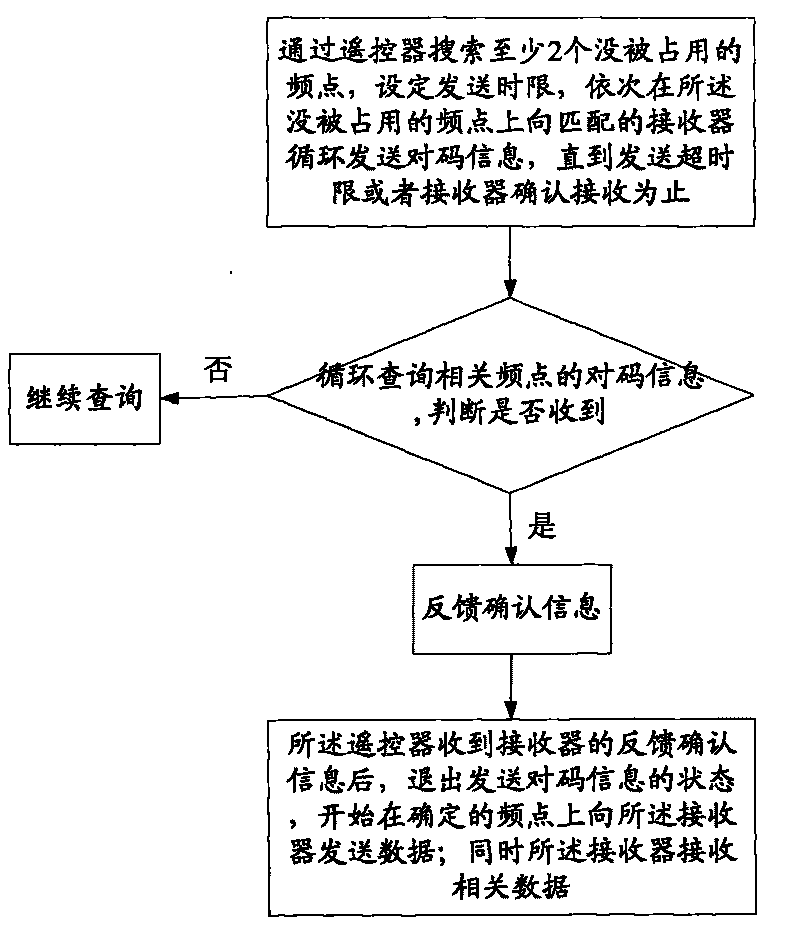

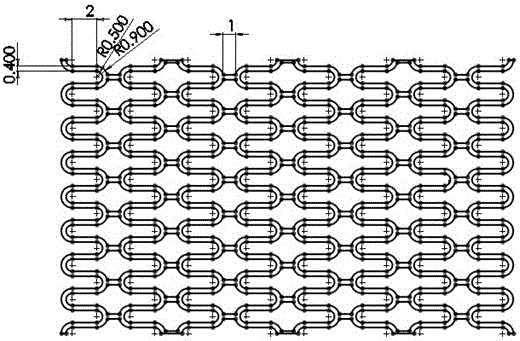

Remote control method and system capable of automatically adjusting frequency and distributing ID

The invention discloses a remote control method and a system capable of automatically adjusting frequency and distributing ID. The method comprises the following steps: (1) searching at least two frequency points which are not occupied by a remote control, setting a sending time limit, successively and circularly sending dual code information to a matched receiver from the frequency points which are not occupied until sending exceeds the time limit or the receiver confirms to receive; (2) searching the dual code information of the relevant frequency point by the receiver to judge whether the dual code information of the relevant frequency point is searched, if yes, feeding back confirmation information, otherwise continuously searching; (3) after the remote control receives the confirmation information fed back by the receiver, retracting the state of sending the dual code information, beginning to send data to the receiver on the determined frequency point, and simultaneously receiving the relevant data by the receiver. The system has the functions of automatically adjusting frequency and automatically distributing ID as well as the memory function of wireless channel ID data, has wide frequency band and high channel utilization ratio and strengthens system antijamming capability.

Owner:GUANGZHOU WALKERA TECH CO LTD

Method for preparing biodegradable polymer self-expansion type intravascular stent based on 3D printing technology

InactiveCN105771003AImprove long-term patencyAvoid axial shorteningSurgeryPharmaceutical delivery mechanismBiocompatibility TestingBiodegradable polymer

The invention relates to a method for preparing a biodegradable polymer self-expansion type intravascular stent based on 3D printing technology.The method includes the specific steps of synthesizing polylactic acid-based shape-memory polyurethane / Fe304 nanocomposite material with good biocompatibility and biodegradability, and making the composite material into the intravascular stent through the Fused Deposition Modeling technology.In addition, in order to increase the blood vessel endothelium repair speed, sirolimus, heparin, endothelial growth factors or the like are selectively introduced to the stent surface through electrostatic spinning.A 'time'dimension is added for the shape-memory function of the base material, and combined with the 3D printing technology, a 4D forming concept is given to the stent.By means of the magnetocaloric effect of Fe304, shape recovery of the shape-memory polymer can be remotely excited, so that the intravascular stent expands automatically, balloon dilatation is not required during stent implantation, axial shortening during balloon dilatation and radial resilience during withdraw of the stent are avoided, and damage of blood vessels is reduced to a minimum level.In addition, the introduction of Fe304 solves the problem that a polymer stent has poor development.

Owner:TONGJI UNIV

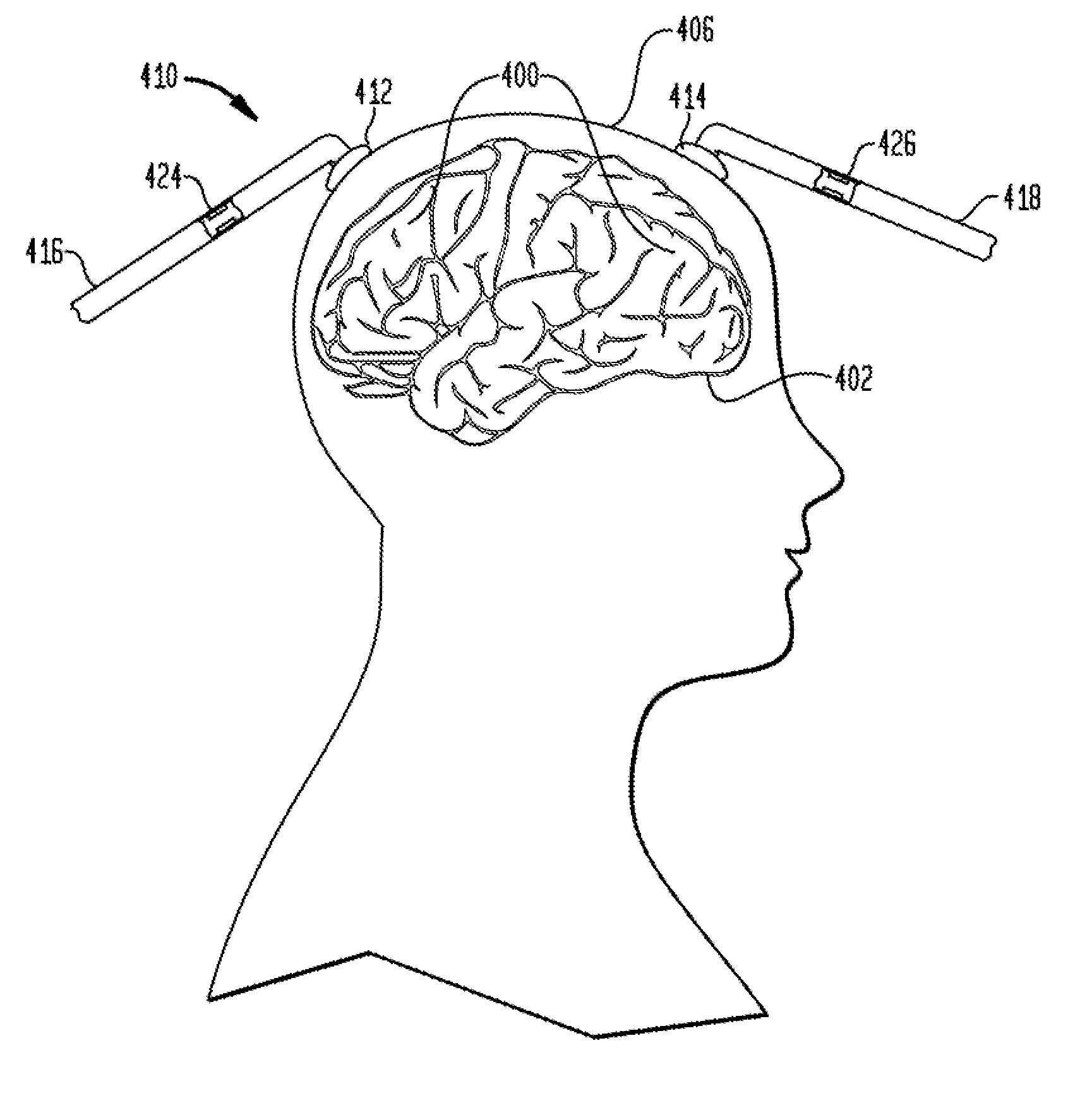

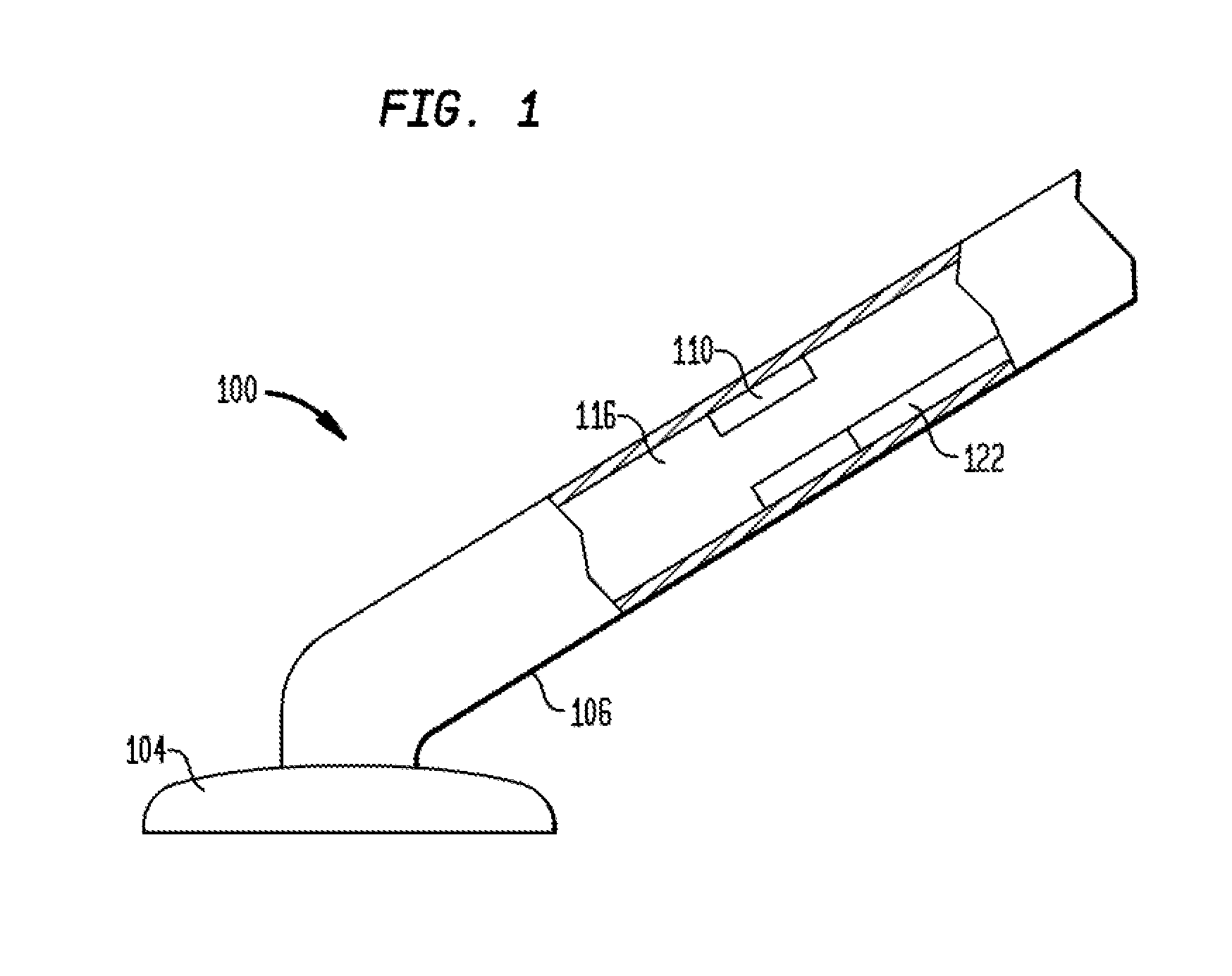

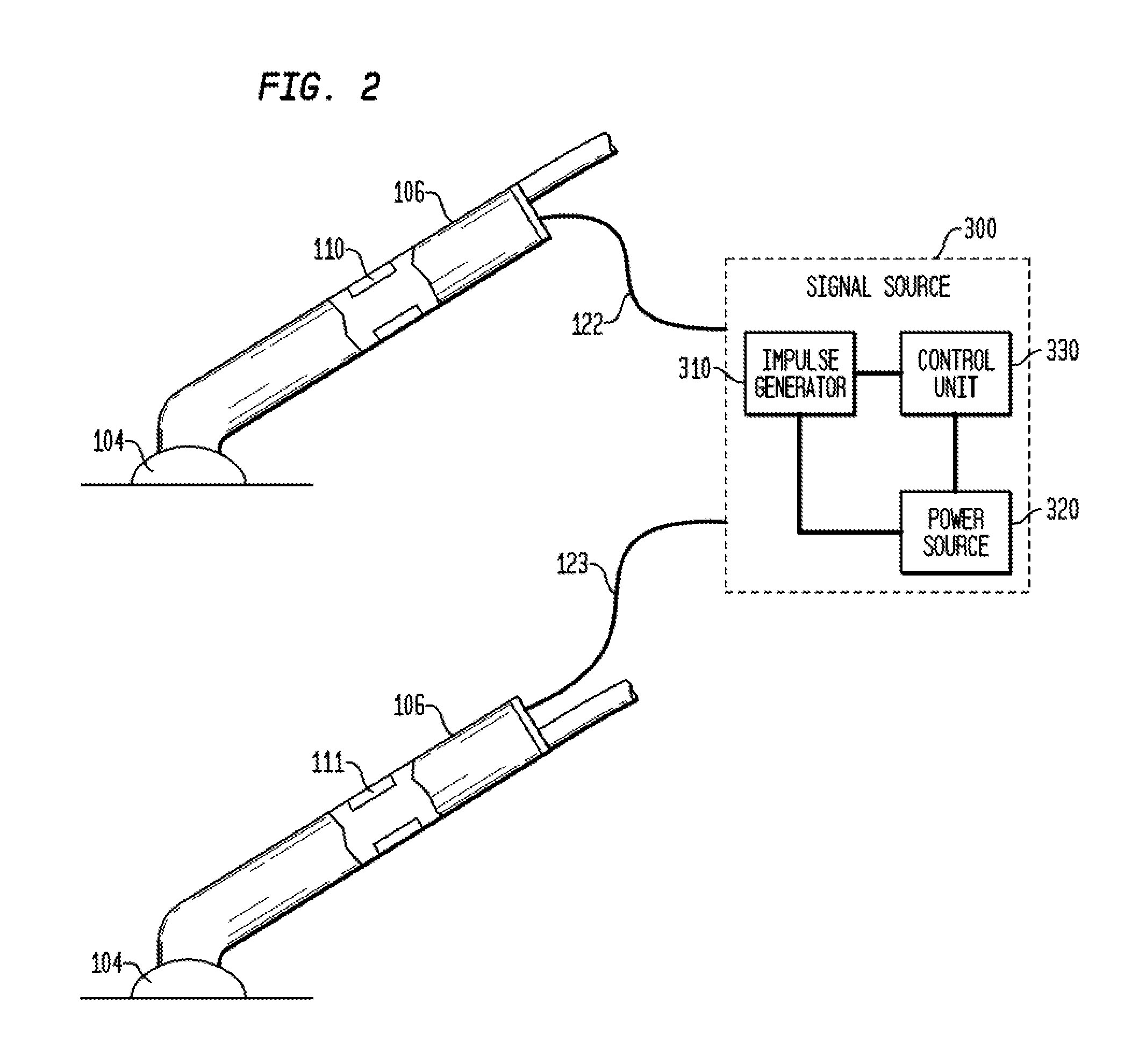

Methods and apparatus for transcranial stimulation

The present invention provides systems, apparatus and methods for applying electric current to neurons in the brain to treat disorders and to improve motor and / or memory functions in a patient. In a method according to the invention, an electrode is positioned adjacent to and spaced from the skin surface of the patient's head and an electric current is applied through the electrode to a target region in the brain to modulate one or more neurons in the target region. The electrode is housed within an enclosure and spaced from the skin surface so that the electrode does not directly contact the patient's tissue, which reduces the potential for collateral tissue damage or necrosis and shields the electrode from the patient's tissue which substantially inhibits Faradic products (e.g., H+, OH−, H2O2) of the electrode from reaching the target site.

Owner:ELECTROCORE

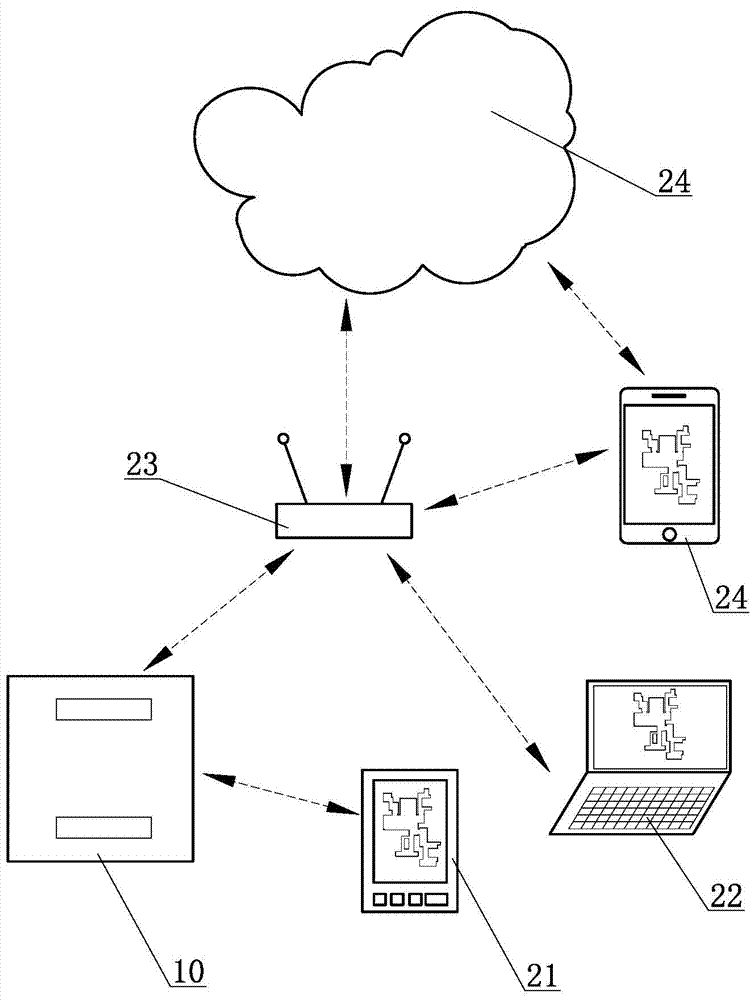

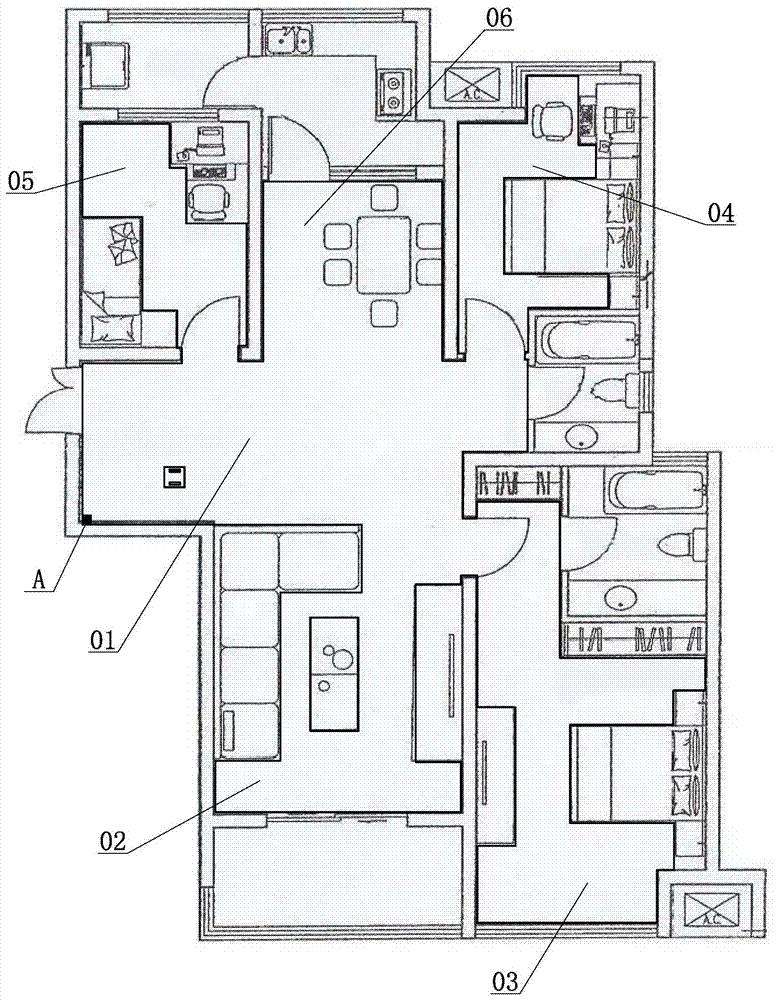

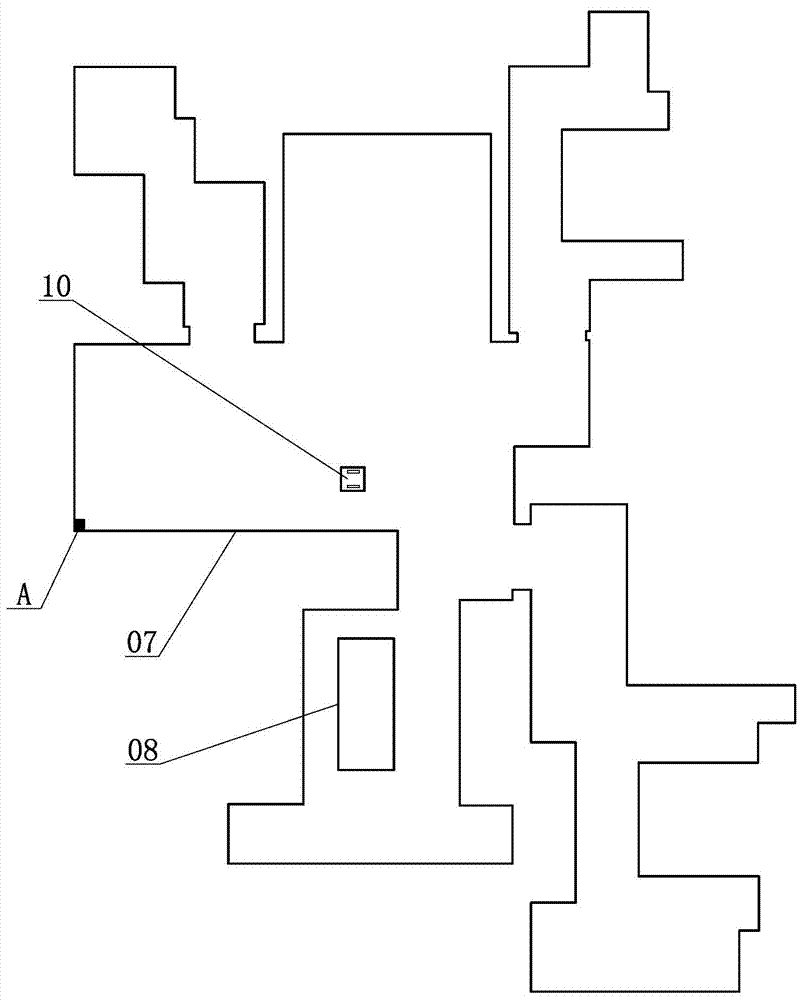

Area cleaning image control method of robot cleaner

ActiveCN106983460AAvoid influenceControl sweeping operationsDrawing from basic elementsMachine detailsImaging processingRemote control

The invention relates to an area cleaning image control method of a robot cleaner. The robot cleaner has a cleaning path memory function, a working face image generating function and a working face image processing function, and the robot cleaner is provided with a cleaning control terminal; initial cleaning is conducted on a working face by the robot cleaner, and a cleaning path is recorded; according to the cleaning path, a working face area image is generated, a copy of the working face area image is transmitted to the cleaning control terminal, the cleaning control terminal selects a cleaning area in the working face area image, and the robot cleaner matches the selected cleaning area with the working face area image so as to determine a travelling path. The method has the advantages that the robot cleaner creates the working face area image and the corresponding cleaning path according to a specified house, so that the situation that control is out of operation due to the influence of environmental factors is avoided; the cleaning control terminal controls the robot cleaner in a remote control mode, the robot cleaner can be flexibly controlled to clean a specified area, and the influence on activities of indoor people is avoided.

Owner:XIAOGOU ELECTRIC INTERNET TECH BEIJING CO LTD

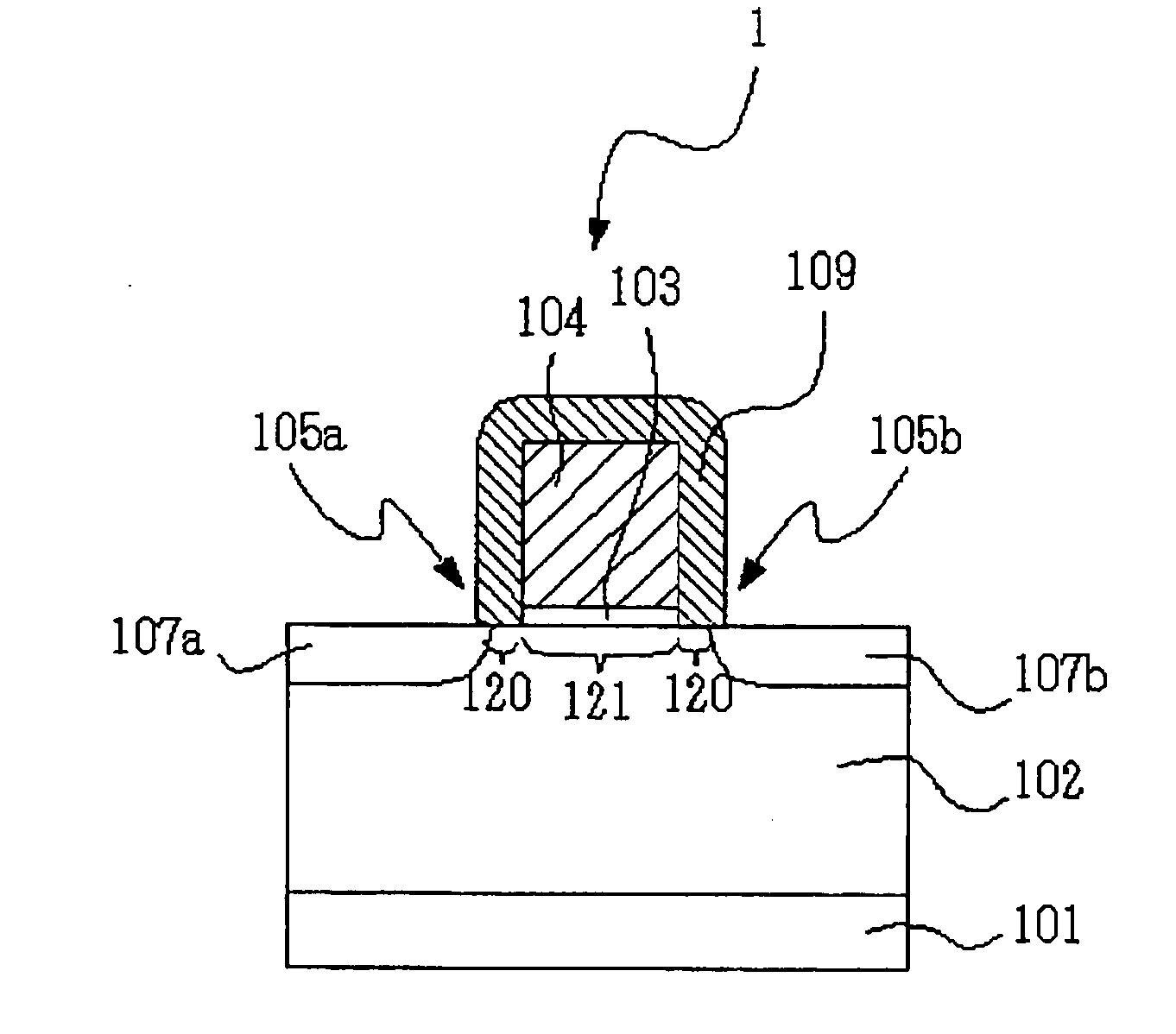

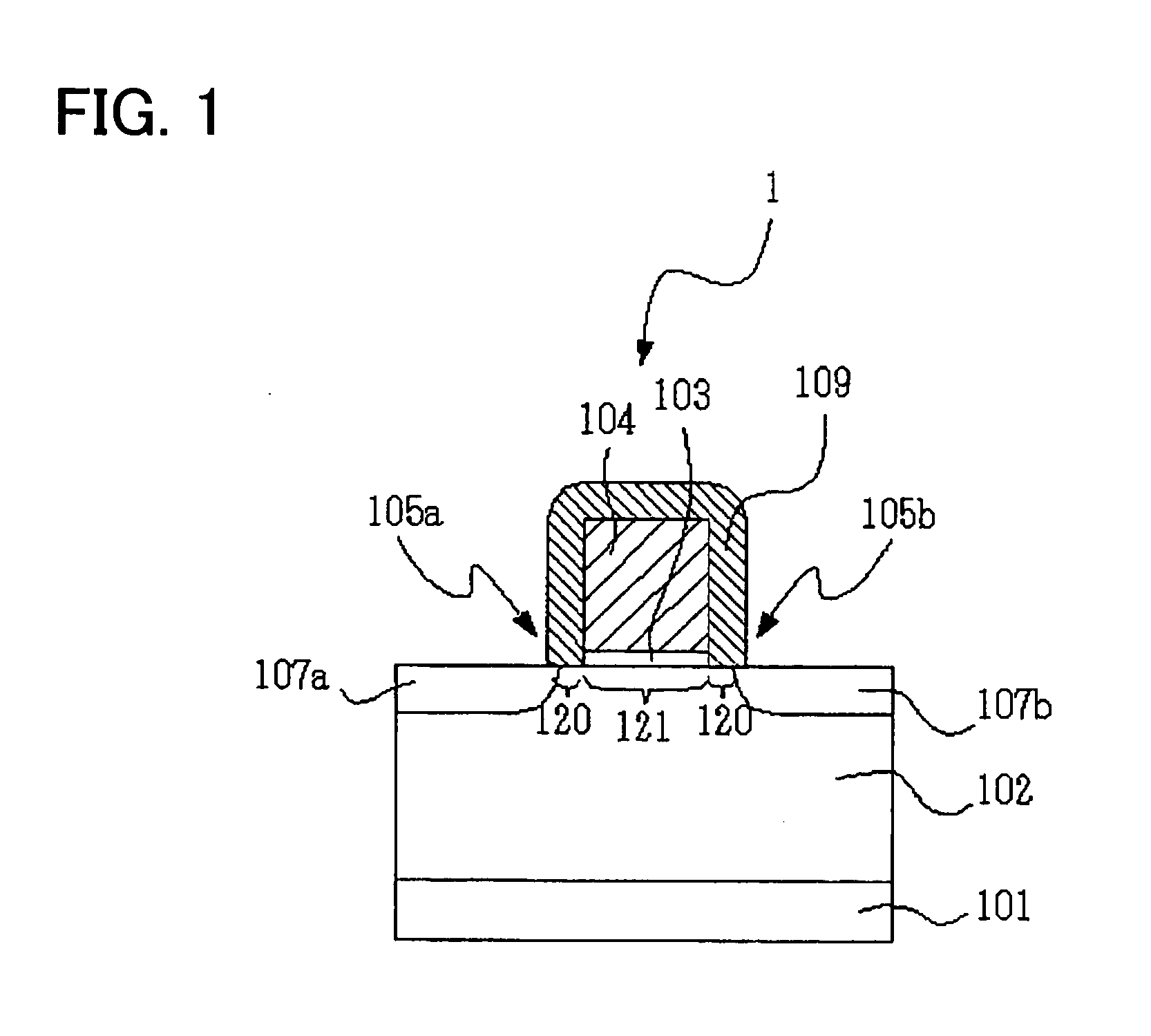

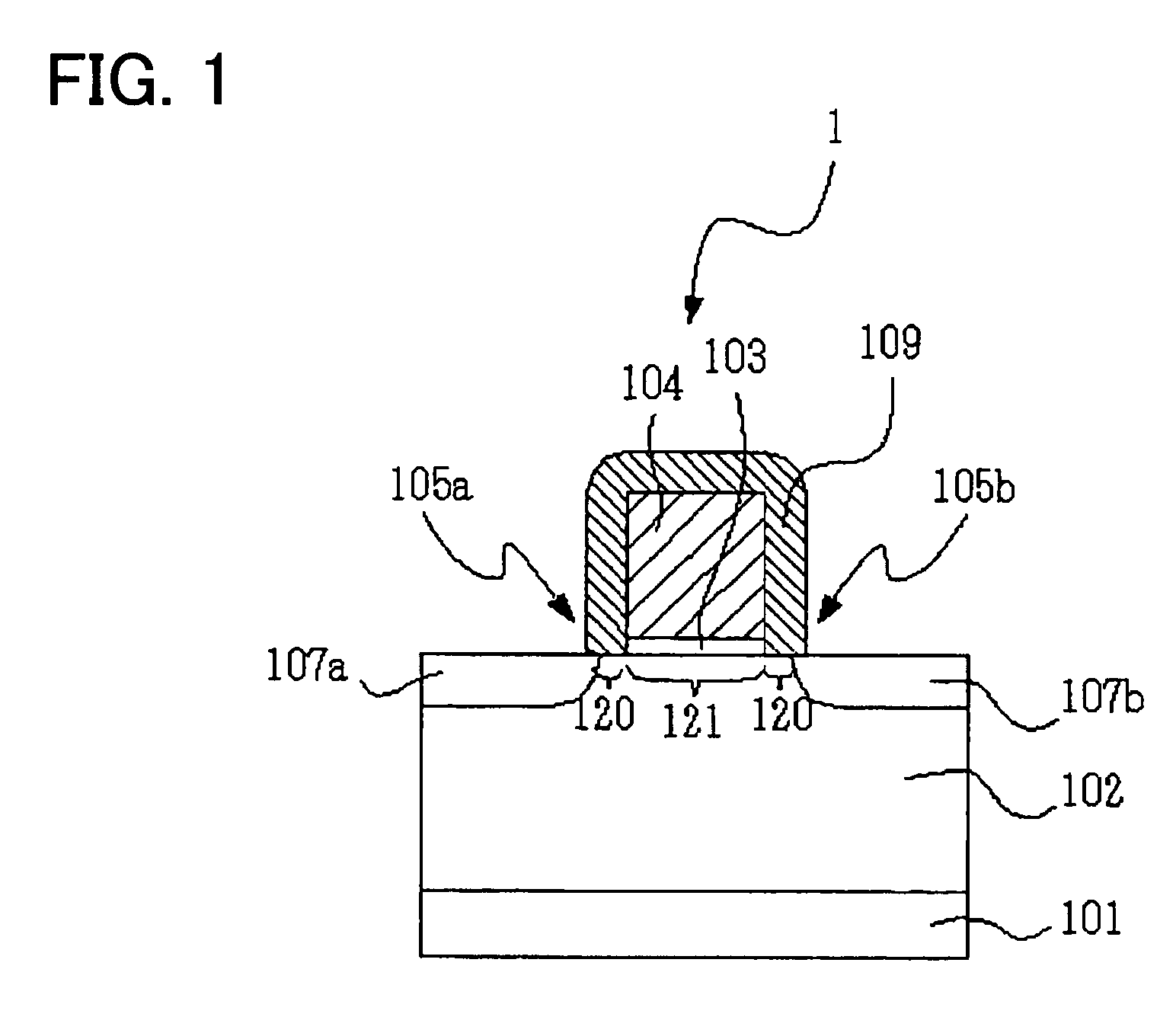

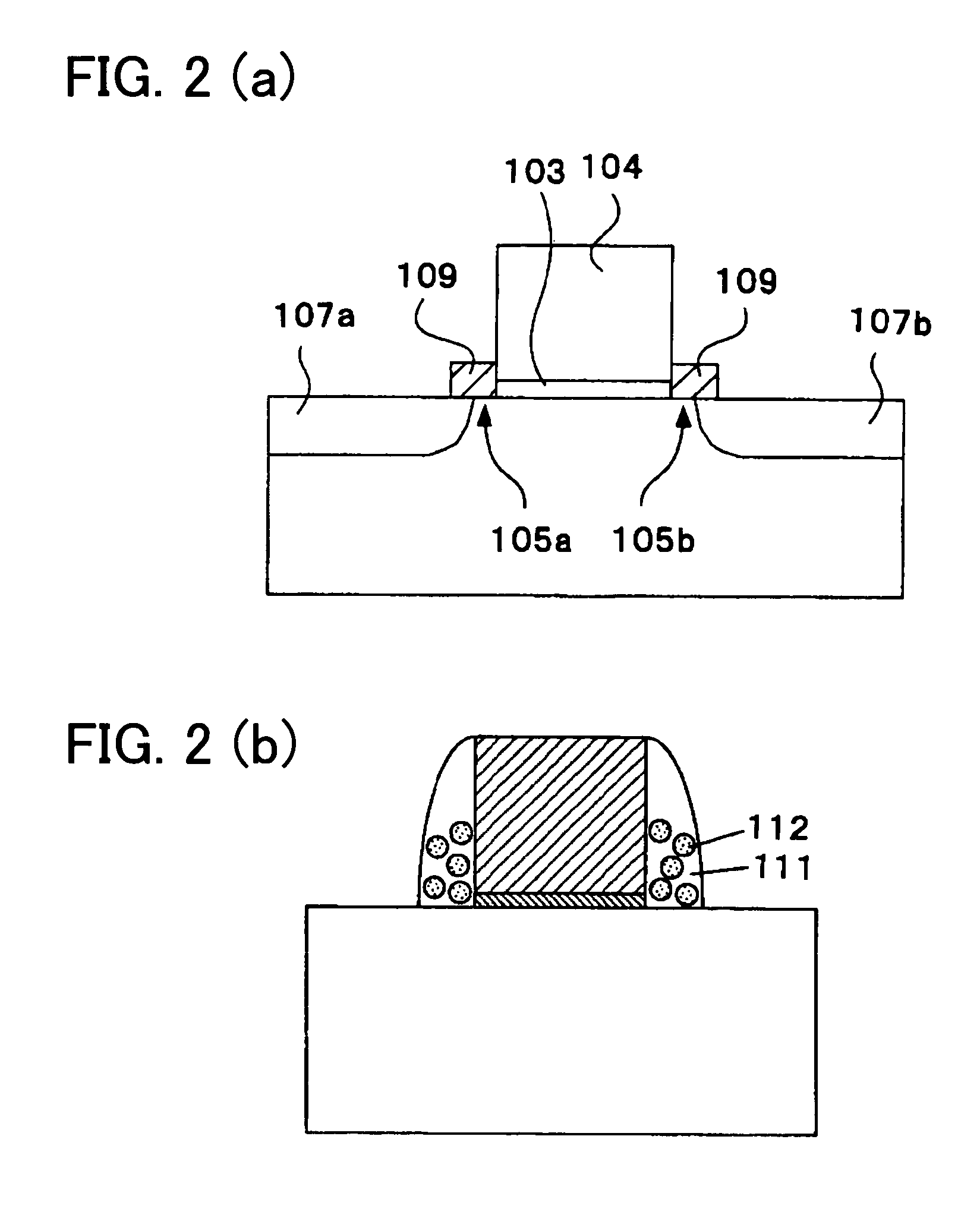

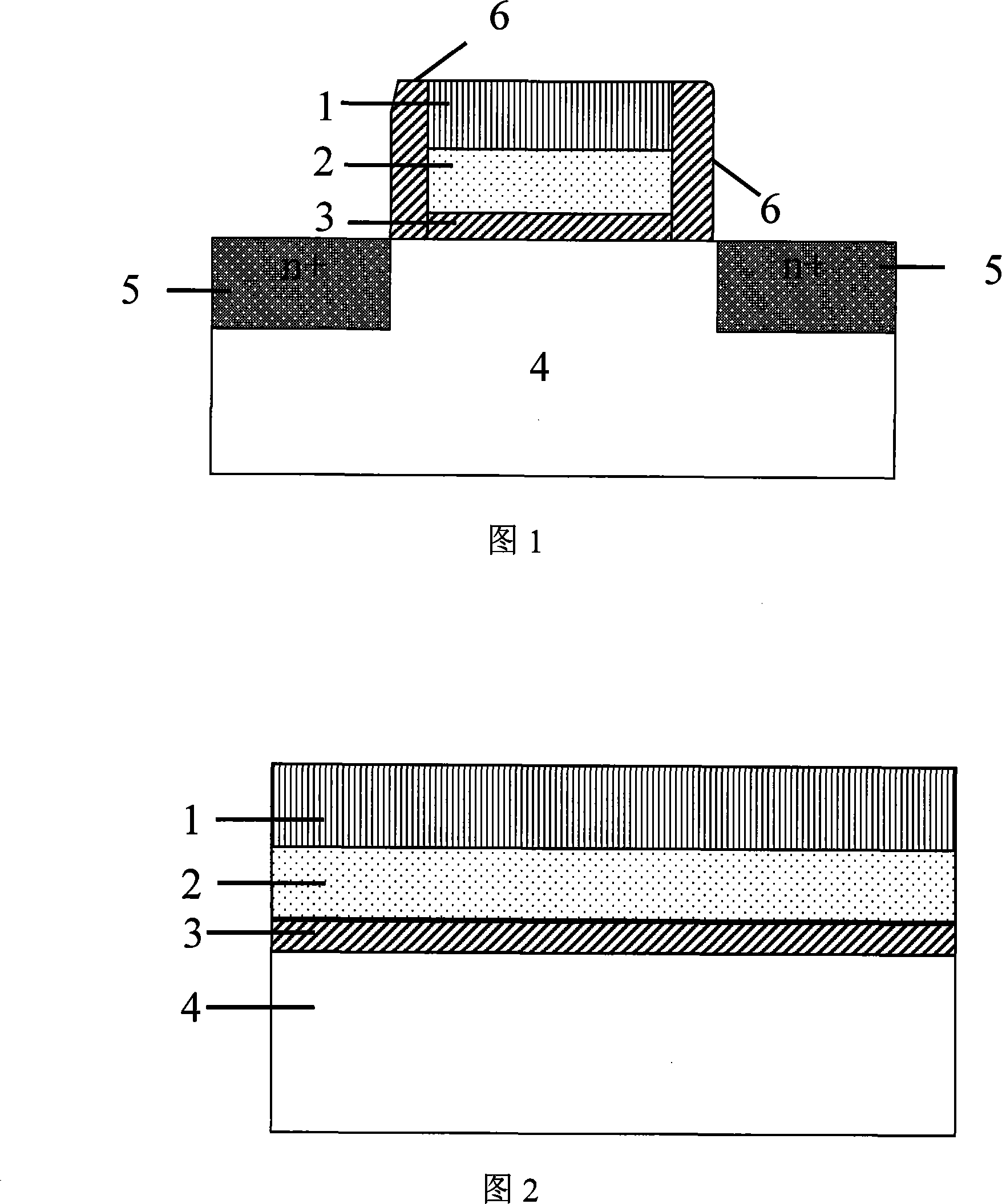

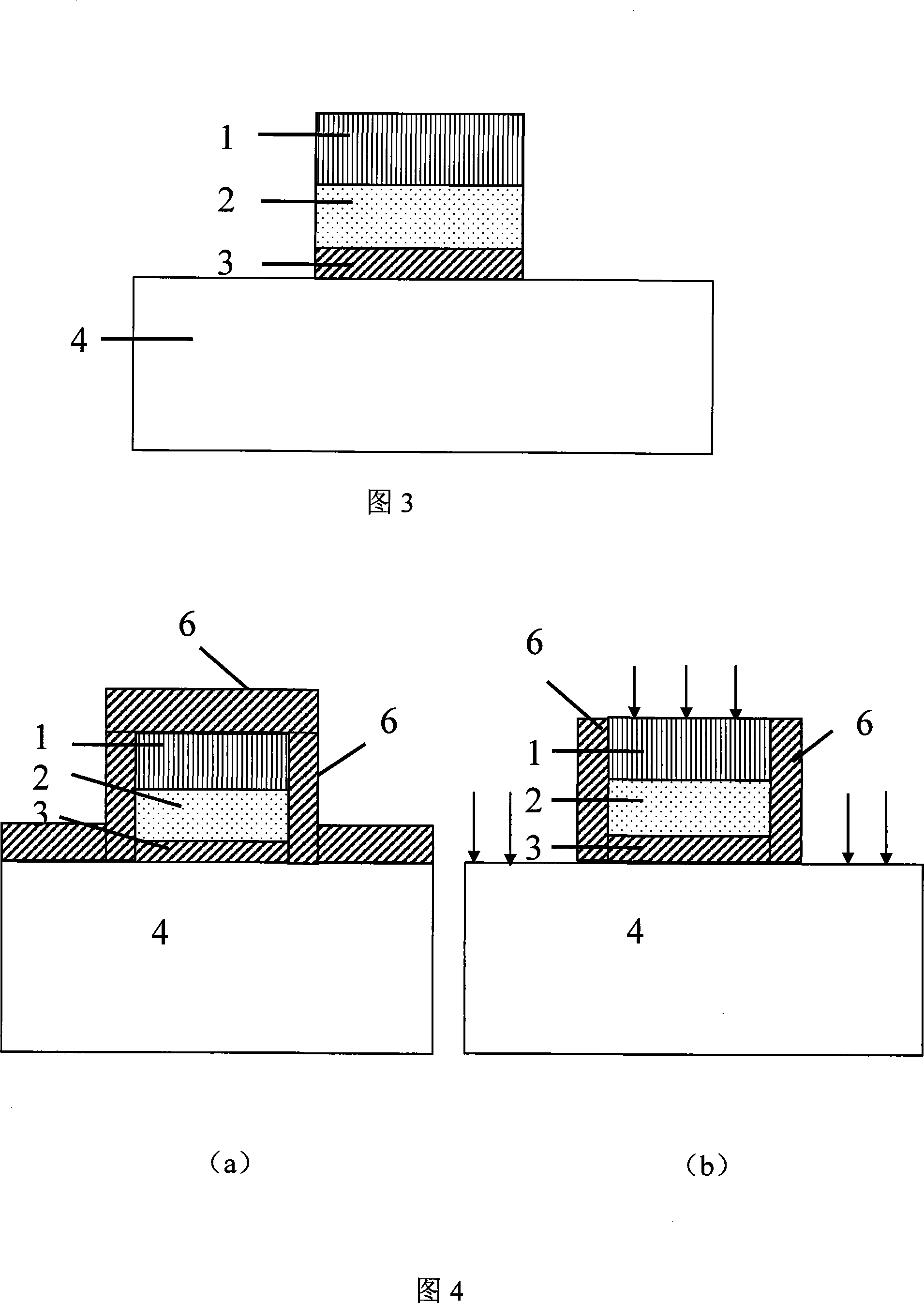

Field-effect tranisistor realizing memory function and method of producing the same

InactiveCN101179095AImprove reliabilityMeet functional applicationsSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyField-effect transistor

The invention provides a field effect transistor that achieves the storage function and the preparation method, which belongs to the filed of semiconductor integrated circuit and manufacturing technology. The transistor comprises a source region, a drain region and a control grid, wherein the control grid utilizes a grid stepped construction which comprises a bottom layer of a tunneling oxidizing layer, an interface layer of a resistance-varying material layer and a top layer of a conductive electrode layer. The field effect transistor obtains an electrically programmable multi-threshold function, the source and drain currents of which are different when a same reading voltage is imposed on the grid, thereby achieving the information storage on two different states or other functions. Utilizing the invention, a plurality of devices and circuits with new functions, high performance and high reliability can be composed, thereby meeting the application of different circuit functions. Meanwhile the invention can adopt the compatibility with the CMOS technology of the conventional PN source or drain junction structure, and can also adopt the compatibility with the CMOS technology of the Schottky source or drain junction structure, with a greater flexibility in technology selection.

Owner:PEKING UNIV

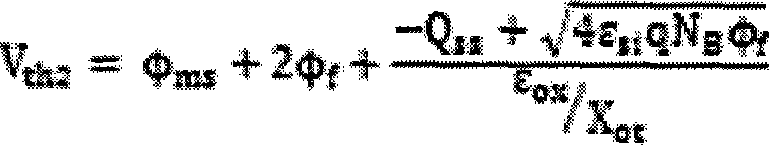

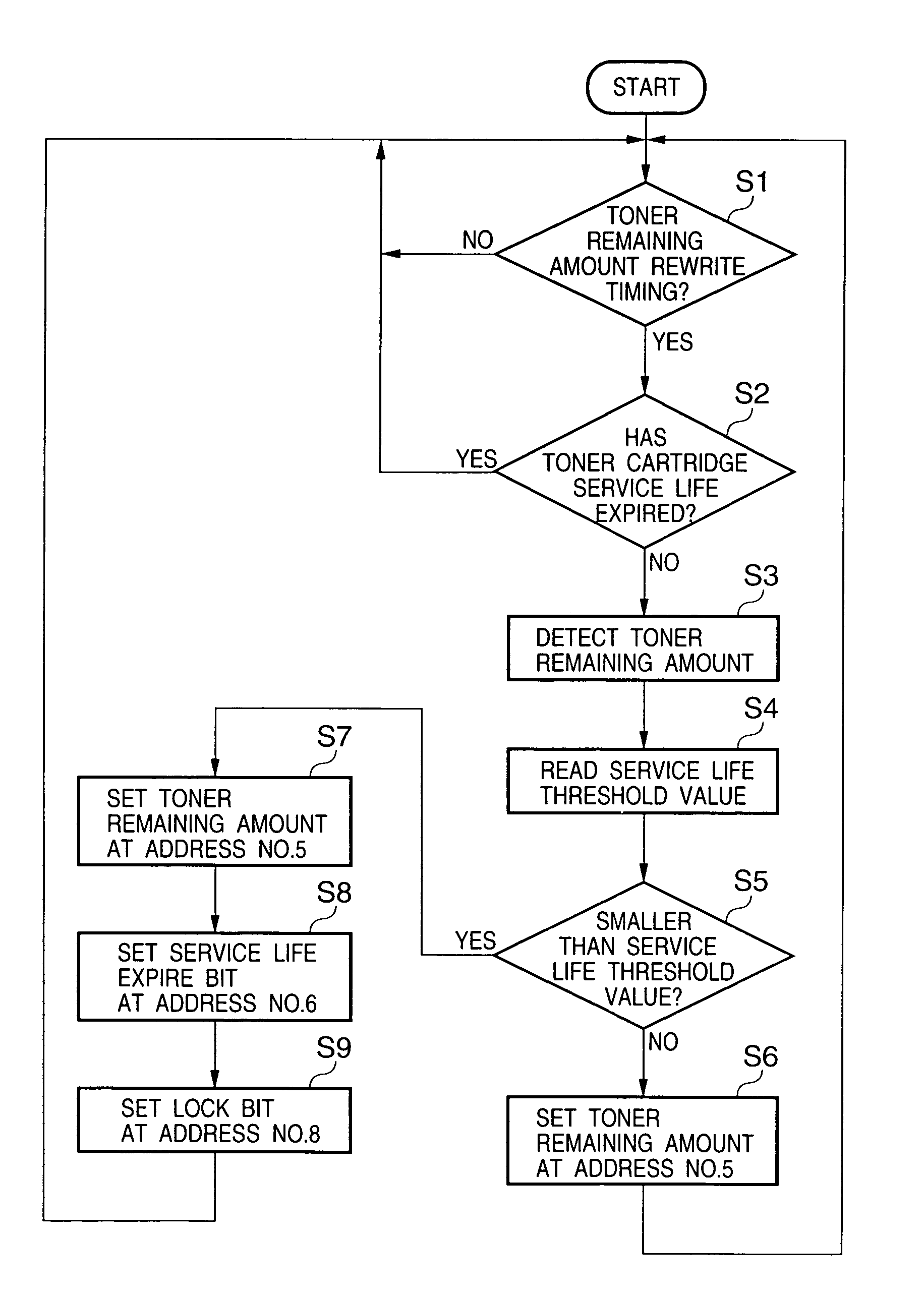

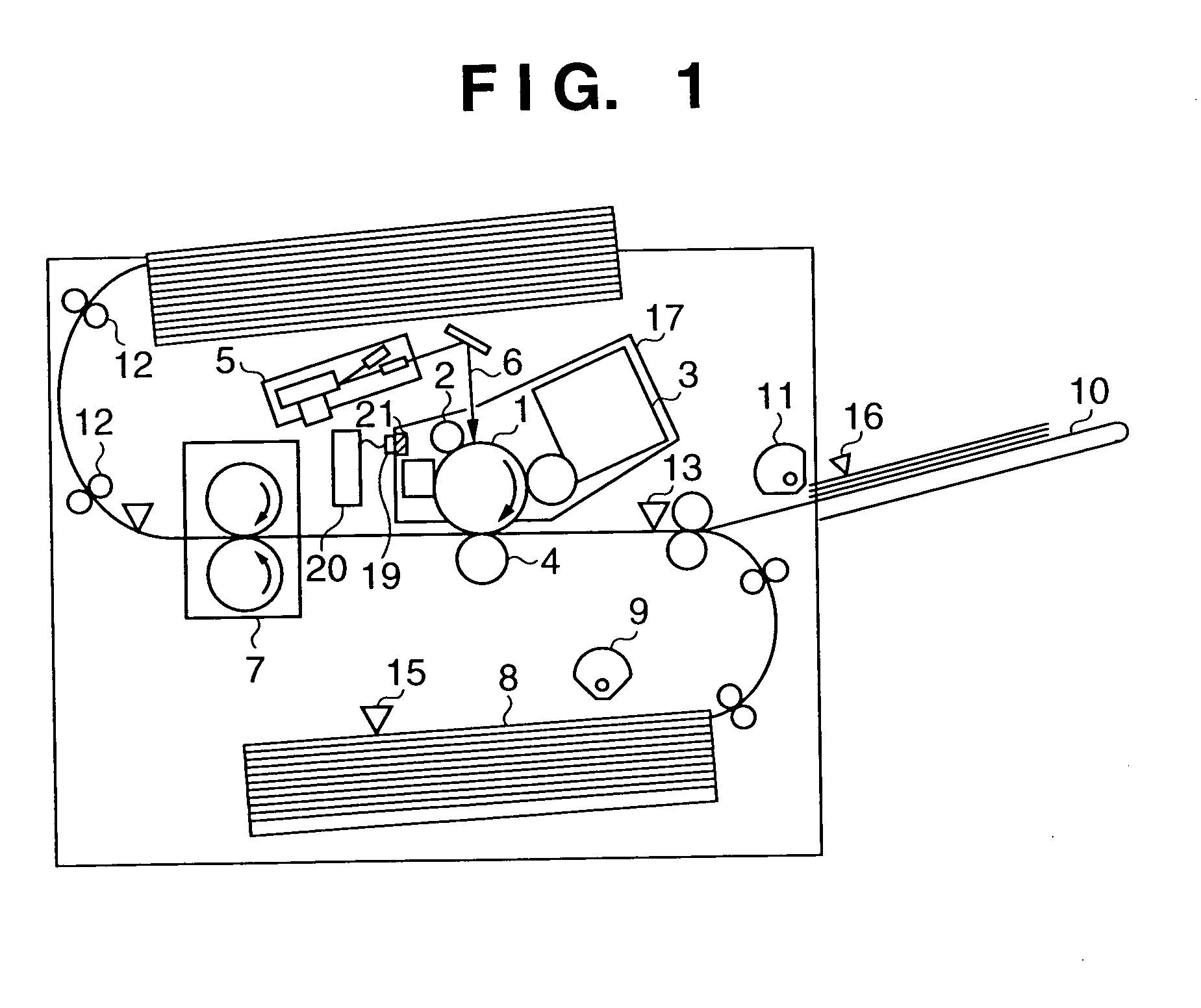

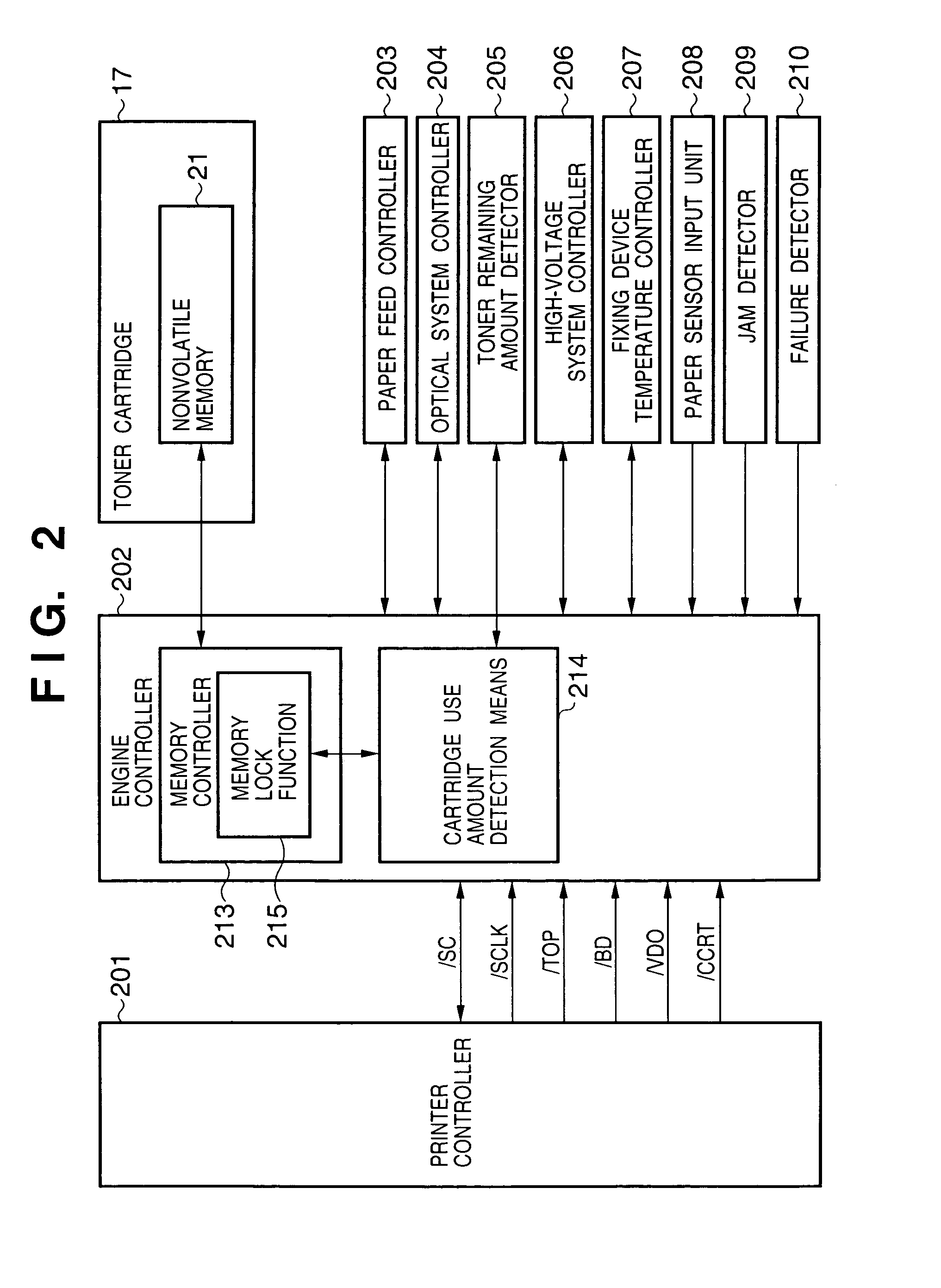

Printing apparatus and its control method, and expendable attached to printing apparatus and having memory

This invention provides a printing apparatus which controls to inhibit any inadvertent write to a memory in an expendable so as to securely manage the exchange timing and the like of the expendable. For this purpose, the expendable such as a toner cartridge or the like comprises a rewritable nonvolatile memory (21) which holds information indicating whether or not its service life has expired. When the toner cartridge is attached to the printing apparatus, it is ready to communicate with a printer engine controller in the printing apparatus, and write to the nonvolatile memory (21) can be made in accordance with an instruction from a control unit. A lock functional unit (21a) writes information indicating write inhibition at a predetermined address in the nonvolatile memory (21), thus inhibiting write to the address position that stores the information indicating whether or not its service life has expired.

Owner:CANON KK

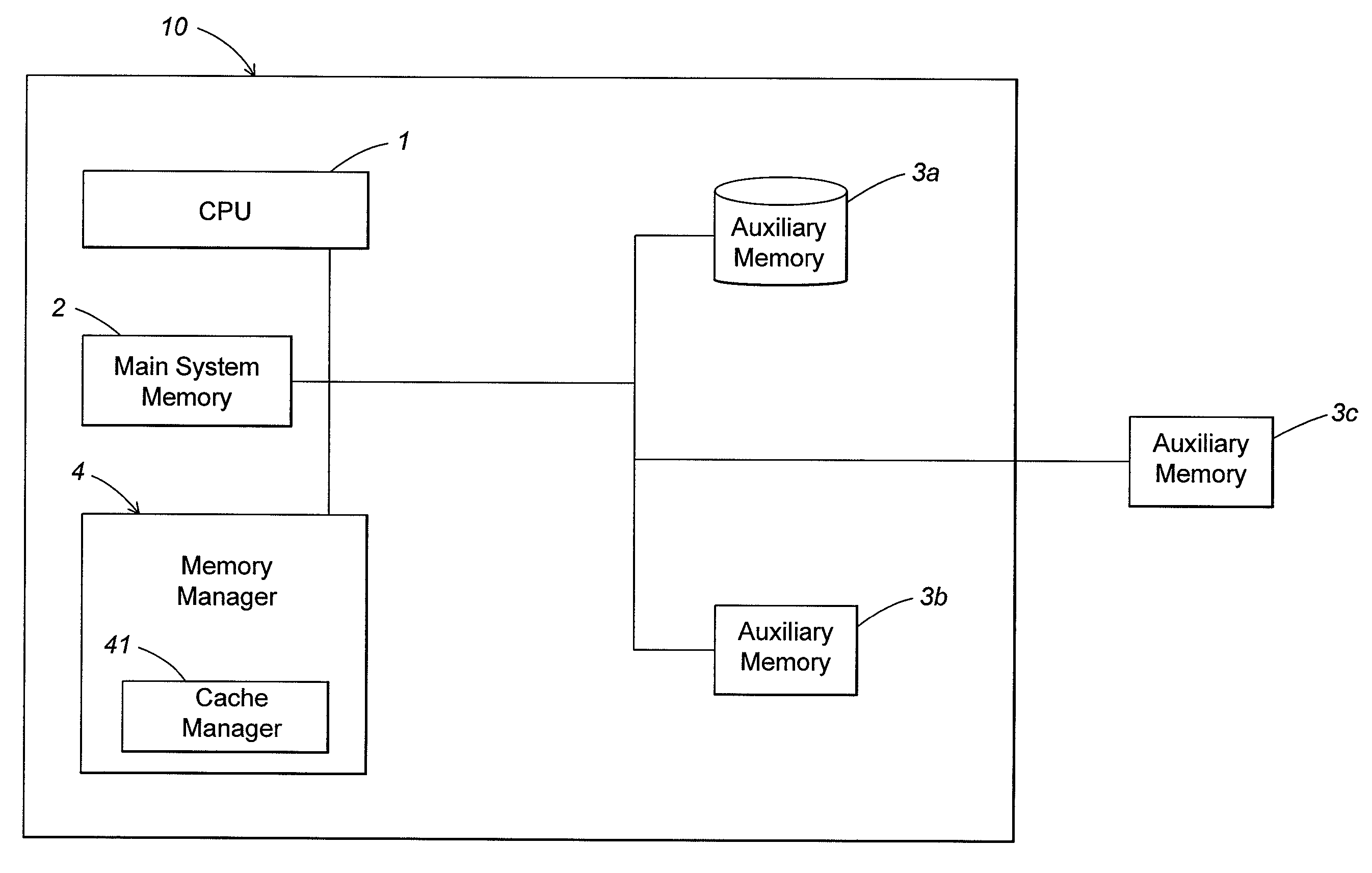

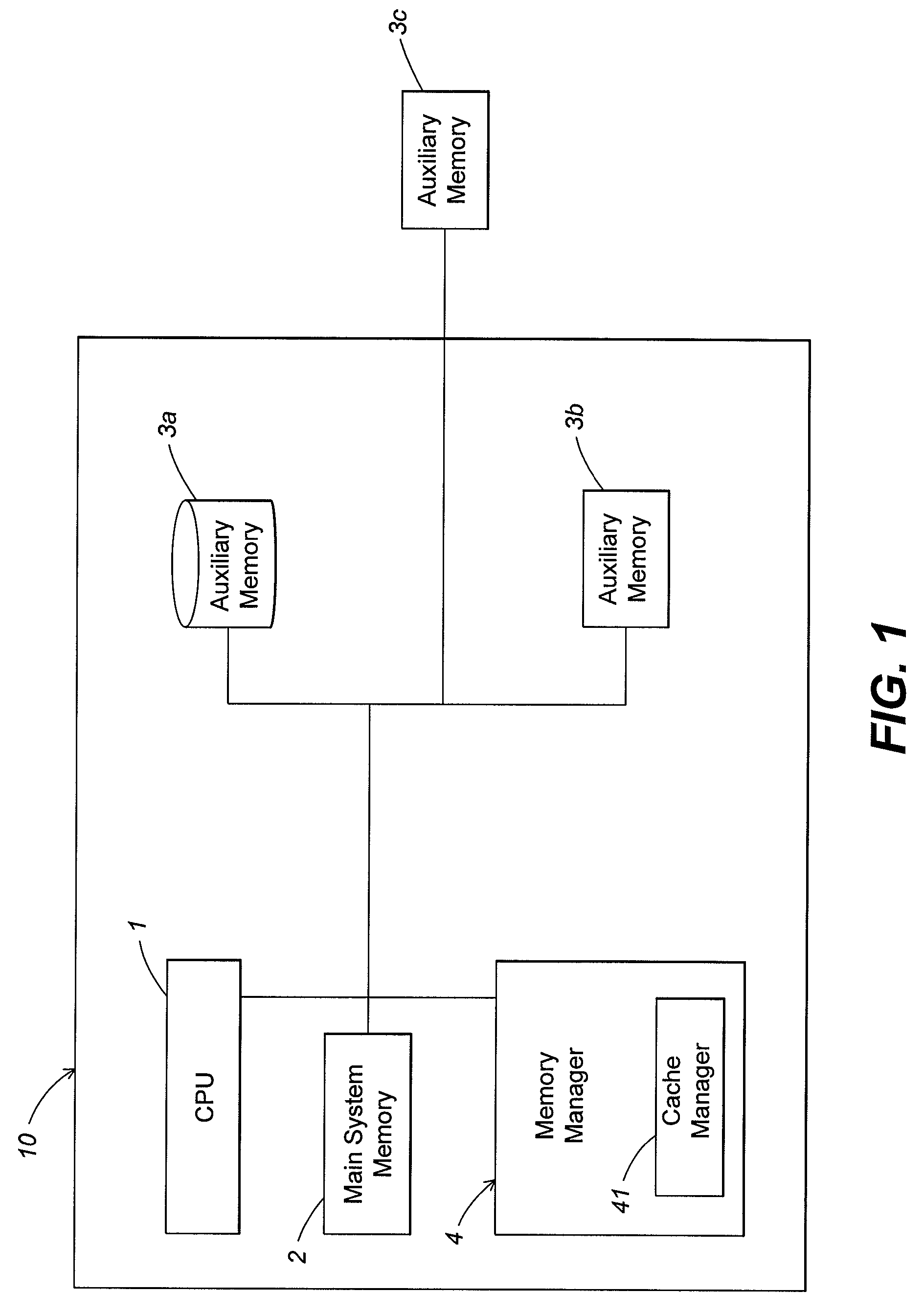

Management of external memory functioning as virtual cache

ActiveUS20090150611A1Improve performanceFaster rateMemory adressing/allocation/relocationPhysical addressAuxiliary memory

A method and apparatus for managing the caching of data on an auxiliary memory of a computer. Pages of data may be cached on an auxiliary memory, such as a flash memory, at a virtual level using an identifier that does not involve a physical address of the pages on a memory. Pages may be cached on auxiliary memory that may be removable from the computer, e.g., by unplugging the memory from the computer. Page data may be encrypted and / or compressed on the auxiliary memory. An authentication indicator may be used to verify the accuracy of cached data in the case of an interrupted connection to the auxiliary memory, e.g., as a result of computer power down, hibernation, removal of the memory from the computer, etc.

Owner:MICROSOFT TECH LICENSING LLC

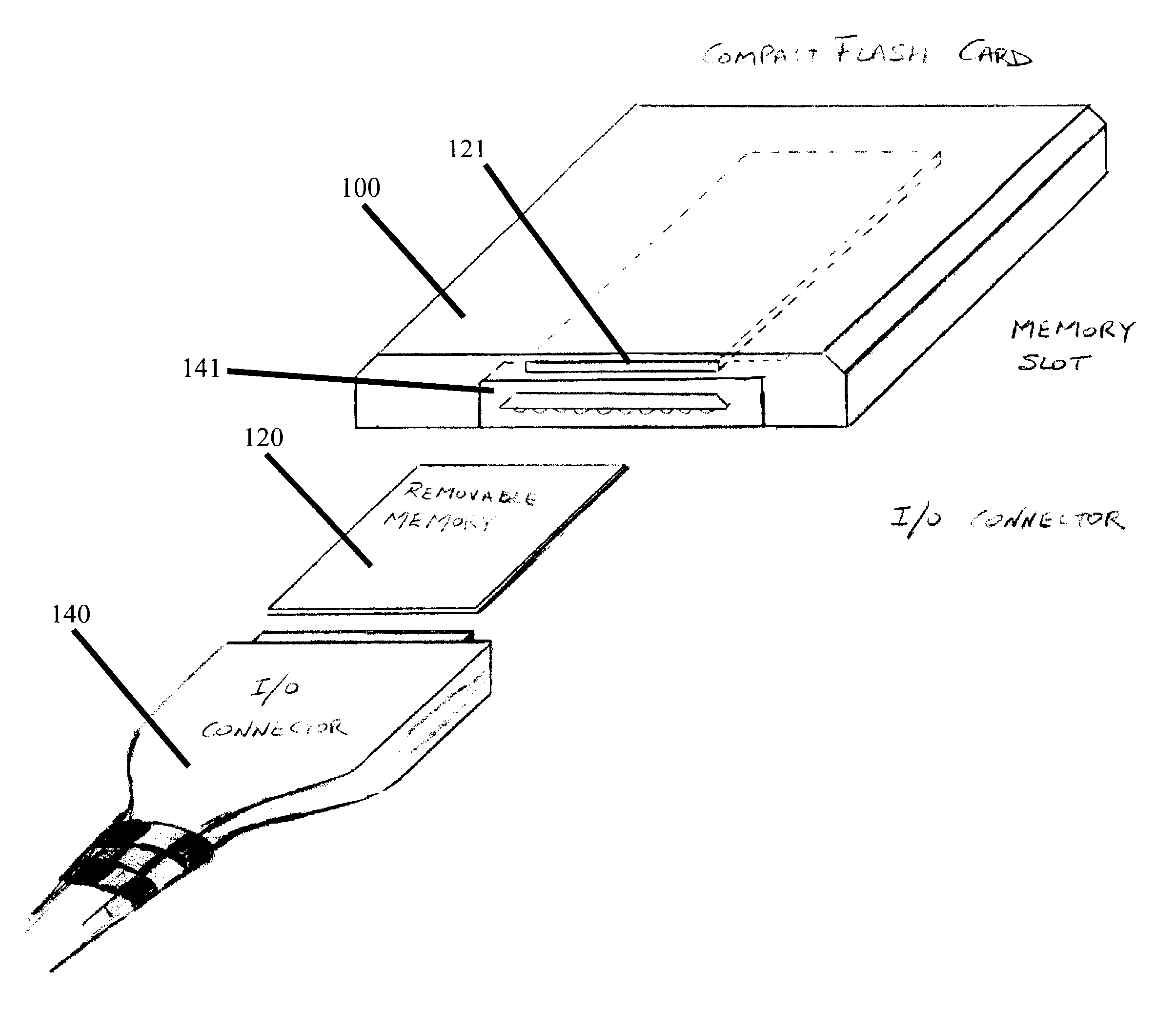

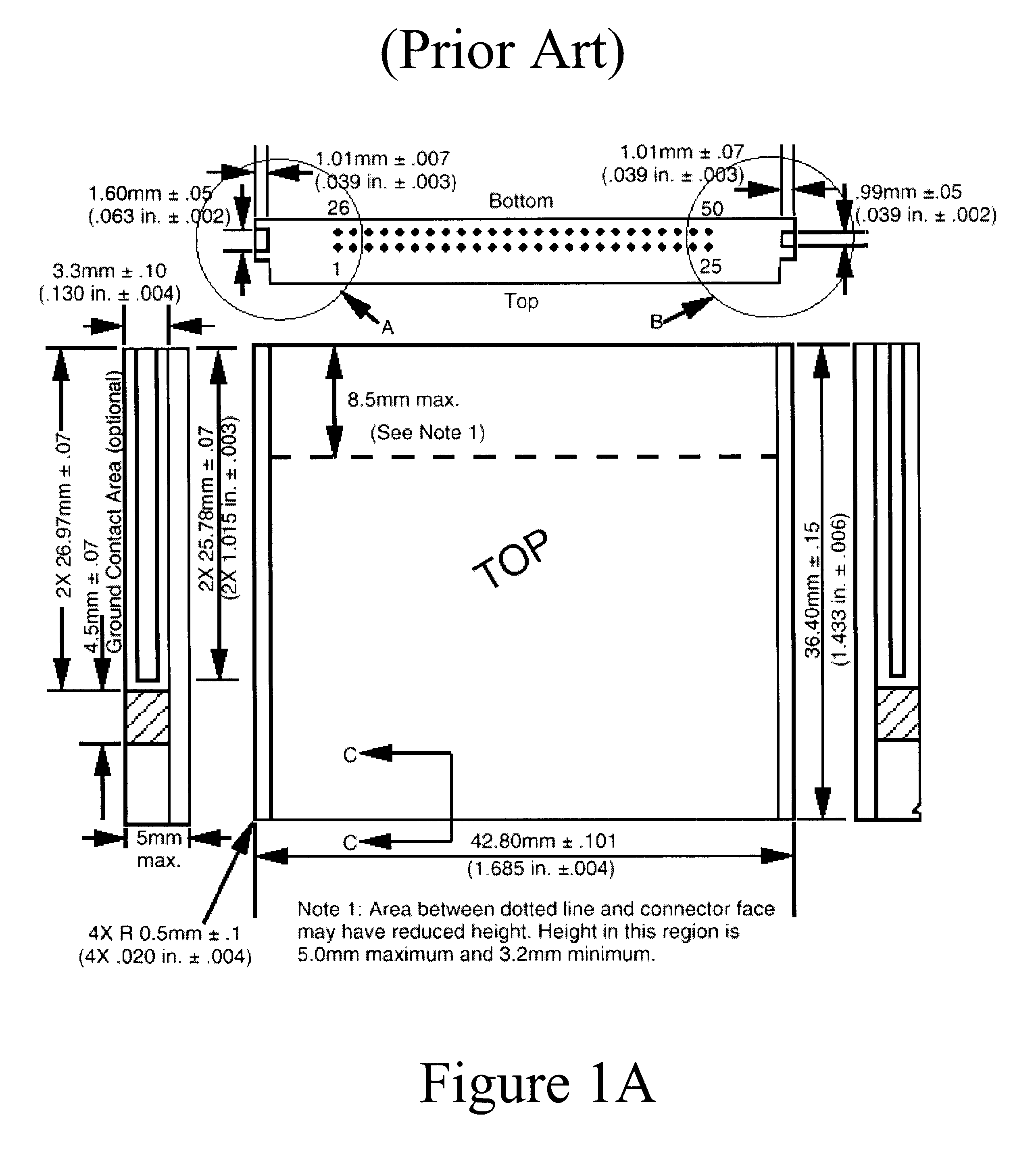

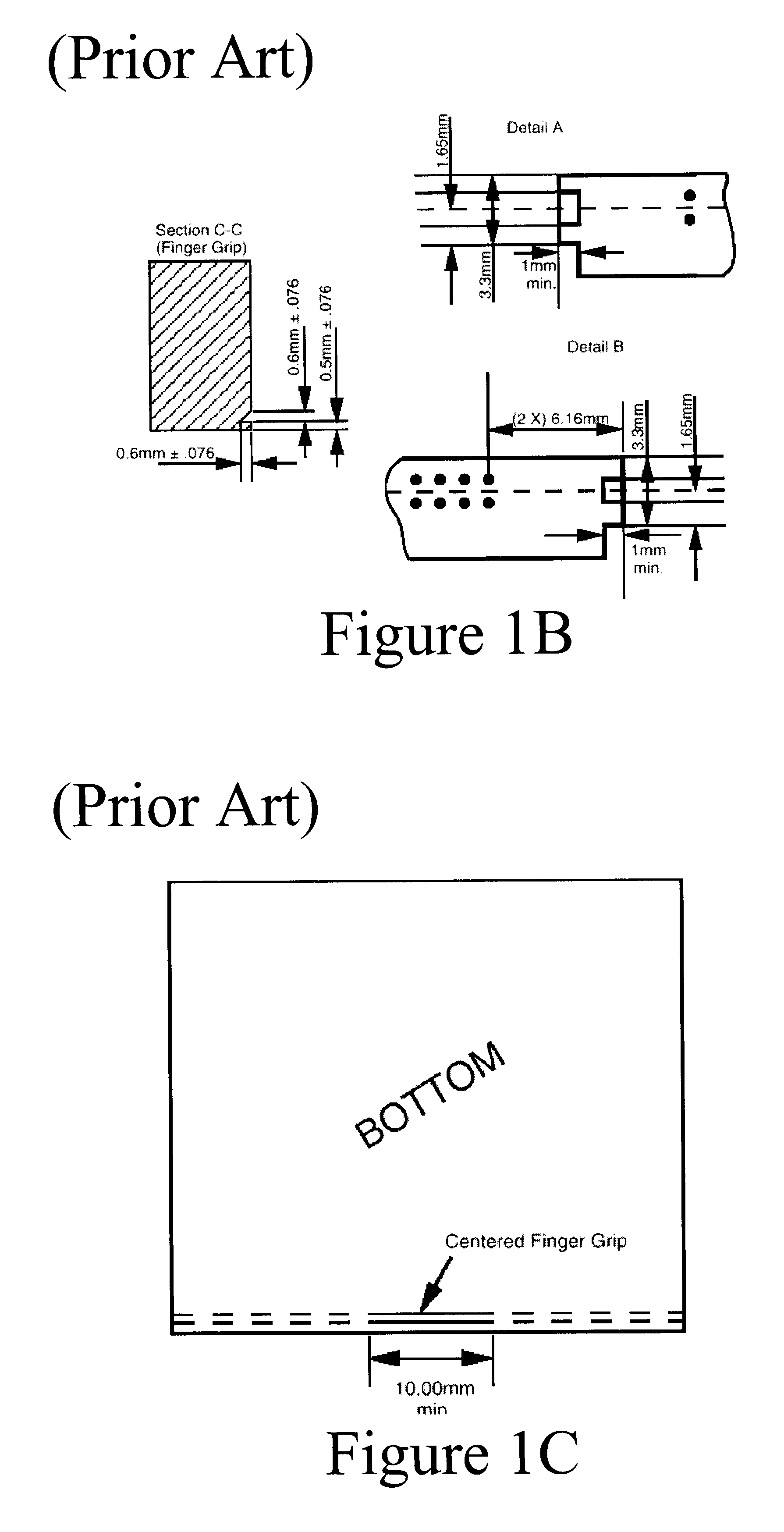

First-level removable module having bar code I/O and second-level removable memory

InactiveUS6691196B2Digital data processing detailsCasings/cabinets/drawers detailsBarcodeRemovable media

Computer hosts, such as PDAs, are customized for use in bar code scanner applications through use of a first-level removable expansion module having bar code related circuitry and a slot and internal connector for a second-level removable memory. In combination with a connected or attached I / O device for scanning bar codes, these modules provide embedded bar code scanning I / O adapter and / or application-specific functions as well as second-level removable memory functions. The removable memory may be used to store a backup copy of the scanned data for restoration in the event the original scan data is lost or corrupted. Restoration may occur using any interface compatible with the removable memory. The removable memory may also be used by the bar code scanner application specific circuitry within the first-level removable expansion module. In illustrative embodiments, an industry standard physical and electrical interface couples the application specific module to the computer host, which provides user interface functions for the application.

Owner:SOCKET MOBILE

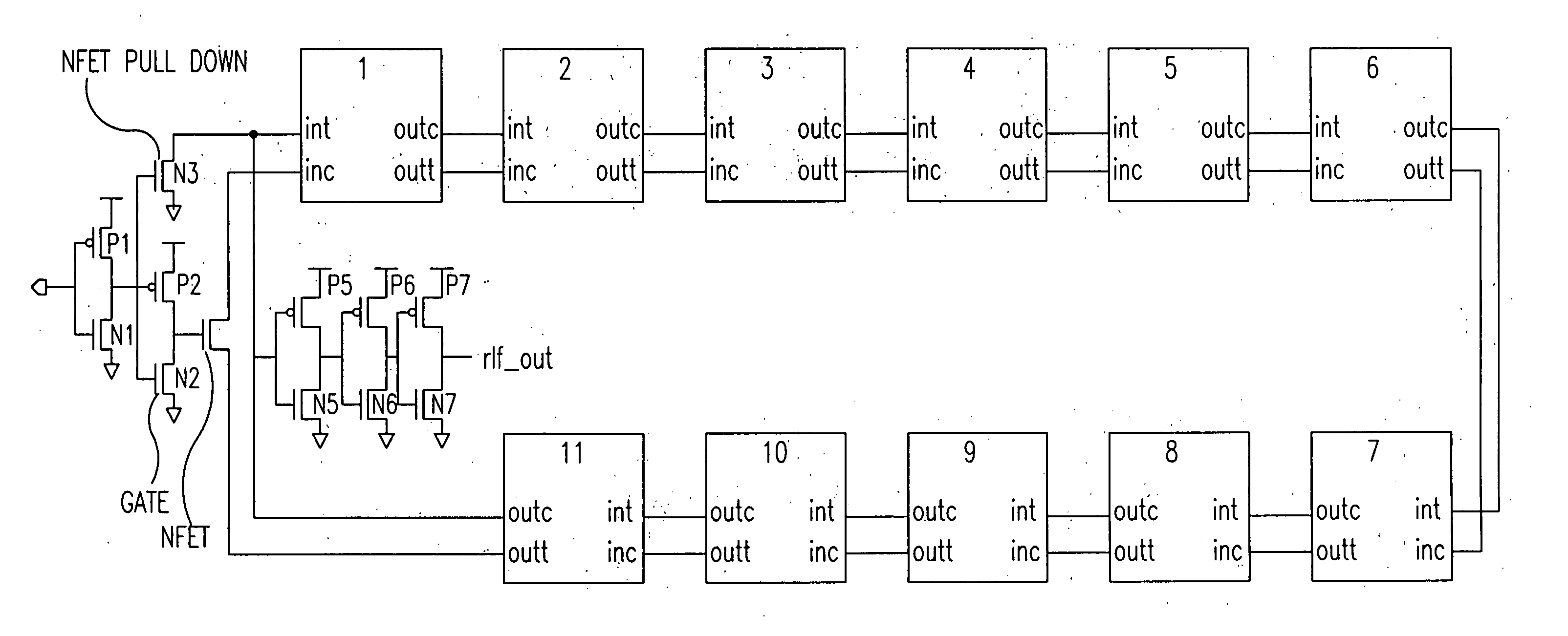

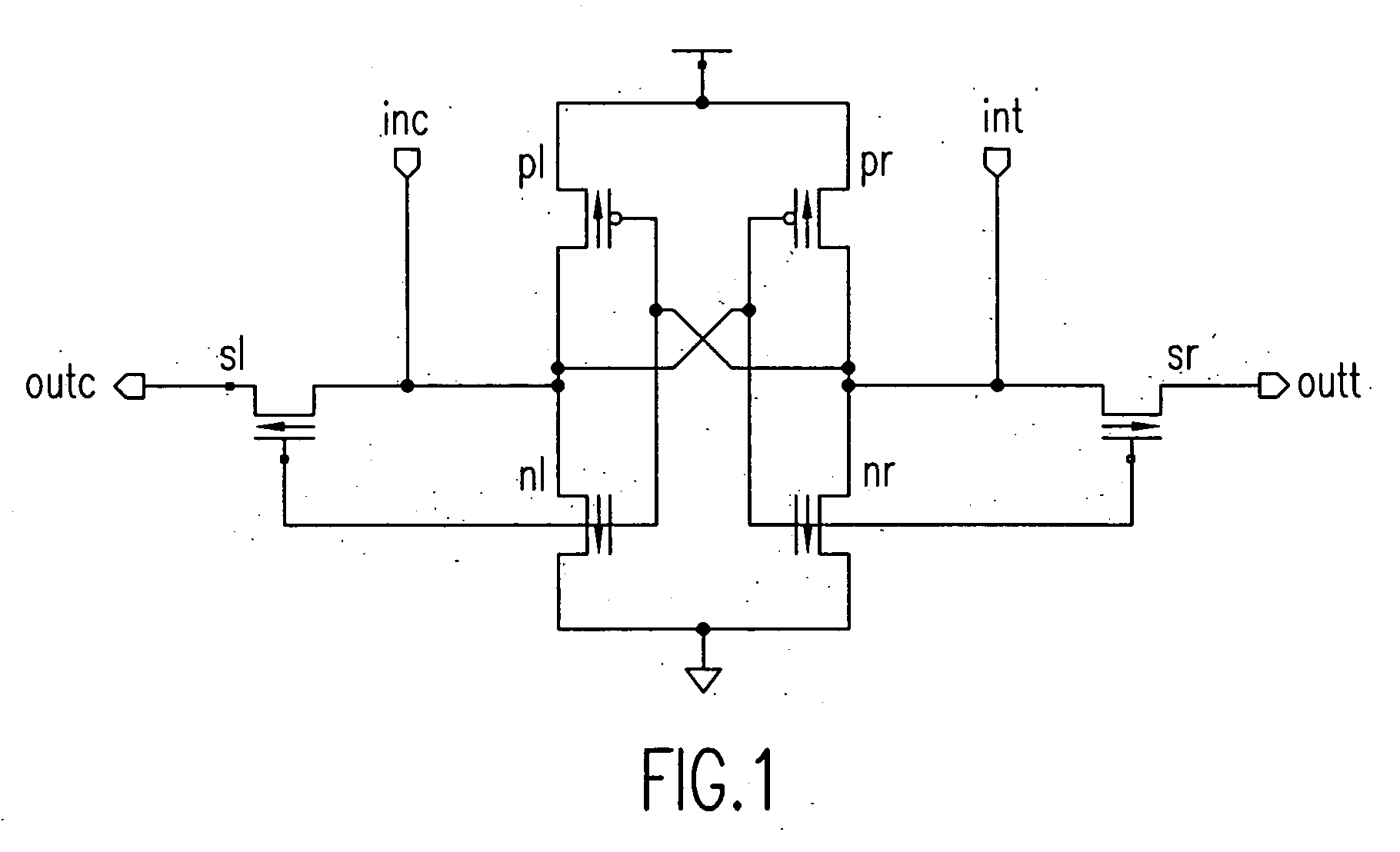

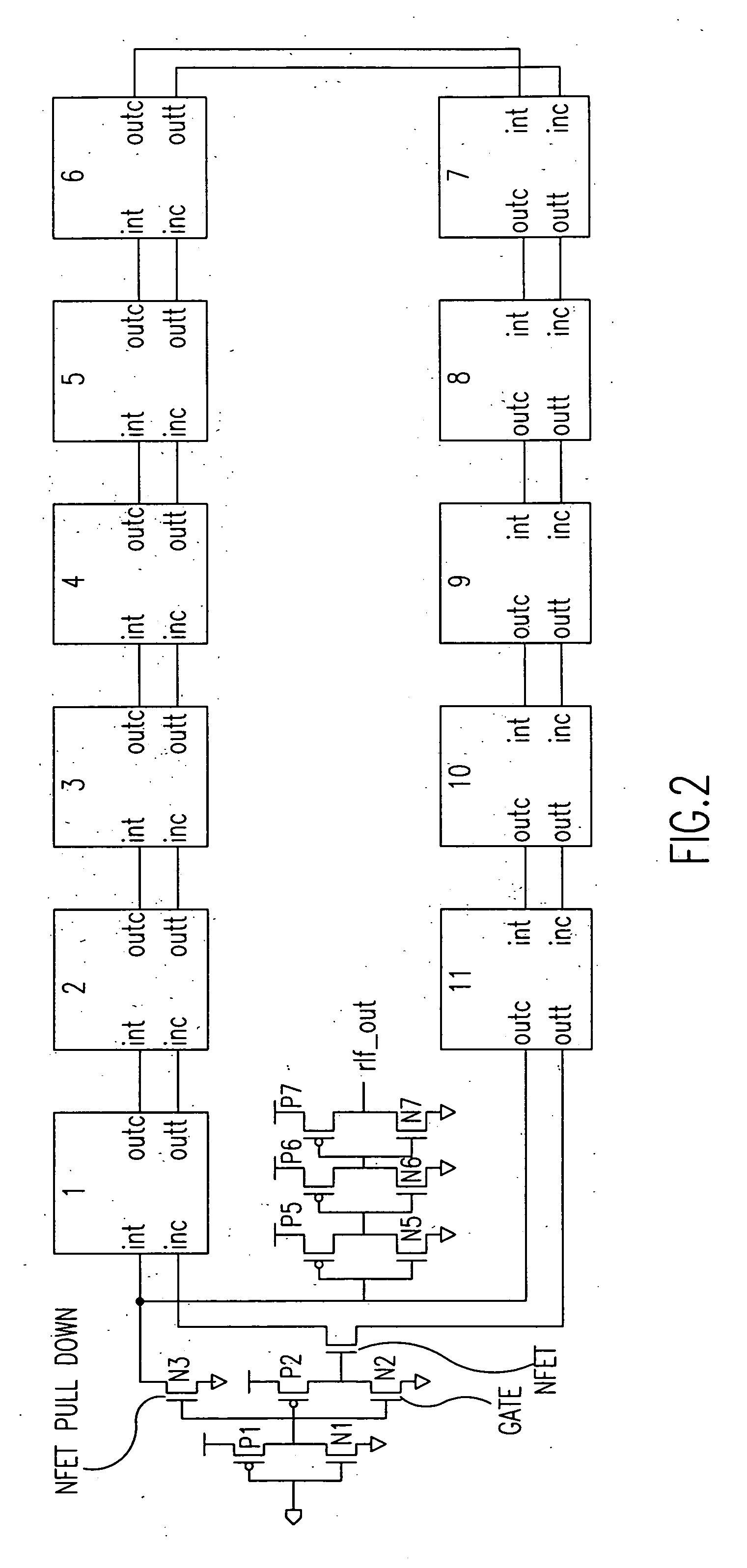

Sram ring oscillator

ActiveUS20060097802A1Easy to buildHigh yieldPulse generation by logic circuitsFrequency analysisCell designField-effect transistor

An SRAM design evaluation circuit topology has the gates of the SRAM cell pass Gate Field Effect Transistors (FETs) connected to the cross-coupled gates of the inverter pair of the SRAM cell. This evaluation circuit typology is used in a full cell implementation. A series of full cells are interconnected one to another in a loop to form a ring oscillator. The output of the ring is frequency divided and measured to study the read and write behavior of the cell design. Similarly, half-cells, with the gates of their pass gates grounded, are interconnected one to another to form a ring oscillator, the output of which is frequency divided and measured to help isolate pass gate impact on memory function. The modified SRAM cell topology, connected as a ring oscillator in hardware, can be used to fully characterize an SRAM cell design, without the use of peripheral read / write circuitry.

Owner:GLOBALFOUNDRIES US INC

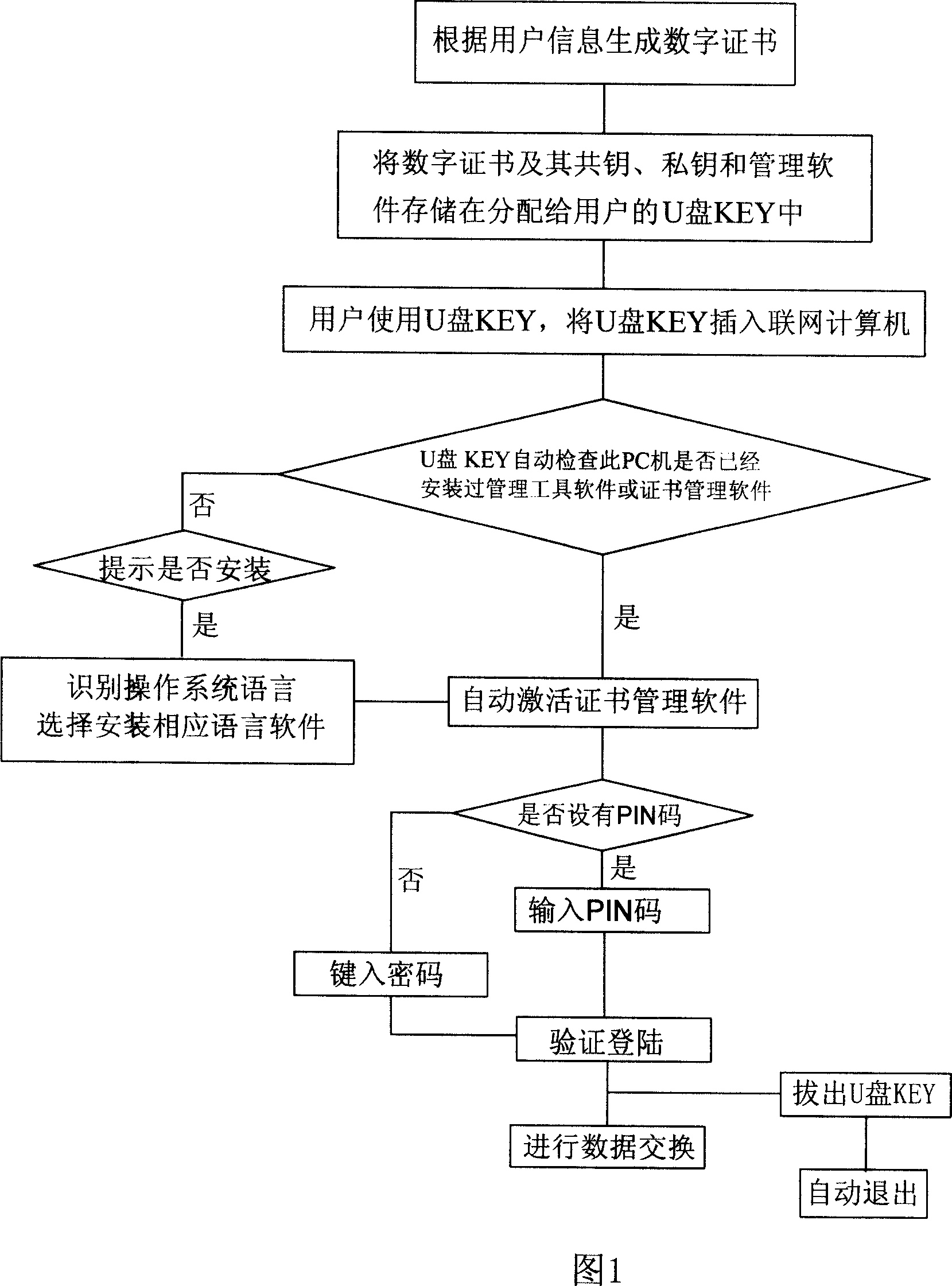

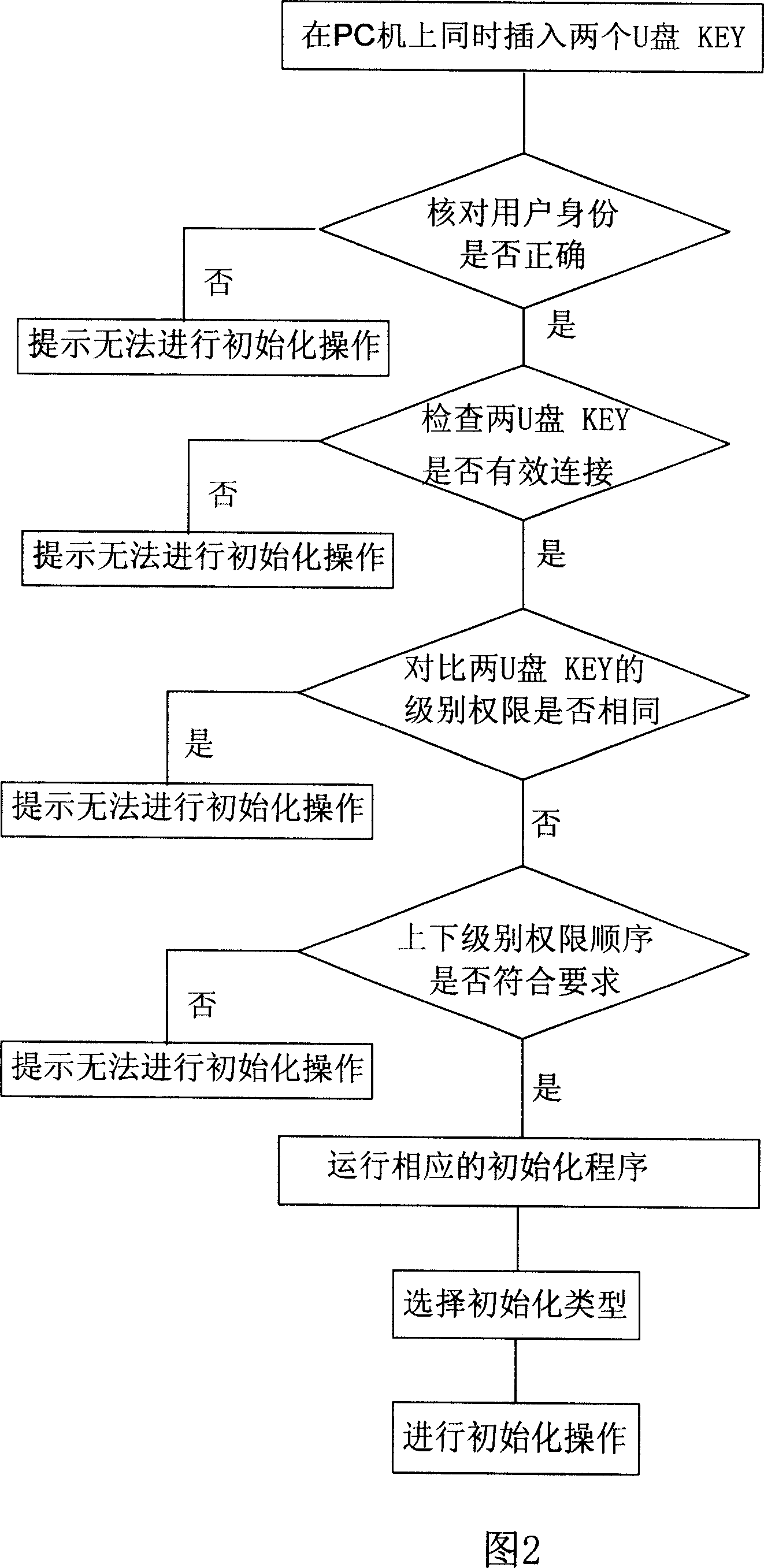

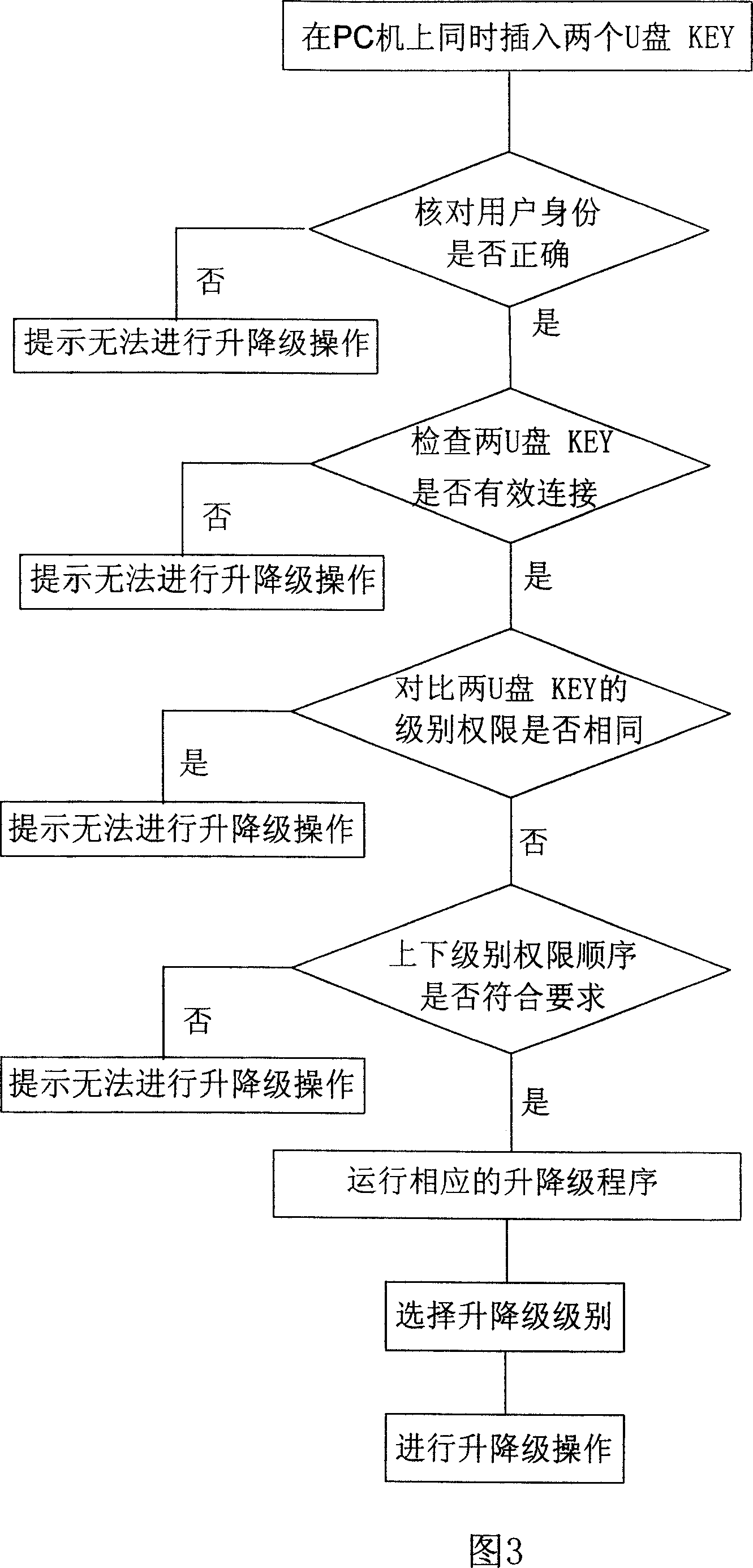

Internet bank U disc KEY ciphering, authentication device and method

InactiveCN101127111AAvoid the risk of forgetting to log out of the systemWith U disk storage functionFinanceDigital data protectionSoftware engineeringUSB

The utility model discloses an encryption and authentication method for U disk KEYS used at the internet banking, which comprising following steps: 1) a digital certificate is generated according to the information of the users; 2) the generated digital certificate in the first step and a public key, together with a private key, and a management software are stored in the U disk KEY allocated to the users; 3) when used, data processing at the internet banking is done after the users are identified with the U disk KEY. The utility model also discloses an encryption and authentication apparatus for the U disk KEY at the internet banking, mainly comprising a U disk KEY, a mainframe, a networked computer and an application server. Through the utility model, the ordinary USB KEY and the U disk memory chip are organically integrated as a whole which has a memory function of the U disk; the necessary management software for the use of the USB KEY and other programs are stored and used as a whole, and the process of the software installation is rapid and simple just by maintaining the necessary selection procedures in the installation process of the users, moreover, coding rules for passwords are not constrained and the ways for certificates management are more reasonable and easy to be operated.

Owner:CHINA CITIC BANK