Virtual memory address translation mechanism with controlled data persistence

a technology of virtual memory address and data persistence, applied in the field of virtual memory address translation mechanism with controlled data persistence, can solve the problem that the access of a particular program which holds the key is also at cache speed, and achieve the effect of facilitating journalling and related data protection and less prone to address errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

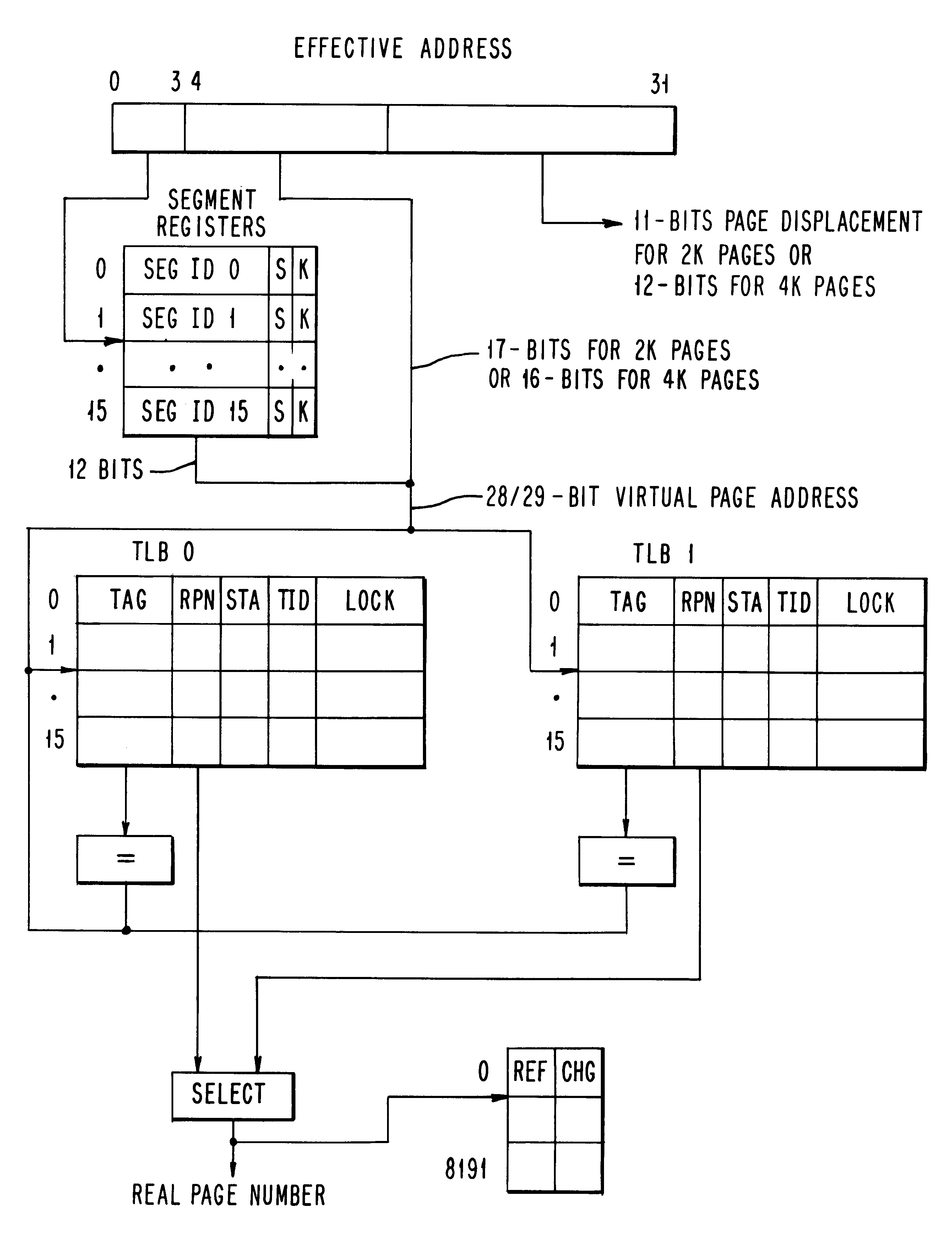

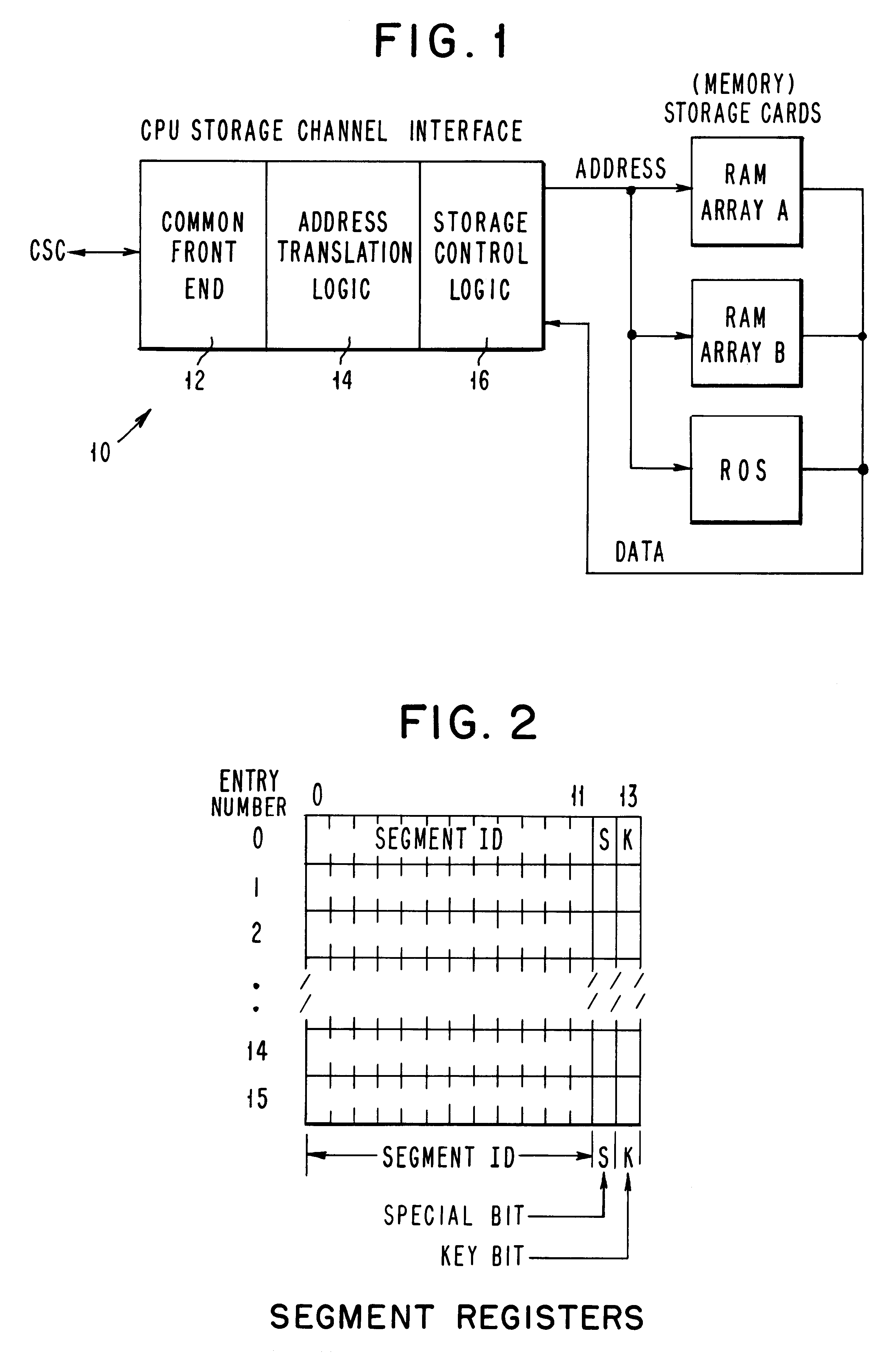

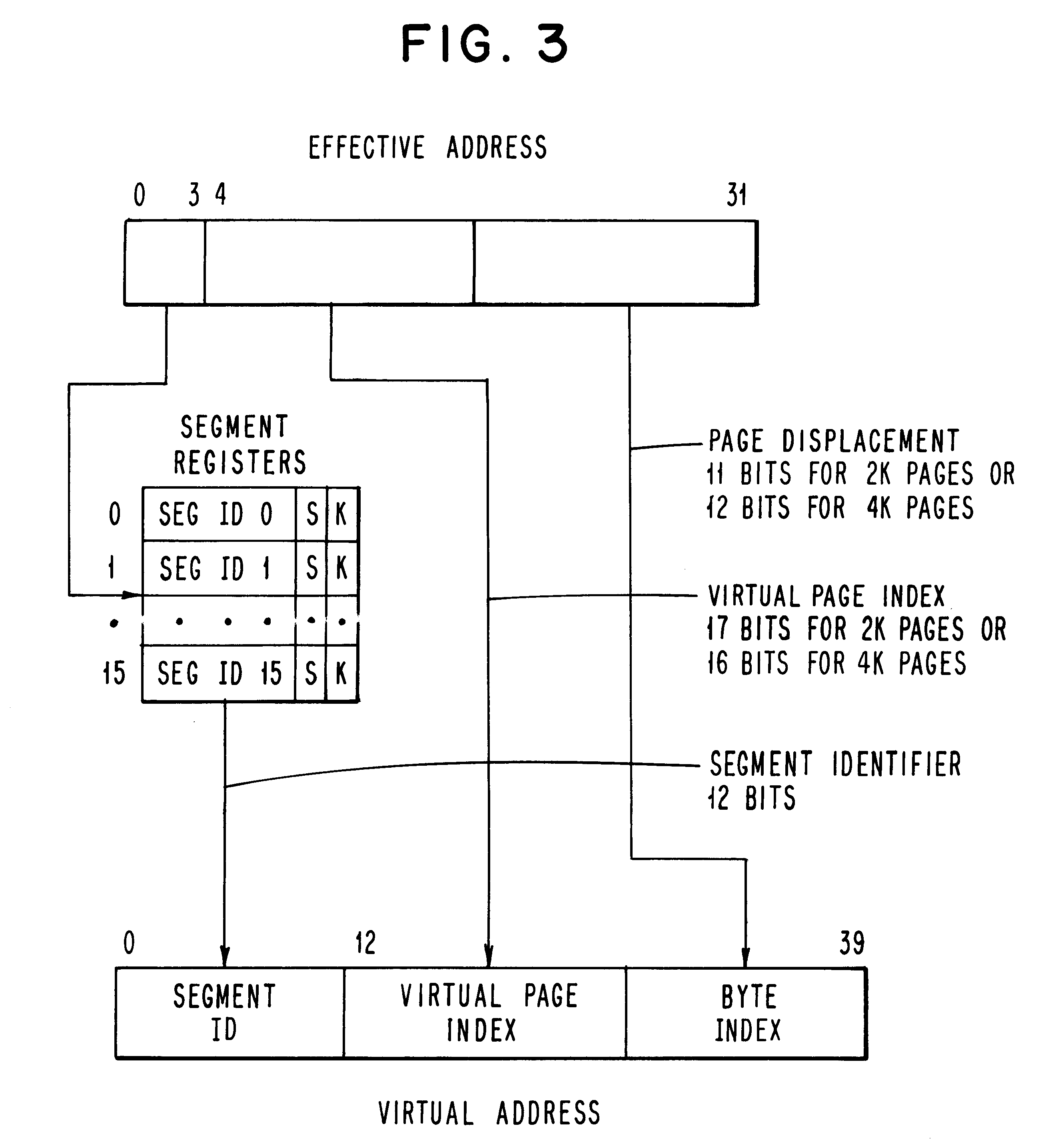

The objects of the present invention are accomplished in general by the herein disclosed storage controller that attaches to a host CPU Storage Channel which implements the address translation architecture described in general terms previously, and which will be described in greater detail subsequently. The translating mechanism contains the logic required to interface with up to 16M bytes of storage. Storage can be interleaved or non-interleaved, and static or dynamic. The translation mechanism is functionally divided into three sections (see FIG. 1). The CPU storage channel interface (CSC) 10 logic consists of the Common Front End (CFE), section 12 which provides the proper protocol from the storage channel to the Address Translation Logic 14 and Storage Control Logic 16. All communication to and from the storage channel is handled by this logic. The Address Translation Logic provides the translation from a virtual address received from the storage channel to a real address used t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More